Patents

Literature

7814 results about "Control logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Control logic is a key part of a software program that controls the operations of the program. The control logic responds to commands from the user, and it also acts on its own to perform automated tasks that have been structured into the program.

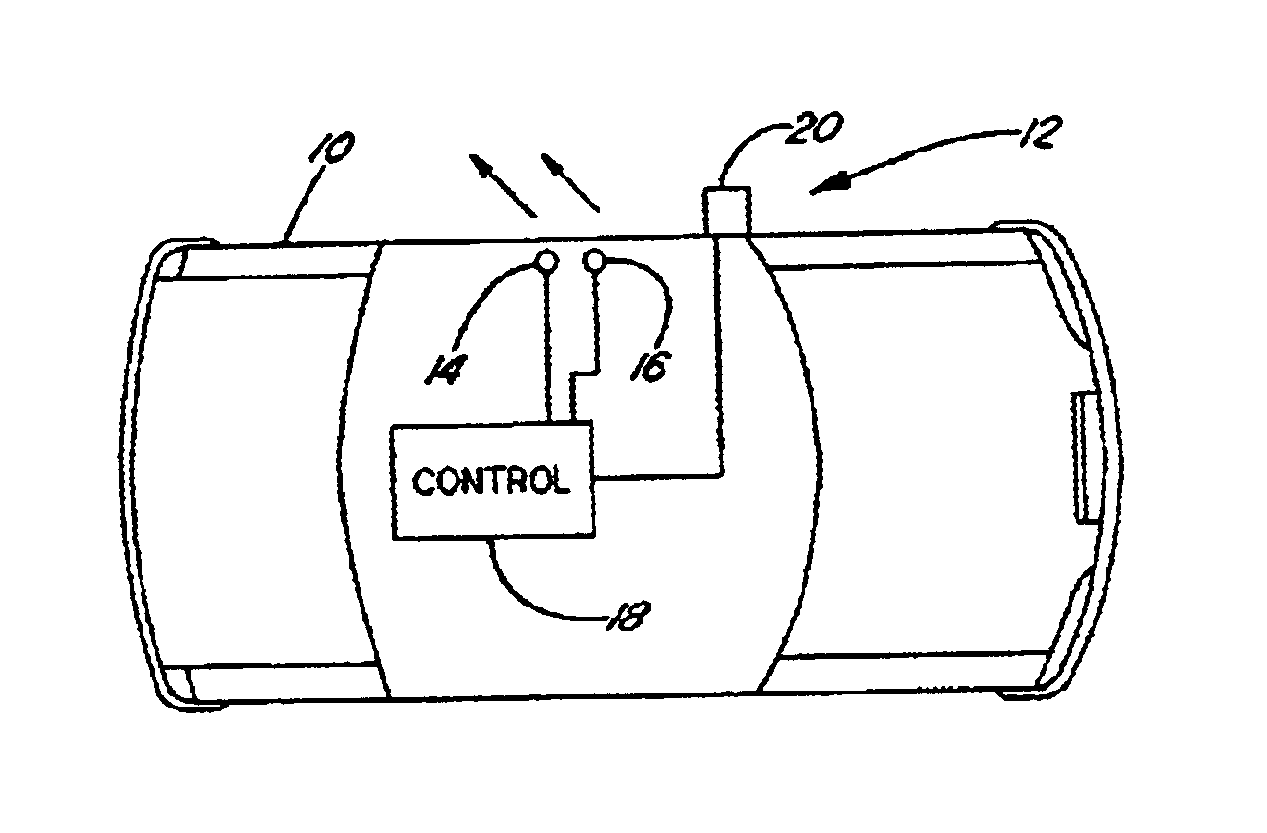

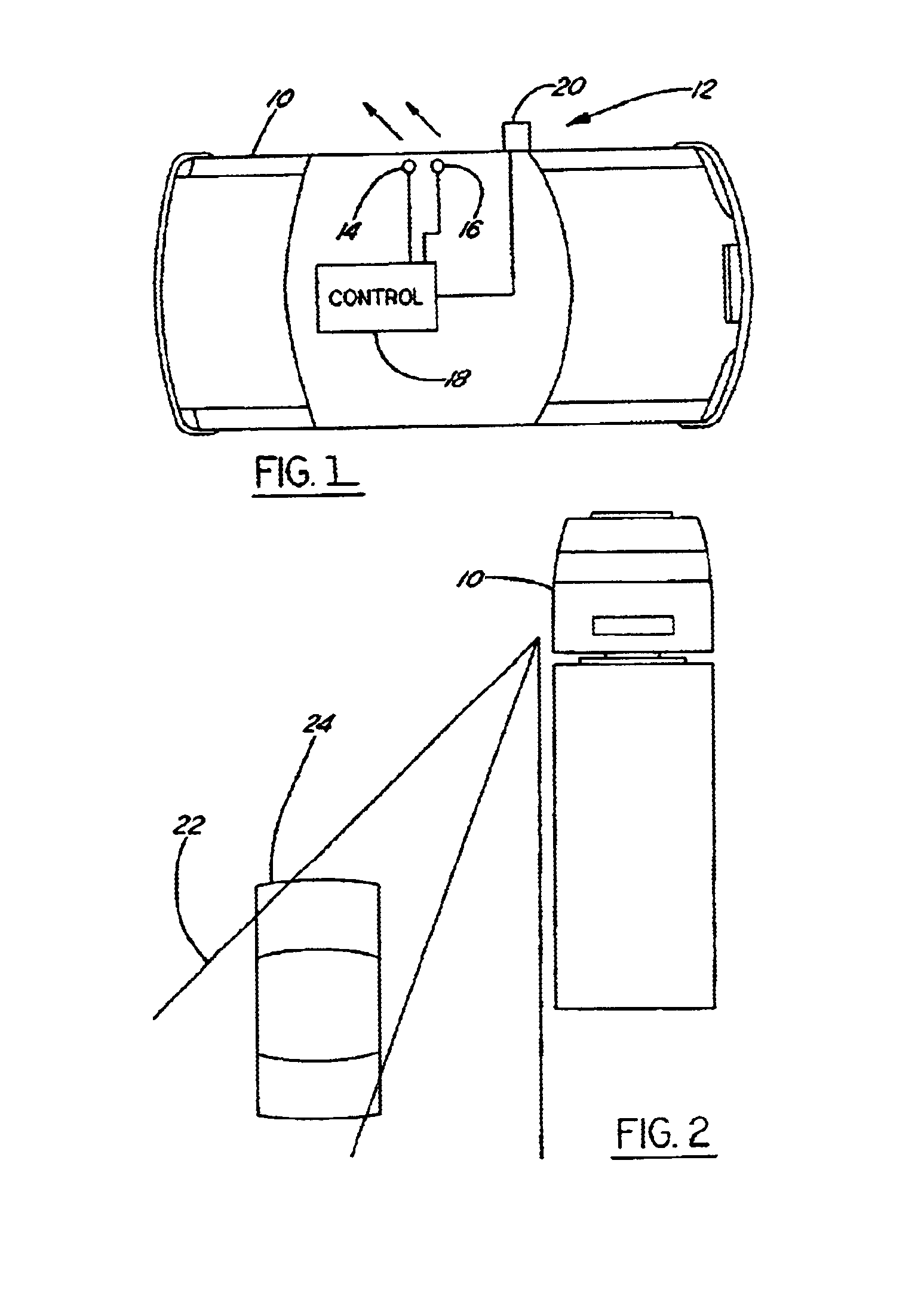

Vehicle blind spot monitoring system

InactiveUS6737964B2Improve securityAnti-collision systemsCharacter and pattern recognitionMonitoring systemDisplay device

A blind spot monitoring system for a vehicle includes two pairs of stereo cameras, two displays and a controller. The stereo cameras monitor vehicle blind spots and generate a corresponding pair of digital signals. The display shows a rearward vehicle view and may replace, or work in tandem with, a side view mirror. The controller is located in the vehicle and receives two pairs of digital signals. The controller includes control logic operative to analyze a stereopsis effect between each pair of stereo cameras and the optical flow over time to control the displays. The displays will show an expanded rearward view when a hazard is detected in the vehicle blind spot and show a normal rearward view when no hazard is detected in the vehicle blind spot.

Owner:FORD GLOBAL TECH LLC

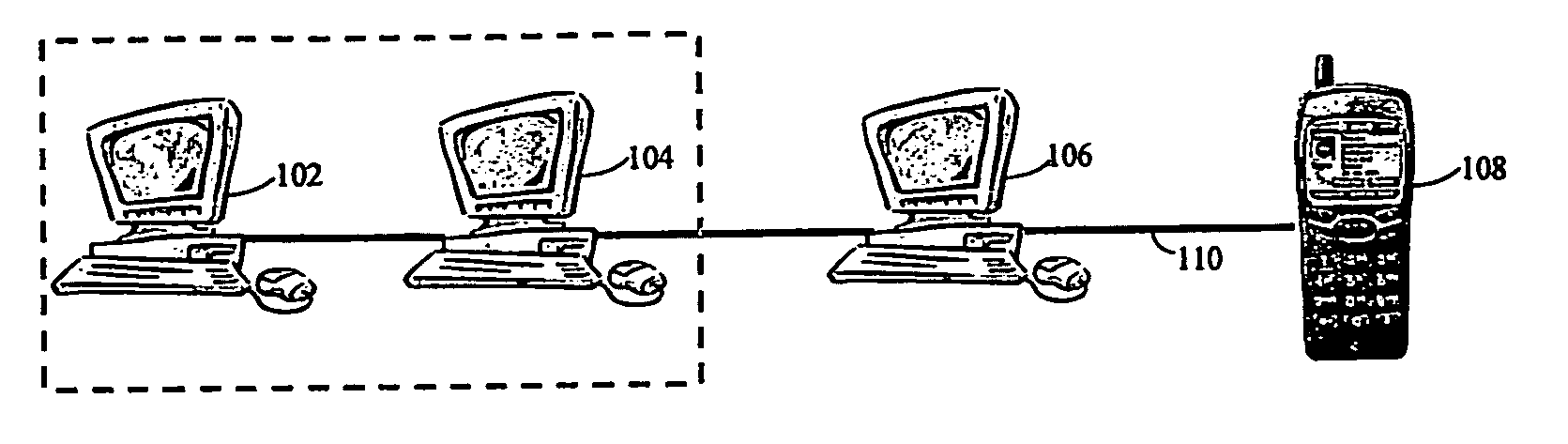

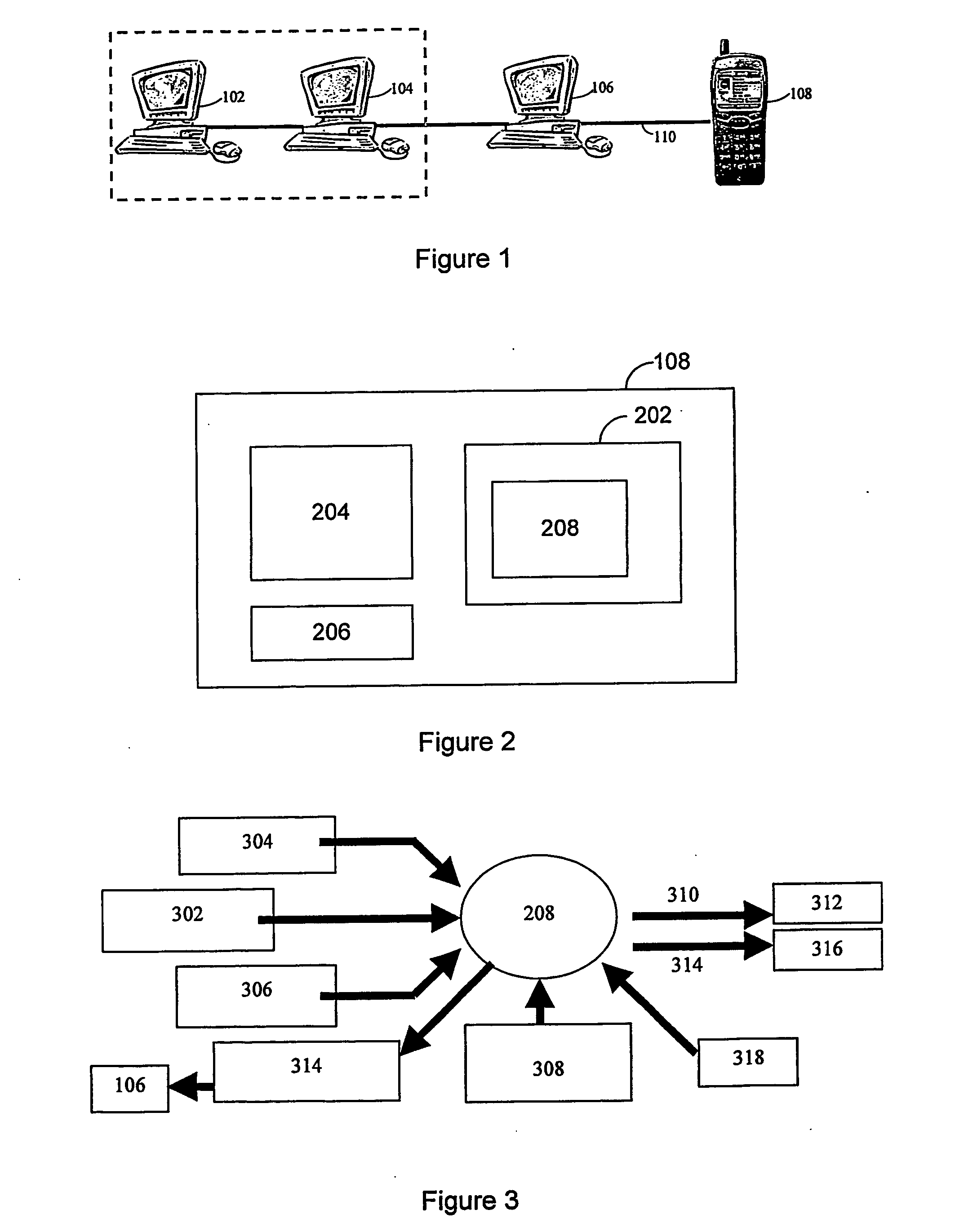

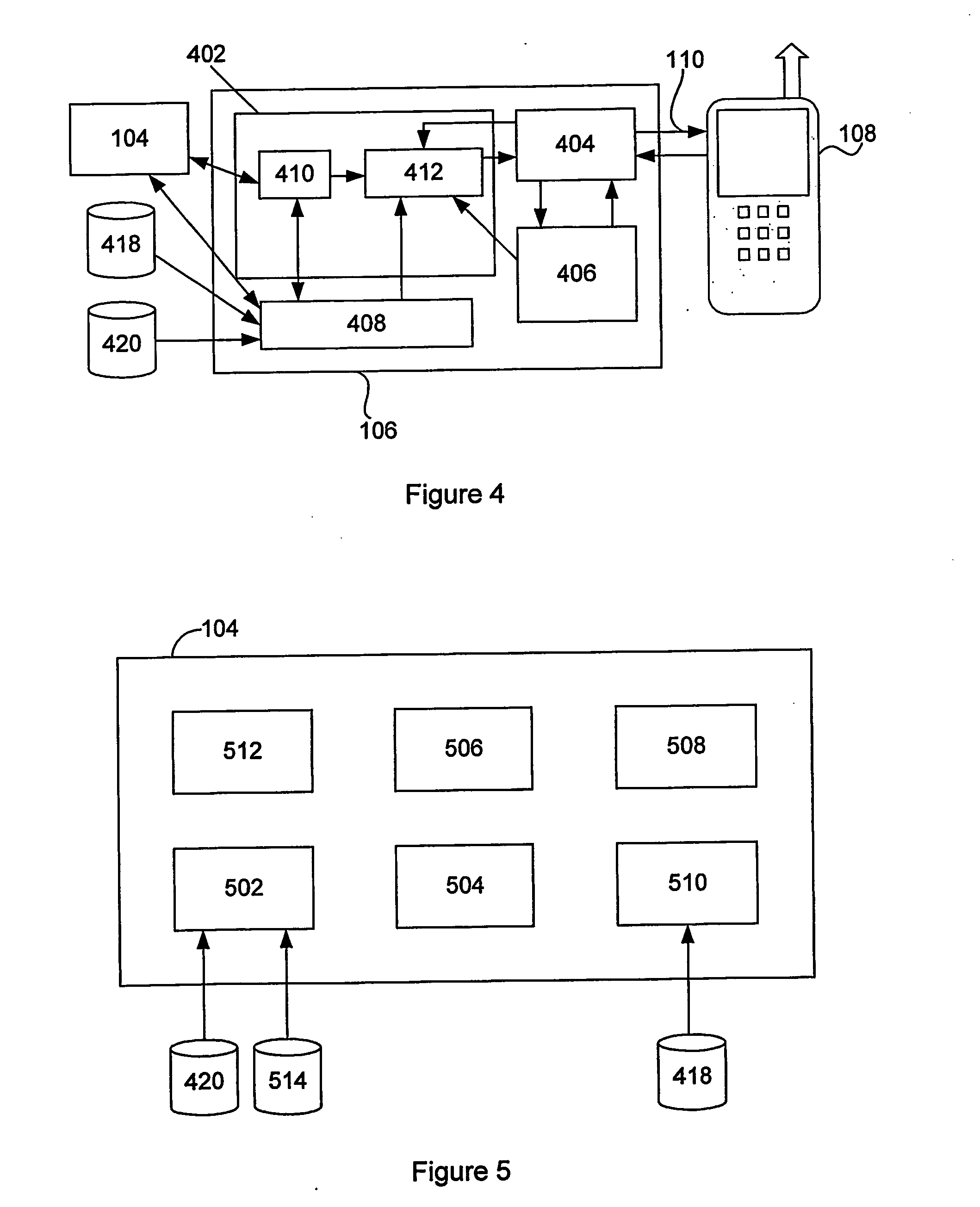

Multimedia publishing system for wireless devices

InactiveUS20060256130A1Cathode-ray tube indicatorsWebsite content managementComputer networkApplication software

A dynamic publishing system for delivery and presentation of multimedia on a wireless device, such as a PDA or mobile telephone. A presentation server dynamically compiles application data based on scene description data for one or more media objects, and sends the application data to the wireless device for presentation of the media objects. The wireless device has a media player that is able to process the application data at an object level for the objects in response to events, and control the presentation. The application data includes content, layout and control logic data for the media objects.

Owner:ACTIVESKY

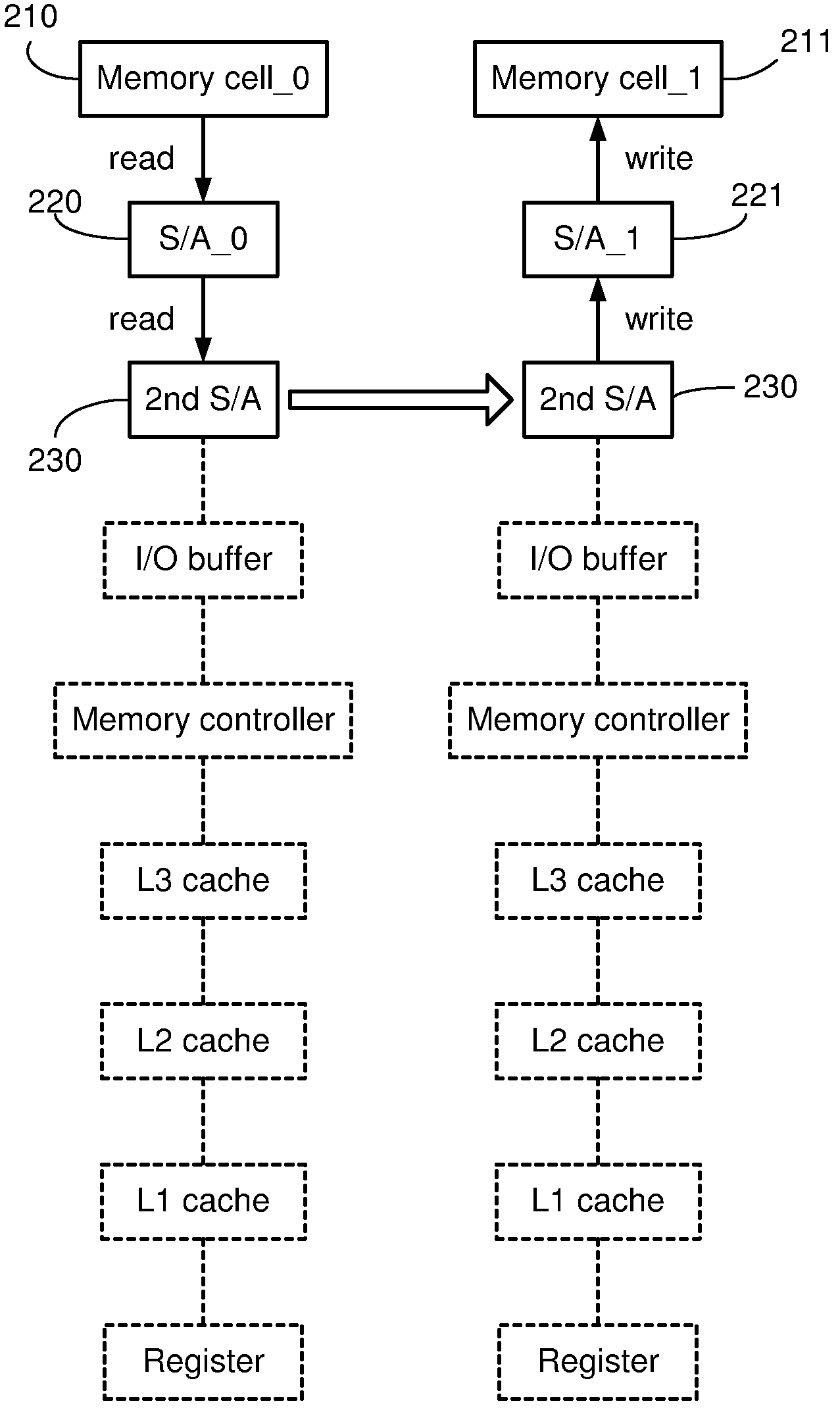

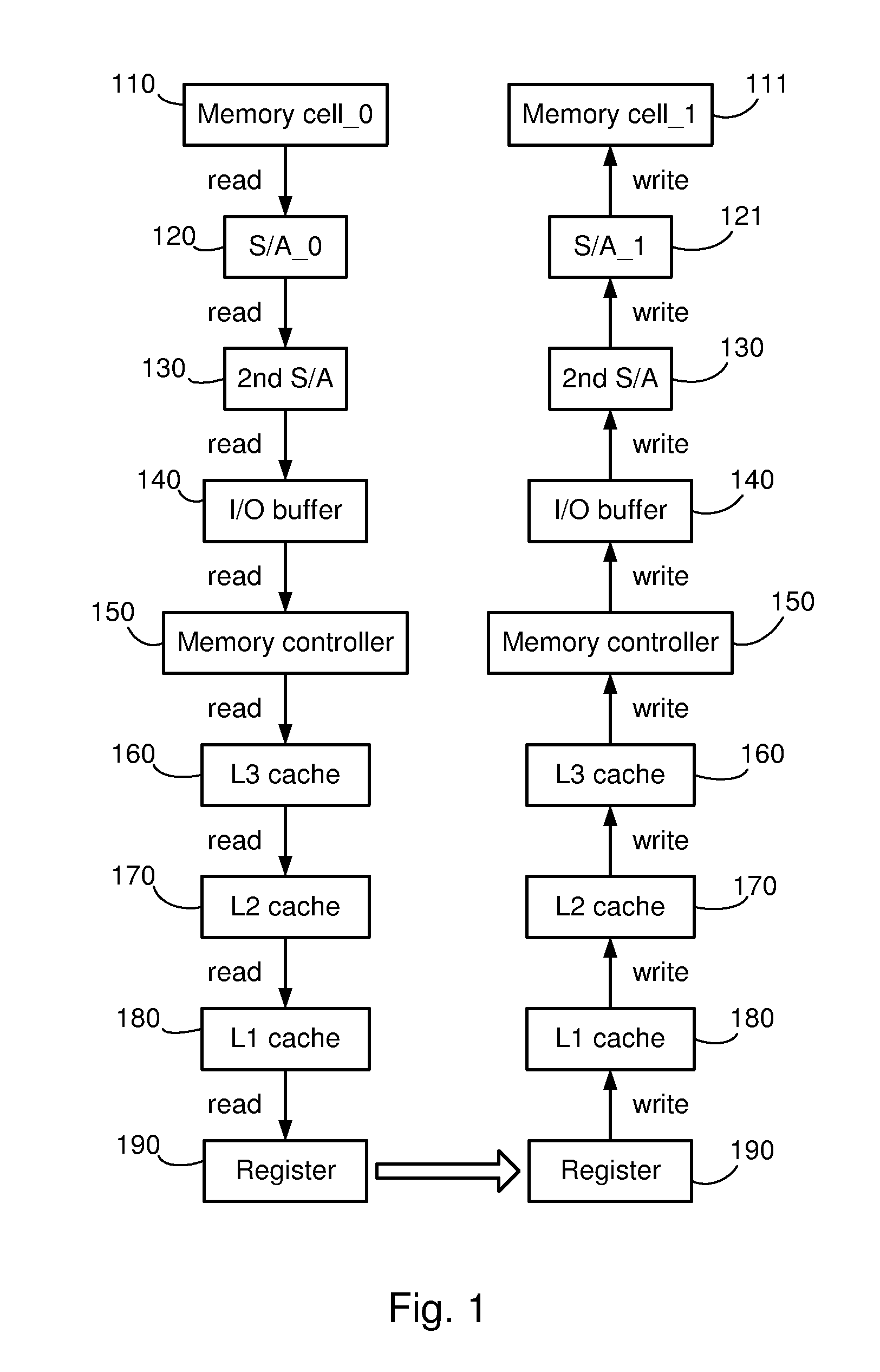

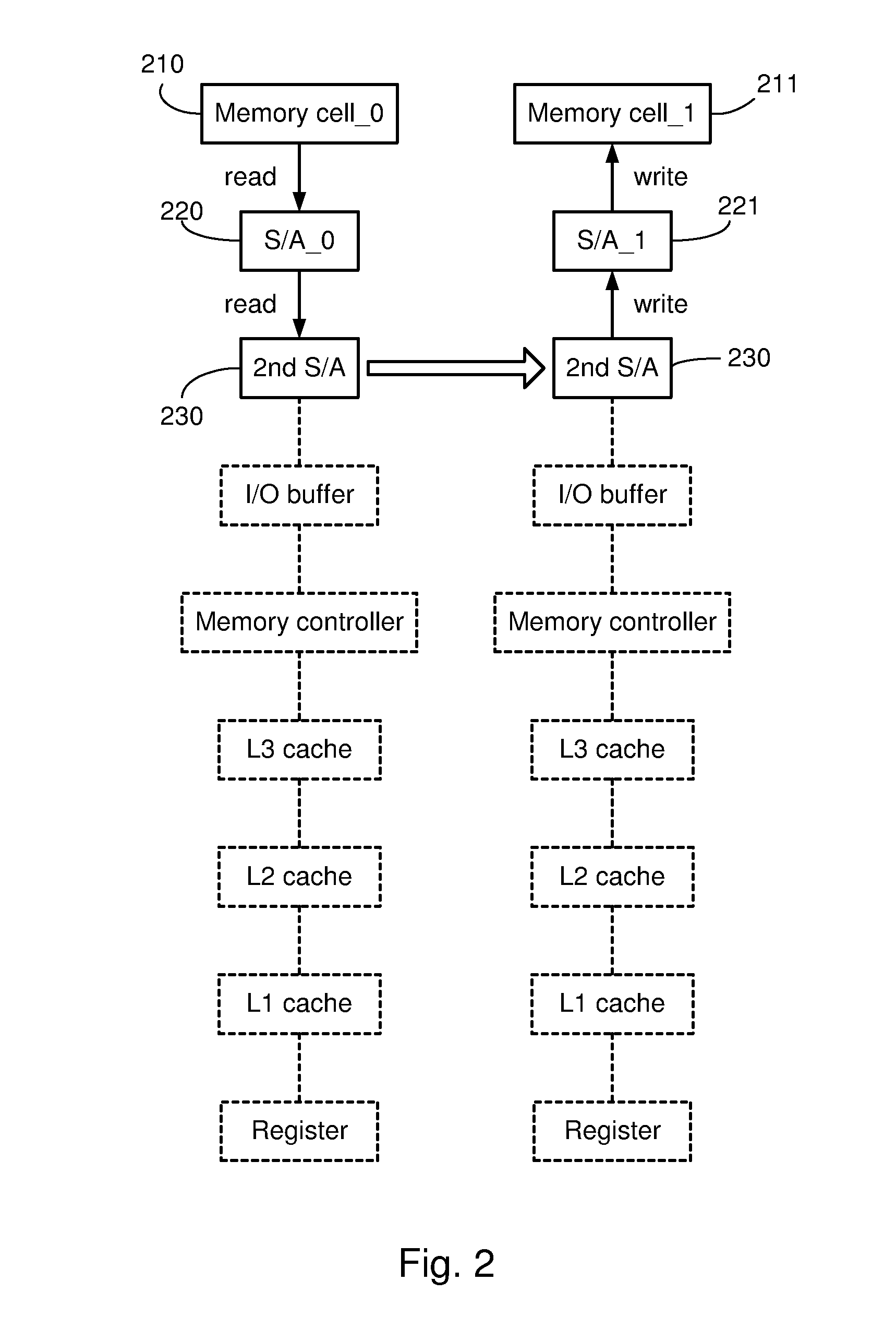

Systems and methods for data transfers between memory cells

Systems and methods for reducing the latency of data transfers between memory cells by enabling data to be transferred directly between sense amplifiers in the memory system. In one embodiment, a memory system uses a conventional DRAM memory structure having a pair of first-level sense amplifiers, a second-level sense amplifier and control logic for the sense amplifiers. Each of the sense amplifiers is configured to be selectively coupled to a data line. In a direct data transfer mode, the control logic generates control signals that cause the sense amplifiers to transfer data from a first one of the first-level sense amplifiers (a source sense amplifier) to the second-level sense amplifier, and from there to a second one of the first-level sense amplifiers (a destination sense amplifier.) The structure of these sense amplifiers is conventional, and the operation of the system is enabled by modified control logic.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

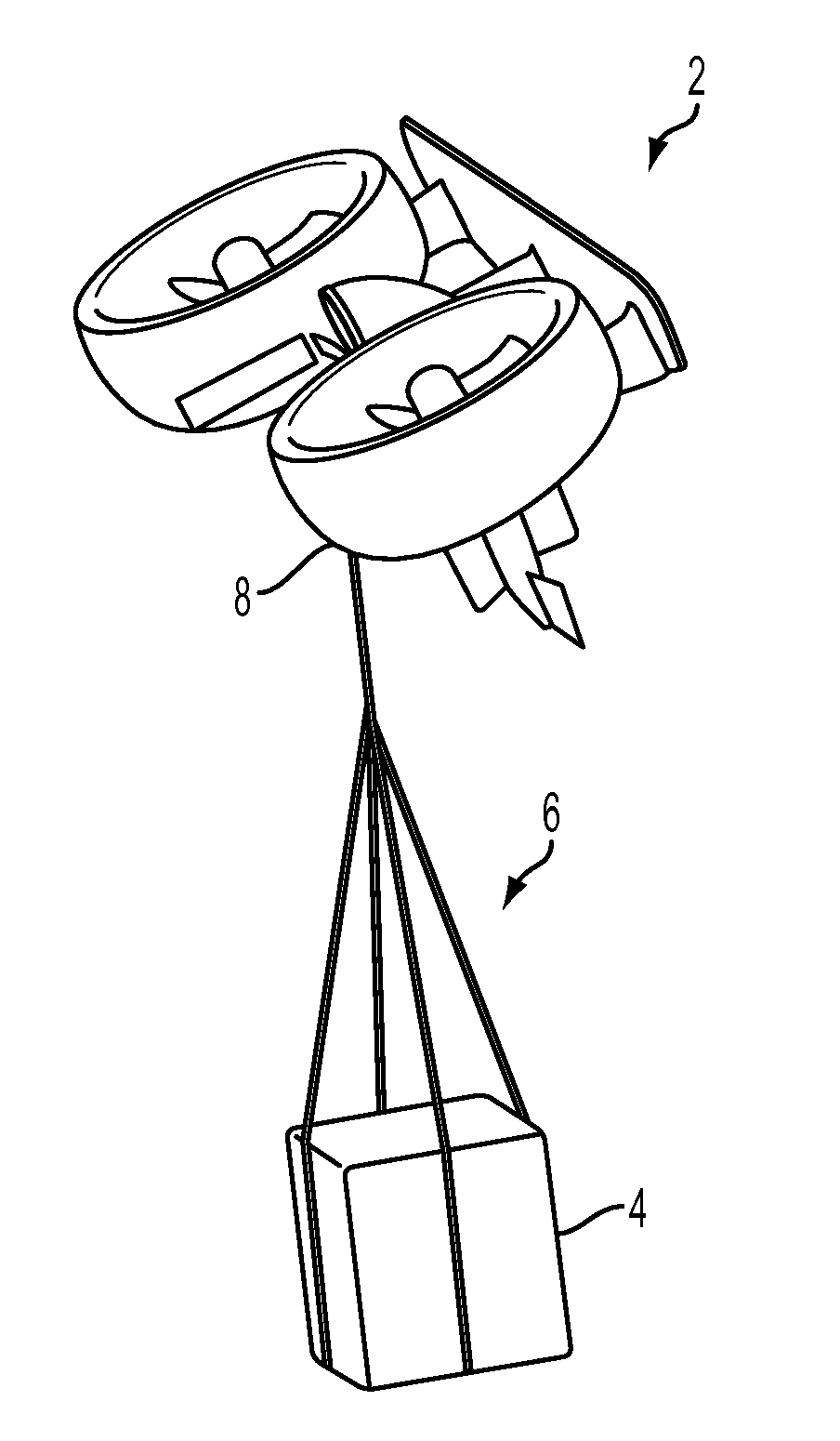

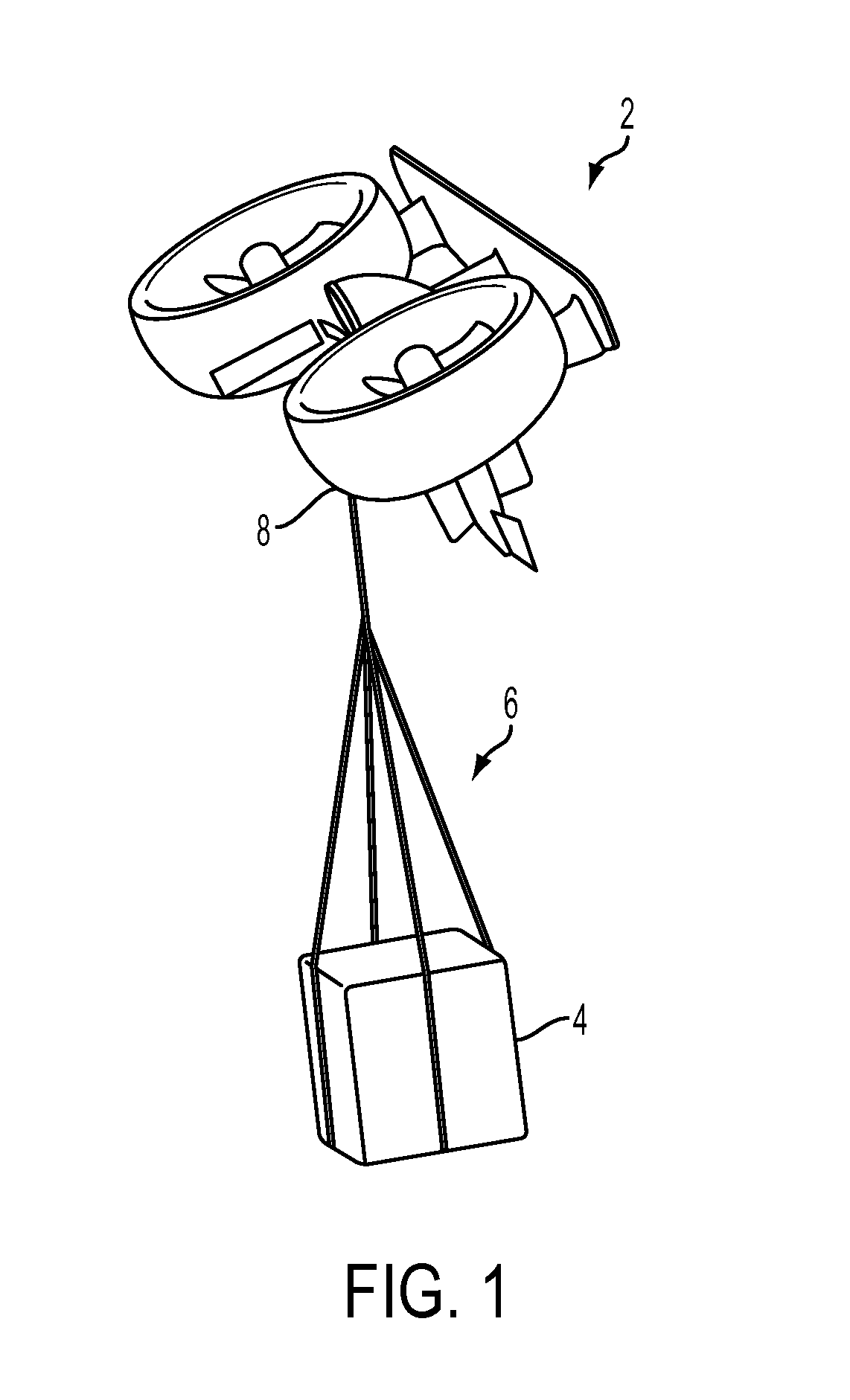

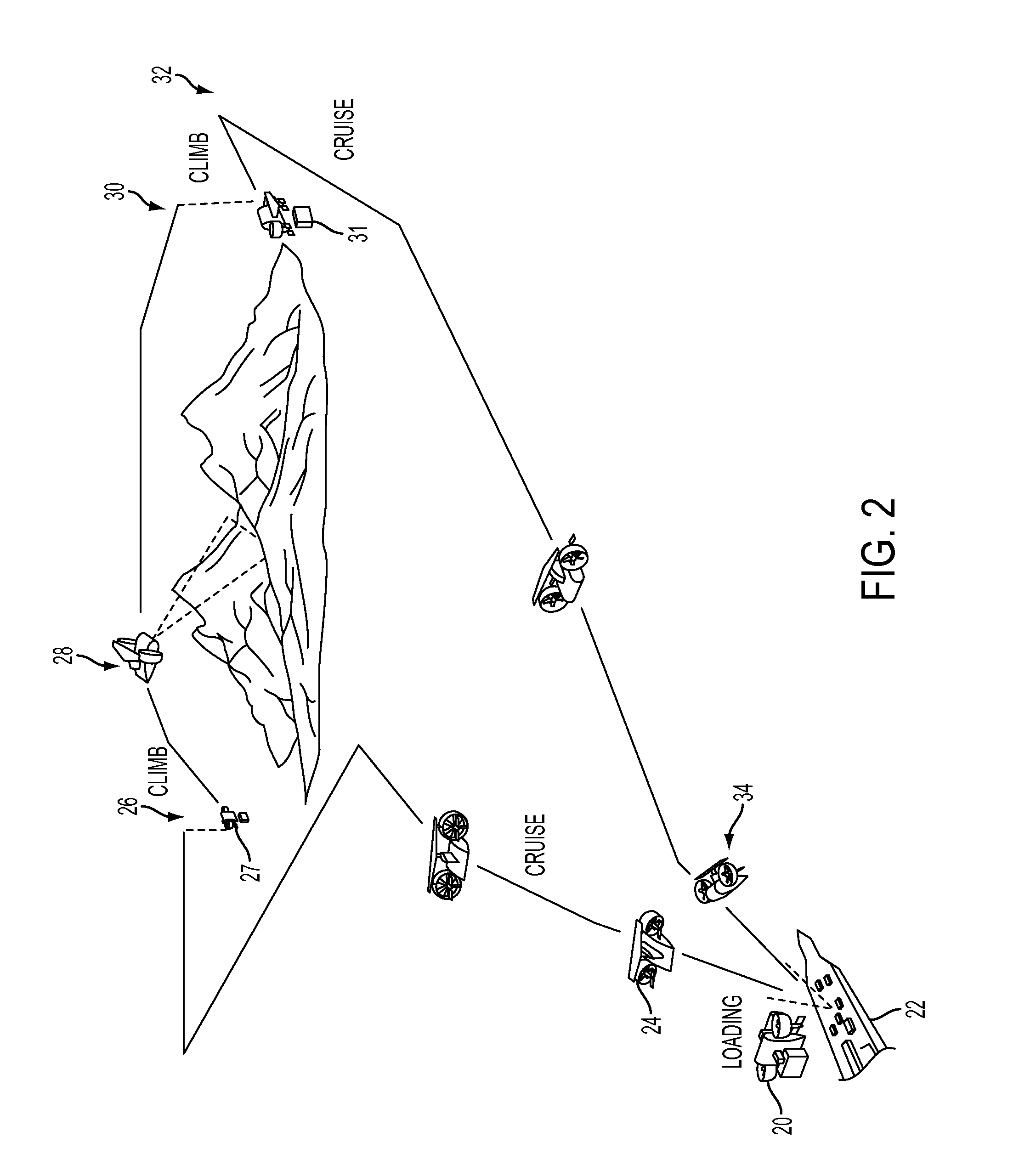

Autonomous Payload Parsing Management System and Structure for an Unmanned Aerial Vehicle

InactiveUS20110084162A1Improve versatilityIncrease in sizeStatic/dynamic balance measurementRemote controlled aircraftManagement systemControl logic

An unmanned aerial vehicle (UAV) for making partial deliveries of cargo provisions includes a UAV having one or more ducted fans and a structural interconnect connecting the one or more fans to a cargo pod. The cargo pod has an outer aerodynamic shell and one or more internal drive systems for modifying a relative position of one or more cargo provisions contained within the cargo pod. Control logic is configured to, after delivery of a partial portion of the cargo provisions contained within the cargo pod, vary a position of at least a portion of the remaining cargo provisions to maintain a substantially same center of gravity of the UAV relative to a center of gravity prior to delivery of the partial portion. Other center of gravity compensation mechanisms may also be controlled by the control logic to aid in maintaining the center of gravity of the UAV.

Owner:HONEYWELL INT INC

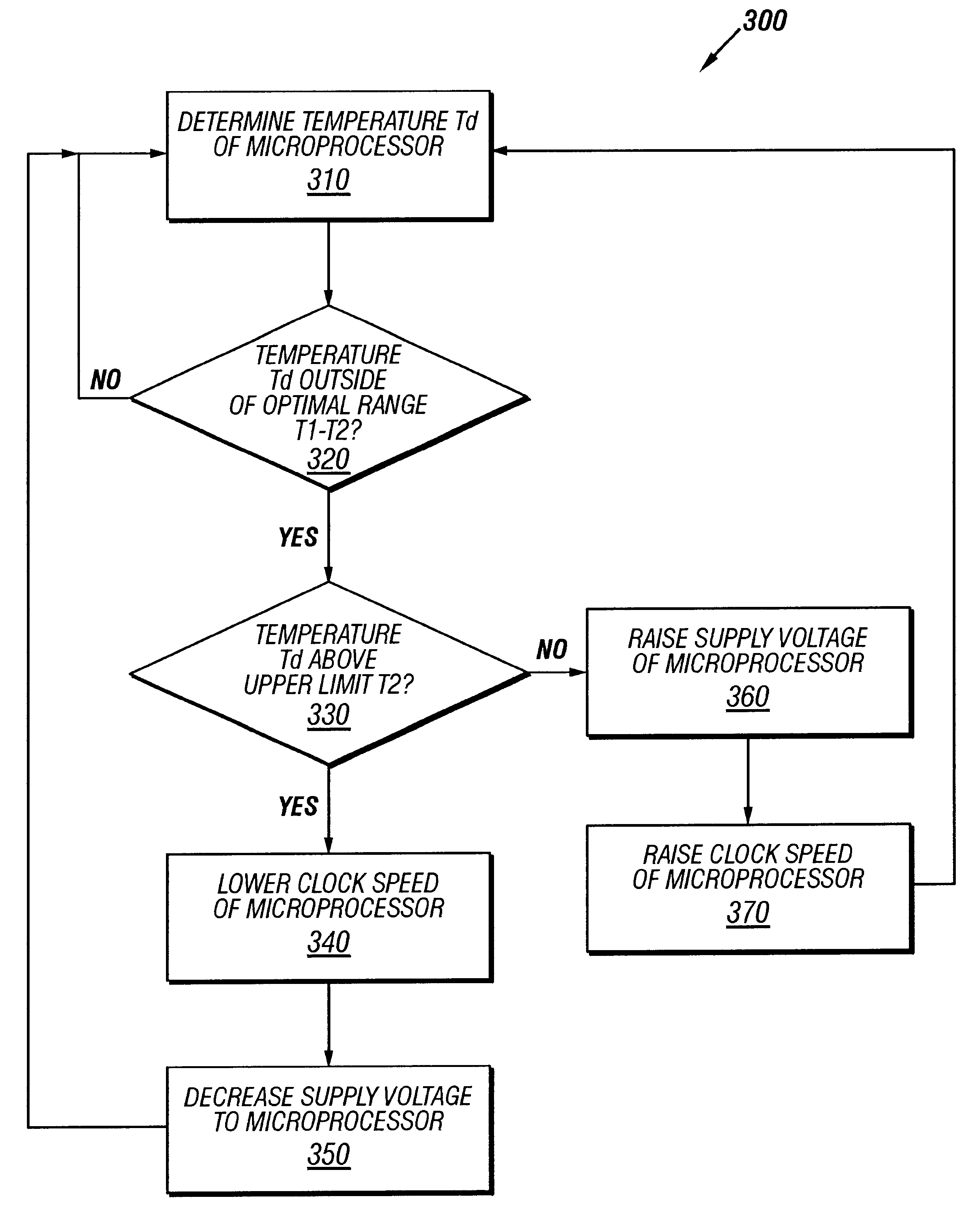

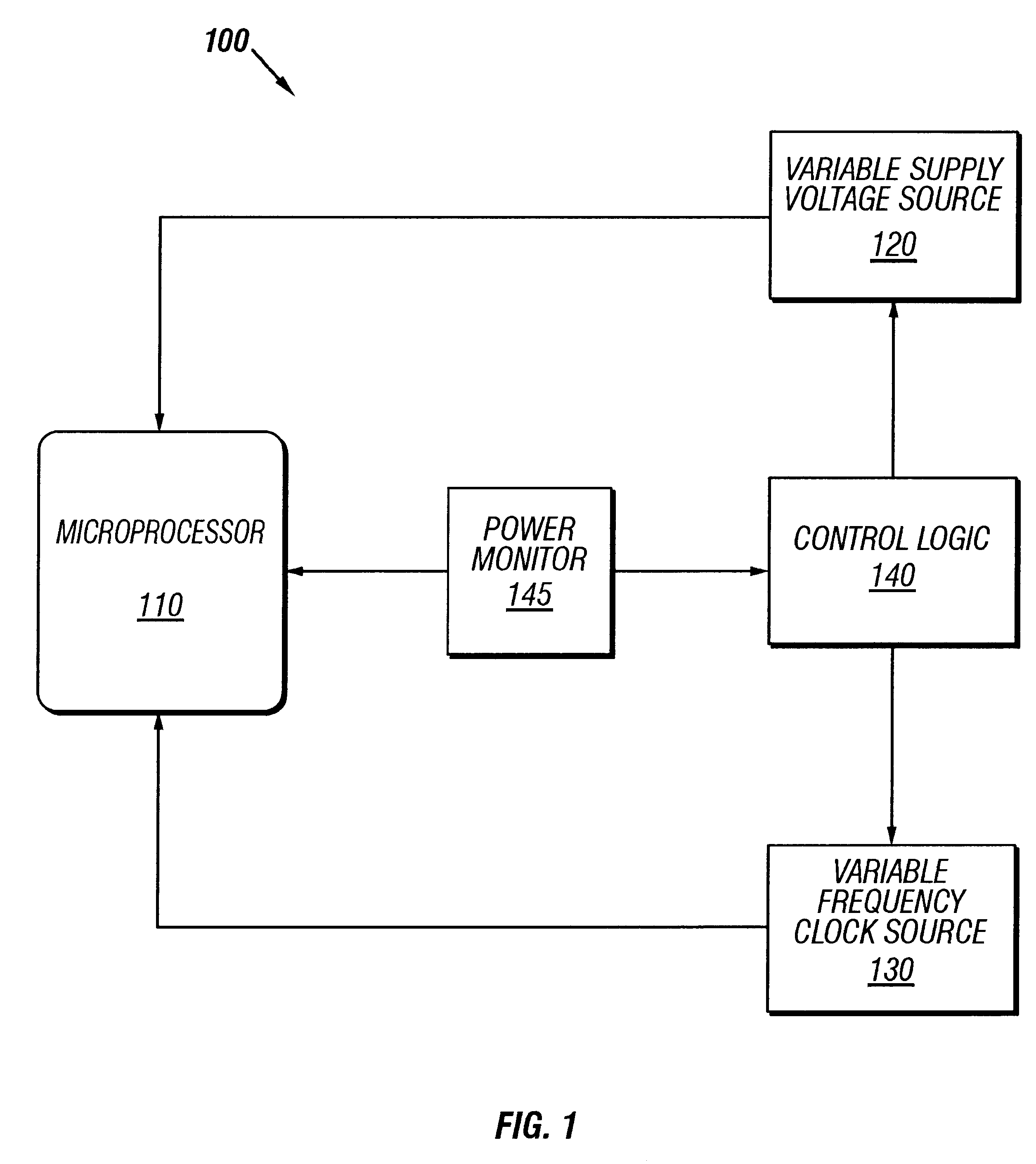

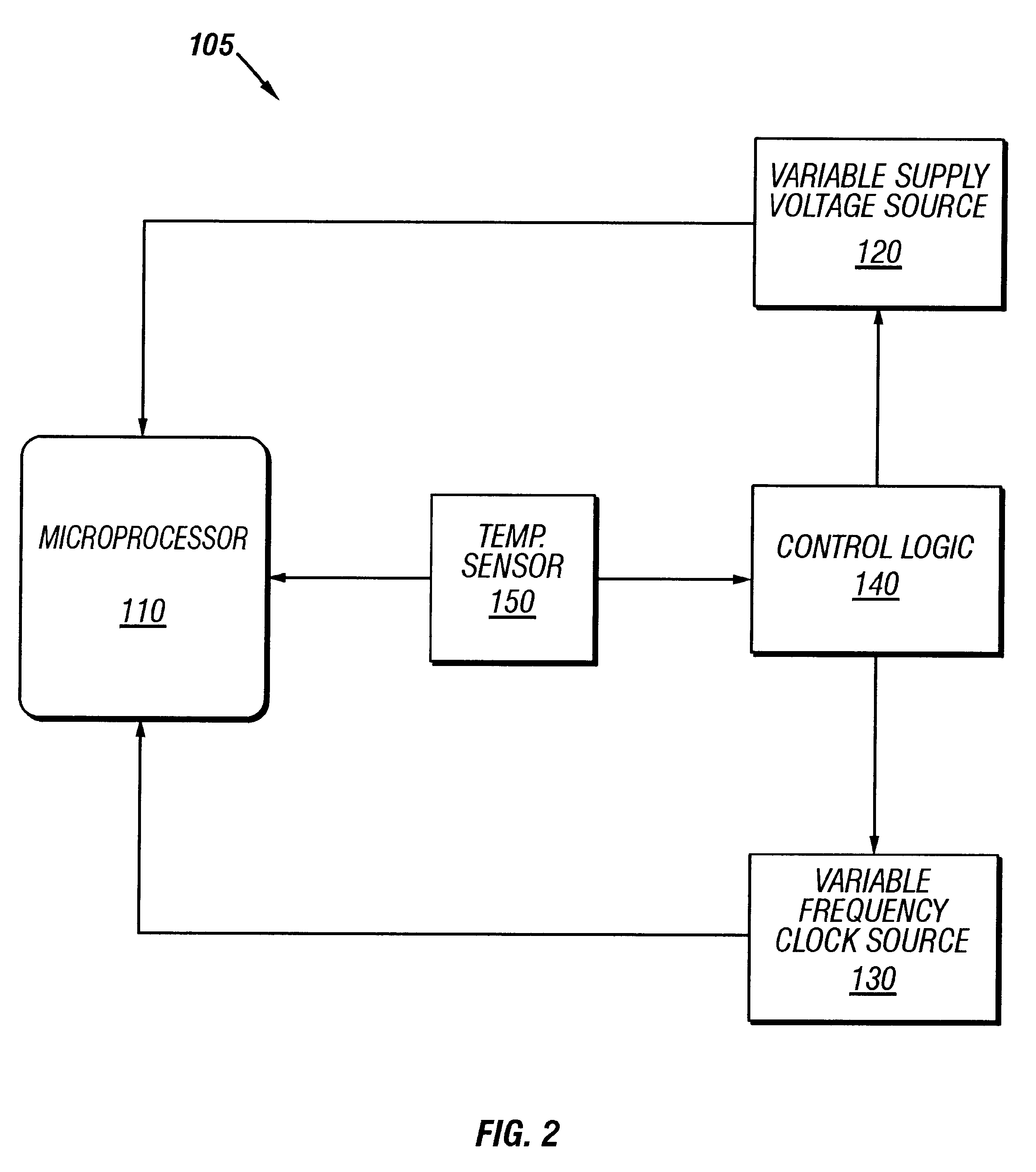

Method and apparatus for power throttling in a microprocessor using a closed loop feedback system

A method and apparatus for power throttling in a microprocessor. A voltage source supplies voltage to the microprocessor, and a clock source operates the microprocessor at a desired frequency. In one embodiment, a power monitor is configured to measure the short term power consumption of the microprocessor. In another embodiment, a temperature sensor measures the temperature of the microprocessor. Control logic is coupled to the voltage source and the clock source. The control logic receives an indication of the power consumption or temperature, as applicable, and compares it to a predetermined value. In response to the comparison, the control logic varies the supply voltage and the frequency.

Owner:INTEL CORP

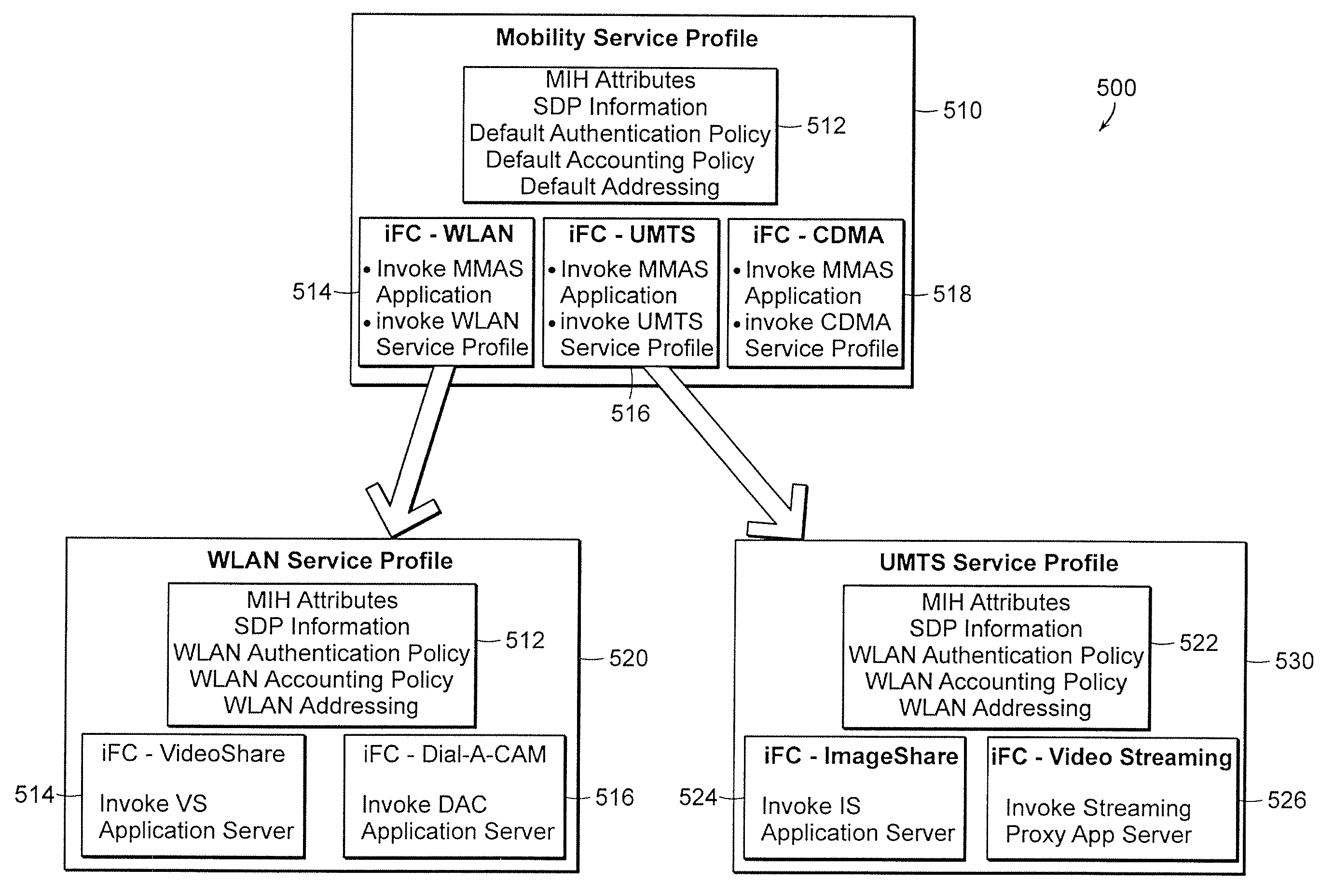

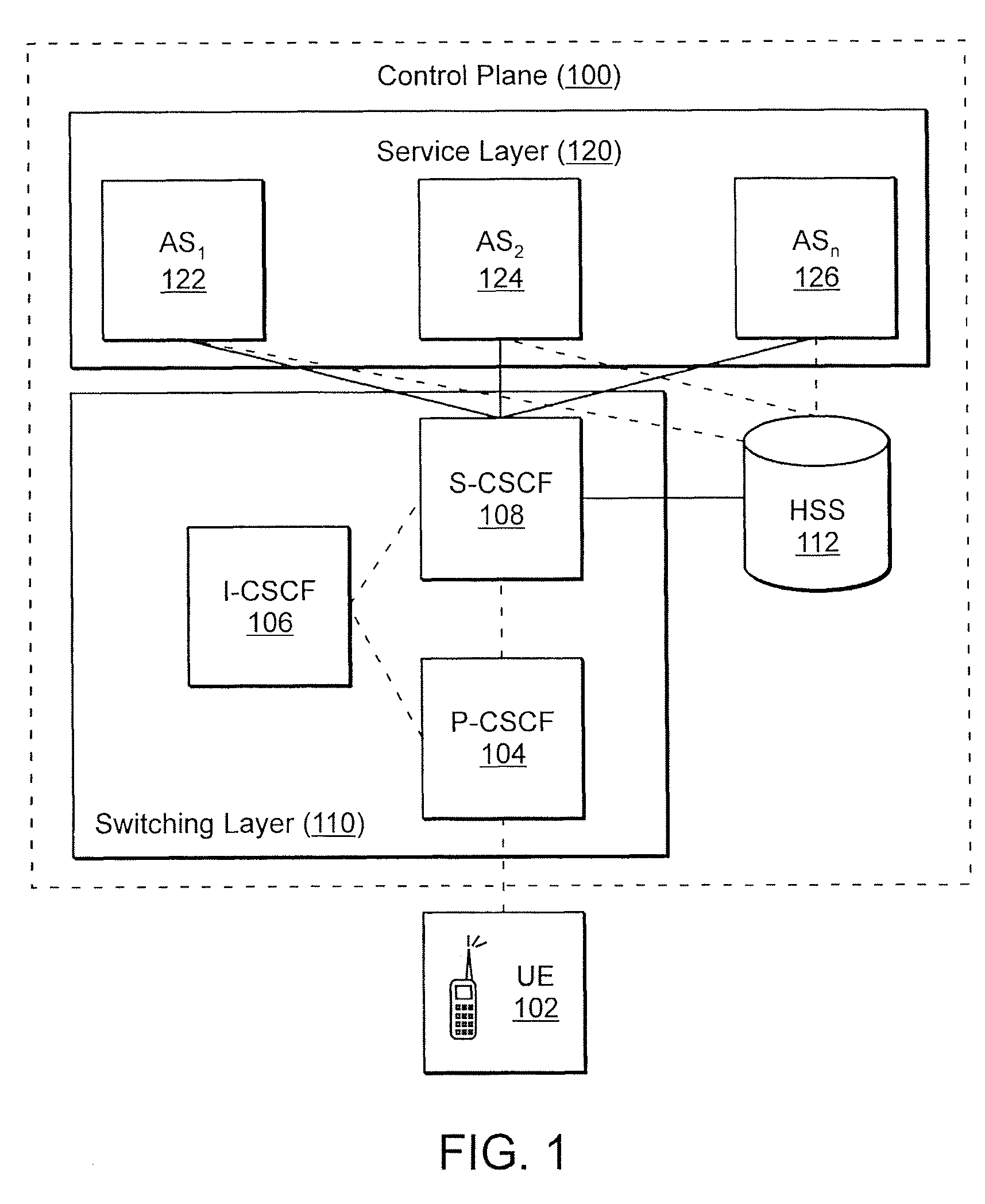

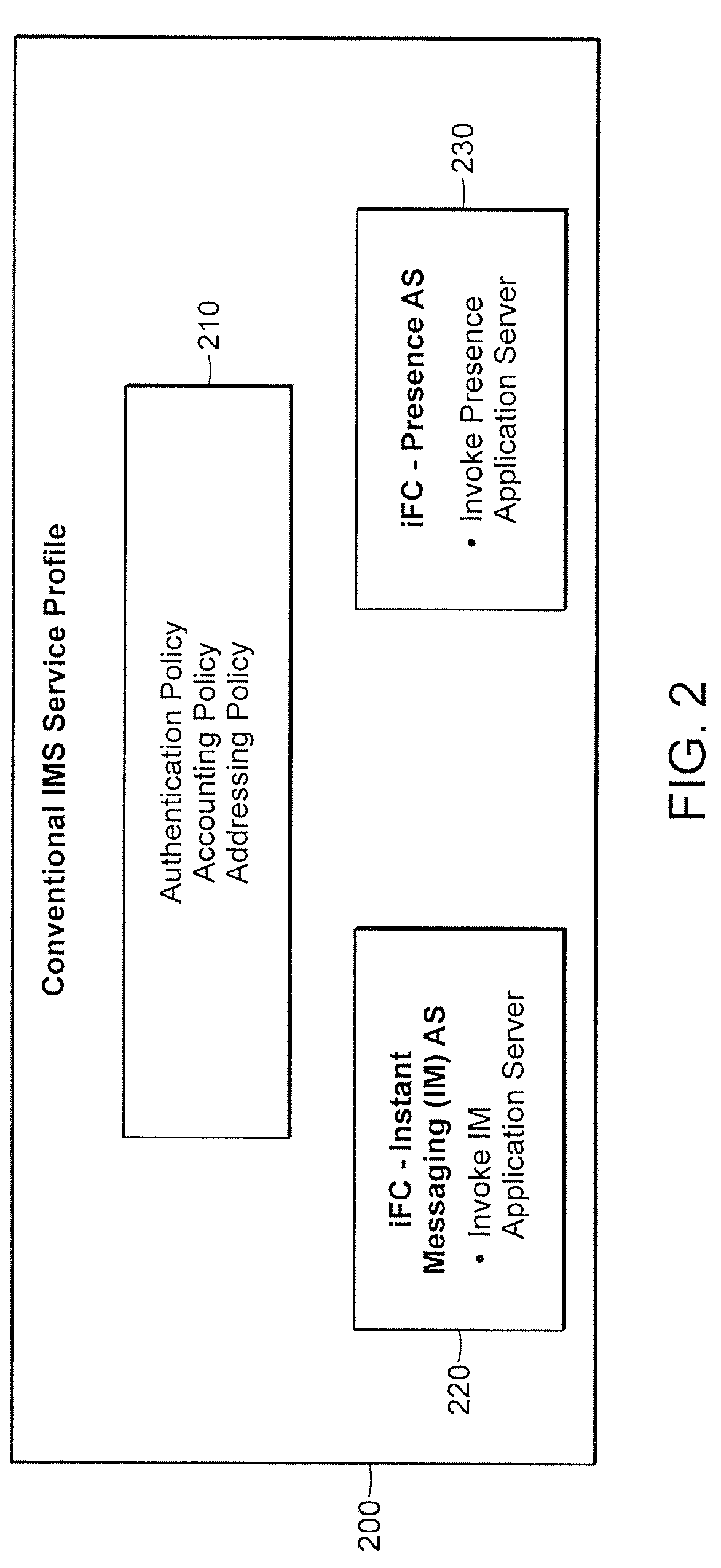

Systems and methods for IMS user sessions with dynamic service selection

ActiveUS7856226B2Multiplex system selection arrangementsSpecial service provision for substationApplication serverSession control

Owner:AYLUS NETWORKS

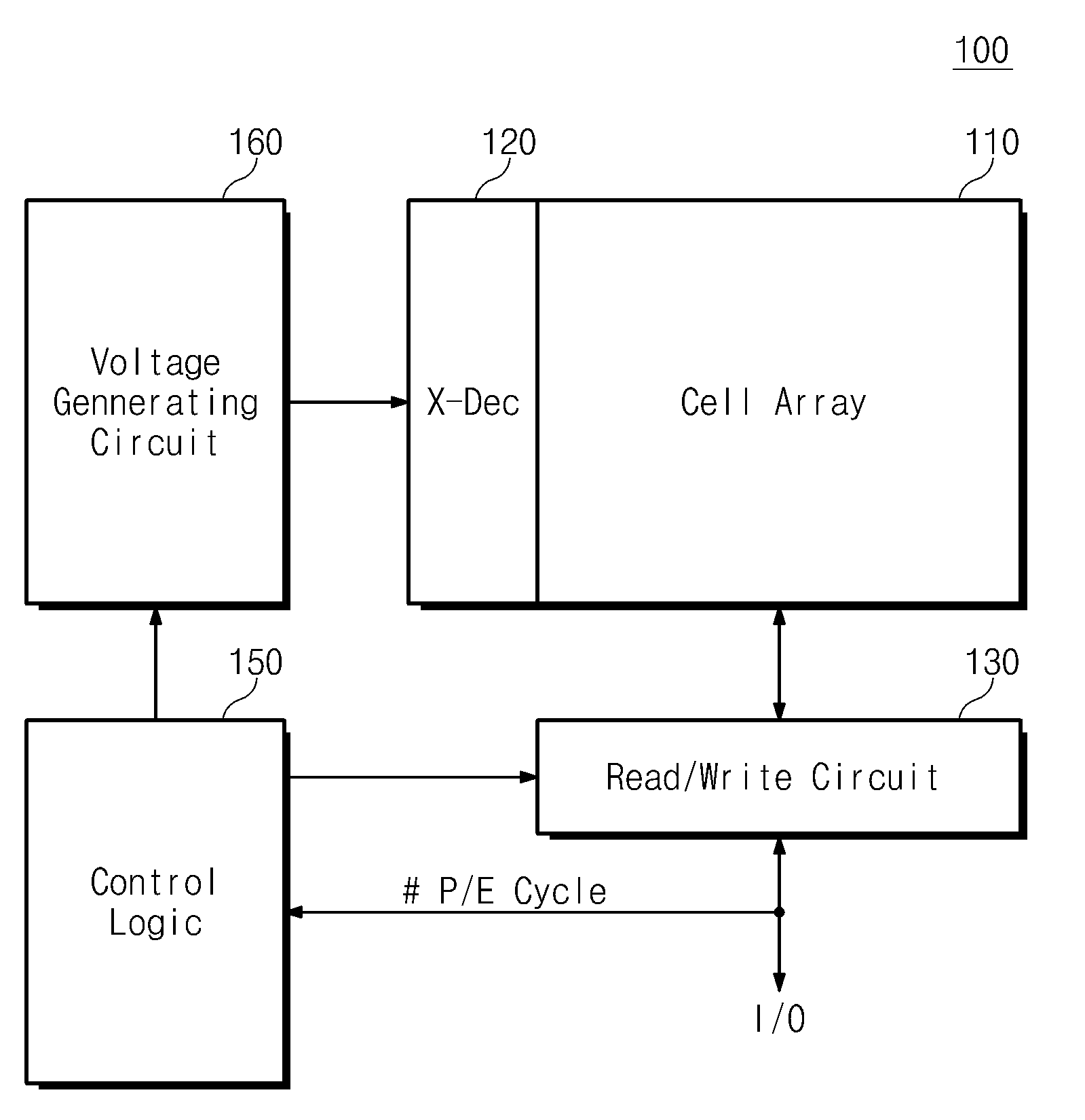

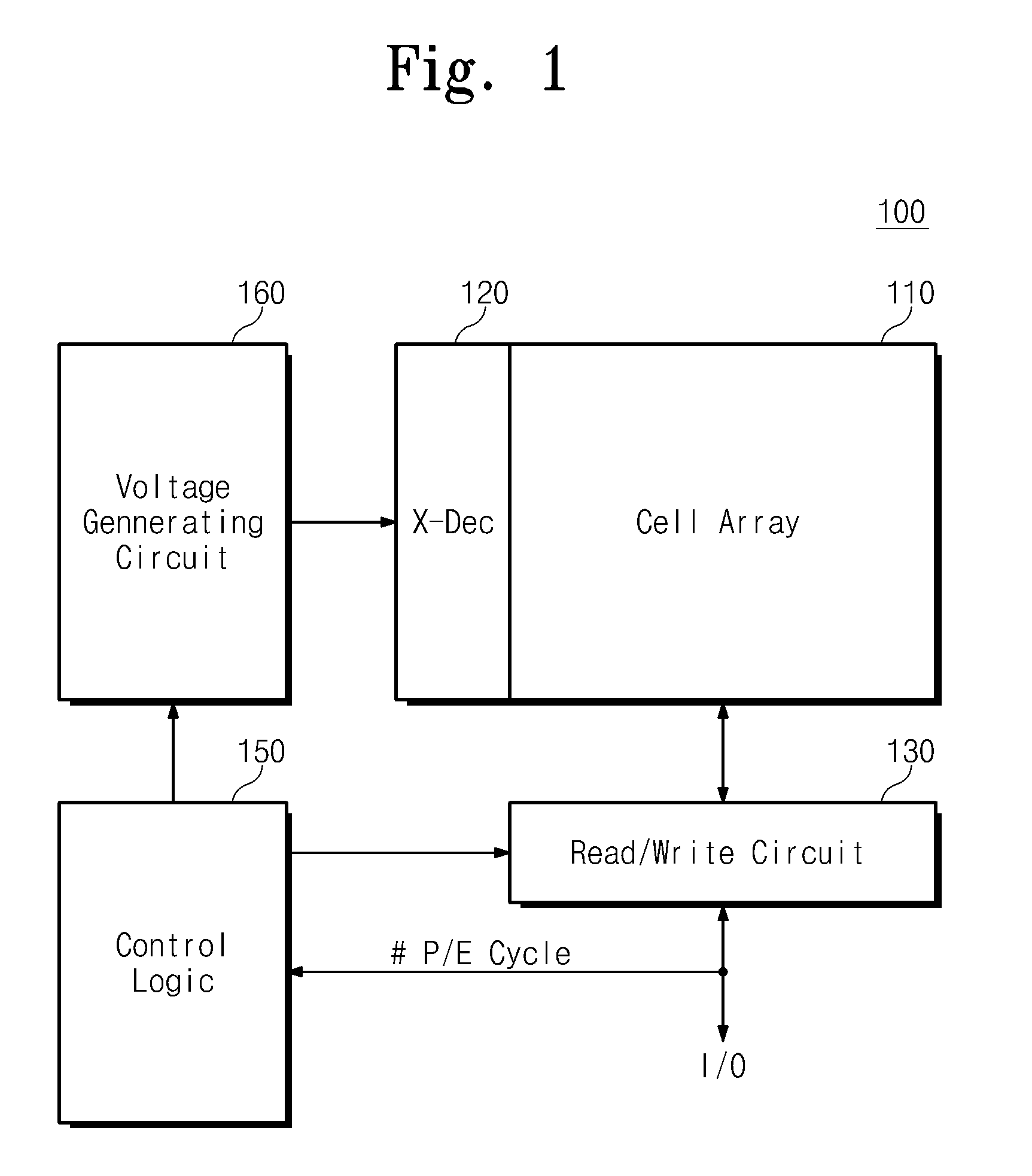

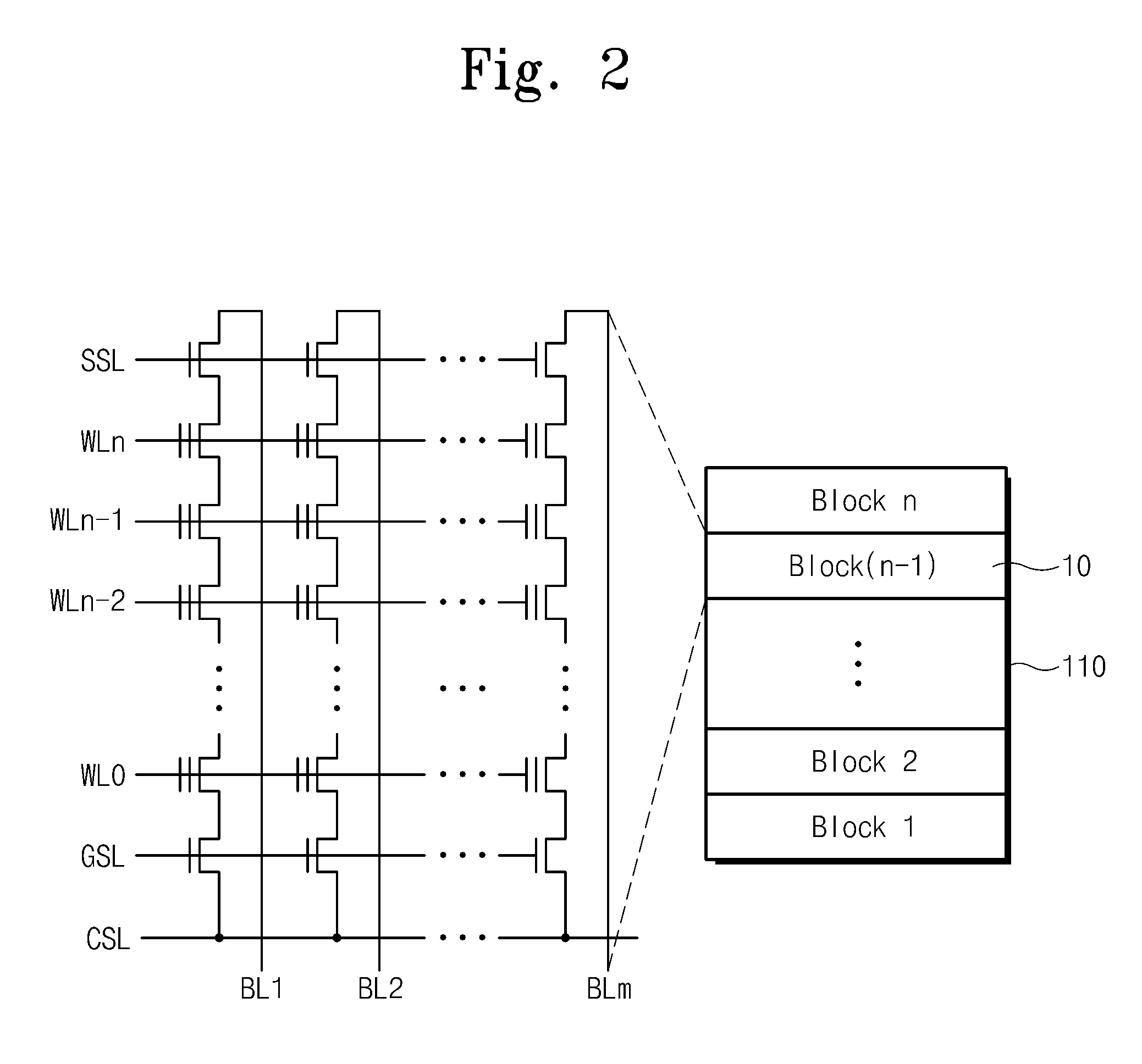

Nonvolatile memory device and related programming method

A nonvolatile memory device comprises a memory cell array comprising a plurality of memory blocks each divided into a plurality of regions, and a control logic component. The control logic component selects a memory block to be programmed based on program / erase cycles of the memory blocks, and selects a program rule used to program the regions of the selected memory block.

Owner:SAMSUNG ELECTRONICS CO LTD

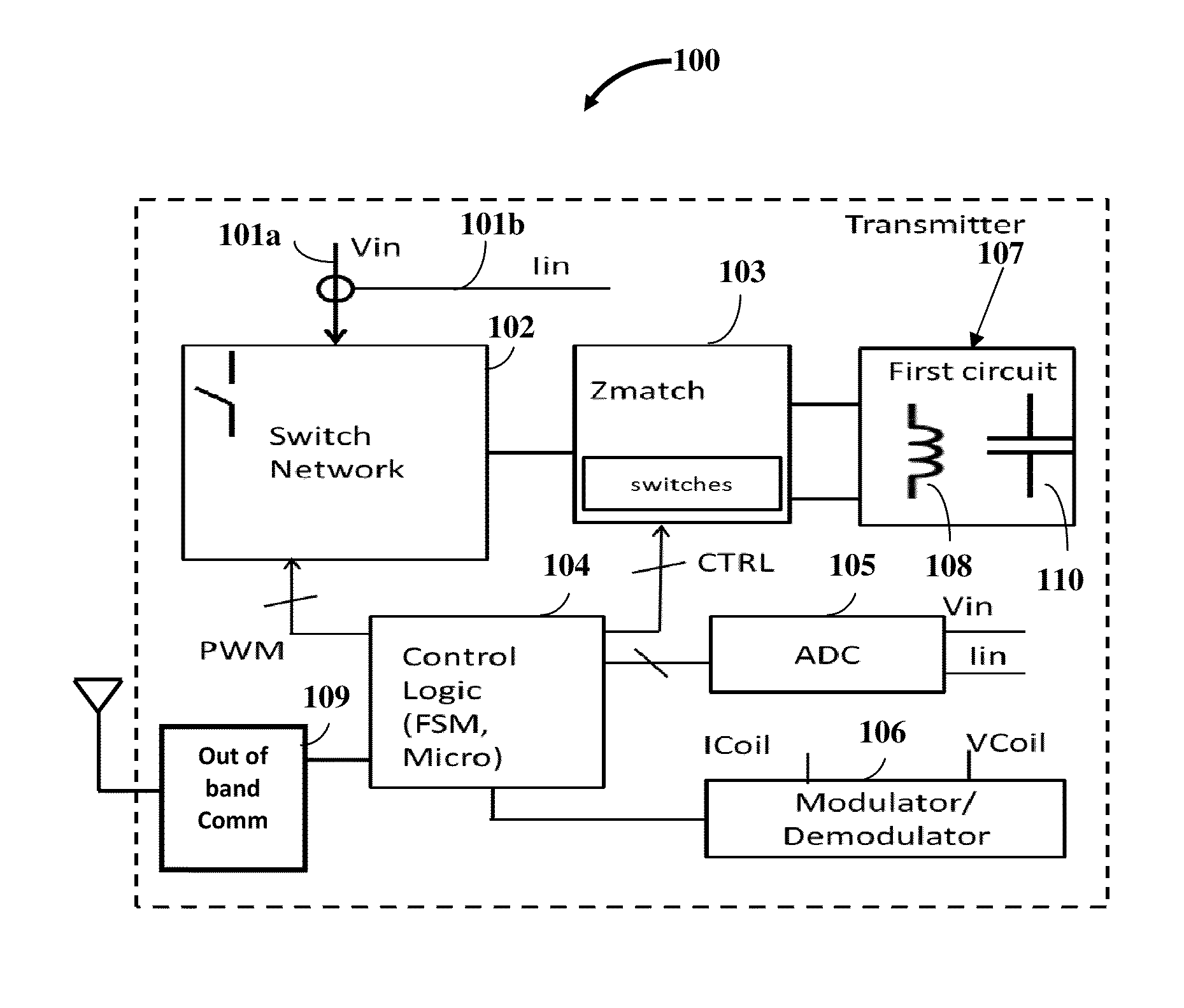

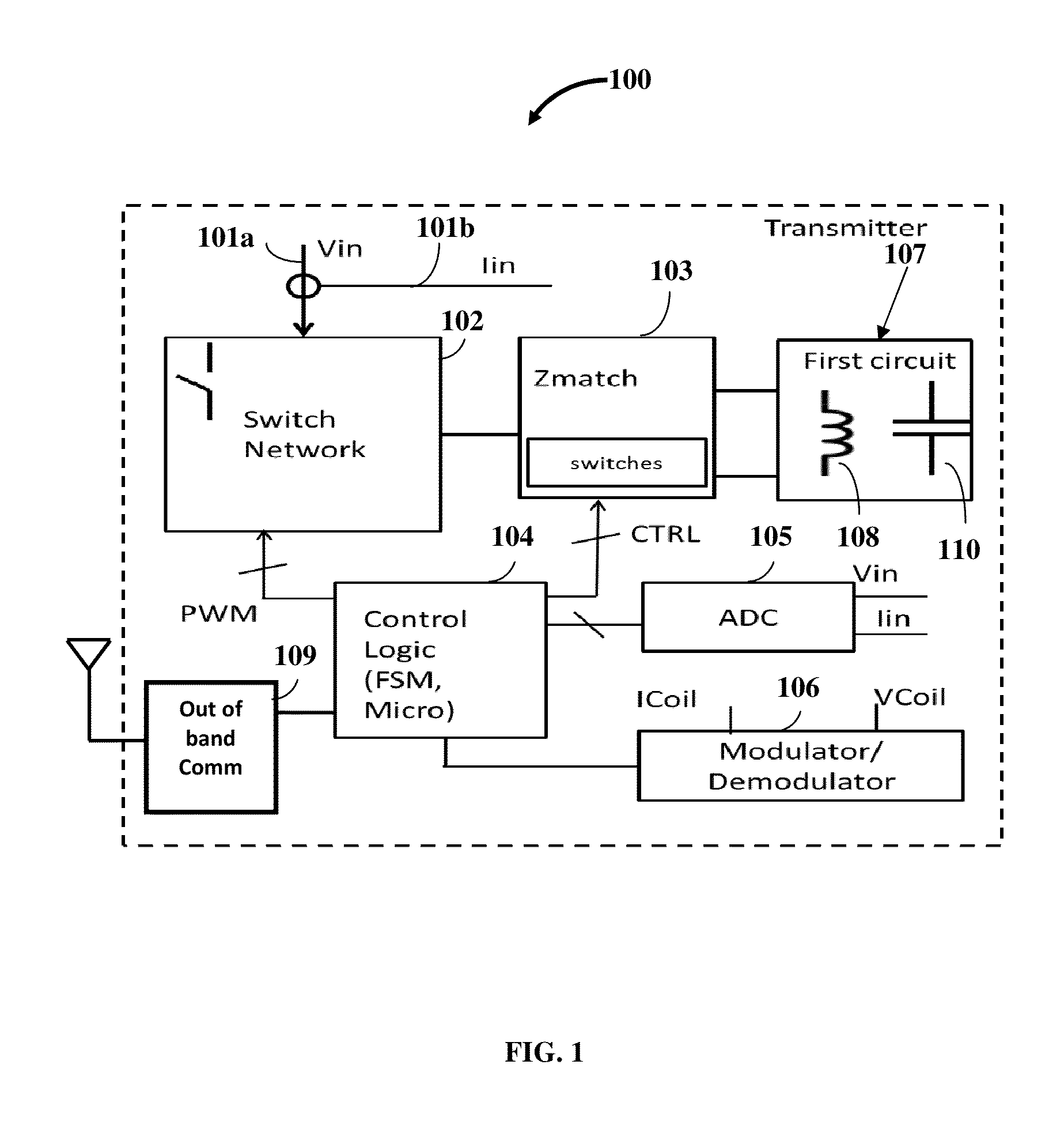

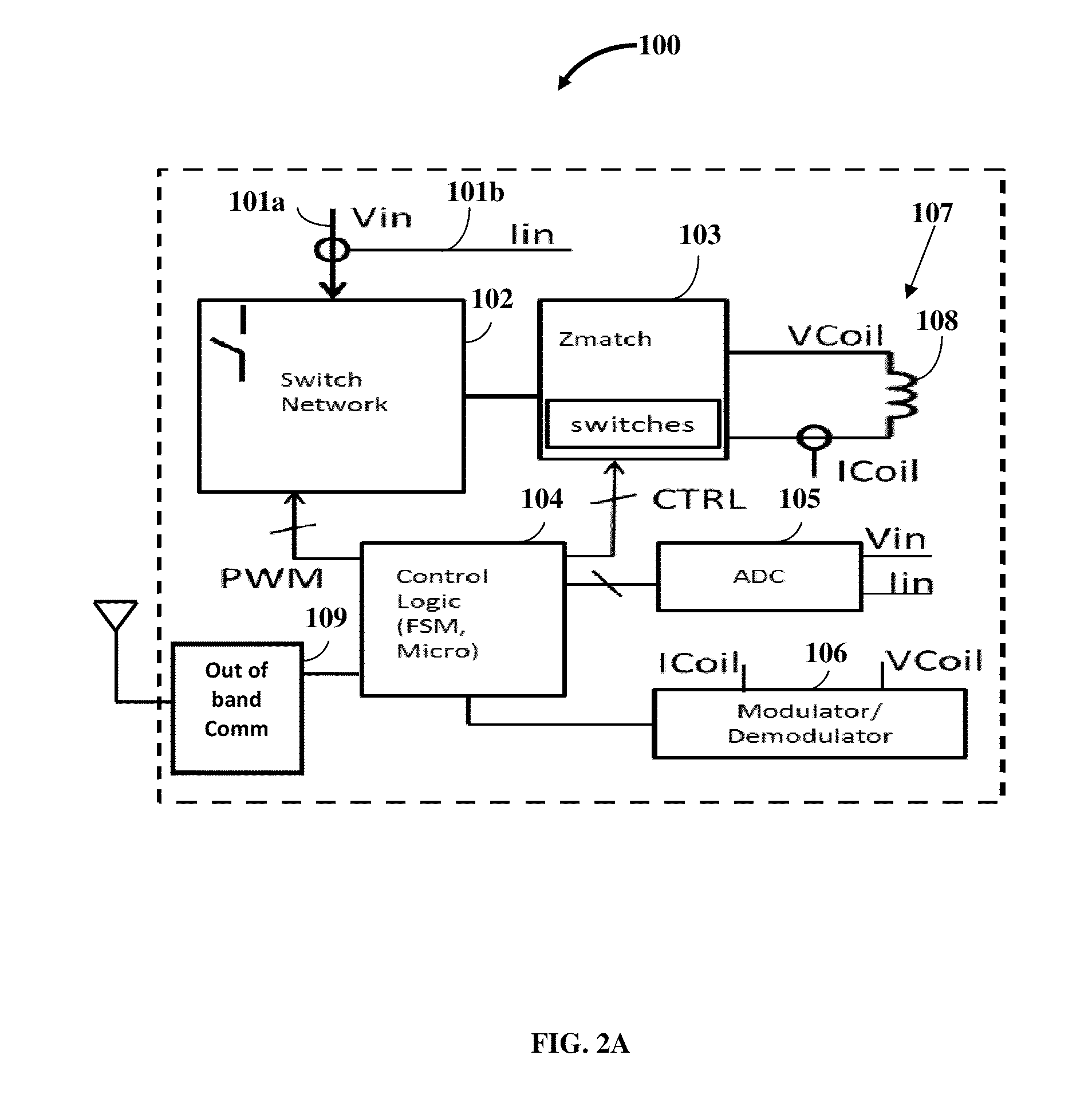

Multi-mode Multi-coupling Multi-protocol Ubiquitous Wireless Power Transmitter

InactiveUS20140139034A1Transmit power can be effectivelyGuaranteed normal transmissionBatteries circuit arrangementsElectromagnetic wave systemExchange networkTransmitted power

A multi-mode multi-coupling multi-protocol wireless power transmitter (WPT) and its embodiments transmit power to a wireless power receiver (WPR) in a power transfer mode (PTM) and a wireless power protocol (WPP) of the WPR. A first circuit of the WPT includes inductors or capacitors emanating power via a magnetic field or electric field PTM respectively. The WPT sequentially parses a test condition to identify a PTM, a power coupling linkage (PCL) between the WPT and the WPR, and a WPP of the WPR. The WPT identifies a match if the PTM of the first circuit and the WPP of the switch network, the variable matching circuit, a modulator / demodulator block or an out-of-band communication block, and a control logic circuit of the WPT match the PTM and the WPP of the WPR to transmit power to the WPR based on the match.

Owner:WIPQTUS

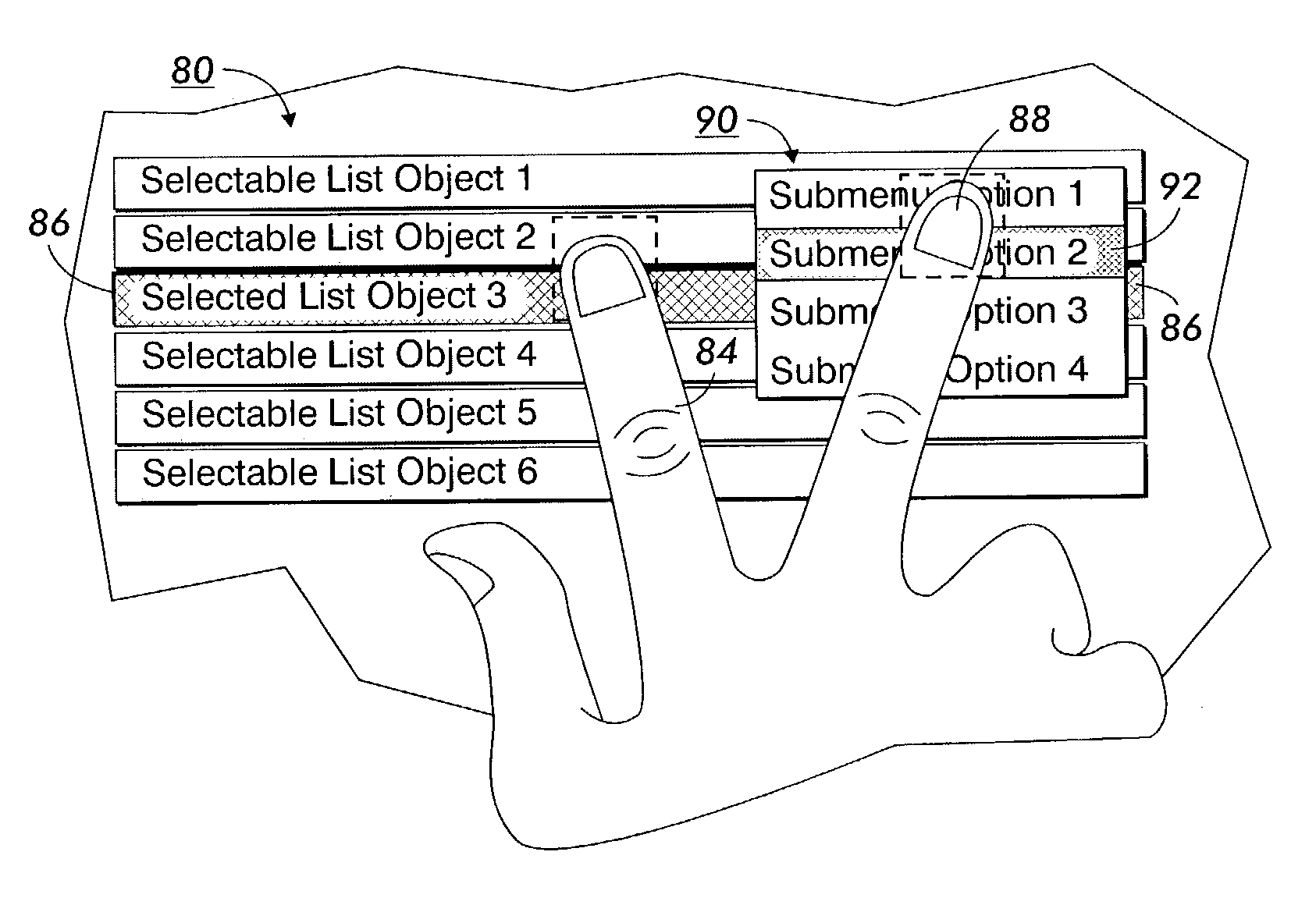

Secondary touch contextual sub-menu navigation for touch screen interface

ActiveUS7158123B2Cathode-ray tube indicatorsElectrographic process apparatusContact positionTouchscreen

A touch sensitive user interface of the type having a display screen for displaying images representative of menus and selectable list objects, for example; control logic responsive to the touch sensitive user interface for determining the contact position of a first probe and a second probe, such as two separate fingers, thereon, displaying menus including list objects representing primary and secondary features or functions respectively, so that a user may touch a selection on the primary menu with the first probe and subsequently touch an area on the display screen where a contextually related secondary menu is displayed for selection of contextually related features or functions.

Owner:TAHOE RES LTD

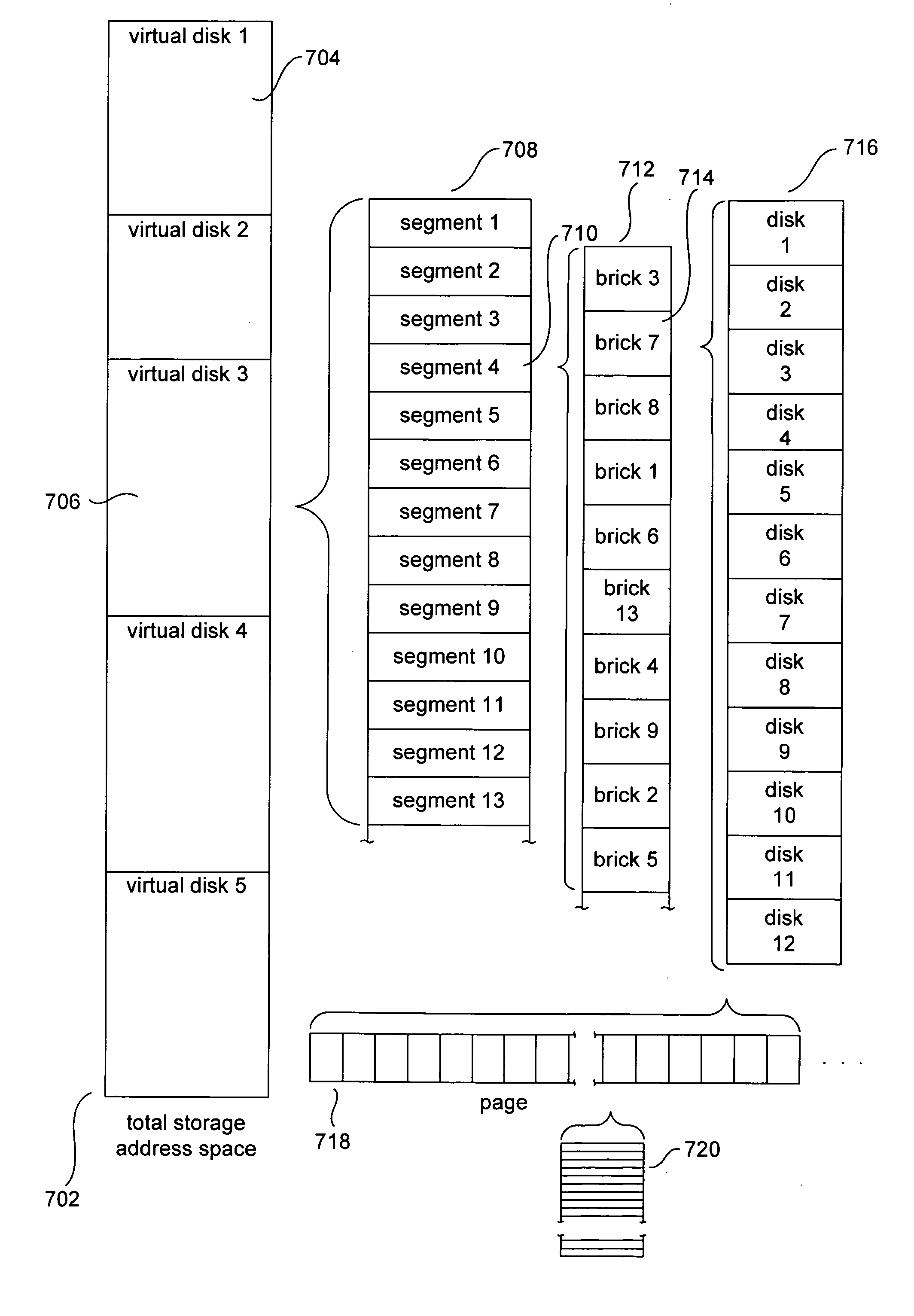

Methods and systems for hierarchical management of distributed data

Various method and system embodiments of the present invention are directed to hierarchical control logic within each component data-storage system of a distributed data-storage system composed of networked component data-storage systems over which virtual disks, optionally replicated as virtual-disk images, composed of data segments in turn composed of data blocks, are distributed at the granularity of segments. Each data segment is distributed according to a configuration. The hierarchical control logic includes, in one embodiment of the present invention, a top-level coordinator, a virtual-disk-image-level coordinator, a segment-configuration-node-level coordinator, a configuration-group-level coordinator, and a configuration-level coordinator.

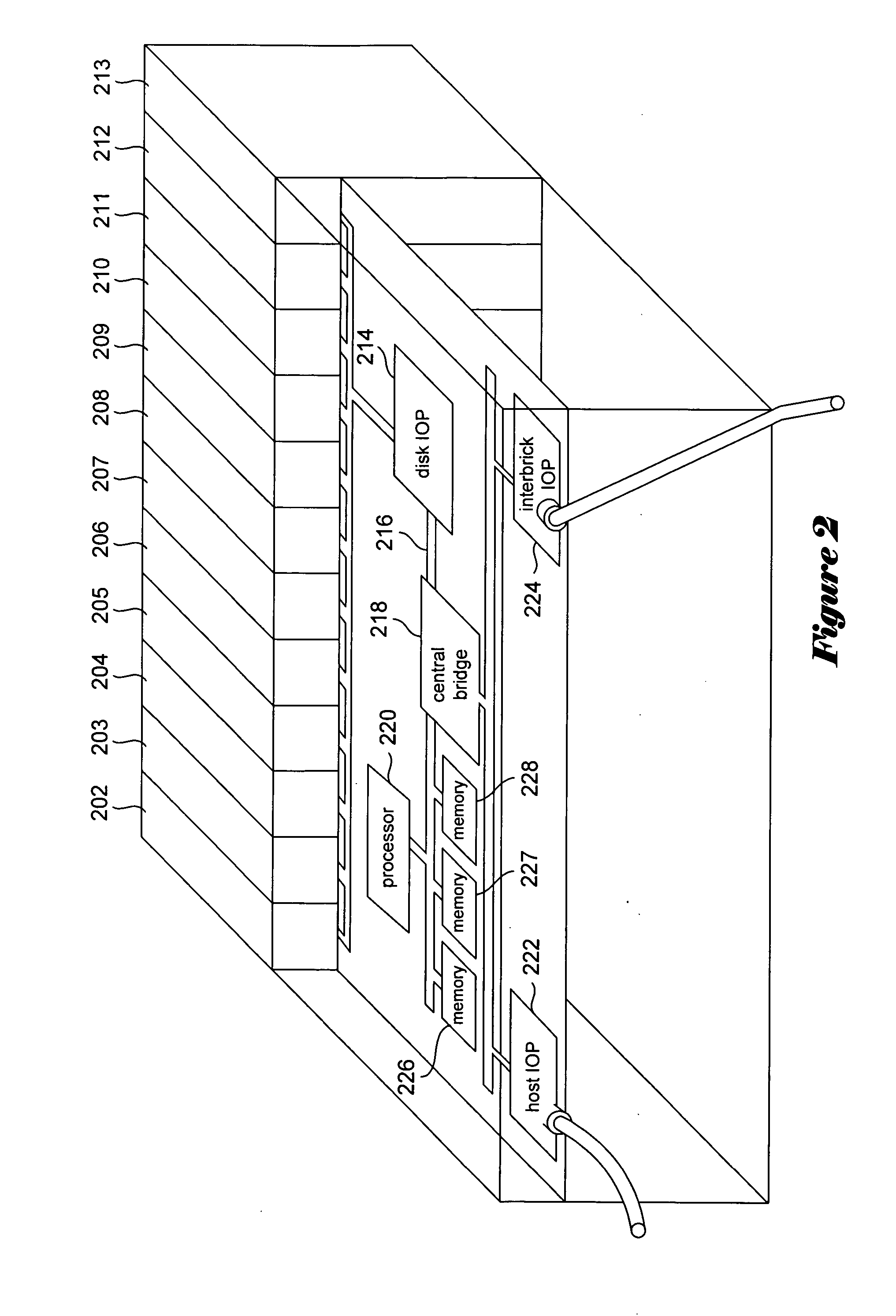

Owner:HEWLETT PACKARD DEV CO LP

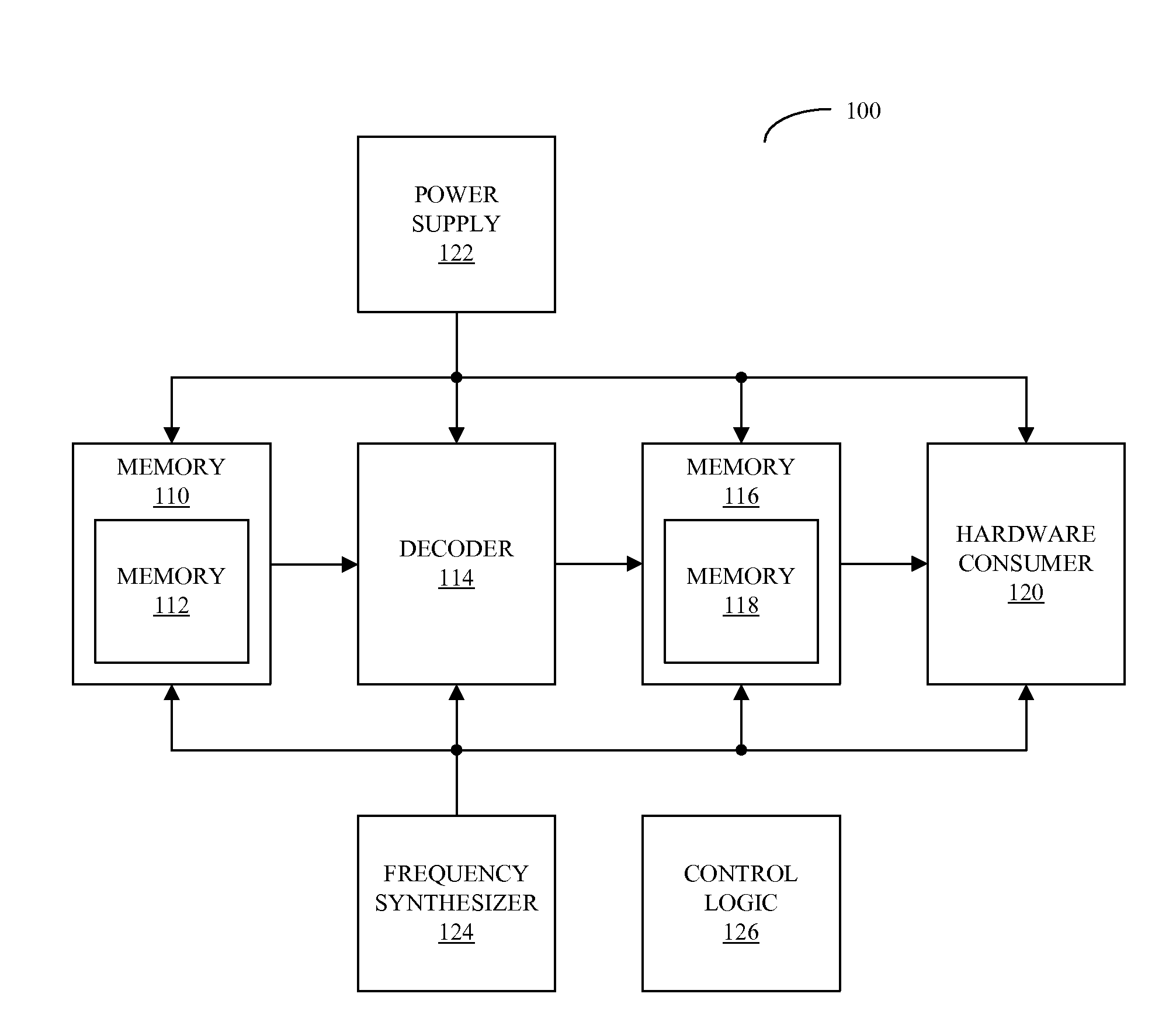

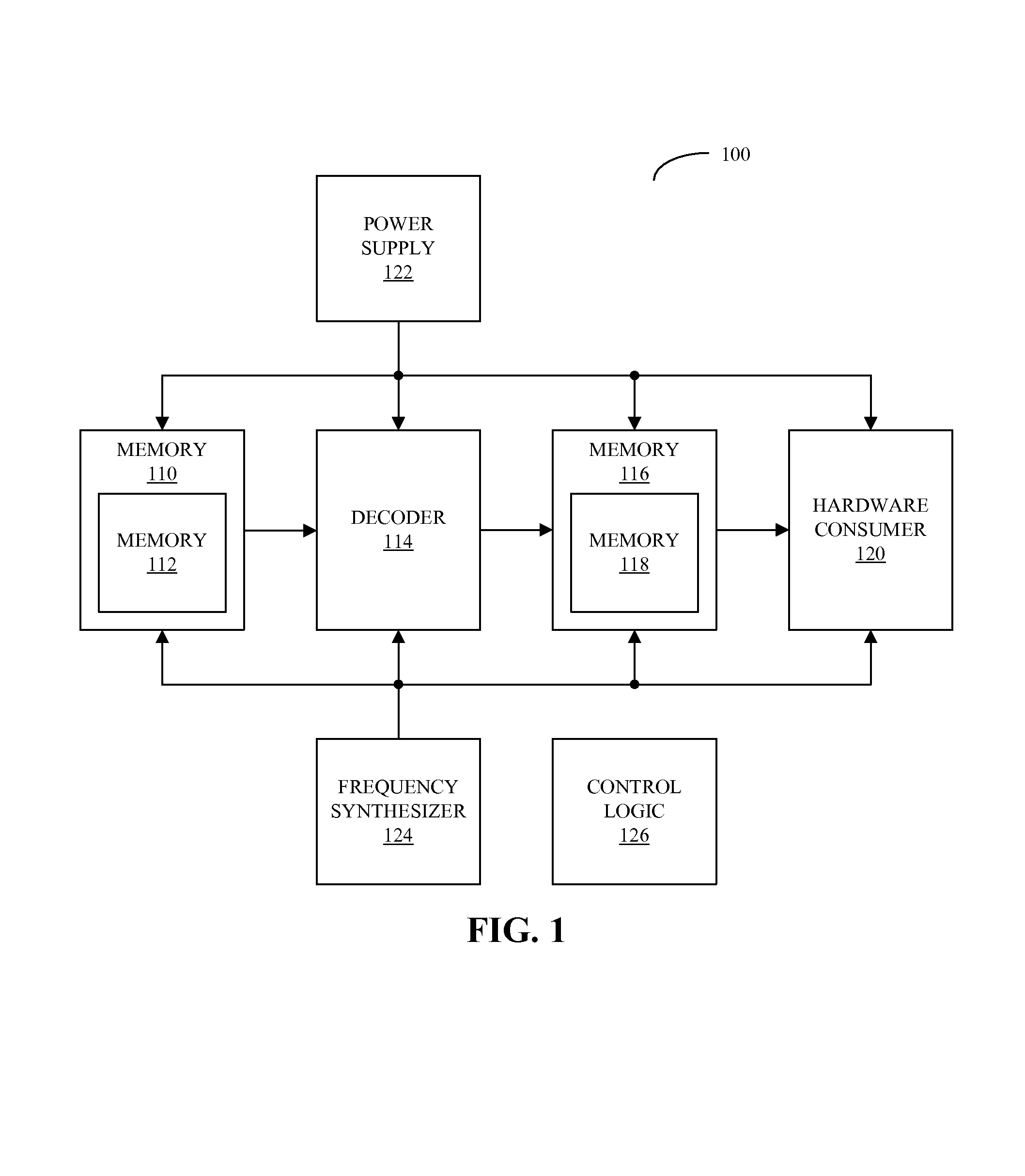

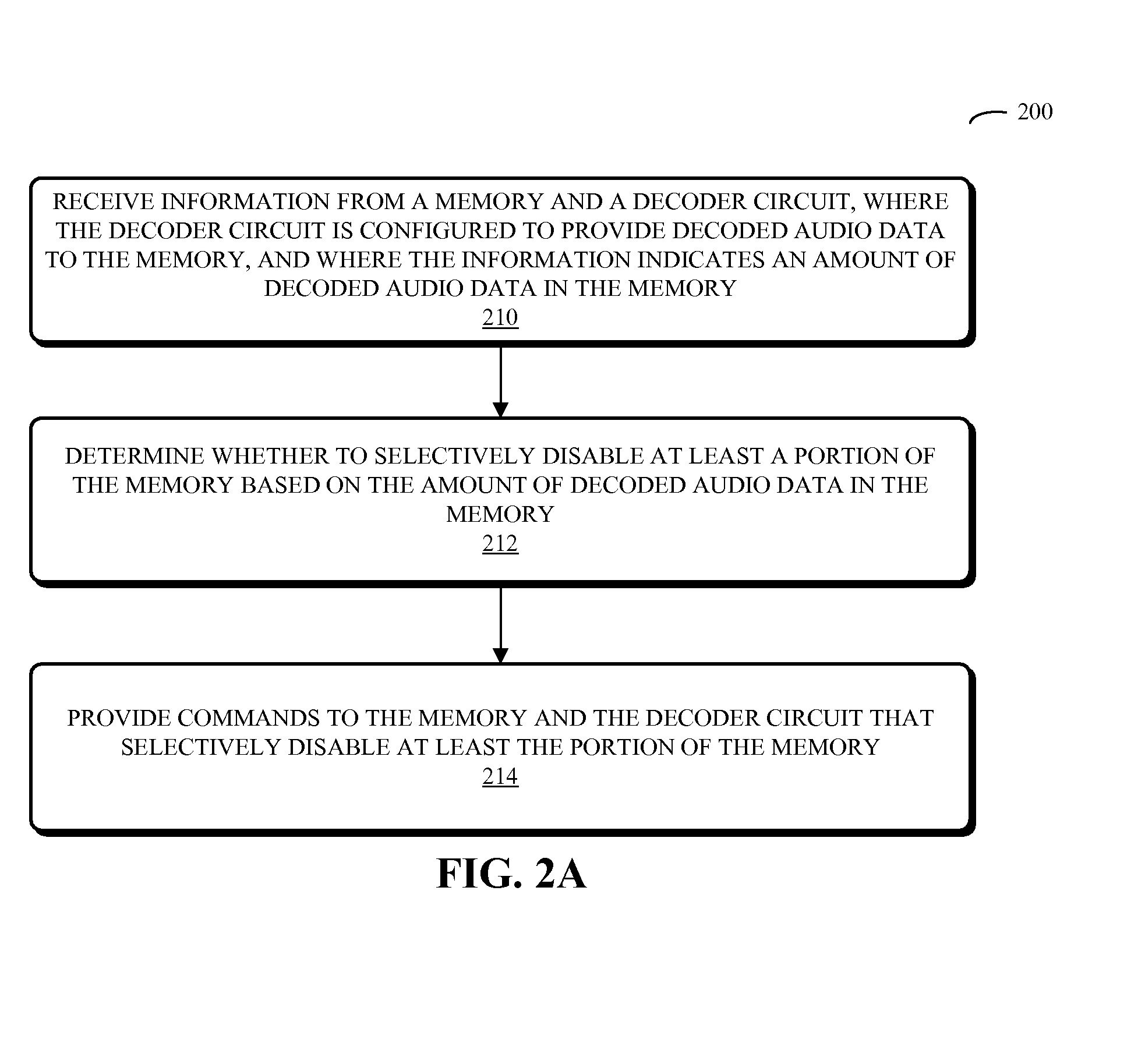

Power-gating media decoders to reduce power consumption

ActiveUS20090003115A1Reduce power consumptionEnergy efficient ICTDigital data processing detailsElectricityHemt circuits

Embodiments of a system that reduces power consumption by power-gating media decoders are described. During operation of the system, a decoder circuit receives encoded audio data and outputs corresponding decoded audio data to a memory, which is electrically coupled to the decoder circuit. Moreover, control logic, which is electrically coupled to the memory and the decoder circuit, provides commands to the memory and the decoder circuit that selectively disable at least a portion of the memory based on an amount of decoded audio data in the memory.

Owner:APPLE INC

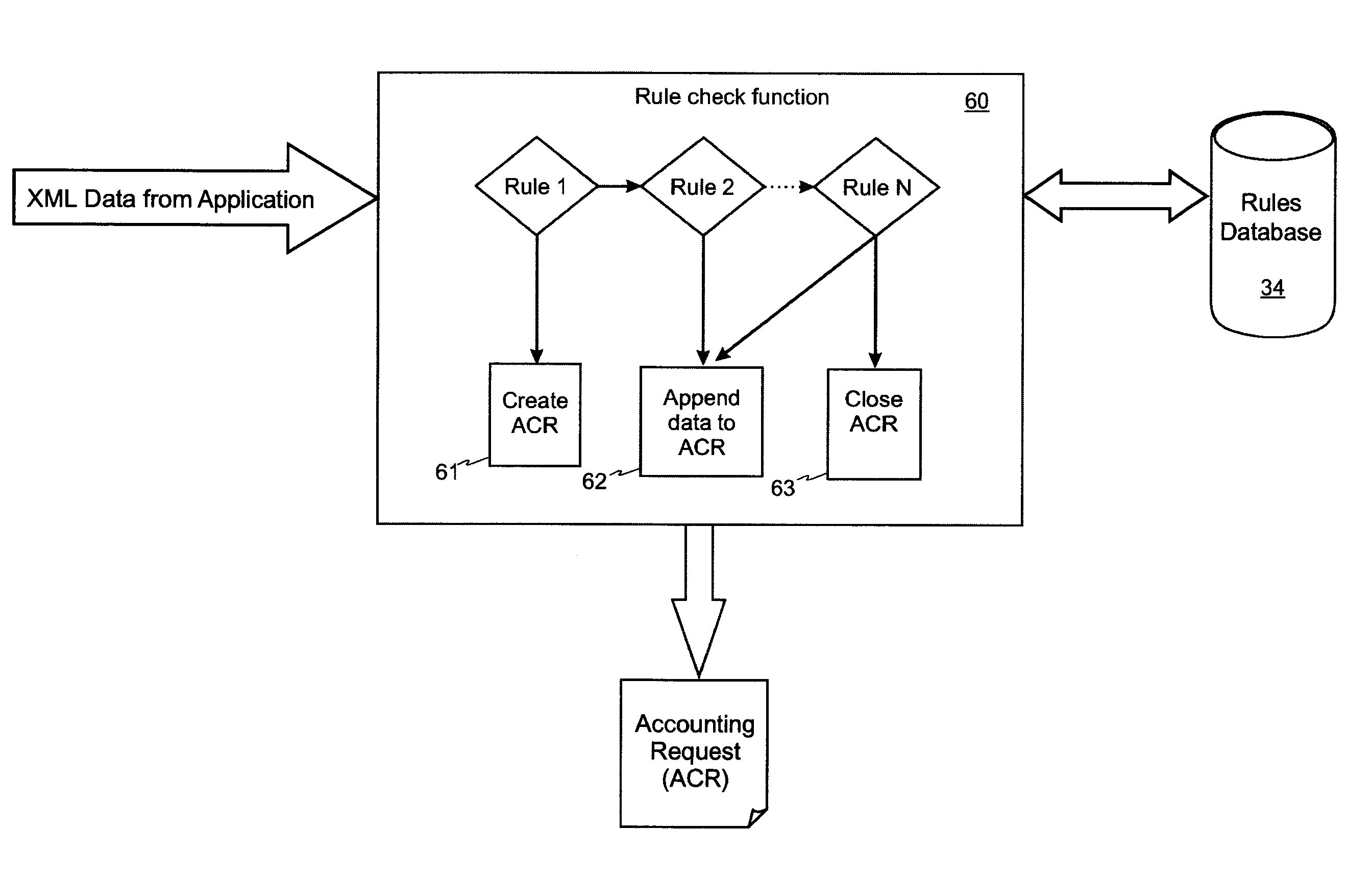

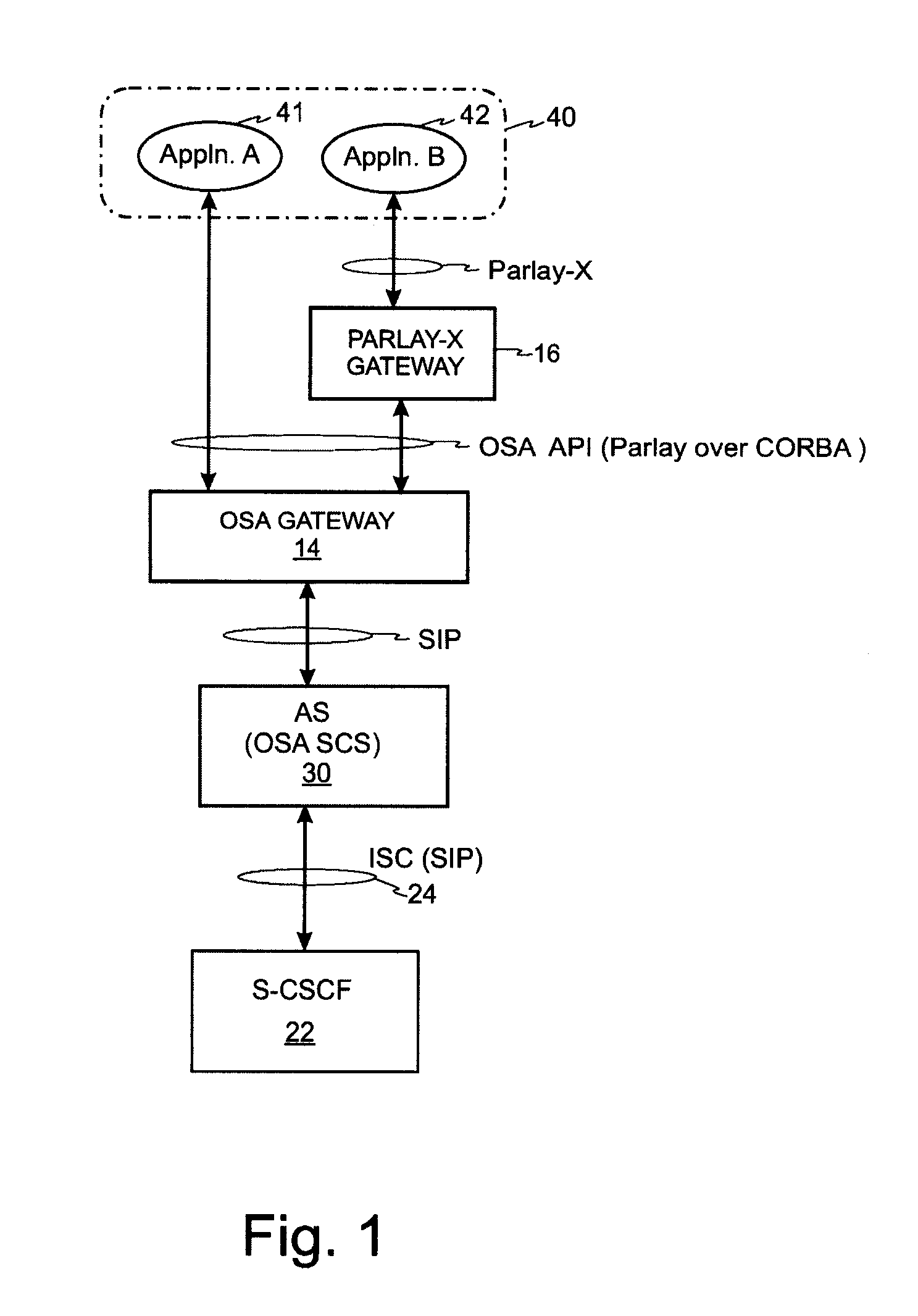

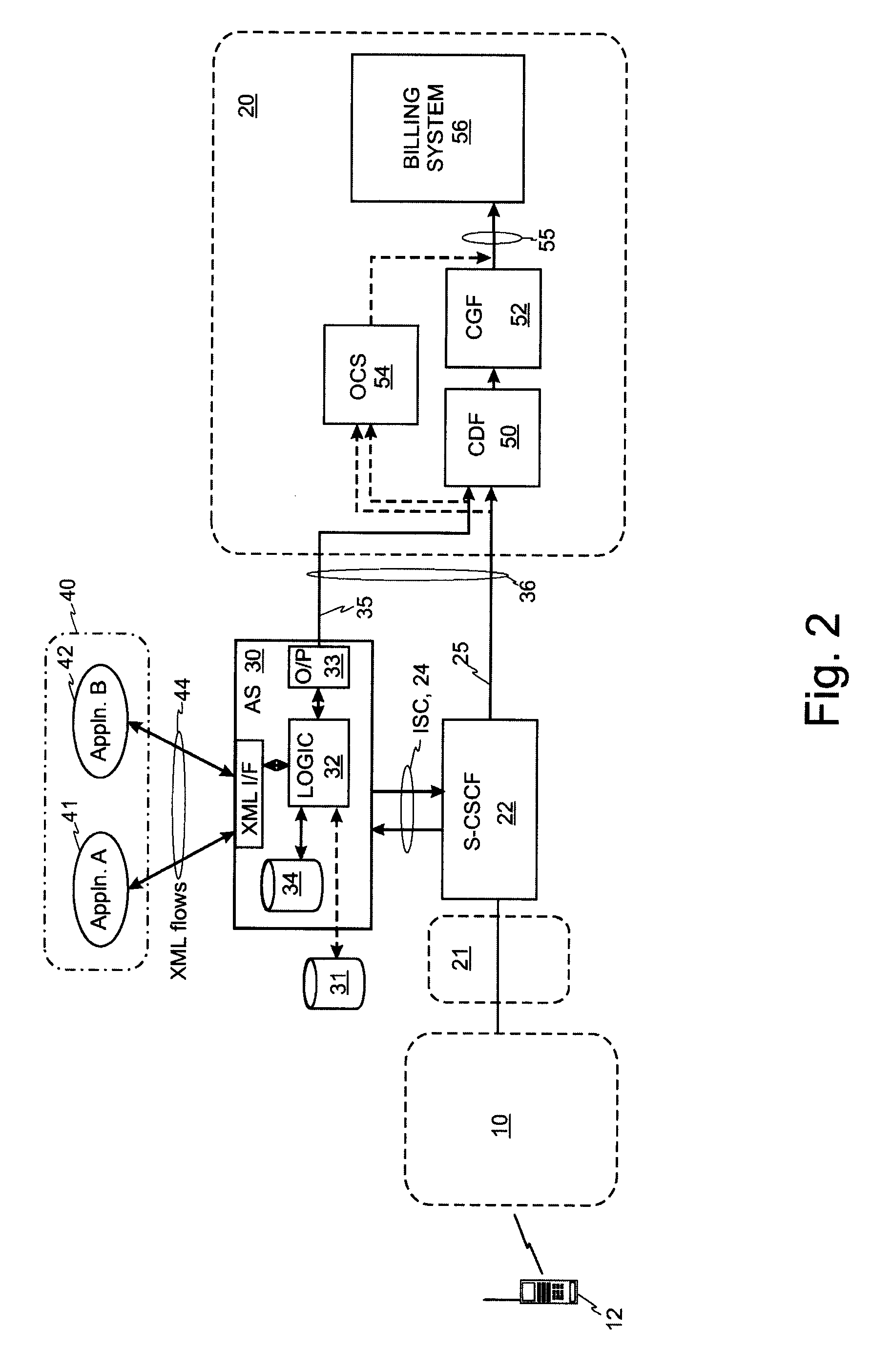

Application Server Billing

InactiveUS20080082643A1Accurate monitoringAvoid the needCredit schemesMultiple digital computer combinationsApplication serverParlay X

An Application Server entity in an IP Multimedia Subsystem (IMS) network comprises an interface for interfacing with an application and control logic which is arranged to inspect signalling information received from the application via the interface in the form of Extensible Markup Language (XML). The received signalling information is compared with stored rule data which specifies a relationship between an element in the signalling information and an action that should be taken and output data is generated based on the comparison. The Application Server can output operational measurements and / or charging information which more accurately reflect usage made of the Application Server resources. The need for a separate OSA / Parlay-X gateway can be avoided.

Owner:RPX CLEARINGHOUSE

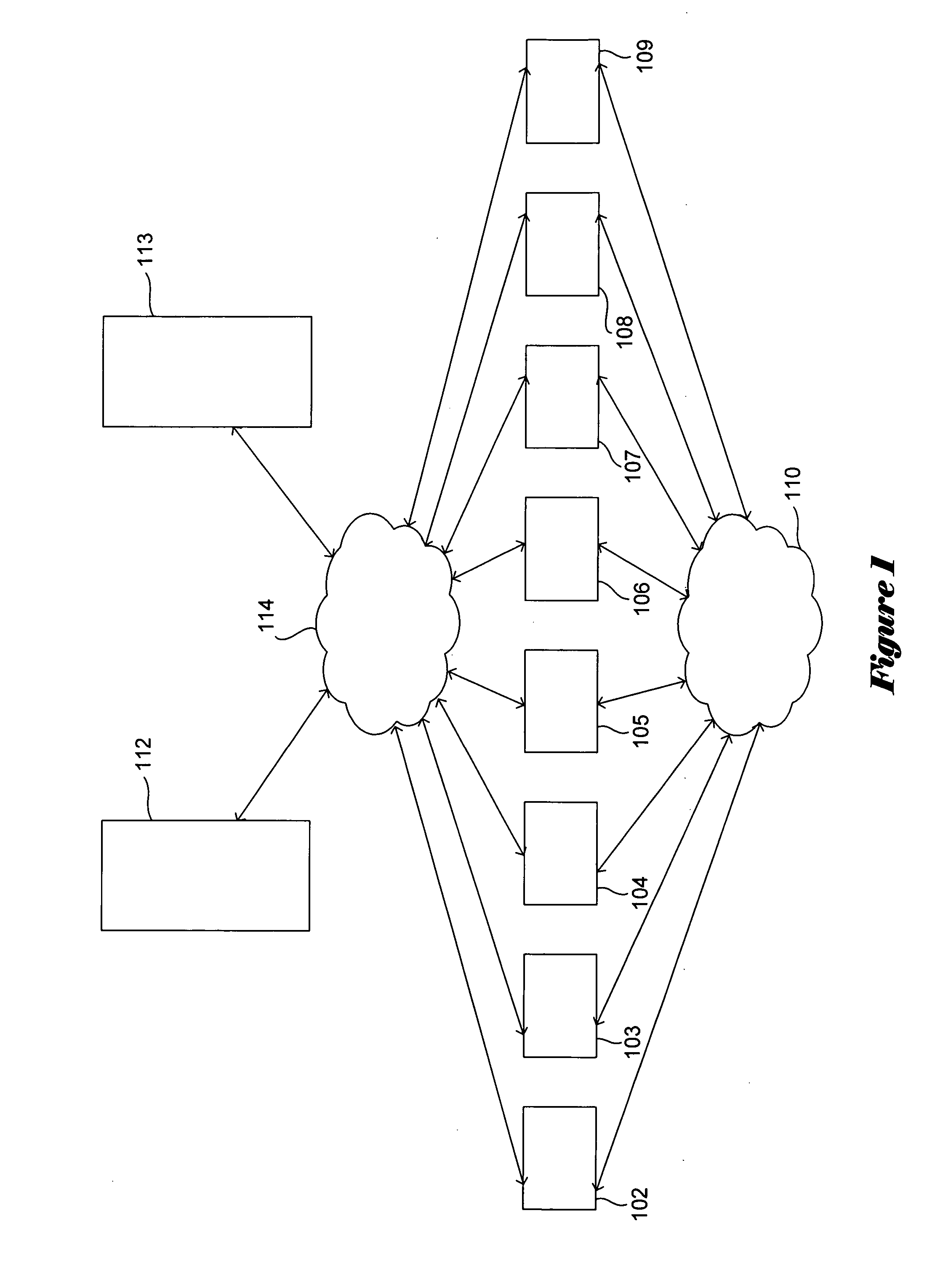

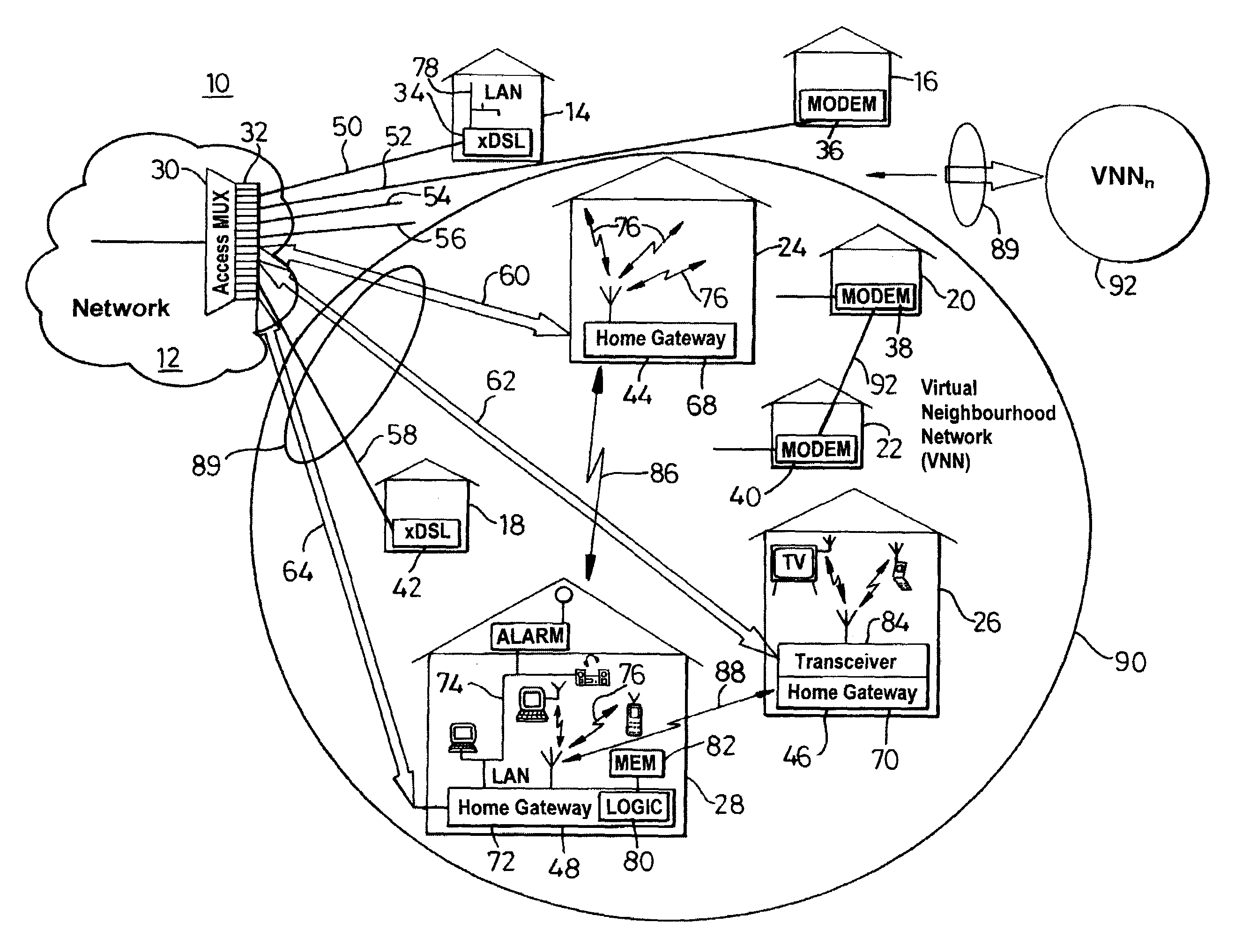

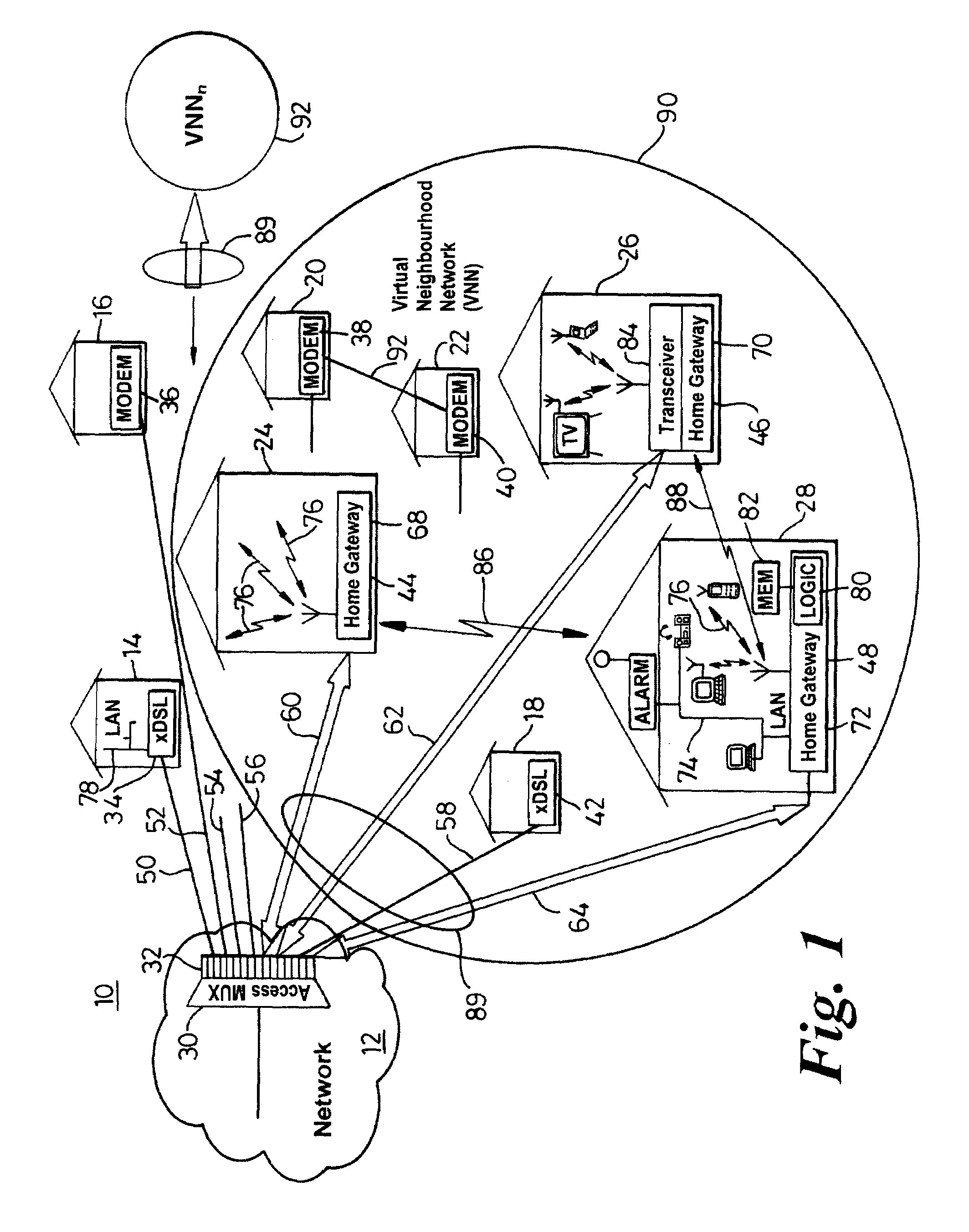

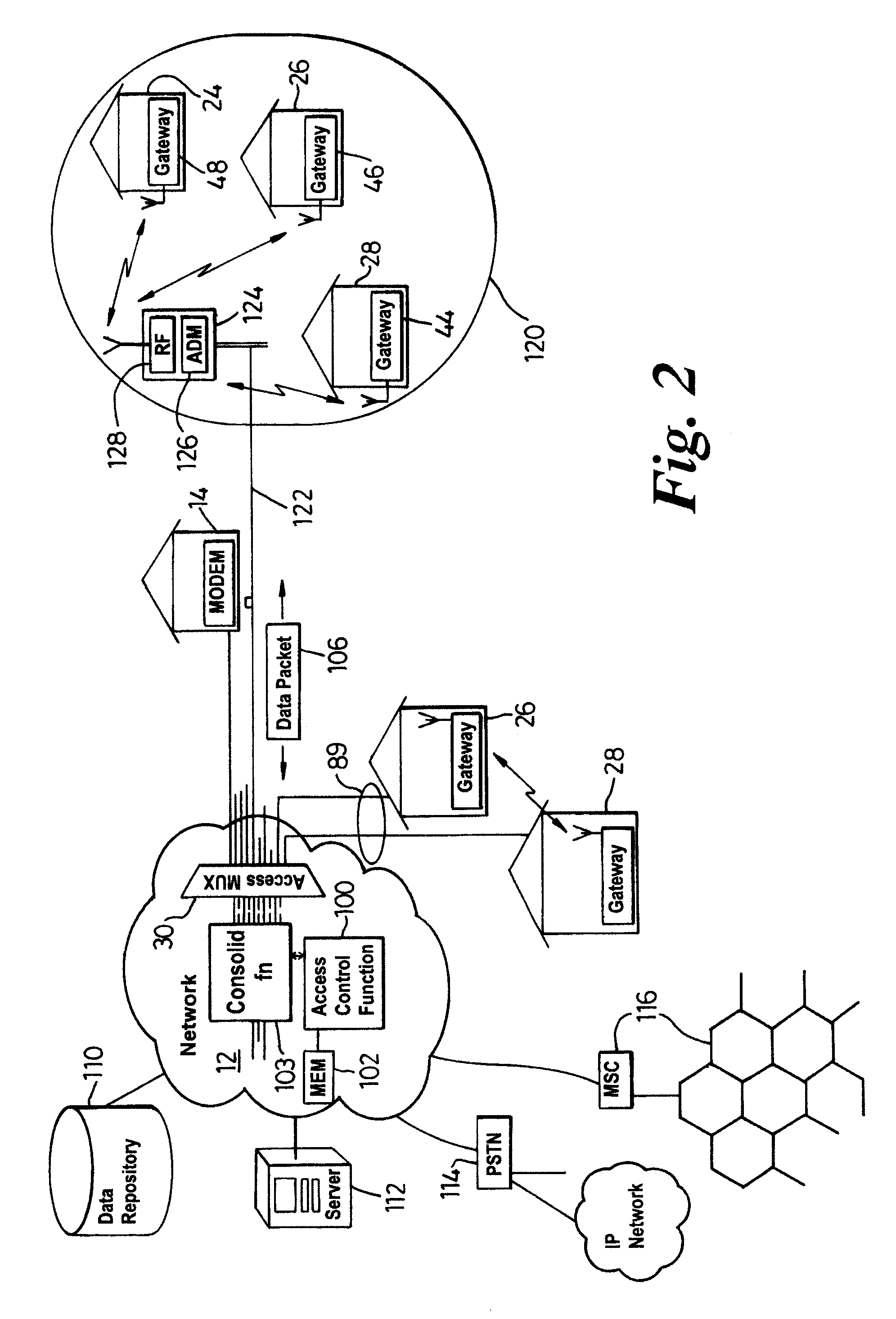

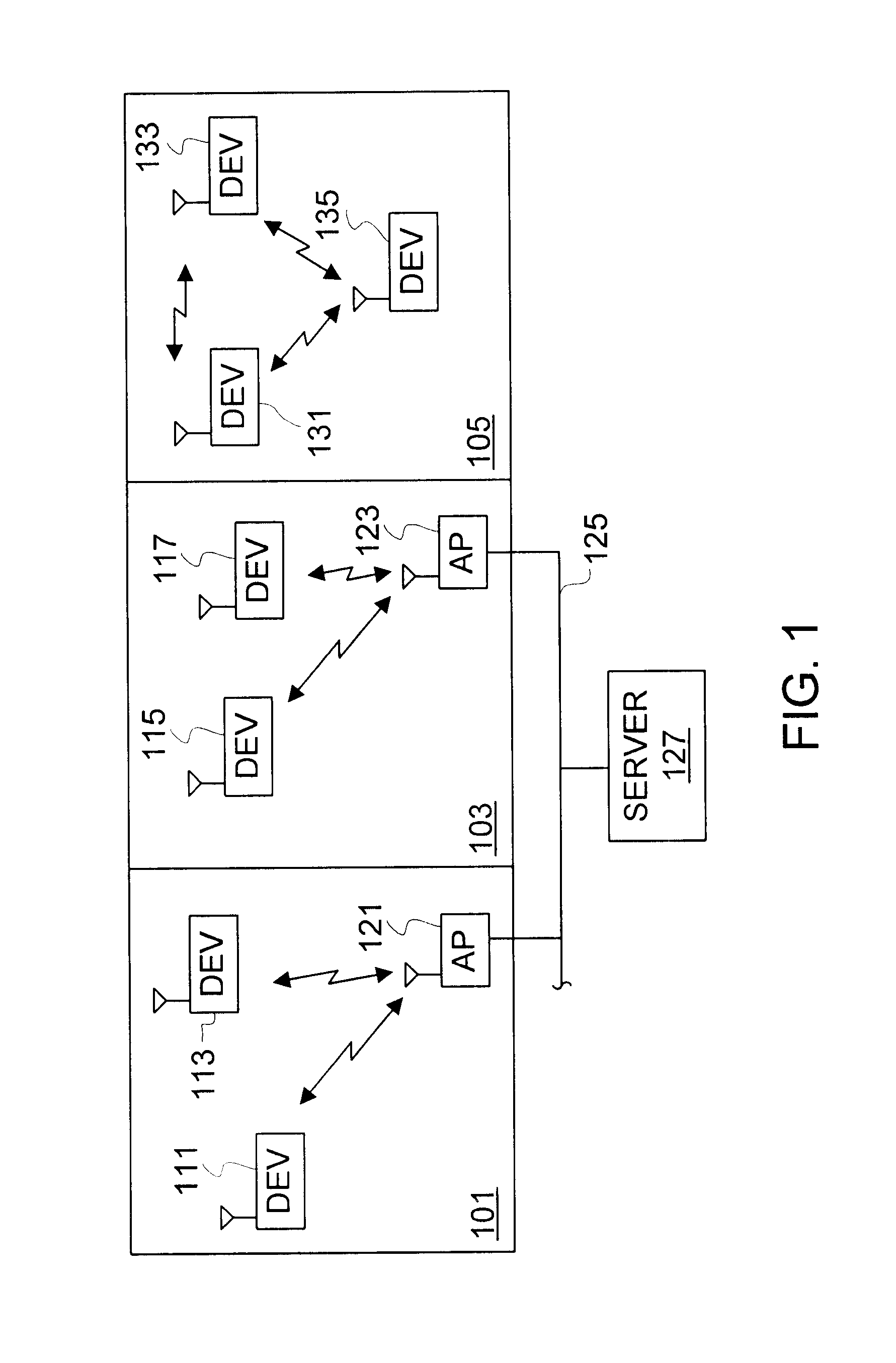

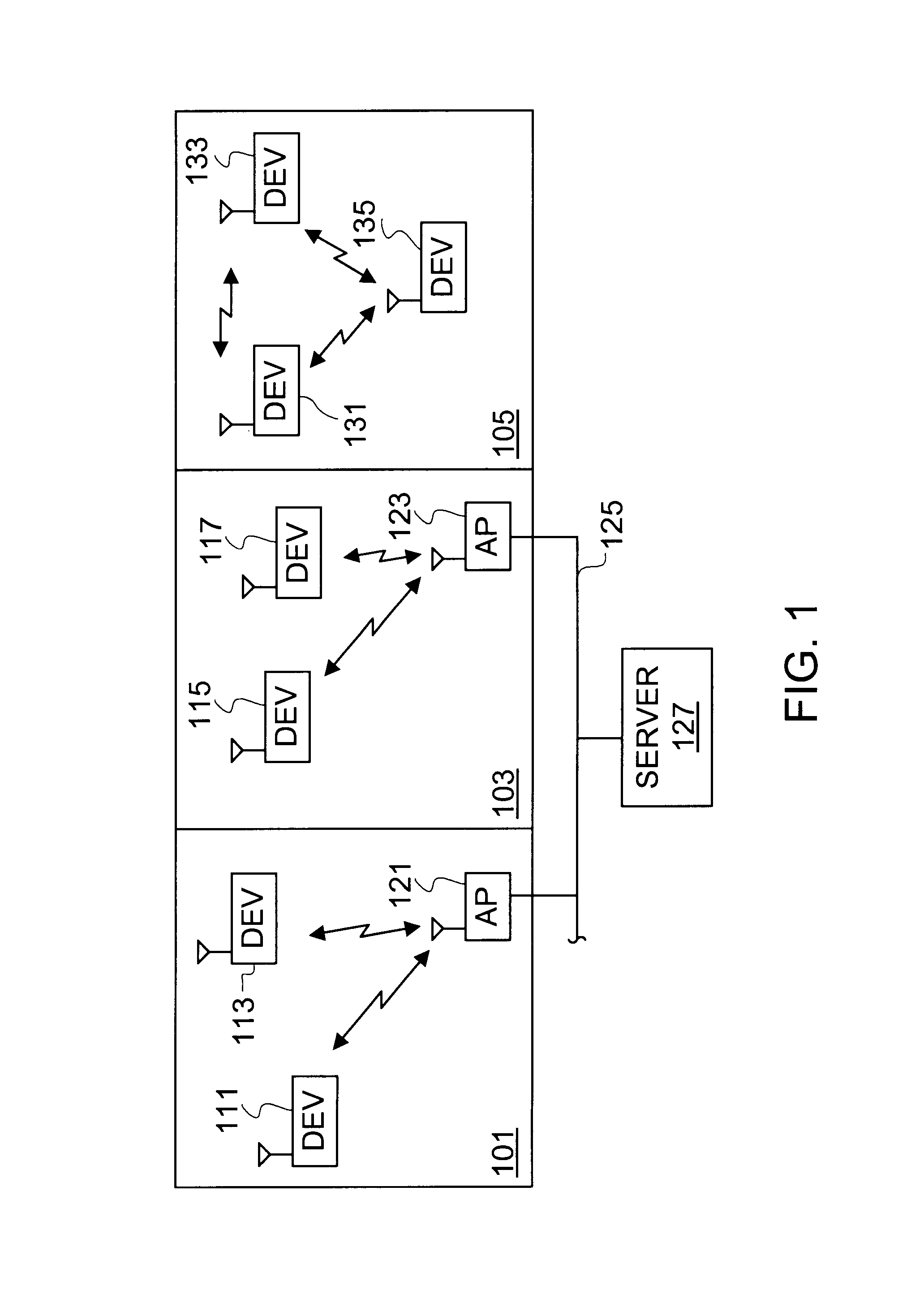

Communication system architecture and operating methodology providing a virtual neighborhood network

InactiveUS7142503B1Overcome bandwidth limitationIncreased peak bandwidth capacityError preventionFrequency-division multiplex detailsEnd-to-end encryptionTransceiver

A communication system (10) supports the provision of a plurality of dedicated communication resources (50–64), such as copper drops, RF links and optical fibers, to dedicated home-gateway devices (44–48) or distribution points (124). The communication resources (50–64) support broadband interconnection (104) between the dedicated home-gateway devices (44–48) or distribution points (124) and an access multiplexor (30) in a network (12). Each gateway device (44–48) or distribution point (124) generally includes a local RF transceiver (84) and associated control logic (80–82) that allows local communication (86) between gateway devices (44–48) and hence statistically multiplexed access (60–64, 89) to multiple communication resources, thereby providing increased bandwidth in uplink and / or downlink directions. With the control logic (80) operable to provide a routing and prioritisation / arbitration function, each gateway (44–48) is able to selectively engage use of supplemental, non-reserved communication resources usually associated with a dedicated ono-to-one connection between the access network (12) and at least one secondary gateway. Physical layer access to information routed via a secondary gateway within a virtual neighborhood network (90–92) comprising several gateways is restricted through an end-to-end encryption algorithm between an originating gateway and, at least, the access multilpexor (30).

Owner:RPX CLEARINGHOUSE

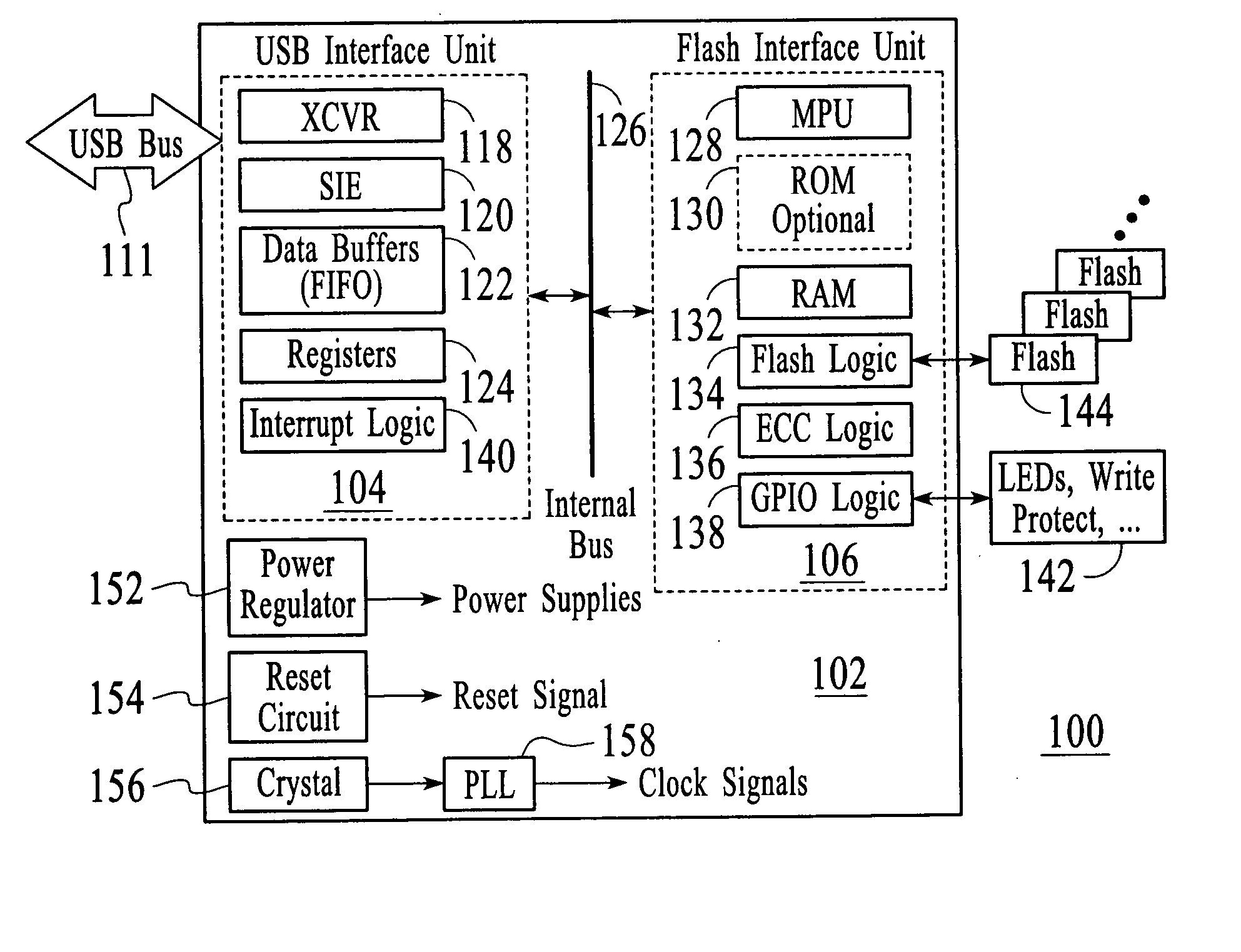

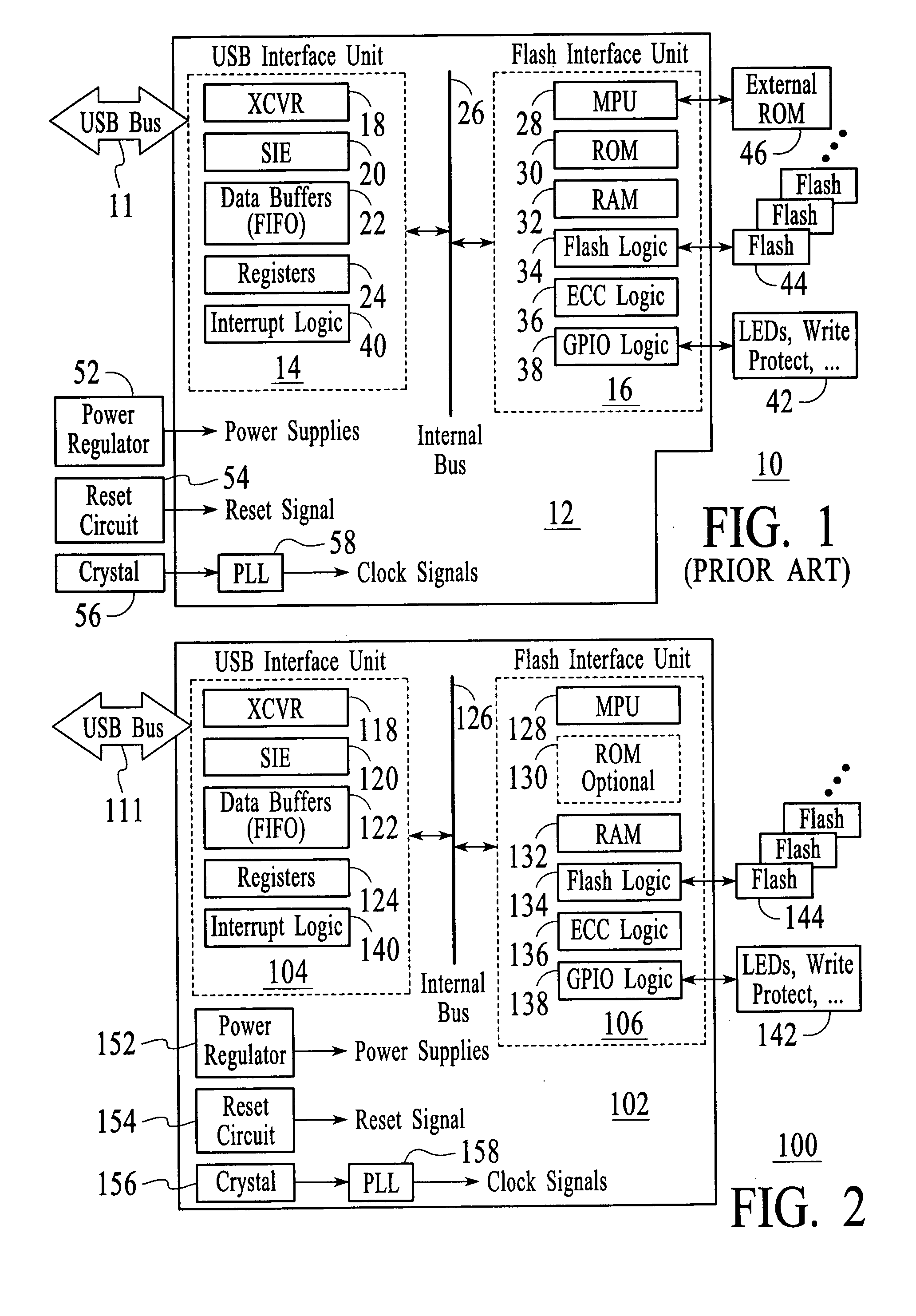

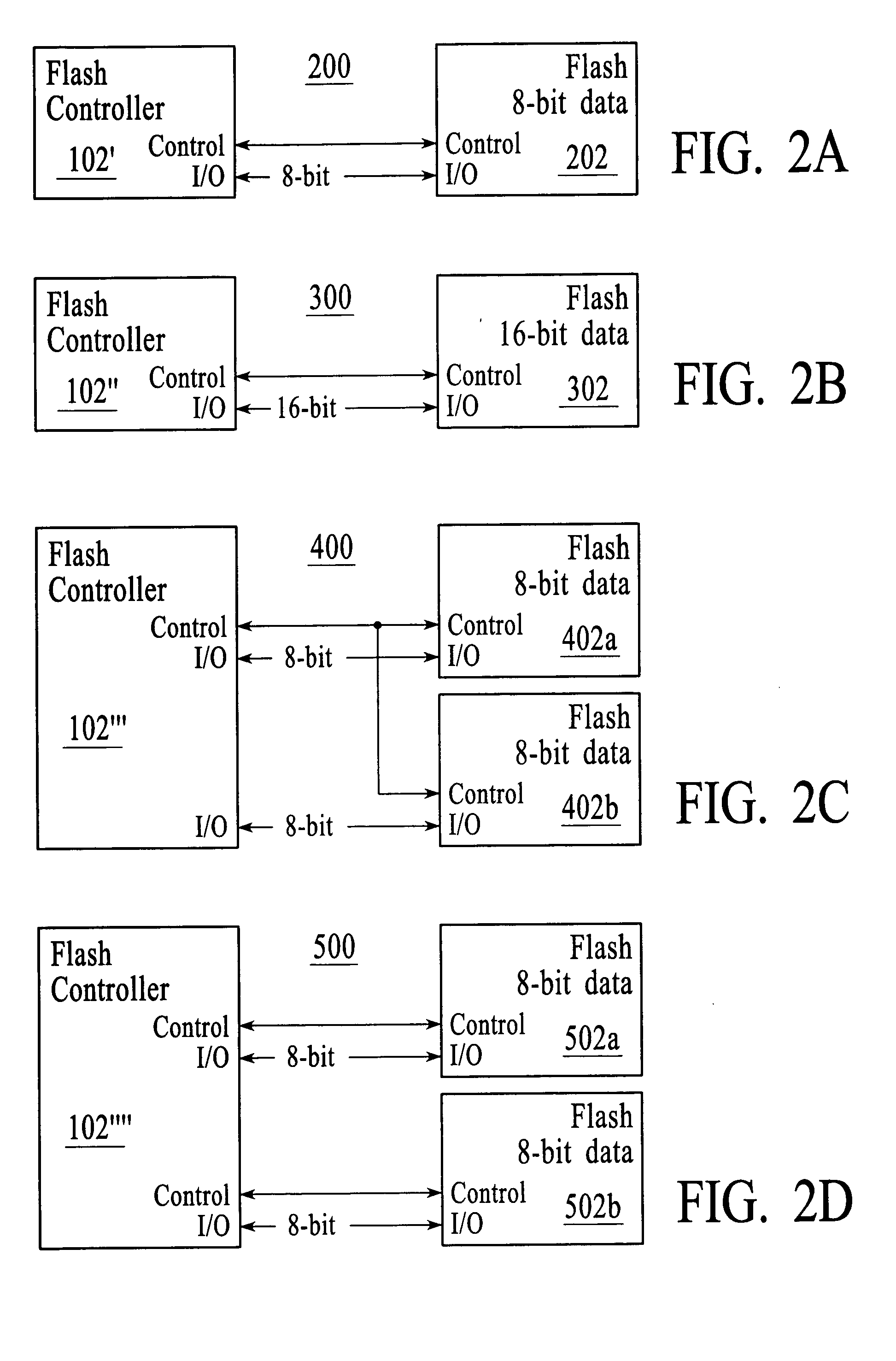

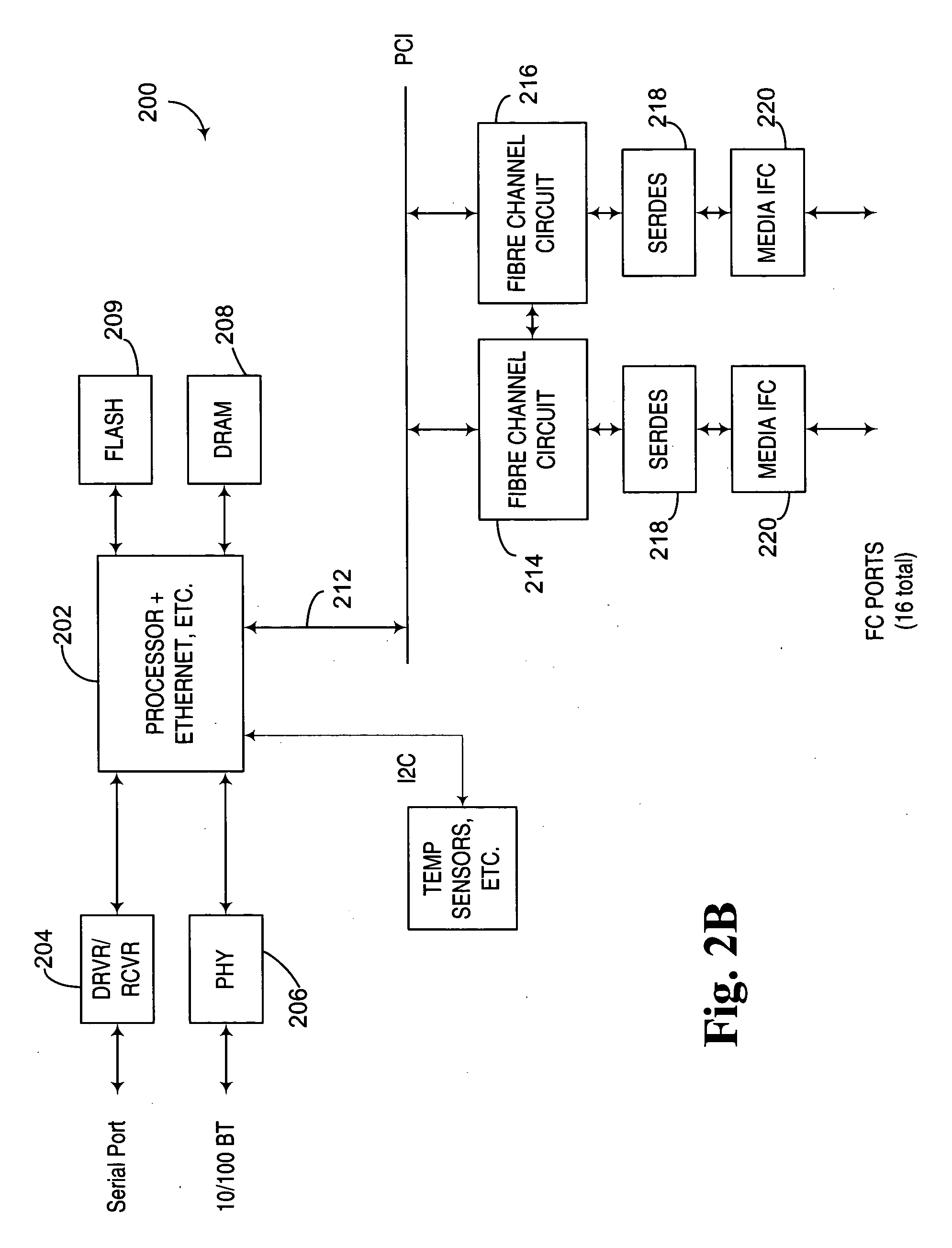

Highly integrated mass storage device with an intelligent flash controller

InactiveUS20050160218A1Increases serial throughputImprove throughputInput/output to record carriersMemory systemsMass storageFlash memory controller

A FLASH controller is disclosed. The controller comprises a USB interface unit. The USB interface unit implements a USB standard that has a bus speed equal or greater than 12 Mb / s. The controller includes an internal bus coupled to the USB interface unit; and a FLASH interface unit coupled to the internal bus. The FLASH interface unit includes FLASH controller logic that allows the throughput for access to the FLASH memory to match the speed of the USB standard. Advantages of the FLASH controller in accordance with the present invention include (1) utilizing the higher speed USB interface such as the USB 2.0 standard, which substantially increases the serial throughput between USB host and FLASH controller; (2) utilizing more advanced FLASH control logic which is implemented to raise the throughput for the FLASH memory access; (3) utilizing an intelligent algorithm to detect and access the different FLASH types, which broadens the sourcing and the supply of FLASH memory; (4) by storing the software program along with data in FLASH memory which results in the cost of the controller being reduced, and also makes the software program field changeable and upgradeable; and (5) providing high integration, which substantially reduces the overall space needed and reduces the complexity and the cost of manufacturing.

Owner:SUPER TALENT ELECTRONICS

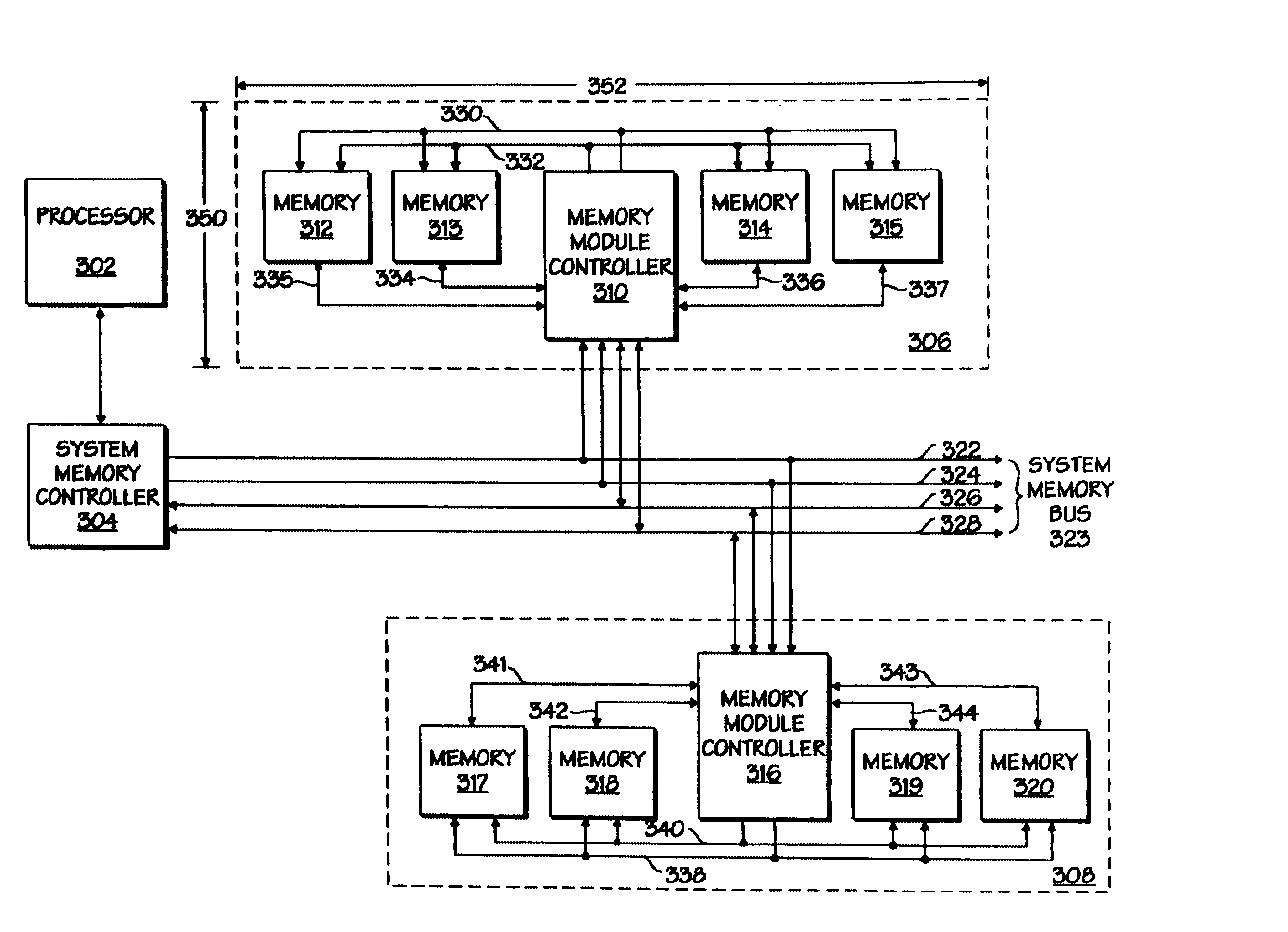

Memory module controller for providing an interface between a system memory controller and a plurality of memory devices on a memory module

A memory module controller for providing interface between a system memory controller and a plurality of memory devices on a memory module. The memory module includes first interface circuitry and control logic. The first interface circuitry is configured to receive from the system memory controller a first memory transaction in a first format. The control logic is coupled to the first interface circuitry and configured to convert the first memory transaction into a second memory transaction in a second format for the plurality of memory devices. The second format of the second memory transaction is different than the first format of the first memory transaction.

Owner:INTEL CORP

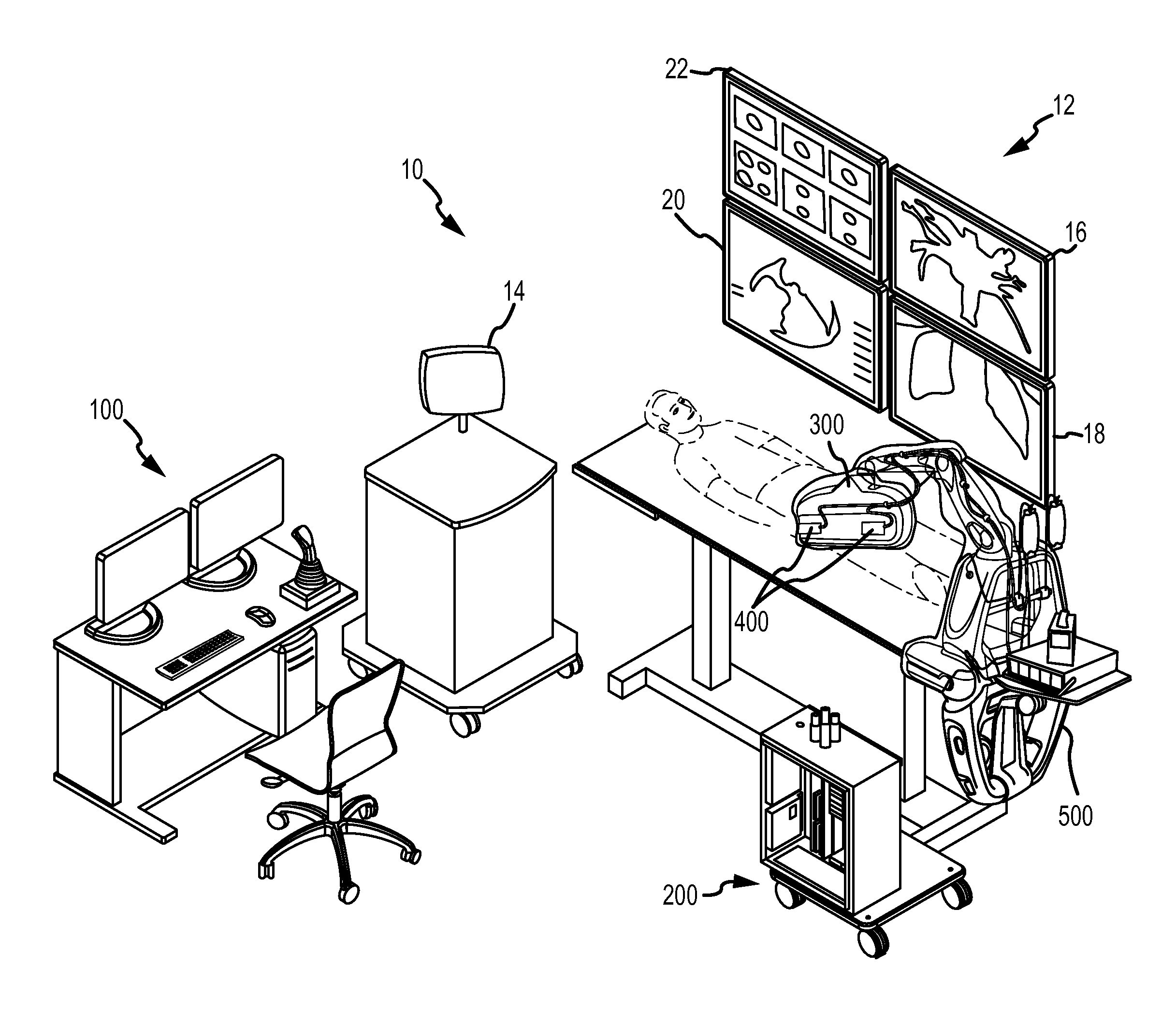

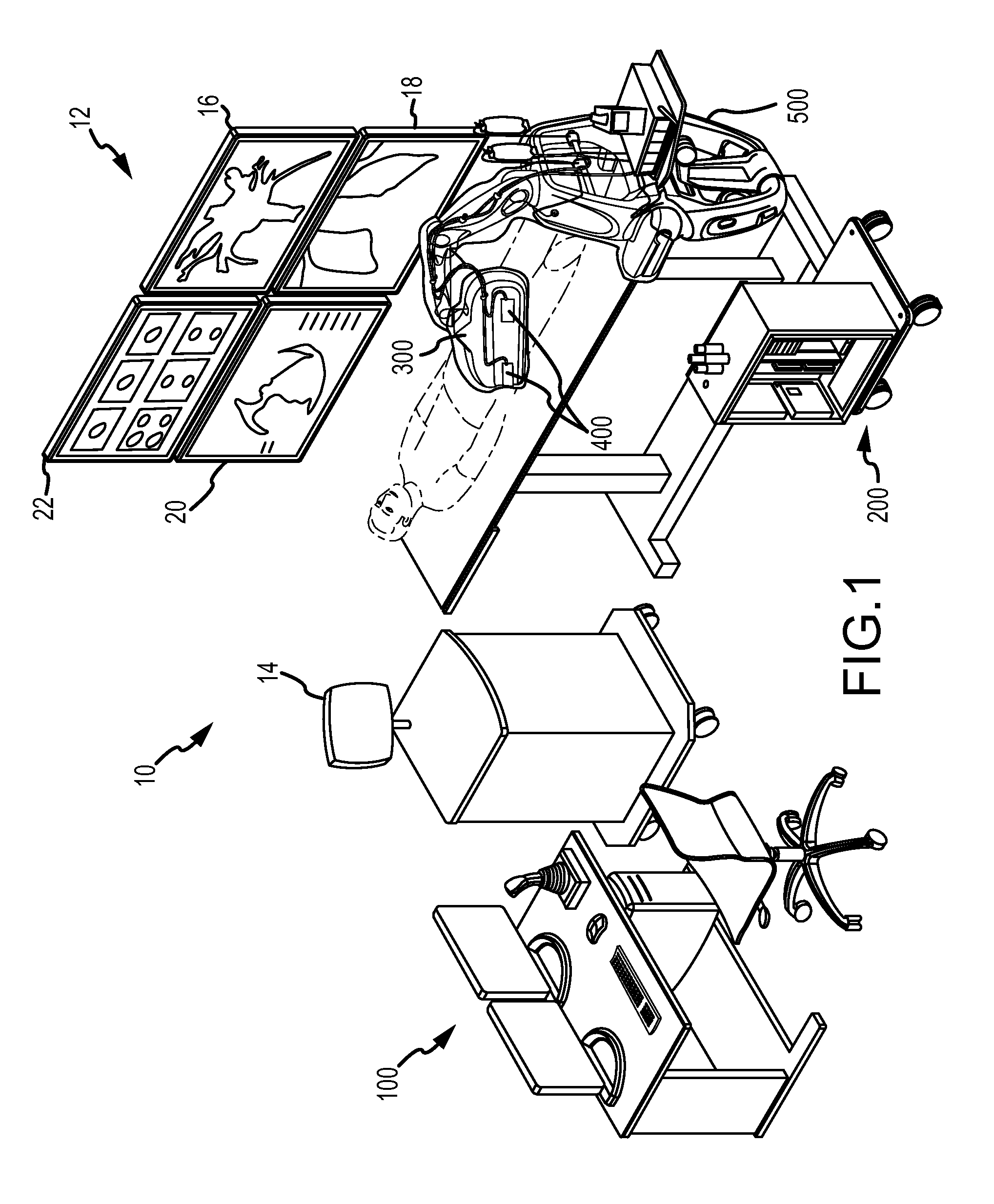

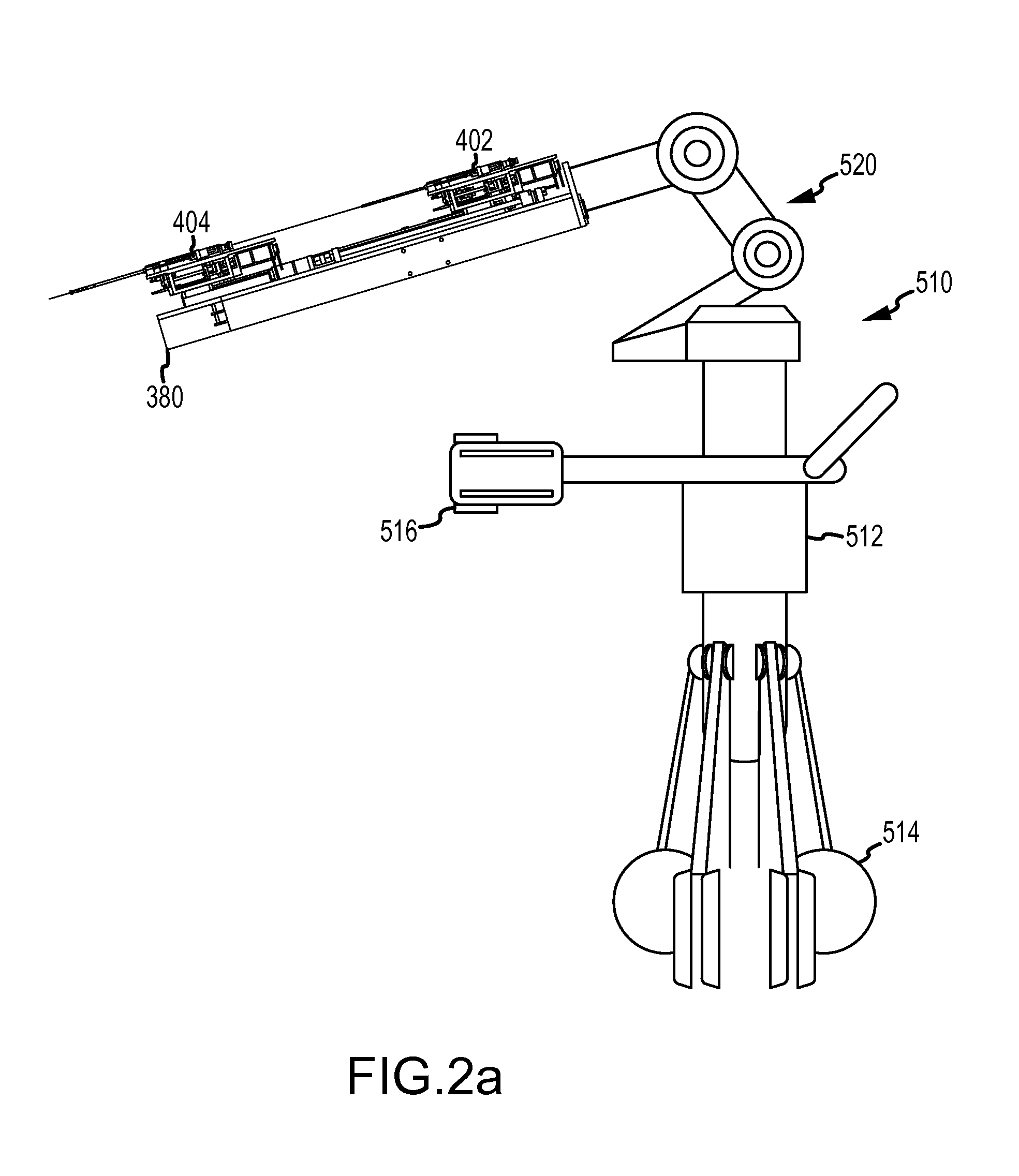

Intuitive user interface control for remote catheter navigation and 3D mapping and visualization systems

The present disclosure relates to a control system for user-guided robotic control of a medical device and includes an electronic control unit, a computer-readable memory coupled to the ECU, and a visualization system configured to provide a view of an anatomical model. The memory contains user interface logic configured to be executed by the ECU, and configured to obtain input from a touch screen display with respect to the view of an anatomical model. Control logic stored in the memory is also configured to be executed by said ECU and is configured to produce an actuation control signal responsive to the input to control actuation of a manipulator assembly so as to move the medical device.

Owner:ST JUDE MEDICAL ATRIAL FIBRILLATION DIV

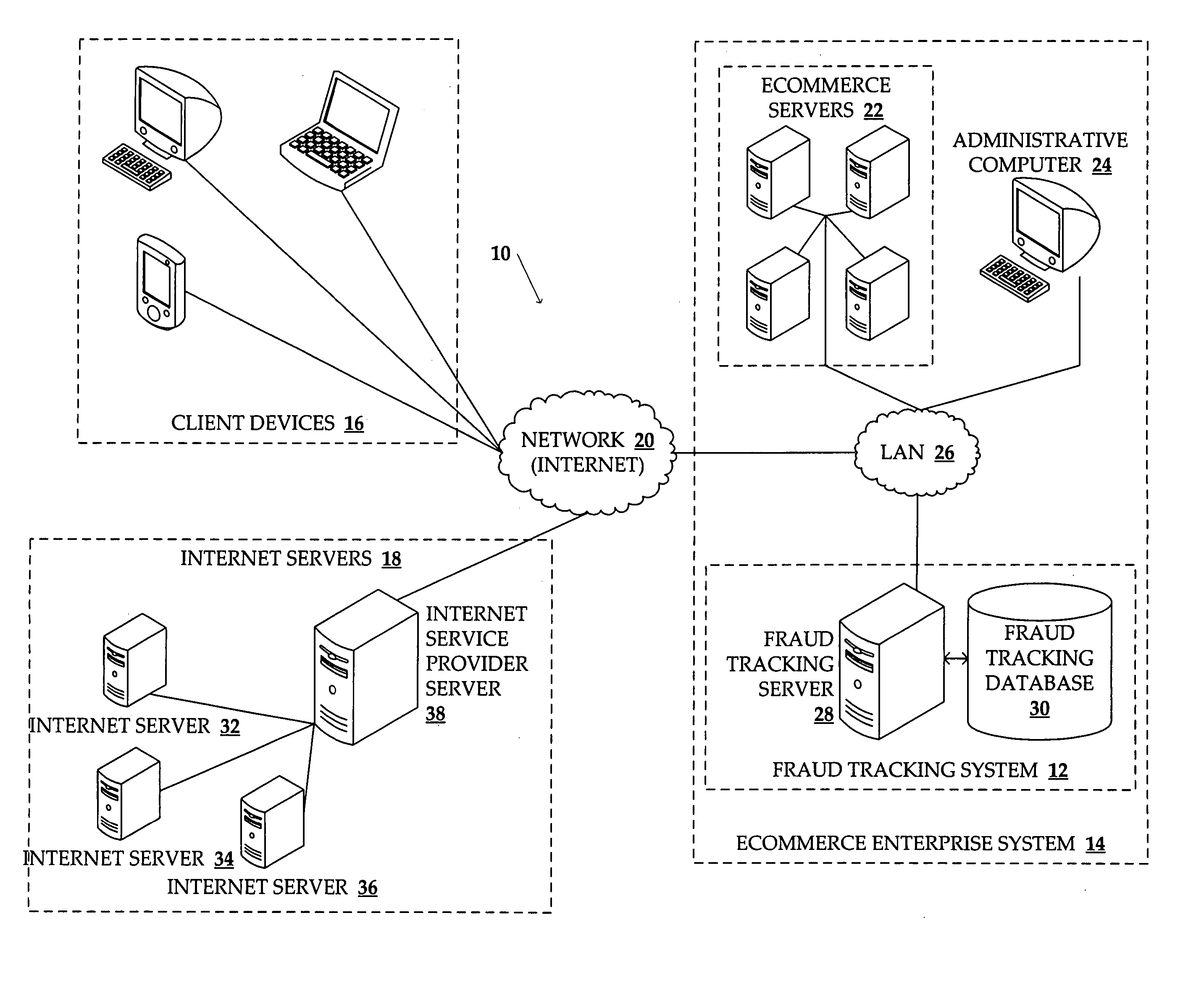

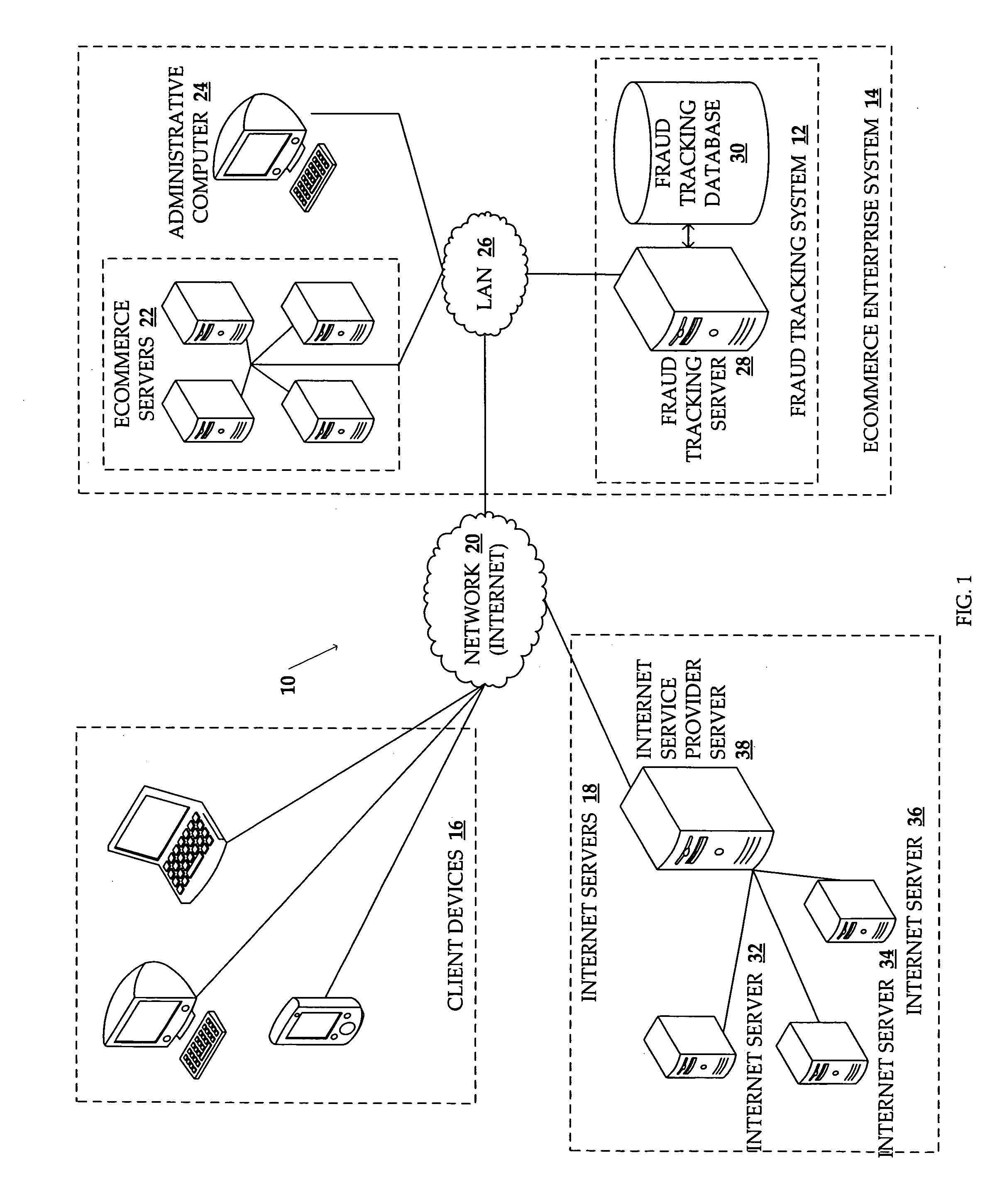

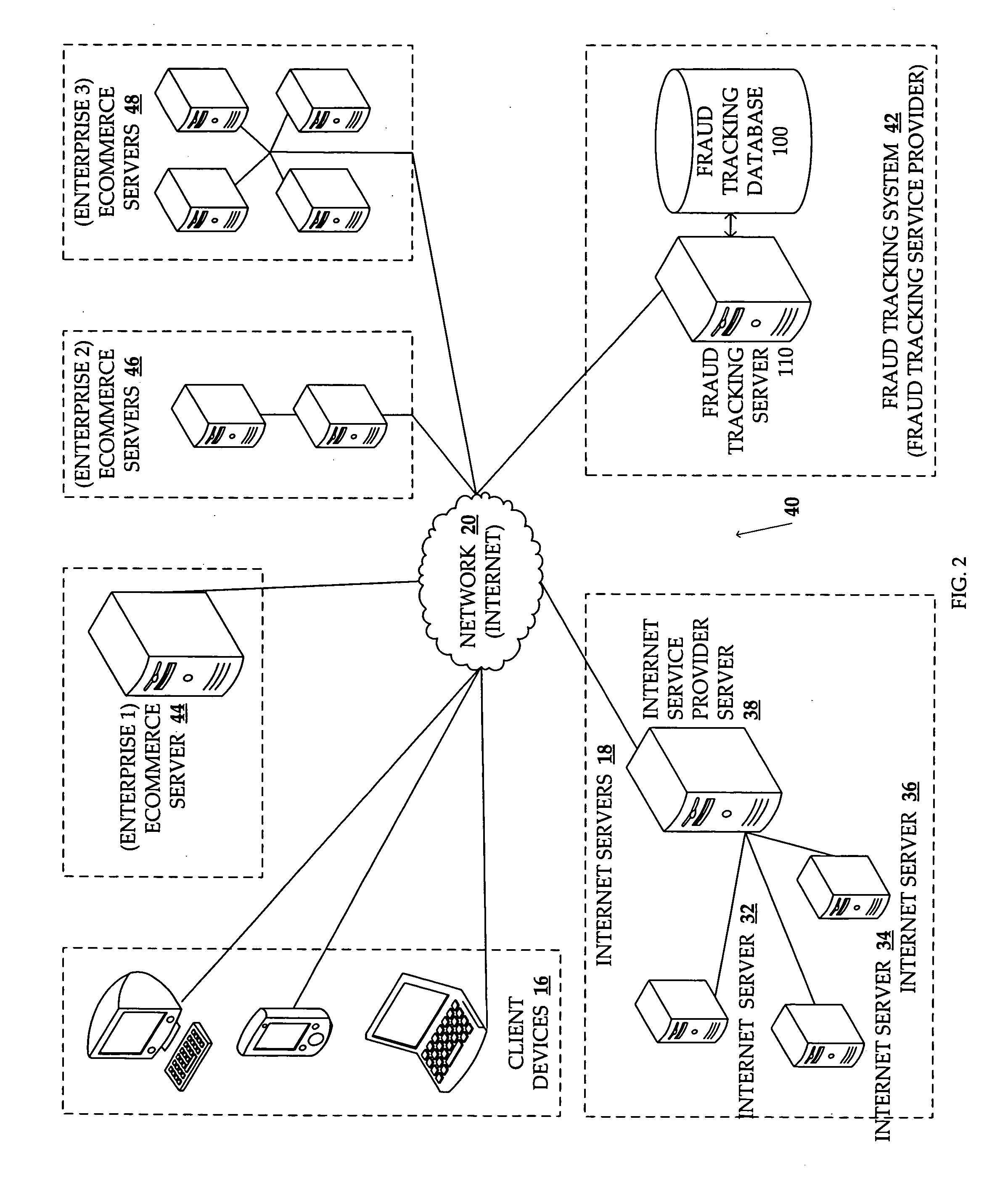

Method and system for tracking fraudulent activity

A method and system for tracking potentially fraudulent activities associated with one or more web sites is disclosed. The system includes a fraud tracking server connected to a fraud tracking database. The fraud tracking server includes a communications module to facilitate the exchange of data between the server and multiple client devices. The fraud tracking server receives data from one or more client devices that identifies a potential spoof site. The fraud tracking server also includes control logic to generate a spoof site tracking record in the fraud tracking database. The spoof site tracking record includes the data identifying the potential spoof site. After the spoof site tracking record has been created, the fraud tracking server notifies an administrator of the potential spoof site by communicating the data received and stored in the fraud tracking database to an administrator.

Owner:PAYPAL INC

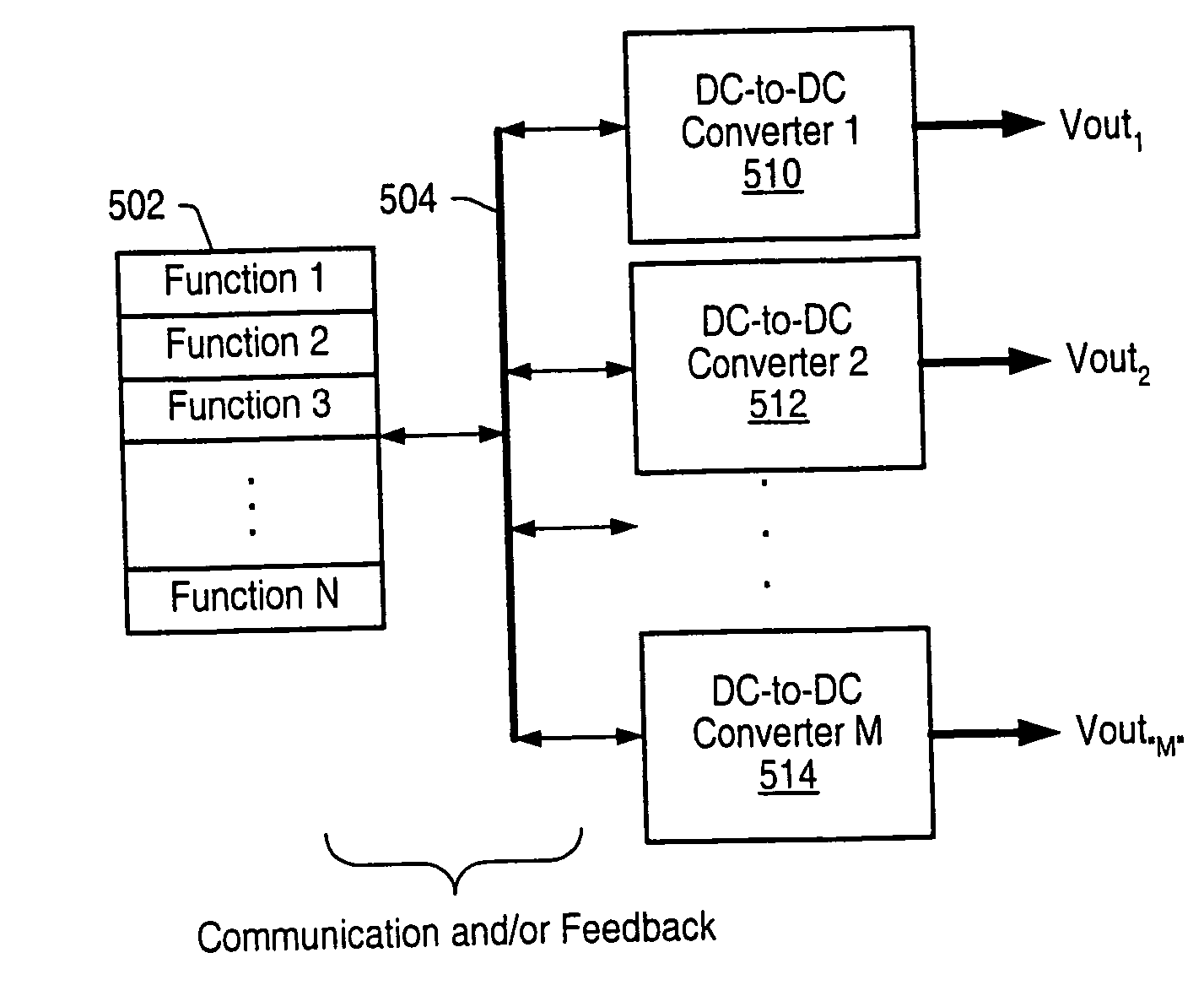

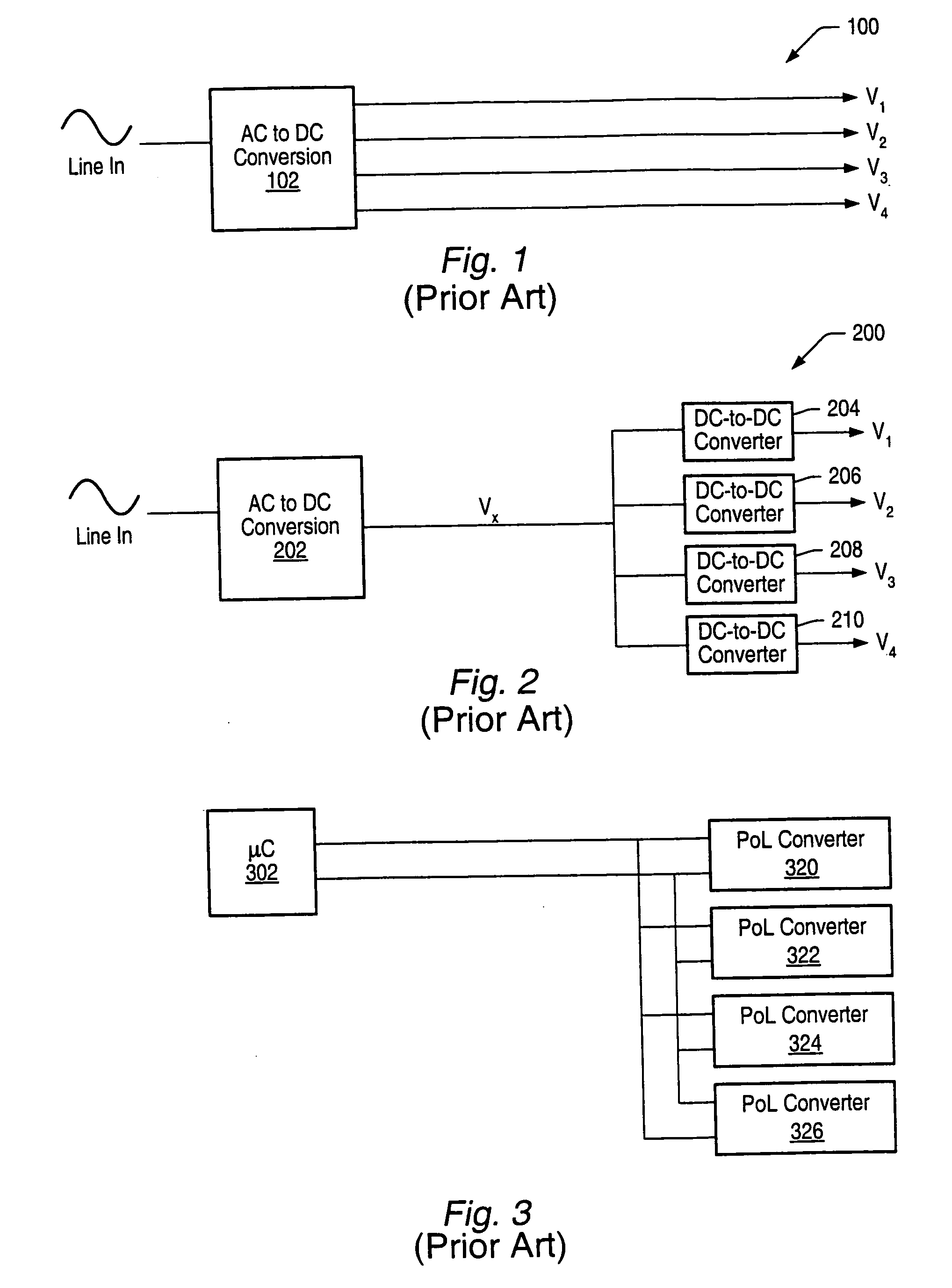

Point of load regulator having a pinstrapped configuration and which performs intelligent bus monitoring

ActiveUS20060149396A1Low costVolume/mass flow measurementHardware monitoringPoint of loadVoltage converter

A new system-level approach to managing the delivery of DC voltage and current. Several system level functions may be enabled without requiring separate ICs to perform those functions. Supervisory functions for a voltage converter may be performed by a central control module or chip that may be coupled to point-of-load voltage converters comprised in digital power management devices (DPMD) through a serial digital bus. The DPMDs may also use the high-speed serial digital bus to provide real-time feedback information to the central control module or chip. Single DPMDs may be combined together in a current sharing configuration in a “plug-and-play” fashion, where the control logic in each DPMD is capable of automatically establishing control loops required a multi-phase supply. Feedback necessary for establishing control may be transmitted across the digital bus coupling the devices. The supervisory functions may be included in each DPMD, which may communicate with each other over a serial digital bus, where the DPMDs singly or together may operate to perform control of their respective POLs, enabling configurations that do not require a central control module.

Owner:INTERSIL INC

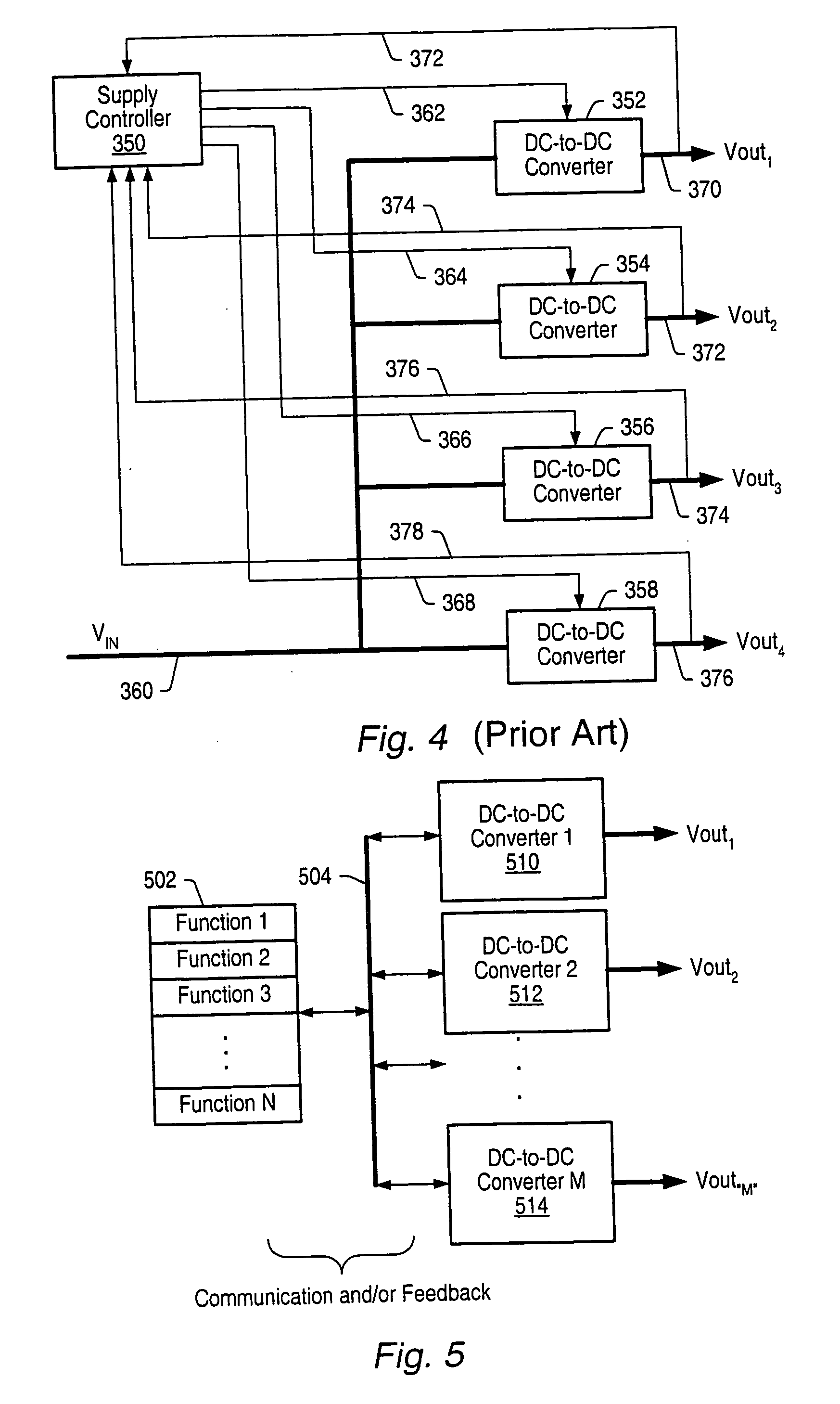

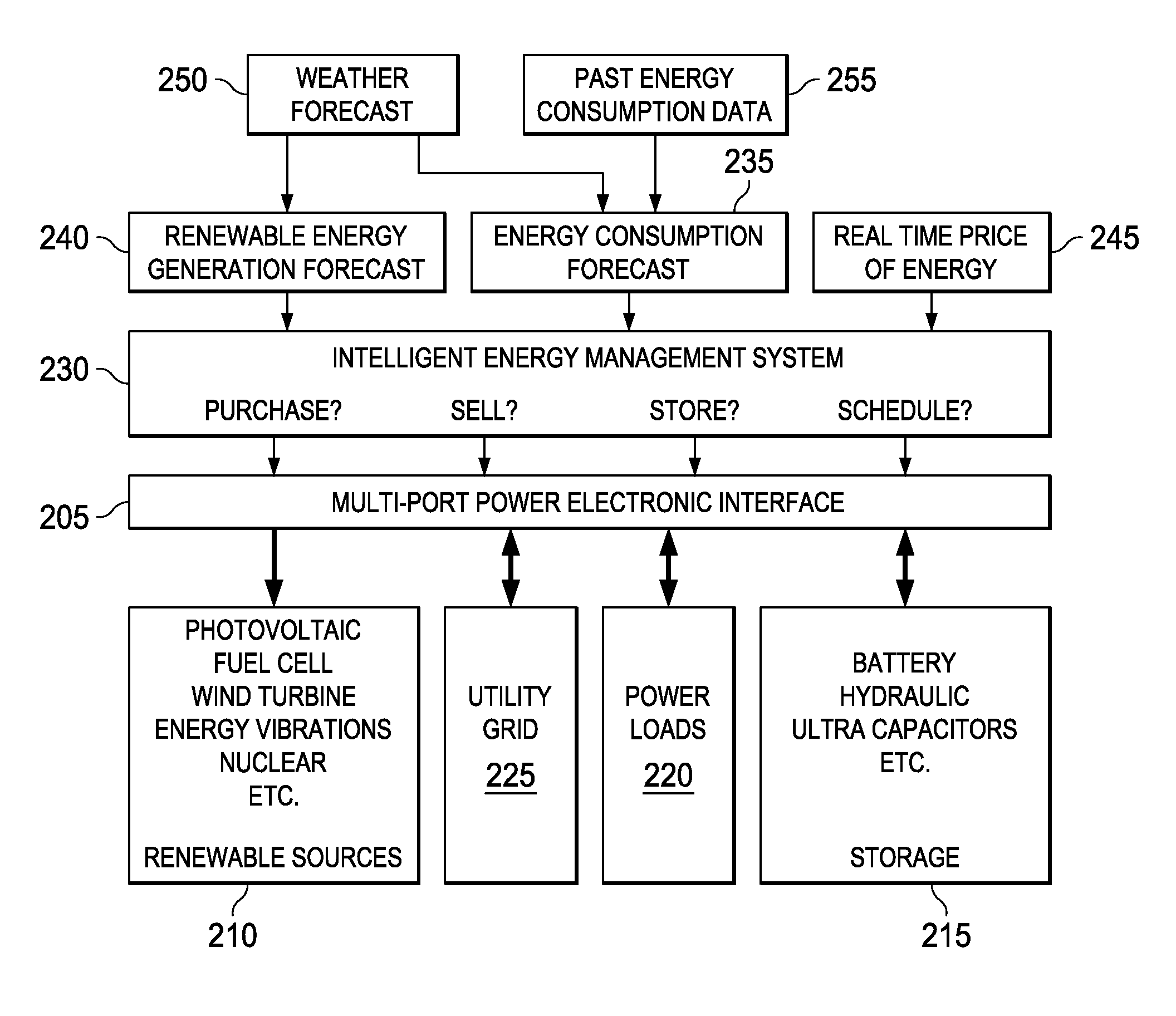

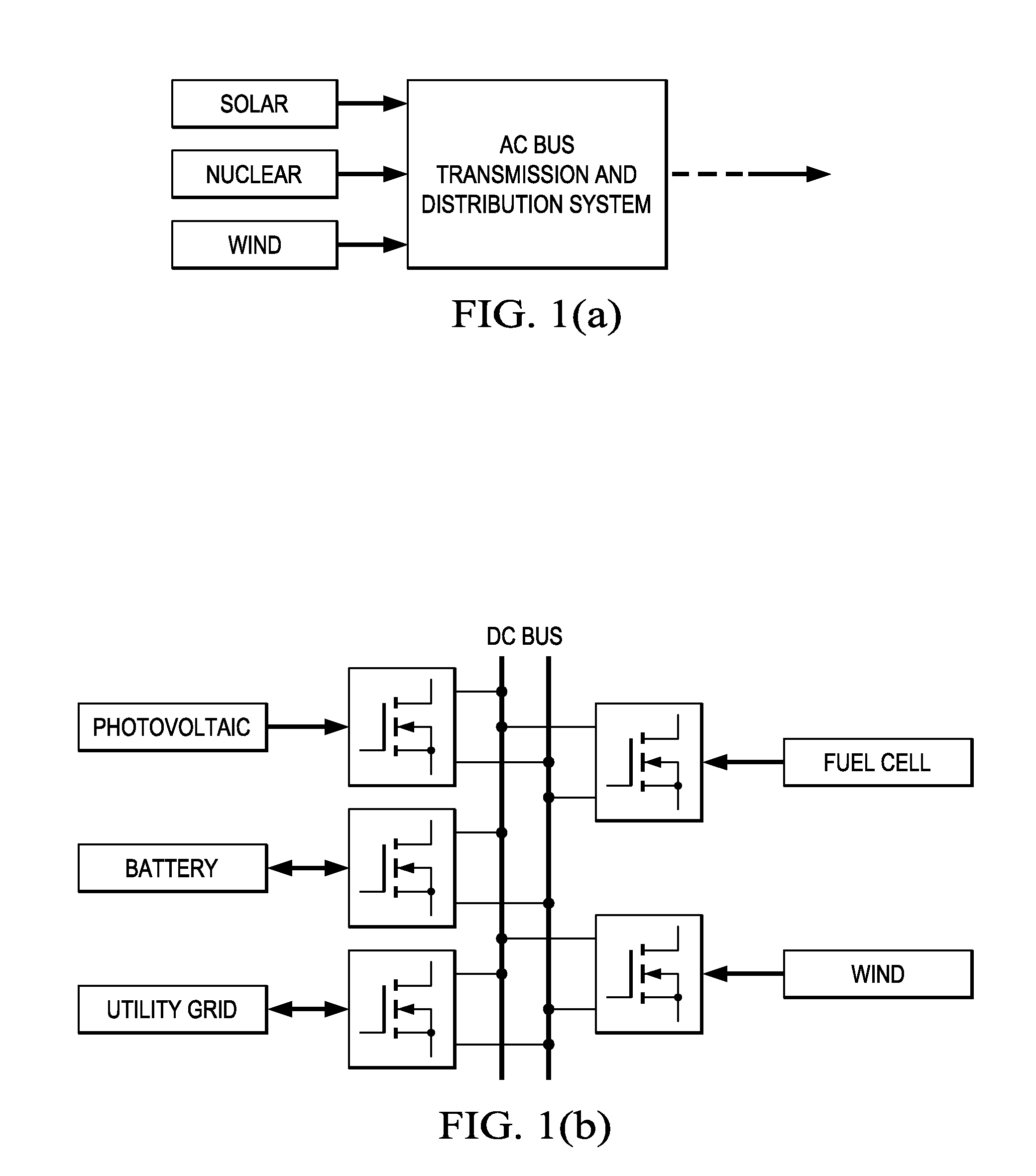

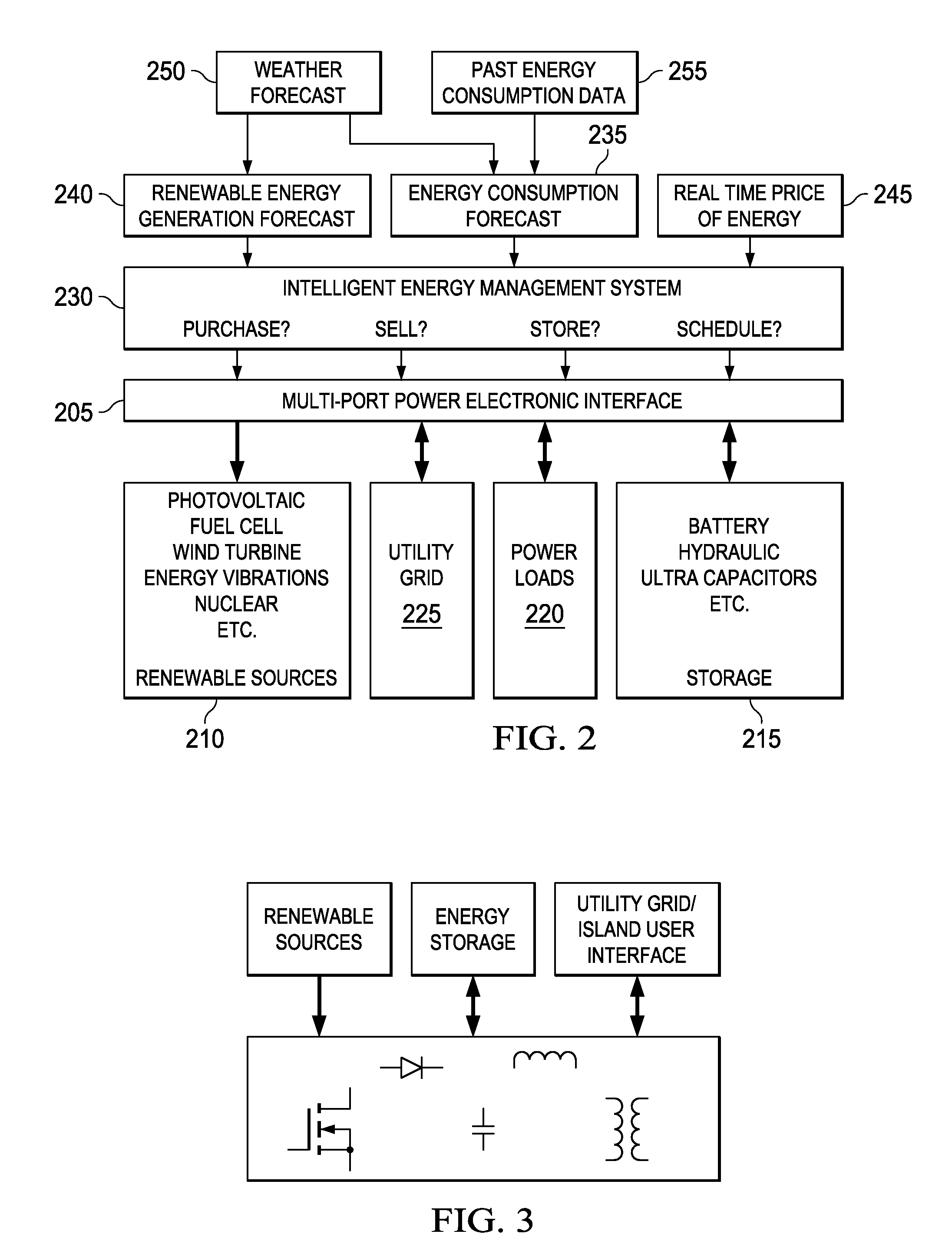

Methods and Apparatus for Design and Control of Multi-port Power Electronic Interface for Renewable Energy Sources

Methods and systems for energy management are disclosed. An example system includes a first port connected to an energy storage device for bidirectional flow of energy, a second port connected to an energy source device for unidirectional flow of energy, a third port connected to a utility grid for bidirectional flow of energy, and a unified control system with control logic configured to simultaneously control energy flow between the first, second, and third ports based on at least two factors from the group consisting of: a state of charge of the energy storage device, a state of the energy source device, and a state of the utility grid. Other embodiments are described and claimed.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

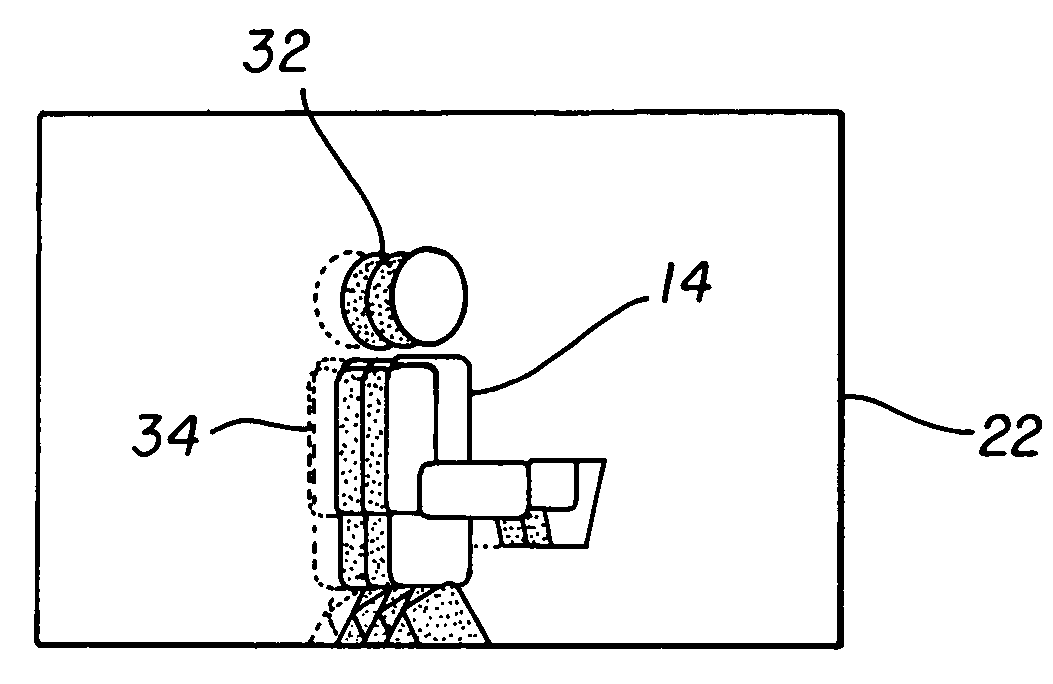

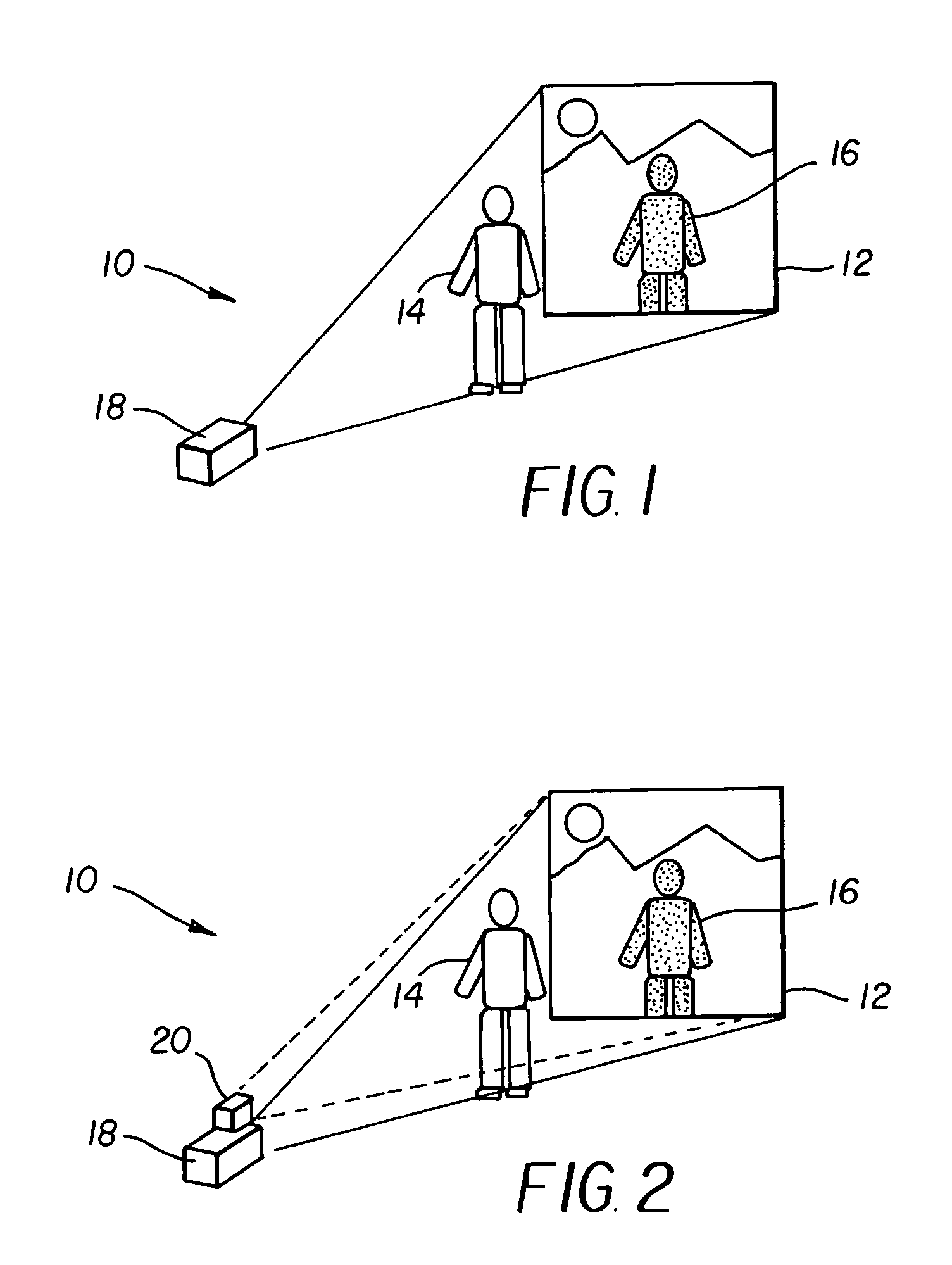

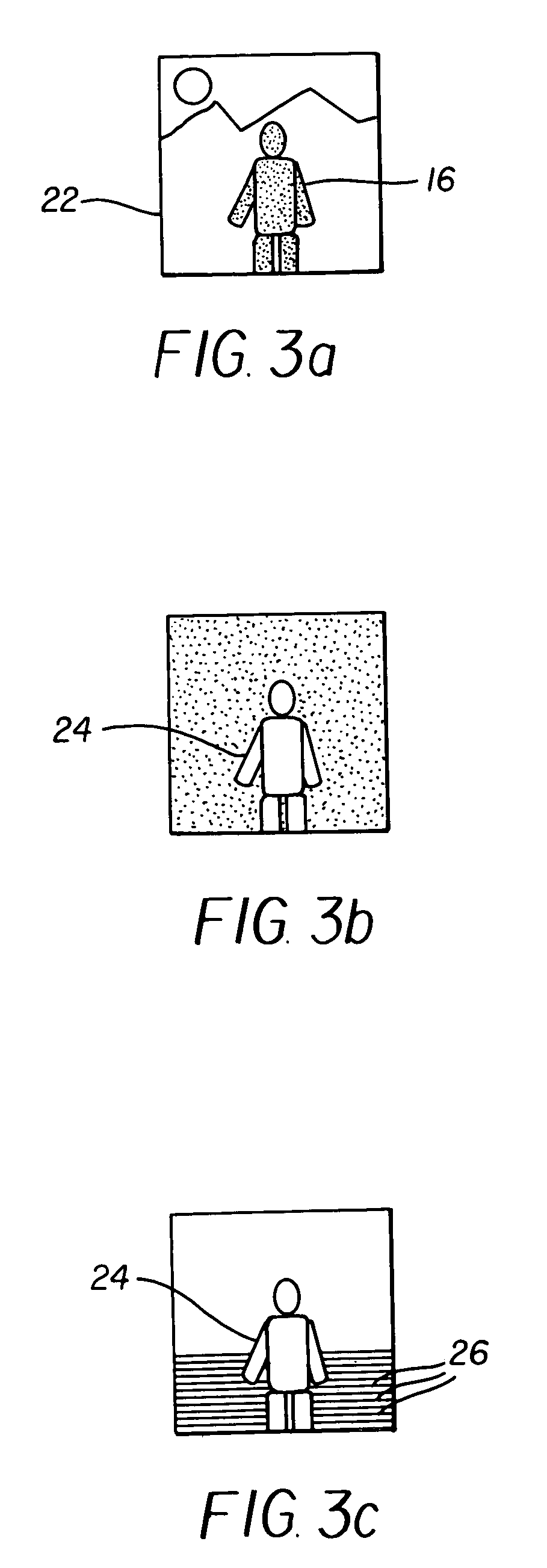

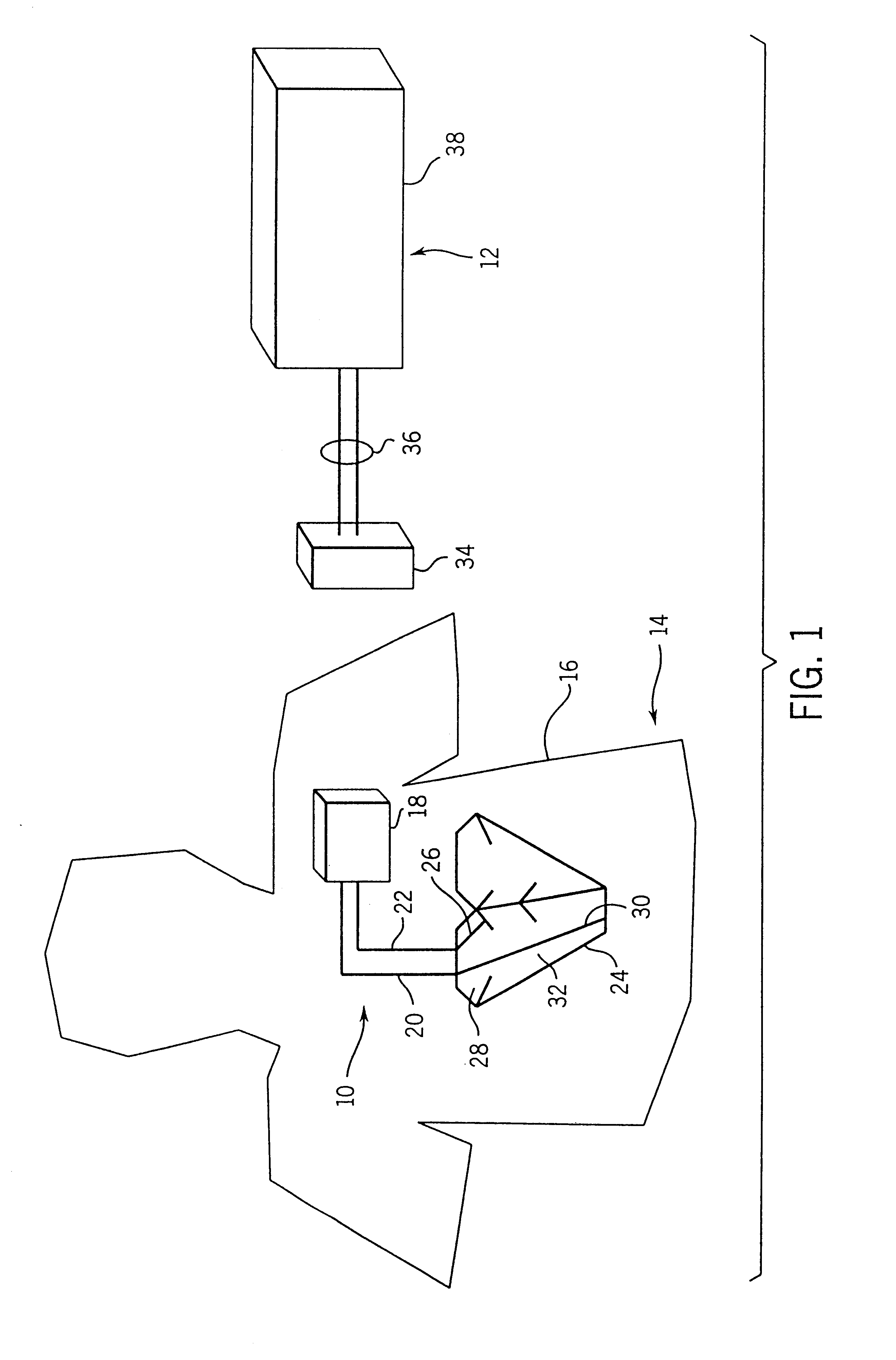

Laser projector having silhouette blanking for objects in the output light path

A projection apparatus (18) forms an image frame (22) on a display surface (12), where the image frame (22) is a two-dimensional array of pixels. The projection apparatus (18) has a laser (40) light source, an image modulator (42) for forming an image-bearing beam according to scanned line data, and projection optics (44) for projecting the image-bearing beam toward the display surface (12). A camera (20) obtains a sensed pixel array by sensing the two-dimensional array of pixels from the display surface (12). A control logic processor (28) compares the sensed pixel array with corresponding image data to identify any portion of the image-bearing beam that is obstructed from the display surface (12) and to disable obstructed portions of the image-bearing beam for at least one subsequent image frame (22).

Owner:IMAX THEATERS INT

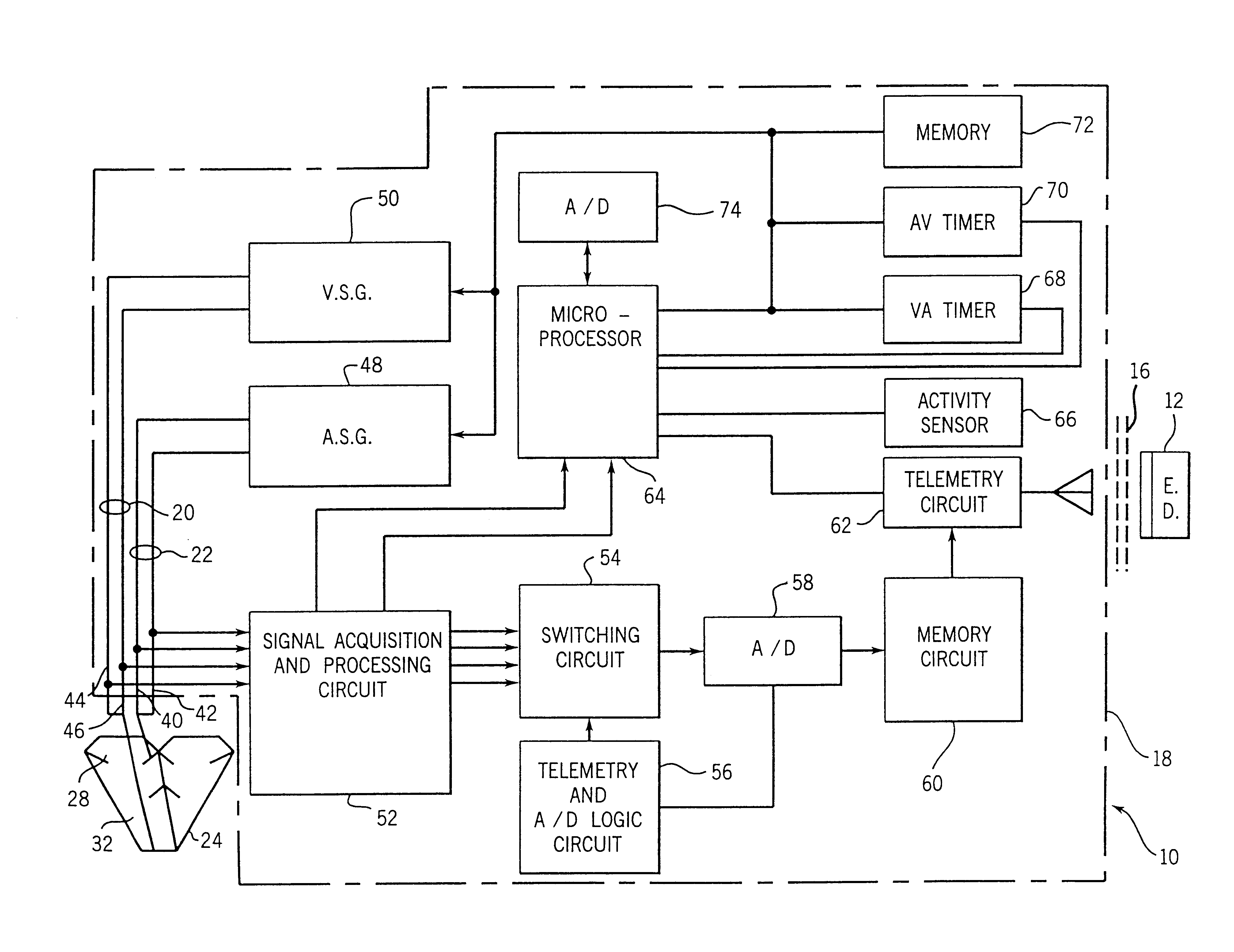

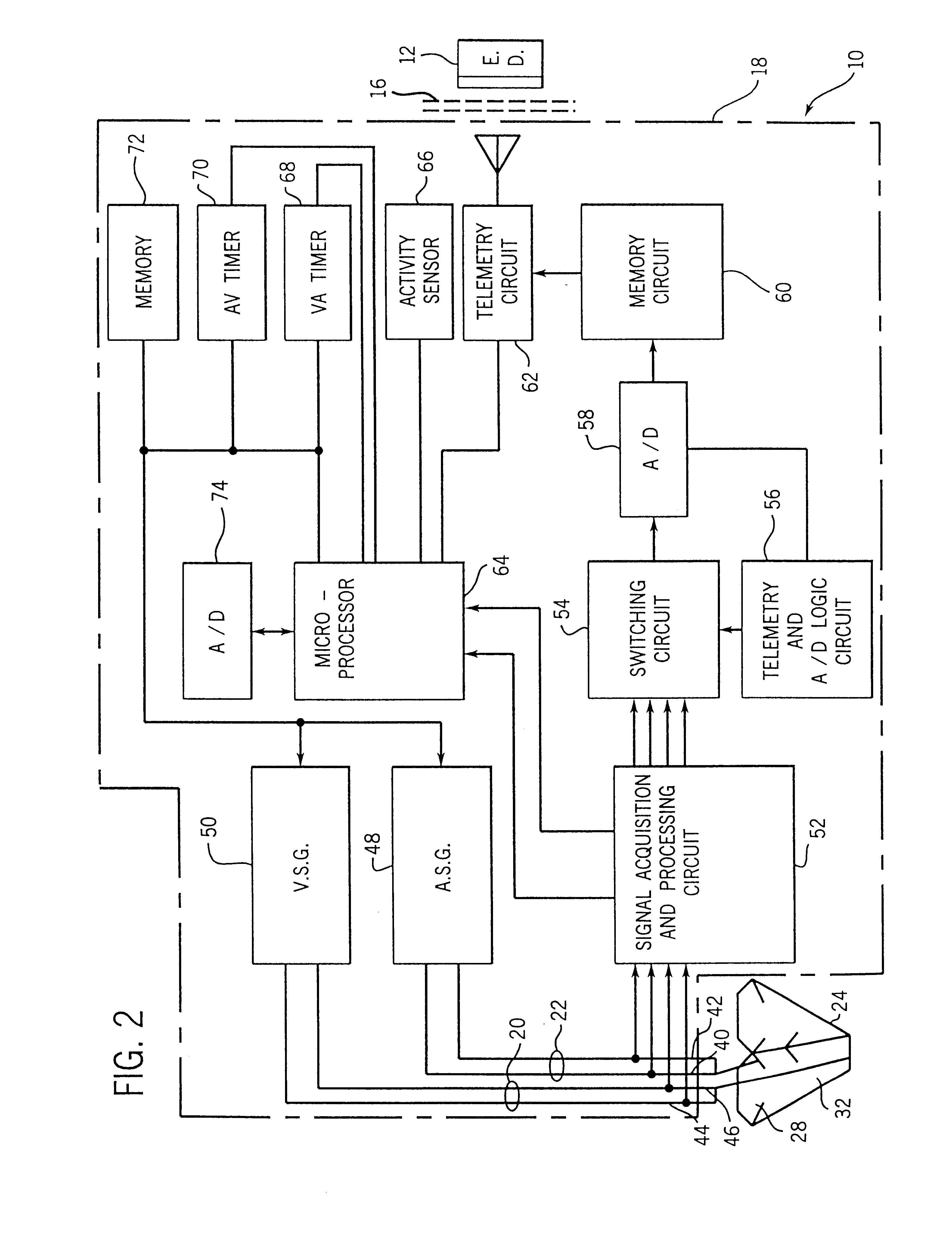

Implantable device with digital waveform telemetry

A technique for acquiring and accessing information from a medical implantable device is provided. Analog waveforms of interest are sensed and processed by signal acquisition circuitry. Analog parameters of interest are applied to selector switches which are controlled by a logic circuit. The logic circuit is also coupled an A / D converter for converting the analog signals to digital values. The digital values are stored in dedicated registers and are available for telemetry to an external device upon receipt of a request or prompt signal. When a digitized value is accessed and telemetered, the control logic circuit changes the conductive state of the selector switches to apply the corresponding analog signal to the A / D converter. The resulting digital value is applied to the corresponding register to refresh the accessed and telemetered value. The technique permits the external device to request and configure the implanted device to send only digitized values of interest. The technique also makes efficient use of the A / D converter, which consumes energy only as needed to refresh the memory when digital values are accessed and telemetered.

Owner:INTERMEDICS

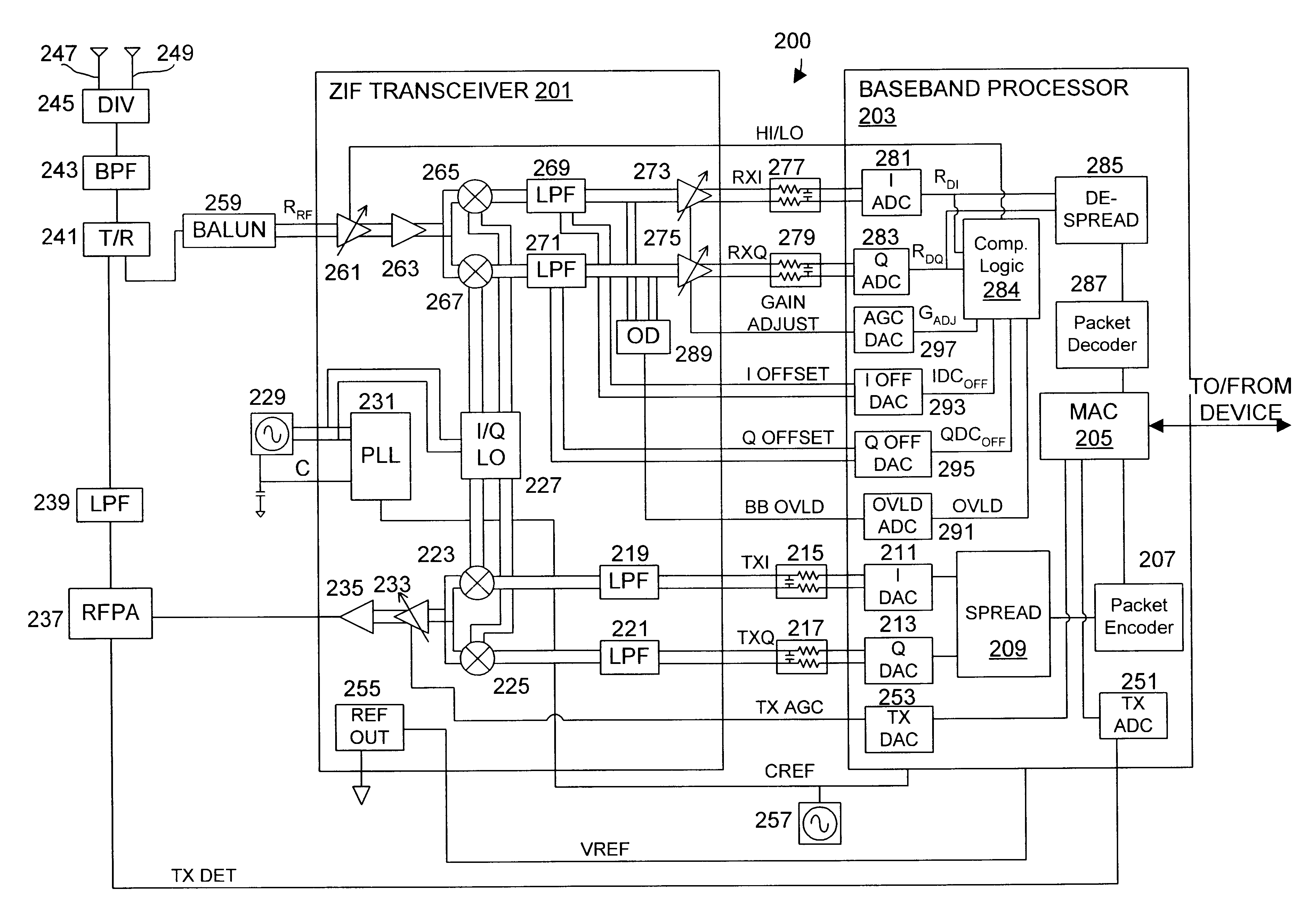

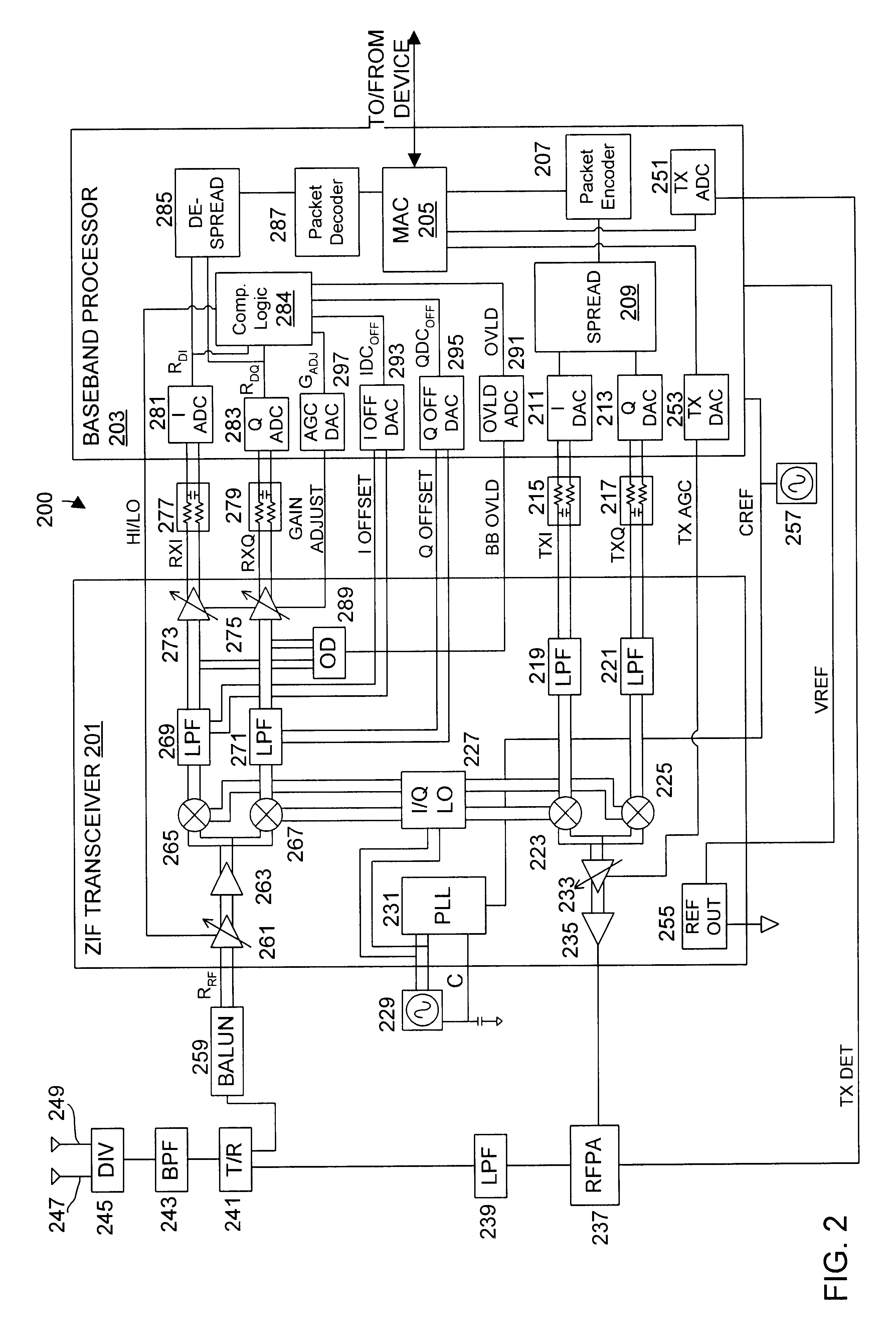

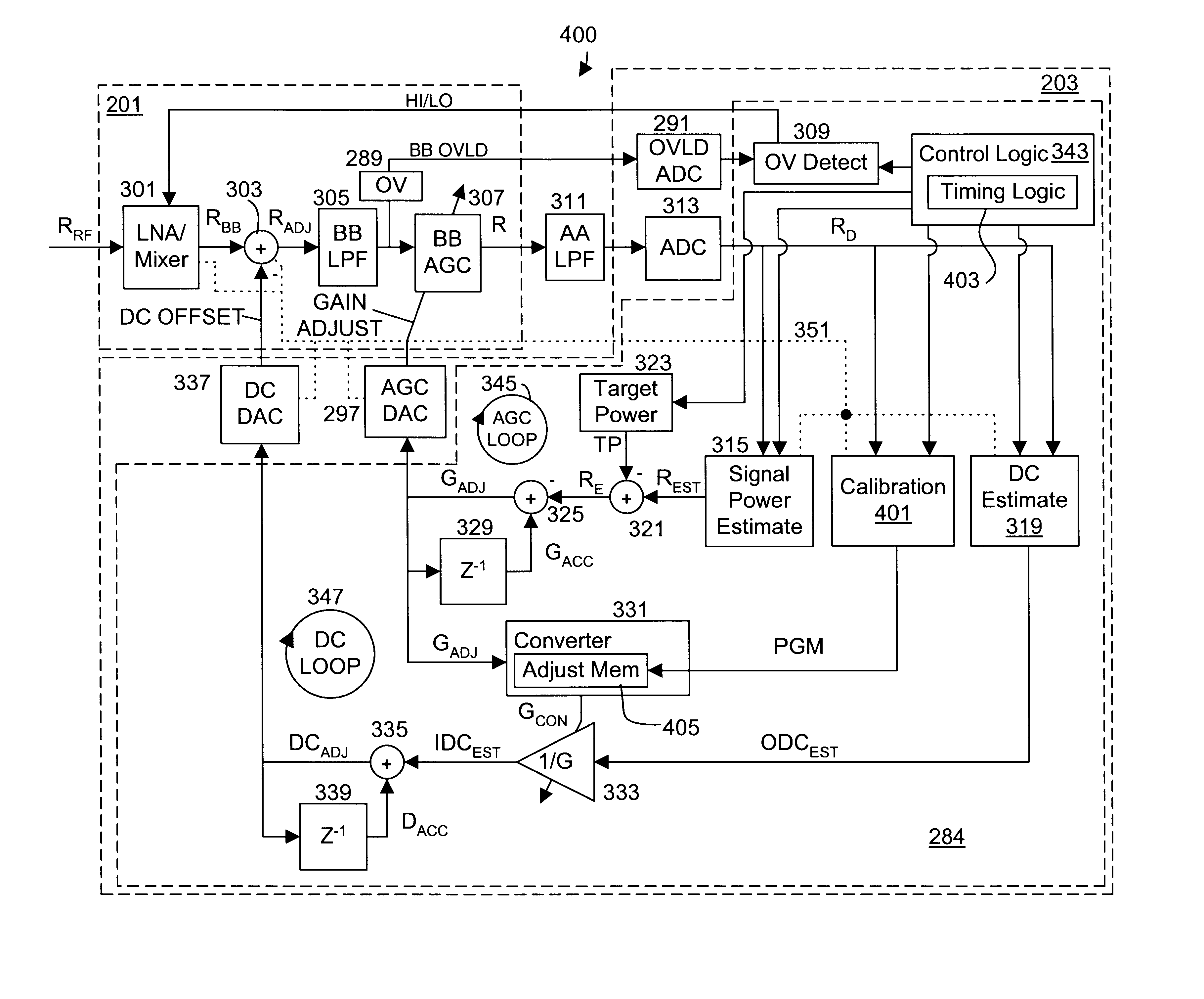

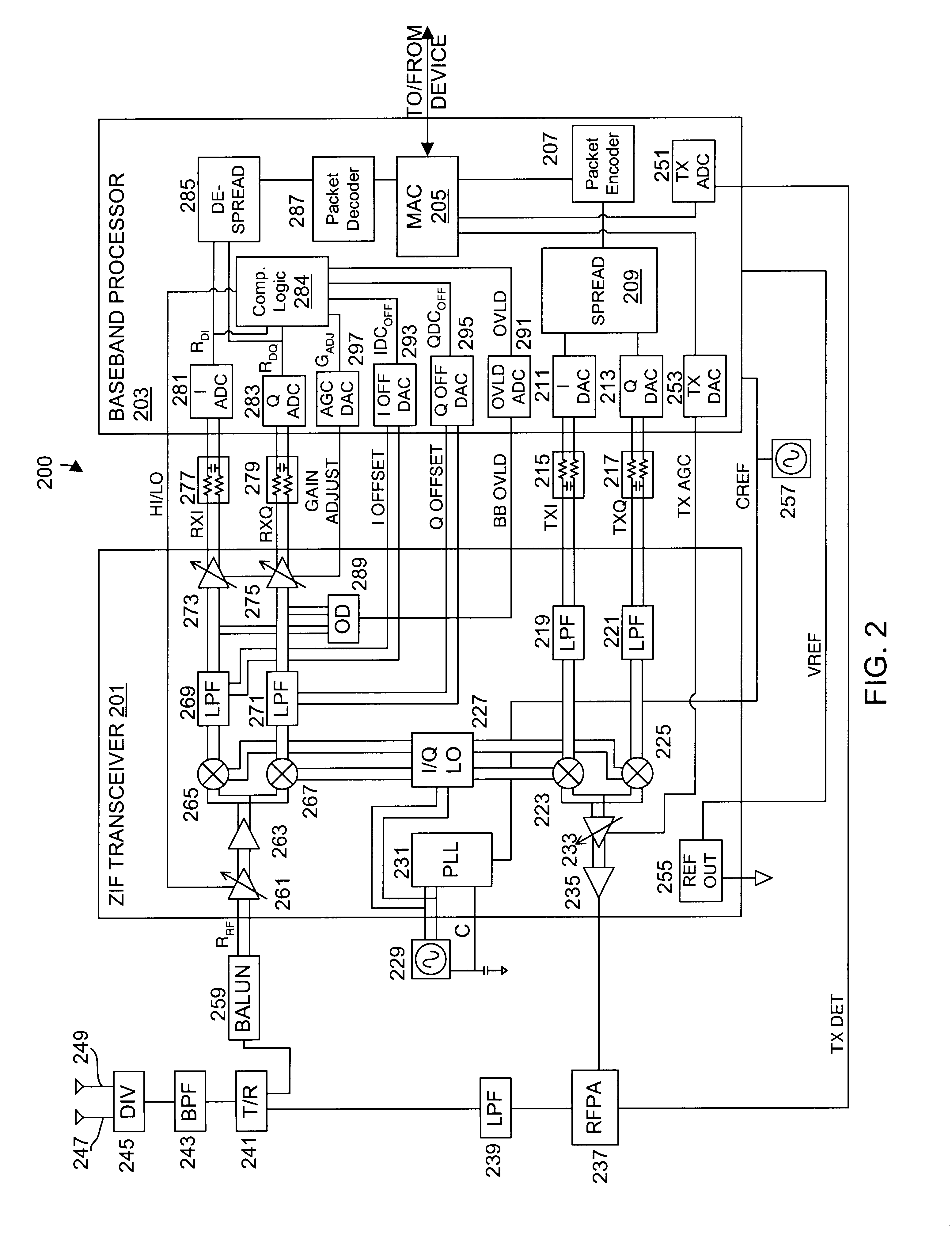

DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6560448B1Low costMaximum performanceGain controlAmplitude-modulated carrier systemsTransceiverAudio power amplifier

A wireless communication device including a radio frequency (RF) circuit, a ZIF transceiver and a baseband processor. The ZIF transceiver includes an RF mixer circuit that converts the RF signal to a baseband input signal, a summing junction that subtracts a DC offset from the baseband input signal to provide an adjusted baseband input signal, and a baseband amplifier that receives the adjusted baseband input signal and that asserts an amplified input signal based on a gain adjust signal. The baseband processor includes gain control logic, DC control logic and a gain interface. The gain control logic receives the amplified input signal, estimates input signal power and asserts the gain adjust signal in an attempt to keep the input signal power at a target power level. The DC control logic estimates an amount of DC in the amplified input signal and provides the DC offset in an attempt to reduce DC in the amplified input signal. The gain interface converts gain levels between the gain control logic and the DC control logic. The RF signal may include in-phase (I) and quadrature (Q) portions, where the RF mixer circuit splits I and Q baseband input signals from the RF signal. Operation is substantially identical for both I and Q channels. The DC control logic operates to remove or otherwise eliminate DC from the received signal that is provided to decoders in the baseband processor.

Owner:M RED INC

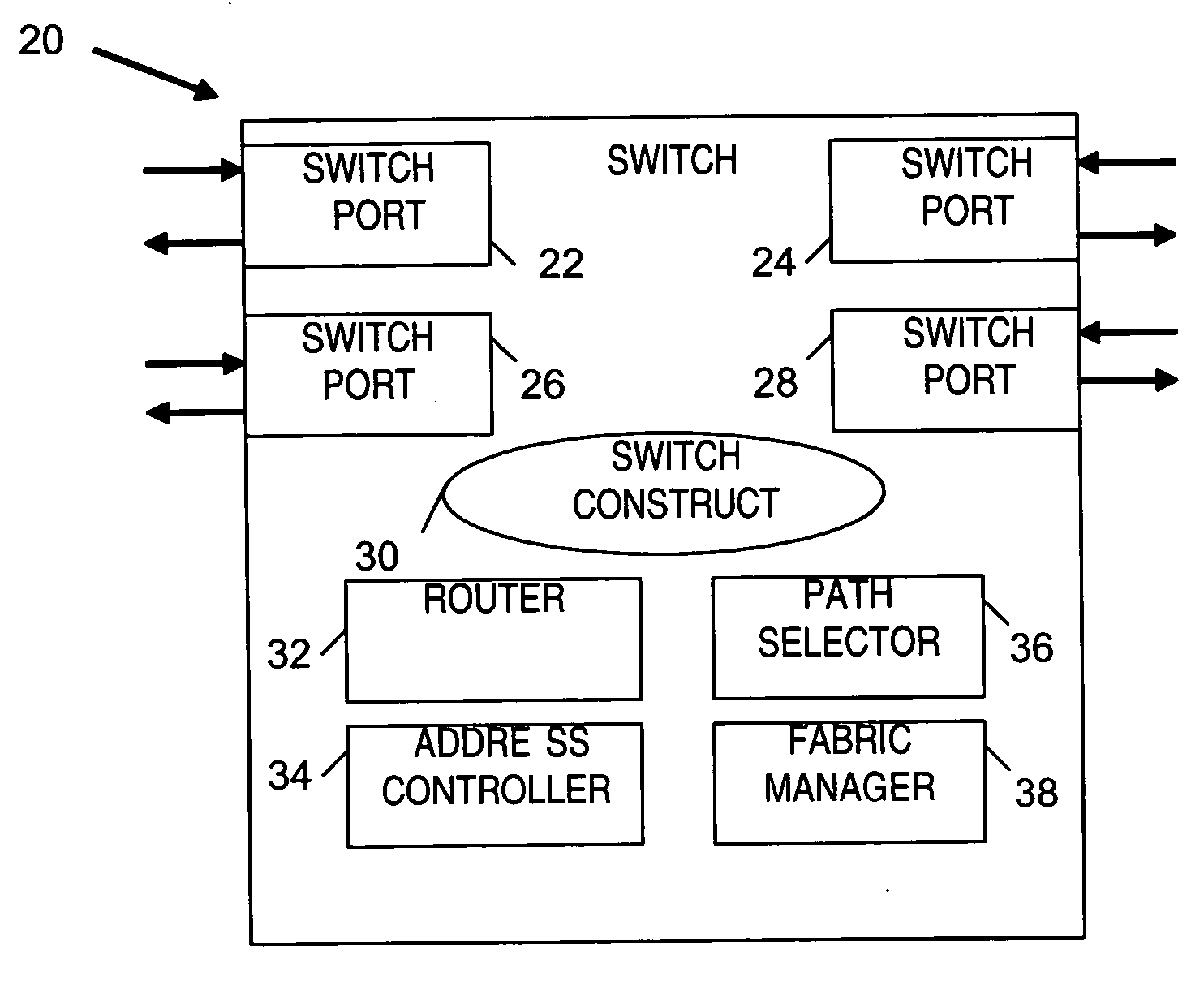

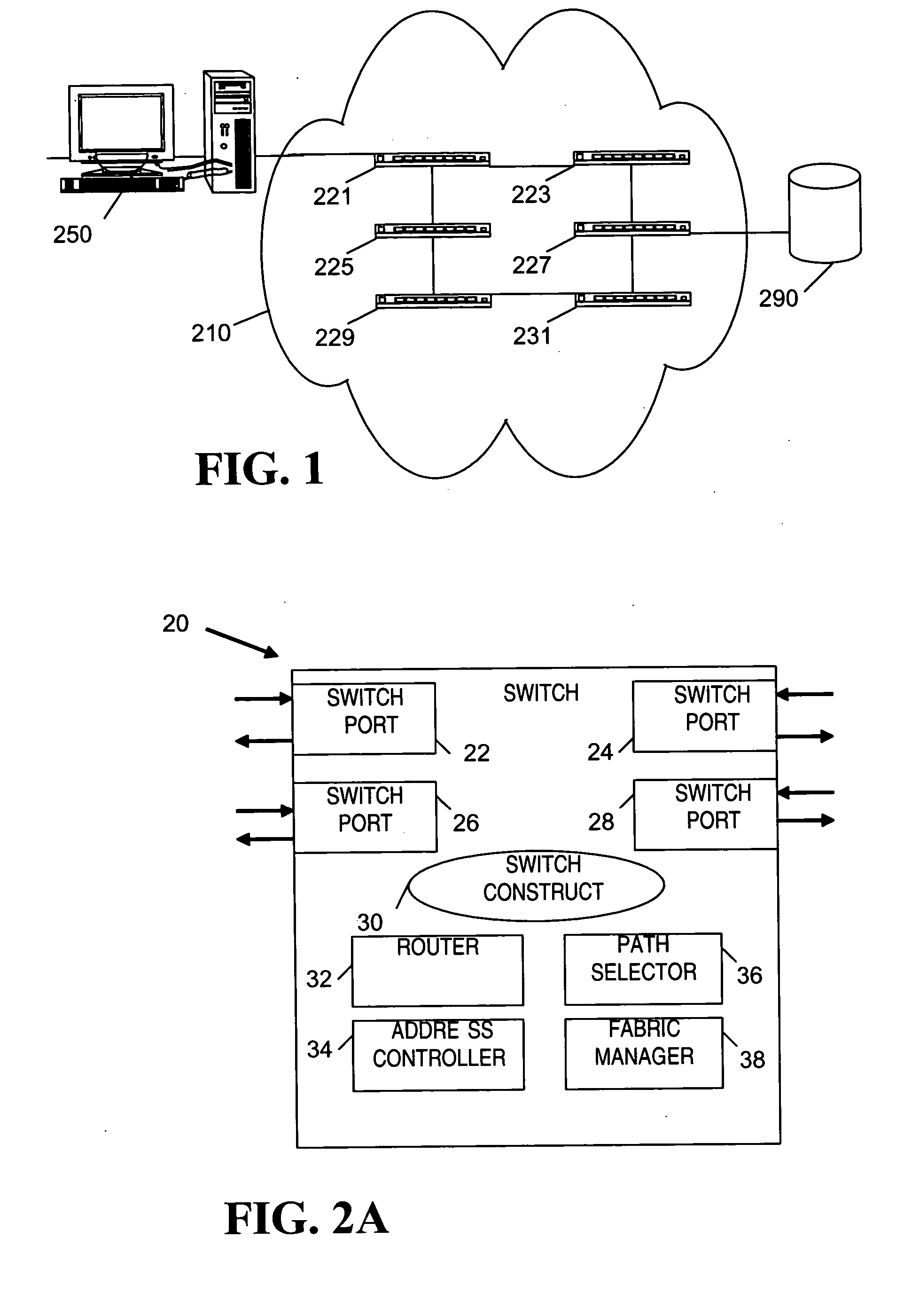

Network path tracing method

Systems and methods for gathering troubleshooting information through one or more networks are disclosed. In one embodiment, the method comprises a switch port configured to receive a frame that has information added by another switch. As the frame traverses the network, control logic in the switch adds additional information into the frame from the current switch.

Owner:AVAGO TECH INT SALES PTE LTD

Device configuration

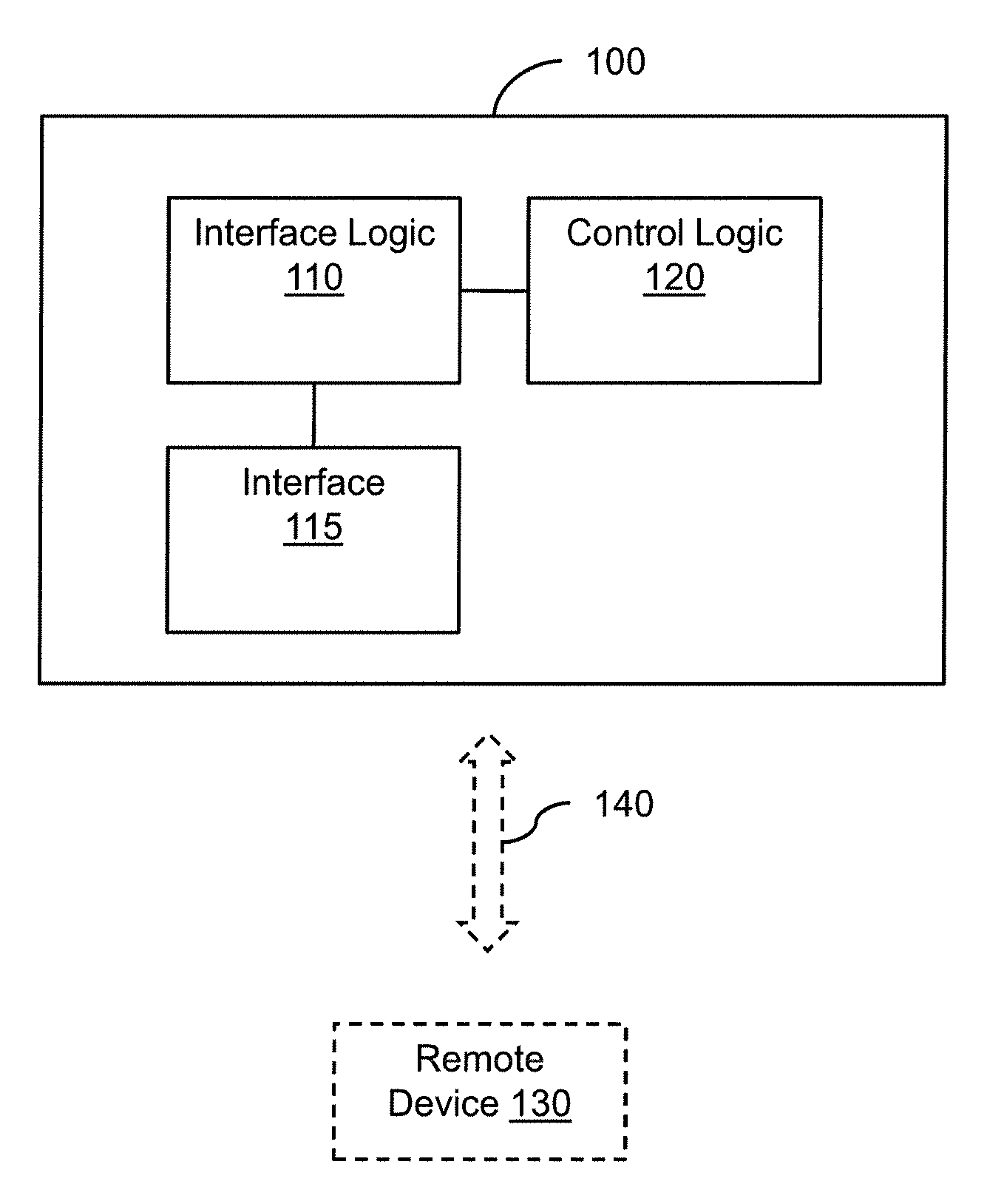

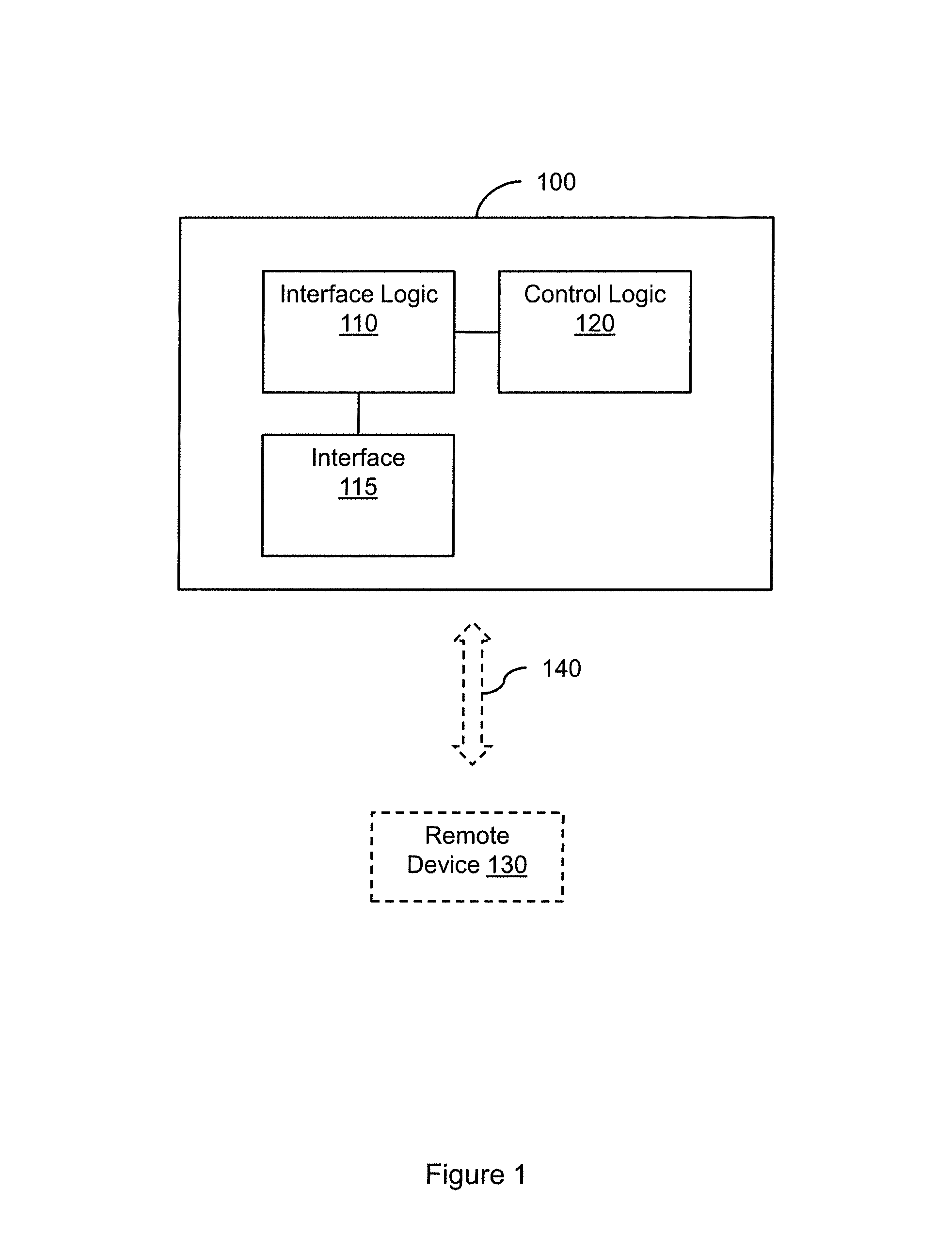

Devices, systems, methods, and other embodiments associated with configuring devices are described. One example apparatus is configured with an interface logic and a control logic. The interface logic is to detect a remote device. When a remote device is detected, the interface logic transmits an interface to the remote device that converts the remote device to be a remote control device. The remote control device provides selected configuration information for controlling an image device. The control logic is to provide control signals for reconfiguring the image device based, at least in part, on the selected configuration information received from the remote device.

Owner:MARVELL ASIA PTE LTD

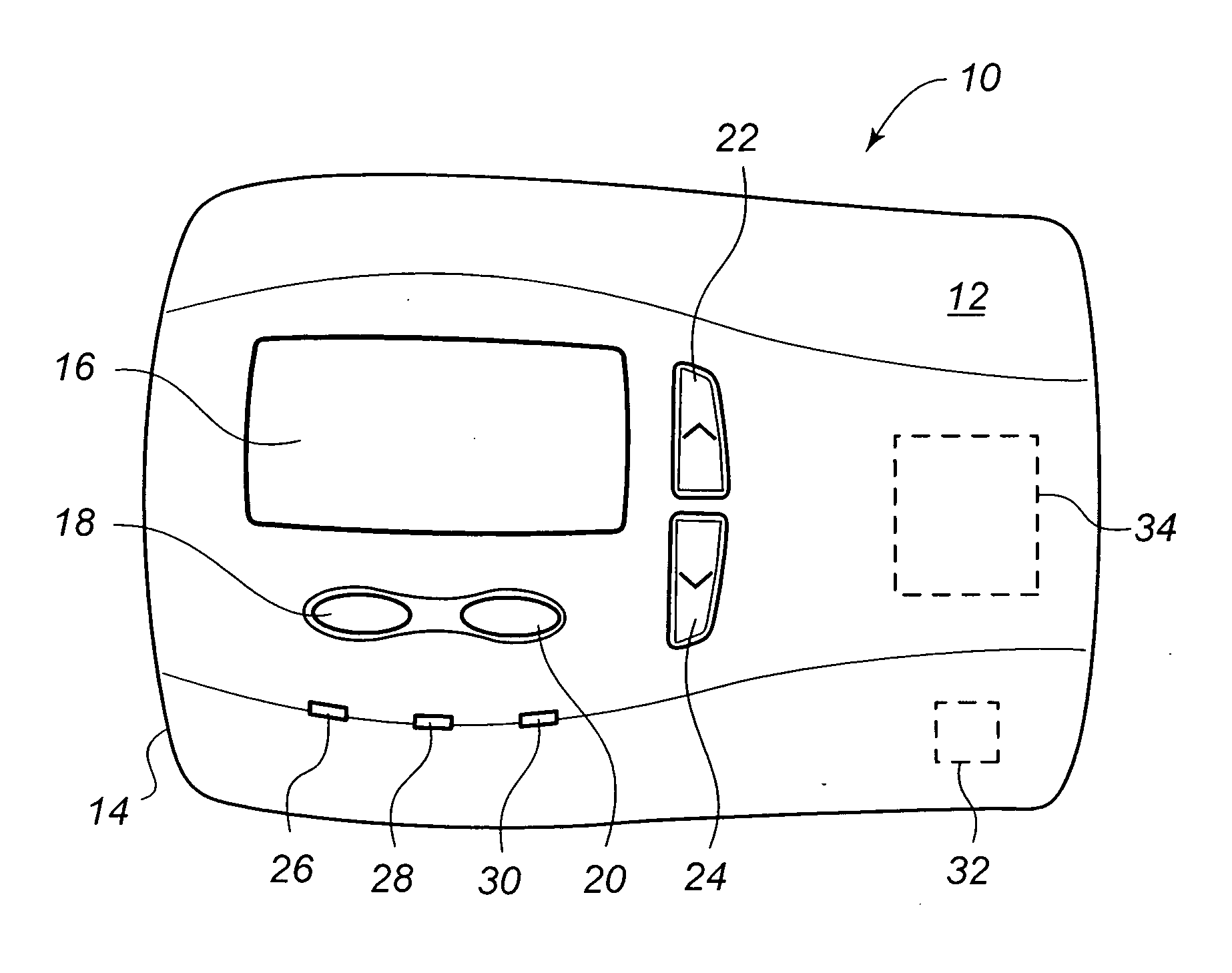

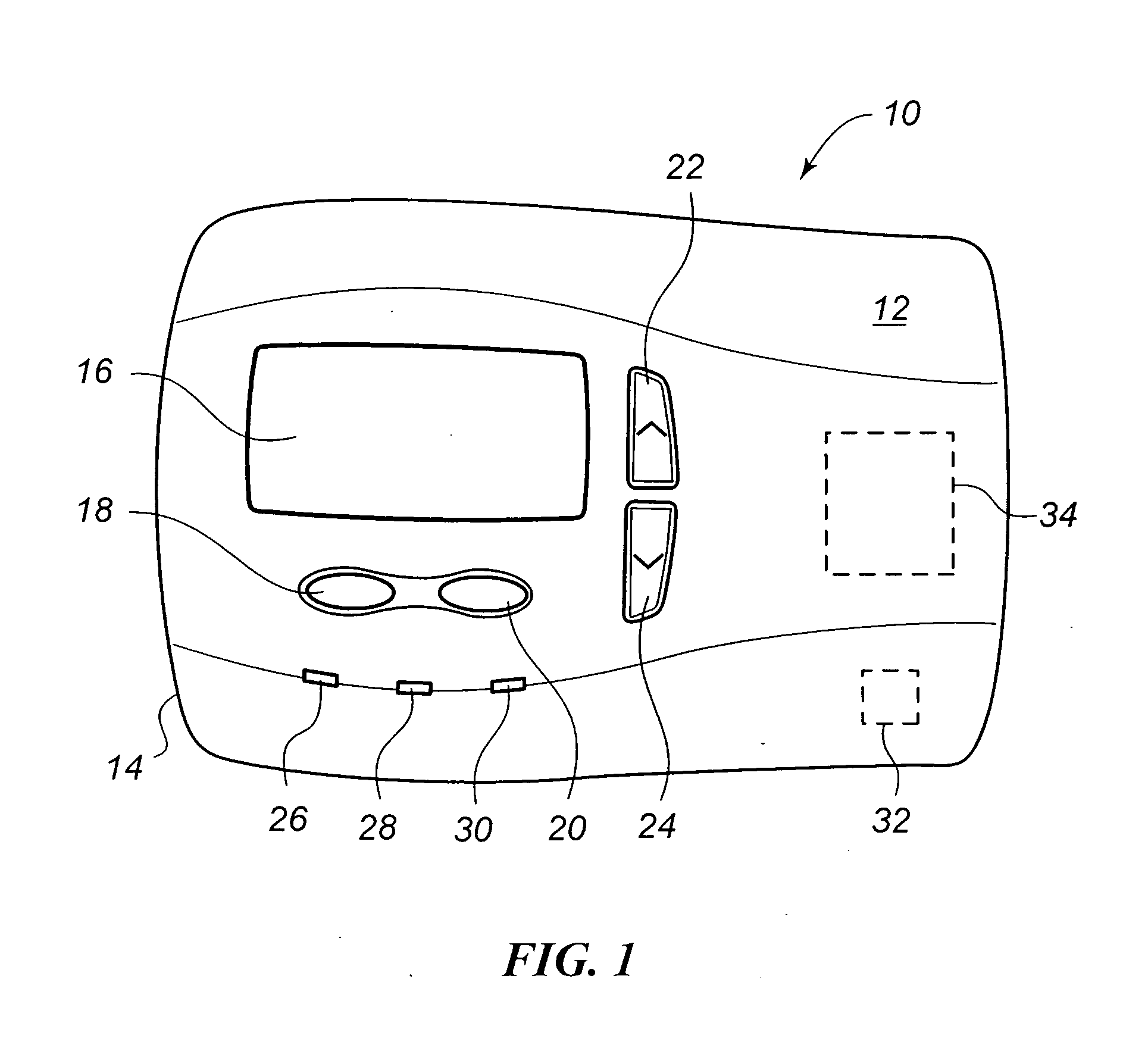

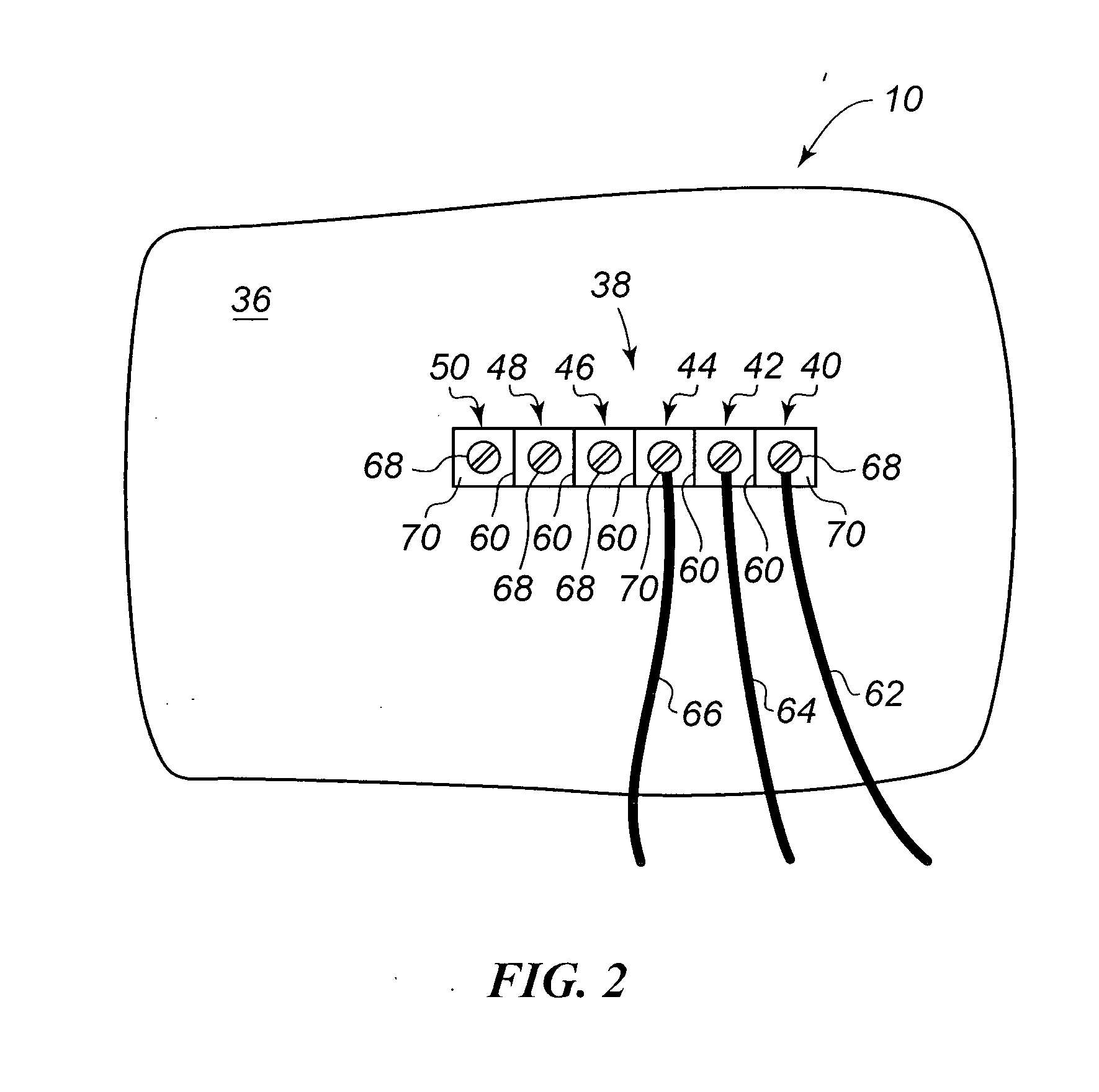

Connector terminal system and wiring method for thermostat

InactiveUS20070221741A1Easily and quickly and conveniently connectedIntuitive experienceMechanical apparatusSpace heating and ventilation safety systemsEngineeringThermostat

A thermostat having a terminal connection mechanism and method that provides ease of installation of the thermostat and the heating, ventilating and air conditioning (HVAC) wiring is provided. One embodiment allows any wire to be attached to any terminal. This thermostat includes logic for determining an identity of the wire connected to an HVAC system component. The control logic determines a characteristic of the HVAC system component and compares the characteristic to a known characteristic of the HVAC system component. Environmental responses may also be monitored to identify the HVAC component. The terminal of the thermostat may be color coded to further ease installation. Tool-less terminal connectors may also be used to still further ease installation.

Owner:RANCO OF DELAWARE

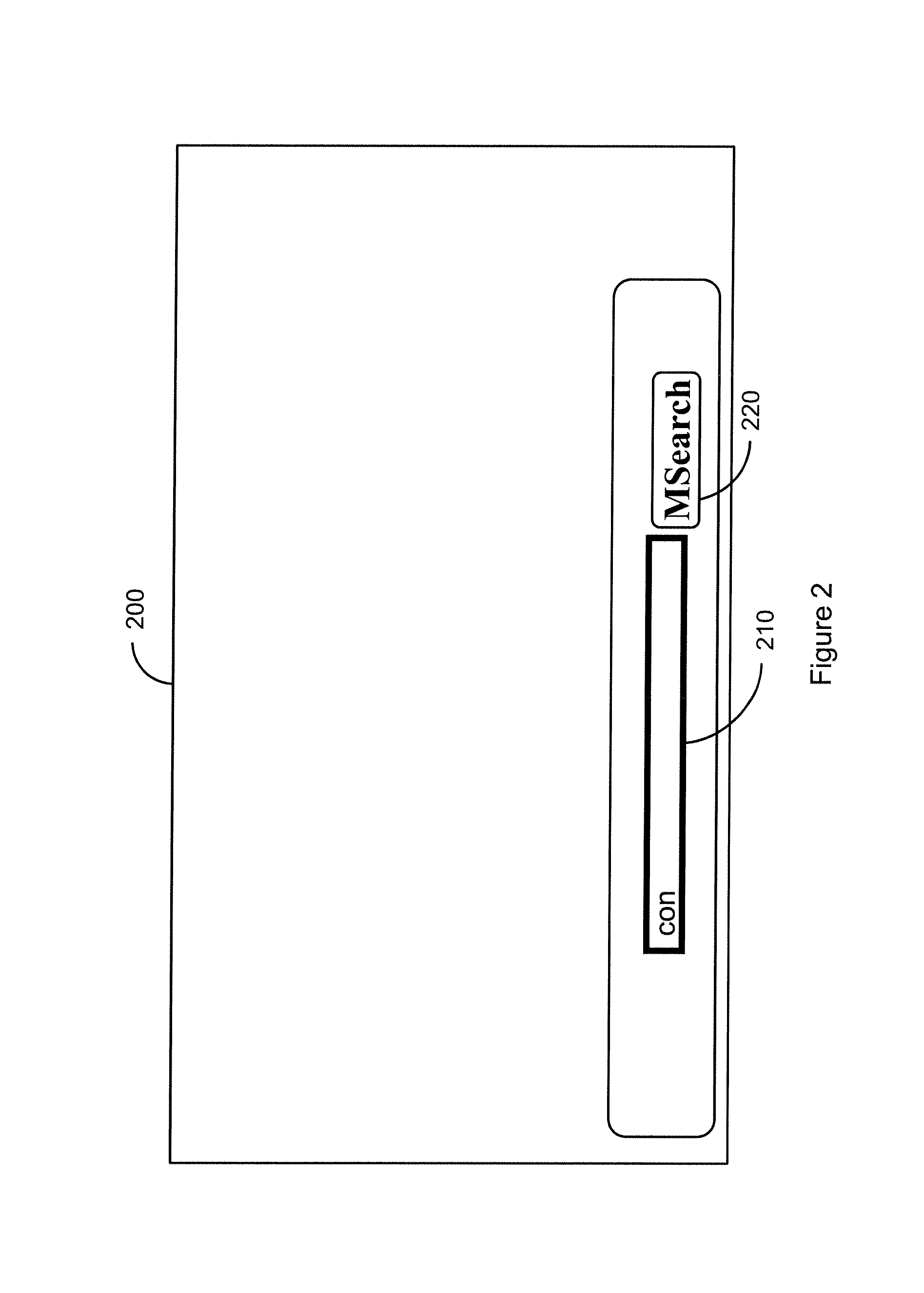

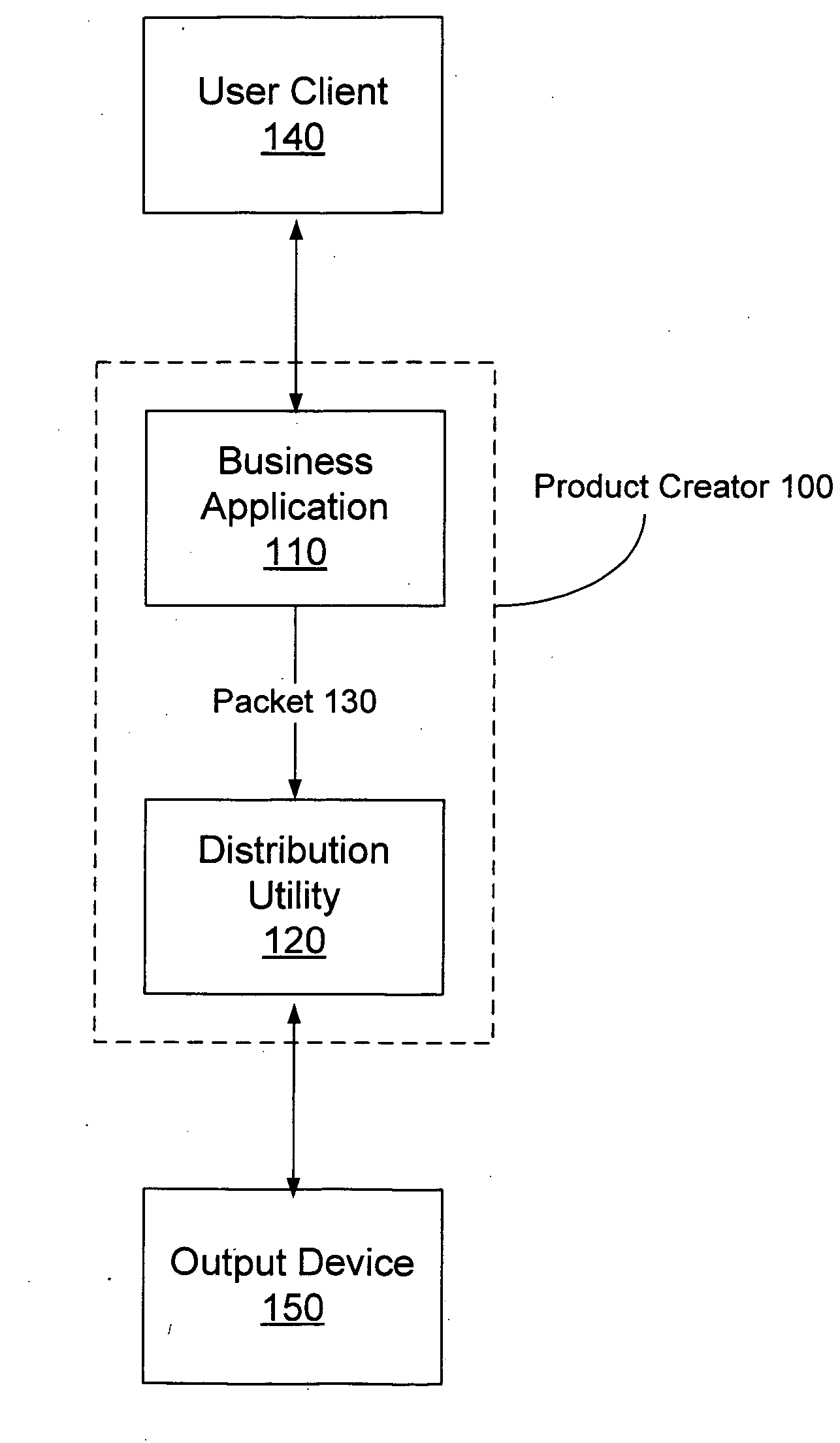

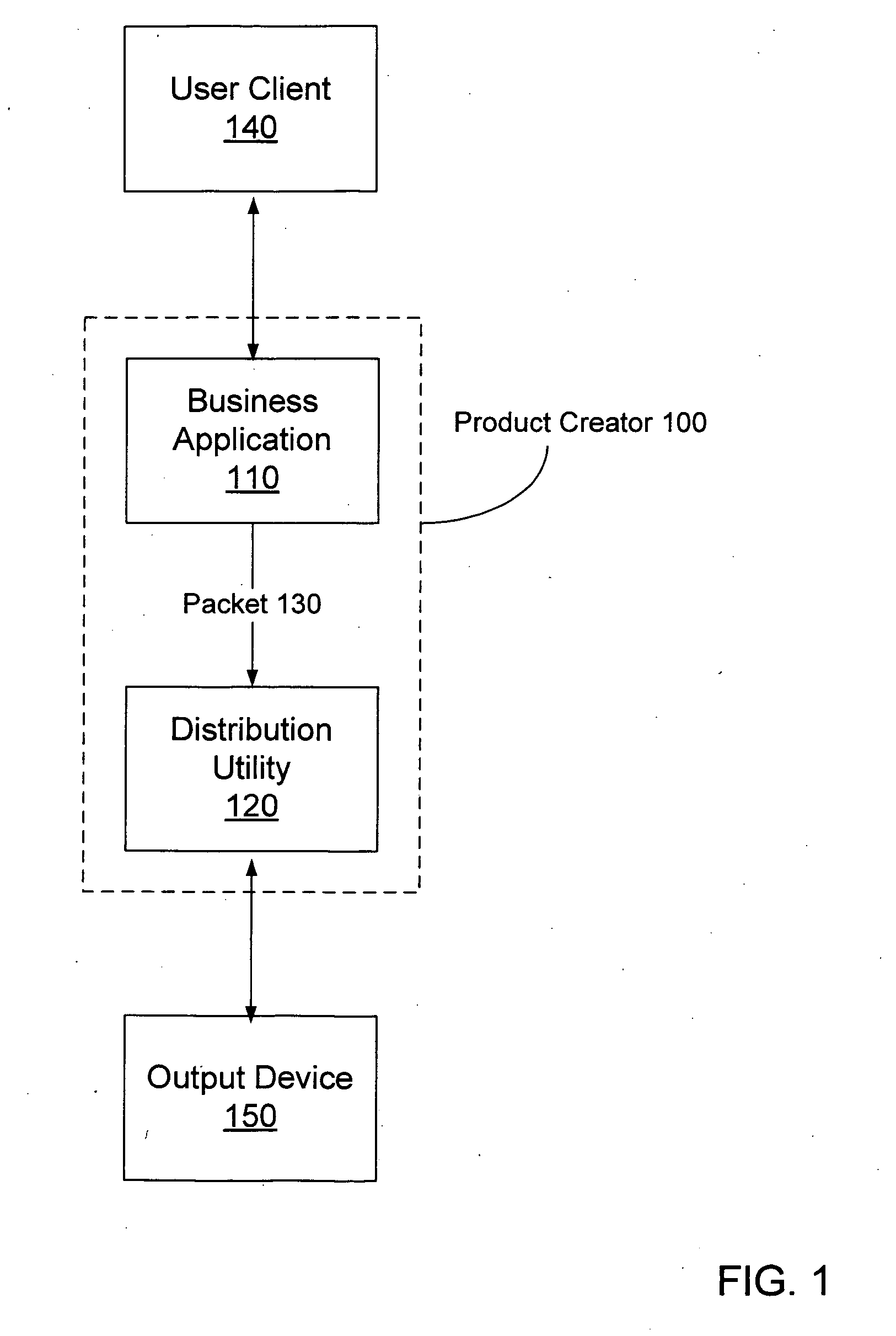

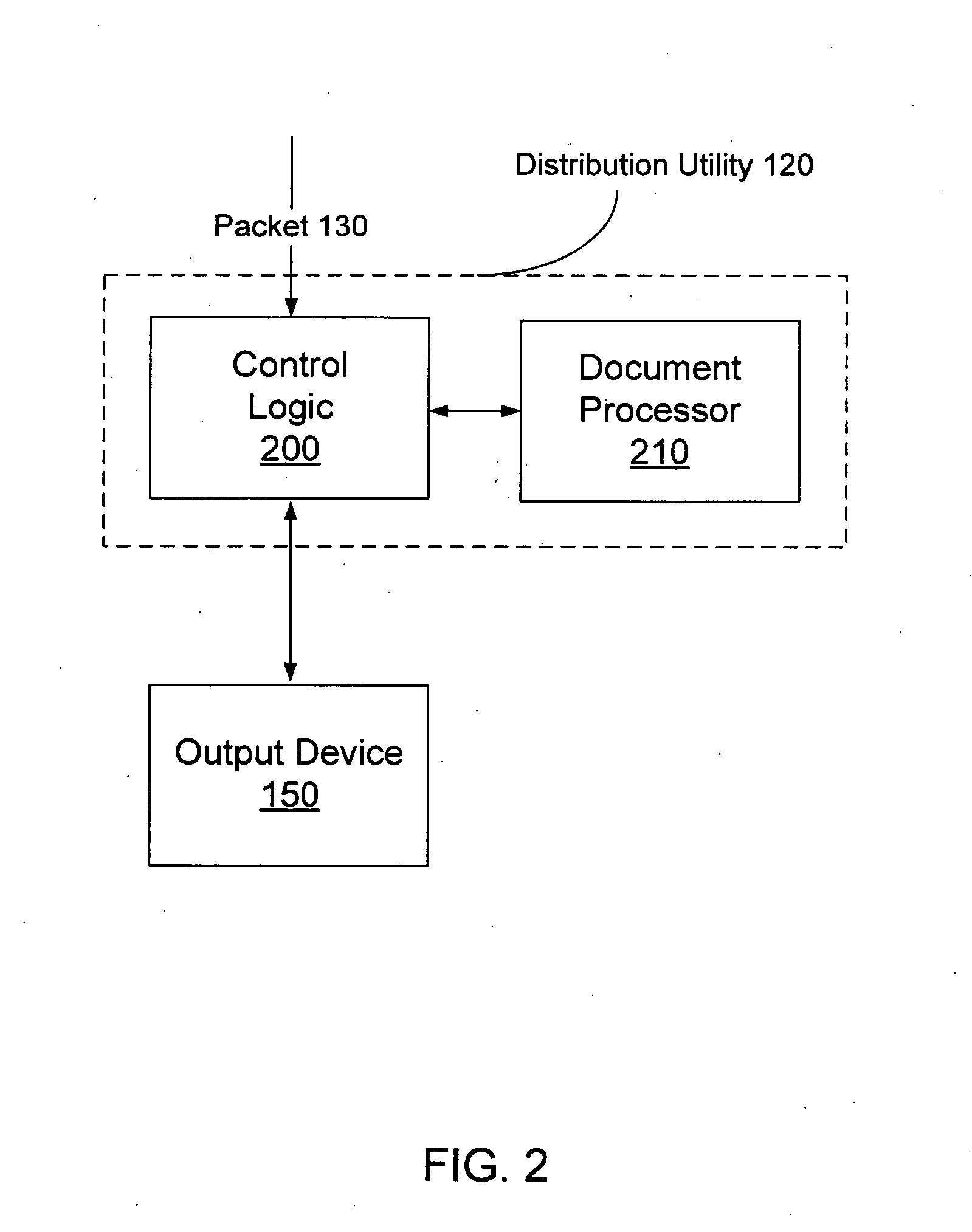

Dynamic variable-content publishing

A product creator system includes a business application and a distribution utility. The business application enables a user to specify and / or edit (via a user client) a document. The business application generates a packet that is transmitted to the distribution utility. The packet describes the document, such as a document of a particular type (where the document is based on variable content and / or variable layout), and a distribution method for the document. Distribution methods include print, ship, mail, fax, email, and save. The distribution utility generates and distributes the document (via an output device) based on the packet. The business application, which can be used with a variety of distribution utilities, includes a web front-end and a packet generator. The distribution utility, which can be used with a variety of business applications, includes control logic and a document processor. The document processor helps generate the document.

Owner:UHLIG

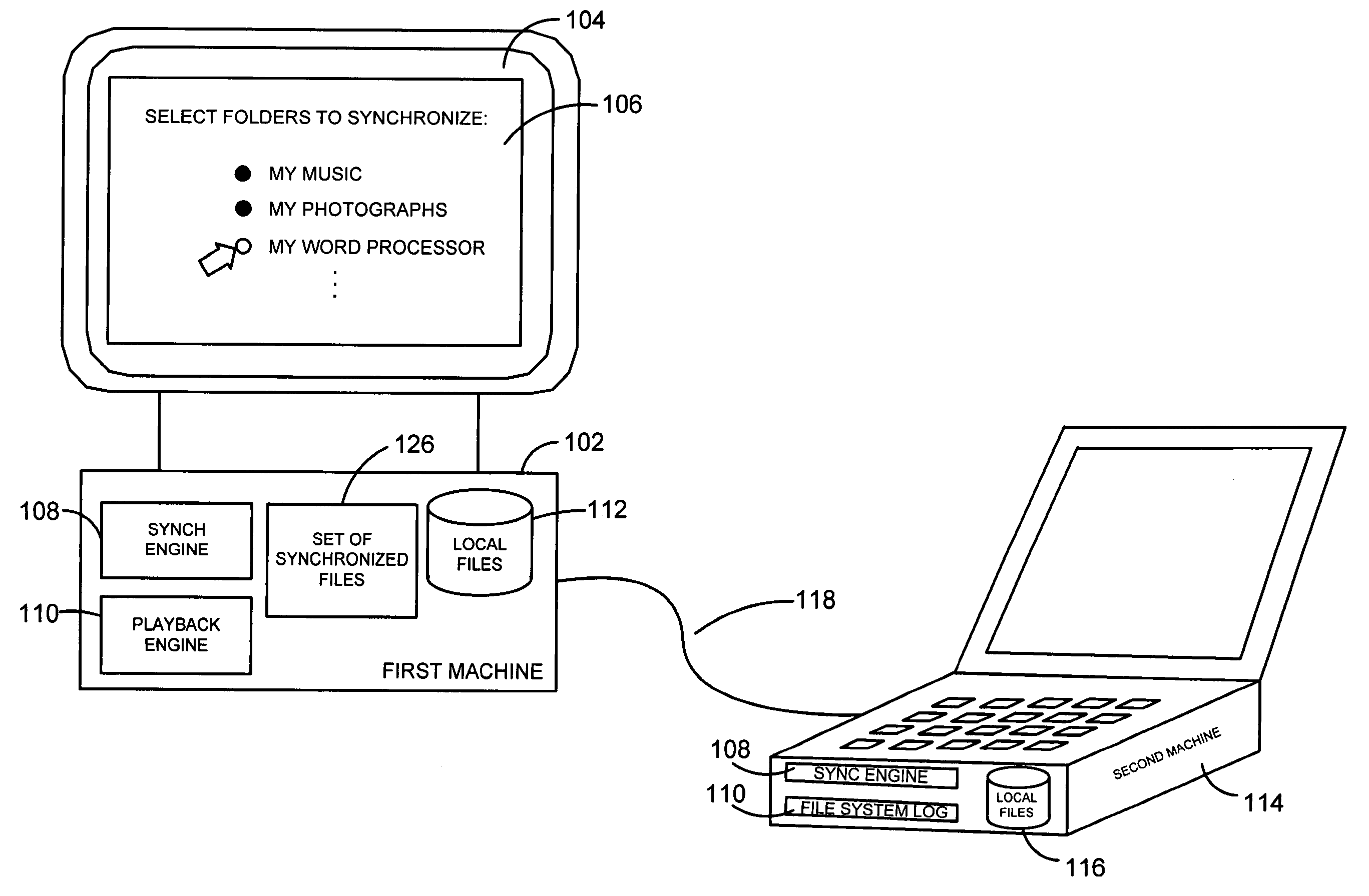

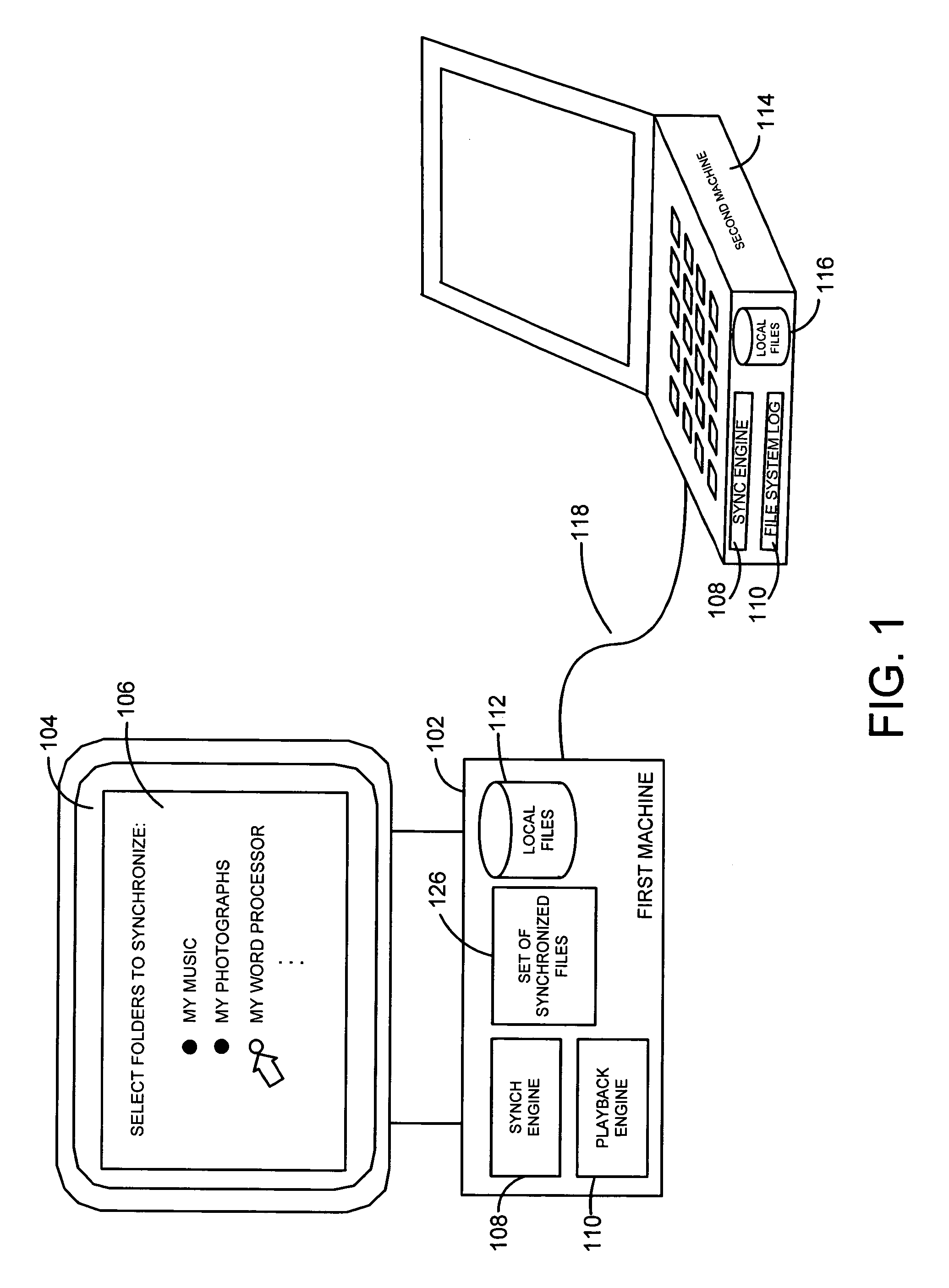

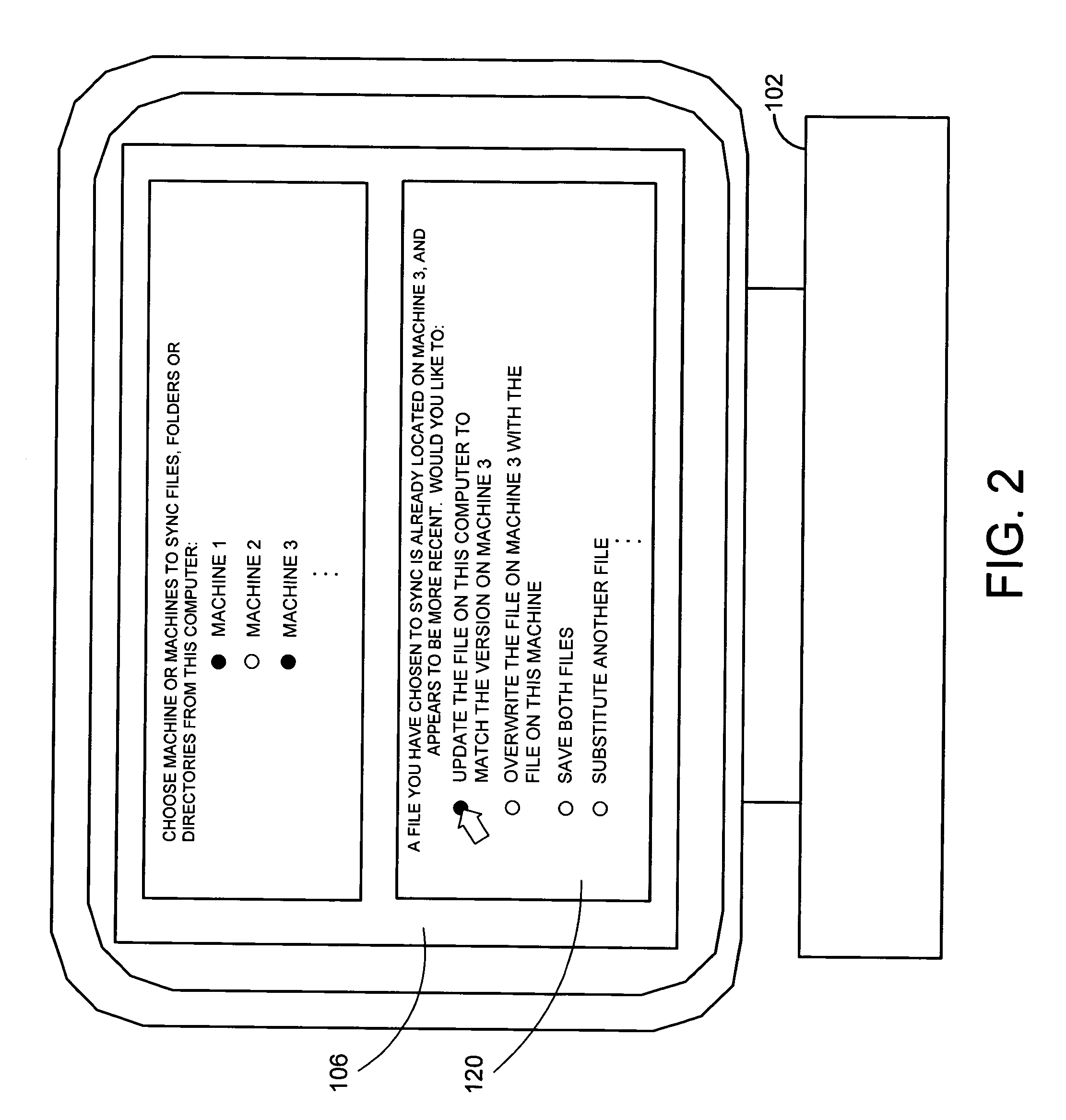

System and method for peer to peer synchronization of files

InactiveUS20060242206A1Currency is bulkyMinimum configuration effortDigital data information retrievalData processing applicationsFile synchronizationOperational system

A system and related techniques provide a seamless, peer-to-peer file synchronization capability for sharing files, folders, directories or other stored content between machines. According to embodiments of the invention in one regard, a sync engine or other file management logic may be integrated into the operating system or other resources of a user's desktop, laptop, network-enabled cellular device or other computer, client, machine or other hardware. The sync engine may accept user designations of files, folders, directories or other contents which they wish to share, sync or roam between two or more selected machines, on an automatically consistent basis. The sync engine or other control logic may maintain a file system log to record the state of files which have been designated for sharing, to indicate for example whether a transmission of the file has been made, to which target machine or machines it has been transmitted, and other variables regarding the state of file or other content. According to embodiments of the invention in one regard, the sync engine may apply version management logic when files located on a target or destination machine, may, for example, reflect newer or more complete content than the file which is designated for roaming to that machine, or other under conditions. A user may therefore readily and with a comparative minimum of configuration effort select and effectuate the sharing of a set of frequently used or otherwise desired files to an arbitrary set of machines which they own or use, without a need to invoke a remote server or other control or storage to back up and synchronize that content.

Owner:MICROSOFT TECH LICENSING LLC

Method and apparatus for controlling a display of a device

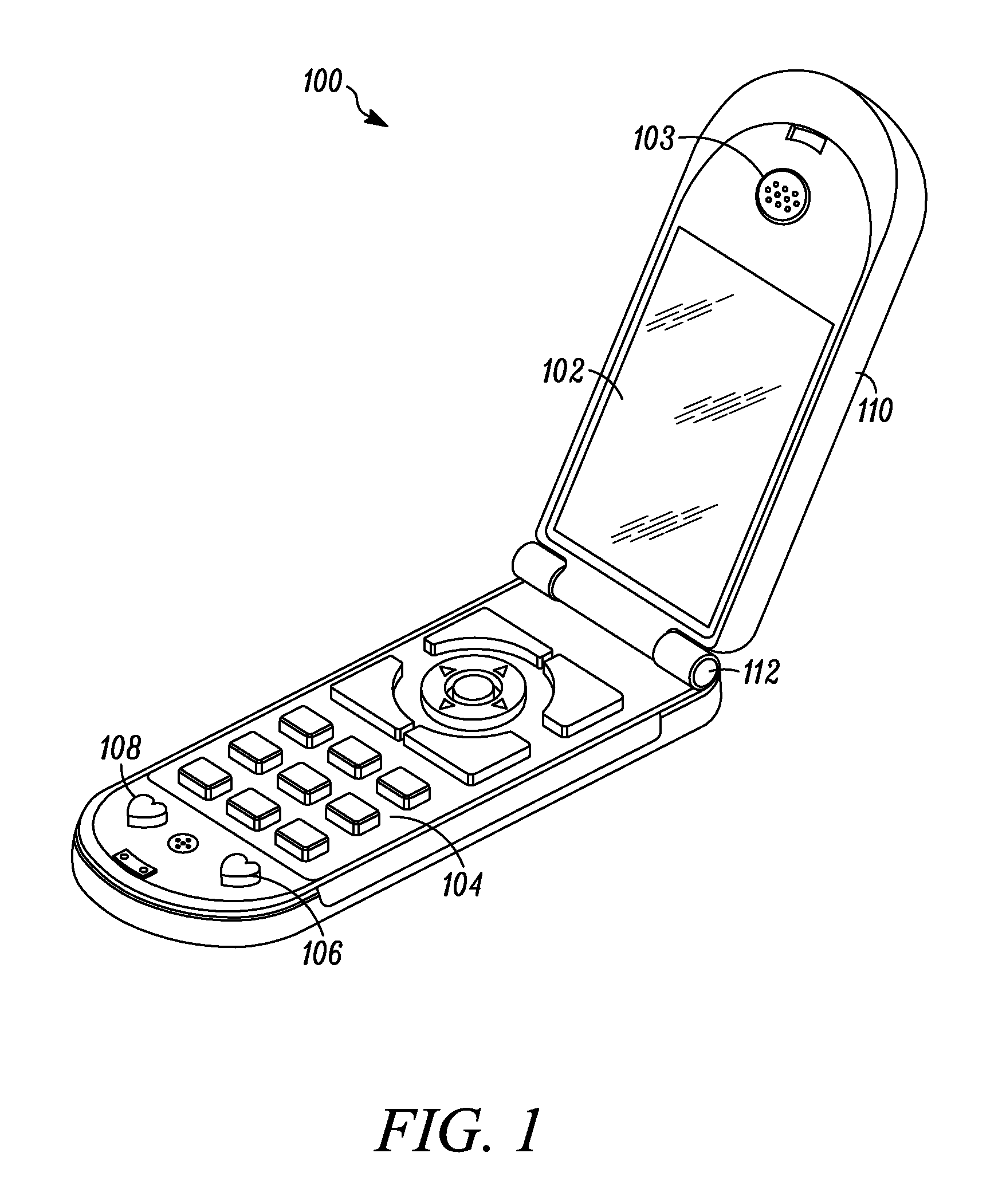

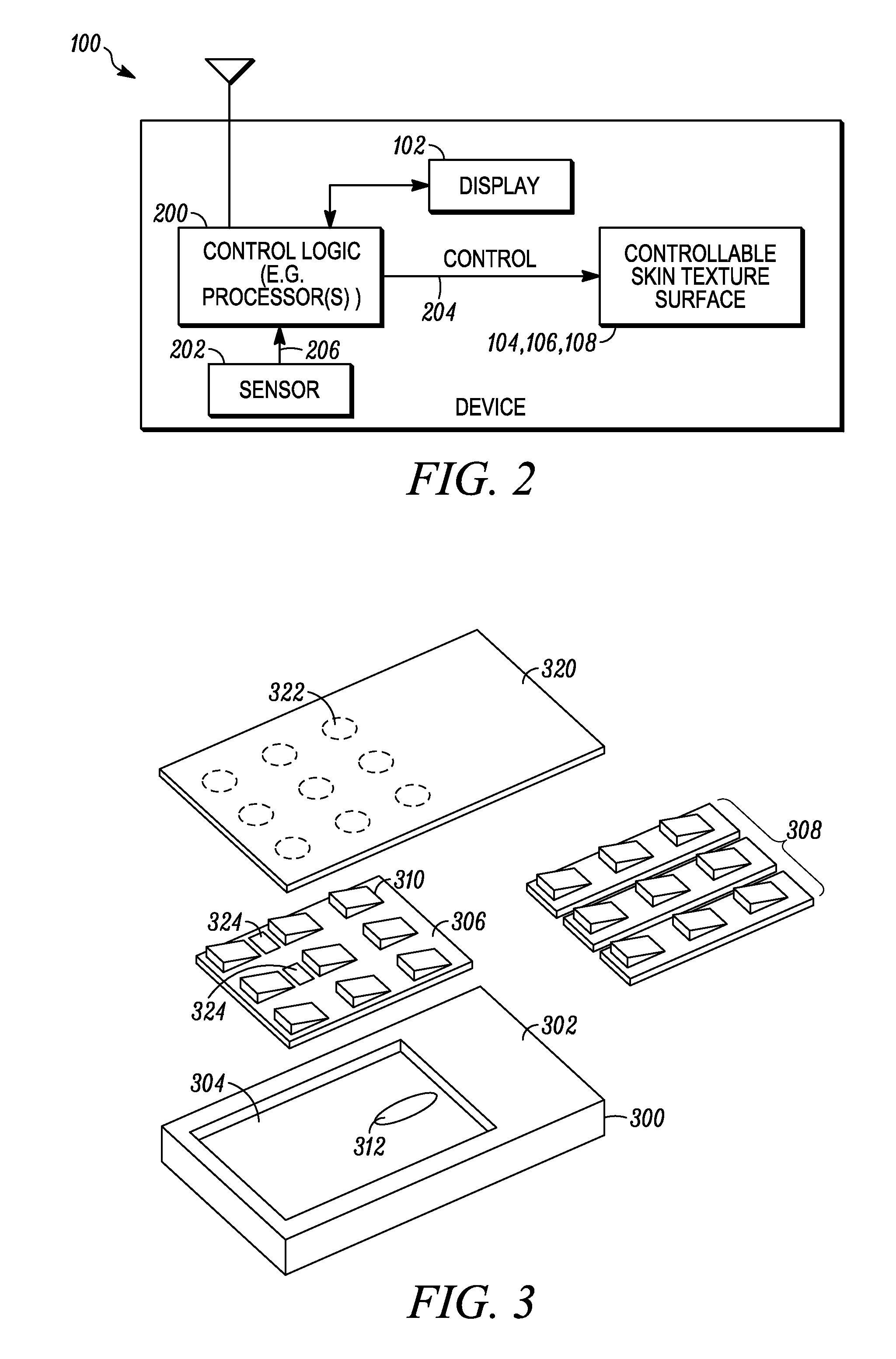

InactiveUS20090015560A1Input/output for user-computer interactionCathode-ray tube indicatorsDisplay deviceSkin texture

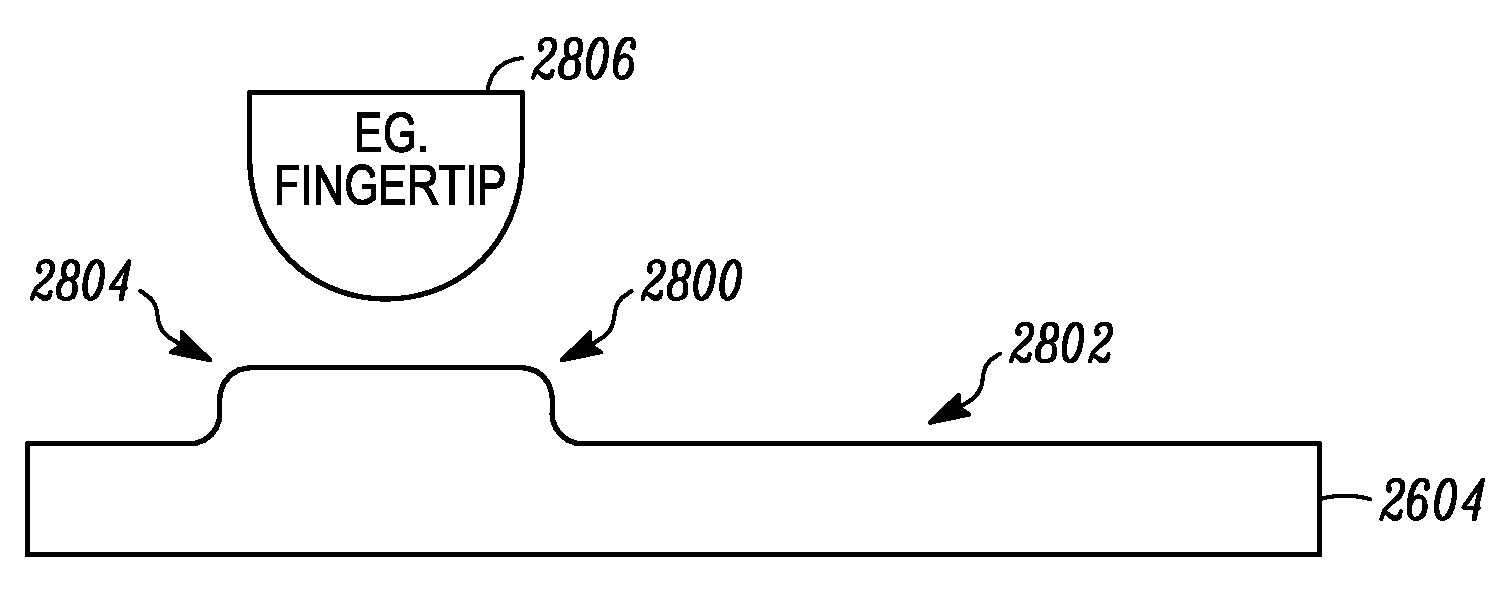

A device (2600) includes a controllable skin texture surface (2616), a non-keypad display (2618), and control logic (200). The non-keypad display displays non-keypad information representing at least one selectable element (2800, 2900). The selectable element represents additional display information (2610, 2614). The control logic is operatively coupled to the non-keypad display and the controllable skin texture surface. The control logic controls at least a portion of the controllable skin texture surface to protrude at a location corresponding to the selectable element to provide a protruding selectable element (2804, 2902). In one example, the device includes a sensor (2602). The sensor is operatively coupled to the control logic. The sensor senses a user activating the selectable element. The control logic controls the non-keypad display to display the additional information in response to the sensor sensing the user activating the selectable element.

Owner:GOOGLE TECH HLDG LLC

Calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6735422B1Low costMaximum performancePulse automatic controlGain controlTransceiverAudio power amplifier

A calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency (ZIF) architecture. The device includes a ZIF transceiver and a baseband processor, which further includes a calibrator that periodically performs a calibration procedure. The baseband processor includes gain control logic, DC control logic, a gain converter and the calibrator. The gain converter converts gain between the gain control logic and the DC control logic. The calibrator programs the gain converter with values determined during the calibration procedure. The gain converter may be a lookup table that stores gain conversion values based on measured gain of a baseband gain amplifier of the ZIF transceiver. The gain control logic may further include a gain adjust limiter that limits change of a gain adjust signal during operation based on a maximum limit or on one or more gain change limits. A second lookup table stores a plurality of DC adjust values, which are added during operation to further reduce DC offset. The calibration procedure includes sampling an output signal for each gain step of the baseband amplifier at two predetermined range values and corresponding DC offsets using successive approximation. The data is used to calculate gain, DC offset and DC differential values, which are used to determine the conversion values programmed into the lookup tables or the gain adjust limiter.

Owner:M RED INC

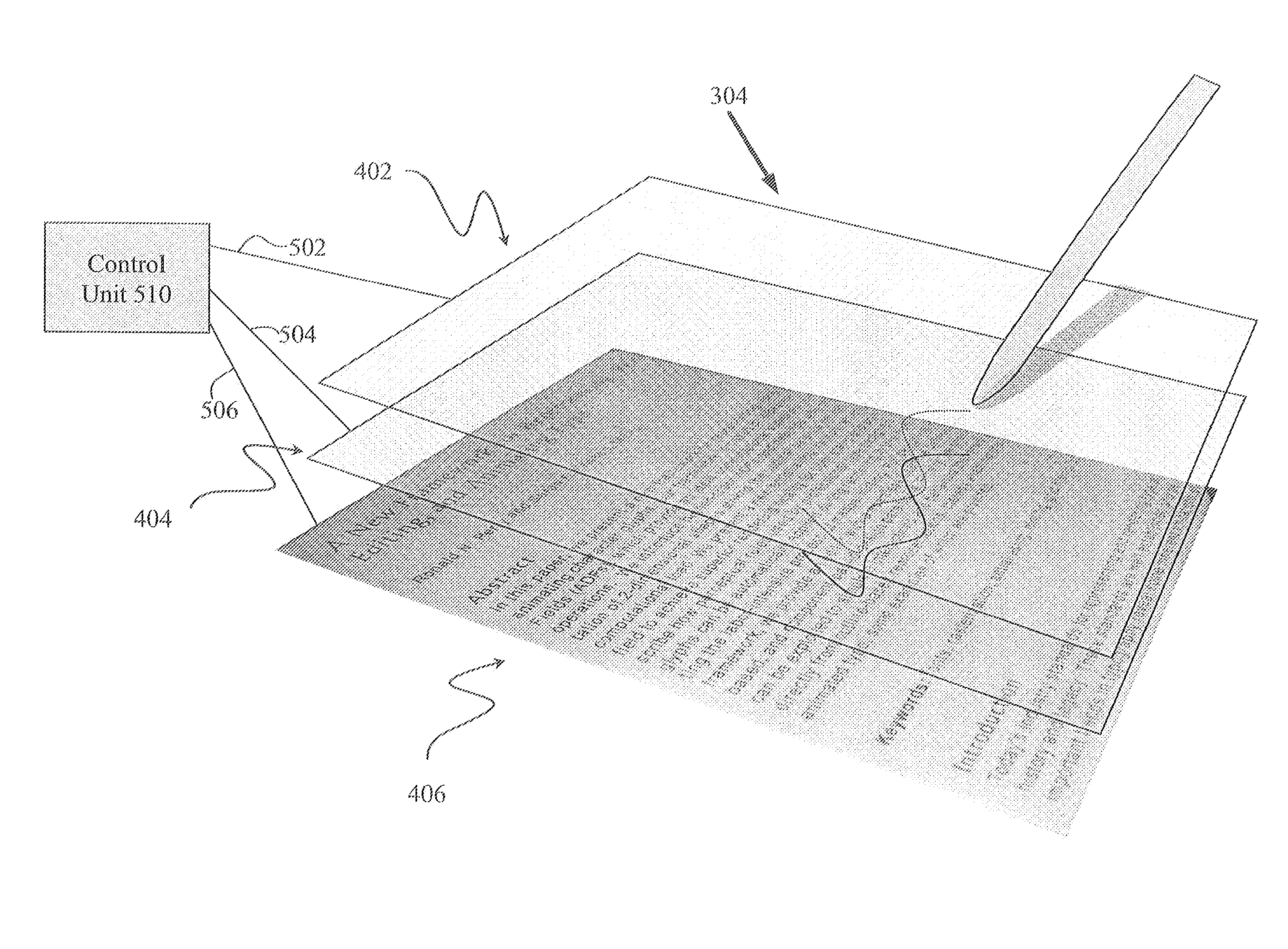

Thin multiple layer input/output device

A multilayer input / output device with a low power and a high resolution display suitable for use in paper-like computing includes a first display layer, a second display layer, an input layer and control logic. The first display layer is a low power display. The second display layer is a fast, transparent display positioned on top of the first layer. The input layer is a layer for detecting input movements or gestures by the user. The control logic is coupled to the first display layer, the second display layer and the input layer for controlling their operation according the method of the present invention. The method of the present invention selectively operates the second display layer to present movement detected by the input layer. At a predetermined time, the information presented on the second display is transferred to and presented on the first display.

Owner:E INK CORPORATION