Patents

Literature

409results about How to "Maximum performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

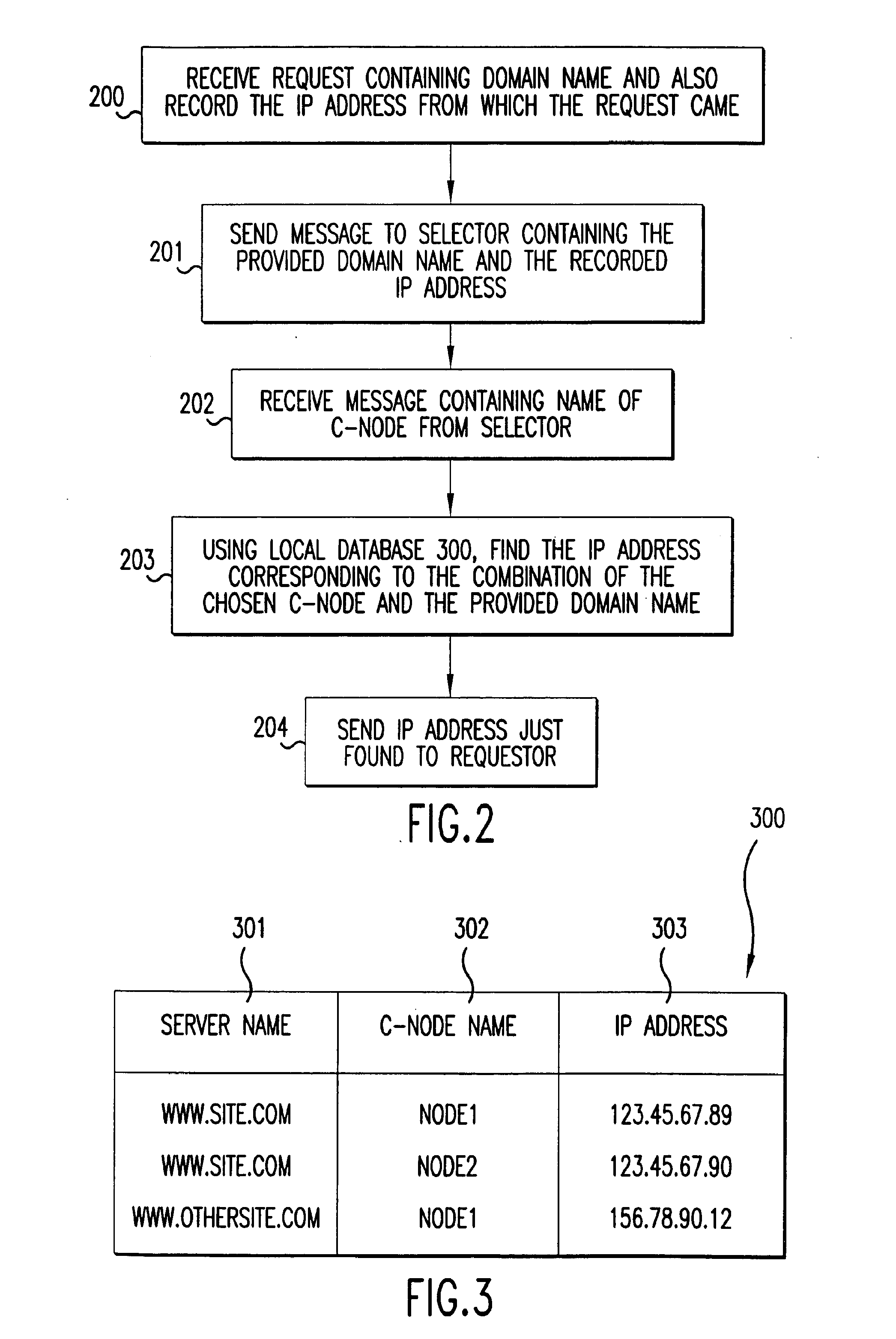

Method for high-performance delivery of web content

InactiveUS20050044270A1Improve performanceReduce deliveryDigital computer detailsData switching networksWeb serviceWeb cache

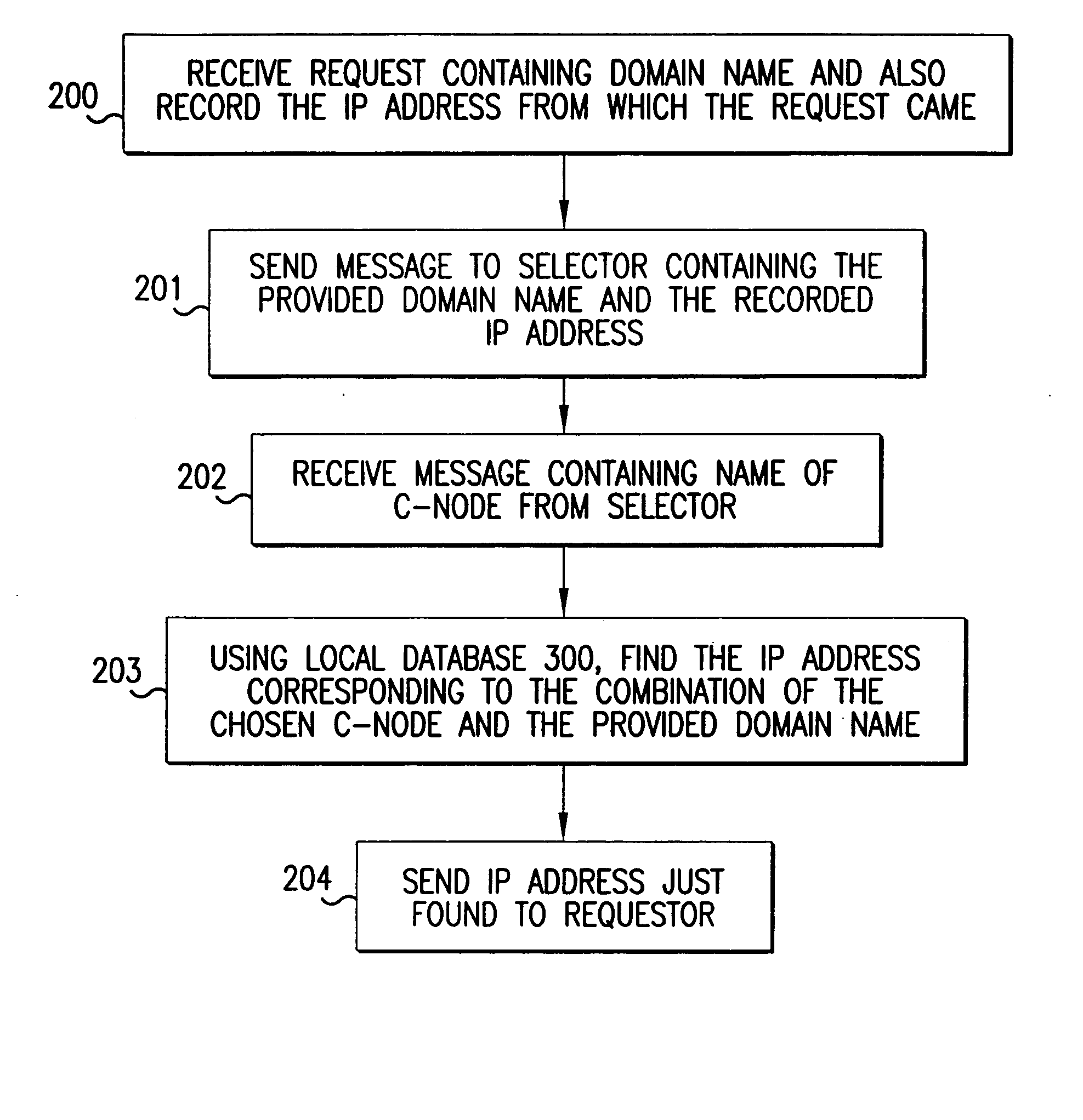

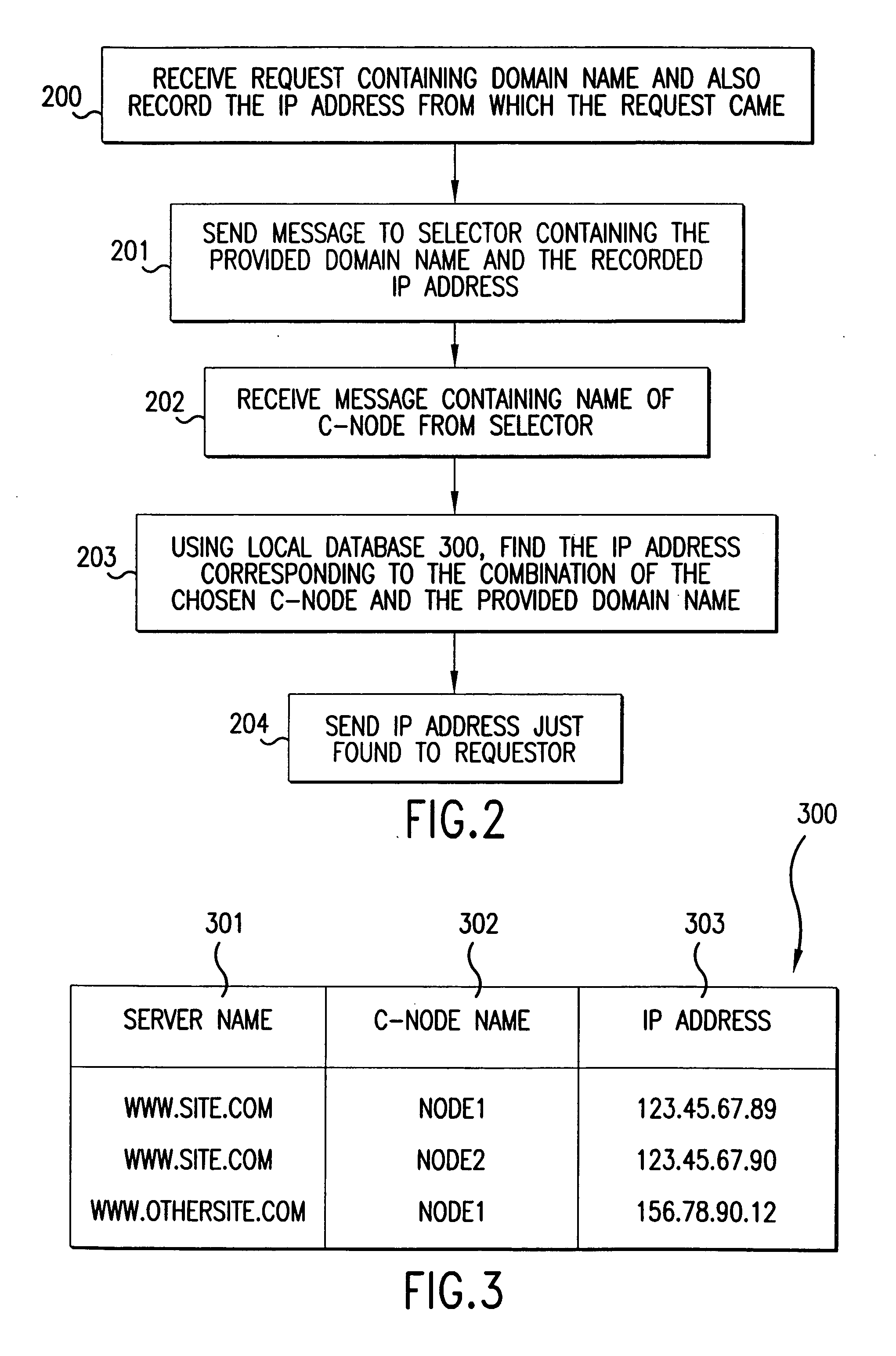

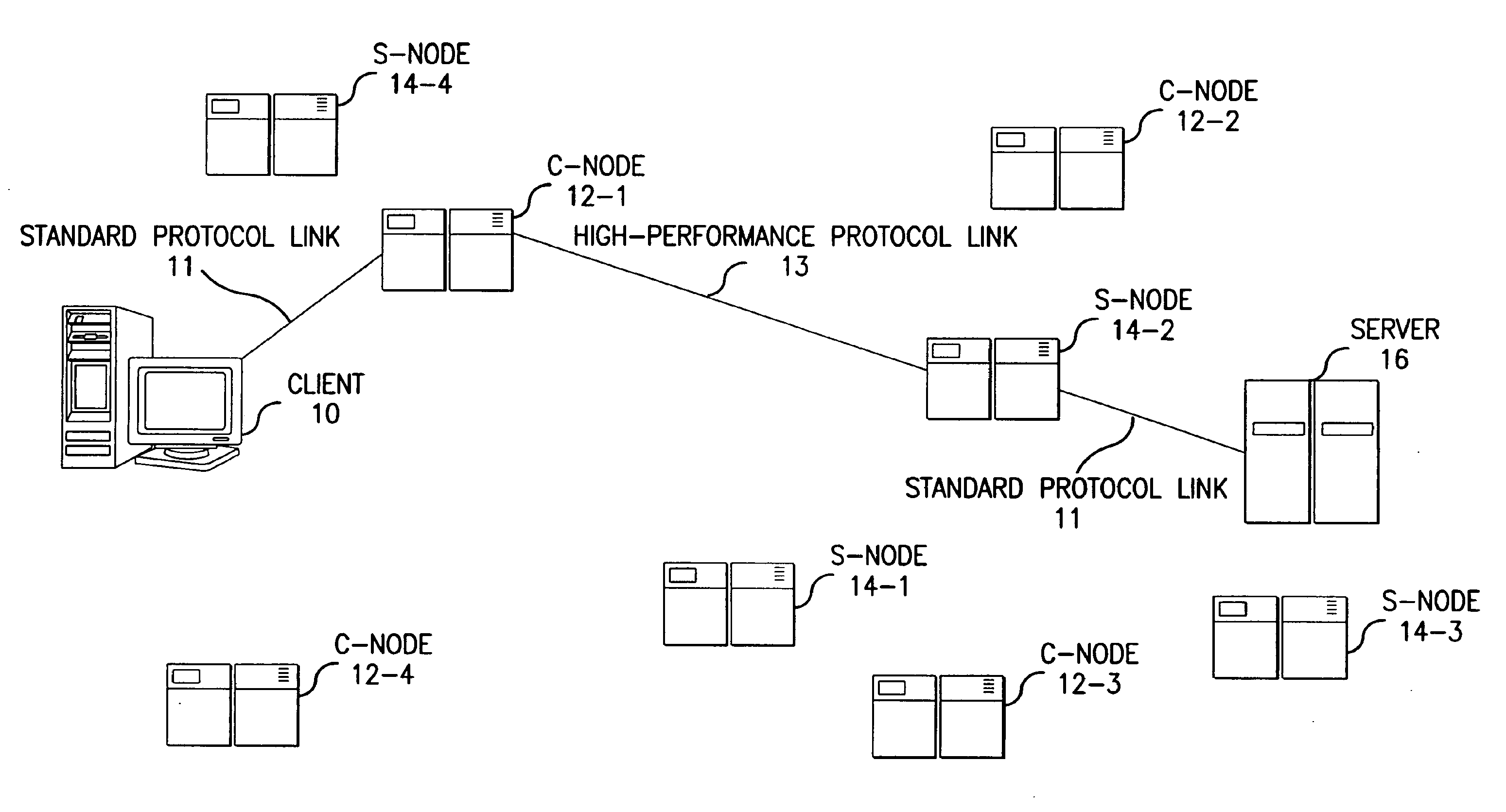

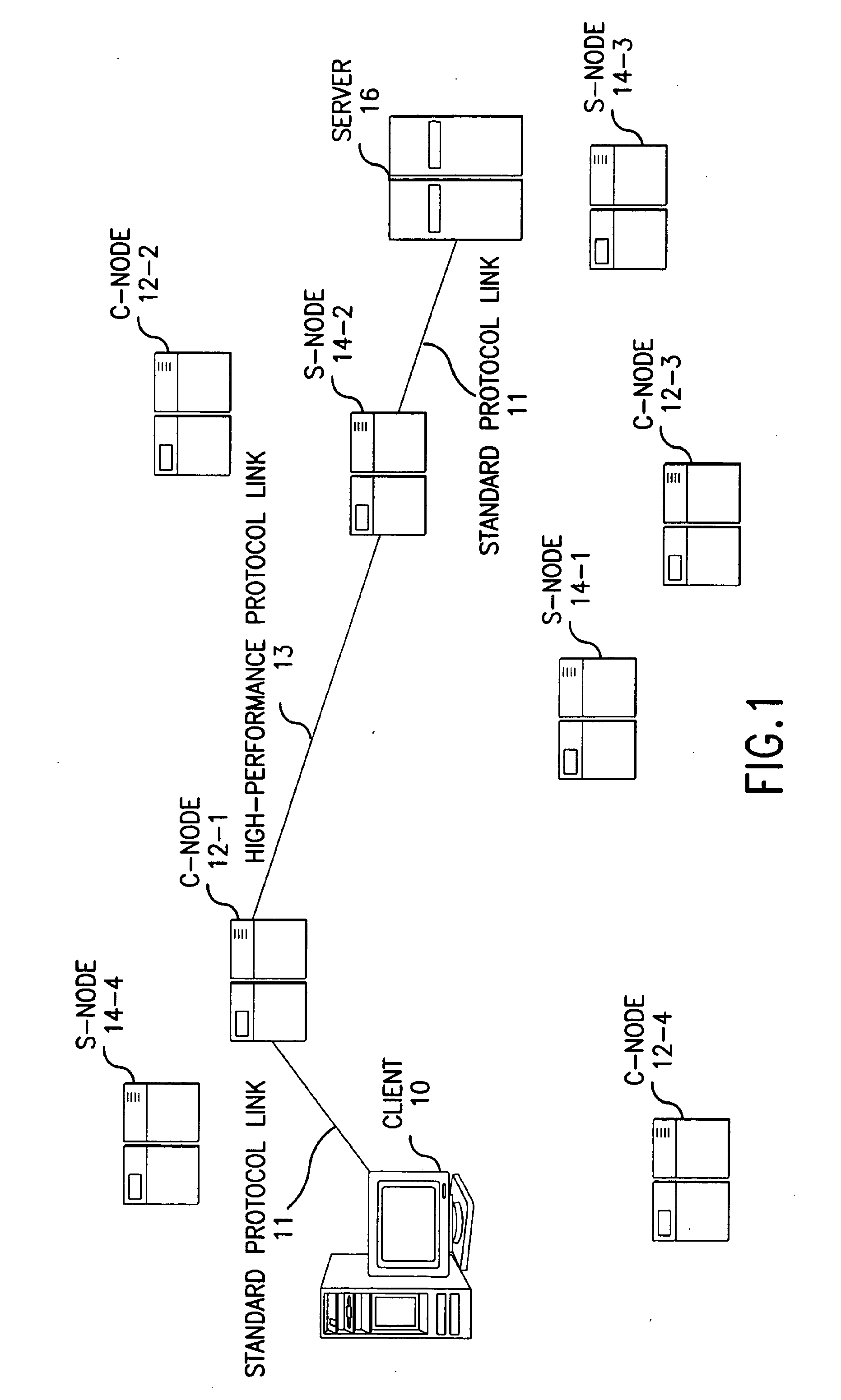

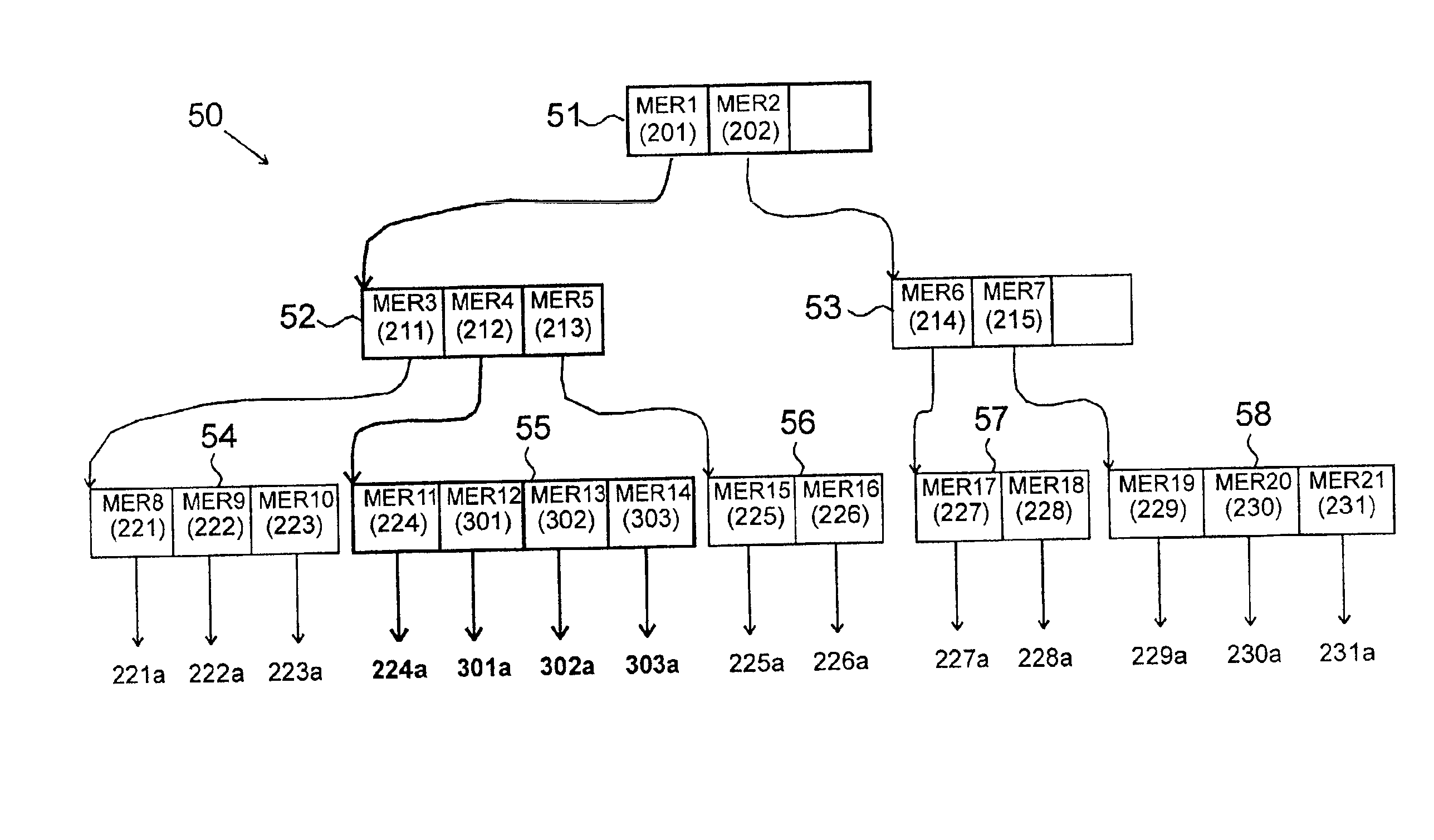

The present invention provides a method and apparatus for increasing the performance of world-wide-web traffic over the Internet. A distributed network of specialized nodes of two types is dispersed around the Internet. A web client's requests are directed to a node of the first type chosen to be close to the client, and the client communicates with this node using a standard protocol such as HTTP. This first node receives the request, and communicates the request to a node of the second type chosen to be close to the request's ultimate destination (e.g., a web server capable of generating a response to the request.) The first node communicates the request to the second node using a different, specialized, protocol that has been designed for improved performance and specifically to reduce traffic volume and to reduce latency. The second node receives communication from the first node using this specialized protocol, converts it back to a standard protocol such as HTTP, and forwards the request to the destination computer or server. Responses from the destination to the client take the corresponding reverse route, and also are carried over a specialized protocol between the two nodes. In addition, these nodes can employ other techniques such as web caches that avoid or improve some communication steps. Thus, specialized, proprietary, or complex protocols and techniques can be quickly deployed to enhance web performance without requiring significant changes to the clients or servers.

Owner:AKAMAI TECH INC

Method for high-performance delivery of web content

InactiveUS20070050522A1Improve performanceReduce deliveryMultiple digital computer combinationsData switching networksWeb serviceWeb cache

The present invention provides a method and apparatus for increasing the performance of world-wide-web traffic over the Internet. A distributed network of specialized nodes of two types is dispersed around the Internet. A web client's requests are directed to a node of the first type chosen to be close to the client, and the client communicates with this node using a standard protocol such as HTTP. This first node receives the request, and communicates the request to a node of the second type chosen to be close to the request's ultimate destination (e.g., a web server capable of generating a response to the request.) The first node communicates the request to the second node using a different, specialized, protocol that has been designed for improved performance and specifically to reduce traffic volume and to reduce latency. The second node receives communication from the first node using this specialized protocol, converts it back to a standard protocol such as HTTP, and forwards the request to the destination computer or server. Responses from the destination to the client take the corresponding reverse route, and also are carried over a specialized protocol between the two nodes. In addition, these nodes can employ other techniques such as web caches that avoid or improve some communication steps. Thus, specialized, proprietary, or complex protocols and techniques can be quickly deployed to enhance web performance without requiring significant changes to the clients or servers.

Owner:AKAMAI TECH INC

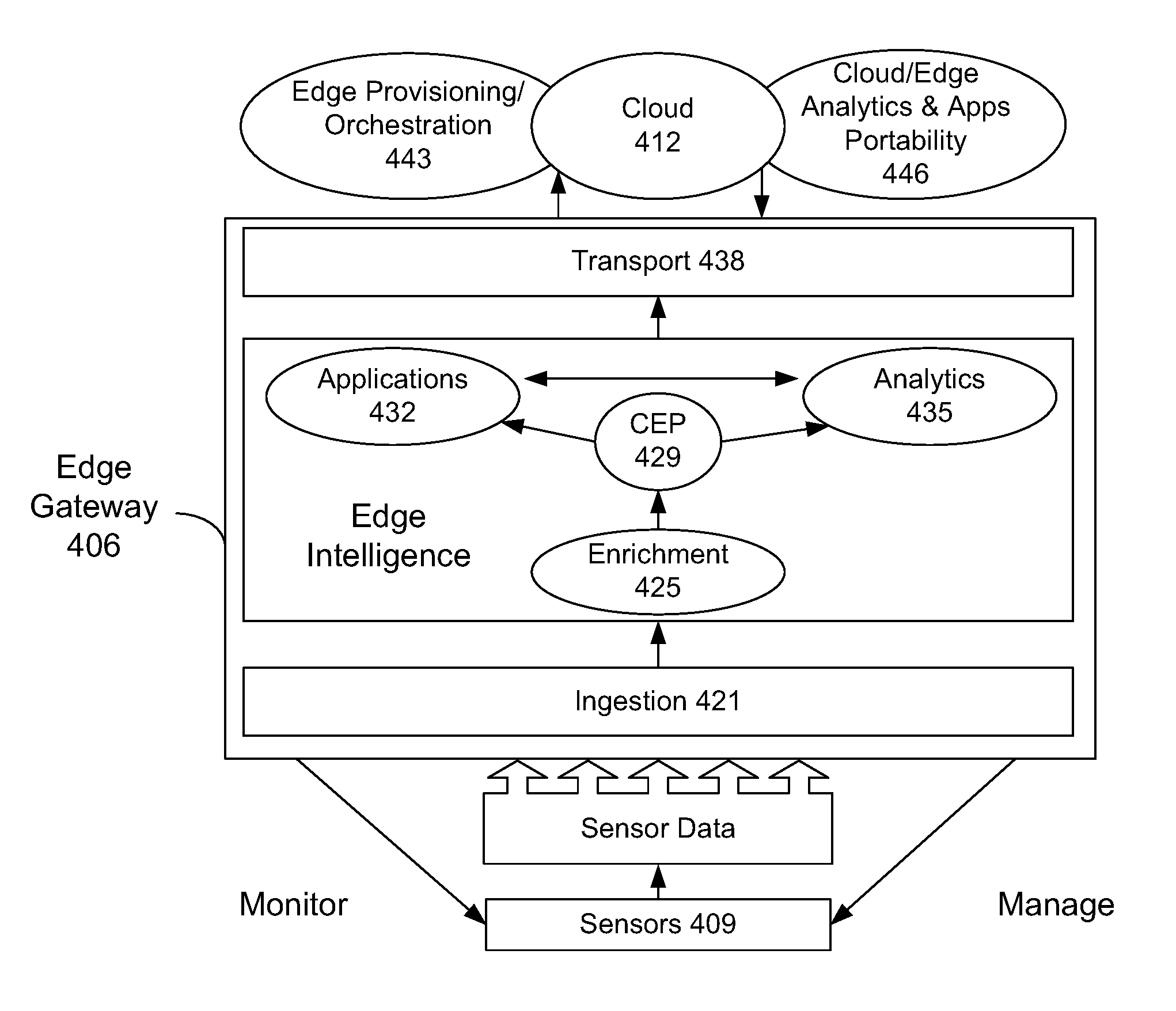

Edge Intelligence Platform, and Internet of Things Sensor Streams System

ActiveUS20170060574A1Delay minimizationMaximum performanceDigital data information retrievalParticular environment based servicesAnalytical expressionsApplication software

A method for enabling intelligence at the edge. Features include: triggering by sensor data in a software layer hosted on either a gateway device or an embedded system. Software layer is connected to a local-area network. A repository of services, applications, and data processing engines is made accessible by the software layer. Matching the sensor data with semantic descriptions of occurrence of specific conditions through an expression language made available by the software layer. Automatic discovery of pattern events by continuously executing expressions. Intelligently composing services and applications across the gateway device and embedded systems across the network managed by the software layer for chaining applications and analytics expressions. Optimizing the layout of the applications and analytics based on resource availability. Monitoring the health of the software layer. Storing of raw sensor data or results of expressions in a local time-series database or cloud storage. Services and components can be containerized to ensure smooth running in any gateway environment.

Owner:JOHNSON CONTROLS TYCO IP HLDG LLP

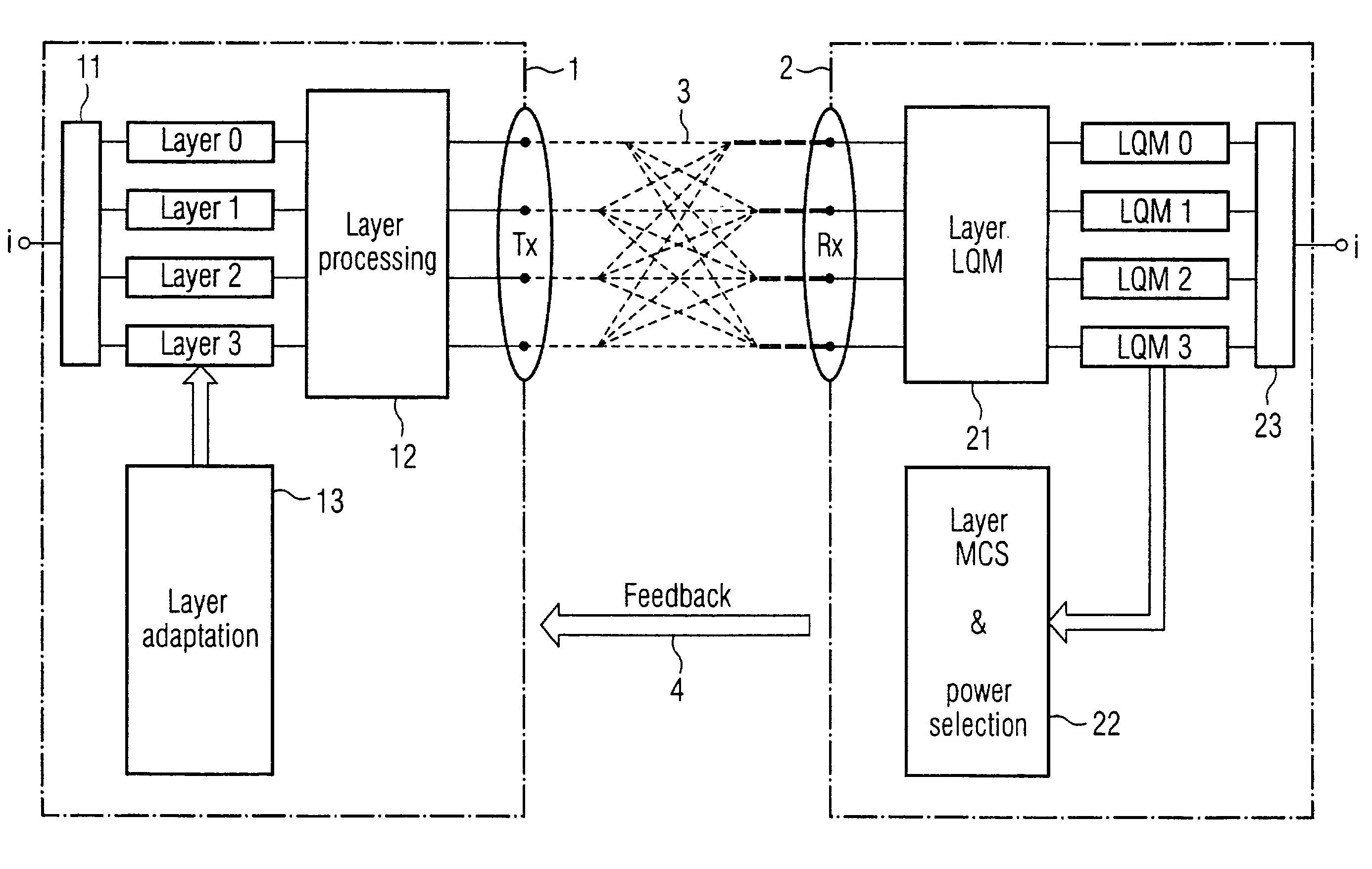

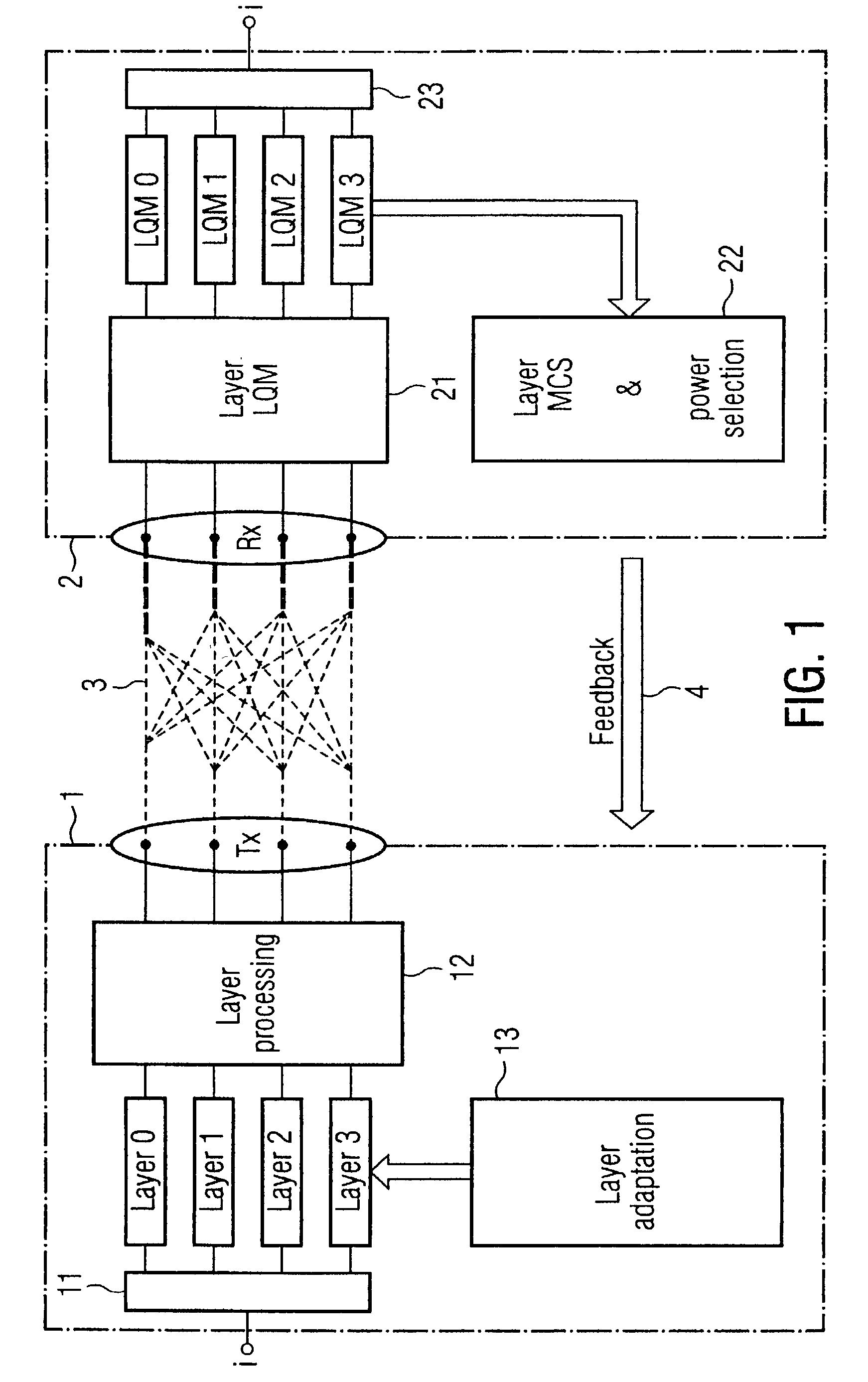

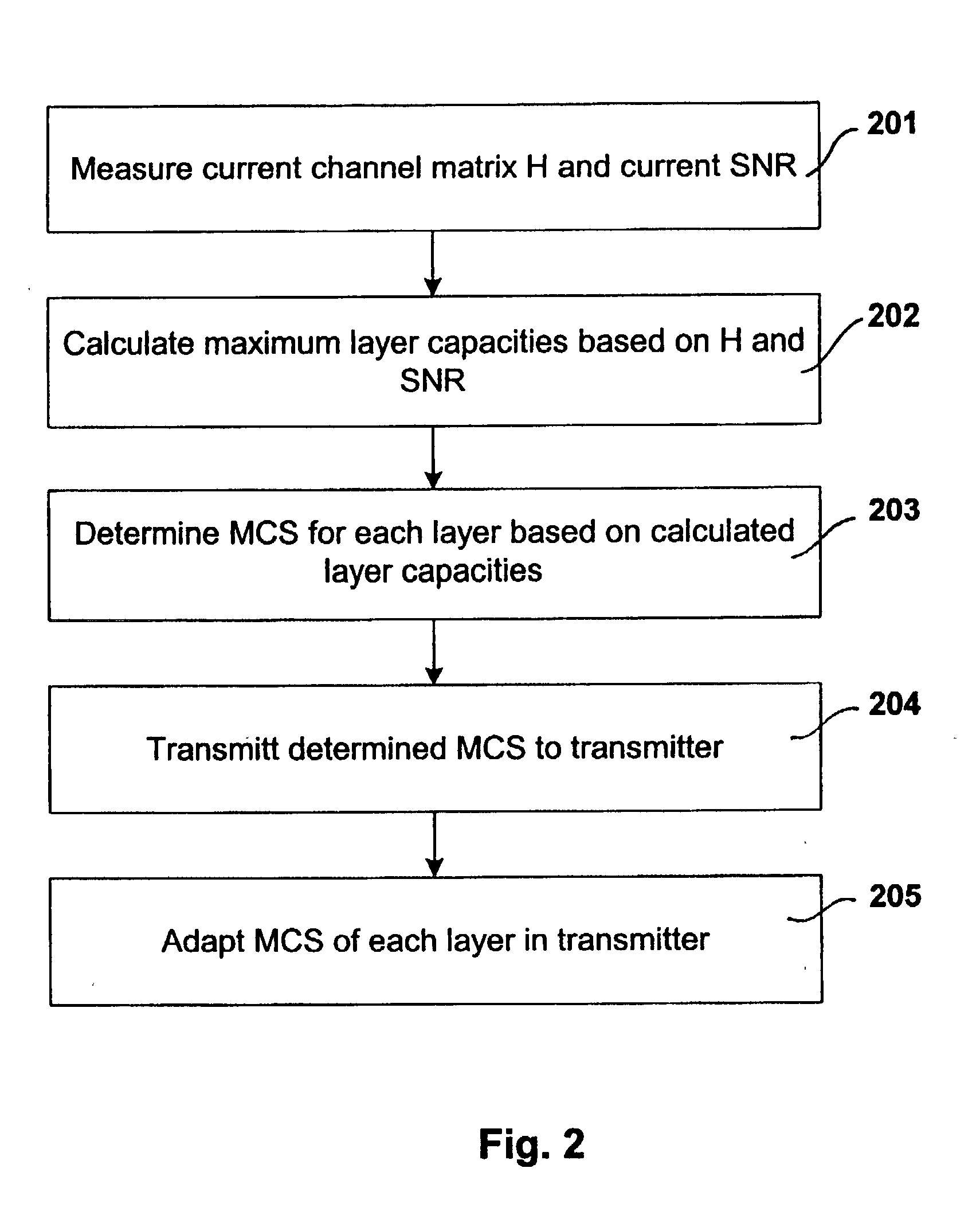

Link adaptation for MIMO transmission schemes

ActiveUS20030003863A1Reduce in quantitySmall rateError prevention/detection by using return channelSpatial transmit diversityCommunications systemMimo transmission

MIMO transmission methods are applied to communicaiton systems in which a transmitter has more than one transmit antenna and a receiver has more than one receive antenna. Information to be transmitted is divided into a plurality of subsignals according to the number of used transmit antennas and each subsignal is processed separately before it is emitted by the respective transmit antenna. In the receiver the different receive signals are processed thus that subsignals are detected and decoded and the contribution of each detected and decoded subsignal is subtracted from the receive signals and whereby a feedback channel from receiver to transmitter is used to send control information to the transmitter depending on the receive situation. In order to optimize the usage of the MIMO channel the invention proposes the in the receiver the link quality of each subsignal is determined and information of each subsignal is transmitted to the receiver via the feedback channel and that in the transmitter properties of the subsignals are controlled by the link quality information.

Owner:TELEFON AB LM ERICSSON (PUBL)

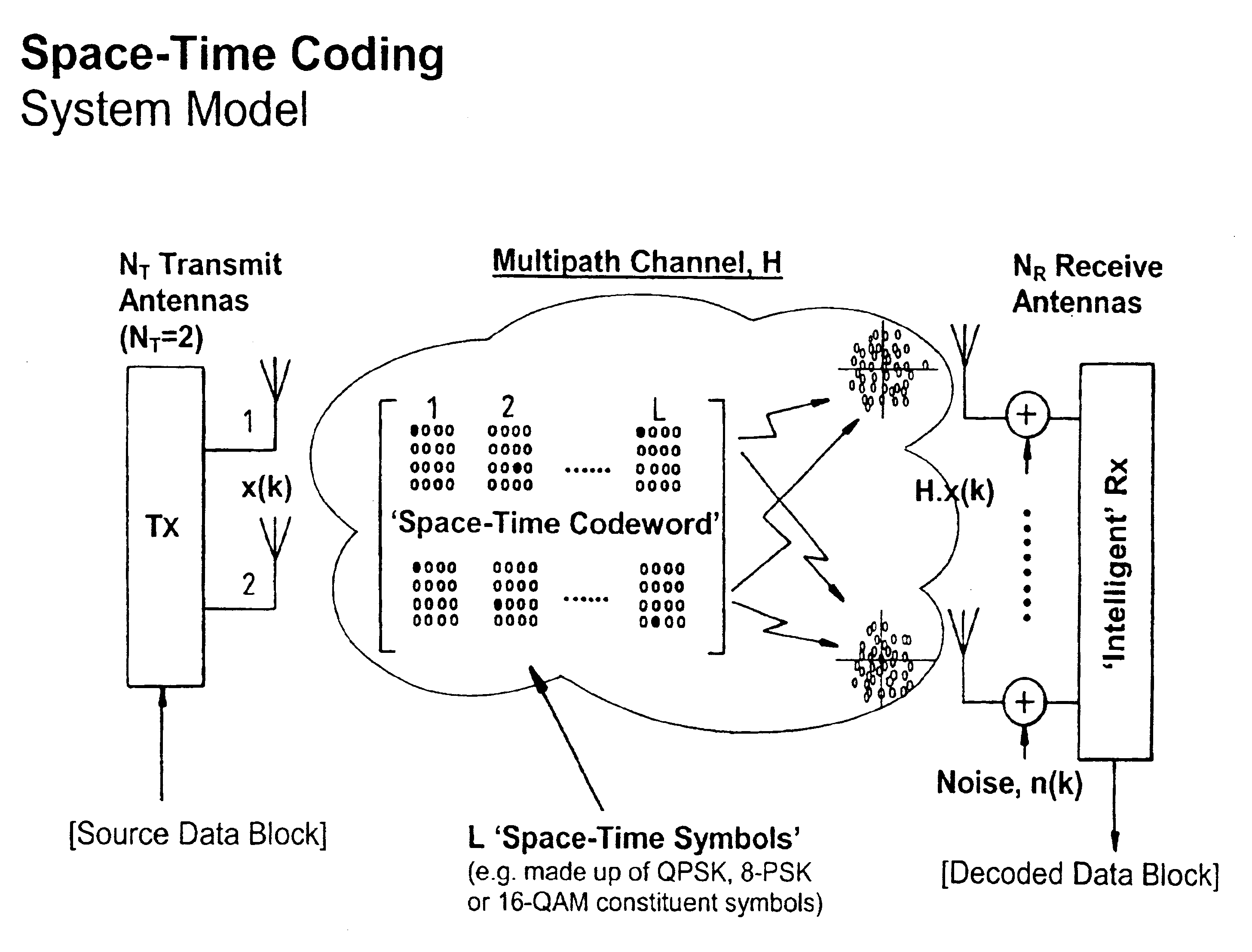

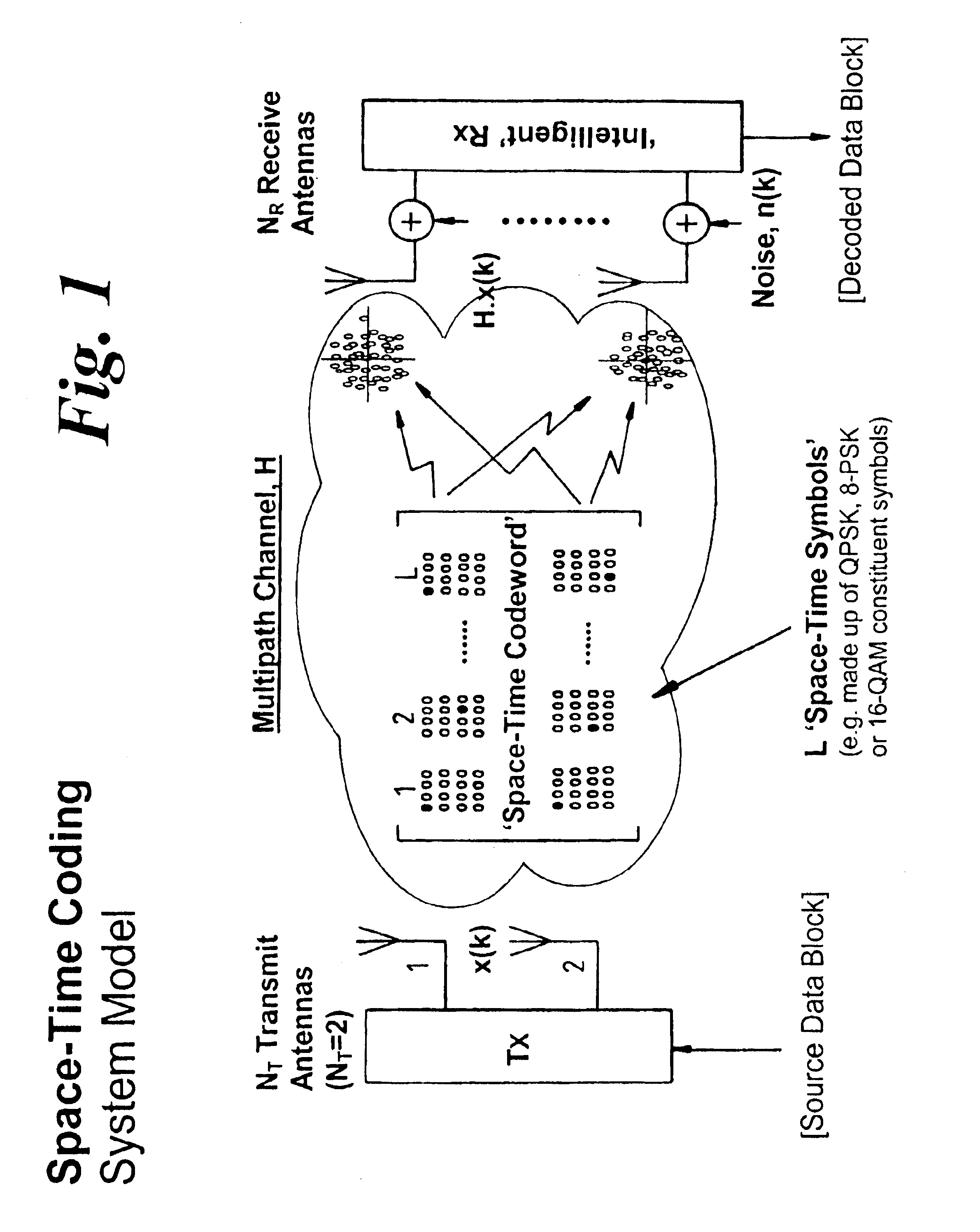

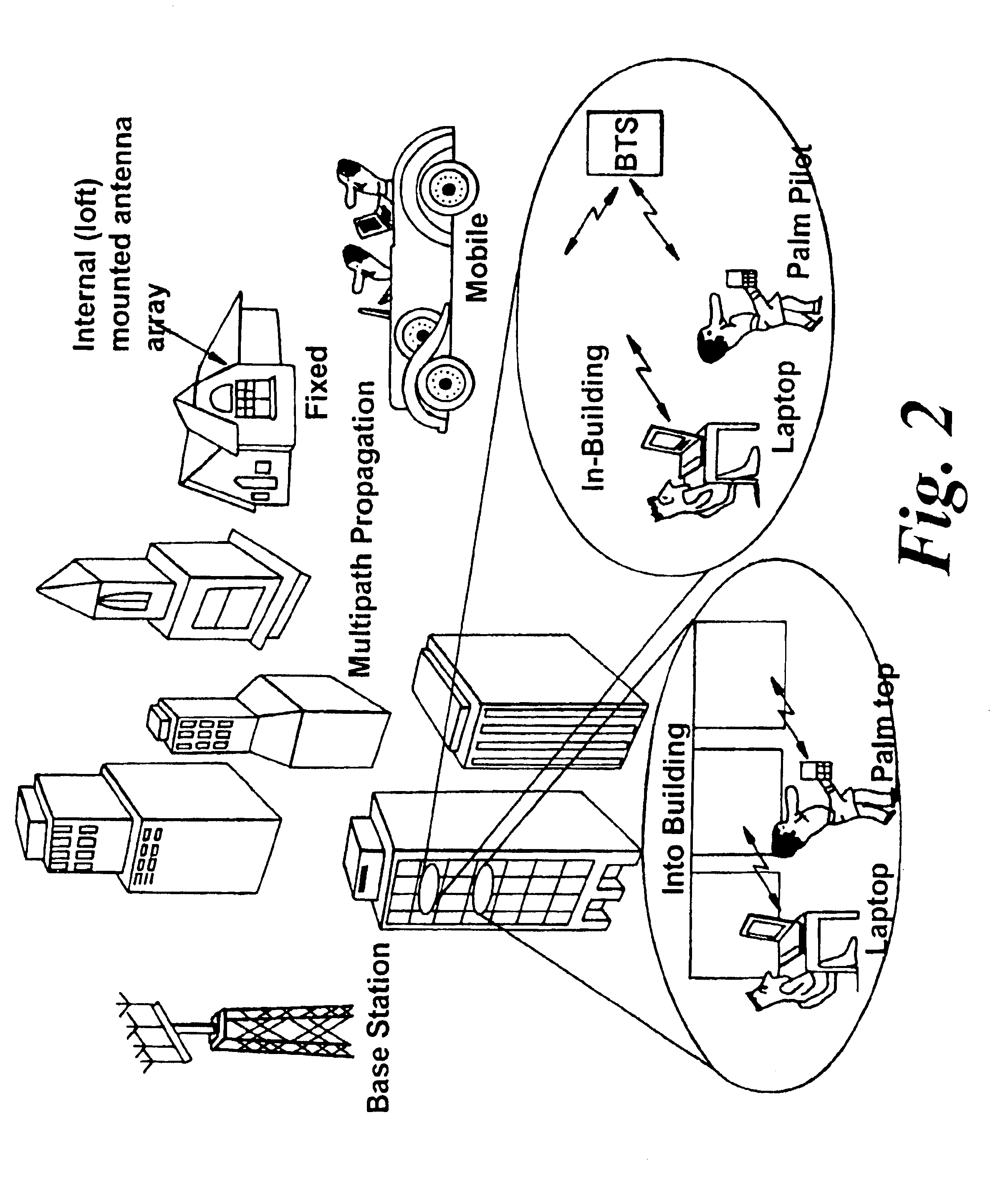

Space-time coding and channel estimation scheme, arrangement and method

InactiveUS6891897B1Improve spectral efficiencyIncreased improved bandwidth efficiencySpatial transmit diversityChannel estimationHigh rateFrequency spectrum

The evolution of high rate data services within future wireless networks will call for new RF access technologies to enable substantial increases in overall system spectral efficiency at an acceptably low cost to the user. Space-Time Coding (STC) is an antenna array processing technology currently simulating considerable Interest across the wireless industry. The invention provides a space-time coding apparatus having an input, a trellis encoder, a modulator, a demultiplexer, and a set of signal outputs wherein the input is operable to receive a stream of data. This allows de-multiplexing to take place after coding and modulation has been performed. The trellis encoder comprises a convolutional encoder operable to sequentially group data to provide coded bits to provide QPSK symbols. By the selection of convolutional encoder rates and / or modulation alphabets STCs of any desired dimensionality may be produced including multi-dimensional codes.

Owner:APPLE INC

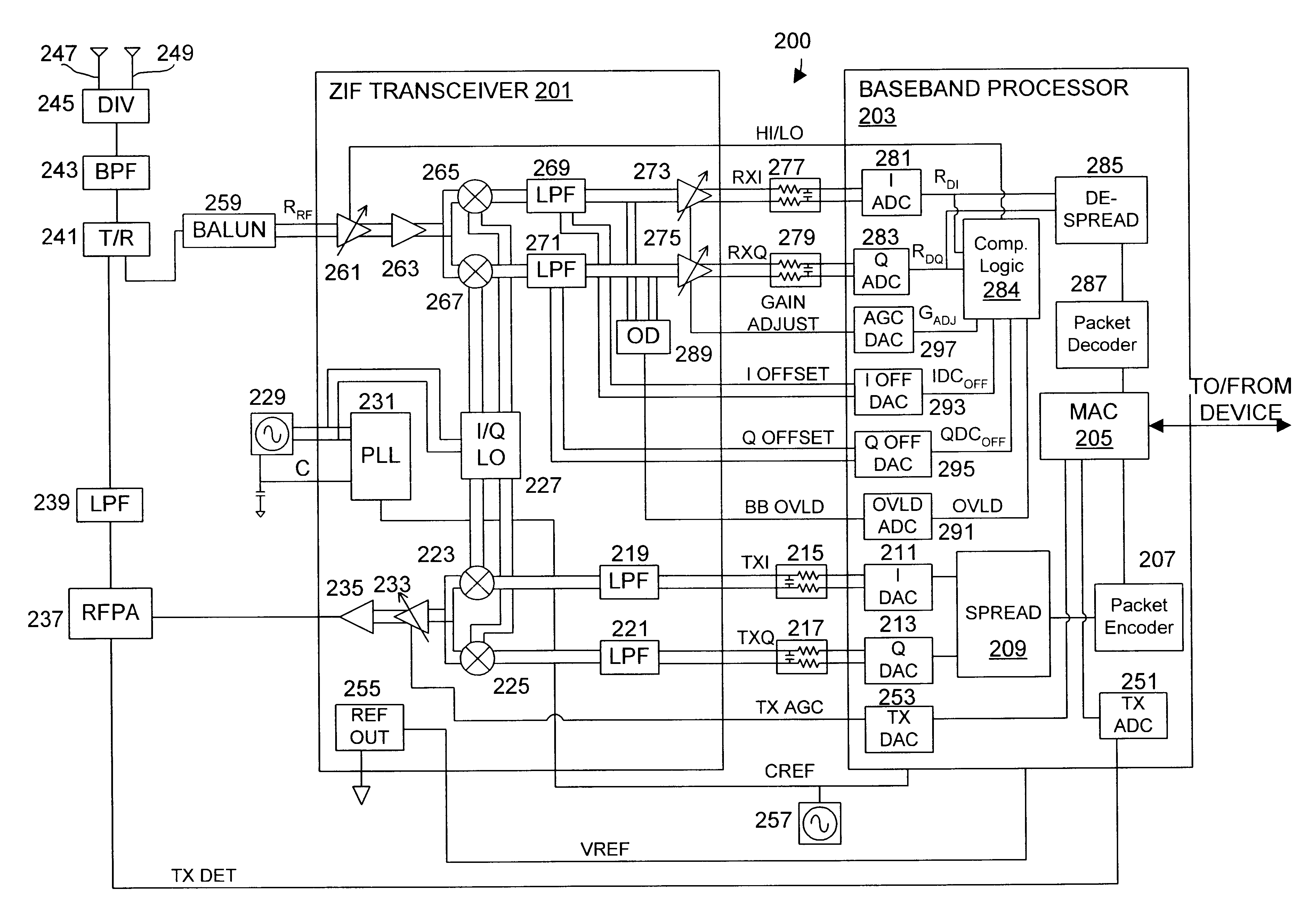

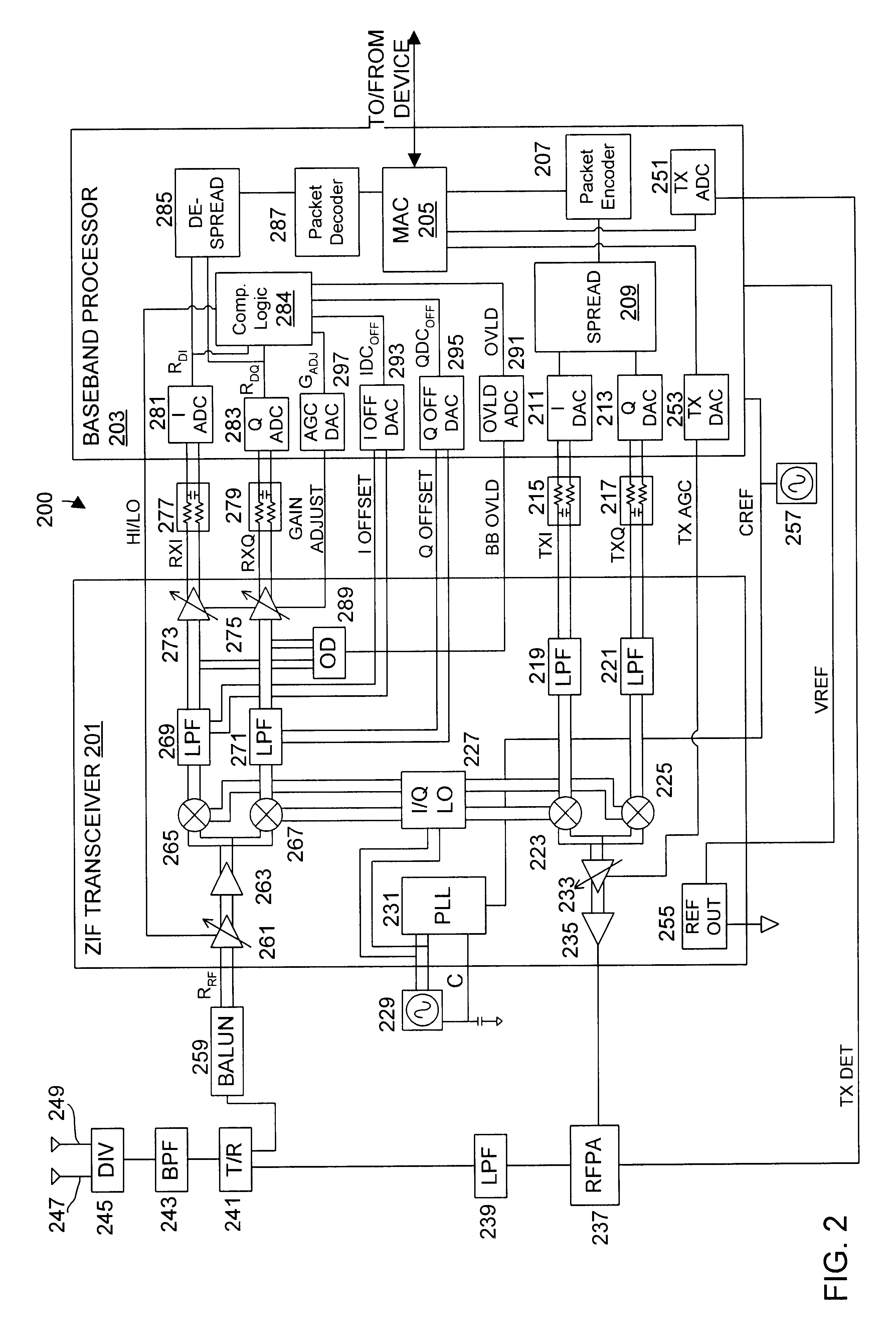

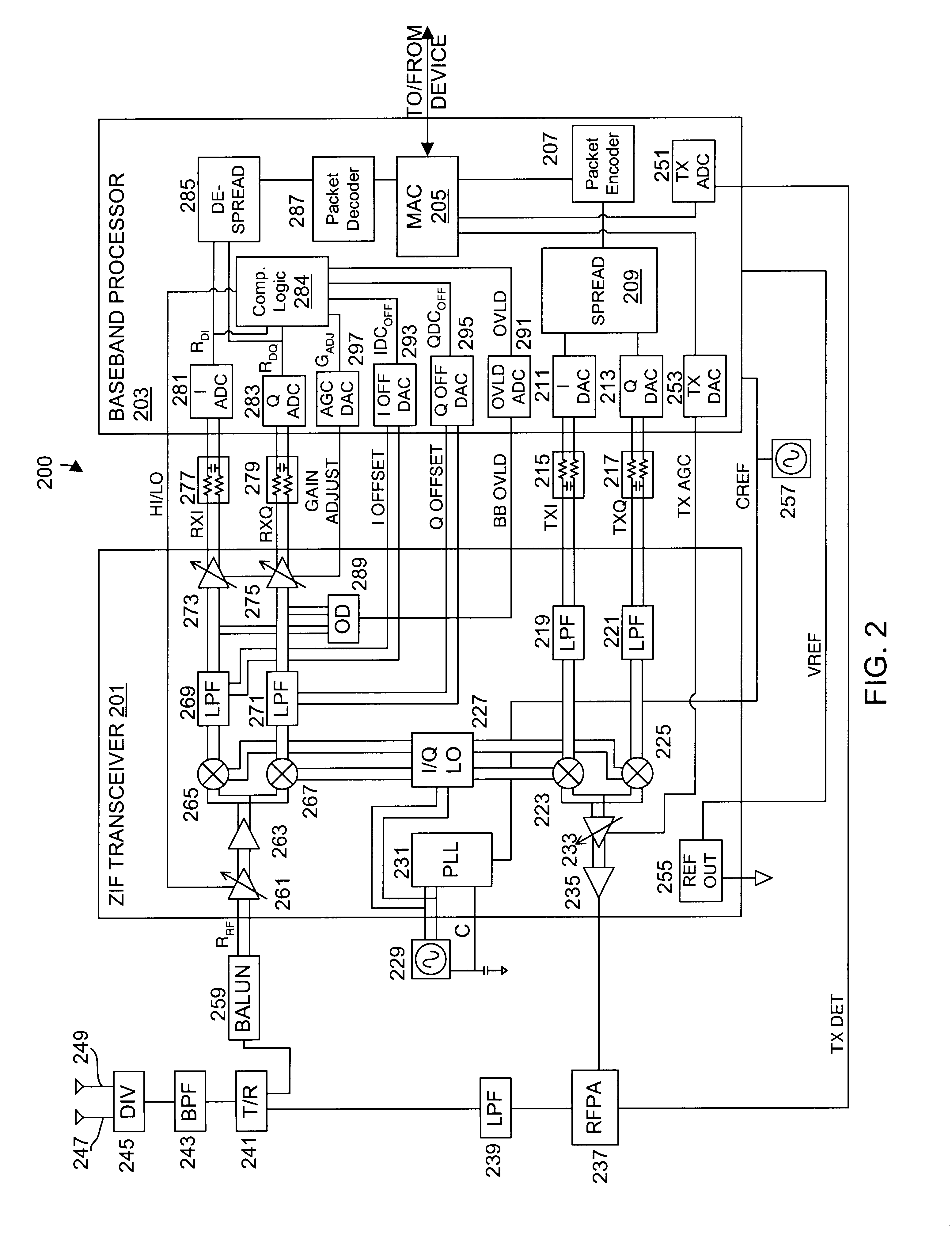

DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6560448B1Low costMaximum performanceGain controlAmplitude-modulated carrier systemsTransceiverAudio power amplifier

A wireless communication device including a radio frequency (RF) circuit, a ZIF transceiver and a baseband processor. The ZIF transceiver includes an RF mixer circuit that converts the RF signal to a baseband input signal, a summing junction that subtracts a DC offset from the baseband input signal to provide an adjusted baseband input signal, and a baseband amplifier that receives the adjusted baseband input signal and that asserts an amplified input signal based on a gain adjust signal. The baseband processor includes gain control logic, DC control logic and a gain interface. The gain control logic receives the amplified input signal, estimates input signal power and asserts the gain adjust signal in an attempt to keep the input signal power at a target power level. The DC control logic estimates an amount of DC in the amplified input signal and provides the DC offset in an attempt to reduce DC in the amplified input signal. The gain interface converts gain levels between the gain control logic and the DC control logic. The RF signal may include in-phase (I) and quadrature (Q) portions, where the RF mixer circuit splits I and Q baseband input signals from the RF signal. Operation is substantially identical for both I and Q channels. The DC control logic operates to remove or otherwise eliminate DC from the received signal that is provided to decoders in the baseband processor.

Owner:M RED INC

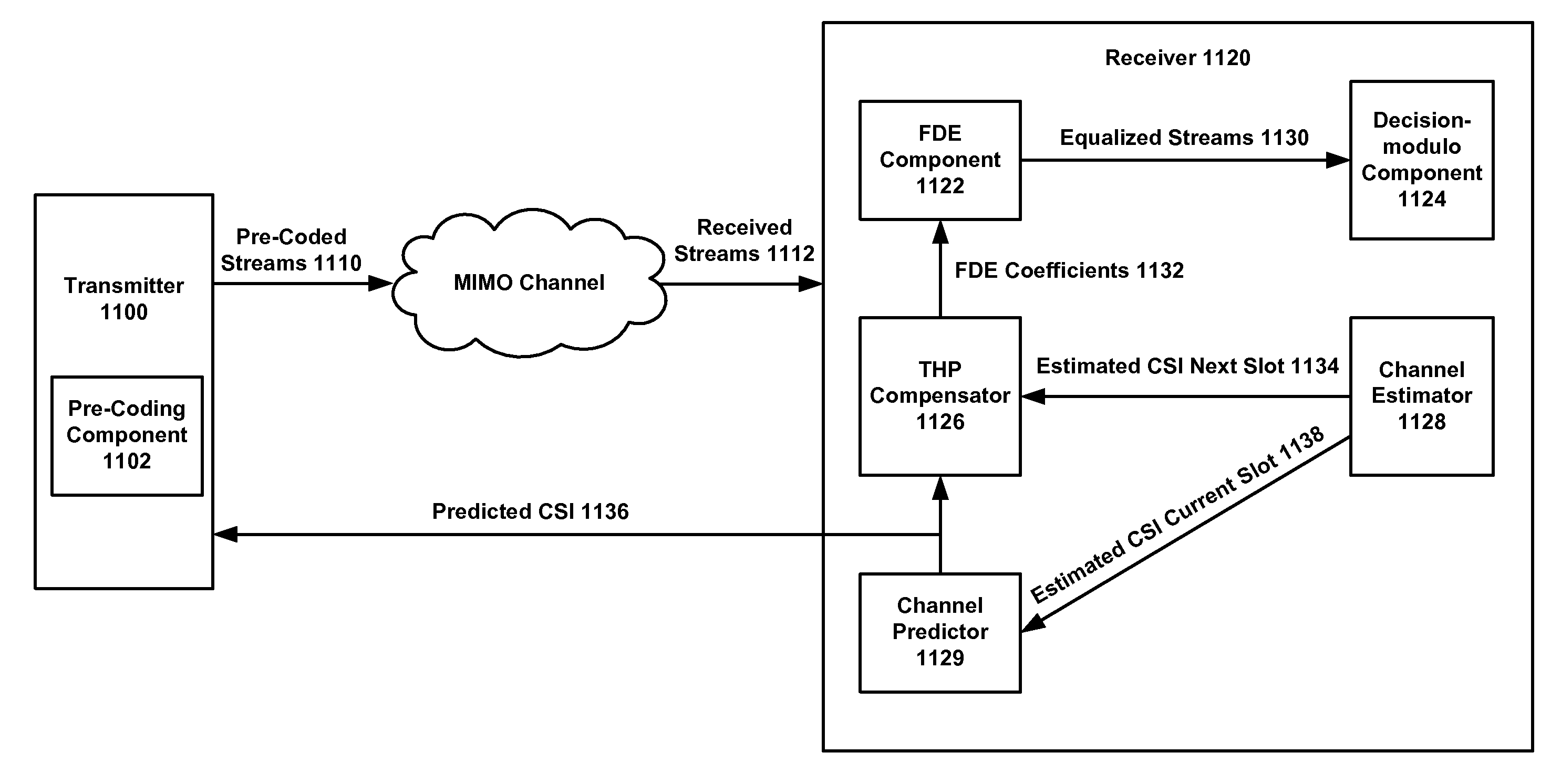

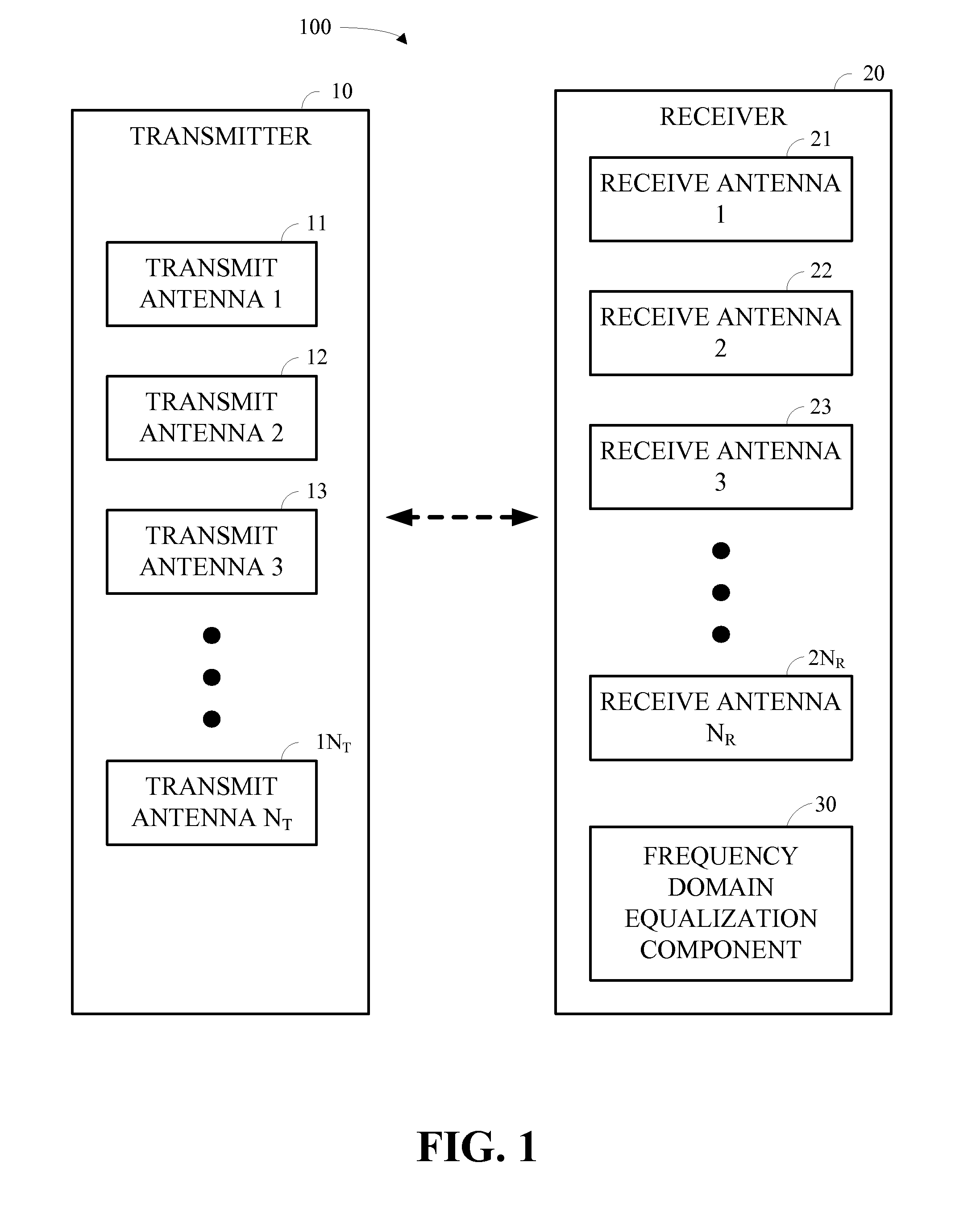

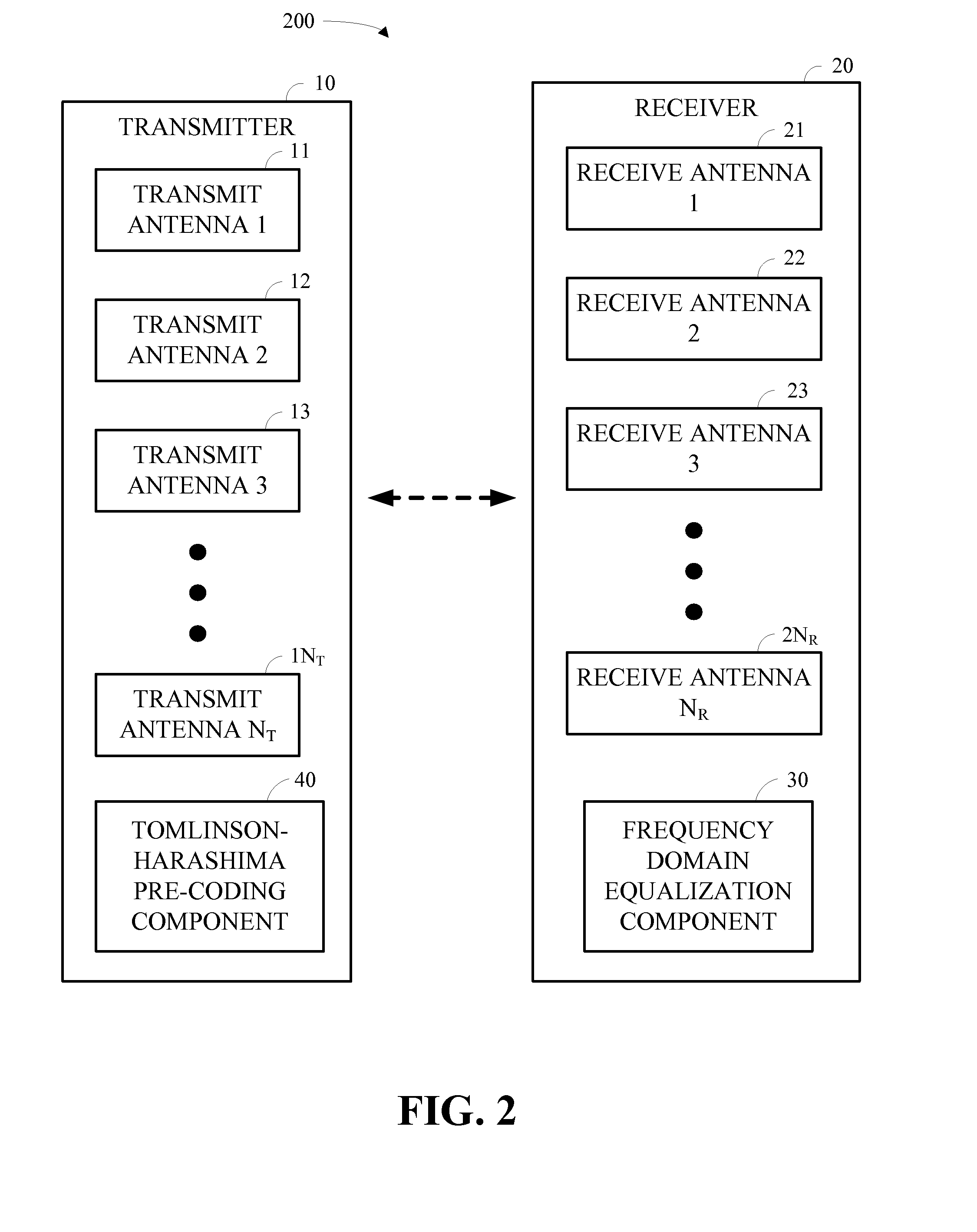

Frequency domain equalization with transmit precoding for high speed data transmission

InactiveUS20090122854A1Avoid error problemsMaximum performanceMultiple-port networksDelay line applicationsMIMOSC-FDE

Various embodiments of multi input multi output (MIMO) communication systems include a transmit Tomlinson-Harashima Precoding (THP) technique and a single carrier frequency domain equalization (SC-FDE) technique. Parallel THP-FDE and successive THP-FDE are proposed based on the minimum mean square error (MMSE) criterion. For the successive THP-FDE technique, where all transmit streams are subsequently precoded, both suboptimal and optimal MMSE ordering algorithm are set forth. Since the feedback processing is performed at the transmitter, no error propagation problem exists in the THP-FDE MIMO techniques, yielding significant performance improvements over conventional FDE MIMO techniques. Applying channel prediction and THP compensation techniques can also further enhance performance.

Owner:YIM TU INVESTMENTS

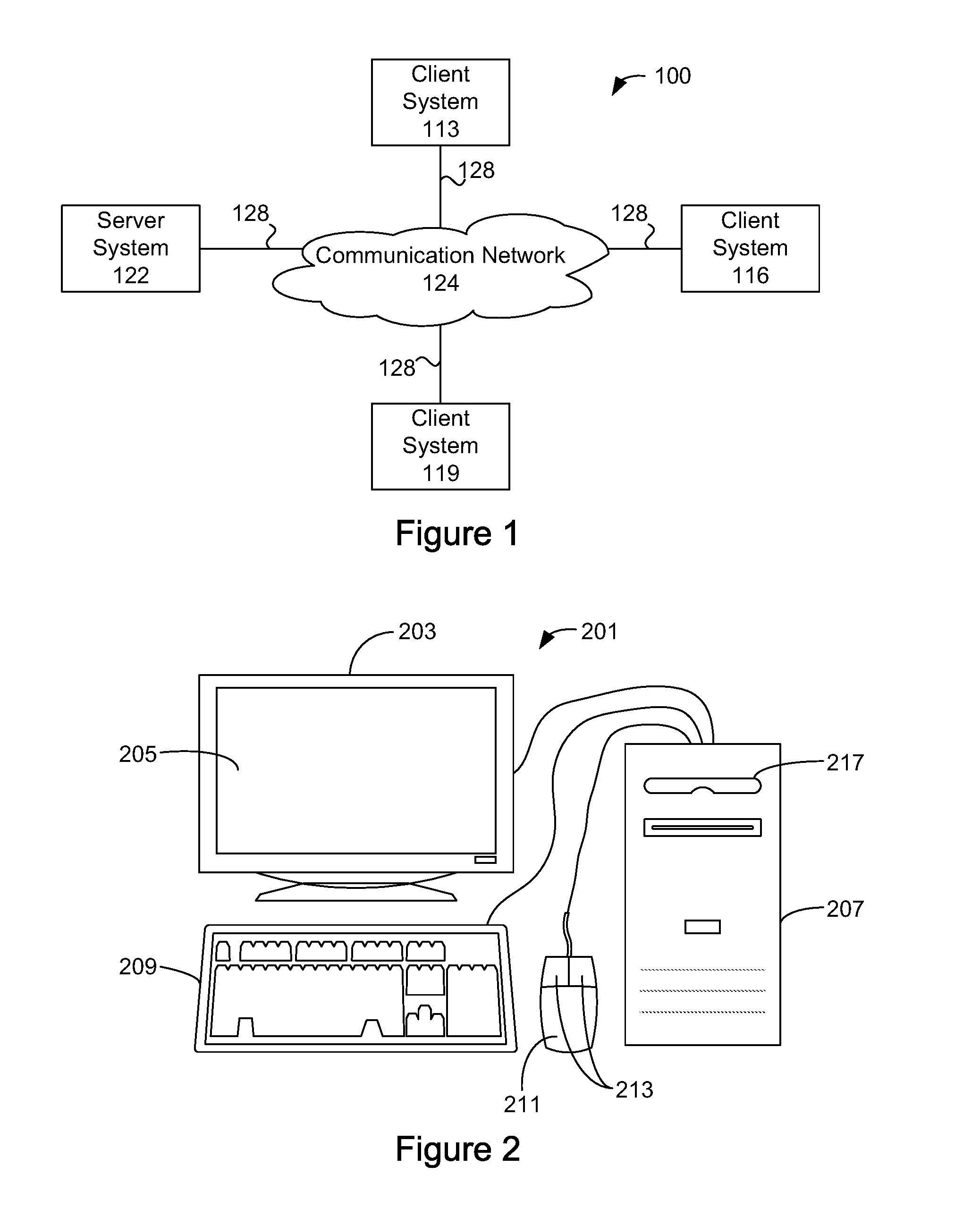

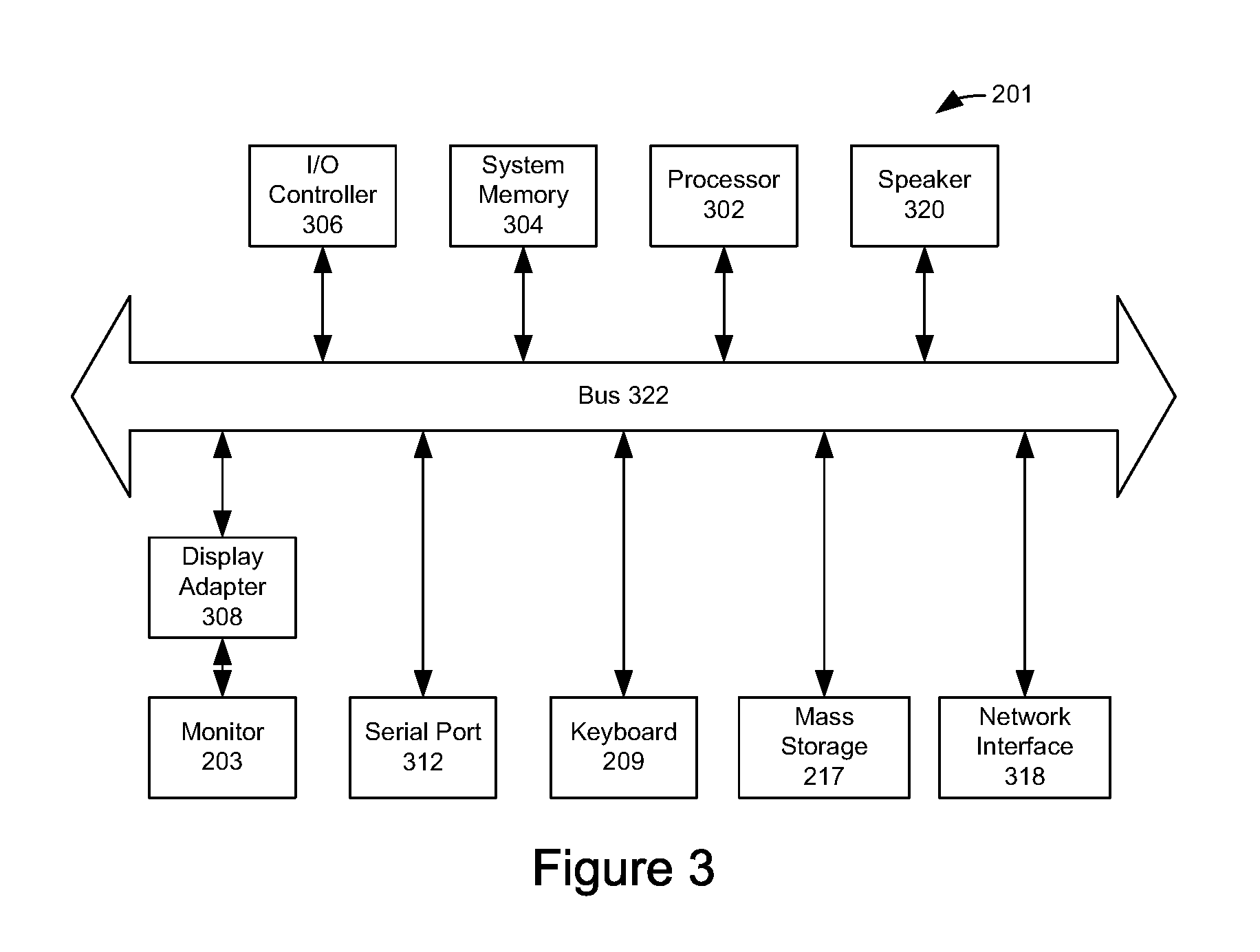

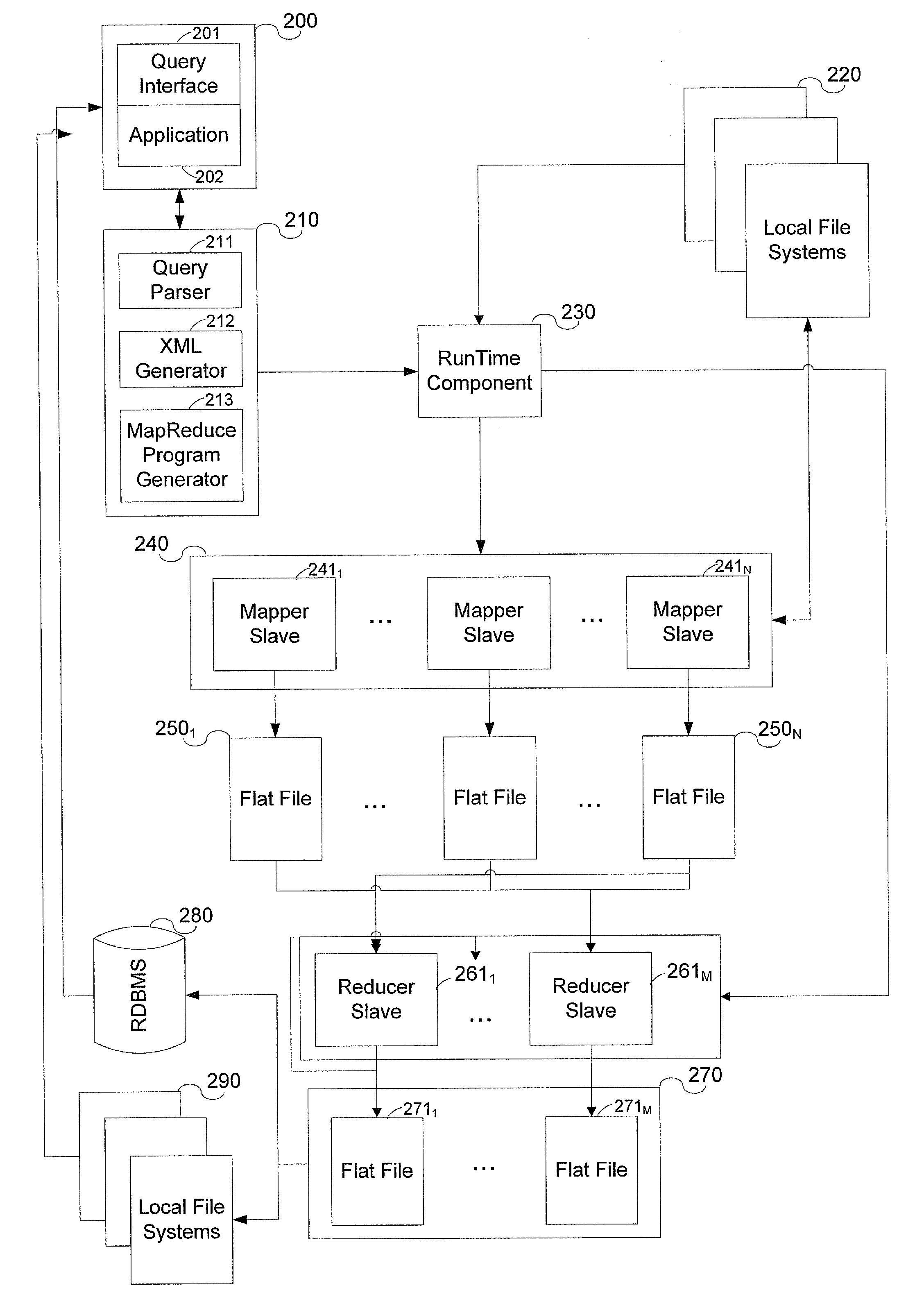

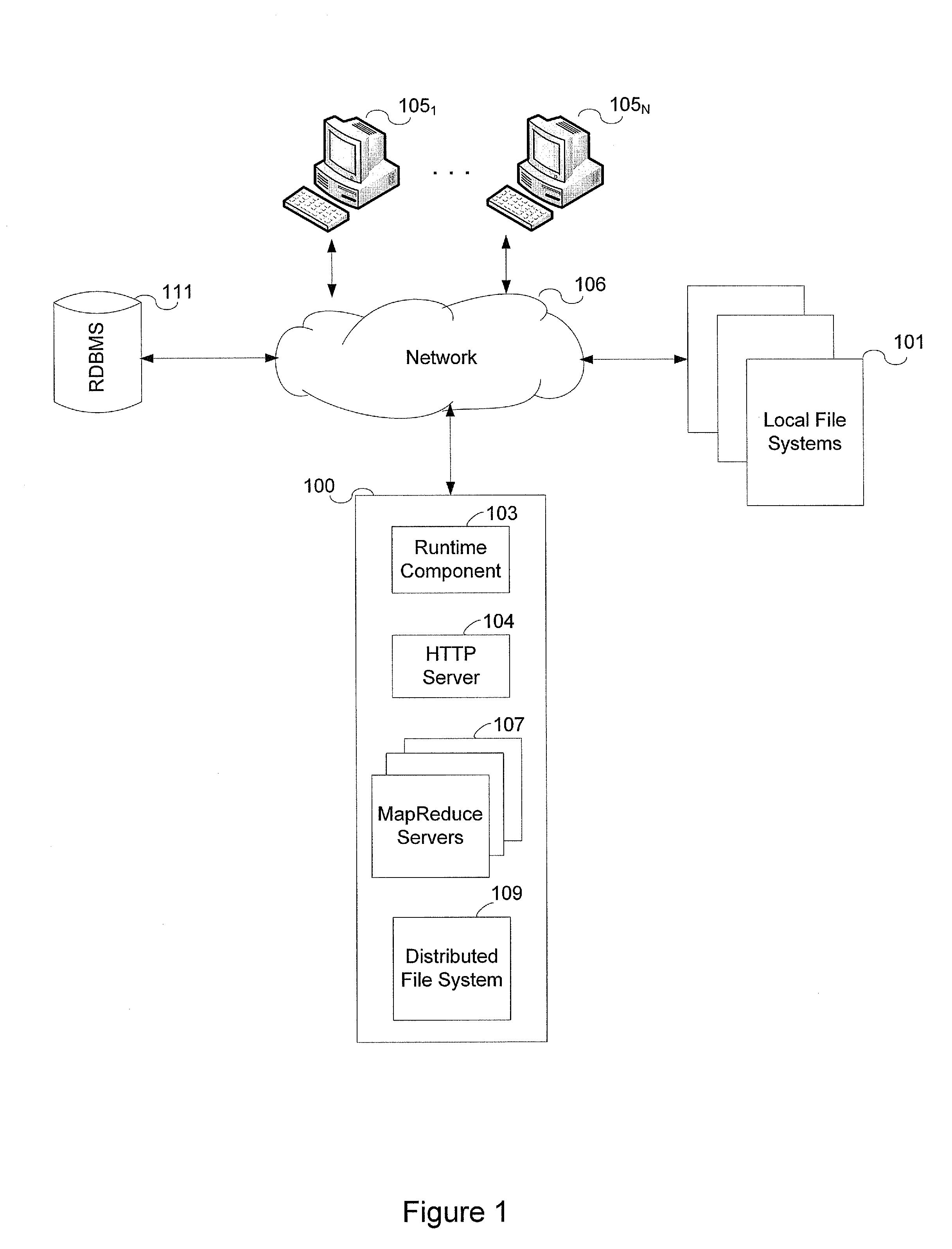

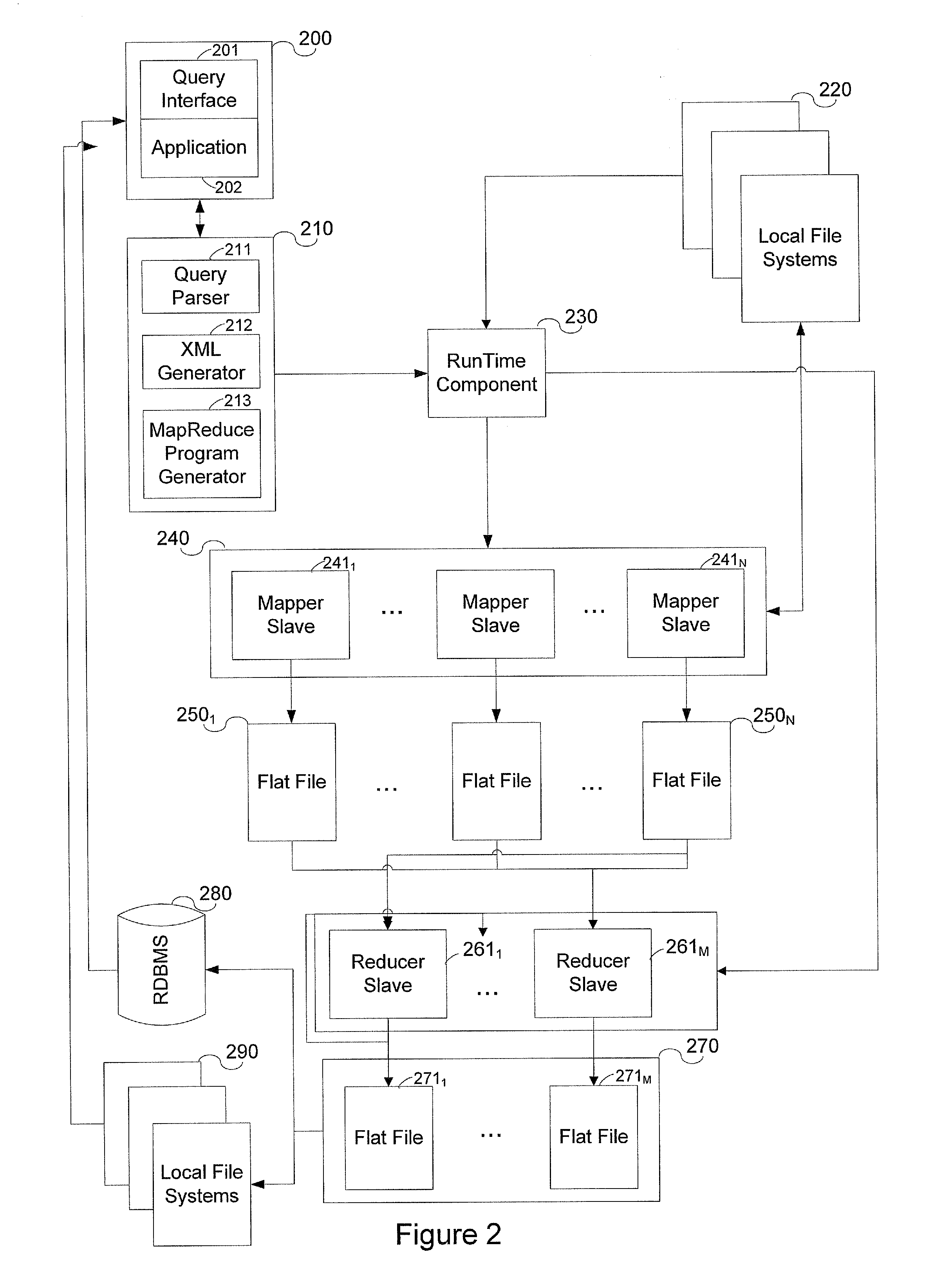

System and method for data warehousing and analytics on a distributed file system

ActiveUS20090055370A1Significant performance bottleneckProcess is time-consume and expensiveDigital data information retrievalDigital data processing detailsData warehouseMap reduce

A computer implemented method for executing an ANSI SQL expression belonging to the SELECT-WHERE-equi-JOIN class on data residing in a distributed file system, said method comprising the steps of entering the ANSI SQL expression into a user interface; converting the ANSI SQL expression into a map-reduce program; running the map-reduce program on the distributed file system; storing the result set of the program in the distributed file system; and presenting the result set through a user interface.

Owner:THRYV INC

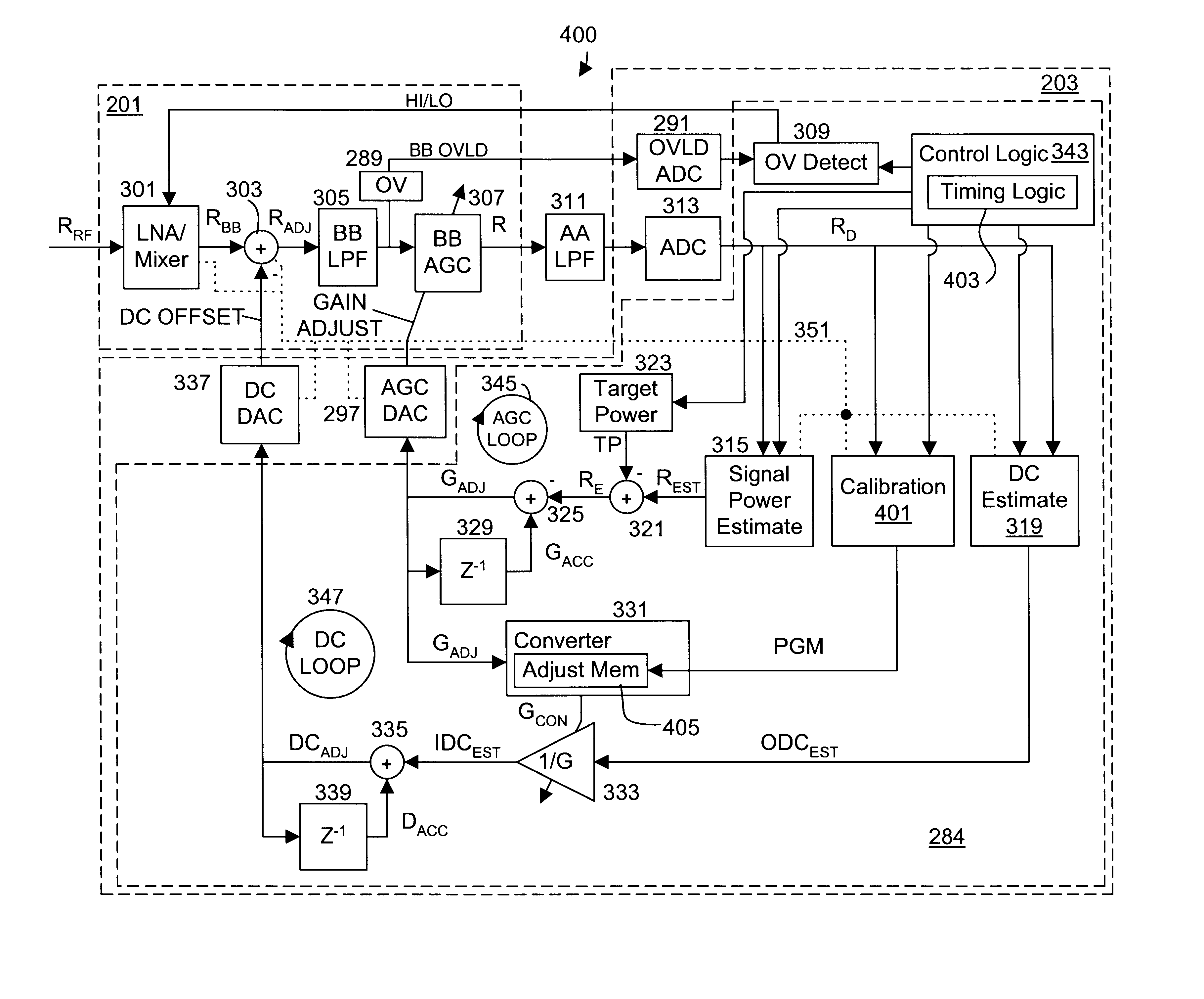

Calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6735422B1Low costMaximum performancePulse automatic controlGain controlTransceiverAudio power amplifier

A calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency (ZIF) architecture. The device includes a ZIF transceiver and a baseband processor, which further includes a calibrator that periodically performs a calibration procedure. The baseband processor includes gain control logic, DC control logic, a gain converter and the calibrator. The gain converter converts gain between the gain control logic and the DC control logic. The calibrator programs the gain converter with values determined during the calibration procedure. The gain converter may be a lookup table that stores gain conversion values based on measured gain of a baseband gain amplifier of the ZIF transceiver. The gain control logic may further include a gain adjust limiter that limits change of a gain adjust signal during operation based on a maximum limit or on one or more gain change limits. A second lookup table stores a plurality of DC adjust values, which are added during operation to further reduce DC offset. The calibration procedure includes sampling an output signal for each gain step of the baseband amplifier at two predetermined range values and corresponding DC offsets using successive approximation. The data is used to calculate gain, DC offset and DC differential values, which are used to determine the conversion values programmed into the lookup tables or the gain adjust limiter.

Owner:M RED INC

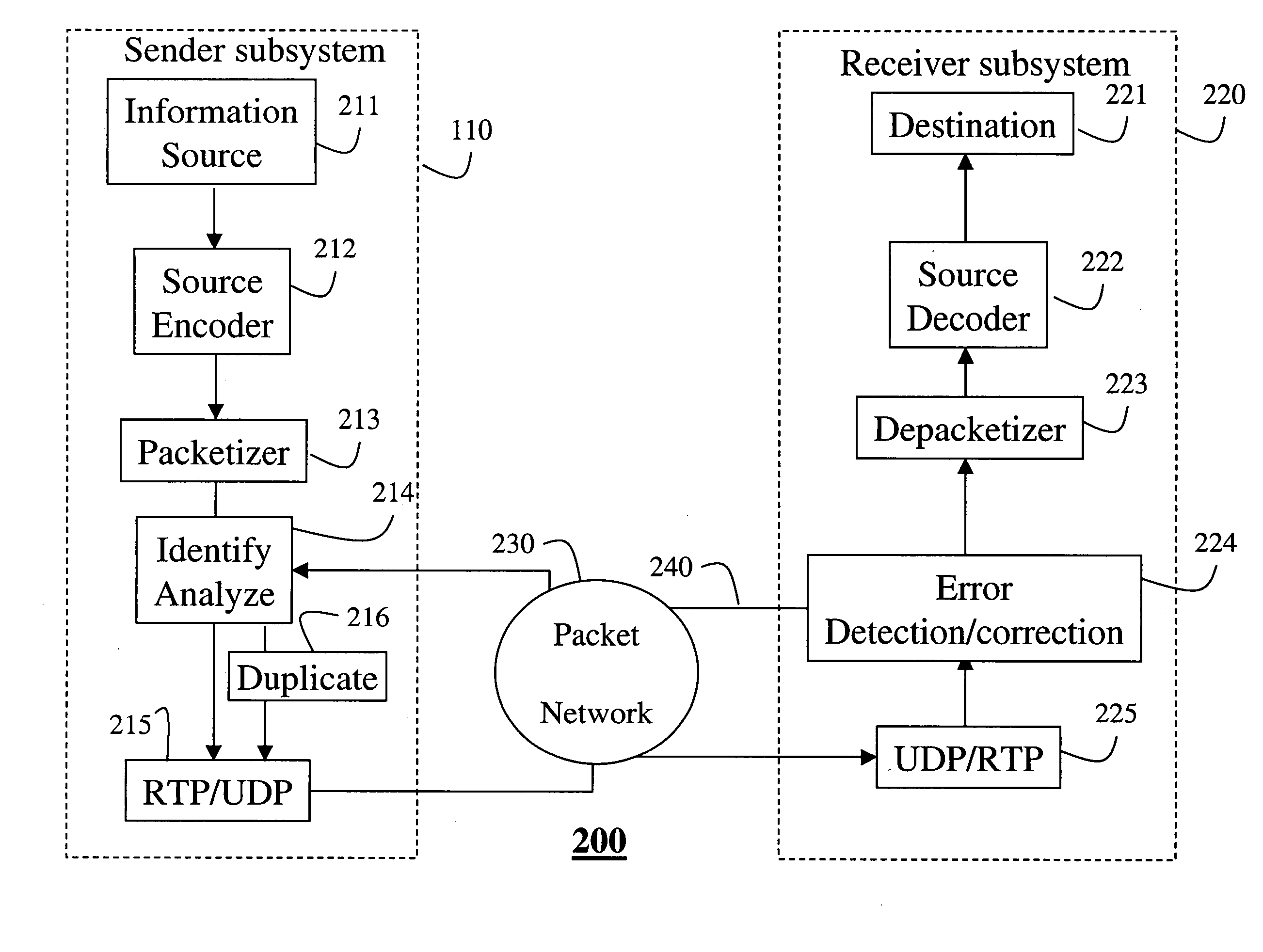

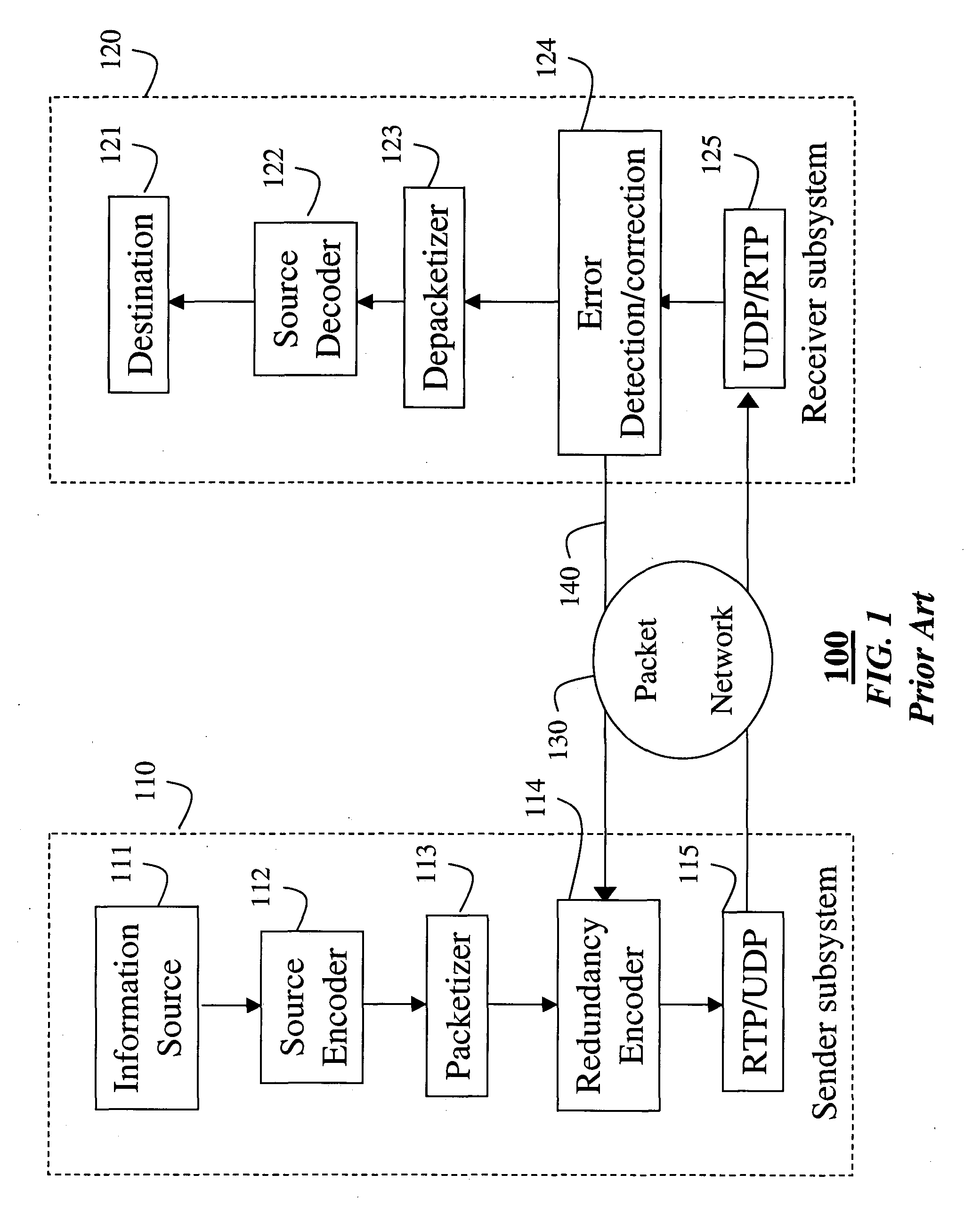

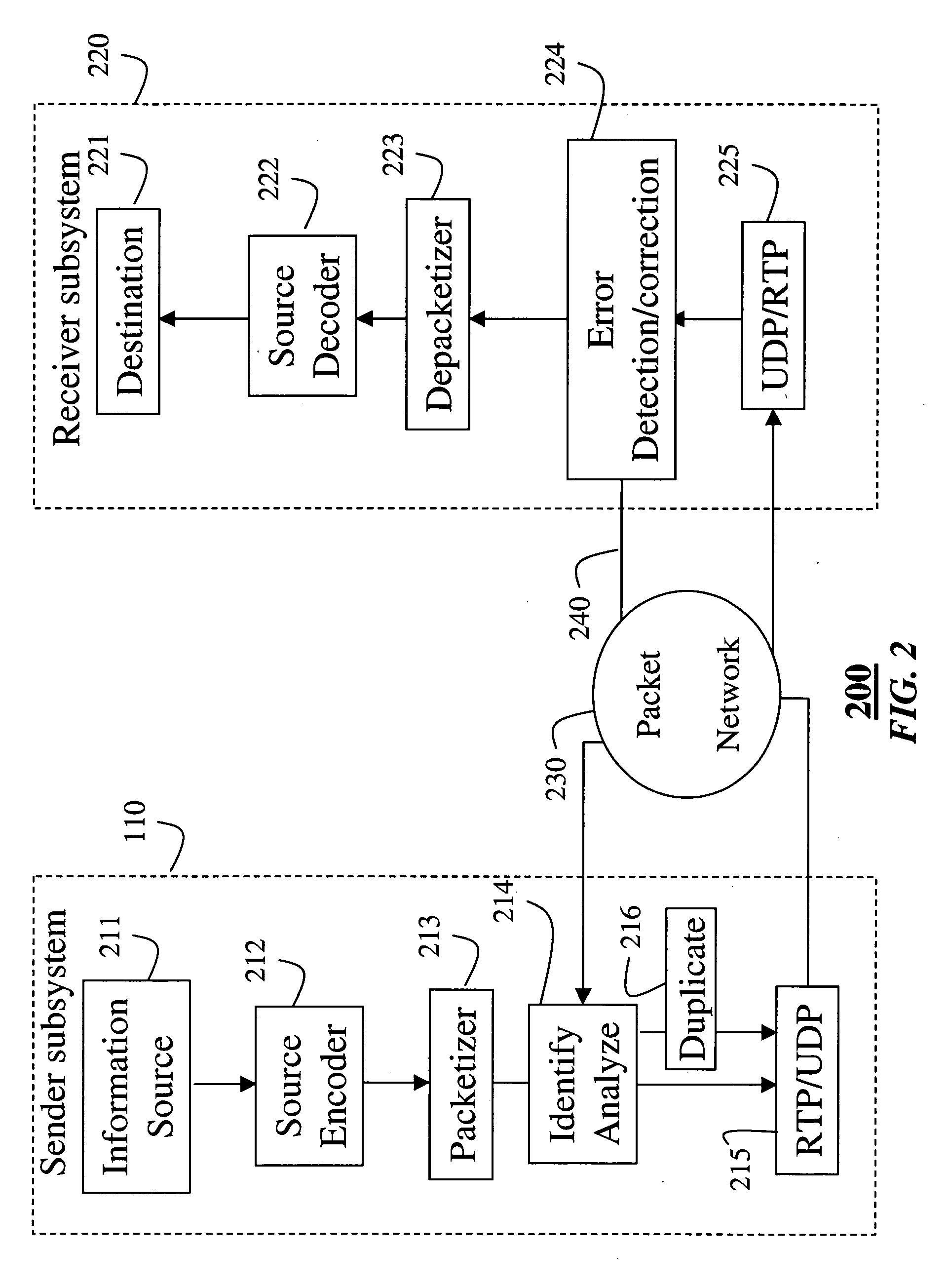

Redundant packets for streaming video protection

InactiveUS20050013249A1Reduce complexitySimple methodError prevention/detection by using return channelTransmission systemsPacket lossLive feedback

A method transmits a video over a network as a bit stream of packets. Real-time feedback information on conditions of the network is received while transmitting the packets. A probability of packet loss is based on the real-time feedback. Then, redundant packets are generated for selected packets of the bit stream if the probability of packet loss is greater than a predetermined threshold.

Owner:MITSUBISHI ELECTRIC RES LAB INC

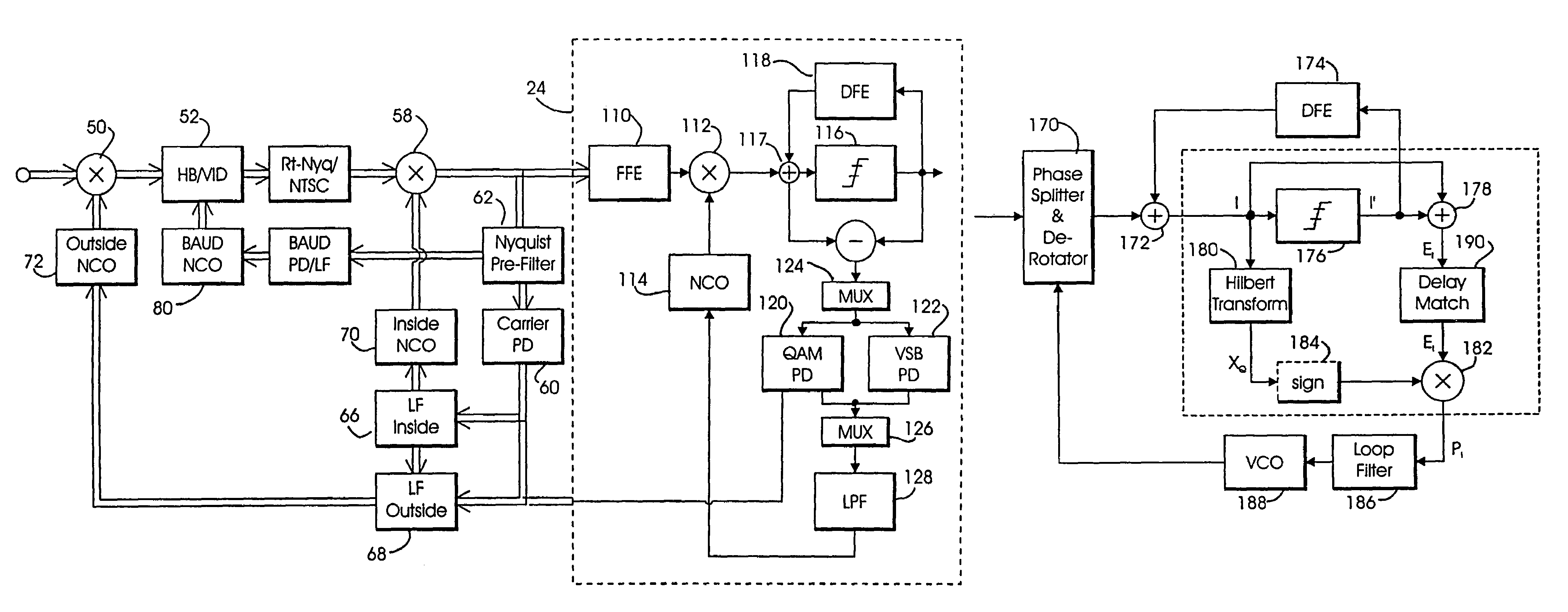

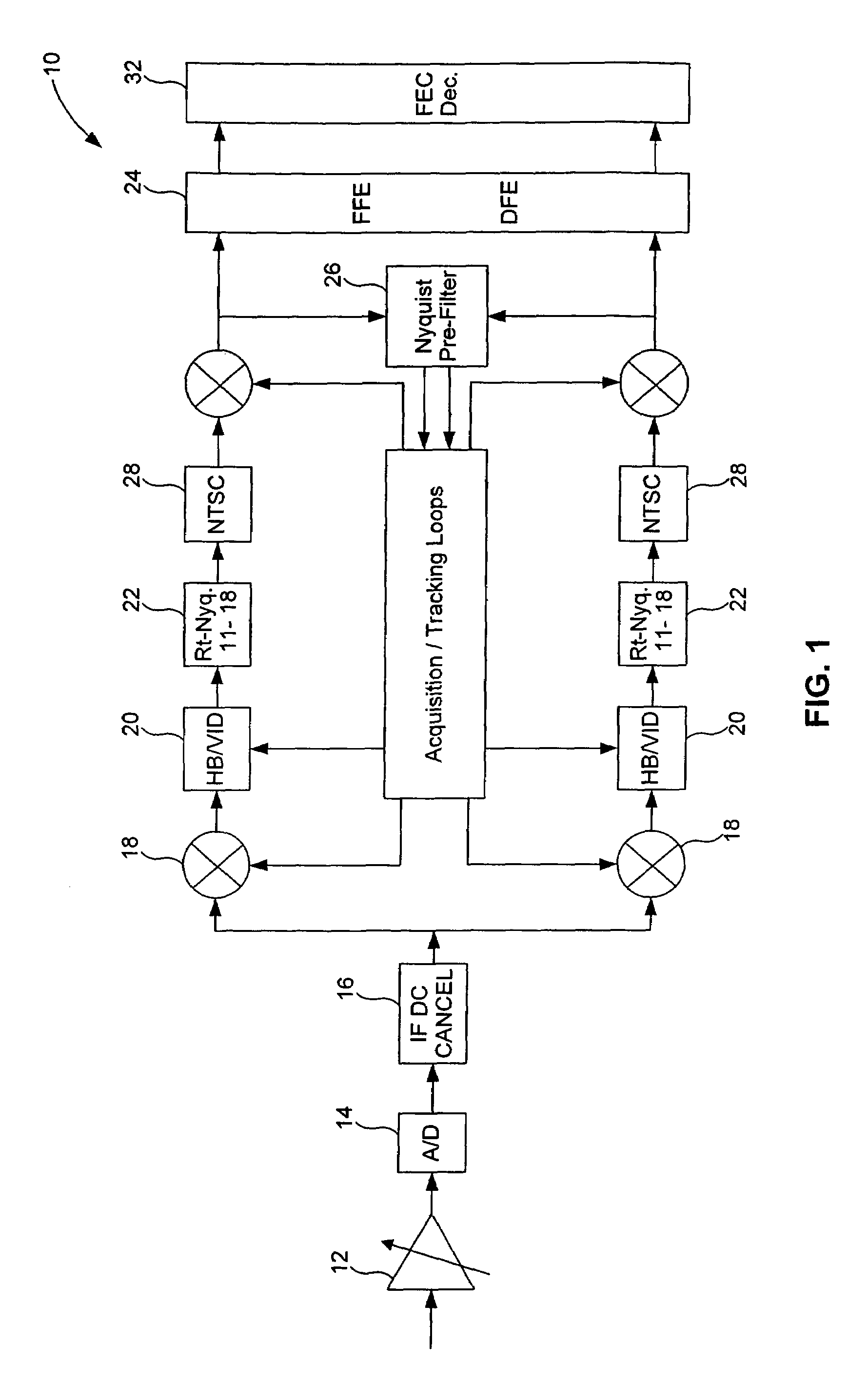

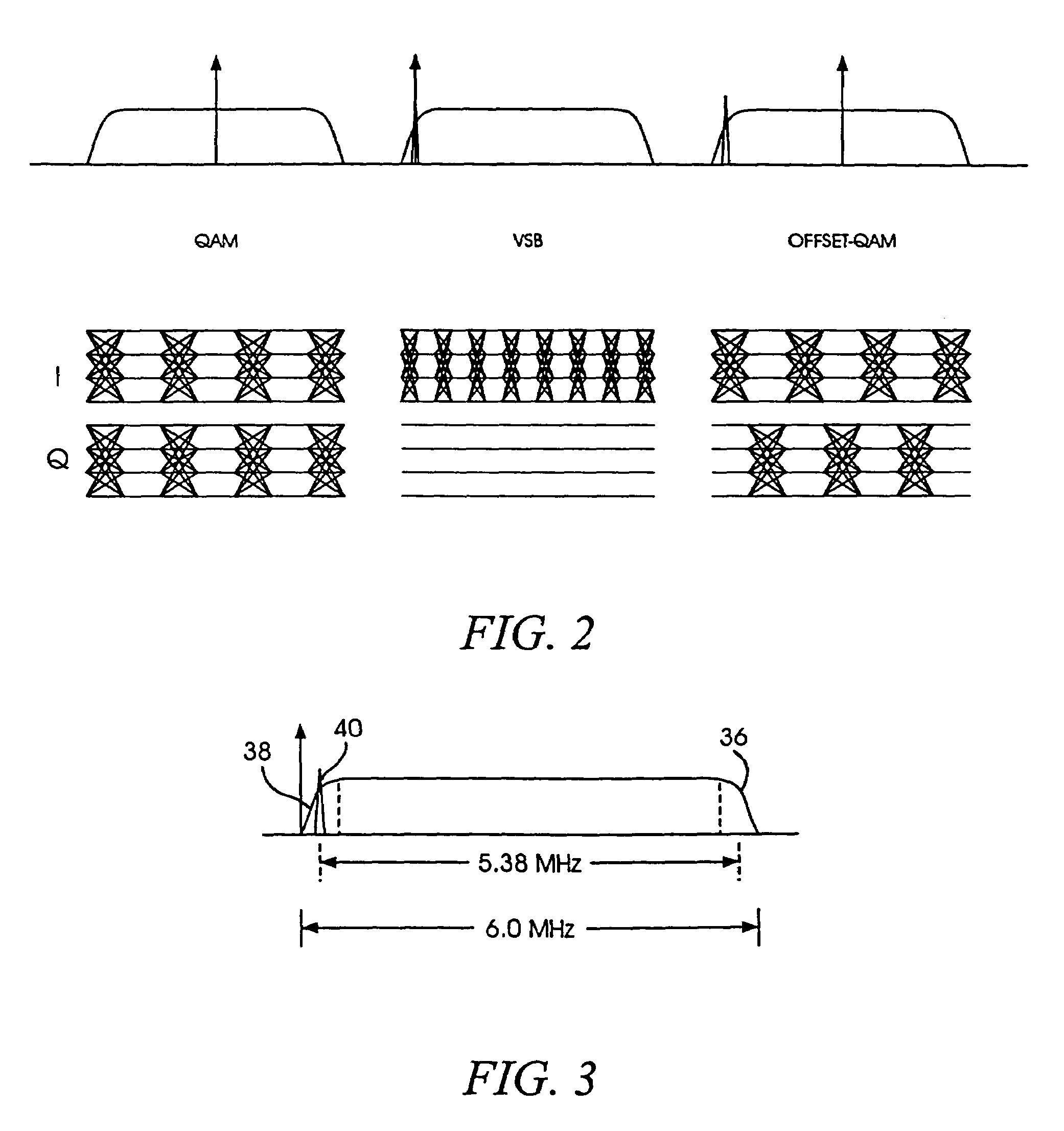

Equalization and decision-directed loops with trellis demodulation in high definition TV

InactiveUS7474695B2Improve reliabilityIncrease delay timeTelevision system detailsMultiple-port networksHigh definition tvHigh-definition television

Improved decision feedback equalizer and decision directed timing recovery systems and methods suitable for use in connection with a dual mode QAM / VSB receiver system are disclosed. A trellis decoder operates in conjunction with a decision feedback equalizer circuit on trellis coded 8-VSB modulated signals. The trellis decoder includes a 4-state traceback memory circuit outputting a maximum likelihood decision as well as a number of intermediate decisions based upon the maximum likelihood sequence path. Any number of decisions, along the sequence, may be provided as an input signal to timing recovery system loops, with the particular decision along the sequence chosen on the basis of its delay through the trellis decoder. Variable delay circuitry is coupled to the other input of the timing recovery system loops in order to ensure that both input signals bear the same timestamp. Final decisions are output from the trellis decoder to a DFE in order to enhance the DFE's ability to operate in low SNR environments. A decision sequence estimation error signal is also generated and used to drive the tap updates of both the DFE and an FFE portion of the equalizer.

Owner:AVAGO TECH INT SALES PTE LTD

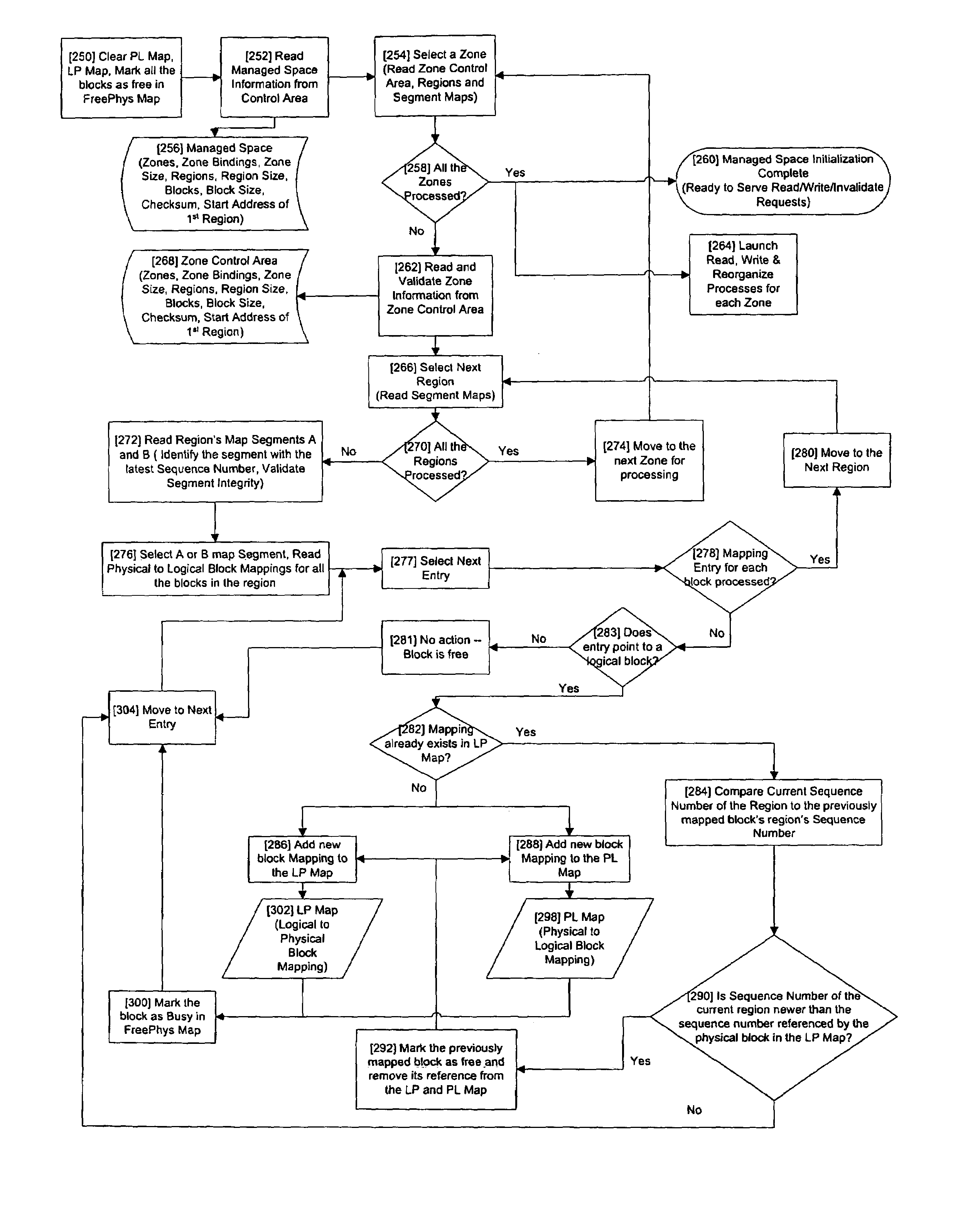

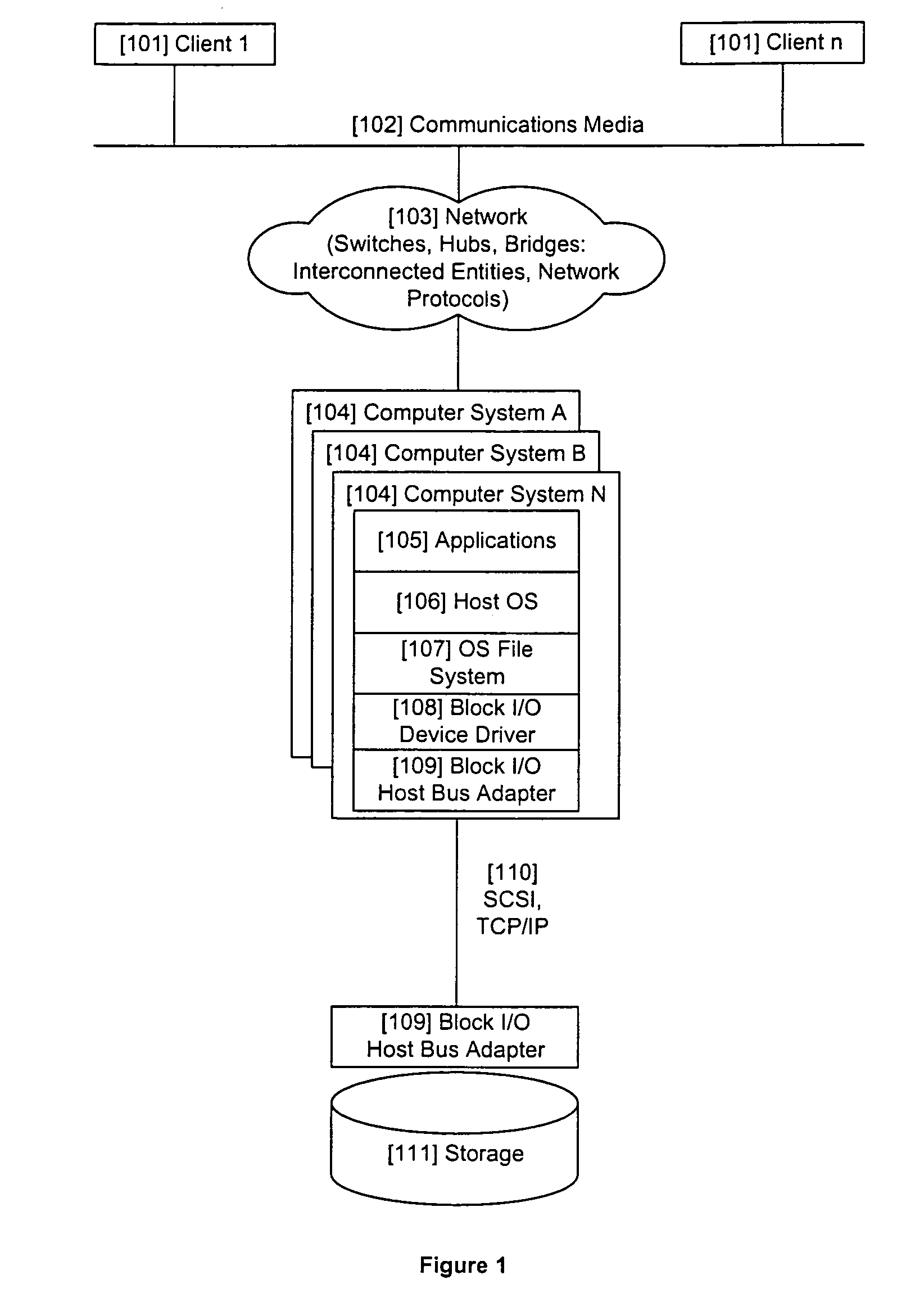

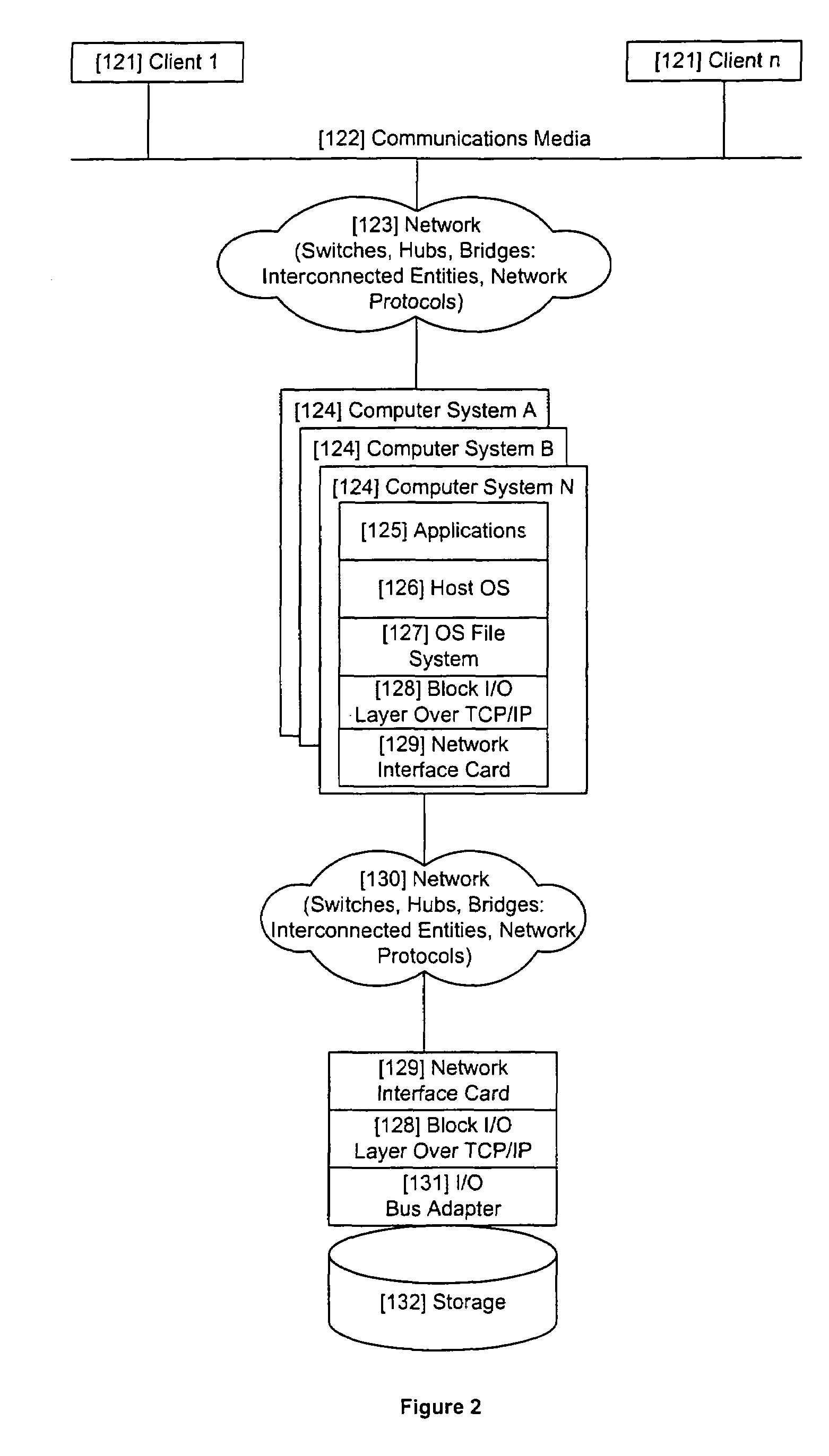

Method and apparatus for improving update performance of non-uniform access time persistent storage media

InactiveUS7328307B2Improve performanceImprove random access performanceInput/output to record carriersMemory adressing/allocation/relocationRAIDAccess time

A high volume storage system is described which continuously remaps where data is stored. The remapping is designed so that writing occurs on an optimum speed basis tuned to the storage system being utilized, e.g., the writes occur in substantially sequential disk storage locations to the extent possible. By remapping data on a substantially continuous basis writes advantageously occur nearer the sequential performance limits of the particular drive or devices being utilized. A methodology is described which improves the external performance of a random access storage system, such as a RAID array. The illustrative embodiments introduce a continuous, optimized dynamic reorganization of the storage media that converts concurrent updates from one or more logical volumes to one or more sequential streams, as appropriate to the number of physical devices and channels over which the updates can be dispersed and thereby minimize the number of seek operations necessary on each physical device.

Owner:UNIFIED PATENTS

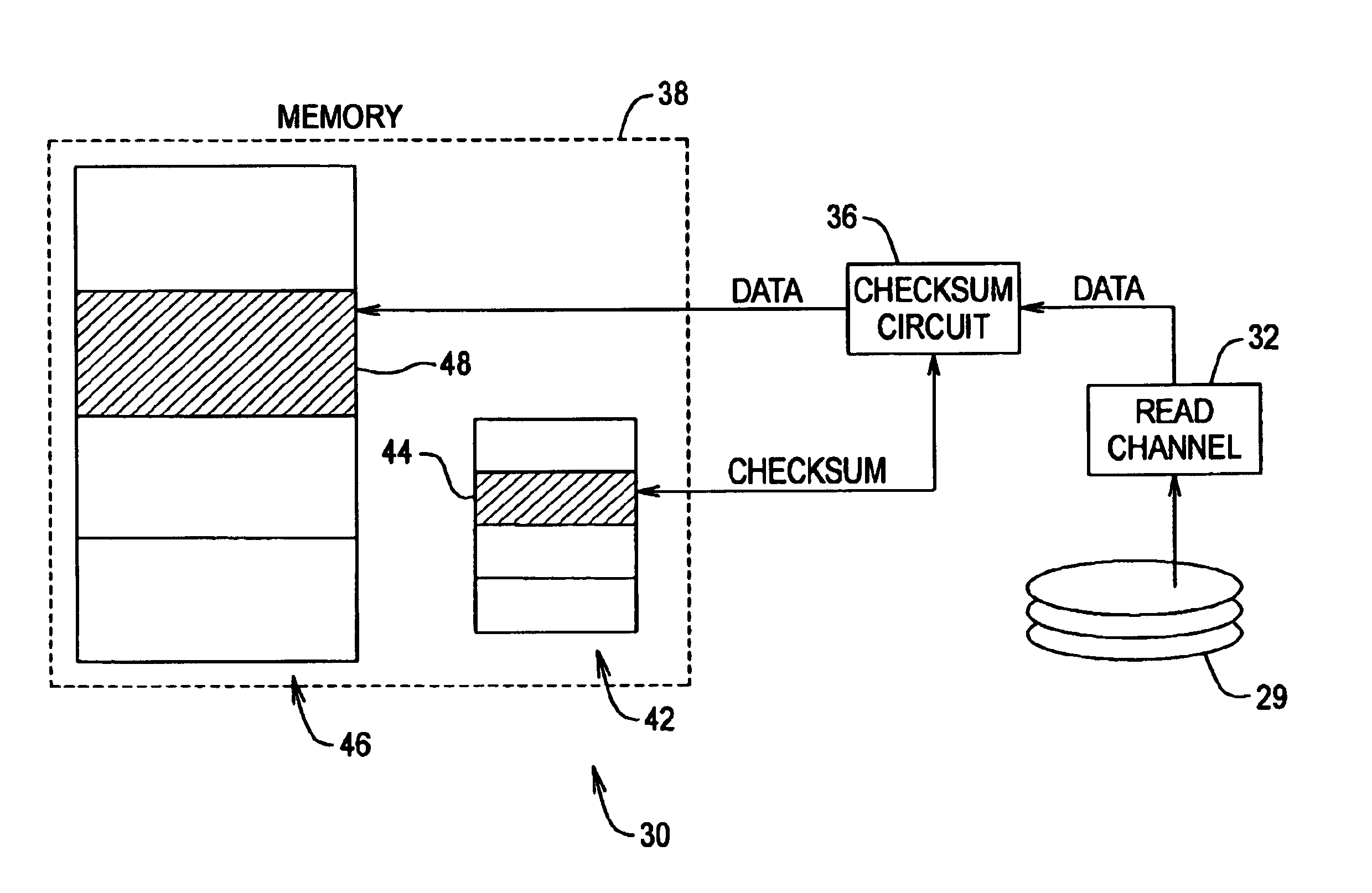

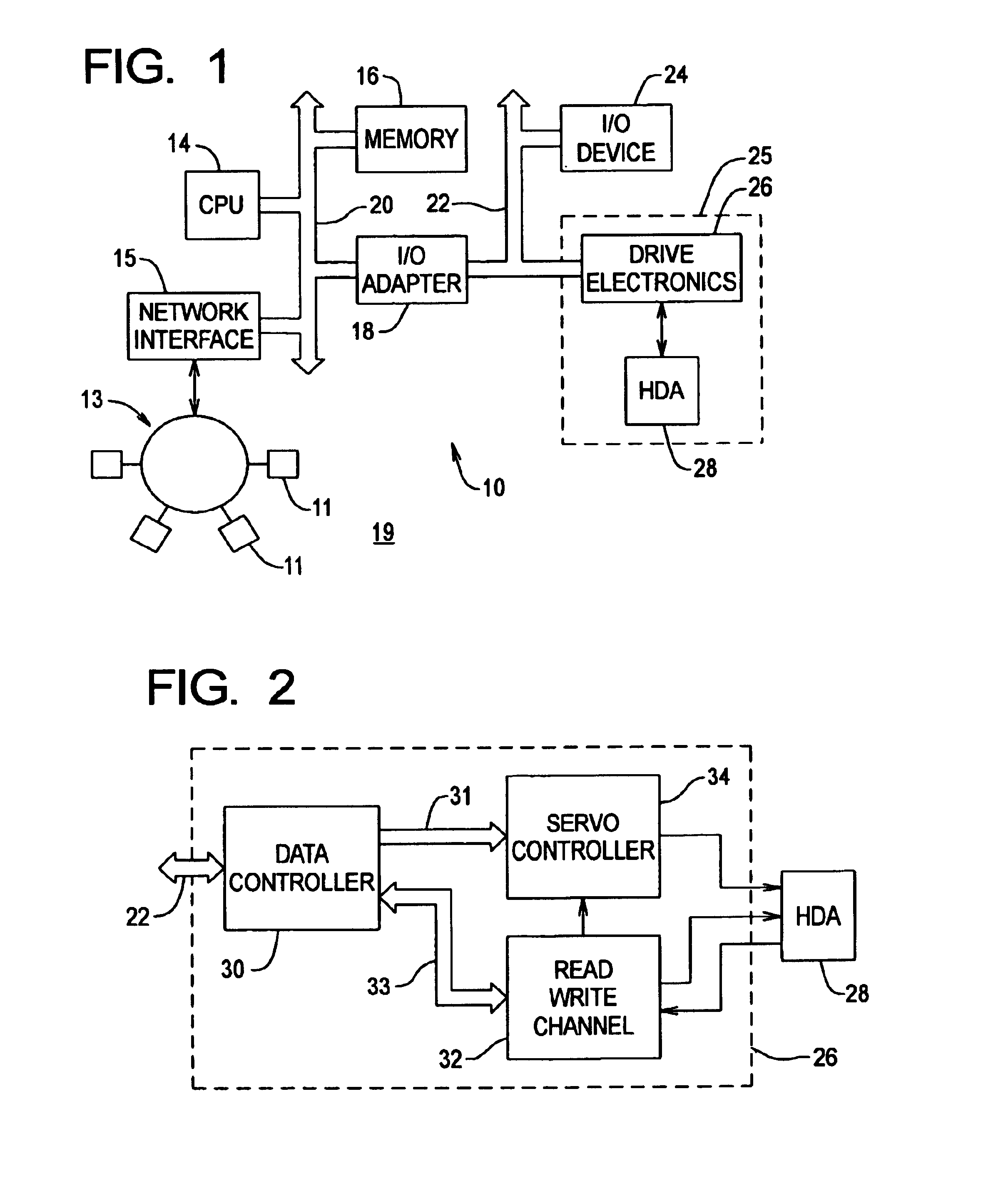

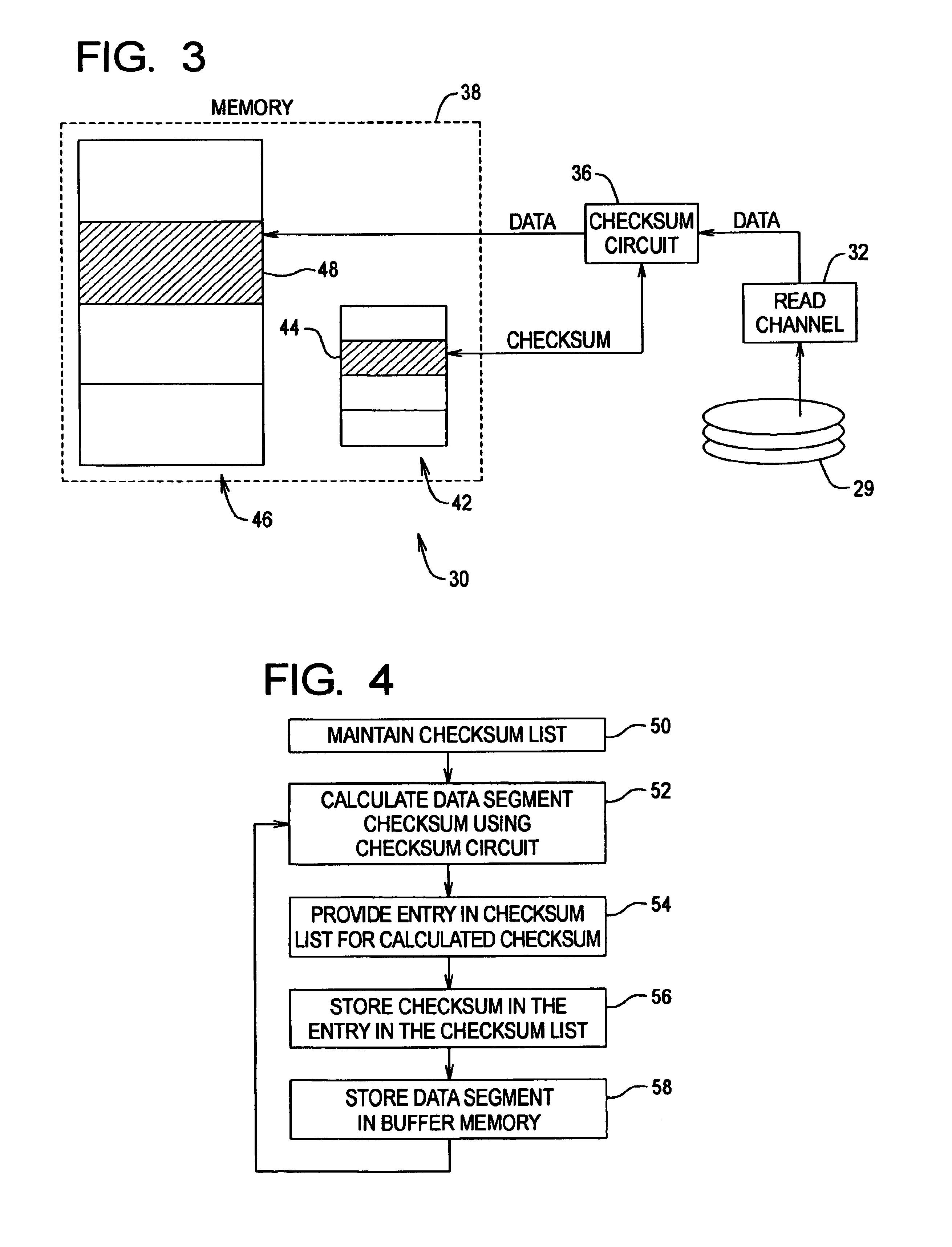

Data checksum method and apparatus

InactiveUS6964008B1Reduce memory bandwidthReduce data transfer latencyCode conversionCoding detailsChecksumData store

A method and apparatus for generating checksum values for data segments retrieved from a data storage device for transfer into a buffer memory, is provided. A checksum list is maintained to contain checksum values, wherein the checksum list includes a plurality of entries corresponding to the data segments stored in the buffer memory, each entry for storing a checksum value for a corresponding data segment stored in the buffer memory. For each data segment retrieved from the storage device: a checksum value is calculated for that data segment using a checksum circuit; an entry in the checksum list corresponding to that data segment is selected; the checksum value is stored in the selected entry in the checksum list; and that data segment is stored in the buffer memory. Preferably, the checksum circuit calculates the checksum for each data segment as that data segment is transferred into the buffer memory.

Owner:MAXTOR

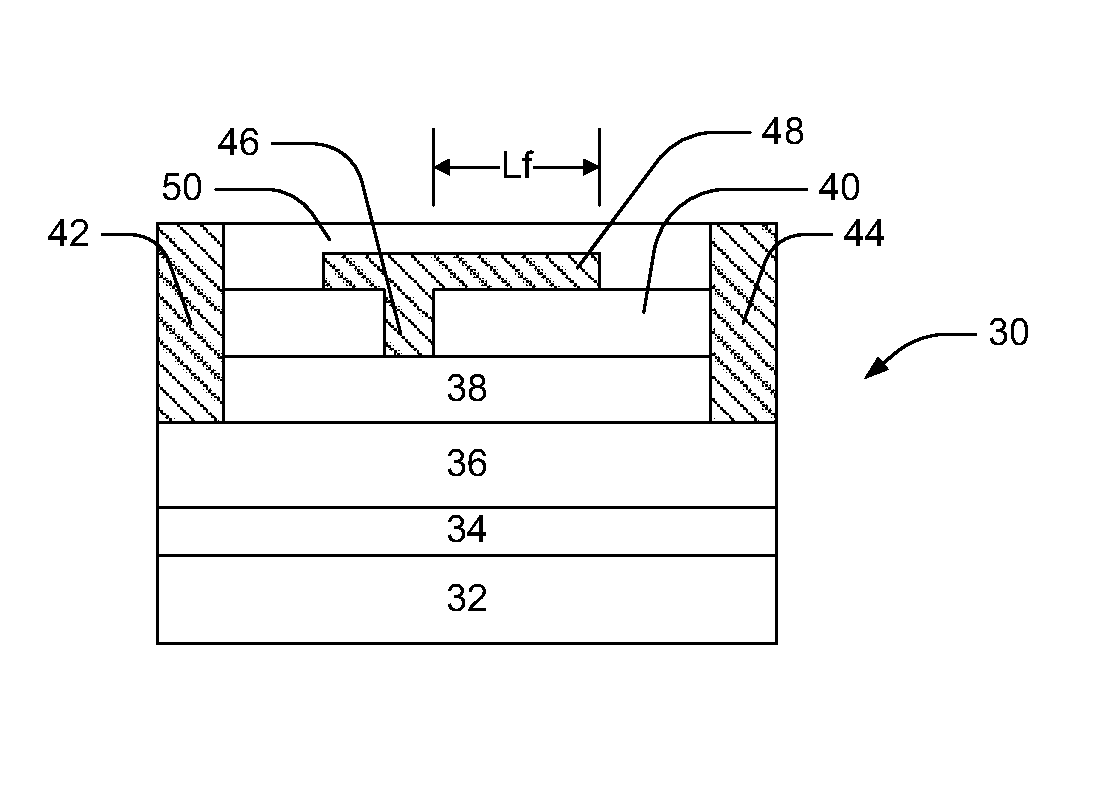

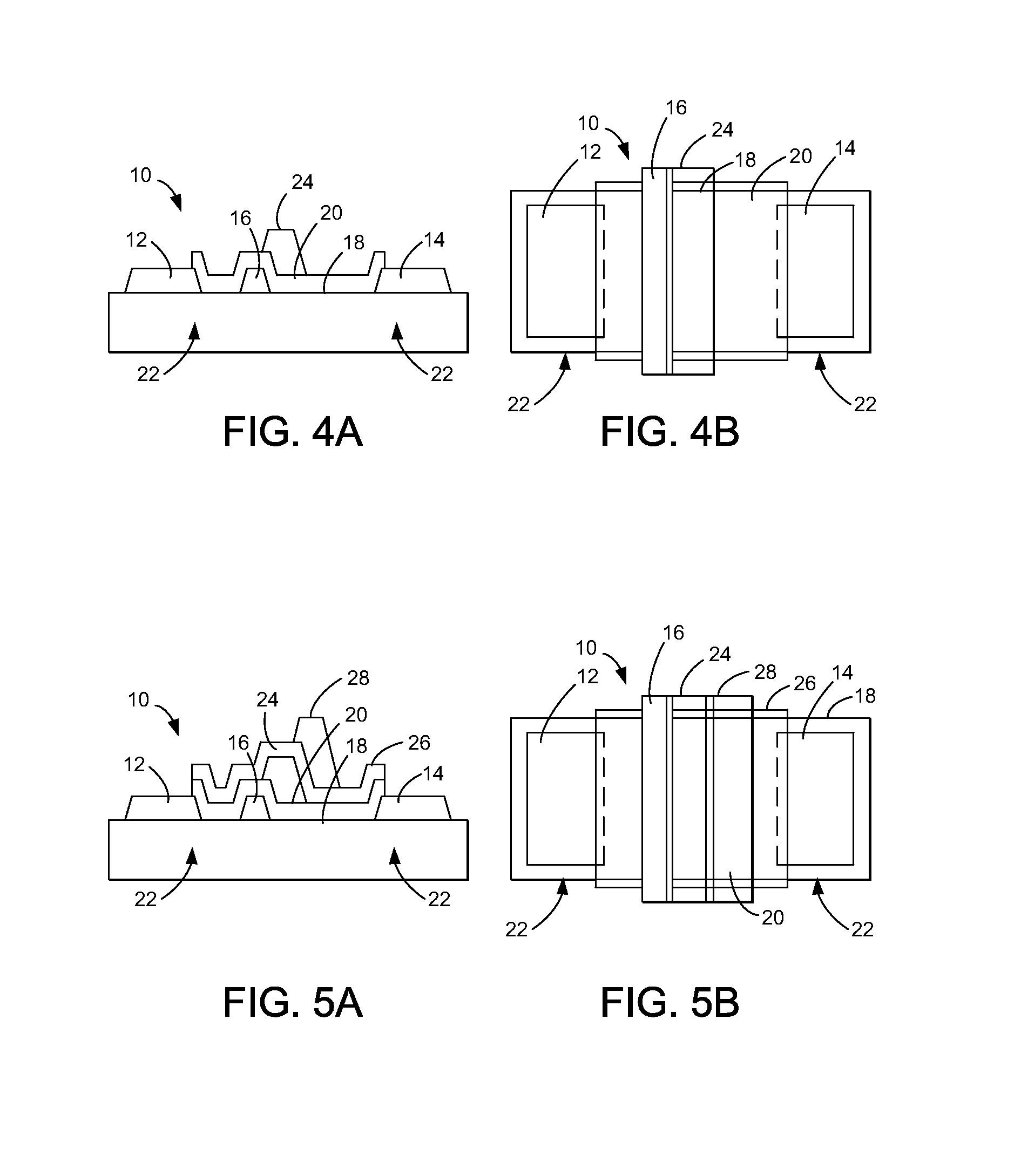

Fabrication of single or multiple gate field plates

ActiveUS7812369B2Strict controlLower gate resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDielectricManufacturing technology

A process for fabricating single or multiple gate field plates using consecutive steps of dielectric material deposition / growth, dielectric material etch and metal evaporation on the surface of a field effect transistors. This fabrication process permits a tight control on the field plate operation since dielectric material deposition / growth is typically a well controllable process. Moreover, the dielectric material deposited on the device surface does not need to be removed from the device intrinsic regions: this essentially enables the realization of field-plated devices without the need of low-damage dielectric material dry / wet etches. Using multiple gate field plates also reduces gate resistance by multiple connections, thus improving performances of large periphery and / or sub-micron gate devices.

Owner:RGT UNIV OF CALIFORNIA +1

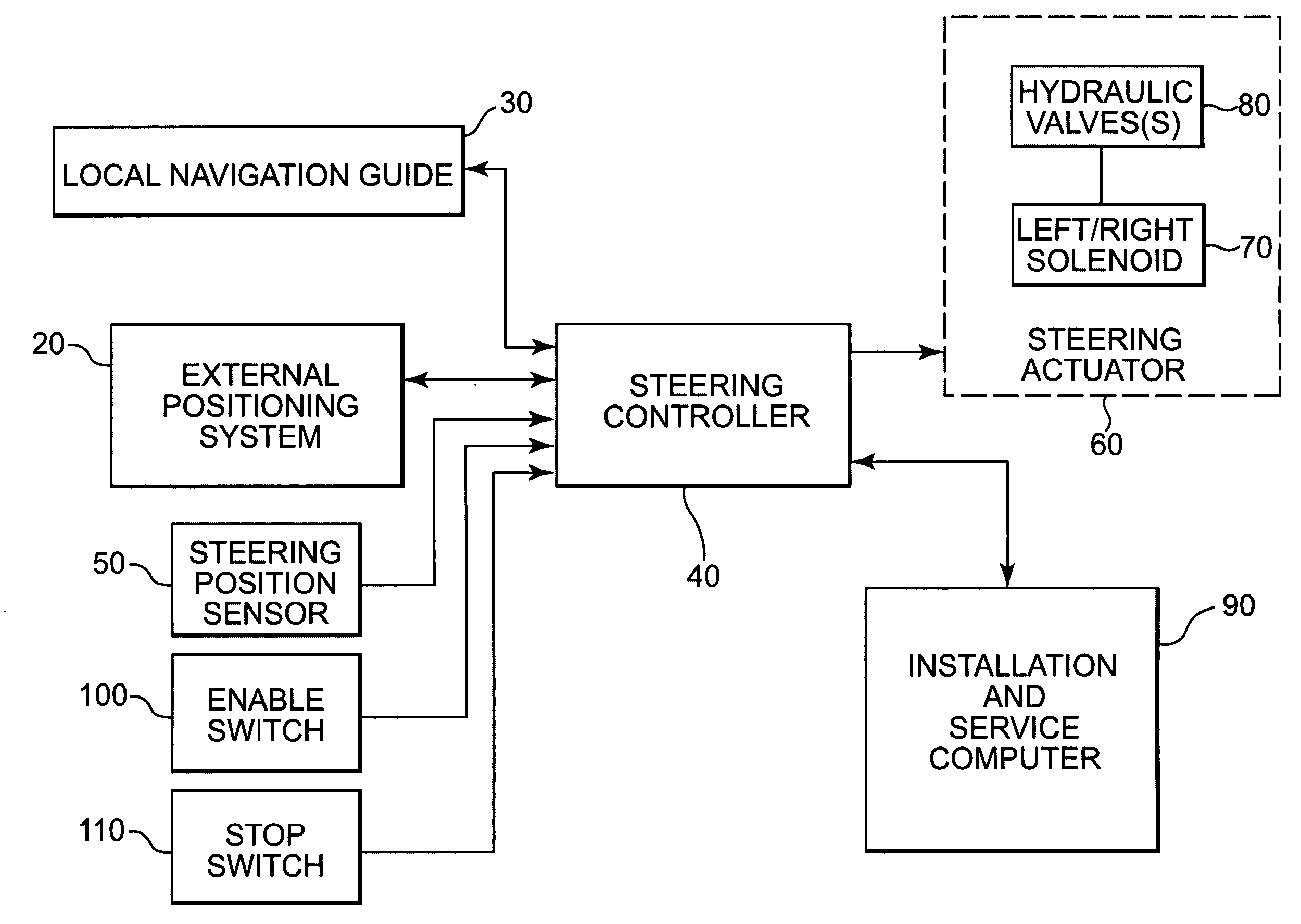

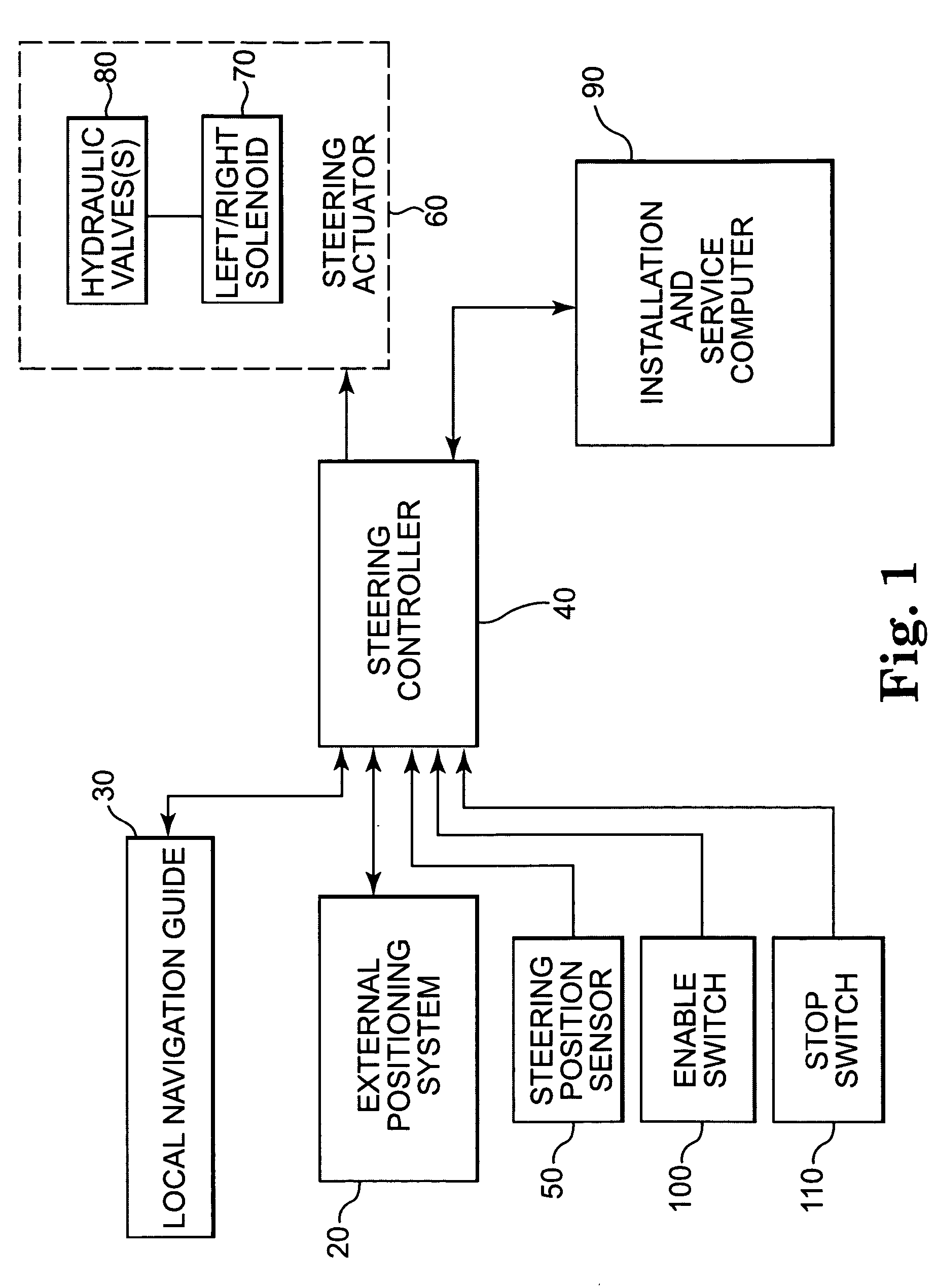

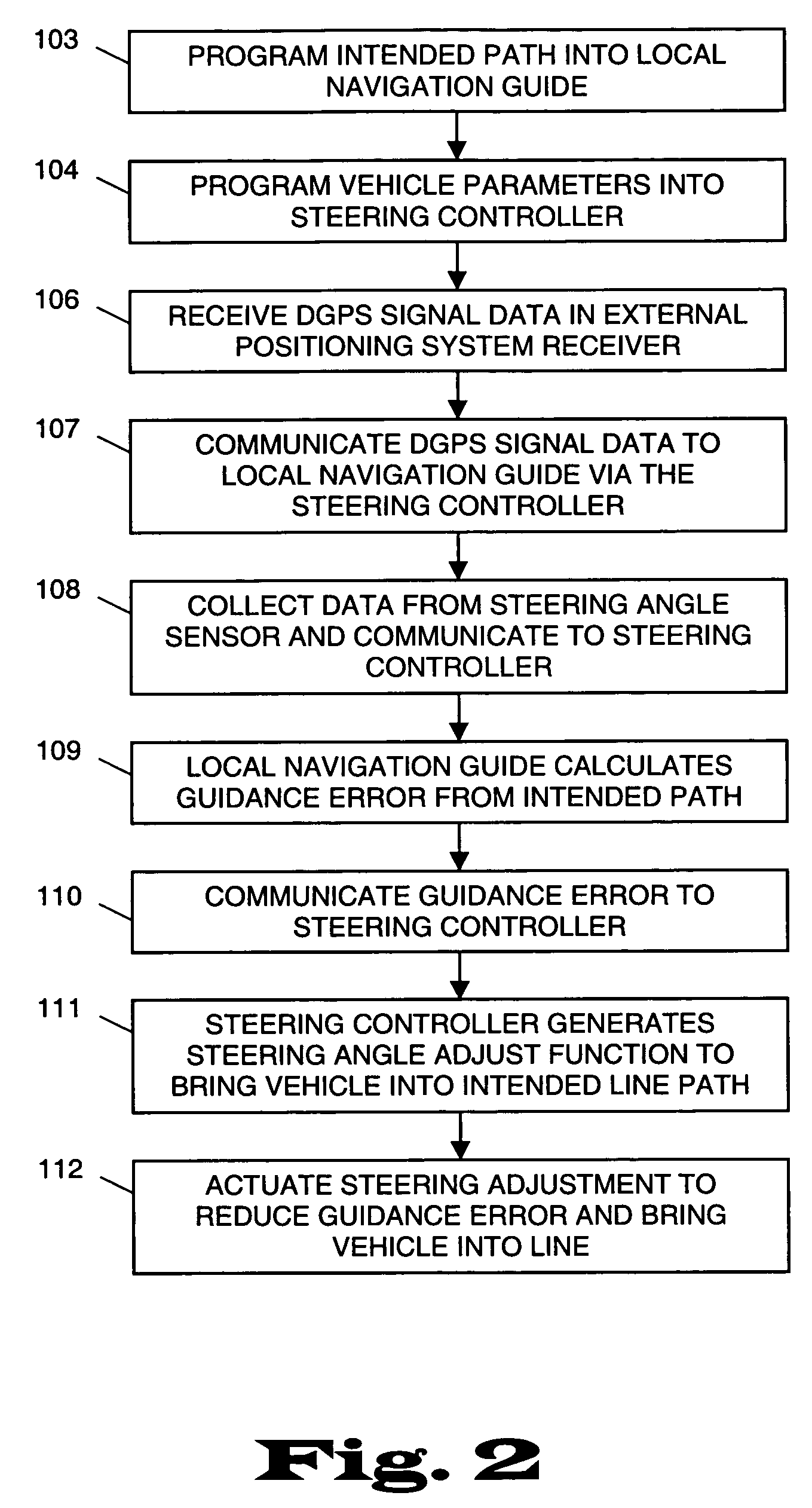

Architecturally partitioned automatic steering system and method

InactiveUS20060167600A1Delay variationMaximum performanceDigital data processing detailsAutomatic steering controlAutomatic steeringSteering angle

A system and method for automatically steering a vehicle along an intended path is provided. The system is architecturally partitioned. The partitioned design allows each of the system elements to be designed and maintained independently while allowing variation and flexibility in system configuration. An embodiment of the system elements may comprise a local navigation guidance unit, an external positioning system, a steering controller, and an installation and service computer. Additional elements of an embodiment of the system may comprise a steering position sensor, and at least one steering actuator. The system allows the operator to enter an intended target path and certain vehicle parameters. The local navigation guidance unit receives positional data from an external positioning system, preferably DGPS, indicative of a navigational path traversed by the vehicle. The guidance unit compares the positional data with the intended target path to obtain guidance error and transmits the guidance error to the steering controller. The system allows for determination of the current steering angle and generation of a steering angle adjustment based upon the intended target, the navigational path traversed by the vehicle, the vehicle parameters, the steering angle and the guidance error. The steering angle adjustment is used to actuate a steering mechanism to smoothly guide the vehicle along the intended target path.

Owner:RAVEN INDUSTRIES INC

High-performance location management platform

InactiveUS6868410B2Quick translationEliminate mass-storage accessesData processing applicationsDigital computer detailsMass storageLongitude

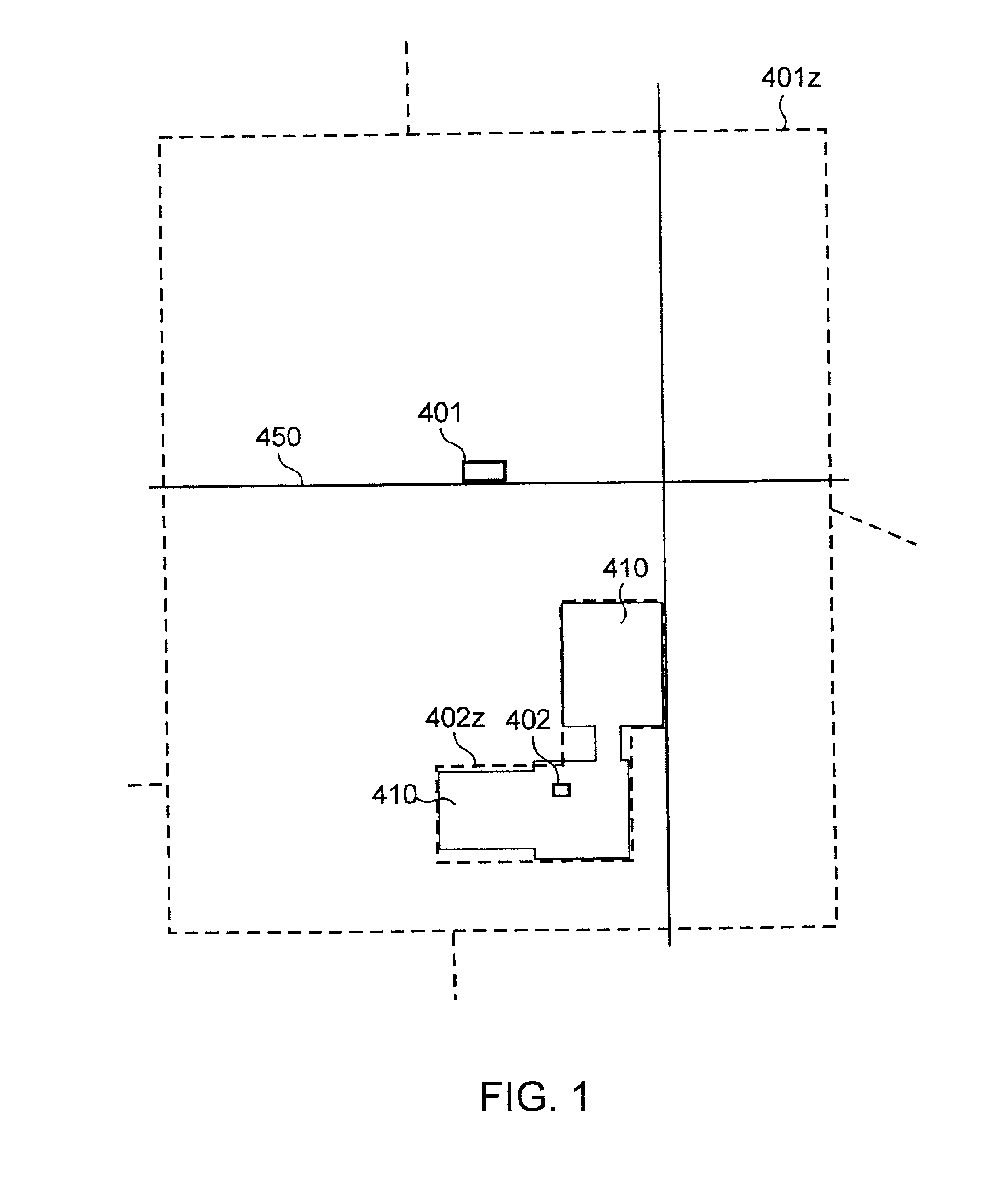

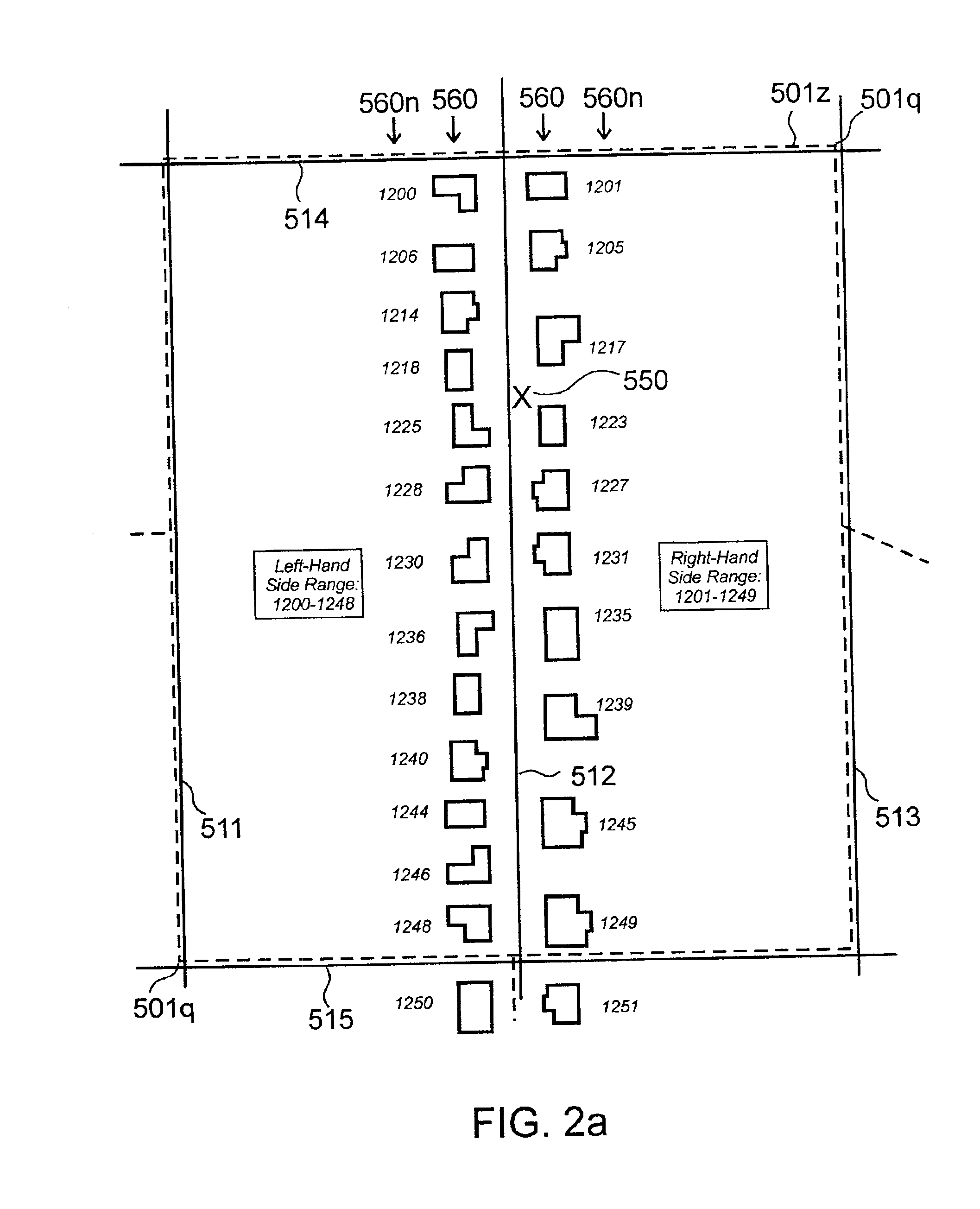

An apparatus and method for rapid translation of geographic latitude and longitude into any of a number of application-specific location designations or location classifications, including street address, nearest intersection, PSAP (Public Safety Answering Point) zone, telephone rate zone, franchise zone, or other geographic, administrative, governmental or commercial division of territory. The speed of translation meets call-setup requirements for call-processing applications such as PSAP determination, and meets caller response expectations for caller queries such as the location of the nearest commercial establishment of a given type. To complete its translation process in a timely manner, a memory-stored spatial database is used to eliminate mass-storage accesses during operation, a spatial indexing scheme such as an R-tree over the spatial database is used to locate a caller within a specific rectangular area, and an optimized set of point-in-polygon algorithms is used to narrow the caller's location to a specific zone identified in the database. Additional validation processing is supplied to verify intersections or street addresses returned for a given latitude and longitude. Automatic conversion of latitude-longitude into coordinates in different map projection systems is provided.The memory-stored database is built in a compact and optimized form from a relational spatial database as required. The R-tree spatial indexing of the memory-stored database allows for substantially unlimited scalability of database size without degradation of response time. Maximum performance for database retrievals is assured by isolating the retrieval process from all updating and maintenance processes. Hot update of the in-memory database is provided without degradation of response time.

Owner:PRECISELY SOFTWARE INC +1

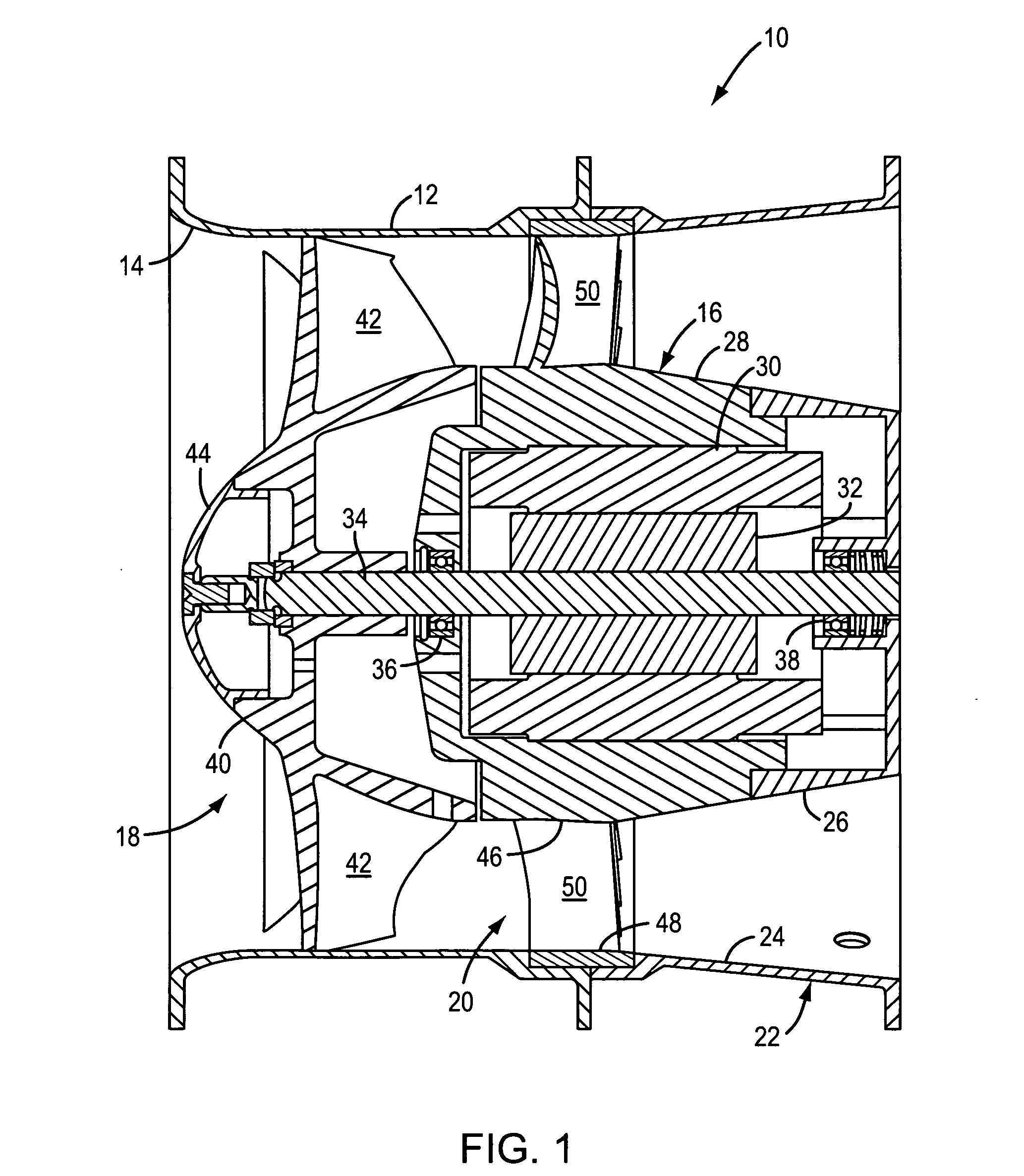

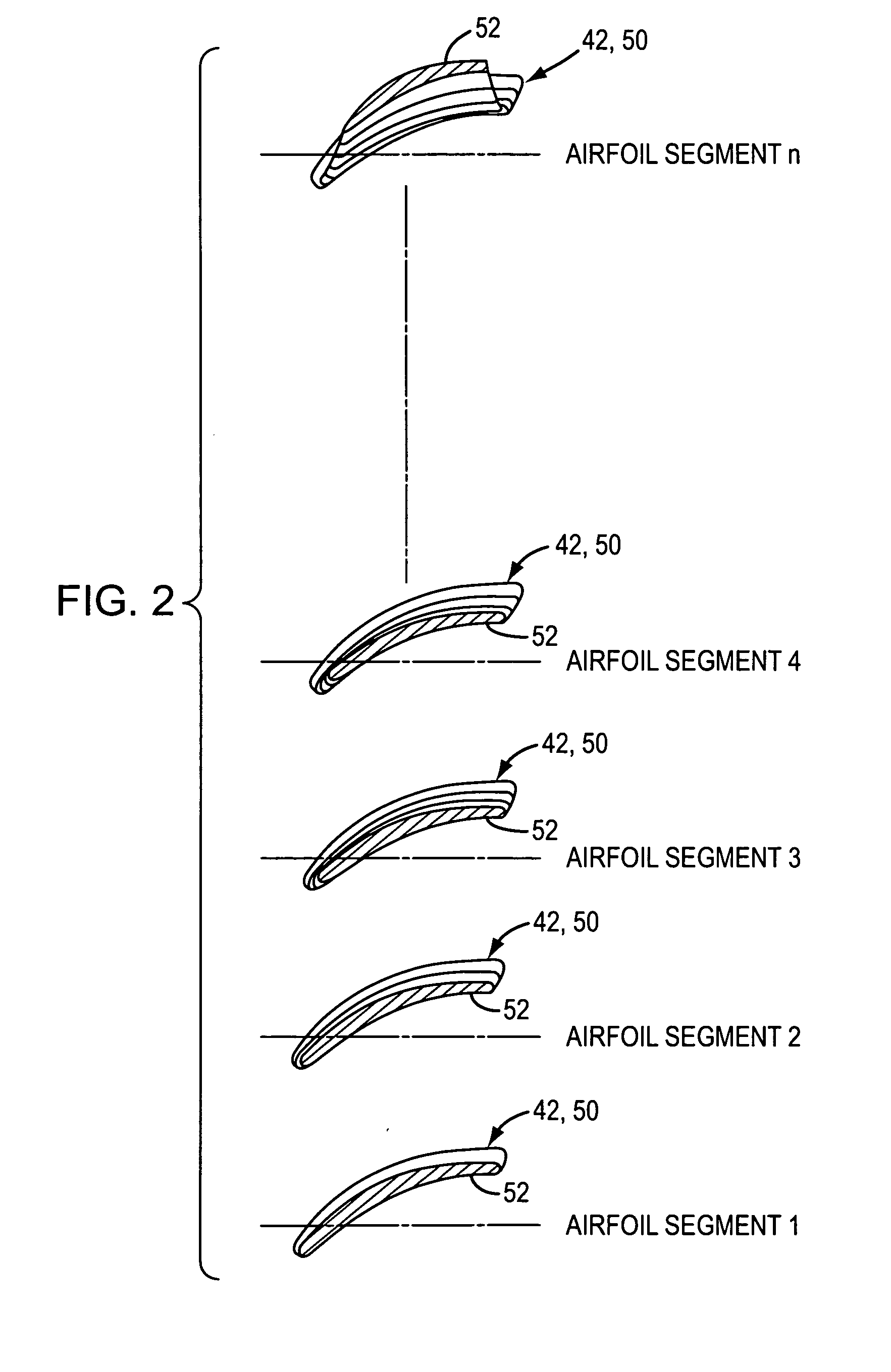

High efficiency cooling fan

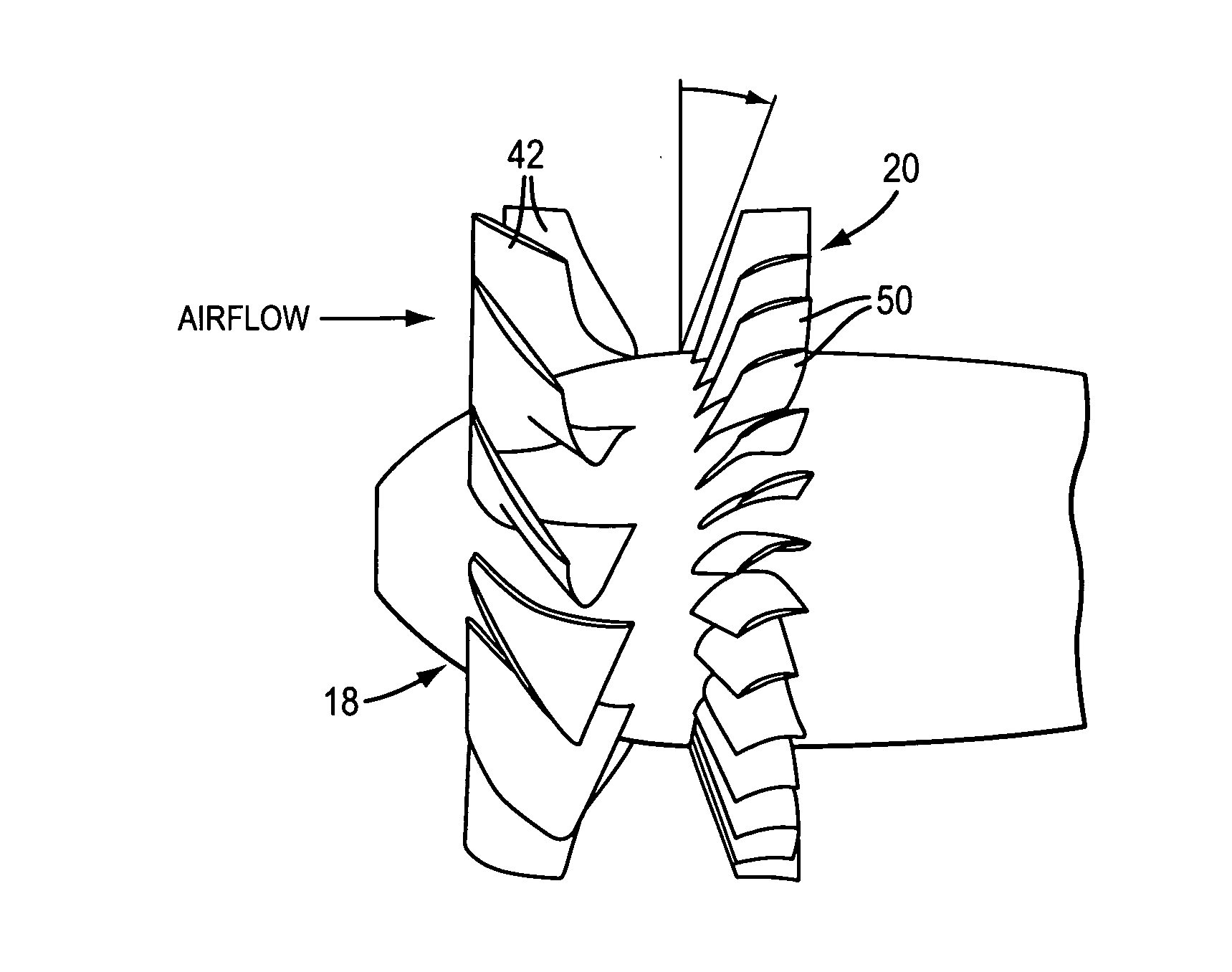

ActiveUS20080226454A1Reduce the amount of noiseMinimize flowPropellersPump componentsImpellerEngineering

A cooling fan includes an impeller which comprises a plurality of radially extending blades, each of which includes a blade hub, a blade tip and a blade midspan approximately midway between the hub and the tip. In addition, each blade includes a camber of between about 60° and 90° at the blade hub, between about 15° and 40° at the blade midspan and between about 15° and 40° at the blade tip.

Owner:BASCOM HUNTER TECH INC

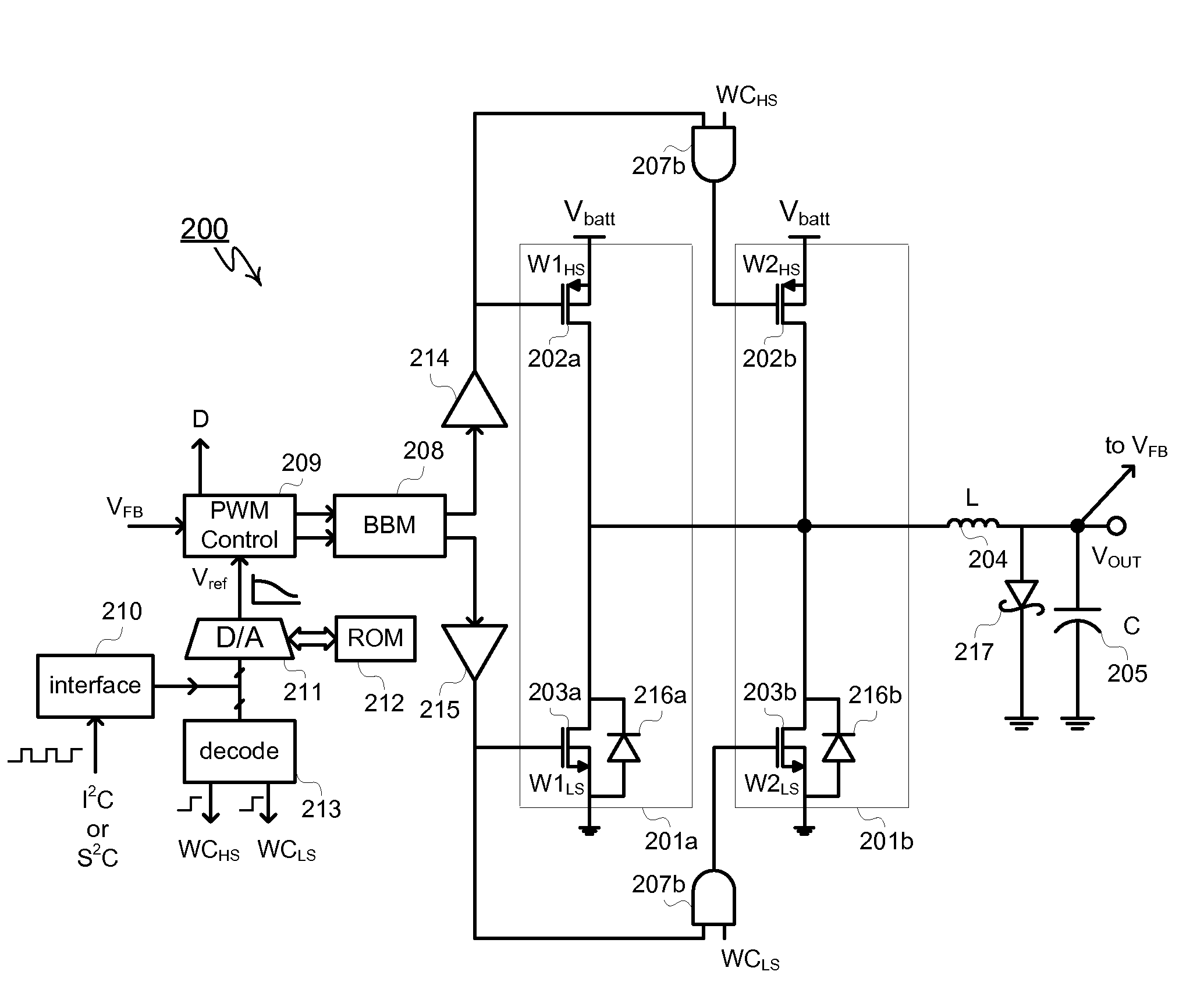

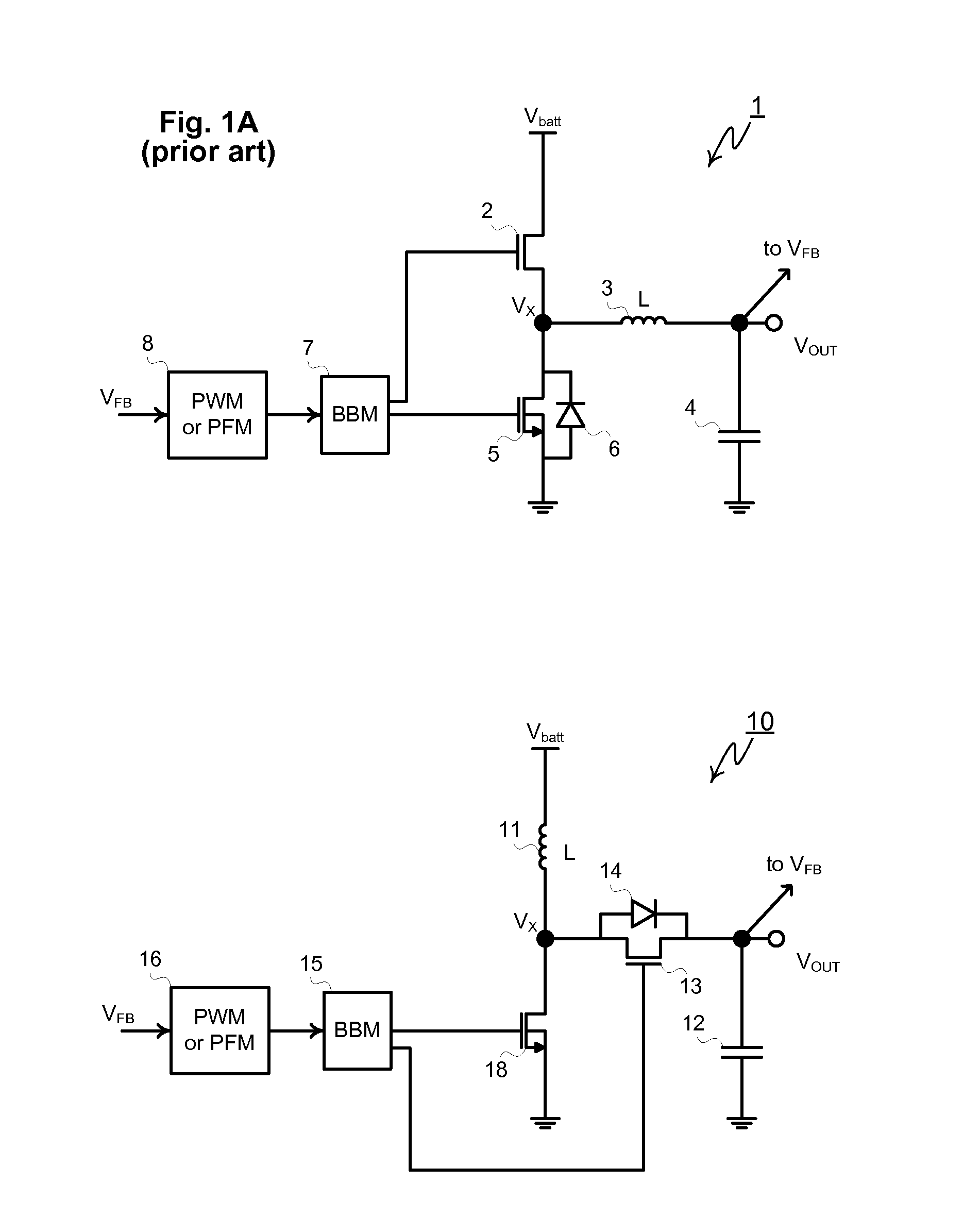

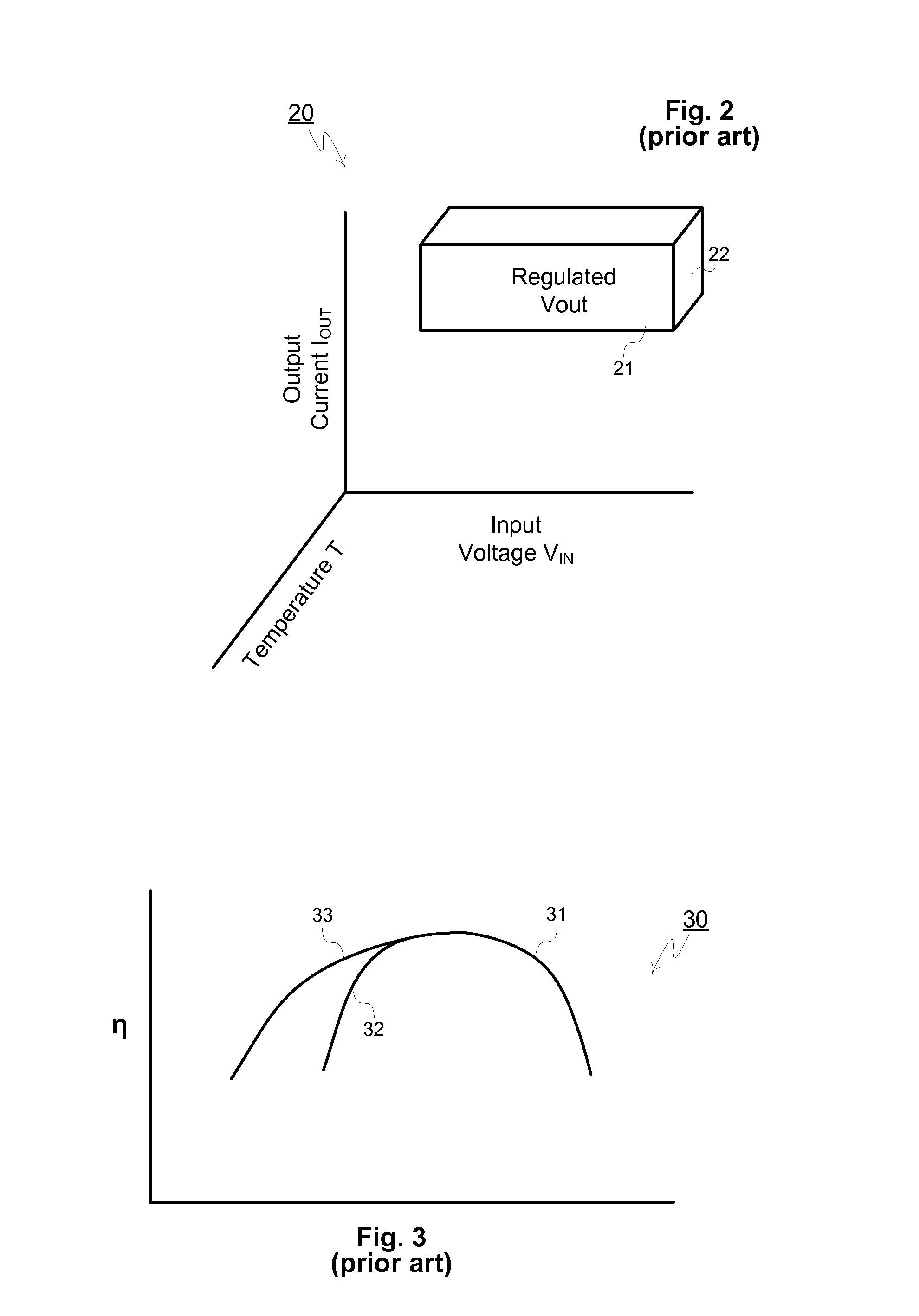

Programmable Step-Down Switching Voltage Regulators with Adaptive Power MOSFETs

InactiveUS20100001704A1Tight regulationPeak efficiencyDc-dc conversionElectric variable regulationControl signalVoltage regulation

A step-down switching voltage regulator includes M high-side switches connected between an input voltage and a node; N synchronous rectifiers connected between the node Vx and a ground voltage and an inductor connected between an input voltage and a node Vx and an inductor connected between the node Vx and an output node. An interface circuit decodes a control signal to identify: 1) a subset (m) of the high-side switches, 2) a subset (n) of the synchronous rectifiers. A control circuit drives the high-side switches and synchronous rectifiers in a repeating sequence that includes an inductor charging phase where the high-side switches in the subset m are activated to connect the node Vx to the input voltage; and an inductor discharging phase where the synchronous rectifiers in the subset n are activated to connect the node Vx to the ground voltage.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

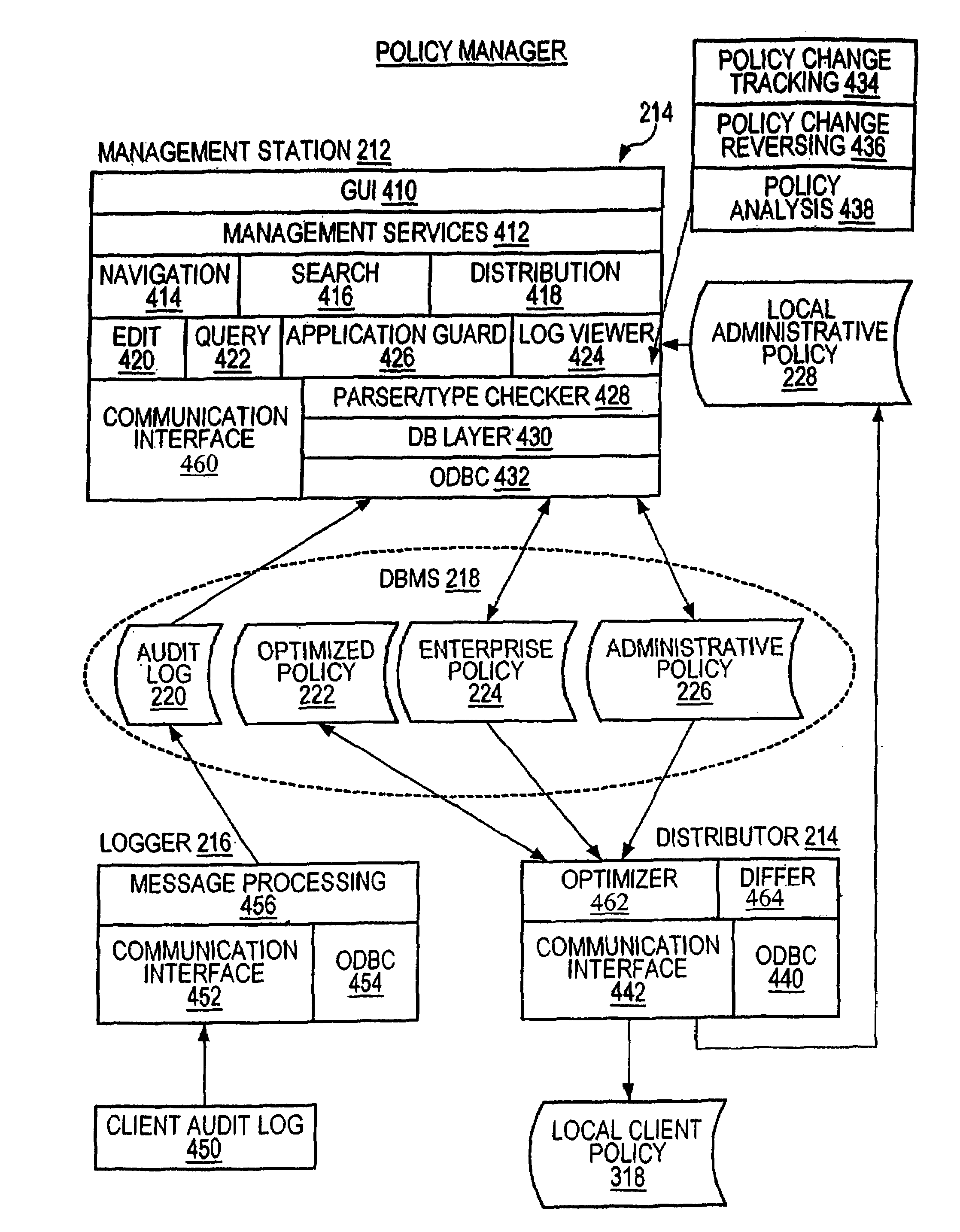

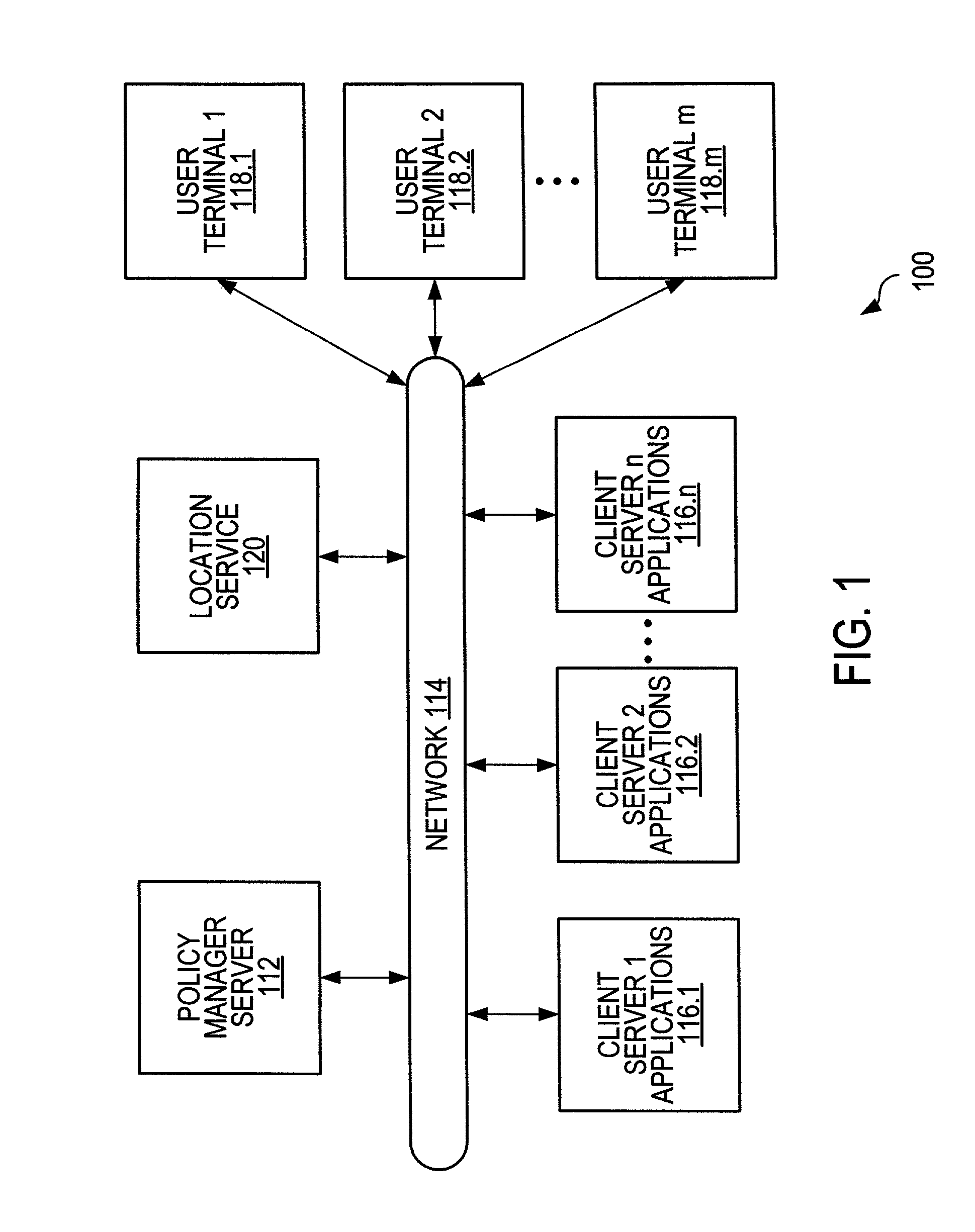

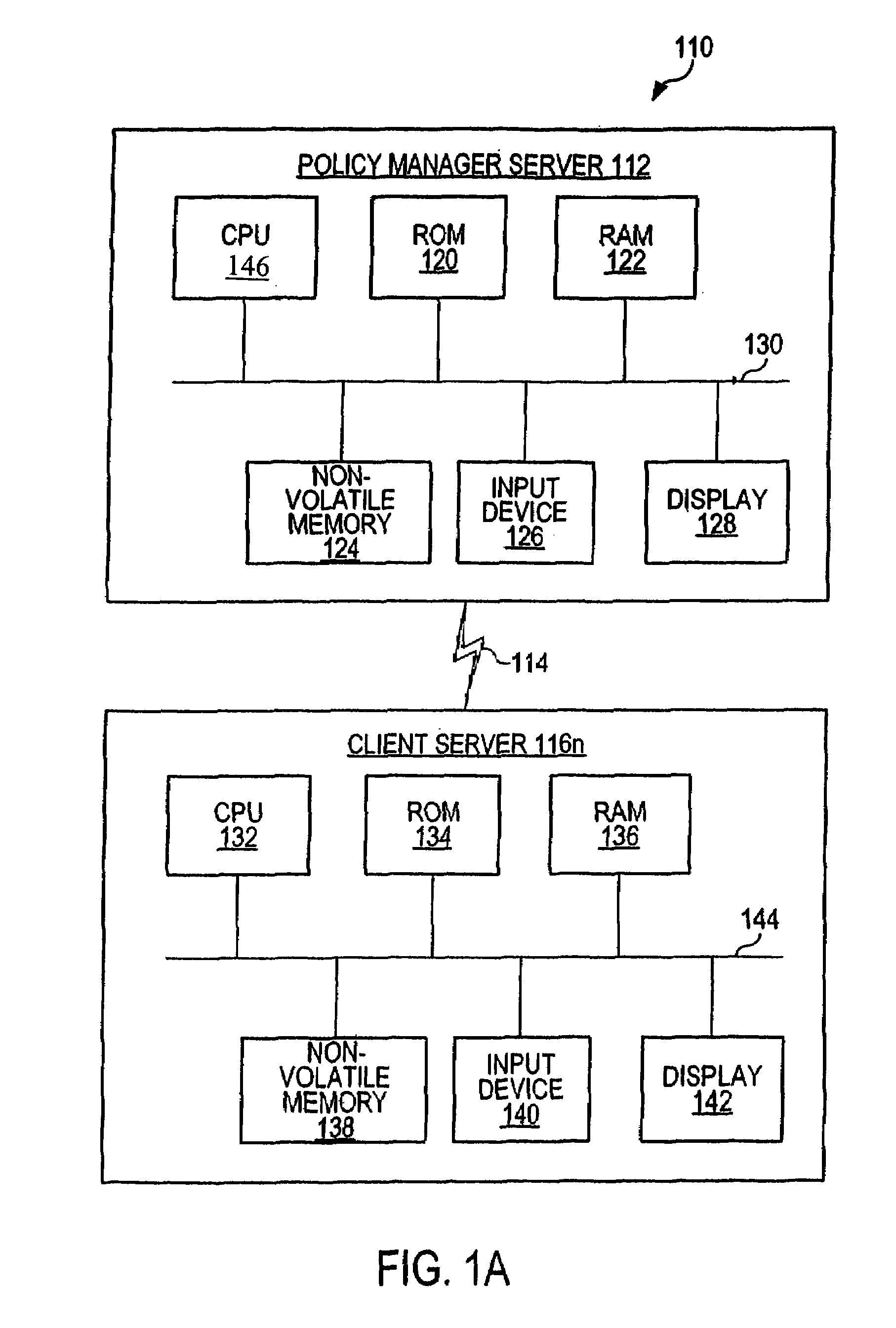

System and method for maintaining security in a distributed computer network

InactiveUS7673323B1Maximum performanceScalability maximumDigital data processing detailsSemiconductor/solid-state device manufacturingDistributed Computing EnvironmentNative client

A system and method for maintaining security in a distributed computing environment comprises a policy manager located on a server for managing and distributing a security policy, and an application guard located on a client for managing access to securable components as specified by the security policy. In the preferred embodiment, a global policy specifies access privileges of the user to securable components. The policy manager may then preferably distribute a local client policy based on the global policy to the client. An application guard located on the client then manages access to the securable components as specified by the local policy.

Owner:ORACLE INT CORP

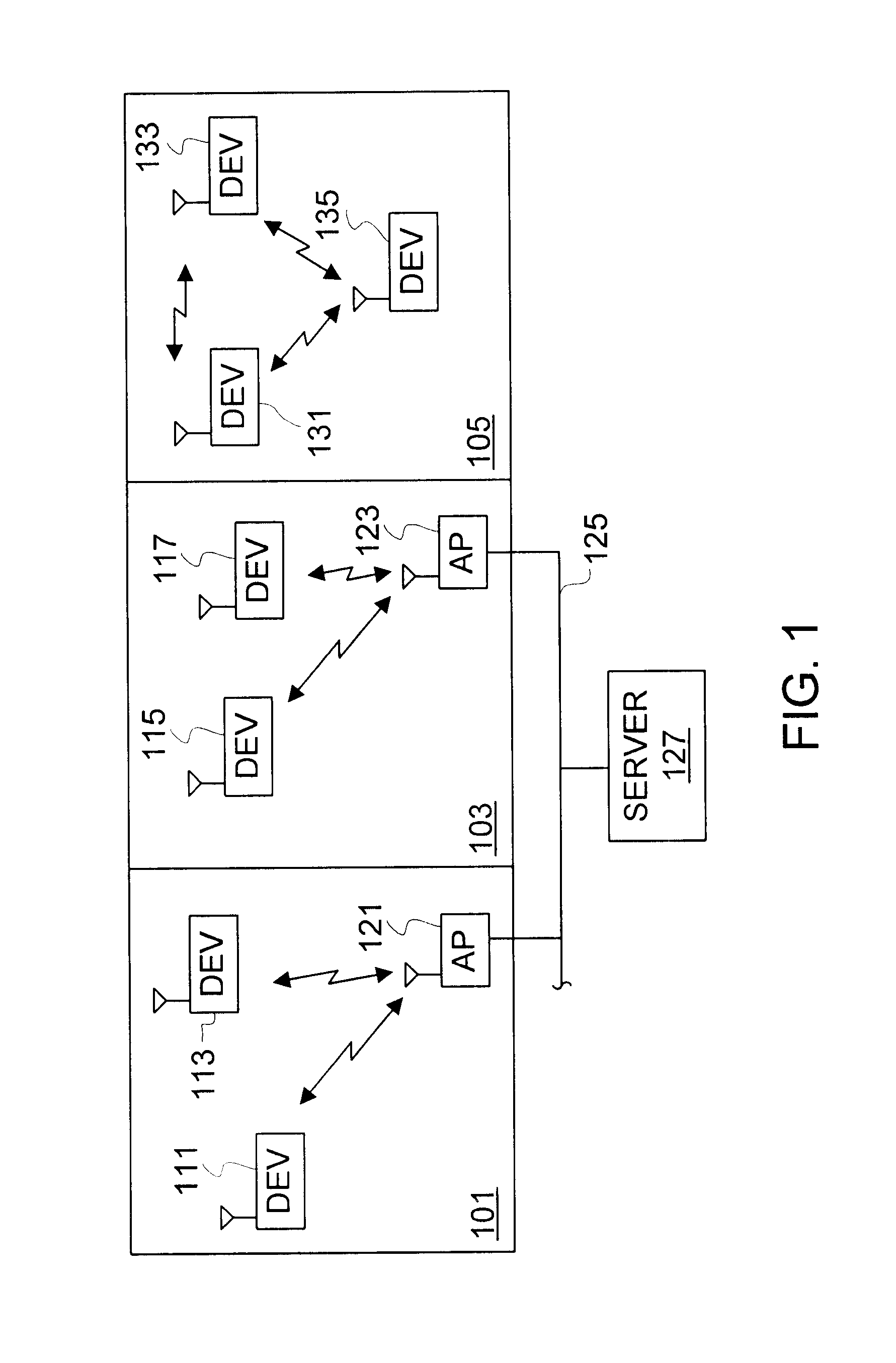

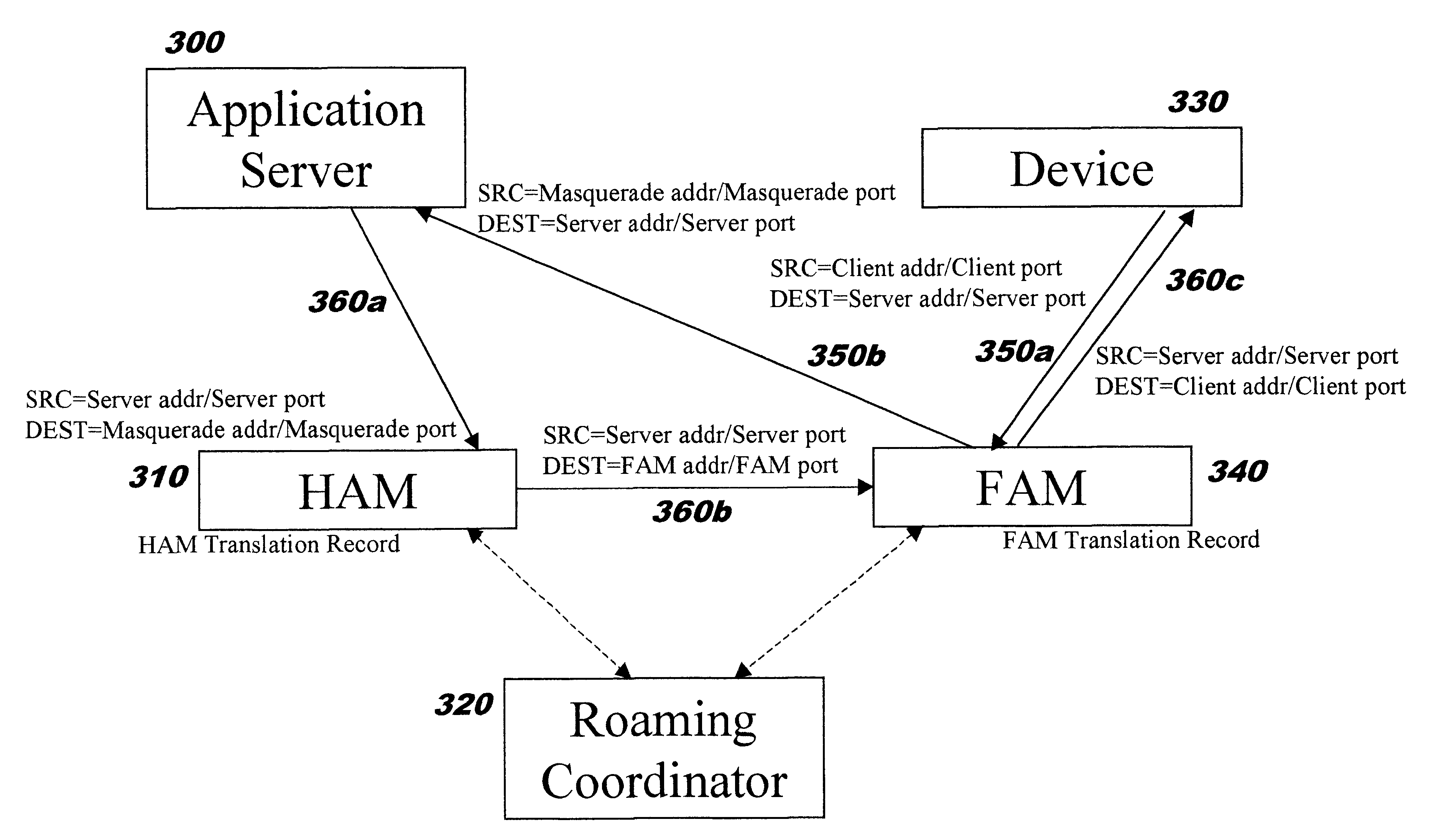

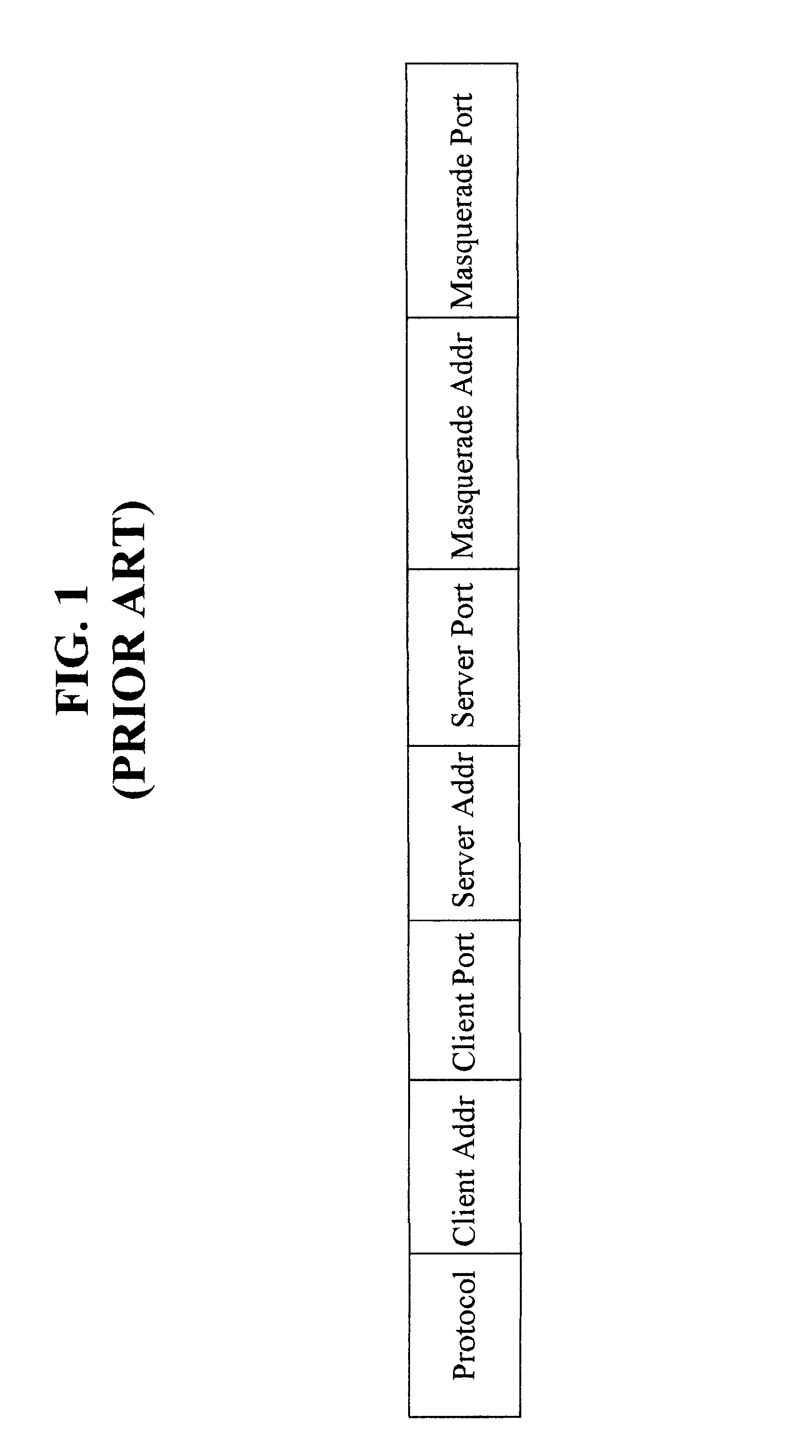

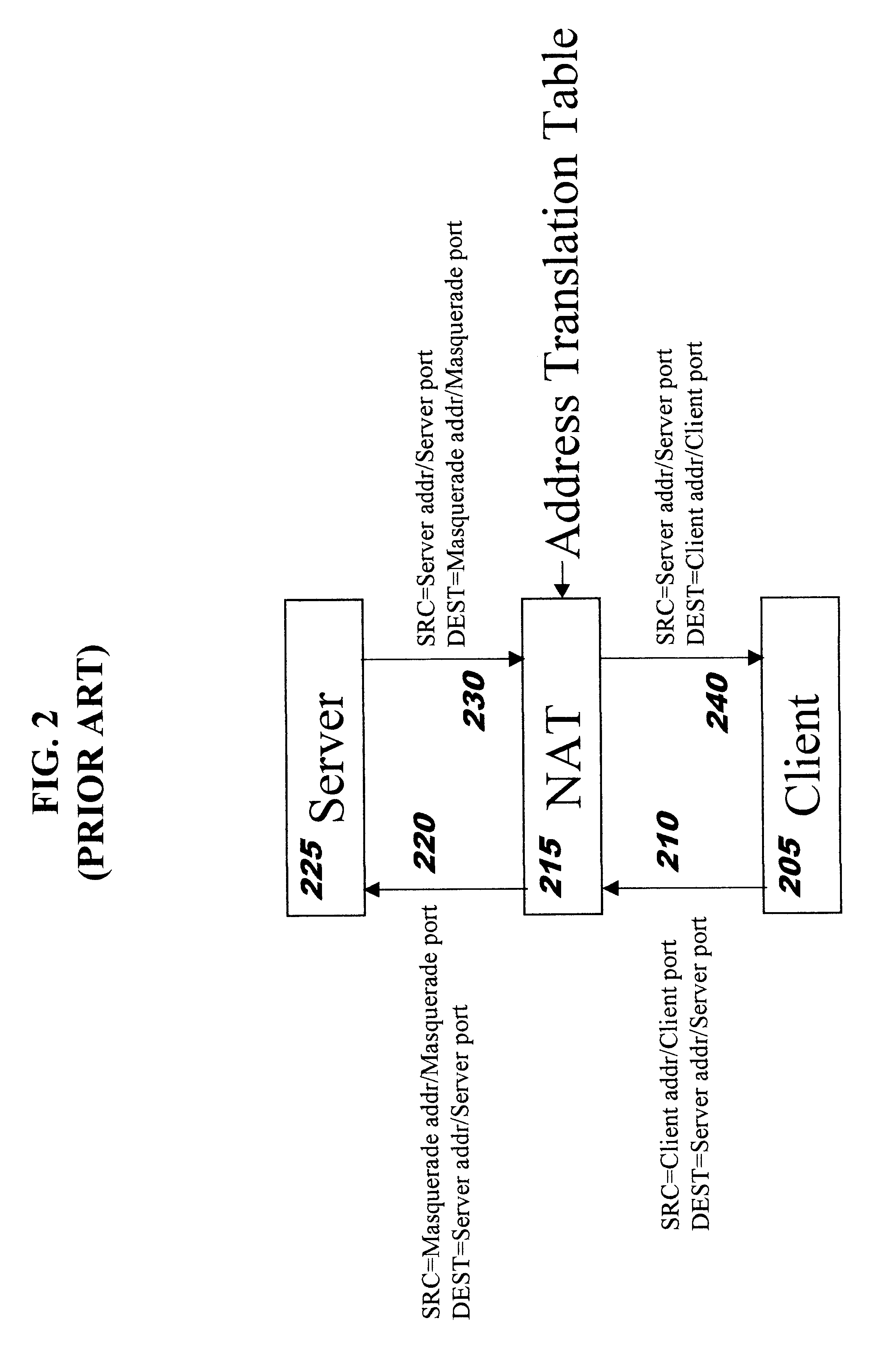

Providing secure network access for short-range wireless computing devices

InactiveUS6851050B2Improve system performanceImprove scalabilityKey distribution for secure communicationUser identity/authority verificationEncrypted functionClient-side

The present invention provides methods, systems, and computer program instructions for providing location-independent packet routing and secure access in a wireless networking environment (such as that encountered within a building), enabling client devices to travel seamlessly within the environment. Each client device uses a constant address. An address translation process that is transparent to the client and server is automatically performed as the device roams through the environment, enabling efficient client migration from one supporting access point to another. The secure access techniques provide user-centric authentication and allow policy-driven packet filtering, while taking advantage of encryption capabilities that are built in to the hardware at each endpoint.

Owner:REEFEDGE

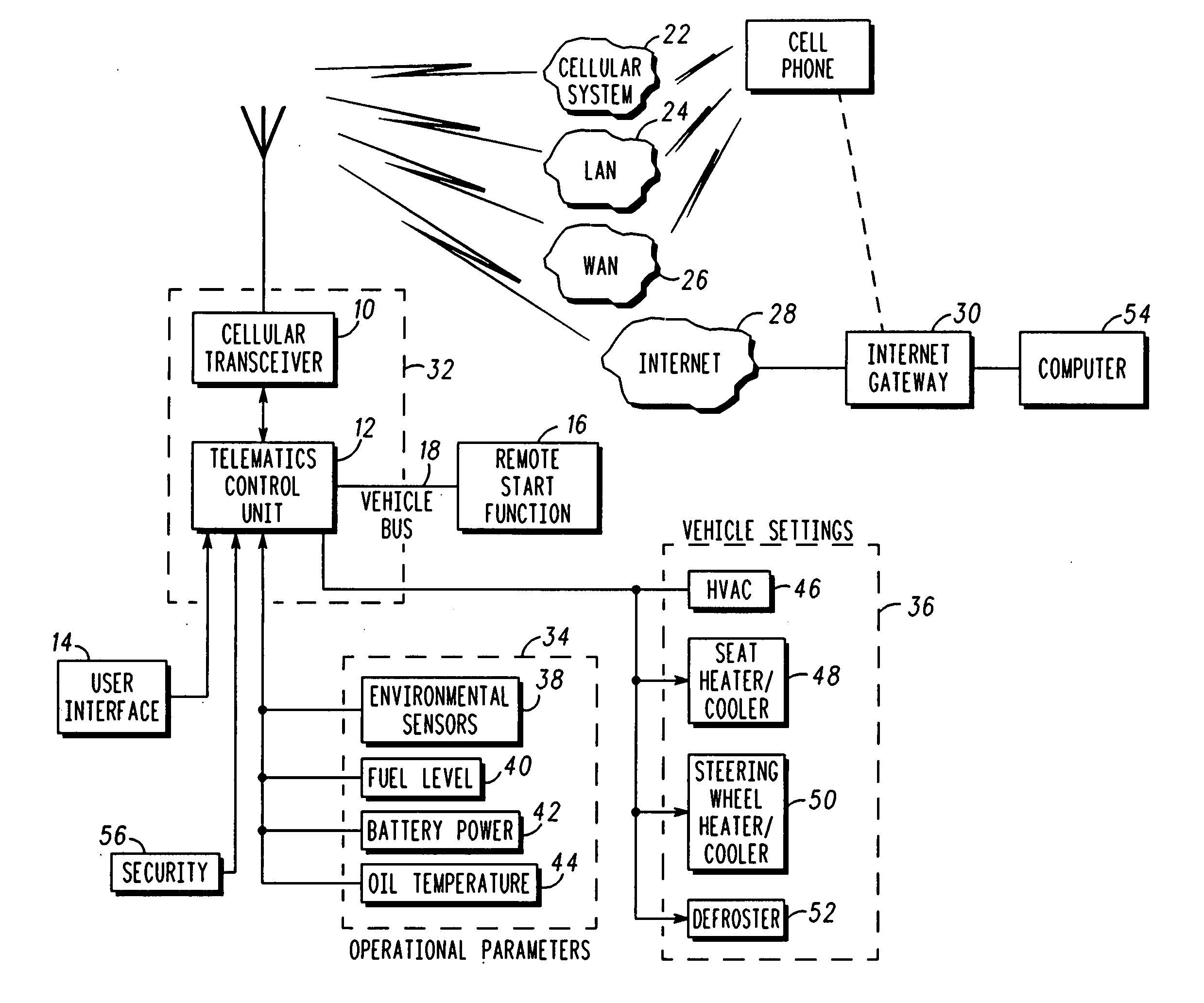

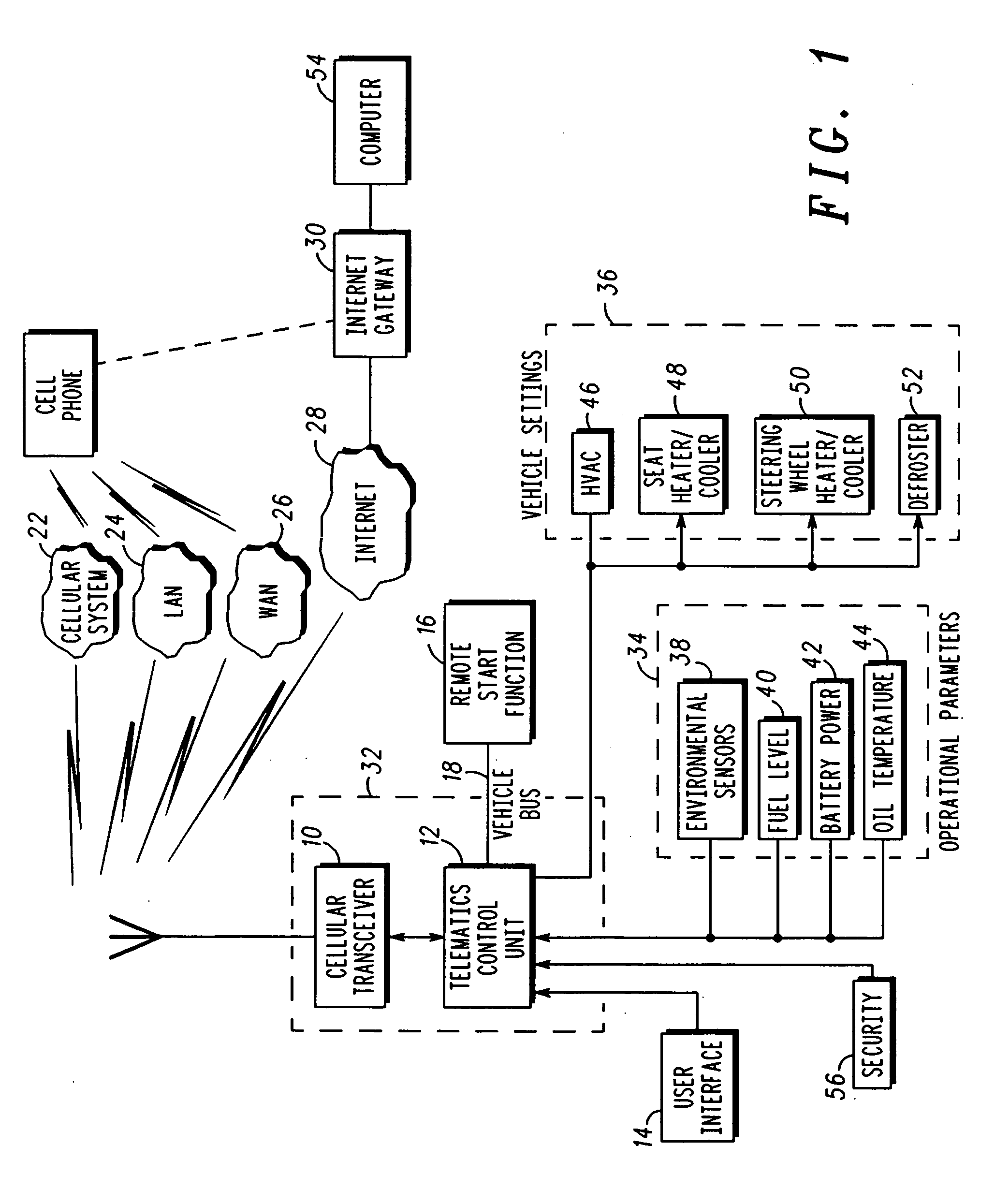

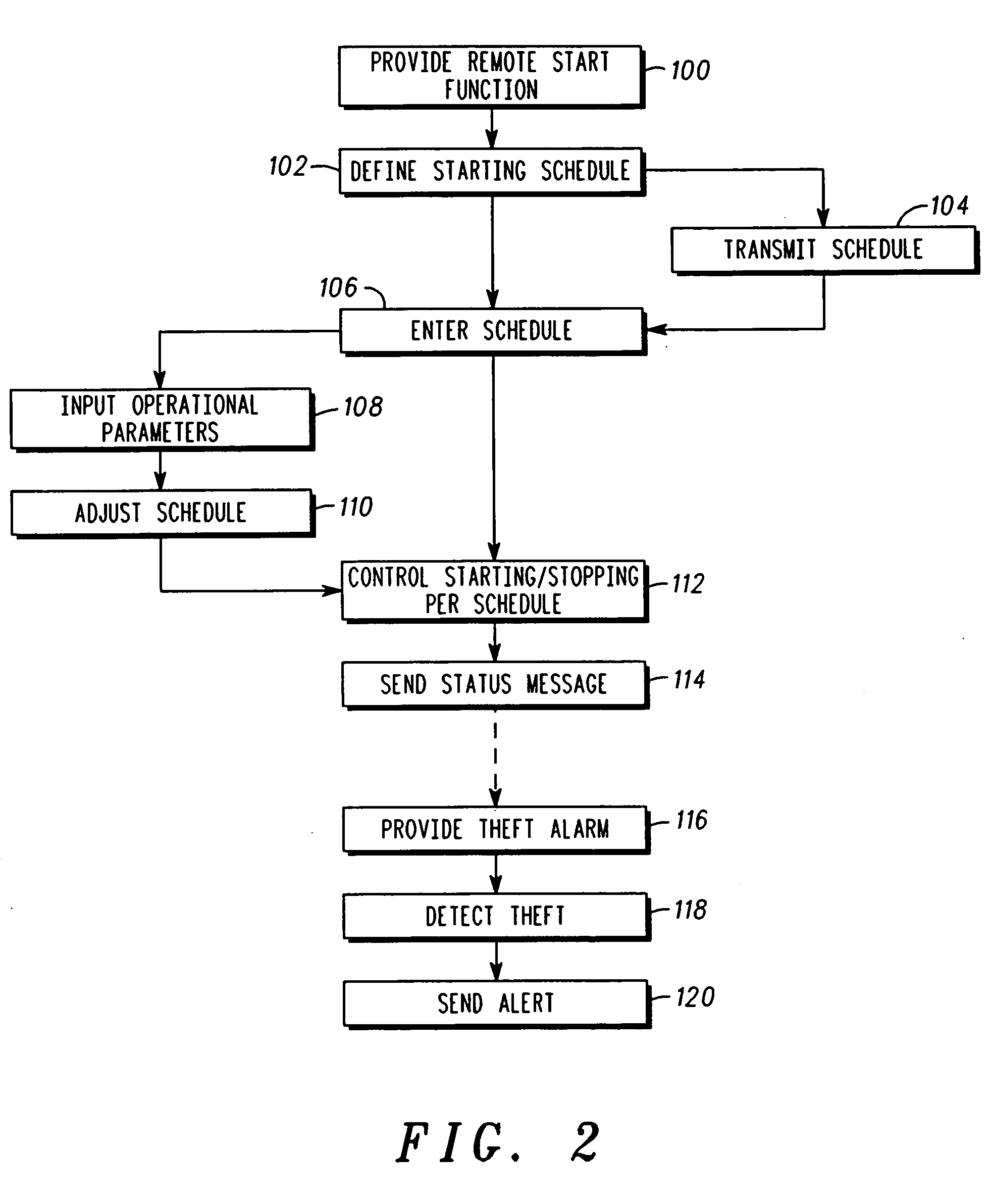

Scheduling remote starting of vehicle

ActiveUS20060080007A1Comfortable environmentMaximum performanceDigital data processing detailsAnti-theft devicesStart timeEngineering

A method is described for scheduling the remote starting of an engine of a vehicle. The vehicle includes a remote starting device and a controller coupled to a communication device and to the remote starting device. The remote starting device is responsive to commands from the controller. The method includes a first step of defining a schedule of starting times. A next step includes entering the schedule in the controller. A next step includes controlling an operation of the remote starting device in accordance with the schedule.

Owner:CONTINENTAL AUTOMOTIVE SYST INC

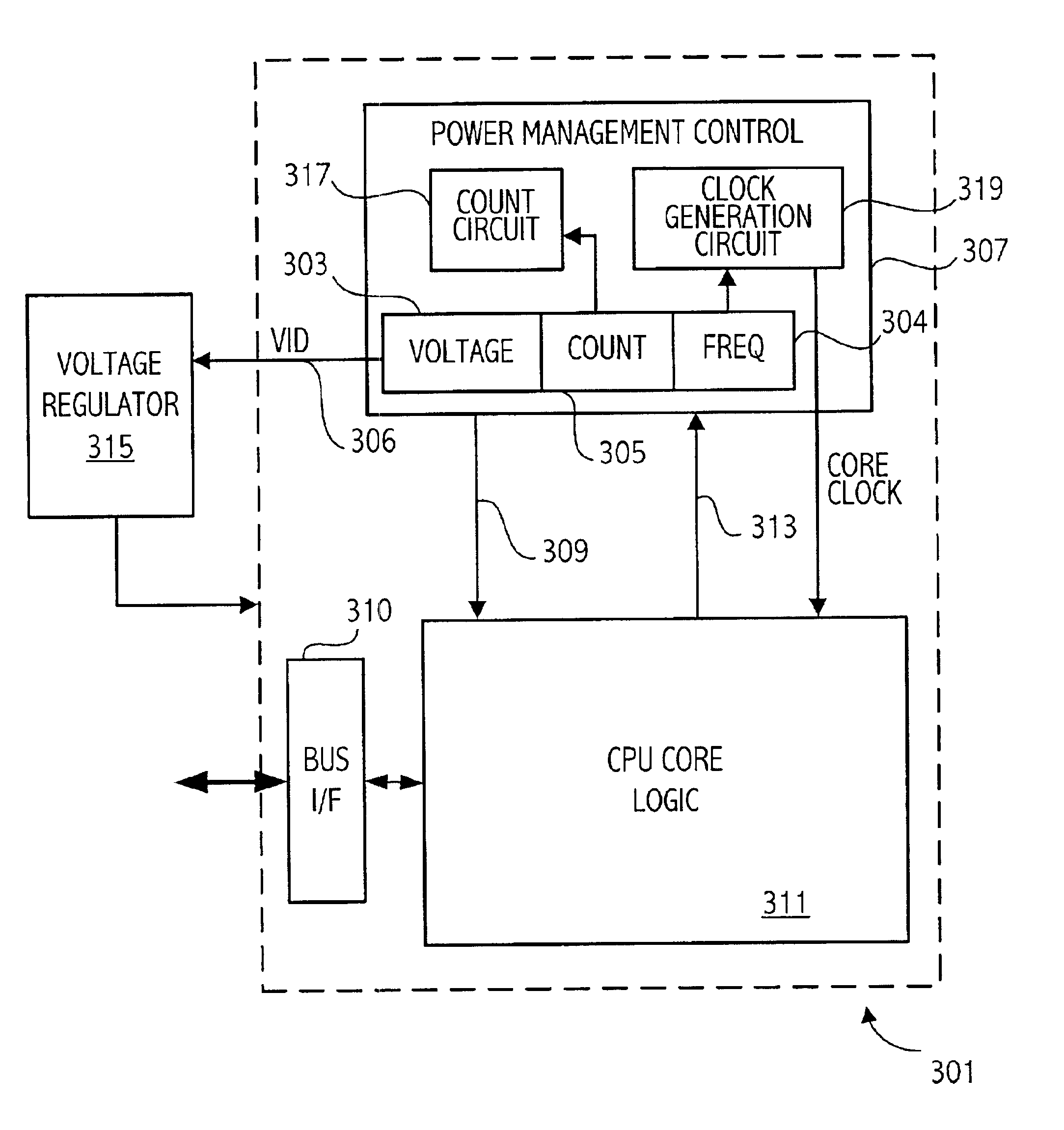

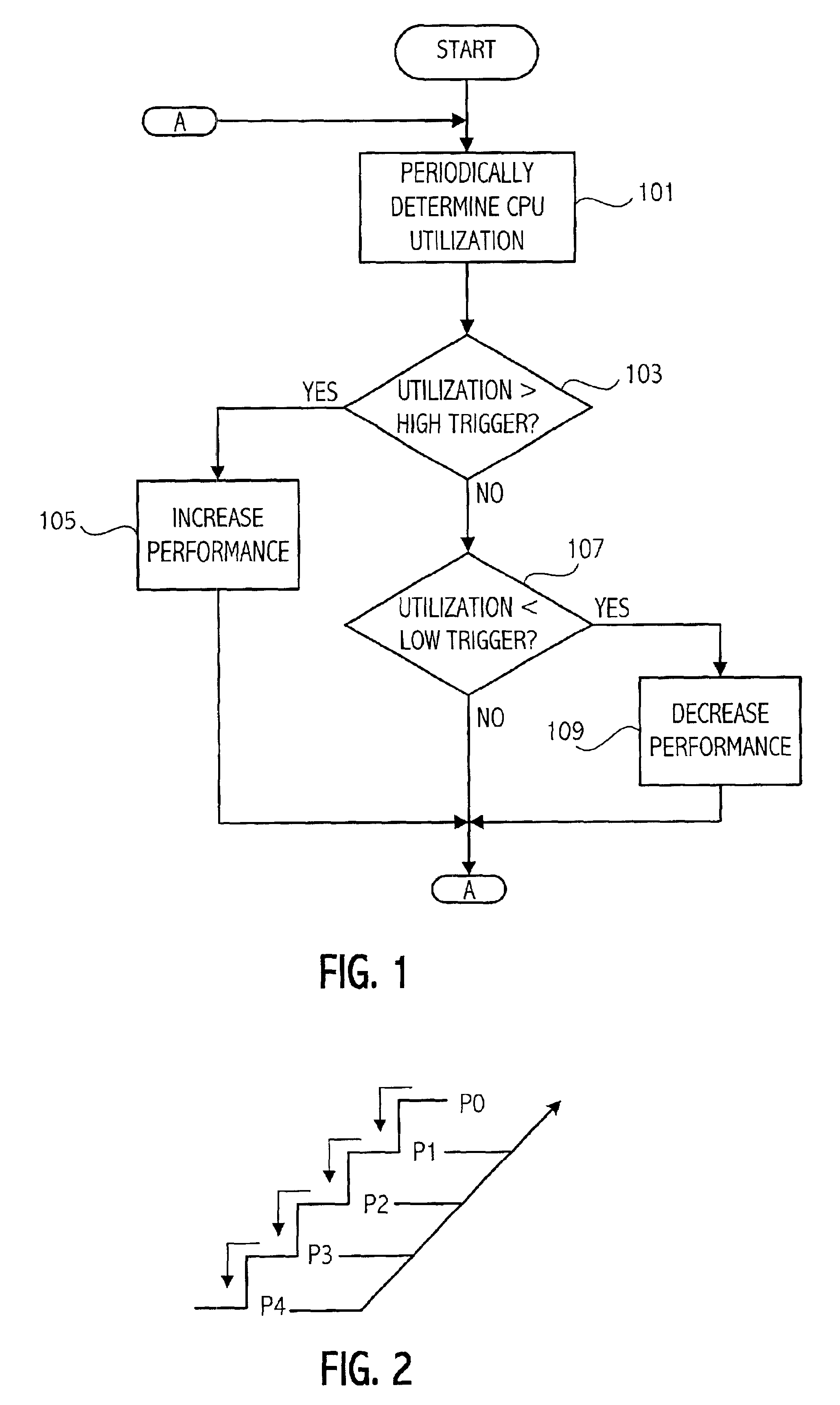

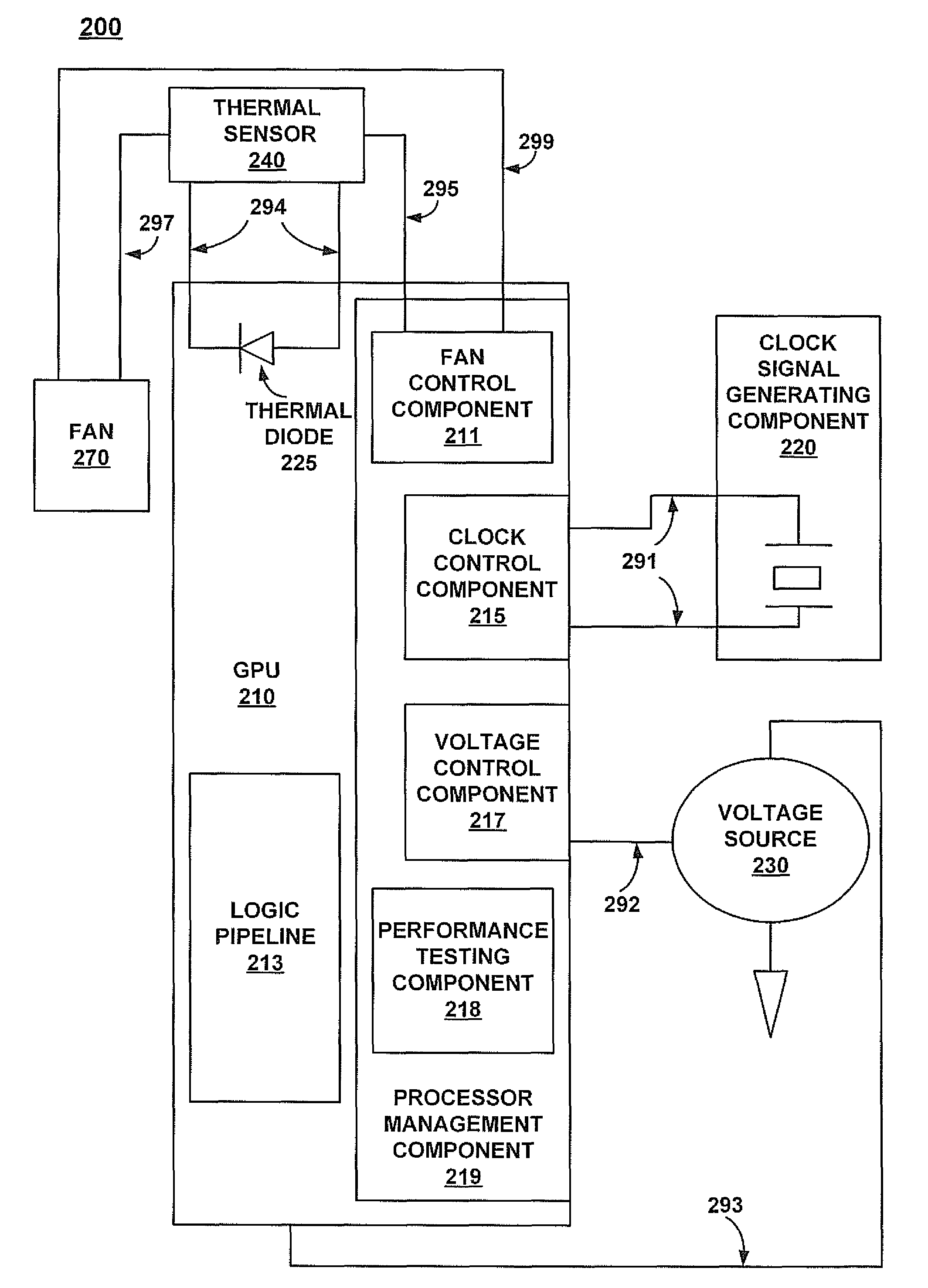

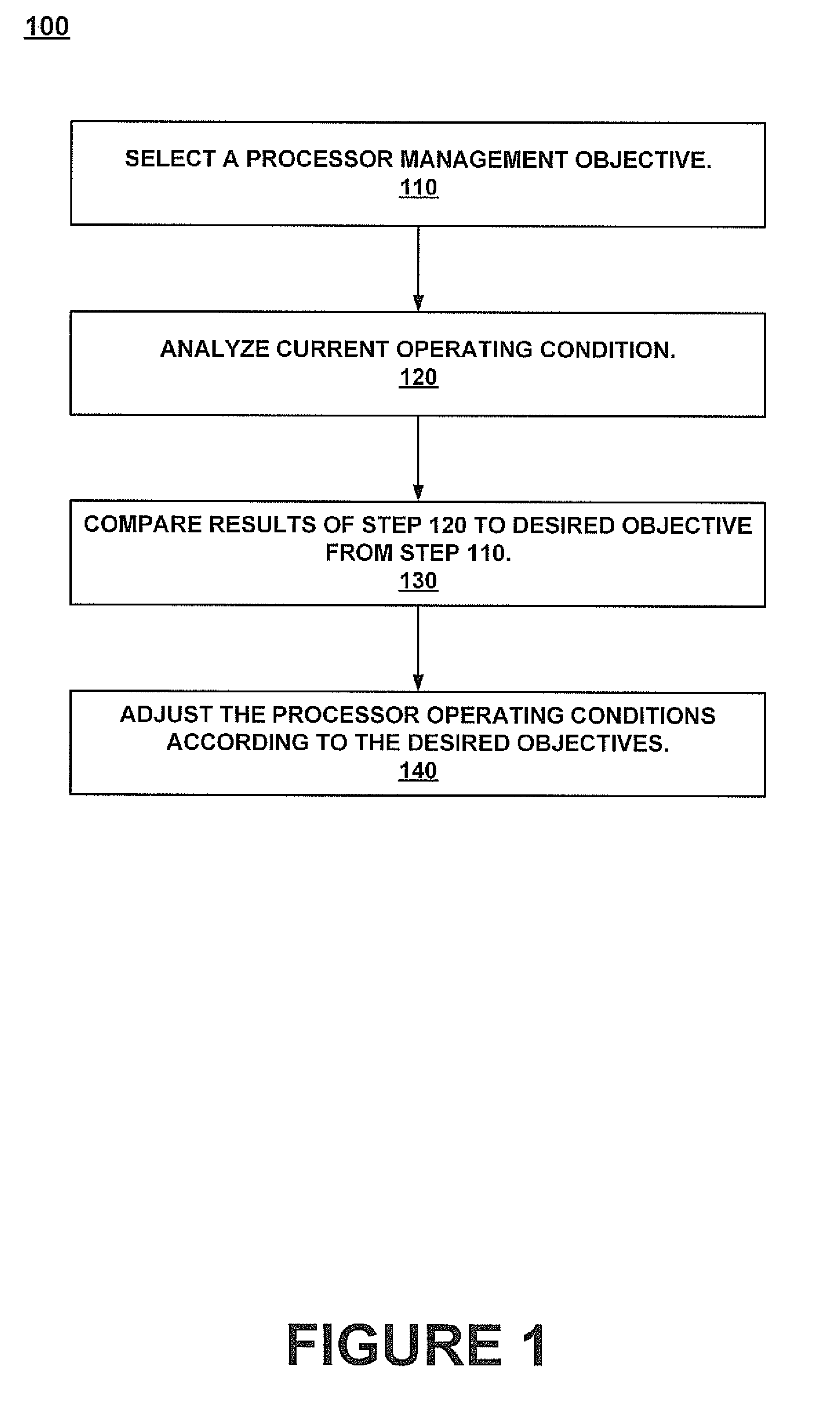

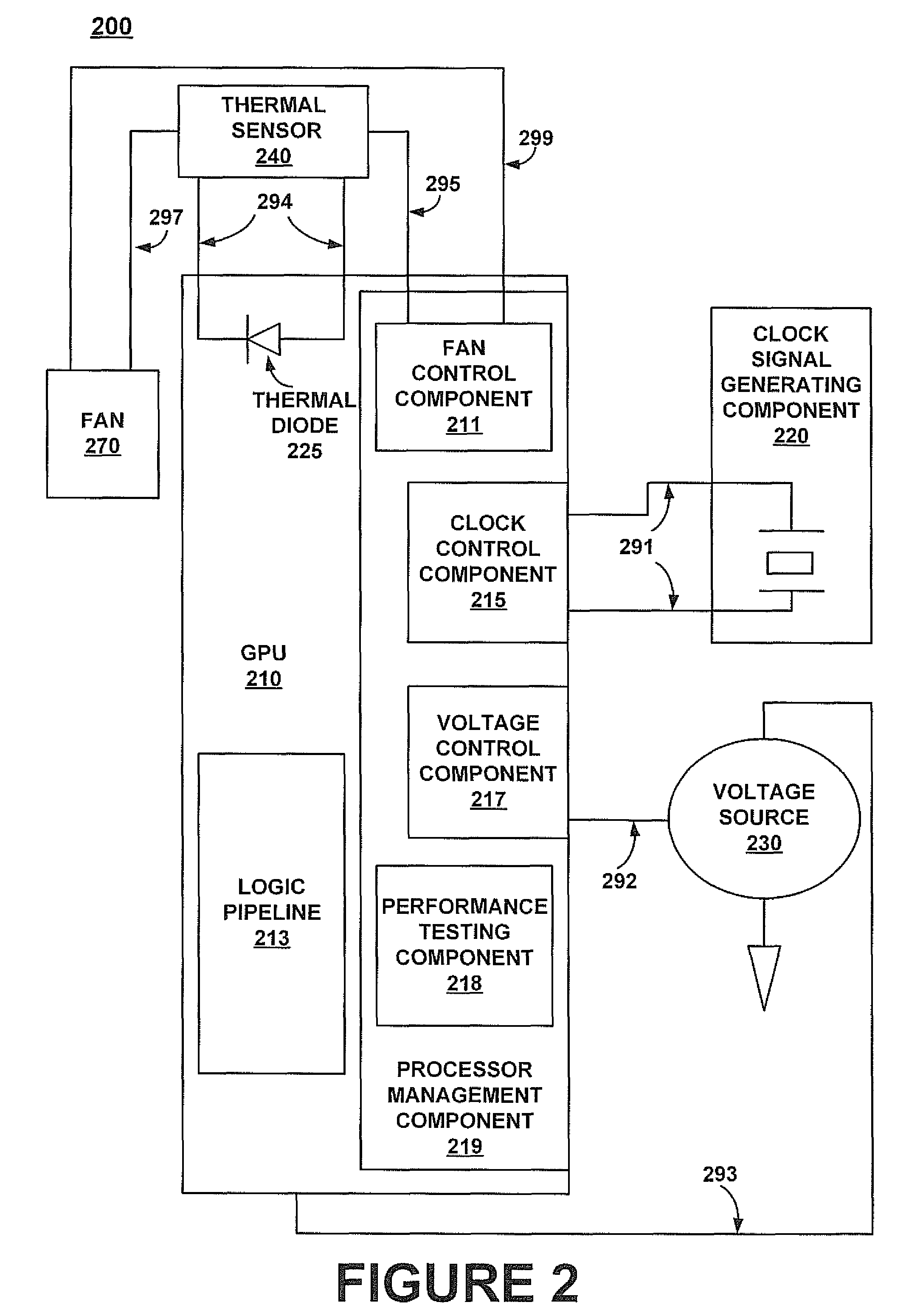

Variable maximum die temperature based on performance state

InactiveUS6889332B2Maximum performanceMaximum performance stateThermometer detailsEnergy efficient ICTEngineeringThermal threshold

The maximum performance state available to a processor in a computer system, in terms of operating frequency and / or voltage, changes according to thermal criteria. When the temperature increases above a predetermined threshold, the maximum performance state available is reduced. Multiple temperature thresholds may be utilized providing for a gradually reduced maximum performance state as temperature increases. When the temperature returns to a lower level, the maximum performance state available is increased. Changing the maximum available performance state according to temperature provides for more gradual reduction in performance as temperature increases, which results in higher average system performance as temperature increases. Thus, a more gradual reduction in performance is provided while still maintaining a high speed rating of the processor in more ideal conditions. In normal operating conditions, high processor performance is provided, while slightly reduced performance is provided in abnormal operating conditions.

Owner:ADVANCED MICRO DEVICES INC

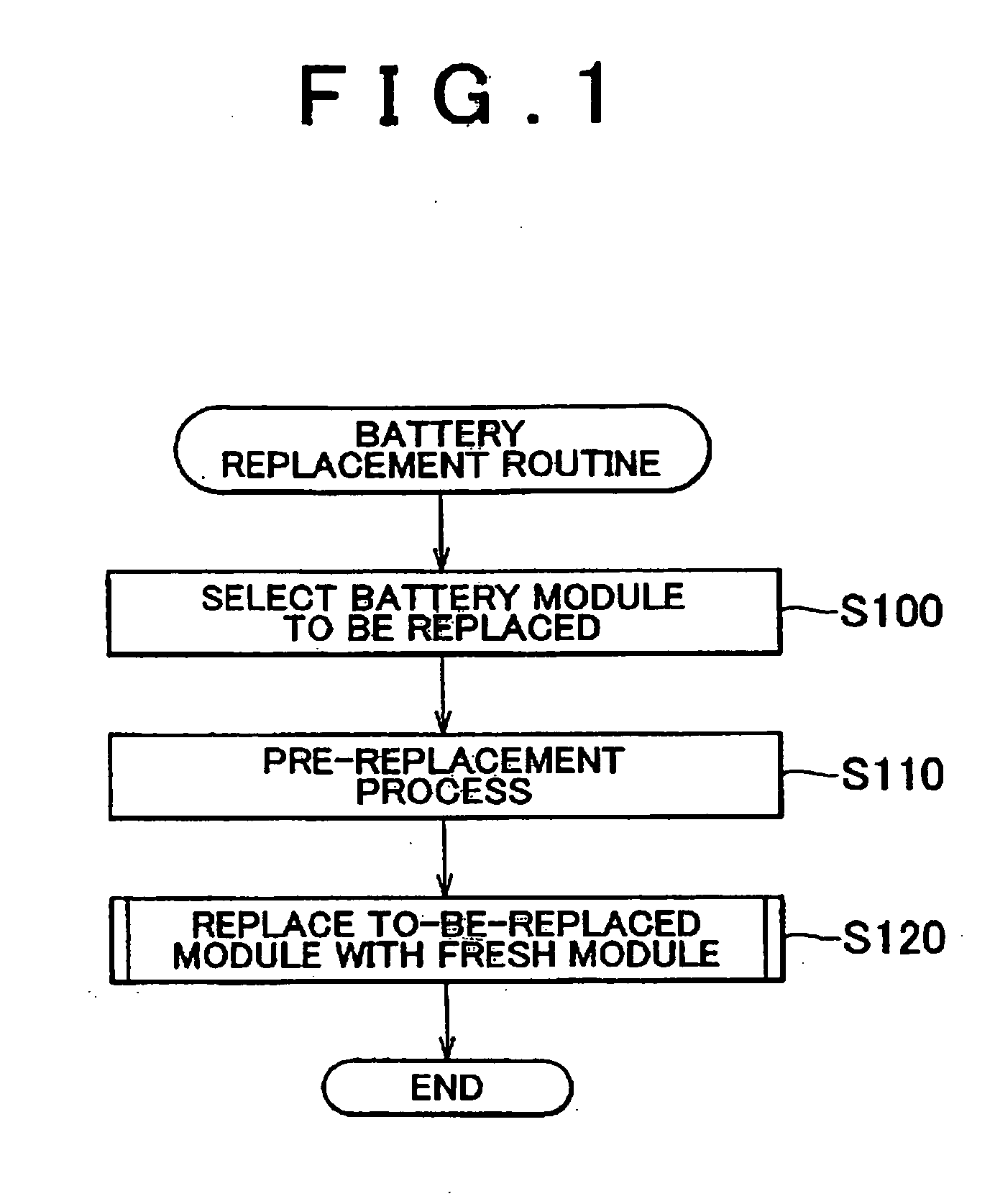

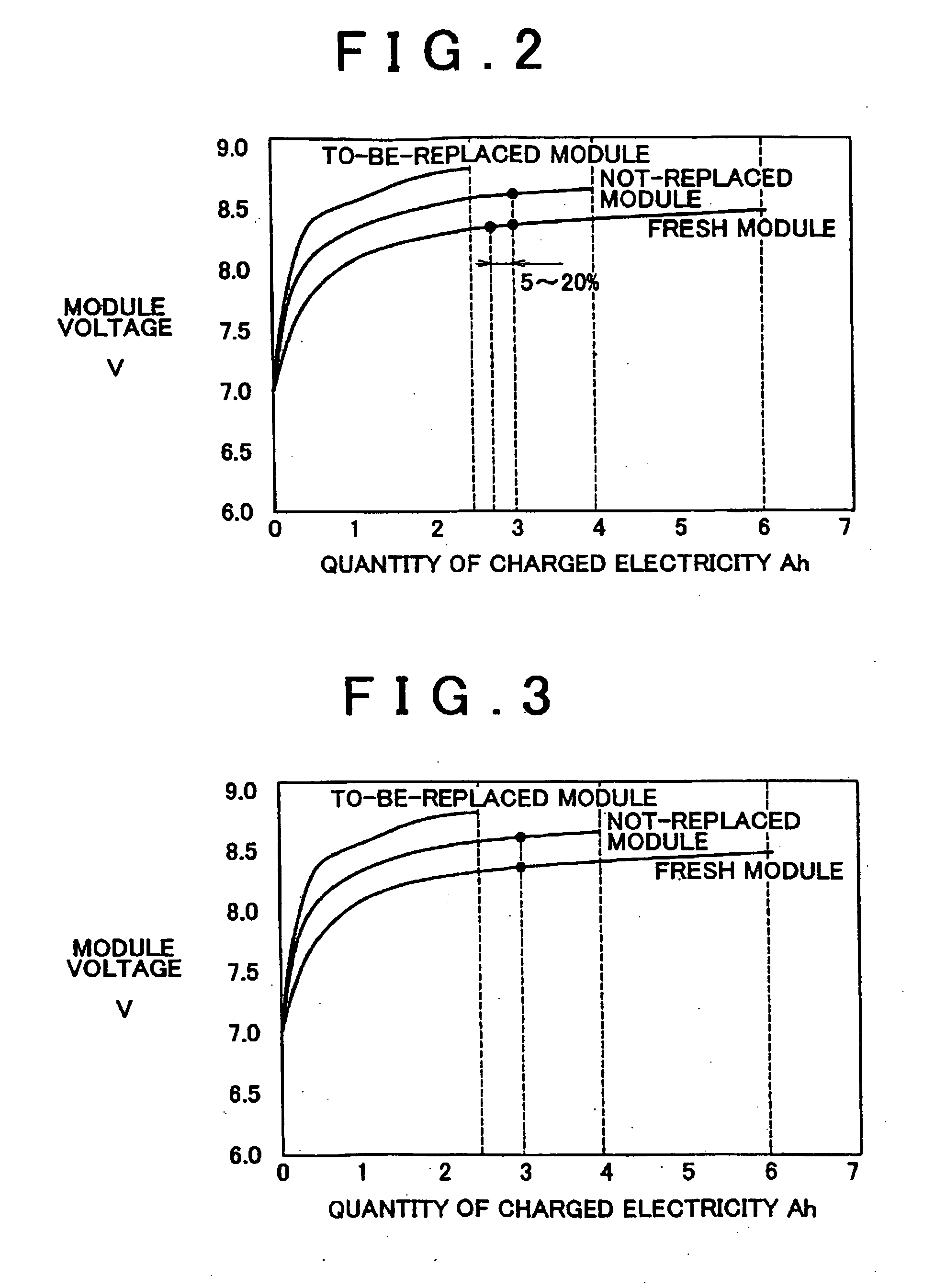

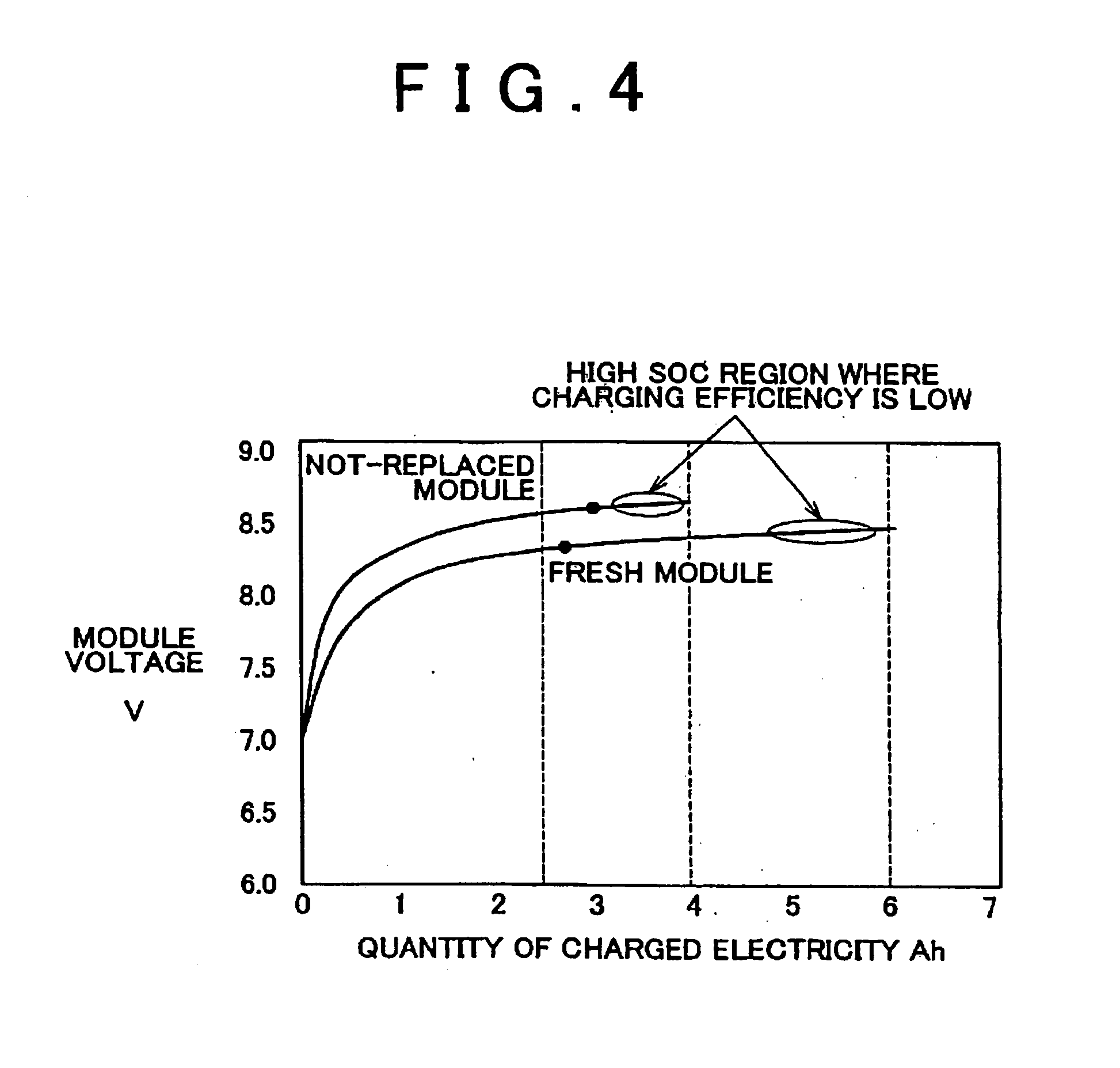

Secondary battery replacement method

ActiveUS20060012330A1Maximum performance of batteryPrevent false detectionParallel/serial switchingElectrical testingElectricityEngineering

A replacement method is provided for replacing a to-be-replaced battery module with a replacing fresh battery module in a battery assembly formed by electrically connecting a plurality of battery modules in series or parallel. The method includes the step (S110) of charging the fresh battery module so that the quantity of charged electricity of the fresh battery module is 5 to 20% less than the quantity of charged electricity of a battery module other than the to-be-replaced battery module, and the step (S120) of replacing the to-be-replaced battery module with the charged fresh battery module.

Owner:TOYOTA JIDOSHA KK

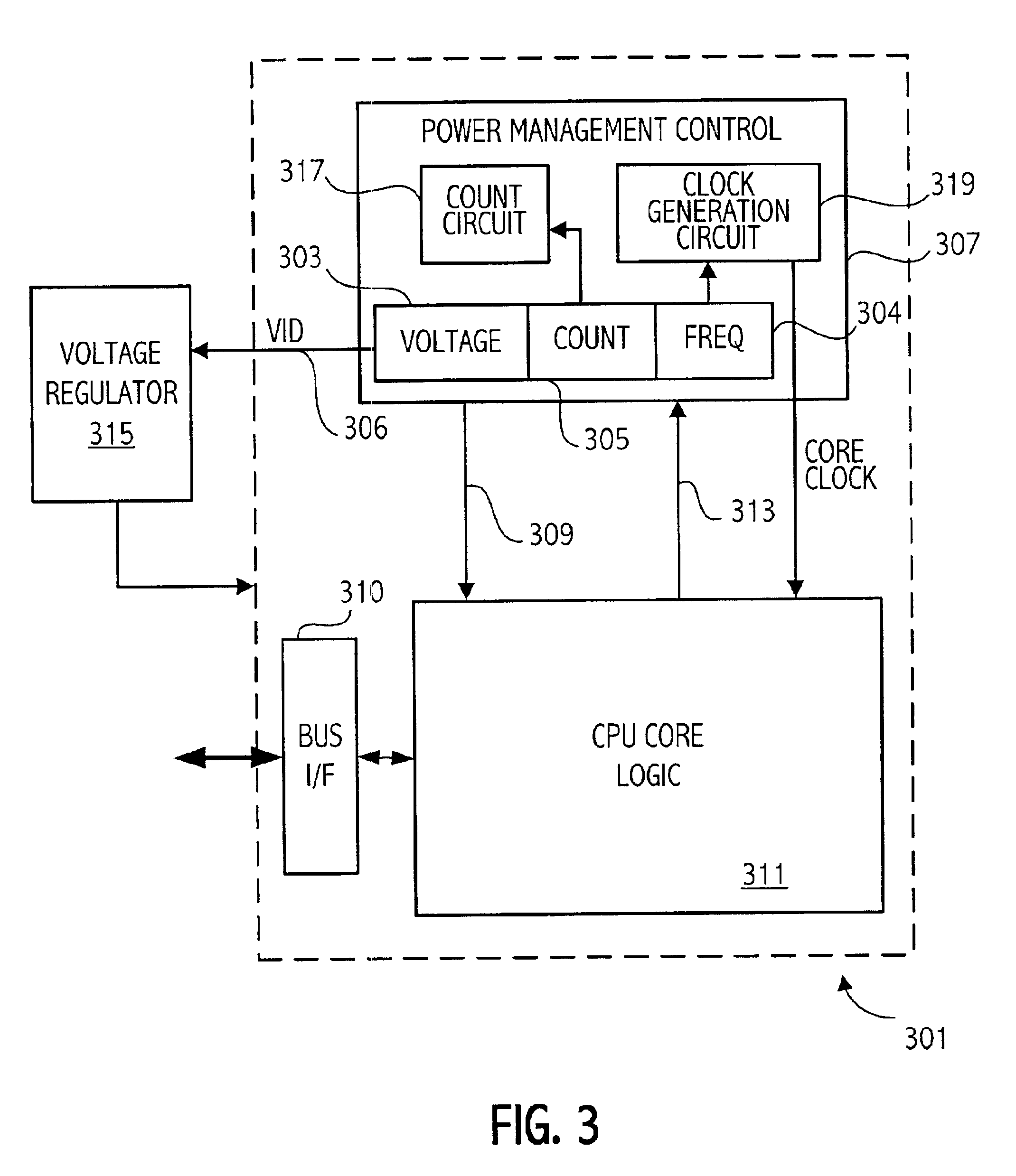

Method and system for dynamic power supply voltage adjustment for a semiconductor integrated circuit device

InactiveUS6947865B1Reduce performance limiting effect of crosstalk and jitter and noiseImprove the level ofThermometer detailsCurrent/voltage measurementSemiconductorCrosstalk

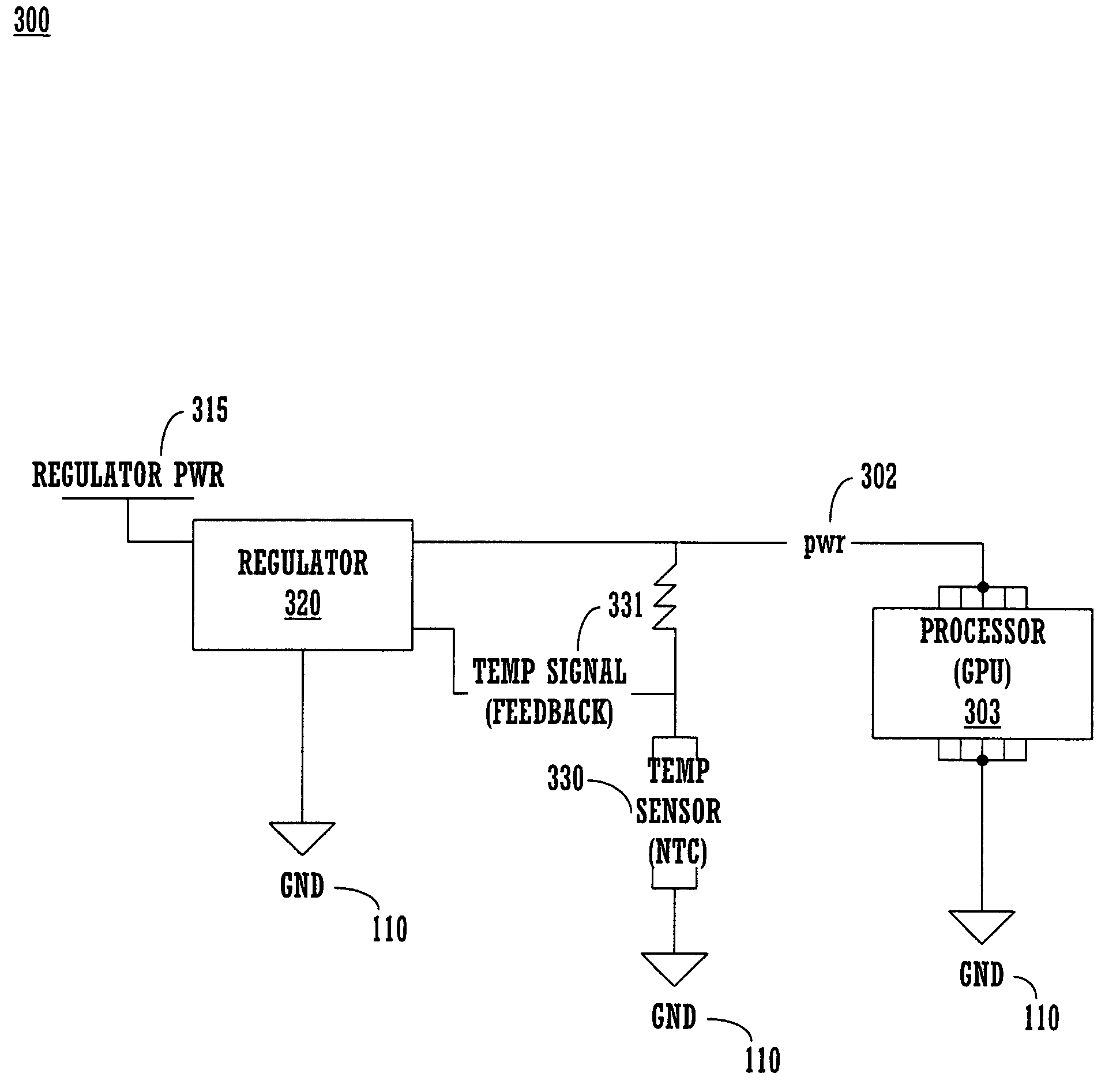

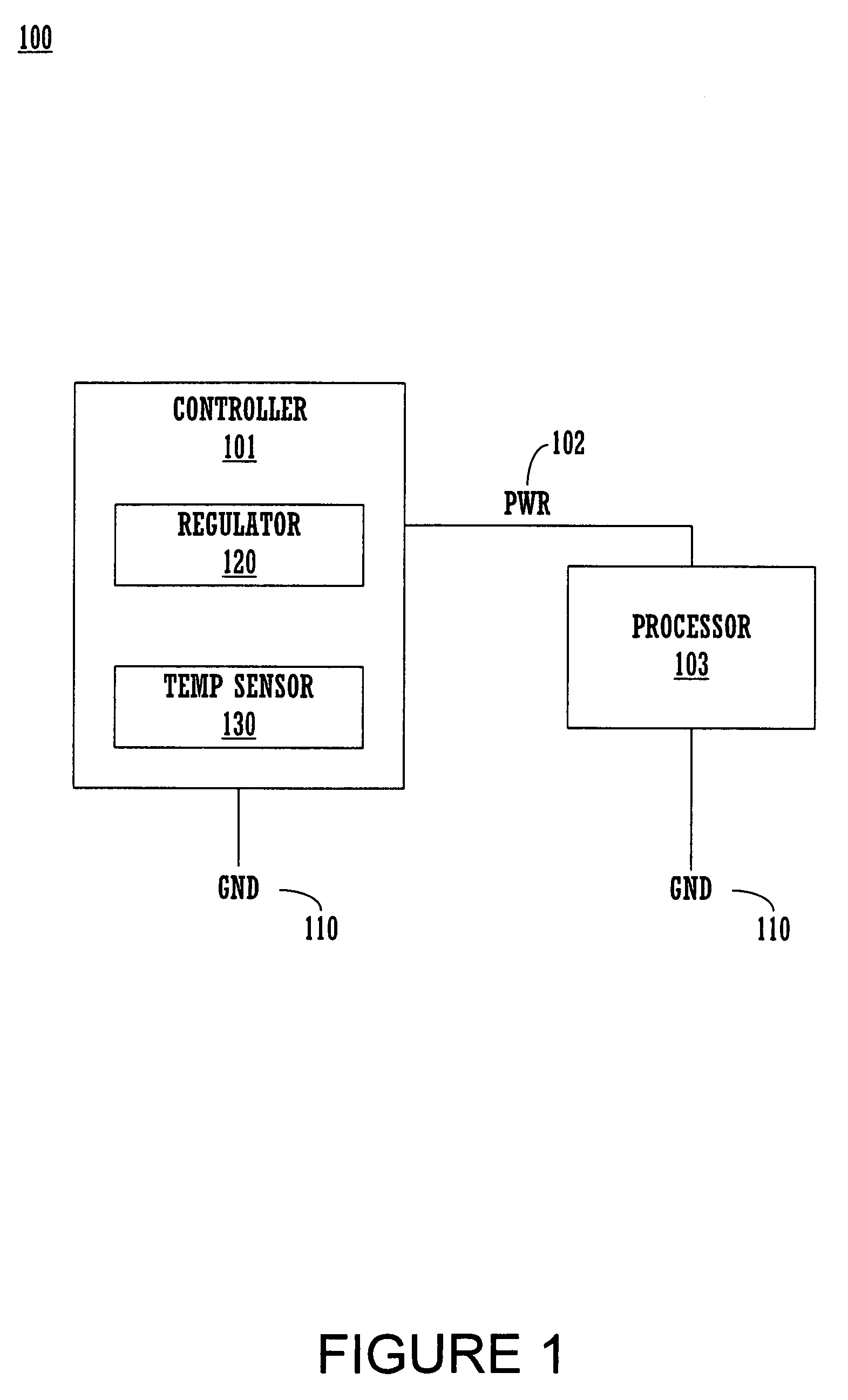

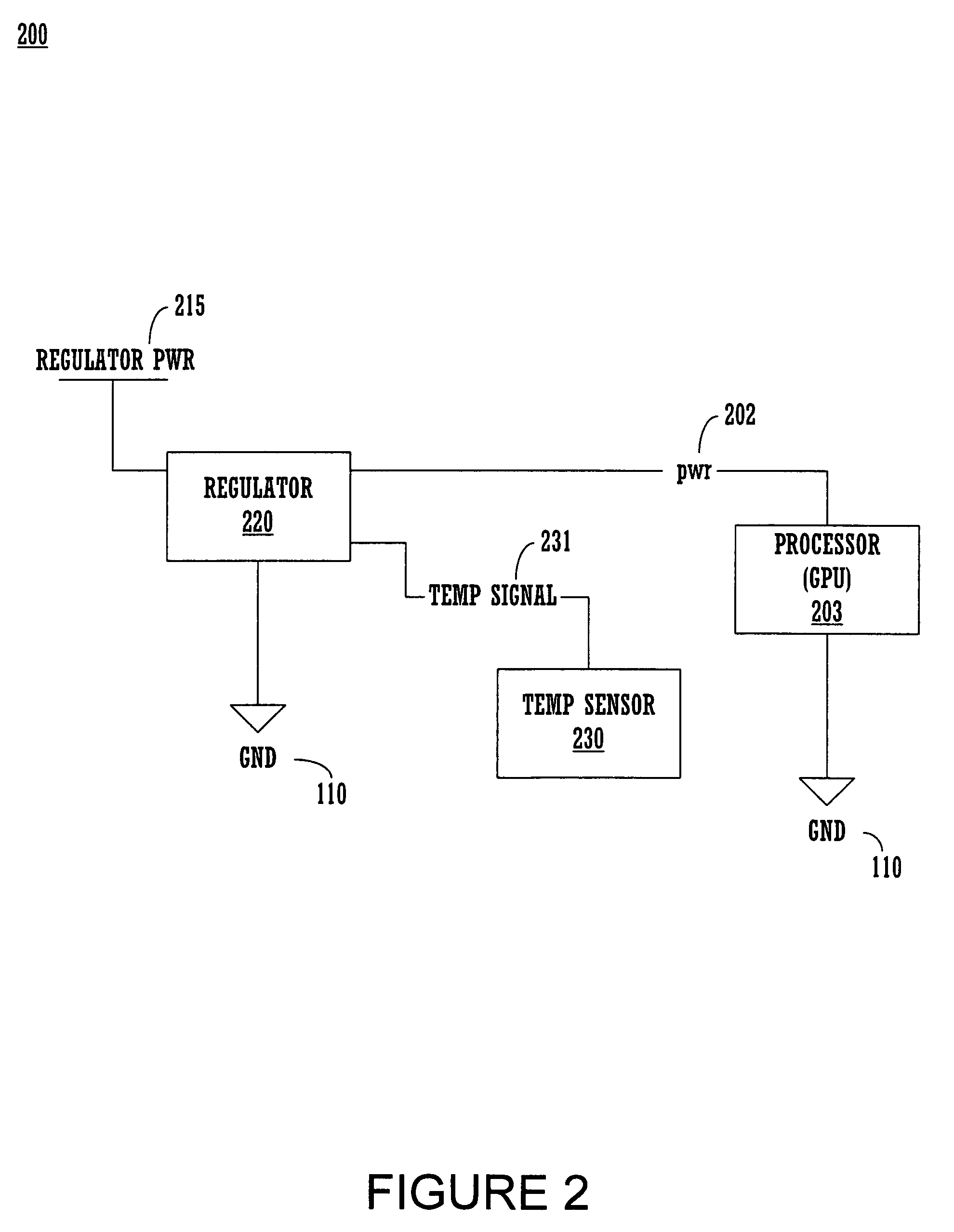

A processor power supply voltage controller. The controller includes a temperature sensor configured to sense a temperature of a processor and generate a temperature signal in accordance therewith. A regulator is coupled to provide a power supply voltage to the processor. The regulator is coupled to receive the temperature signal and control the power supply voltage to maintain a substantially stable crosstalk level within the processor.

Owner:NVIDIA CORP

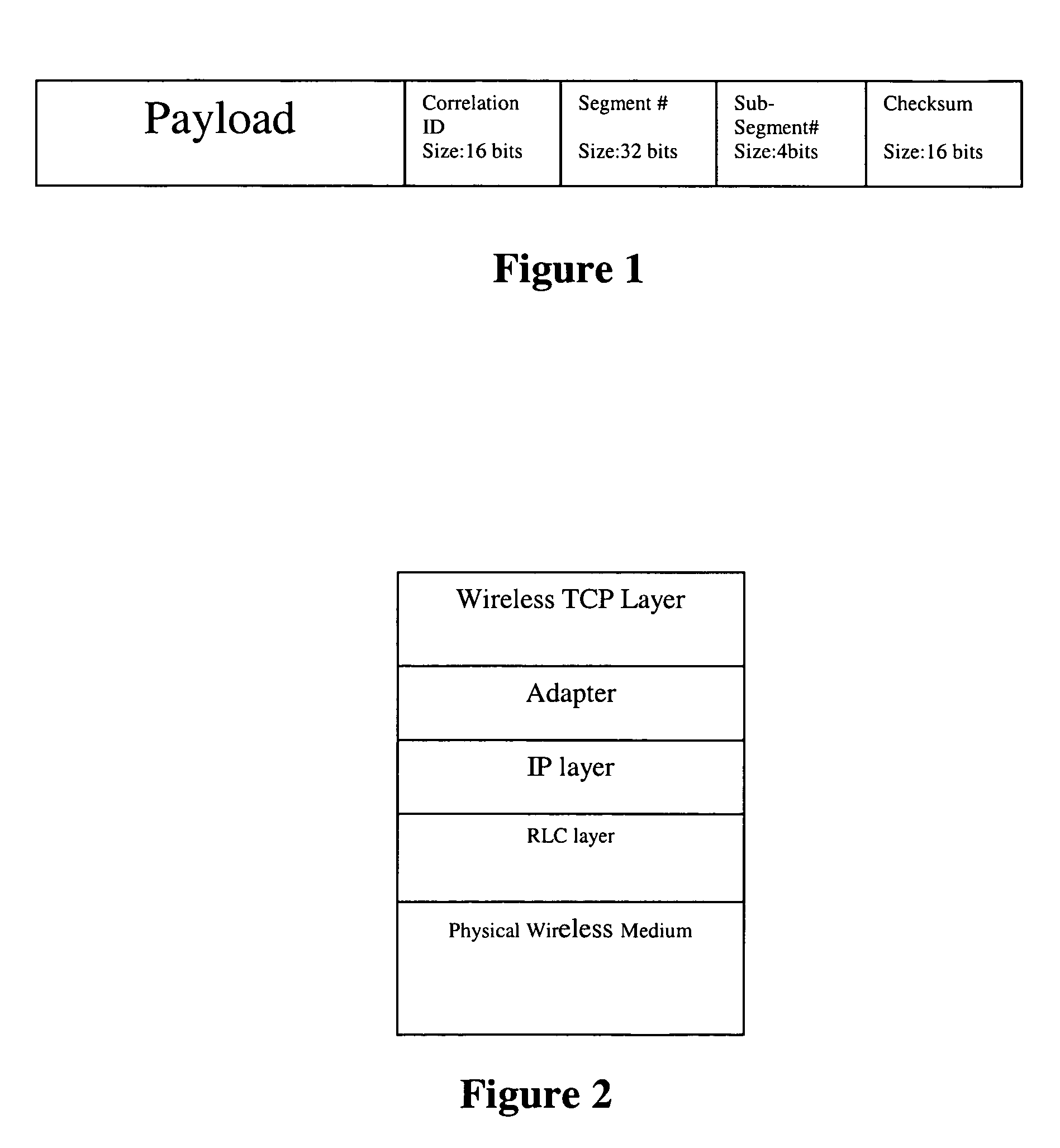

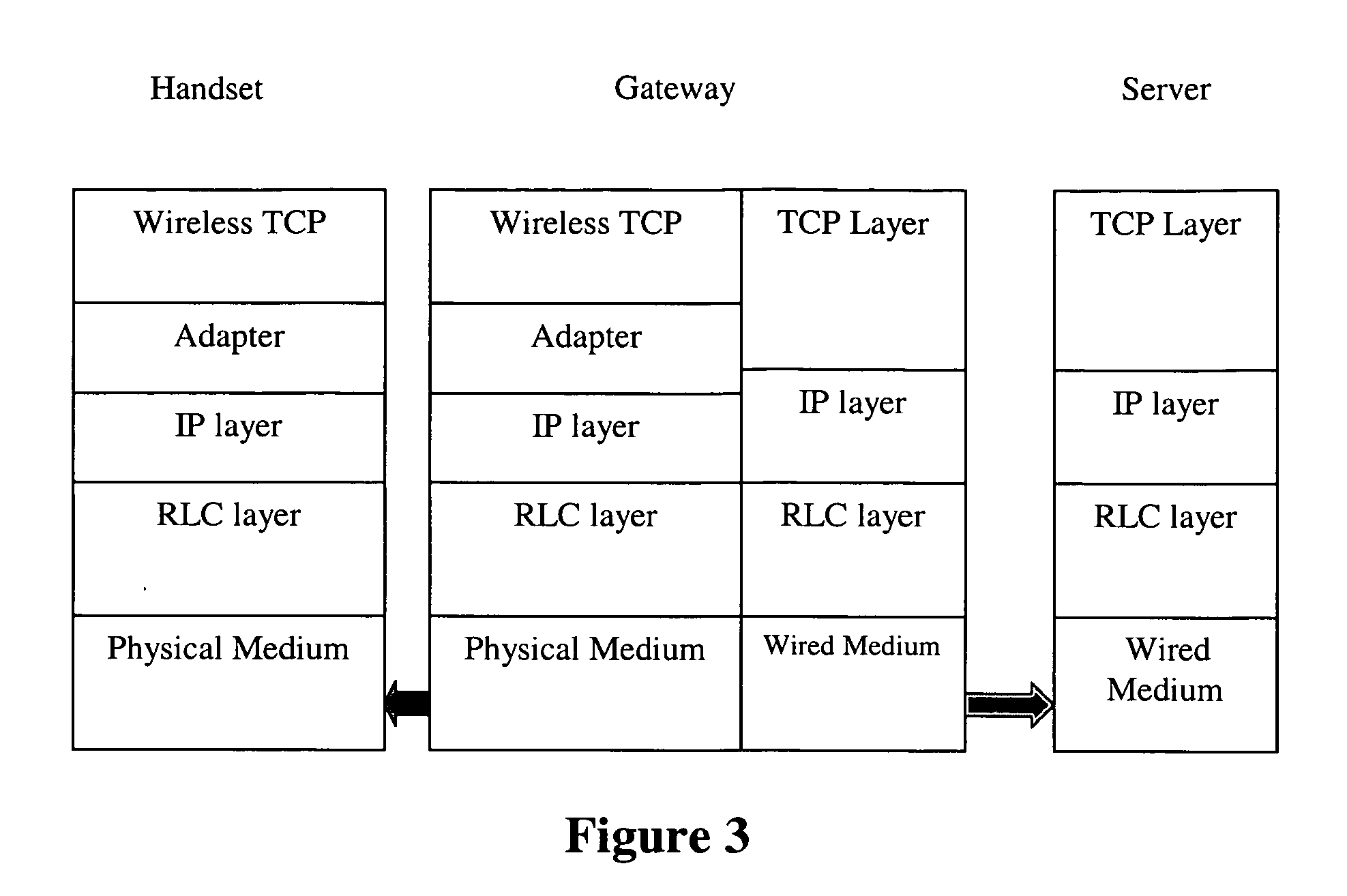

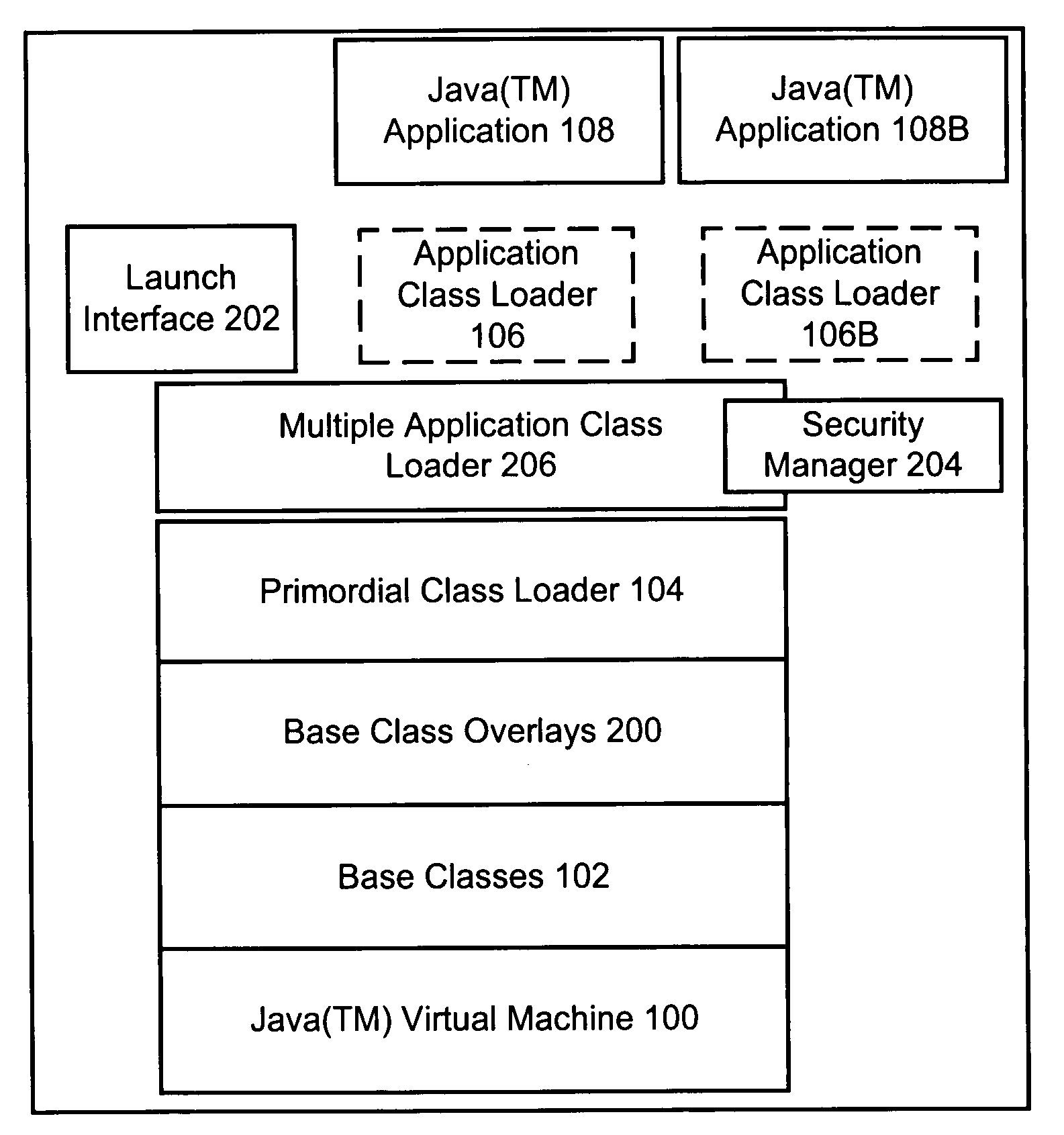

Sub-segment based transport layer protocol for wireless medium

InactiveUS20050265353A1Maximum performanceSave bandwidthEnergy efficient ICTNetwork traffic/resource managementTransport layerPacket loss

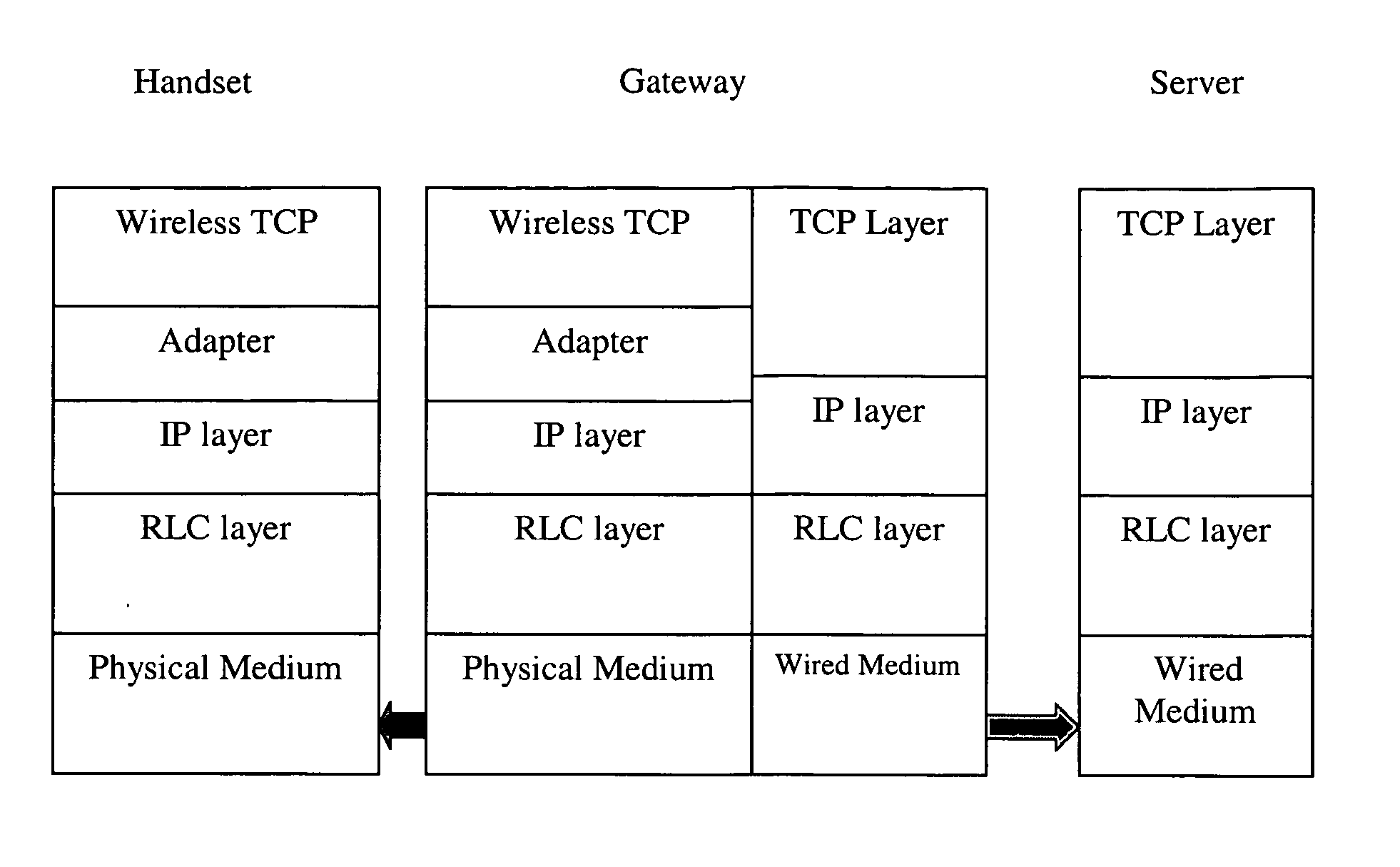

The invention enables the use of TCP protocol for reliable transport of data over a wireless network, resolving the problems associated with frequent packet loss. Additional benefits include delivery of significant performance improvement, bandwidth saving and backward compatibility compared to the wire-line TCP protocol, and contribution to power savings in wireless handsets and devices. To make the retransmission process more granular, transport layer segments are subdivided into sub-segments. The invention utilizes a split TCP based approach and produces a series of smaller-sized segments that share the same transport layer header. A NACK-based message exchange, a new header format and a special windowing protocol are used to achieve reliability, flow-control, and efficient buffer handling.

Owner:NEW JERSEY INSTITUTE OF TECHNOLOGY

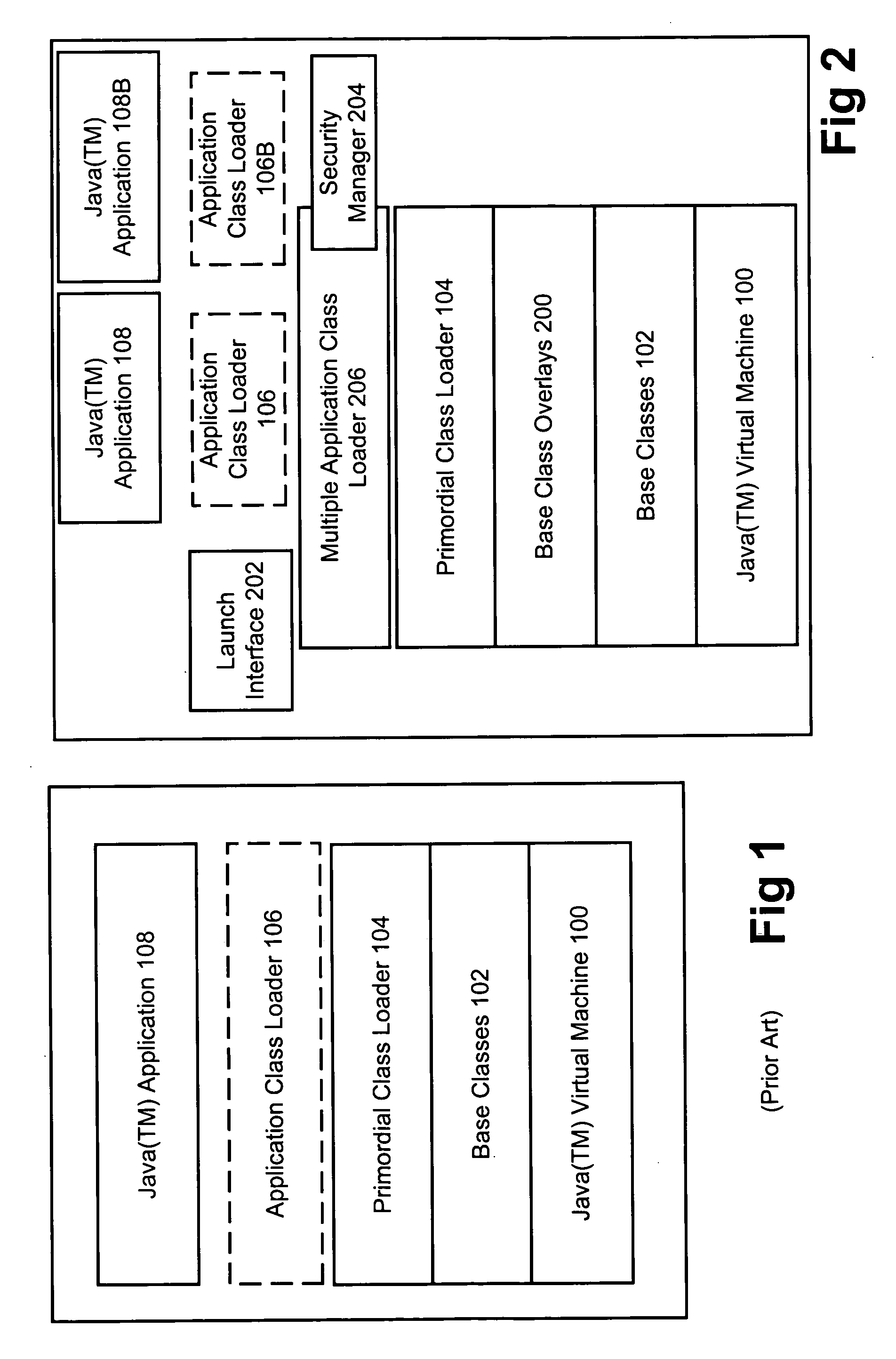

Method and apparatus for executing multiple JAVA((TM)) applications on a single JAVA((TM)) virtual machine

InactiveUS6931544B1Big memorySignificant performance improvementProgram loading/initiatingSoftware simulation/interpretation/emulationOverlayUser Privilege

A modified JAVA(™) execution environment is described. The modified environment supports multiple JAVA(™) applications on a single JAVA(™) virtual machine (JVM). This modified environment provides significant memory and performance improvements when running multiple applications on a single computer system. Notably, no changes are needed to the source code of an application to take advantage of the modified environment. Further, embodiments of the invention may support shared access to base classes through the use of overlays. Additionally, system resource permissions can be enforced based upon the user permissions associated with a running application. Notably, embodiments of the invention allow multiple applications to share the abstract window toolkit (AWT) on a per display basis. Since only a single garbage collection routine is necessary, applications see improved performance relative to running in different JVMs. Further, the shared base classes eliminate significant memory overhead.

Owner:APPLE INC

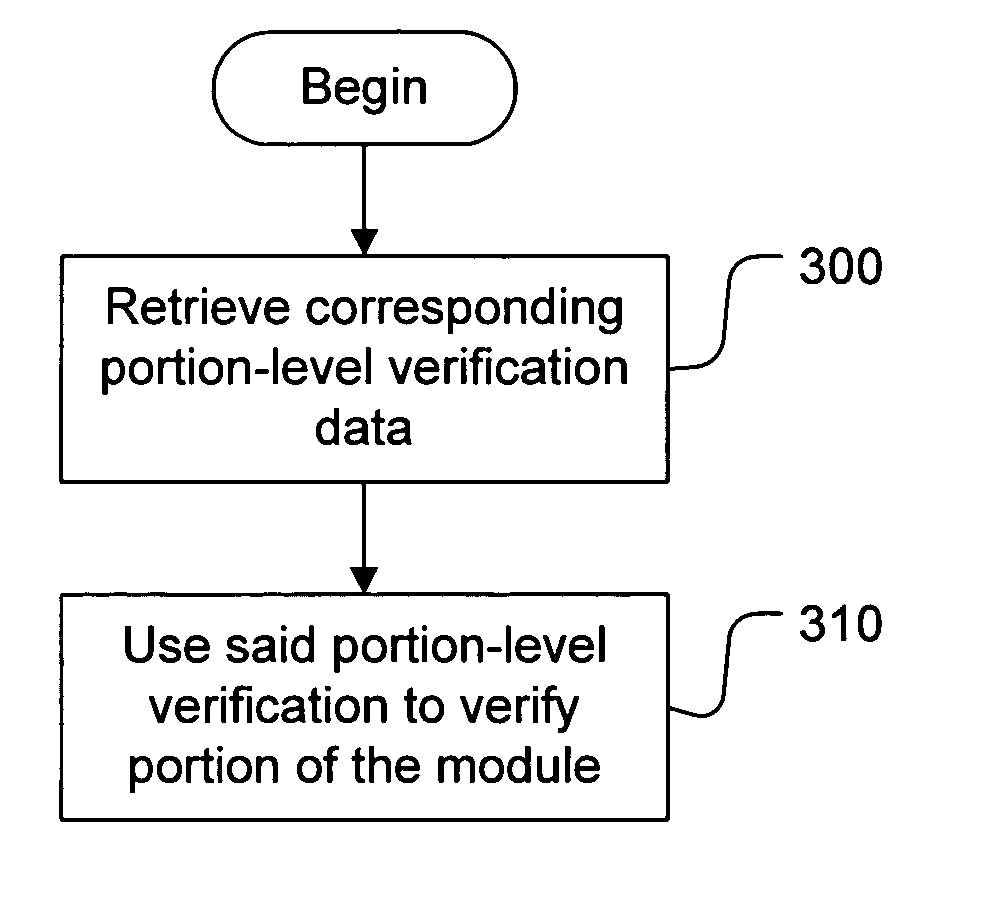

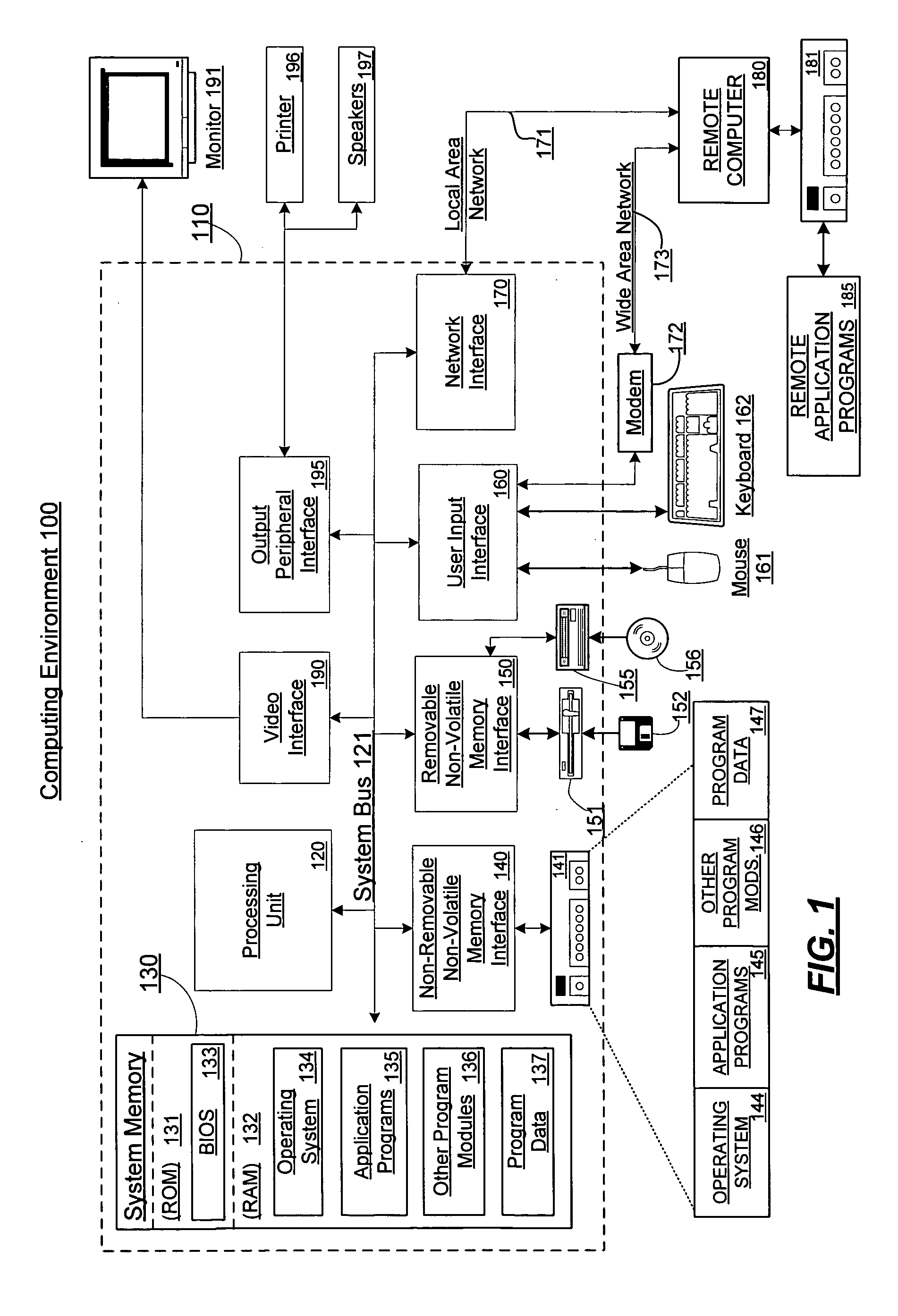

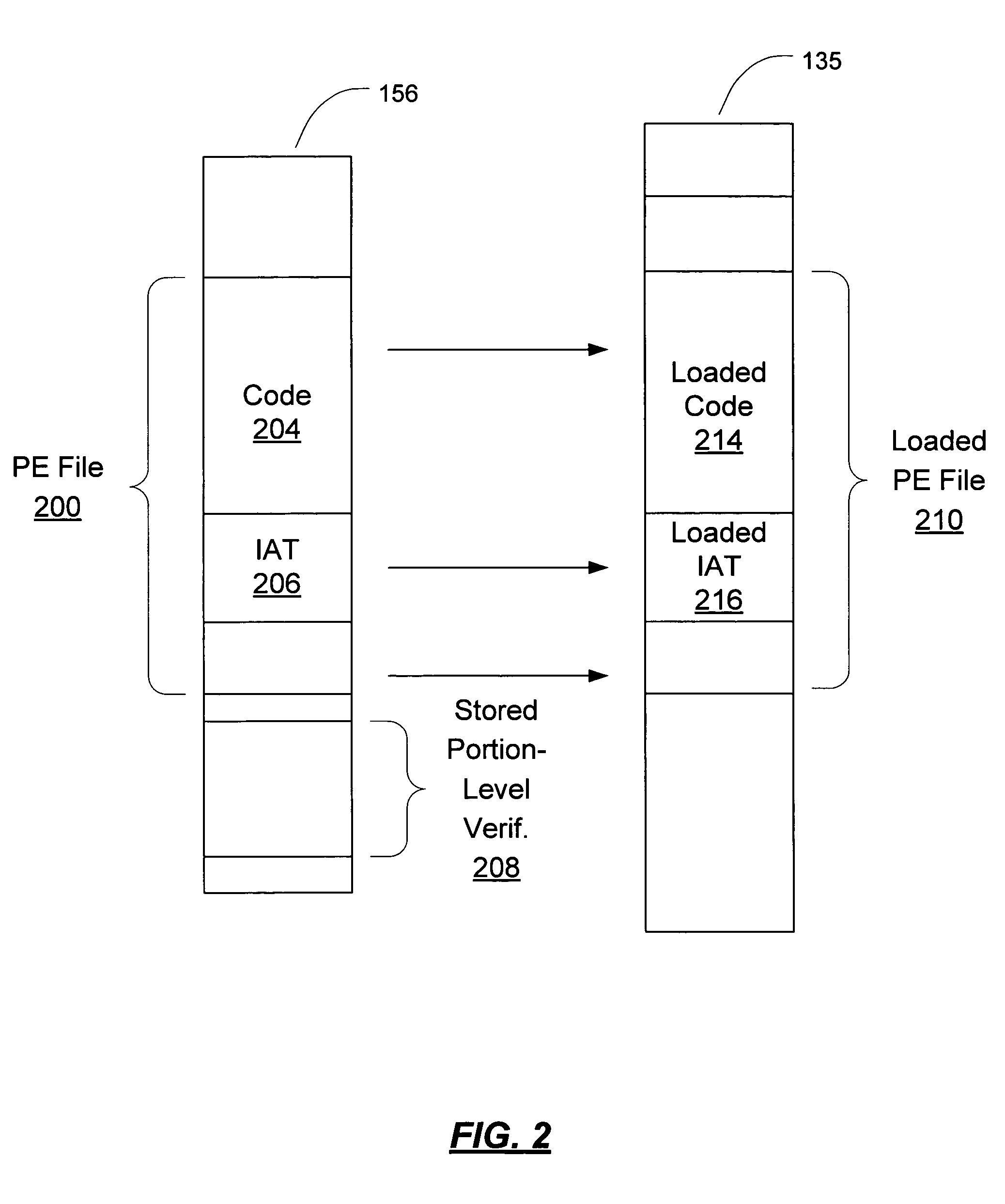

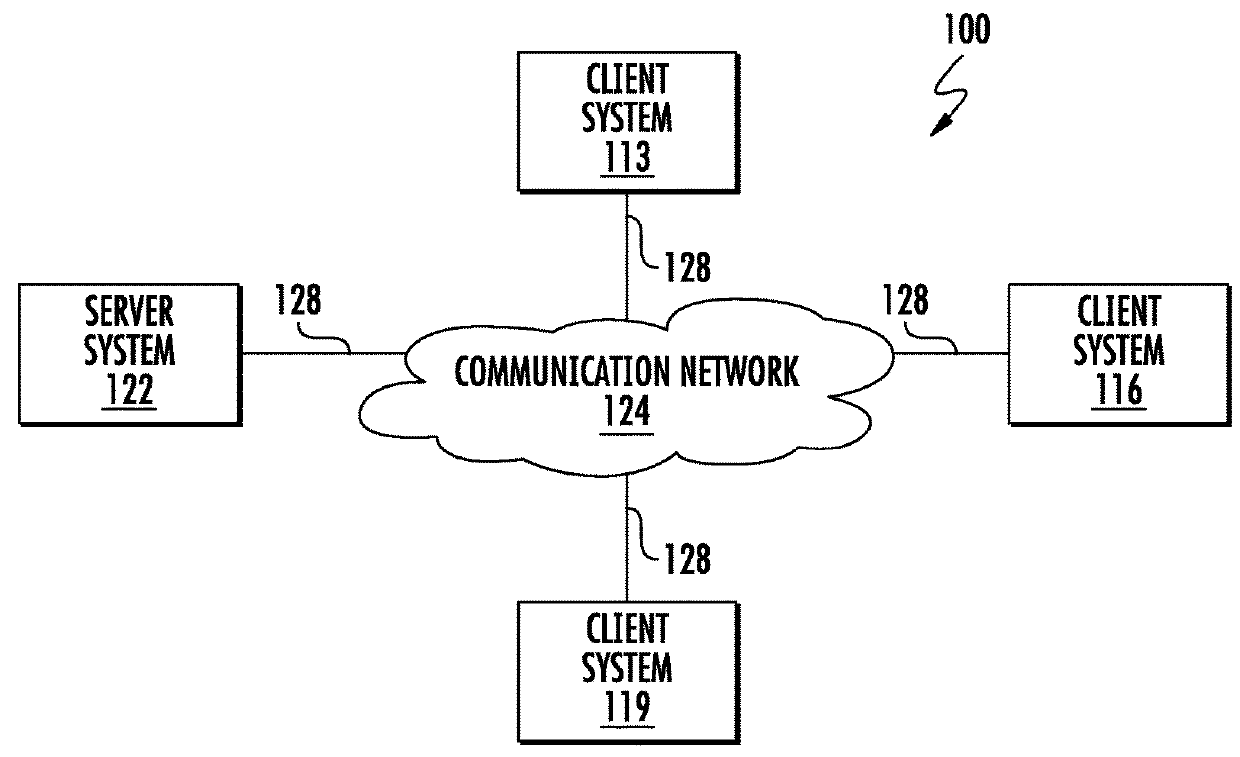

Portion-level in-memory module authentication

ActiveUS20060026569A1Efficient techniqueMaximum performanceMemory loss protectionUser identity/authority verificationOperational systemDigital signature

Dynamic run-time verification of a module which is loaded in memory (in whole or in part) for execution is enabled by using pre-computed portion-level verification data for portions of the module smaller than the whole (e.g. at the page-level). A portion of the module as loaded into memory for execution can be verified. Pre-computed portion-level verification data is retrieved from storage and used to verify the loaded portions of the executable. Verification data may be, for example, a digitally signed hash of the portion. Where the operating system loader has modified the portion for execution, the modifications are reversed, removing any changes performed by the operating system. If the portion has not been tampered, this will return the portion to its original pre-loaded state. This version is then used to determine validity using the pre-computed portion-level verification. Additionally, during execution of the module, new portions / pages of the module which are loaded can be verified to ensure that they have not been changed, and a list of hot pages of the module can be made, including pages to be continually reverified, in order to ensure that no malicious changes have been made in the module.

Owner:MICROSOFT TECH LICENSING LLC

Edge intelligence platform, and internet of things sensor streams system

ActiveUS10007513B2Low costSave levelParticular environment based servicesInterprogram communicationAnalytical expressionsResource based

A method for enabling intelligence at the edge. Features include: triggering by sensor data in a software layer hosted on either a gateway device or an embedded system. Software layer is connected to a local-area network. A repository of services, applications, and data processing engines is made accessible by the software layer. Matching the sensor data with semantic descriptions of occurrence of specific conditions through an expression language made available by the software layer. Automatic discovery of pattern events by continuously executing expressions. Intelligently composing services and applications across the gateway device and embedded systems across the network managed by the software layer for chaining applications and analytics expressions. Optimizing the layout of the applications and analytics based on resource availability. Monitoring the health of the software layer. Storing of raw sensor data or results of expressions in a local time-series database or cloud storage. Services and components can be containerized to ensure smooth running in any gateway environment.

Owner:JOHNSON CONTROLS TYCO IP HLDG LLP

Processor temperature adjustment system and method

ActiveUS7886164B1Facilitates processor speed adjustmentEasy maintenanceEnergy efficient ICTVolume/mass flow measurementEngineeringThermal threshold

The present invention facilitates processor speed adjustments within acceptable temperature ranges. In one embodiment, a present invention system includes a temperature sensor that senses the temperature of the processor. When the temperature sensor senses the processor temperature approaching predetermined levels one or more adjustments are performed. For example, the adjustment can include automatically increasing or decreasing a voltage level in response to crossing a temperature threshold.

Owner:NVIDIA CORP

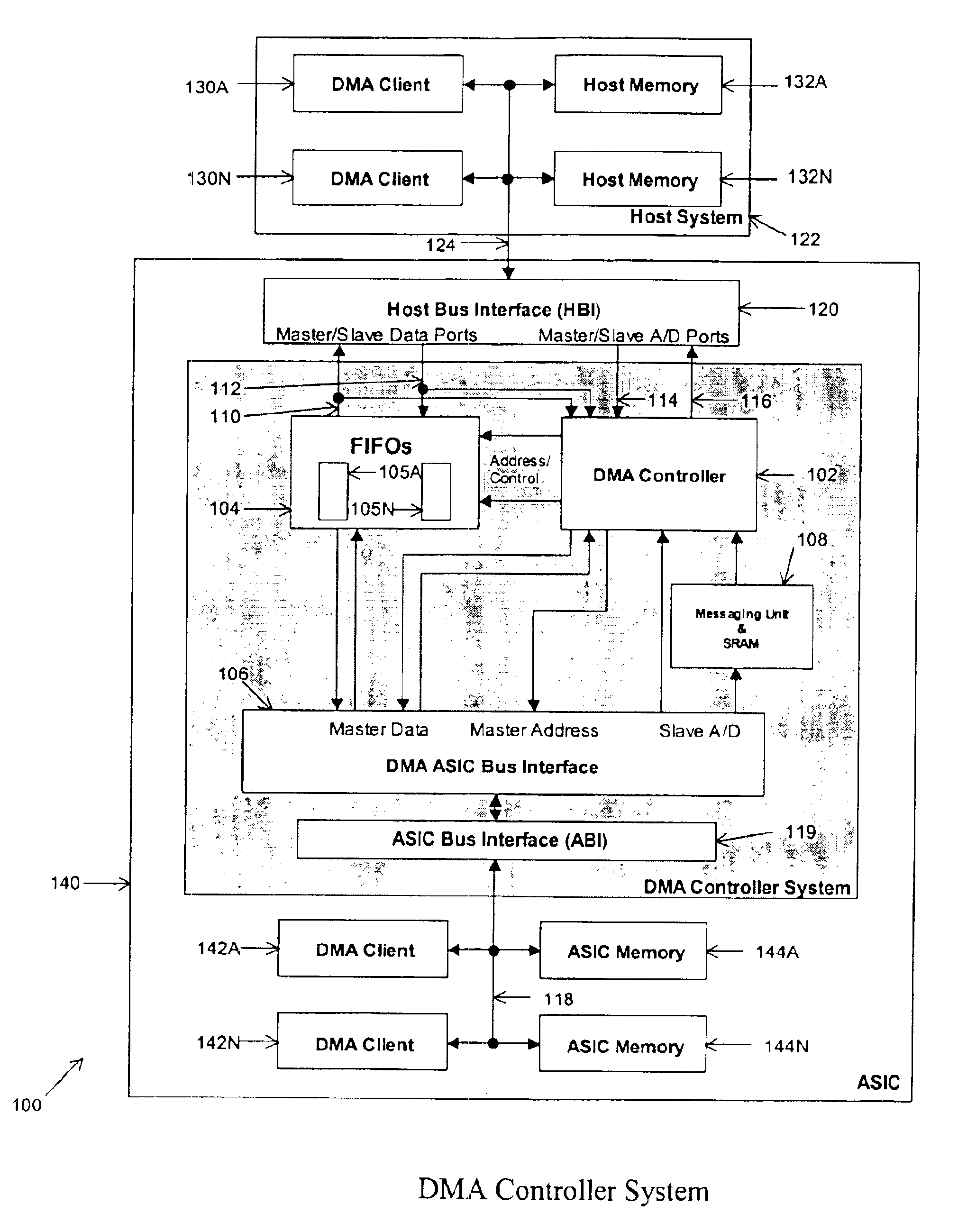

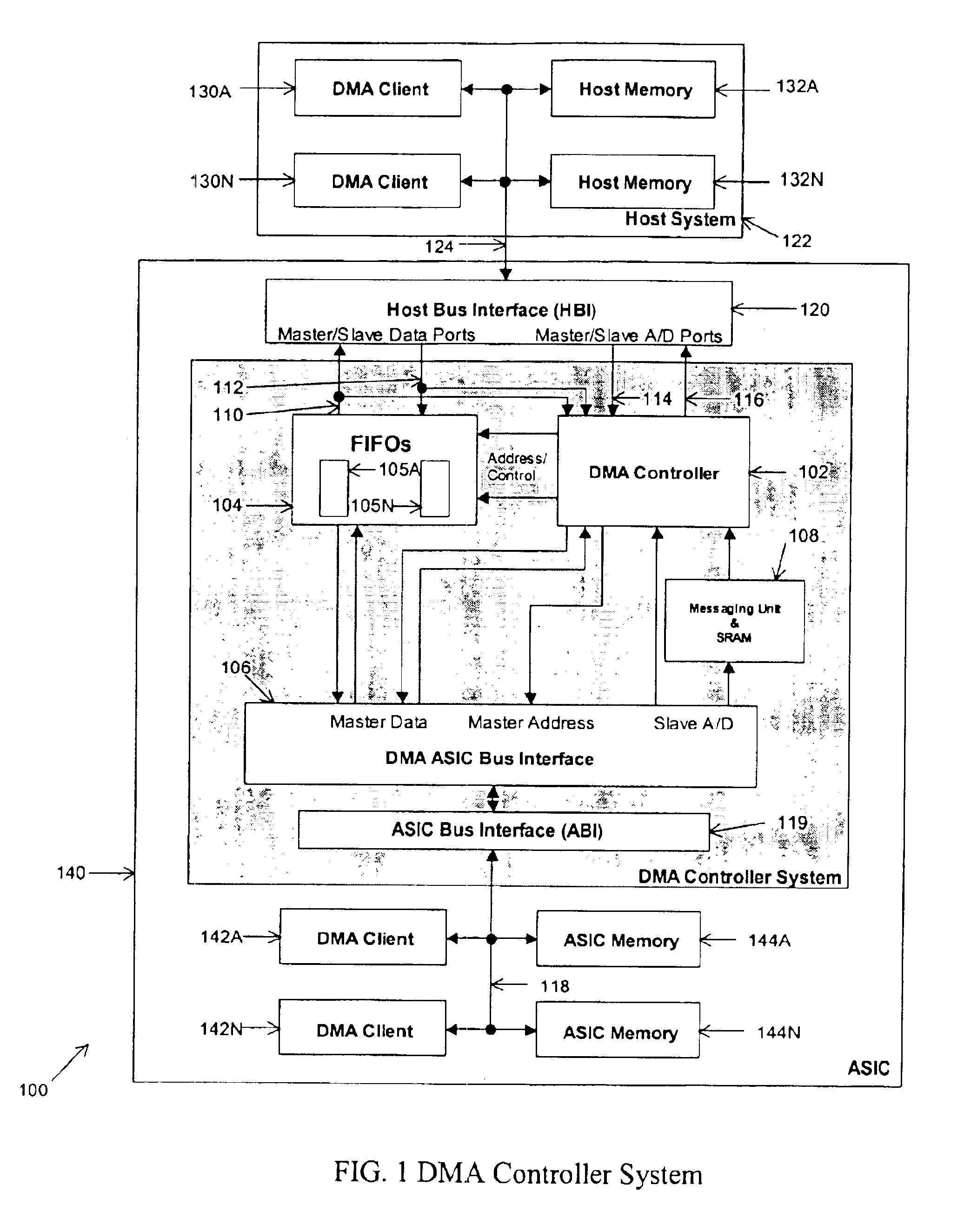

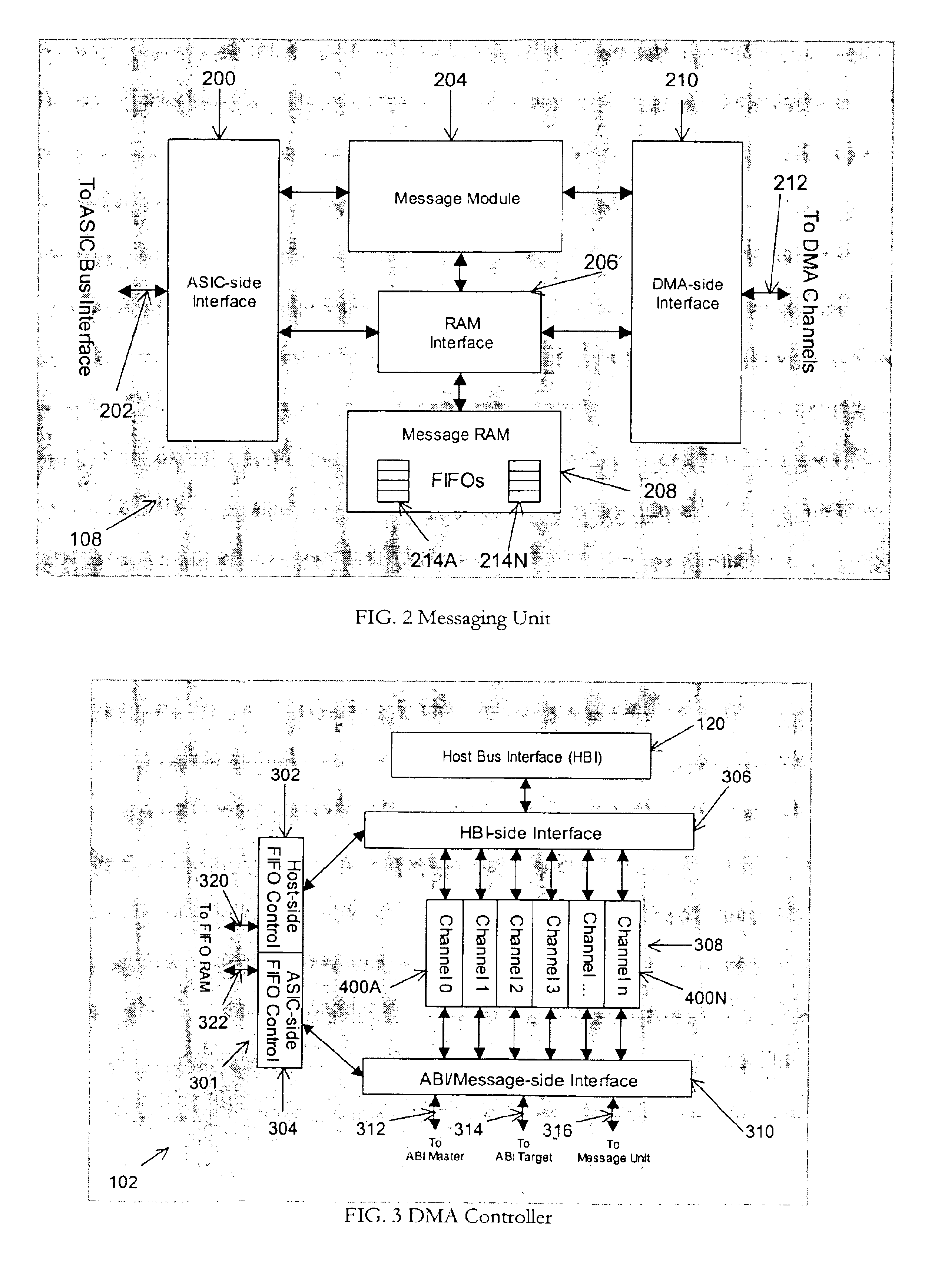

Direct memory access controller system with message-based programming

InactiveUS6874054B2Performance advantageEasy to operateProgram initiation/switchingRedundant data error correctionDirect memory accessTransfer system

A data transfer system comprising a first bus interface, a second bus interface, a first-in-first-out memory, a controller and a message unit. The message unit is operable to queue a plurality of data transfer request messages from the first bus interface and the second bus interface. The controller is operable to process each data transfer request message and transfer data between the first bus interface, the first-in-first-out memory and the second bus interface. The controller is configured to calculate error detection codes (EDCs) and chain EDC values.

Owner:AVAGO TECH INT SALES PTE LTD