Patents

Literature

234results about How to "Lower gate resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

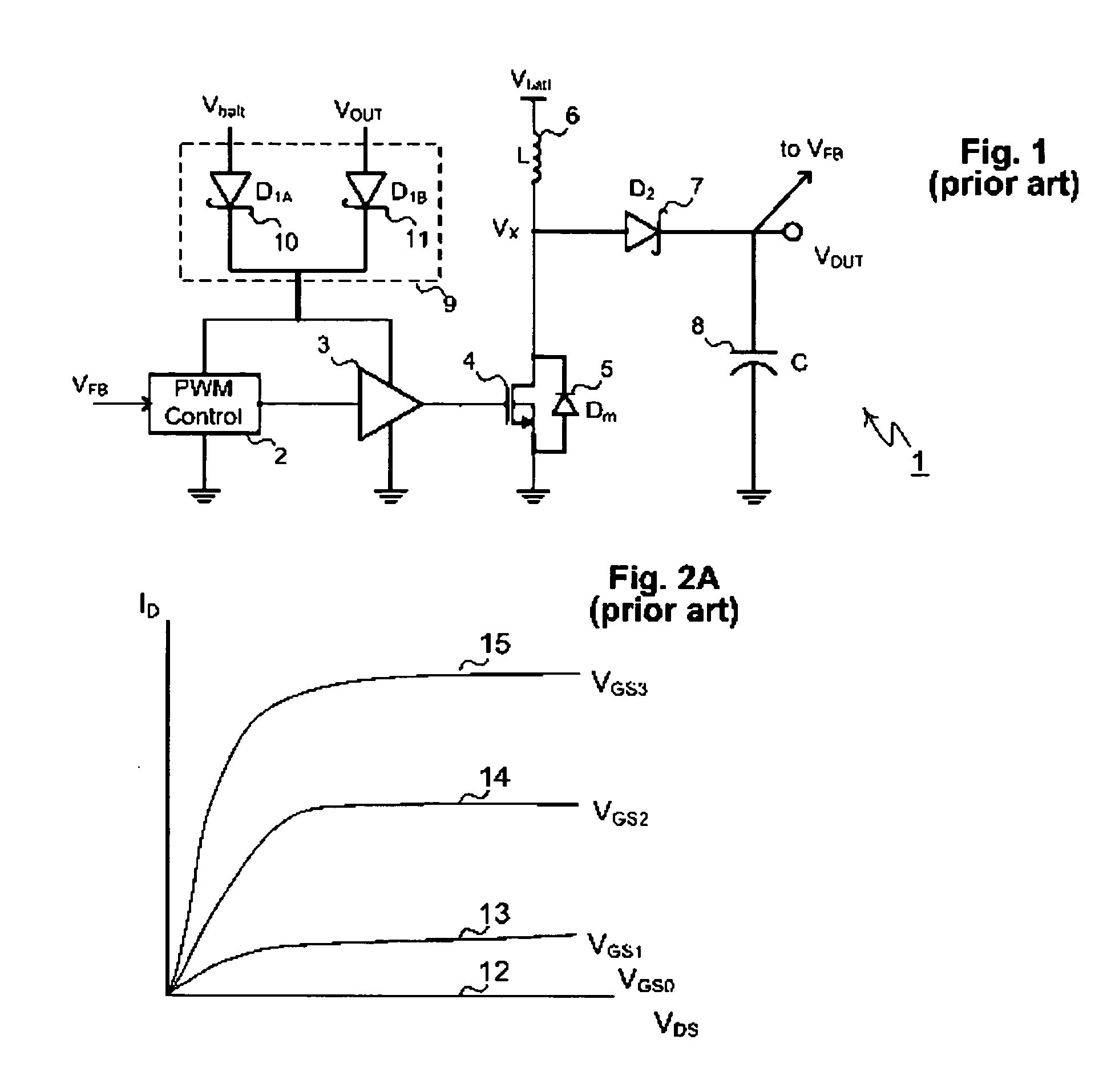

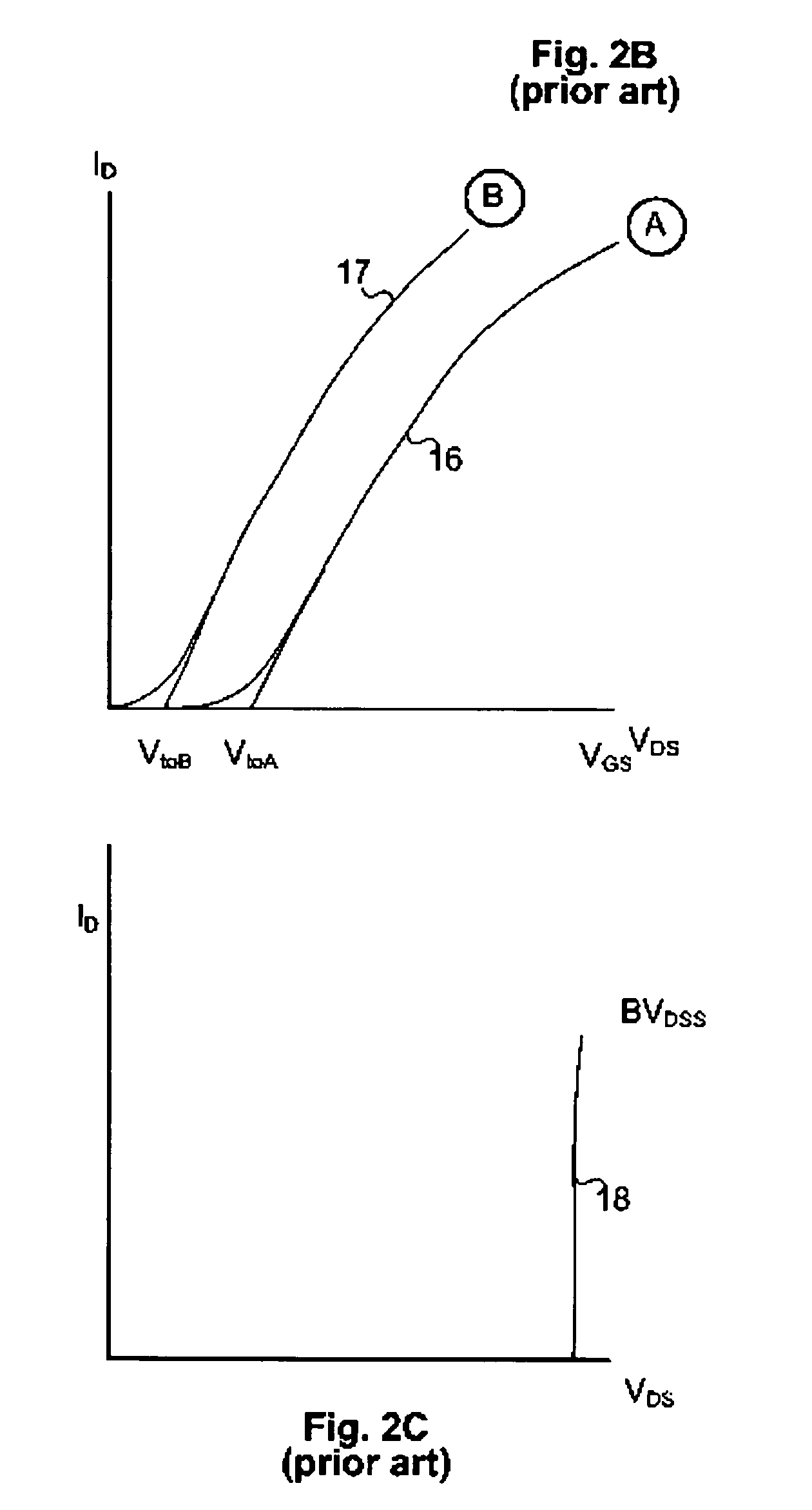

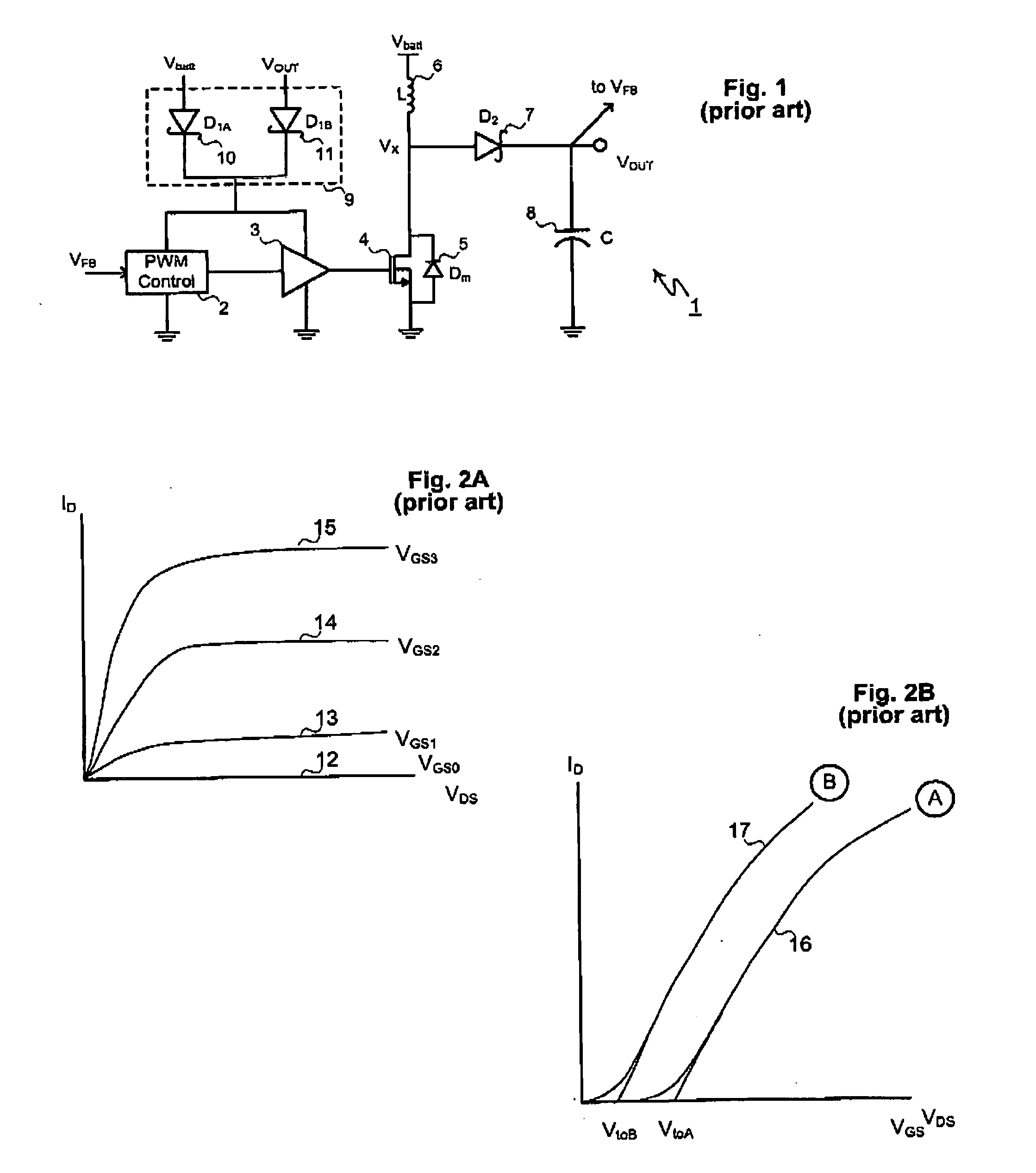

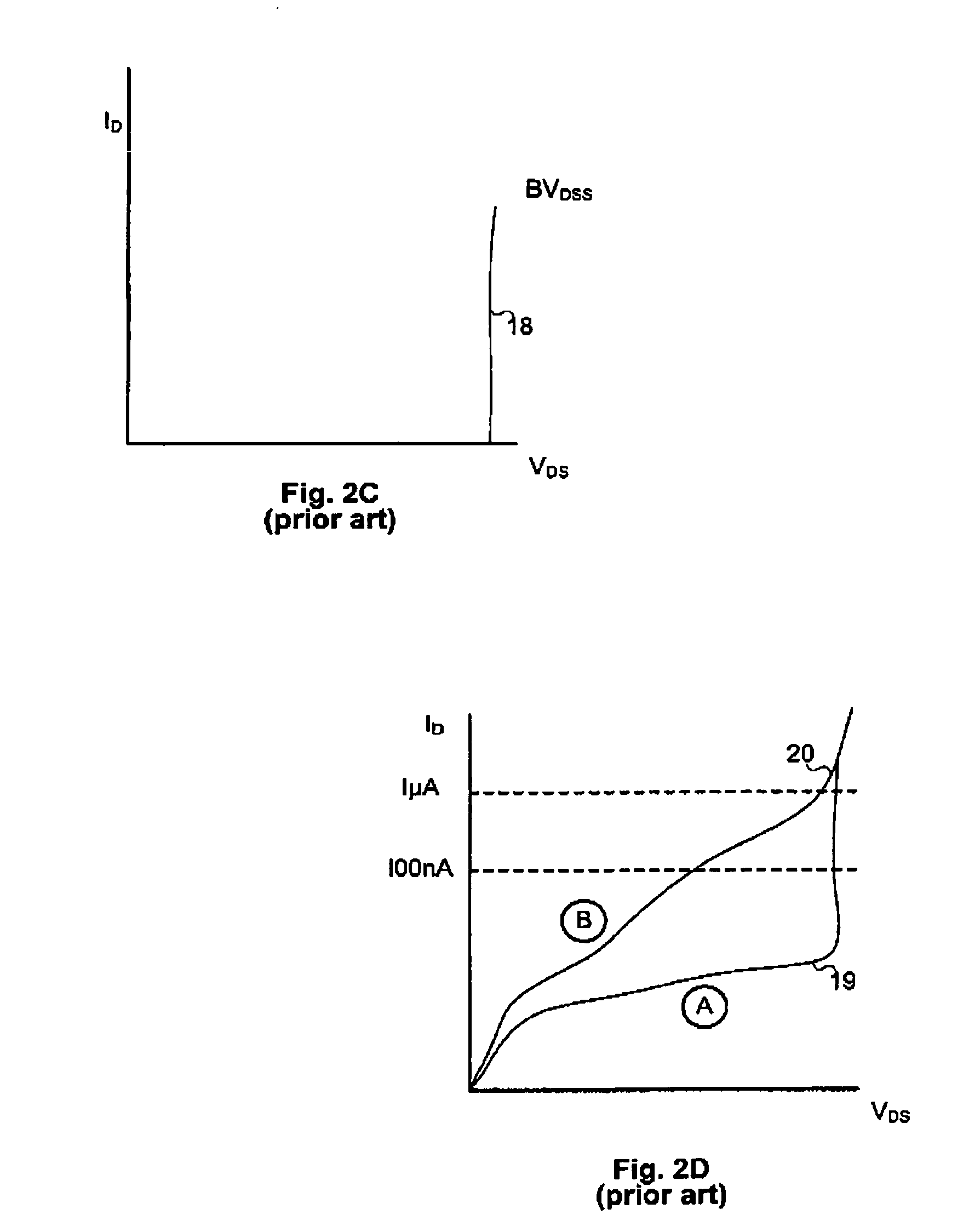

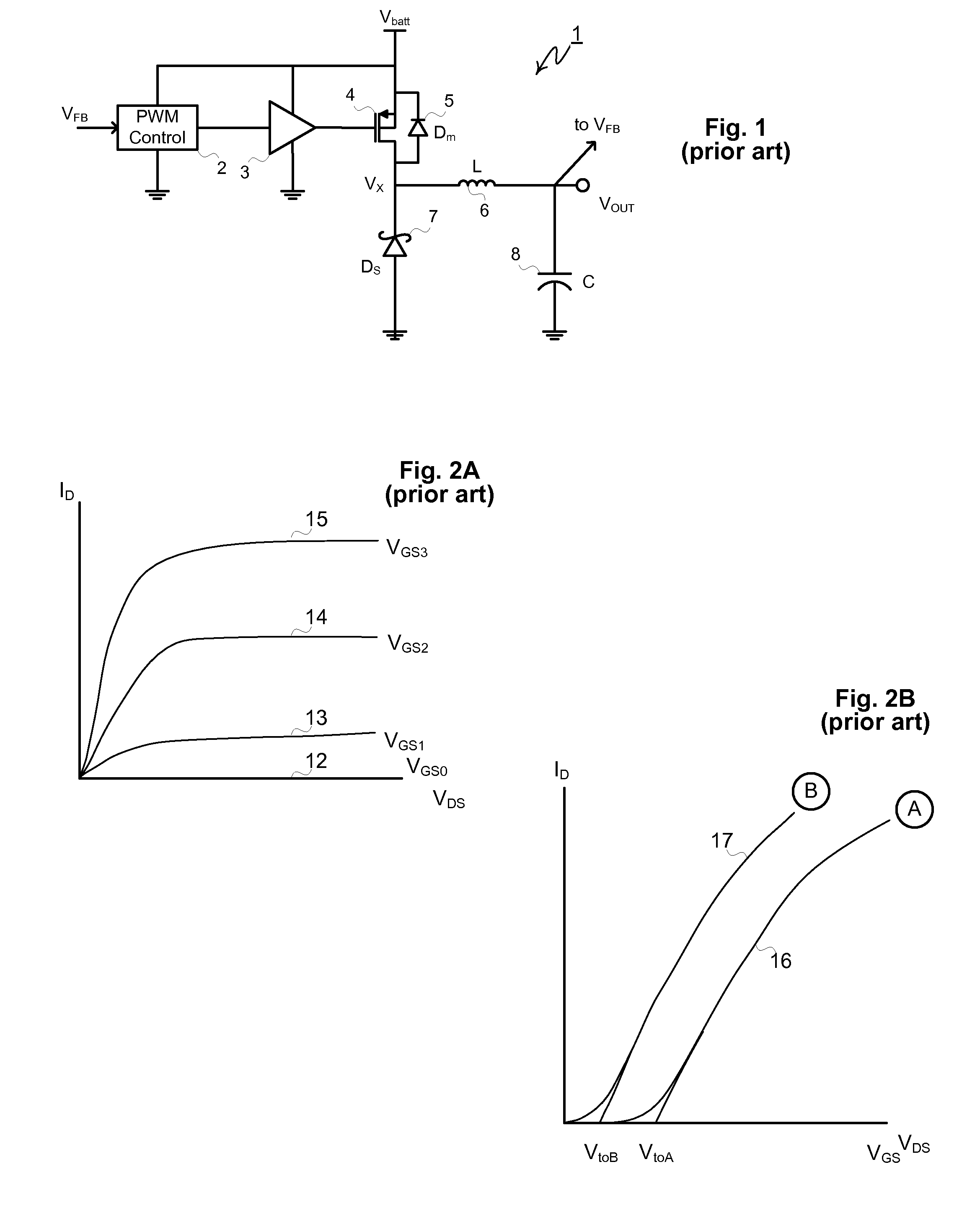

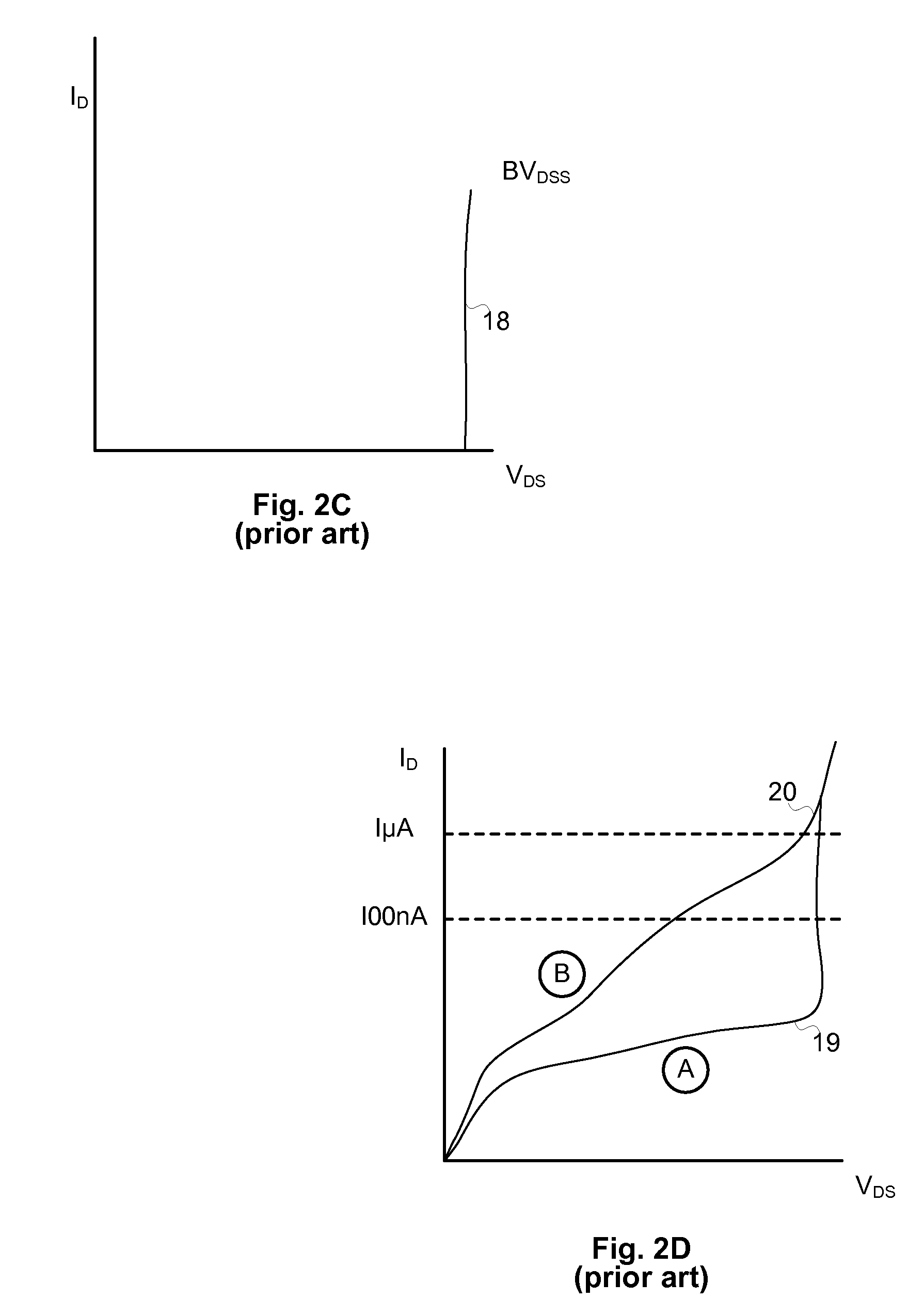

High-Frequency Power MESFET Boost Switching Power Supply

InactiveUS20080186004A1Lower on-resistanceLow off-state drain leakageTransistorDc-dc conversionMOSFETHigh frequency power

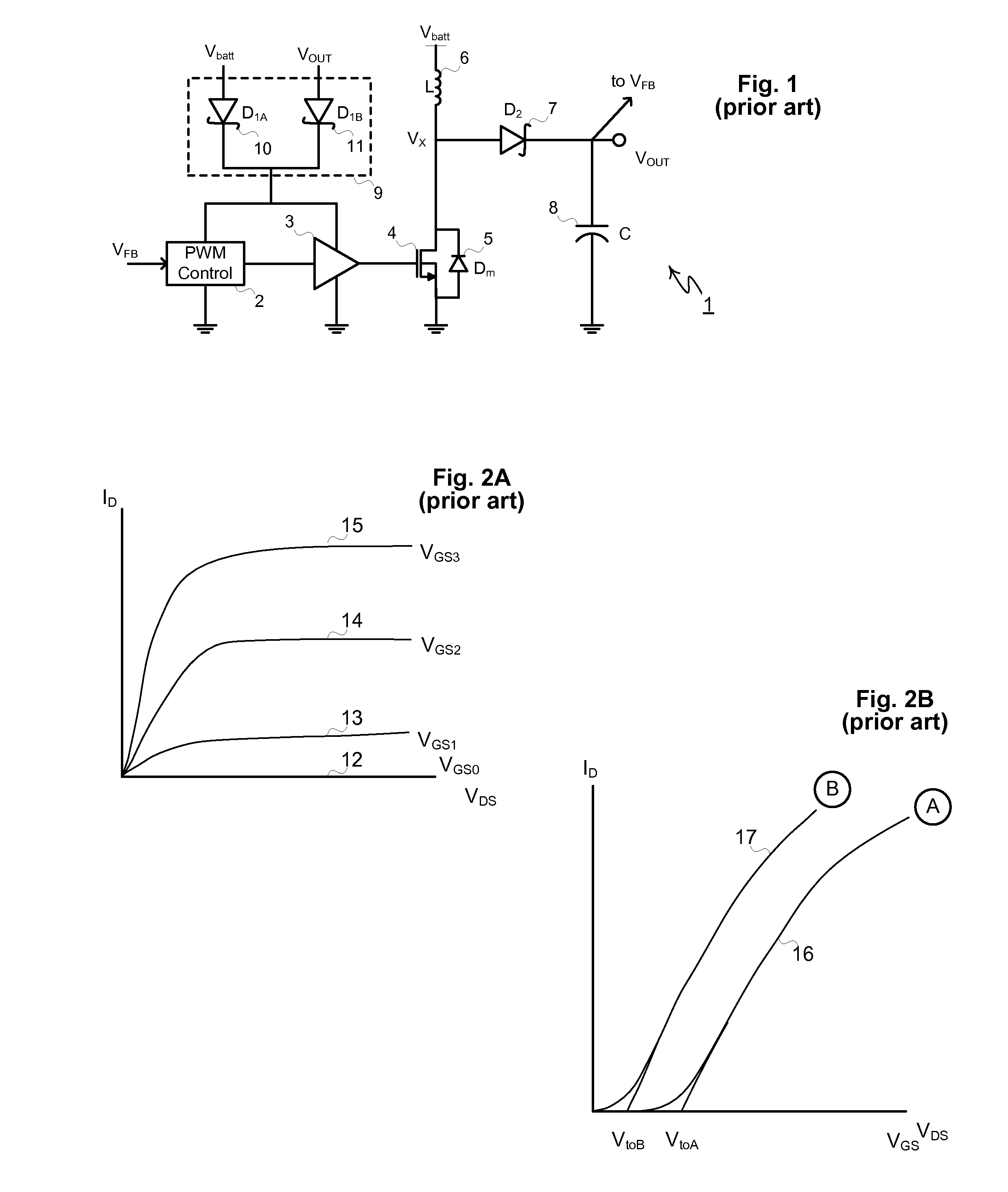

A MESFET based boost converter includes an N-channel MESFET connected to a node Vx. An inductor connects the node Vx to a battery or other power source. The node Vx is also connected to an output node via a Schottky diode or a second MESFET or both. A control circuit drives the MESFET (and the second MESFET) so that the inductor is alternately connected to ground and to the output node. The maximum voltage impressed across the low side MESFET is optionally clamped by a Zener diode. In some implementations, the MESFET is connected in series with a MOSFET. The MOSFET is switched off during sleep or standby modes to minimize leakage current through the MESFET. The MOSFET is therefore switched at a low frequency compared to the MESFET and does not contribute significantly to switching losses in the converter. In other implementations, more than one MESFET is connected in series with a MOSFET, the MOSFETs being switched off during periods of inactivity to suppress leakage currents.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

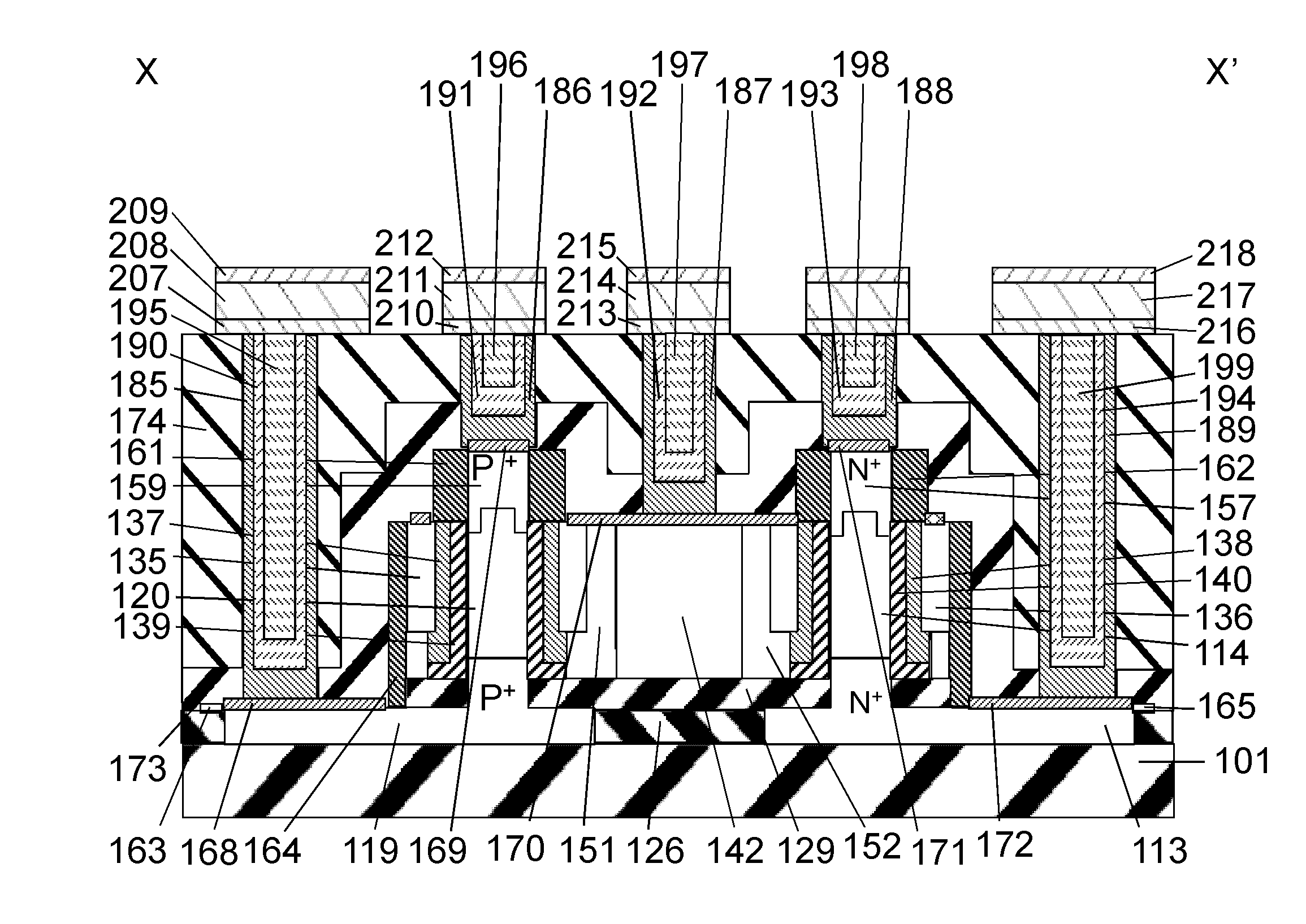

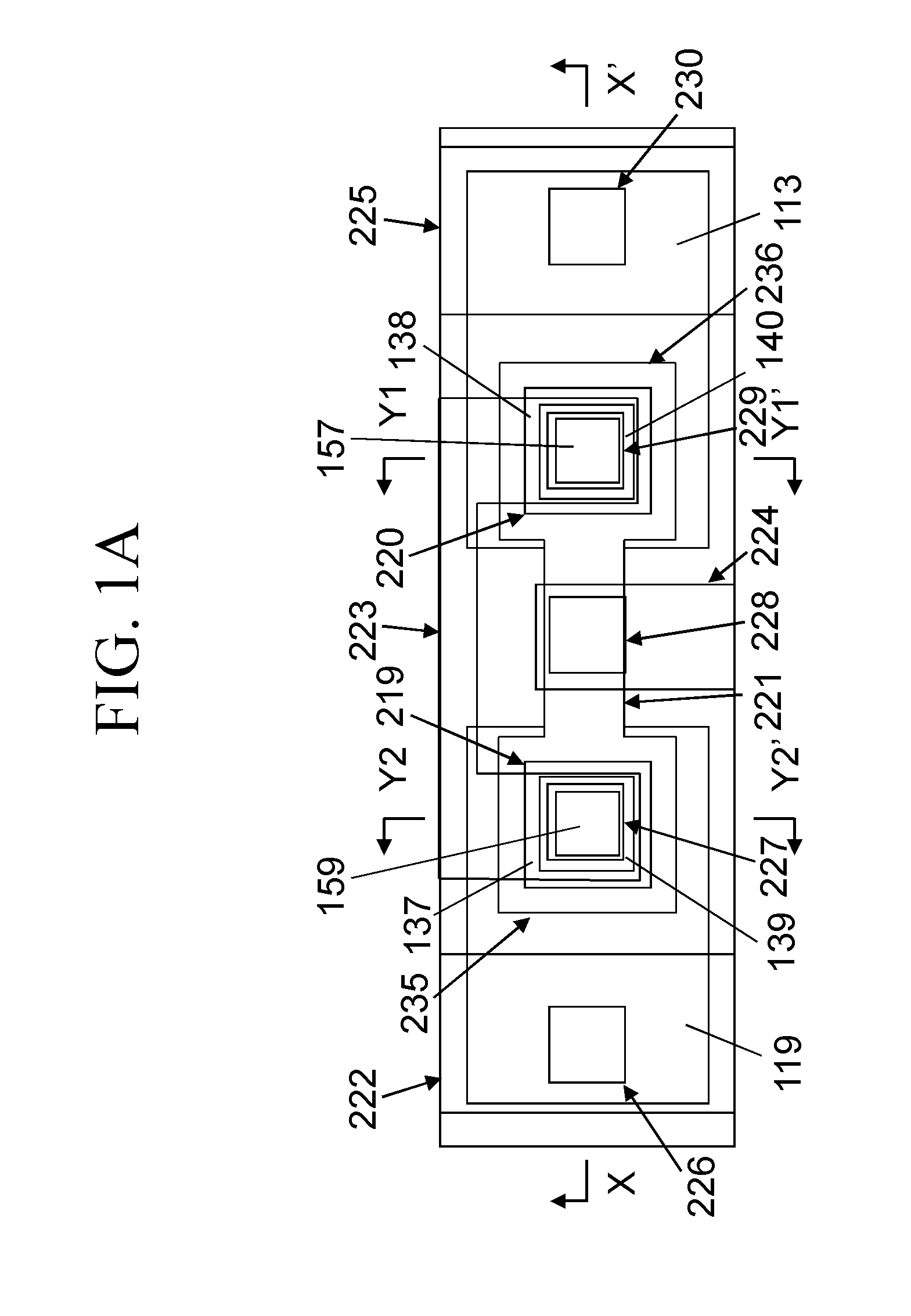

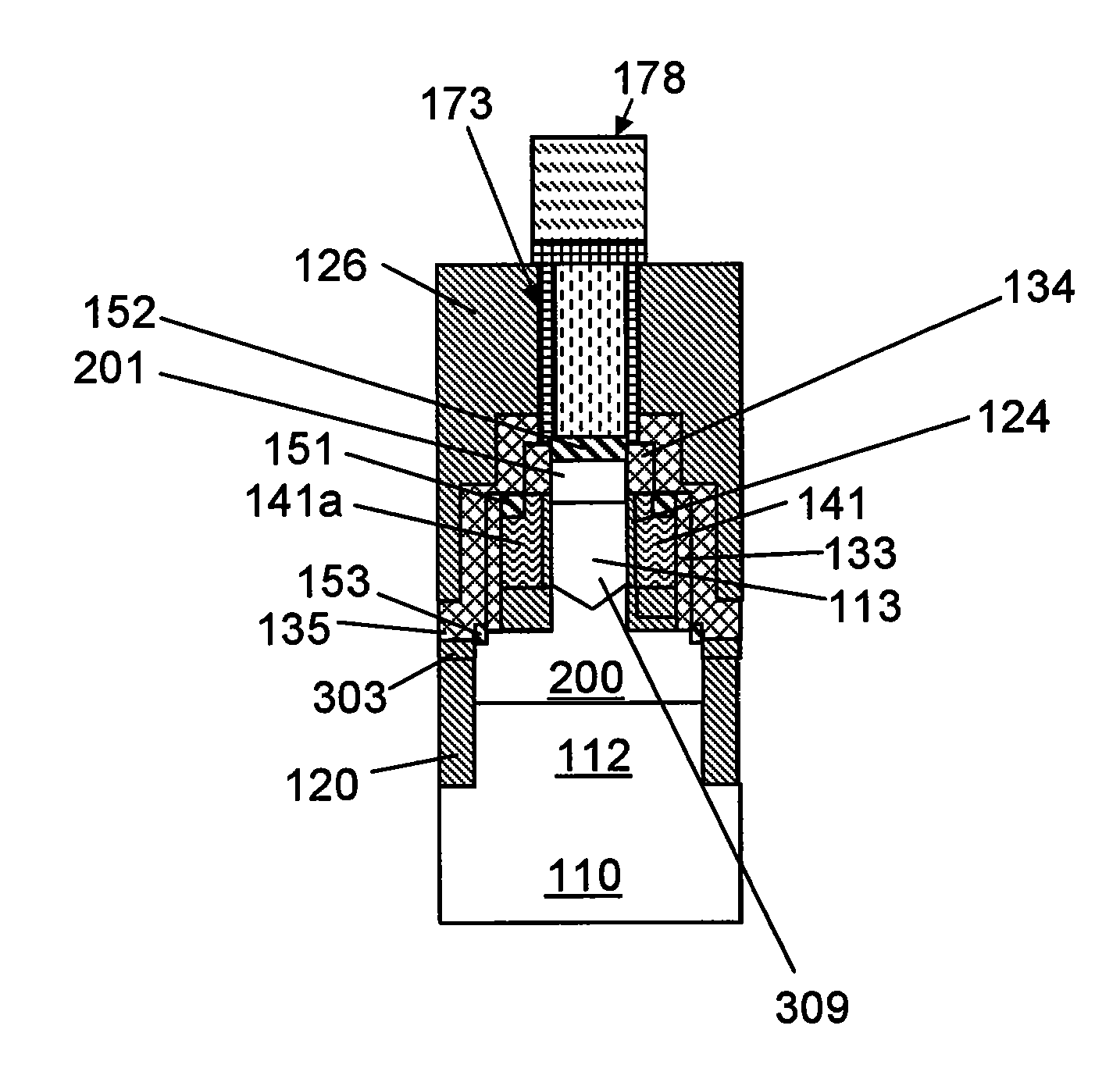

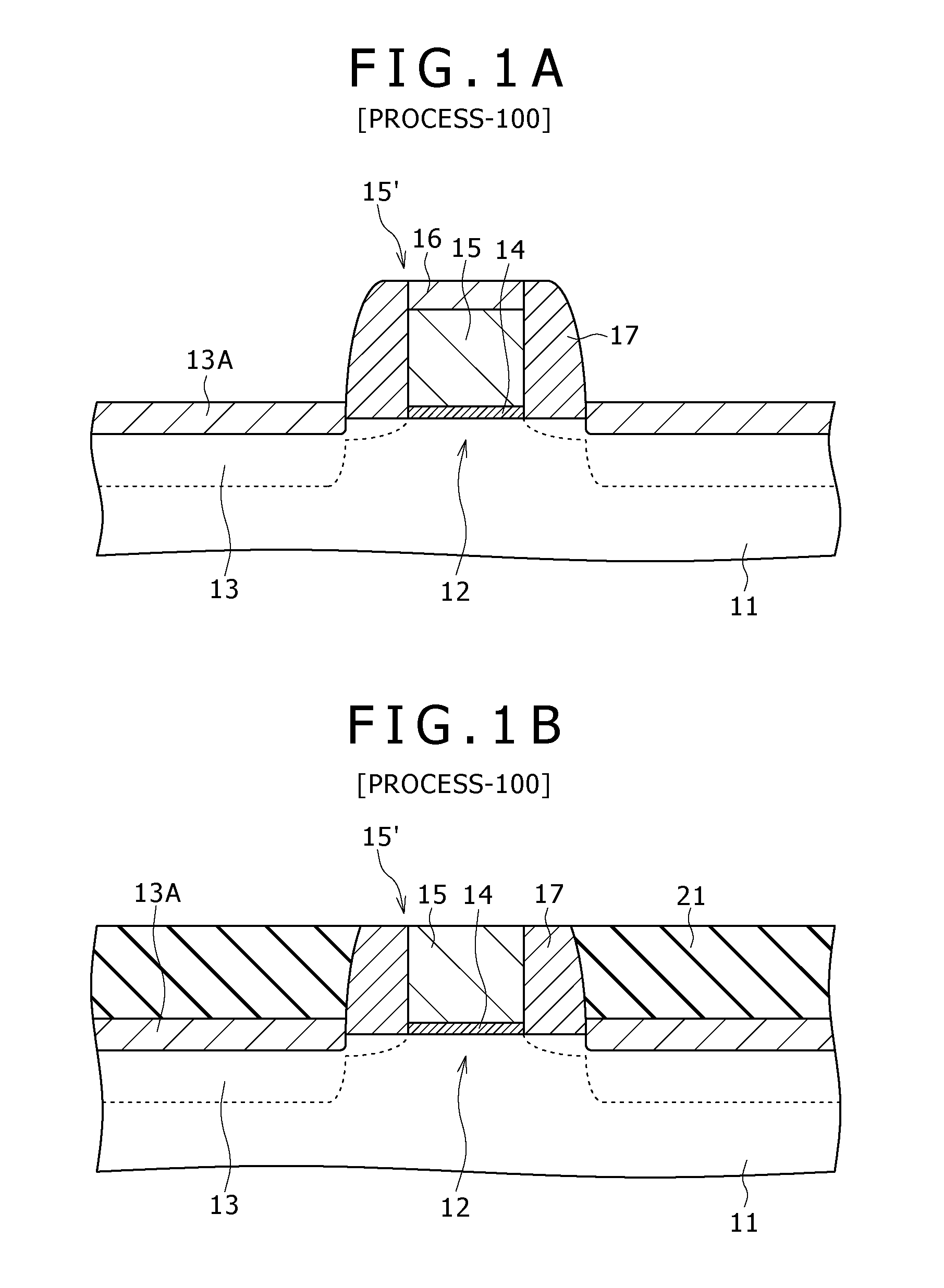

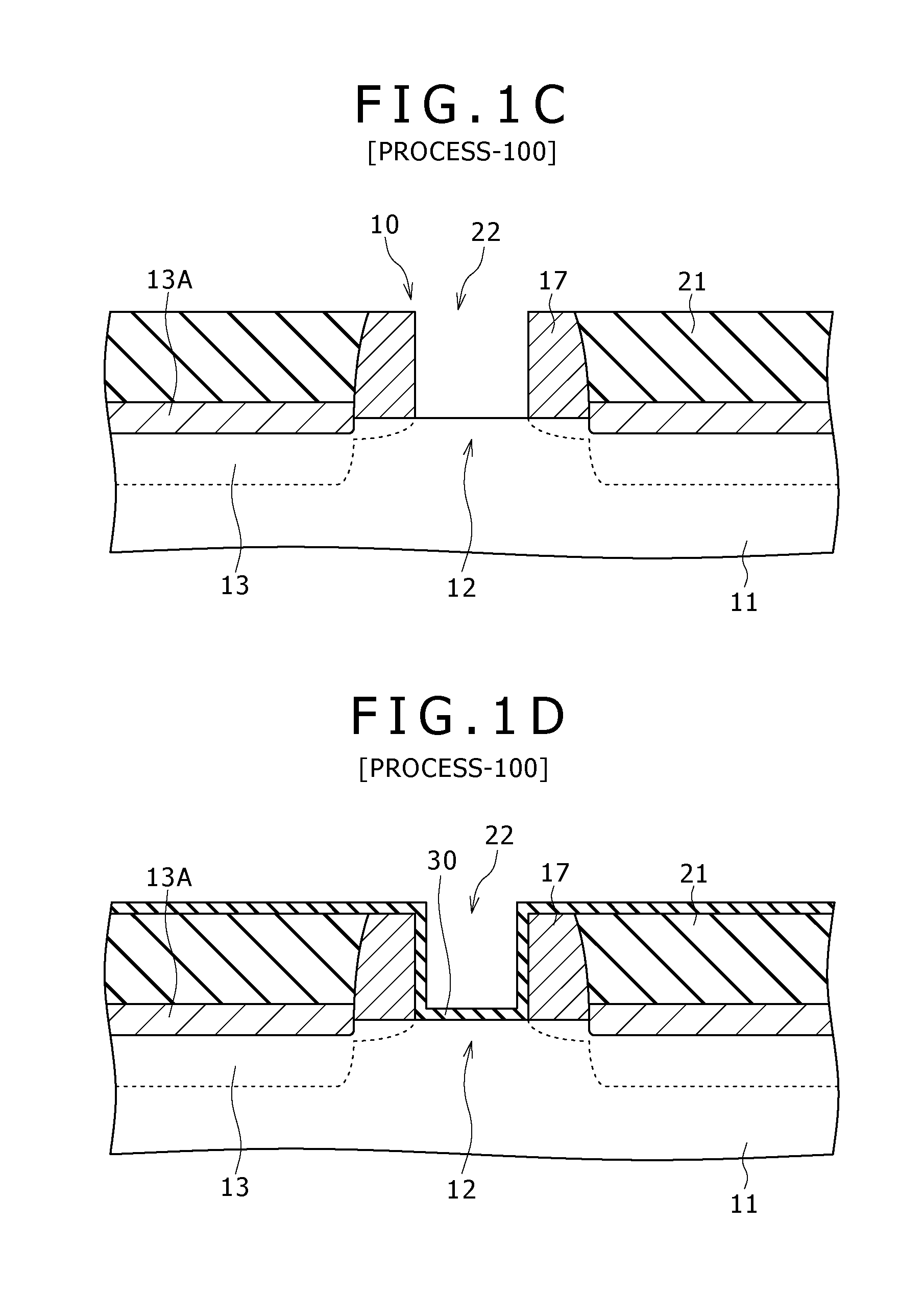

Semiconductor device and production method

ActiveUS20110303973A1Limitation on gate lengthReduce metal pollutionTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceSilicon

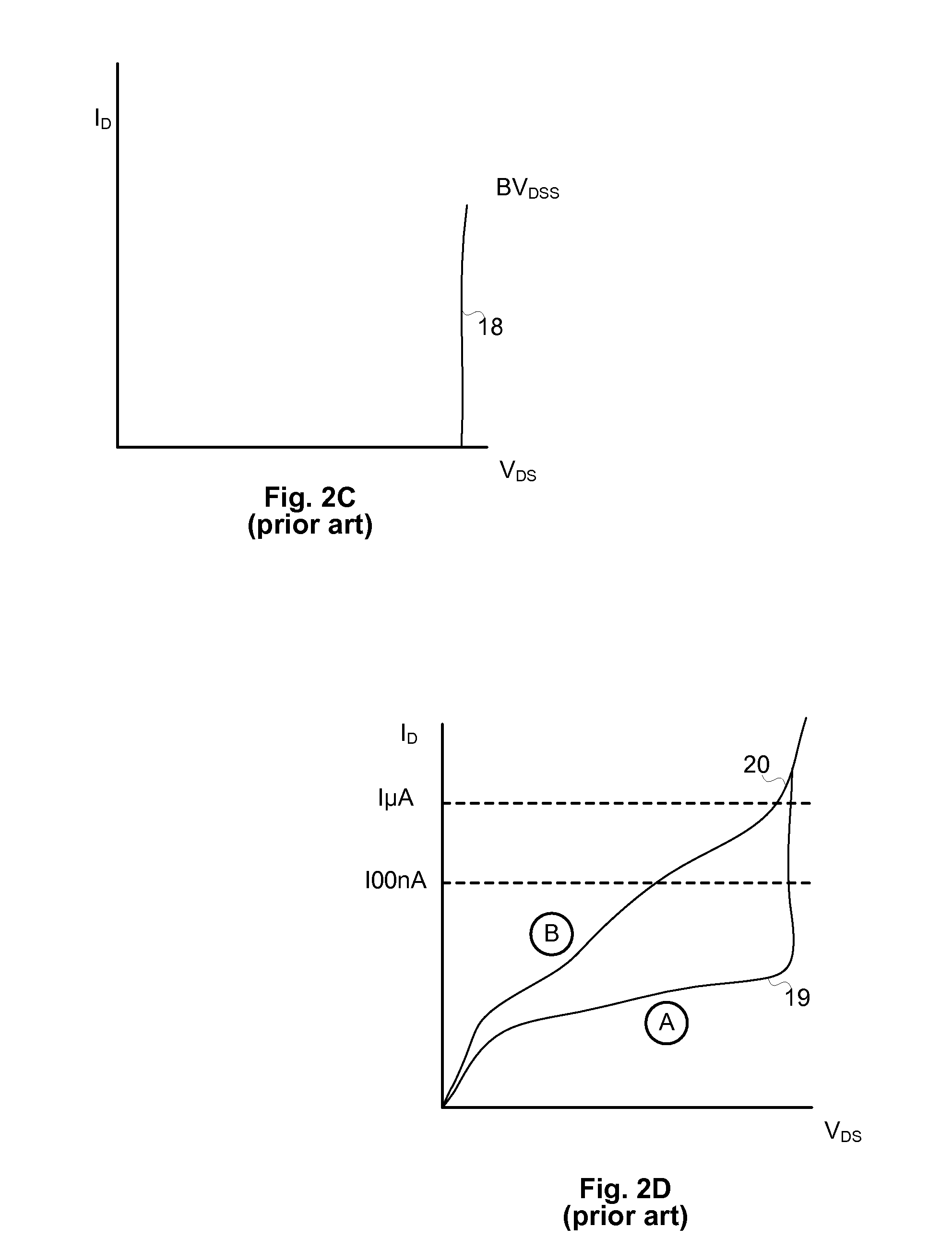

The semiconductor device according to the present invention is an nMOS SGT and is composed of a first n+ type silicon layer, a first gate electrode containing metal and a second n+ type silicon layer arranged on the surface of a first columnar silicon layer positioned vertically on a first planar silicon layer. Furthermore, a first insulating film is positioned between the first gate electrode and the first planar silicon layer, and a second insulating film is positioned on the top surface of the first gate electrode. In addition, the first gate electrode containing metal is surrounded by the first n+ type silicon layer, the second n+ type silicon layer, the first insulating film and the second insulating film.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

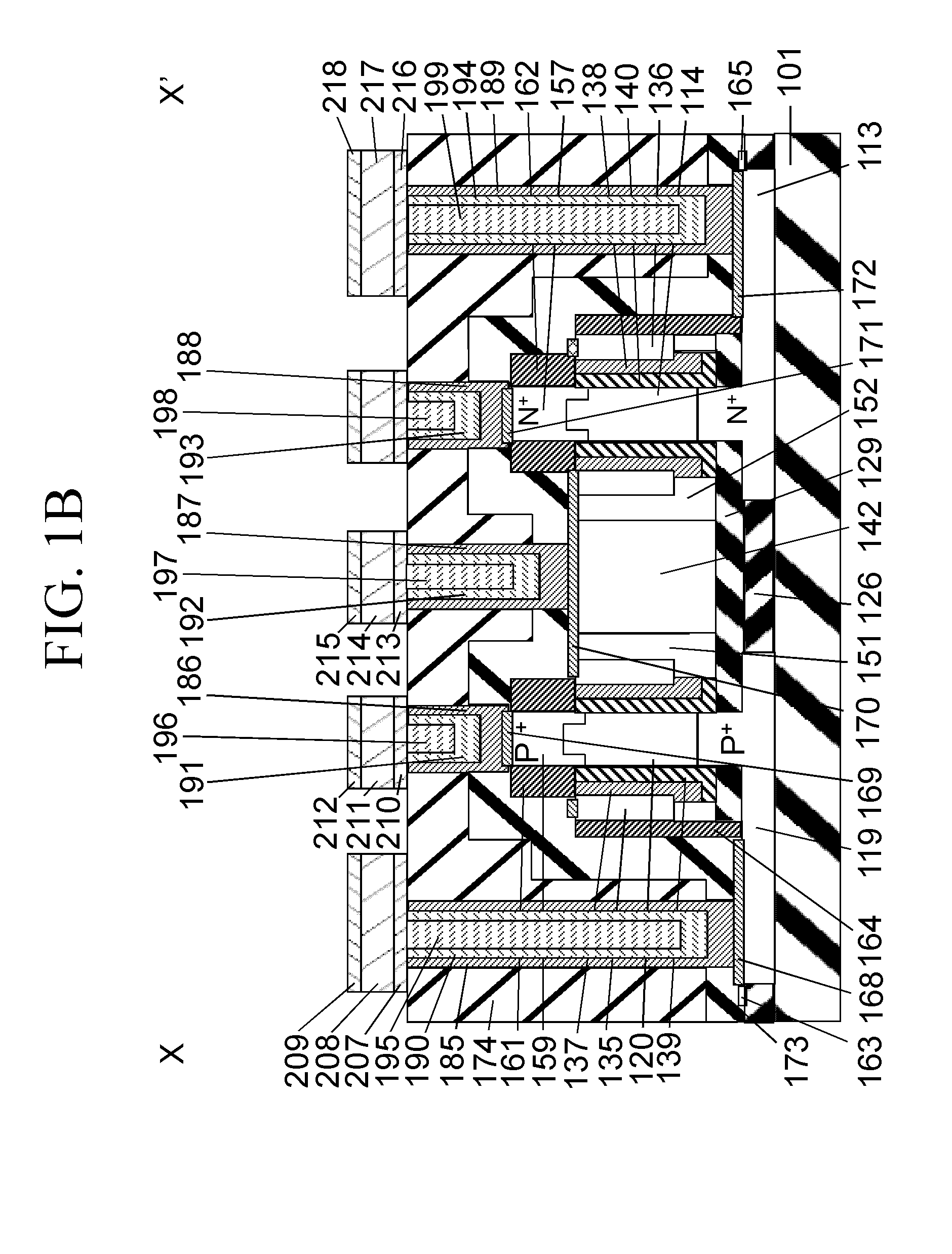

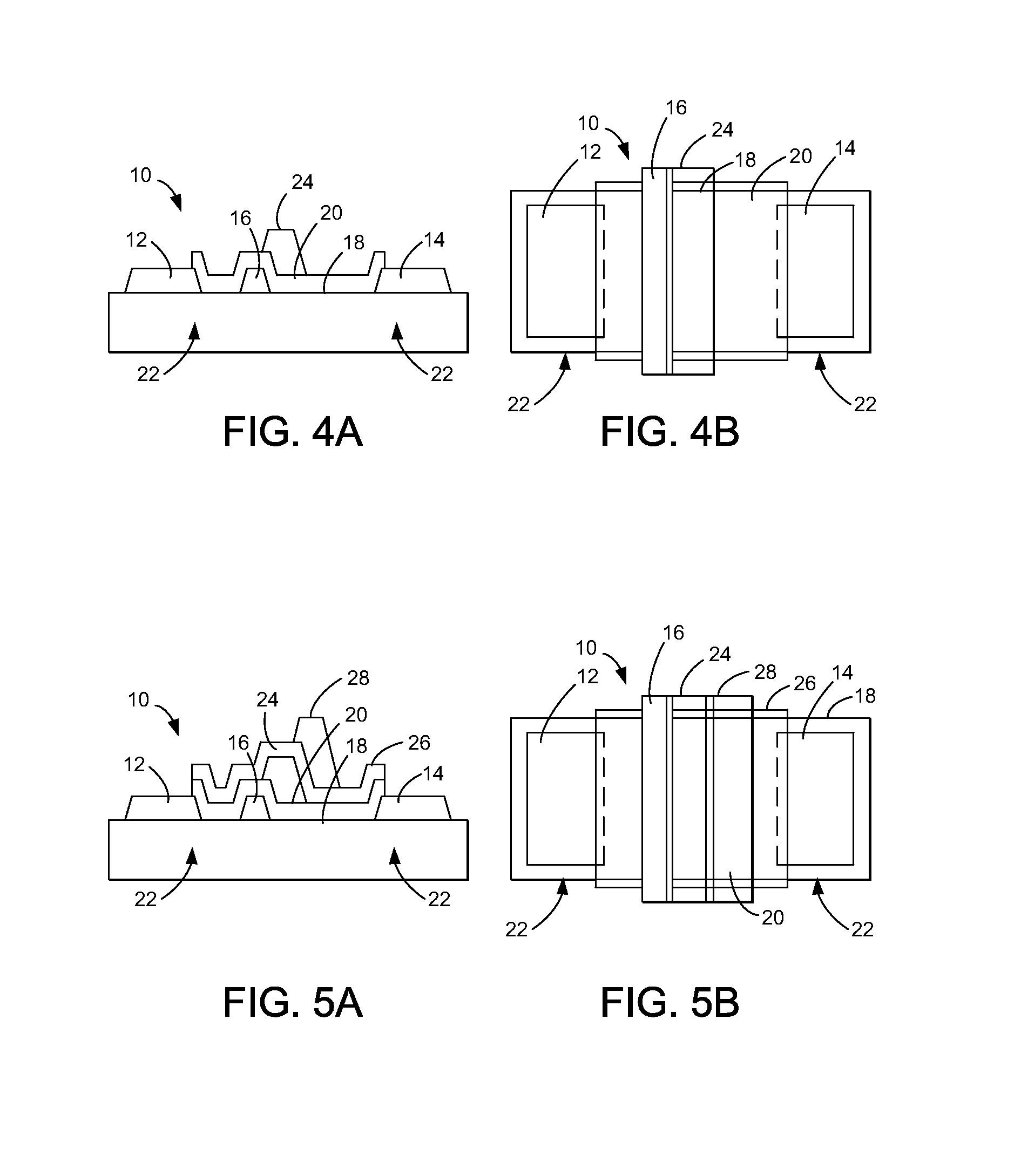

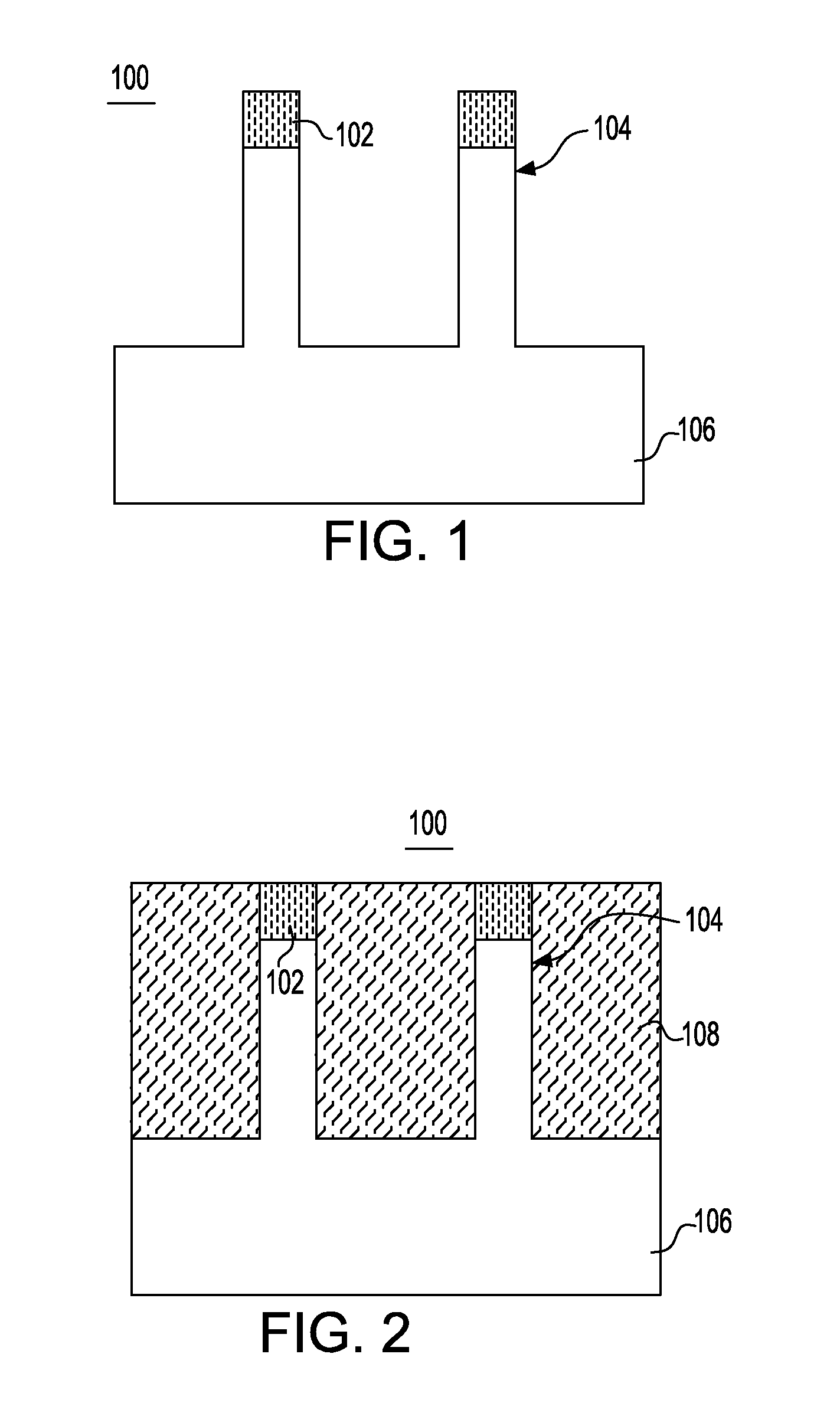

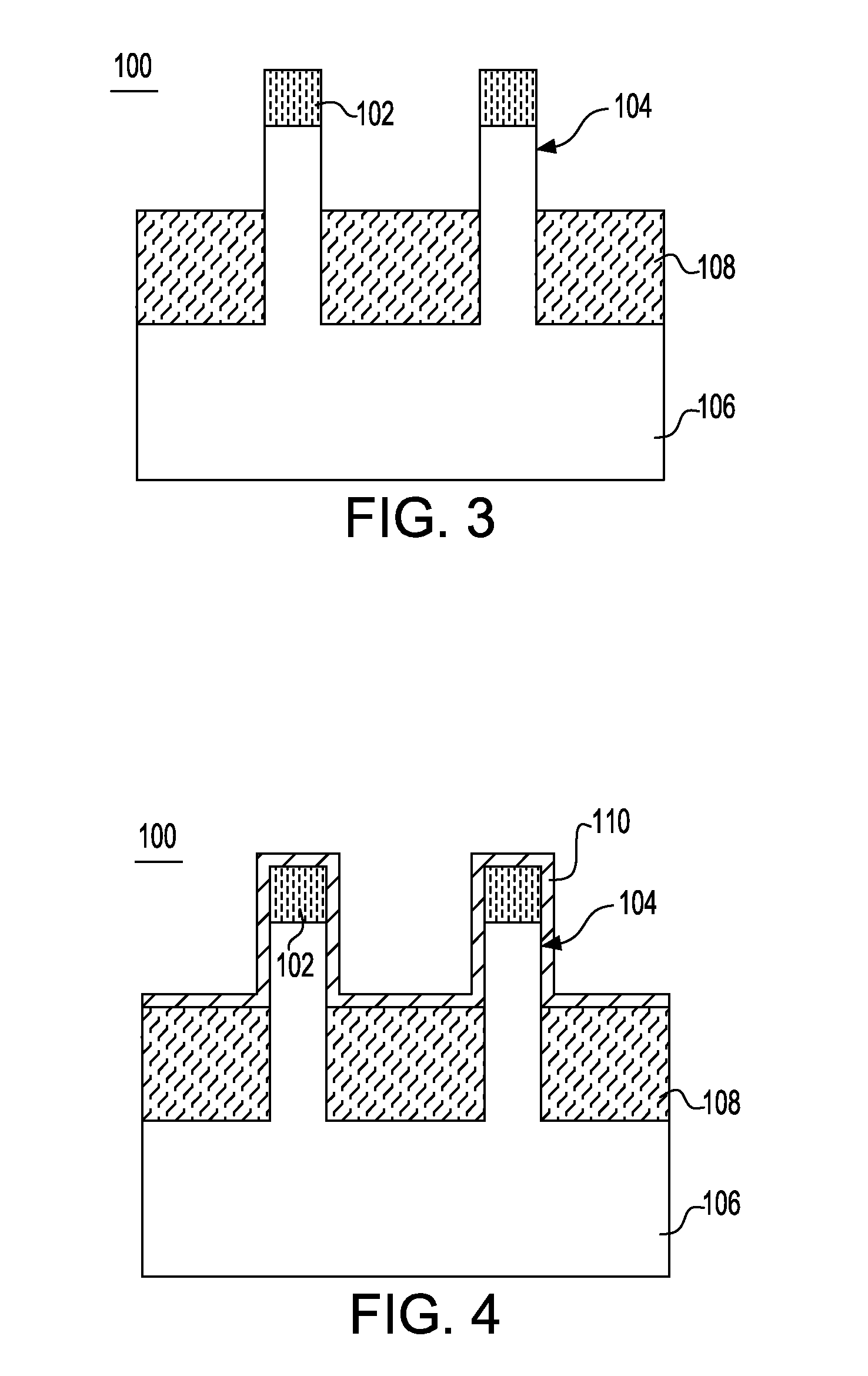

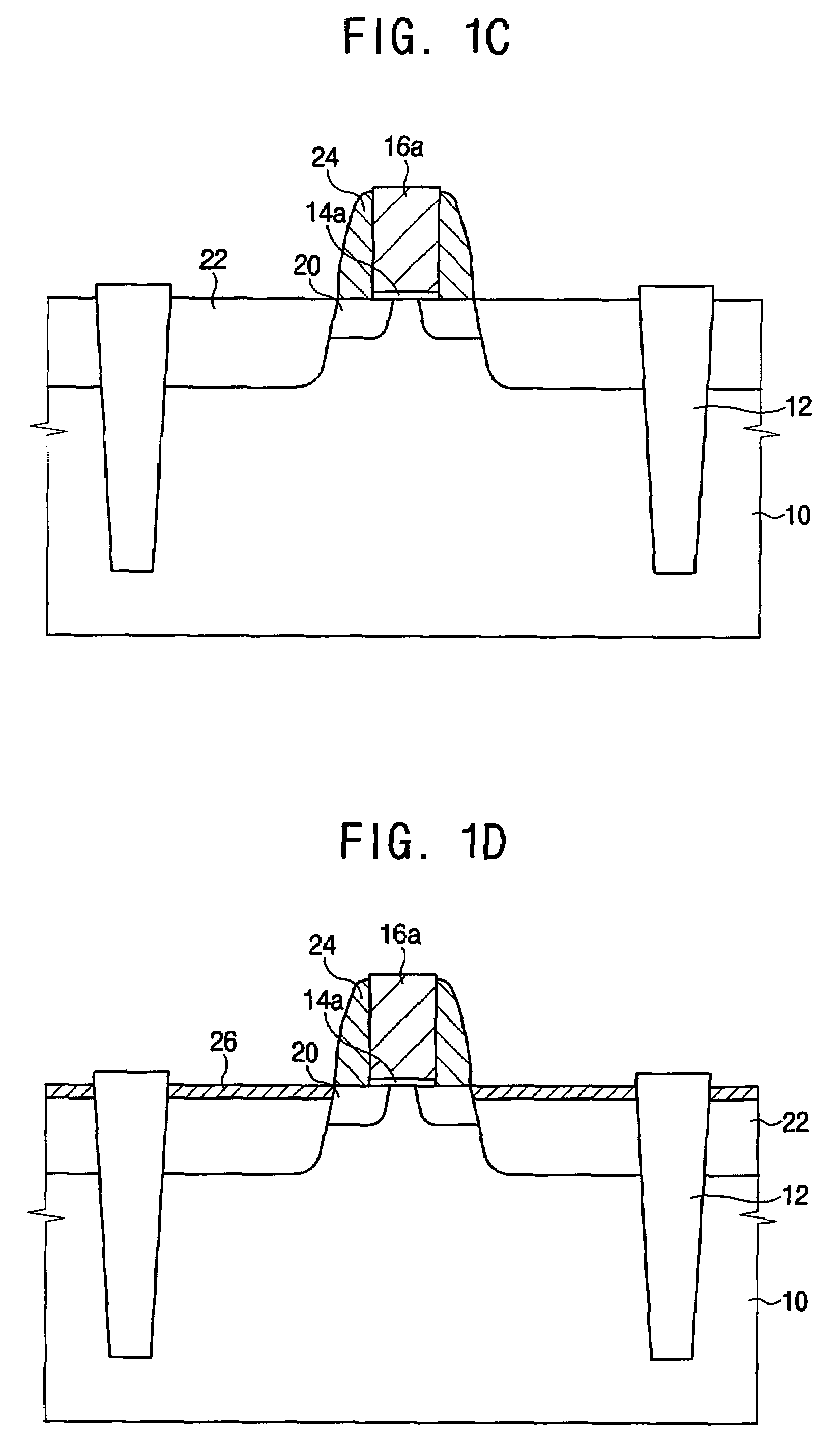

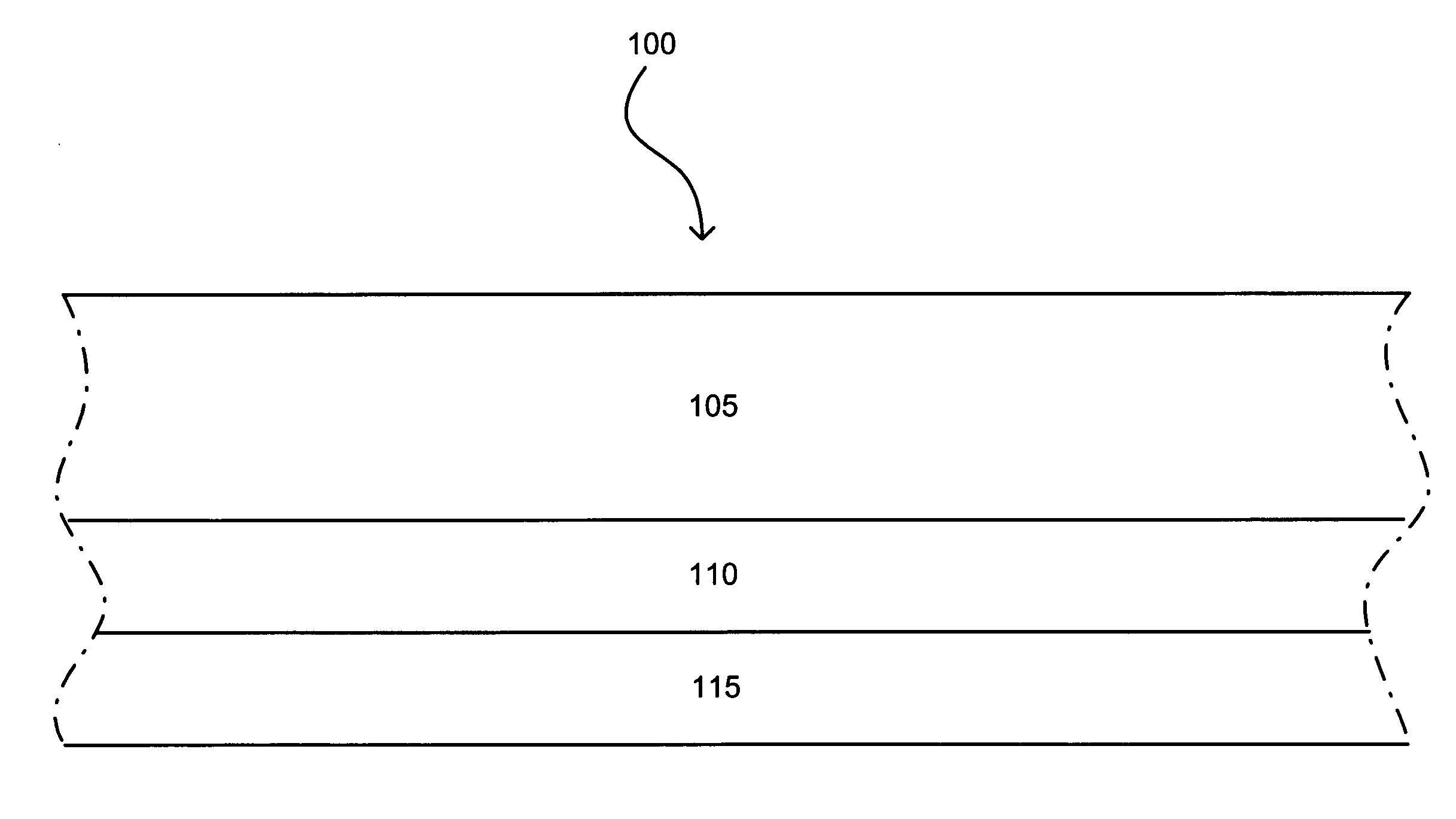

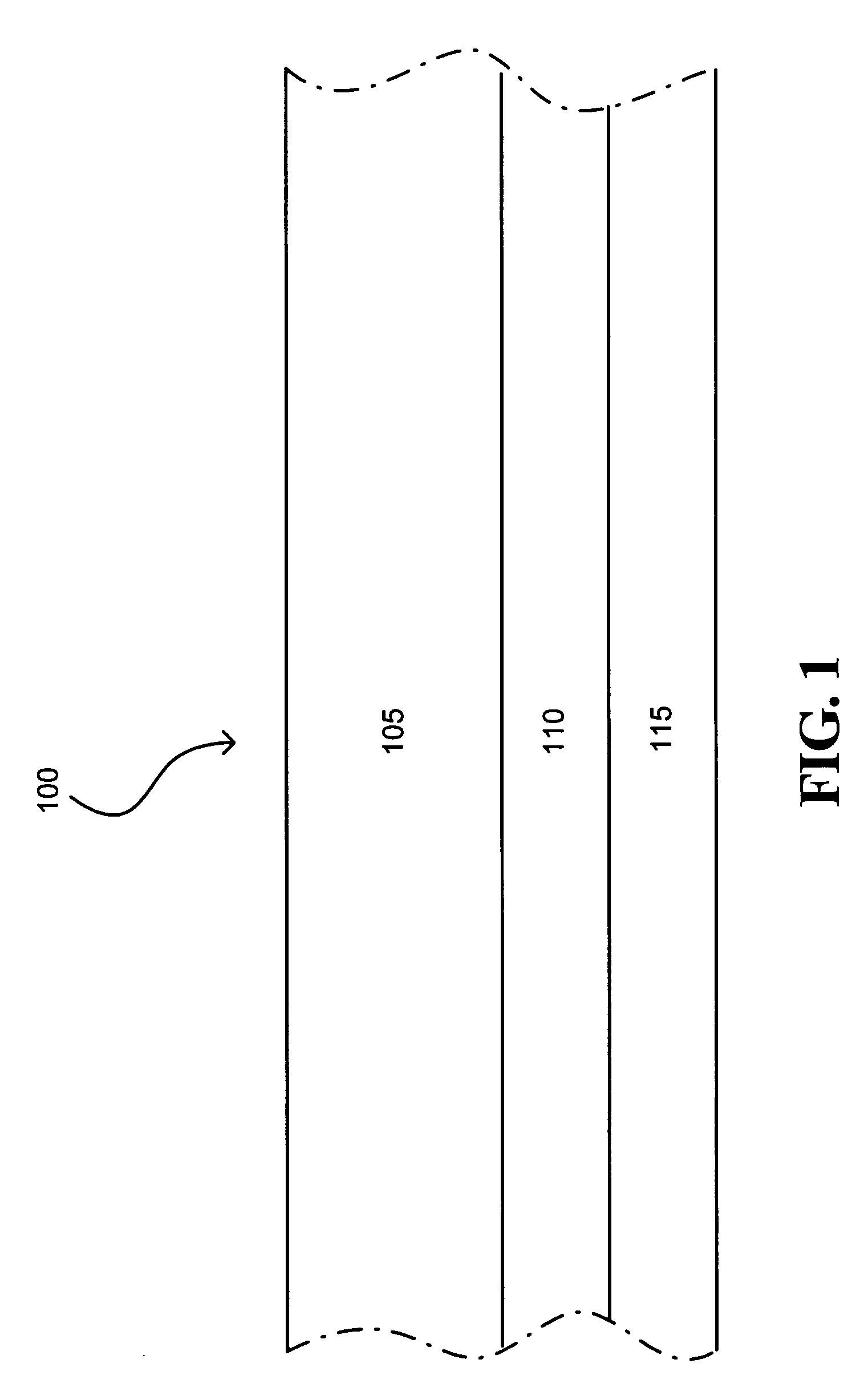

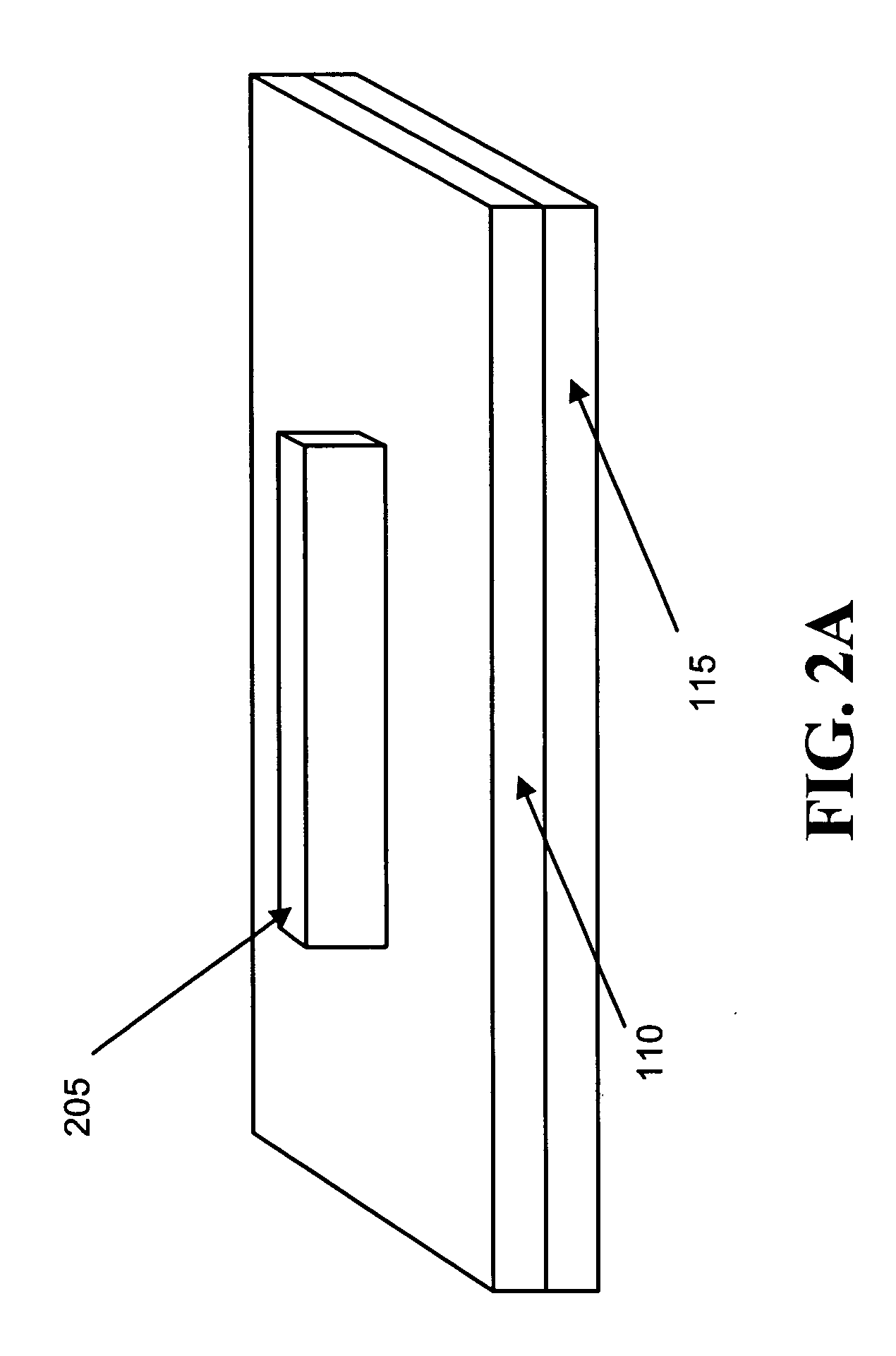

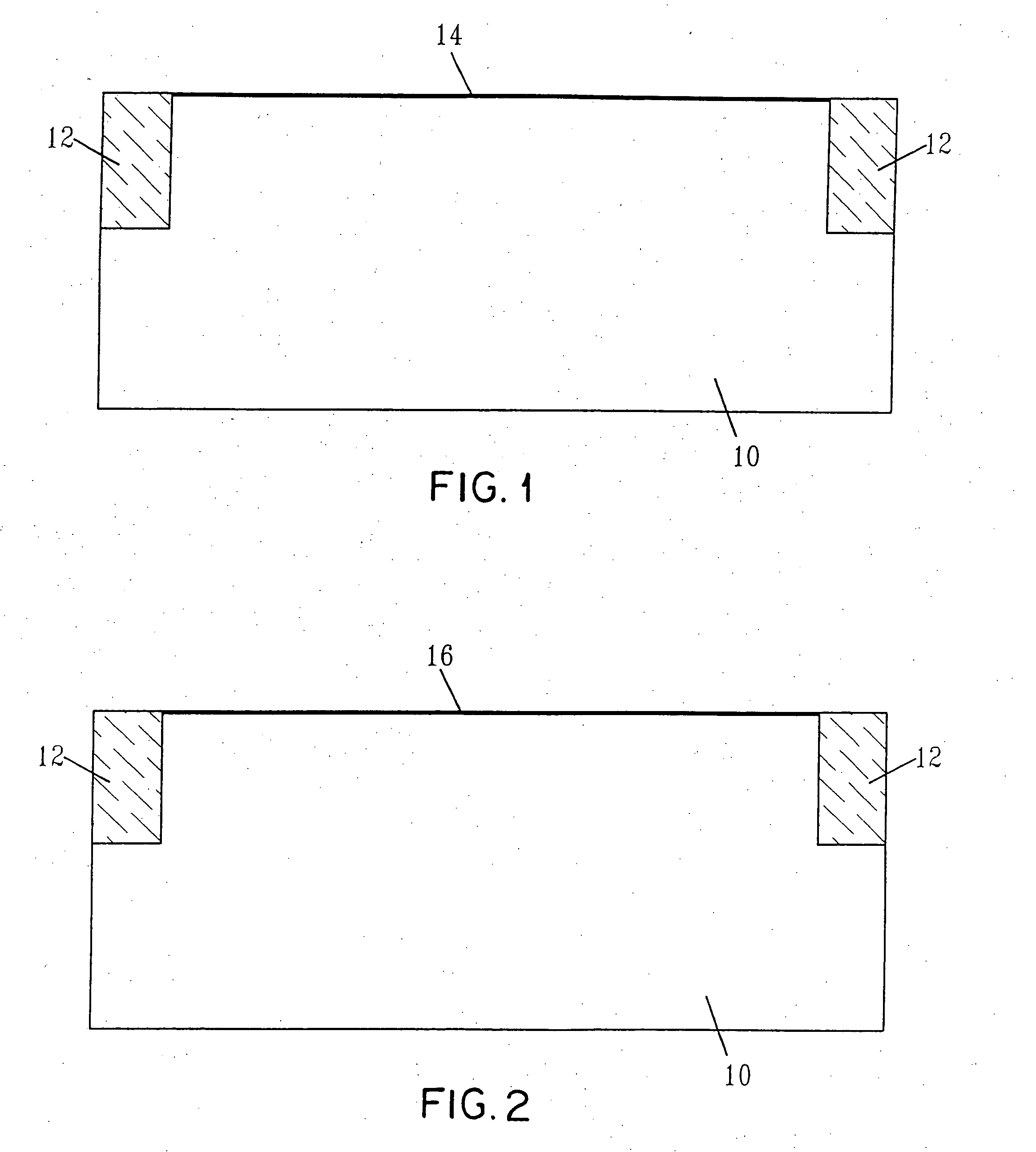

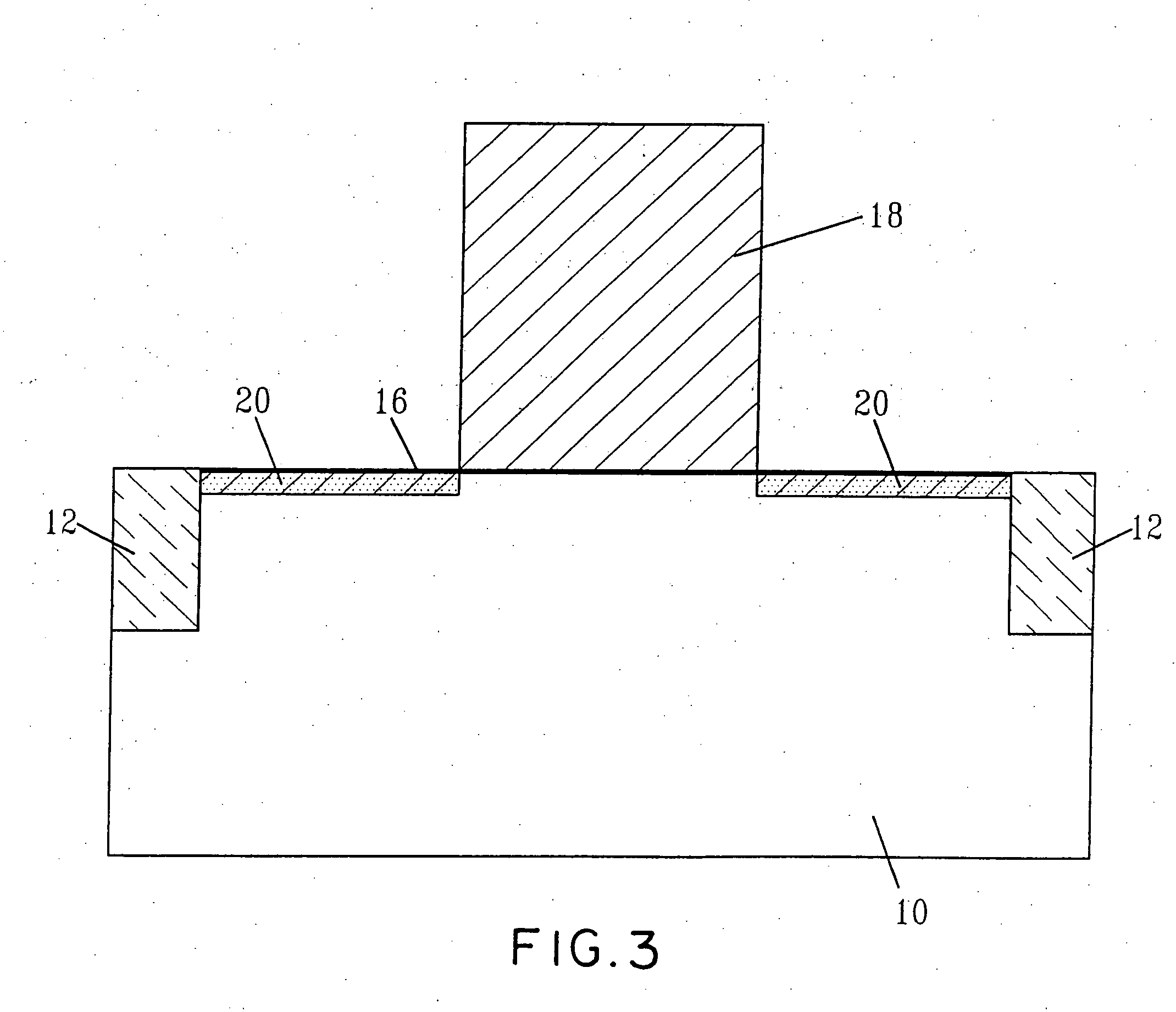

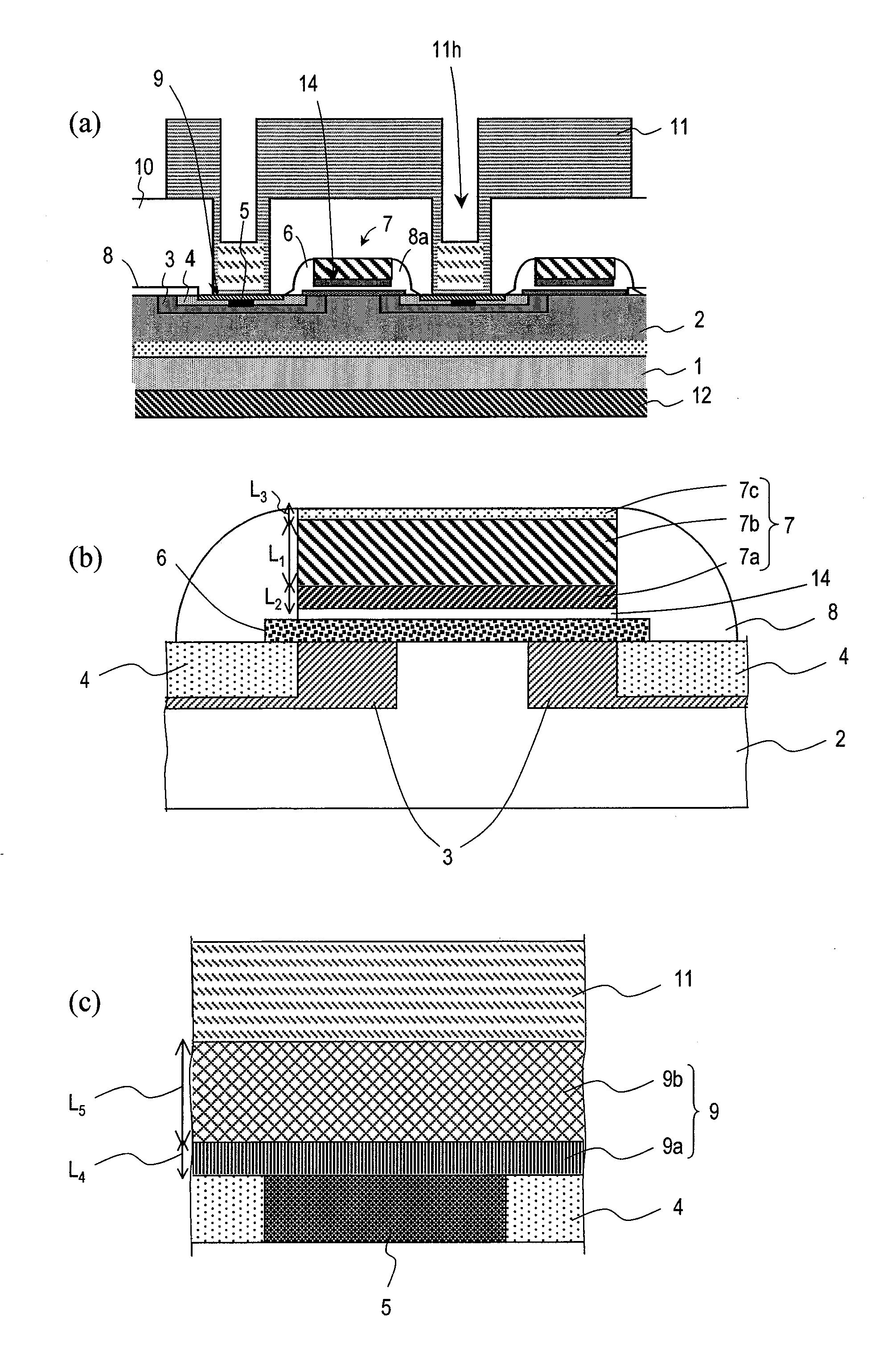

Fabrication of single or multiple gate field plates

ActiveUS7812369B2Strict controlLower gate resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDielectricManufacturing technology

A process for fabricating single or multiple gate field plates using consecutive steps of dielectric material deposition / growth, dielectric material etch and metal evaporation on the surface of a field effect transistors. This fabrication process permits a tight control on the field plate operation since dielectric material deposition / growth is typically a well controllable process. Moreover, the dielectric material deposited on the device surface does not need to be removed from the device intrinsic regions: this essentially enables the realization of field-plated devices without the need of low-damage dielectric material dry / wet etches. Using multiple gate field plates also reduces gate resistance by multiple connections, thus improving performances of large periphery and / or sub-micron gate devices.

Owner:RGT UNIV OF CALIFORNIA +1

High Frequency Power MESFET Gate Drive Circuits

InactiveUS20070146020A1Lower on-resistanceRobust avalancheTransistorDc-dc conversionDriver circuitHigh frequency power

A series of gate drive circuits for MESFETs are provided. The gate drive circuits are intended to be used in switching regulators where at least one switching device is an N-channel MESFET. For regulators of this type, the gate drive circuits provide gate drive at the correct voltage to ensure that MESFETs are neither under driven (resulting in incorrect circuit operation) nor over driven (resulting in MESFET damage or excess current or power loss).

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

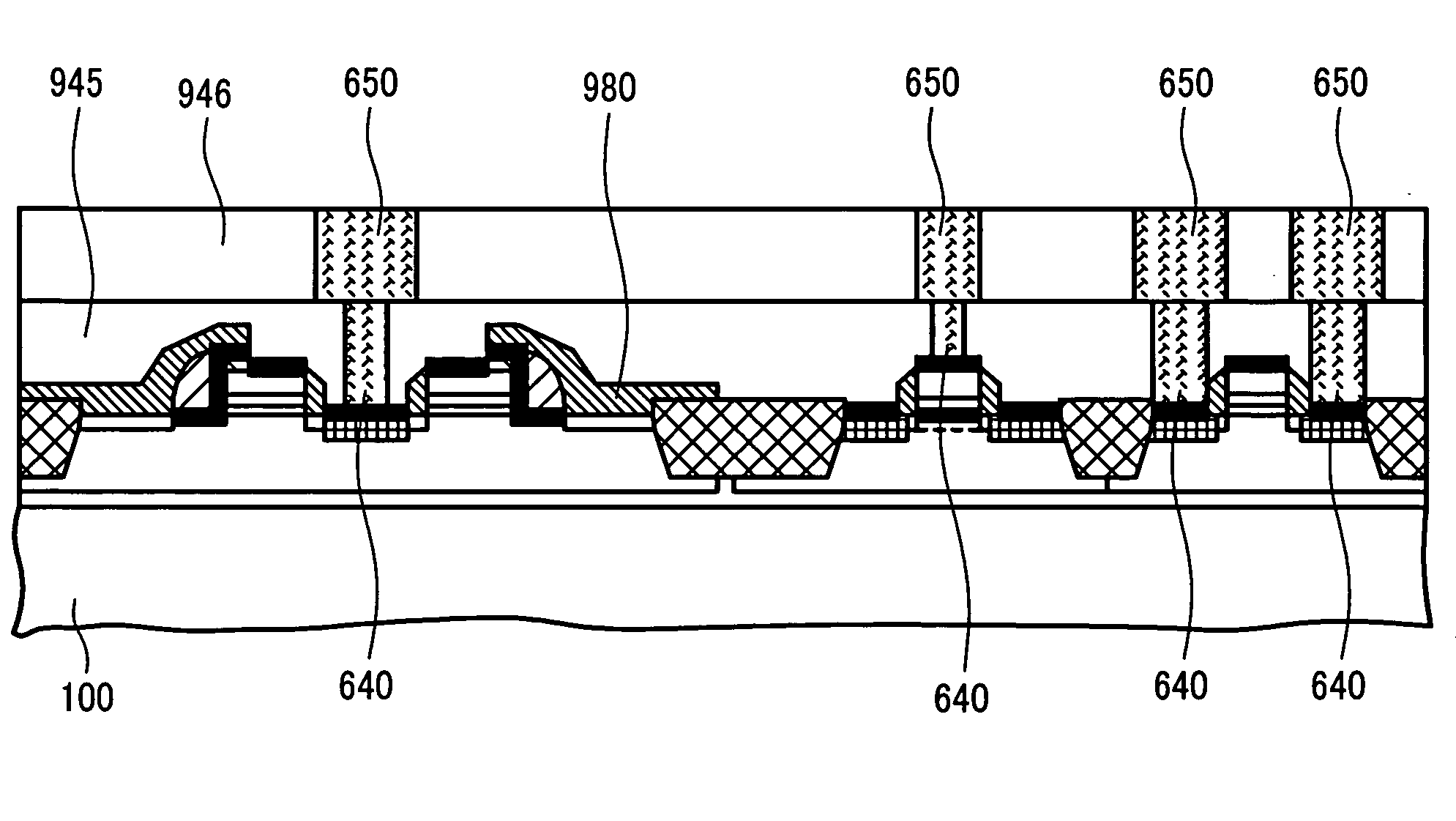

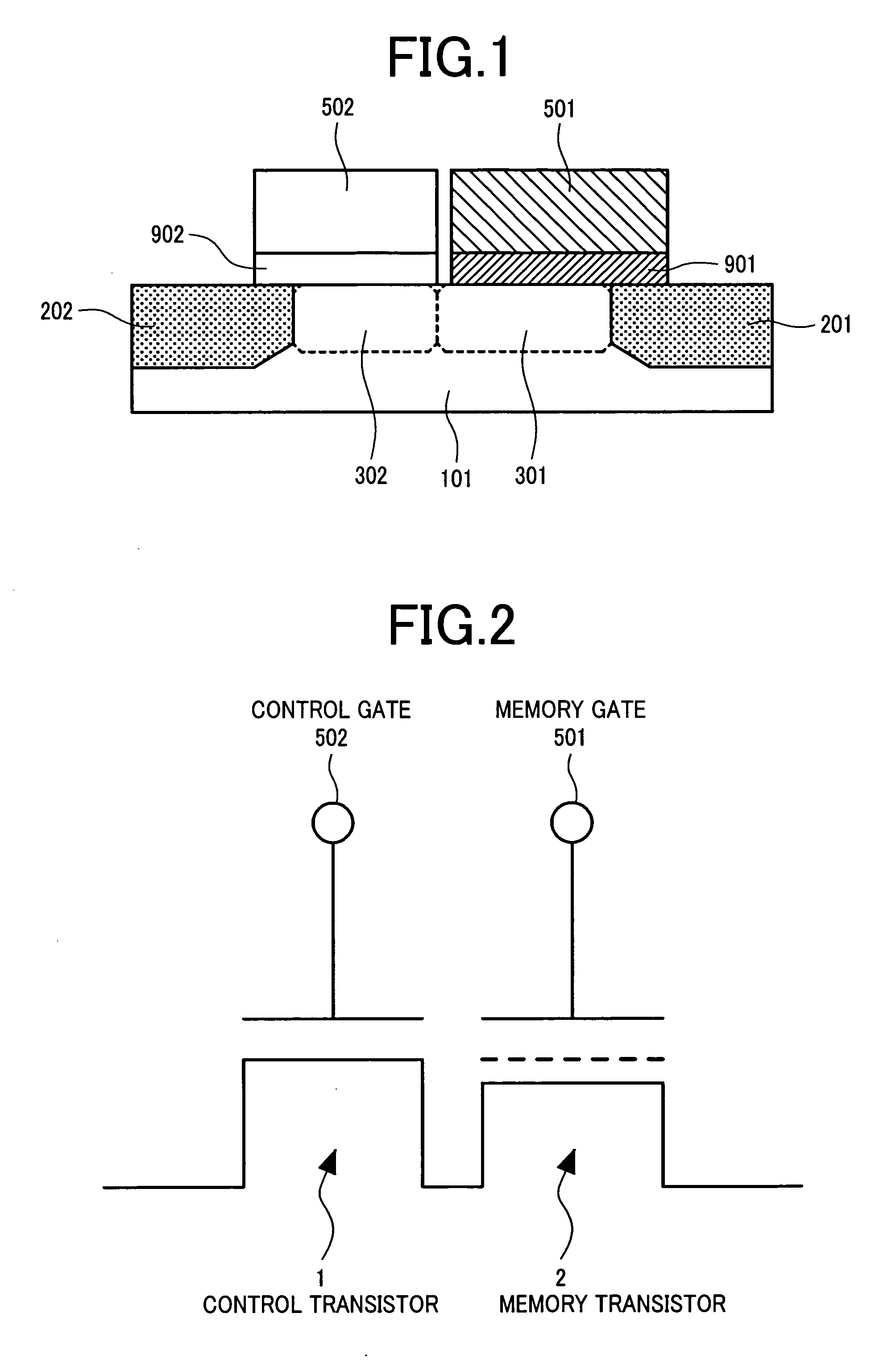

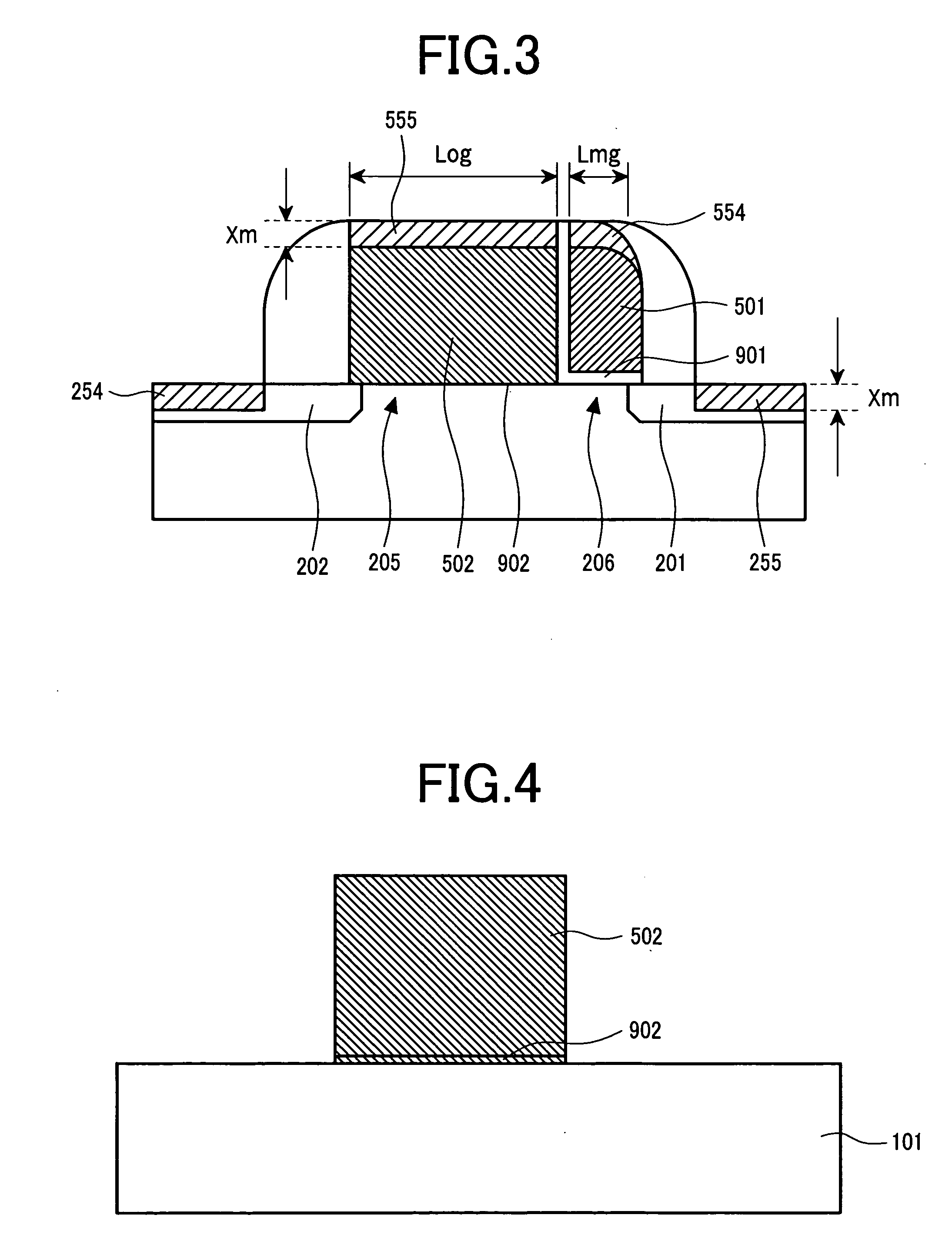

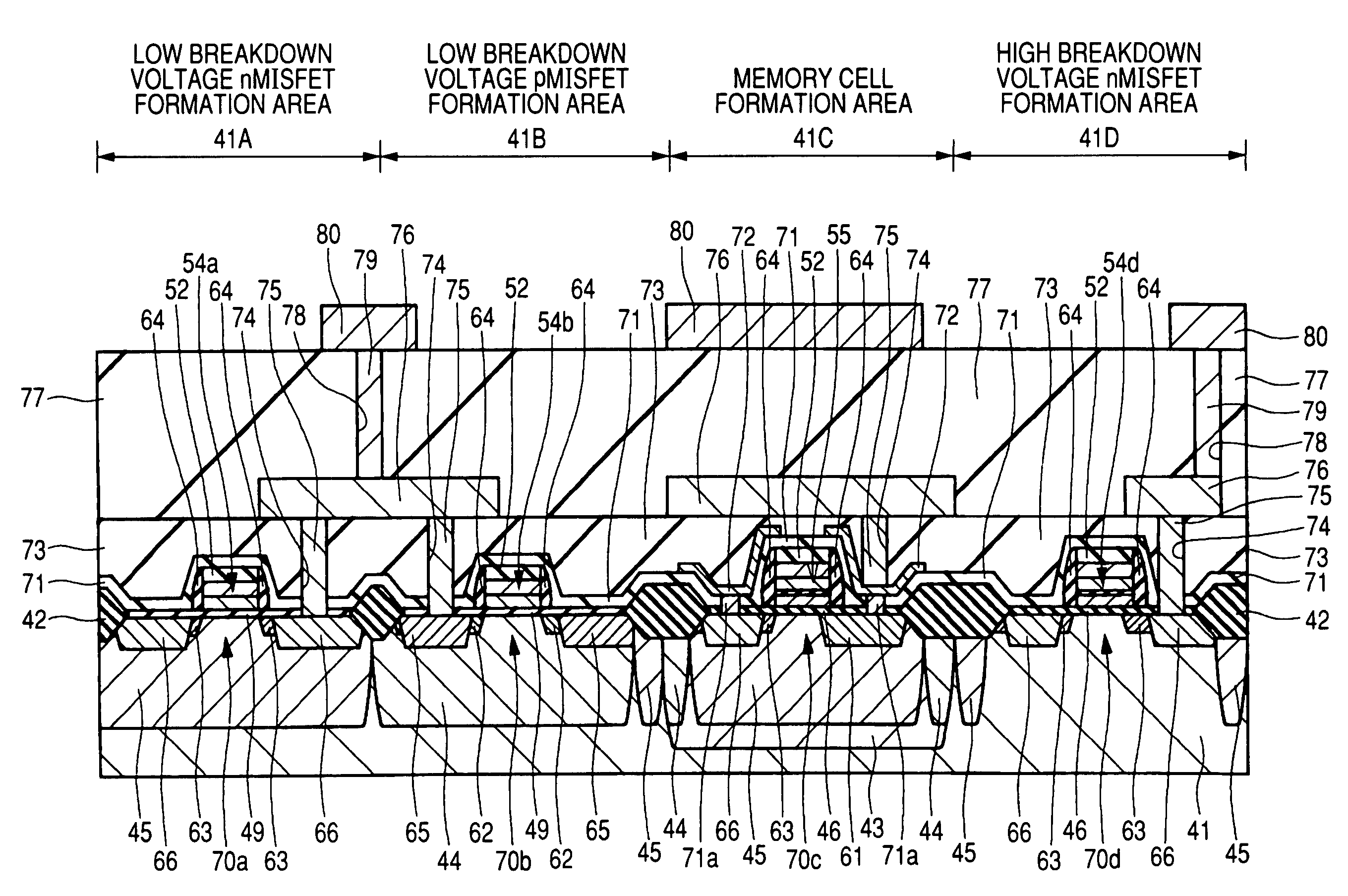

Nonvolatile semiconductor memory and making method thereof

InactiveUS20050176202A1Lower resistanceMaximizing thicknessTransistorSolid-state devicesDiffusion layerLow resistance

A nonvolatile semiconductor memory device of a split gate structure having a gate of low resistance suitable to the arrangement of a memory cell array is provided. When being formed of a side wall spacer, a memory gate is formed of polycrystal silicon and then replaced with nickel silicide. Thus, its resistance can be lowered with no effect on the silicidation to the selection gate or the diffusion layer.

Owner:RENESAS ELECTRONICS CORP

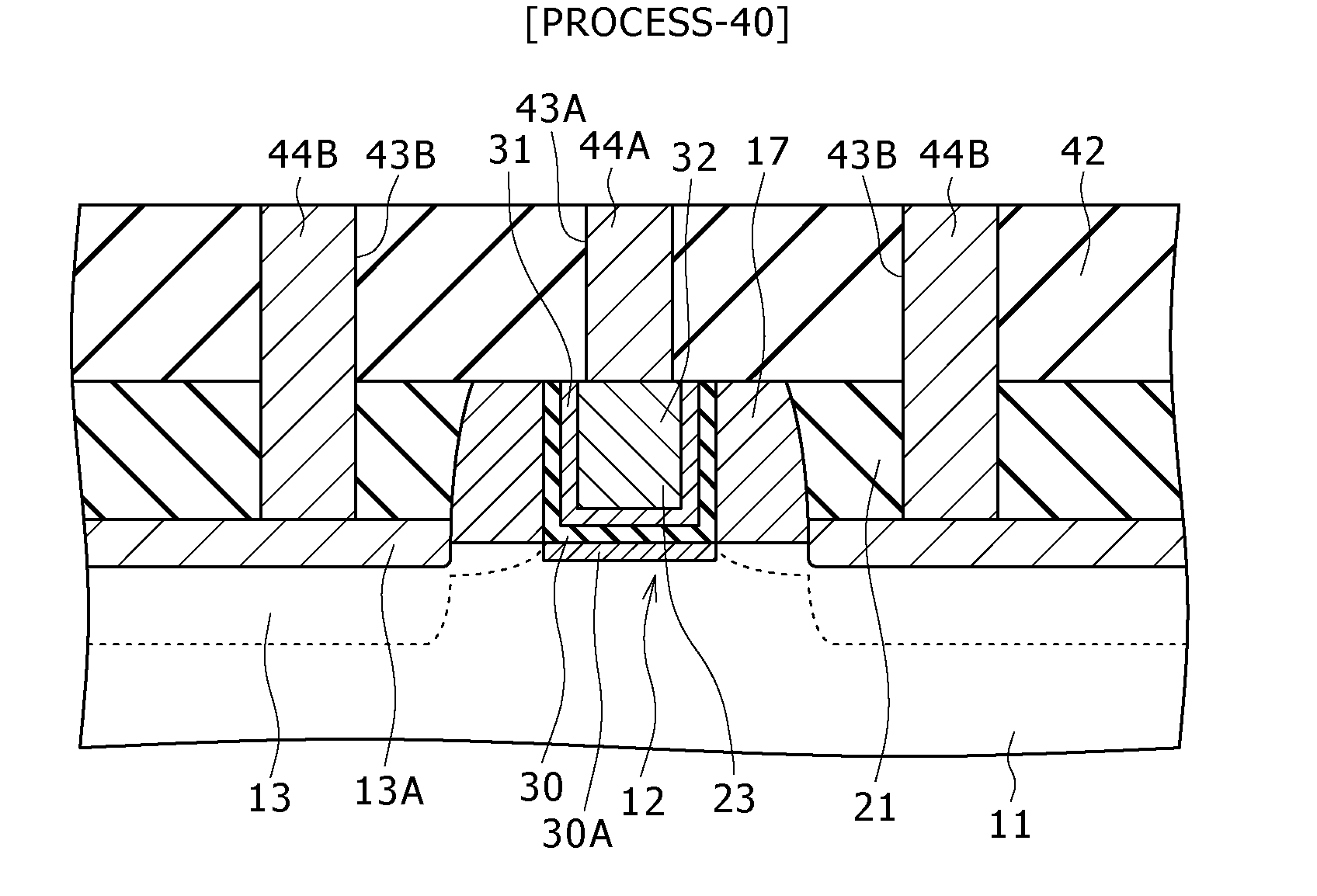

Semiconductor device and manufacturing method thereof

ActiveUS20100264485A1Lower gate resistanceReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor package

This invention provides a method of manufacturing a semiconductor device, which comprises the steps of: forming a first columnar semiconductor layer on a first flat semiconductor layer; forming a first semiconductor layer of a second conductive type in a lower portion of the first columnar semiconductor layer; forming a first insulating film around a lower sidewall of the first columnar silicon layer; forming a gate insulating film and a gate electrode around the first columnar silicon layer; forming a sidewall-shaped second insulating film to surround an upper sidewall of the first columnar silicon layer; forming a semiconductor layer of a first conductive type between the first semiconductor layer of the second conductive type and a second semiconductor layer of the second conductive type; and forming a metal-semiconductor compound on an upper surface of the first semiconductor layer of the second conductive type.

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD

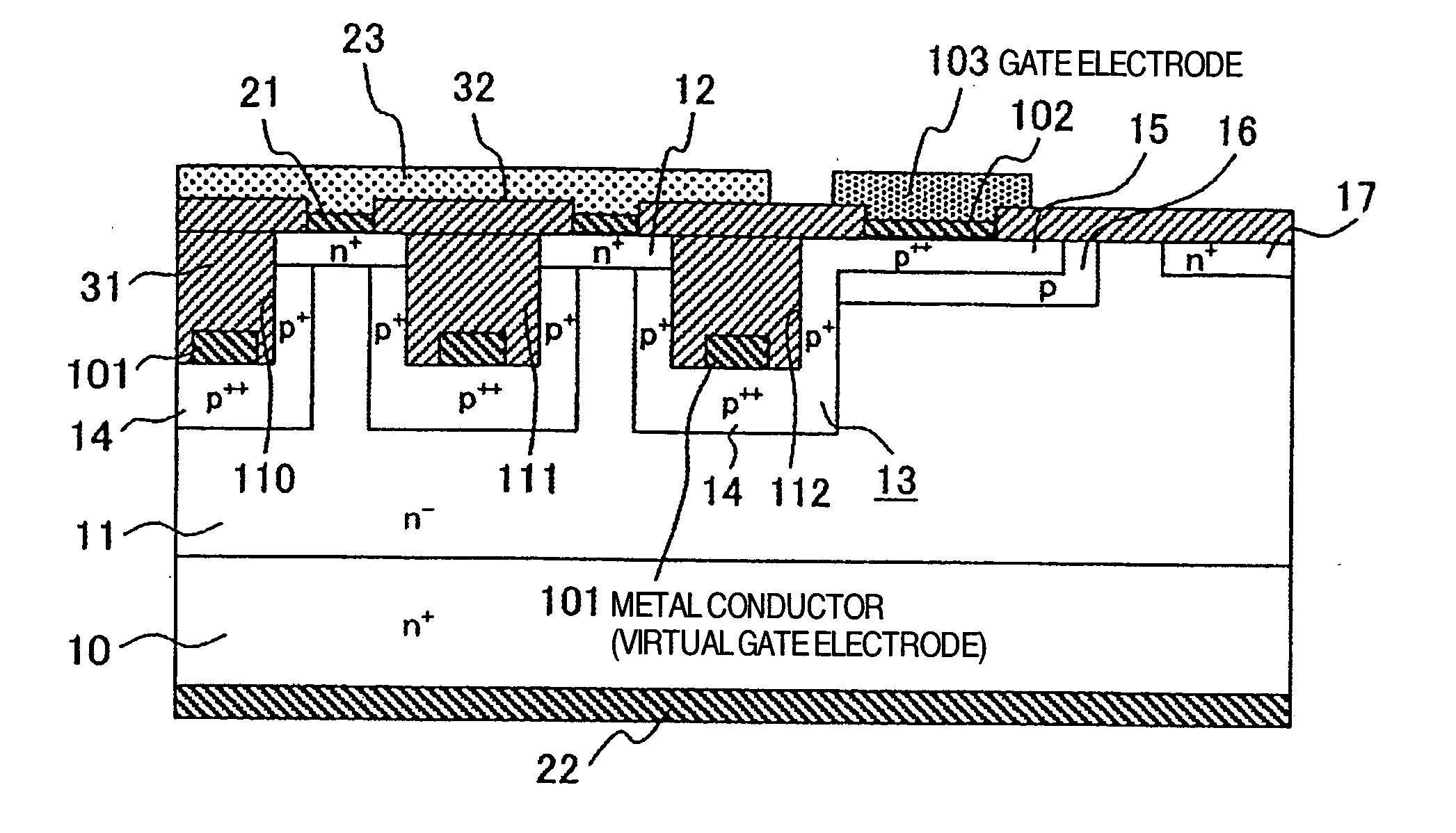

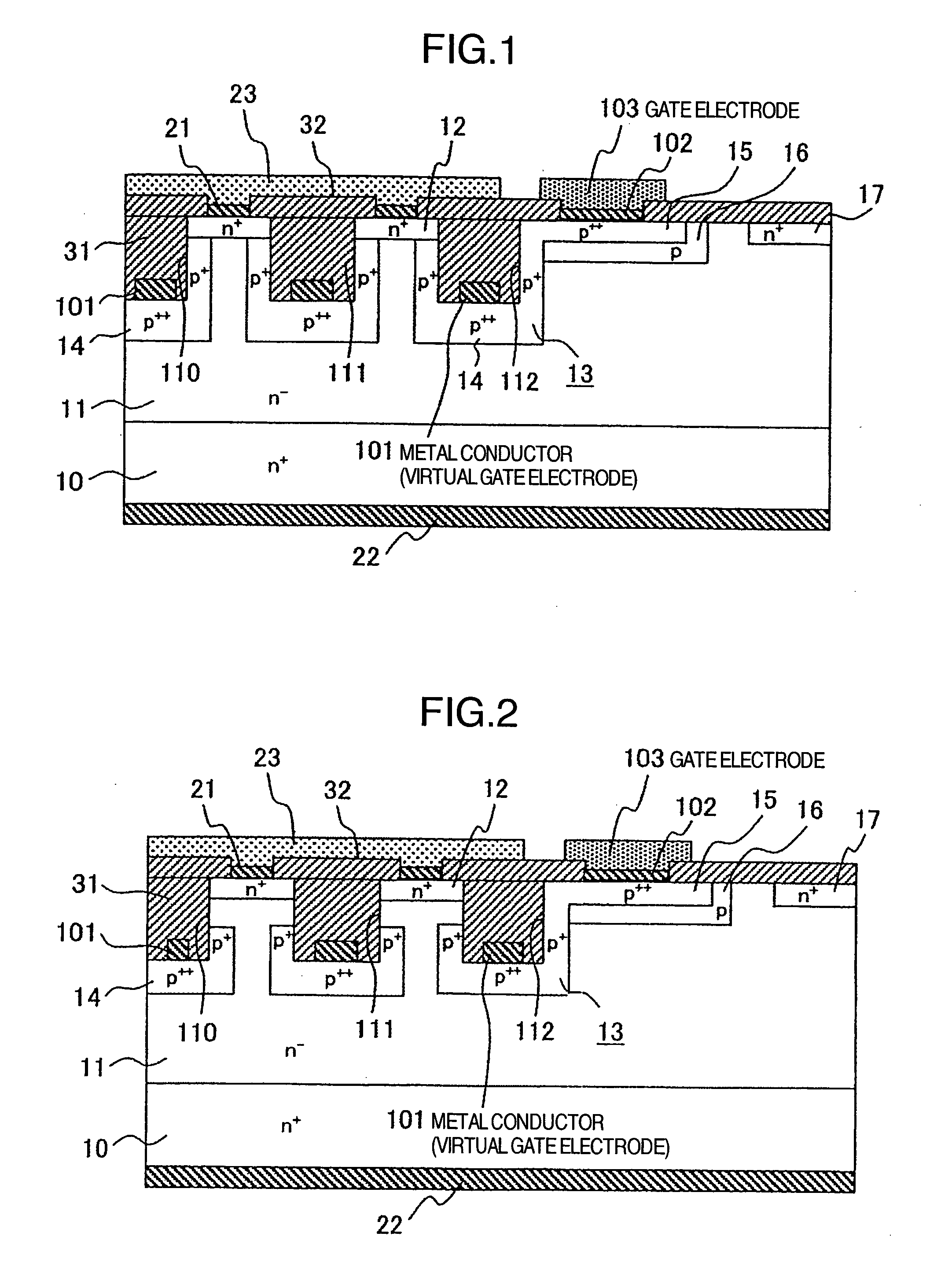

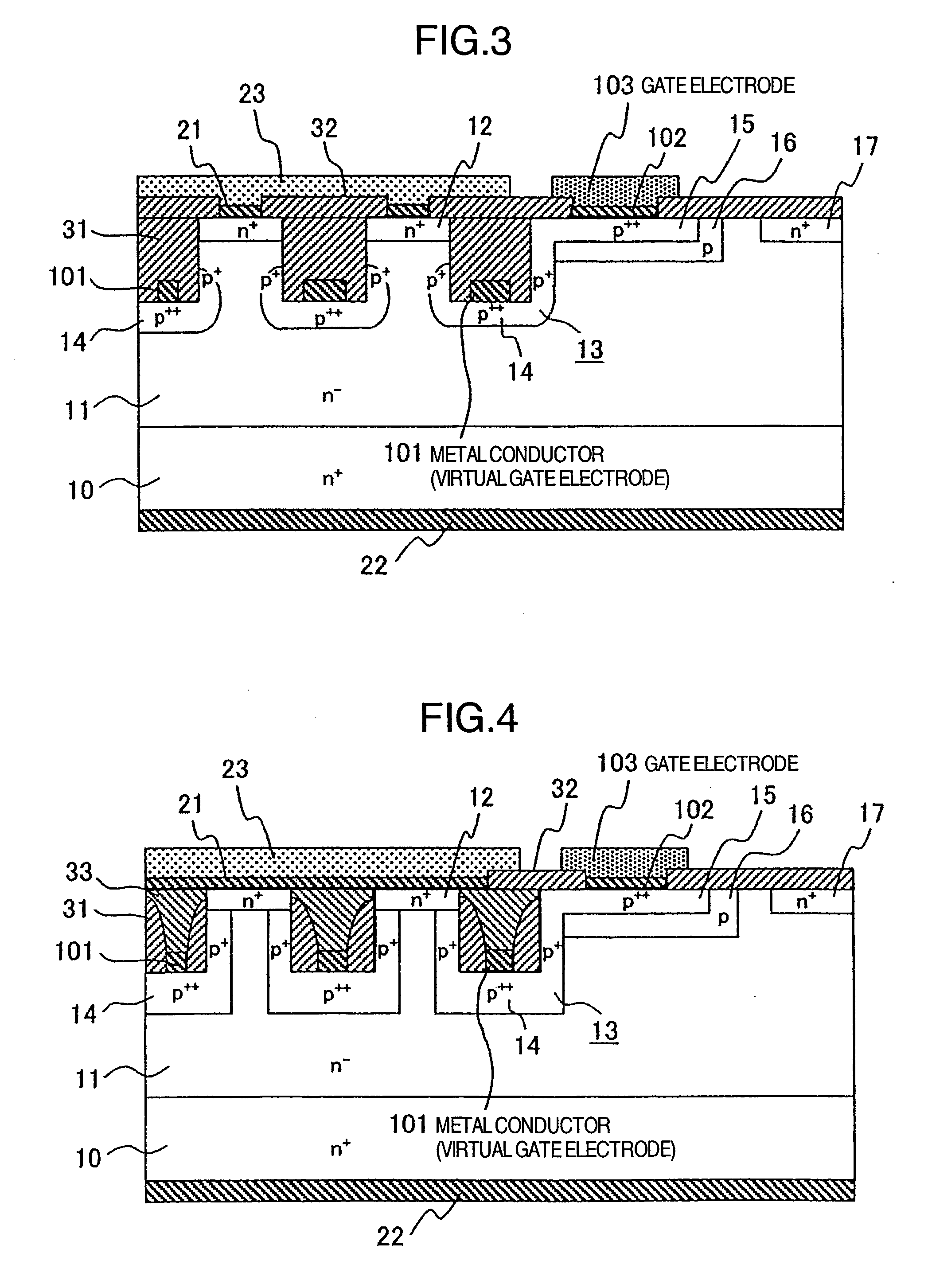

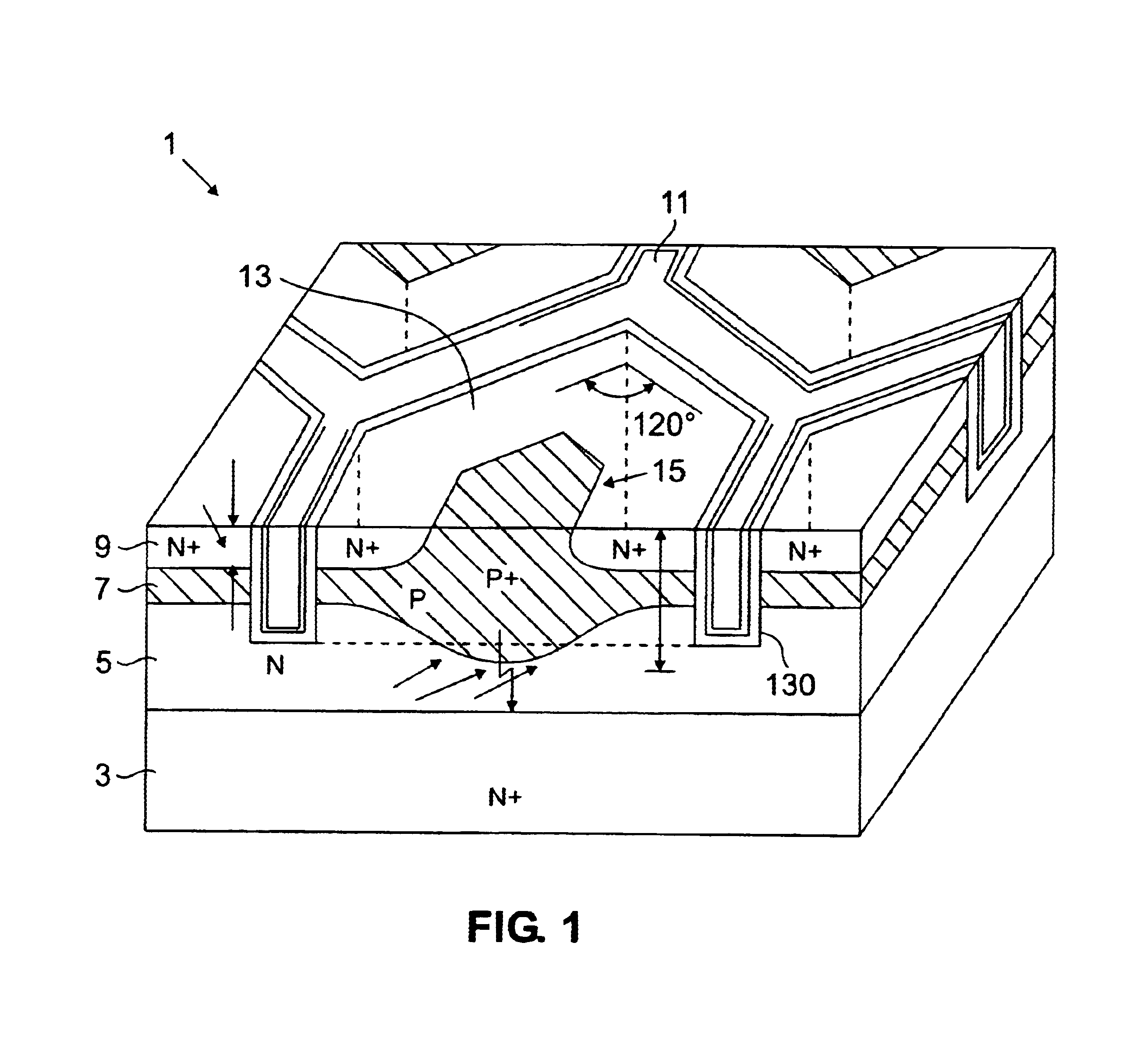

Semiconductor devices

InactiveUS20060060884A1Increase current densityLower gate resistanceThyristorElectrical conductorDevice material

A silicon carbide semiconductor device such as JFET, SIT and the like is provided for accomplishing a reduction in on-resistance and high-speed switching operations. In the JFET or SIT which turns on / off a current with a depletion layer extending in a channel between a gate region formed along trench grooves, a gate contact layer and a gate electrode, which can be supplied with voltages from the outside, are formed on one surface of a semiconductor substrate or on the bottom of the trench groove. A metal conductor (virtual gate electrode) is formed in ohmic contact with a p++ contact layer of the gate region on the bottom of the trench grooves independently of the gate electrode. The virtual gate electrode is electrically isolated from the gate electrode and an external wire.

Owner:DENSO CORP +1

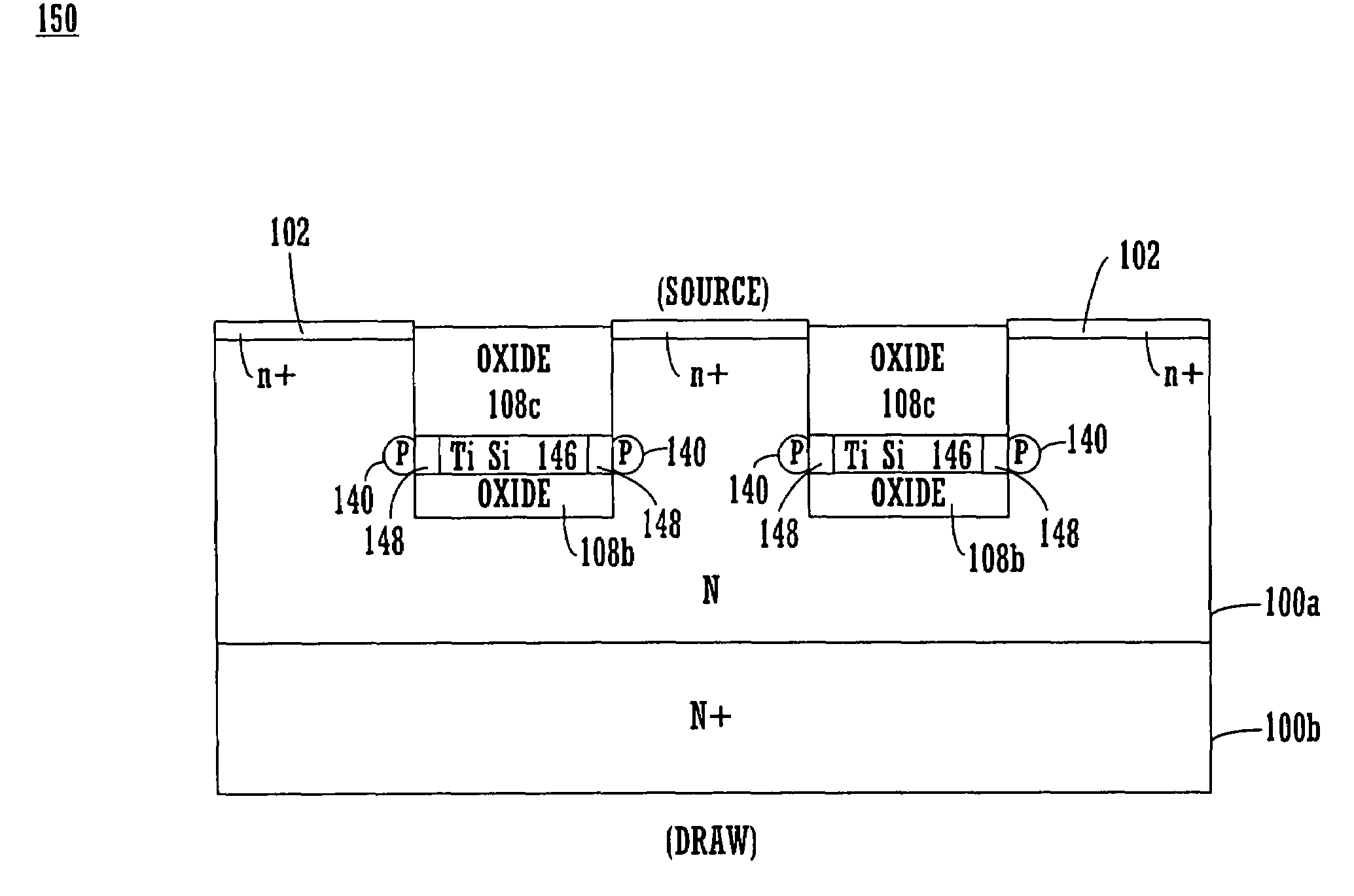

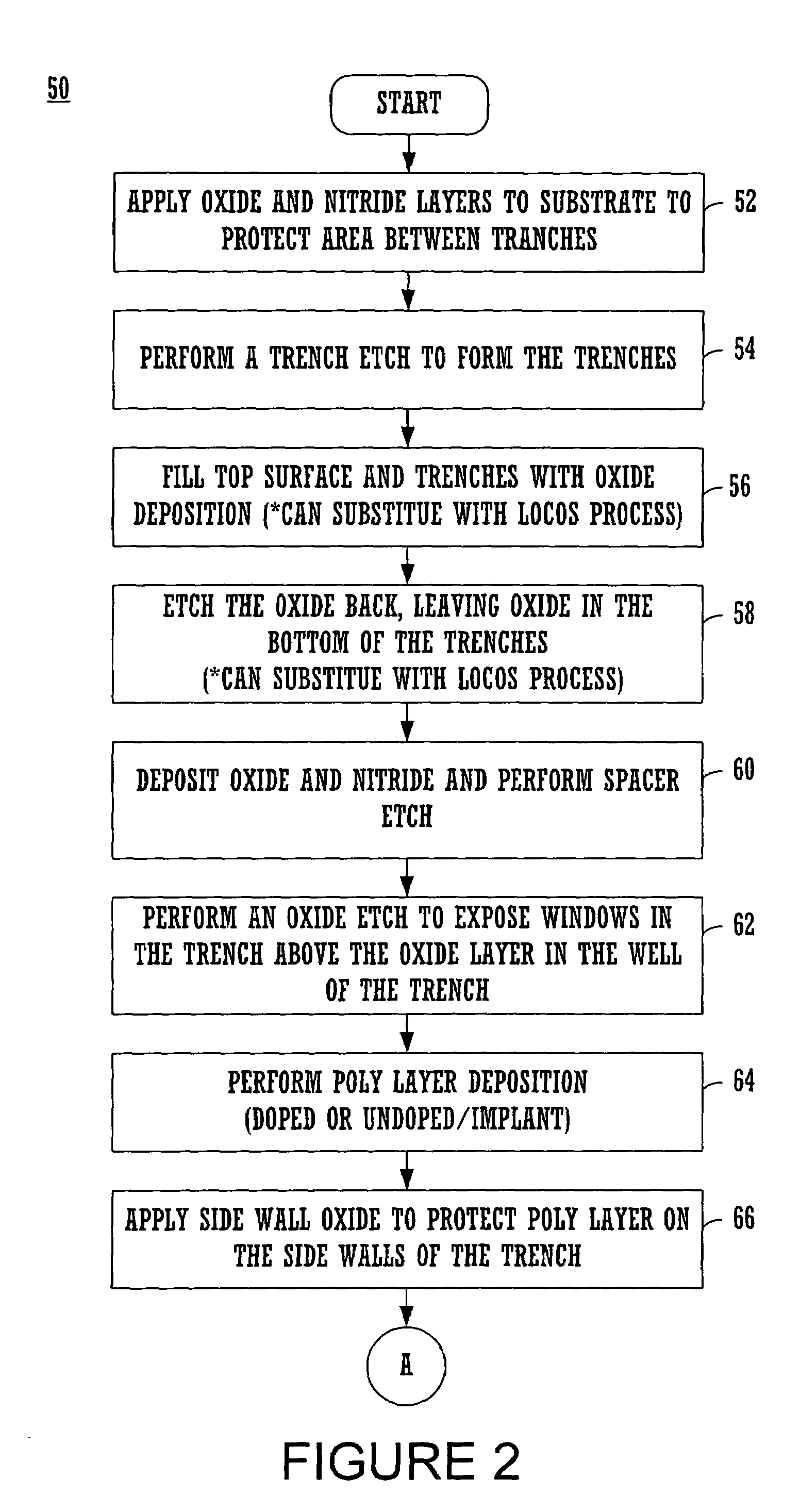

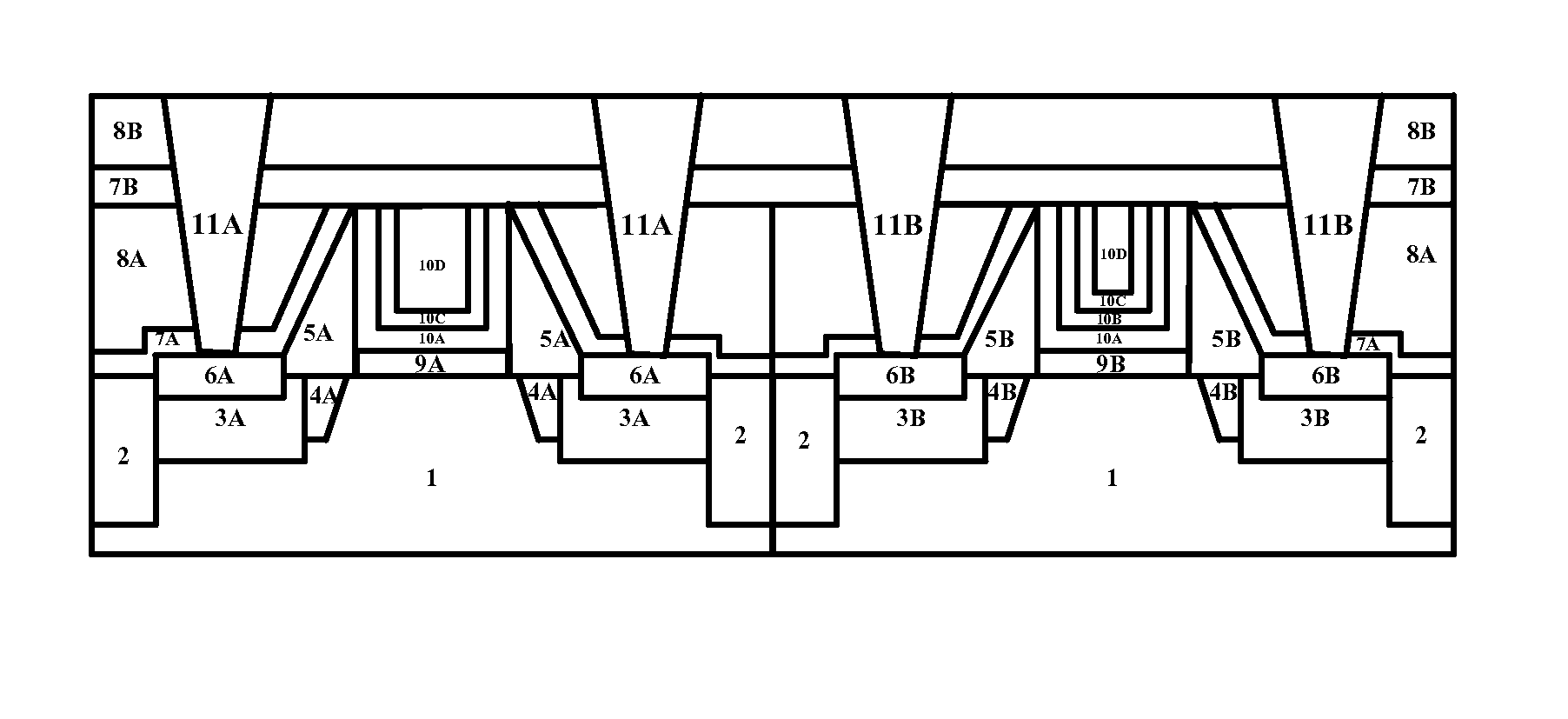

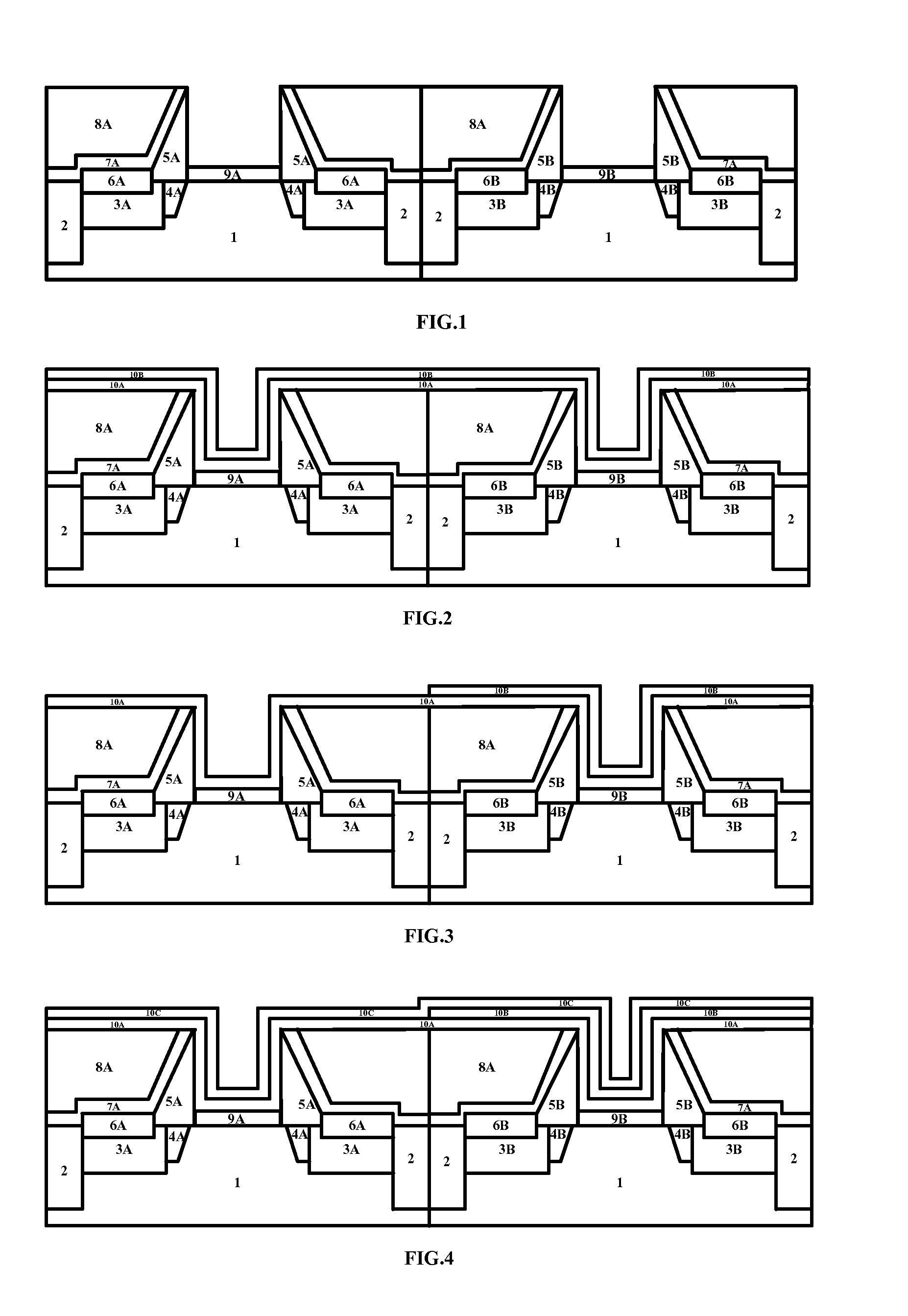

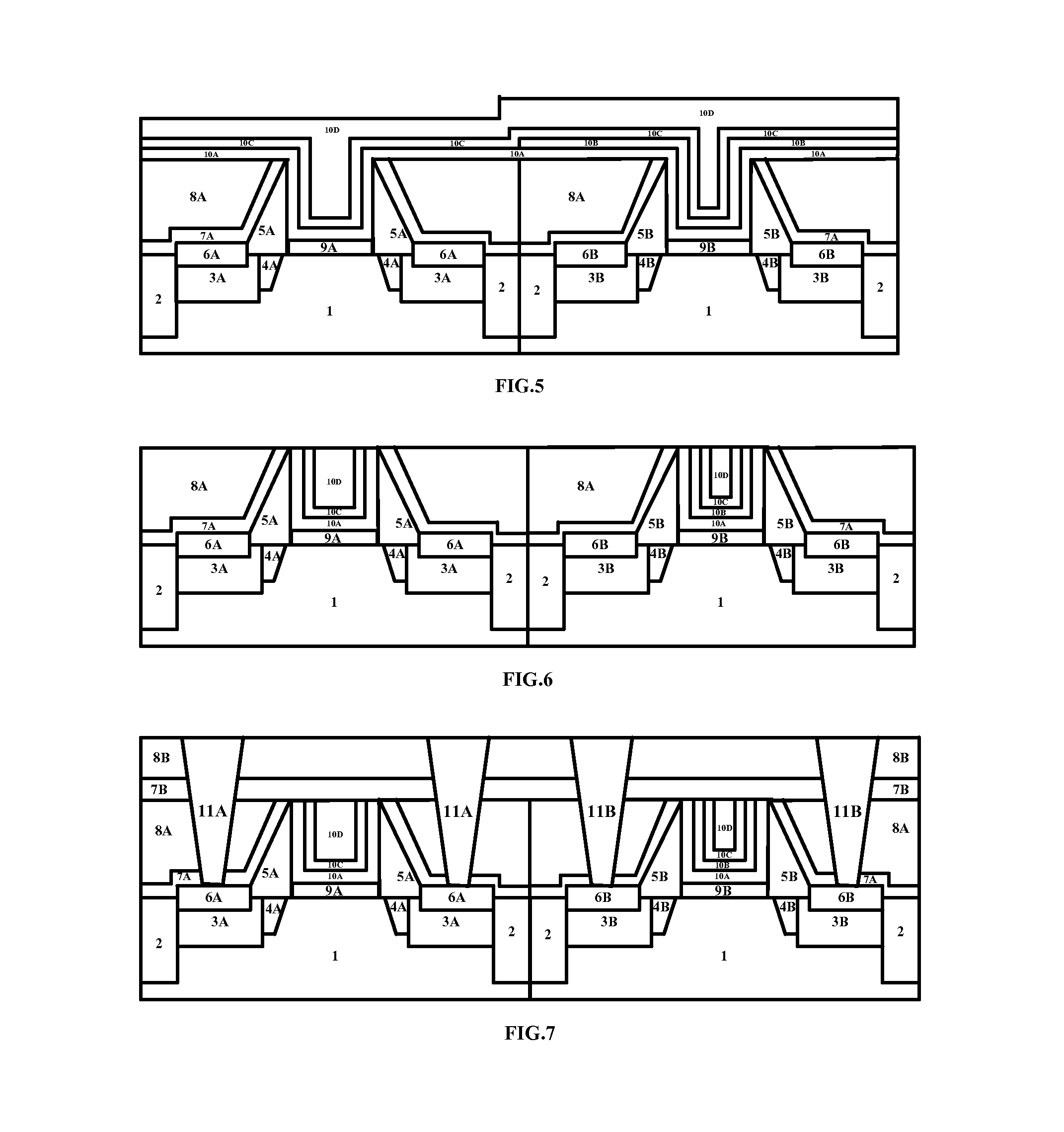

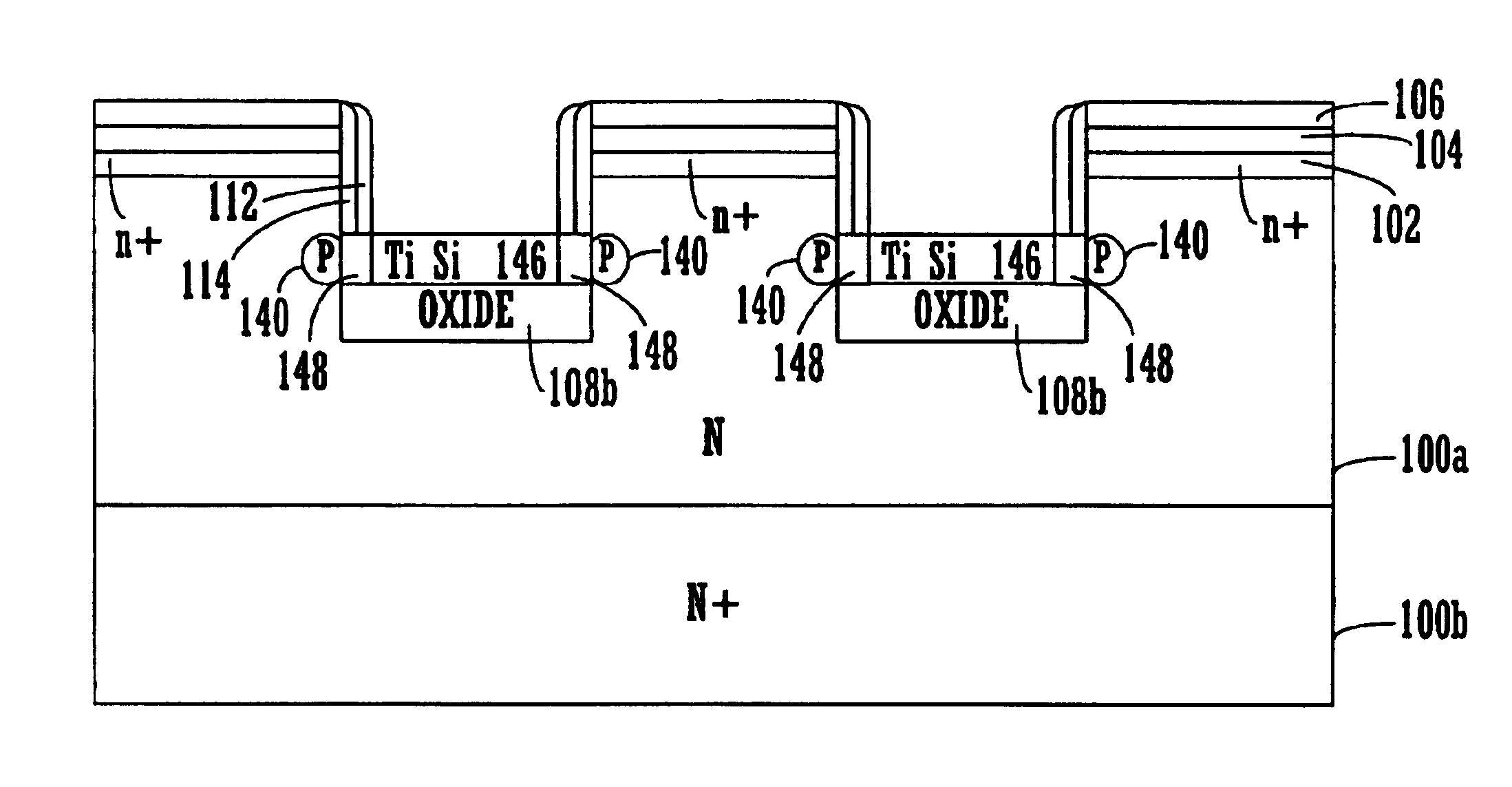

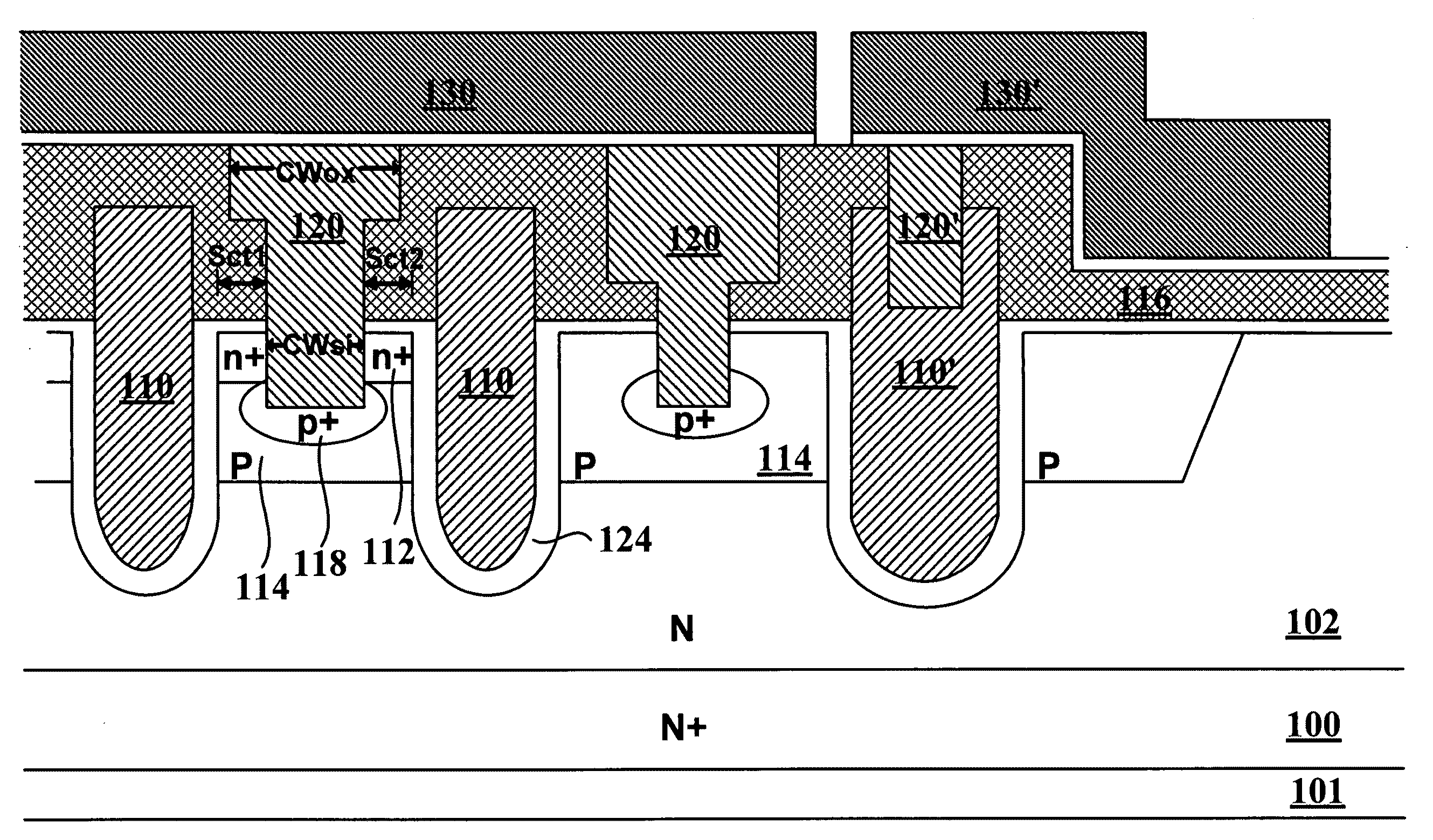

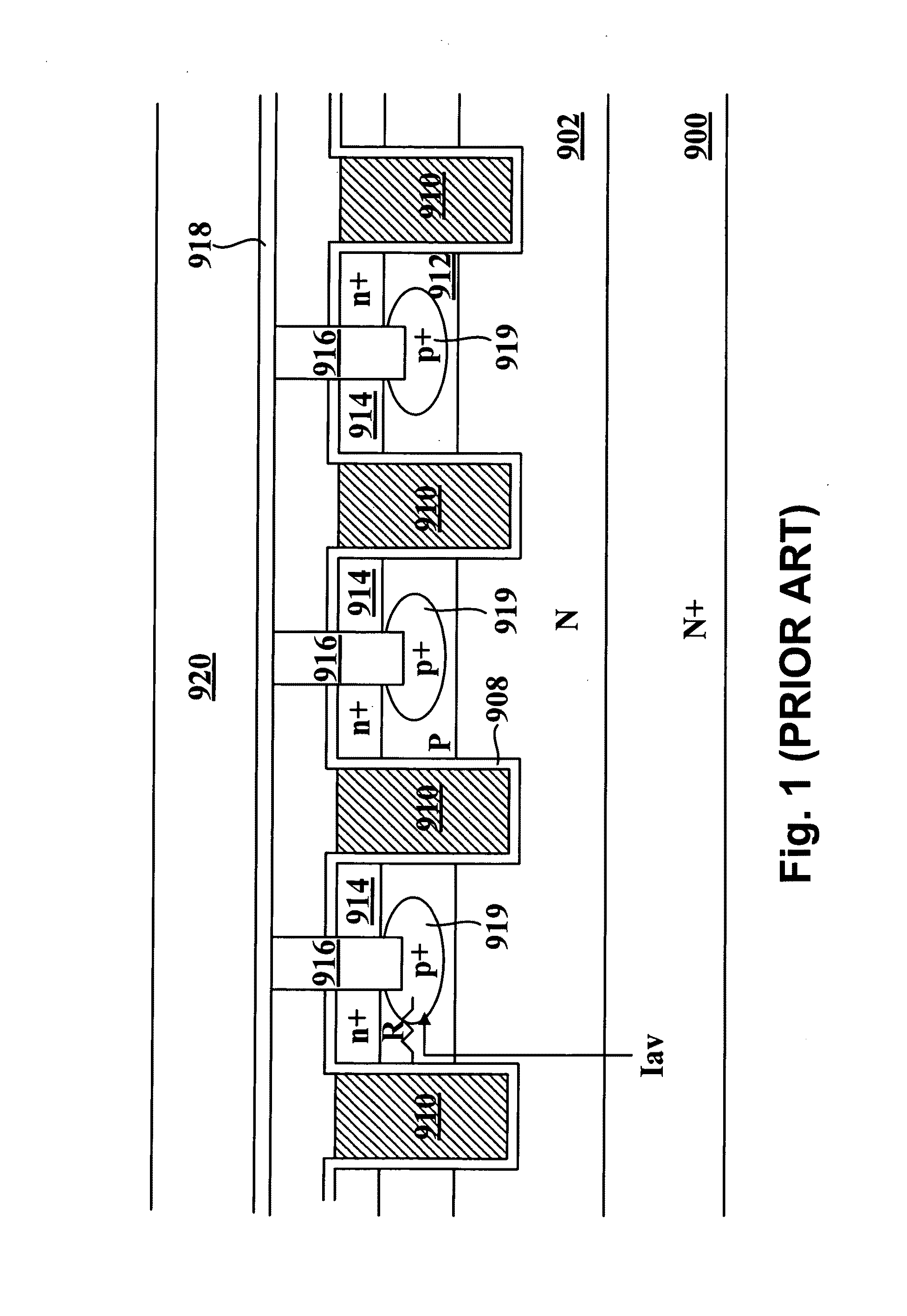

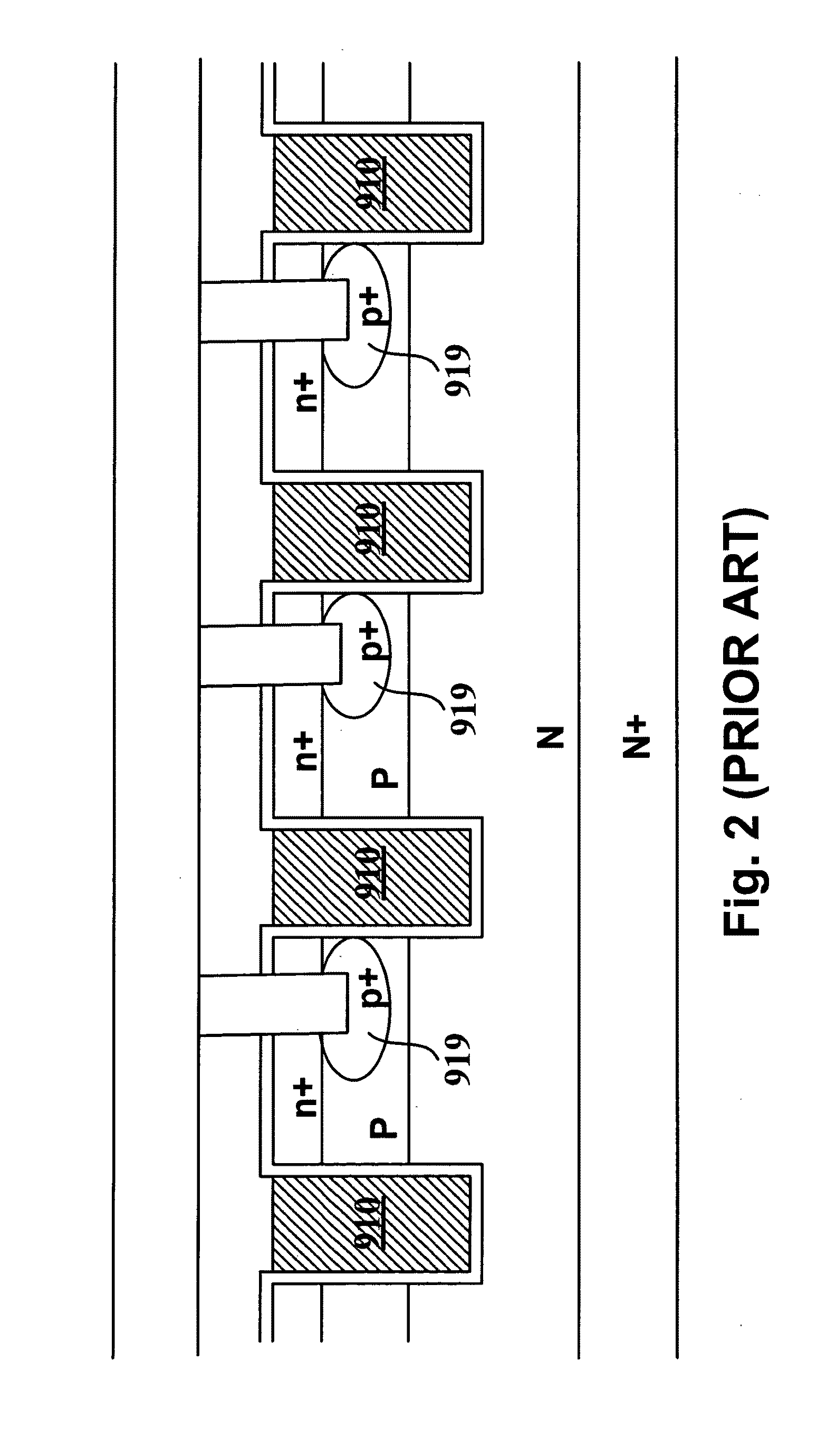

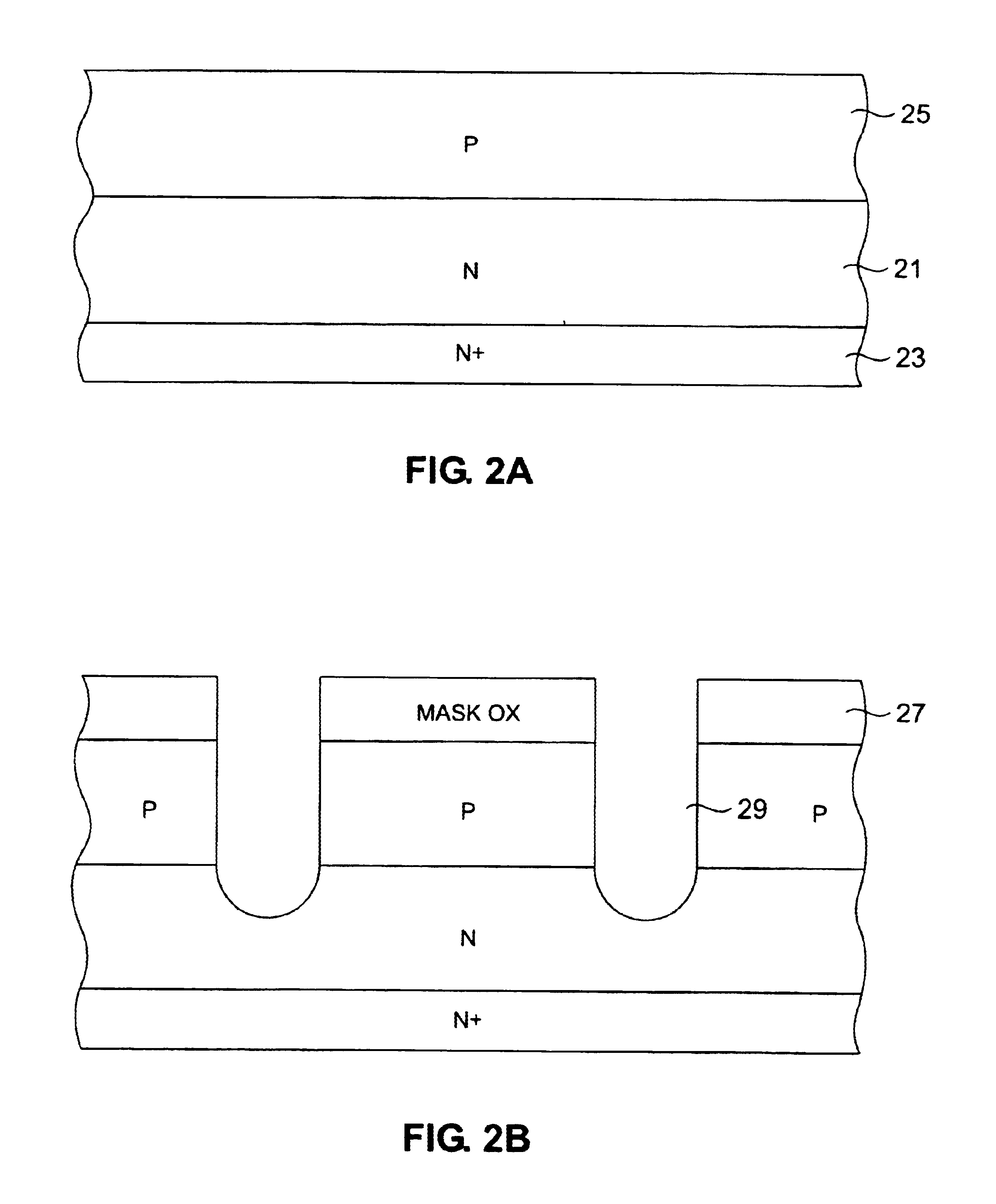

JFET and MESFET structures for low voltage high current and high frequency applications

InactiveUS7045397B1Easy to controlLower junction capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceLow voltage

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

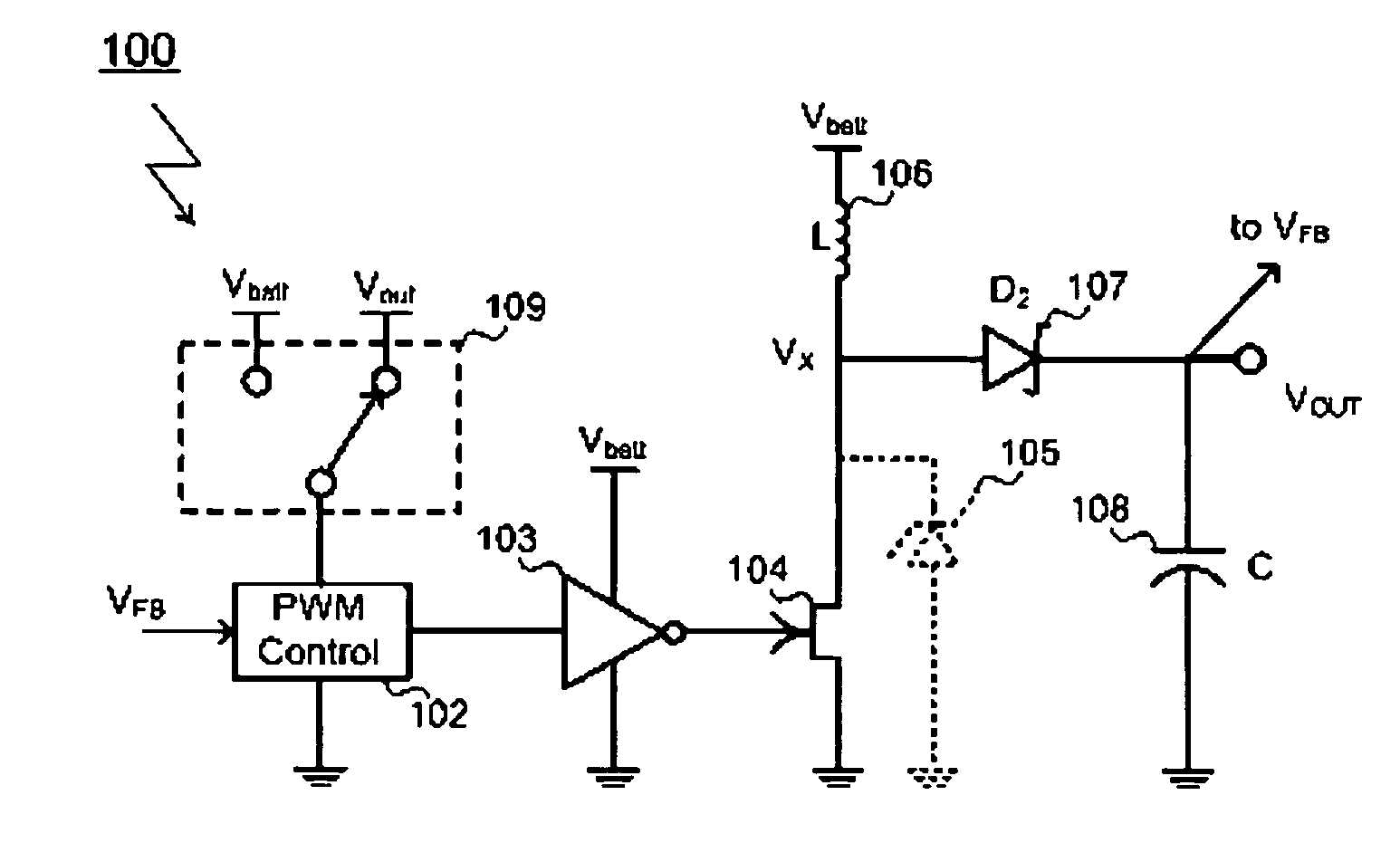

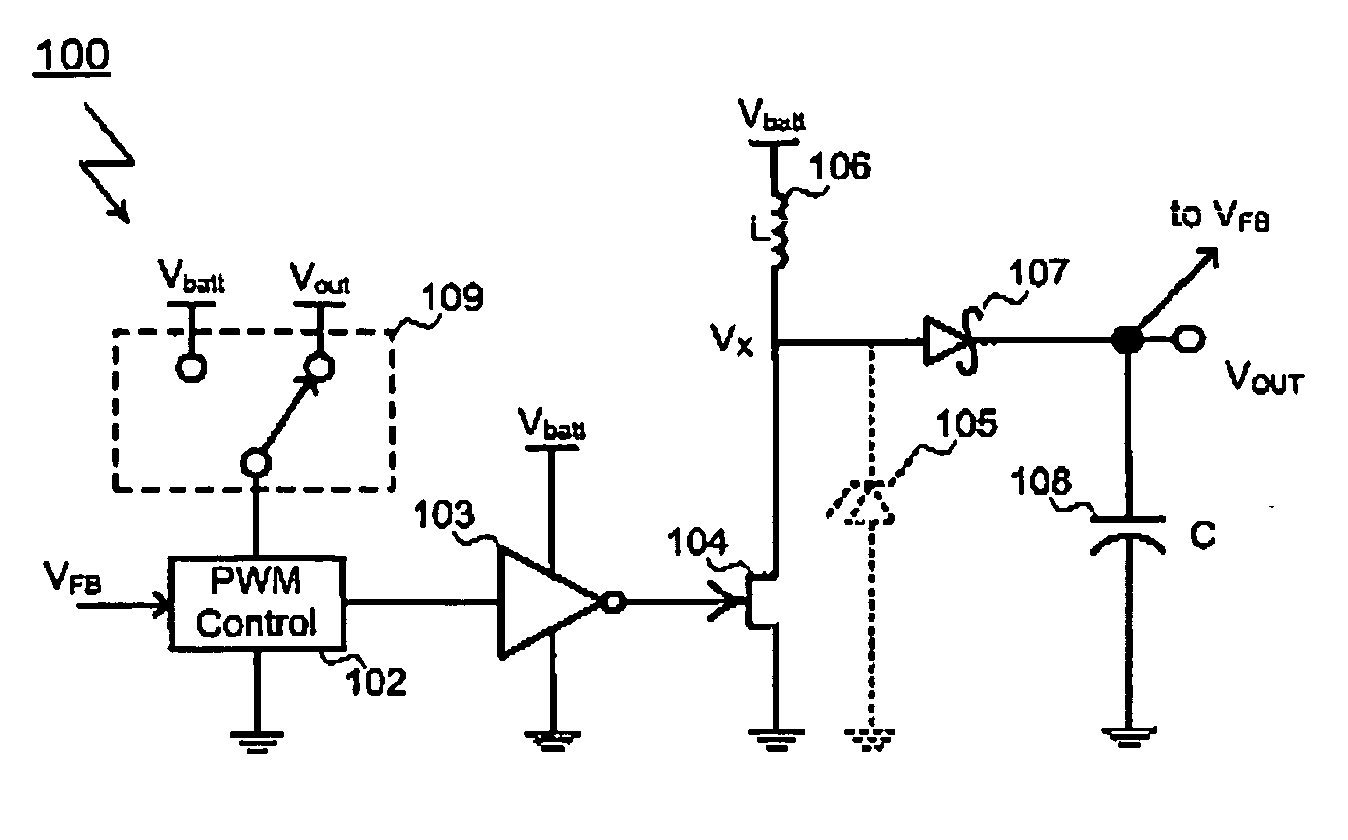

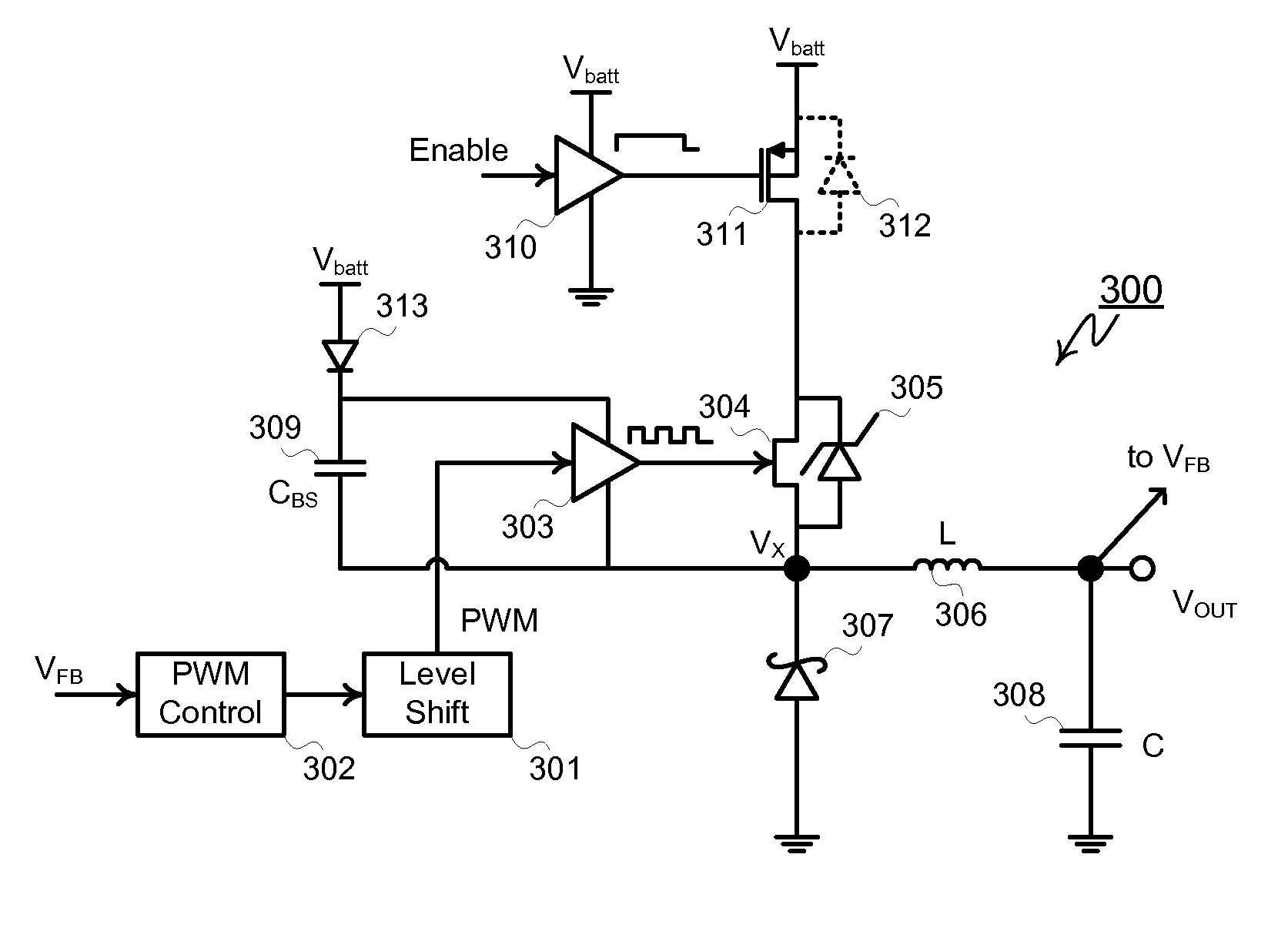

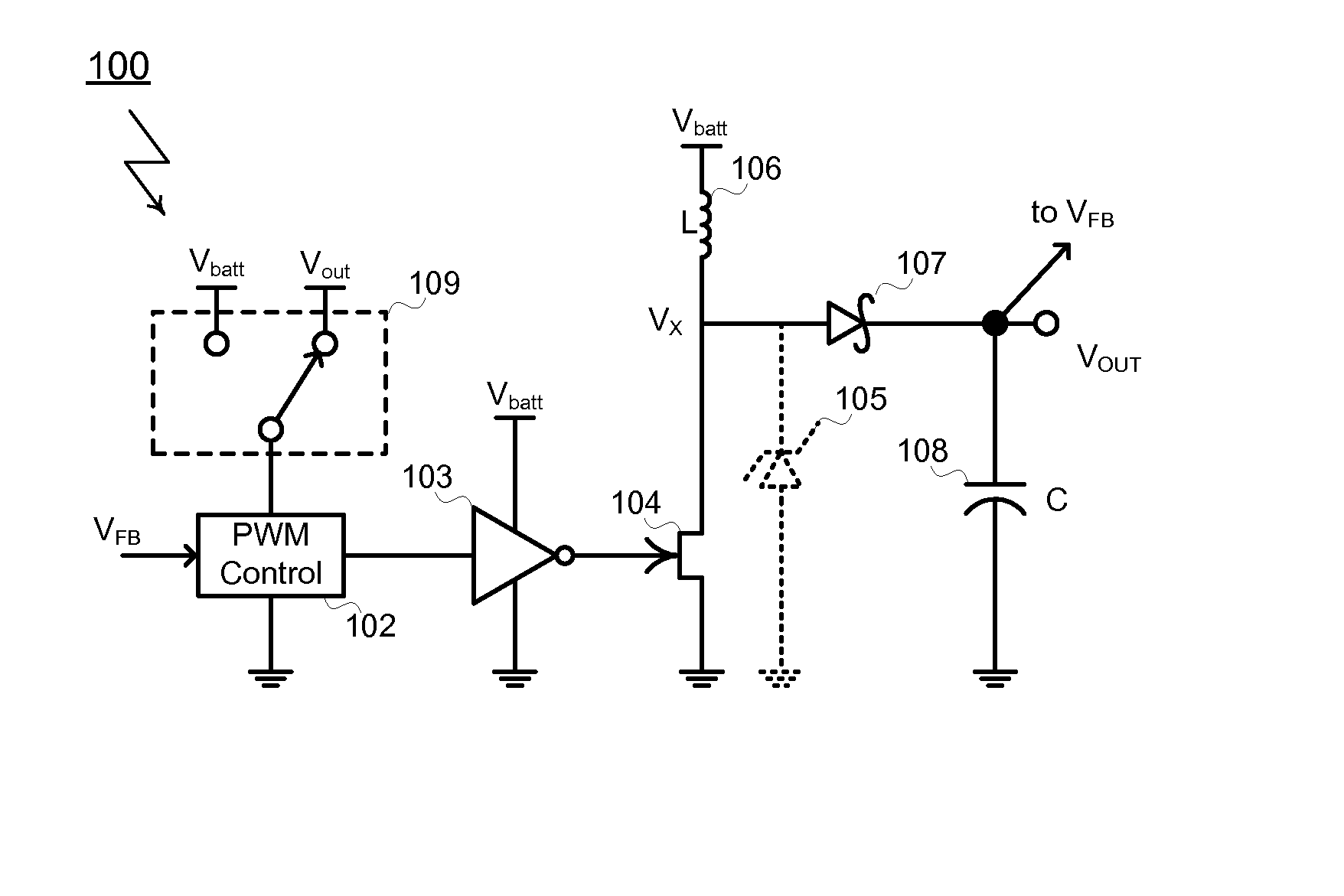

High-Frequency Buck Converter that Includes a Cascode MESFET-MOSFET Power Switch

InactiveUS20080191679A1Lower on-resistanceLow off-state drain leakageDc-dc conversionElectric variable regulationMOSFETElectrical battery

A Buck converter that includes a cascode switch comprising a series connected MESFET and MOSFET power switch. The cascode power switch is typically connected in between a power source and a node Vx. The node Vx is connected to an output node via an inductor and to ground via a Schottky diode or a second MESFET or both. A control circuit drives the MESFET (and the second MESFET) so that the inductor is alternately connected to the battery and to ground. The MOSFET is switched off during sleep or standby modes to minimize leakage current through the MESFET. The MOSFET is therefore switched at a low frequency compared to the MESFET and does not contribute significantly to switching losses in the converter.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

DC-DC Converter that Includes a High Frequency Power MESFET Gate Drive Circuit

InactiveUS20080203991A1Lower on-resistanceLow off-state drain leakageTransistorDc-dc conversionDc dc converterHigh frequency power

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

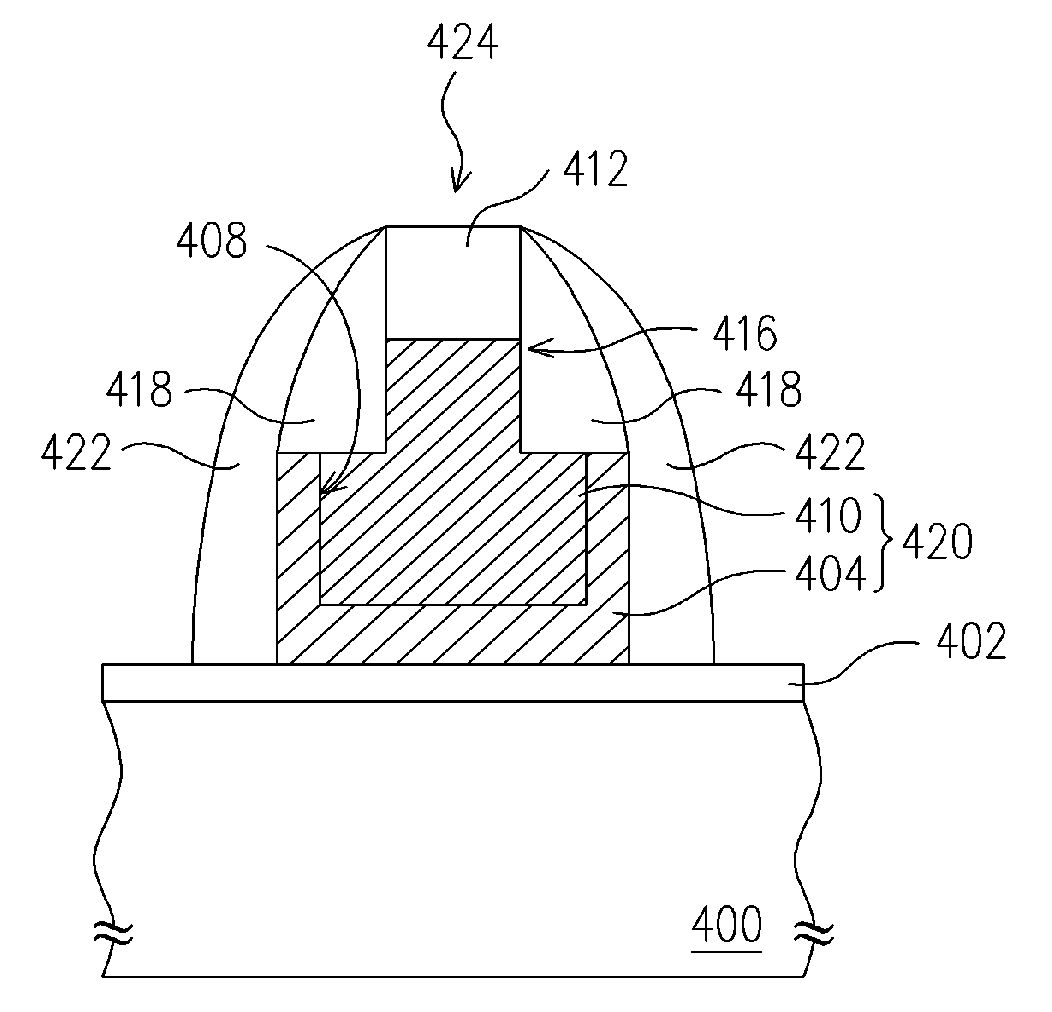

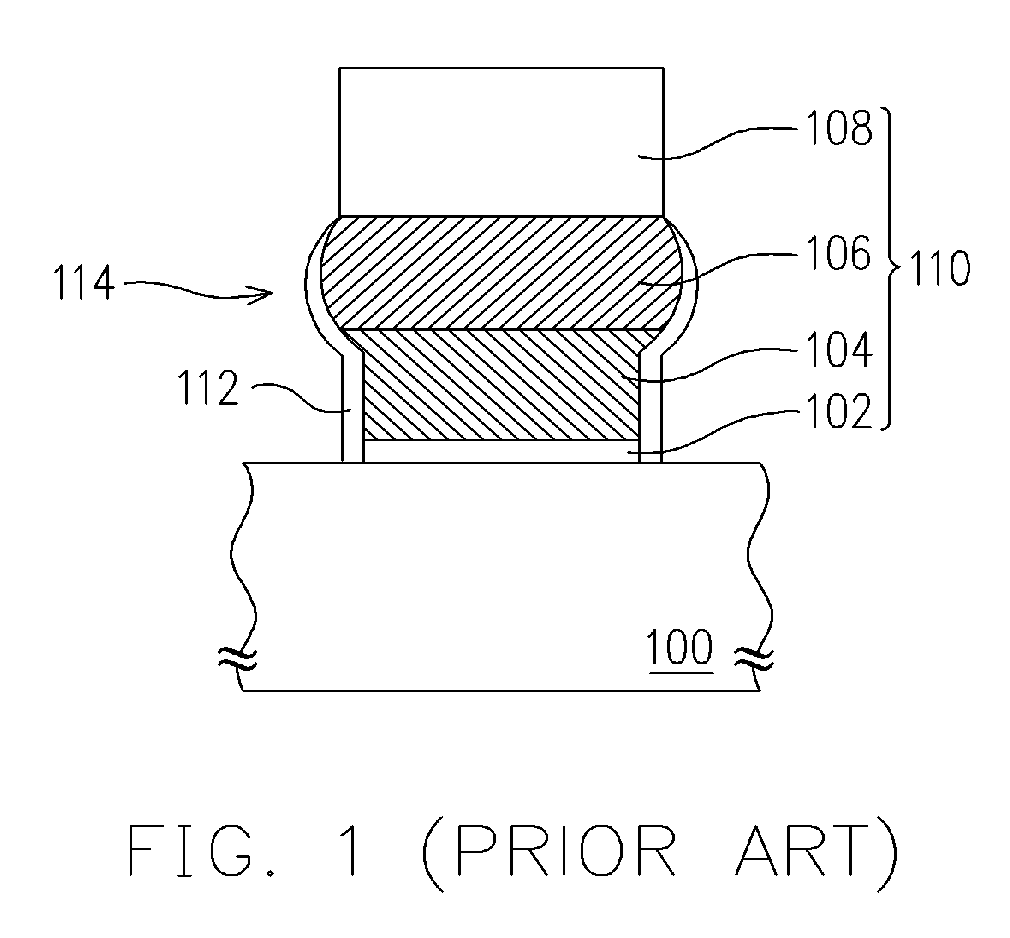

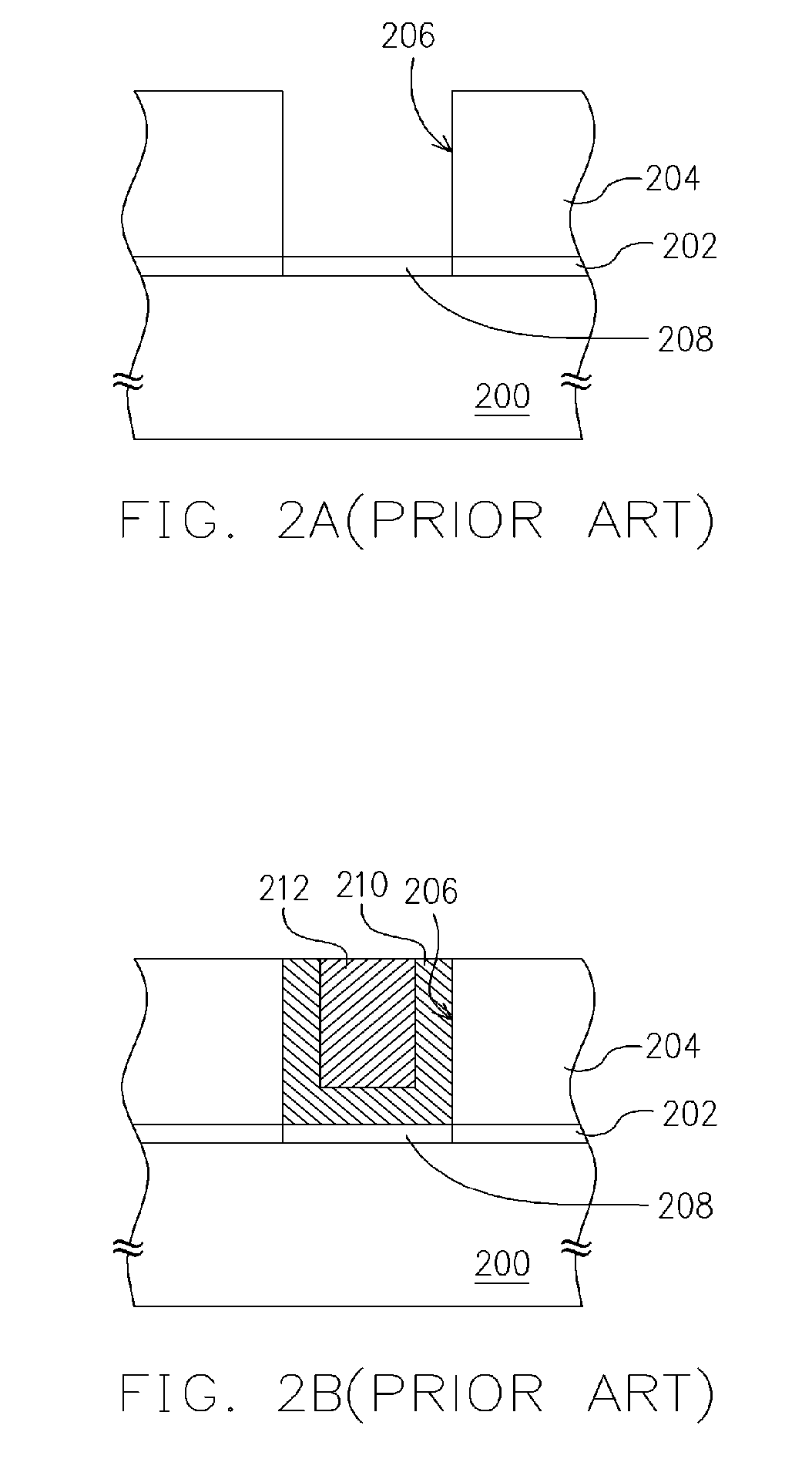

Gate structure and fabricating method thereof

ActiveUS20070104862A1Gate resistance be lowerLower gate resistancePretreated surfacesSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

A gate structure comprising a substrate, a gate dielectric layer, a first conductive layer, a second conductive layer, a cap layer and a first insulating spacer is provided. The gate dielectric layer is disposed on the substrate. The first conductive layer is disposed on the gate dielectric layer and has an opening. Part of the second conductive layer is disposed in the opening. The second conductive layer has an extrusion that protrudes above the opening of the first conductive layer. The extrusion has a cross-sectional width less than the width of the second conductive layer inside the opening. The cap layer is disposed on the extrusion. The first insulating spacer is disposed on part of the first conductive layer and covers the sidewalls of the extrusion. The inclusion of the extrusion in the second conductive layer decreases the resistance of the gate structure and promotes the efficiency of the device.

Owner:PROMOS TECH INC

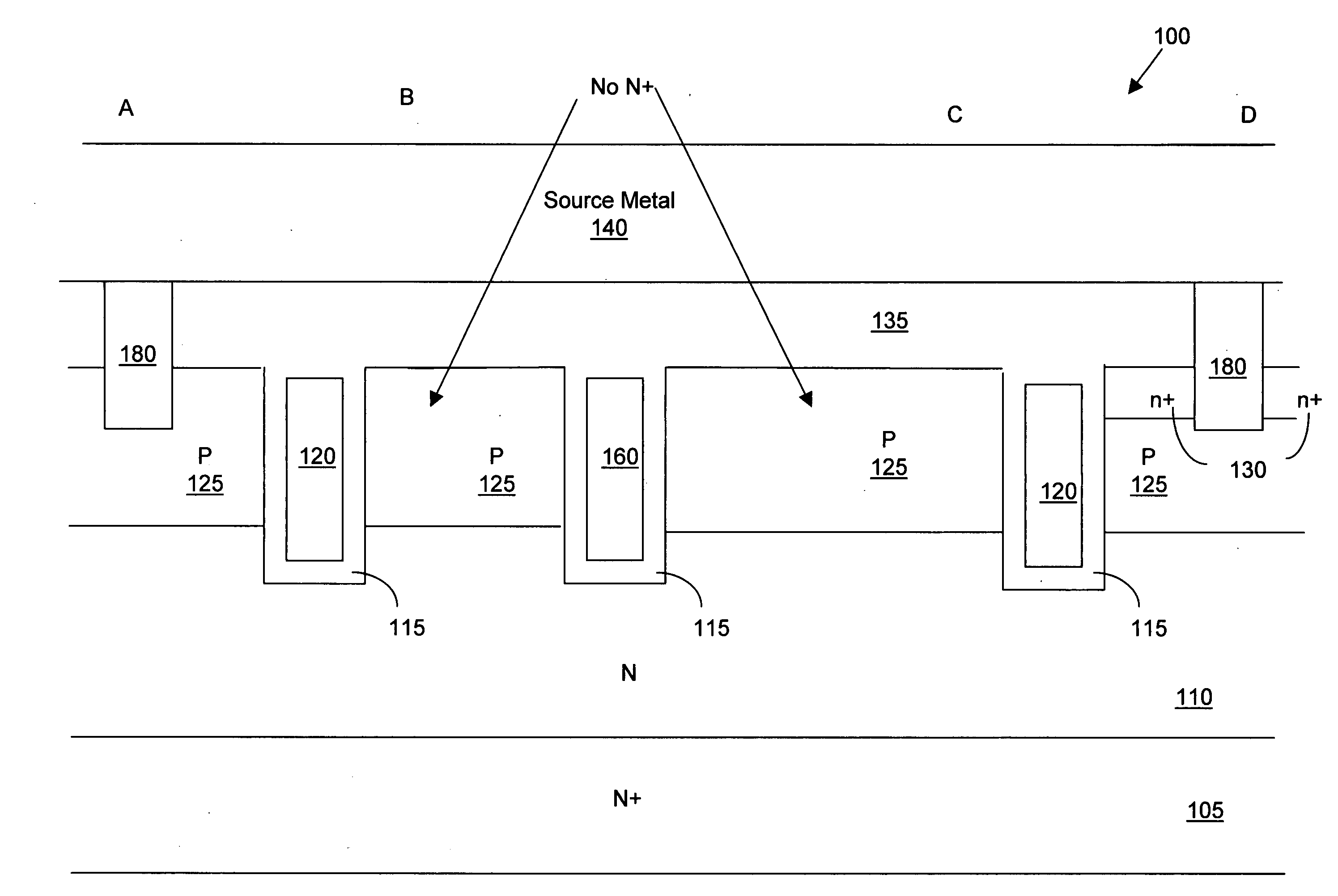

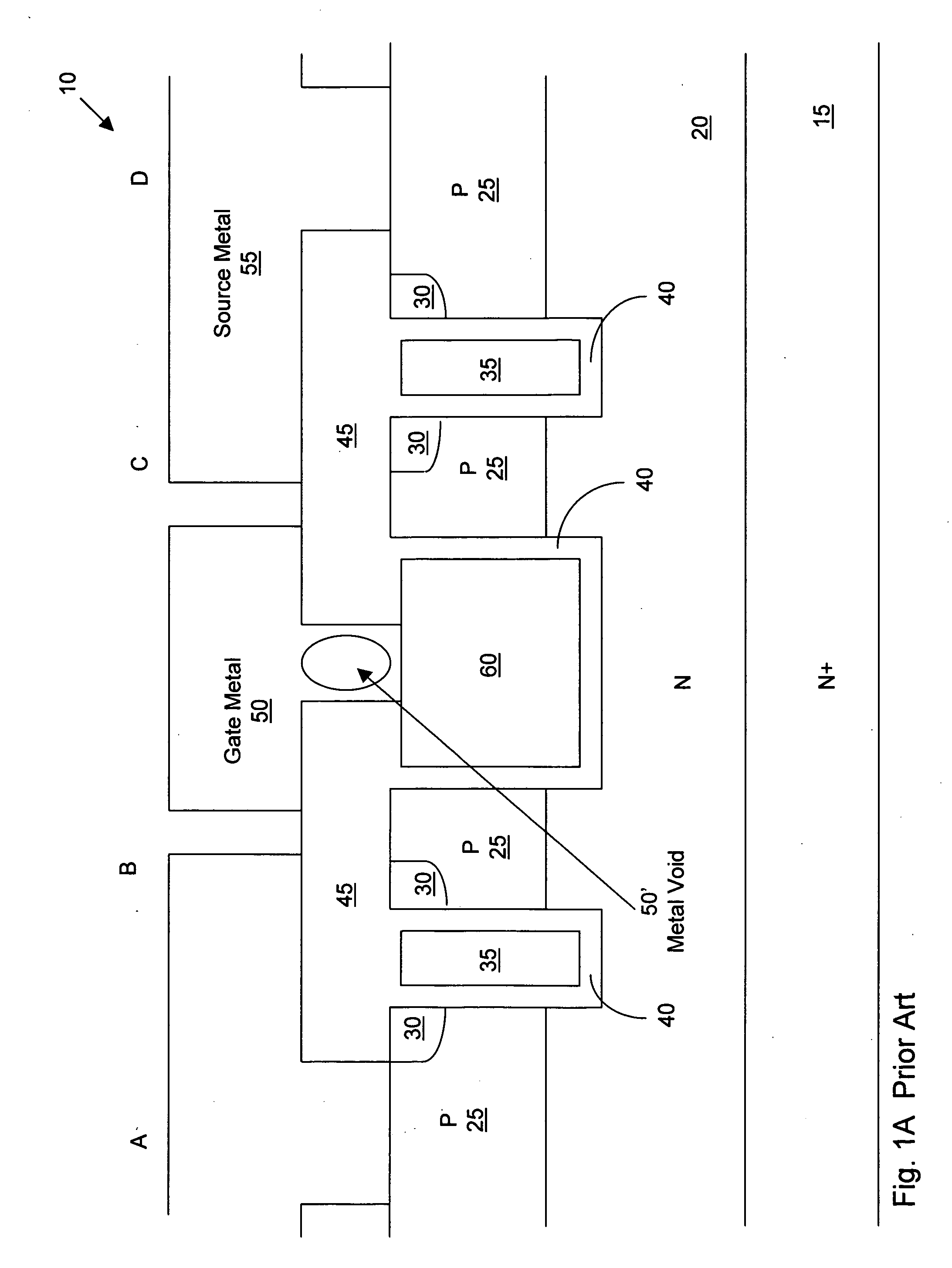

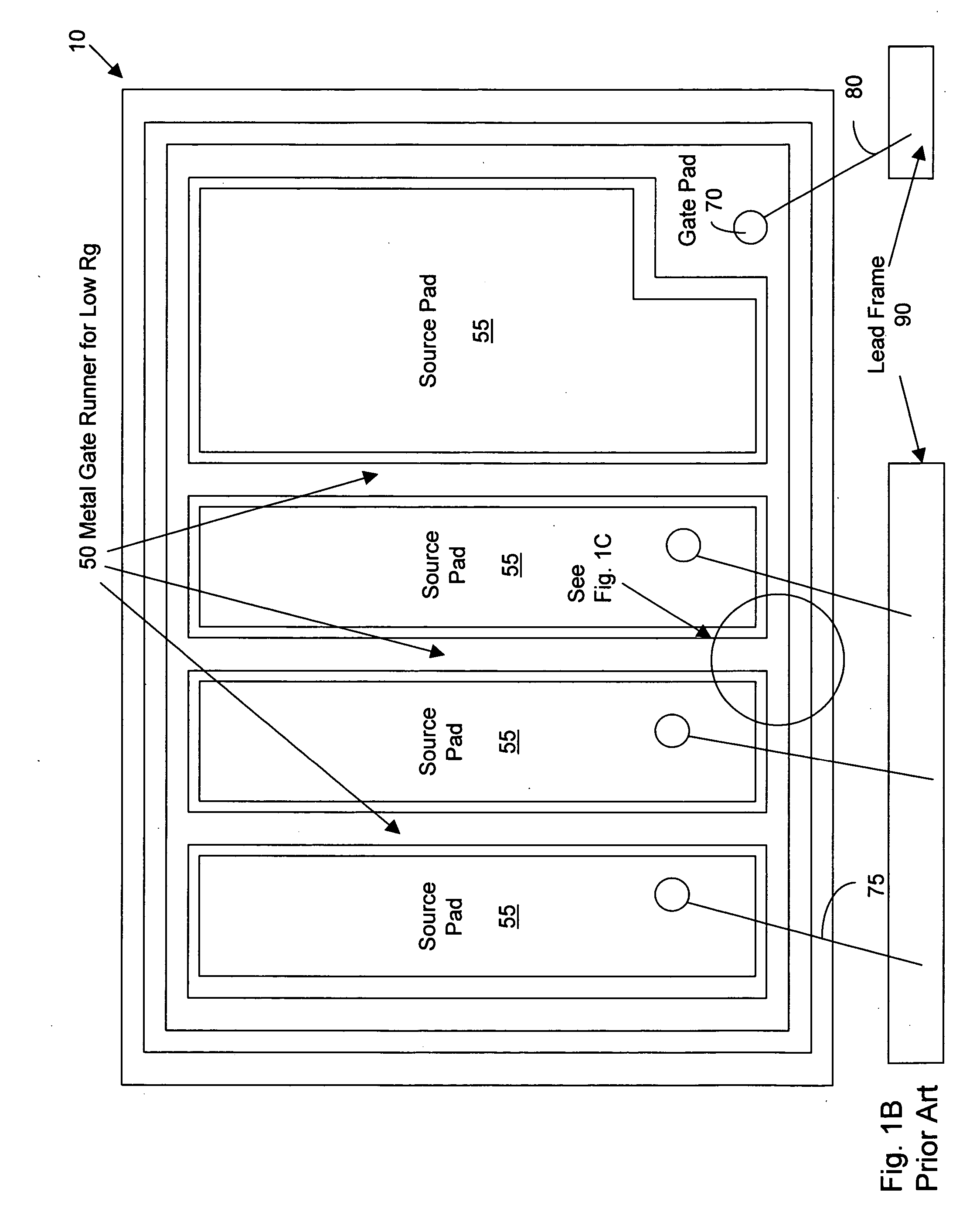

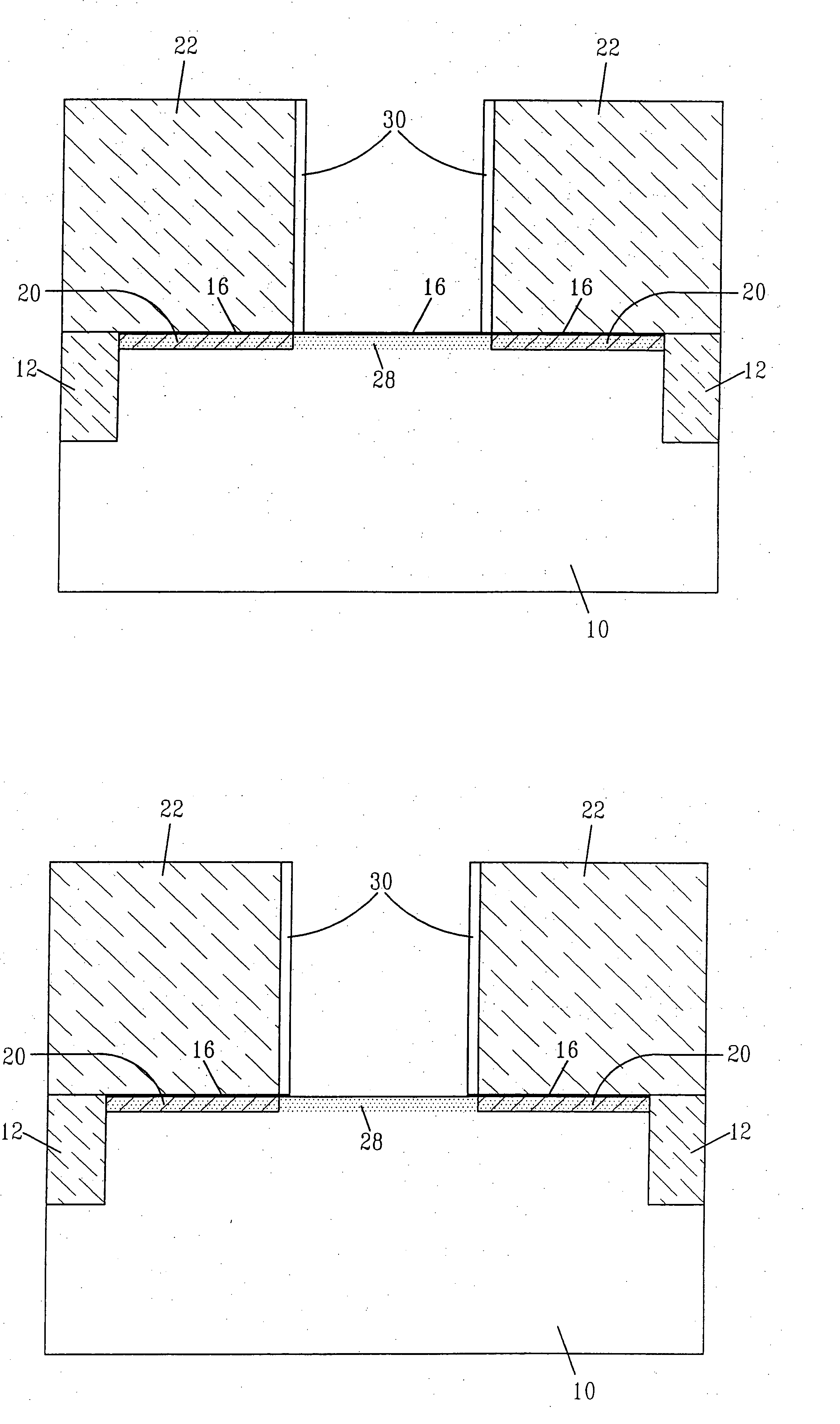

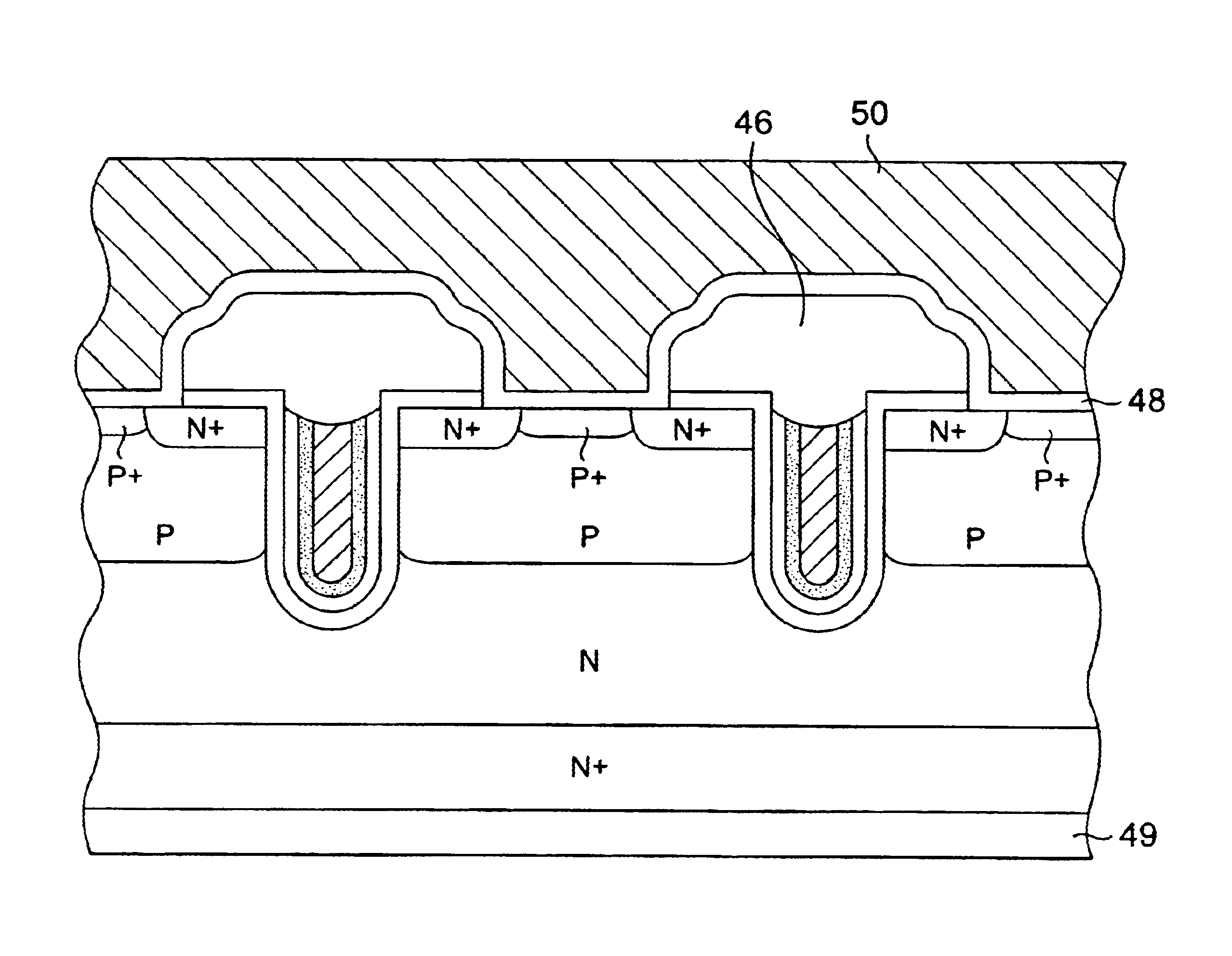

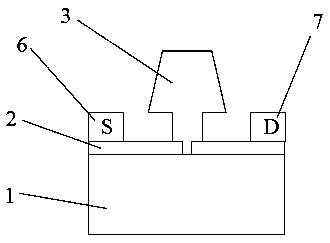

Gate contact and runners for high density trench MOSFET

InactiveUS20060273390A1Lower gate resistanceReduce source-body resistanceSolid-state devicesSemiconductor devicesTrench mosfetHigh density

A trenched metal oxide semiconductor field effect transistor (MOSFET) cell that includes a trenched gate surrounded by a source region encompassed in a body region above a drain region disposed on a bottom surface of a substrate. The MOSFET cell further includes a buried trench-poly gate runner electrically contacting to a trench gate of the trenched MOSFET. The buried trench-poly gate runner for functioning as a gate runner to increase gate transmission area and a contact area to a gate contact metal for reducing a gate resistance.

Owner:M MOS SEMICON

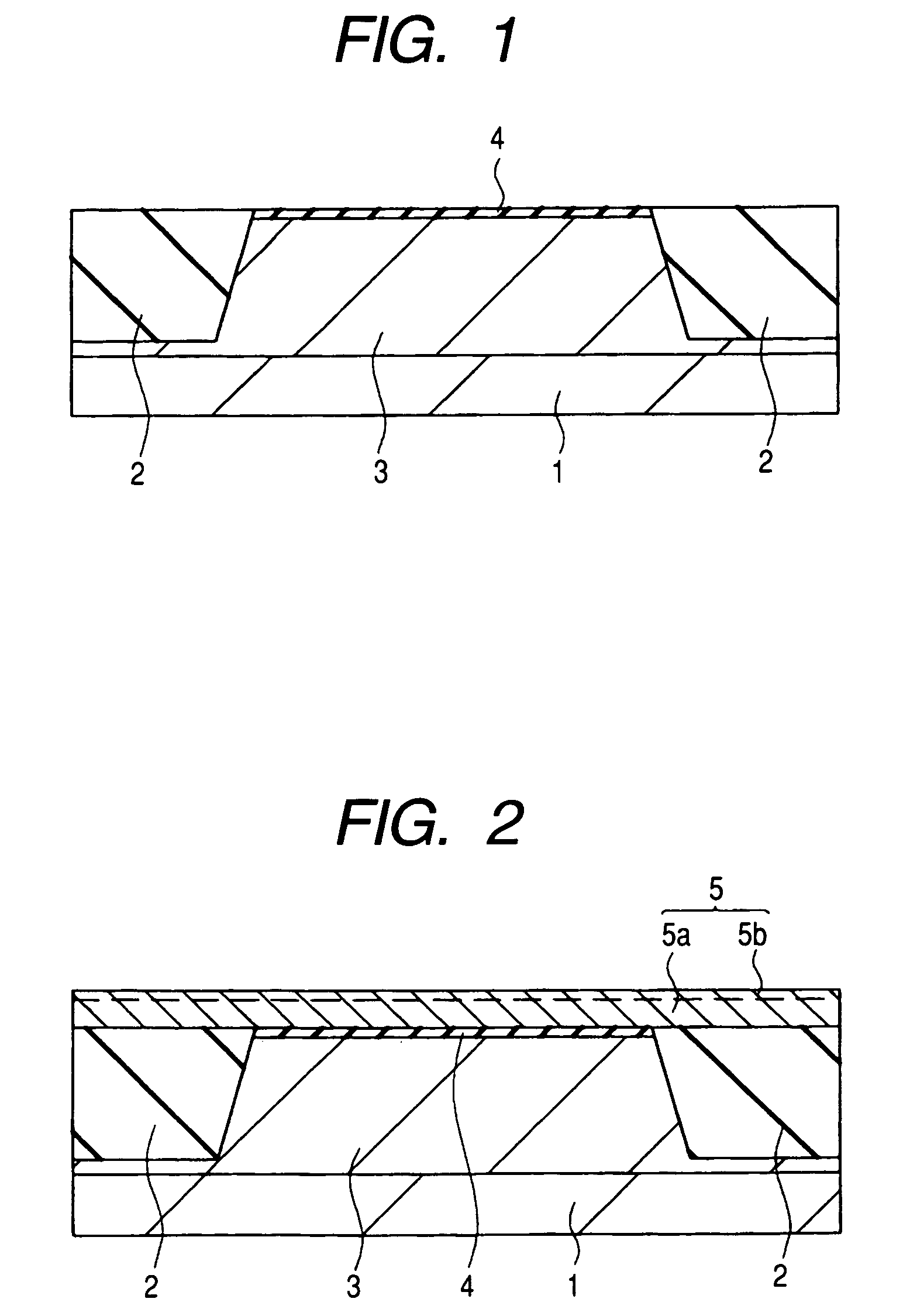

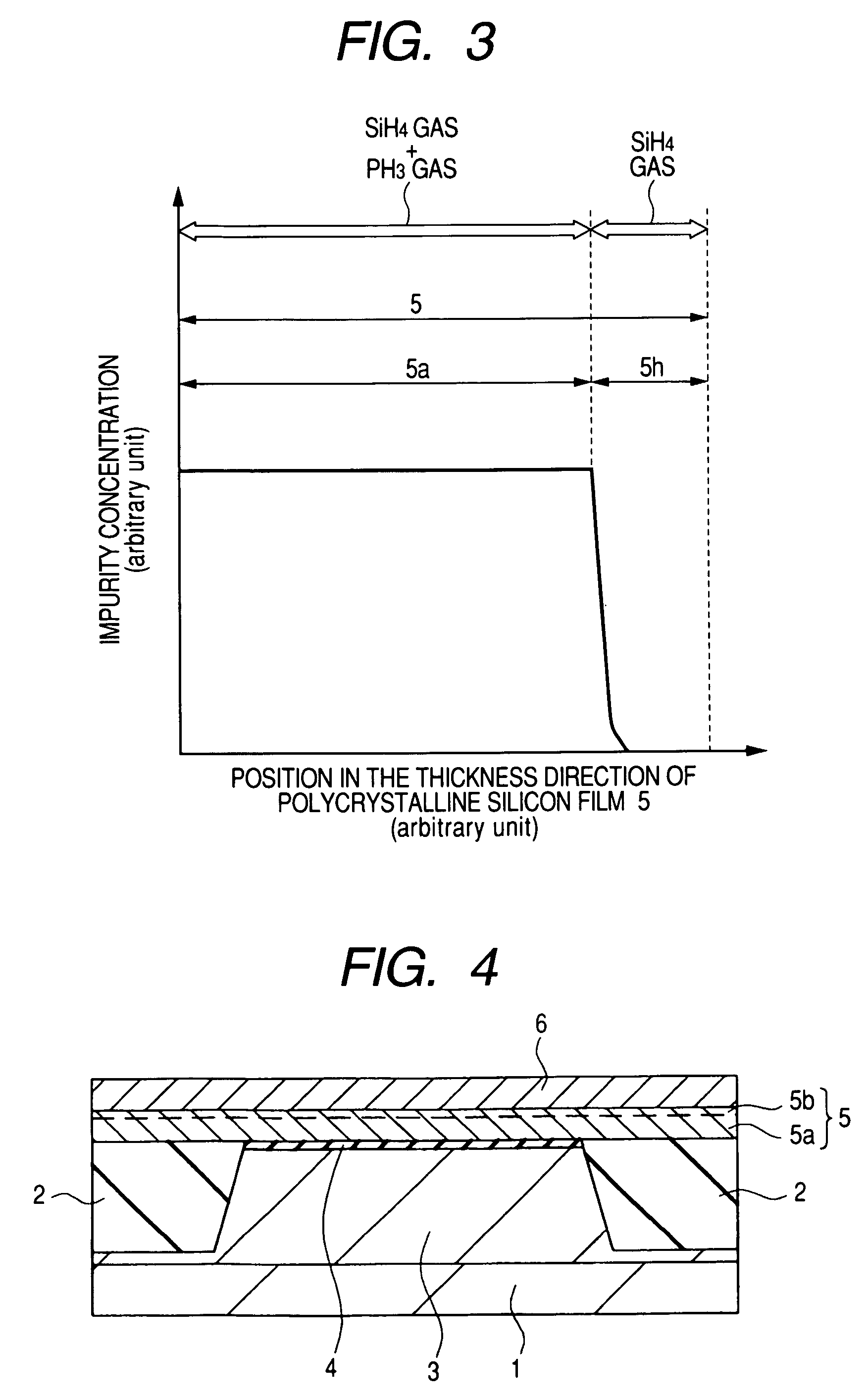

Method of manufacturing a semiconductor device

ActiveUS7256125B2Lower gate resistanceLow reliabilityTransistorSolid-state devicesNon dopedSemiconductor

For improving the reliability of a semiconductor device having a stacked structure of a polycrystalline silicon film and a tungsten silicide film, the device is manufactured by forming a polycrystalline silicon film, a tungsten silicide film and an insulating film successively over a gate insulating film disposed over the main surface of a semiconductor substrate, and patterning them to form a gate electrode having a stacked structure consisting of the polycrystalline silicon film and tungsten silicide film. The polycrystalline silicon film has two regions, one region formed by an impurity-doped polycrystalline silicon and the other one formed by non-doped polycrystalline silicon. The tungsten silicide film is deposited so that the resistivity of it upon film formation would exceed 1000 μΩcm.

Owner:RENESAS ELECTRONICS CORP +1

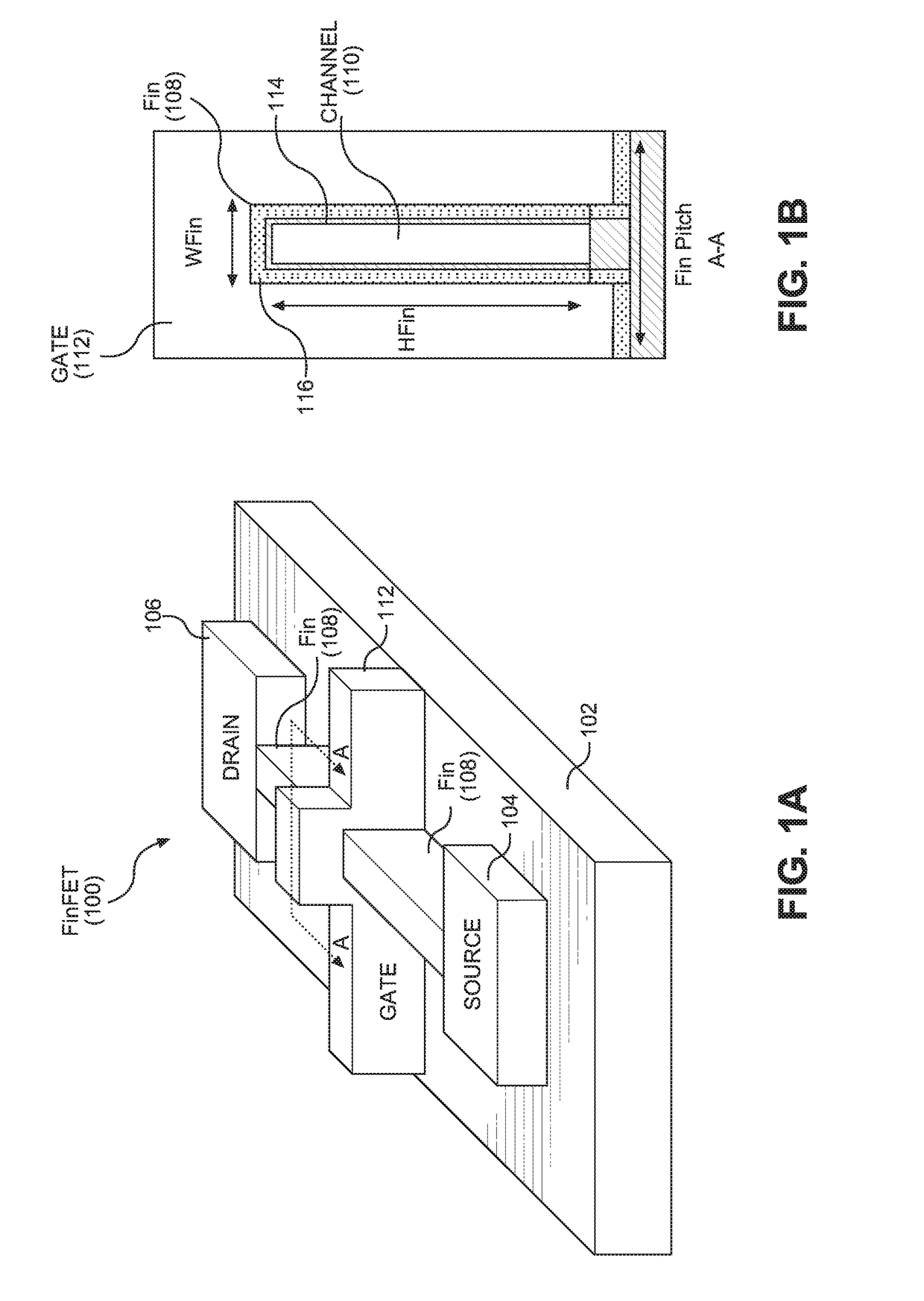

Method and structure to enhance gate induced strain effect in multigate device

ActiveUS20150206953A1Increase currentImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCharge carrier mobilityHigh stress

A FinFet formed by depositing a thin layer of polycrystalline silicon followed by depositing a stress containing material, including a high Ge percentage silicon germanium film and / or a high stress W film on top of a polycrystalline silicon film. Freeing space between fins allows stressor films to be deposited closer to the transistor channel, improving the proximity of the stress containing material to the transistor channel and enhancing the stress coupling efficiency by defining a ratio between stress level in the stressor film and stress transferred to the channel for a mobility enhancement. The stress level is enhanced by patterning by removing the n-type workfunction metal from the p-FinFET. After stripping off the soft or hard mask, the p-type workfunction metal is deposited in the n- and p-FinFET regions. The freed space specifically for p-FinFet between the fins achieves an even higher stressor coupling to further boost the carrier mobility.

Owner:IBM CORP

Method of forming a metal gate in a semiconductor device

ActiveUS7361565B2Increase speedReduce voltageTransistorSemiconductor/solid-state device manufacturingEngineeringPhotolithography

In a method of forming a metal gate in a semiconductor device, a gate insulation pattern and a dummy gate pattern are formed on a substrate. An insulation interlayer is formed on the dummy gate pattern to cover the dummy gate pattern. The insulation interlayer is polished such that a top surface of the dummy gate pattern is exposed, and the dummy gate pattern is selectively removed to form a trench on the substrate. A gate spacer is formed on an inner sidewall of the trench for determining a gate length of the metal gate. A metal is deposited to a sufficient thickness to fill the trench to form a metal layer. The metal layer is polished to remain in the trench. Accordingly, the gate length of the metal gate may be reduced no more than the resolution limit of the photolithography exposing system.

Owner:SAMSUNG ELECTRONICS CO LTD

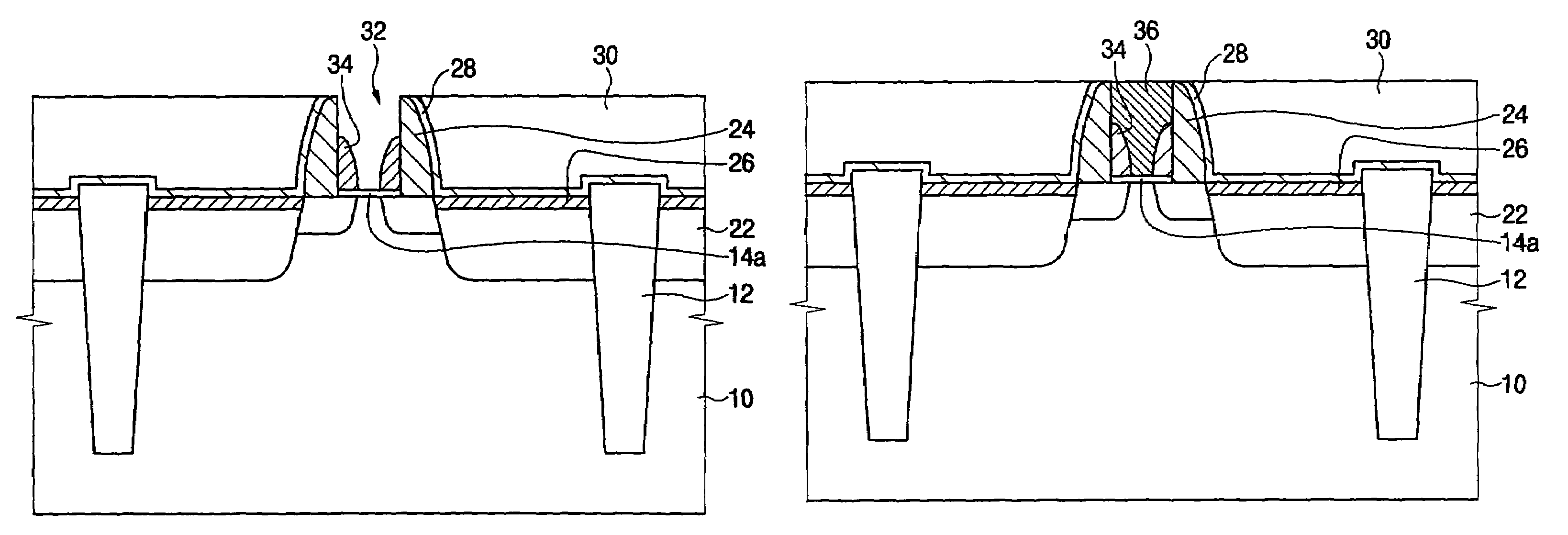

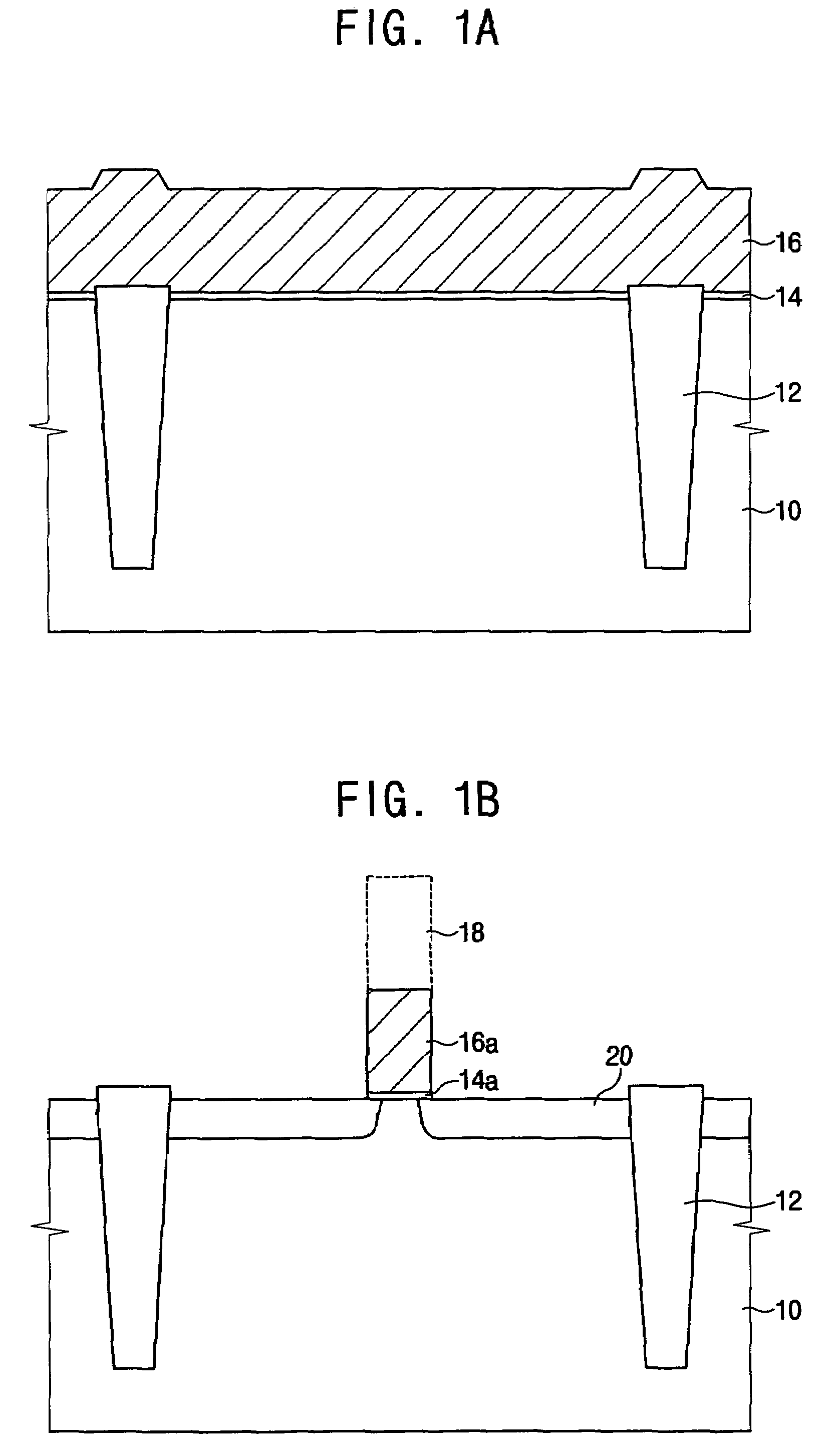

Method for manufacturing insulated gate field effect transistor

ActiveUS20080197426A1Reduce contact resistanceReduce gate capacitanceTransistorSolid-state devicesEngineeringConductive materials

Disclosed herein is a method for manufacturing an insulated gate field effect transistor, the method including the steps of: (a) preparing a base that includes source / drain regions, a channel forming region, a gate insulating film formed on the channel forming region, an insulating layer covering the source / drain regions, and a gate electrode formation opening provided in a partial portion of the insulating layer above the channel forming region; (b) forming a gate electrode by burying a conductive material layer in the gate electrode formation opening; (c) removing the insulating layer; and (d) depositing a first interlayer insulating layer and a second interlayer insulating layer sequentially across an entire surface, wherein in the step (d), the first interlayer insulating layer is deposited in a deposition atmosphere containing no oxygen atom.

Owner:SONY CORP

Semiconductor device and method of manufacturing the same

ActiveUS20140027857A1Lower gate resistanceIncrease paddingTransistorSemiconductor/solid-state device manufacturingWork functionBlocking layer

The present invention discloses a semiconductor device, comprising a substrate, a plurality of gate stack structures on the substrate, a plurality of gate spacer structures on both sides of each gate stack structure, a plurality of source and drain regions in the substrate on both sides of each gate spacer structure, the plurality of gate stack structures comprising a plurality of first gate stack structures and a plurality of second gate stack structures, characterized in that each of the first gate stack structures comprises a first gate insulating layer, a first blocking layer, a first work function regulating layer and a resistance regulating layer, and each of the second gate stack structures comprises a second gate insulating layer, a first blocking layer, a second work function regulating layer, a first work function regulating layer and a resistance regulating layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

JFET and MESFET structures for low voltage, high current and high frequency applications

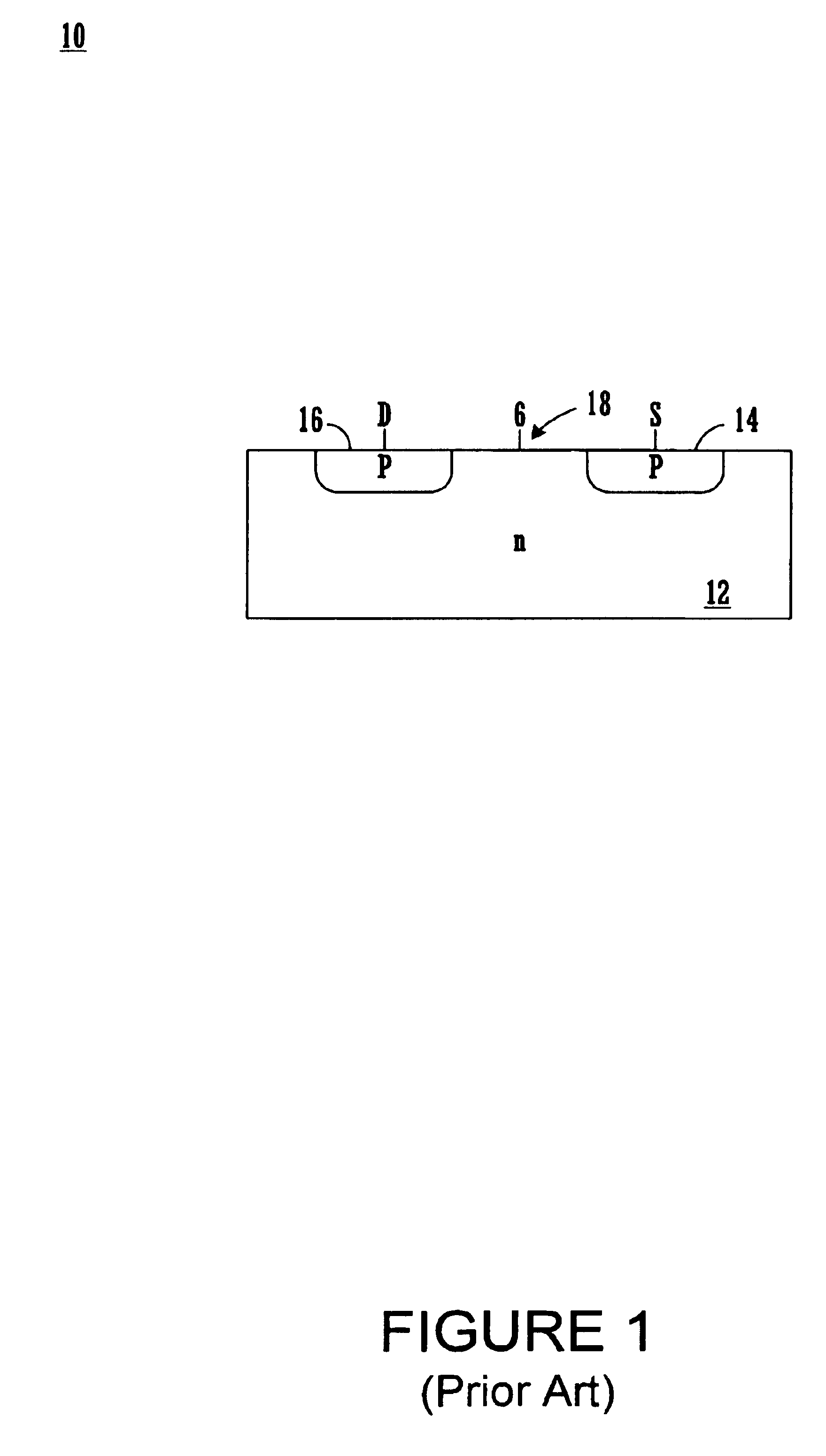

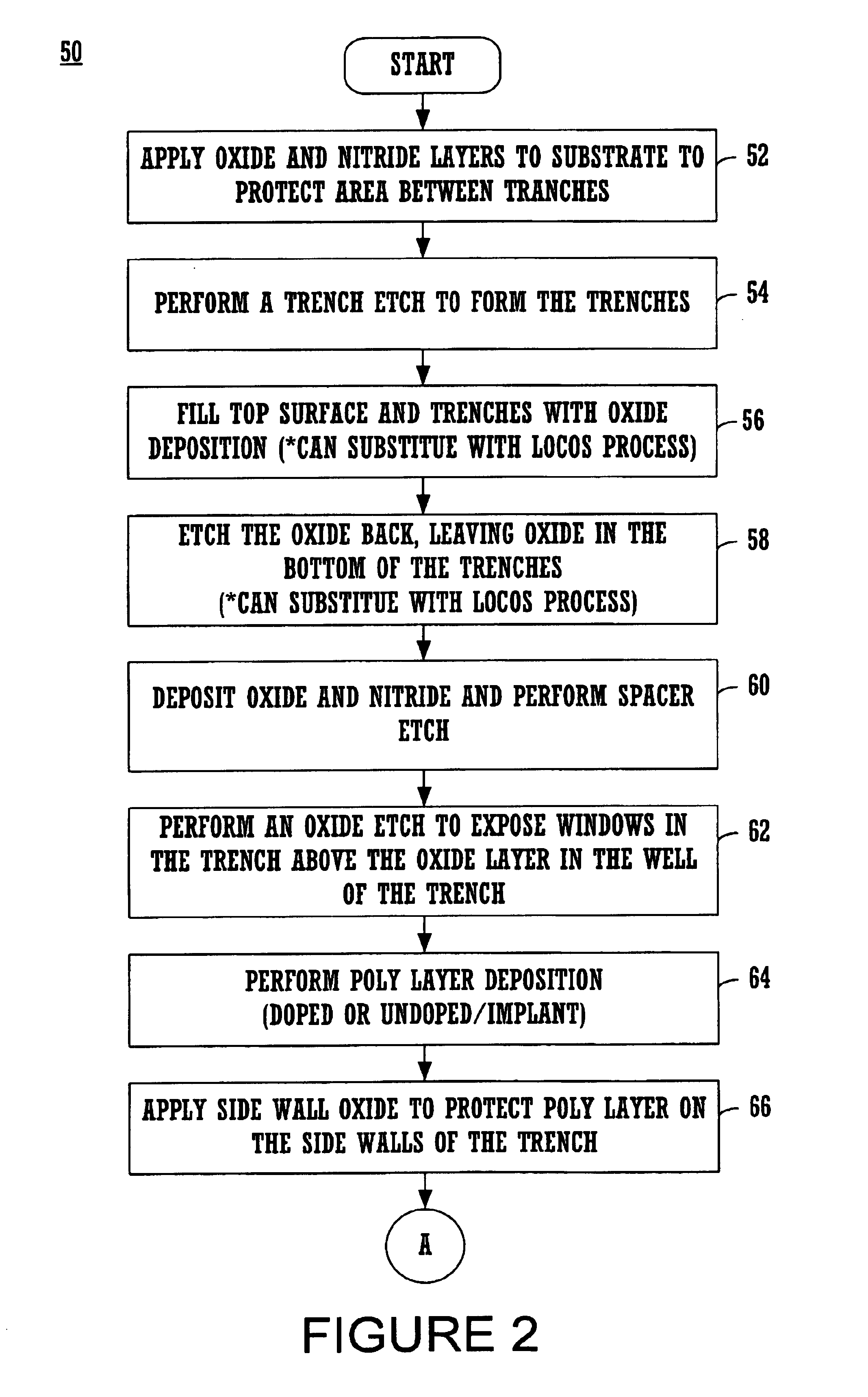

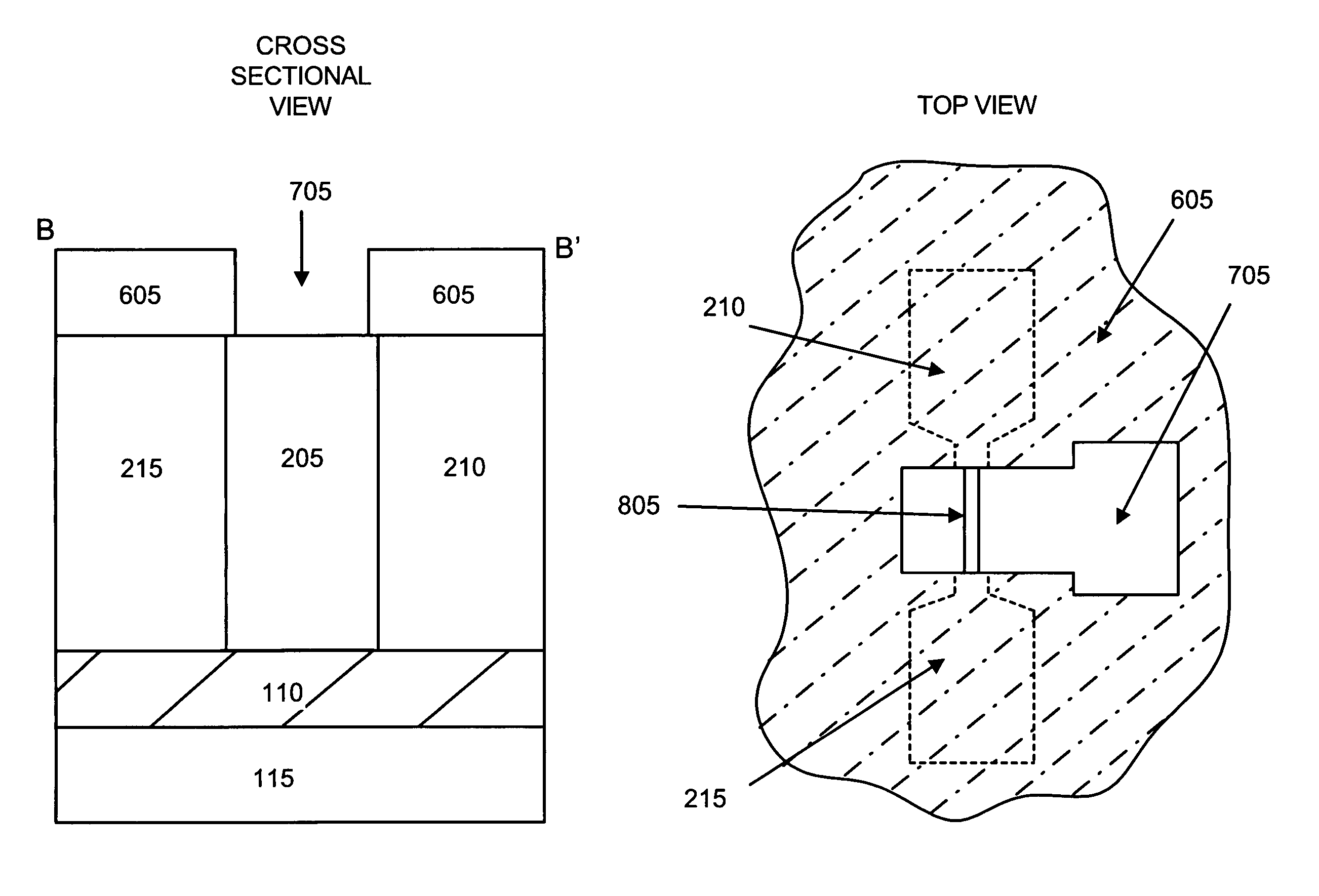

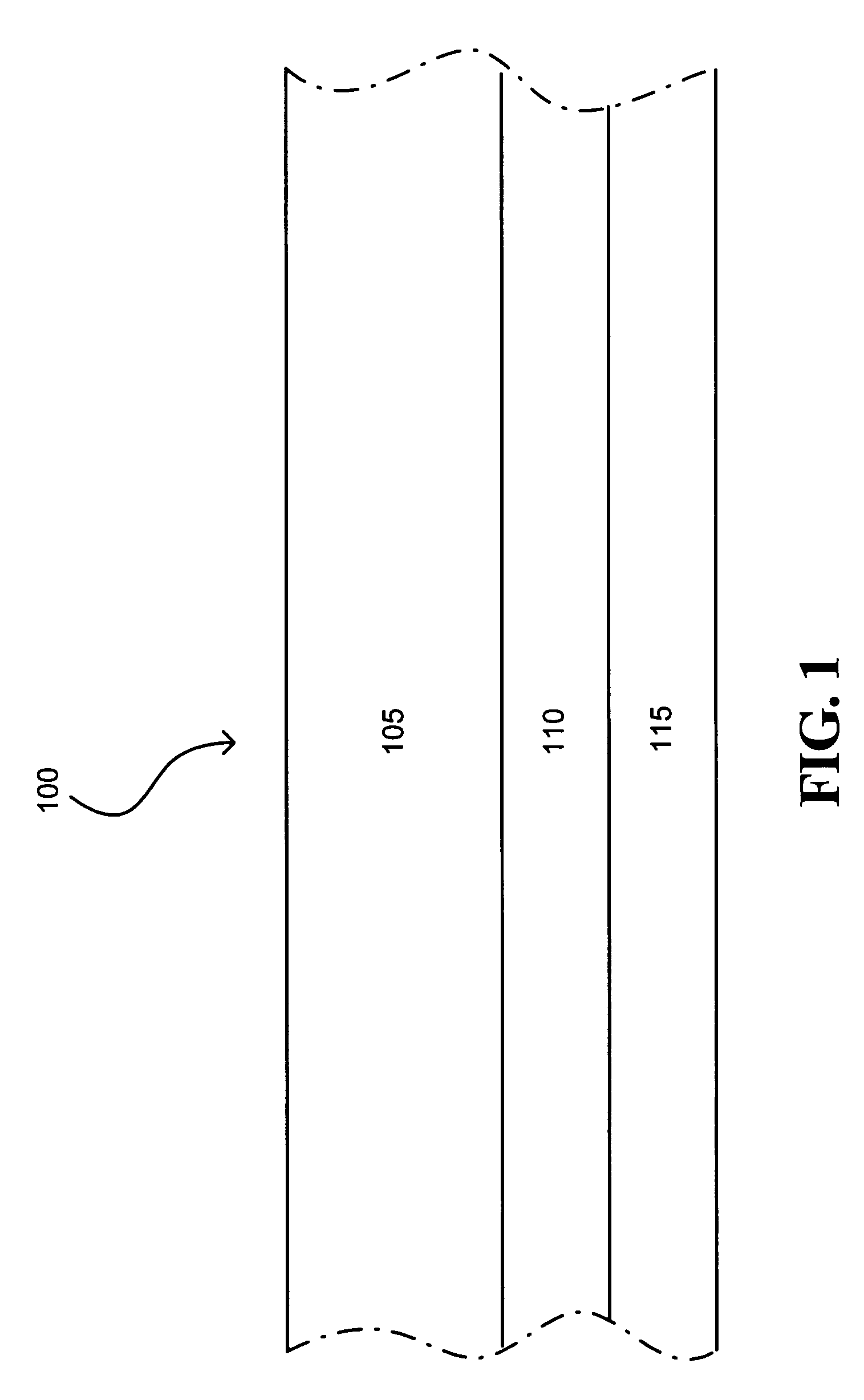

InactiveUS6921932B1Easy to controlLower junction capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceLow voltage

JFET and MESFET structures, and processes of making same, for low voltage, high current and high frequency applications. The structures may be used in normally-on (e.g., depletion mode) or normally-off modes. The structures include an oxide layer positioned under the gate region which effectively reduces the junction capacitance (gate to drain) of the structure. For normally off modes, the structures reduce gate current at Vg in forward bias. In one embodiment, a silicide is positioned in part of the gate to reduce gate resistance. The structures are also characterized in that they have a thin gate due to the dipping of the spacer oxide, which can be below 1000 angstroms and this results in fast switching speeds for high frequency applications.

Owner:POWER INTEGRATIONS INC

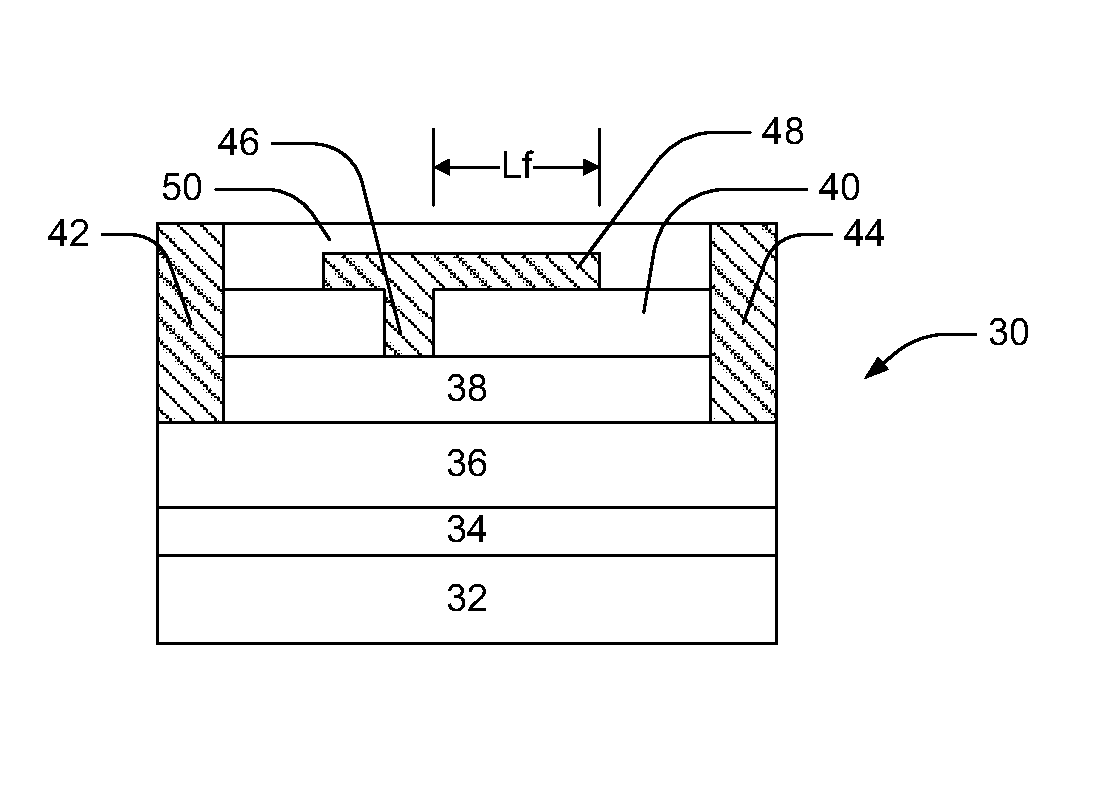

Narrow-body damascene tri-gate FinFET

ActiveUS7186599B2Process controlHigher drive currentTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

A method of forming a fin field effect transistor includes forming a fin and forming a source region on a first end of the fin and a drain region on a second end of the fin. The method further includes forming a dummy gate with a first semi-conducting material in a first pattern over the fin and forming a dielectric layer around the dummy gate. The method also includes removing the first semi-conducting material to leave a trench in the dielectric layer corresponding to the first pattern, thinning a portion of the fin exposed within the trench, and forming a metal gate within the trench.

Owner:ADVANCED MICRO DEVICES INC

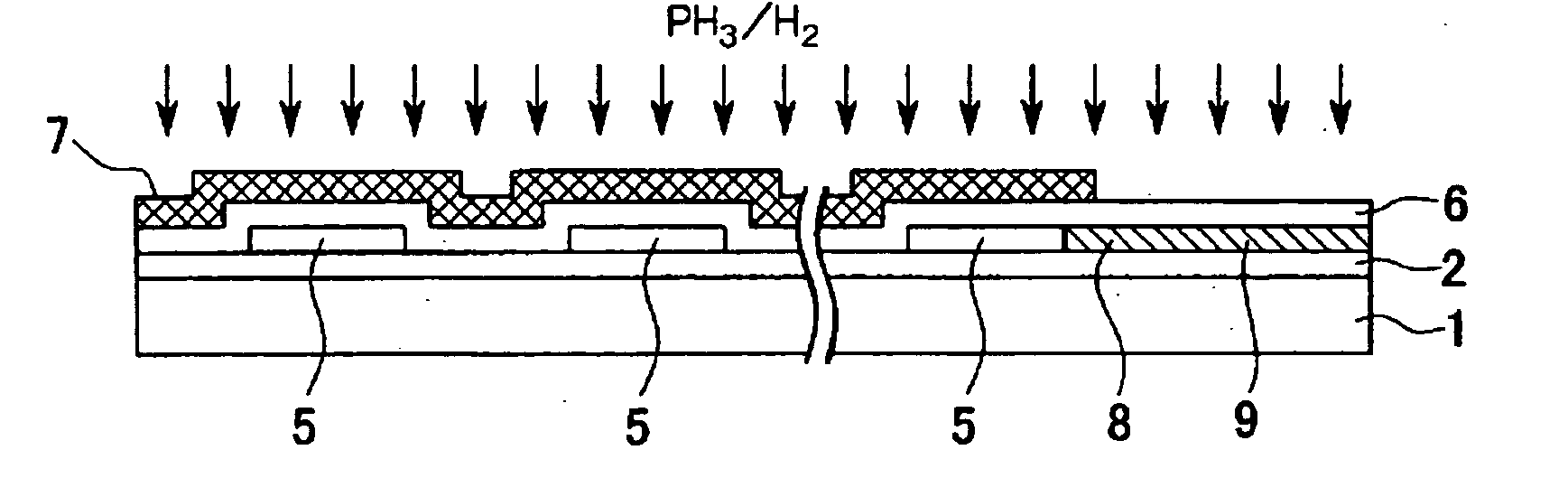

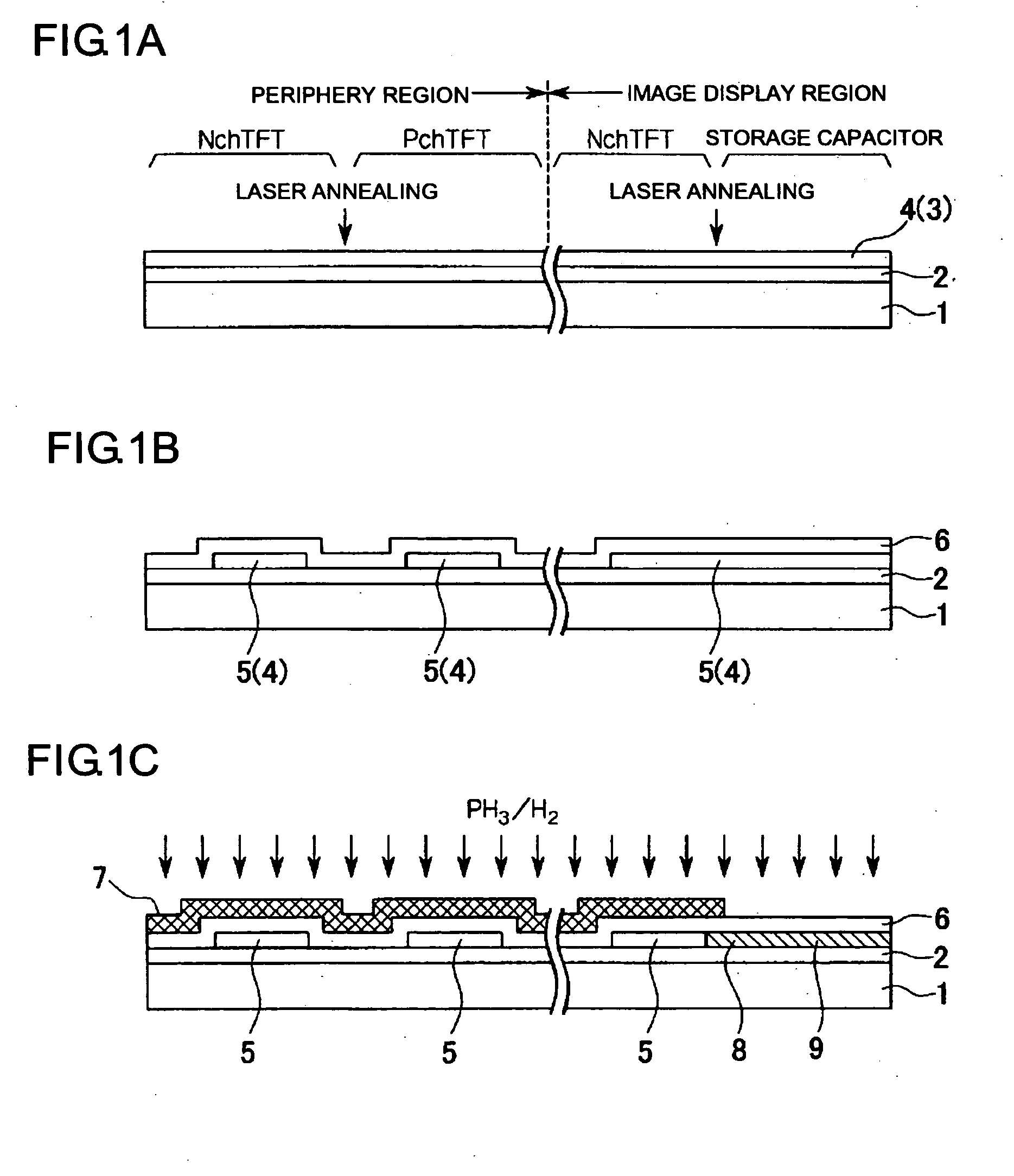

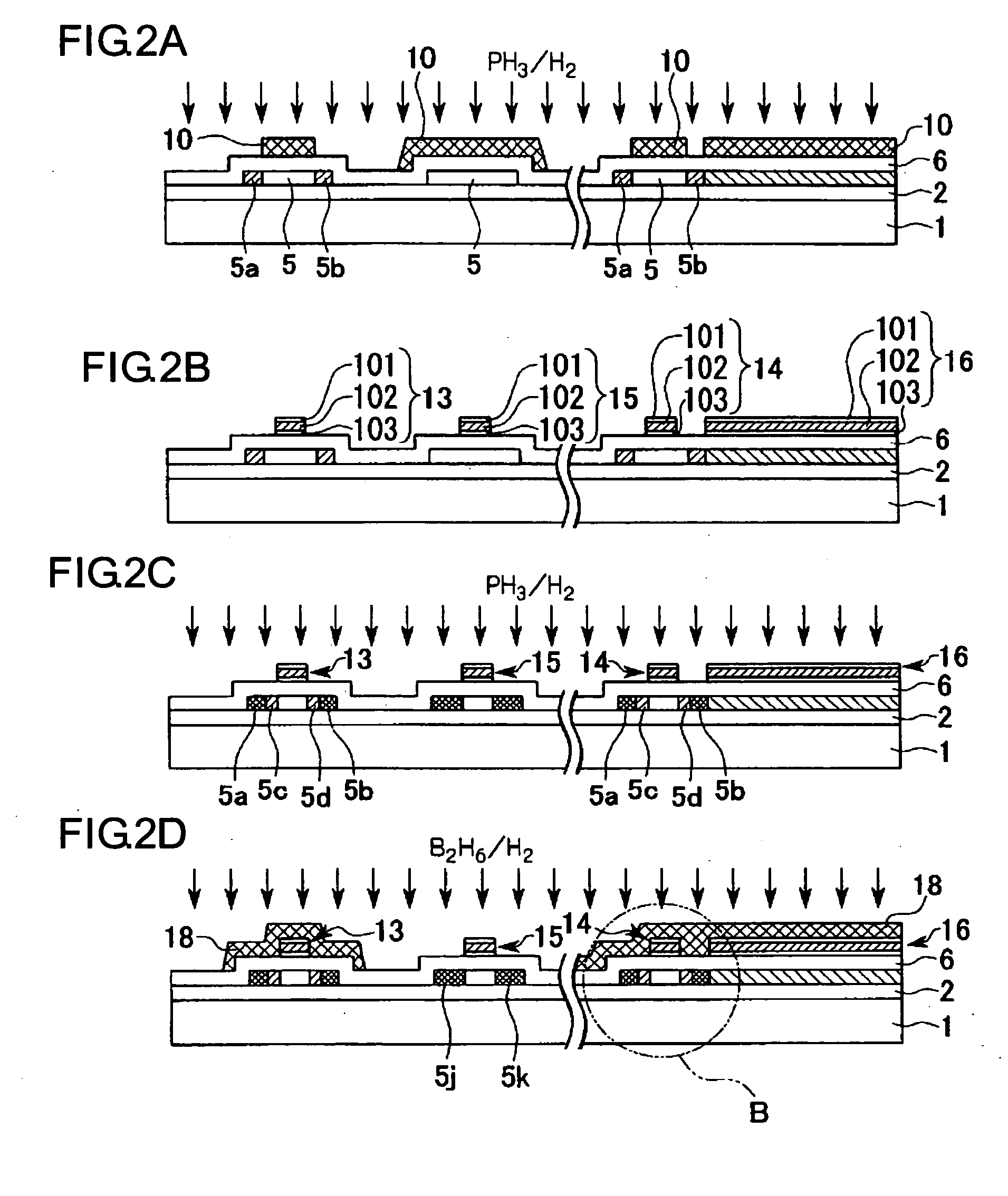

Thin film semiconductor element and method of manufacturing the same

ActiveUS20050035352A1Excellent etching propertiesPrevent leakageTransistorSolid-state devicesCapacitanceEngineering

The invention provides a thin film semiconductor element and a method of manufacturing the same to achieve lowering the resistance of gate electrodes, lowering the capacitance of source electrodes, and enhancing etching characteristics. The thin film semiconductor element can include a semiconductor film provided on a substrate, source and drain electrodes connected to the semiconductor film, and a gate electrode provided on the semiconductor film with an insulating film interposed therebetween. The film thickness of the source and drain electrodes can be smaller than the film thickness of the gate electrode.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Narrow-body damascene tri-gate FinFET

ActiveUS20050153485A1Process controlHigher drive currentTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsEngineering

A method of forming a fin field effect transistor includes forming a fin and forming a source region on a first end of the fin and a drain region on a second end of the fin. The method further includes forming a dummy gate with a first semi-conducting material in a first pattern over the fin and forming a dielectric layer around the dummy gate. The method also includes removing the first semi-conducting material to leave a trench in the dielectric layer corresponding to the first pattern, thinning a portion of the fin exposed within the trench, and forming a metal gate within the trench.

Owner:ADVANCED MICRO DEVICES INC

Low resistance T-gate MOSFET device using a damascene gate process and an innovative oxide removal etch

InactiveUS20050170659A1Increase the areaLow-sheet resistance poly-gatesTransistorSemiconductor/solid-state device manufacturingMOSFETLow resistance

The present invention provides a method for fabricating low-resistance, sub-0.1 μm channel T-gate MOSFETs that do not exhibit any poly depletion problems. The inventive method employs a damascene-gate processing step and a chemical oxide removal etch to fabricate such MOSFETs. The chemical oxide removal may be performed in a vapor containing HF and NH3 or a plasma containing HF and NH3.

Owner:IBM CORP

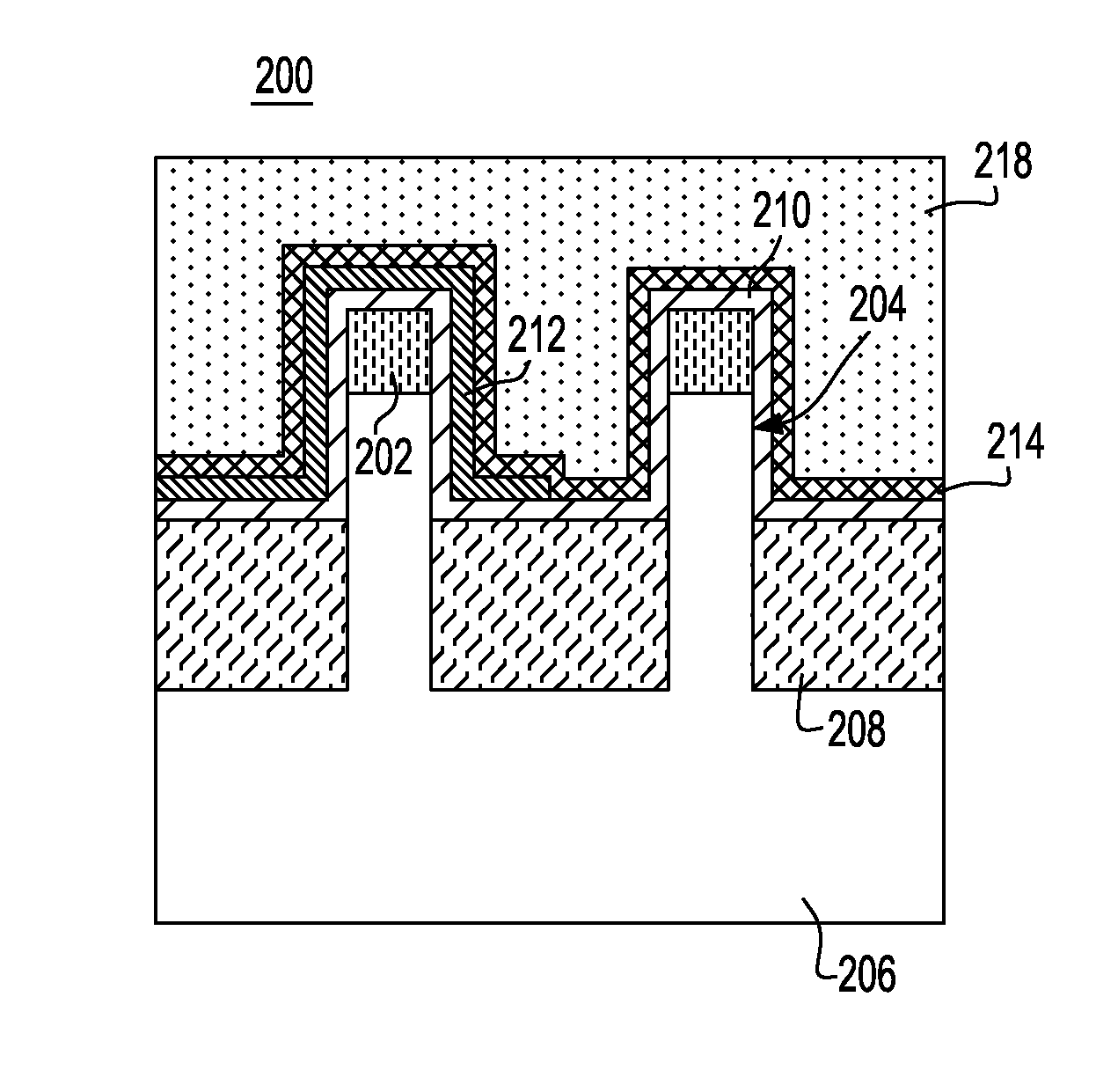

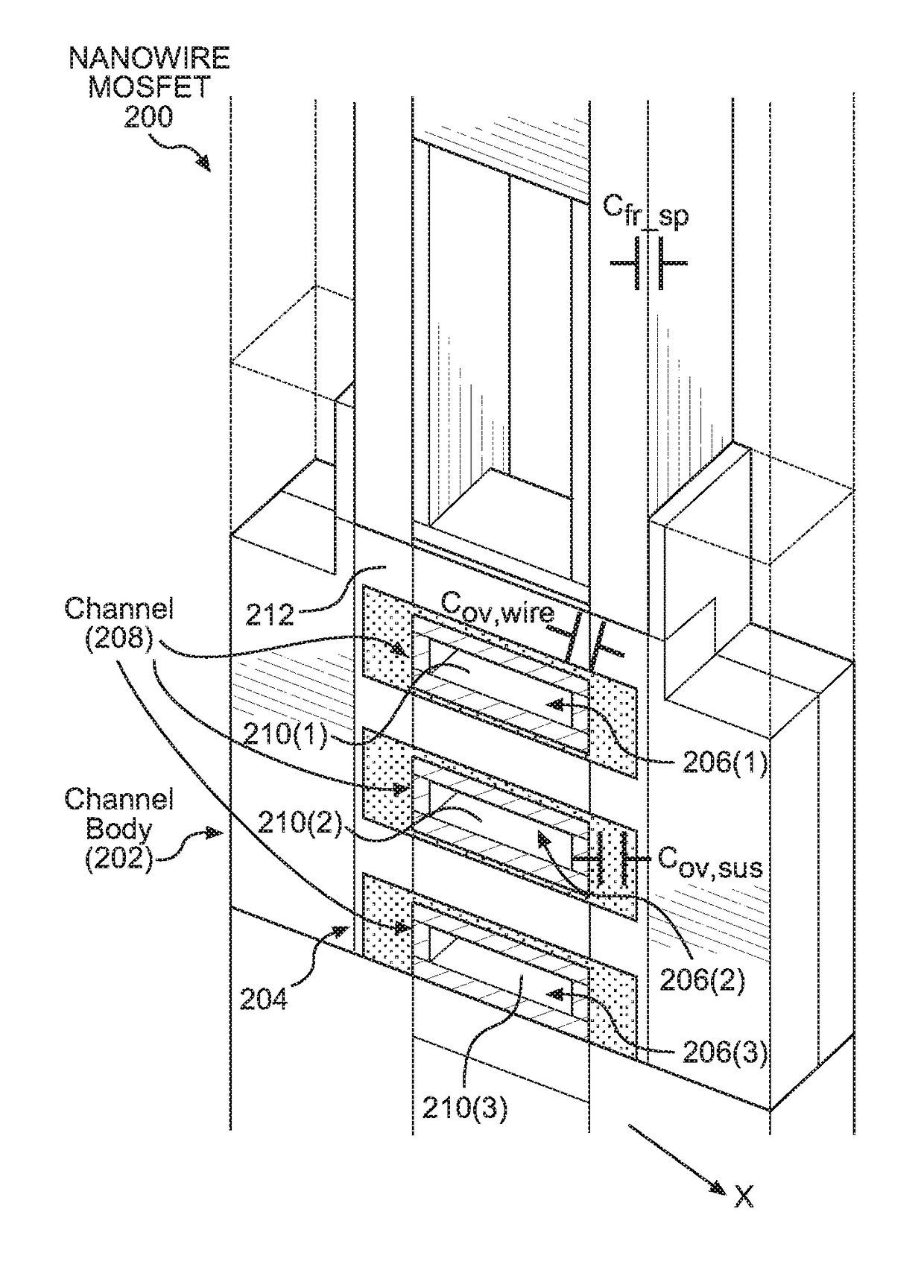

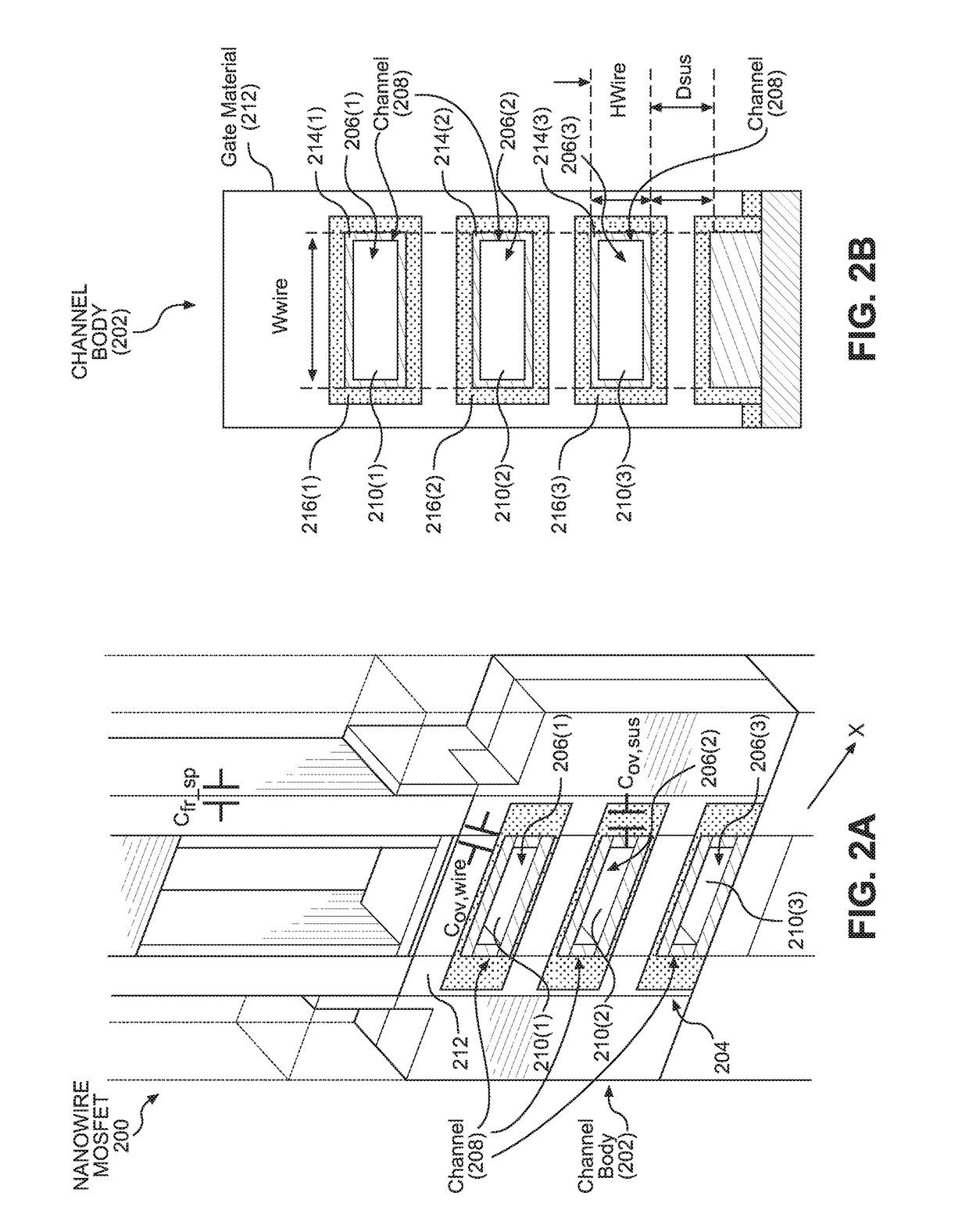

NANOWIRE METAL-OXIDE SEMICONDUCTOR (MOS) FIELD-EFFECT TRANSISTORS (FETs) (MOSFETs) EMPLOYING A NANOWIRE CHANNEL STRUCTURE EMPLOYING RECESSED CONDUCTIVE STRUCTURES FOR CONDUCTIVELY COUPLING NANOWIRE STRUCTURES

InactiveUS20170207313A1Increase widthIncrease channel current densitySemiconductor devicesMOSFETNanowire

Nanowire metal-oxide semiconductor (MOS) Field-Effect Transistors (FETs) (MOSFETs) employing a nanowire channel structure employing recessed conductive structures for conductively coupling nanowire structures are disclosed. Conductive structures are disposed between adjacent nanowire structures to conductively couple nanowire structures. Providing conductive structures in the nanowire channel structure increases the average cross-sectional area of nanowire structures, as compared to a similar nanowire channel structure not employing conductive structures, thus increasing effective channel width and drive strength for a given channel structure height. The precision of a gate material filling process is also eased, because gate material does not have to be disposed in areas between adjacent nanowire structures occupied by conductive structures. The conductive structure width can also be recessed with regard to width of nanowire structures in the nanowire channel structure to allow for a thicker metal gate to lower the gate resistance, while providing excellent electrostatic gate control of the channel.

Owner:QUALCOMM INC

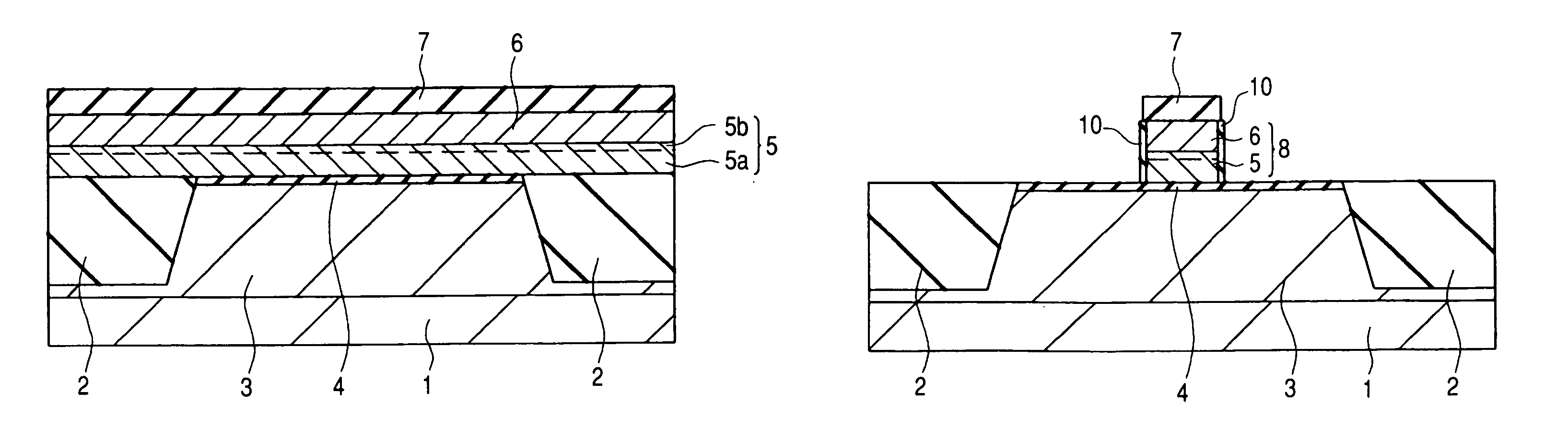

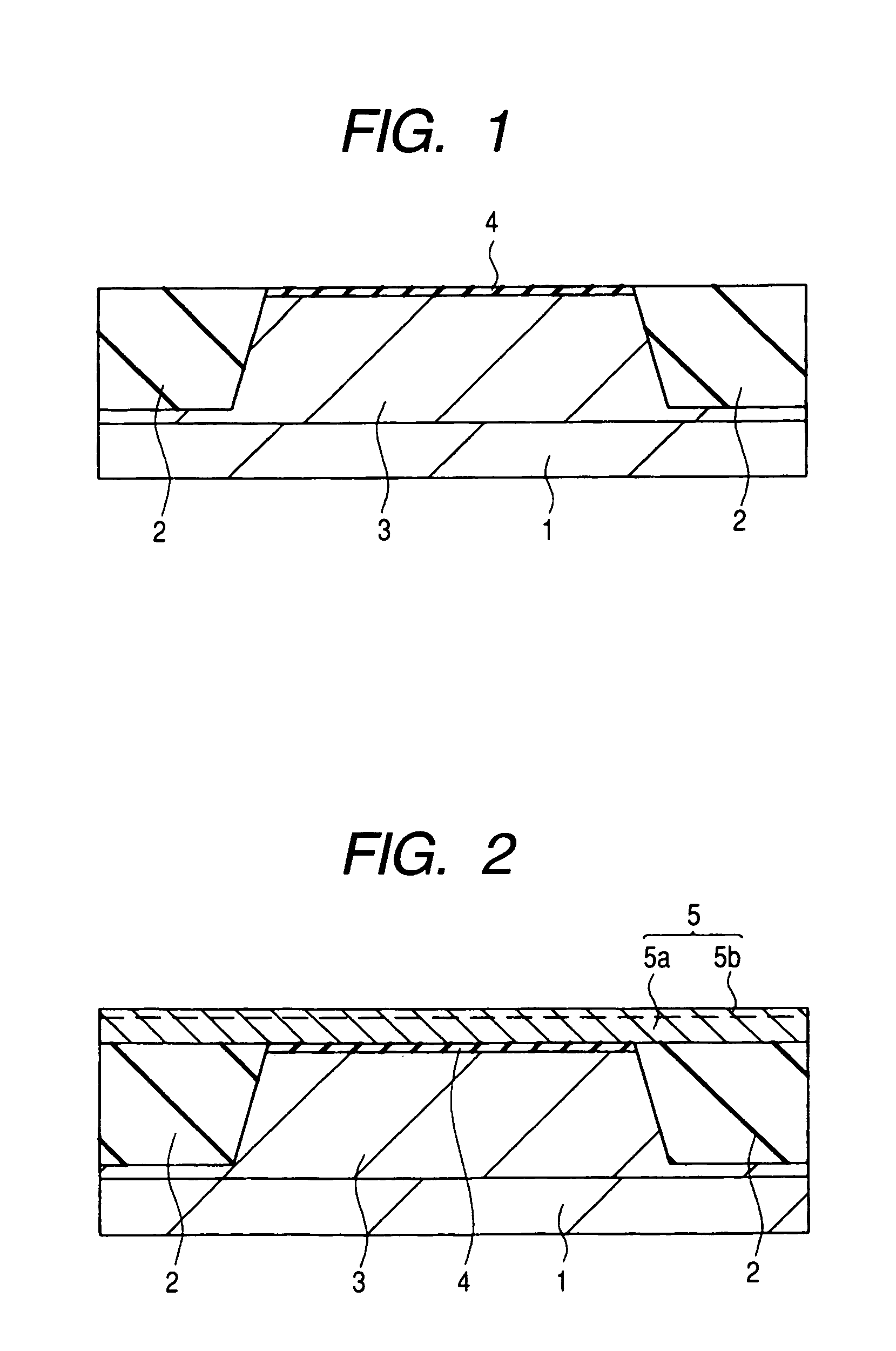

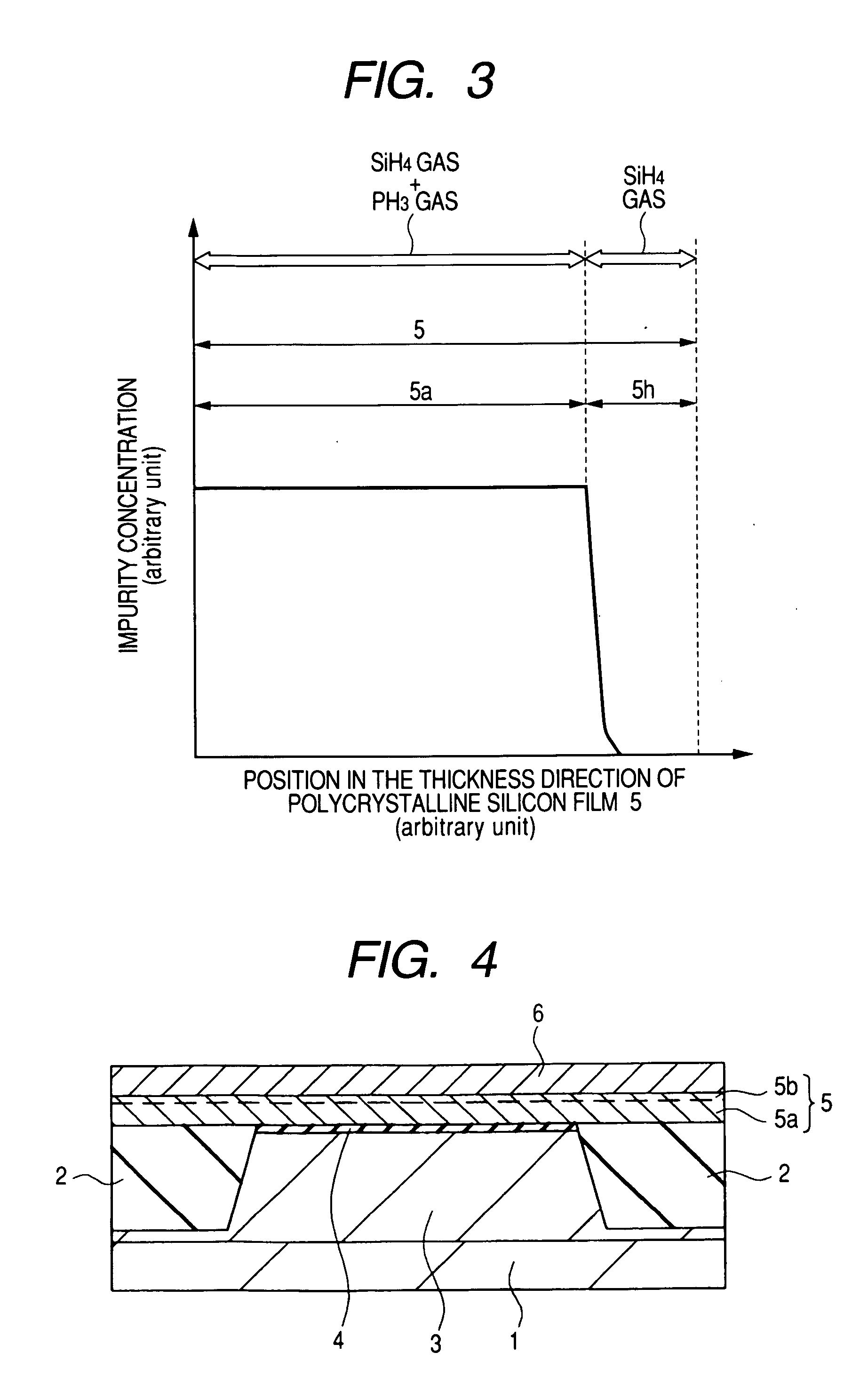

Method of manufacturing a semiconductor device

ActiveUS20050048708A1Lower gate resistanceLow reliabilityTransistorSolid-state devicesDevice materialNon doped

For improving the reliability of a semiconductor device having a stacked structure of a polycrystalline silicon film and a tungsten silicide film, the device is manufactured by forming a polycrystalline silicon film, a tungsten silicide film and an insulating film successively over a gate insulating film disposed over the main surface of a semiconductor substrate, and patterning them to form a gate electrode having a stacked structure consisting of the polycrystalline silicon film and tungsten silicide film. The polycrystalline silicon film has two regions, one region formed by an impurity-doped polycrystalline silicon and the other one formed by non-doped polycrystalline silicon. The tungsten silicide film is deposited so that the resistivity of it upon film formation would exceed 1000 μΩcm.

Owner:RENESAS ELECTRONICS CORP +1

Trench MOSFET with terrace gate and self-aligned source trench contact

InactiveUS20100127324A1Reduce manufacturing costLower gate resistanceTransistorSemiconductor/solid-state device manufacturingTrench mosfetTrench gate

A trench MOSFET with terrace gate is disclosed for self-aligned contact. When refilling the gate trenches, the deposited polysilicon layer is higher than the sidewalls of the trenches to be used as a terrace gate of the MOSFET. The source contact width is determined by mesa width between two adjacent trenches minus 2 times of the oxide thickness deposited on the mesa instead of contact mask width which is wider than silicon contact width. Therefore, the position of source contact is still unchanged even if the misalignment of trench mask happens. At the same time, by using terrace gates, the Rg is thus reduced because the terrace gate provides more polysilicon as gate material than the conventional trench gate.

Owner:FORCE MOS TECH CO LTD

High speed trench DMOS

InactiveUS6849899B2Lower gate resistanceReduce gate capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePropagation delay

A method for making trench DMOS is provided that utilizes polycide and refractory techniques to make trench DMOS which exhibit low gate resistance, low gate capacitance, reduced distributed RC gate propagation delay, and improved switching speeds for high frequency applications.

Owner:GEN SEMICON

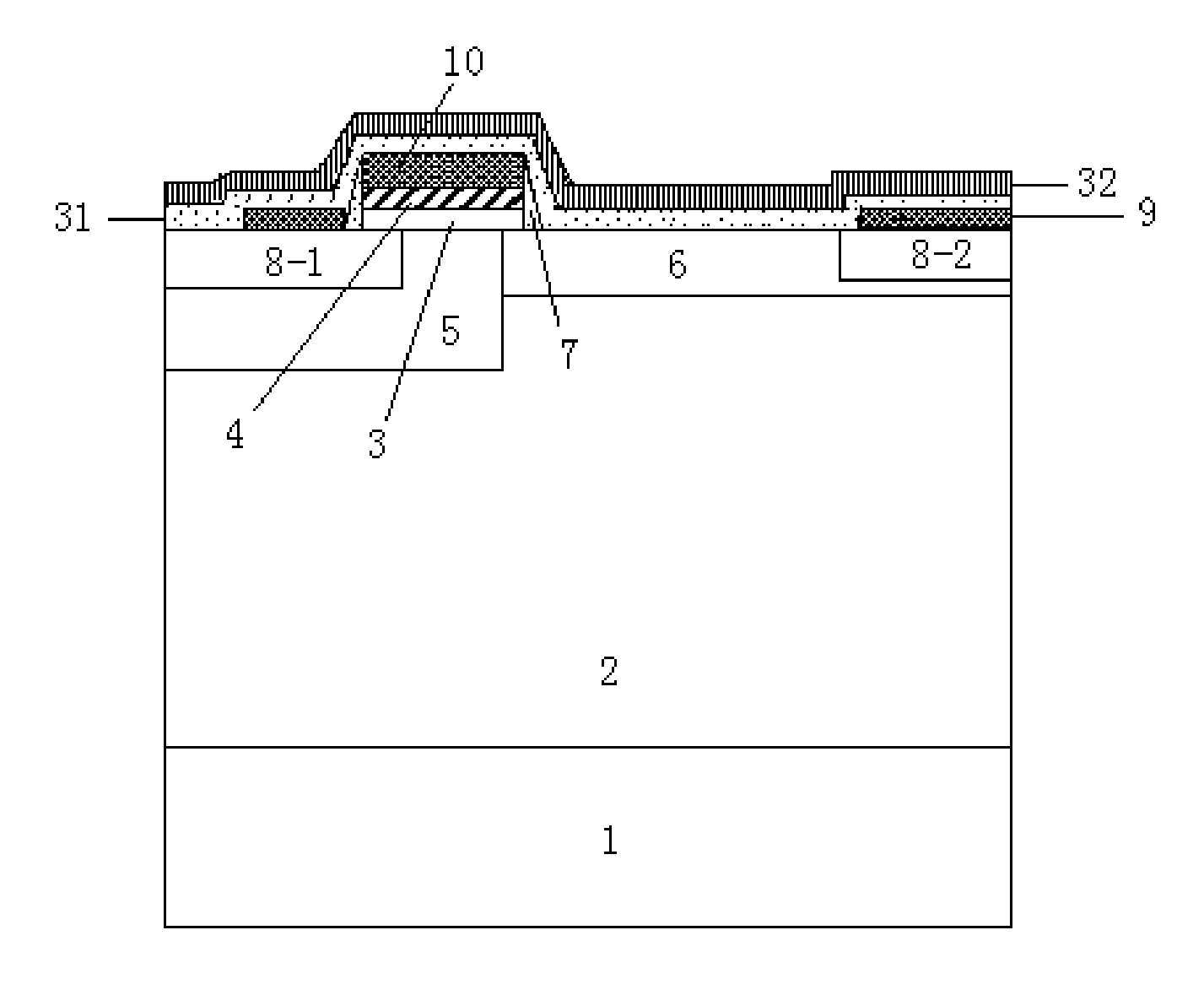

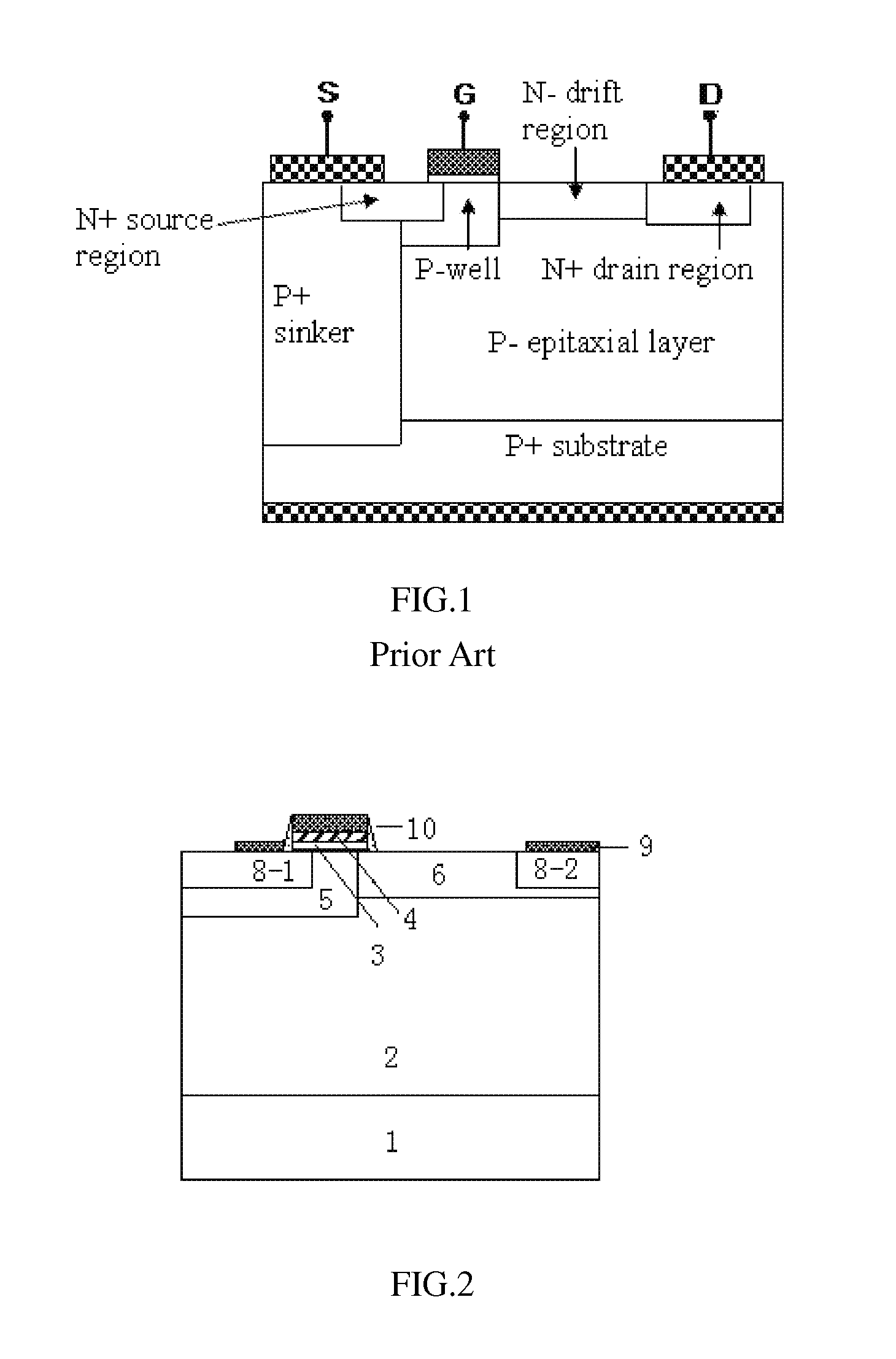

Semiconductor device and method for fabricating the same

ActiveUS20140048878A1Reduce horizontal sizeImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A semiconductor device includes: a P+ substrate; a P− epitaxial layer over the P+ substrate; a P-well and an N− drift region in the P− epitaxial layer and laterally adjacent to each other; an N+ source region in the P-well and connected to a front-side metal via a first contact electrode; an N+ drain region in the N− drift region and connected to the front-side metal via a second contact electrode; a gate structure on the P− epitaxial layer and connected to the front-side metal via a third contact electrode; and a metal plug through the P− epitaxial layer and having one end in contact with the P+ substrate and the other end connected to the front-side metal, the metal plug being adjacent to one side of the N+ source region that is farther from the N− drift region. A method for fabricating the semiconductor device is also disclosed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

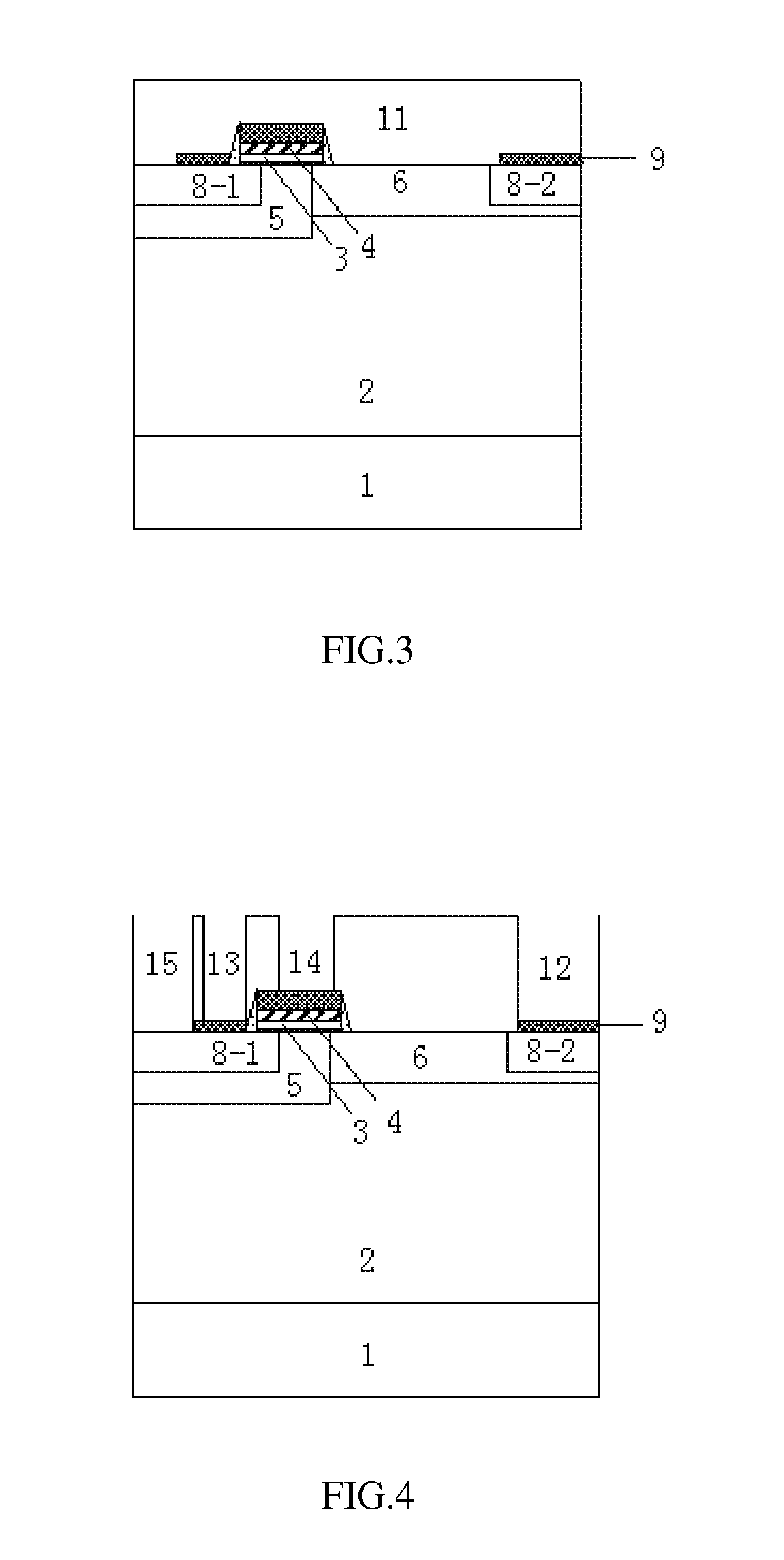

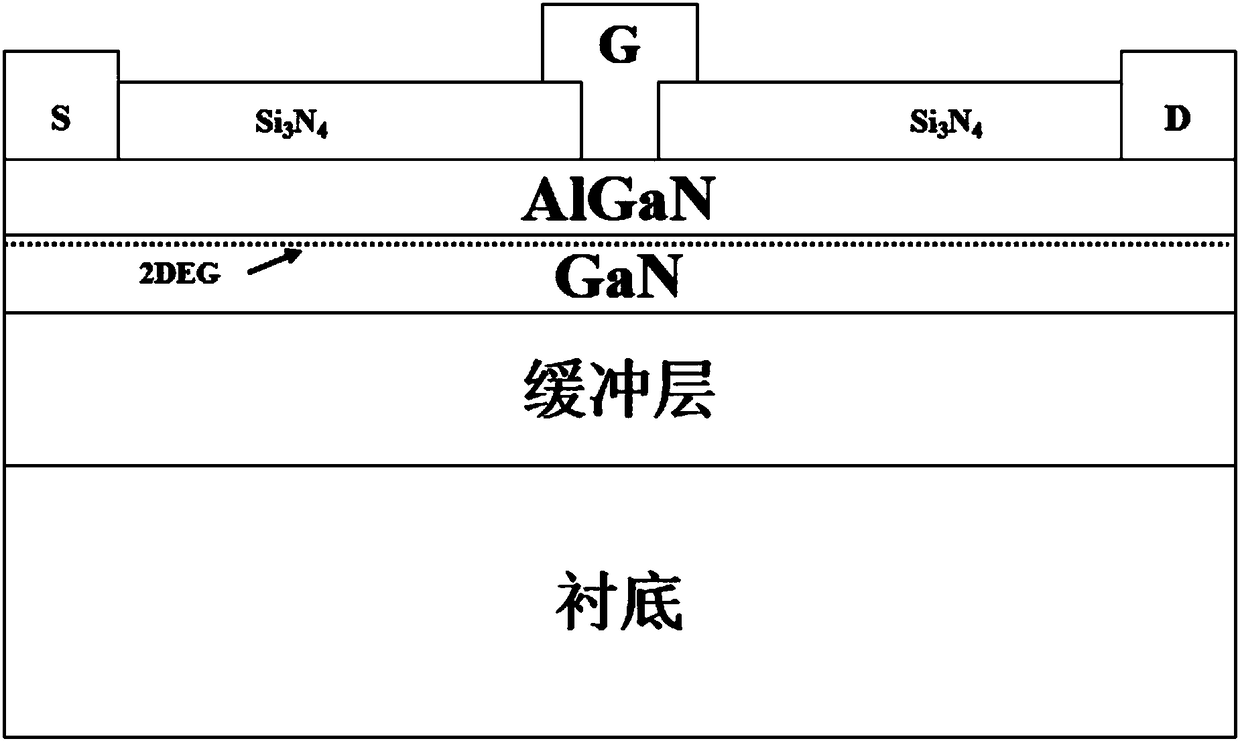

GaN-based T-type gate high-frequency device, preparation method thereof and application thereof

InactiveCN108565283ASolve problems such as low production efficiencyReduce processing difficultySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionHigh resistance

The invention discloses a GaN-based T-type gate high-frequency device, a preparation method and application thereof. The GaN-based T-type gate high-frequency device includes a heterojunction includinga first semiconductor and a second semiconductor formed on the first semiconductor, a P-type semiconductor and a high-resistance semiconductor formed on a heterojunction, and a source electrode, a drain electrode and a gate, wherein the second semiconductor has a band gap wider than the first semiconductor, two-dimensional electron gas is formed in the heterojunction, the P-type semiconductor islocated in a gate lower region and is connected to the gate, the length of the gate is larger than the length of the P-type semiconductor, the P-type semiconductor is used for depleting the two-dimensional electron gas in the gate lower region, the high-resistance semiconductor is located between the P-type semiconductor and the source electrode or the drain electrode, and the source electrode andthe drain electrode can be electrically connected through the two-dimensional electronic gas. According to the GaN-based T-type gate high-frequency device, the preparation method and the applicationthereof, the etching of the gate lower region is not needed, the problems of uniformity, repeatability and damage introduced by an etching process are avoided, the electron beam exposure technology isnot needed, and the problems of low production efficiency and the like are solved.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Semiconductor device and method for manufacturing the same

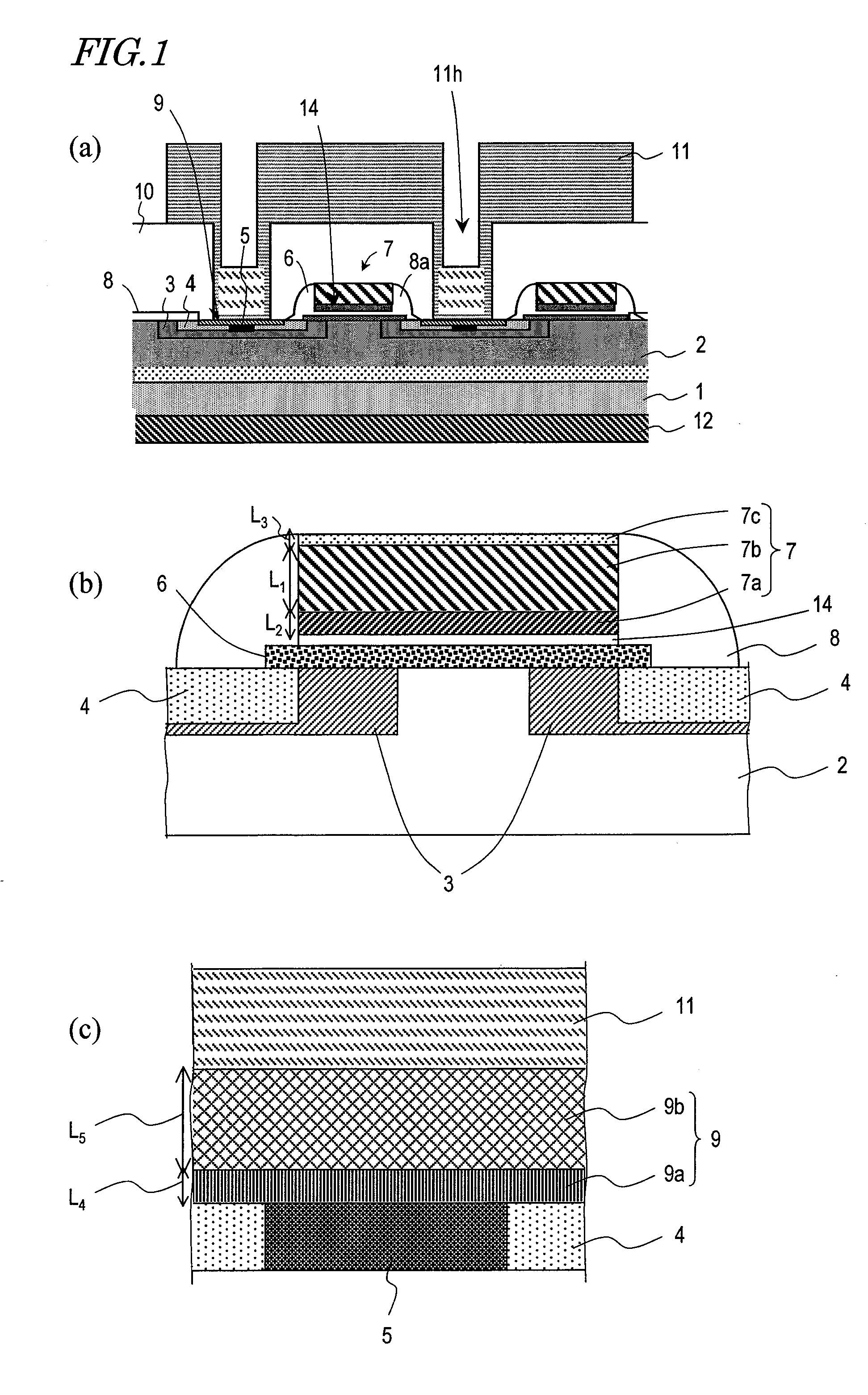

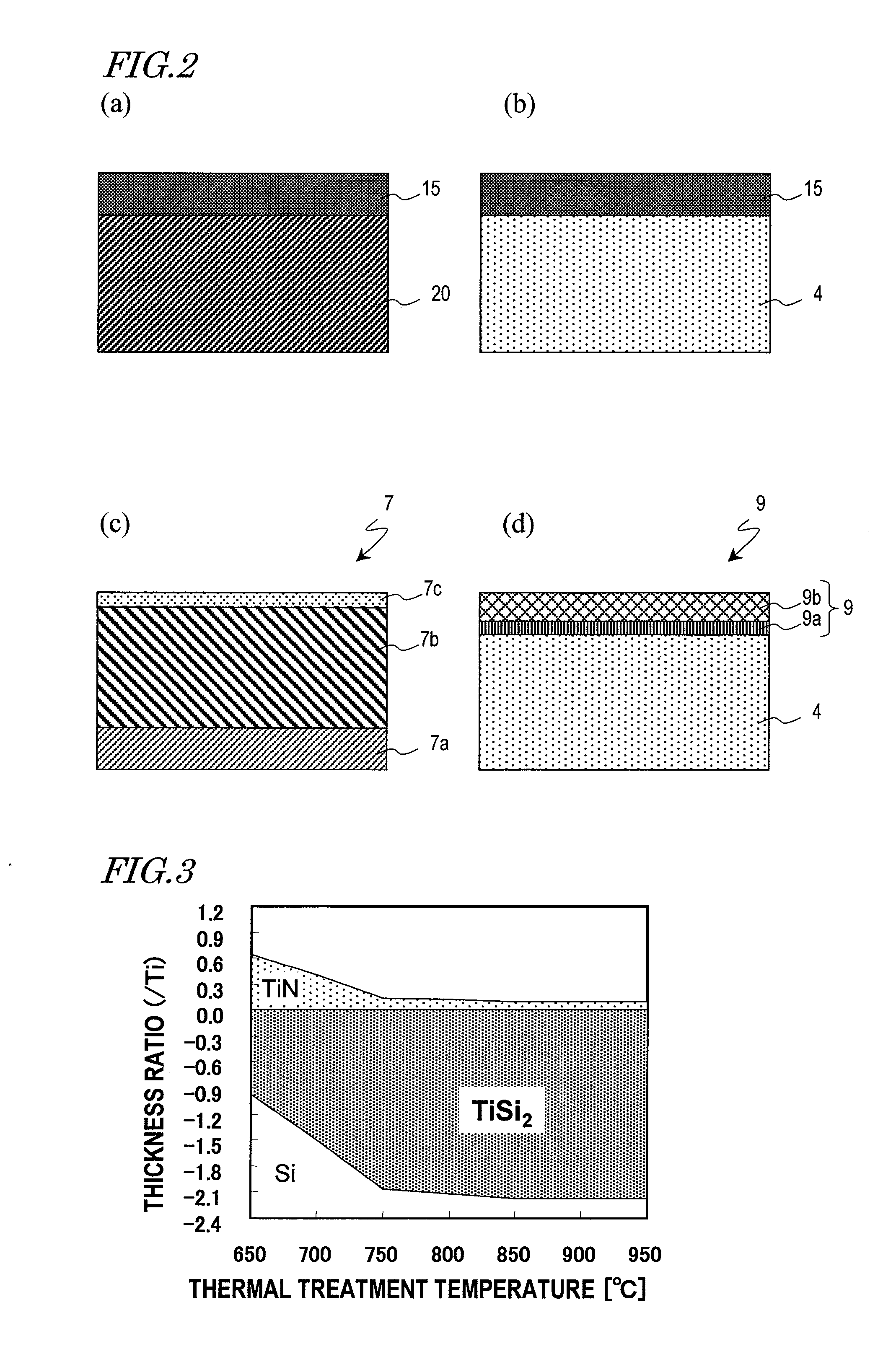

ActiveUS20100244048A1Adhesiveness decreaseDecrease gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTitaniumHigh concentration

A semiconductor device according to the present invention comprises a silicon carbide semiconductor substrate (1) including a silicon carbide layer (2); a high-concentration impurity region (4) provided in the silicon carbide layer (2); an ohmic electrode (9) electrically connected with the high-concentration impurity region (4); a channel region electrically connected with the high-concentration impurity region; a gate insulating layer (14) provided on the channel region; and a gate electrode (7) provided on the gate insulating layer (14). The ohmic electrode (9) contains an alloy of titanium, silicon and carbon, and the gate electrode (7) contains titanium silicide.

Owner:PANASONIC CORP

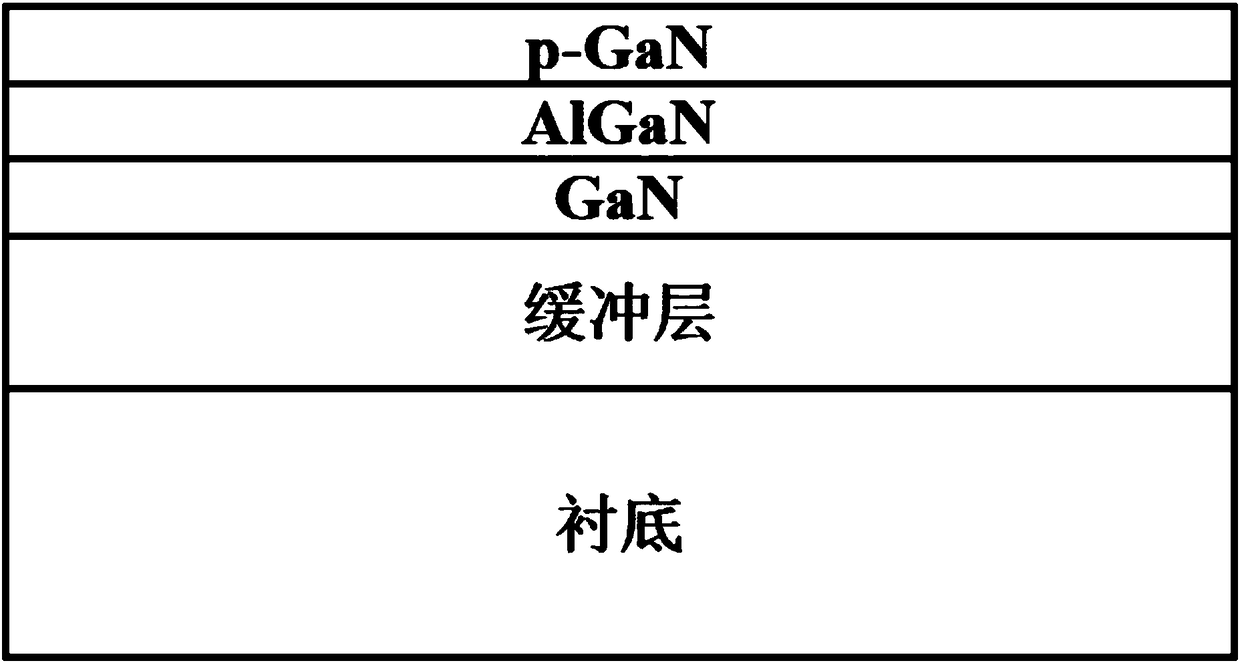

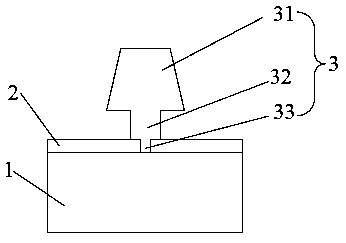

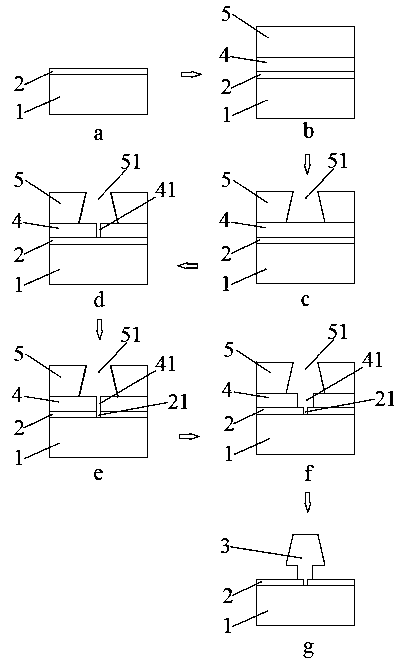

A double T-shaped gate, and a manufacturing method and an application thereof

InactiveCN109103245AImprove the problem of low exposure efficiencyIncrease production capacitySemiconductor devicesParasitic capacitanceEngineering

A double T-shaped gate, and a manufacturing method and an application thereof are provided. The double T-shaped gate comprises a gate foot, a gate root and a gate cap, wherein the gate foot and the gate root form a first level T-shaped gate, the gate root and the gate cap form a second level T-shaped gate, the gate cap is suspended, and the gate foot grows on a substrate through a dielectric passivation layer. The invention can reduce the gate resistance, and the manufacturing method thereof not only can effectively realize the small line width gate, reduce the gate parasitic capacitance, butalso can improve the efficiency of the gate fabrication.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT