Patents

Literature

118results about How to "Reduce gate capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

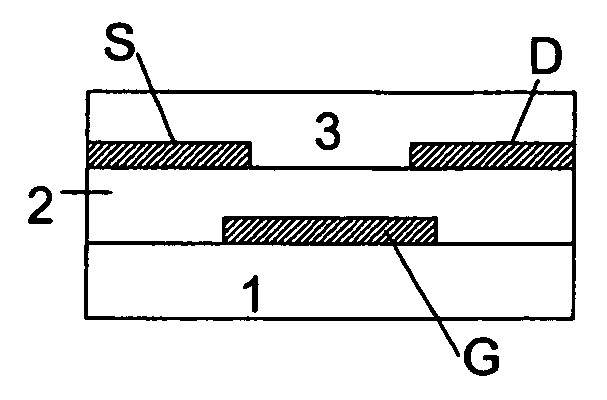

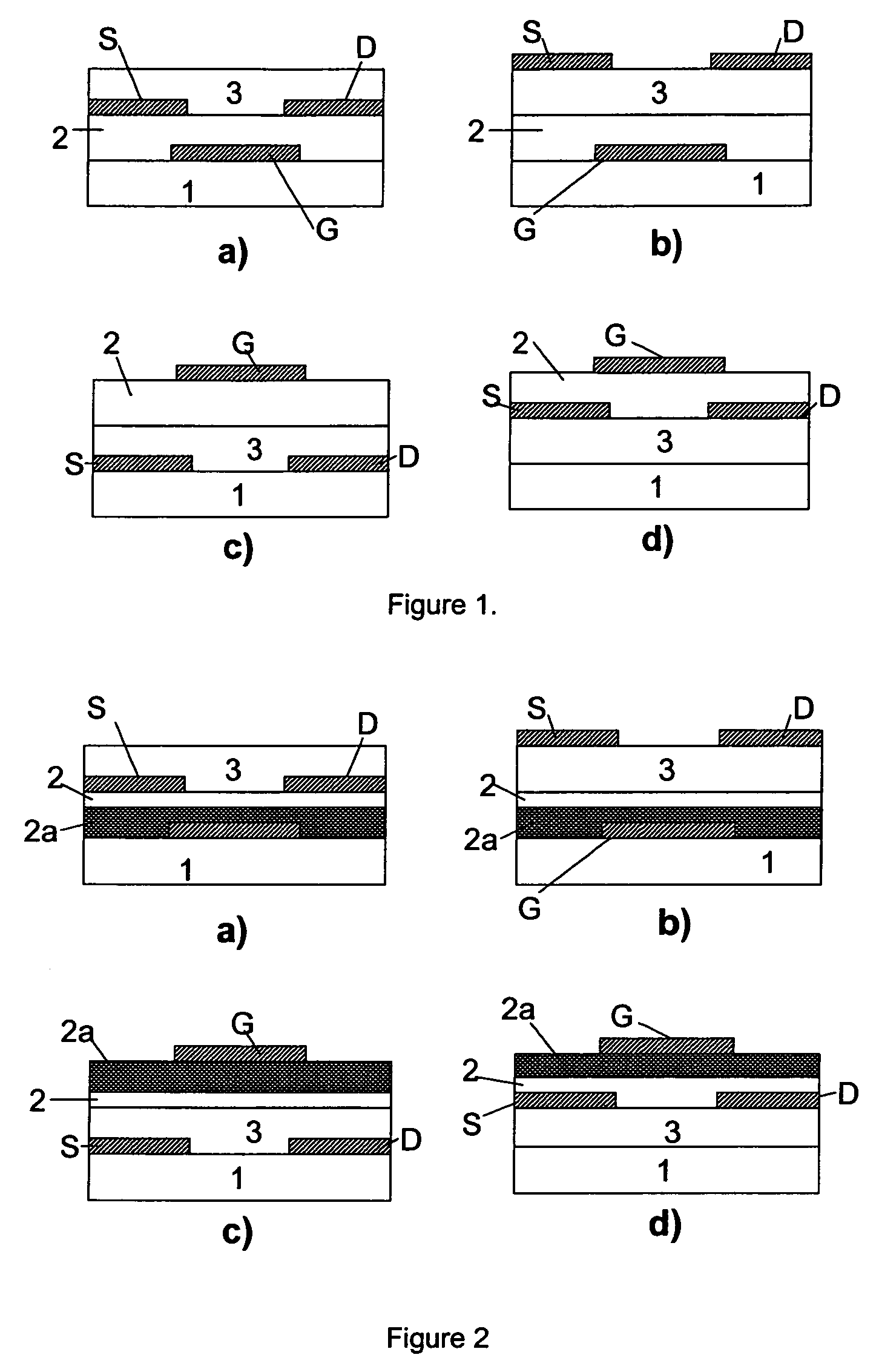

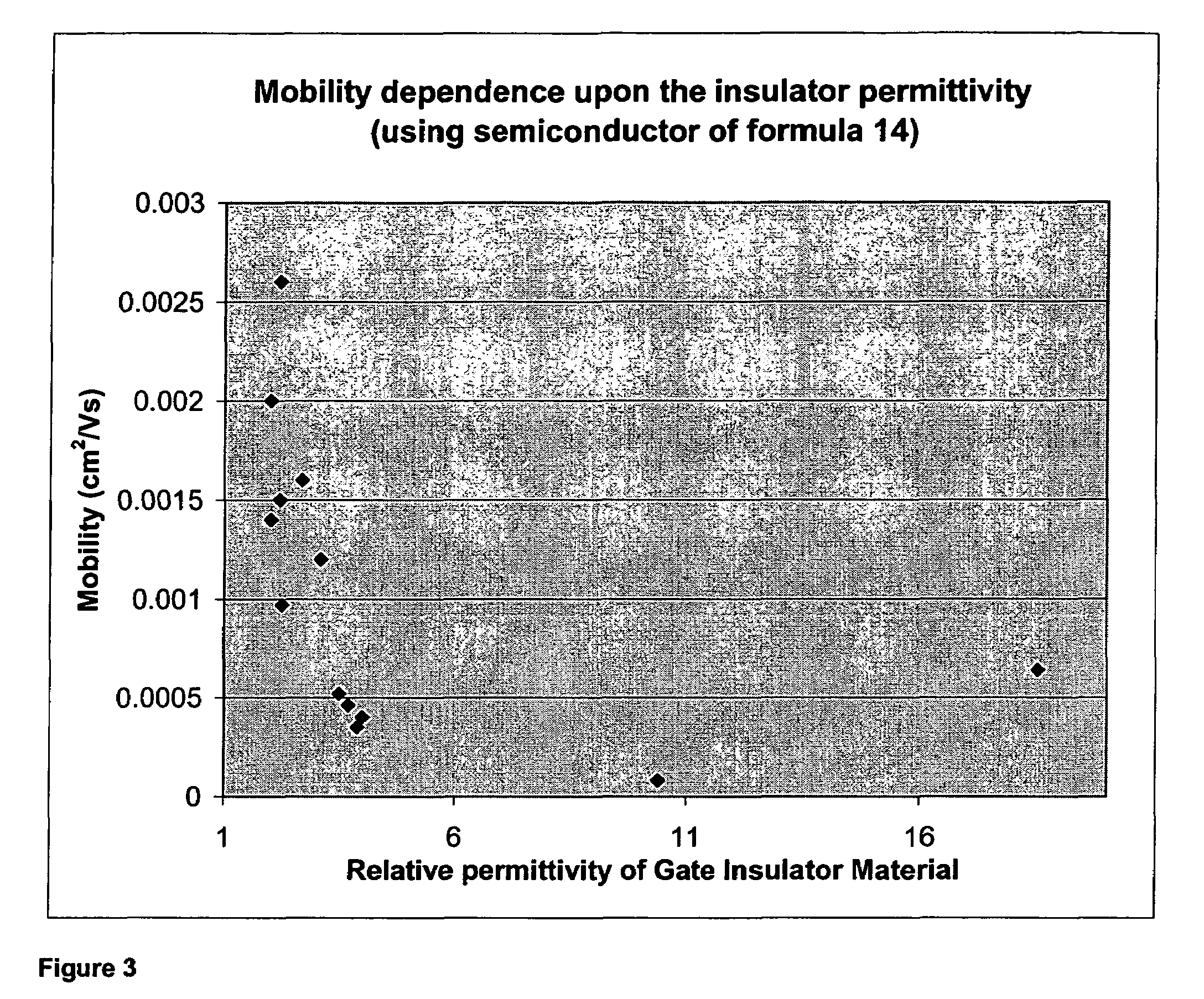

Organic field effect transistor with an organic dielectric

InactiveUS7029945B2Improve performancePreventing modulationTransistorSolid-state devicesOrganic field-effect transistorGate insulator

A process of manufacturing an organic field effect device is provided comprising the steps of (a) depositing from a solution an organic semiconductor layer; and (b) depositing from a solution a layer of low permittivity insulating material forming at least a part of a gate insulator, such that the low permittivity insulating material is in contact with the organic semiconductor layer, wherein the low permittivity insulating material is of relative permittivity from 1.1 to below 3.0. In addition, an organic field effect device manufactured by the process is provided.

Owner:MERCK PATENT GMBH

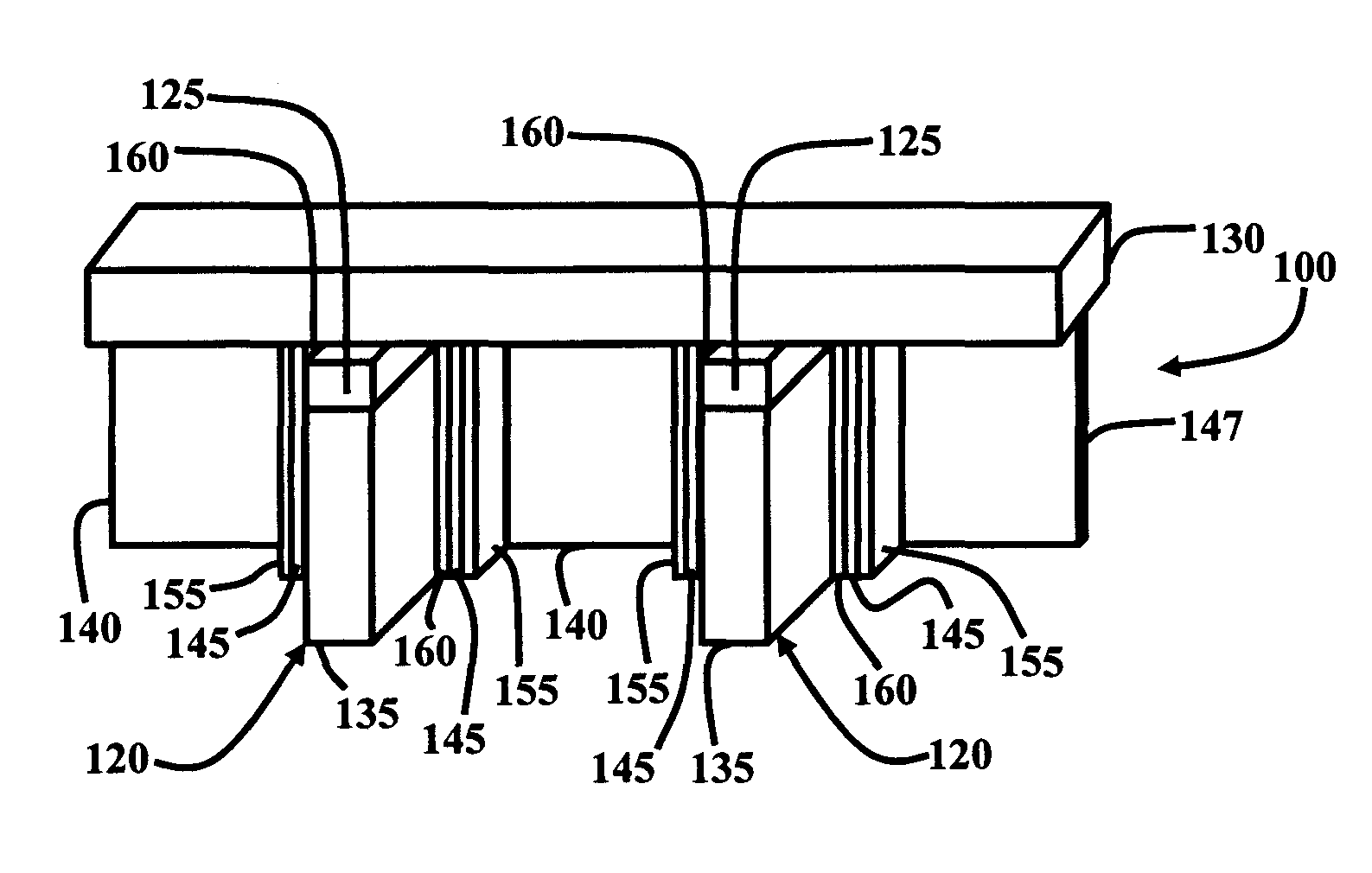

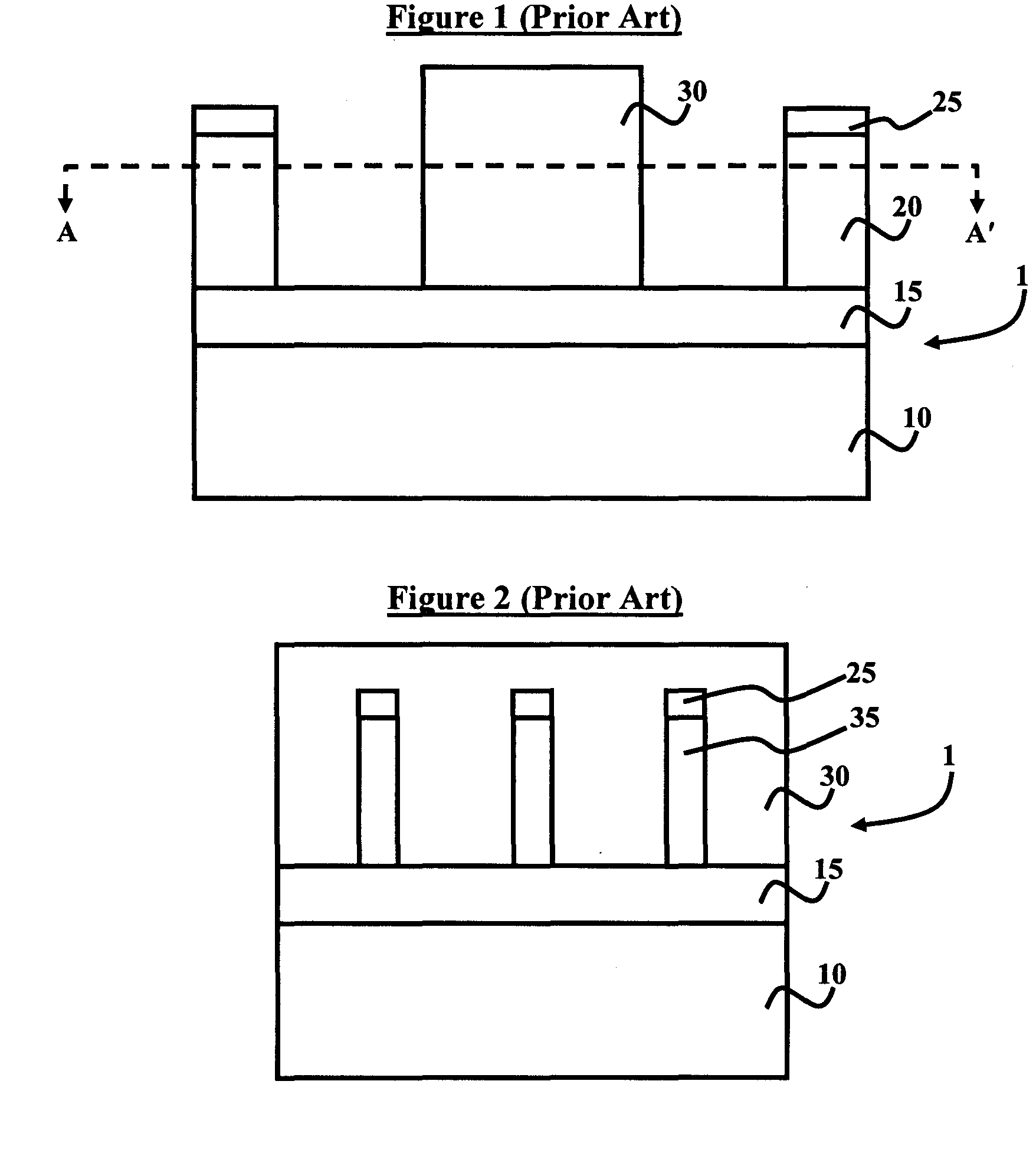

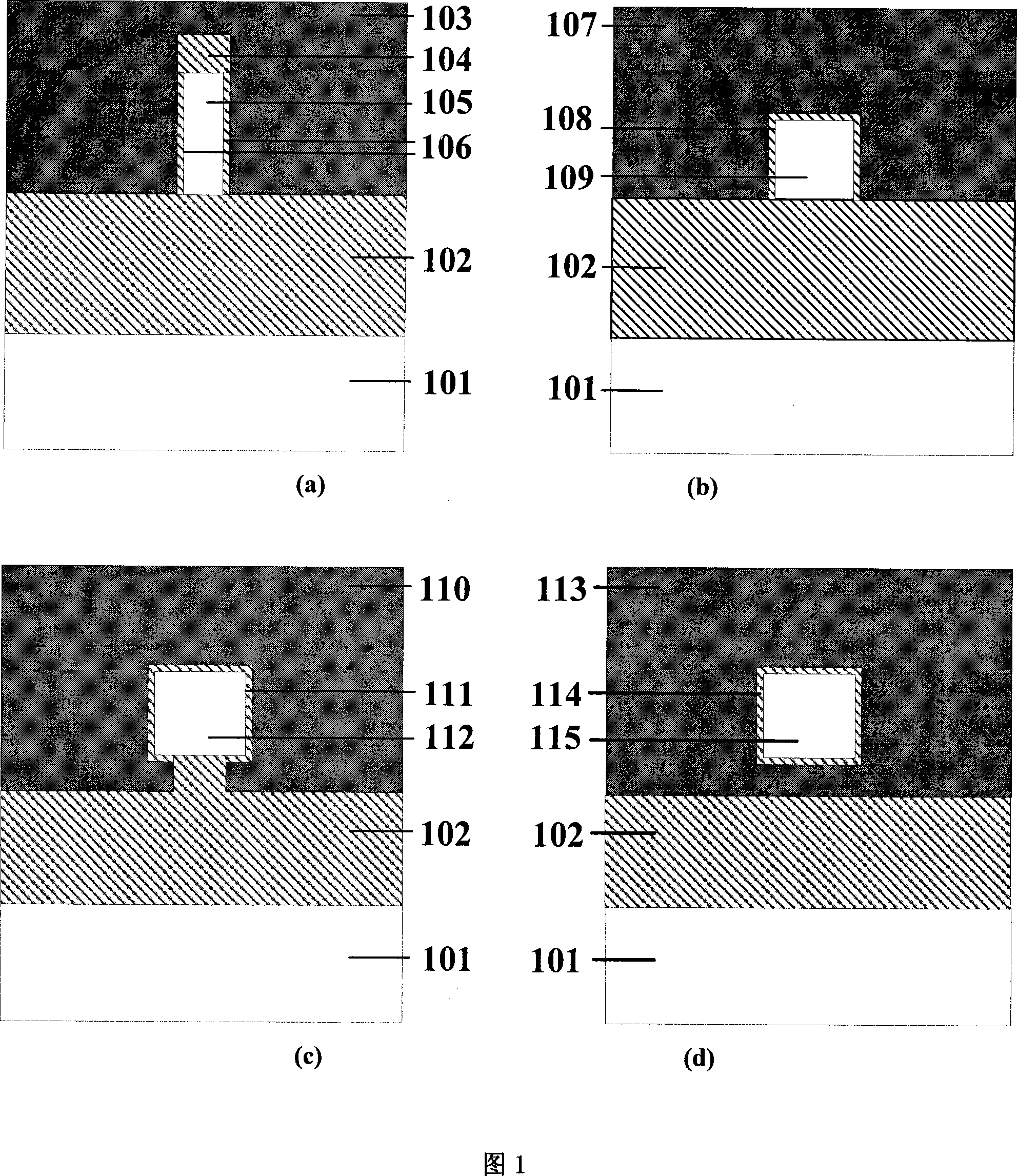

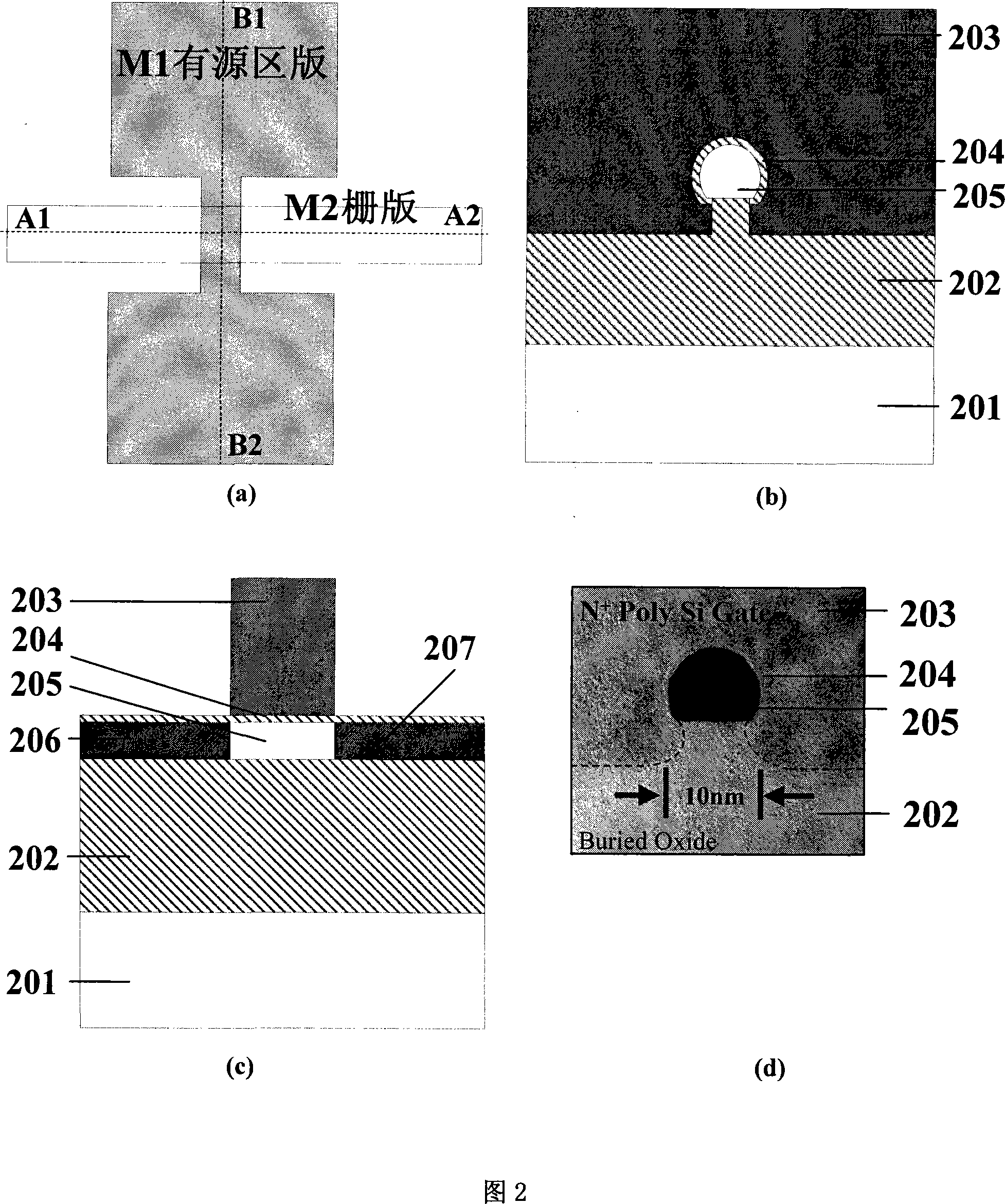

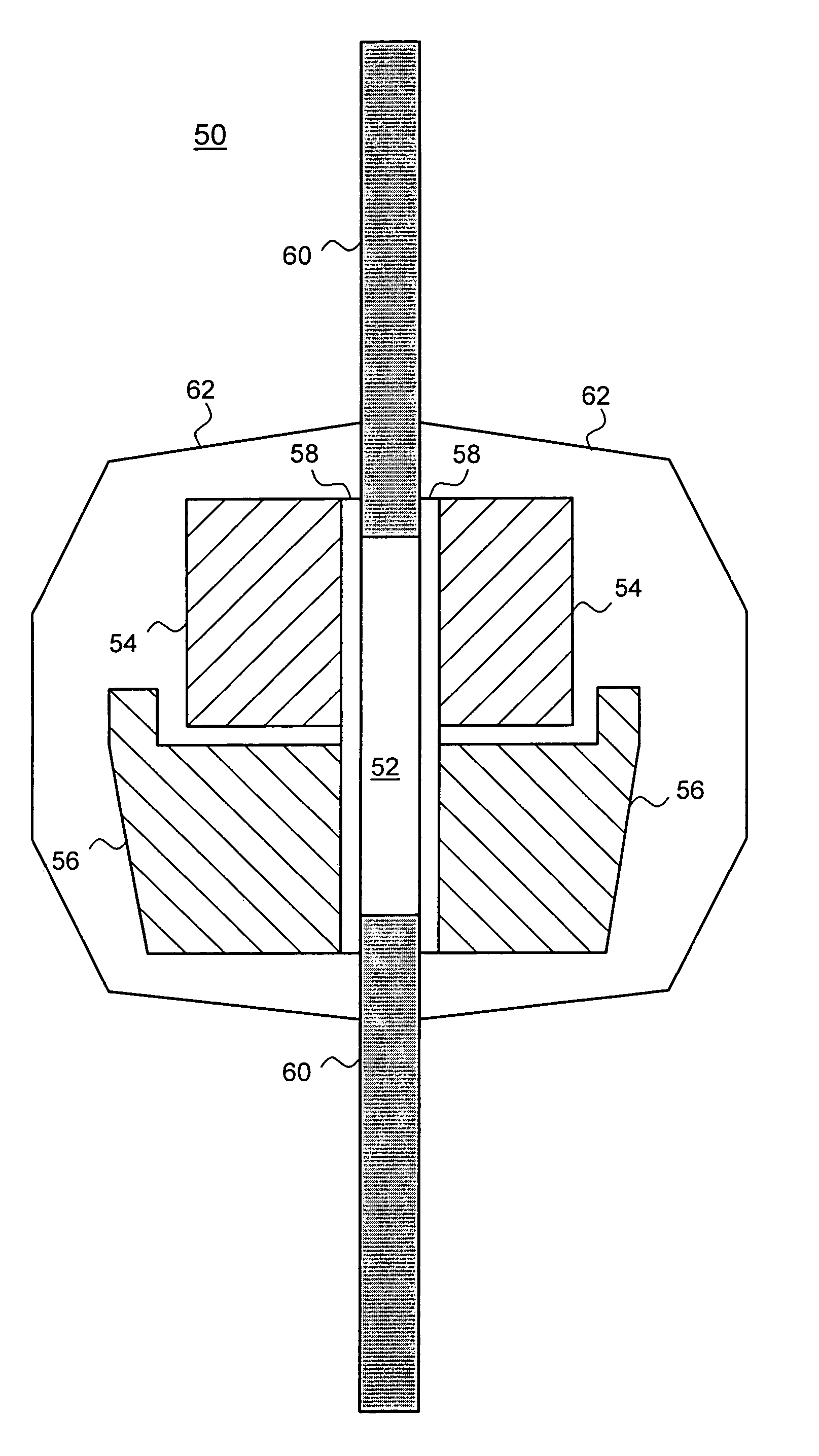

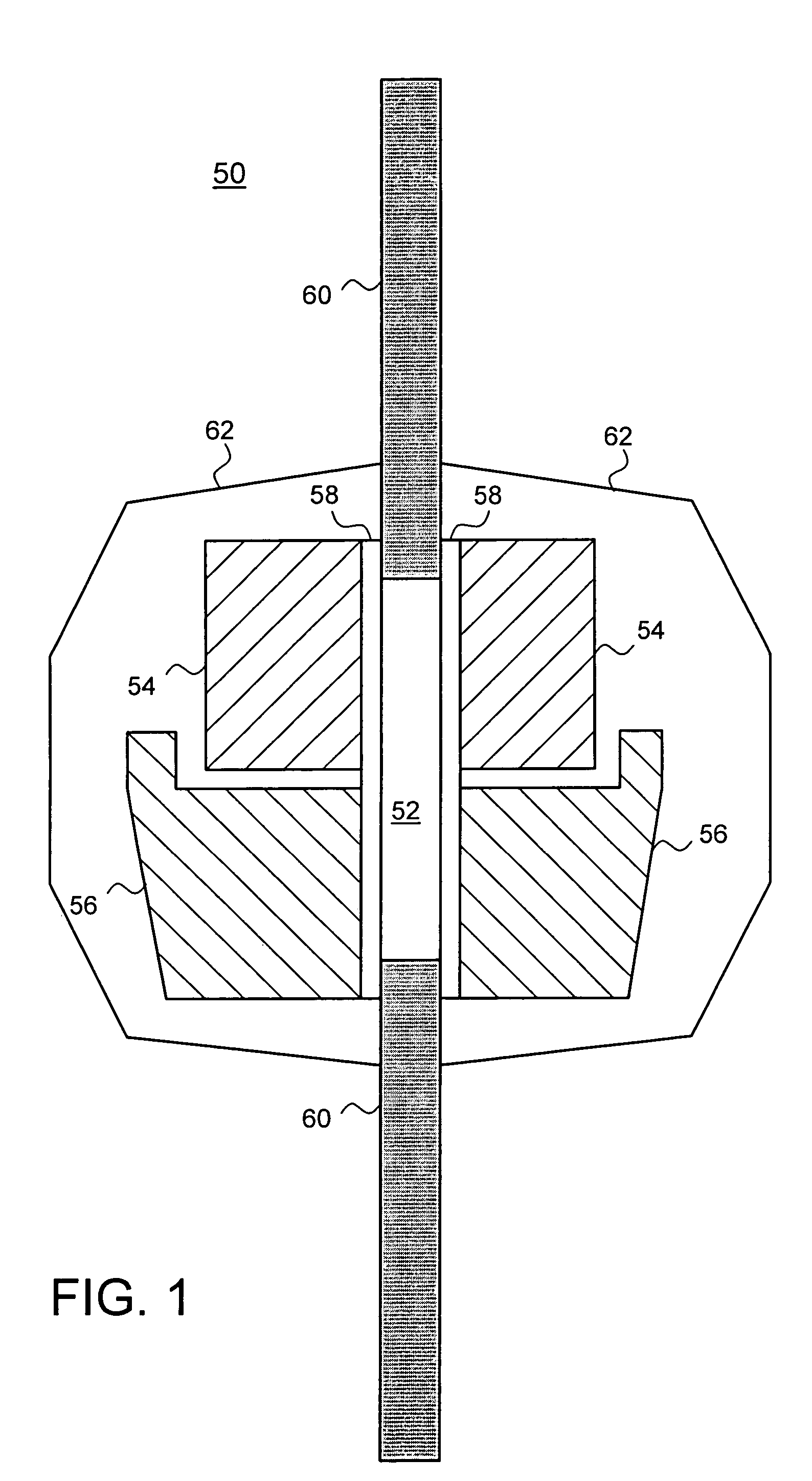

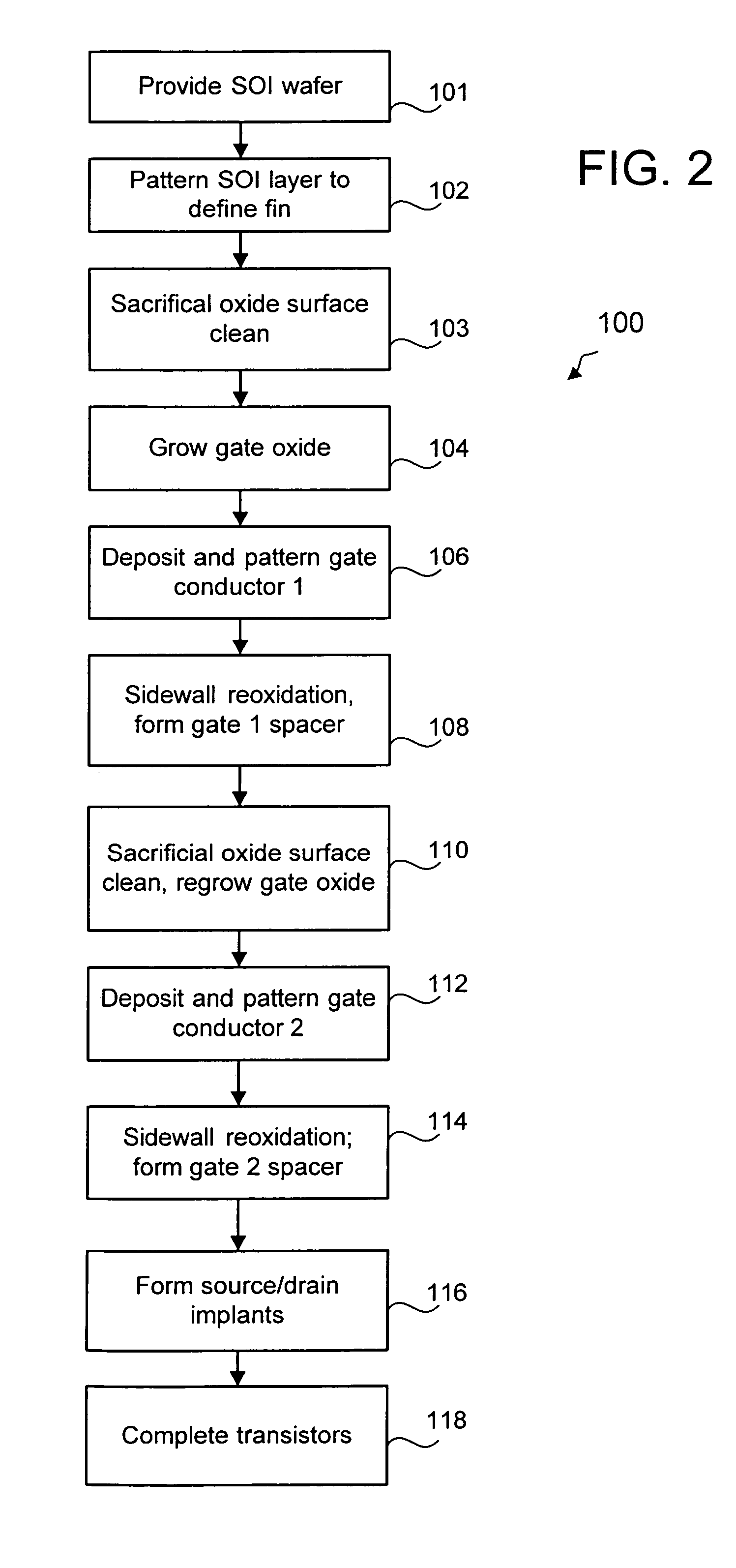

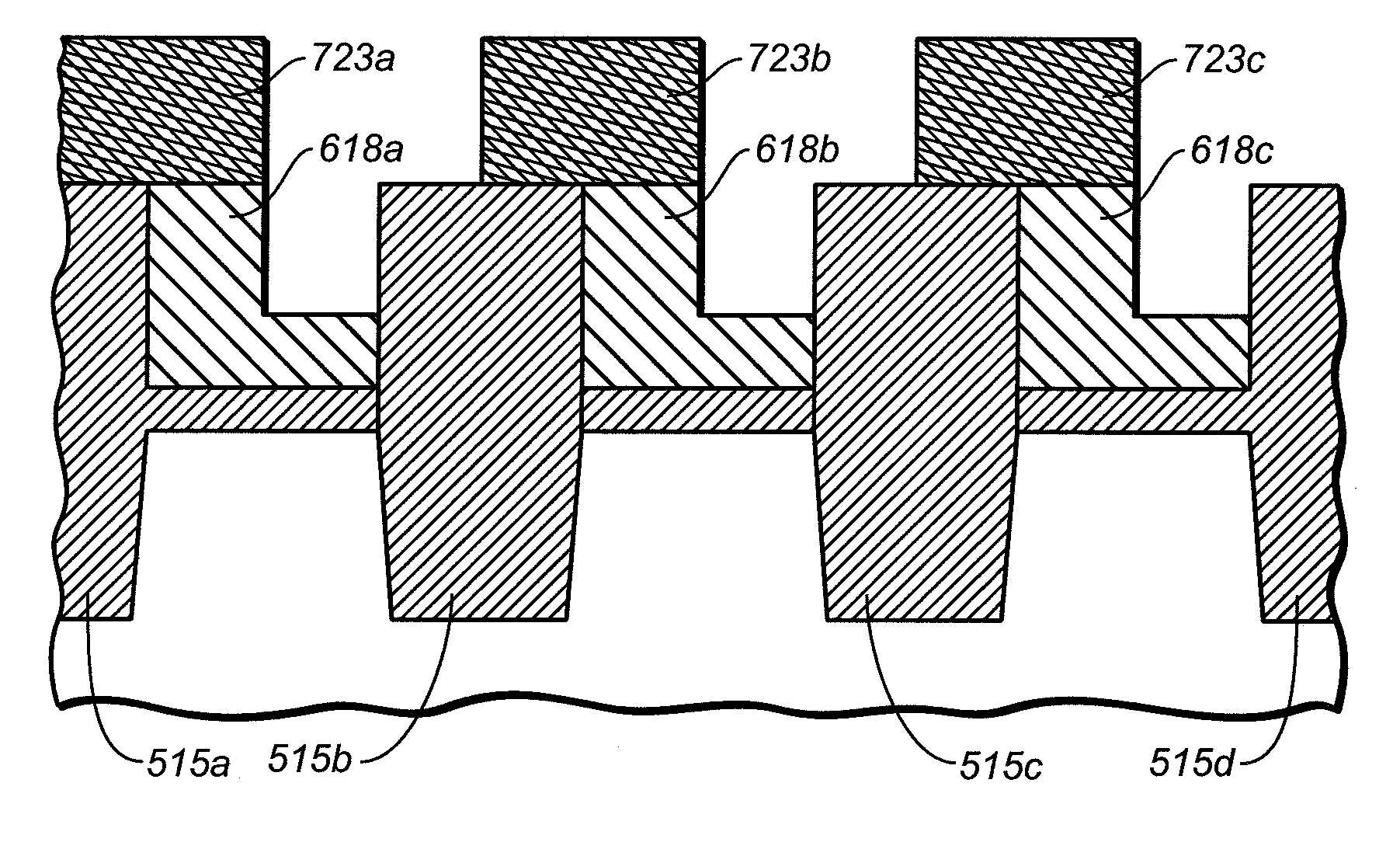

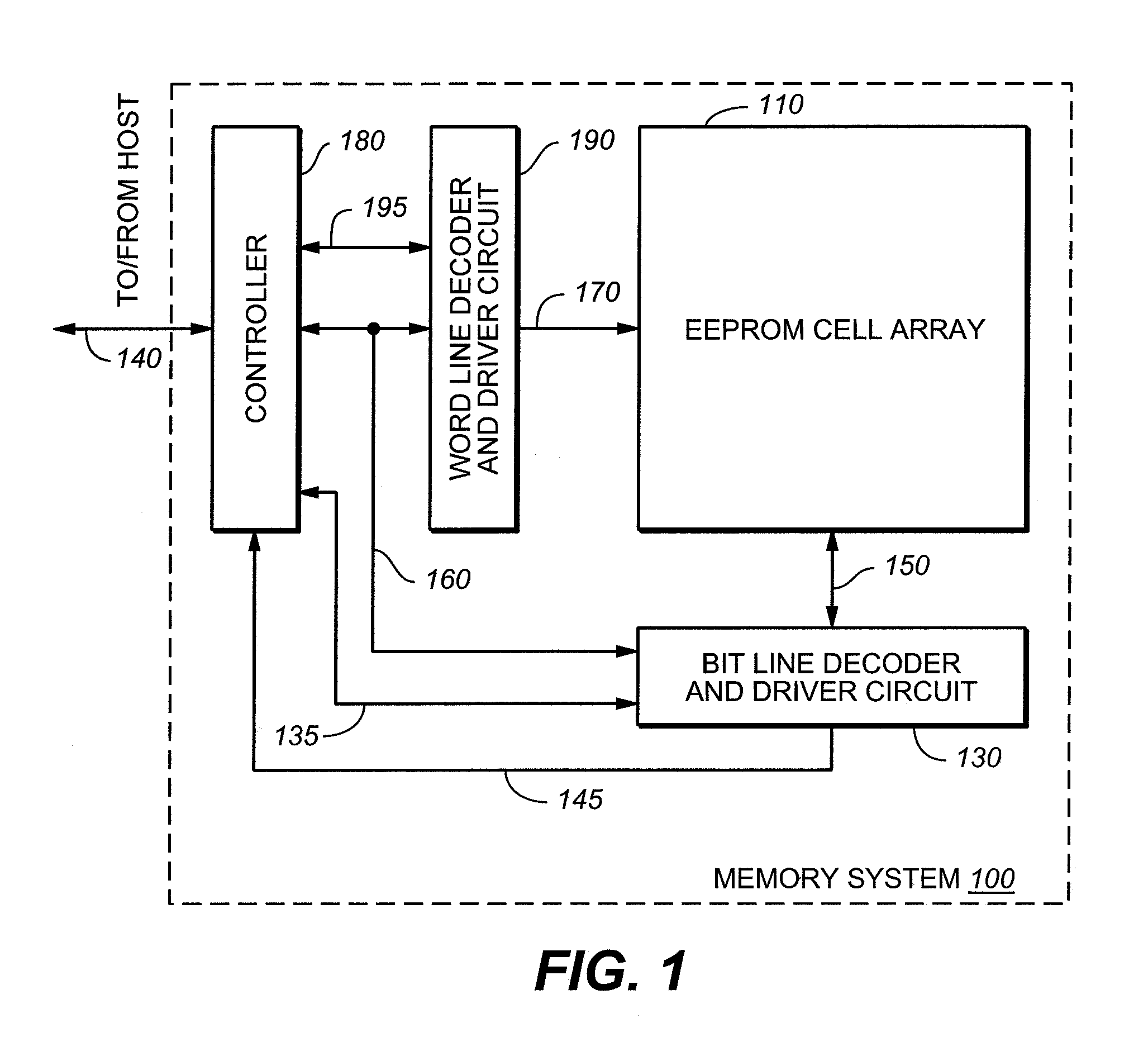

FinFET with low gate capacitance and low extrinsic resistance

ActiveUS7105934B2Reduce gate capacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate insulator

A FinFET device and a method of lowering a gate capacitance and extrinsic resistance in a field effect transistor, wherein the method comprises forming an isolation layer comprising a BOX layer over a substrate, configuring source / drain regions above the isolation layer, forming a fin structure over the isolation layer, configuring a first gate electrode adjacent to the fin structure, disposing a gate insulator between the first gate electrode and the fin structure, positioning a second gate electrode transverse to the first gate electrode, and depositing a third gate electrode on the fin structure, the first gate electrode, and the second gate electrode, wherein the isolation layer is formed beneath the insulator, the first gate electrode, and the fin structure. The method further comprises sandwiching the second gate electrode with a dielectric material. The fin structure is formed by depositing an oxide layer over a silicon layer.

Owner:MICROSOFT TECH LICENSING LLC

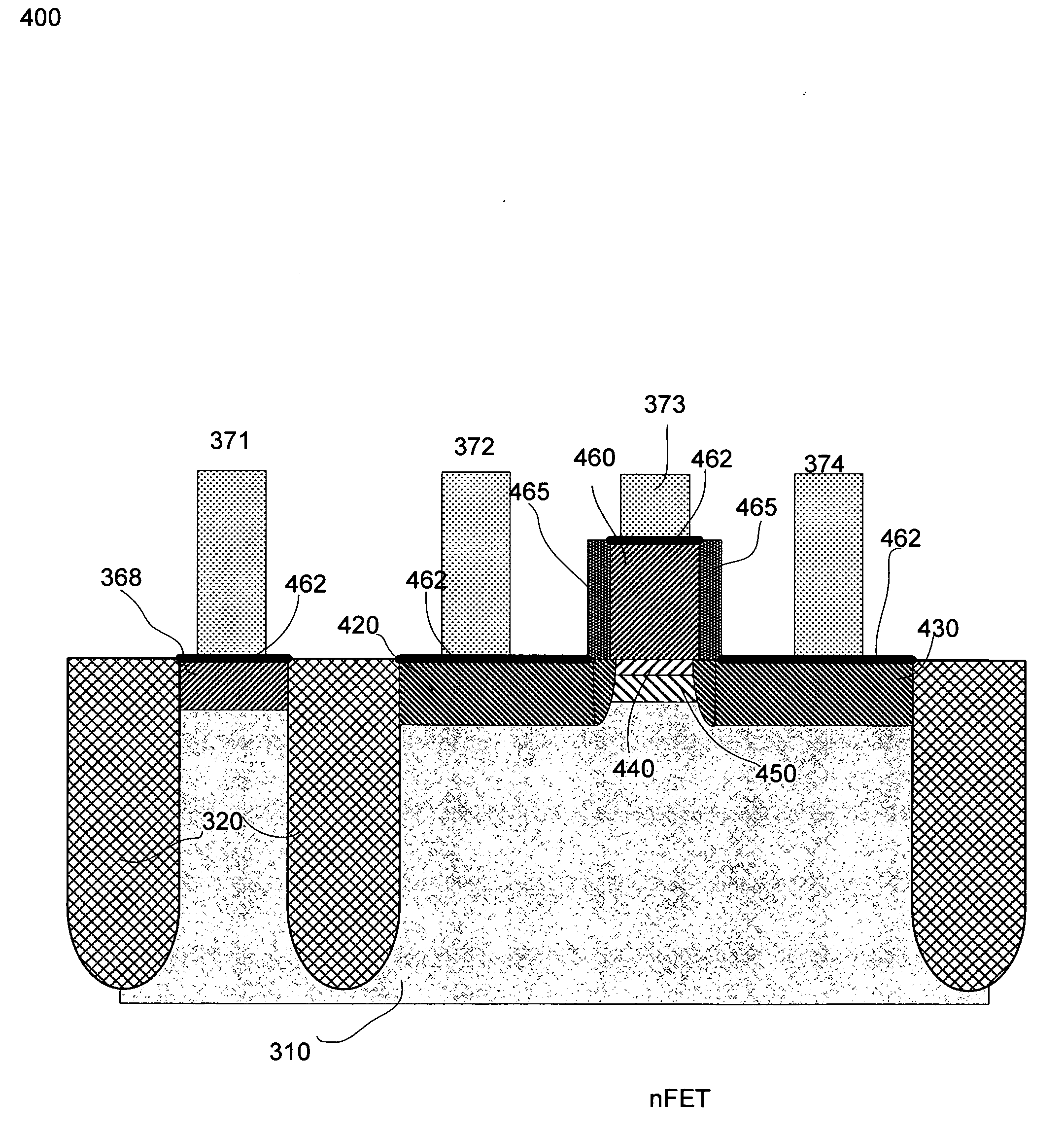

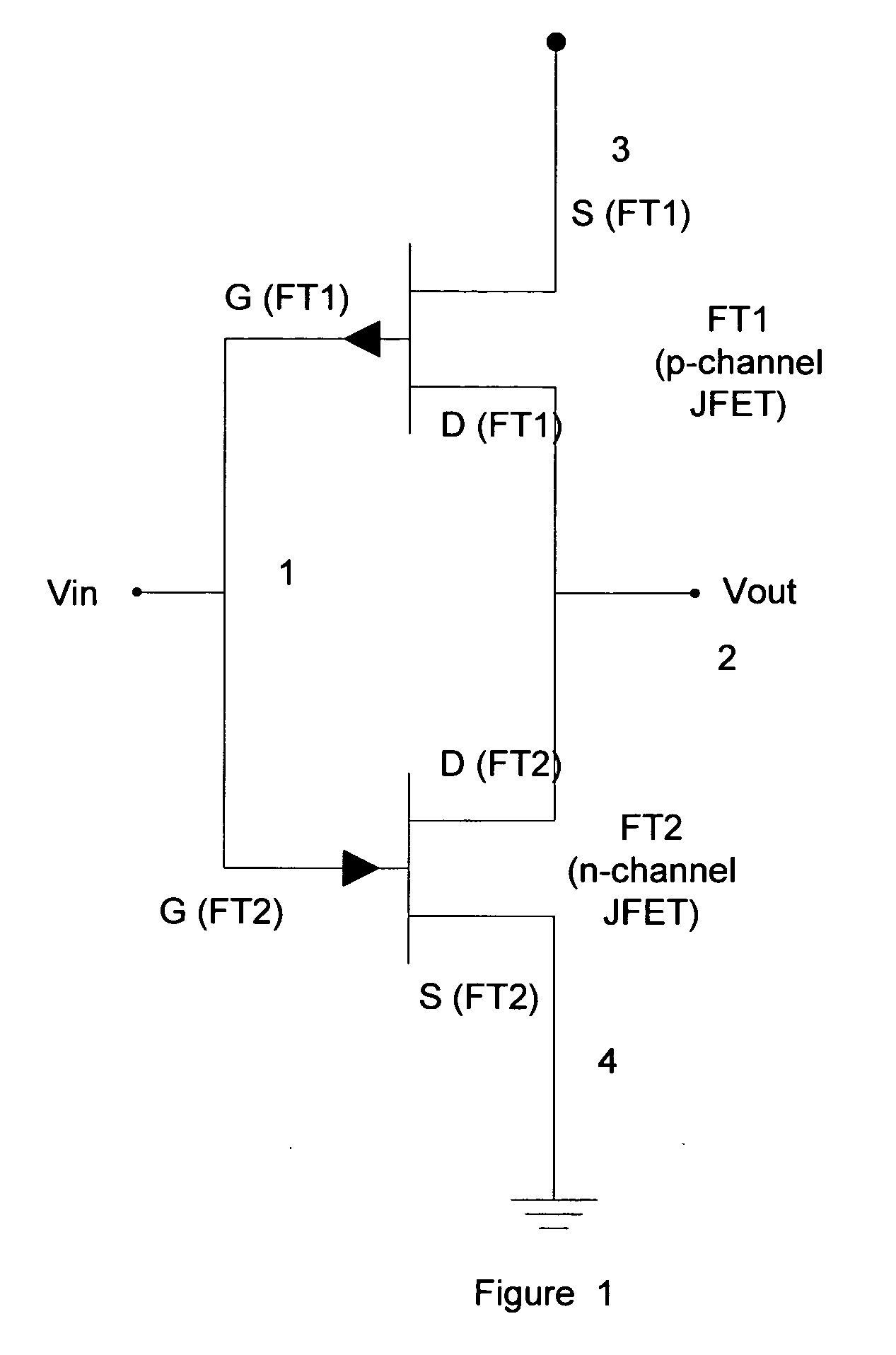

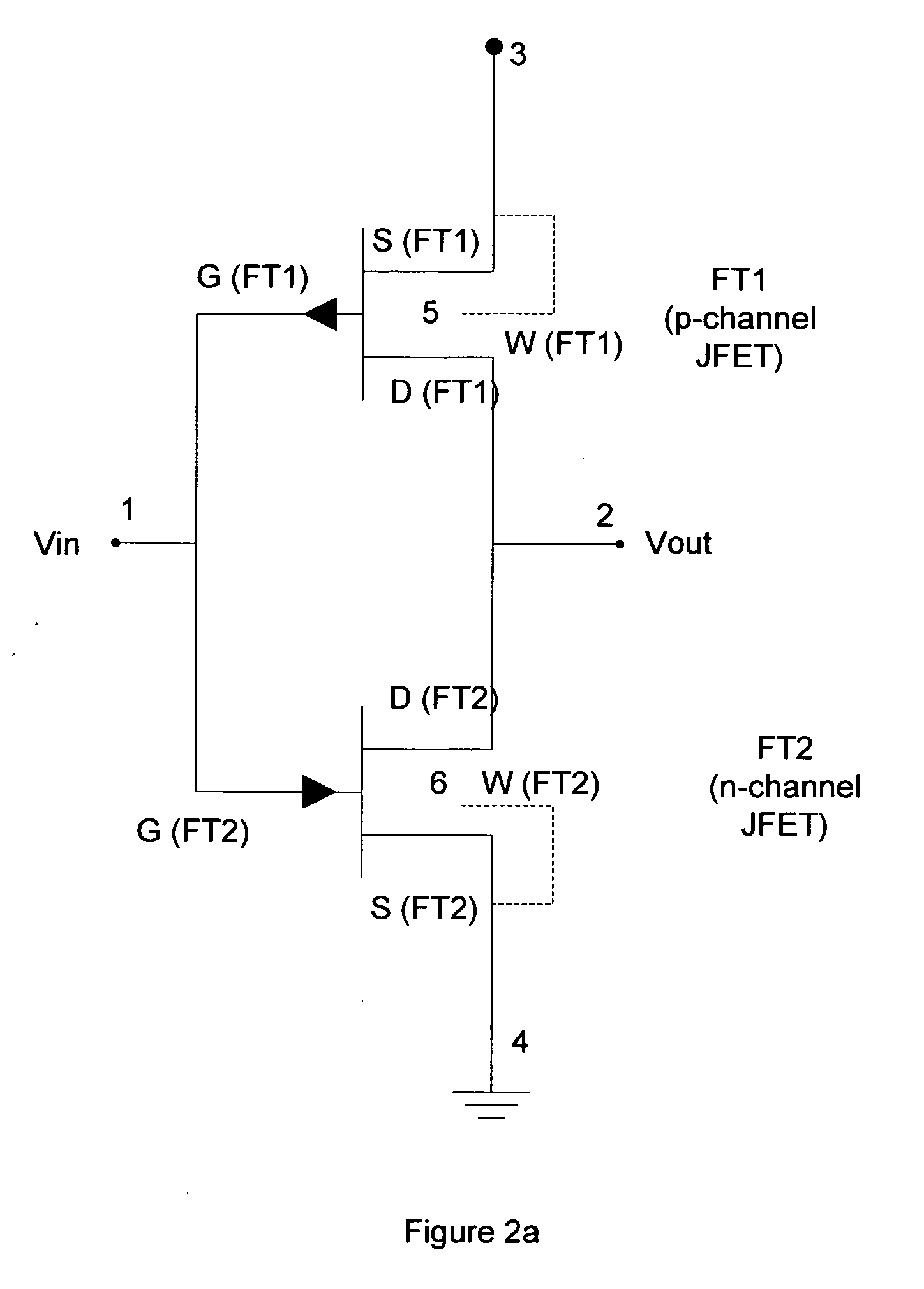

Integrated circuit using complementary junction field effect transistor and MOS transistor in silicon and silicon alloys

InactiveUS20070096144A1Reduce power consumptionReduce gate capacitanceTransistorSolid-state devicesCMOSSilicon alloy

This invention describes a method of building complementary logic circuits using junction field effect transistors in silicon. This invention is ideally suited for deep submicron dimensions, preferably below 65 nm. The basis of this invention is a complementary Junction Field Effect Transistor which is operated in the enhancement mode. The speed-power performance of the JFETs becomes comparable with the CMOS devices at sub-70 nanometer dimensions. However, the maximum power supply voltage for the JFETs is still limited to below the built-in potential (a diode drop). To satisfy certain applications which require interface to an external circuit driven to higher voltage levels, this invention includes the structures and methods to build CMOS devices on the same substrate as the JFET devices.

Owner:MIE FUJITSU SEMICON

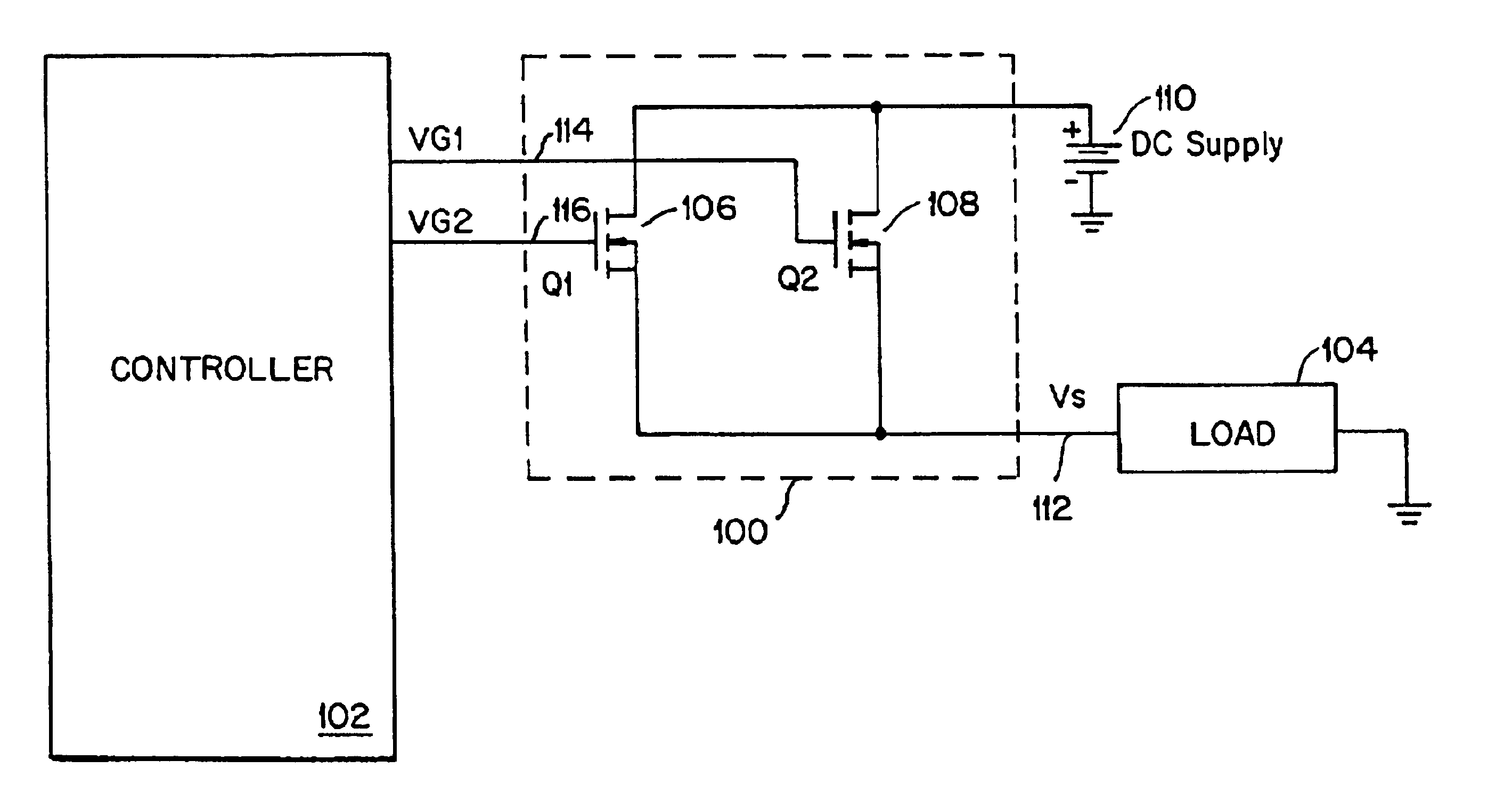

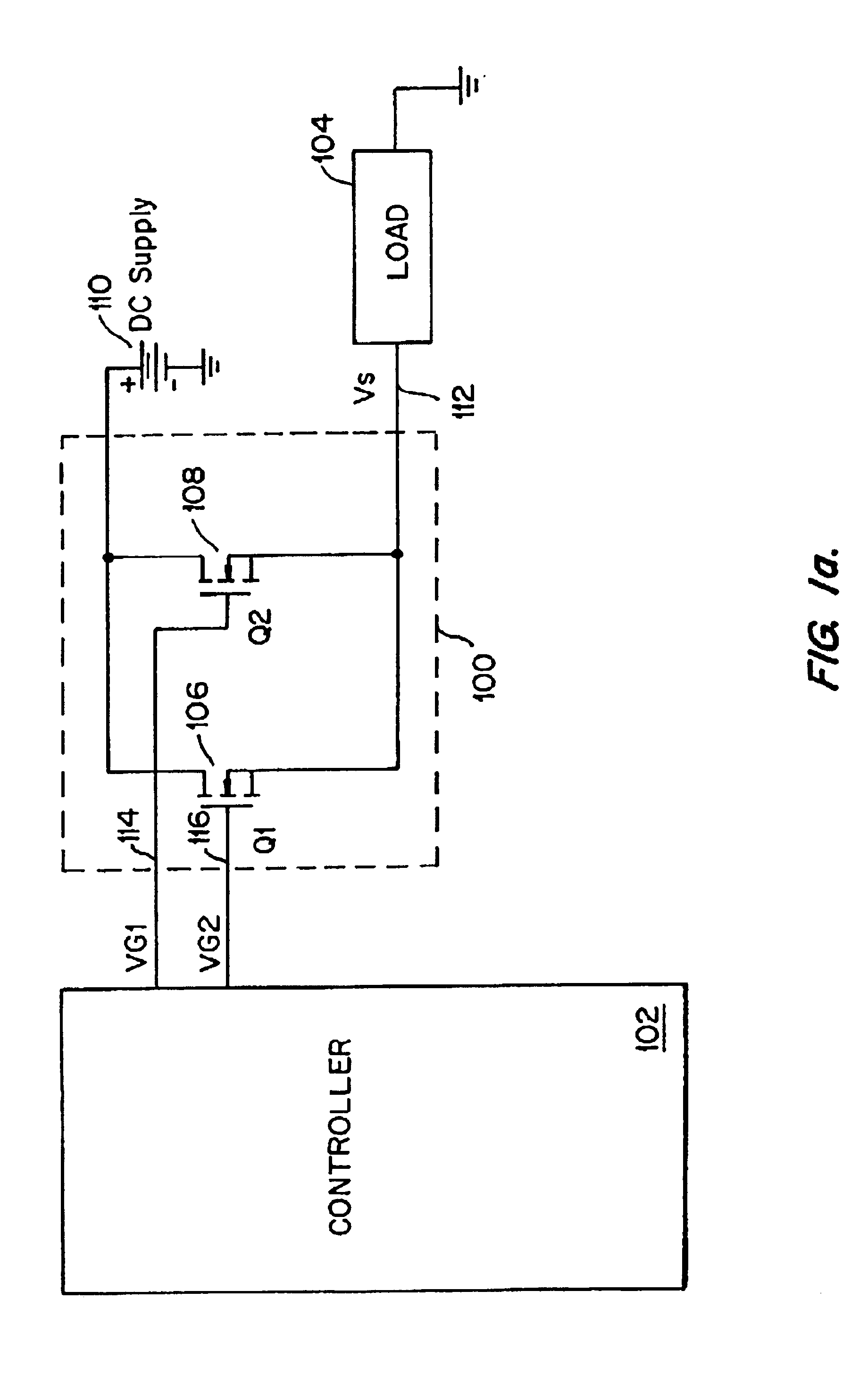

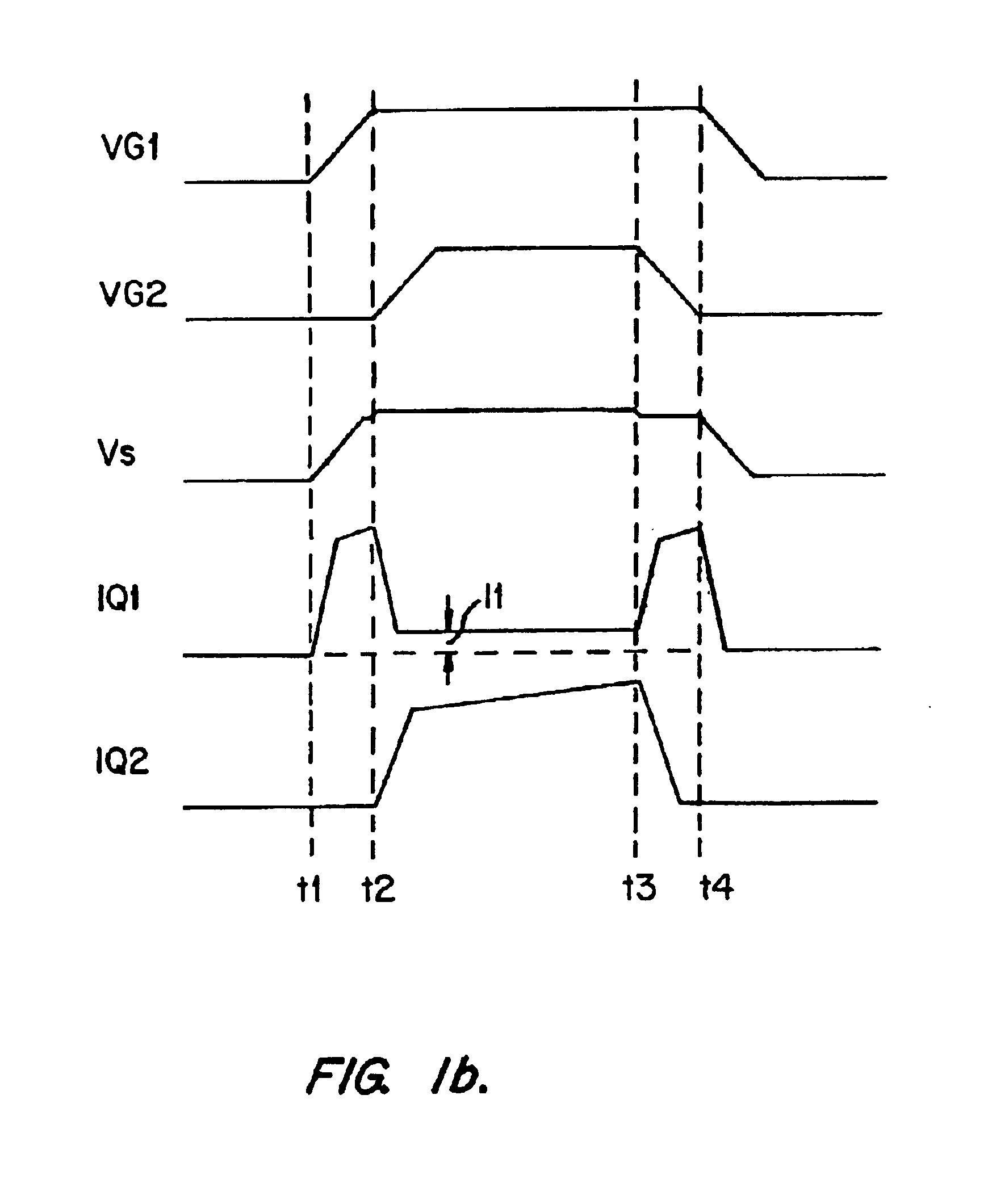

Method and circuit for reducing losses in DC-DC converters

InactiveUS6930473B2Reduction of gate capacitance switching lossReduce conduction lossElectronic switchingApparatus without intermediate ac conversionCapacitanceLow load

In accordance with the present invention, a switching converter includes two transistors Q1 and Q2 parallel-connected between two terminals. Transistor Q1 is optimized to reduce the dynamic loss and transistor Q2 is optimized to reduce the conduction loss. Q1 and Q2 are configured and operated such that the dynamic loss of the converter is dictated substantially by Q1 and the conduction loss of the converter is dictated substantially by Q2. Thus, the tradeoff between these two types of losses present in conventional techniques is eliminated, allowing the dynamic and conduction losses to be independently reduced. Further, the particular configuration and manner of operation of Q1 and Q2 enable reduction of the gate capacitance switching loss when operating under low load current conditions.

Owner:SEMICON COMPONENTS IND LLC

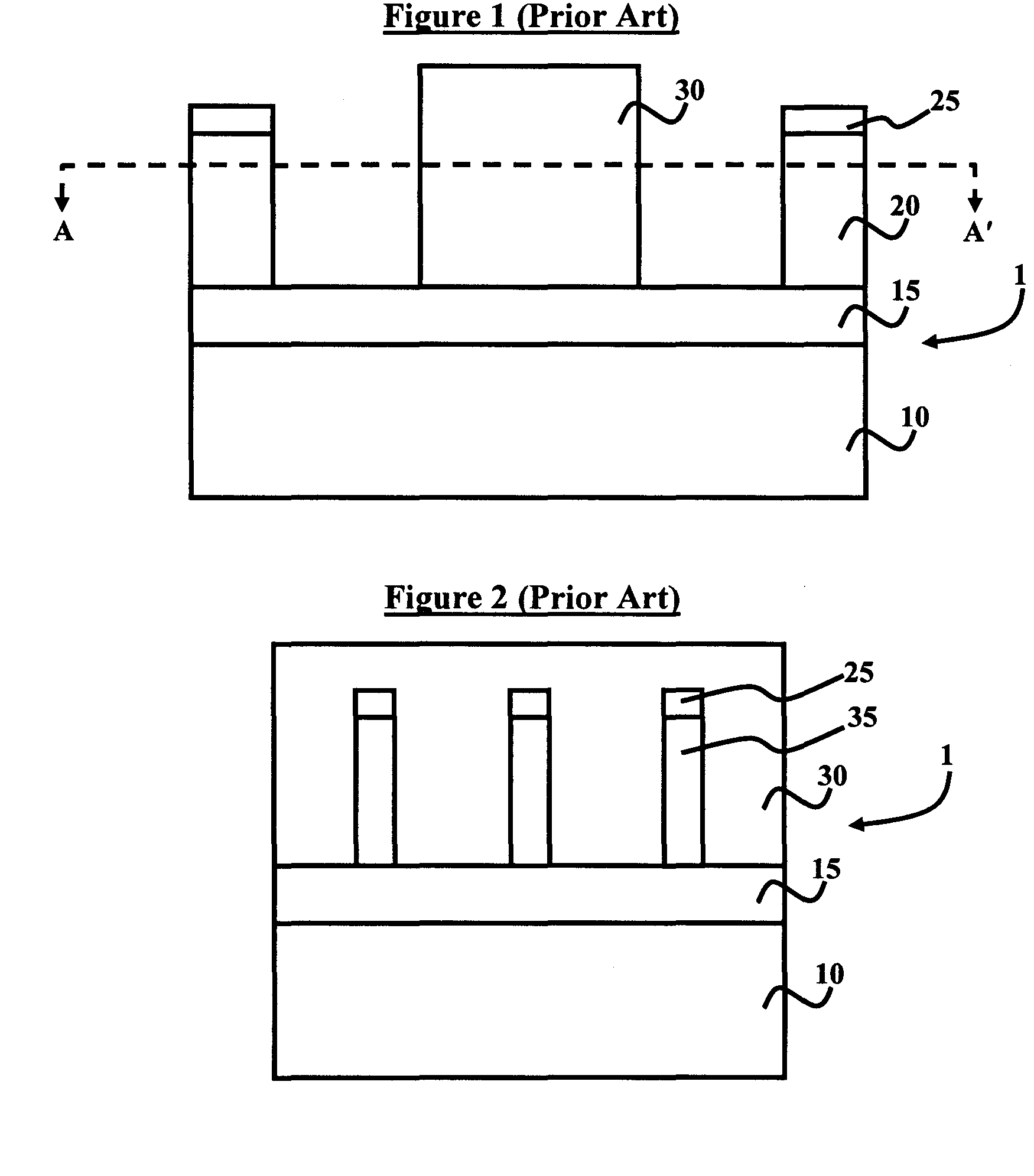

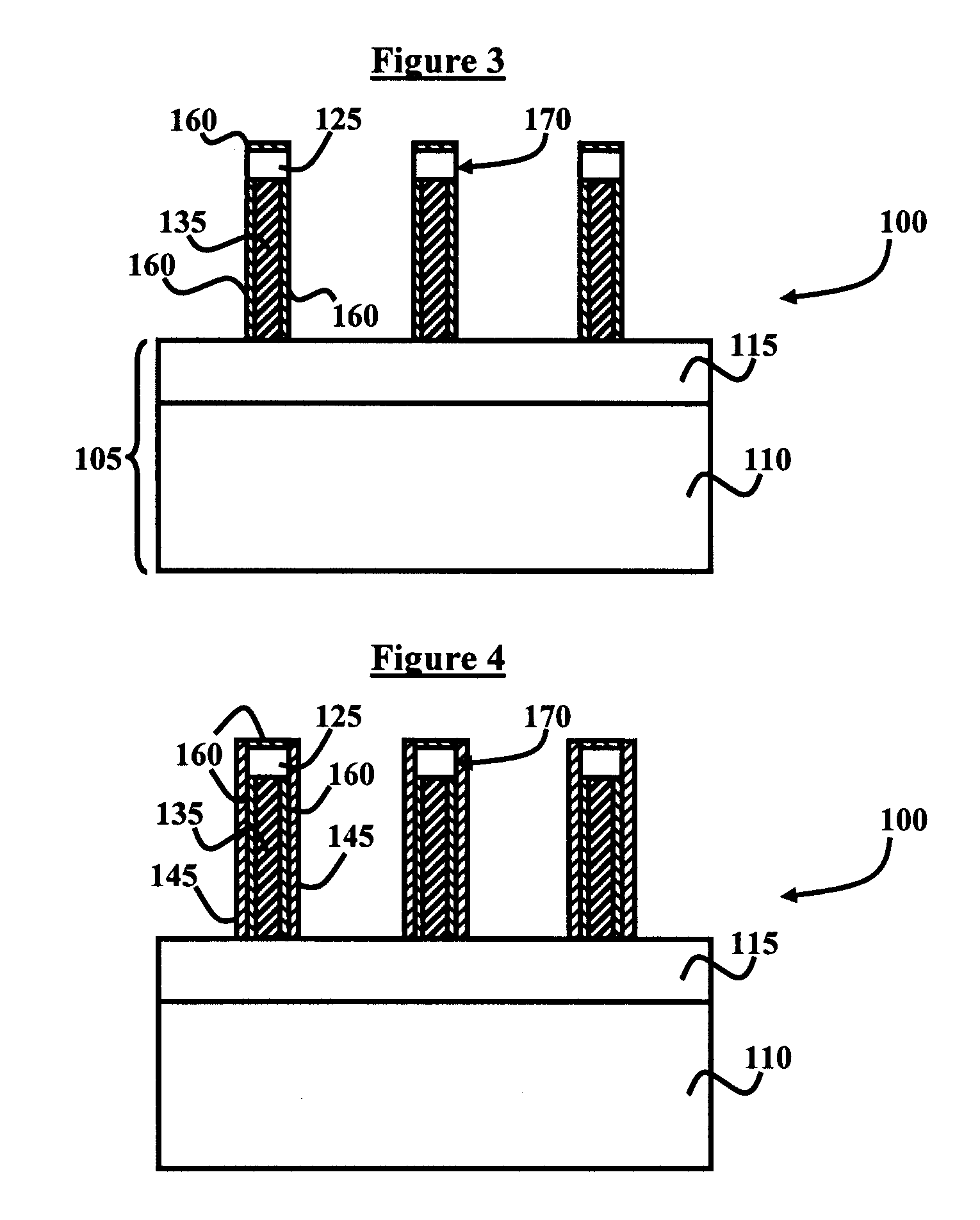

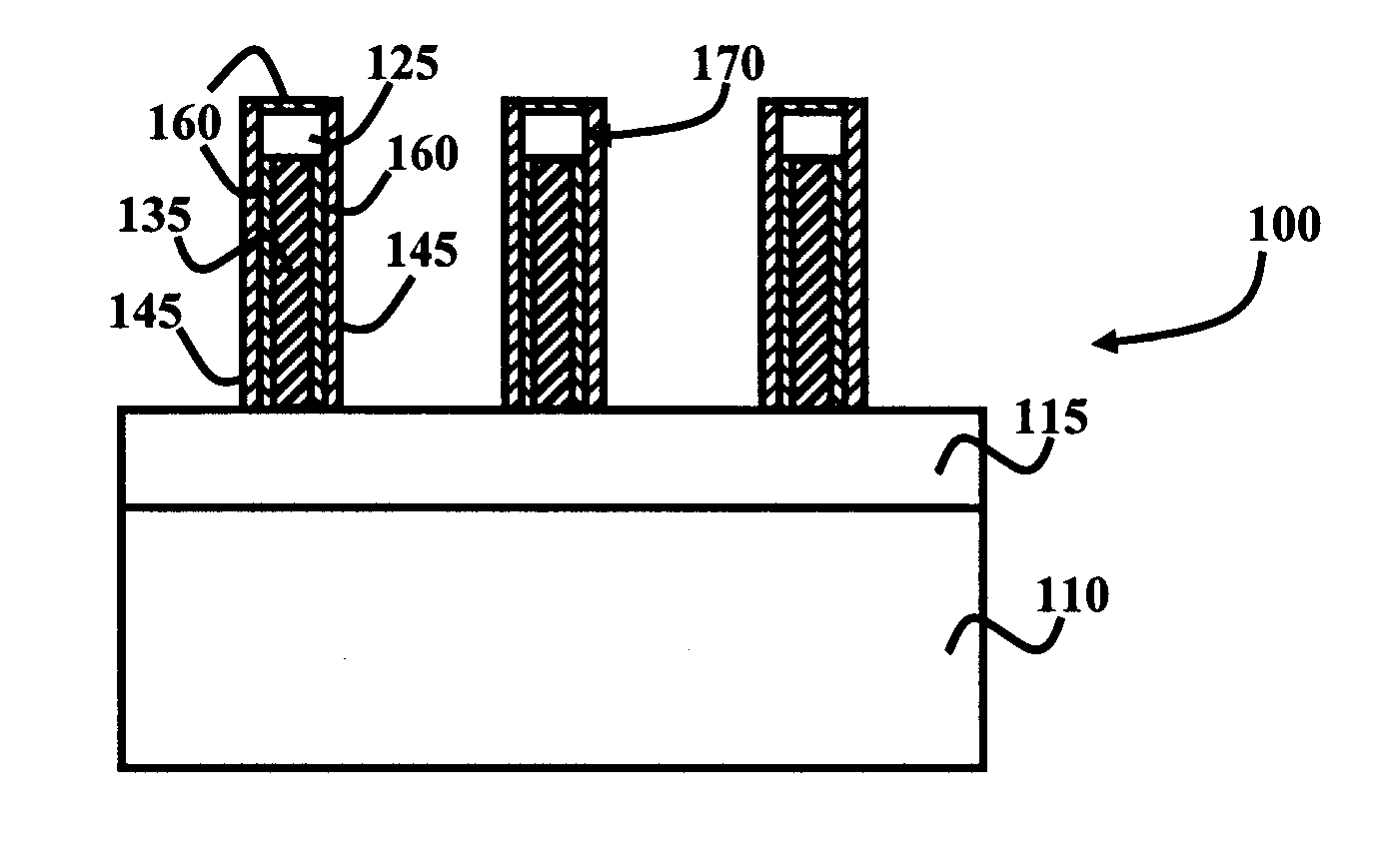

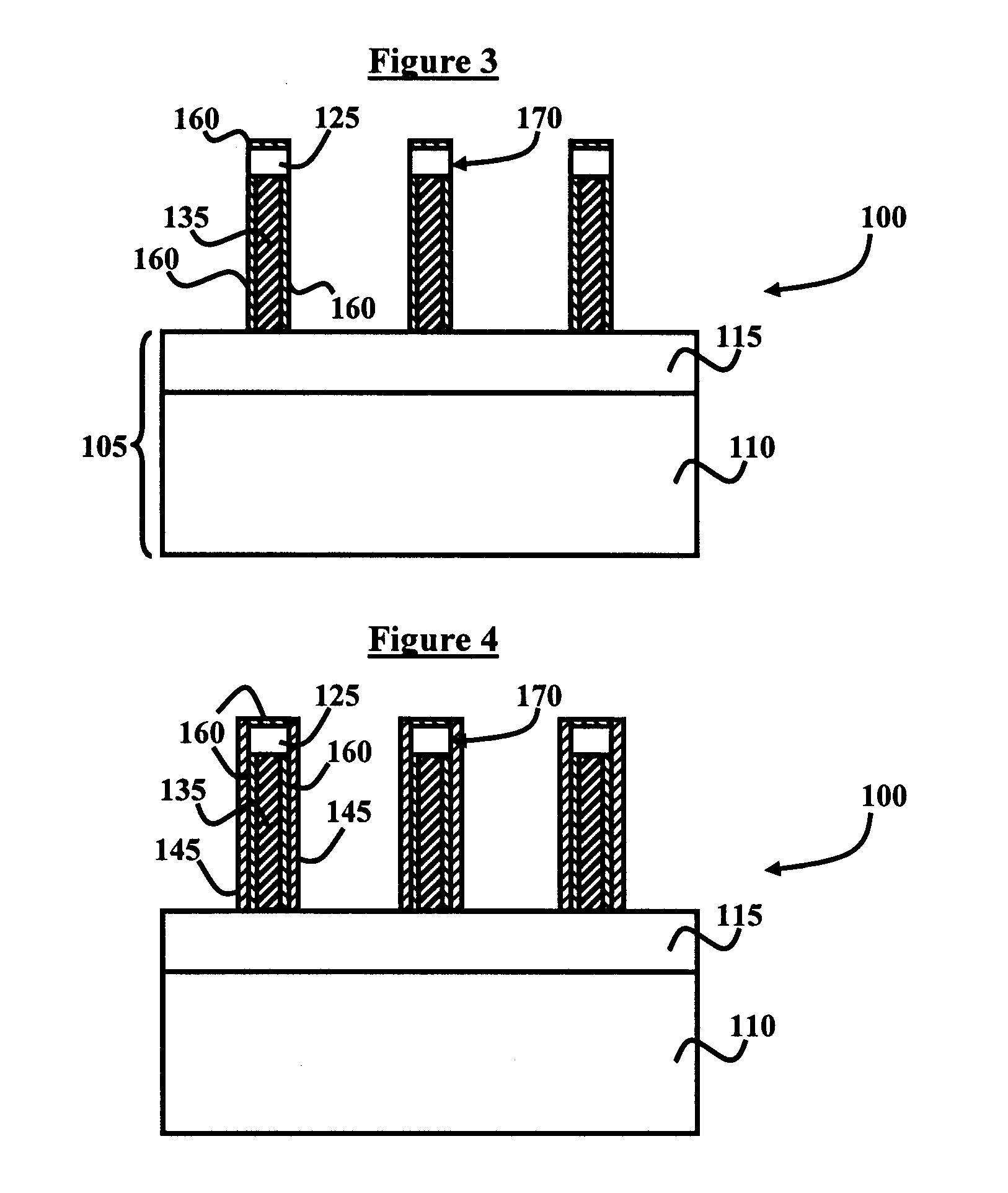

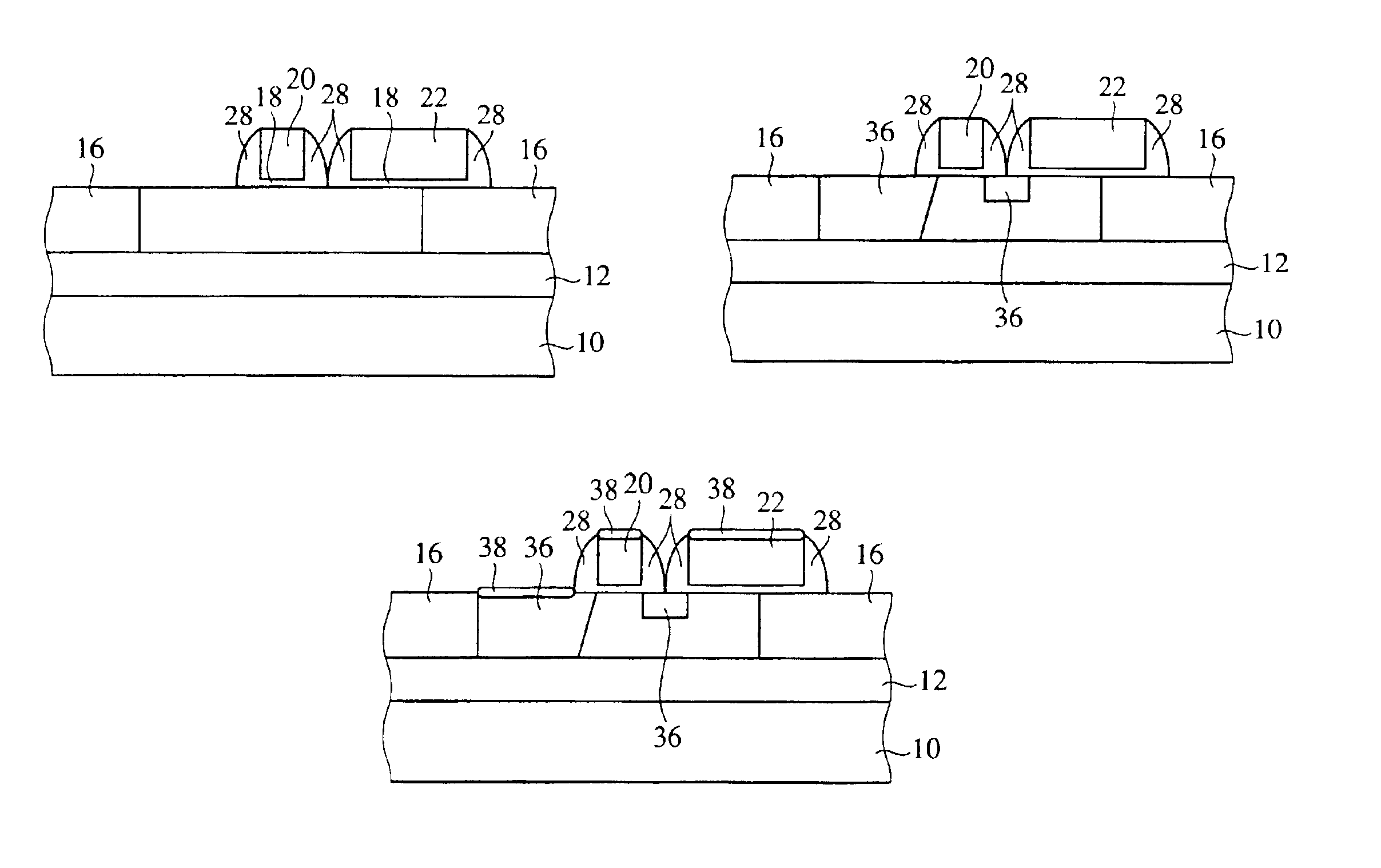

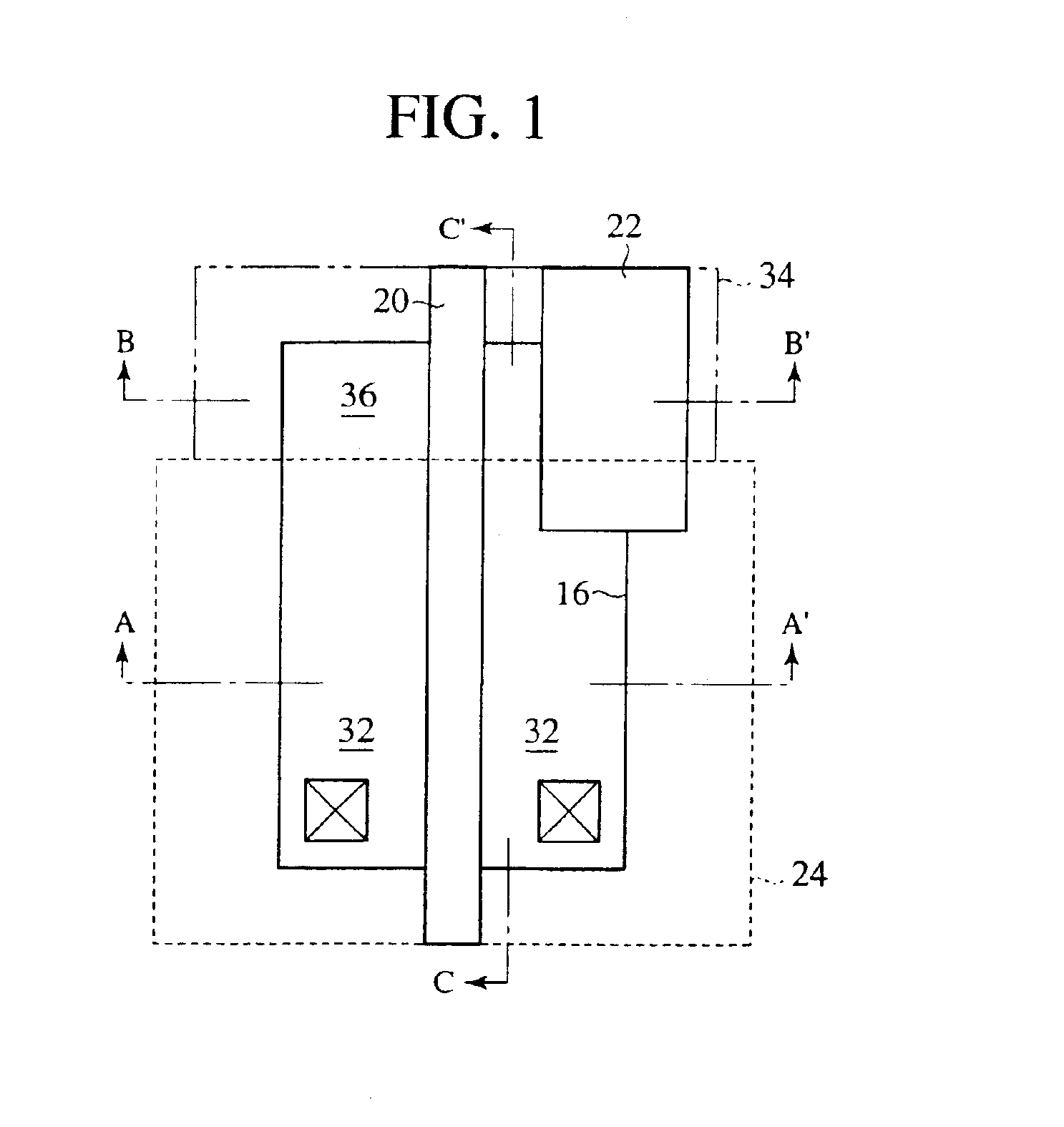

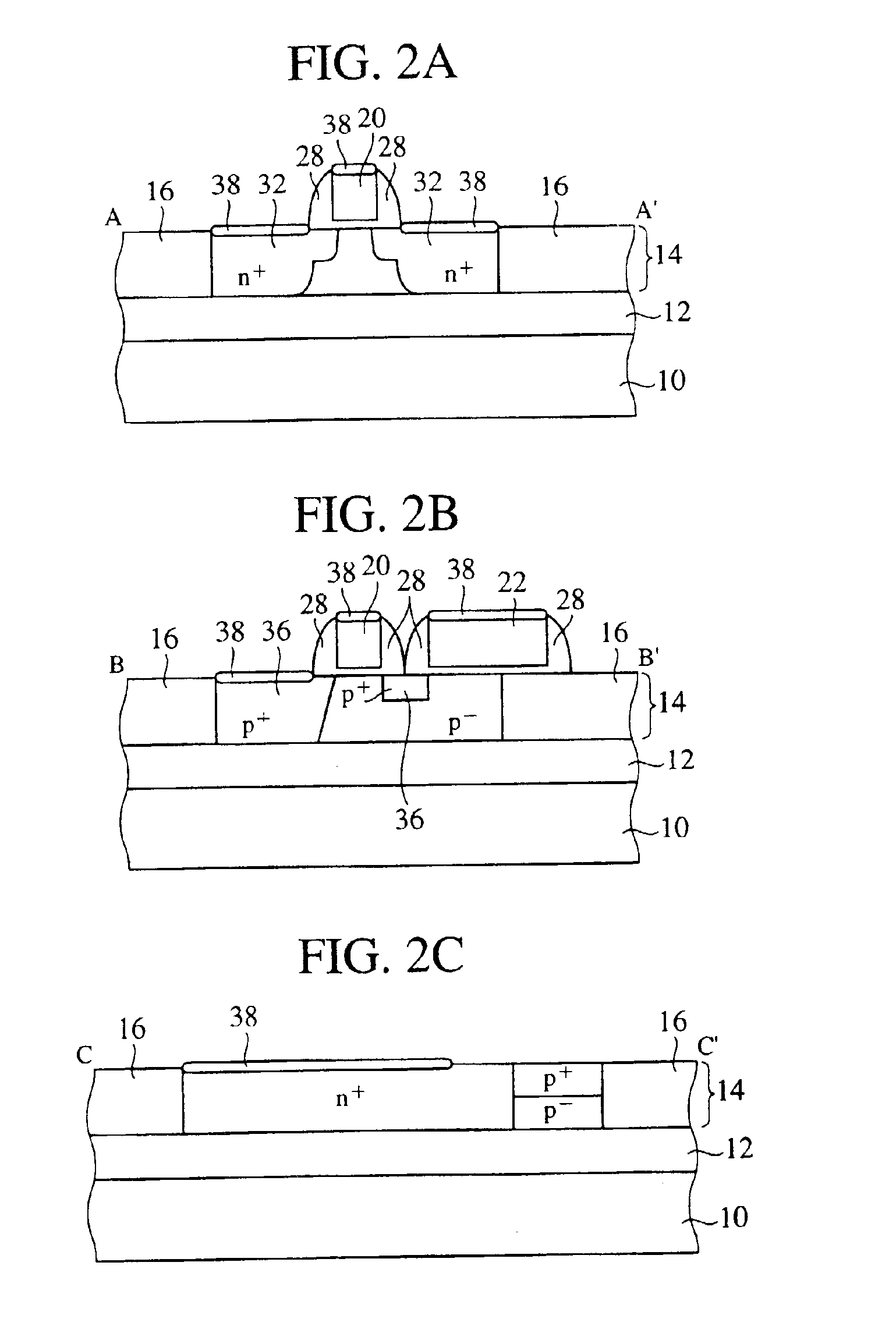

Finfet with low gate capacitance and low extrinsic resistance

ActiveUS20060043616A1Reduce gate capacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate insulator

A FinFET device and a method of lowering a gate capacitance and extrinsic resistance in a field effect transistor, wherein the method comprises forming an isolation layer comprising a BOX layer over a substrate, configuring source / drain regions above the isolation layer, forming a fin structure over the isolation layer, configuring a first gate electrode adjacent to the fin structure, disposing a gate insulator between the first gate electrode and the fin structure, positioning a second gate electrode transverse to the first gate electrode, and depositing a third gate electrode on the fin structure, the first gate electrode, and the second gate electrode, wherein the isolation layer is formed beneath the insulator, the first gate electrode, and the fin structure. The method further comprises sandwiching the second gate electrode with a dielectric material. The fin structure is formed by depositing an oxide layer over a silicon layer.

Owner:MICROSOFT TECH LICENSING LLC

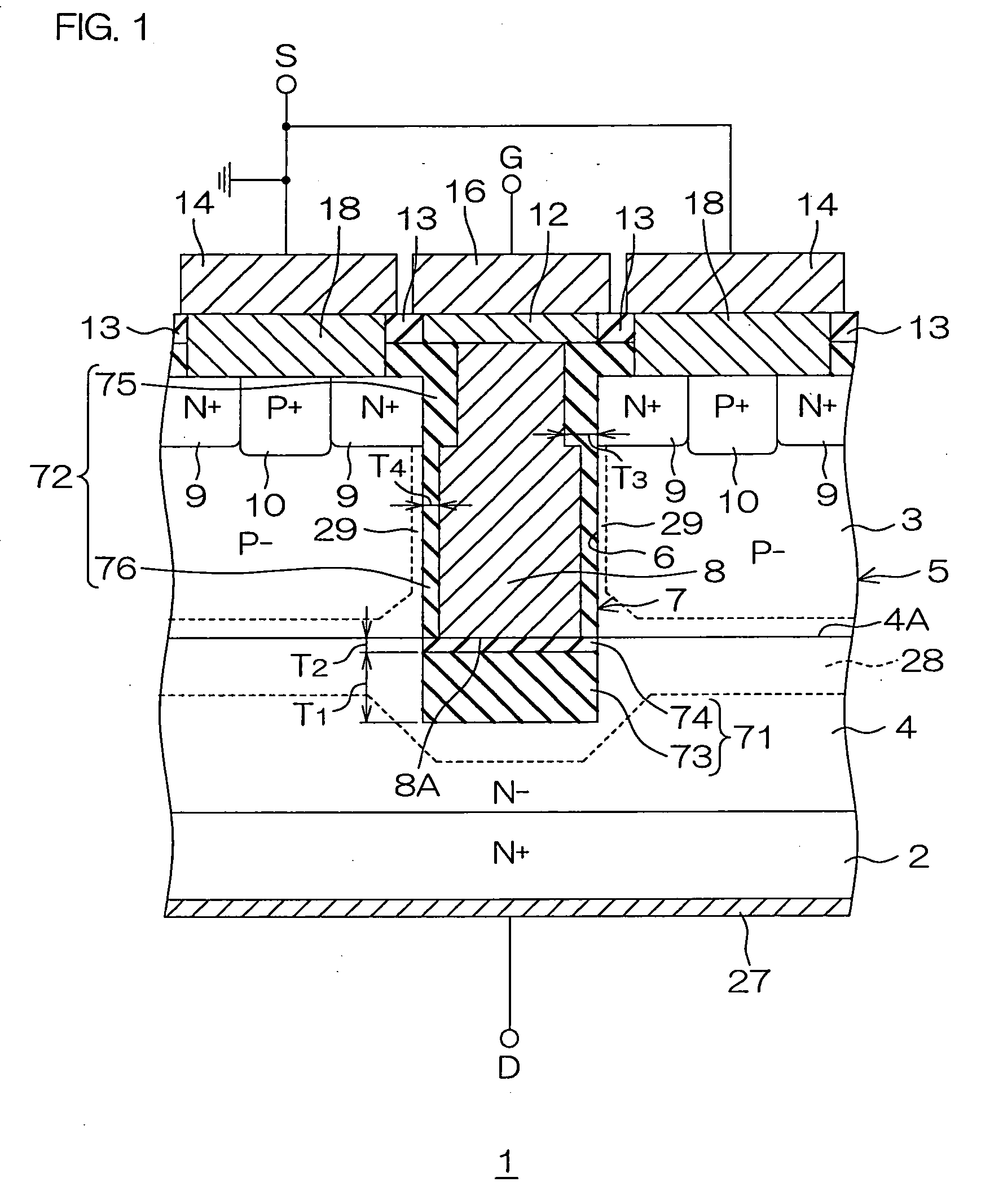

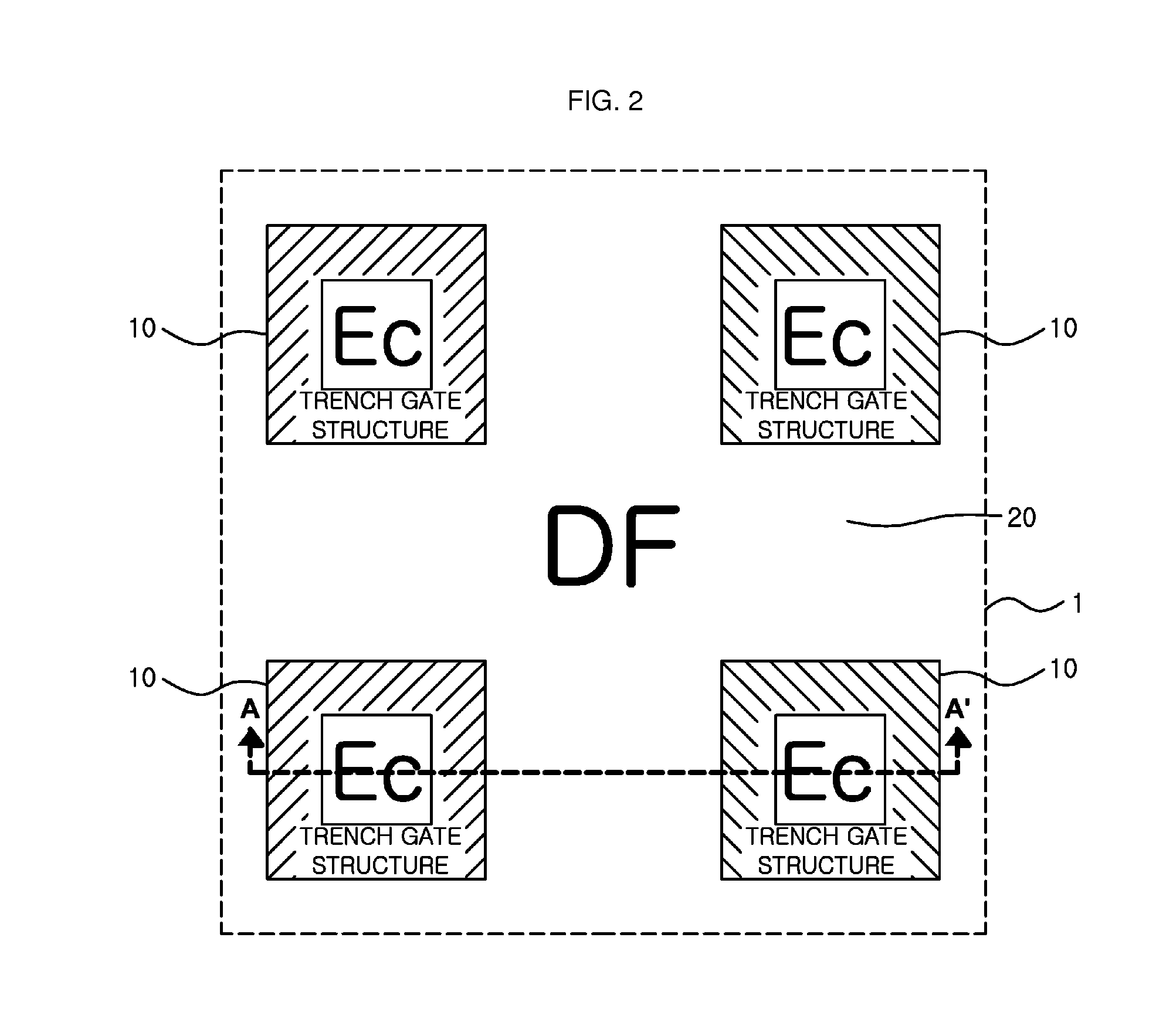

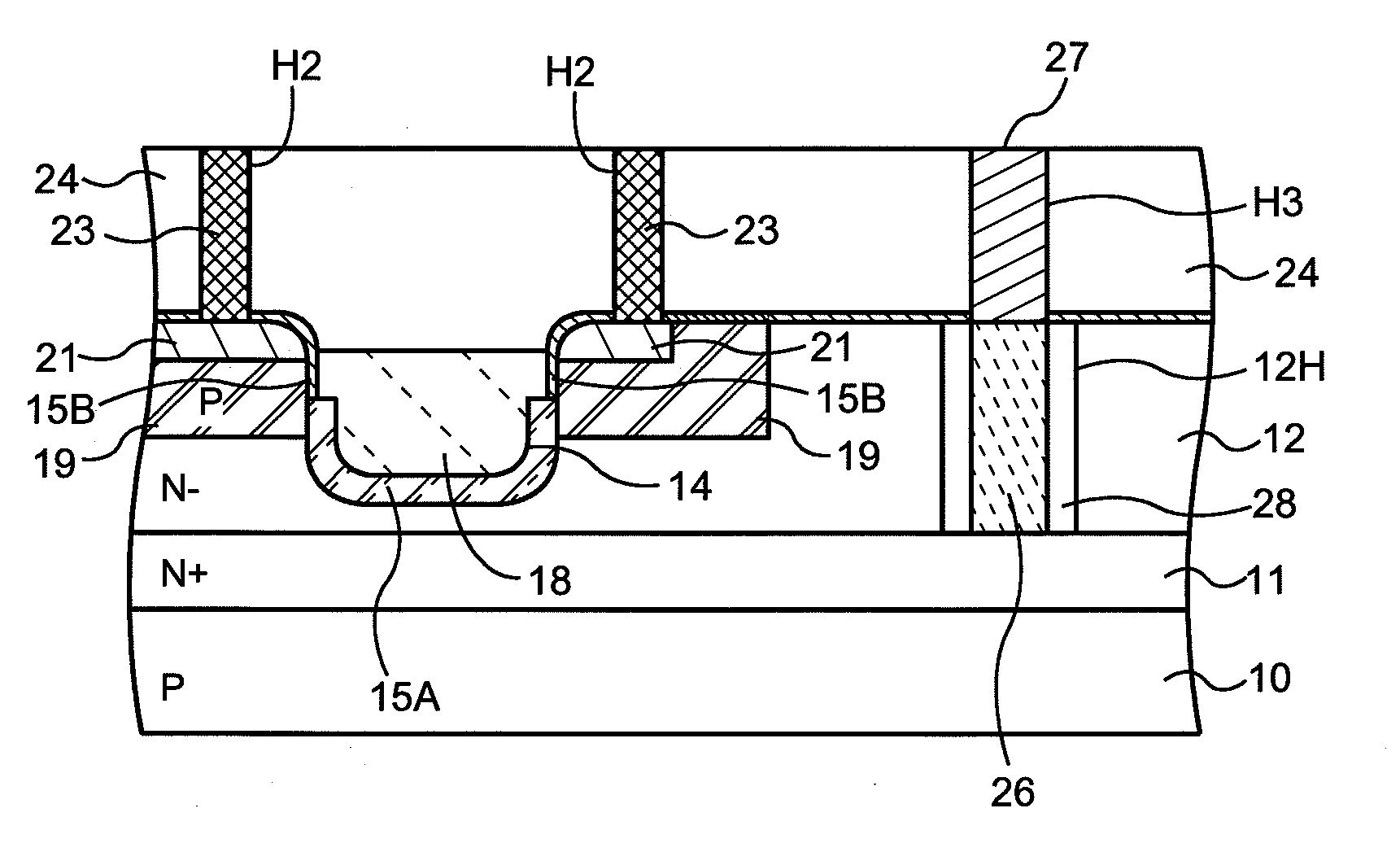

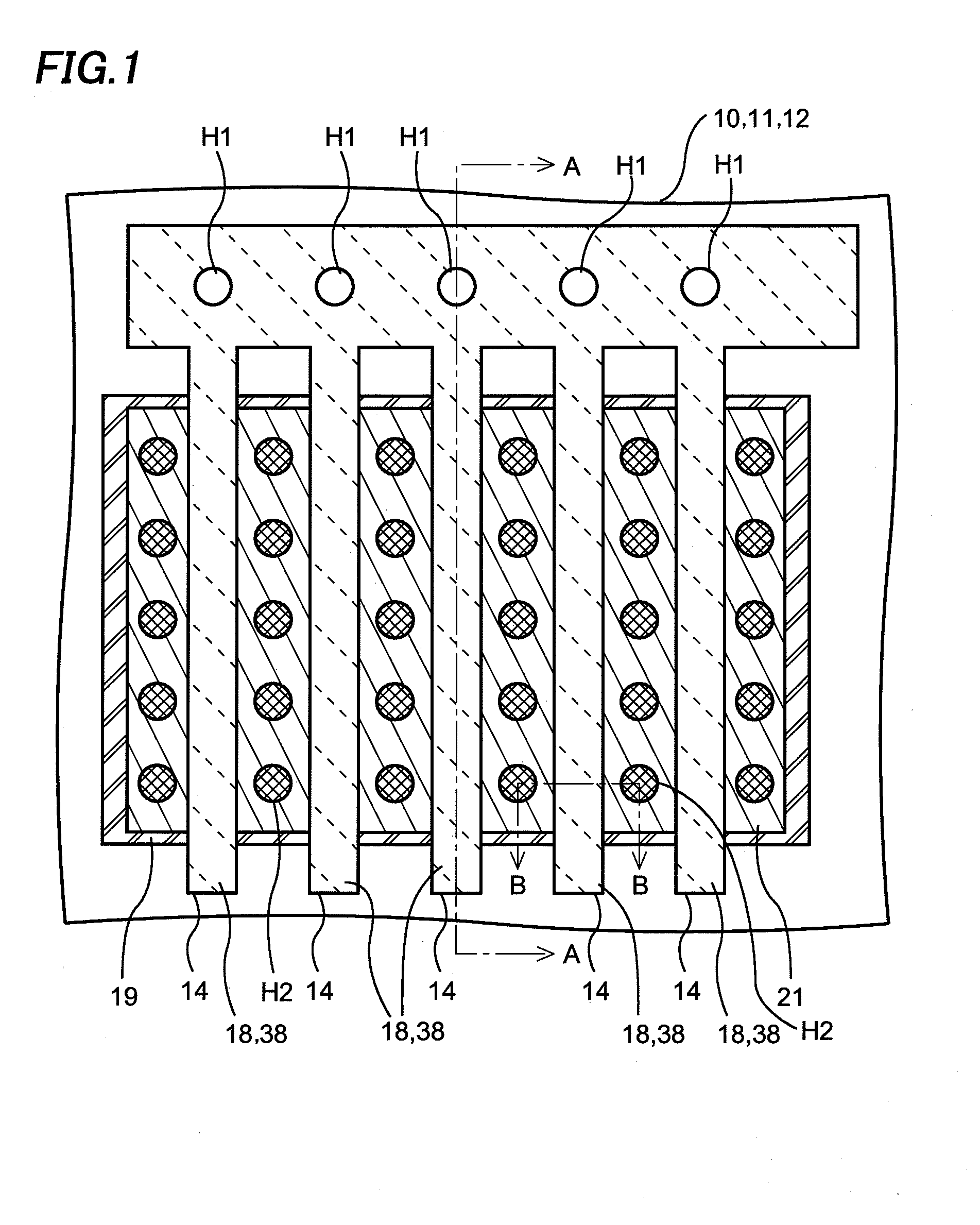

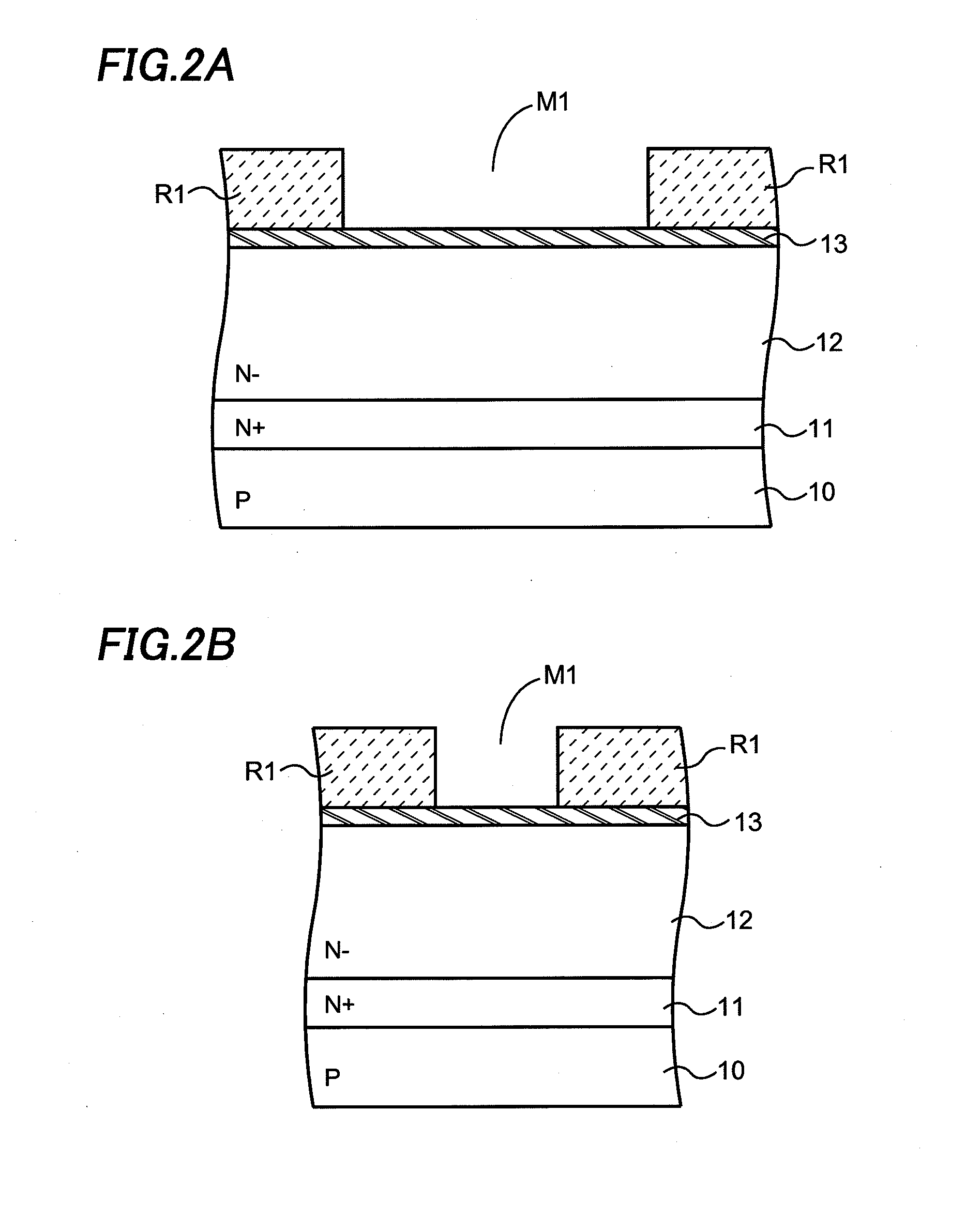

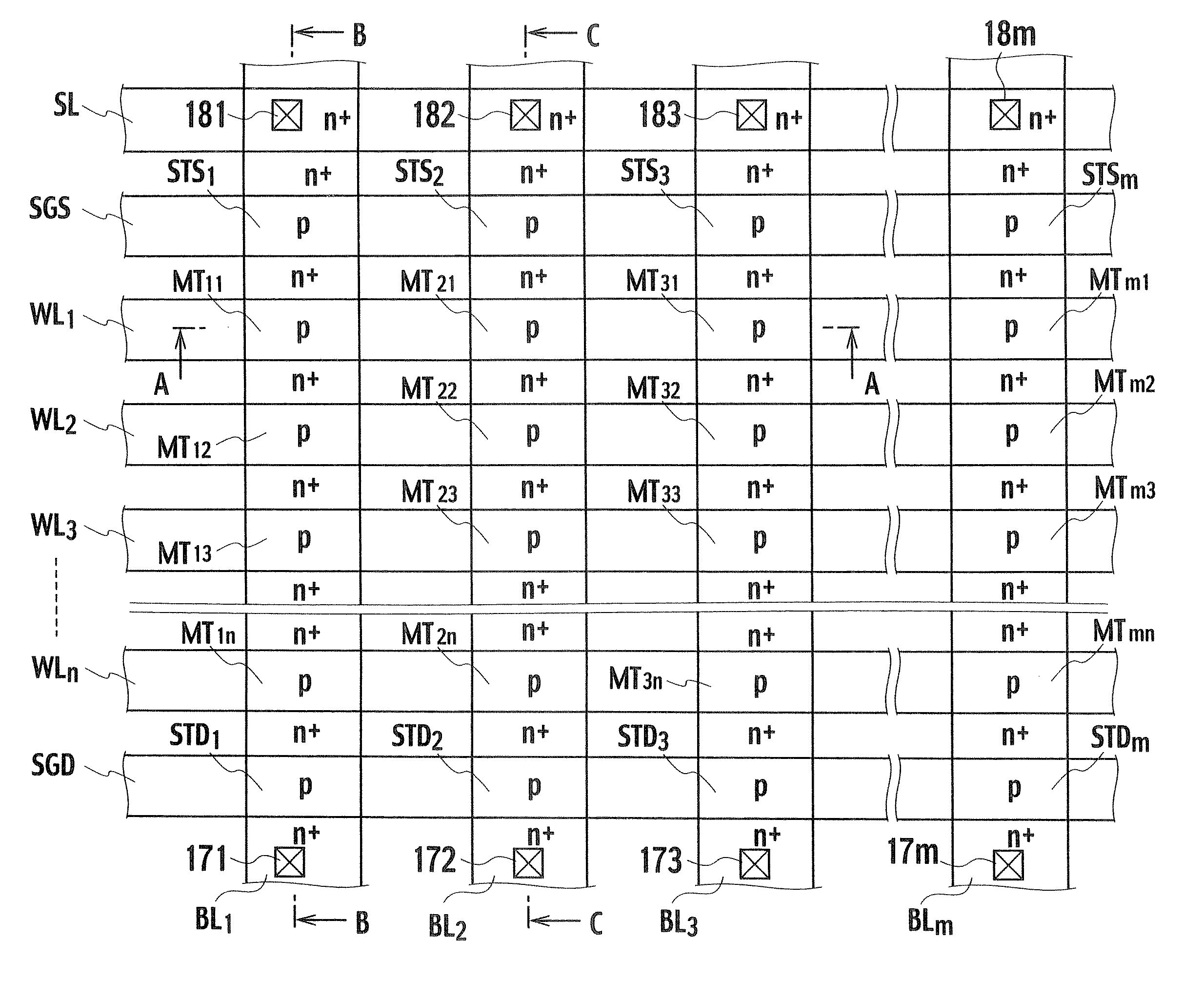

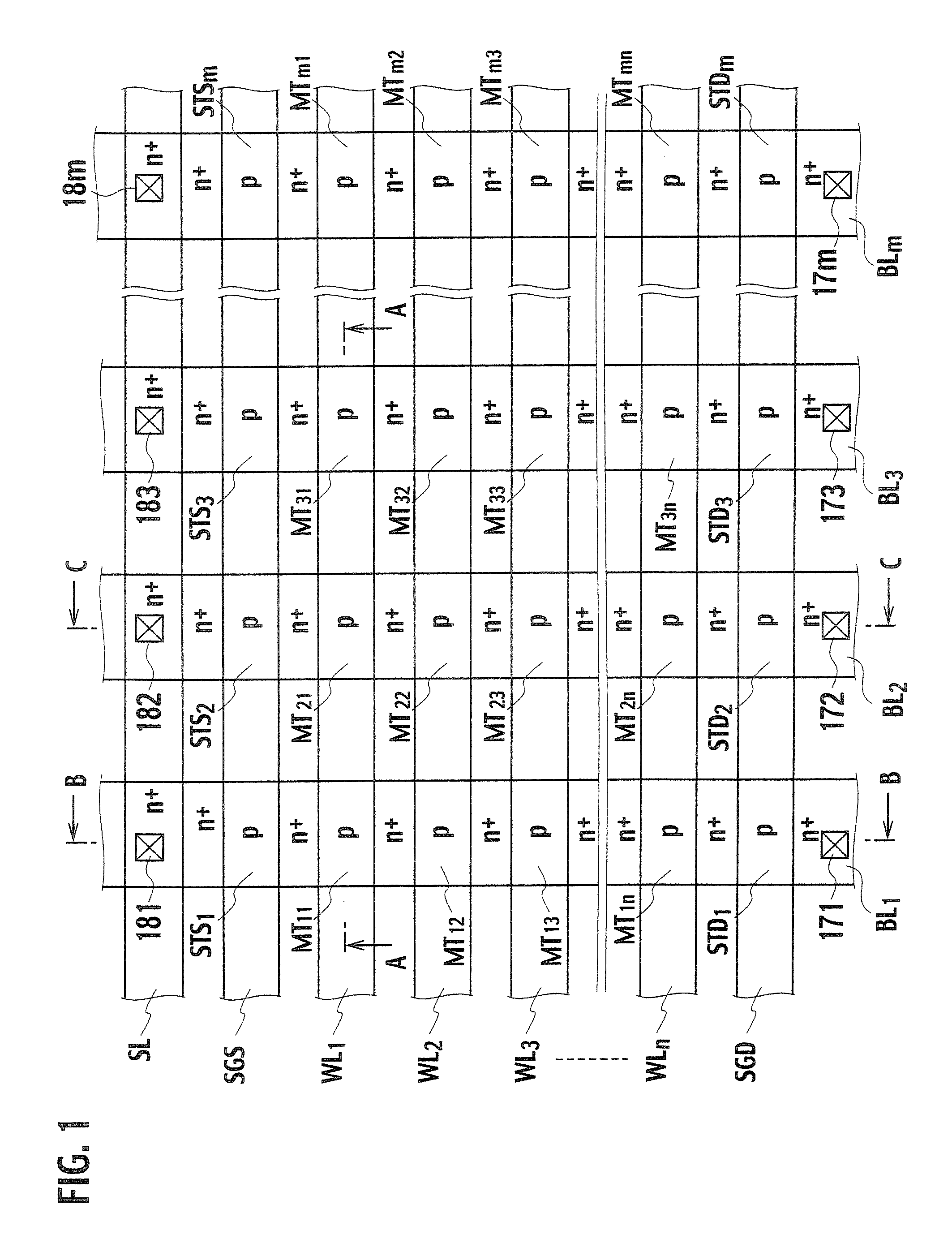

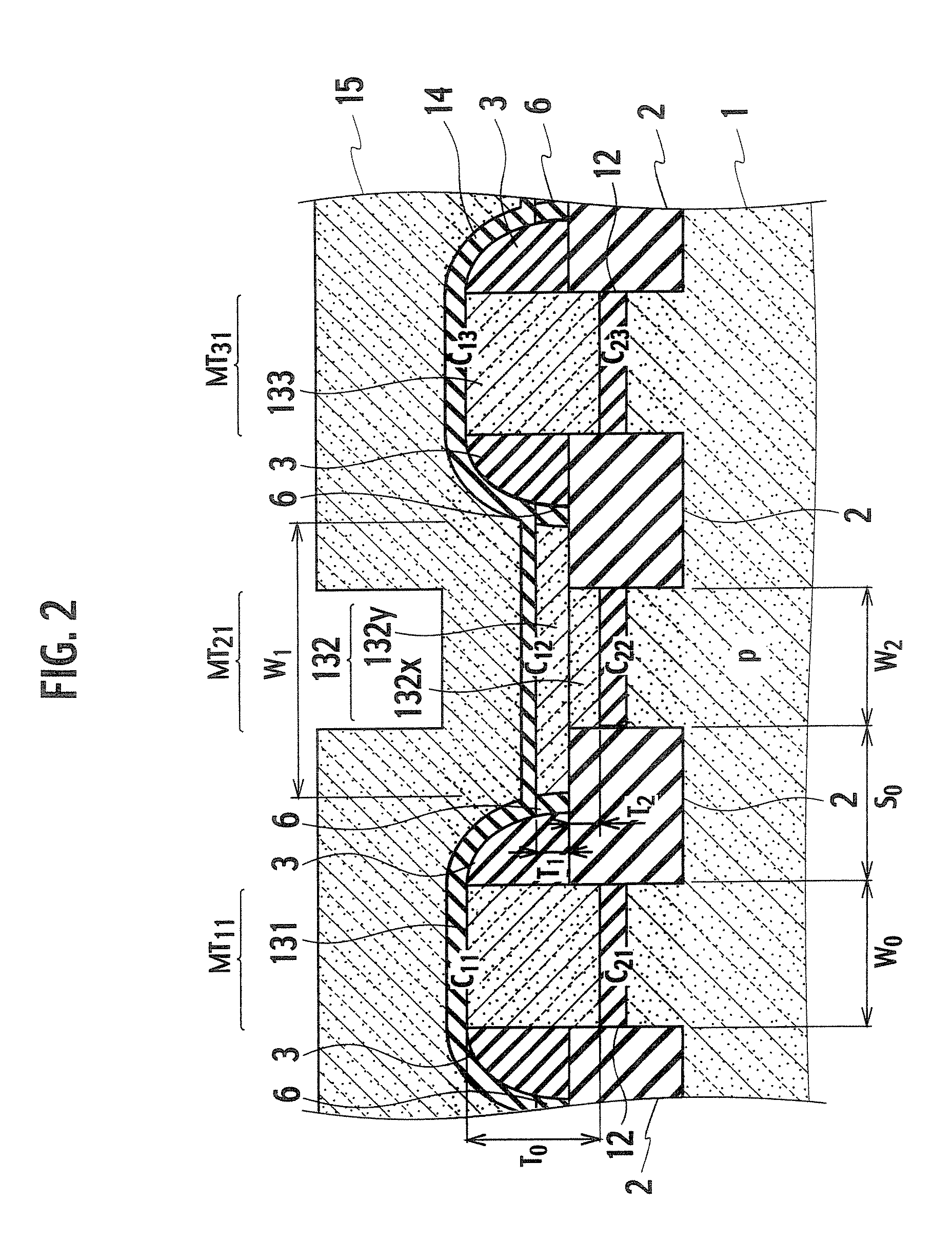

Semiconductor device and method of manufacturing semiconductor device

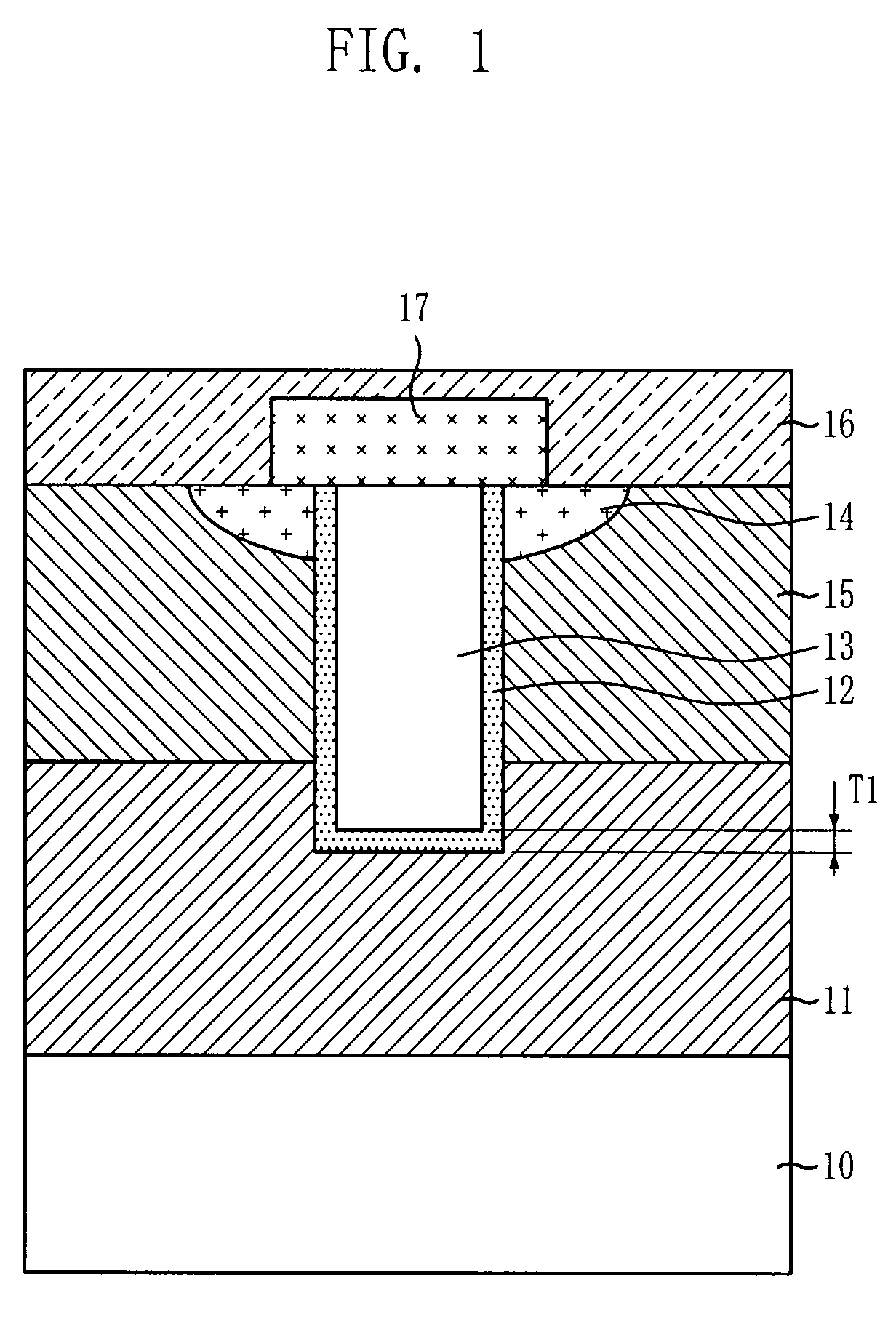

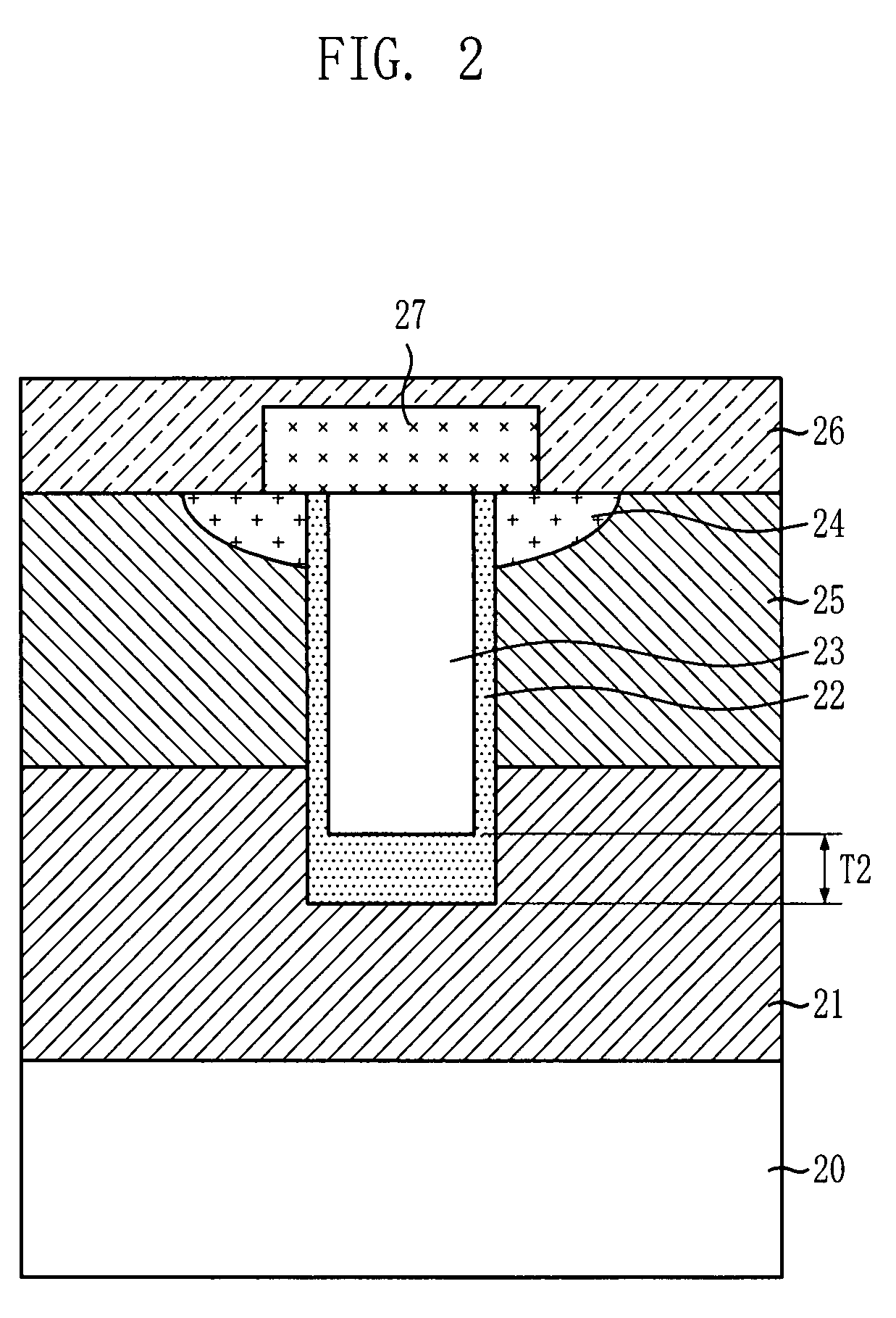

ActiveUS20090078995A1Lower on-resistanceReduce gate capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerSemiconductor

A semiconductor device includes a first conductivity type layer of a first conductivity type, a body layer of a second conductivity type formed on the first conductivity type layer, a gate trench passing through the body layer so that the deepest portion thereof reaches the first conductivity type layer, a source region of the first conductivity type formed around the gate trench on the surface layer portion of the body layer, a gate insulating film formed on the bottom surface and the side surface of the gate trench, and a gate electrode embedded in the gate trench through the gate insulating film, and the bottom surface of the gate electrode and the upper surface of the first conductivity type layer are flush with each other.

Owner:ROHM CO LTD

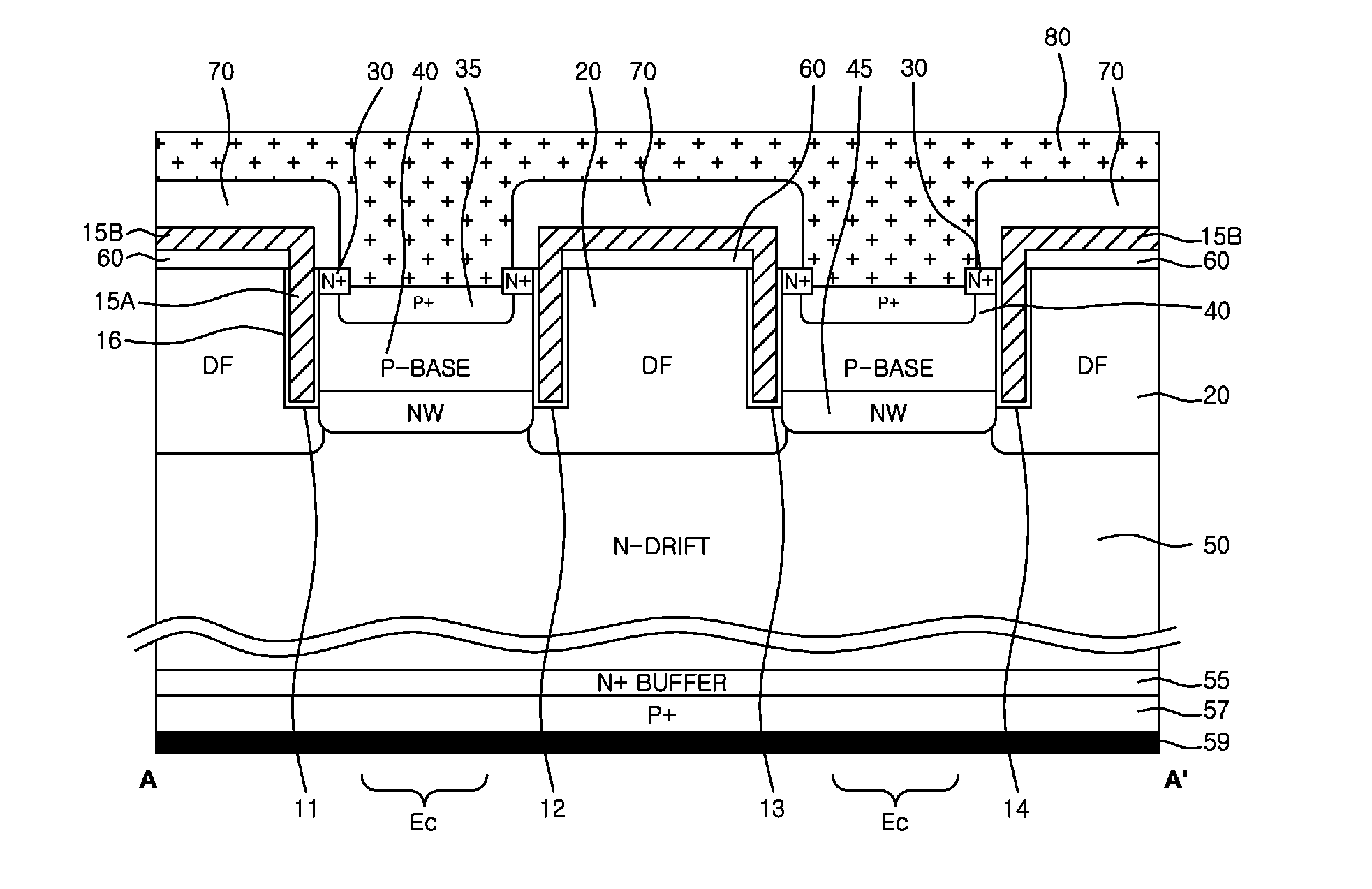

Power semiconductor device

ActiveUS20160336393A1Reduce gate capacitanceSolve the large consumptionSemiconductor/solid-state device detailsSolid-state devicesCapacitancePower semiconductor device

The present examples relate to a power semiconductor device. The present examples also relate to a power semiconductor device that maintains a breakdown voltage and reduces a gate capacitance through improving the structure of an Injection Enhanced Gate Transistor (IEGT), and thereby reduces strength of an electric field compared to alternative technologies. Accordingly, the present examples provide a power semiconductor device with a small energy consumption and with an improved switching functionality.

Owner:MAGNACHIP SEMICONDUCTOR LTD

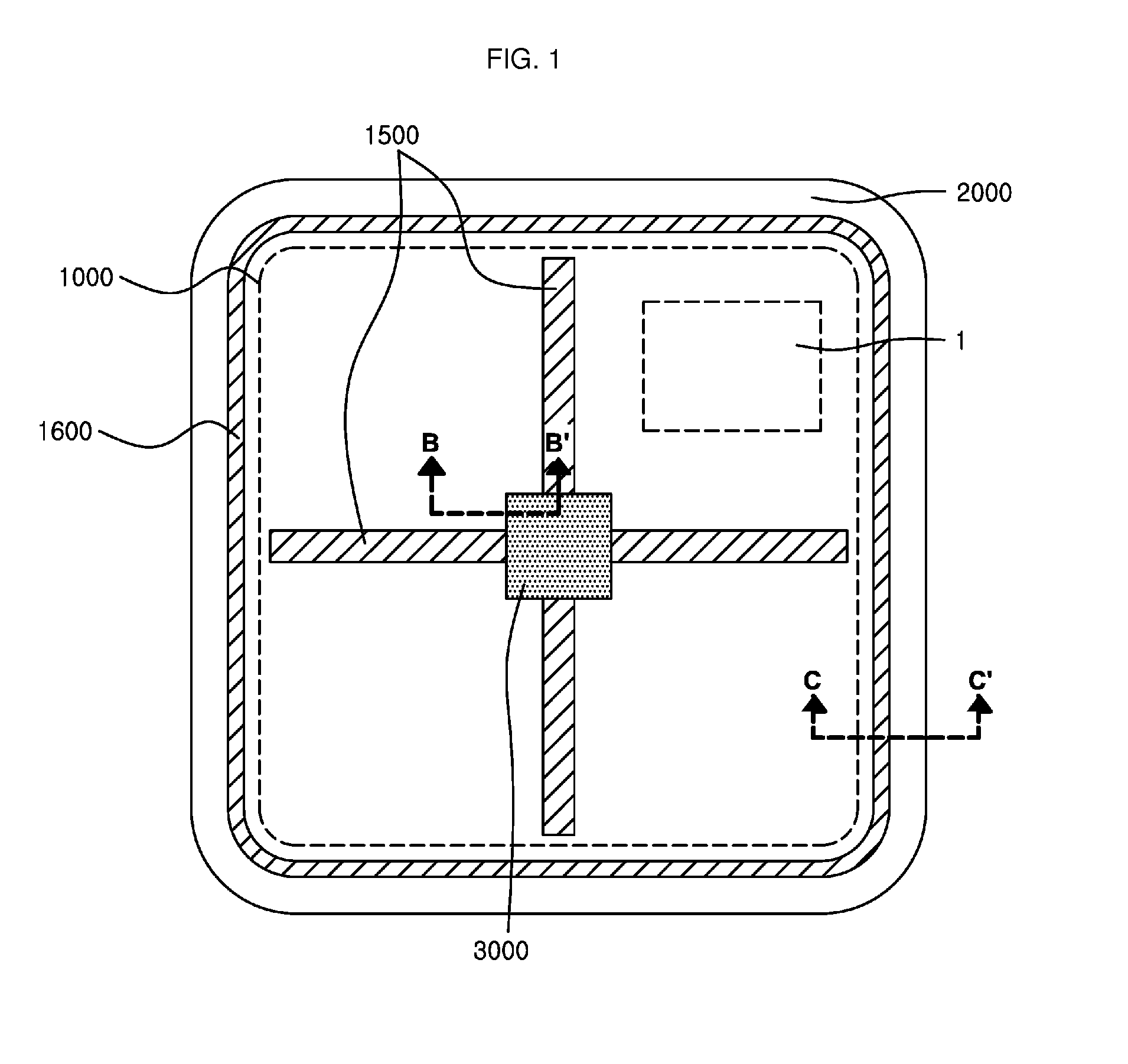

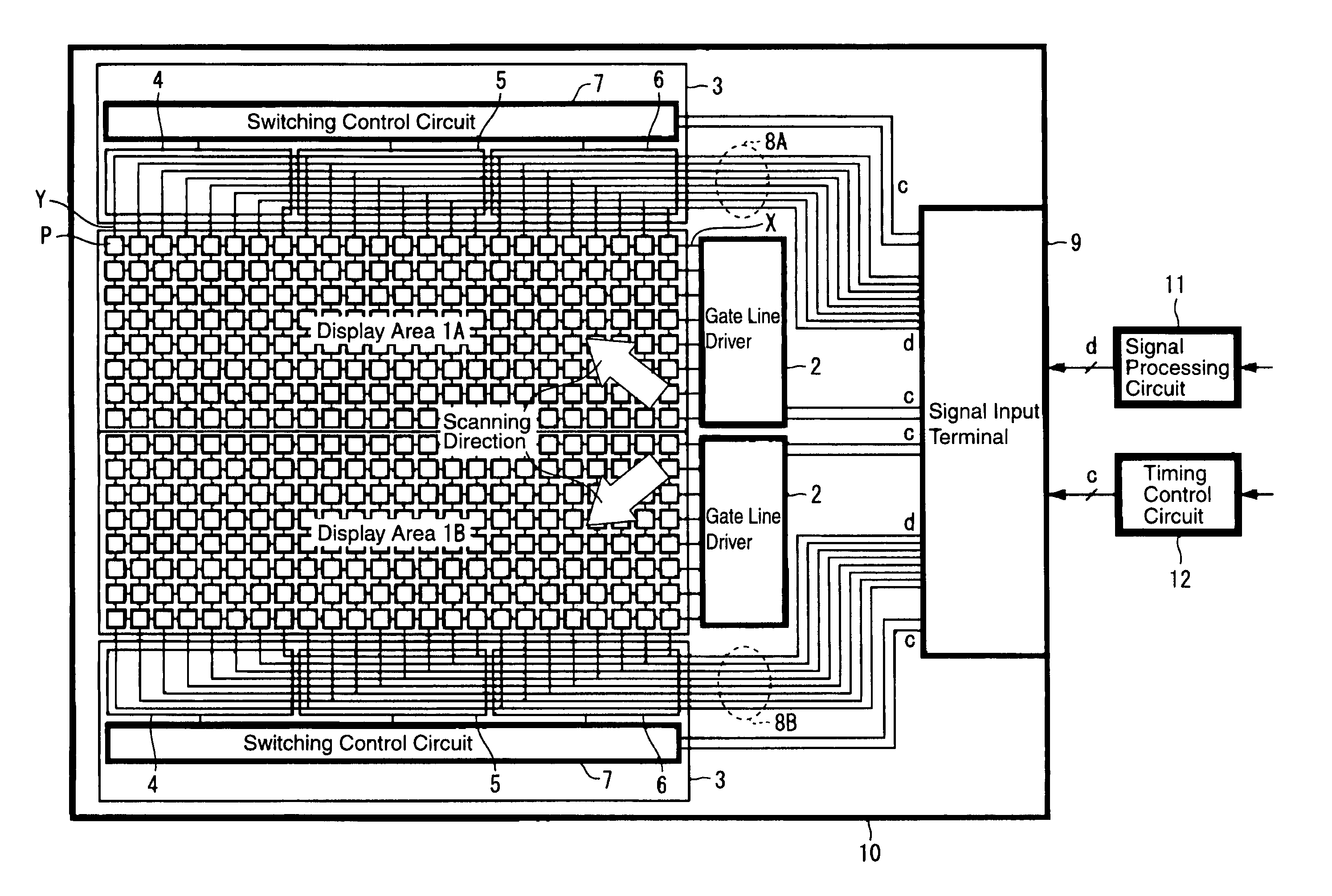

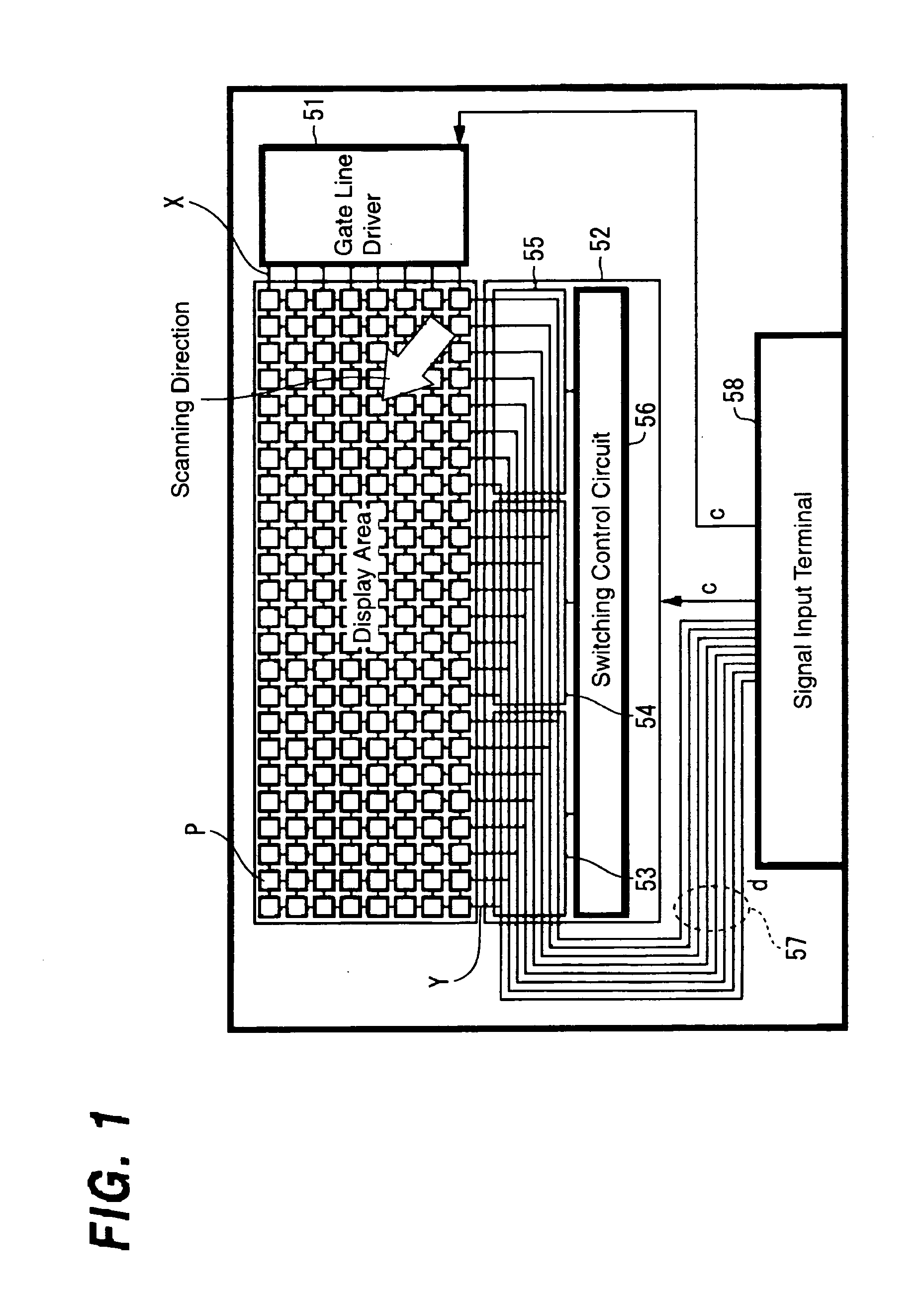

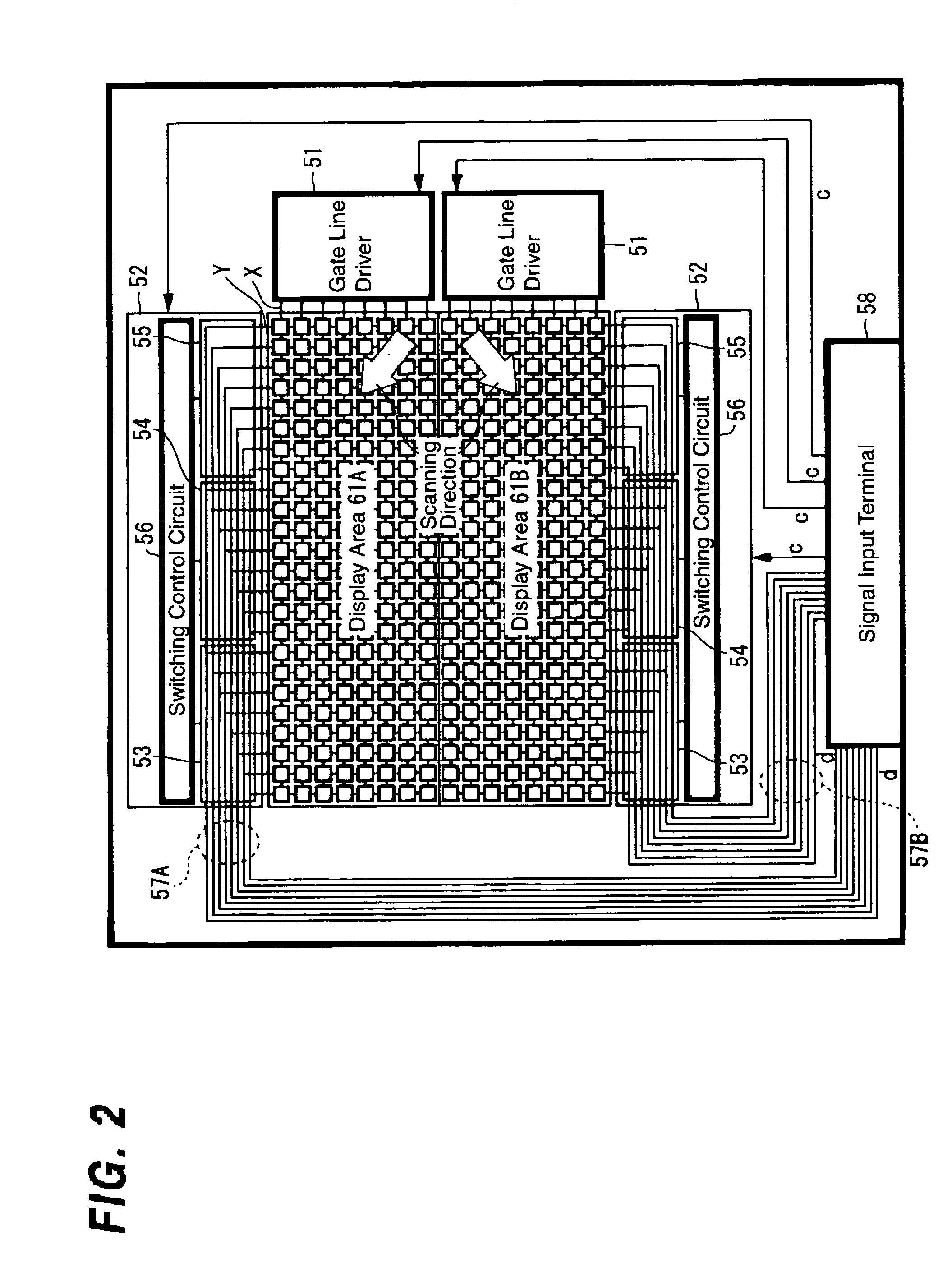

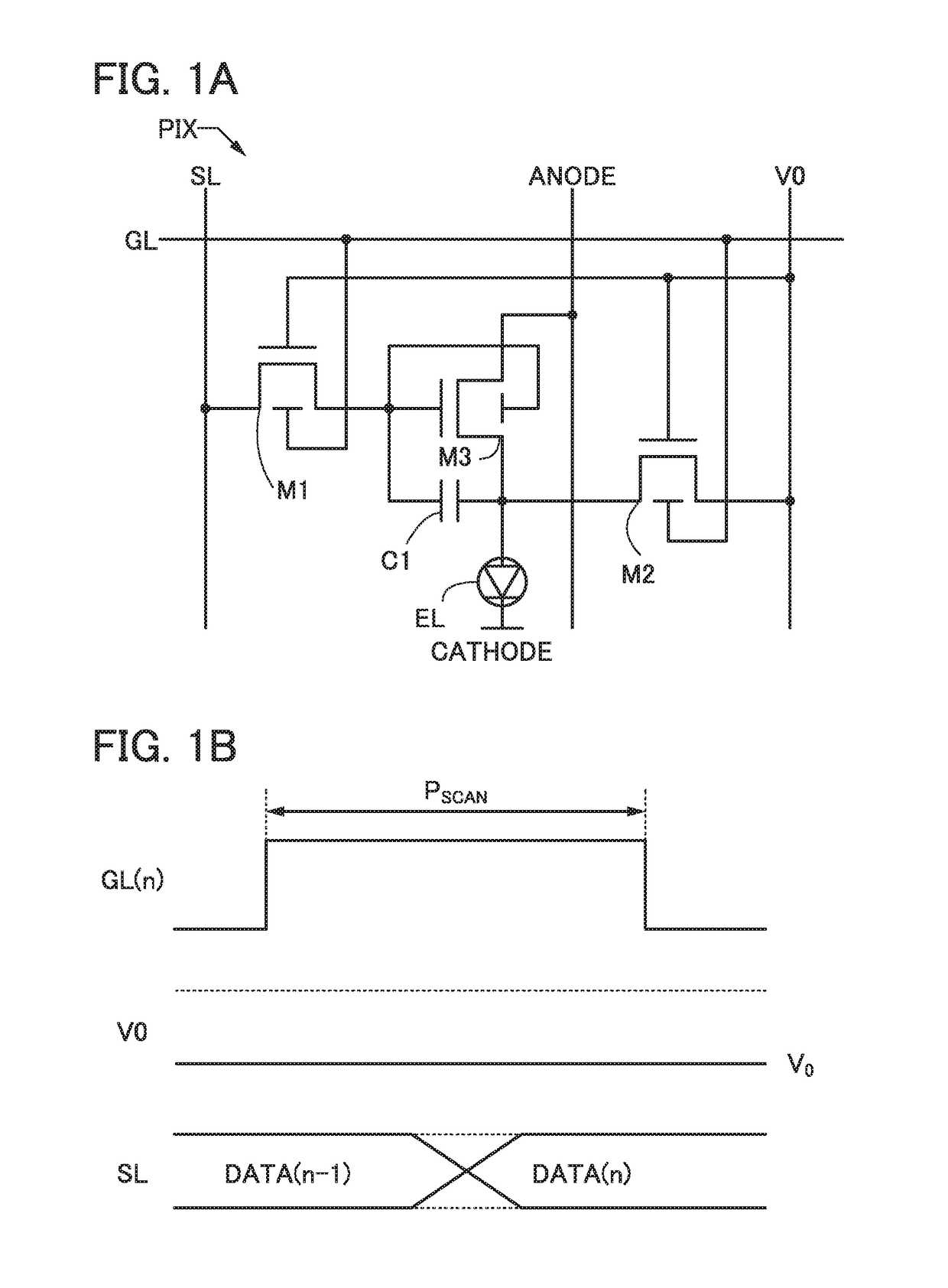

Display device and projection type display apparatus

InactiveUS20050248556A1Improve picture qualityCapacitance can be smallProjectorsCathode-ray tube indicatorsLiquid-crystal displayDisplay device

A display device having extremely short writing time to a pixel such as the liquid crystal display device of a dot sequential drive method using a single-crystal silicon transistor as a switching element is provided in which in the case where a display area is divided into two or more areas, the degradation of picture quality is prevented to perform a high definition display. In a display device of a matrix drive method in which gate lines X in the row direction and data lines Y in the column direction are arranged in matrix shape and a pixel P is arranged at the intersection of the gate line and the data line, a display area is divided into two or more areas 1A and 1B which are driven independently from each other; wiring layout of signal lines 8A and 8B which transfer display data d to each of the areas 1A and 1B is approximately symmetrical with a division boundary line of those areas positioned in between; and control unit 12 which makes a control to perform writing of the display data at least to the pixels P next to each other with the division boundary line positioned in between at approximately the same timing.

Owner:SONY CORP

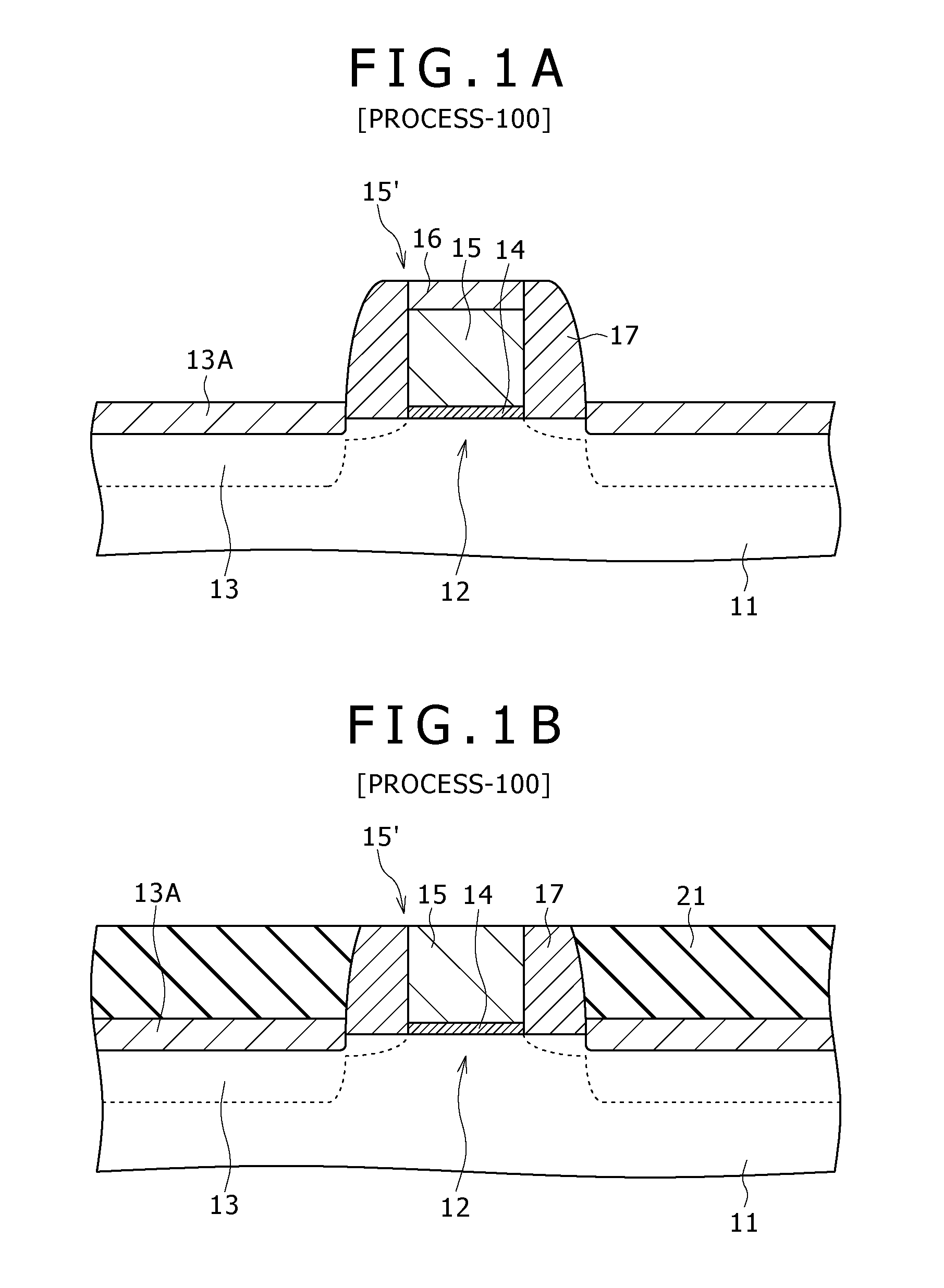

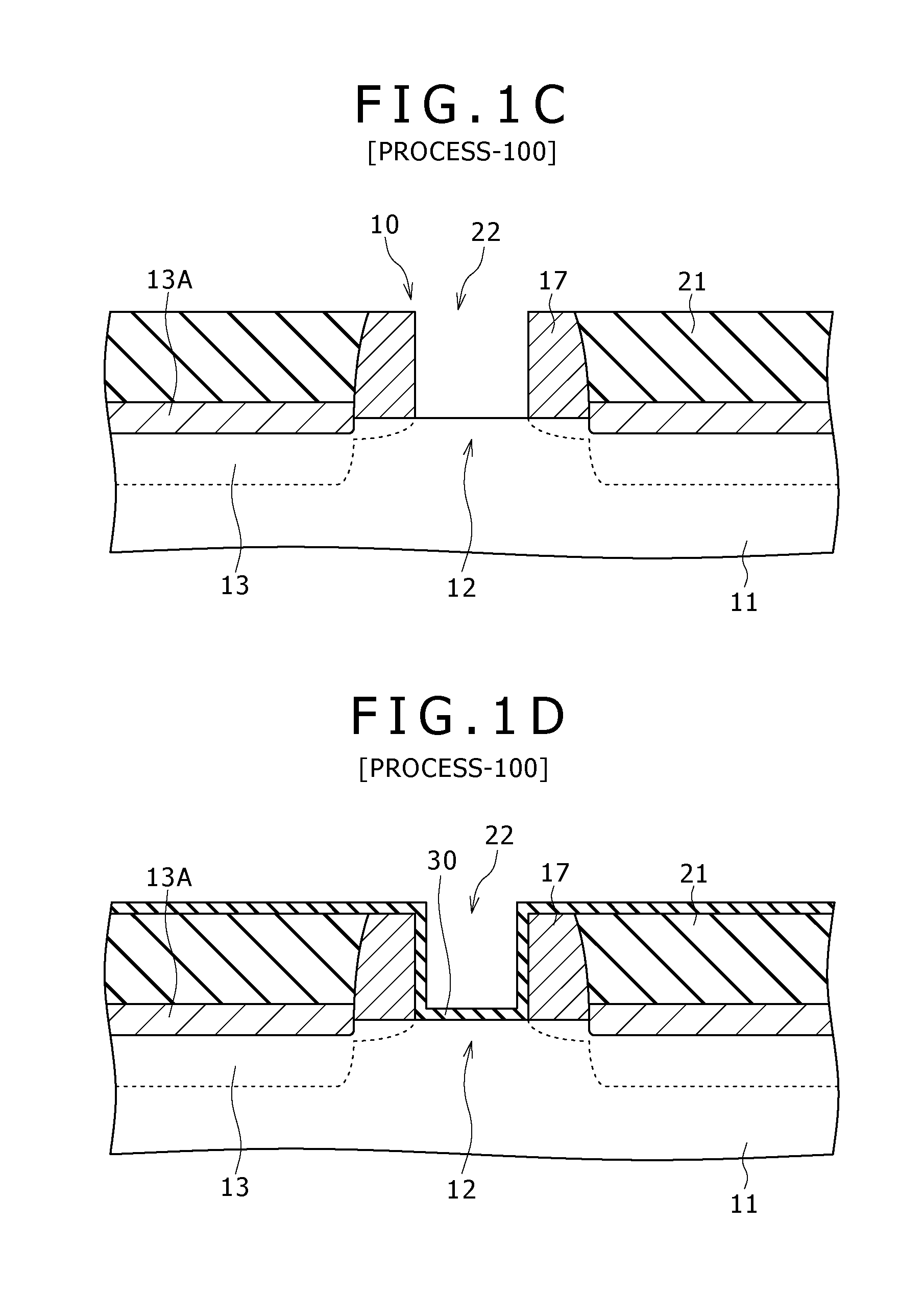

Method for manufacturing insulated gate field effect transistor

ActiveUS20080197426A1Reduce contact resistanceReduce gate capacitanceTransistorSolid-state devicesEngineeringConductive materials

Disclosed herein is a method for manufacturing an insulated gate field effect transistor, the method including the steps of: (a) preparing a base that includes source / drain regions, a channel forming region, a gate insulating film formed on the channel forming region, an insulating layer covering the source / drain regions, and a gate electrode formation opening provided in a partial portion of the insulating layer above the channel forming region; (b) forming a gate electrode by burying a conductive material layer in the gate electrode formation opening; (c) removing the insulating layer; and (d) depositing a first interlayer insulating layer and a second interlayer insulating layer sequentially across an entire surface, wherein in the step (d), the first interlayer insulating layer is deposited in a deposition atmosphere containing no oxygen atom.

Owner:SONY CORP

Air-gap grapheme transistor and manufacturing method thereof

InactiveCN102074584ALow dielectric constantSmall overall permittivitySemiconductor/solid-state device manufacturingSemiconductor devicesIntegrated circuit manufacturingAND gate

The invention belongs to the technical field of carbon integrated circuit manufacturing, in particular relates to an air-gap grapheme transistor and a manufacturing method thereof. In the method, gate electrodes and gate medium grow on a silicon base and then source and drain graphics are formed; grapheme is transformed to the formed source and drain graphics so as to separate the grapheme from the gate medium; and the air-gap is used to separate the grapheme from the gate medium so as to eliminate the growth process of a buffer layer on the grapheme, thus high mobility of carriers in the grapheme is retained maximally, and deterioration for the surface properties of the grapheme is reduced, thereby further improving electrical properties of grapheme devices.

Owner:FUDAN UNIV

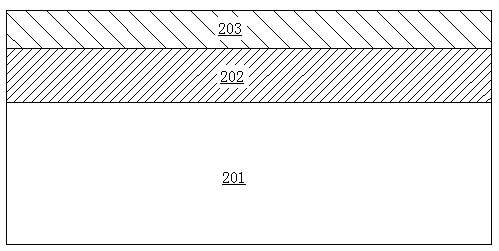

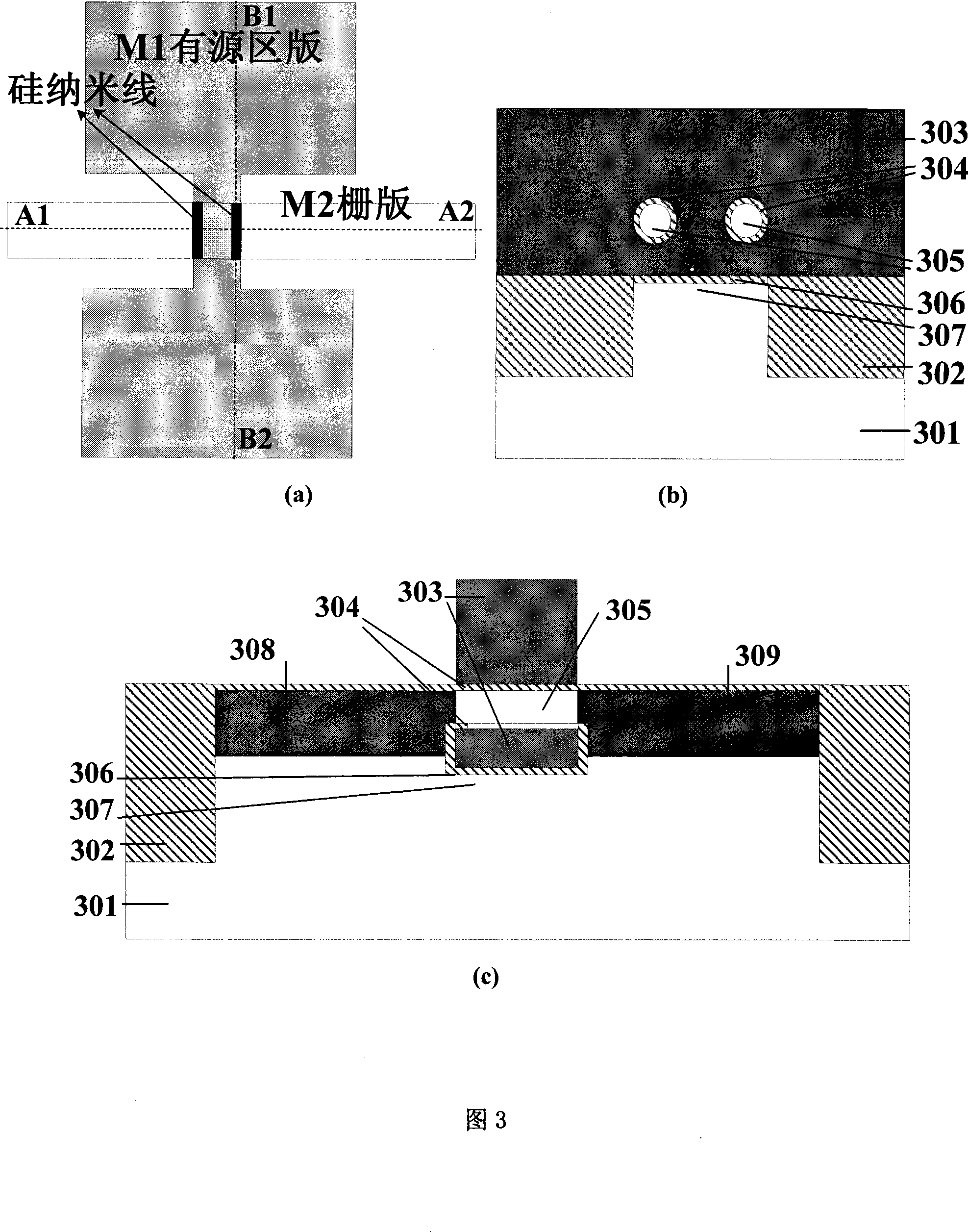

A double silicon nanowire wrap gate field-effect transistor and its manufacture method

InactiveCN101060135AImprove featuresLow costSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETSoi cmos technology

The provided double-silicon nano line enclose-grid FET belonged to MOSFET technique in ULSI comprises: a silicon substrate, double silicon lines as the channels, a grid anode and multicrystal silicon grid enclosing the nano lines to form the enclose-grid structure, both source and drain connecting with the substrate, and a thick SiO2 layer between the right bottom of channel and substrate. This invention is compatible to common CMOS technique, reduces cost and power consumption, and has wide application.

Owner:PEKING UNIV

Dual double gate transistor and method for forming

InactiveUS7101741B2High densityImprove device performanceTransistorSolid-state devicesElectric currentDual gate

The present invention provides a dual gate transistor and a method for forming the same that results in improved device performance and density. The present invention uses a double gate design to implement a dual gate transistor. A double gate is a gate which is formed on both sides of the transistor body. The present invention thus provides a transistor with two double gates in series that provide improved current control over traditional dual gate designs. The preferred embodiment of the present invention uses a fin type body with dual double-gates. In a fin type structure, the double gates are formed on each side of a thin fin shaped body, with the body being disposed horizontally between the gates.

Owner:GLOBALFOUNDRIES US INC

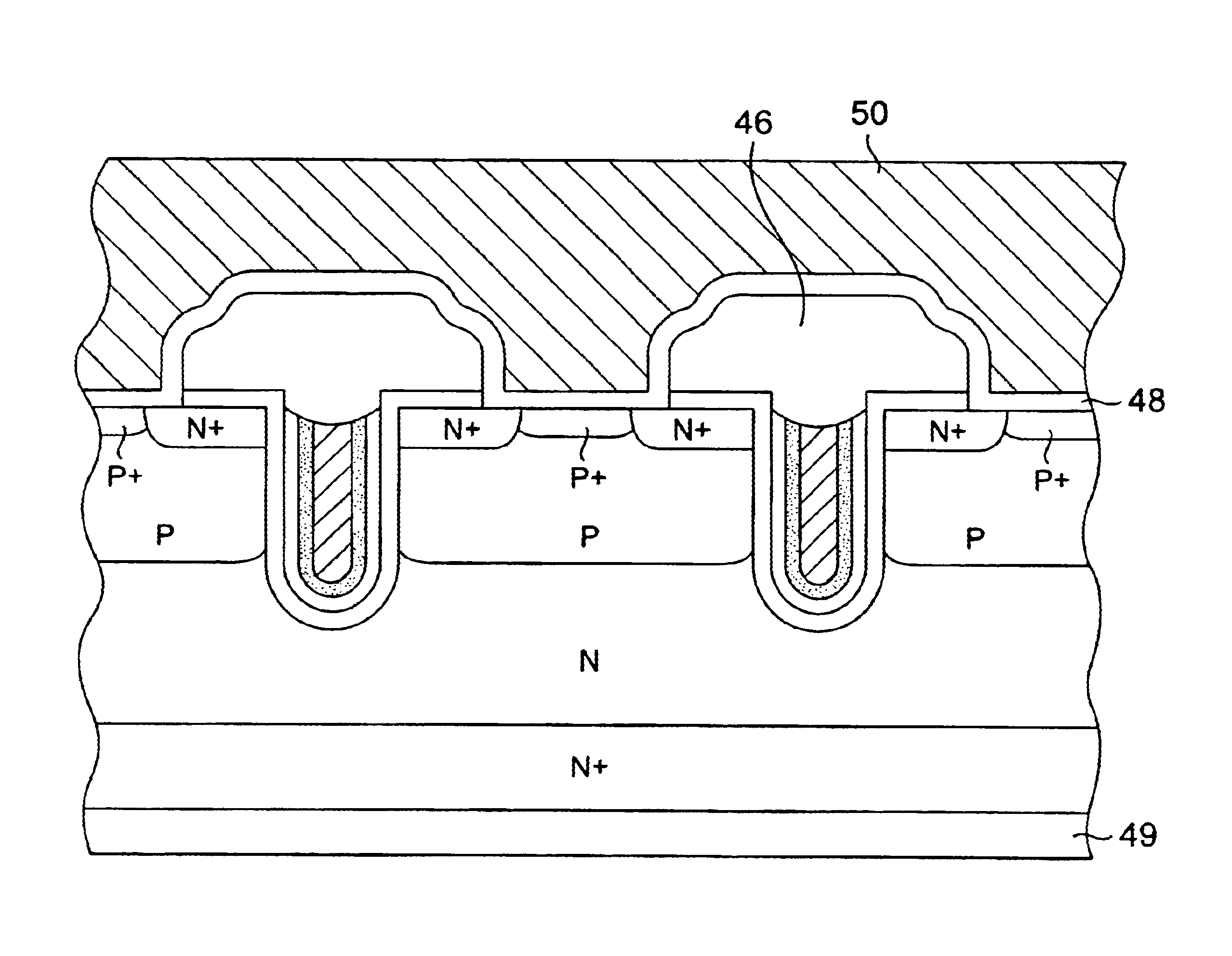

High speed trench DMOS

InactiveUS6849899B2Lower gate resistanceReduce gate capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePropagation delay

A method for making trench DMOS is provided that utilizes polycide and refractory techniques to make trench DMOS which exhibit low gate resistance, low gate capacitance, reduced distributed RC gate propagation delay, and improved switching speeds for high frequency applications.

Owner:GEN SEMICON

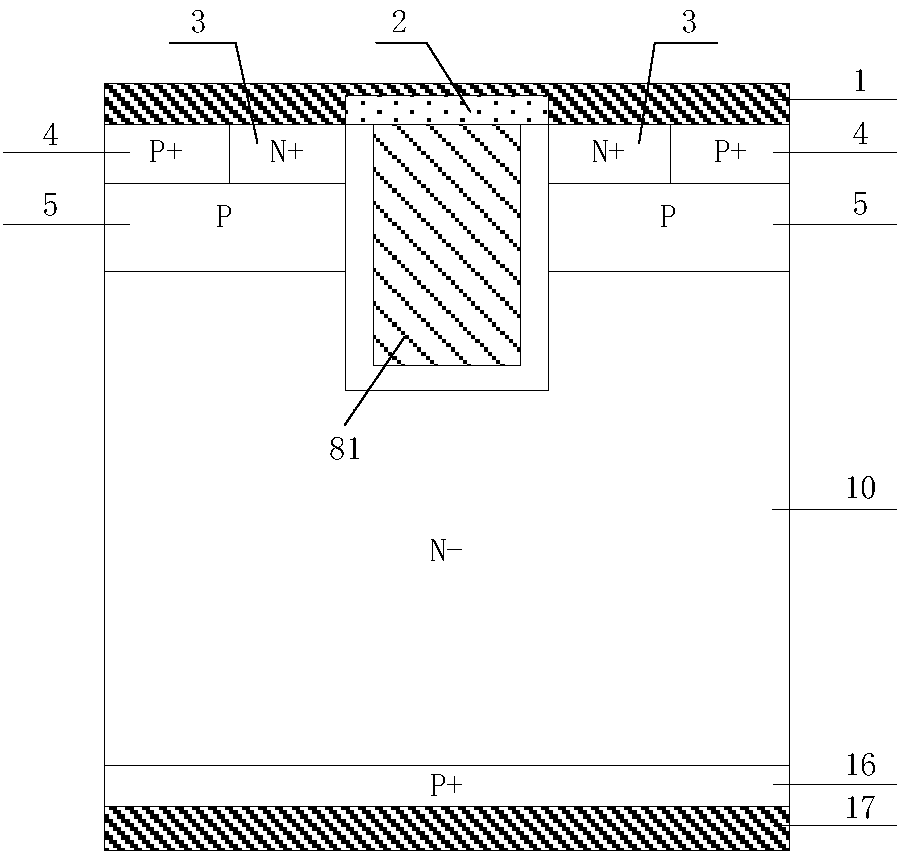

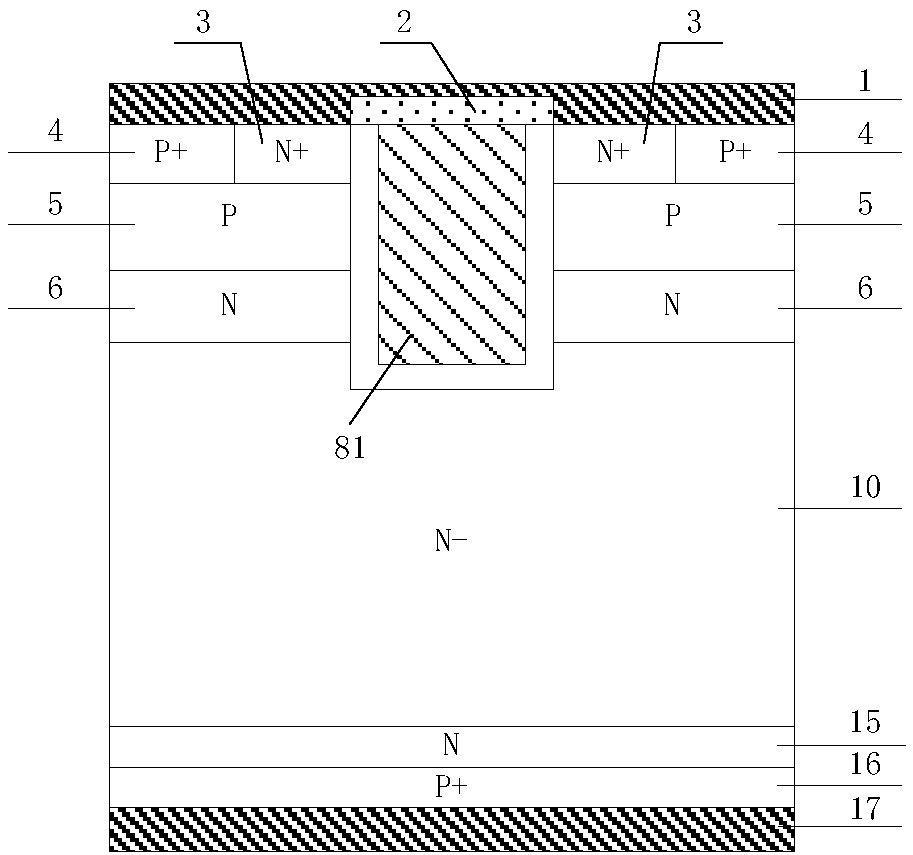

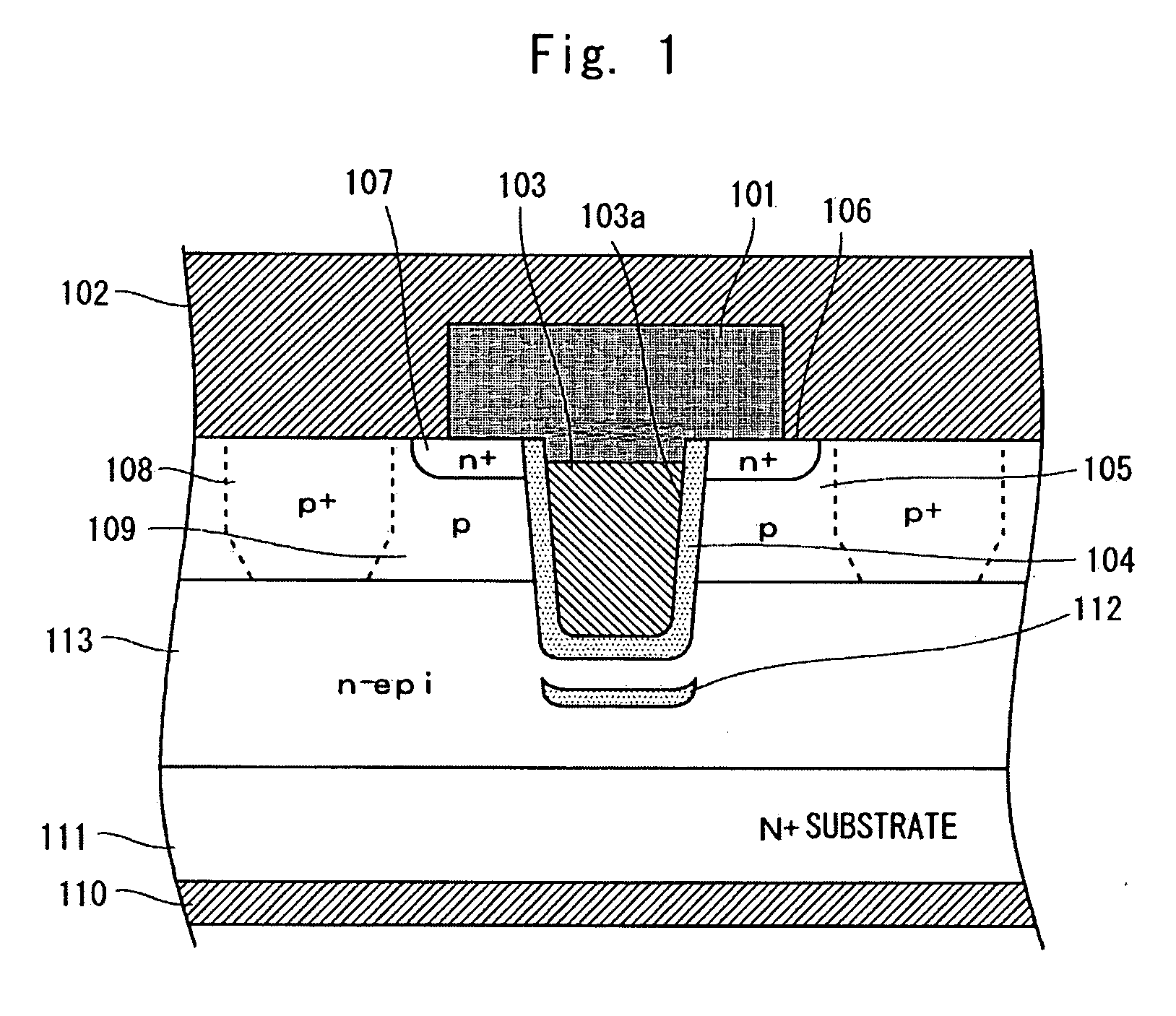

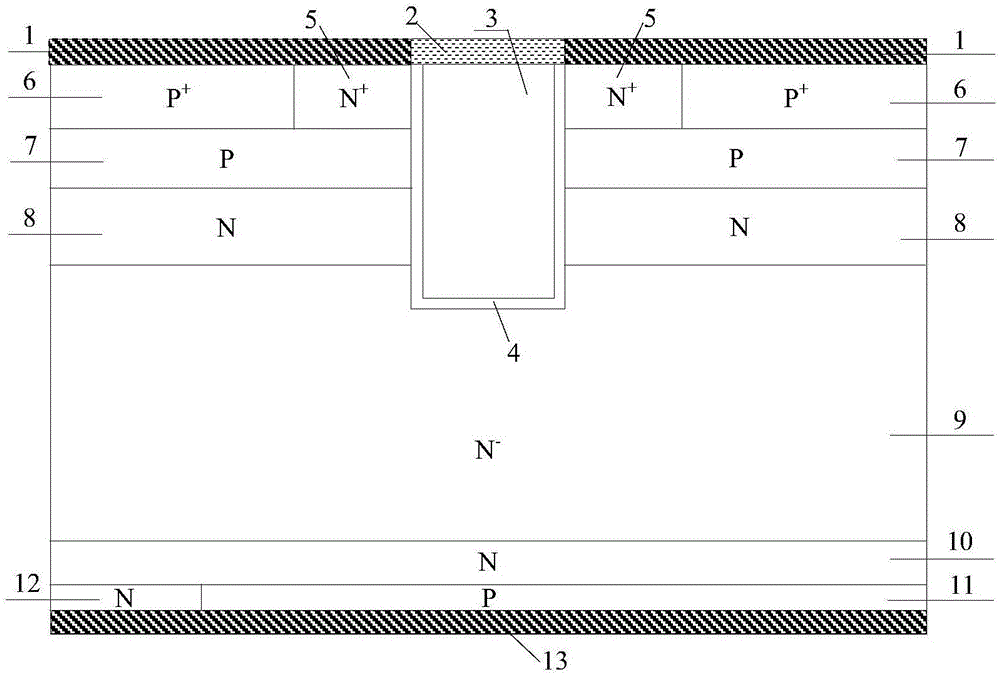

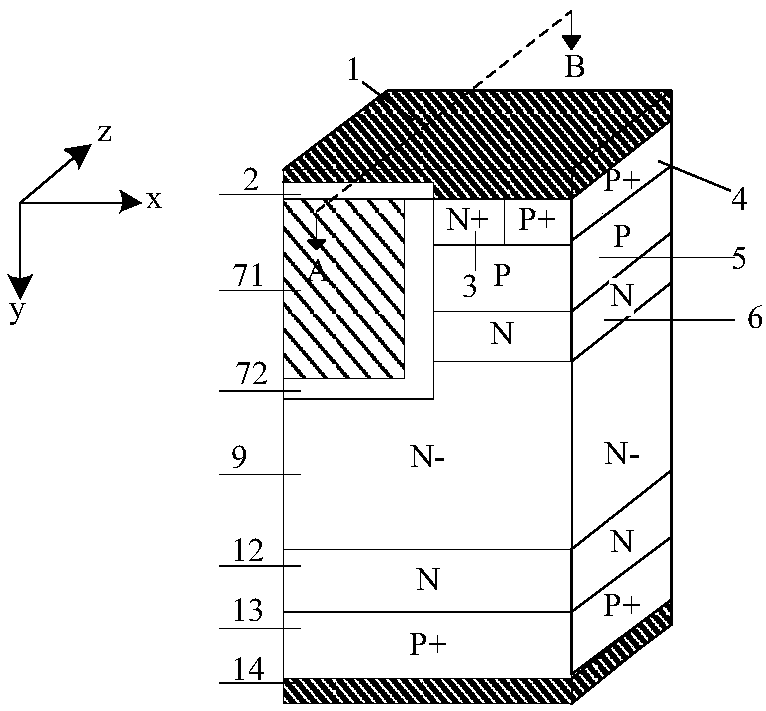

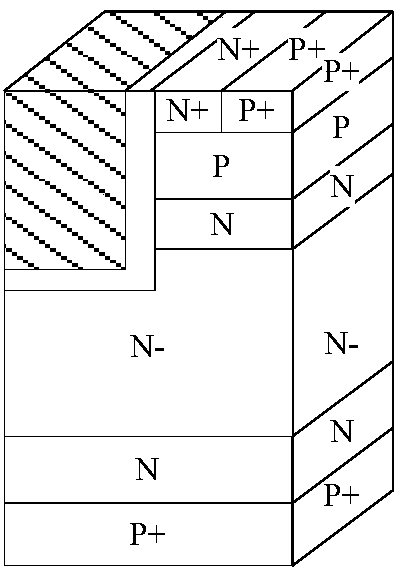

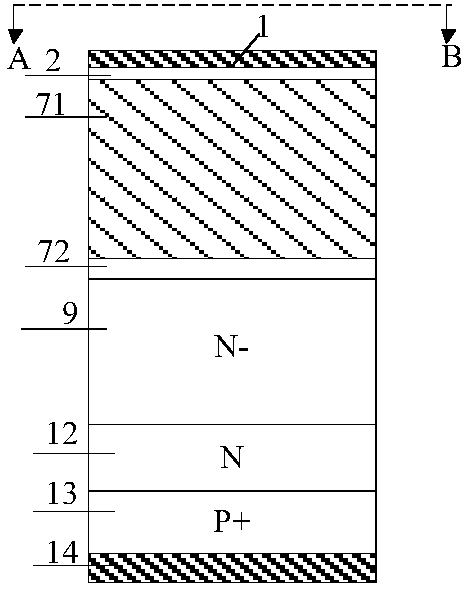

Reverse blocking type IGBT and manufacturing method therefor

ActiveCN107799587AImprove reverse breakdown voltageGood positive characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower semiconductor device

The invention discloses a reverse blocking type IGBT and a manufacturing method therefor, and belongs to the technical field of a power semiconductor device. By introducing a floating P type body region on one side of a trench gate and introducing a trench collector structure in a collector region and a field stop layer, the positive breakdown voltage of a device is improved without influencing the threshold voltage and switch-on of an IGBT device; the gate-collector capacitance is lowered, and adverse influence caused by a Miller effect can be relieved; the overall gate capacitance is lowered, the switching speed of the device is improved, the switching loss of the device is lowered, and the compromising relation between forward switch-on voltage drop and switch-off loss of the conventional CSTBT device is improved; the problems of current, voltage oscillation and EMI in the device starting dynamic process can be avoided, and device reliability is improved; the current carrier enhancement effect at the emitter end of the device is improved, the current carrier concentration distribution in a drift region can be improved, and compromising between forward switch-on voltage drop andswitch-off loss can be further improved; and the reverse breakdown voltage of the device is improved, and high forward characteristic of the device is ensured while excellent reverse blocking performance is obtained.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

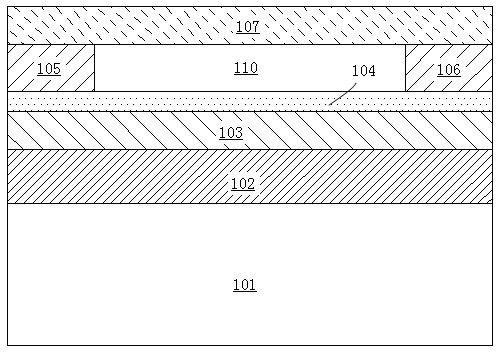

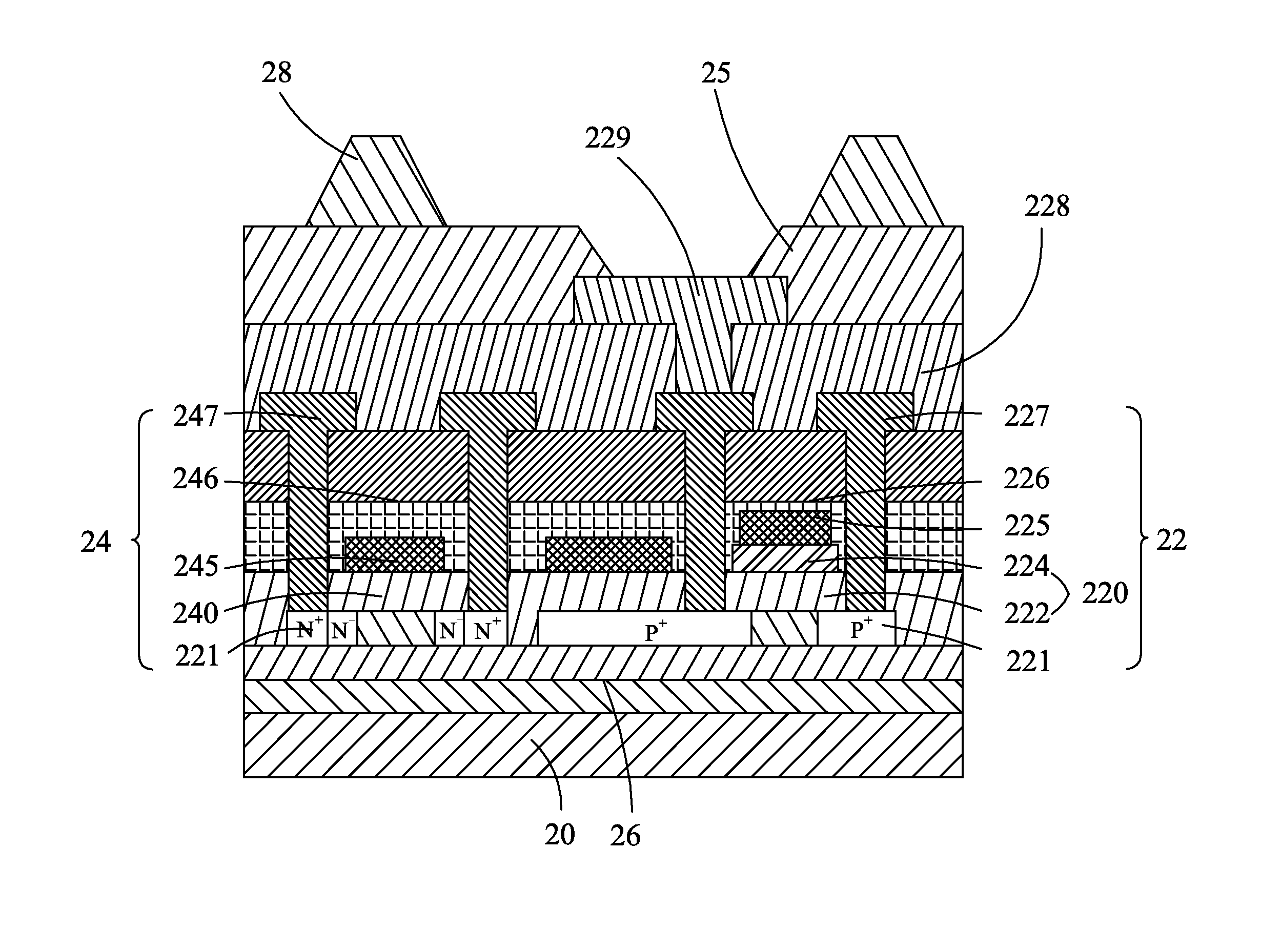

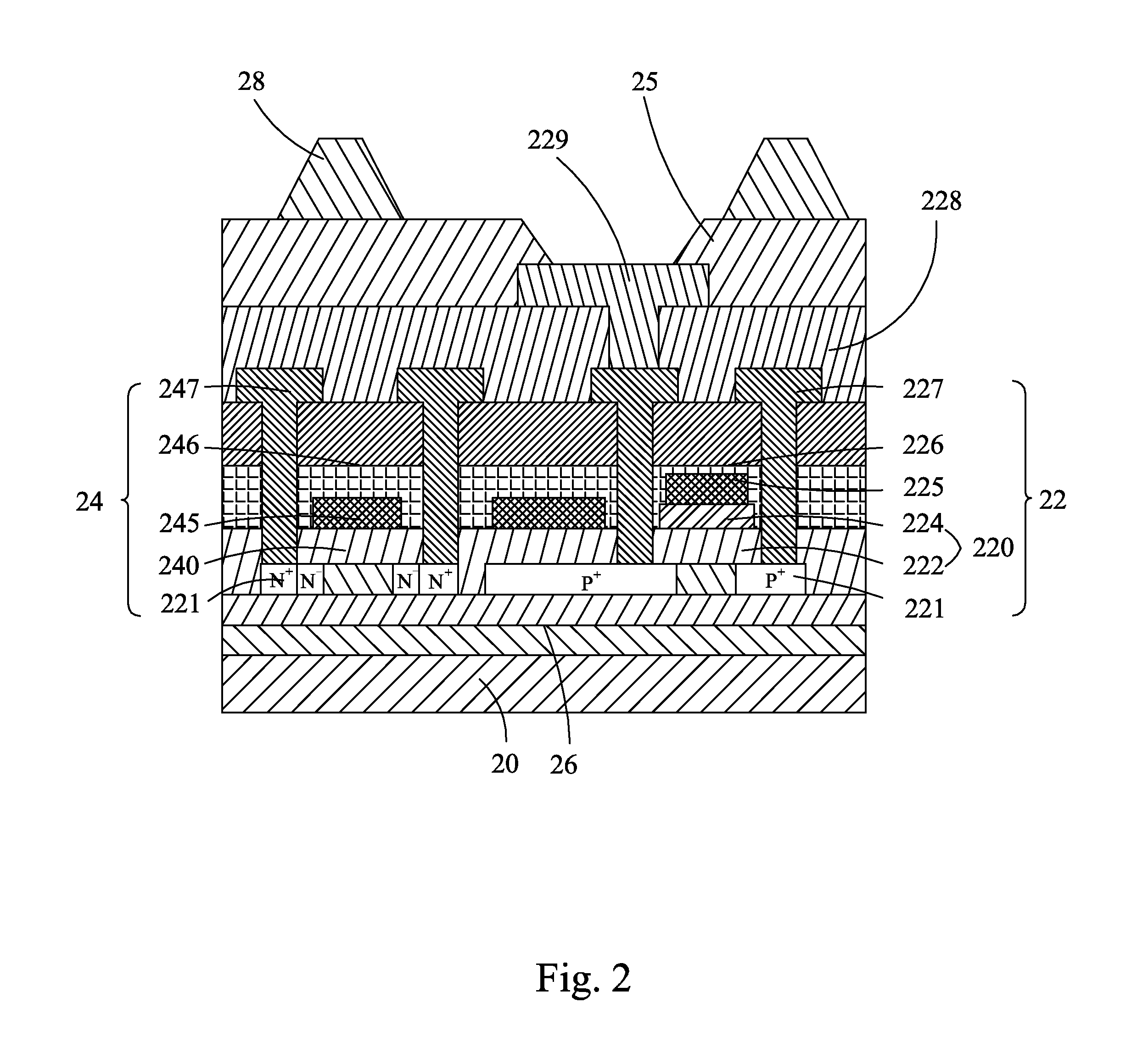

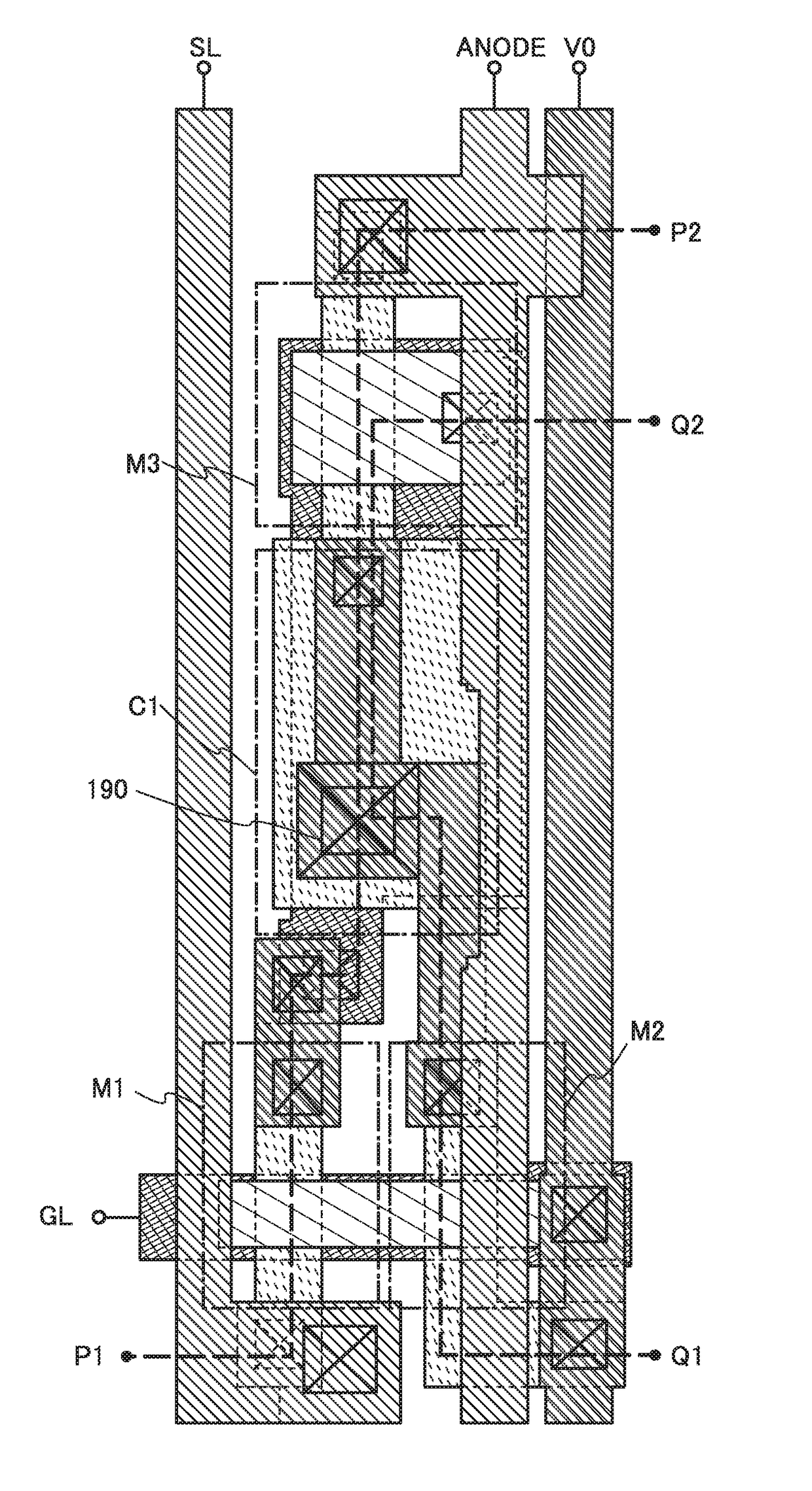

Active organic electroluminescence device back panel and manufacturing method thereof

ActiveUS20150069335A1Simple structureSimple definitionSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceInsulation layer

The present invention provides an active organic electroluminescence device back panel and a manufacturing method thereof. The device back panel includes: a substrate (20), a plurality of active TFT pixel arrays formed on the substrate (20), and organic planarization layers (228), organic electroluminescence electrodes (229), pixel definition layers (25), and support bodies (28) formed on the active TFT pixel arrays. Each of the active TFT pixel arrays includes a driving TFT (22) and a switch TFT (24). The driving TFT (22) has a gate insulation layer (220) that has a thickness greater than a thickness of a gate insulation layer (240) of the switch TFT (24). Through thickening the gate insulation layer of the driving TFT, the gate capacitance of the driving TFT can be reduced and the sub-threshold swing of the driving TFT is increased to realize well definition of grey levels. Further, the thickness of the gate insulation layer of the switch TFT can be kept unchanged so that the sub-threshold swing of the switch TFT maintains relatively small so as to lower down the operating voltage and increase the circuit operation speed to thereby effectively improve the quality of the organic electroluminescence device.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

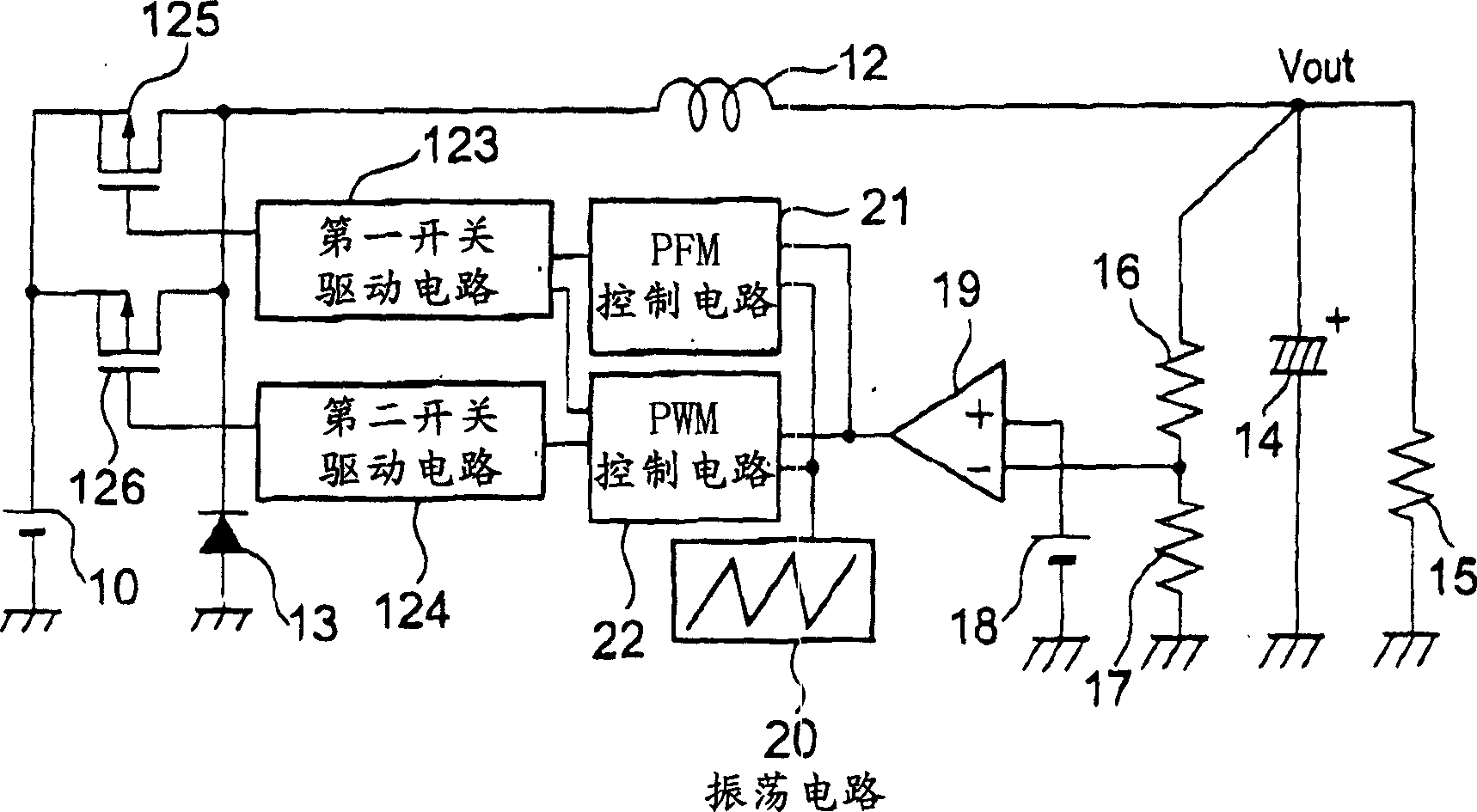

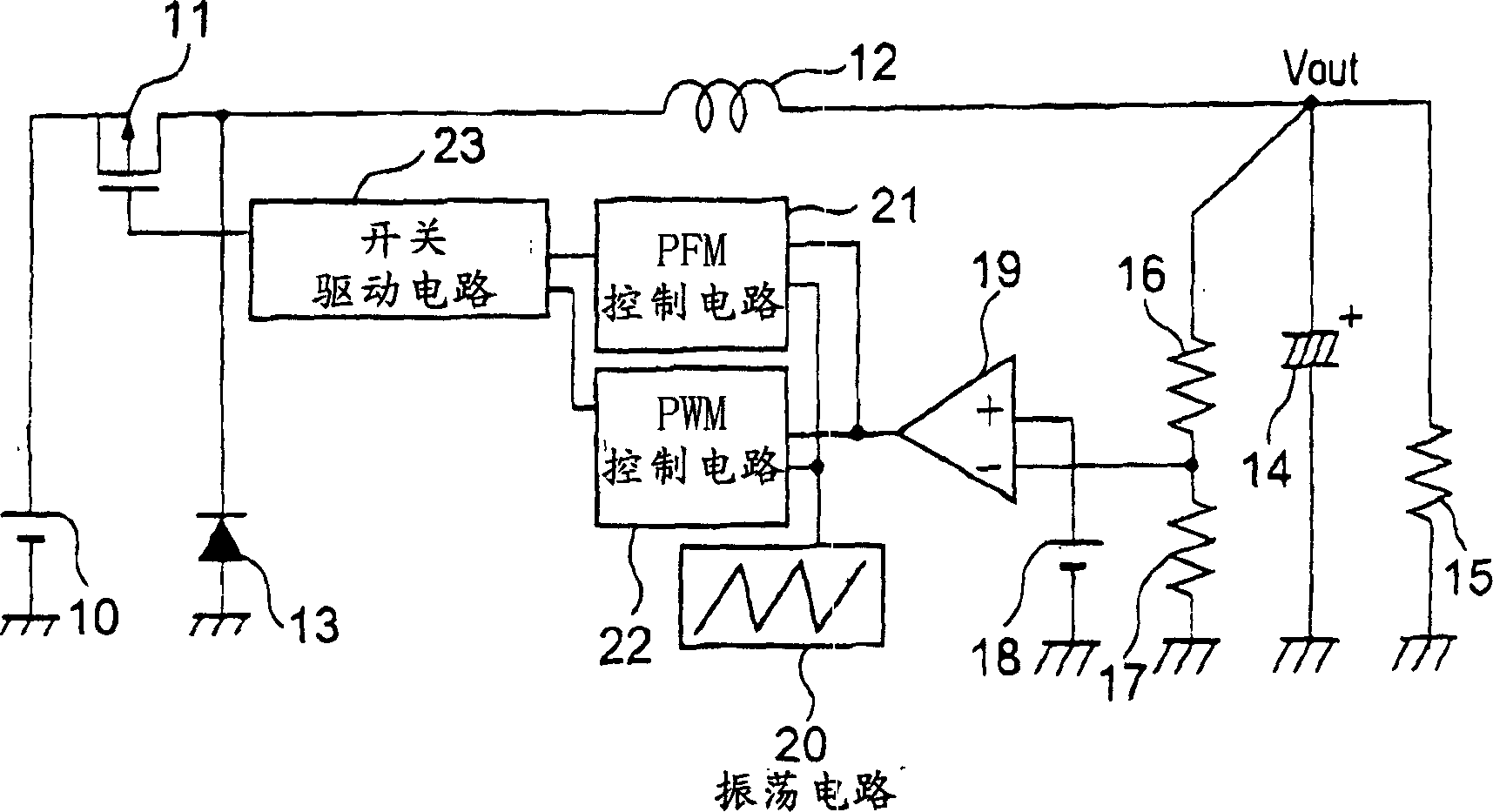

Switching regulator control circuit

InactiveCN1578086AIncrease the on-resistanceReduce gate capacitanceEfficient power electronics conversionDc-dc conversionCapacitanceControl theory

The present invention provides an SW regulator control circuit that is efficient in both of the cases where the load is heavy and where the load is light. Two switch MOS transistors are disposed as switching elements of the SW regulator in parallel which are large in an on-resistance and small in a gate capacity, and in the case where a load of the SW regulator is heavy, the two switch MOS transistors are driven in parallel to lessen the on-resistance whereas in the case where the load is light, one of the two switch MOS transistors is driven to lessen the gate capacity.

Owner:SEIKO INSTR INC

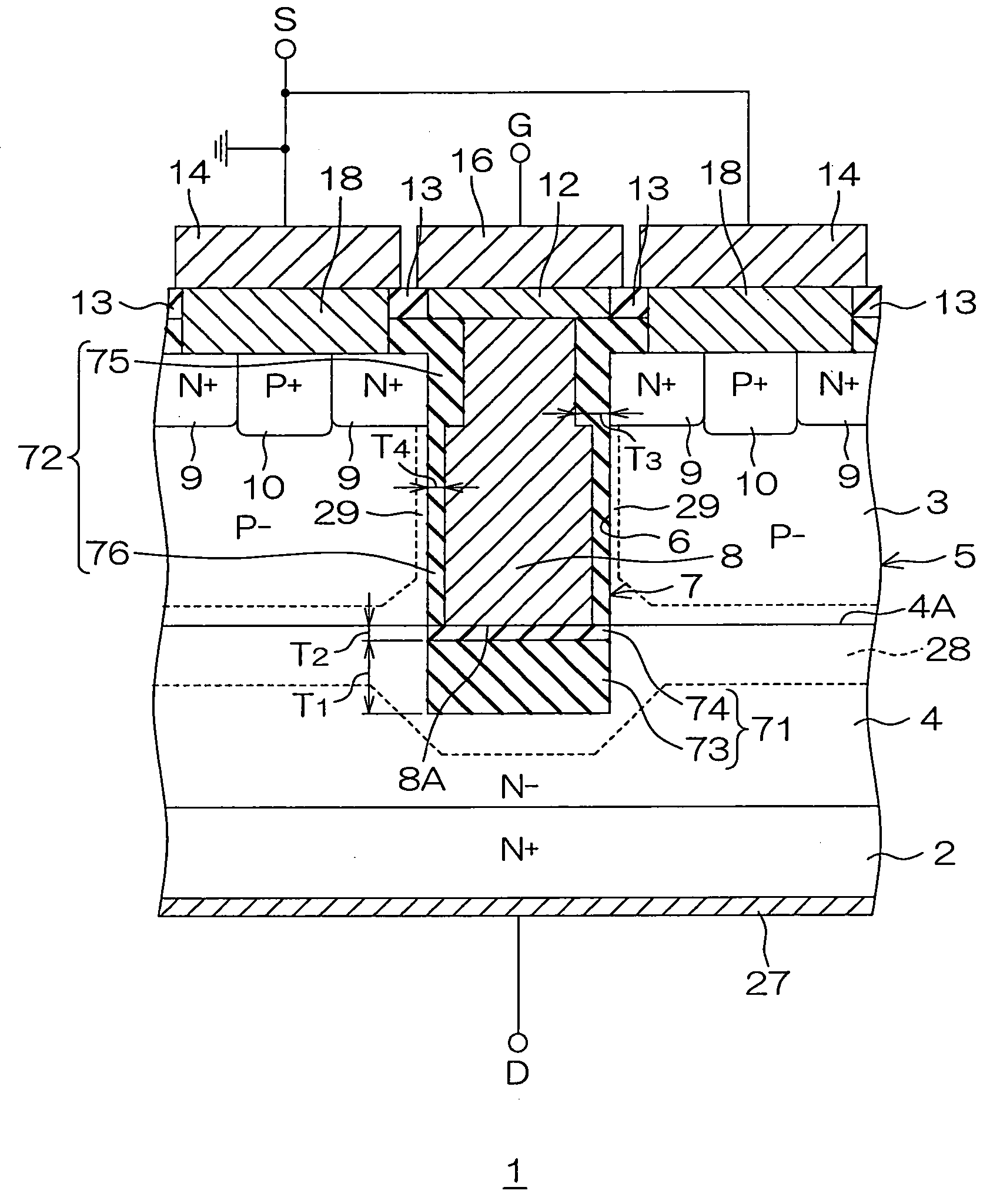

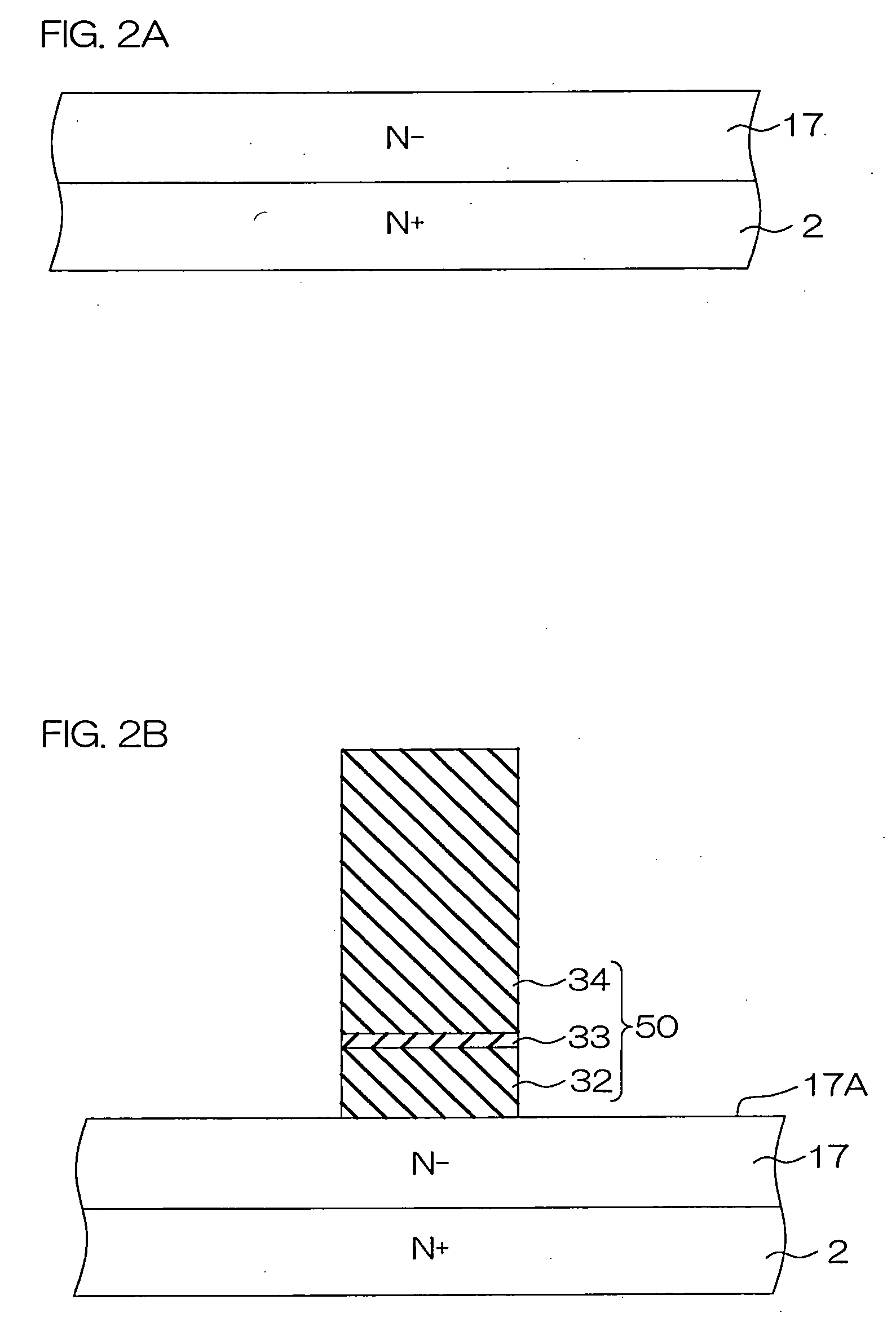

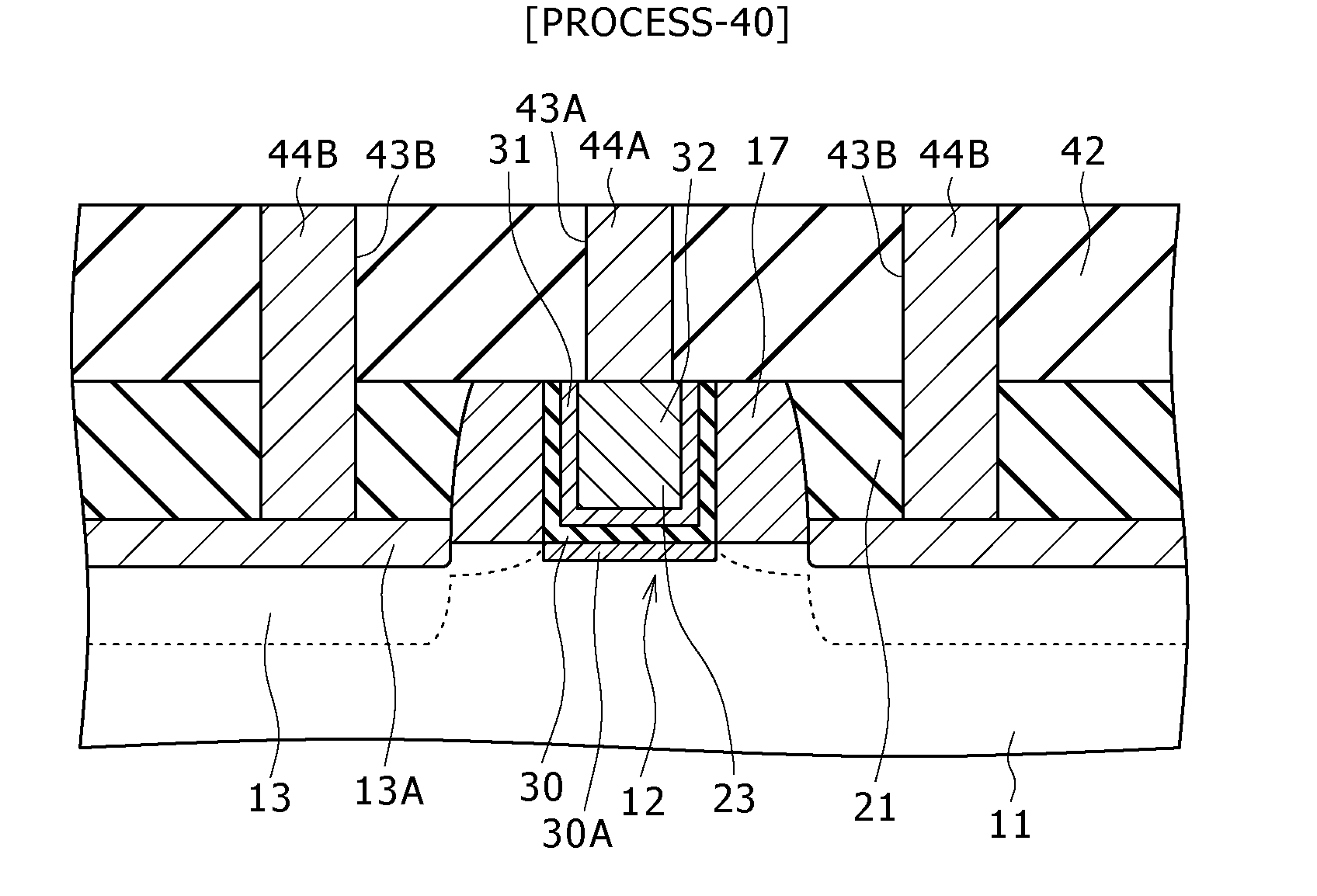

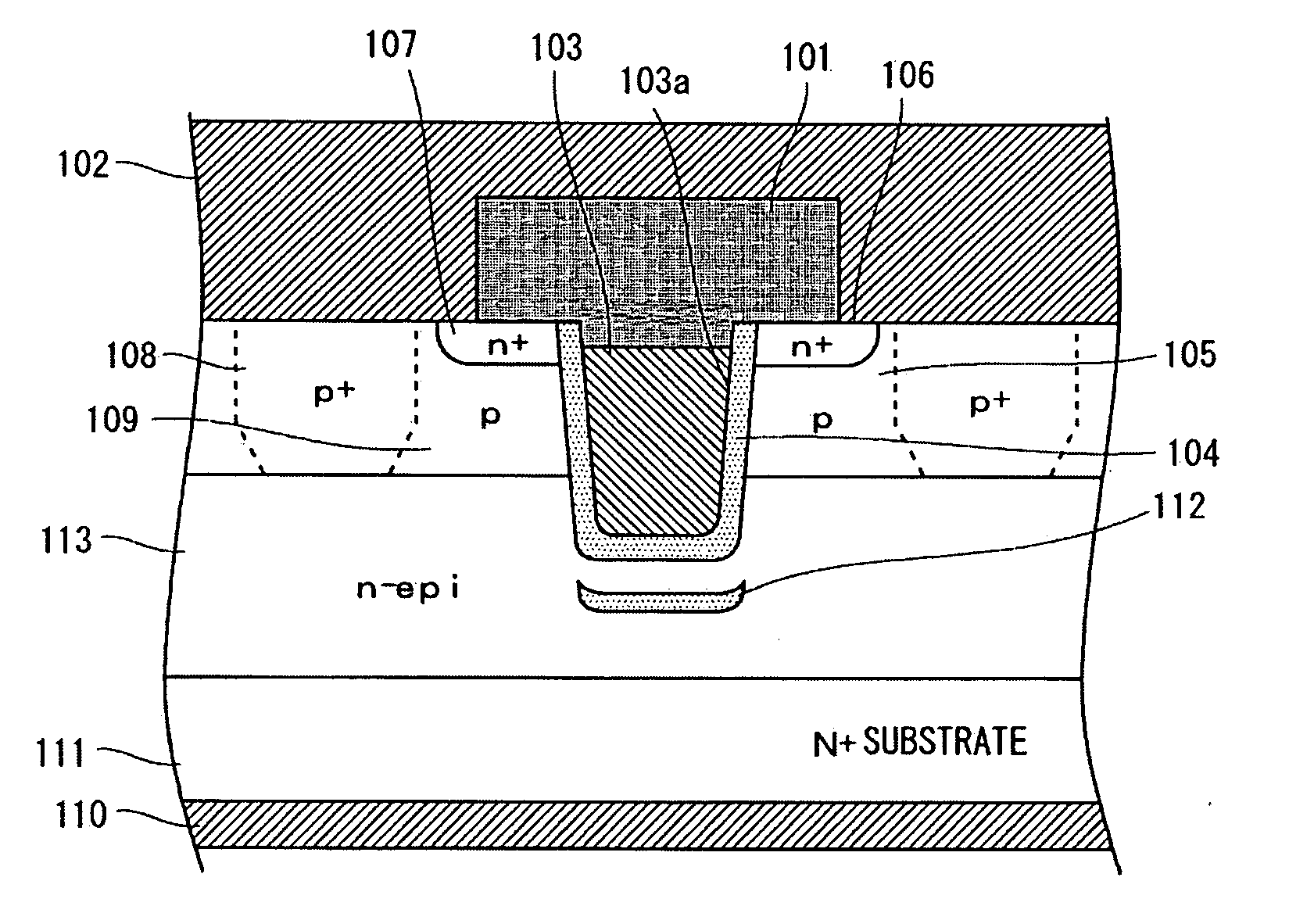

Trench gate type transistor and method of manufacturing the same

ActiveUS20100059816A1Reduce gate capacitanceImprove gate breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGate capacitanceElectric field

The invention provides a trench gate type transistor in which the gate capacitance is reduced, the crystal defect is prevented and the gate breakdown voltage is enhanced. Trenches are formed in an N− type semiconductor layer. A uniformly thick silicon oxide film is formed on the bottom of each of the trenches and near the bottom, being round at corner portions. A silicon oxide film is formed on the upper portion of the sidewall of each of the trenches, which is thinner than the silicon oxide film and round at corner portions. Gate electrodes are formed from inside the trenches onto the outside thereof. The thick silicon oxide film reduces the gate capacitance, and the thin silicon oxide film on the upper portion provides good transistor characteristics. Furthermore, with the round corner portions, the crystal defect does not easily occur, and the gate electric field is dispersed to enhance the gate breakdown voltage.

Owner:SEMICON COMPONENTS IND LLC

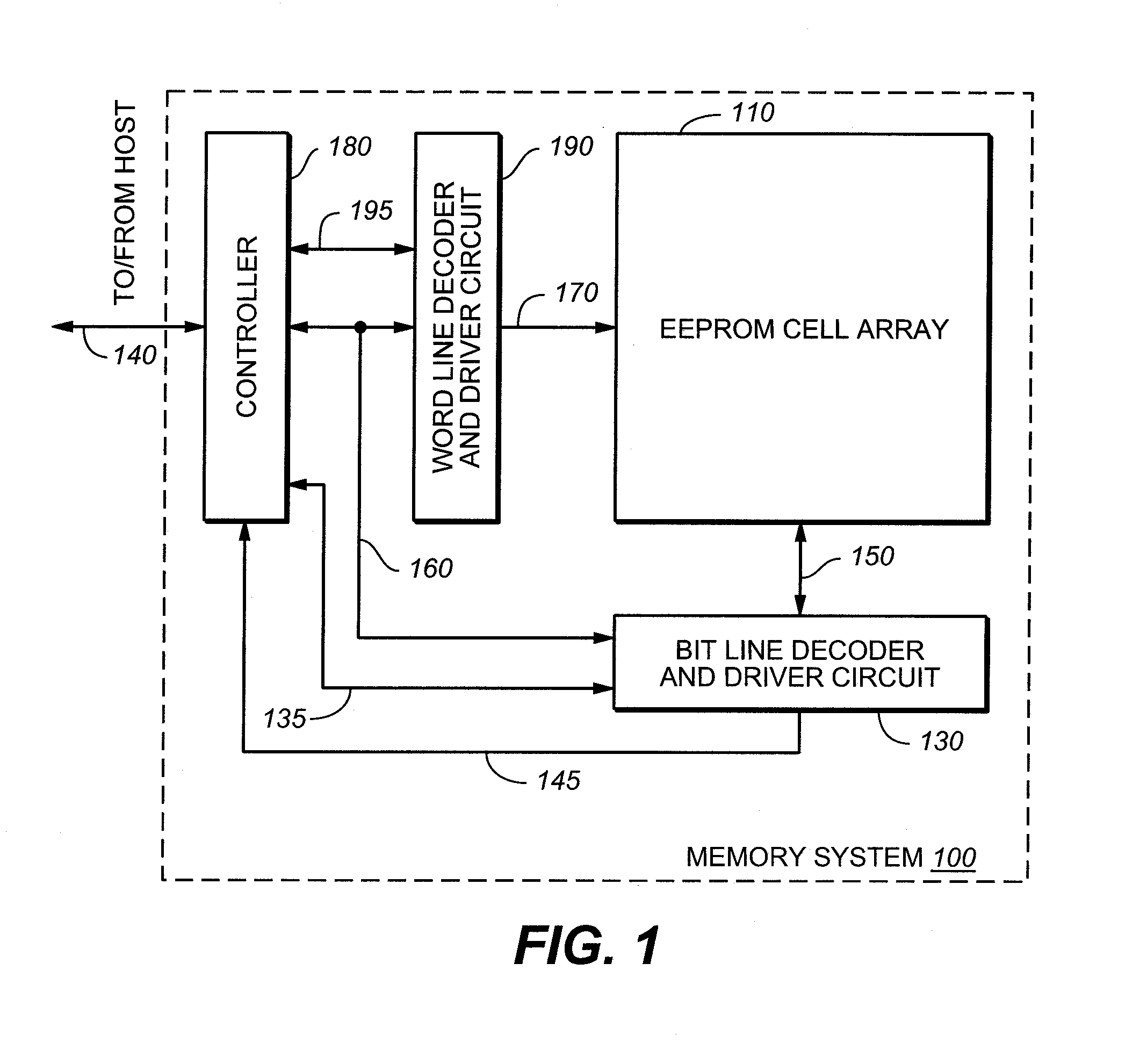

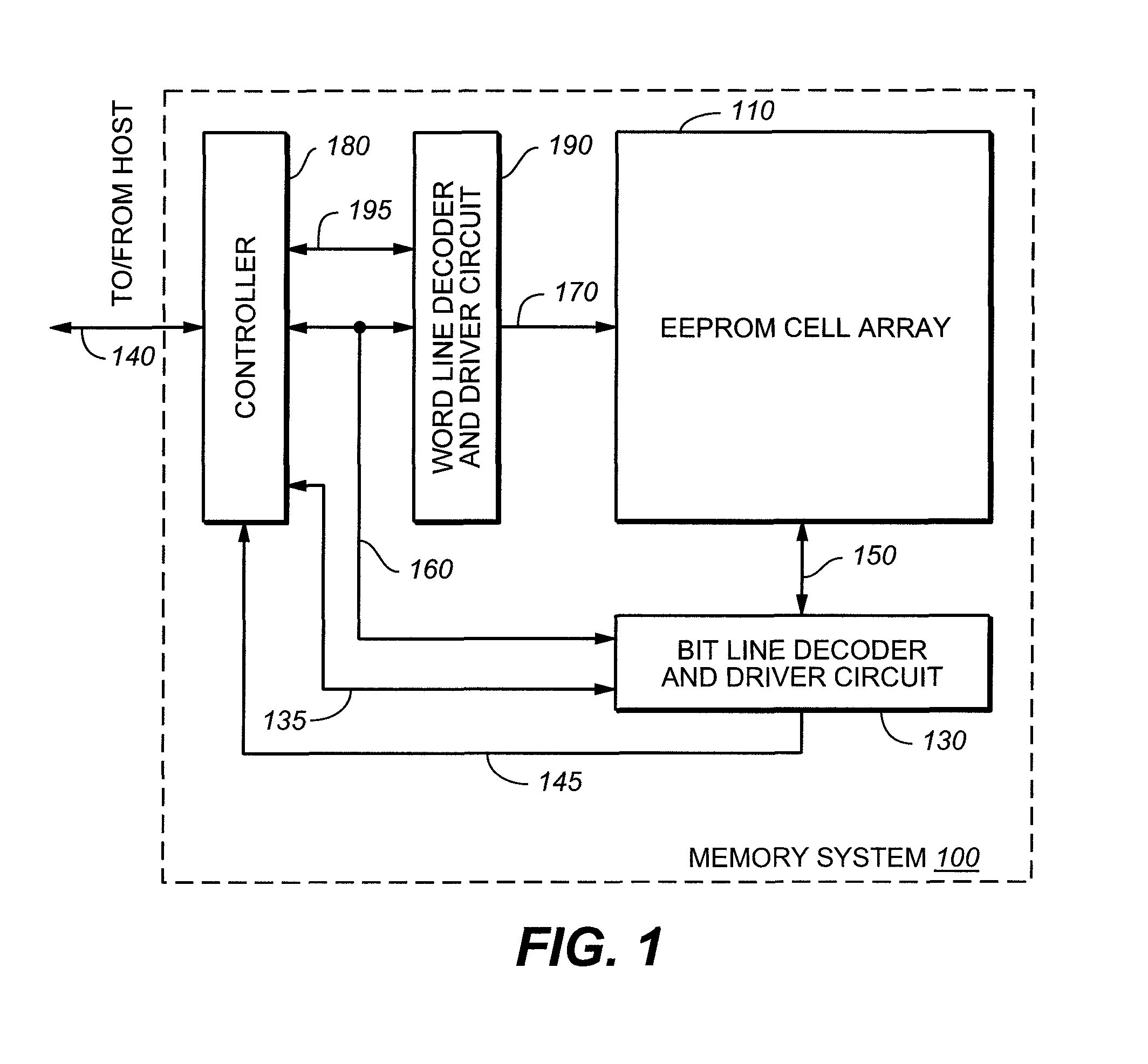

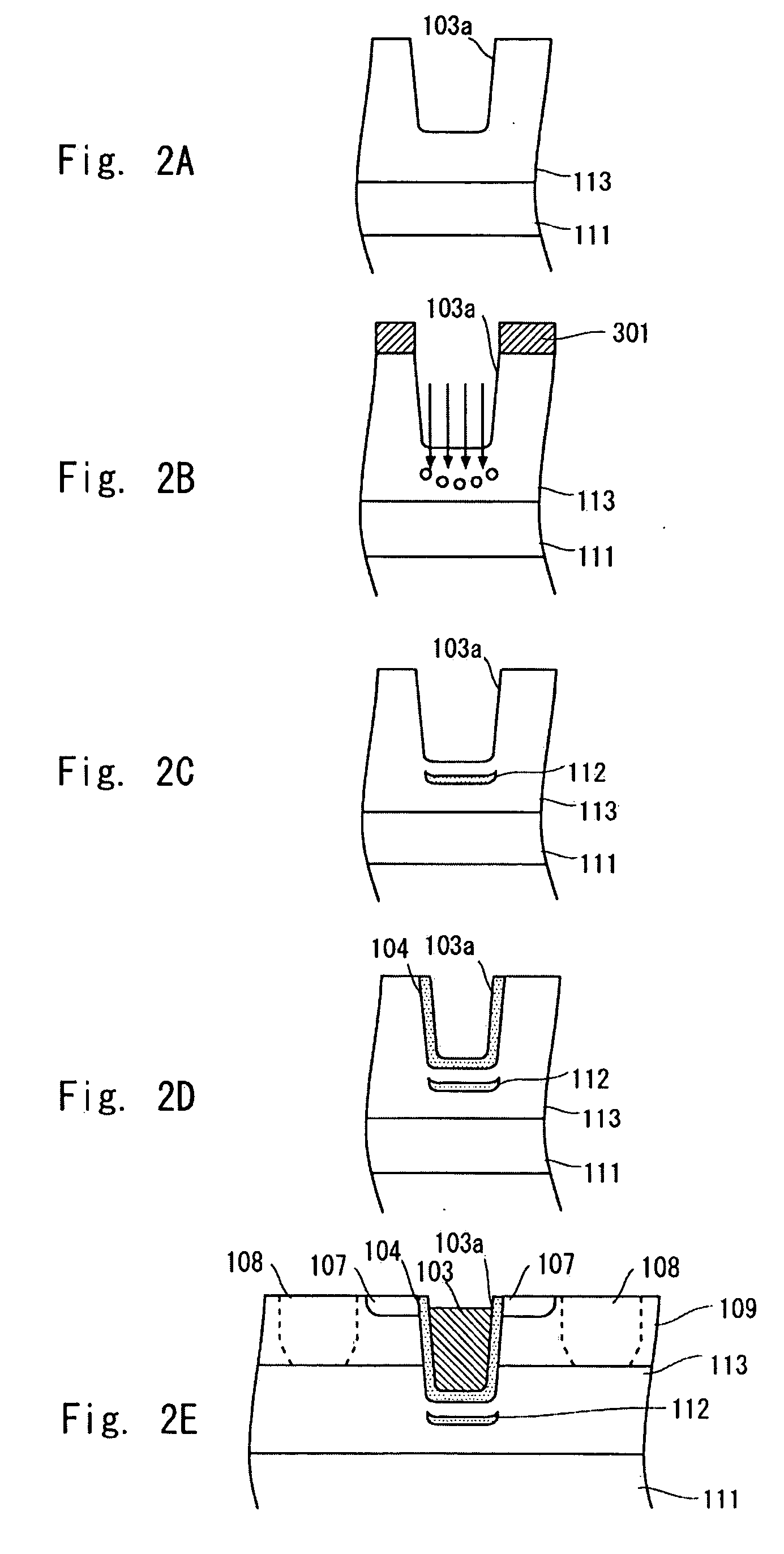

Semiconductor memory and method for manufacturing a semiconductor memory

InactiveUS20070198766A1Efficient driveReduce gate capacitanceSolid-state devicesRead-only memoriesEngineeringSemiconductor

A semiconductor memory includes: a first memory cell transistor including: a first floating gate electrode provided on and insulated from the substrate; and a first control gate electrode provided on and insulated from the first floating gate electrode; and a second memory cell transistor including: a second floating gate electrode provided on and insulated from the substrate, an upper surface being larger than a lower surface, and the upper surface being lower than an upper surface of the first floating gate electrode; and a second control gate electrode provided on and insulated from the second floating gate electrode.

Owner:KK TOSHIBA

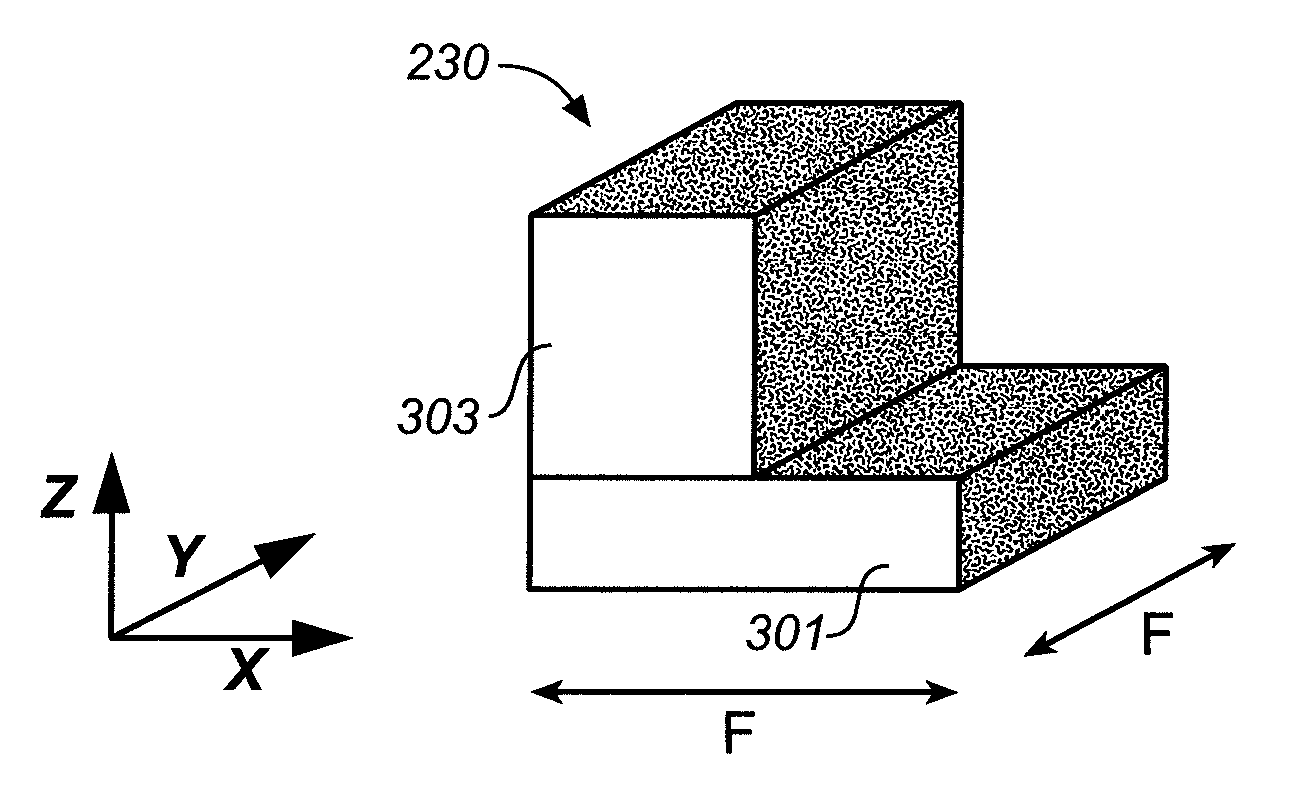

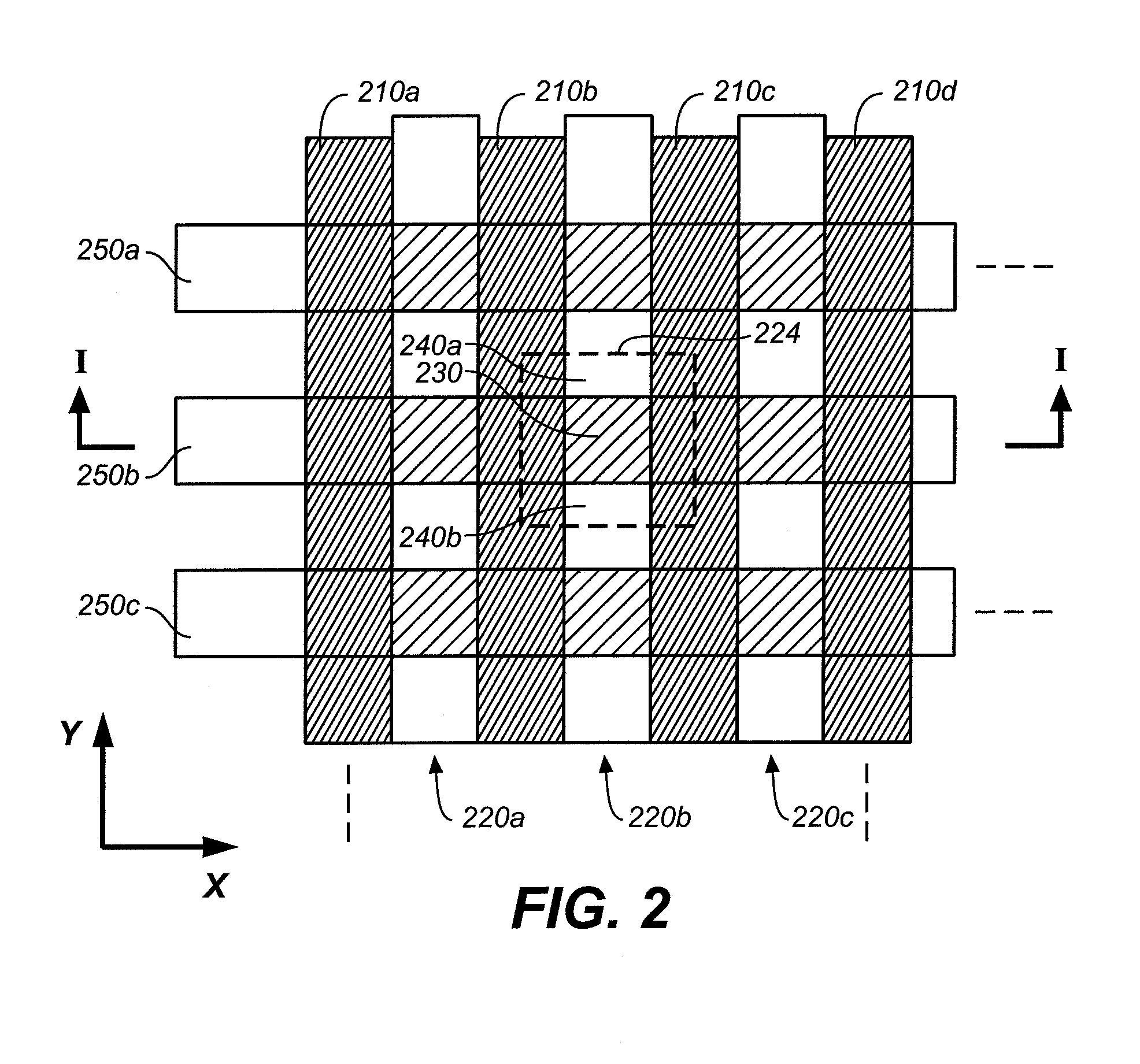

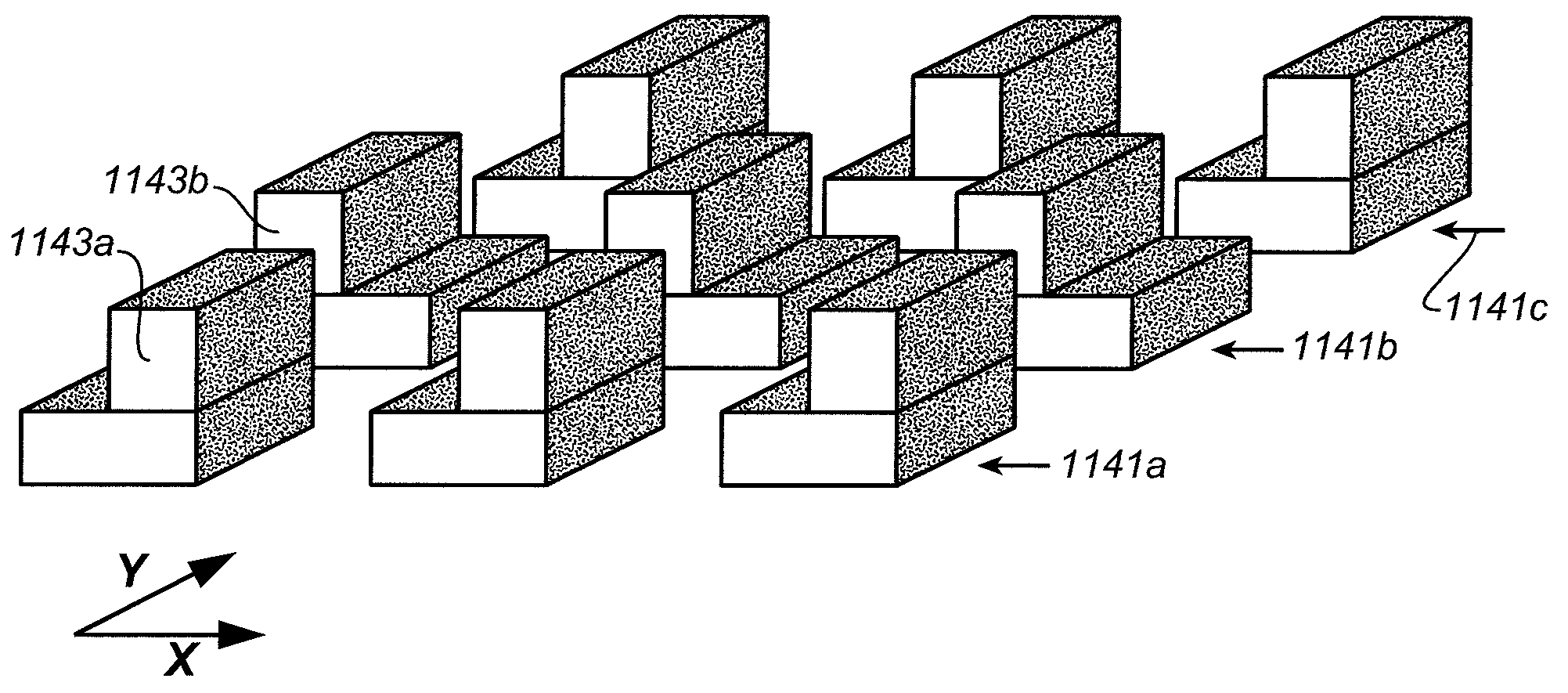

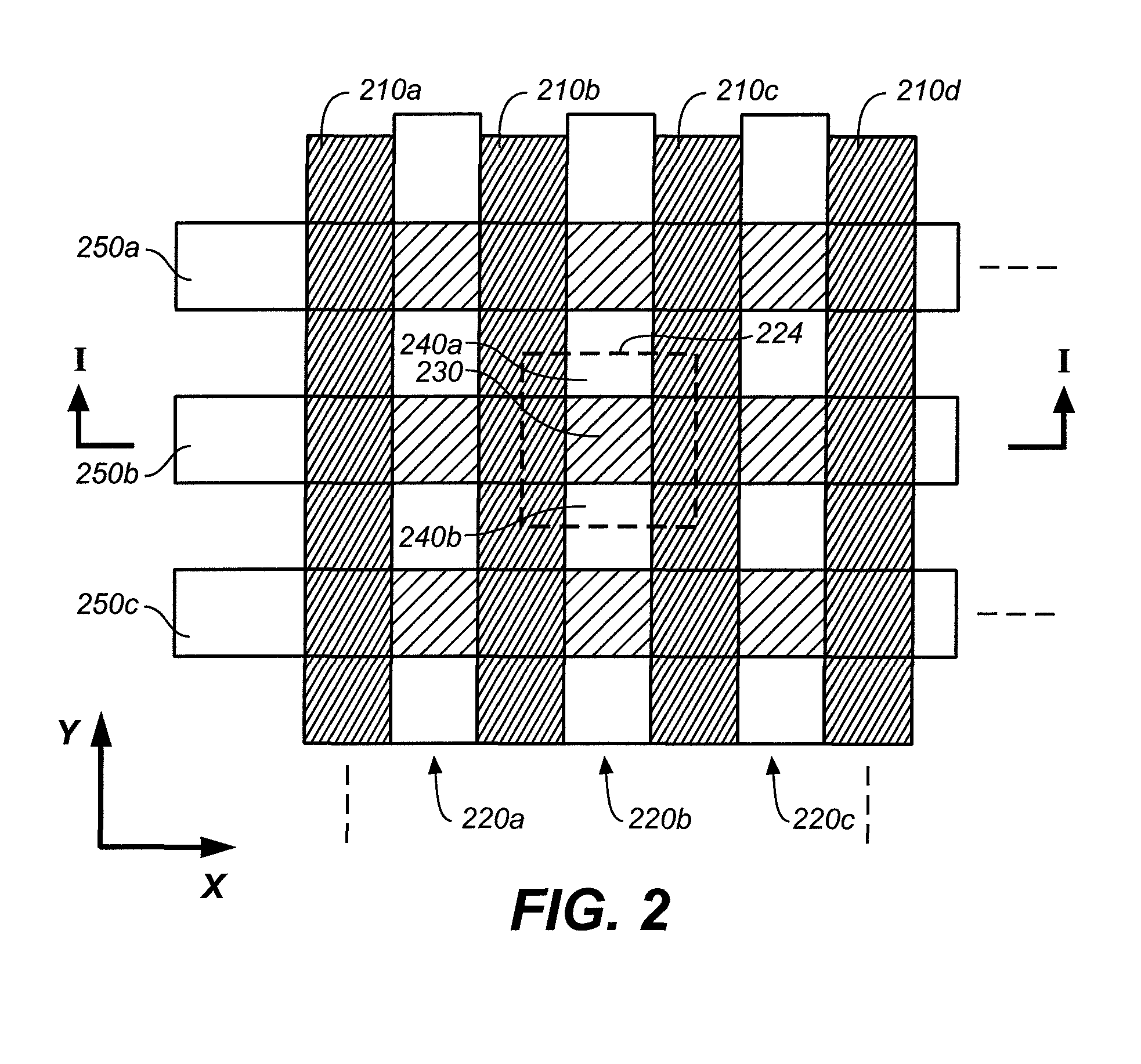

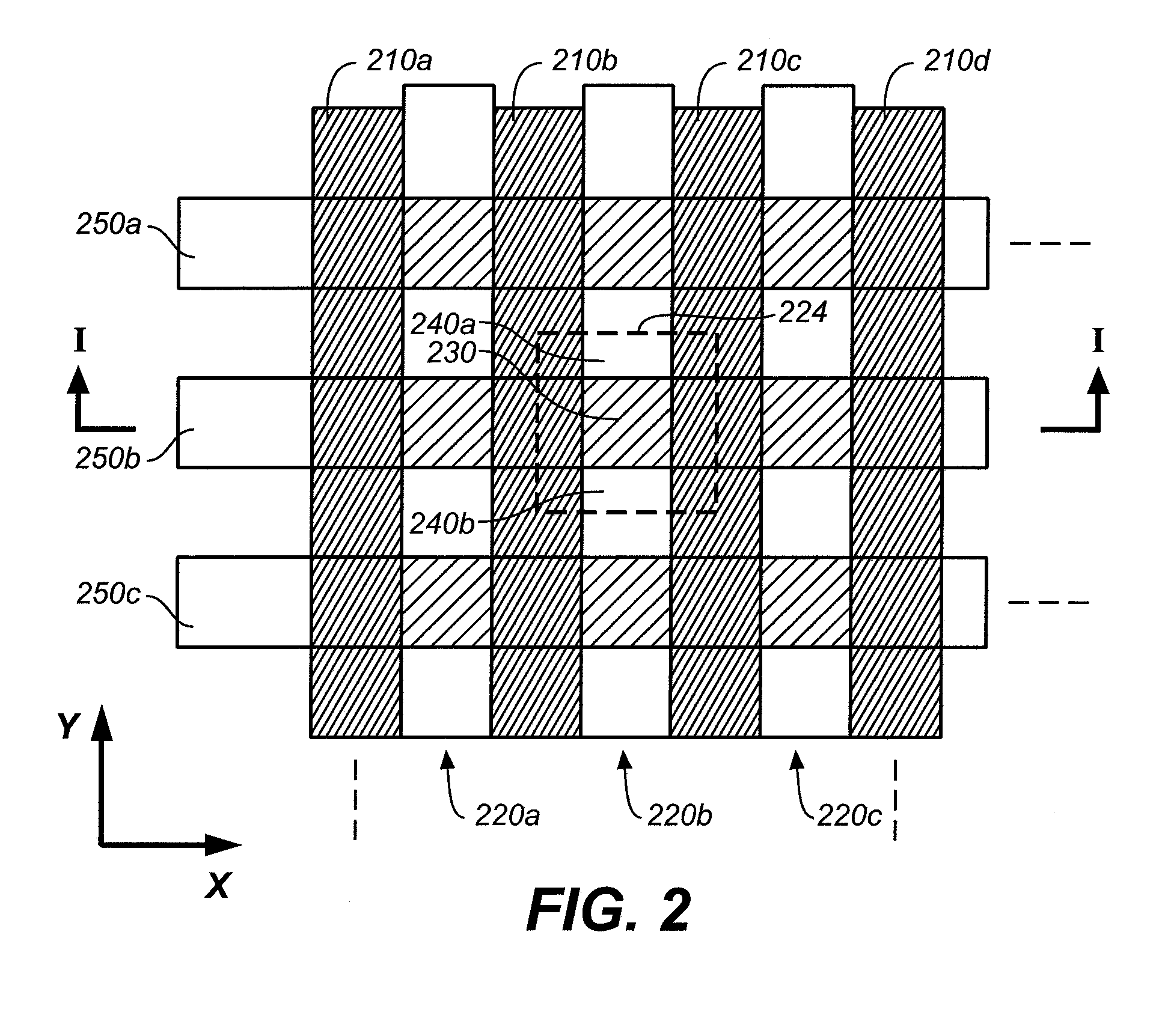

Nonvolatile Memories with Shaped Floating Gates

InactiveUS20080042183A1Reduce areaReduce gate capacitanceTransistorSolid-state devicesBit lineNon-volatile memory

In a nonvolatile memory using floating gates to store charge, individual floating gates are L-shaped. Orientations of L-shaped floating gates may alternate in the bit line direction and may also alternate in the word line direction. L-shaped floating gates are formed by etching conductive portions using etch masks of different patterns to obtain floating gates of different orientations.

Owner:WODEN TECH INC

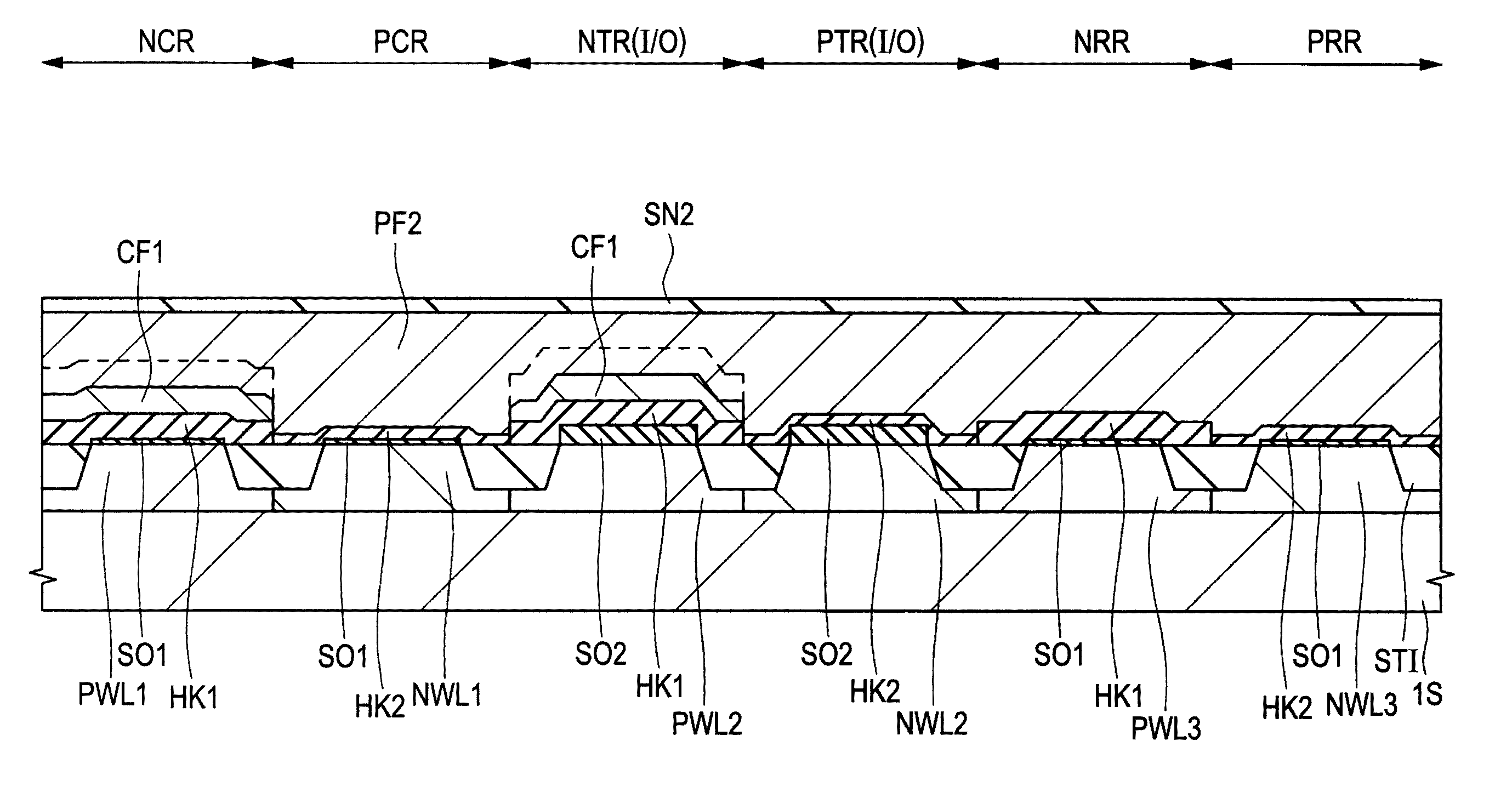

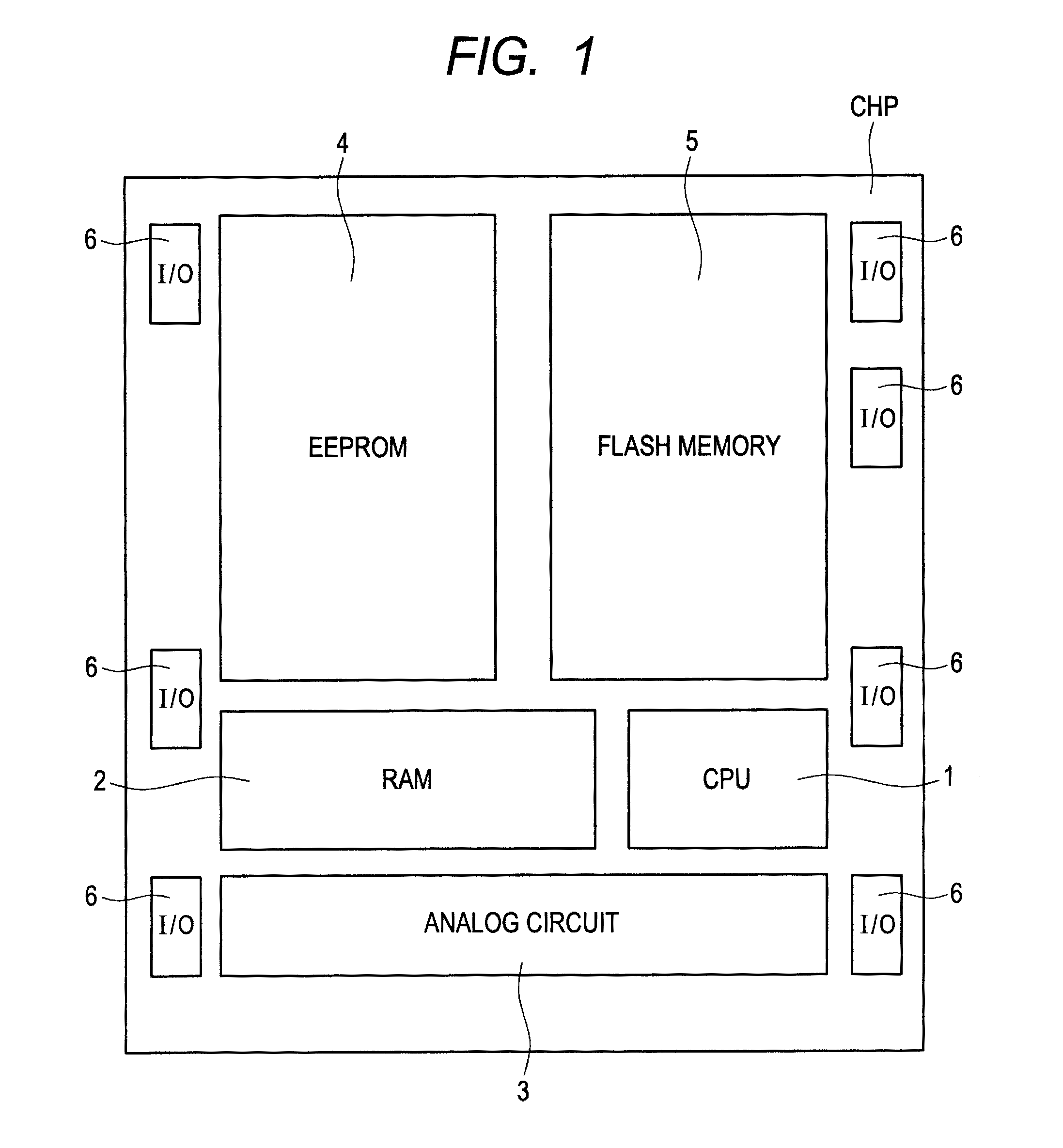

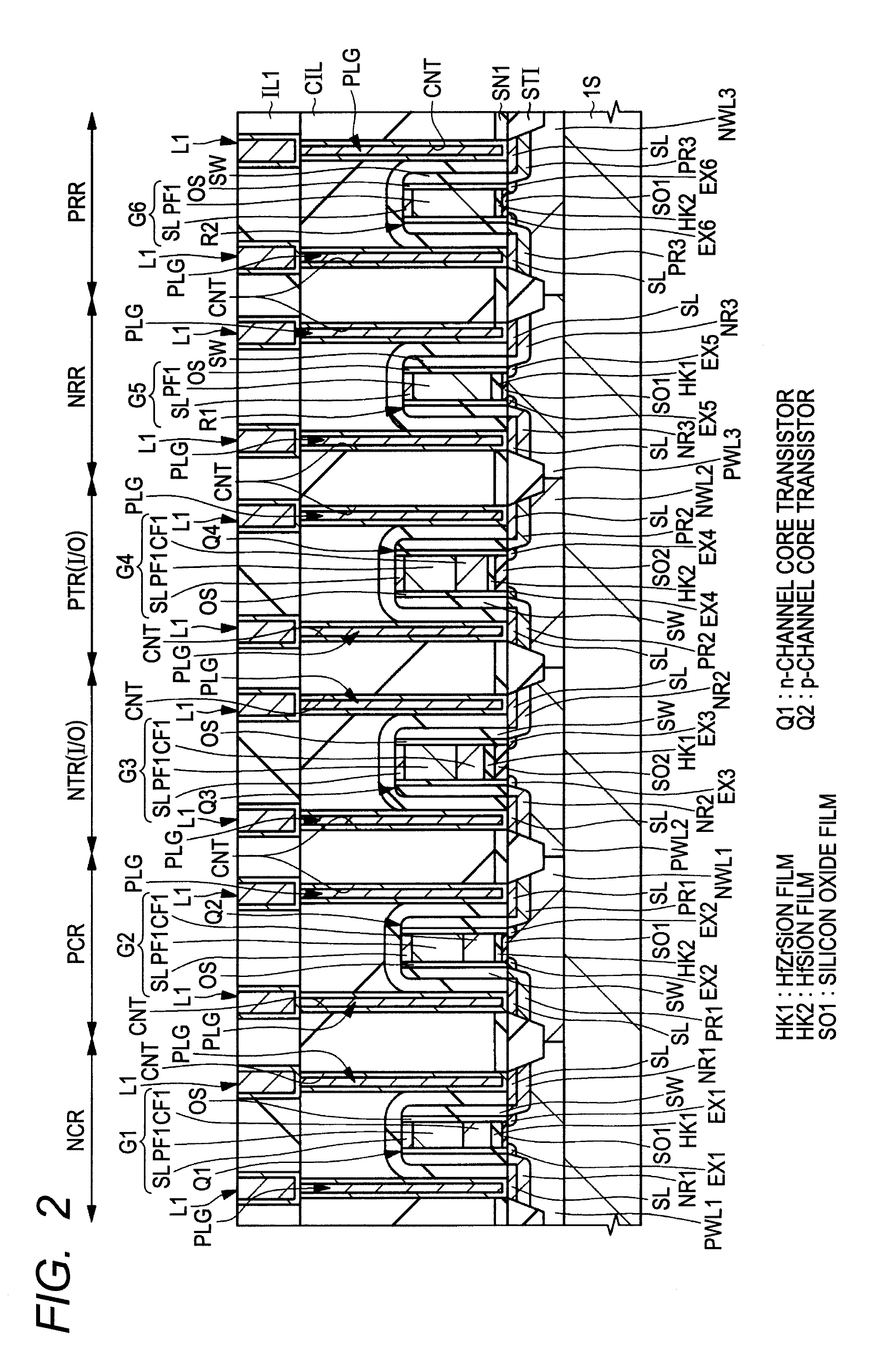

Semiconductor device and manufacturing method thereof

InactiveUS20120056268A1Improve reliabilityReduce thicknessTransistorSolid-state devicesPower semiconductor deviceHafnium

There is provided a technology capable of achieving, in a semiconductor device having a MISFET using an insulating film containing hafnium as a gate insulating film, an improvement in the reliability of a MISFET. In the present invention, the gate insulating film of an n-channel core transistor is provided with a structure different from that of the gate insulating film of a p-channel core transistor. Specifically, in the n-channel core transistor, as the gate insulating film thereof, a laminate film of a silicon oxide film and a HfZrSiON film is used. On the other hand, in the p-channel core transistor, as the gate insulating film thereof, a laminate film of a silicon oxide film and a HfSiON film is used.

Owner:RENESAS ELECTRONICS CORP

Nonvolatile memories with shaped floating gates

InactiveUS7755132B2Reduce areaReduce gate capacitanceTransistorSolid-state devicesBit lineEngineering

In a nonvolatile memory using floating gates to store charge, individual floating gates are L-shaped. Orientations of L-shaped floating gates may alternate in the bit line direction and may also alternate in the word line direction. L-shaped floating gates are formed by etching conductive portions using etch masks of different patterns to obtain floating gates of different orientations.

Owner:WODEN TECH INC

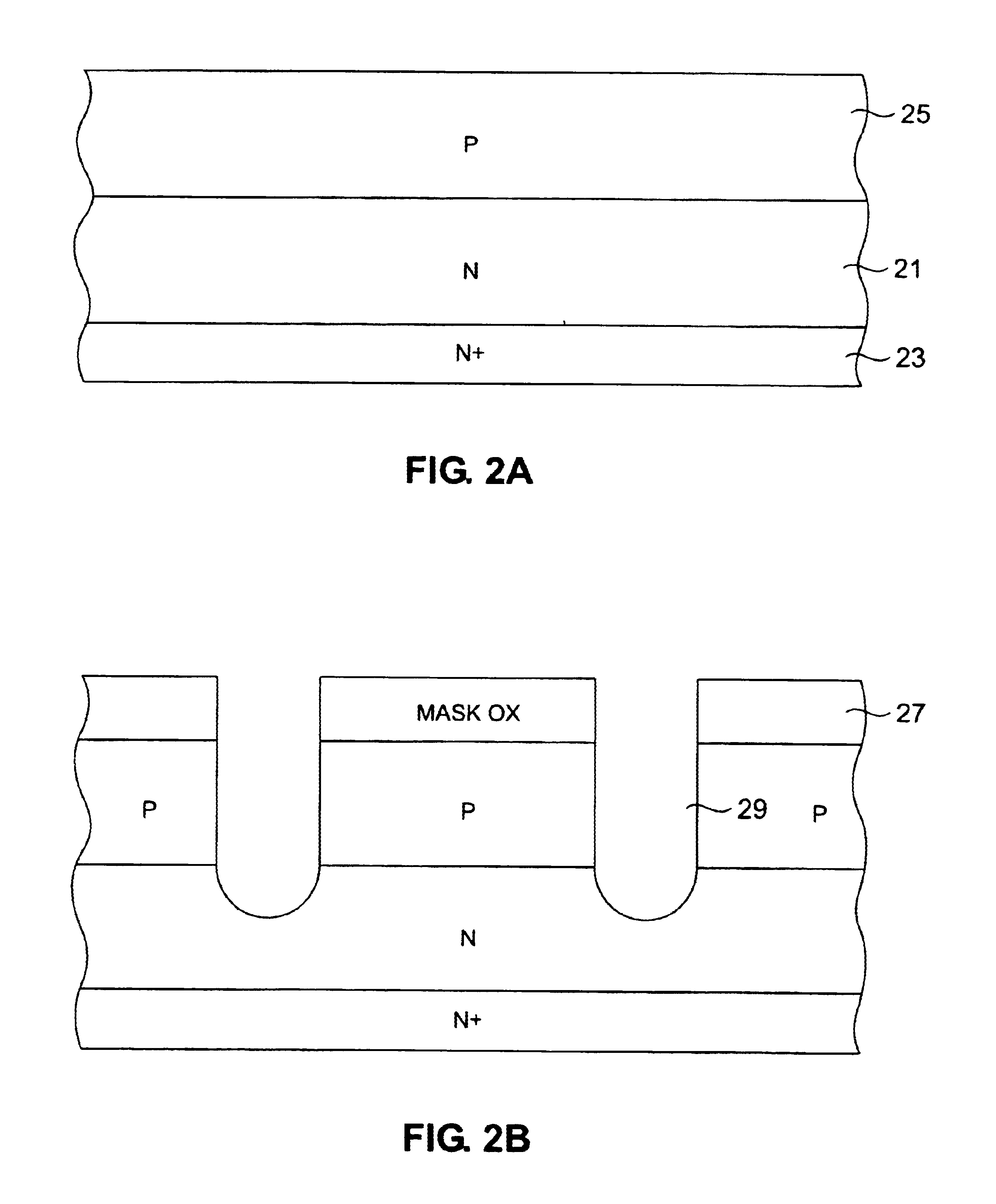

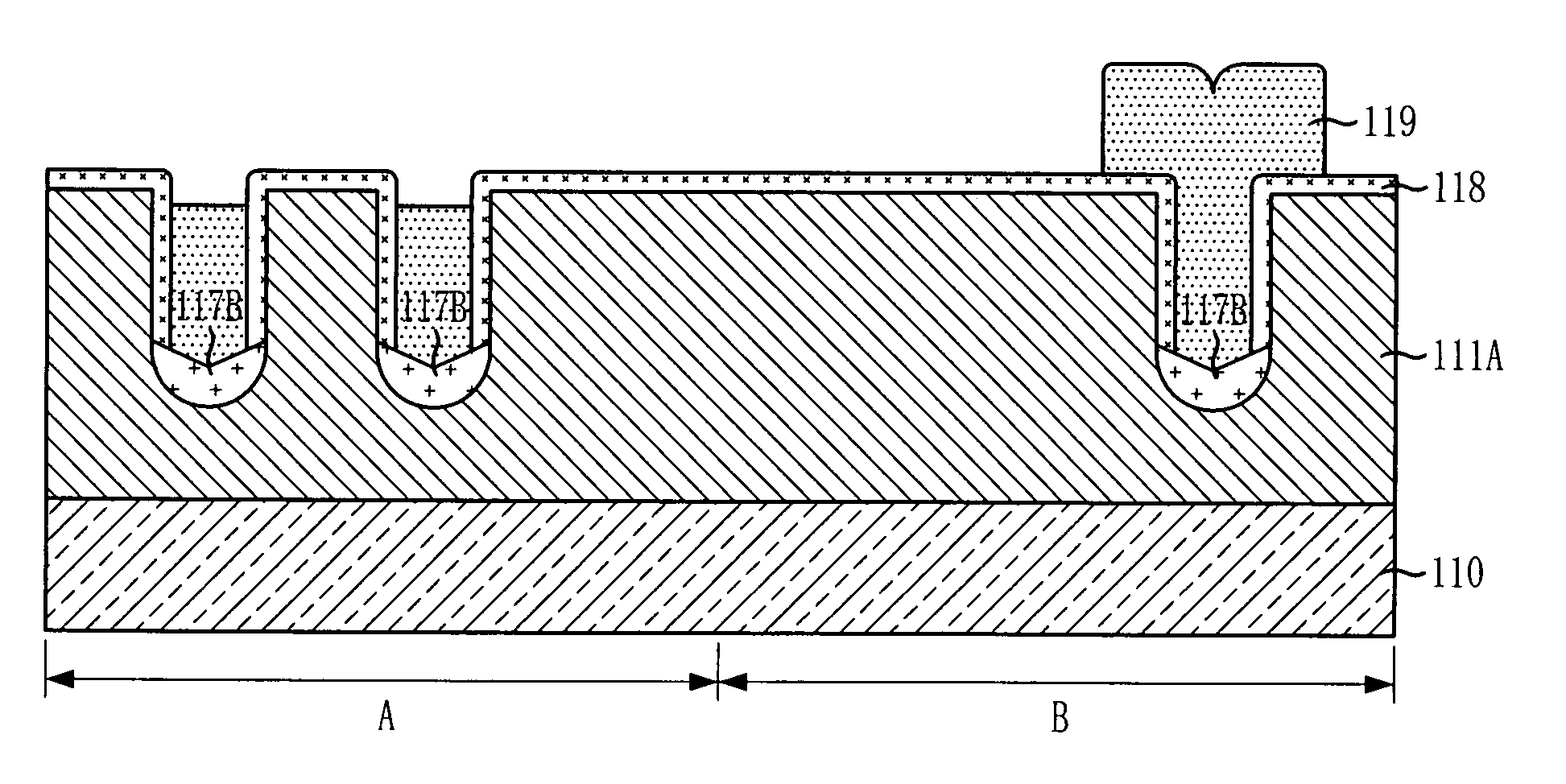

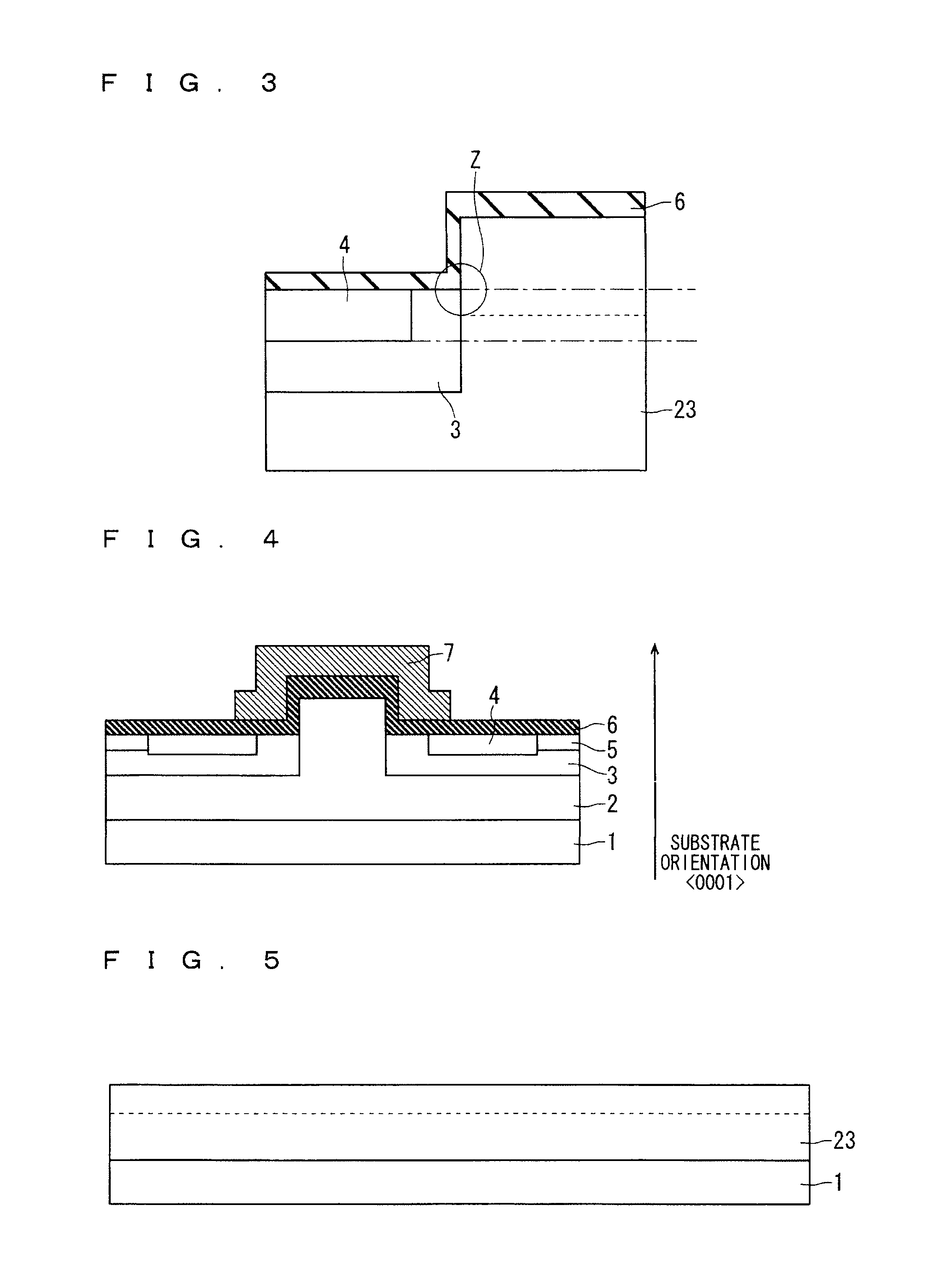

Semiconductor device and manufacturing method for semiconductor device

ActiveUS20060208314A1Reduce gate capacitanceAvoid failureSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

To provide a semiconductor device capable of reducing a gate capacitance, and preventing breakdown of a gate oxide film if a large amount of current flows. A semiconductor device according to an embodiment of the present invention includes: an epitaxial layer; a channel region formed on the epitaxial layer; a trench extending from a surface of the channel region to the epitaxial layer; a gate oxide film that covers an inner surface of the trench; a gate electrode filled into the trench; and a buried insulating film formed below the gate electrode and away from the gate oxide film.

Owner:RENESAS ELECTRONICS CORP

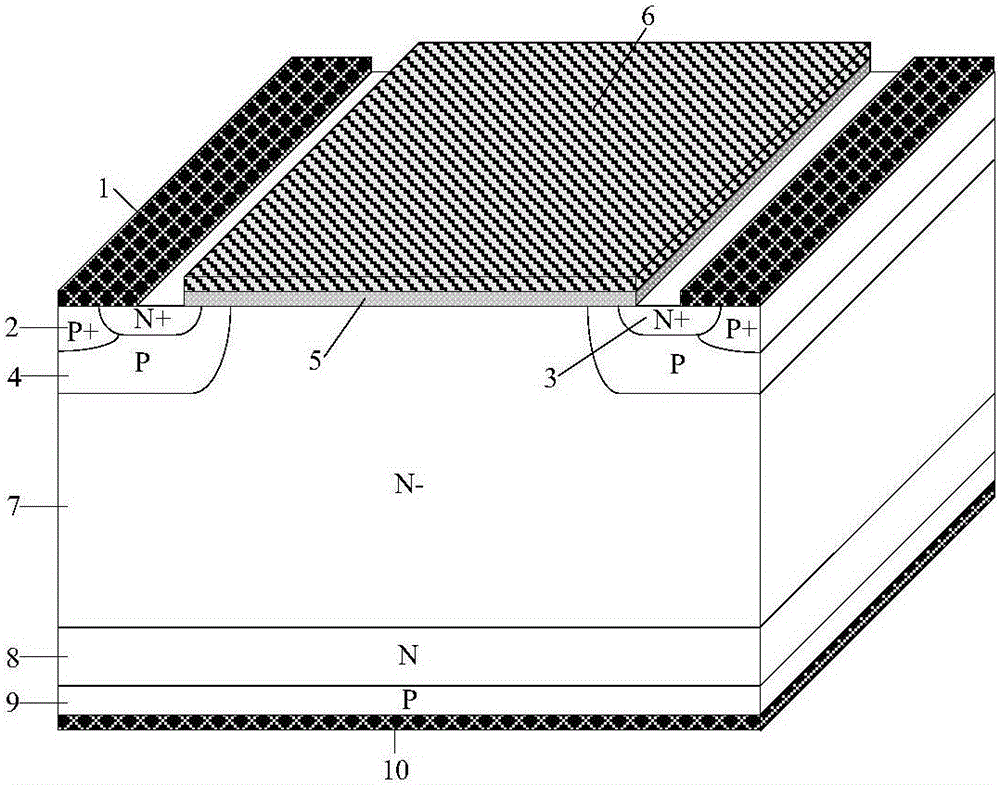

Plane gate IGBT and manufacturing method therefor

InactiveCN105932055AReduce gate capacitanceFast switching speedTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceCapacitance

The invention belongs to the technical field of a power semiconductor device, and relates to a plane gate IGBT and a manufacturing method therefor. On the basis of the conventional plane gate IGBT device structure, a surface recombination device structure is introduced, so that the gate electrode capacitance, particularly the gate electrode-collector electrode capacitance of the device is reduced, the switching speed of the device is improved, and the switching loss of the device is lowered; and meanwhile, the forward conduction voltage drop and the drift region carrier concentration distribution of the device are improved, the performance of the device is enhanced, and degradation of the blocking performance of the device is prevented.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

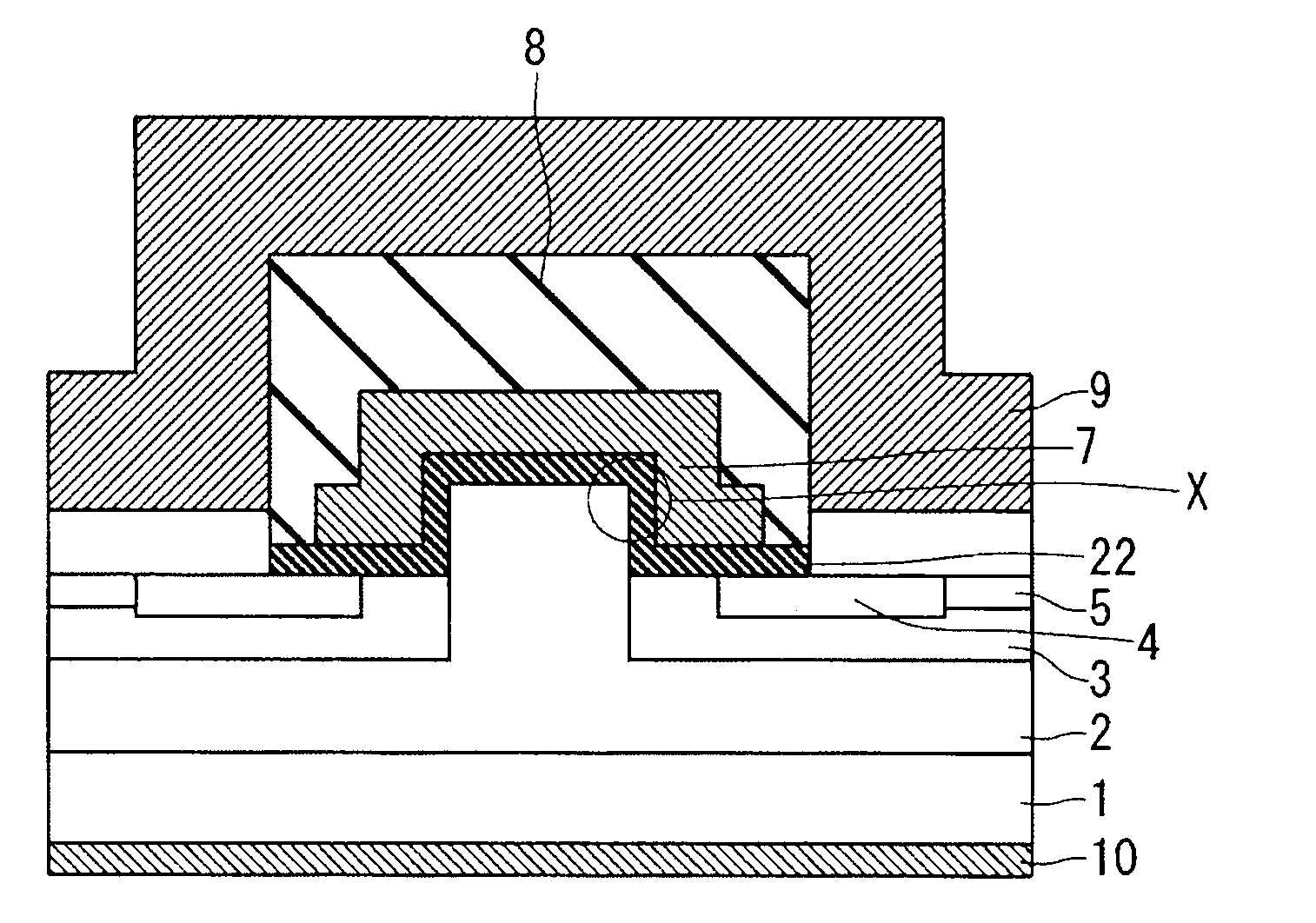

Semiconductor device and method for fabricating the same

InactiveUS6867106B2Suppress speed performance deteriorationGate capacitance is smallTransistorSemiconductor/solid-state device detailsBody contactBody region

The semiconductor device comprises: a conducting layer including: a channel region; a source region and a drain region sandwiching the channel region; and a body region connected to the channel region and being adjacent to the source region and the drain region; a gate electrode formed above the channel region interposing a gate insulation film therebetween; a dummy electrode formed on the body region near the interface between at least the drain region and the body region, and electrically insulated with the gate electrode; and a body contact region formed in the body region except a region where the dummy electrode is formed. The gate electrode and the dummy electrode are electrically insulated with each other, whereby the semiconductor device having body contacts can have a gate capacitance much decreased. Accordingly, deterioration of the speed performance of the transistors can be suppressed.

Owner:FUJITSU SEMICON LTD

Transistor having recess channel and fabricating method thereof

ActiveUS7767530B2Increase speedReduce gate capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerTransistor

A transistor includes a substrate including a trench, an insulation layer filled in a portion of the trench, the insulation layer having a greater thickness over an edge portion of a bottom surface of the trench than over a middle portion of the bottom surface of the trench, a gate insulation layer formed over inner sidewalls of the trench, the gate insulation layer having a thickness smaller than the insulation layer, and a gate electrode filled in the trench.

Owner:KEY FOUNDRY CO LTD

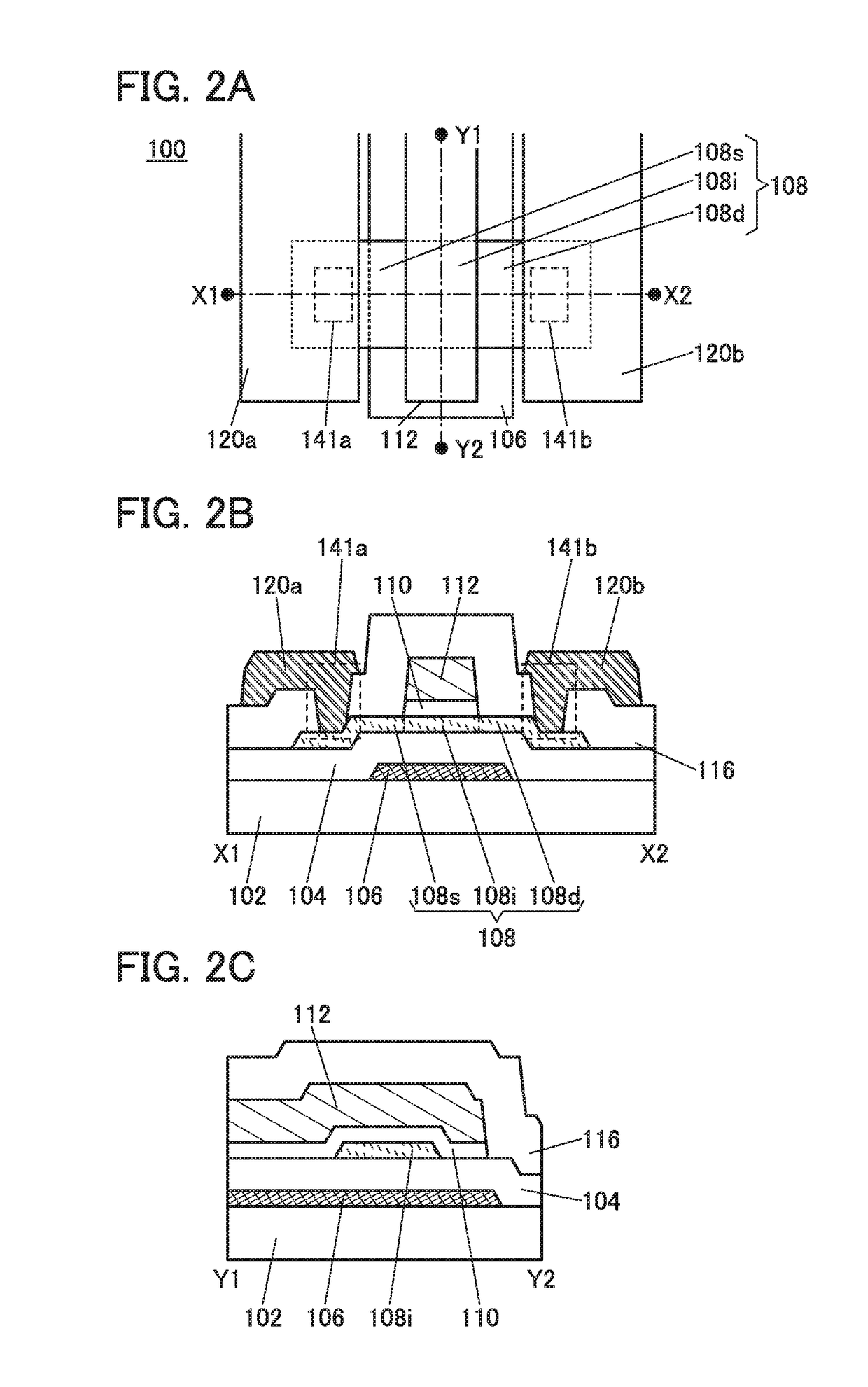

Display device, display module, and electronic device

ActiveUS20170186777A1High field-effect mobilityImprove reliabilityTransistorStatic indicating devicesCapacitanceOxygen vacancy

A novel display device or the like in which a transistor connected to a scan line has small gate capacitance is provided. A novel display device or the like in which a scan line has low resistance is provided. A novel display device or the like in which pixels can be arranged with high density is provided. A novel display device or the like that can be manufactured without an increase in cost is provided. In a transistor including a first gate electrode and a second gate electrode, the first gate electrode is formed using a metal material with low resistance and the second gate electrode is formed using a metal oxide material that can reduce oxygen vacancies in an oxide semiconductor layer. The first gate electrode is connected to the scan line, and the second gate electrode is connected to a wiring to which a constant potential is supplied.

Owner:SEMICON ENERGY LAB CO LTD

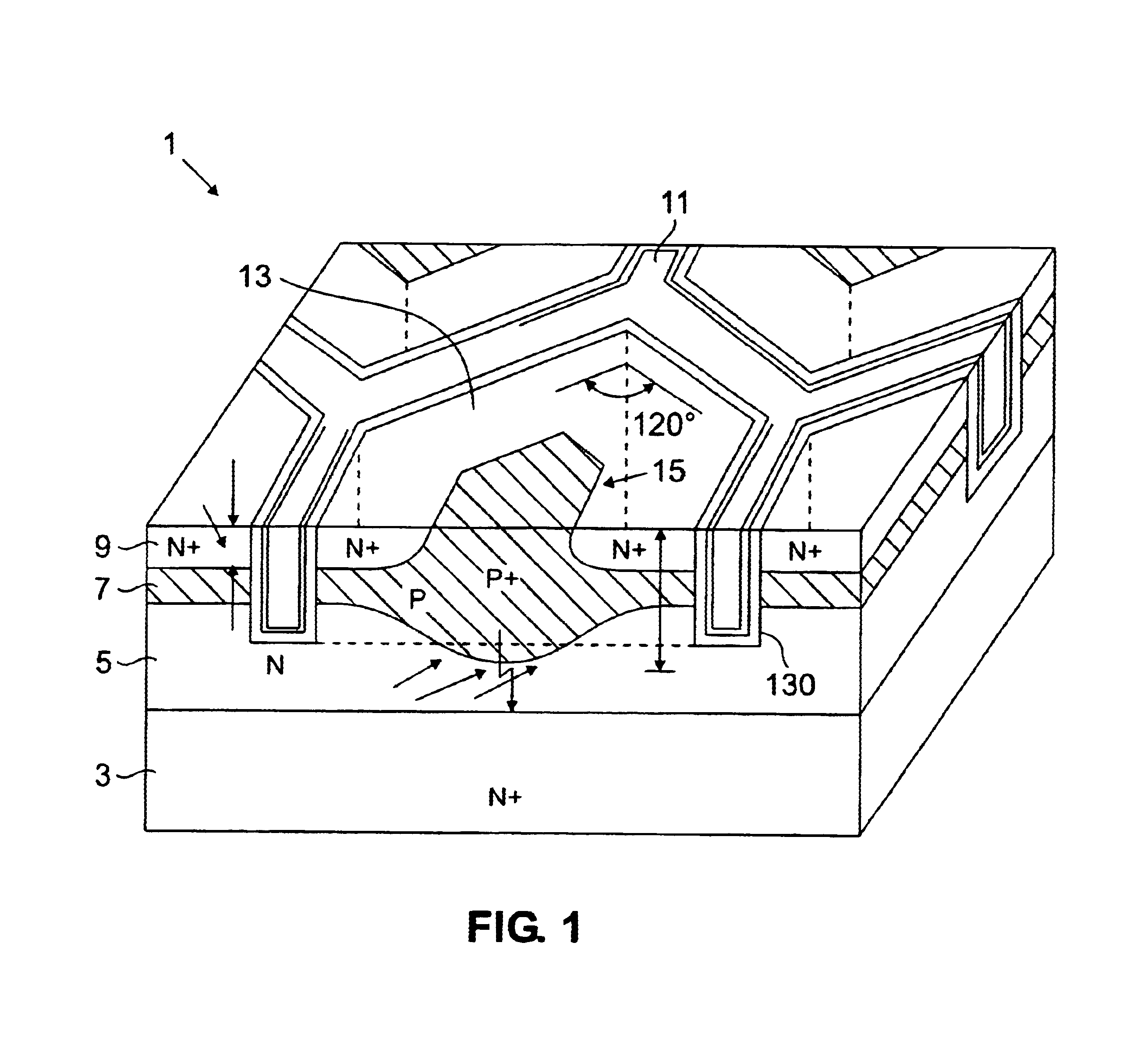

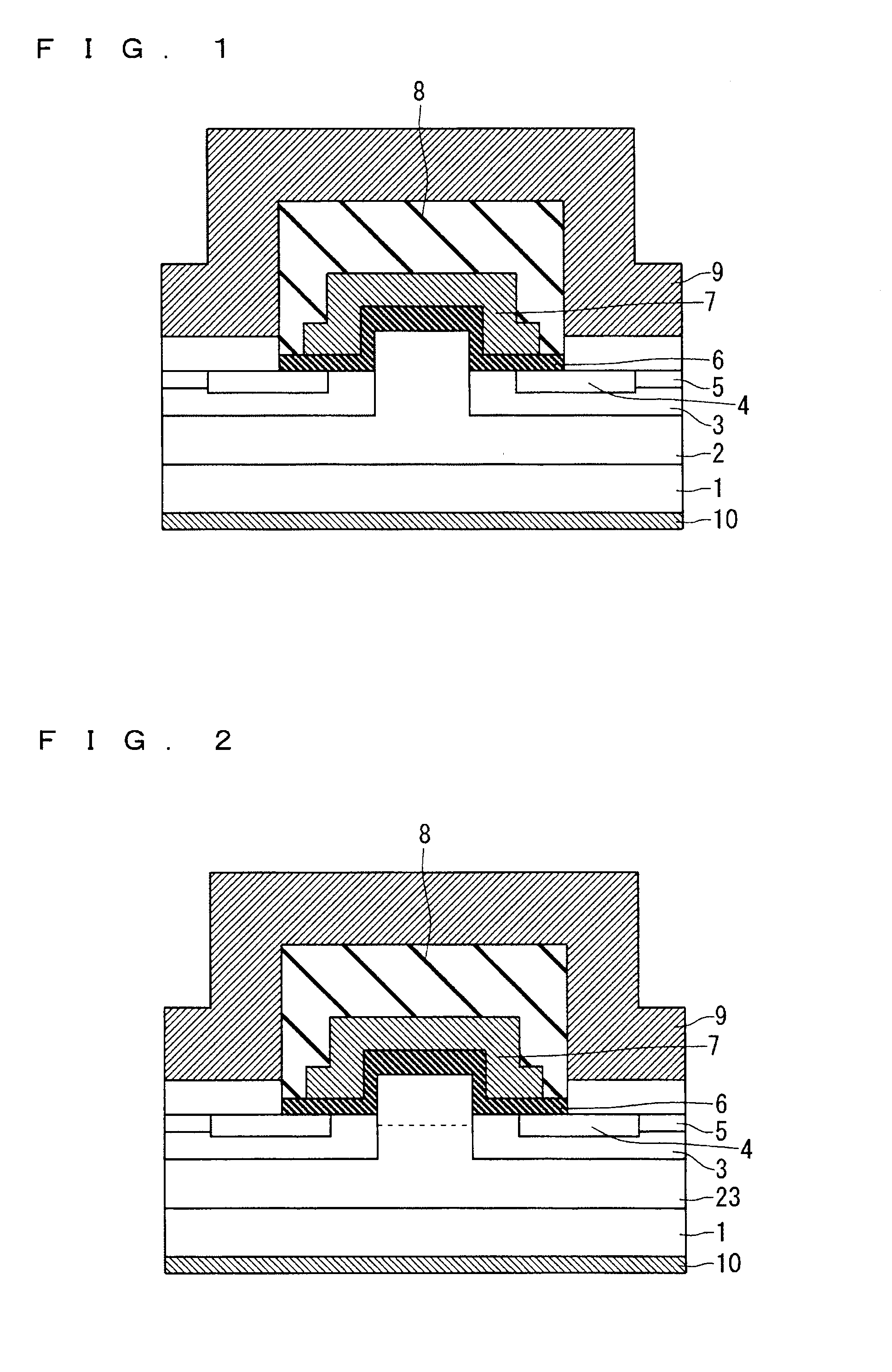

Semiconductor device and method for manufacturing the same

ActiveUS20120112266A1Lowered intensity of electric fieldSuppressing gate capacitanceSemiconductor/solid-state device detailsSolid-state devicesPhysicsSemiconductor

A semiconductor device of the present invention includes: a semiconductor substrate of a first conductive type; an epitaxial layer of the first conductive type formed on the semiconductor substrate and having a protrusion formed on a surface thereof; a well region of a second conductive type formed on the surface of the epitaxial layer at each side of the protrusion; a source region of the first conductive type selectively formed in a surface of the well region; a gate insulating film formed so as to cover at least the protrusion and the surface of the well region; and a gate electrode formed on a part of the gate insulating film corresponding to the protrusion. The gate insulating film is thicker in a region thereof corresponding to an upper surface of the protrusion than the other regions thereof.

Owner:MITSUBISHI ELECTRIC CORP

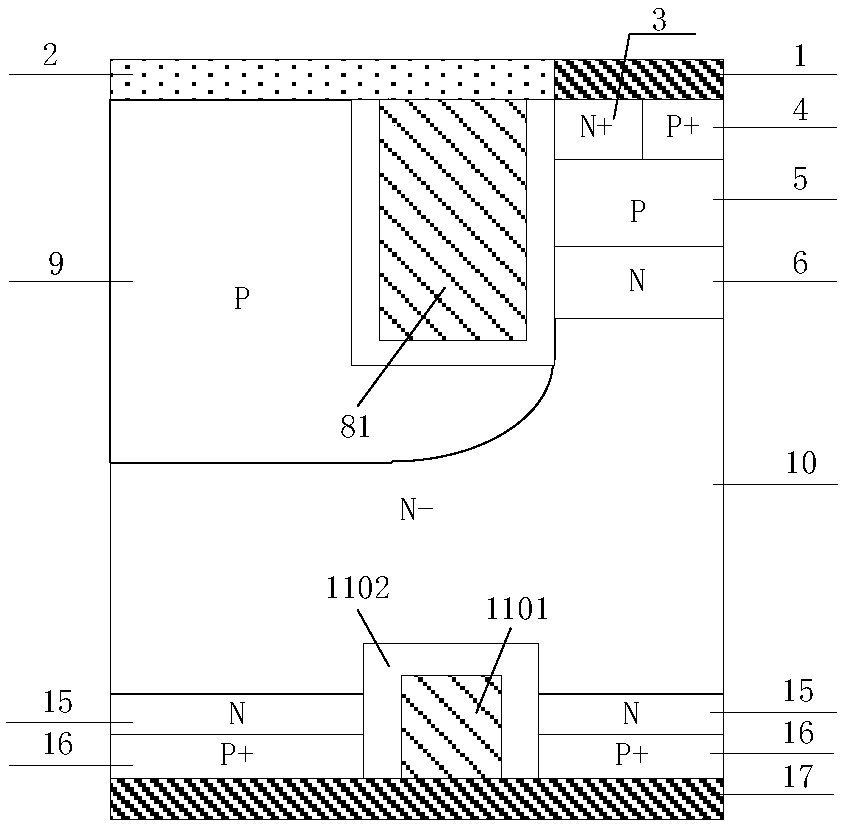

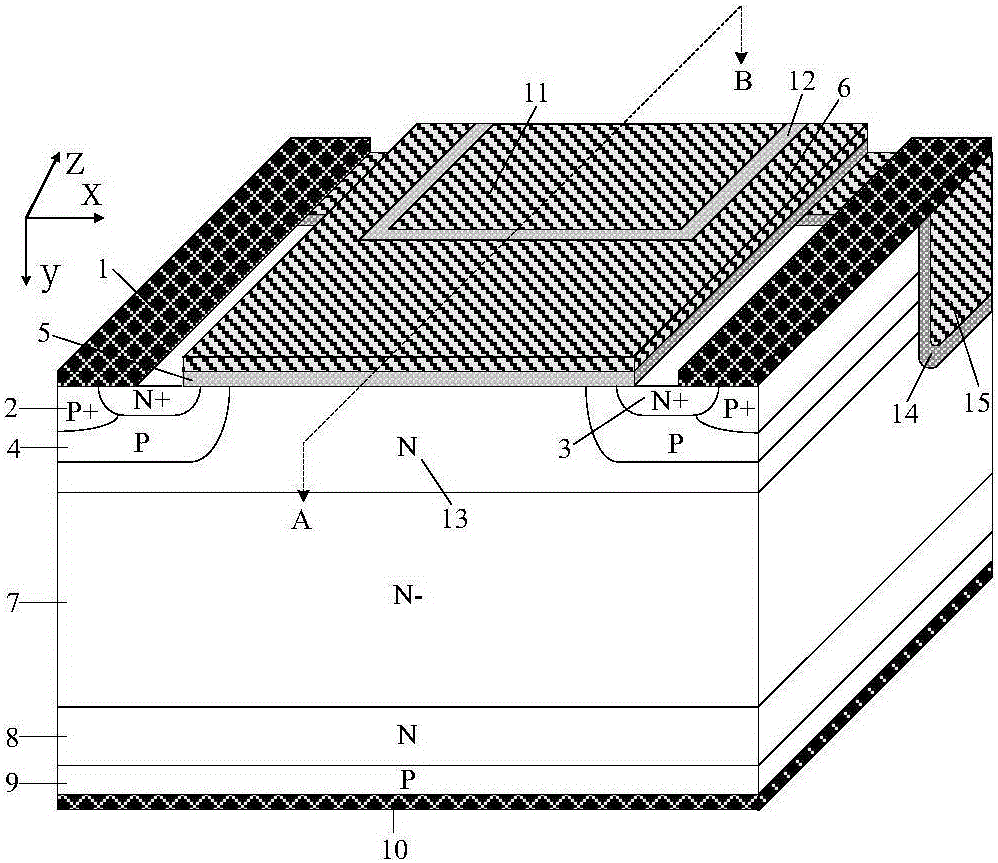

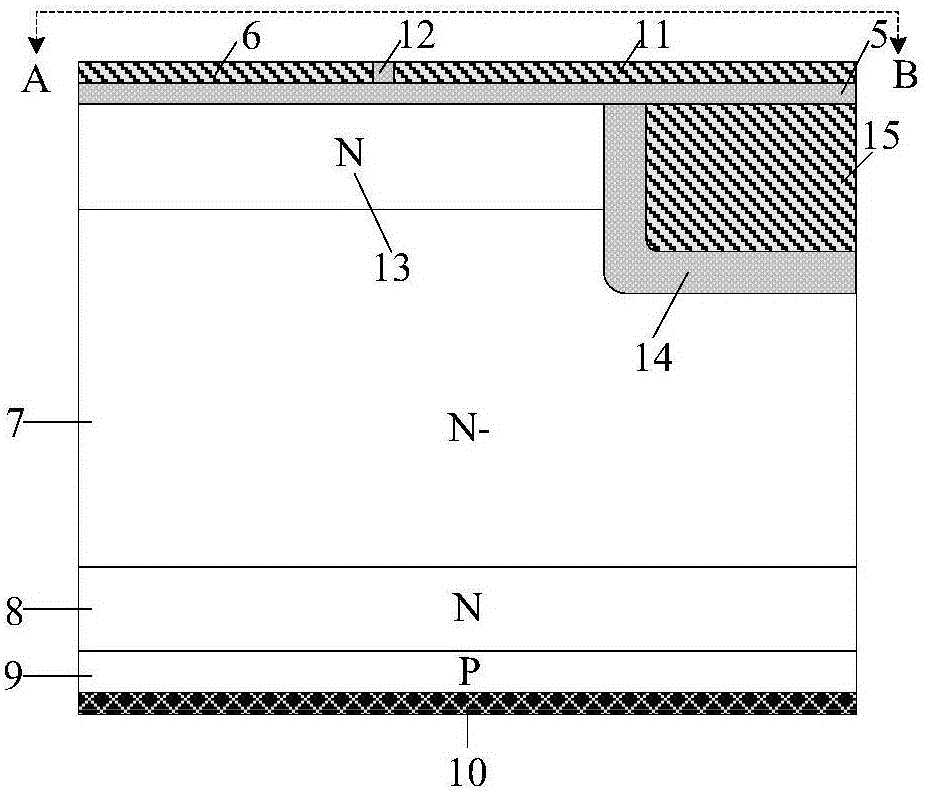

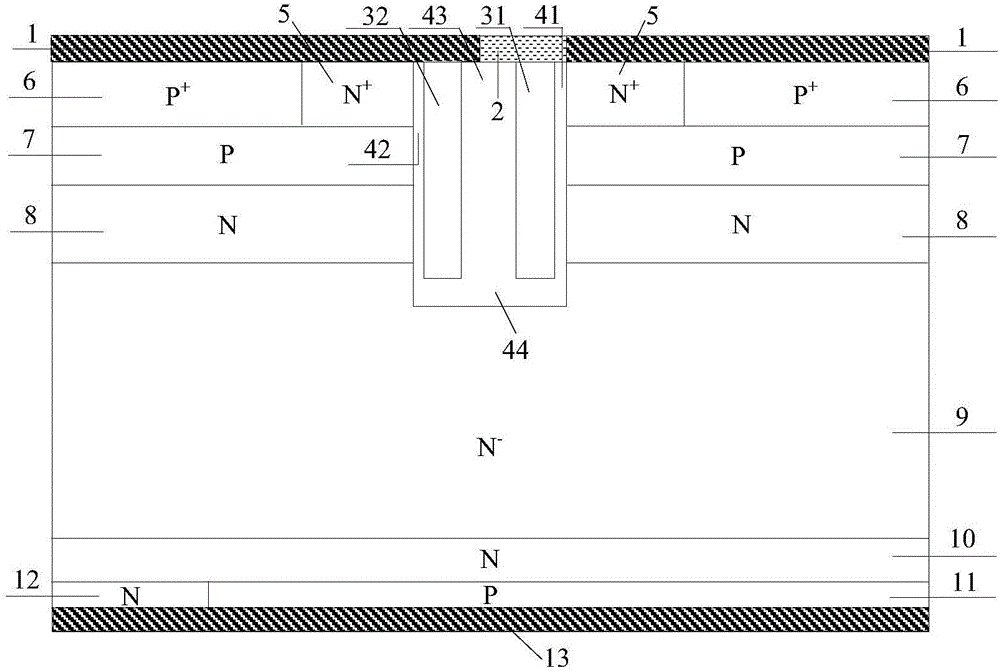

Trench gate charge storage reverse-conducting insulated-gate bipolar transistor (RC-IGBT) and fabrication method thereof

ActiveCN105870179AReduce gate capacitanceLow densitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower semiconductor device

The invention belongs to the technical field of a power semiconductor device, in particular relates to a reverse-conducting trench gate charge storage insulated-gate bipolar transistor (IGBT). By introducing a side-surfaces split electrode connected with an emitter into a trench on the condition of a certain device trench depth and a certain trench metal oxide semiconductor (MOS) structure density, the gate capacitance of the device is reduced, the switching speed of the device is increased, the switching loss is reduced, and the positive conduction voltage drop and the average switching loss are improved; meanwhile, the density of an MOS channel is reduced, the short-circuit safety working region of the IGBT is improved, and the performance and the reliability of the device are improved; and a reverse freewheeling diode works in multiple submodes in a working mode of the reverse freewheeling diode, the IGBG has low diode conduction voltage drop, and the reverse recovery characteristic of the freewheeling diode is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Methods of forming nonvolatile memories with L-shaped floating gates

In a nonvolatile memory using floating gates to store charge, individual floating gates are L-shaped. Orientations of L-shaped floating gates may alternate in the bit line direction and may also alternate in the word line direction. L-shaped floating gates are formed by etching conductive portions using etch masks of different patterns to obtain floating gates of different orientations.

Owner:WODEN TECH INC

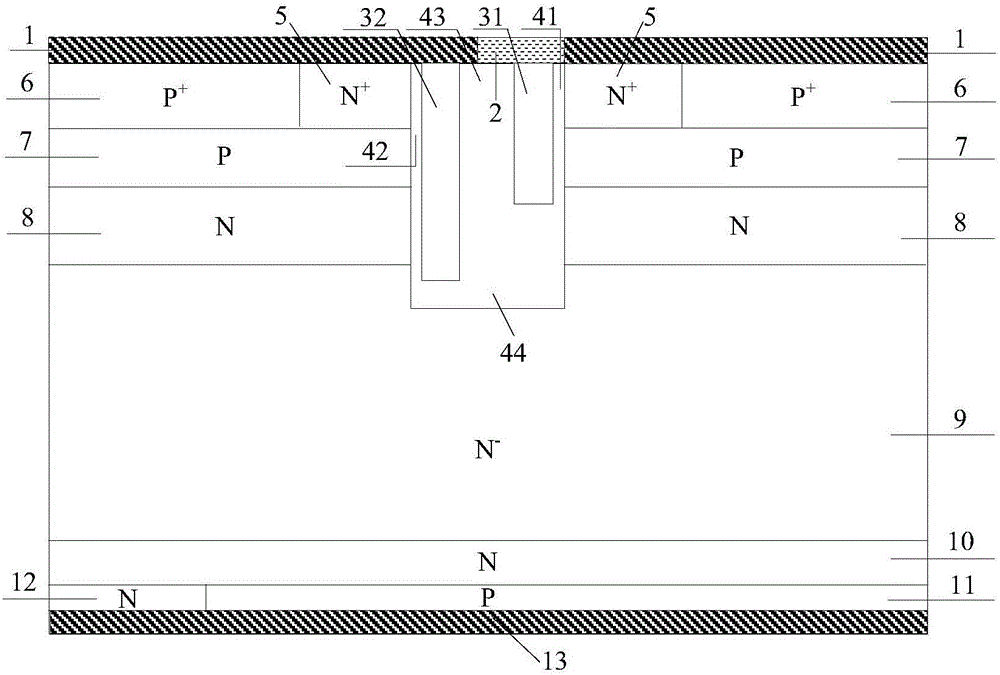

Trench gate charge storage type IGBT and manufacturing method thereof

ActiveCN108461537AIncreased injection enhancementImprove concentration distributionSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The invention discloses a trench gate charge storage type IGBT, and belongs to the technical field of semiconductor power devices. A conventional trench gate structure is widened, and a side wall gateelectrode structure is employed for forming a mesa structure located below a base region. moreover, a shielding trench structure for shielding the electric field of a charge storage layer is introduced, thereby improving the carrier injection enhancement effect, and improving the compromise between a forwarding ON voltage drop Vceon and the OFF loss Eoff. The electric field concentration effect at the tip of the bottom of a trench is alleviated, and the breakdown voltage of a device is effectively improved. The gate capacitance of the device, especially the Miller capacitance CGC and the gatecharge QG, is reduced, the switching speed of the device is improved, the switching loss of the device is reduced, and the requirements for the capability of a gate drive circuit are reduced. The constraint on the doping concentration of an N-type charge storage layer and the withstand voltage of the device from the thickness are avoided, the saturation current density is reduced, and a short-circuit safe operating region (SCSOA) of the device is improved. Moreover, an EMI effect is effectively inhibited when the device is turned on. In addition, the manufacturing method is compatible with aconventional trench gate charge storage type IGBT manufacturing method.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA