A double silicon nanowire wrap gate field-effect transistor and its manufacture method

A technology of field-effect transistors and silicon nanowires, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of reducing device switching speed, increasing gate capacitance, and increasing leakage current, so as to improve the performance of devices. Effects of switching speed, reduction of parasitic gate capacitance, and reduction of leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0074] The double silicon nanowire gate field effect transistor provided by the present invention and its preparation method will be described in detail below with reference to the accompanying drawings, but this does not constitute a limitation to the present invention.

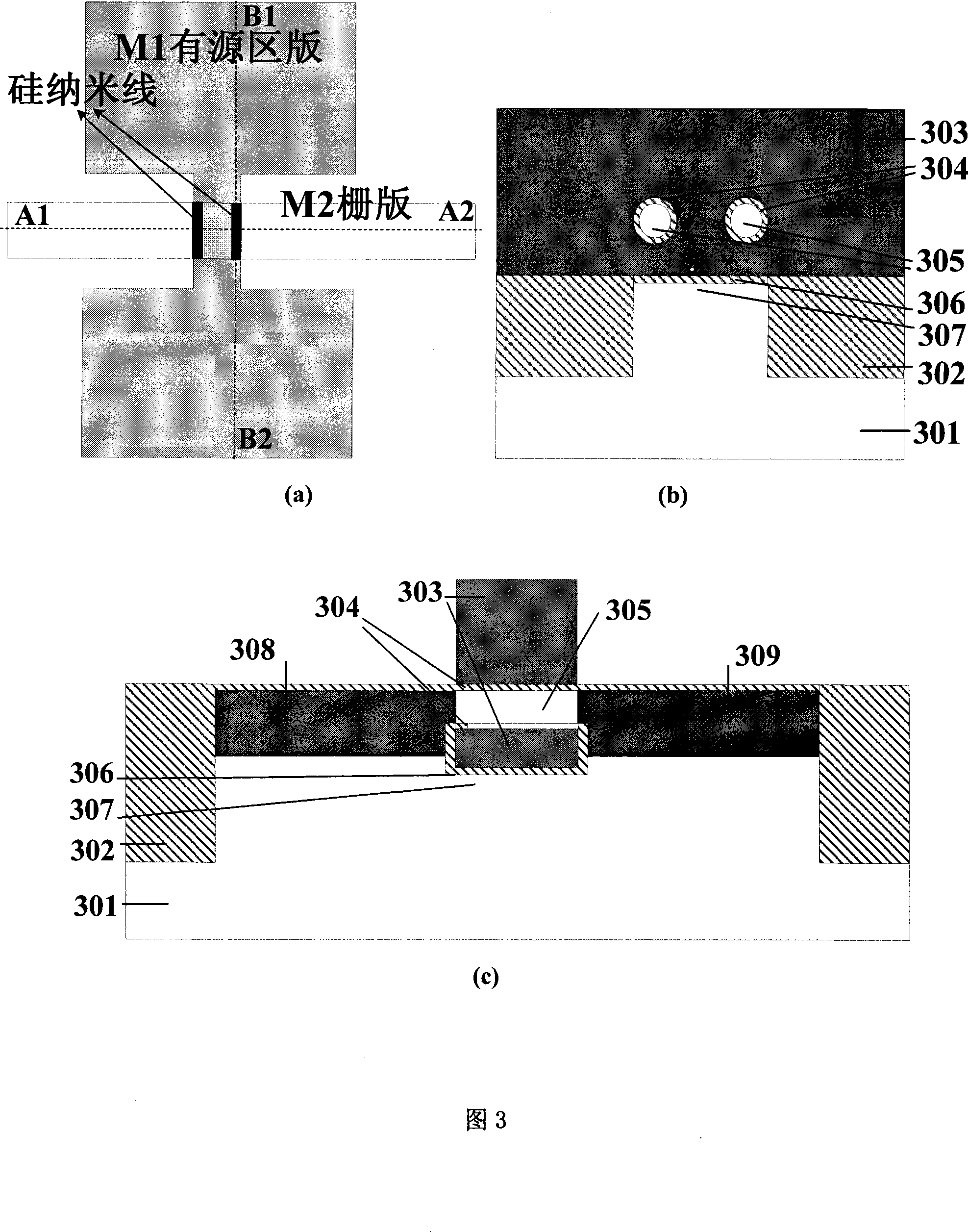

[0075] As shown in FIG. 4 , it is the double silicon nanowire gate device of this embodiment. Figure 4(a) shows the layout of the device. The part of the M1 active region plate covered by the M2 gate plate is the channel region, and the uncovered part is the source region and drain region. The width of the channel region (A1A2 direction) is 50nm, and the length of the channel region (B1B2 direction), that is, the gate length is 30nm. Figure 4(b) and (c) respectively show the cross-sectional structure of the device along the vertical direction of the channel (A1A2 direction) and along the channel direction (B1B2 direction). As shown in Figure 4(b): the cross section of the double silicon nanowire 405 as a ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More