Patents

Literature

850 results about "Silicon nanowires" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Silicon nanowires, also referred to as SiNWs, are a type of semiconductor nanowire most often formed from a silicon precursor by etching of a solid or through catalyzed growth from a vapor or liquid phase. Such nanowires have promising applications in lithium ion batteries, thermoelectrics and sensors.Initial synthesis of SiNWs is often accompanied by thermal oxidation steps to yield ...

Electrode Including Nanostructures for Rechargeable Cells

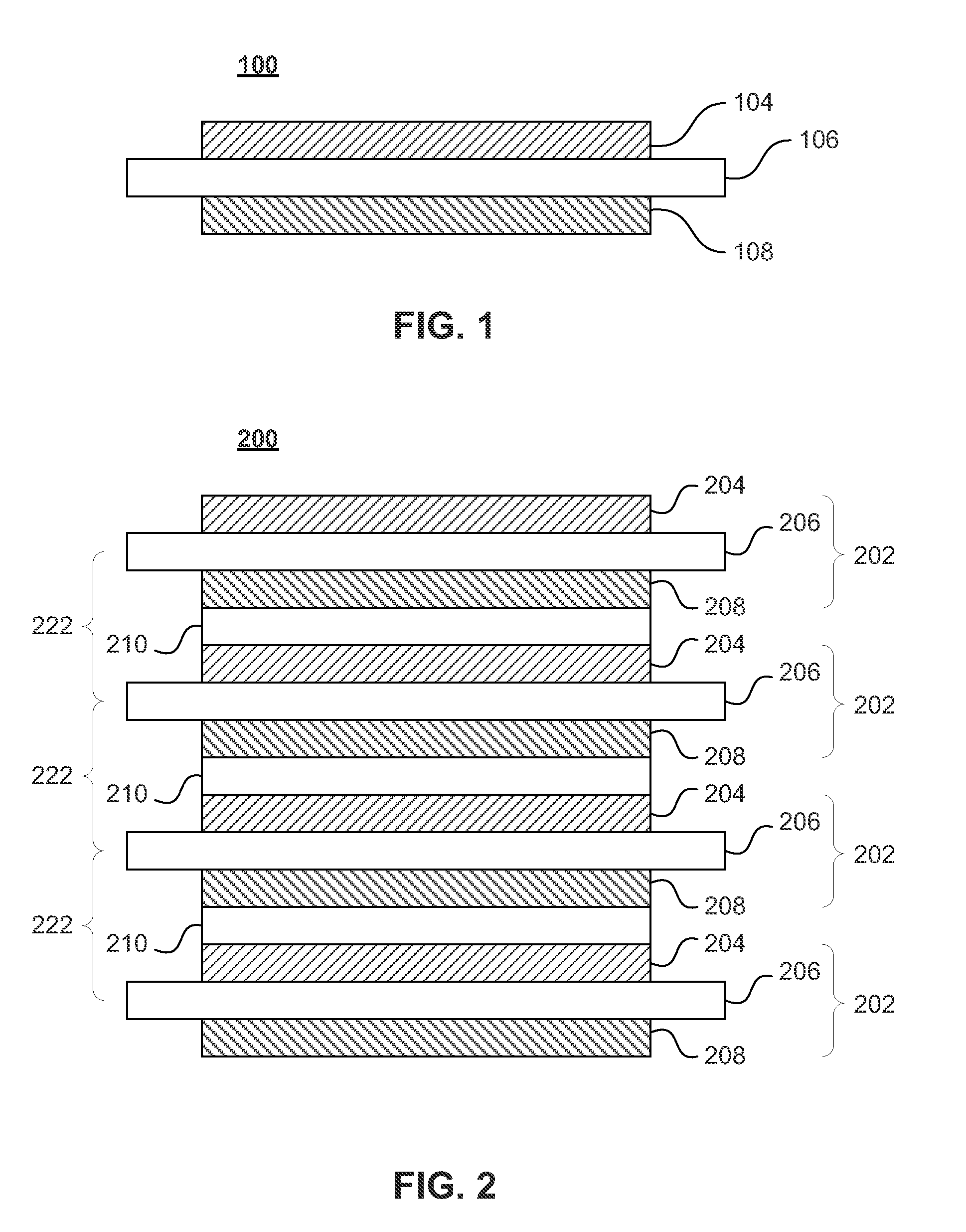

InactiveUS20100285358A1Lower resistanceNanostructure manufactureMicroscopic fiber electrodesRechargeable cellSilicon nanowires

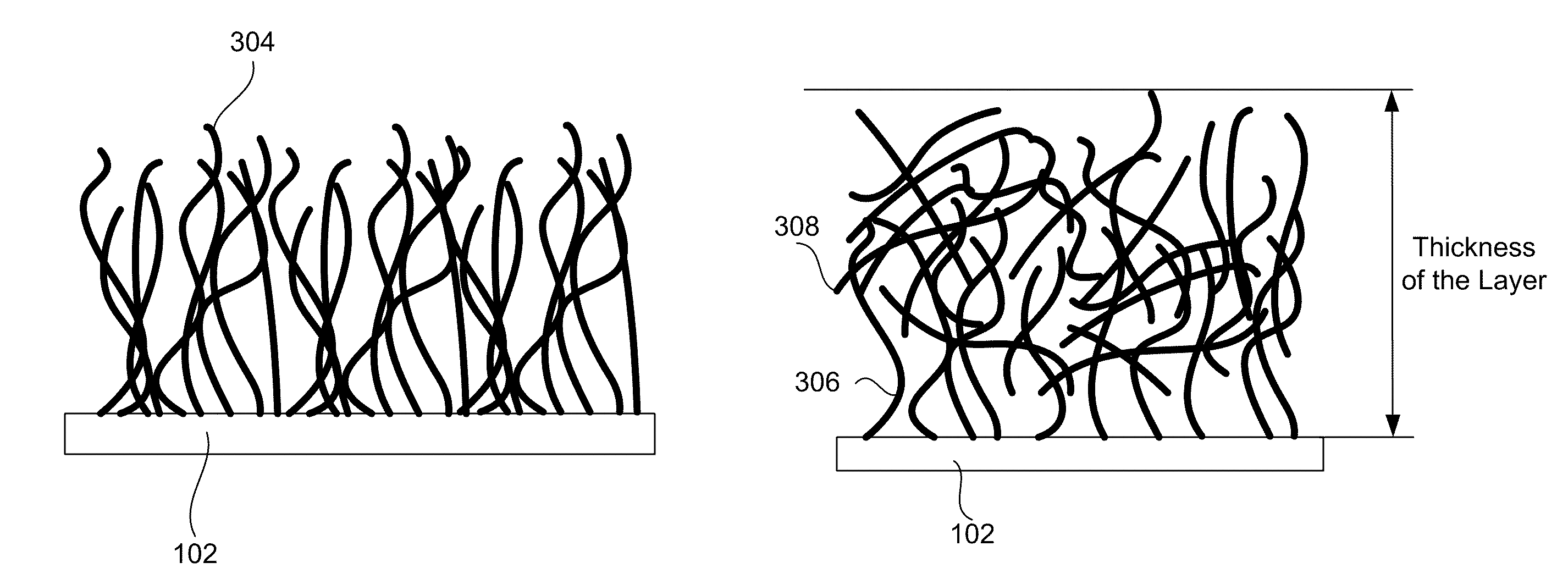

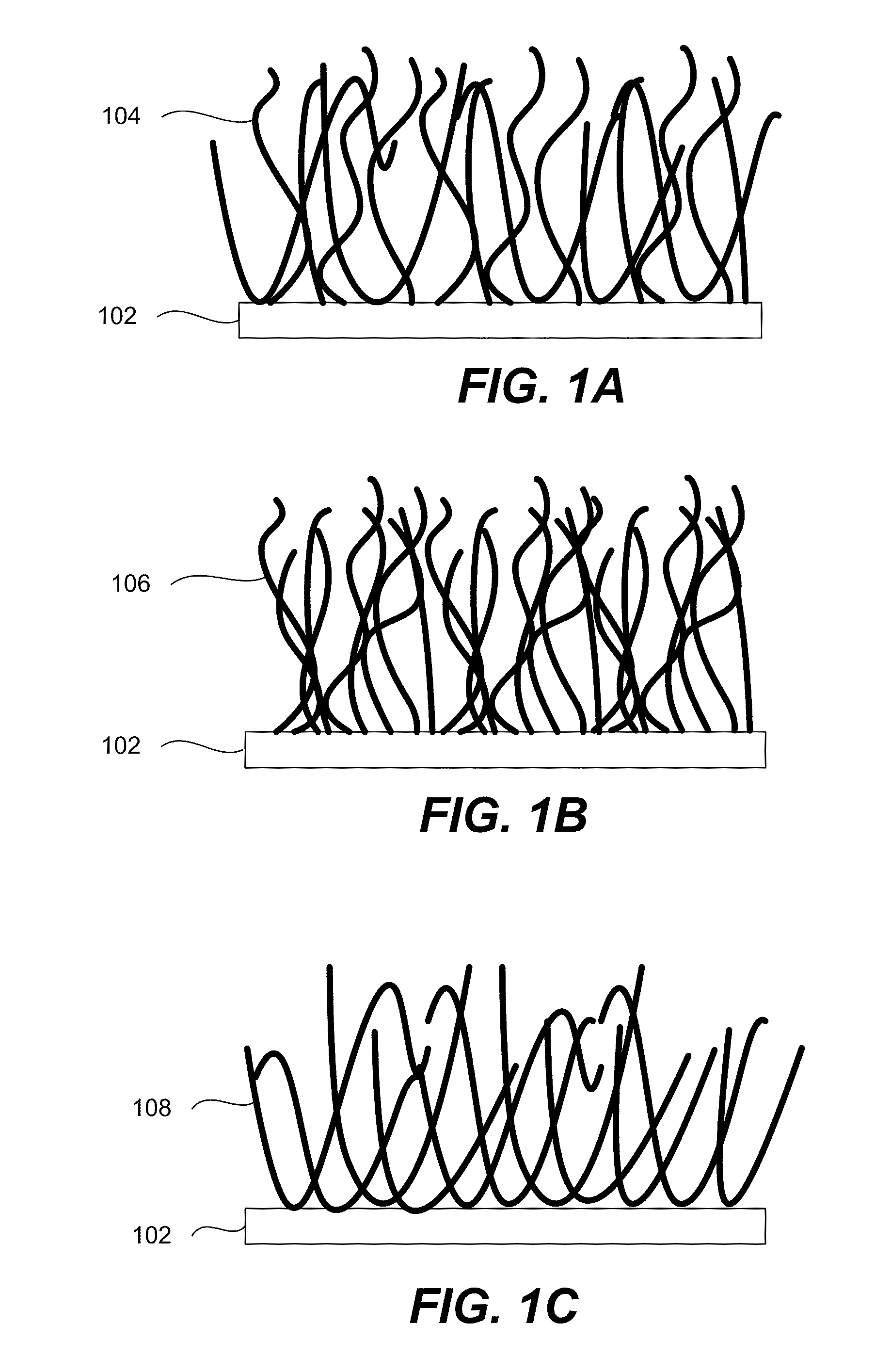

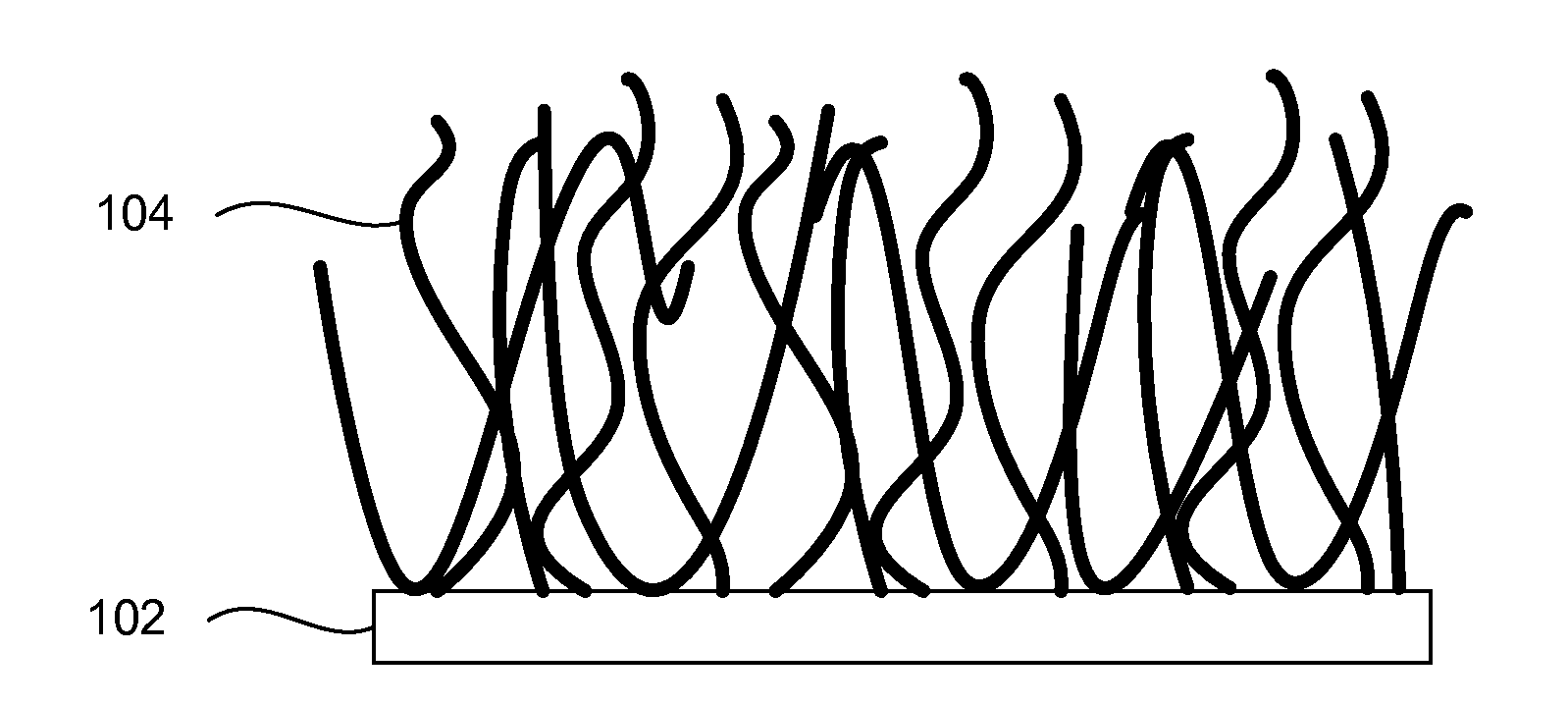

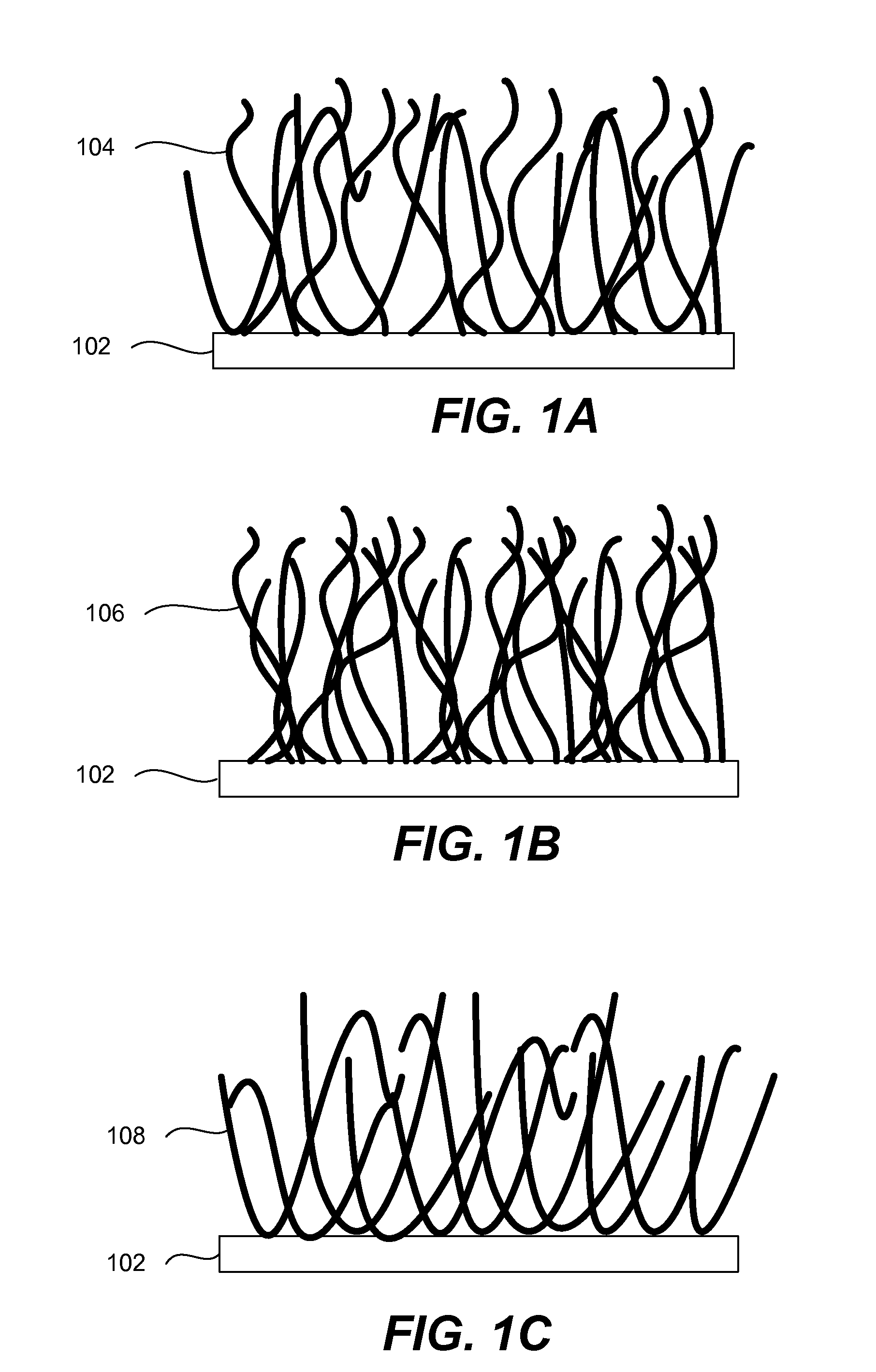

A lithium ion battery electrode includes silicon nanowires used for insertion of lithium ions and including a conductivity enhancement, the nanowires growth-rooted to the conductive substrate.

Owner:AMPRIUS INC

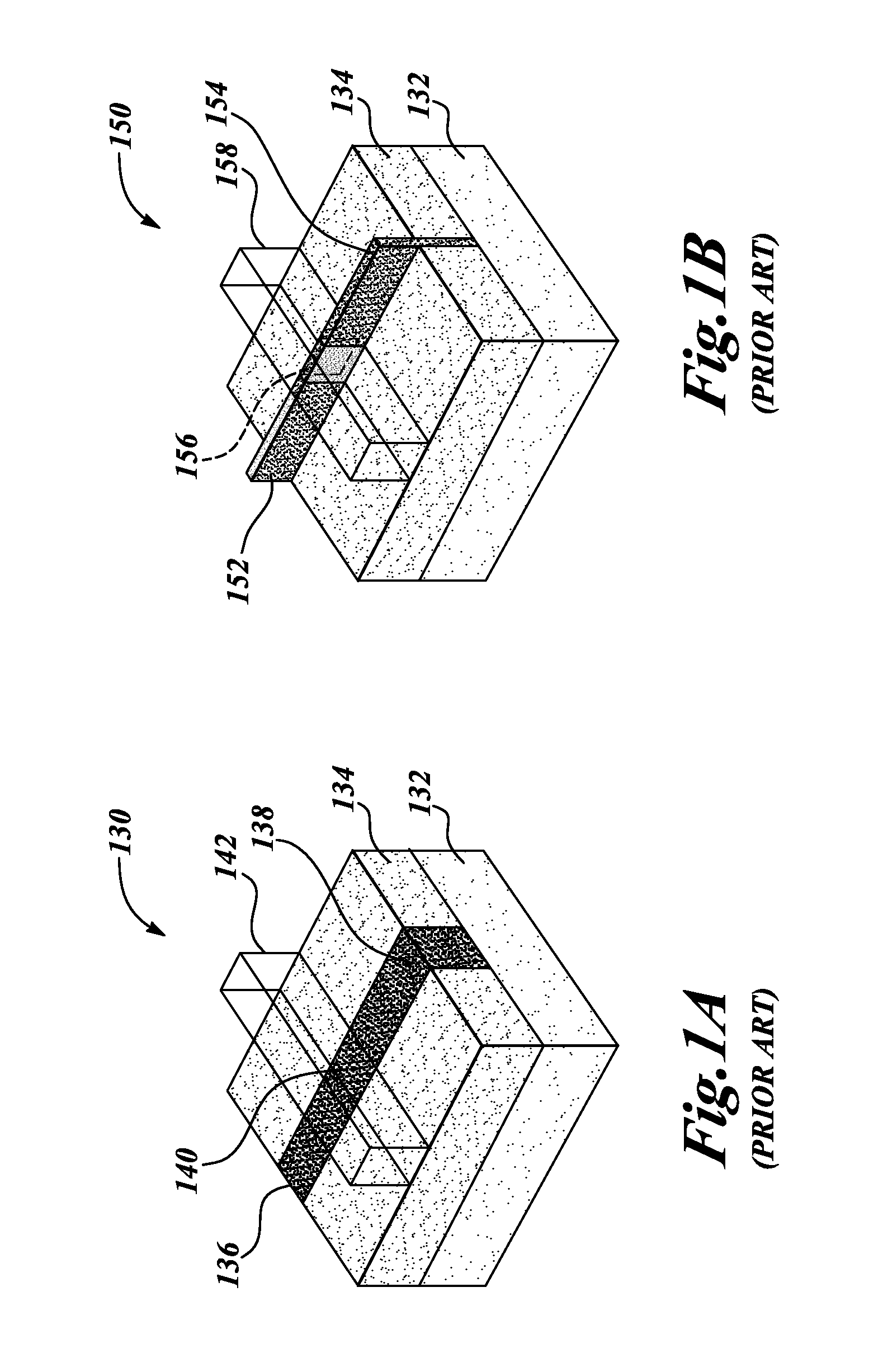

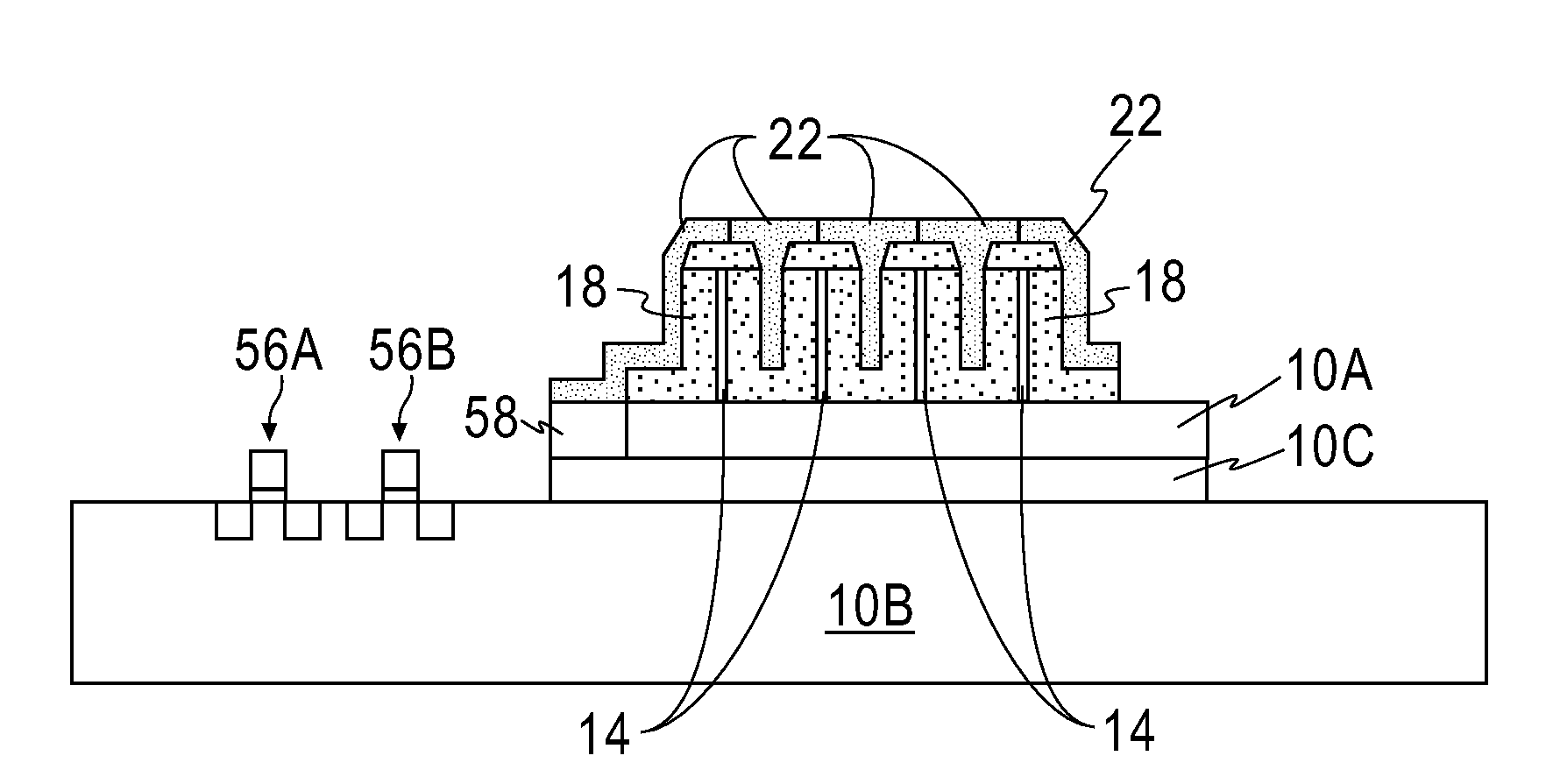

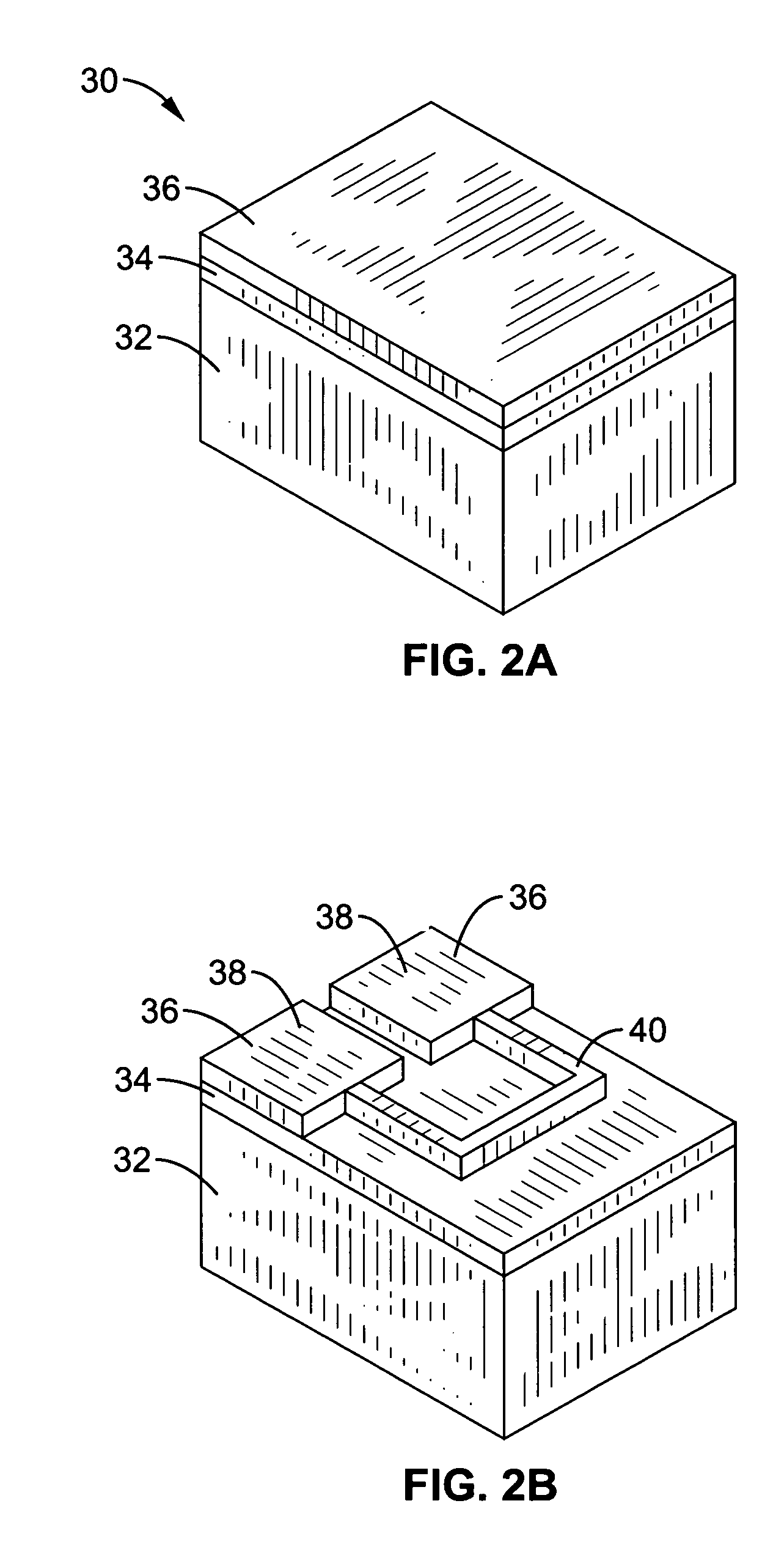

Multi-channel gate-all-around fet

ActiveUS20150372104A1Low working voltageImprove reliabilityNanoinformaticsSolid-state devicesSilicon nanowiresPower flow

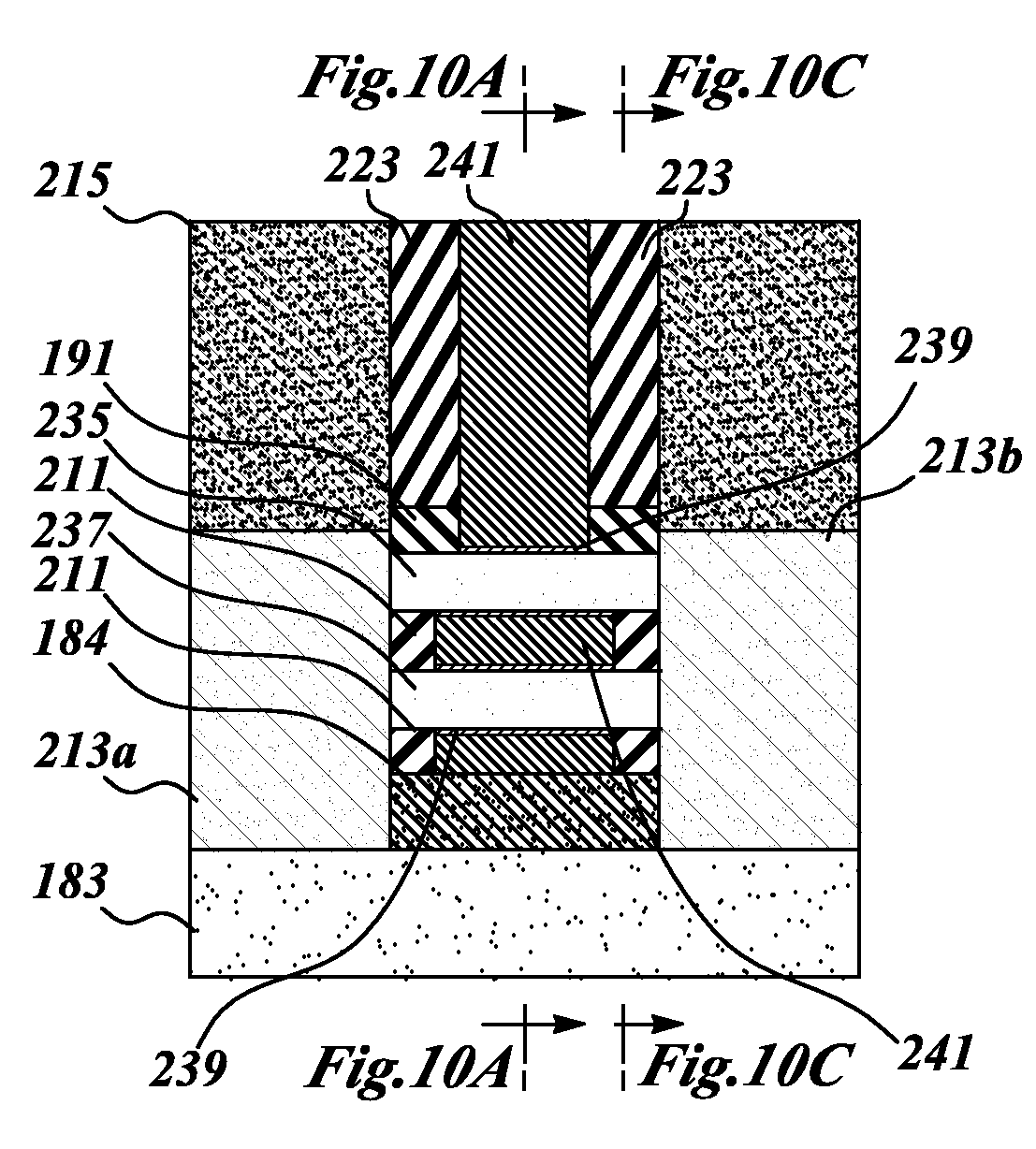

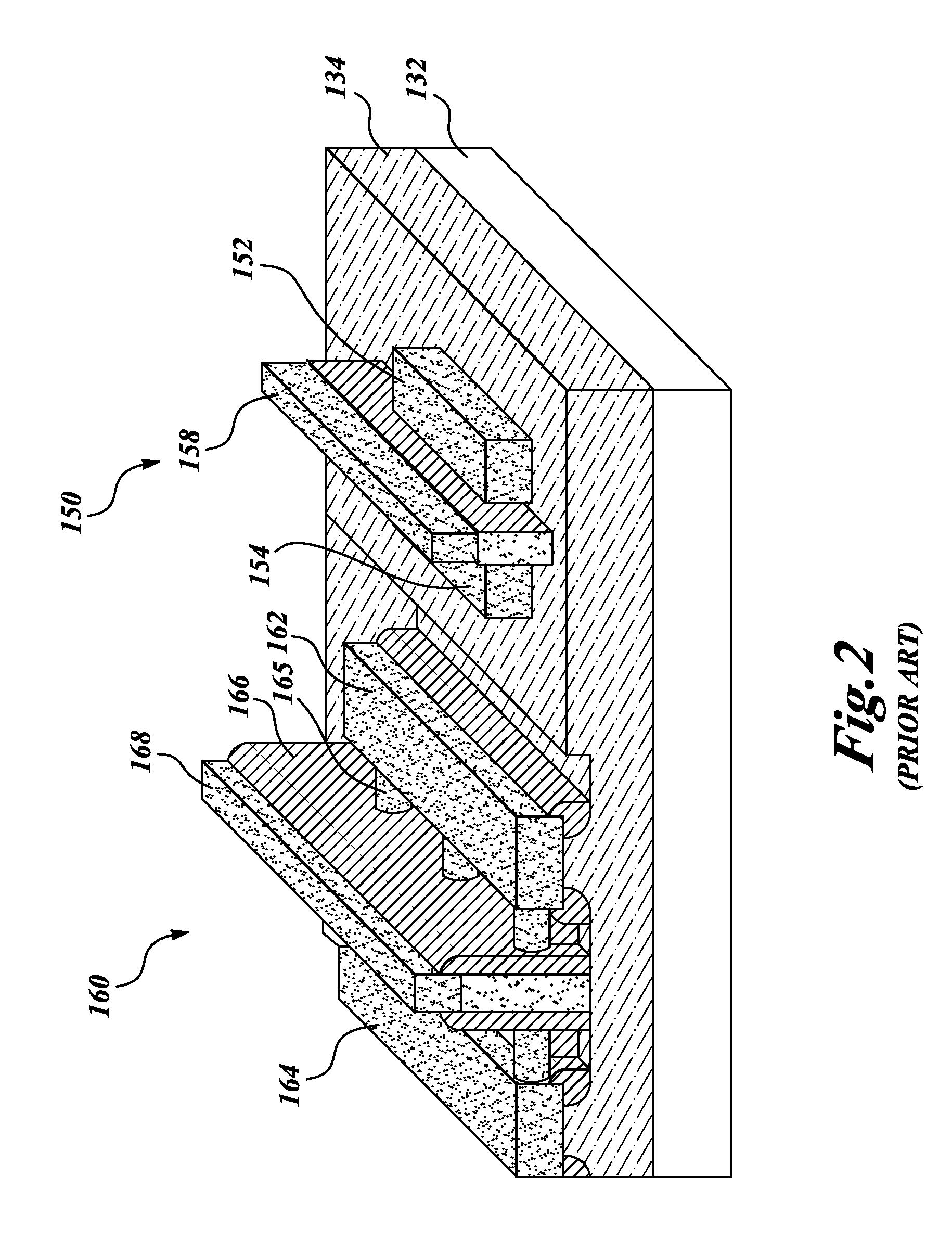

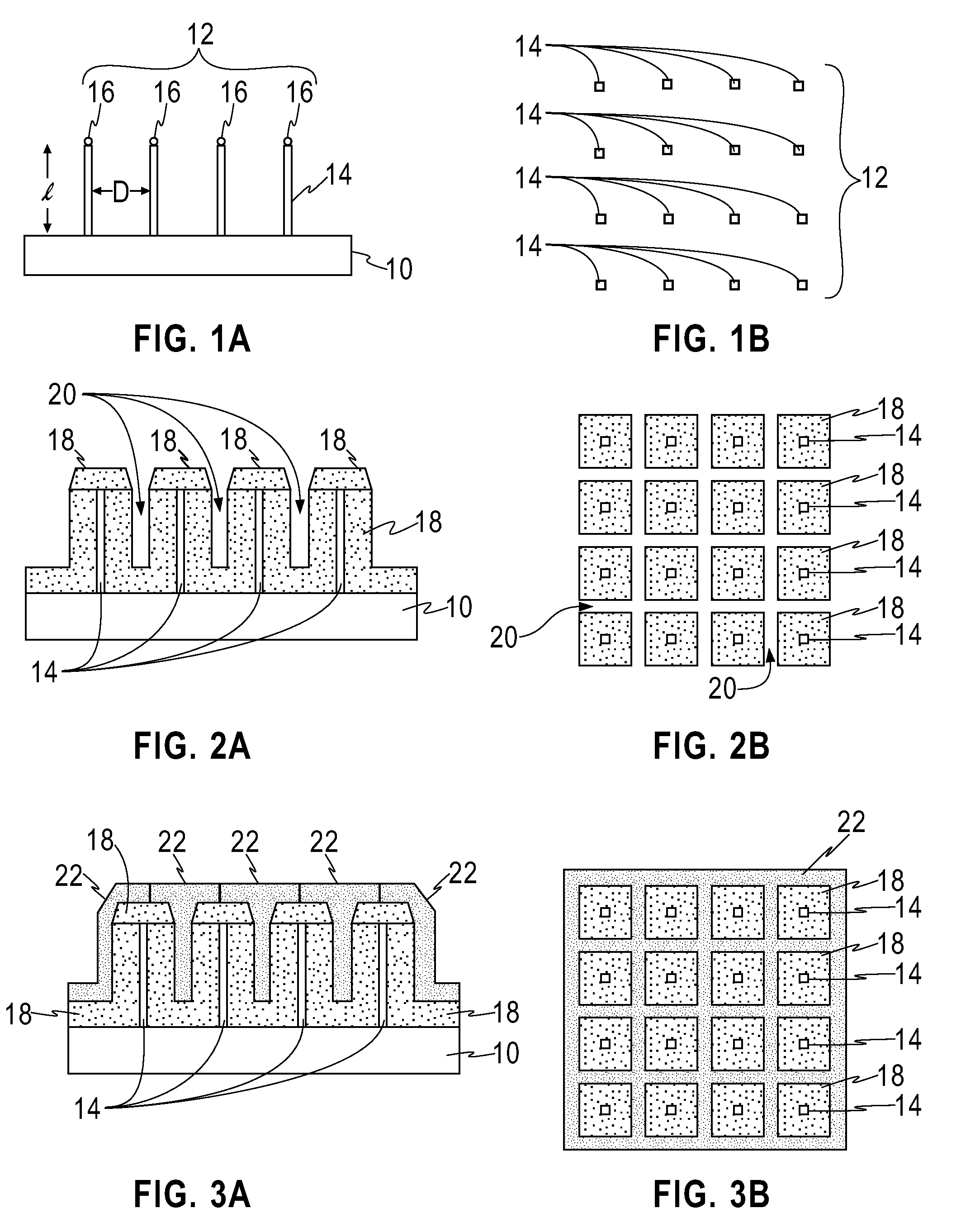

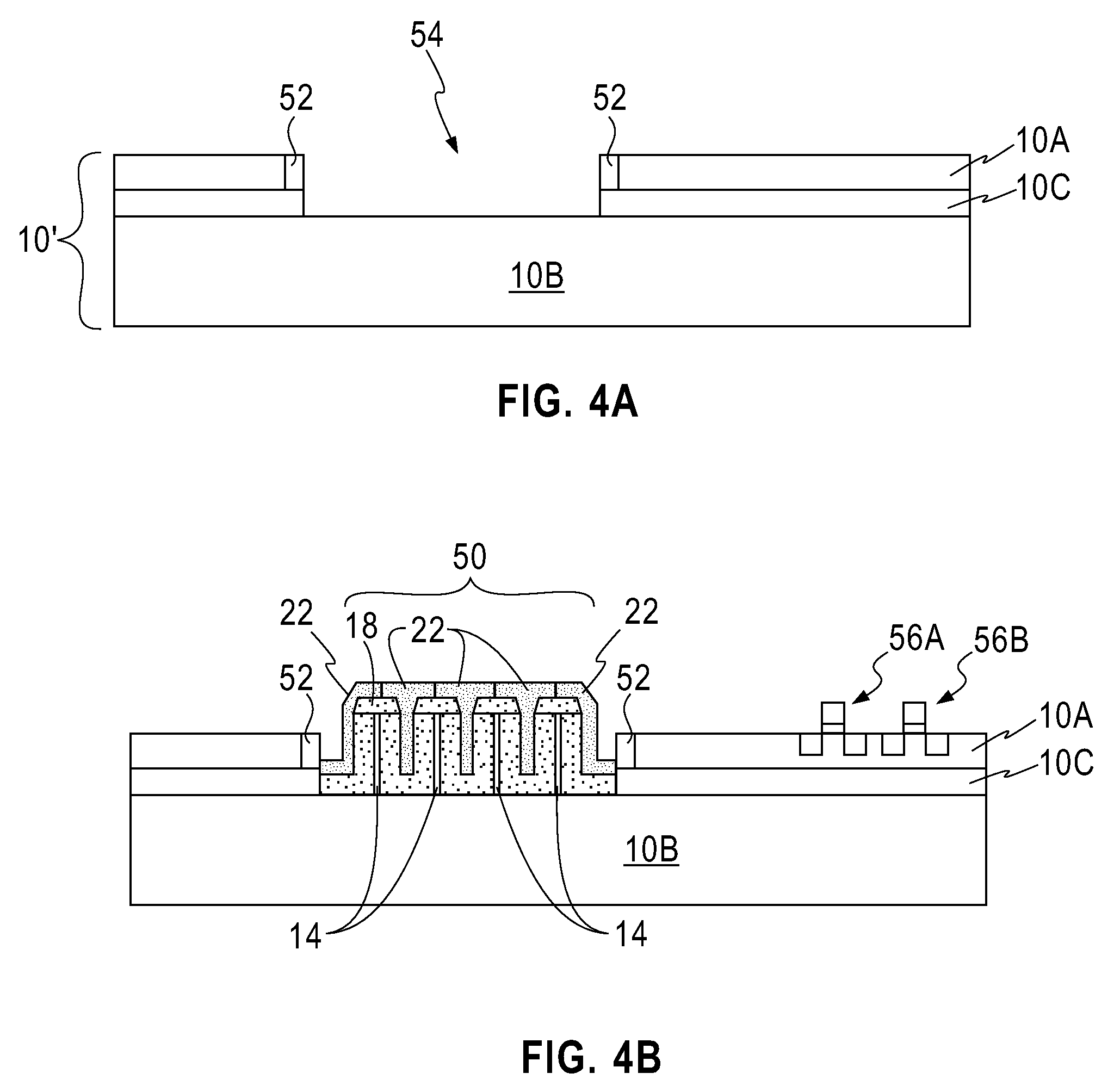

A high performance GAA FET is described in which vertically stacked silicon nanowires carry substantially the same drive current as the fin in a conventional FinFET transistor, but at a lower operating voltage, and with greater reliability. One problem that occurs in existing nanowire GAA FETs is that, when a metal is used to form the wrap-around gate, a short circuit can develop between the source and drain regions and the metal gate portion that underlies the channel. The vertically stacked nanowire device described herein, however, avoids such short circuits by forming insulating barriers in contact with the source and drain regions, prior to forming the gate. Through the use of sacrificial films, the fabrication process is almost fully self-aligned, such that only one lithography mask layer is needed, which significantly reduces manufacturing costs.

Owner:IBM CORP +2

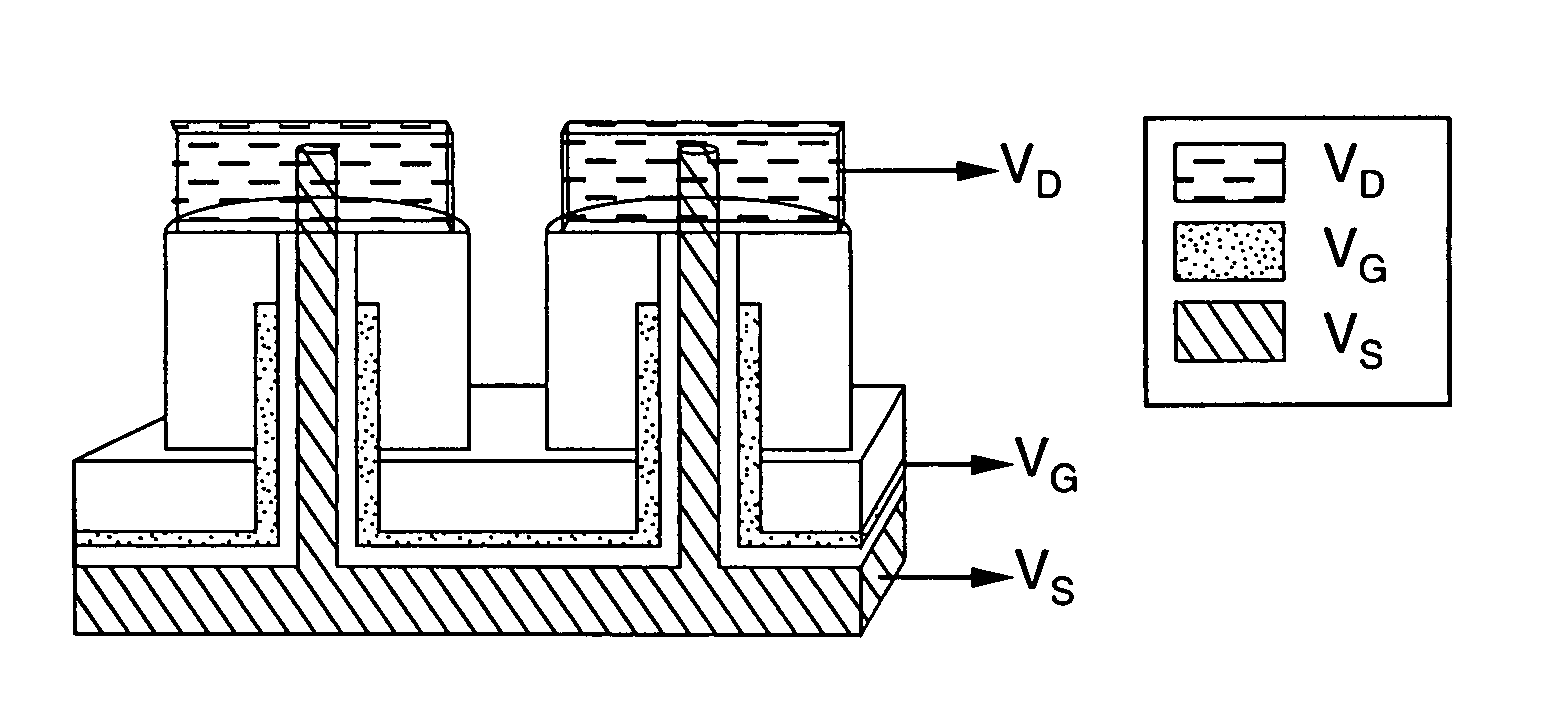

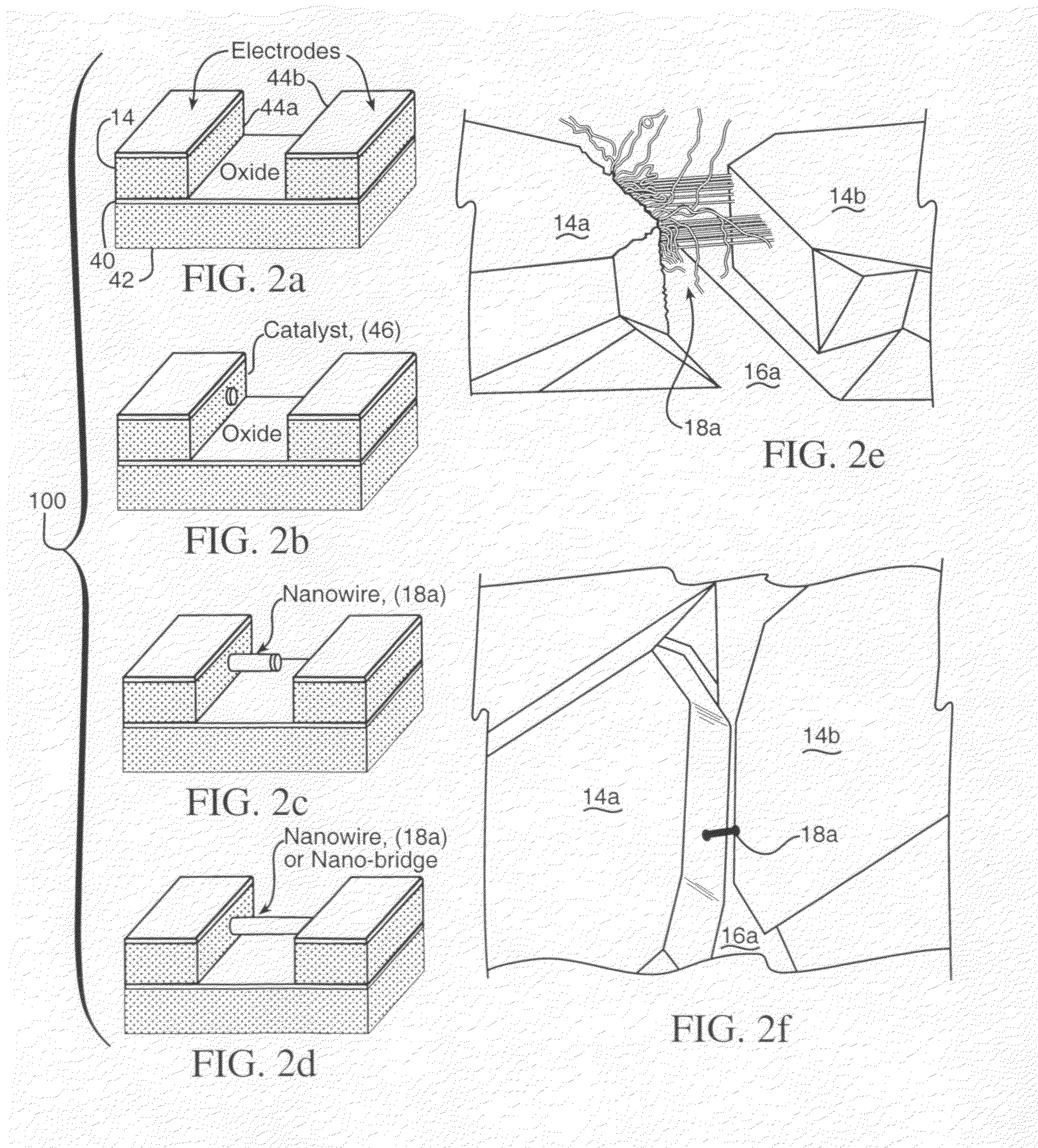

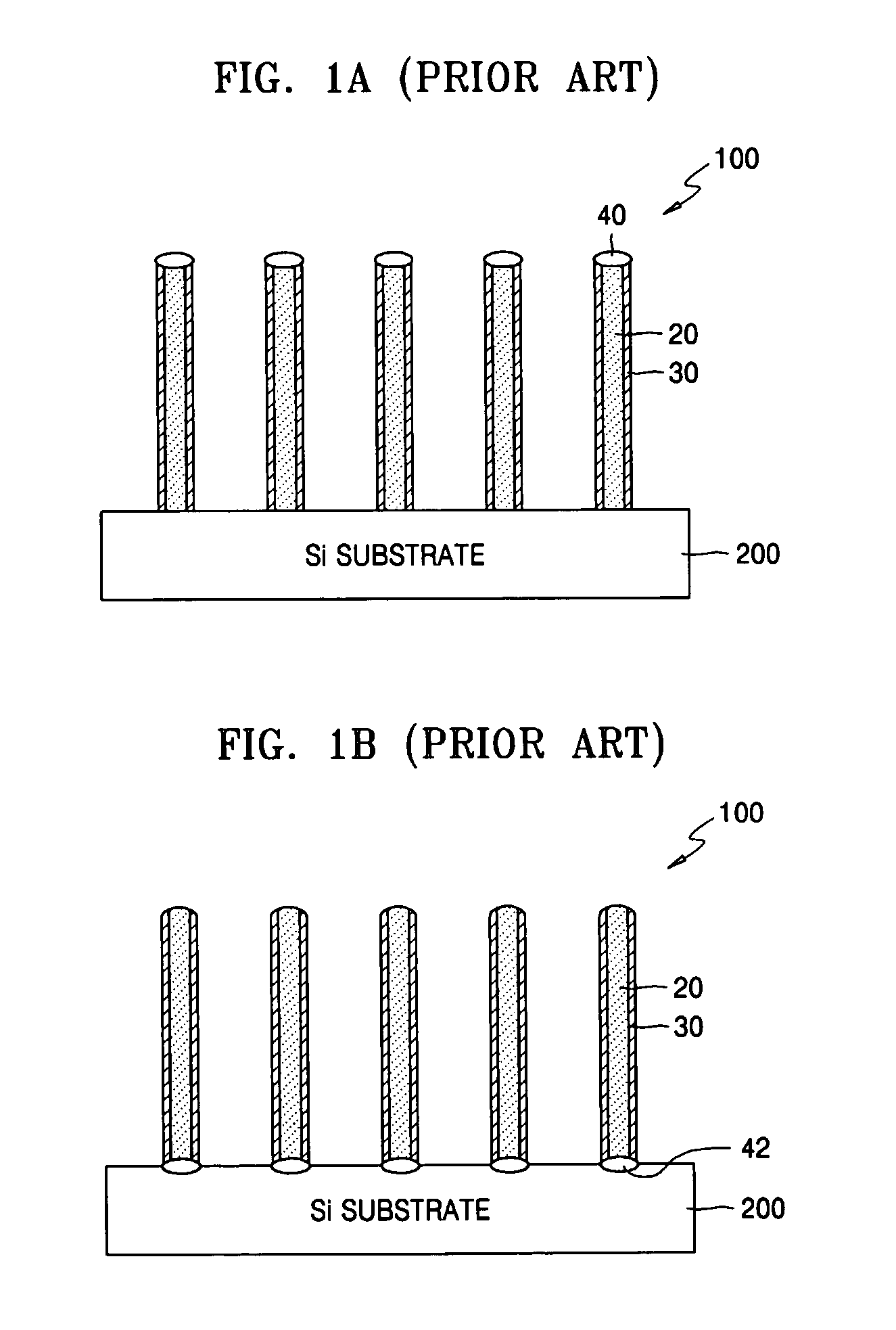

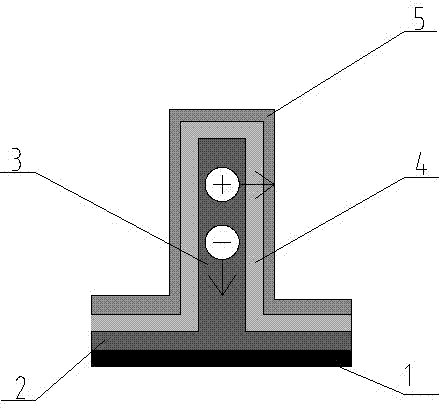

Vertical integrated silicon nanowire field effect transistors and methods of fabrication

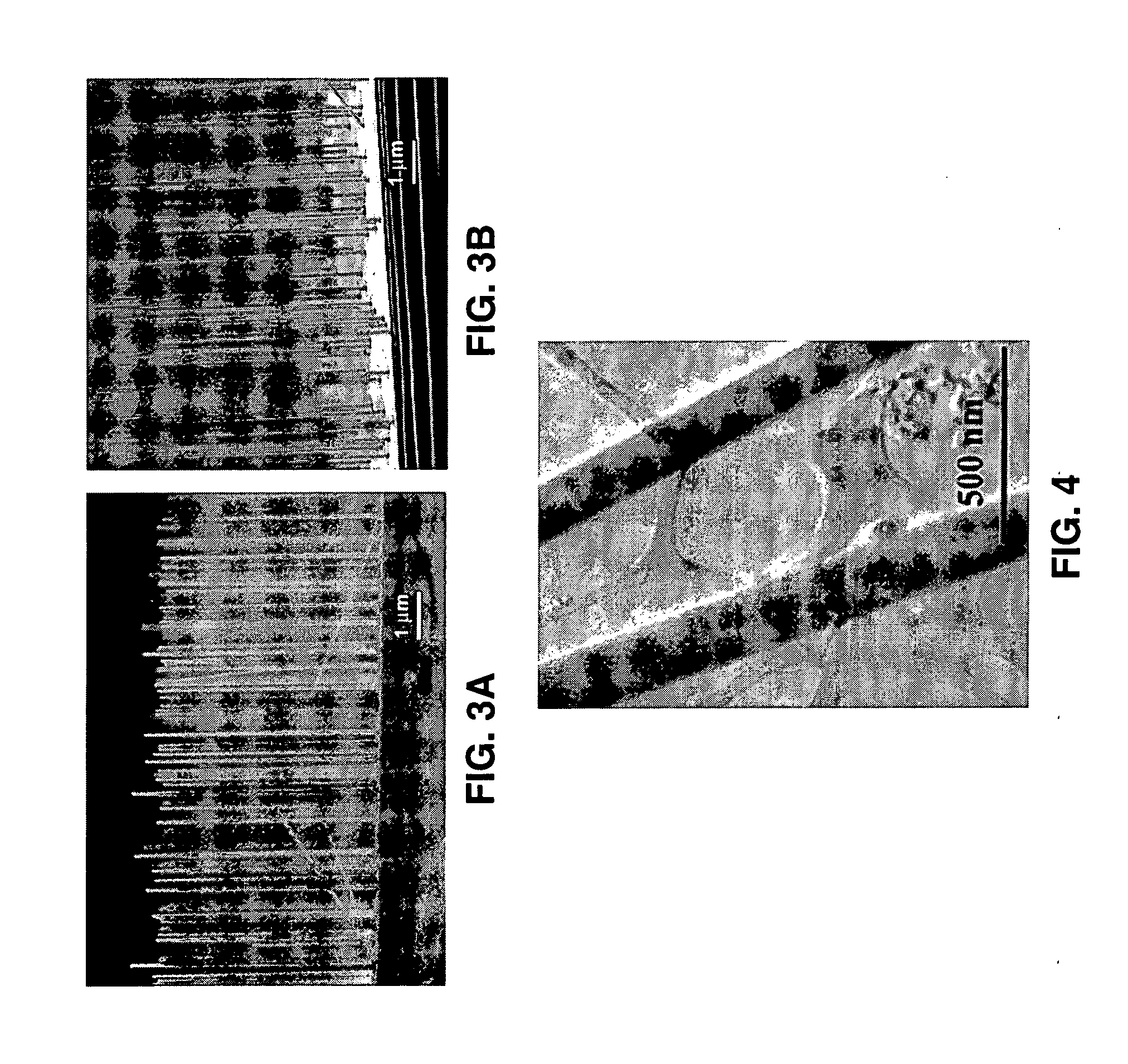

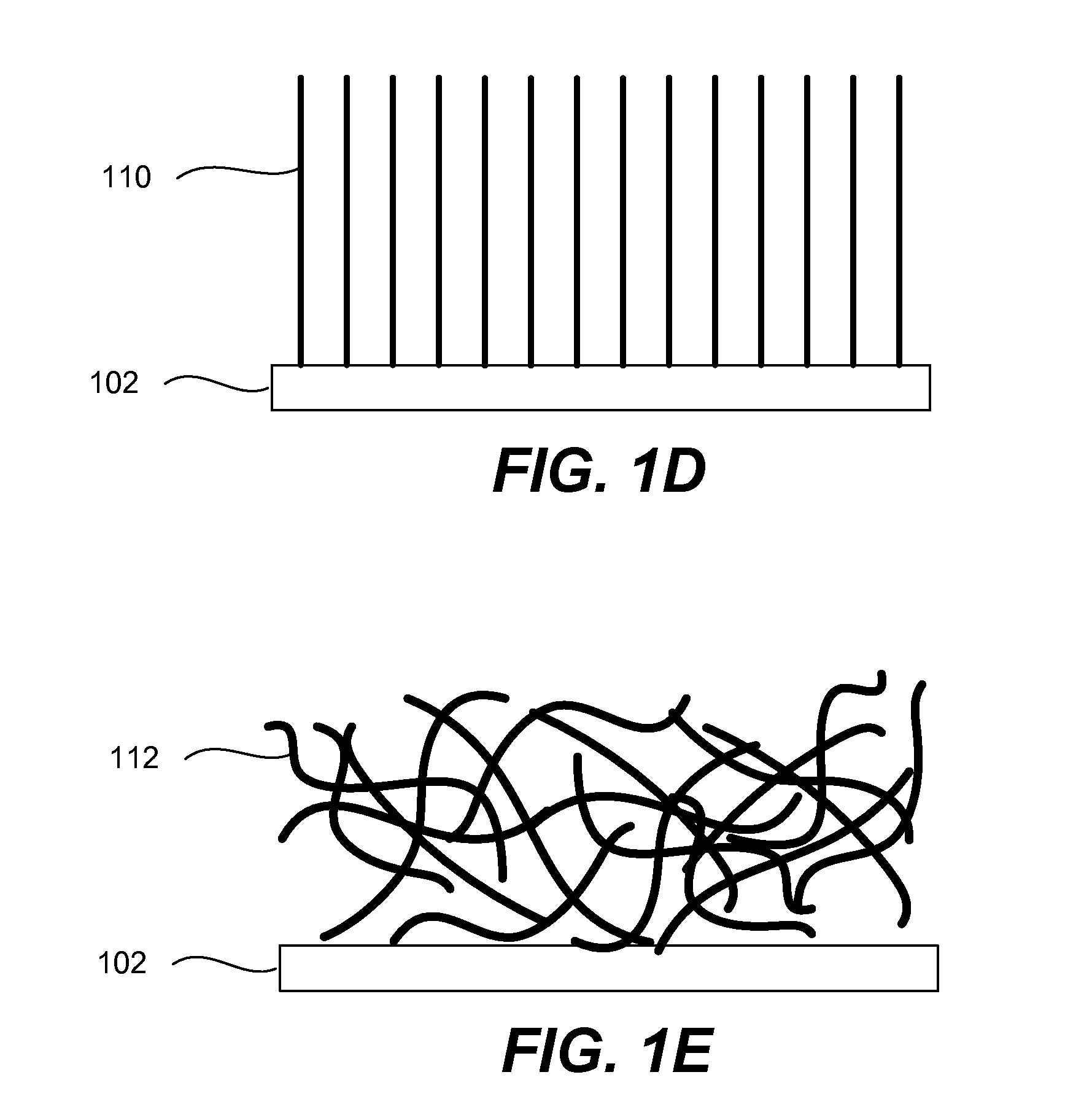

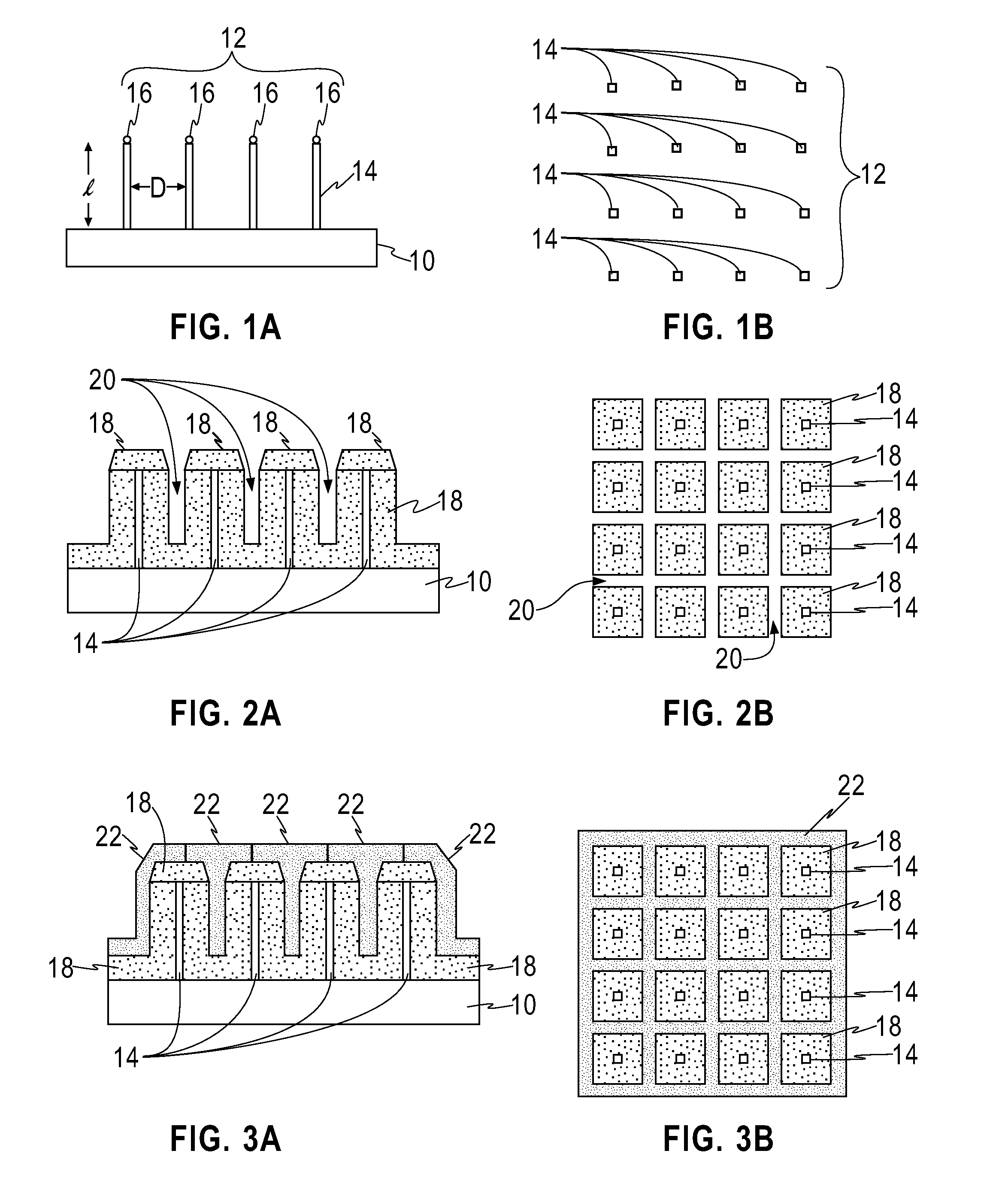

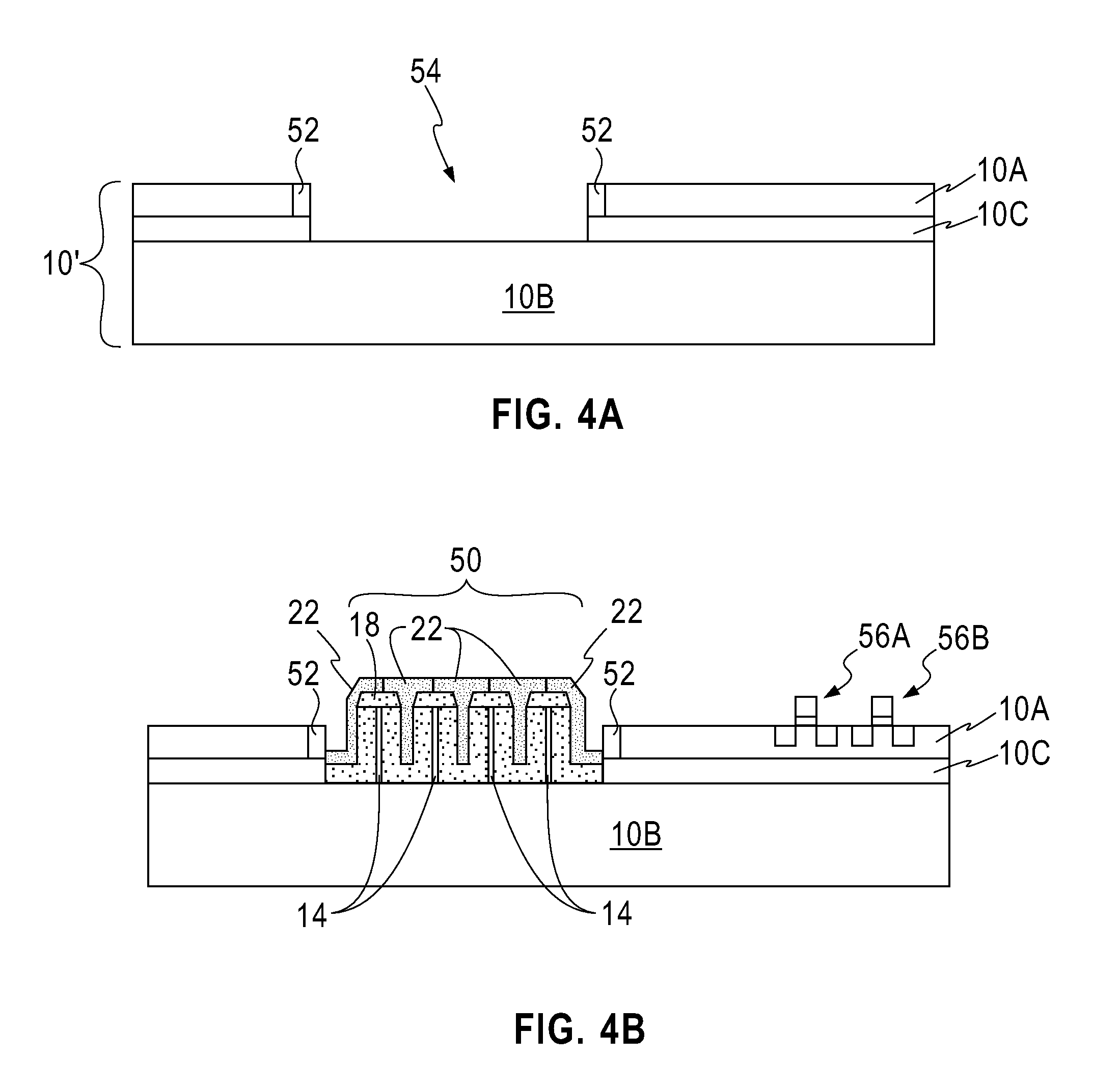

Vertical integrated field effect transistor circuits and methods are described which are fabricated from Silicon, Germanium, or a combination Silicon and Germanium based on nanowires grown in place on the substrate. By way of example, vertical integrated transistors are formed from one or more nanowires which have been insulated, had a gate deposited thereon, and to which a drain is coupled to the exposed tips of one or more of the nanowires. The nanowires are preferably grown over a surface or according to a desired pattern in response to dispersing metal nanoclusters over the desired portions of the substrate. In one preferred implementation, SiCl4 is utilized as a gas phase precursor during the nanowire growth process. In place nanowire growth is also taught in conjunction with structures, such as trenches, while bridging forms of nanowires are also described.

Owner:RGT UNIV OF CALIFORNIA

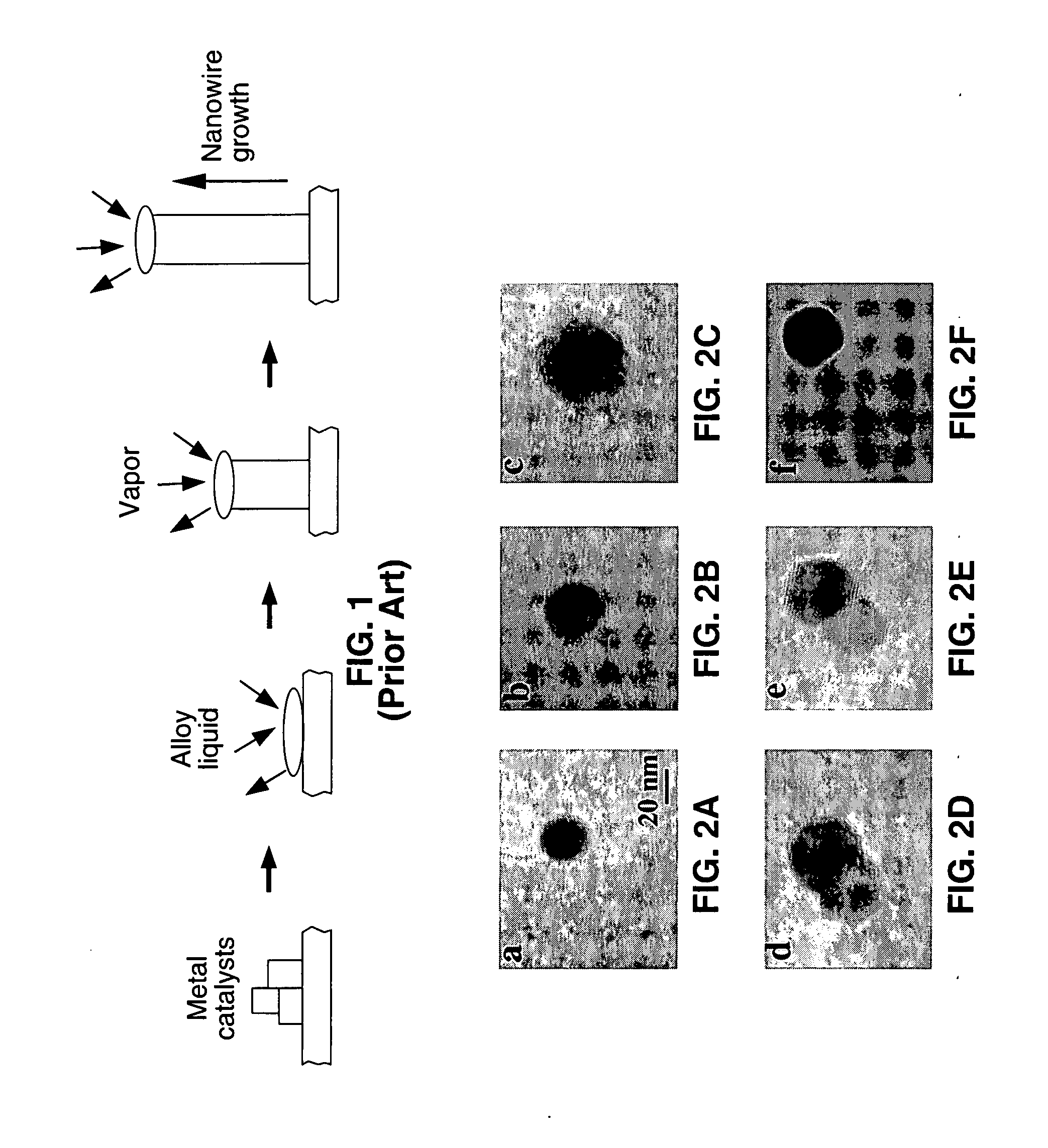

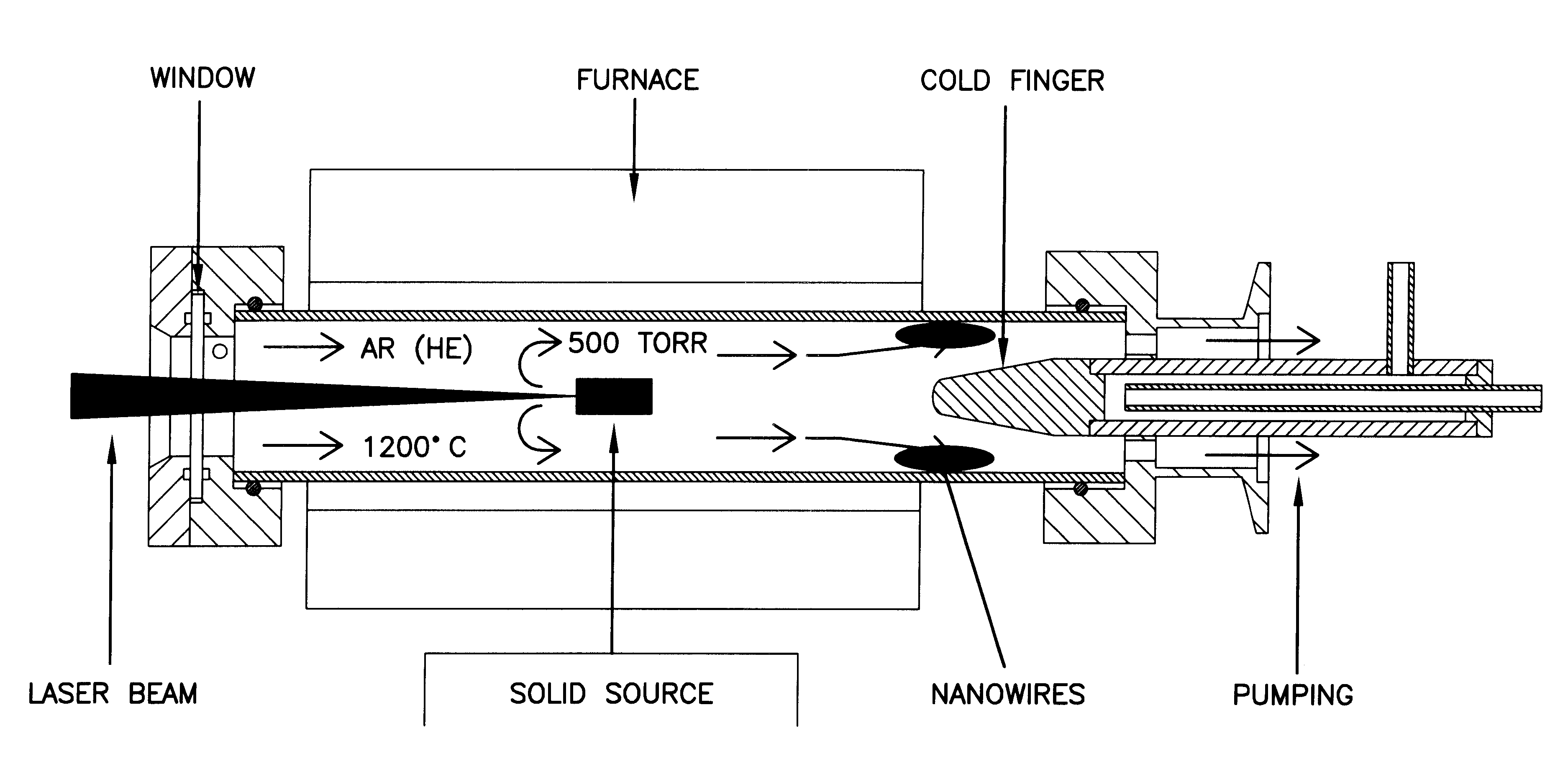

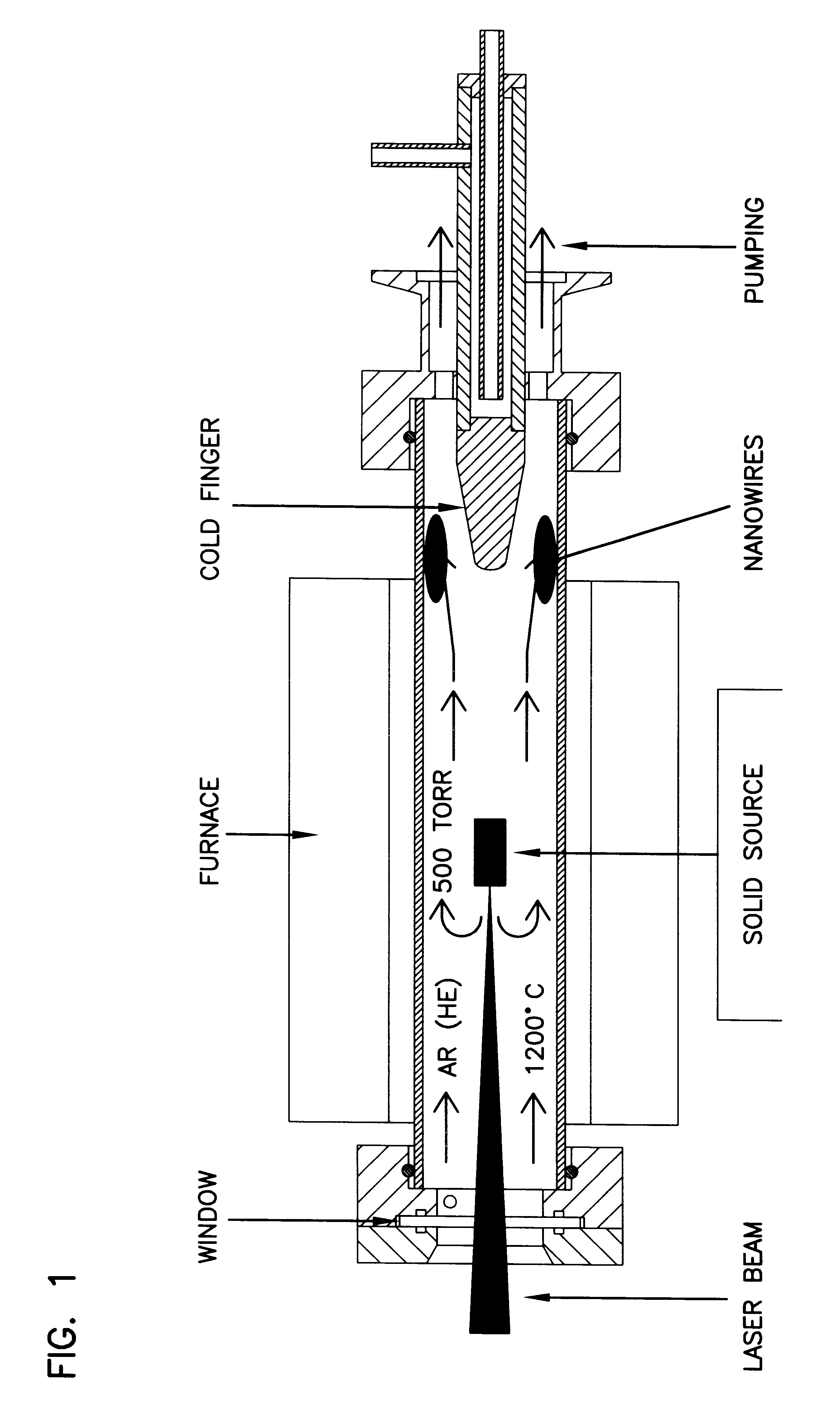

Growth method for silicon nanowires and nanoparticle chains from silicon monoxide

InactiveUS6313015B1Enhance one-dimensional growthLowering of total energy of systemPolycrystalline material growthNanotechSputteringSilicon monoxide

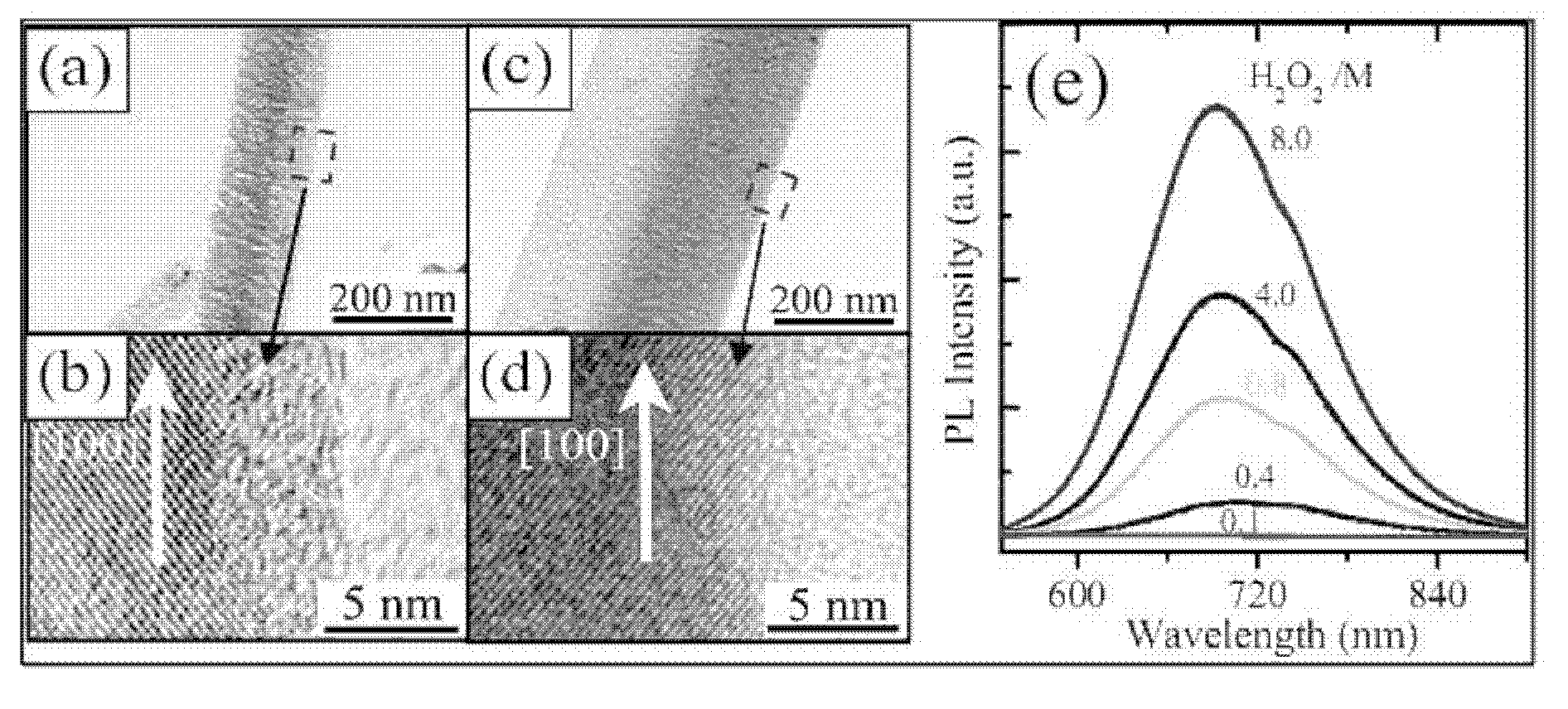

Silicon nanowires and silicon nanoparticle chains are formed by the activation of silicon monoxide in the vapor phase. The silicon monoxide source may be solid or gaseous, and the activation may be by thermal excitation, laser ablation, plasma or magnetron sputtering. The present invention produces large amounts of silicon nanowires without requiring the use of any catalysts that may cause contamination.

Owner:HONG KONG CITY UNIV OF

Tunnel effect transistors based on silicon nanowires

InactiveUS20080067495A1Optimize architectureReduce power consumptionTransistorNanoinformaticsMOSFETLattice mismatch

Tunnel field-effect transistors (TFETs) are regarded as successors of metal-oxide semiconductor field-effect transistors (MOSFETs), but silicon-based TFETs typically suffer from low on-currents, a drawback related to the large resistance of the tunnel barrier. To achieve higher on-currents a nanowire-based TFET with a germanium (Ge) tunnel barrier in an otherwise silicon (Si) channel is used. A nanowire is introduced such that the lattice mismatch between silicon and germanium does not result in a highly defective interface. A dynamic power reduction as well as a static power reduction can result, compared to conventional MOSFET configurations. Multiple layers of logic can therefore be envisioned with these nanowire Si / Ge TFETs resulting in ultra-high on-chip transistor densities.

Owner:KATHOLIEKE UNIV LEUVEN

Graded hybrid amorphous silicon nanowire solar cells

InactiveUS20080135089A1Raise VocIncrease IscPV power plantsSemiconductor/solid-state device manufacturingAmorphous siliconSilicon nanowires

In some embodiments, the present invention is directed to compositionally-graded hybrid nanostructure-based photovoltaic devices comprising elongated semiconductor nanostructures and an amorphous semiconductor single layer with continuous gradation of doping concentration across its thickness from substantially intrinsic to substantially conductive. In other embodiments, the present invention is directed to methods of making such photovoltaic devices, as well as to applications which utilize such devices (e.g., solar cell modules).

Owner:GENERAL ELECTRIC CO

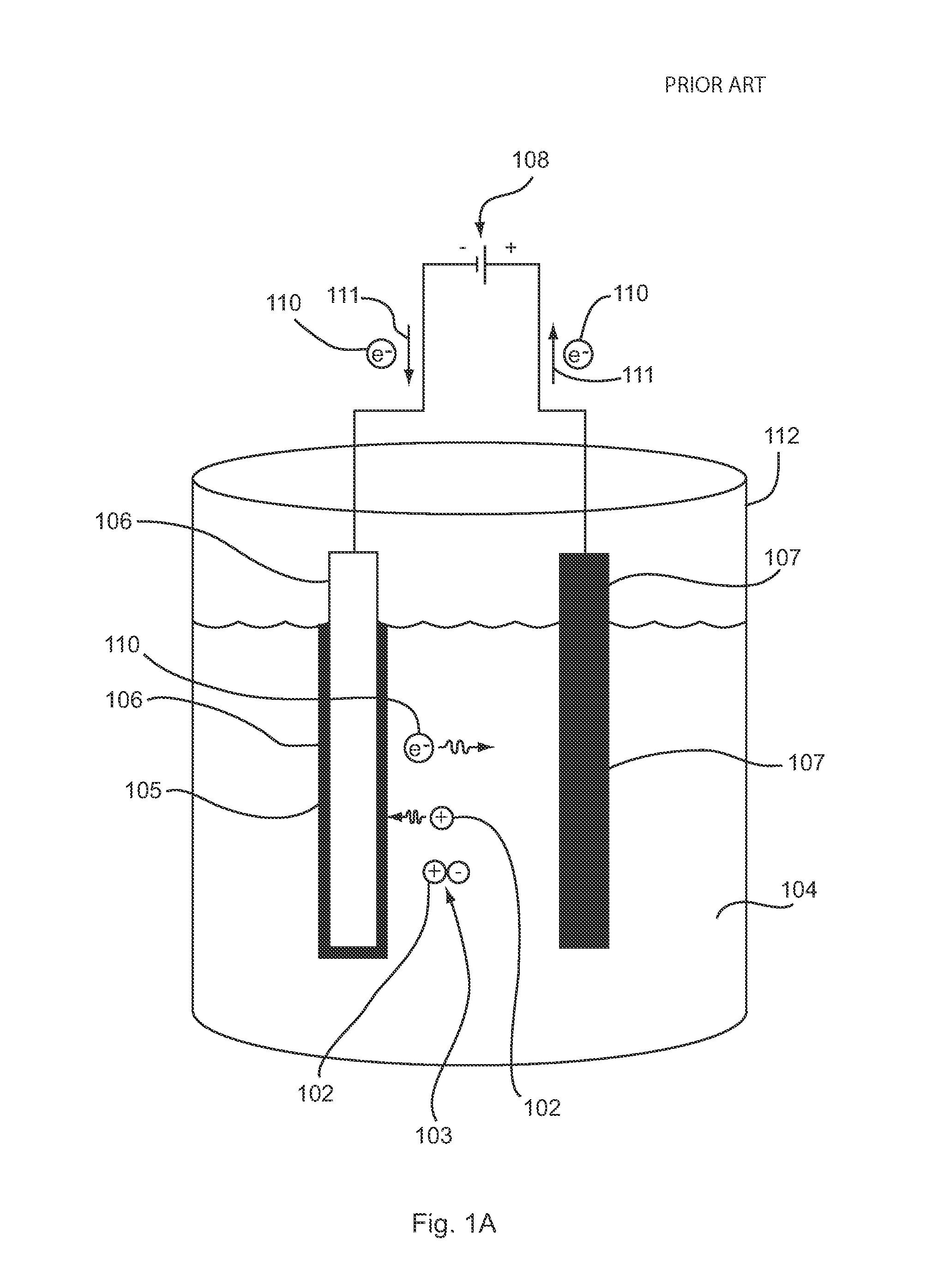

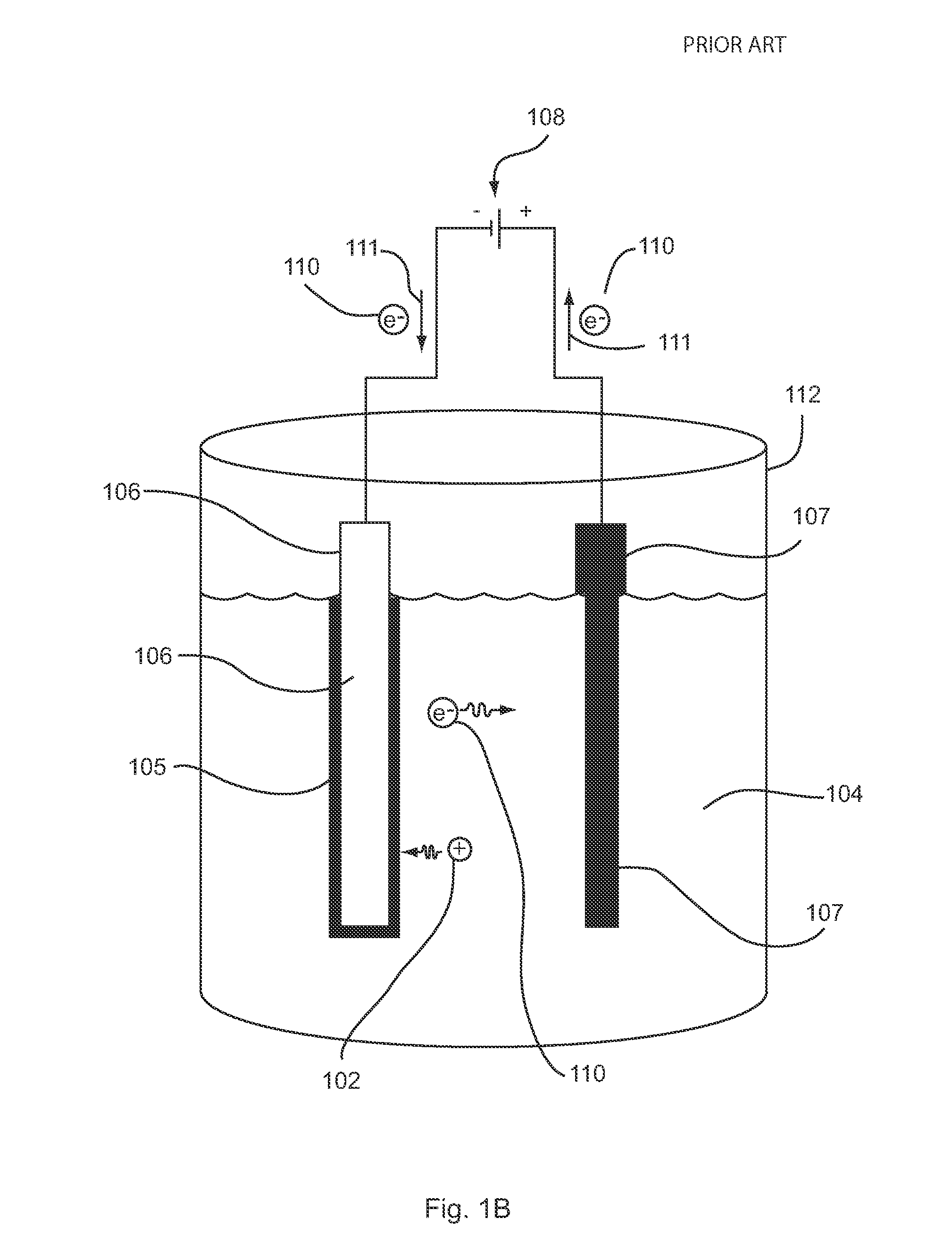

Electrode including nanostructures for rechargeable cells

ActiveUS20120183856A1Lower resistanceMaterial nanotechnologyNanostructure manufactureRechargeable cellSilicon nanowires

A lithium ion battery electrode includes silicon nanowires used for insertion of lithium ions and including a conductivity enhancement, the nanowires growth-rooted to the conductive substrate.

Owner:AMPRIUS TECH INC

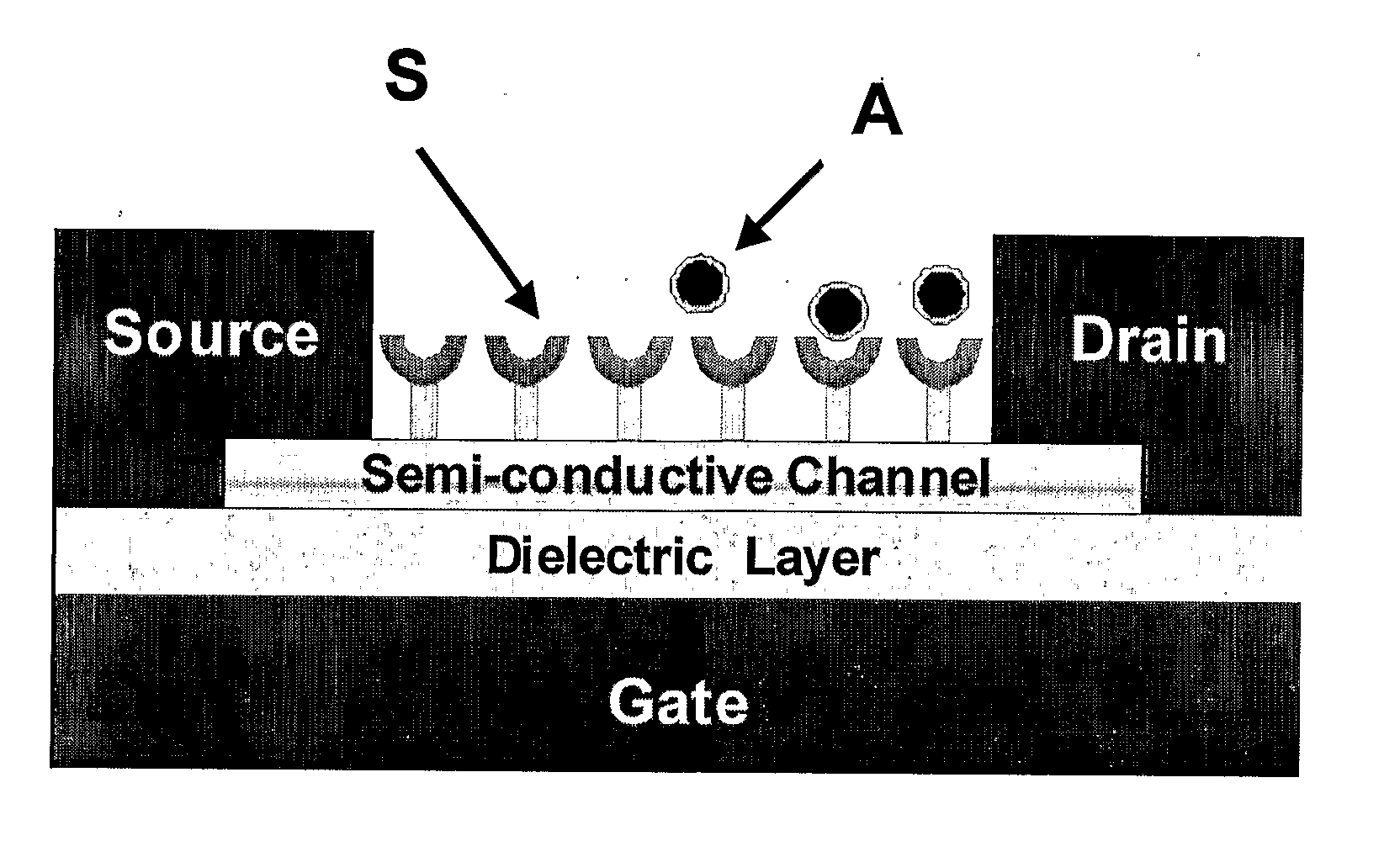

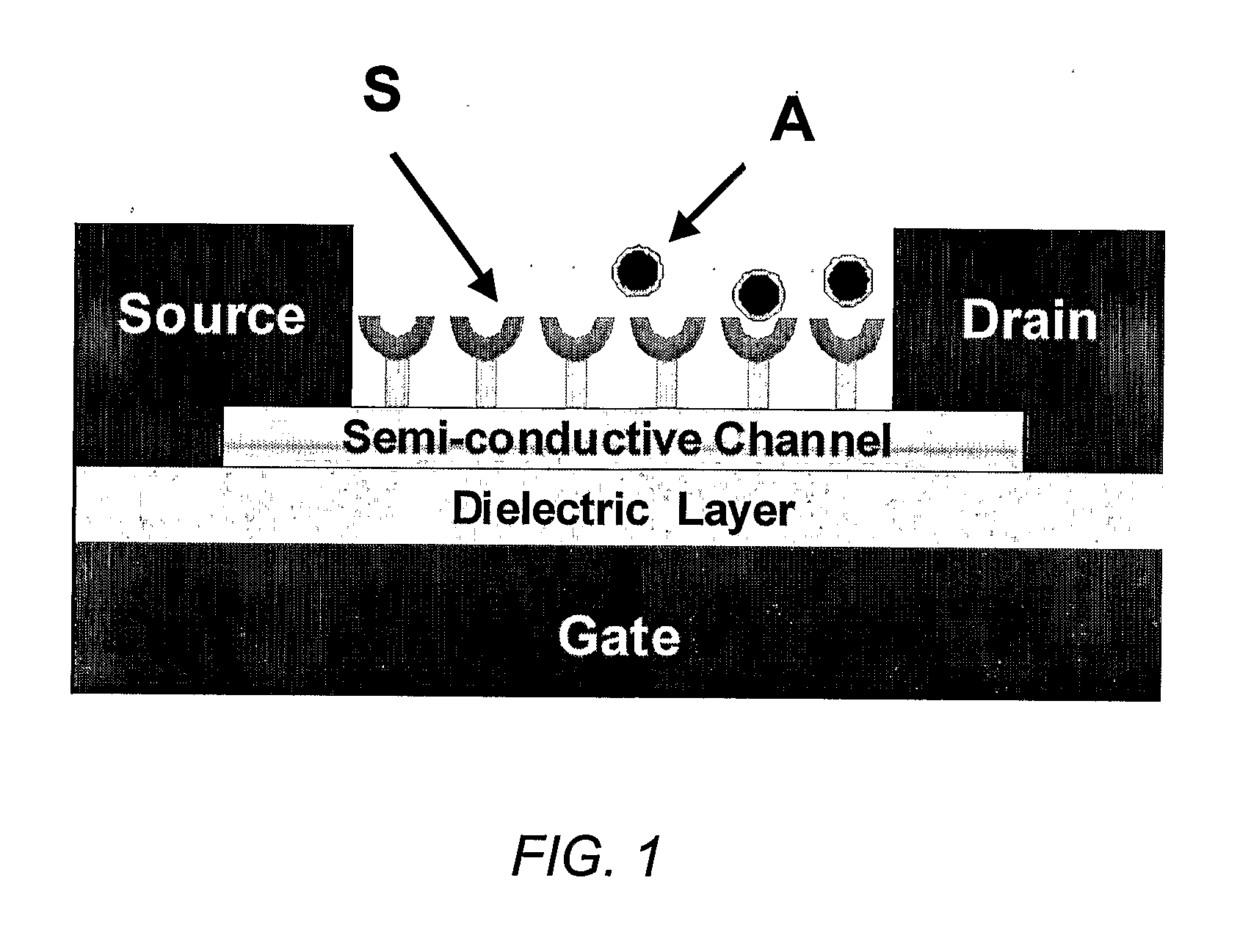

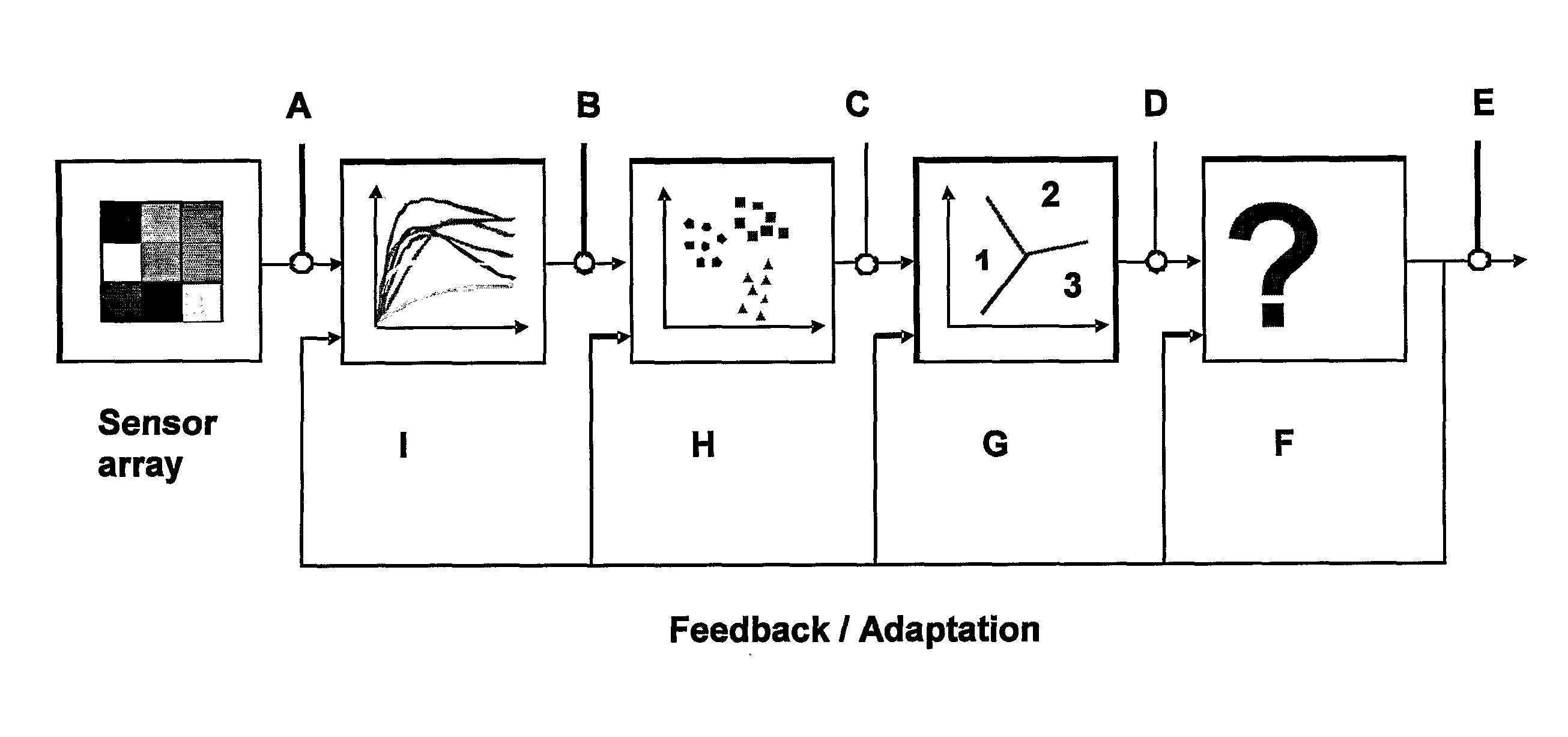

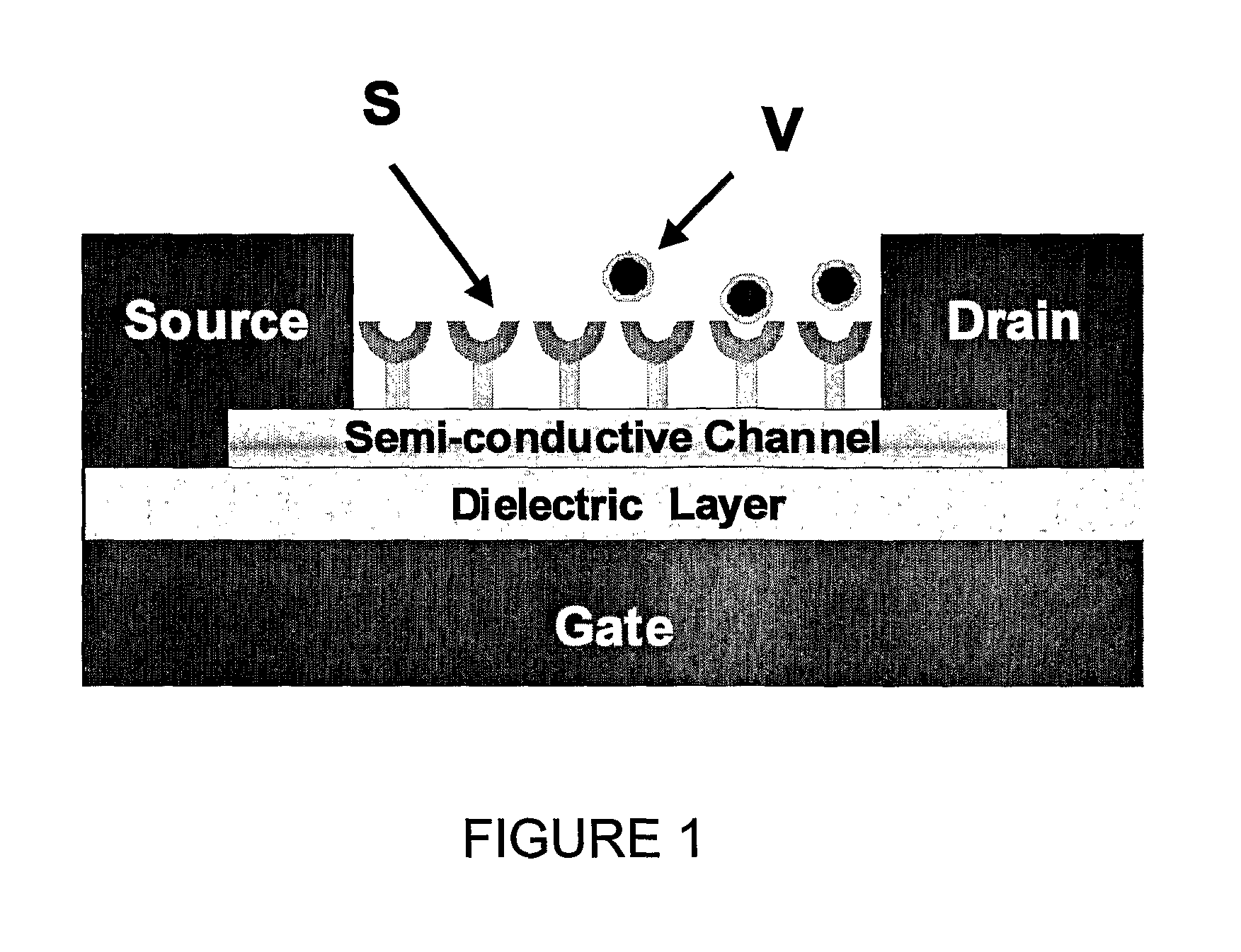

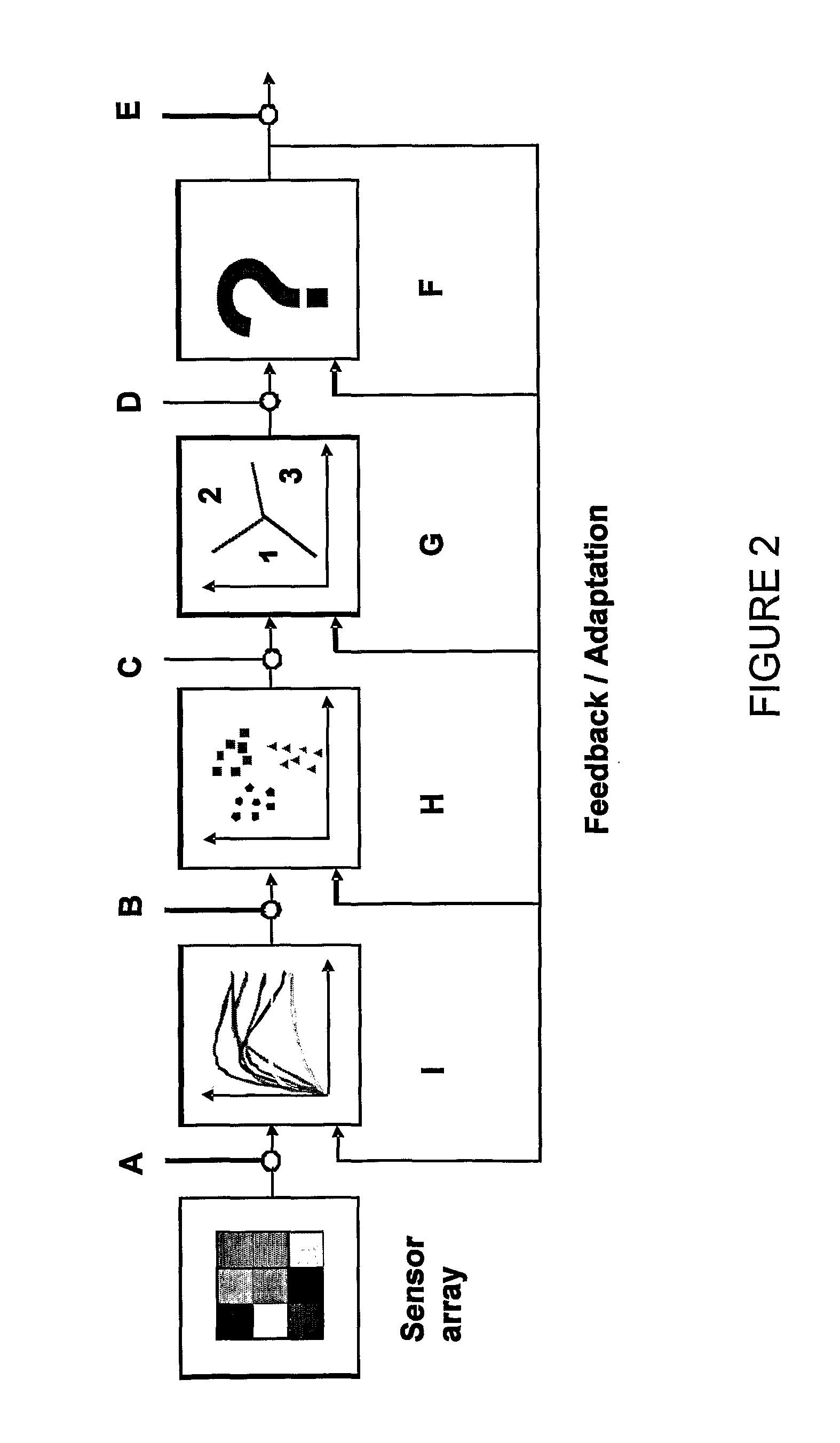

Chemically sensitive field effect transistors and uses thereof in electronic nose devices

ActiveUS20100198521A1High sensitivityImprove Sensing PerformanceMaterial nanotechnologyMaterial analysis by electric/magnetic meansDiseaseMedicine

The present invention provides an electronic nose device based on chemically sensitive field effect transistors. In particular, the sensors of the electronic nose device are composed of non-oxidized, functionalized silicon nanowires which can detect volatile organic compounds with very high sensitivity. Methods of use in diagnosing diseases including various types of cancer are disclosed.

Owner:TECHNION RES & DEV FOUND LTD

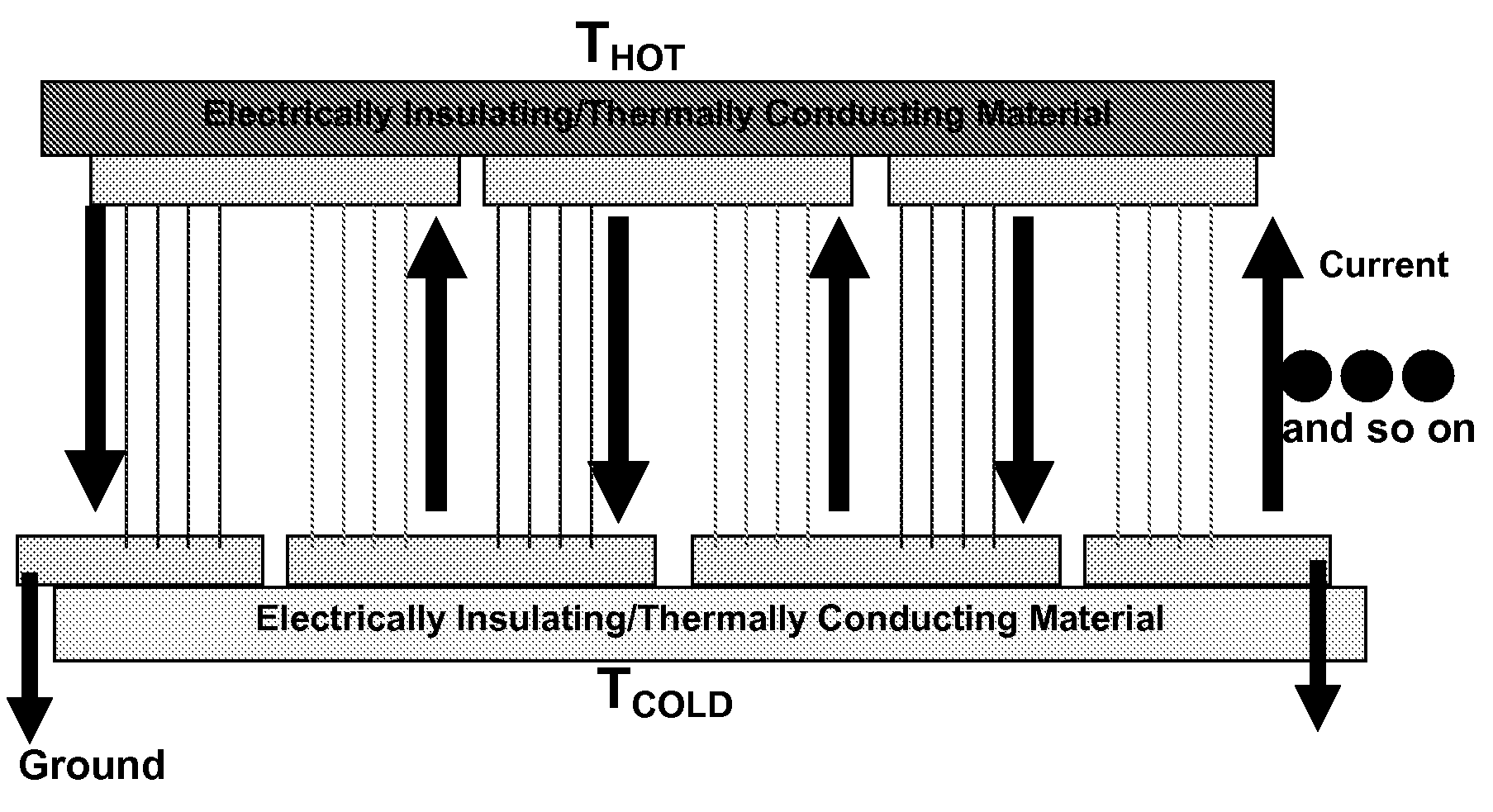

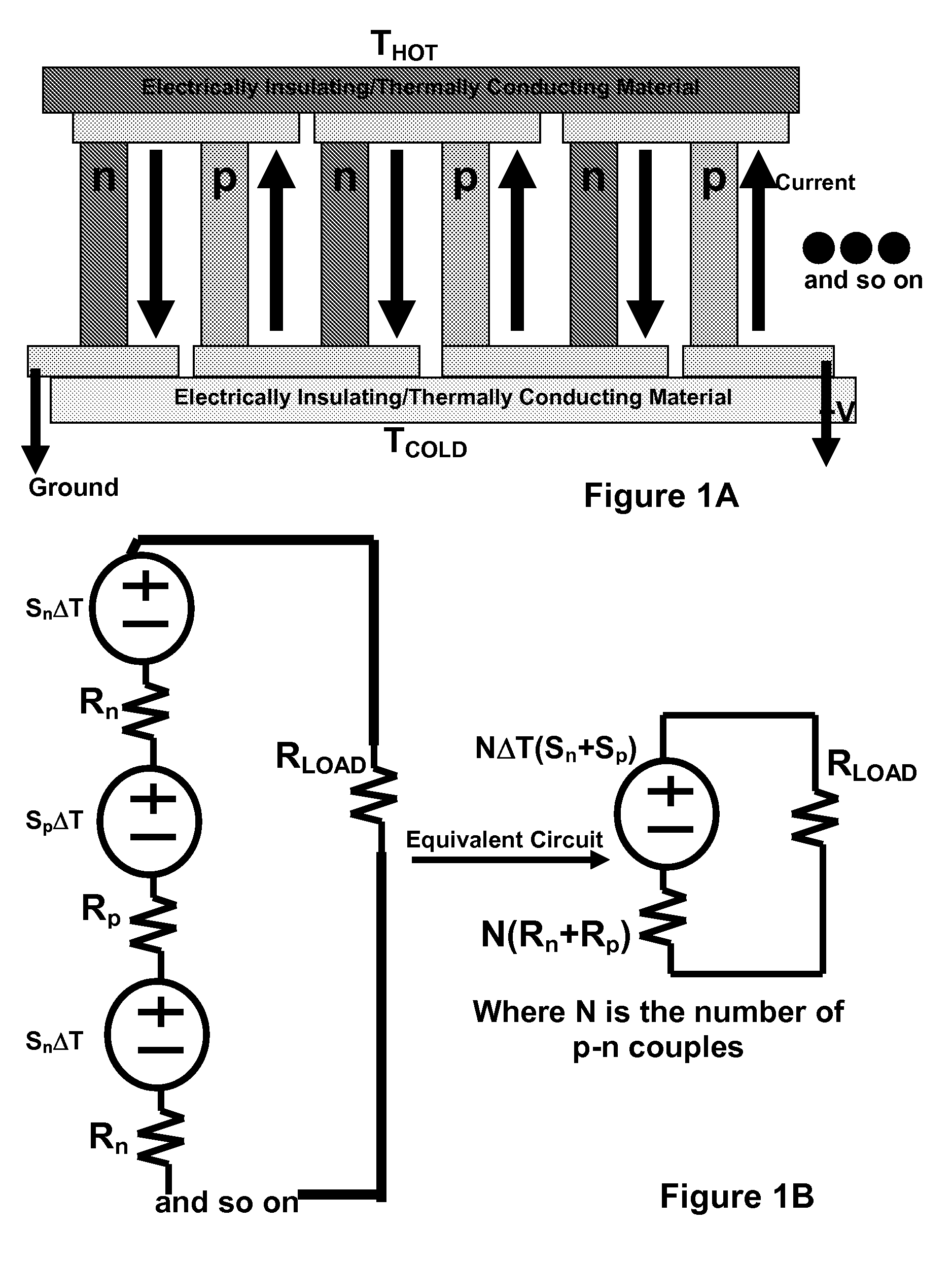

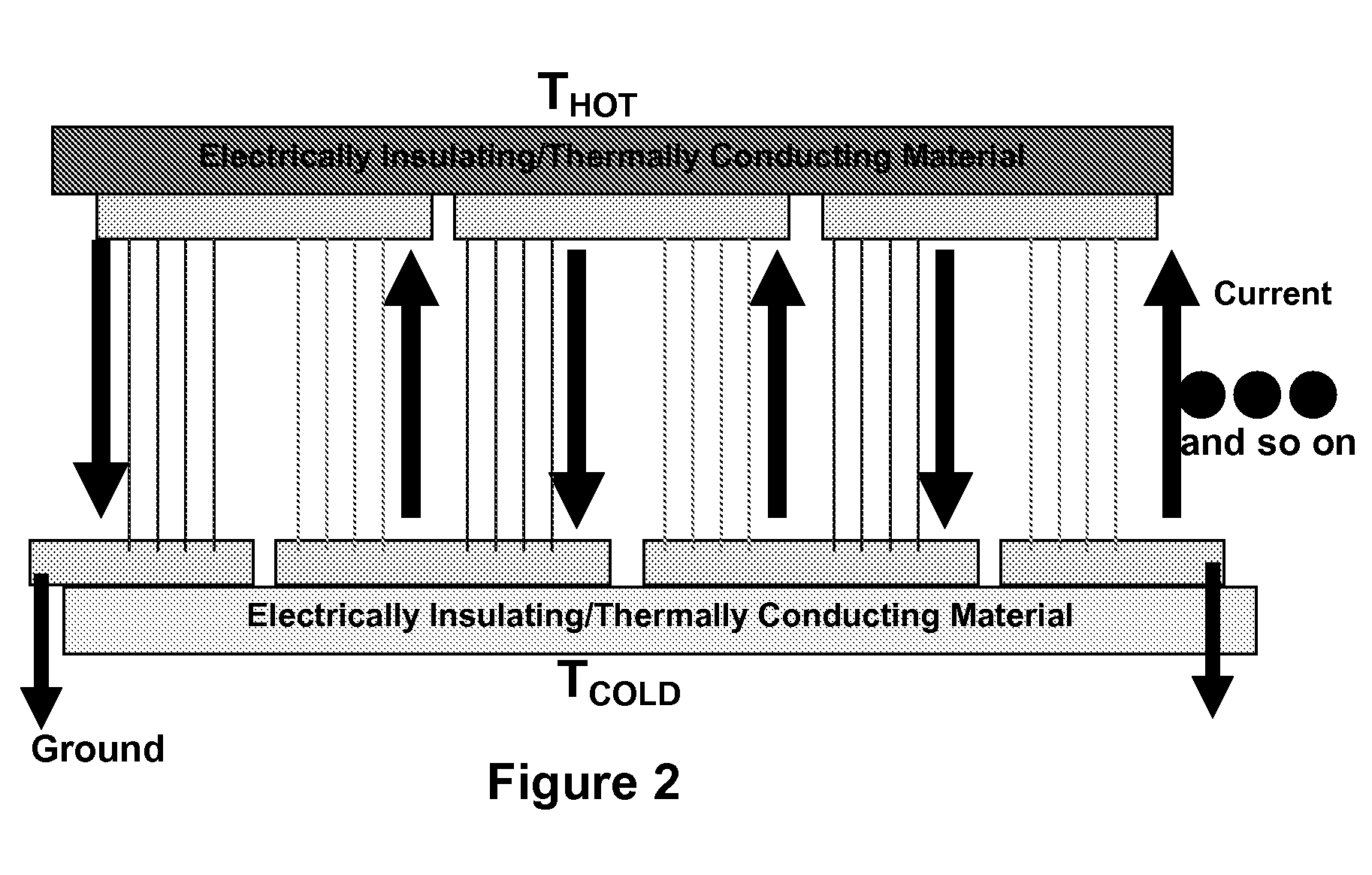

Methods and devices for controlling thermal conductivity and thermoelectric power of semiconductor nanowires

ActiveUS20090020148A1High thermoelectric efficiencyThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentSilicon nanowiresThermocouple

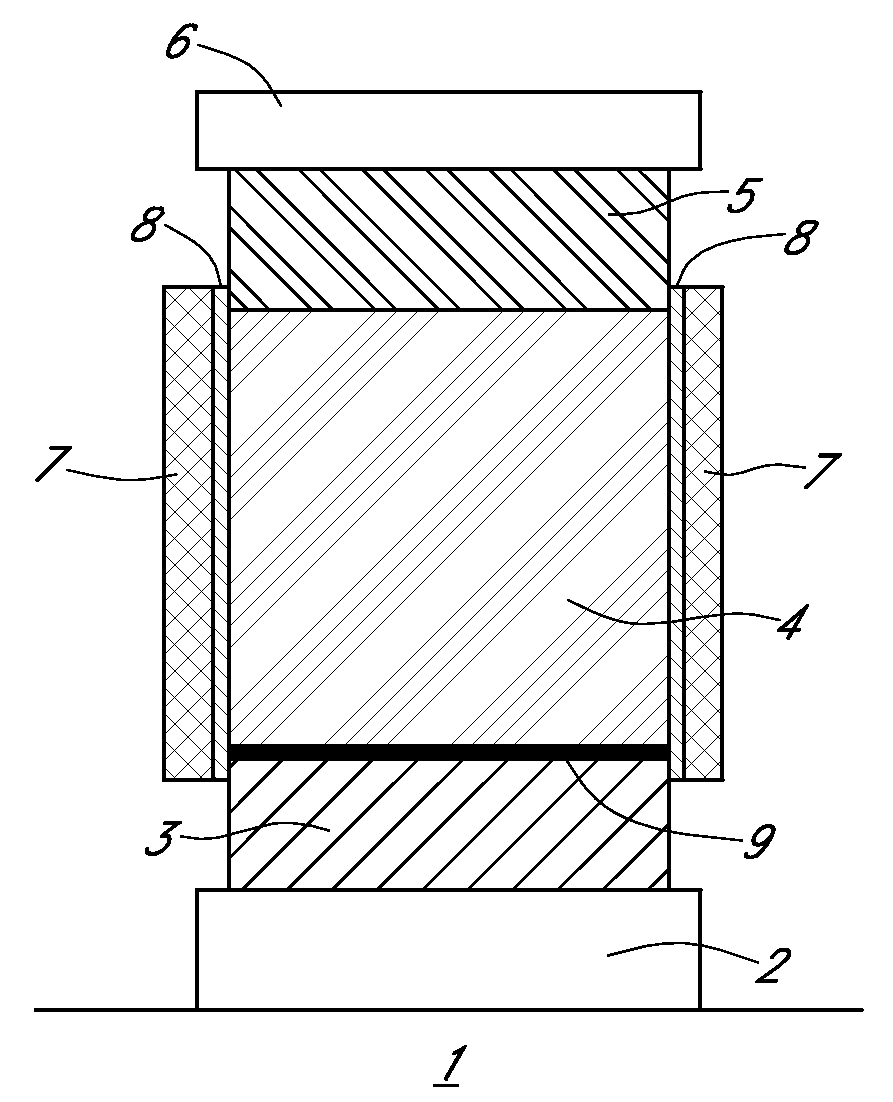

Methods and devices for controlling thermal conductivity and thermoelectric power of semiconductor nanowires are described. The thermal conductivity and the thermoelectric power are controlled substantially independently of the electrical conductivity of the nanowires by controlling dimensions and doping, respectively, of the nanowires. A thermoelectric device comprising p-doped and n-doped semiconductor nanowire thermocouples is also shown, together with a method to fabricate alternately p-doped and n-doped arrays of silicon nanowires.

Owner:CALIFORNIA INST OF TECH

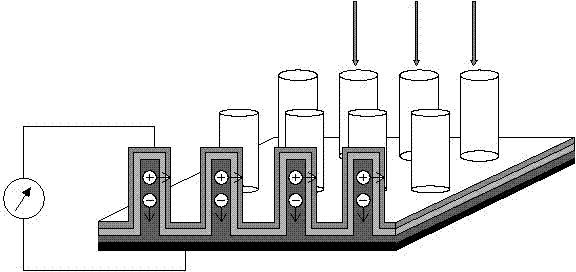

Method for manufacturing and integrating multichannel high-sensitive biosensor

InactiveCN101592627AHigh sensitivityExtend your lifeSemi-permeable membranesNanostructure manufactureField-effect transistorMicrofluidic channel

The invention provides a method for manufacturing and integrating a multichannel high-sensitive biosensor. The method comprises the following steps: firstly, based on an SOI silicon chip, adopting a top-down method to manufacture an FET field effect transistor of a silicon nanometer wire; secondly, utilizing polydimethylsiloxane (PDMS) to manufacture a plurality of microfluid channels; and finally, modifying the silicon nanometer wires in different microfluid channels to allow the silicon nanometer wire to be modified with different detecting antibodies and small molecules for detecting different target molecules. The sensor manufacture by the method can be used for simultaneously detecting relevant factors (such as DNA, RNA, protein and the like) or virus of different types of diseases and has the characteristics of high sensitivity, stability, easy integration and the like.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

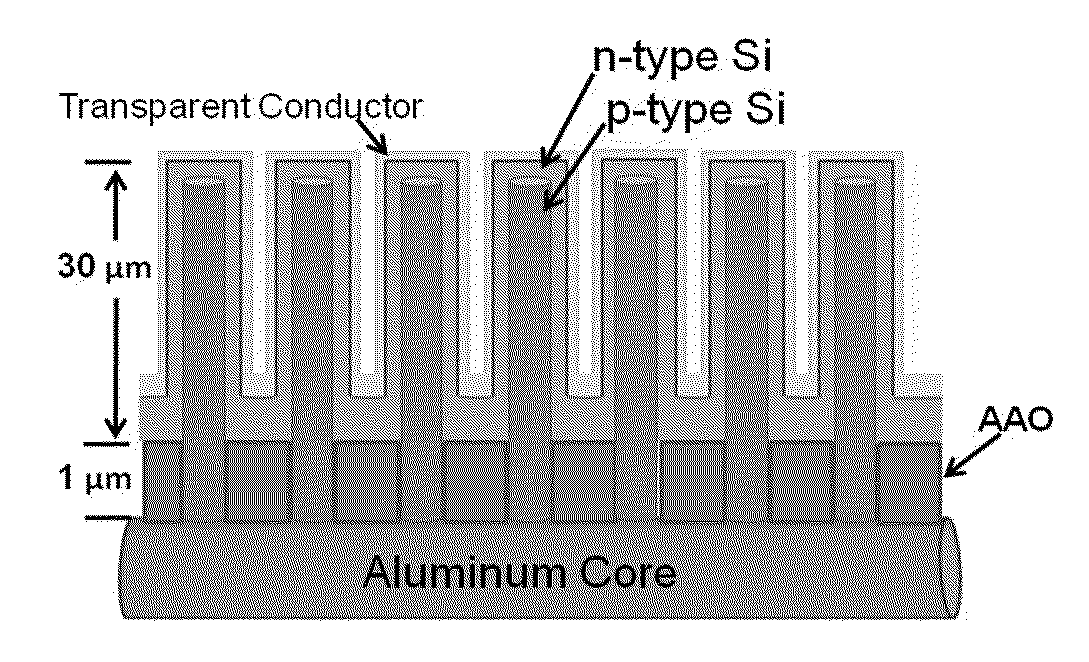

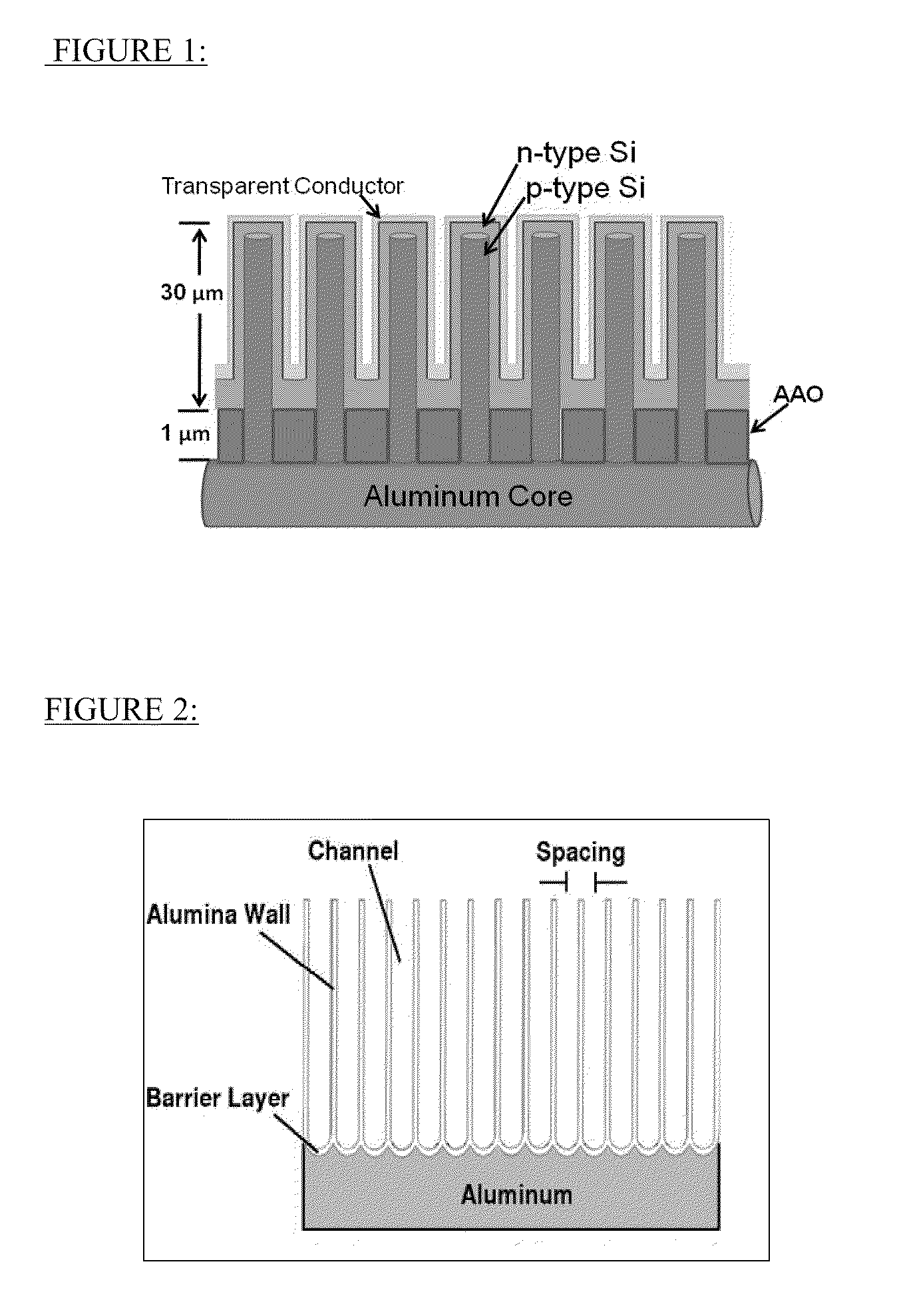

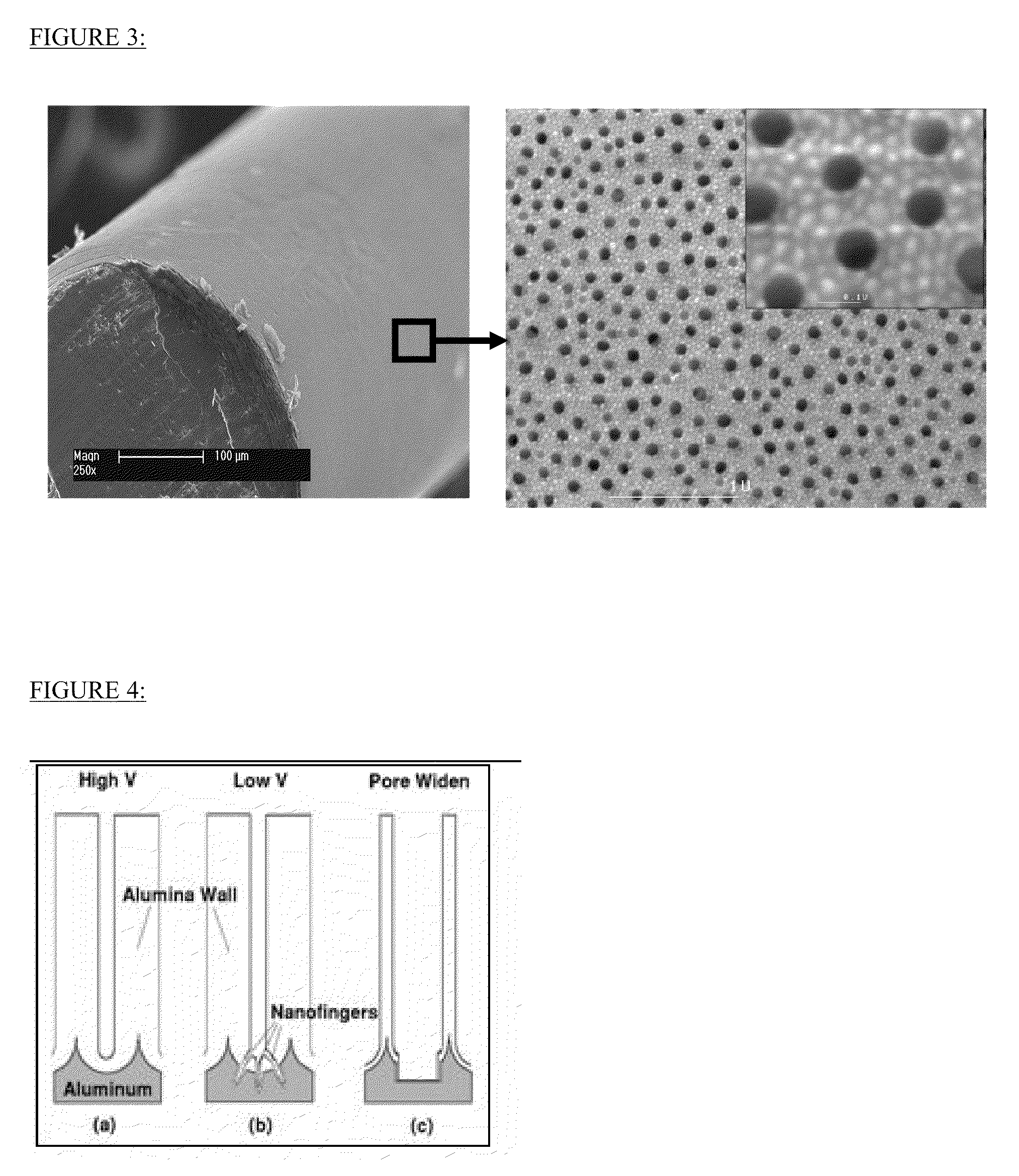

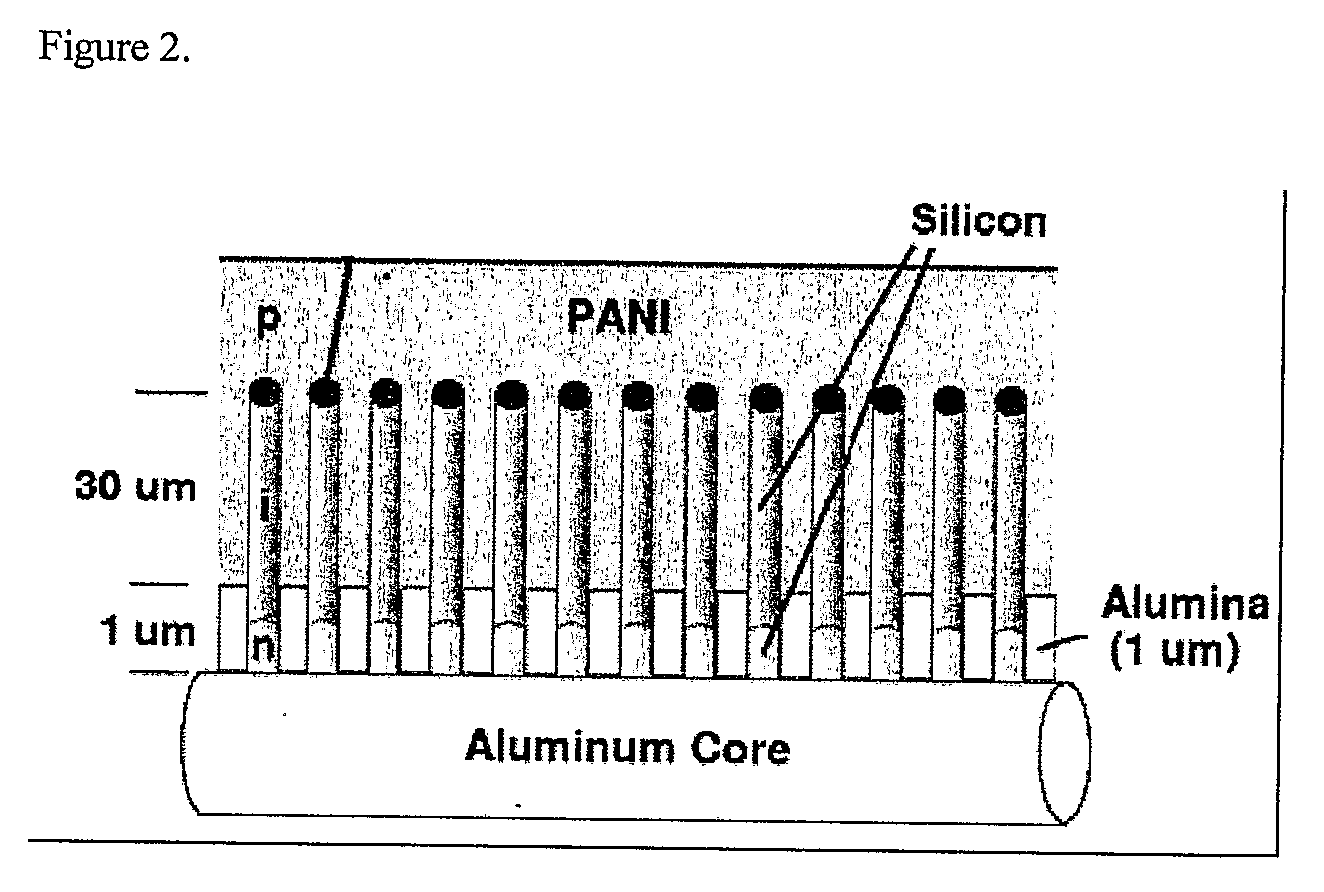

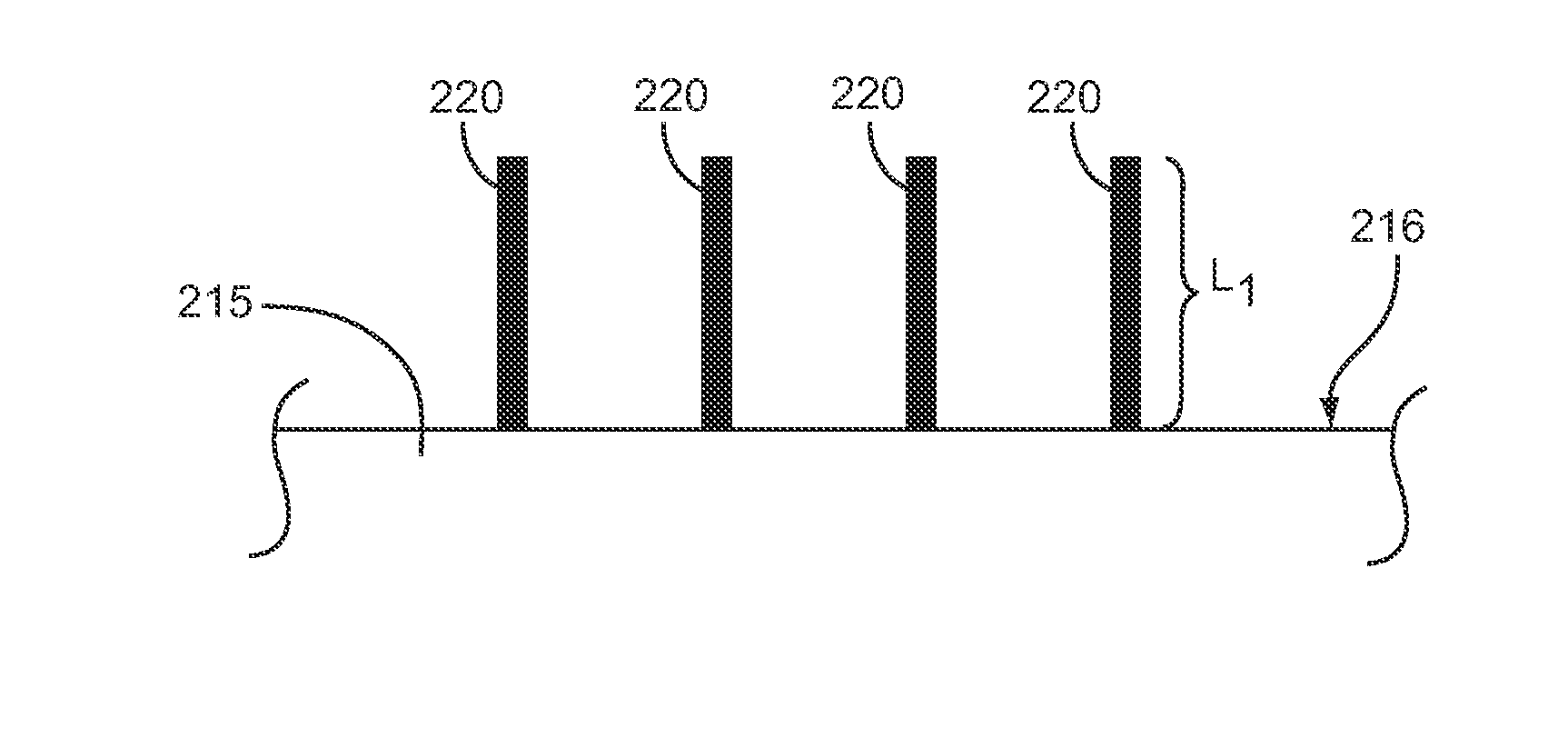

Semiconducting nanowire arrays for photovoltaic applications

InactiveUS20100193768A1Novel design attributeEasy to produceSolid-state devicesSemiconductor/solid-state device manufacturingDopantSilicon nanowires

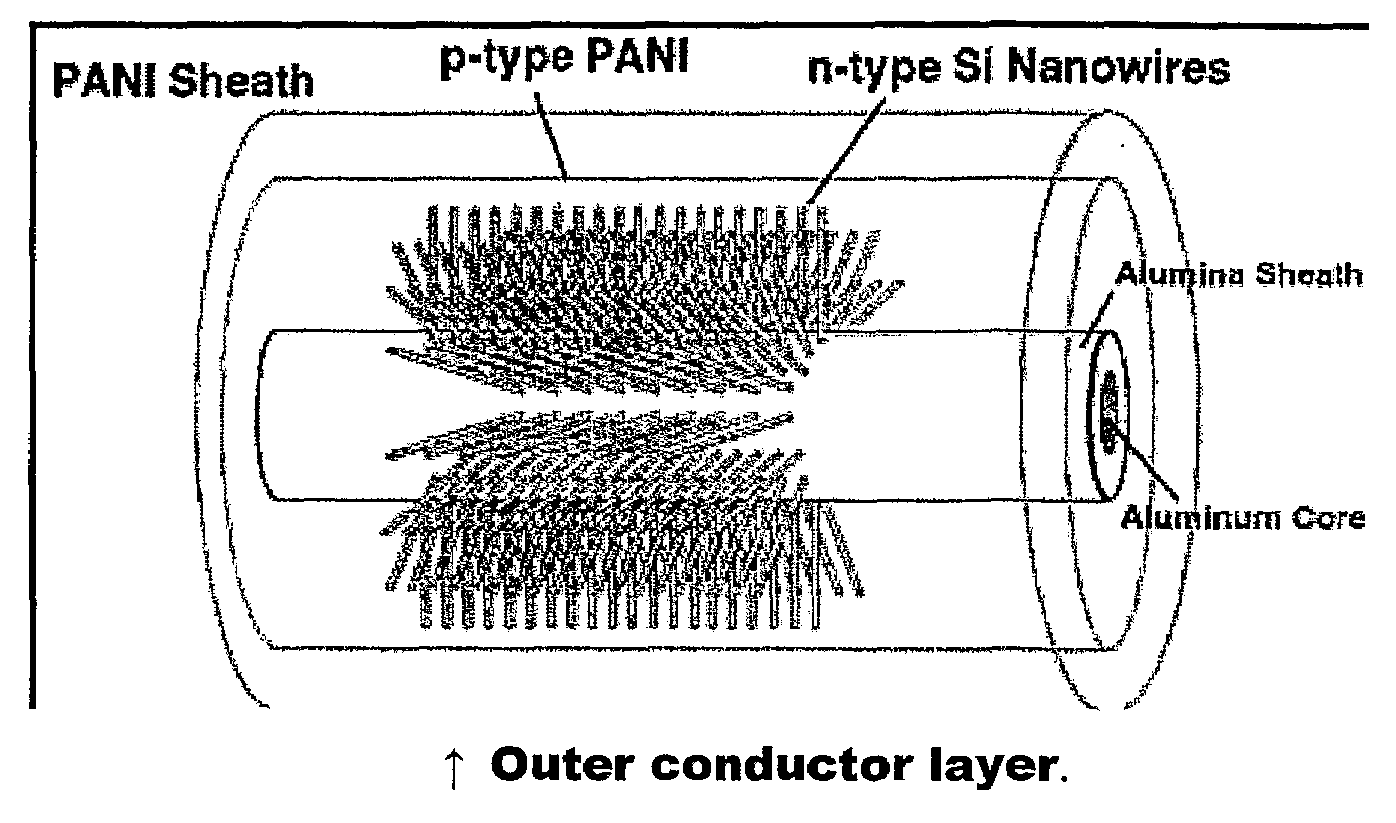

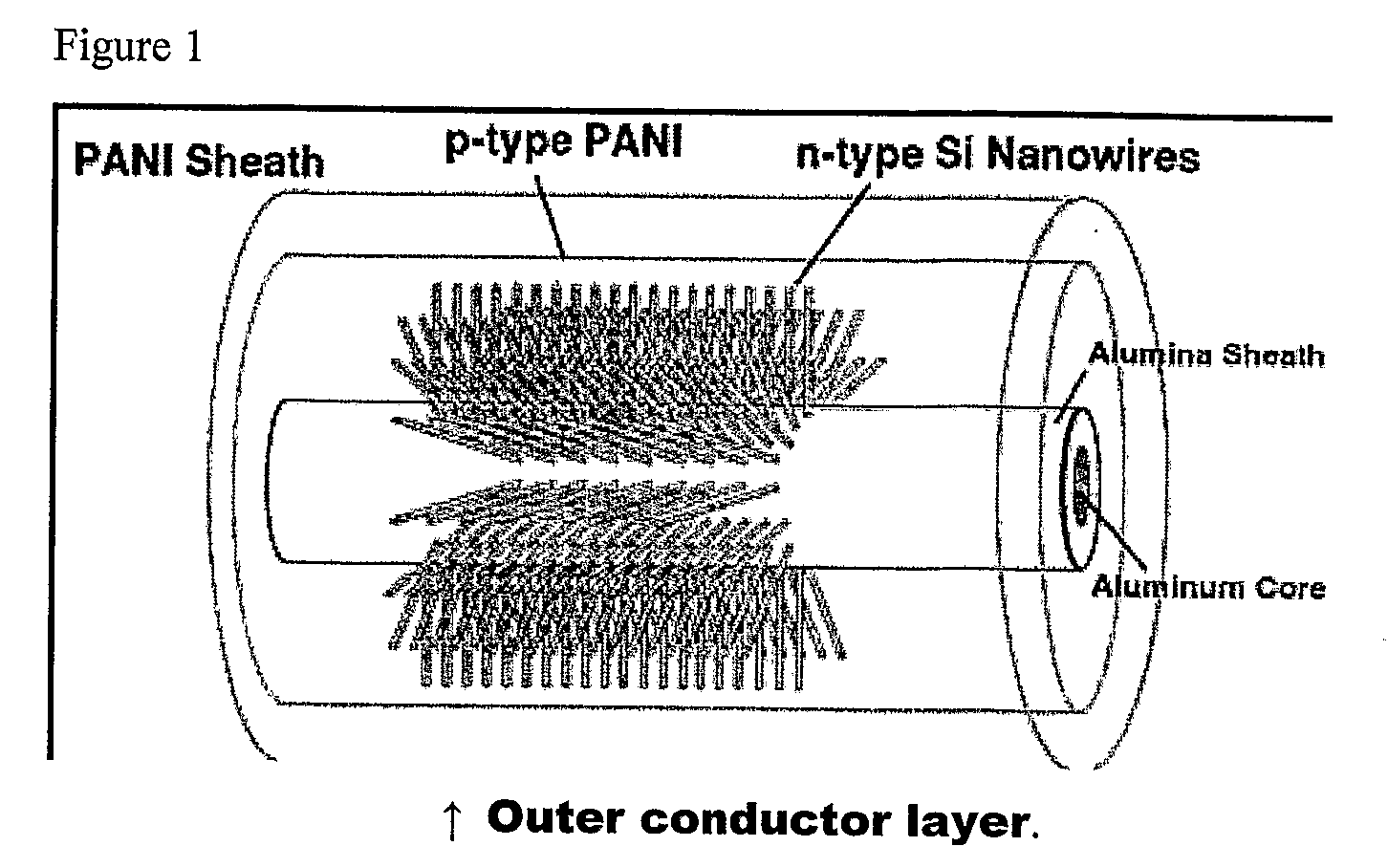

This invention relates to the fabrication of nanowires for electrical and electronic applications. A method of growing silicon nanowires using an alumina template is disclosed whereby the aluminum forming the alumina is also used as the catalyst for growing the silicon nanowires in a VLS (CVD) process and as the semiconductor dopant. In addition, various techniques for masking off parts of the aluminum and alumina in order to maintain electrical isolation between device layers is disclosed.

Owner:ILLUMINEX CORP

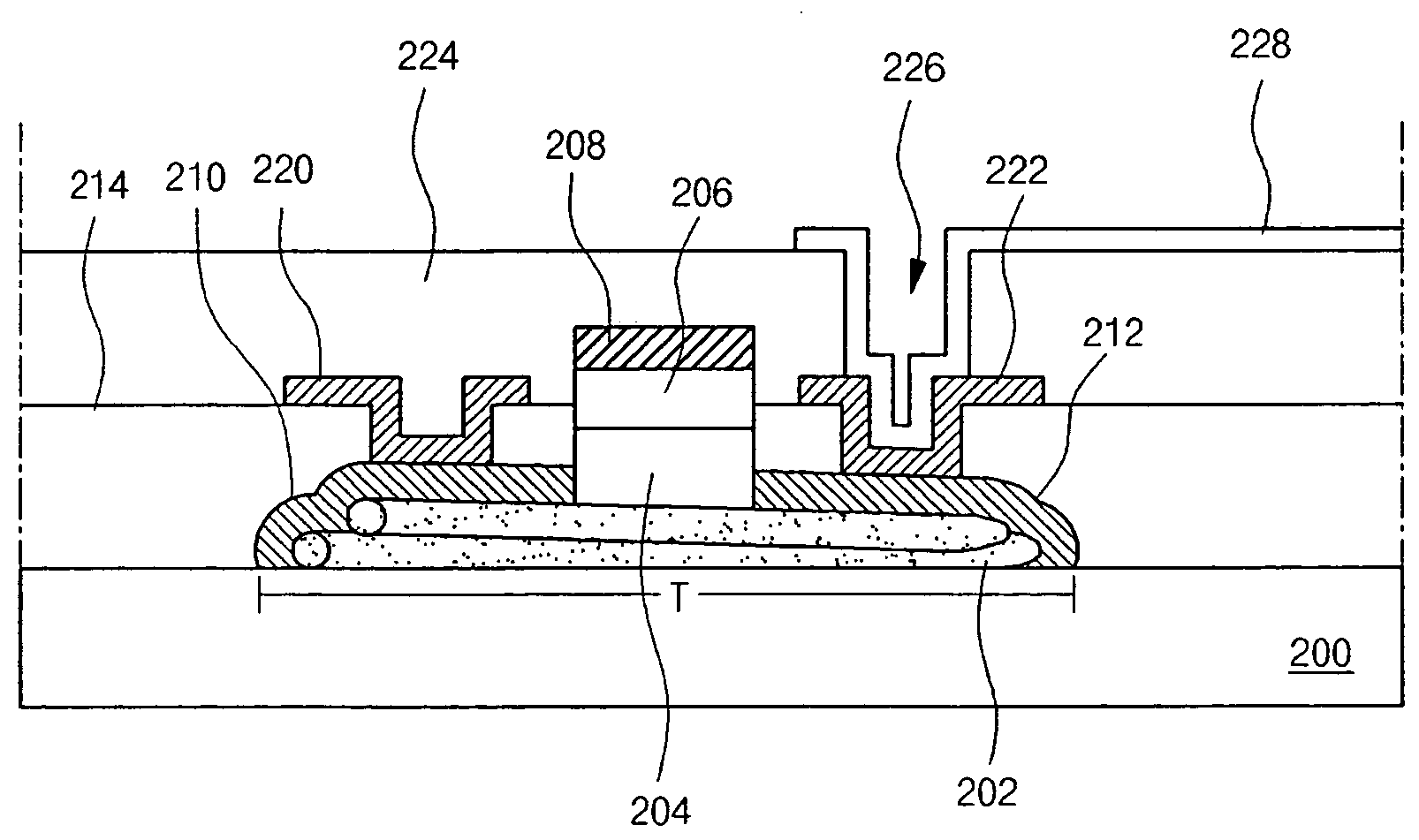

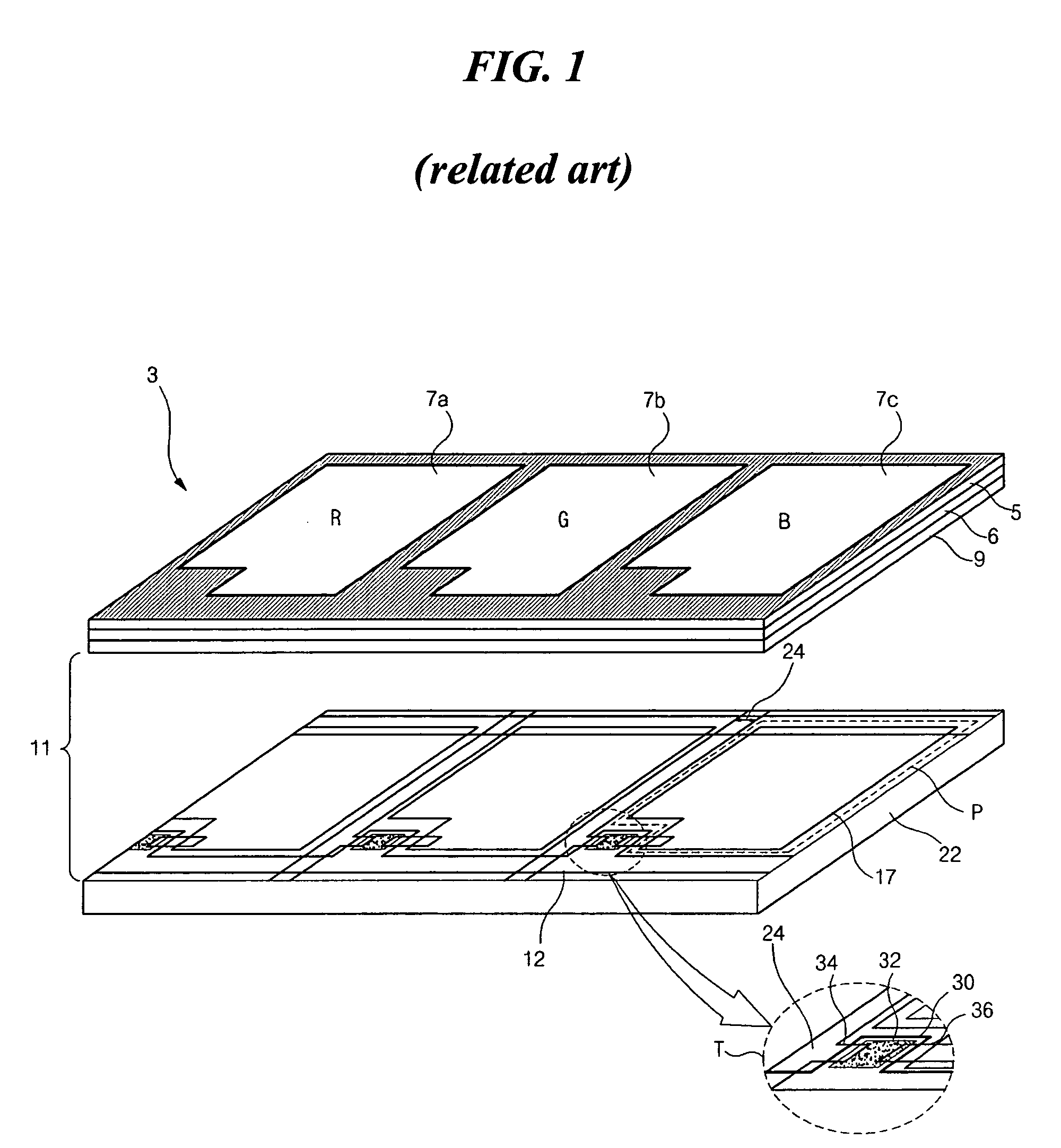

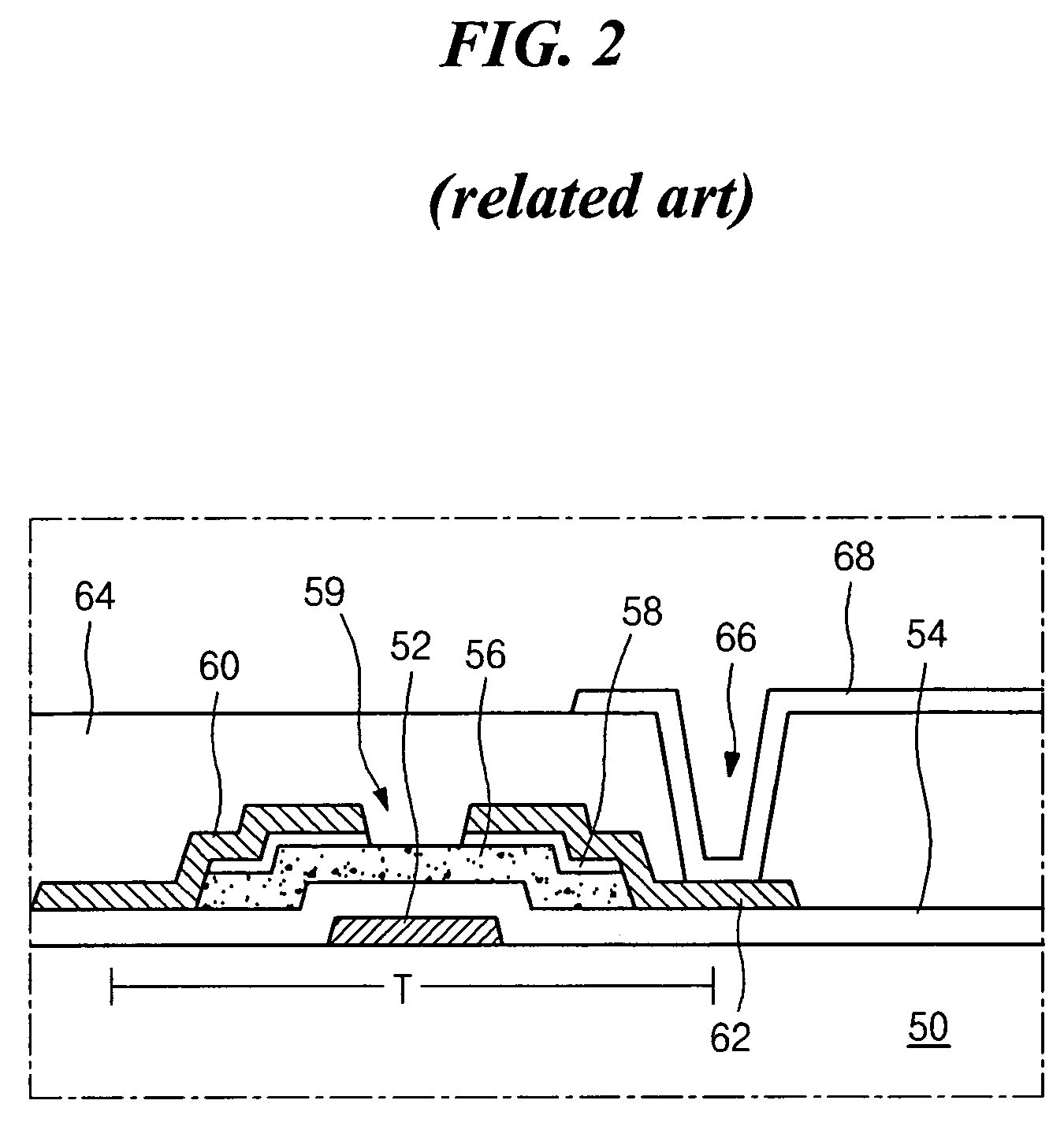

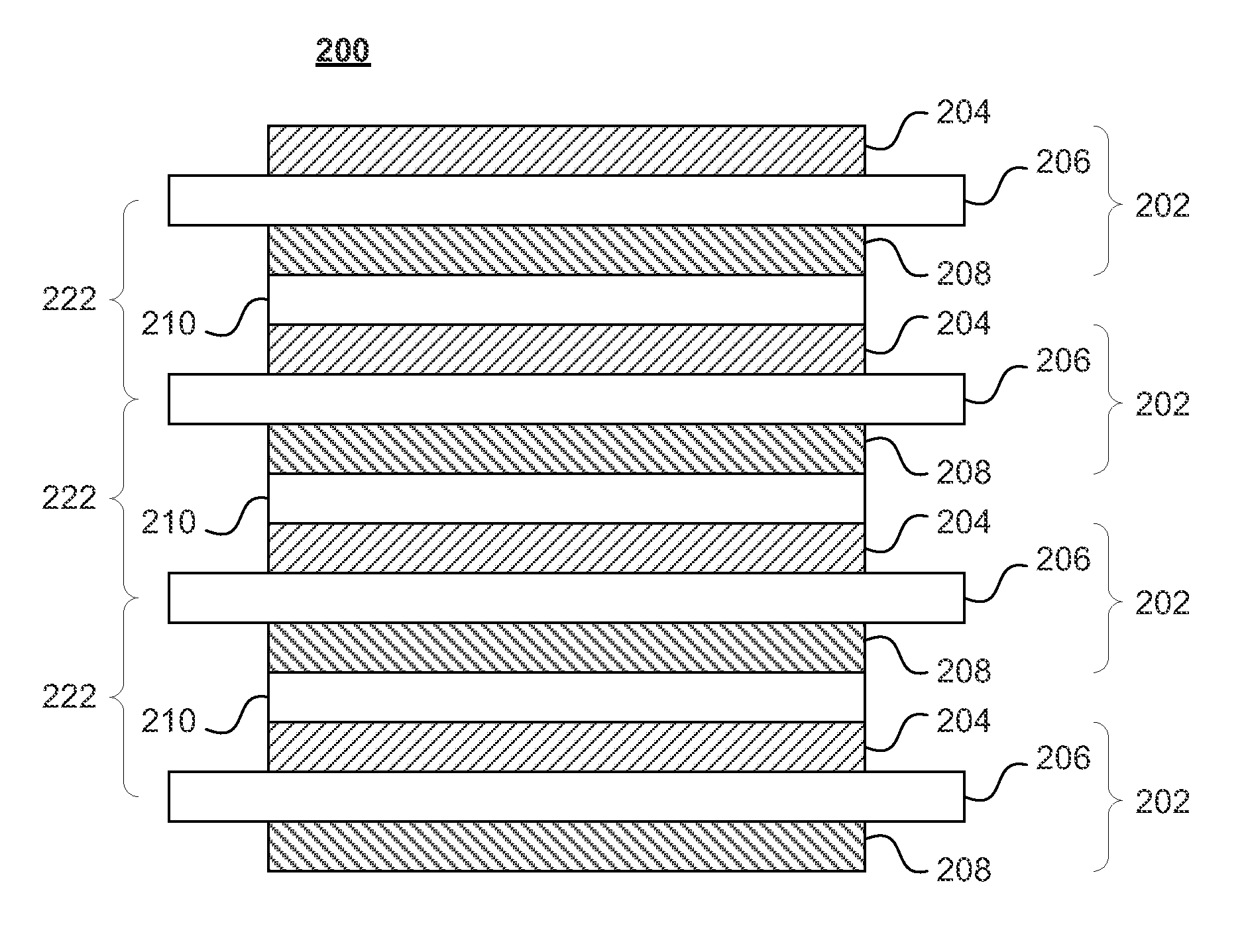

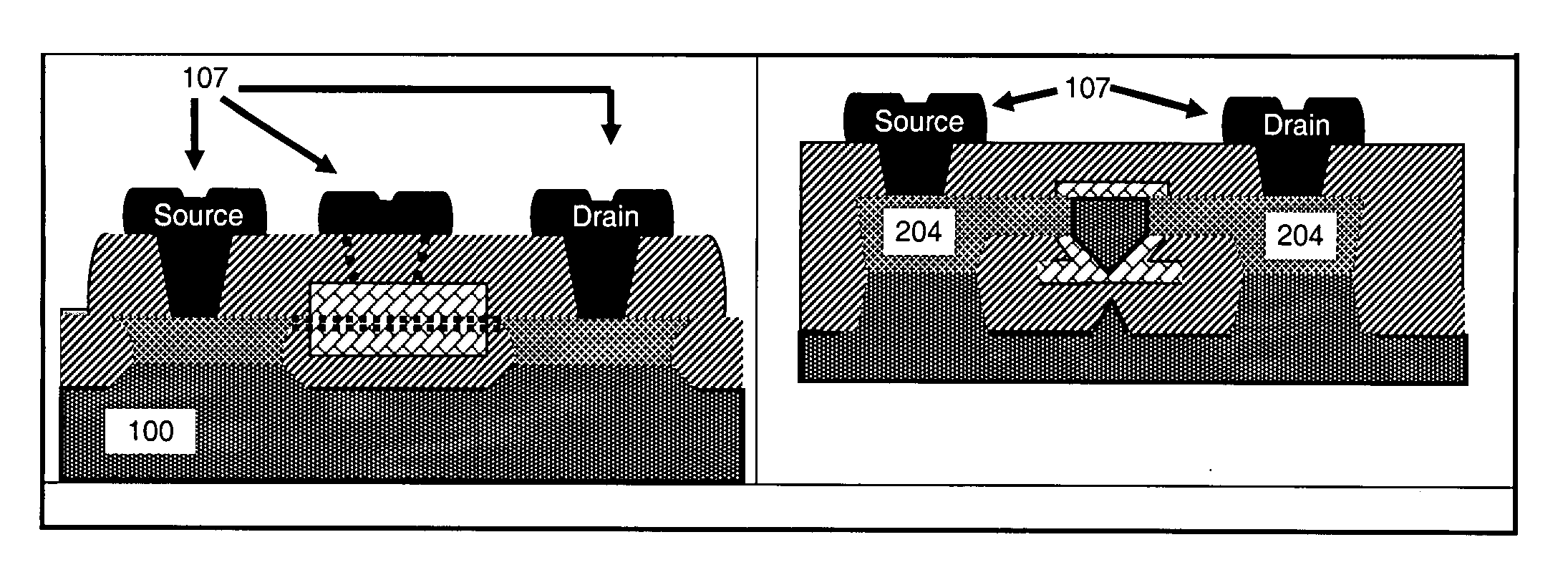

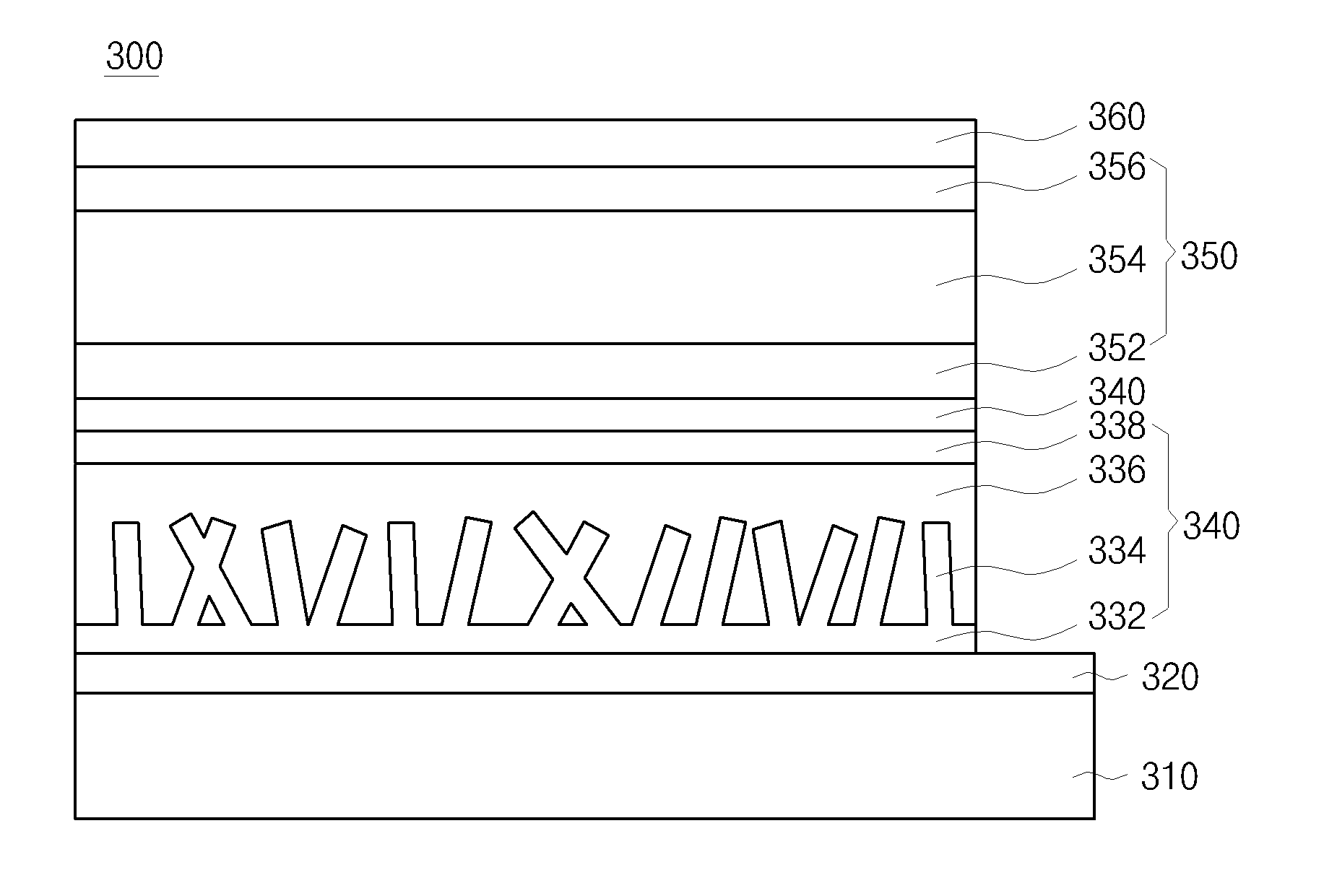

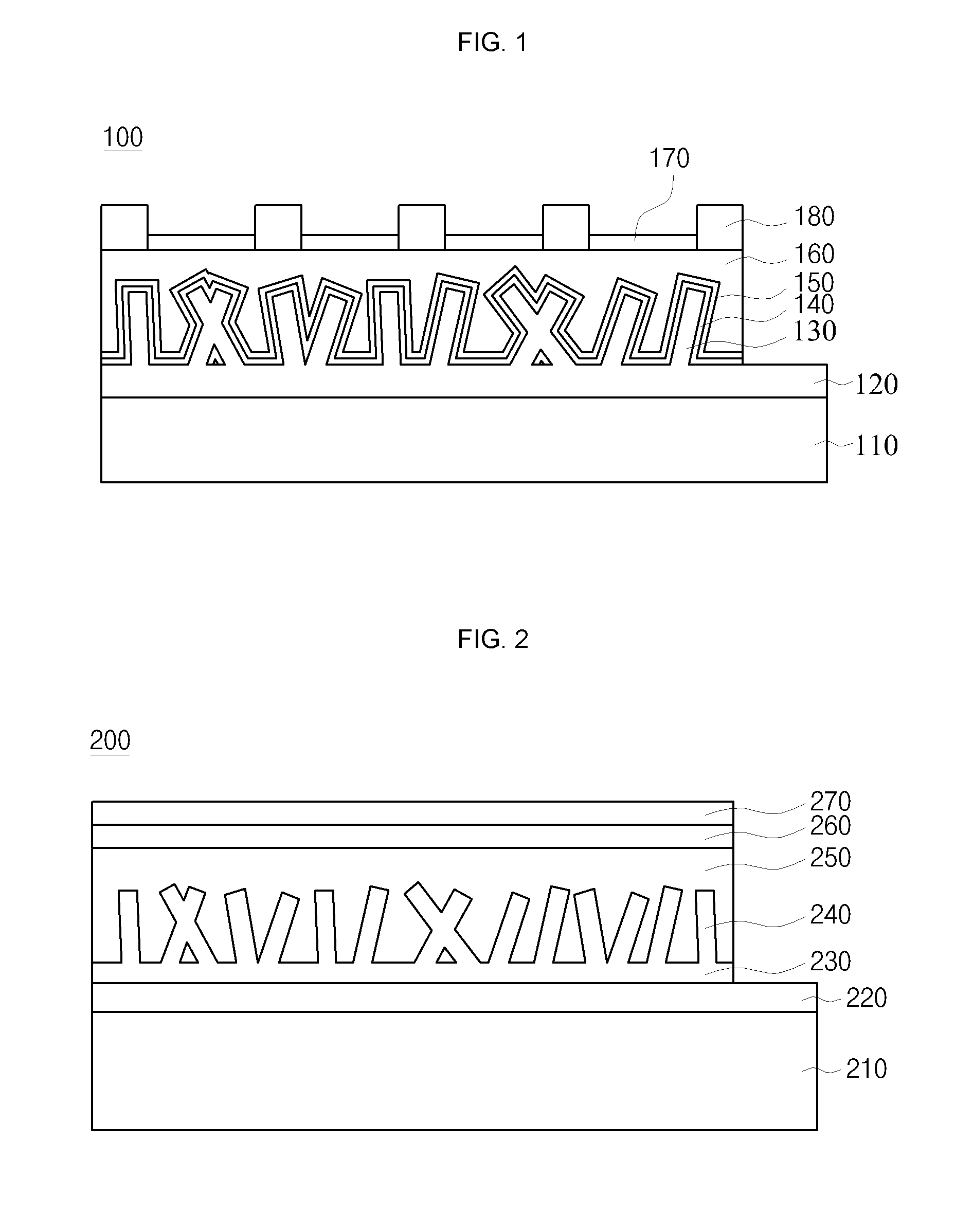

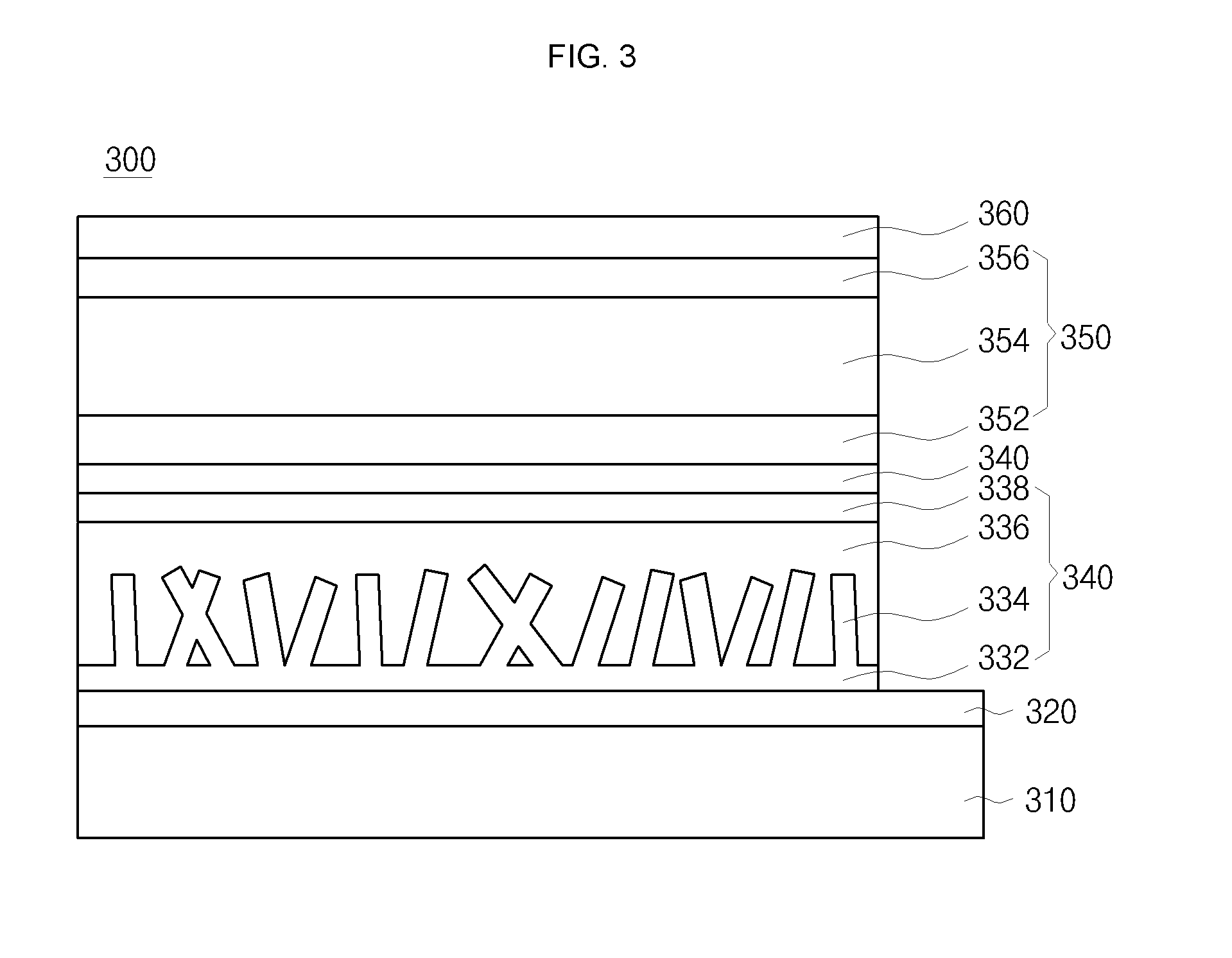

Thin film transistor having silicon nanowire and method of fabricating the same

InactiveUS7704806B2Guaranteed uptimeInterferenceNanoinformaticsSolid-state devicesSilicon nanowiresTransistor

A thin film transistor includes: a silicon nanowire on a substrate, the silicon nanowire having a central portion and both side portions of the central portion; a gate electrode on the central portion; and a source electrode and a drain electrode spaced apart from the source electrode on the both side portions, the source electrode and the drain electrode electrically connected to the silicon nanowire, respectively.

Owner:LG DISPLAY CO LTD

High performance electrodes

InactiveUS20110070488A1Improve electronic conductivityImprove thermal conductivityActive material electrodesElectrode collector coatingCarbon nanotubeSlurry

Techniques, arrangements and compositions are provided to incorporate nanostructured materials into electrodes for energy storage devices. Materials such as, for example, carbon nanotubes, silicon nanowires, silicon carbide nanowires, zinc nanowires, and other materials may be used to modify electrode properties such as electronic conductivity, thermal conductivity, or durability, for example. In some embodiments, nanostructured materials may be added to electrode formulations such as, for example, slurries or powders. Nanostructured materials may be deposited directly onto active material particles or electrode components. In some embodiments, coatings may be used to assist in deposition.

Owner:G4 SYNERGETICS INC

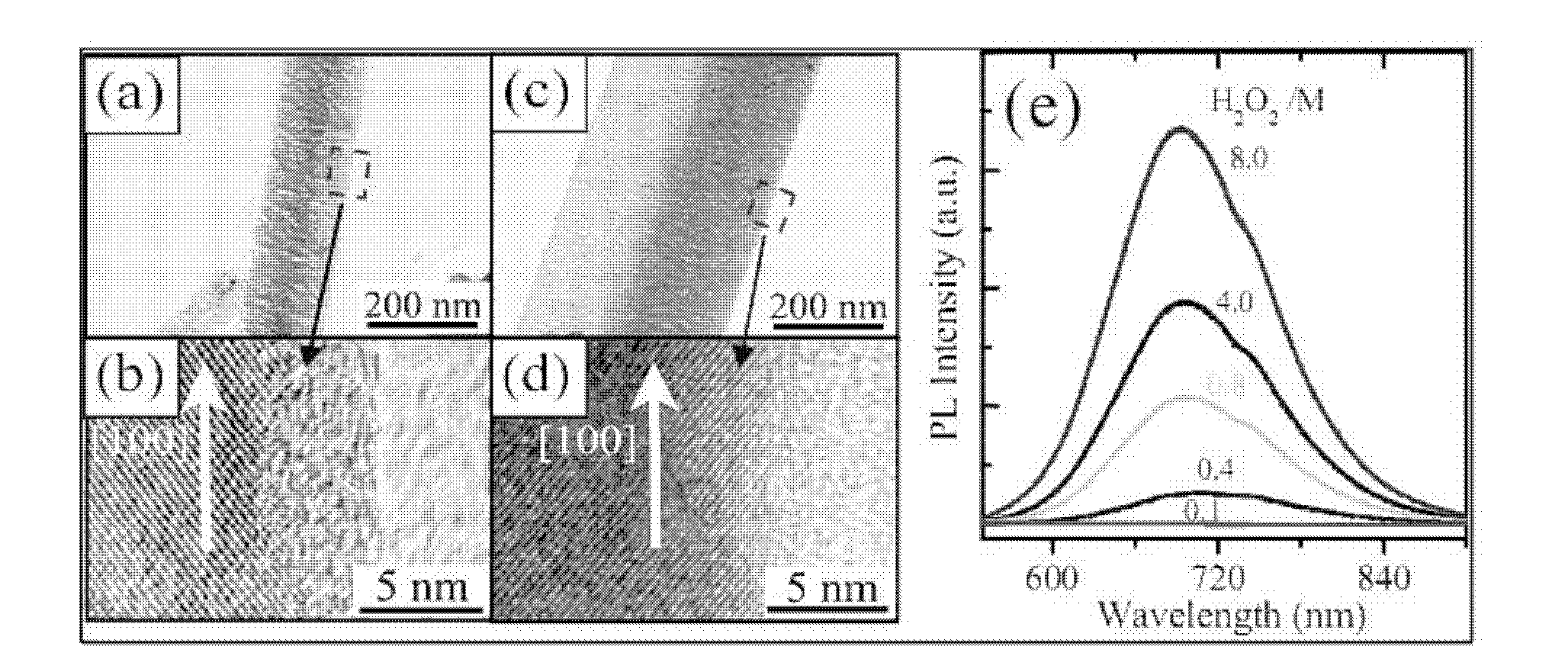

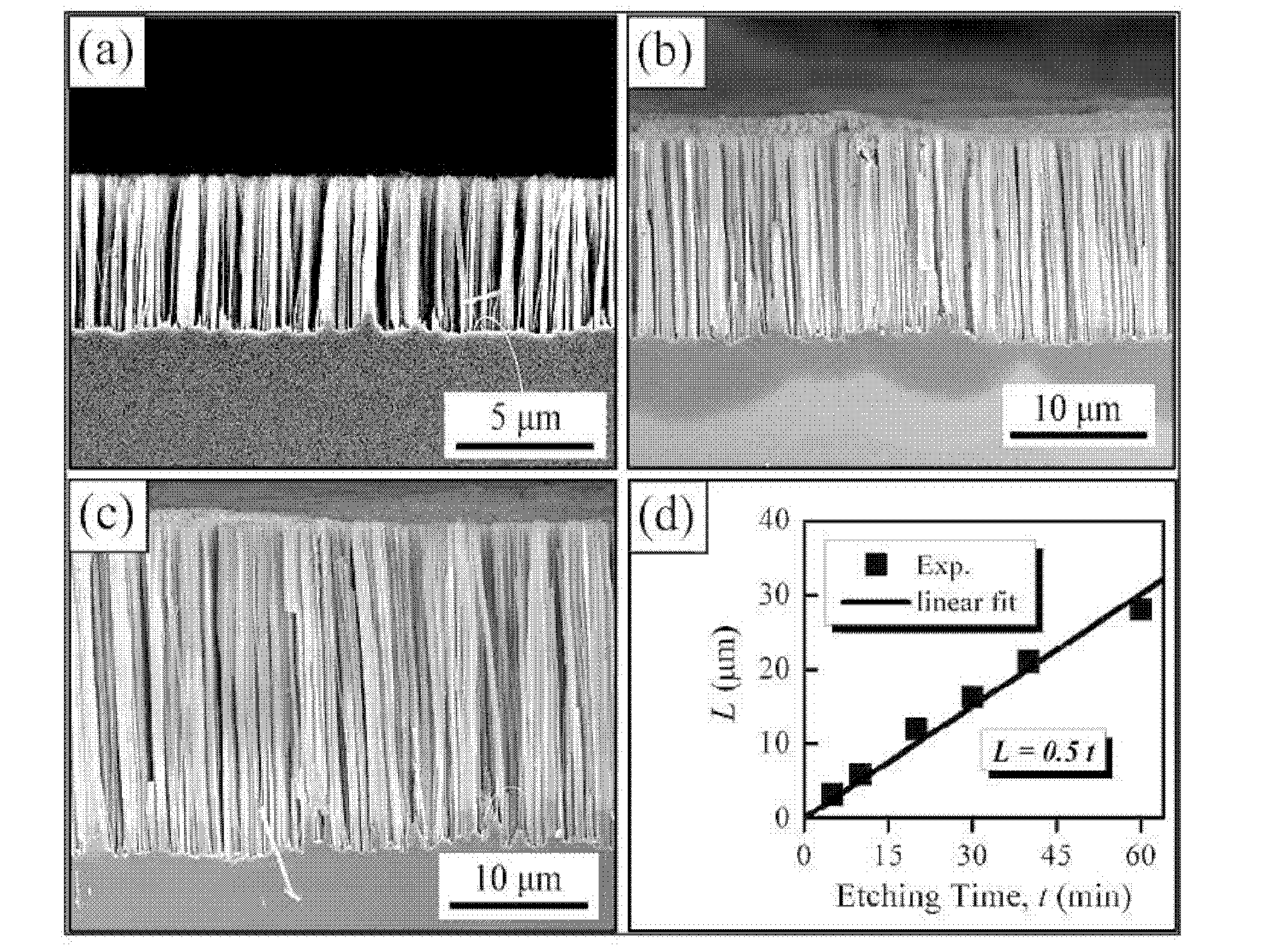

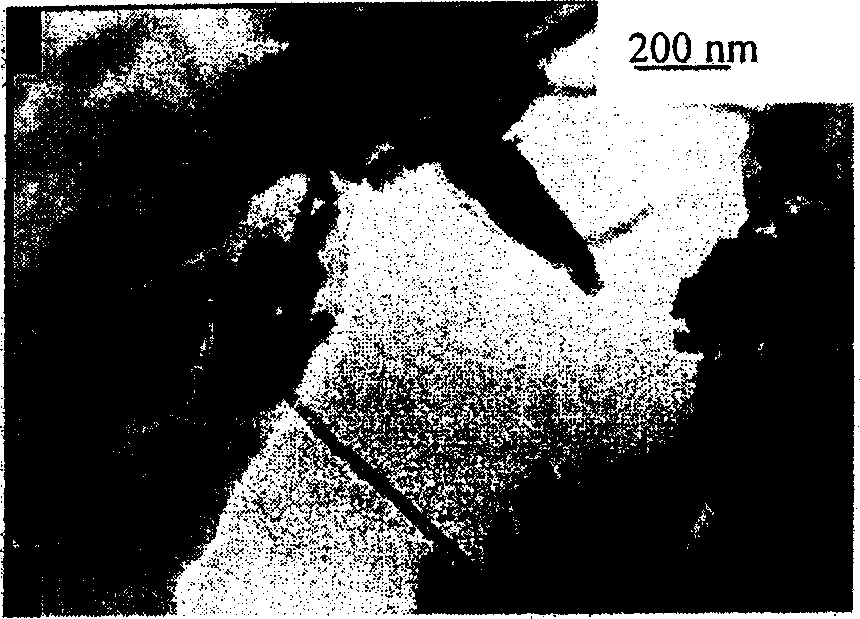

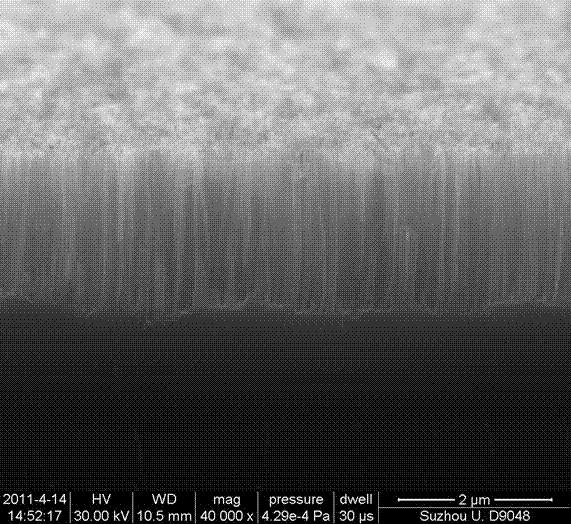

Method for preparing silicon nanowire array with smooth surface

The invention relates to a method for preparing a length-controlled silicon nanowire array with a smooth surface, and belongs to the technology of the preparation of nanometer materials. The method comprises the following steps of: firstly, performing wet chemical cleaning on a silicon wafer; secondly, depositing a silver nanometer granular layer on the surface of the silicon wafer in mixed solution containing hydrofluoric acid and silver nitrate by an electroless chemical deposition method; thirdly, performing chemical etching by mixed solution containing the hydrofluoric acid and hydrogen peroxide; and finally, removing silver nanometer granules by using nitric acid to obtain the silicon nanowire array. In the method, length-controlled silicon nanowires with the smooth surfaces are prepared by regulating the concentration and etching time of the hydrogen peroxide serving as an oxidant simply in a chemical etch system, so the technical problem of preparing the silicon nanowires with fewer surface defects in metal-assisted chemical etching is solved.

Owner:SHANGHAI JIAO TONG UNIV

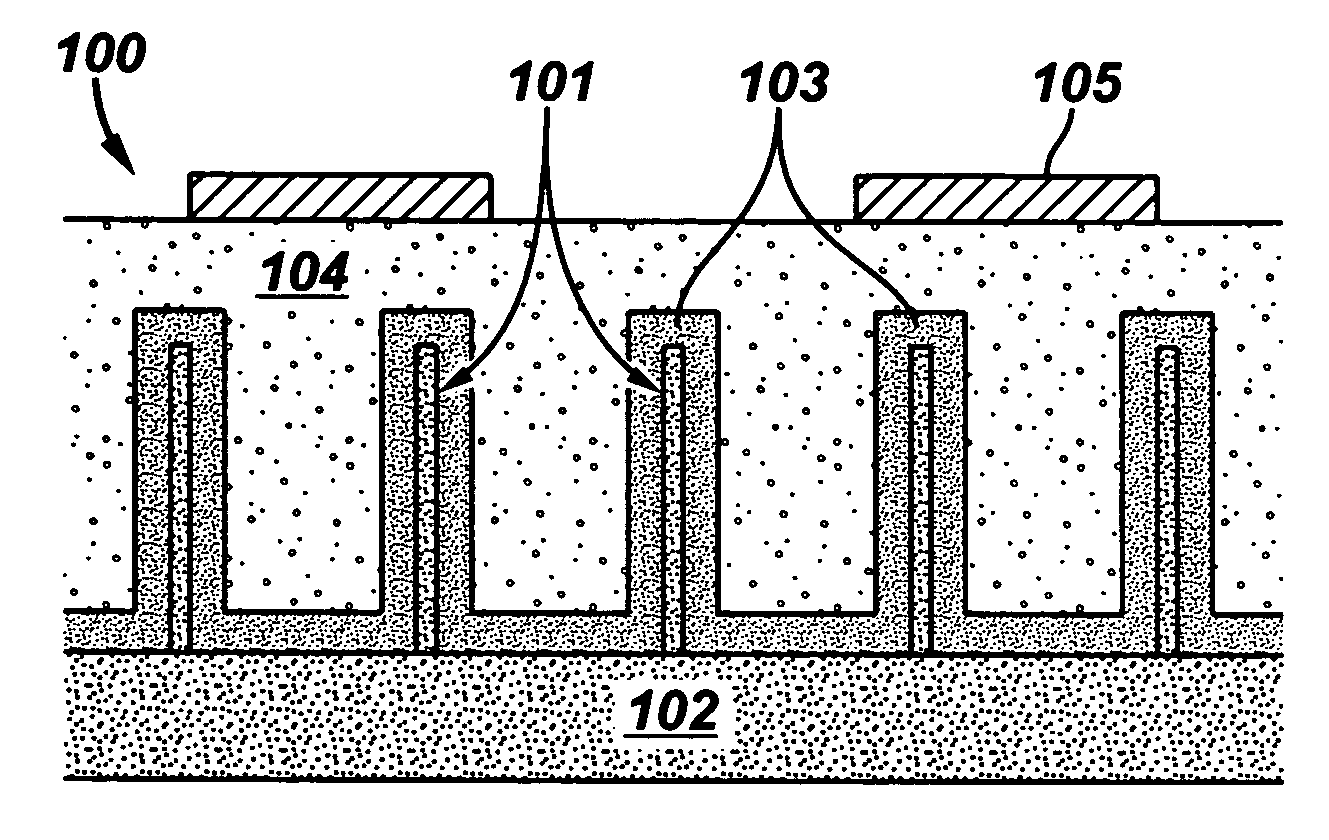

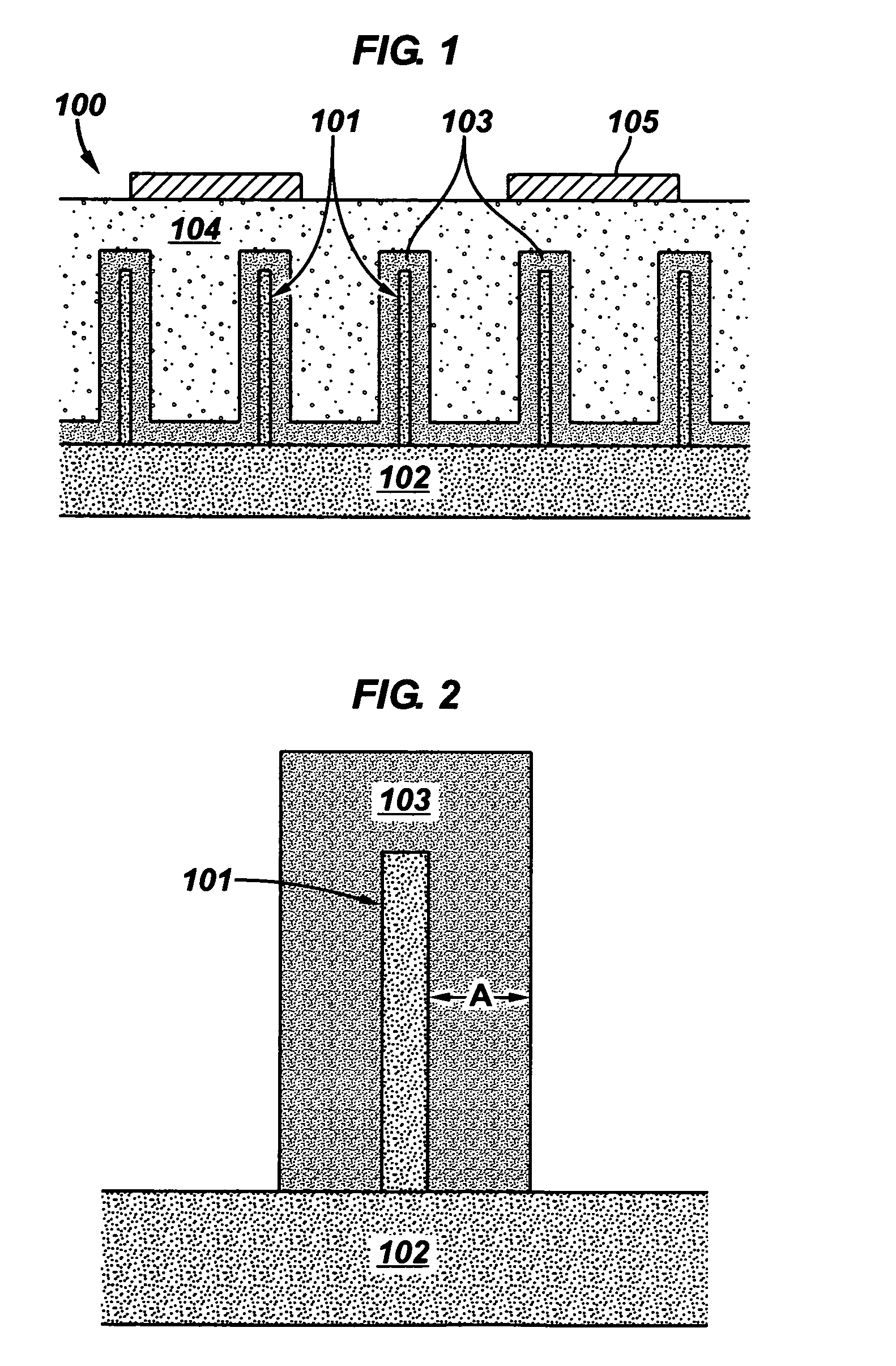

Fast p-i-n photodetector with high responsitivity

InactiveUS20090289320A1Eliminate the problemHigh recombination rateTransistorFinal product manufactureSemiconductor materialsPhotodetector

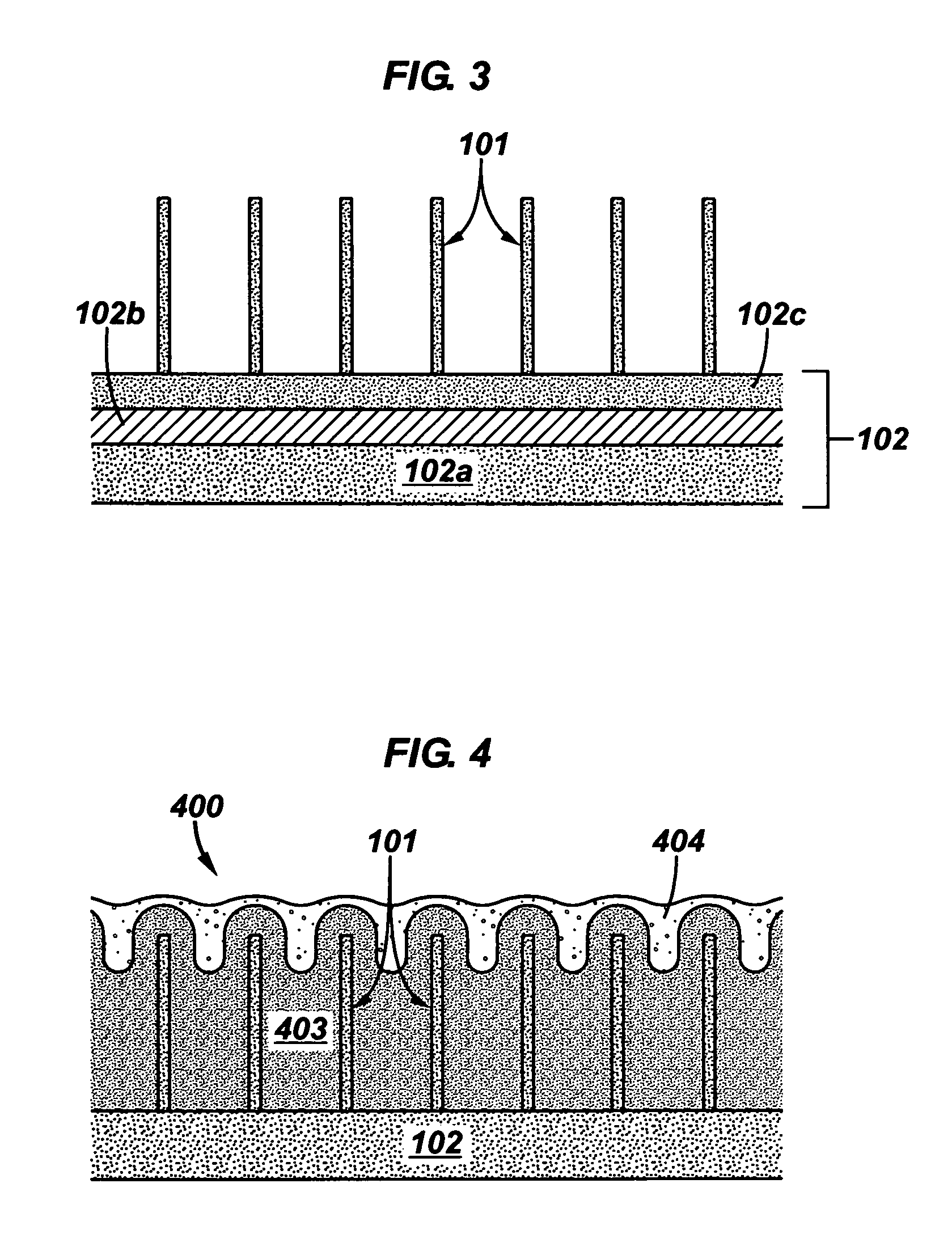

A lateral p-i-n photodetector is provided that includes an array of vertical semiconductor nanowires of a first conductivity type that are grown over a semiconductor substrate also of the first conductivity type. Each vertically grown semiconductor nanowires of the first conductivity type is surrounded by a thick epitaxial intrinsic semiconductor film. The gap between the now formed vertically grown semiconductor nanowires-intrinsic semiconductor film columns (comprised of the semiconductor nanowire core surrounded by intrinsic semiconductor film) is then filled by forming an epitaxial semiconductor material of a second conductivity type which is different from the first conductivity type. In a preferred embodiment, the vertically grown semiconductor nanowires of the first conductivity type are n+ silicon nanowires, the intrinsic epitaxial semiconductor layer is comprised of intrinsic epitaxial silicon, and the epitaxial semiconductor material of the second conductivity type is comprised of p+ silicon.

Owner:IBM CORP

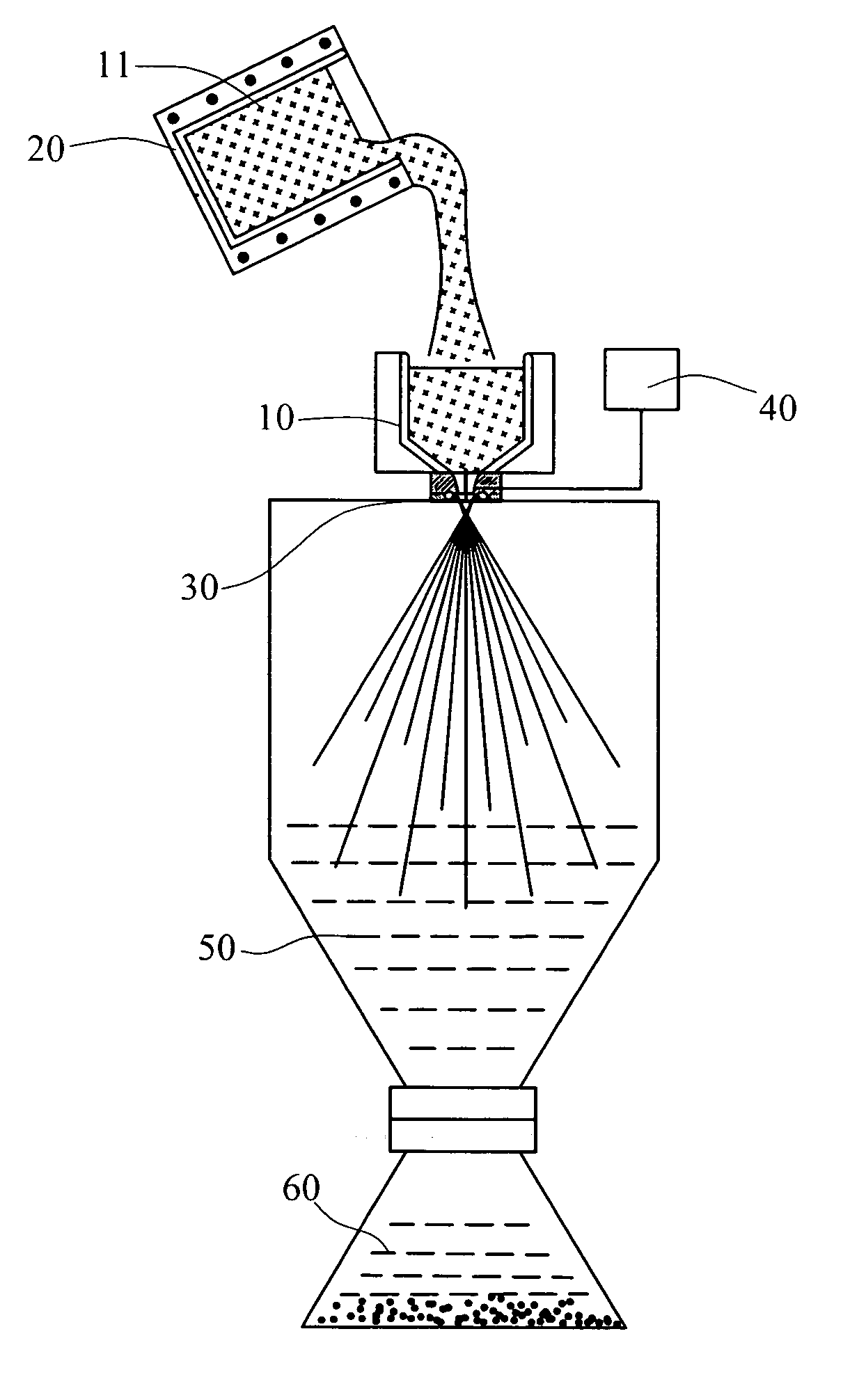

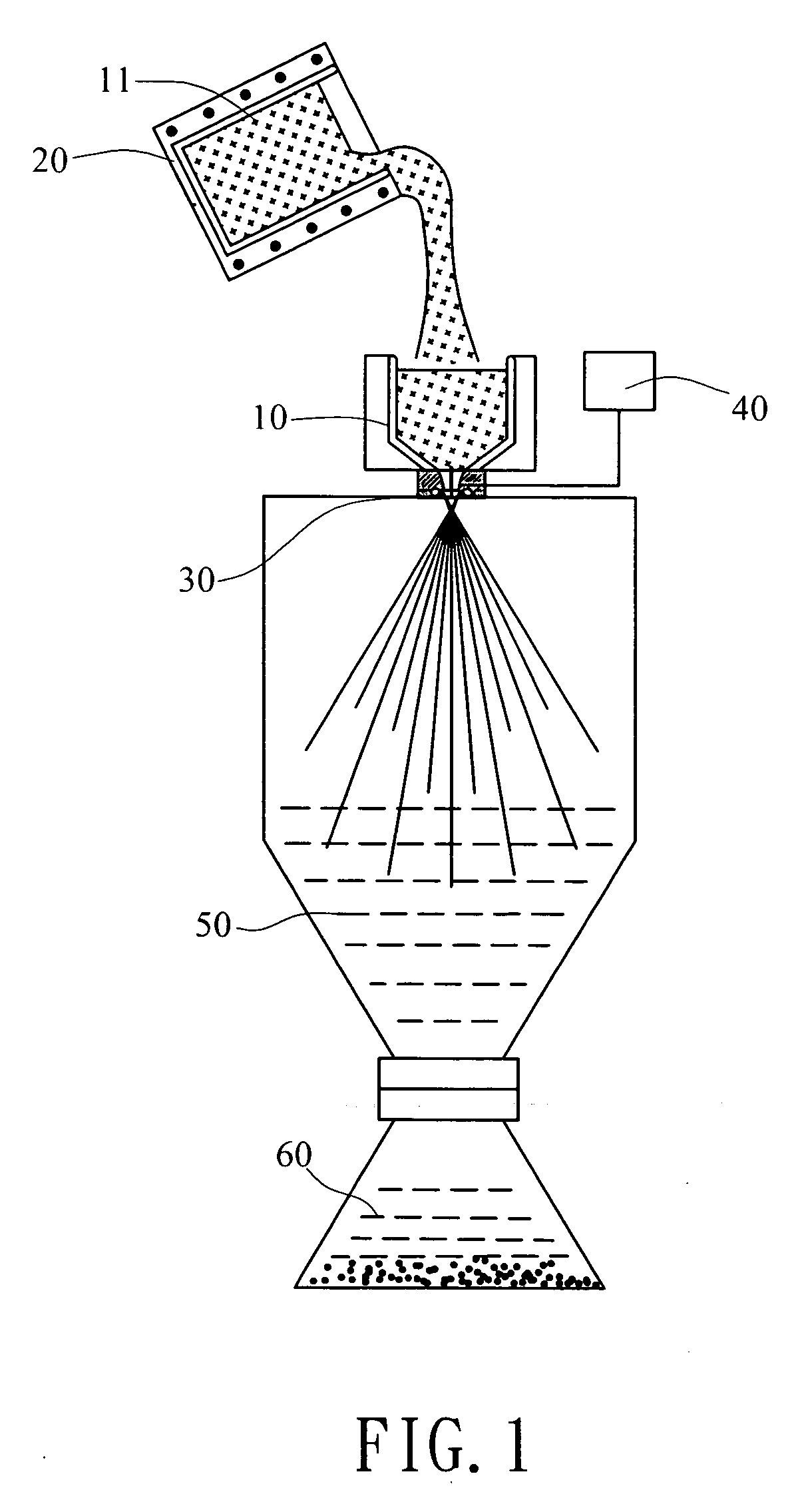

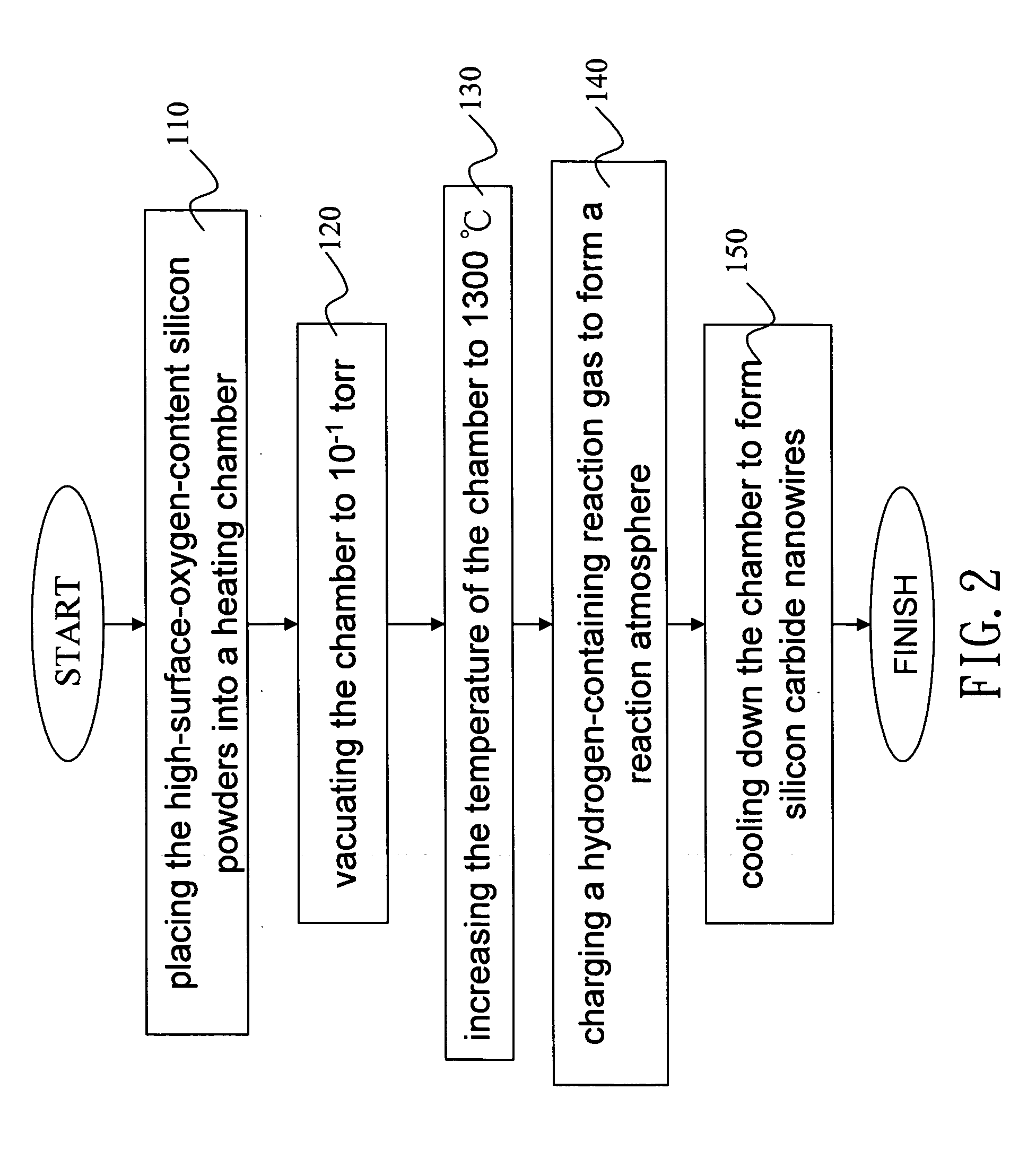

Process of forming silicon-based nanowires

InactiveUS20050176264A1Low costHeating equipmentPolycrystalline material growthSemiconductor/solid-state device manufacturingSolid reactionSilicon nanowires

A process of forming silicon-based nanowires heats high-surface-oxygen-content silicon powders to initiate vapor-solid reaction to form nanowires. The reaction gas is charged to react with the Si powders to form the silicon-based nanowires such as silicon nanowires or SiC nanowires. With control of the reaction gas, the components of the nanowires can be exactly controlled without the addition of metallic catalysts. Thereby, the nanowires can be made with reduced cost.

Owner:IND TECH RES INST

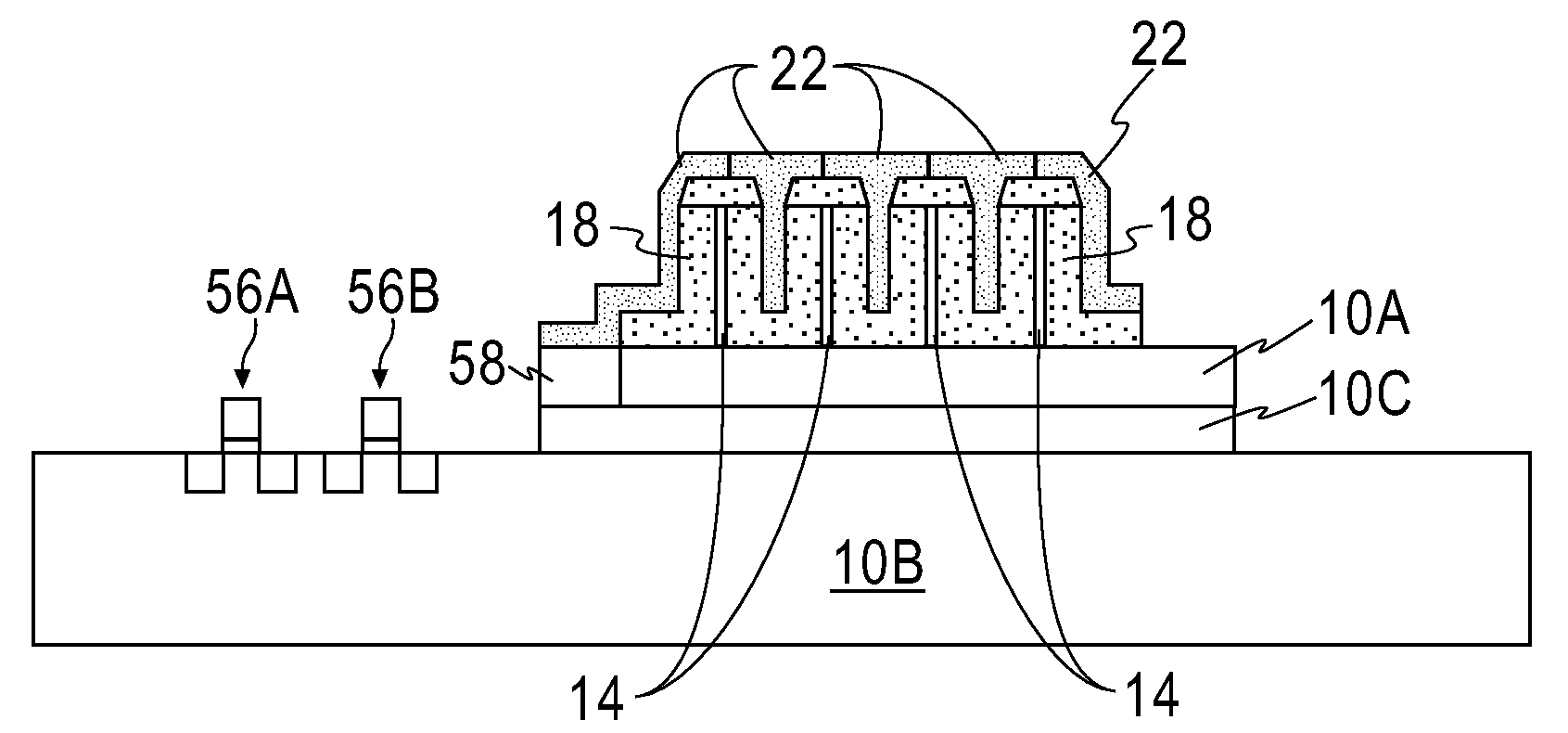

Fast p-i-n photodetector with high responsitivity

ActiveUS20090305454A1Easy to integrateHigh rateFinal product manufactureNanoinformaticsSemiconductor materialsPhotodetector

A lateral p-i-n photodetector is provided that includes an array of vertical semiconductor nanowires of a first conductivity type that are grown over a semiconductor substrate also of the first conductivity type. Each vertically grown semiconductor nanowires of the first conductivity type is surrounded by a thick epitaxial intrinsic semiconductor film. The gap between the now formed vertically grown semiconductor nanowires-intrinsic semiconductor film columns (comprised of the semiconductor nanowire core surrounded by intrinsic semiconductor film) is then filled by forming an epitaxial semiconductor material of a second conductivity type which is different from the first conductivity type. In a preferred embodiment, the vertically grown semiconductor nanowires of the first conductivity type are n+ silicon nanowires, the intrinsic epitaxial semiconductor layer is comprised of intrinsic epitaxial silicon, and the epitaxial semiconductor material of the second conductivity type is comprised of p+ silicon.

Owner:IBM CORP

Photovoltaic wire

InactiveUS20090266411A1Efficient and economic use of materialEnhanced light absorptionSolid-state devicesPhotovoltaic energy generationPolymeric surfaceElectrical conductor

A photovoltaic wire is presented where the active layers coat a metallic wire, preferably aluminum. The active layers are an array of doped silicon nanowires electrically attached to the metallic wire that extend from the surface of the wire into a layer of semiconducting polymer, preferably polyaniline. The surface of the polymer is coated with a transparent conductor to complete the photovoltaic circuit.

Owner:ILLUMINEX CORP

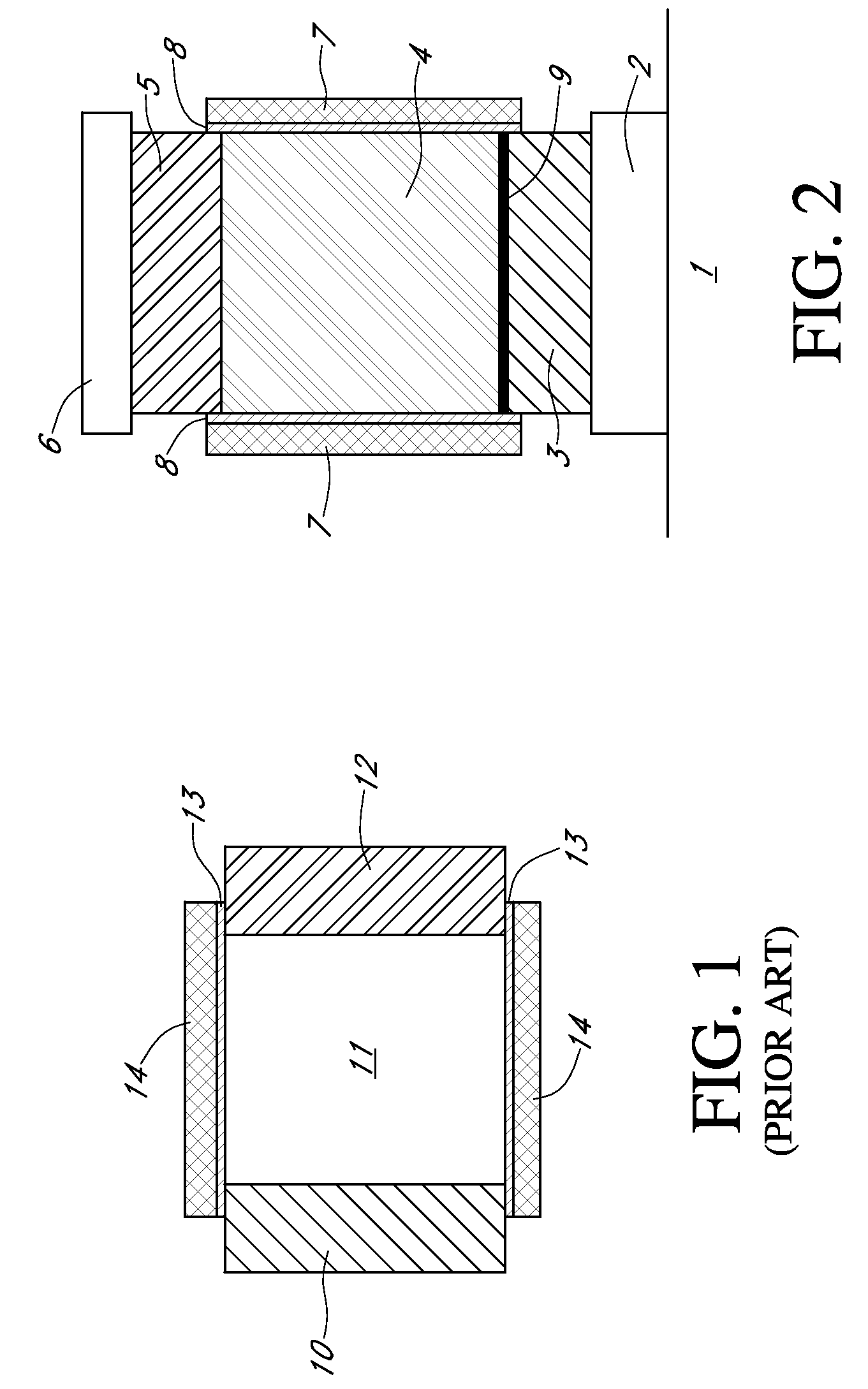

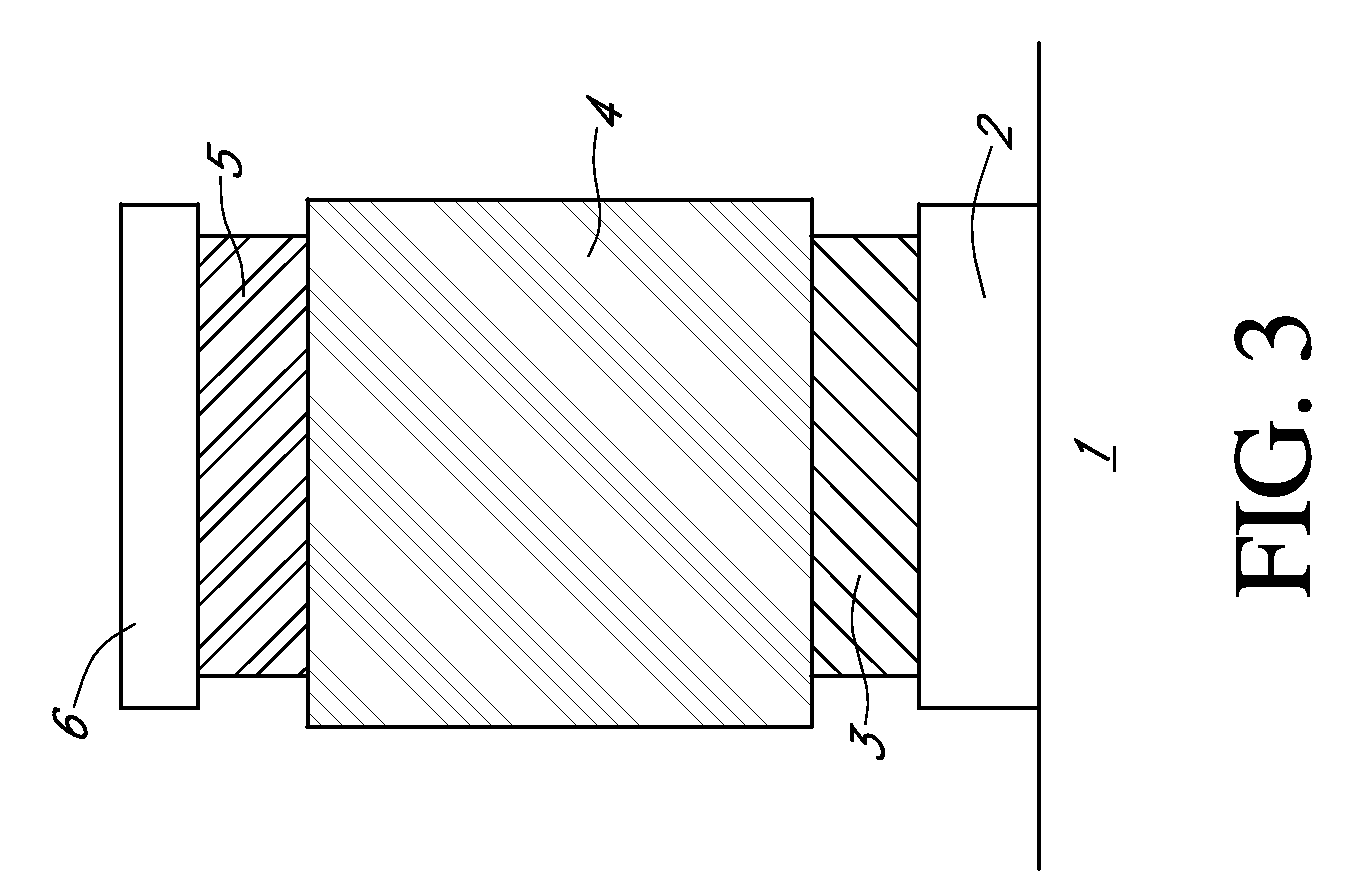

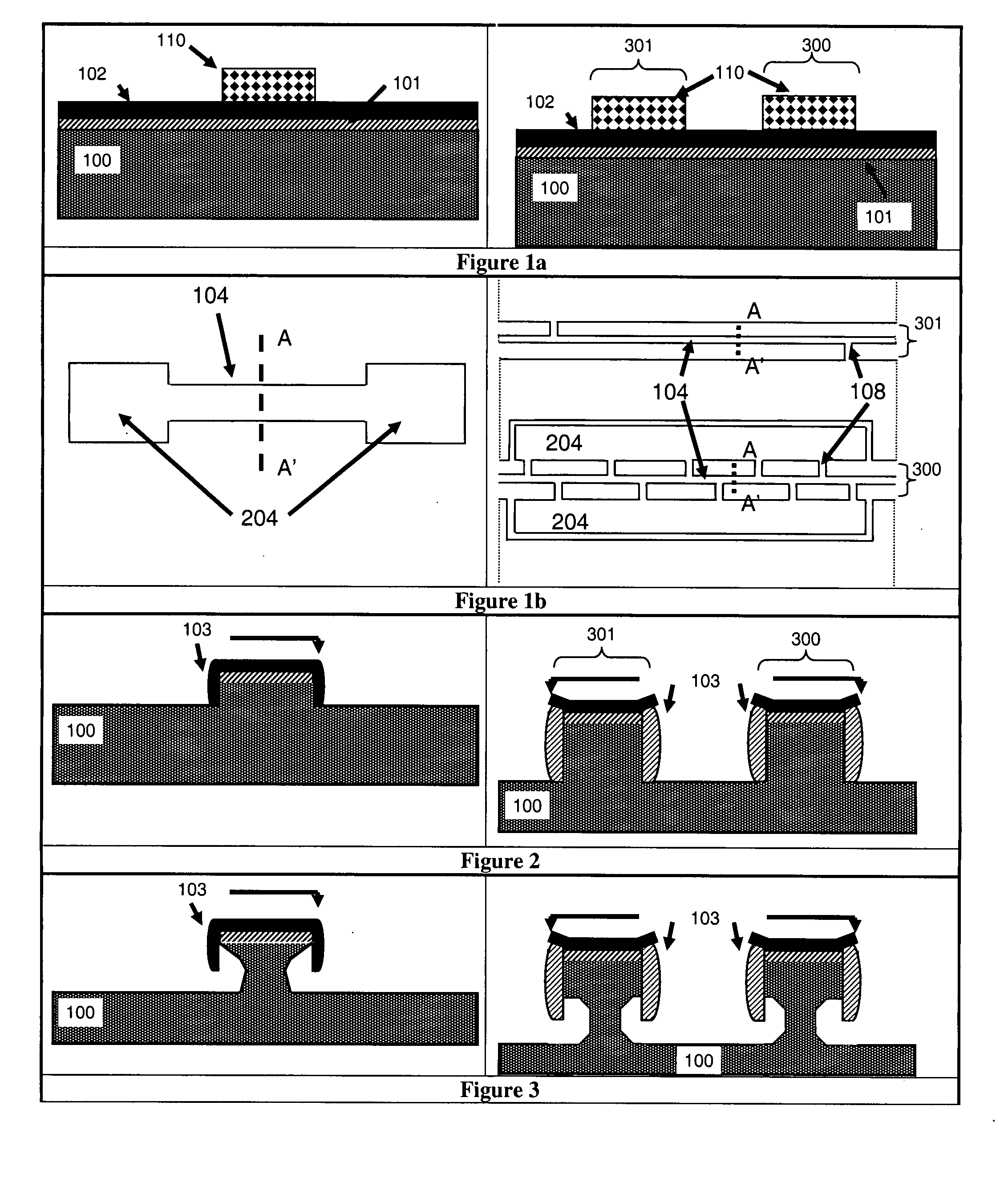

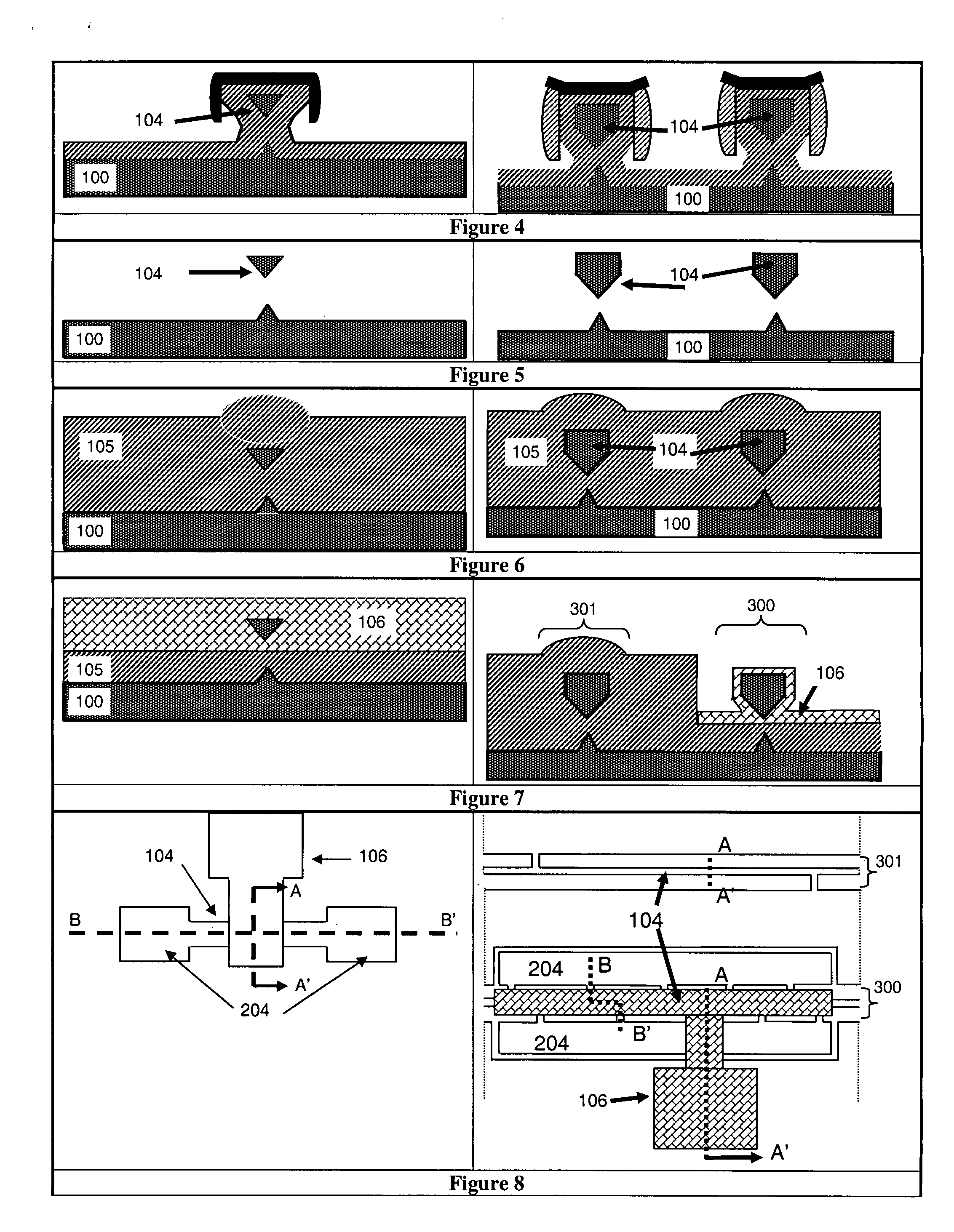

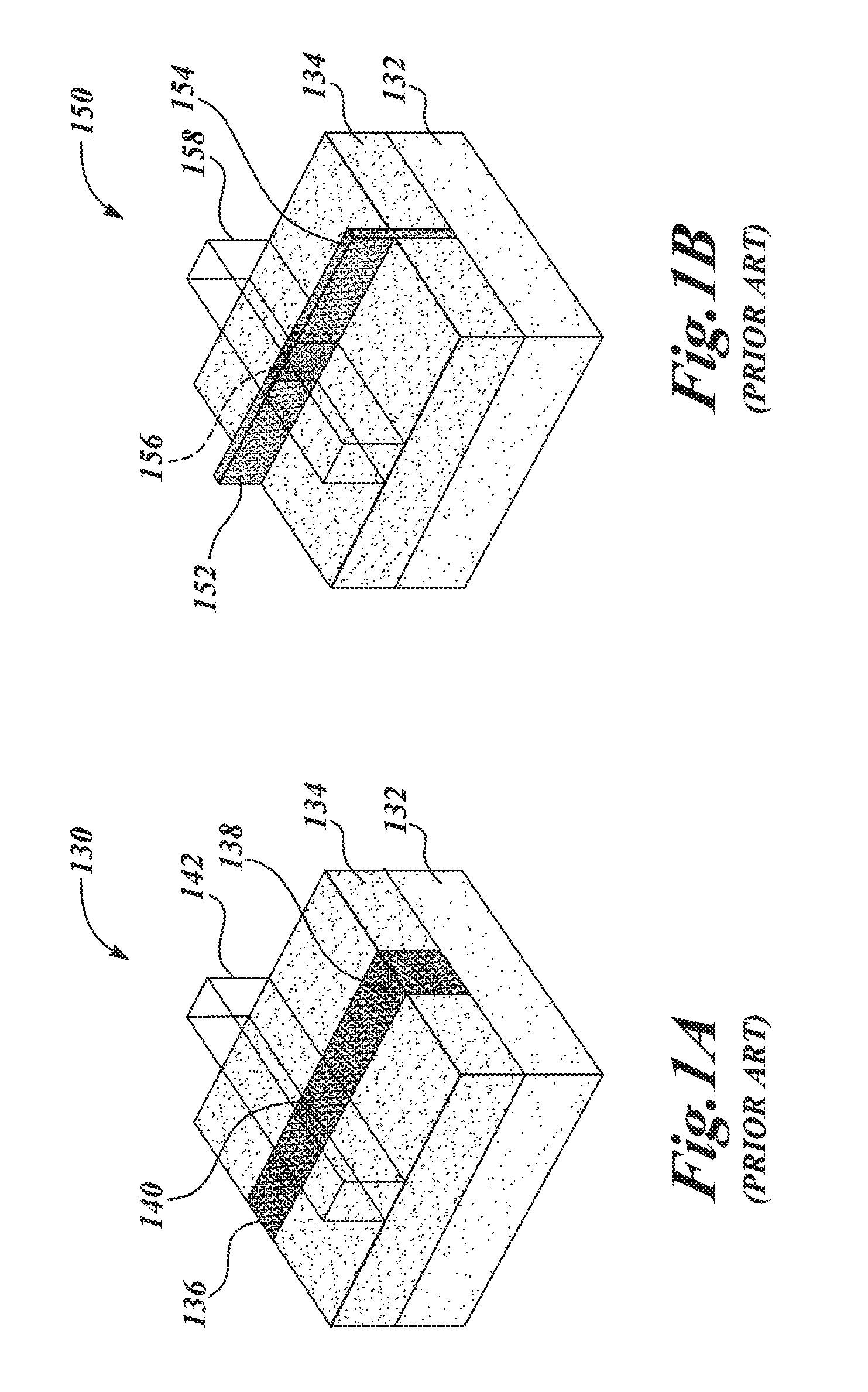

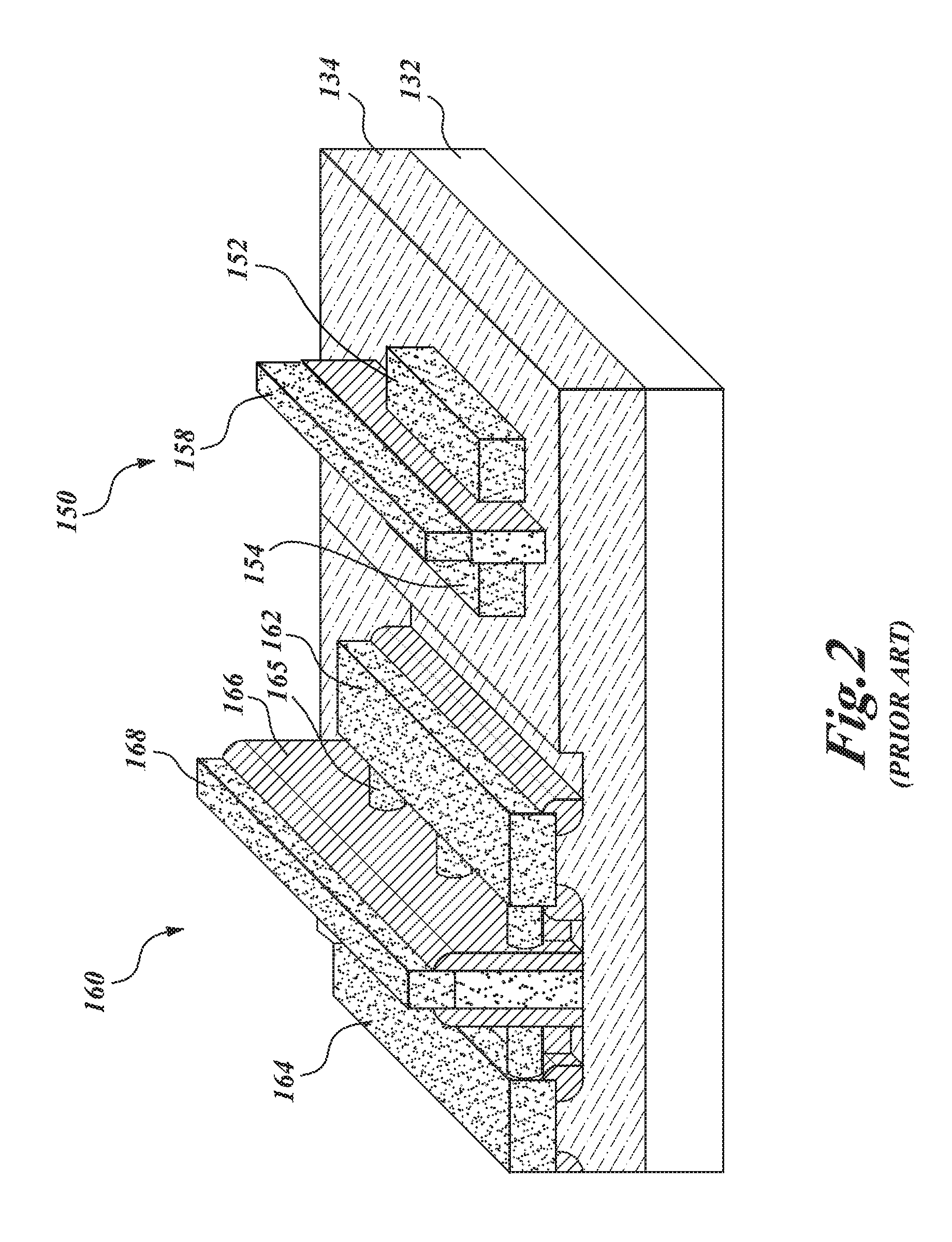

Fabrication of silicon nano wires and gate-all-around MOS devices

InactiveUS20070298551A1Quality improvementEnhance the quantum effectNanoinformaticsSemiconductor/solid-state device manufacturingMOSFETCapacitance

The invention relates to methods for manufacturing semiconductor devices. Processes are disclosed for implementing suspended single crystal silicon nano wires (NWs) using a combination of anisotropic and isotropic etches and spacer creation for sidewall protection. The core dimensions of the NWs are adjustable with the integration sequences: they can be triangular, rectangular, quasi-circular, or an alternative polygonal shape. Depending on the length of the NWs, going from the sub-micron to millimeter range, the NWs may utilize support from anchors to the side, during certain processing steps. By changing the lithographic dimensions of the anchors compared to the NWs, the anchors may be reduced or eliminated during processing. The method covers, among other things, the integration of Gate-All-Around NW (GAA-NW) MOSFETs on a bulk semiconductor. The GAA structure may consist of a silicon core fabricated as specified in the invention, surrounded by any usable gate dielectric, and finally by a gate material, such as polysilicon or metal. The source and drain of the GAA-NW may be connected to the bulk semiconductor to avoid self heating of the device over a wide range of operating conditions. The GAA-NW MOS capacitor can also be used for the integration of a Gate-All-Around optical phase modulator (GAA modulator). The working principle for the optical modulator is modulation of the refractive index by free carrier accumulation or inversion in a MOS capacitive structure, which changes the phase of the propagating light.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

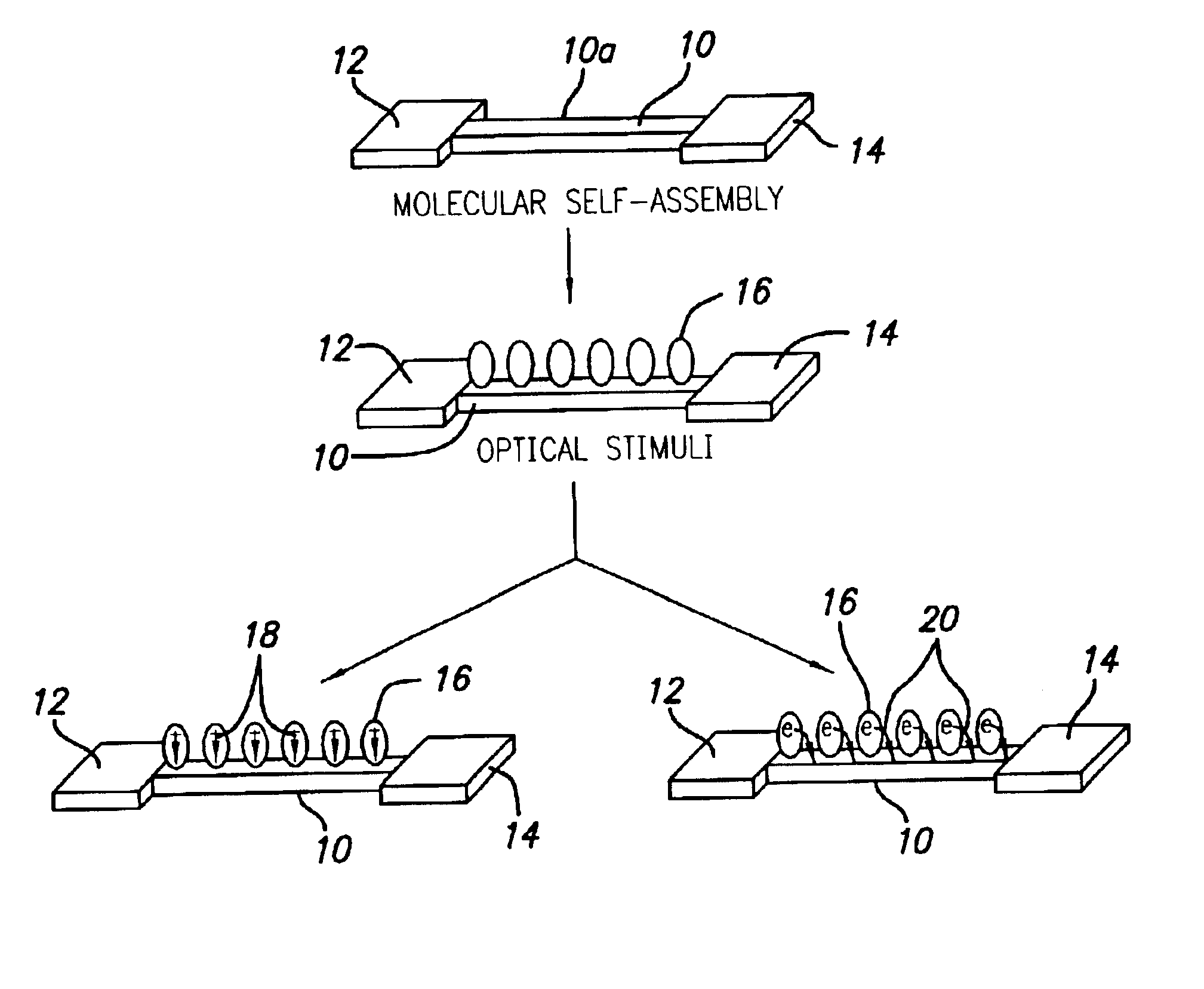

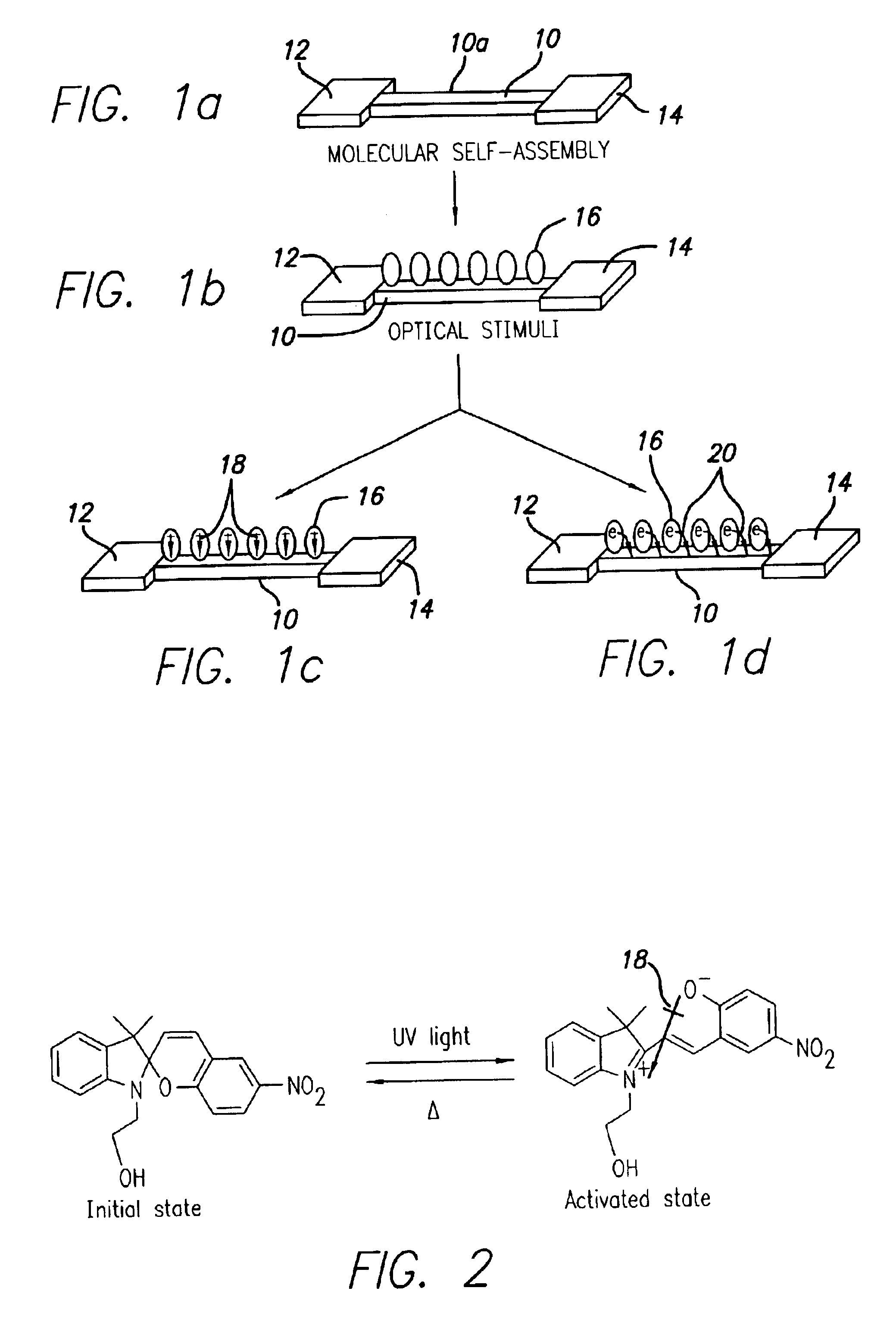

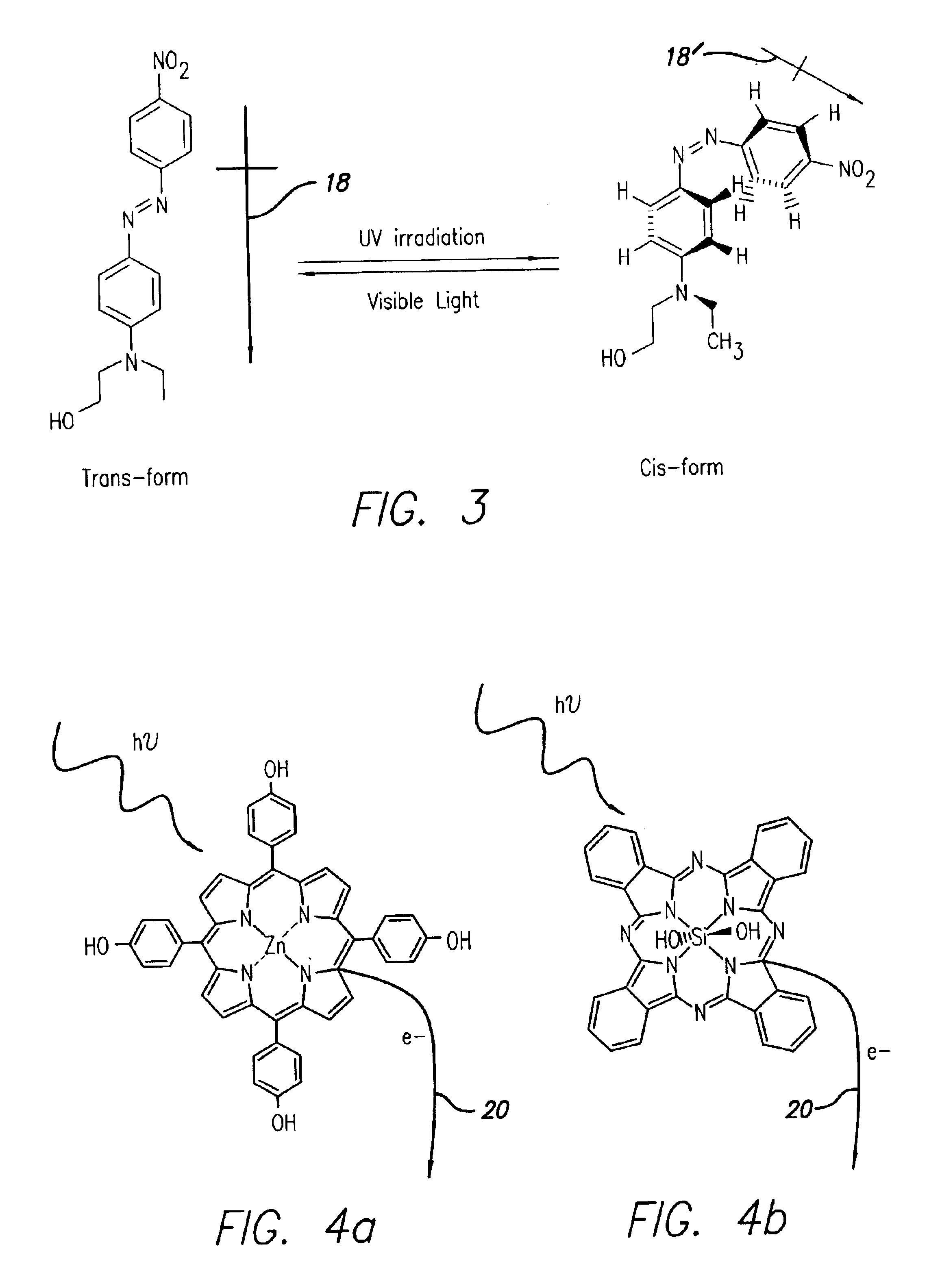

Nano optical sensors via molecular self-assembly

InactiveUS6815706B2High density and sensitivityIndividual molecule manipulationSolid-state devicesEnergy transferSilicon nanowires

An optical sensor is provided, comprising (a) a silicon nanowire of finite length having an electrical contact pad at each end thereof; and (b) a plurality of self-assembled molecules on a surface of the silicon nanowire, the molecules serving to modulate electrical conductivity of the silicon nanowire by either a reversible change in dipole moment of the molecules or by a reversible molecule-assisted electron / energy transfer from the molecules onto the silicon nanowire. Further, a method of making the optical sensor is provided. The concept of molecular self-assembly is applied in attaching functional molecules onto silicon nanowire surfaces, and the requirement of molecule modification (hydroxy group in molecules) is minimal from the point view of synthetic difficulty and compatibility. Self-assembly will produce well-ordered ultra-thin films with strong chemical bonding on a surface that cannot be easily achieved by other conventional methods.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

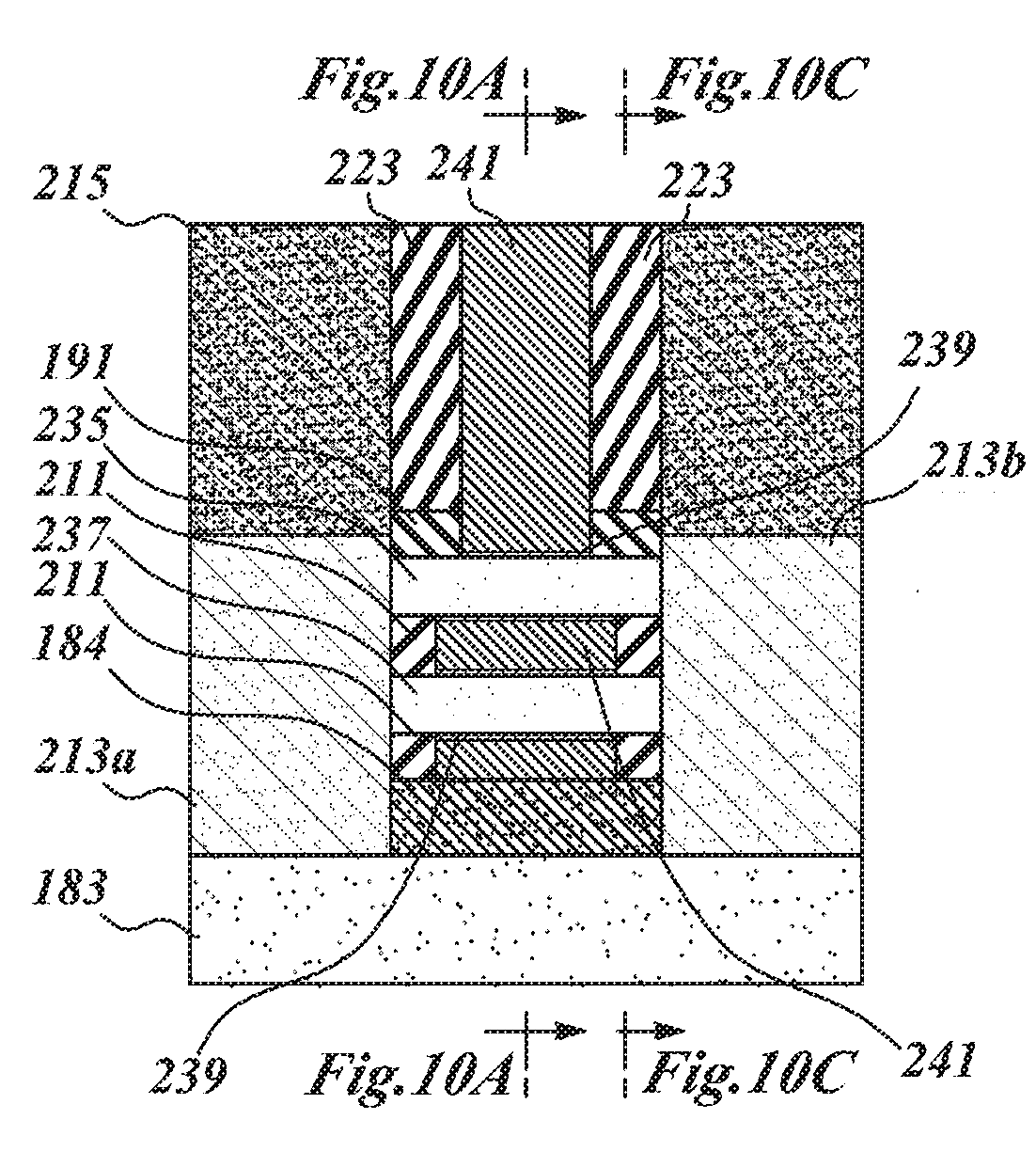

Multi-channel gate-all-around fet

ActiveUS20160111513A1Low working voltageImprove reliabilityTransistorNanoinformaticsDriving currentPower flow

A high performance GAA FET is described in which vertically stacked silicon nanowires carry substantially the same drive current as the fin in a conventional FinFET transistor, but at a lower operating voltage, and with greater reliability. One problem that occurs in existing nanowire GAA FETs is that, when a metal is used to form the wraparound gate, a short circuit can develop between the source and drain regions and the metal gate portion that underlies the channel. The vertically stacked nanowire device described herein, however, avoids such short circuits by forming insulating barriers in contact with the source and drain regions, prior to forming the gate. Through the use of sacrificial films, the fabrication process is almost fully self-aligned, such that only one lithography mask layer is needed, which significantly reduces manufacturing costs.

Owner:TAIWAN SEMICON MFG CO LTD

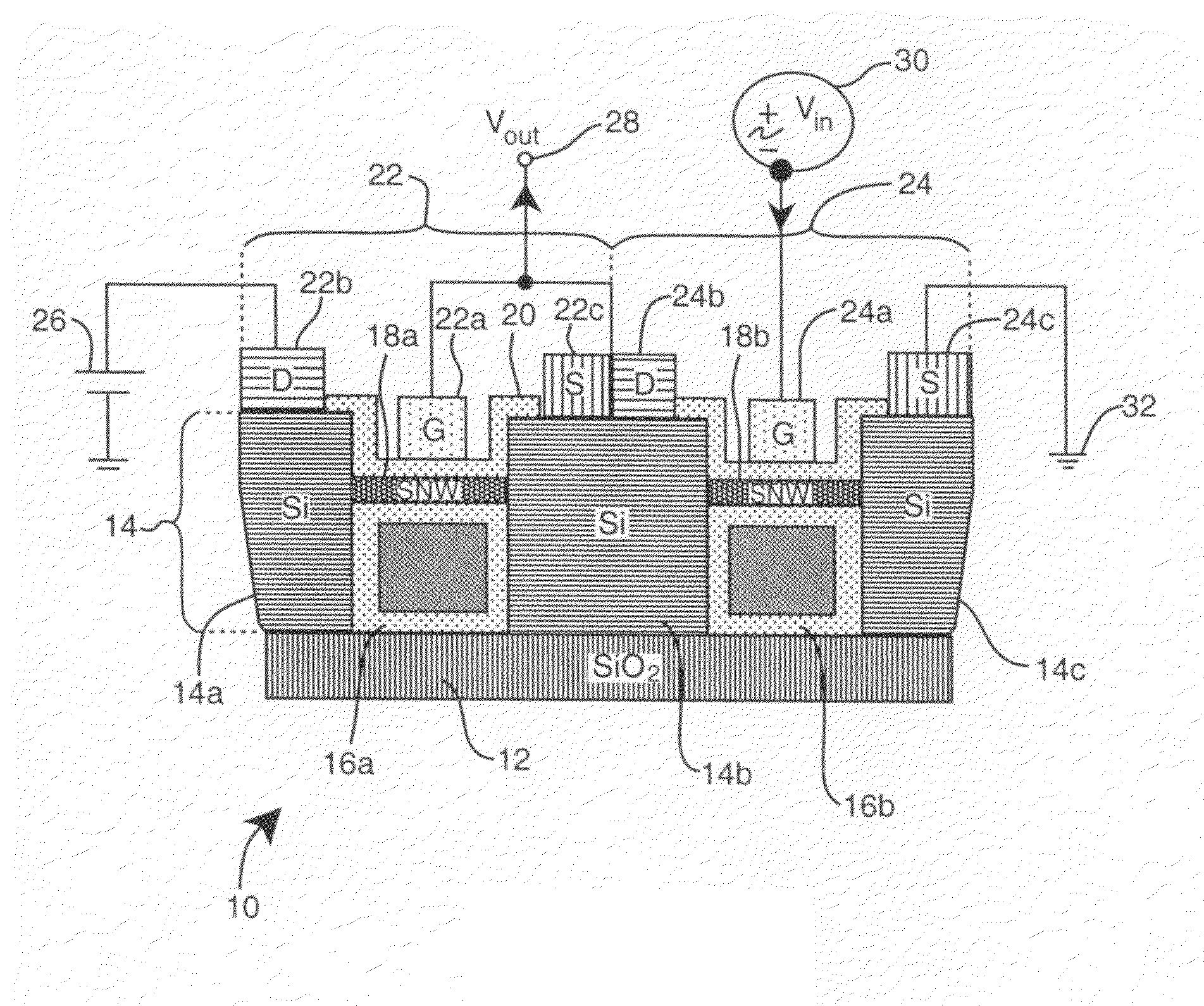

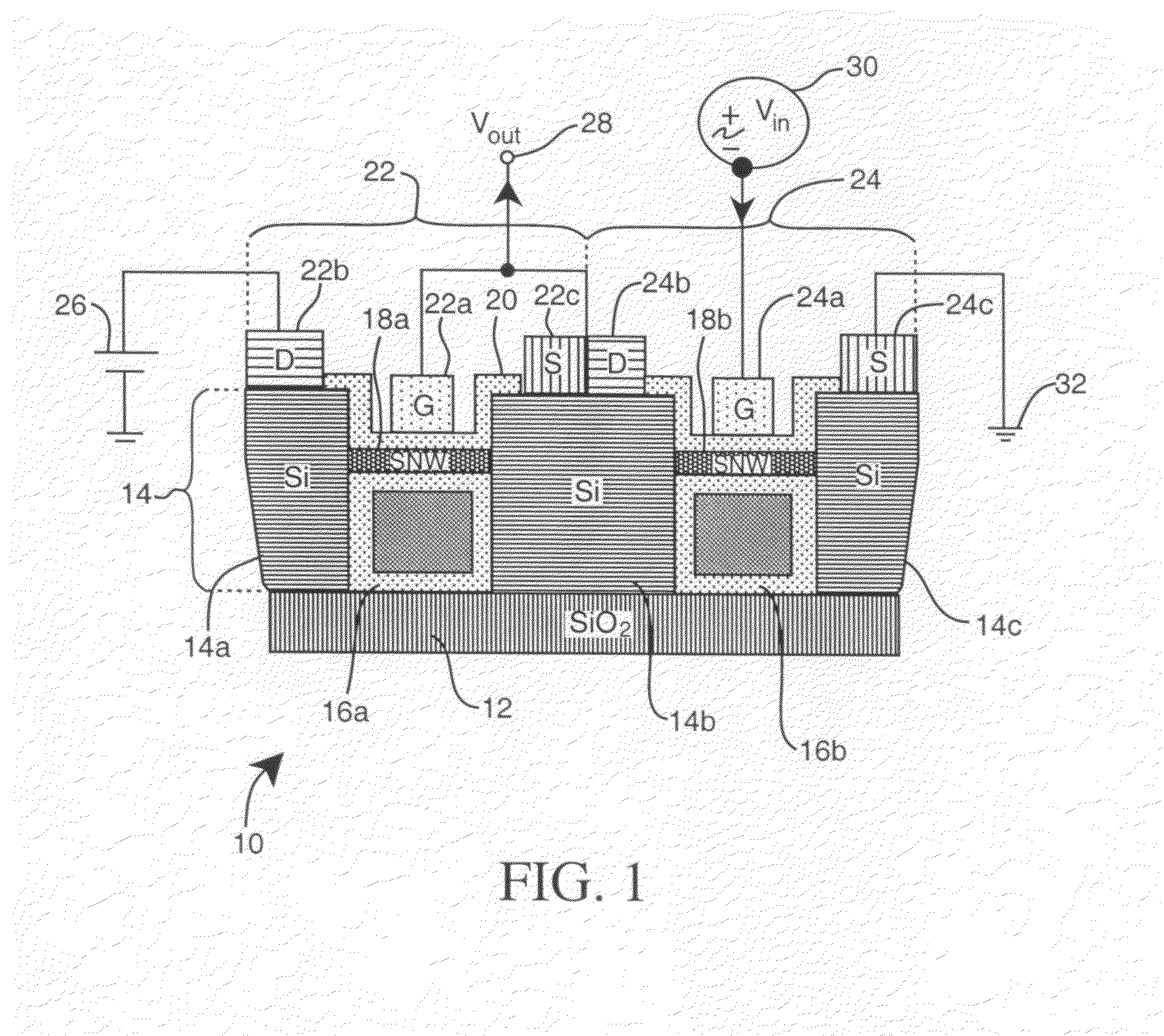

Insulated gate silicon nanowire transistor and method of manufacture

An insulated gate silicon nanowire transistor amplifier structure is provided and includes a substrate formed of dielectric material. A patterned silicon material may be disposed on the substrate and includes at least first, second and third electrodes uniformly spaced on the substrate by first and second trenches. A first nanowire formed in the first trench operates to electrically couple the first and second electrodes. A second nanowire formed in the second trench operates to electrically couple the second and third electrodes. First drain and first source contacts may be respectively disposed on the first and second electrodes and a first gate contact may be disposed to be capacitively coupled to the first nanowire. Similarly, second drain and second source contacts may be respectively disposed on the second and third electrodes and a second gate contact may be disposed to be capacitively coupled to the second nanowire.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

Silicon Nanostructure Active Materials for Lithium Ion Batteries and Processes, Compositions, Components and Devices Related Thereto

ActiveUS20140248543A1Highly controllableAvoid irreversibleElectrochemical processing of electrodesElectrode carriers/collectorsCopper electrodeGraphite particle

The present invention relates to nanostructured materials for use in rechargeable energy storage devices such as lithium batteries, particularly rechargeable secondary lithium batteries, or lithium-ion batteries (LIBs). The present invention includes materials, components, and devices, including nanostructured materials for use as battery active materials, and lithium ion battery (LIB) electrodes comprising such nanostructured materials, as well as manufacturing methods related thereto. Exemplary nanostructured materials include silicon-based nanostructures such as silicon nanowires and coated silicon nanowires, nanostructures disposed on substrates comprising active materials or current collectors such as silicon nanowires disposed on graphite particles or copper electrode plates, and LIB anode composites comprising high-capacity active material nanostructures formed on a porous copper and / or graphite powder substrate.

Owner:ONED MATERIAL INC

Nitrogen oxide sensitive field effect transistors for explosive detection comprising functionalized non-oxidized silicon nanowires

InactiveUS20100325073A1Improve overall senseHigh selectivityMaterial analysis by electric/magnetic meansDigital computer detailsChemical compoundSilicon nanowires

An apparatus for detecting volatile compounds derived from explosive materials with very high sensitivity. The apparatus is composed of field effect transistors of non-oxidized silicon nanowires modified with specific functional groups including, in particular, amine, imine and / or carboxyl moieties. Further a system is provided comprising the apparatus in conjunction with learning and pattern recognition algorithms and methods of use thereof for detecting and quantifying specific explosive compounds.

Owner:TECHNION RES & DEV FOUND LTD

Silicon nano wire having a silicon-nitride shell and method of manufacturing the same

InactiveUS20060182966A1Excellent luminous propertiesEasy to controlMaterial nanotechnologyPolycrystalline material growthSilicon nanowiresOptoelectronics

Silicon nano wires having silicon nitride shells and a method of manufacturing the same are provided. Each silicon nano wire has a core portion formed of silicon, and a shell portion formed of silicon nitride surrounding the core portion. The method includes removing silicon oxide formed on the shell of the silicon nano wire and forming a silicon nitride shell.

Owner:SAMSUNG ELECTRONICS CO LTD

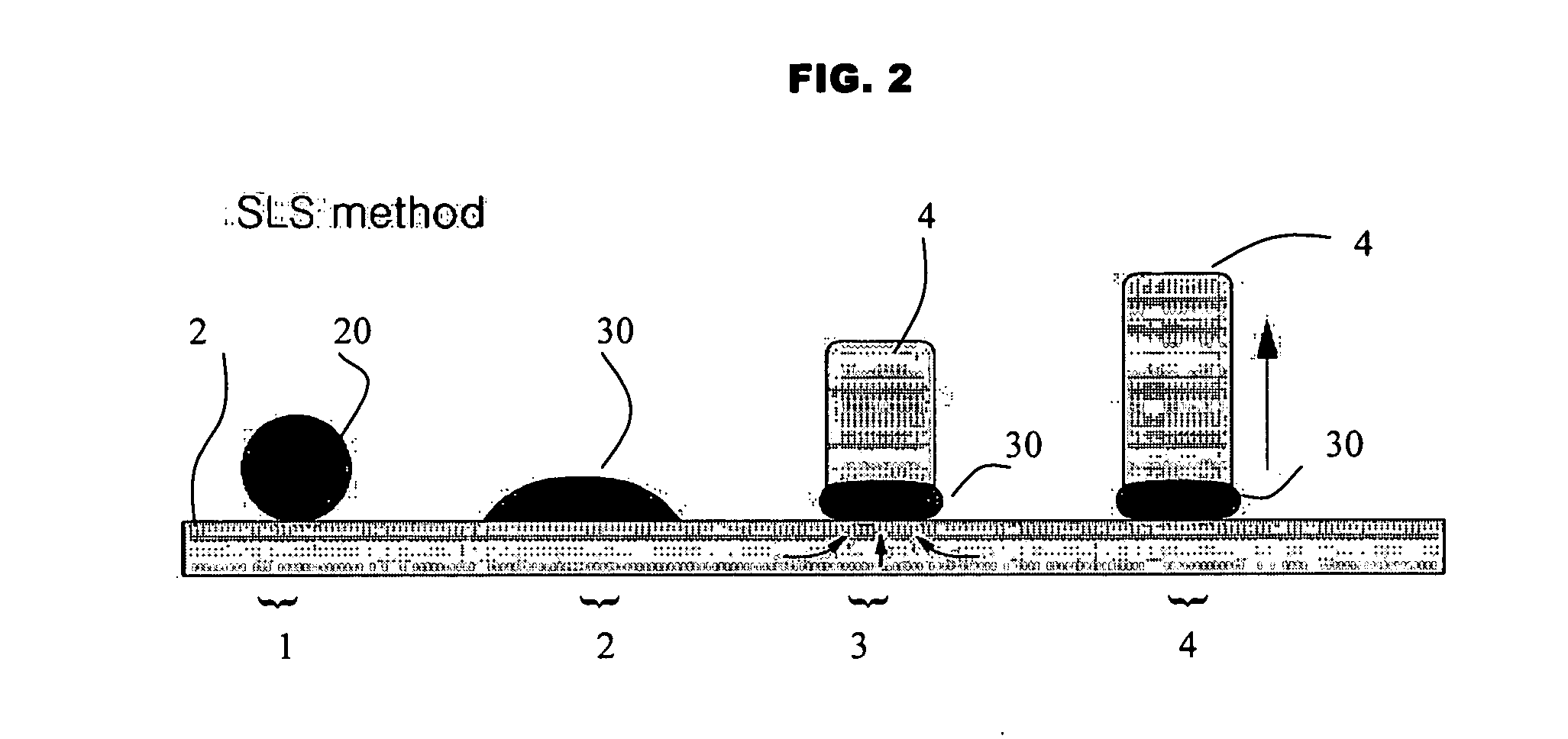

Method of manufacturing silicon nanowires using porous glass template and device comprising silicon nanowires formed by the same

InactiveUS20070232028A1Increasing structural efficiency of structureMaterial nanotechnologyPolycrystalline material growthVapor liquidPhotovoltaic detectors

A method of manufacturing silicon nanowires is characterized in that silicon nanowires are formed and grown through a solid-liquid-solid process or a vapor-liquid-solid process using a porous glass template having nanopores doped with erbium or an erbium precursor. In addition, a device including silicon nanowires formed using the above exemplary method according to the present invention can be effectively applied to various devices, for example, electronic devices such as field effect transistors, sensors, photodetectors, light emitting diodes, laser diodes, etc.

Owner:SAMSUNG ELECTRONICS CO LTD

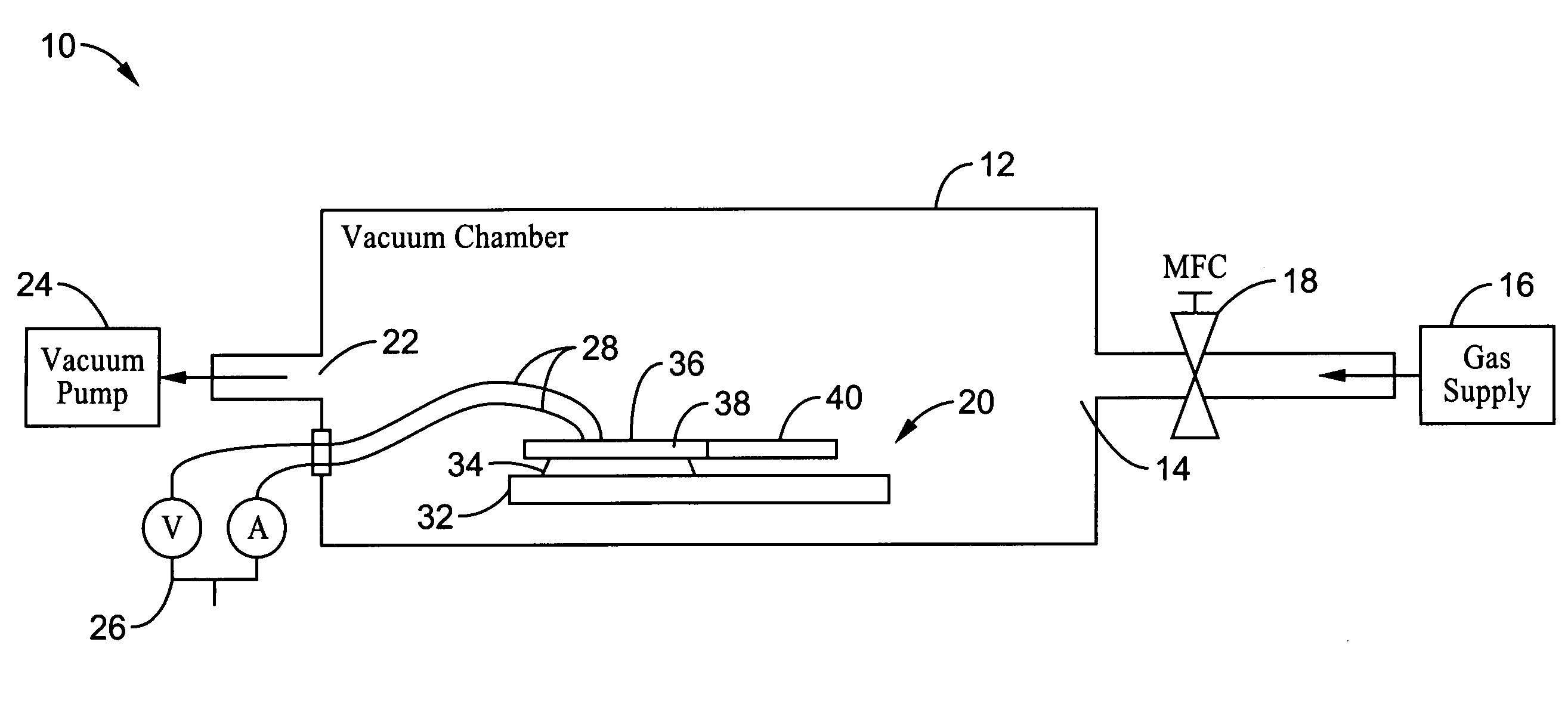

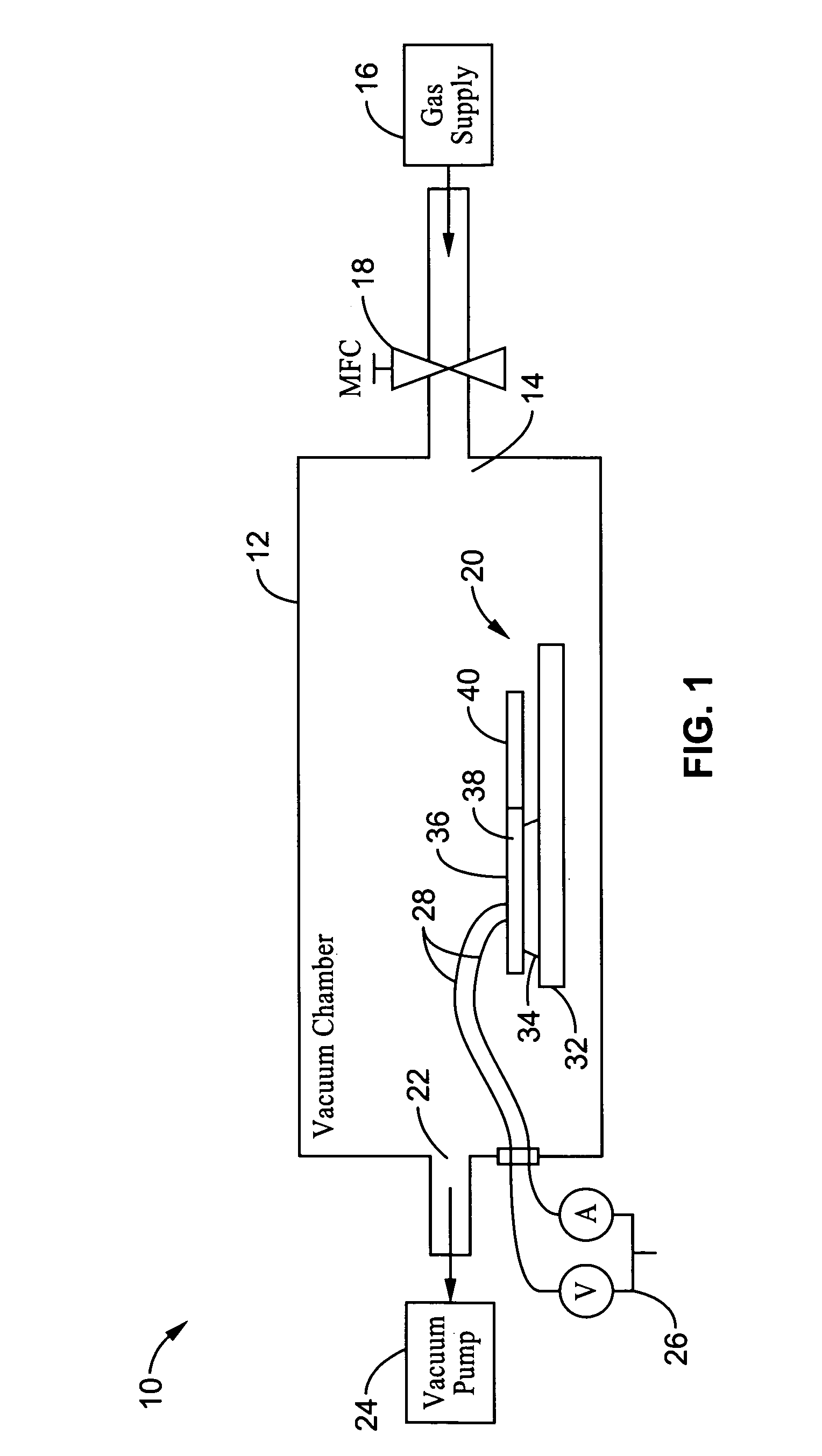

Method for preparing one-dimensional nanostructure in anode alumina template

InactiveCN1669920AImprove qualitySynthesis temperature is lowAnodisationPolycrystalline material growthSilanesHoneycomb structure

The invention discloses a method for preparing a one-dimensional silicon nanostructure in a anodic aluminum oxide mold, which comprises the following steps: growing the one-dimensional silicon nanostructure in low-temperature by the method of plasma chemical depositing with the spacing limited function of porous aluminium oxide, including the silicon nanowire and silicon nanotube, preparing a porous aluminum oxide mold with honeycomb structure by anodic oxidation process, wherein openings arrange ordered, apertures are coherent and vertical the surfaces of the mold, imbedding the mold into a plasma enhanced chemical depositing reaction chamber, growing the silicon nanowire or silicon nanotube at a temperature of 300 Deg. C by controlling the gas flow with the perhydrous diluting silane as the growth air supply.

Owner:ZHEJIANG UNIV

A kind of organic-inorganic hybrid solar cell and preparation method thereof

InactiveCN102263204ALow purity requirementReduce dosageSolid-state devicesSemiconductor/solid-state device manufacturingSolar batteryP–n junction

The invention discloses an organic-inorganic hybridization solar battery which comprises a metal backing electrode, an n-type silicon substrate layer, a silicon nanometer wire array and a battery positive electrode and also comprises a p-type cavity transmission shell layer, wherein the p-type cavity transmission shell layer is a conjugated organic matter semiconductor thin film; the metal backing electrode is arranged on the lower surface of the n-type silicon substrate layer; the silicon nanometer wire array is arranged on the upper surface of the n-type silicon substrate layer; the surfaceof a silicon nanometer wire in the silicon nanometer wire array is covered by the layer of p-type cavity transmission shell layer; and the battery positive electrode is arranged on the p-type cavity transmission shell layer. As a three-dimensional radial p-n junction hybridization structure formed by the silicon nanometer wire array and the conjugated organic matter is adopted in the organic-inorganic hybridization solar battery, on one hand, the absorption of light is increased, the usage amount of silicon is reduced, the purify requirement on the silicon is reduced, on the other hand, the transmission range of current carriers is shortened, the problem that the current carriers are easy to combine is reduced, and the photoelectric conversion efficiency is improved.

Owner:SUZHOU UNIV

Localized synthesis and self-assembly of nanostructures

ActiveUS7311776B2Hot spotMaterial nanotechnologyPolycrystalline material growthGas phaseSilicon nanowires

Systems and methods for local synthesis of silicon nanowires and carbon nanotubes, as well as electric field assisted self-assembly of silicon nanowires and carbon nanotubes, are described. By employing localized heating in the growth of the nanowires or nanotubes, the structures can be synthesized on a device in a room temperature chamber without the device being subjected to overall heating. The method is localized and selective, and provides for a suspended microstructure to achieve the thermal requirement for vapor deposition synthesis, while the remainder of the chip or substrate remains at room temperature. Furthermore, by employing electric field assisted self-assembly techniques according to the present invention, it is not necessary to grow the nanotubes and nanowires and separately connect them to a device. Instead, the present invention provides for self-assembly of the nanotubes and nanowires on the devices themselves, thus providing for nano-to micro-integration.

Owner:RGT UNIV OF CALIFORNIA

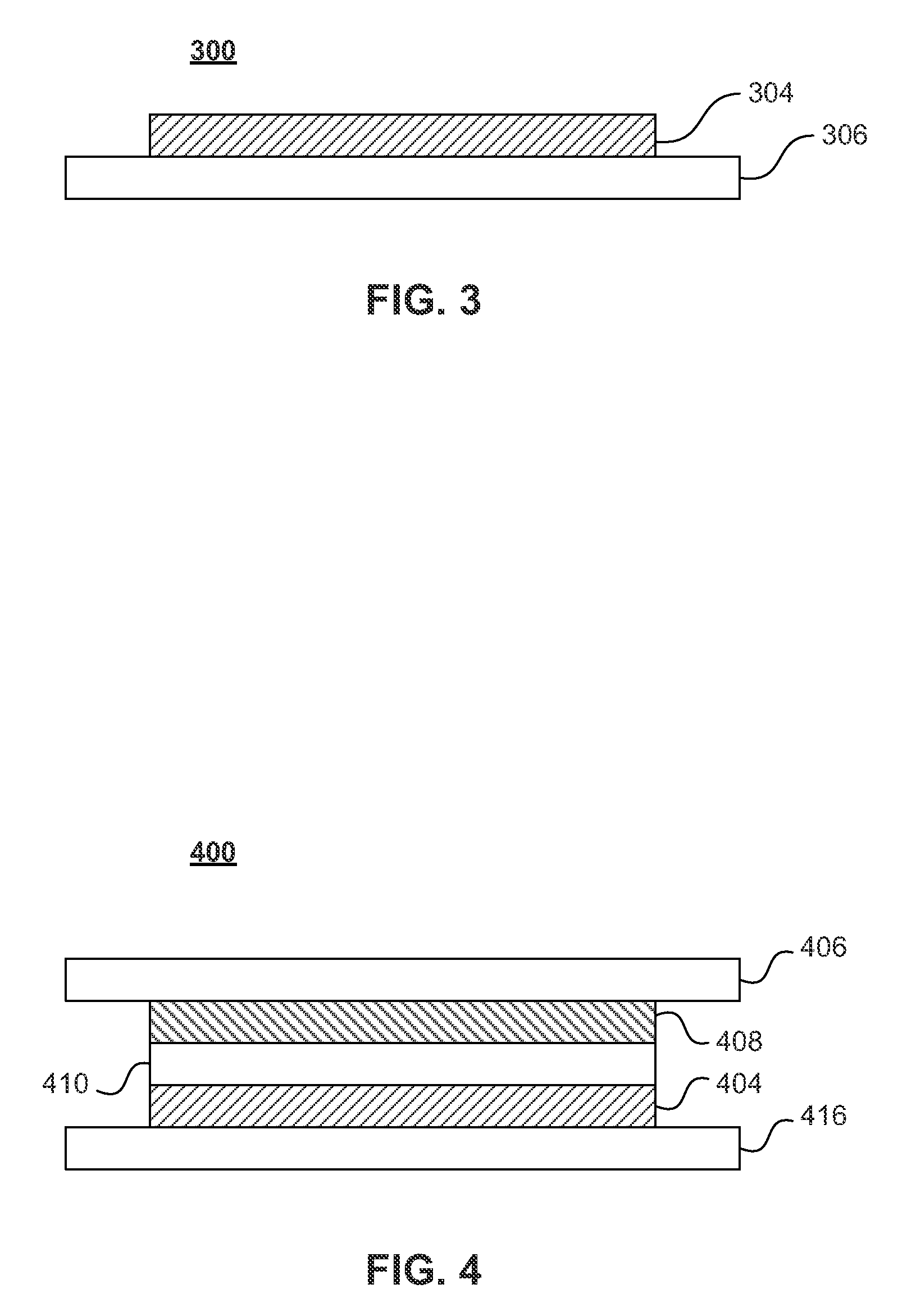

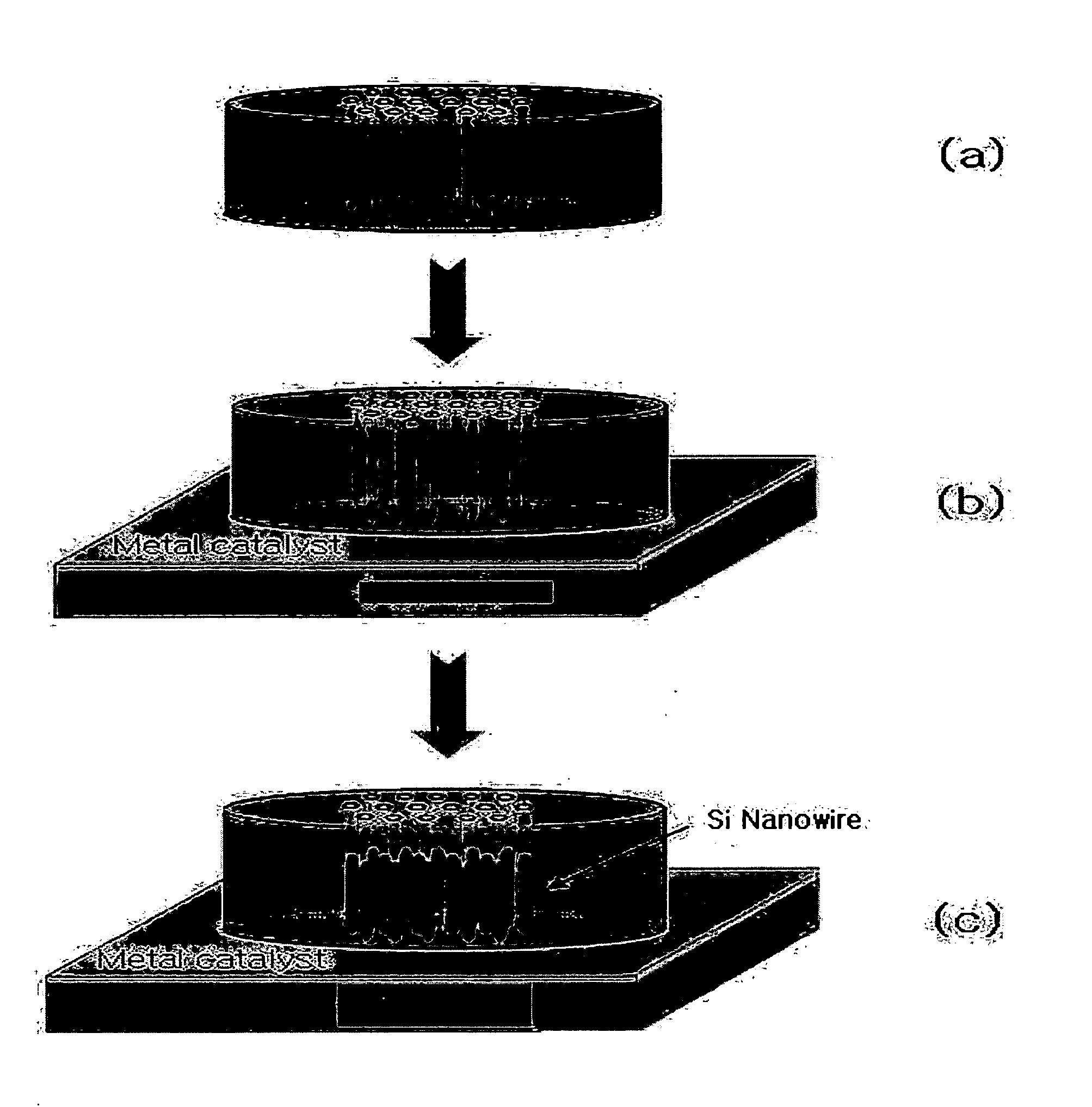

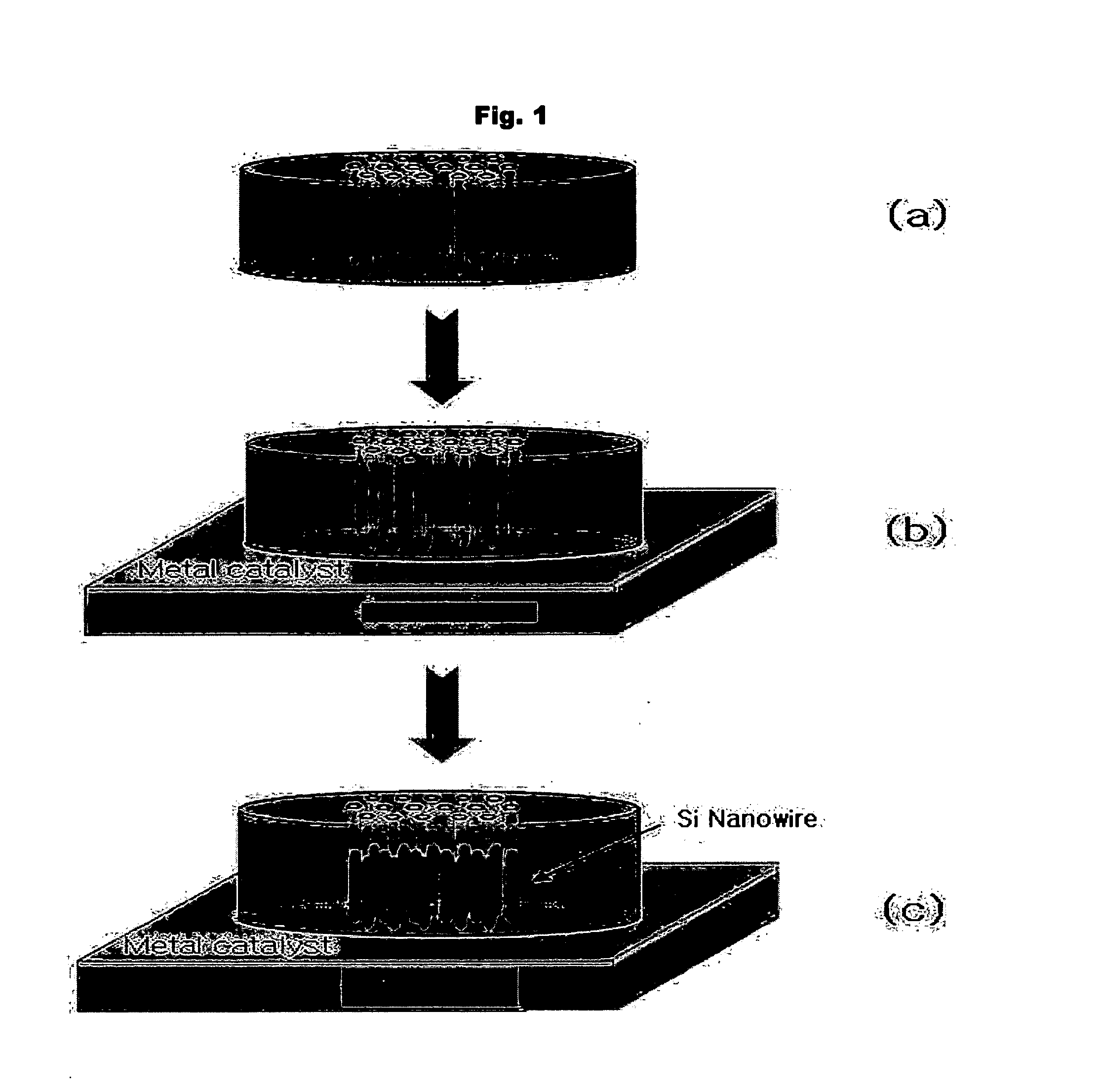

Method for fabricating silicon NANO wire, solar cell including silicon NANO wire and method for fabricating solar cell

InactiveUS20100206367A1Final product manufactureSemiconductor/solid-state device manufacturingSilicon nanowiresSolar cell

A method for fabricating a silicon nano wire, a solar cell including the silicon nano wire and a method for fabricating the solar cell. The solar cell includes a substrate, a first++-type poly-Si layer formed on the substrate, a first-type silicon nano wire layer including a first-type silicon nano wire grown from the first++-type poly-Si layer, an intrinsic layer formed on the substrate having the first-type silicon nano wire layer, and a second-type doping layer formed on the intrinsic layer.

Owner:KOREA INST OF IND TECH