Patents

Literature

2302 results about "P–n junction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A p–n junction is a boundary or interface between two types of semiconductor materials, p-type and n-type, inside a single crystal of semiconductor. The "p" (positive) side contains an excess of holes, while the "n" (negative) side contains an excess of electrons in the outer shells of the electrically neutral atoms there. This allows electrical current to pass through the junction only in one direction. The p-n junction is created by doping, for example by ion implantation, diffusion of dopants, or by epitaxy (growing a layer of crystal doped with one type of dopant on top of a layer of crystal doped with another type of dopant). If two separate pieces of material were used, this would introduce a grain boundary between the semiconductors that would severely inhibit its utility by scattering the electrons and holes.

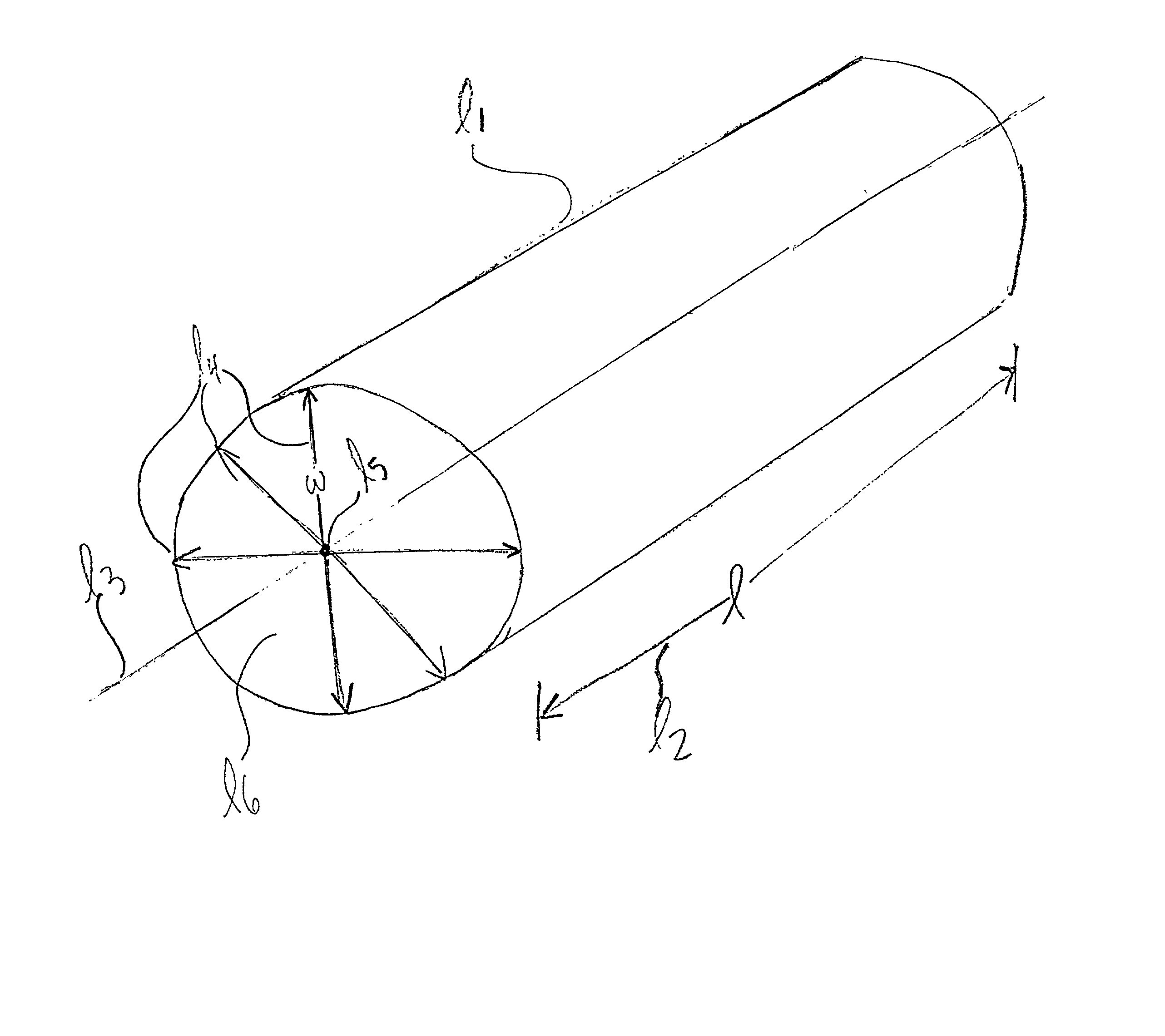

Doped elongated semiconductors, growing such semiconductors, devices including such semiconductors and fabricating such devices

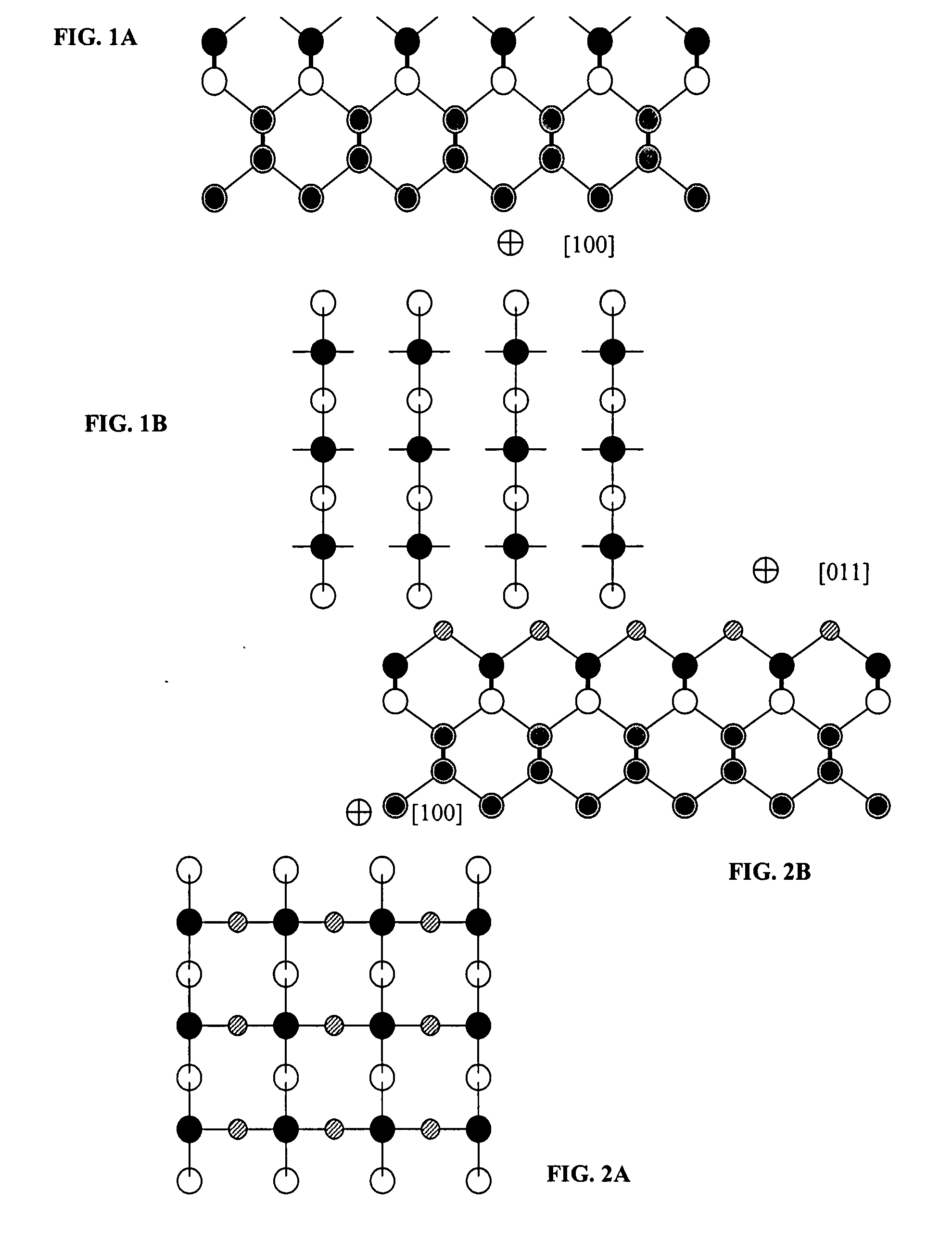

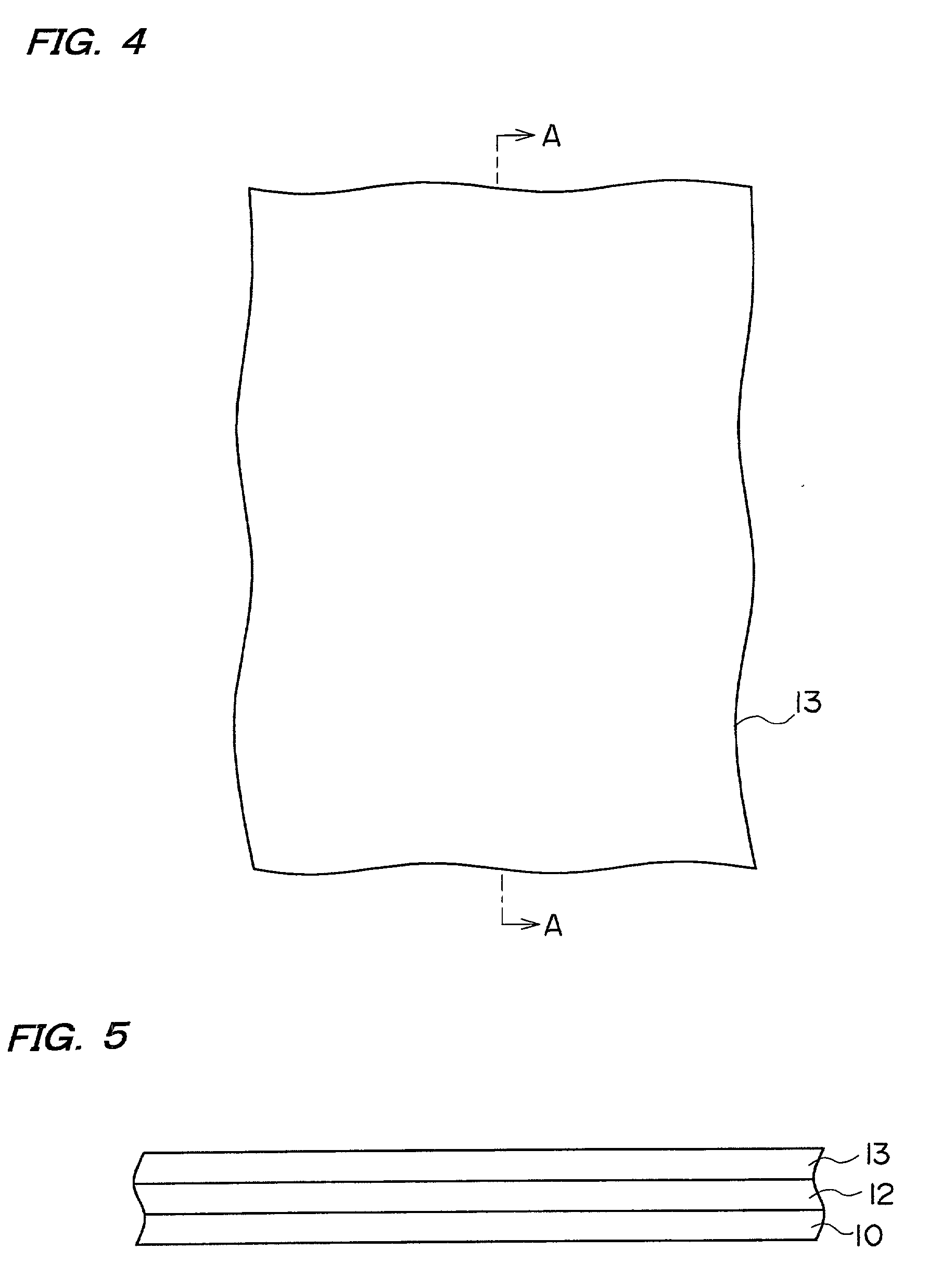

A bulk-doped semiconductor that is at least one of the following: a single crystal, an elongated and bulk-doped semiconductor that, at any point along its longitudinal axis, has a largest cross-sectional dimension less than 500 nanometers, and a free-standing and bulk-doped semiconductor with at least one portion having a smallest width of less than 500 nanometers. Such a semiconductor may comprise an interior core comprising a first semiconductor; and an exterior shell comprising a different material than the first semiconductor. Such a semiconductor may be elongated and my have, at any point along a longitudinal section of such a semiconductor, a ratio of the length of the section to a longest width is greater than 4:1, or greater than 10:1, or greater than 100:1, or even greater than 1000:1. At least one portion of such a semiconductor may a smallest width of less than 200 nanometers, or less than 150 nanometers, or less than 100 nanometers, or less than 80 nanometers, or less than 70 nanometers, or less than 60 nanometers, or less than 40 nanometers, or less than 20 nanometers, or less than 10 nanometers, or even less than 5 nanometers. Such a semiconductor may be a single crystal and may be free-standing. Such a semiconductor may be either lightly n-doped, heavily n-doped, lightly p-doped or heavily p-doped. Such a semiconductor may be doped during growth. Such a semiconductor may be part of a device, which may include any of a variety of devices and combinations thereof, and, and a variety of assembling techniques may be used to fabricate devices from such a semiconductor. Two or more of such a semiconductors, including an array of such semiconductors, may be combined to form devices, for example, to form a crossed p-n junction of a device. Such devices at certain sizes may exhibit quantum confinement and other quantum phenomena, and the wavelength of light emitted from one or more of such semiconductors may be controlled by selecting a width of such semiconductors. Such semiconductors and device made therefrom may be used for a variety of applications.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

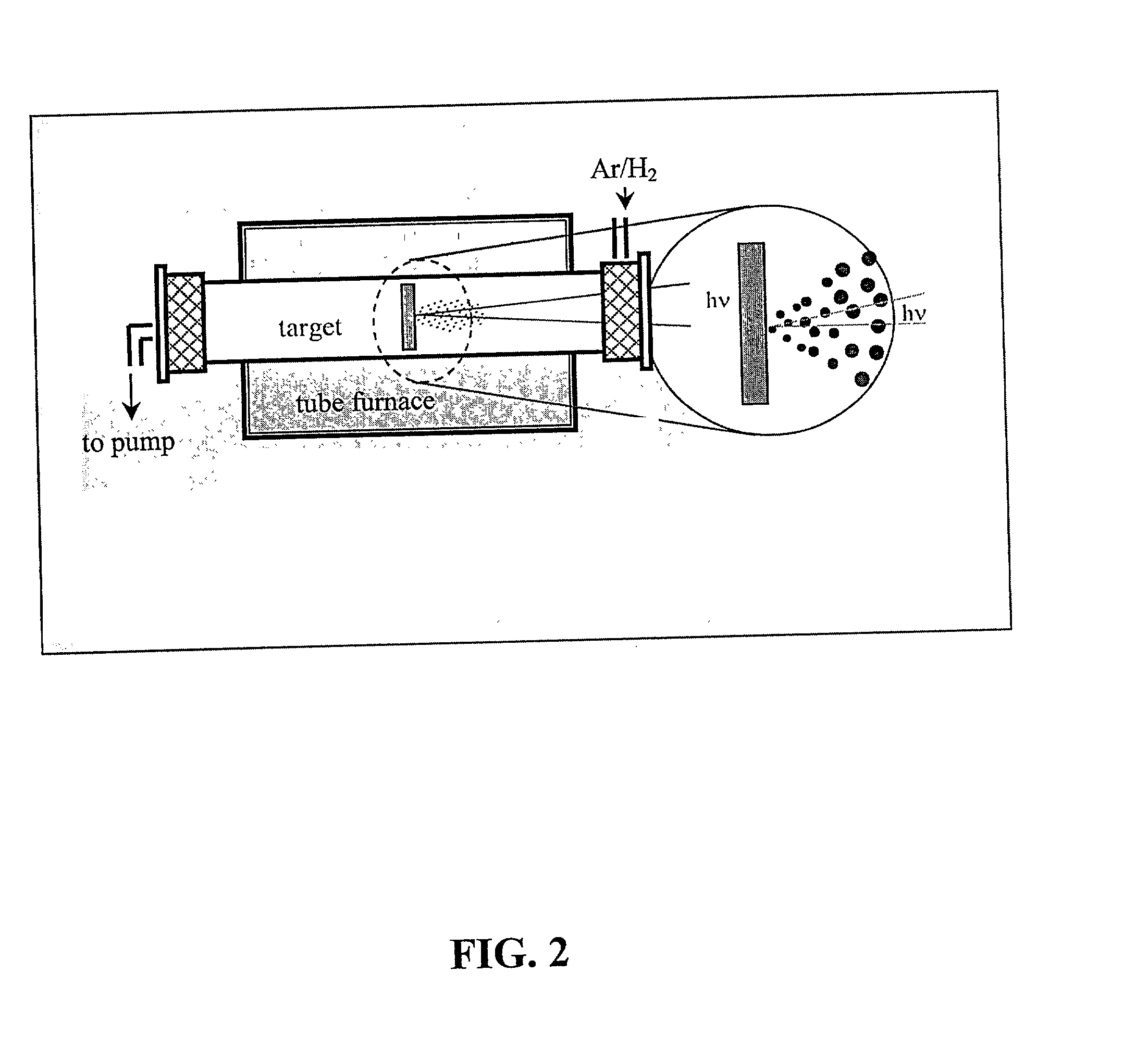

LED lighting system

InactiveUS20060193130A1Reduce heat resistance requirementsImprove cooling effectPoint-like light sourceLighting heating/cooling arrangementsHeat resistanceAdhesive

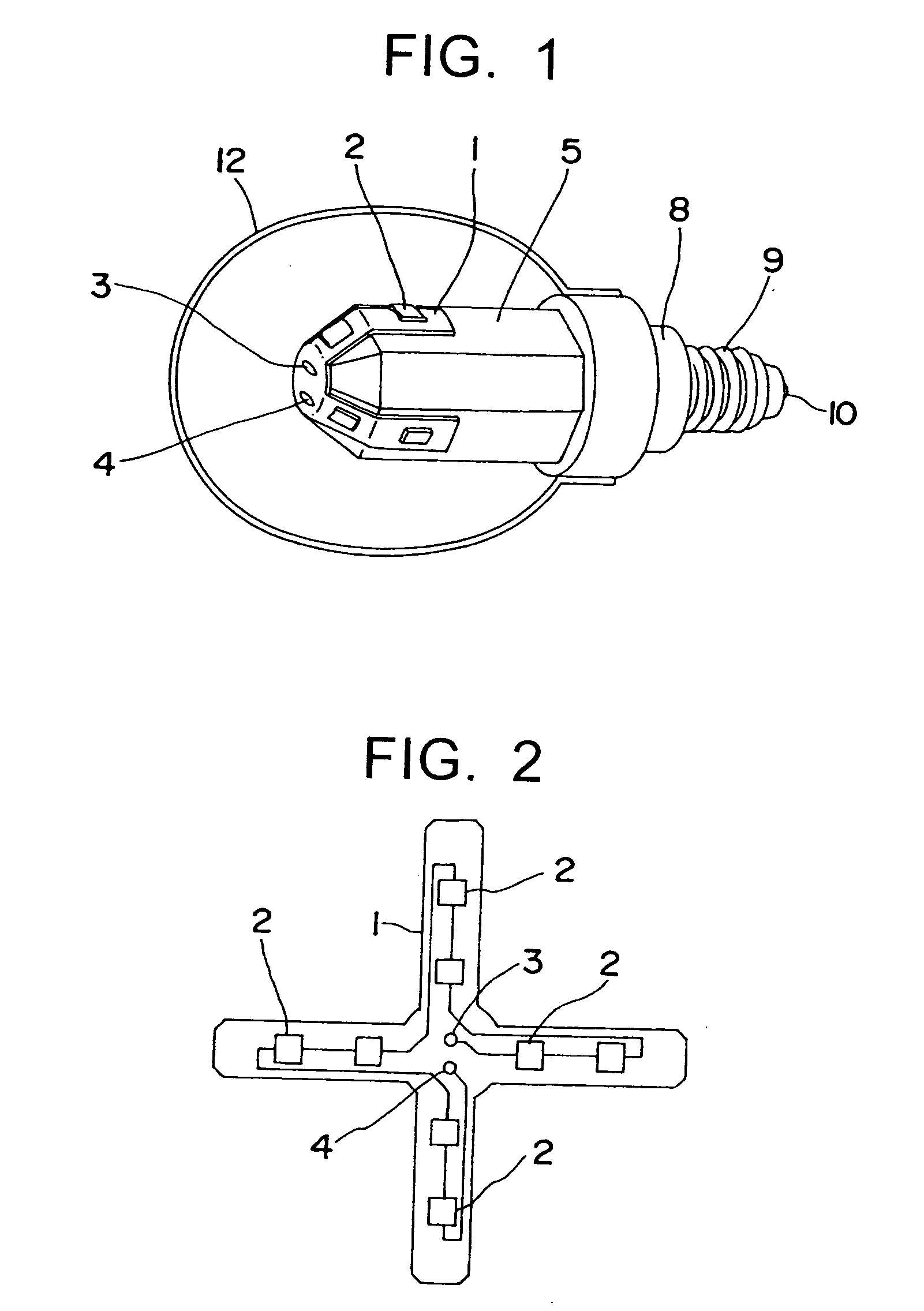

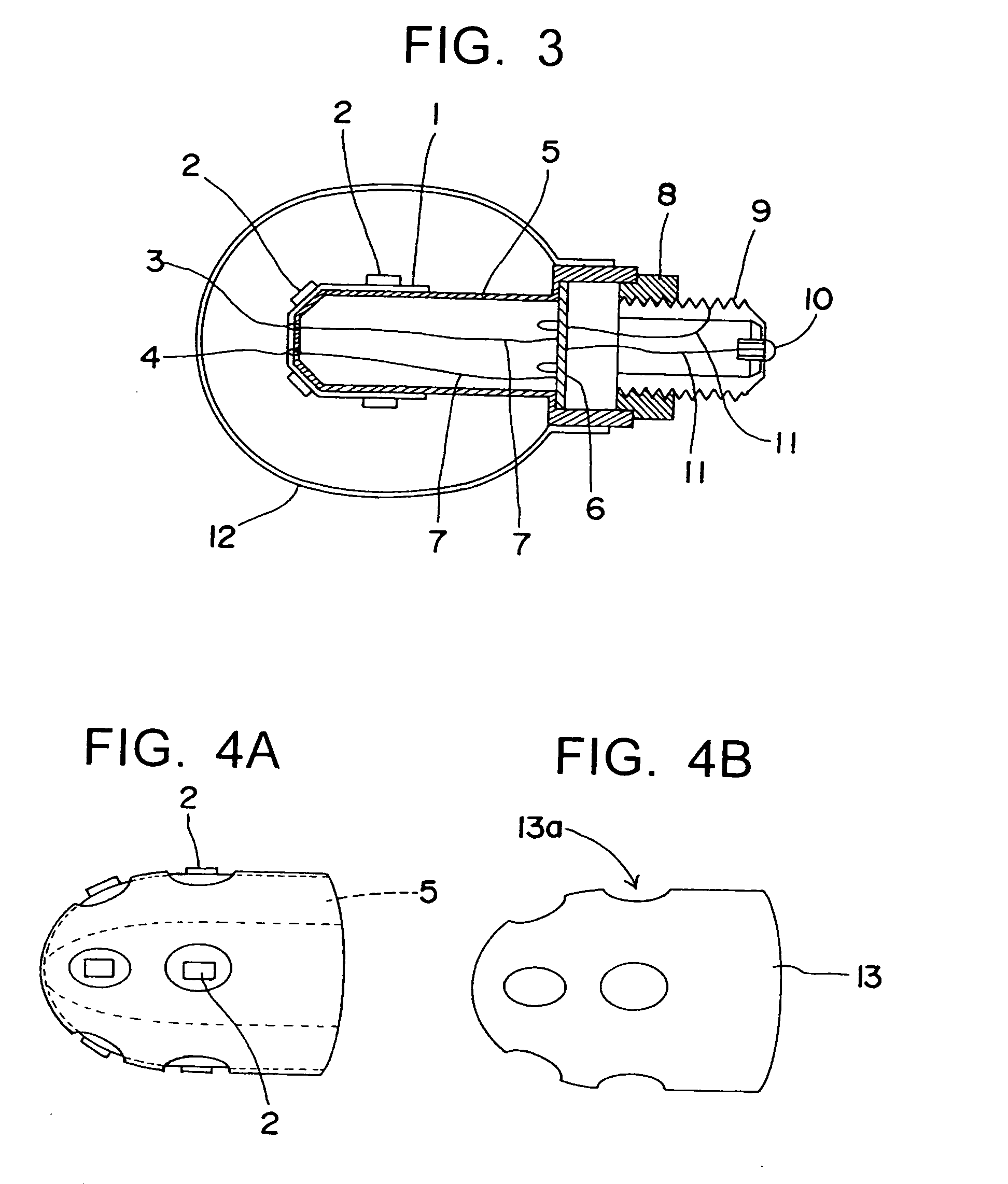

Provided is an LED lighting system with a smaller heat resistance of the LED, which can be produced by simpler mounting steps and is capable of three-dimensionally arranging the LEDs depending on required directivity of each system. A plurality of LEDs 2 are mounted on an FPC 1 which has a radial shape and can be flat when developed. The LEDs 2 connected by printed wiring to each other and linked to terminals 3 and 4 are attached on a surface of a core 5 made of a material having a high thermal conductivity. Heat generated at a p-n junction of the LEDs 2 is transmitted to the core 5 via the FPC 1 and a thermal-conductive adhesive.

Owner:ATEX CO LTD

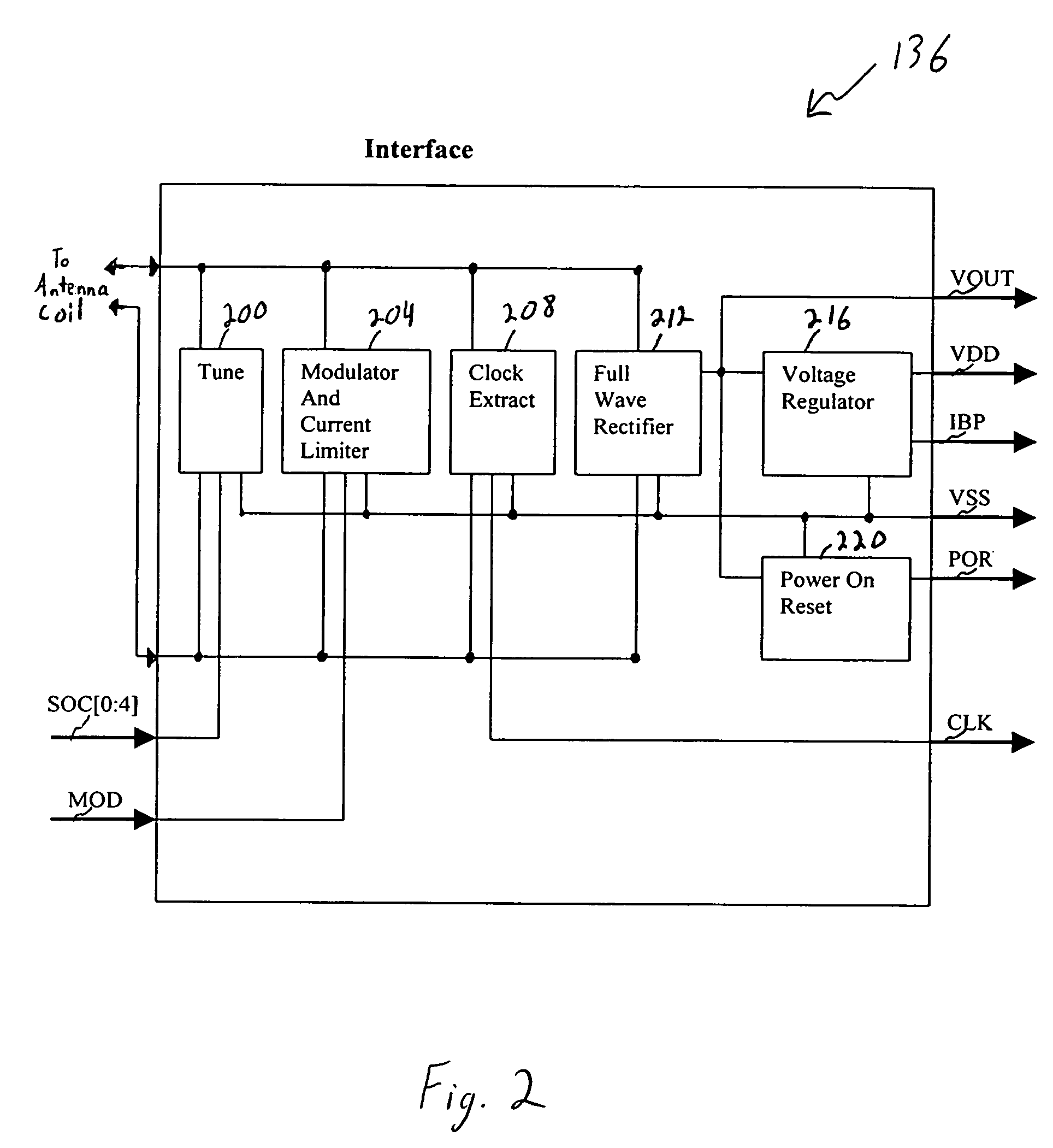

Method and apparatus for sensing and transmitting a body characteristic of a host

InactiveUS7015826B1Thermometer detailsElectric signal transmission systemsP–n junctionIntegrated circuit

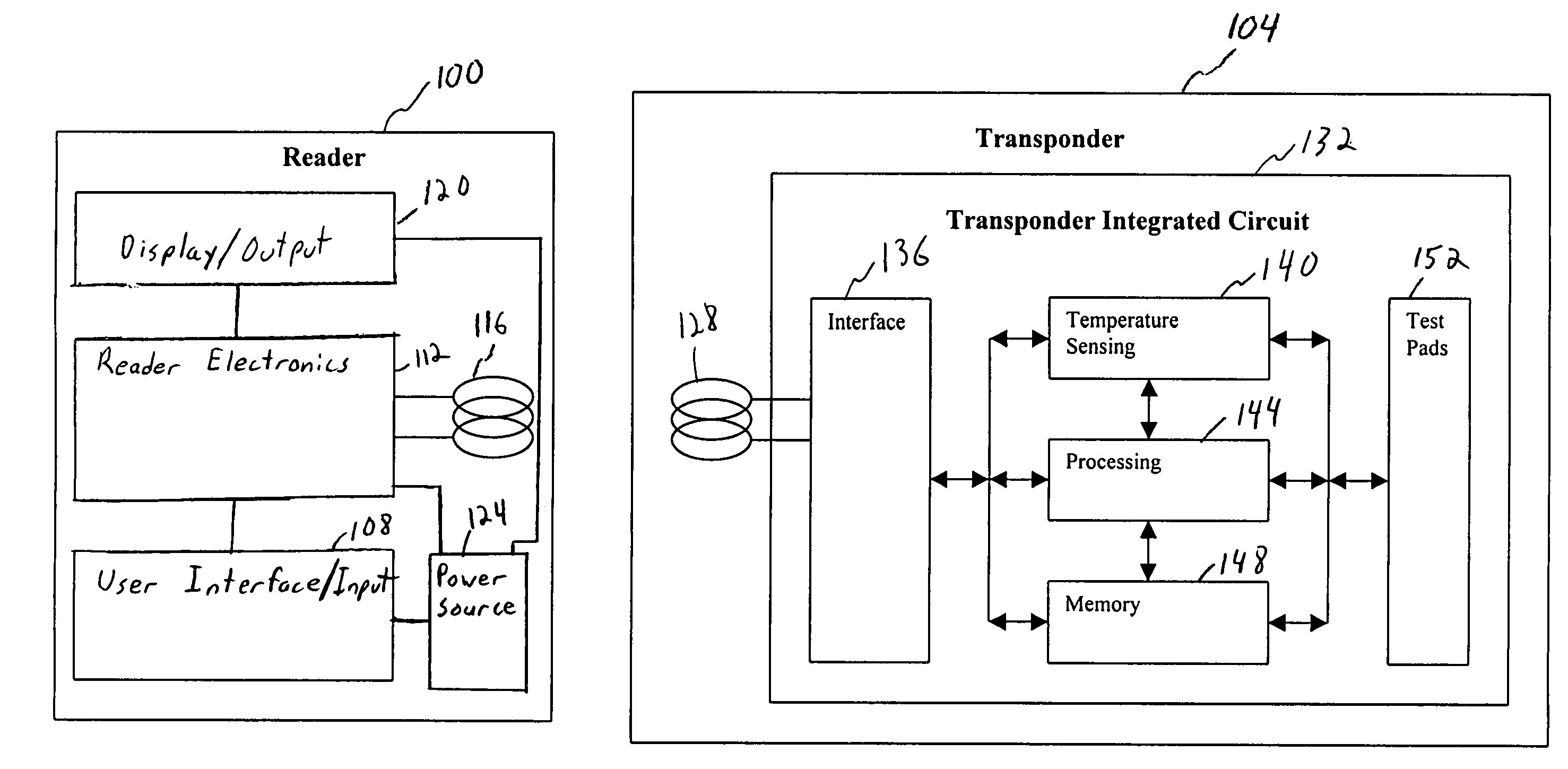

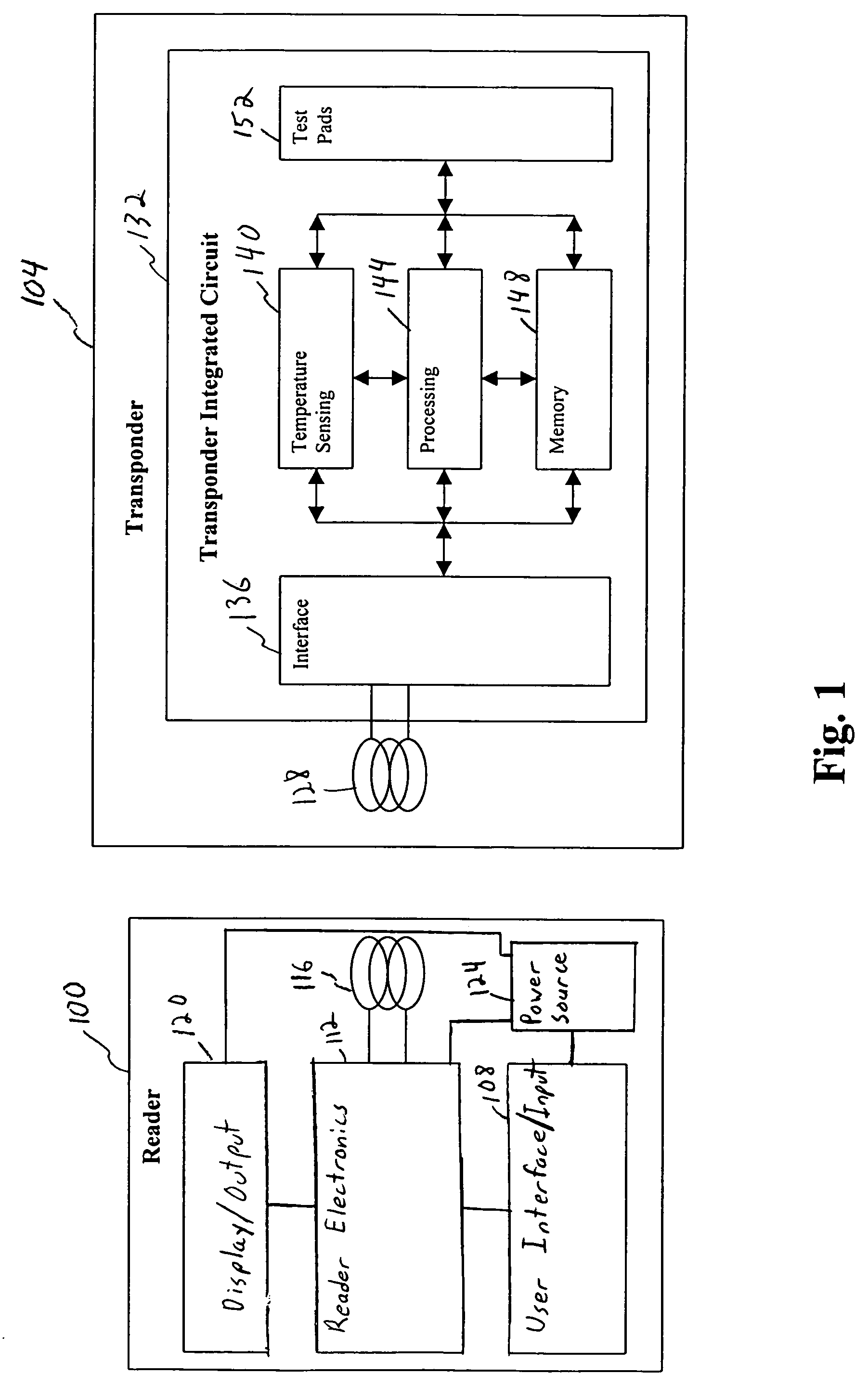

A passive transponder including an integrated sensor is disclosed. The transponder receives an interrogation signal from a scanner, and is operable to transmit identification information and body characteristic information to a scanner. The scanner is operable to receive the identification and body characteristic information and display and / or store the information. The sensor is integrated into the transponder. If temperature is to be sensed, the transponder determines the temperature of the host using the temperature dependent characteristics of the P-N junction of the integrated circuit.

Owner:VERICHIP CORPORATION

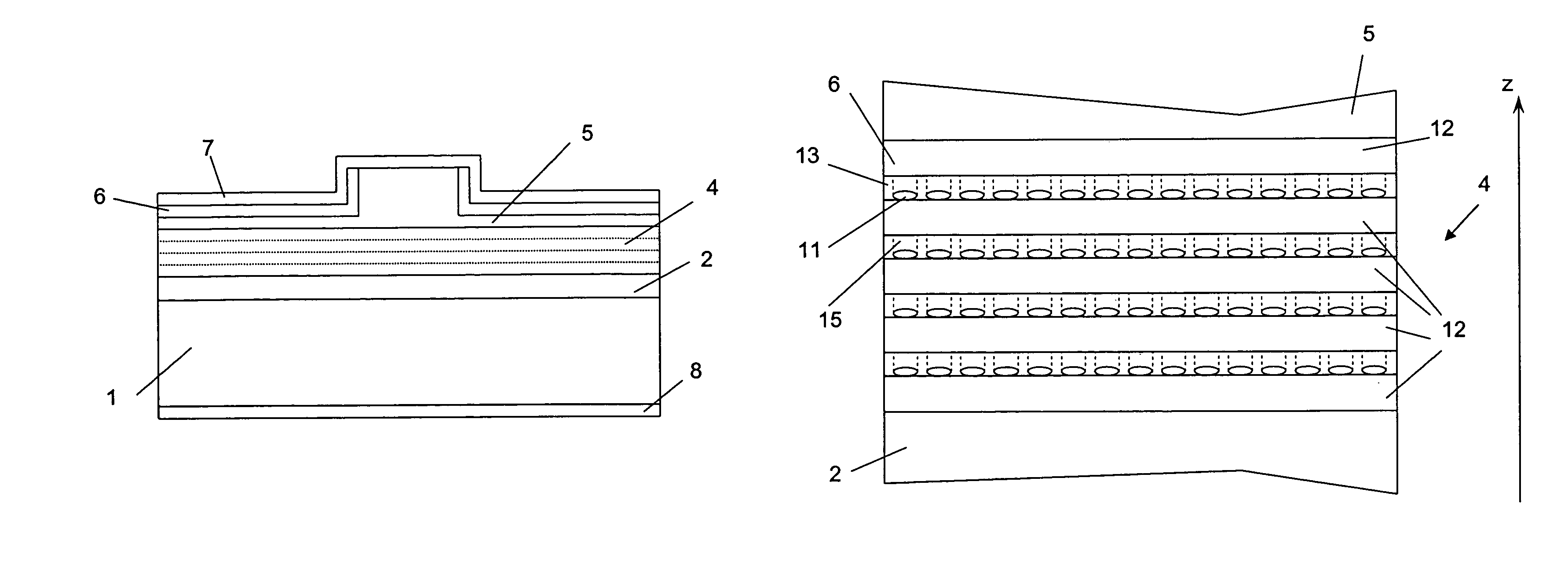

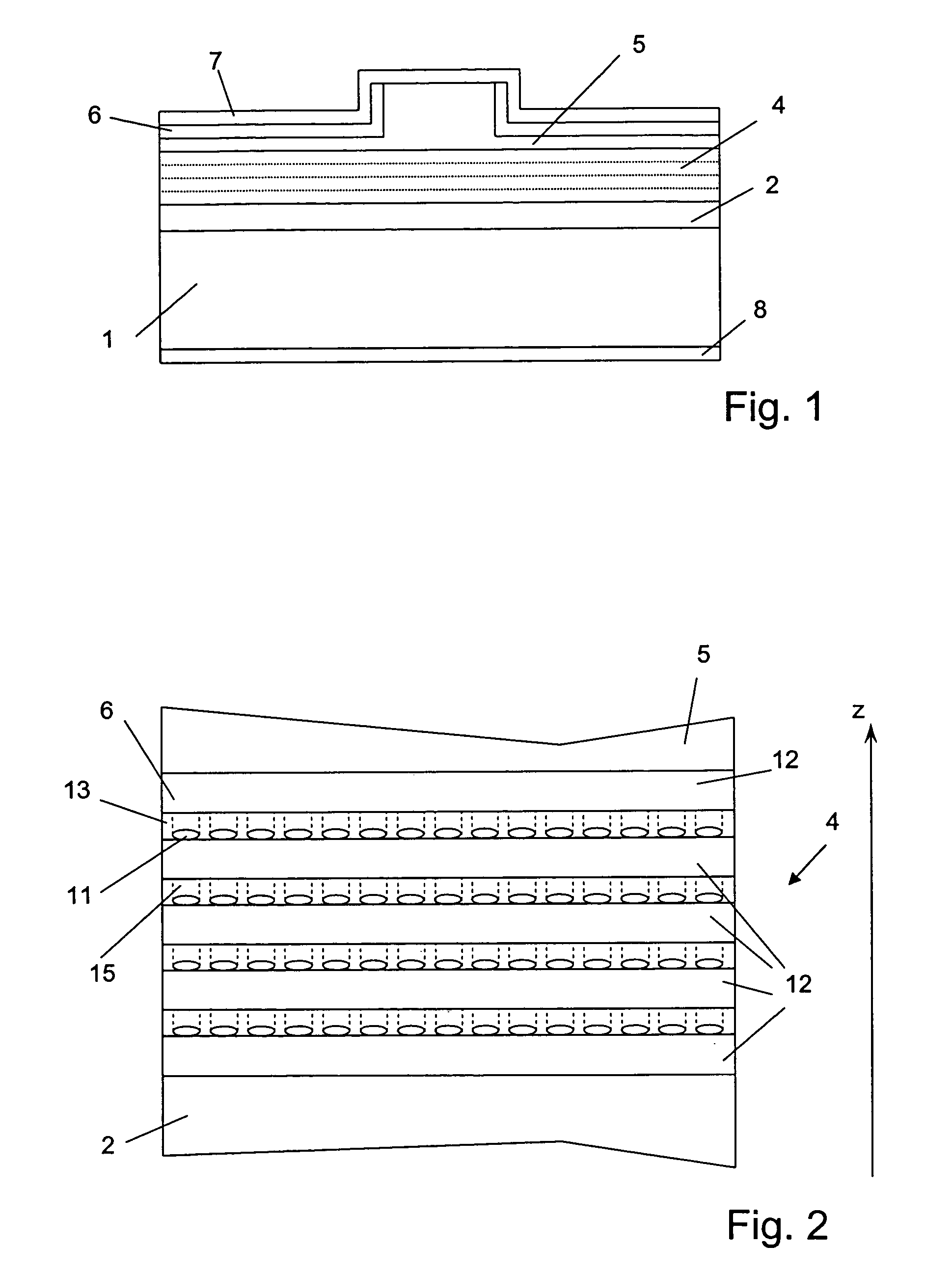

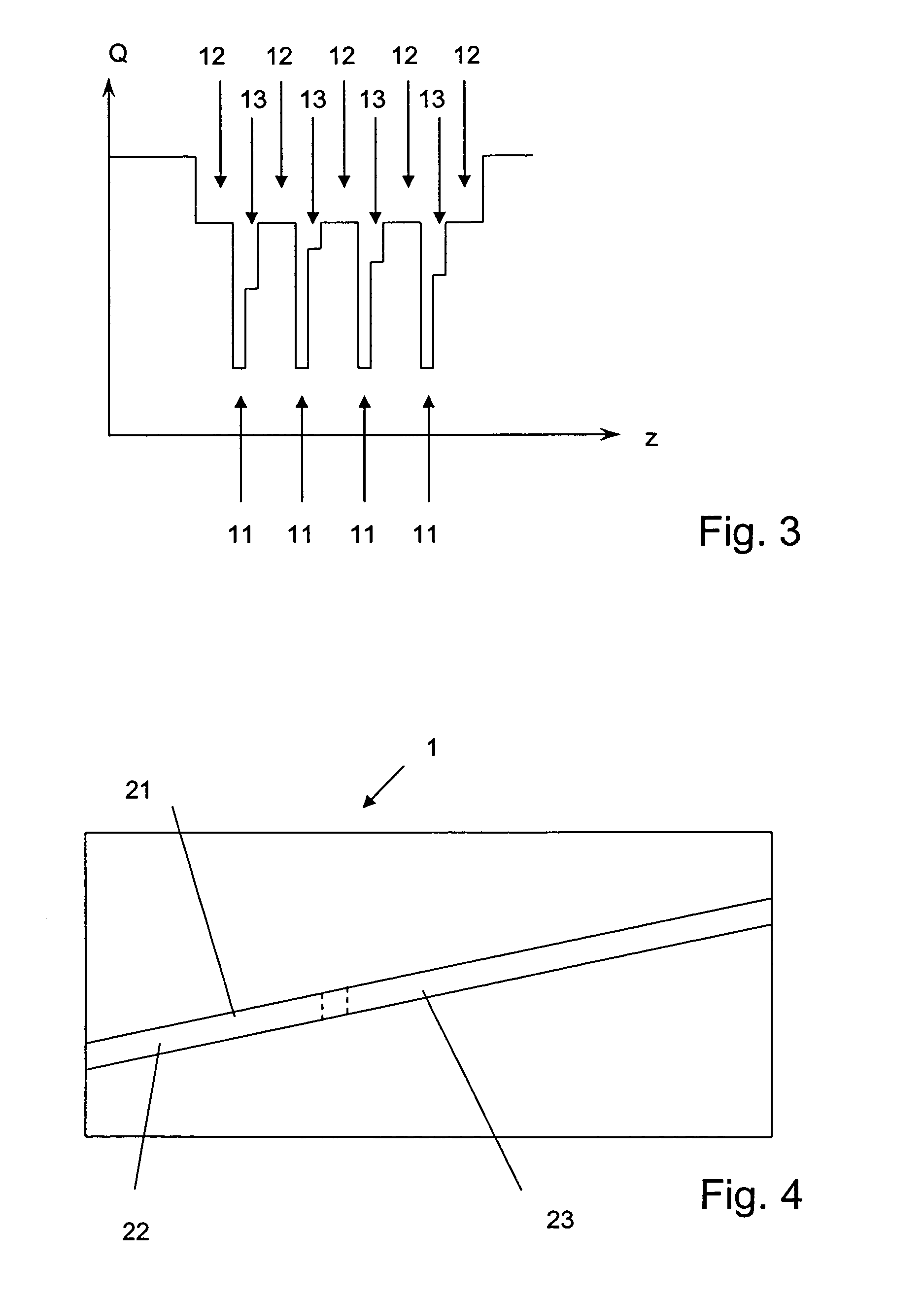

Broadband light emitting device

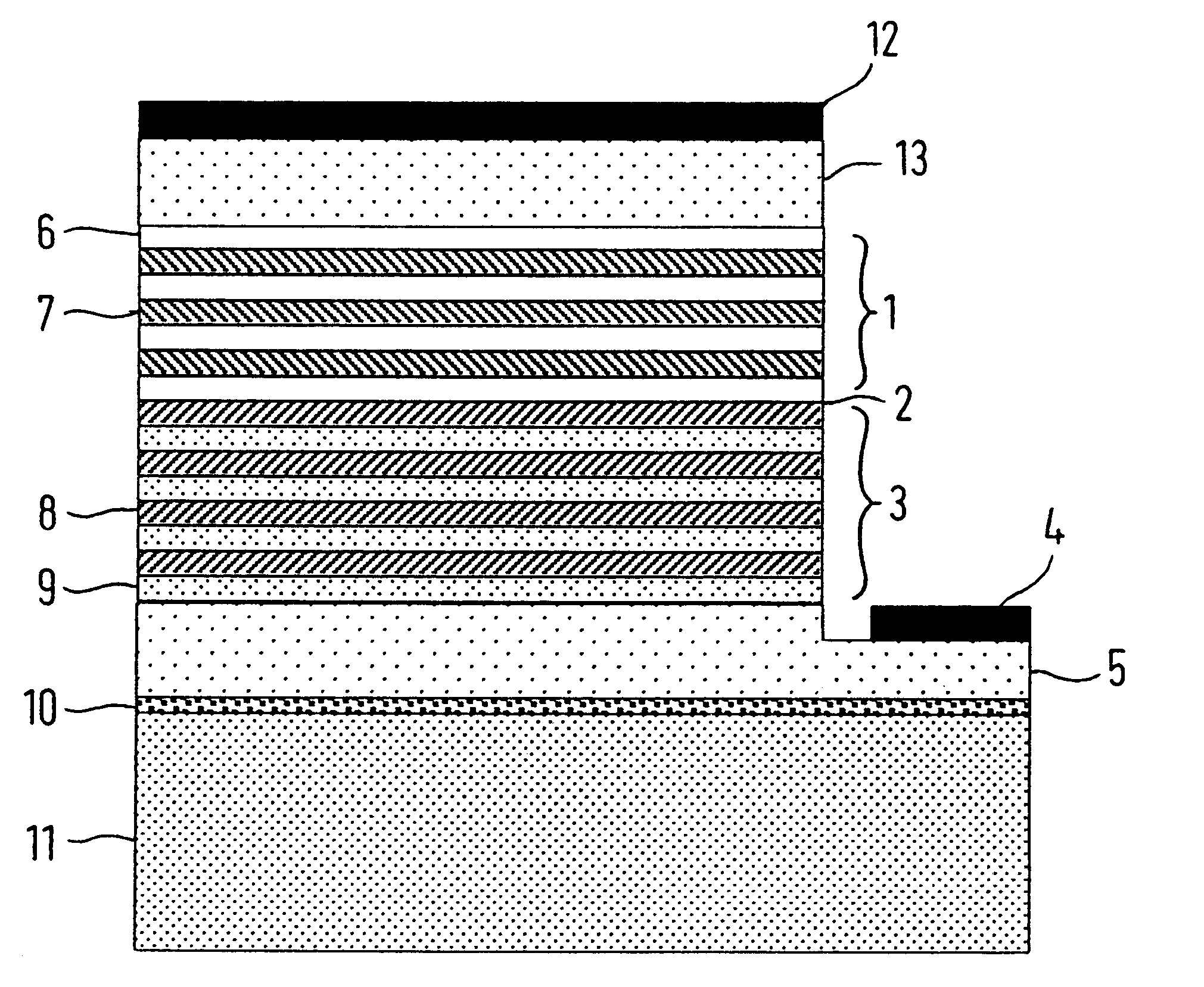

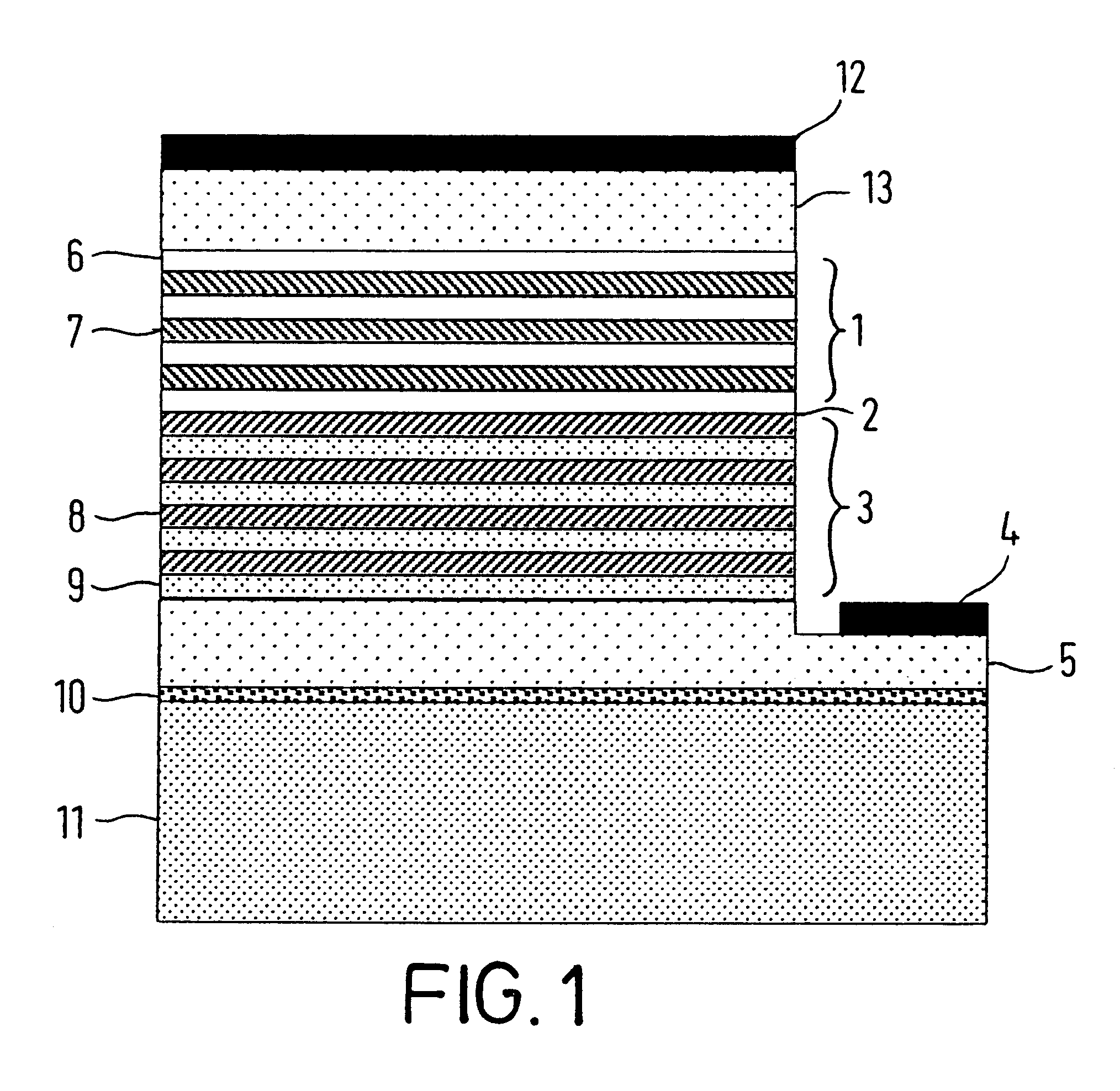

ActiveUS7019325B2Increase heightBroad emission spectrumLaser detailsLaser optical resonator constructionStimulated emissionP–n junction

The invention concerns a superluminescent light emitting diode (SLED) comprising a semiconductor heterostructure forming a PN junction and a waveguide. The semiconductor heterostructure includes a gain region with a contact means for biasing the PN junction so as to produce light emission including stimulated emission from an active zone of the gain region, and in the active zone a plurality of quantum dot layers, each quantum dot layer made up of a plurality of quantum dots and a plurality of adjoining layers, each adjoining layer adjacent to one of said quantum dot layers. The material composition or a deposition parameter of at least two adjoining layers is different. This ensures an enhanced emission spectral width.

Owner:EXALOS

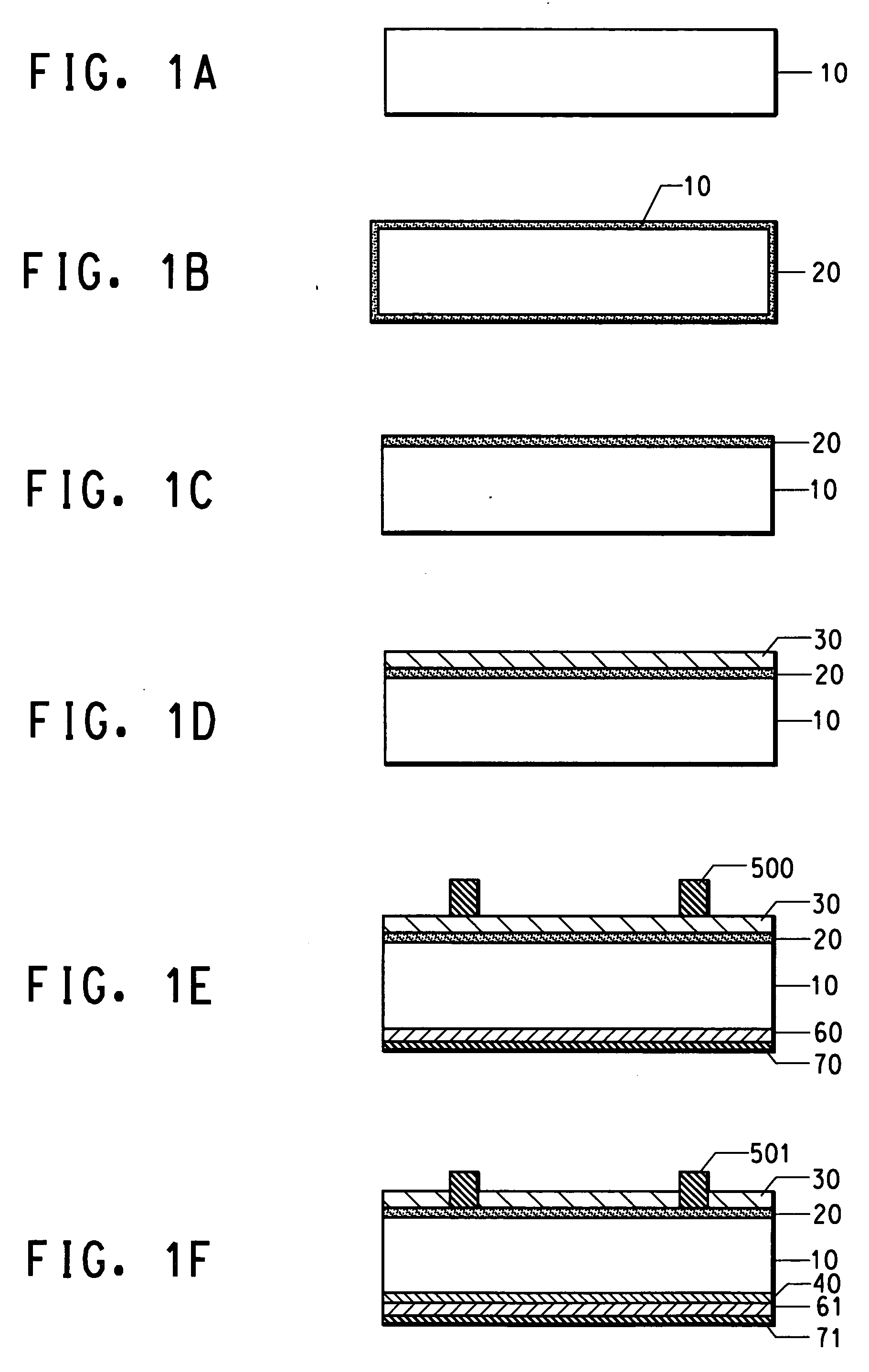

Low temperature fabrication of discrete silicon-containing substrates and devices

InactiveUS20070262363A1Less timeLess moneySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEtching

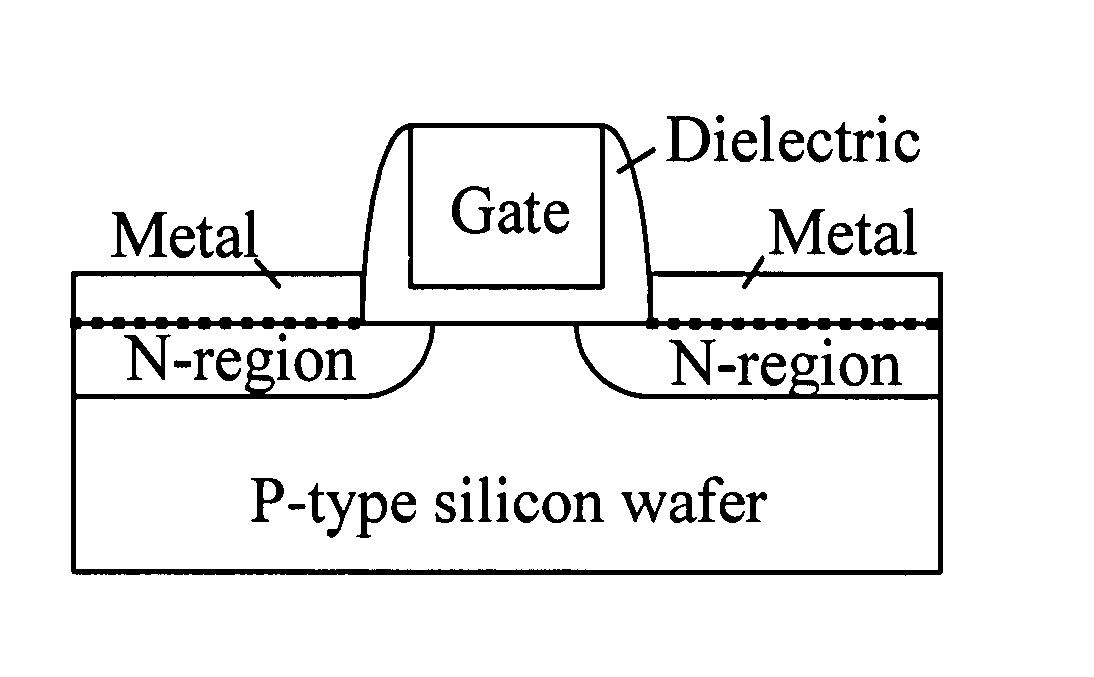

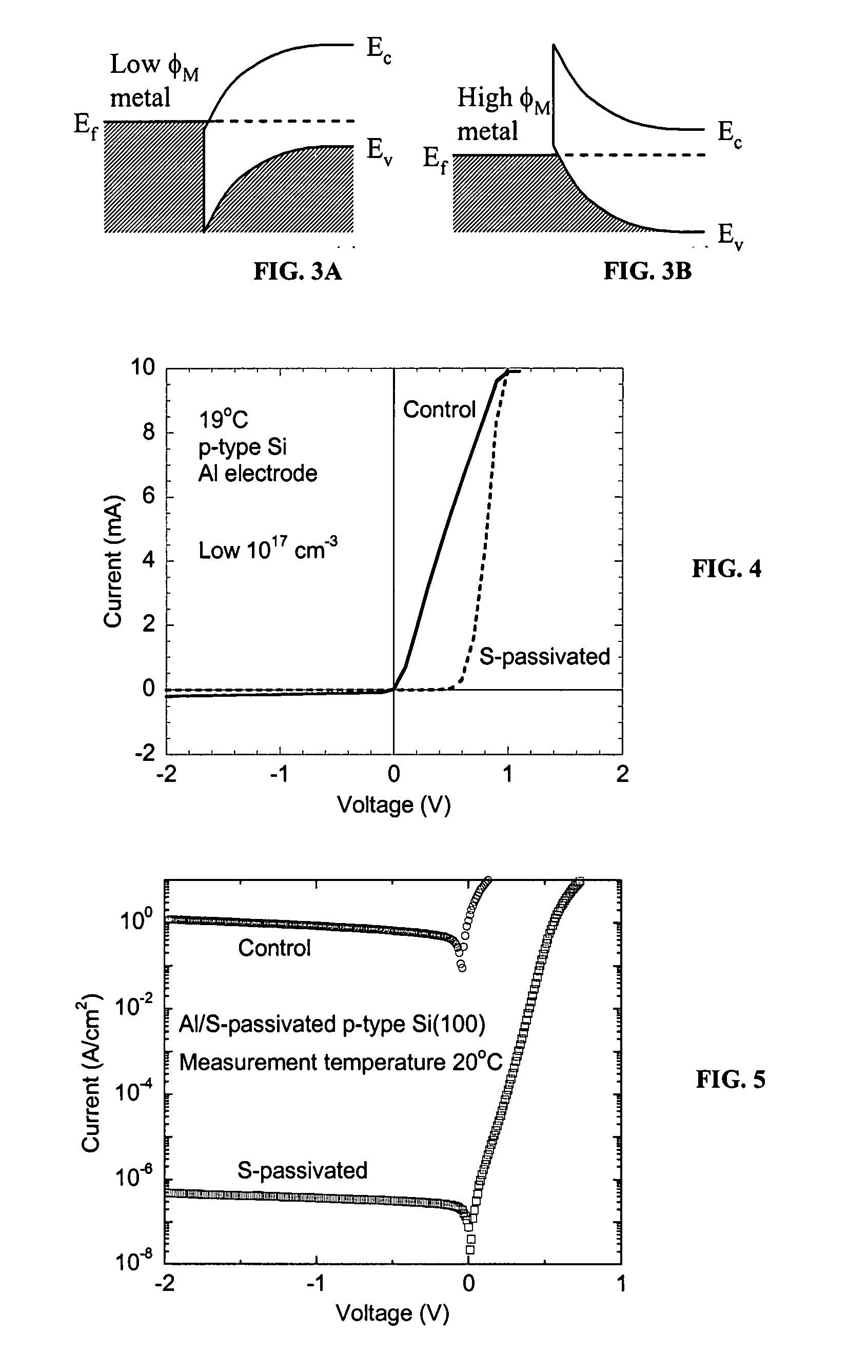

Fabrication methods and processes are described, the methods and processes occurring at a low-temperature and involving passivation. The methods and processes easily incorporate annealing, deposition, patterning, lithography, etching, oxidation, epitaxy and chemical mechanical polishing for forming suitable devices, such as diodes and MOSFETs. Such fabrication is a suitable and more cost-effective alternative to a process of diffusion or doping, typical for forming p-n junctions. The process flow does not require temperatures above 700 degrees Centigrade. Formation of p-n junctions in discrete silicon diodes and MOSFETs are also provided, fabricated at low temperatures in the absence of diffusion or doping.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

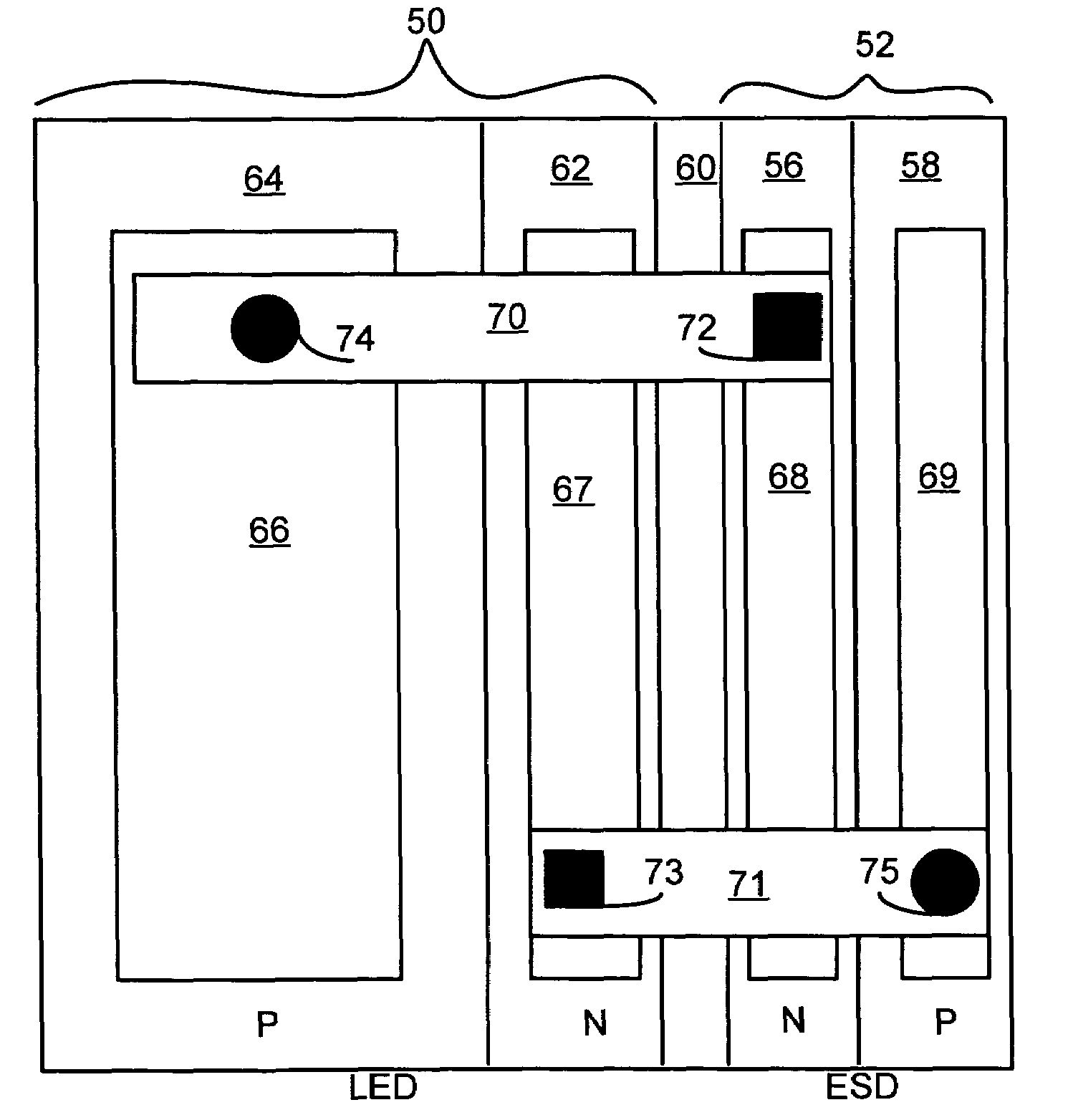

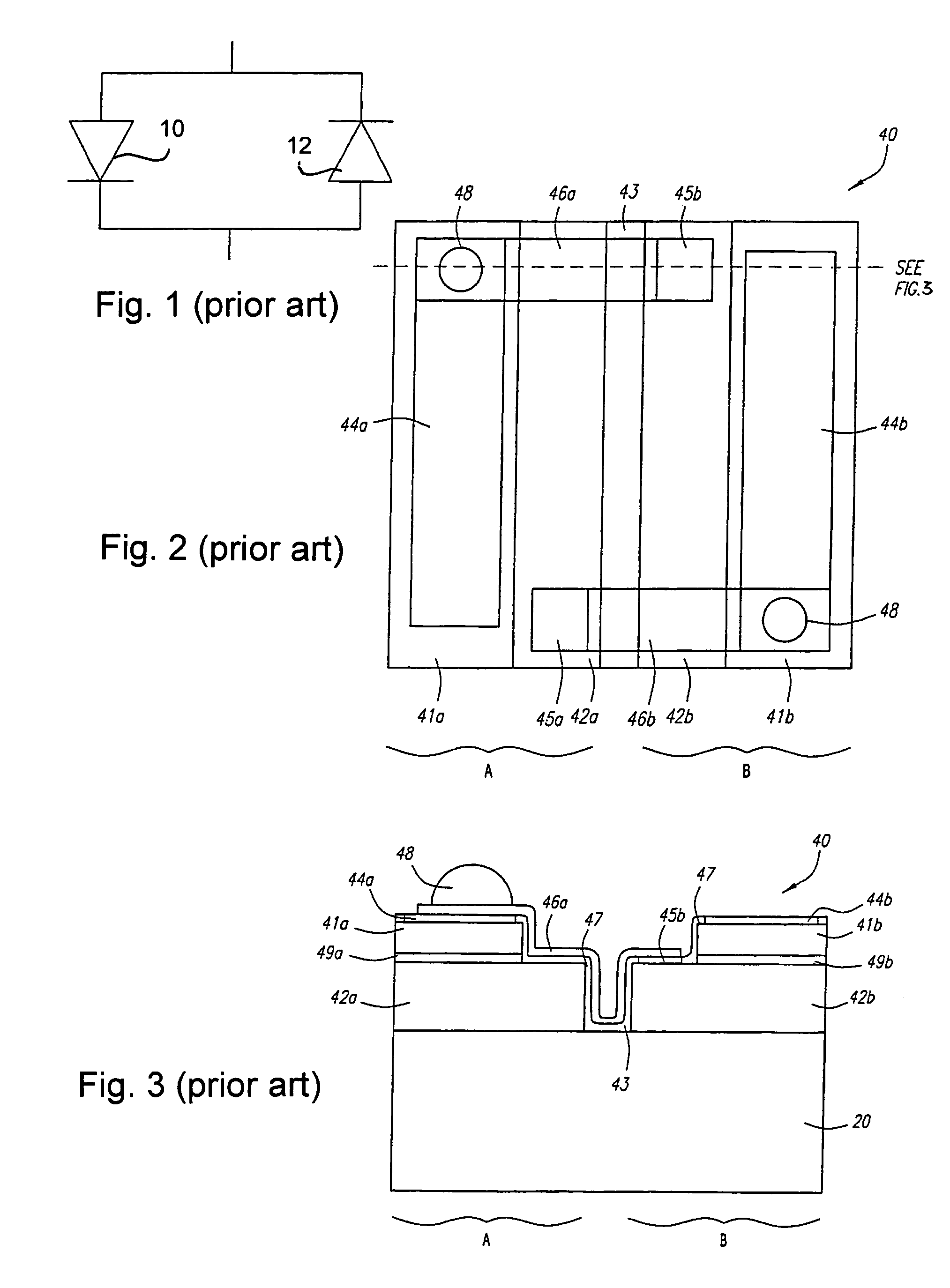

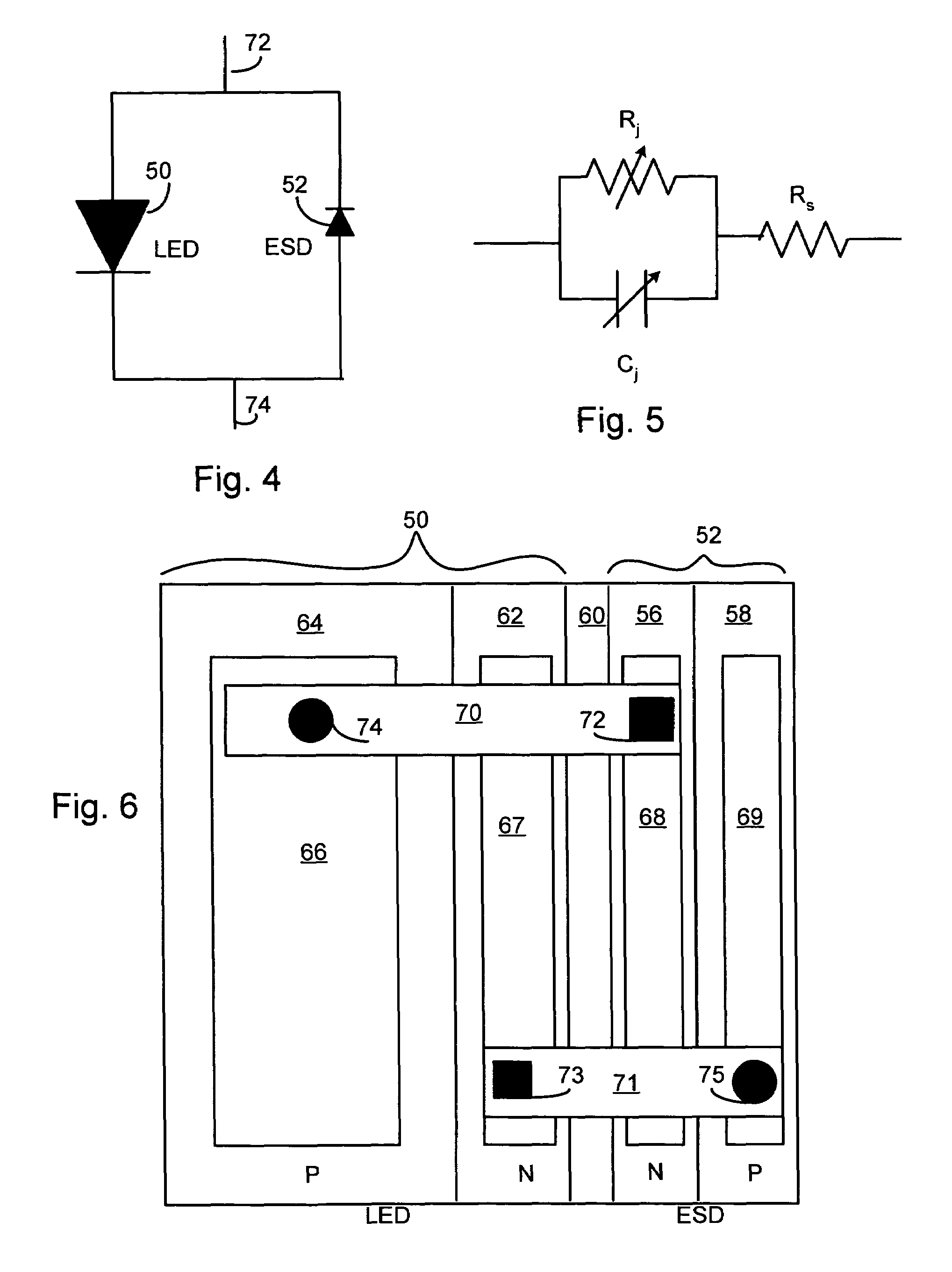

LED chip with integrated fast switching diode for ESD protection

ActiveUS7064353B2Reduced series resistanceIncrease widthSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsP–n junction

Owner:JANSSEN PHARMA NV +1

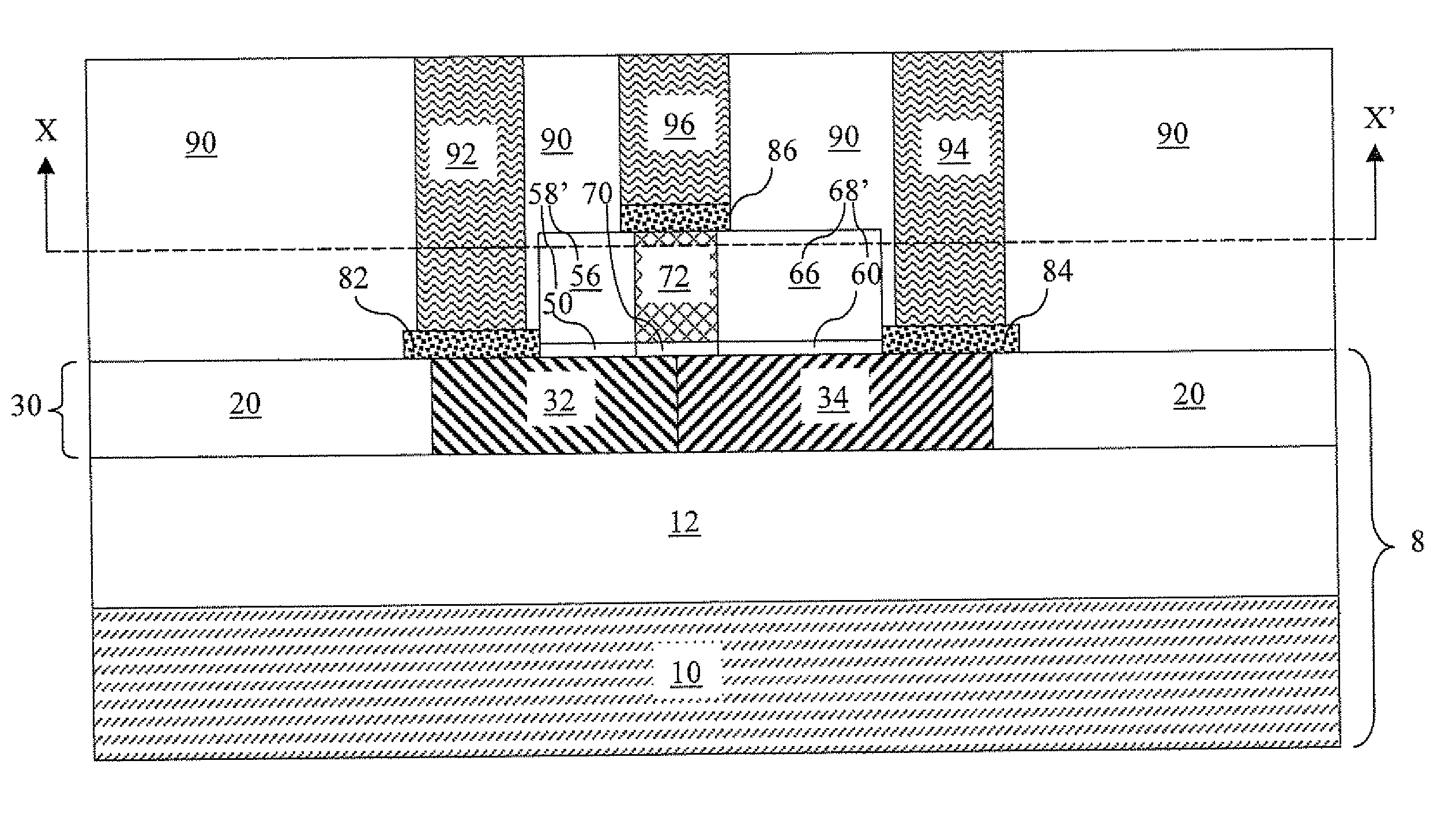

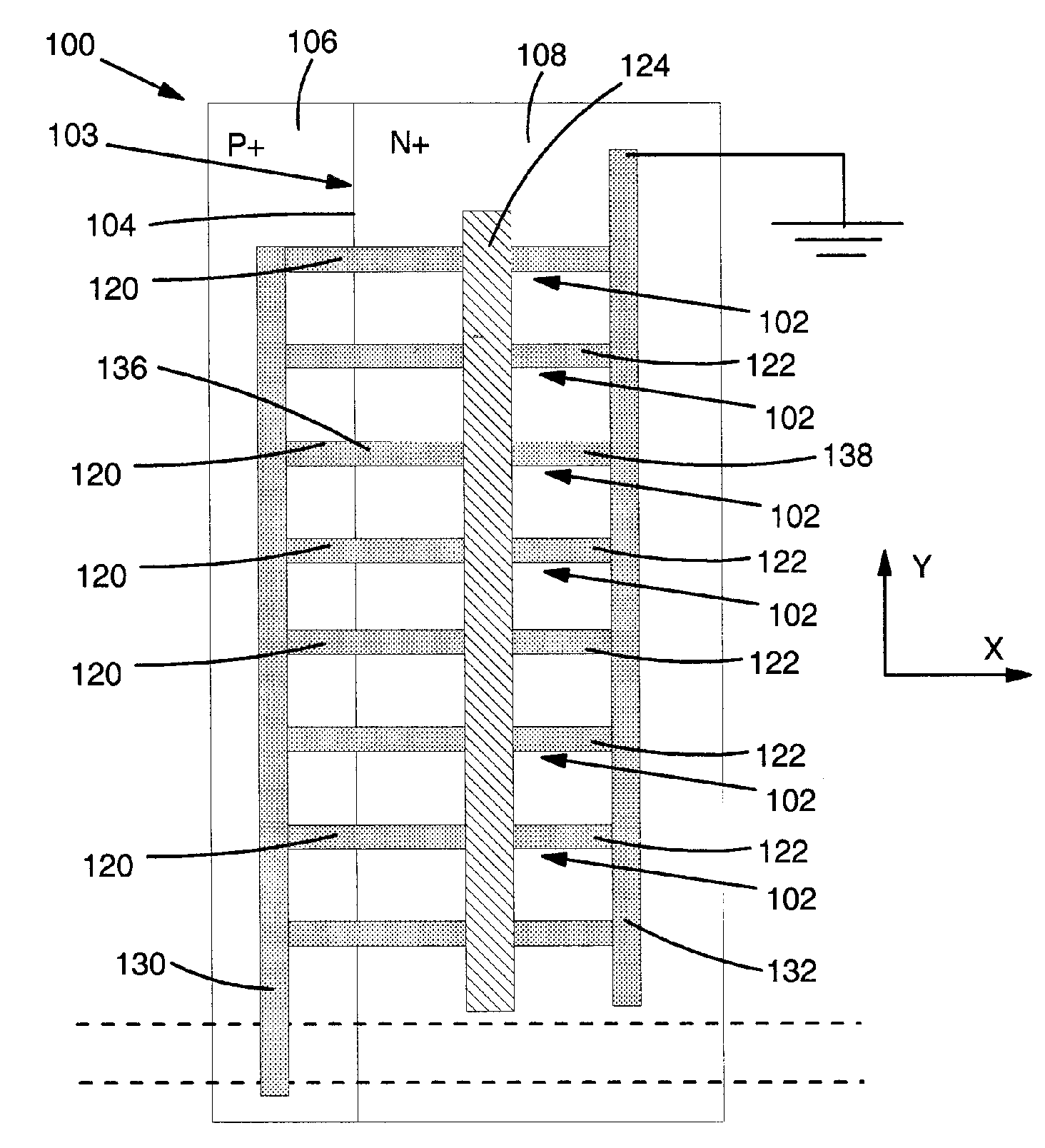

Memory cell access device having a pn-junction with polycrystalline and single-crystal semiconductor regions

ActiveUS20100117048A1Inhibited DiffusionImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSingle crystalP–n junction

A memory device includes a driver comprising a pn-junction in the form of a multilayer stack including a first doped semiconductor region having a first conductivity type, and a second doped semiconductor region having a second conductivity type opposite the first conductivity type, the first and second doped semiconductors defining a pn-junction therebetween, in which the first doped semiconductor region is formed in a single-crystalline semiconductor, and the second doped semiconductor region includes a polycrystalline semiconductor. Also, a method for making a memory device includes forming a first doped semiconductor region of a first conductivity type in a single-crystal semiconductor, such as on a semiconductor wafer; and forming a second doped polycrystalline semiconductor region of a second conductivity type opposite the first conductivity type, defining a pn-junction between the first and second regions.

Owner:MACRONIX INT CO LTD

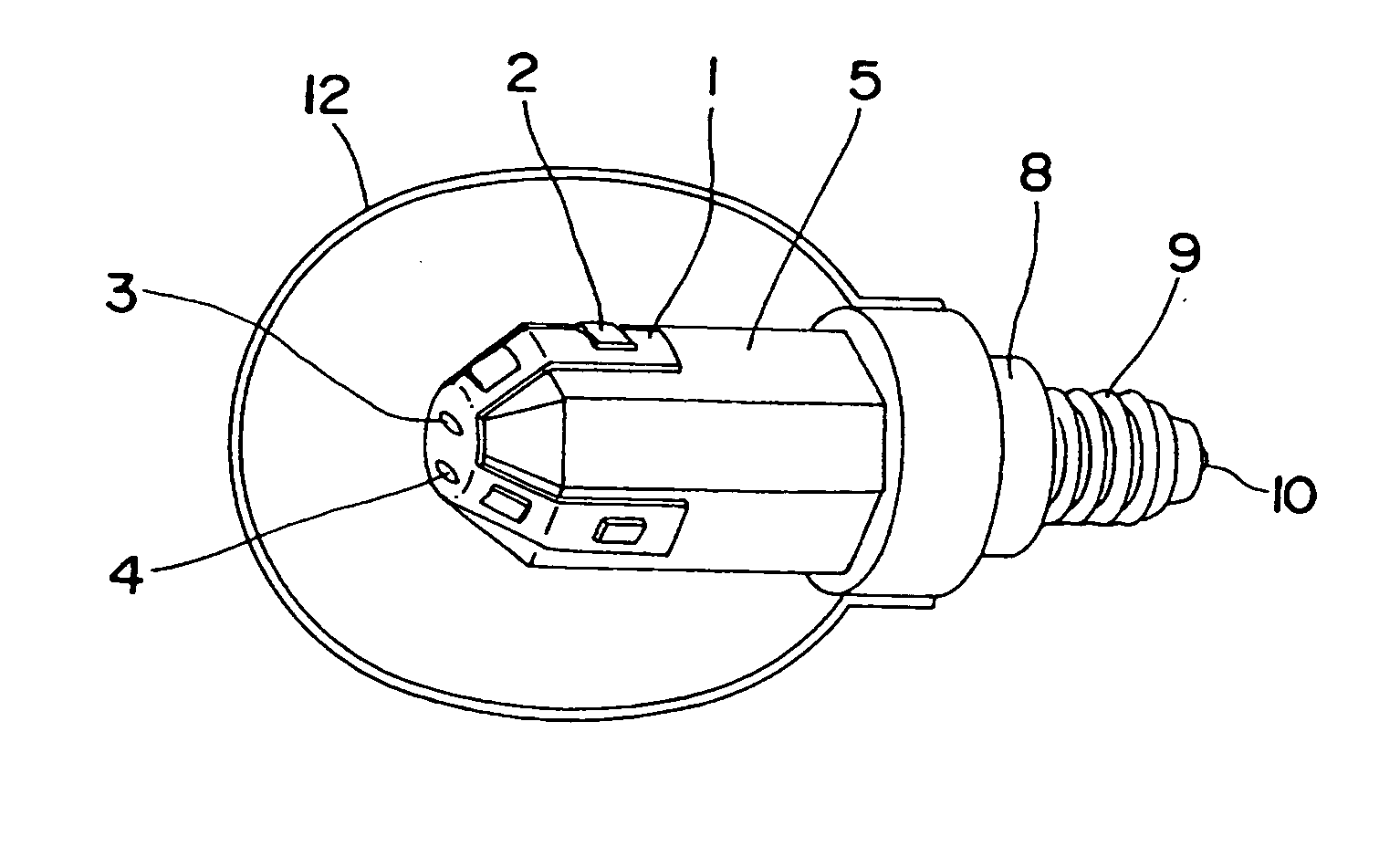

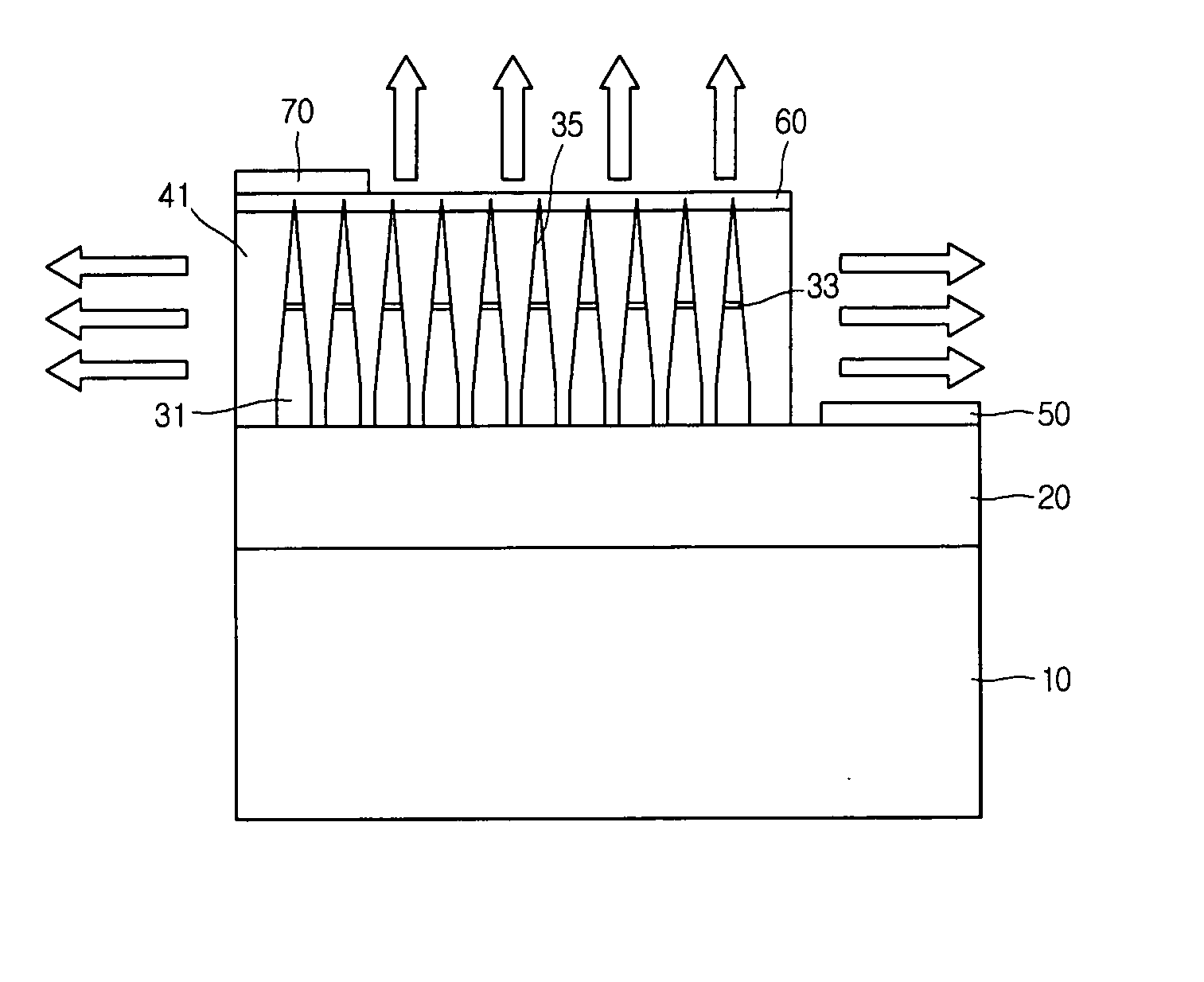

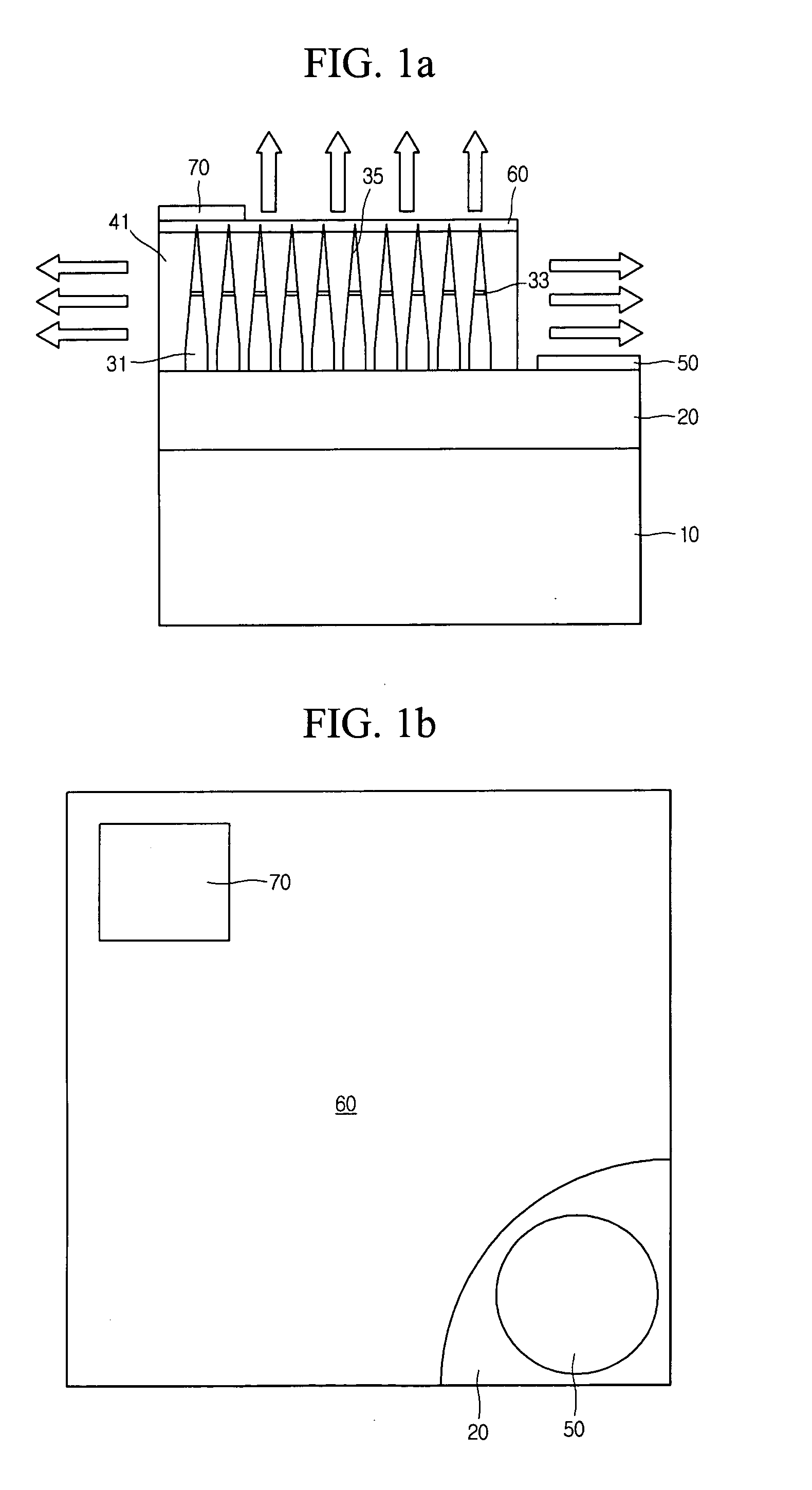

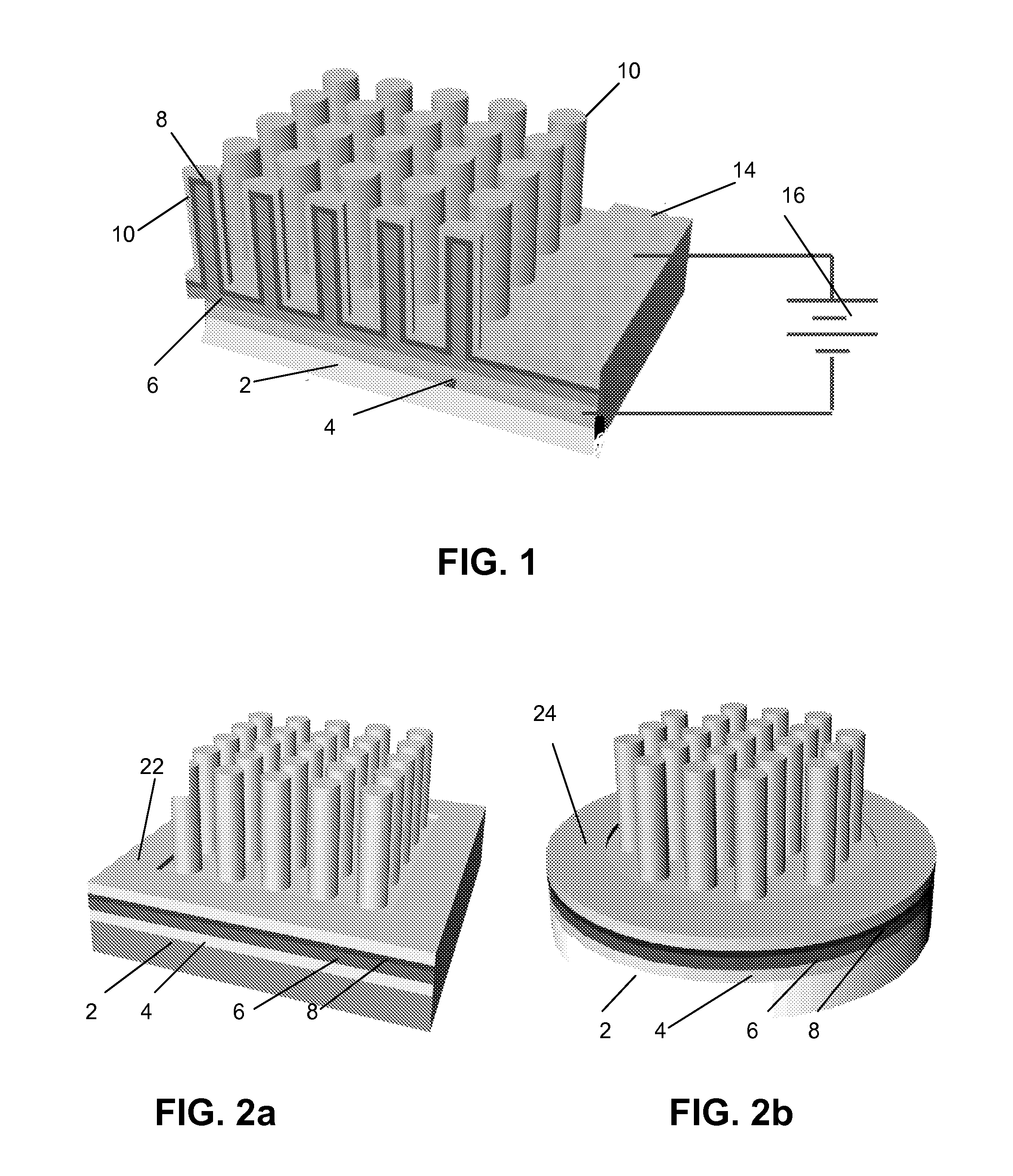

Super bright light emitting diode of nanorod array structure having InGaN quantum well and method for manufacturing the same

ActiveUS20050194598A1Increase brightnessHigh light emitting efficiencyMaterial nanotechnologySemiconductor/solid-state device detailsNanowireQuantum well

An GaN light emitting diode (LED) having a nanorod (or, nanowire) structure is disclosed. The GaN LED employs GaN nanorods in which a n-type GaN nanorod, an InGaN quantum well and a p-type GaN nanorod are subsequently formed in a longitudinal direction by inserting the InGaN quantum well into a p-n junction interface of the p-n junction GaN nanorod. In addition, a plurality of such GaN nanorods are arranged in an array so as to provide an LED having much greater brightness and higher light emission efficiency than a conventional laminated-film GaN LED.

Owner:DONGGUK UNIV IND ACADEMIC COOPERATION FOUND

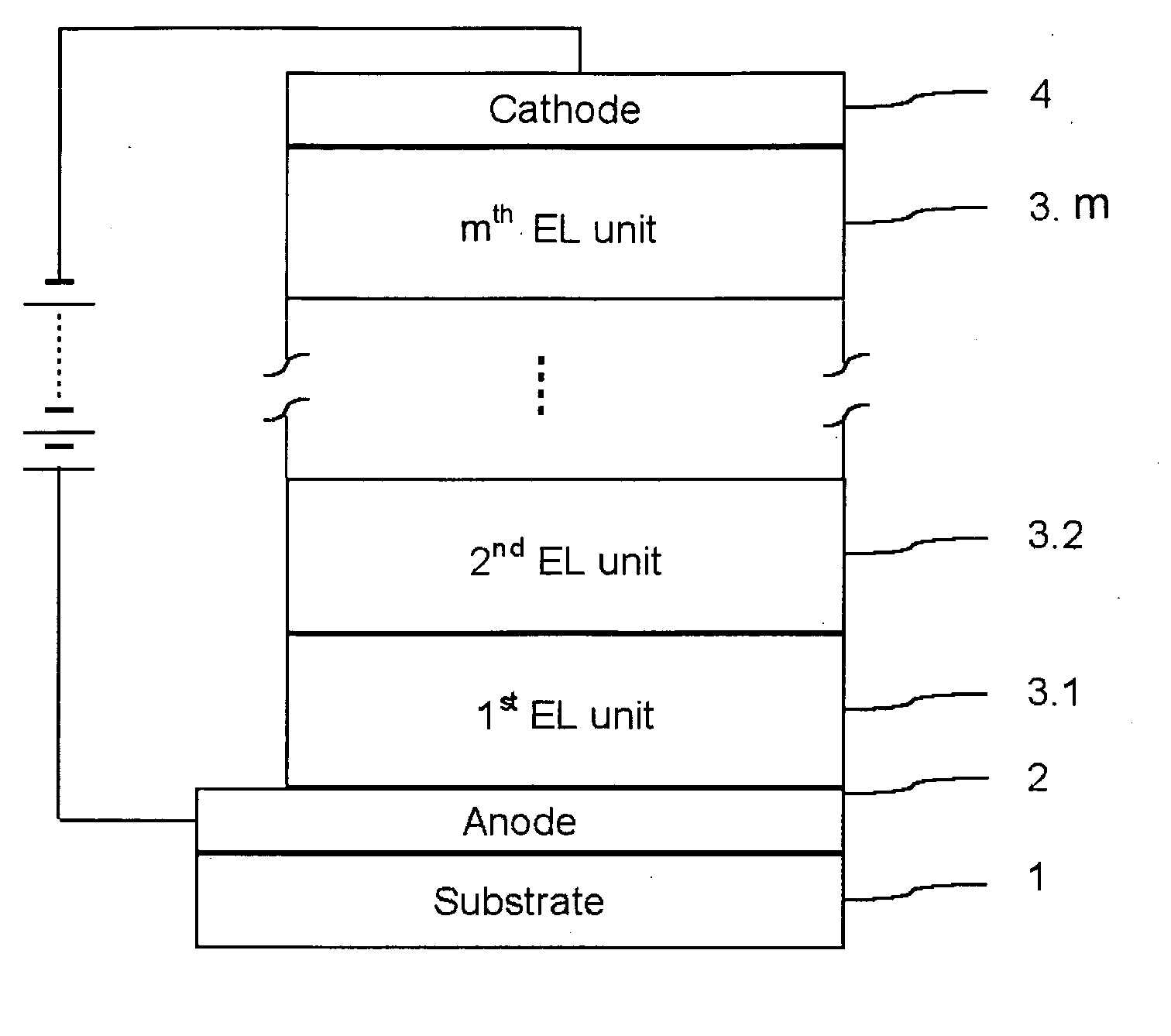

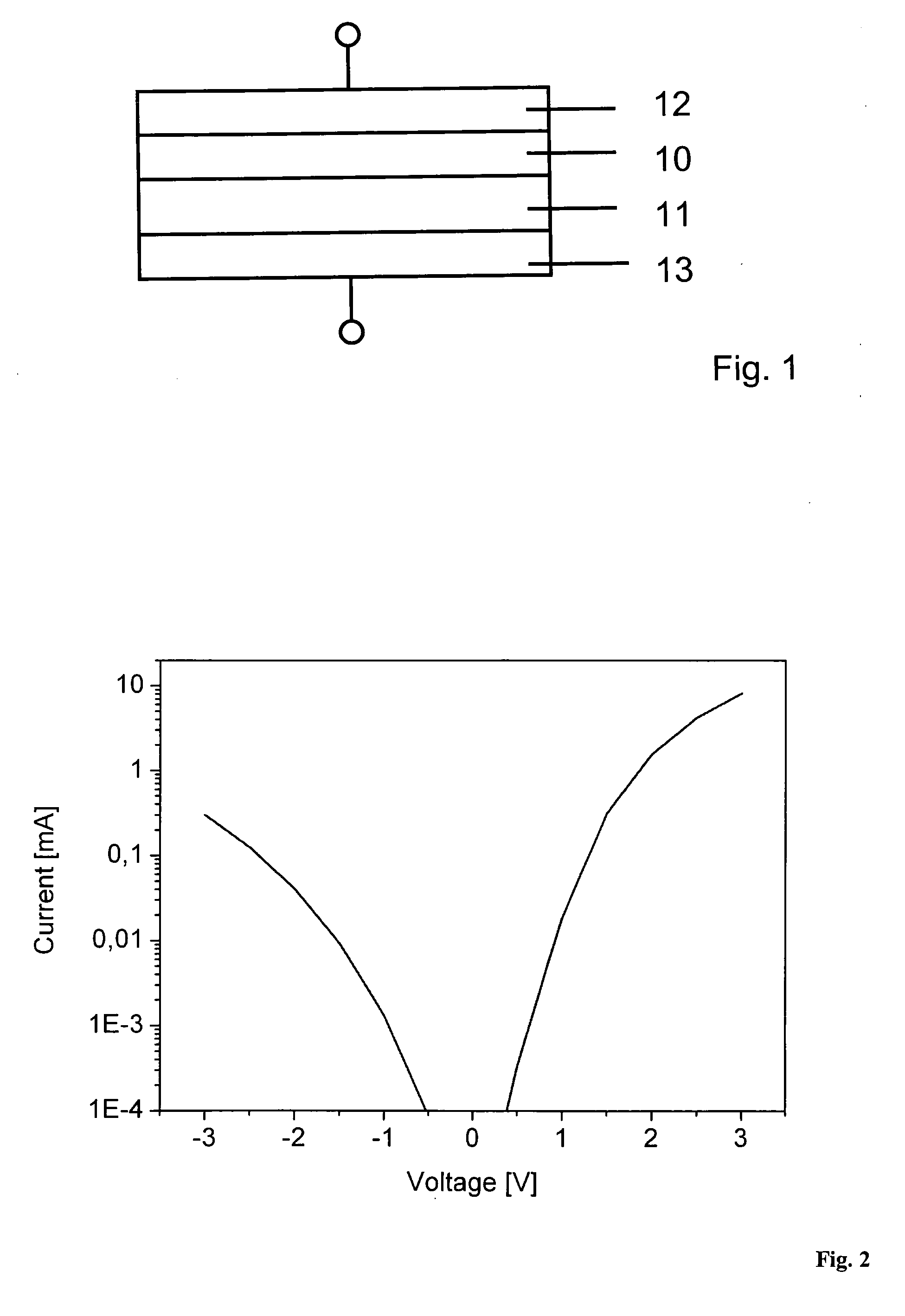

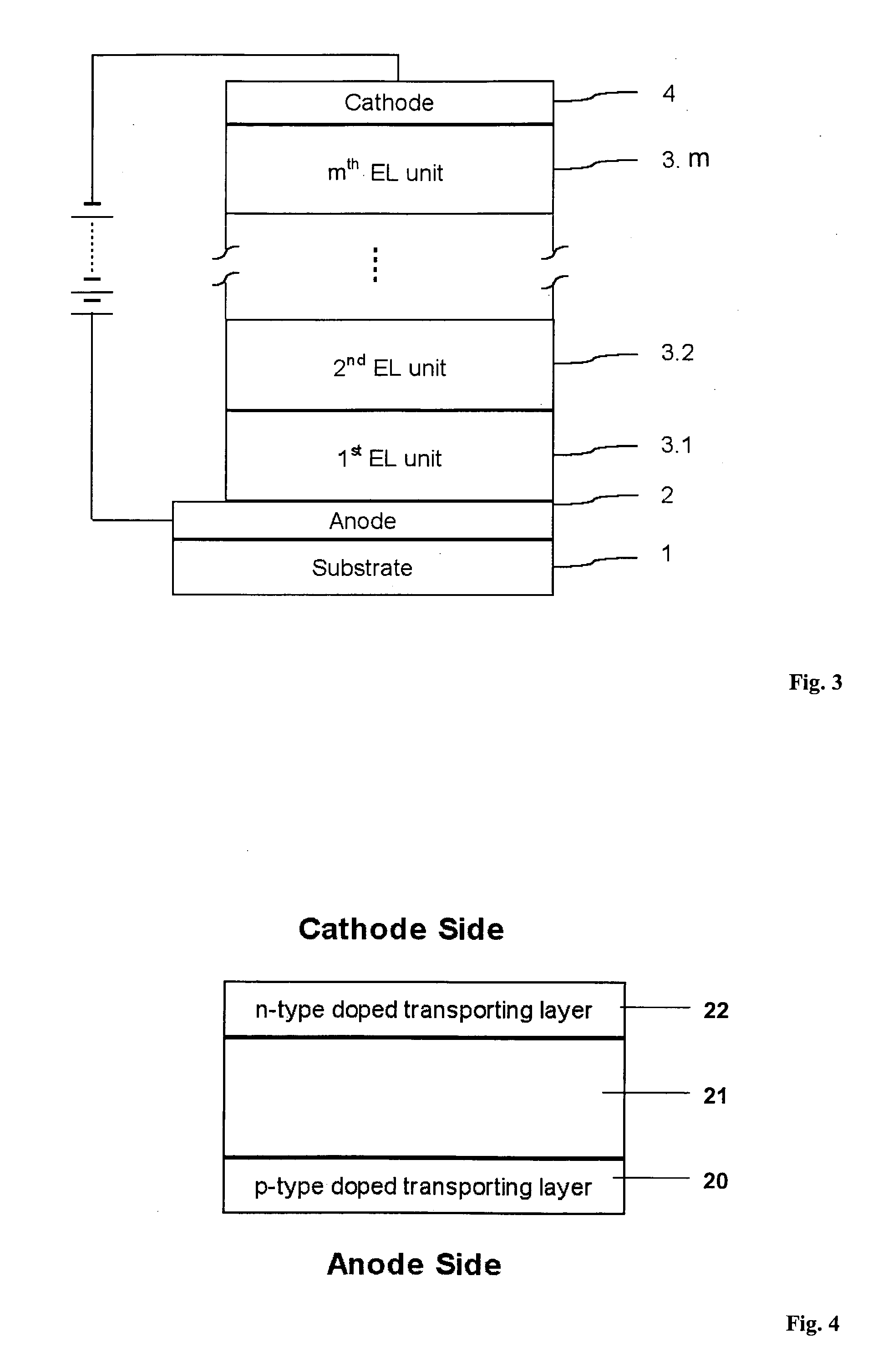

Electronic device with a layer structure of organic layers

ActiveUS20090045728A1Need long operating lifetimesTailoring of interface stabilityDischarge tube luminescnet screensLamp detailsDopantOrganic layer

The invention relates to an electronic device comprising a layer structure of organic layers, wherein said layer structure comprises a p-n-junction between an n-type doped organic layer provided as an organic matrix material doped with an n-type dopant and a p-type doped organic layer provided as a further organic matrix material doped with a p-type dopant, and wherein the n-type dopant and the p-type dopant both are molecular dopants, a reduction potential of the p-type dopant is equal or larger than about 0 V vs. Fc / Fc+, and an oxidation potential of the n-type dopant is equal or smaller than about −1.5 V vs. Fc / Fc+.

Owner:NOVALED AG

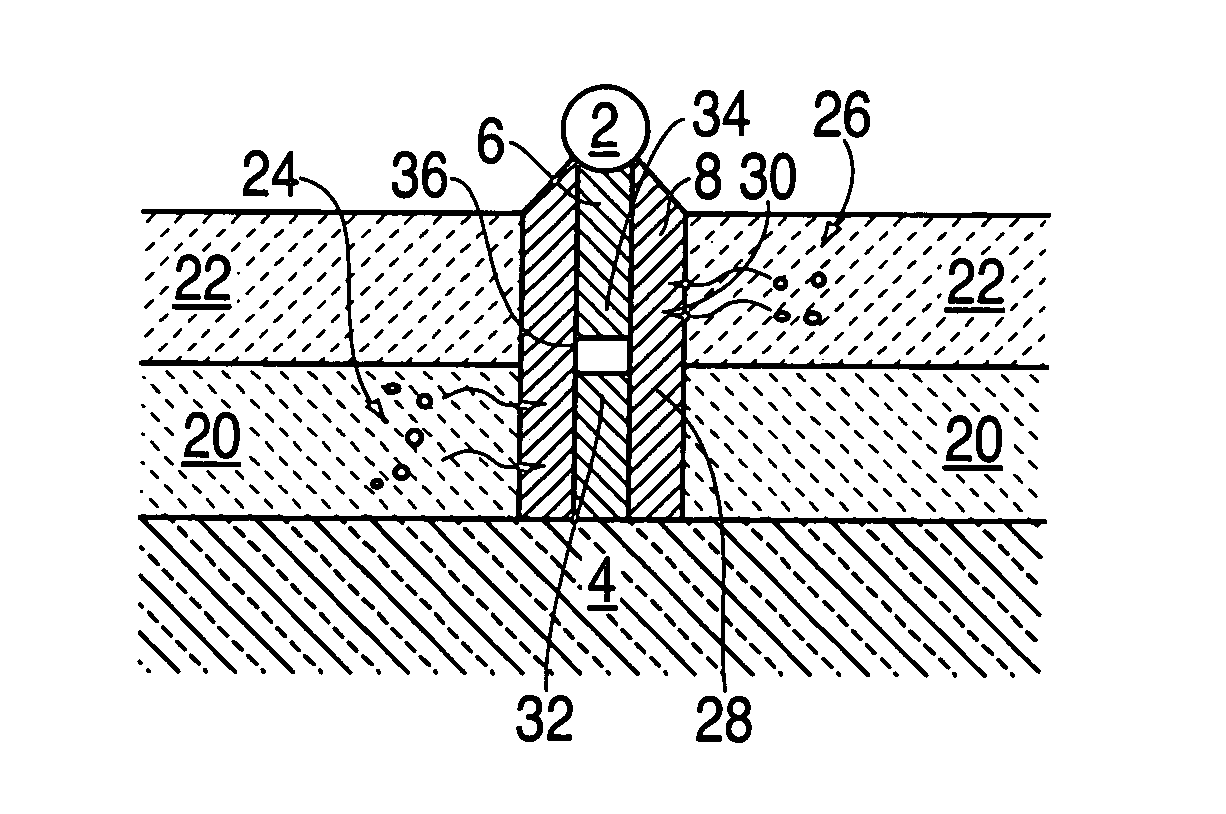

Tunneling effect transistor with self-aligned gate

ActiveUS7700466B2Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingField-effect transistorP–n junction

In one embodiment, a mandrel and an outer dummy spacer may be employed to form a first conductivity type region. The mandrel is removed to form a recessed region wherein a second conductivity type region is formed. In another embodiment, a mandrel is removed from within shallow trench isolation to form a recessed region, in which an inner dummy spacer is formed. A first conductivity type region and a second conductivity region are formed within the remainder of the recessed region. An anneal is performed so that the first conductivity type region and the second conductivity type region abut each other by diffusion. A gate electrode is formed in self-alignment to the p-n junction between the first and second conductivity regions. The p-n junction controlled by the gate electrode, which may be sublithographic, constitutes an inventive tunneling effect transistor.

Owner:TWITTER INC

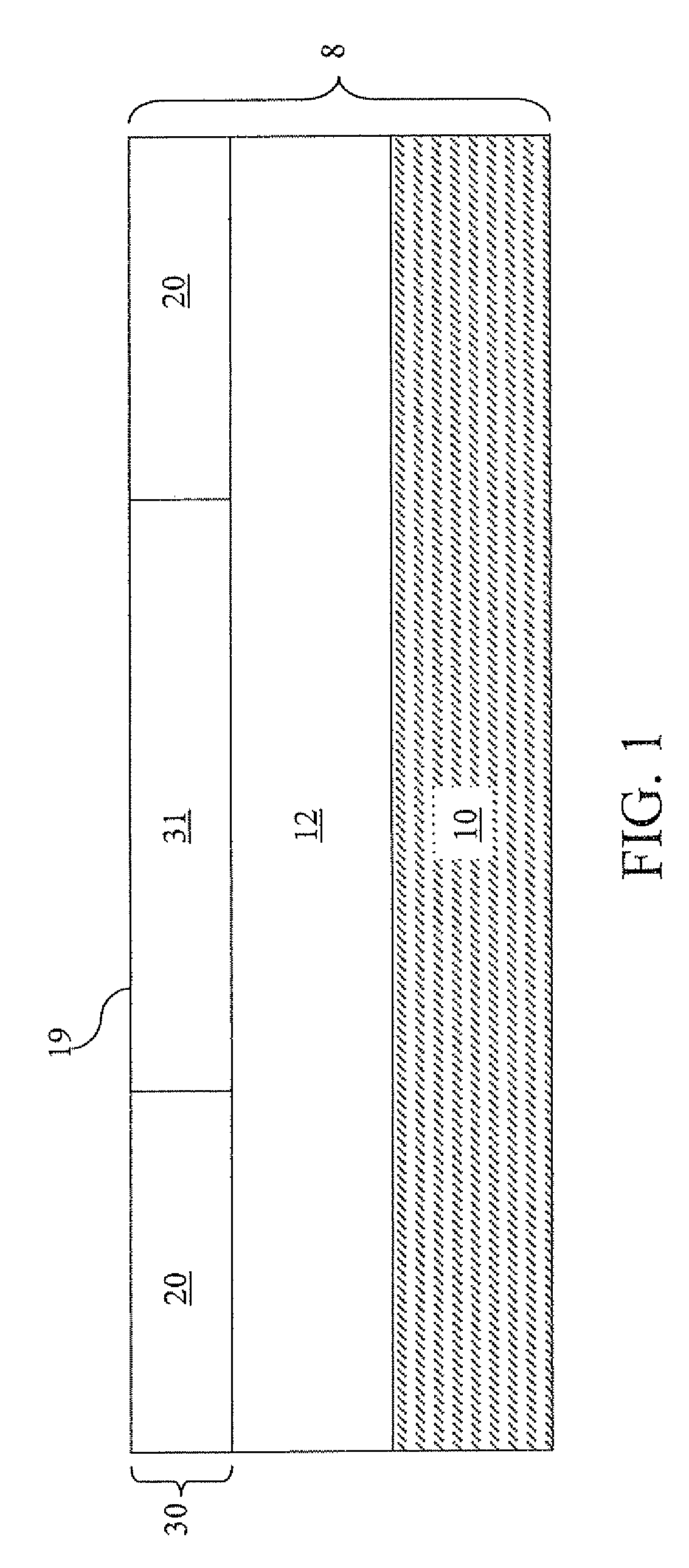

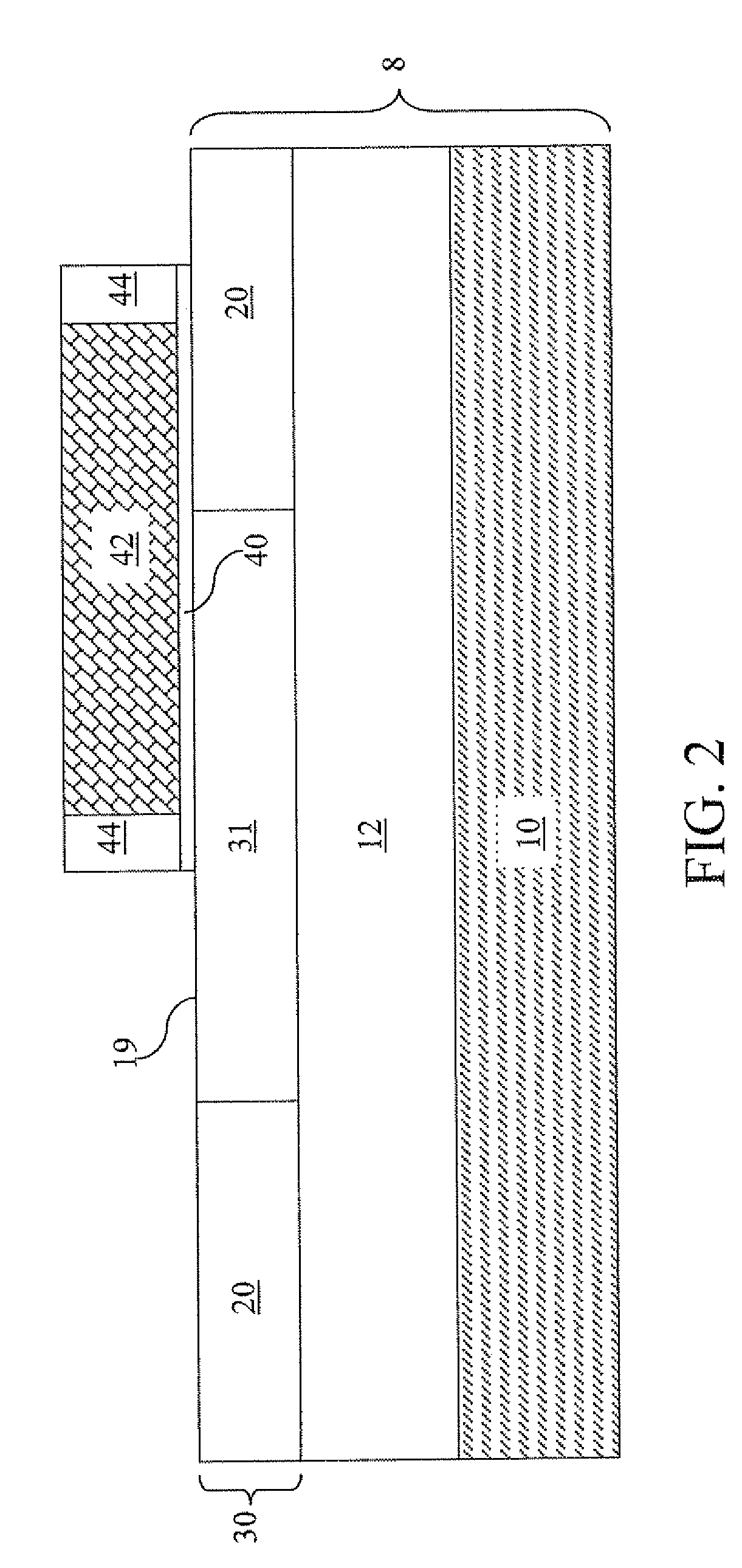

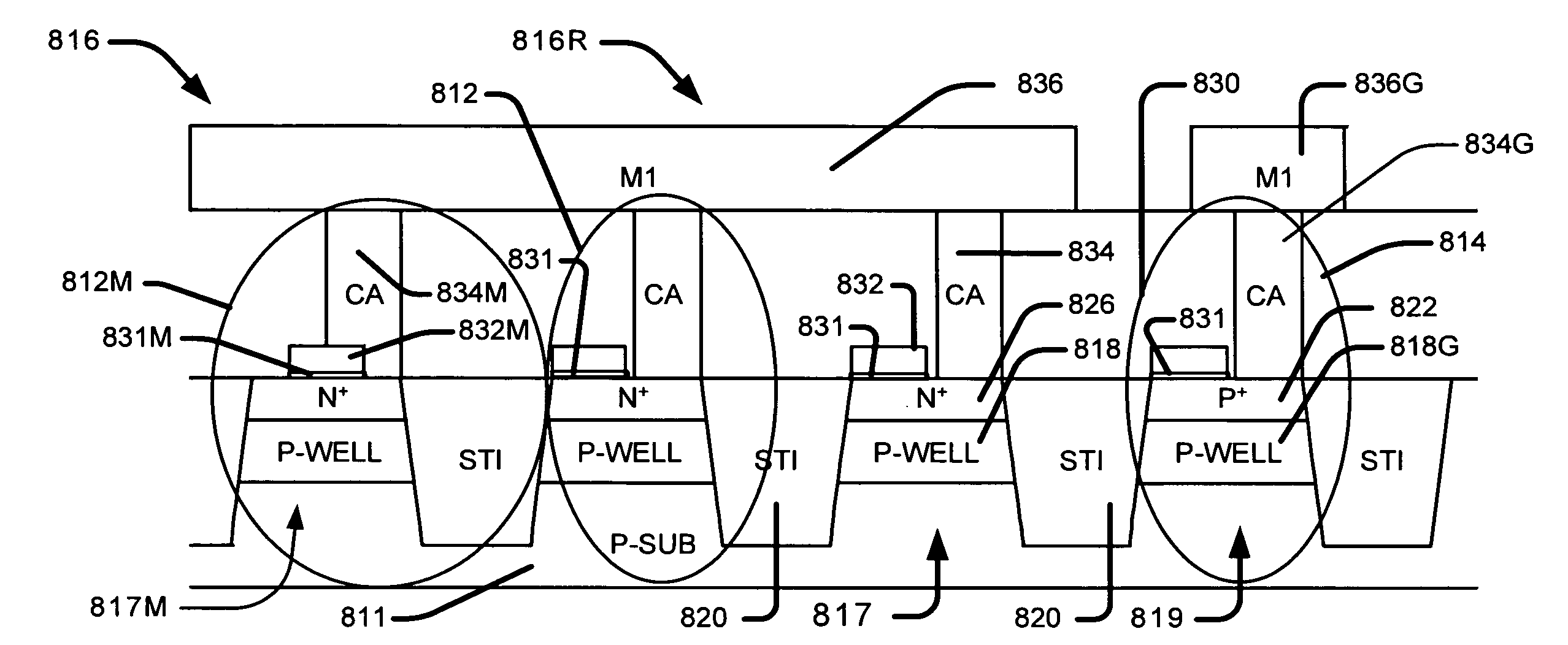

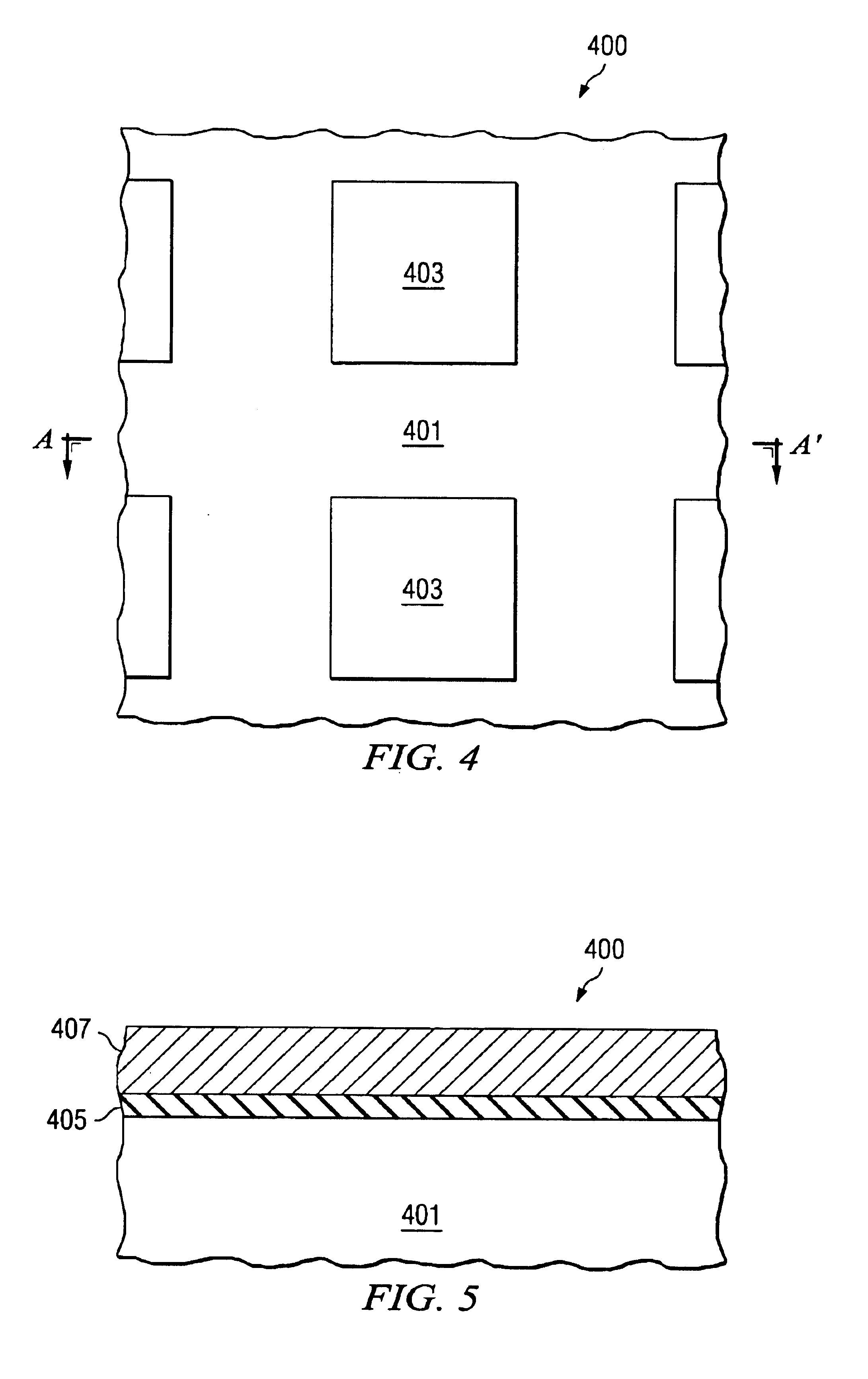

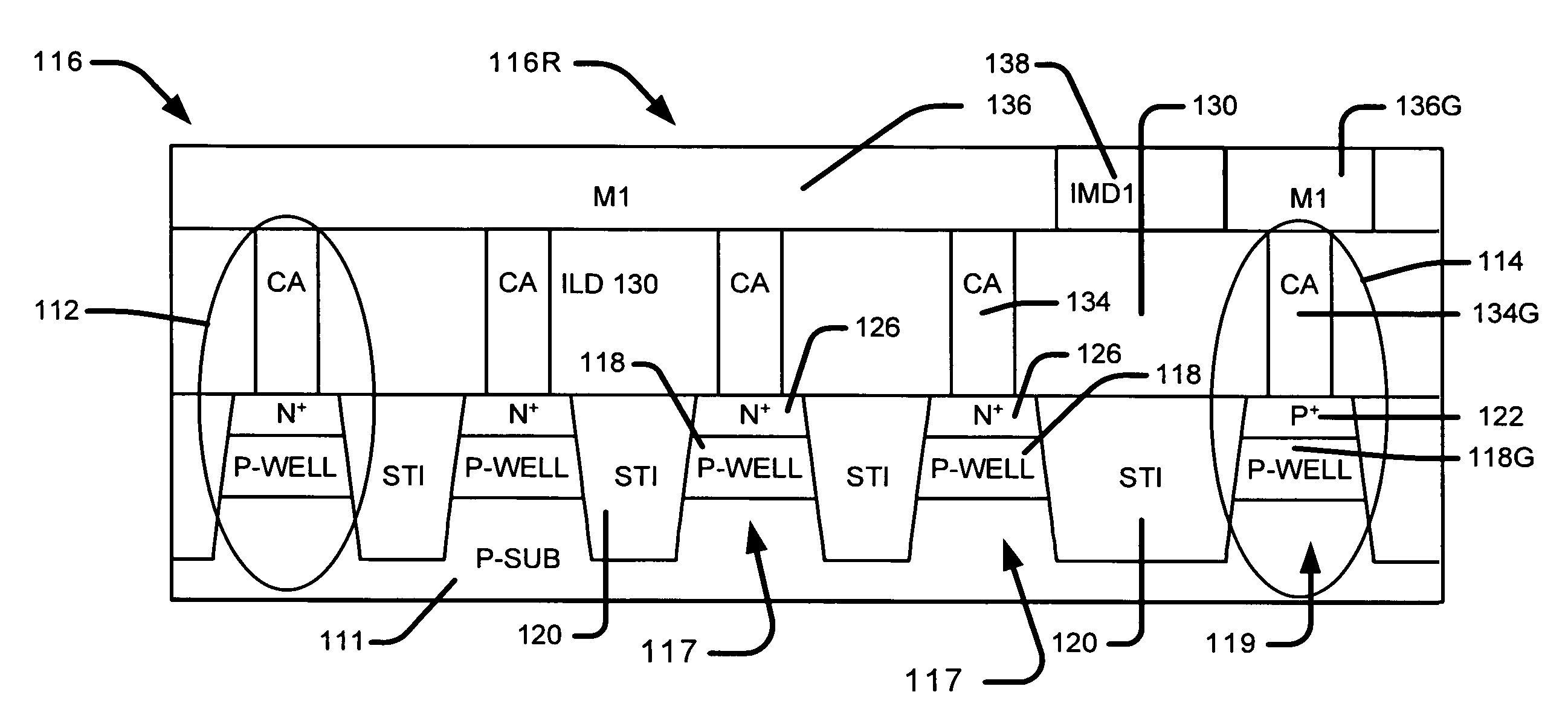

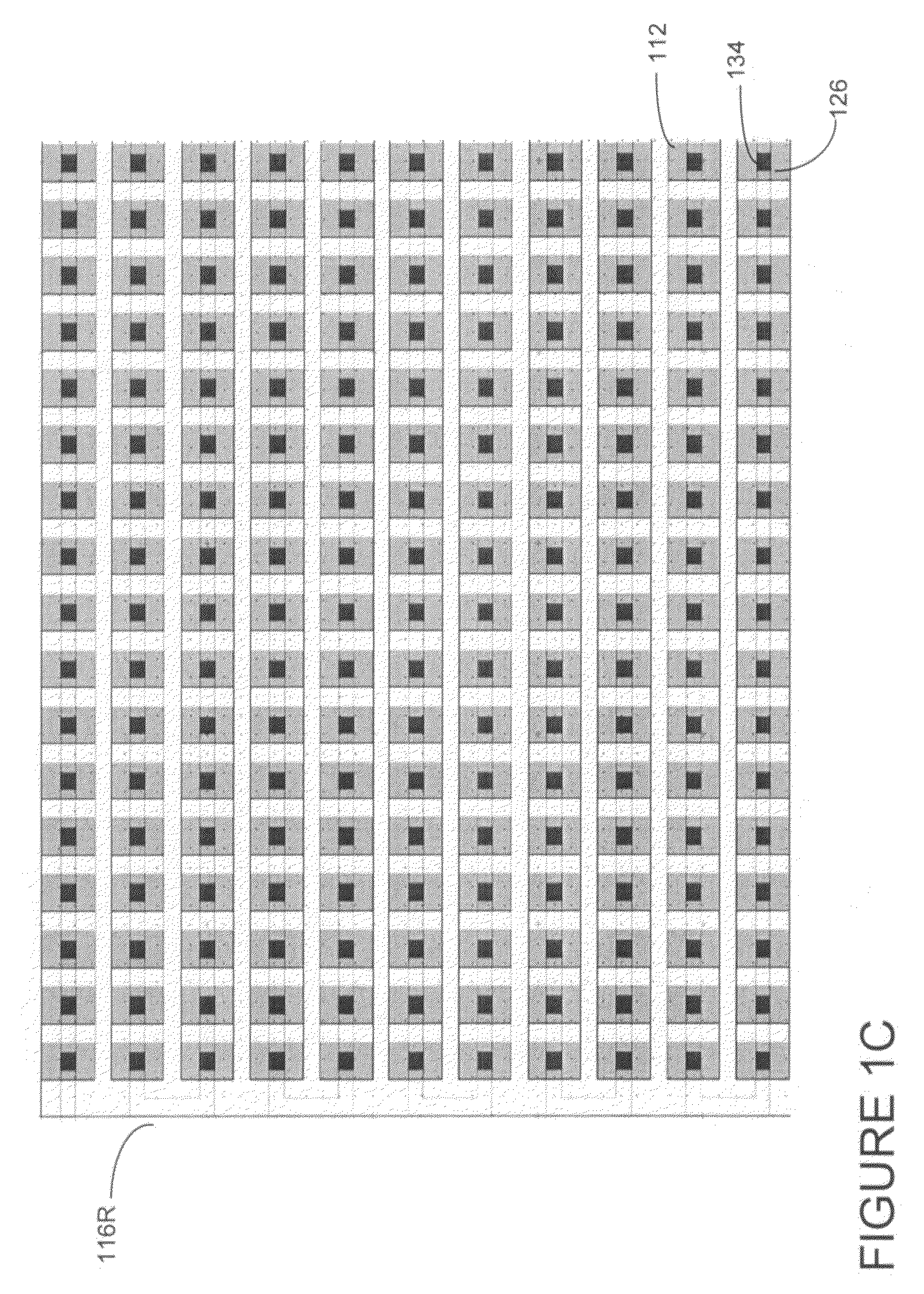

Buried short location determination using voltage contrast inspection

Structure and methods of determining the complete location of a buried short using voltage contrast inspection are disclosed. In one embodiment, a method includes providing a test structure having a PN junction thereunder; and using the PN junction to determine the location of the buried short using voltage contrast (VC) inspection. A test structure may include a plurality of test elements each having a PN junction thereunder, wherein a location of the buried short within the test structure can be determined using the PN junction and the VC inspection. The PN junction forces a change in illumination brightness of a test element including the buried short, thus allowing determination of the complete location of a buried short.

Owner:GLOBALFOUNDRIES INC

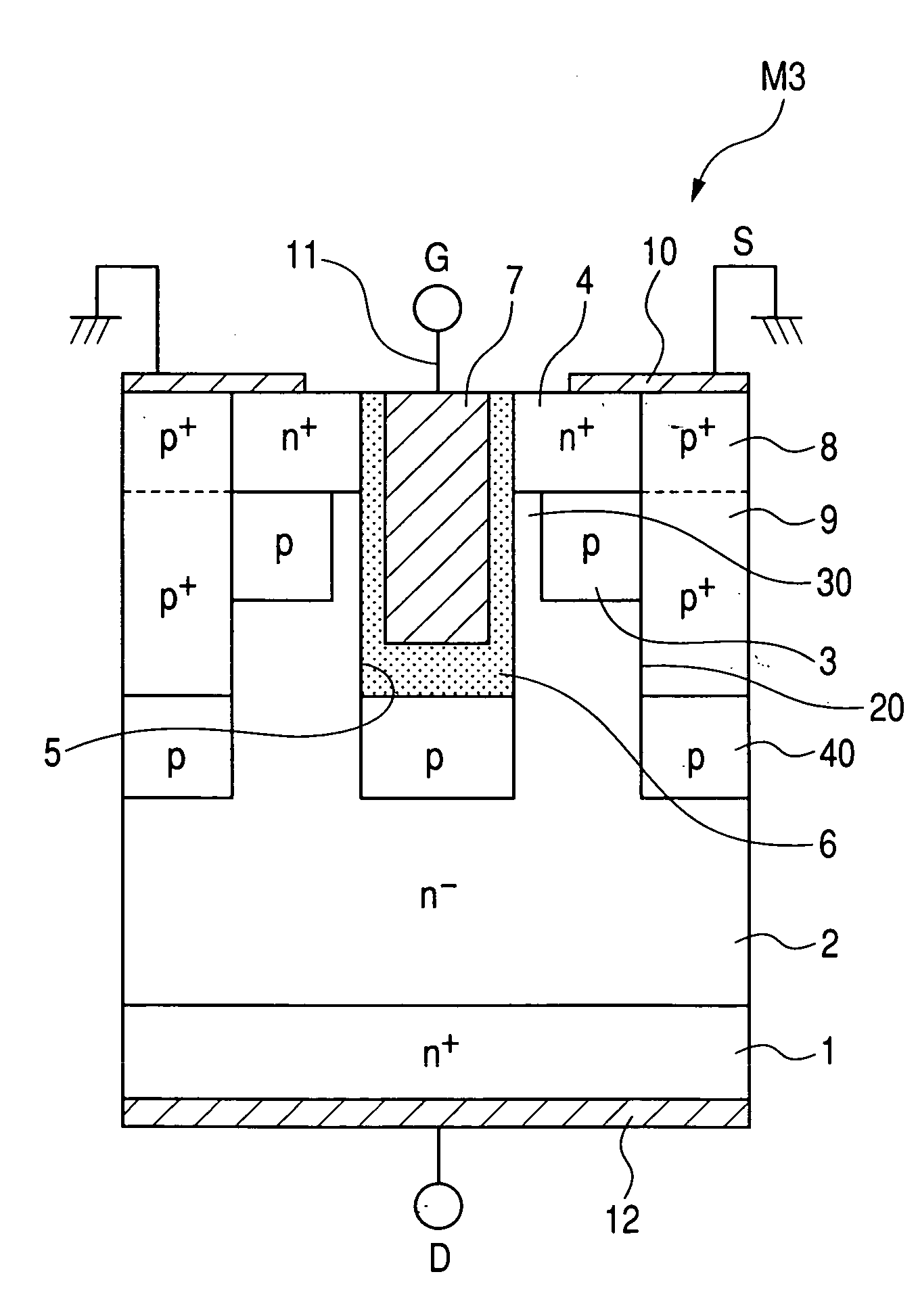

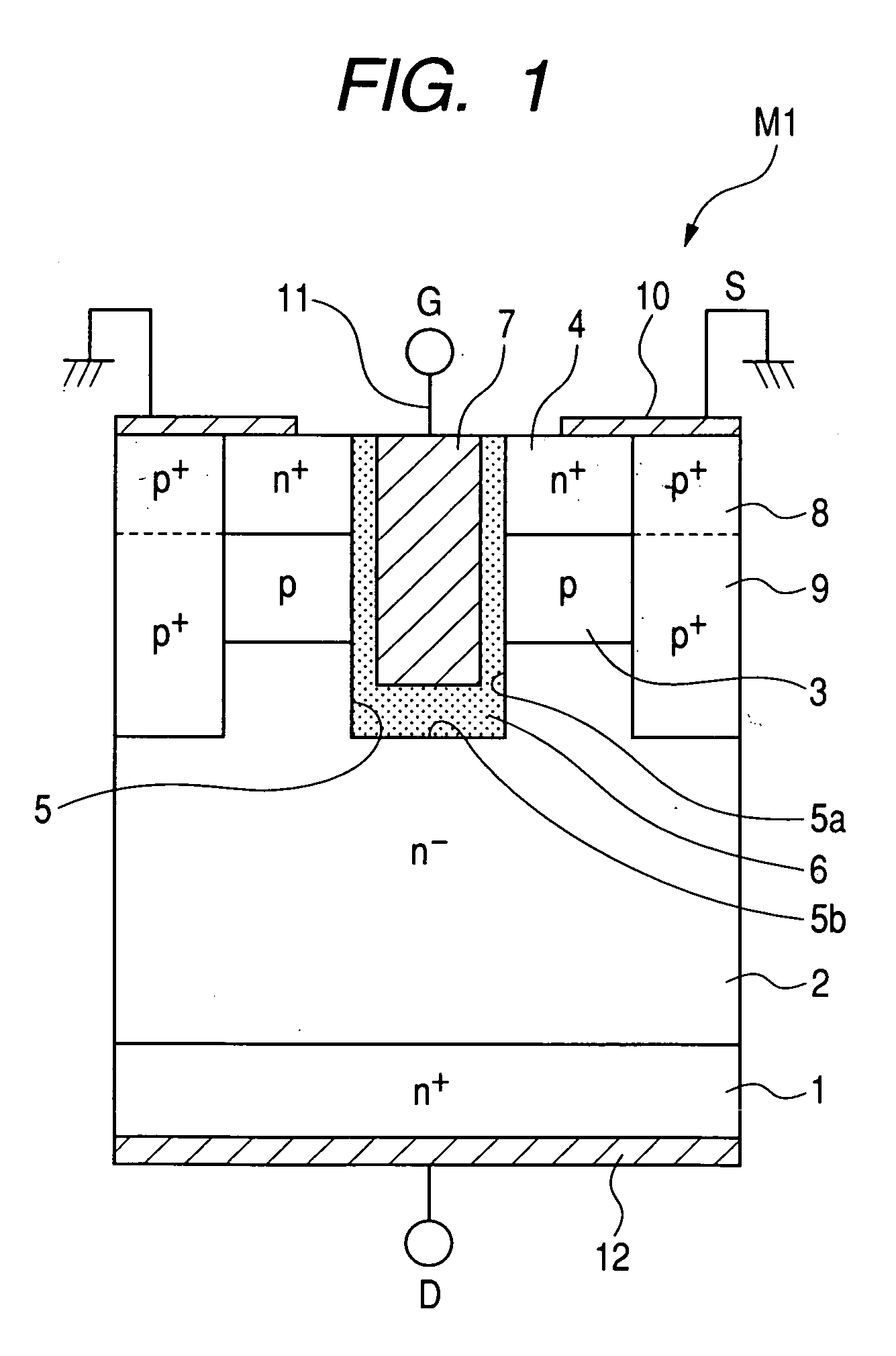

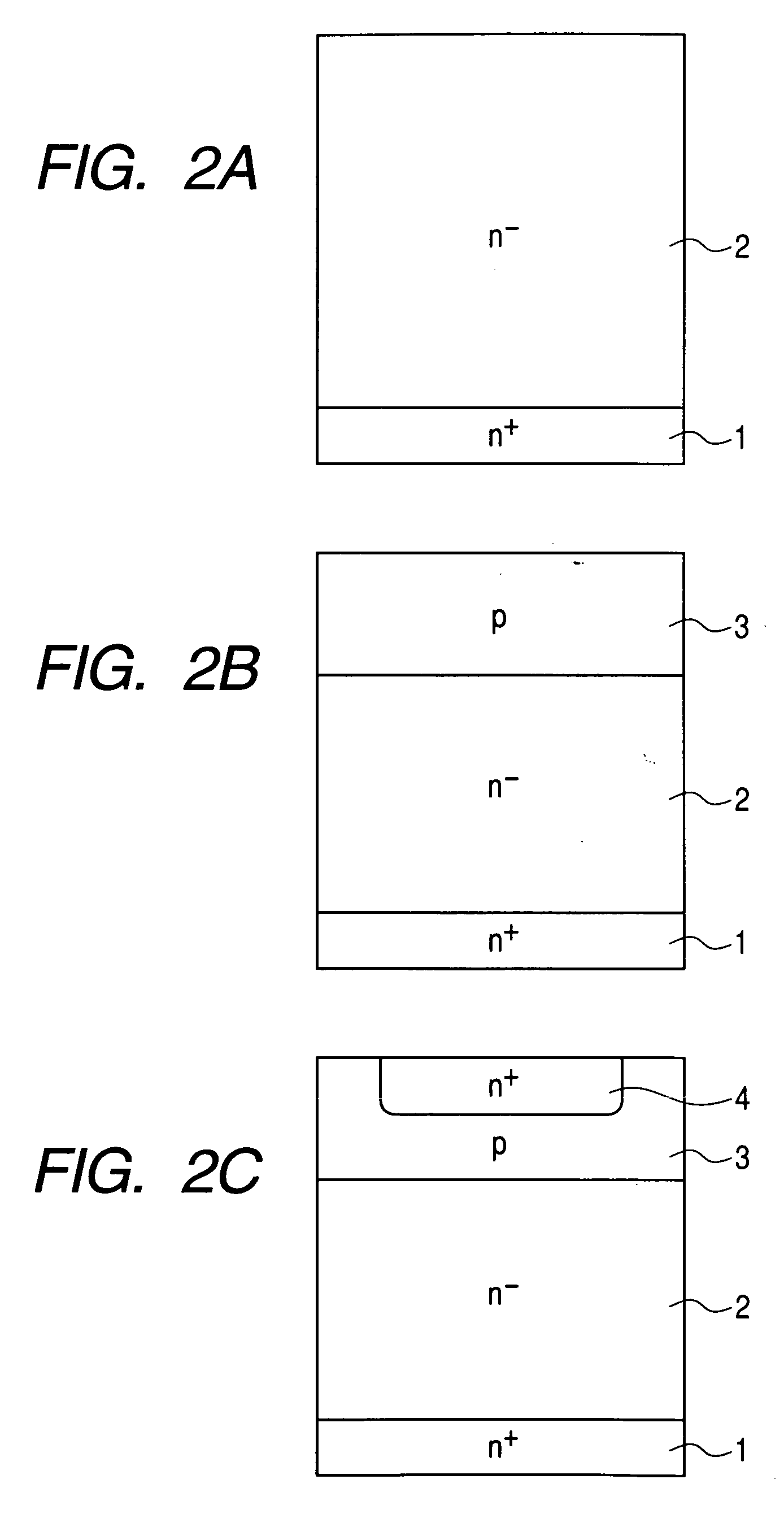

Silicon carbide semiconductor device and related manufacturing method

ActiveUS20090114969A1Increase concentrationReduce concentrationTransistorSolid-state devicesP–n junctionGate oxide

An SiC semiconductor device and a related manufacturing method are disclosed having a structure provided with a p+-type deep layer formed in a depth equal to or greater than that of a trench to cause a depletion layer between at a PN junction between the p+-type deep layer and an n−-type drift layer to extend into the n−-type drift layer in a remarkable length, making it difficult for a high voltage, resulting from an adverse affect arising from a drain voltage, to enter a gate oxide film. This results in a capability of minimizing an electric field concentration in the gate oxide film, i.e., an electric field concentration occurring at the gate oxide film at a bottom wall of the trench.

Owner:DENSO CORP

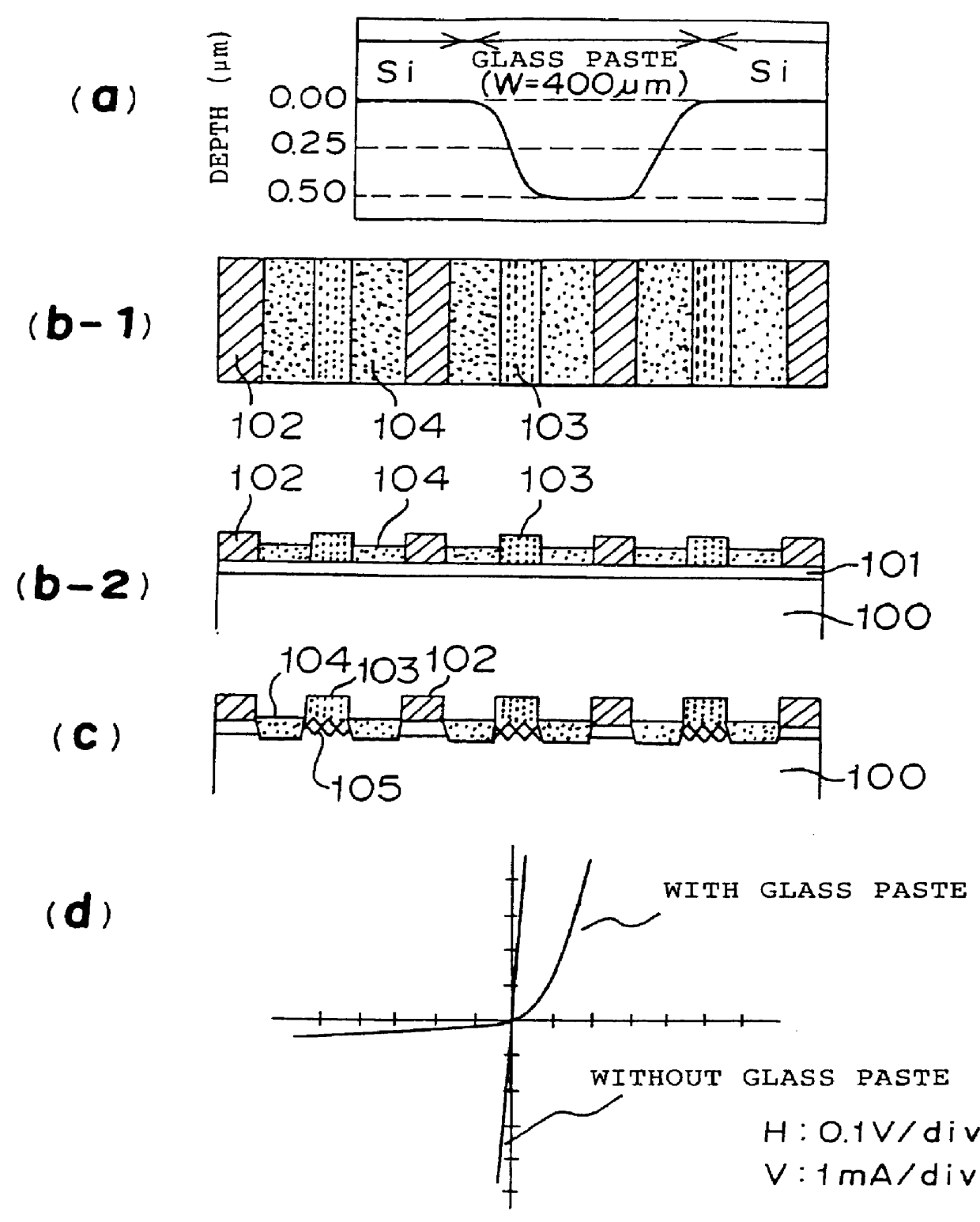

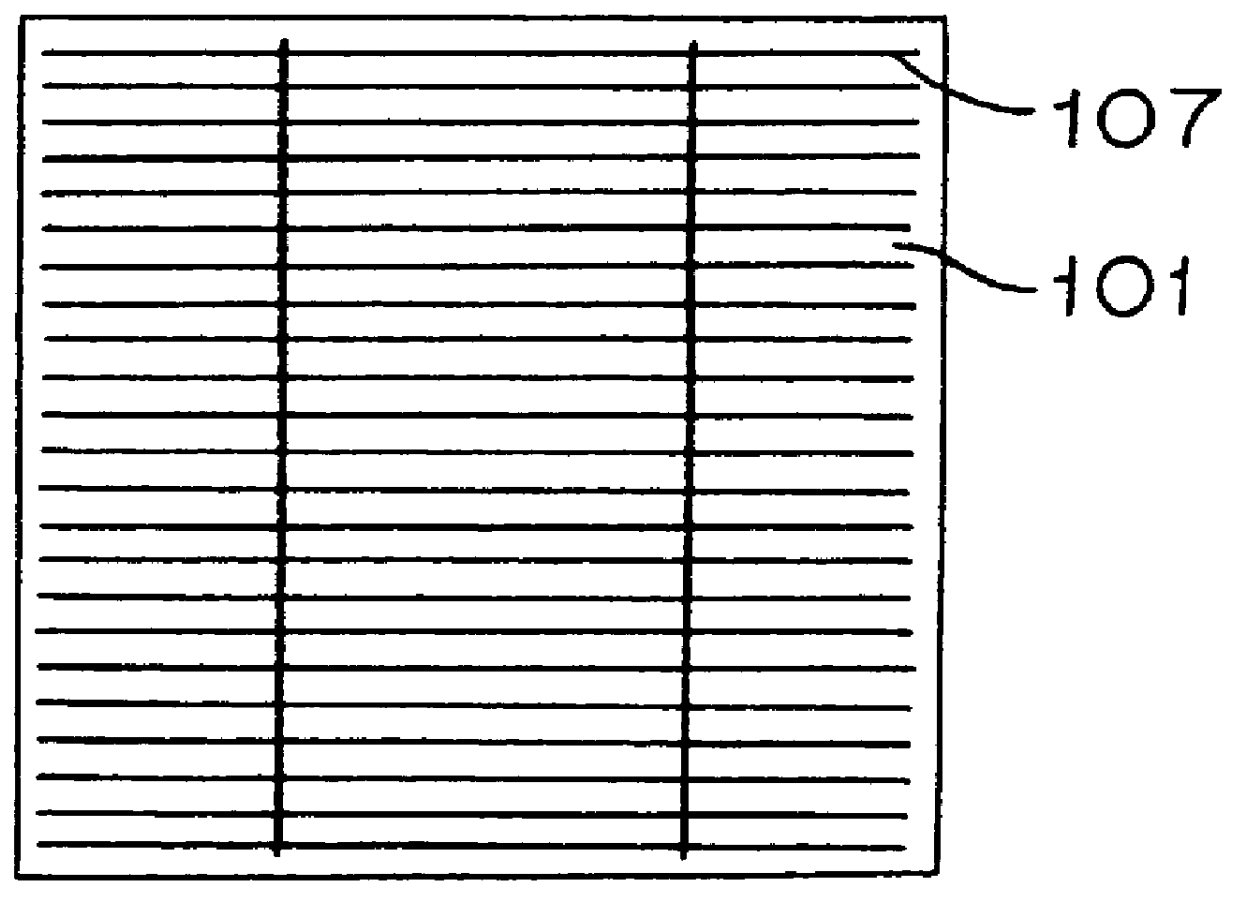

Method of manufacture of semiconductor device and conductive compositions used therein

InactiveUS20060231804A1Semiconductor/solid-state device detailsConductive materialDevice materialFrit

The present invention is directed to a thick film conductive composition comprising: (a) electrically conductive silver powder; (b) Zn-containing additive wherein the particle size of said zinc-containing additive is in the range of 7 nanometers to less than 100 nanometers; (c) glass frit wherein said glass frit has a softening point in the range of 300 to 600° C.; dispersed in (d) organic medium. The present invention is further directed to a semiconductor device and a method of manufacturing a semiconductor device from a structural element composed of a semiconductor having a p-n junction and an insulating film formed on a main surface of the semiconductor comprising the steps of (a) applying onto said insulating film the thick film composition as describe above; and (b) firing said semiconductor, insulating film and thick film composition to form an electrode.

Owner:EI DU PONT DE NEMOURS & CO

E-beam inspection structure for leakage analysis

InactiveUS20090057664A1Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementElectricityGate dielectric

A testing structure, and method of using the testing structure, where the testing structure comprised of at least one of eight test structures that exhibits a discernable defect characteristic upon voltage contrast scanning when it has at least one predetermined structural defect. The eight test structures being: 1) having an Active Area (AA) / P-N junction leakage; 2) having an isolation region to ground; 3) having an AA / P-N junction and isolation region; 4) having a gate dielectric leakage and gate to isolation region to ground; 5) having a gate dielectric leakage through AA / P-N junction to ground leakage; 6) having a gate dielectric to ground and gate / one side isolation region leakage to ground; 7) having an oversized gate dielectric through AA / P-N junction to ground leakage; and 8) having an AA / P-N junction leakage gate dielectric leakage.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

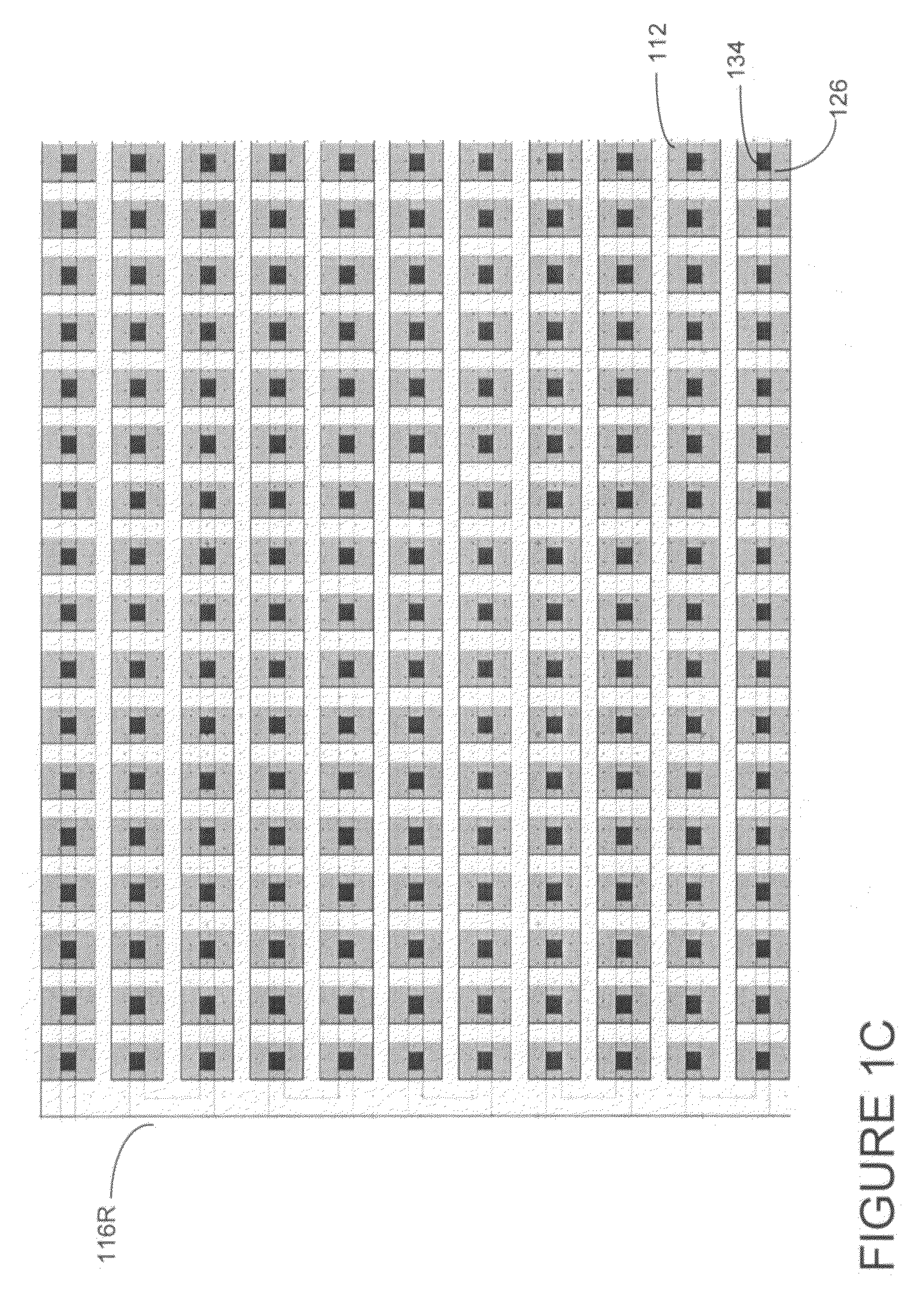

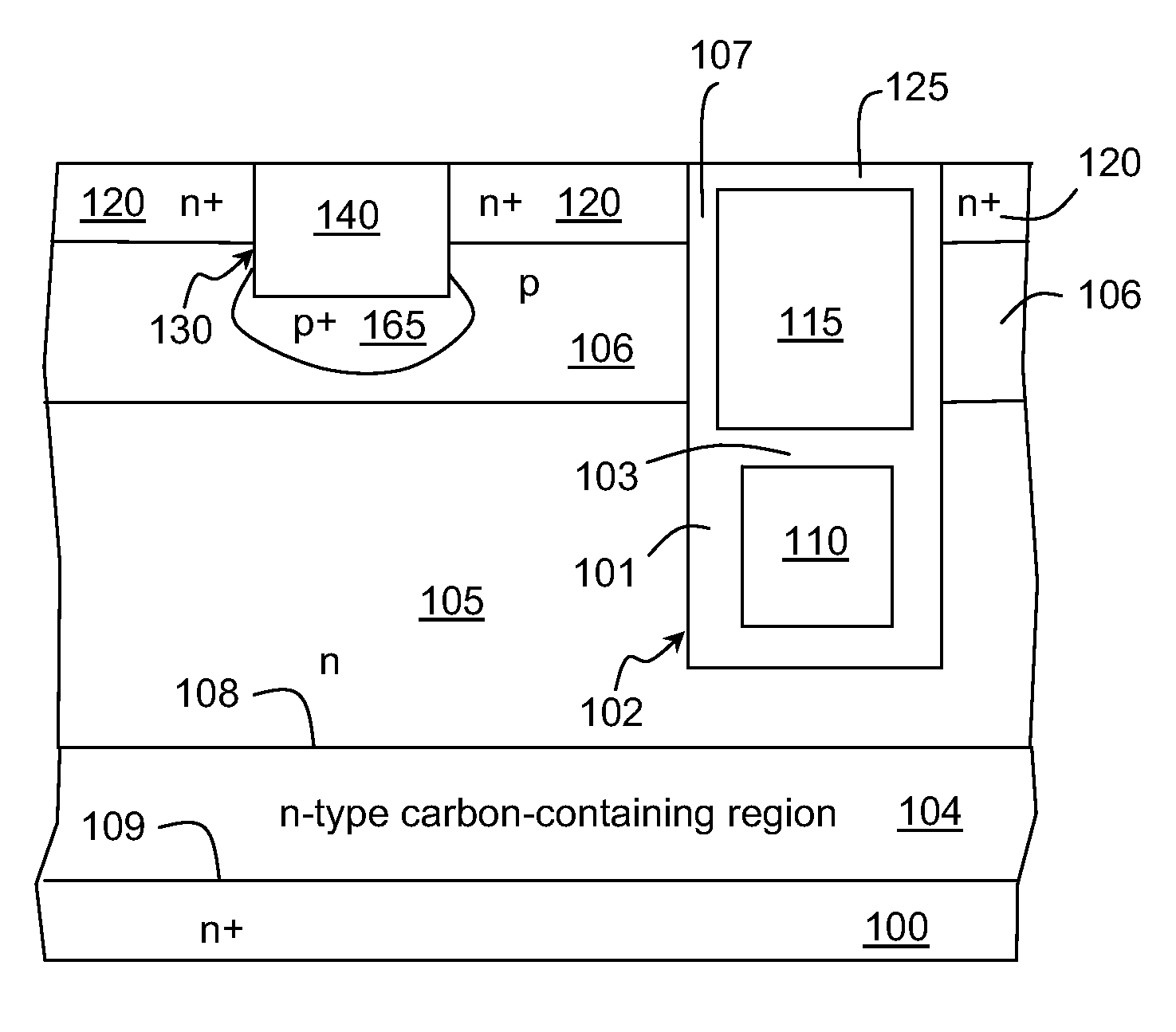

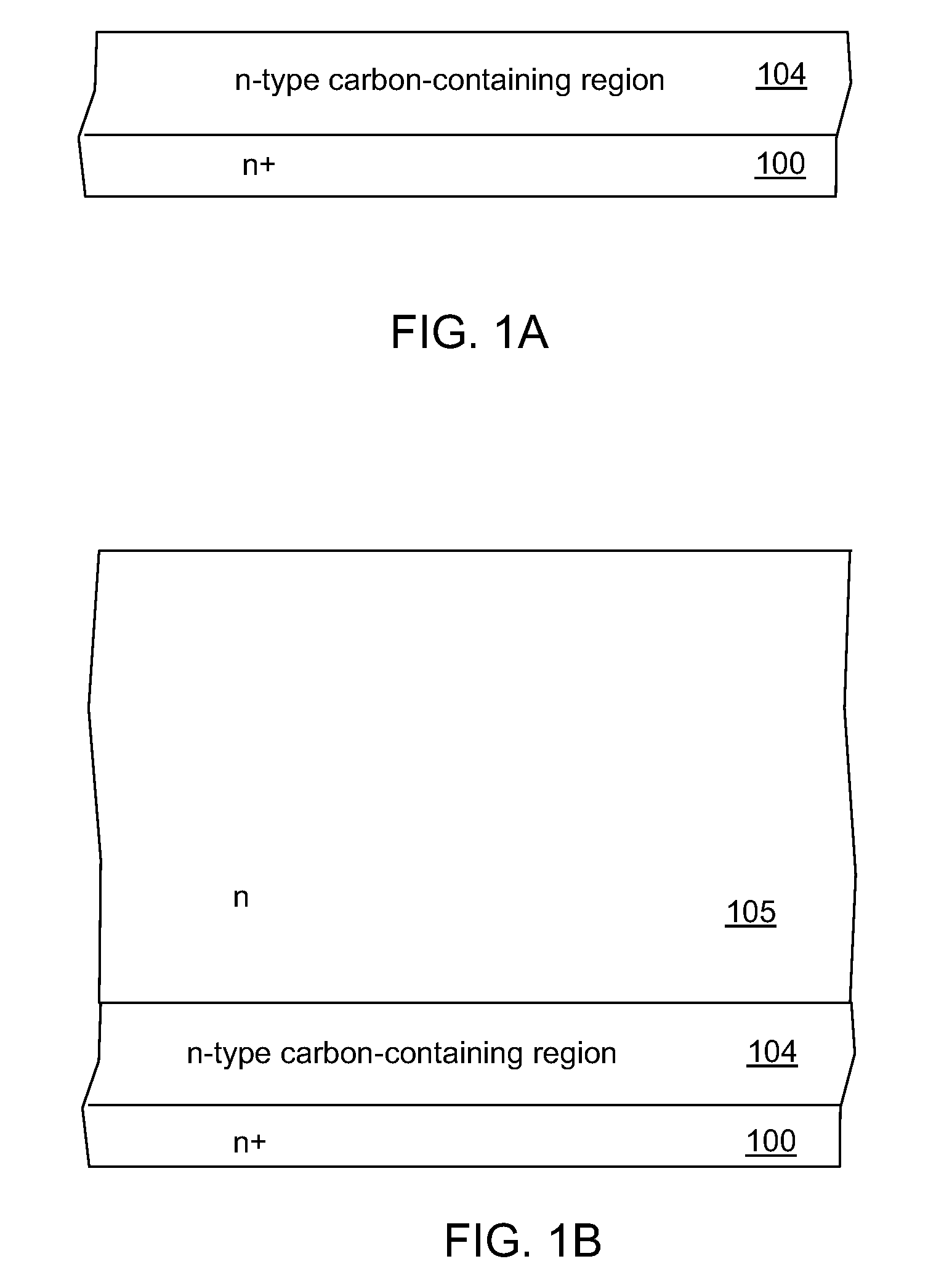

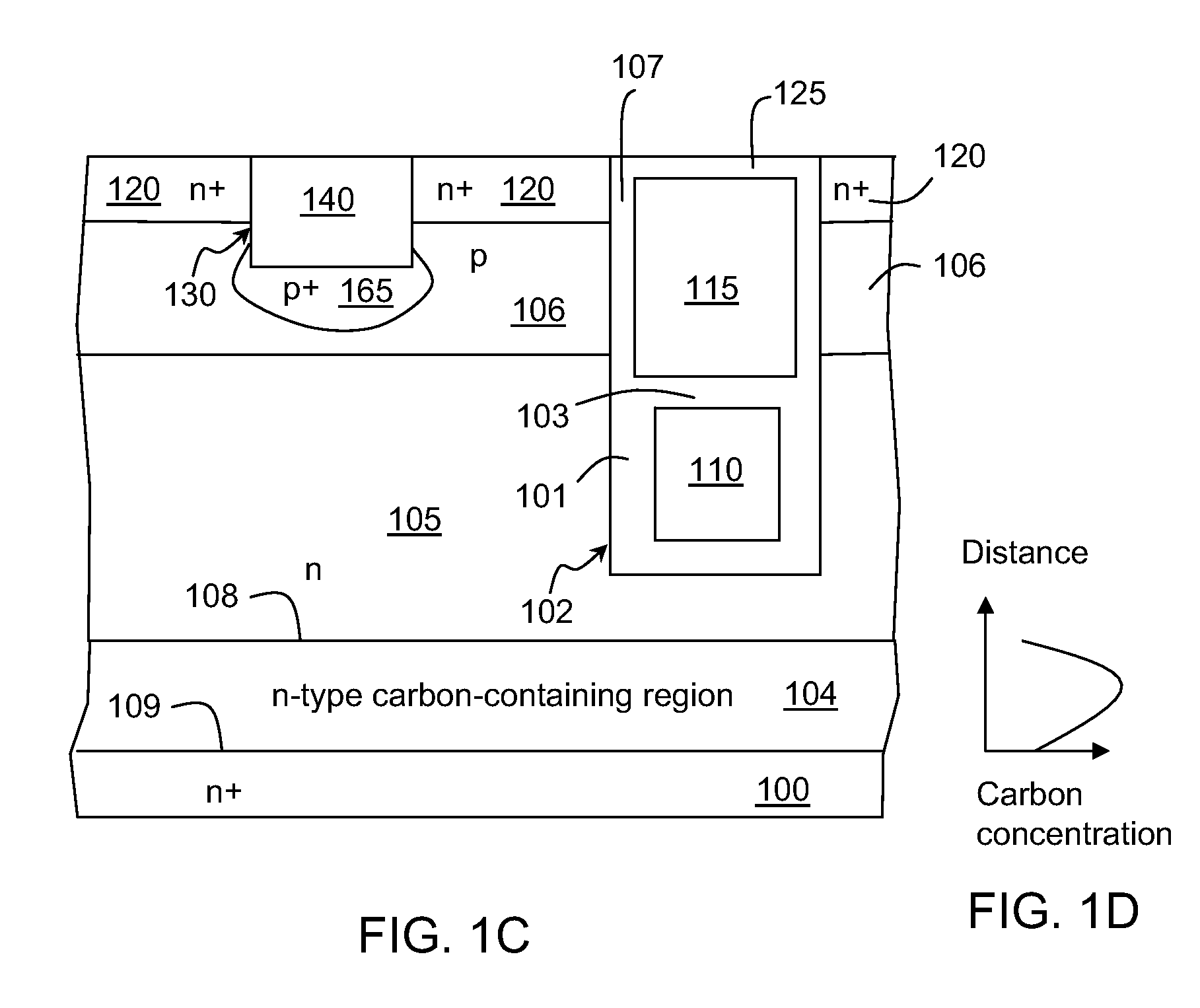

Structure and method for forming power devices with carbon-containing region

ActiveUS7994573B2Solid-state devicesSemiconductor/solid-state device manufacturingGate dielectricField-effect transistor

Owner:SEMICON COMPONENTS IND LLC

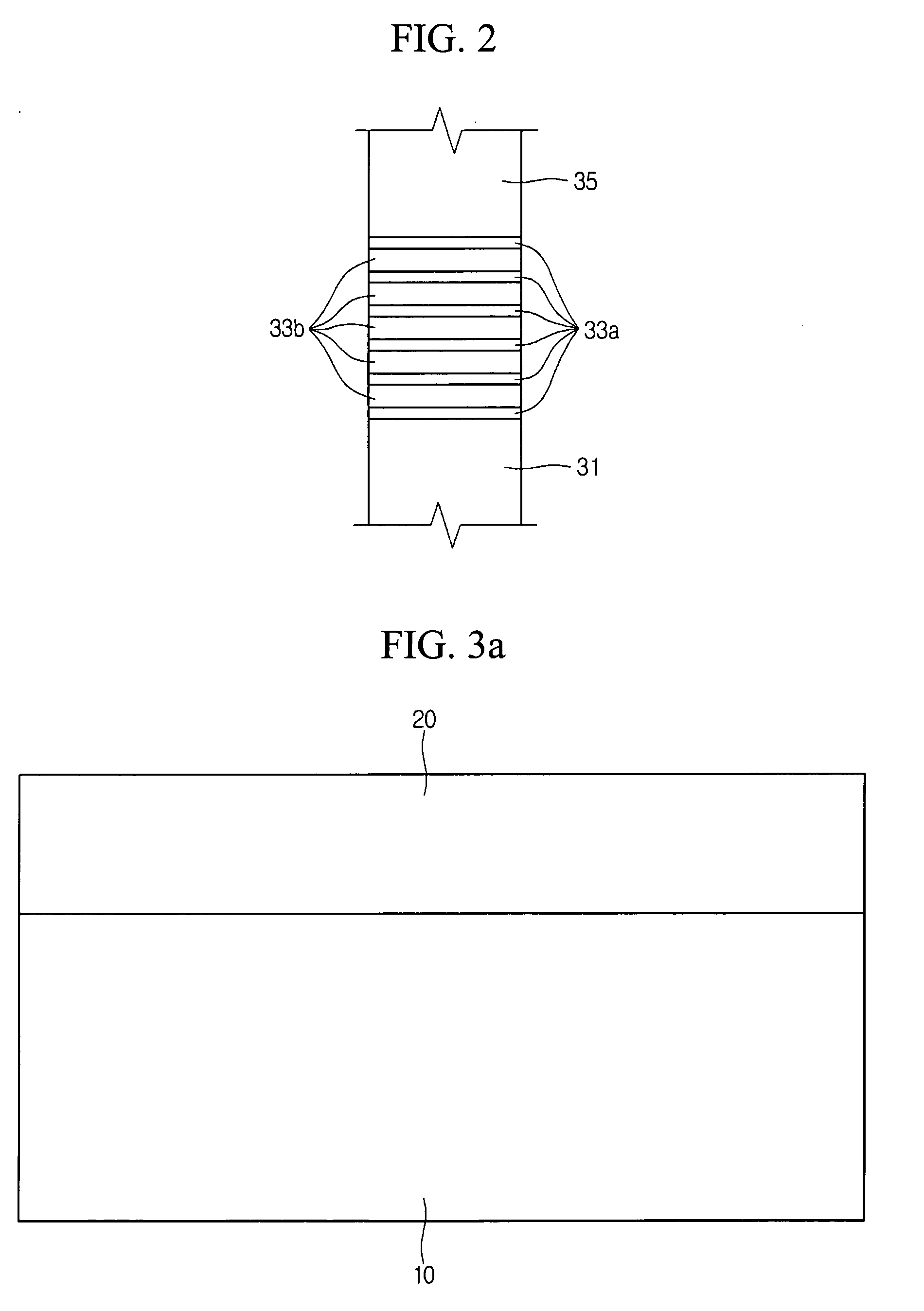

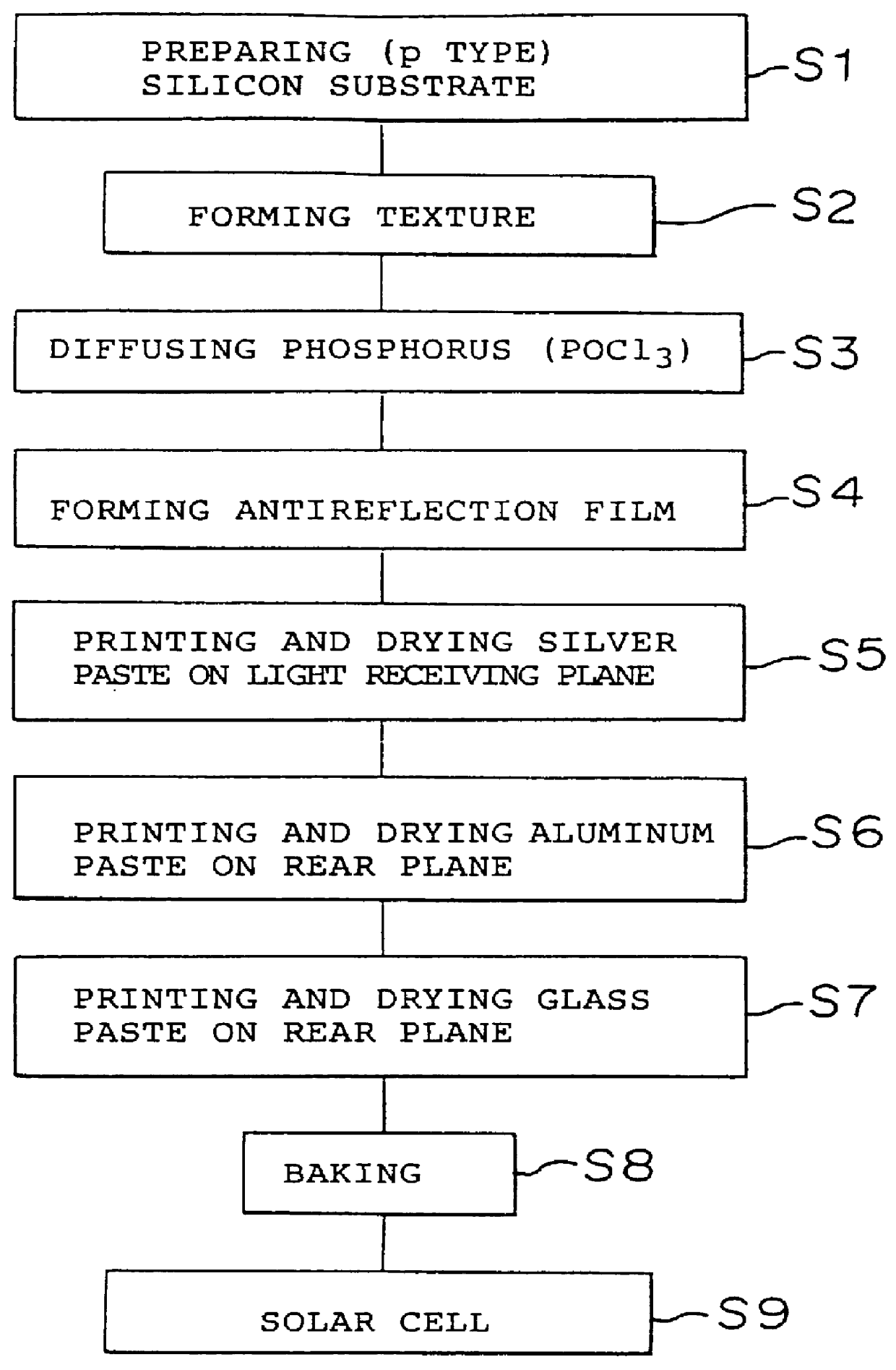

Method of producing a solar cell; a solar cell and a method of producing a semiconductor device

InactiveUS6093882ASemiconductor/solid-state device manufacturingPhotovoltaic energy generationSilver pasteSolar cell

Owner:MITSUBISHI ELECTRIC CORP

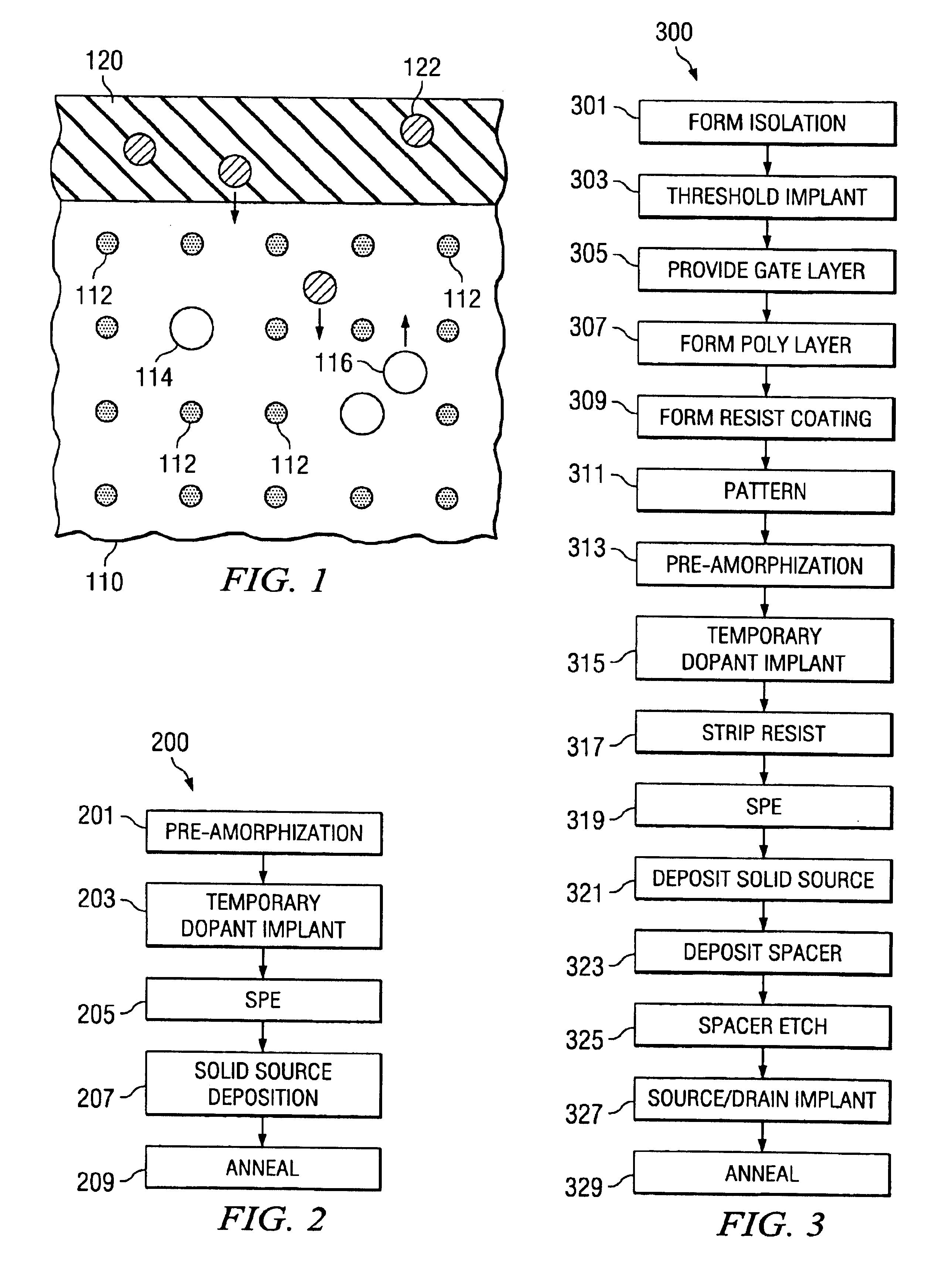

Fabrication of abrupt ultra-shallow junctions

InactiveUS6852603B2Promote formationFaster diffusing speciesSemiconductor/solid-state device manufacturingDiffusionDopant

One aspect of the invention relates to a method of forming P-N junctions within a semiconductor substrate. The method involves providing a temporary impurity species, such as fluorine, within the semiconductor crystal matrix prior to solid source in-diffusion of the primary dopant, such as boron. The impurity atom is a faster diffusing species relative to silicon atoms. During in-diffusion, the temporary impurity species acts to reduce the depth to which the primary dopant diffuses and thereby facilitates the formation of very shallow junctions.

Owner:TEXAS INSTR INC

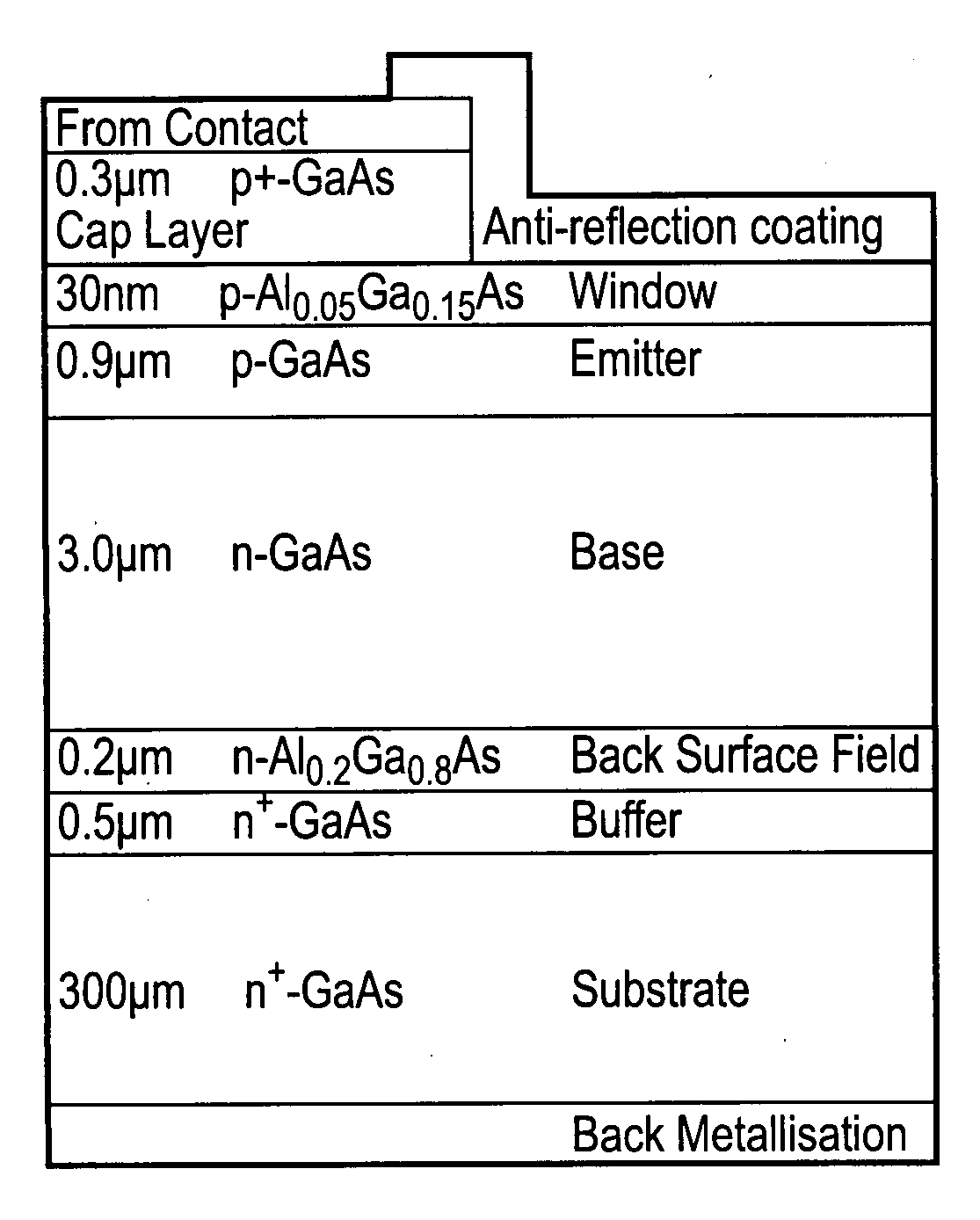

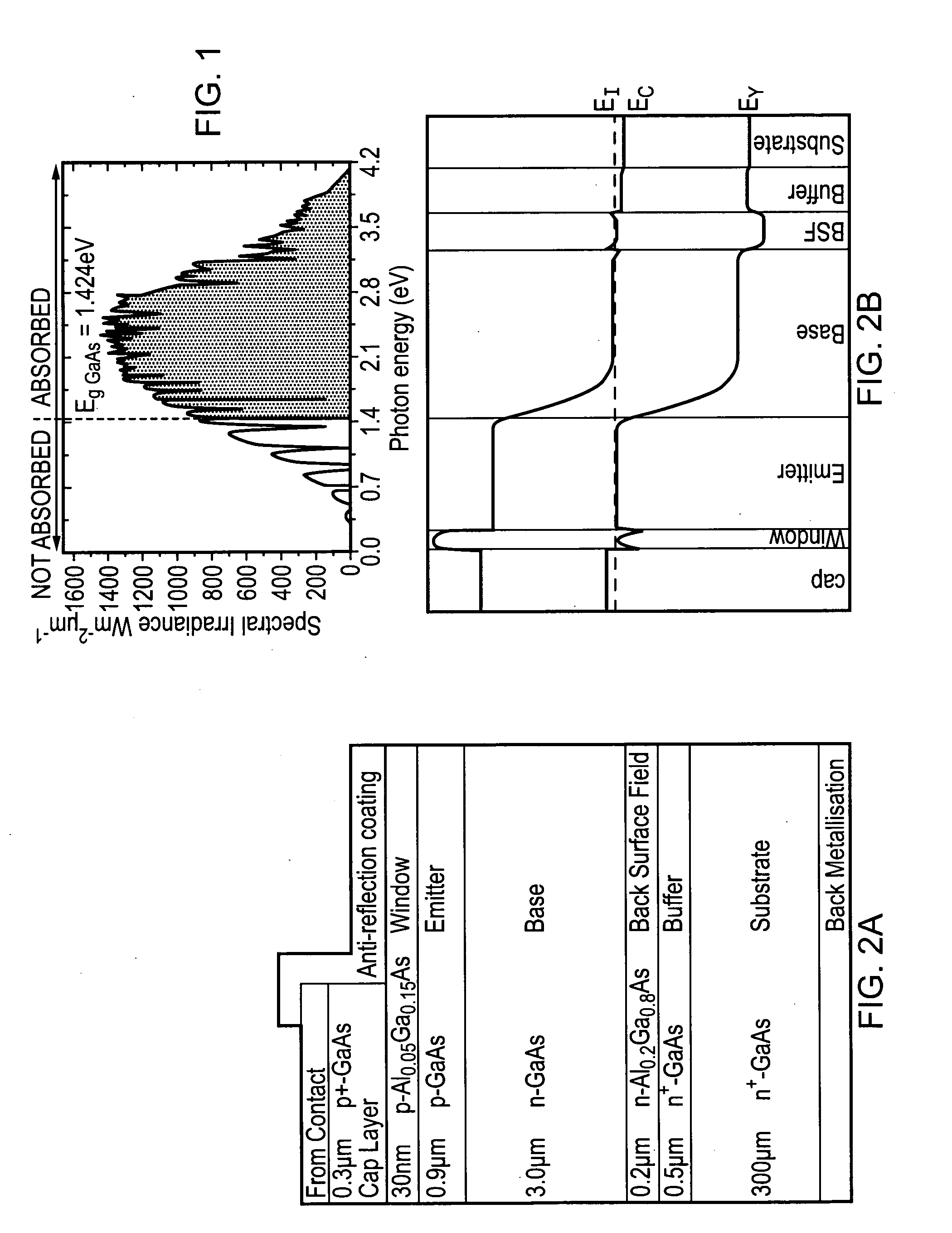

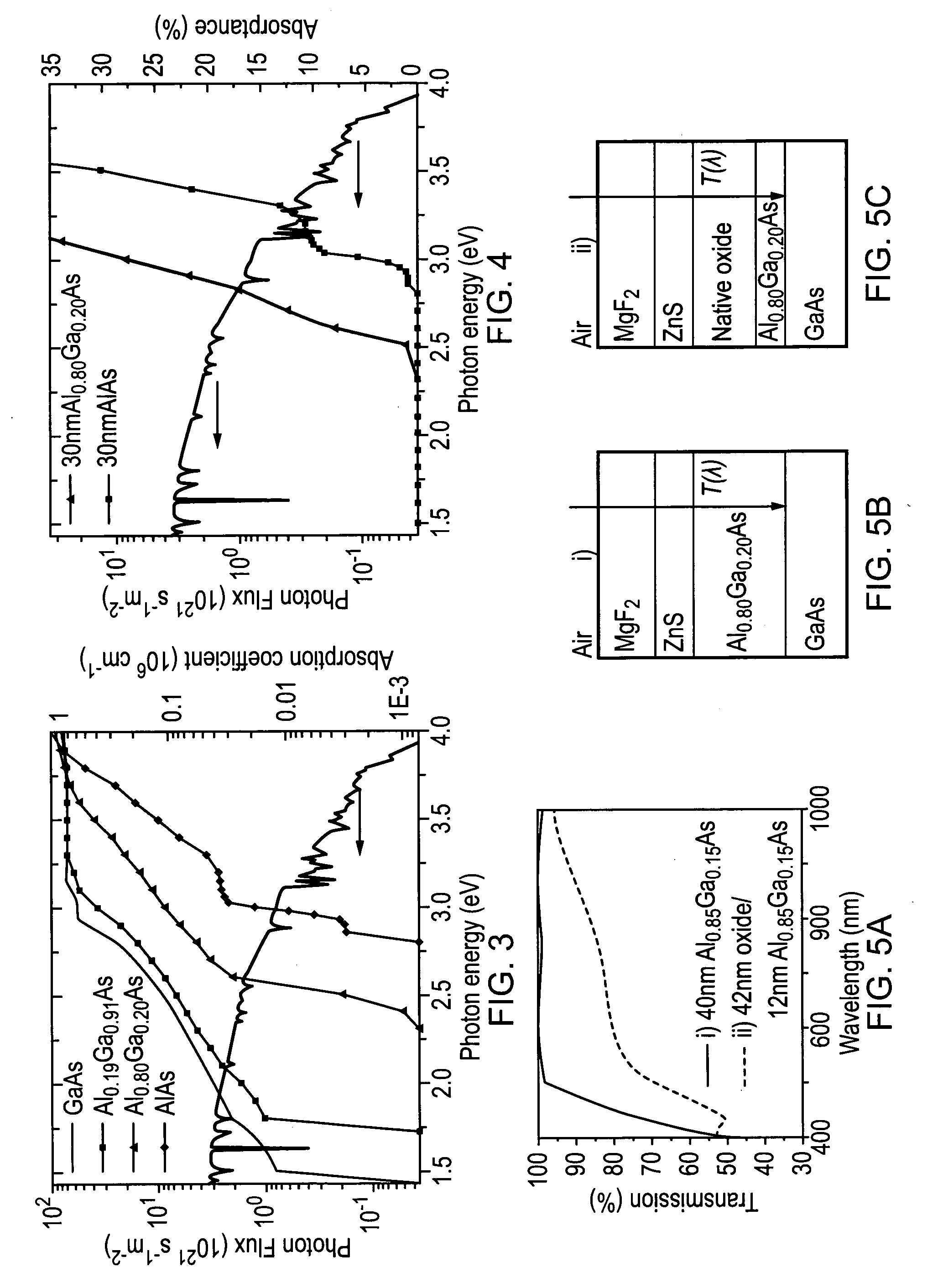

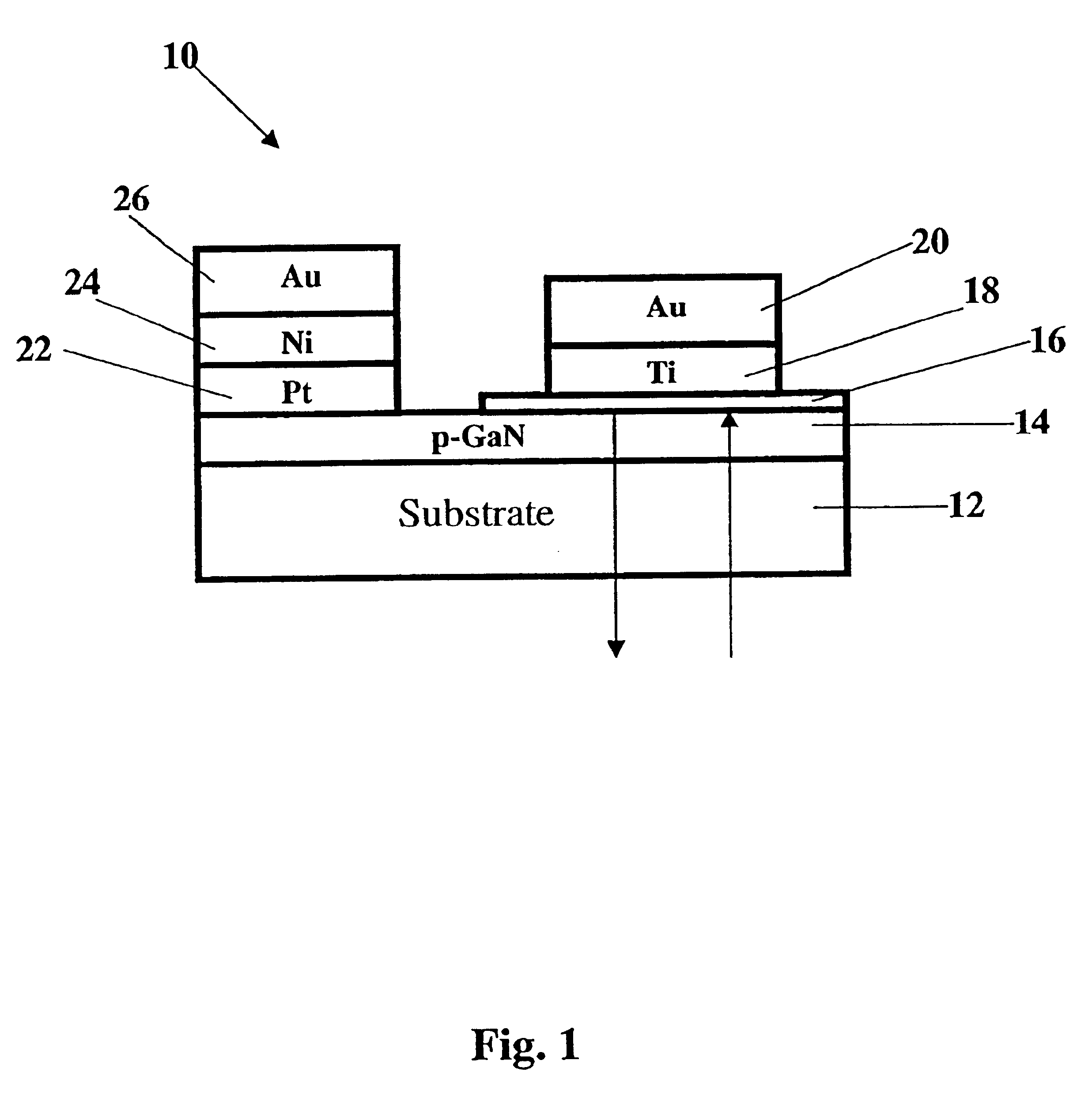

Semiconductor optoelectronic devices and methods for making semiconductor optoelectronic devices

InactiveUS20100218819A1Solar photon flux is reducingImprove device performanceFinal product manufactureSemiconductor/solid-state device manufacturingCharge carrierSolar cell

A semiconductor-based optoelectronic device such as a solar cell has an n-type layer and a p-type layer, together forming a p-n junction. Contact regions are formed on the device, with light-receiving regions between contact regions. A window layer is formed over the n-type layer or the p-type layer at the light-receiving region, the window layer promoting reduced carrier recombination at the surface of the n-type or p-type layer, and / or reflection of minority carriers in the n-type or p-type layer towards the p-n junction. The device has a window protection layer formed over the window layer, the window protection layer providing protection from degradation of the window layer during manufacture and / or operation of the device. For GaAs-based devices the window layer may be Al0.9Ga0.1As and the window protection layer may be GaAs. Additionally, an AlAs etch stop layer may be provided over the window protection layer.

Owner:THE UNIV COURT OF THE UNIV OF GLASGOW

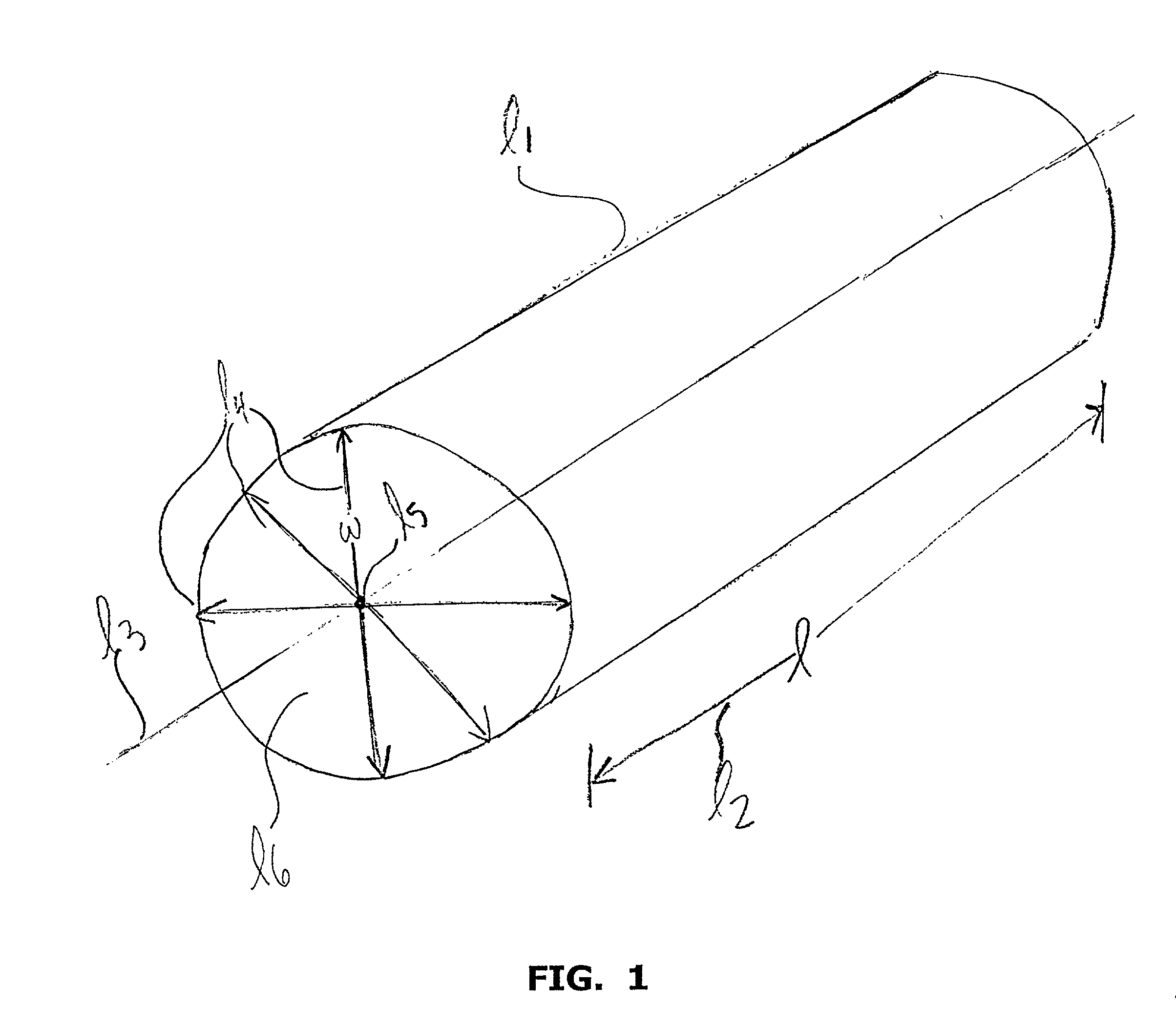

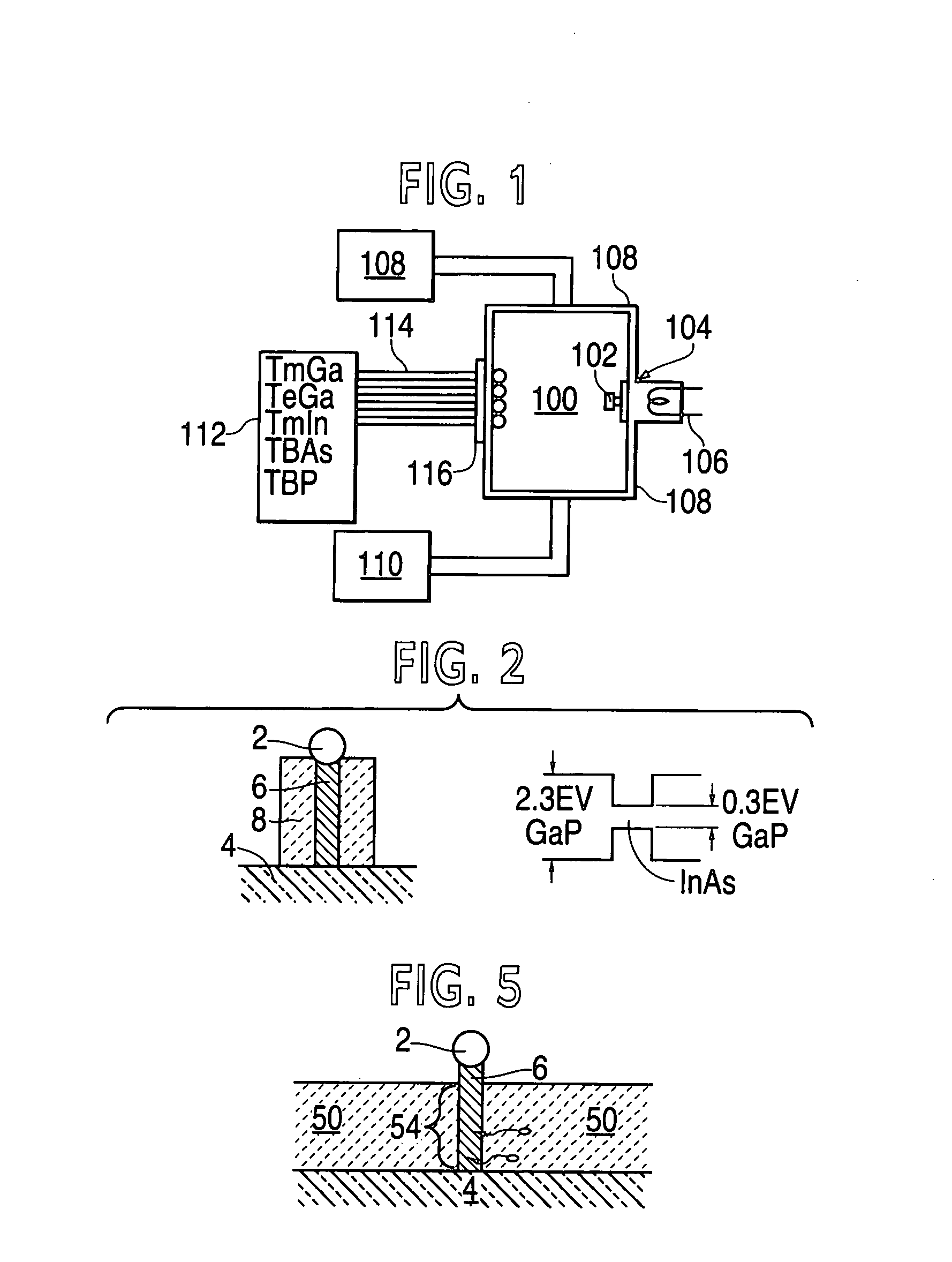

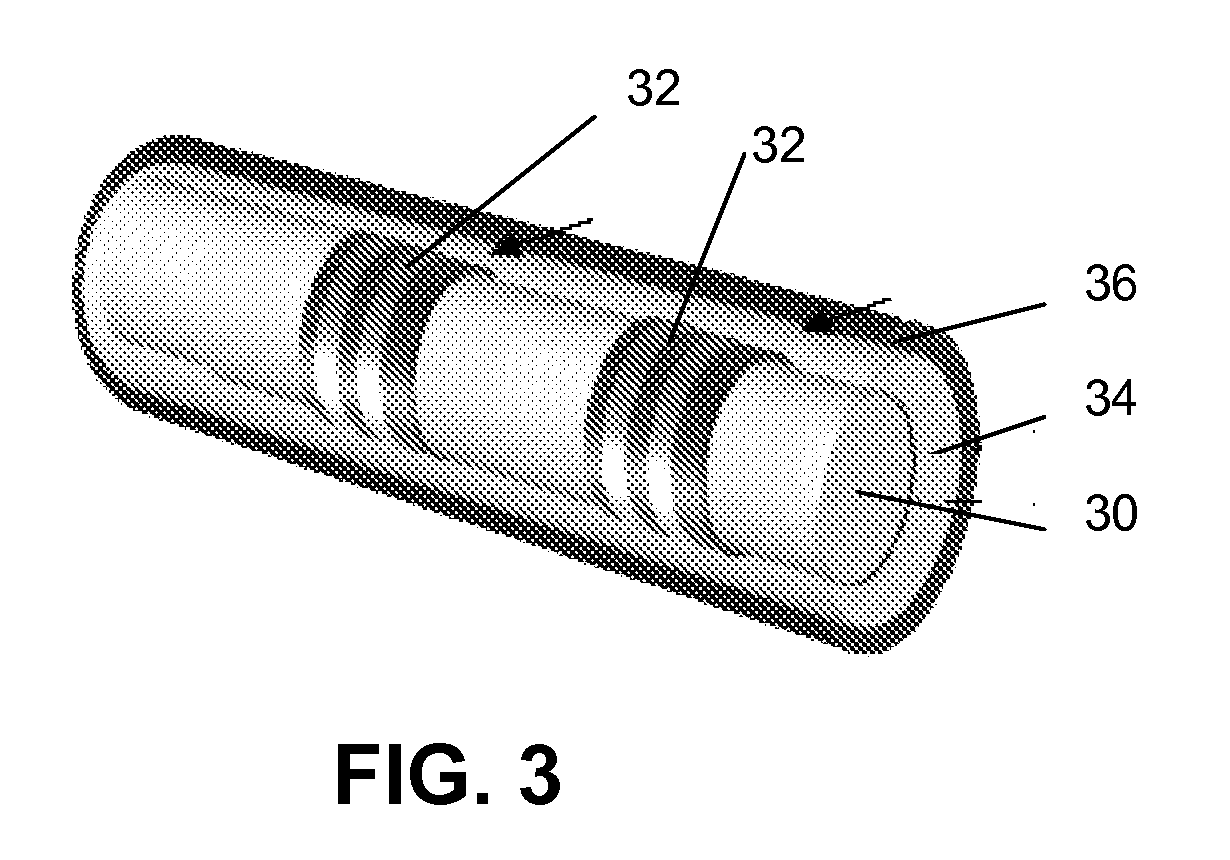

Nanowhiskers with PN junctions, doped nanowhiskers, and methods for preparing them

InactiveUS20050006673A1Good electrical conductivityPermitted diffusionPolycrystalline material growthNanoinformaticsHeterojunctionP–n junction

Nano-engineered structures are disclosed, incorporating nanowhiskers of high mobility conductivity and incorporating pn junctions. In one embodiment, a nanowhisker of a first semiconducting material has a first band gap, and an enclosure comprising at least one second material with a second band gap encloses said nanoelement along at least part of its length, the second material being doped to provide opposite conductivity type charge carriers in respective first and second regions along the length of the of the nanowhisker, whereby to create in the nanowhisker by transfer of charge carriers into the nanowhisker, corresponding first and second regions of opposite conductivity type charge carriers with a region depleted of free carriers therebetween. The doping of the enclosure material may be degenerate so as to create within the nanowhisker adjacent segments having very heavy modulation doping of opposite conductivity type analogous to the heavily doped regions of an Esaki diode. In another embodiment, a nanowhisker is surrounded by polymer material containing dopant material. A step of rapid thermal annealing causes the dopant material to diffuse into the nanowhisker. In a further embodiment, a nanowhisker has a heterojunction between two different intrinsic materials, and Fermi level pinning creates a pn junction at the interface without doping.

Owner:QUNANO

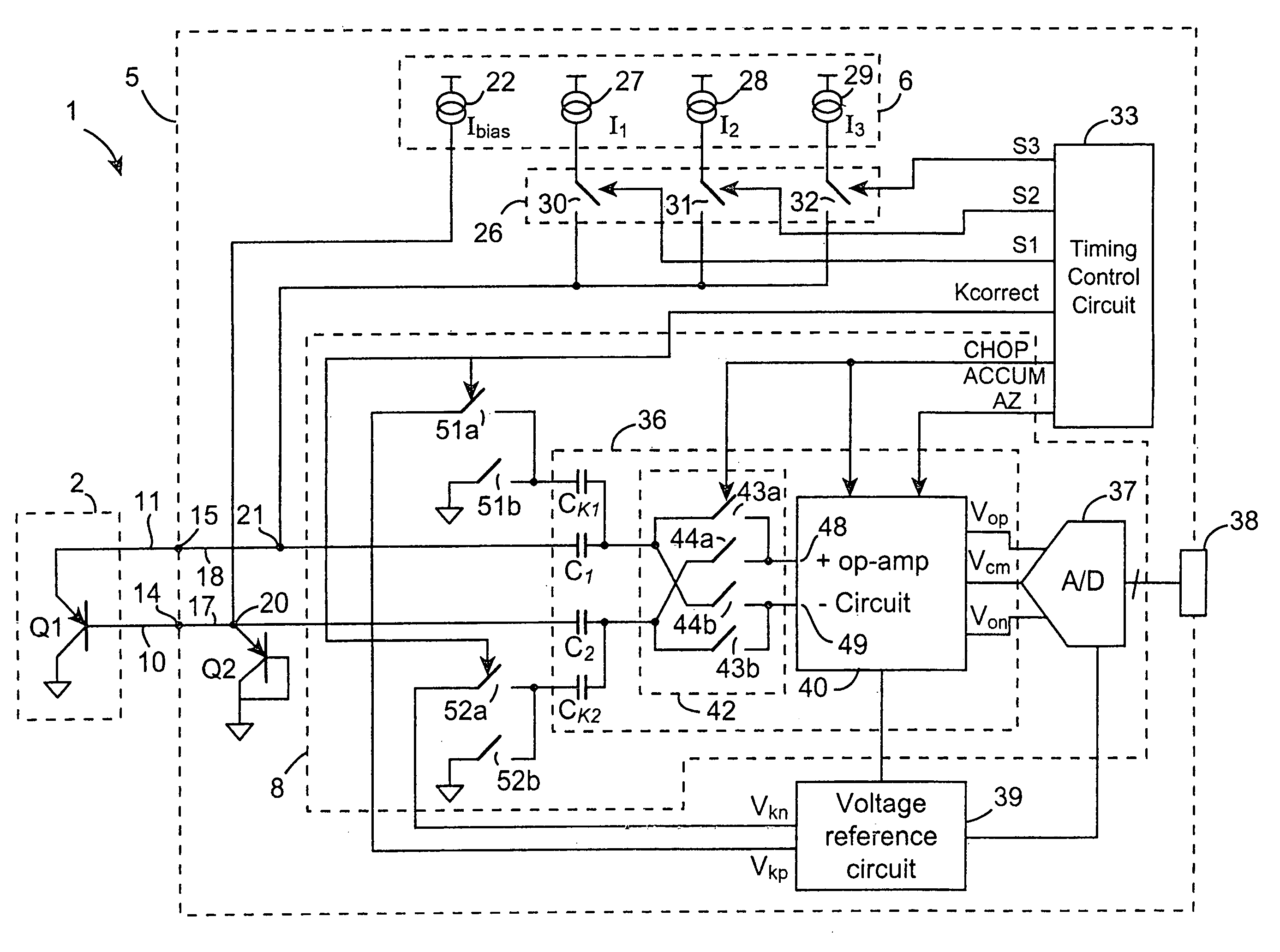

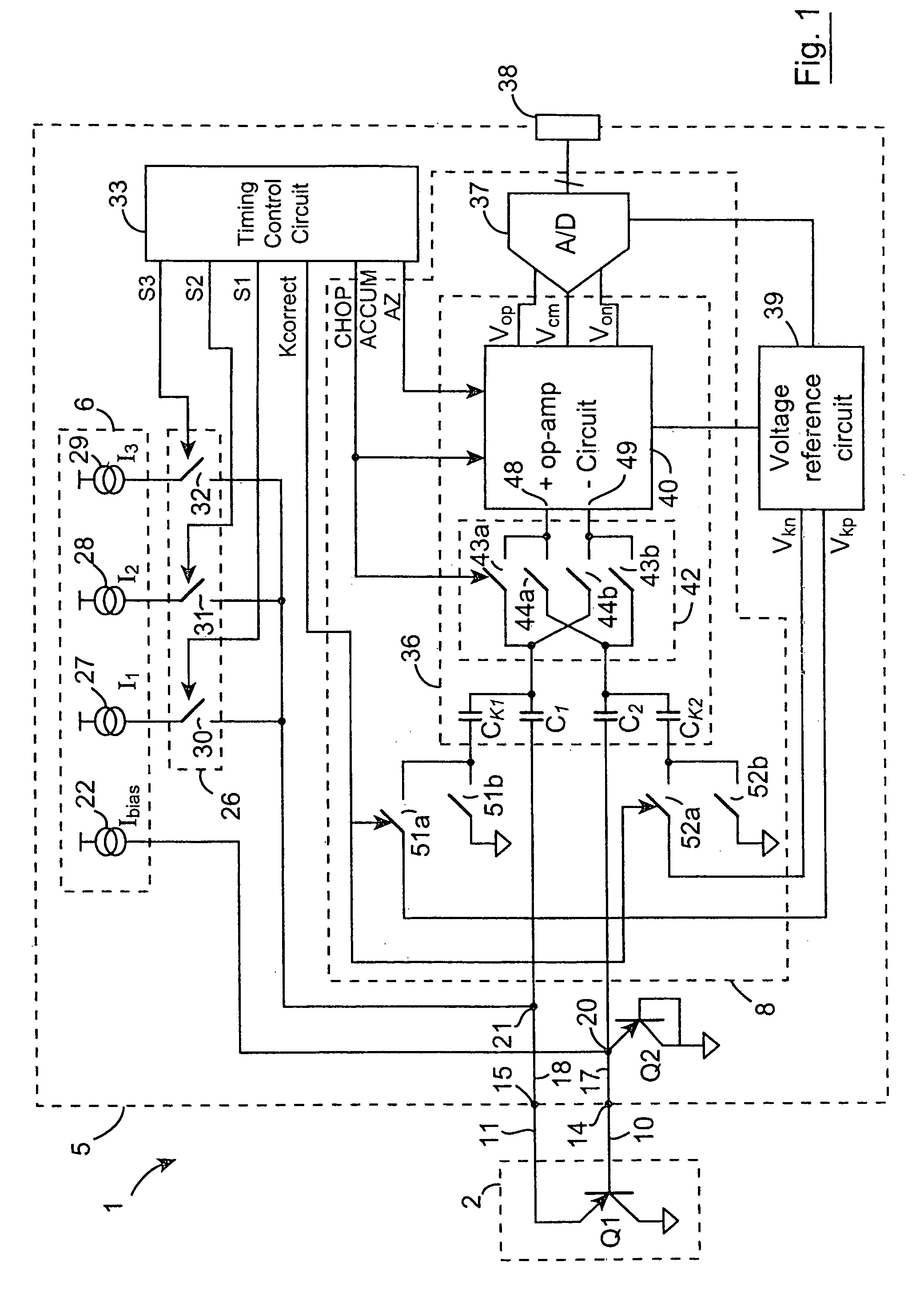

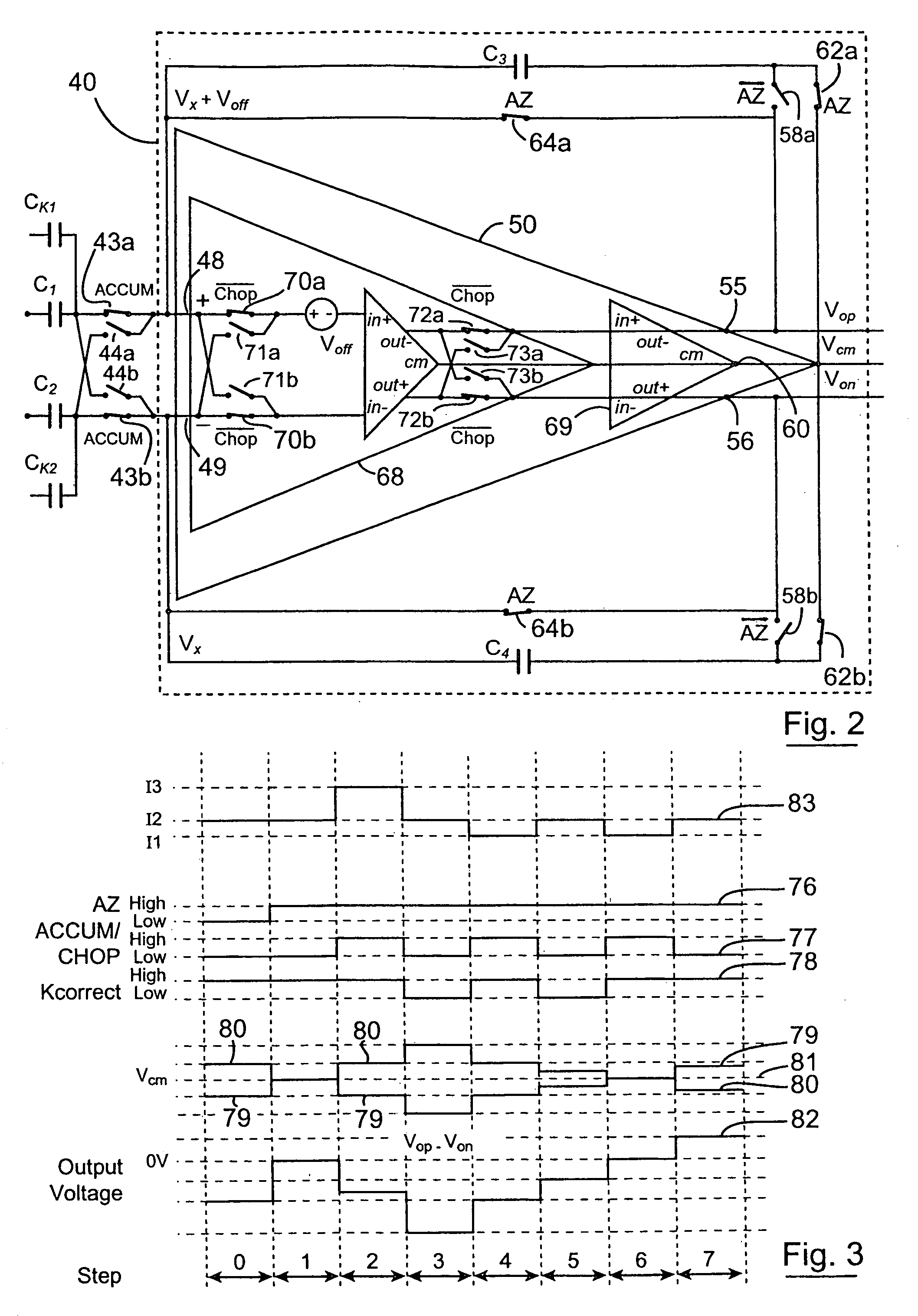

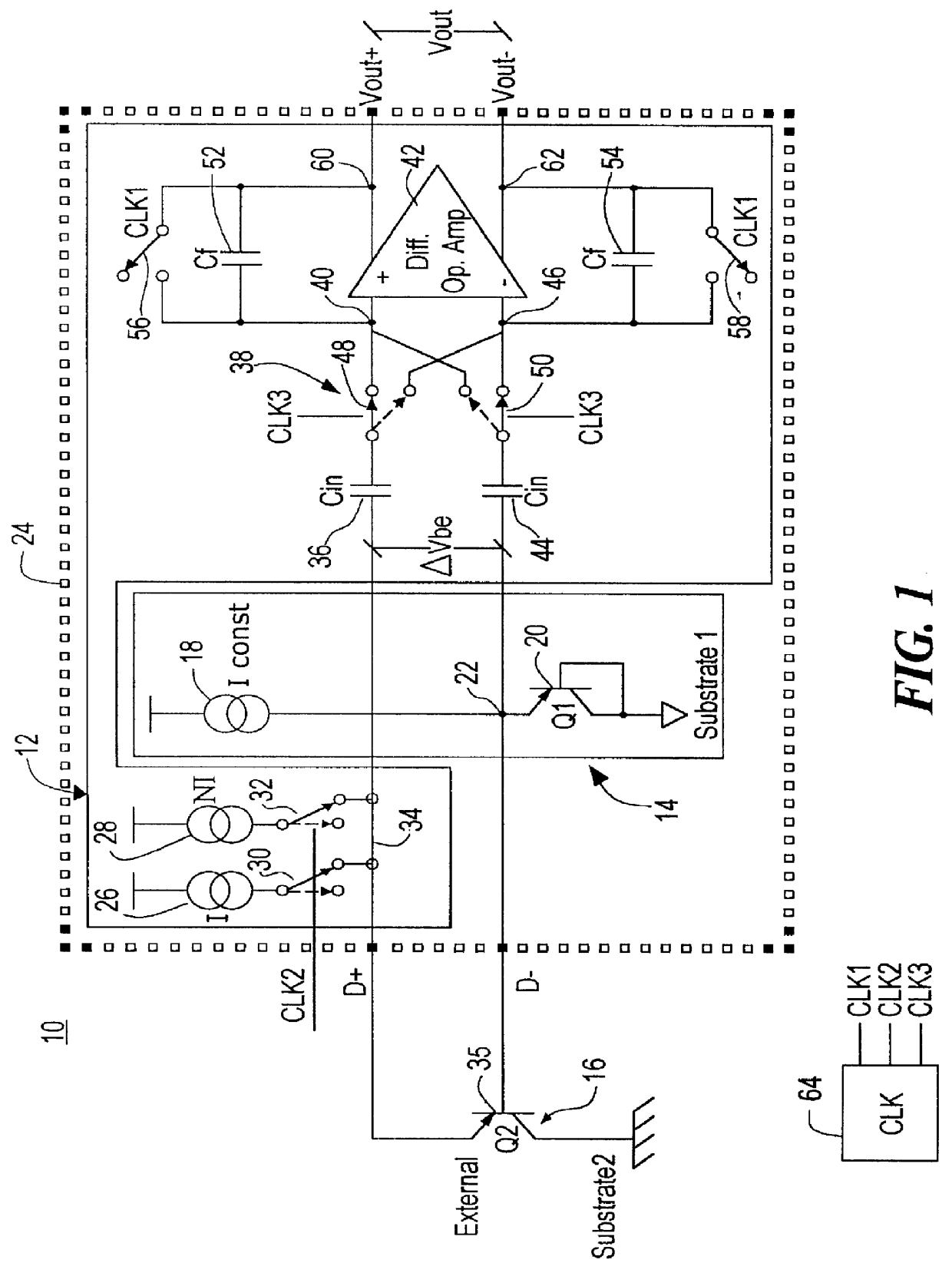

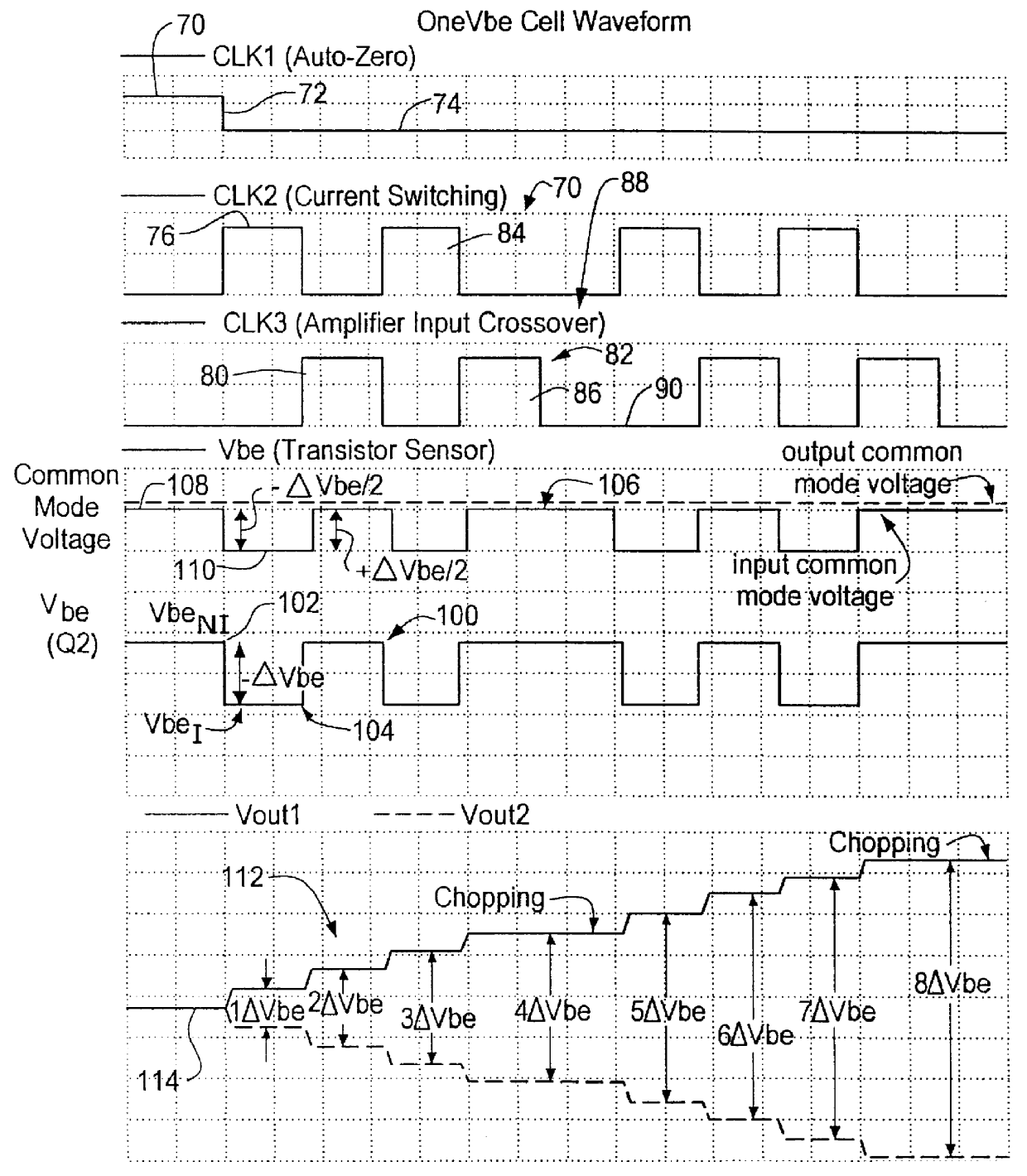

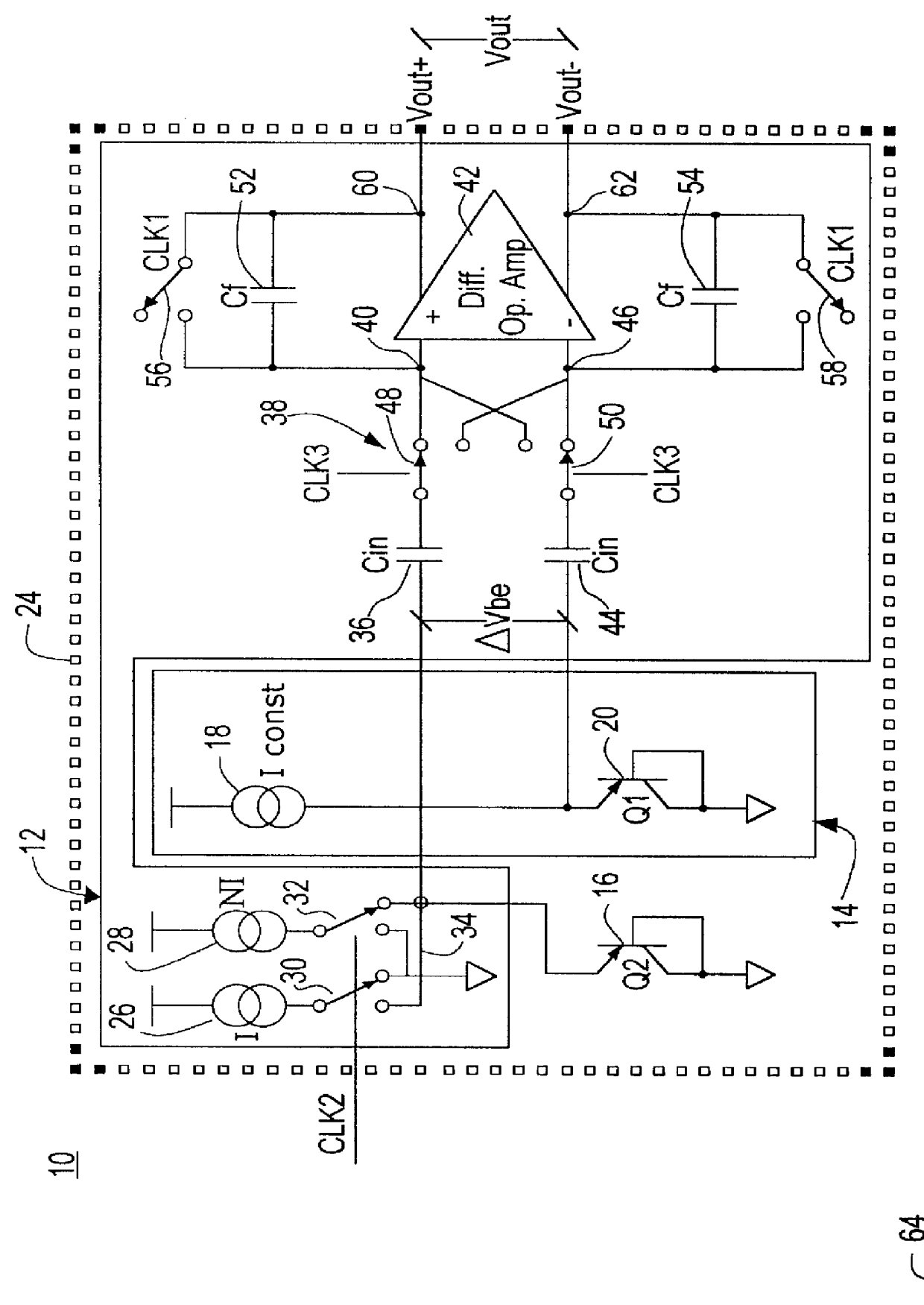

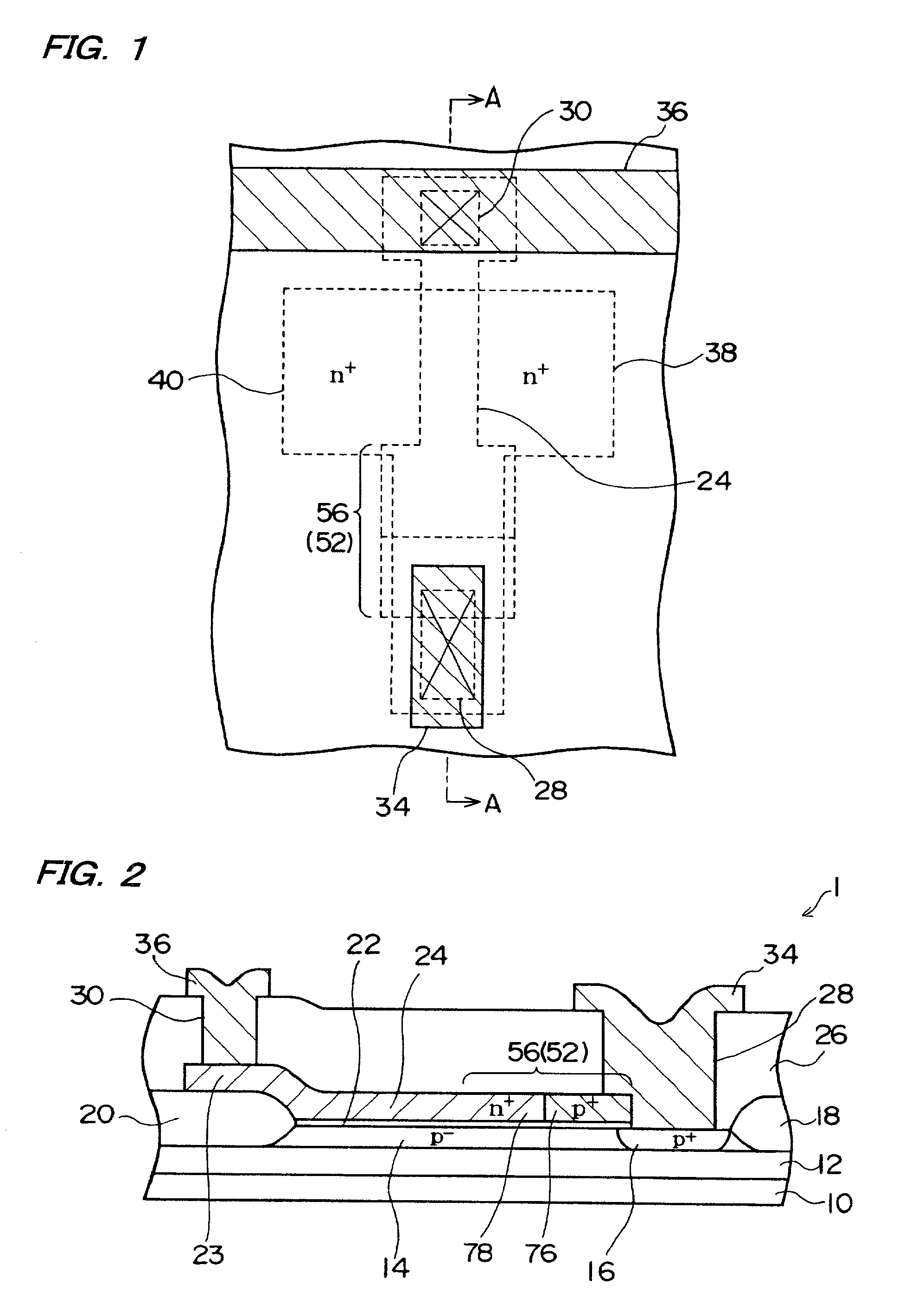

Method and a measuring circuit for determining temperature from a PN junction temperature sensor, and a temperature sensing circuit comprising the measuring circuit and a PN junction

ActiveUS7010440B1Accurate representationEliminate the effects ofThermometer detailsThermometers using material expansion/contactionSwitched currentExcitation current

A switched current temperature sensing circuit (1) comprises a measuring transistor (Q1) which is located remotely of a measuring circuit (5) which applies three excitation currents (I1,I2,I3) of different values to the measuring transistor (Q1) in a predetermined current sequence along lines (10,11). Resulting base / emitter voltages from the measuring transistor (Q1) are applied to the measuring circuit (5) along the same two lines (10,11) as the excitation currents are applied to the measuring transistor (Q1). Voltage differences ΔVbe of successive base / emitter voltages resulting from the excitation currents are integrated in an integrating circuit (36) of the measuring circuit (5) to provide an output voltage indicative of the temperature of the measuring transistor (Q1). By virtue of the fact that the measuring transistor (Q1) is excited by excitation currents of three different values, the effect of current path series resistance in the lines (10,11) on the output voltage indicative of temperature is eliminated. The predetermined current sequence in which the excitation currents are applied to the measuring transistor (Q1) is selected to minimize the voltages in the integrating circuit (36) during integration of the voltage differences ΔVbe.

Owner:ANALOG DEVICES INC

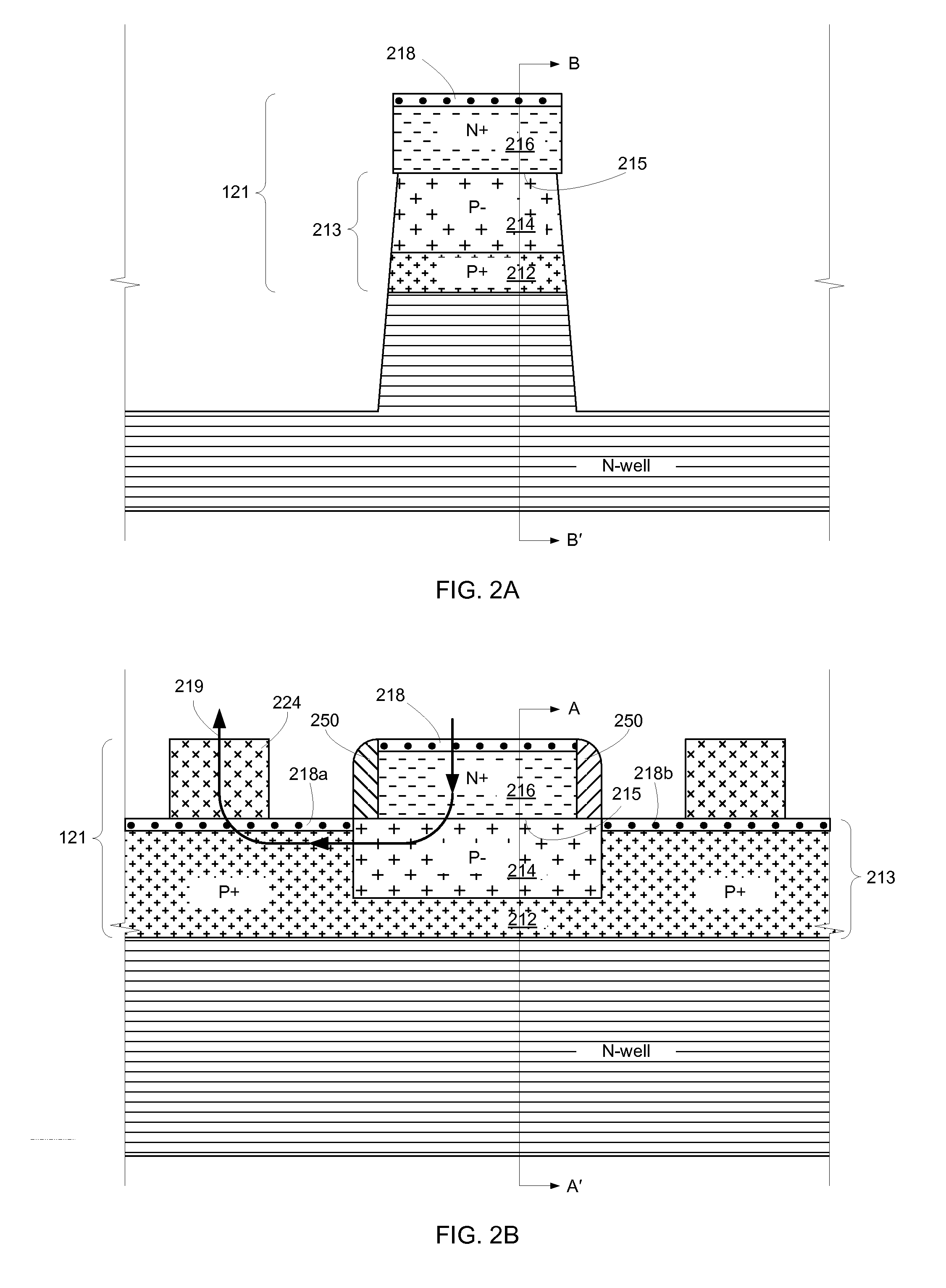

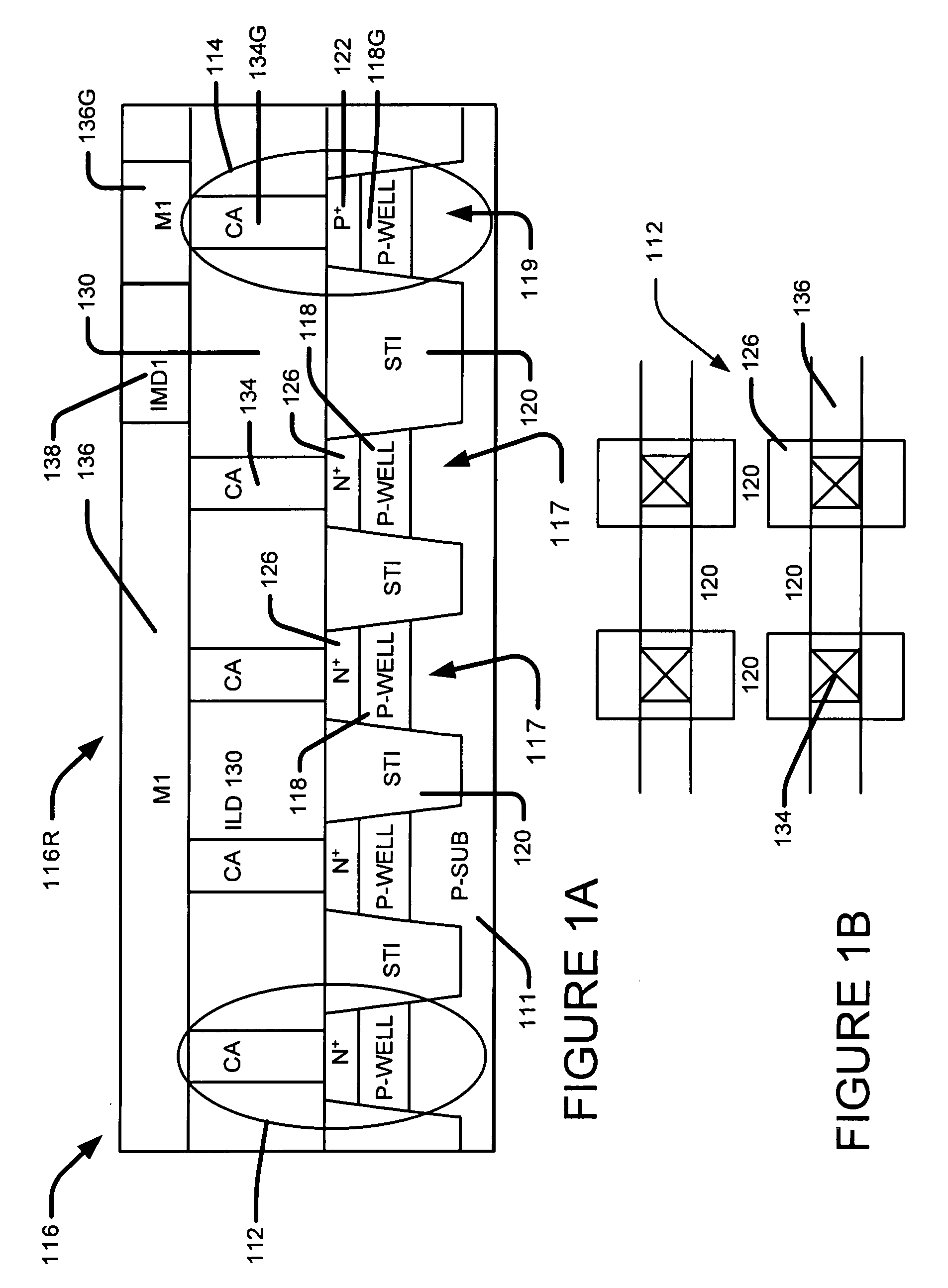

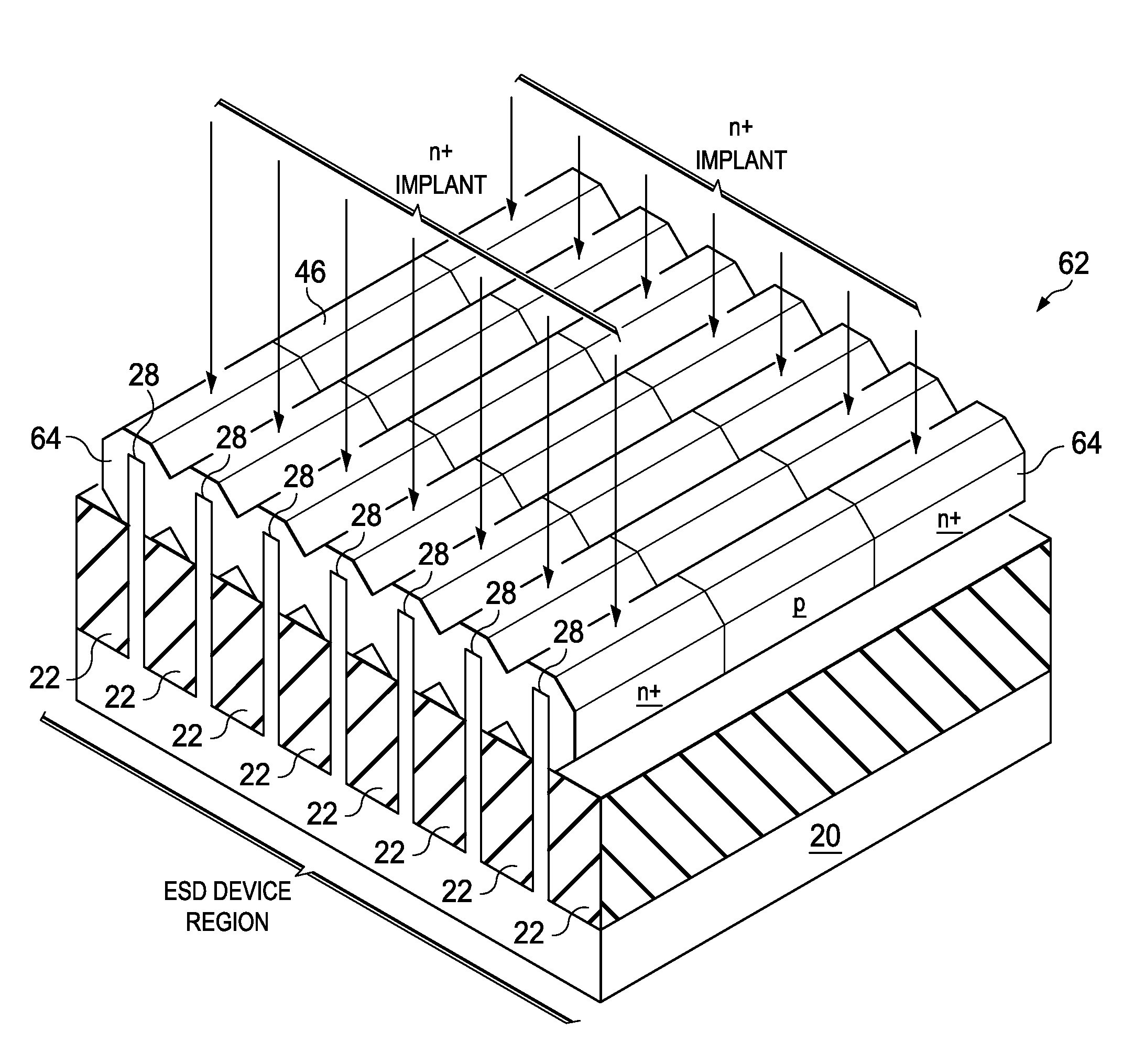

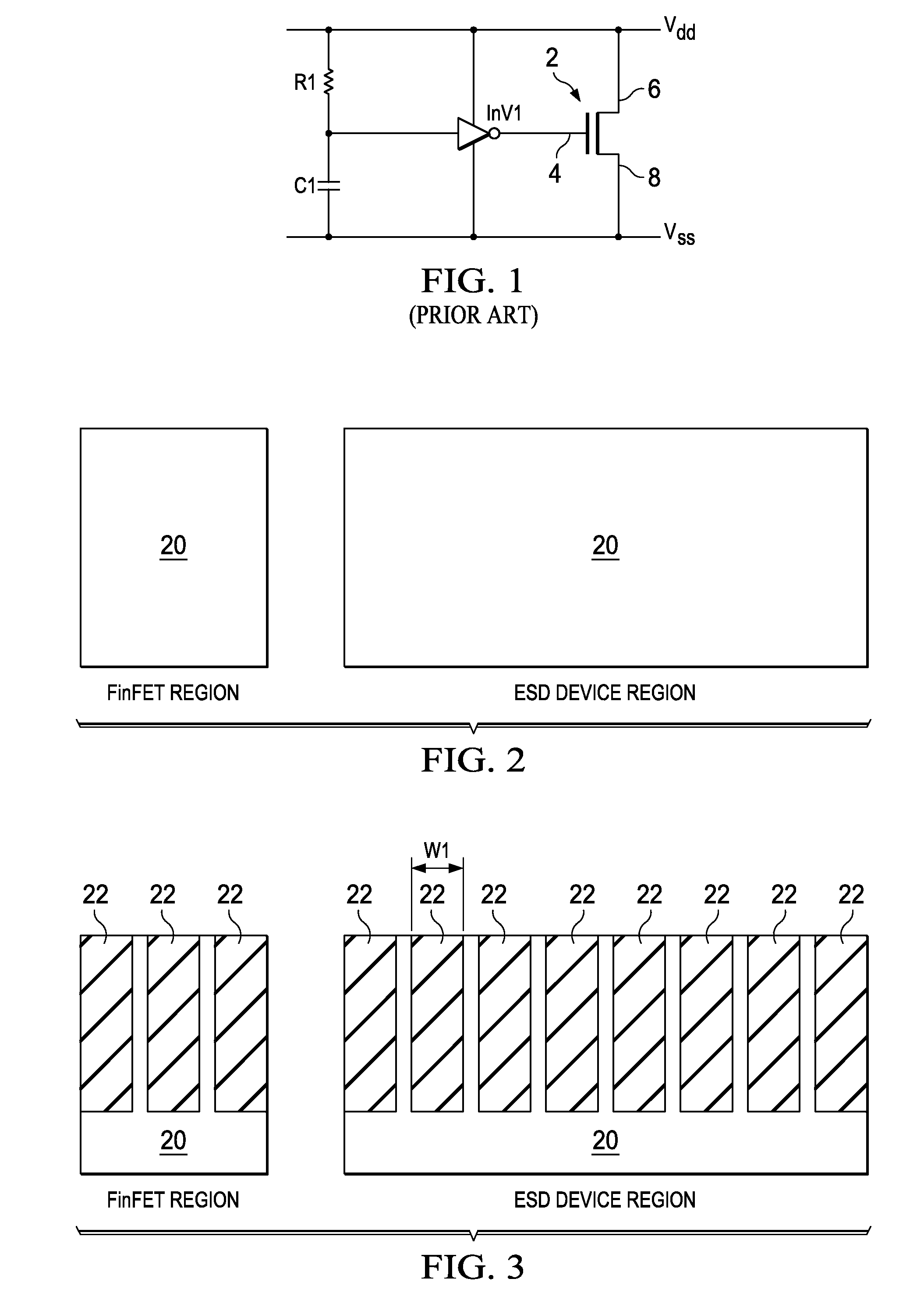

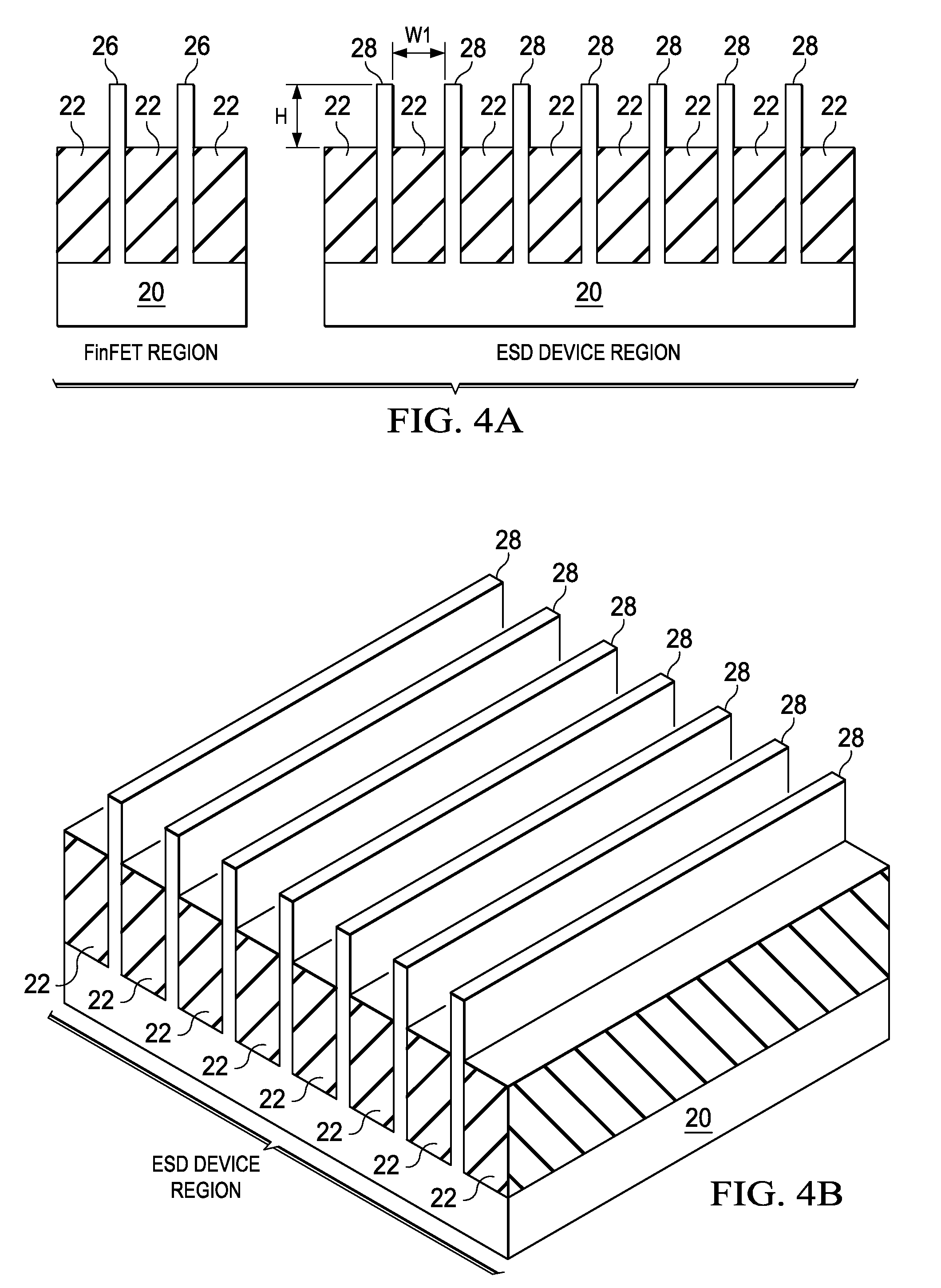

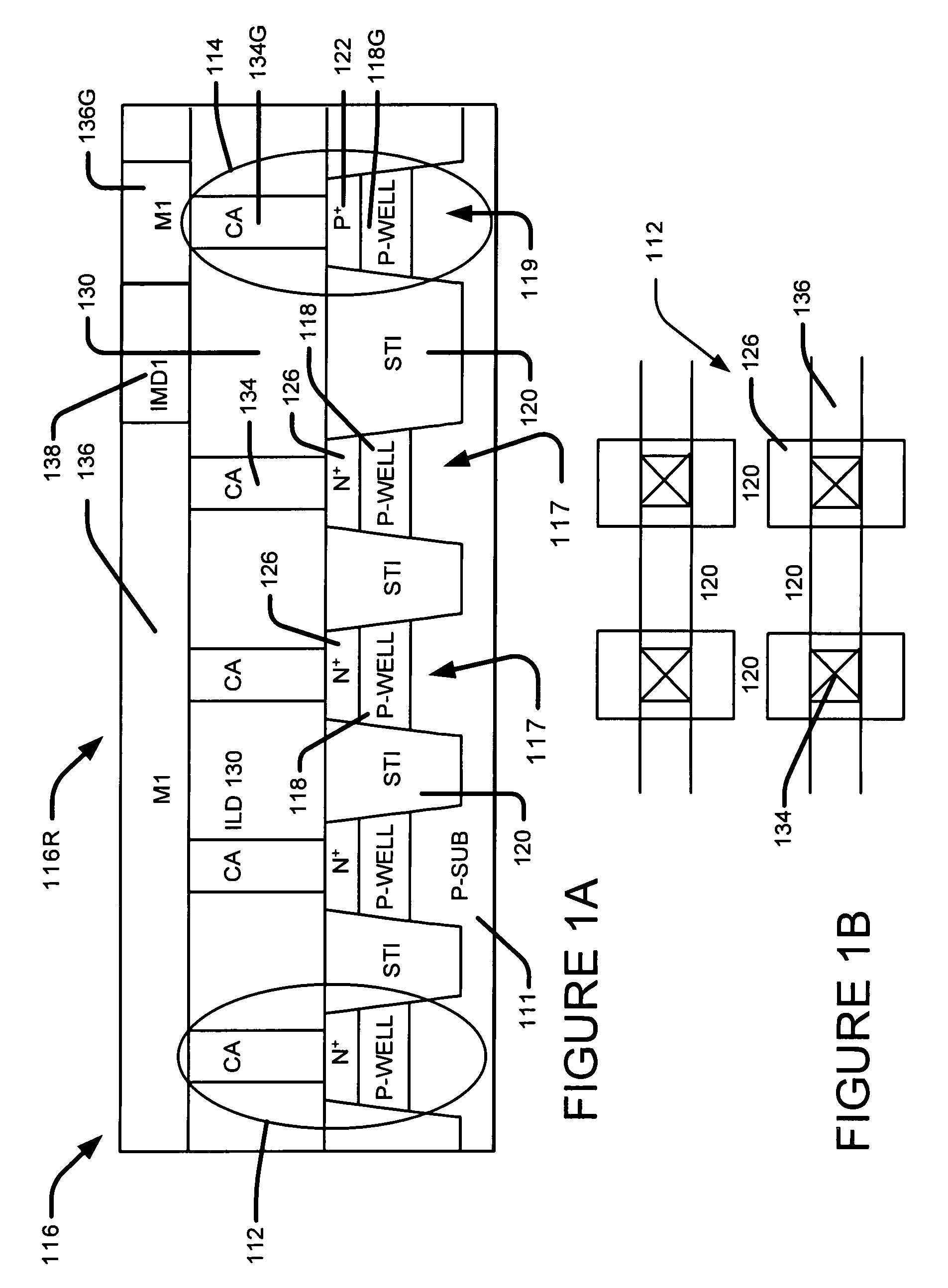

Forming ESD Diodes and BJTs Using FinFET Compatible Processes

InactiveUS20090315112A1Improved ESD currentIncrease currentSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor materials

A method of forming an electrostatic discharging (ESD) device includes forming a first and a second semiconductor fin over a substrate and adjacent to each other; epitaxially growing a semiconductor material on the first and the second semiconductor fins, wherein a first portion of the semiconductor material grown from the first semiconductor fin joins a second portion of the semiconductor material grown from the second semiconductor fin; and implanting a first end and a second end of the semiconductor material and first end portions of the first and the second semiconductor fins to form a first and a second implant region, respectively. A P-N junction is formed between the first end and the second end of the semiconductor material. The P-N junction is a junction of an ESD diode, or a junction in an NPN or a PNP BJT.

Owner:TAIWAN SEMICON MFG CO LTD

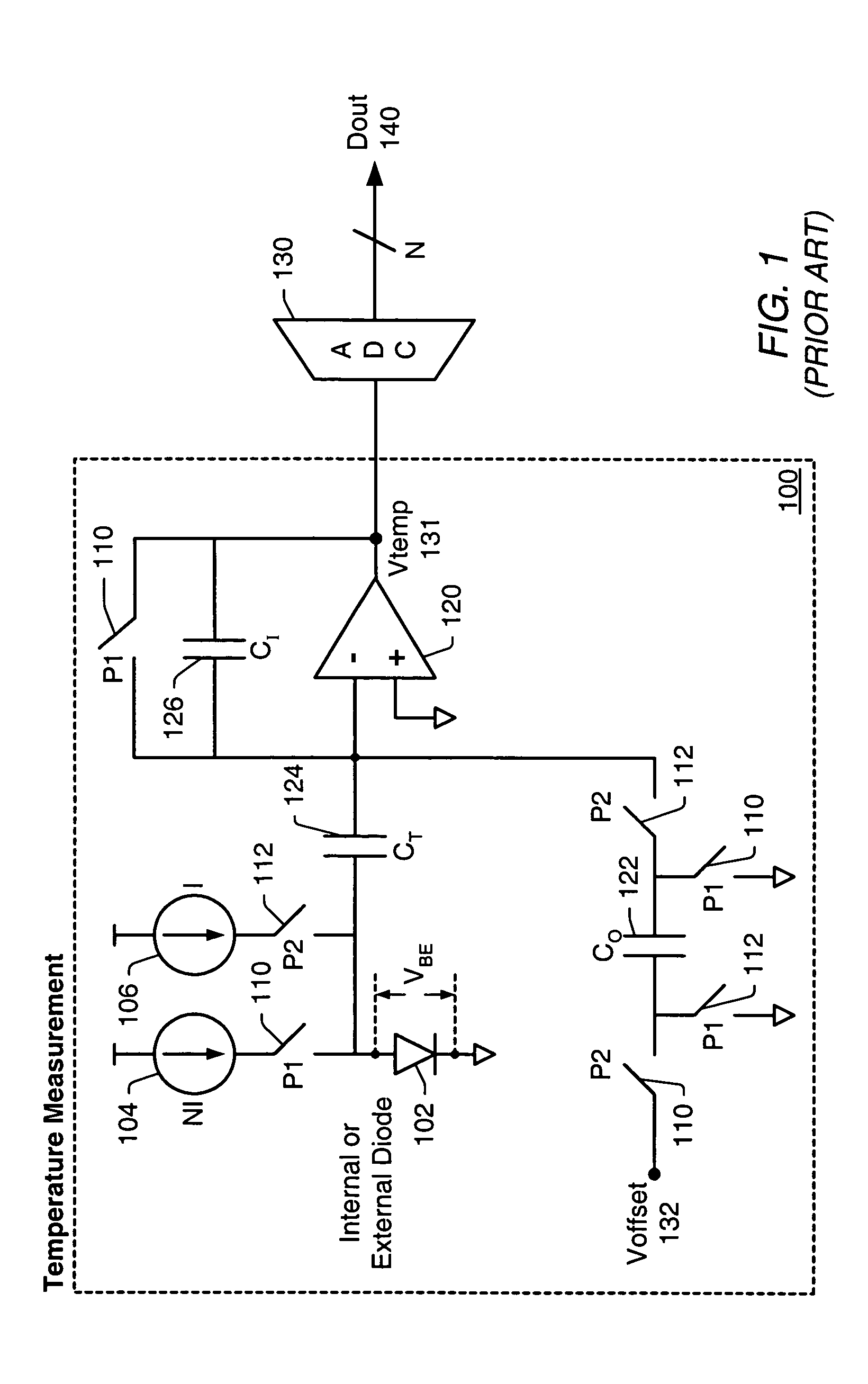

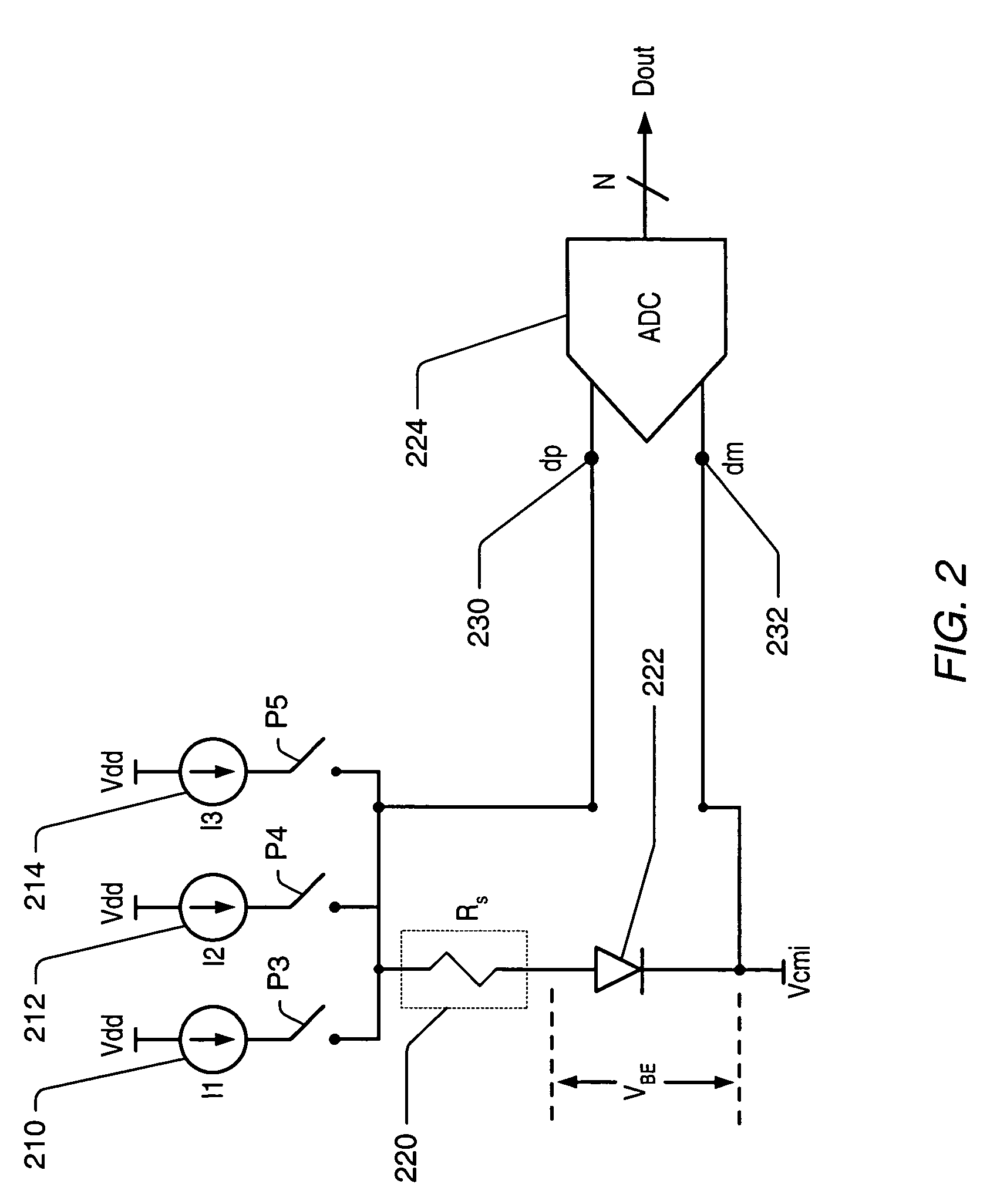

Integrated resistance cancellation in temperature measurement systems

ActiveUS7281846B2Eliminate needThermometers using electric/magnetic elementsUsing electrical meansElectrical resistance and conductanceIntegrator

A temperature measurement device may be implemented by coupling a PN-junction, which may be comprised in a diode, to an analog-to-digital converter (ADC) that comprises an integrator. Different currents may be successively applied to the diode, resulting in different VBE values across the diode. The ΔVBE values thus obtained may be successively integrated. Appropriate values for the different currents may be determined based on a set of mathematical equations, each equation relating the VBE value to the temperature of the diode, the current applied to the diode and parasitic series resistance associated with the diode. When the current sources with the appropriate values are sequentially applied to the diode and the resulting diode voltage differences are integrated by the integrator comprised in the ADC, the error in the temperature measurement caused by series resistance is canceled in the ADC, and an accurate temperature reading of the diode is obtained from the output of the ADC.

Owner:MICROCHIP TECH INC

Decoupled switched current temperature circuit with compounded DELTA V be

InactiveUS6097239AThermometers using electric/magnetic elementsElectronic switchingDelta-vAudio power amplifier

A decoupled switched current temperature circuit with compounded DELTA Vbe includes an amplifier having an inverting input with corresponding non-inverting output and a non-inverting input with a corresponding inverting output; a PN junction connected to the non-inverting input through a first input capacitor and a voltage reference circuit is connected to the inverting input through a second input capacitor; a current supply includes a low current source and a high current source; a switching device applies the high current source to the PN junction and applies the low current source to the PN junction for providing the DELTA Vbe of the PN junction to the first capacitor; a first feedback capacitor is interconnected between the inverting output and the non-inverting input and a second feedback capacitor is interconnected between the non-inverting output and inverting input of the amplifier to define the gain on each of the inputs to produce a differential voltage across the outputs representative of the temperature of the PN junction; first and second reset switching devices discharge the first and second feedback capacitors, respectively, and a multi-phase switched device alternately interchanges the connection of the first and second input capacitors with the amplifier inputs for compounding the single DELTA Vbe .

Owner:ANALOG DEVICES INC

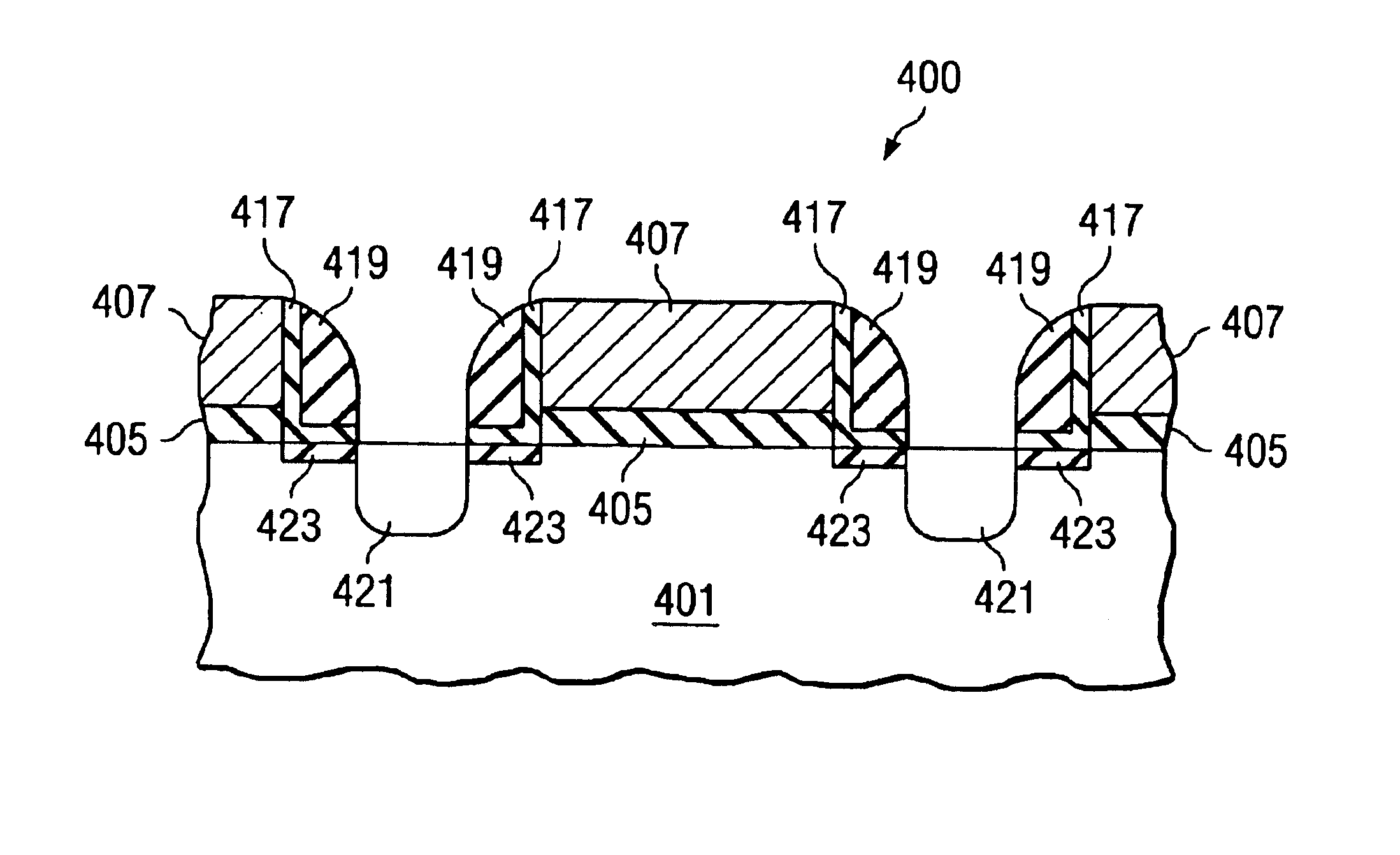

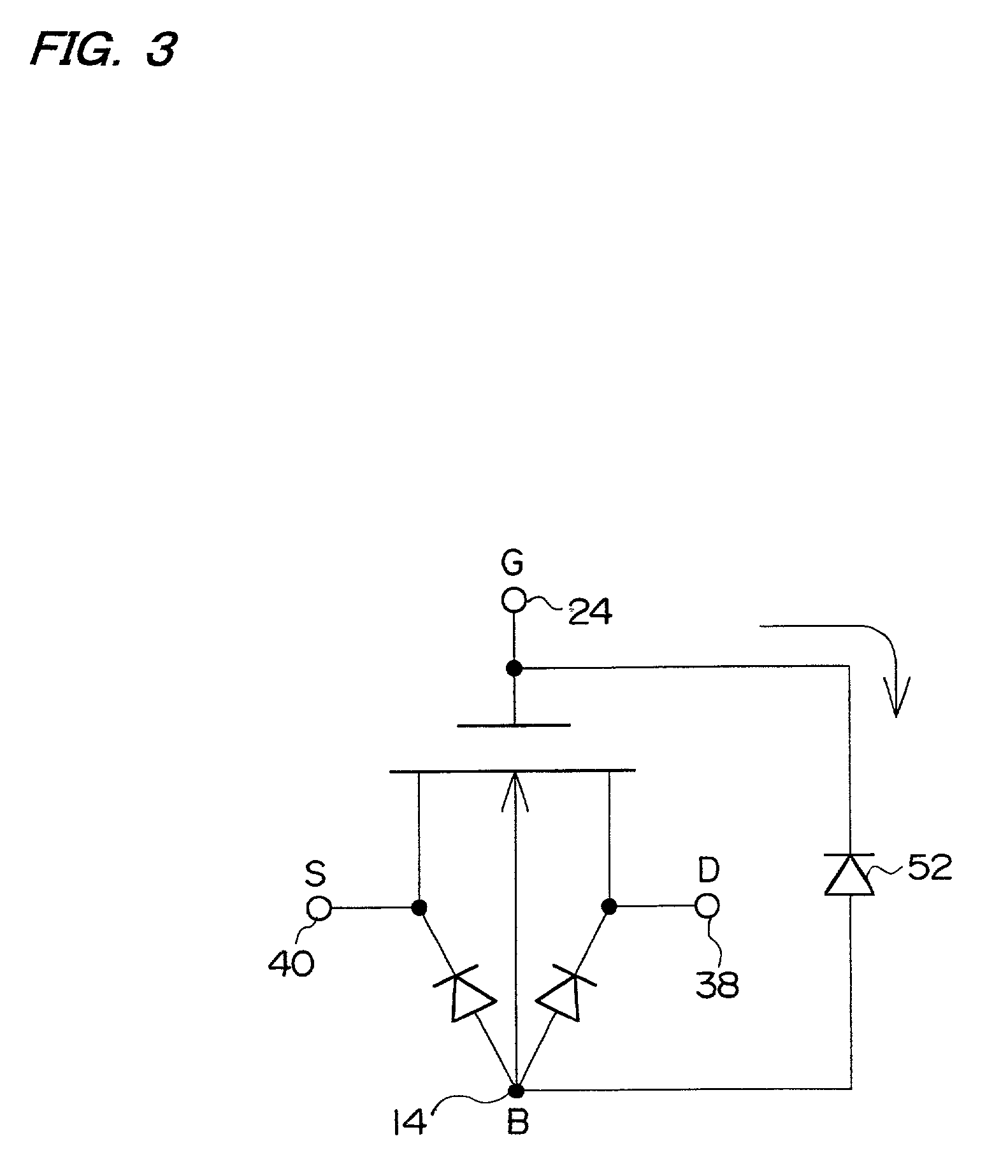

SOI-structure MIS field-effect transistor and method of manufacturing the same

A SOI-structure MOS field-effect transistor. In this transistor, agate electrode and a p- region that is a body region are placed into electrical contact by a PN junction portion. An n+-type portion of the PN junction portion is in electrical contact with the gate electrode and a p+-type portion of the PN junction portion is in electrical contact with a p- region. When a positive voltage is applied to the gate electrode, the above configuration ensures that a reverse voltage is applied to the PN junction portion, so that only a small current on the order of the reverse leakage current of the PN junction flows along the path from the gate electrode, to the PN junction portion and the body region, and into the source region.

Owner:SEIKO EPSON CORP

E-beam inspection structure for leakage analysis

InactiveUS7939348B2Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementGate dielectricVoltage contrast

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

One-chip micro-integrated optoelectronic sensor

InactiveUS6881979B2High sensitivityLaser detailsFinal product manufactureOptical reflectionPhotovoltaic detectors

This disclosure describes one-chip micro-integrated optoelectronic sensors and methods for fabricating and using the same. The sensors may include an optical emission source, optical filter and a photodetector fabricated on the same transparent substrate using the same technological processes. Optical emission may occur when a bias voltage is applied across a metal-insulator-semiconductor Schottky contact or a p-n junction. The photodetector may be a Schottky contact or a p-n junction in a semiconductor. Some sensors can be fabricated on optically transparent substrate and employ back-side illumination. In the other sensors provided, the substrate is not transparent and emission occurs from the edge of a p-n junction or through a transparent electrode. The sensors may be used to measure optical absorption, optical reflection, scattering or fluorescence. The sensors may be fabricated and operated to provide a selected spectrum of light emitted and a multi-quantum well heterostructure may be fabricated to filter light reaching the photodetector.

Owner:HOUSTON UNIV OF

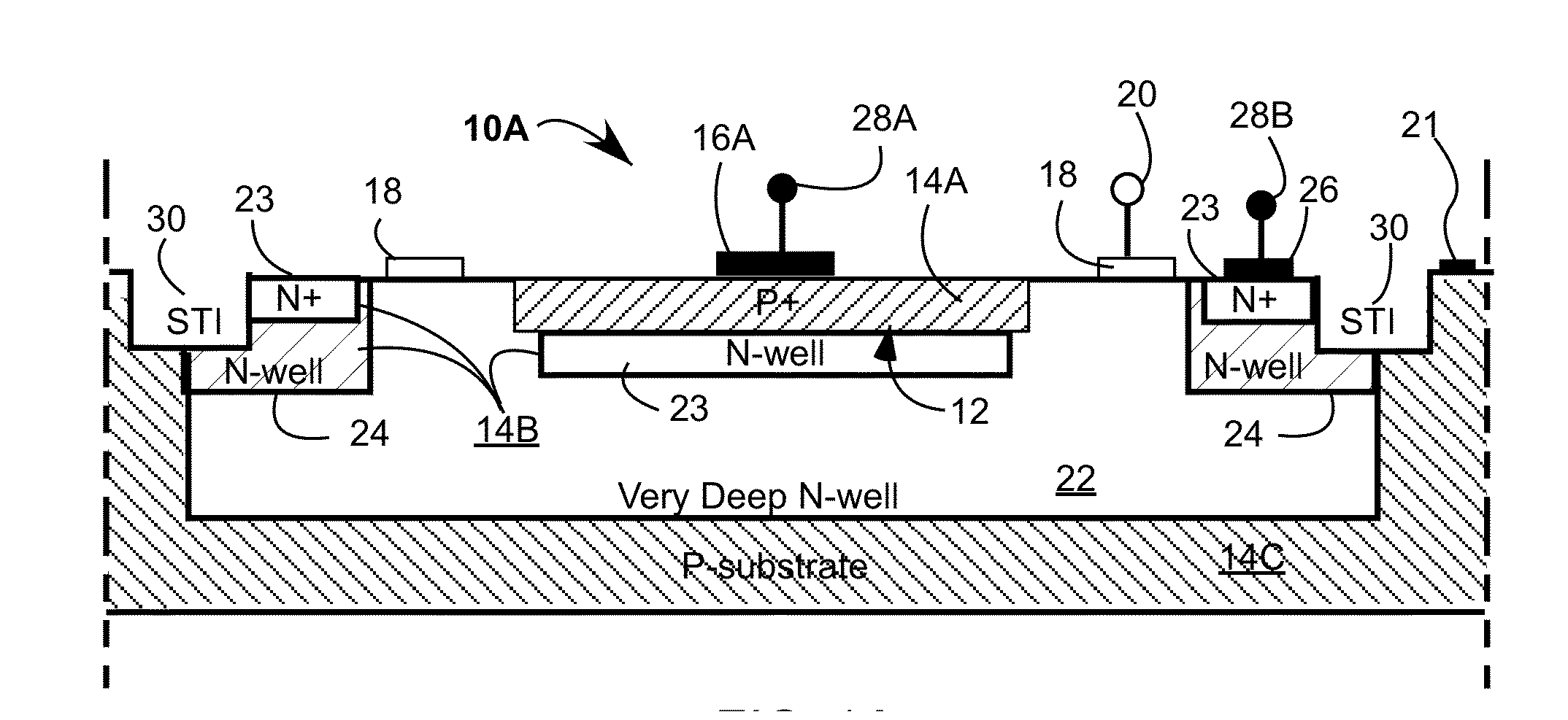

Clamped Avalanche Photodiode

ActiveUS20160218236A1Solid-state devicesRadiation controlled devicesP–n junctionCondensed matter physics

An avalanche photodiode device operated in Geiger-mode, the device comprising a P-N junction formed on a substrate with a first semiconductor region and a second semiconductor region with an anode and cathode. The device further comprising a third semiconductor region, the third semiconductor region in physical contact with the second region, not in physical contact with the first region, and being the same semiconductor-type as the first semiconductor region. Additionally comprising a diode on the second semiconductor region and having a turn-on voltage than the P-N junction.

Owner:LADARSYST INC

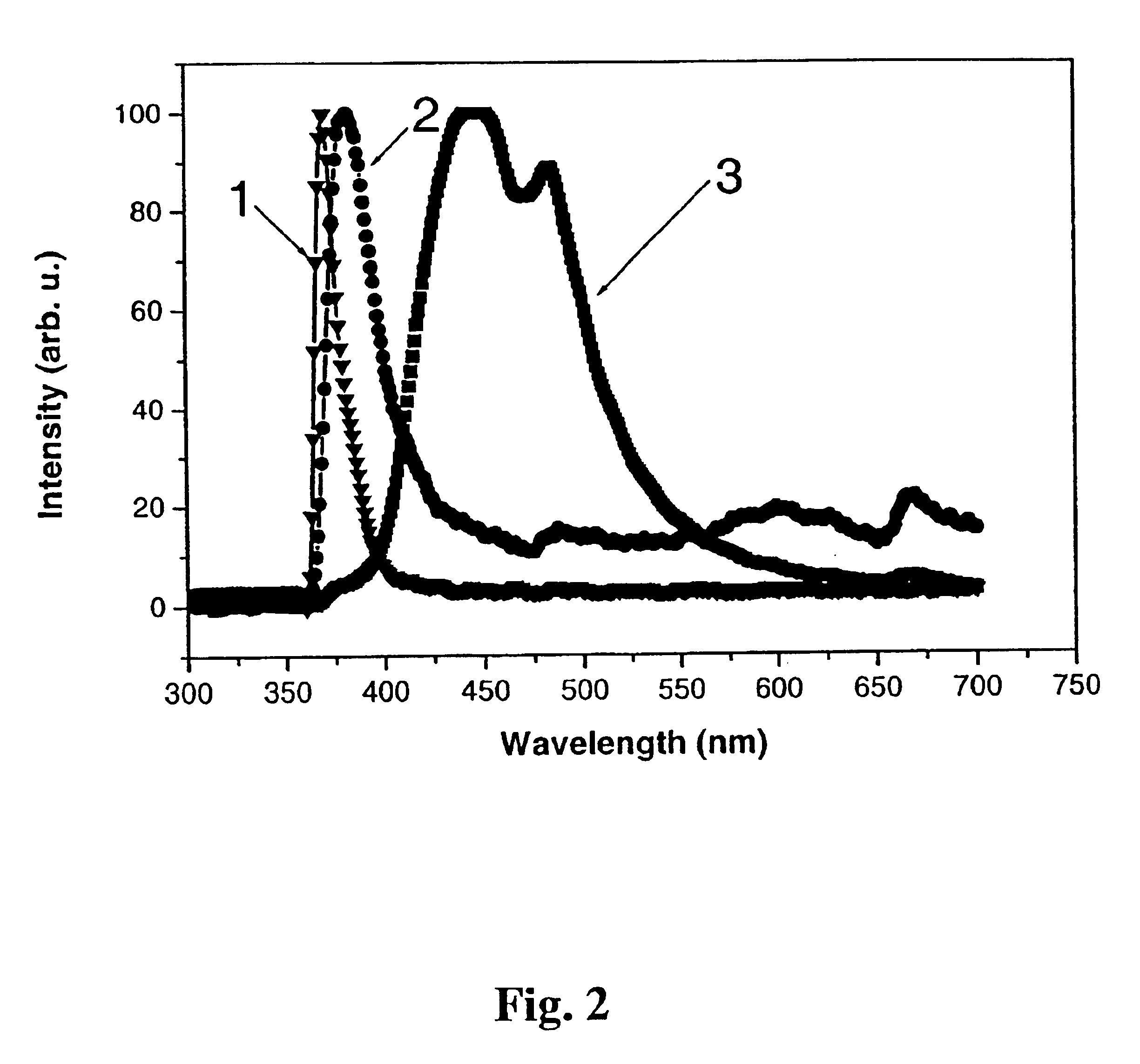

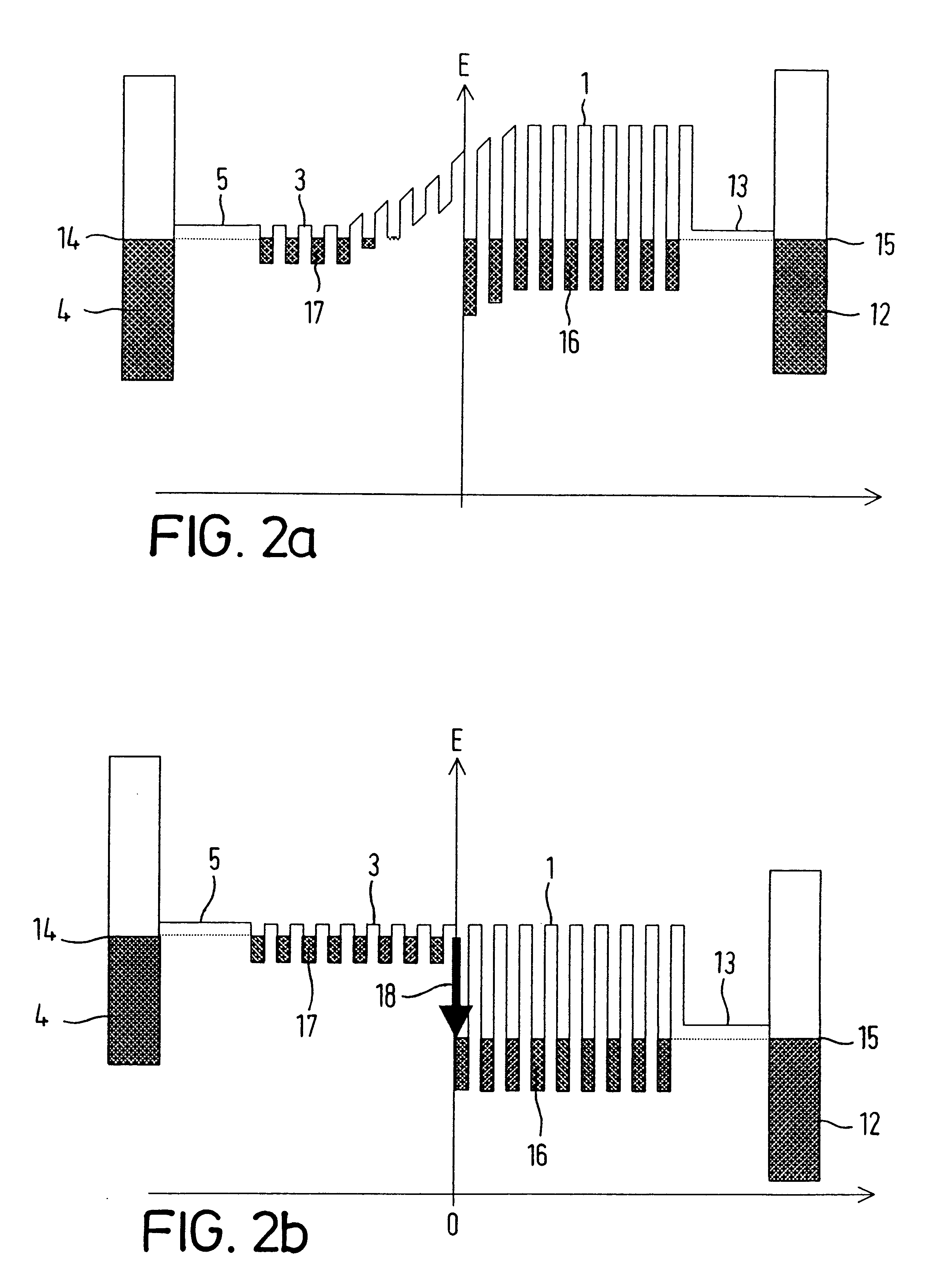

Unipolar light emitting devices based on III-nitride semiconductor superlattices

InactiveUS6455870B1Laser detailsSemiconductor/solid-state device manufacturingElectron holeP–n junction

The fabrication of unipolar light emitting devices (ULEDs) based on III-nitride semiconductors is disclosed using an effective "p-n junction" between two n-type III-nitride semiconductor superlattices. Such a device works like a usual light emitting diode at forward bias but the radiation arises not due to recombination of electrons and holes but due to electron transitions from a shallow sub-band superlattice into a deep sub-band superlattice.

Owner:ARIMA OPTOELECTRONICS

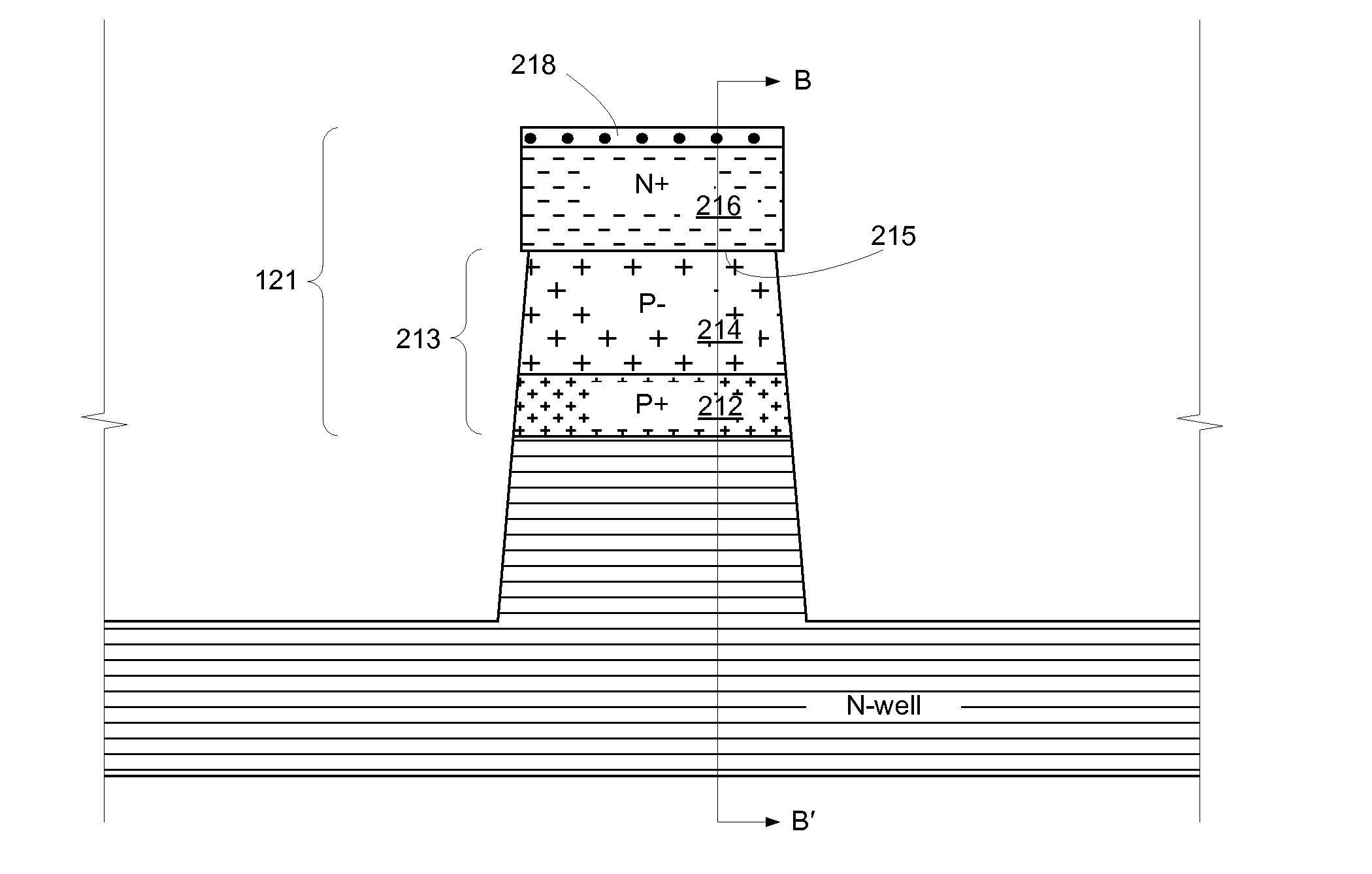

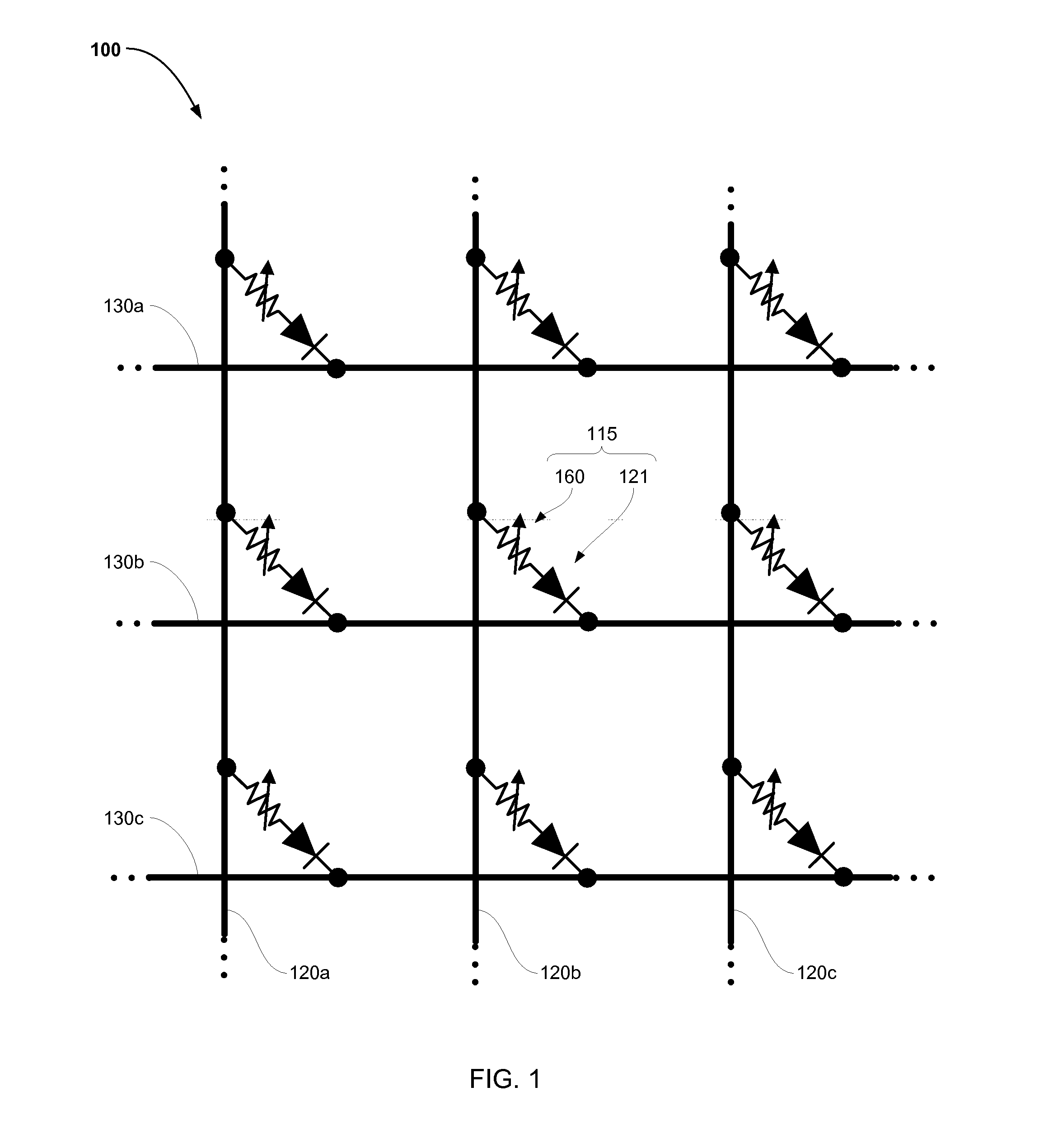

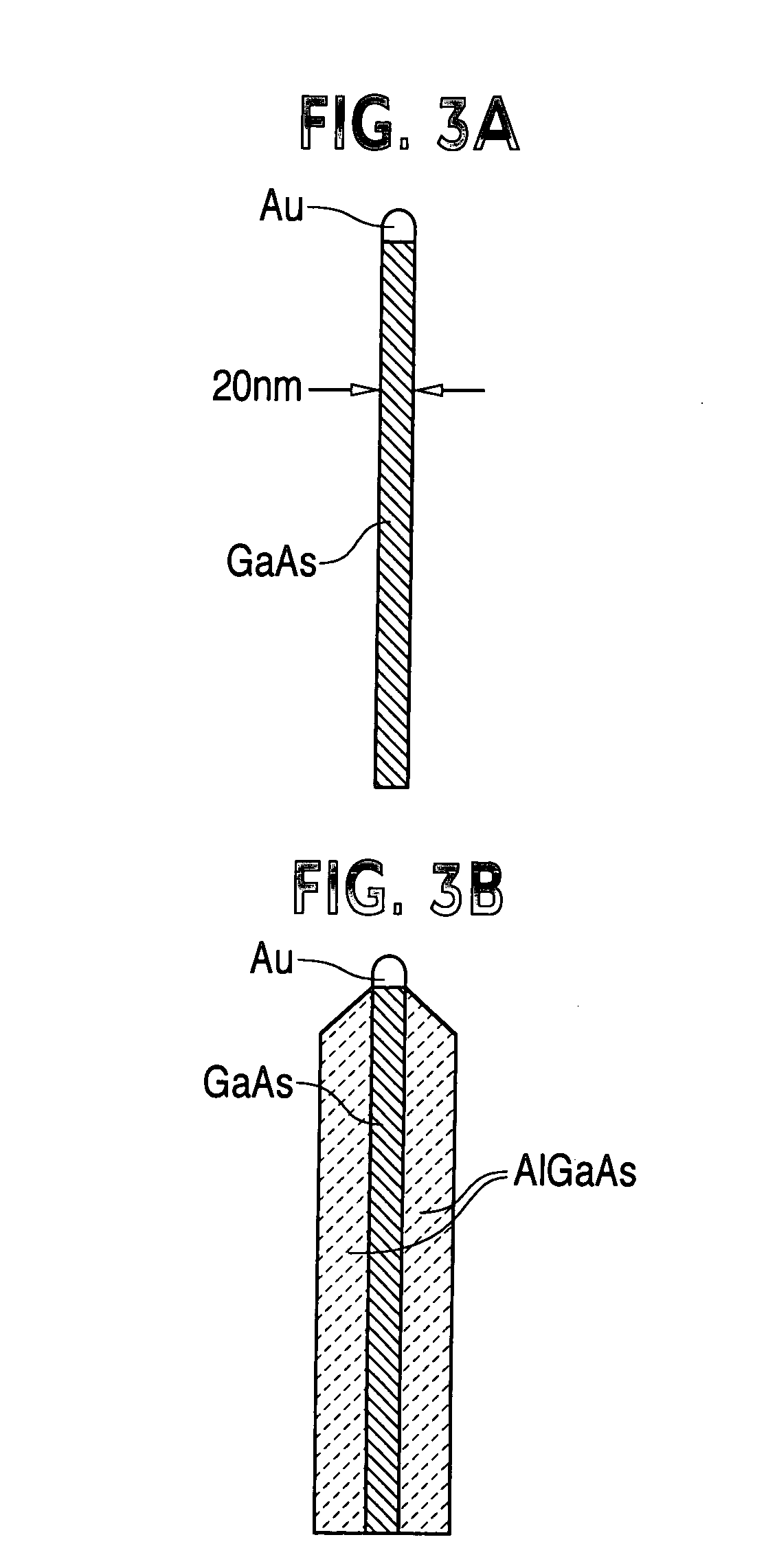

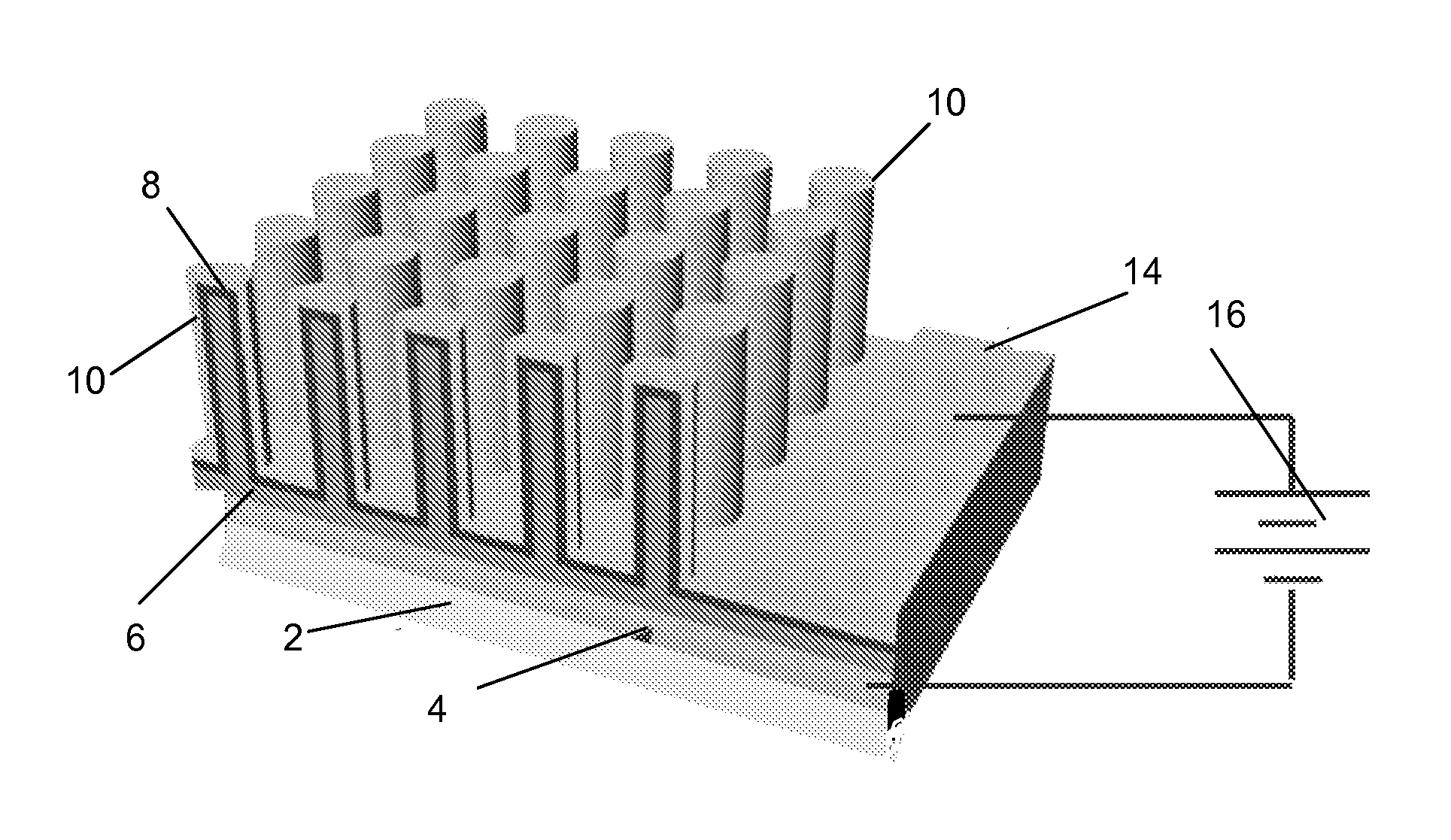

Nanowire Array-Based Light Emitting Diodes and Lasers

InactiveUS20110163292A1Reduce the lasing thresholdImprove efficiencyMaterial nanotechnologySemiconductor/solid-state device manufacturingQuantum wellP–n junction

Semiconductor nanowire arrays are used to replace the conventional planar layered construction for fabrication of LEDs and laser diodes. The nanowire arrays are formed from III-V or II-VI compound semiconductors on a conducting substrate. For fabrication of the device, an electrode layer is deposited on the substrate, a core material of one of a p-type and n-type compound semiconductor material is formed on top of the electrode as a planar base with a plurality of nanowires extending substantially vertically therefrom. A shell material of the other of the p-type and n-type compound semiconductor material is formed over an outer surface of the core material so that a p-n junction is formed across the planar base and over each of the plurality of nanowires. An electrode coating is formed an outer surface of the shell material for providing electrical contact to a current source. Heterostructures and superlattices grown along the lengths of the nanowires allow the confinement of photons in the quantum well to enhance the efficiency and as well as color tuning.

Owner:RGT UNIV OF CALIFORNIA

Thin film photodetector, method and system

InactiveUS20070290287A1High proportionMaterial nanotechnologyThermoelectric device with peltier/seeback effectPhotodetectorCharge carrier

A photodetector, comprises a first section comprising at least one p-n junction that converts photon energy into a separate charge carrier and hole carrier; and another section of semiconductors of opposing conductivity type connected electrically in series and thermally in parallel in a heat dissipating and electric generating relationship to the cell to augment generation of electric energy of the first section.

Owner:FREEDMAN PHILIP D