Patents

Literature

25193results about "Radiation controlled devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device and manufacturing method thereof

ActiveUS20070108446A1Low resistance of wireLower resistanceTransistorElectroluminescent light sourcesAlloySilicon oxide

To provide a semiconductor device in which a defect or fault is not generated and a manufacturing method thereof even if a ZnO semiconductor film is used and a ZnO film to which an n-type or p-type impurity is added is used for a source electrode and a drain electrode. The semiconductor device includes a gate insulating film formed by using a silicon oxide film or a silicon oxynitride film over a gate electrode, an Al film or an Al alloy film over the gate insulating film, a ZnO film to which an n-type or p-type impurity is added over the Al film or the Al alloy film, and a ZnO semiconductor film over the ZnO film to which an n-type or p-type impurity is added and the gate insulating film.

Owner:SEMICON ENERGY LAB CO LTD

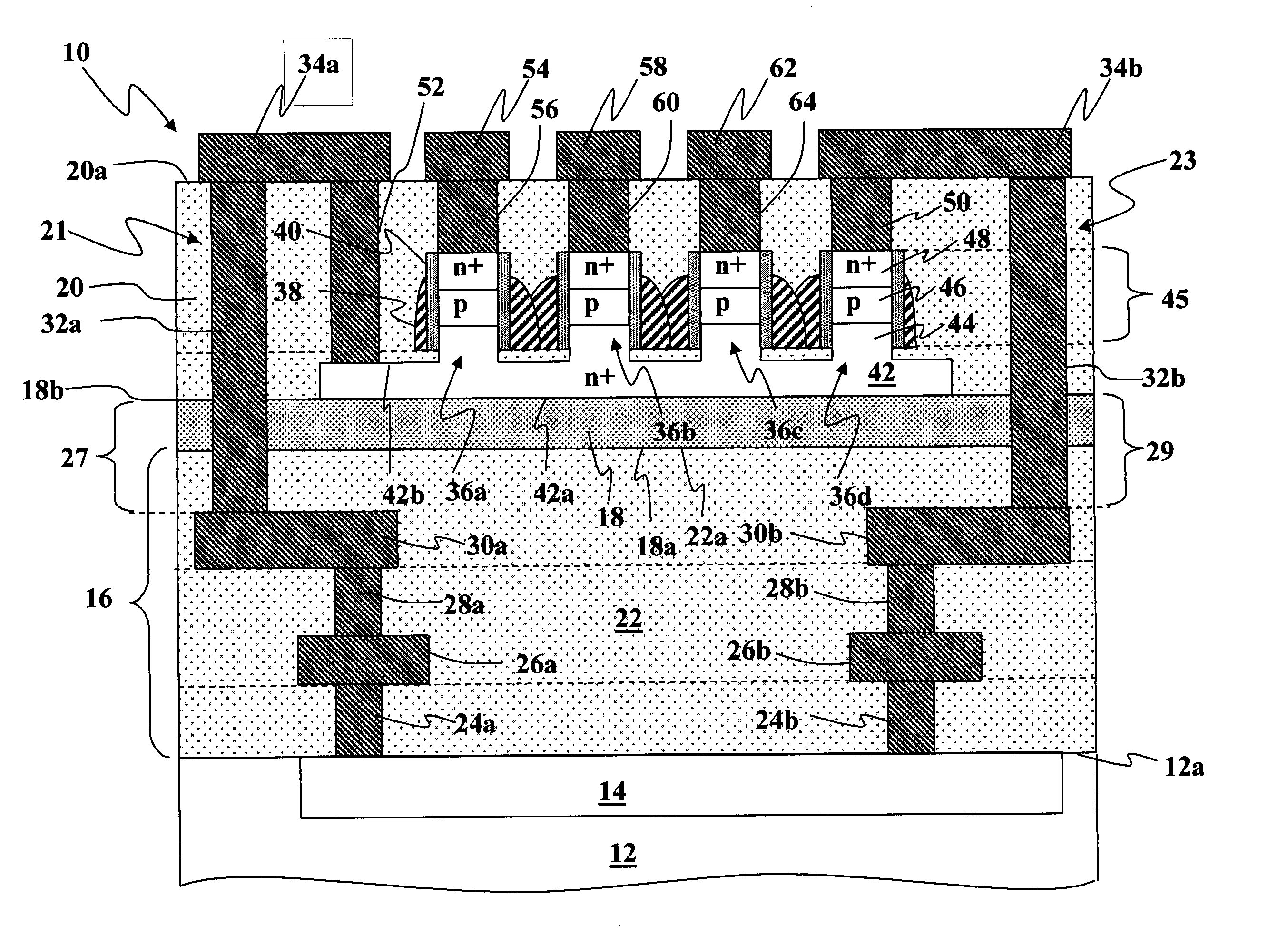

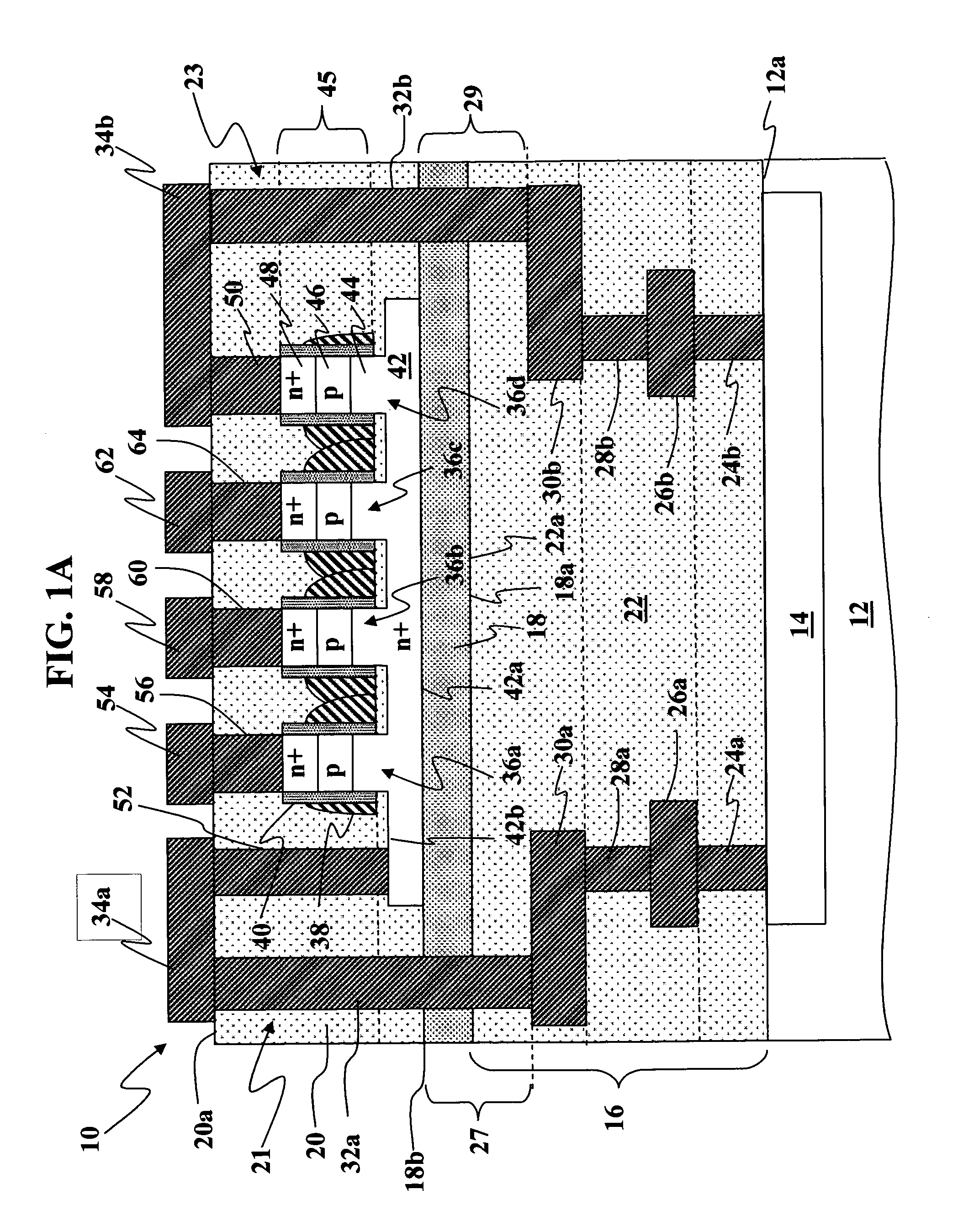

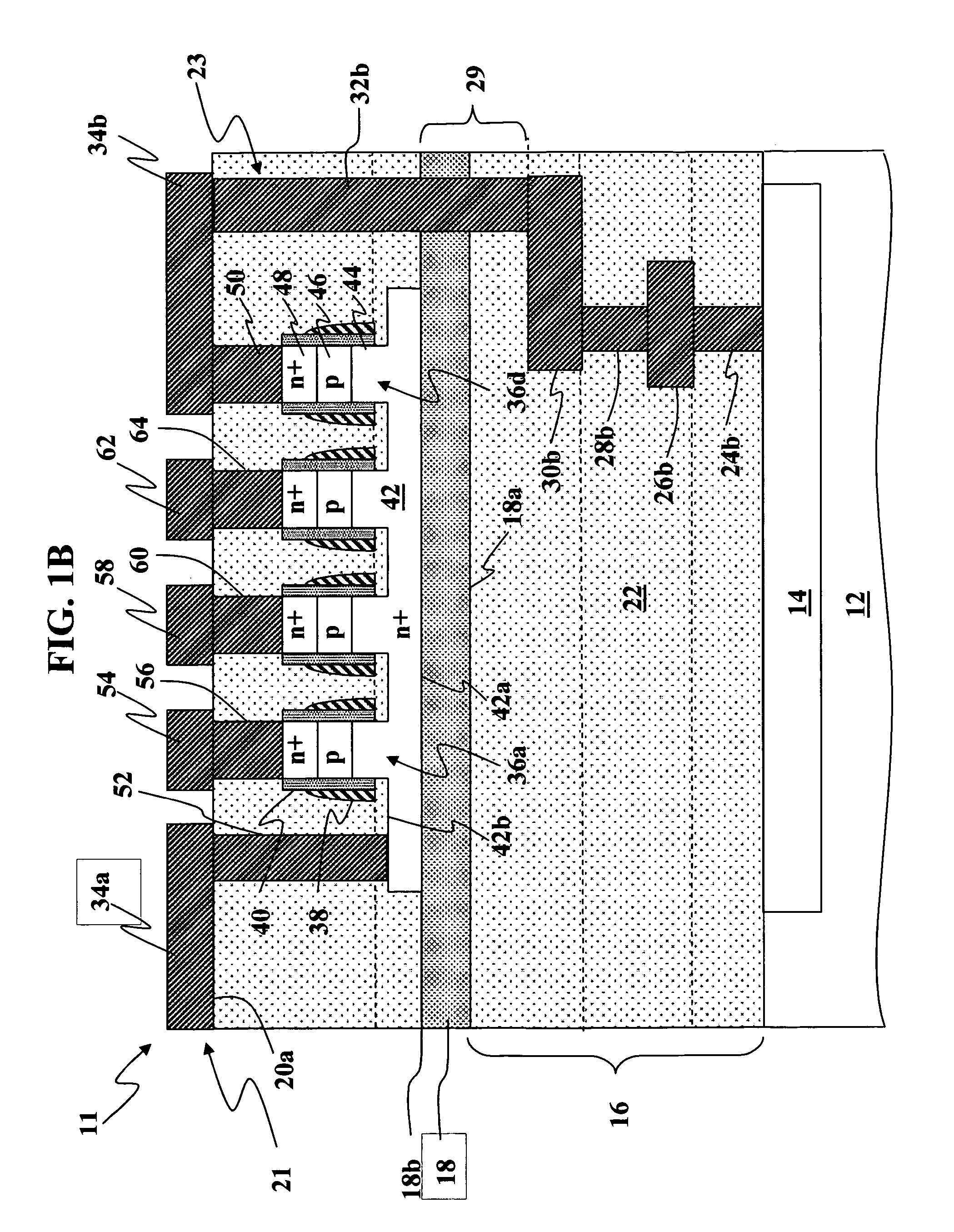

High-density three-dimensional memory cell

InactiveUS6952030B2High densityReduce the overall heightTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

A three dimensional monolithic memory comprising a memory cell allowing for increased density is disclosed. In the memory cell of the present invention, a bottom conductor preferably comprising tungsten is formed. Above the bottom conductor a semiconductor element preferably comprises two diode portions and an antifuse. Above the semiconductor element are additional conductors and semiconductor elements in multiple stones of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

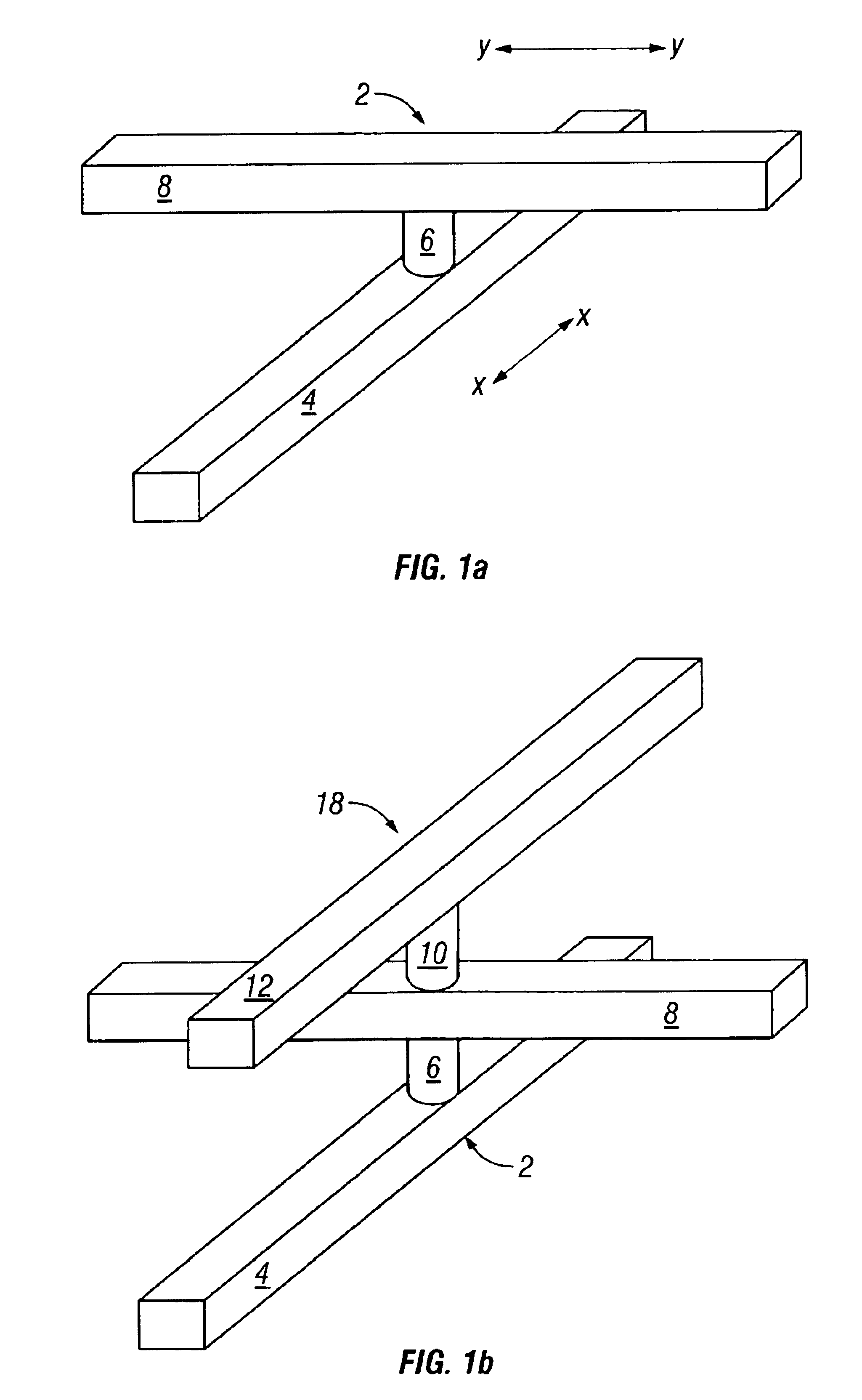

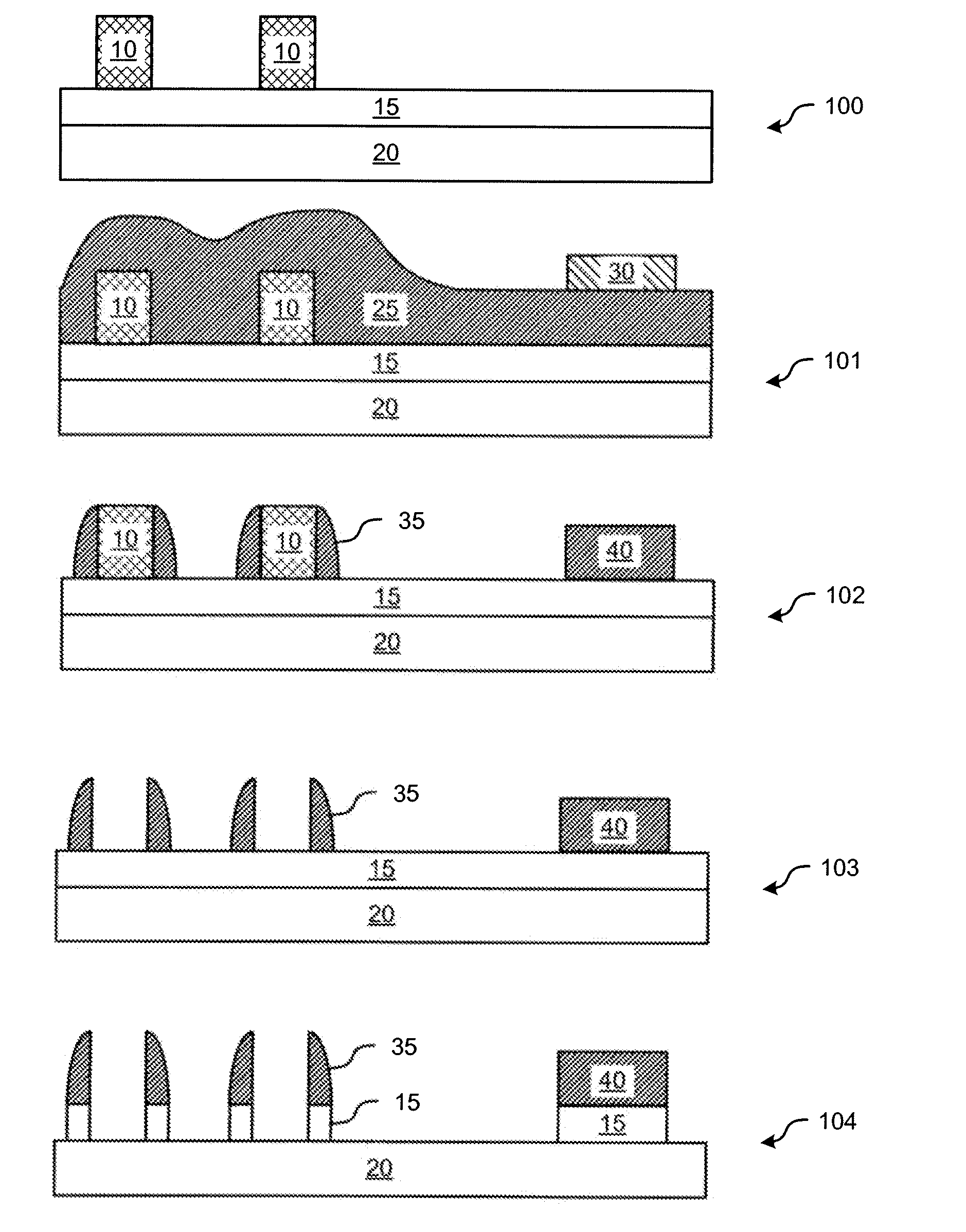

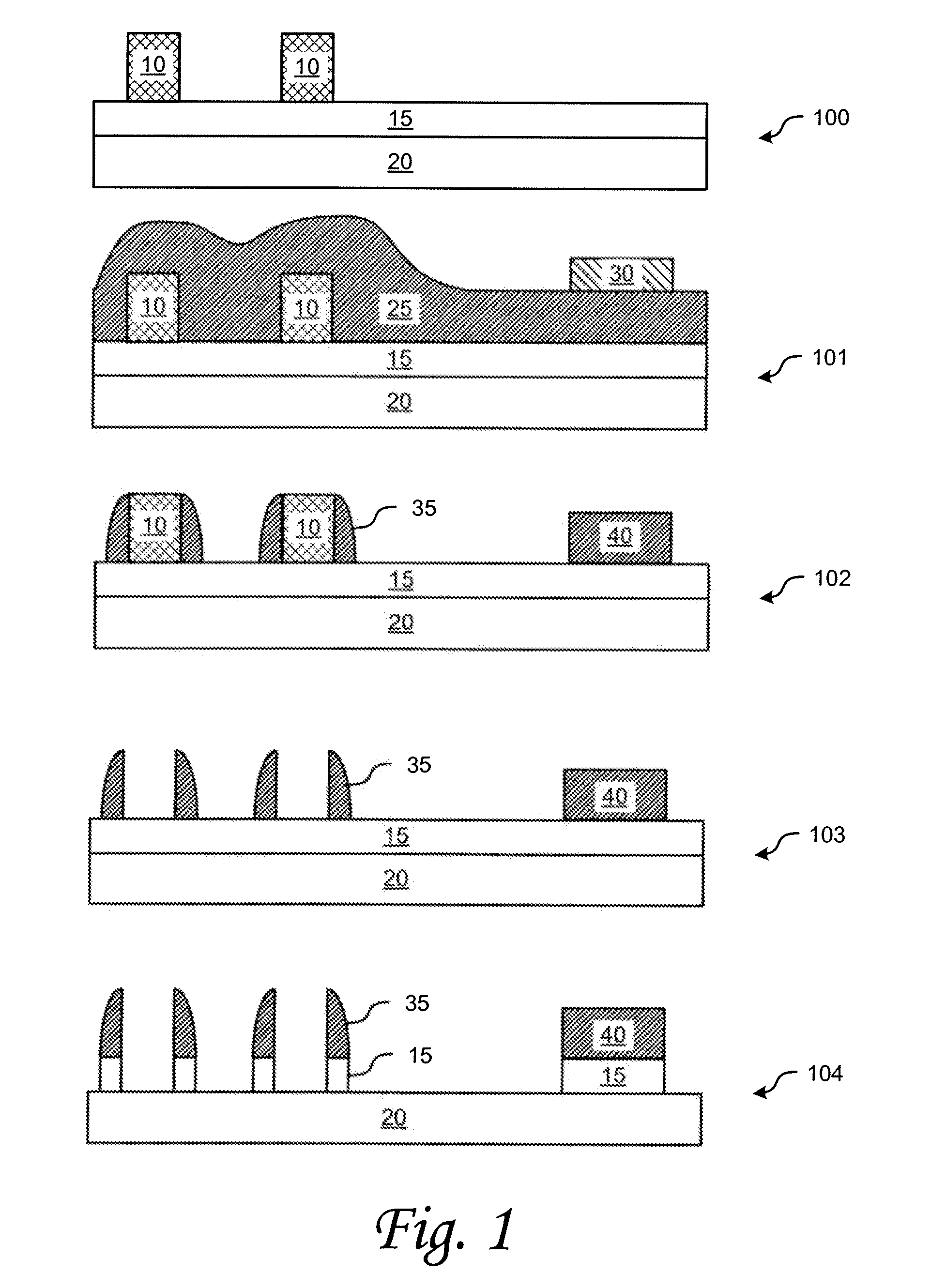

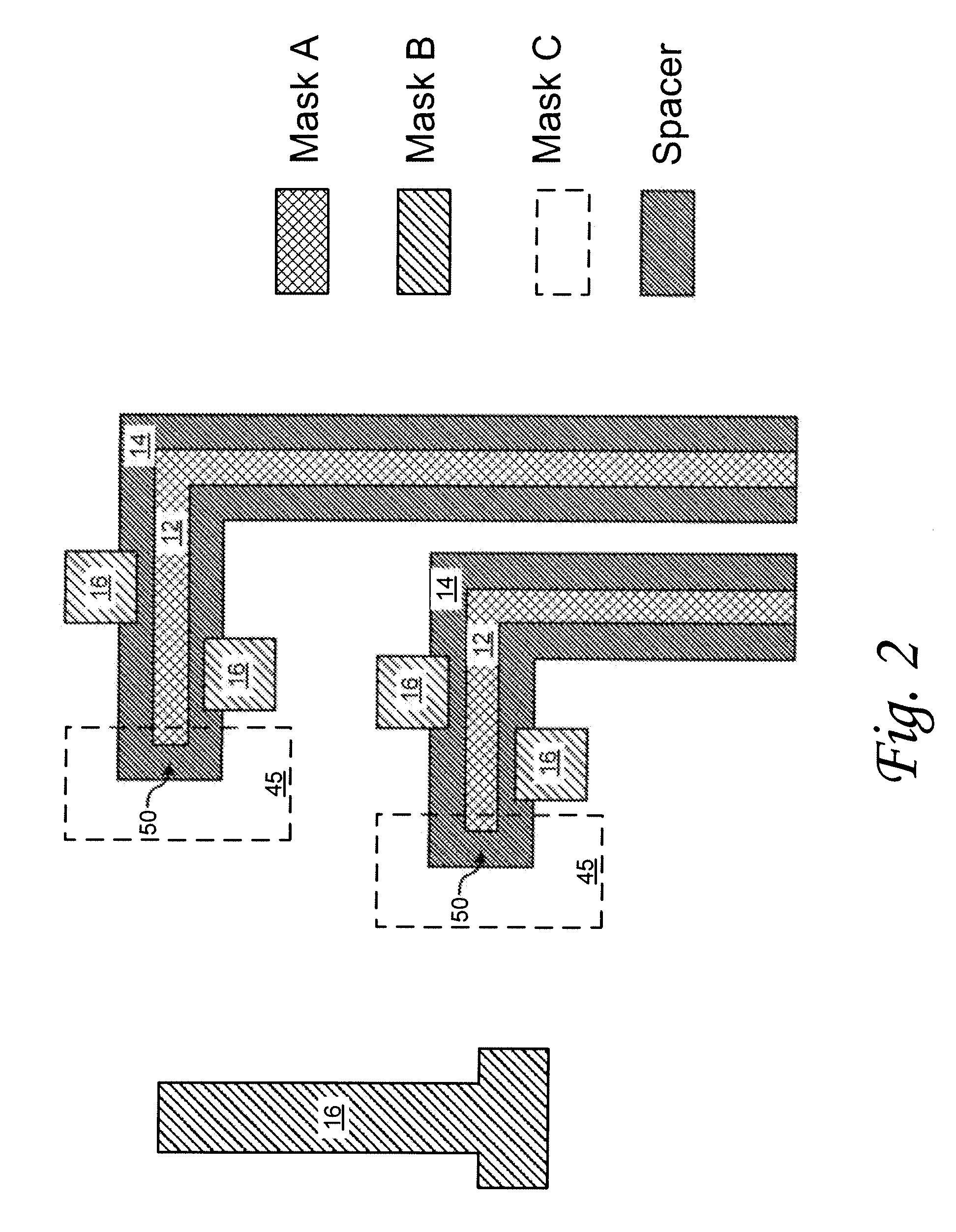

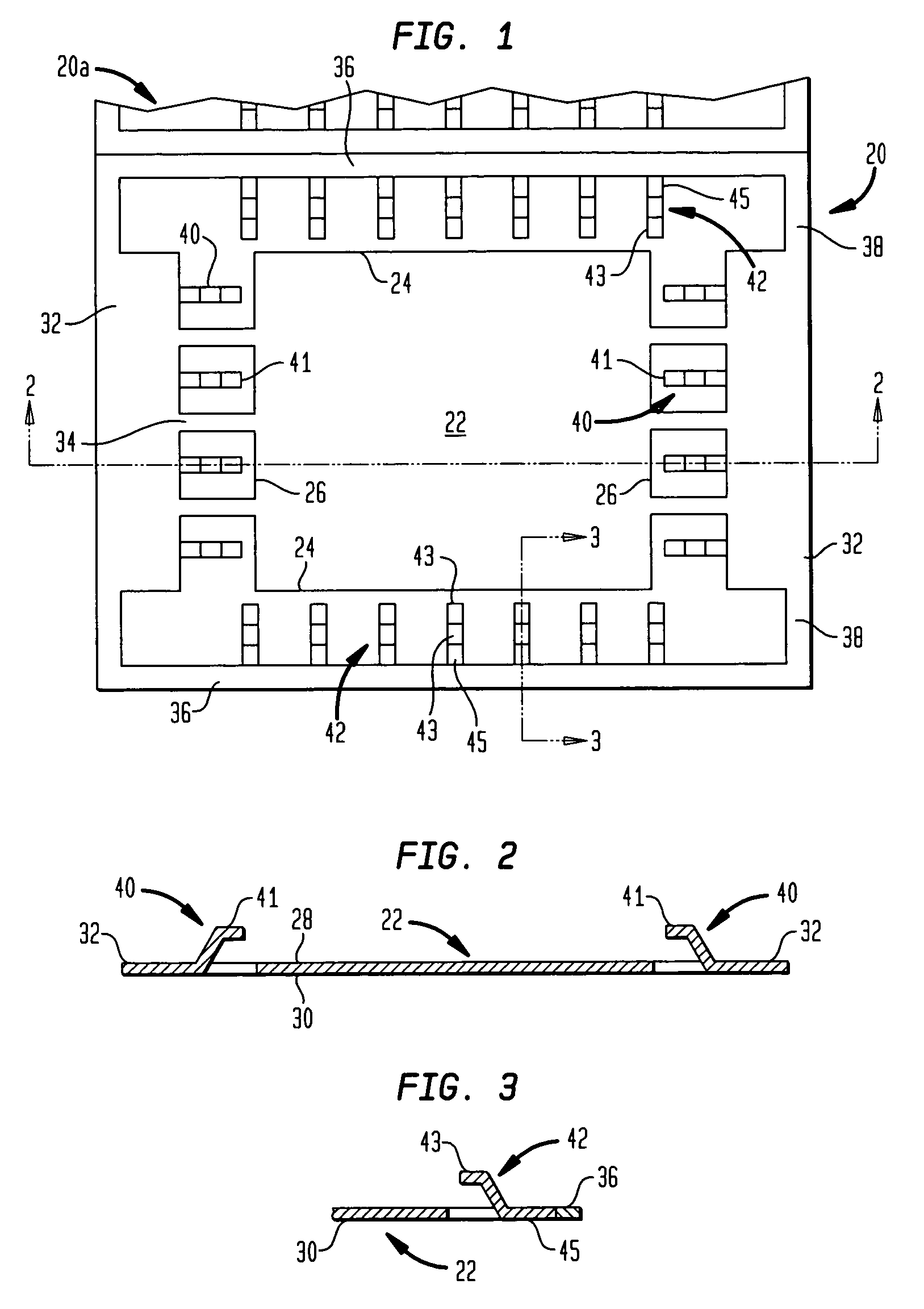

Single spacer process for multiplying pitch by a factor greater than two and related intermediate IC structures

Single spacer processes for multiplying pitch by a factor greater than two are provided. In one embodiment, n, where n≧2, tiers of stacked mandrels are formed over a substrate, each of the n tiers comprising a plurality of mandrels substantially parallel to one another. Mandrels at tier n are over and parallel to mandrels at tier n−1, and the distance between adjoining mandrels at tier n is greater than the distance between adjoining mandrels at tier n−1. Spacers are simultaneously formed on sidewalls of the mandrels. Exposed portions of the mandrels are etched away and a pattern of lines defined by the spacers is transferred to the substrate.

Owner:MICRON TECH INC

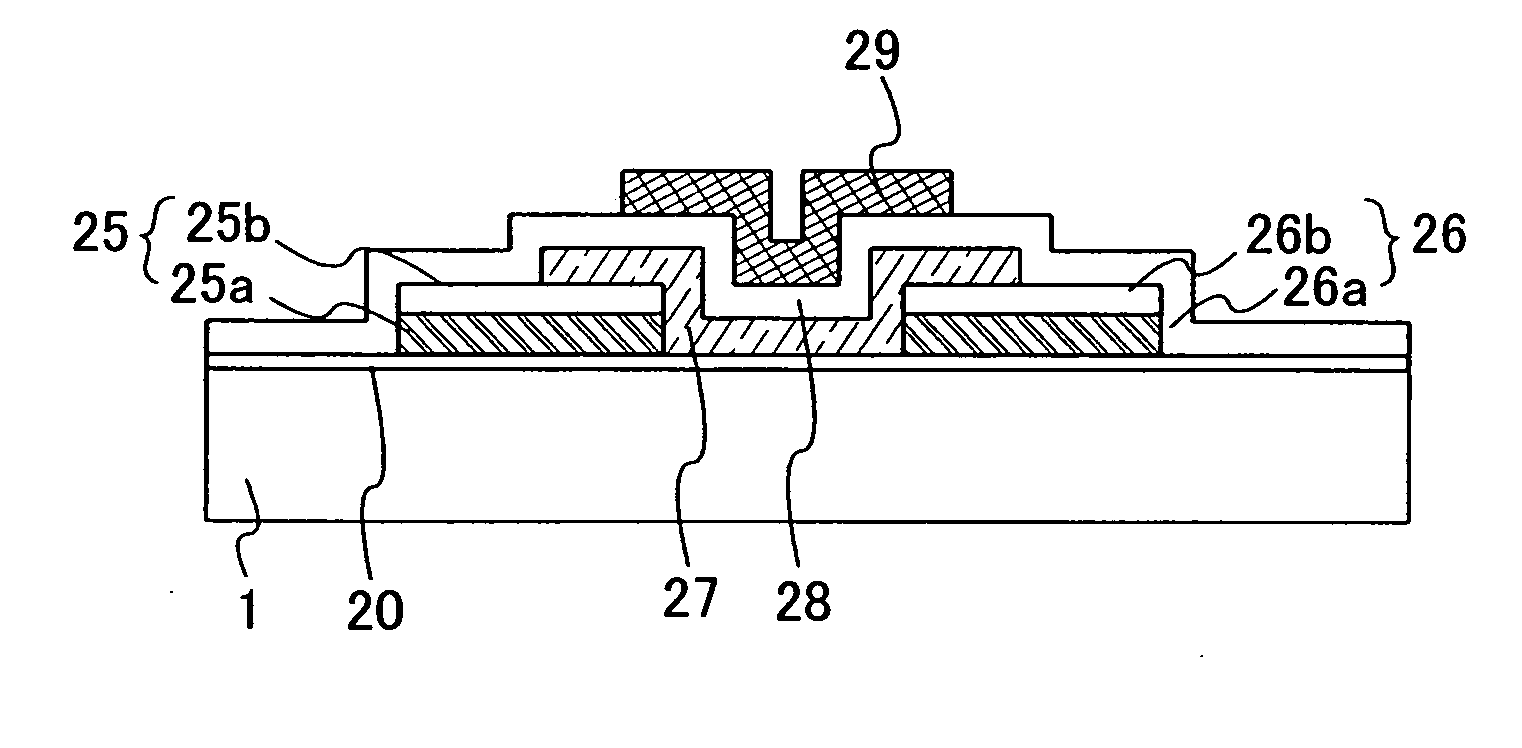

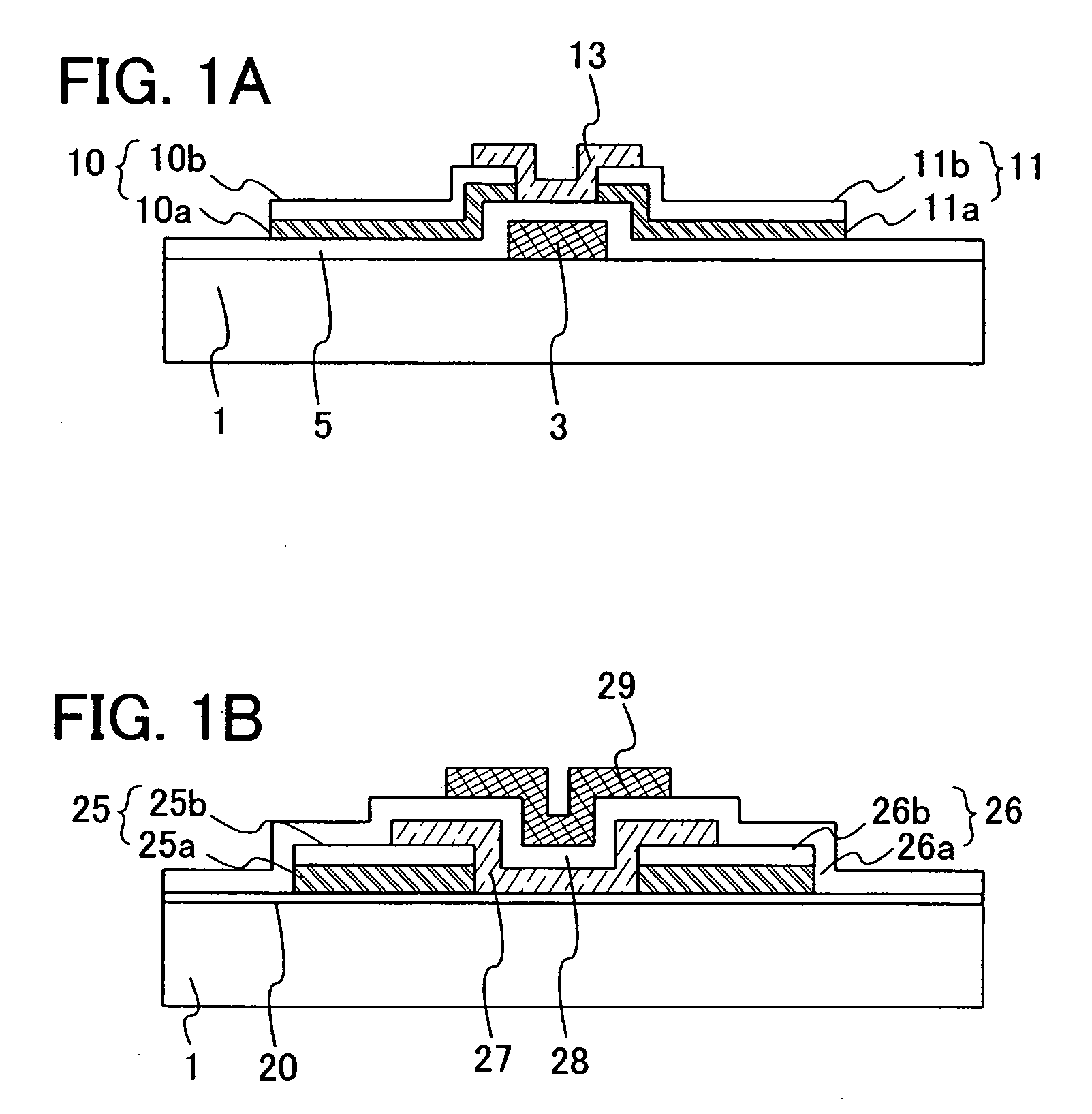

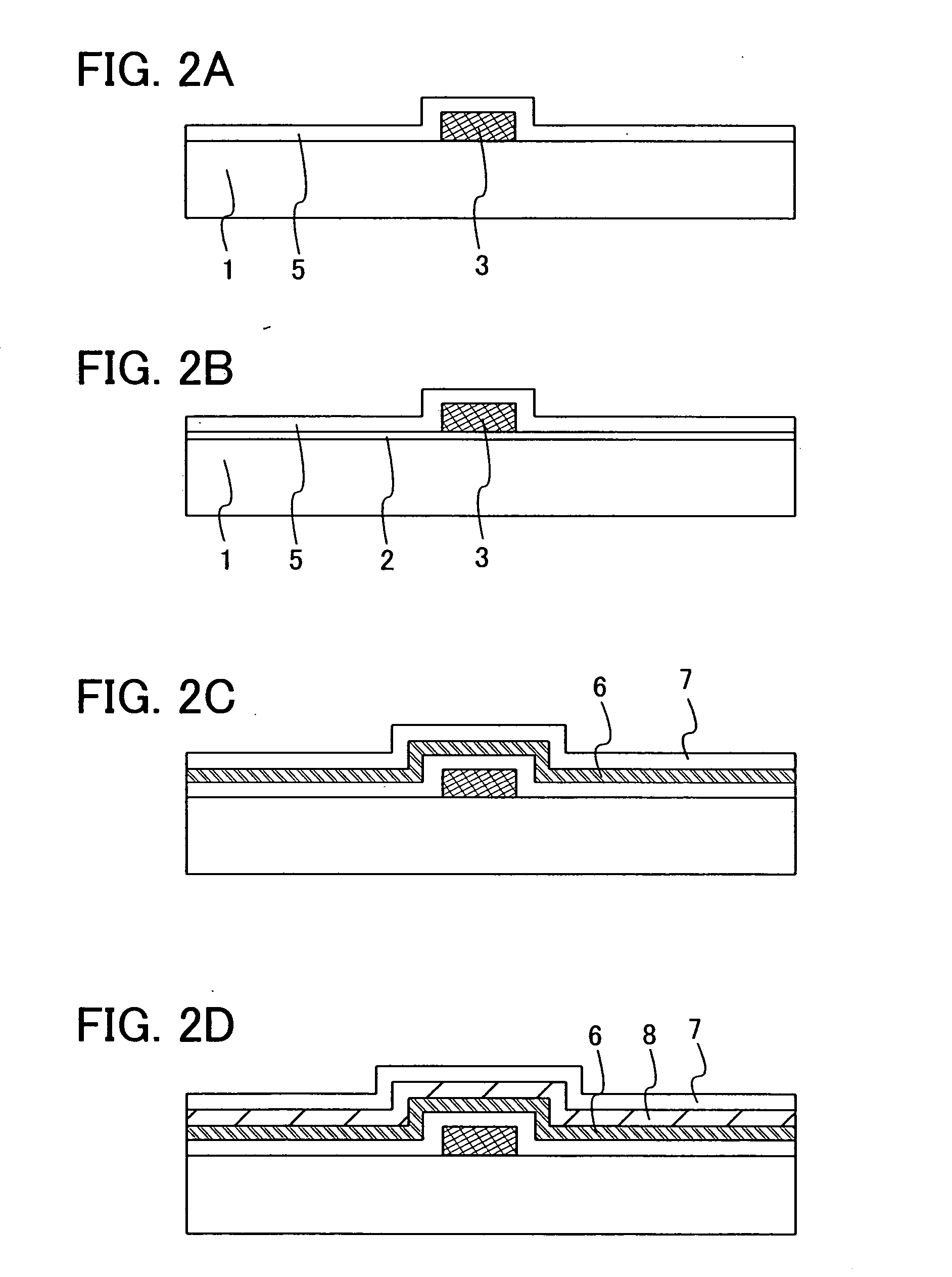

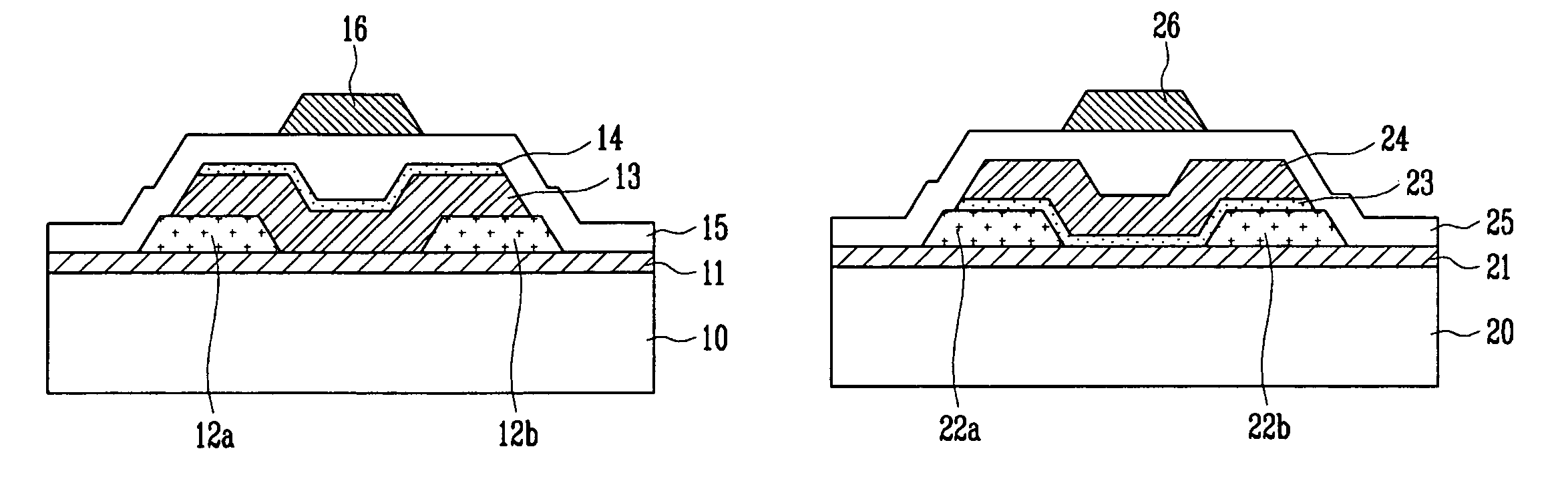

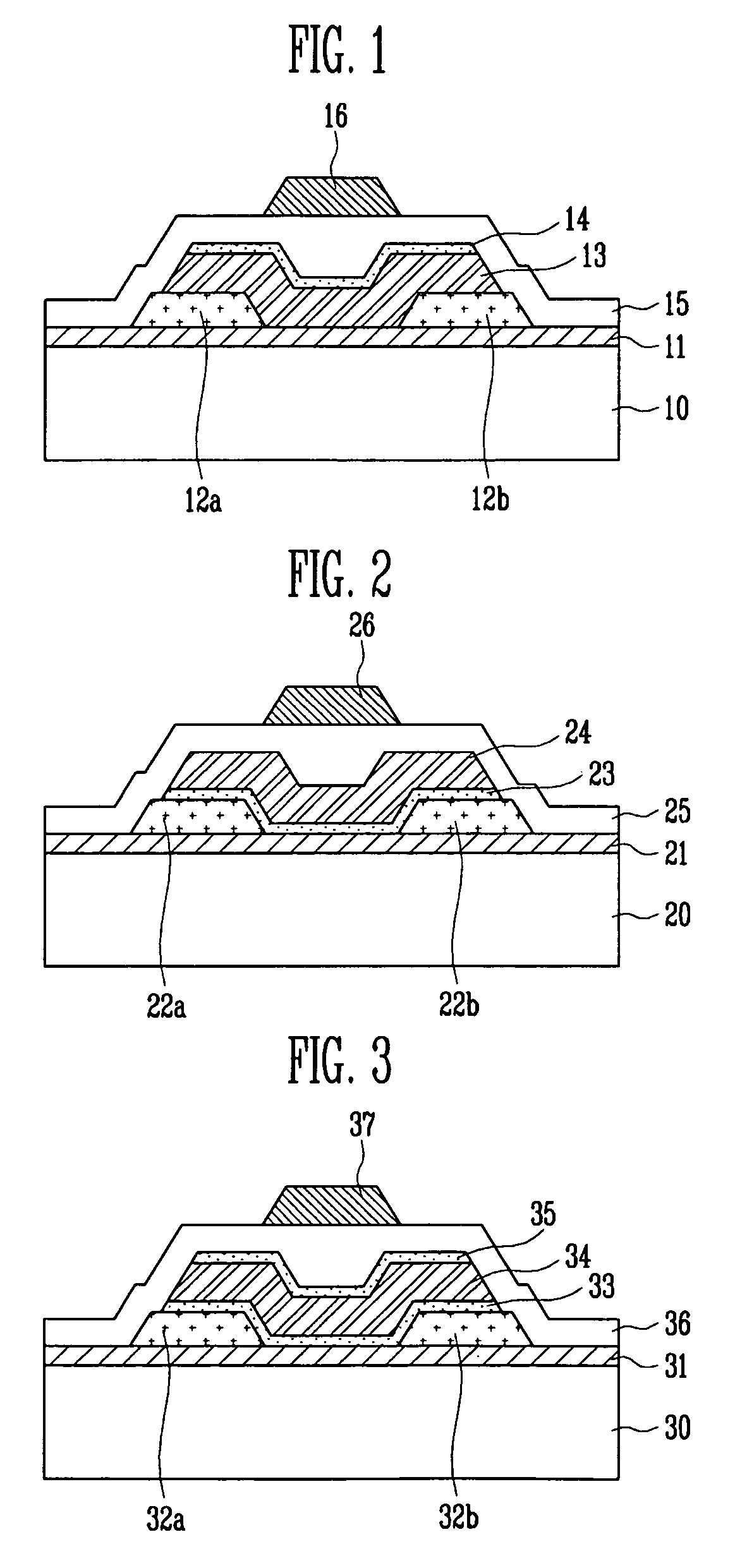

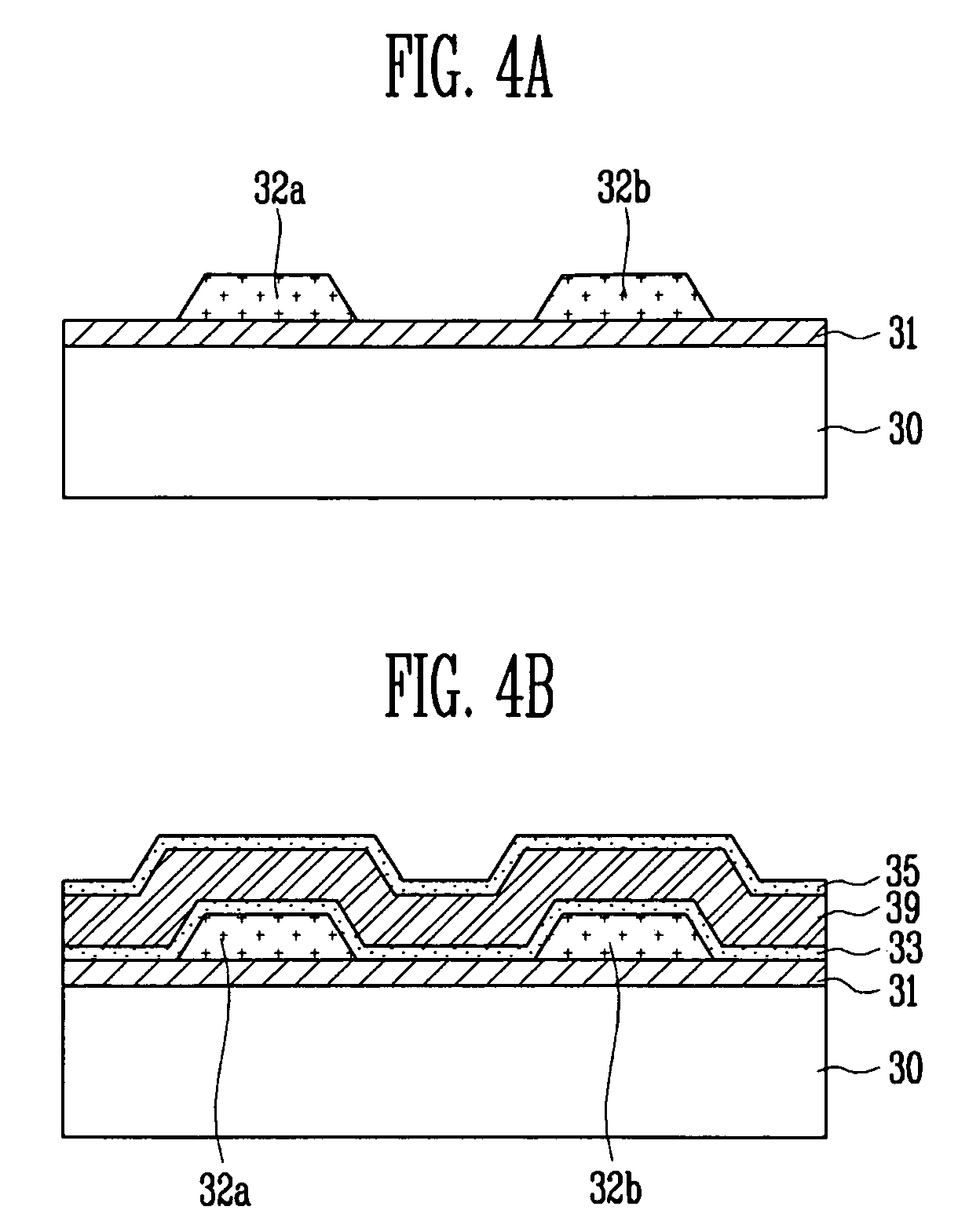

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS7994500B2Improve featuresAvoid chargingSemiconductor/solid-state device detailsSolid-state devicesTrappingOxide thin-film transistor

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

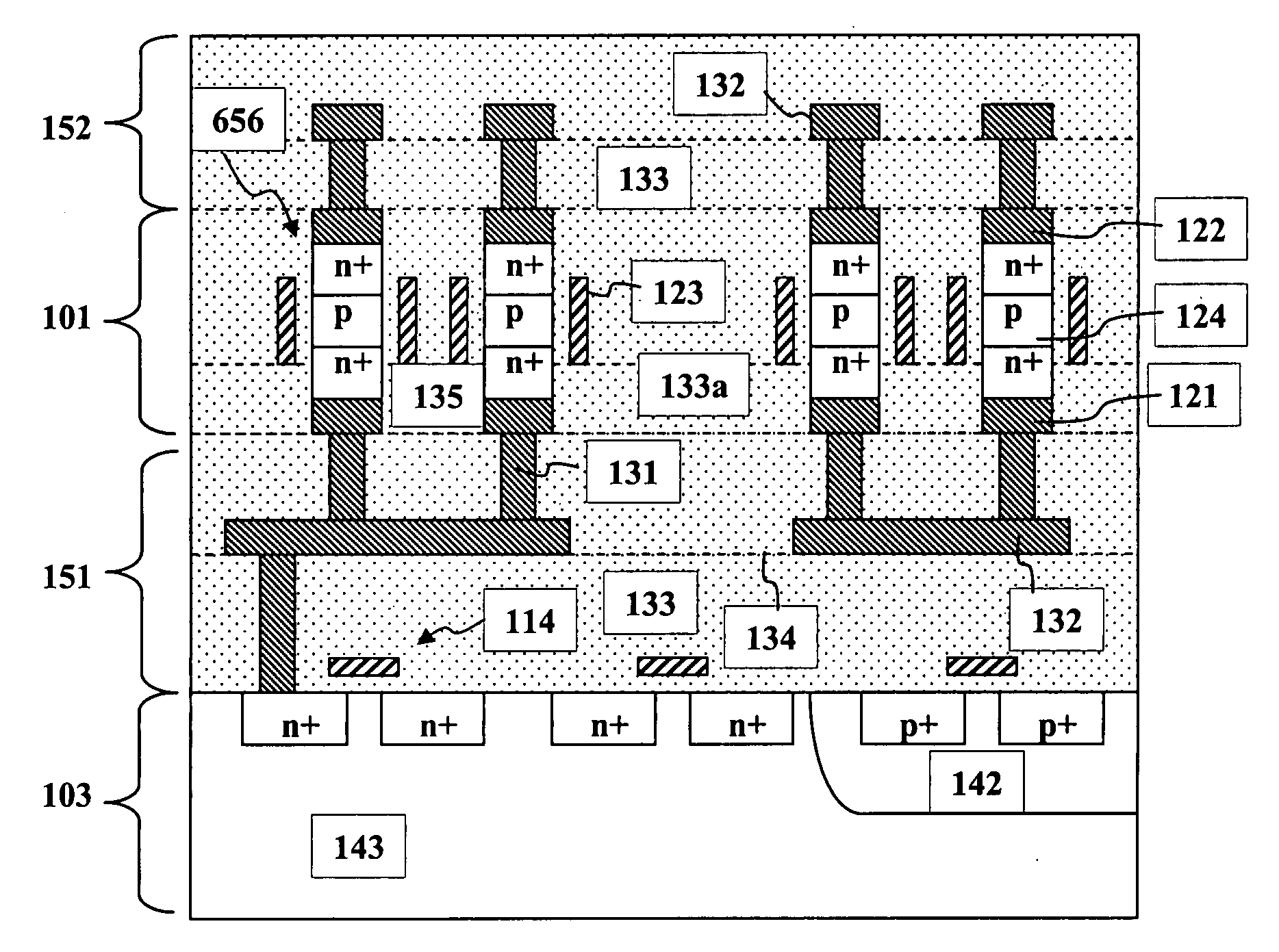

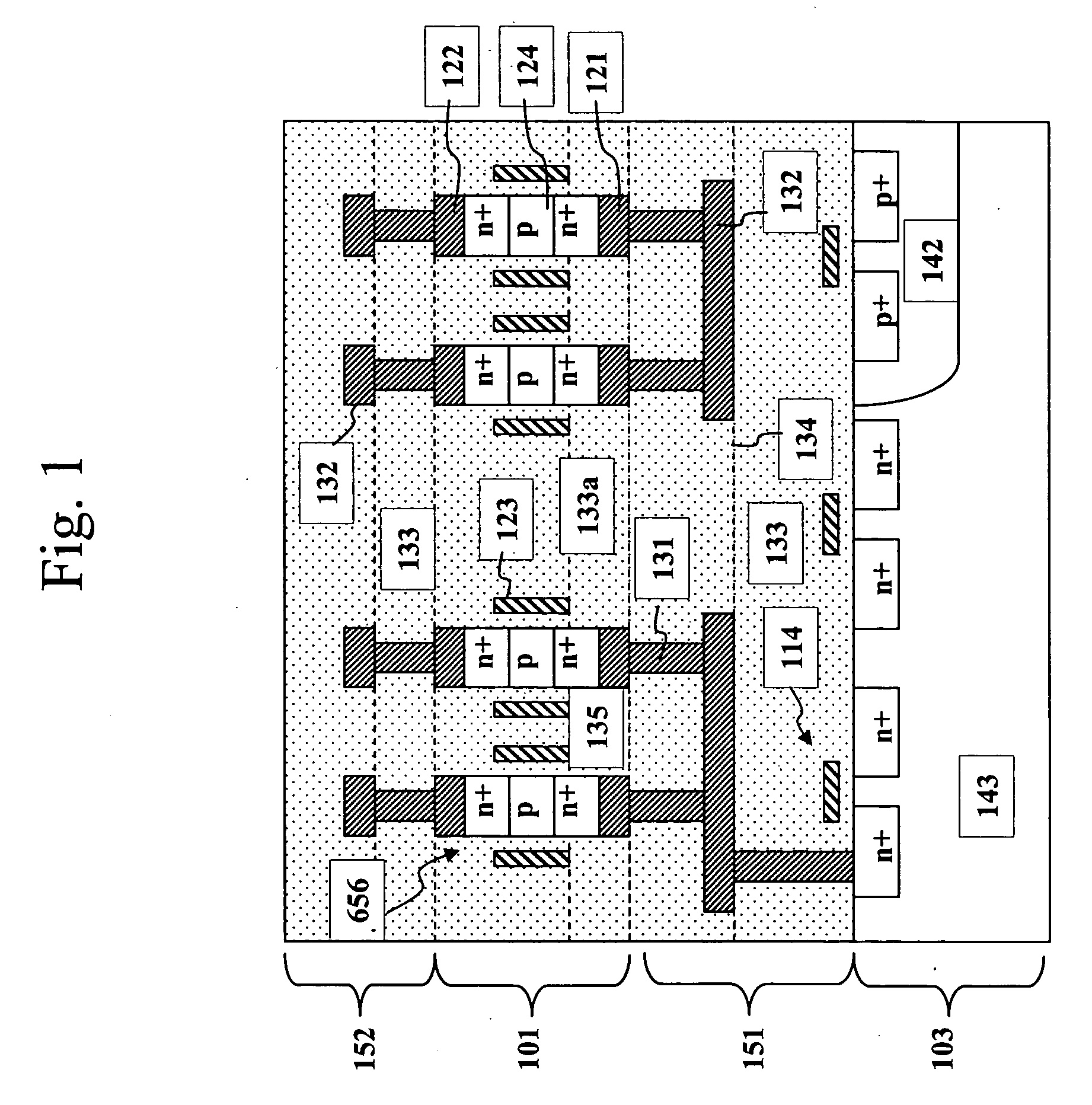

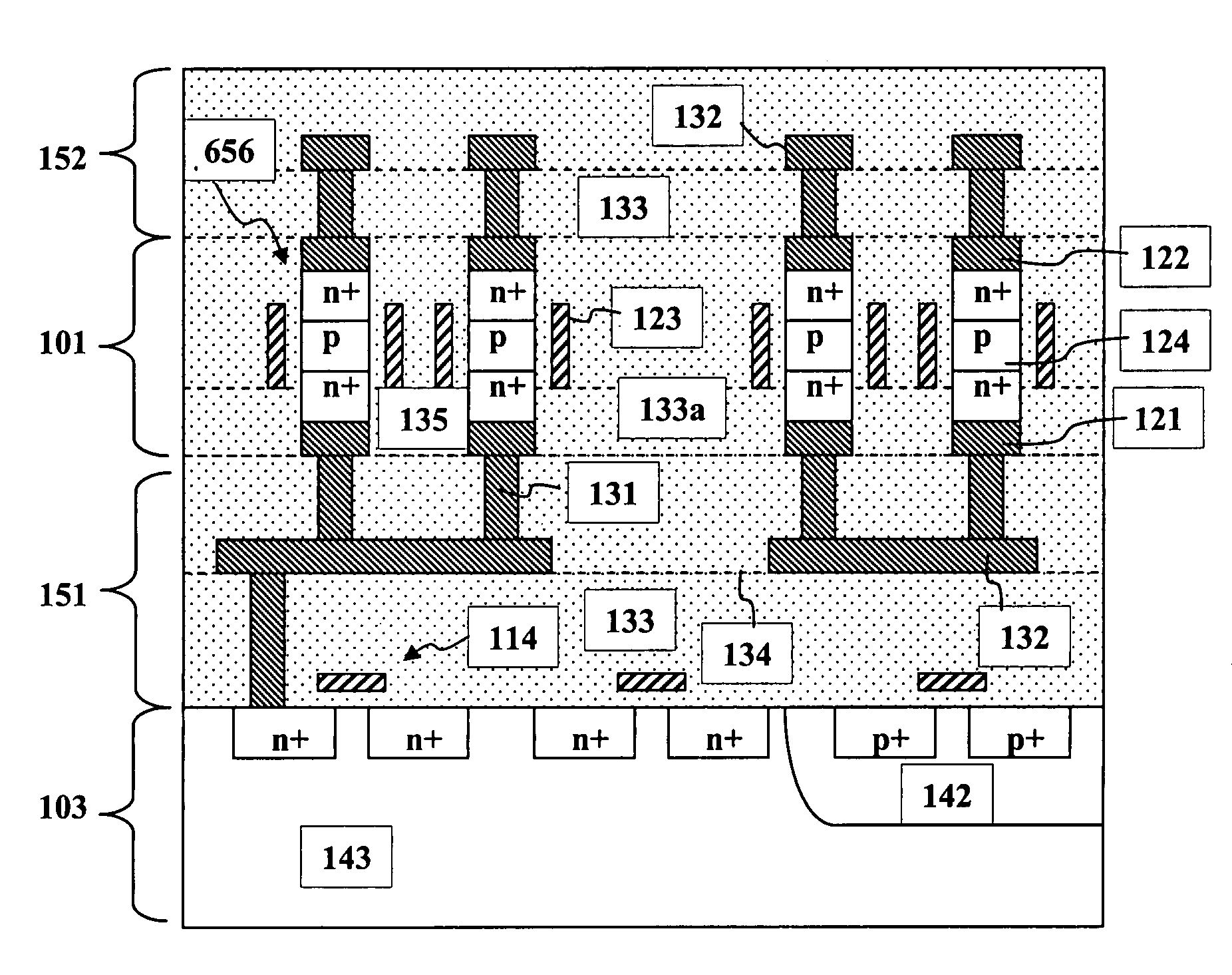

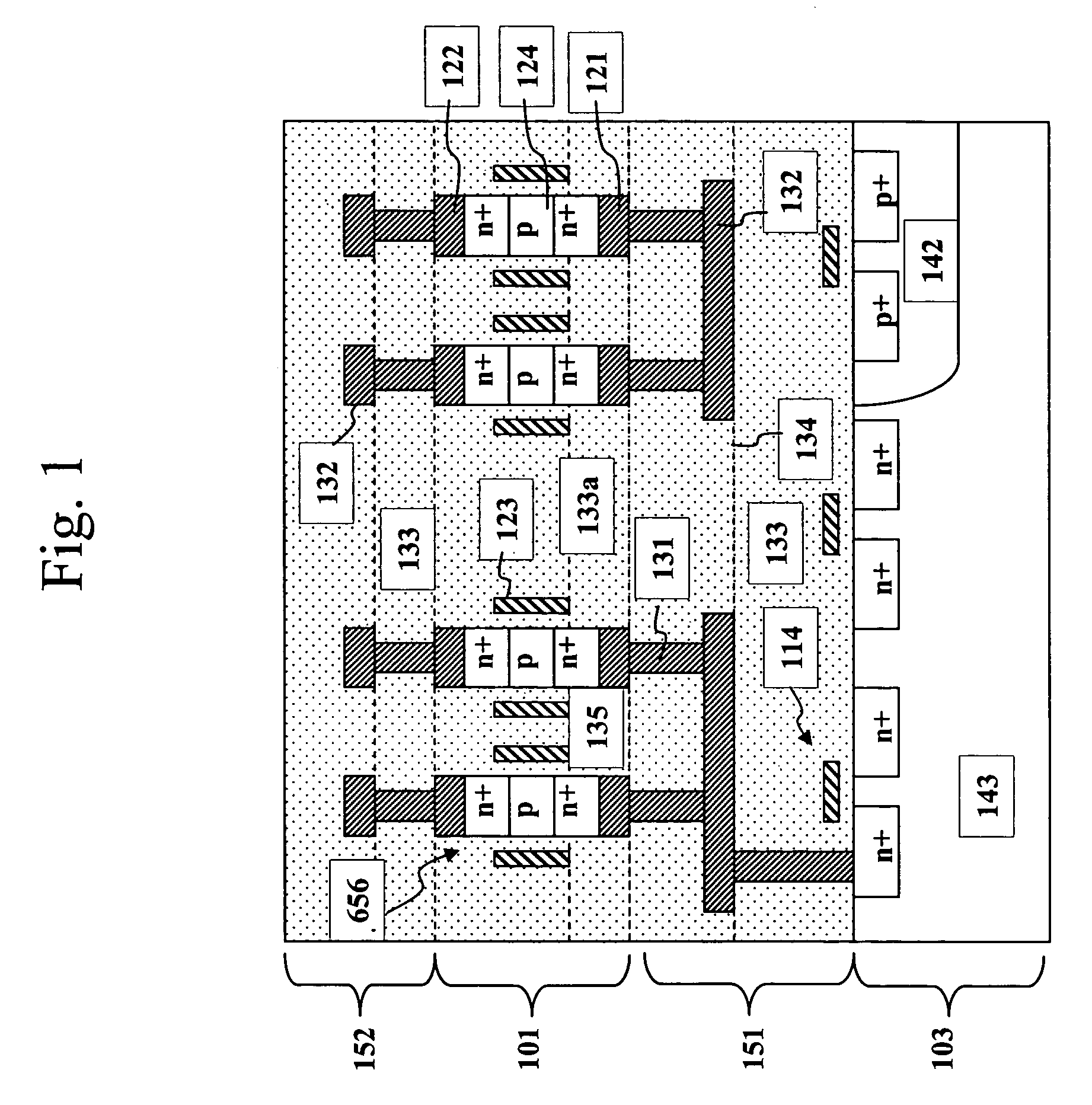

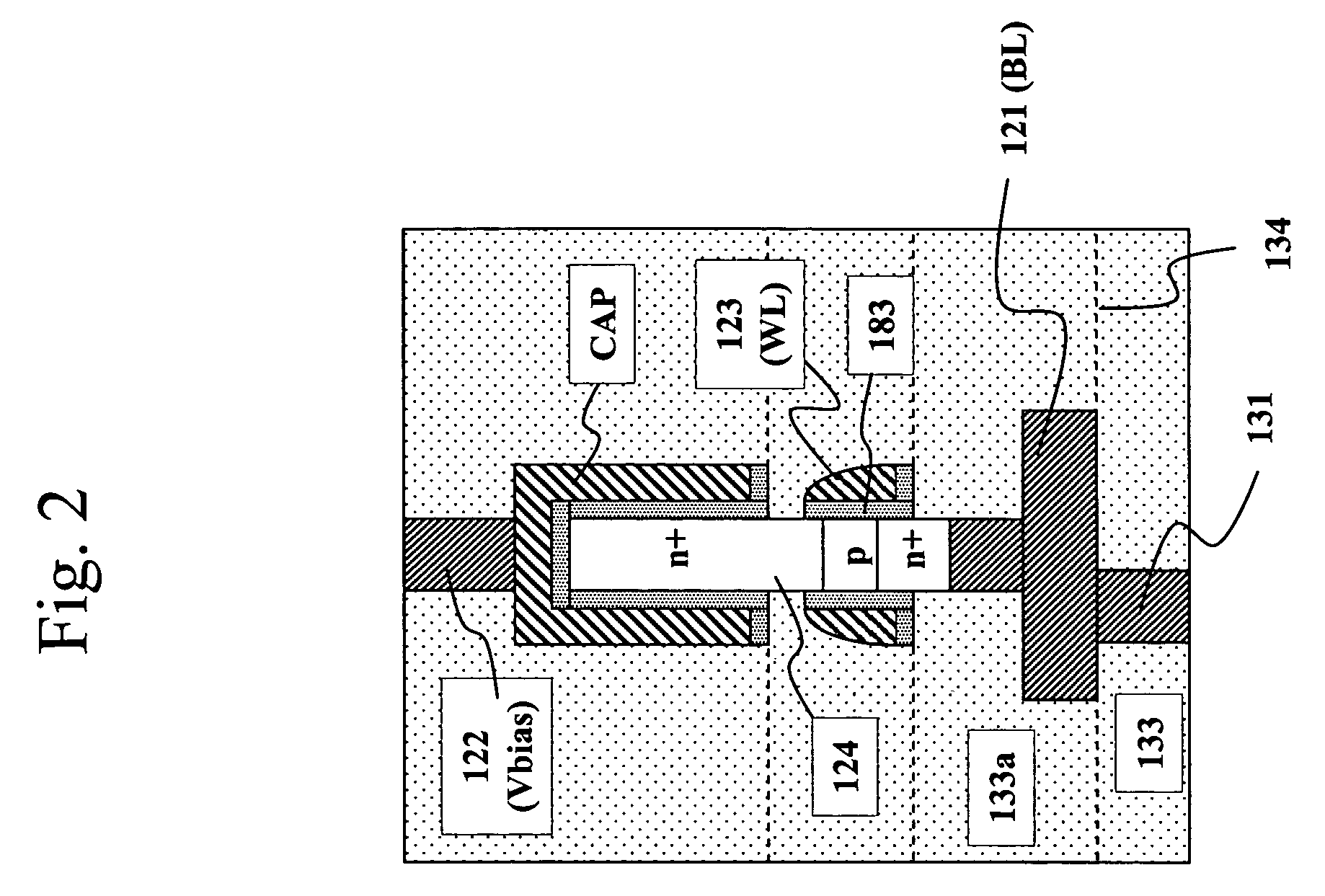

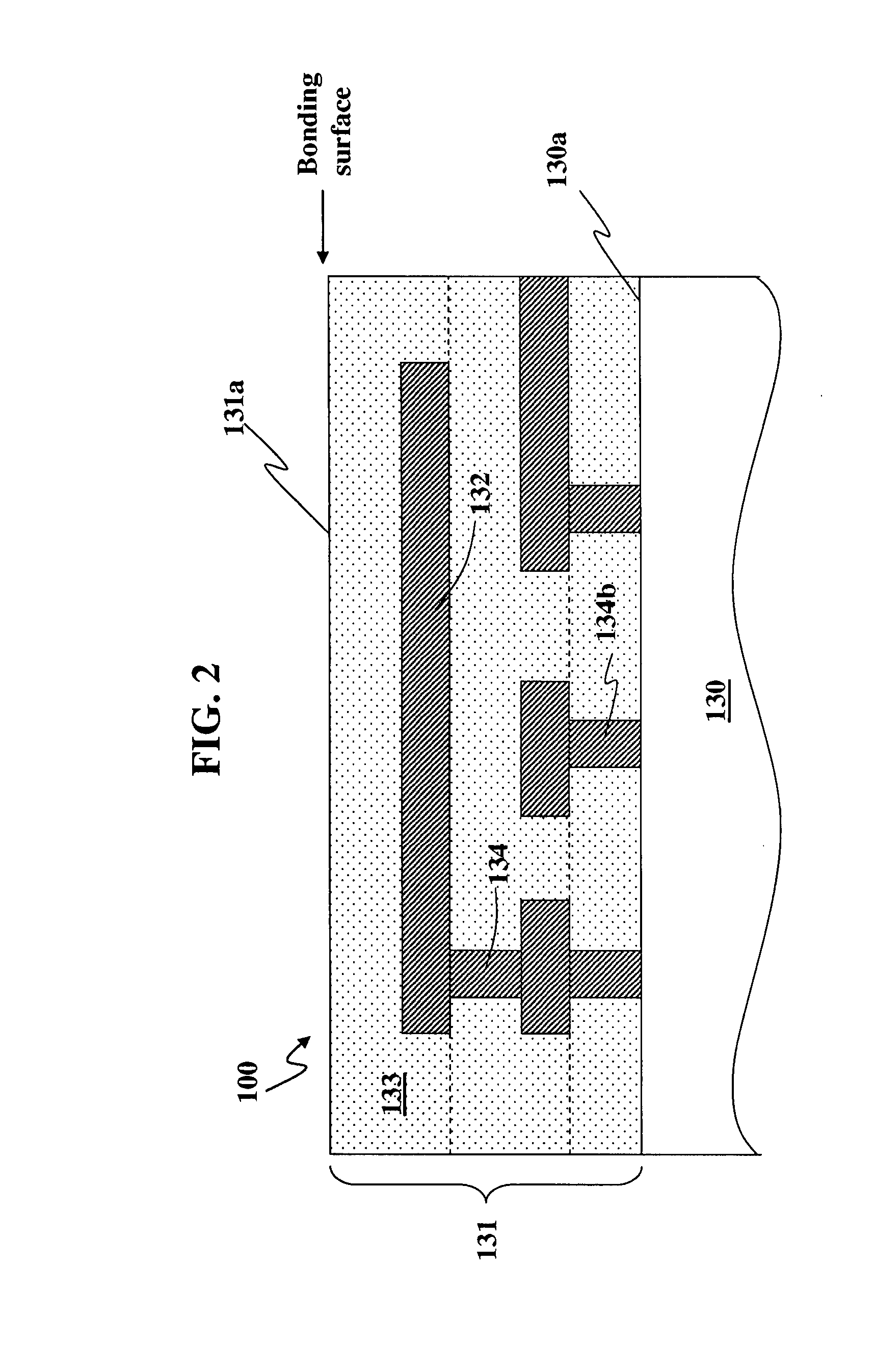

Vertical memory device structures

Vertically oriented semiconductor memory cells are added to a separately fabricated substrate that includes electrical devices and / or interconnect. The plurality of vertically oriented semiconductor memory cells are physically separated from each other, and are not disposed within the same semiconductor body. The plurality of vertically oriented semiconductor memory cells can be added to the separately fabricated substrate as a thin layer including several doped semiconductor regions which, subsequent to attachment, are etched to produce individual doped stack structures, which are then supplied with various dielectric coatings, gate electrodes, and contacts by means of further processing operations. Alternatively, the plurality of vertically oriented semiconductor memory cells may be completely fabricated prior to attachment. DRAMs, SRAMs, non-volatile memories, and combinations of memory types can be provided.

Owner:BESANG

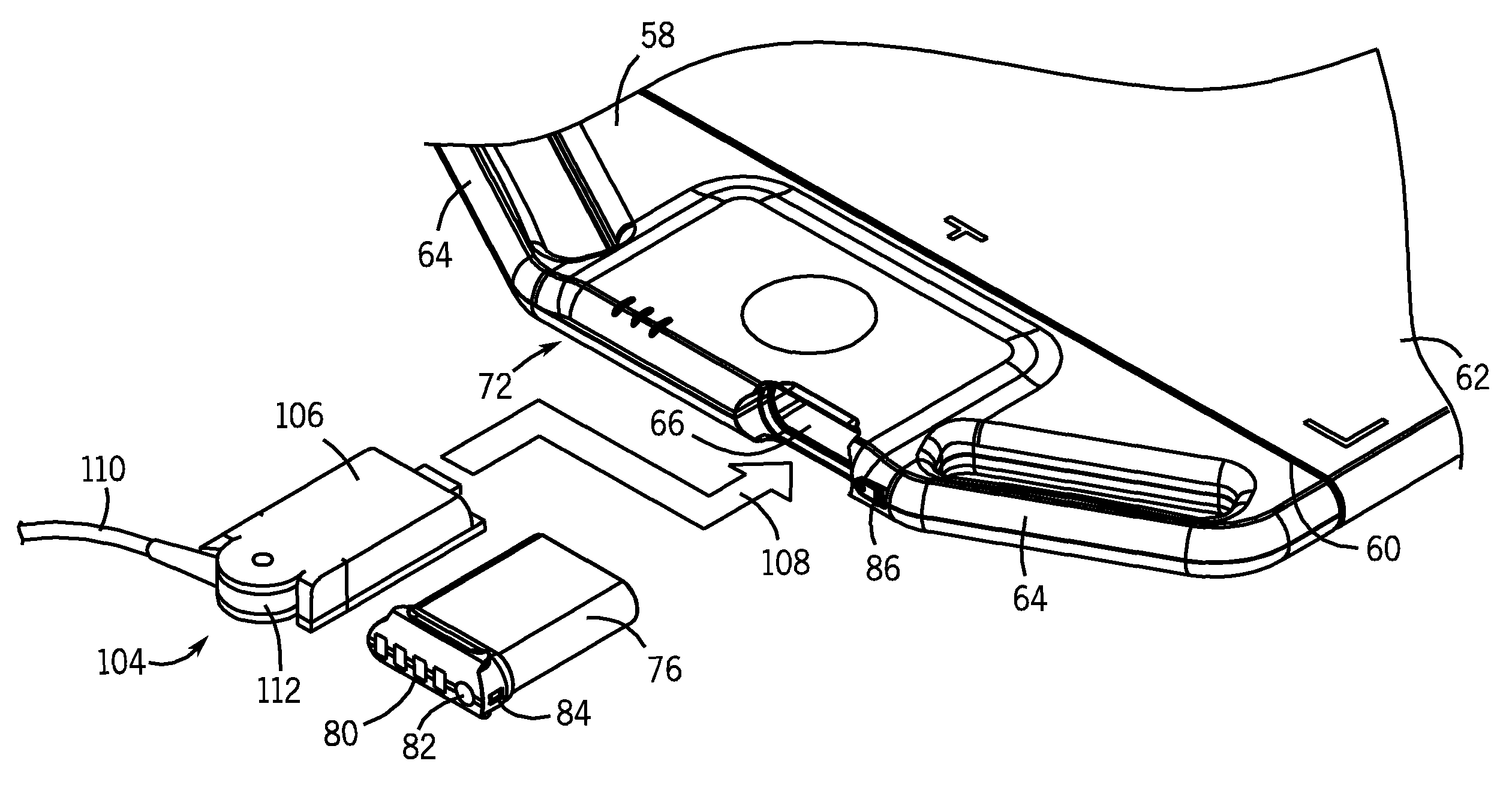

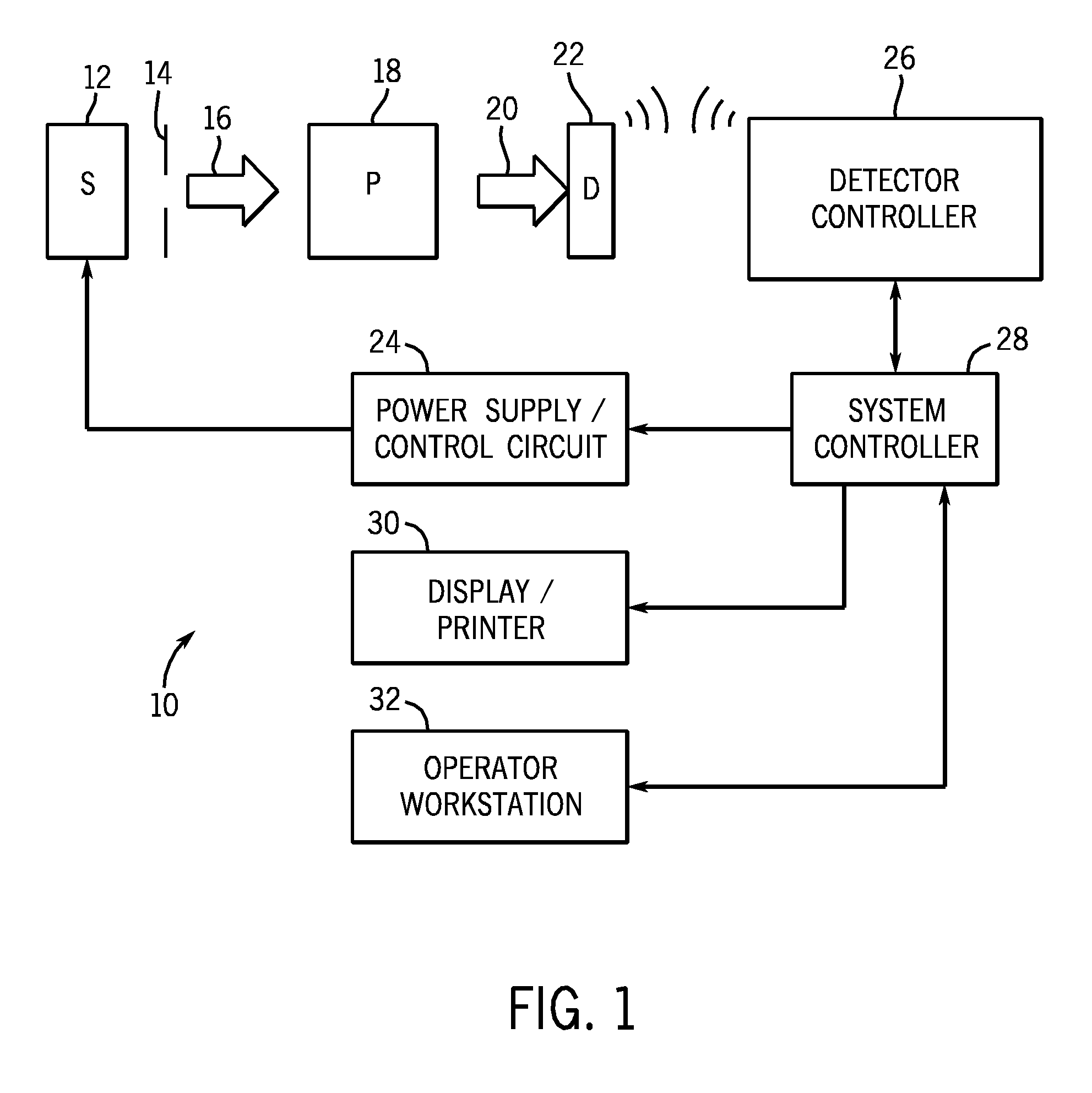

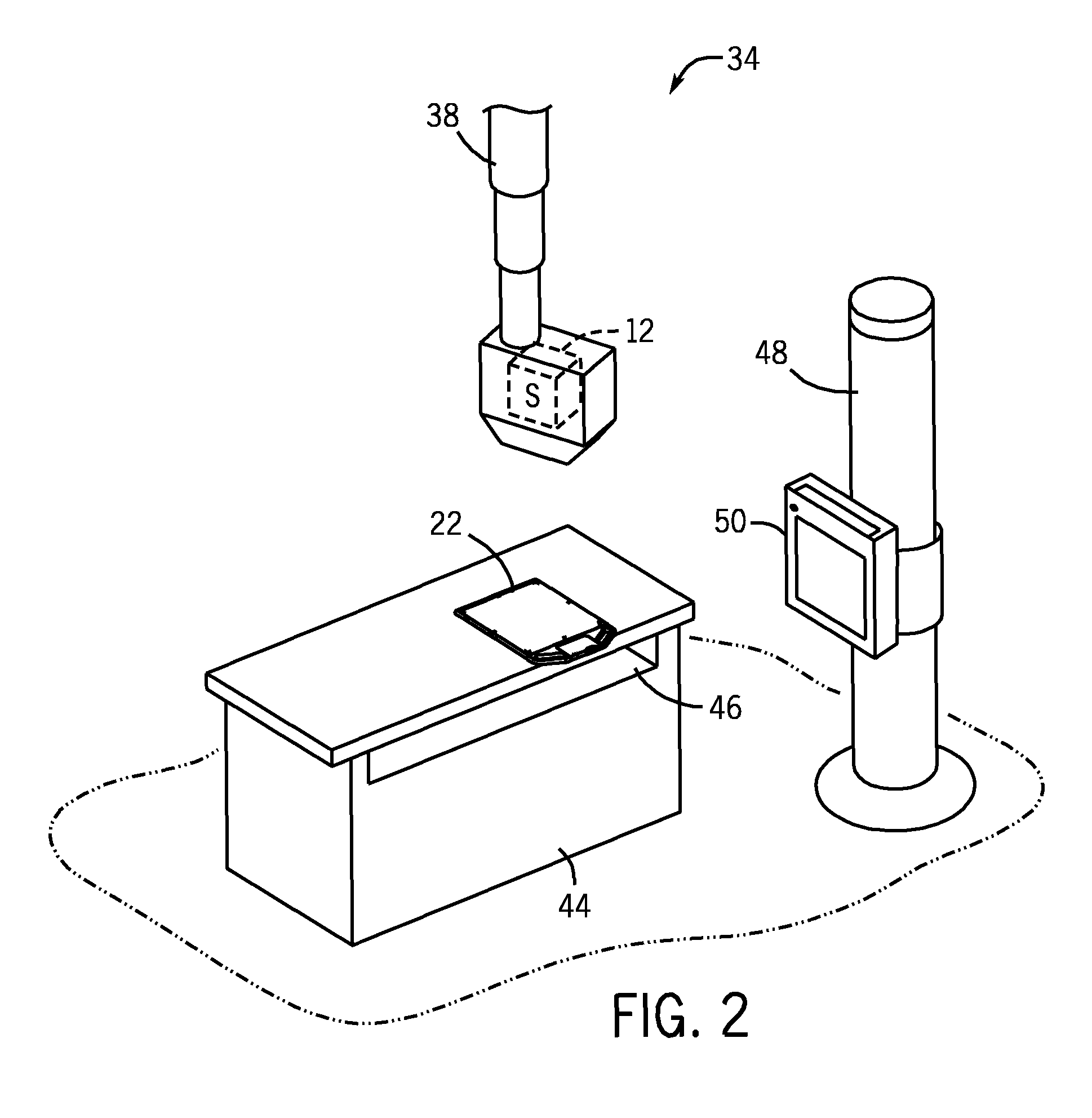

Digital image detector

ActiveUS8324585B2Radiation diagnosis data transmissionSolid-state devicesDigital imagingWireless data

A digital detector of a digital imaging system is provided. In one embodiment, a digital detector includes a detector array disposed in a housing and configured to generate image data based on received radiation. The digital detector may also include a battery configured to be disposed within a receptacle of the housing and to supply operating power to the detector array. In one embodiment, the battery or the detector may provide for wireless data communication. In certain embodiments, a tethered plug configured to be disposed within the receptacle may be provided. In one such embodiment, the tether may be rotatable relative to the plug. Additional systems, methods, and devices are also disclosed.

Owner:GENERAL ELECTRIC CO

Method of eliminating a lithography operation

ActiveUS20090146322A1Semiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

Methods of semiconductor device fabrication are disclosed. An exemplary method includes processes of depositing a first pattern on a semiconductor substrate, wherein the first pattern defines wide and narrow spaces; depositing spacer material over the first pattern on the substrate; etching the spacer material such that the spacer material is removed from horizontal surfaces of the substrate and the first pattern but remains adjacent to vertical surfaces of a wide space defined by the first pattern and remains within narrow a space defined by the first pattern; and removing the first pattern from the substrate. In one embodiment, the first pattern can comprise sacrificial material, which can include, for example, polysilicon material. The deposition can comprise physical vapor deposition, chemical vapor deposition, electrochemical deposition, molecular beam epitaxy, atomic layer deposition or other deposition techniques. According to another embodiment, features for lines and logic device components having a width greater than that of the lines are formed in the spacer material in the same mask layer.

Owner:CADENCE DESIGN SYST INC

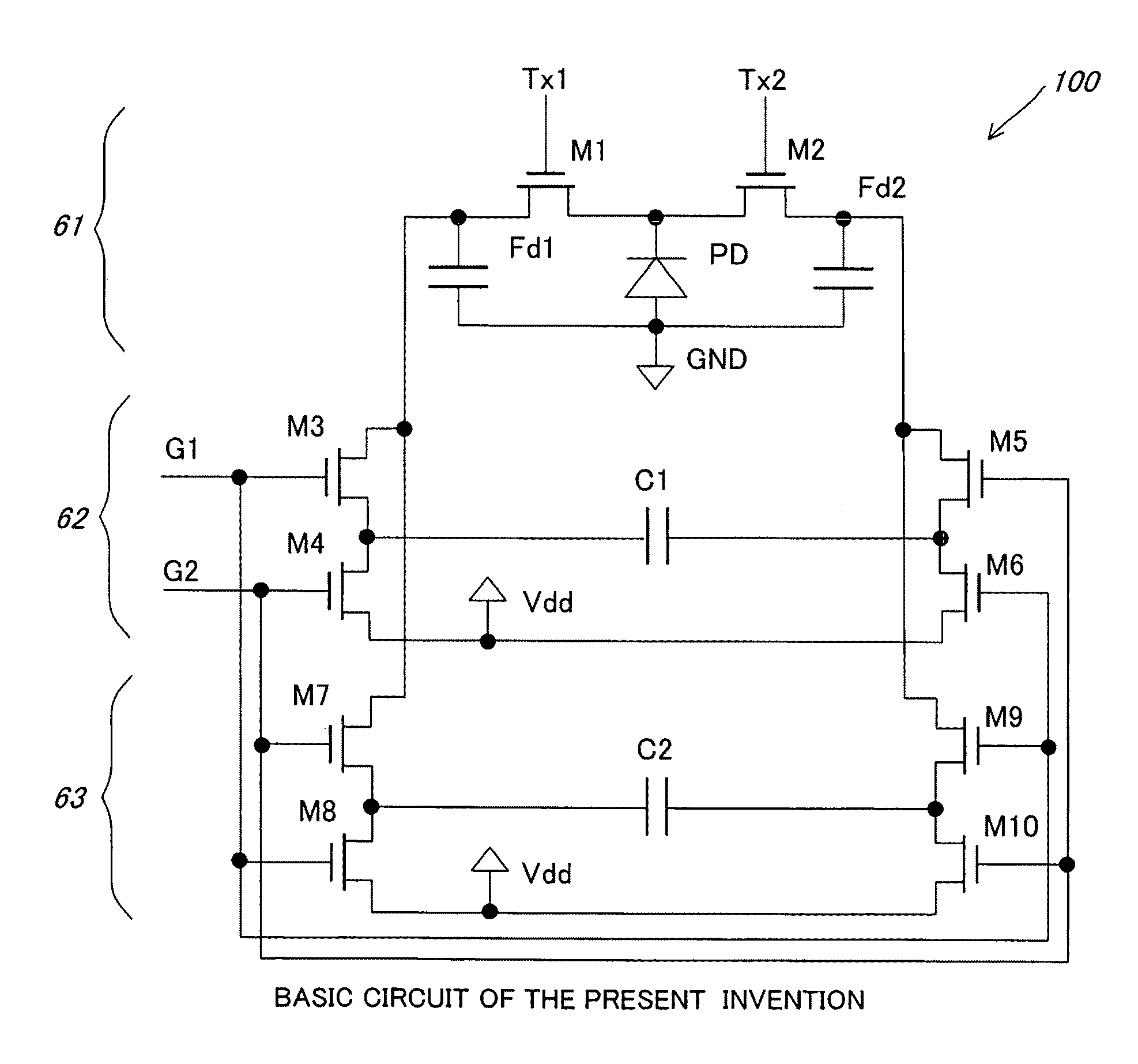

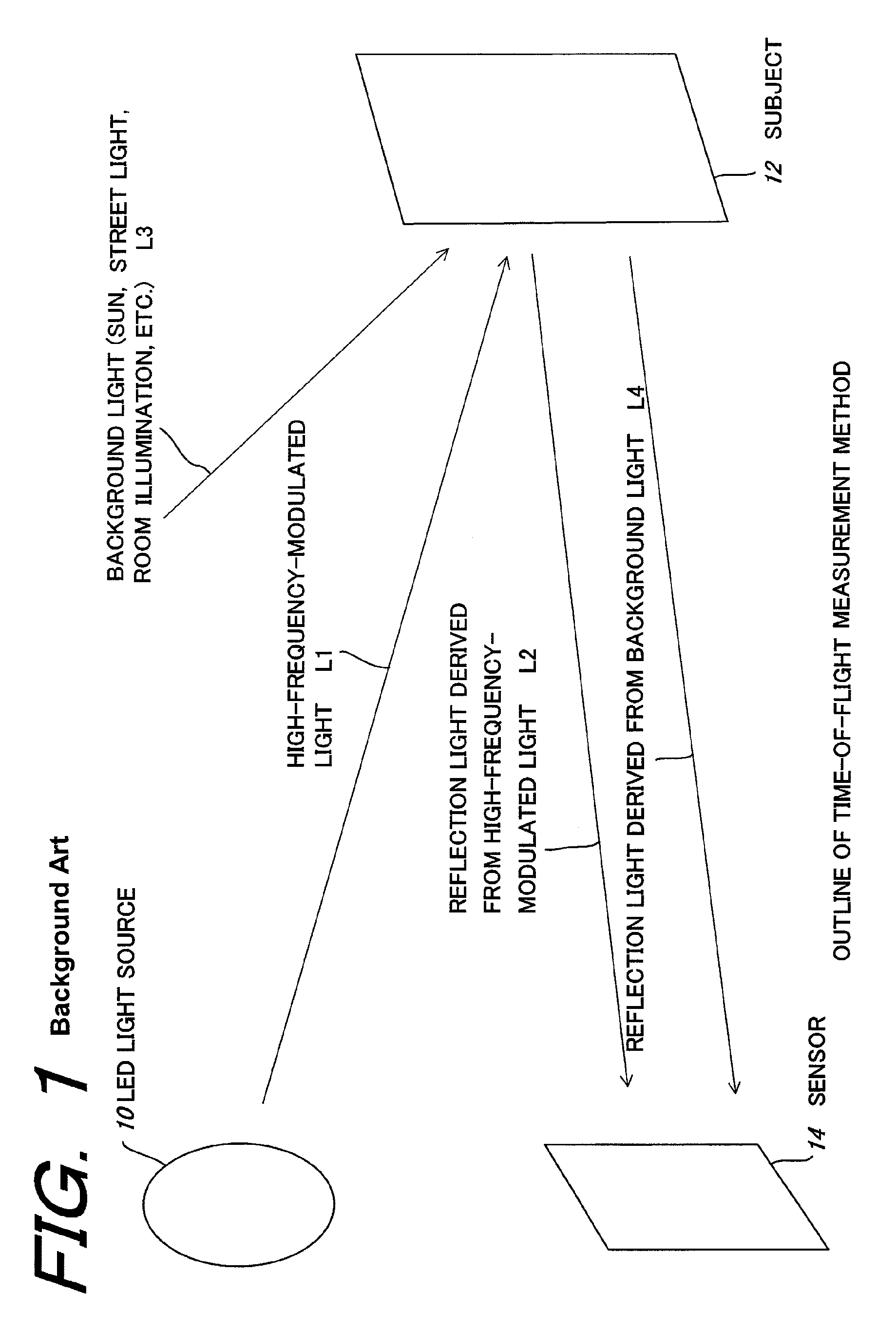

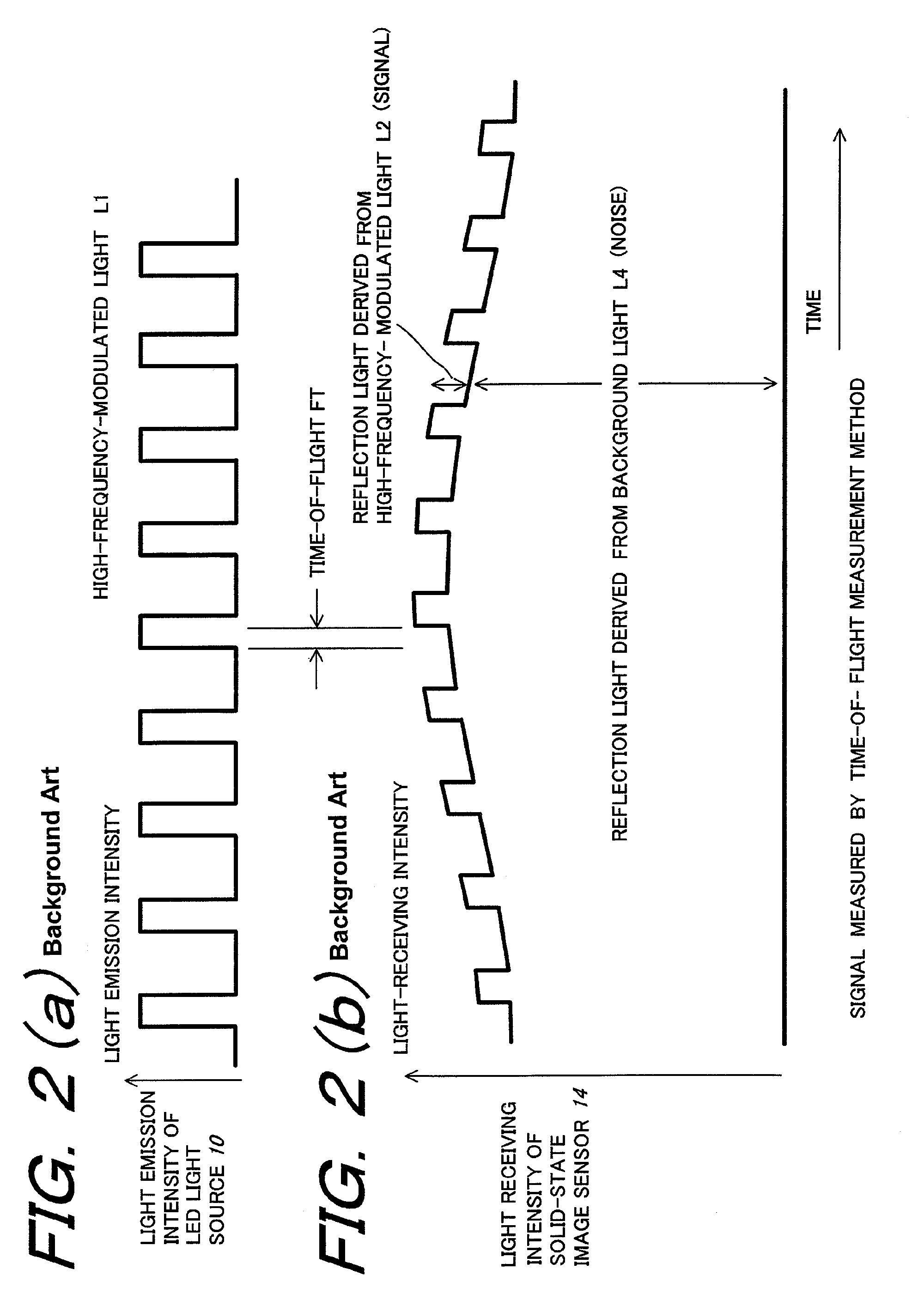

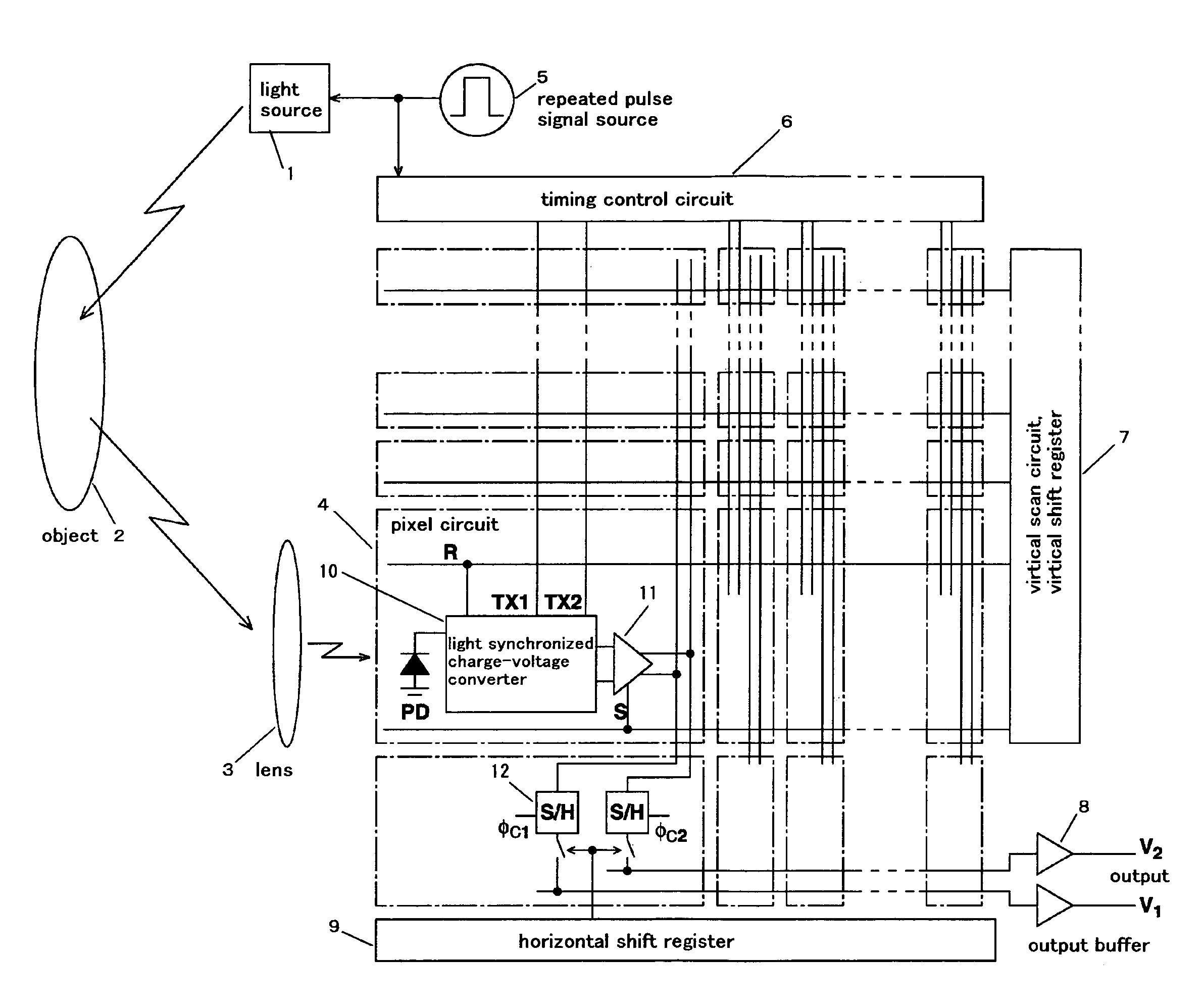

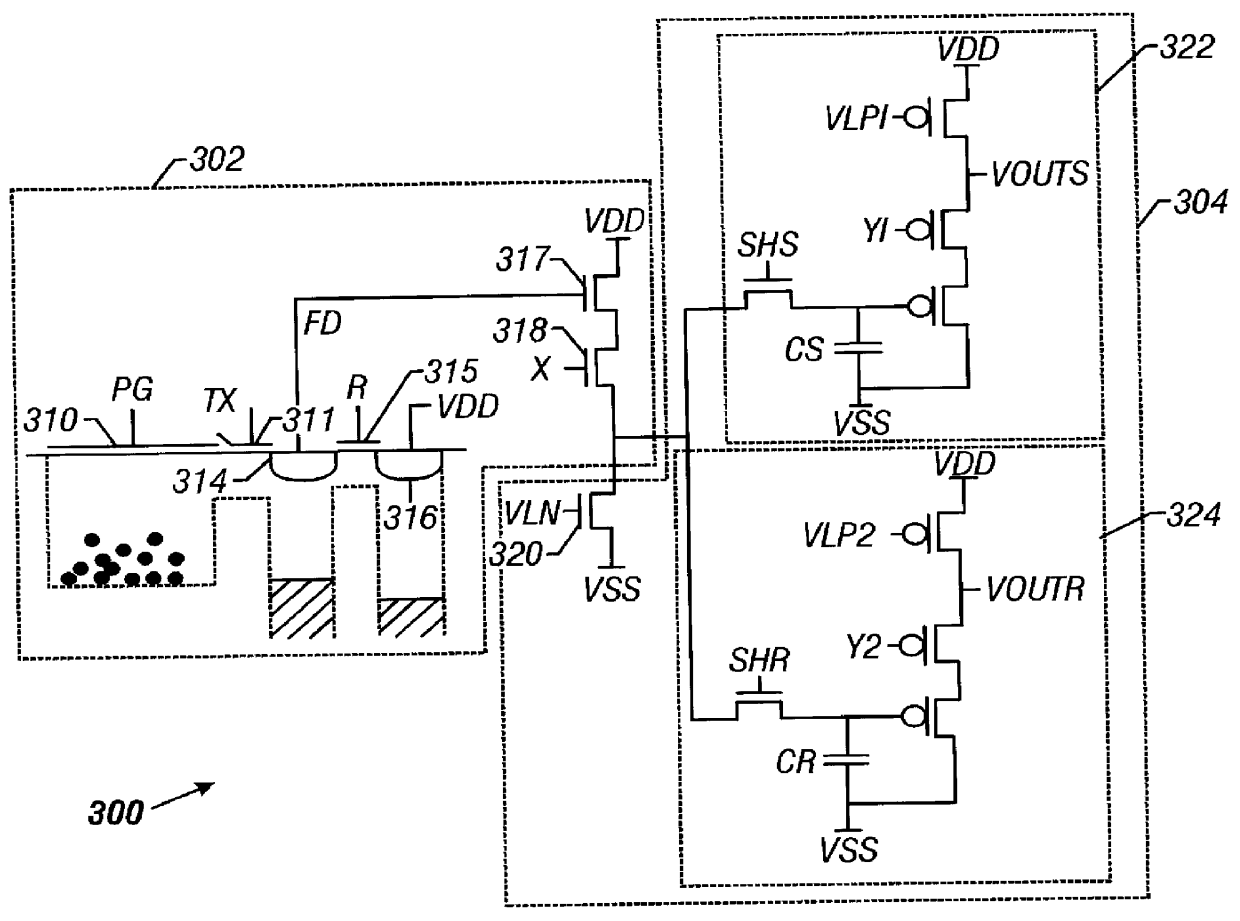

Solid-state image sensor

ActiveUS7683954B2Efficient extractionCancel noiseTelevision system detailsOptical rangefindersLow noiseCapacitor

A solid-state image sensor of a charge sorting method used in a time-of-flight measurement method, in which noise derived from background light, which is caused by the reflection light from the subject derived from background light is eliminated, reflection light from the subject derived from a predetermined light source, which is previously set in the solid-state image sensor, is effectively extracted as a signal component to achieve high sensitivity and low noise, which is a solid-state image sensor that is equipped with a plurality of charge-storage sections, discriminates photoelectrons generated by incoming light on the incoming timing and sort to the above-described plurality of charge-storage sections, and measures the timing of the incoming light, in which the sensor has: a plurality of capacitors that capable of conducting to the plurality of charge-storage sections; and a control section that controls a conducted state between the above-described plurality of charge-storage sections and the above-described plurality of capacitors, in which by selectively conducting the above-described plurality of charge-storage sections and the above-described plurality of capacitors by the control of the above-described control section, the difference component of charge stored in the above-described plurality of charge-storage sections is extracted.

Owner:STANLEY ELECTRIC CO LTD

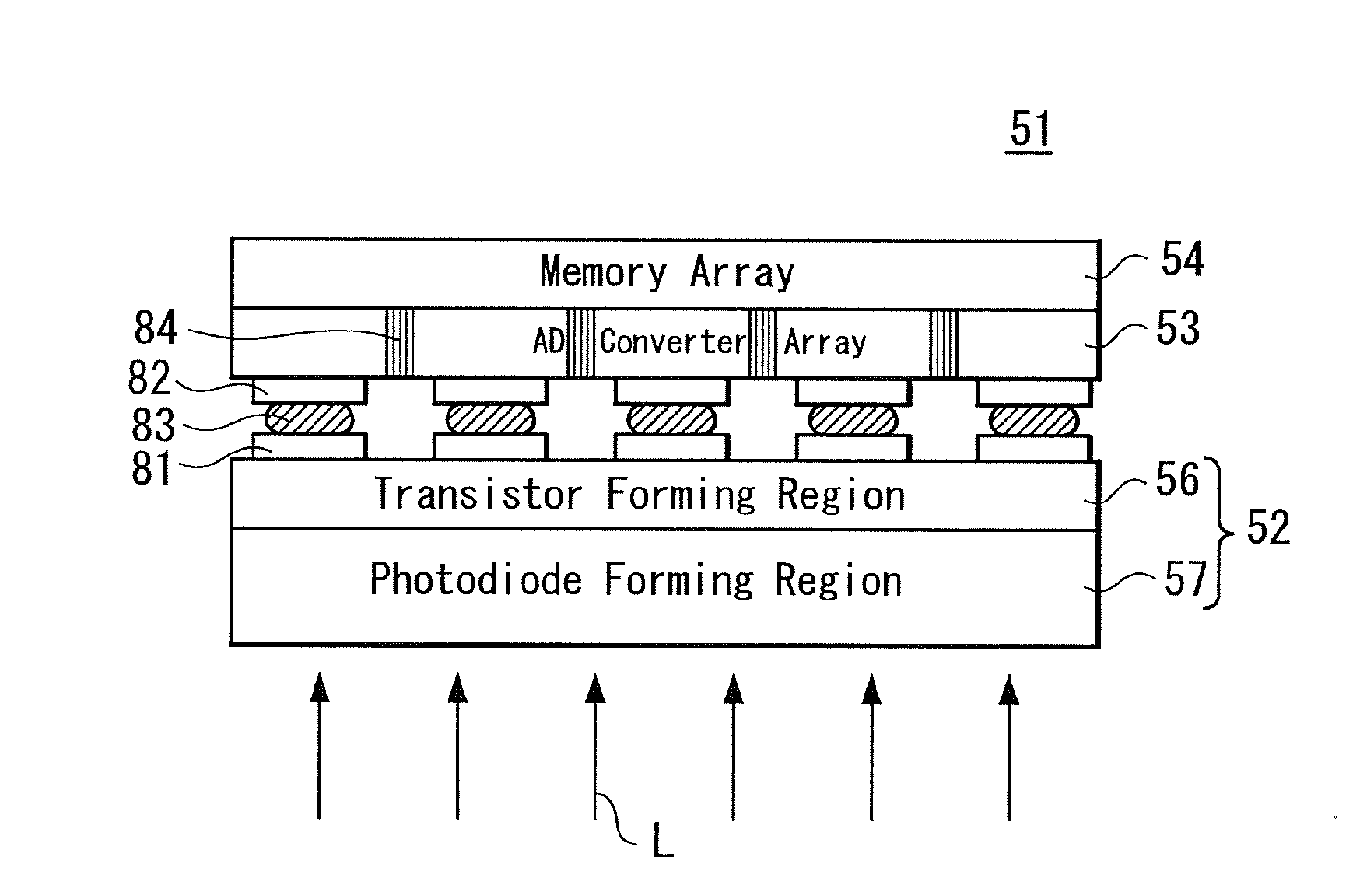

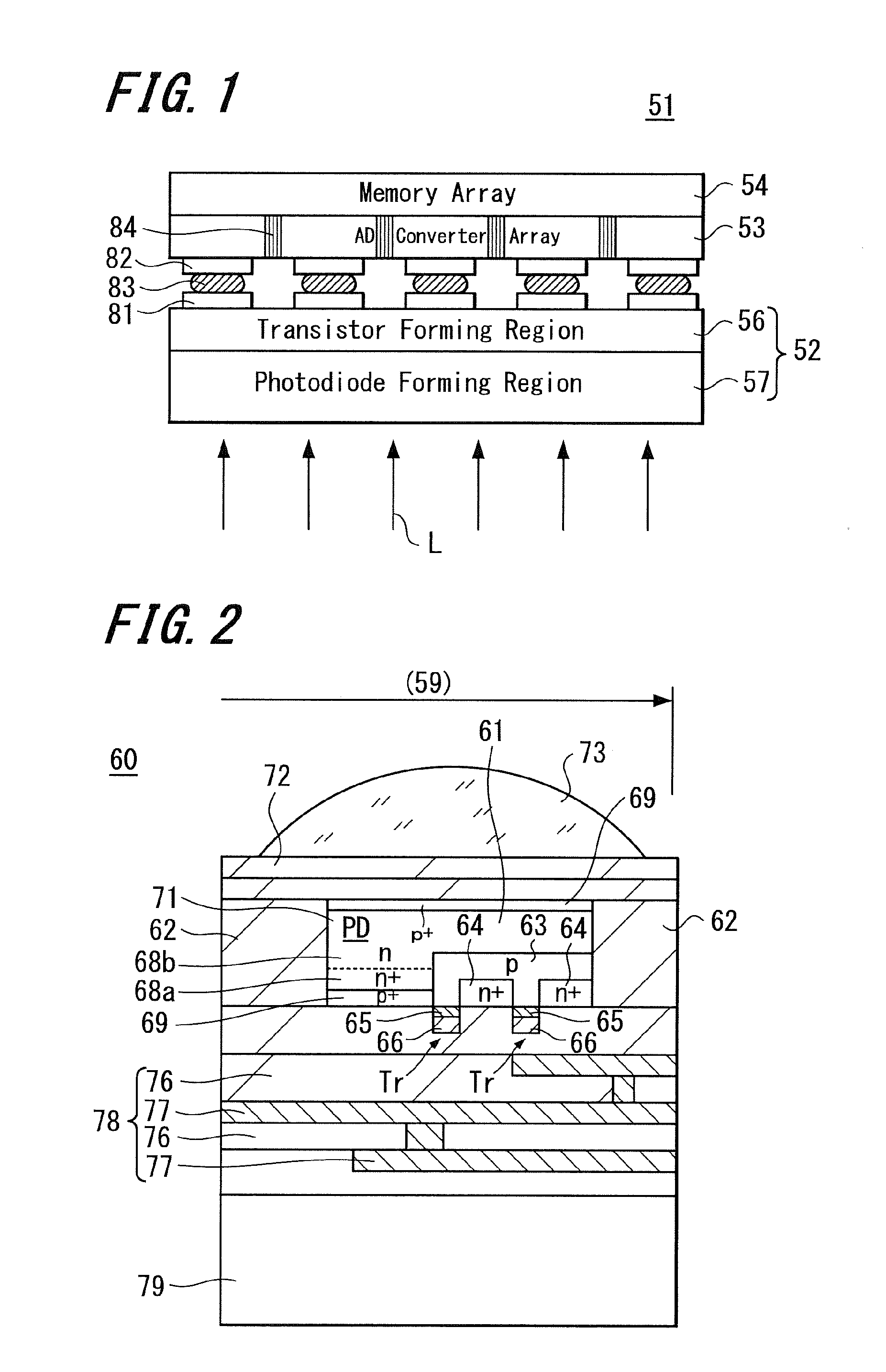

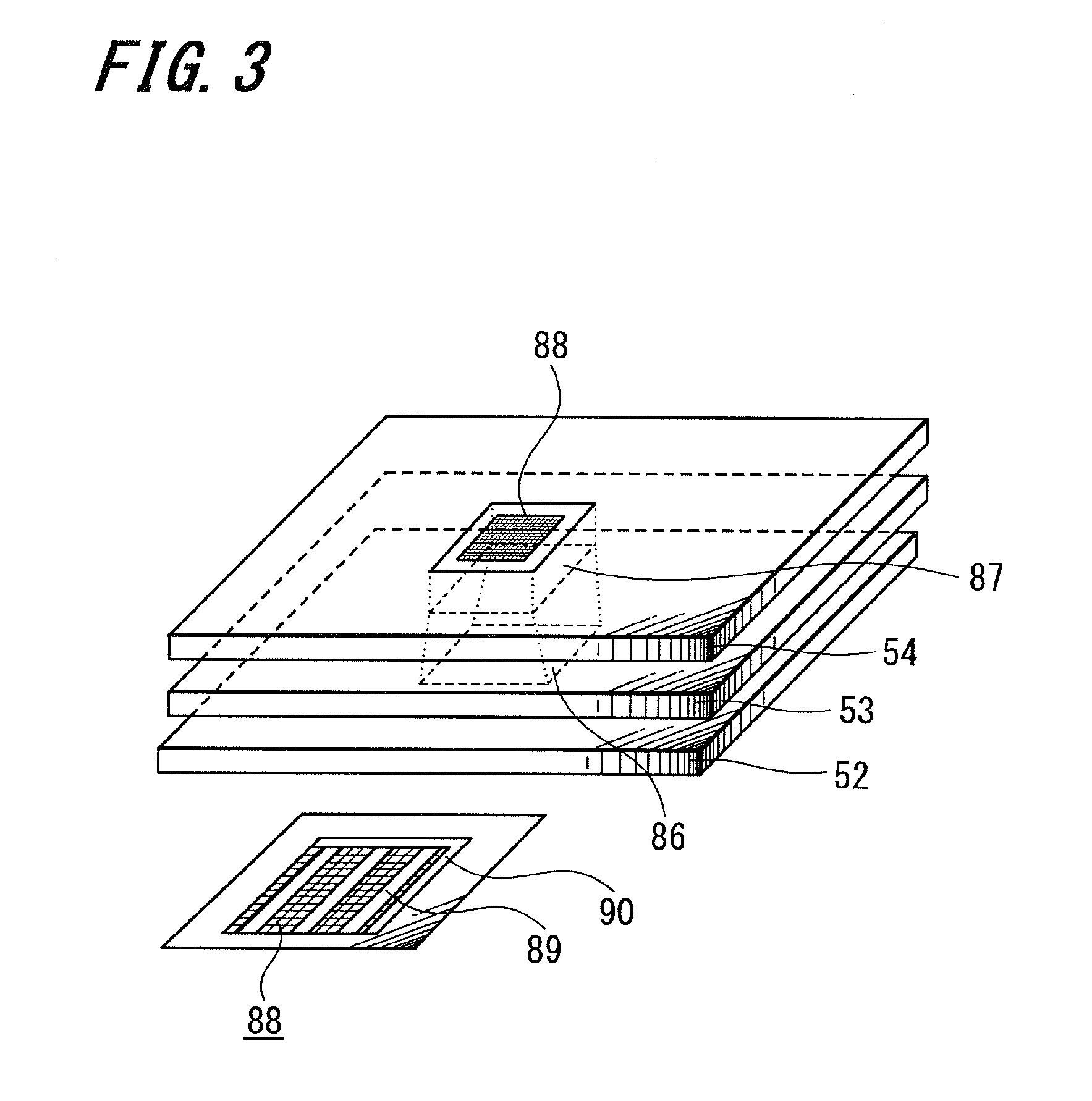

Semiconductor image sensor module and method of manufacturing the same

ActiveUS20100276572A1Increase the aperture ratioIncrease profitTransistorTelevision system detailsCMOSSemiconductor chip

A CMOS type semiconductor image sensor module wherein a pixel aperture ratio is improved, chip use efficiency is improved and furthermore, simultaneous shutter operation by all the pixels is made possible, and a method for manufacturing such semiconductor image sensor module are provided. The semiconductor image sensor module is provided by stacking a first semiconductor chip, which has an image sensor wherein a plurality of pixels composed of a photoelectric conversion element and a transistor are arranged, and a second semiconductor chip, which has an A / D converter array. Preferably, the semiconductor image sensor module is provided by stacking a third semiconductor chip having a memory element array. Furthermore, the semiconductor image sensor module is provided by stacking the first semiconductor chip having the image sensor and a fourth semiconductor chip having an analog nonvolatile memory array.

Owner:SONY CORP

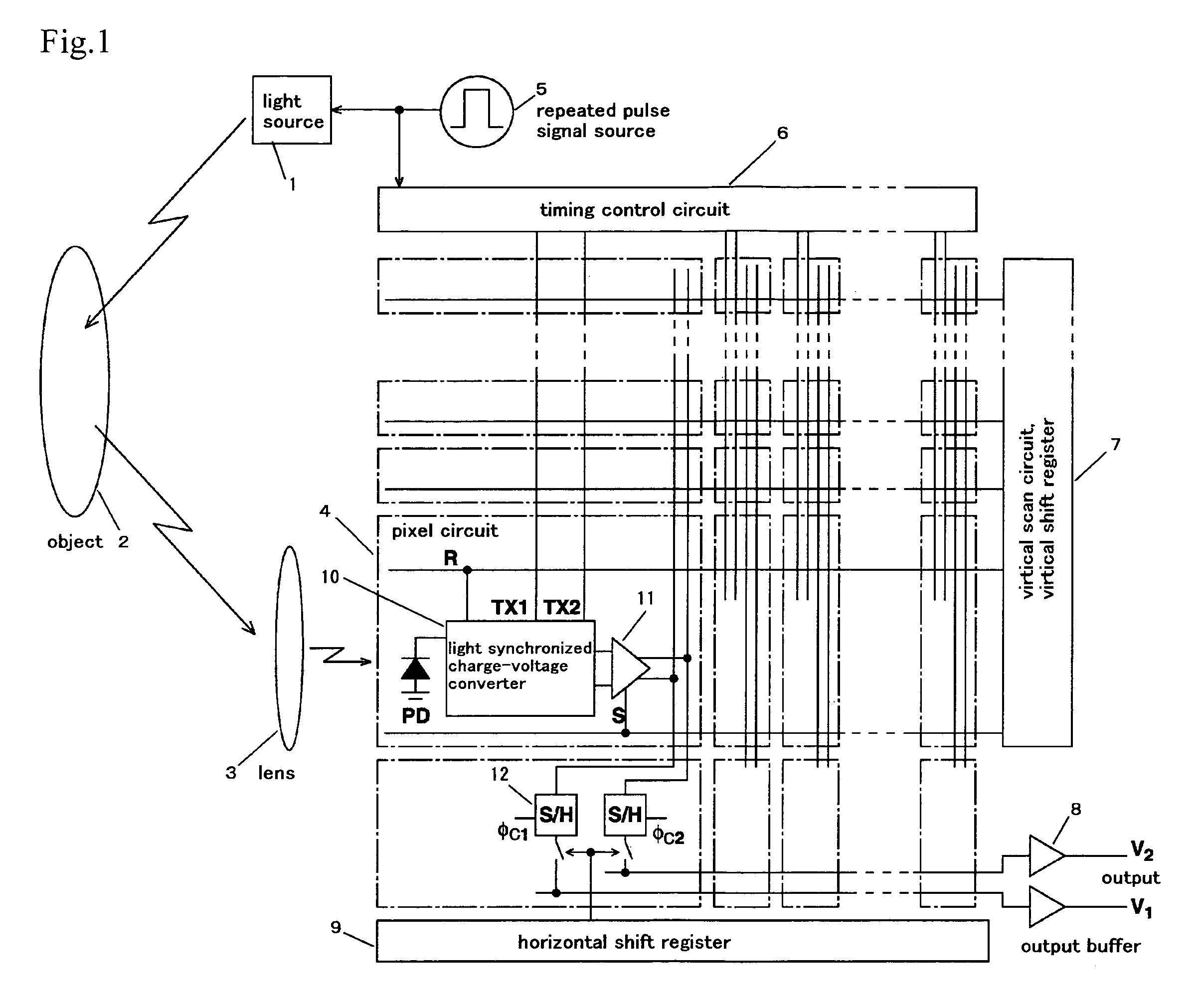

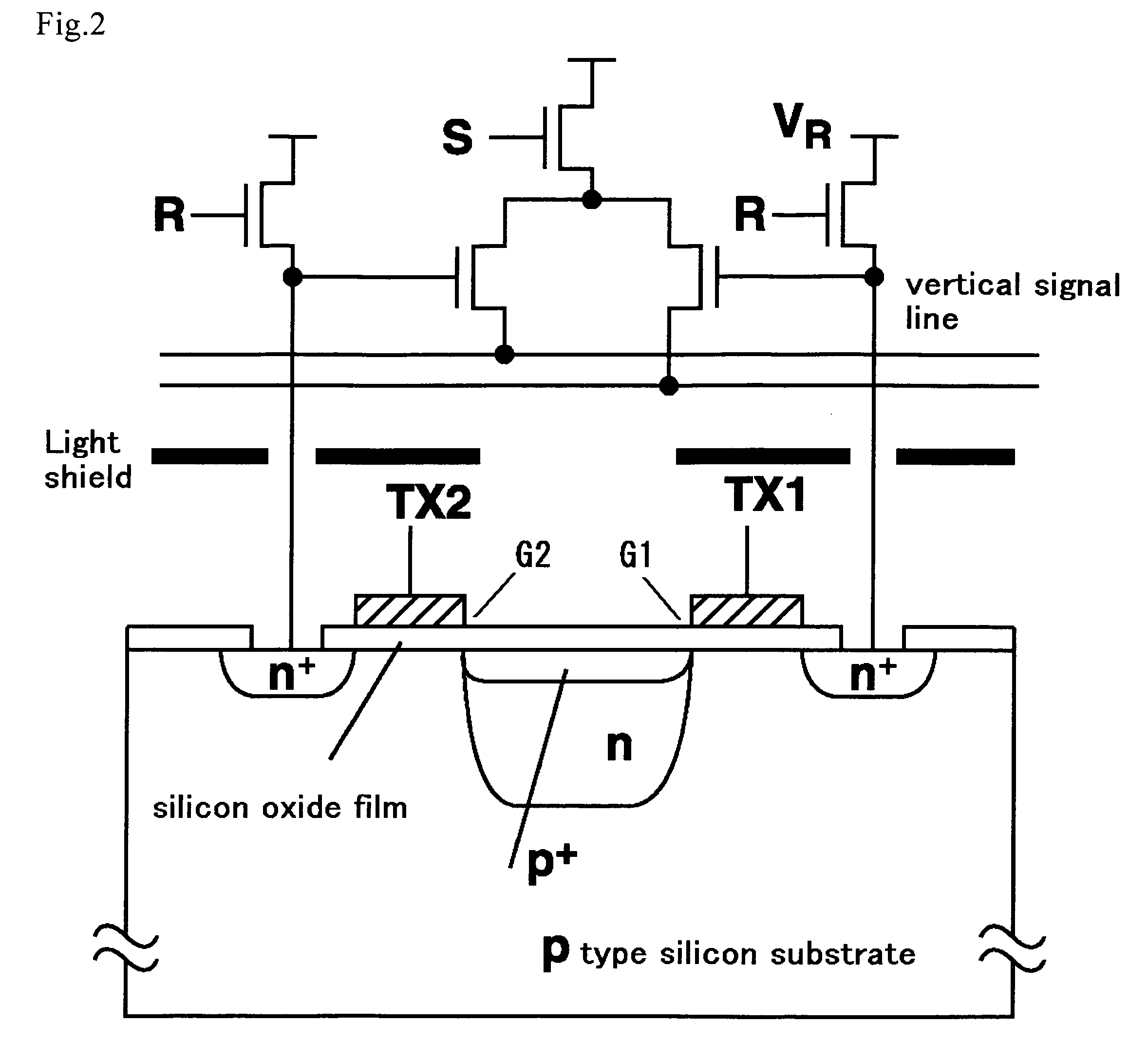

Distance image sensor

ActiveUS7436496B2High sensitivityEnhanced charge transferTelevision system detailsOptical rangefindersAudio power amplifierDelayed time

A distance image sensor for removing the background light and improving the charge transfer efficiency in a device for measuring the distance to an object by measuring the time-of-flight of the light.In a distance image sensor for determining the signals of two charge storage nodes which depend on the delay time of the modulated light, a signal by the background light is received from the third charge storage node or the two charge storage nodes in a period when the modulated light does not exist, and is subtracted from the signal which depends on the delay time of the two charge storage nodes, so as to remove the influence of the background. Also by using a buried diode as a photo-detector, and using an MOS gate as gate means, the charge transfer efficiency improves. The charge transfer efficiency is also improved by using a negative feedback amplifier where a capacitor is disposed between the input and output.

Owner:NAT UNIV CORP SHIZUOKA UNIV

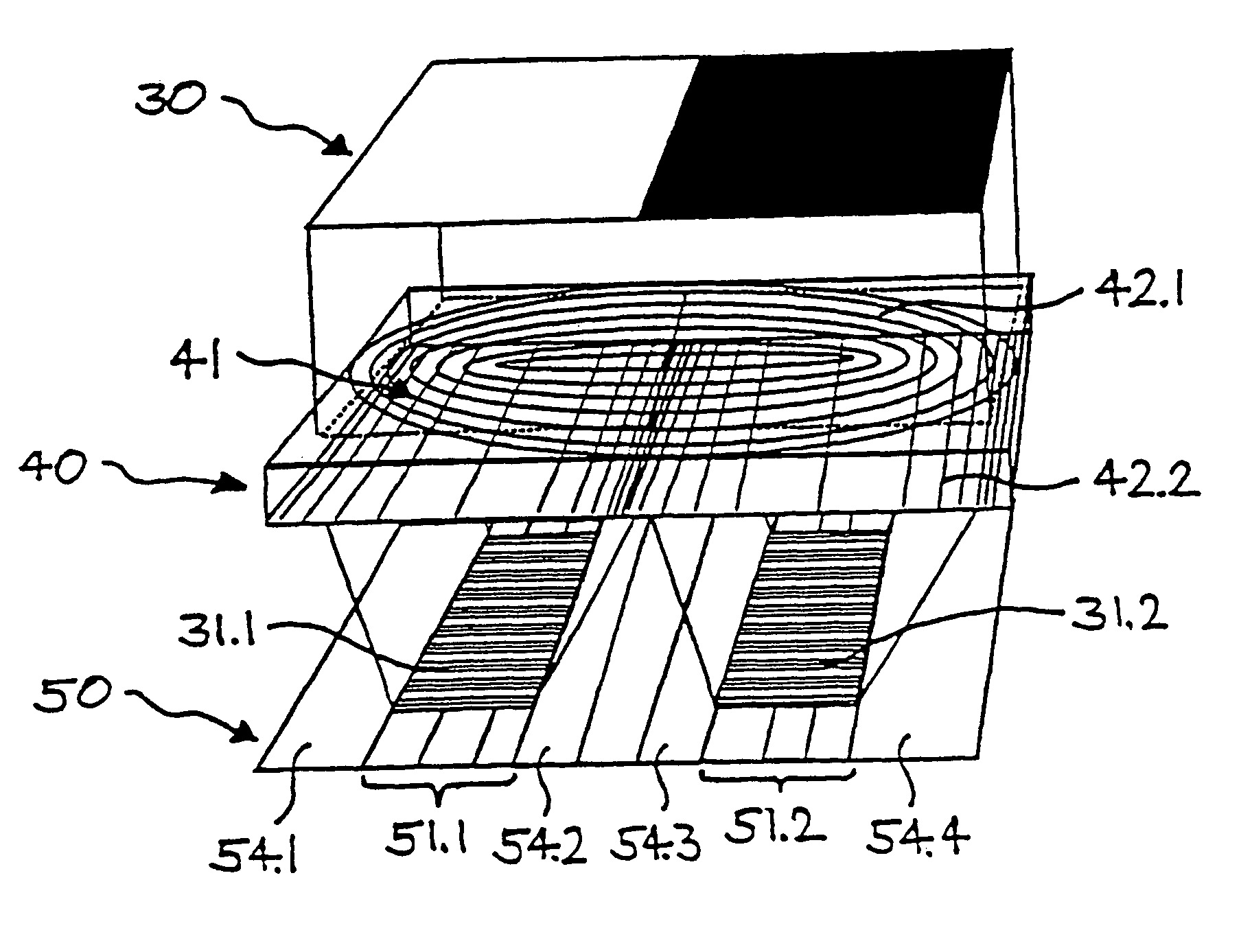

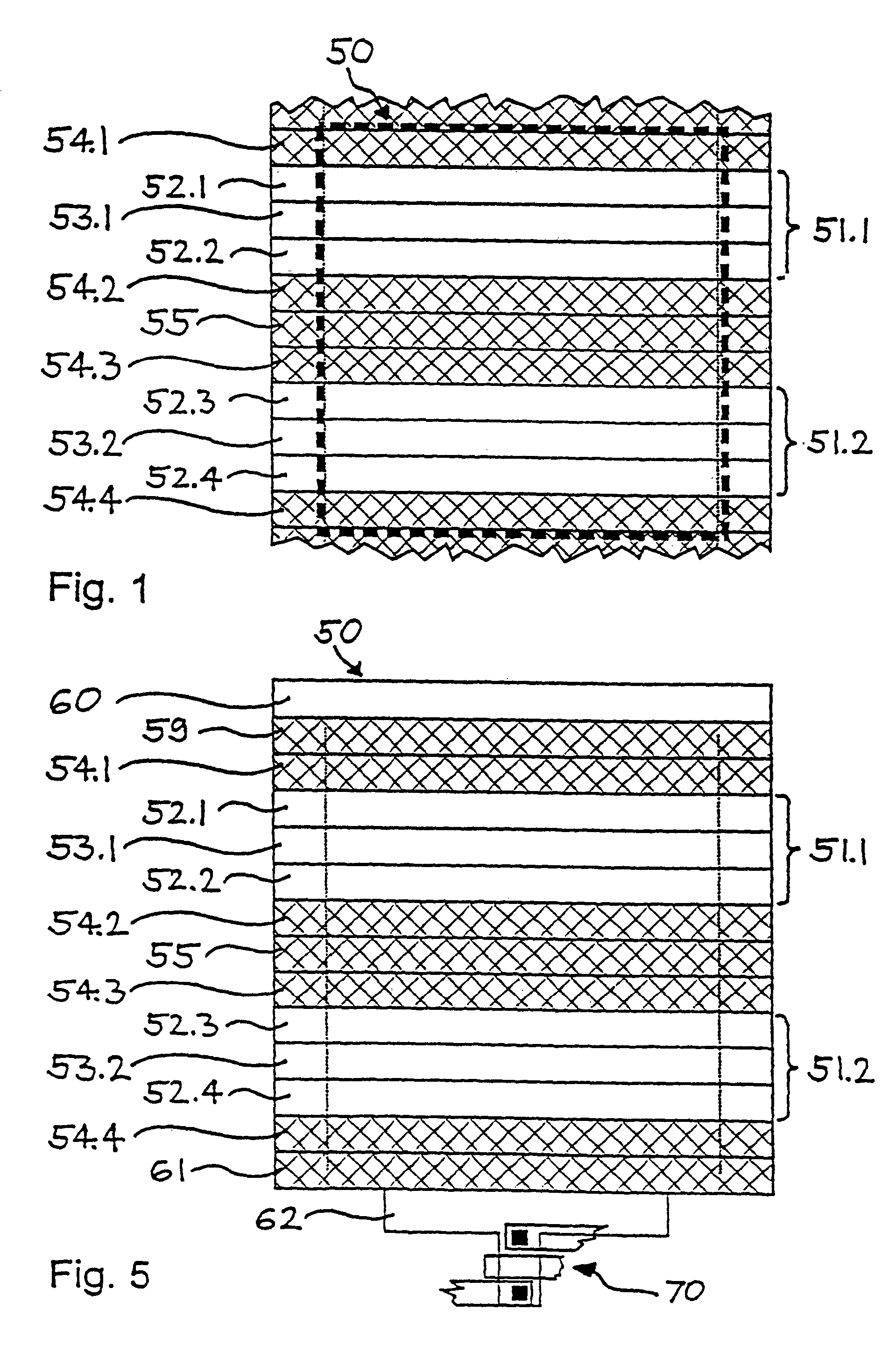

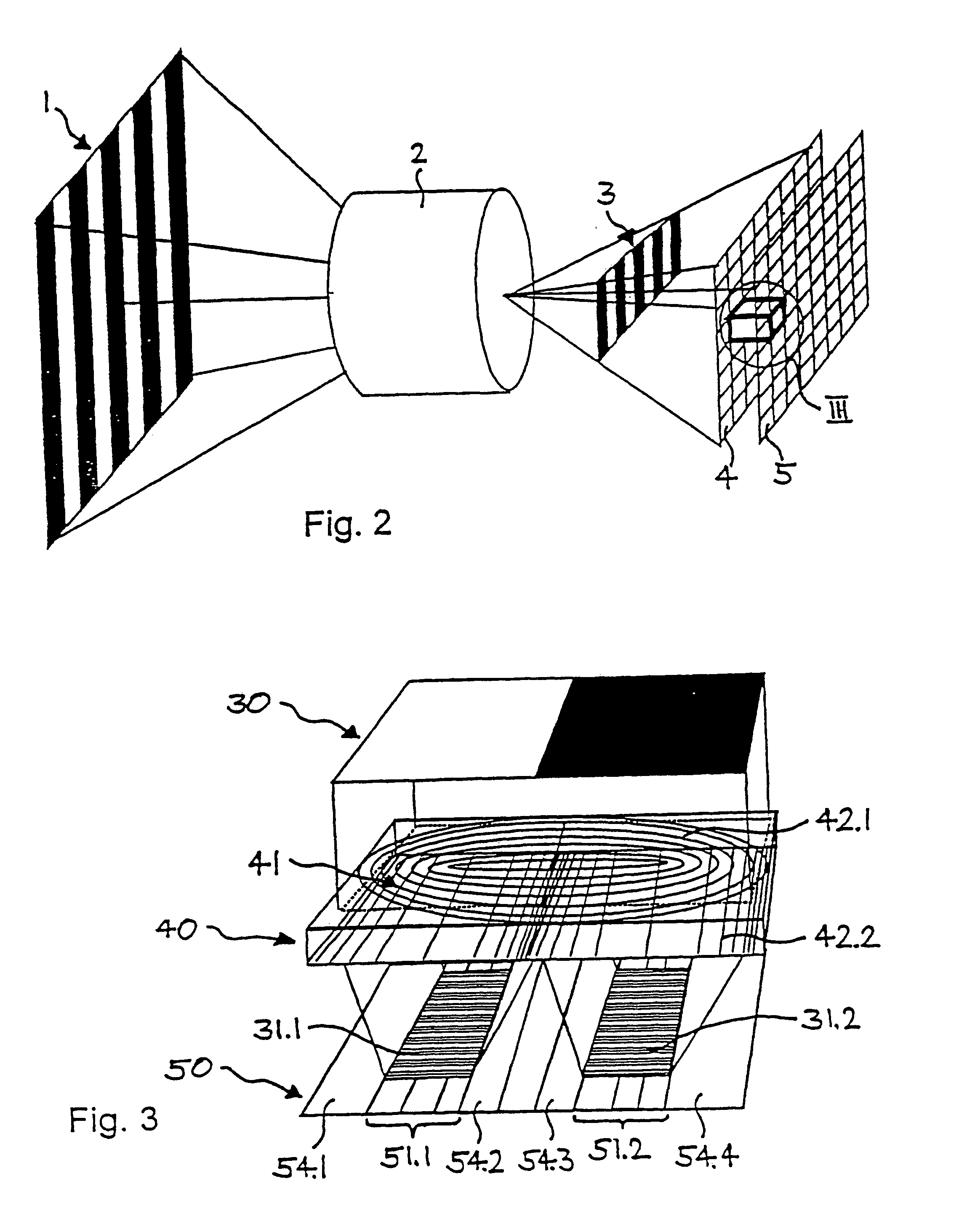

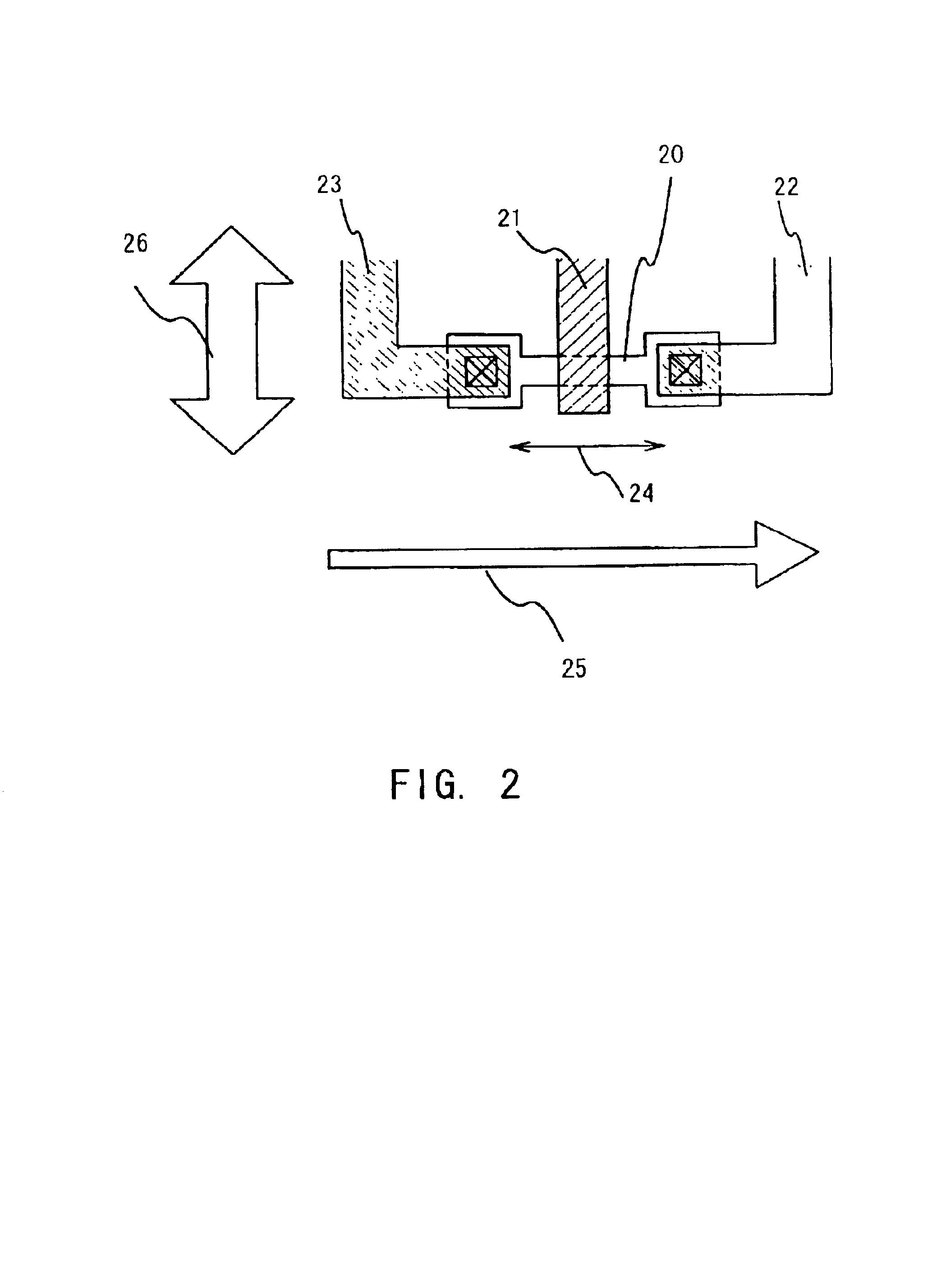

Device and method for spatially resolved photodetection and demodulation of modulated electromagnetic waves

InactiveUS7060957B2Low lighting powerExtend integration timePrismsSolid-state devicesPulse radiationData acquisition

A device and method for spatially resolved photodetection and demodulation of temporally modulated electromagnetic waves makes it possible to measure phase, amplitude and offset of a temporally modulated, spatially coded radiation field. A micro-optical element (41) spatially averages a portion (30) of the scene and equally distributes the averaged intensity on two photo sites (51.1.51.2) close to each other. Adjacent to each of these photo sites (51.1) are two storage areas (54.1, 54.2) into which charge from the photo site can be moved quickly (with a speed of several MHz to several tens or even hundreds of MHz) and accumulated essentially free of noise. This is possible by employing the charge-coupled device (CCD) principle. The device combines a high optical fill factor, insensitivity to offset errors, high sensitivity even with little light, simultaneous data acquisition, small pixel size, and maximum efficiency in use of available signal photons for sinusoidal as well as pulsed radiation signals. The device and method may be used in a time-of-flight (TOF) range imaging system without moving parts, offering 2D or 3D range data.

Owner:AMS SENSORS SINGAPORE PTE LTD

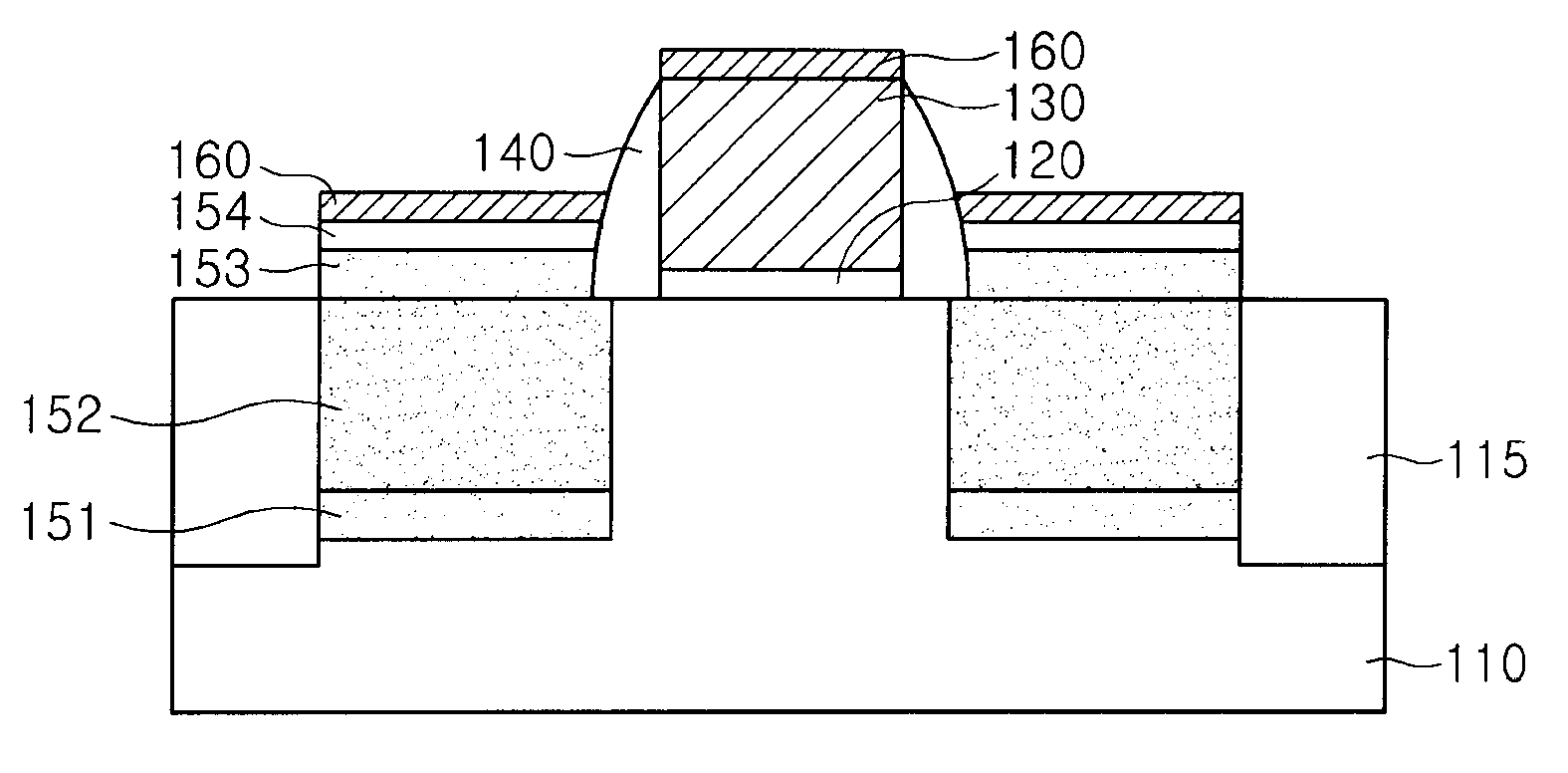

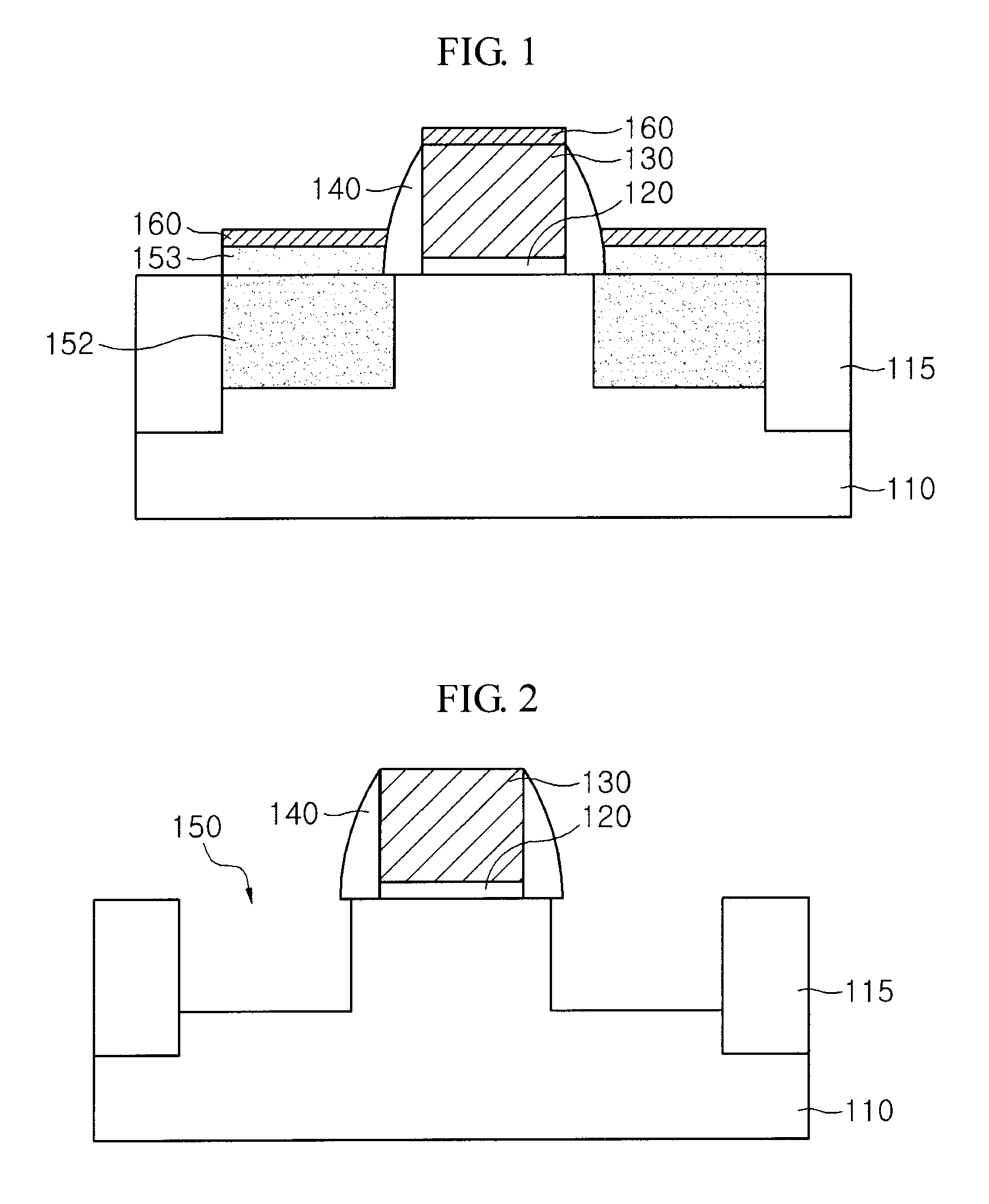

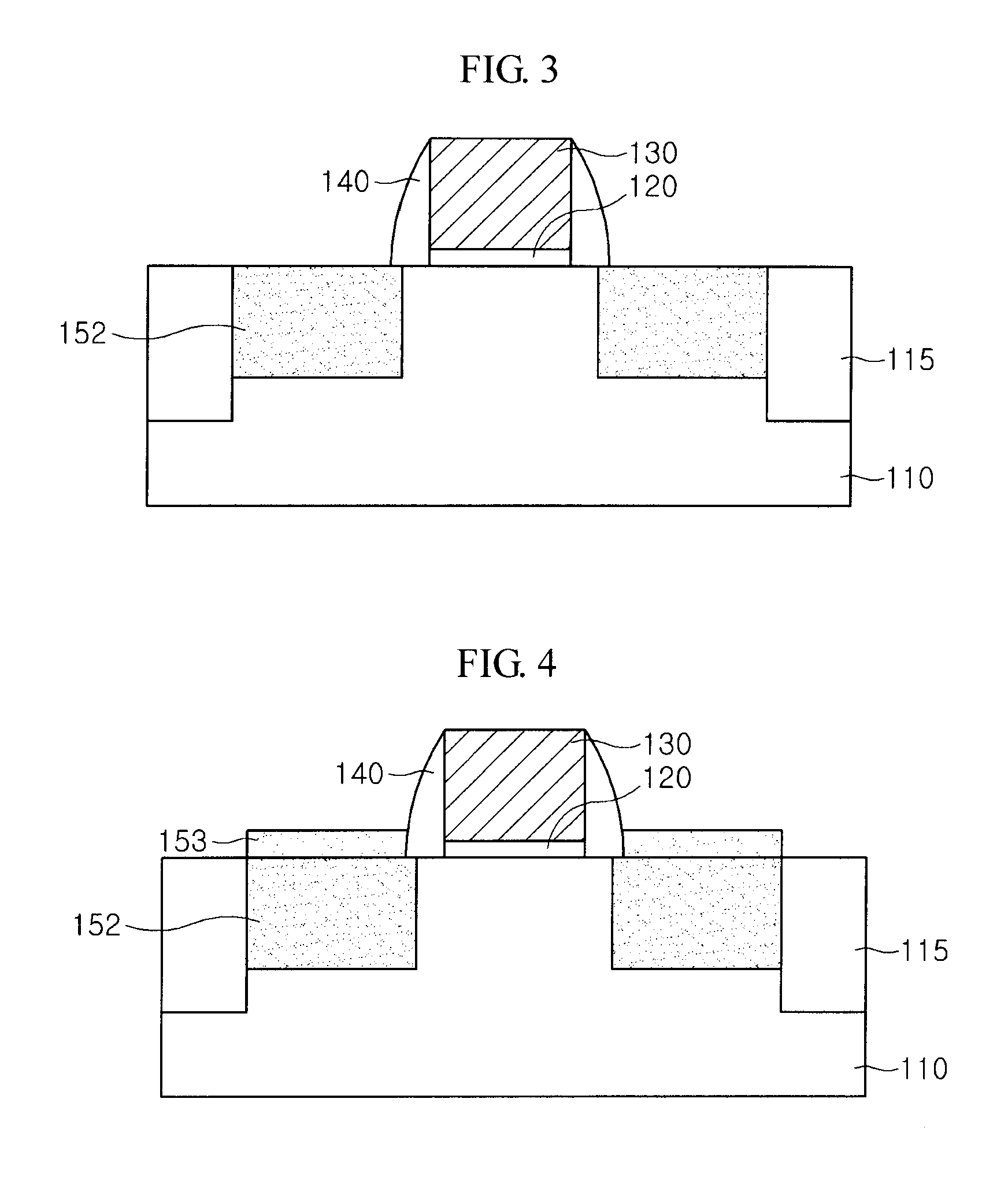

Transistor and method of fabricating the same

ActiveUS20090108308A1Improve performanceIncrease resistanceSolid-state devicesSemiconductor/solid-state device manufacturingSiliconTransistor

A transistor and a method of fabricating the same are provided. The transistor includes a SiGe epitaxial layer formed in a recess region of a substrate at both side of a gate electrode and a SiGe capping layer formed on the SiGe epitaxial layer. The transistor further includes a SiGe seed layer formed under the SiGe epitaxial layer and a silicon capping layer formed on the SiGe capping layer.

Owner:JUSUNG ENG

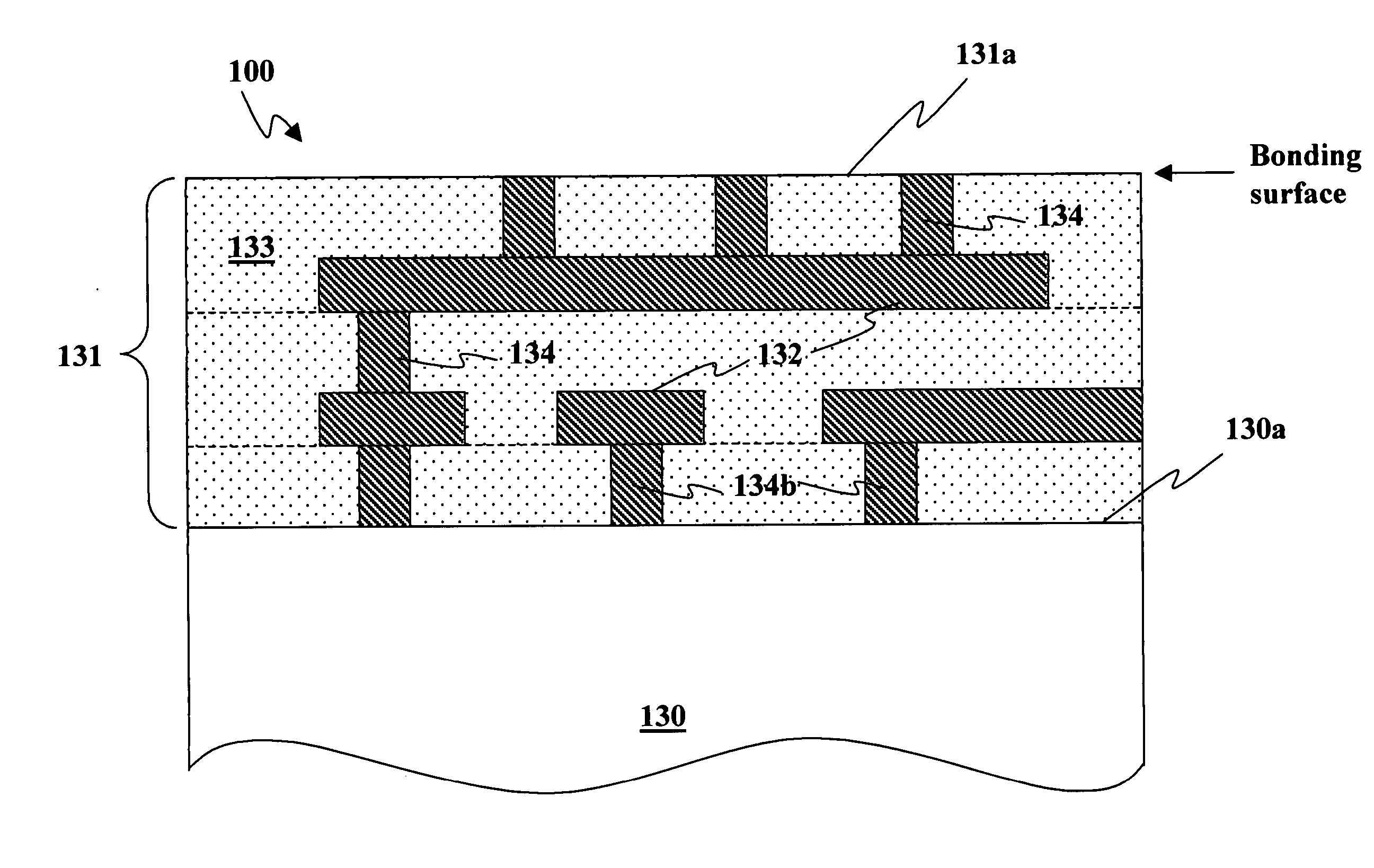

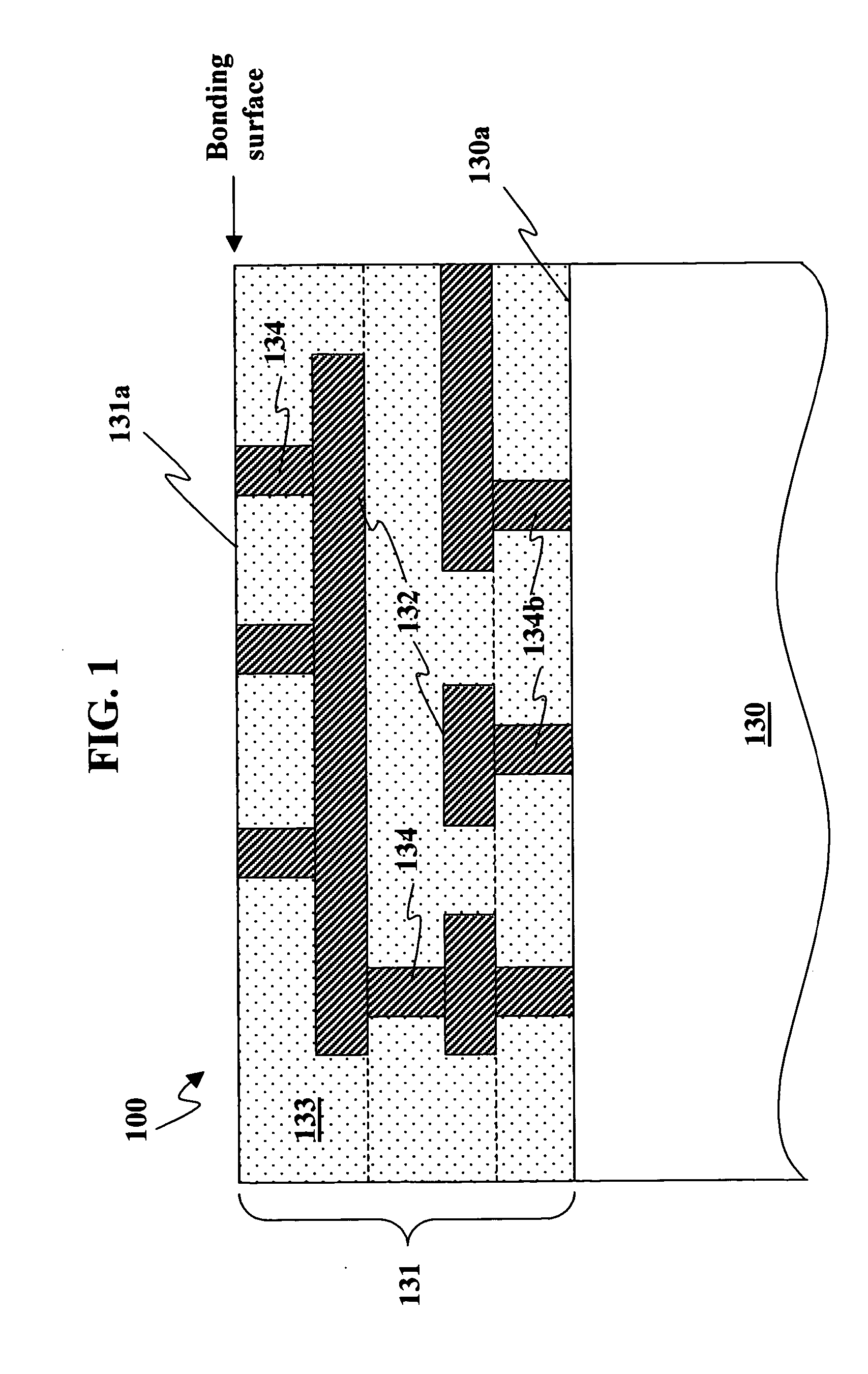

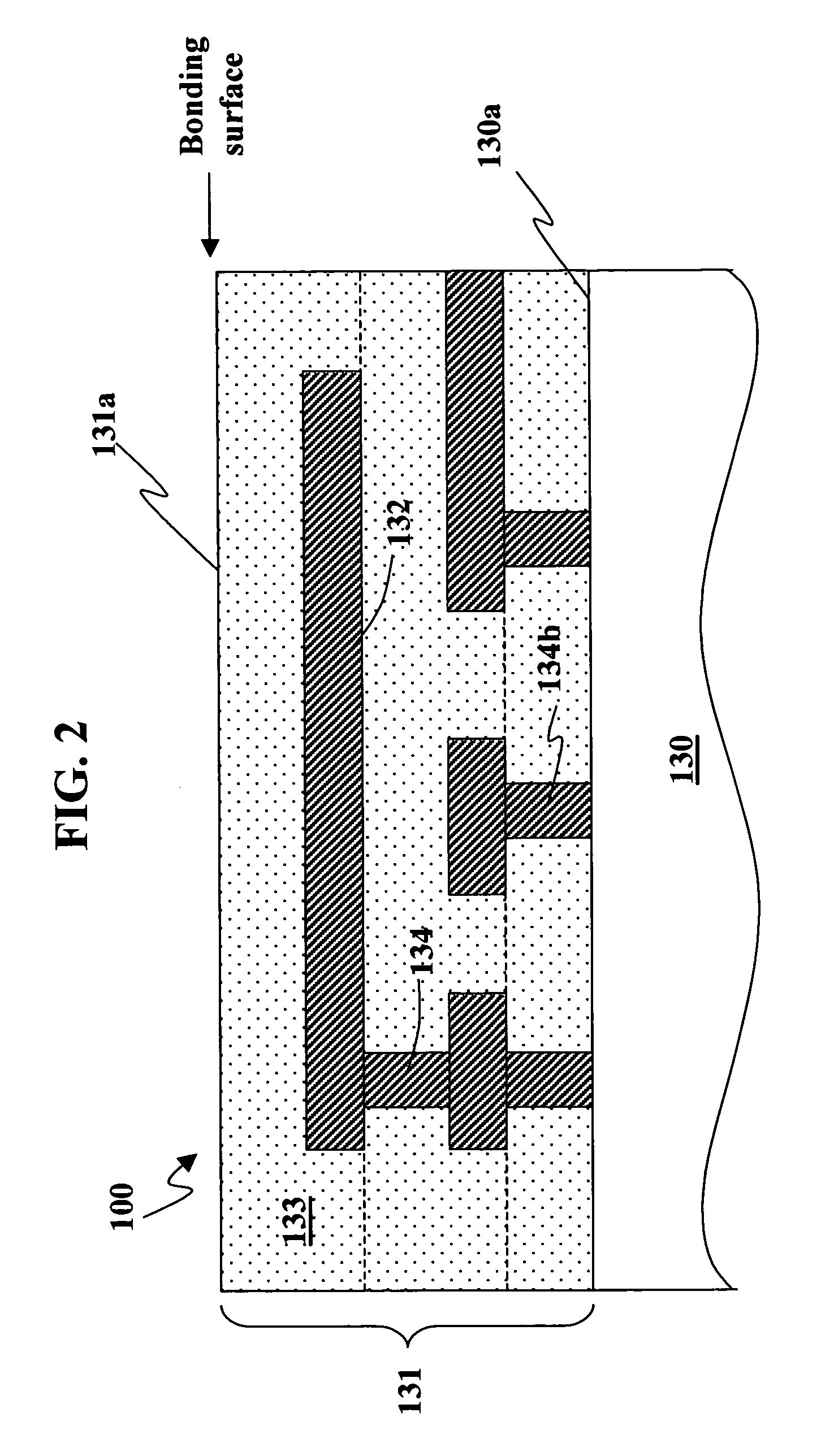

Vertical memory device structures

Vertically oriented semiconductor memory cells are added to a separately fabricated substrate that includes electrical devices and / or interconnect. The plurality of vertically oriented semiconductor memory cells are physically separated from each other, and are not disposed within the same semiconductor body. The plurality of vertically oriented semiconductor memory cells can be added to the separately fabricated substrate as a thin layer including several doped semiconductor regions which, subsequent to attachment, are etched to produce individual doped stack structures, which are then supplied with various dielectric coatings, gate electrodes, and contacts by means of further processing operations. Alternatively, the plurality of vertically oriented semiconductor memory cells may be completely fabricated prior to attachment. DRAMs, SRAMs, non-volatile memories, and combinations of memory types can be provided.

Owner:BESANG

Highly sensitive, fast pixel for use in an image sensor

ActiveUS7560701B2Overcomes speed limitationReasonable sensitivitySolid-state devicesMaterial analysis by optical meansElectric signalDemodulation

Owner:AMS SENSORS SINGAPORE PTE LTD

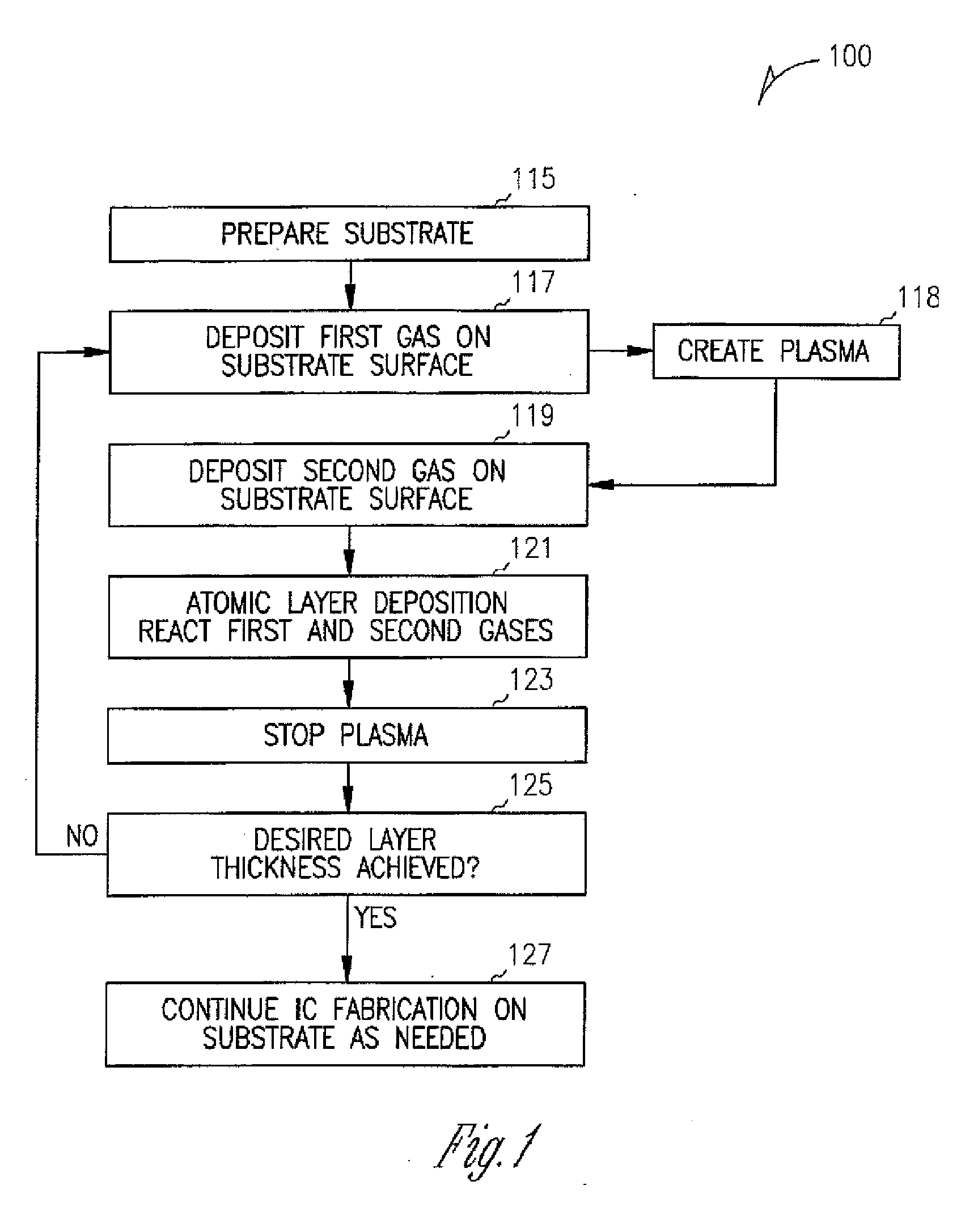

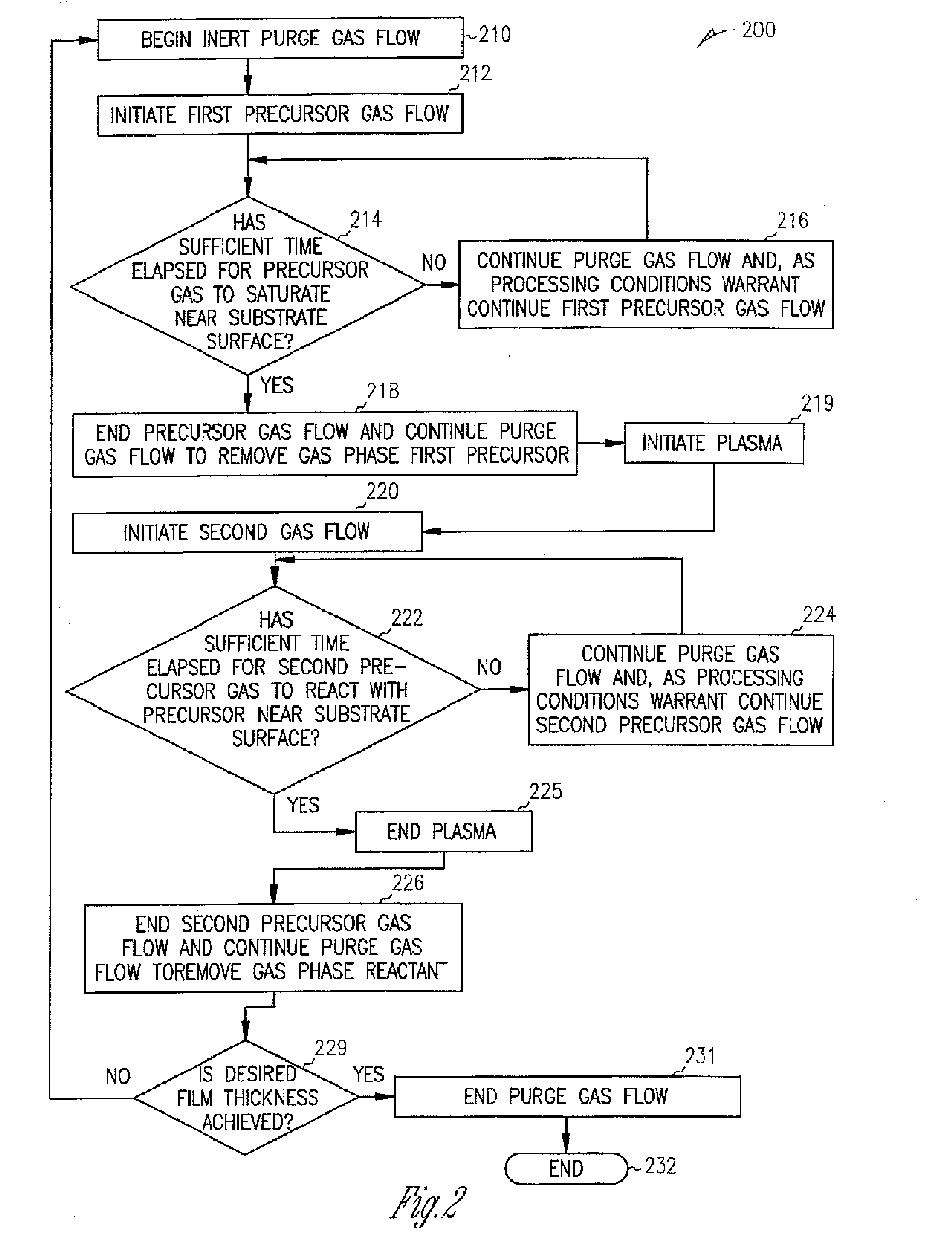

Enhanced atomic layer deposition

InactiveUS20110108929A1Enhance ALD reactionTransistorSolid-state devicesThermal energyCelsius Degree

Atomic layer deposition is enhanced using plasma. Plasma begins prior to flowing a second precursor into a chamber. The second precursor reacts with a first precursor to deposit a layer on a substrate. The layer may include at least one element from each of the first and second precursors. The layer may be TaN, and the precursors may be TaF5 and NE3. The plasma may begin during purge gas flow between a pulse of the first precursor and a pulse of the second precursor. Thermal energy assists the reaction of the precursors to deposit the layer on the substrate. The thermal energy may be greater than generally accepted for ALD (e.g., more than 300 degrees Celsius).

Owner:ROUND ROCK RES LLC

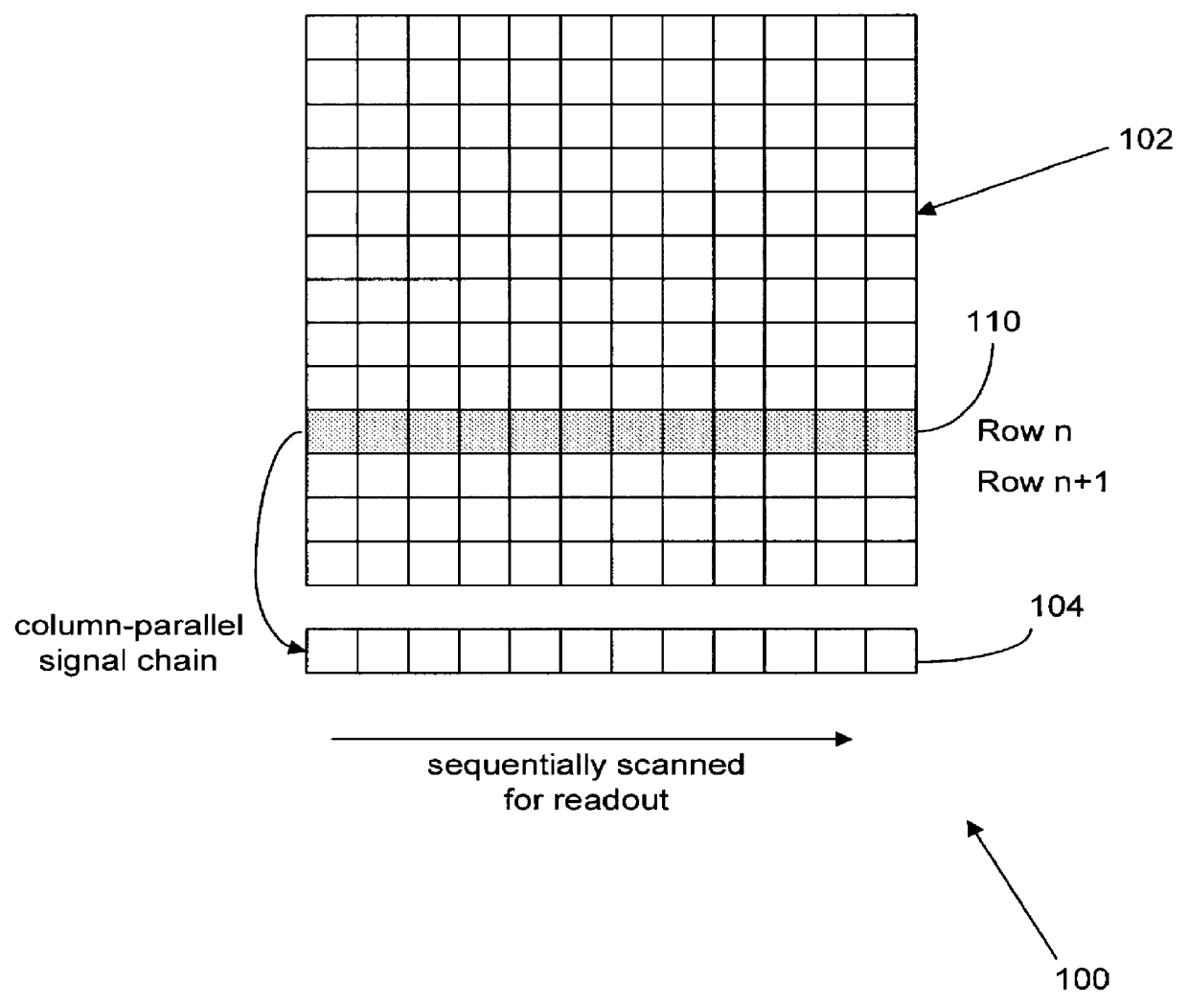

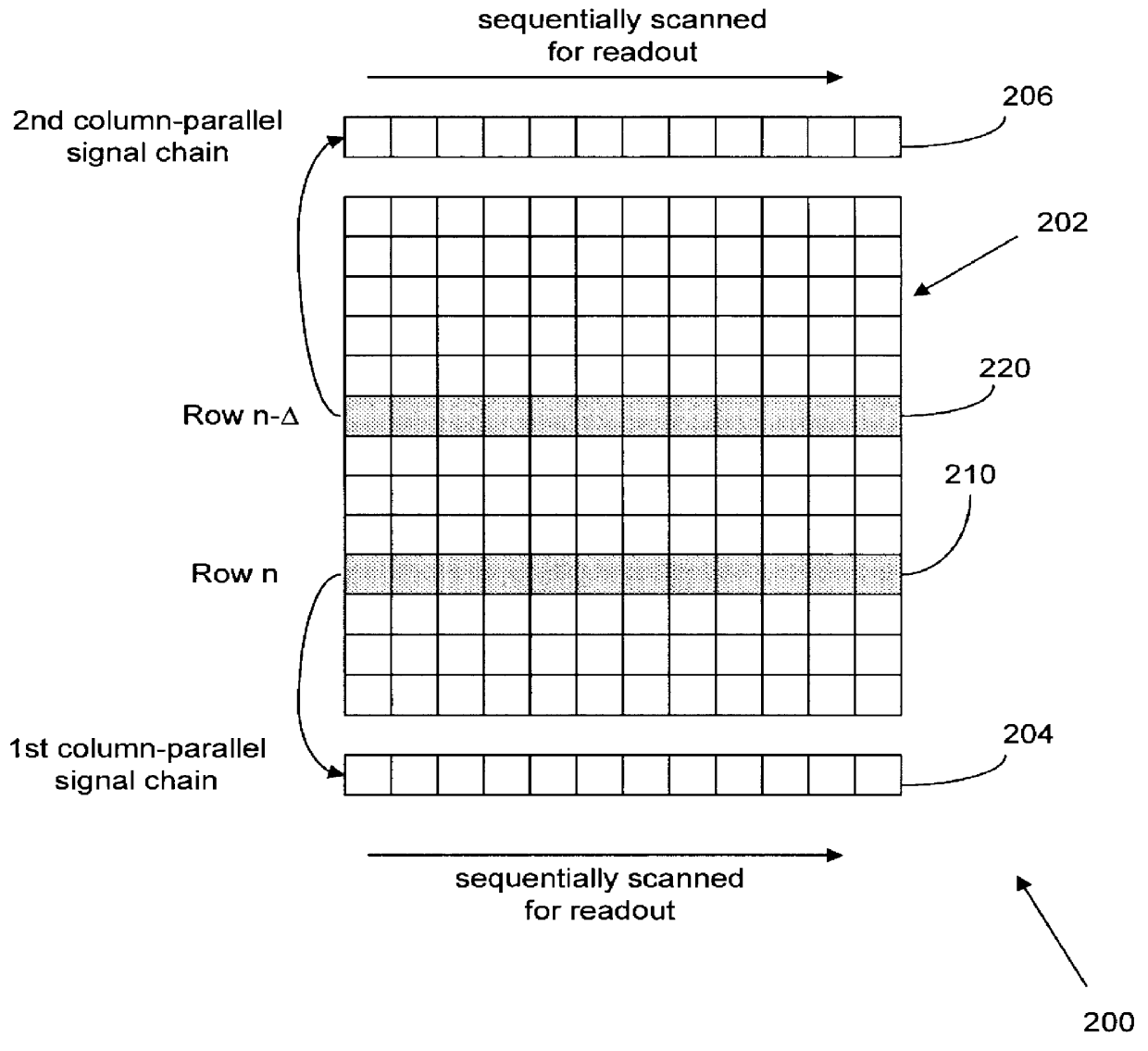

Image sensor producing at least two integration times from each sensing pixel

InactiveUS6115065AIncrease flexibilityImprove performanceTelevision system detailsTelevision system scanning detailsHigh frame rateComputer science

Designs and operational methods to increase the dynamic range of image sensors and APS devices in particular by achieving more than one integration times for each pixel thereof. An APS system with more than one column-parallel signal chains for readout are described for maintaining a high frame rate in readout. Each active pixel is sampled for multiple times during a single frame readout, thus resulting in multiple integration times. The operation methods can also be used to obtain multiple integration times for each pixel with an APS design having a single column-parallel signal chain for readout. Furthermore, analog-to-digital conversion of high speed and high resolution can be implemented.

Owner:CALIFORNIA INST OF TECH

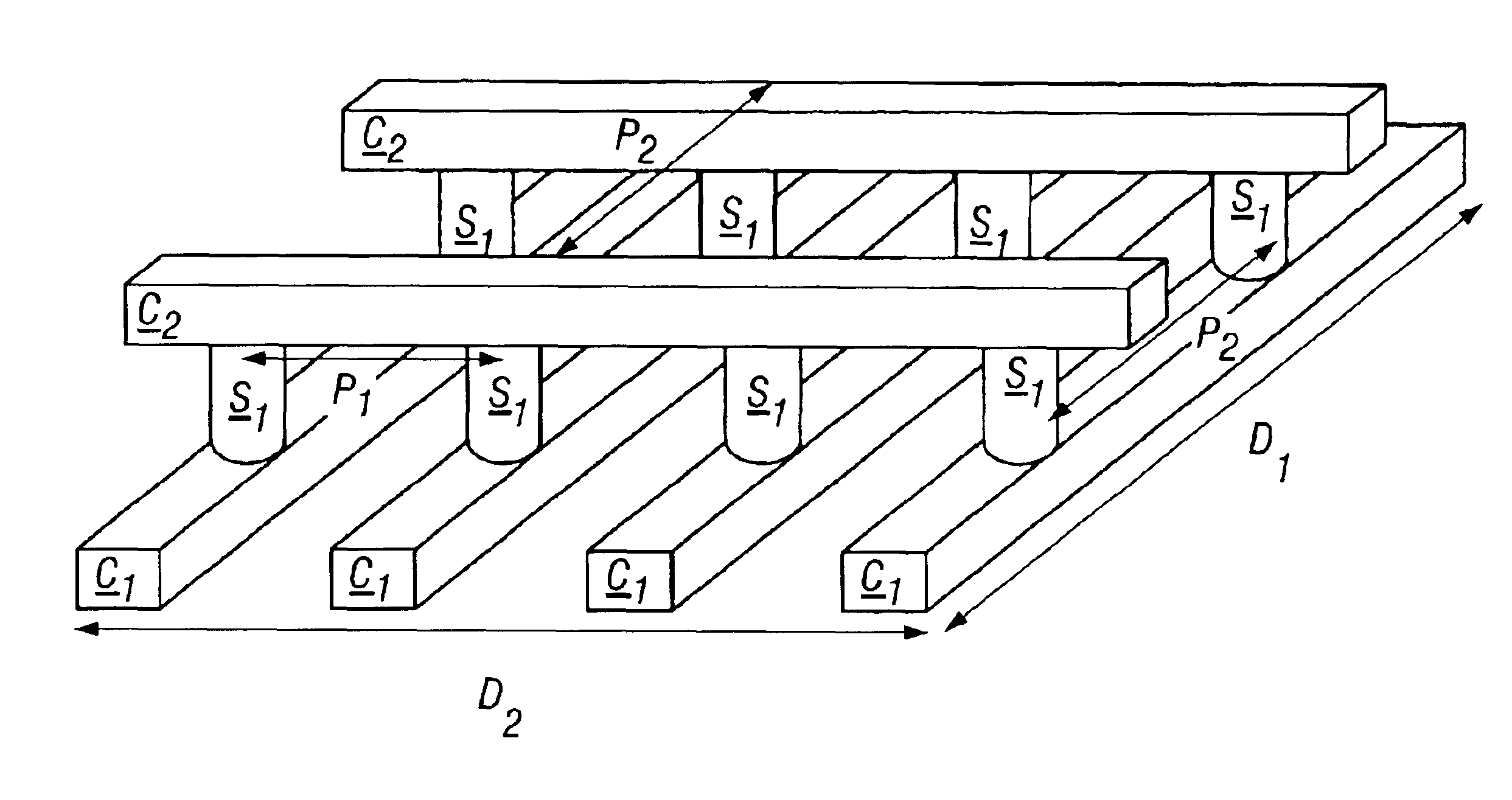

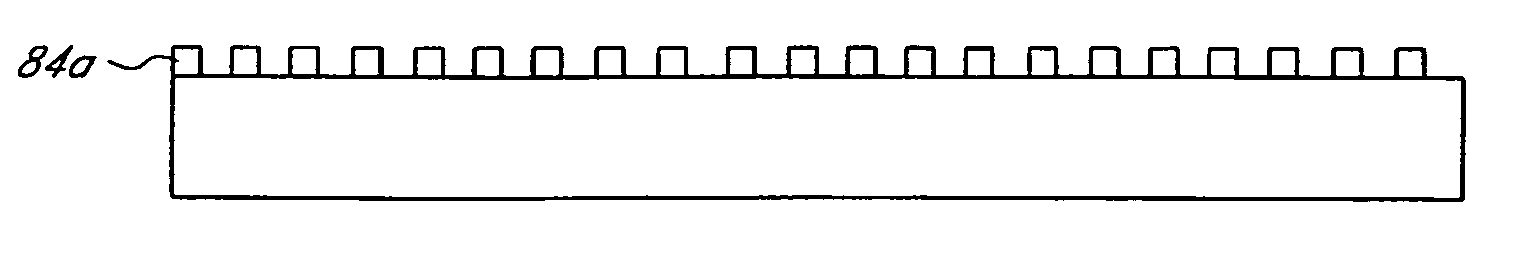

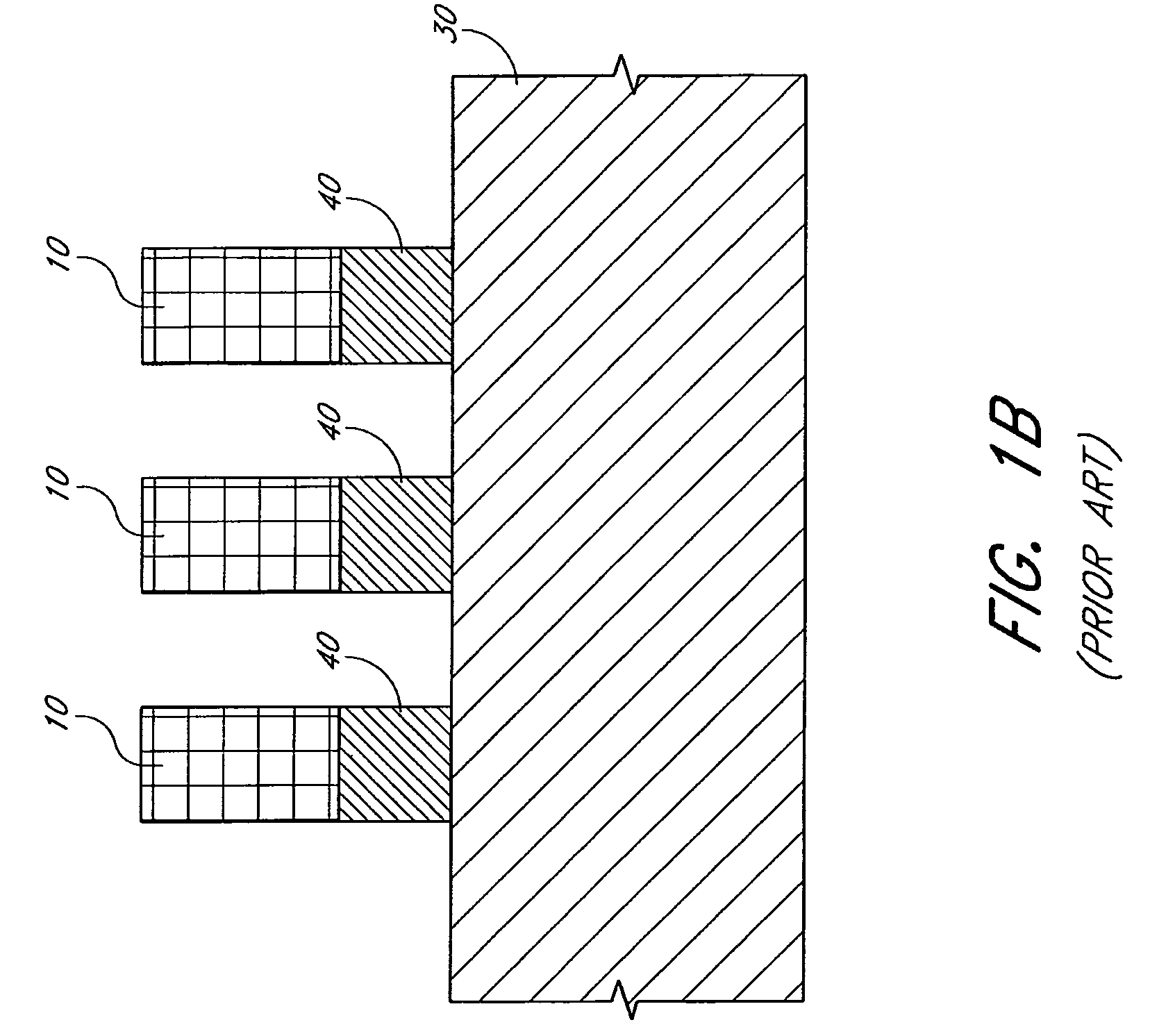

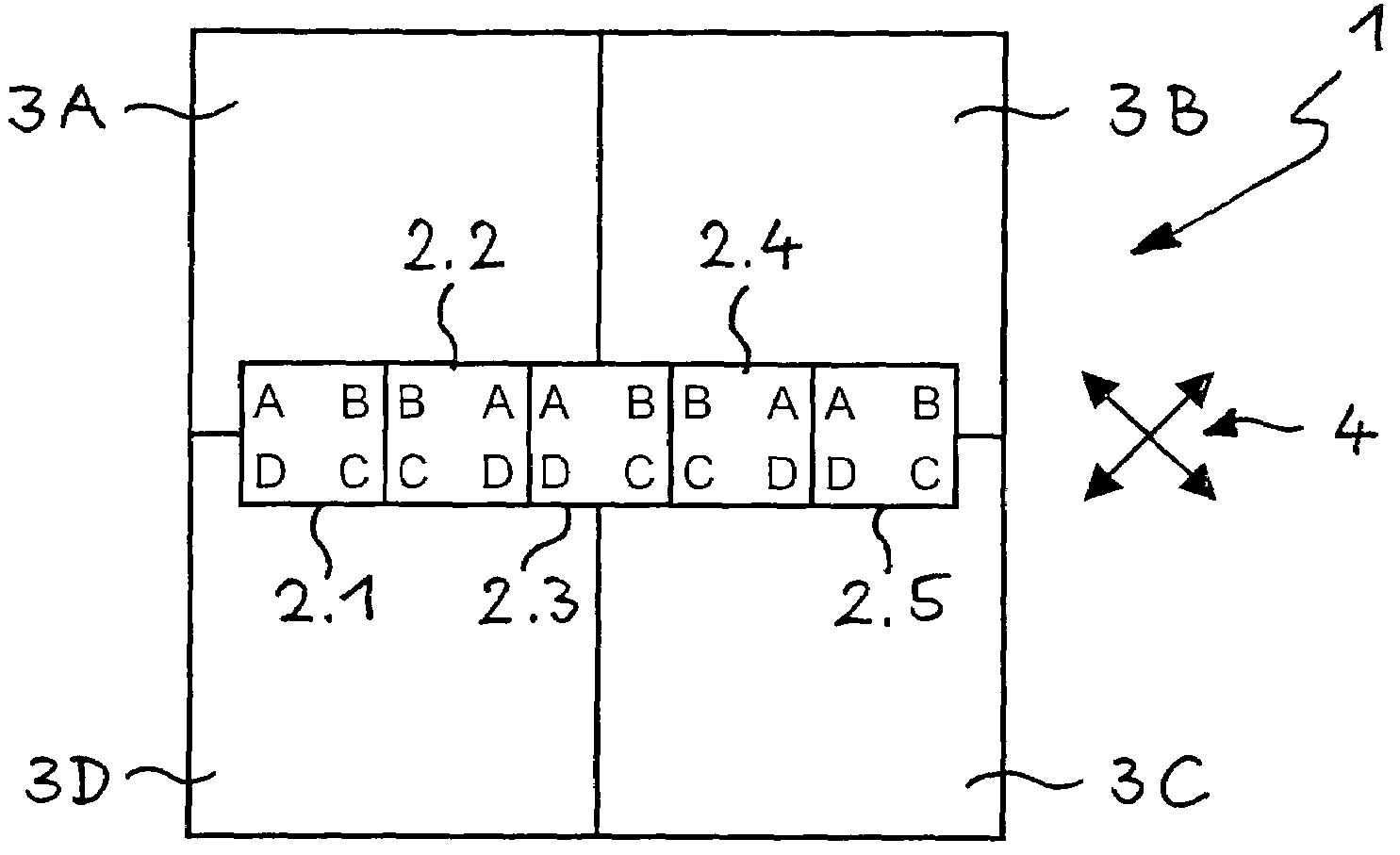

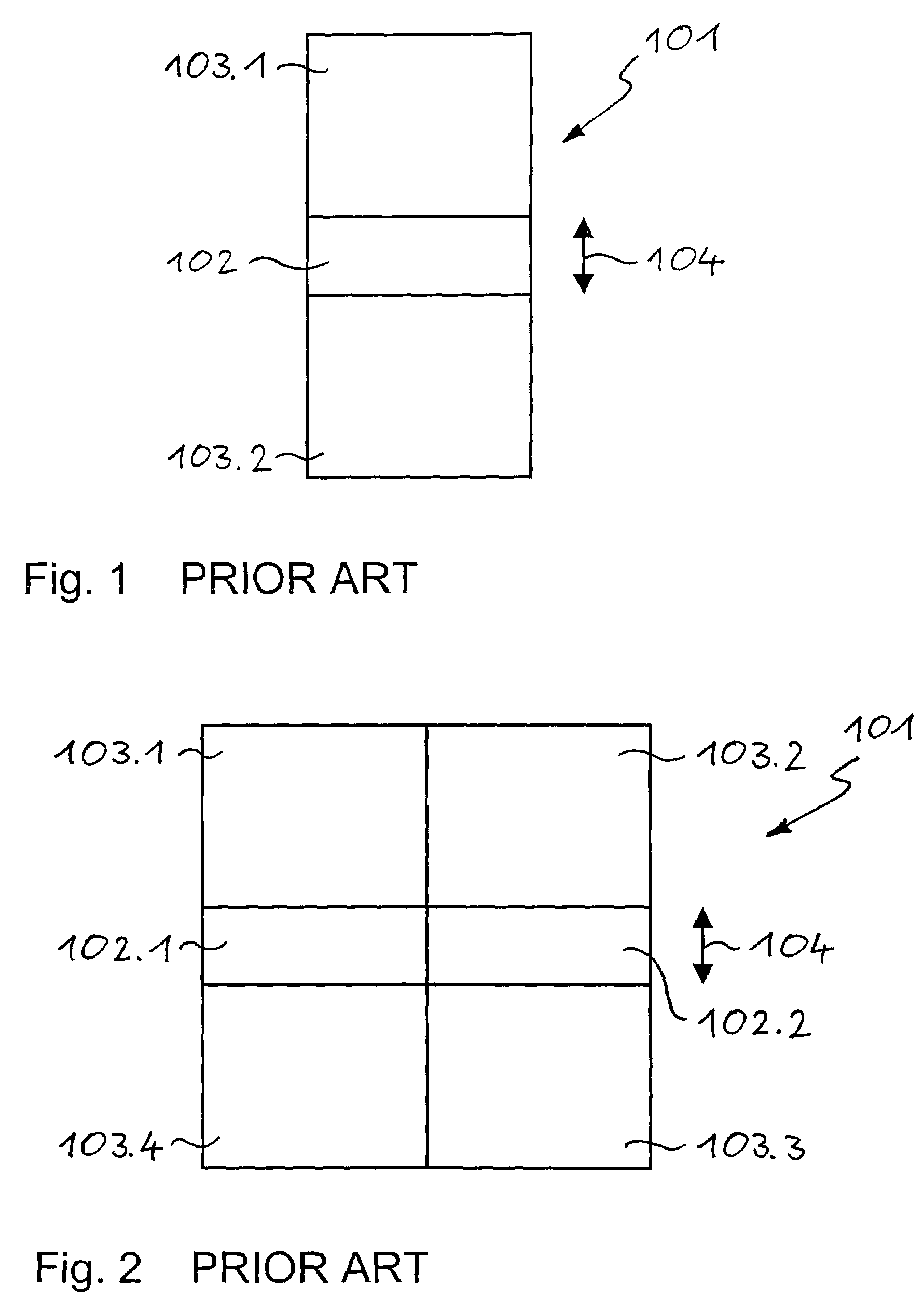

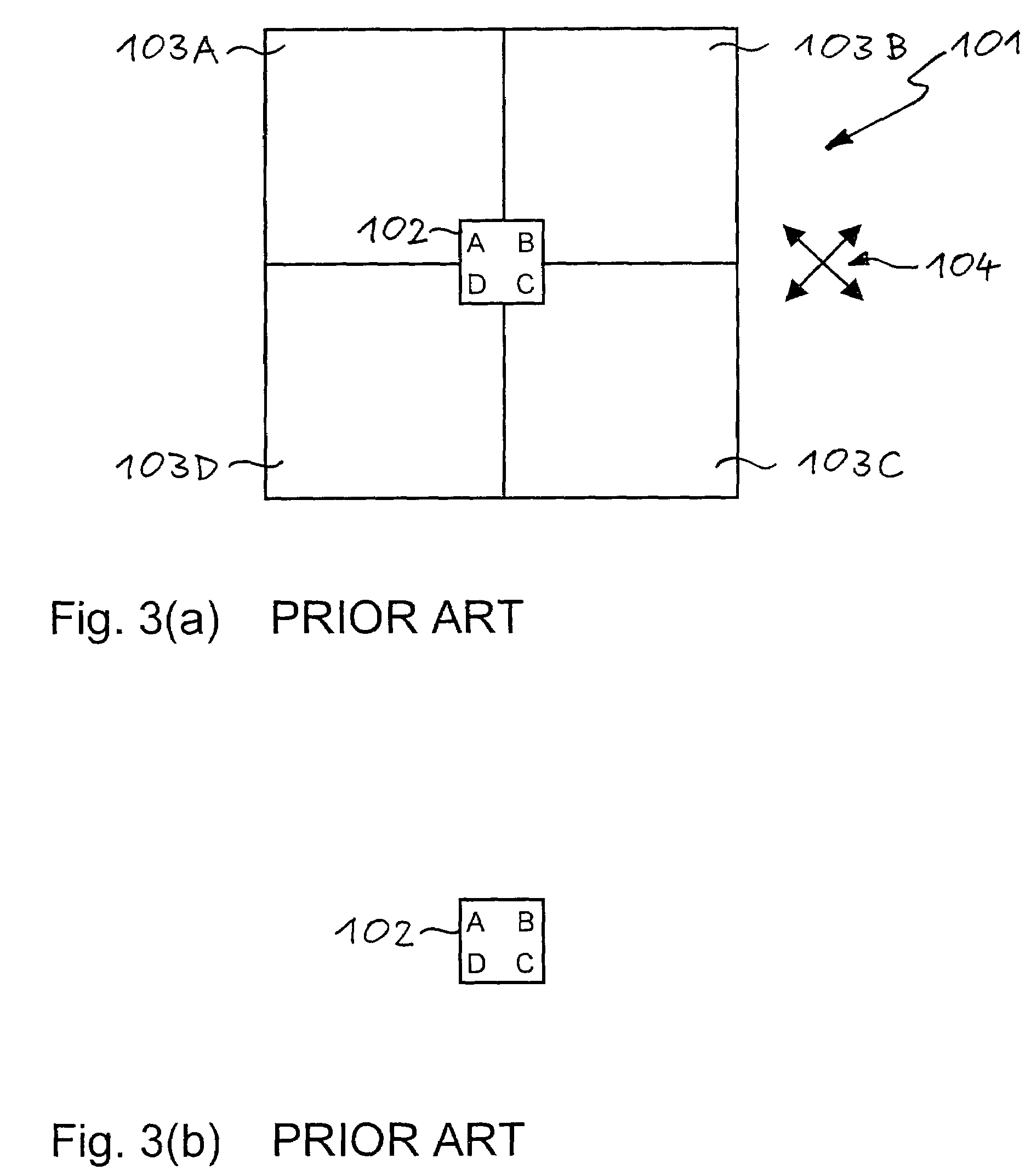

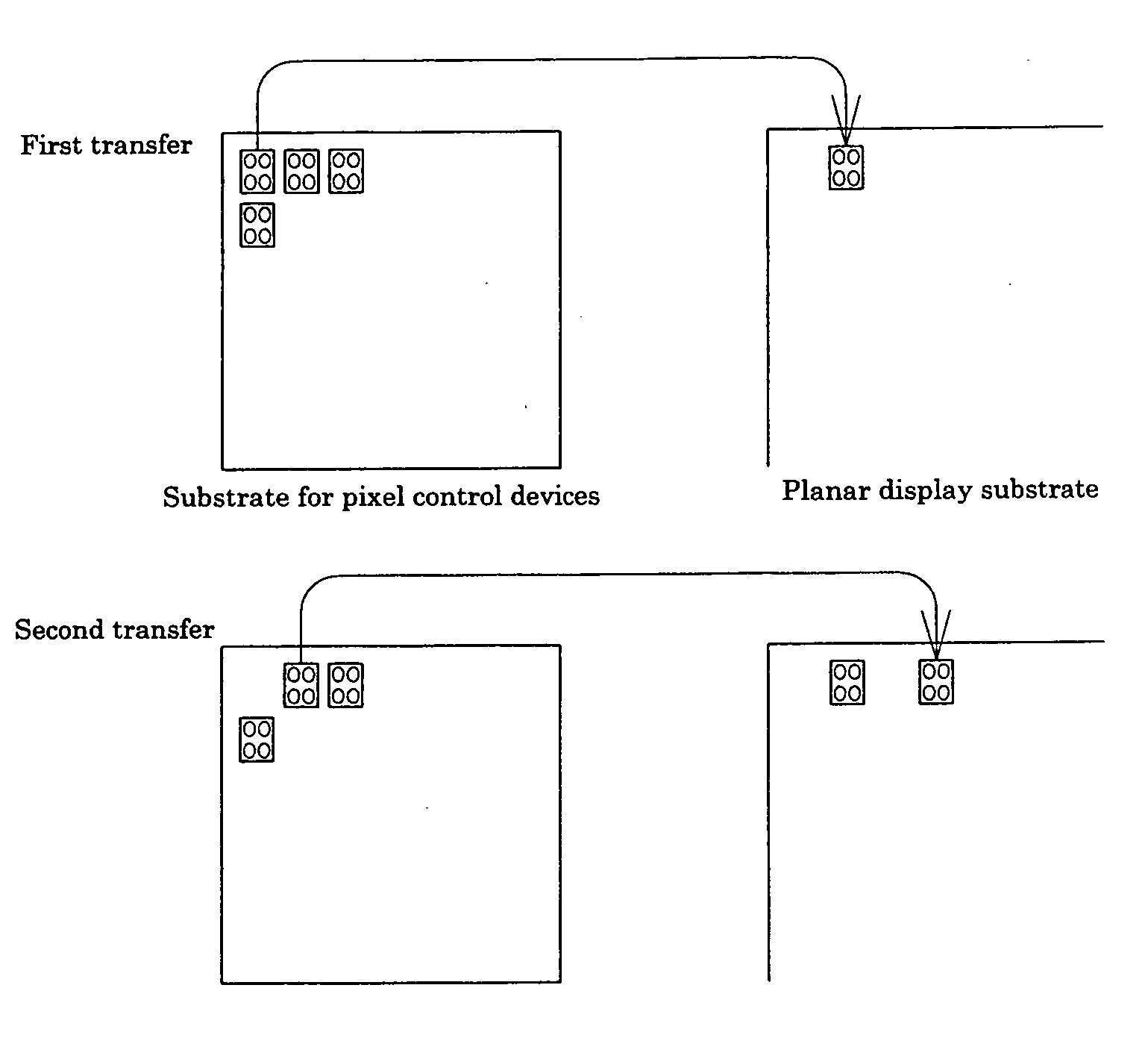

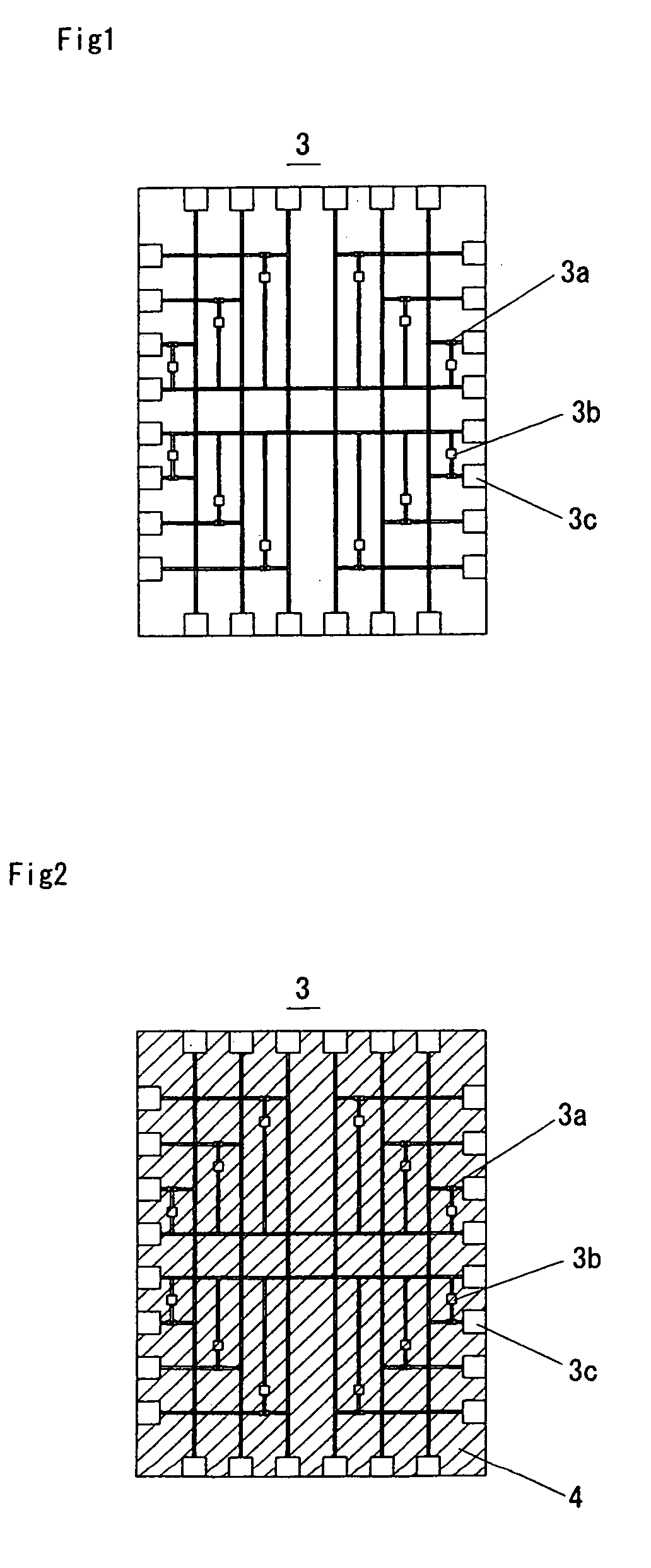

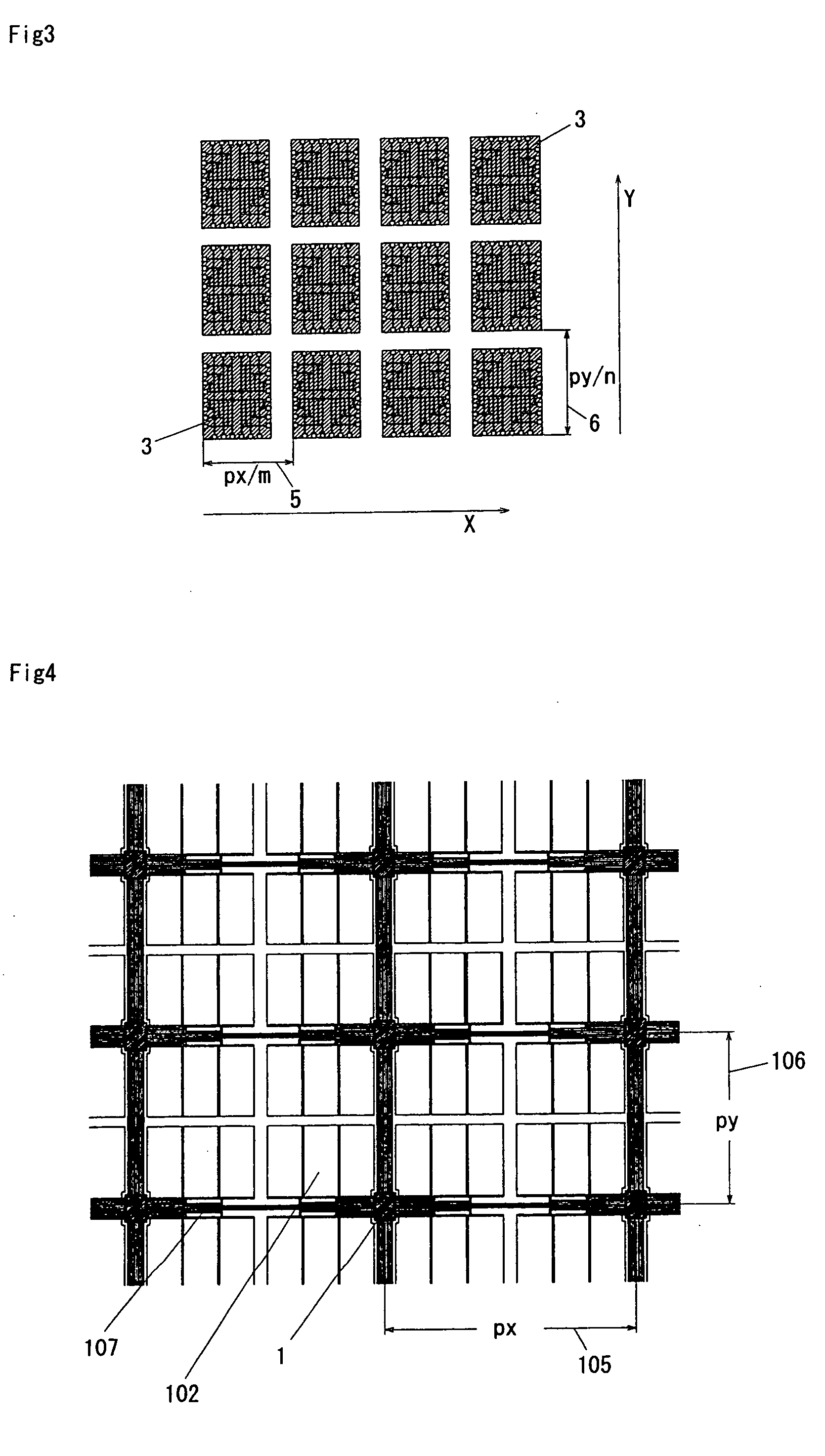

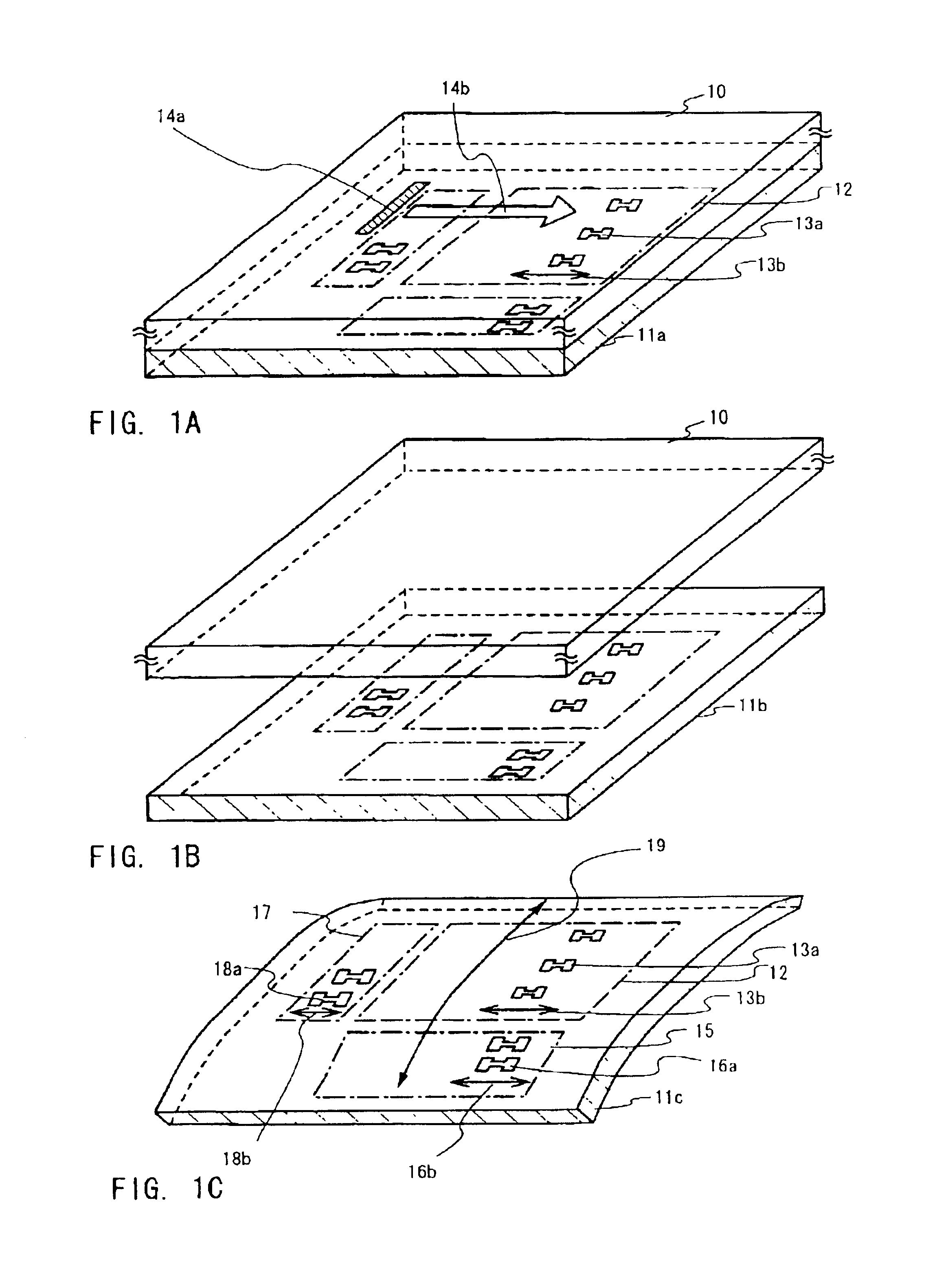

Pixel control element selection transfer method, pixel control device mounting device used for pixel control element selection transfer method, wiring formation method after pixel control element transfer, and planar display substrate

InactiveUS20060055864A1Stable formationEasy to operateSolid-state devicesSemiconductor/solid-state device manufacturingComputer science

There is provided a method for selectively transferring pixel control devices onto a planar display substrate, which method enables prepared pixel control devices to be easily, reliably and inexpensively mounted without inducing any loss of pixel control devices. The pixel control devices (1) are formed in a large number at pitches (5, 6) obtained respectively by dividing pitches (105, 106) on the planar display substrate (100) by natural numbers. The pixel control devices corresponding to the number of the pitches (105, 106) on the planar display substrate (100) are picked up, retained on a transparent thermoplastic resin film (101) formed on the planar display substrate (100) utilizing the plastic deformation of the film and fixed at the peripheries thereof with a transparent ultraviolet curing resin film (104).

Owner:MATSUMURA HIDEKI

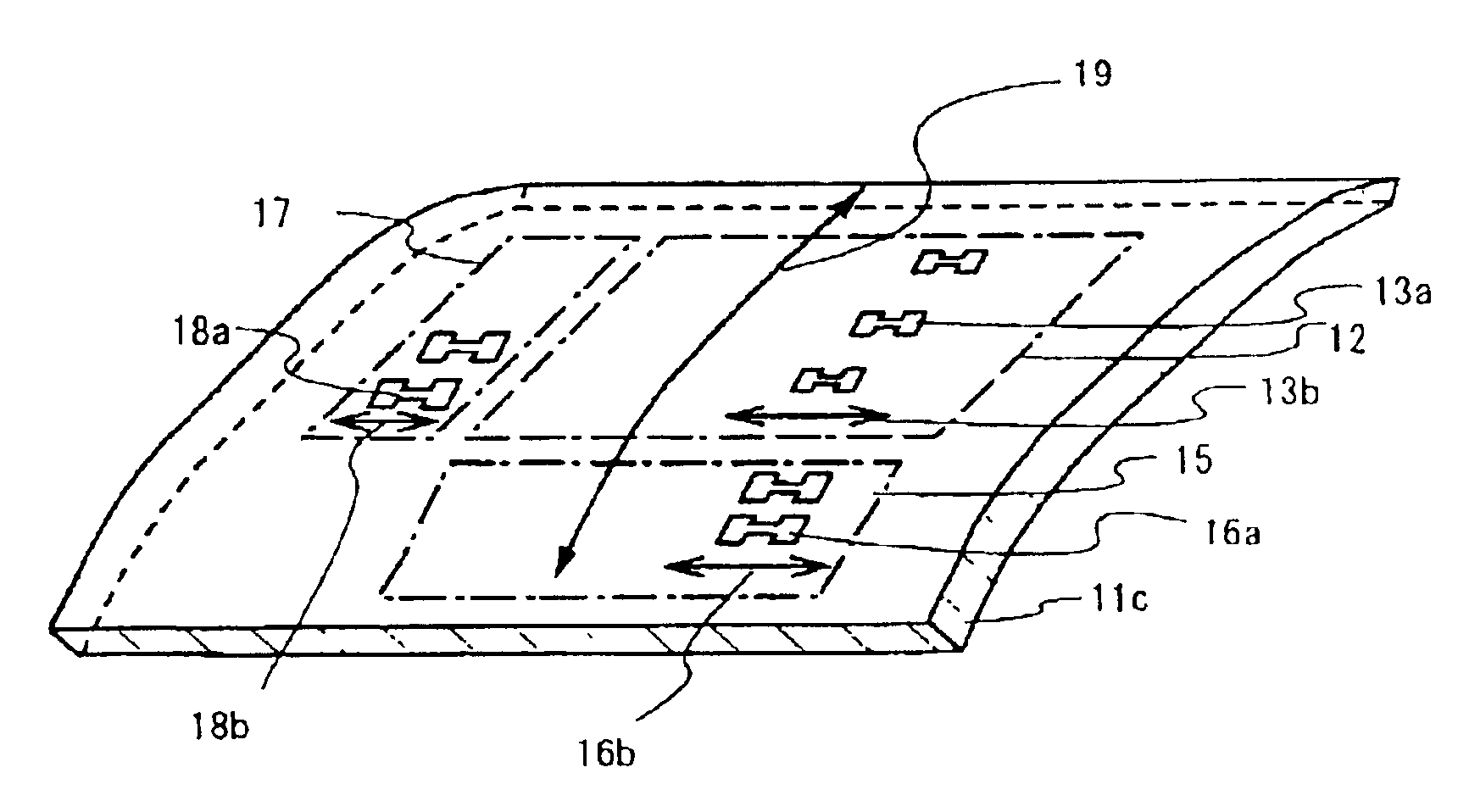

Semiconductor device and manufacturing method thereof

InactiveUS7180091B2Minimize impactSeparate cleanTransistorSolid-state devicesDriver circuitEngineering

The invention relates to a semiconductor device including a plurality of thin film transistors provided on a base member having a curved surface. The surface may be bent in either a convex shape or a concave shape. All channel length directions of the plurality of thin film transistors may also be aligned in the same direction. Further, the channel length direction may be different from the direction in which the base member is bent. A pixel portion and a driver circuit portion may also be provided on the base member. The invention also includes a method of manufacturing a semiconductor device including forming a layer to be peeled including an element of a substrate, bonding a support member to the layer to be peeled, and bonding a transfer body to the layer to be peeled.

Owner:SEMICON ENERGY LAB CO LTD

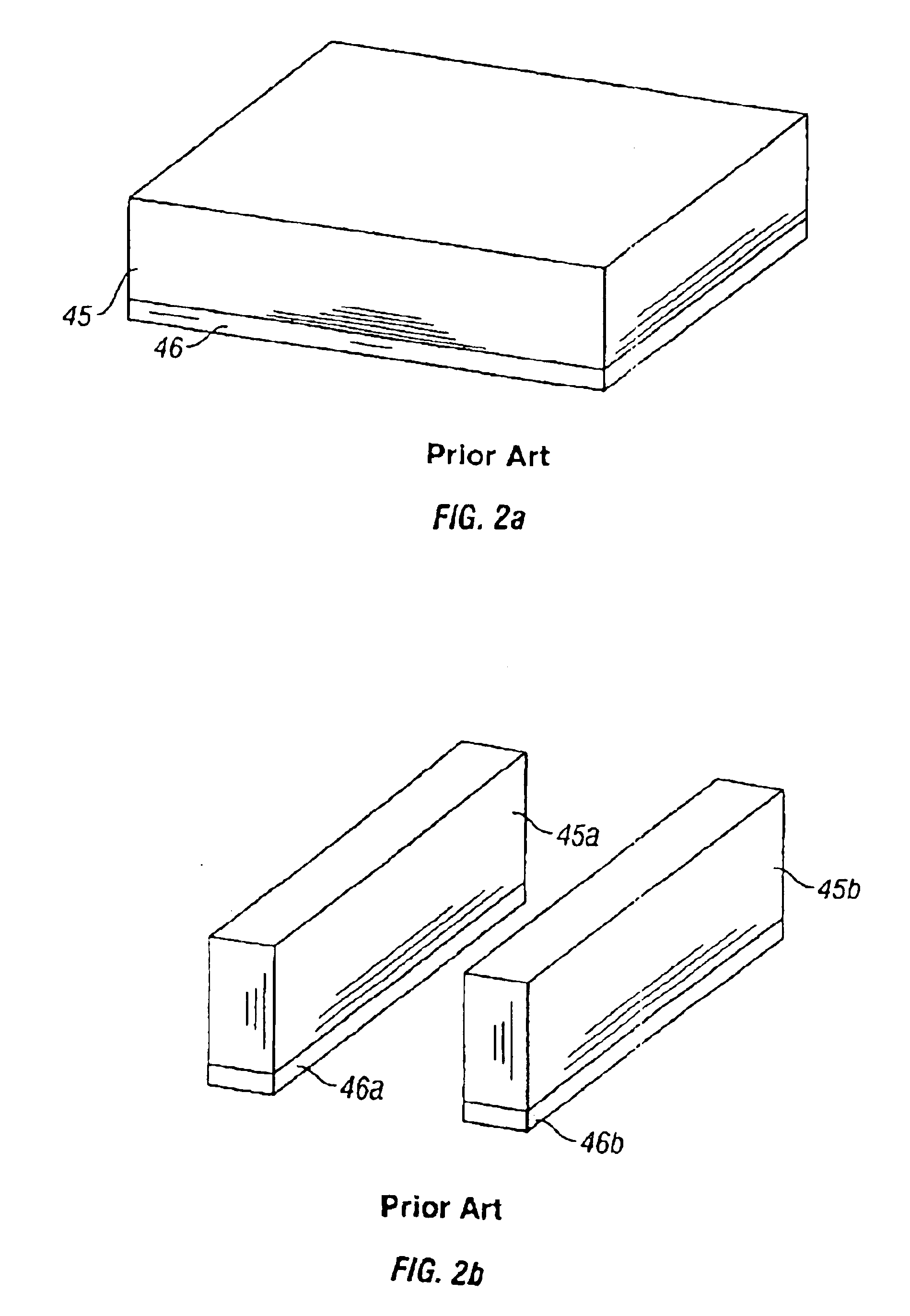

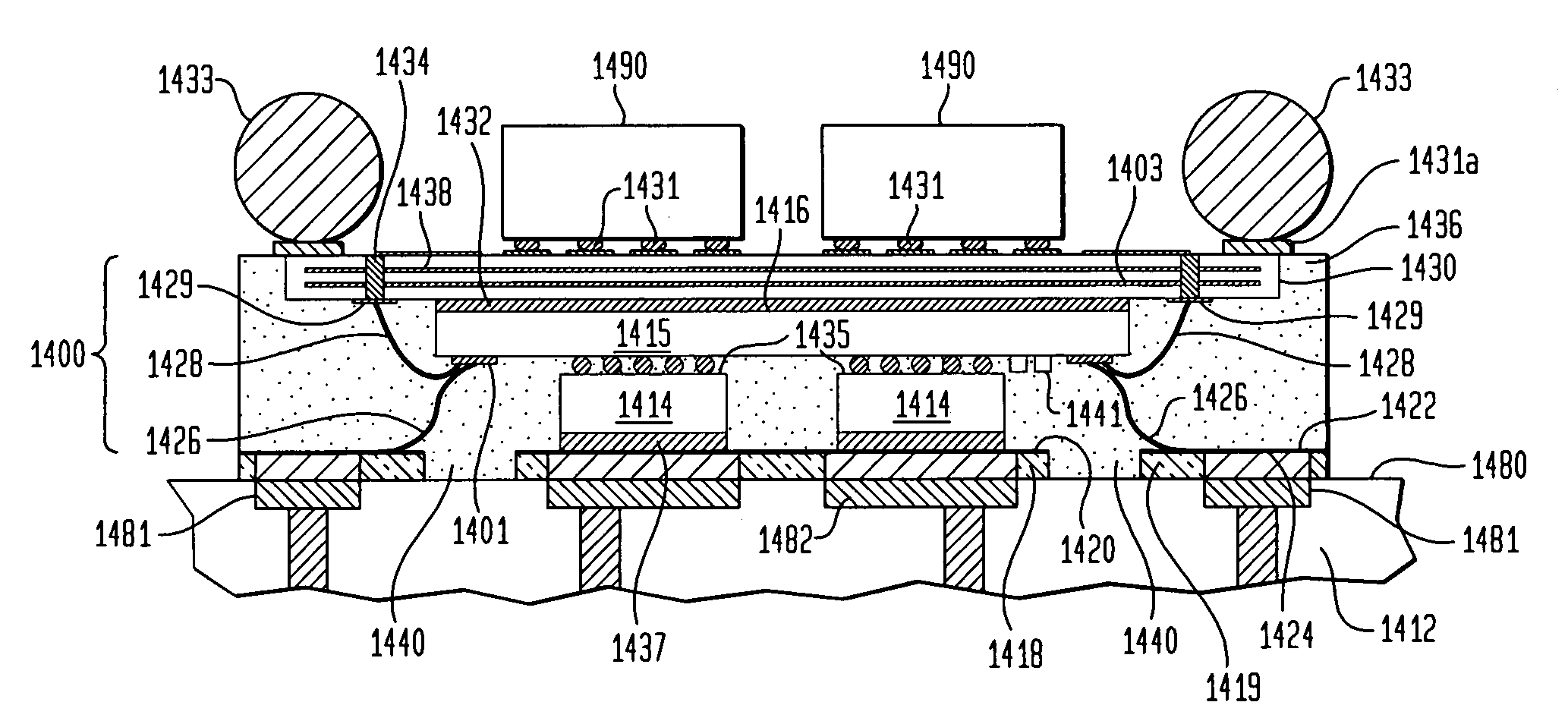

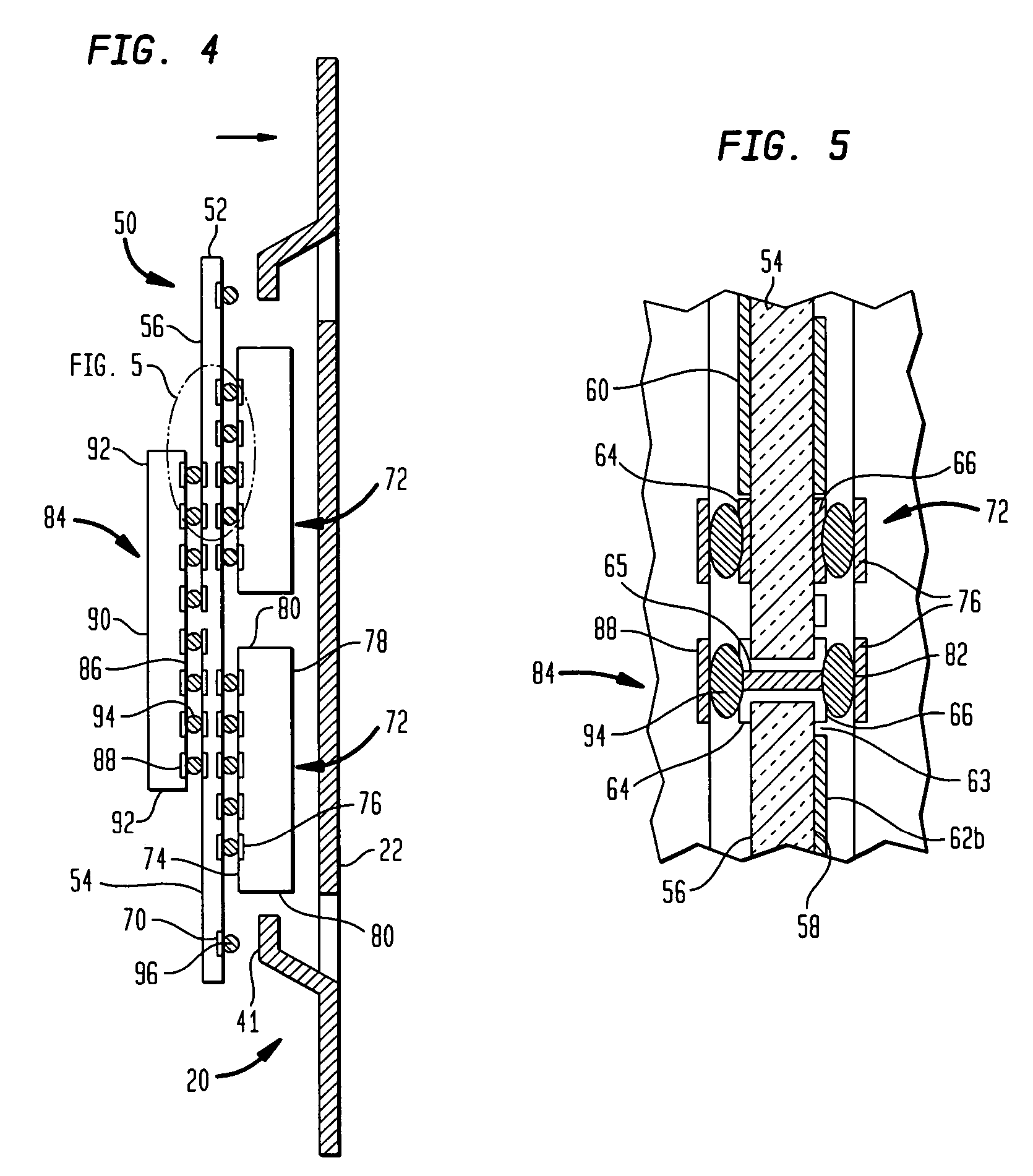

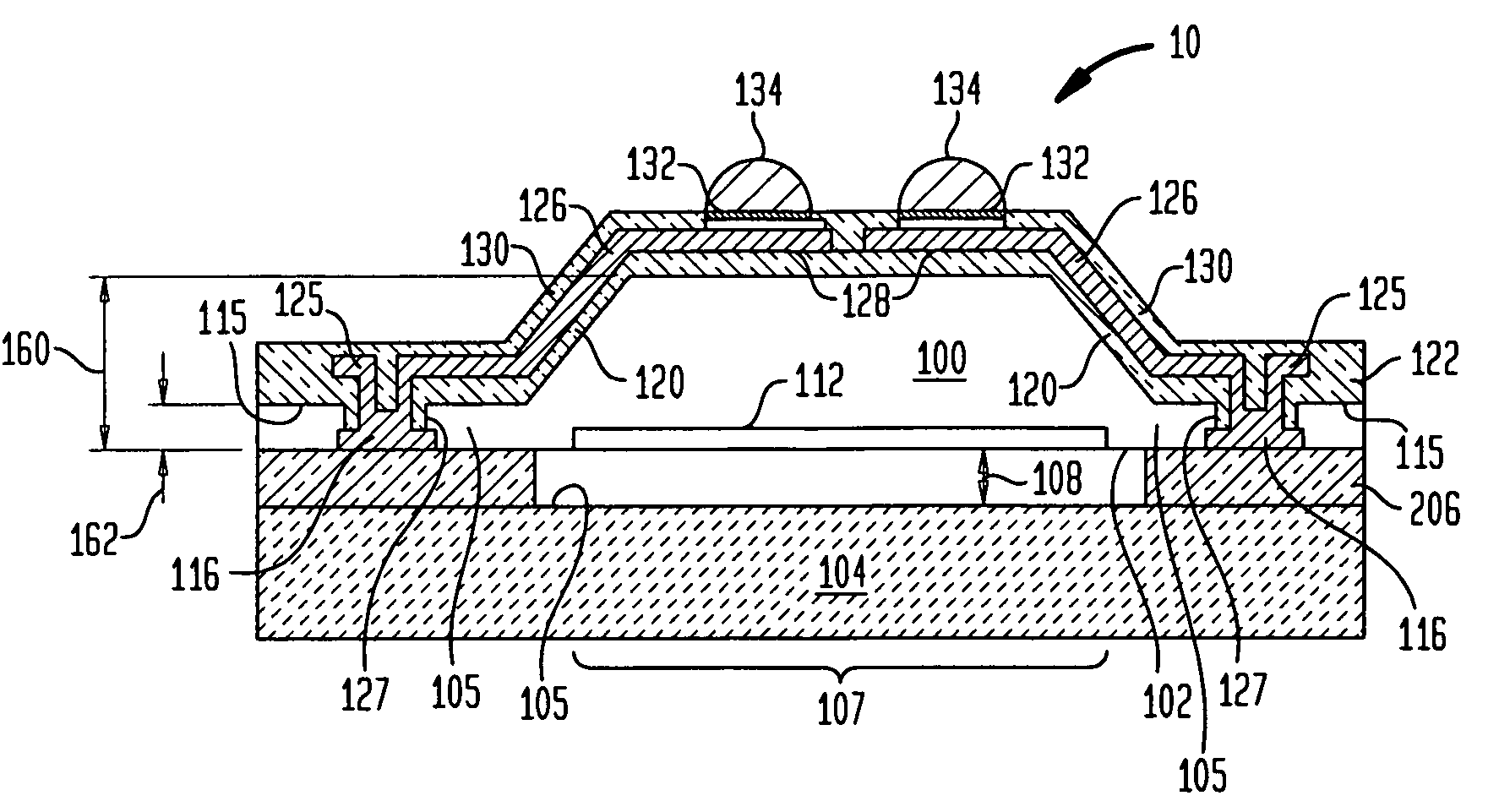

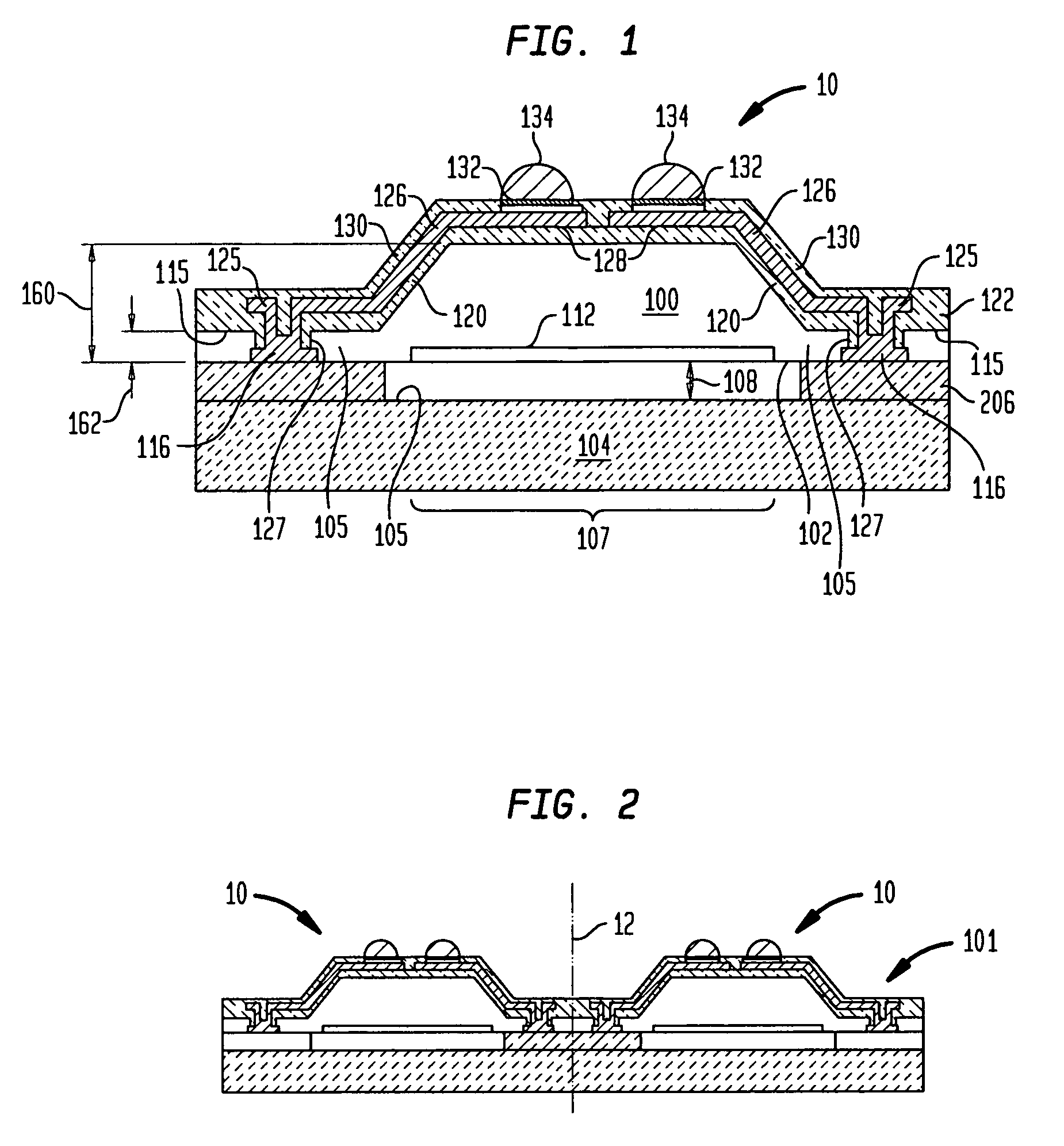

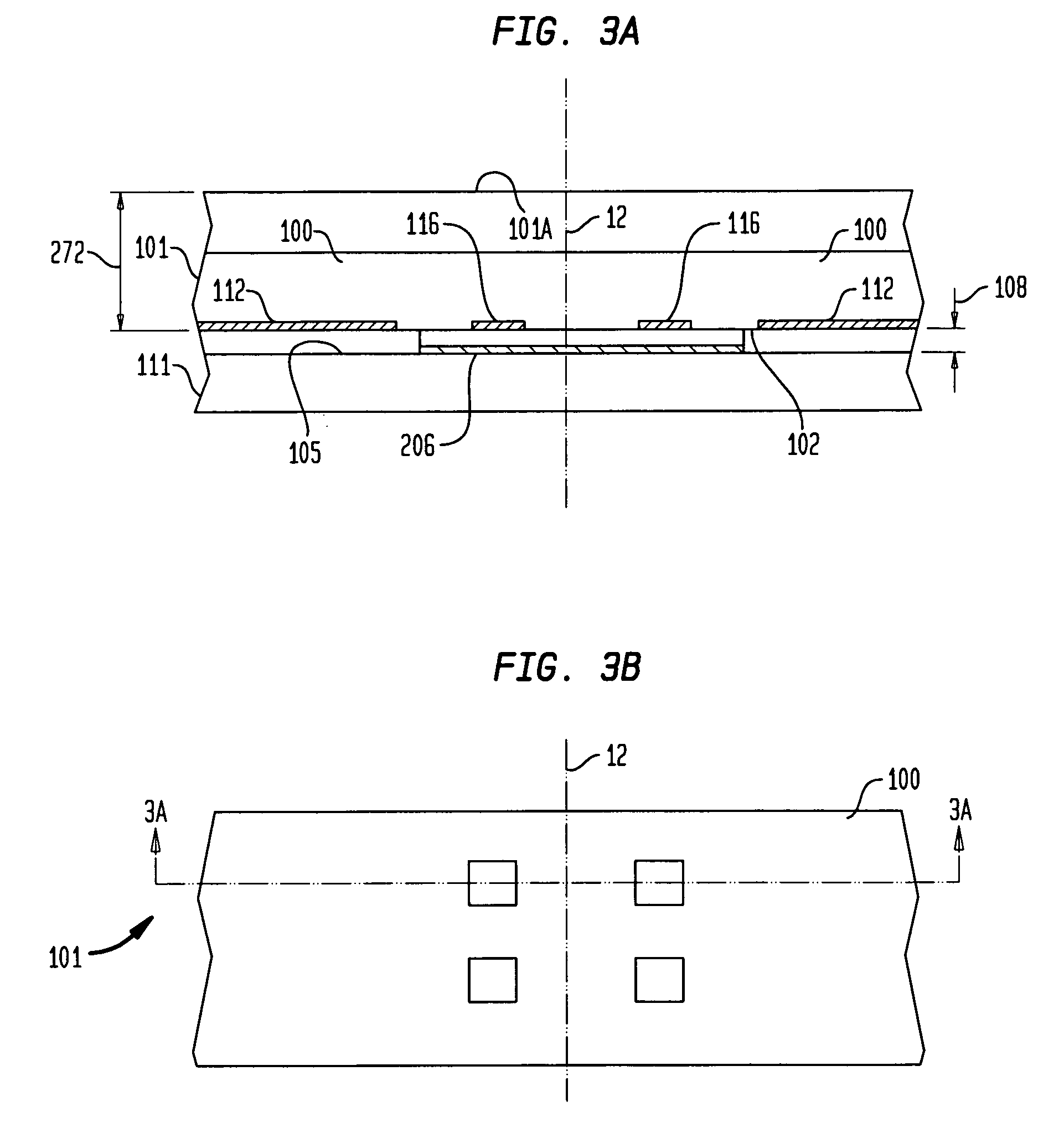

High frequency chip packages with connecting elements

InactiveUS7176506B2Reduce packaging costsLow impedance connectionImpedence networksSemiconductor/solid-state device detailsFlexible circuitsSurface mounting

A radio frequency chip package is formed by assembling a connecting element such as a circuit board or flexible circuit tape having chips thereon with a bottom plane element such as a lead frame incorporating a large thermally-conductive plate and leads projecting upwardly from the plane of the plate. The assembly step places the rear surfaces of the chips on the bottom side of the connecting element into proximity with the thermal conductor and joins the conductive traces on the connecting element with the leads. The resulting assembly is encapsulated, leaving terminals at the bottom ends of the leads exposed. The encapsulated assembly may be surface-mounted to a circuit board. The leads provide robust electrical connections between the connecting element and the circuit board.

Owner:TESSERA INC

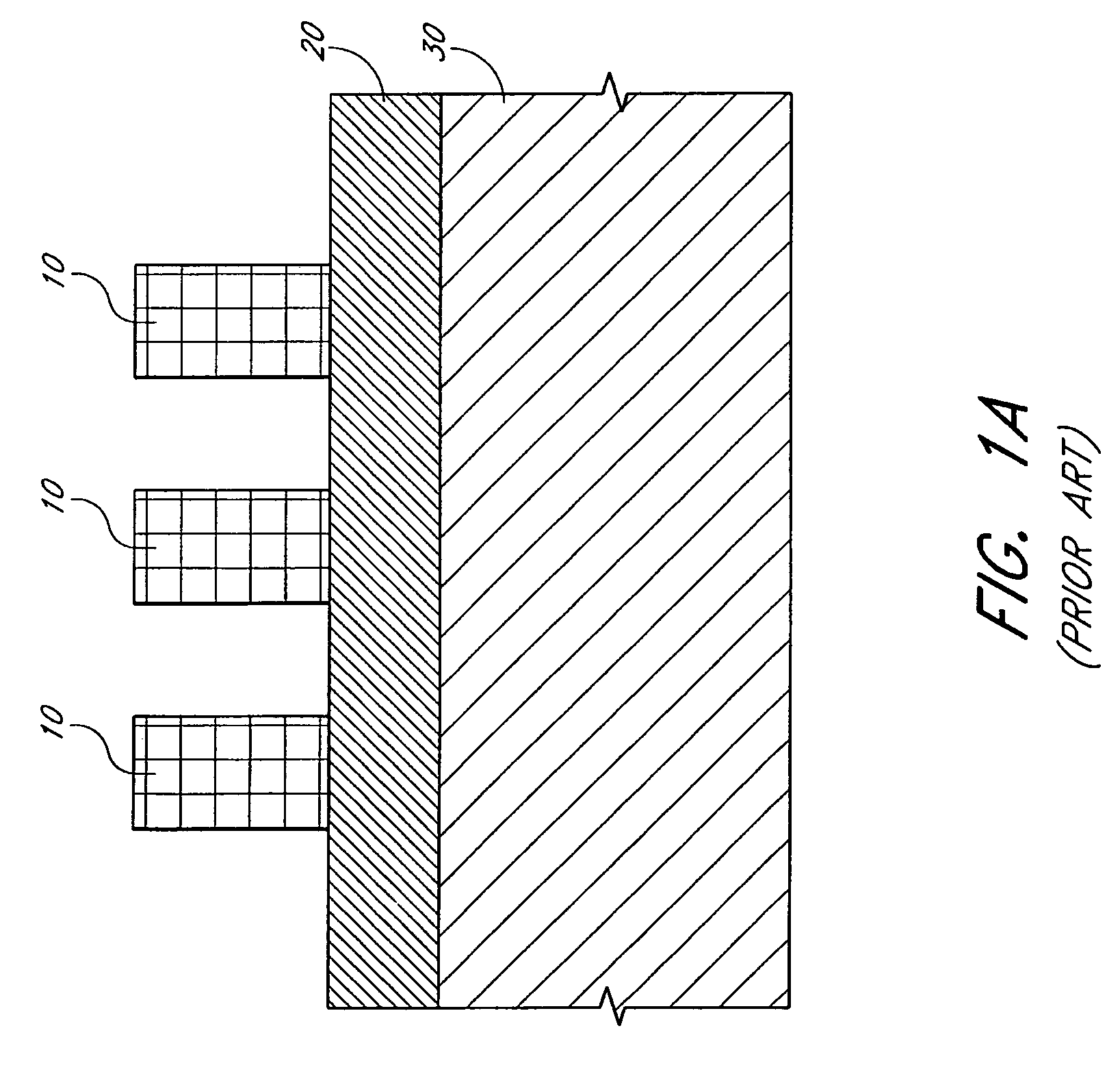

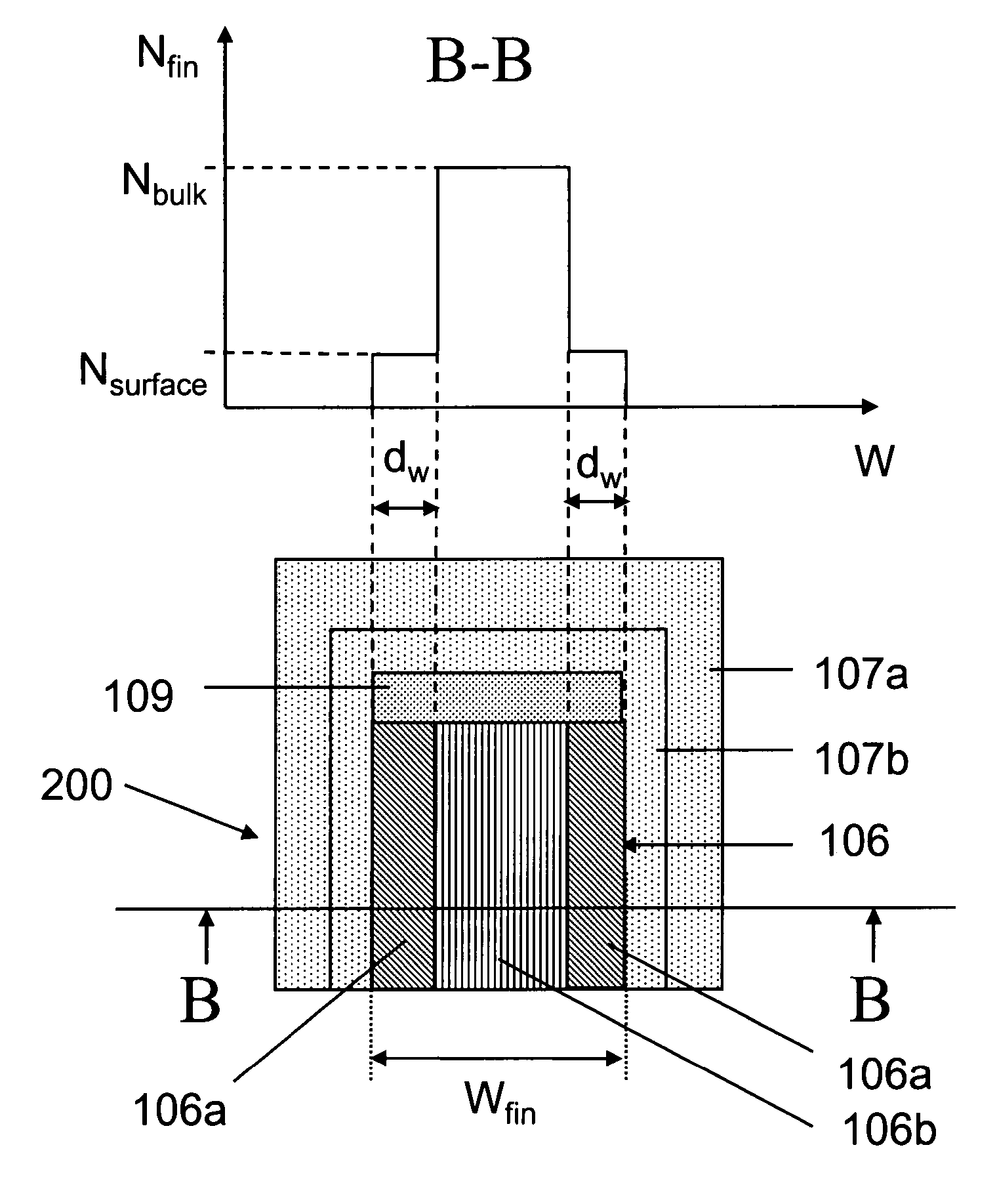

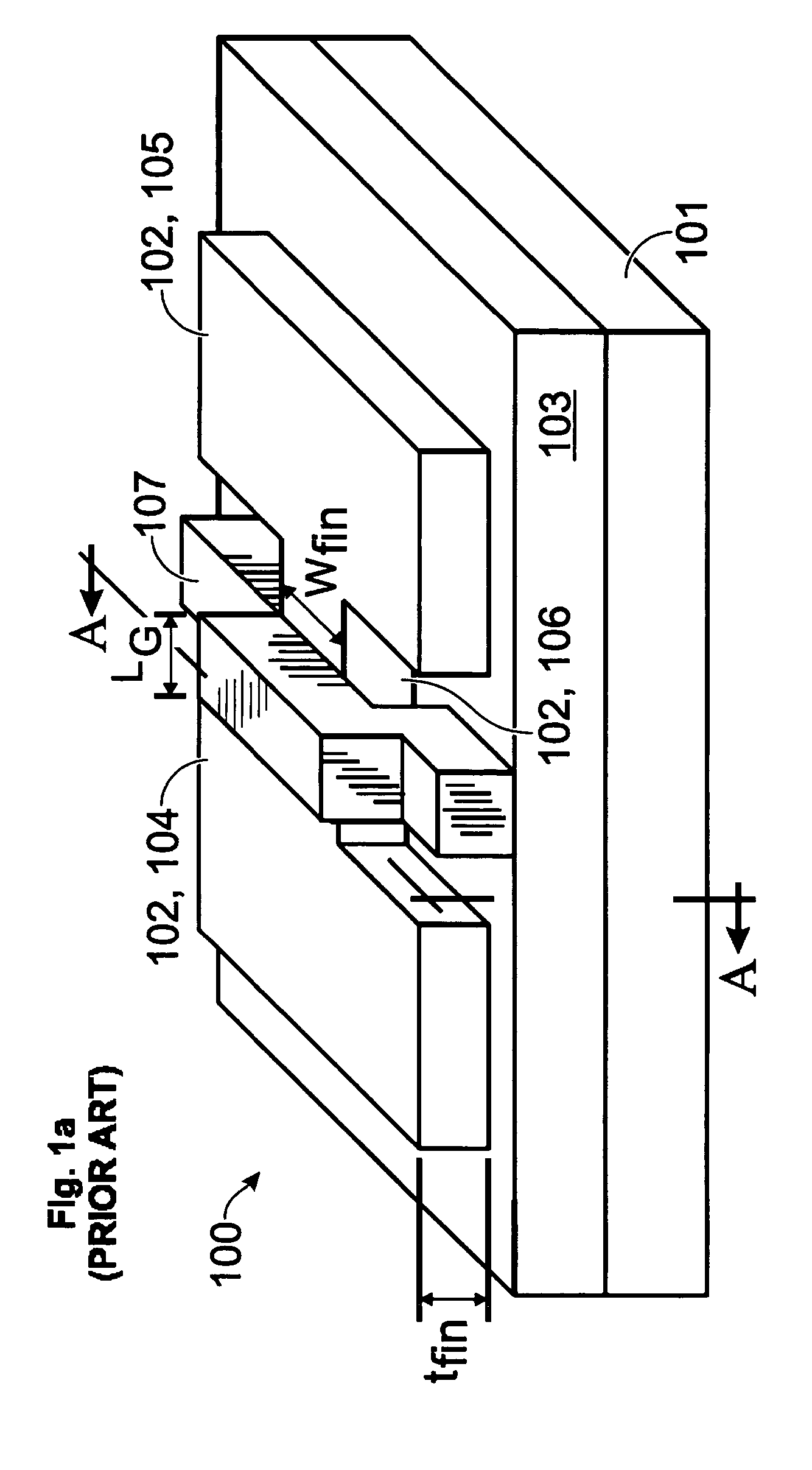

Multiple gate semiconductor device and method for forming same

A multiple gate semiconductor device. The device includes at least two gates. The dopant distribution in the semiconductor body of the device varies from a low value near the surface of the body towards a higher value inside the body of the device.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Chips having rear contacts connected by through vias to front contacts

InactiveUS20080246136A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor device

A microelectronic unit is provided in which front and rear surfaces of a semiconductor element may define a thin region which has a first thickness and a thicker region having a thickness at least about twice the first thickness. A semiconductor device may be present at the front surface, with a plurality of first conductive contacts at the front surface connected to the device. A plurality of conductive vias may extend from the rear surface through the thin region of the semiconductor element to the first conductive contacts. A plurality of second conductive contacts can be exposed at an exterior of the semiconductor element. A plurality of conductive traces may connect the second conductive contacts to the conductive vias.

Owner:INVENSAS CORP

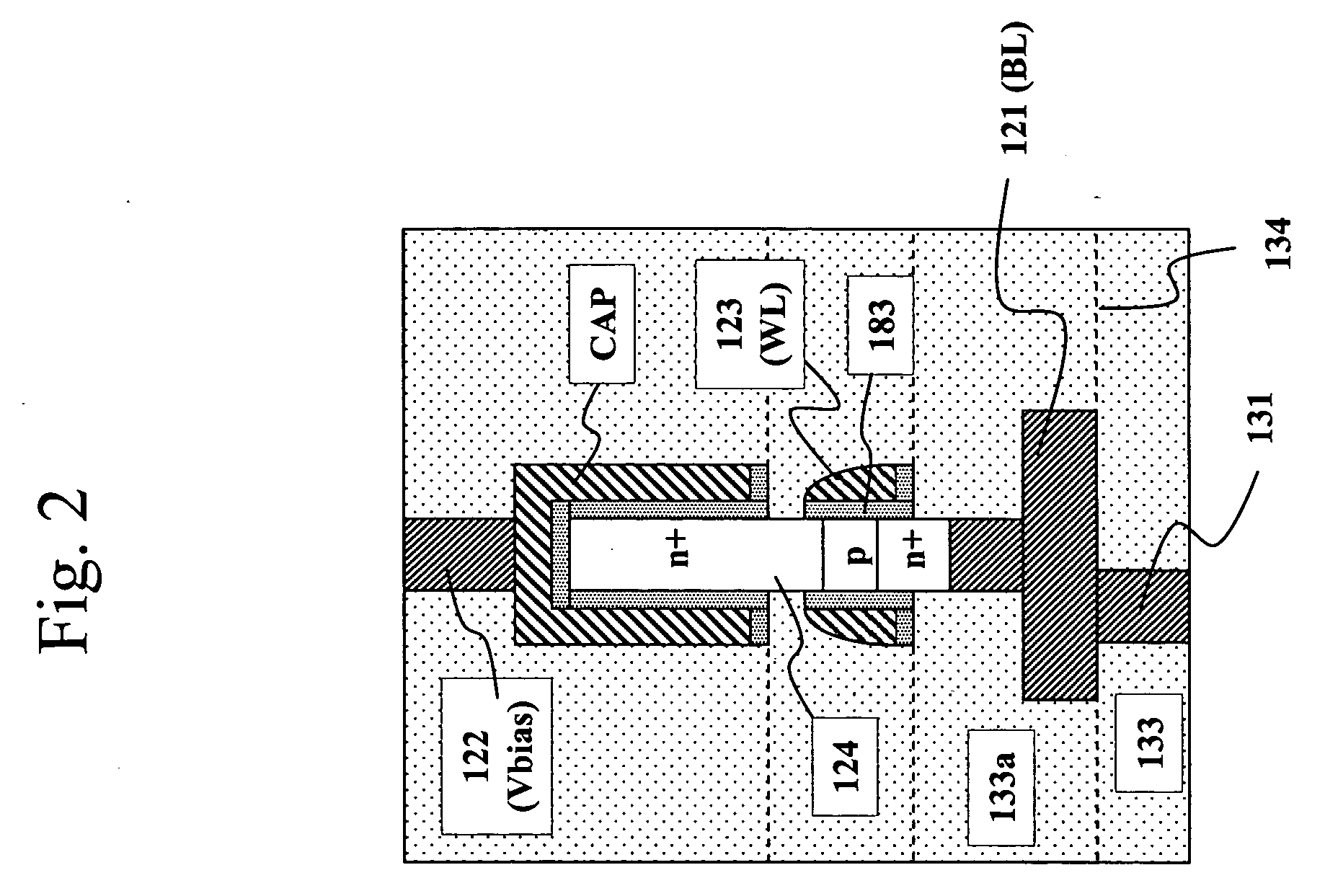

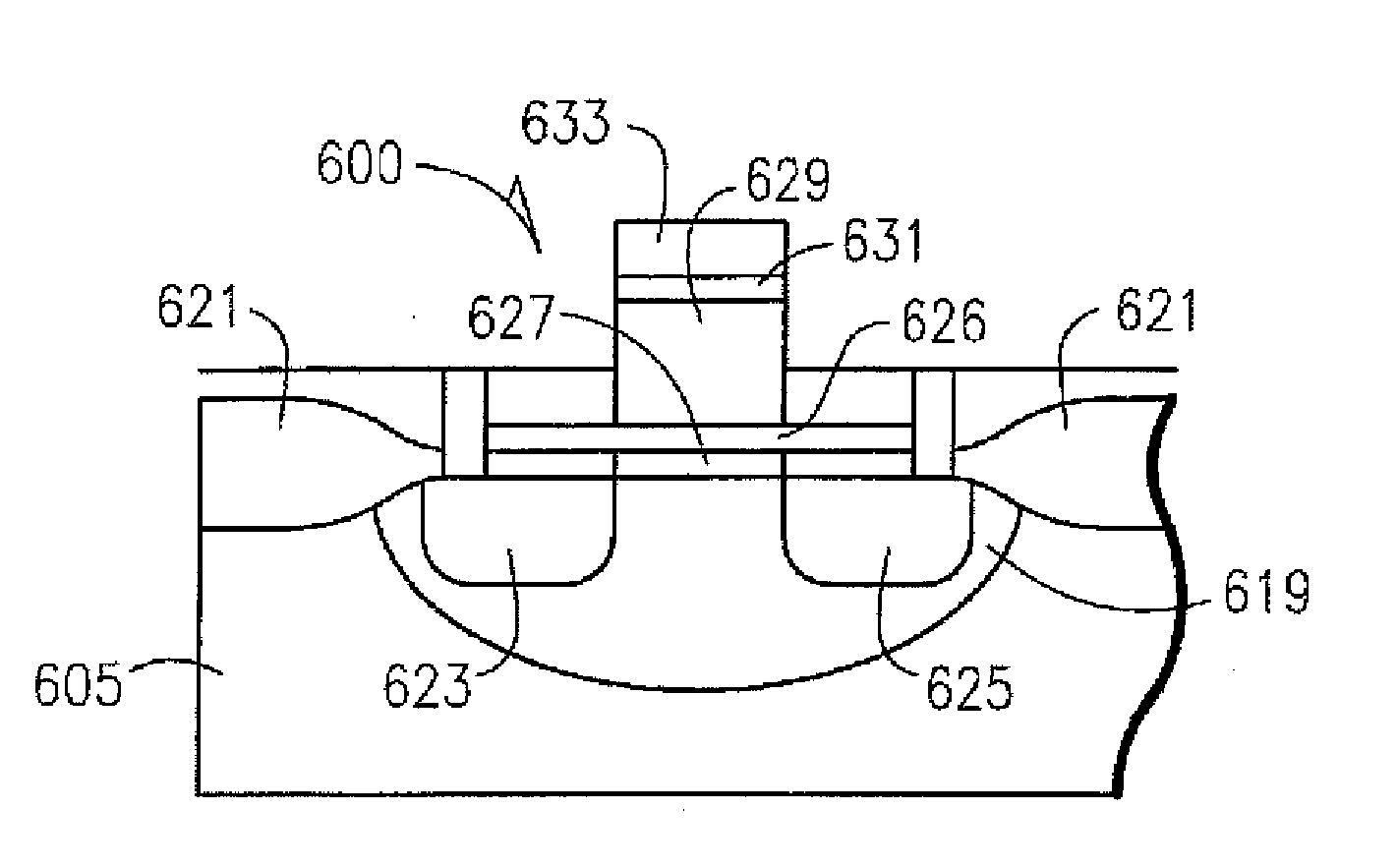

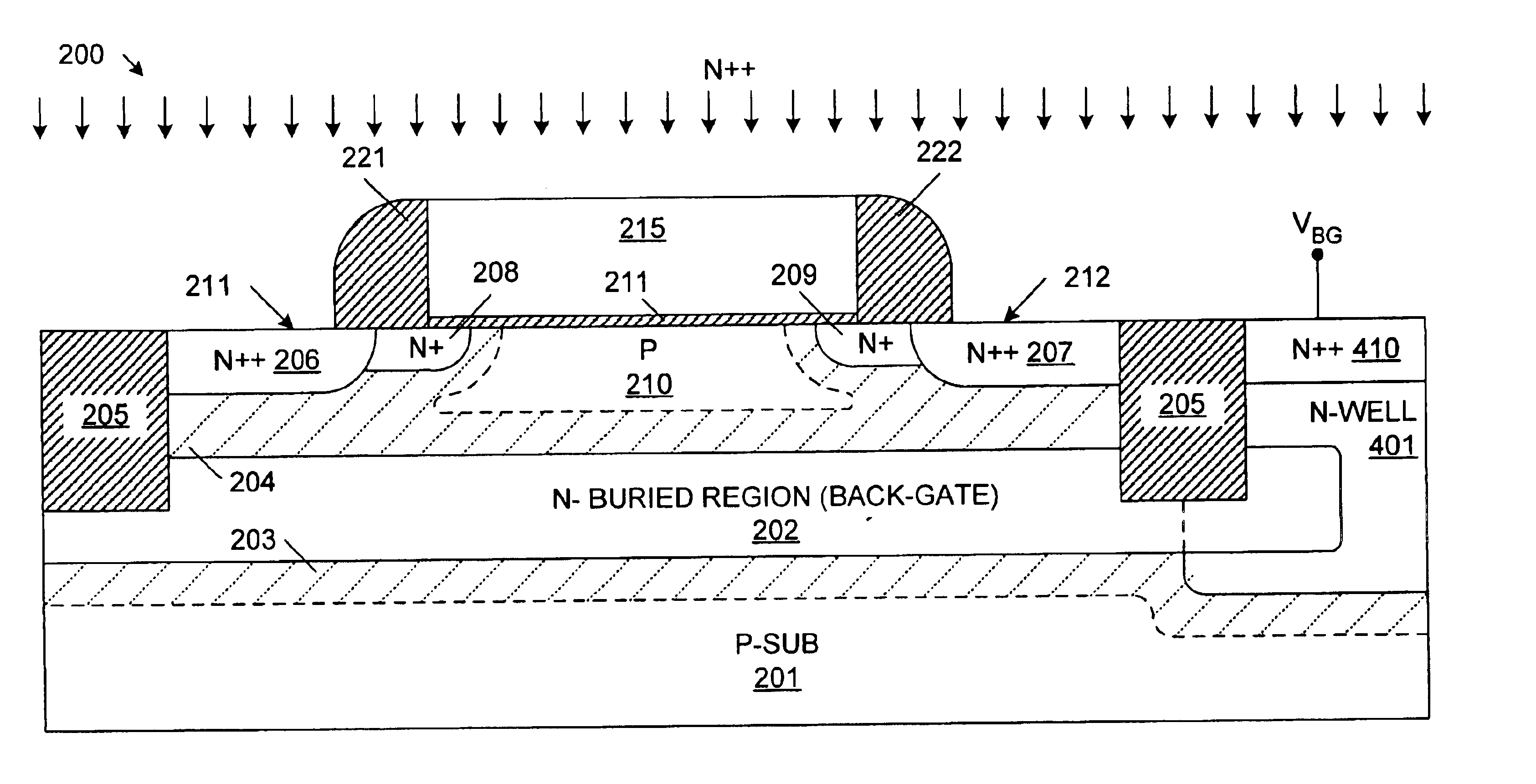

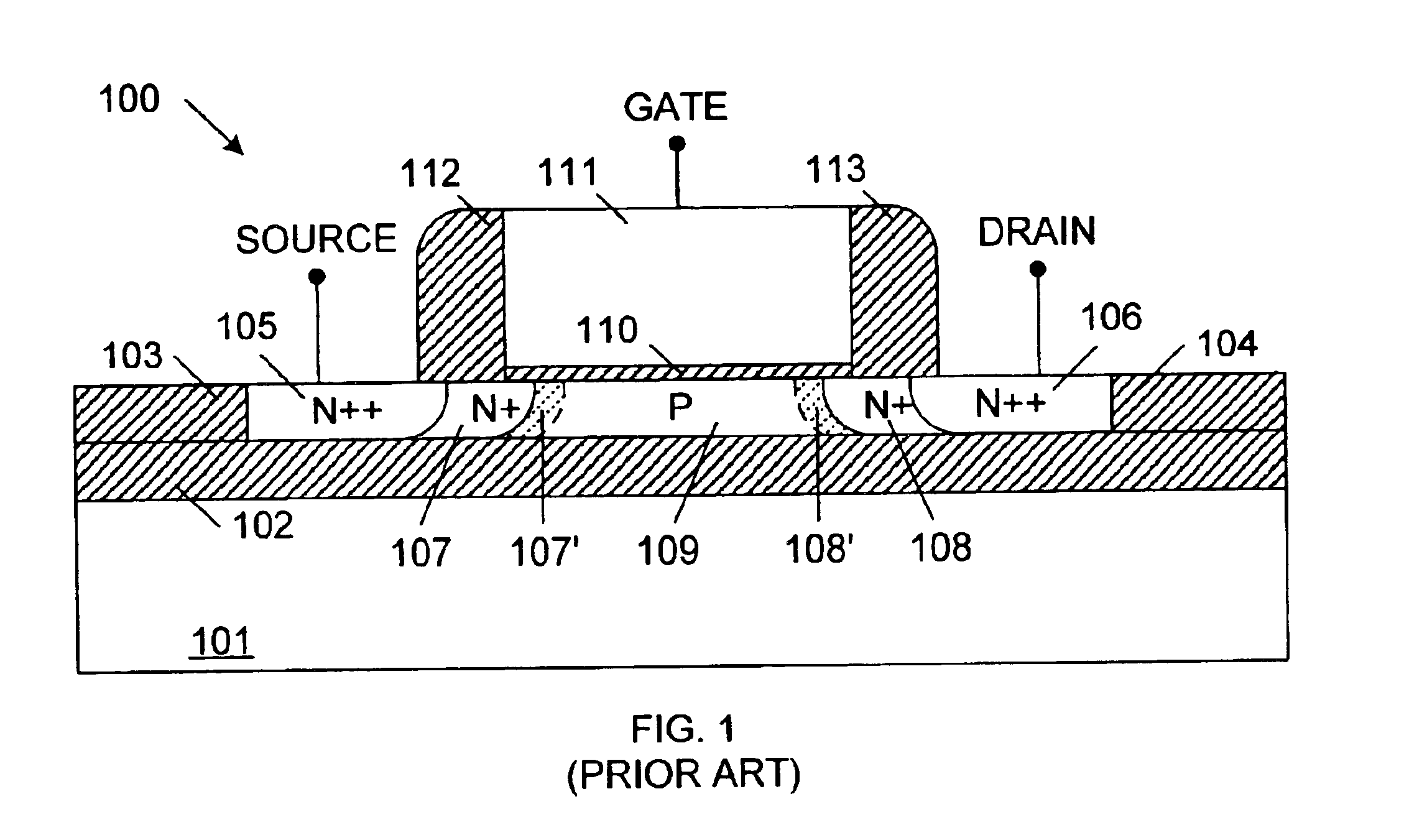

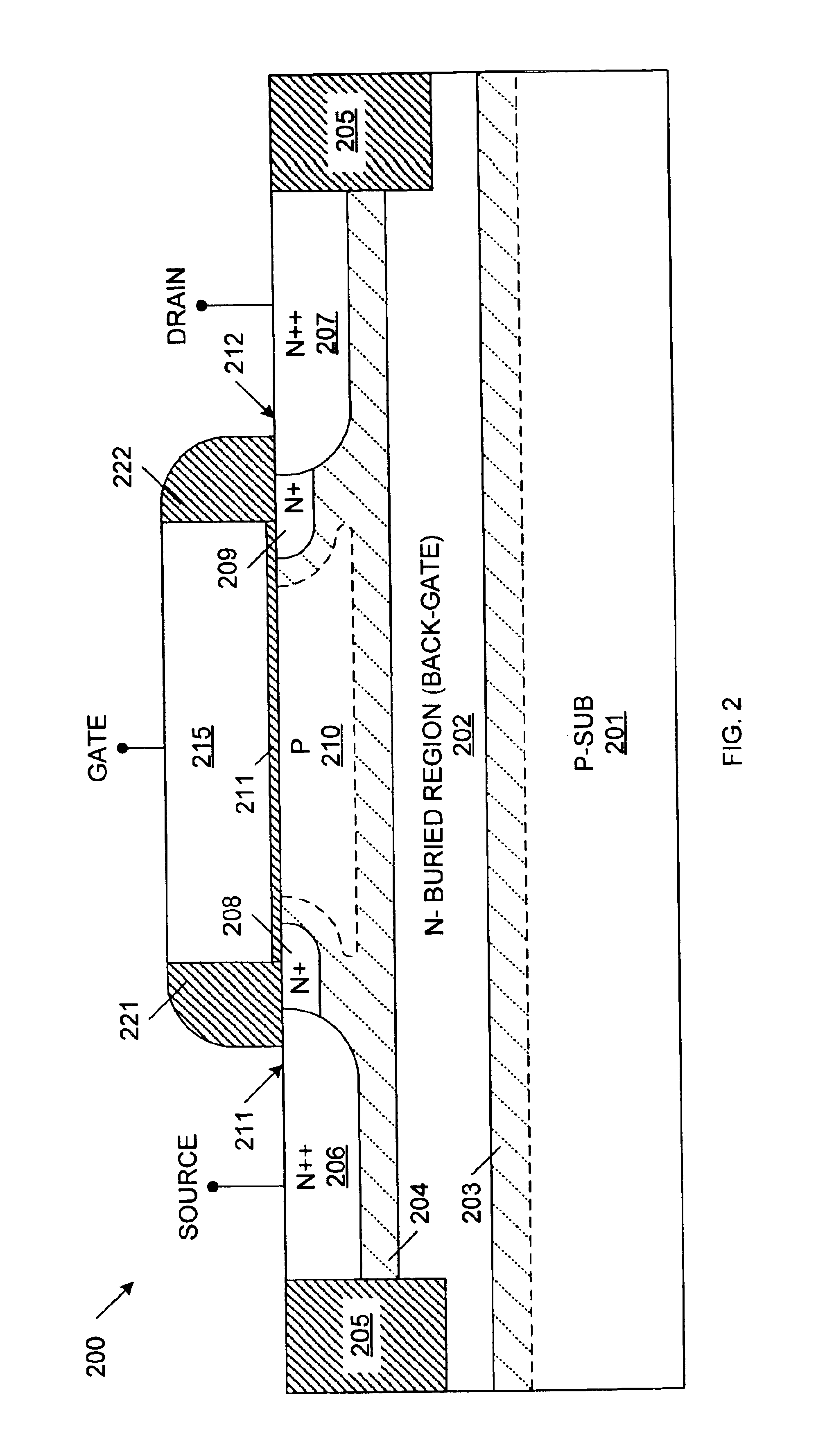

Method of fabricating a one transistor floating-body DRAM cell in bulk CMOS process with electrically isolated charge storage region

InactiveUS6913964B2Limiting leakage currentEnsure adequate isolationTransistorSolid-state devicesEngineeringField-effect transistor

A one-transistor, floating-body (1T / FB) dynamic random access memory (DRAM) cell is provided that includes a field-effect transistor fabricated using a process compatible with a standard CMOS process. The field-effect transistor includes a source region and a drain region of a first conductivity type and a floating body region of a second conductivity type, opposite the first conductivity type, located between the source region and the drain region. A buried region of the first conductivity type is located under the source region, drain region and floating body region. The buried region helps to form a depletion region, which is located between the buried region and the source region, the drain region and the floating body region. The floating body region is thereby isolated by the depletion region. A bias voltage can be applied to the buried region, thereby controlling leakage currents in the 1T / FB DRAM cell.

Owner:MOSYS INC

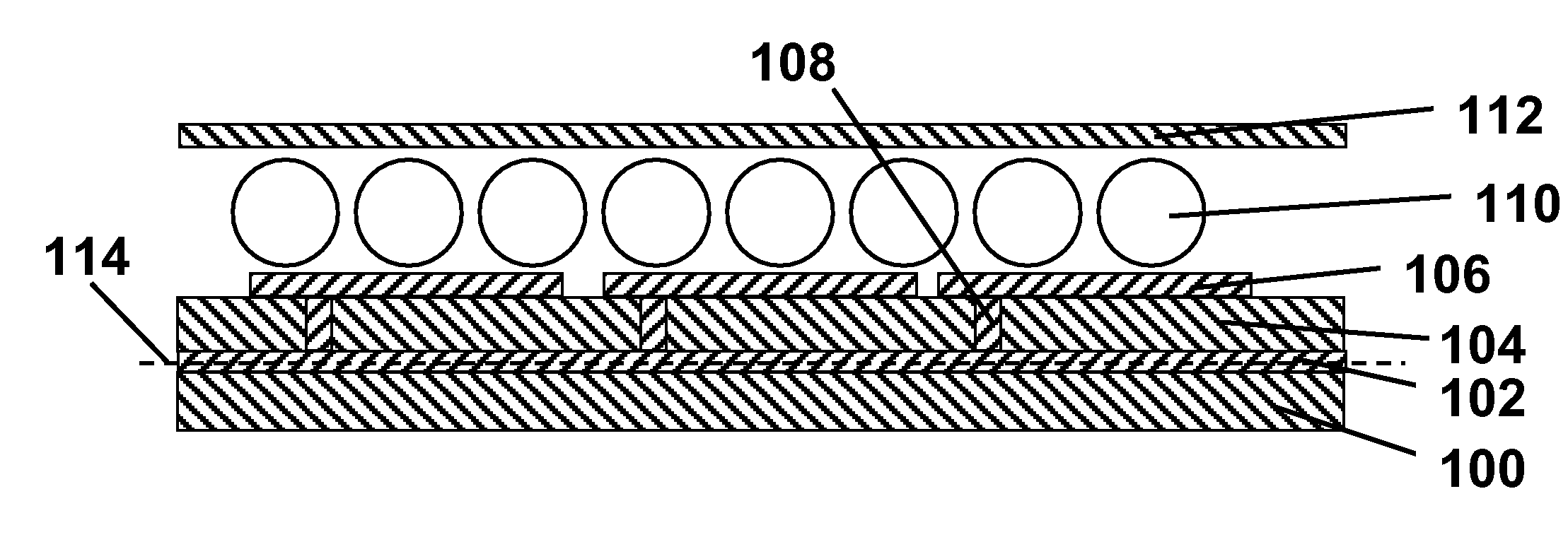

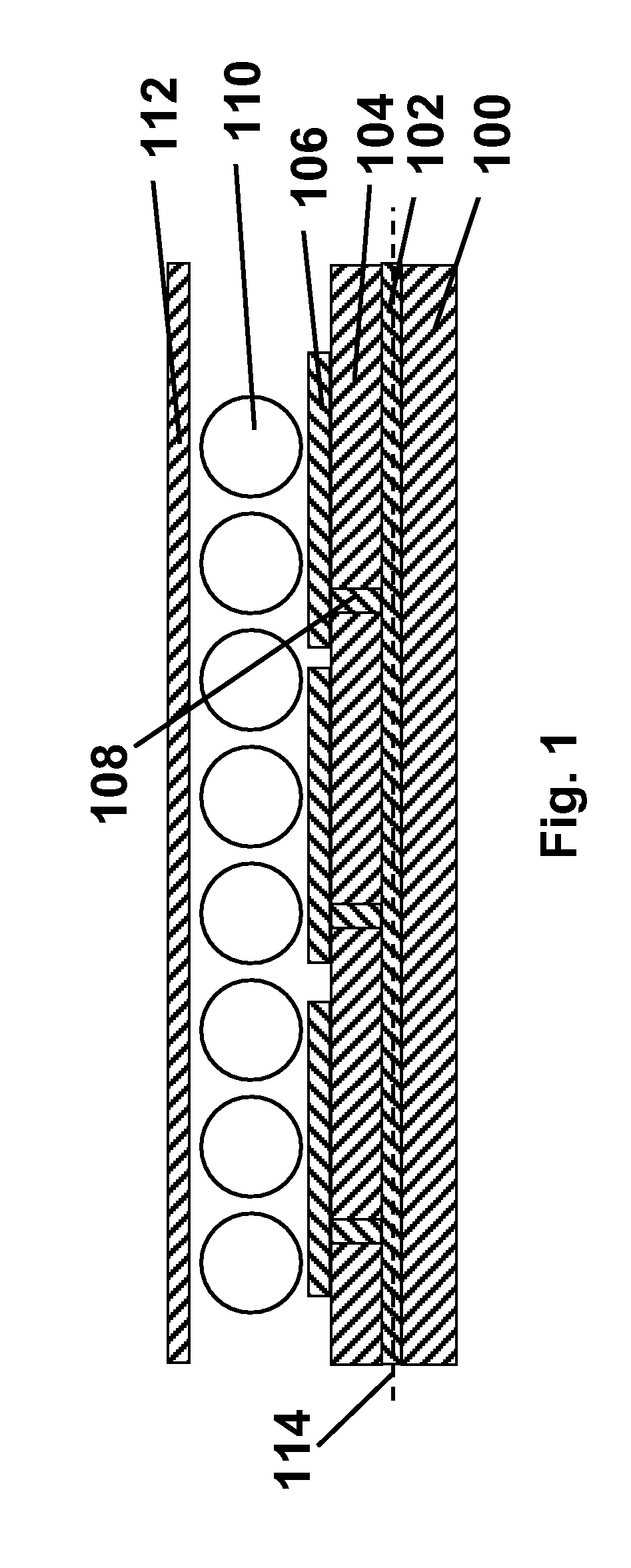

Electro-optic displays, and components for use therein

InactiveUS7190008B2Change conductivitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceNeutral plane

An electro-optic display comprises a substrate (100), non-linear devices (102) disposed substantially in one plane on the substrate (100), pixel electrodes (106) connected to the non-linear devices (102), an electro-optic medium (110) and a common electrode (112) on the opposed side of the electro-optic medium (110) from the pixel electrodes (106). The moduli of the various parts of the display are arranged so that, when the display is curved, the neutral axis or neutral plane lies substantially in the plane of the non-linear devices (102).

Owner:E INK CORPORATION

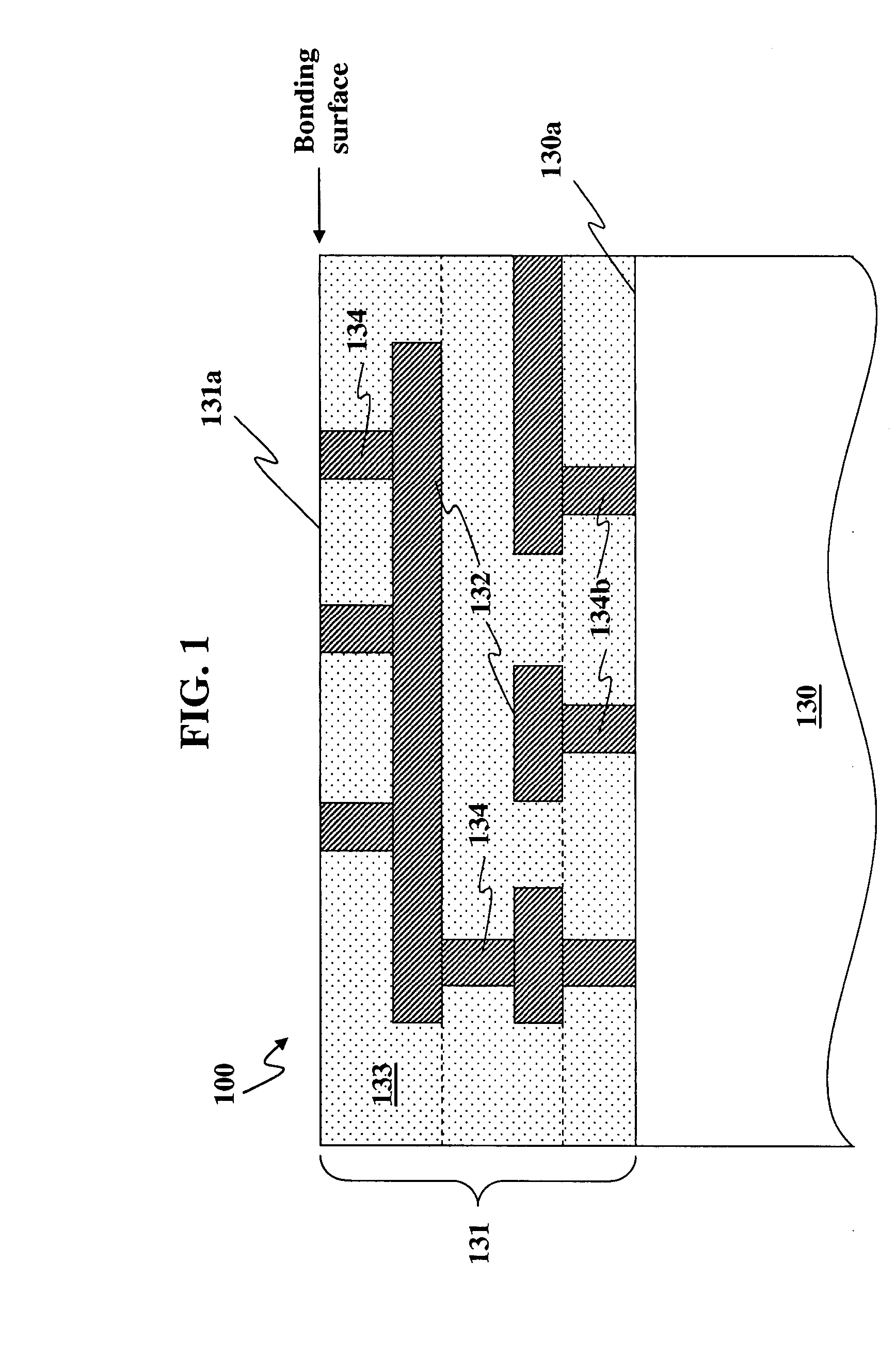

Semiconductor bonding and layer transfer method

The present invention provides a method of coupling substrates together. The method includes providing first and second substrates and then coupling the first and second substrates together. One of the first and second substrates includes devices with an interconnect region positioned thereon and the other substrate carries a device structure.

Owner:BESANG

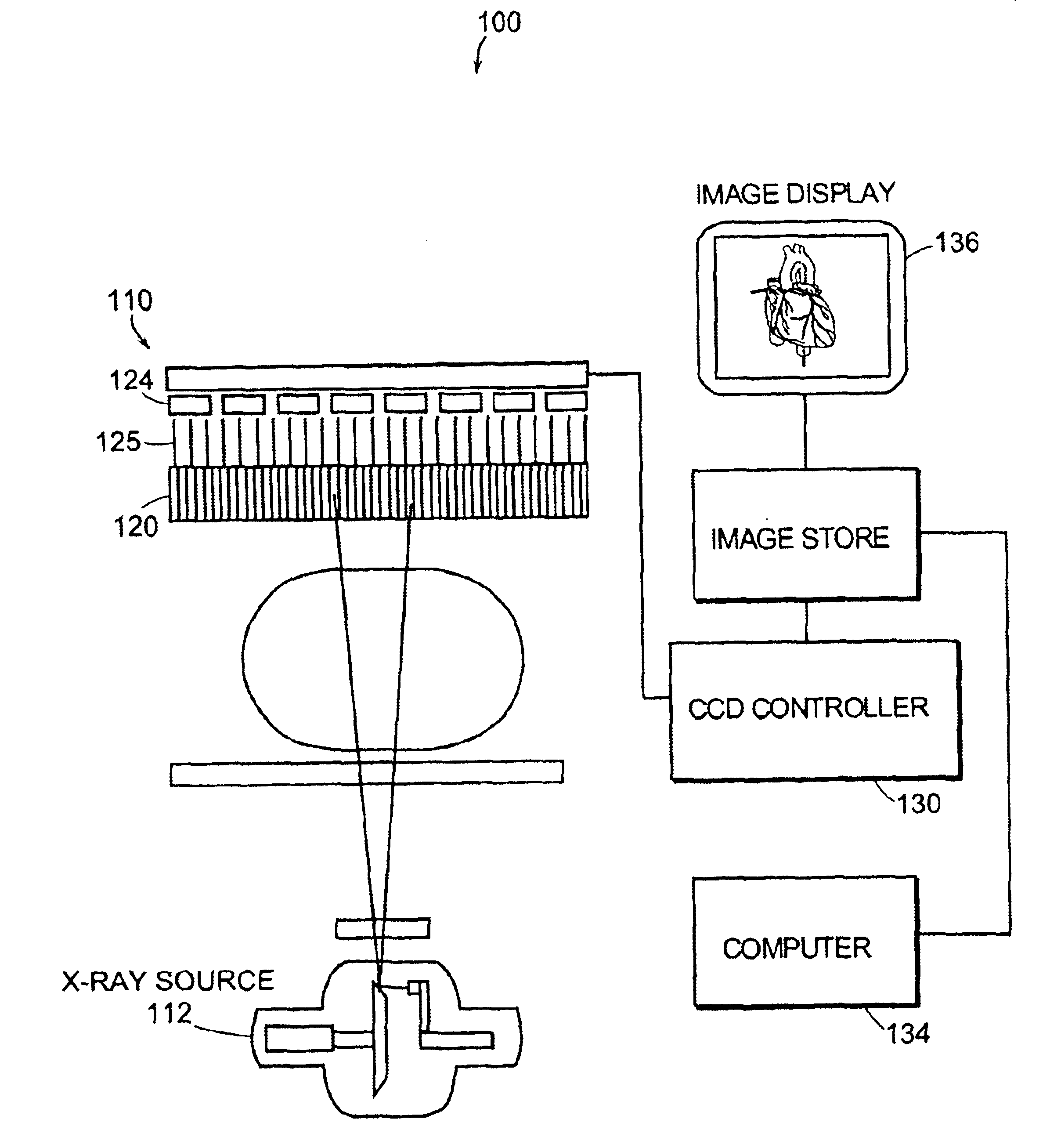

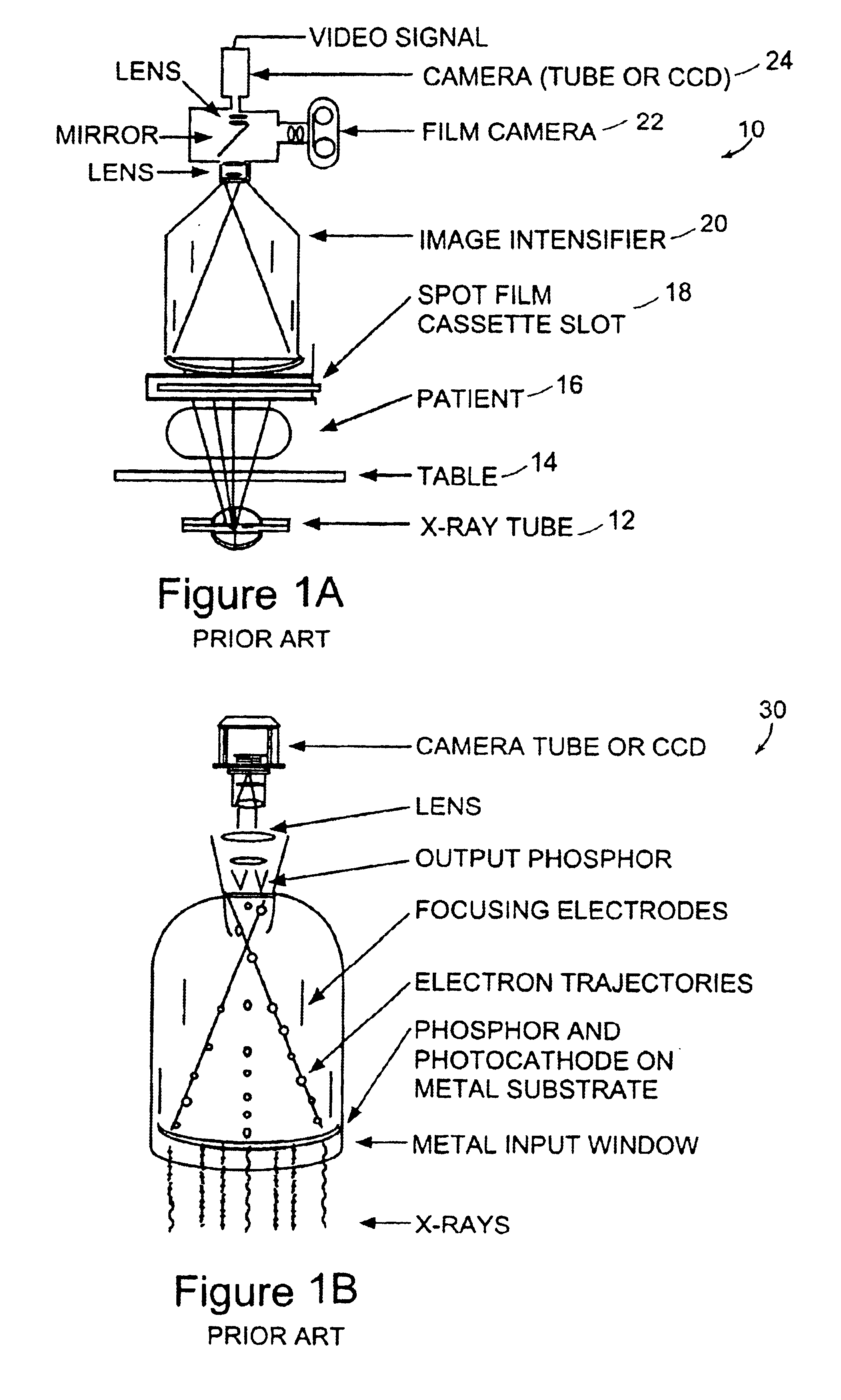

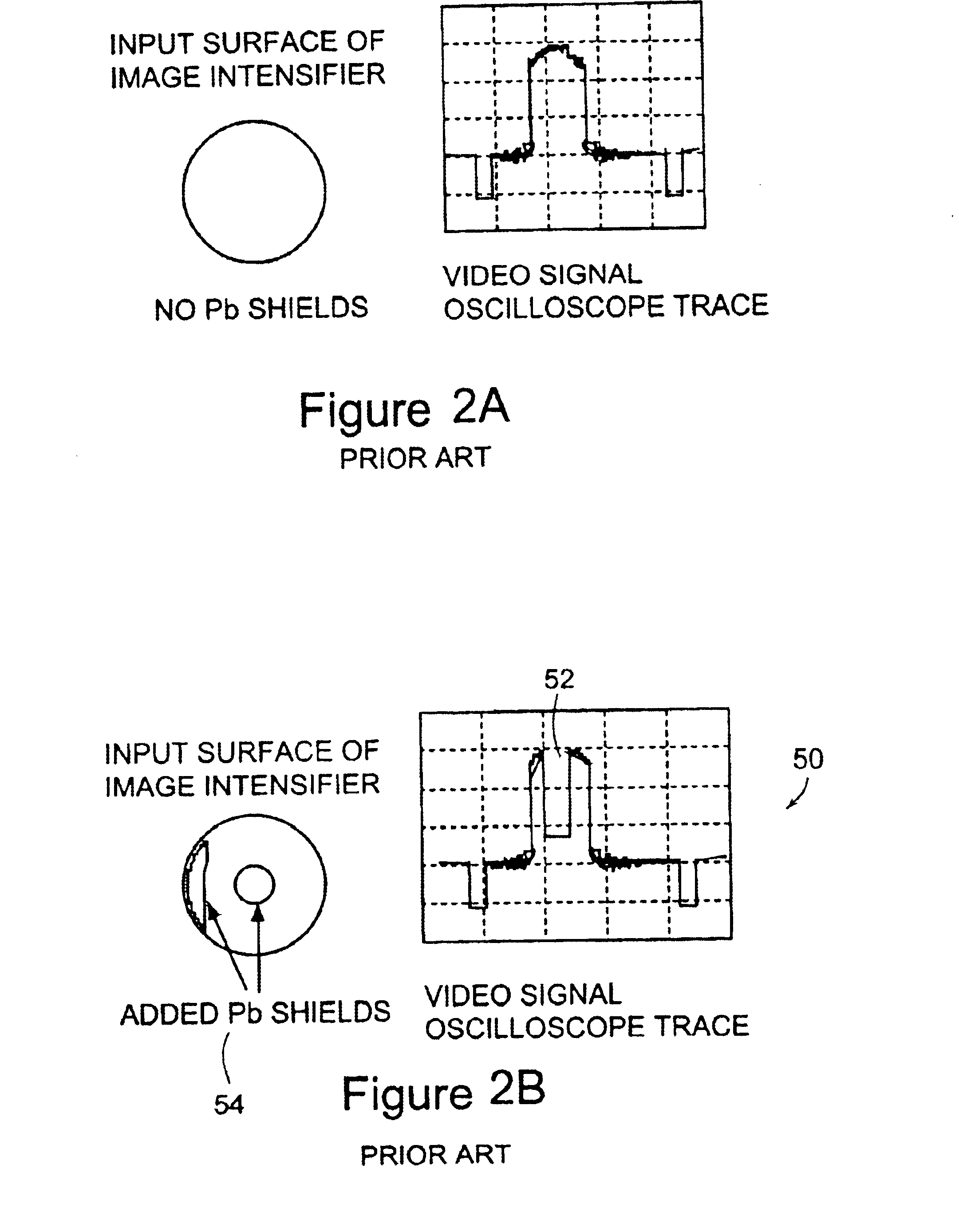

System and method for x-ray fluoroscopic imaging

InactiveUS6895077B2Increase frame rateAccurate imagingTelevision system detailsSolid-state devicesFluorescenceX-ray

A system for x-ray fluoroscopic imaging of bodily tissue in which a scintillation screen and a charge coupled device (CCD) is used to accurately image selected tissue. An x-ray source generates x-rays which pass through a region of a subject's body, forming an x-ray image which reaches the scintillation screen. The scintillation screen re-radiates a spatial intensity pattern corresponding to the image, the pattern being detected by the CCD sensor. In a preferred embodiment the imager uses four 8×8-cm three-side buttable CCDs coupled to a CsI:T1 scintillator by straight (non-tapering) fiberoptics and tiled to achieve a field of view (FOV) of 16×16-cm at the image plane. Larger FOVs can be achieved by tiling more CCDs in a similar manner. The imaging system can be operated in a plurality of pixel pitch modes such as 78, 156 or 234-μm pixel pitch modes. The CCD sensor may also provide multi-resolution imaging. The image is digitized by the sensor and processed by a controller before being stored as an electronic image. Other preferred embodiments may include each image being directed on flat panel imagers made from but not limited to, amorphous silicon and / or amorphous selenium to generate individual electronic representations of the separate images used for diagnostic or therapeutic applications.

Owner:UNIV OF MASSACHUSETTS MEDICAL CENT

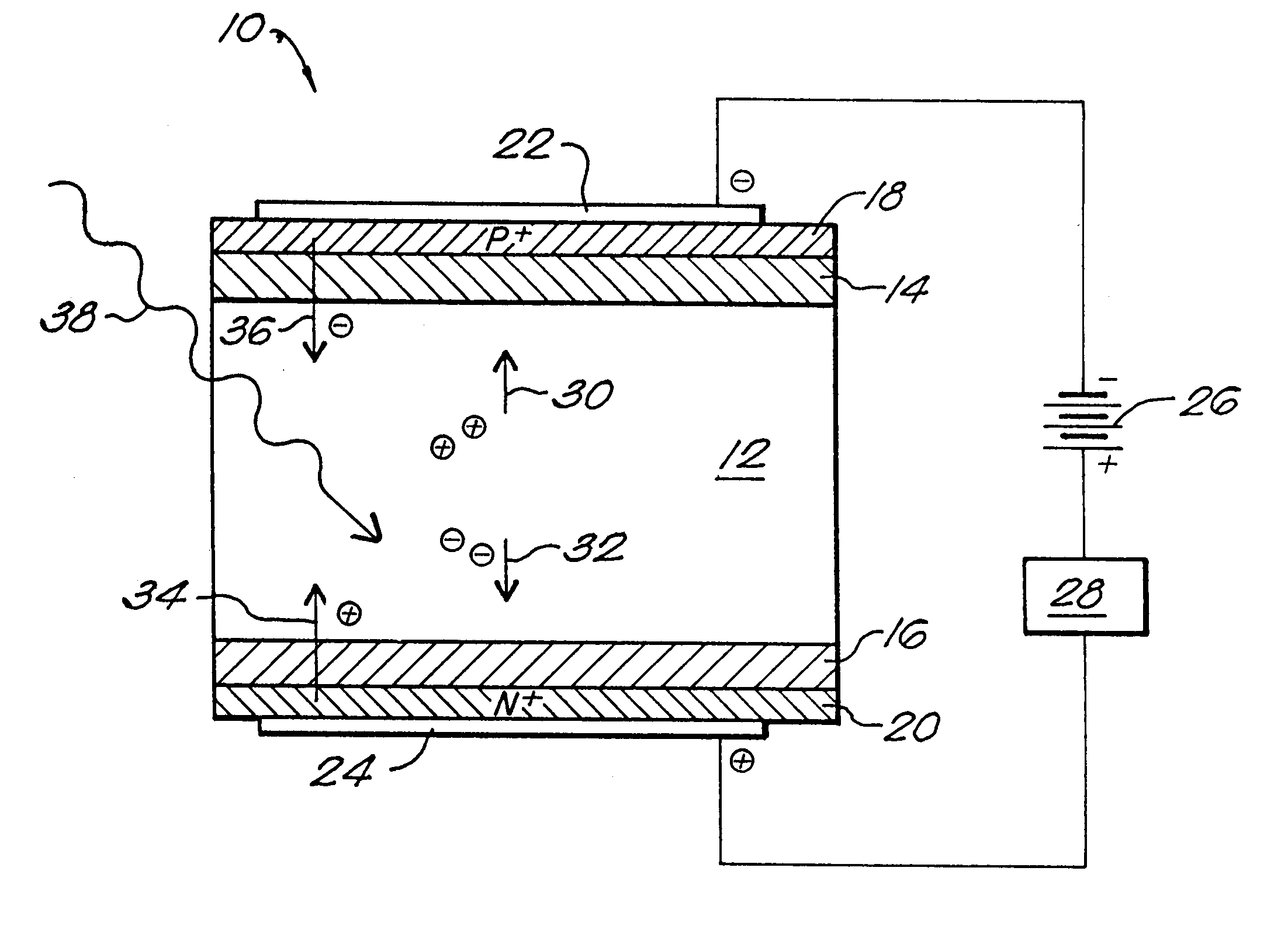

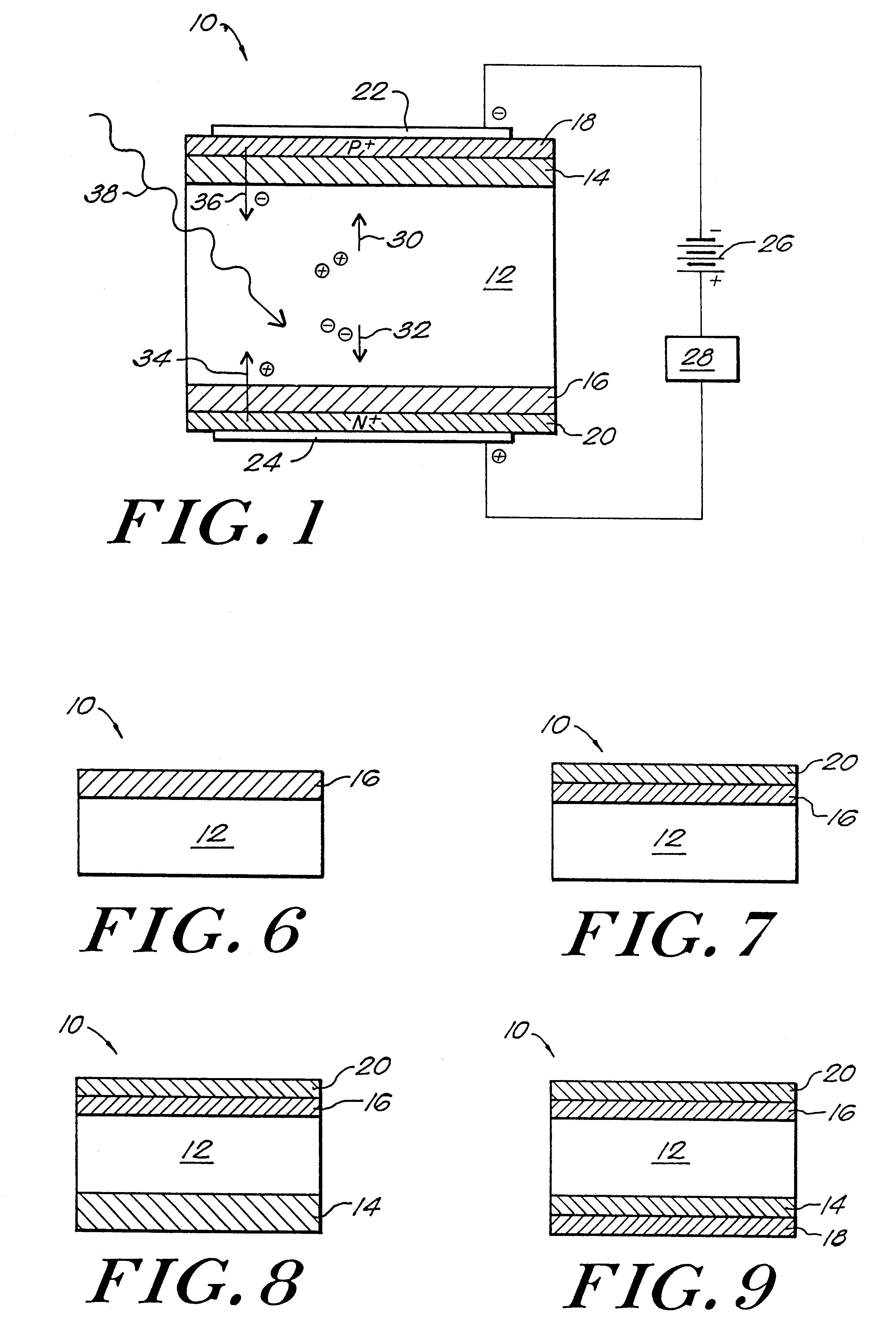

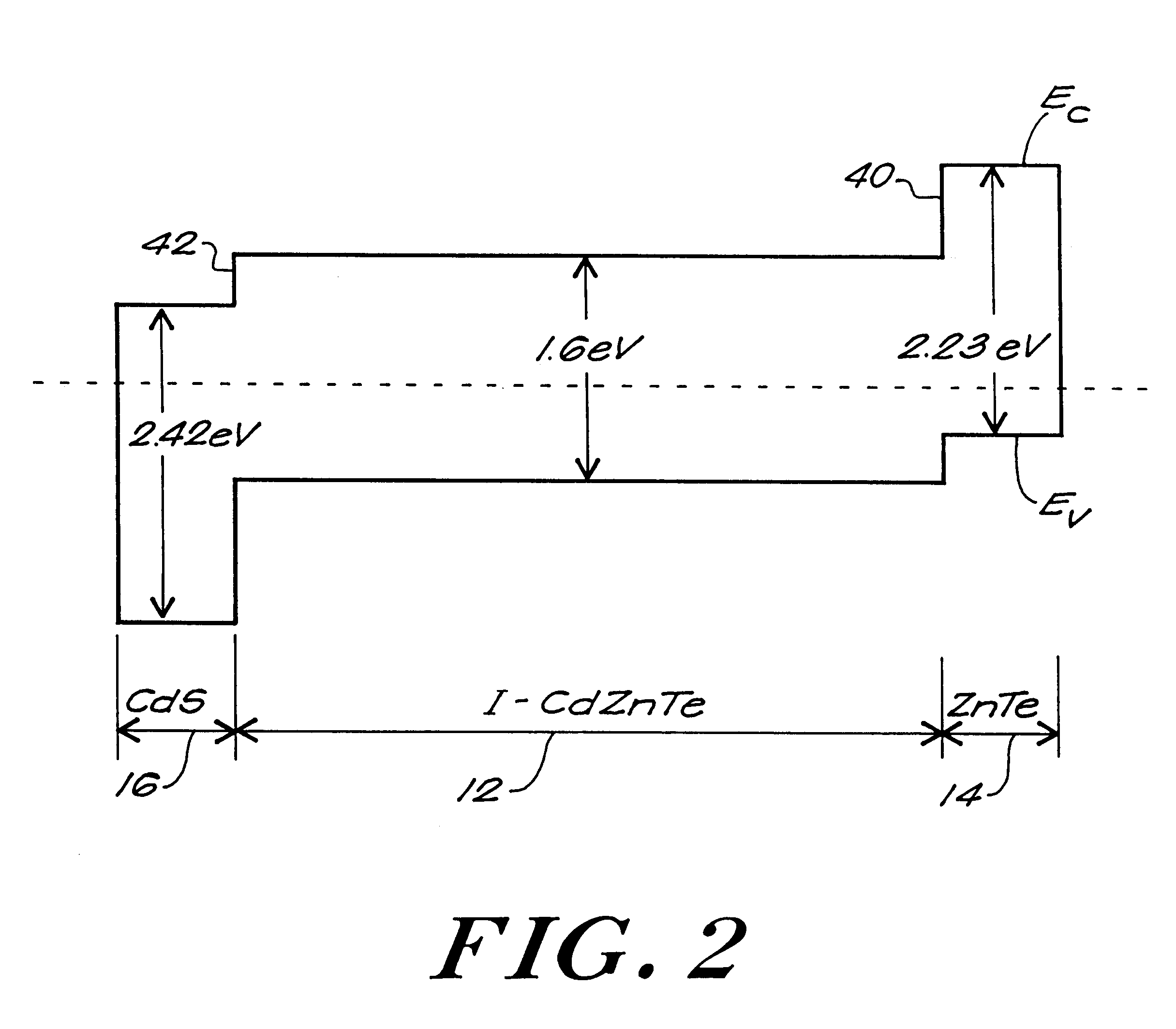

Semiconductor P-I-N detector

InactiveUS6255708B1Reduce leakage currentMitigating dopant diffusionSolid-state devicesSemiconductor/solid-state device manufacturingDopantIndium

A semiconductor P-I-N detector including an intrinsic wafer, a P-doped layer, an N-doped layer, and a boundary layer for reducing the diffusion of dopants into the intrinsic wafer. The boundary layer is positioned between one of the doped regions and the intrinsic wafer. The intrinsic wafer can be composed of CdZnTe or CdTe, the P-doped layer can be composed of ZnTe doped with copper, and the N-doped layer can be composed of CdS doped with indium. The boundary layers is formed of an undoped semiconductor material. The boundary layer can be deposited onto the underlying intrinsic wafer. The doped regions are then typically formed by a deposition process or by doping a section of the deposited boundary layer.

Owner:MASIMO SEMICON +2

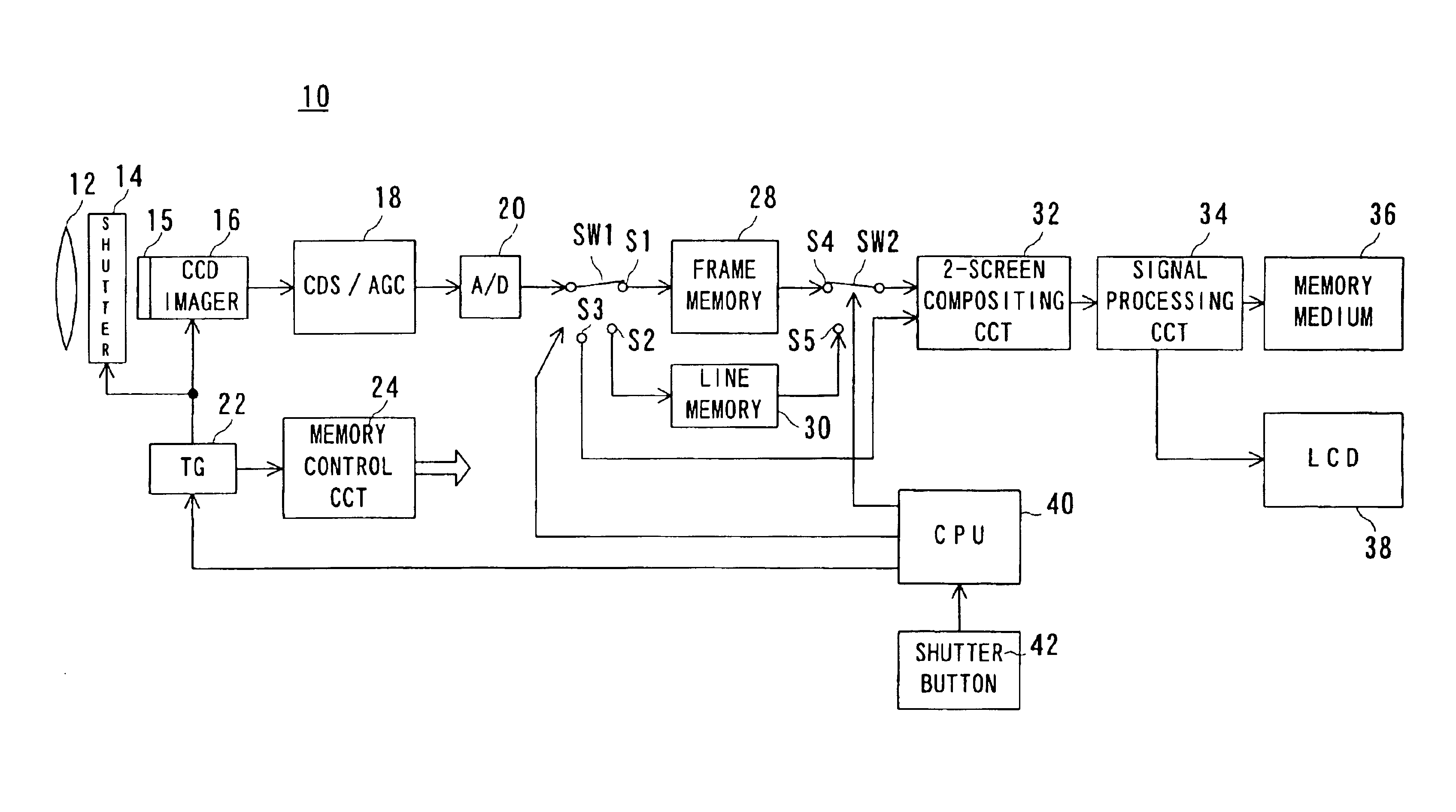

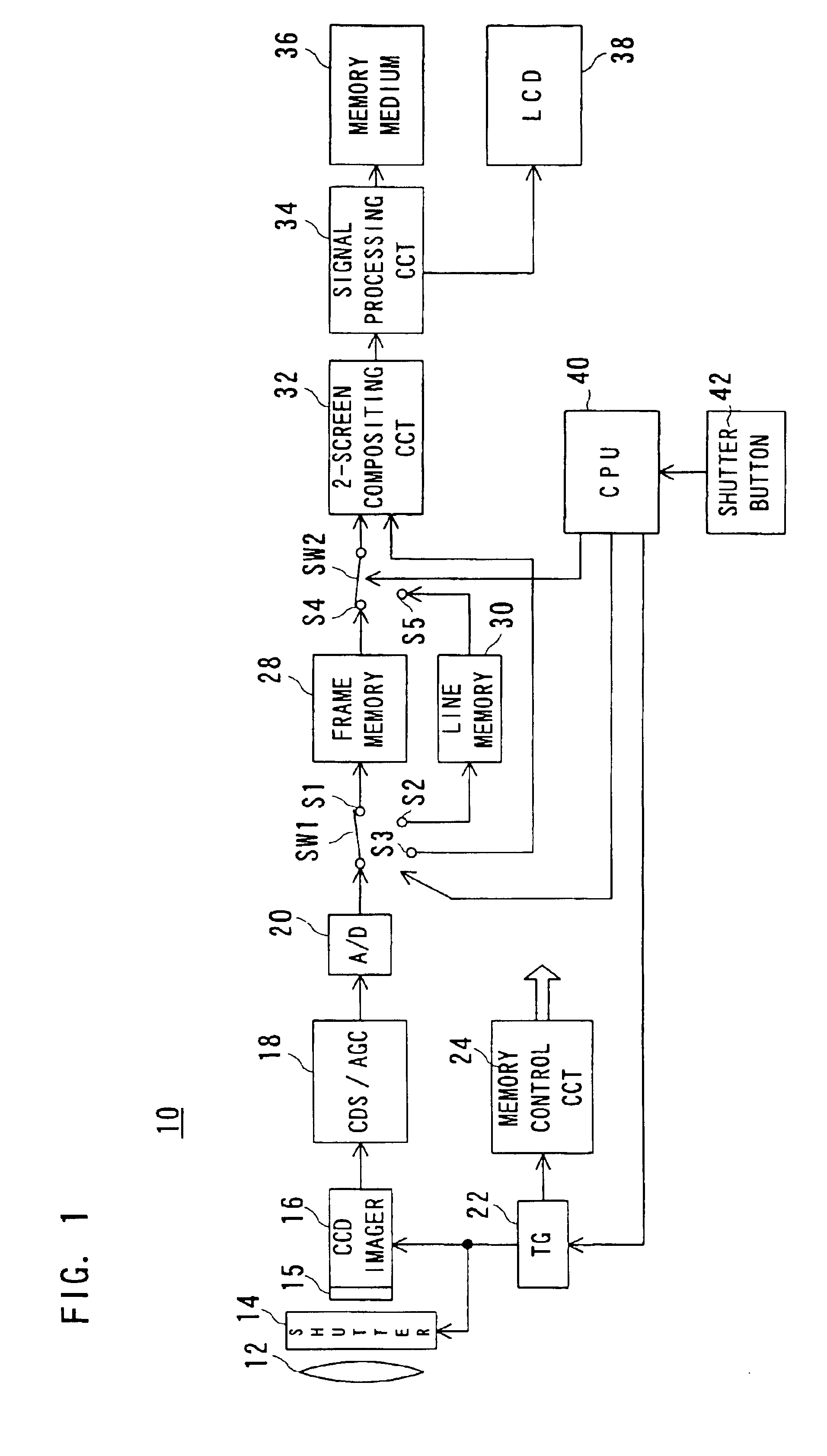

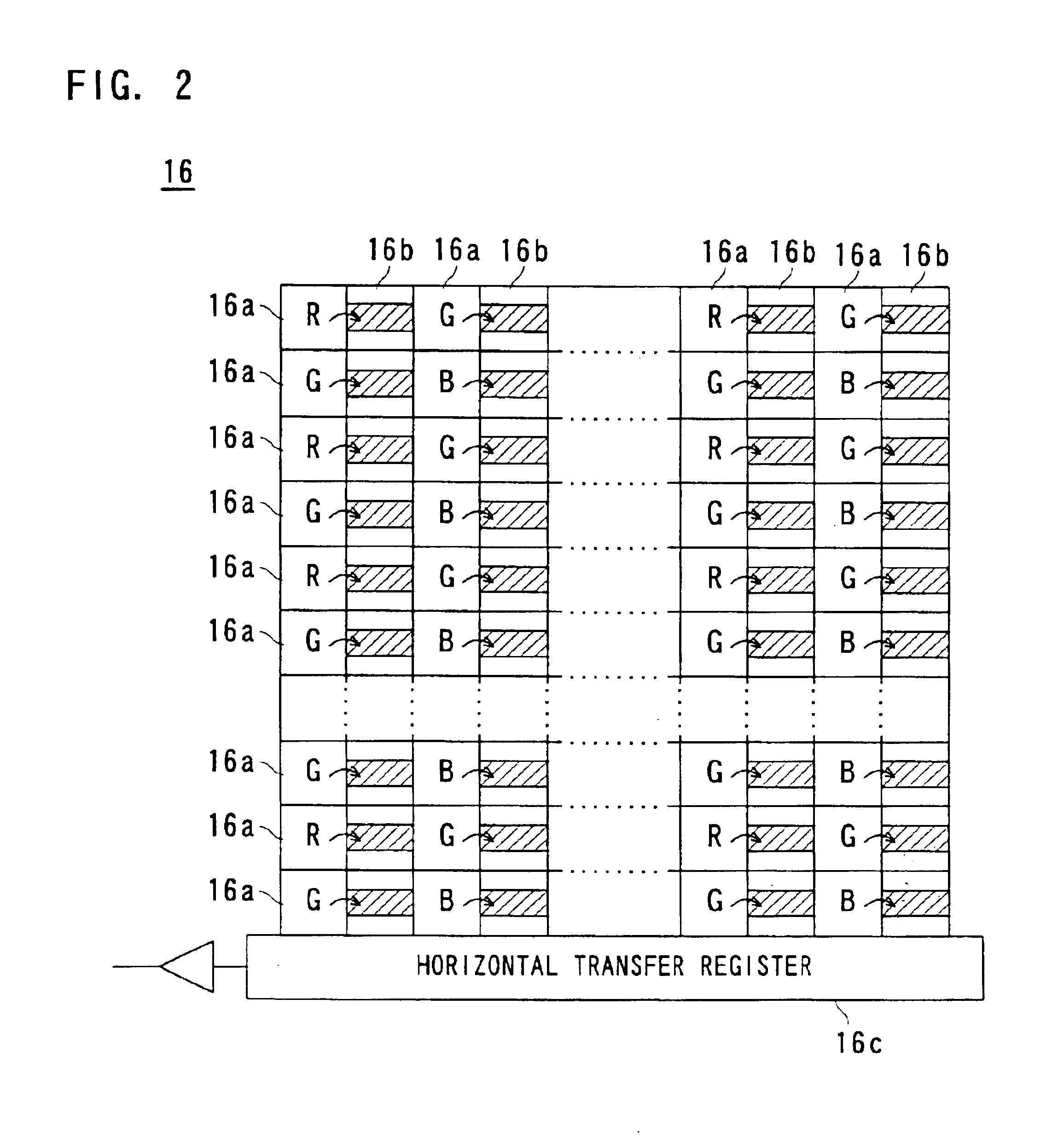

Digital camera which produces a single image based on two exposures

InactiveUS6903770B1Improve dynamic rangeTelevision system detailsTelevision system scanning detailsSingle imageSingle exposure

A digital camera includes a CCD imager having an interline transfer scheme. A first charge produced due to first exposure is read from light receiving elements positioned vertically intermittently. A second charge produced due to second exposure is also read from the same light receiving elements to vertical transfer regions. Here, the first charge is vertically moved simultaneously with or prior to reading out the second charge. The moving distance, at this time, is equal to or greater than a distance that the light receiving elements continue in the vertical direction. As a result of this, the second charge will not be mixed with the first charge. The first and second charges are subjected to a compositing process to display a composite image on an LCD.

Owner:XACTI CORP

Semiconductor bonding and layer transfer method

The present invention provides a method of coupling substrates together. The method includes providing first and second substrates and then coupling the first and second substrates together. One of the first and second substrates includes devices with an interconnect region positioned thereon and the other substrate carries a device structure.

Owner:BESANG

Semiconductor device with base support structure

InactiveUS20050280156A1TransistorSemiconductor/solid-state device detailsDevice materialSemiconductor chip

An apparatus includes a semiconductor chip with a base support structure having a surface and an opposed surface. At least one device structure extends from the surface of the base support structure. A first conductive region is coupled to the base support structure. At least a portion of the first conductive region extends below the opposed surface.

Owner:BESANG

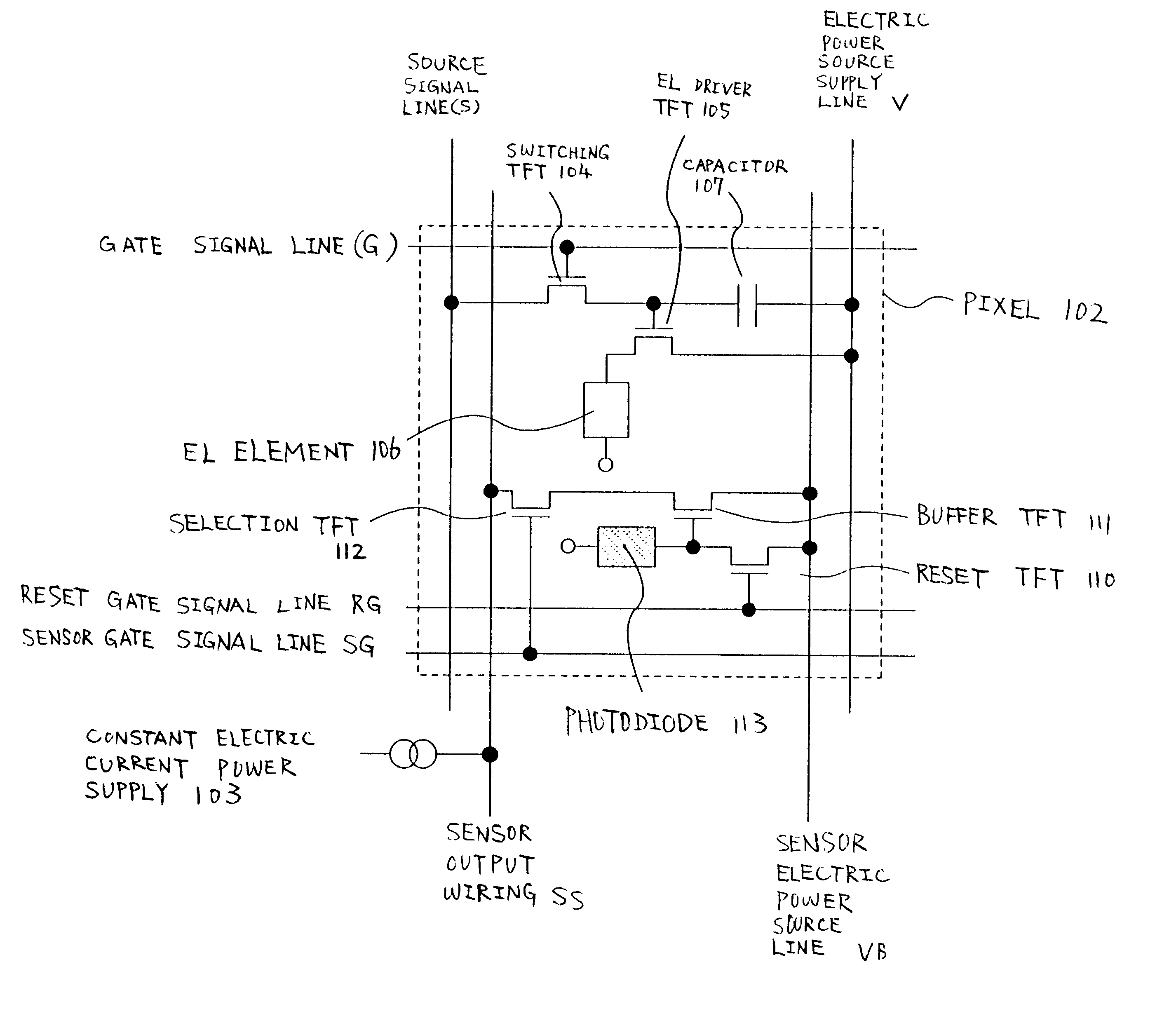

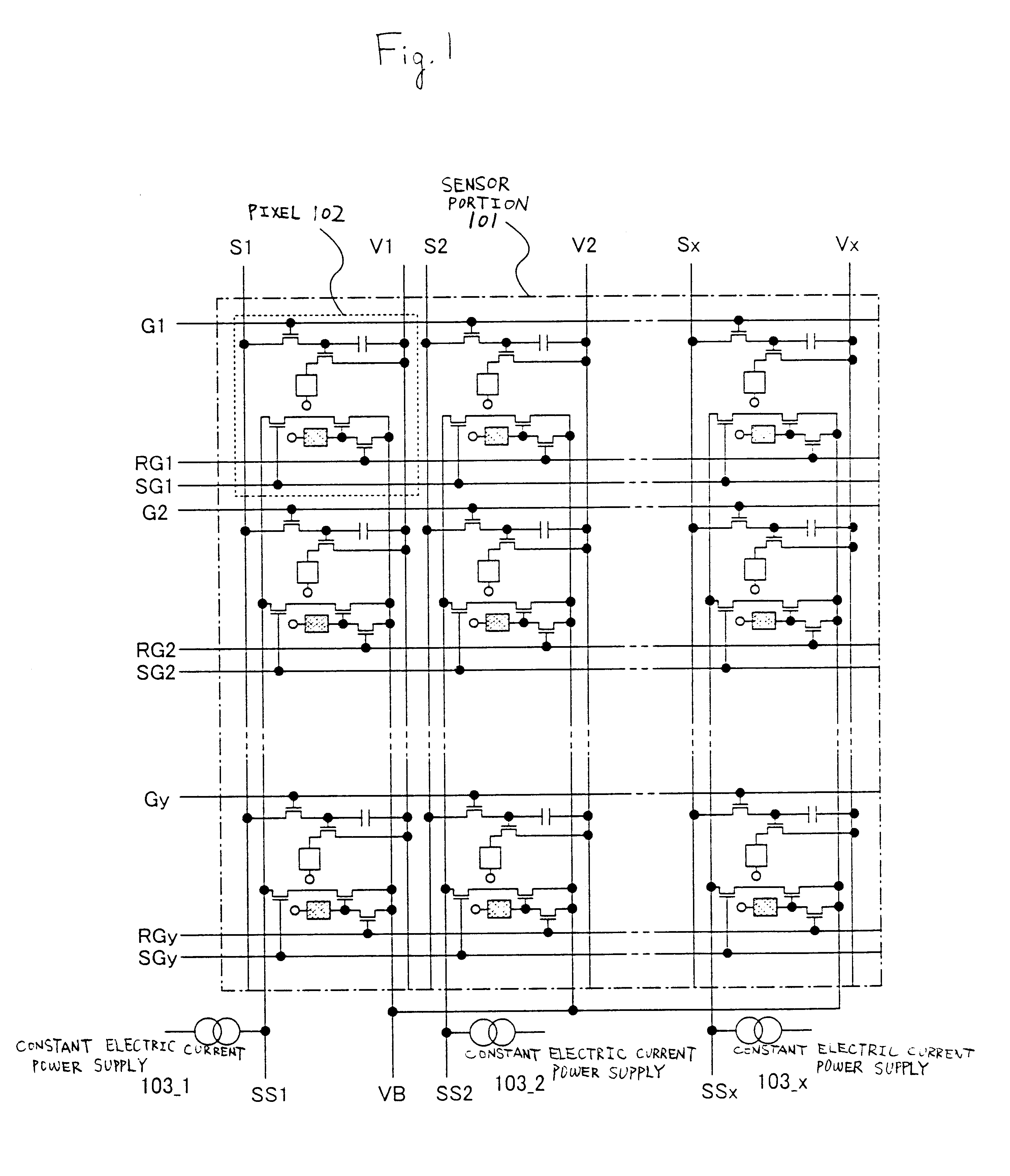

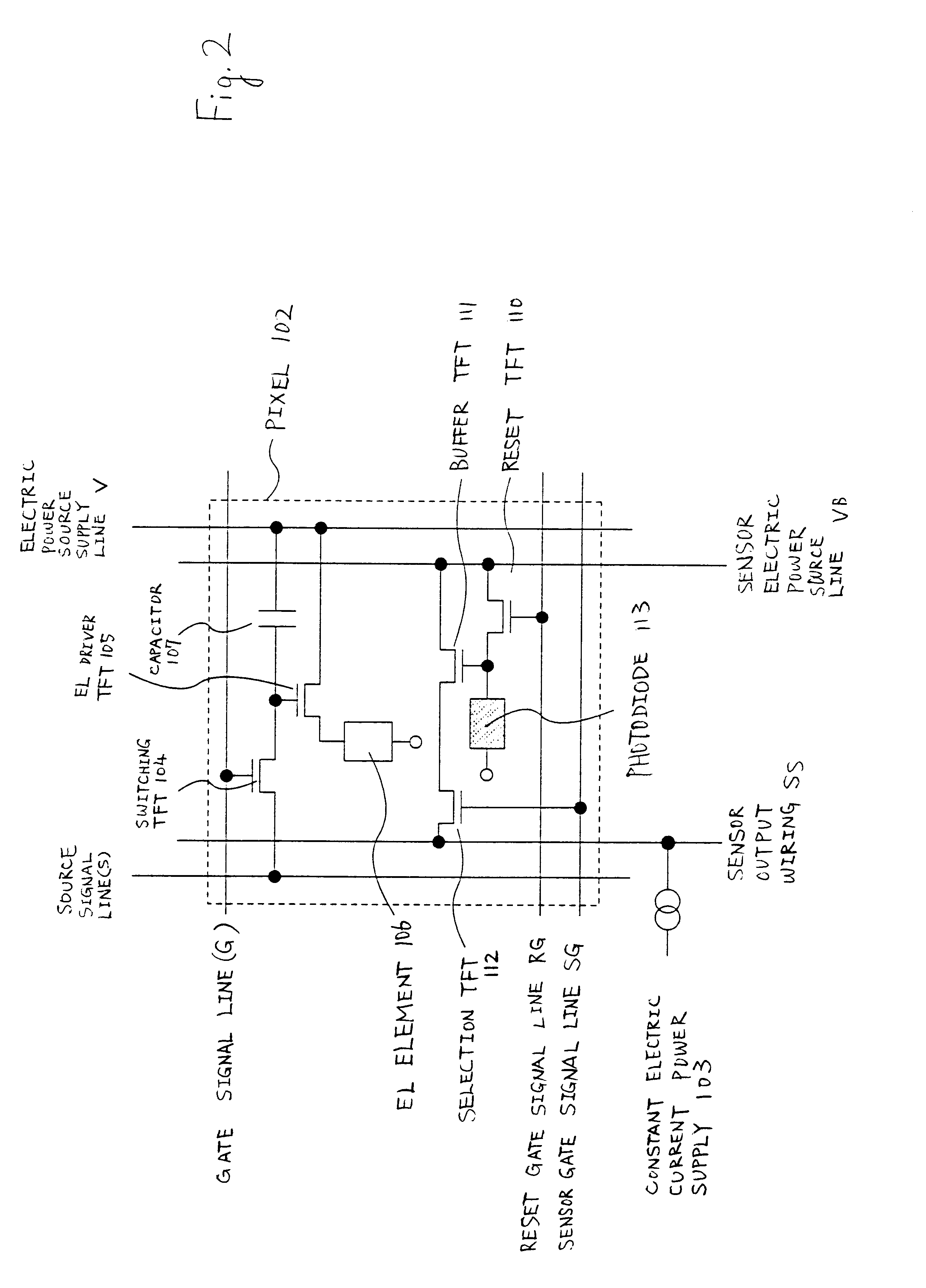

Adhesion type area sensor and display device having adhesion type area sensor

InactiveUS6747638B2Television system detailsTelevision system scanning detailsDisplay deviceEngineering

A lightweight, thin, small size adhesion type area sensor is provided. A pixel of the area sensor has an EL element as a light source, and a photodiode as a photoelectric conversion element. A TFT is used with the adhesion type area sensor for controlling the operation of the EL element and the photodiode.

Owner:SEMICON ENERGY LAB CO LTD