Patents

Literature

2584 results about "Dynamic random-access memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

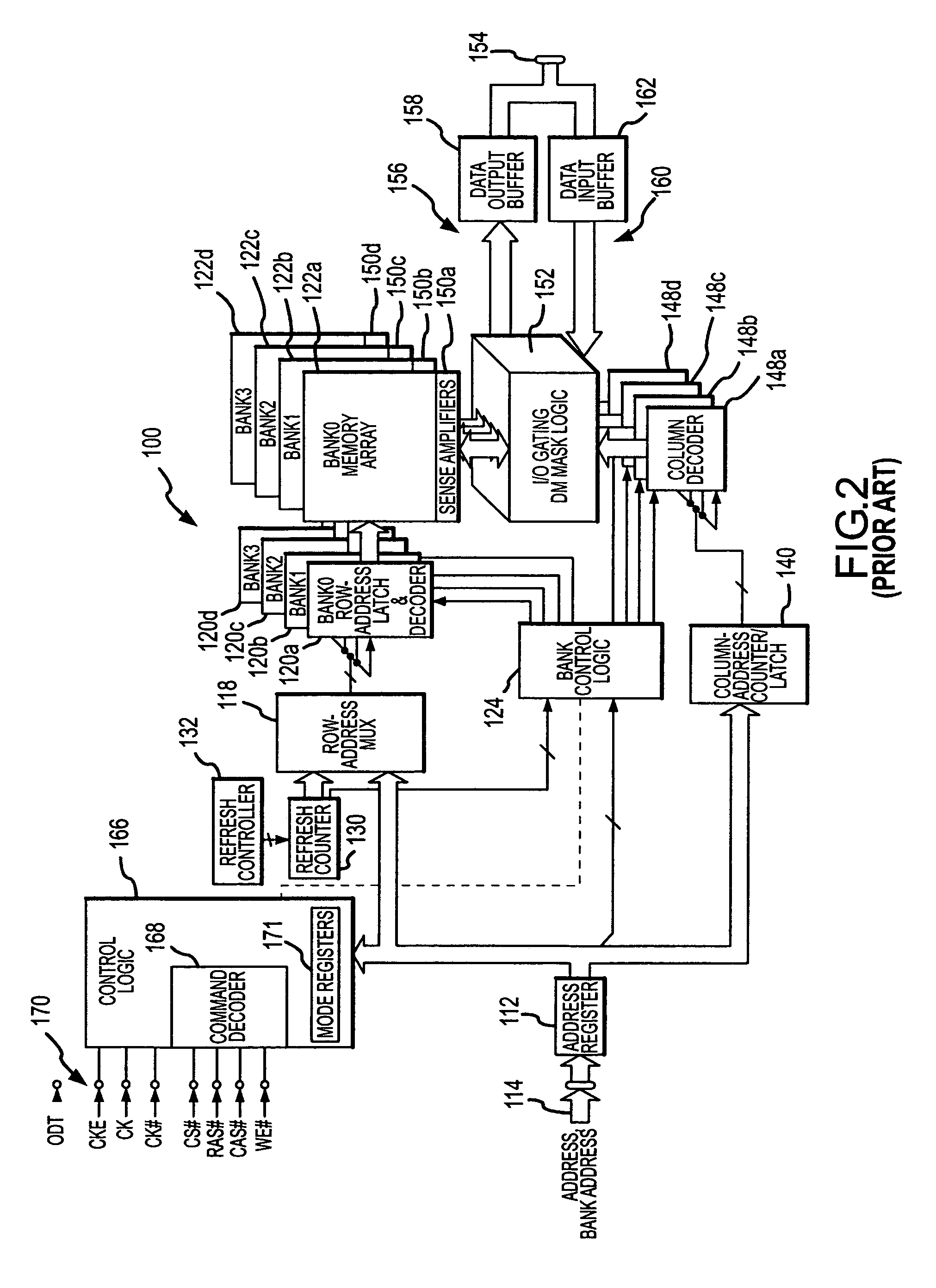

Dynamic random-access memory (DRAM) is a type of random access semiconductor memory that stores each bit of data in a memory cell consisting of a tiny capacitor and a transistor, both typically based on metal-oxide-semiconductor (MOS) technology. The capacitor can either be charged or discharged; these two states are taken to represent the two values of a bit, conventionally called 0 and 1. The electric charge on the capacitors slowly leaks off, so without intervention the data on the chip would soon be lost. To prevent this, DRAM requires an external memory refresh circuit which periodically rewrites the data in the capacitors, restoring them to their original charge. This refresh process is the defining characteristic of dynamic random-access memory, in contrast to static random-access memory (SRAM) which does not require data to be refreshed. Unlike flash memory, DRAM is volatile memory (vs. non-volatile memory), since it loses its data quickly when power is removed. However, DRAM does exhibit limited data remanence.

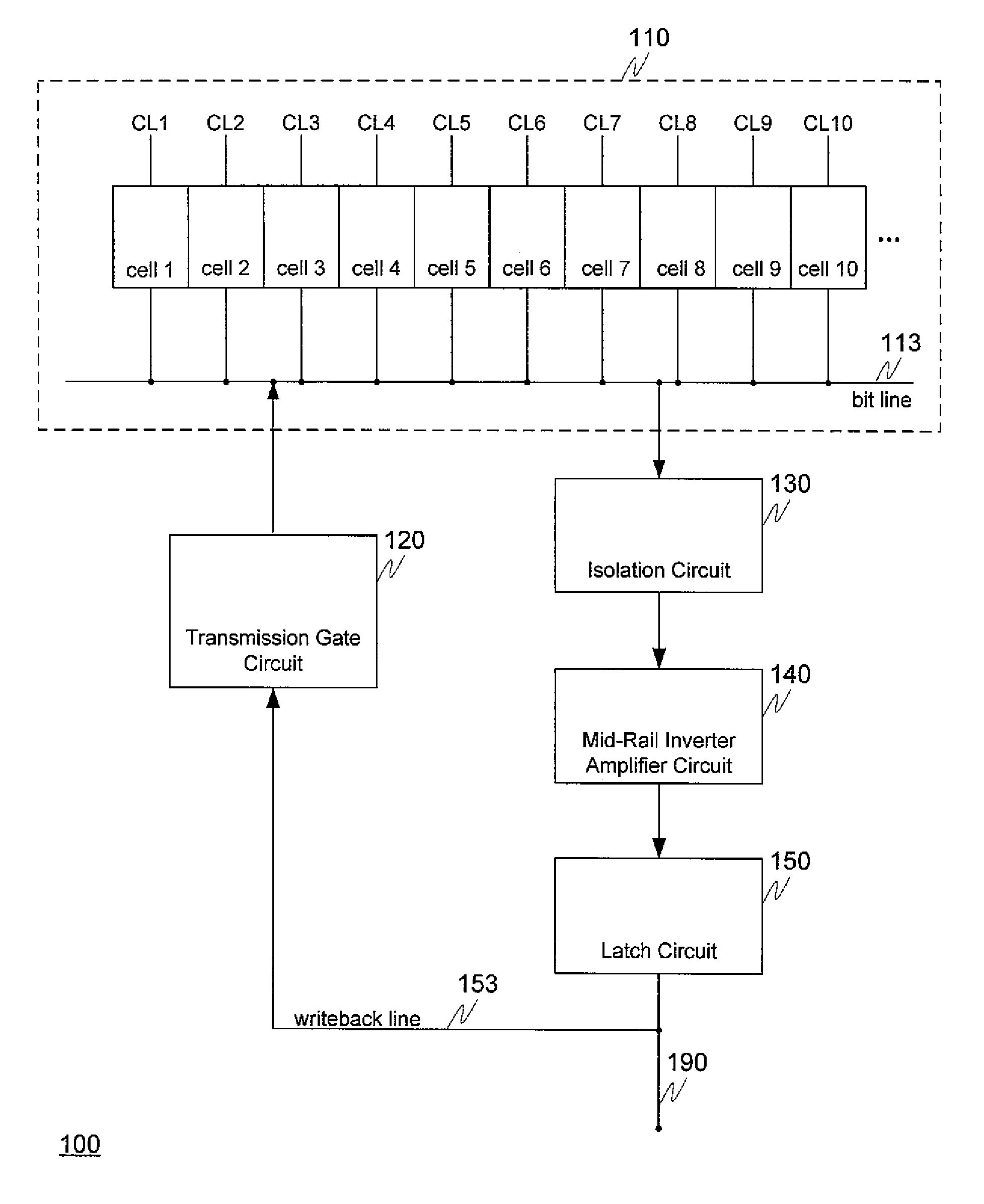

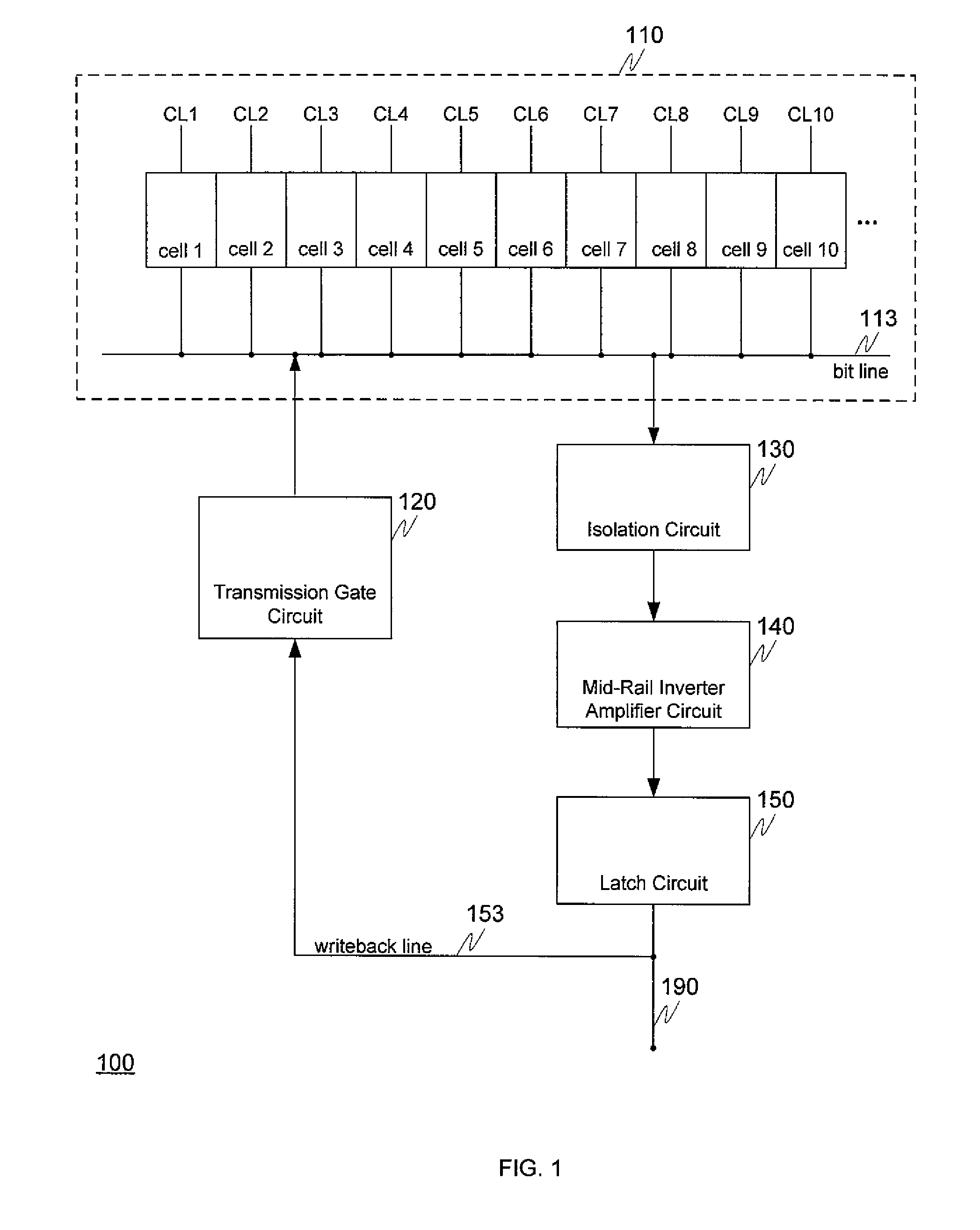

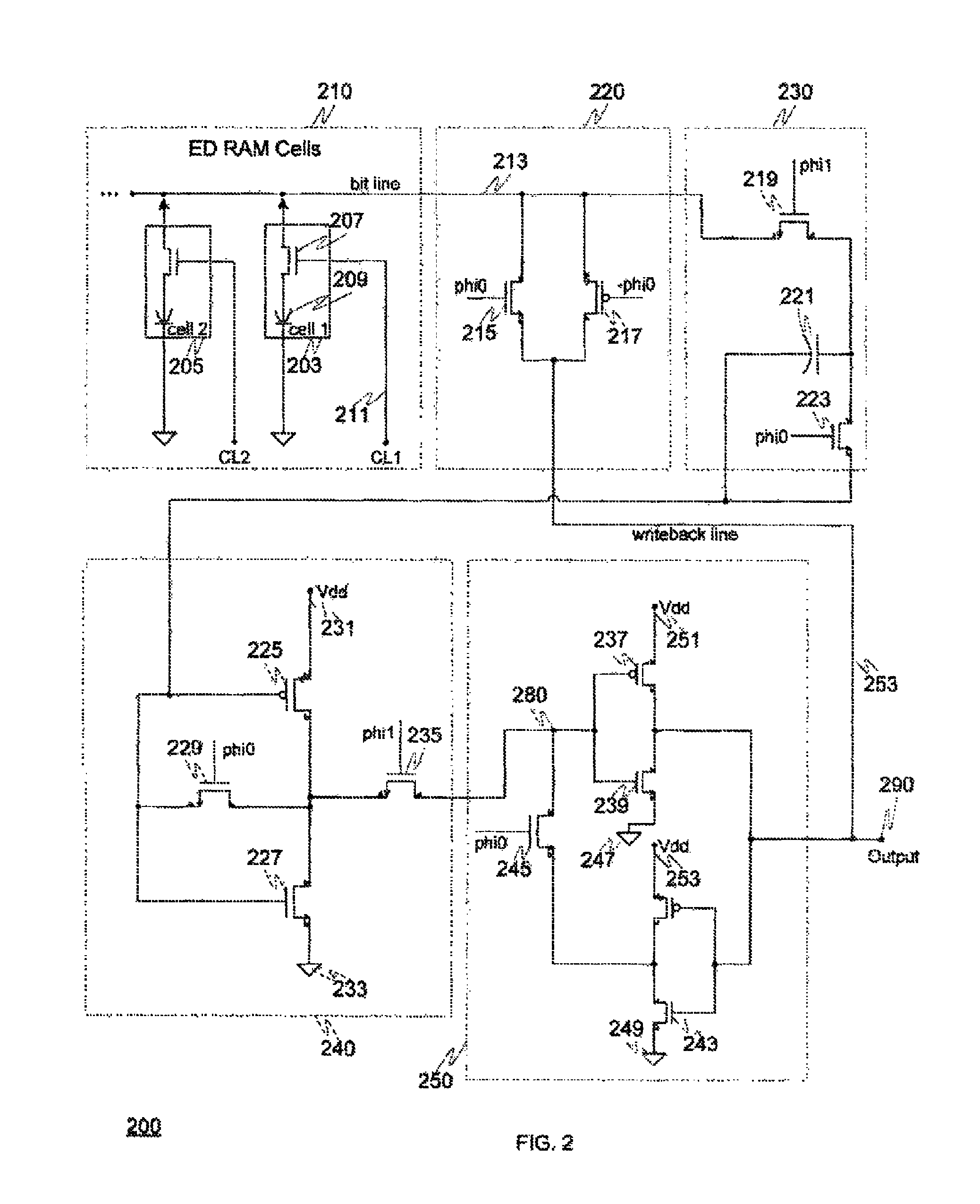

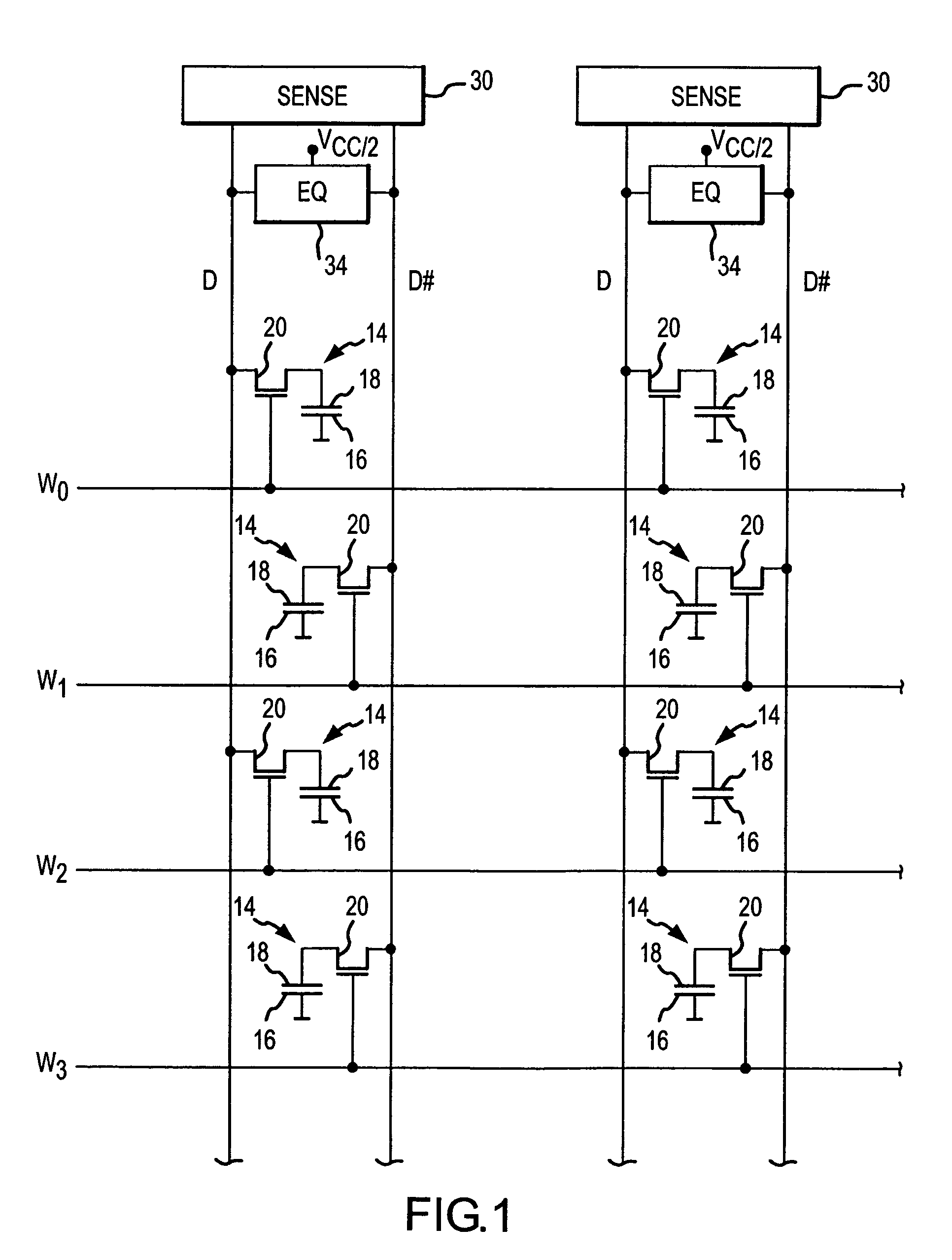

High performance eDRAM sense amplifier

Embedded dynamic random access memory (eDRAM) sense amplifier circuitry in which a bit line connected to each of a first plurality of eDRAM cells is controlled by cell control lines tied to each of the cells. During a READ operation the eDRAM cell releases its charge indicating its digital state. The digital charge propagates through the eDRAM sense amplifier circuitry to a mid-rail amplifier inverter circuit which amplifies the charge and provides it to a latch circuit. The latch circuit, in turn, inverts the charge to correctly represent at its output the logical value stored in the eDRAM cell being read, and returns the charge through the eDRAM sense amplifier circuitry to replenish the eDRAM cell.

Owner:INT BUSINESS MASCH CORP

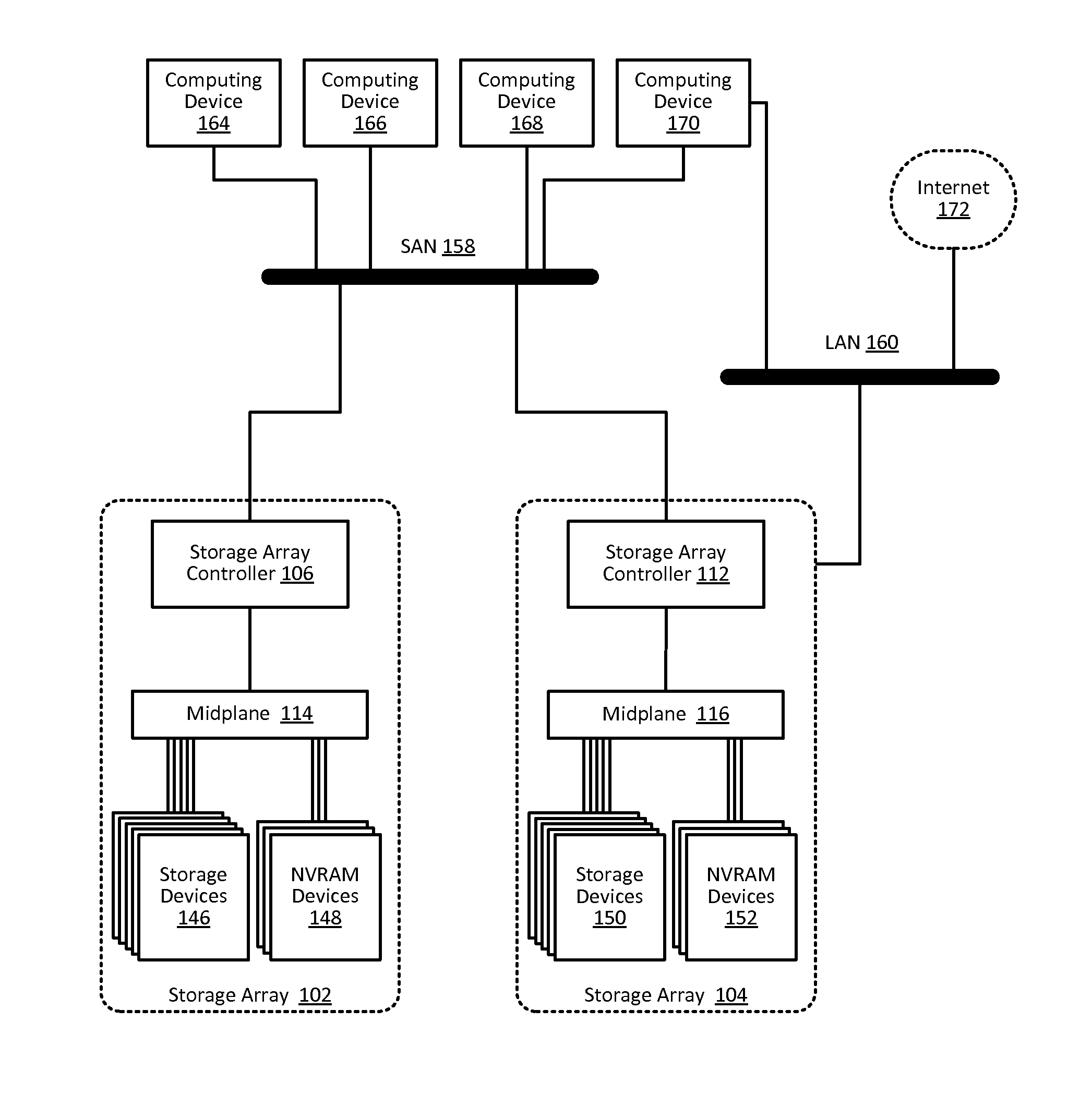

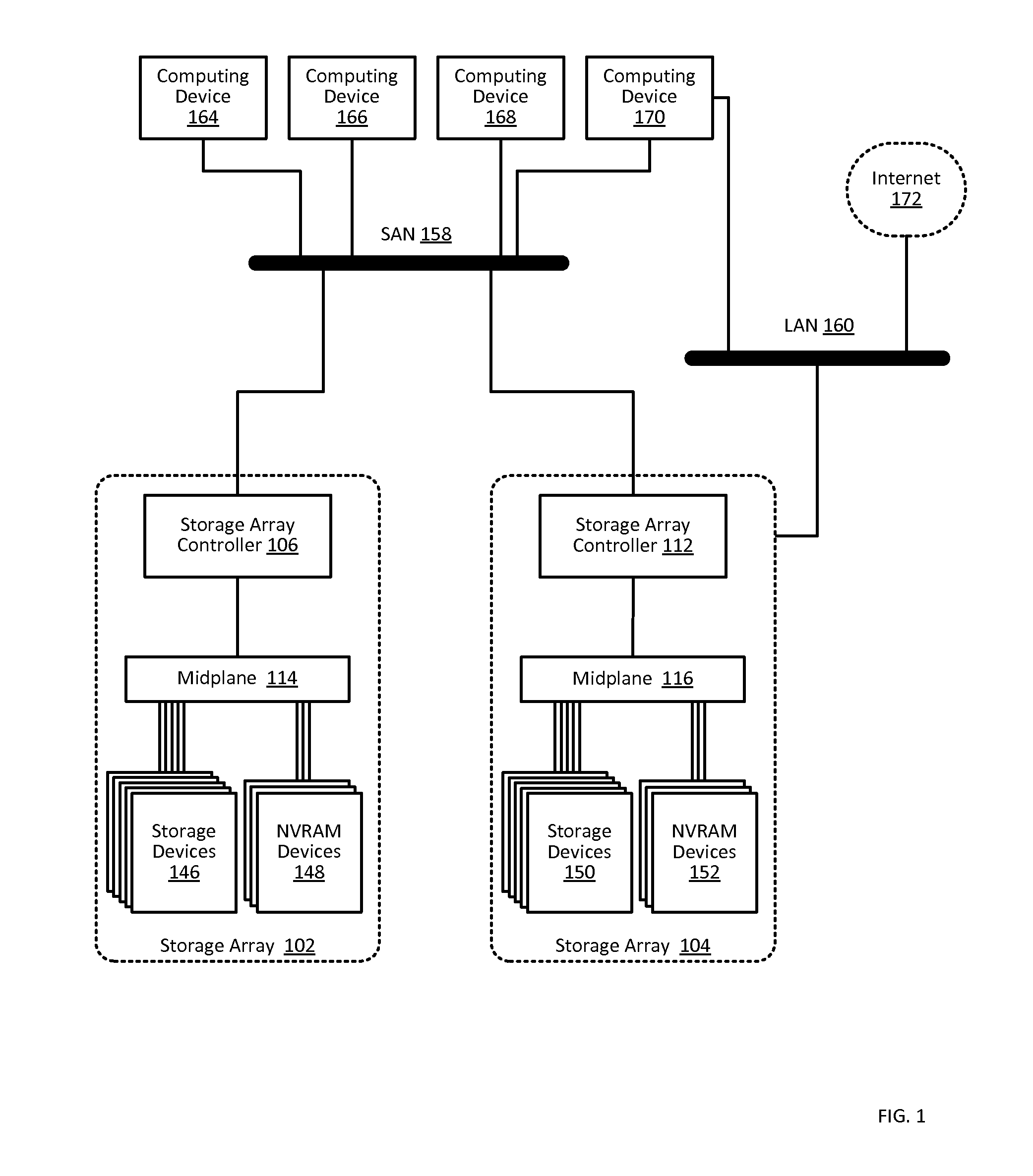

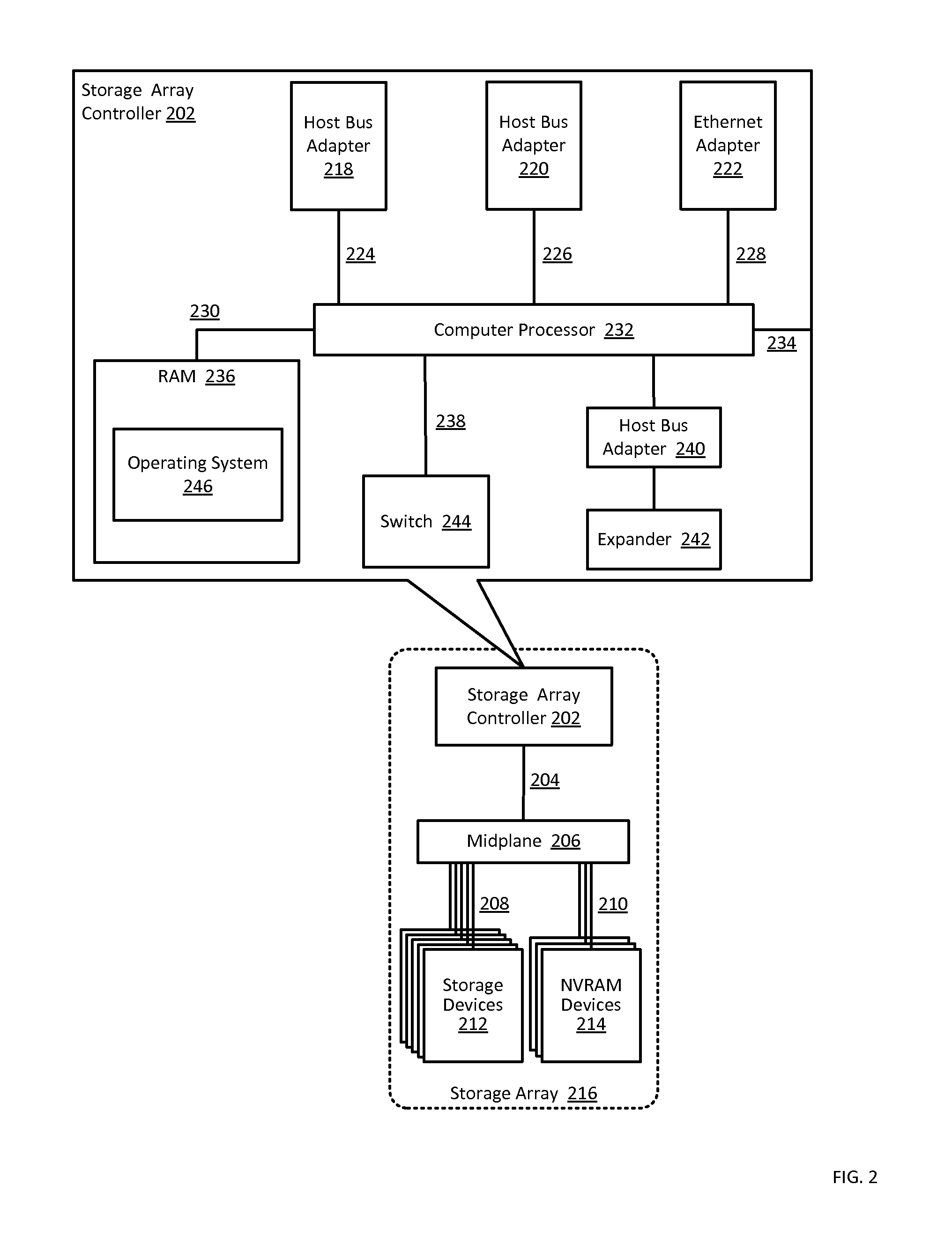

Buffering data to be written to an array of non-volatile storage devices

InactiveUS20160350009A1Input/output to record carriersError detection/correctionComputer hardwareStandby power

Buffering data to be written to an array of non-volatile storage devices, including: receiving a request to write data to the array of non-volatile storage devices; sending, to a non-volatile random access memory (‘NVRAM’) device, an instruction to write the data to dynamic random access memory (‘DRAM’) in the NVRAM device, the DRAM configured to receive power from a primary power source, the DRAM further configured to receive power from a backup power source in response to the primary power source failing; and writing the data to the DRAM in the NVRAM device.

Owner:PURE STORAGE

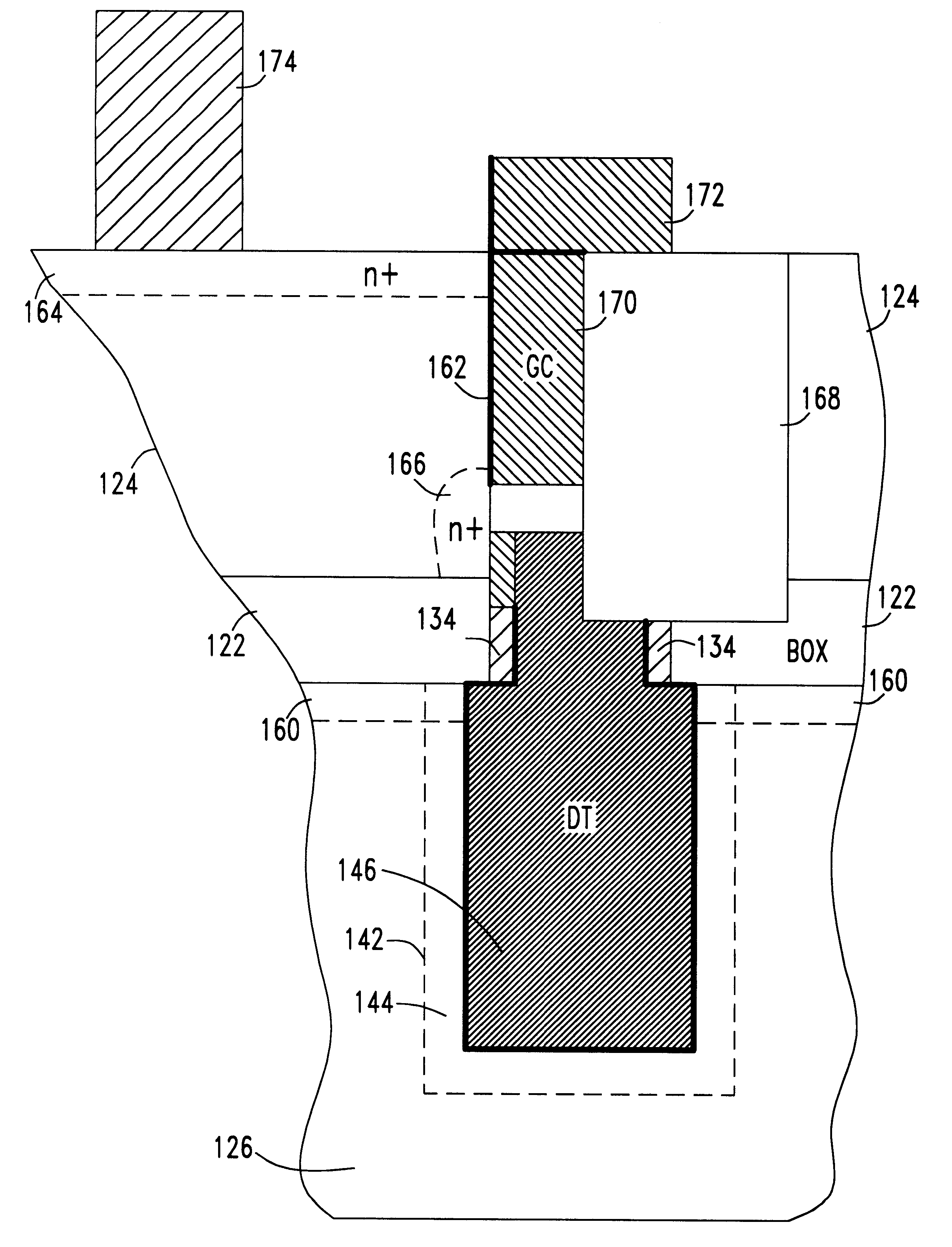

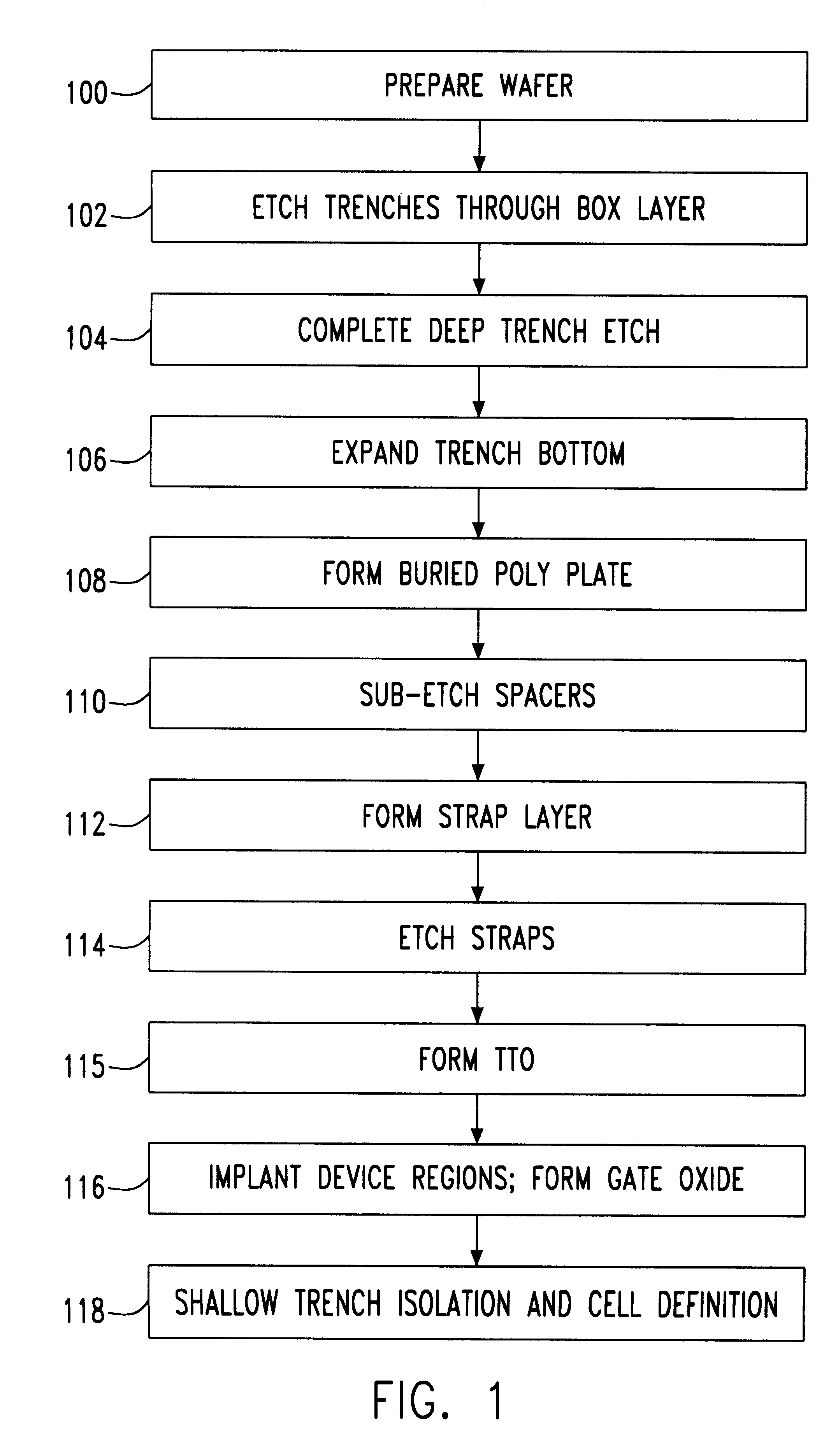

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

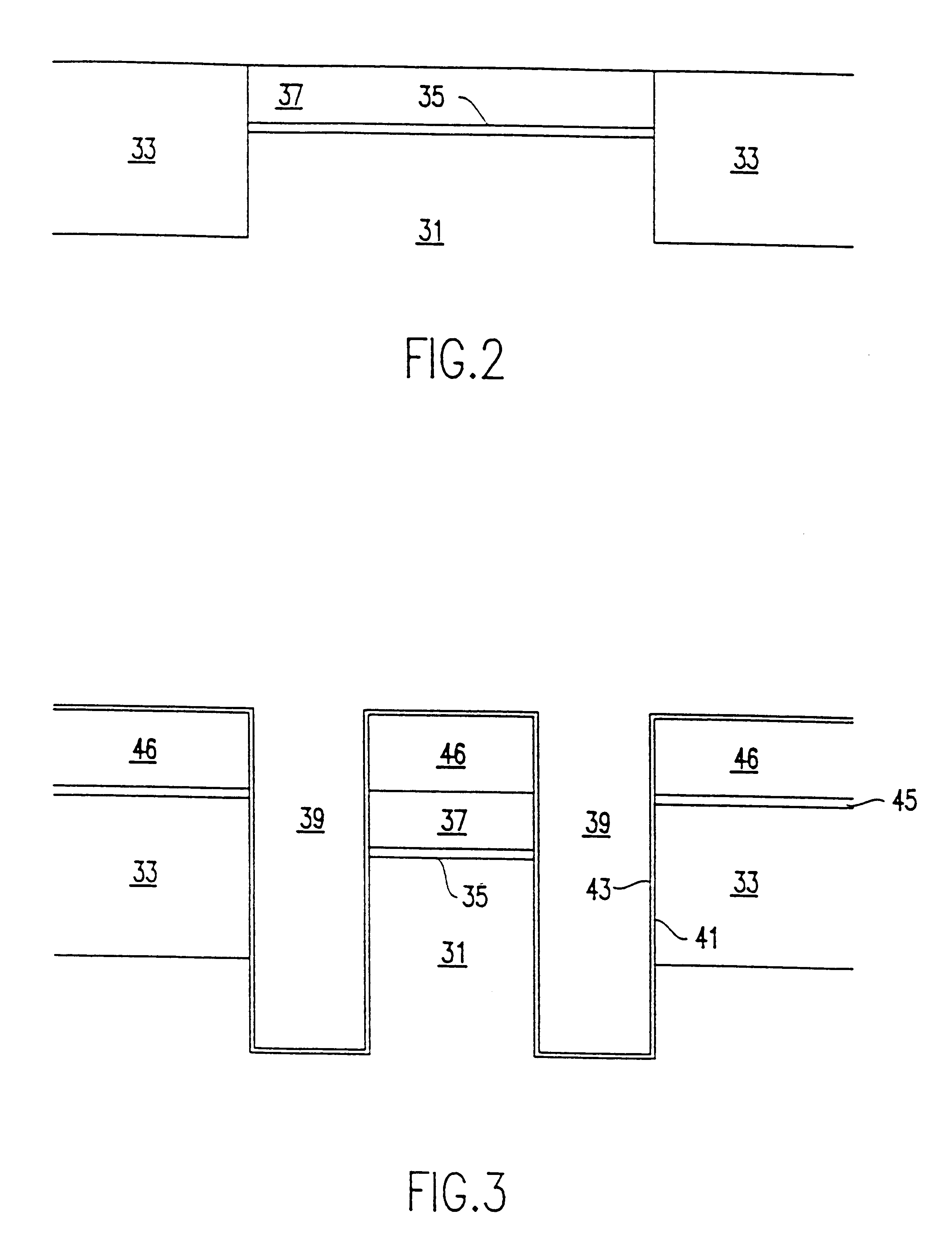

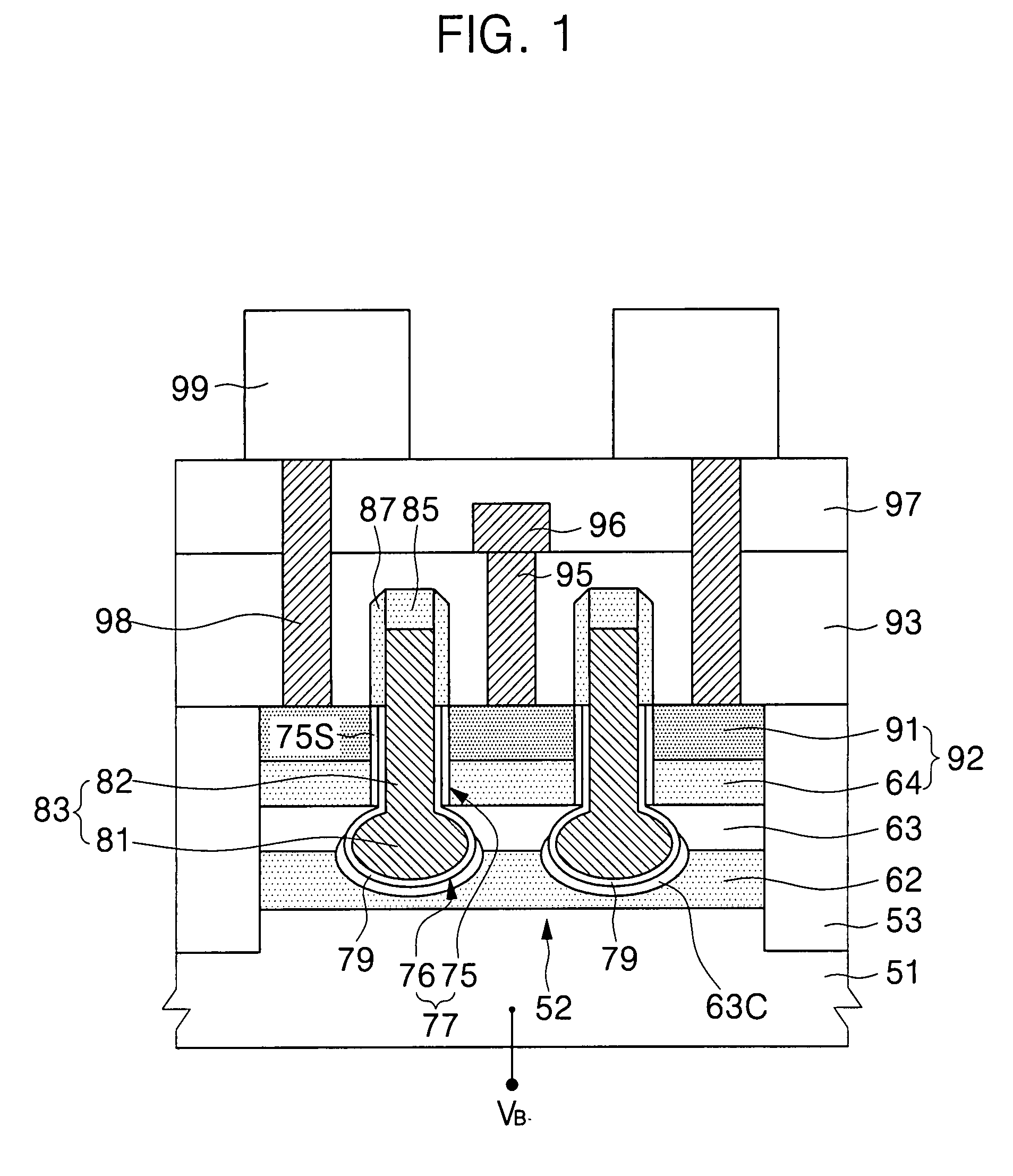

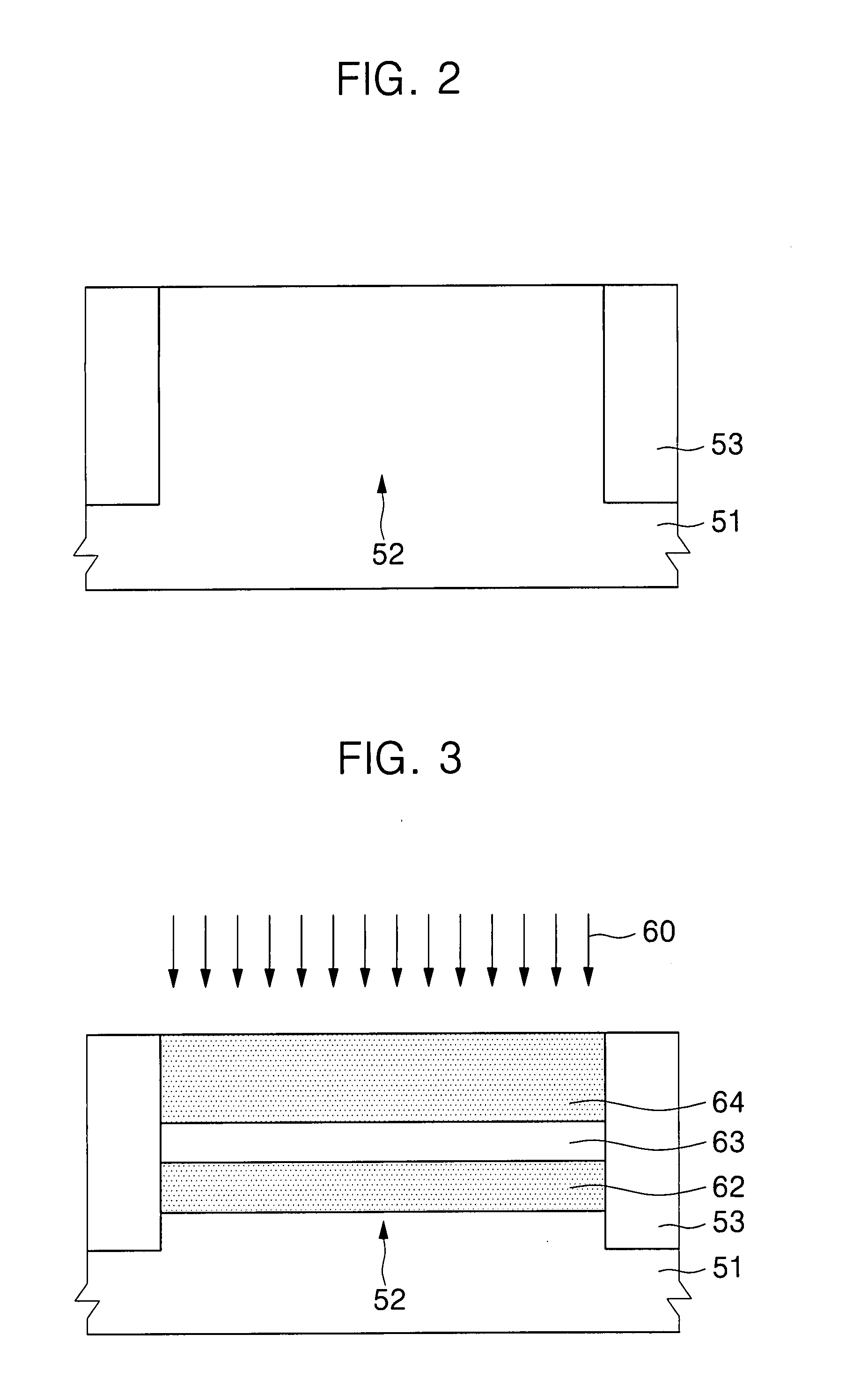

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

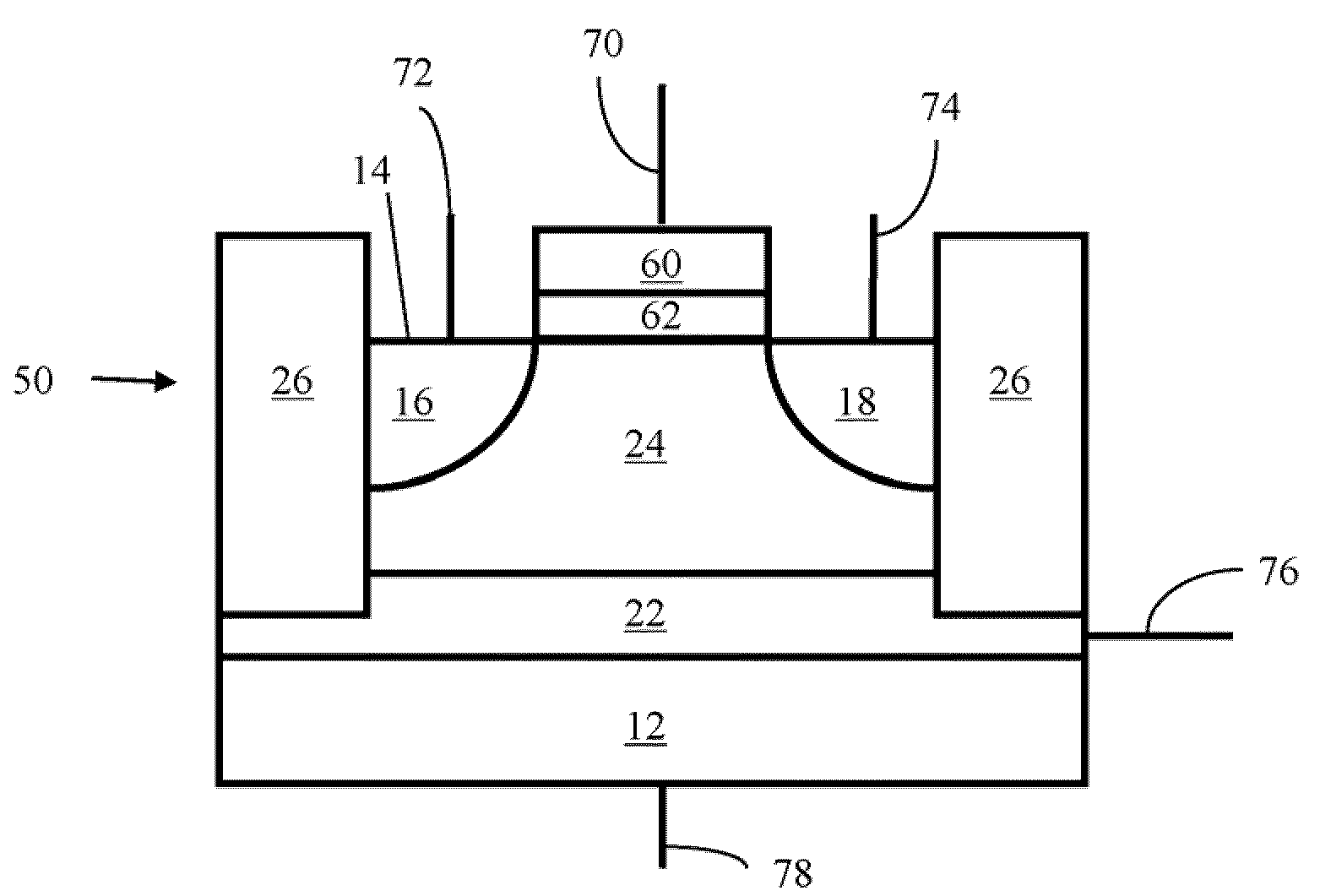

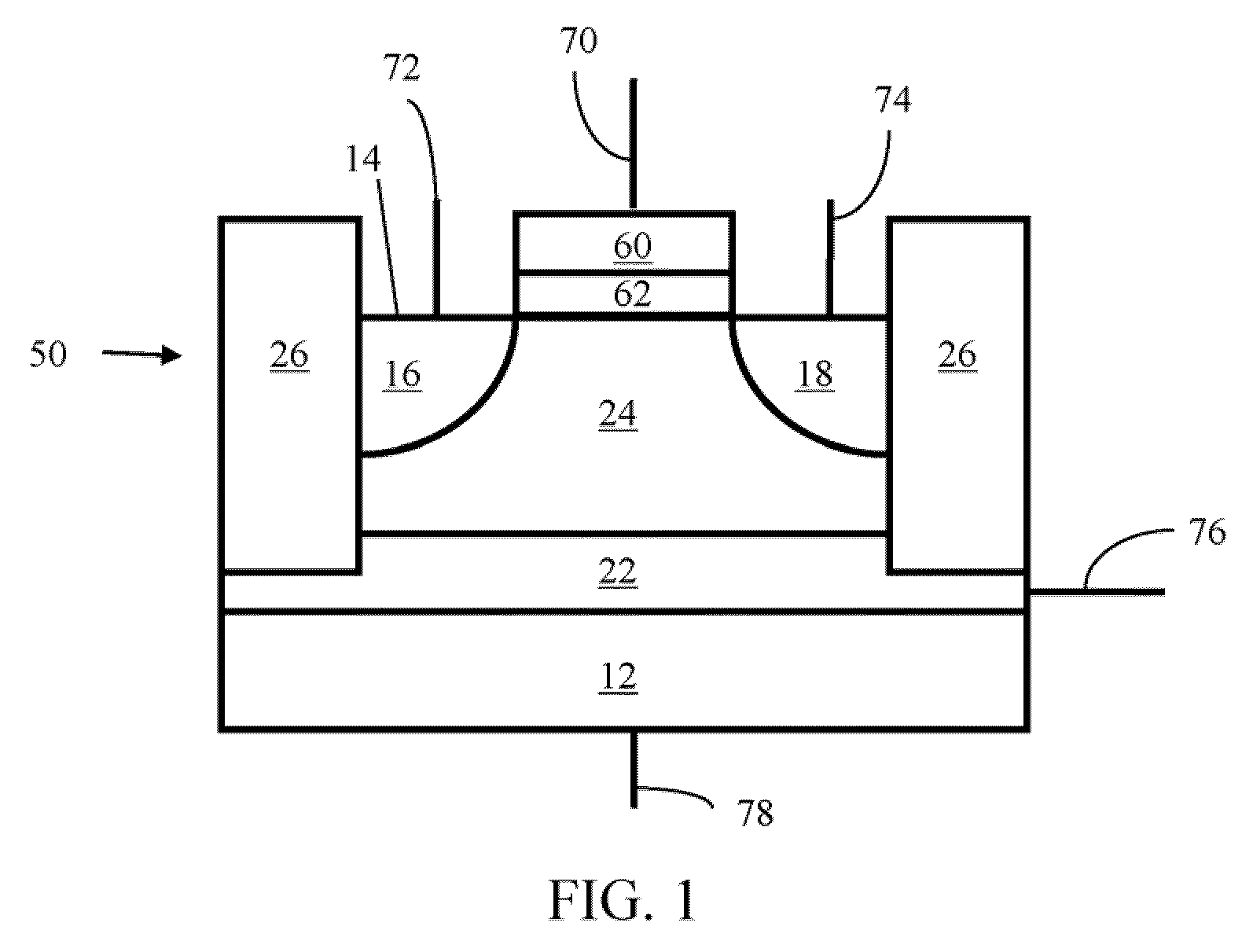

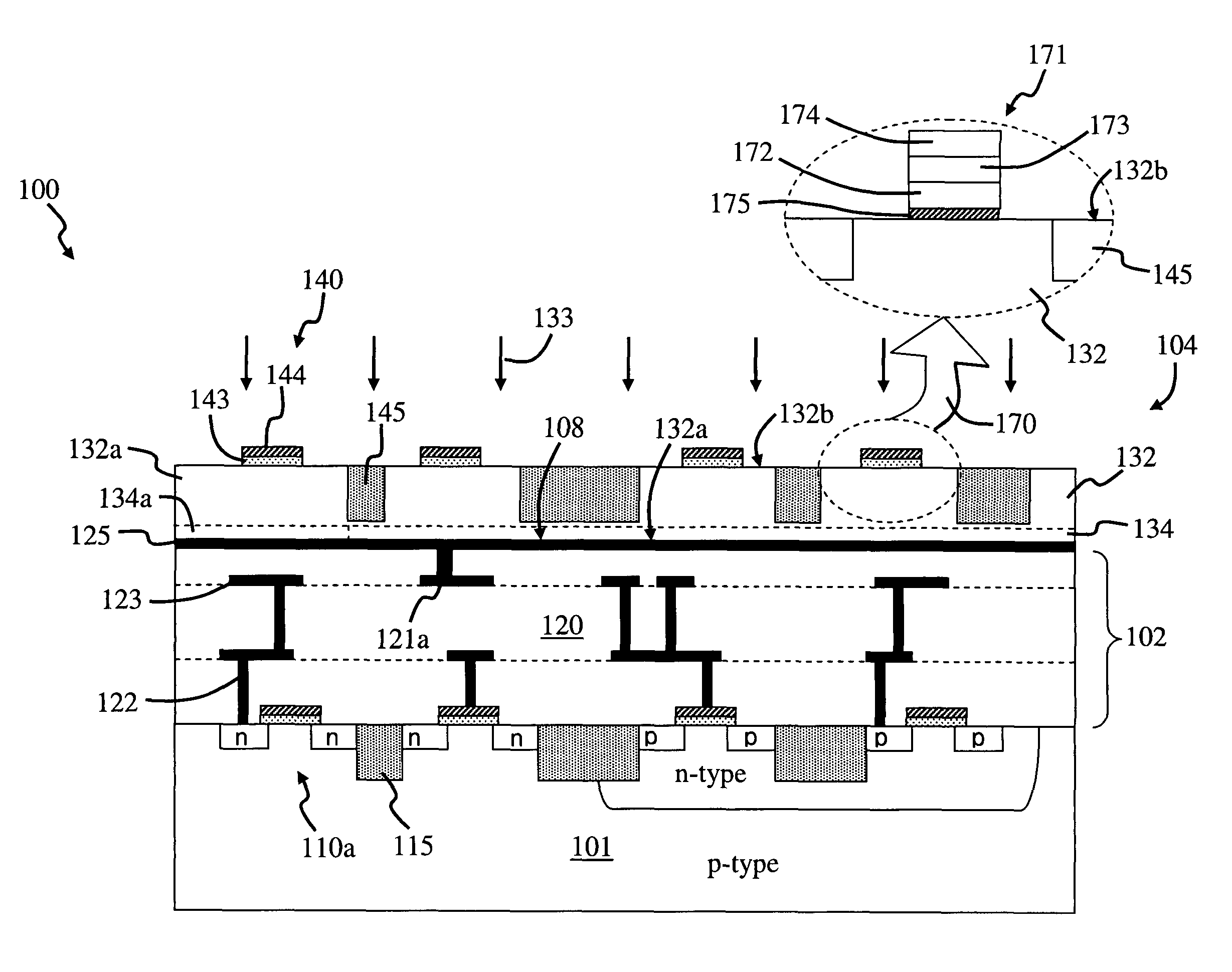

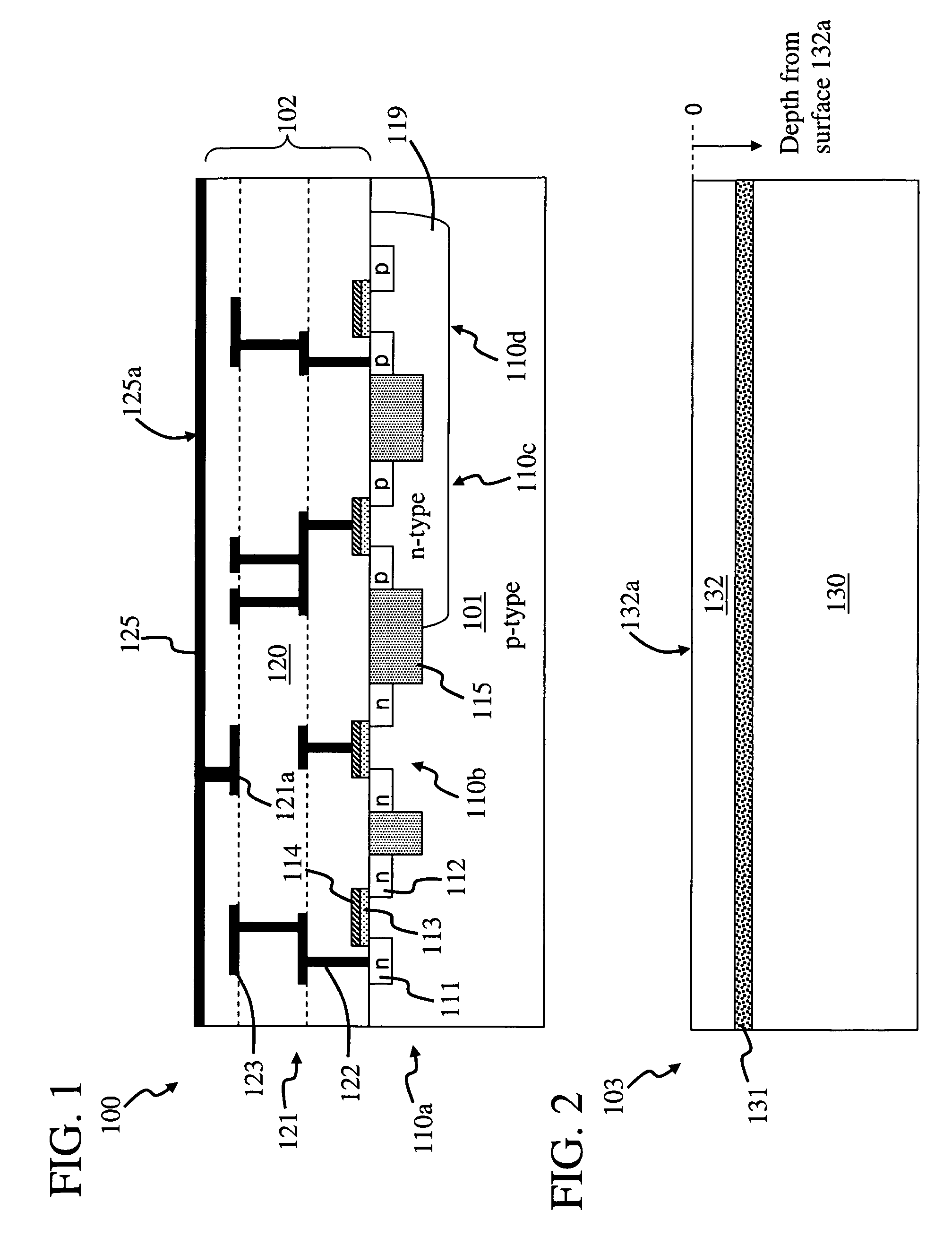

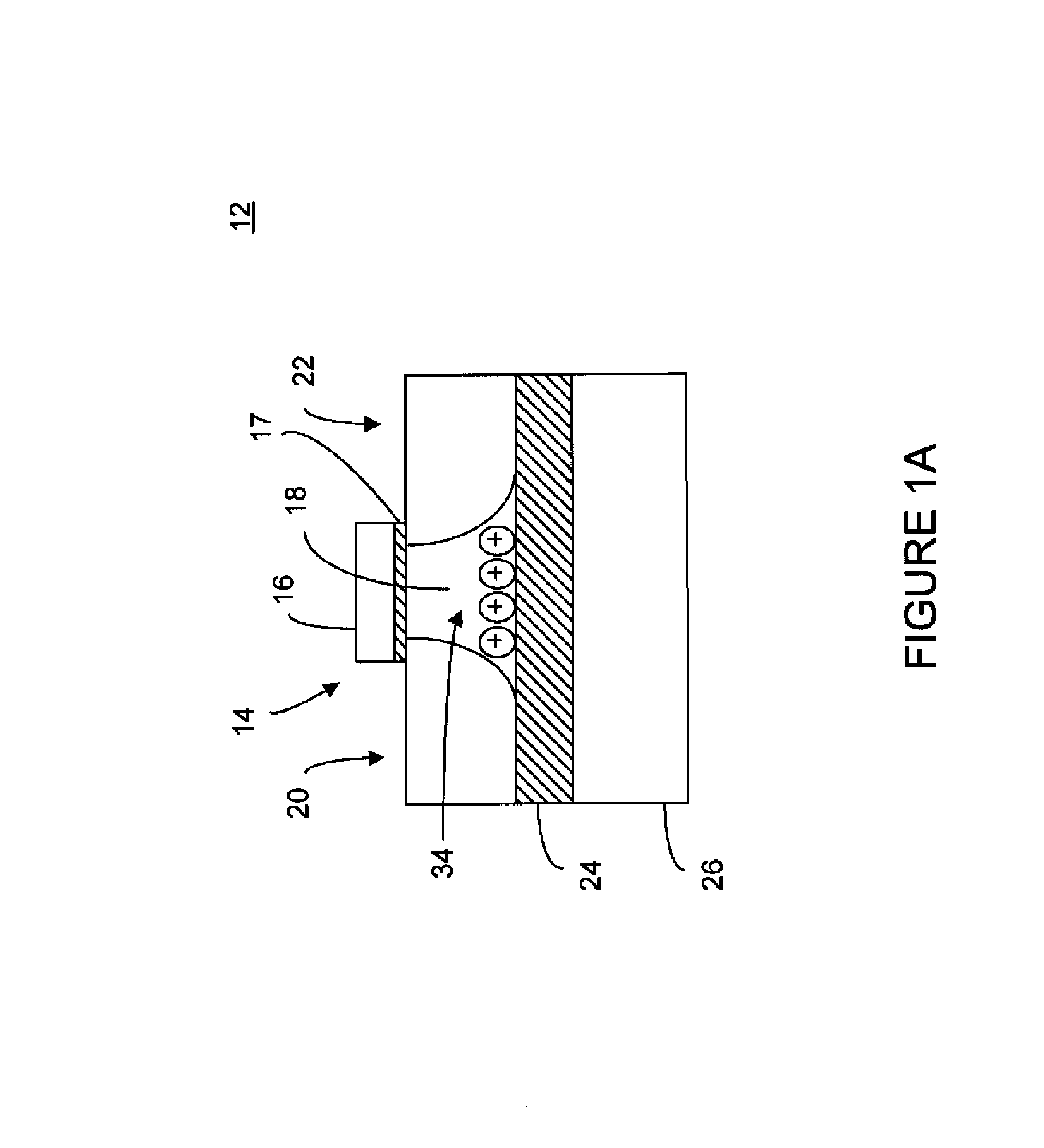

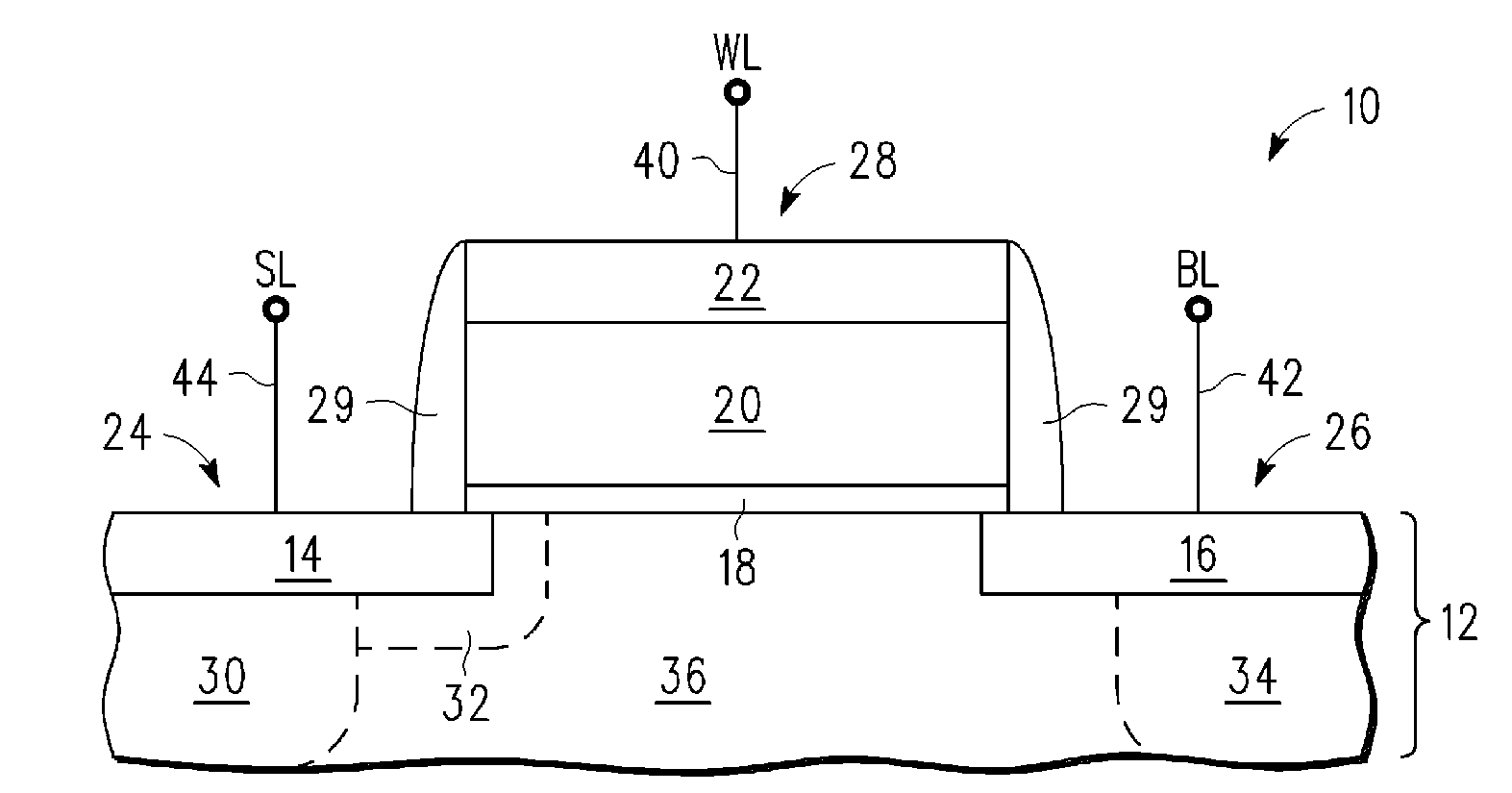

Method of fabricating a one transistor floating-body DRAM cell in bulk CMOS process with electrically isolated charge storage region

InactiveUS6913964B2Limiting leakage currentEnsure adequate isolationTransistorSolid-state devicesEngineeringField-effect transistor

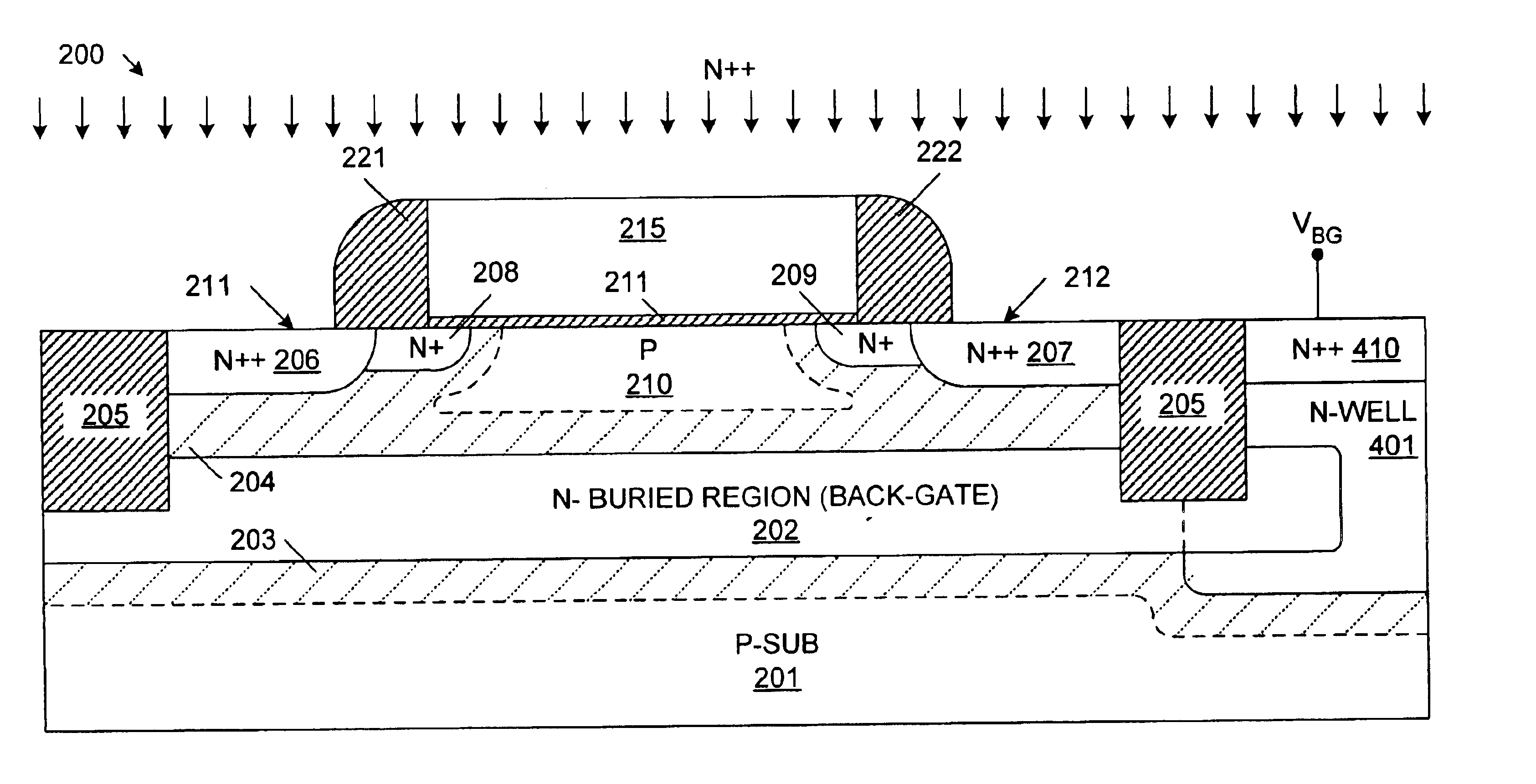

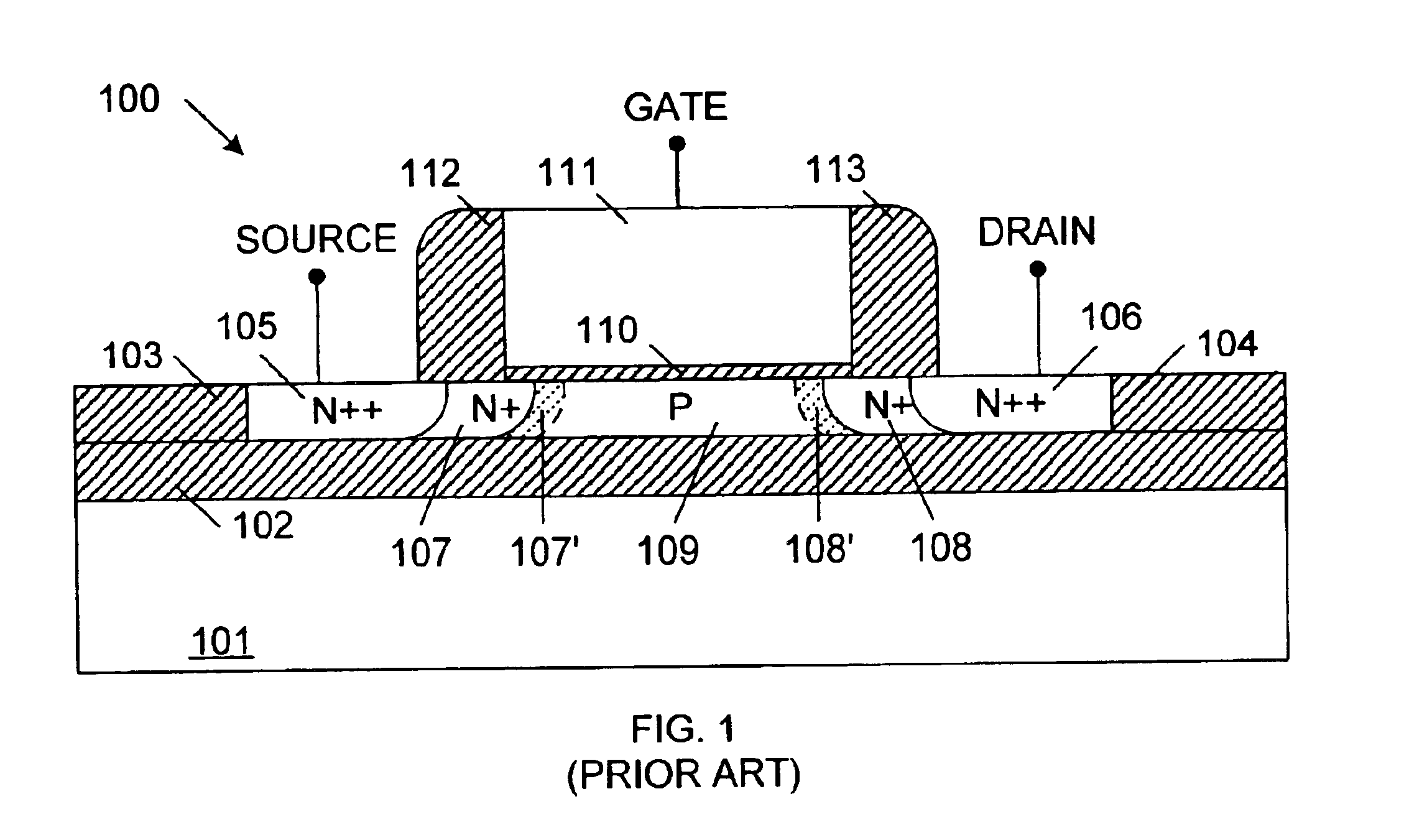

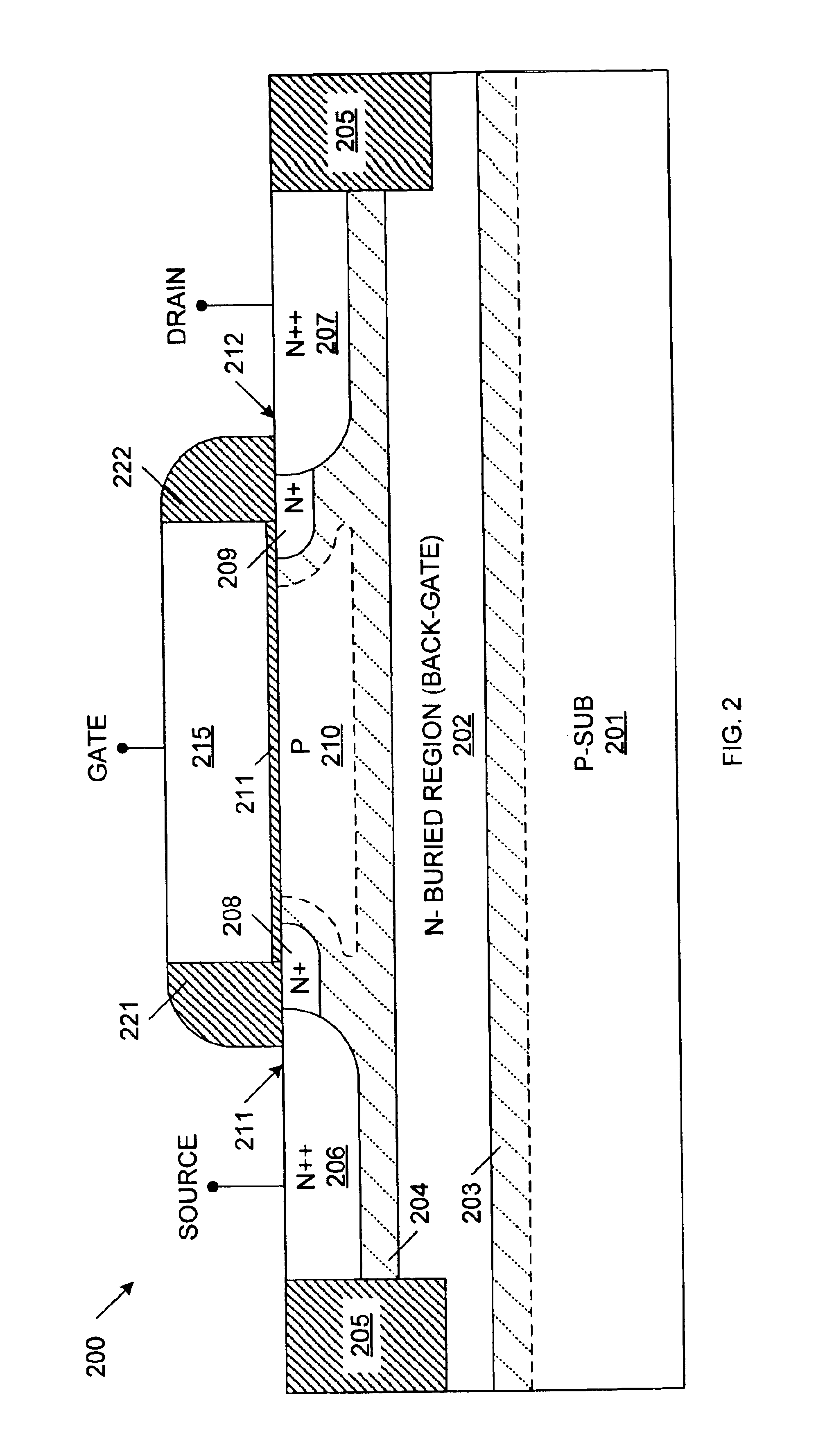

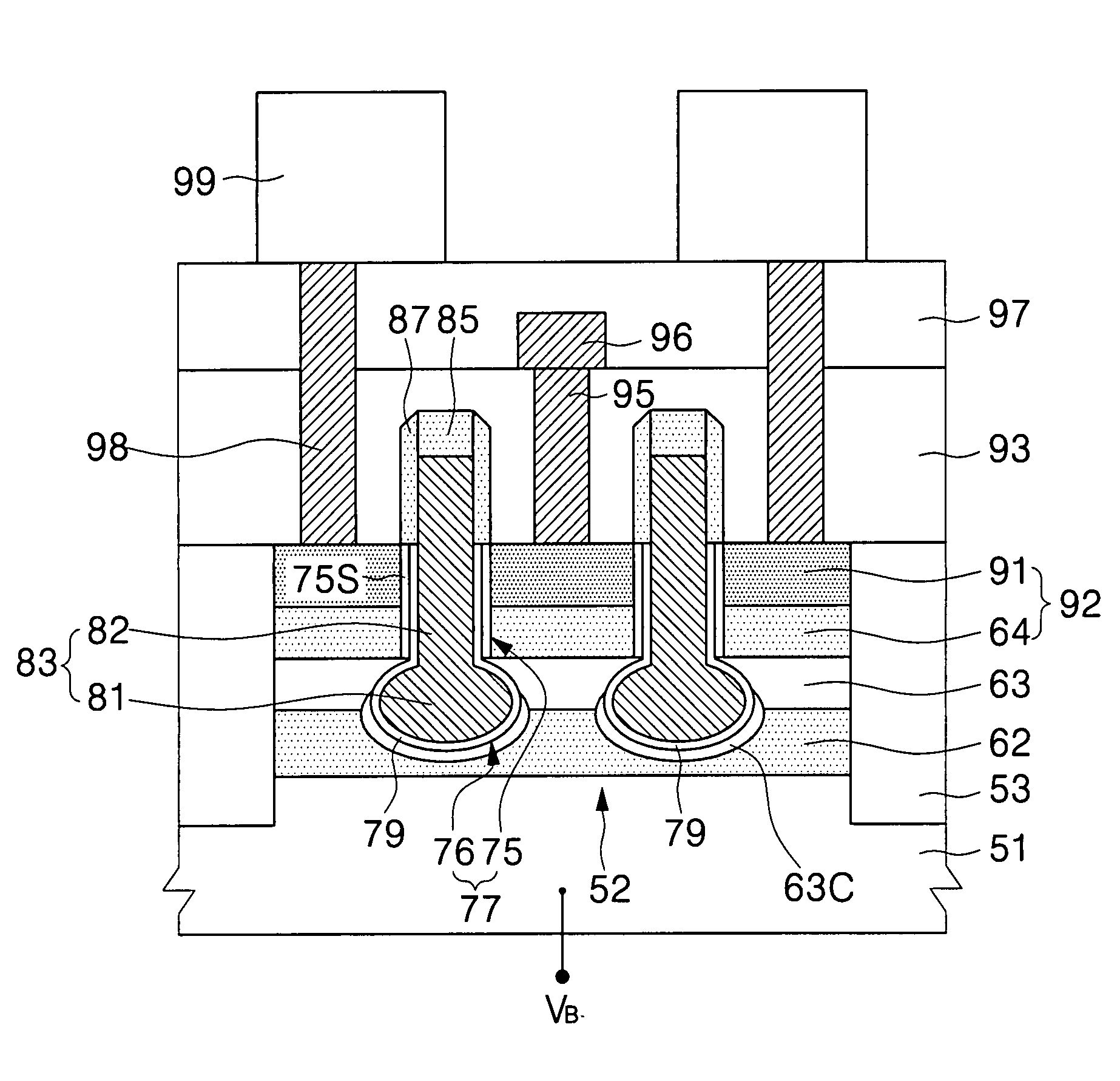

A one-transistor, floating-body (1T / FB) dynamic random access memory (DRAM) cell is provided that includes a field-effect transistor fabricated using a process compatible with a standard CMOS process. The field-effect transistor includes a source region and a drain region of a first conductivity type and a floating body region of a second conductivity type, opposite the first conductivity type, located between the source region and the drain region. A buried region of the first conductivity type is located under the source region, drain region and floating body region. The buried region helps to form a depletion region, which is located between the buried region and the source region, the drain region and the floating body region. The floating body region is thereby isolated by the depletion region. A bias voltage can be applied to the buried region, thereby controlling leakage currents in the 1T / FB DRAM cell.

Owner:MOSYS INC

Semiconductor circuit

InactiveUS20080191312A1Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceEngineering

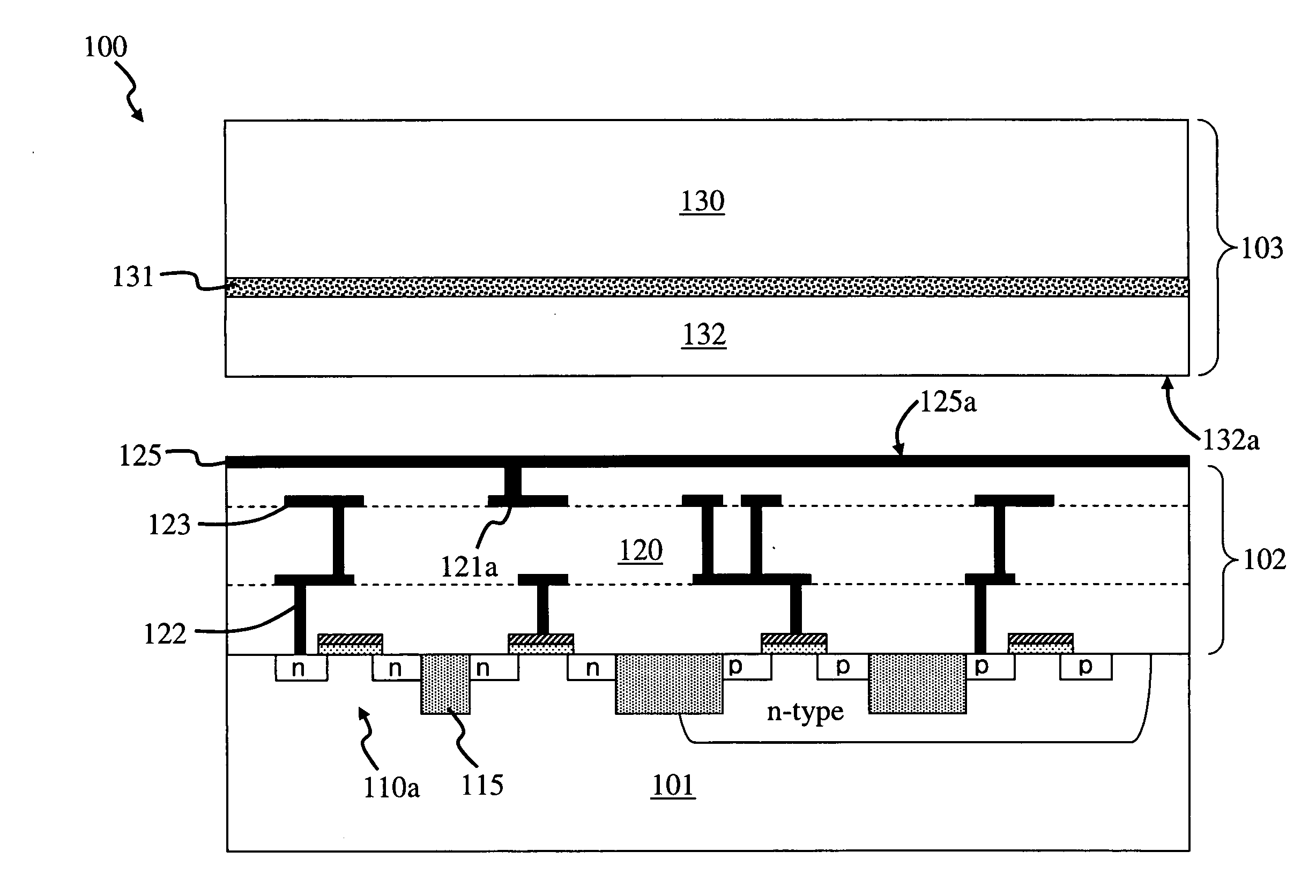

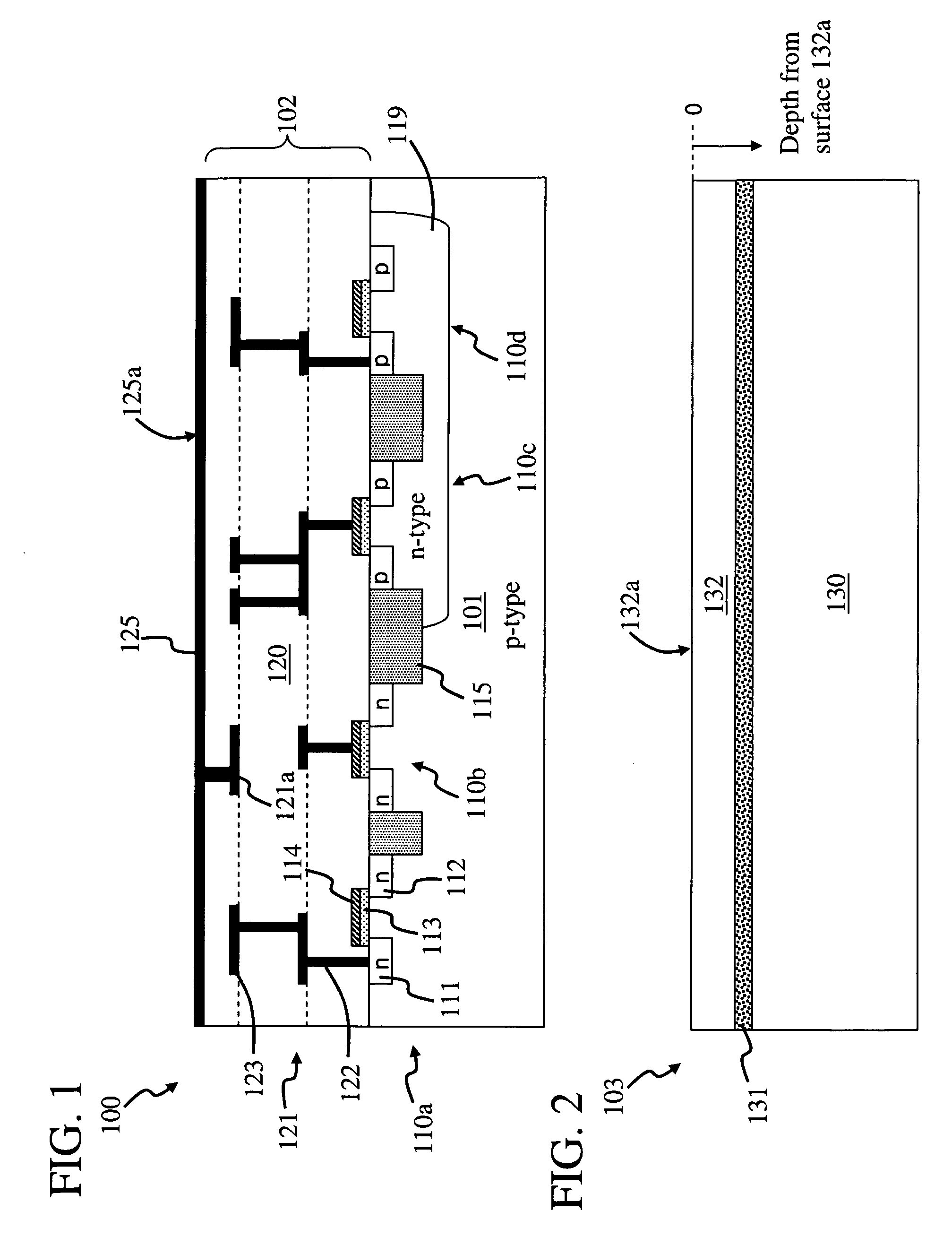

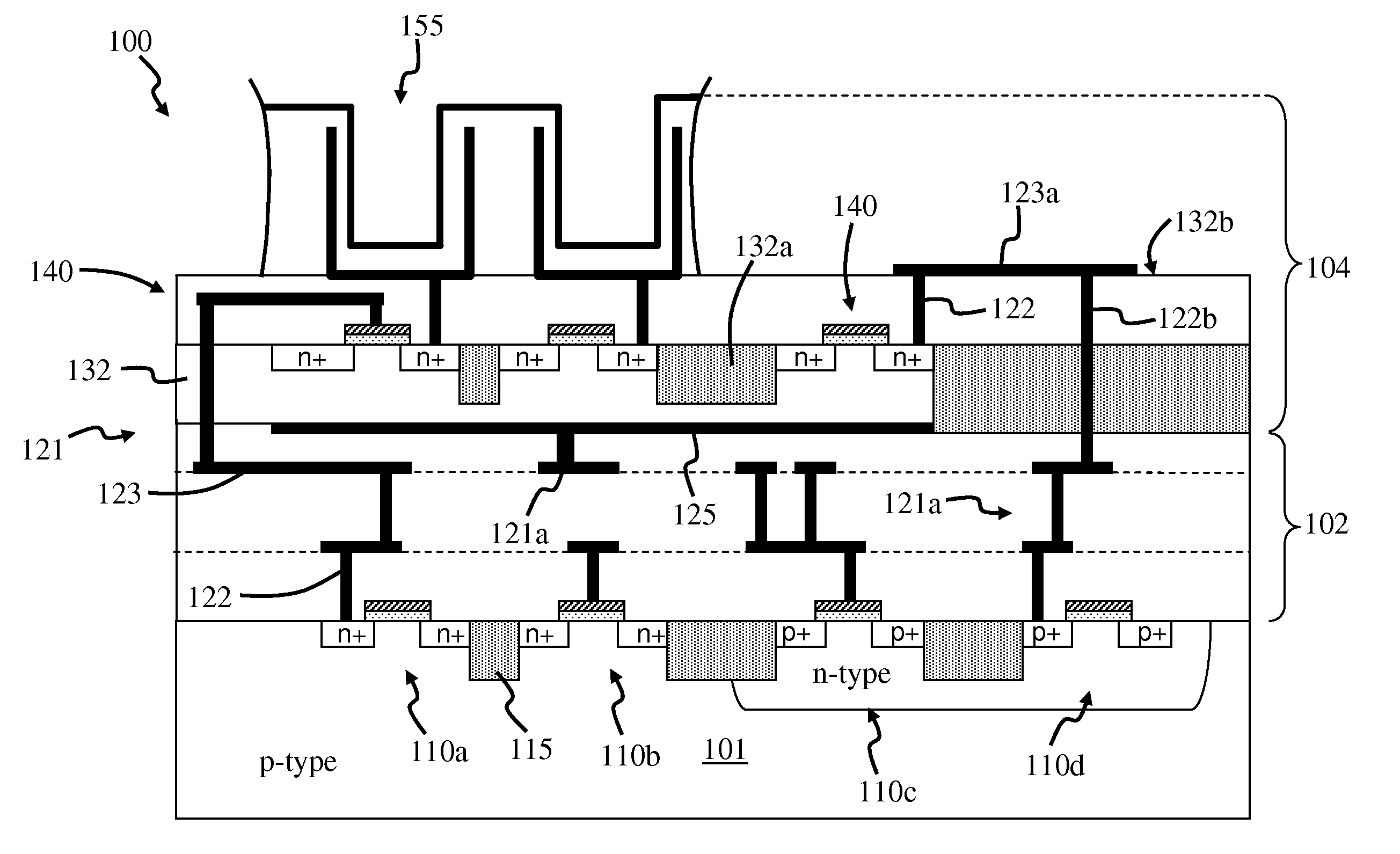

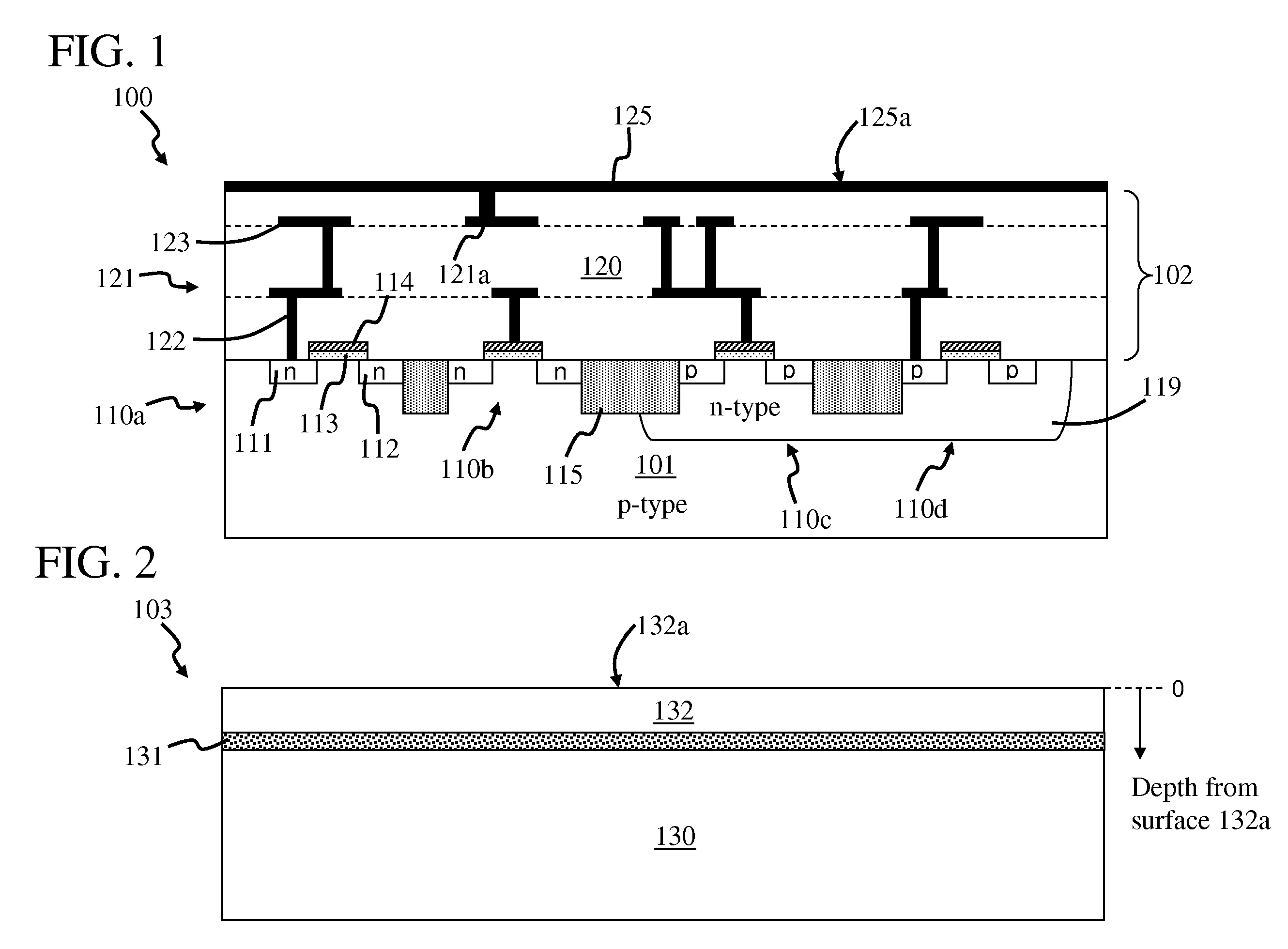

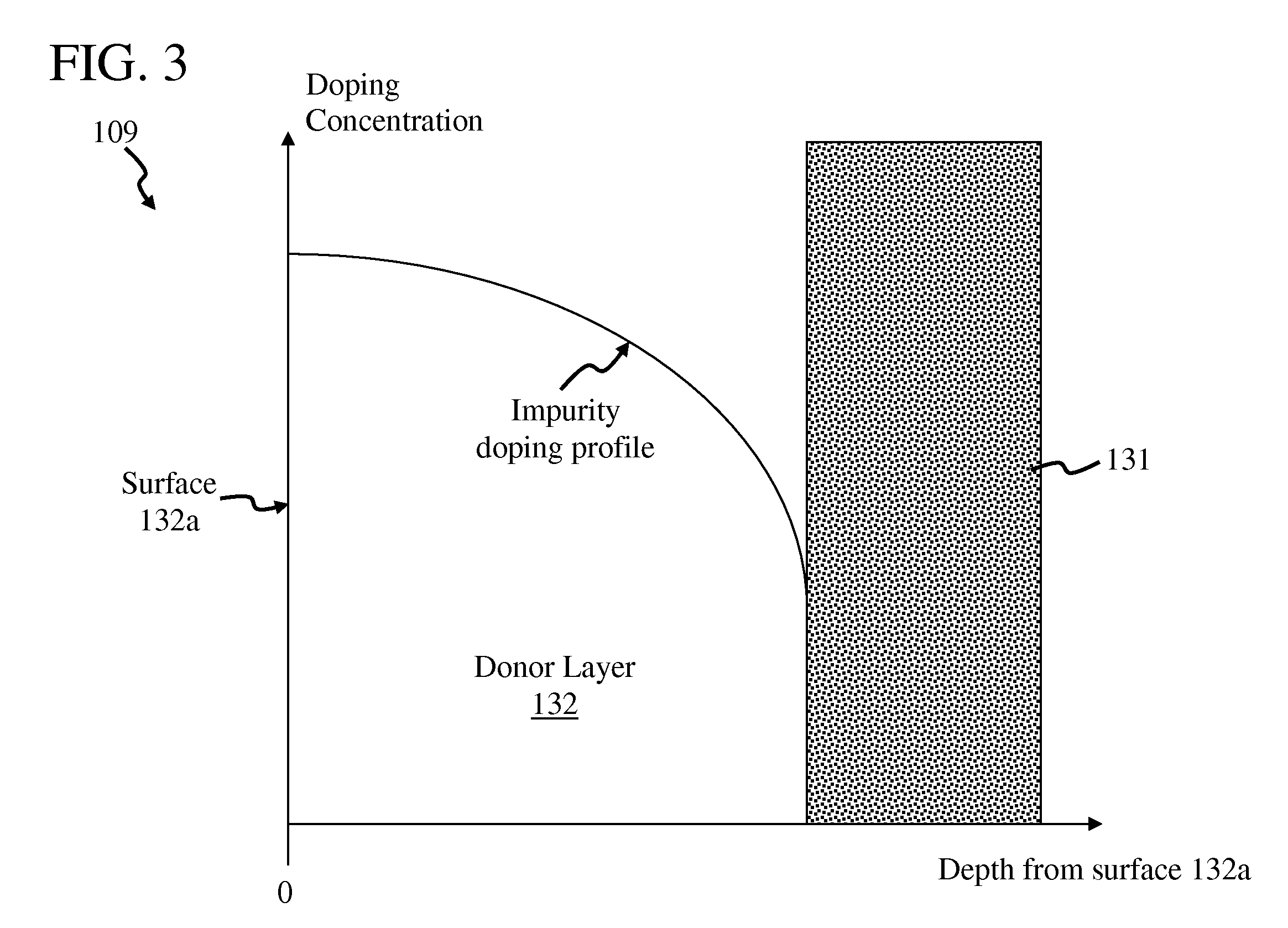

A semiconductor memory device includes a substrate and an interconnect region carried by the substrate. A donor layer is coupled to the interconnect region through a bonding interface. An electronic device is formed with the donor layer, wherein the electronic device is formed after the bonding interface is formed. A capacitor is connected to the electronic device so that the electronic device and capacitor operate as a dynamic random access memory device.

Owner:BESANG

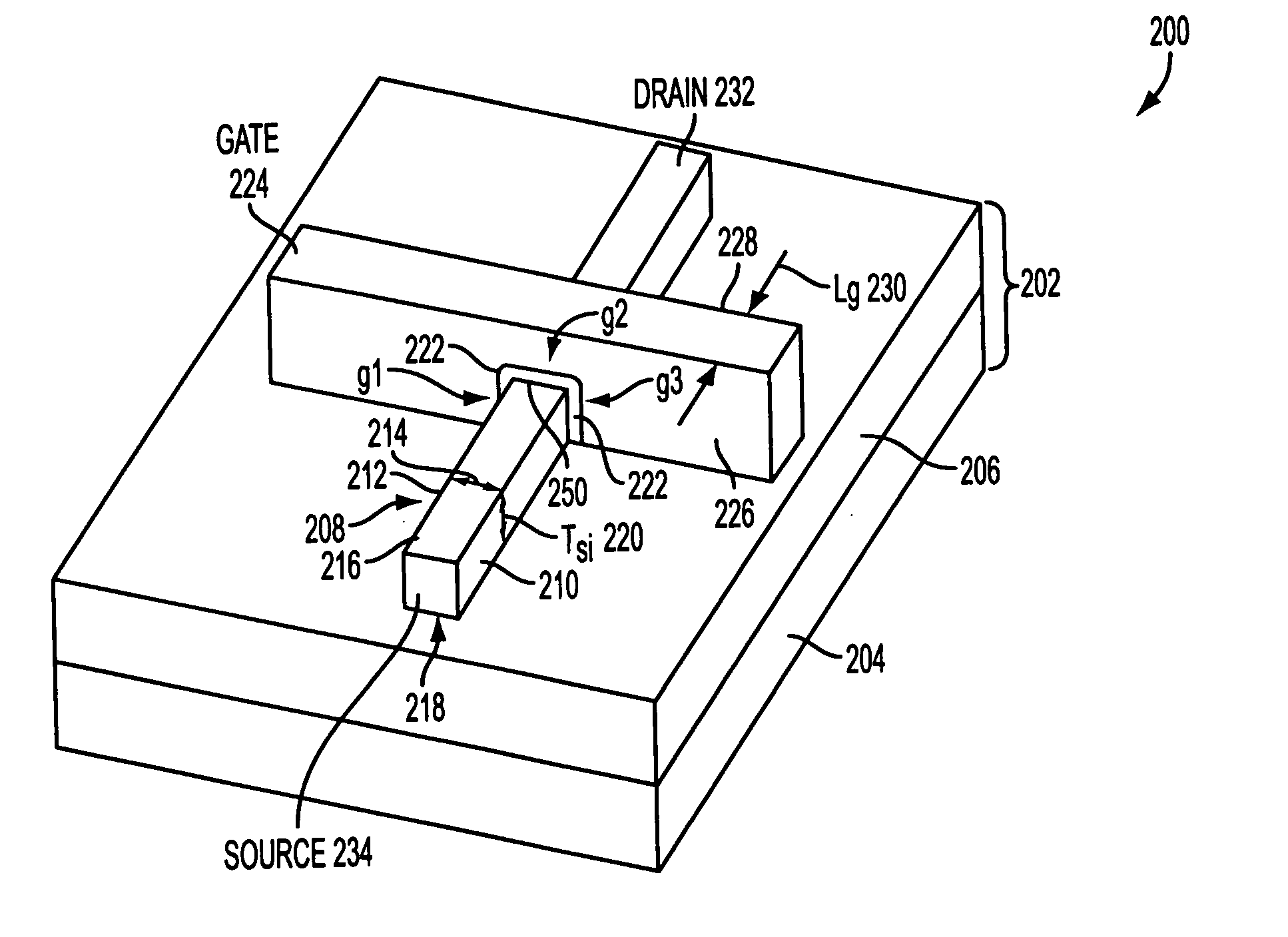

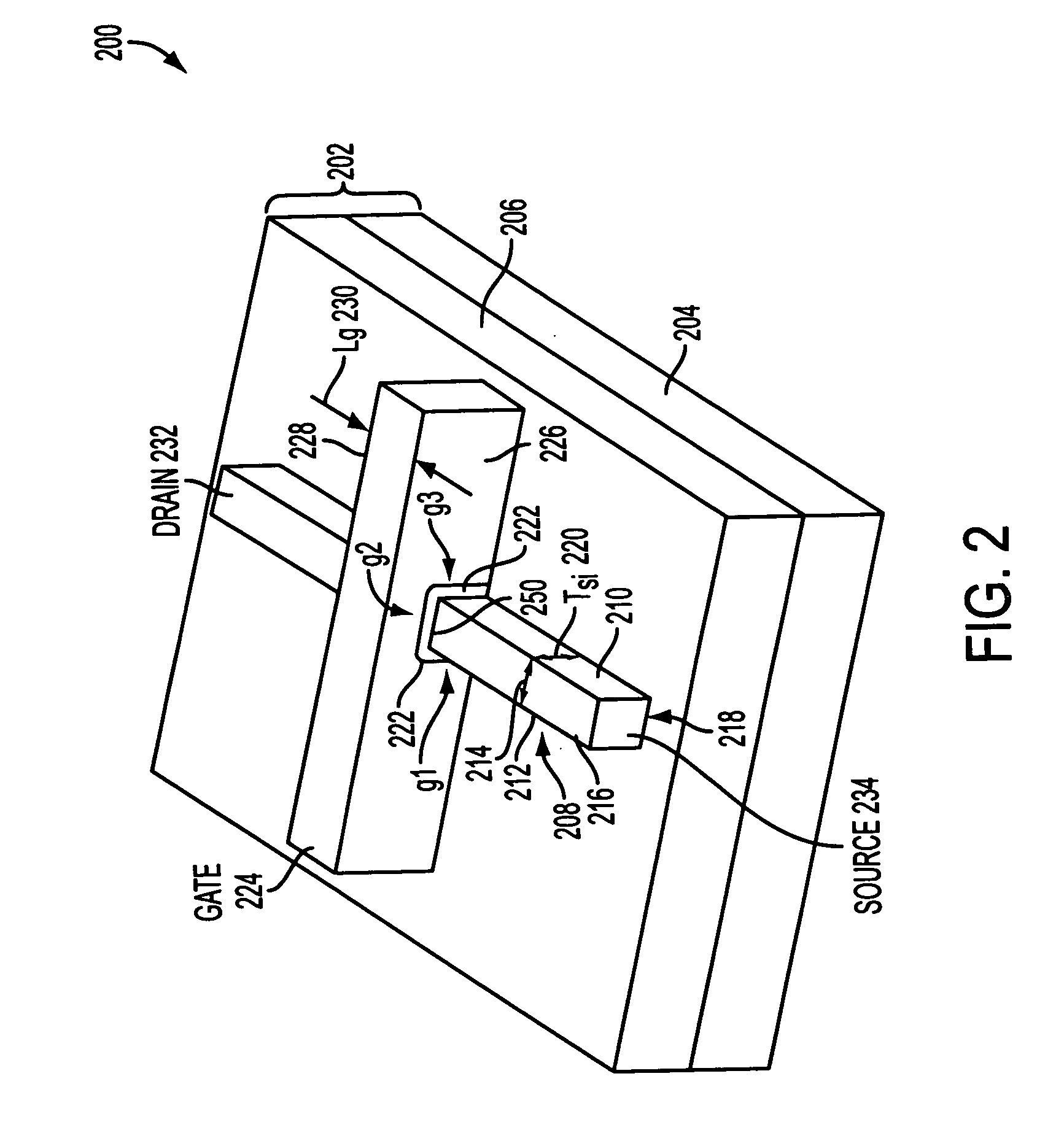

Floating-body DRAM in tri-gate technology

A floating-body dynamic random access memory device may include a semiconductor body having a top surface and laterally opposite sidewalls formed on a substrate. A gate dielectric layer may be formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode may be formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body. The gate electrode may only partially deplete a region of the semiconductor body, and the partially depleted region may be used as a storage node for logic states.

Owner:INTEL CORP

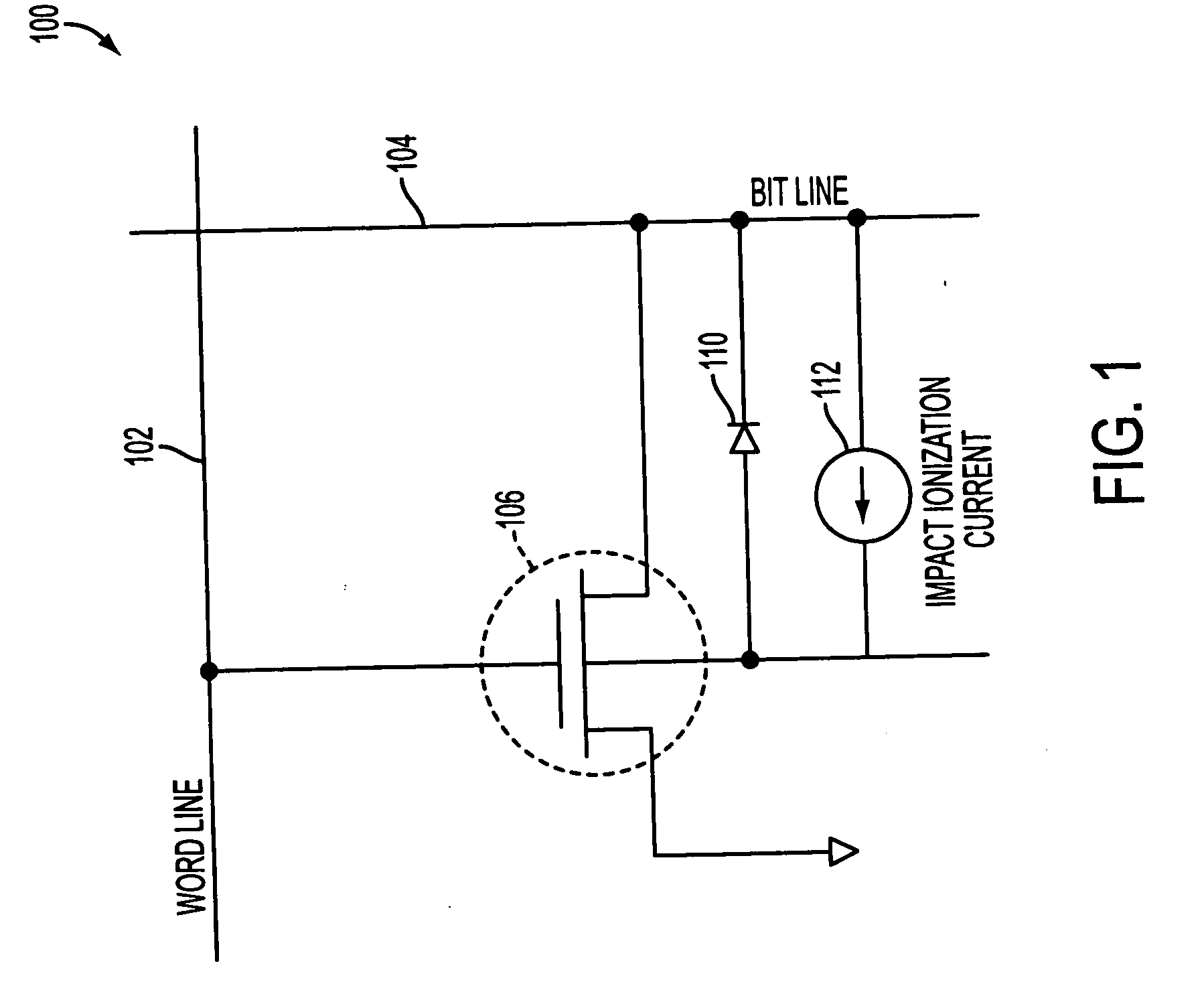

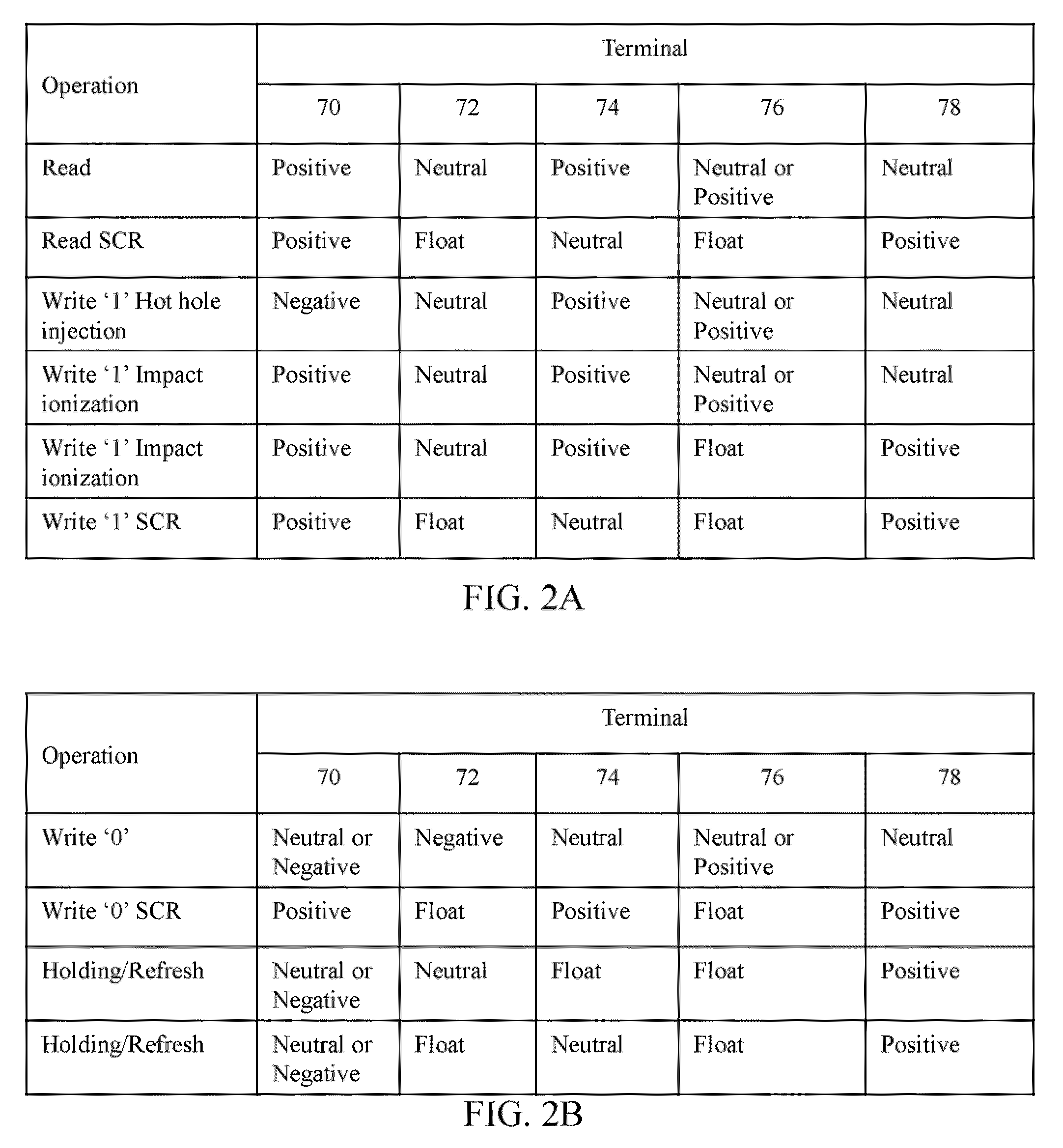

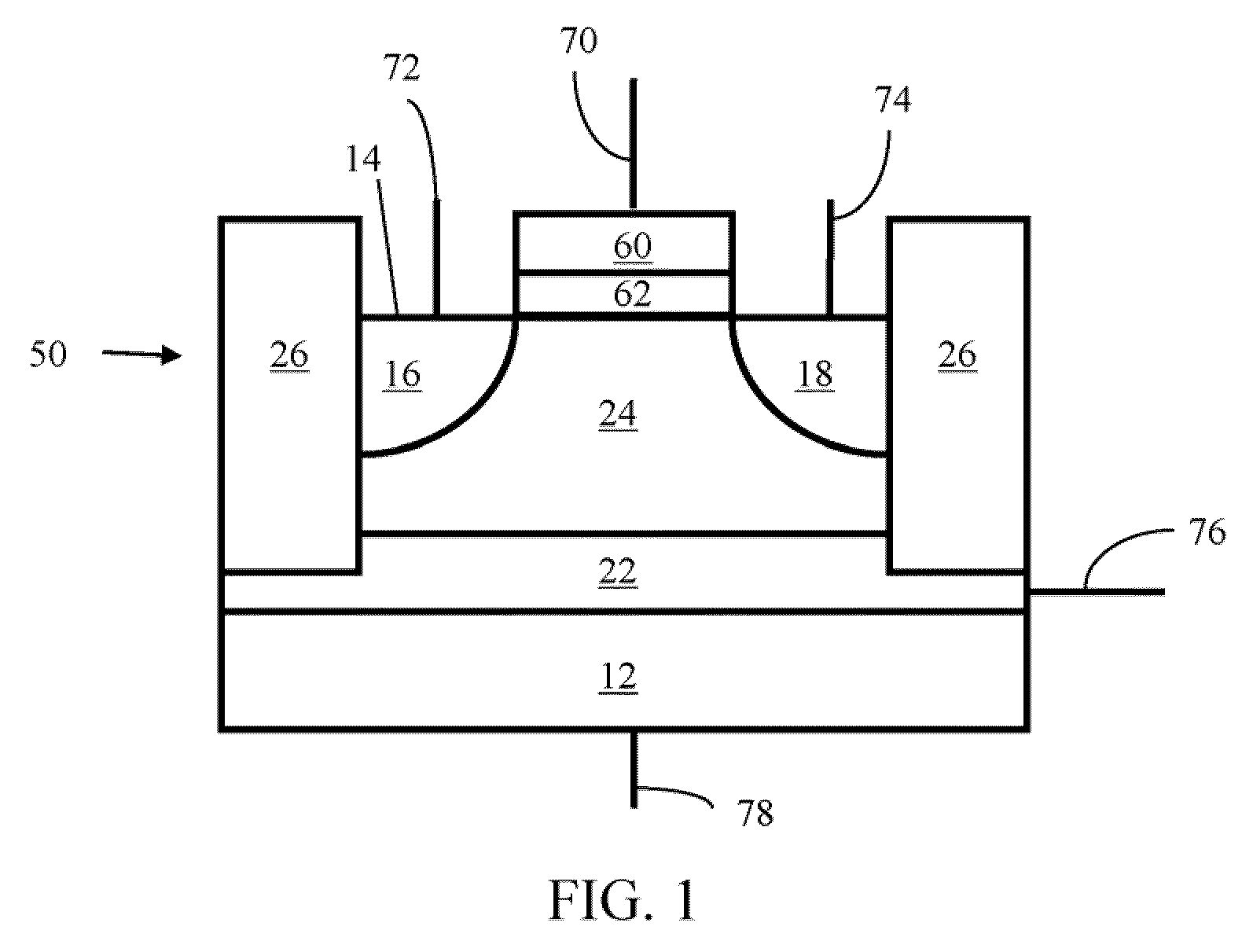

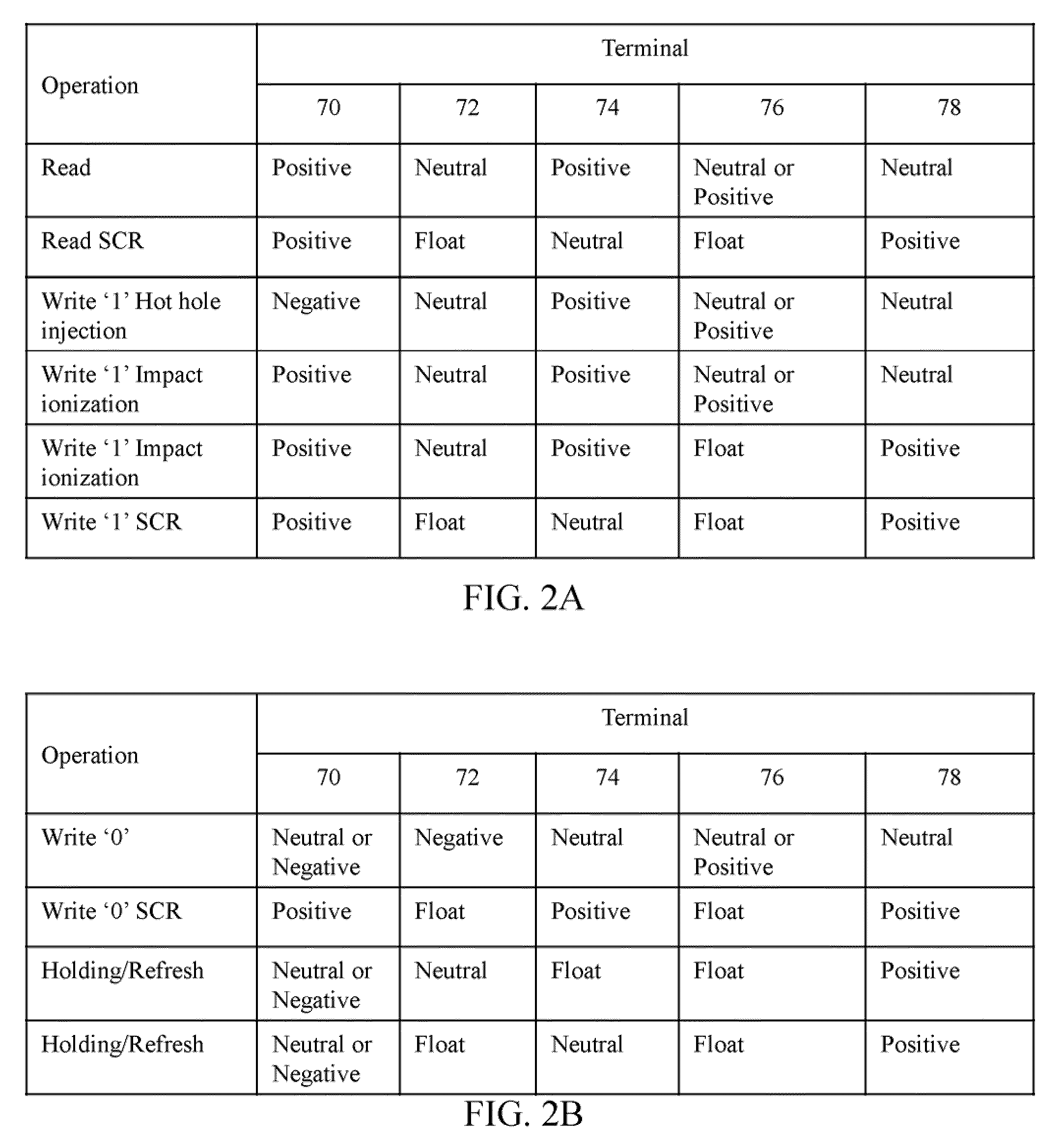

Method of operating semiconductor memory device with floating body transistor using silicon controlled rectifier principle

Methods of operating semiconductor memory devices with floating body transistors, using a silicon controlled rectifier principle are provided, as are semiconductor memory devices for performing such operations. A method of maintaining the data state of a semiconductor dynamic random access memory cell is provided, wherein the memory cell comprises a substrate being made of a material having a first conductivity type selected from p-type conductivity type and n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type; a second region having the second conductivity type, the second region being spaced apart from the first region; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; and a gate positioned between the first and second regions and adjacent the body region. The memory cell is configured to store a first data state which corresponds to a first charge in the body region in a first configuration, and a second data state which corresponds to a second charge in the body region in a second configuration. The method includes: providing the memory cell storing one of the first and second data states; and applying a positive voltage to a substrate terminal connected to the substrate beneath the buried layer, wherein when the body region is in the first state, the body region turns on a silicon controlled rectifier device of the cell and current flows through the device to maintain configuration of the memory cell in the first memory state, and wherein when the memory cell is in the second state, the body region does not turn on the silicon controlled rectifier device, current does not flow, and a blocking operation results, causing the body to maintain the second memory state.

Owner:ZENO SEMICON

Semiconductor circuit

InactiveUS20110053332A1Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceEngineering

A semiconductor memory device includes a substrate and an interconnect region carried by the substrate. A donor layer is coupled to the interconnect region through a bonding interface. An electronic device is formed with the donor layer, wherein the electronic device is formed after the bonding interface is formed. A capacitor is connected to the electronic device so that the electronic device and capacitor operate as a dynamic random access memory device.

Owner:BESANG

Semiconductor circuit

InactiveUS7800199B2Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceCapacitor

A semiconductor memory device includes a substrate and an interconnect region carried by the substrate. A donor layer is coupled to the interconnect region through a bonding interface. An electronic device is formed with the donor layer, wherein the electronic device is formed after the bonding interface is formed. A capacitor is connected to the electronic device so that the electronic device and capacitor operate as a dynamic random access memory device.

Owner:BESANG

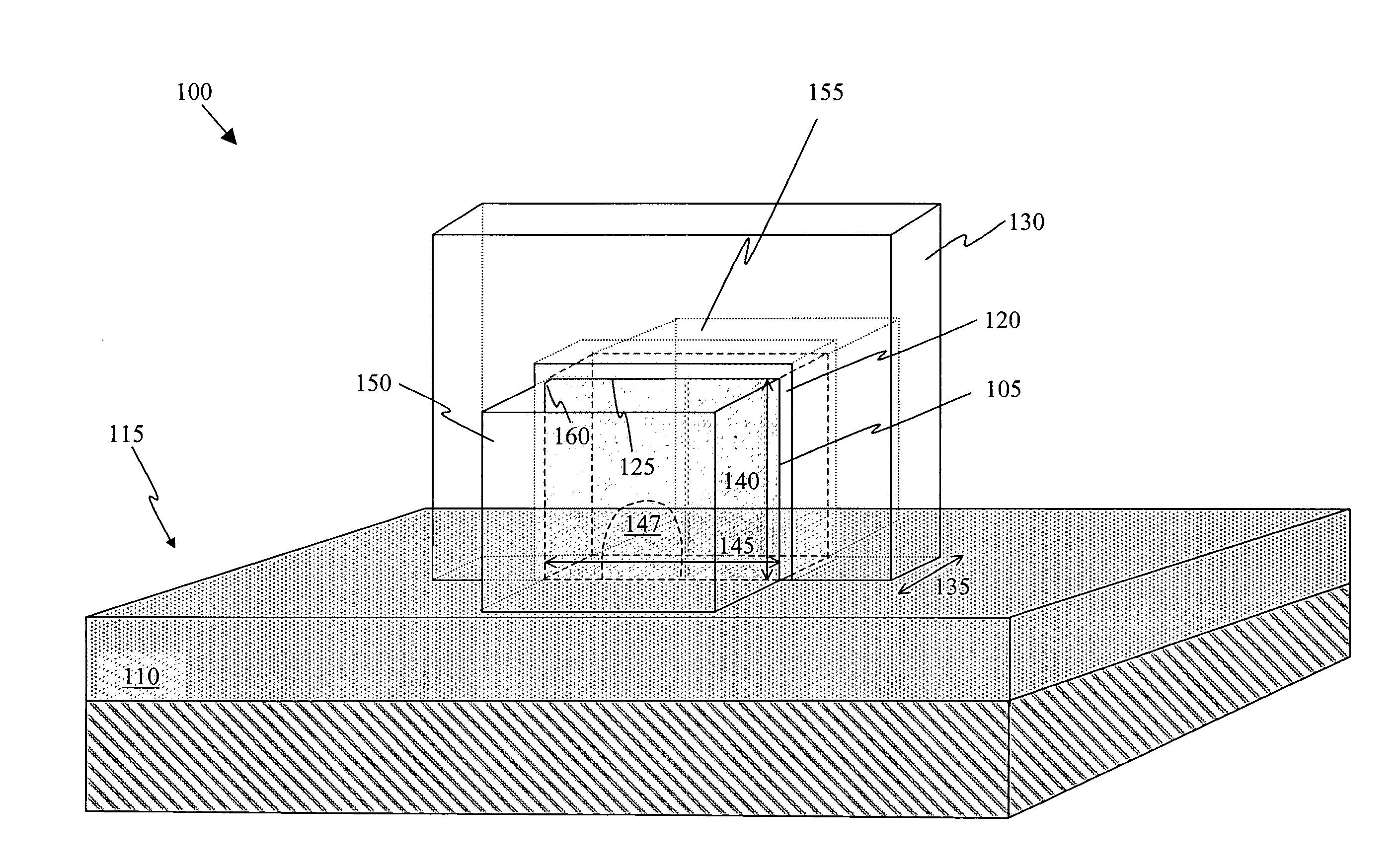

Multi-gate one-transistor dynamic random access memory

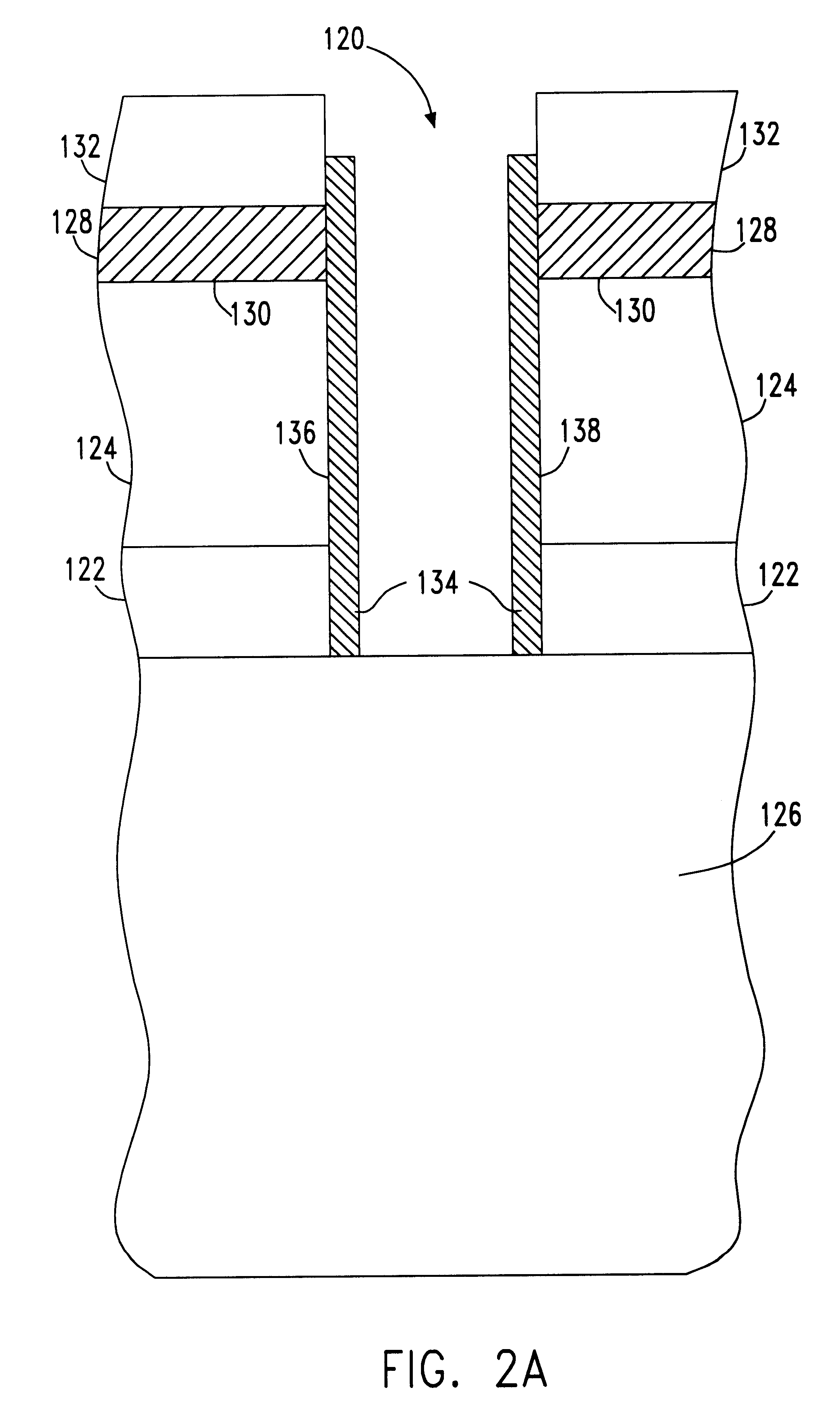

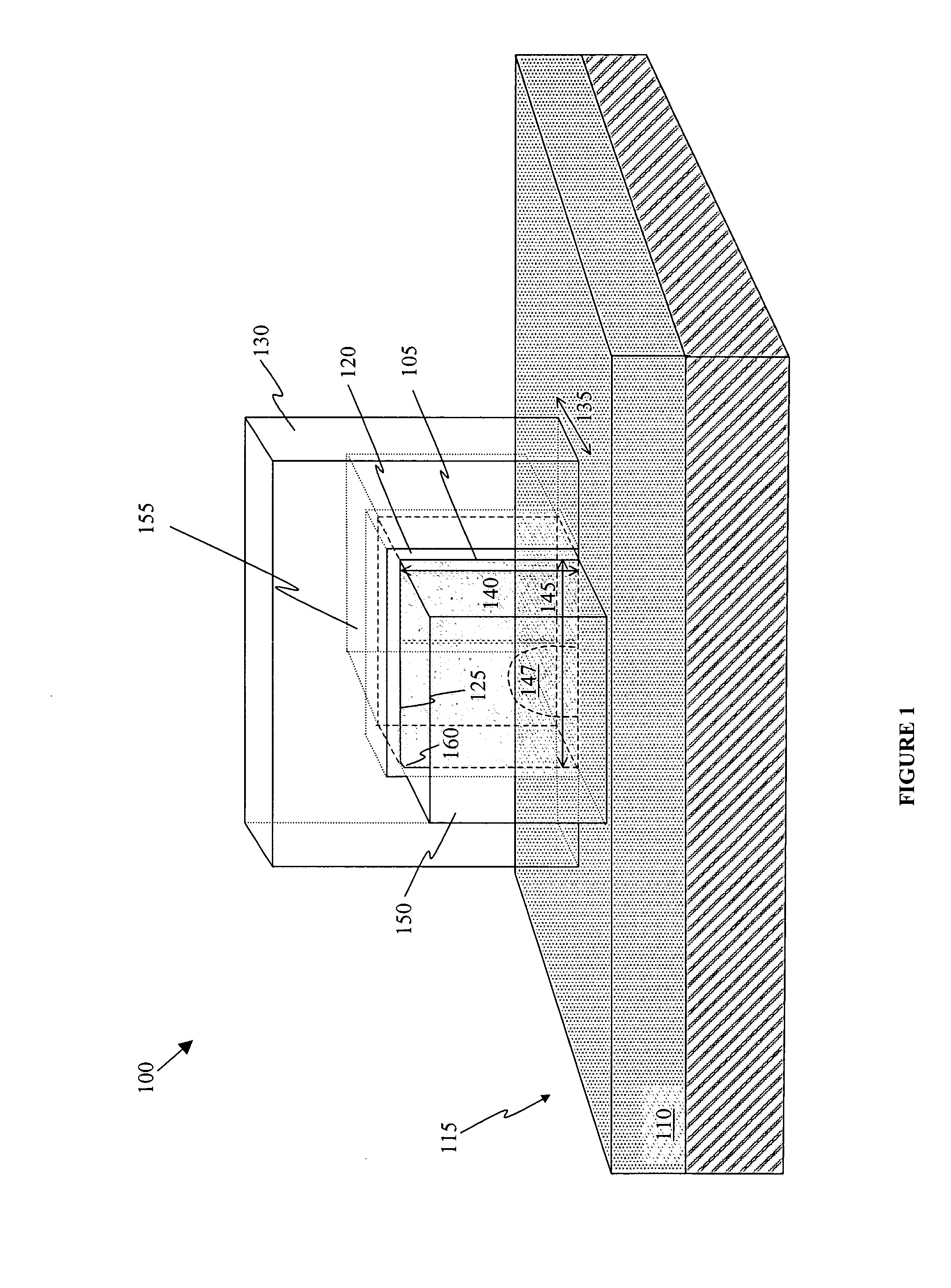

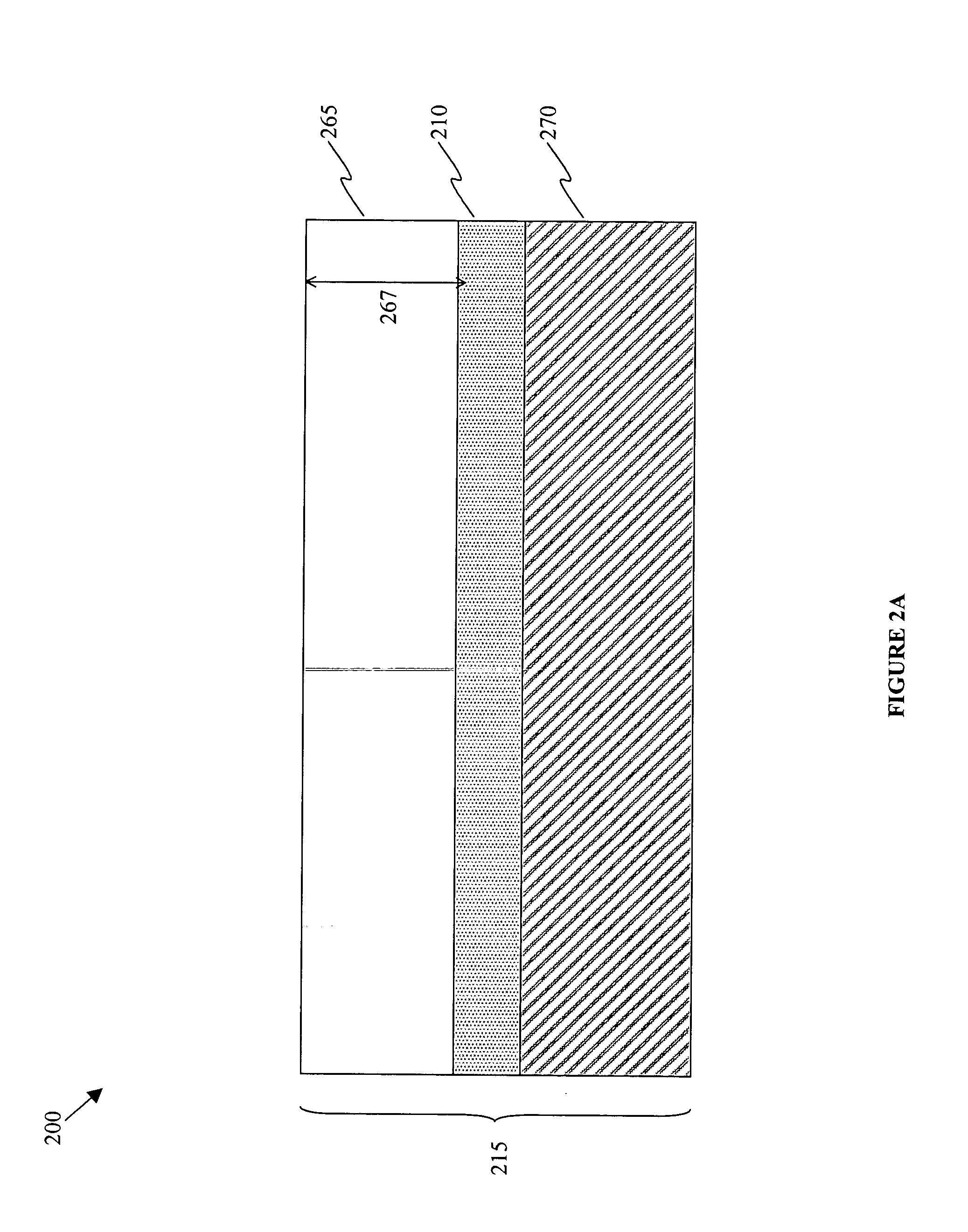

The present invention provides a one-transistor dynamic random access memory (1T DRAM) device (100). The 1T DRAM device (100) includes a body region (105) insulated (110) from a substrate (115) and an insulating layer (120) on a surface of the body region (125). A gate structure (130) is on the insulating layer (120) and conformally surrounding portions of the body region (105). A width of the body region (145) is sufficient to provide a not fully depleted region. Other embodiments include a method of manufacturing a 1T DRAM device (200) and an integrated circuit (300).

Owner:TEXAS INSTR INC

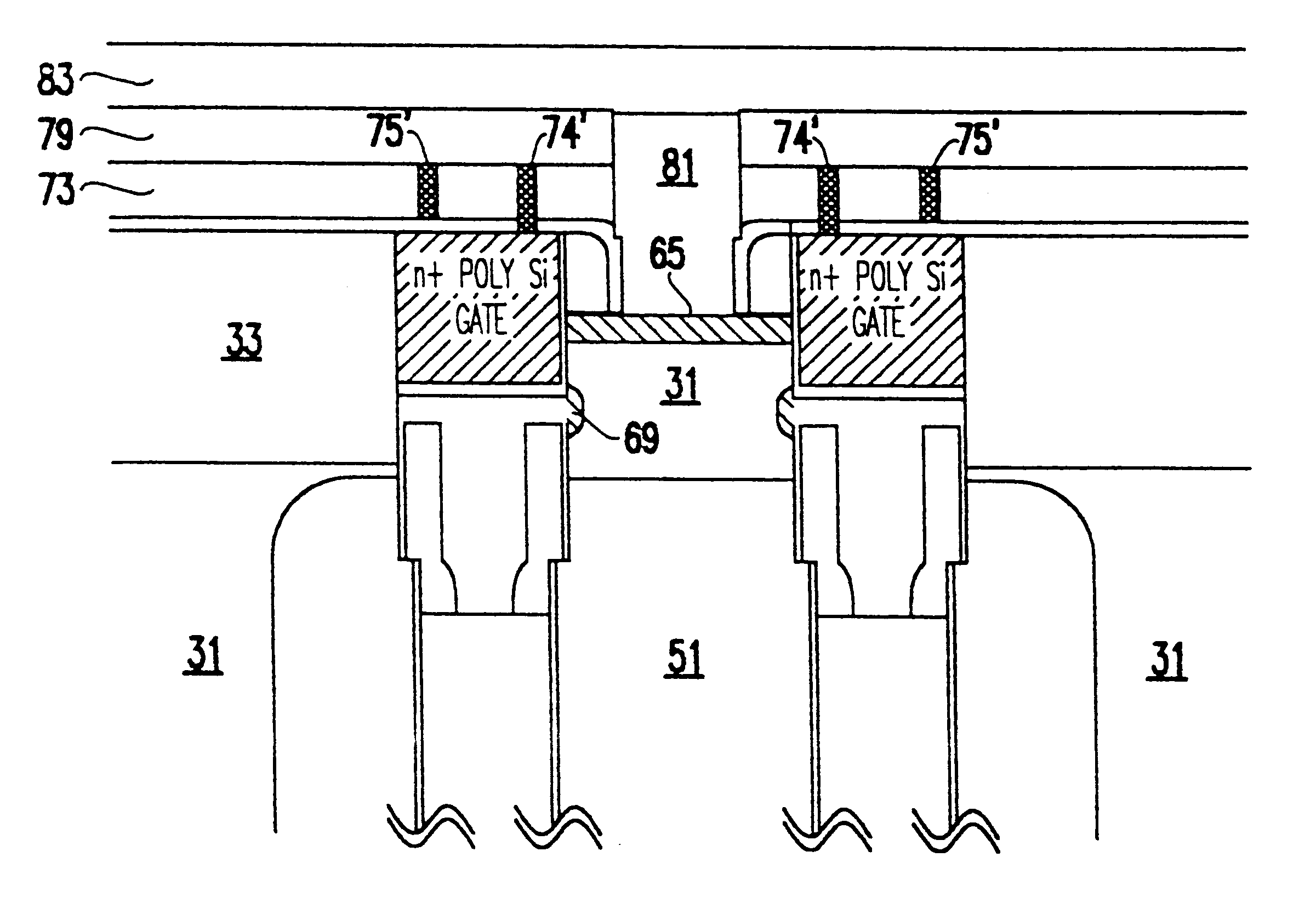

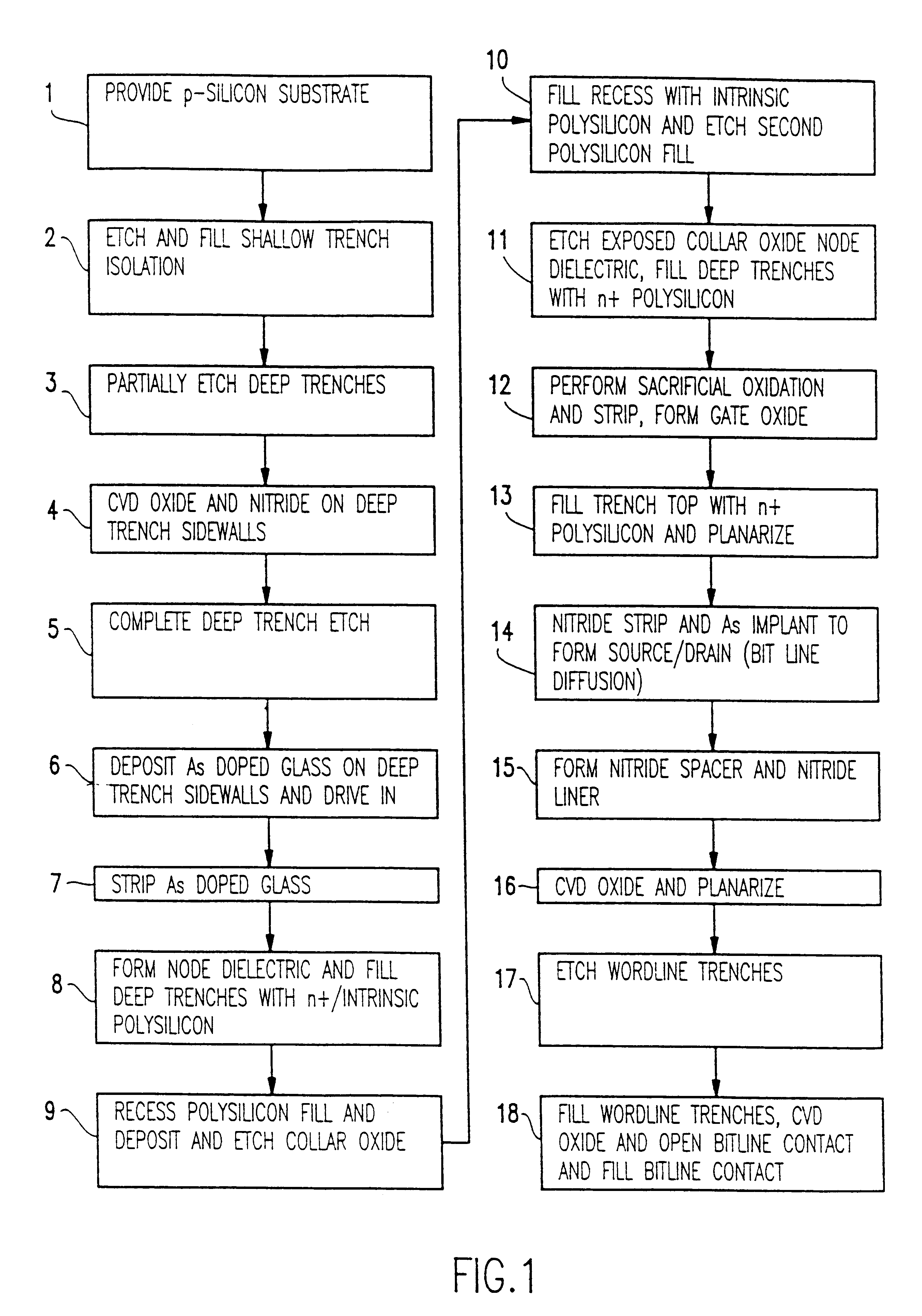

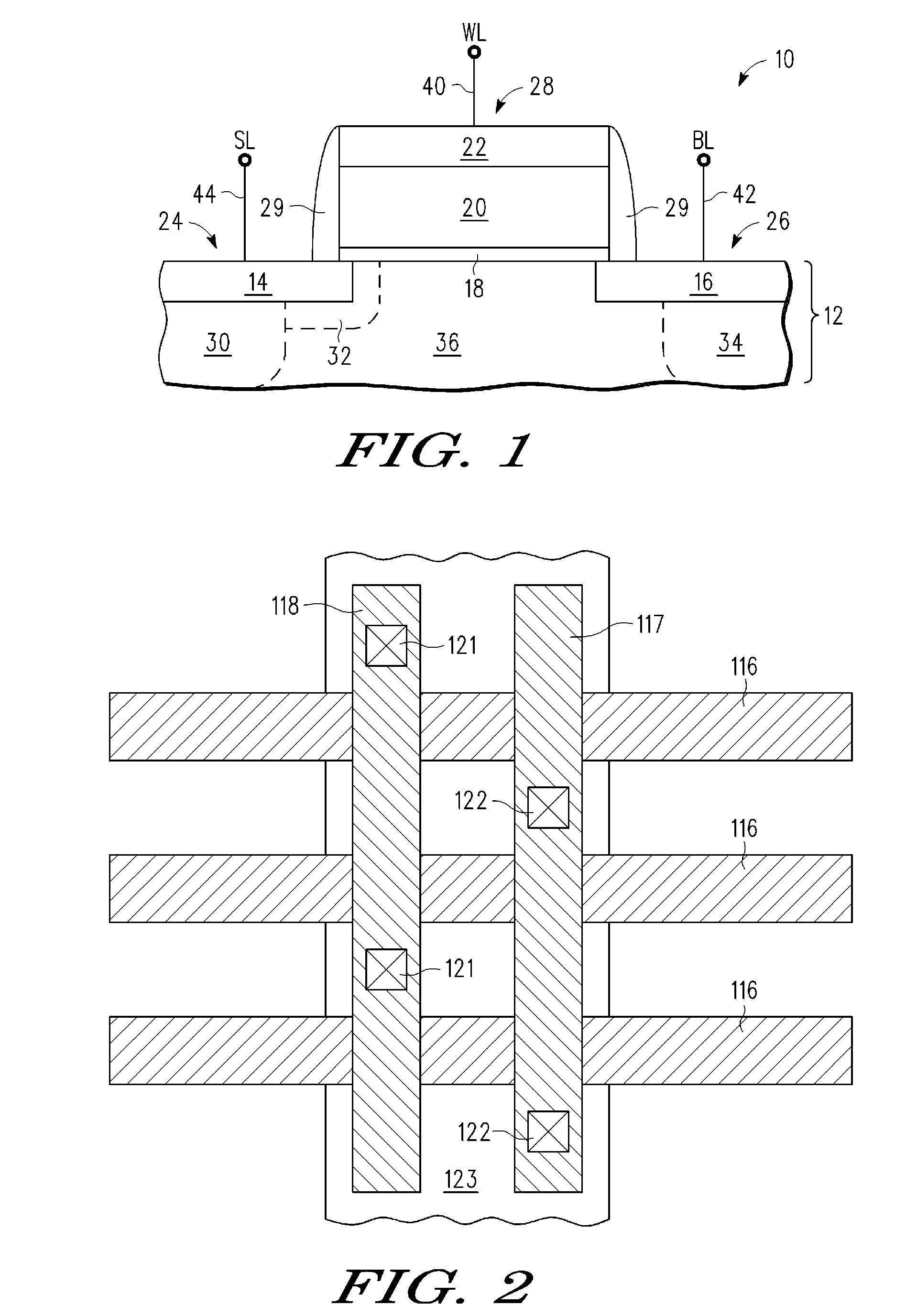

Trench storage dynamic random access memory cell with vertical transfer device

InactiveUS6225158B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringDeep trench

A trench storage dynamic random access memory cell with vertical transfer device can be formed in a wafer having prepared shallow trench isolation. Vertical transfer device is built as the deep trenches are formed. Using square printing to form shallow trench isolation and deep trenches, allows for scaling of the cell to very small dimensions.

Owner:GLOBALFOUNDRIES INC

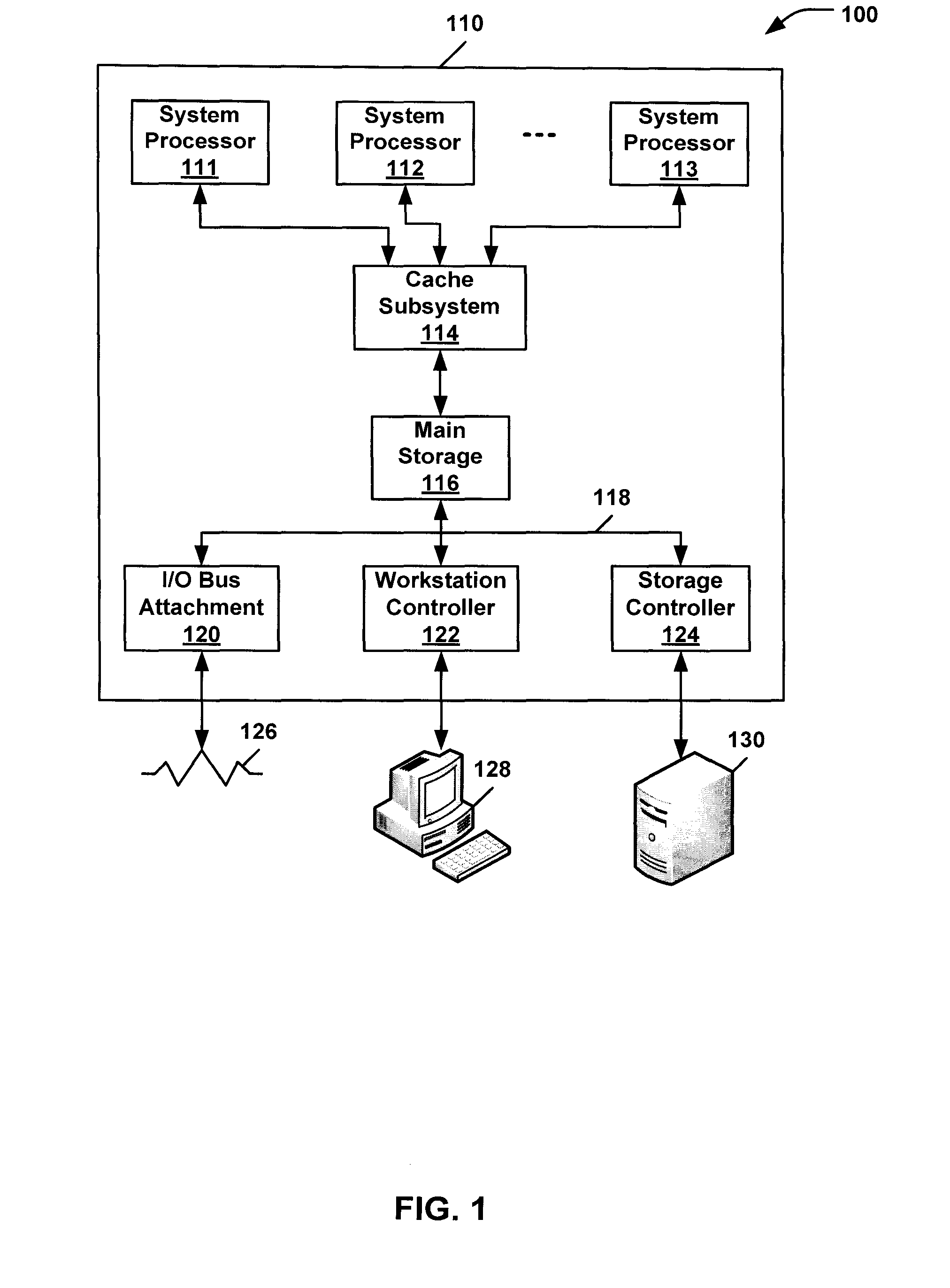

Redistribution of memory to reduce computer system power consumption

InactiveUS20070106860A1Limited amount of powerLowering thermal profileEnergy efficient ICTVolume/mass flow measurementDIMMPower mode

A method, apparatus and system are disclosed for redistributing memory allocation to portions of dynamic random access memory (DRAM) and dual in-line memory module (DIMM) devices that are underutilized, in order to balance memory usage more evenly amongst active devices so as to limit the amount of power and the thermal load consumed by an individual memory component. The disclosed method, apparatus and system are capable of identifying and tracking memory usage to minimize power consumption in a way that lessens the detrimental effects of “throttling” or reduced power modes for memory devices.

Owner:LENOVO GLOBAL TECH INT LTD

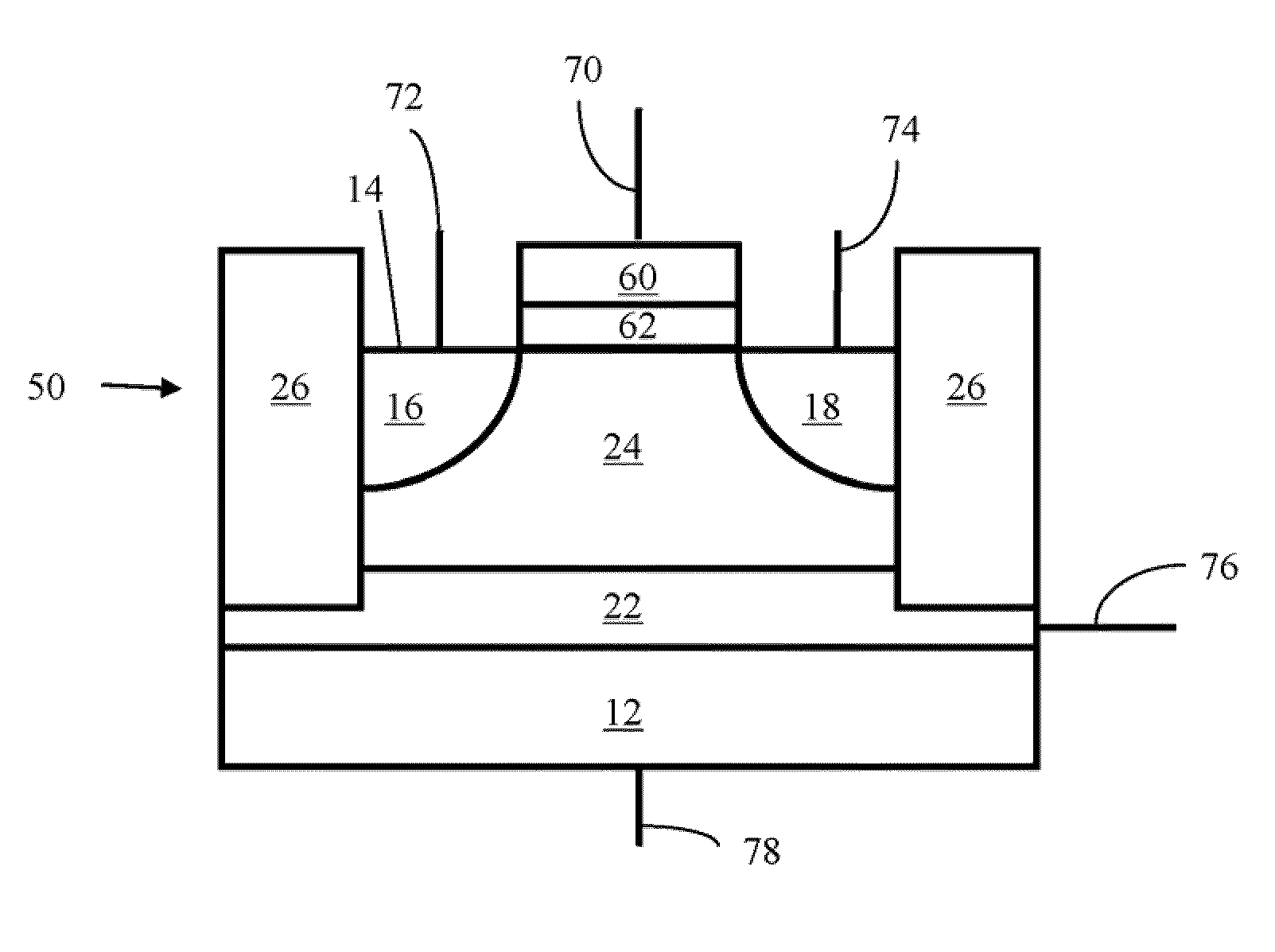

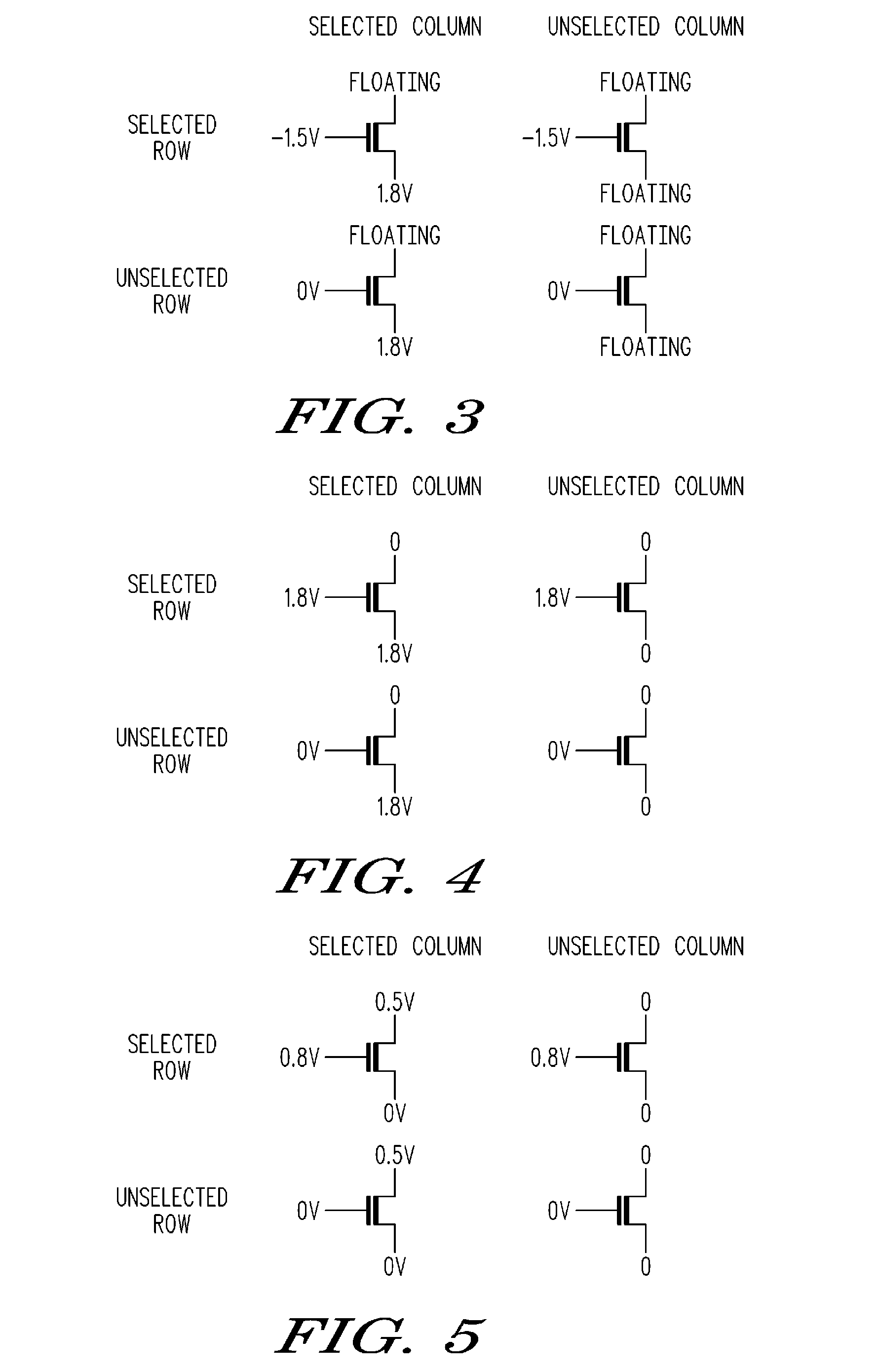

Techniques for reducing a voltage swing

Techniques for reducing a voltage swing are disclosed. In one particular exemplary embodiment, the techniques may be realized as an apparatus for reducing a voltage swing comprising: a plurality of dynamic random access memory cells arranged in arrays of rows and columns, each dynamic random access memory cell including one or more memory transistors. The one or more memory transistors of the apparatus for reducing a voltage swing may comprise: a first region coupled to a source line, a second region coupled to a bit line, a first body region disposed between the first region and the second region, wherein the first body region may be electrically floating, and a first gate coupled to a word line spaced apart from, and capacitively coupled to, the first body region. The apparatus for reducing a voltage swing may also comprise a first voltage supply coupled to the source line configured to supply a first voltage and a second voltage to the source line, wherein a difference between the first voltage and the second voltage may be less than 3.5V.

Owner:MICRON TECH INC

Method of operating semiconductor memory device with floating body transistor using silicon controlled rectifier principle

A method of maintaining the data state of a semiconductor dynamic random access memory cell is provided, wherein the memory cell comprises a substrate being made of a material having a first conductivity type selected from p-type conductivity type and n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type; a second region having the second conductivity type, the second region being spaced apart from the first region; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; and a gate positioned between the first and second regions and adjacent the body region.

Owner:ZENO SEMICON

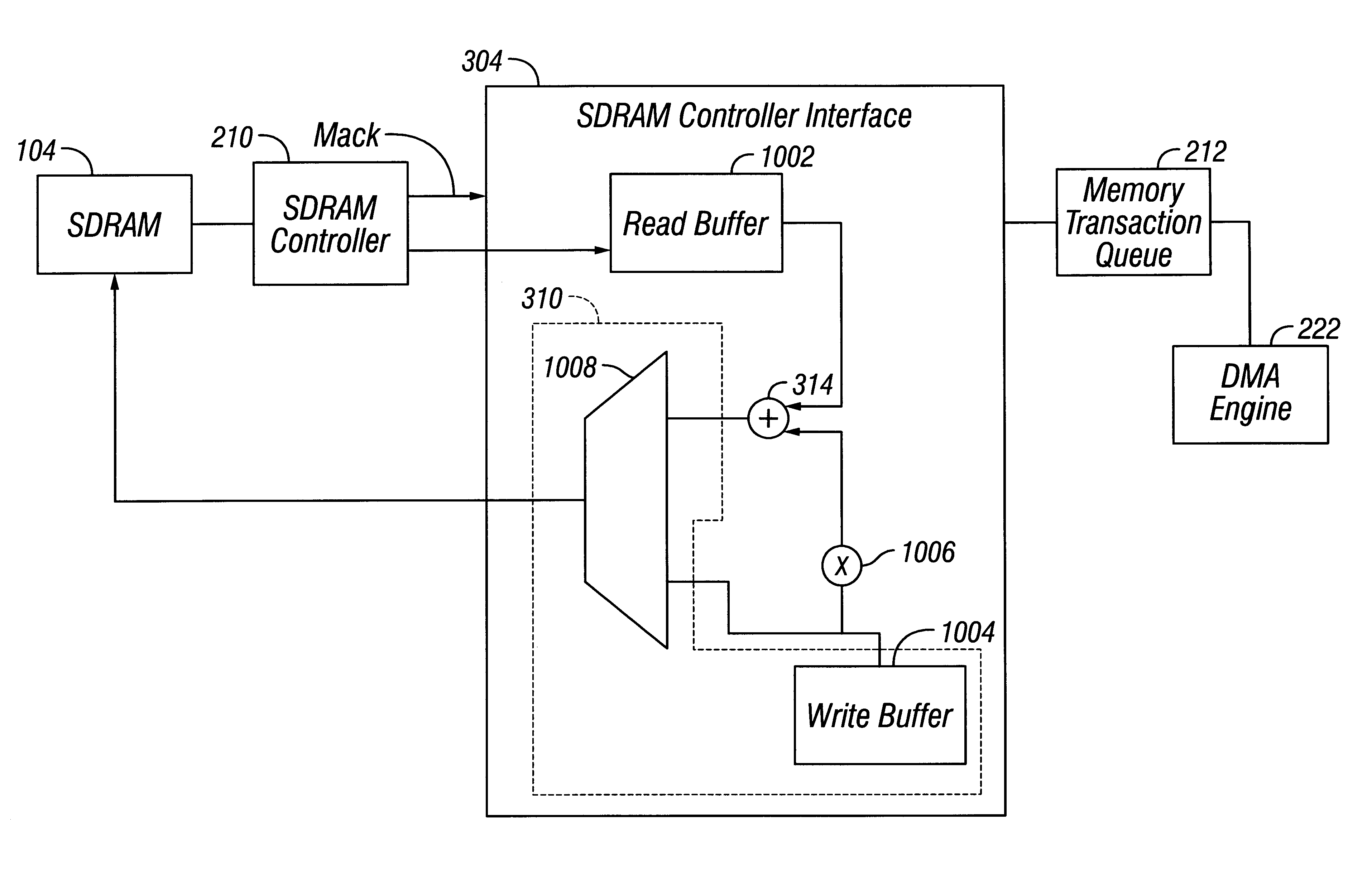

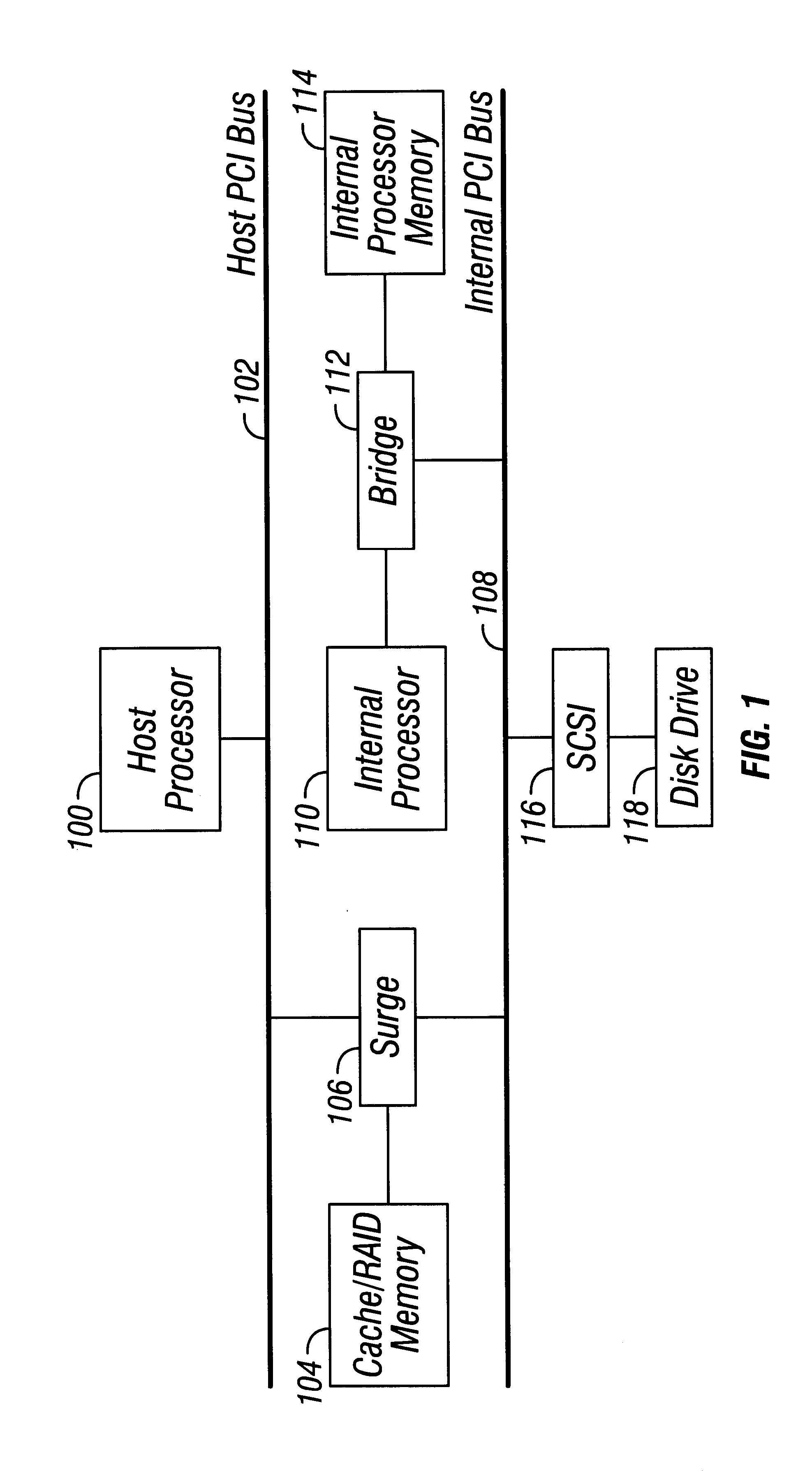

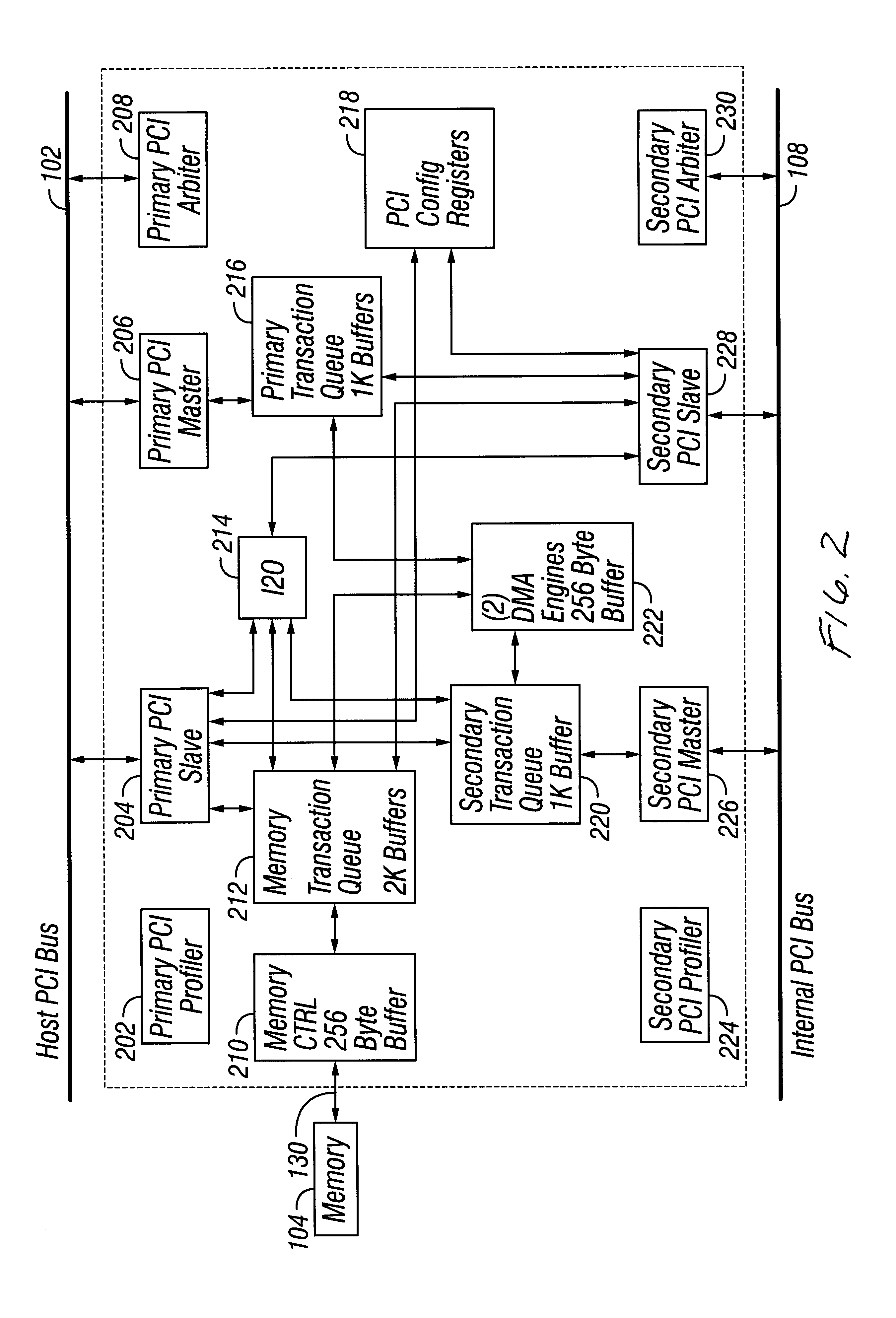

Raid XOR operations to synchronous DRAM using a read buffer and pipelining of synchronous DRAM burst read data

A memory interface controller includes a read buffer to pipeline data from a synchronous dynamic random access memory (DRAM) in response to a plurality of consecutive SDRAM burst read requests, a write buffer to store write data, an exclusive or (XOR) engine to XOR the write data with the data from the read buffer, and a write interface to write resulting data from XORing the write data and the data from the read buffer to the synchronous DRAM. Data is pipelined in the read buffer by repeatedly issuing an SDRAM burst read request before data is transferred out of the synchronous DRAM in response to a previous SDRAM burst read request until a desired amount of data is stored in the read buffer. The memory interface controller thus can perform an external read-modify-write cycle for the synchronous DRAM. The synchronous DRAM can serve as a RAID (Redundant Array s of Inexpensive Disks) memory.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

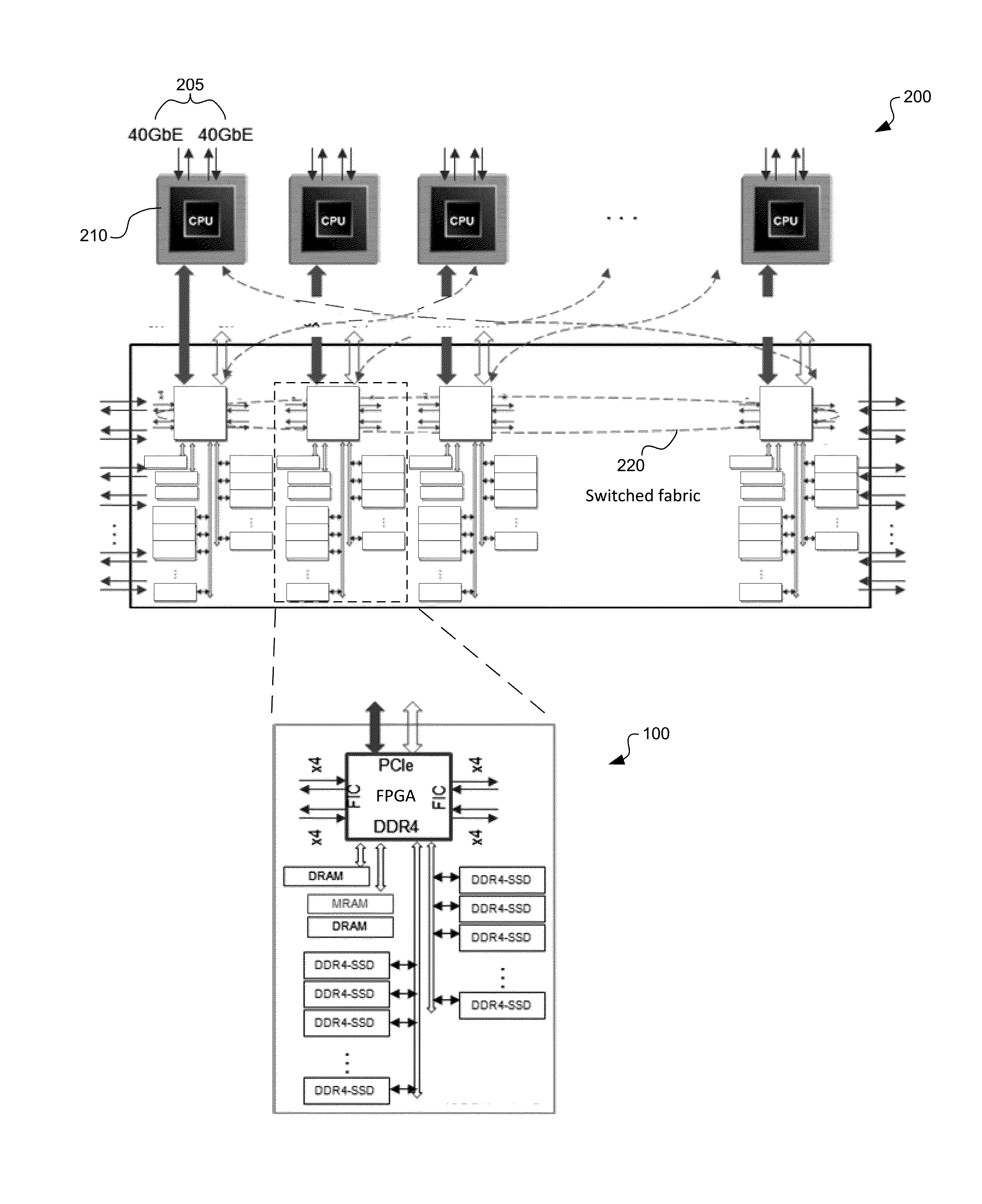

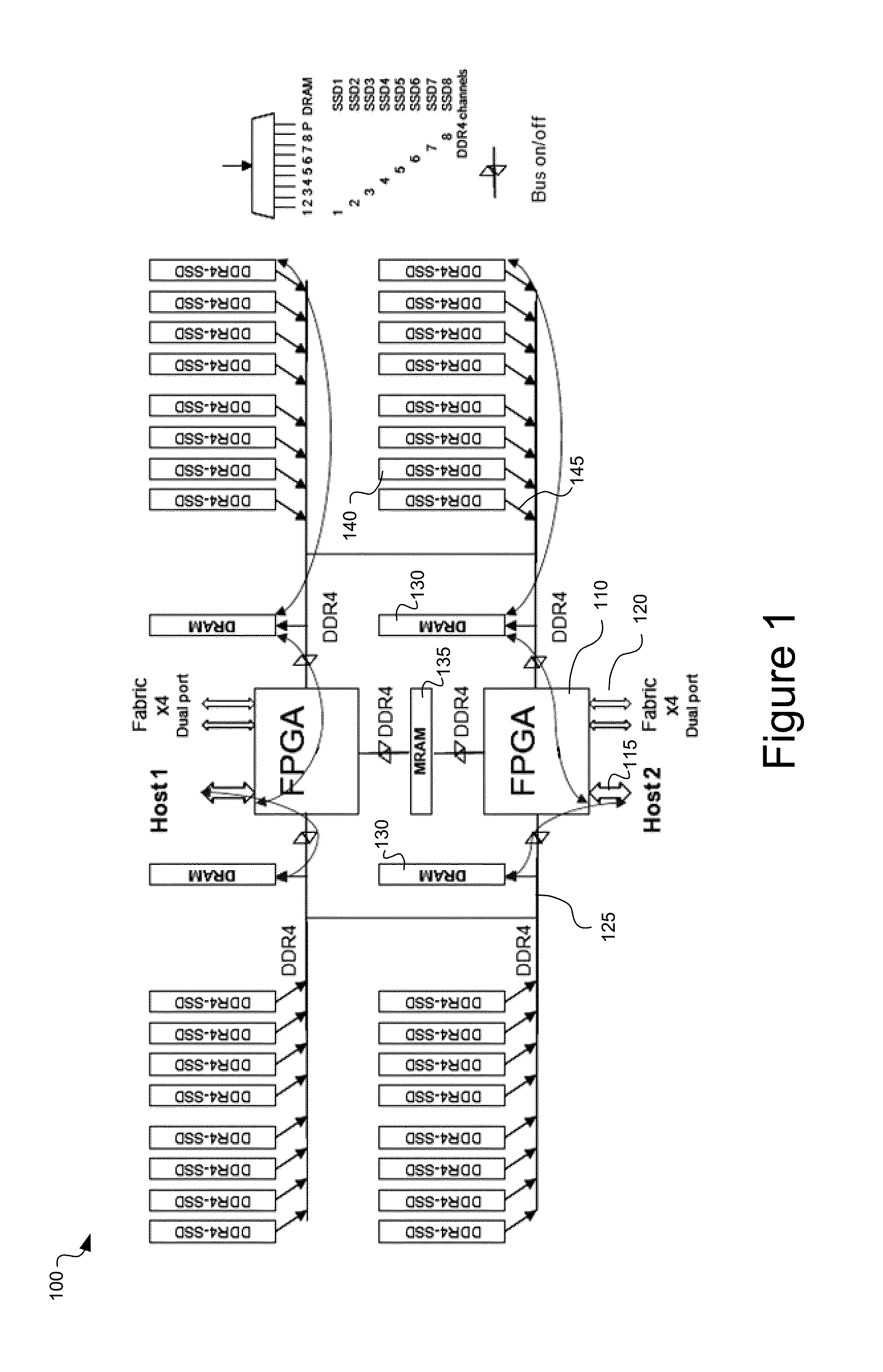

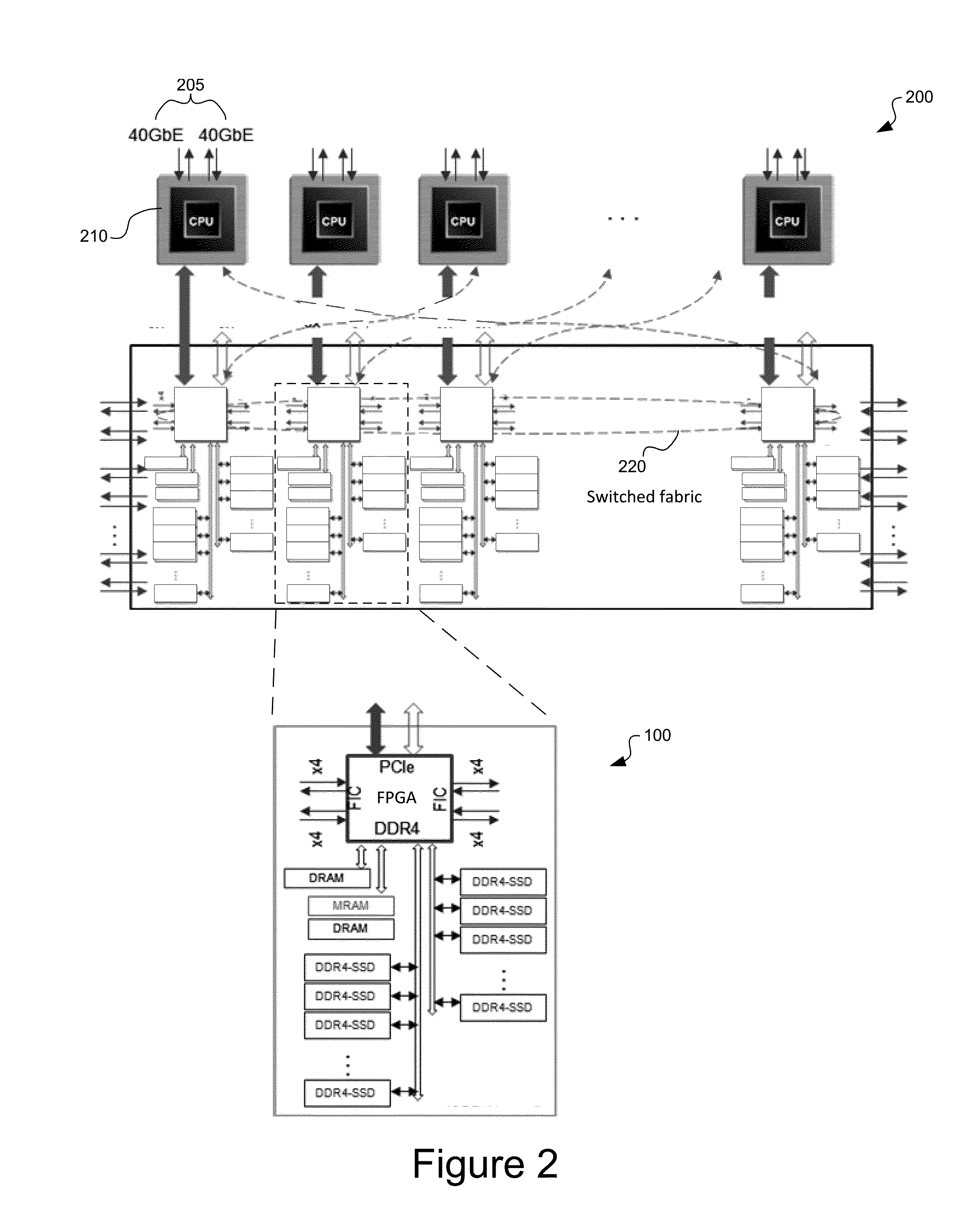

Rdma-ssd dual-port unified memory and network controller

ActiveUS20150254003A1Increase storage capacityLower latencyMemory architecture accessing/allocationInput/output to record carriersMagnetic reluctanceData memory

System and method for a unified memory and network controller for an all-flash array (AFA) storage blade in a distributed flash storage clusters over a fabric network. The unified memory and network controller has 3-way control functions including unified memory buses to cache memories and DDR4-AFA controllers, a dual-port PCIE interconnection to two host processors of gateway clusters, and four switch fabric ports for interconnections with peer controllers (e.g., AFA blades and / or chassis) in the distributed flash storage network. The AFA storage blade includes dynamic random-access memory (DRAM) and magnetoresistive random-access memory (MRAM) configured as data read / write cache buffers, and flash memory DIMM devices as primary storage. Remote data memory access (RDMA) for clients via the data caching buffers is enabled and controlled by the host processor interconnection(s), the switch fabric ports, and a unified memory bus from the unified controller to the data buffer and the flash SSDs.

Owner:FUTUREWEI TECH INC

Combined command set

InactiveUS20030217223A1Memory adressing/allocation/relocationDigital storageStatic random-access memoryMemory bank

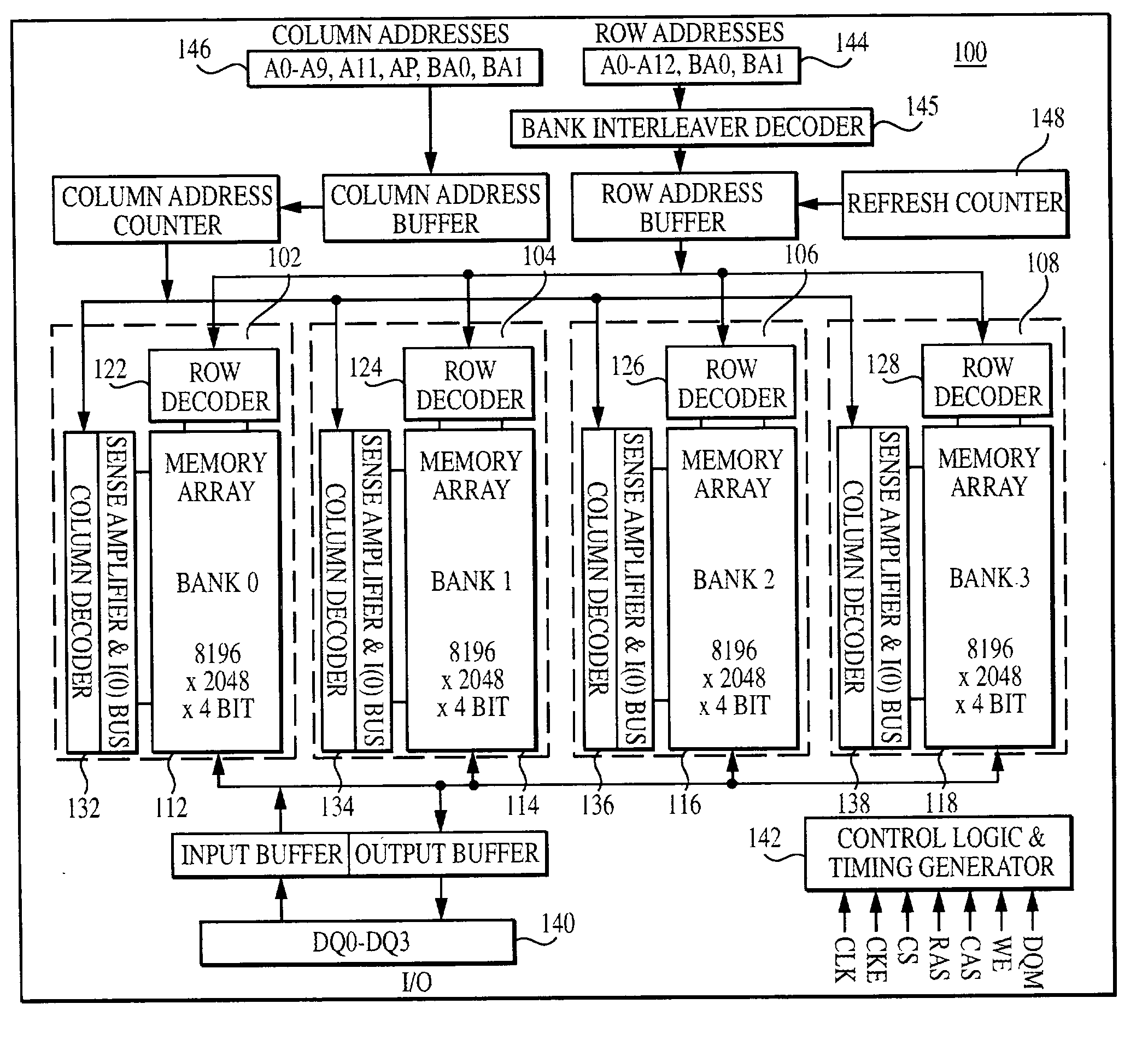

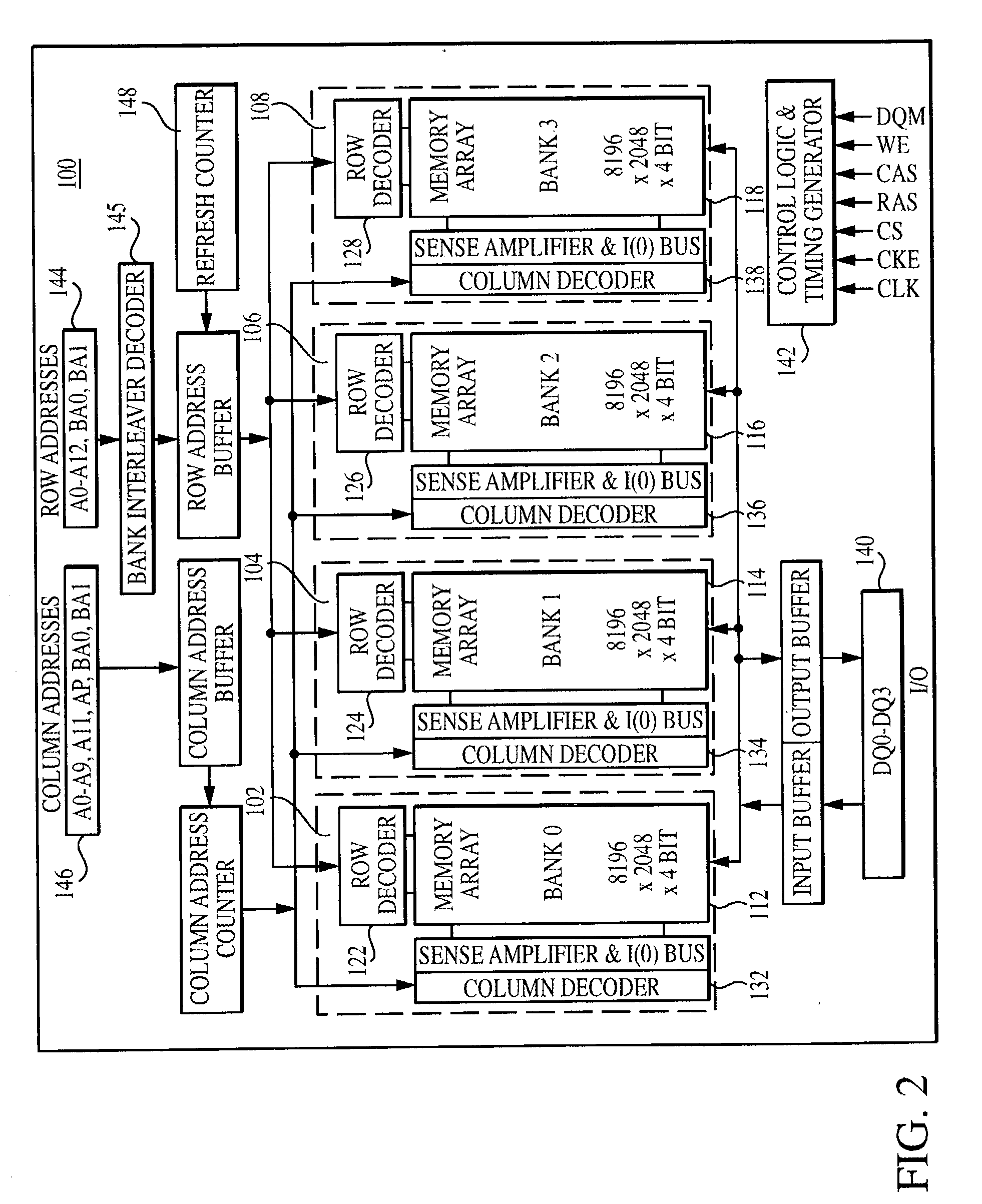

A circuit and method of operation for combining commands in a DRAM (dynamic random access memory) are revealed. The method applies to DRAMs having a plurality of memory banks or arrays. The method combines commands to rows on different memory banks, and the method also combines row and column commands on different memory banks. The method eliminates steps in a sequence of commands, and may significantly increase speed of input / output to a DRAM.

Owner:INFINEON TECH AG

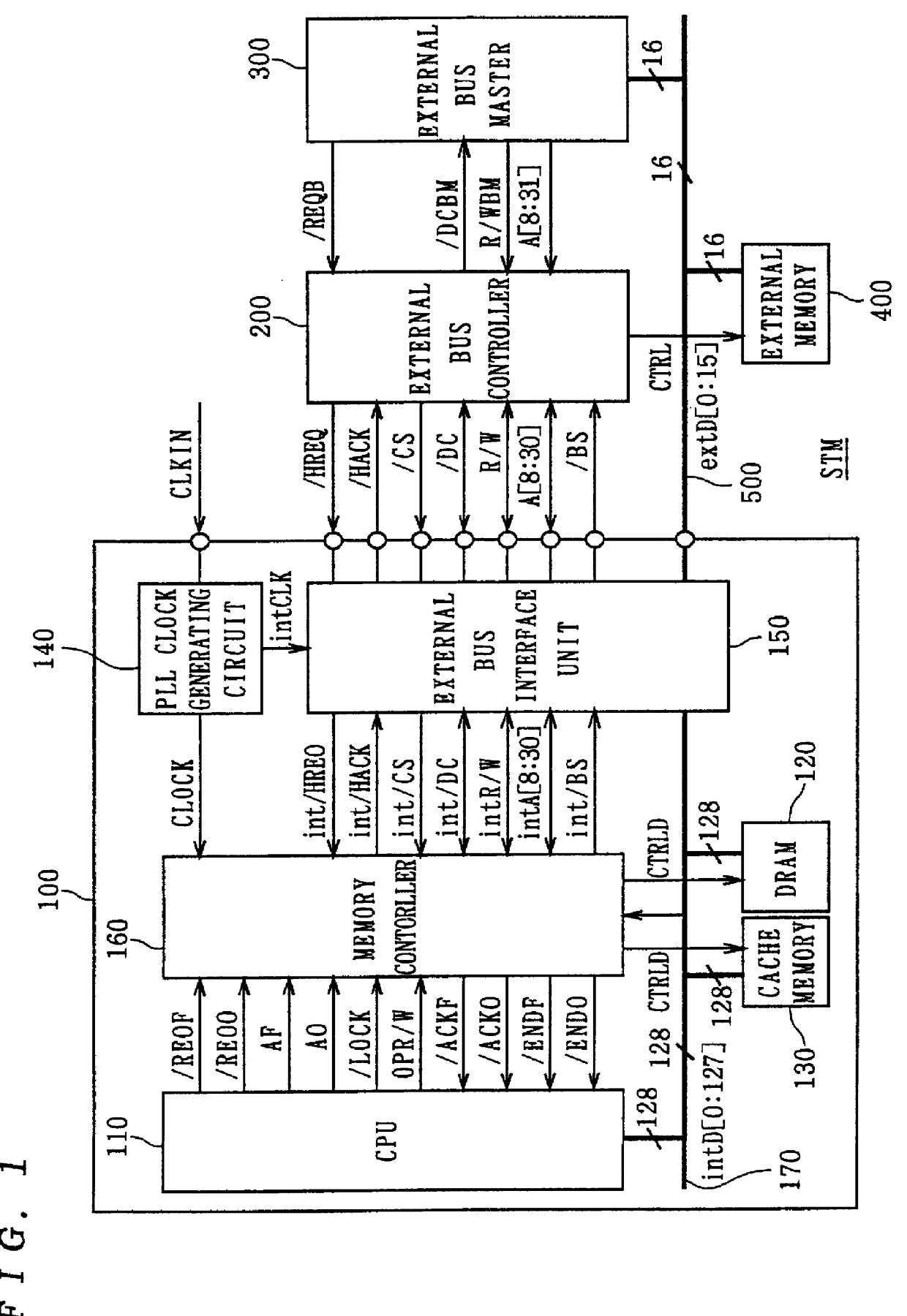

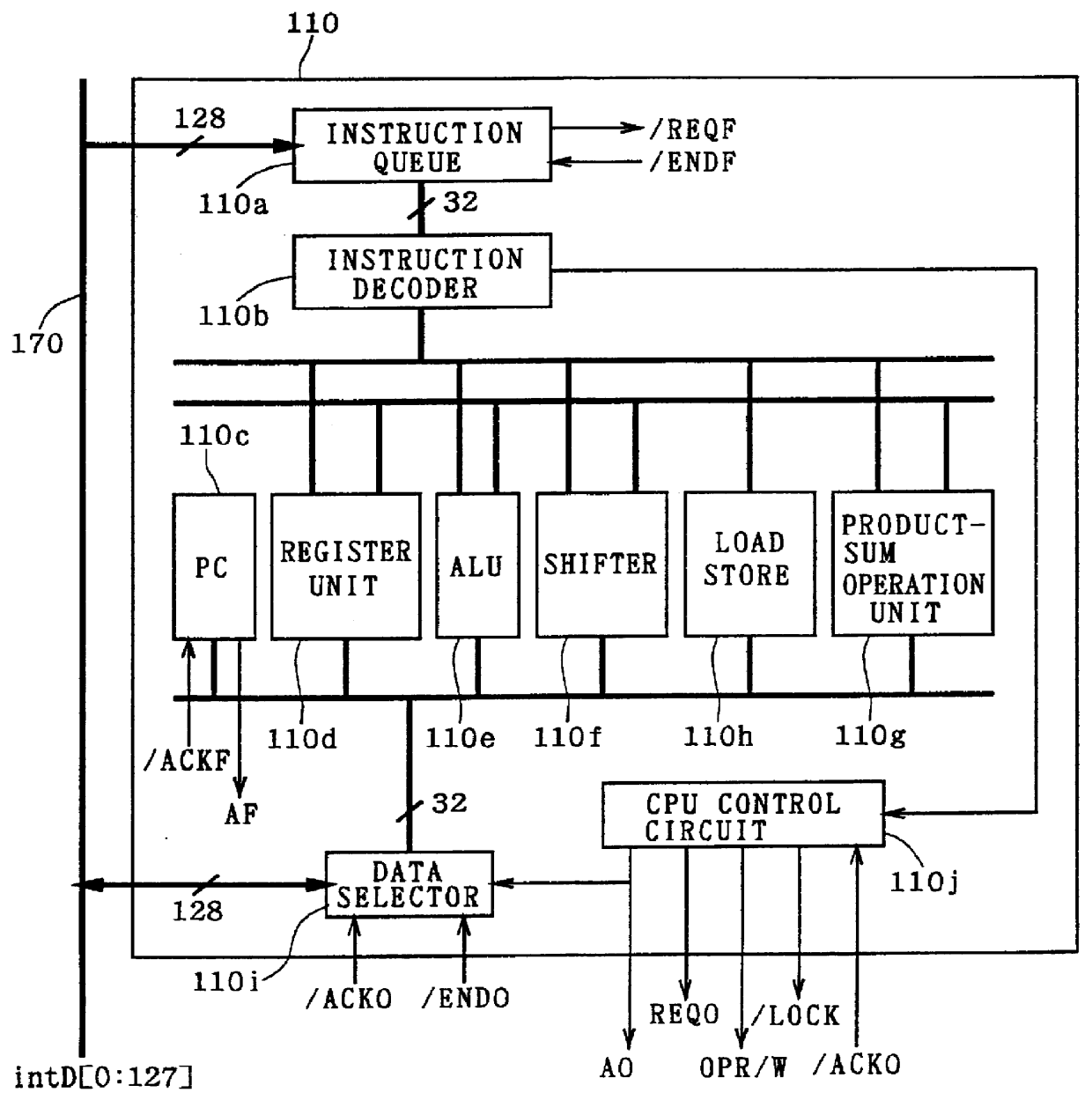

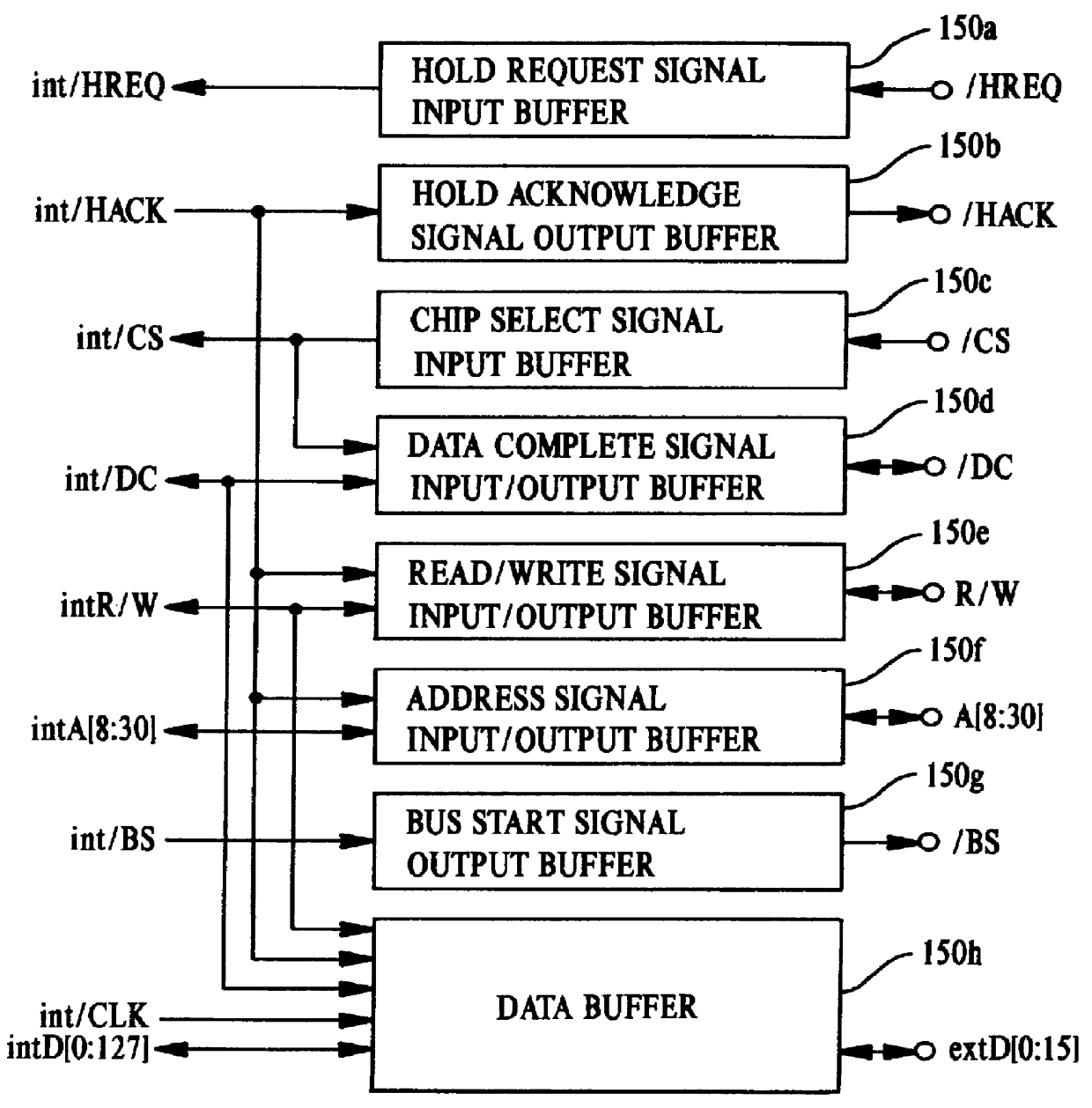

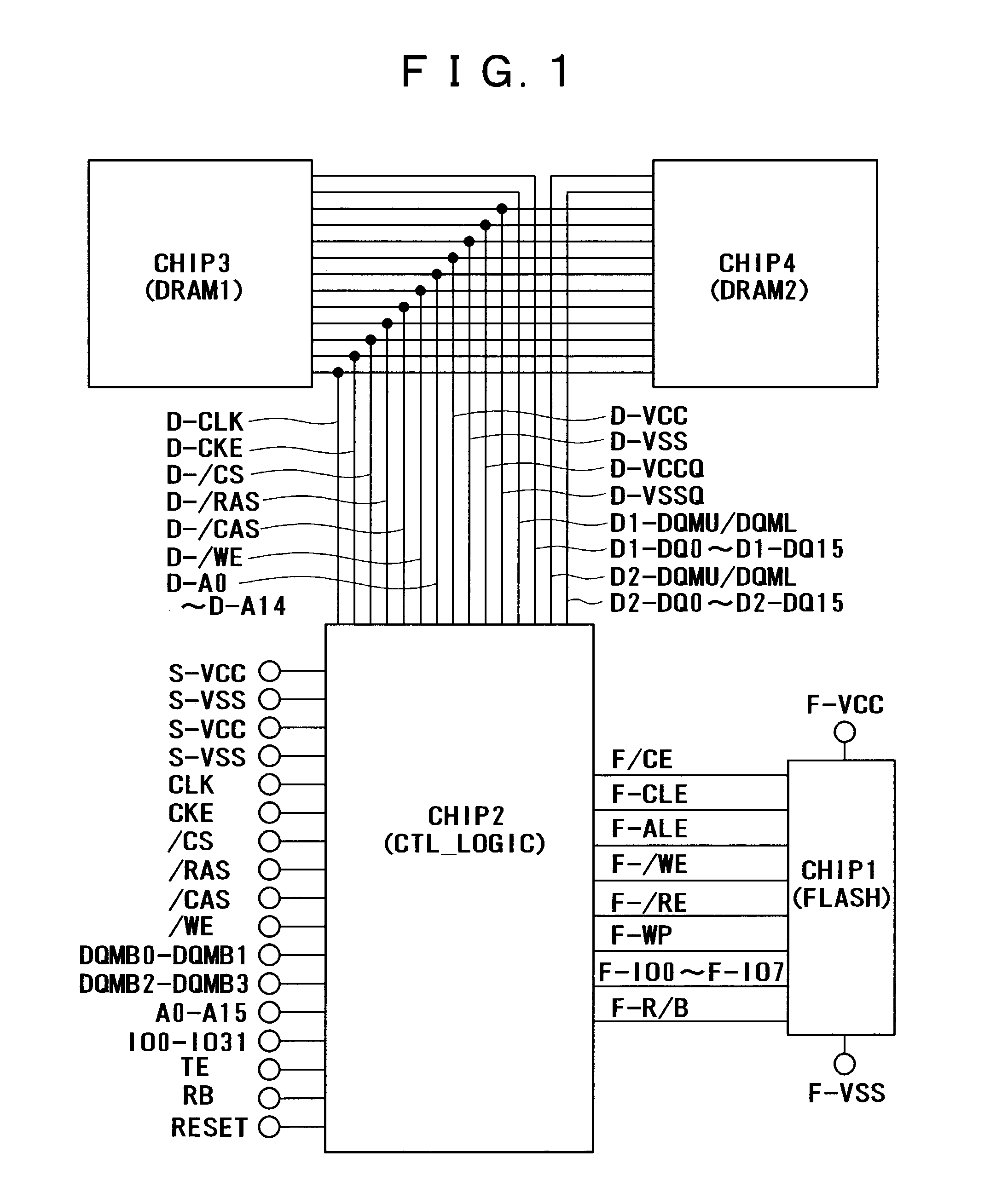

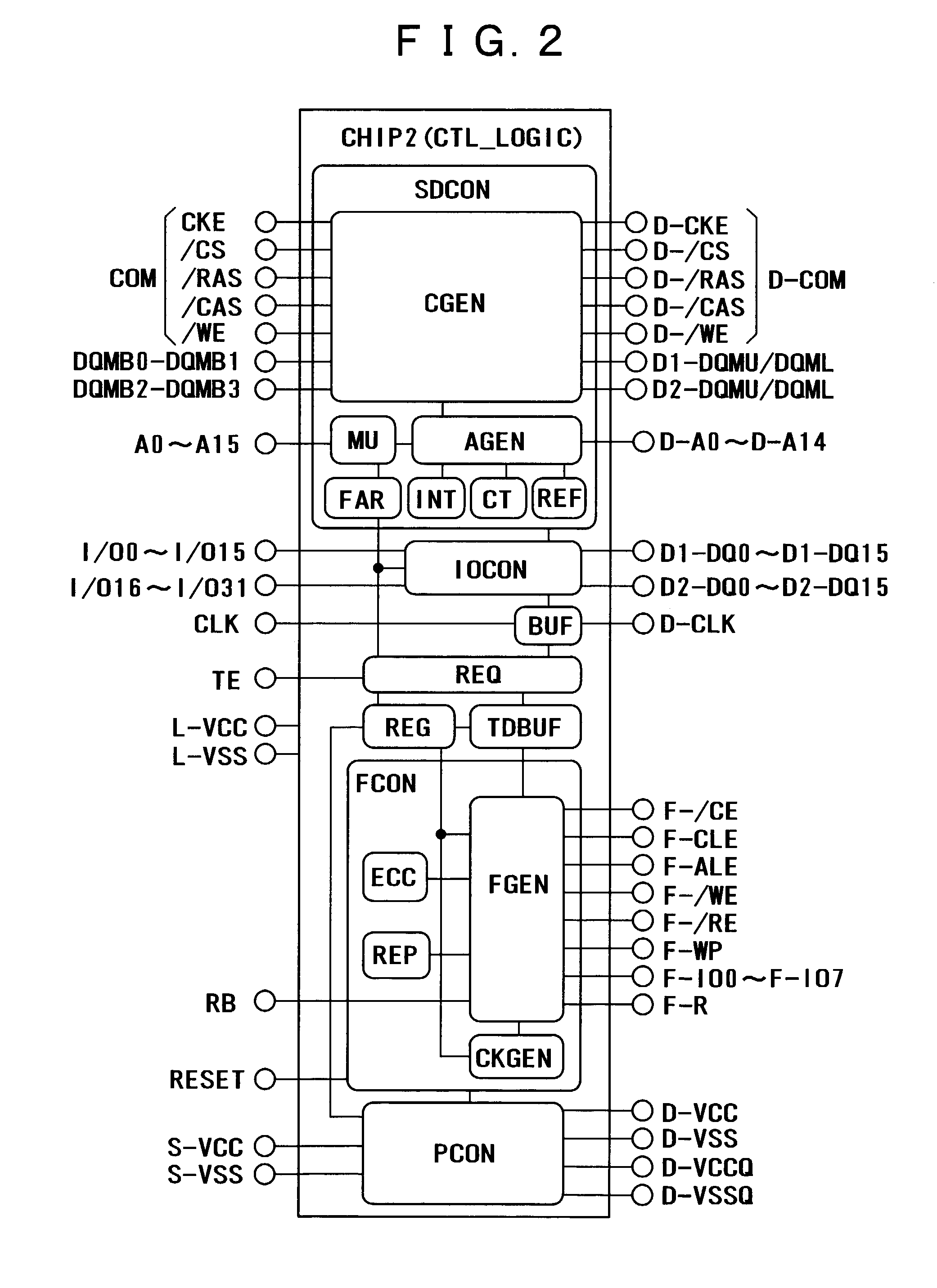

Computer system and semiconductor device on one chip including a memory and central processing unit for making interlock access to the memory

InactiveUS6101584AUnauthorized memory use protectionMultiple digital computer combinationsChip selectComputerized system

A central processing unit (CPU) having a built-in dynamic random-access memory (DRAM) with exclusive access to the DRAM when the CPU performs an interlock access to the DRAM. A memory controller prevents the DRAM from being externally accessed while the CPU is performing the interlock access. When the memory controller receives an external request for accessing the DRAM during a time when the CPU is performing an interlock access to the DRAM, the memory controller outputs a response signal indicating that external access to the DRAM is excluded or inhibited. The request signal can be a hold request signal for requesting a bus right or can be a chip select signal. The response signal can be a hold acknowledge signal or a data complete signal. The memory controller can be switched to and from first and second lock modes, where hold request and hold acknowledge signals are used during the first lock mode and chip select and data complete signals are used in the second lock mode.

Owner:MITSUBISHI ELECTRIC CORP

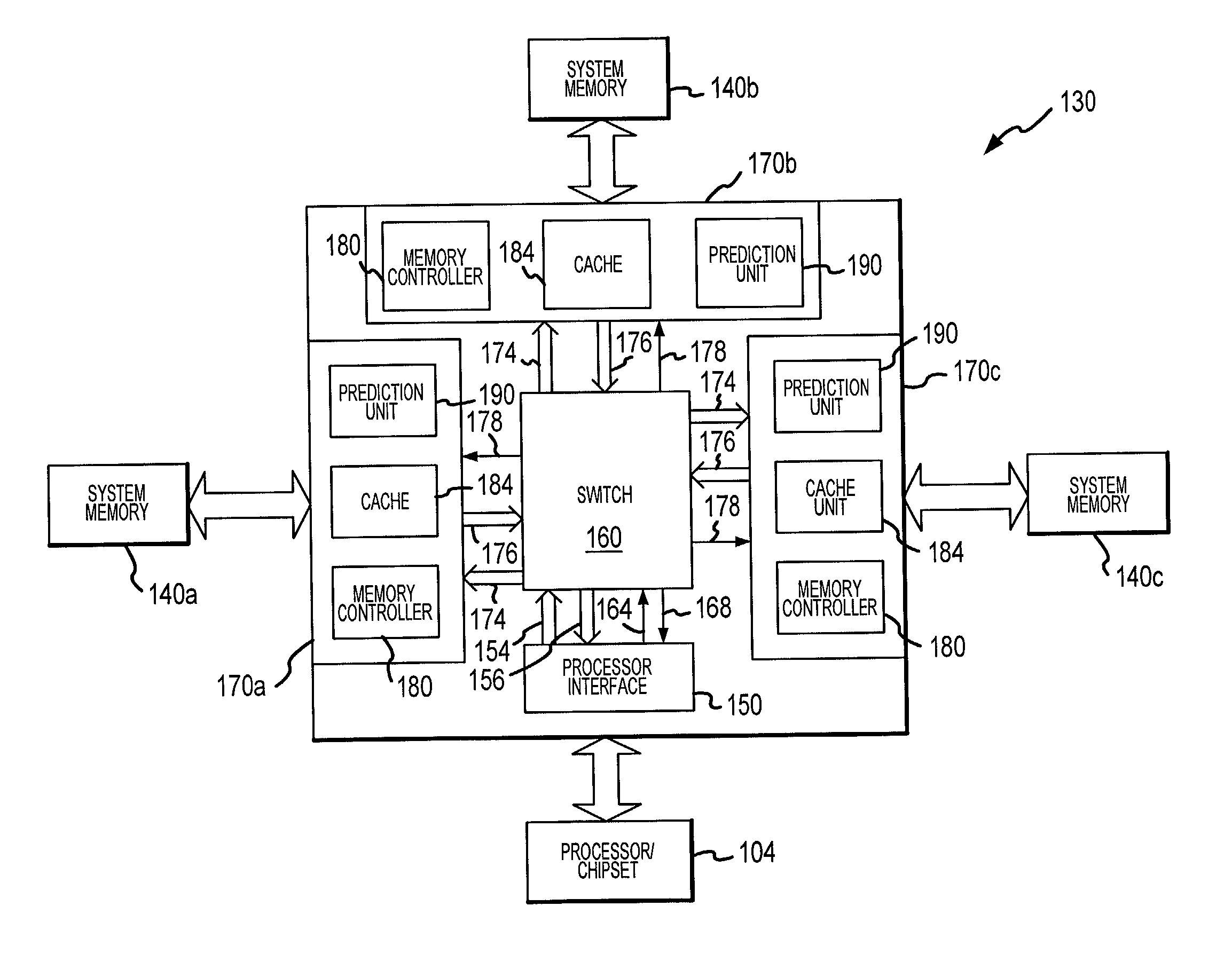

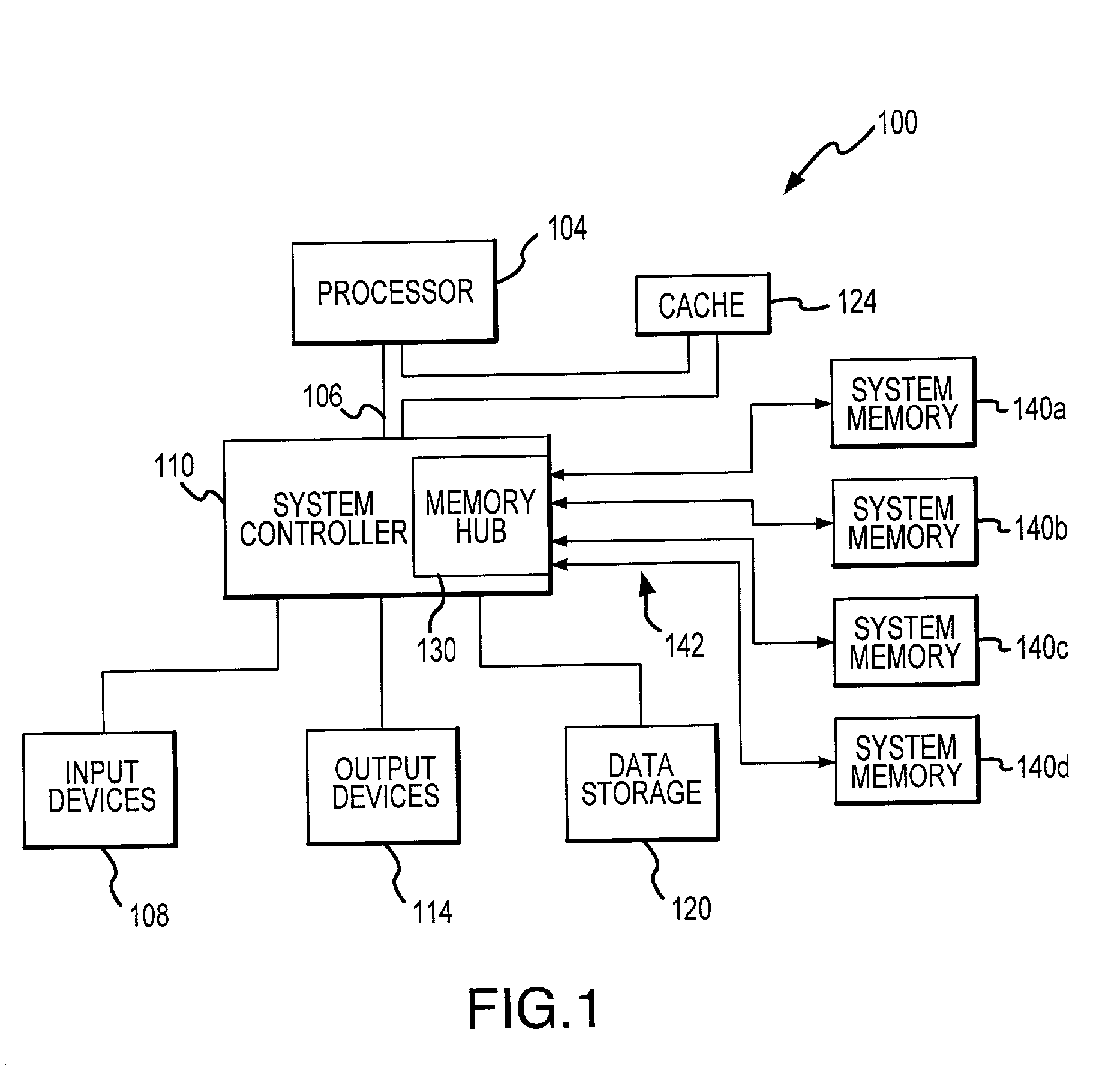

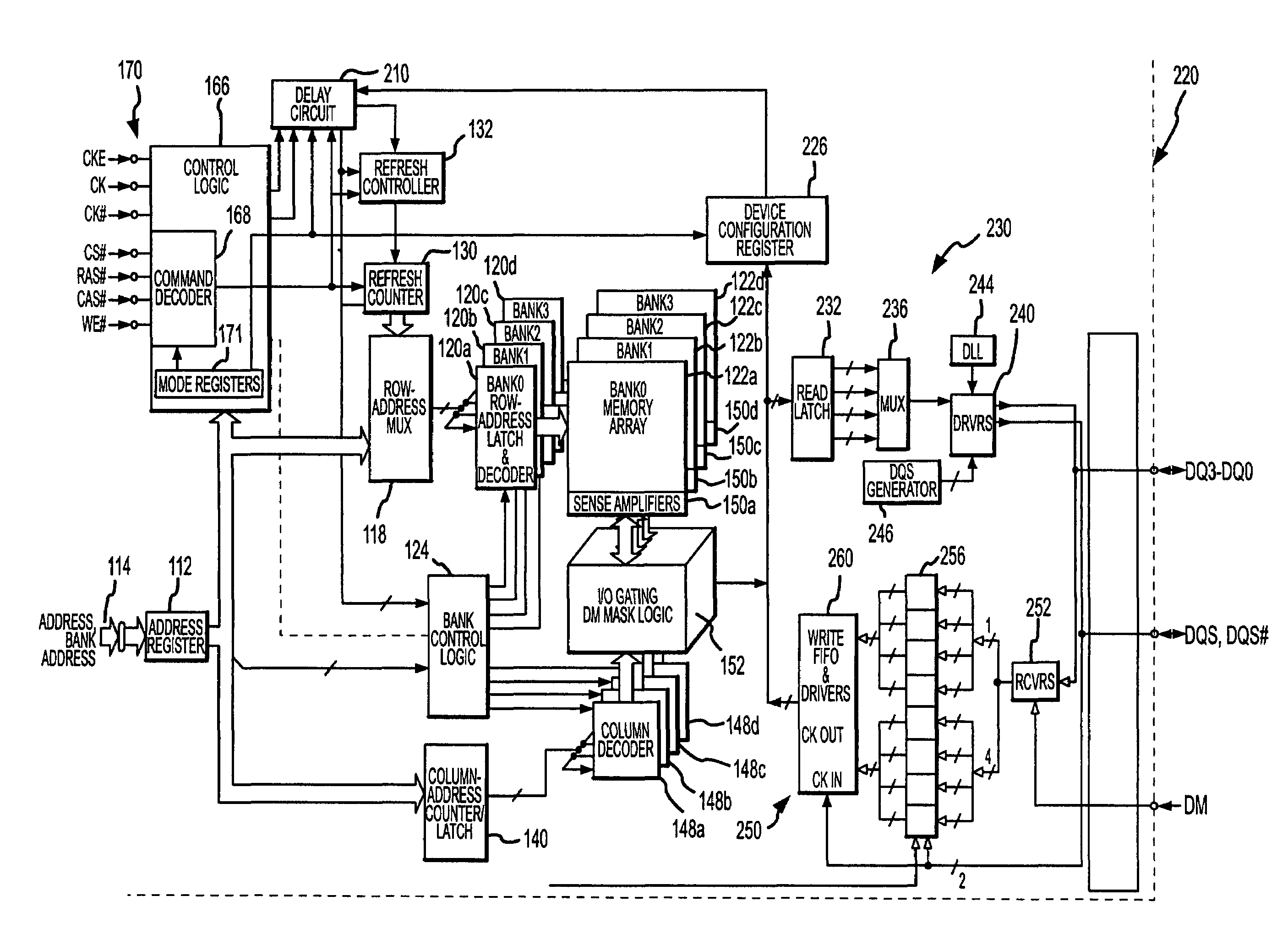

Memory hub with internal cache and/or memory access prediction

InactiveUS7133972B2Memory adressing/allocation/relocationMultiple digital computer combinationsRandom access memoryMemory interface

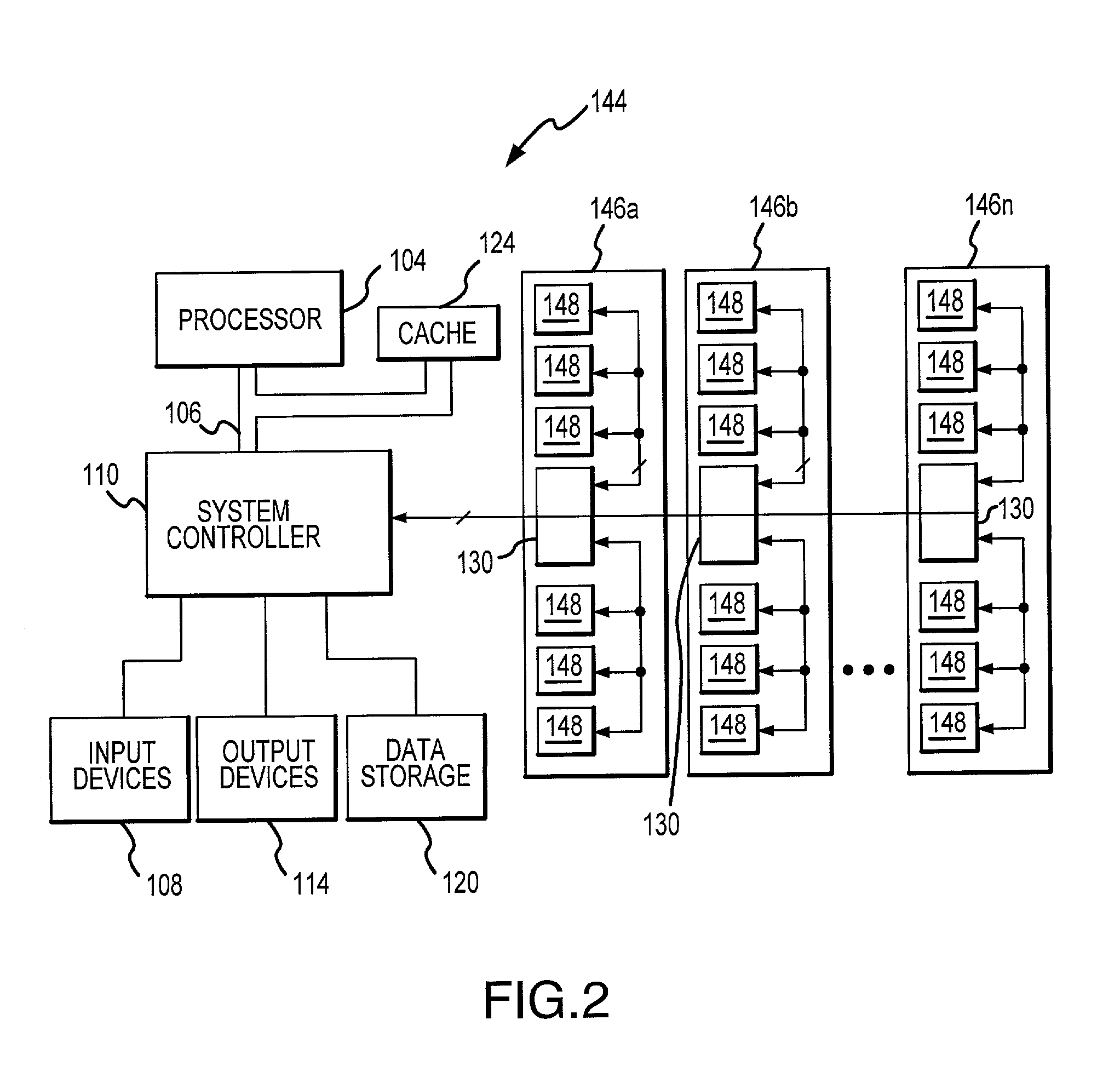

A computer system includes a memory hub for coupling a processor to a plurality of synchronous dynamic random access memory (“SDRAM”) devices. The memory hub includes a processor interface coupled to the processor and a plurality of memory interfaces coupled to respective SDRAM devices. The processor interface is coupled to the memory interfaces by a switch. Each of the memory interfaces includes a memory controller, a cache memory, and a prediction unit. The cache memory stores data recently read from or written to the respective SDRAM device so that it can be subsequently read by processor with relatively little latency. The prediction unit prefetches data from an address from which a read access is likely based on a previously accessed address.

Owner:ROUND ROCK RES LLC

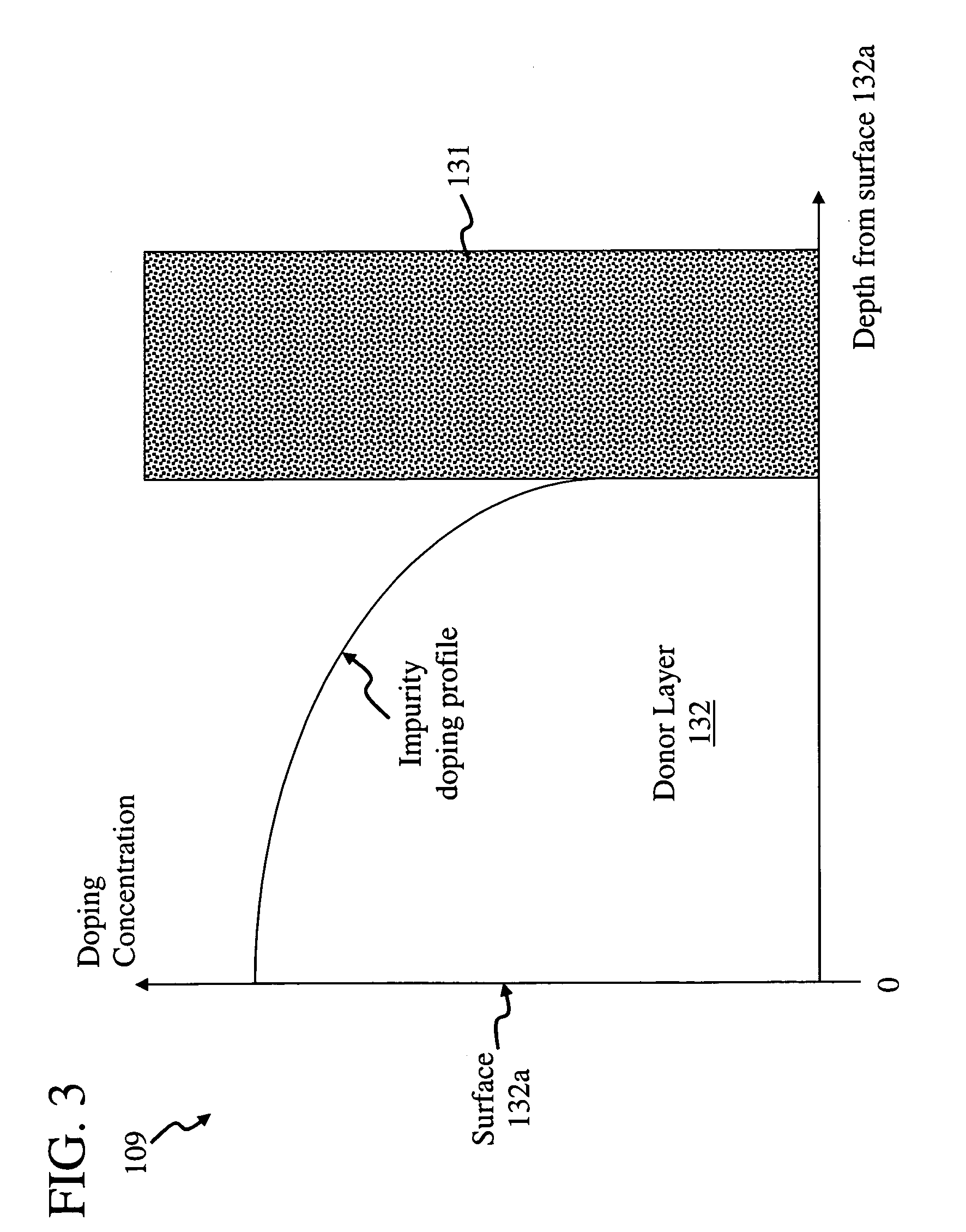

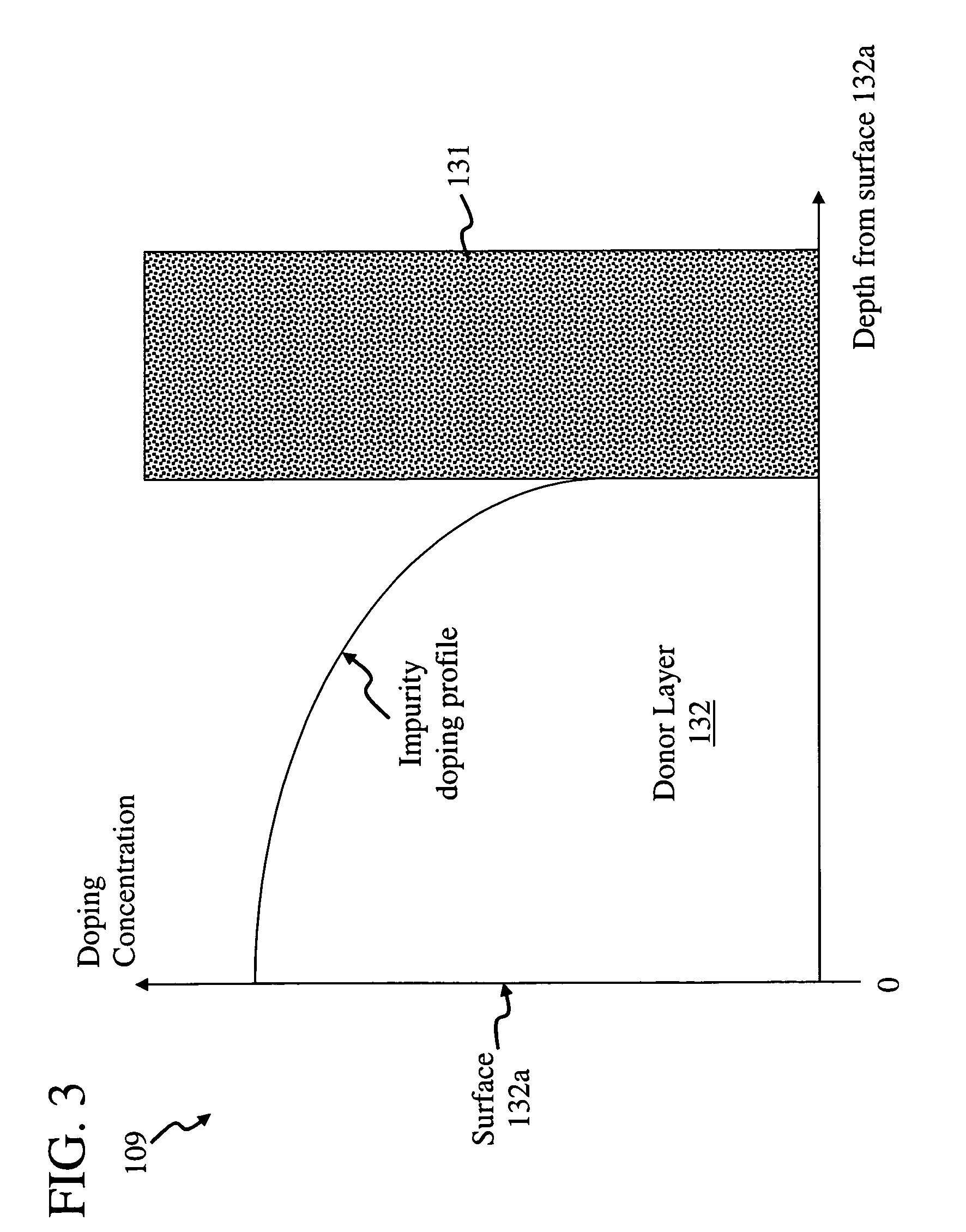

Semiconductor devices and dynamic random access memories having a retrograde region and methods of forming the same

InactiveUS20080169493A1Raise the threshold voltageEasy to limitTransistorFuel supply apparatusDevice materialImpurity ions

Semiconductor devices include an active region defined in a semiconductor substrate having first type impurity ions. A retrograde region is in the active region and has second type impurity ions. An upper channel region is on the retrograde region in the active region and has the first type impurity ions. Source and drain regions are on the upper channel region in the active region and spaced apart from each other. A gate electrode fills a gate trench formed in the active region. The gate electrode is disposed between the source and drain regions and extends into the retrograde region through the upper channel region. DRAM devices and methods are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

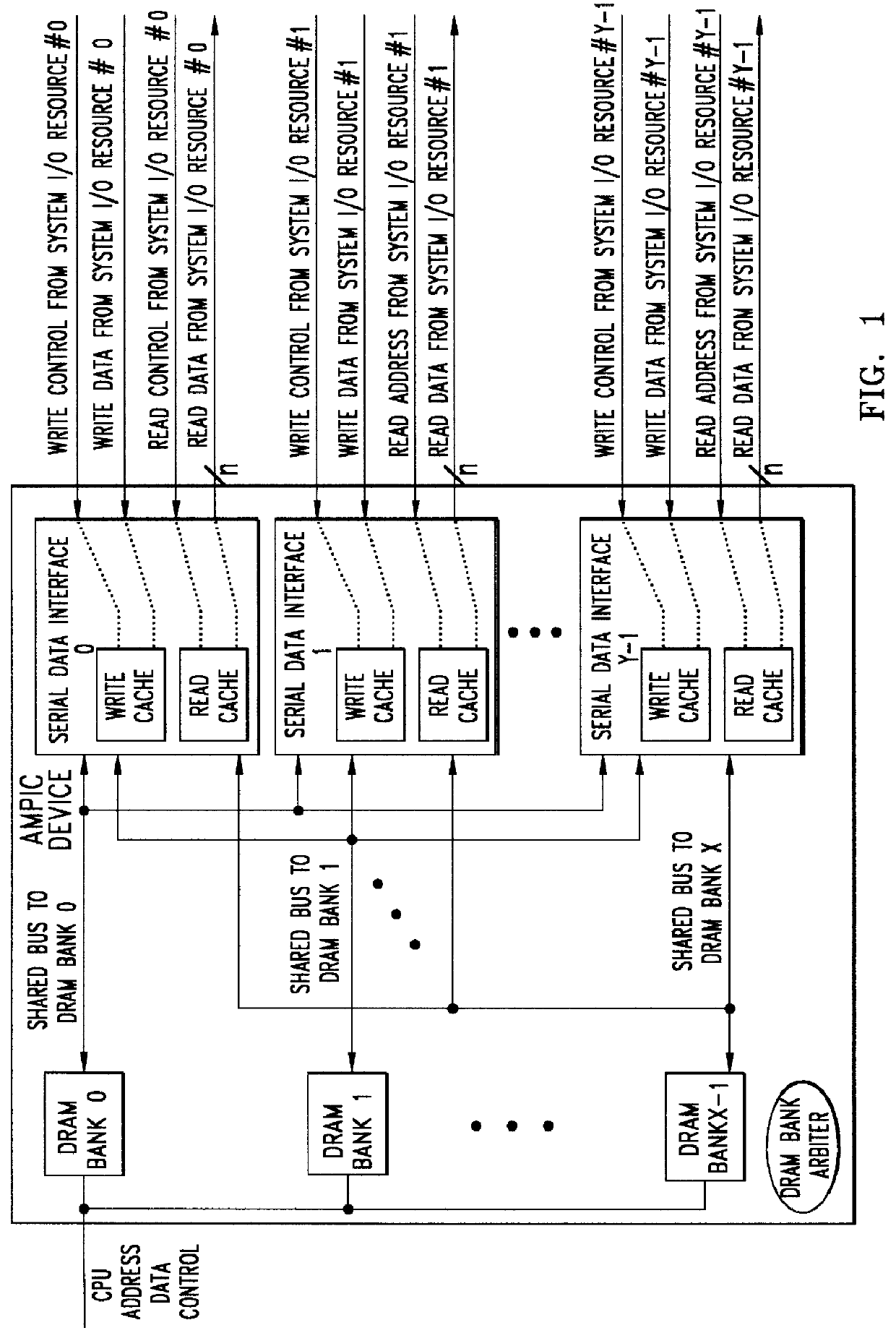

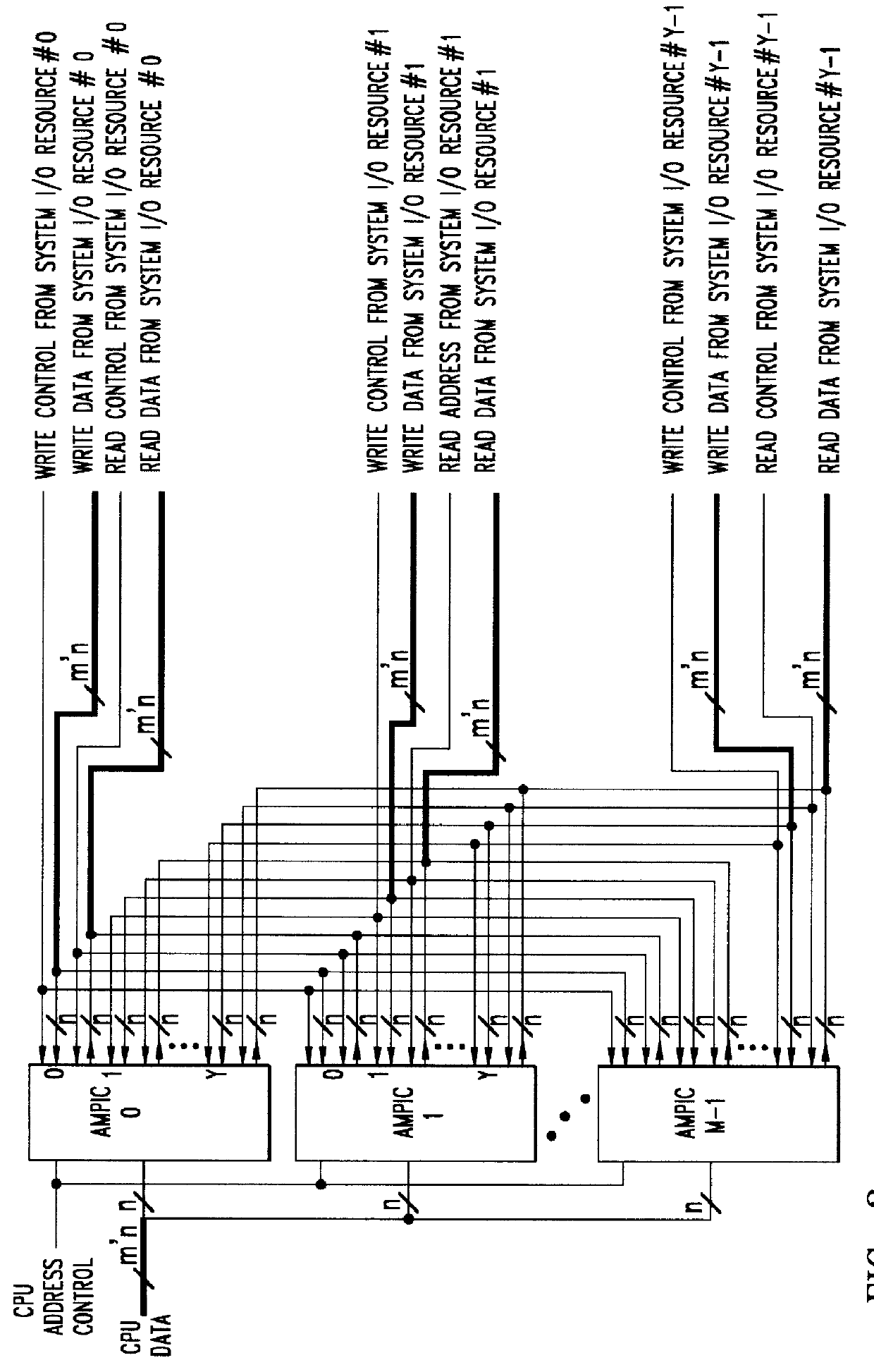

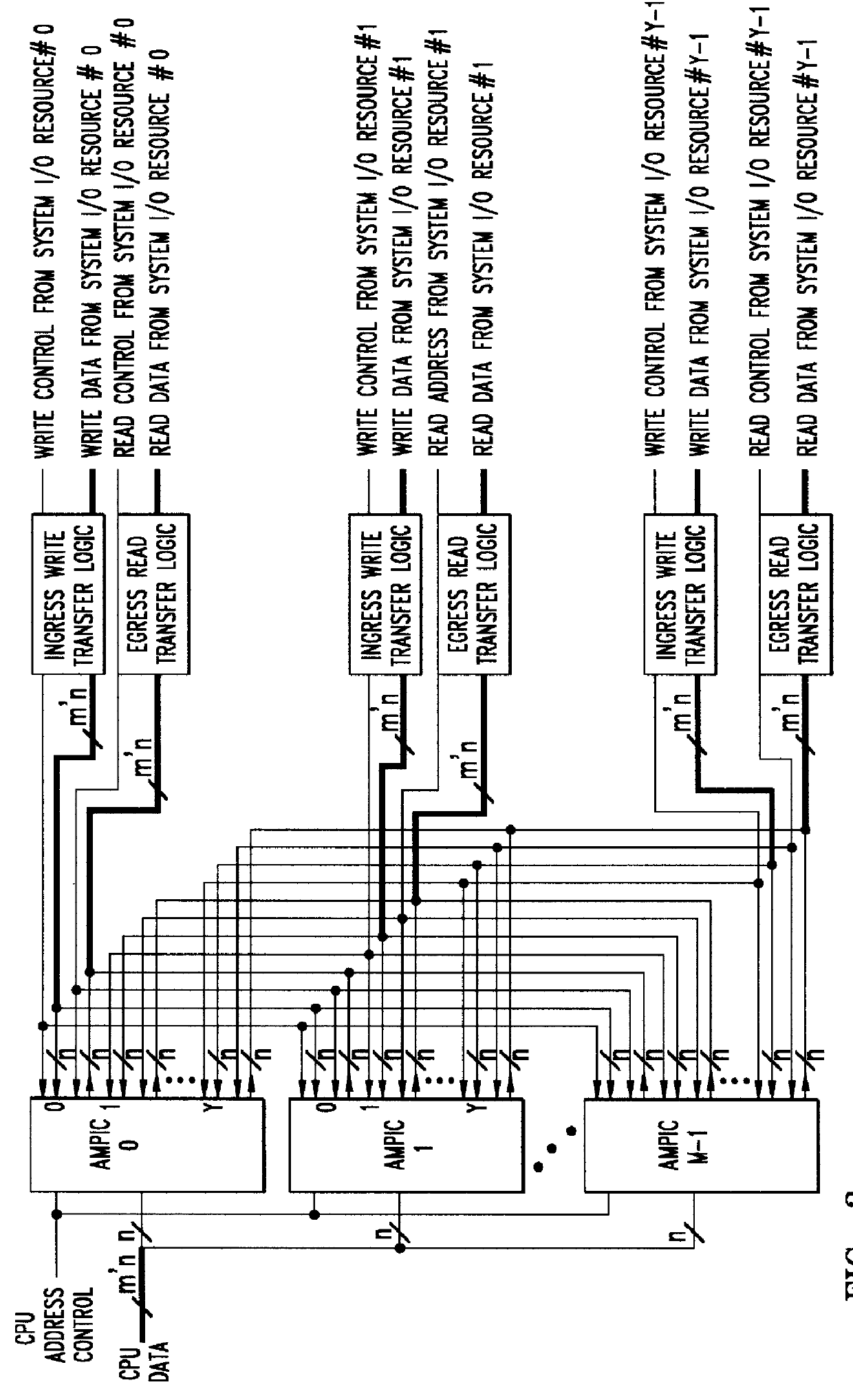

Method of and apparatus for validating data read out of a multi port internally cached dynamic random access memory (AMPIC DRAM)

InactiveUS6085290AEliminates race conditionMemory architecture accessing/allocationMemory adressing/allocation/relocationData validationStatic random-access memory

An apparatus for and method of enhancing the performance of a multi-port internal cached DRAM (AMPIC DRAM) by providing an internal method of data validation within the AMPIC memories themselves to guarantee that only valid requested data is returned from them, or properly marked invalid data. A modified technique for identifying bad data that has been read out of AMPIC memory devices in the system.

Owner:NEXABIT NETWORKS +1

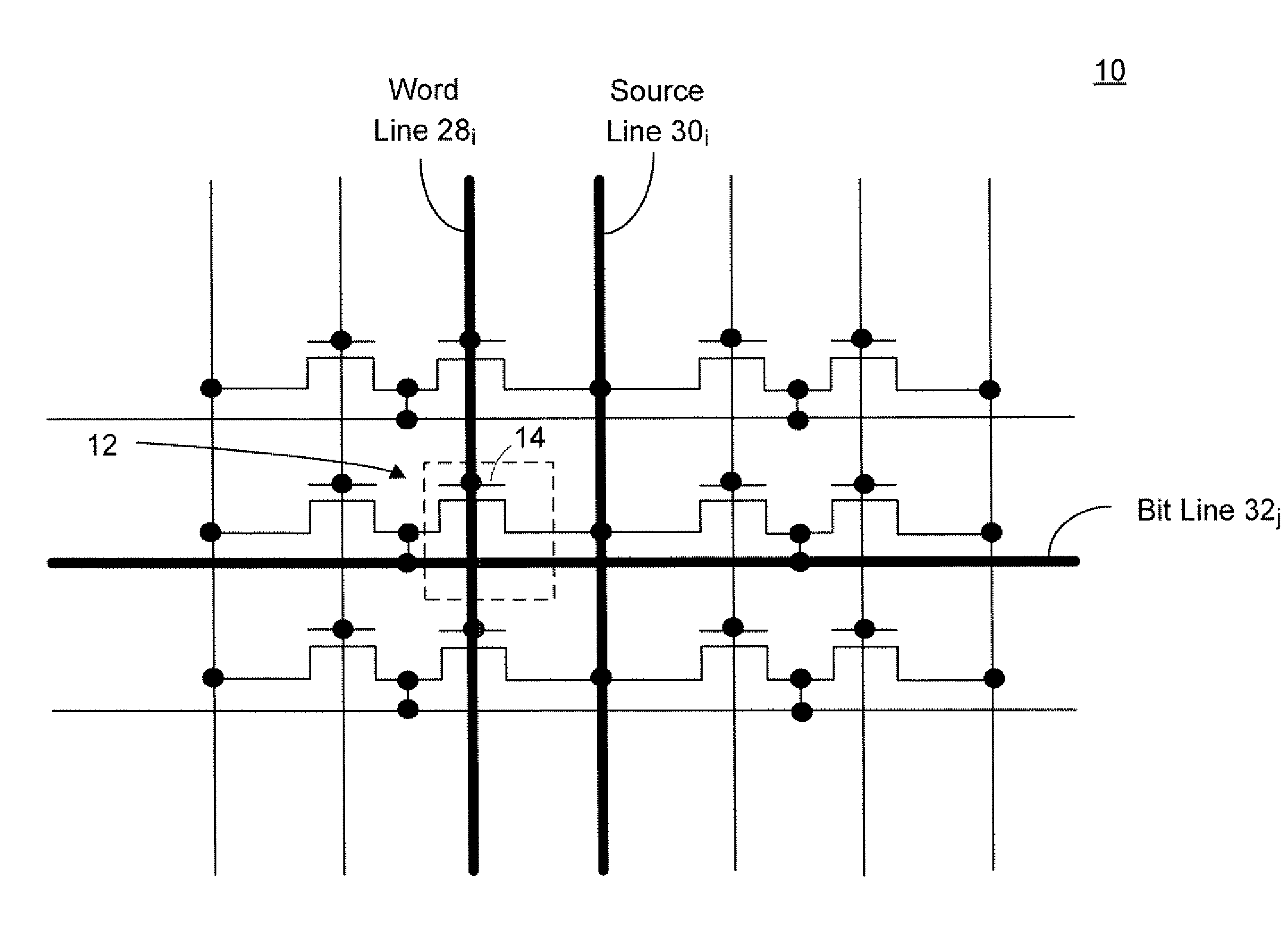

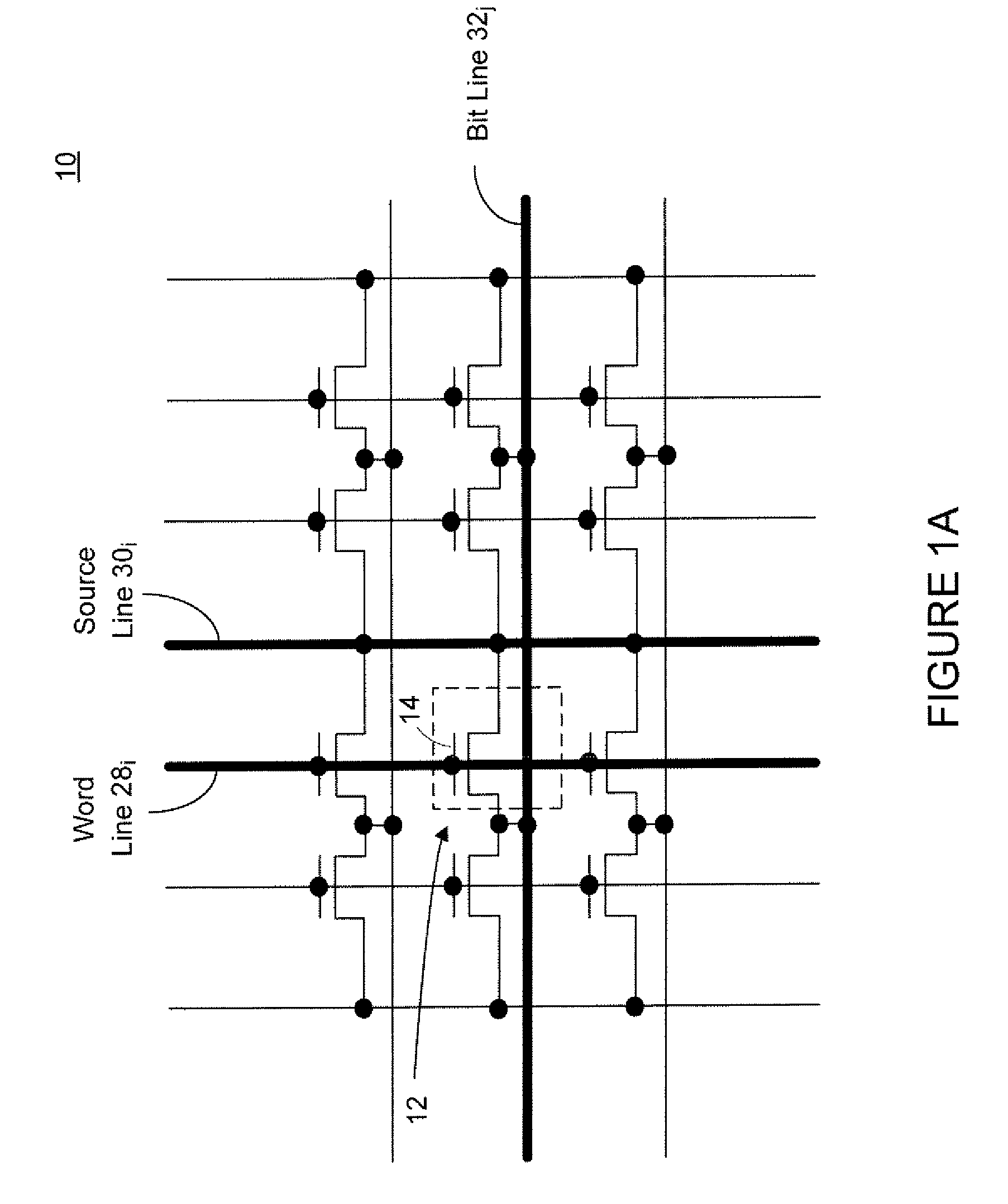

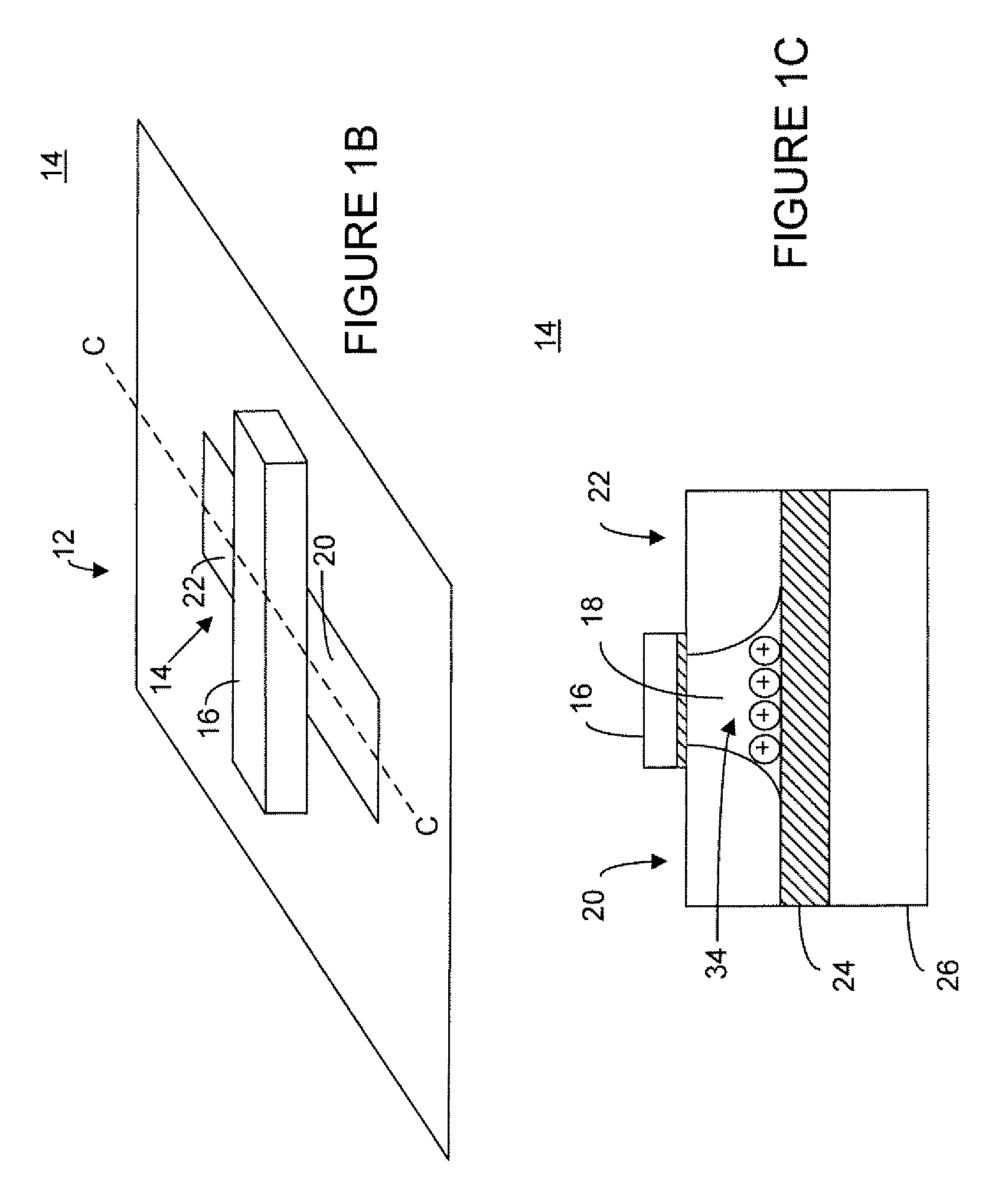

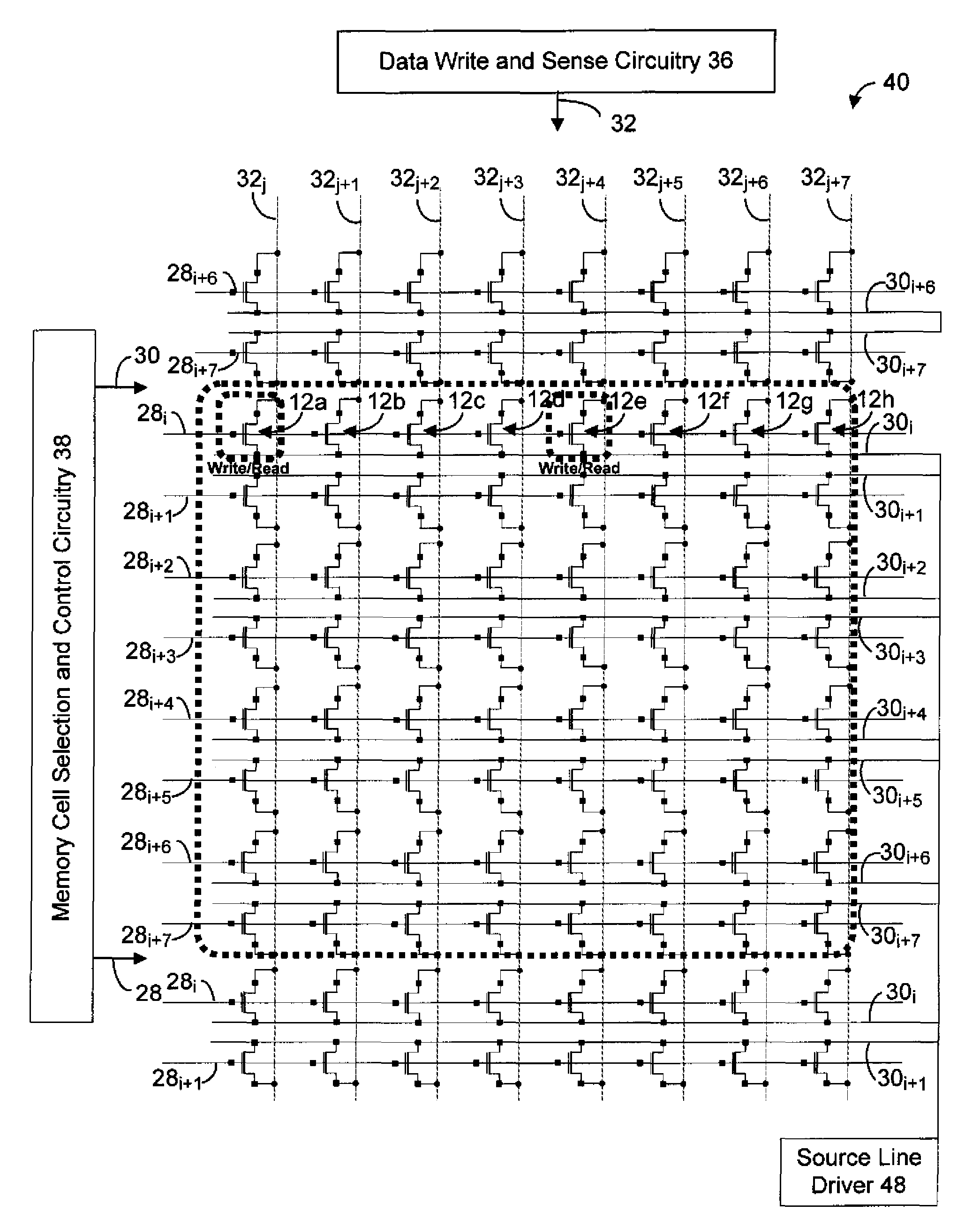

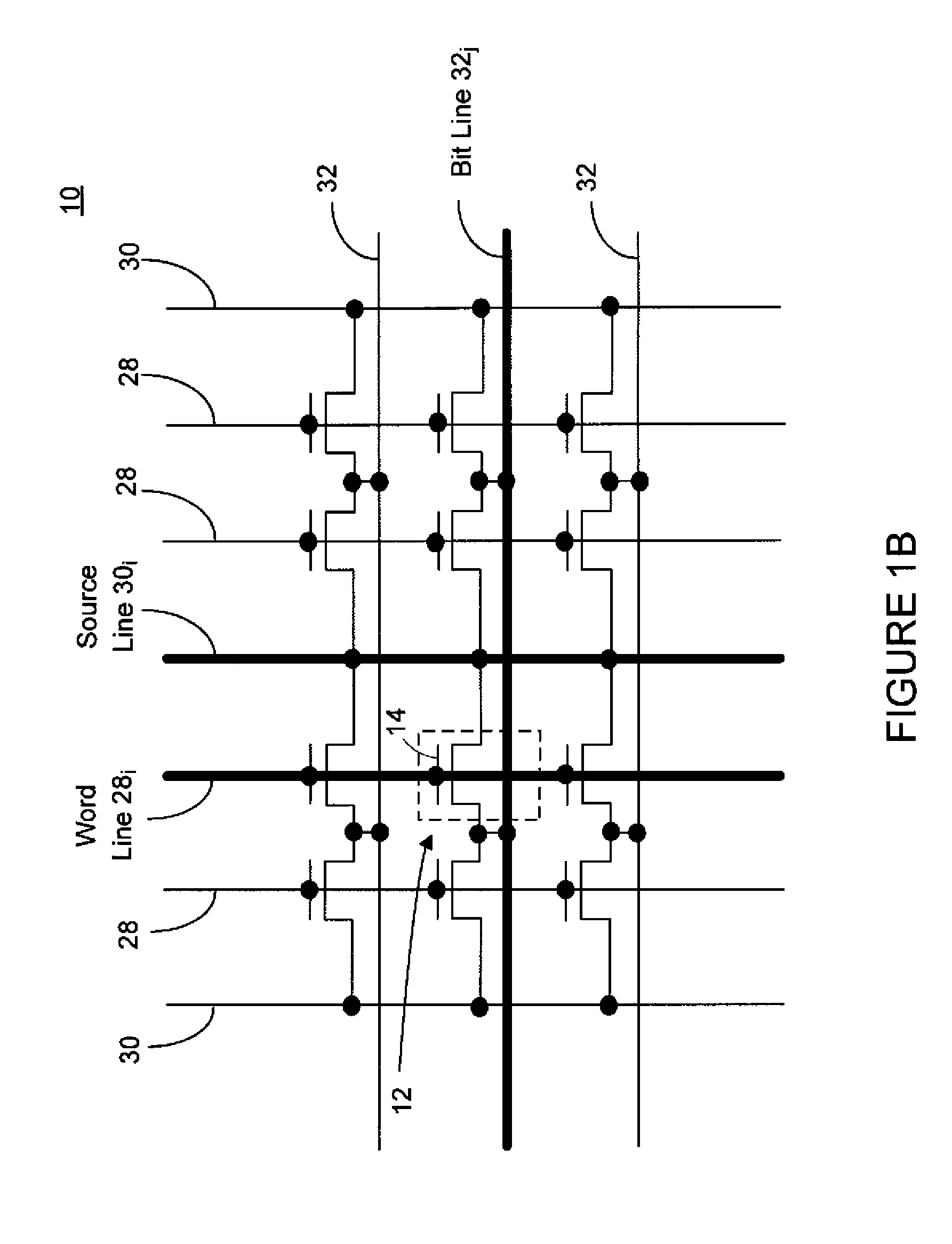

Techniques for simultaneously driving a plurality of source lines

Techniques for simultaneously driving a plurality of source lines are disclosed. In one particular exemplary embodiment, the techniques may be realized as an apparatus for simultaneously driving a plurality of source lines. The apparatus may include a plurality of source lines coupled to a single source line driver. The apparatus may also include a plurality of dynamic random access memory cells arranged in an array of rows and columns, each dynamic random access memory cell including one or more memory transistors. Each of the one or more memory transistors may include a first region coupled to a first source line of the plurality of source lines, a second region coupled to a bit line, a body region disposed between the first region and the second region, wherein the body region may be electrically floating, and a gate coupled to a word line and spaced apart from, and capacitively coupled to, the body region.

Owner:MICRON TECH INC

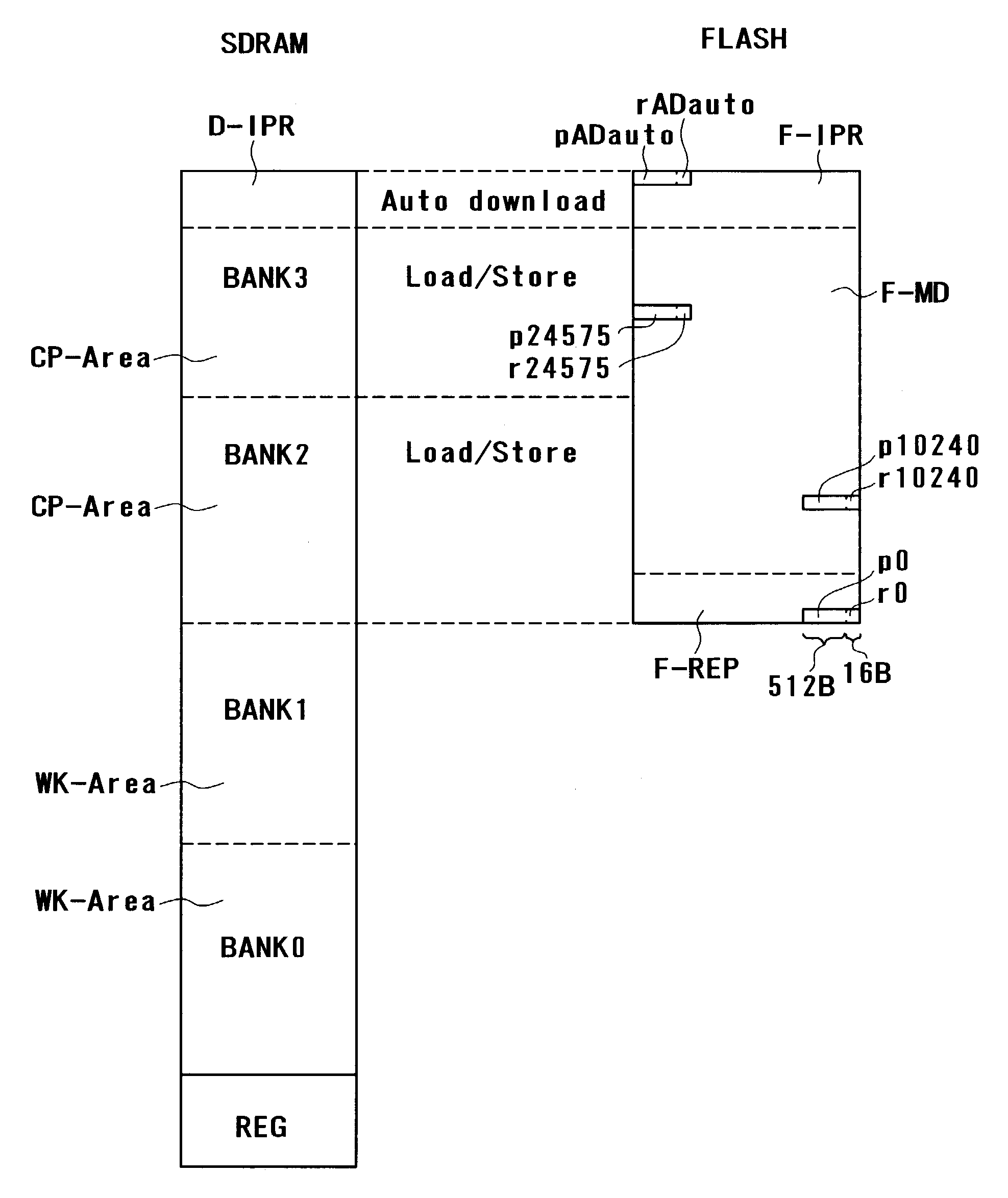

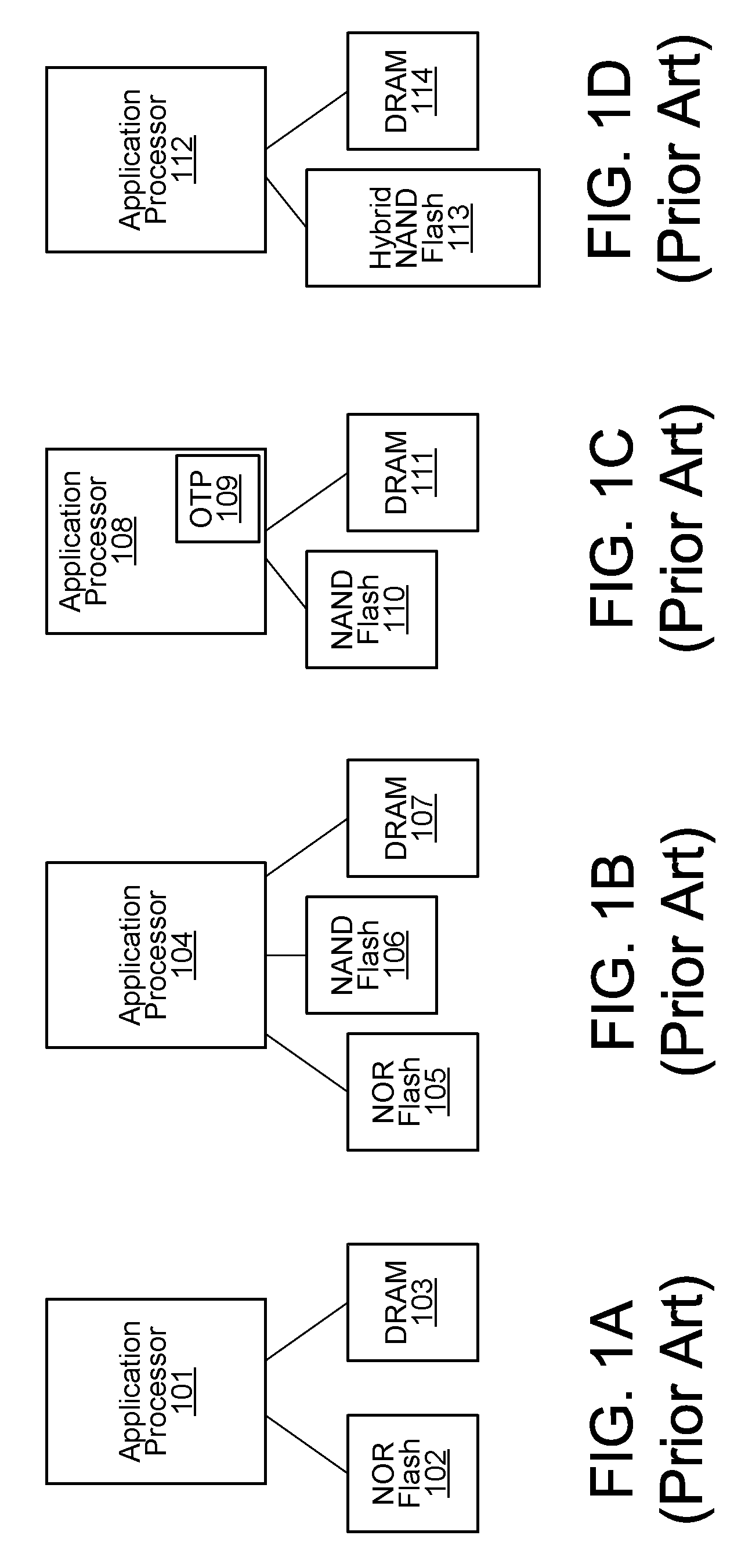

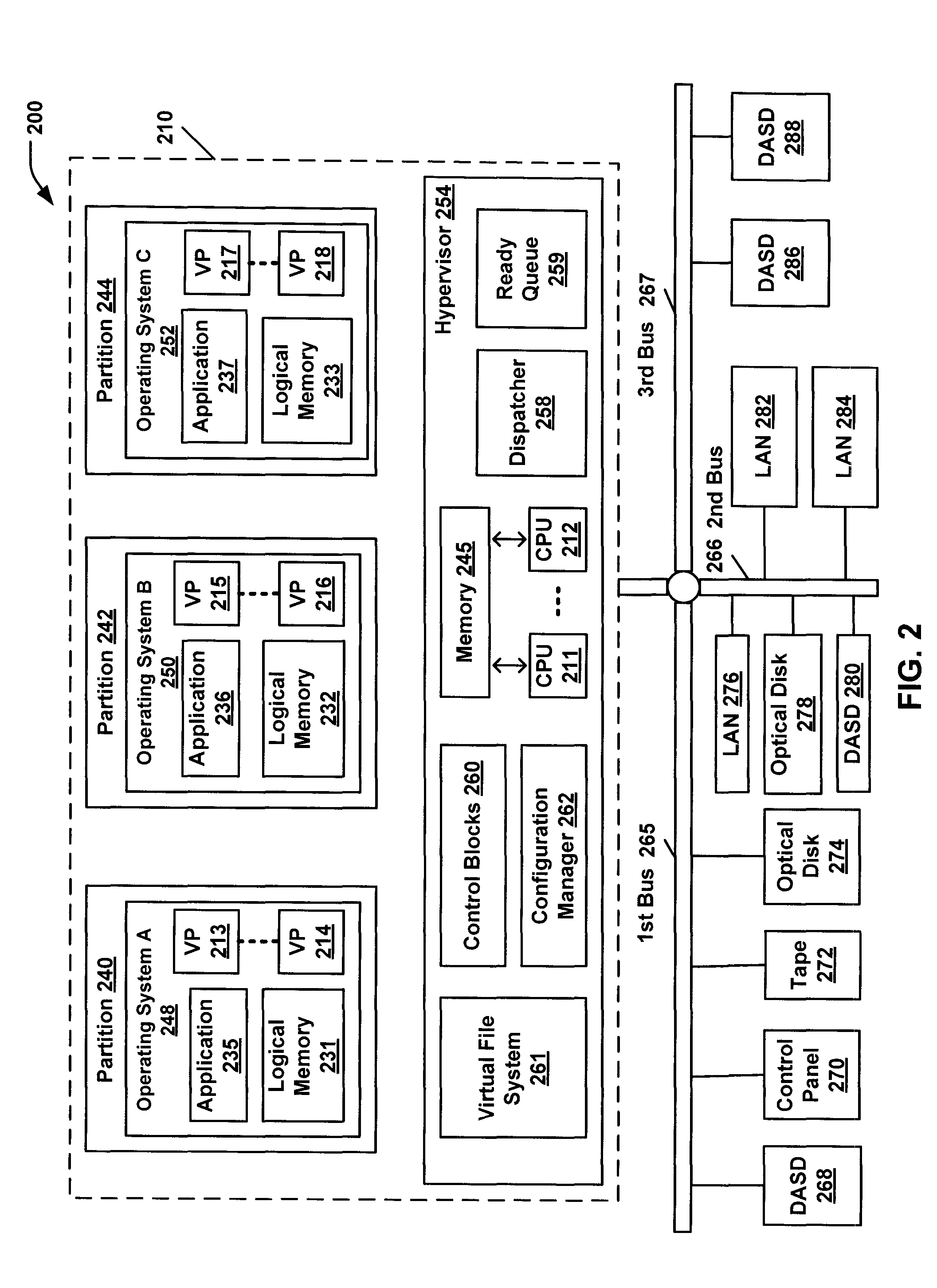

System and method for using dynamic random access memory and flash memory

InactiveUS7136978B2Increase storage capacityIncrease speedEnergy efficient ICTMemory loss protectionRandom access memorySynchronous dynamic random-access memory

A system and method are provided for using dynamic random access memory and flash memory. In one example, the memory system comprises a nonvolatile memory; synchronous dynamic random access memories; circuits including a control circuit which is coupled with the nonvolatile memory and the synchronous dynamic random access memories, and controls accesses to the nonvolatile memory and the synchronous dynamic random access memories; and a plurality of input / output terminals coupled with the circuits, wherein in data transfer from the nonvolatile memory to the synchronous dynamic random access memories, error corrected data is transferred.

Owner:HITACHI ULSI SYST CO LTD +1

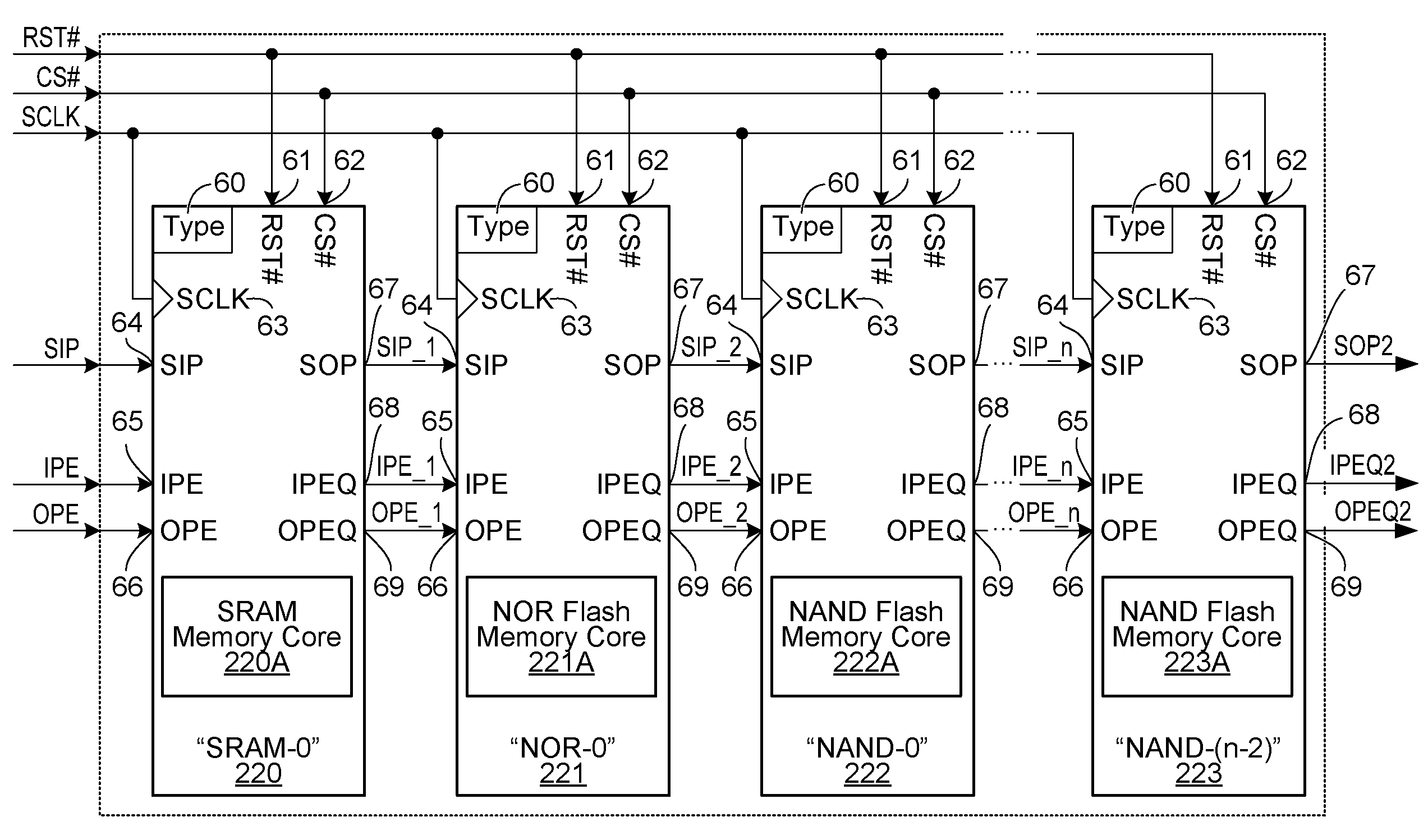

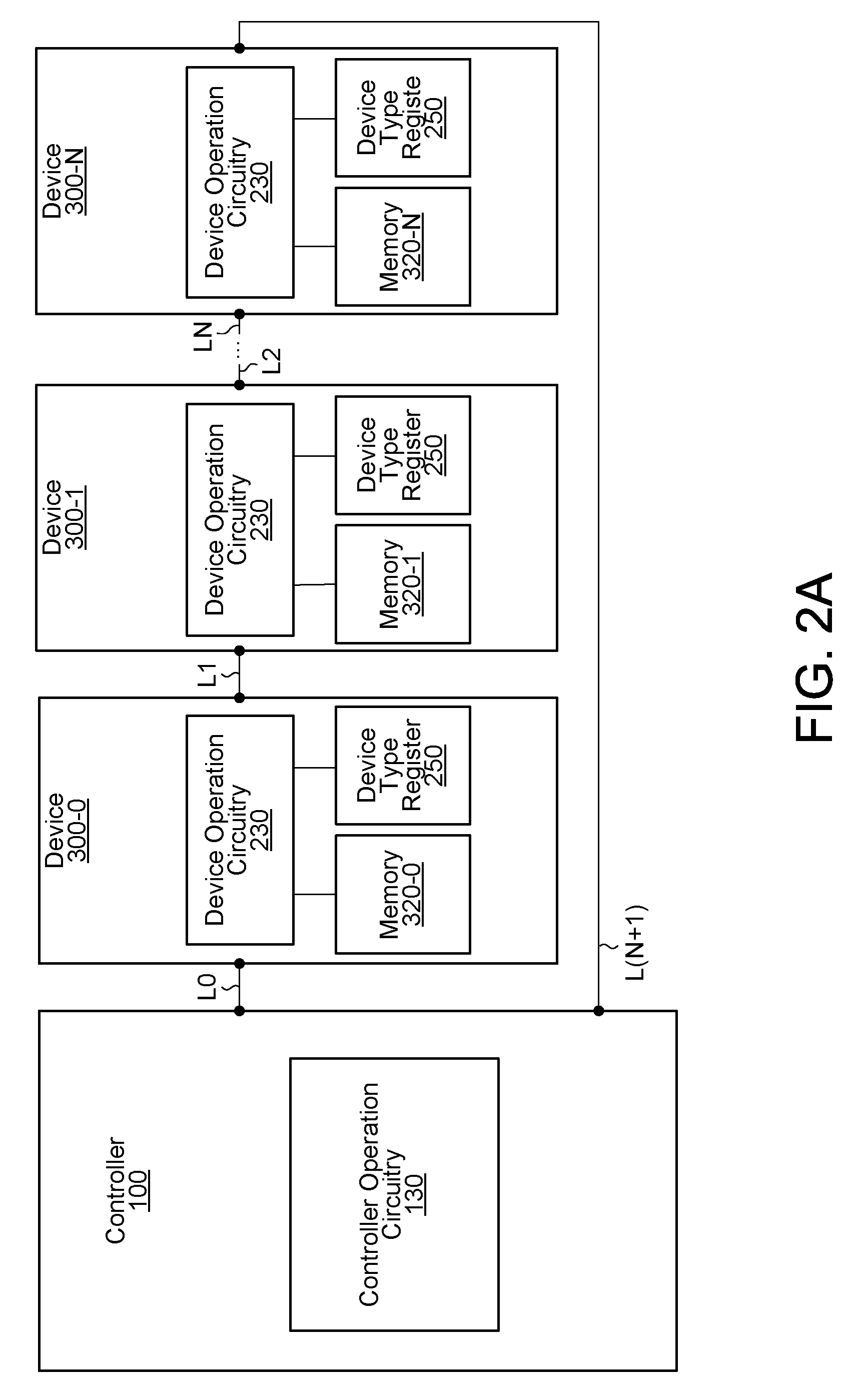

System and method of operating memory devices of mixed type

InactiveUS20080140916A1Memory adressing/allocation/relocationRead-only memoriesHybrid typeStatic random-access memory

A memory system architecture is provided in which a memory controller controls memory devices in a serial interconnection configuration. The memory controller has an output port for sending memory commands and an input port for receiving memory responses for those memory commands requisitioning such responses. Each memory device includes a memory, such as, for example, NAND-type flash memory, NOR-type flash memory, random access memory and static random access memory. Each memory command is specific to the memory type of a target memory device. A data path for the memory commands and the memory responses is provided by the interconnection. A given memory command traverses memory devices in order to reach its intended memory device of the serial interconnection configuration. Upon its receipt, the intended memory device executes the given memory command and, if appropriate, sends a memory response to a next memory device. The memory response is transferred to the memory controller.

Owner:CONVERSANT INTPROP MANAGEMENT INC

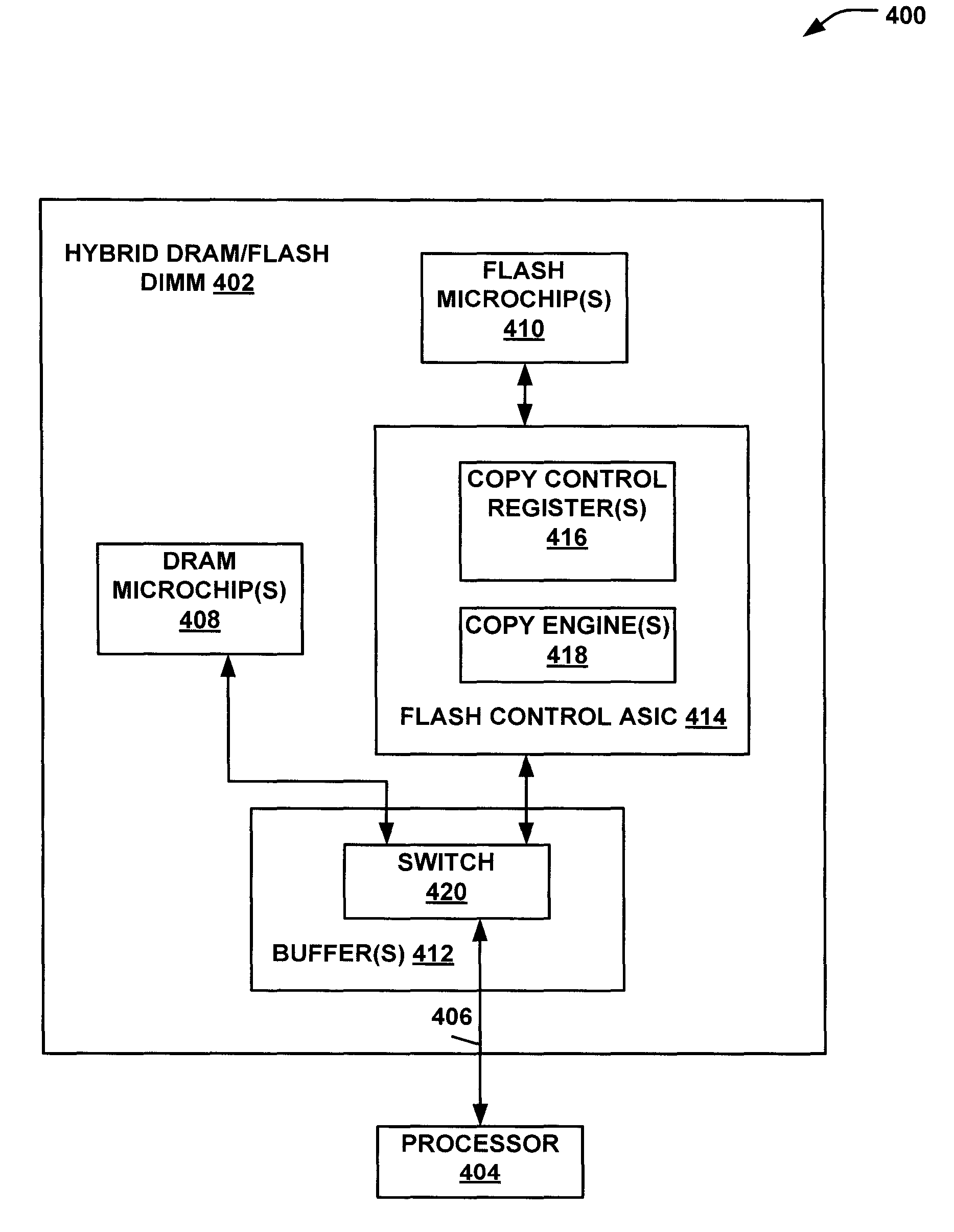

Flash memory dual in-line memory module management

InactiveUS20140095769A1Improve work performanceImprove system performanceRead-only memoriesDigital storageDIMMComputer module

Systems and methods to manage memory on a dual in-line memory module (DIMM) are provided. A particular method may include receiving at a flash application-specific integrated circuit (ASIC) a request from a processor to access data stored in a flash memory of a DIMM. The data may be transferred from the flash memory to a switch of the DIMM. The data may be routed to a dynamic random-access memory (DRAM) of the DIMM. The data may be stored in the DRAM and may be provided from the DRAM to the processor.

Owner:LENOVO ENTERPRISE SOLUTIONS SINGAPORE

Method and system for reducing the peak current in refreshing dynamic random access memory devices

InactiveUS7200062B2Limiting peak current consumptionDigital storageComputer hardwareComputer science

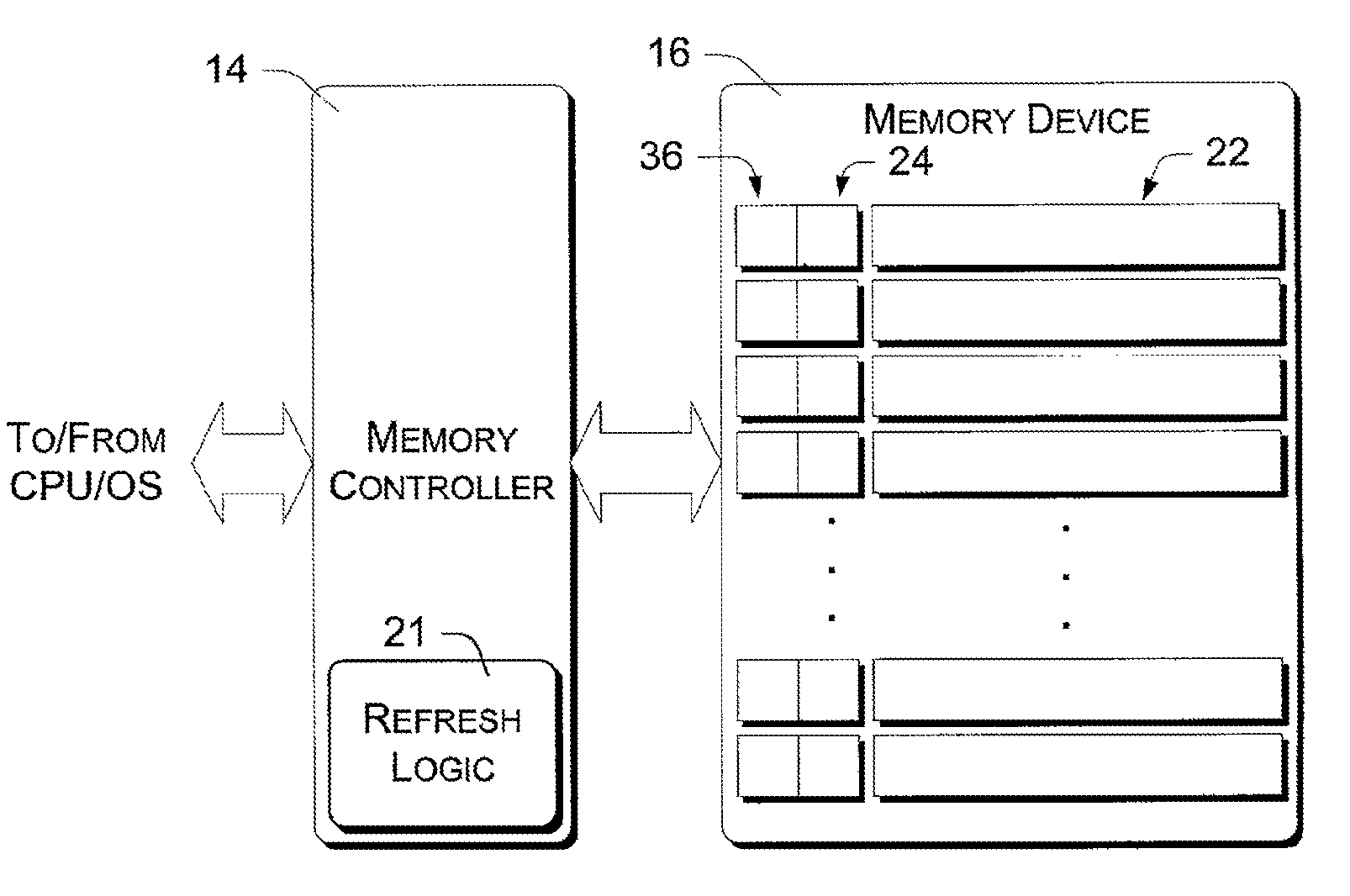

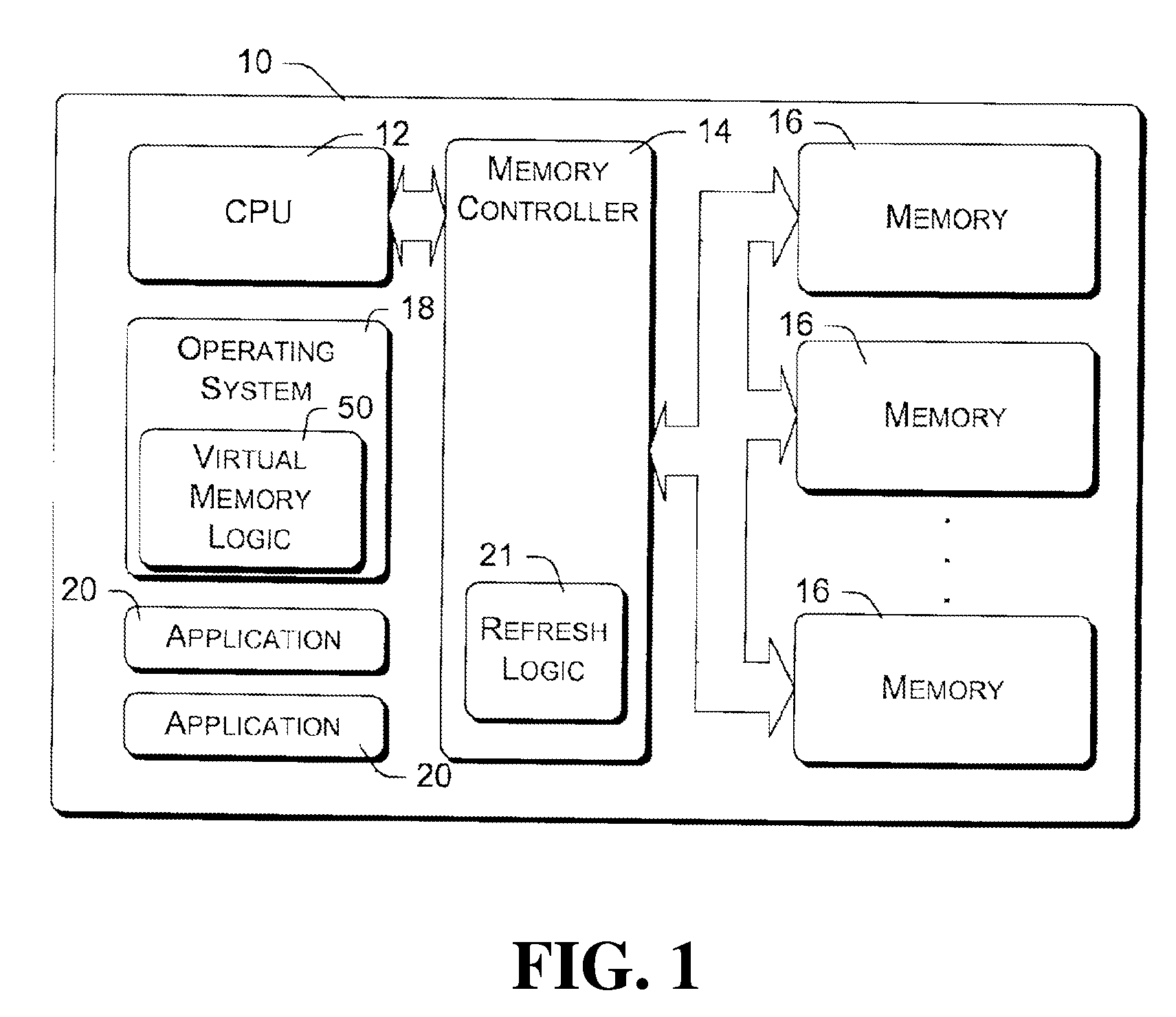

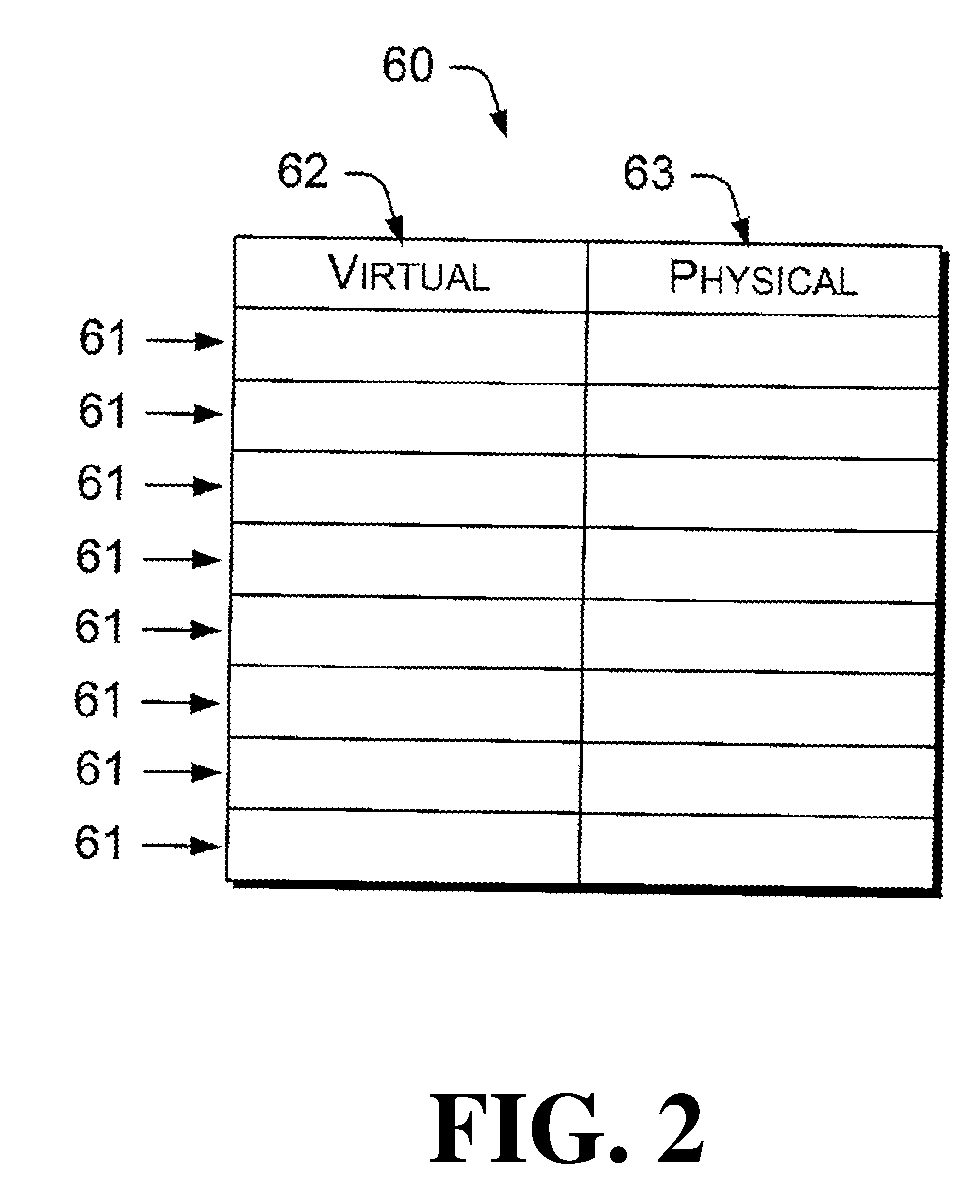

A dynamic random access memory device includes a mode register that is programmed with a delay value. In some embodiments, a offset code is also stored in the memory device. The memory device uses the delay value, which may be added to or multiplied by the offset code, to delay the initiation of a received auto-refresh or self-refresh command. A large number of dynamic random access memory devices in a system may be provided with different delay values and possibly offset codes so that the memory device do not all perform refreshes simultaneously in response to an auto-refresh or self-refresh command issued to all of the memory devices simultaneously. As a result, the peak current drawn by the memory devices resulting from the auto-refresh command or self-refresh command is maintained at a relatively low value.

Owner:ROUND ROCK RES LLC

One transistor dram cell structure and method for forming

ActiveUS20080099808A1Simple and compact designGuaranteed uptimeTransistorSolid-state devicesSchottky diodeBody region

A one-transistor dynamic random access memory (DRAM) cell includes a transistor which has a first source / drain region, a second source / drain region, a body region between the first and second source / drain regions, and a gate over the body region. The first source / drain region includes a Schottky diode junction with the body region and the second source / drain region includes an n-p diode junction with the body region.

Owner:NXP USA INC

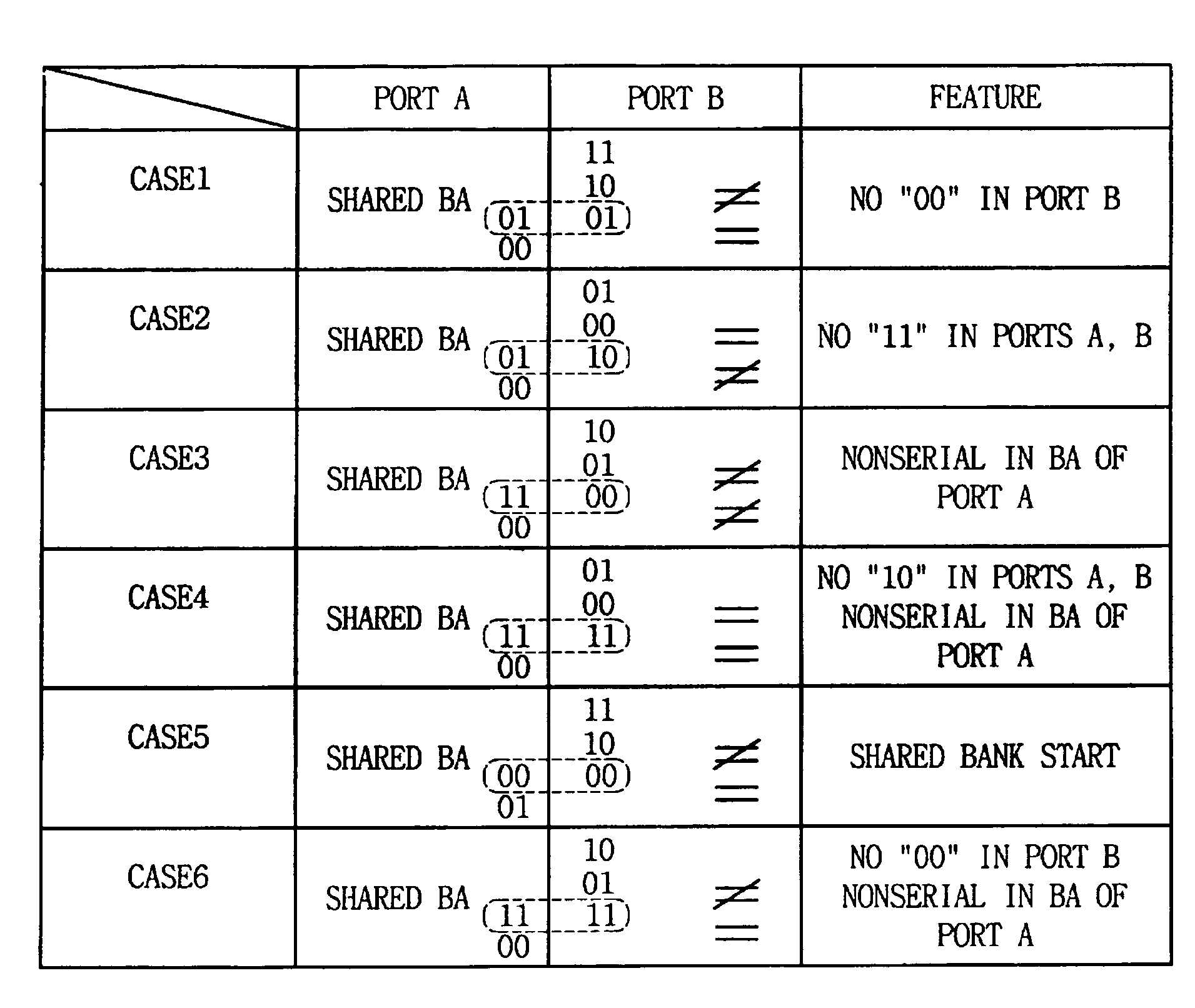

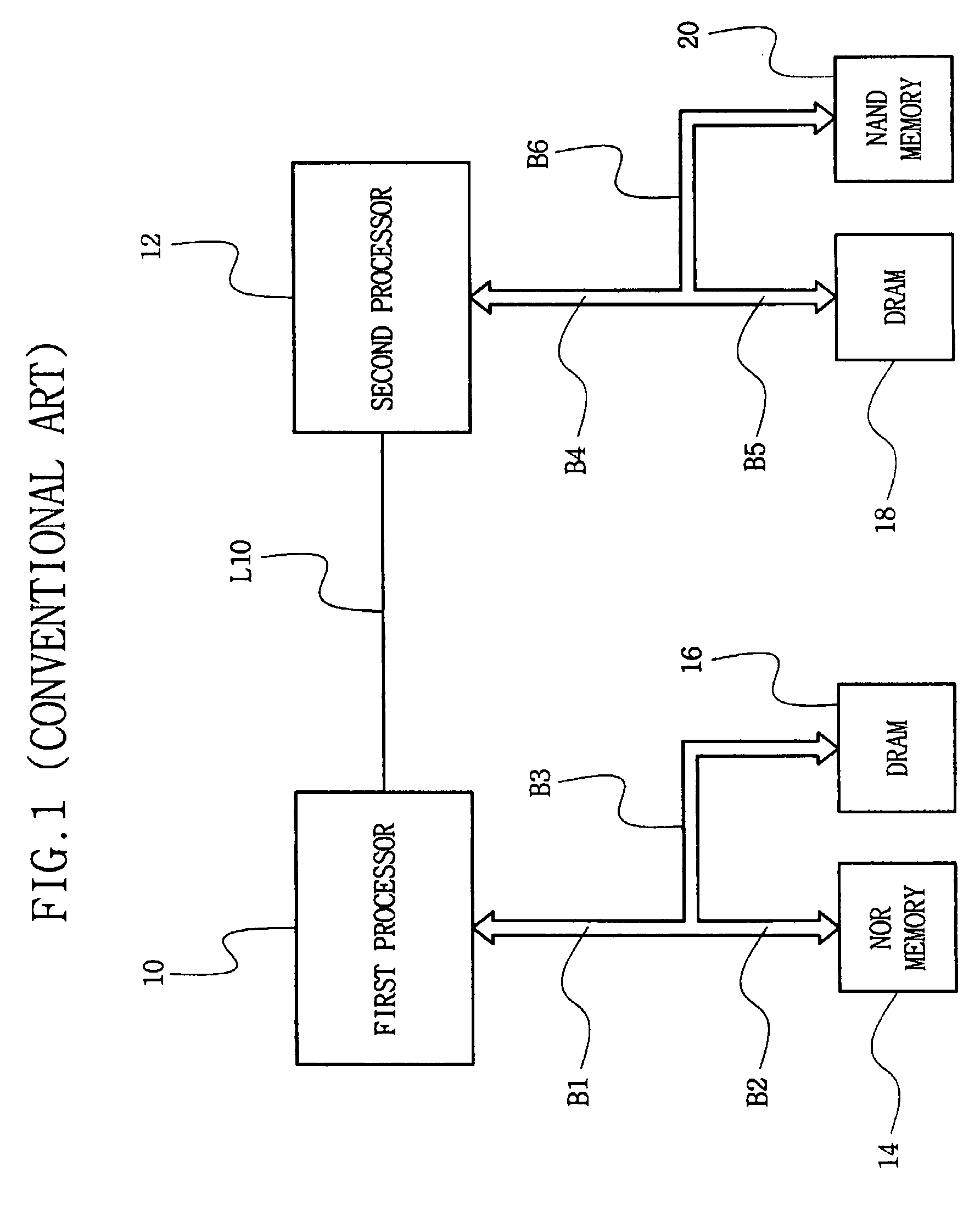

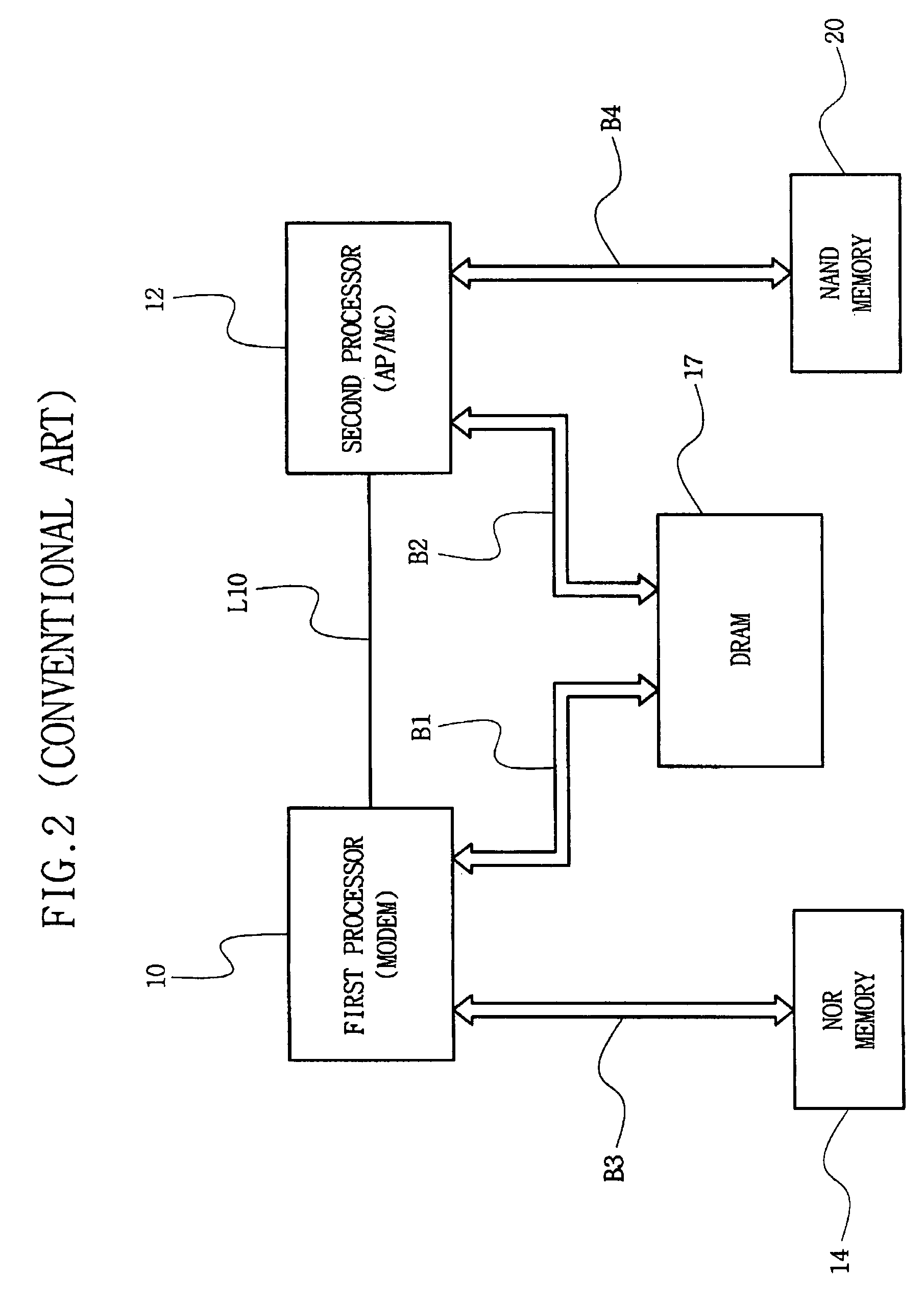

Multiprocessor system and method thereof

A multiprocessor system and method thereof are provided. The example multiprocessor system may include first and second processors, a dynamic random access memory having a memory cell array, the memory cell array including a first memory bank coupled to the first processor through a first port, second and fourth memory banks coupled to the second processor through a second port, and a third memory bank shared and connected with the first and second processors through the first and second ports, and a bank address assigning unit for assigning bank addresses to select individually the first and second memory banks, as the same bank address through the first and second ports, so that starting addresses for the first and second memory banks become equal in booting, and assigning bank addresses to select the third memory bank, as different bank addresses through the first and second ports, and assigning, through the second port, bank addresses to select the fourth memory bank, as the same bank address as a bank address to select the third memory bank through the first port.

Owner:SAMSUNG ELECTRONICS CO LTD

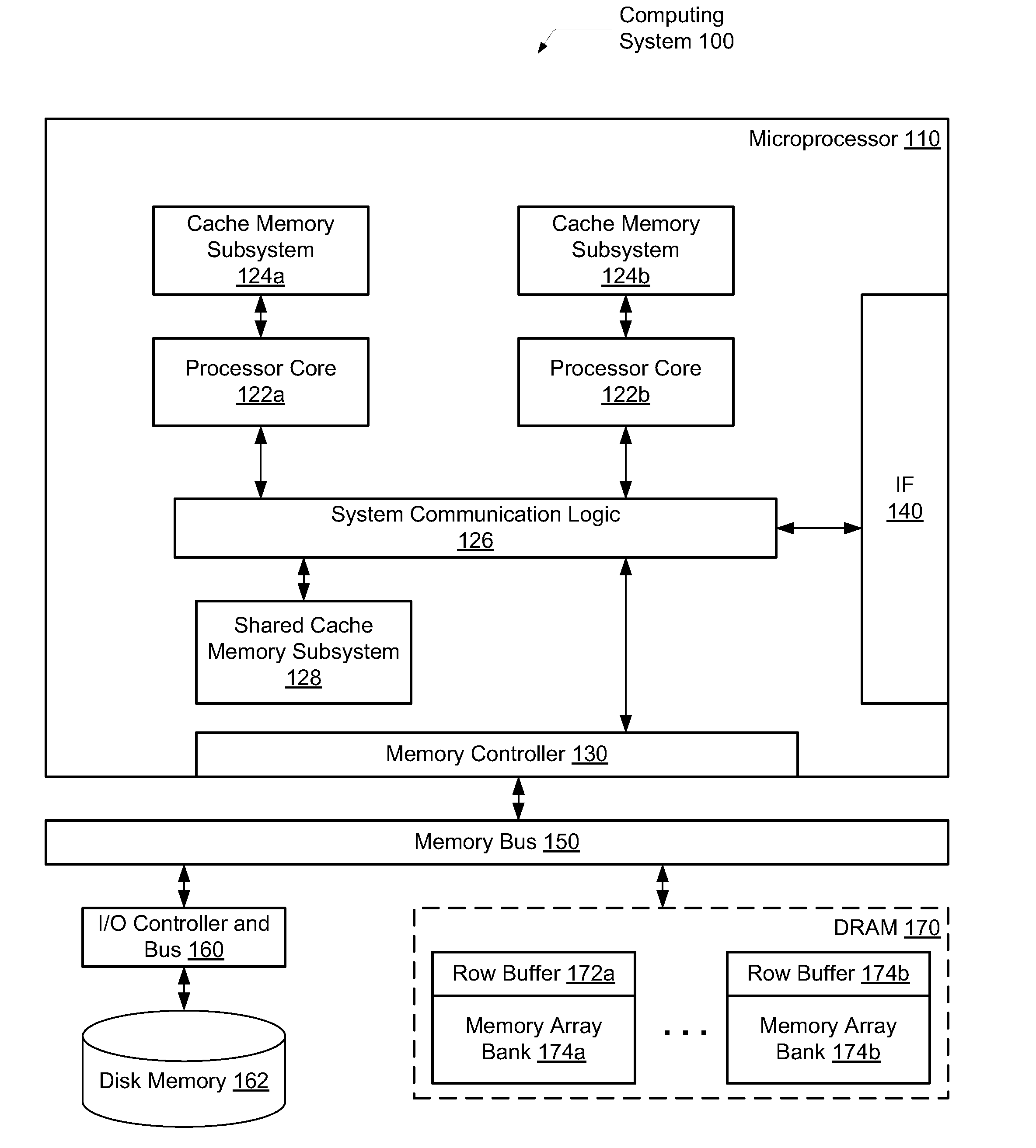

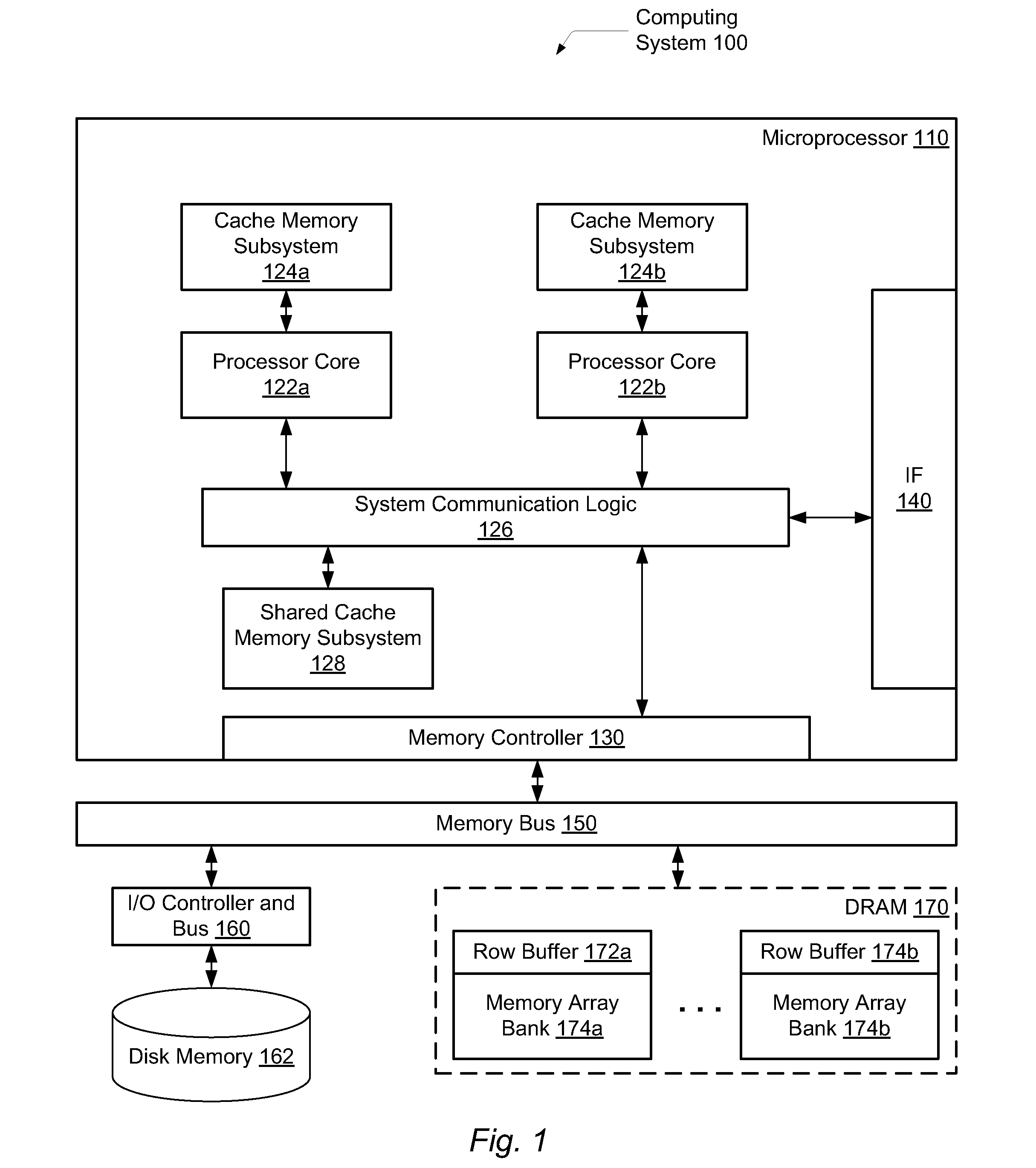

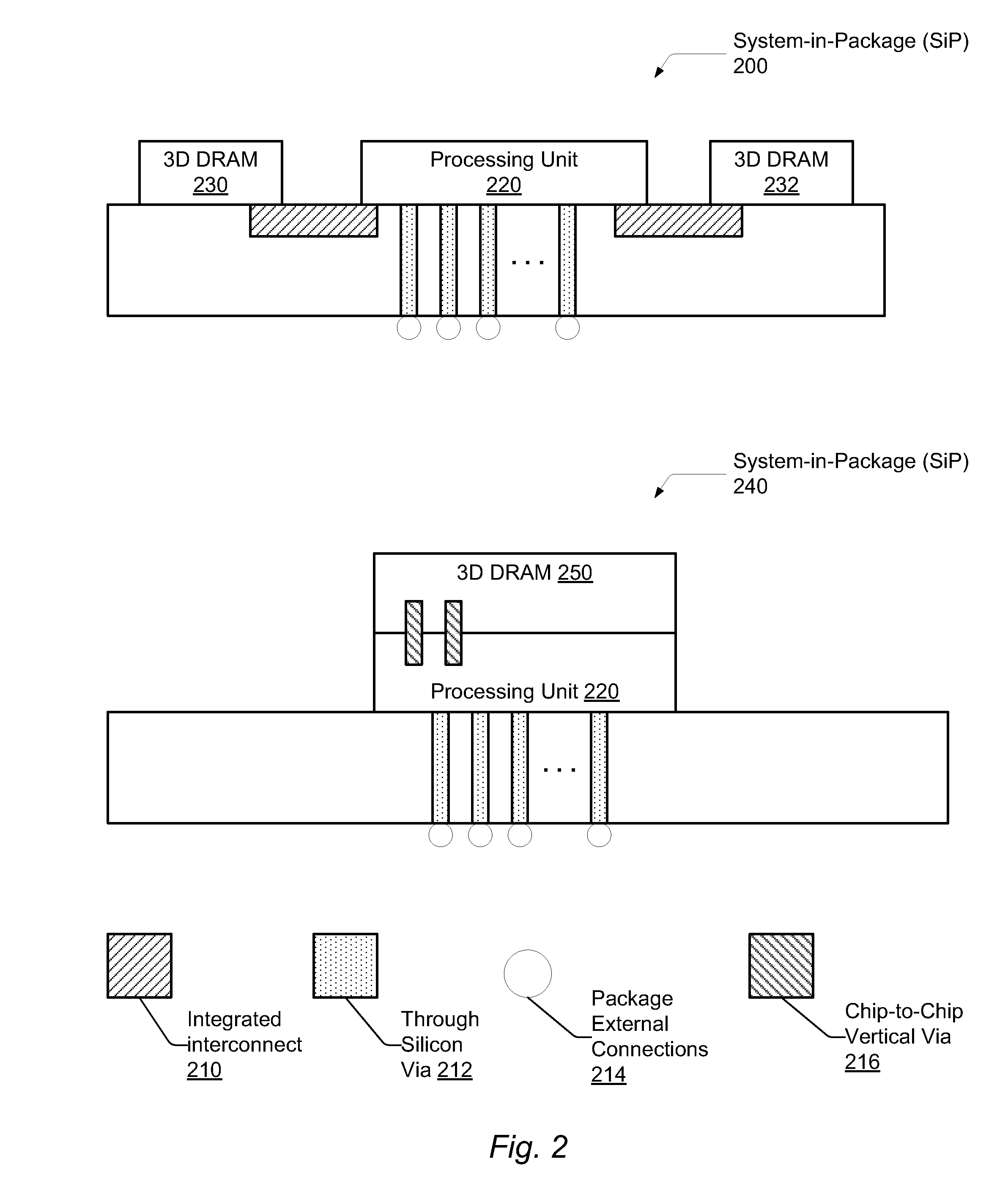

Dram cache with tags and data jointly stored in physical rows

ActiveUS20130138892A1Reduce latencyReduce power consumptionEnergy efficient ICTMemory adressing/allocation/relocationParallel computingData access

A system and method for efficient cache data access in a large row-based memory of a computing system. A computing system includes a processing unit and an integrated three-dimensional (3D) dynamic random access memory (DRAM). The processing unit uses the 3D DRAM as a cache. Each row of the multiple rows in the memory array banks of the 3D DRAM stores at least multiple cache tags and multiple corresponding cache lines indicated by the multiple cache tags. In response to receiving a memory request from the processing unit, the 3D DRAM performs a memory access according to the received memory request on a given cache line indicated by a cache tag within the received memory request. Rather than utilizing multiple DRAM transactions, a single, complex DRAM transaction may be used to reduce latency and power consumption.

Owner:ADVANCED MICRO DEVICES INC

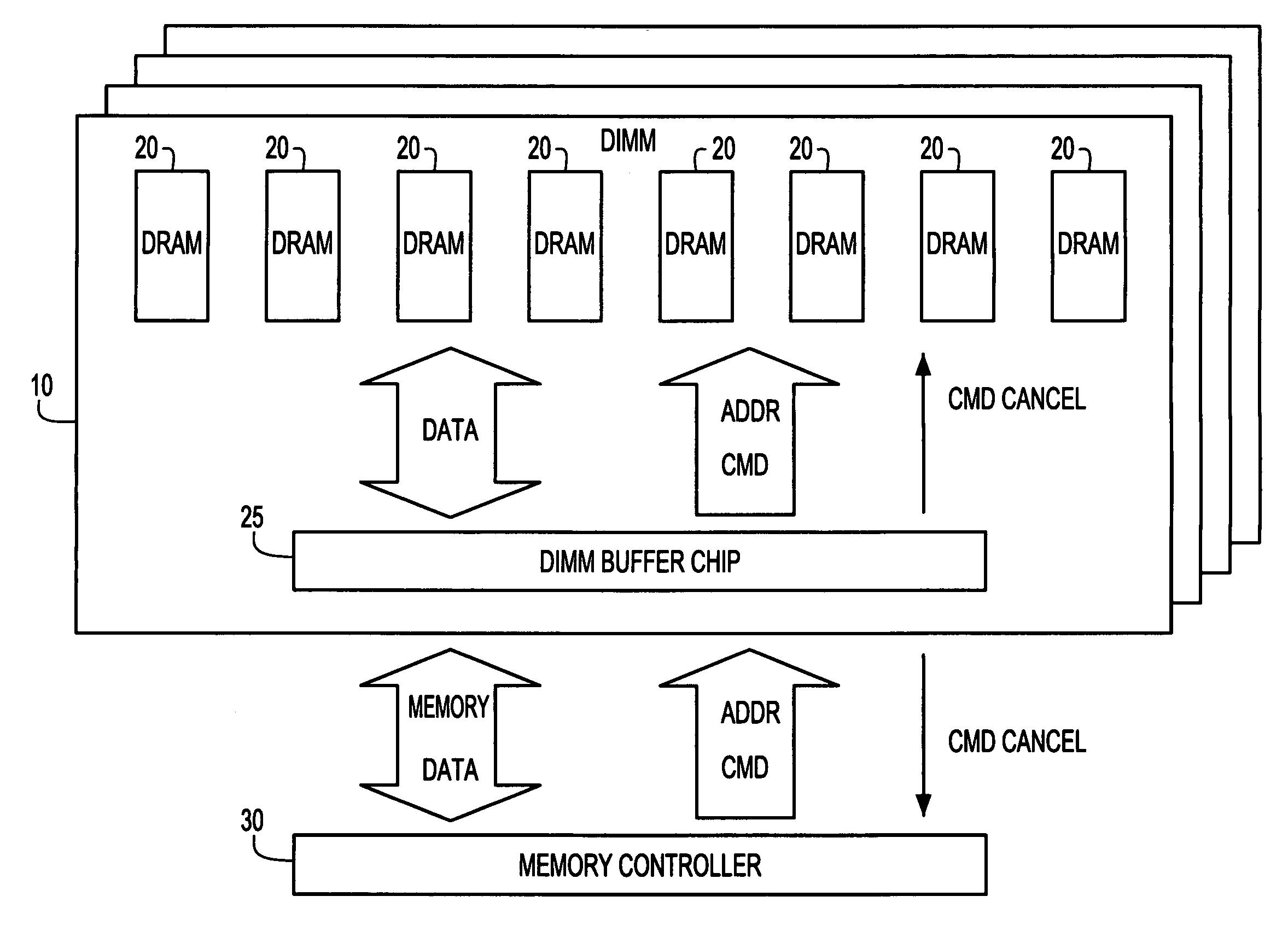

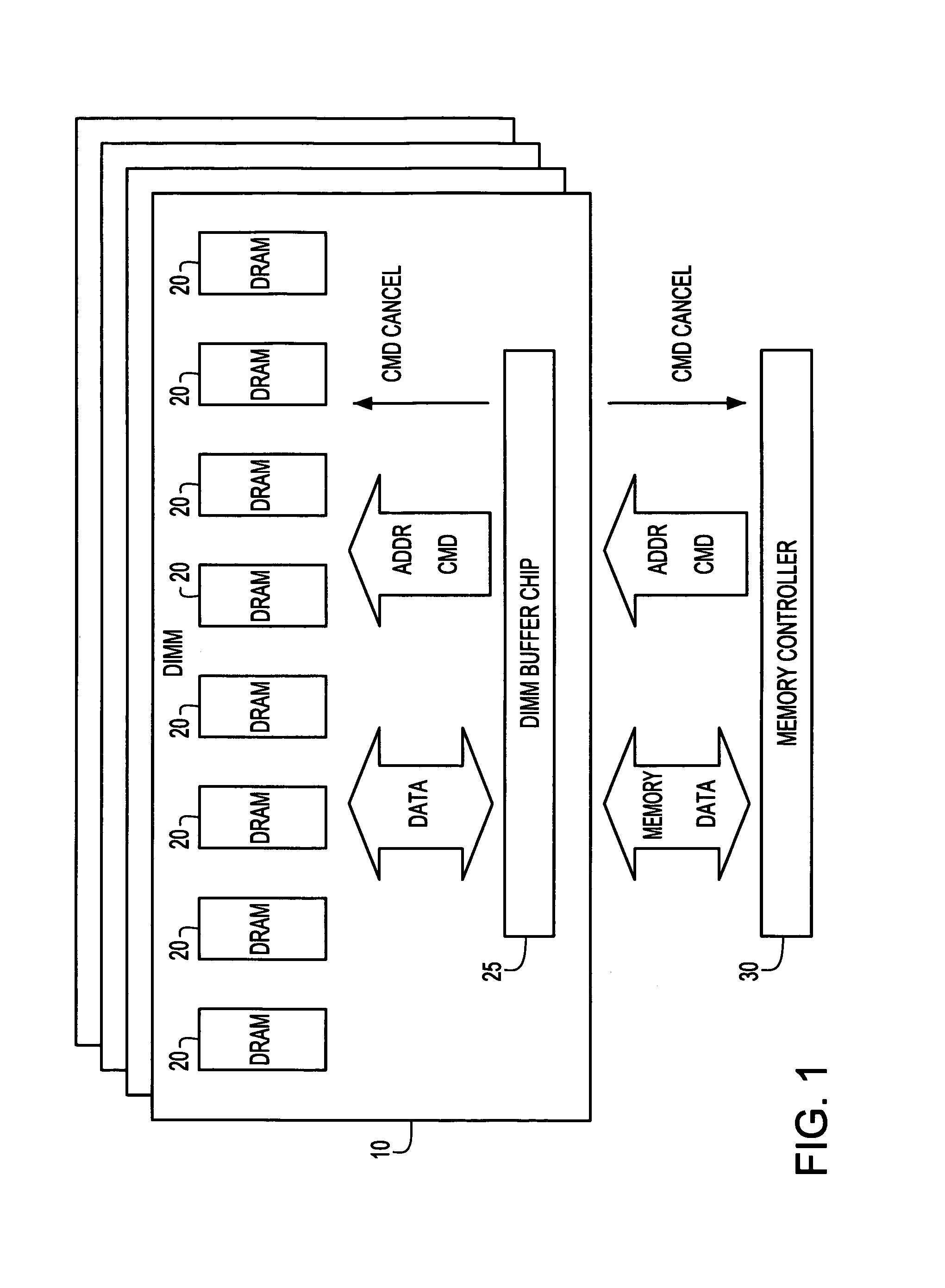

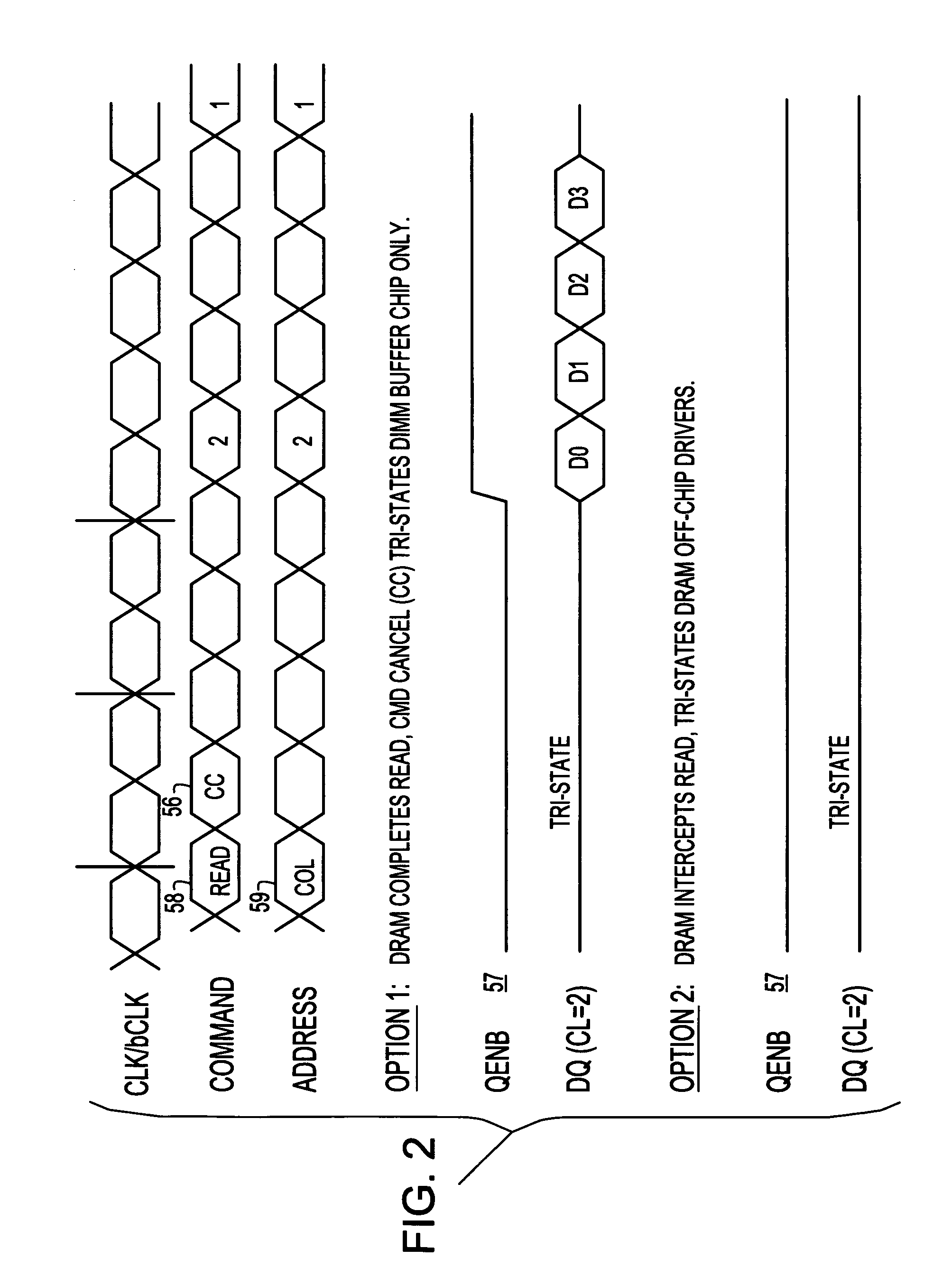

Method for performing a command cancel function in a DRAM

ActiveUS7480774B2Improve overall memory system reliabilityImprove system reliabilityOther printing matterMemory loss protectionClock rate8-bit

A method for performing a common cancel (CC) function on a dynamic random access memory (DRAM) semiconductor device to improve reliability and speed of a memory system. The CC function rakes advantage of the intrinsic delays associated wit memory read operations at high clock frequencies, and the increased write latency commensurate with increased read latencies where non-zero larencies for read and write operations are the norm by permitting address and command ECC structures to operate in parallel with the address and command re-drive circuitt The CC function is extendable to future DDR2 and DDR3 operating requirements in which latency of higher frequency modes will increase due to the shift from 2 bit pre-fetch to 4 and 8 bit pre-fetch architecture.

Owner:MARVELL ASIA PTE LTD