Patents

Literature

920results about How to "Improve system reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

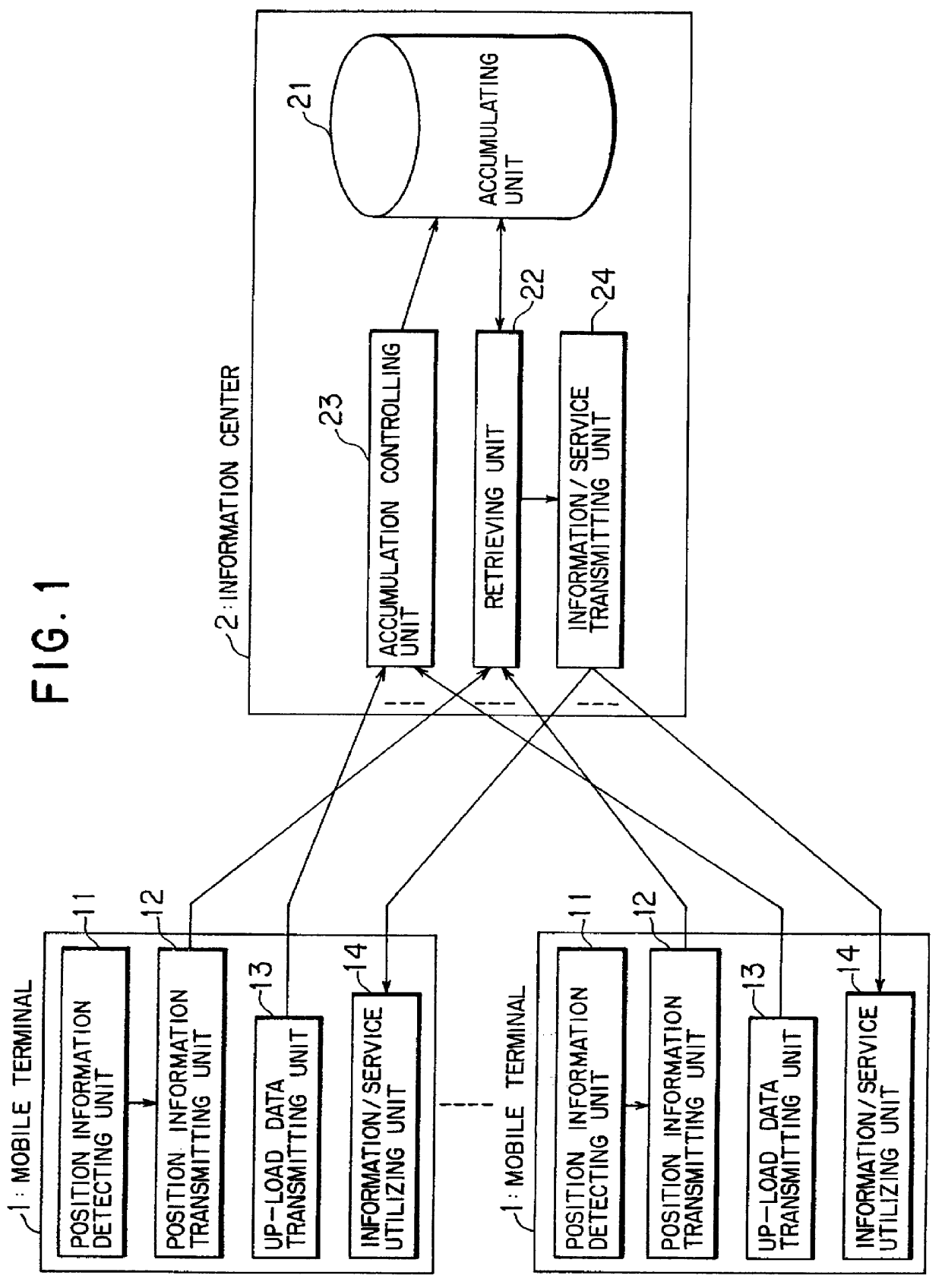

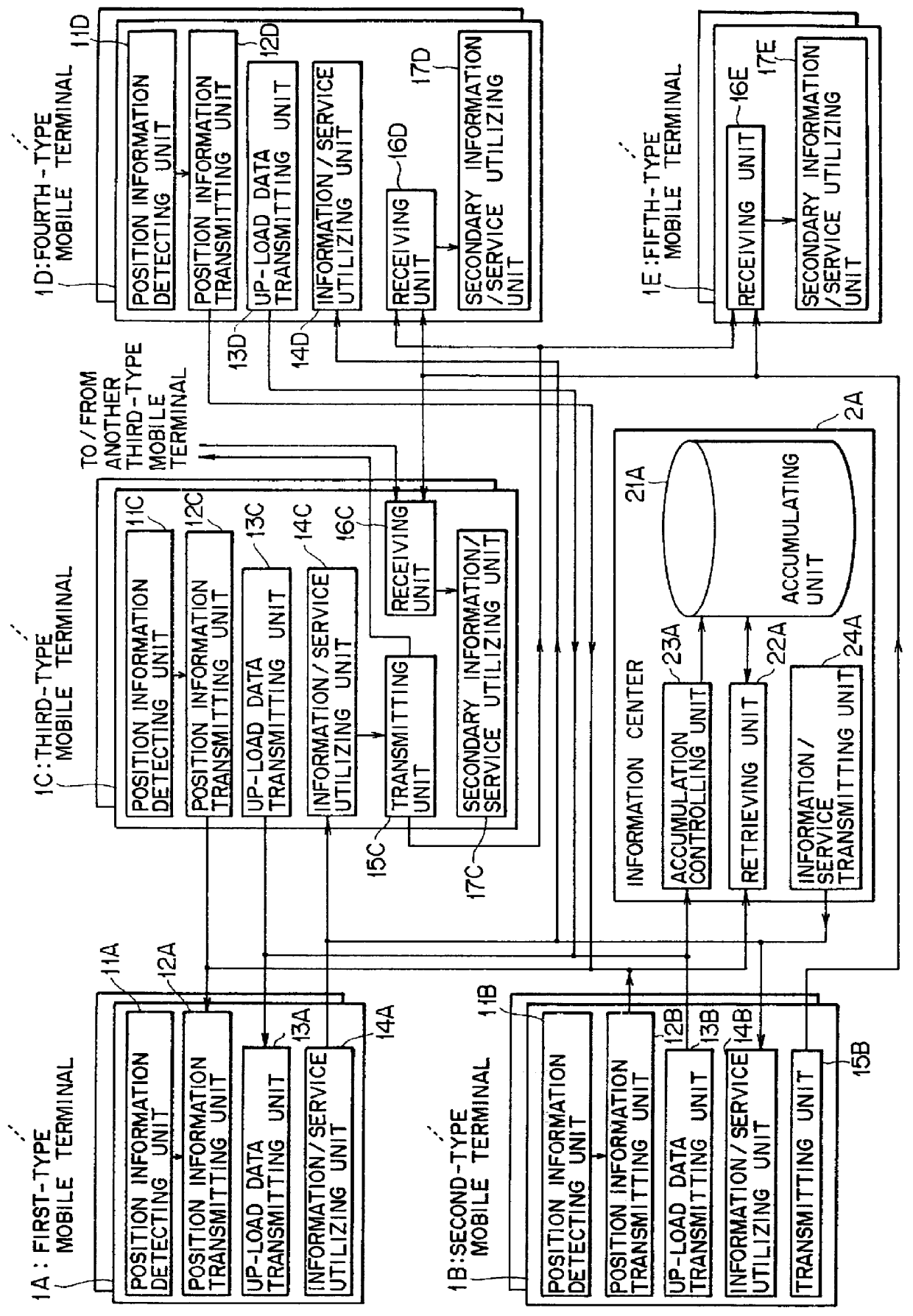

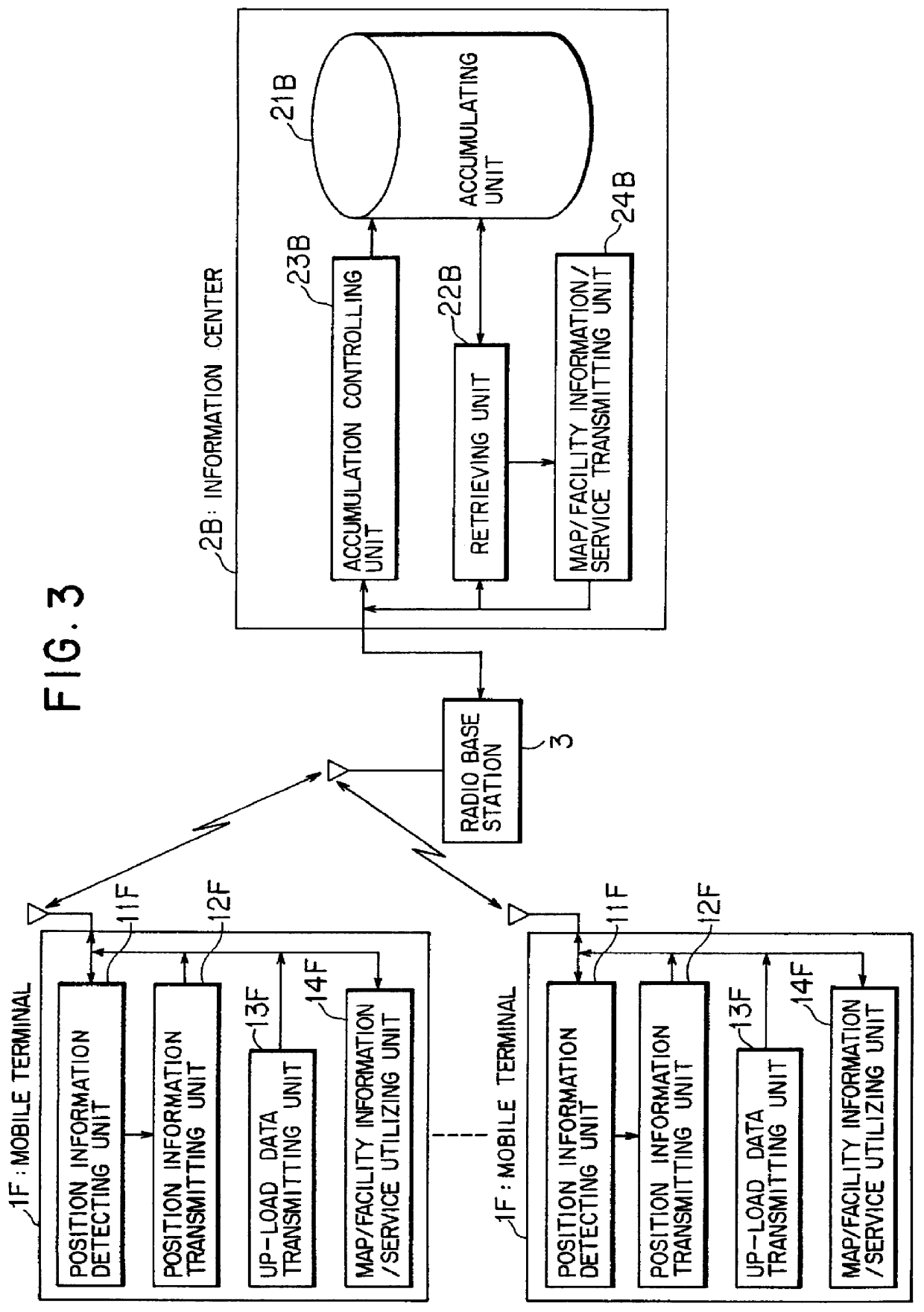

Mobile communication system, and a mobile terminal, an information center and a storage medium used therein

InactiveUS6115611AEasy to operateImprove utilizationInstruments for road network navigationRoad vehicles traffic controlTelecommunicationsComputer terminal

In a mobile communicating system, a mobile terminal has a position information detecting unit for detecting position information, a position information transmitting unit for transmitting the position information to an information center, an up-load data transmitting unit for transmitting up-load data to the information center and an information / service utilizing unit for utilizing information / service from the information center, whereas the information center has an accumulating unit for accumulating information / services, a retrieving unit for receiving the position information from the mobile terminal to retrieve the information / services in the accumulating unit, an accumulation controlling unit for accumulating the up-load data in the accumulating unit, and an information / service transmitting unit for taking out the information / service retrieved by the retrieving unit from the accumulating unit and transmitting it to the mobile terminal, thereby providing not only map information showing the current position of the mobile terminal but also information of facilities on the map to the mobile terminal.

Owner:FUJITSU LTD

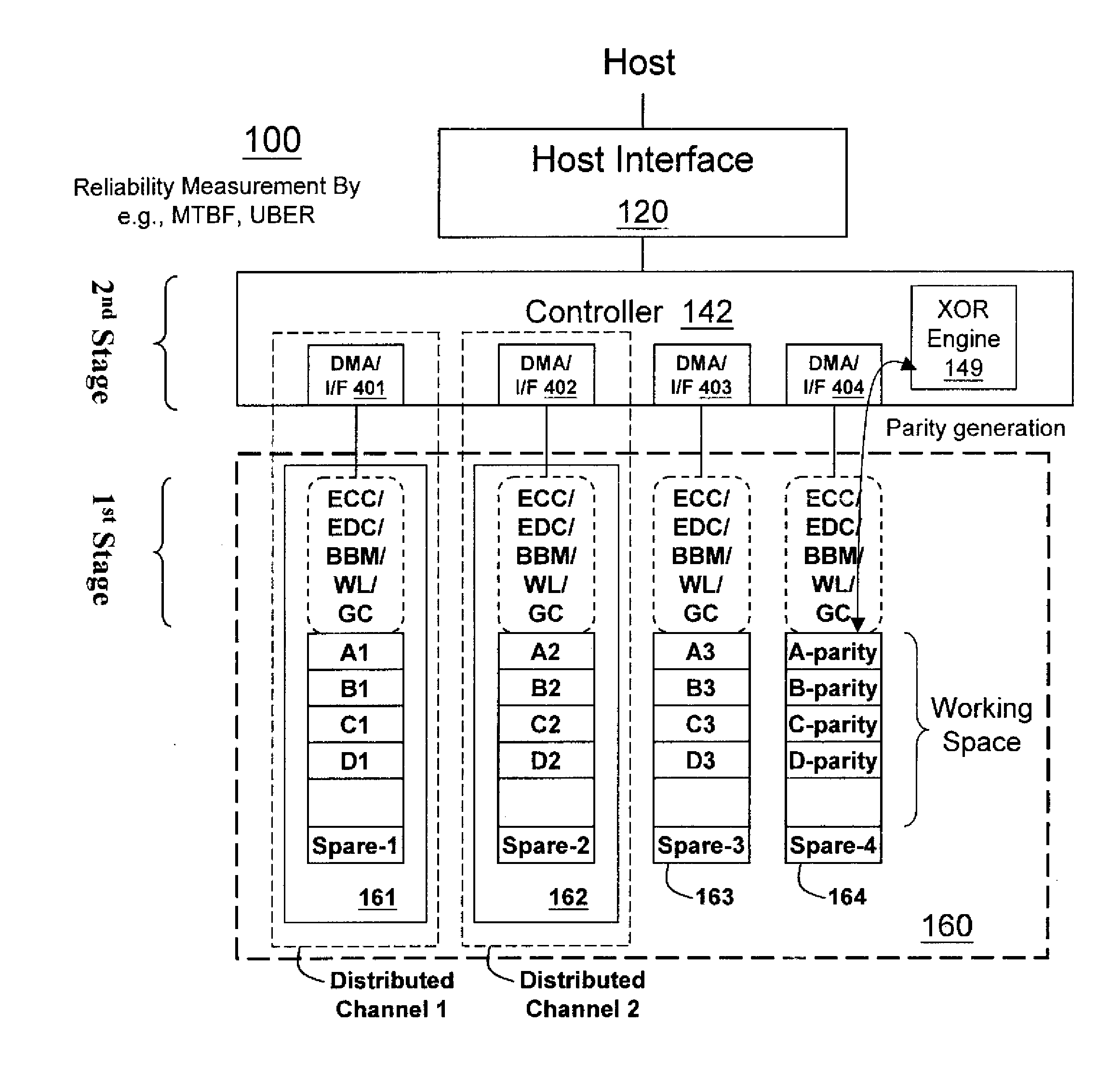

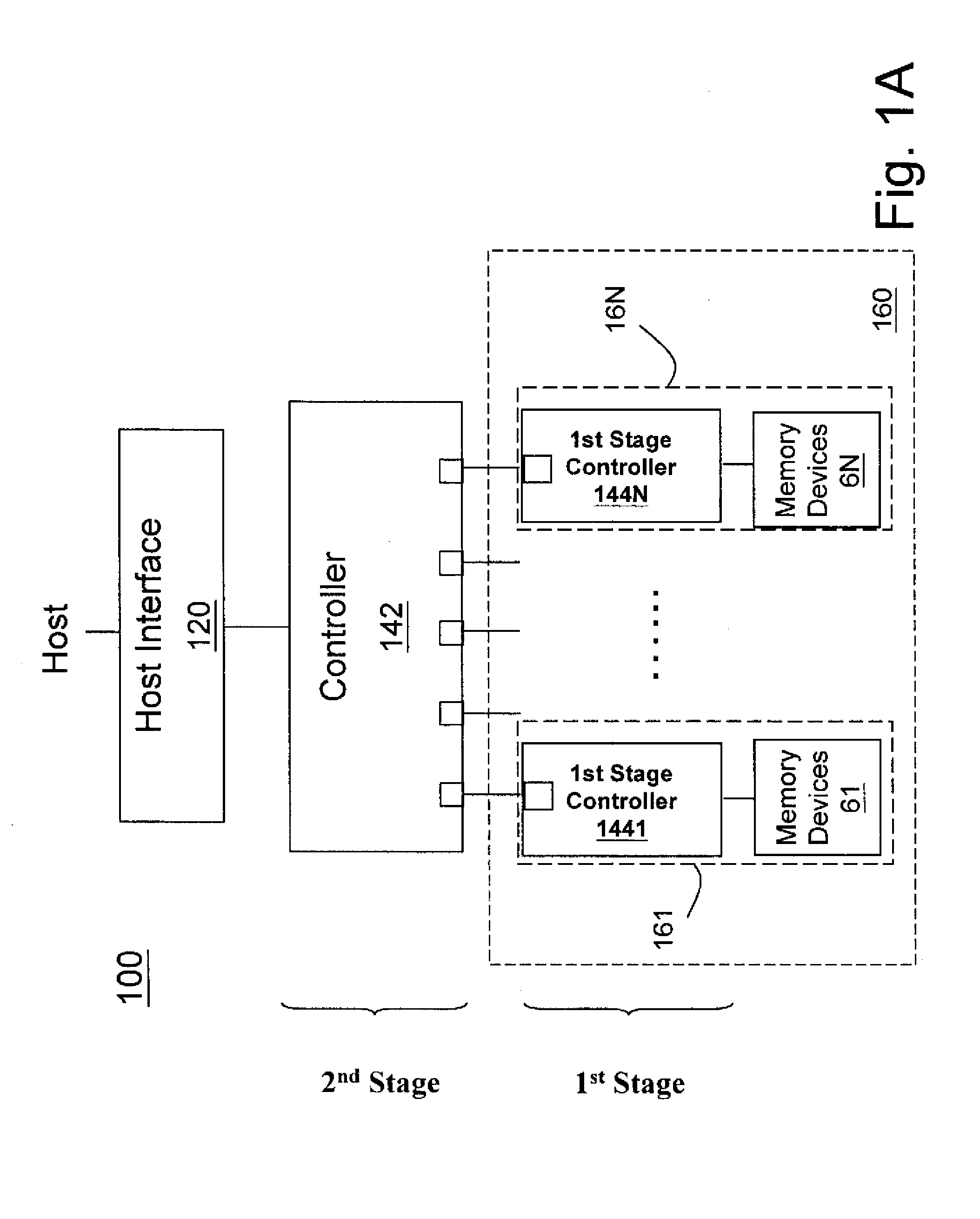

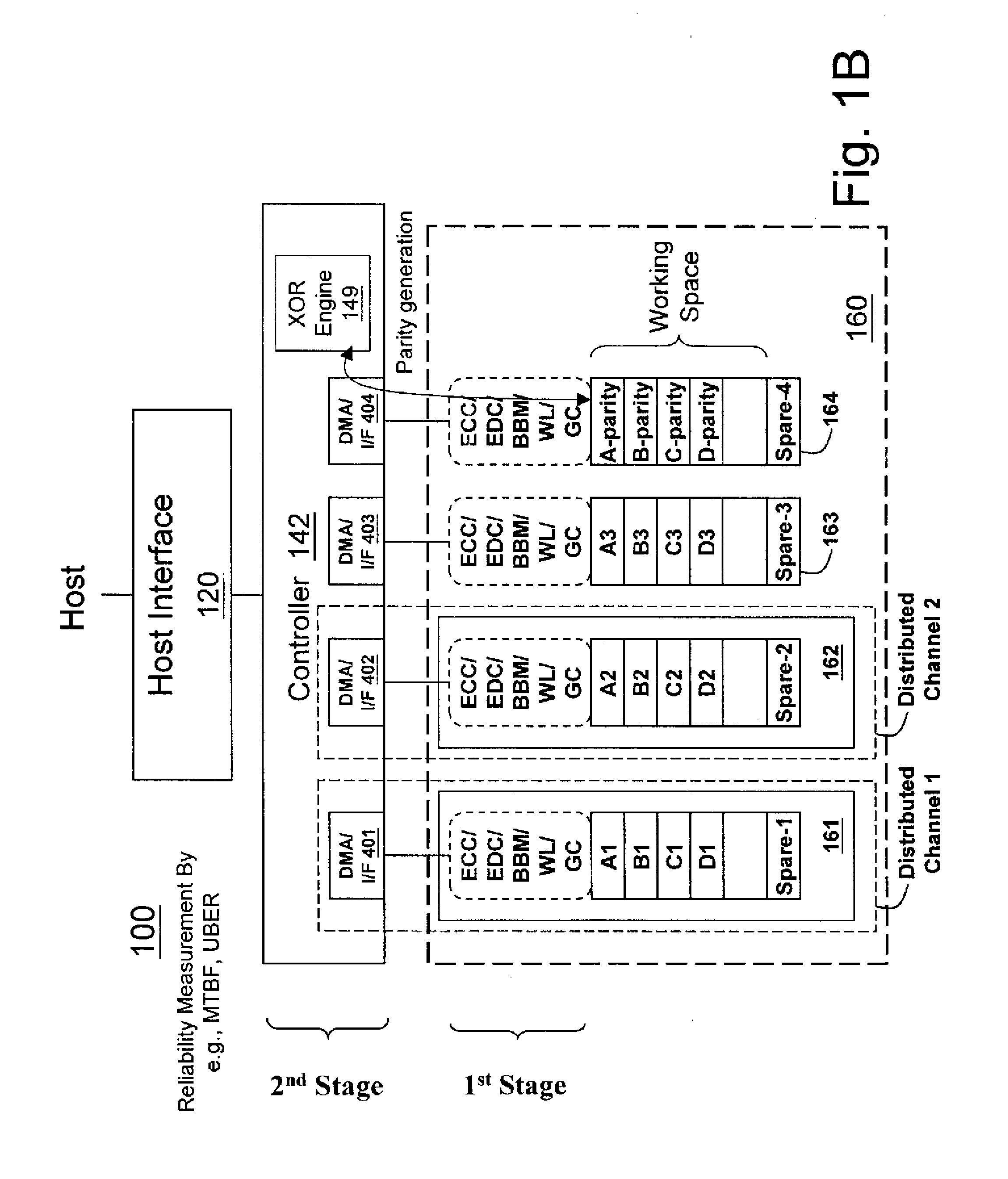

Non-volatile memory data storage system with reliability management

InactiveUS20100017650A1Improve reliabilityReliable managementMemory loss protectionMemory adressing/allocation/relocationRAIDData recovery

A non-volatile memory data storage system, comprising: a host interface for communicating with an external host; a main storage including a first plurality of flash memory devices, wherein each memory device includes a second plurality of memory blocks, and a third plurality of first stage controllers coupled to the first plurality of flash memory devices; and a second stage controller coupled to the host interface and the third plurality of first stage controller through an internal interface, the second stage controller being configured to perform RAID operation for data recovery according to at least one parity.

Owner:NANOSTAR CORP

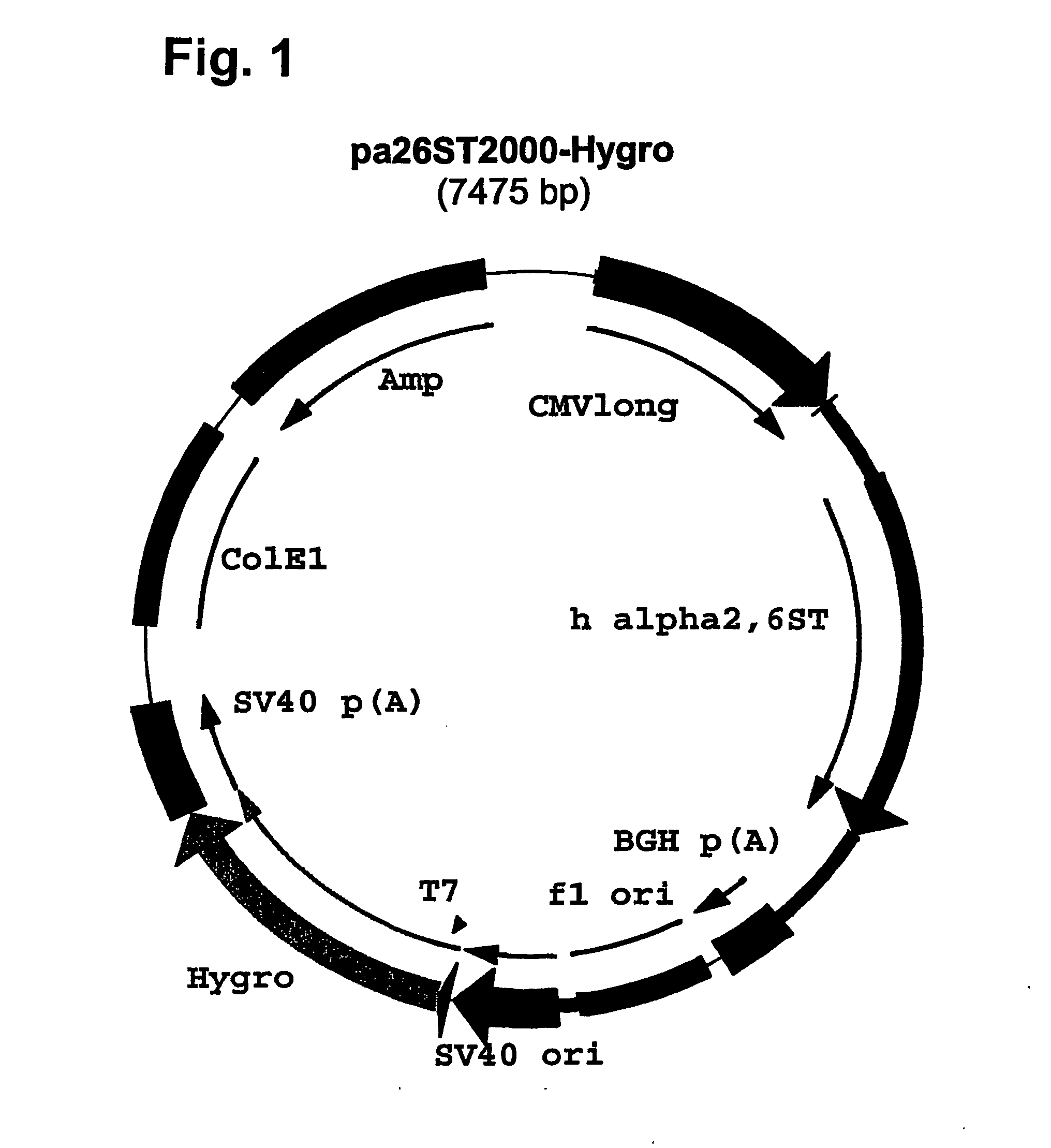

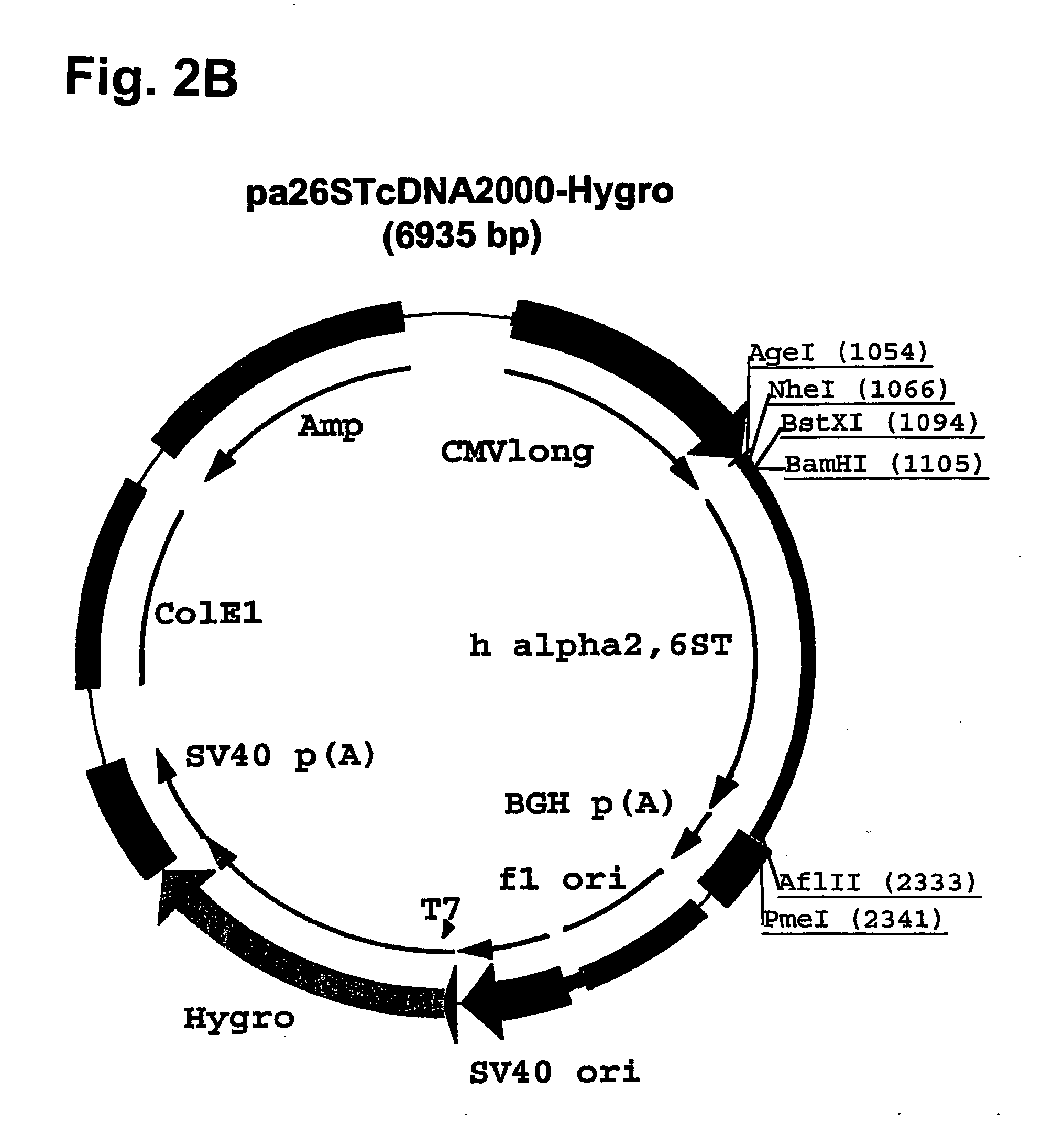

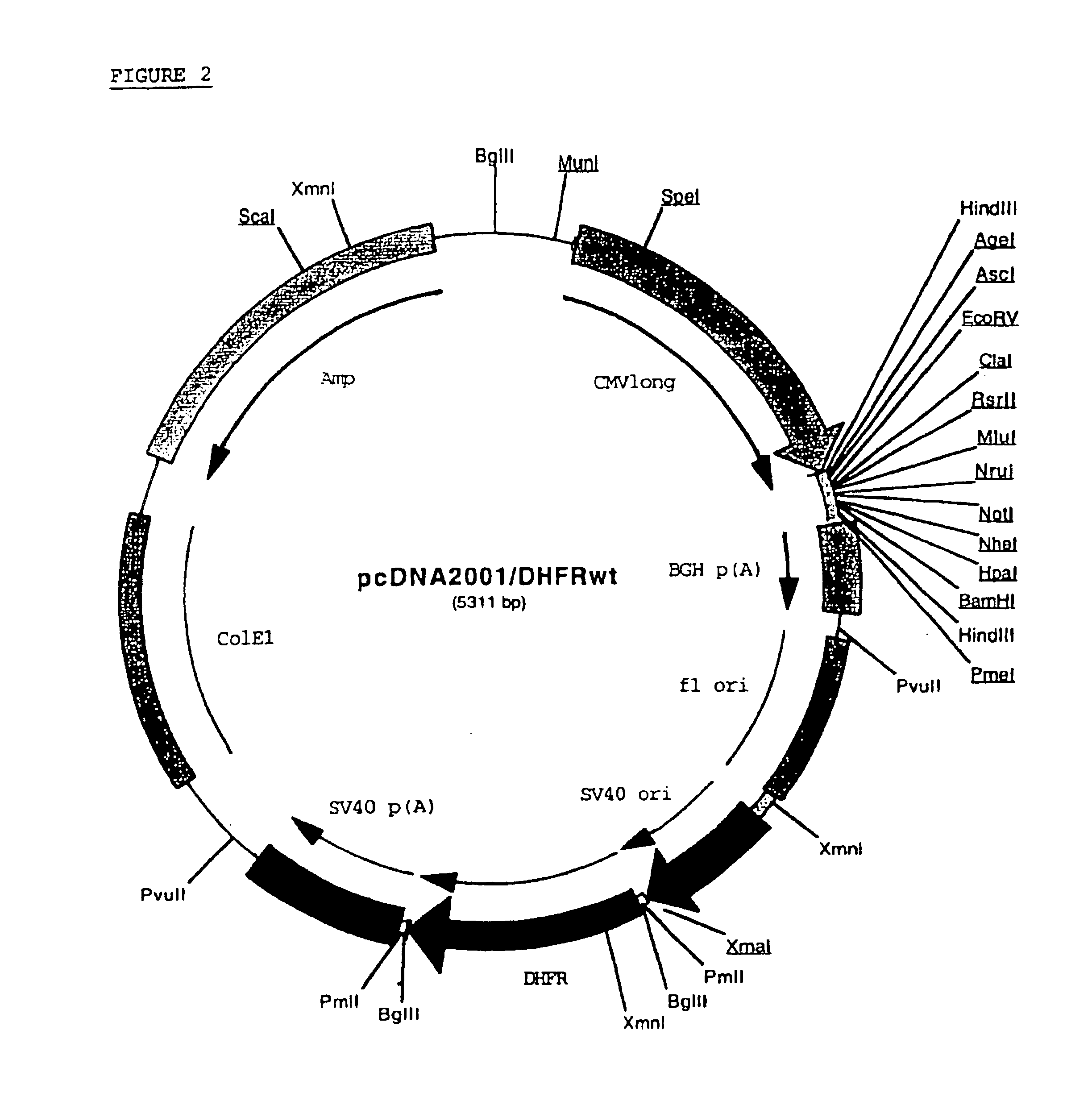

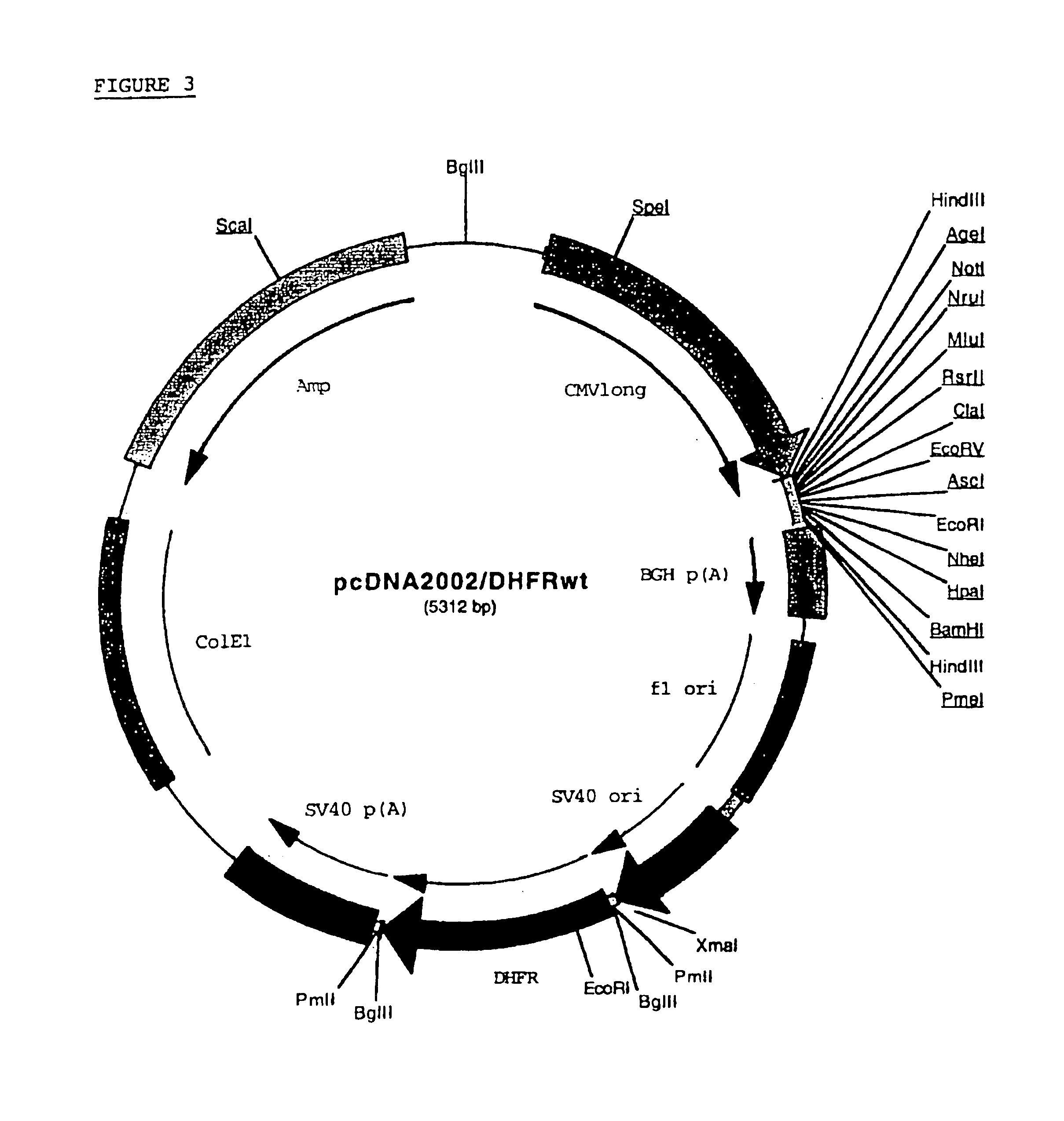

Compositions of erythropoietin isoforms comprising Lewis-X structures and high sialic acid content

InactiveUS20050181359A1Presence can be undesiredImprove system reliabilityOrganic active ingredientsBiocideHeterologousE1A Protein

Disclosed are immortalized human embryonic retina cells, having a nucleic acid sequence encoding an adenoviral E1A protein integrated into the genome of the cells, and further comprising a nucleic acid sequence encoding an enzyme involved in post-translational modification of proteins, such as a sialyltransferase, wherein said nucleic acid sequence encoding the enzyme involved in post-translational modification of proteins is under control of a heterologous promoter. Methods for producing recombinant proteins from such cells and obtaining such recombinant proteins having increased sialylation are provided as are novel compositions of isoforms of erythropoietin .

Owner:JANSSEN VACCINES & PREVENTION BV

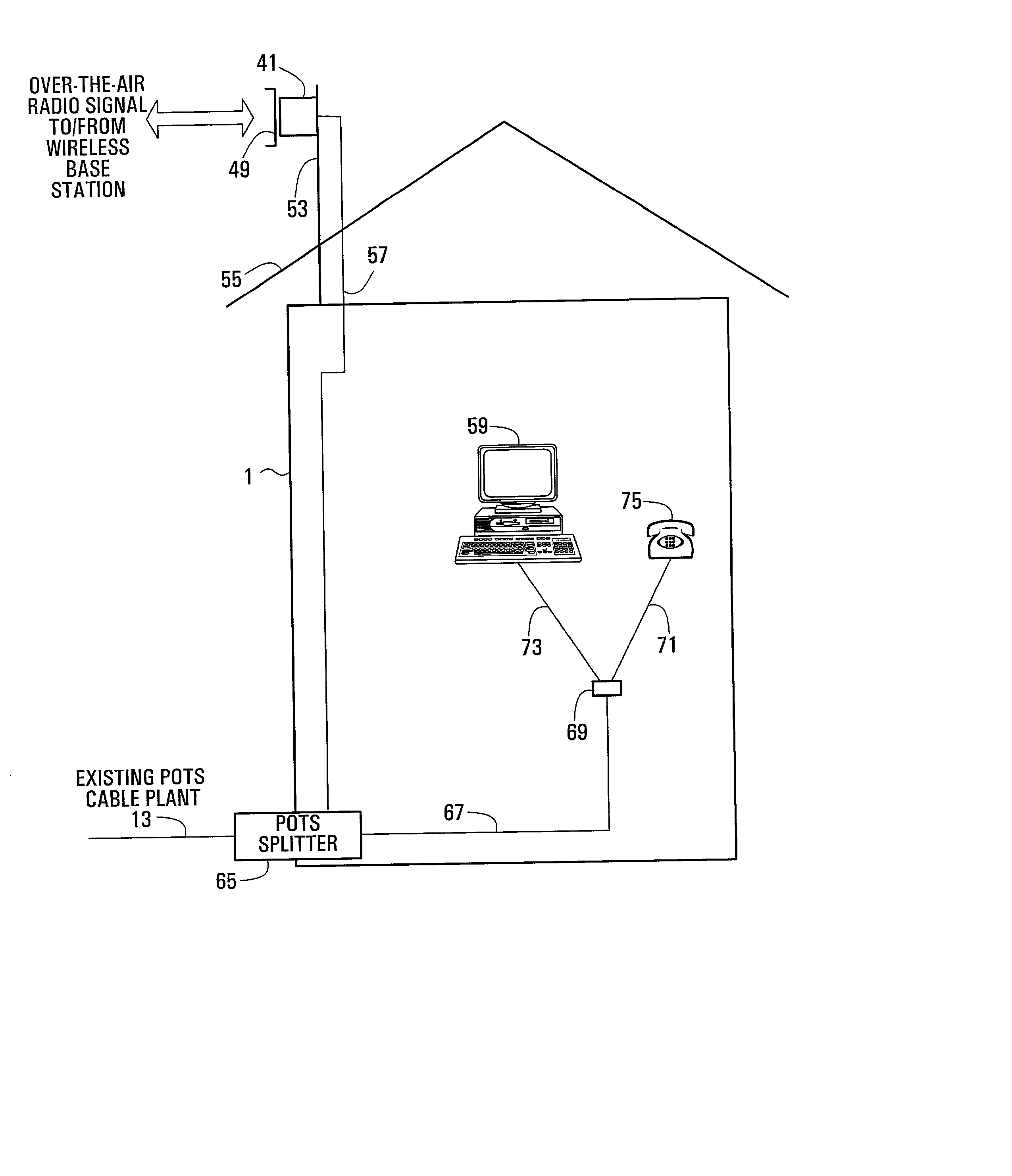

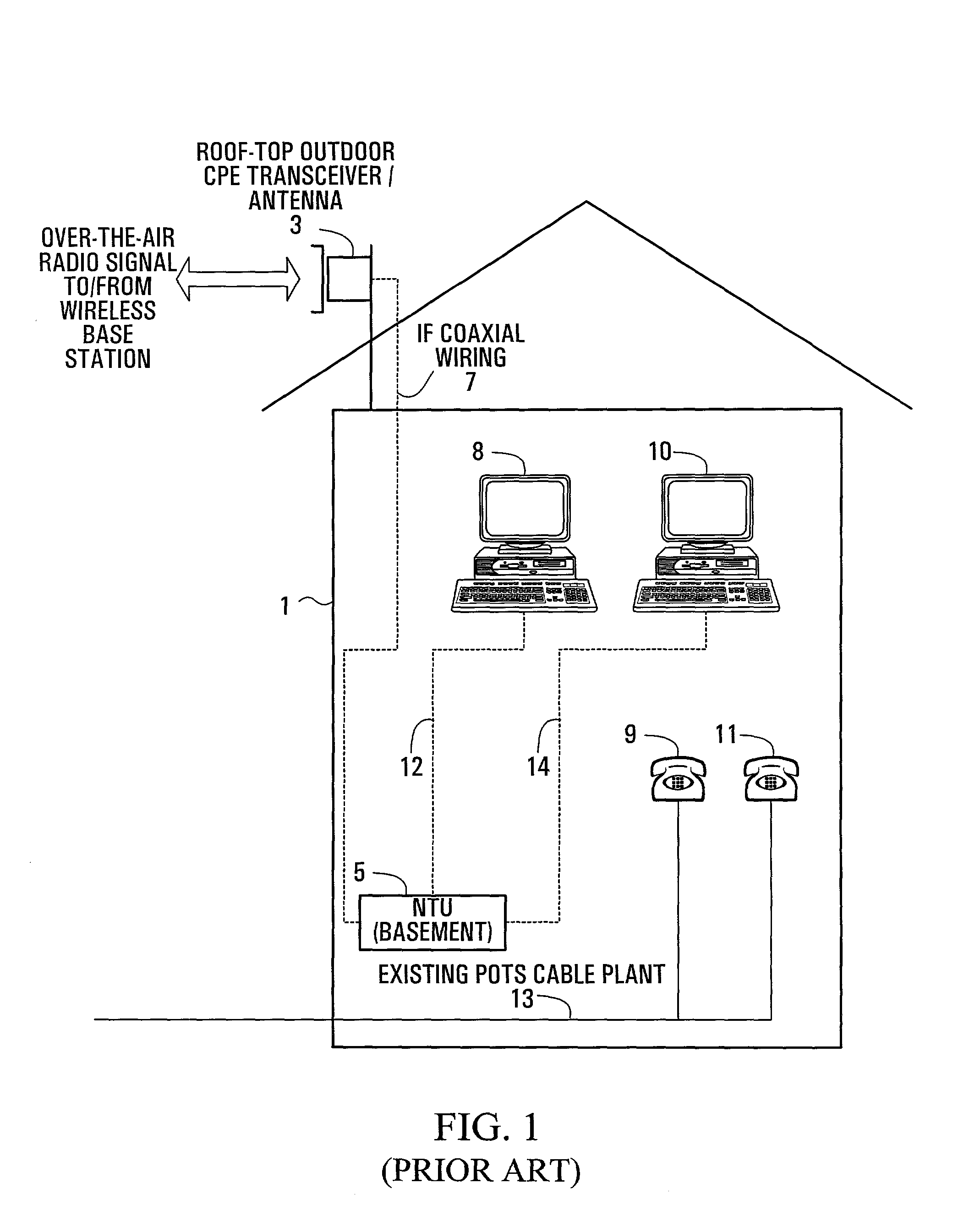

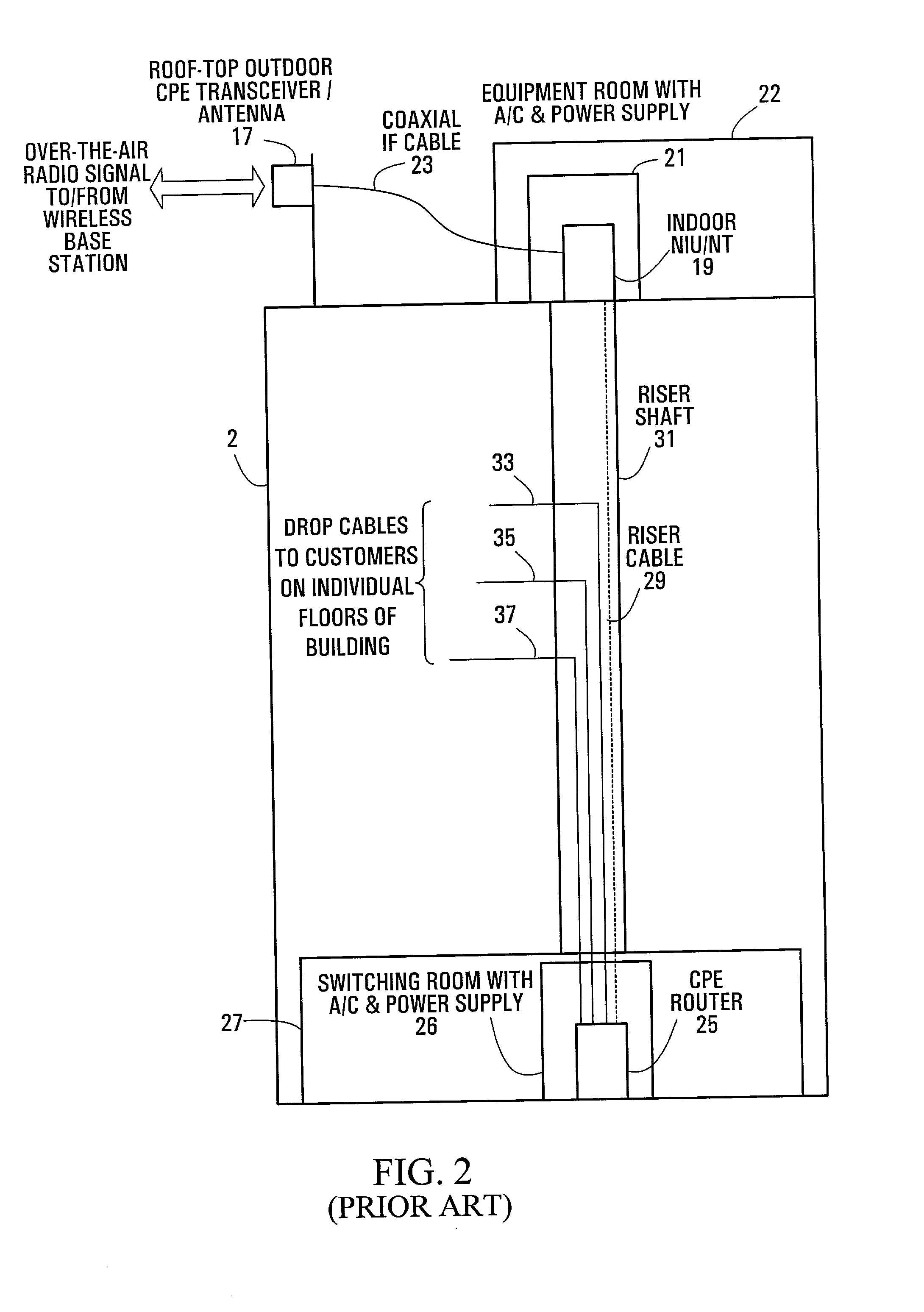

Transceiver for fixed wireless access network applications

InactiveUS20020128009A1Low costConveniently mountedRadio/inductive link selection arrangementsWireless commuication servicesTransceiverWireless transceiver

A combined wireless transceiver and signal conversion unit comprises a radio receiver for receiving a wireless radio signal, and a converter for converting the signal into a form having a communications protocol supported by a communications port of a user digital device. An output device is provided for transmitting the converted signal to a user digital device via a wireline or other suitable medium for carrying the converted signal. The unit includes an input device for receiving a communications signal from the communication port of a user digital device via a wireline or other suitable signal transmission medium, and a transmitter for converting the received signal to a form for wireless transmission.

Owner:DRAGONWAVE

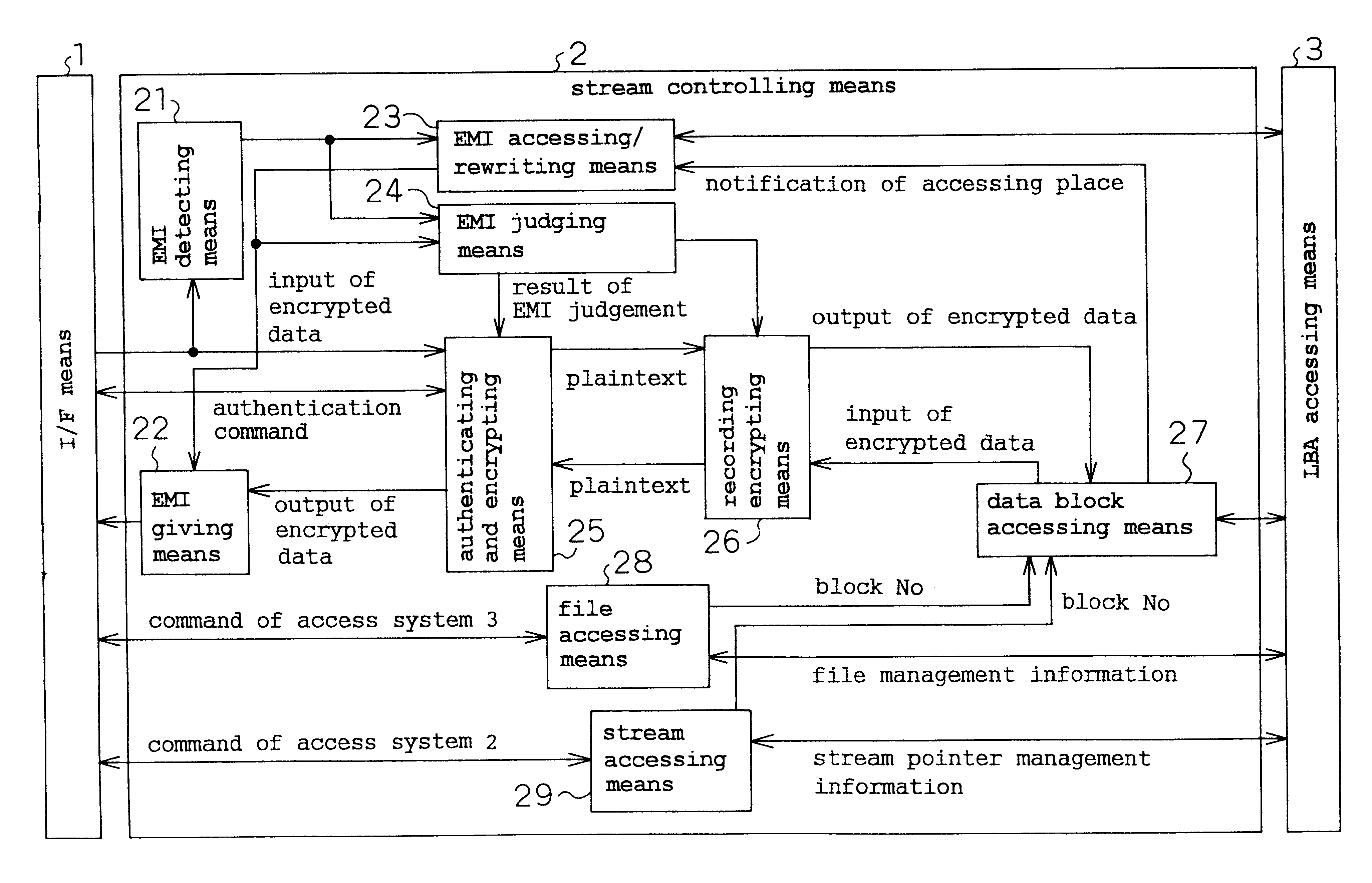

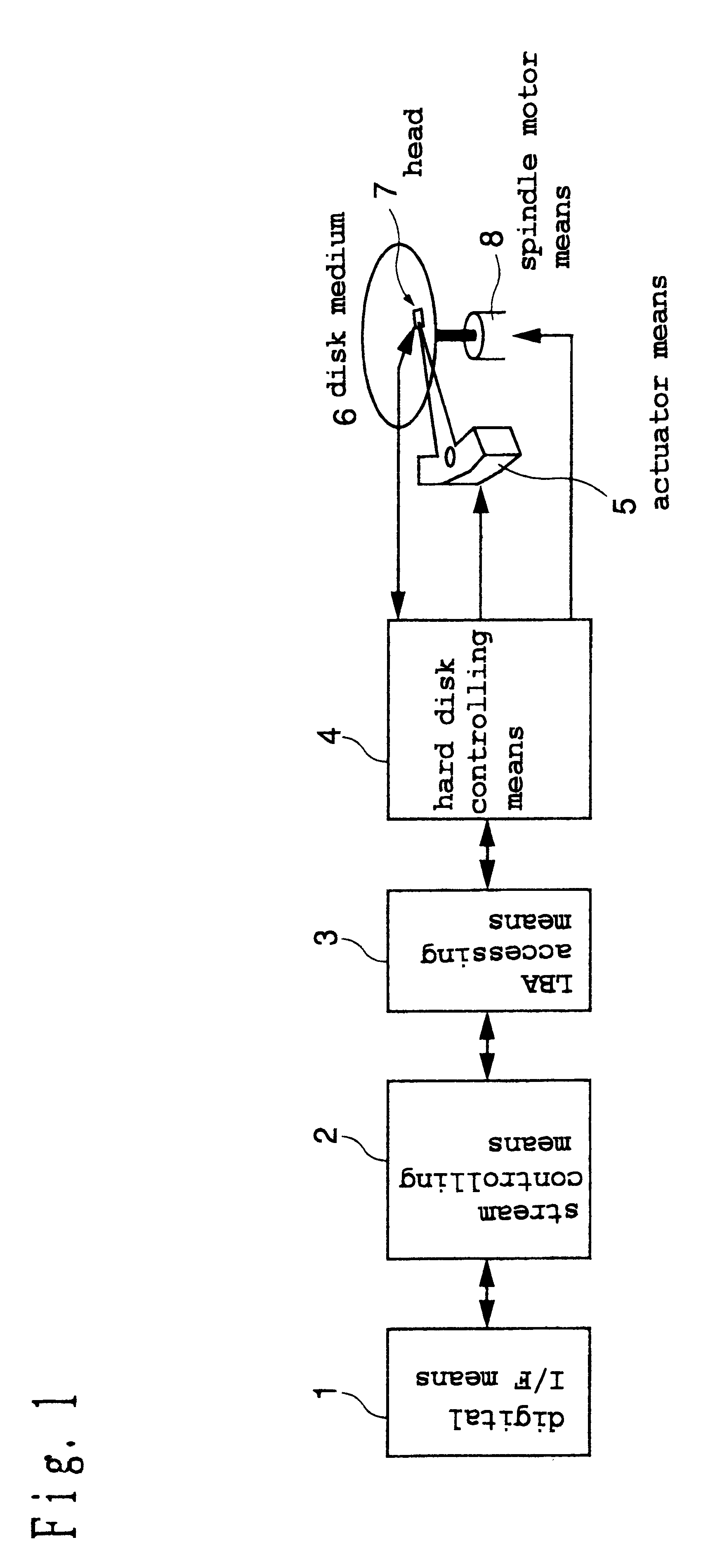

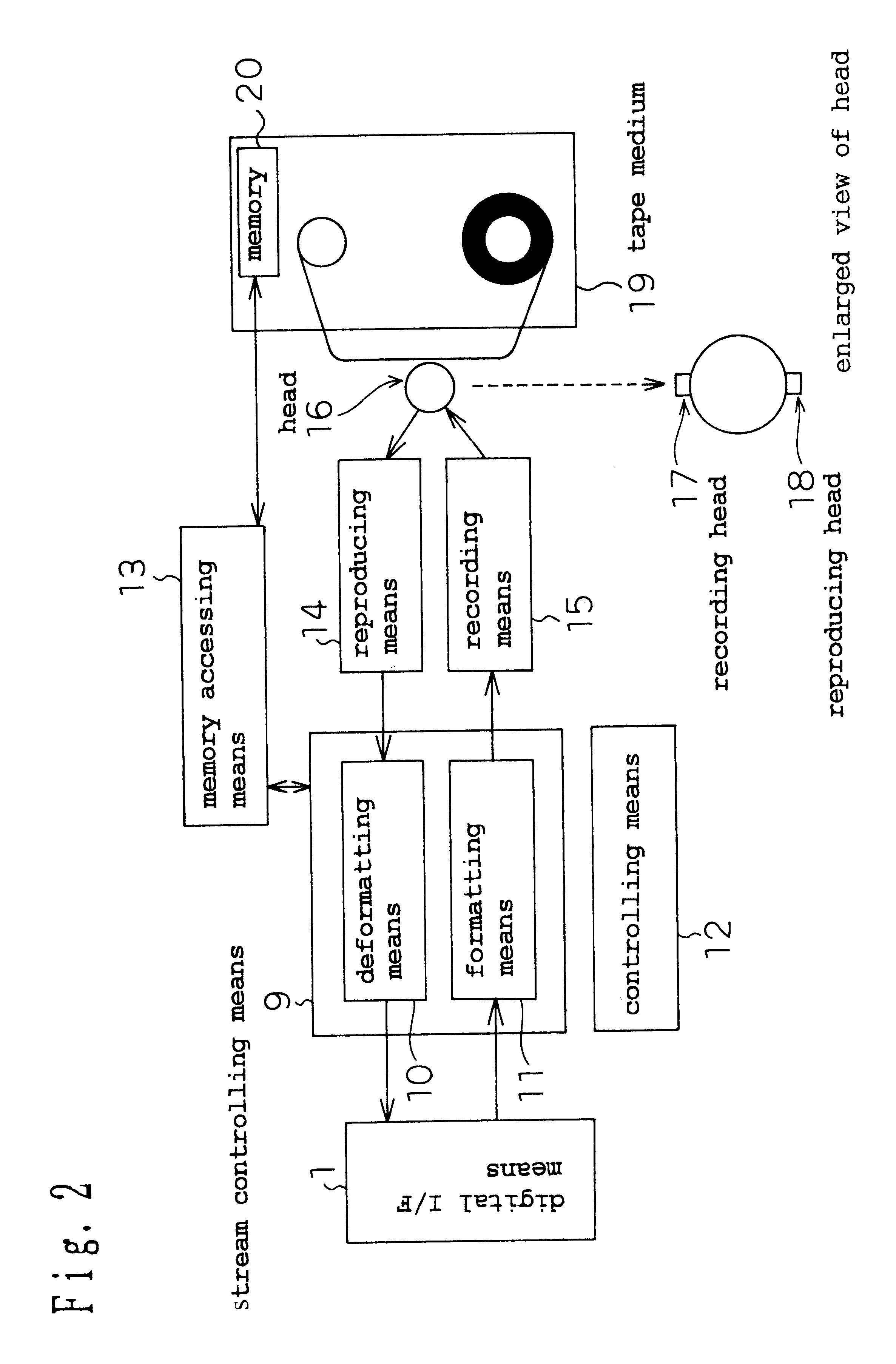

Recording/reproducing apparatus, program recorded medium, recorded medium, cache device, and transmitter

InactiveUS6584552B1Improve system reliabilityImprove reliabilityTelevision system detailsUnauthorized memory use protectionComputer hardwareTransmitter

A recording and reproducing apparatus is characterized in that said apparatus has: inputting means for receiving a packet data which is based on IEEE 1394, and in which signal information for indicating copy right information of an AV data (hereinafter, referred to as EMI) is provided in a header of a packet according to IEEE 1394; and recording and reproducing means for recording and reproducing an AV data and the EMI which are held in the packet data received by said inputting means. Four kinds of EMI are used, and, when an AV data indicating allowance "copy one generation" among them is to be recorded, said recording and reproducing means performs recording while rewriting the EMI to EMI indicating "no more copy."

Owner:INTERTRUST TECH CORP

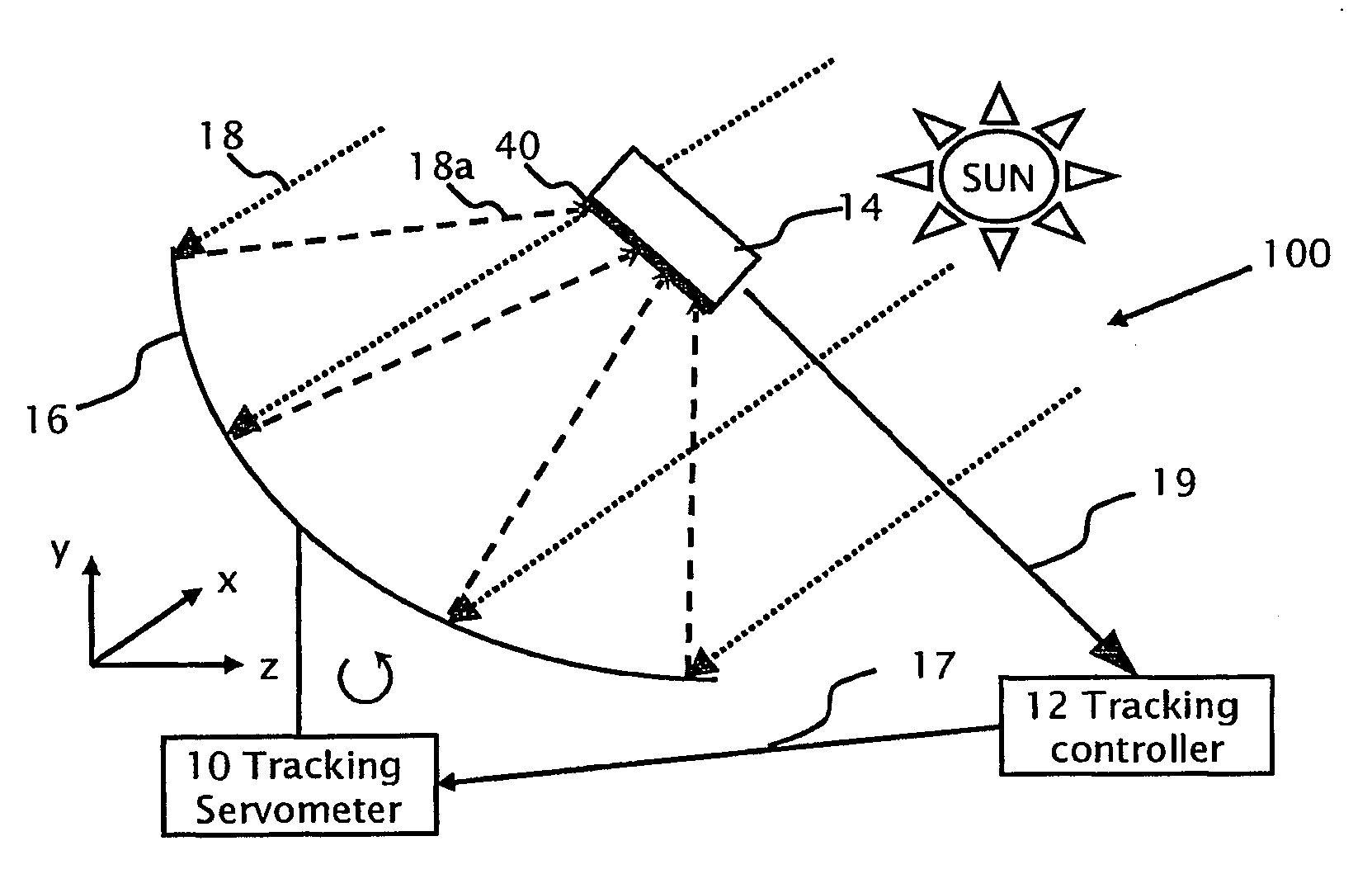

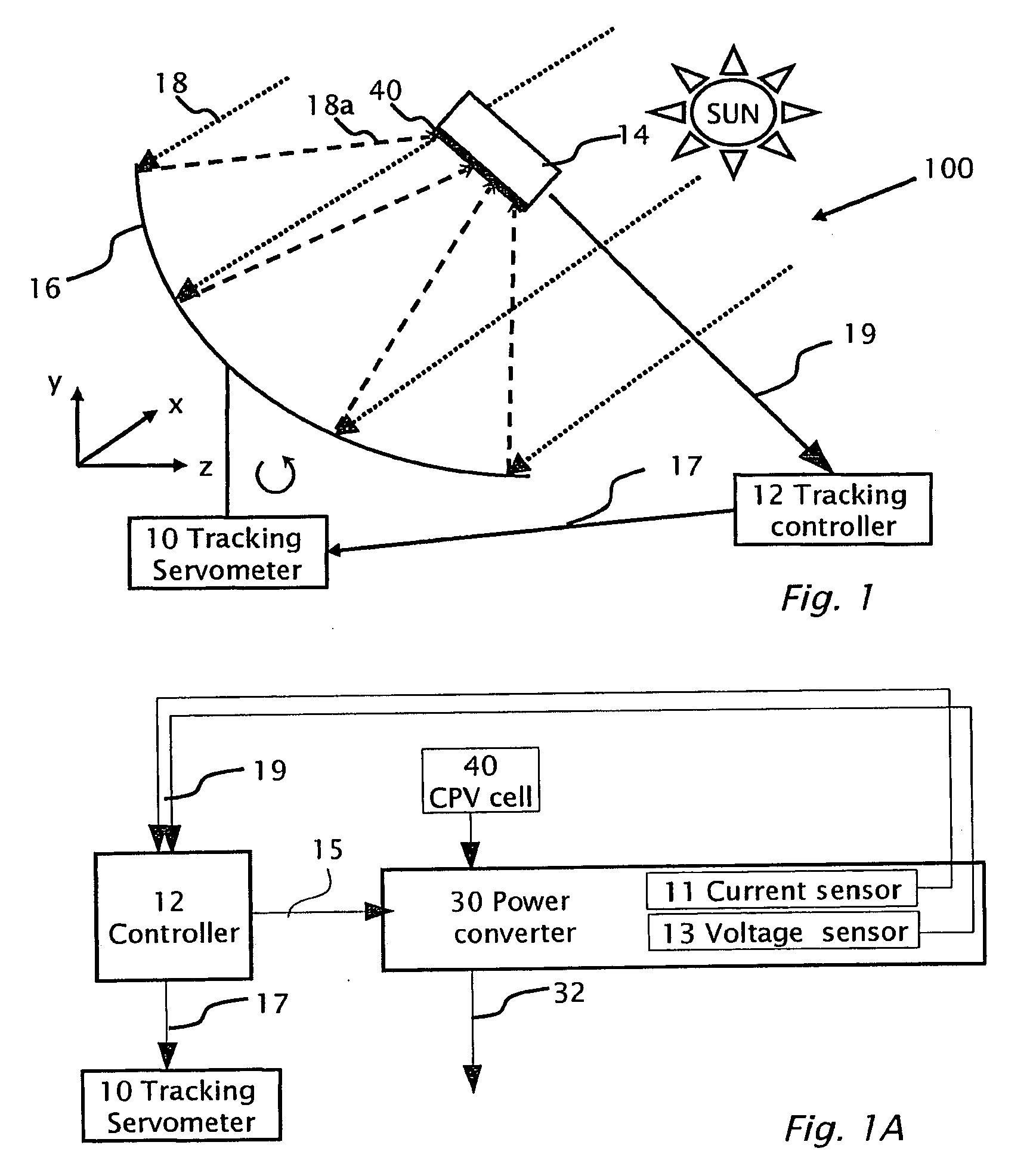

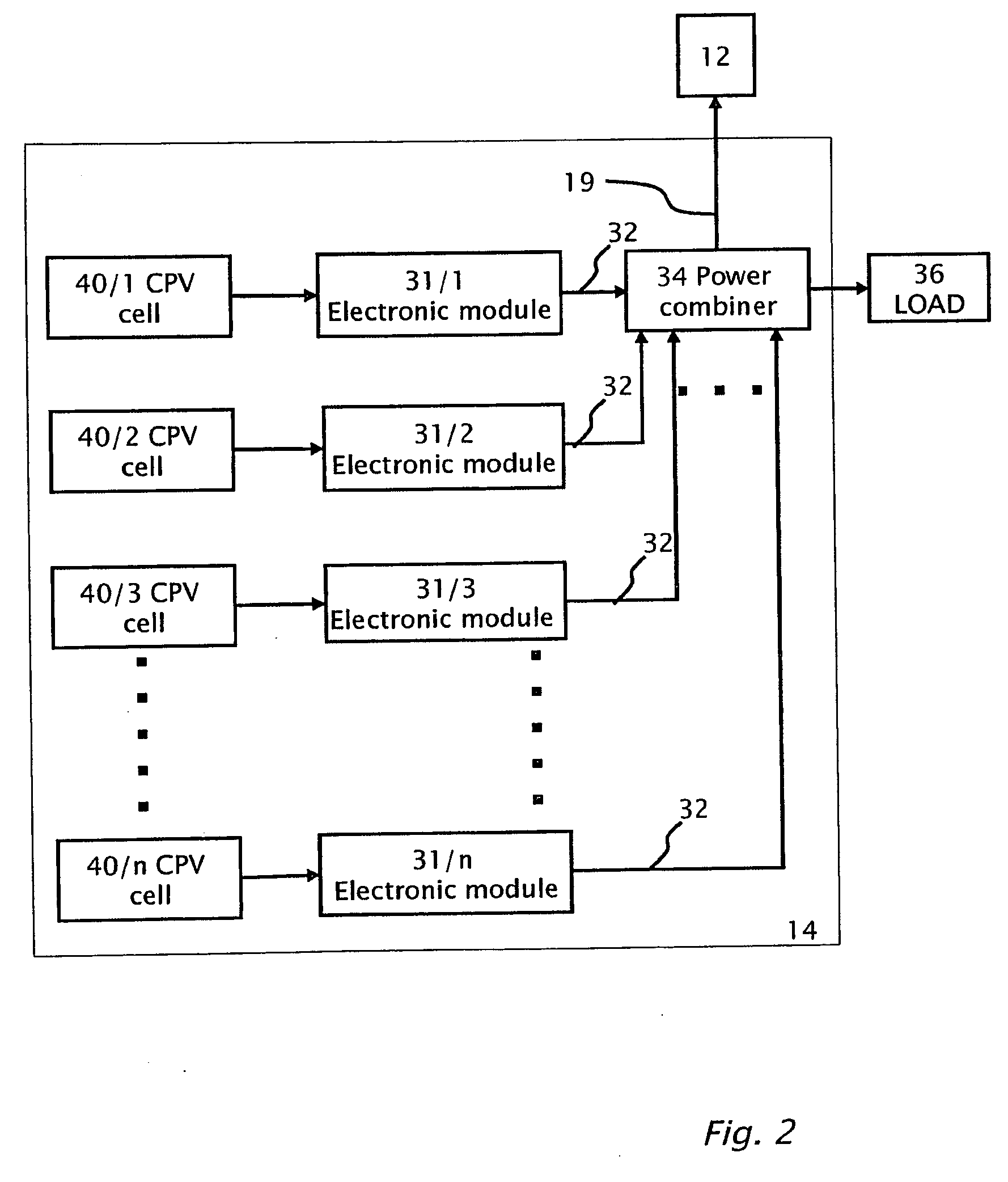

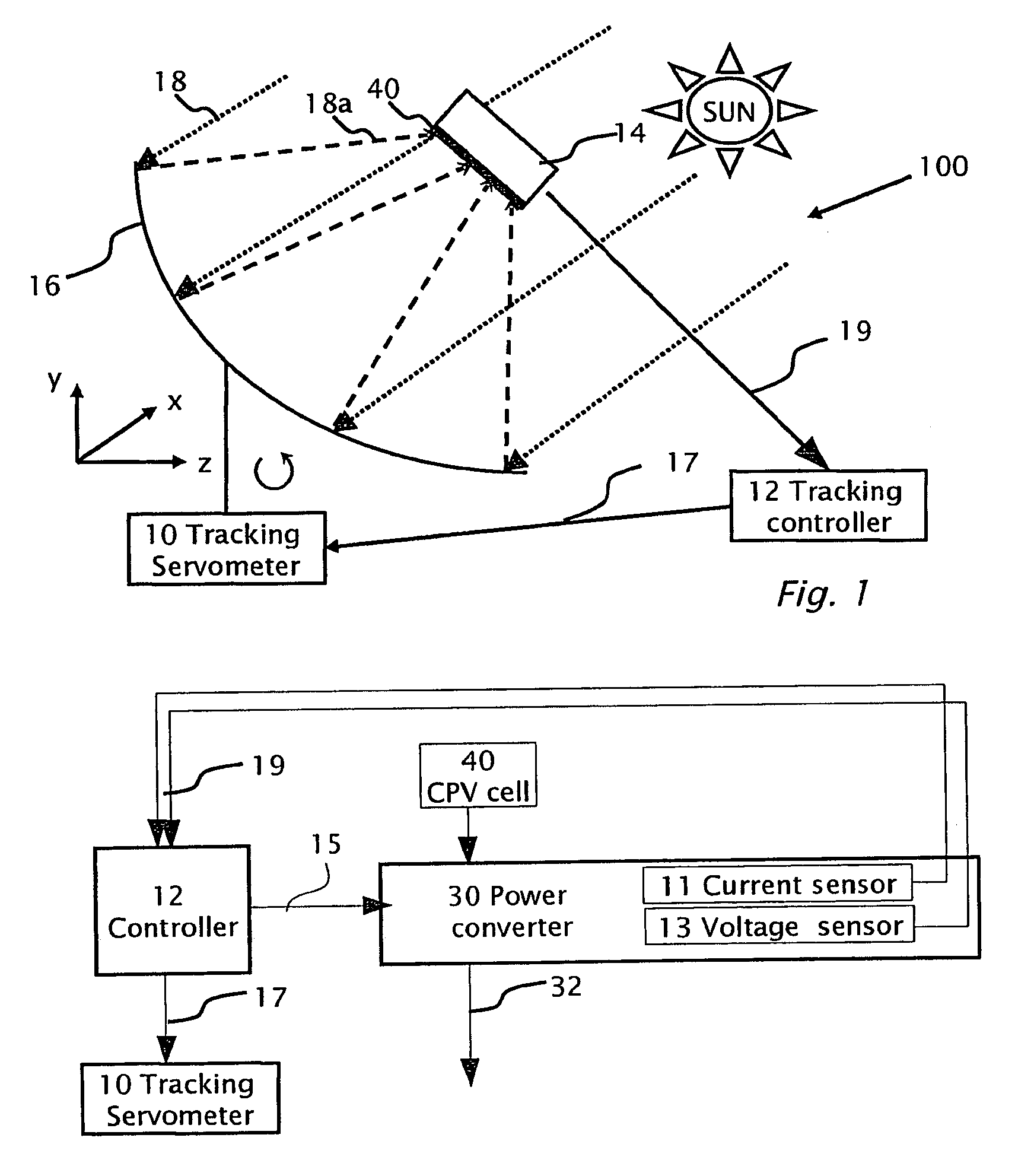

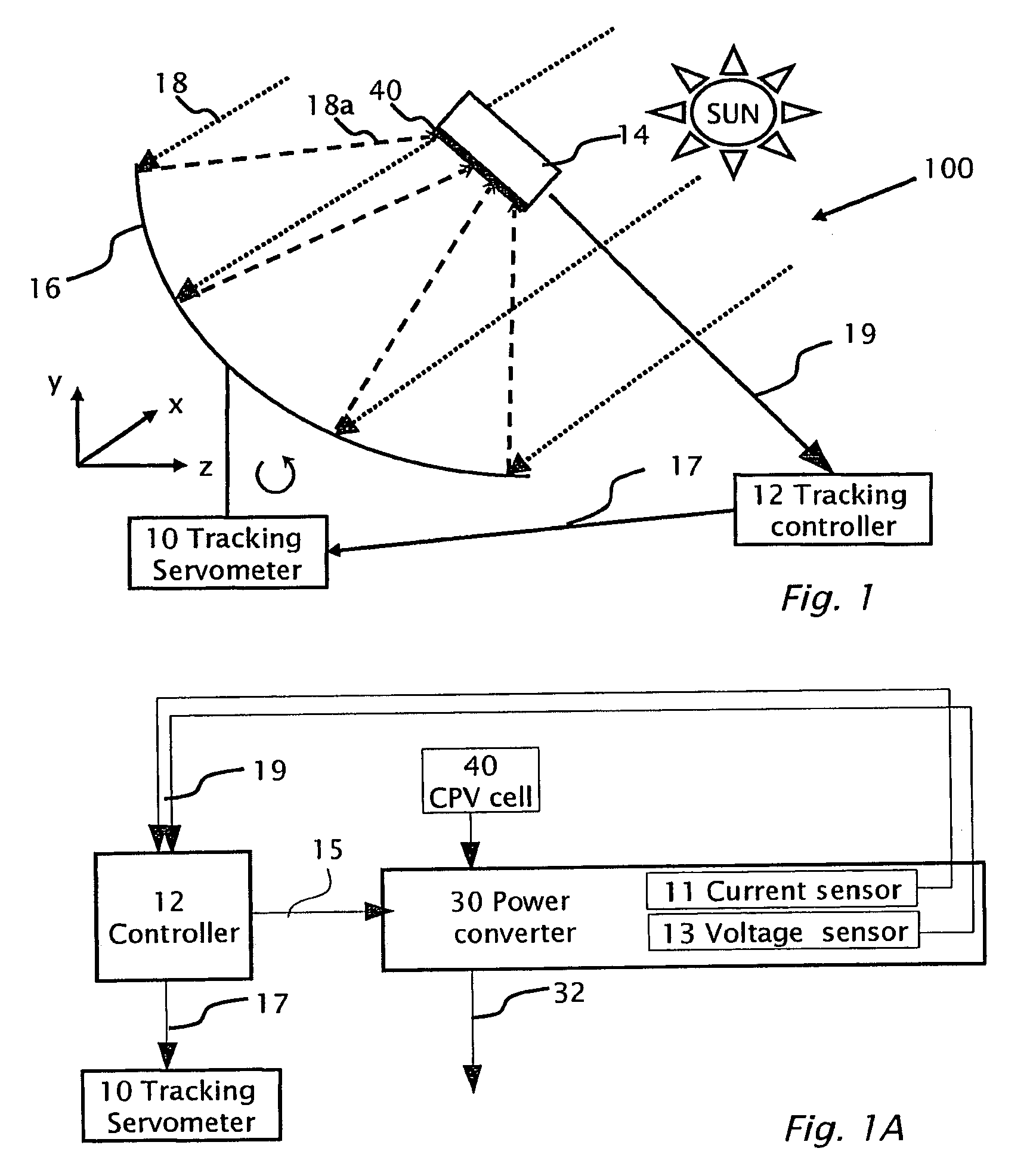

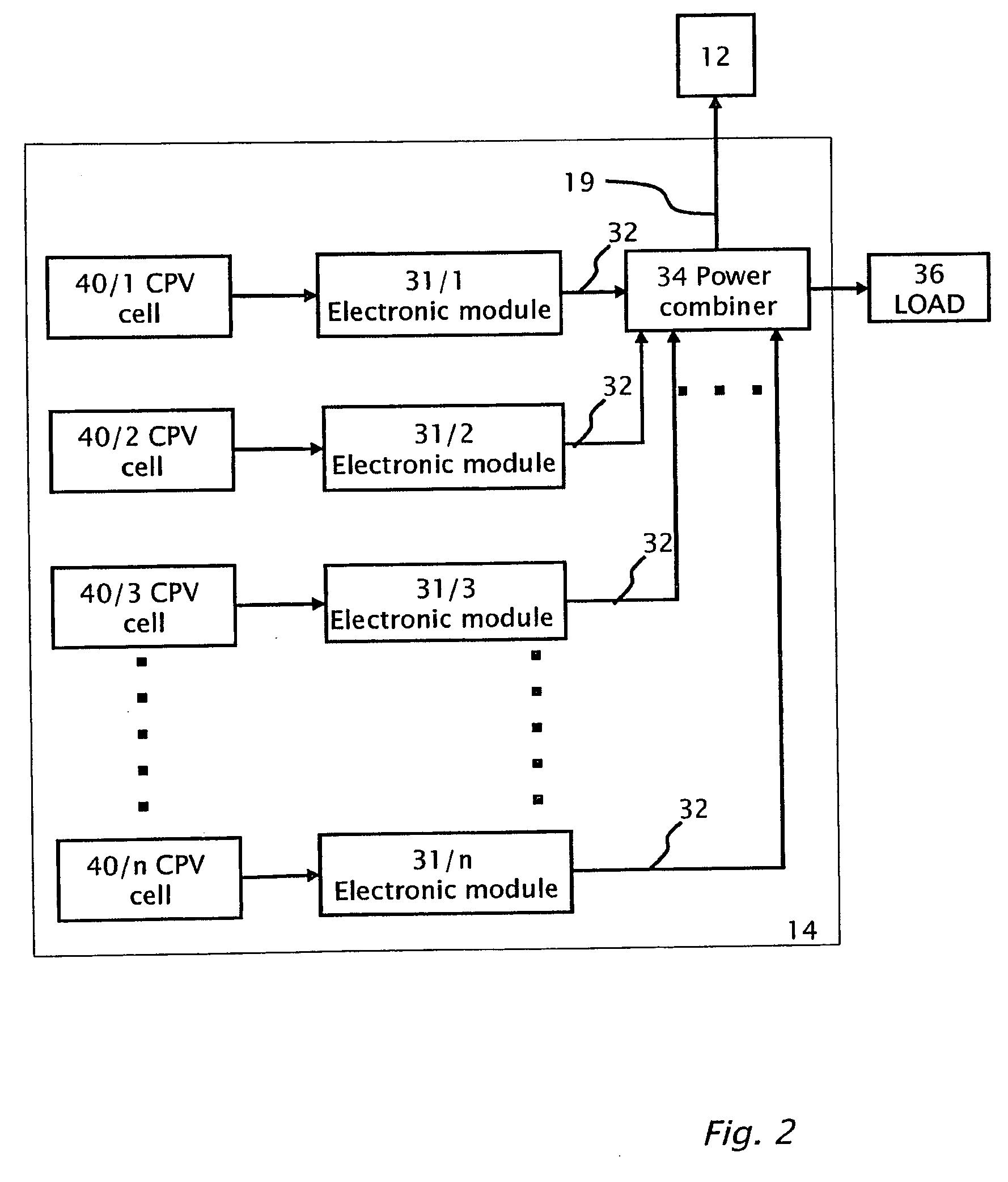

Photovoltaic system power tracking method

ActiveUS20090145480A1Increased electrical powerMaximize solar powerSolar heating energySolar heat collector controllersSolar lightElectrical current

A photovoltaic system including a photovoltaic cell, and an electronic module connected to the photovoltaic cell. The electronic module is adapted to produce at least one control signal indicative of electrical power being generated by the photovoltaic cells. A tracking controller is adapted to receive the control signal(s) and based on the control signal(s), the controller is adapted to control a tracking motor for adjusting the system so that electrical power generated by the photovoltaic cells is increased. The photovoltaic system may include an optical element, adapted for concentrating solar light onto the photovoltaic cells. The electronic module preferably performs direct current (DC) to direct current (DC) power conversion and maximum power point tracking by electrical power, current, or voltage at either their inputs or their outputs. Alternatively, the tracking controller is configured to also perform maximum power point tracking by increasing to a local maximum electrical power by varying at least one of (i) current or voltage output from the photovoltaic cell or (ii) current or voltage output from the electronic module.

Owner:SOLAREDGE TECH LTD

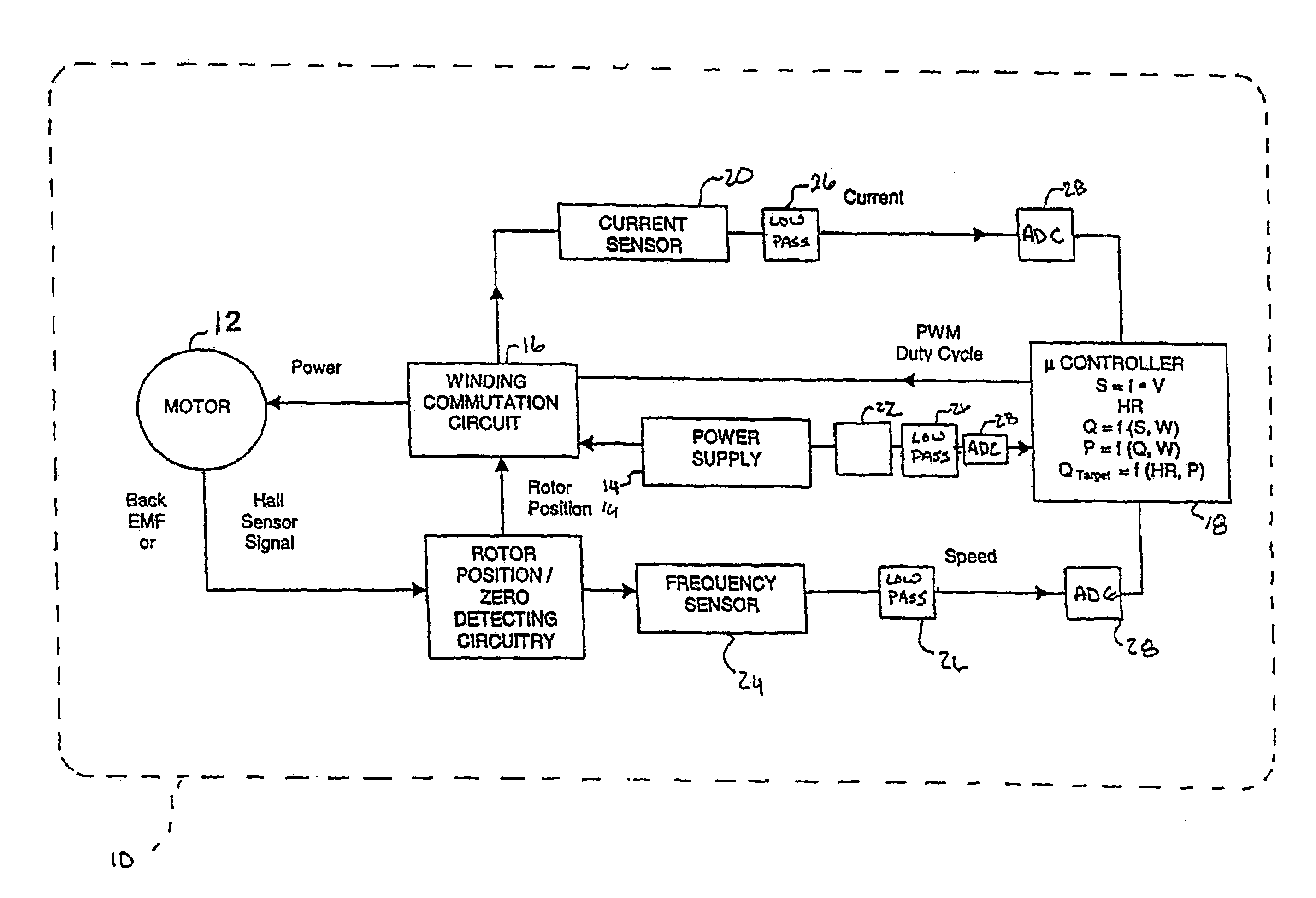

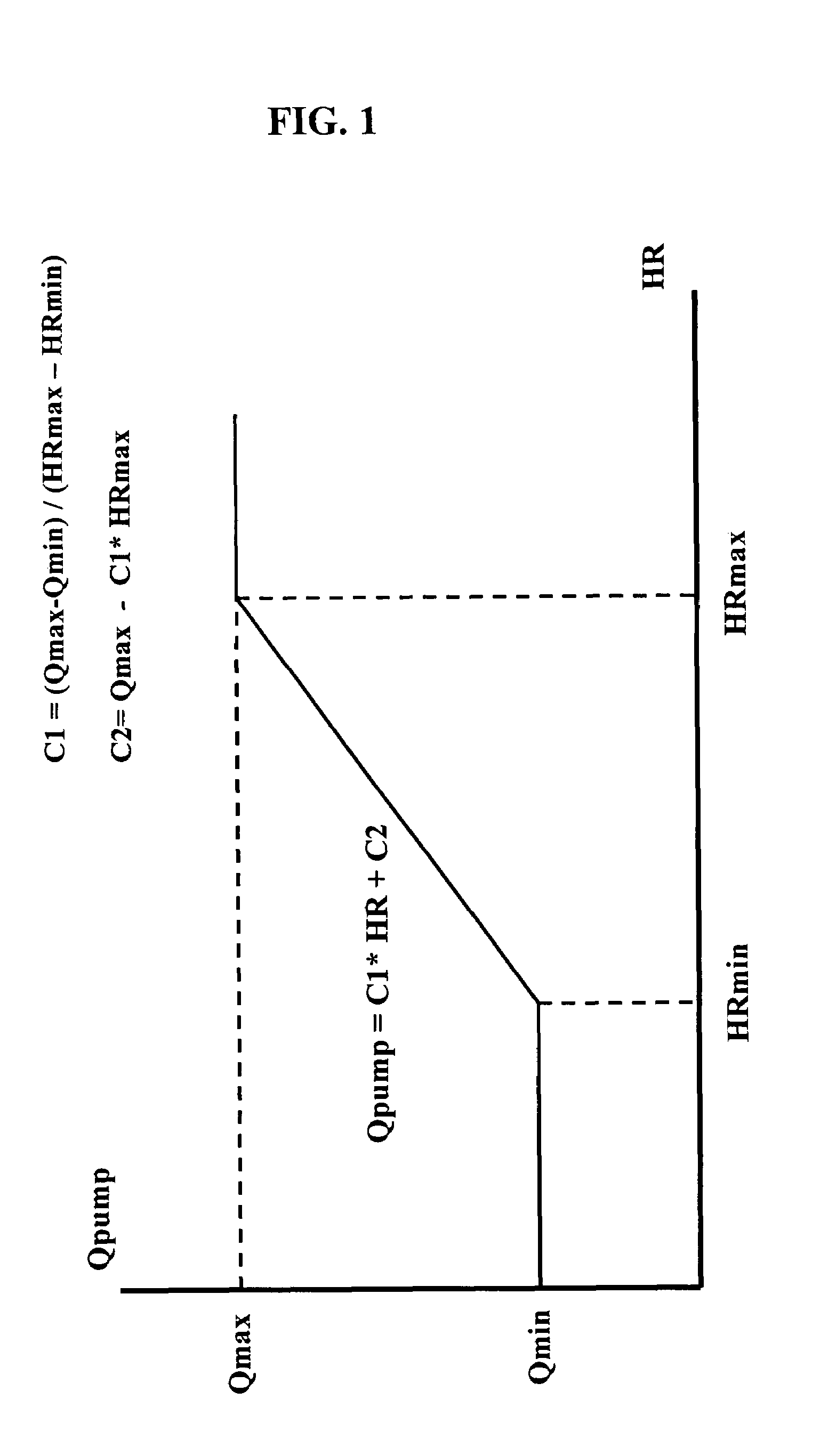

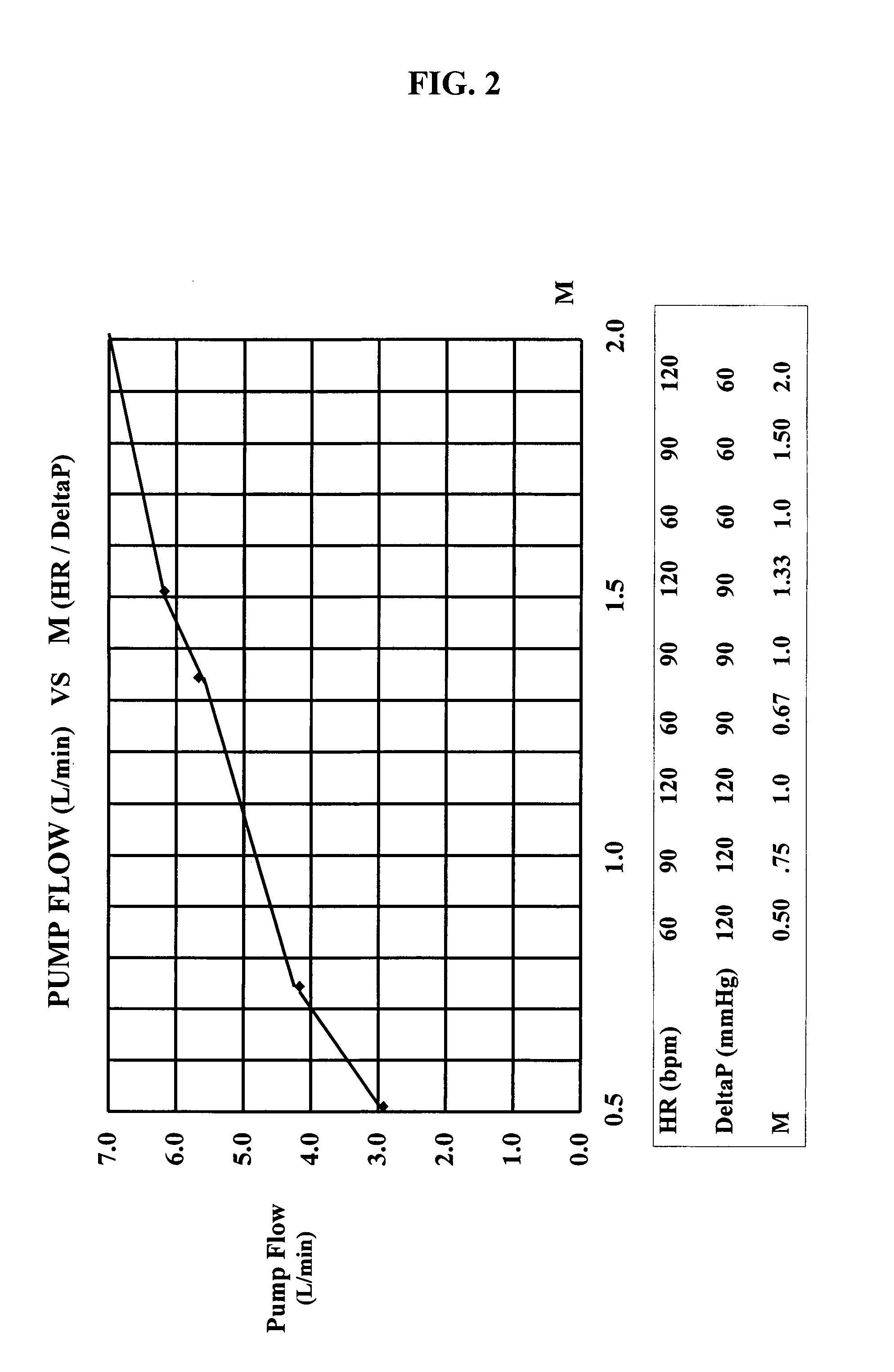

Chronic performance control system for rotodynamic blood pumps

InactiveUS7645225B2Simple control circuitIncrease control flexibilityDC motor speed/torque controlAC motor controlMicrocontrollerMotor speed

In a left ventricular assist device (LVAD) a rotodynamic blood pump (10) is powered by a brushless DC motor (12). A power supply (14) supplies power to the motor (12). Three feedback channels, one for each of voltage, current, and motor speed lead to a microcontroller or microprocessor (18). The three feedback waveforms are analyzed, and from these waveforms, motor input power, patient heart rate, current pump flow rate, and systemic pressure are determined. The microprocessor (18) then calculates a desired flow rate proportional to the patient heart rate. The microprocessor communicates a new power output to a commutation circuit (16), which regulates power to the motor (12). The pump (10) also includes safety checks that are prioritized over desired pump flow. These include prevention of ventricular suction, low pulsatility, minimum and maximum pump speed, minimum speed-relative pump flow, minimum absolute pump flow, minimum and maximum motor input power.

Owner:MEDVEDEV ALEXANDER +2

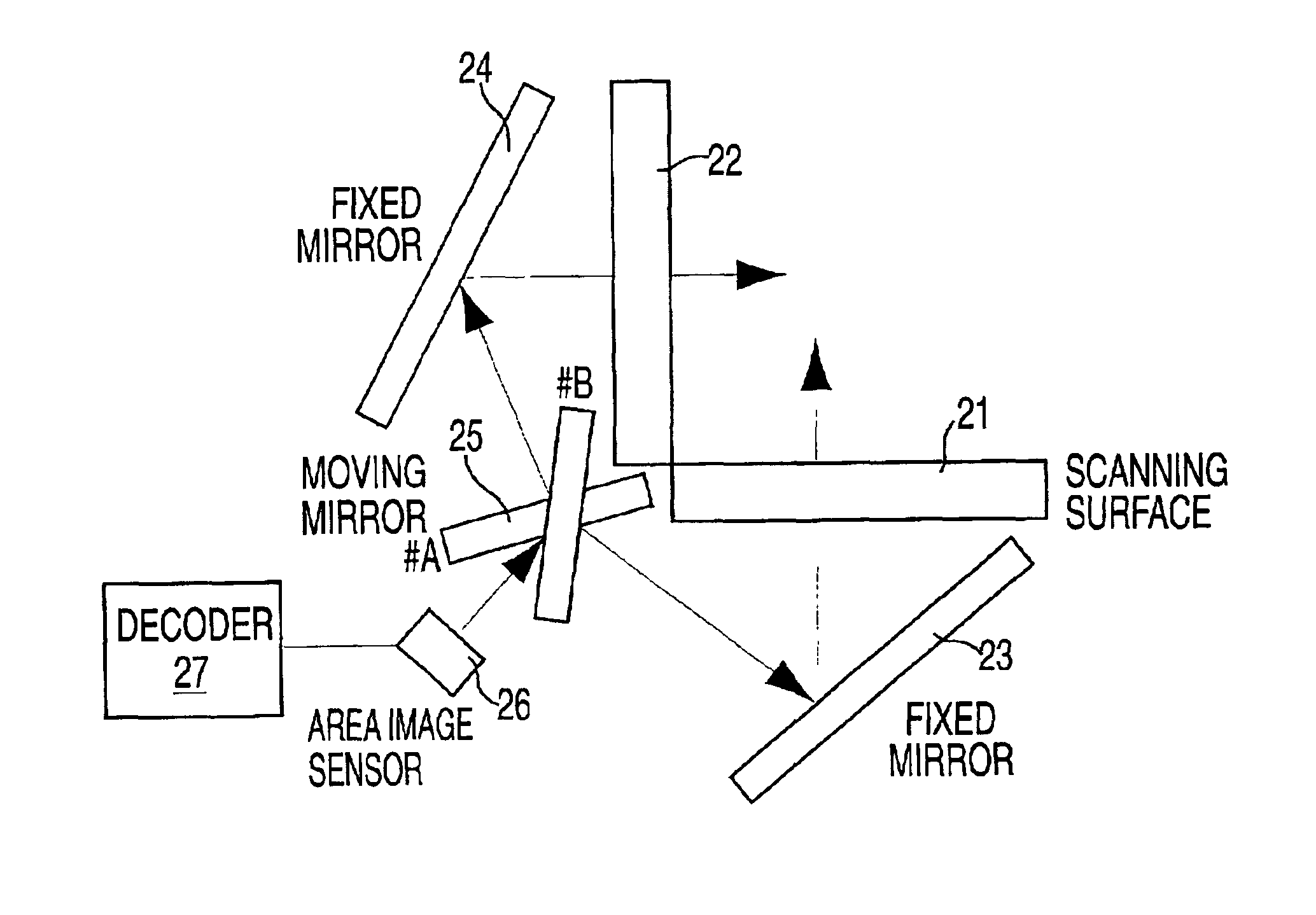

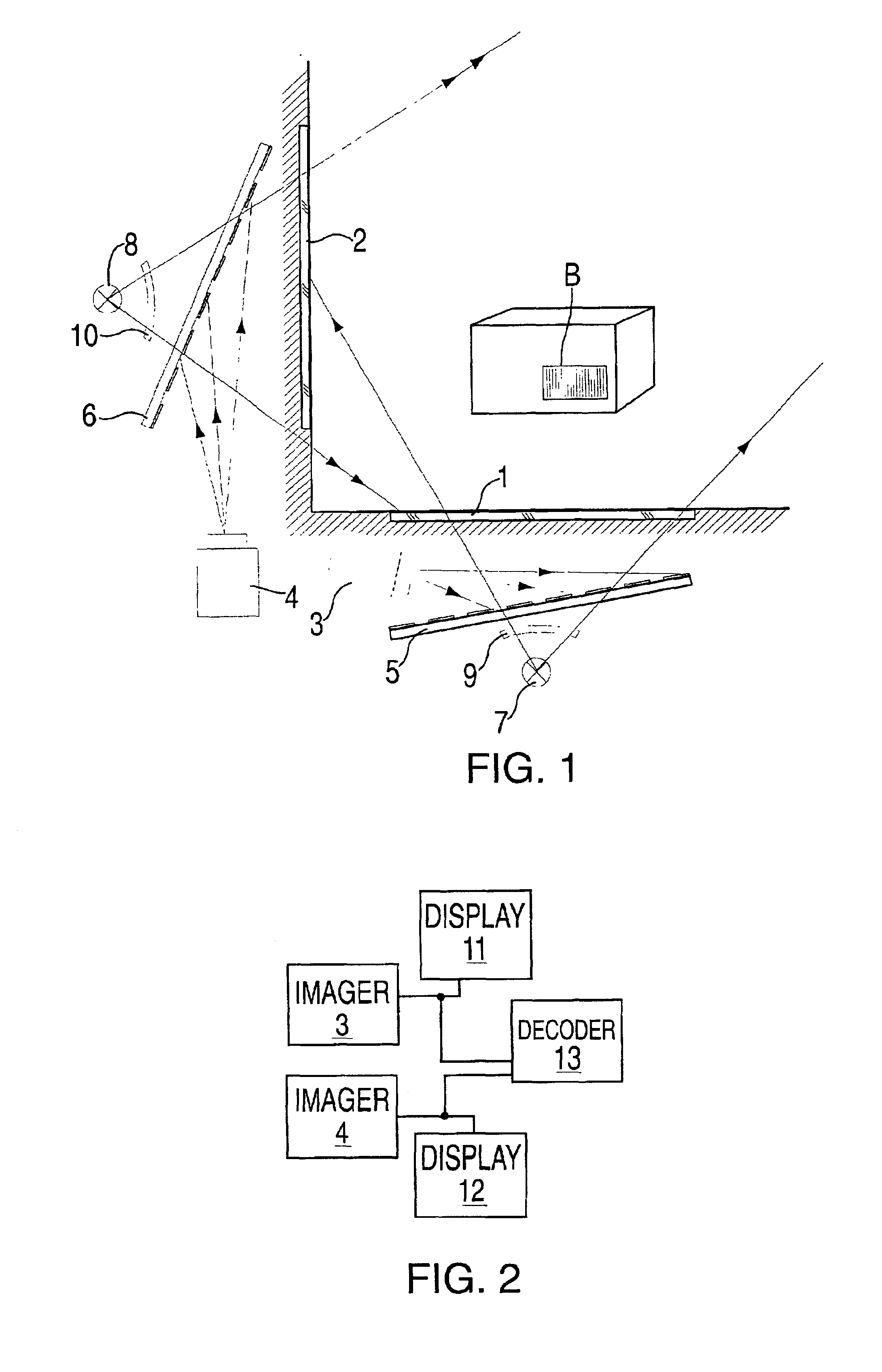

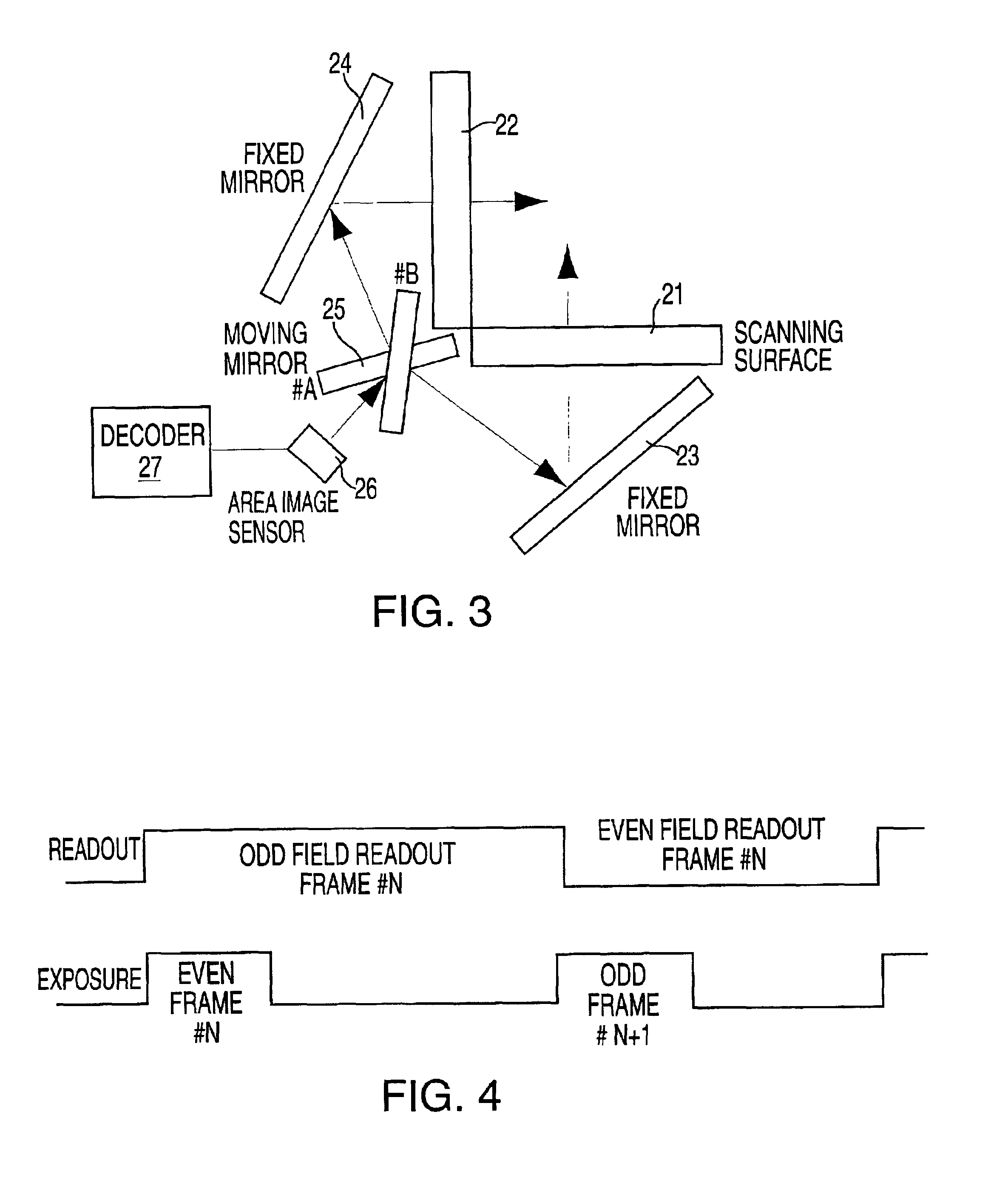

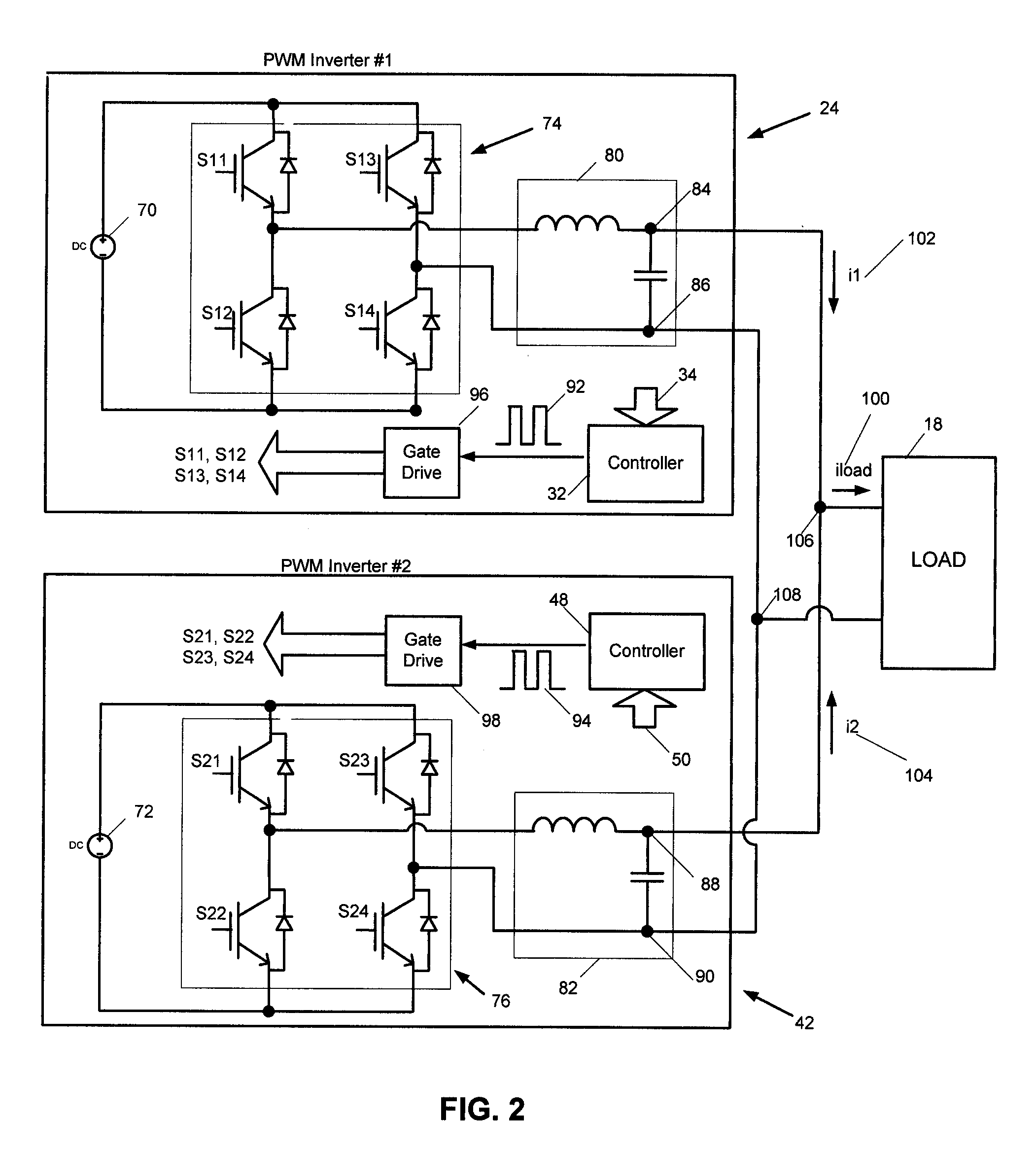

Bioptics bar code reader

InactiveUS6899272B2Increase heightImprove system reliabilityMirrorsCharacter and pattern recognitionBarcodeComputer science

A bioptics bar code reader has first and second windows disposed at an angle to each other, a first imager for the first window and a second imager for the second window and first and second optics for directing light from a bar code in a reading area between the windows to the first and second imagers. The two imagers each obtain an image of the bar code in the reading area.

Owner:SYMBOL TECH LLC

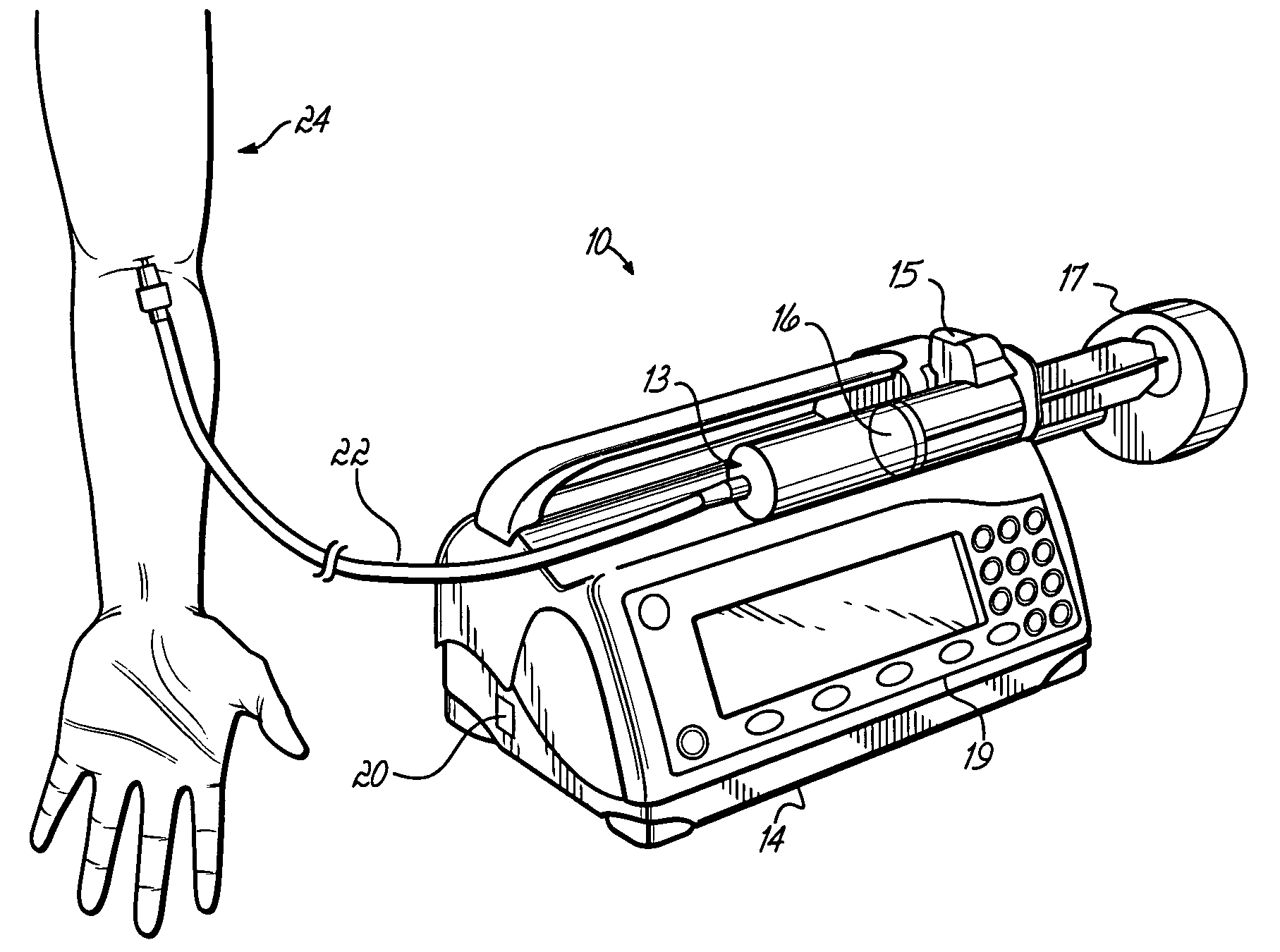

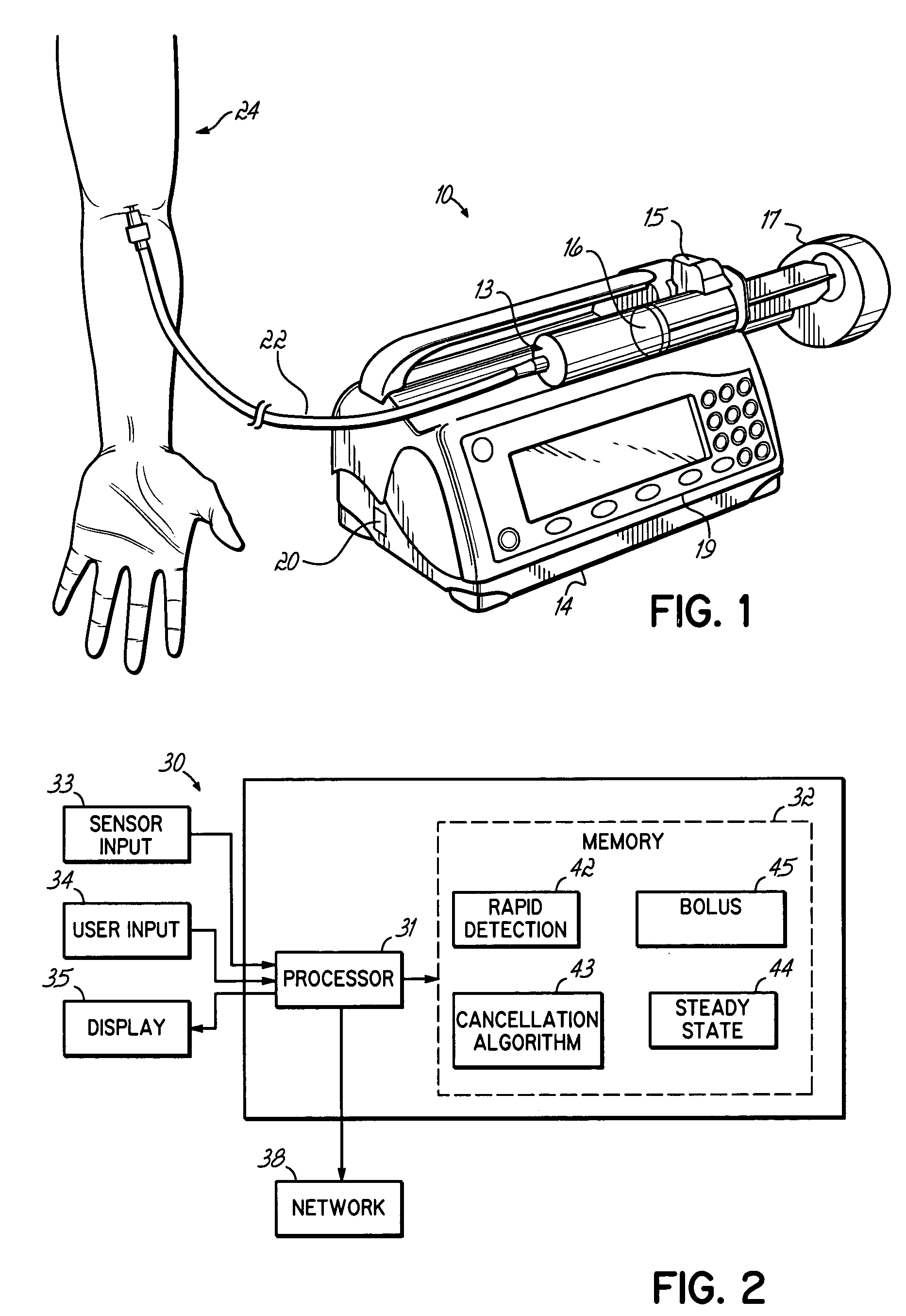

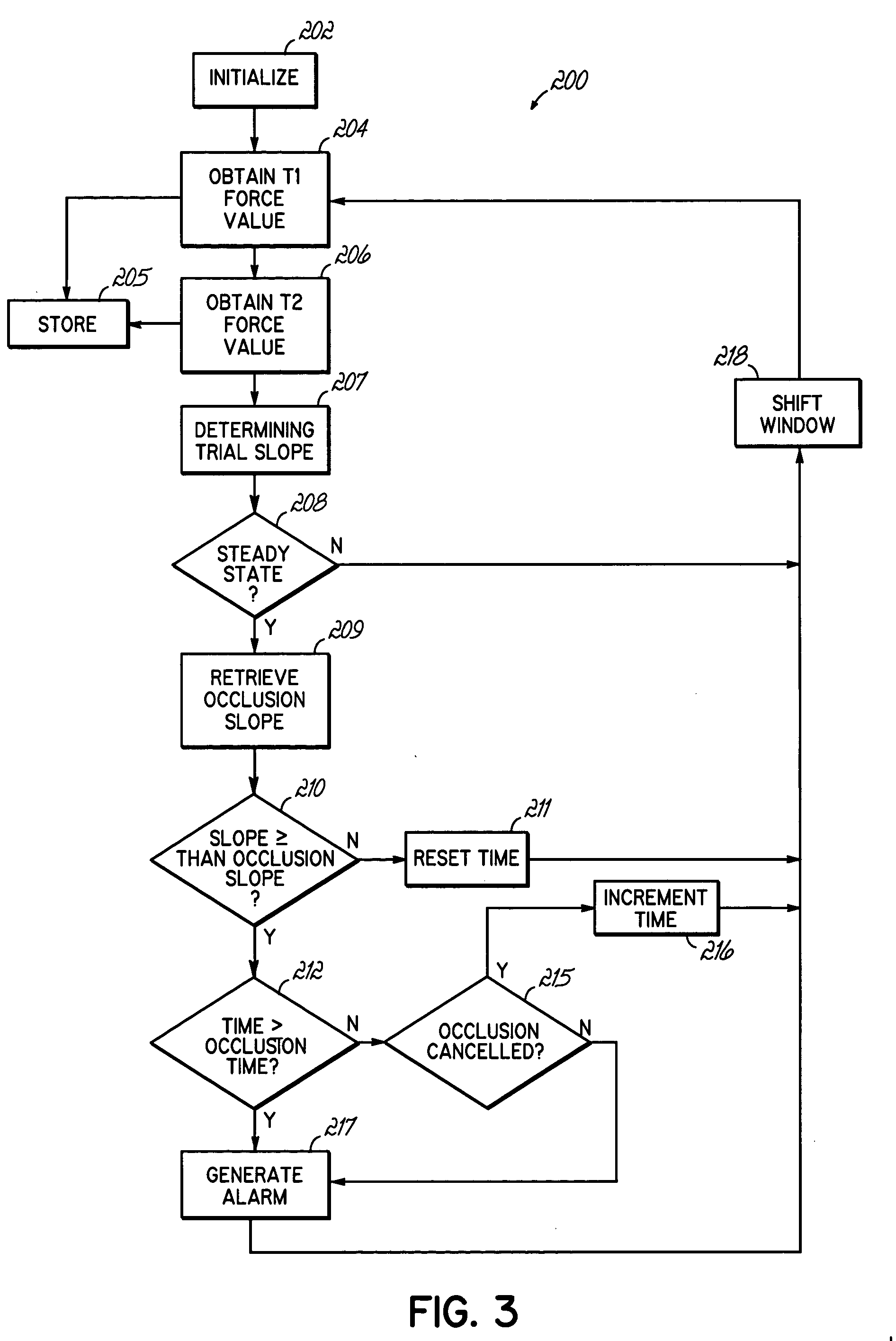

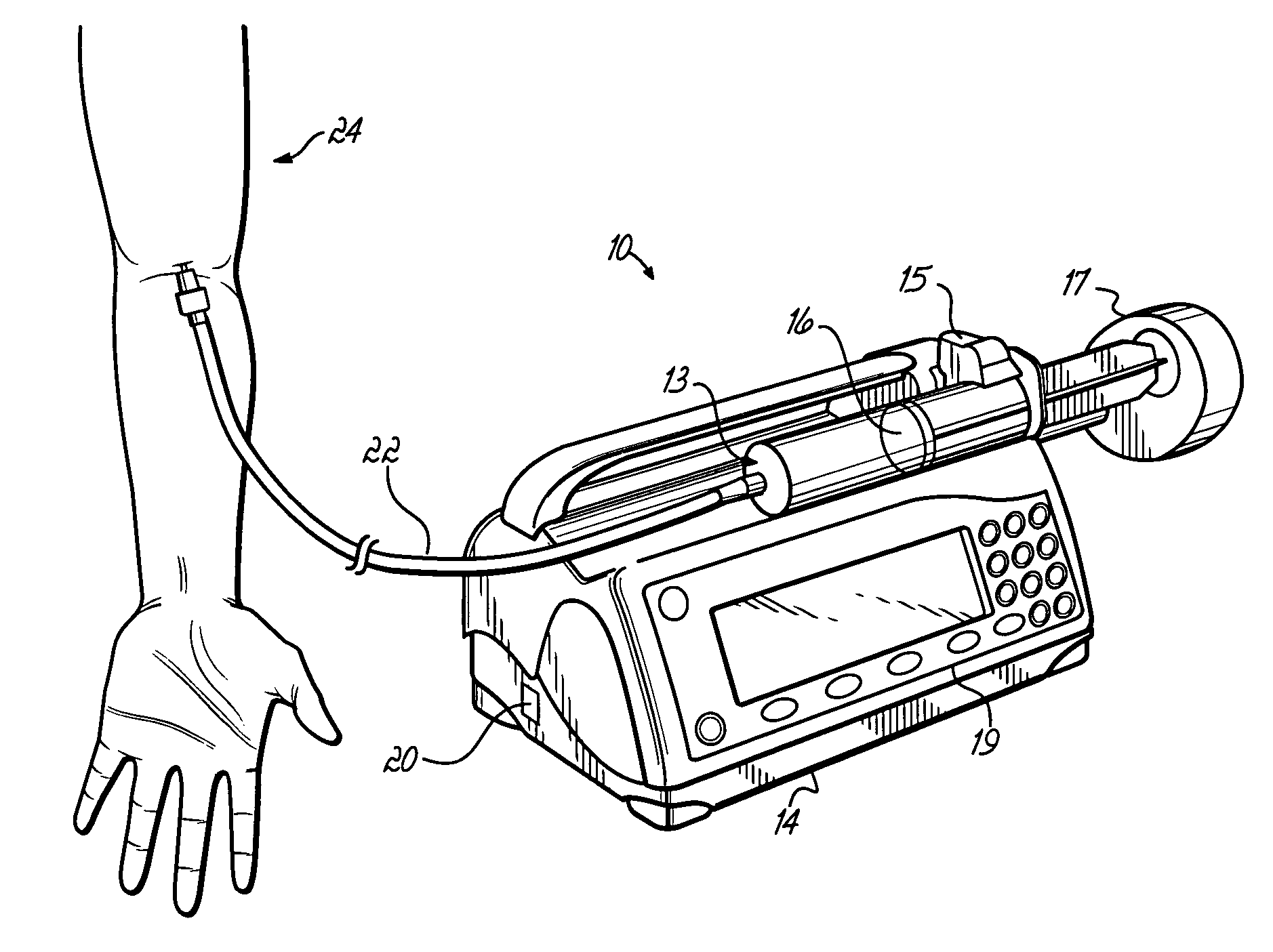

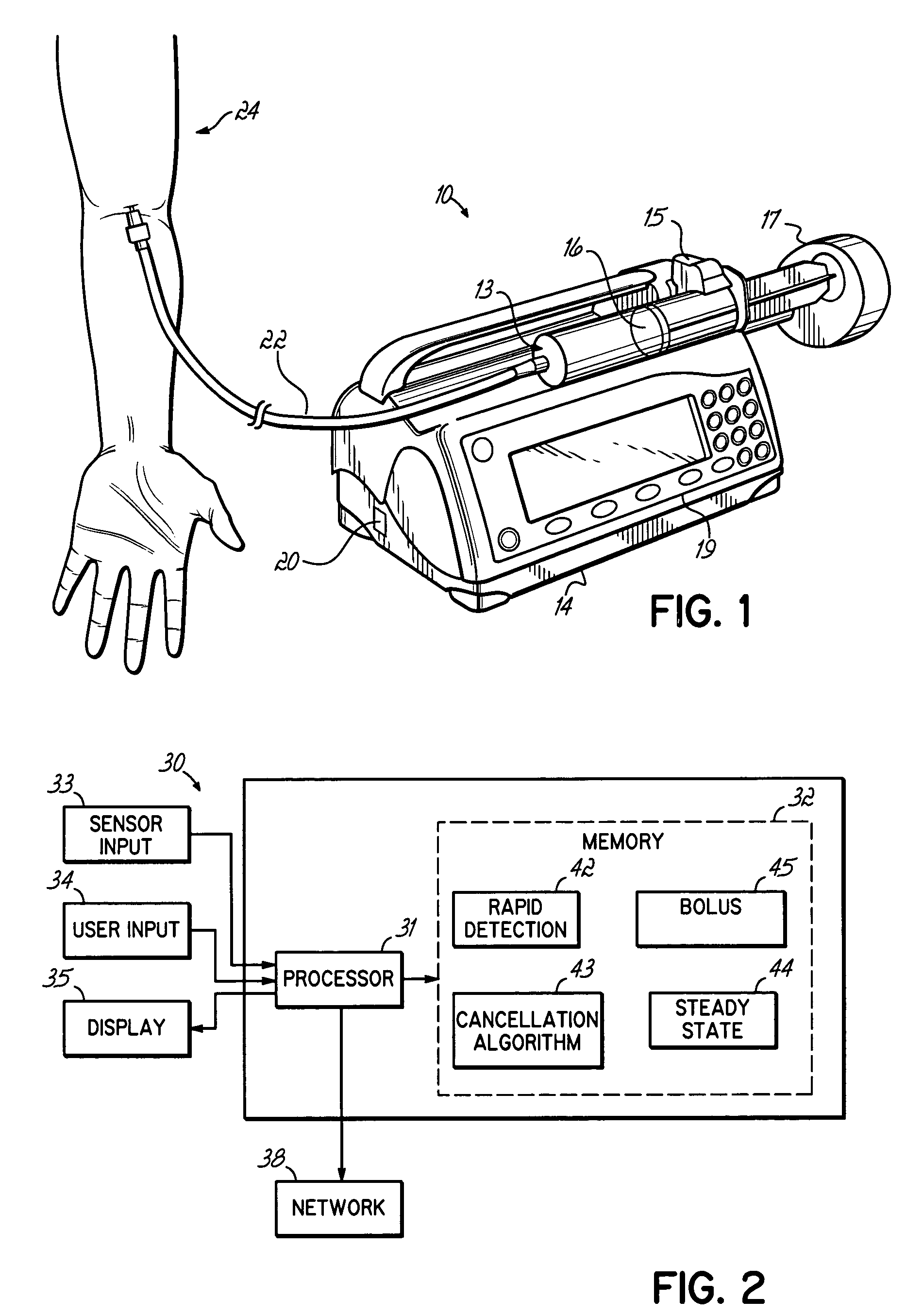

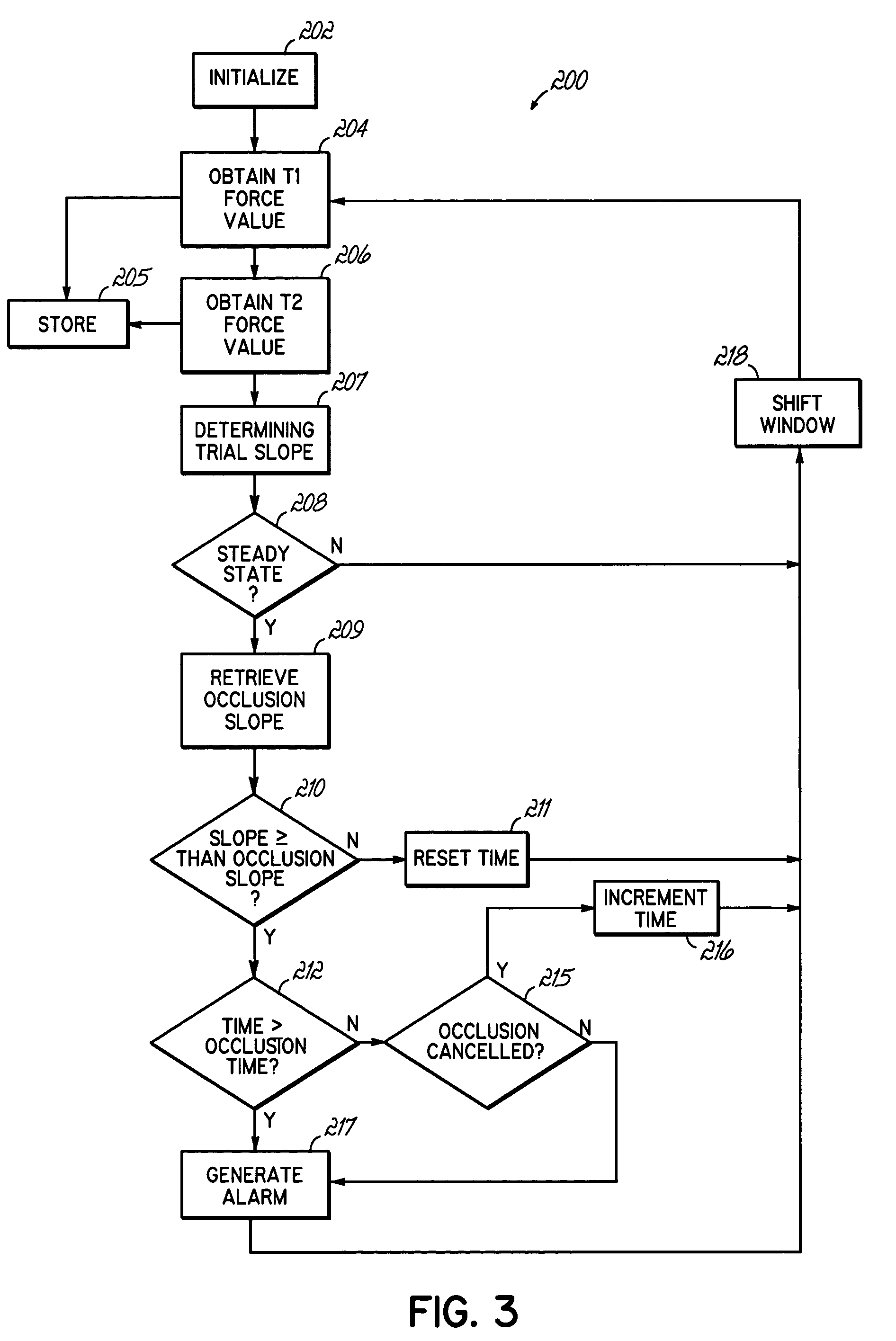

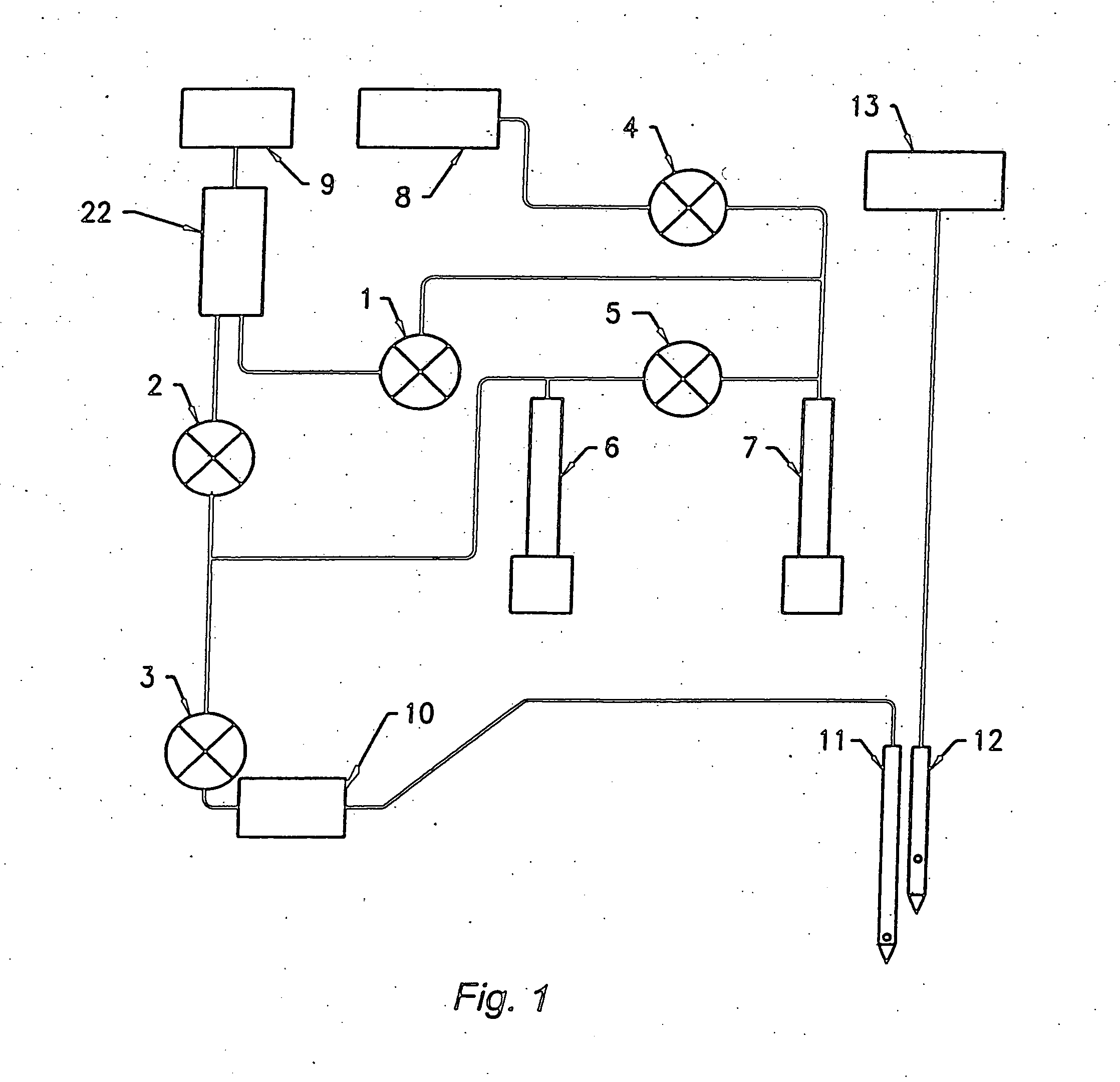

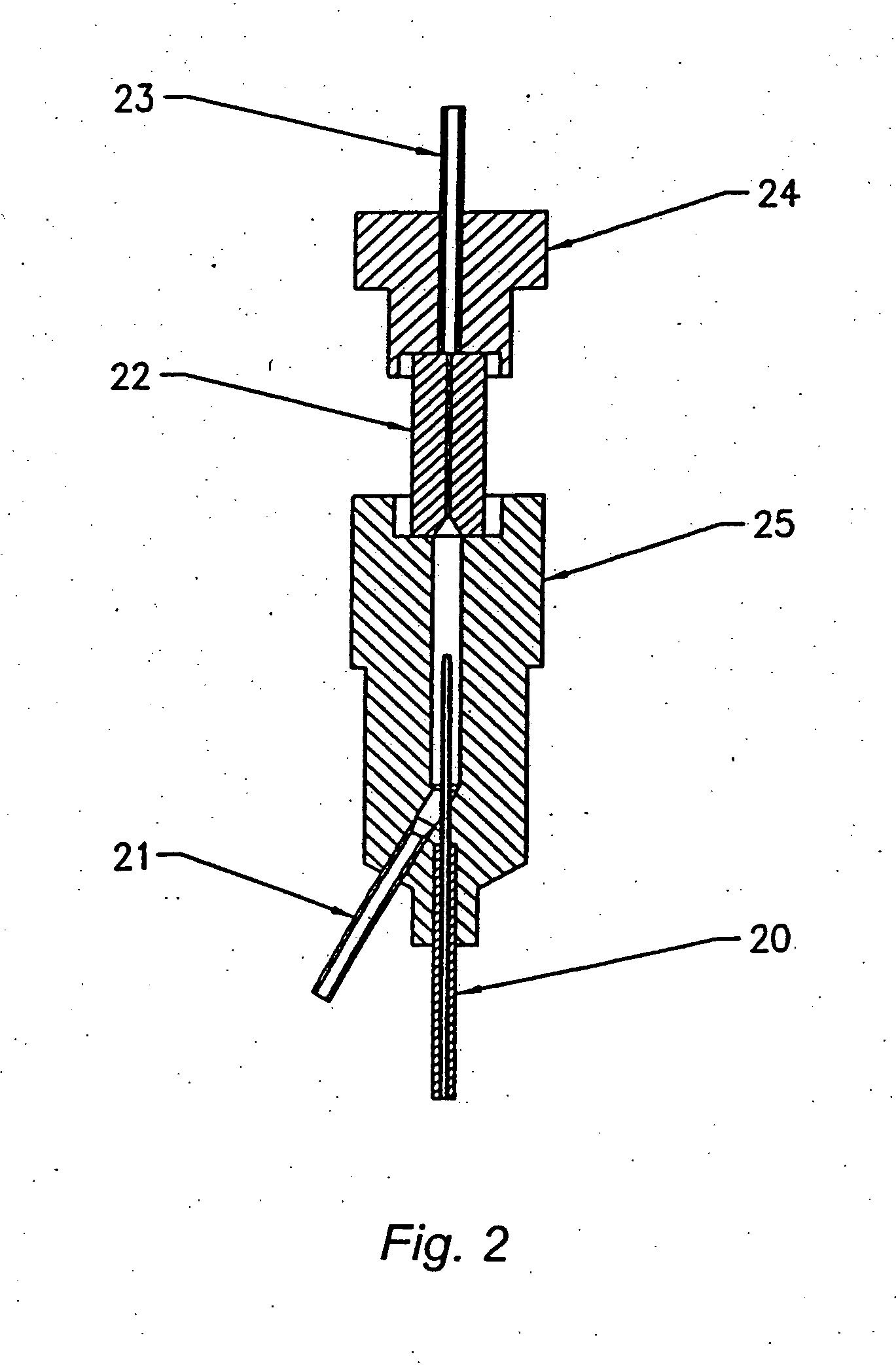

Syringe pump rapid occlusion detection system

ActiveUS20050096593A1Reduces incidenceReduces infusion rateMedical devicesPump controlSyringeOcclusion detection

An apparatus, method and program product detects an occlusion in a fluid line by determining if a relationship between force measurements departs from an expected relationship.

Owner:SMITHS MEDICAL ASD INC

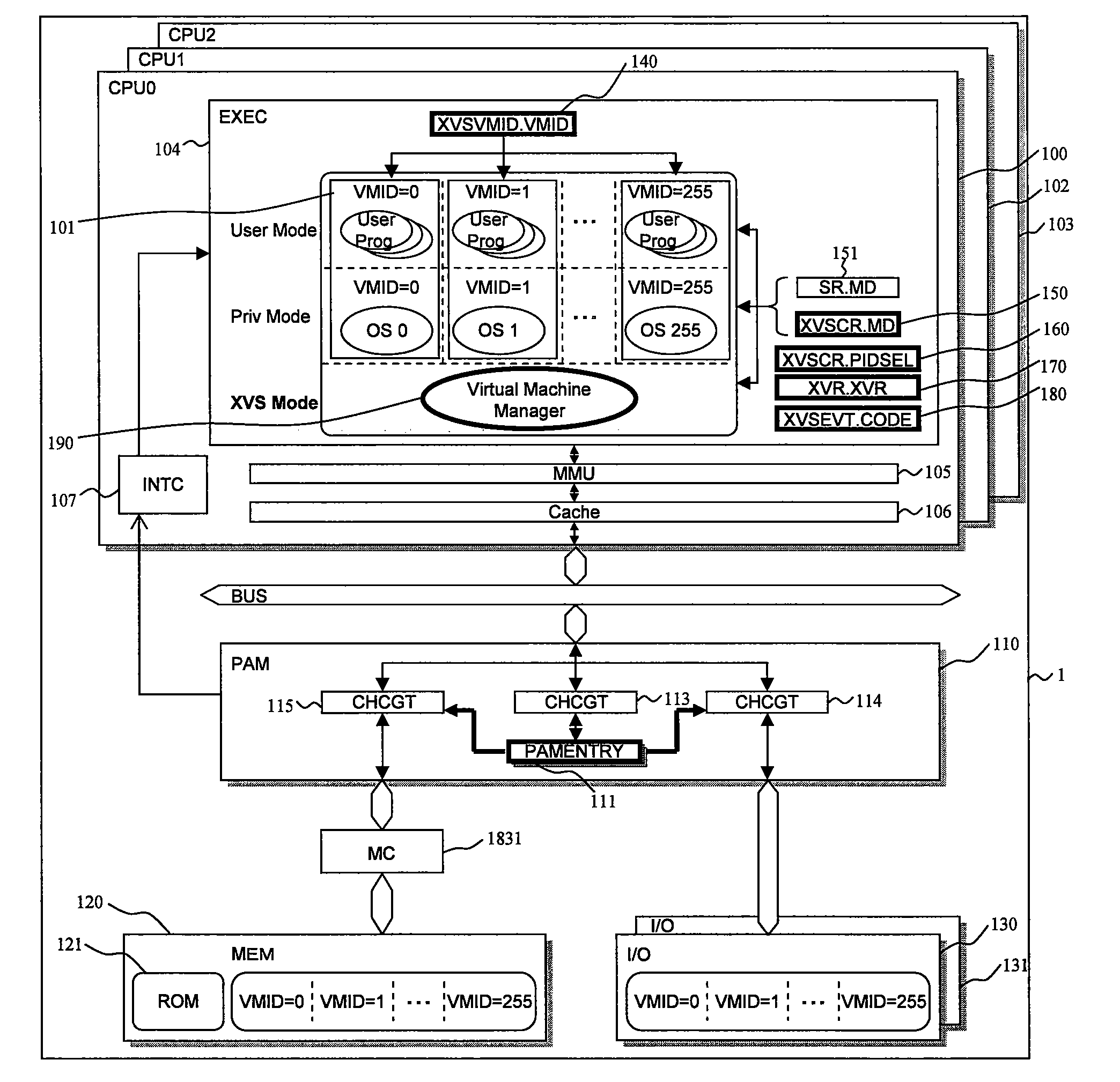

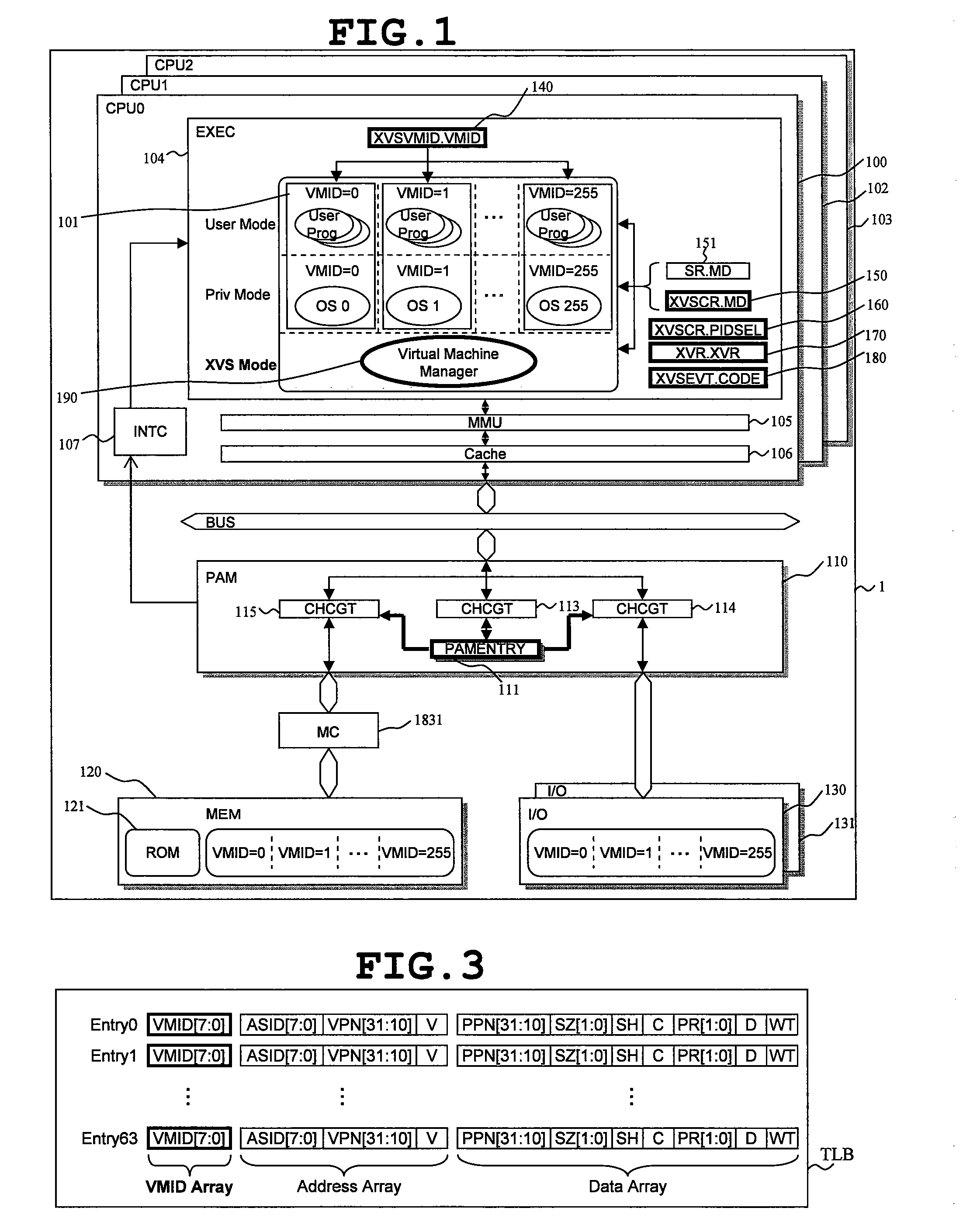

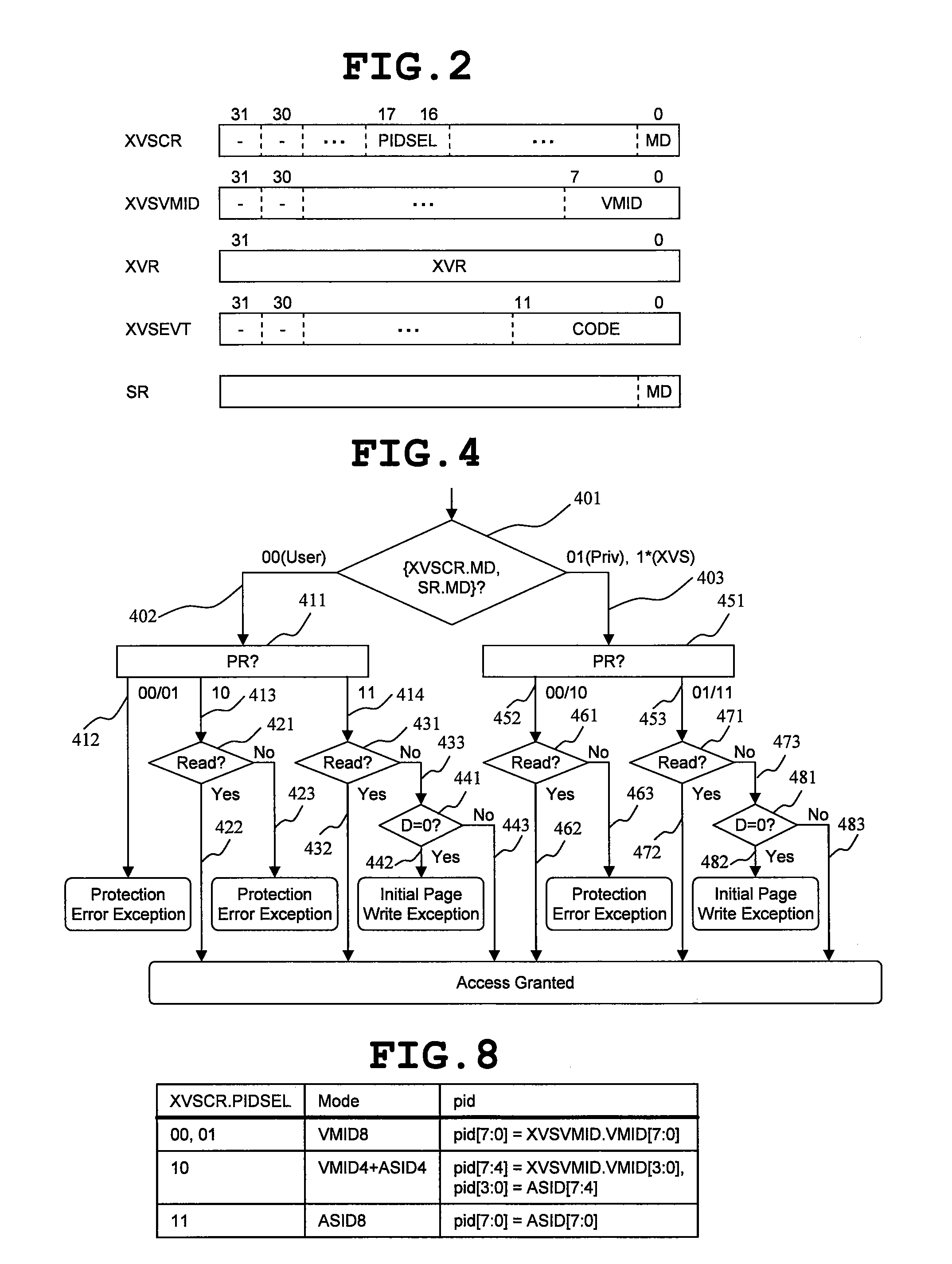

Data processor

ActiveUS20080086729A1Reduce needImprove system reliabilityResource allocationSoftware simulation/interpretation/emulationOperational systemControl register

A data processor includes: a central processing unit (CPU), in which a plurality of virtual machines (101), each running an application program under controls of different operating systems, and a virtual machine manager (190) for controlling the plurality of virtual machines are selectively arranged according to information set in mode registers (140, 150, 151); and a resource access management module (110) for managing access to hardware resource available for the plurality of virtual machines. The resource access management module accepts, as inputs, the information set in the mode registers and access control information of the central processing unit to the hardware resource, compares the information thus input with information set in a control register, and controls whether or not to permit access to the hardware resource in response to the access control information. As a result, redesign involved in changes in system specifications can be reduced, and a malfunction owing to resource contention can be prevented. The invention contributes to increase of security.

Owner:RENESAS ELECTRONICS CORP

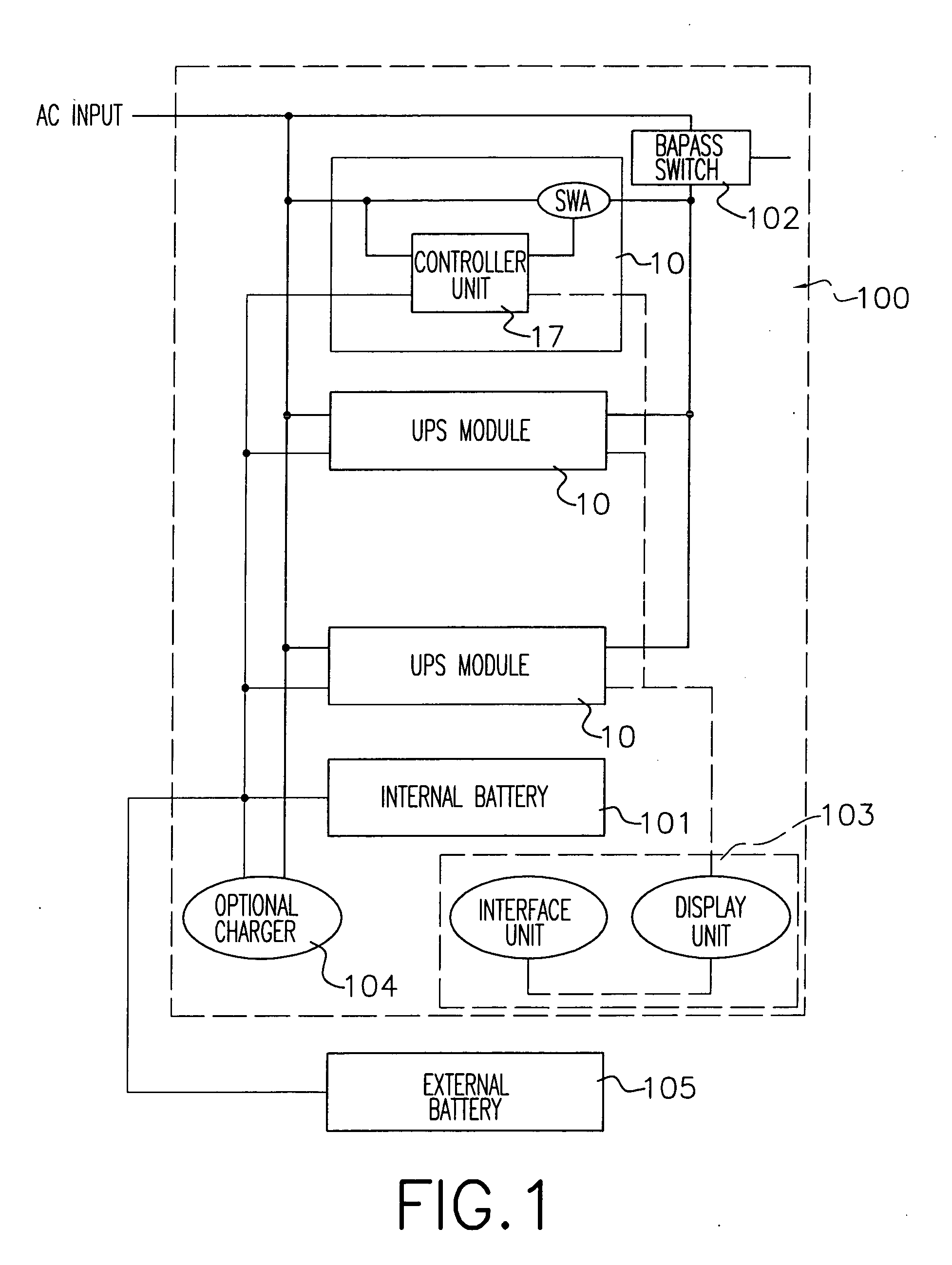

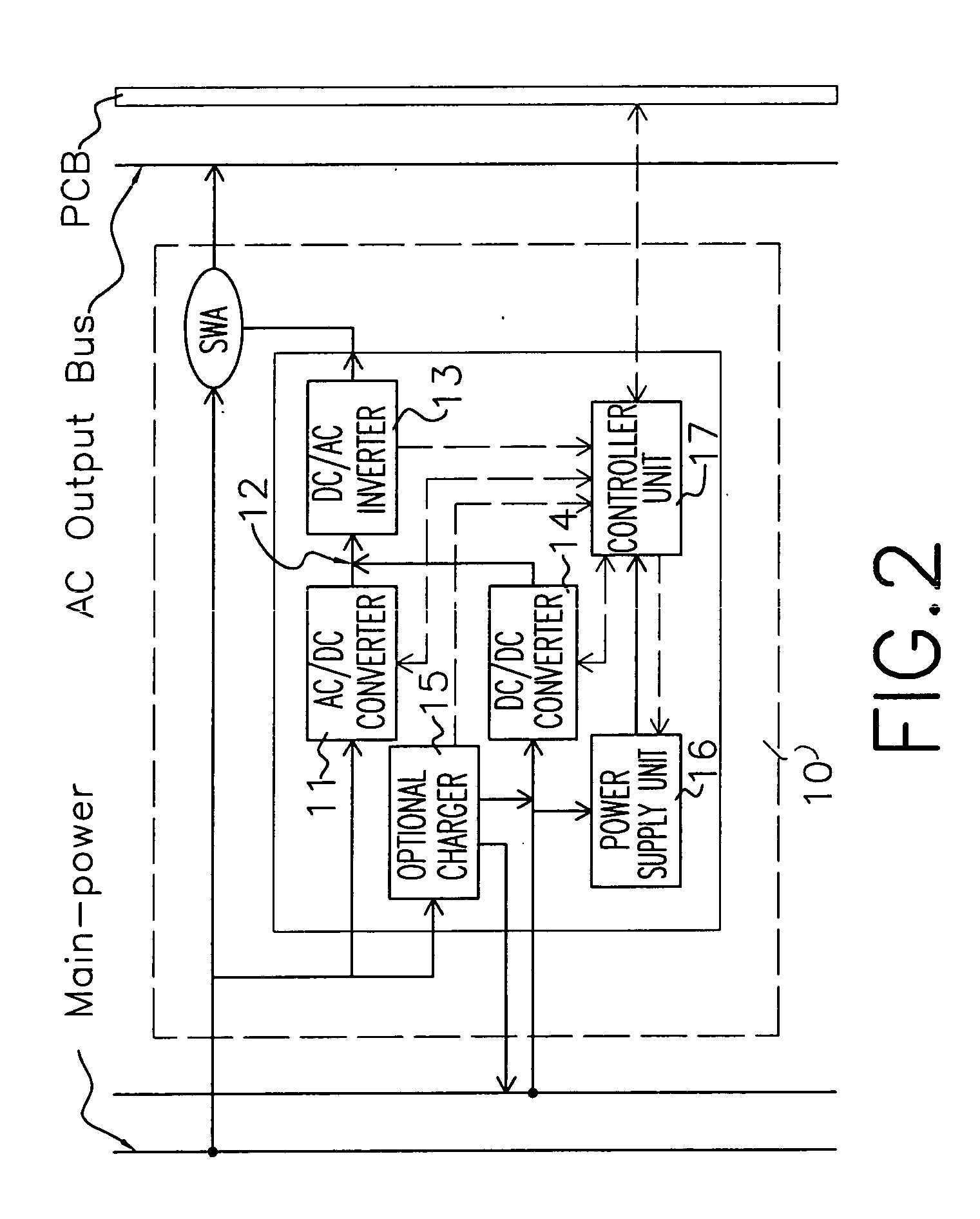

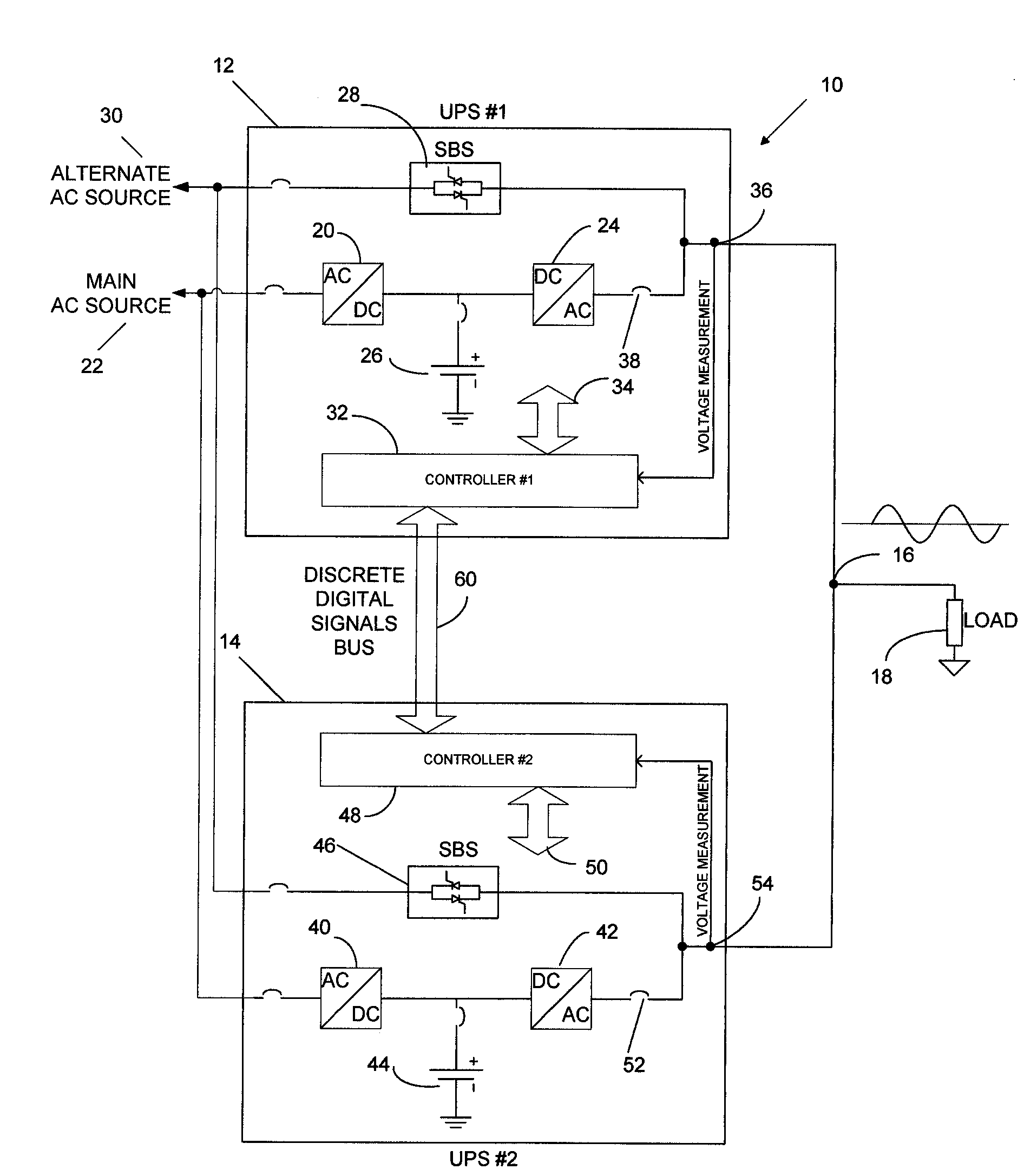

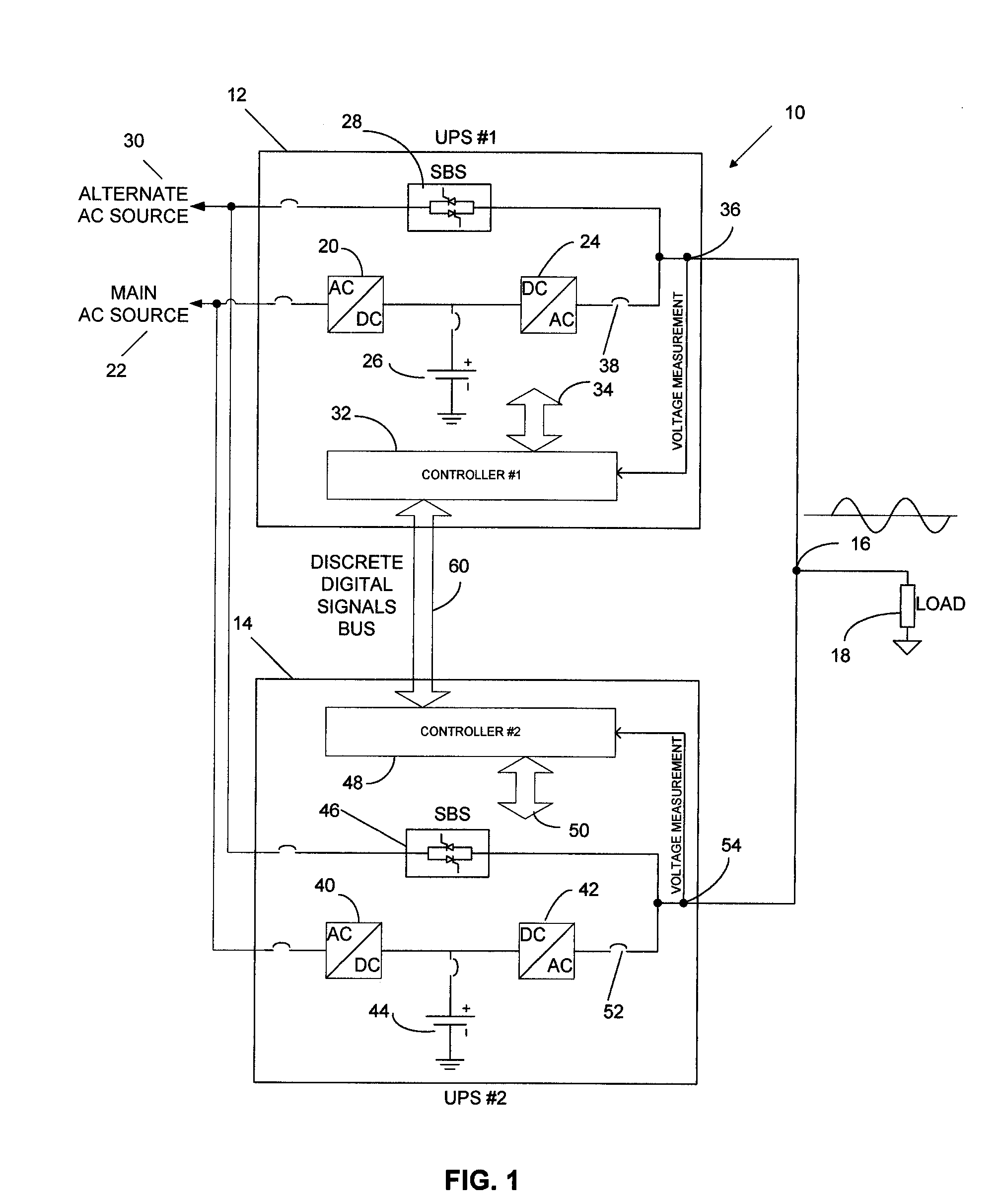

Modular uninterruptible power supply system and control method thereof

InactiveUS20050043859A1Protect the loadImprove fault toleranceMechanical power/torque controlBatteries circuit arrangementsModularityEngineering

An uninterruptible power supply (UPS) system and control method thereof is provided. The system contains a plurality of UPS modules connected in parallel, and each module is equipped with full uninterruptible power supply capabilities, and redundant control logic and functional capabilities for self-initiated role detection, master arbitration and parallel processing. The UPS system is self-initialized through a master arbitration process to elect a virtual master among the peers for maintaining inter-unit signaling between parallel UPS modules and controlling the parallel operation. If the virtual master is failed, other UPS modules will initiate the role detection and master arbitration to re-elect a new virtual master. Parallel operation is accomplished without any external controller; the system can be operated with only one UPS module; distribution of adequate resource to each module is properly arranged, thus the risks of system-level single-point failure are much reduced.

Owner:PHOENIXTEC POWER

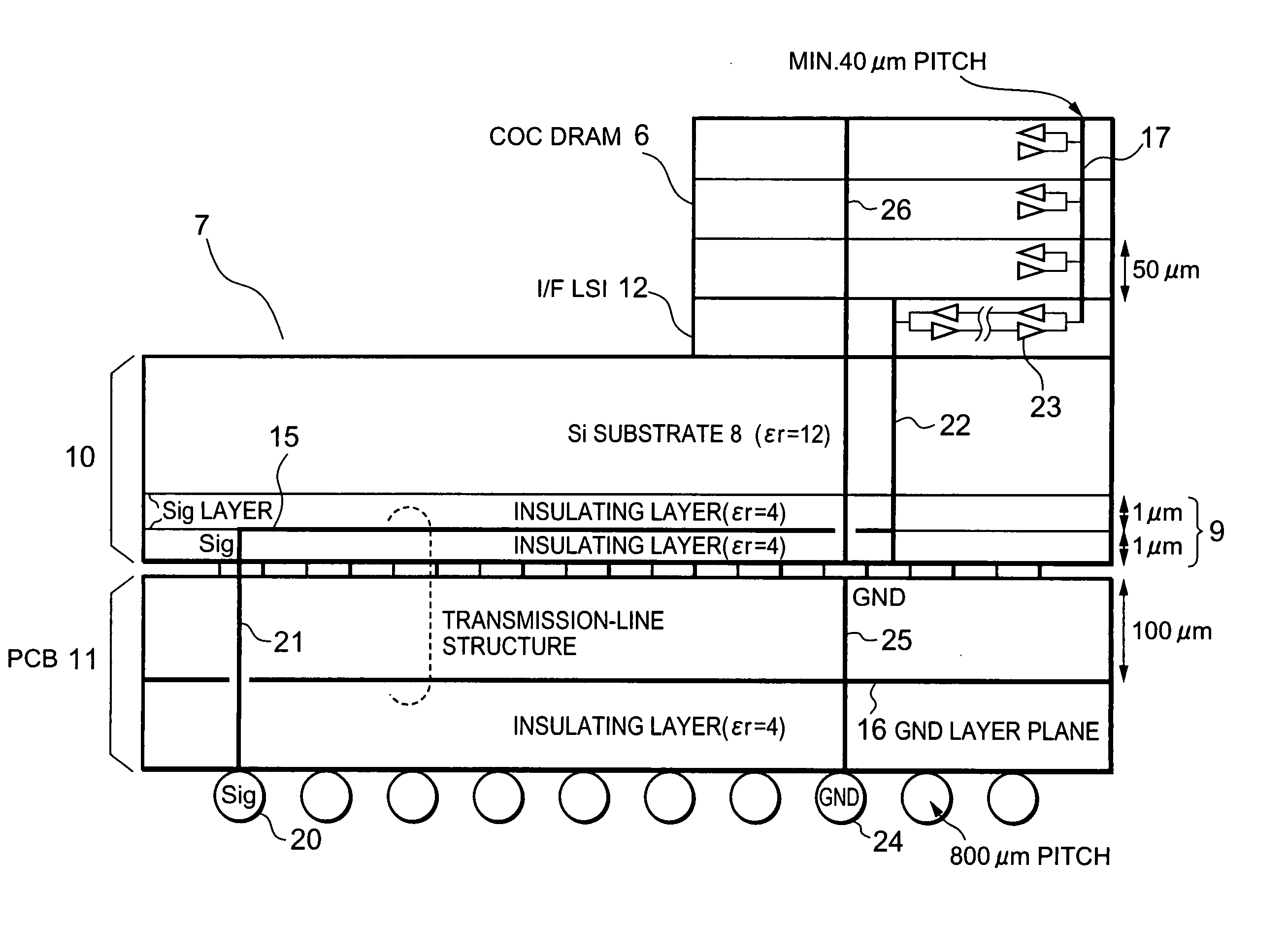

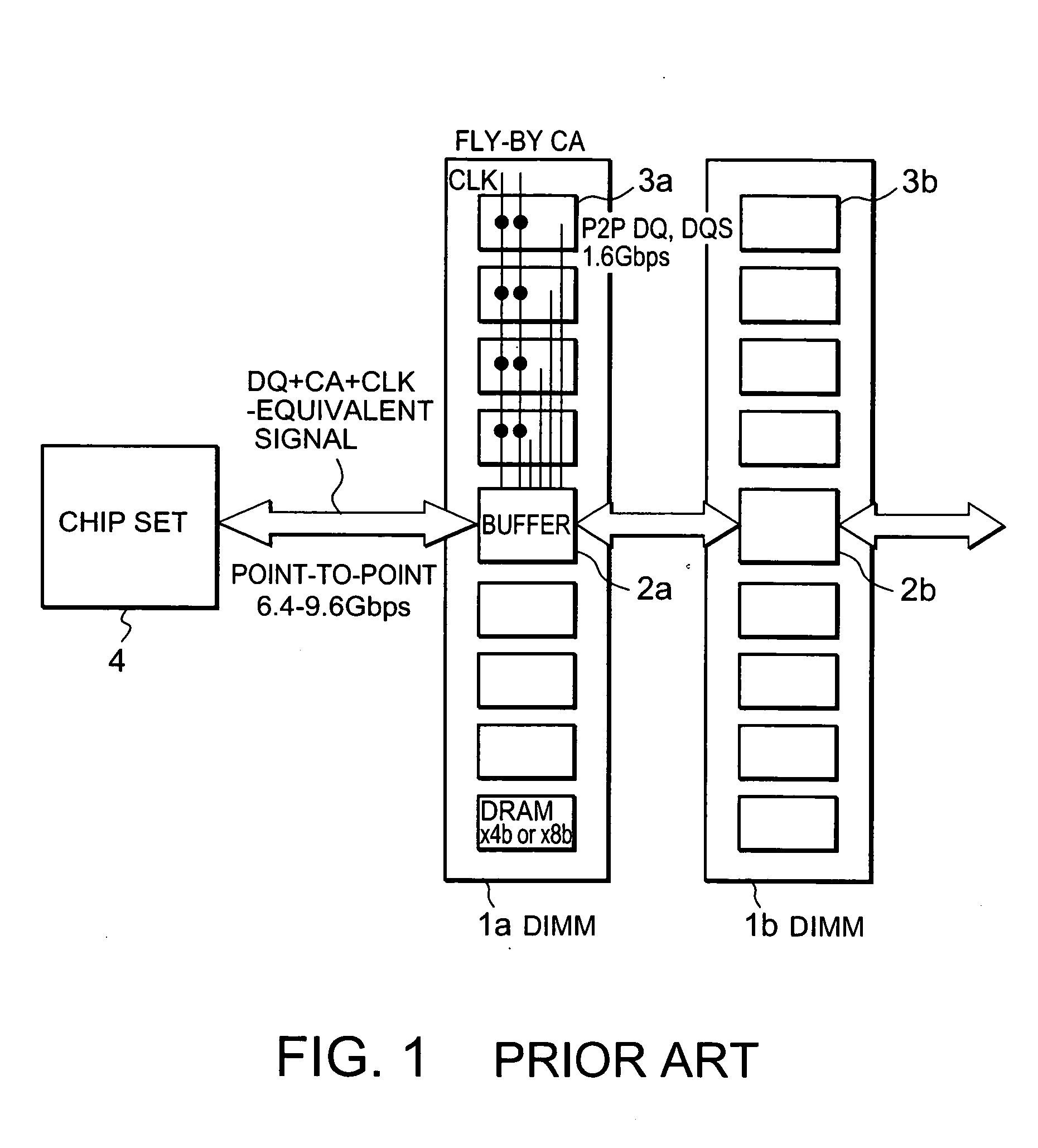

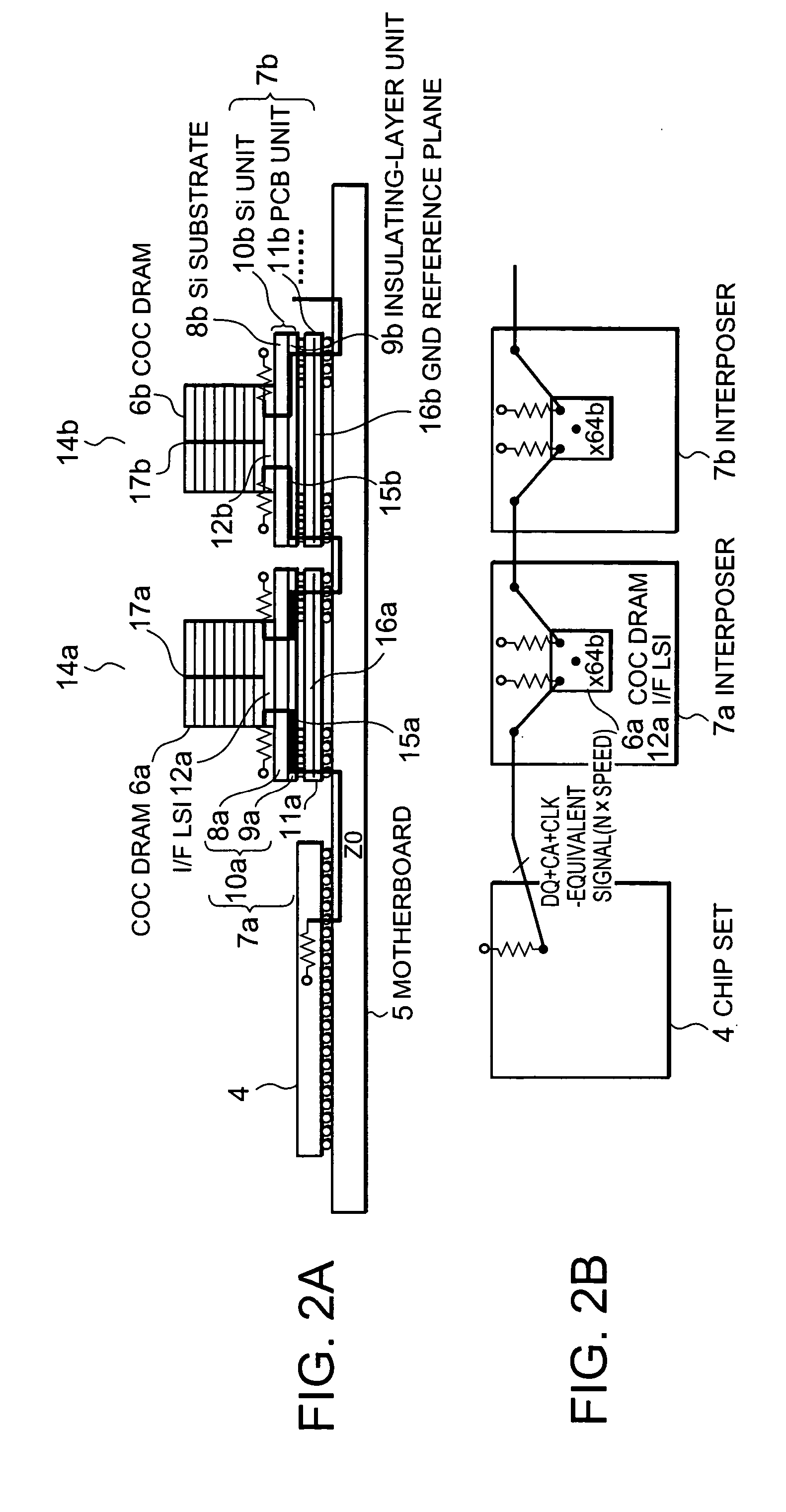

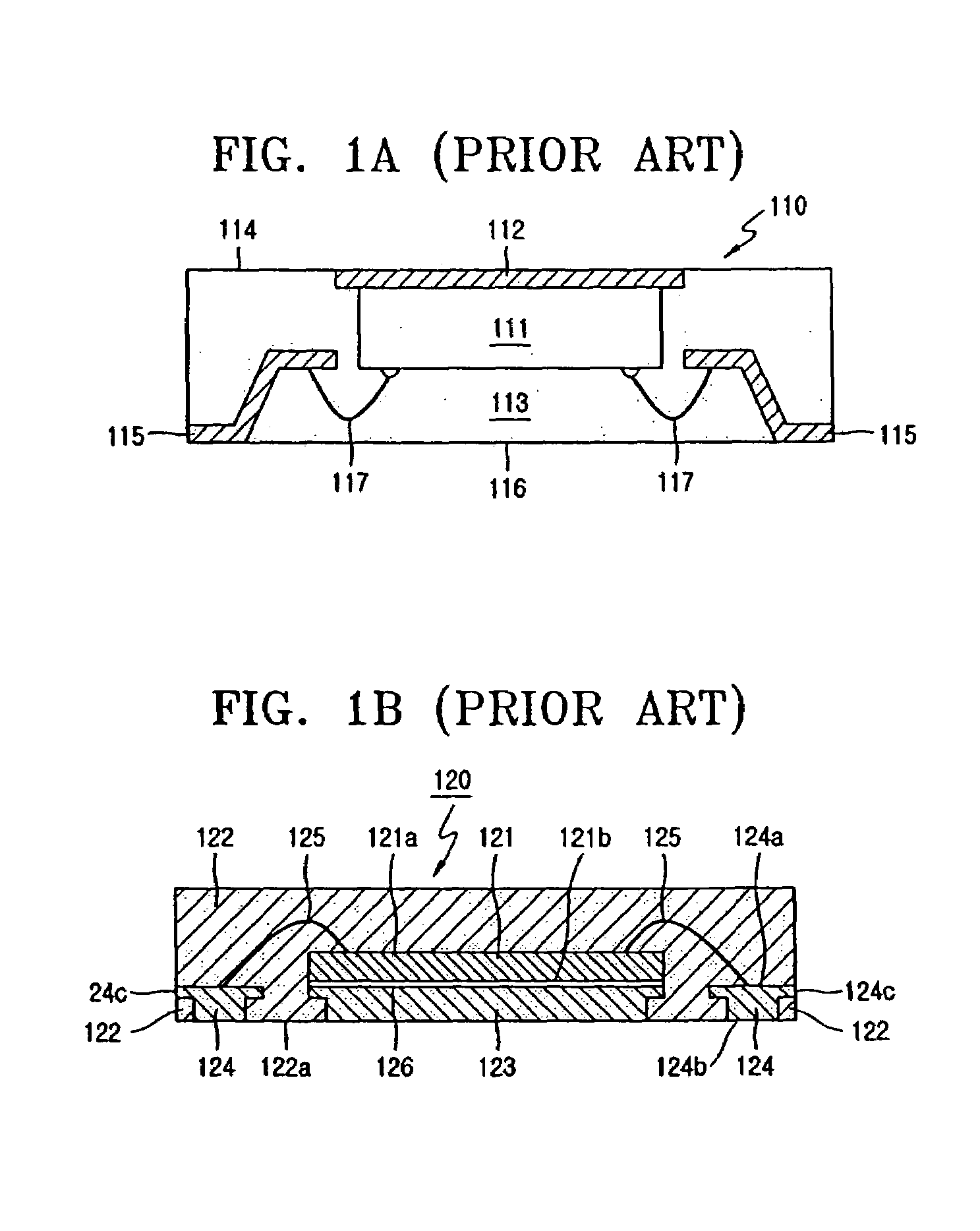

Semiconductor integrated circuit device

InactiveUS20050139977A1Easy impedance matchingReduce signalingTransistorSemiconductor/solid-state device detailsInterposerChipset

A COC DRAM including a plurality of stacked DRAM chips is mounted on a motherboard by using an interposer. The interposer includes a Si unit and a PCB. The Si unit includes a Si substrate and an insulating-layer unit in which wiring is installed. The PCB includes a reference plane for the wiring in the Si unit. The wiring topology between a chip set and the COC DRAM is the same for every signal. Accordingly, a memory system enabling a high-speed operation, low power consumption, and large capacity is provided.

Owner:PS4 LUXCO SARL

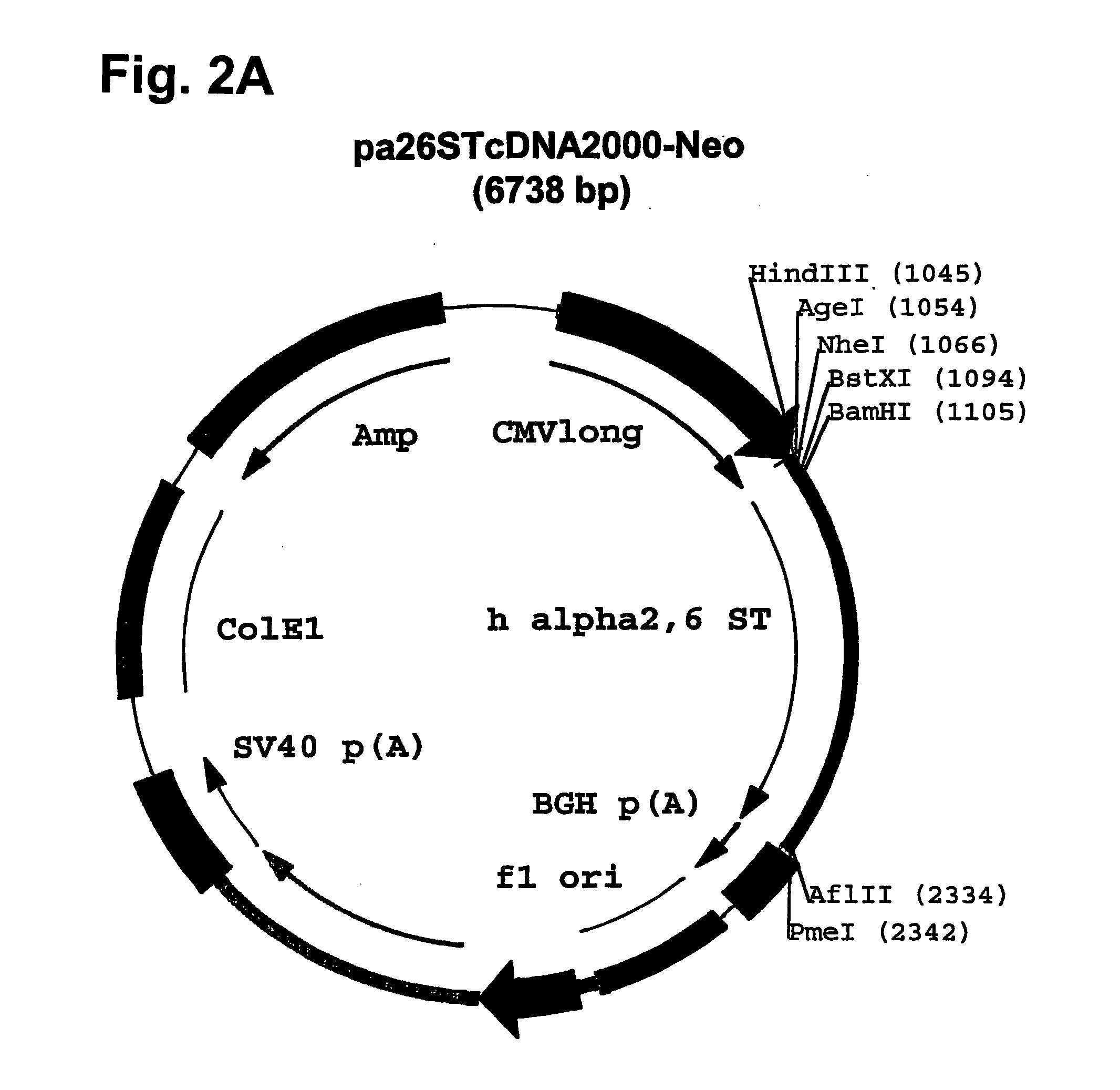

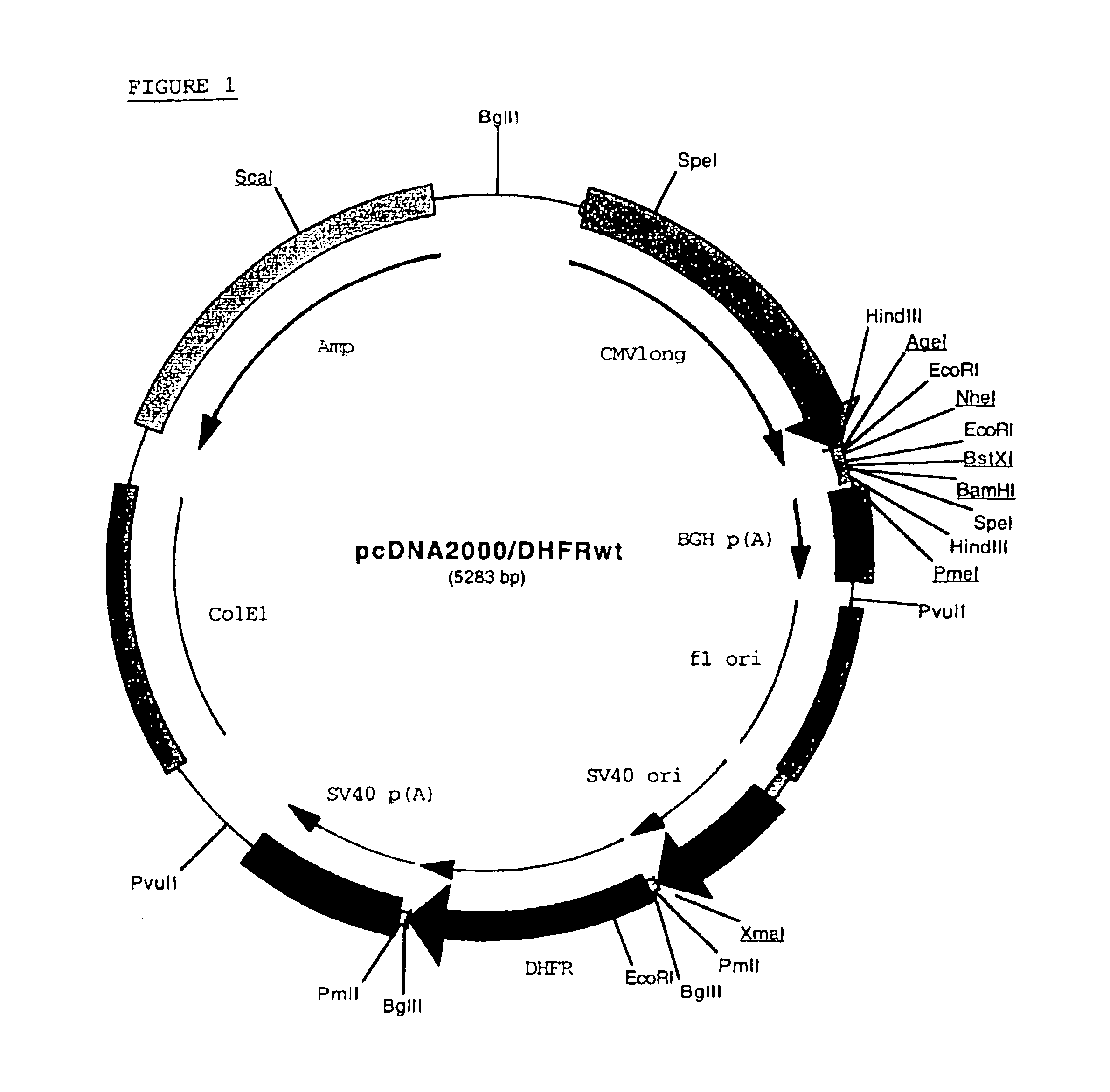

Recombinant protein production in a human cell

InactiveUS6855544B1Easy to handleLarge-scale (continuous) productionSsRNA viruses negative-senseSugar derivativesHamsterHuman cell

Methods and compositions for the production of recombinant proteins in a human cell line. The methods and positions are particularly useful for generating stable expression of human recombinant proteins of interest that are modified post-translationally, for example, by glycosylation. Such proteins may have advantageous properties in comparison with their counterparts produced in non-human systems such as Chinese Hamster Ovary cells.

Owner:JANSSEN VACCINES & PREVENTION BV

Processing system for fabricating compound nitride semiconductor devices

InactiveUS20090194026A1Expands available process windowImprove system throughputAfter-treatment apparatusPolycrystalline material growthCompound structureEngineering

One embodiment of a processing system for fabricating compound nitride semiconductor devices comprises one or more processing chamber operable with form a compound nitride semiconductor layer on a substrate, a transfer chamber coupled with the processing chamber, a loadlock chamber coupled with the transfer chamber, and a load station coupled with the loadlock chamber, wherein the load station comprises a conveyor tray movable to convey a carrier plate loaded with one or more substrates into the loadlock chamber. Compared to a single chamber reactor, the multi-chamber processing system expands the potential complexity and variety of compound structures. Additionally, the system can achieve higher quality and yield by specialization of individual chambers for specific epitaxial growth processes. Throughput is increased by simultaneous processing in multiple chambers.

Owner:APPLIED MATERIALS INC

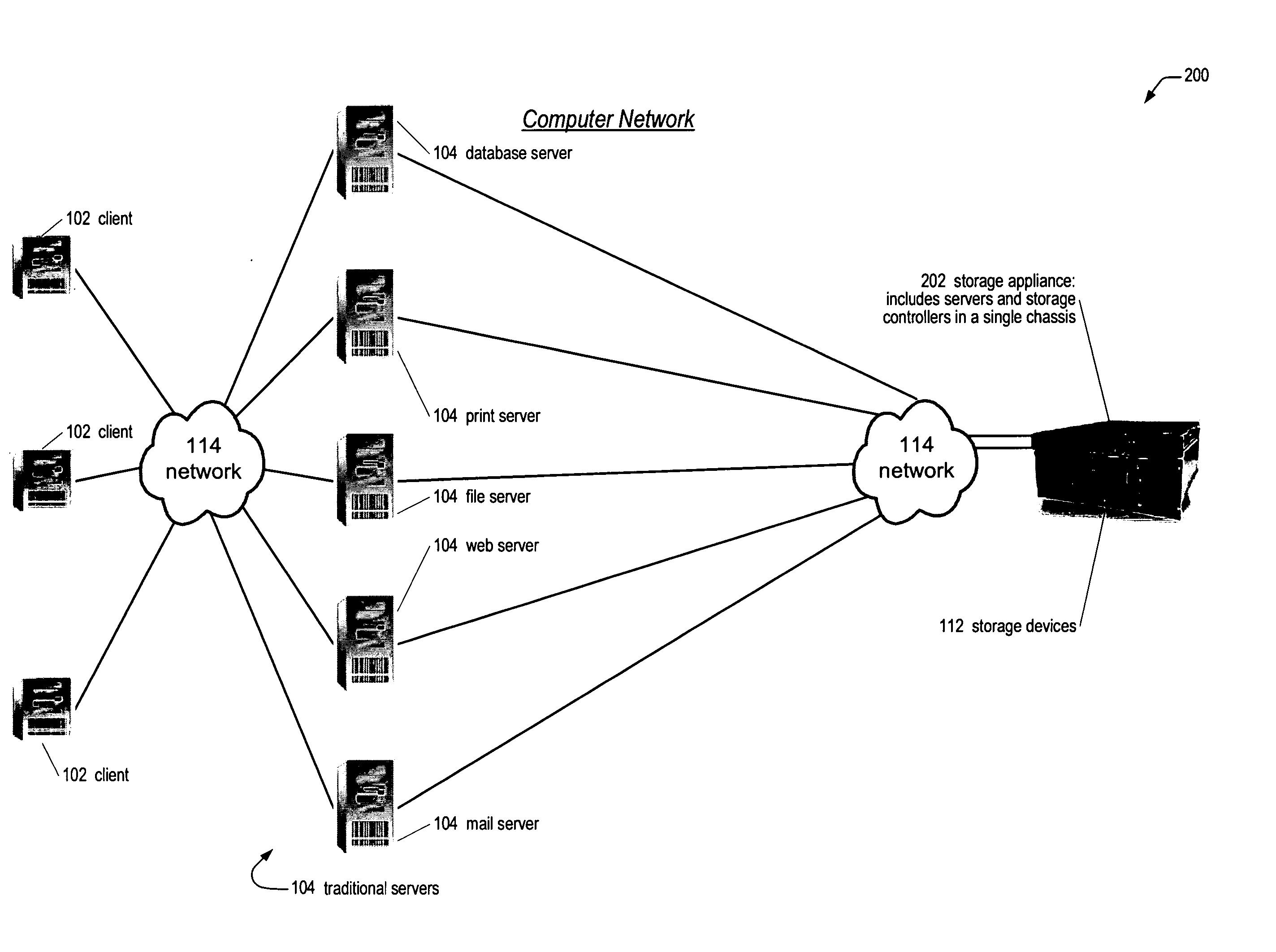

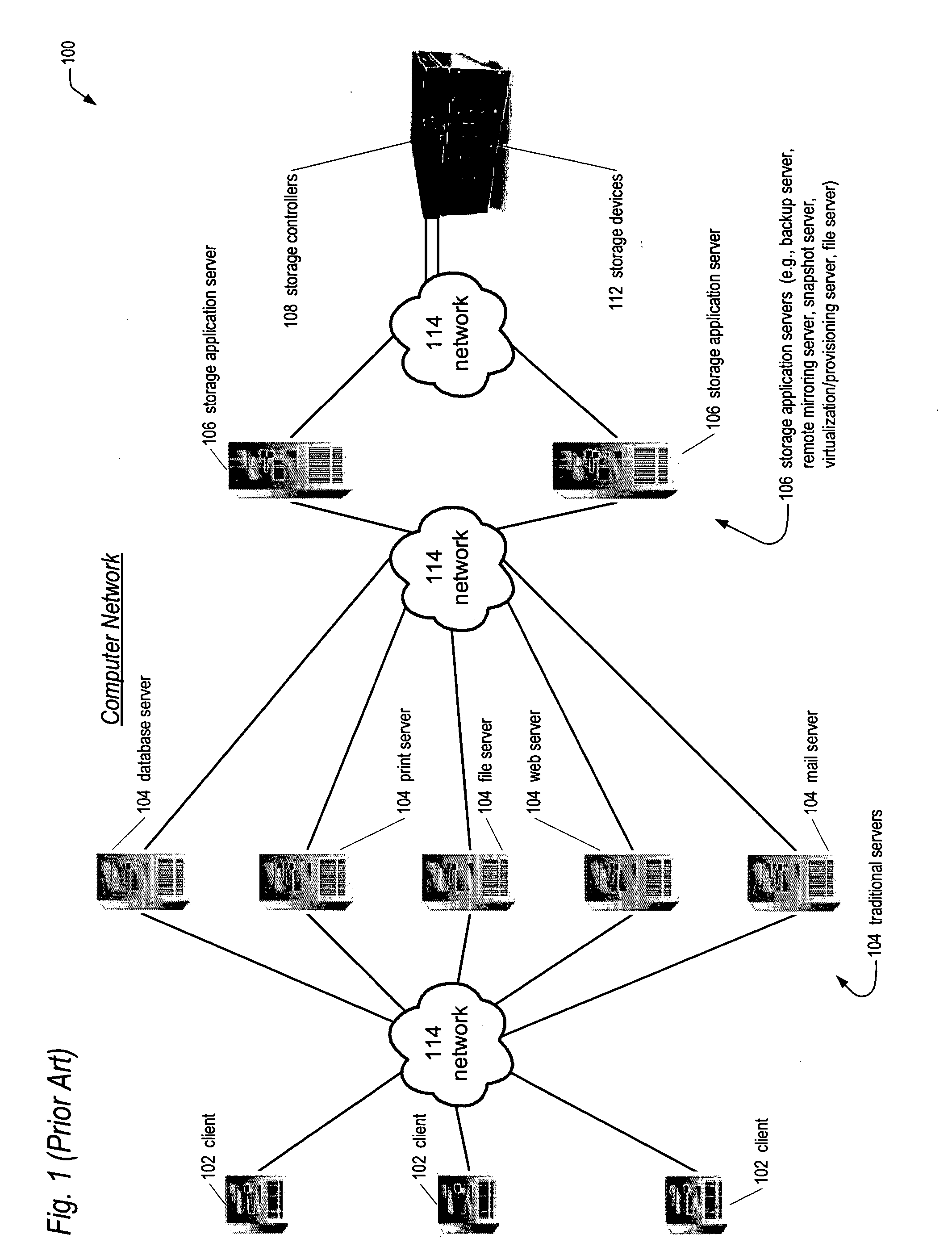

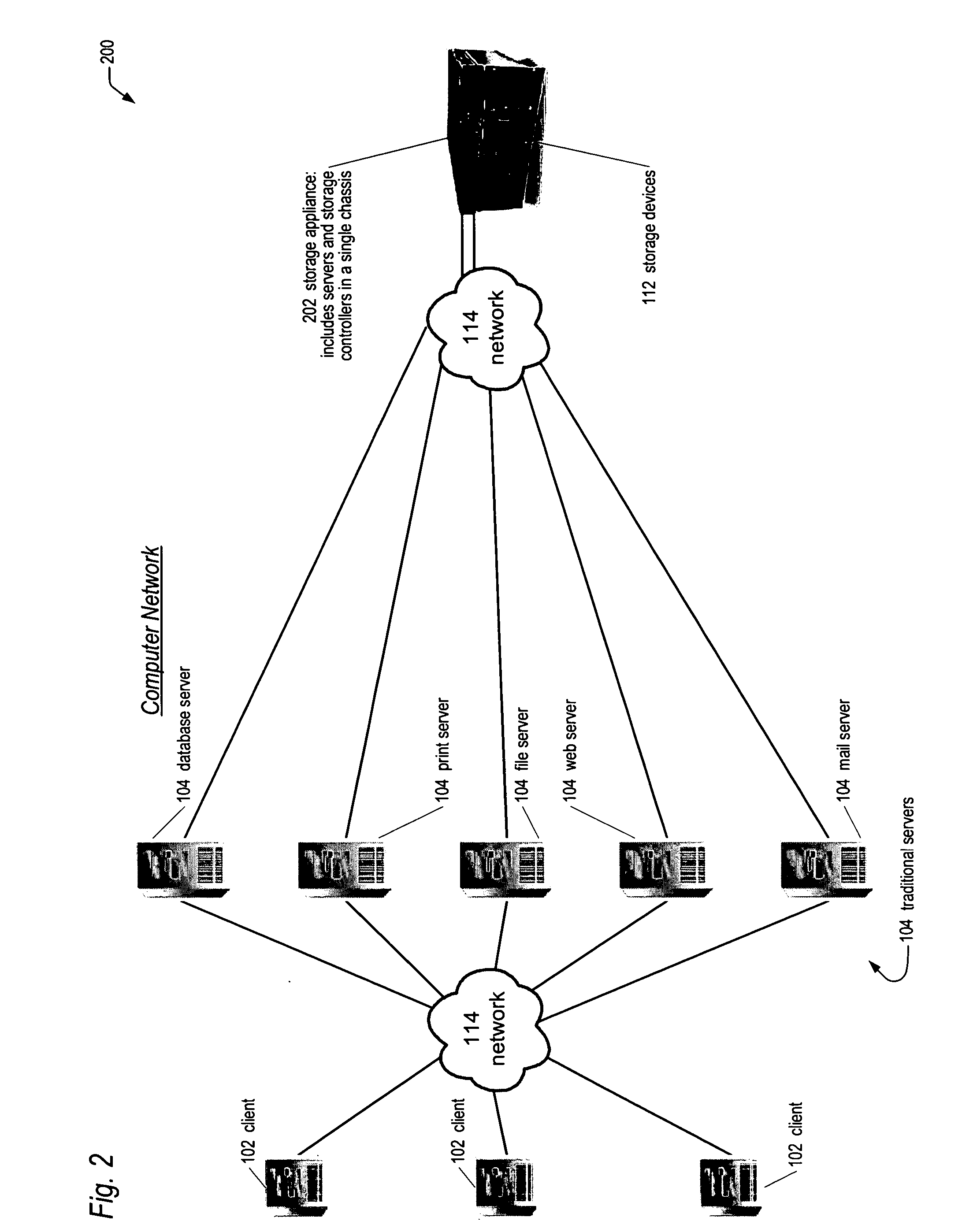

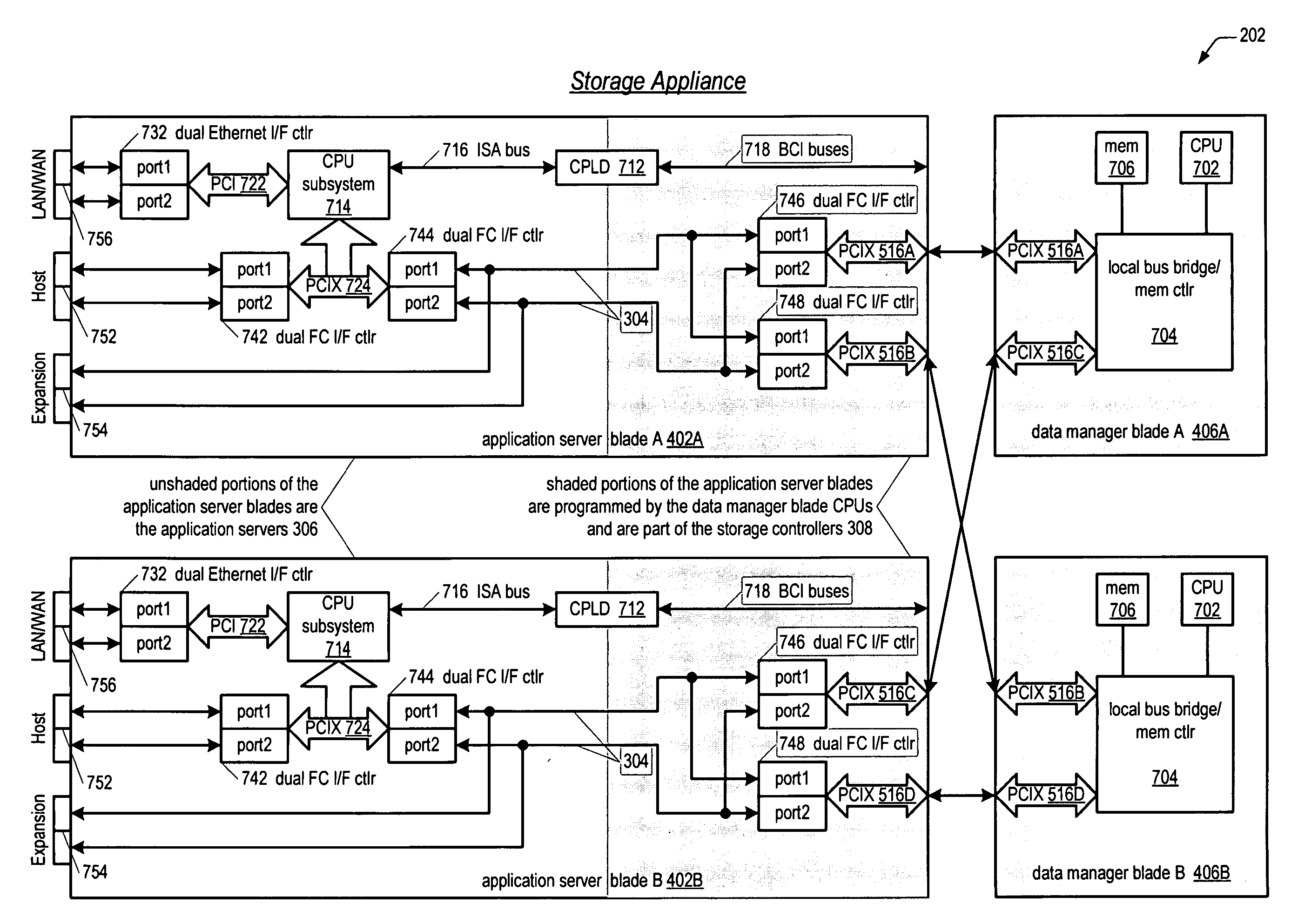

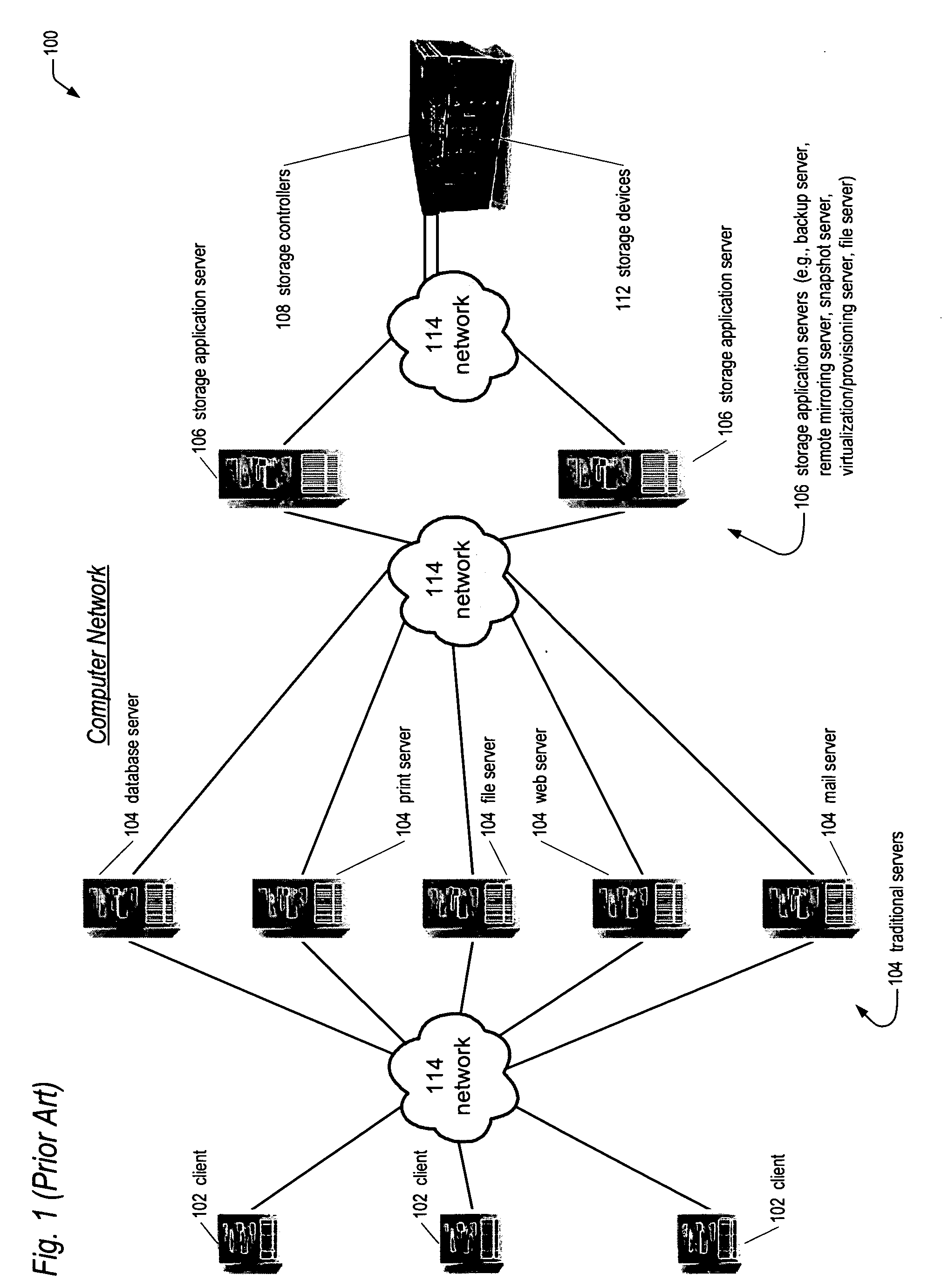

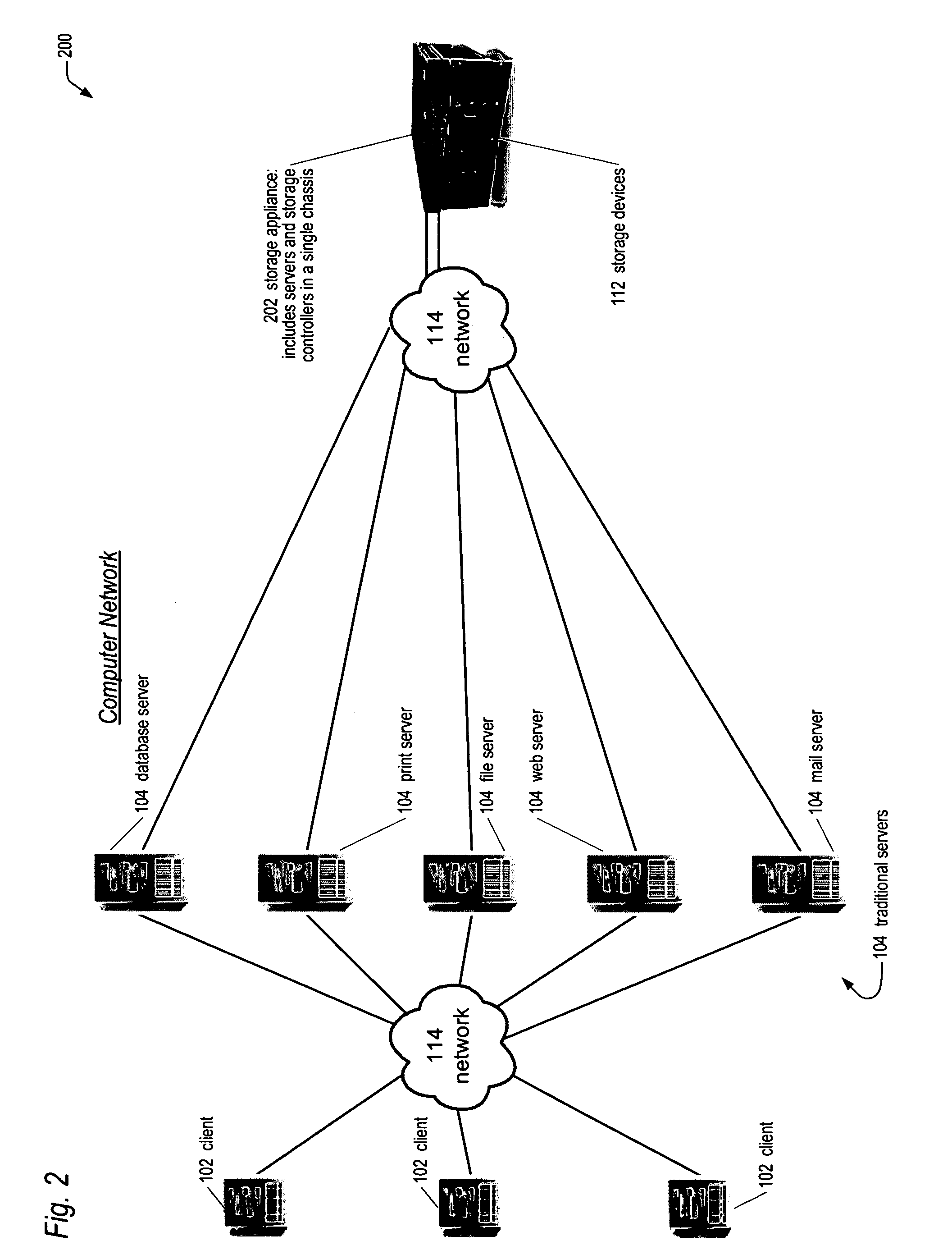

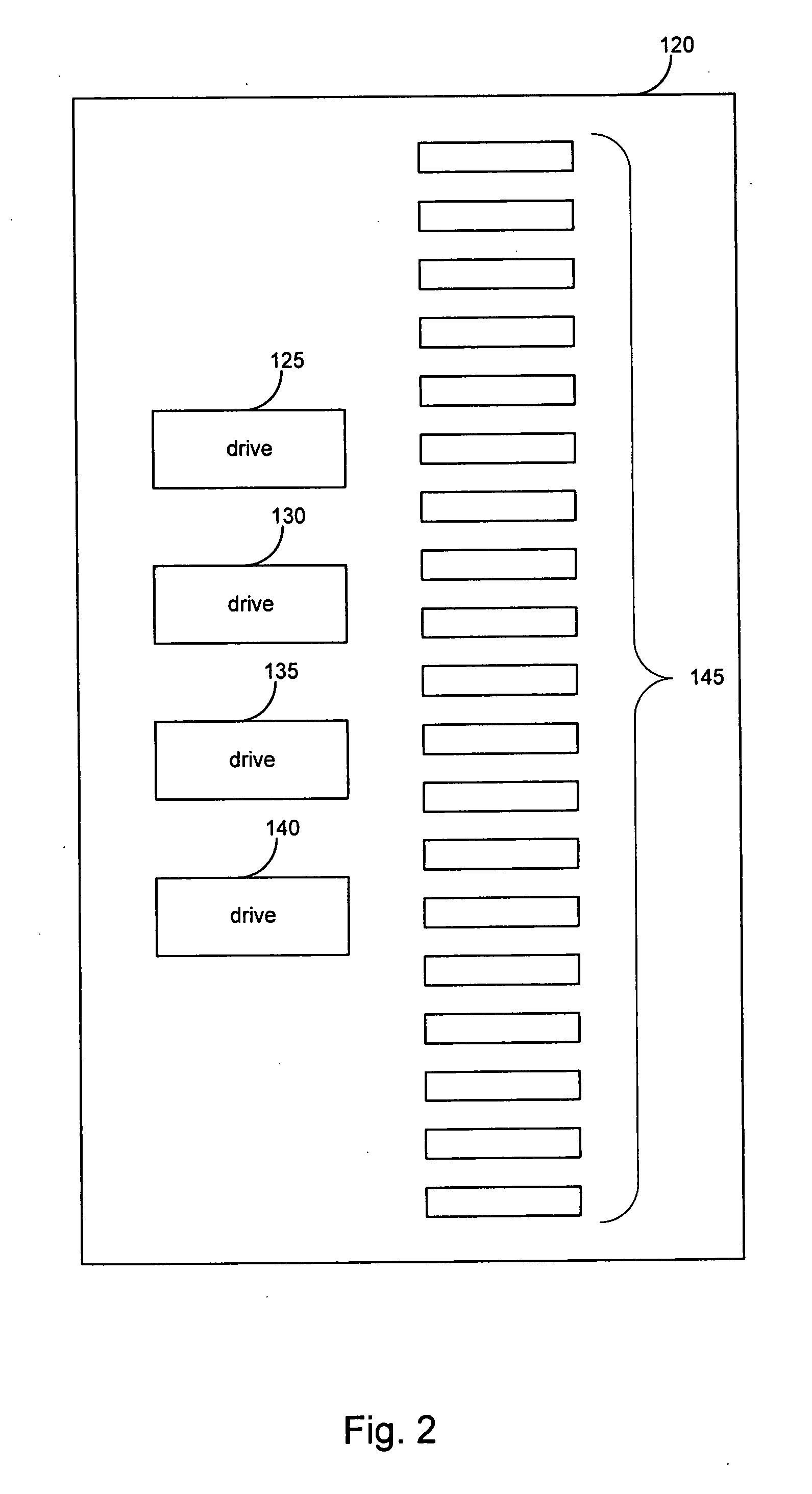

Network storage appliance with integrated redundant servers and storage controllers

ActiveUS20050021606A1Reduce needLow costInput/output to record carriersDigital data processing detailsHard disc driveOff the shelf

A network storage appliance is disclosed. The appliance includes a single chassis that encloses a plurality of servers and a plurality of storage controllers coupled together via a chassis backplane. The storage controllers control the transfer of data between the plurality of servers and a plurality of storage devices coupled to the storage controllers. The servers and storage controllers include a plurality of field replaceable unit (FRUs) hot-pluggable into the backplane such that any one of the FRUs may fail without loss of availability to the storage devices' data. In various embodiments, the chassis fits in a 19″ wide rack; is 1U high; the servers are standard PCs configured to execute off-the-shelf server applications and to facilitate porting of popular operating systems with little modification; the servers include disk-on-chip memory rather than a hard drive; local buses (e.g., PCIX) on the backplane interface the various FRUs.

Owner:DOT HILL SYST

Network storage appliance with integrated server and redundant storage controllers

ActiveUS20050010715A1Improve system reliabilityImprove manageabilityInput/output to record carriersDigital data processing detailsControl storeMagnetic tape

A network storage appliance is disclosed. The appliance includes a chassis enclosing a backplane, and a server enclosed in the chassis and coupled to the backplane. The appliance also includes storage controllers enclosed in the chassis, each coupled to the backplane, which control transfer of data between the server and storage devices coupled to the storage controllers. The storage controllers also control transfer of data between the storage devices and computers networked to the appliance and external to the appliance. The storage controllers and the server comprise a plurality of hot-replaceable blades. Any one of the plurality of blades may be replaced during operation of the appliance without loss of access to the storage devices by the computers. In one embodiment, the server executes storage application software, such as backup software for backing up data on the storage devices, such as to a tape device networked to the server.

Owner:DOT HILL SYST

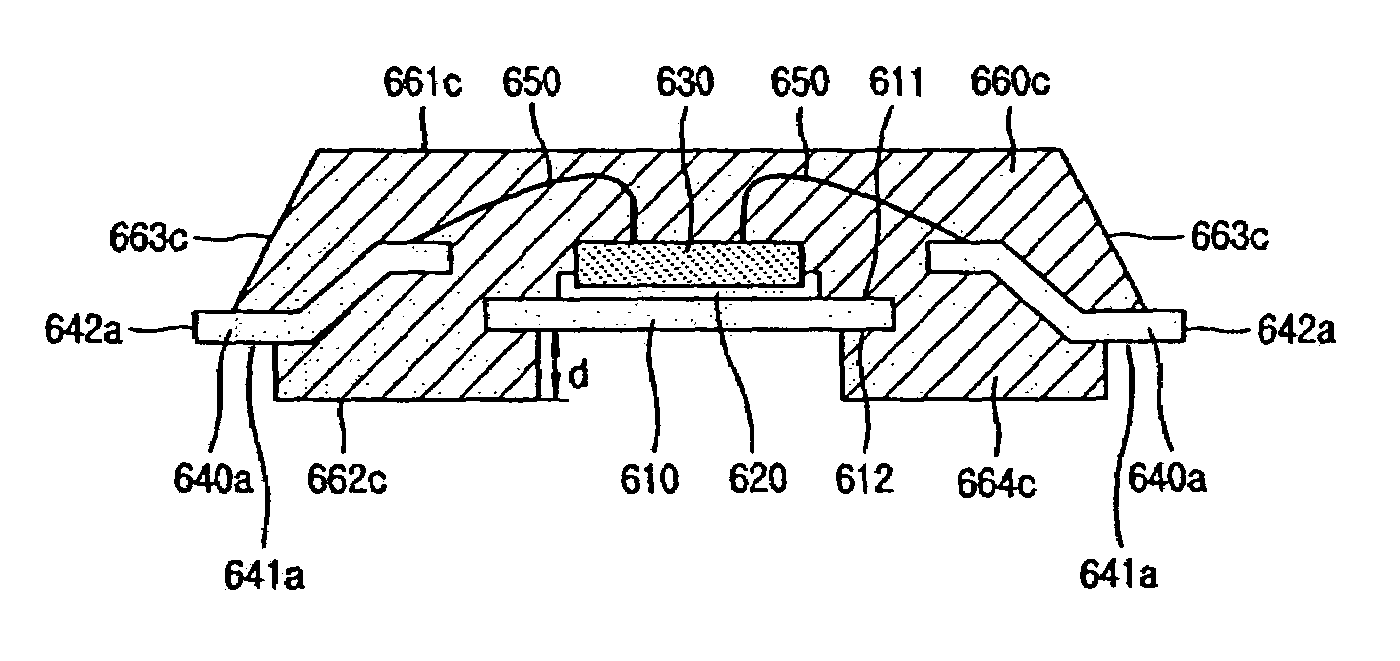

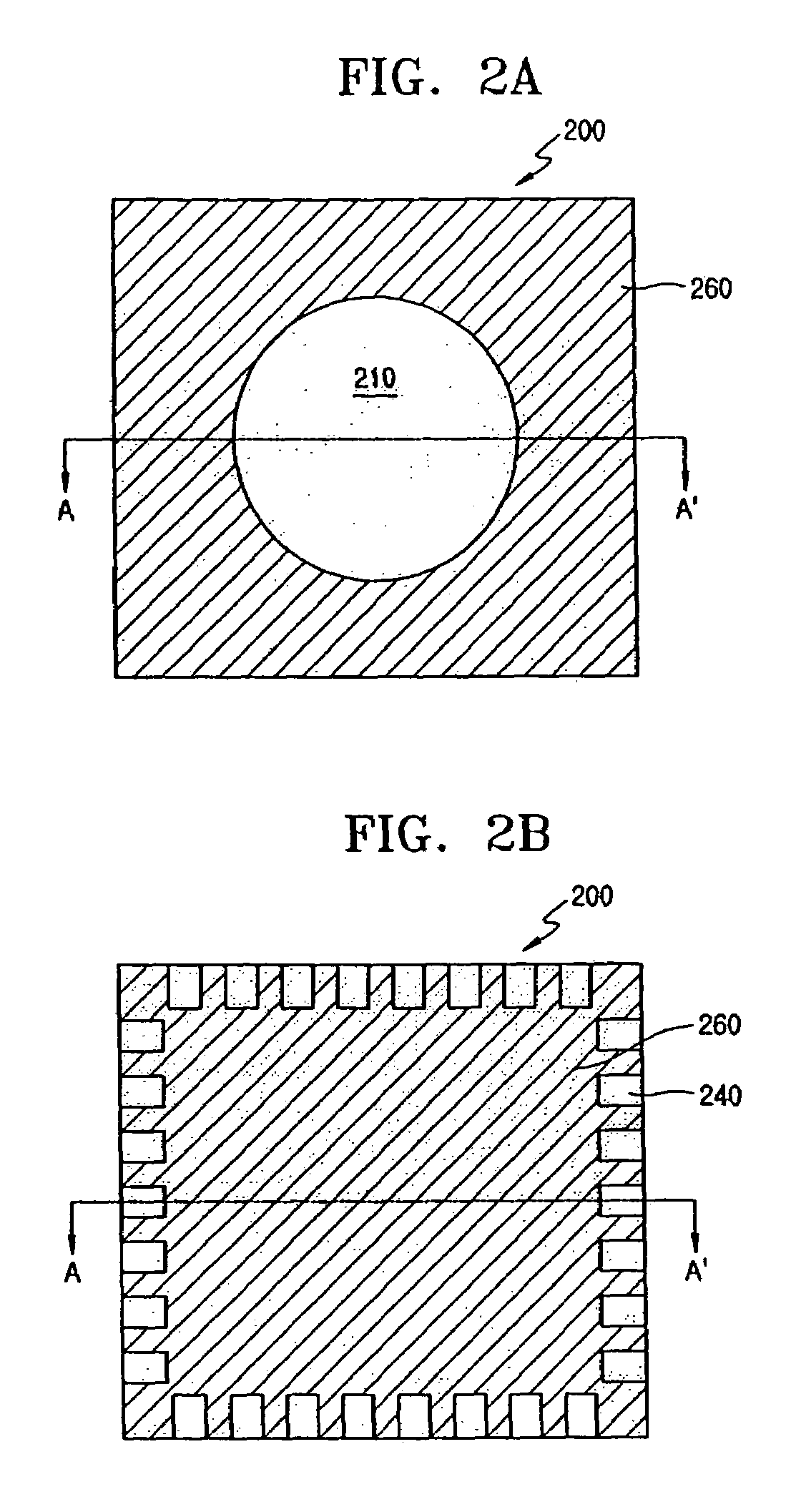

Molded leadless package having a partially exposed lead frame pad

ActiveUS7315077B2Improve reliabilityGood transferabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

Provided are a molded leadless package, and a sawing type molded leadless package and method of manufacturing same. The molded leadless package includes a lead frame pad having first and second surfaces opposite to each other. A semiconductor chip is adhered to the first surface of the lead frame pad. A lead is electrically coupled to the semiconductor chip. A molding material covers the lead frame pad, the semiconductor chip, and the lead and exposes a portion of the lead and a portion of the second surface of the lead frame pad. A step difference is formed between a surface of the molding material covering the second surface of the lead frame pad and the second surface of the lead frame pad itself. The sawing type molded leadless package includes a short-circuit preventing member that is post-shaped or convex, and protruding from the lower surface of the die pad.

Owner:SEMICON COMPONENTS IND LLC

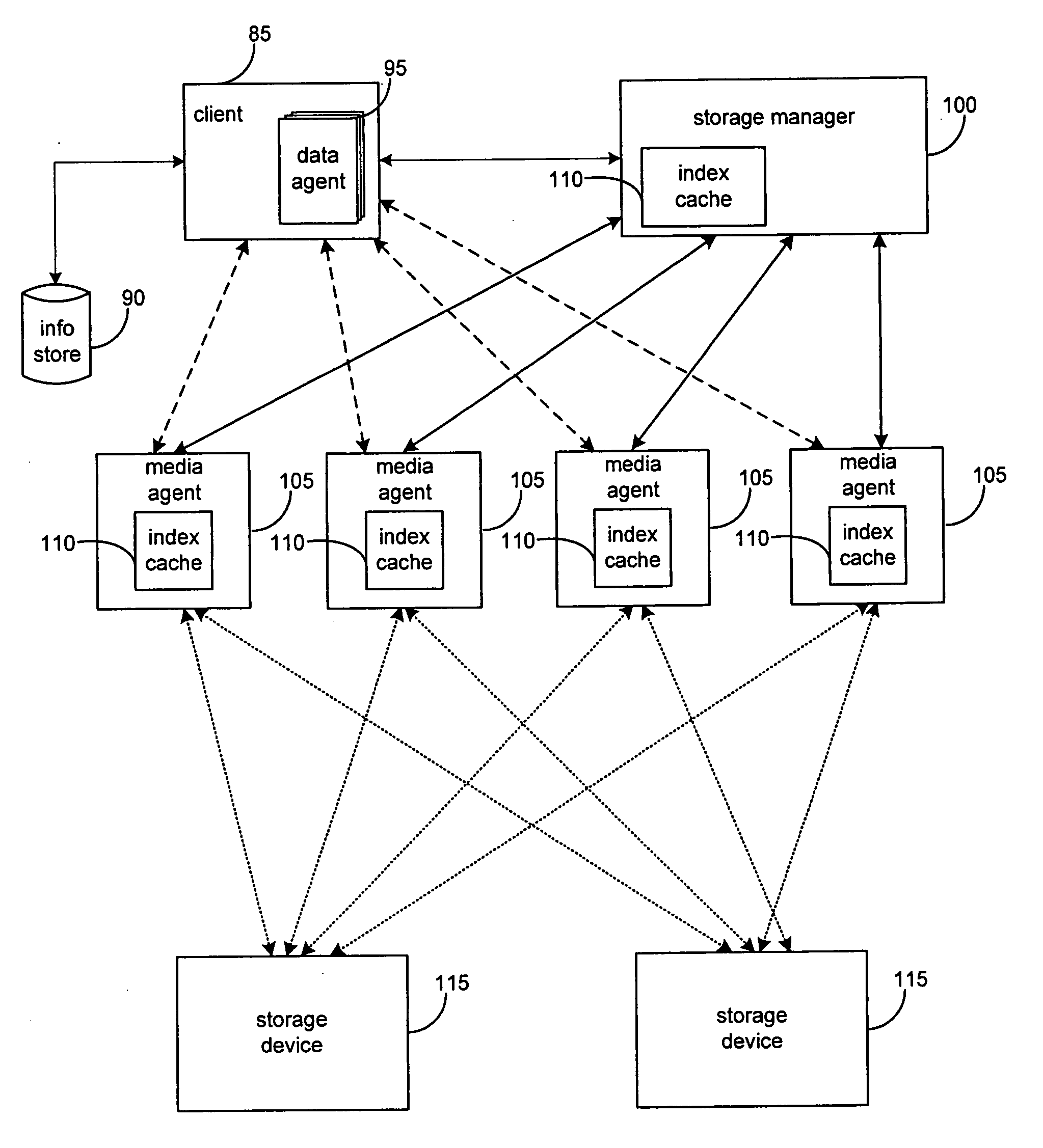

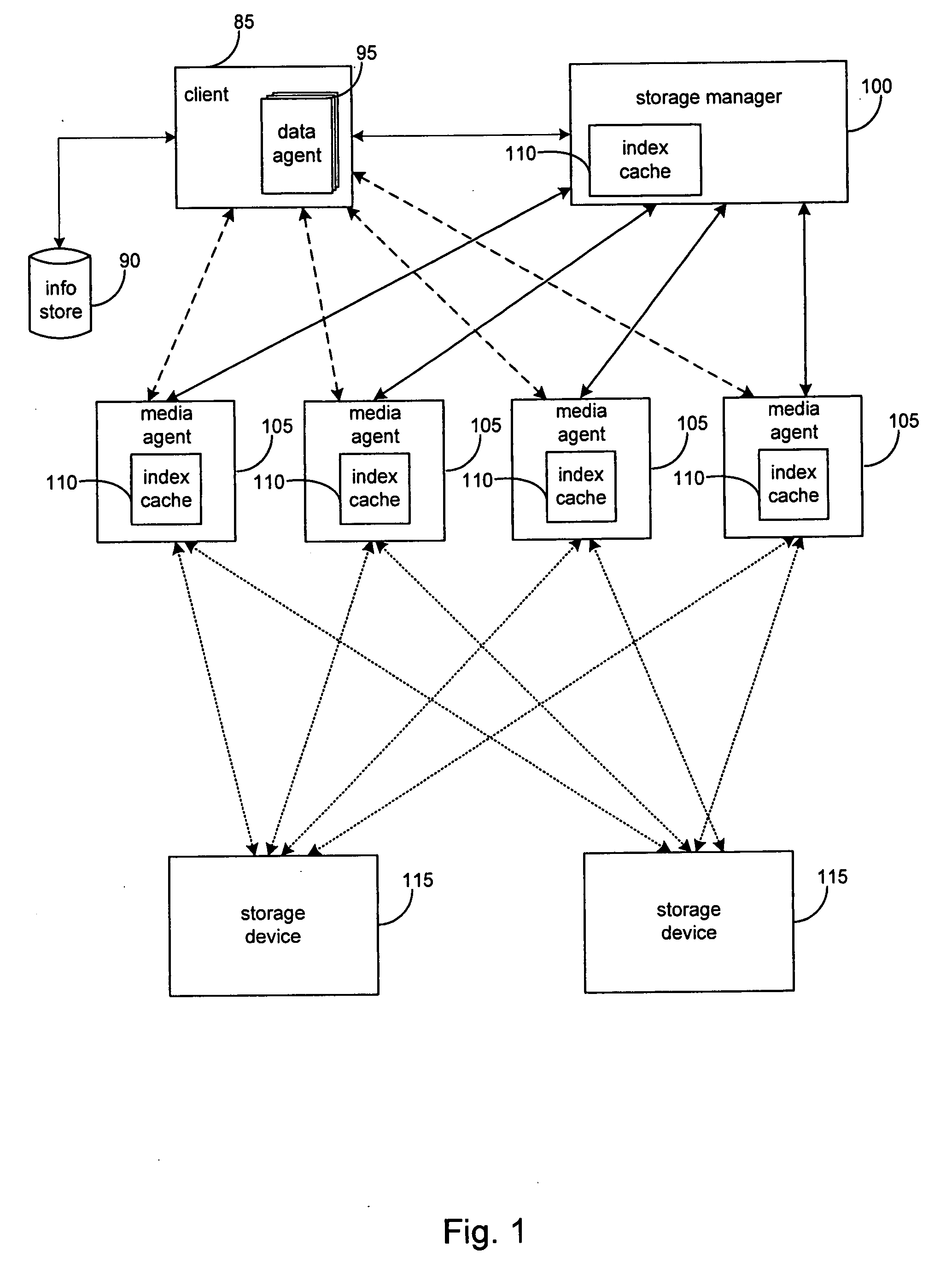

System and methods for granular resource management in a storage network

InactiveUS20080147878A1Improve performanceImprove system reliabilityDigital data information retrievalMultiple digital computer combinationsResource managementDatapath

In accordance with some aspects of the present invention, systems and methods are provided for dynamically and / or automatically selecting and / or modifying data path definitions that are used in performing storage operations on data. Alternate data paths may be specified or selected that use some or all resources that communicate with a particular destination to improve system reliability and performance. The system may also dynamically monitor and choose data path definitions to optimize system performance, conserve storage media and promote balanced load distribution.

Owner:KOTTOMTHARAYIL RAJIV +2

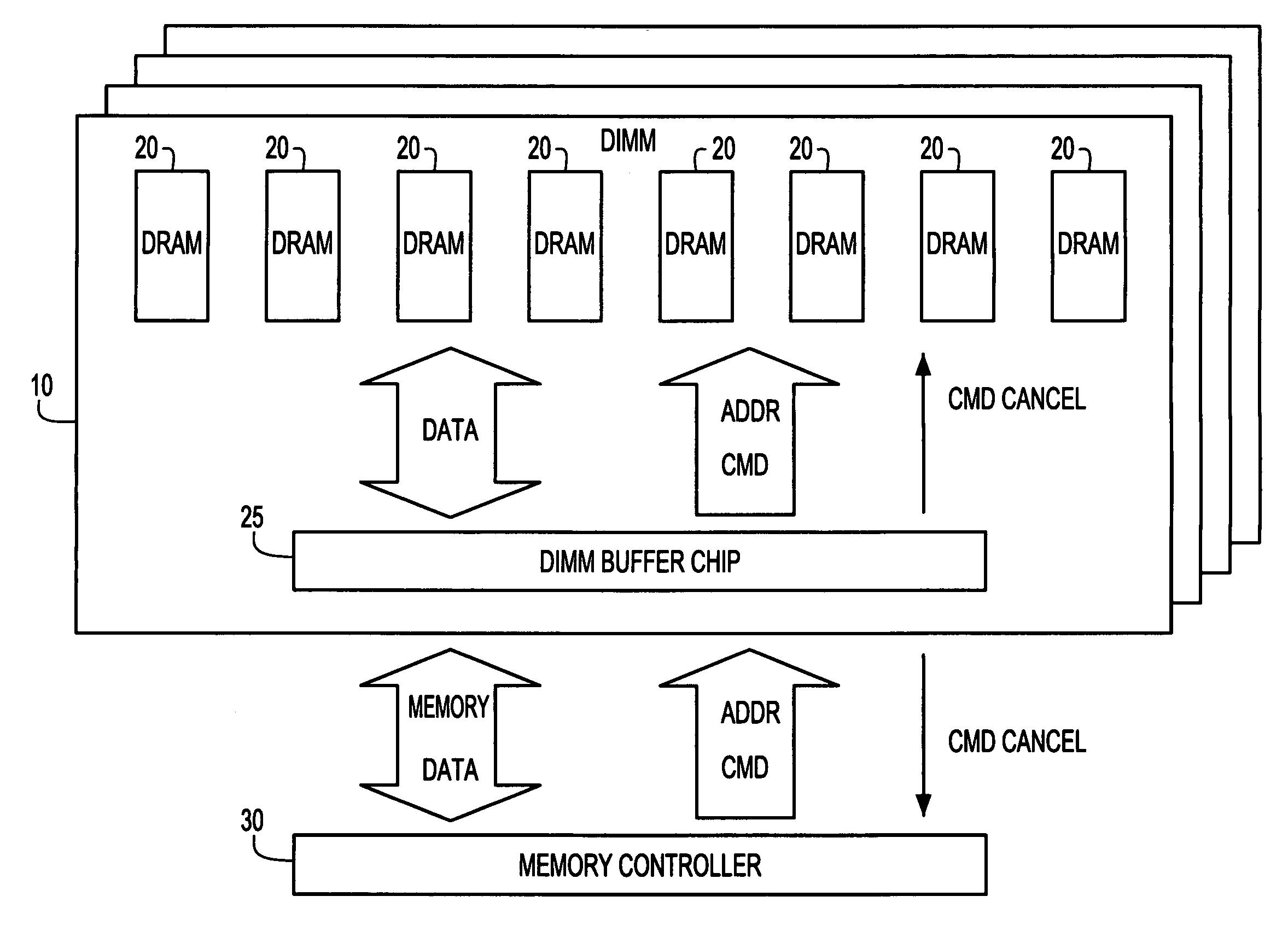

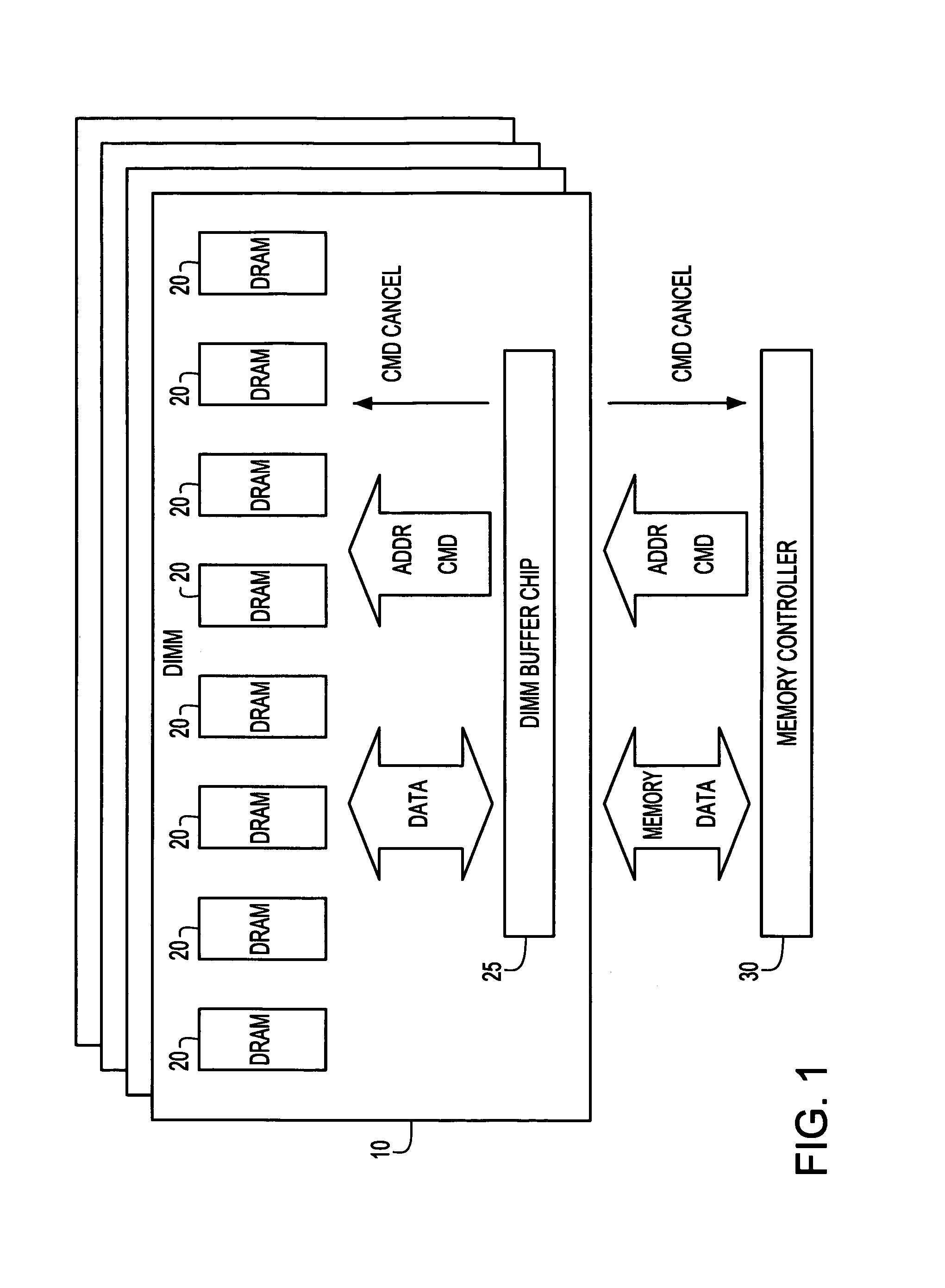

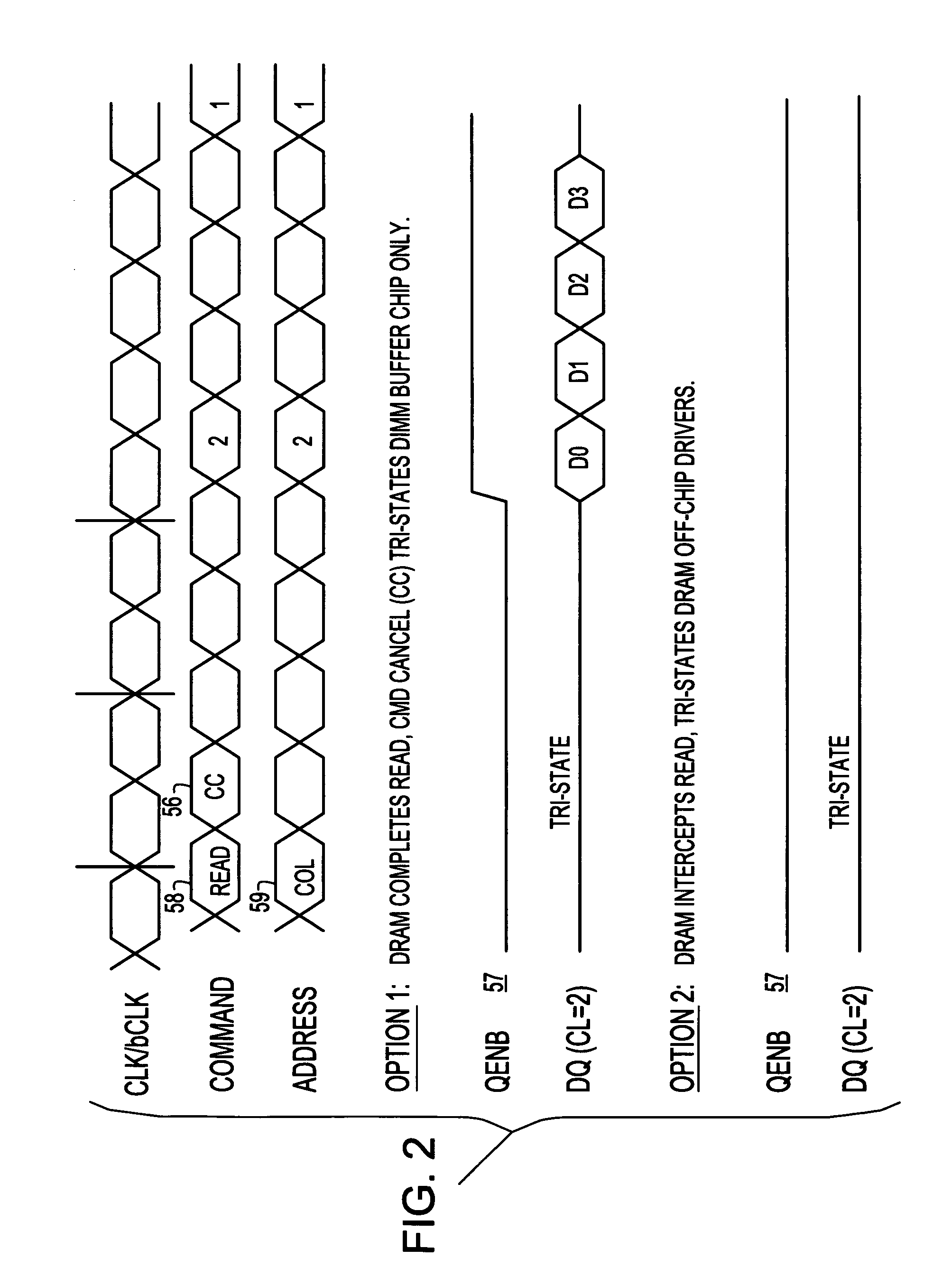

Method for performing a command cancel function in a DRAM

ActiveUS7480774B2Improve overall memory system reliabilityImprove system reliabilityOther printing matterMemory loss protectionClock rate8-bit

A method for performing a common cancel (CC) function on a dynamic random access memory (DRAM) semiconductor device to improve reliability and speed of a memory system. The CC function rakes advantage of the intrinsic delays associated wit memory read operations at high clock frequencies, and the increased write latency commensurate with increased read latencies where non-zero larencies for read and write operations are the norm by permitting address and command ECC structures to operate in parallel with the address and command re-drive circuitt The CC function is extendable to future DDR2 and DDR3 operating requirements in which latency of higher frequency modes will increase due to the shift from 2 bit pre-fetch to 4 and 8 bit pre-fetch architecture.

Owner:MARVELL ASIA PTE LTD

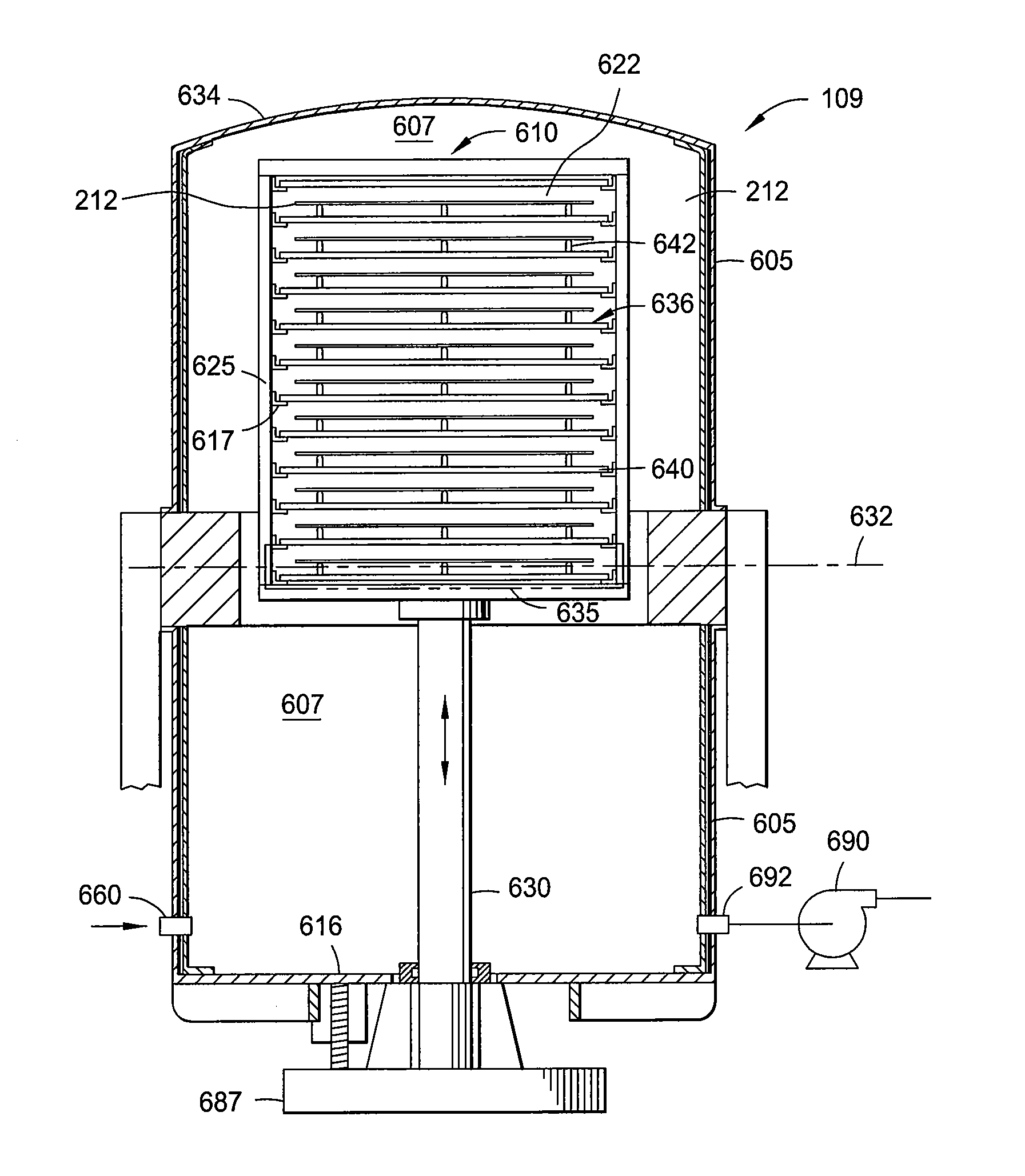

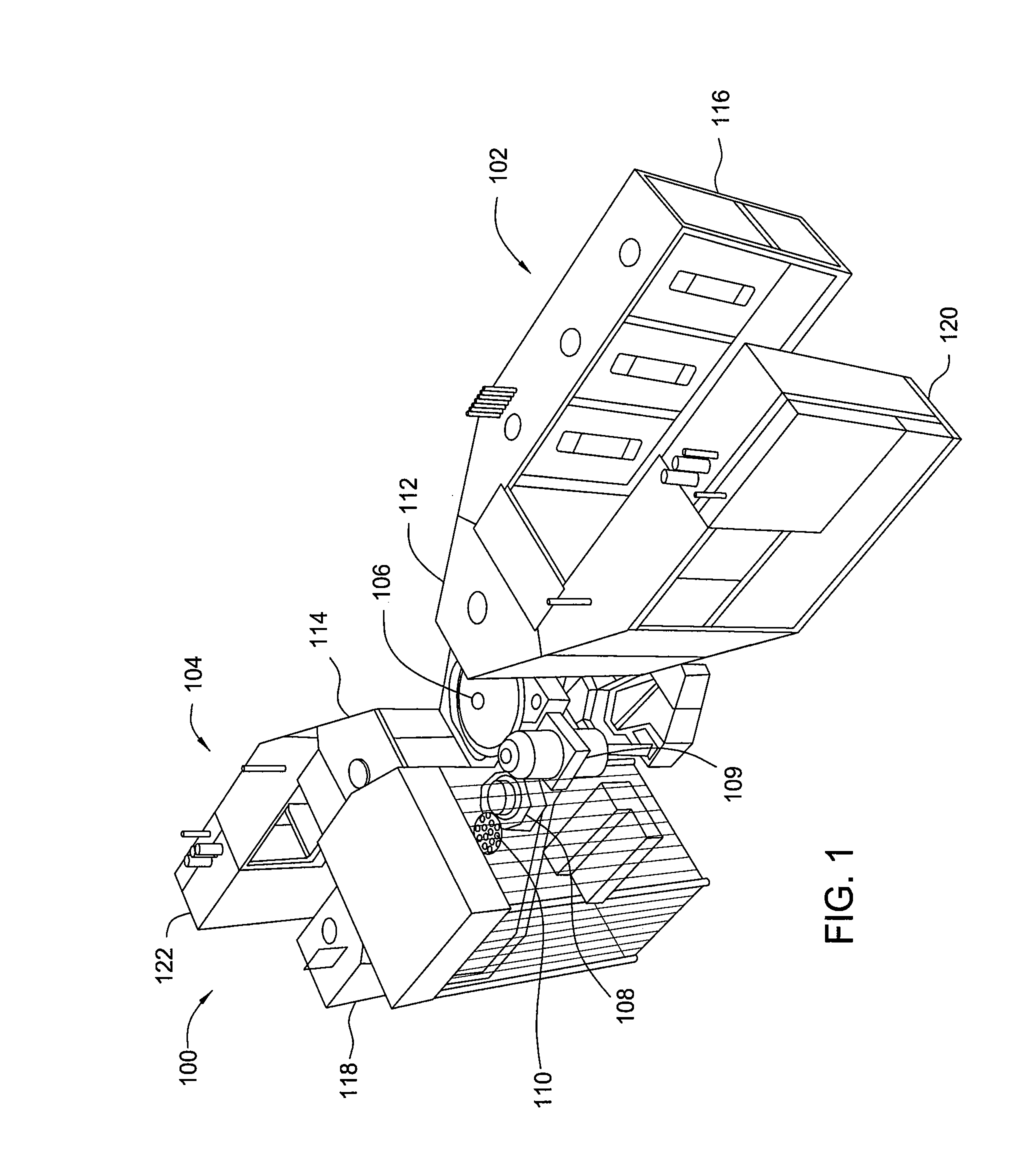

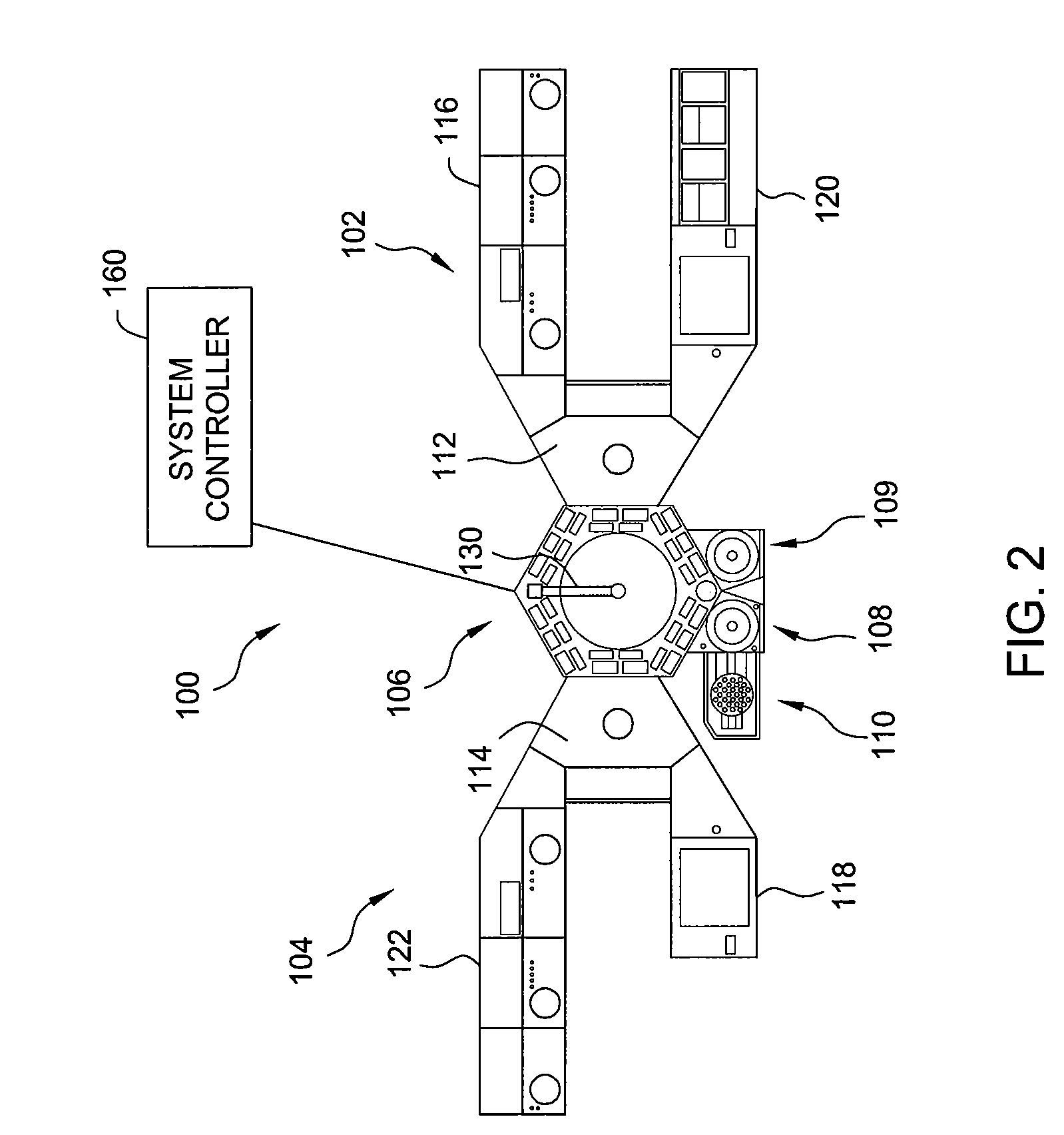

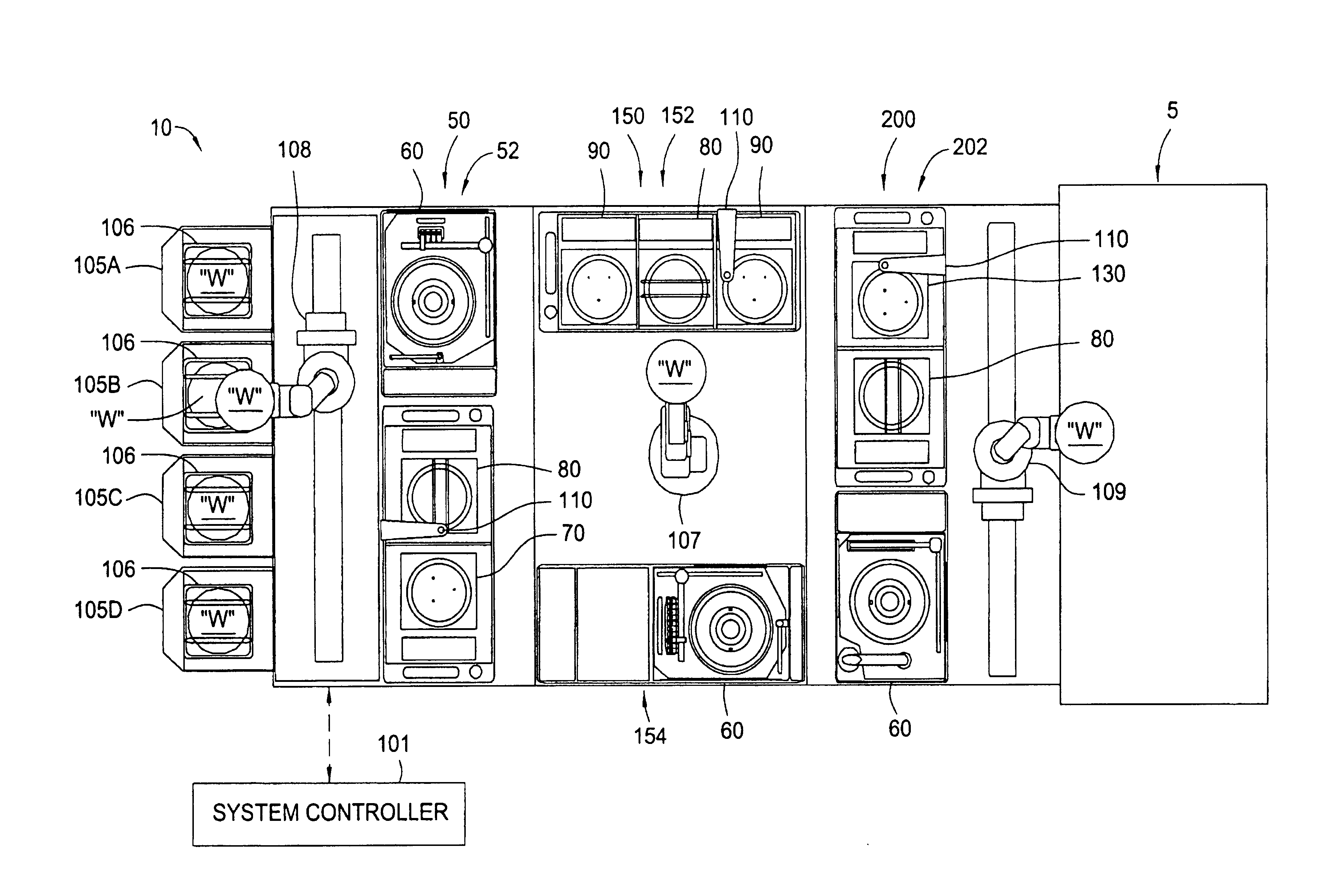

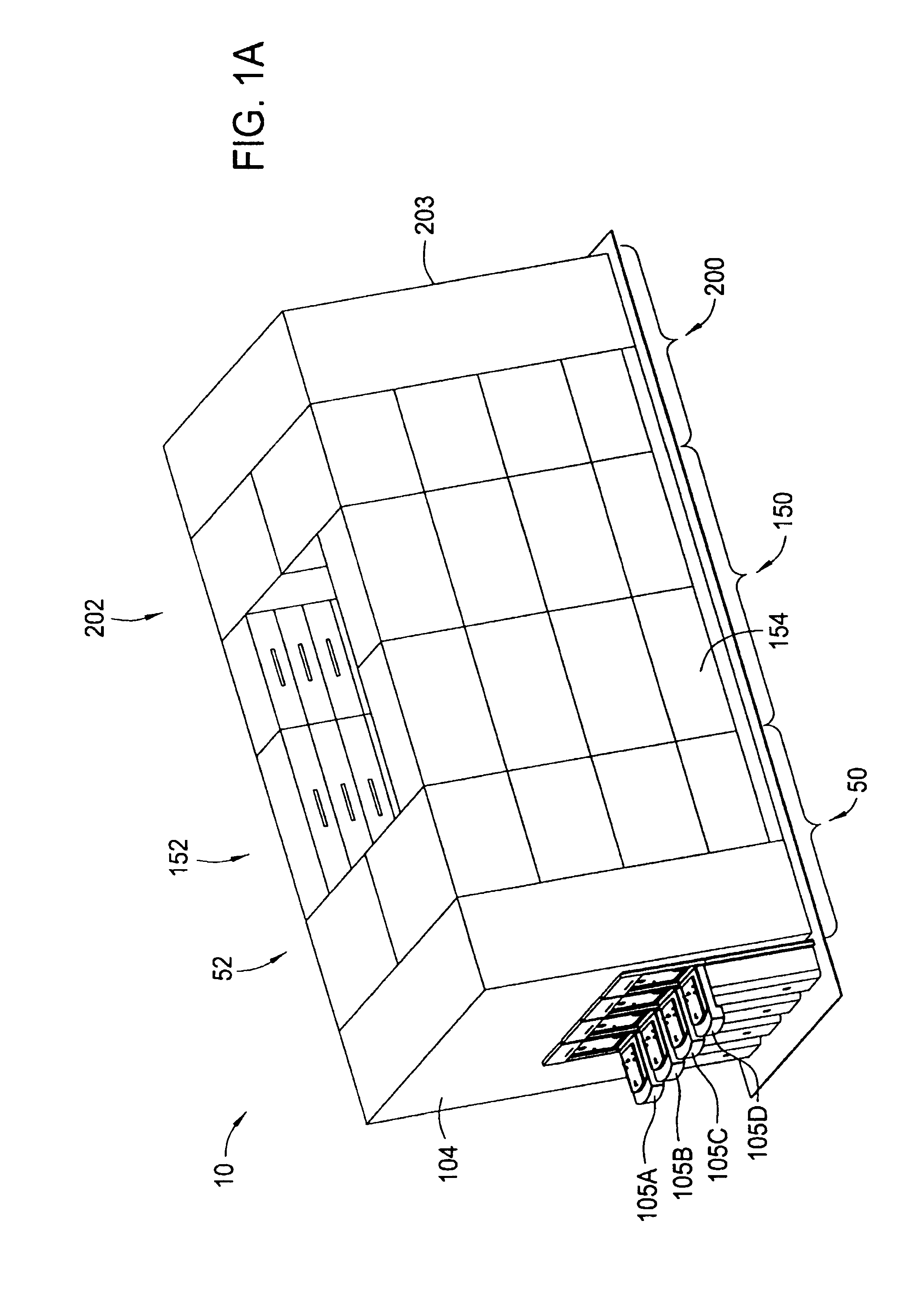

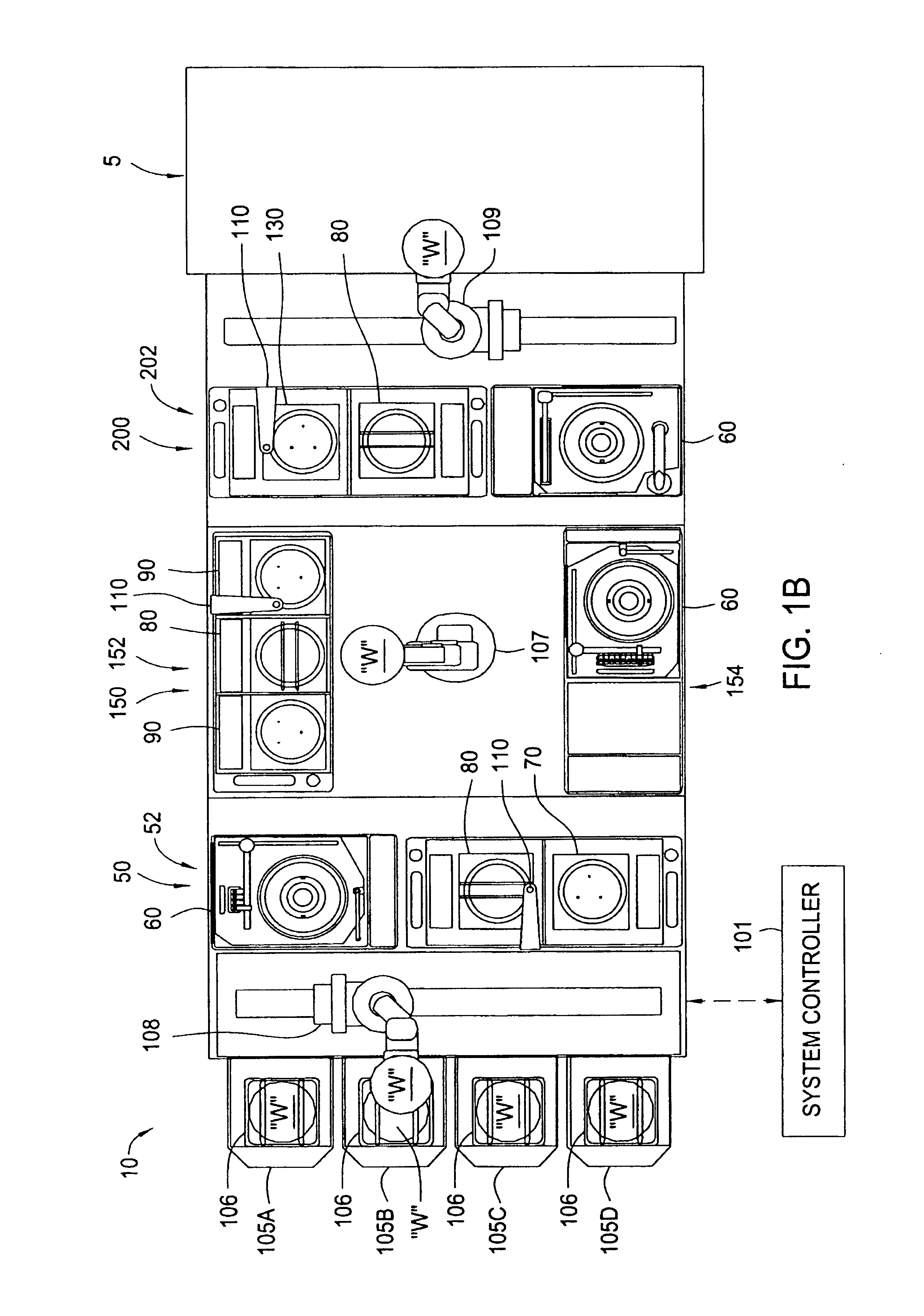

Cluster tool architecture for processing a substrate

ActiveUS20060130750A1Temperature controlMore repeatable wafer processing historyLiquid surface applicatorsSemiconductor/solid-state device testing/measurementLithography processEngineering

Embodiments generally provide an apparatus and method for processing substrates using a multi-chamber processing system (e.g., a cluster tool) that has an increased system throughput, increased system reliability, substrates processed in the cluster tool have a more repeatable wafer history, and also the cluster tool has a smaller system footprint. In one embodiment, the cluster tool is adapted to perform a track lithography process in which a substrate is coated with a photosensitive material, is then transferred to a stepper / scanner, which exposes the photosensitive material to some form of radiation to form a pattern in the photosensitive material, which is then removed in a developing process completed in the cluster tool. In track lithography type cluster tools, since the chamber processing times tend to be rather short, and the number of processing steps required to complete a typical track system process is large, a significant portion of the time it takes to process a substrate is taken up by the processes of transferring the substrates in a cluster tool between the various processing chambers. In one embodiment of the cluster tool, the cost of ownership is reduced by grouping substrates together and transferring and processing the substrates in groups of two or more to improve system throughput, and reduces the number of moves a robot has to make to transfer a batch of substrates between the processing chambers, thus reducing wear on the robot and increasing system reliability. In one aspect of the invention, the substrate processing sequence and cluster tool are designed so that the substrate transferring steps performed during the processing sequence are only made to chambers that will perform the next processing step in the processing sequence. Embodiments also provide for a method and apparatus that are used to improve the coater chamber, the developer chamber, the post exposure bake chamber, the chill chamber, and the bake chamber process results. Embodiments also provide for a method and apparatus that are used to increase the reliability of the substrate transfer process to reduce system down time.

Owner:SCREEN SEMICON SOLUTIONS CO LTD

Photovoltaic system power tracking method

ActiveUS9291696B2Power maximizationImprove system reliabilitySolar heating energyElectric signal transmission systemsSolar lightPower flow

A photovoltaic system including a photovoltaic cell, and an electronic module connected to the photovoltaic cell. The electronic module is adapted to produce at least one control signal indicative of electrical power being generated by the photovoltaic cells. A tracking controller is adapted to receive the control signal(s) and based on the control signal(s), the controller is adapted to control a tracking motor for adjusting the system so that electrical power generated by the photovoltaic cells is increased. The photovoltaic system may include an optical element, adapted for concentrating solar light onto the photovoltaic cells. The electronic module preferably performs direct current (DC) to direct current (DC) power conversion and maximum power point tracking by electrical power, current, or voltage at either their inputs or their outputs. Alternatively, the tracking controller is configured to also perform maximum power point tracking by increasing to a local maximum electrical power by varying at least one of (i) current or voltage output from the photovoltaic cell or (ii) current or voltage output from the electronic module.

Owner:SOLAREDGE TECH LTD

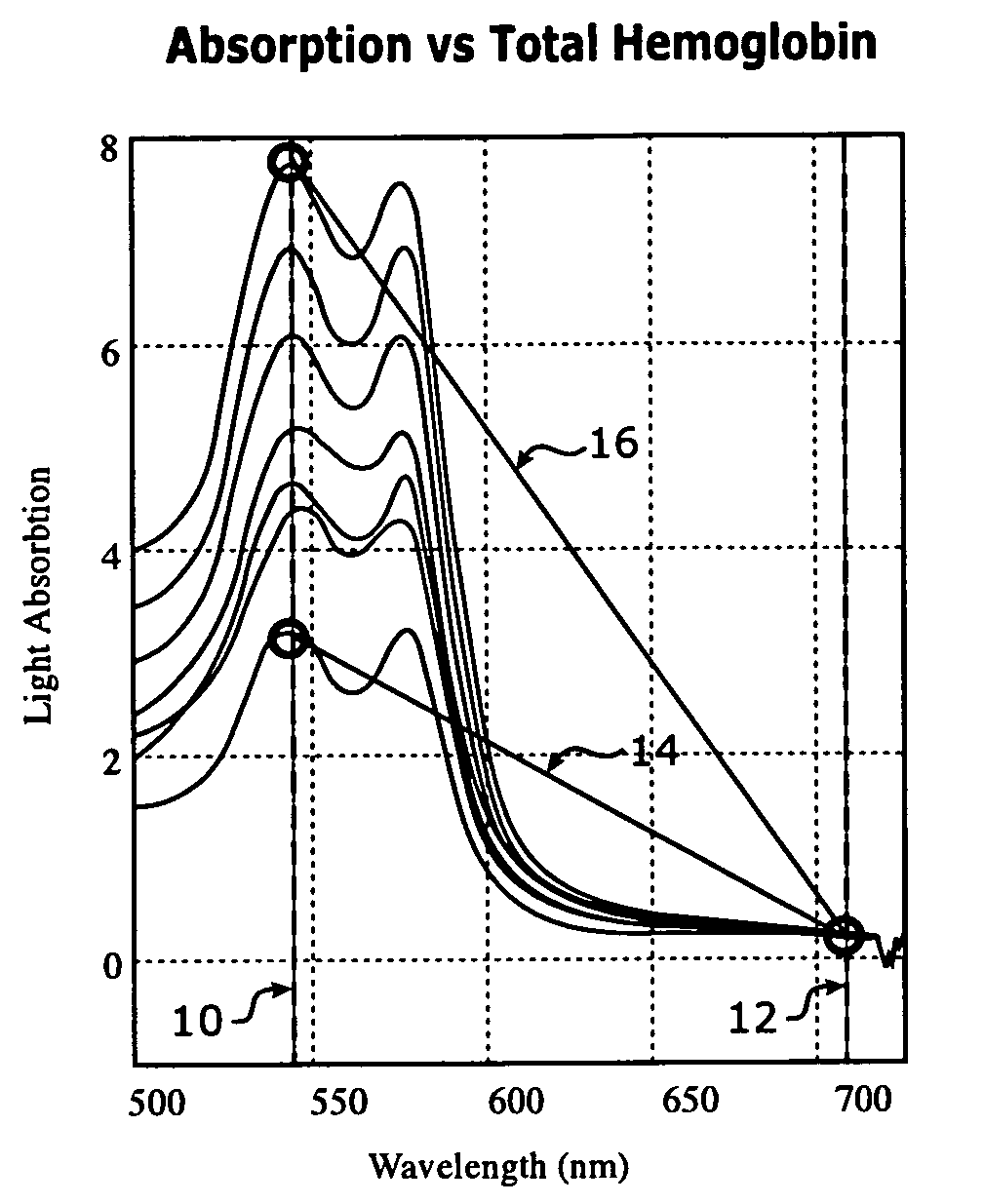

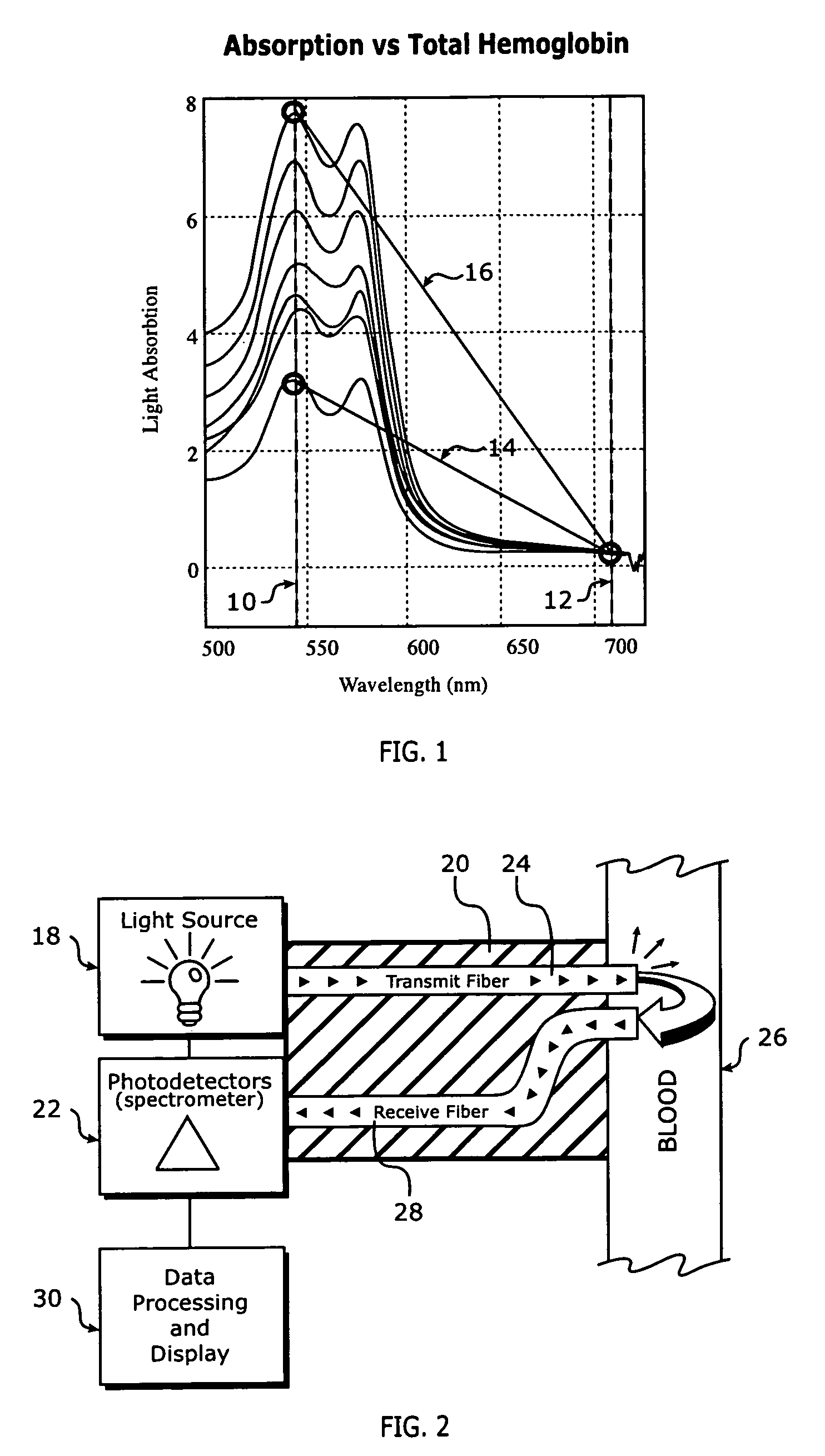

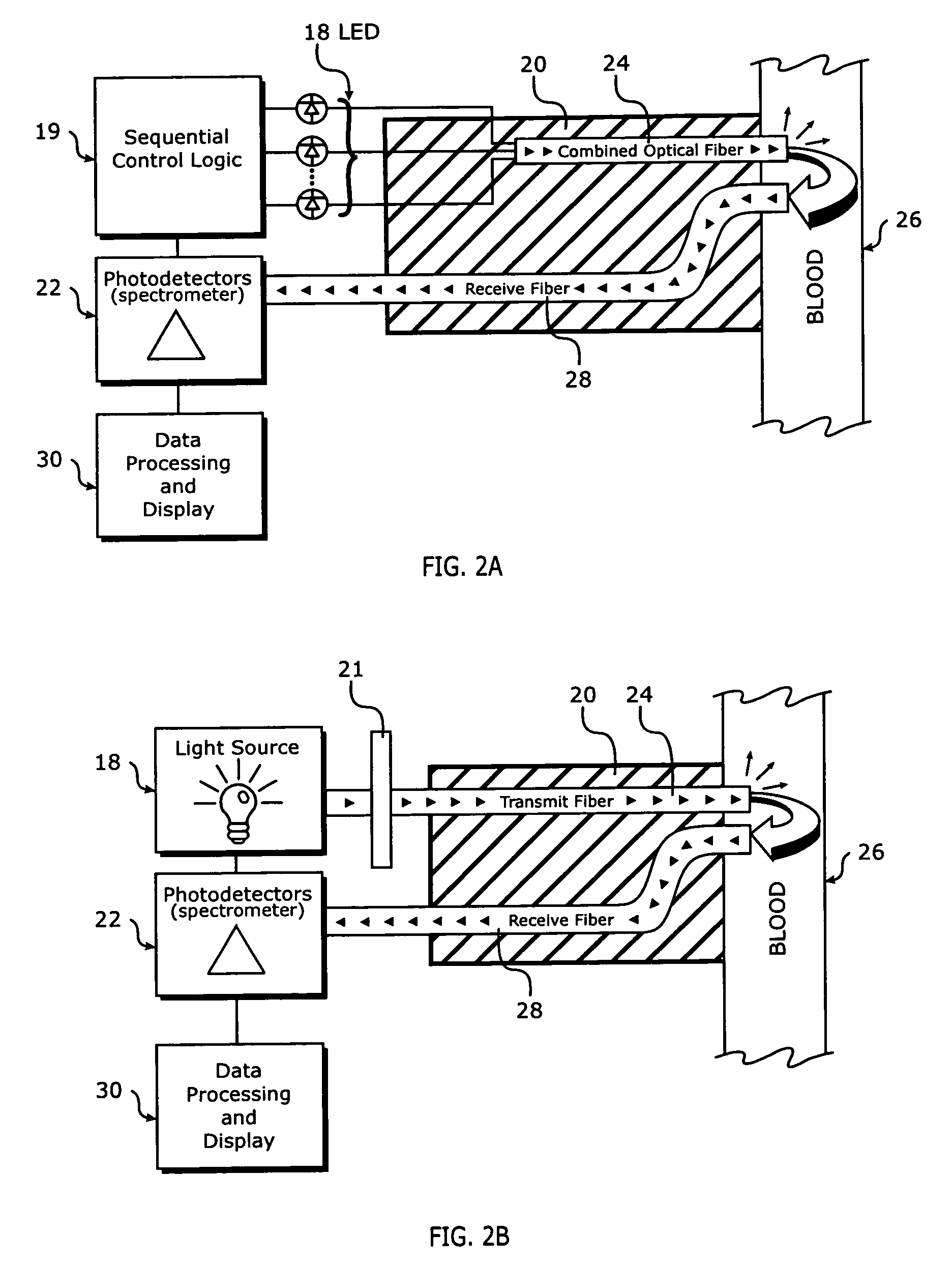

Continuous spectroscopic measurement of total hemoglobin

ActiveUS7319894B2Fast informationEasy to readDiagnostics using spectroscopyCatheterPhotodetectorTotal hemoglobin

Methods for measuring the total hemoglobin of whole blood include measuring reflective light at multiple wavelengths within the visible spectrum, calculating light absorbance at each of the multiple wavelengths, performing a comparison in a change in like absorbance between the multiple wavelengths, and / or relating the comparison to total hemoglobin. A system for measuring total hemoglobin of whole blood may include at least one light source, a catheter, optical fibers, at least one photodetector, data processing circuitry, and / or a display unit.

Owner:EDWARDS LIFESCIENCES CORP

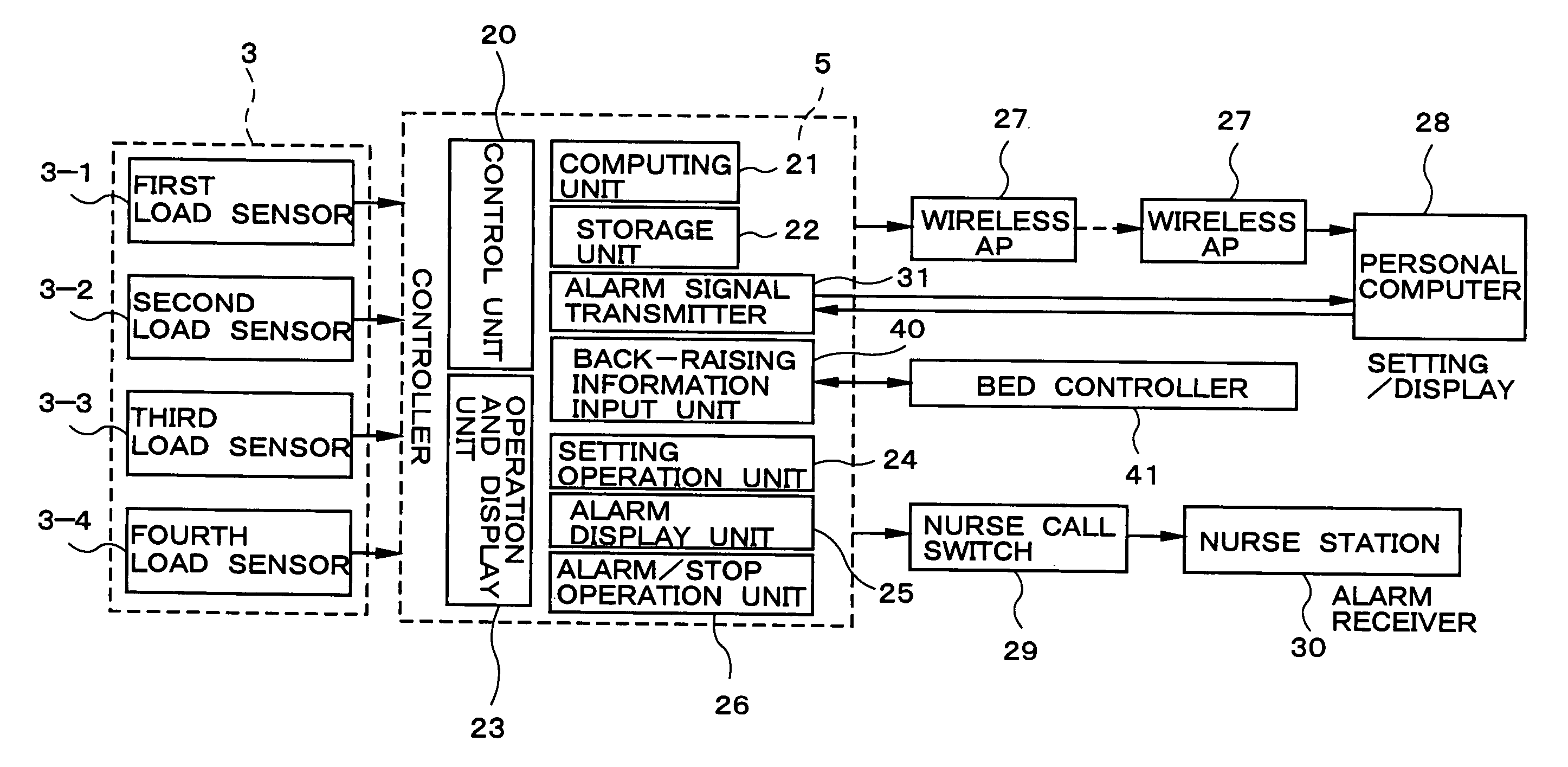

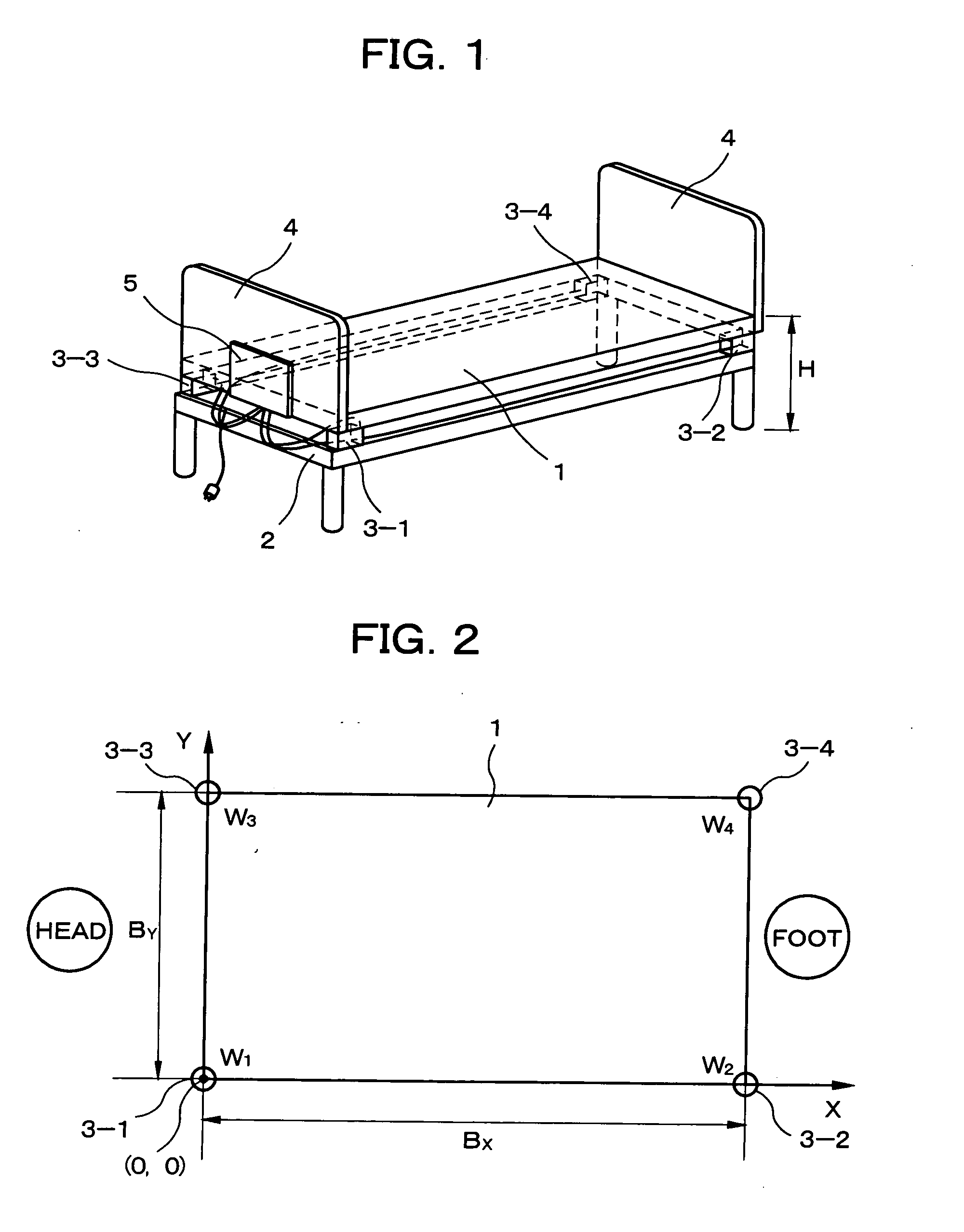

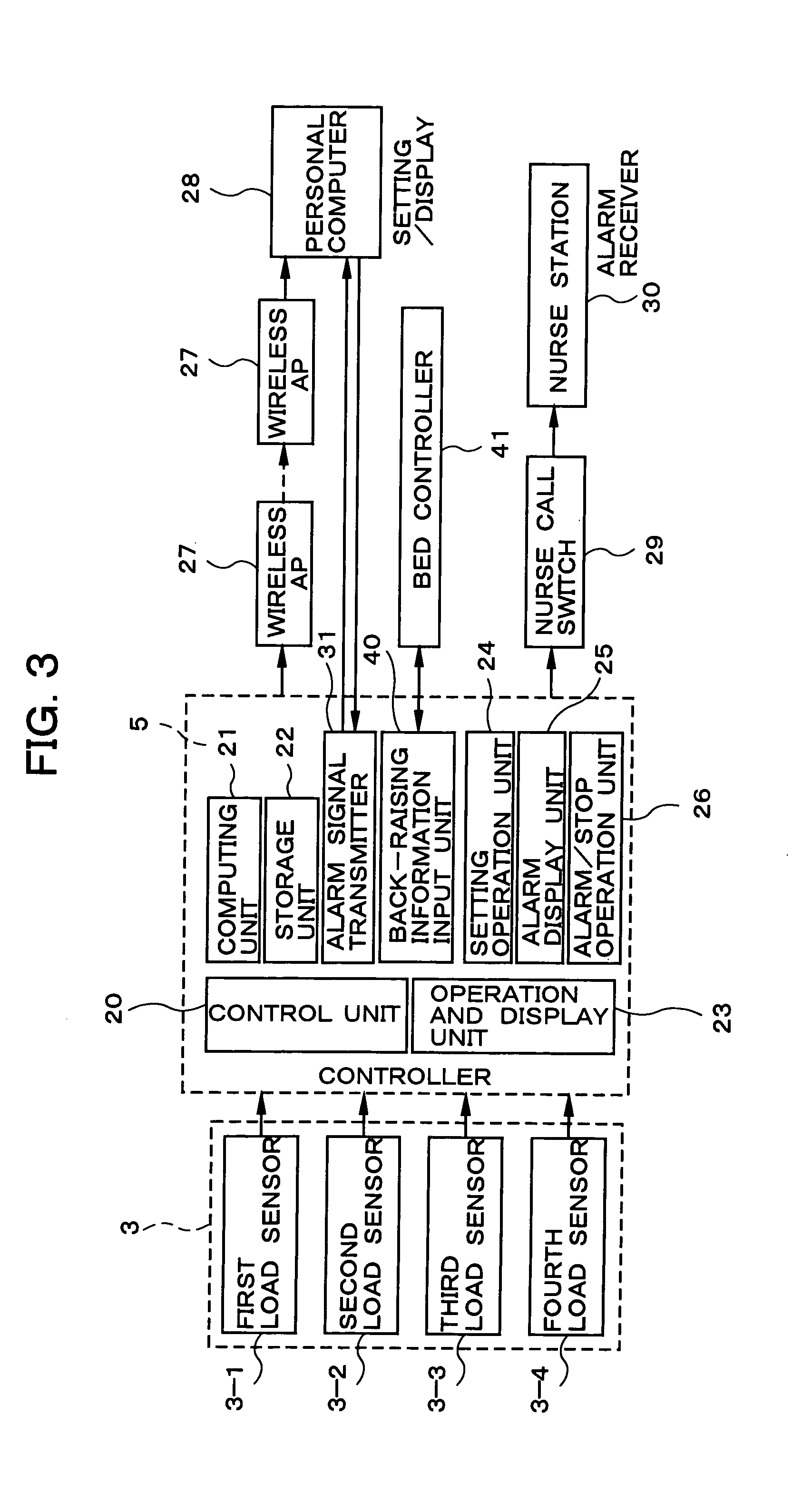

Bed apparatus having movable bedboard

ActiveUS20080204254A1Reduce detection accuracyImprove system reliabilityDiagnostic recording/measuringSensorsAbnormal positionsEngineering

A body weight threshold determination unit determines that the body weight of a user on a bed is at a body weight threshold or higher, and a center-of-gravity position area determination unit determines that the center-of-gravity position thereof has moved to an abnormal position (monitored area). In such a case, the bed user is detected to be in an abnormal position when a body weight center-of-gravity position monitoring unit detects that such a state has continued for a prescribed length of time or longer. When a back-raising operation has been carried out, a movable bedboard determination unit inputs the movable bedboard information, and a monitored area adjustment unit adjusts the monitored area. The monitored area is thereby constantly set to a suitable area in accordance with the state of the movable bedboard. In this manner, the combined information of the body weight information and center-of-gravity position information of the user is determined, whereby the movement of the user can be more accurately monitored with fewer misdetections, high detection accuracy, and high reliability in an electric bed having a movable bedboard.

Owner:PARAMOUNT BED CO LTD

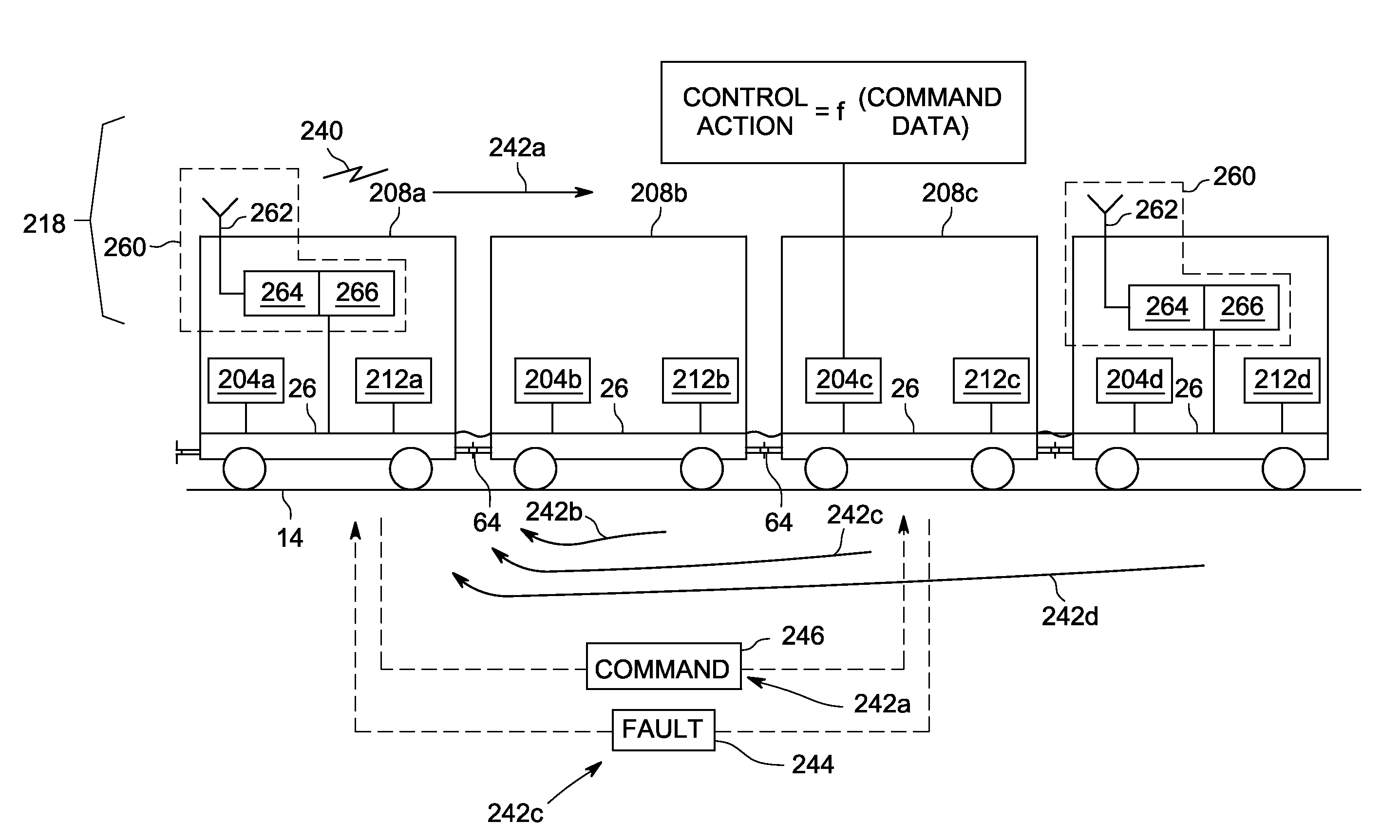

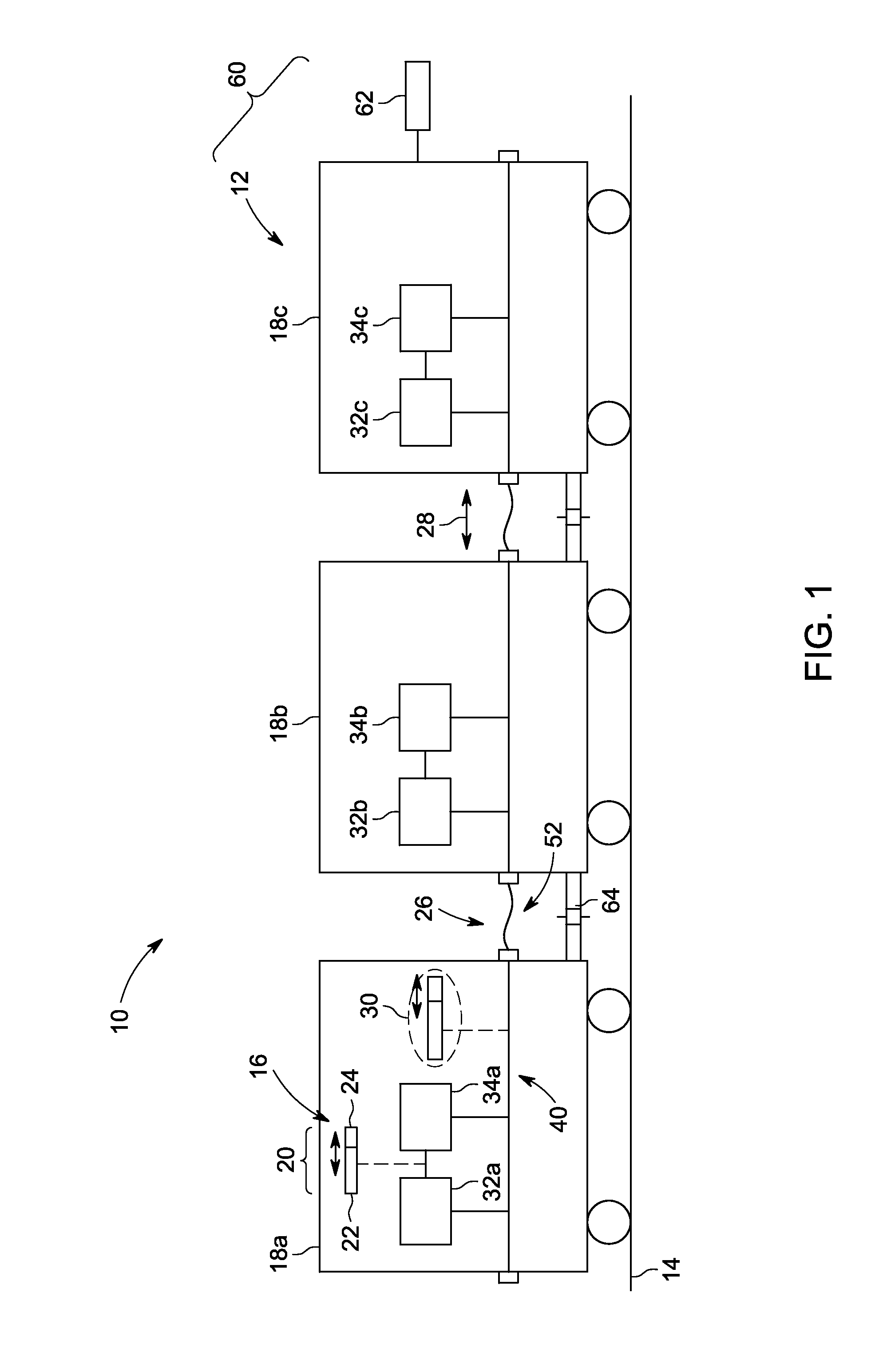

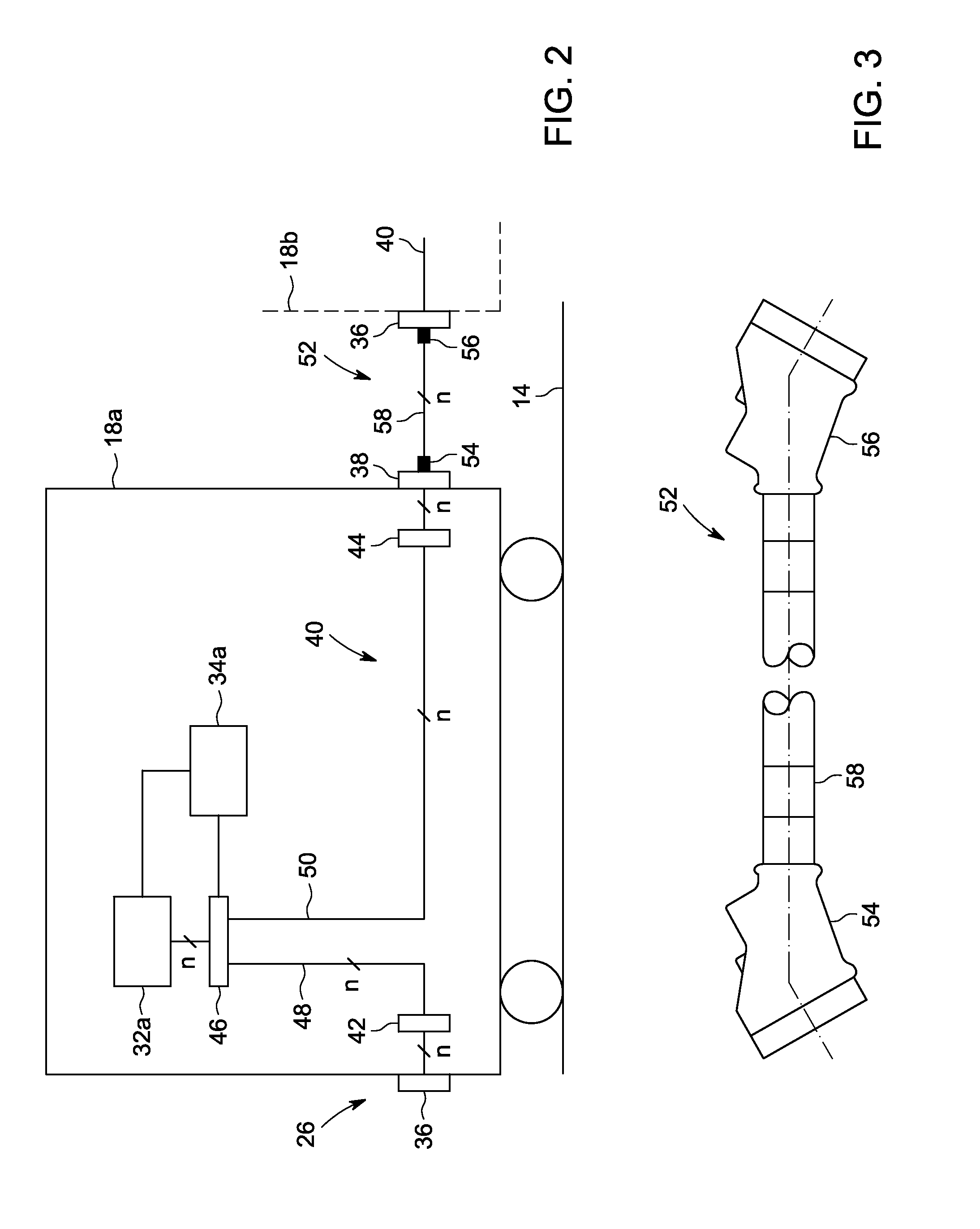

System and method for controlling operations of a vehicle consist based on location data

ActiveUS20110270475A1Improve performanceImprove system reliabilityDigital data processing detailsSignalling indicators on vehicleData systemLocation data

Systems and methods are described for monitoring different conditions that are simultaneously or concurrently experienced by different vehicles in the same consist and using the monitored conditions to locally change operations of one or more of the vehicles. In accordance with one embodiment, operations data related to one or more vehicles of the consist is acquired from one or more of plural different locations in the consist. The operations data and location data related to where the operations data is acquired are communicated to a first vehicle of the consist. Command data is formed based on the operations data and the location data. The command data directs at least one of the vehicles in the consist to change one or more operations of the at least one of the vehicles. The command data is transmitted to one or more of the vehicles of the consist.

Owner:GE GLOBAL SOURCING LLC

Syringe pump rapid occlusion detection system

ActiveUS8182461B2Wide pressure varianceImprove system reliabilityMedical devicesFlow monitorsMedicineOcclusion detection

An apparatus, method and program product detects an occlusion in a fluid line by determining if a relationship between force measurements departs from an expected relationship.

Owner:SMITHS MEDICAL ASD INC

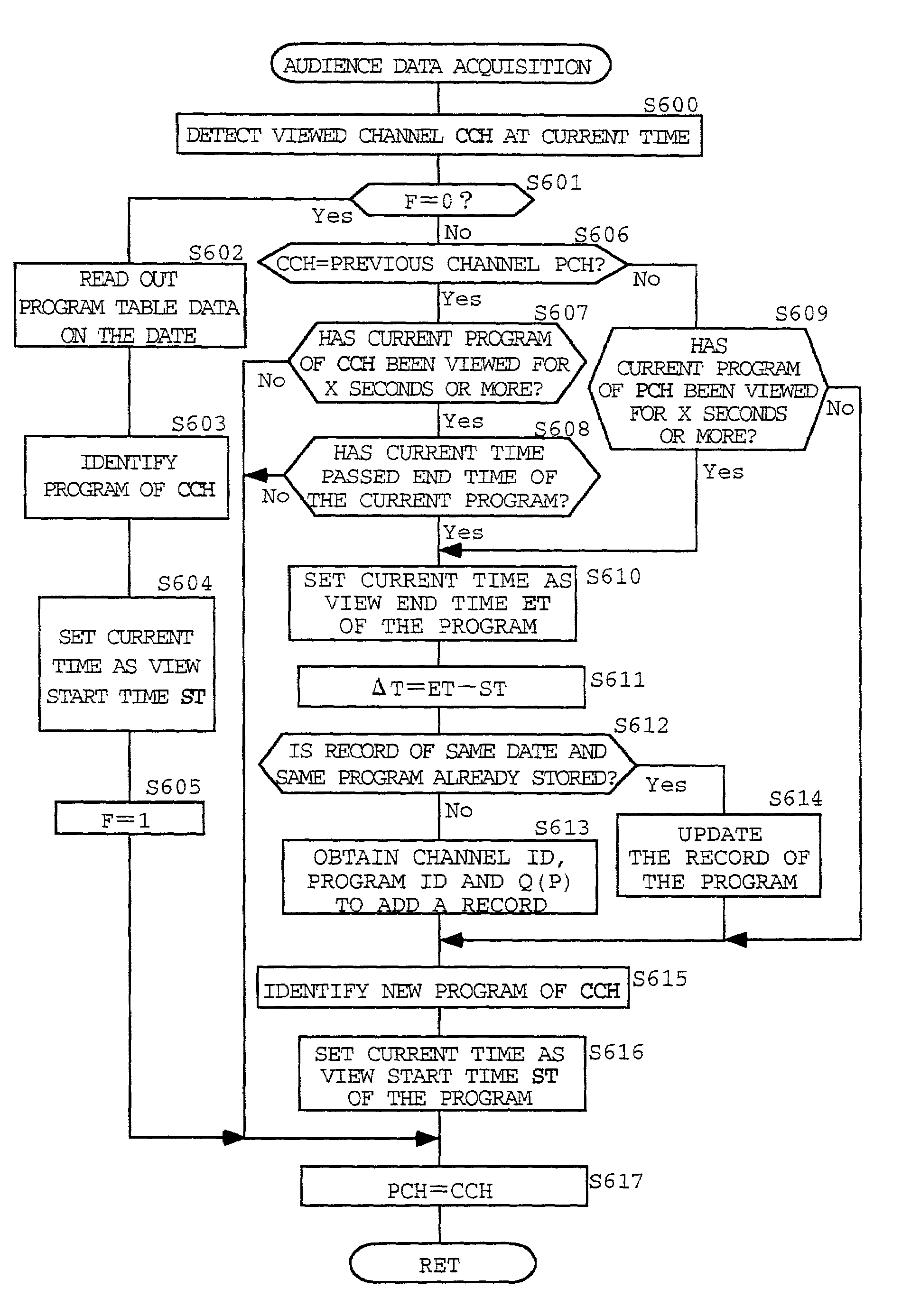

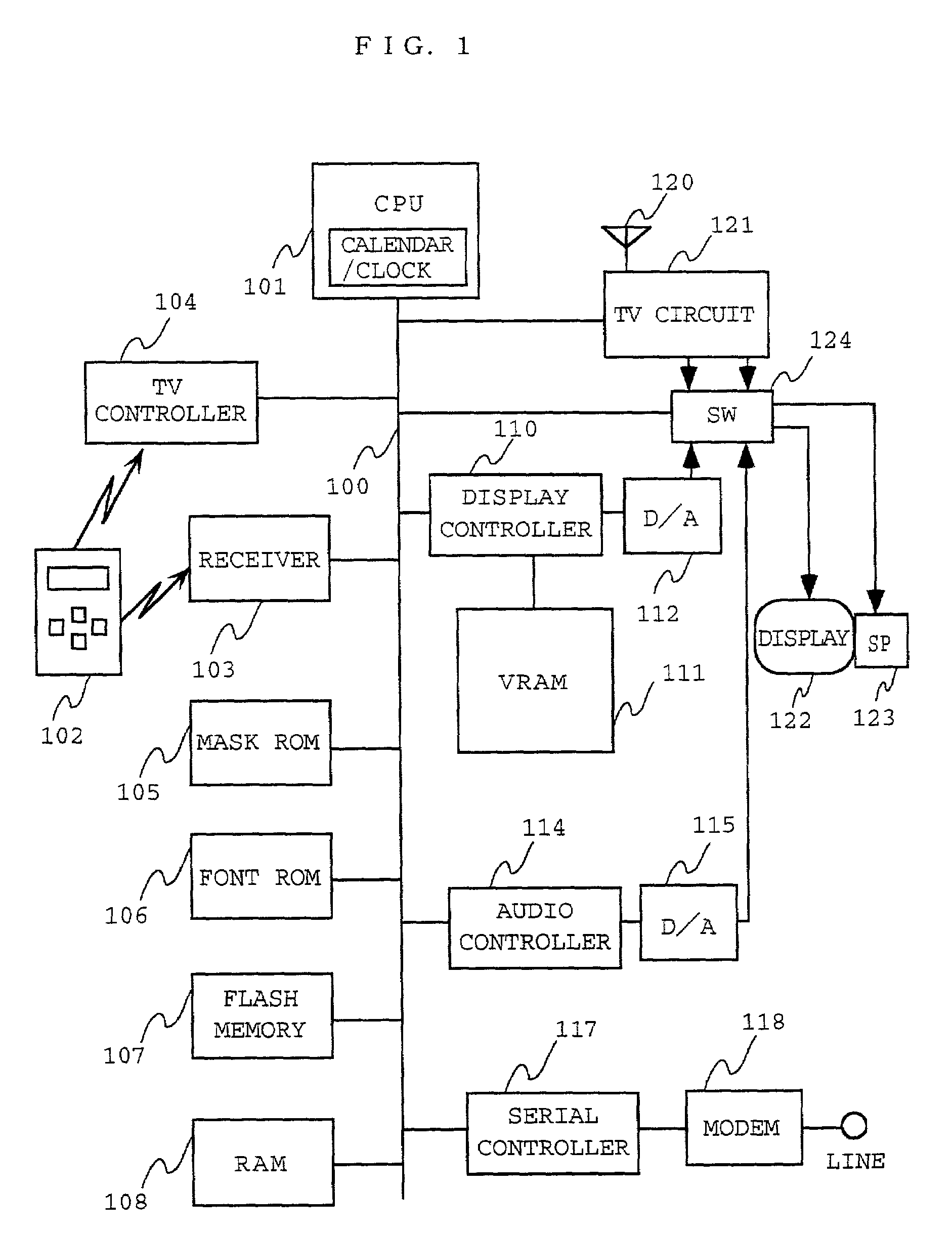

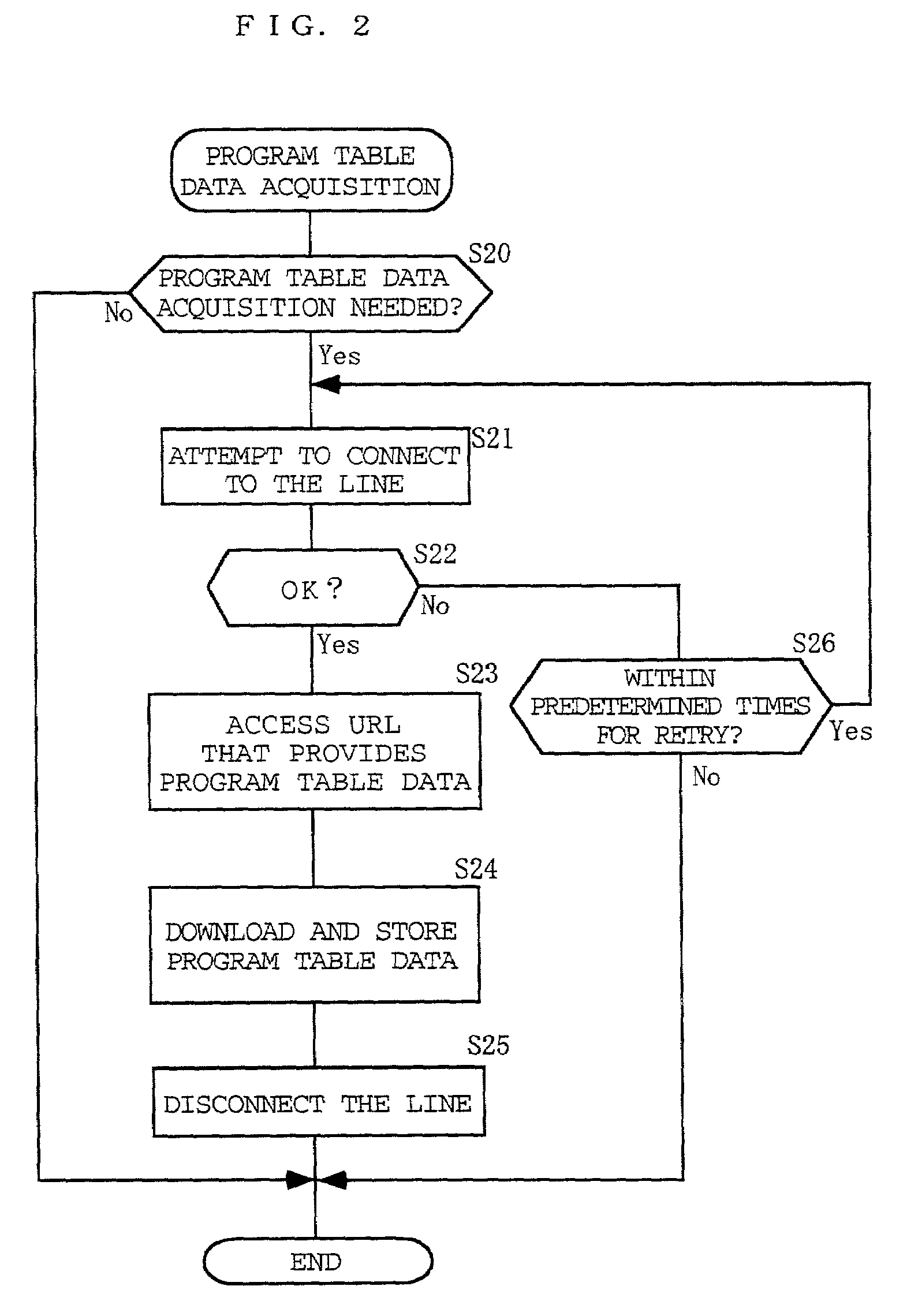

Method and device for obtaining audience data on TV program

InactiveUS7039928B2Reduce congestionReduces telephone chargeTelevision system detailsAnalogue secracy/subscription systemsData packTime information

The TV program table data in the area where a viewer resides are received through the Internet or a broadcasting medium by using the TV set with an internet connection function at the viewer. While the viewer is watching a TV program, the audience data including viewed channel information and viewed time information are automatically obtained. The obtained audience data are compared with the TV program table data to identify the watched program. The program ID of the identified program and the viewed time information are transferred to a data collecting center through the Internet together with the viewer ID data. By utilizing the Internet for the distribution of the TV program table data to the viewers and for the collection of the audience data, the nationwide TV audience data can be easily collected and used to make statistics. Since viewed channel and viewed time information are correlated with programs on the viewer's side, the load of processing the data on the center side can be relieved.

Owner:ACCESS

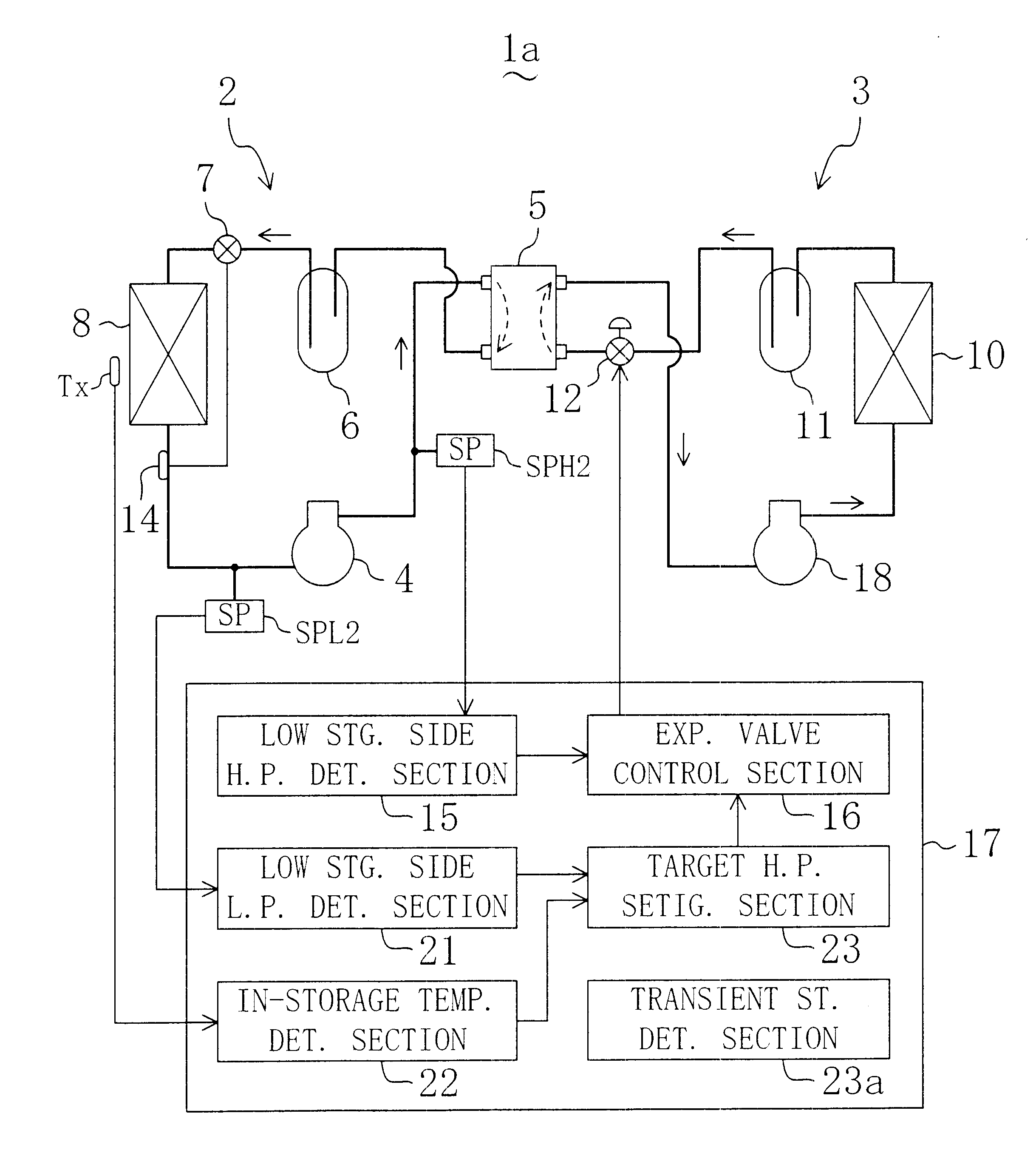

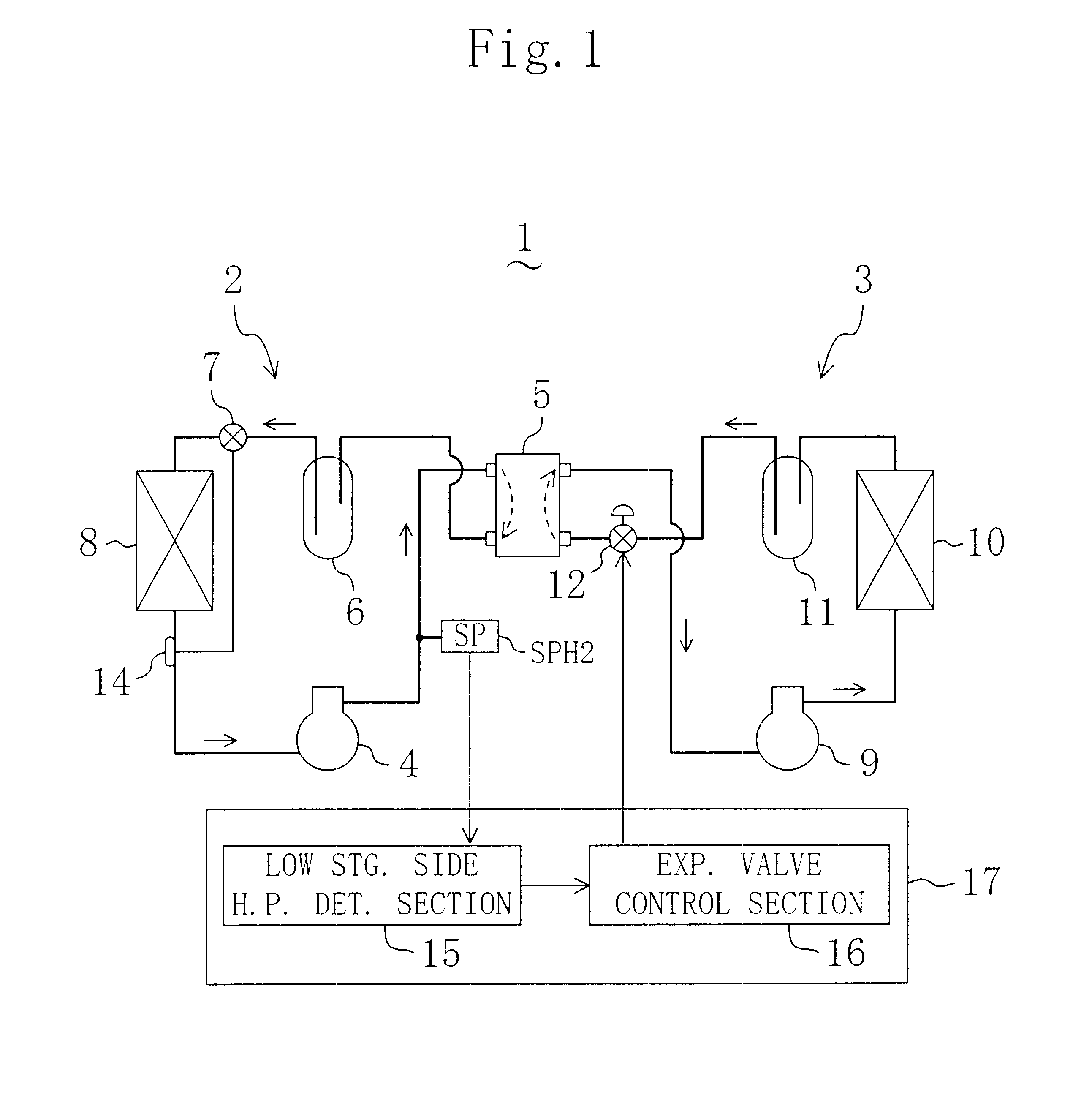

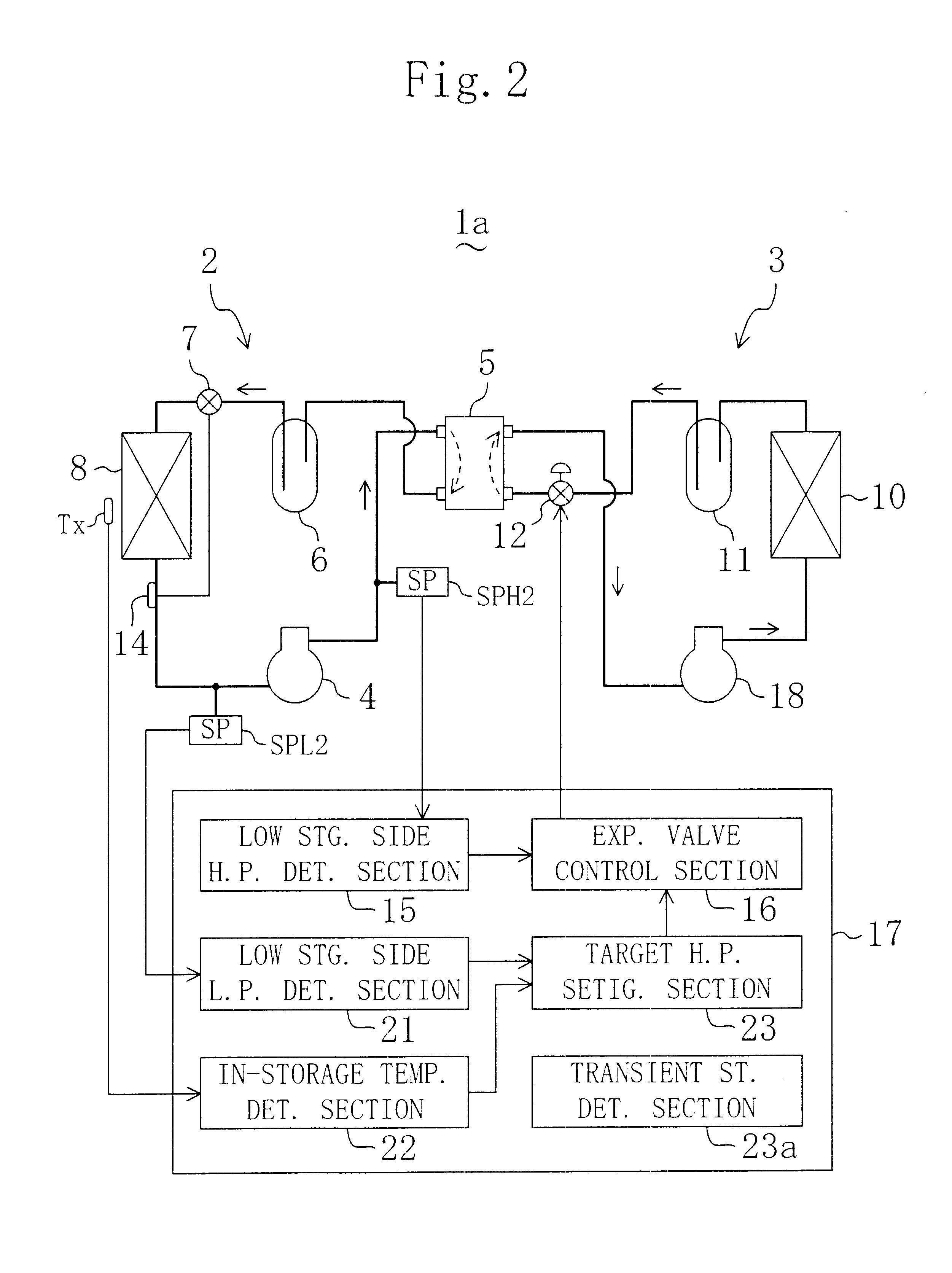

Refrigerating system

InactiveUS6405554B1Improve system reliabilityEasy to implementMechanical apparatusCompression machines with non-reversible cycleEngineeringRefrigerant

The refrigerating system includes a low stage side refrigerant circuit (2) formed by connecting a low stage side compressor (4), a cascade condenser (5), a low stage side receiver (6), a low stage side expansion valve (7) formed of a temperature-sensitive expansion valve and an evaporator (8) in this order. The system also includes a high stage side refrigerant circuit (3) formed by connecting a high stage side compressor (9), a condenser (10), a high stage side receiver (11), a high stage side expansion valve (12) formed of a motor-operated expansion valve and the cascade condenser (5) in this order. The opening of the high stage side expansion valve (12) is adjusted so that the pressure sensed by a high-pressure sensor (SPH2) for sensing the high pressure in the low stage side refrigerant circuit (2) reaches a predetermined target high pressure.

Owner:DAIKIN IND LTD

Method for pulse width modulation synchronization in a parallel ups system

ActiveUS20080265680A1Improve system reliabilityBatteries circuit arrangementsAc-dc conversionPulse width modulatedPhysics

A method for pulse width modulated pulse synchronization in a parallel UPS system uses the locally measured critical bus voltage to detect a zero crossing and adjust the PWM pulse to coincide with the zero crossing. No communication between the units is required to perform synchronization, and no “master” and “slave” relationship exists to thereby increase the total system reliability.

Owner:VERTIV CORP

Flow-cytometry-based hematology system

InactiveUS20060203226A1Reduce wasteLow costWithdrawing sample devicesPreparing sample for investigationMedicine.hematologyFlow cell

Owner:IDEXX LABORATORIES

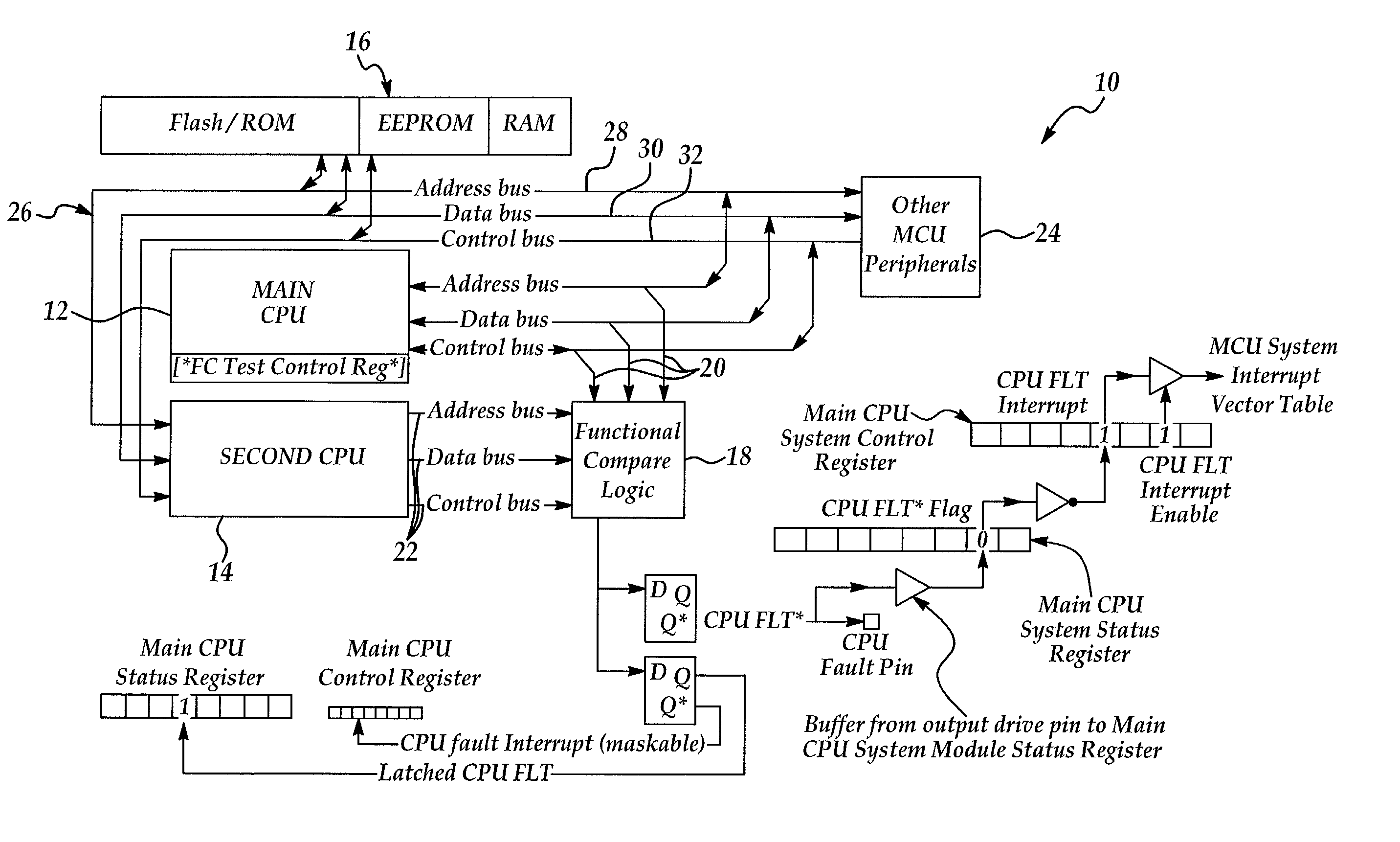

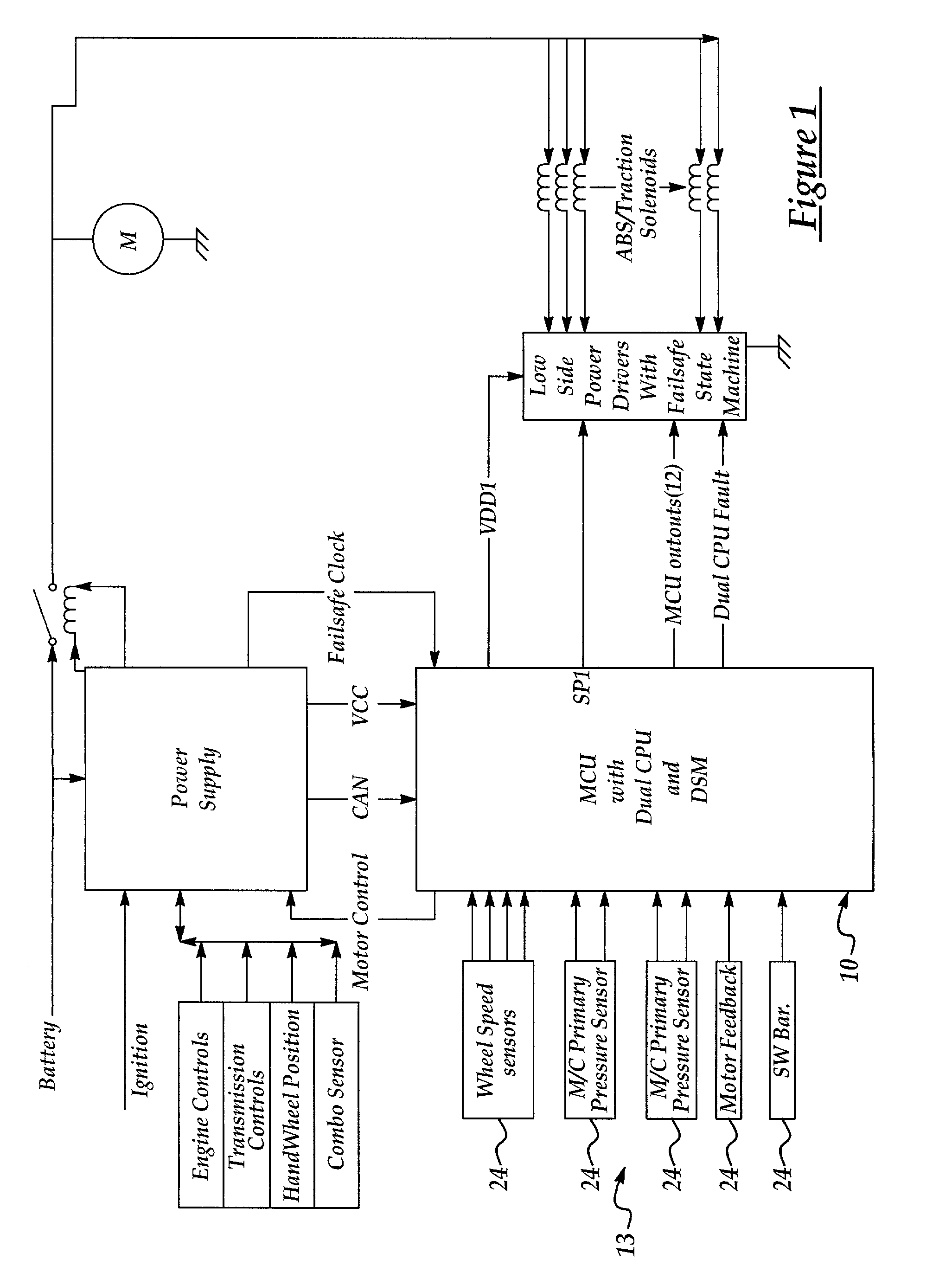

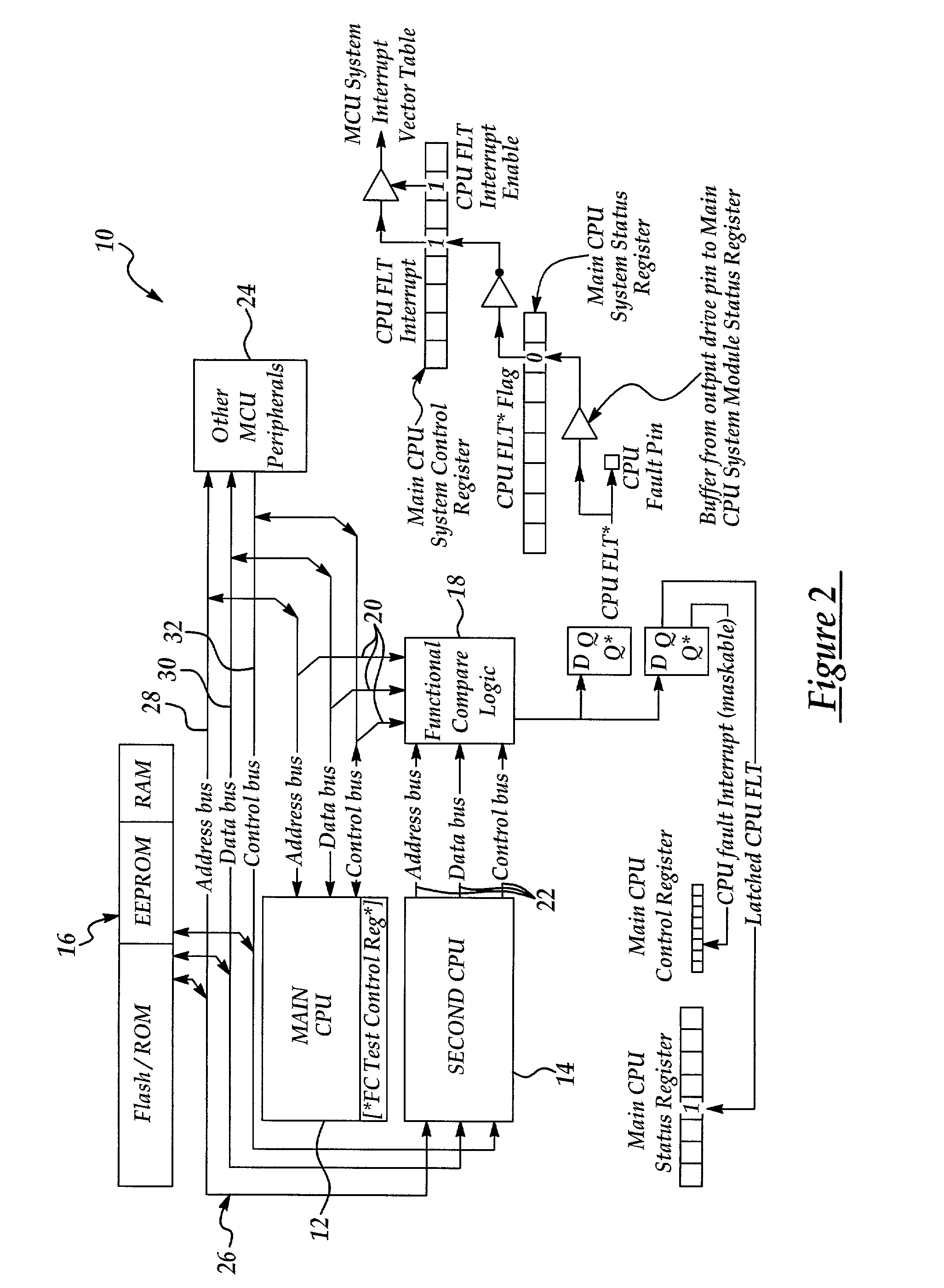

Secured microcontroller architecture

InactiveUS6981176B2Reduce sensitivityImprove system reliabilityVehicle testingRegistering/indicating working of vehiclesMicrocontrollerParallel computing

A microcontroller unit (MCU) having a primary, or main, processing unit, a secondary processing unit coupled to the primary processing unit, and a common memory coupled to the primary and secondary processing units is disclosed. A functional compare module is coupled to the primary processing unit and the secondary processing unit for comparing a primary output of the primary processing unit and a secondary output of the secondary processing units to detect a fault if the primary output and the secondary output are not the same. The invention provides a method for detecting a fault in the MCU including the steps of reading a control algorithm stored in the common memory by the primary processing unit, reading the control algorithm stored in the common memory by the secondary processing unit, comparing the primary output and the secondary output and responsively detecting a fault, if the primary output does not match the second output.

Owner:SAMSUNG ELECTRONICS CO LTD