Patents

Literature

455results about How to "Improve system throughput" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

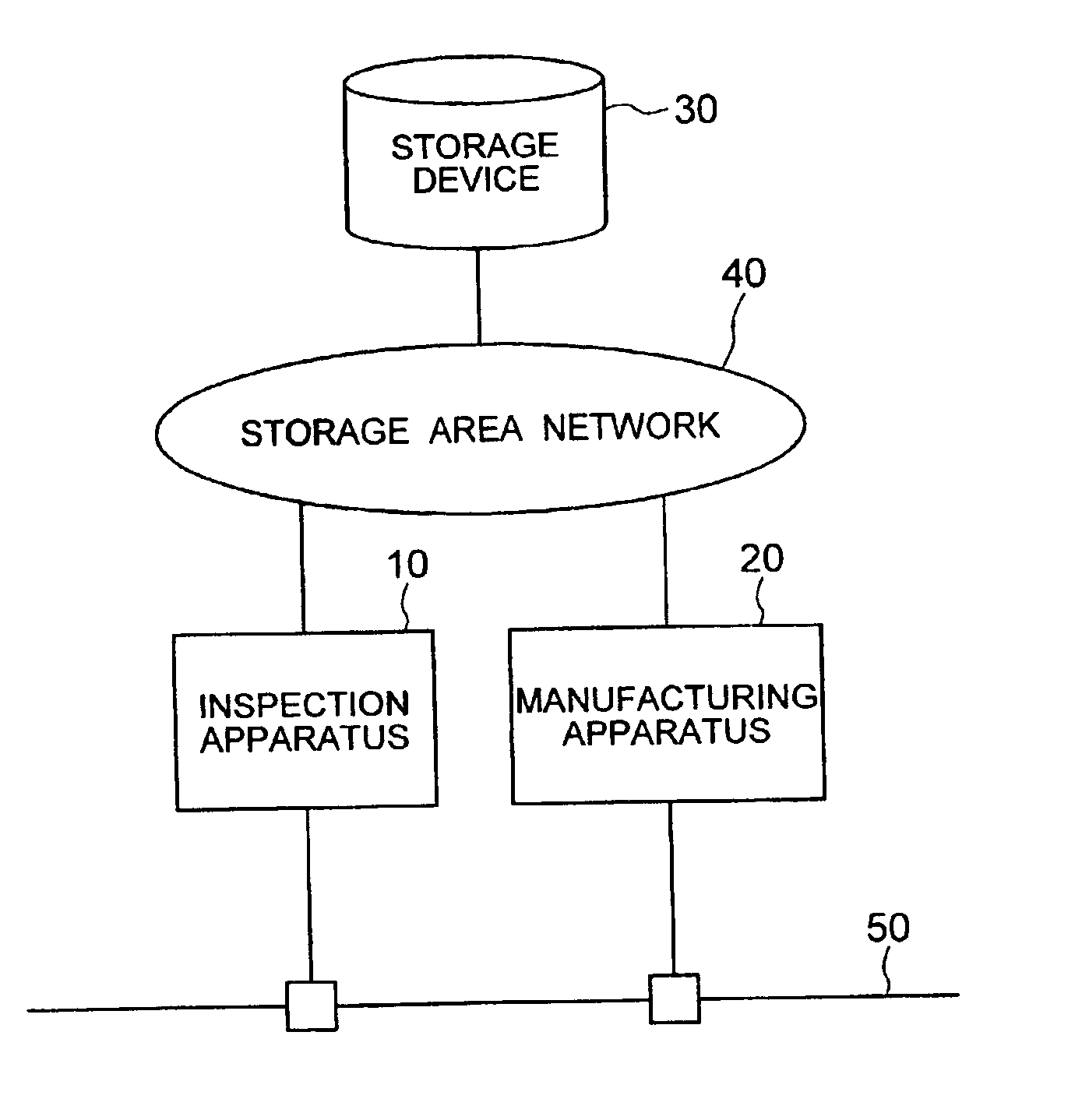

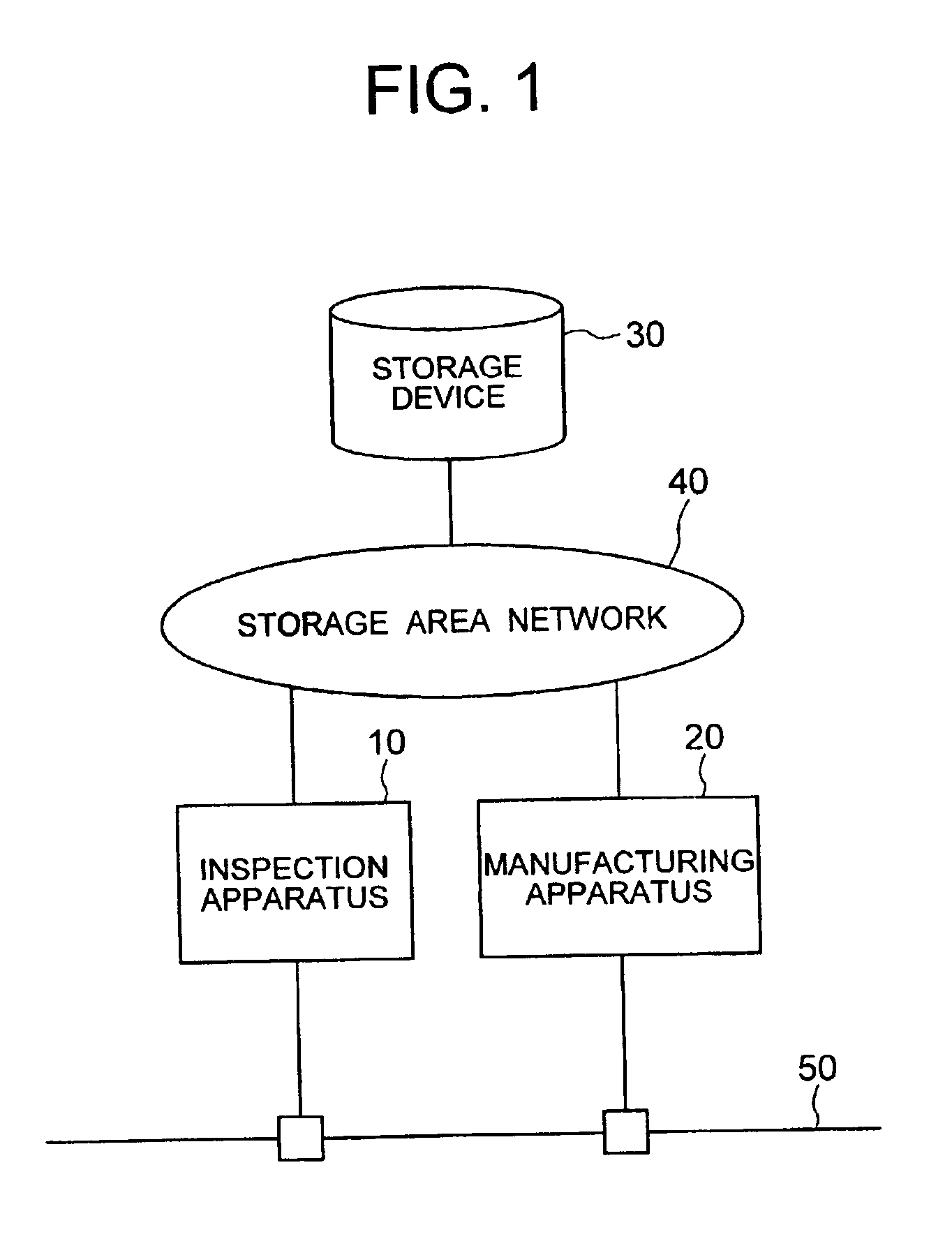

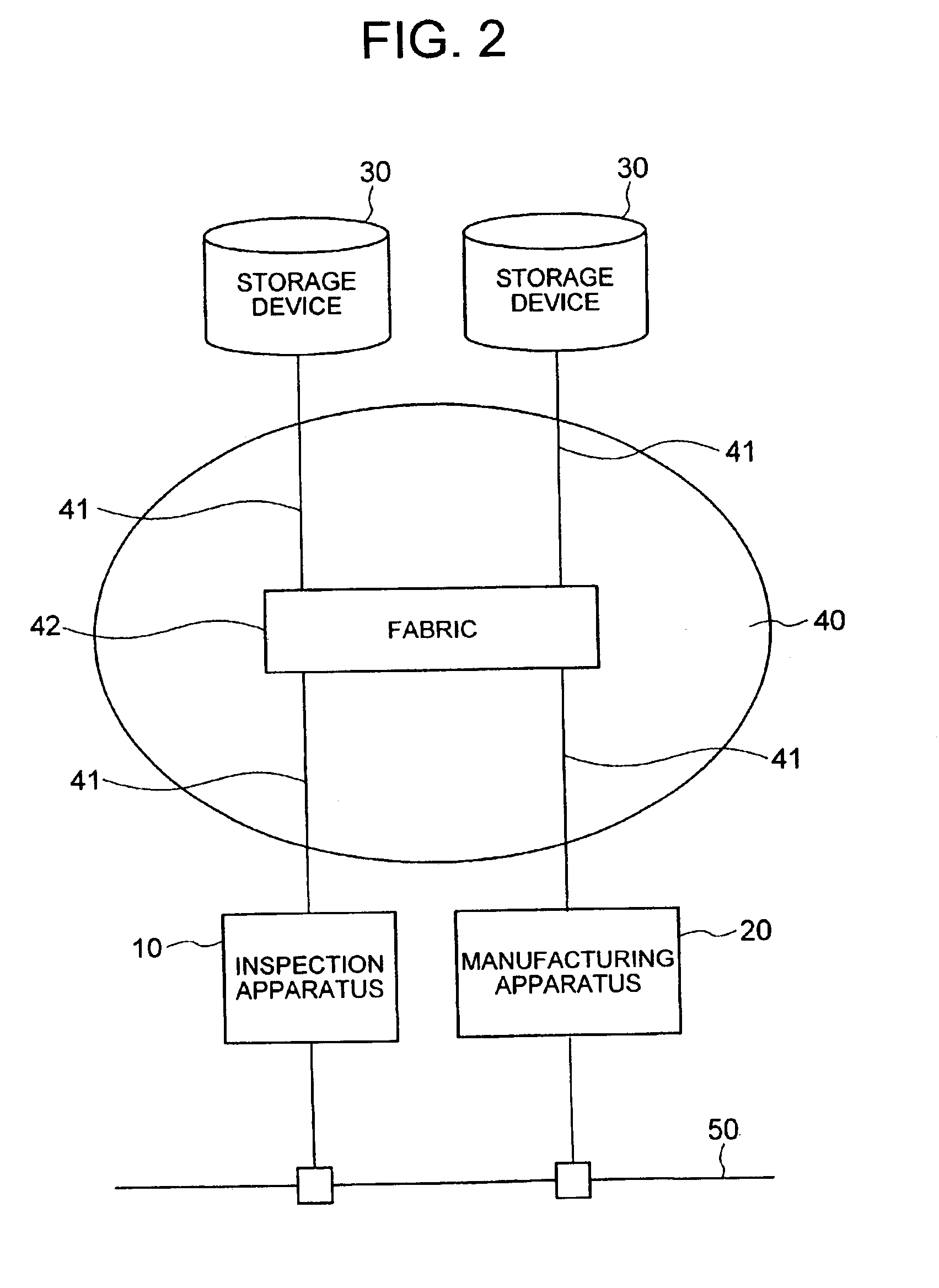

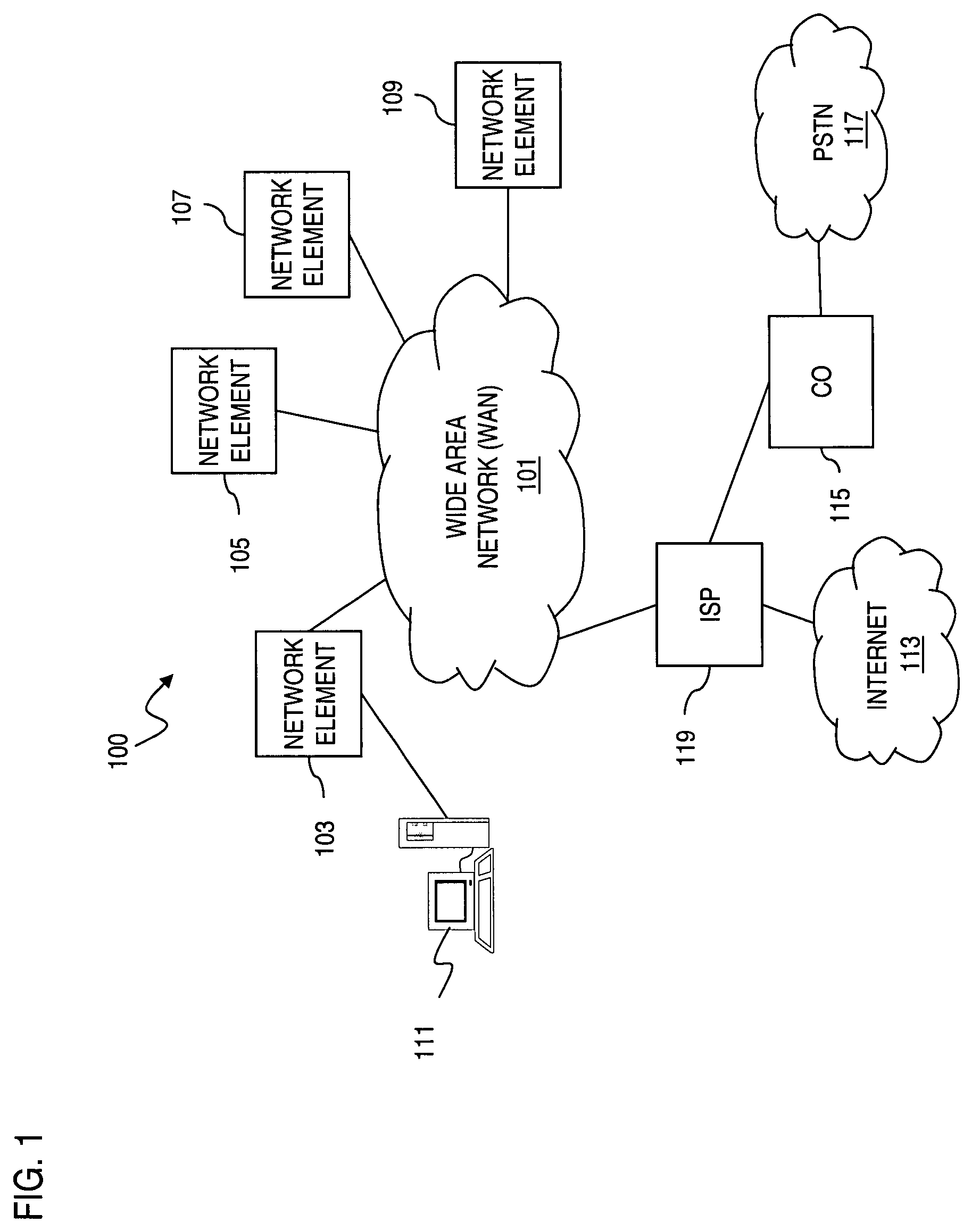

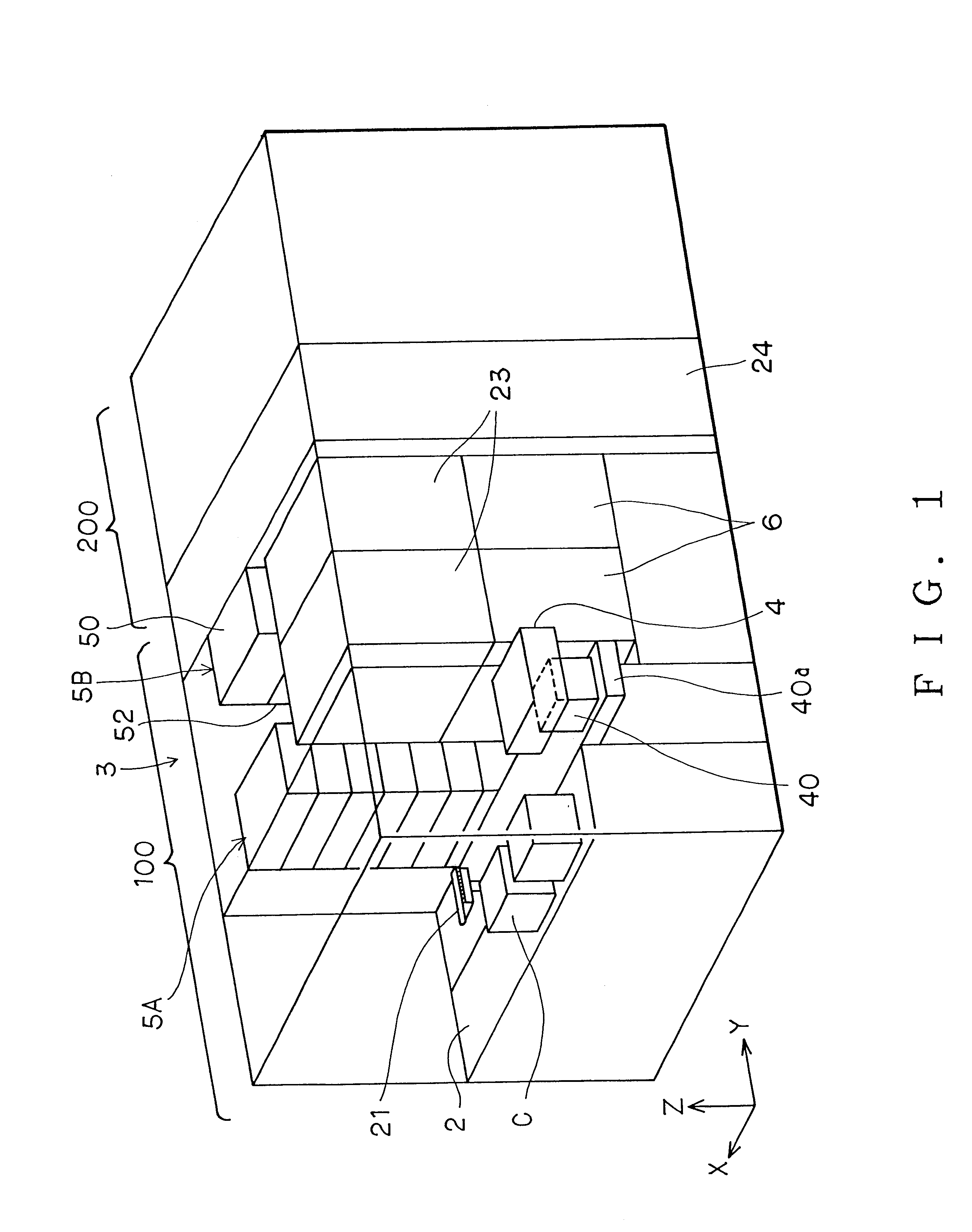

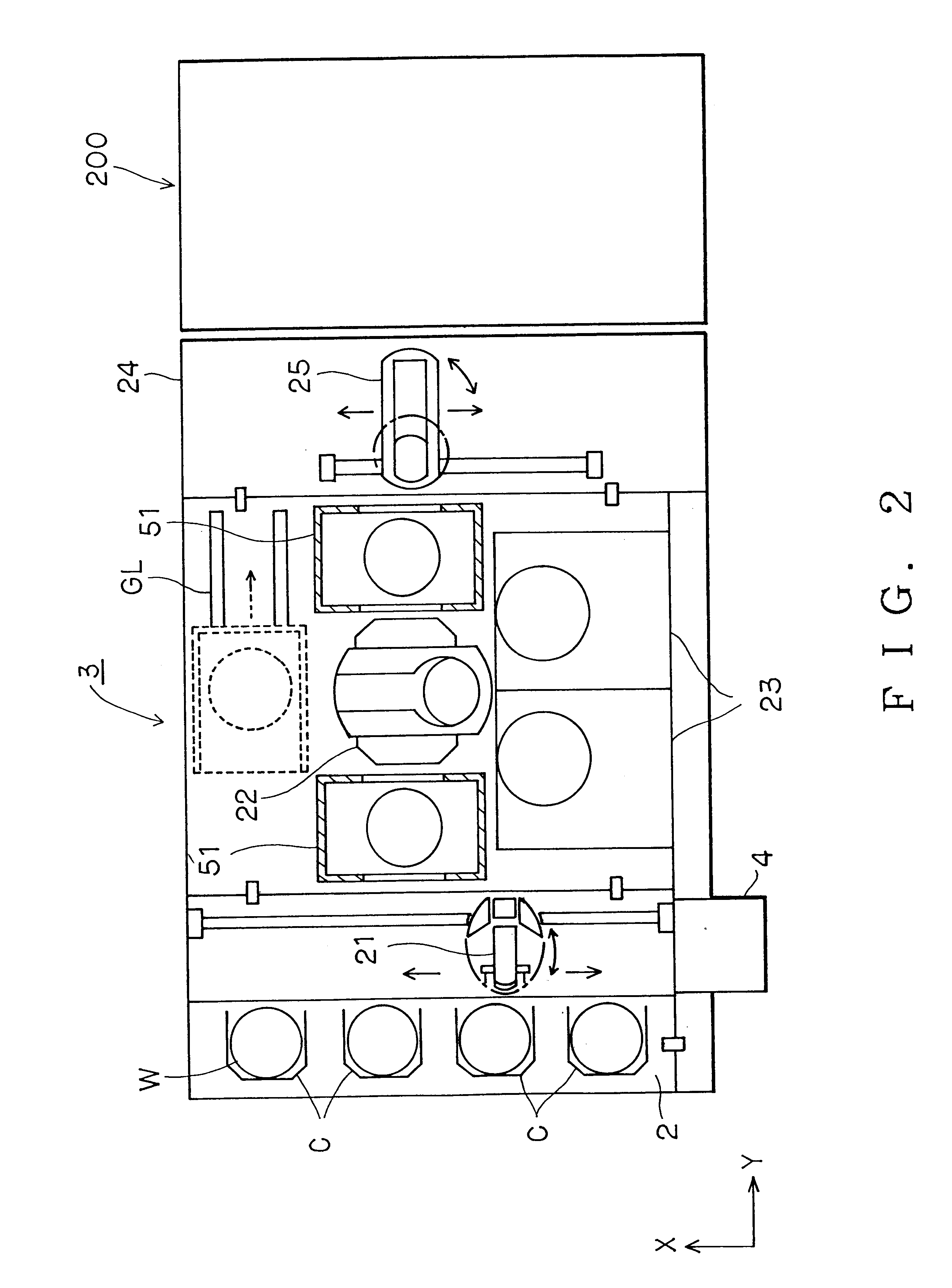

Semiconductor production system

InactiveUS6850854B2Improve system throughputIncrease in sizeSemiconductor/solid-state device testing/measurementElectronic circuit testingStorage area networkObservation unit

A semiconductor production system has a semiconductor manufacturing apparatus having an exposure unit, a control unit for controlling the exposure unit and a storage device; a semiconductor inspection apparatus having an observation unit, a control unit for controlling the observation unit and a storage device; and a storage device commonly used by the semiconductor manufacturing apparatus and the semiconductor inspection apparatus. The manufacturing apparatus, the inspection apparatus and the commonly used storage device are interconnected via a storage area network. With the semiconductor manufacturing apparatus and the storage device linked together via the storage area network, a large volume of image data or design data can be communicated at high speed, thus improving the system throughput.

Owner:HITACHI LTD

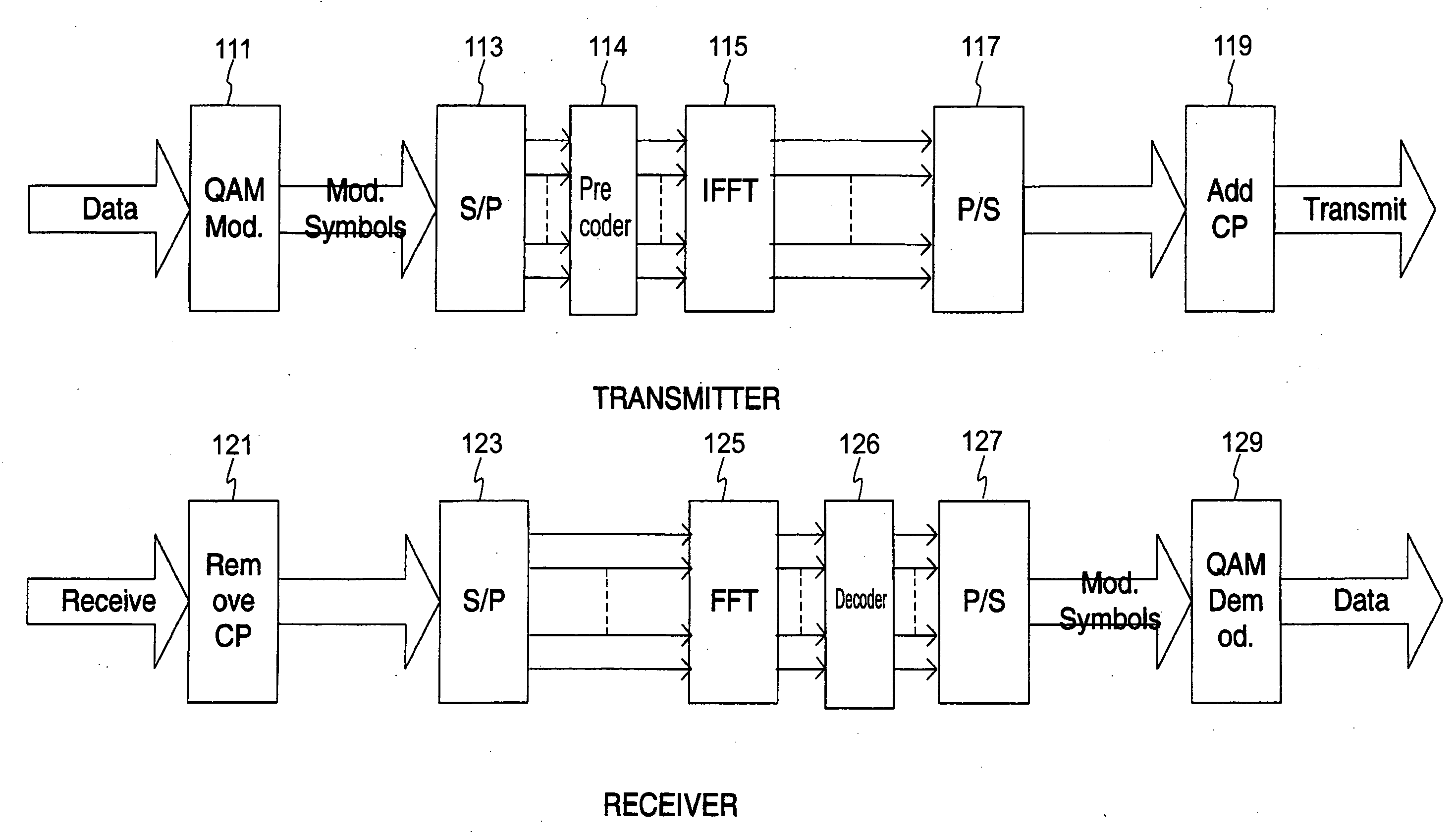

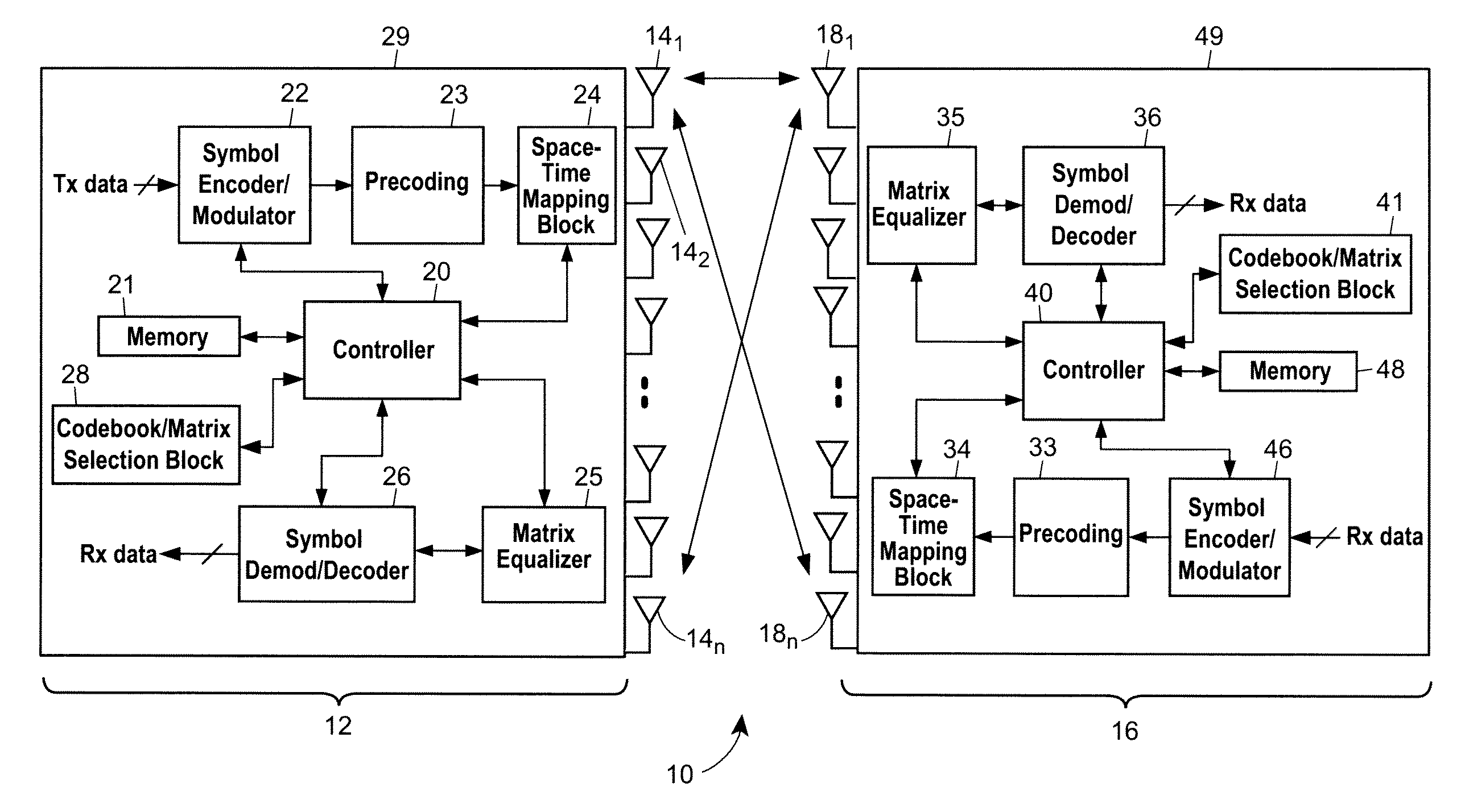

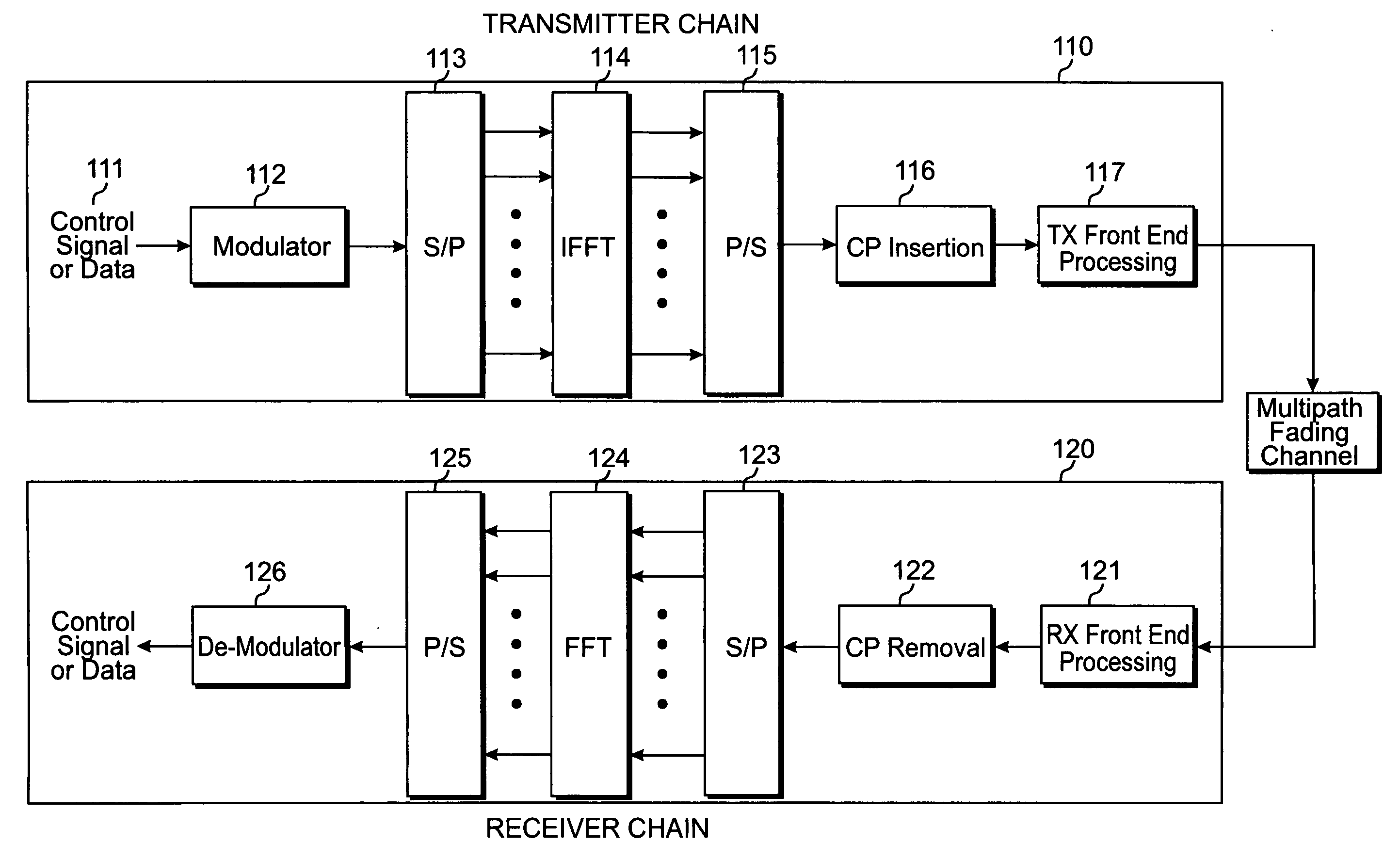

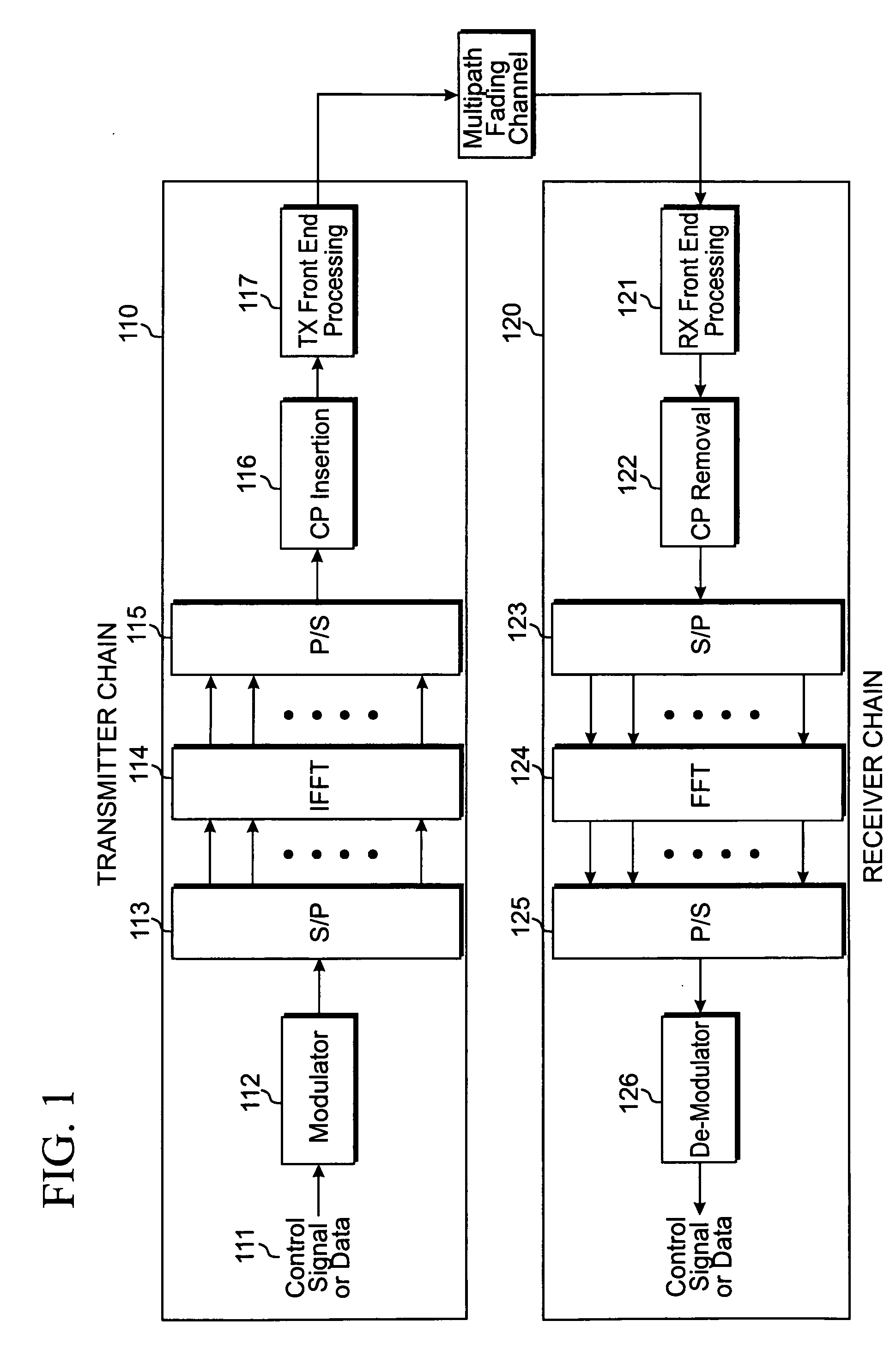

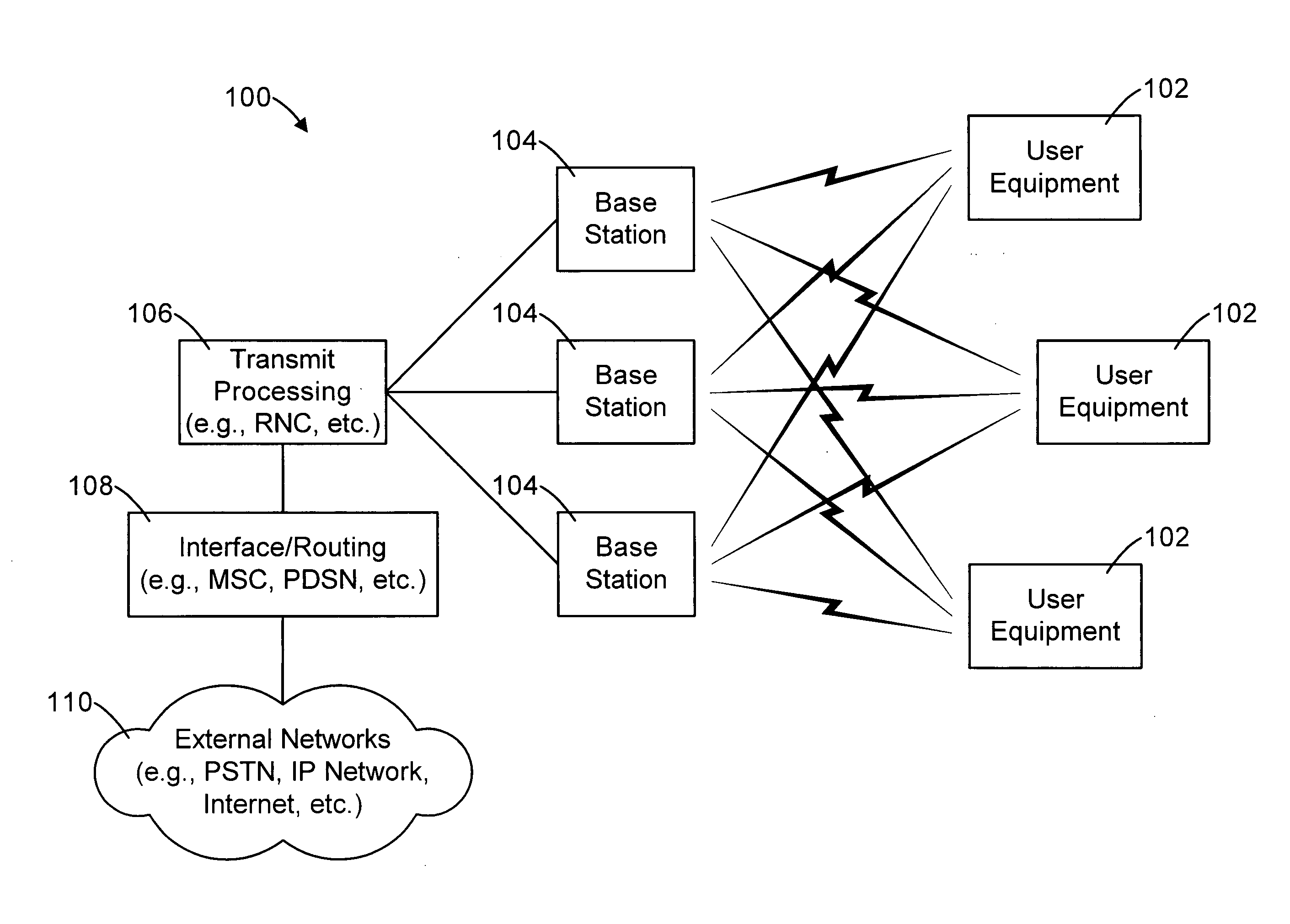

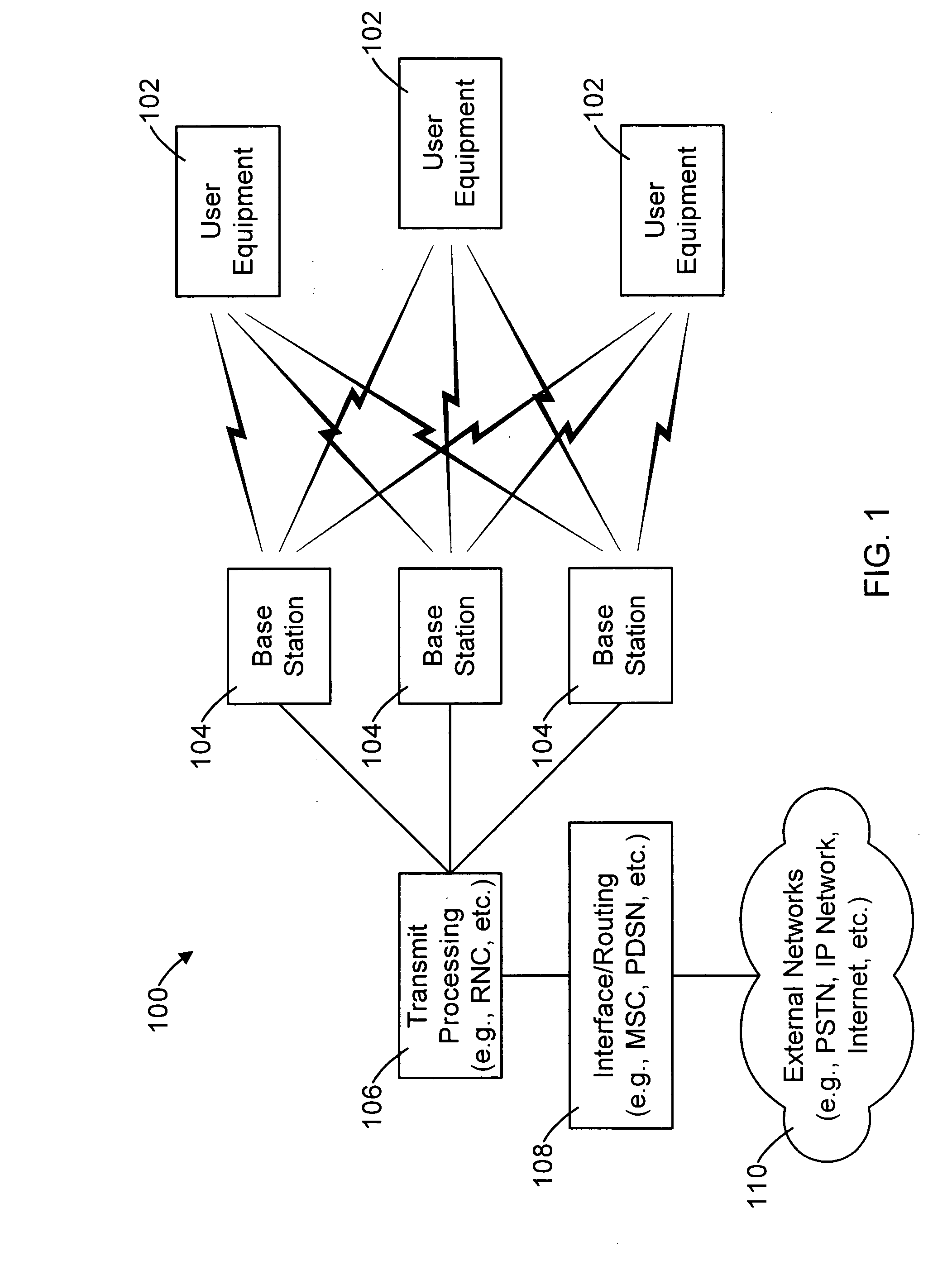

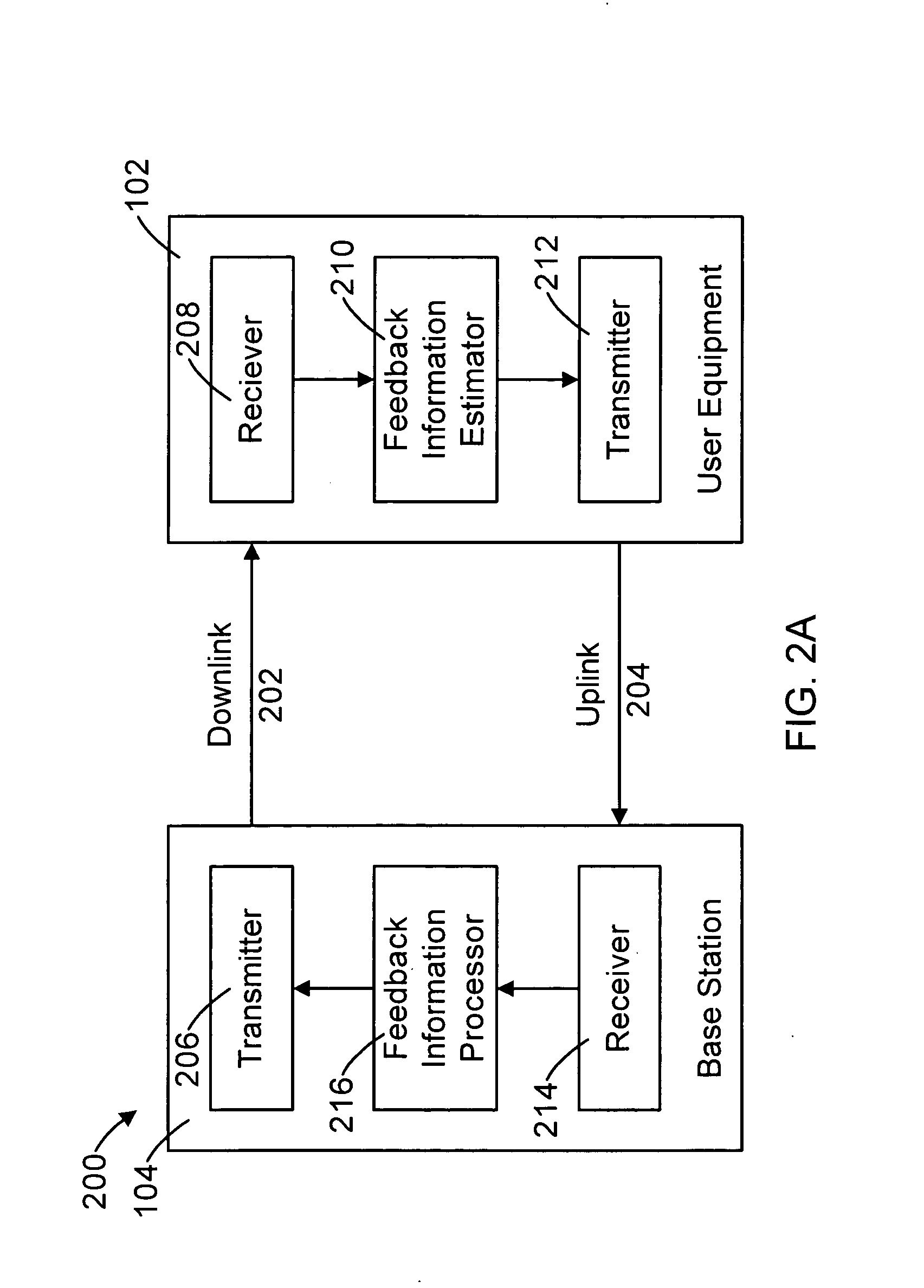

Method and apparatus of codebook-based single-user closed-loop transmit beamforming (SU-CLTB) for OFDM wireless systems

ActiveUS20090041150A1Improve throughputMaximize signal to noise ratioMultiple-port networksAntenna arraysCommunications systemClosed loop

A method includes broadcasting, at a transmitter, messages comprising antenna configuration, antenna spacing and a number of antenna of the transmitter and reference signals; generating, at a receiver, a codebook comprising a plurality of antenna beams based on the broadcasted messages; receiving, at the receiver, the broadcasted reference signals; selecting, at the receiver, an antenna beam among the plurality of antenna beams within the codebook in dependence upon a predetermined performance criteria of a data communication system and in dependence upon the broadcasted reference signals; feedbacking to the transmitter, at the receiver, information comprising the antenna beam selected by the receiver; optimizing, at the transmitter, a beamforming process by utilizing the feedback information from the receiver; transmitting, at the transmitter, data signals by utilizing the optimized beamforming process; and receiving and processing, at the receiver, the data signals in dependence upon the selected antenna beams within the codebook.

Owner:SAMSUNG ELECTRONICS CO LTD

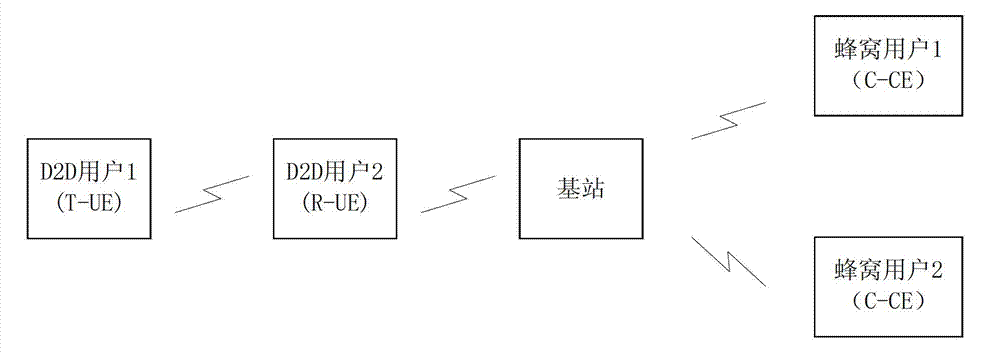

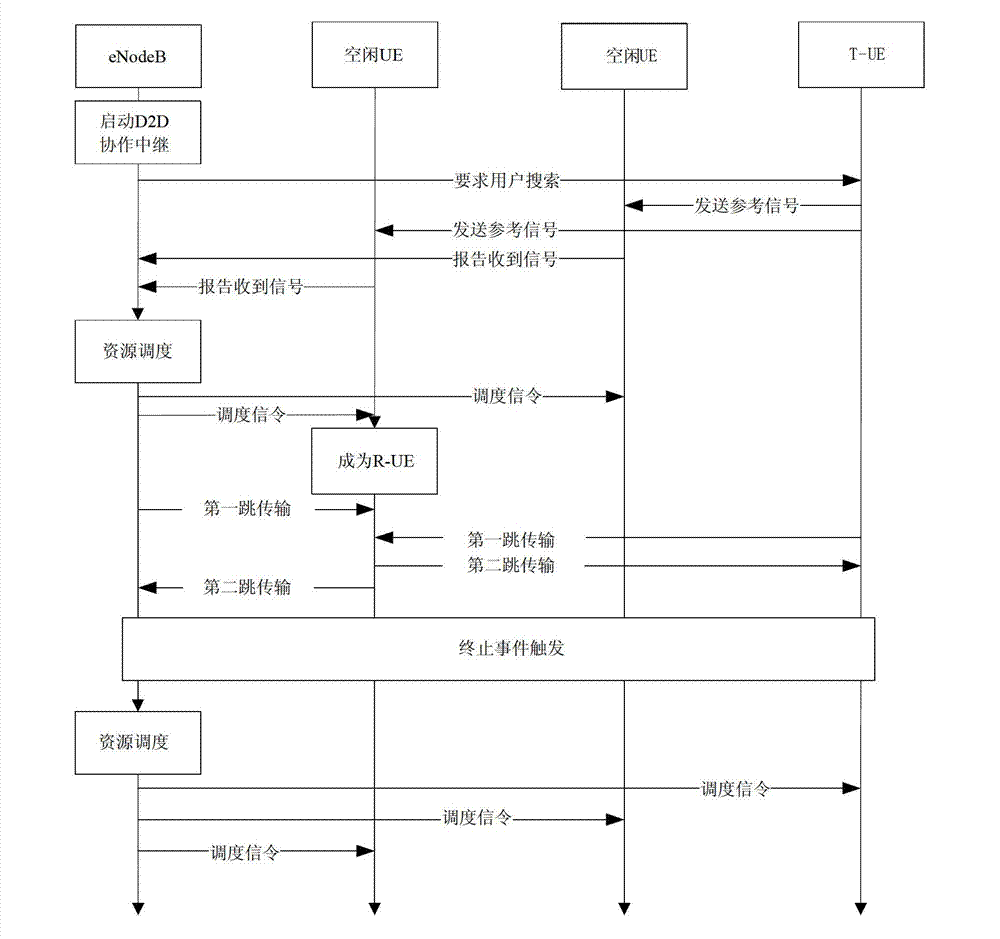

Terminal D2D (device-to-device) cooperation relay communication implementation method in TD-LTE-A (time division-long term evolution-advanced) system

InactiveCN102780993AImprove service qualityImprove system throughputNetwork data managementQuality of serviceTime-Division Long-Term Evolution

The invention discloses a terminal D2D (device-to-device) cooperation relay communication implementation method in a TD-LTE-A (time division-long term evolution-advanced) system, and relates to a relay communication implementation method in the TD-LTE-A system. The method disclosed by the invention aims at realizing communication coverage on terminals in the TD-LTE-A system under a 4G (4th generation) standard and improving service quality and system throughput. According to the method disclosed by the invention, an on-net idle user in a cell is used as a mobile relay, terminal D2D cooperation relay communication is established with a user on the edge of the cell, relay service is provided for the user on the edge of the cell, the coverage range of the cell, the service quality of the user on the edge and the system throughput are significantly improved by resource allocation and time slot allocation of the cell, and the network construction cost of the system can be further greatly reduced. The method disclosed by the invention is suitable for the TD-LTE-A system.

Owner:HARBIN INST OF TECH

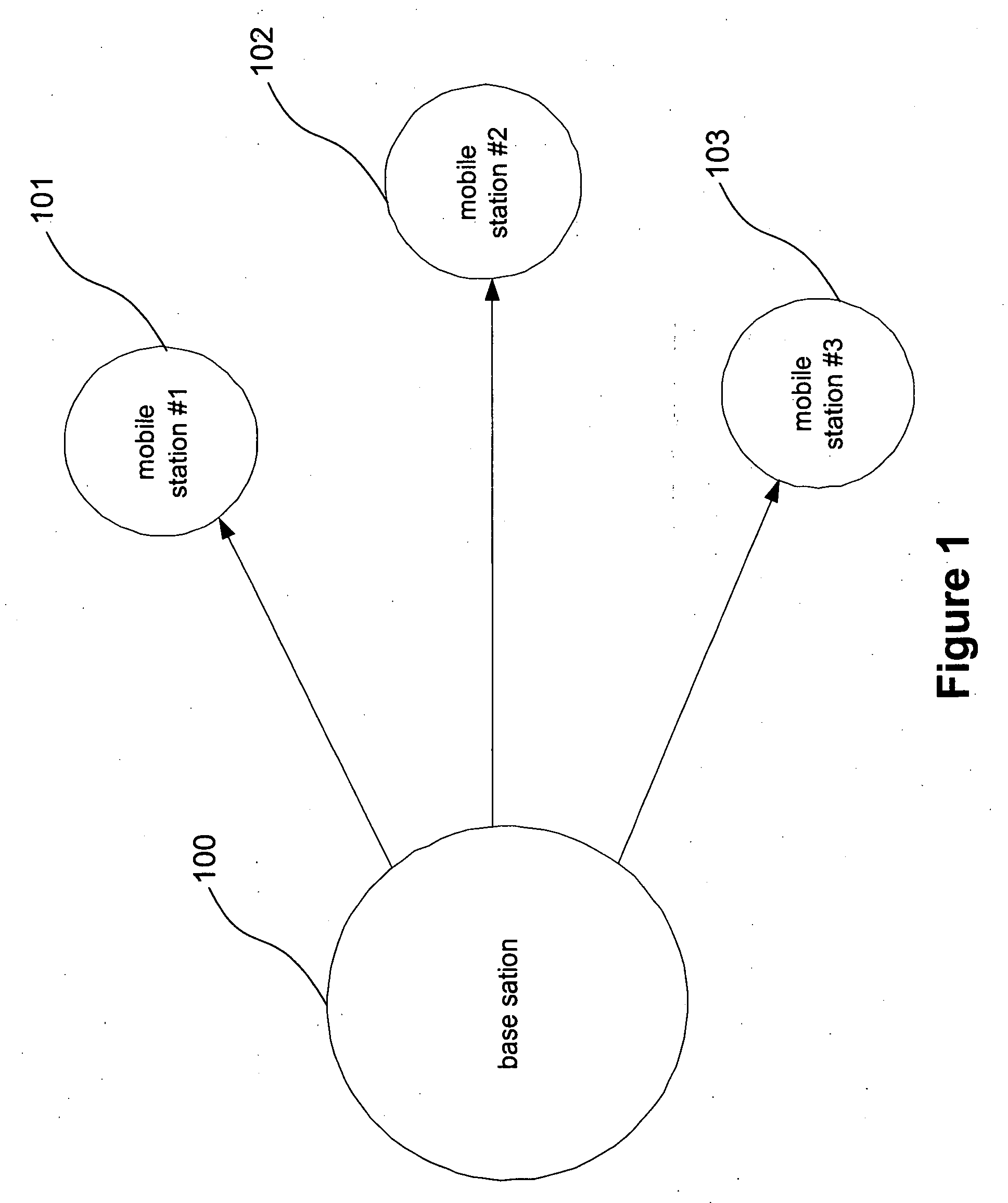

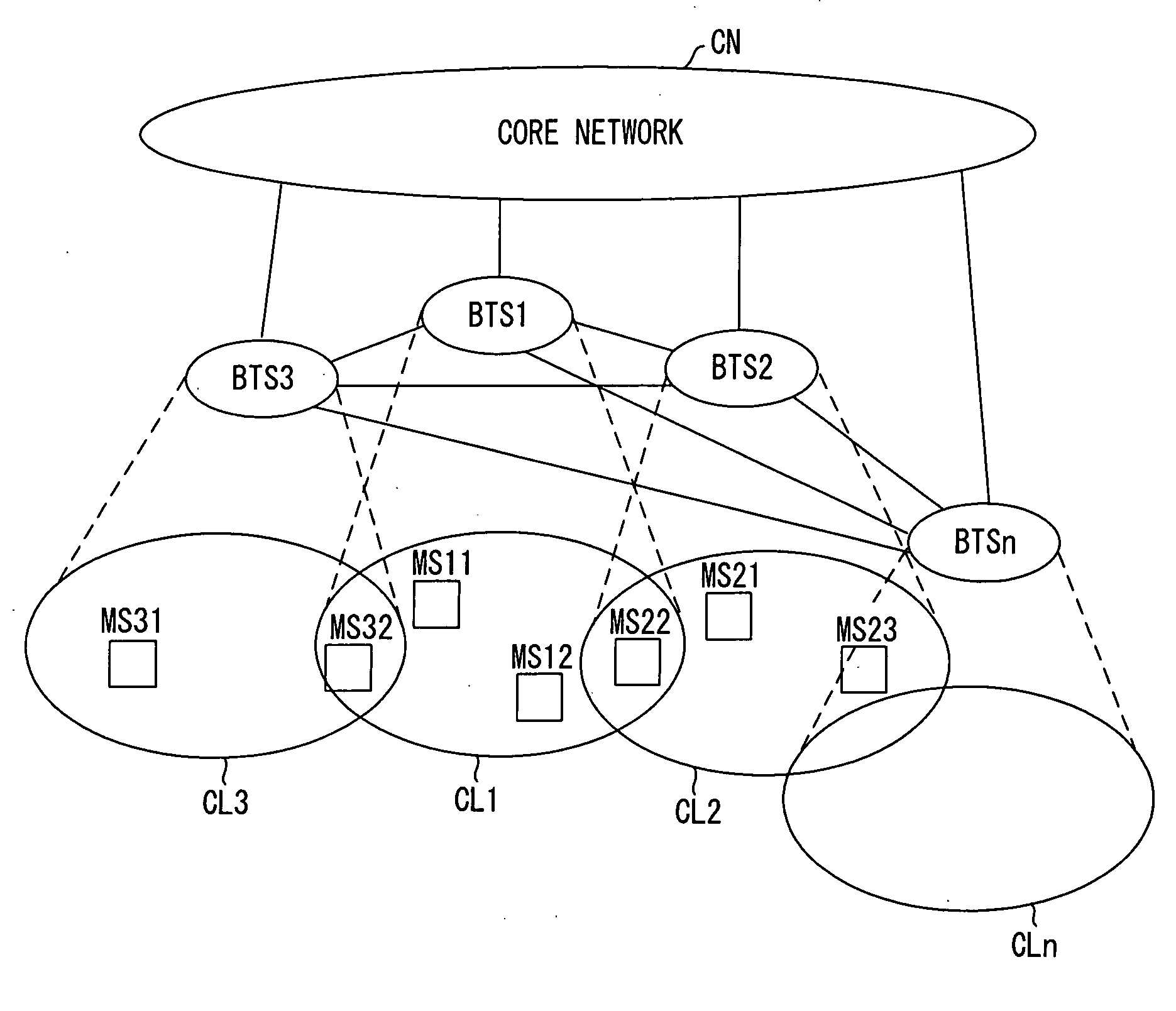

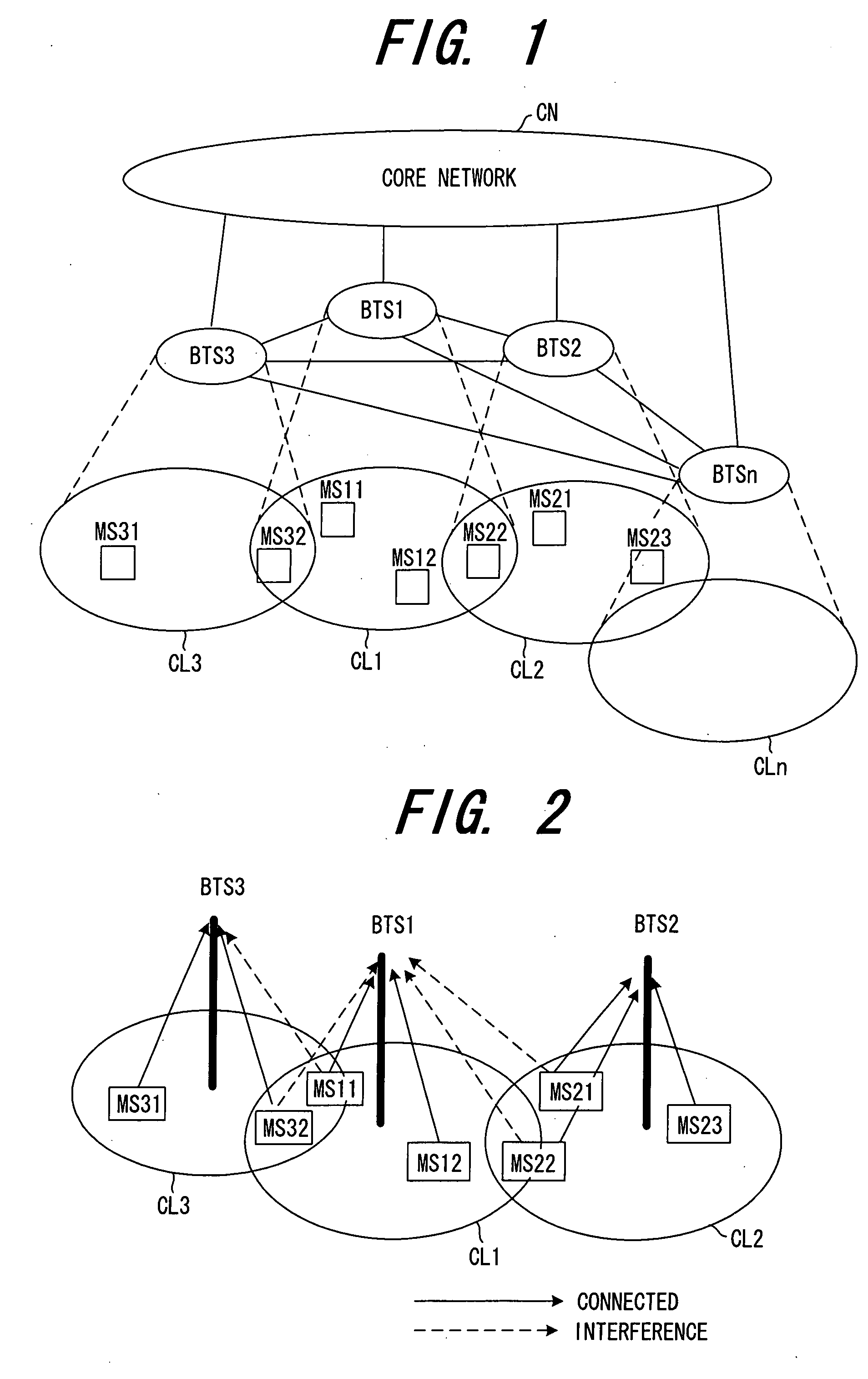

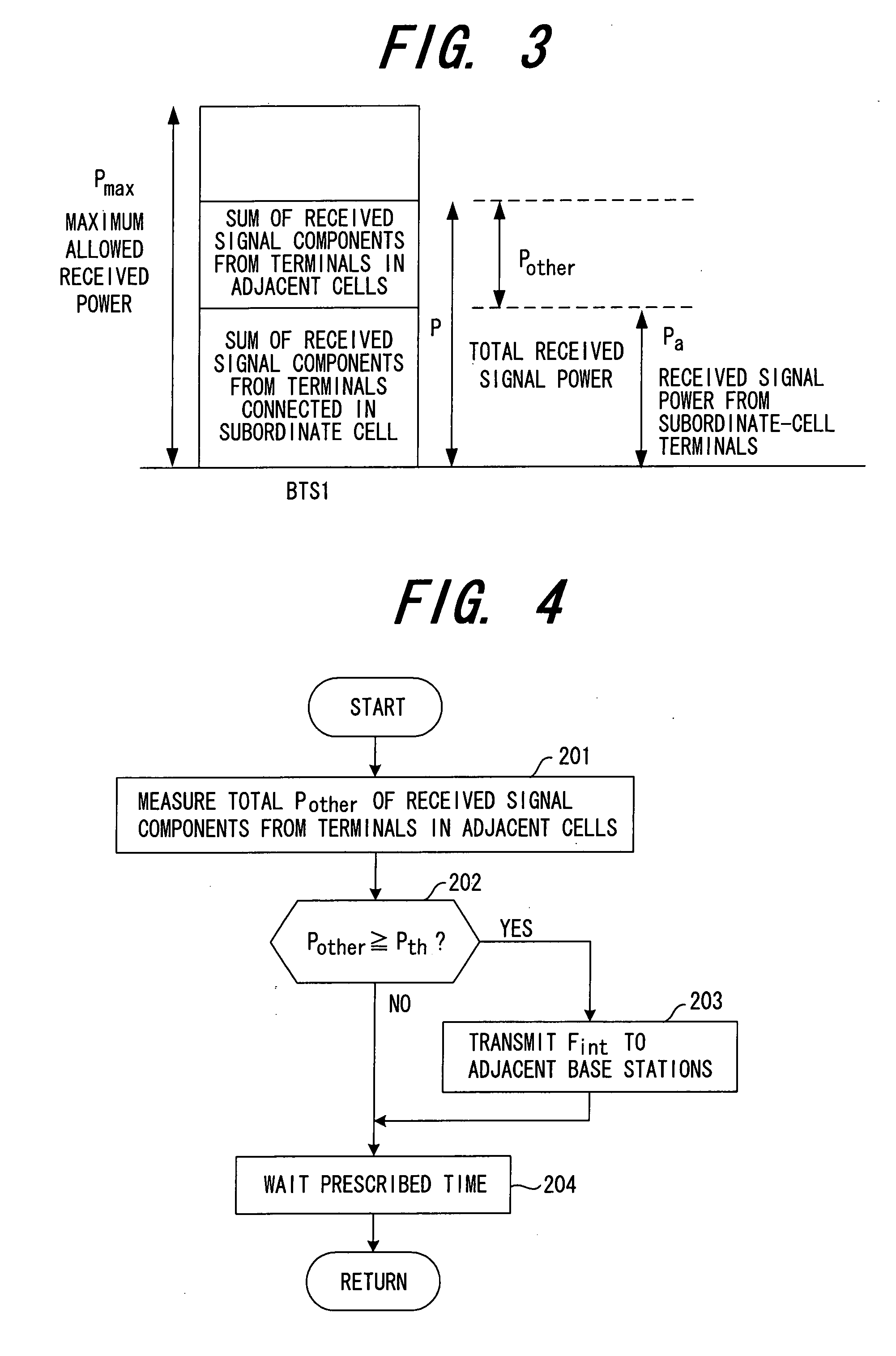

Base station and interference reduction method in base station

InactiveUS20070280170A1Reduce interference powerReduce Interfering SignalsPower managementNetwork traffic/resource managementEngineeringExecution control

A base station communicates with mobile terminals existing within a subordinate cell, and in addition executes control to reduce interference from mobile terminals existing within adjacent cells. The base station measures the total interference power received from mobile terminals in all adjacent cells, and if the total interference power is greater than a preset value, issues a request to the base stations of all adjacent cells to reduce interference. The base station which has received the interference reduction request discriminates mobile terminals which impart interference to the base station which is the source of the interference reduction request, and reduces interference by either temporarily lowering the uplink data transmission rate or temporarily halting uplink data transmission for such mobile terminals.

Owner:FUJITSU LTD

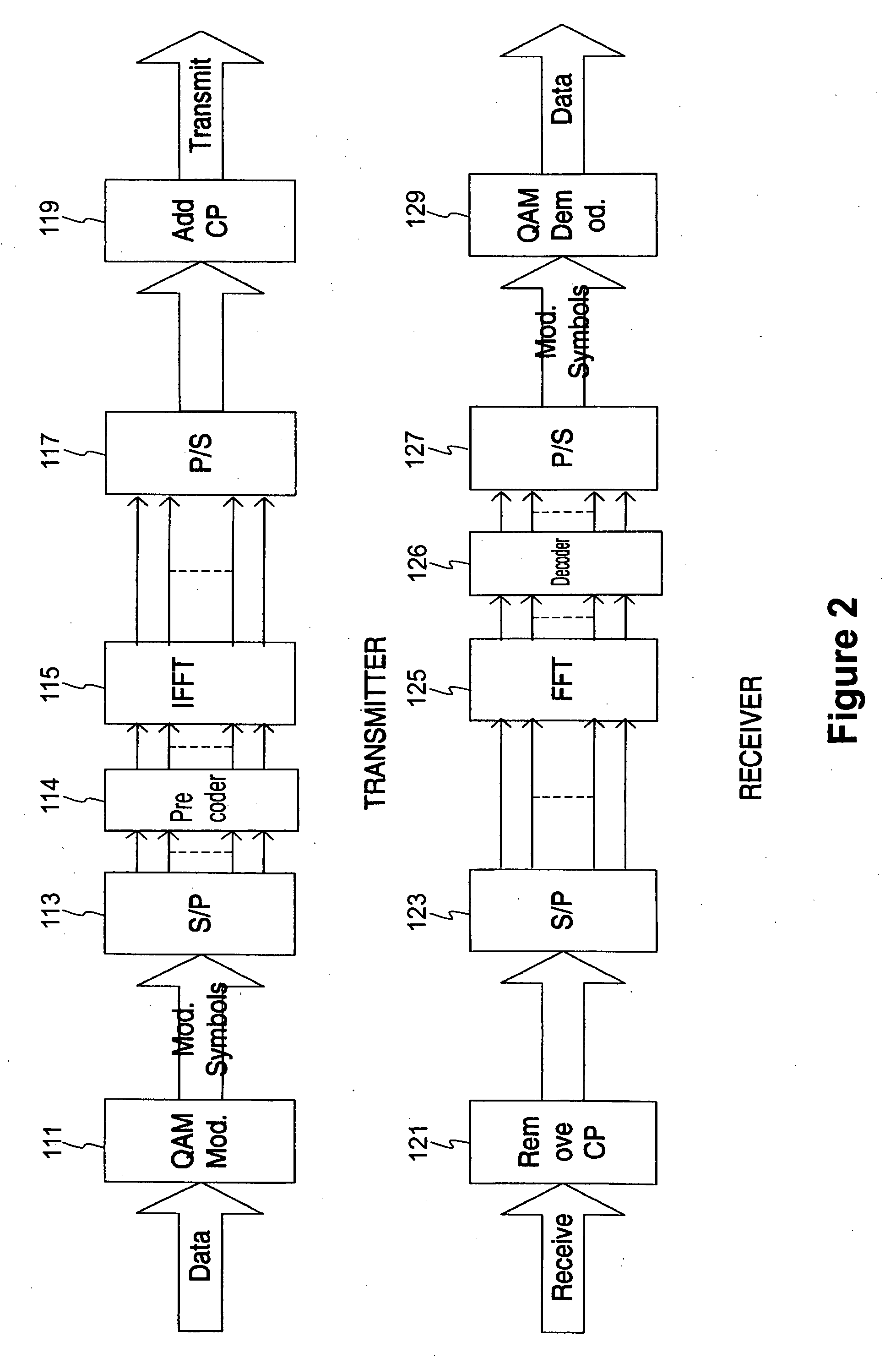

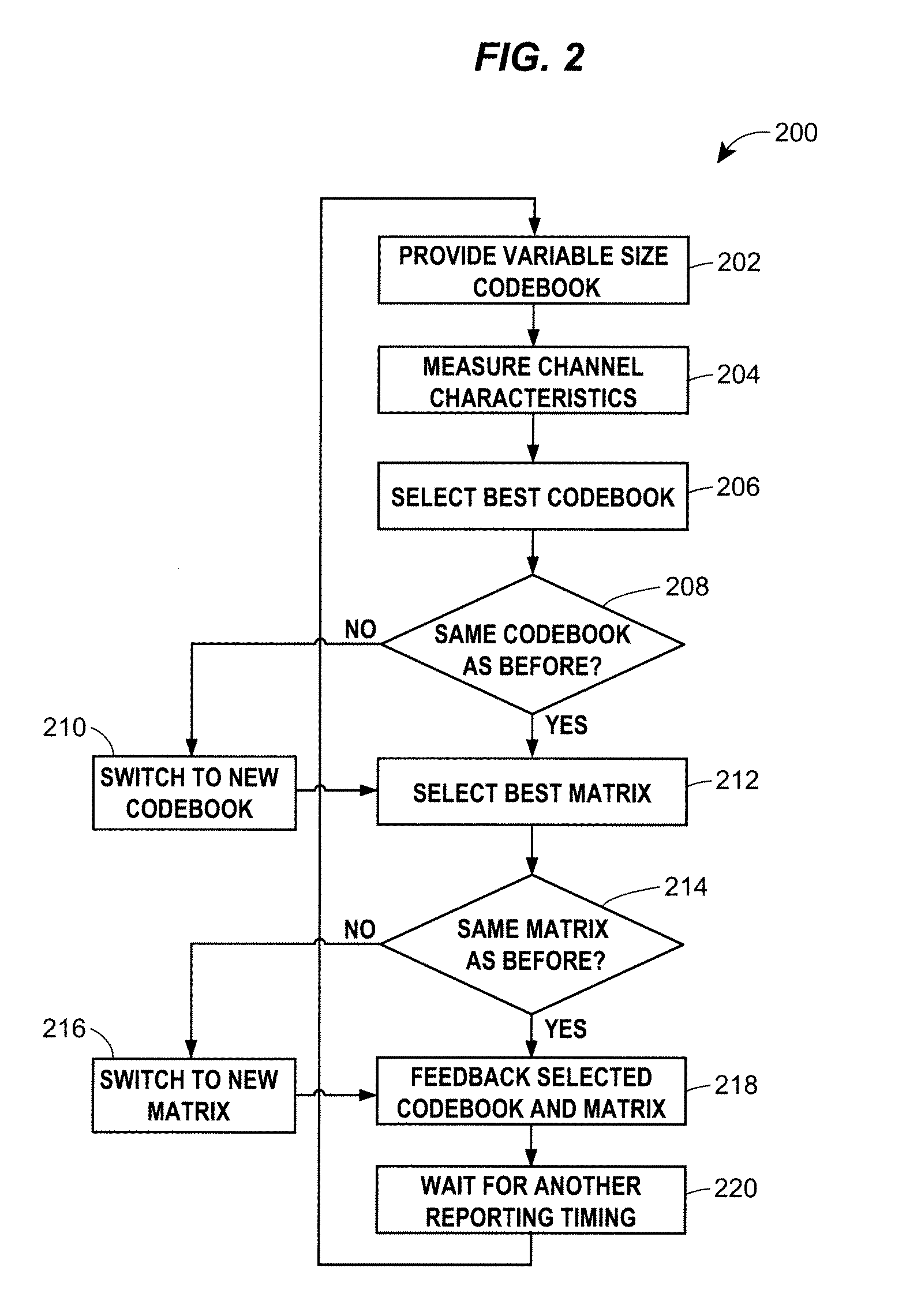

Variable codebook for MIMO system

ActiveUS20080232503A1Reduce channel efficiencyImprove system throughputModulated-carrier systemsTransmission control/equalisingCode bookWireless communication systems

A MIMO wireless communication system employing a variable size preceding codebook is provided. The size of the codebook may be determined by the quality of the wireless transmission channel between a transmitter and a receiver associated with the MIMO wireless communication systems or some other codebook selection criteria. A larger codebook can be employed when the channel quality is high, allowing for significant gains in overall system throughput. In contrast, a smaller codebook can be employed when the cannel quality is poor, so that the added channel overhead associated with a larger code book does not reduce the channel efficiency under circumstances in which a larger codebook would not significantly improve system throughput.

Owner:MARVELL ASIA PTE LTD

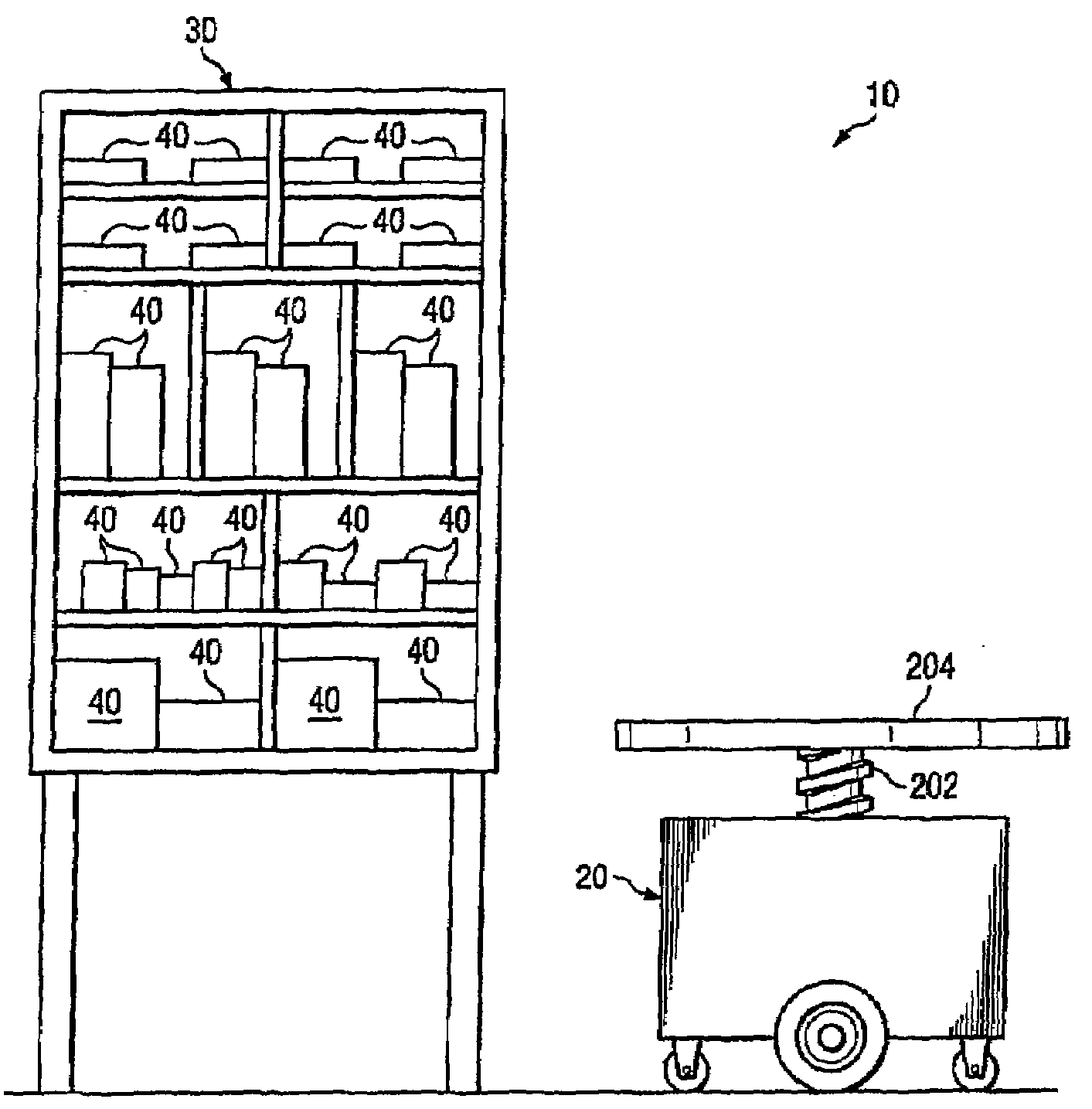

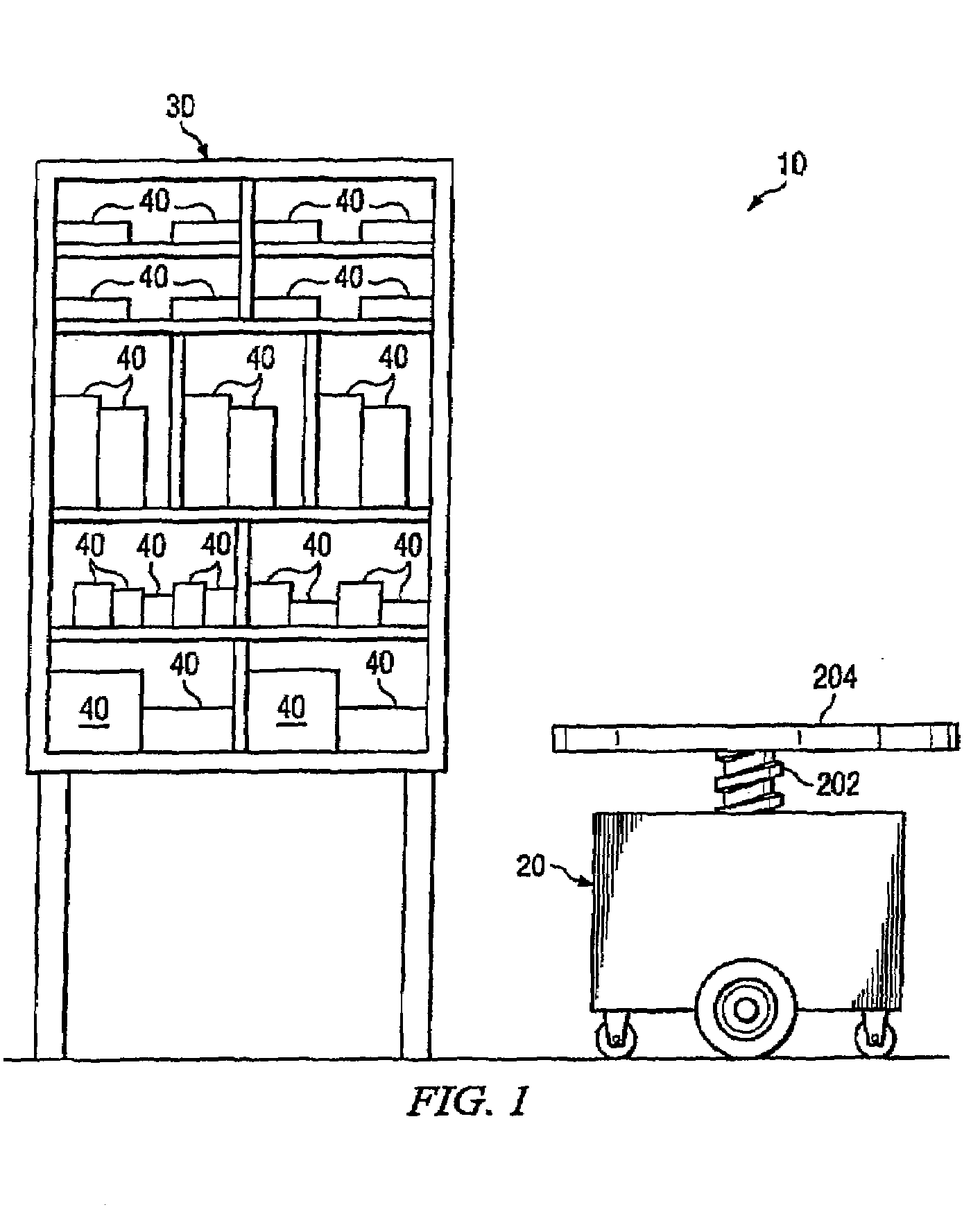

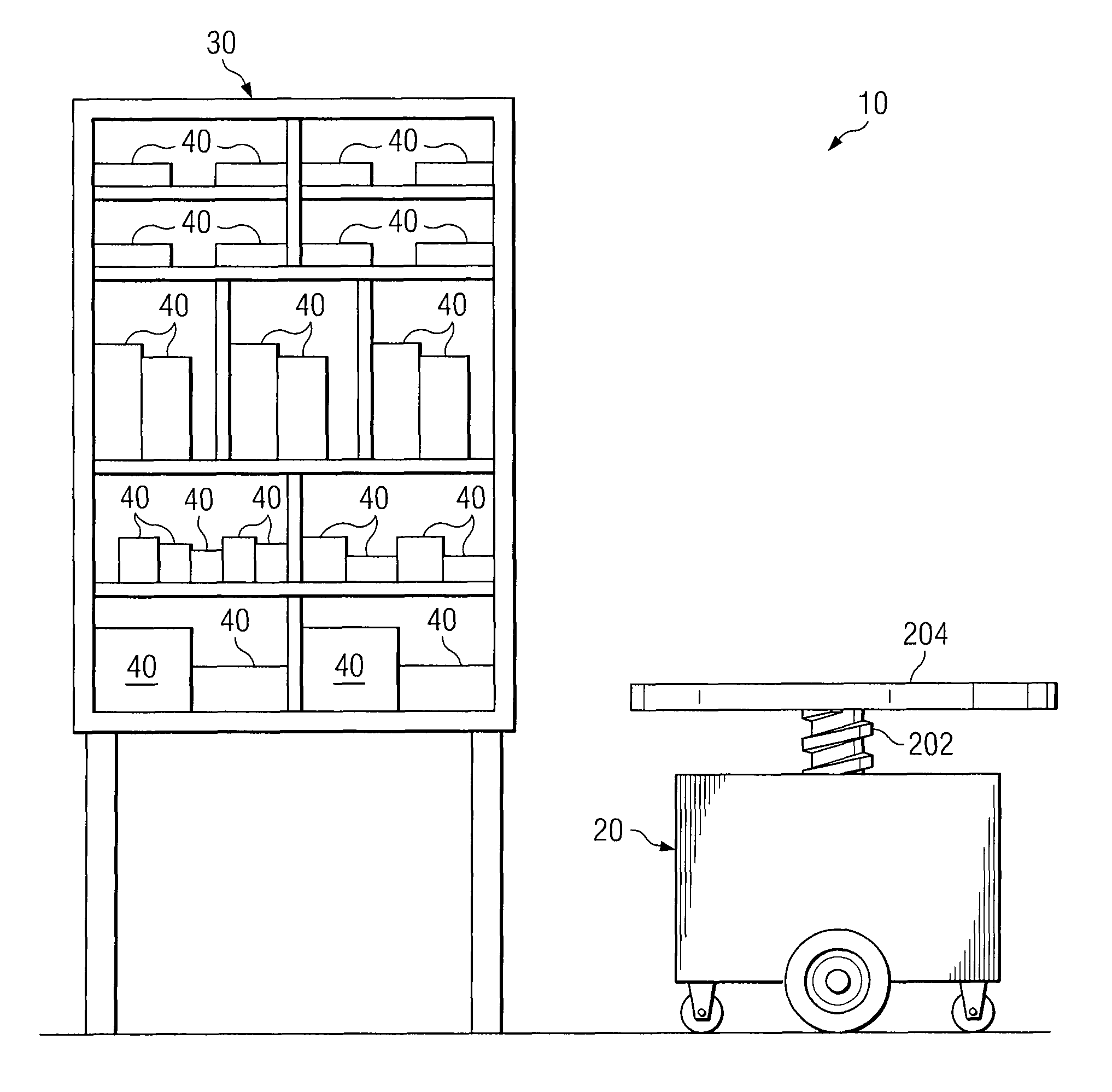

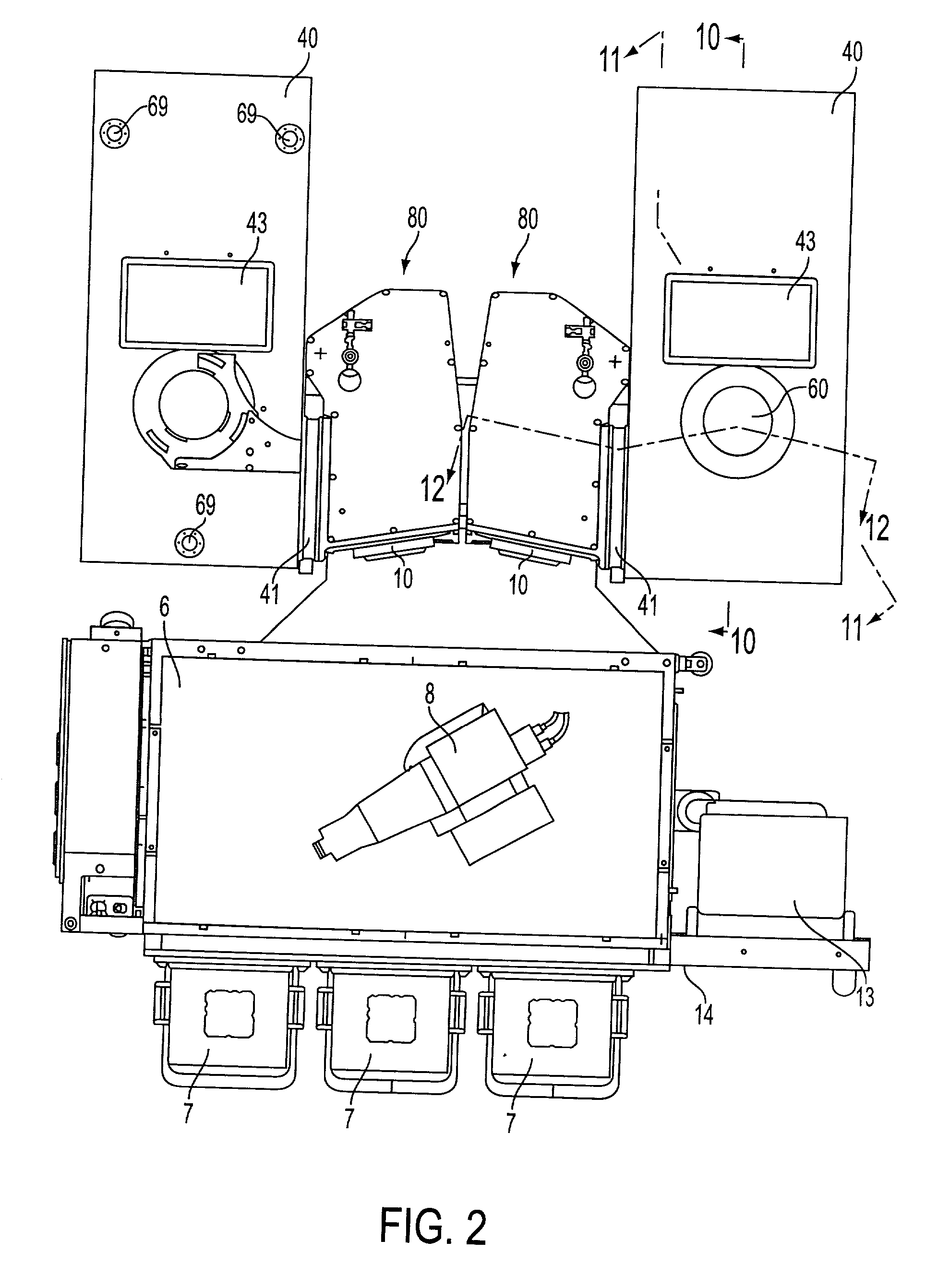

System and method for transporting inventory items

ActiveUS20080166217A1Simple technologyDisadvantages and reduced eliminatedProgramme-controlled manipulatorDigital data processing detailsMechanical engineering

An apparatus for transporting inventory items includes a housing, a drive module, a docking module, an elevating shaft, and a rotation module. The drive module is capable of propelling the apparatus in at least a first direction. The docking head is capable of coupling to or supporting an inventory holder. The rotation module is capable of inducing rotation in the housing relative to the elevating shaft. The elevating shaft connects to the docking head and is capable of raising the docking head when the housing is rotated relative to the elevating shaft.

Owner:AMAZON TECH INC

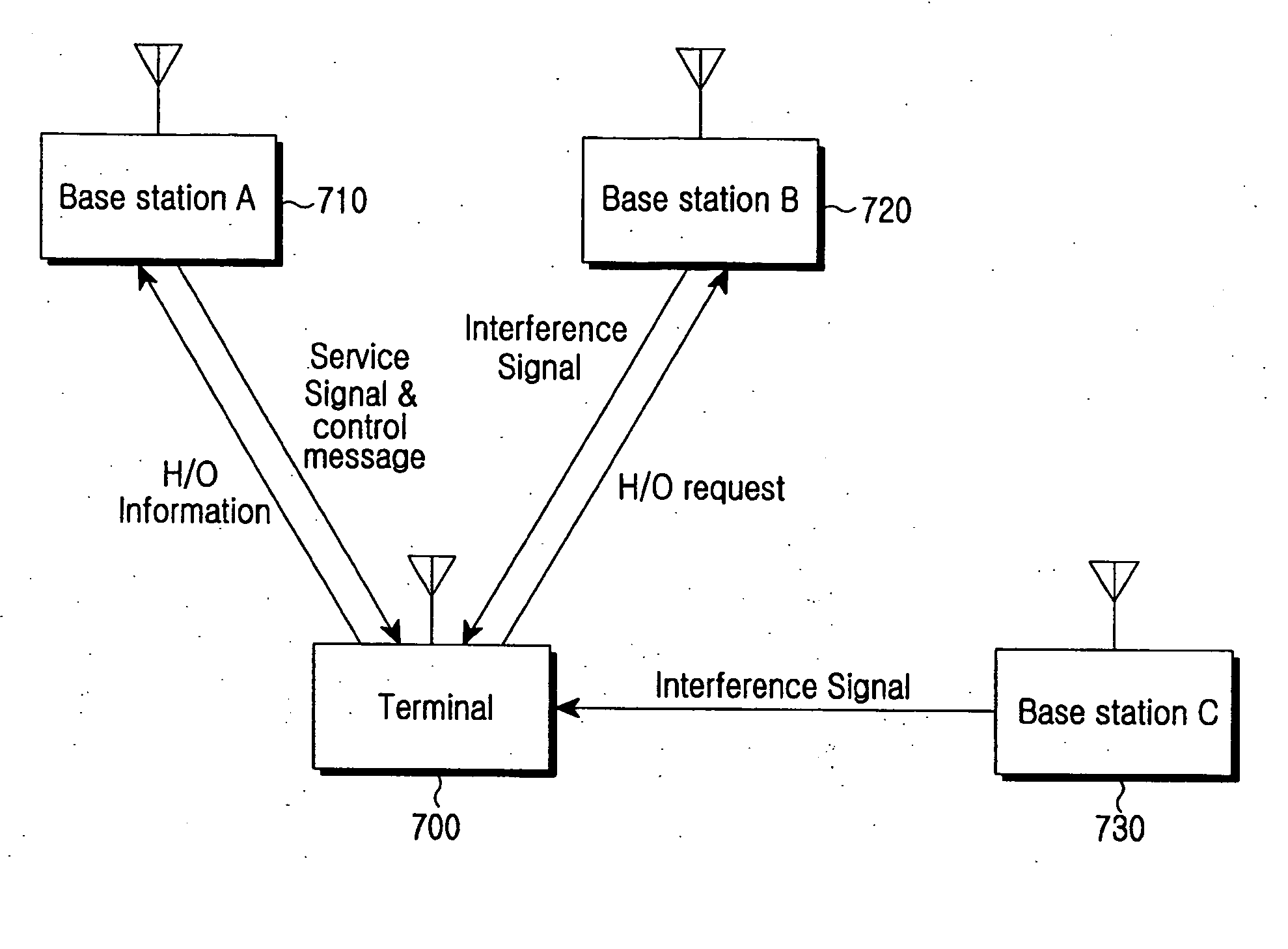

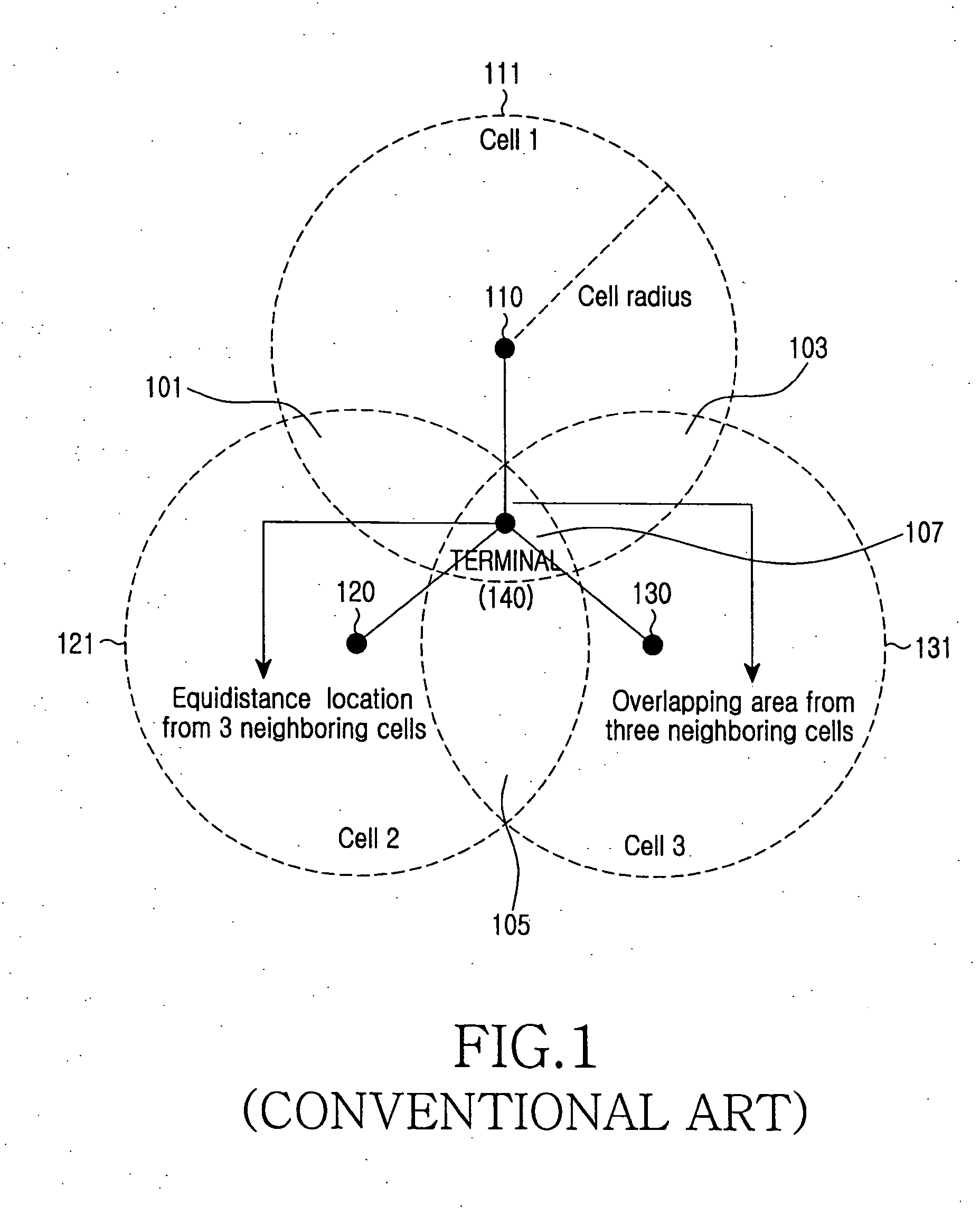

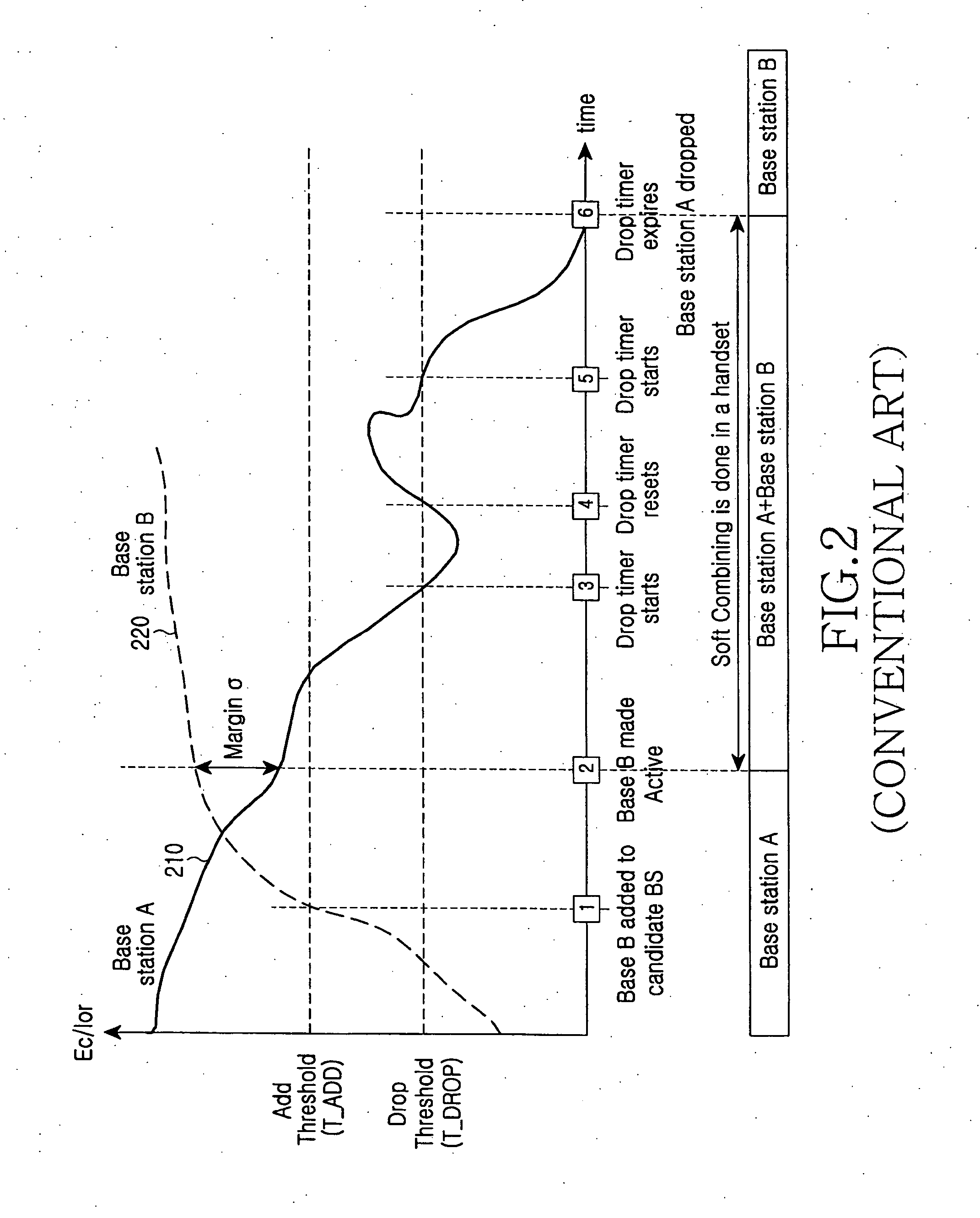

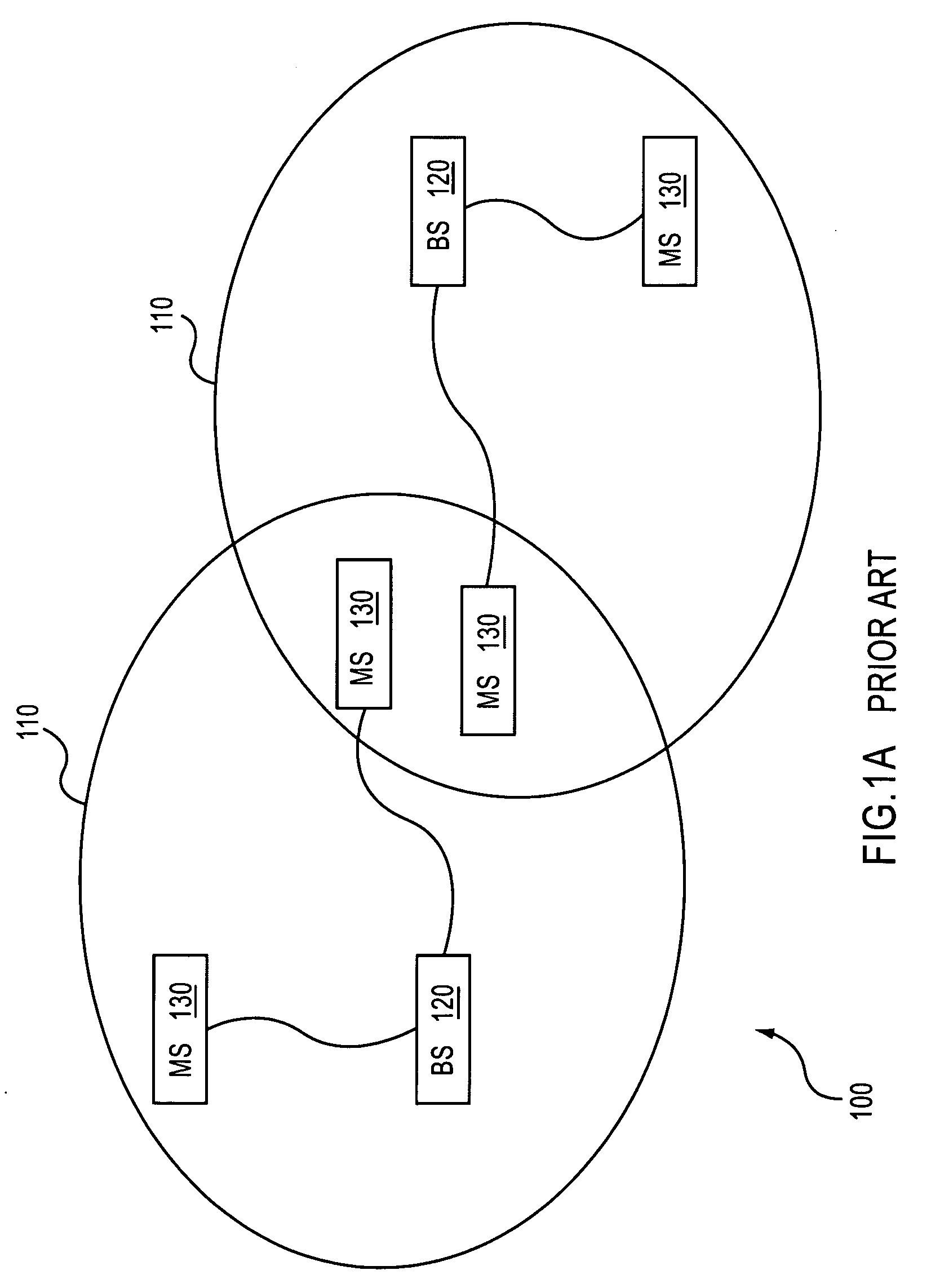

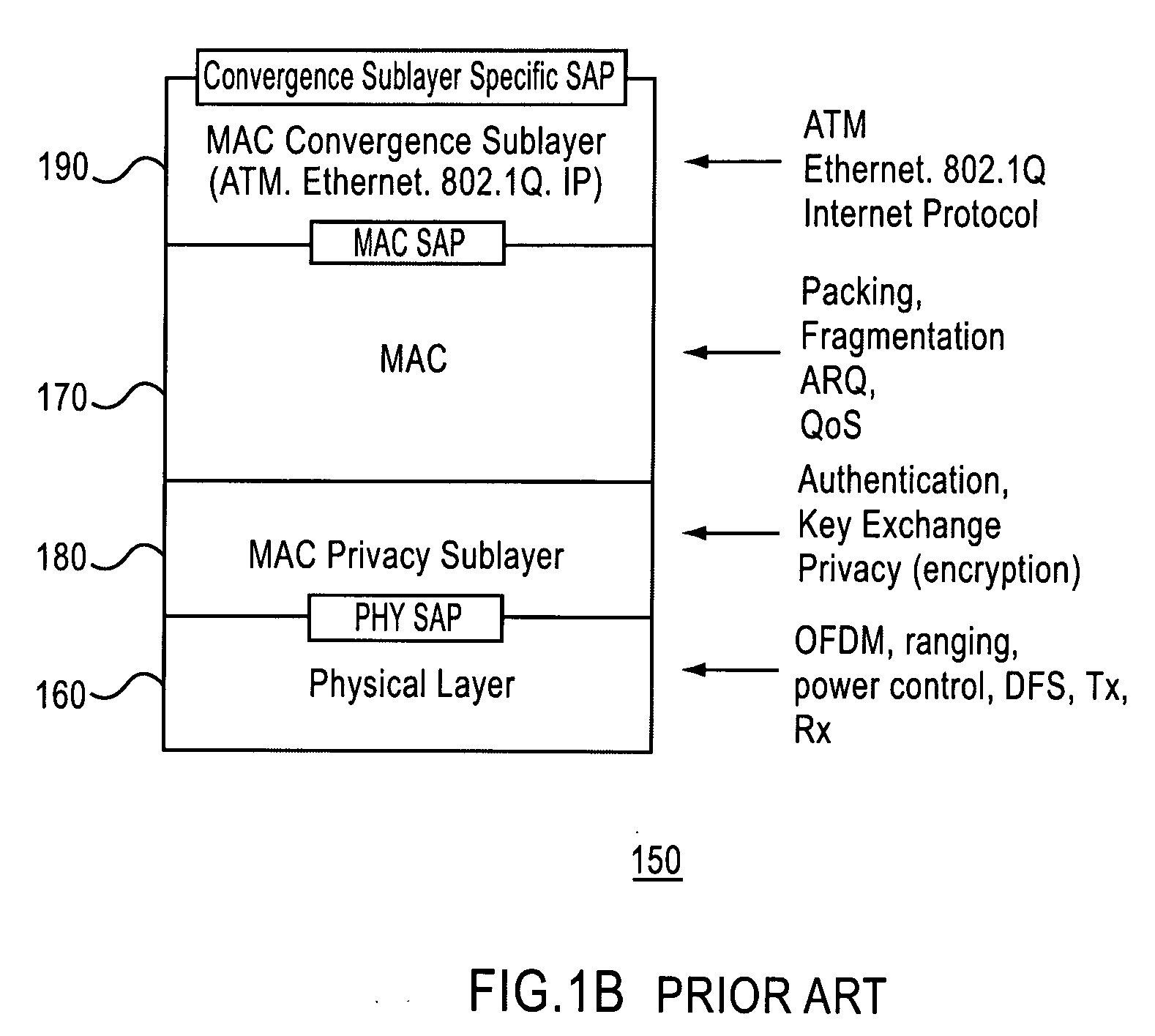

Apparatus and method for hard handover in a wireless communication system

ActiveUS20070135125A1Secure transmissionPreventing a decrease in QoSRadio/inductive link selection arrangementsRadio transmissionCommunications systemSignal-to-noise ratio (imaging)

Provided is a hard handover method in a wireless communication system. The hard handover method includes checking a signal-to-noise ratio (SNR) of a signal received from each of at least one neighboring base station (BS) while in communication with a serving BS, and canceling interference if the SNR of the signal received from each of the at least one neighboring BSs satisfies a select condition; sending a handover request to the serving BS, if a difference between a SNR of the interference-canceled signal and a SNR of the interference signal reaches a handover request threshold; and upon receipt of a handover approval from the serving BS, releasing a communication channel to the serving BS, and connecting a call to a BS that provides an interference signal whose SNR has reached the threshold.

Owner:SAMSUNG ELECTRONICS CO LTD

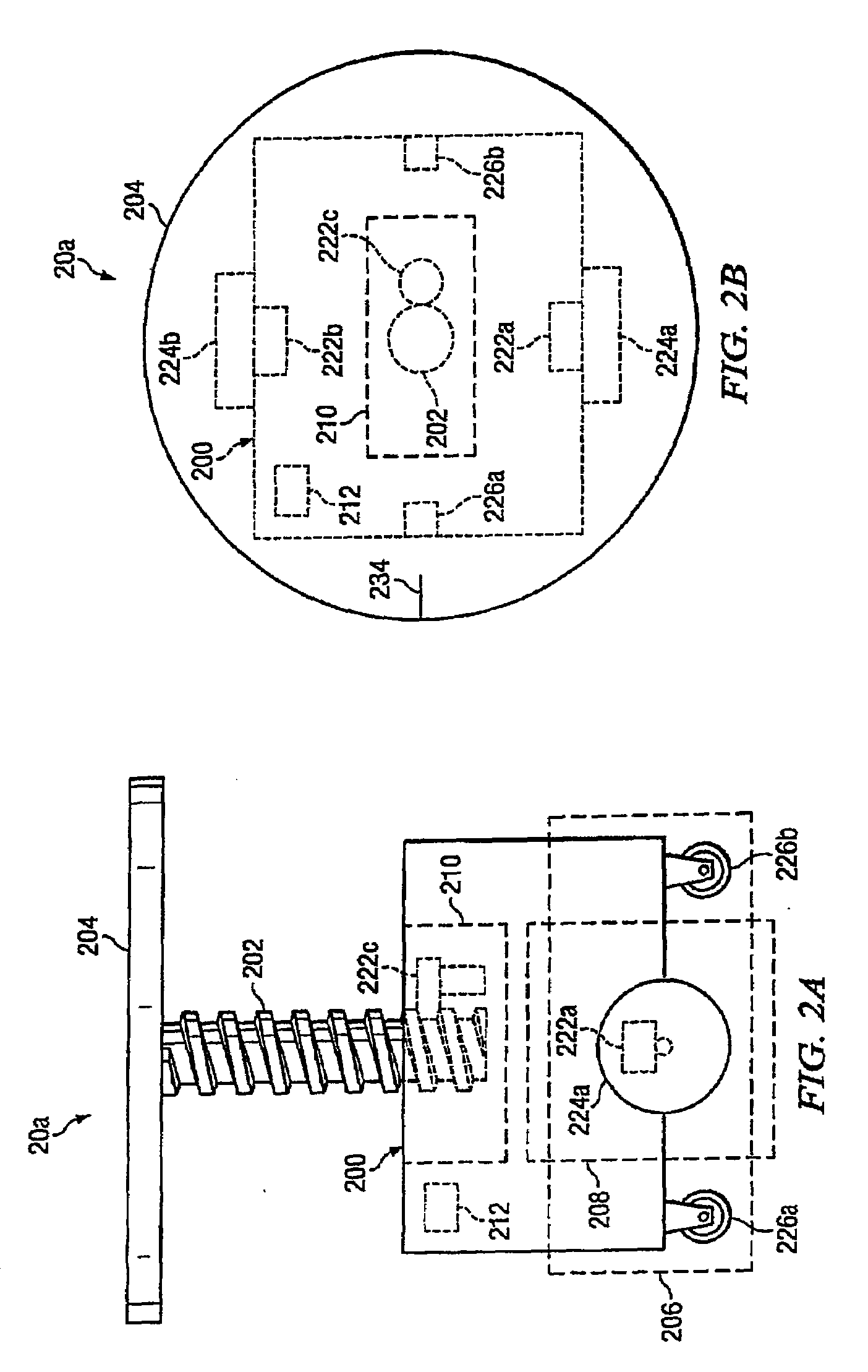

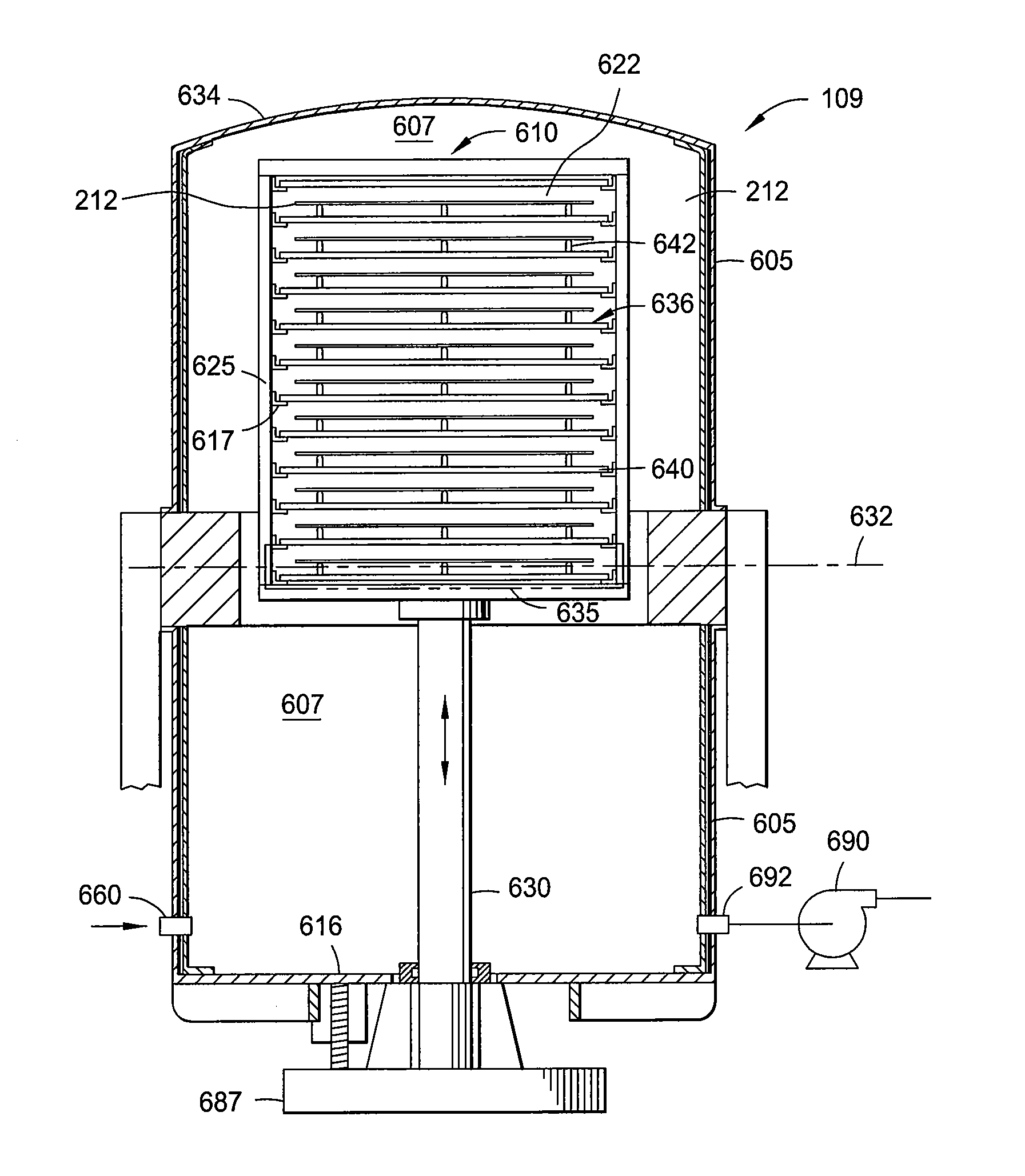

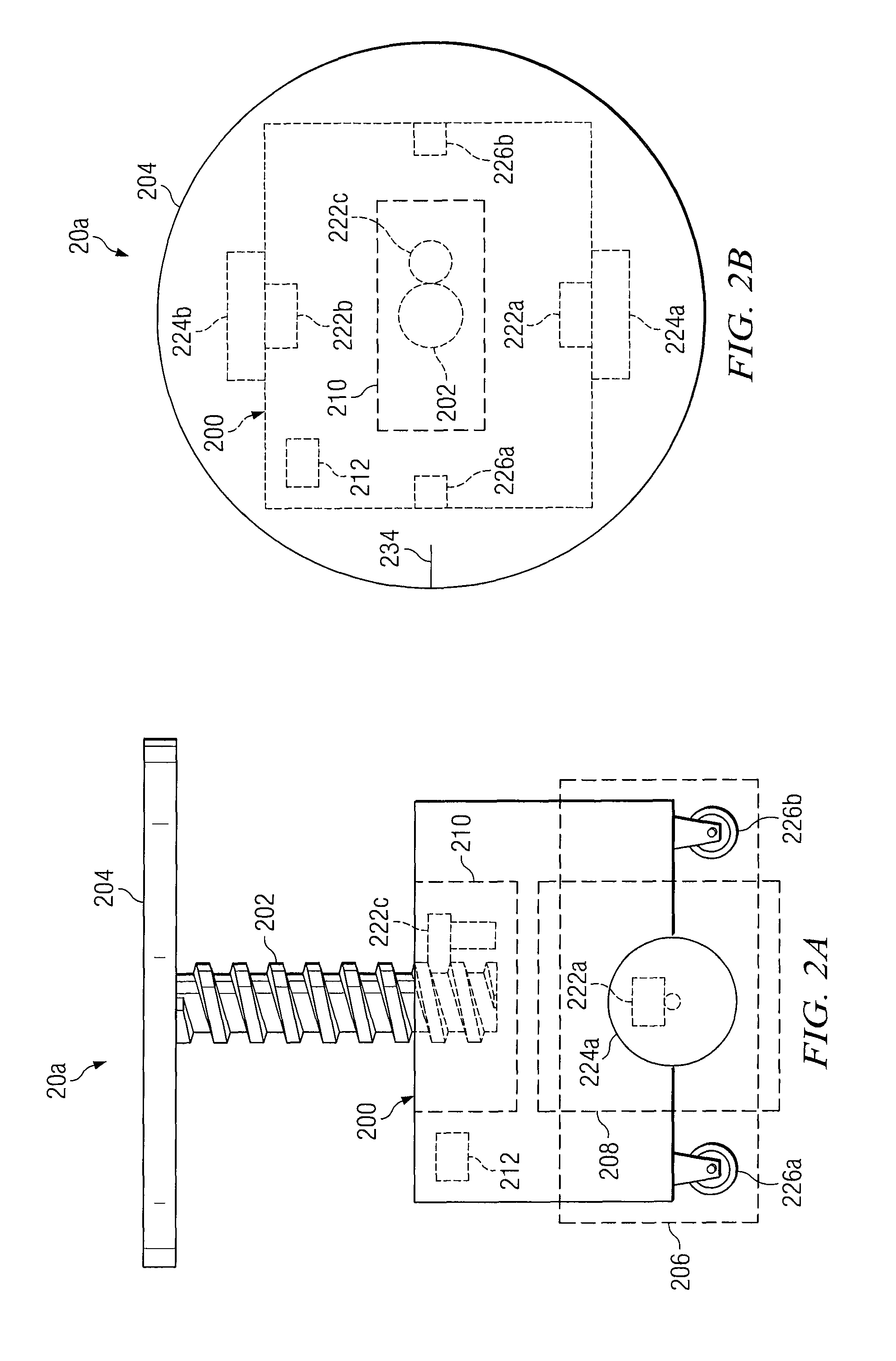

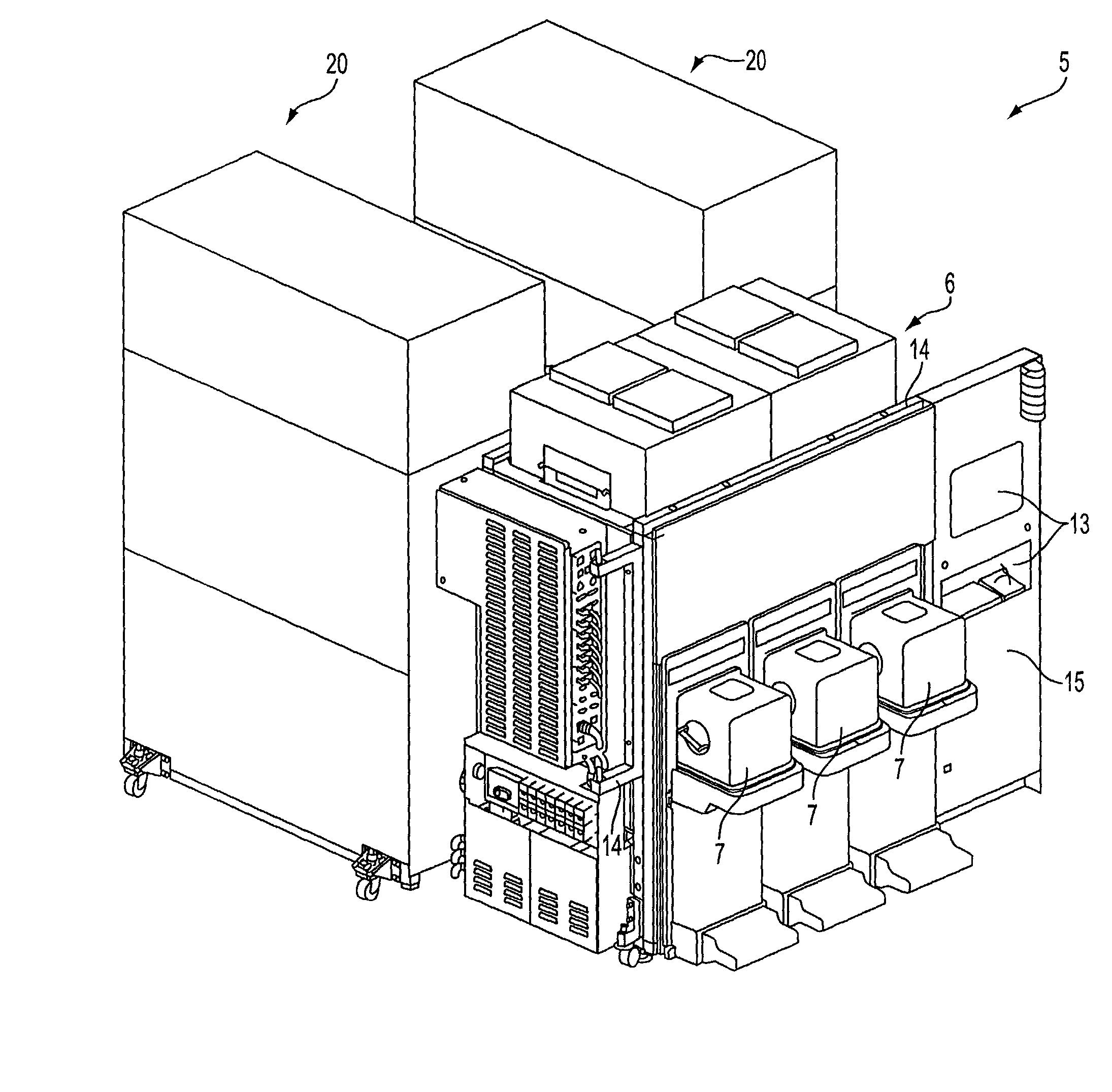

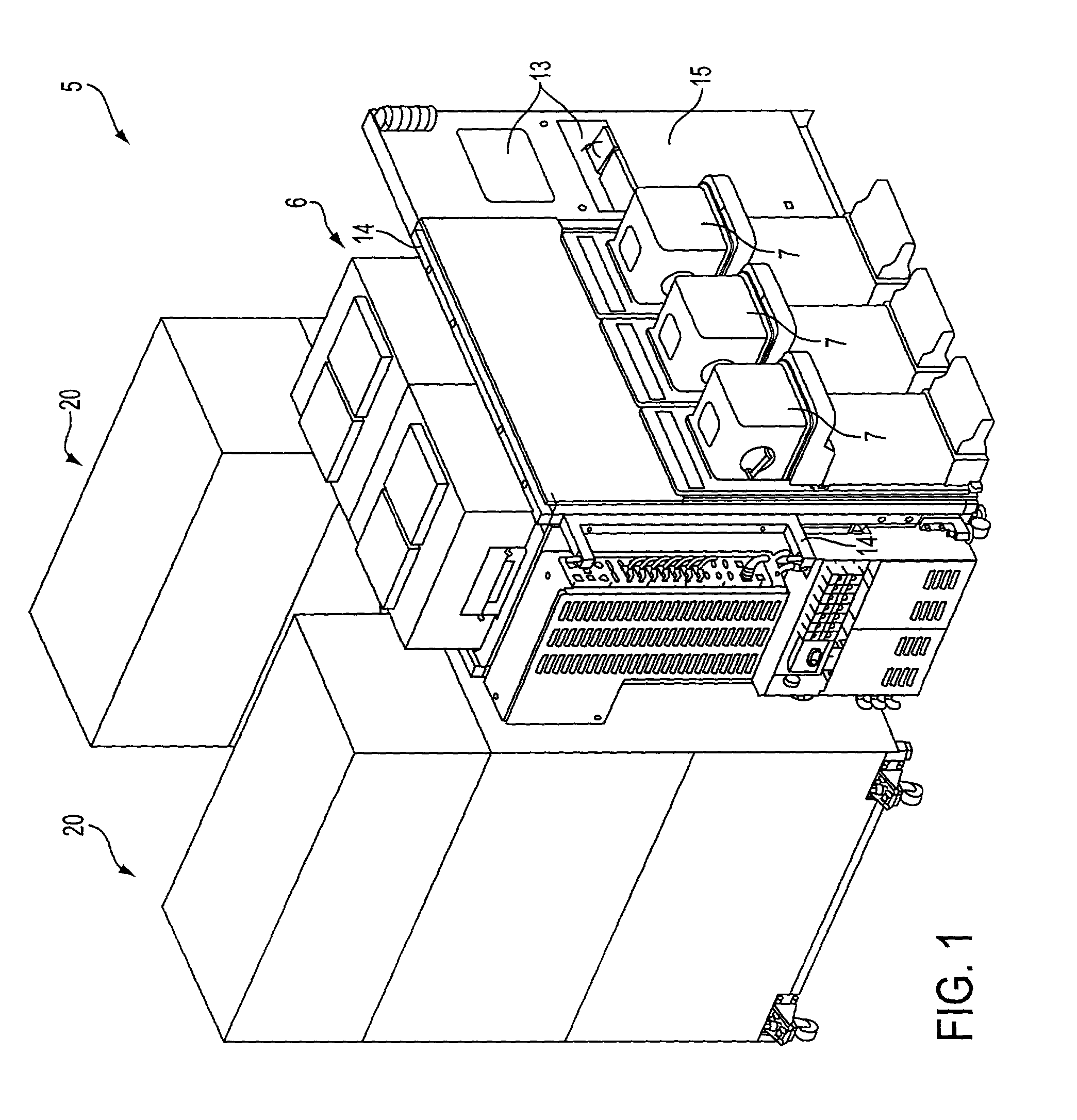

Processing system for fabricating compound nitride semiconductor devices

InactiveUS20090194026A1Expands available process windowImprove system throughputAfter-treatment apparatusPolycrystalline material growthCompound structureEngineering

One embodiment of a processing system for fabricating compound nitride semiconductor devices comprises one or more processing chamber operable with form a compound nitride semiconductor layer on a substrate, a transfer chamber coupled with the processing chamber, a loadlock chamber coupled with the transfer chamber, and a load station coupled with the loadlock chamber, wherein the load station comprises a conveyor tray movable to convey a carrier plate loaded with one or more substrates into the loadlock chamber. Compared to a single chamber reactor, the multi-chamber processing system expands the potential complexity and variety of compound structures. Additionally, the system can achieve higher quality and yield by specialization of individual chambers for specific epitaxial growth processes. Throughput is increased by simultaneous processing in multiple chambers.

Owner:APPLIED MATERIALS INC

Method and apparatus for printing raster lines in a selective deposition modelling system

InactiveUS6136252AImprove system throughputSimple technologyAdditive manufacturing apparatusAuxillary shaping apparatusGratingSelective deposition

Owner:3D SYST INC

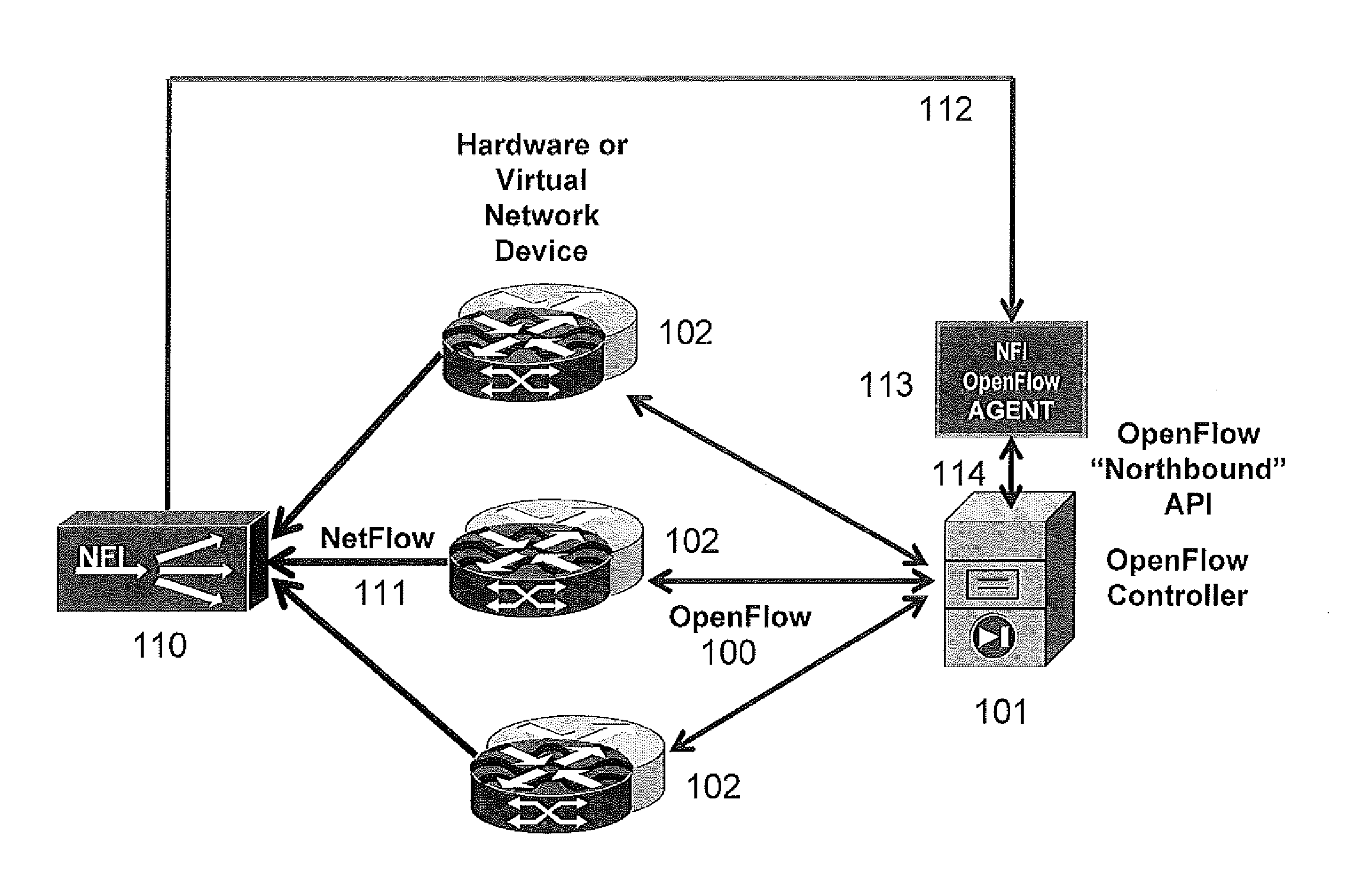

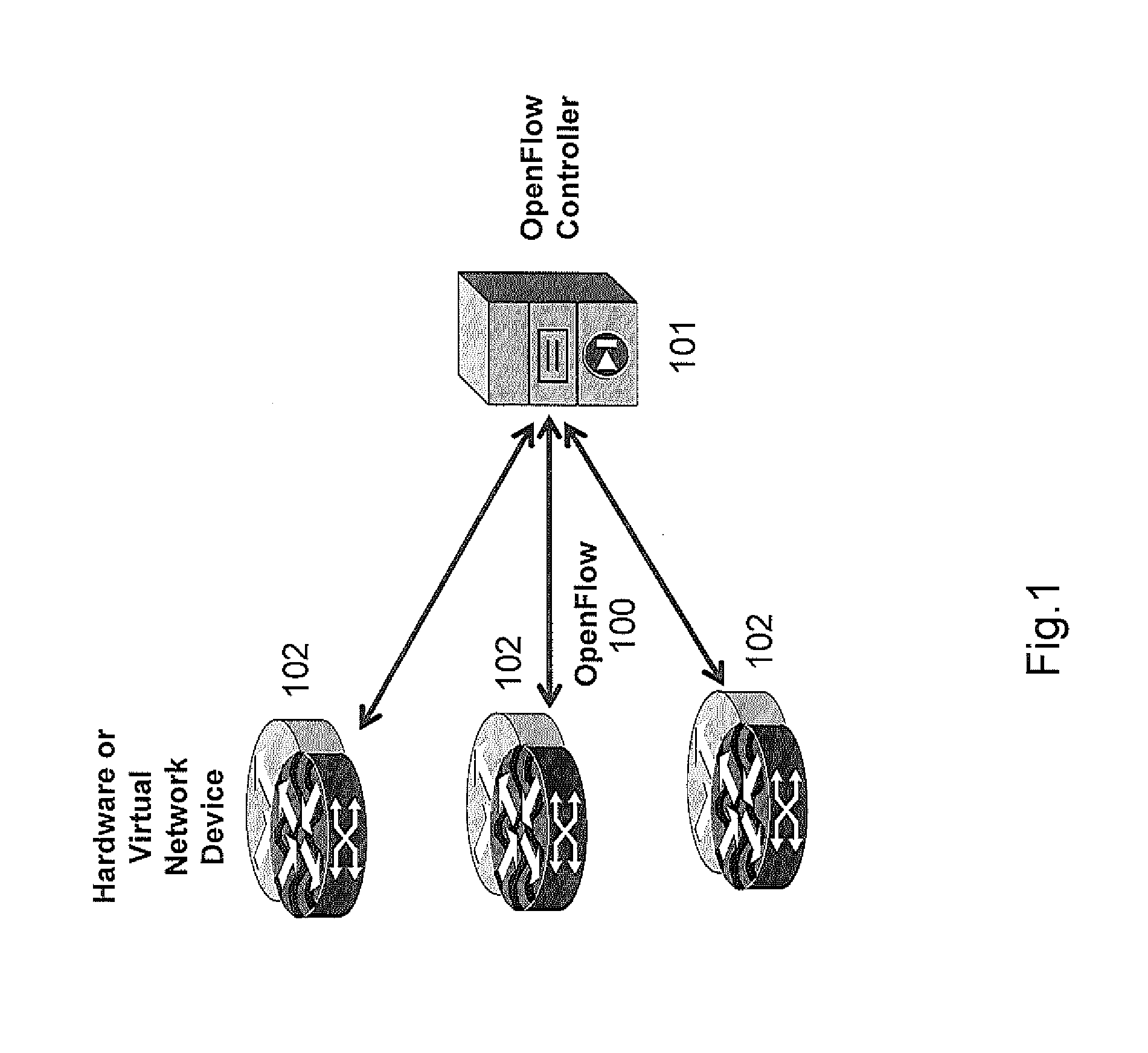

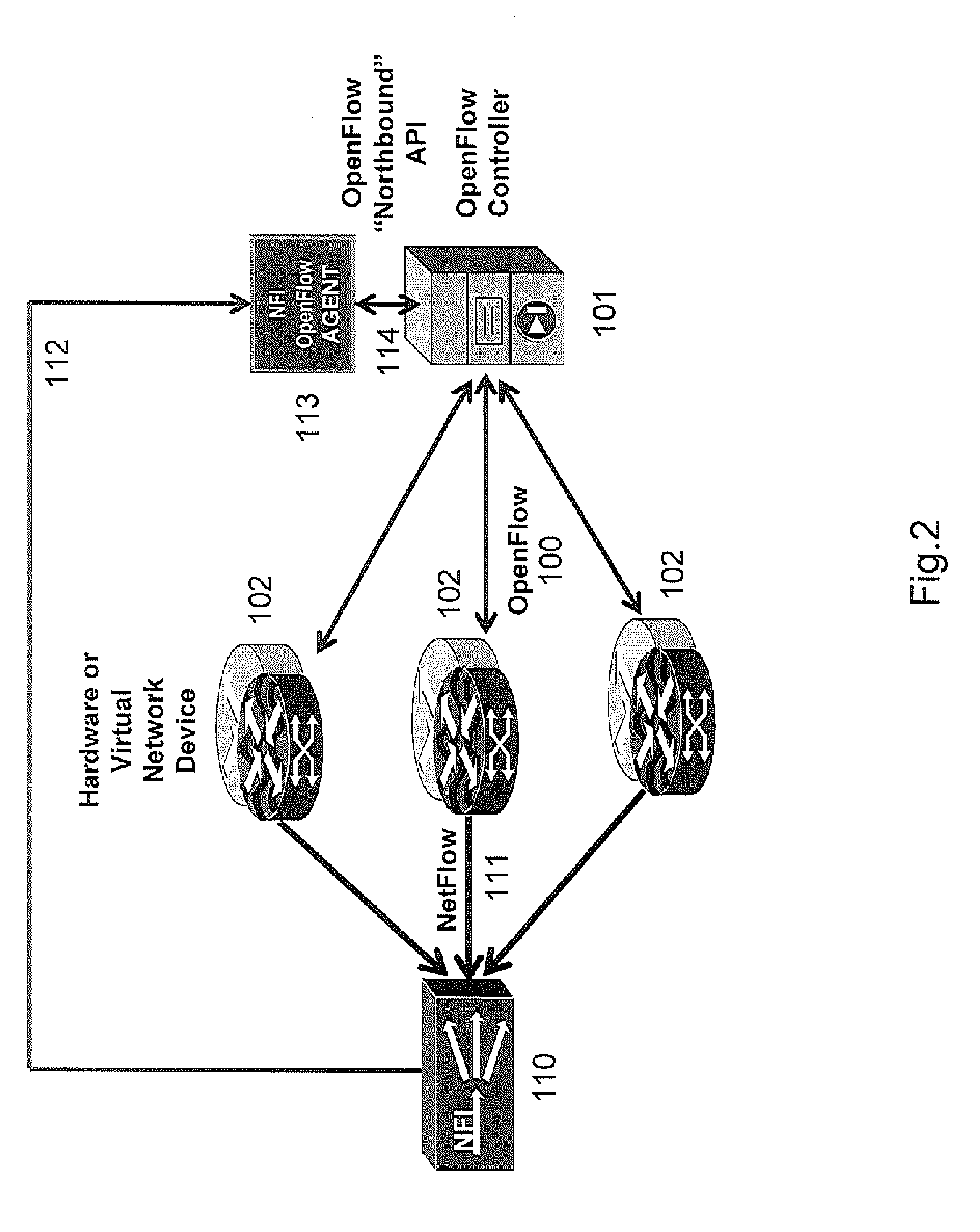

Streaming Method and System for Processing Network Metadata

InactiveUS20140075557A1Easy to deployImprove system throughputMemory loss protectionError detection/correctionInternet trafficTemplate based

An improved method and system for processing network metadata is described. Network metadata may be processed by dynamically instantiated executable software modules which make policy-based decisions about the character of the network metadata and about presentation of the network metadata to consumers of the information carried by the network metadata. The network metadata may be type classified and each subclass within a type may be mapped to a definition by a unique fingerprint value. The fingerprint value may be used for matching the network metadata subclasses against relevant policies and transformation rules. For template-based network metadata such as NetFlow v9, an embodiment of the invention can constantly monitor network traffic for unknown templates, capture template definitions, and informs administrators about templates for which custom policies and conversion rules do not exist. Conversion modules can efficiently convert selected types and / or subclasses of network metadata into alternative metadata formats.

Owner:NETFLOW LOGIC

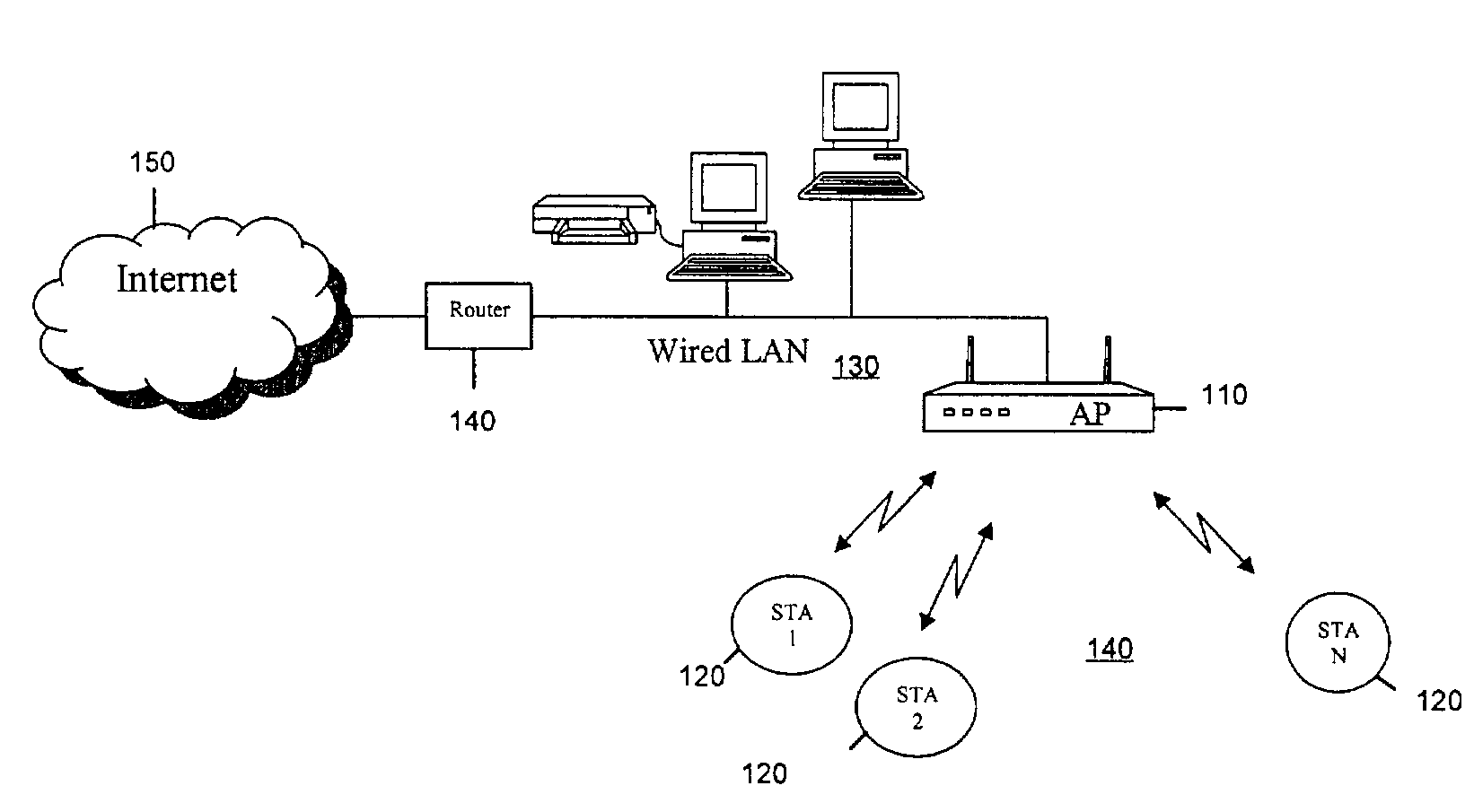

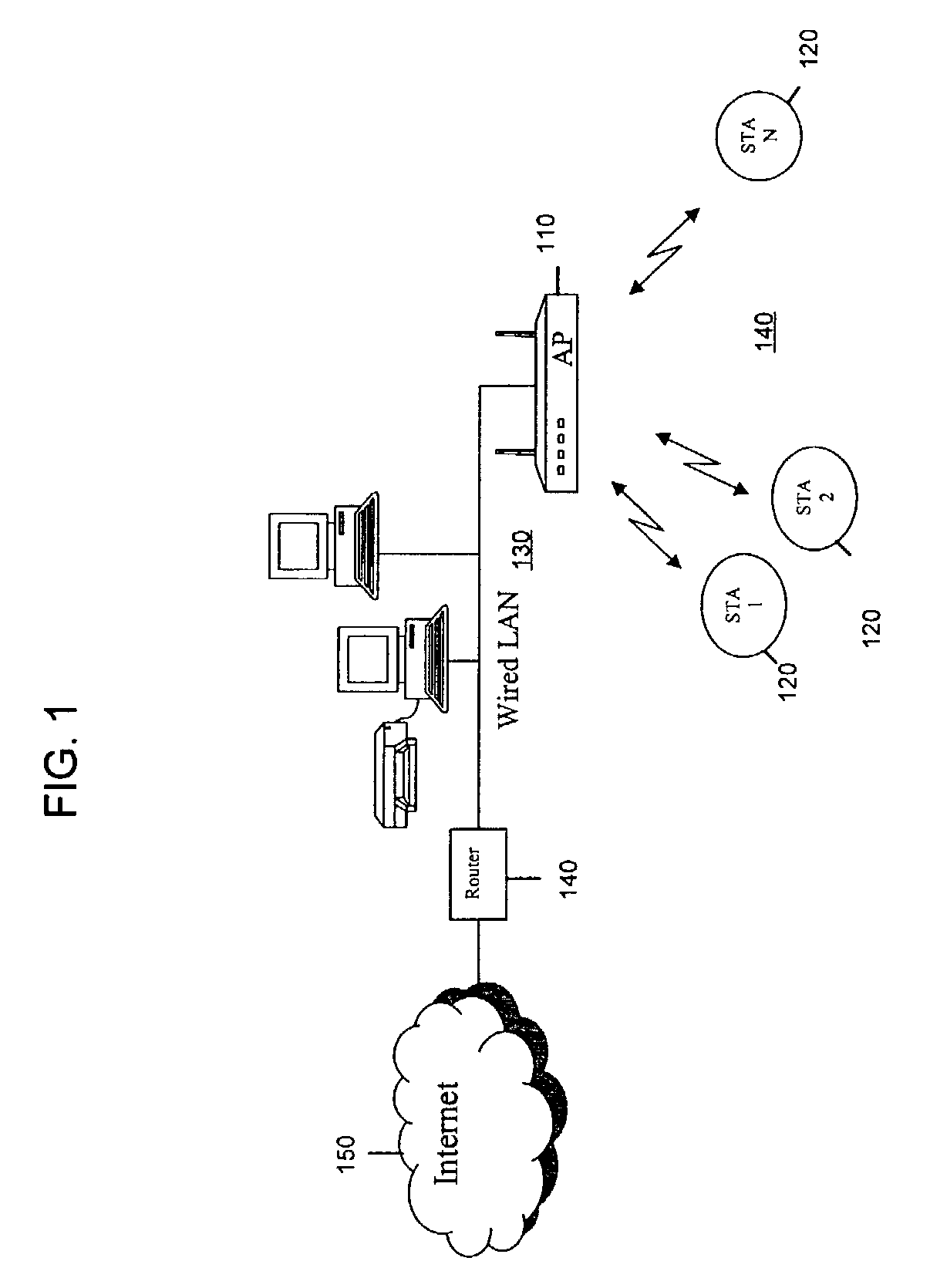

Throughput in multi-rate wireless networks using variable-length packets and other techniques

InactiveUS7248604B2Improve throughputImprove system throughputNetwork traffic/resource managementNetwork topologiesNetwork packetData rate

In a wireless communication network having a plurality of devices operating at different data rates that contend for access to the network, a method is provided that assigns network access parameters to one or more of the devices so as to control throughput on the network. Examples of network access control parameters are the maximum data packet size and the contention window size. Generally, the network access control parameter for slower data rate users is configured so that they do not occupy the network a disproportionate amount of time compared to faster data rate users.

Owner:IPR LICENSING INC

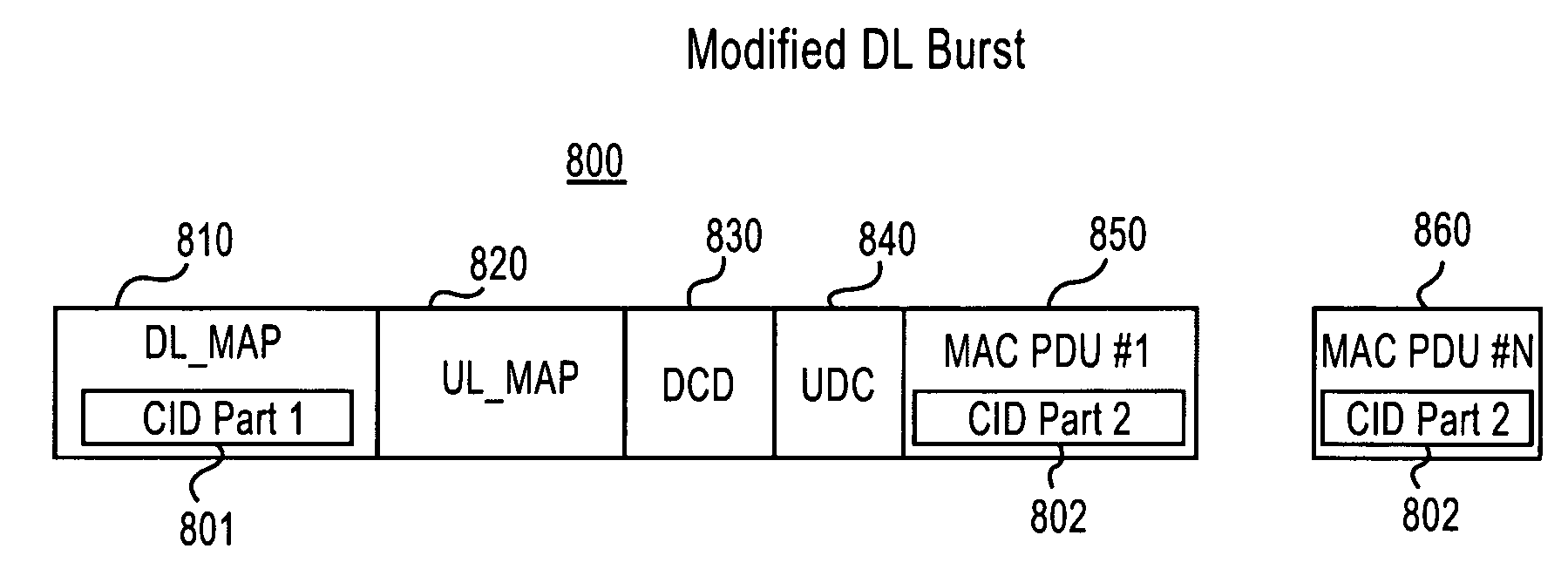

Method and apparatus to reduce system overhead

InactiveUS20090092076A1Improve system throughputReduce system overheadError preventionNetwork traffic/resource managementNetwork packetComputer science

System throughput is improved by decreasing the system overhead by reducing the size of control packets and data packet headers. A connection identifier (CID) is divided into a CID part 1 carried on a MAP IE and a CID part 2 carried on the generic MAC-PDU headers of one or more MAC PDUs. Versions of RCID-IE( ) in MAP messages may used to represent CID part 1. The generic MAX PDU headers (GMH) may vary according to the length of CID part 1, and multiple GMHs in a PHY burst may have different CID parts 2. In addition, the type header field of the GMH may be shortened or removed. Alternatively, a modified GMH may have an extended type sub-header field. In addition, the GMH may use a shorter connection index or a connection index mask instead of a CID.

Owner:NOKIA SOLUTIONS & NETWORKS OY

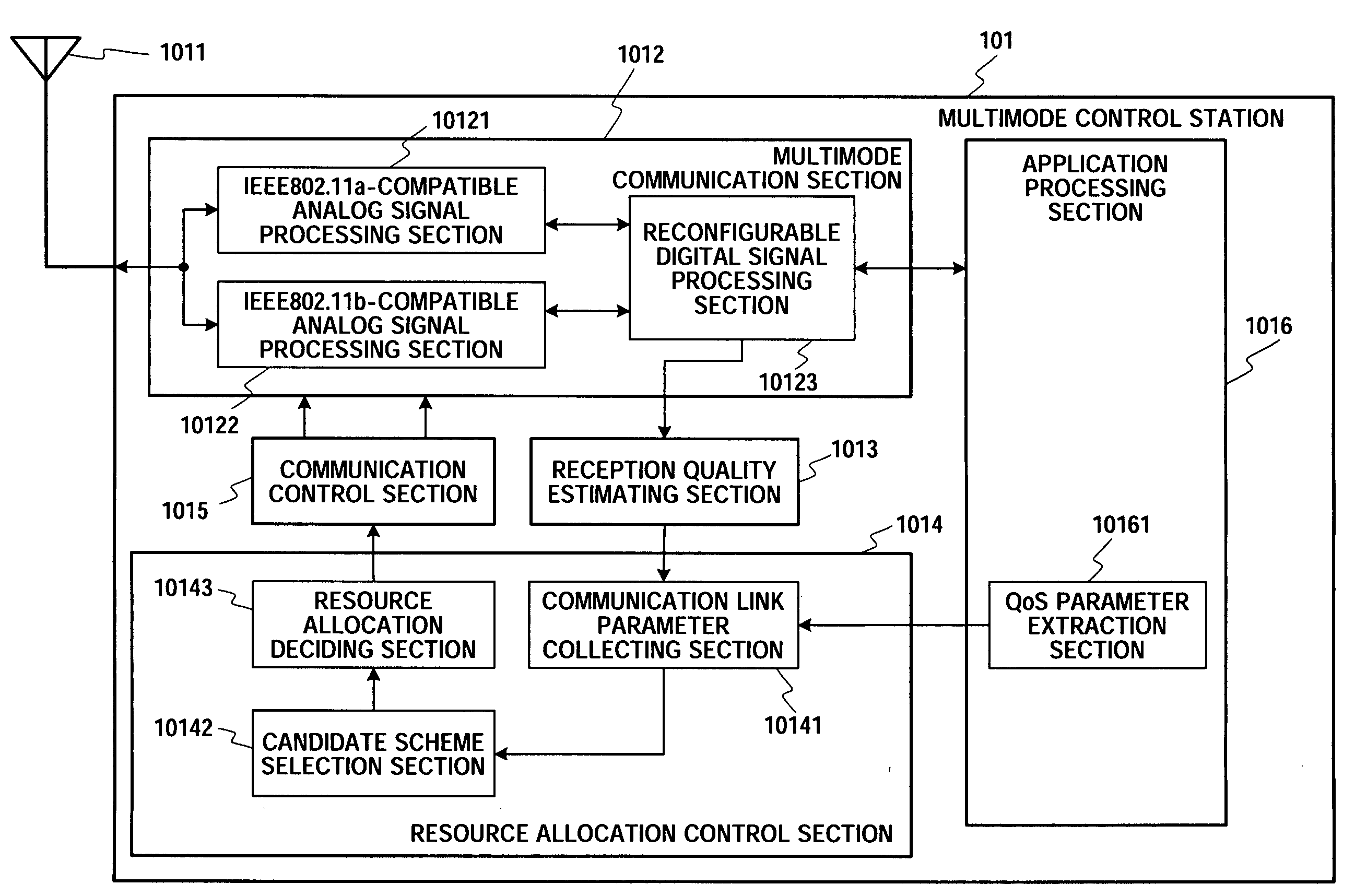

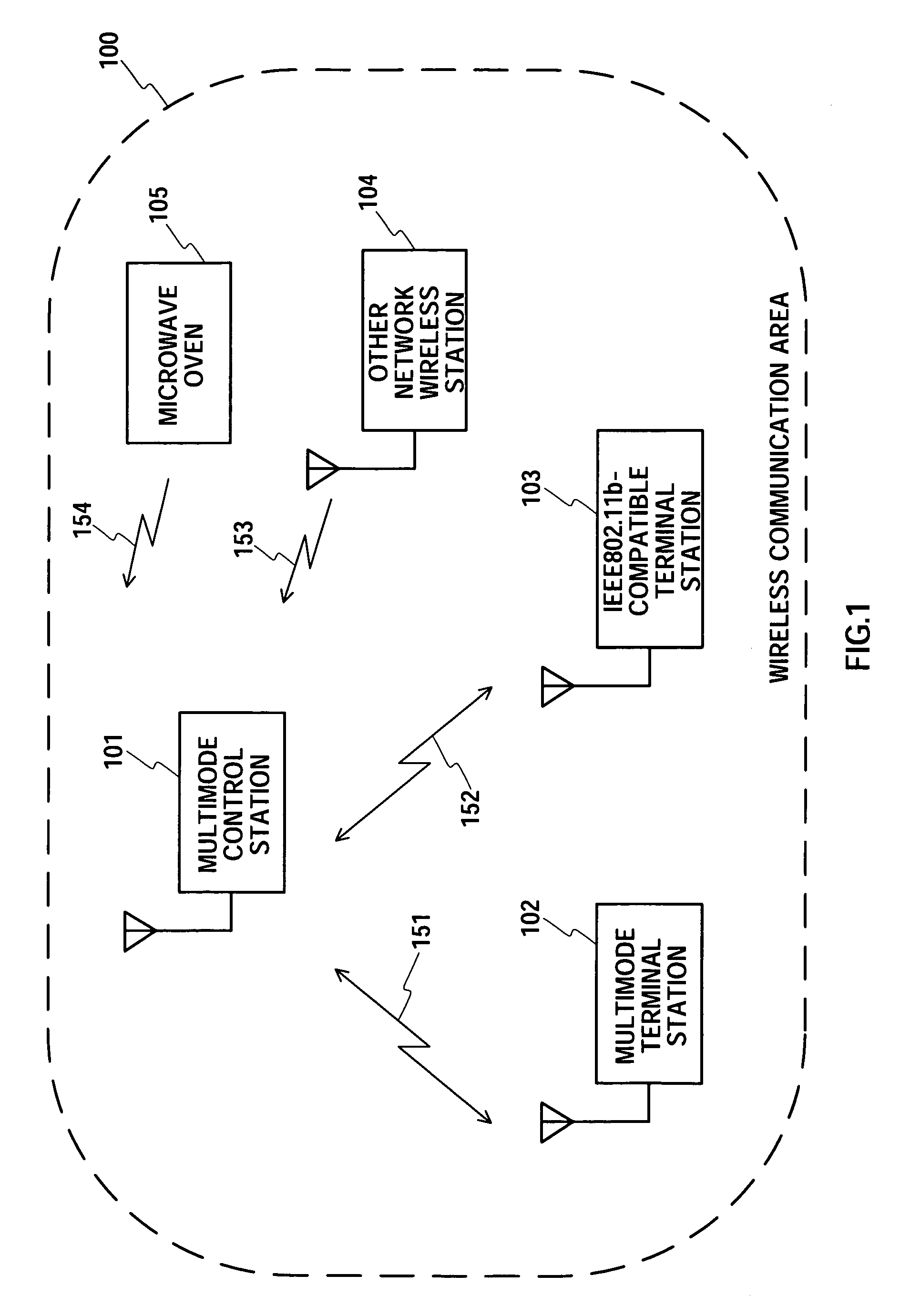

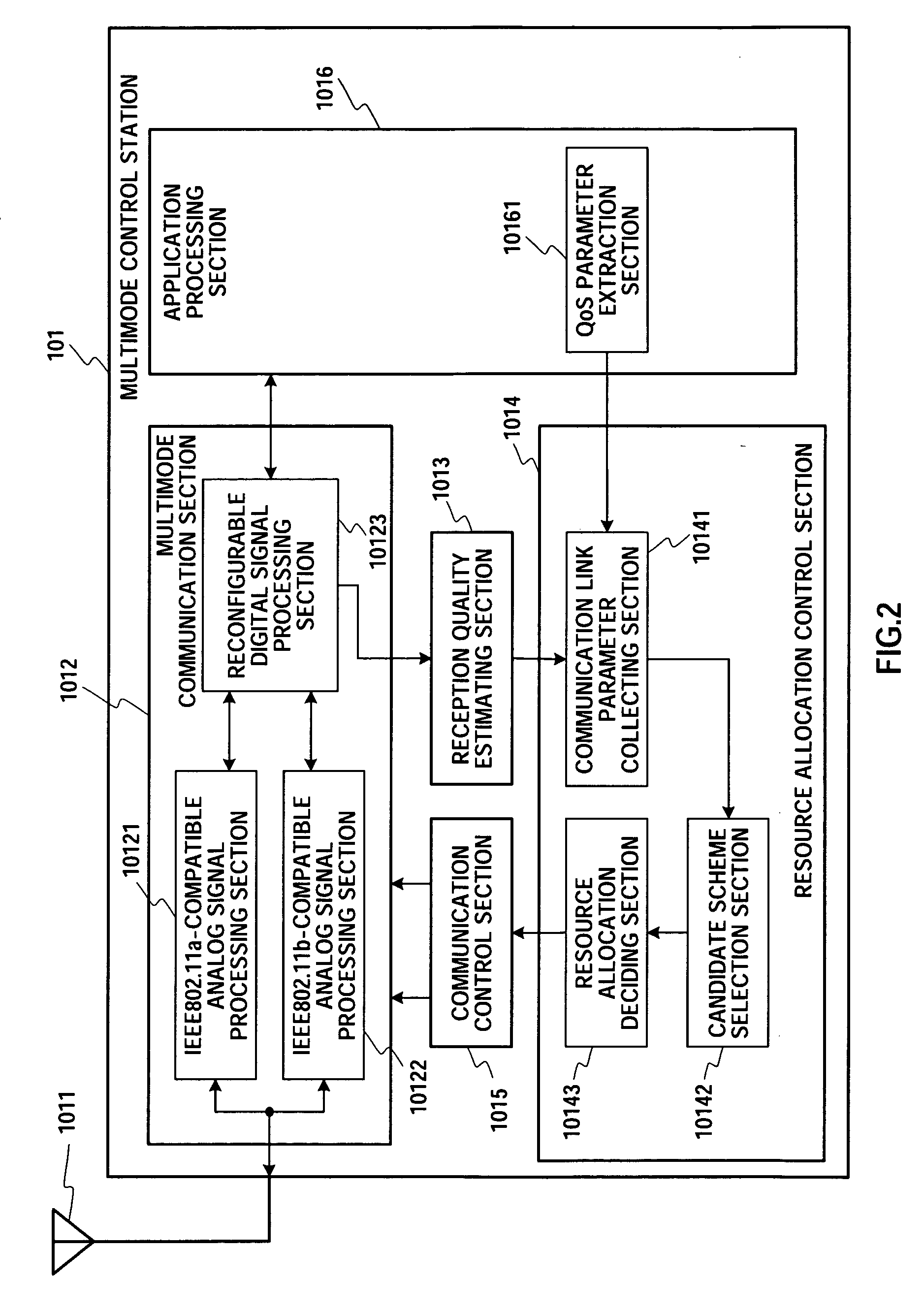

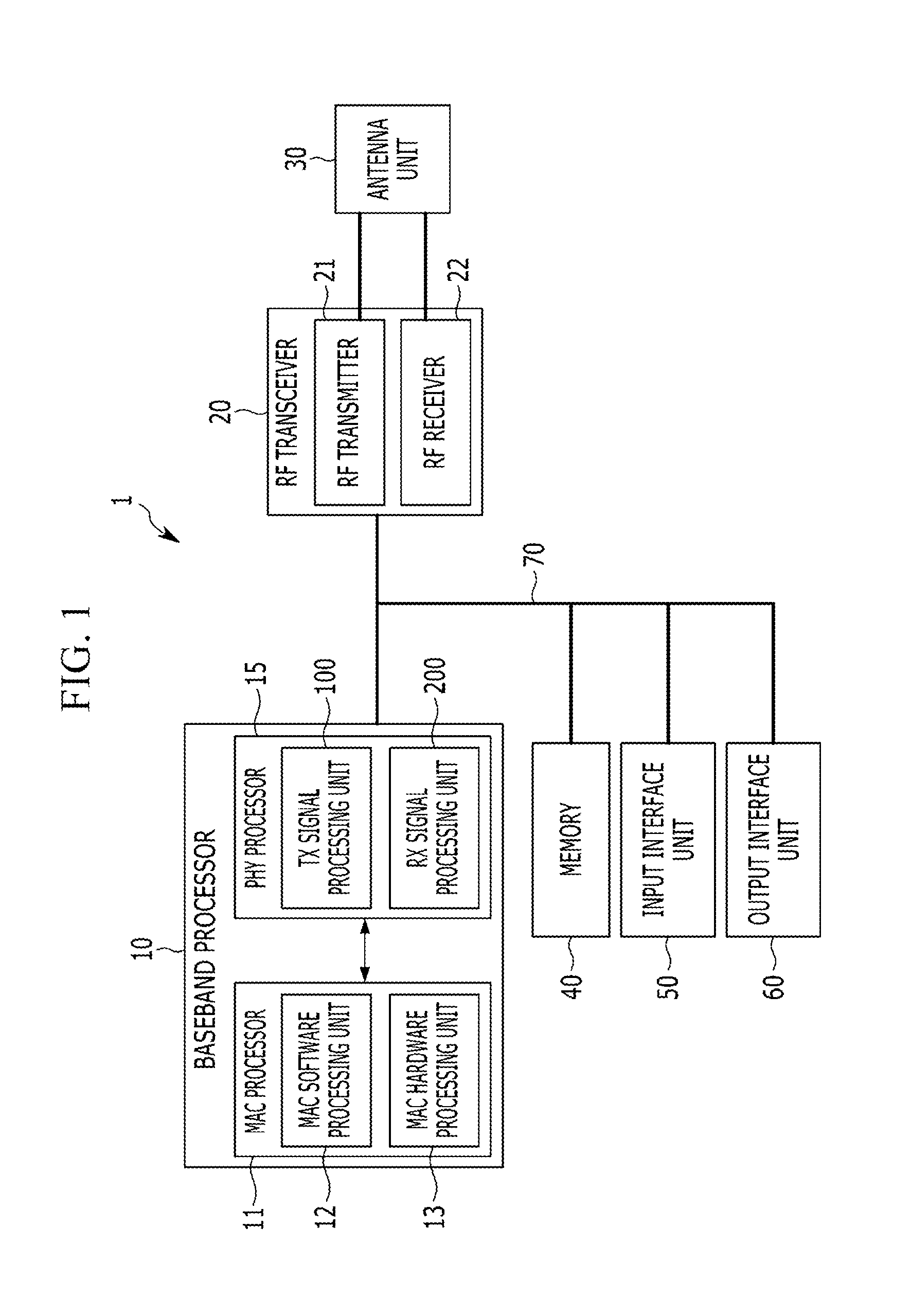

Multi-Mode Control Station, Radio Communication System, Radio Station, and Radio Communication Control Method

InactiveUS20080200195A1Improve system throughputLarge throughputNear-field transmissionTransmission control/equalisingCommunication unitTelecommunications link

The overall throughput of the radio communication traffic in a radio communication area in a radio communication environment where a plurality of types of radio communication systems are mixedly used in a neighboring radio communication area is improved. When a multi-mode control station (101) performs communication with a terminal station in a network through a plurality of types of communication systems, a communication link parameter collecting section (10141) collects parameters indicating the states of the communication links. A resource allocation determining section (10143) determines communication resource allocation for which the throughput is the greatest for each resource allocation period according to the parameters. A communication control section (1015) controls a multi-mode communication unit (1012) according to the result of the determination.

Owner:KOHNO RYUJI +1

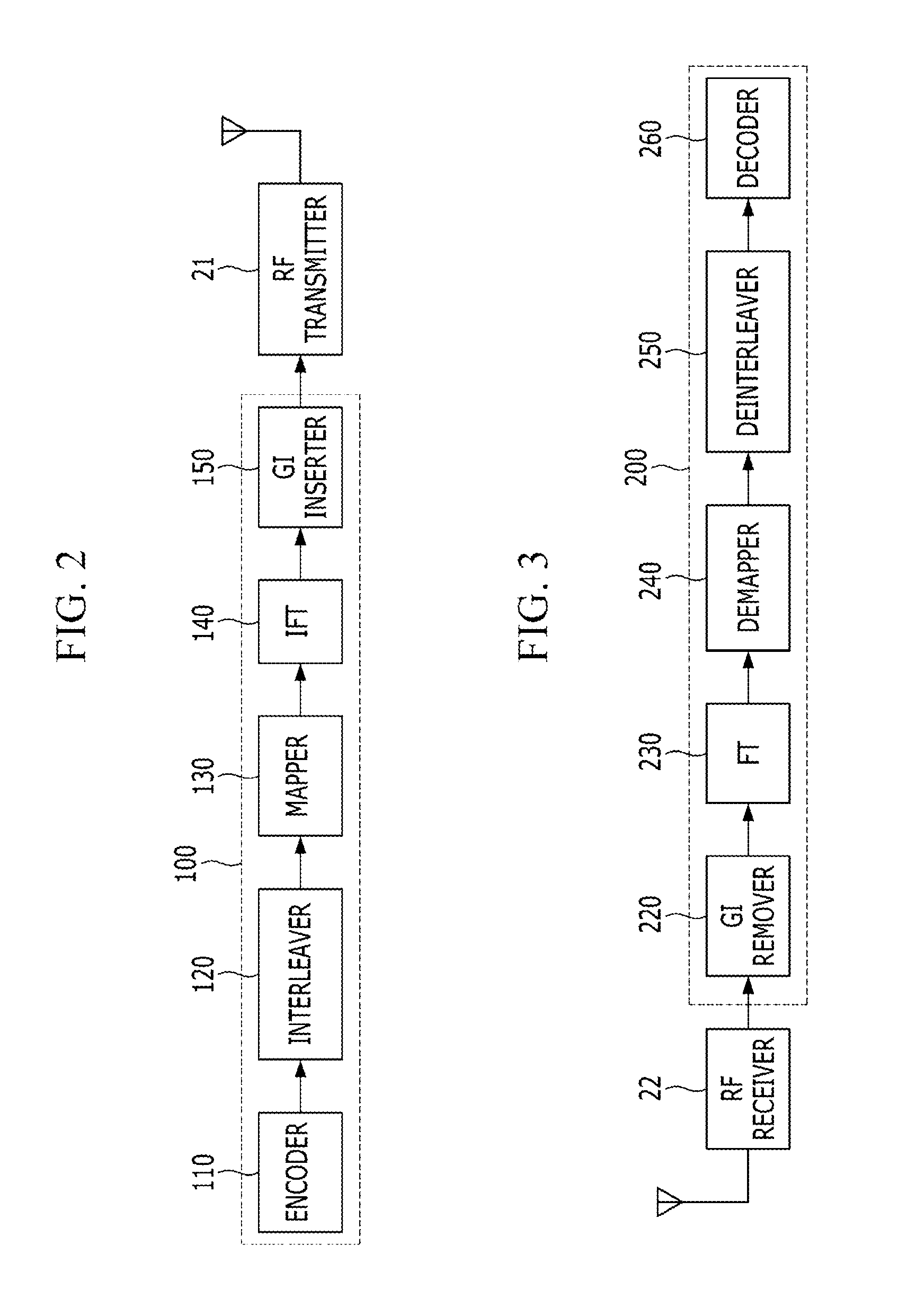

Method for transmitting and receiving frame

ActiveUS20150334708A1Enhance throughputImprove system throughputError preventionNetwork topologiesData fieldComputer science

A frame transmission method is provided by a device in a wireless communication network. The device generates a signal field including a symbol using a 64 FFT and carrying signaling information, and generates a data field including a symbol using a FFT having a larger size than the 64 FFT and carrying data. The device transmits a frame including the signal field and the data field.

Owner:ATLAS GLOBAL TECH LLC

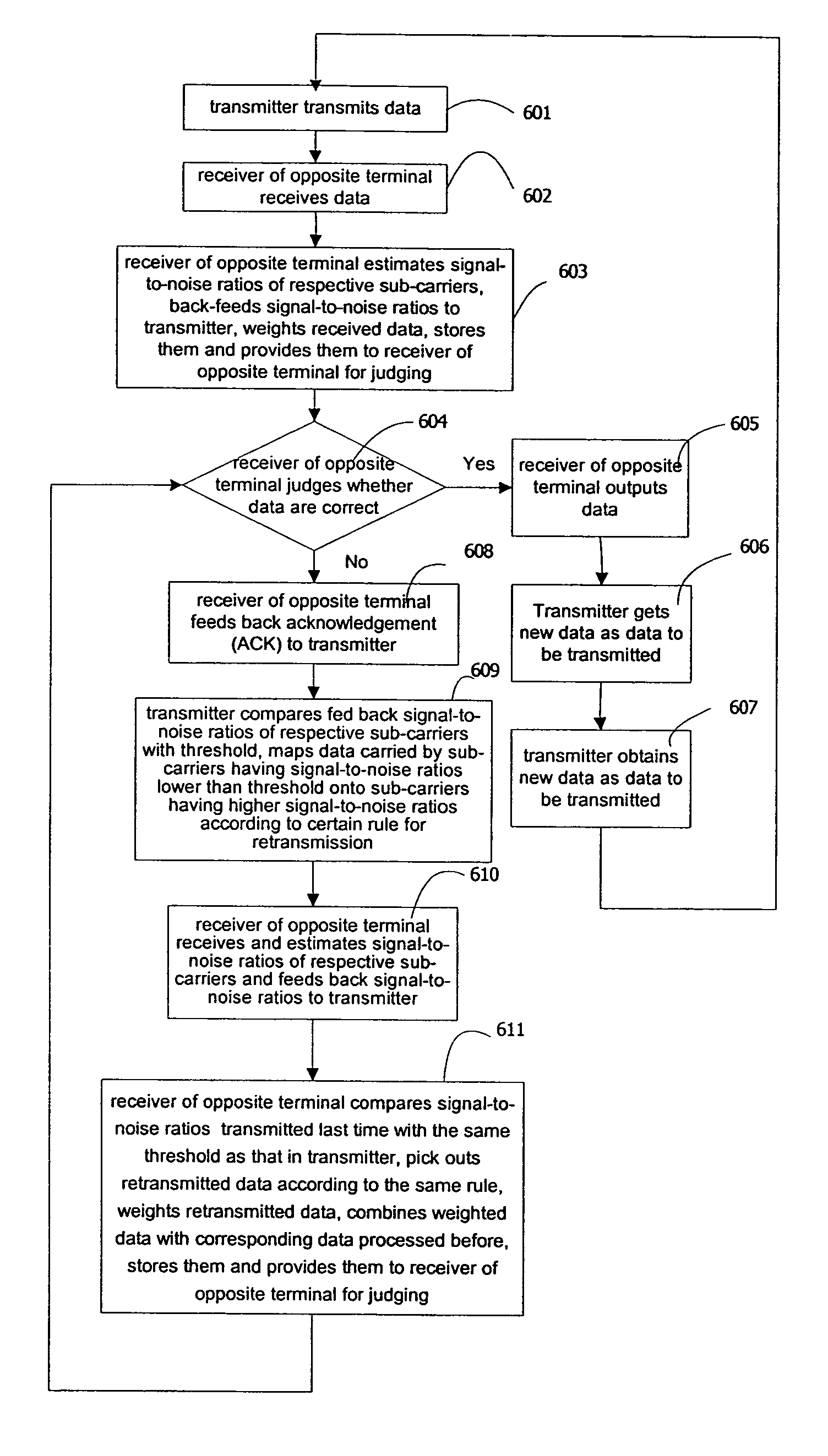

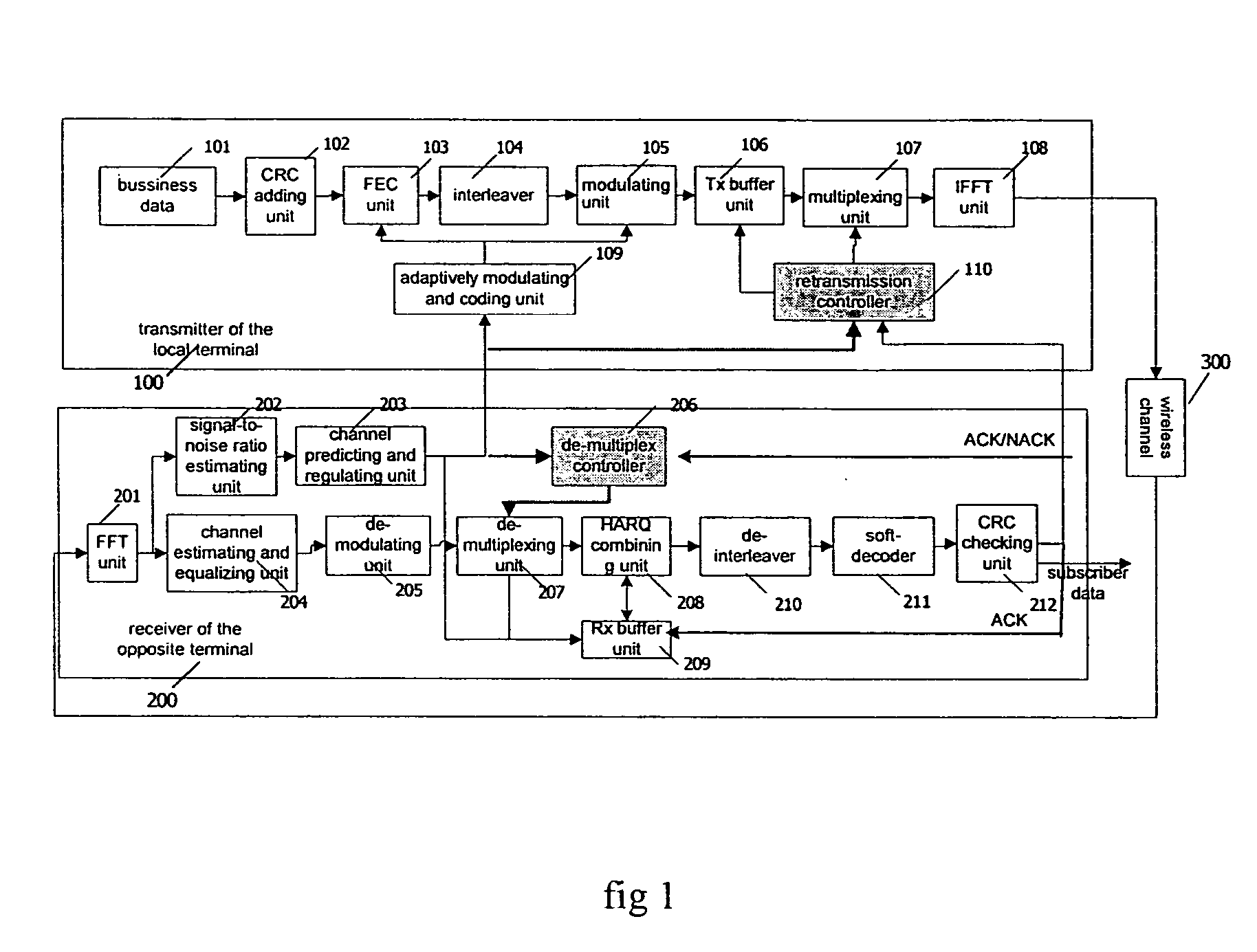

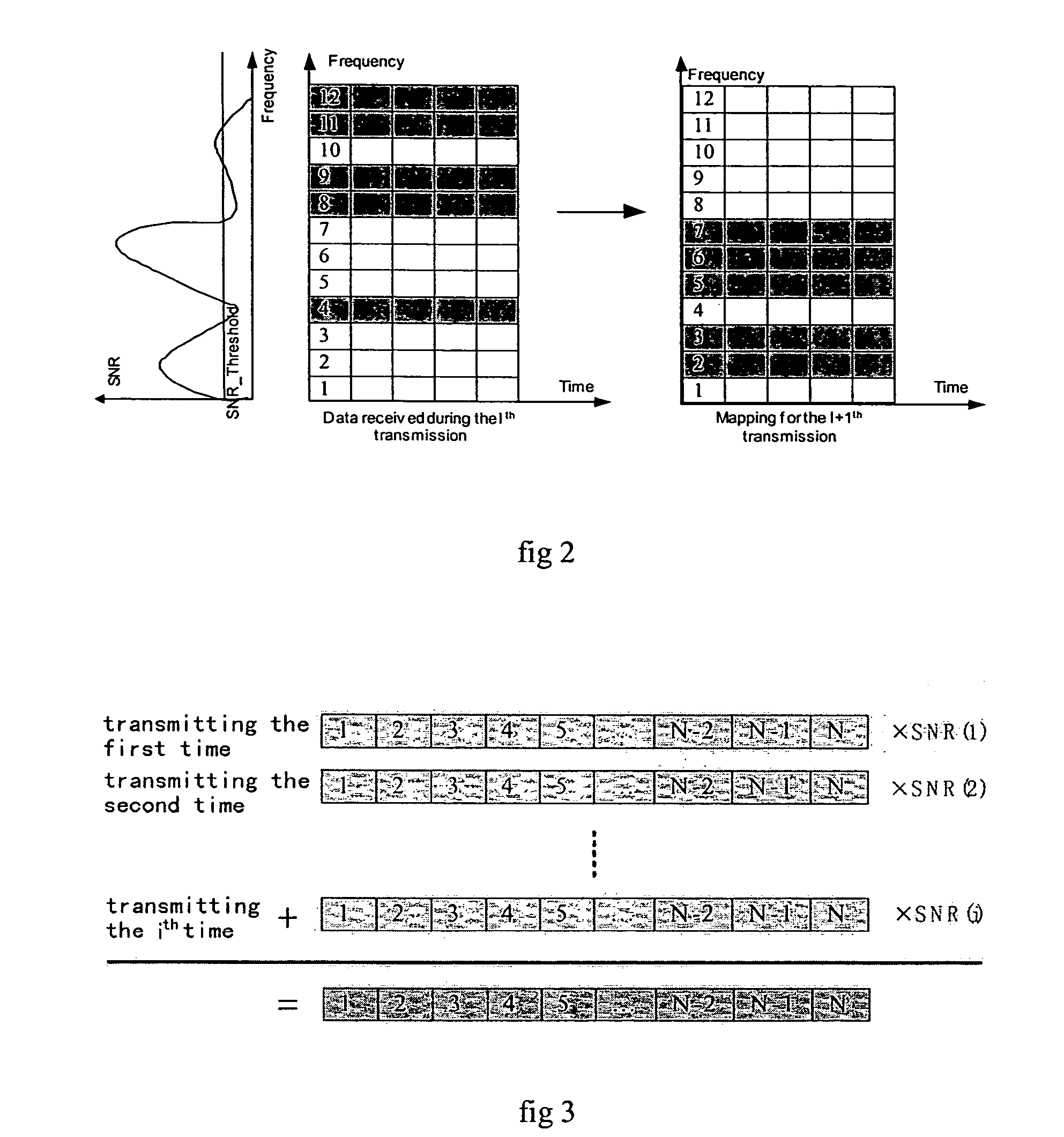

Data transmitting method with hybrid automatic repeat request in multi-carrier system

InactiveUS20050135253A1Reduce amountIncrease system throughputError prevention/detection by using return channelFrequency-division multiplex detailsData transmissionCarrier signal

The present invention provides a data transmitting method with hybrid automatic repeat request in multi-carrier system. In this method, the signal-to-noise ratios of respective sub-carriers are compared with a threshold, the data on the sub-carriers having the signal-to-noise ratios lower than the threshold are selectively retransmitted by mapping these data onto the sub-carriers having the good channel conditions, and then the retransmitted data are combined hybrid-automatically in the receiver of the opposite terminal. By using the method the system throughput can be enhanced effectively without impairing the bit error rate of the system.

Owner:ALCATEL LUCENT SAS

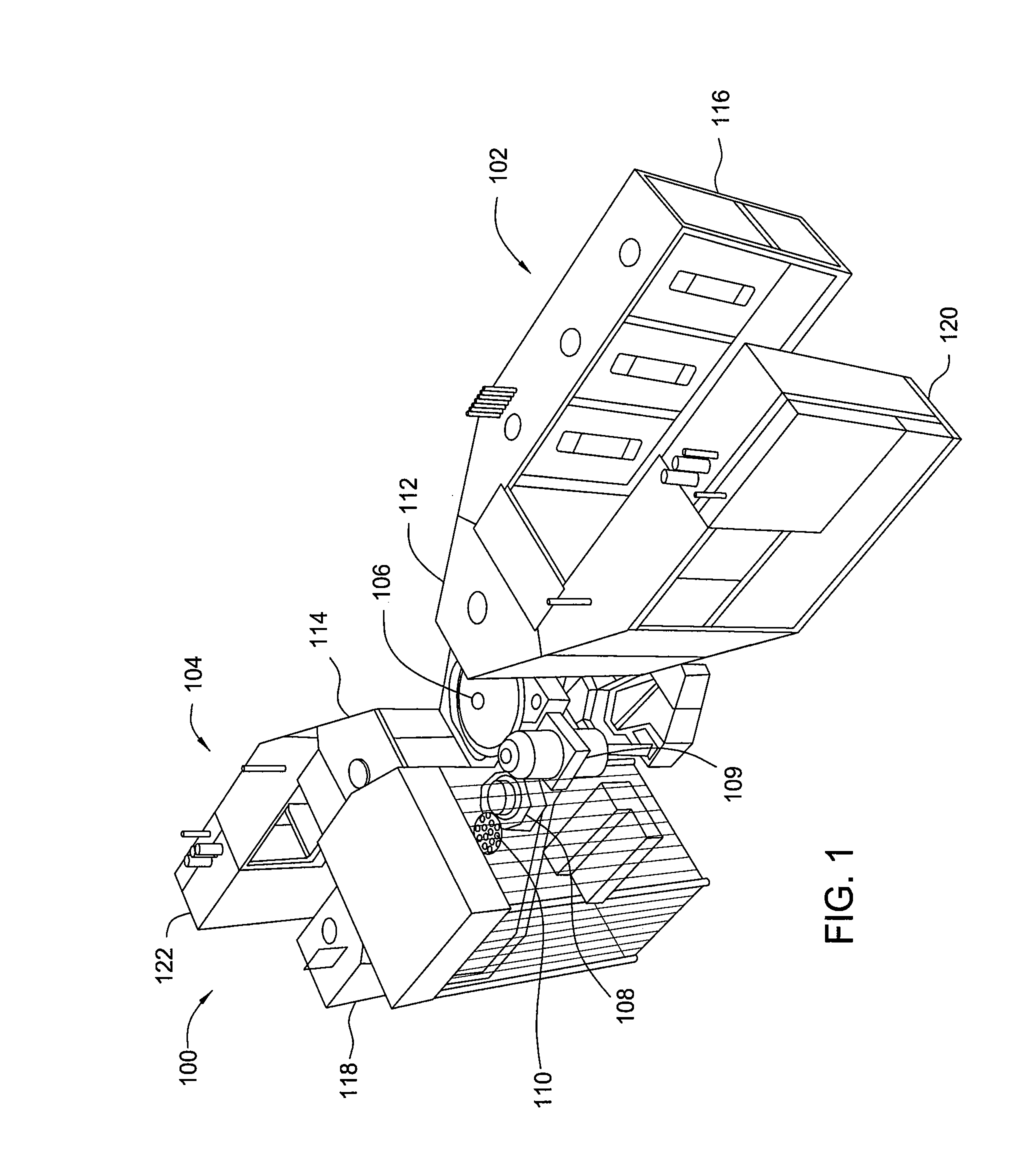

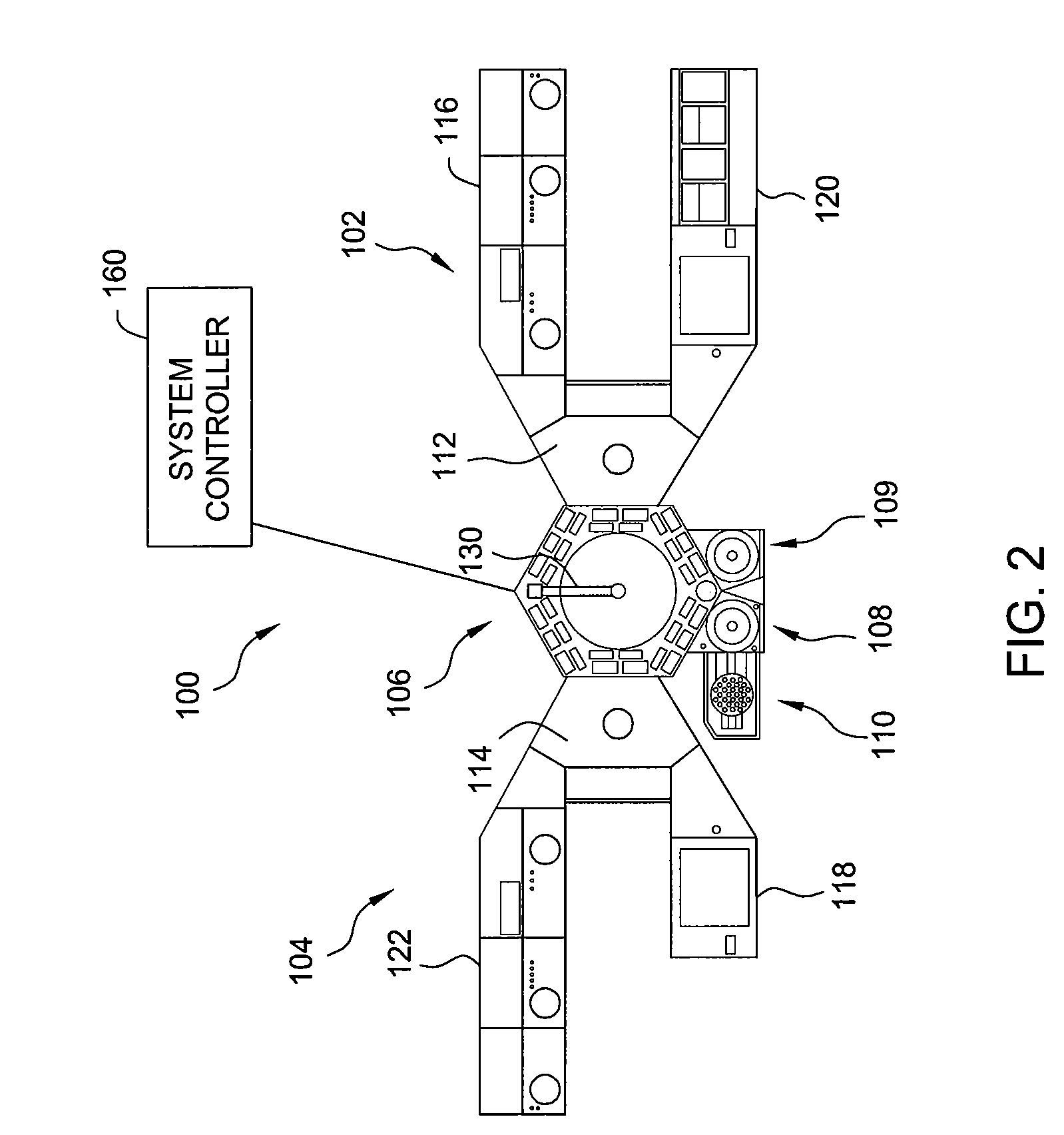

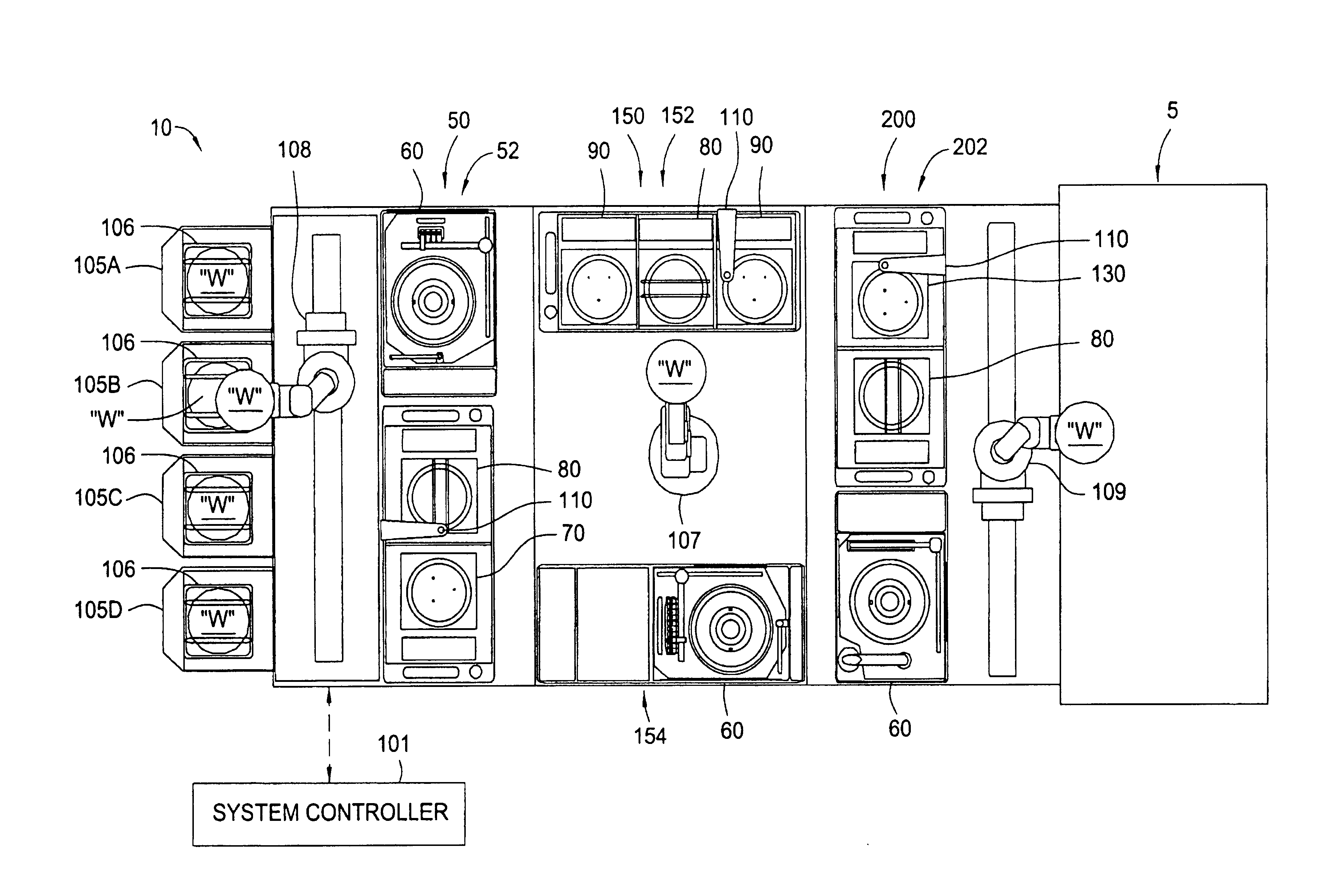

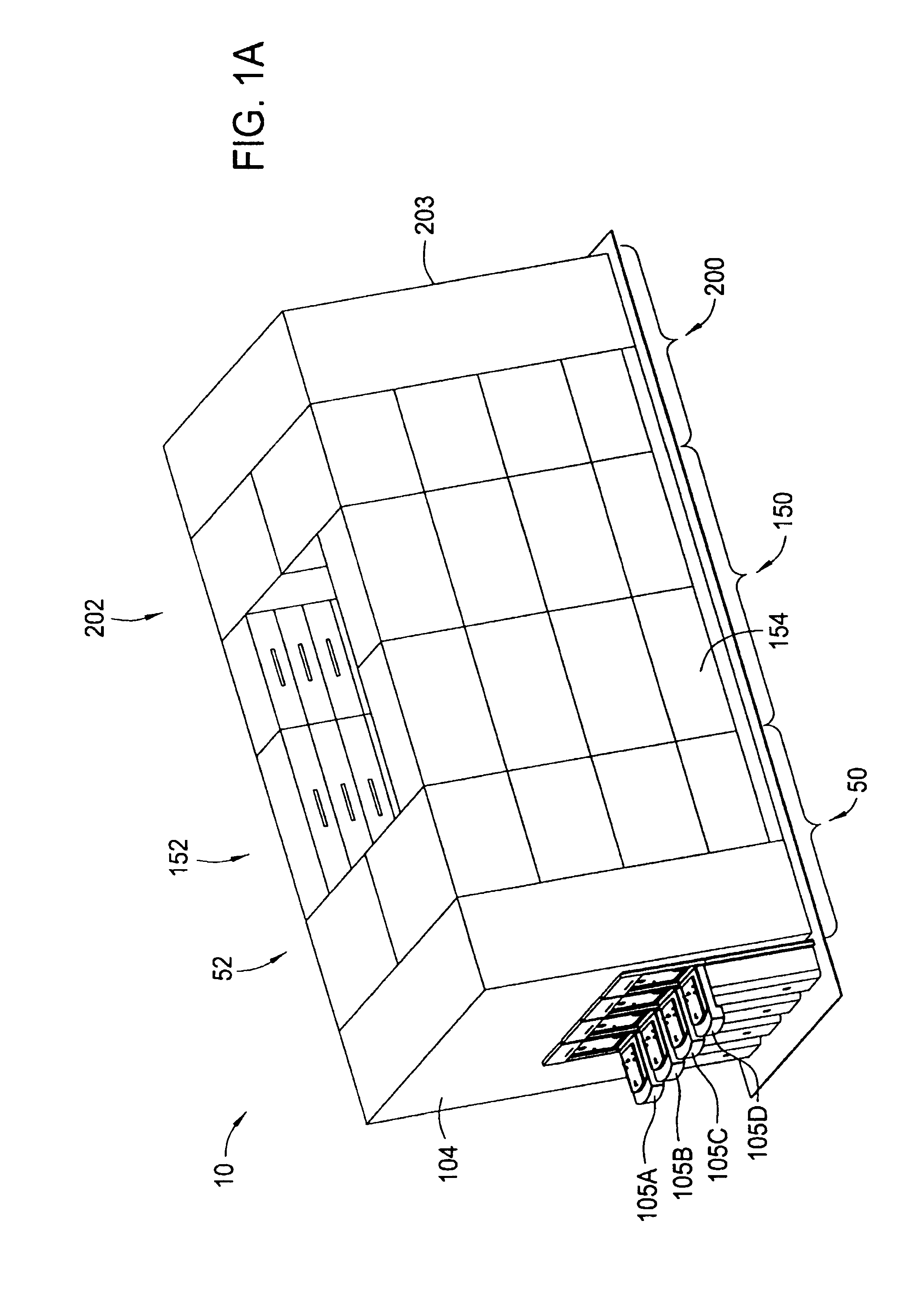

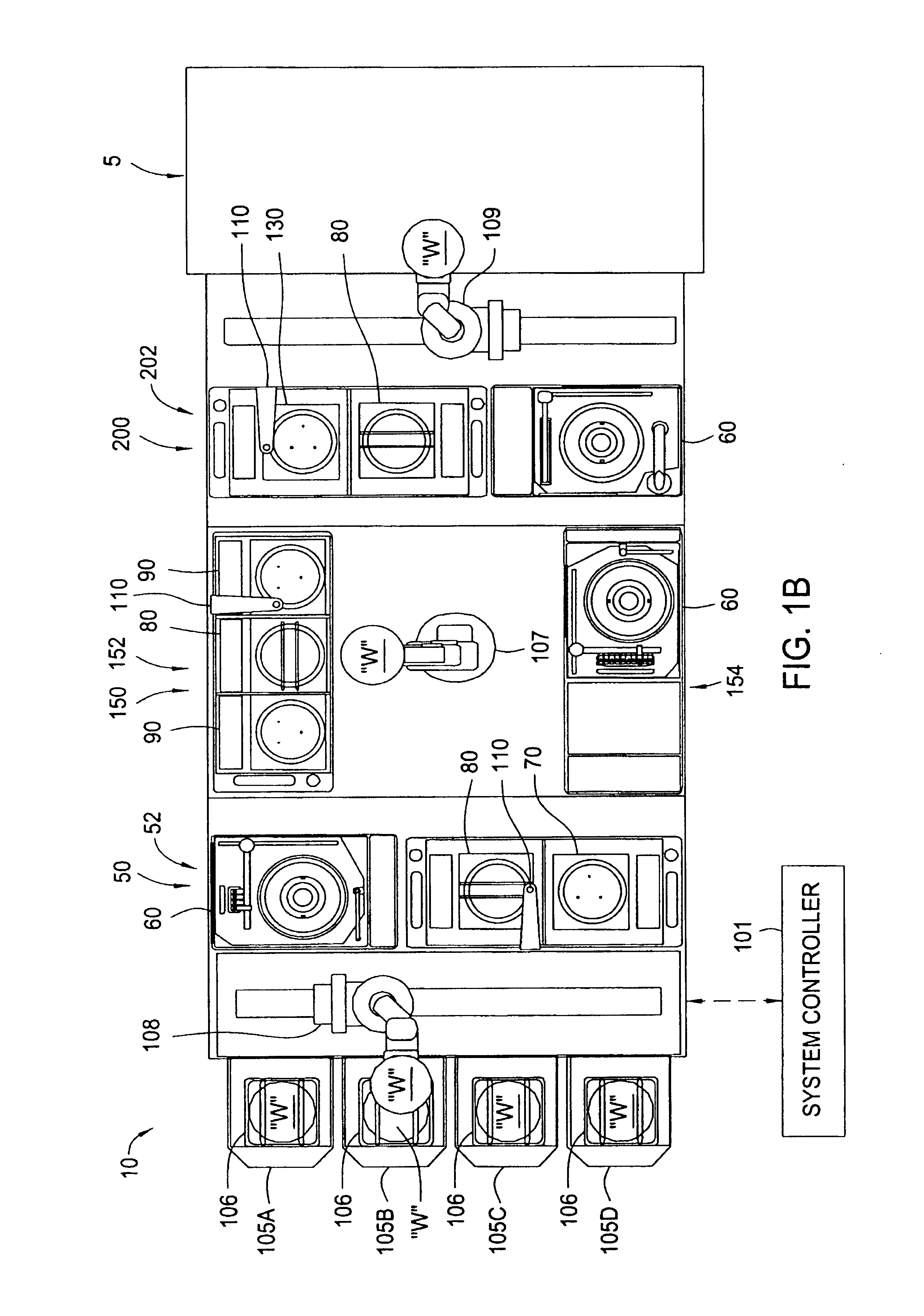

Cluster tool architecture for processing a substrate

ActiveUS20060130750A1Temperature controlMore repeatable wafer processing historyLiquid surface applicatorsSemiconductor/solid-state device testing/measurementLithography processEngineering

Embodiments generally provide an apparatus and method for processing substrates using a multi-chamber processing system (e.g., a cluster tool) that has an increased system throughput, increased system reliability, substrates processed in the cluster tool have a more repeatable wafer history, and also the cluster tool has a smaller system footprint. In one embodiment, the cluster tool is adapted to perform a track lithography process in which a substrate is coated with a photosensitive material, is then transferred to a stepper / scanner, which exposes the photosensitive material to some form of radiation to form a pattern in the photosensitive material, which is then removed in a developing process completed in the cluster tool. In track lithography type cluster tools, since the chamber processing times tend to be rather short, and the number of processing steps required to complete a typical track system process is large, a significant portion of the time it takes to process a substrate is taken up by the processes of transferring the substrates in a cluster tool between the various processing chambers. In one embodiment of the cluster tool, the cost of ownership is reduced by grouping substrates together and transferring and processing the substrates in groups of two or more to improve system throughput, and reduces the number of moves a robot has to make to transfer a batch of substrates between the processing chambers, thus reducing wear on the robot and increasing system reliability. In one aspect of the invention, the substrate processing sequence and cluster tool are designed so that the substrate transferring steps performed during the processing sequence are only made to chambers that will perform the next processing step in the processing sequence. Embodiments also provide for a method and apparatus that are used to improve the coater chamber, the developer chamber, the post exposure bake chamber, the chill chamber, and the bake chamber process results. Embodiments also provide for a method and apparatus that are used to increase the reliability of the substrate transfer process to reduce system down time.

Owner:SCREEN SEMICON SOLUTIONS CO LTD

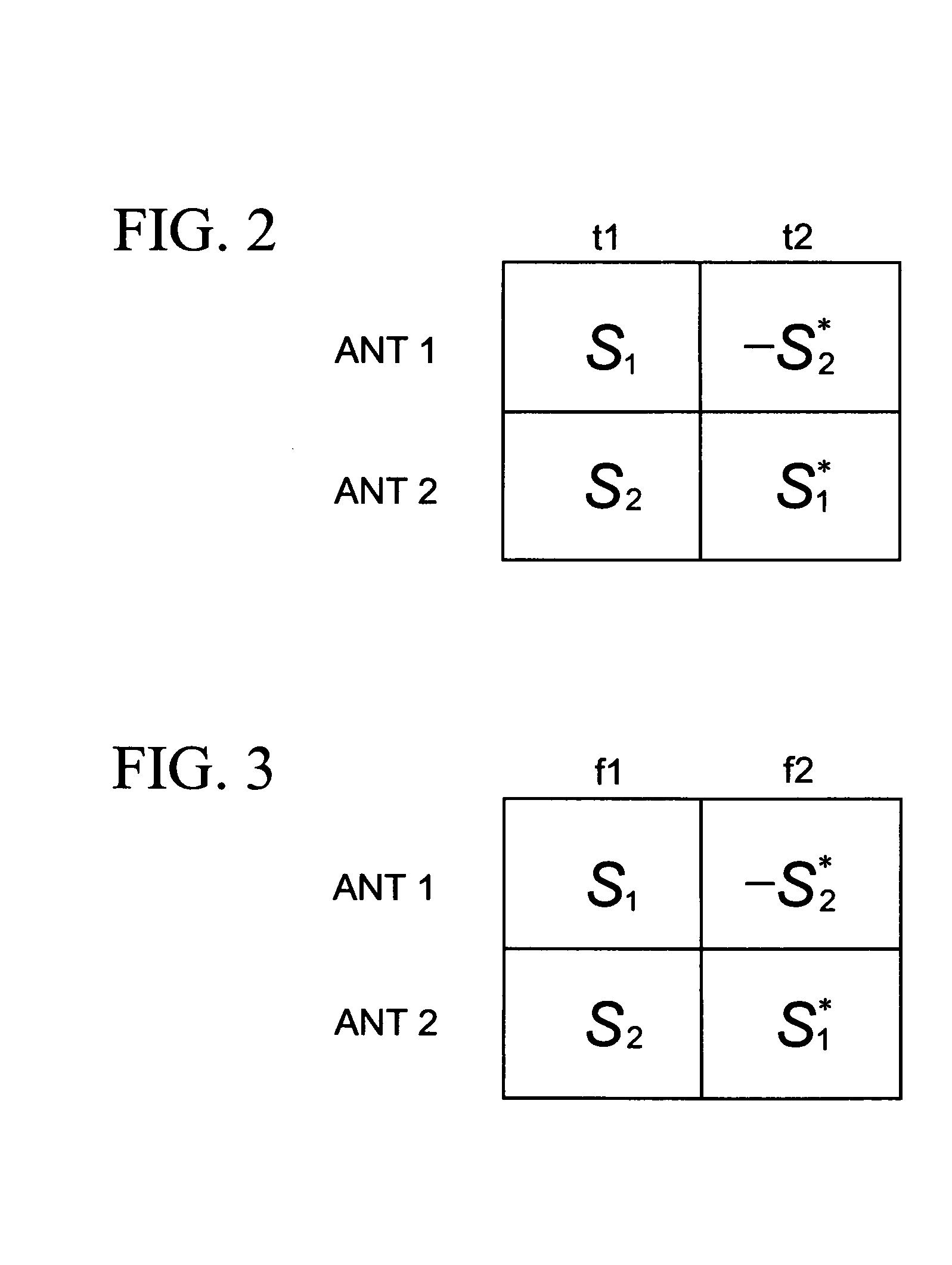

Antenna mapping in a MIMO wireless communication system

InactiveUS20080273452A1Improve transmission performanceImprove system throughputModulated-carrier systemsCode conversionCommunications systemSymbol mapping

A method for transmission is provided to generate a plurality of reference signals for a plurality of antenna ports, with each reference signal corresponding to an antenna port; to map the plurality of reference signals to a plurality of physical antennas in accordance with a selected antenna port mapping scheme, with each reference signal corresponding to a physical antenna, and the plurality of physical antennas being aligned sequentially with equal spacing between two immediately adjacent physical antennas; to demultiplex information to be transmitted into a plurality of stream blocks; to insert a respective cyclic redundancy check to each of the stream blocks; to encode each of the stream blocks according to a corresponding coding scheme; to modulate each of the stream blocks according to a corresponding modulation scheme; to demultiplex the stream blocks to generate a plurality of sets of symbols, with each stream block being demultiplexed into a set of symbols; to map the plurality of sets of symbols into the plurality of antenna ports in accordance with a selected symbol mapping scheme; and to transmit the plurality of sets of symbols via the corresponding antenna ports, with each set of symbols being transmitted via a subset of antenna ports, with, within each subset of antenna ports, the distance between the physical antennas of the corresponding antenna ports being larger than the average distance among the plurality of physical antennas.

Owner:SAMSUNG ELECTRONICS CO LTD

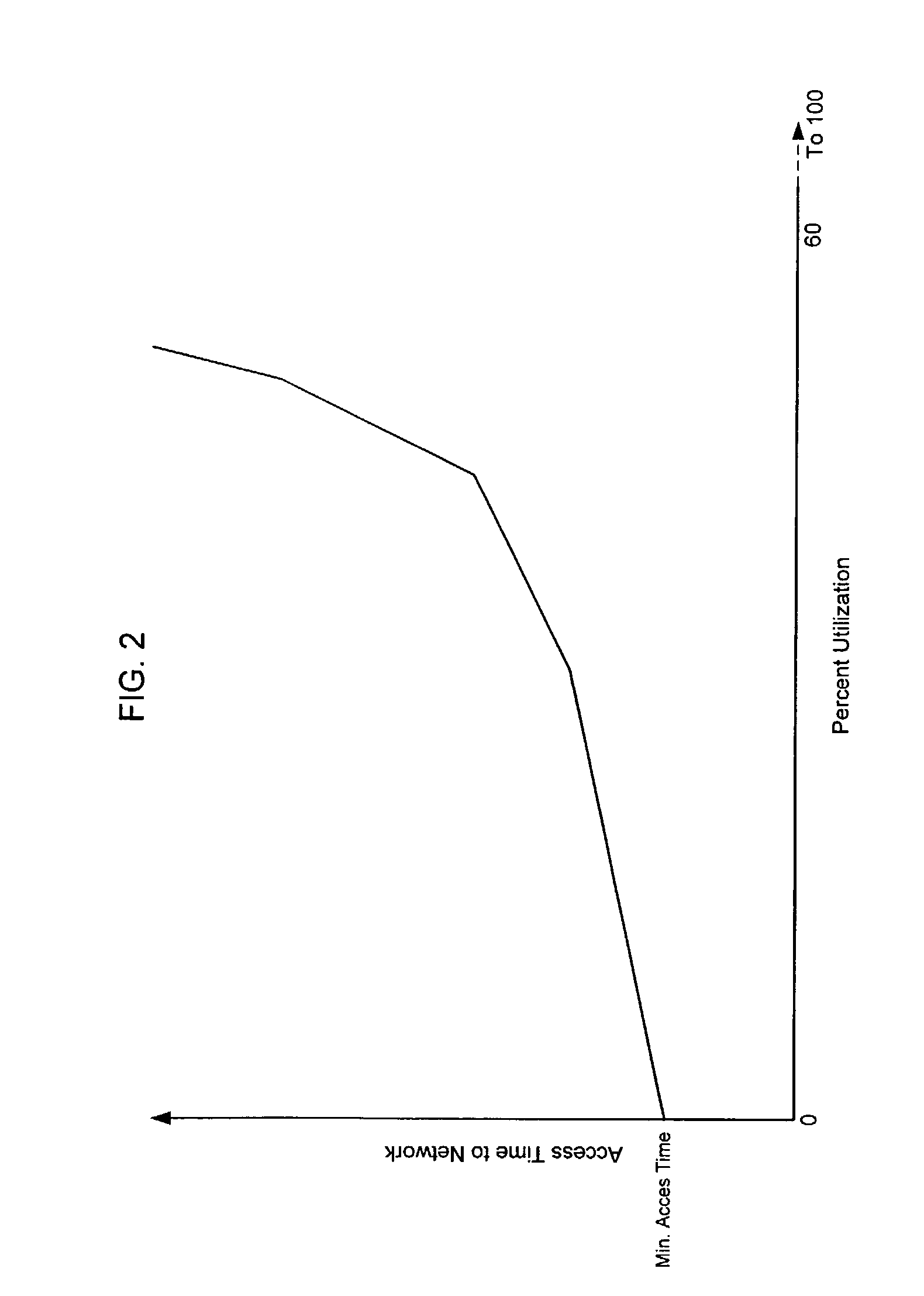

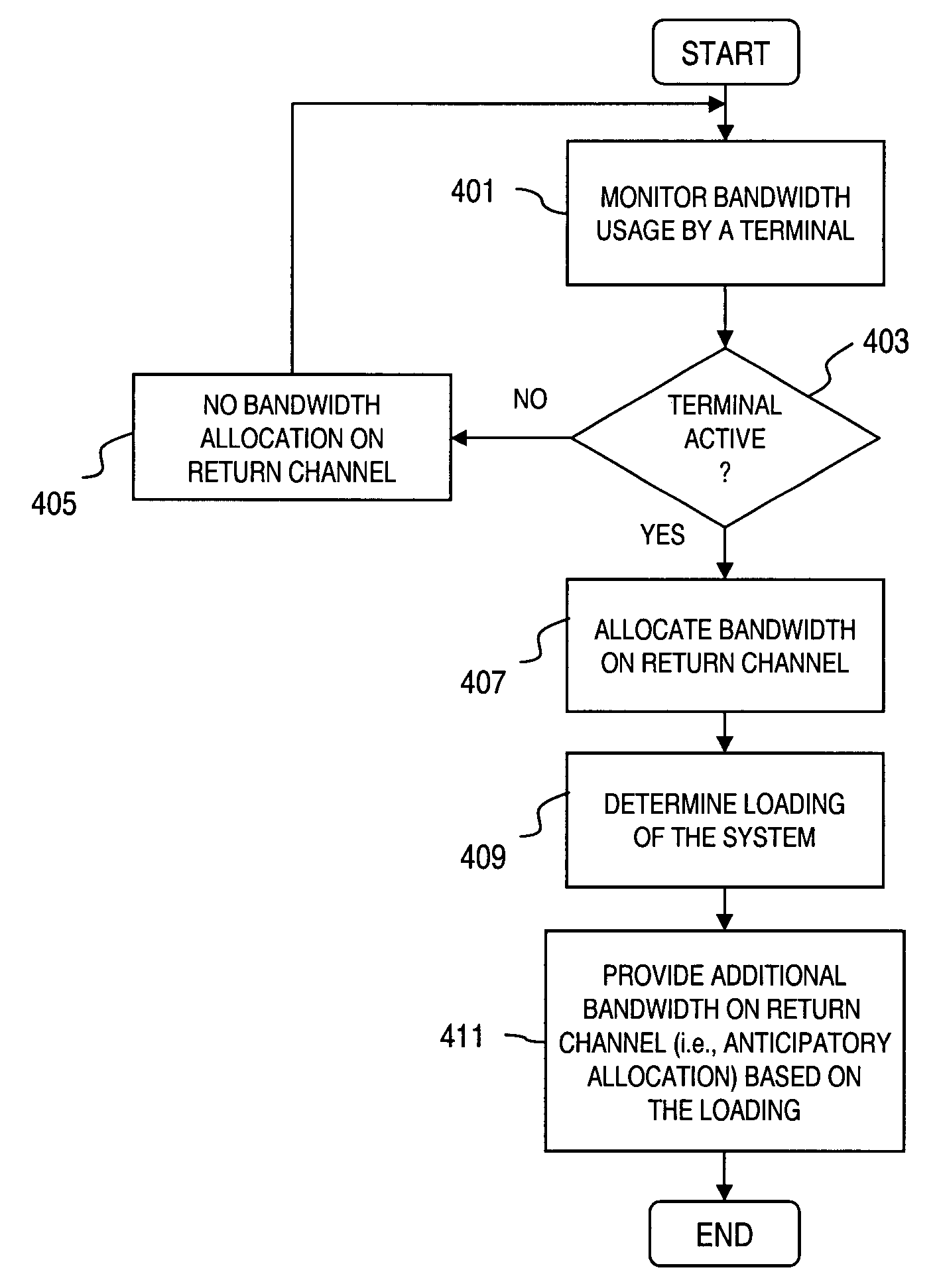

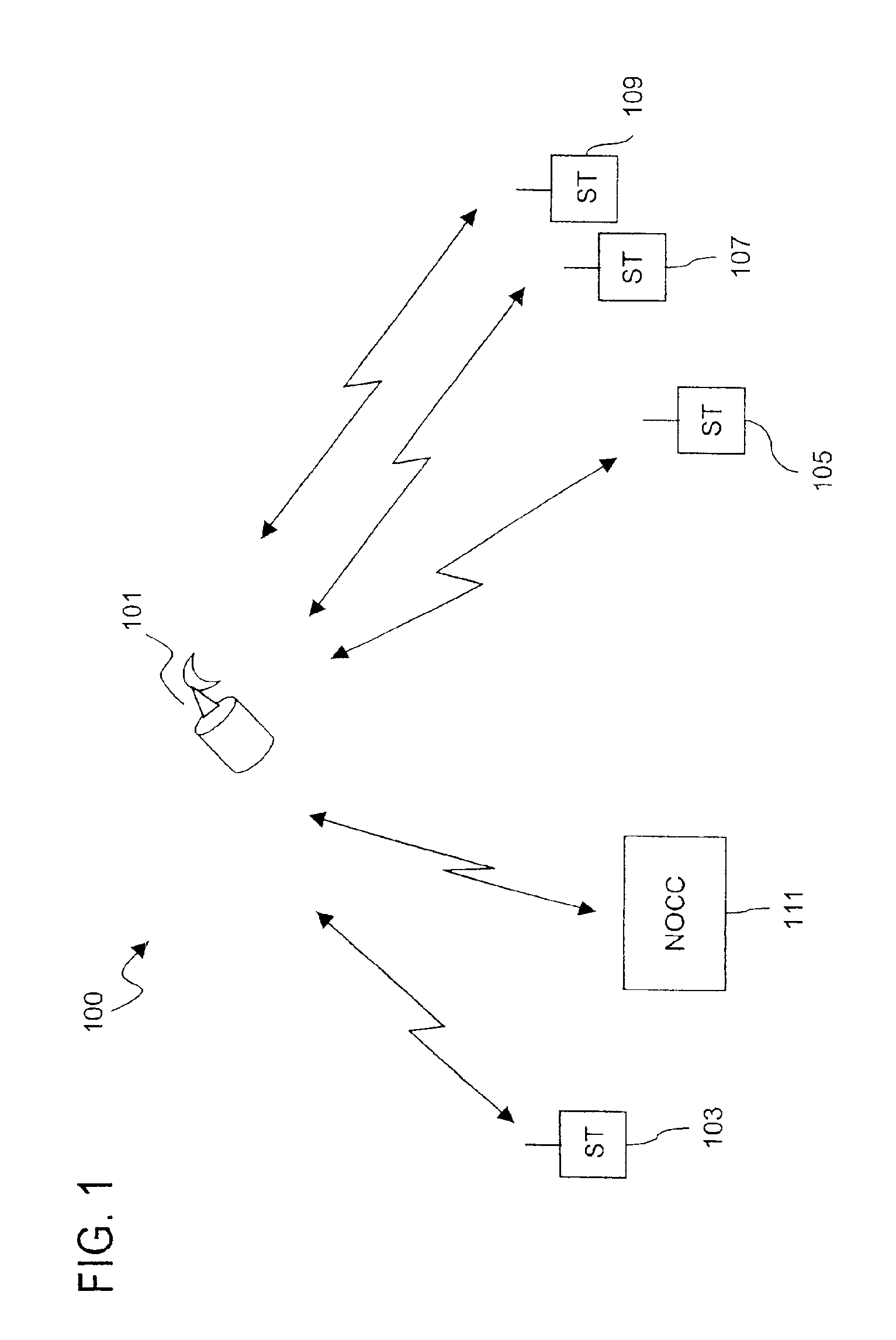

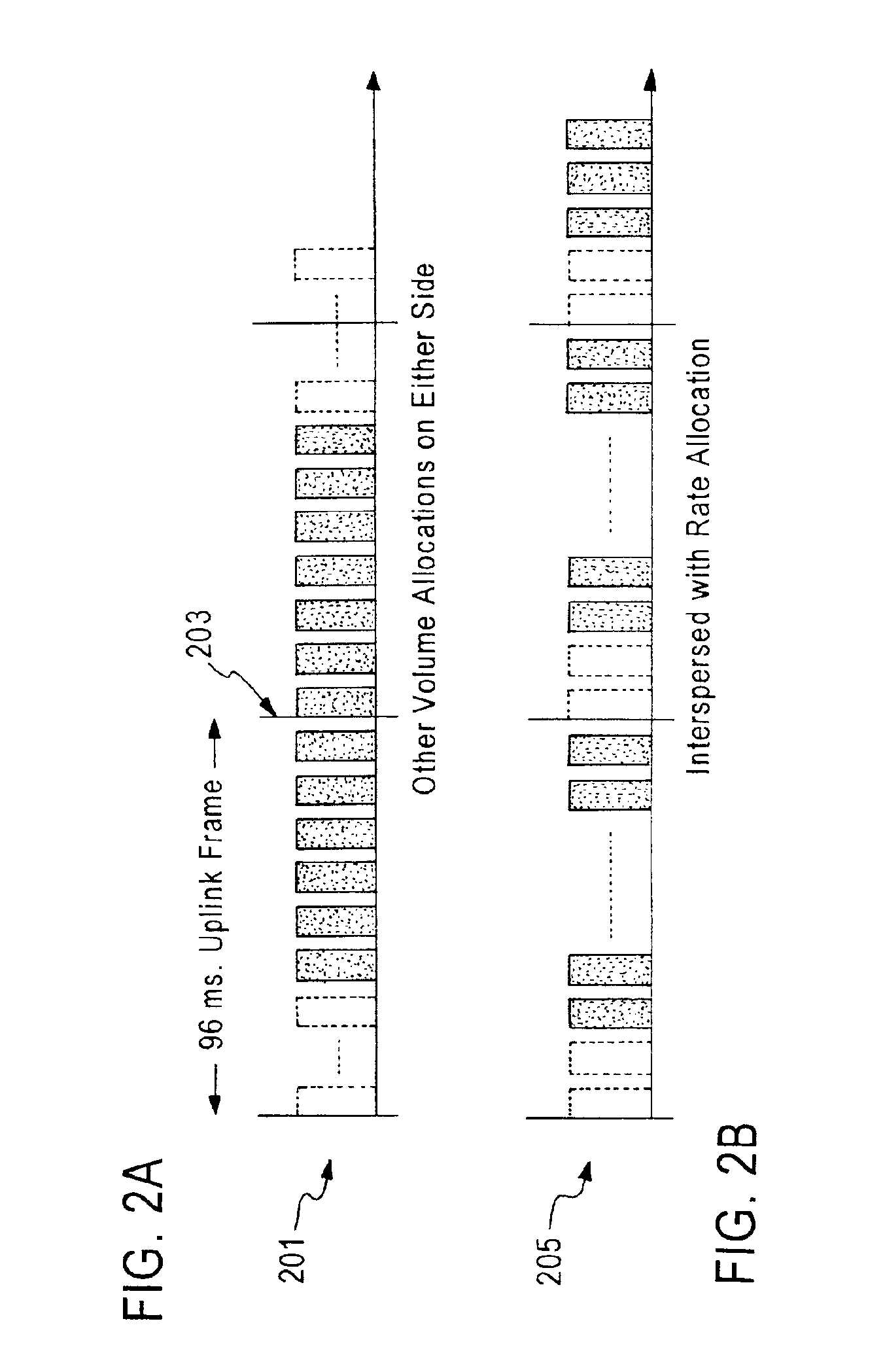

Method and system for providing load-sensitive bandwidth allocation

ActiveUS7336967B2Size be alterEfficient bandwidth utilizationTime-division multiplexRadio/inductive link selection arrangementsBandwidth allocationNetwork management

An approach is provided for managing bandwidth in a data network. Capacity is allocated on a communication channel, which can be utilized for transporting data traffic or support network administrative functions (e.g., ranging), for a terminal to transmit data over the communication channel. In anticipation of the terminal having to transmit additional data, additional capacity is allocated on the communication channel for the terminal prior to receiving a request for bandwidth by the terminal. The anticipatory allocation is determined according to loading of the data network. This approach as particular applicability to shared capacity systems, such as a satellite communication system.

Owner:HUGHES NETWORK SYST

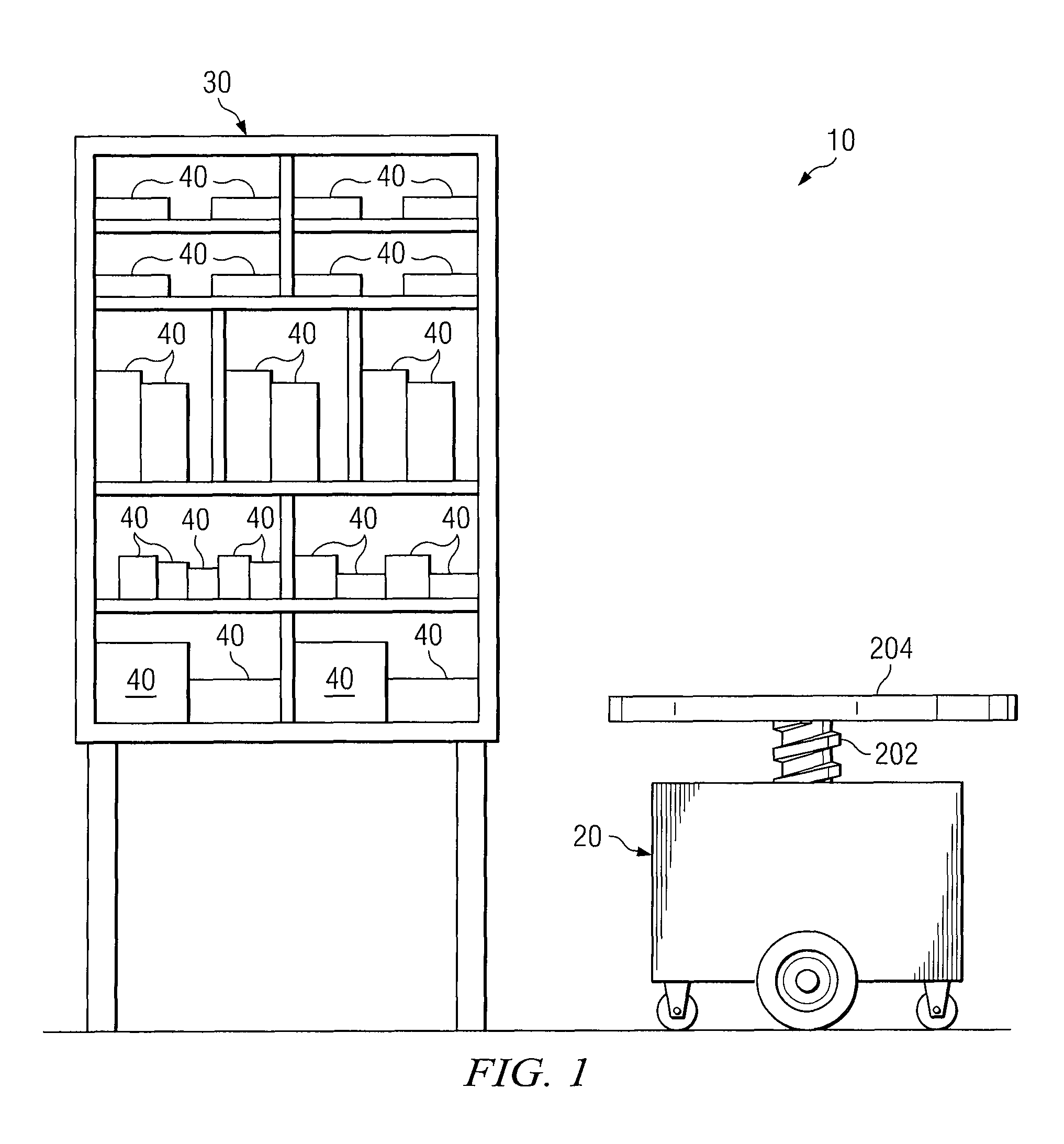

System and method for transporting inventory items

ActiveUS7850413B2Disadvantages and reduced eliminatedInventory reduced eliminatedProgramme-controlled manipulatorDigital data processing detailsEngineeringMechanical engineering

An apparatus for transporting inventory items includes a housing, a drive module, a docking module, an elevating shaft, and a rotation module. The drive module is capable of propelling the apparatus in at least a first direction. The docking head is capable of coupling to or supporting an inventory holder. The rotation module is capable of inducing rotation in the housing relative to the elevating shaft. The elevating shaft connects to the docking head and is capable of raising the docking head when the housing is rotated relative to the elevating shaft.

Owner:AMAZON TECH INC

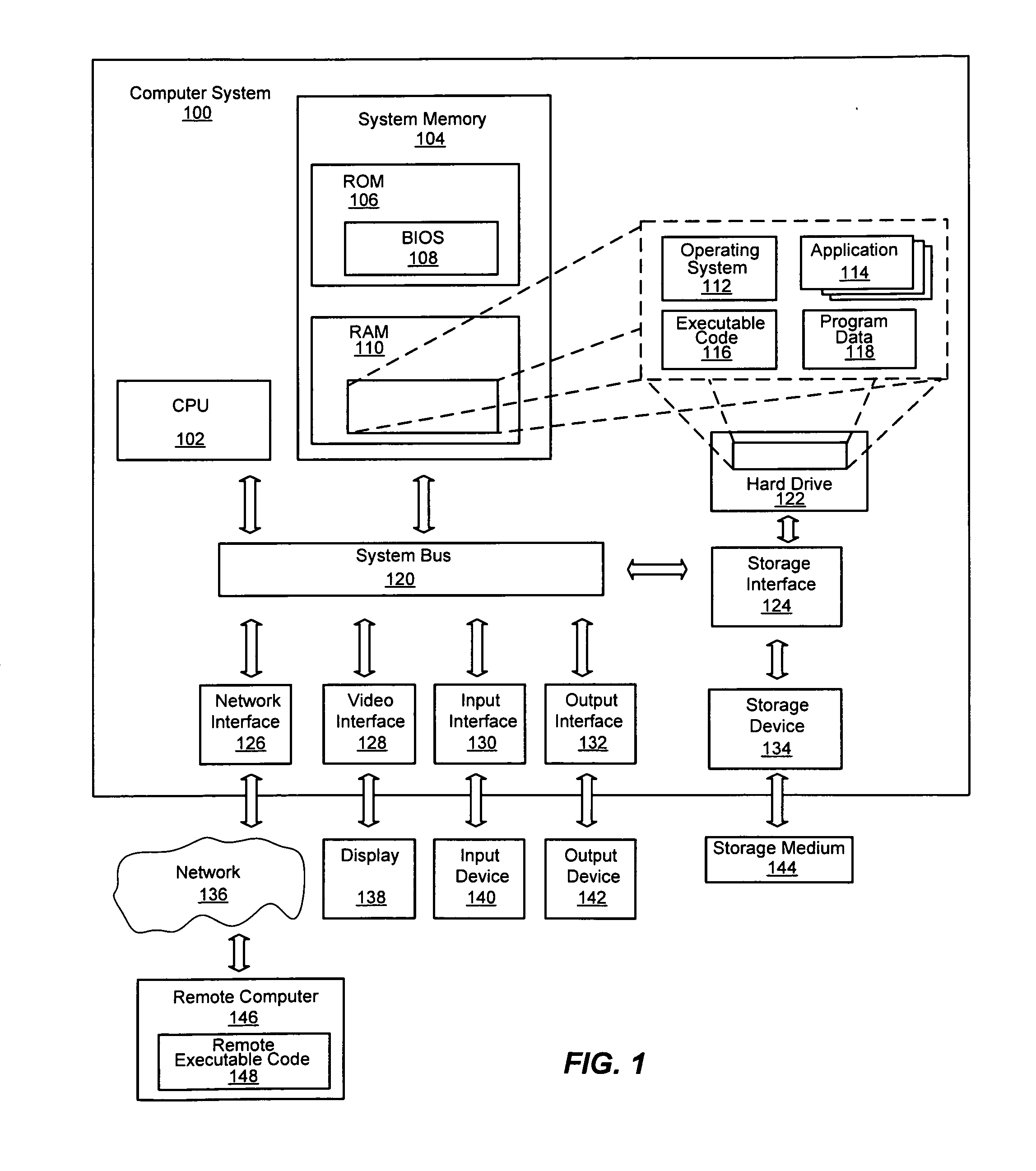

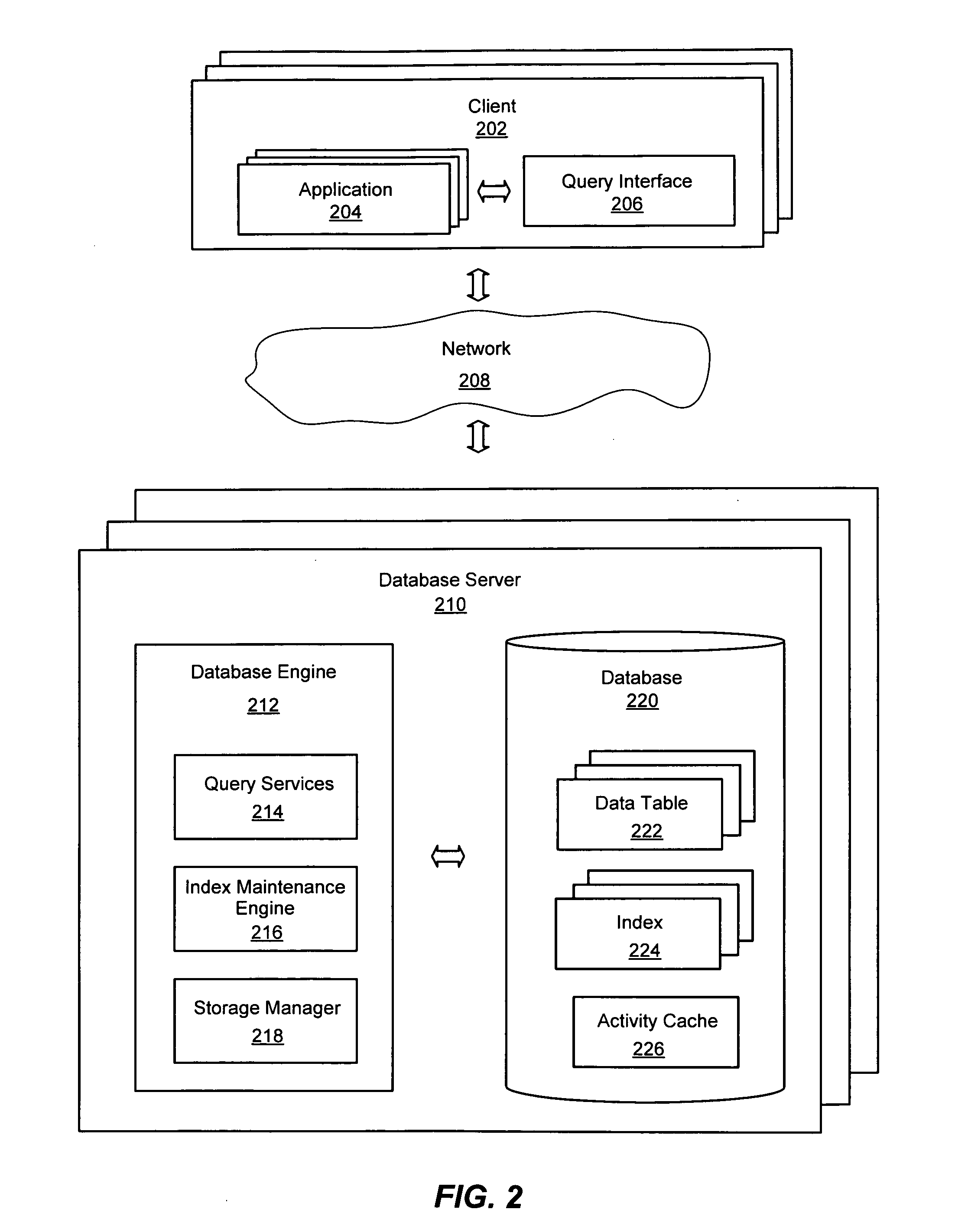

System and method for asynchronous update of indexes in a distributed database

InactiveUS20090210429A1Reduce latencyIncrease throughputDigital data information retrievalSpecial data processing applicationsClient-sideDatabase server

An improved system and method for asynchronous update of indexes in a distributed database is provided. A database server may receive the request to update the data and may update the data in a primary data table of the distributed database. An asynchronous index update of the indexes may be initiated at the time a record is updated in a data table and then control may be returned to a client to perform another data update. An activity cache may be provided for caching the records updated by a client so that when the client requests a subsequent read, the updated records may be available in the activity cache to support the various guarantees for reading the data. Advantageously, the asynchronous index update scheme may provide increased performance and more scalability while efficiently maintaining indexes over database tables in a large scale, replicated, distributed database.

Owner:OATH INC

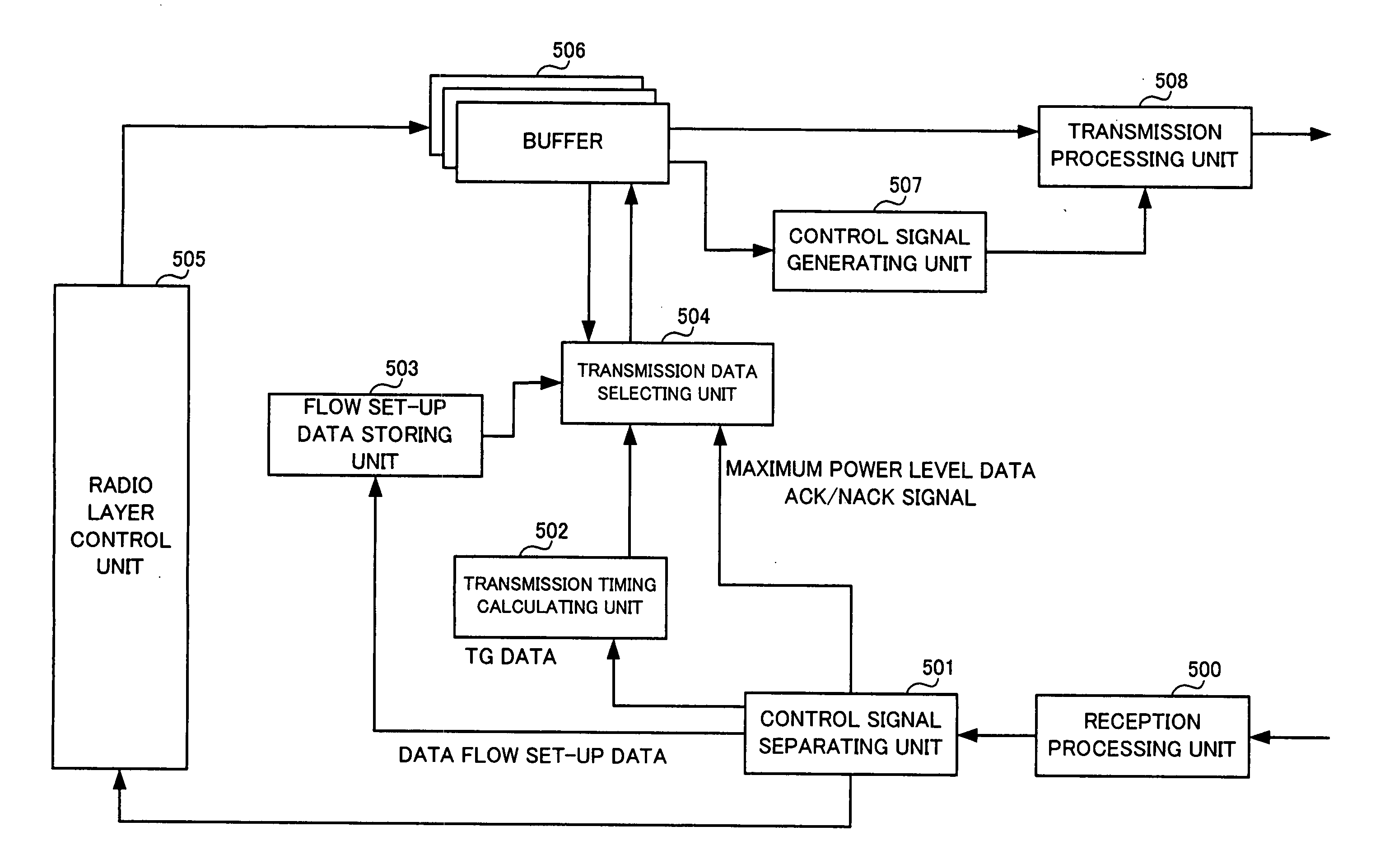

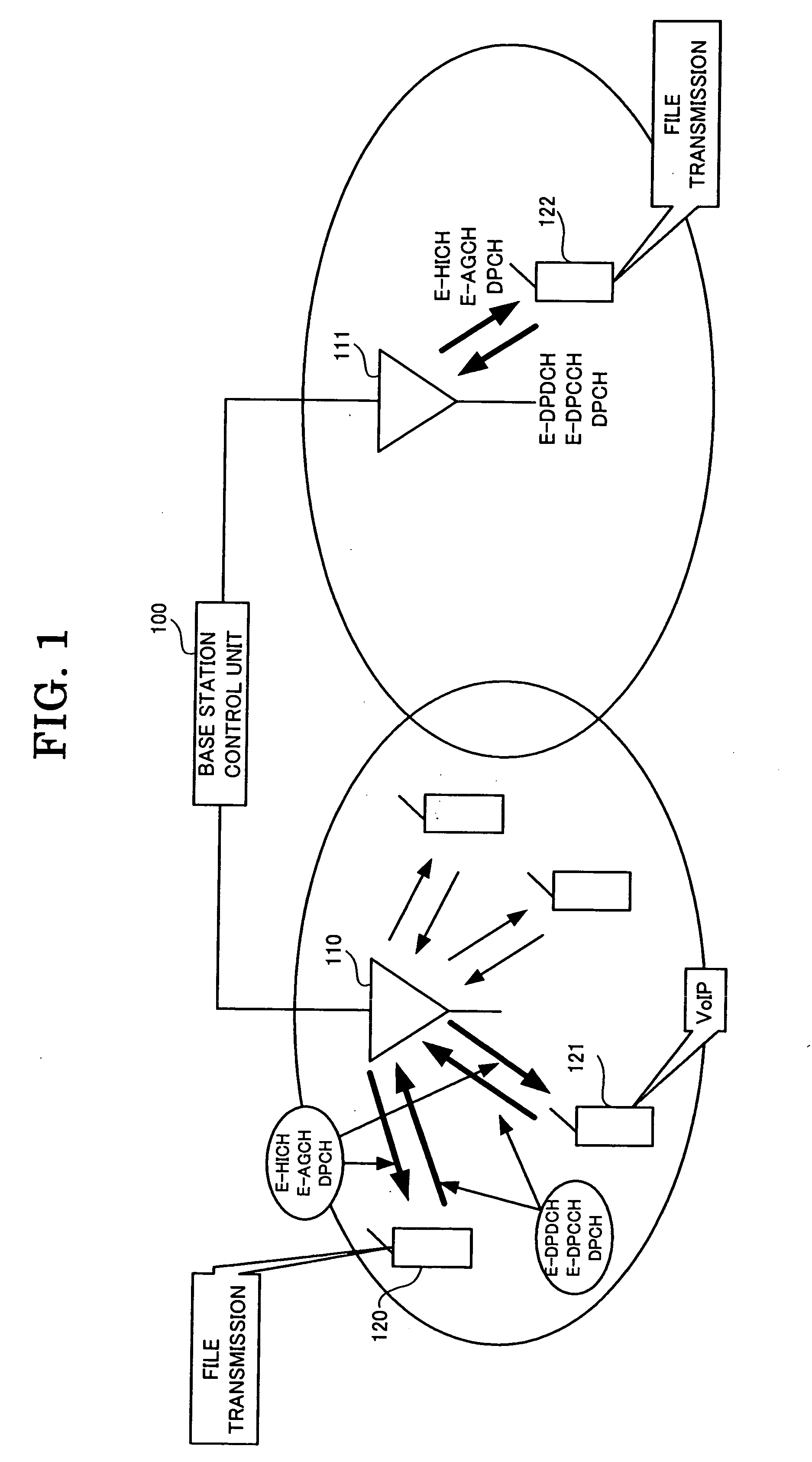

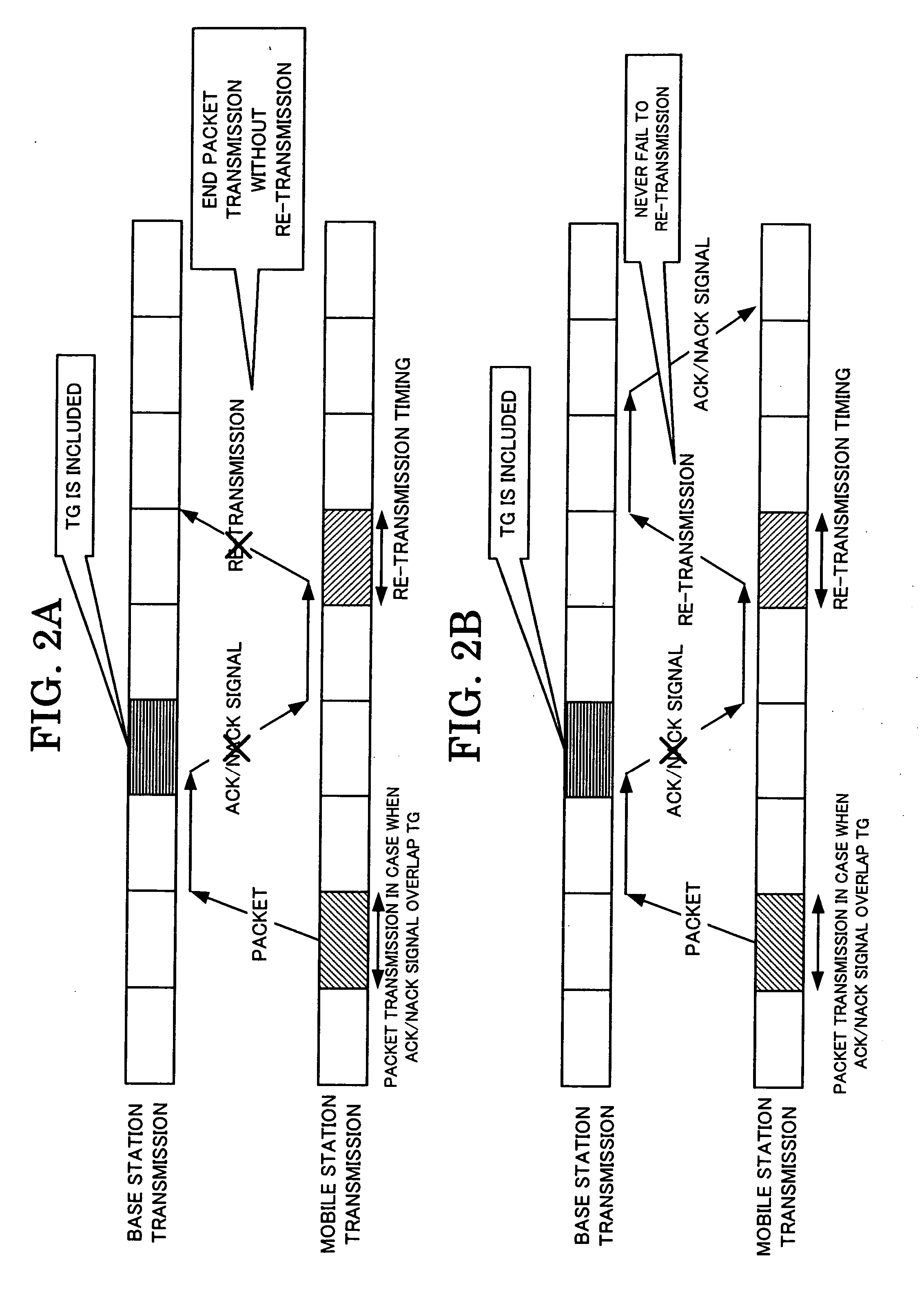

Communication control method, wireless communication system, mobile station, base station and base station control unit

InactiveUS20060146762A1Quality improvementReduce delaysPower managementNetwork traffic/resource managementCommunications systemMobile station

A wireless communication, in which mobile and base stations setup uplink and downlink channels, and the mobile station transmits data flows. The base station interrupts transmission via the downlink setup with the mobile station in the predetermined transmission interruption time interval. The mobile station determines, in response to the data flow, packet transmission in a first transmission time interval for the predetermined time interval determined from the transmission interruption time interval or re-transmission of the packets transmitted in the first transmission time interval. The mobile station transmits packets in response to the determination. The base station transmits an arrival confirmation signal for the transmitted packets. The mobile station performs re-transmission in response to the arrival confirmation signal or to the determination.

Owner:NEC CORP

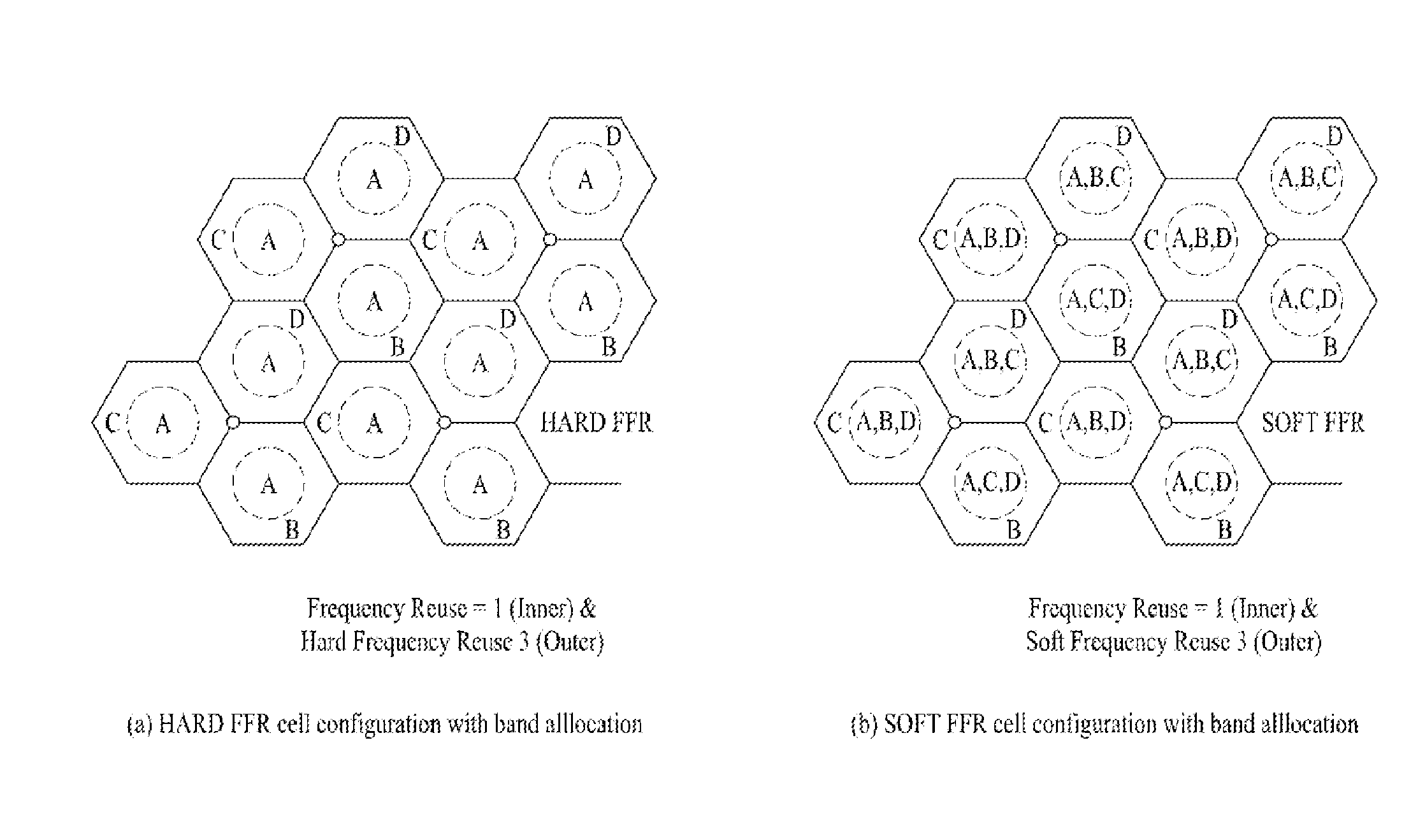

Mobile station apparatus and method for transmitting signals in wireless communication system

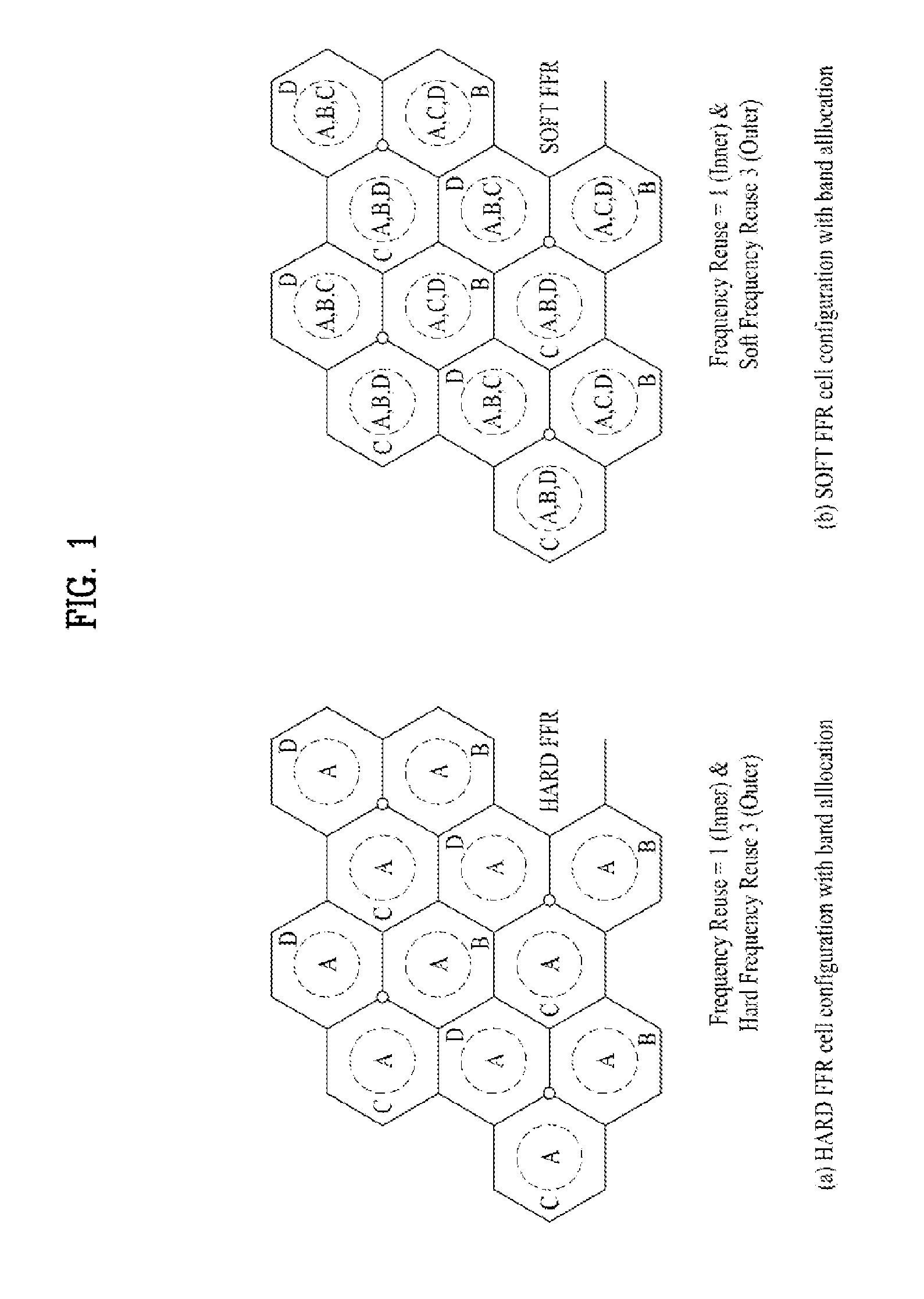

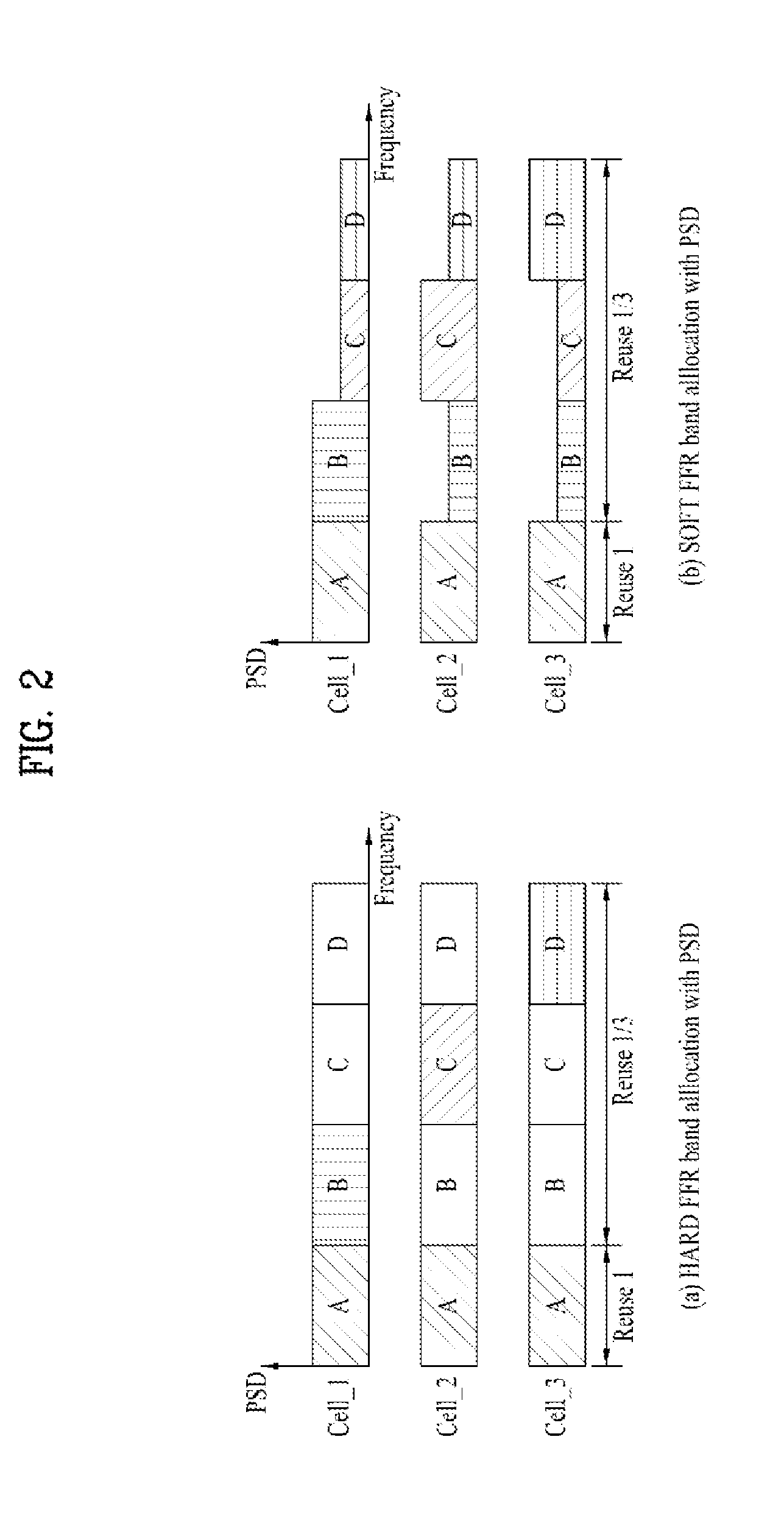

ActiveUS20110194423A1Improve system throughput and cell edge-user throughputImprove system throughputPower managementError preventionControl parametersSignal-to-interference-plus-noise ratio

A method for transmitting signal, at a mobile station, in a wireless communication system is provided. Inter-cell interference level control parameter information may be different for each frequency partition due to use of an FFR scheme. This method is advantageous in that, when uplink transmission is performed, system throughput and cell edge-user throughput are improved and inter-cell interference level control is efficiently performed, thereby improving a Signal to Interference plus Noise Ratio (SINR) at the receiving end.

Owner:LG ELECTRONICS INC

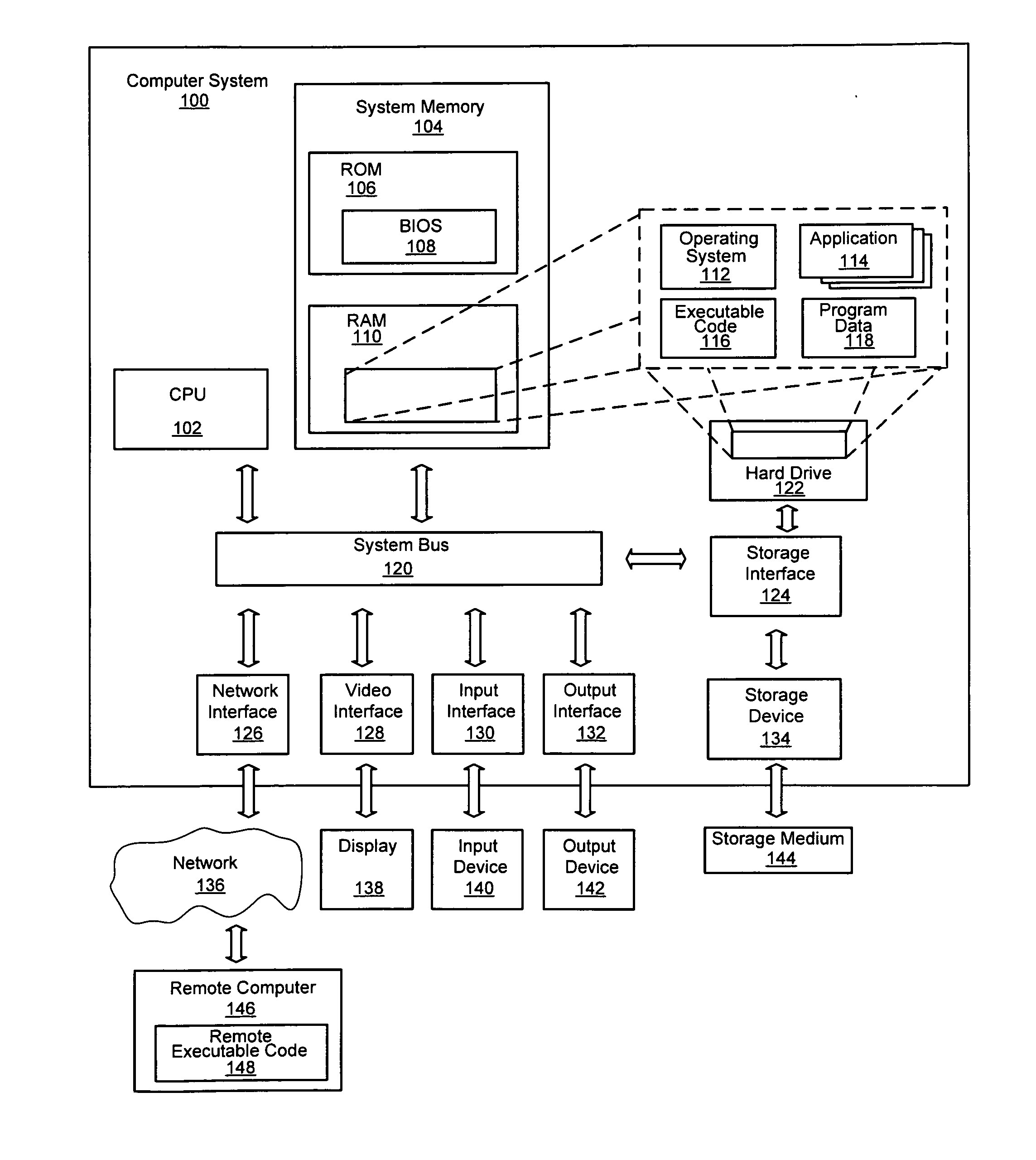

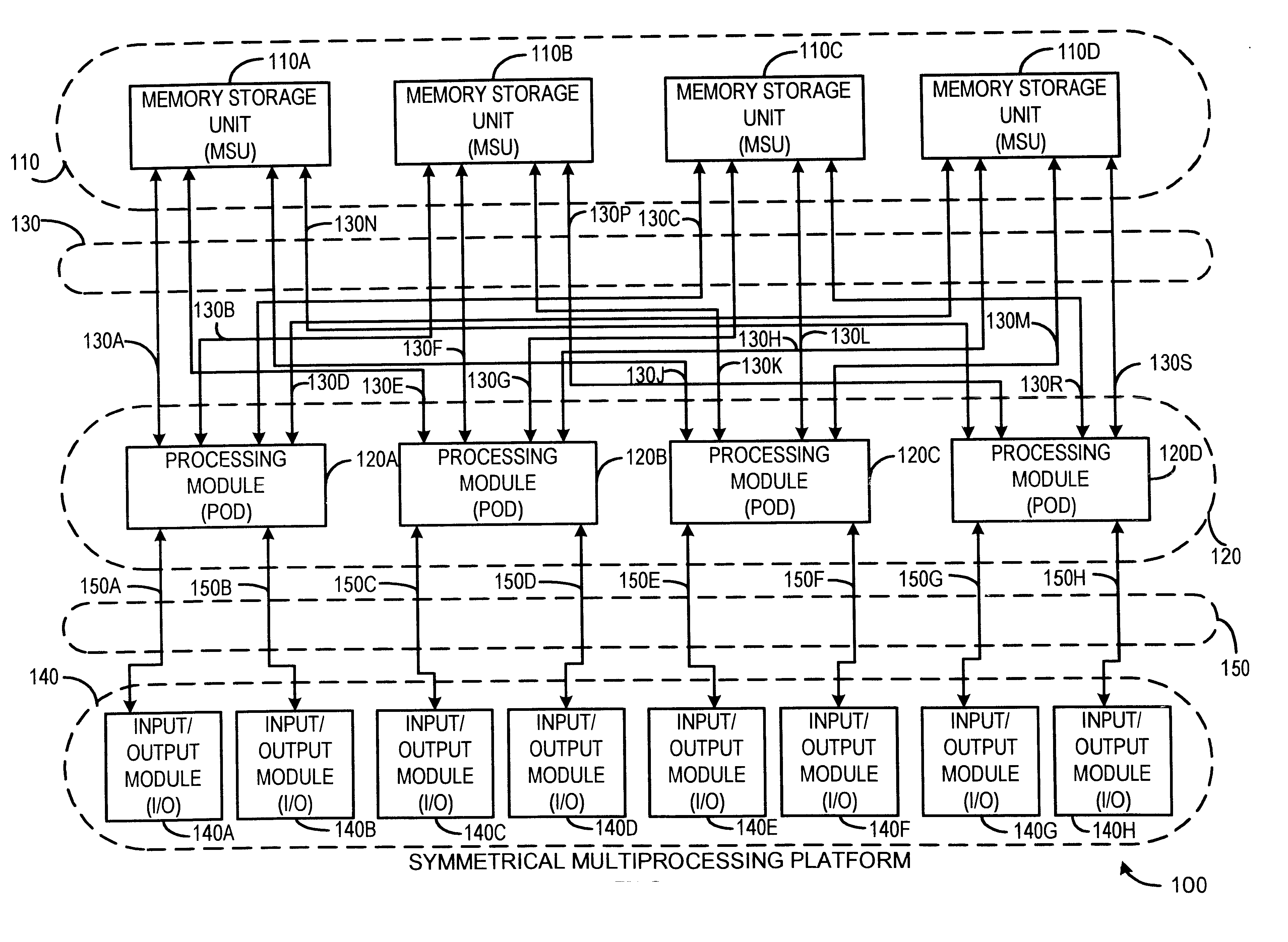

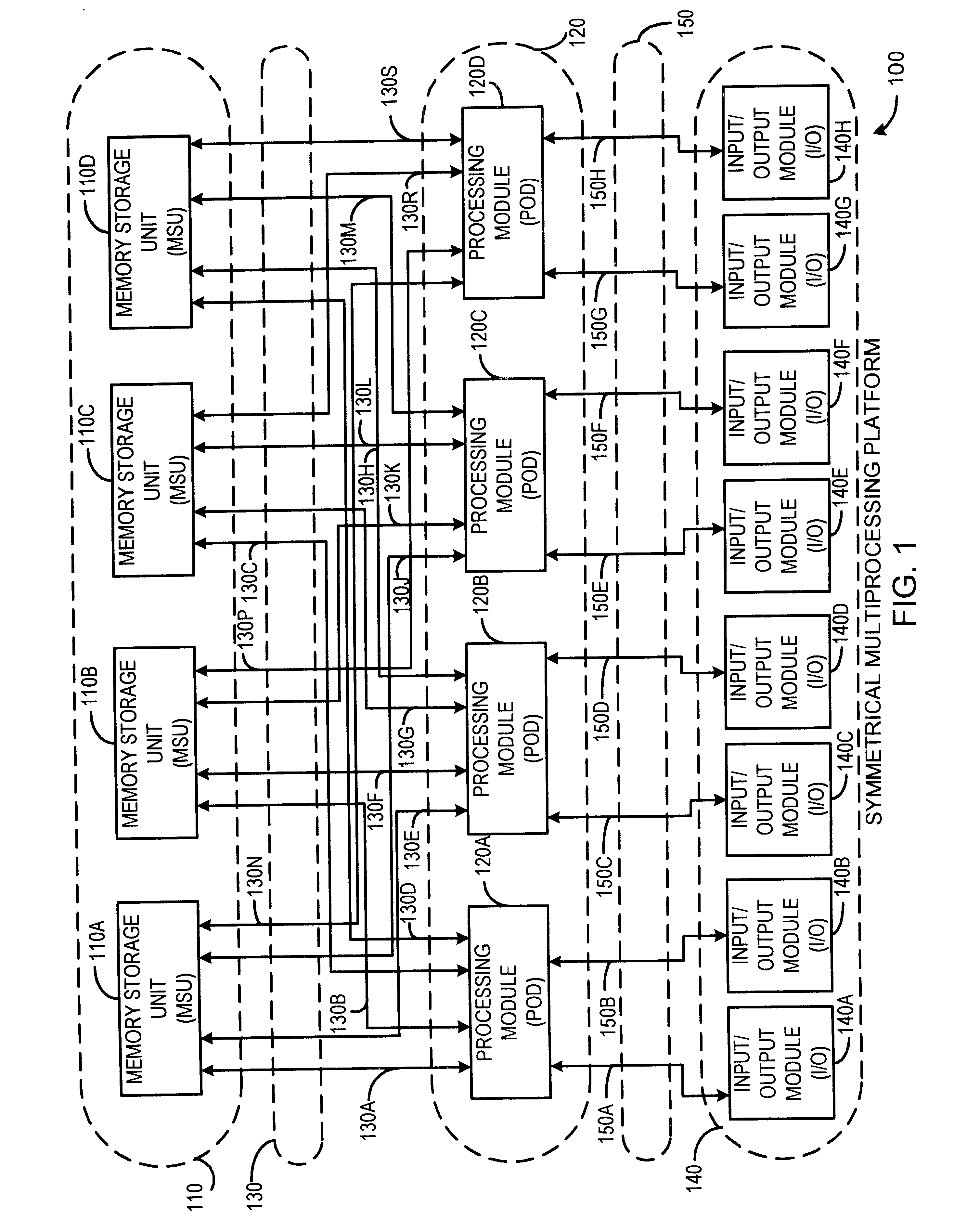

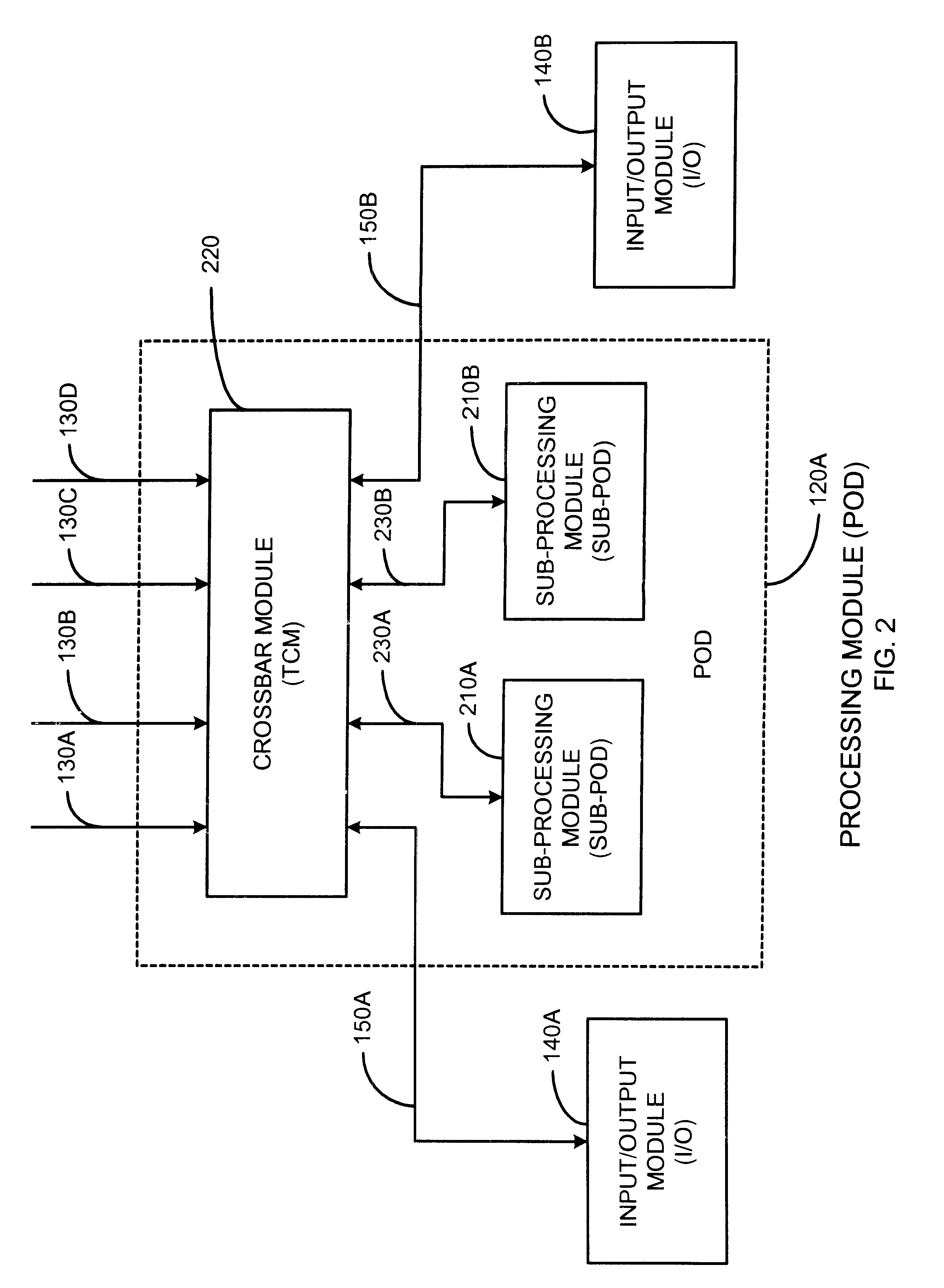

High-speed memory storage unit for a multiprocessor system having integrated directory and data storage subsystems

InactiveUS6415364B1Easy to manageImprove system throughputMemory adressing/allocation/relocationInput/output processes for data processingHigh speed memoryImpact system

A high-speed memory system is disclosed for use in supporting a directory-based cache coherency protocol. The memory system includes at least one data system for storing data, and a corresponding directory system for storing the corresponding cache coherency information. Each data storage operation involves a block transfer operation performed to multiple sequential addresses within the data system. Each data storage operation occurs in conjunction with an associated read-modify-write operation performed on cache coherency information stored within the corresponding directory system. Multiple ones of the data storage operations may be occurring within one or more of the data systems in parallel. Likewise, multiple ones of the read-modify-write operations may be performed to one or more of the directory systems in parallel. The transfer of address, control, and data signals for these concurrently performed operations occurs in an interleaved manner. The use of block transfer operations in combination with the interleaved transfer of signals to memory systems prevents the overhead associated with the read-modify-write operations from substantially impacting system performance. This is true even when data and directory systems are implemented using the same memory technology.

Owner:UNISYS CORP

Semiconductor wafer processing system with vertically-stacked process chambers and single-axis dual-wafer transfer system

InactiveUS20020033136A1Optimize vertical orientation and layoutReduce system footprintSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusTransfer systemComputer module

A semiconductor wafer processing system including a multi-chamber module having vertically-stacked semiconductor wafer process chambers and a loadlock chamber dedicated to each semiconductor wafer process chamber. Each process chamber includes a chuck for holding a wafer during wafer processing. The multi-chamber modules may be oriented in a linear array. The system further includes an apparatus having a dual-wafer single-axis transfer arm including a monolithic arm pivotally mounted within said loadlock chamber about a single pivot axis. The apparatus is adapted to carry two wafers, one unprocessed and one processed, simultaneously between the loadlock chamber and the process chamber. A method utilizing the disclosed system is also provided.

Owner:AVIZA TECHNOLOGY INC

Method, apparatus and system for handling unreliable feedback information in a wireless network

InactiveUS20050181811A1Accurately reflectImprove system throughputError prevention/detection by using return channelPower managementTelecommunicationsWireless network

The present invention provides a method, apparatus and system for handling unreliable feedback information in a wireless network. The present invention adjusts one or more communications (202) with a receiving unit (272) in a wireless communication network by receiving feedback information (302) relating to the receiving unit (102), determining a feedback information offset for the receiving unit (272), and adjusting the one or more communications (202) with the receiving unit (272) based on the feedback information and the feedback information offset (306).

Owner:UNWIRED PLANET

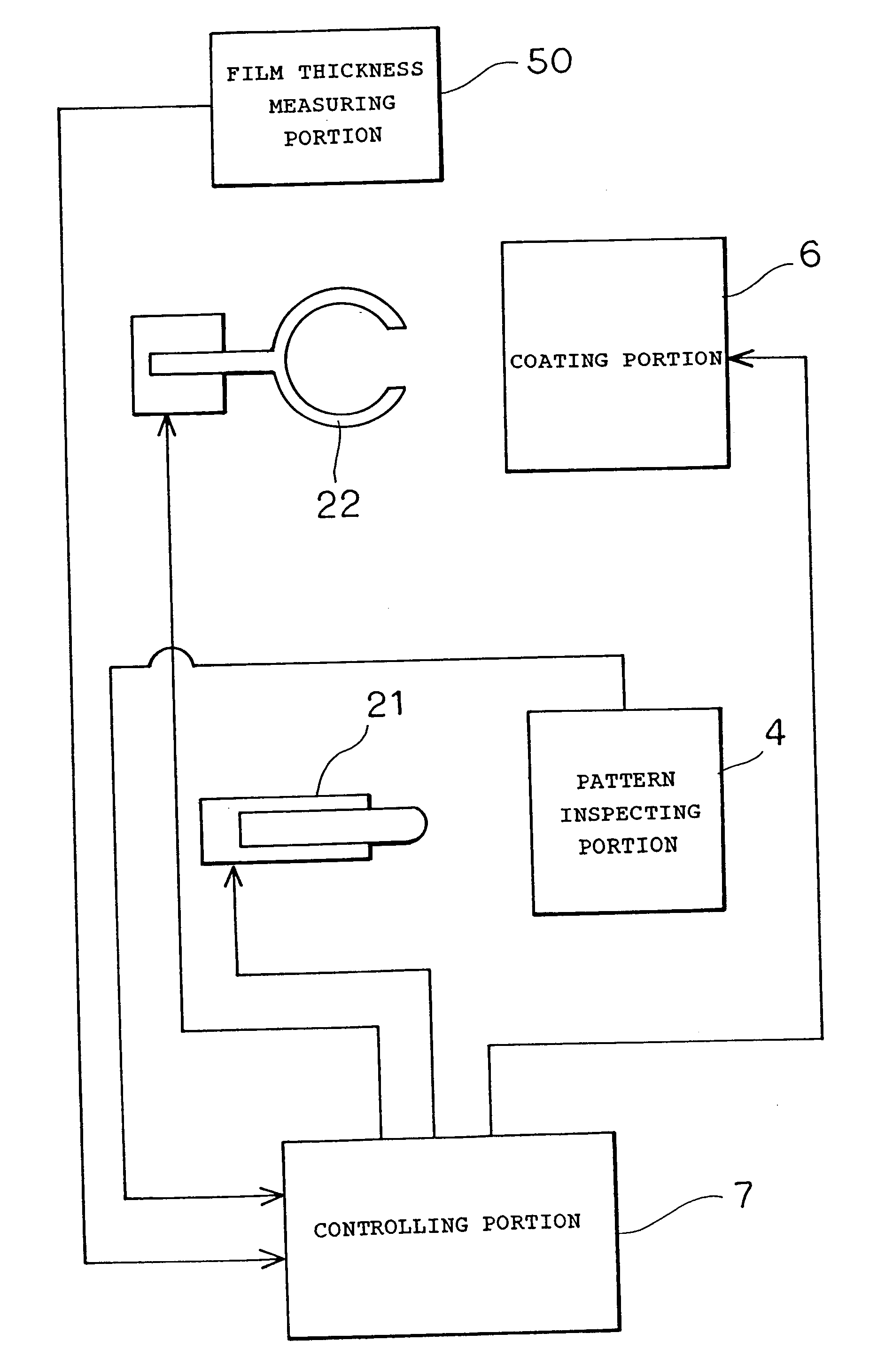

Resist coating and developing unit

InactiveUS6313903B1Improve system throughputFast transferLiquid surface applicatorsSemiconductor/solid-state device manufacturingResistWafering

In a transferring region of a wafer transferring portion that transfers a wafer placed in a carrier loading and unloading portion, a pattern inspecting portion for inspecting a resist pattern and a carrier for accommodating a wafer determined as an unacceptable wafer are disposed. The carrier is conveyed to an external cleaning portion. Resist on the unacceptable wafer is cleaned and removed. The resultant wafer is loaded to the coating and developing unit. The film thickness of a monitor wafer is measured by a film thickness measuring portion disposed in the coating and developing unit. Thereafter, resist on the entire surface of the monitor wafer is removed with thinner supplied from a solvent nozzle. Thus, the monitor wafer is regenerated. Consequently, when the coating and developing unit is operated and a substrate and a monitor substrate that have been processes are inspected, the throughput of the coating and developing unit becomes high and the processes can be automatically performed.

Owner:TOKYO ELECTRON LTD

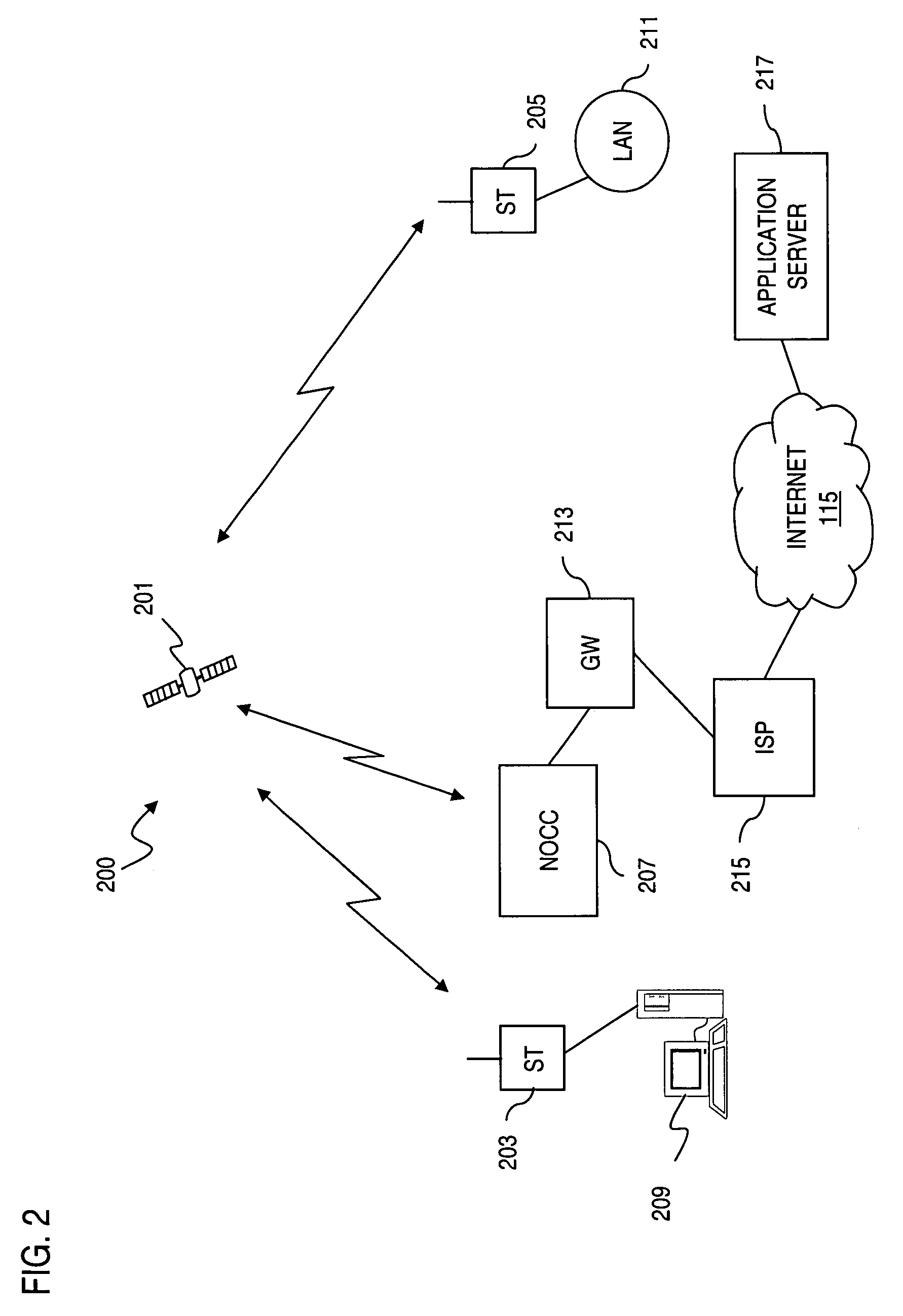

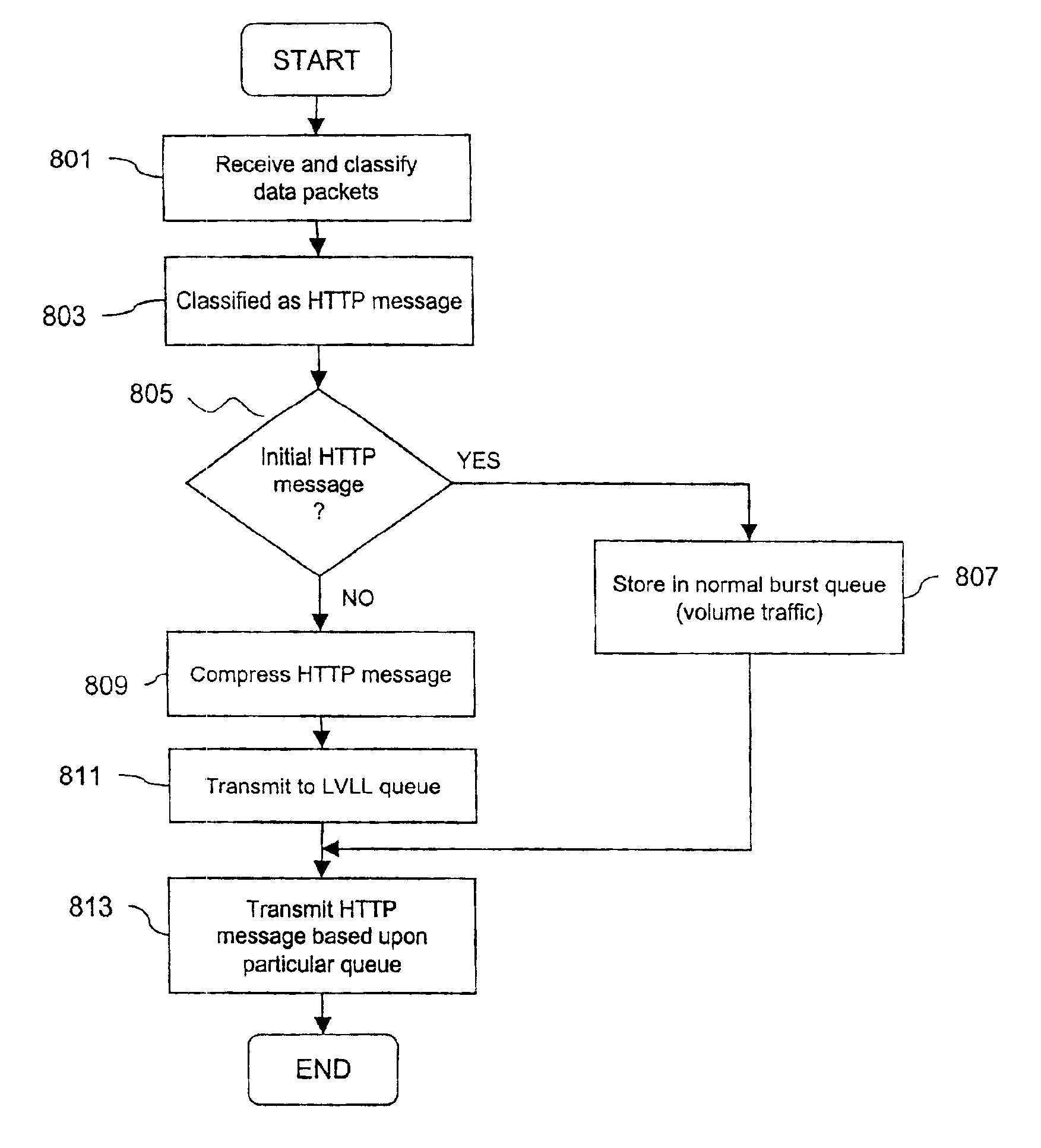

Low latency handling of transmission control protocol messages in a broadband satellite communications system

InactiveUS6961539B2Minimize impactImprove system throughputError prevention/detection by using return channelFrequency-division multiplex detailsCommunications systemLatency (engineering)

An approach for transmitting packets conforming with the TCP (Transmission Control Protocol) over a satellite communications network comprises a plurality of prioritized queues that are configured to store the packets. The packets conform with a predetermined protocol. A classification logic classifies the packets based upon the predetermined protocol. The packet is selectively stored in one of the plurality of queues, wherein the one queue is of a relatively high priority. The packet is scheduled for transmission over the satellite communications network according to the relative priority of the one queue.

Owner:HUGHES NETWORK SYST

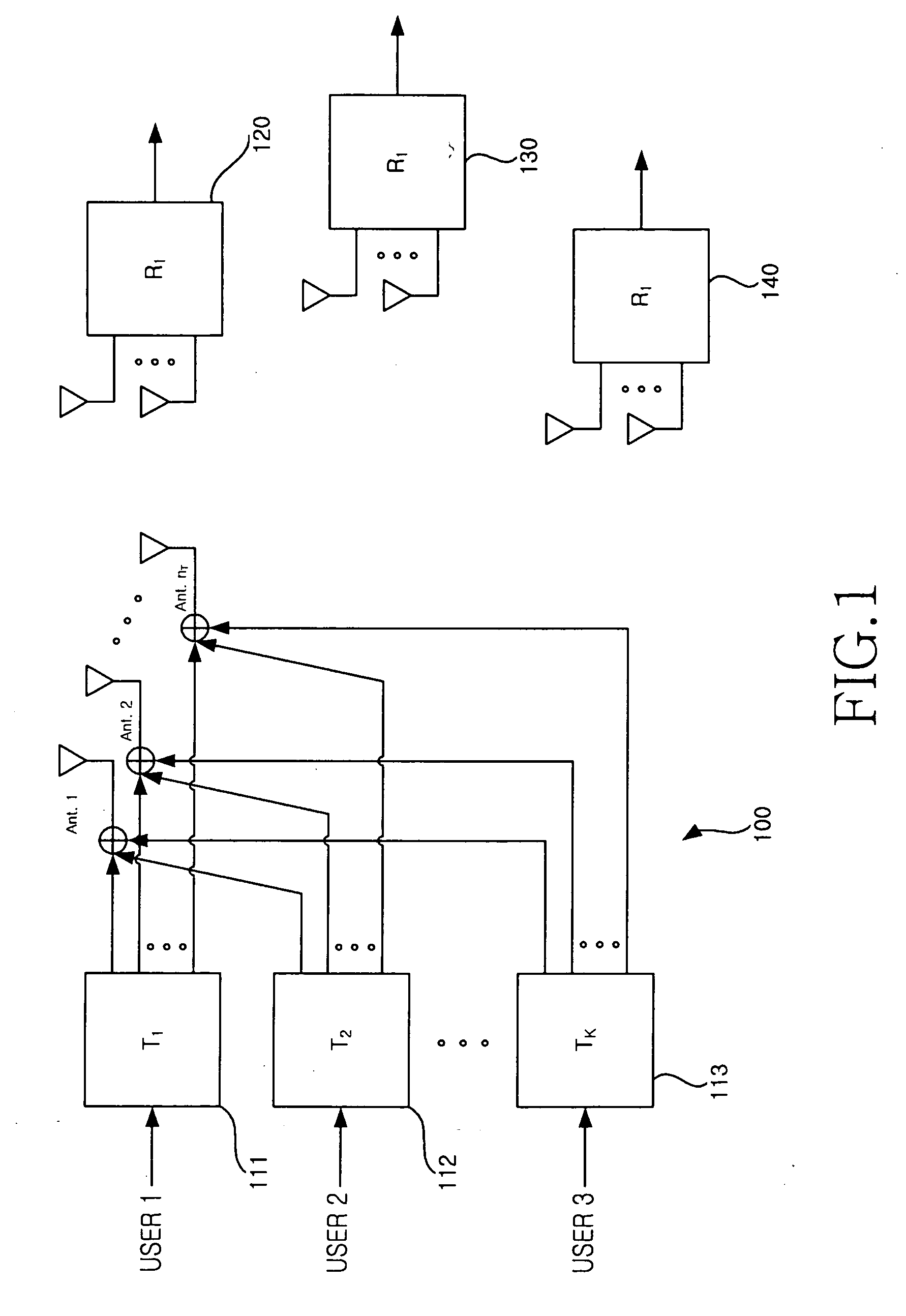

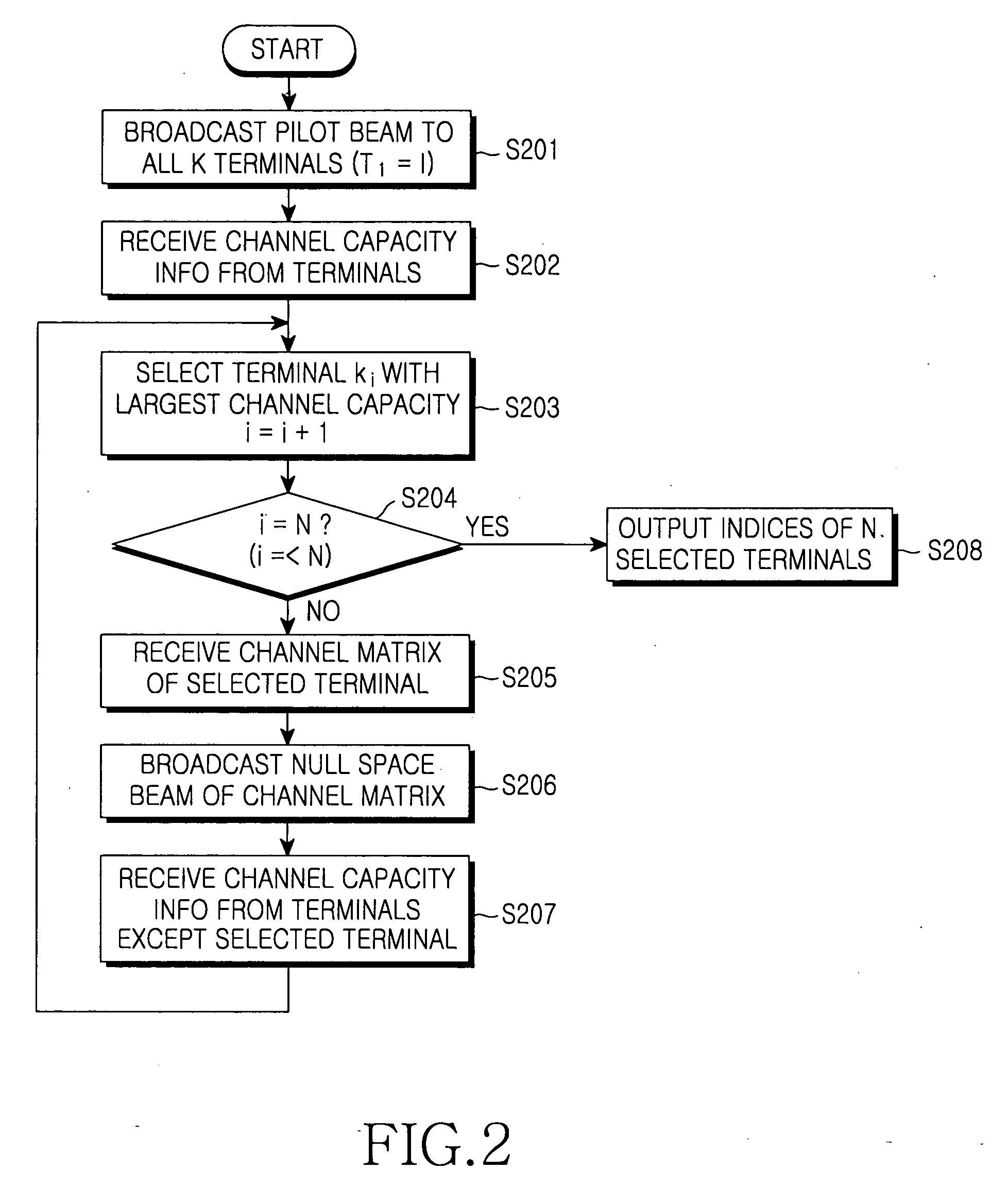

User selection method in a zero-forcing beamforming algorithm

InactiveUS20070058590A1Improve performanceIncrease throughputDiversity/multi-antenna systemsSubstation equipmentChannel capacityEngineering

In a method for selecting a transmission target terminal in a zero-forcing beamforming algorithm, information about a channel capacity of each terminal is received from all K terminals. A terminal with a largest channel capacity is selected as an initial transmission target terminal. A determination is made as to whether the number of currently selected terminals, i, is equal to the predefined number N. If the number of currently selected terminals, i, is different from the predefined number N, information about channel capacities of remaining terminals except previously selected transmission target terminals is received until i is equal to N and a terminal with a largest channel capacity is selected as a transmission target terminal.

Owner:SAMSUNG ELECTRONICS CO LTD +1

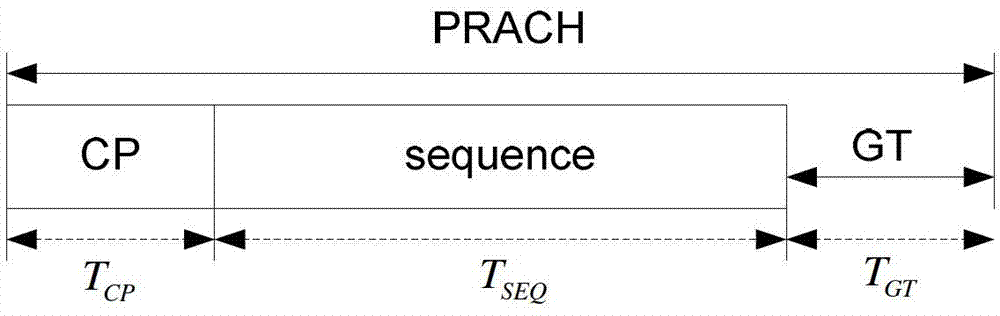

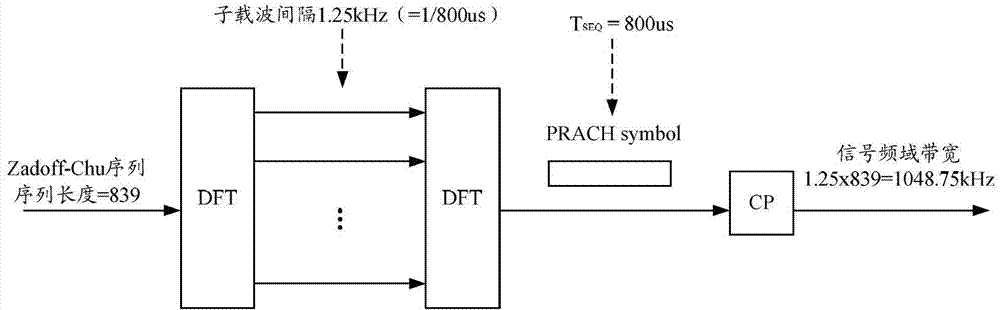

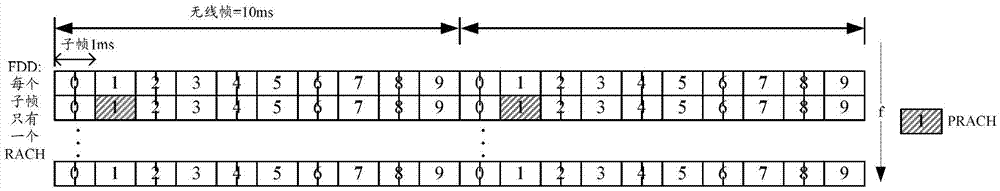

Resource determining method and device for physical random access channel

ActiveCN103716895AImprove resource reuse capacityImprove access efficiencyWireless communicationTime domainTelecommunications

The invention discloses a resource determining method for a physical random access channel. The method comprises the step of configuring a plurality of physical random access channel resources for each piece of user equipment (UE), and the physical random access channel resources include at least one of the following resources: time domain resource, frequency domain resource, code domain resource and space domain resource, wherein the time domain resource is emission sub-frame configuration of a physical random access channel, the frequency domain resource is emission band configuration of the physical random access channel, the code domain resource emission sequence or orthogonal mask configuration of the random access channel, and the space domain resource is space access location configuration of the random access channel. The invention further discloses a resource determining device for a physic al random access channel. The PRACH resource reusing capability in a frequency division duplex system is improved, the PRACH collision probability is reduced, and the terminal access efficiency and the system throughput are improved.

Owner:ZTE CORP

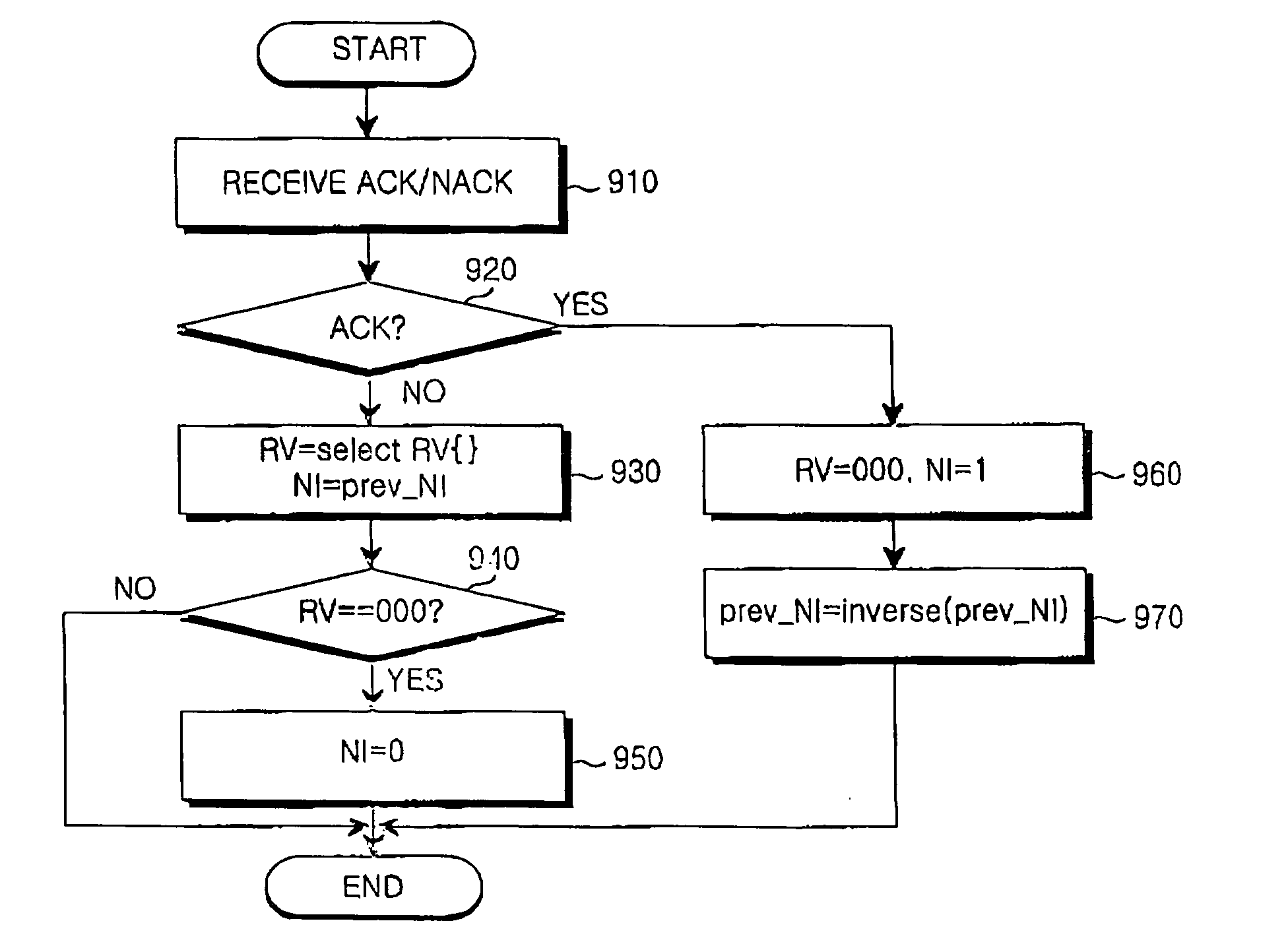

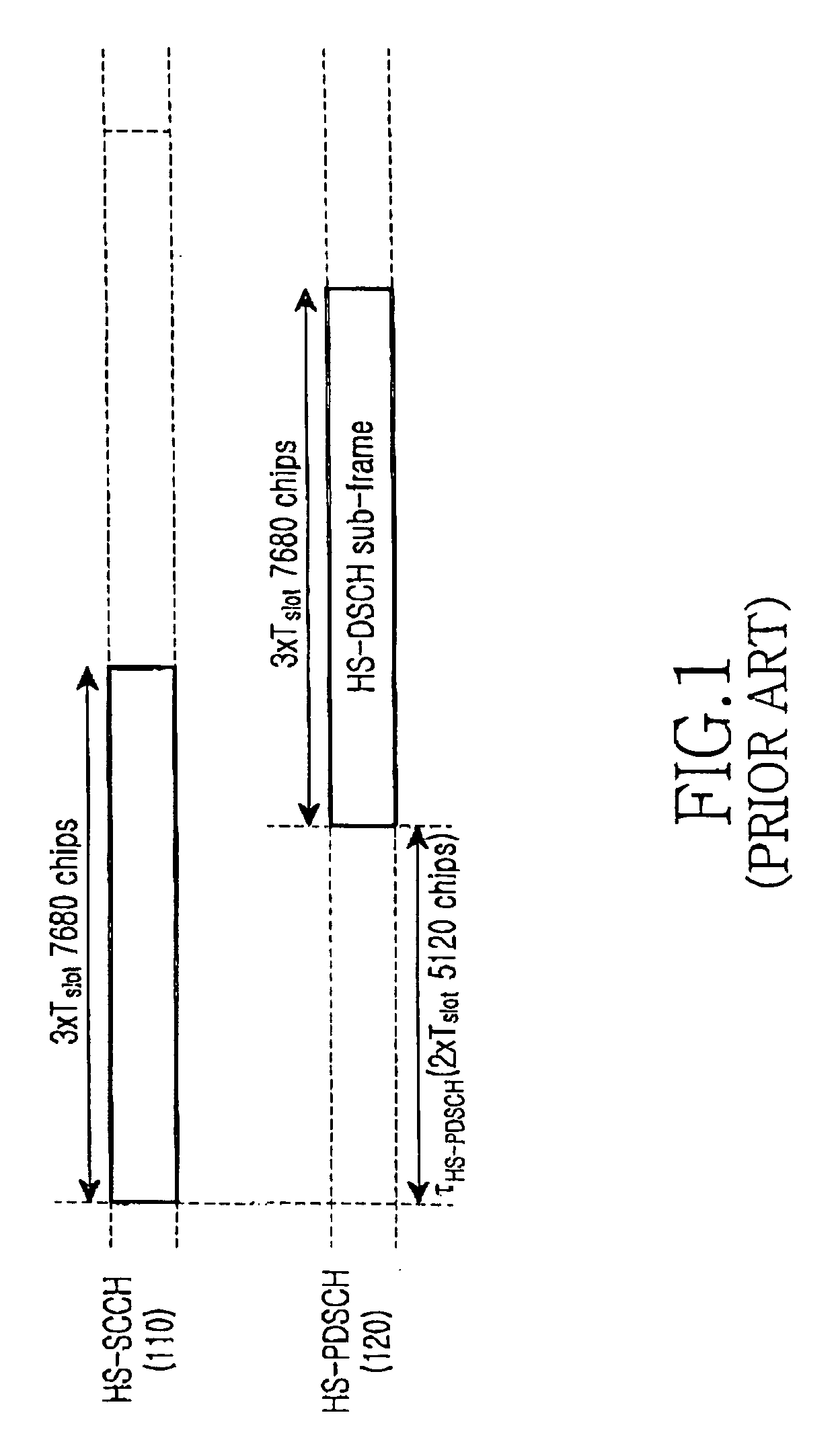

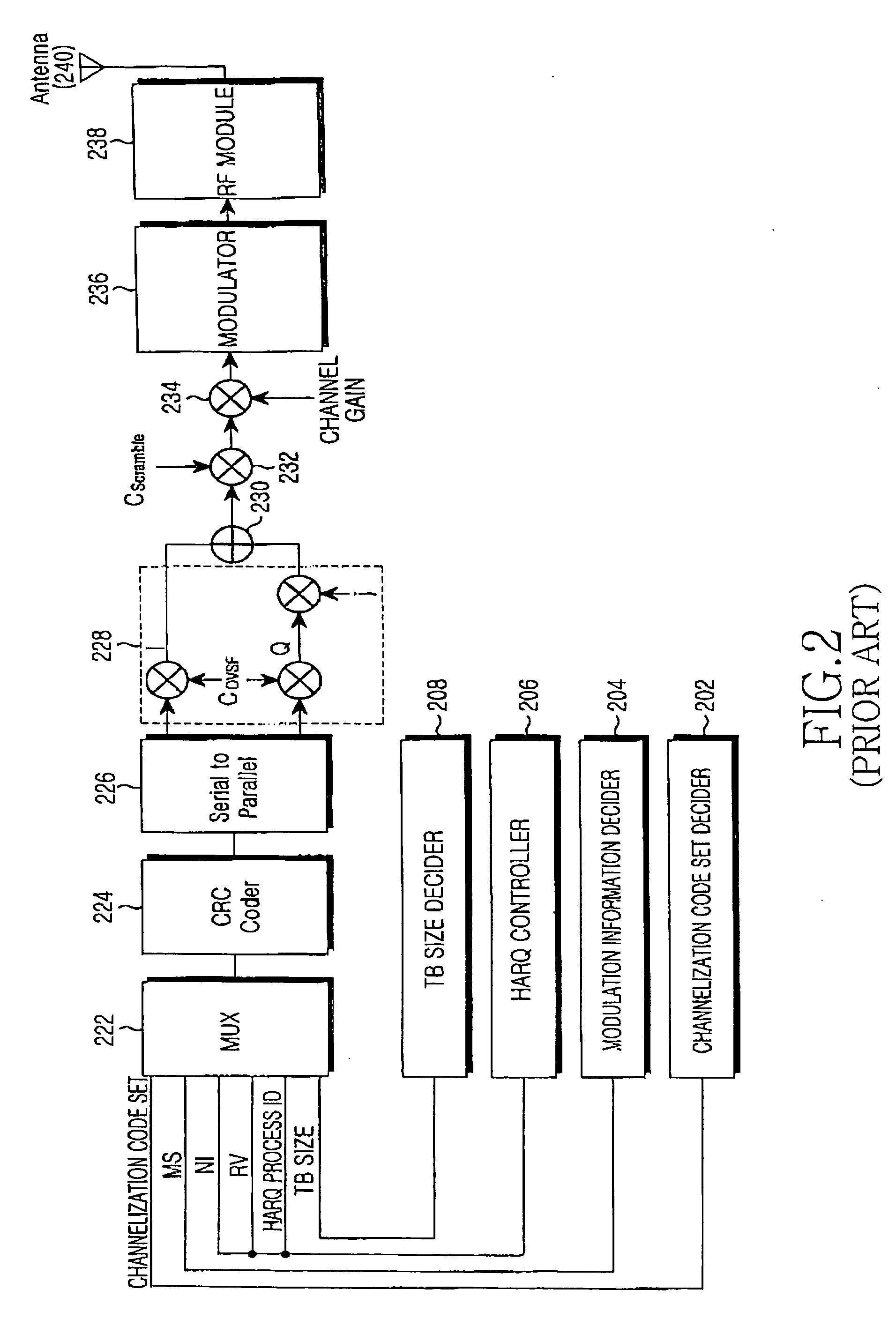

Method and apparatus for transmitting/receiving a control signal on a high speed shared control channel in a hybrid automatic retransmission request system

InactiveUS20050105494A1Avoid packet lossEfficiently control informationError prevention/detection by using return channelNetwork traffic/resource managementCommunications systemControl signal

A method and apparatus for transmitting / receiving control information to support High Speed Downlink Packet Access (HSDPA) in a WCDMA communication system are provided. When transmitting new packet data, a Node B sets a New data Indicator (NI) to a specific bit value indicating an initial transmission for the packet data. Upon receipt of a retransmission request for the packet data, the Node B sets the NI as the inverse of a previous NI. If an redundancy version (RV) representing a constellation and a data type for packet data, is set to a specific value indicating an initial transmission, the Node B set the NI to the inverse of the specific bit value regardless of the previous NI. A User Equipment (UE) receives control information including the NI and the redundancy version (RV) and determines that the packet data is initial transmission data or retransmission data, according to the NI and the RV.

Owner:SAMSUNG ELECTRONICS CO LTD