Patents

Literature

287 results about "Block transfer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A block transfer must be a transfer of two or more people at the same time from one pension scheme to a new pension scheme.

Storage system bus transfer optimization

ActiveUS8751728B1Reduce bus activityInput/output to record carriersConcurrent instruction executionSystem busBlock transfer

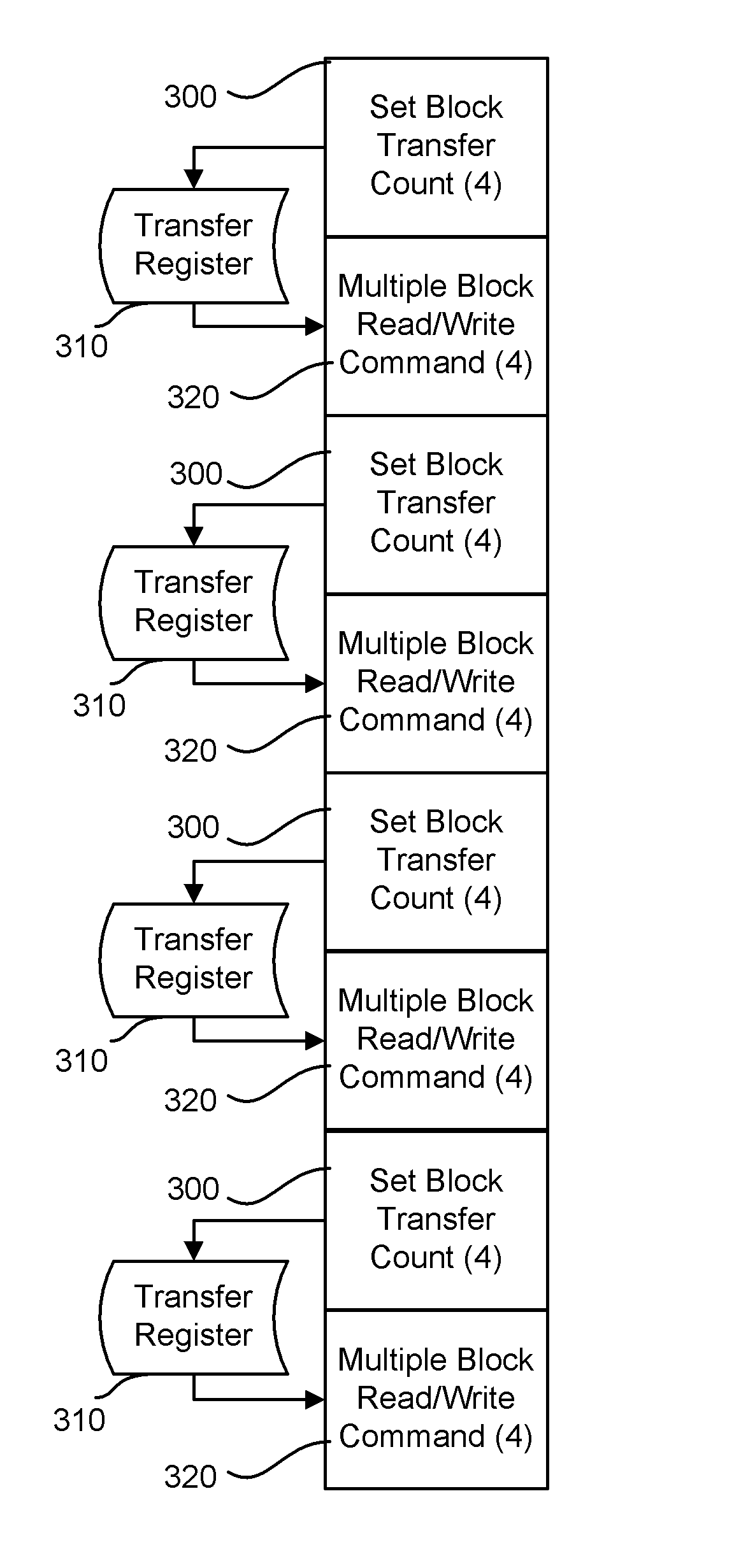

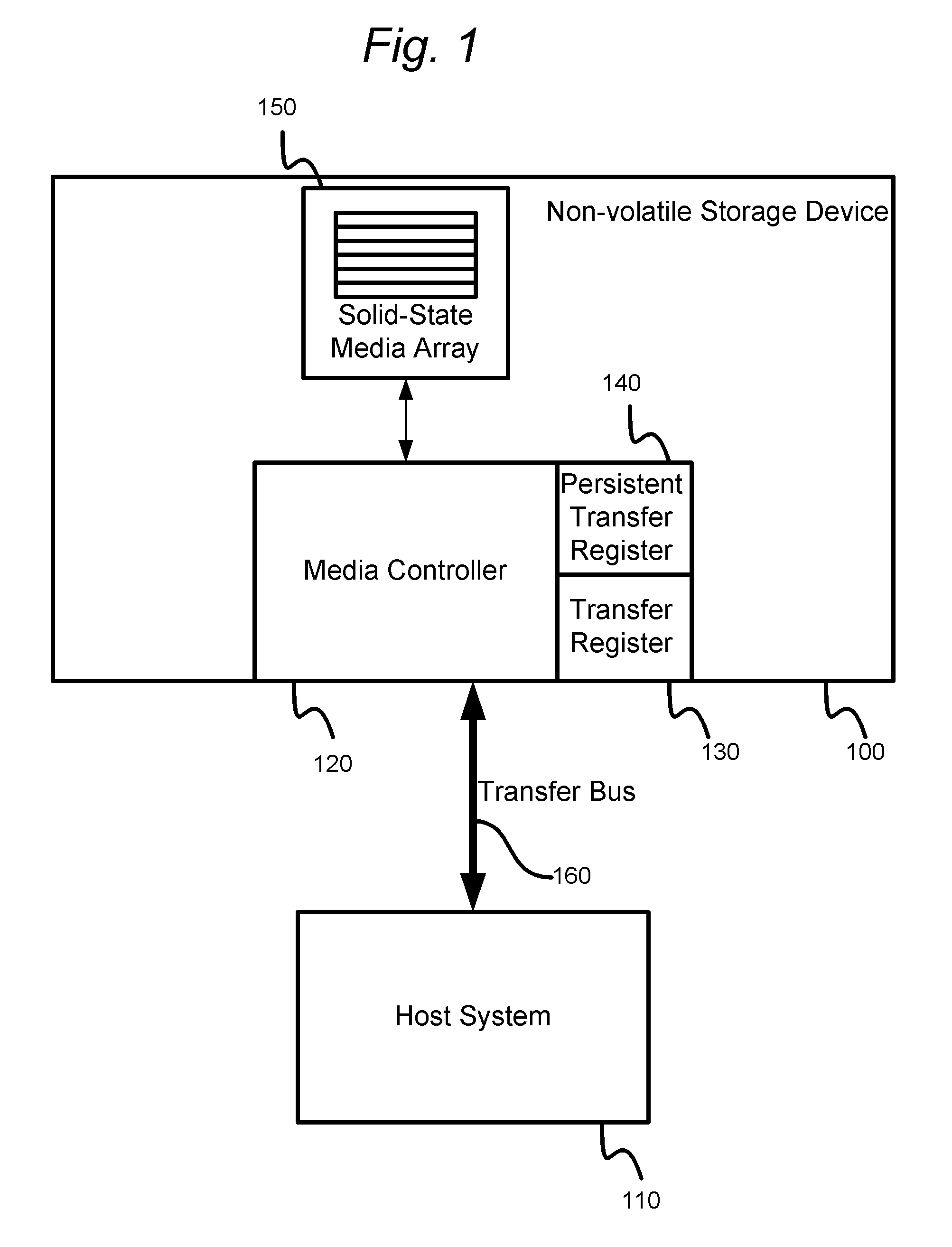

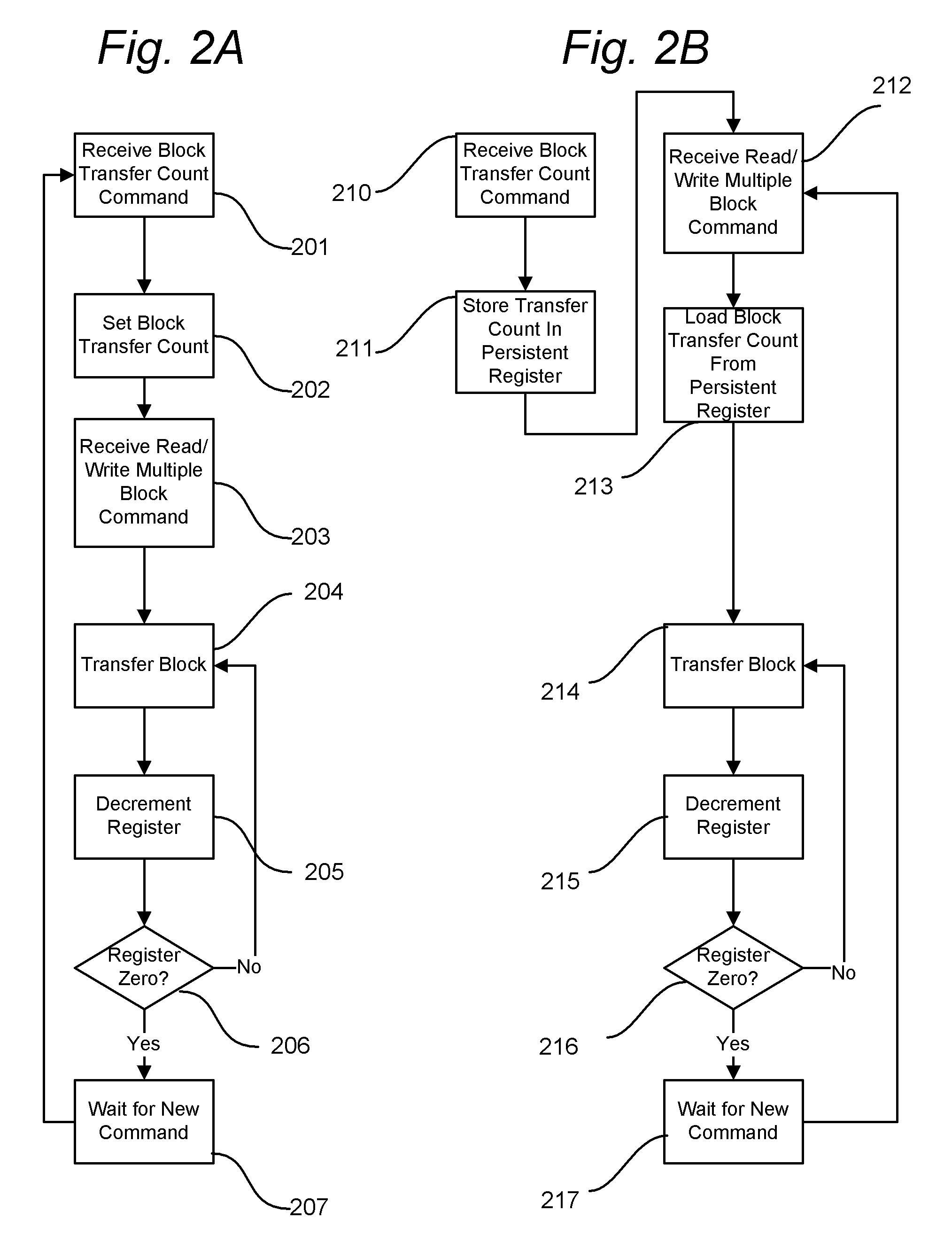

Embodiments of the invention include systems and methods for reducing bus transfers for a storage device. In particular, these systems and methods reduce bus transfers by modifying an interface transfer protocol which designates the size of a multiple block read or write command is transmitted in a separate block transfer size command. Separate block transfer size commands can be omitted where the storage device maintains a record of a previously used block transfer size and reuses the size for subsequent multiple block read or write commands.

Owner:WESTERN DIGITAL TECH INC

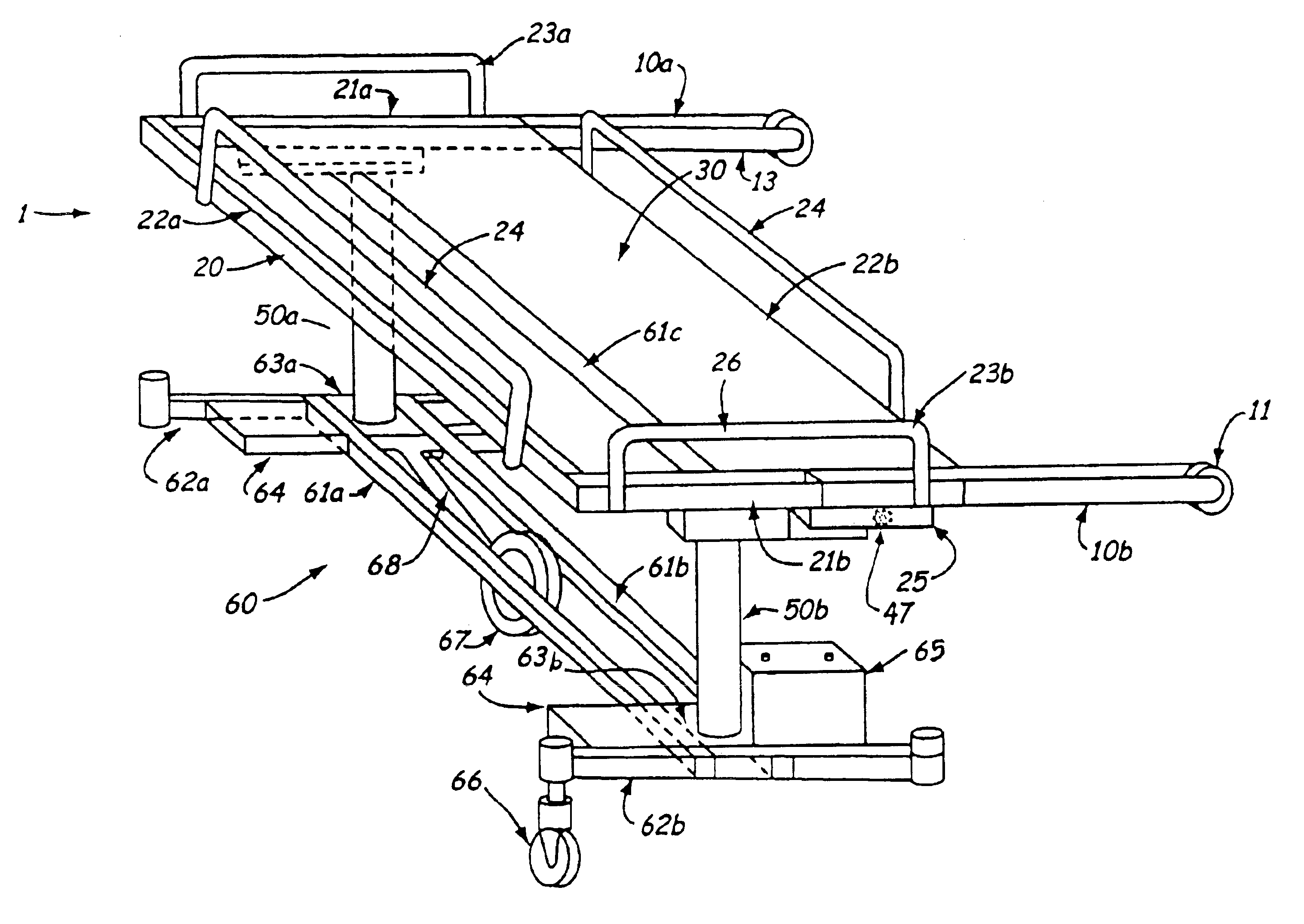

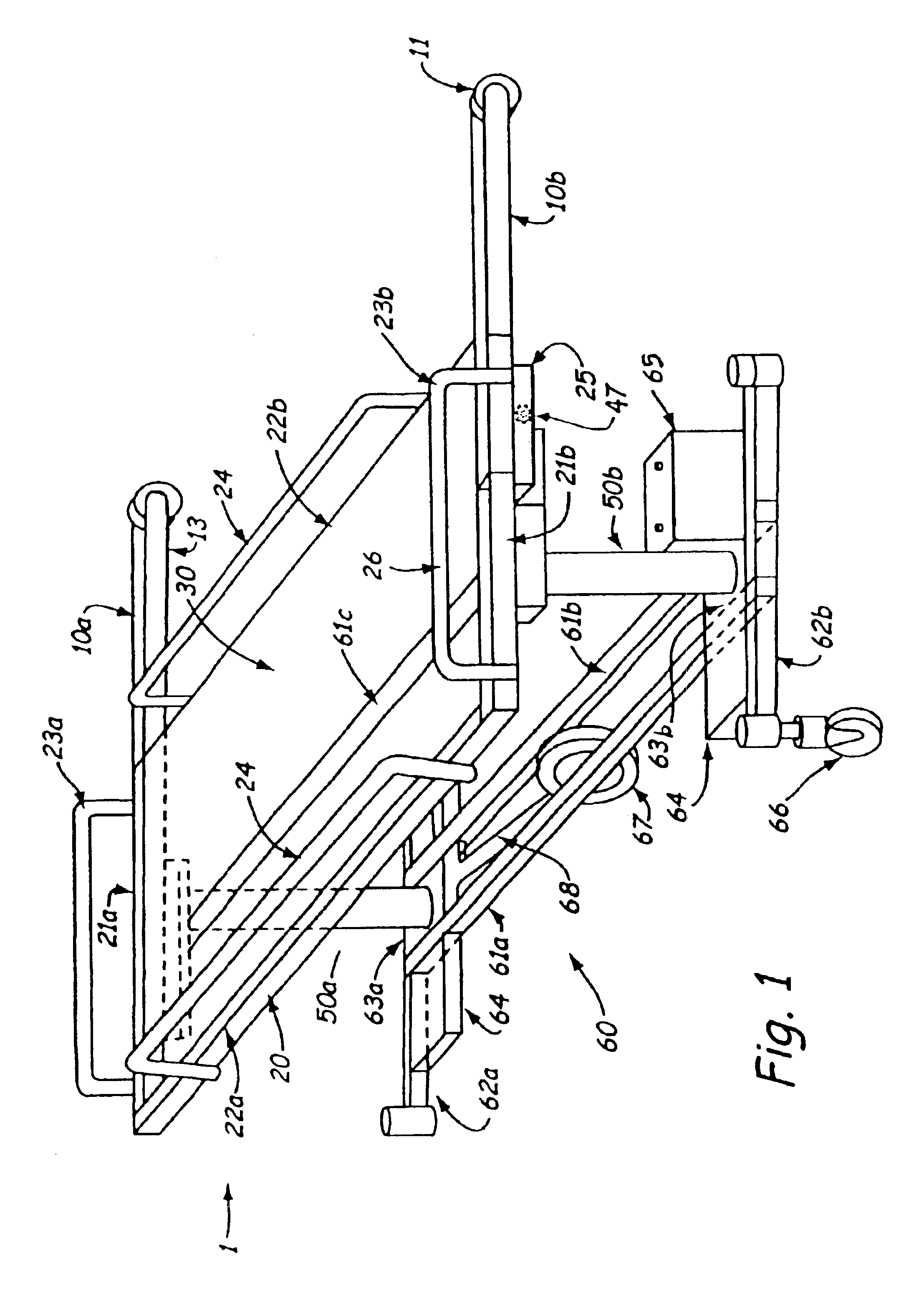

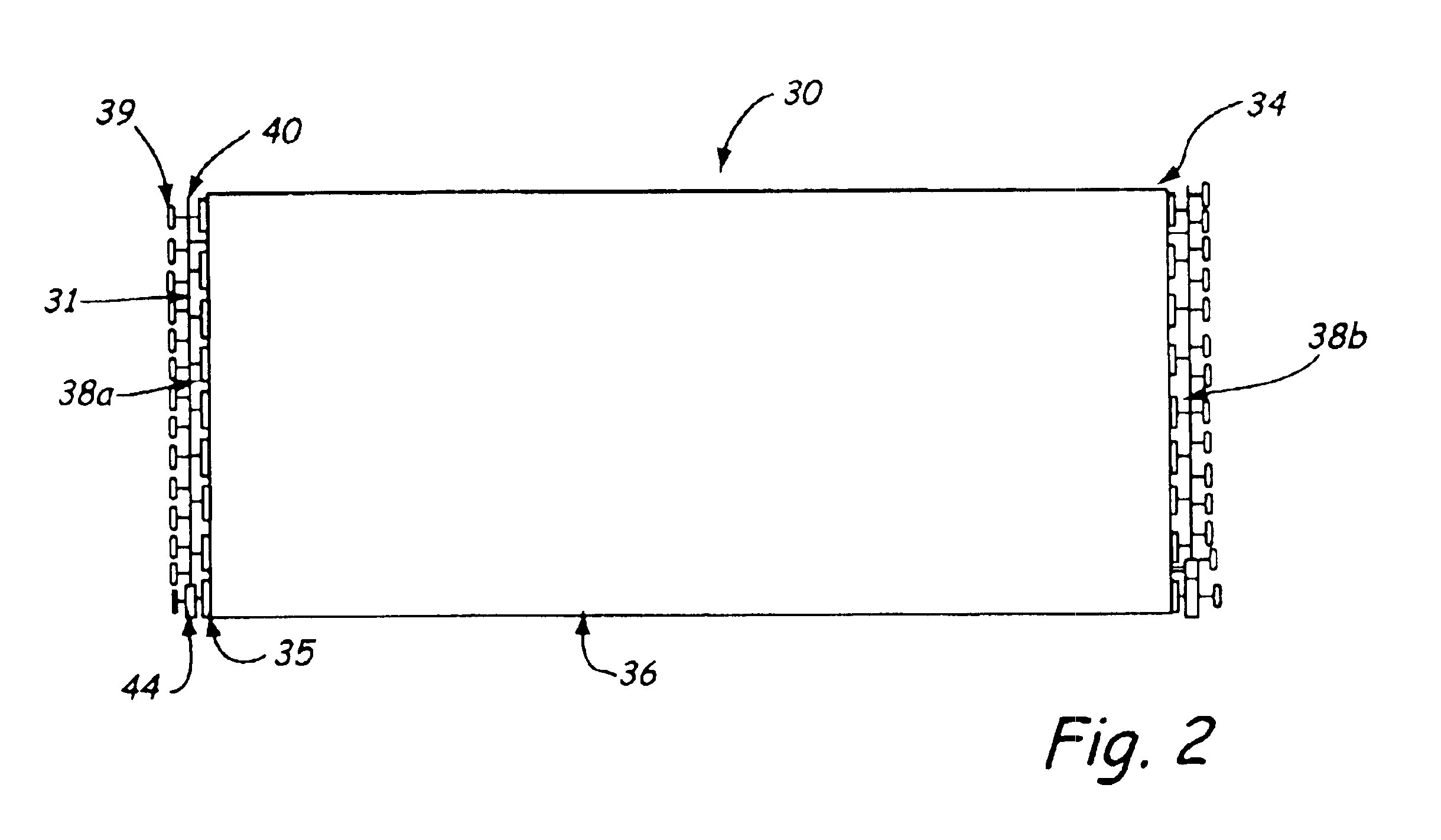

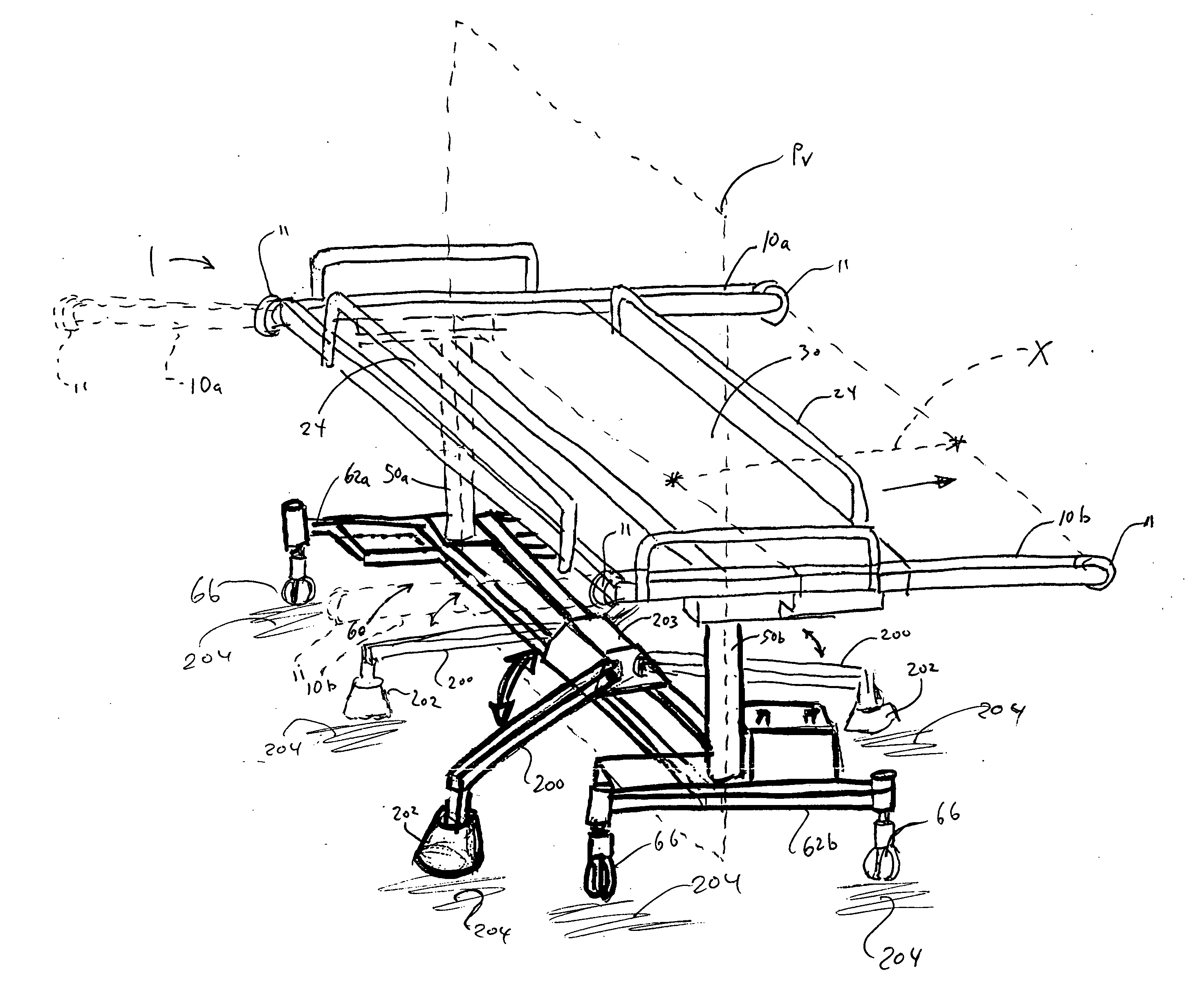

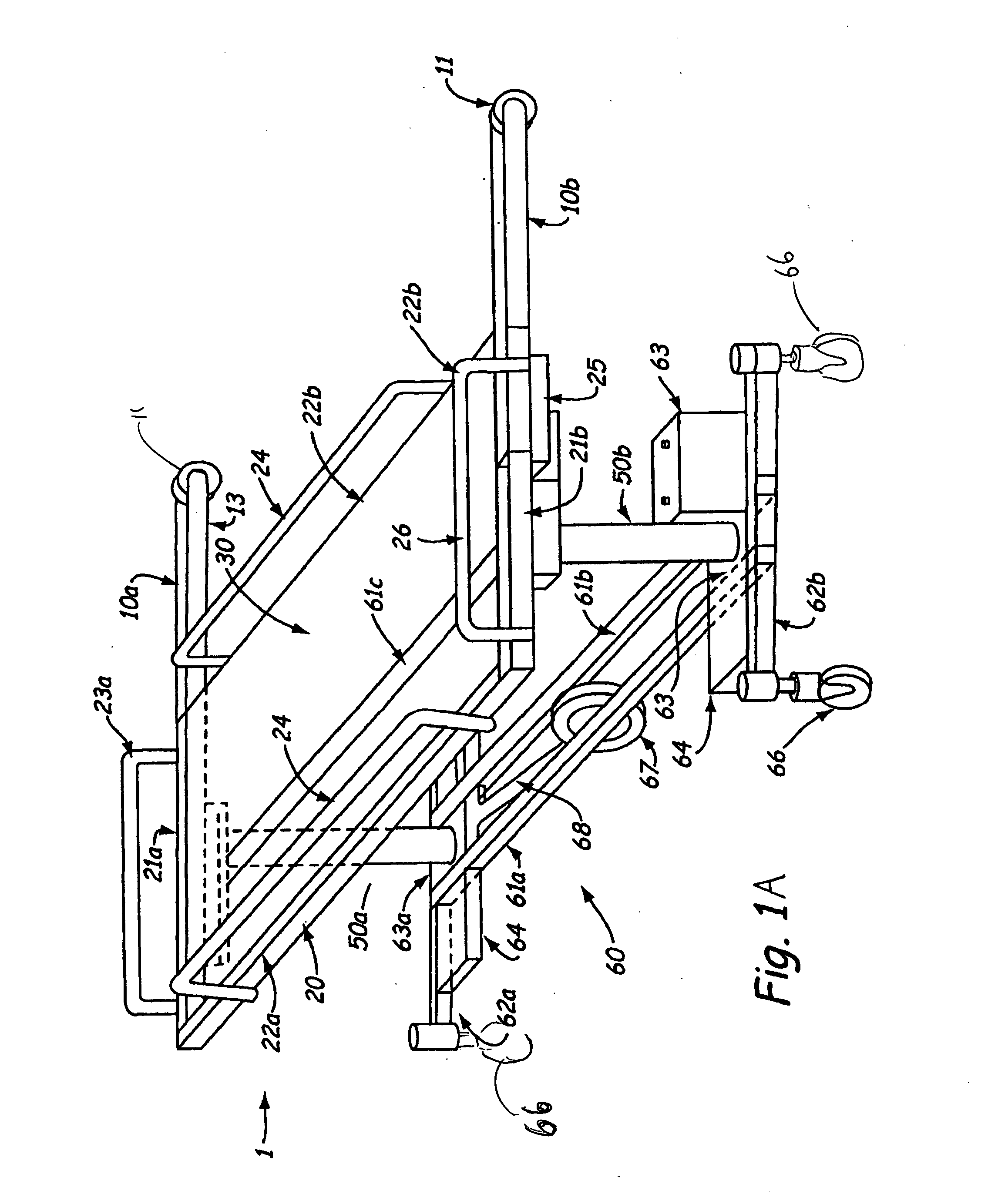

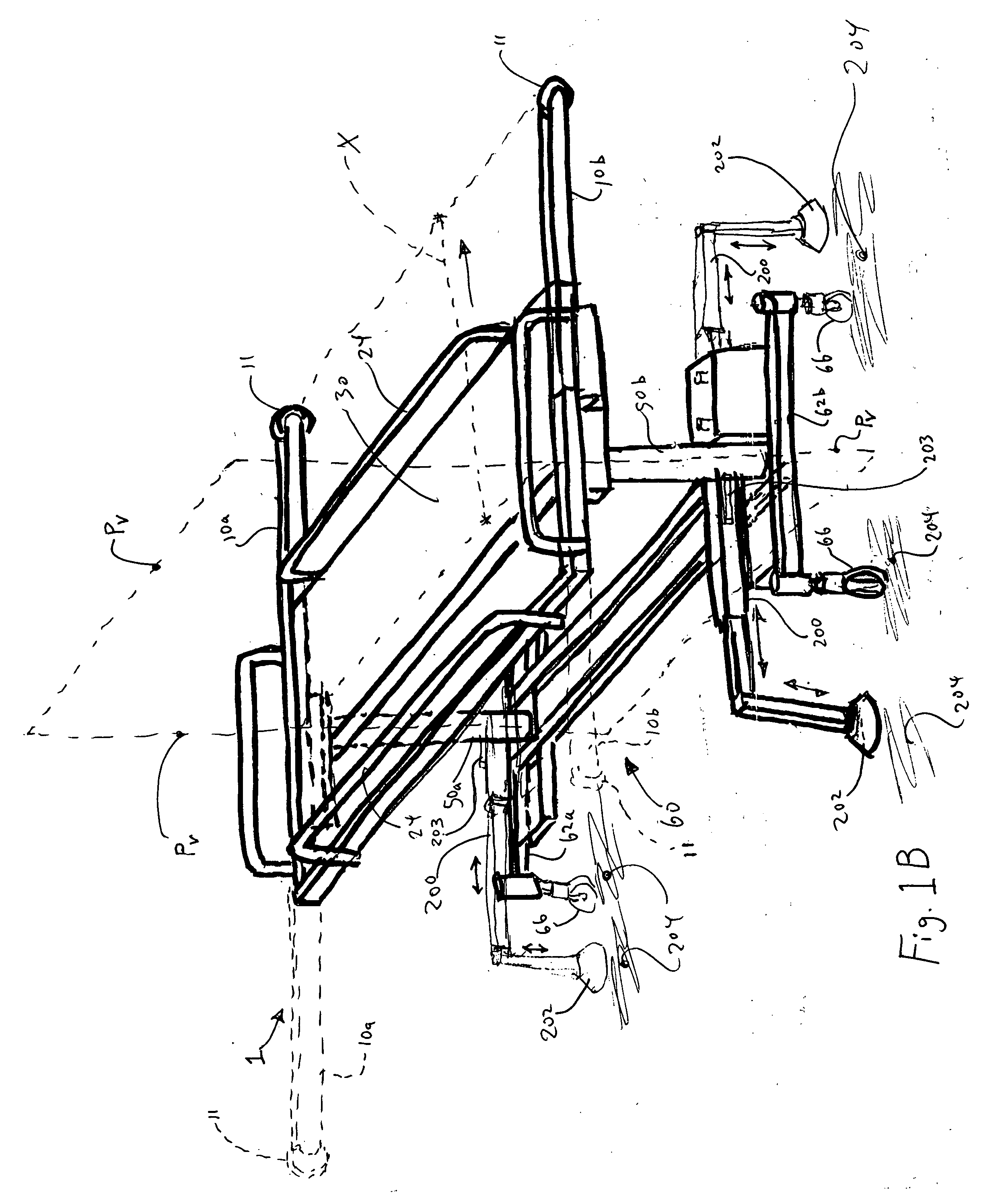

Patient transfer and transport bed

The present invention is a transfer and transport device and method for moving a patient from a bed to another location within a medical facility. The transport device includes an integral transfer mechanism for transferring a patient from a hospital bed to the device and back.

Owner:DANE INDS

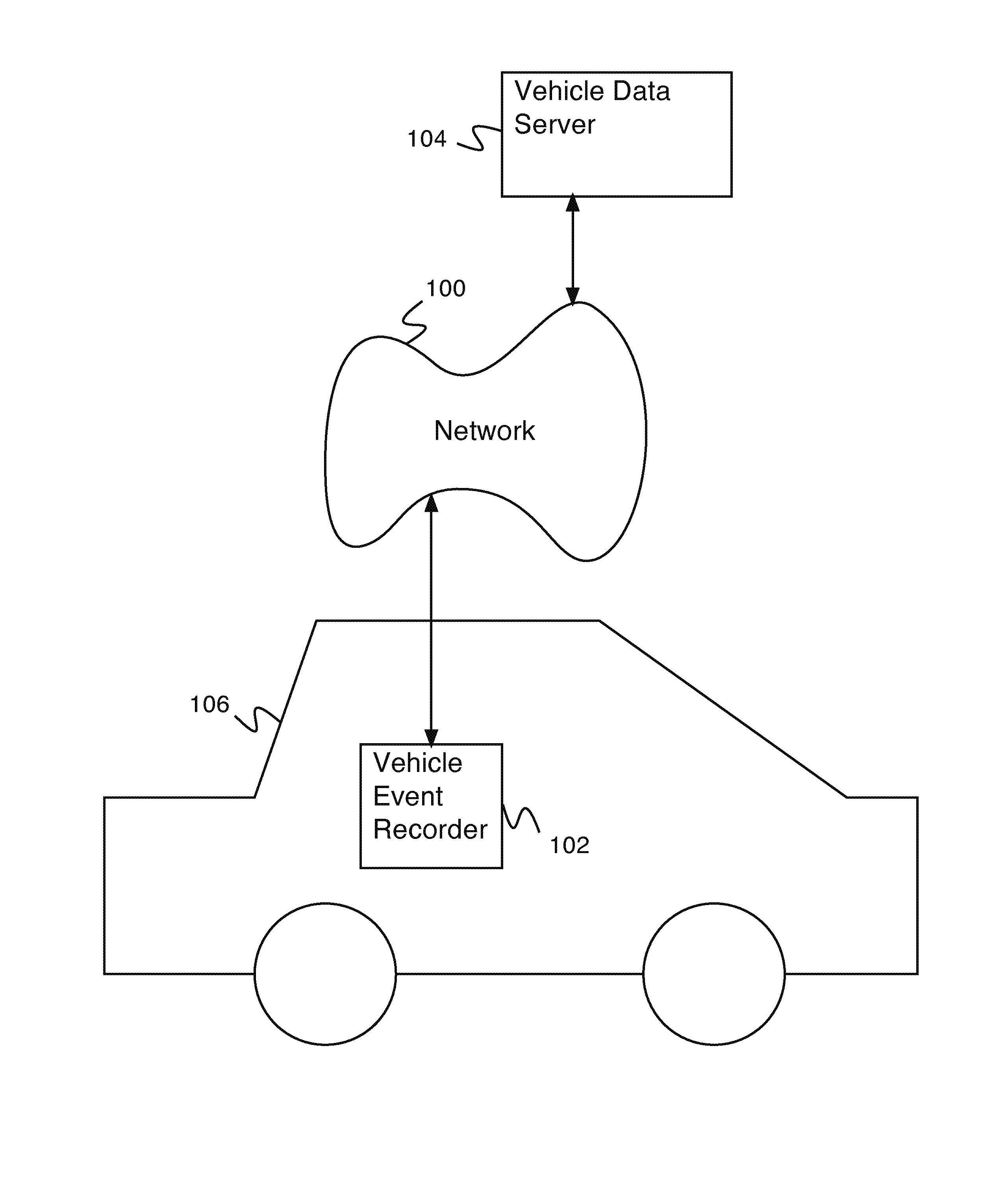

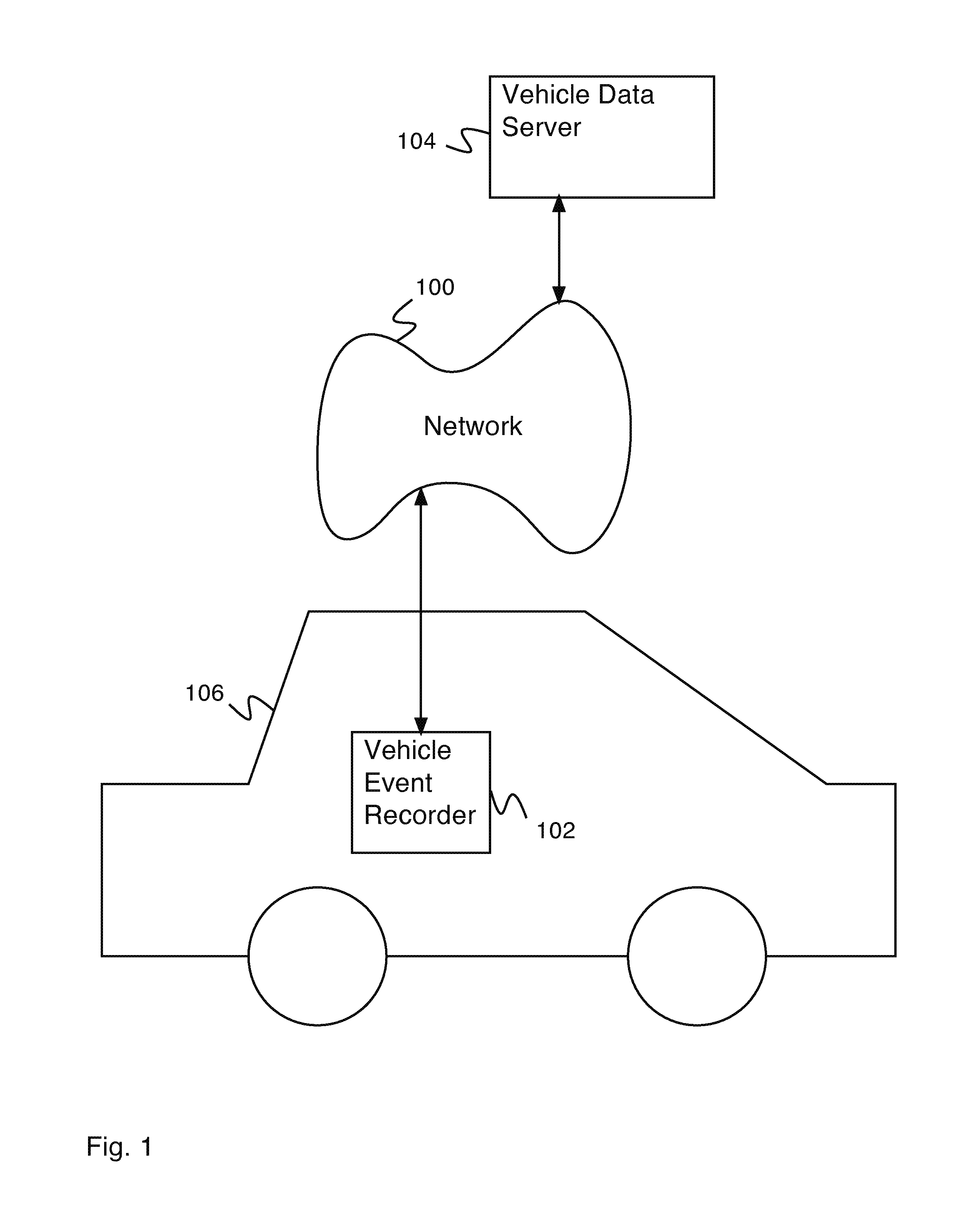

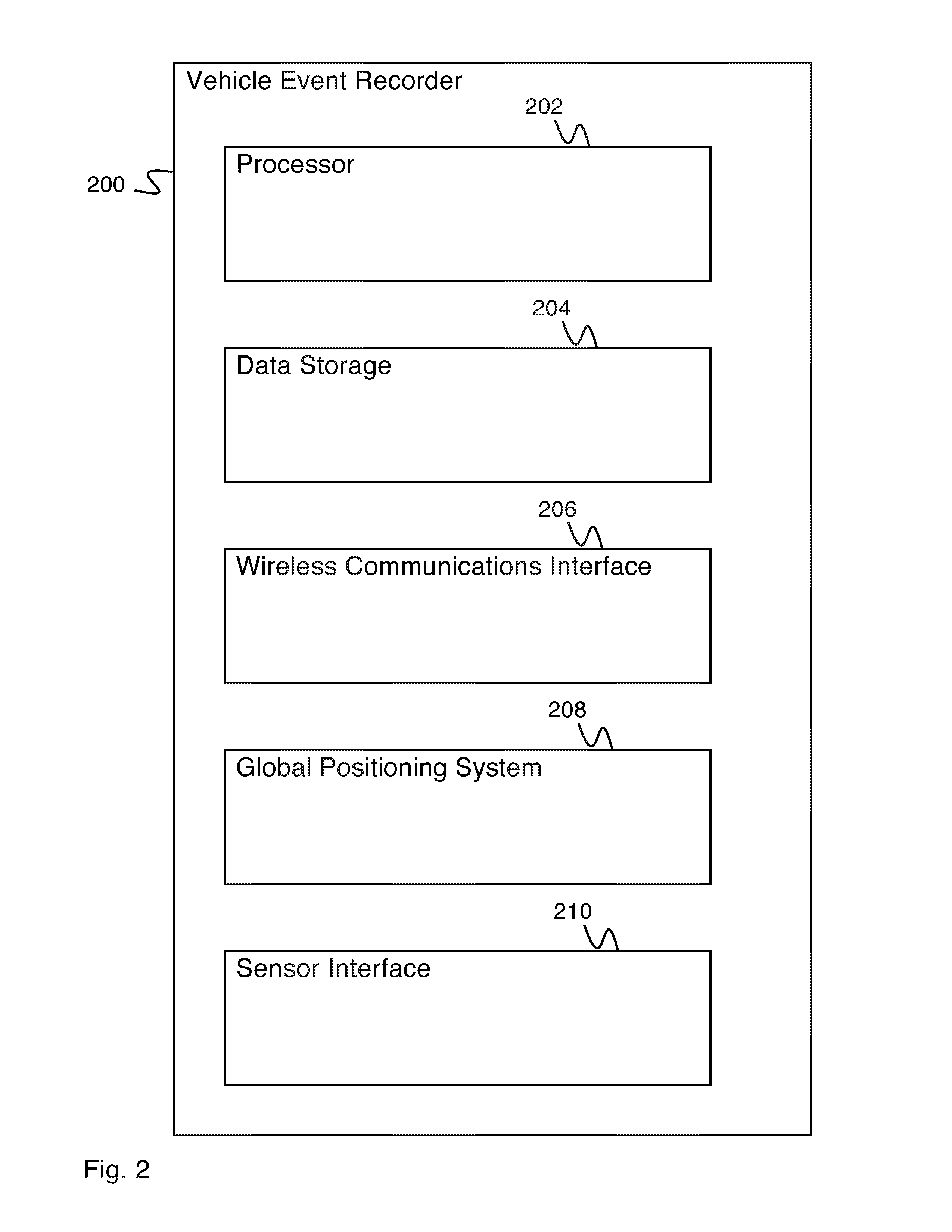

Managing the camera acquiring interior data

ActiveUS8930072B1Television system detailsRegistering/indicating working of vehiclesData transmissionReal-time computing

A system for managing a camera is comprises an input interface configured to detect a change in state; a processor configured to block transfer of data from an inward facing video camera; and an output interface configured to indicate that transfer of data is blocked.

Owner:DRIVECAM

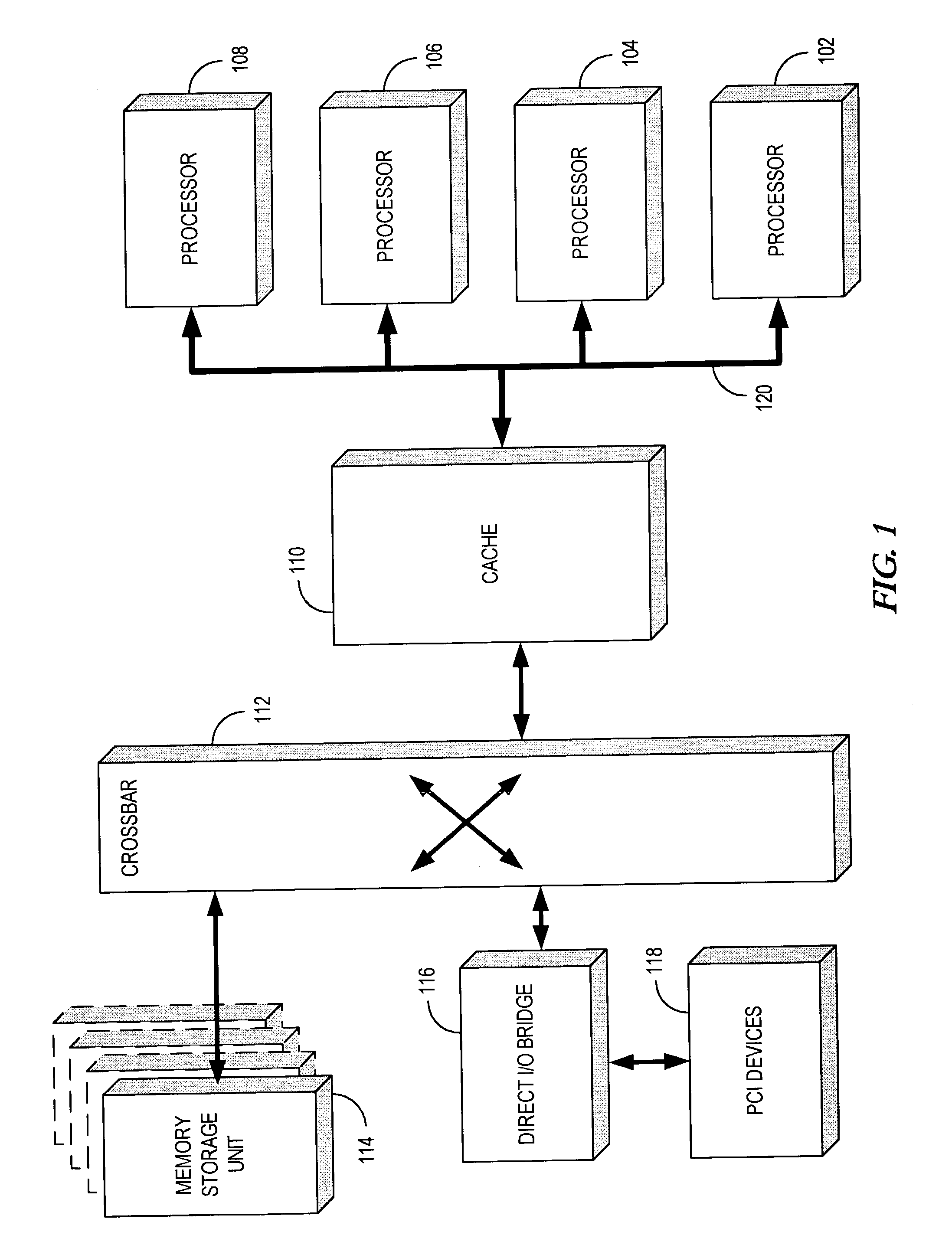

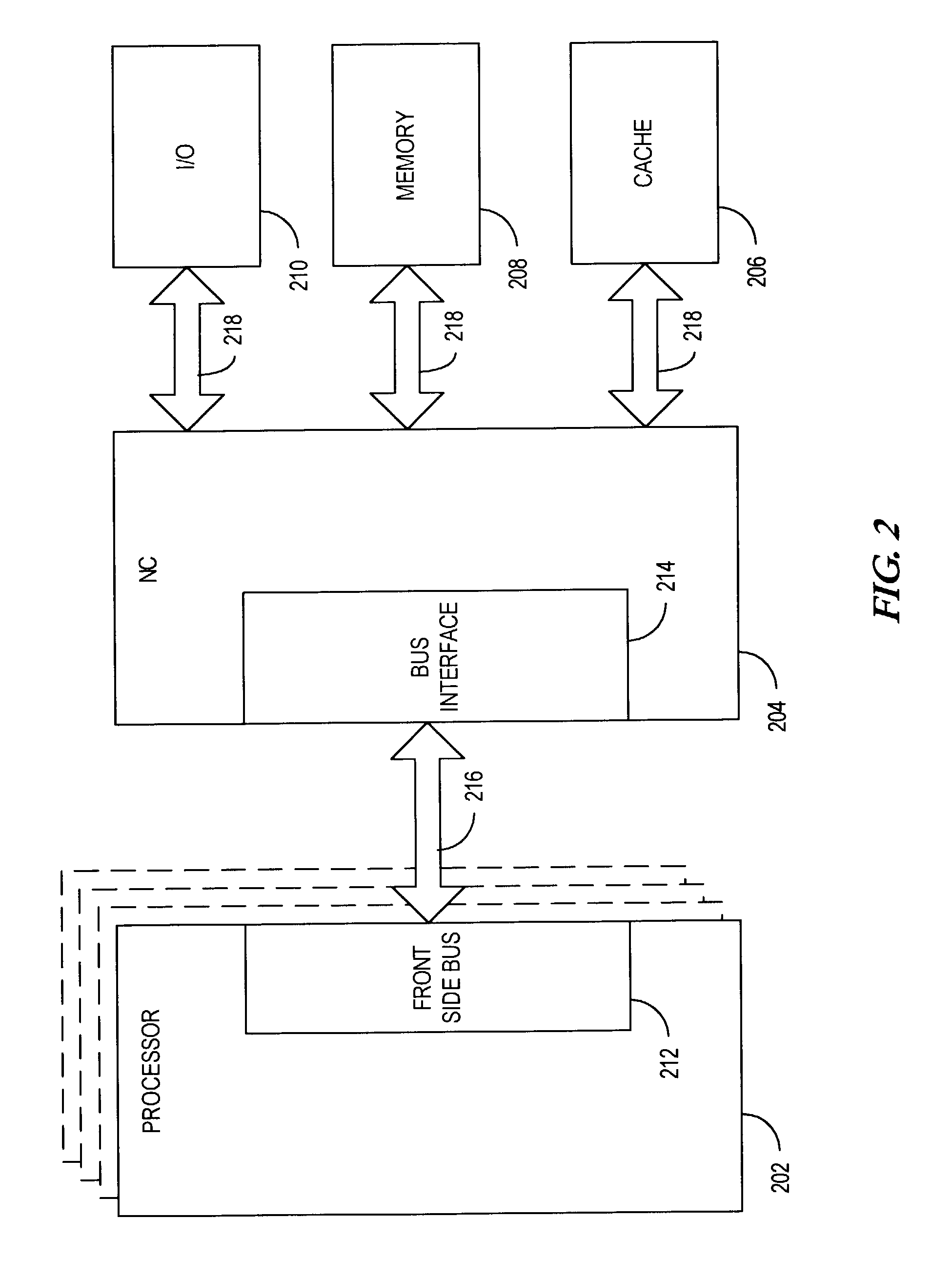

High-speed memory storage unit for a multiprocessor system having integrated directory and data storage subsystems

InactiveUS6415364B1Easy to manageImprove system throughputMemory adressing/allocation/relocationInput/output processes for data processingHigh speed memoryImpact system

A high-speed memory system is disclosed for use in supporting a directory-based cache coherency protocol. The memory system includes at least one data system for storing data, and a corresponding directory system for storing the corresponding cache coherency information. Each data storage operation involves a block transfer operation performed to multiple sequential addresses within the data system. Each data storage operation occurs in conjunction with an associated read-modify-write operation performed on cache coherency information stored within the corresponding directory system. Multiple ones of the data storage operations may be occurring within one or more of the data systems in parallel. Likewise, multiple ones of the read-modify-write operations may be performed to one or more of the directory systems in parallel. The transfer of address, control, and data signals for these concurrently performed operations occurs in an interleaved manner. The use of block transfer operations in combination with the interleaved transfer of signals to memory systems prevents the overhead associated with the read-modify-write operations from substantially impacting system performance. This is true even when data and directory systems are implemented using the same memory technology.

Owner:UNISYS CORP

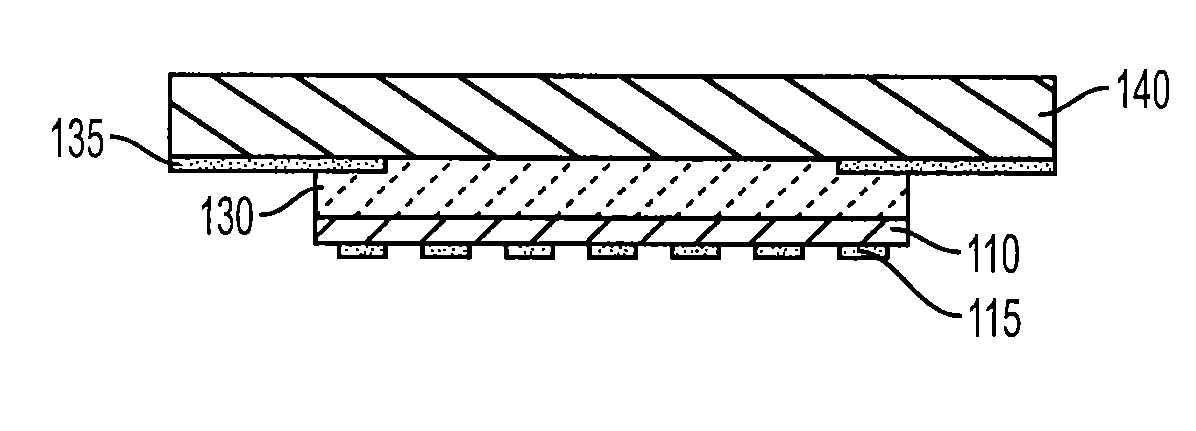

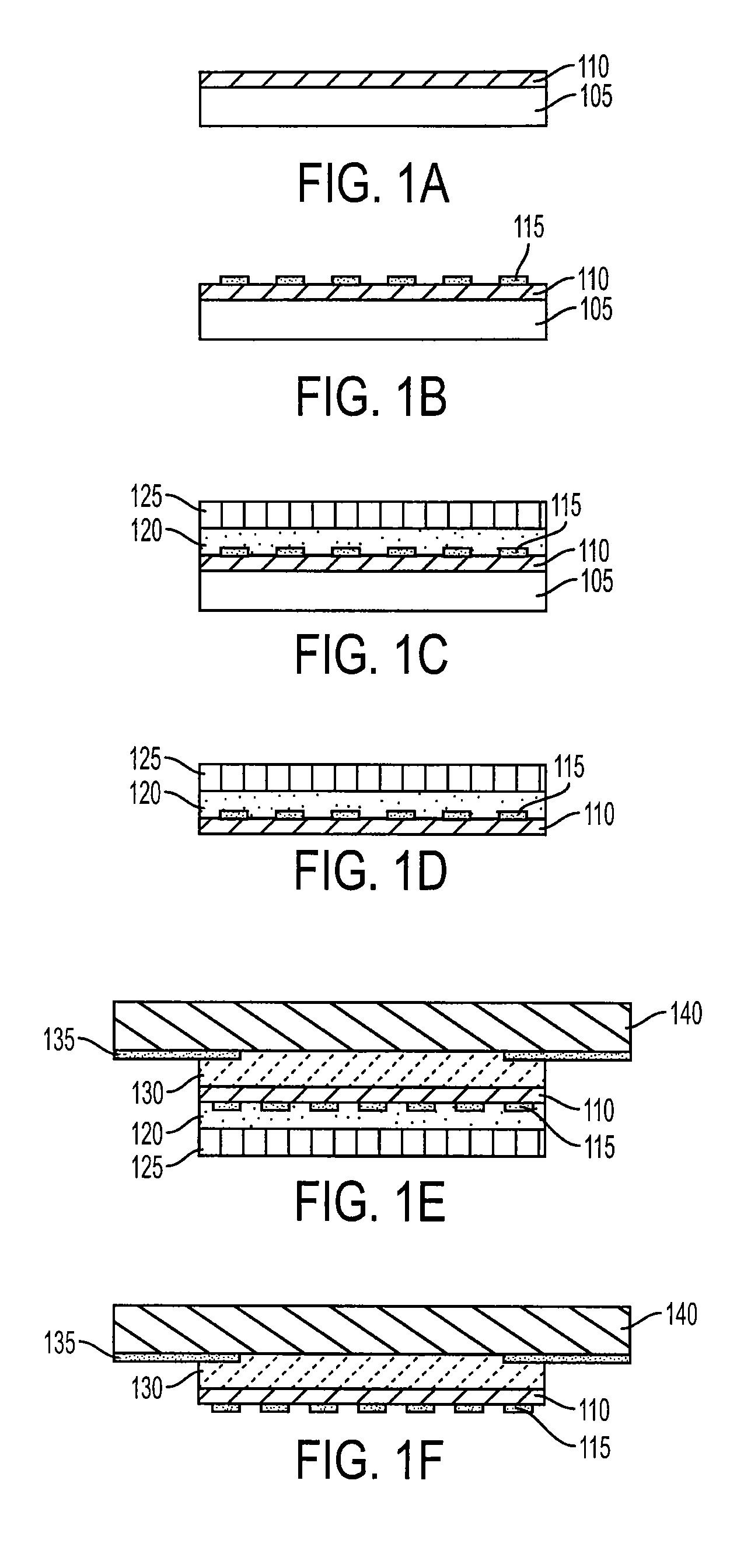

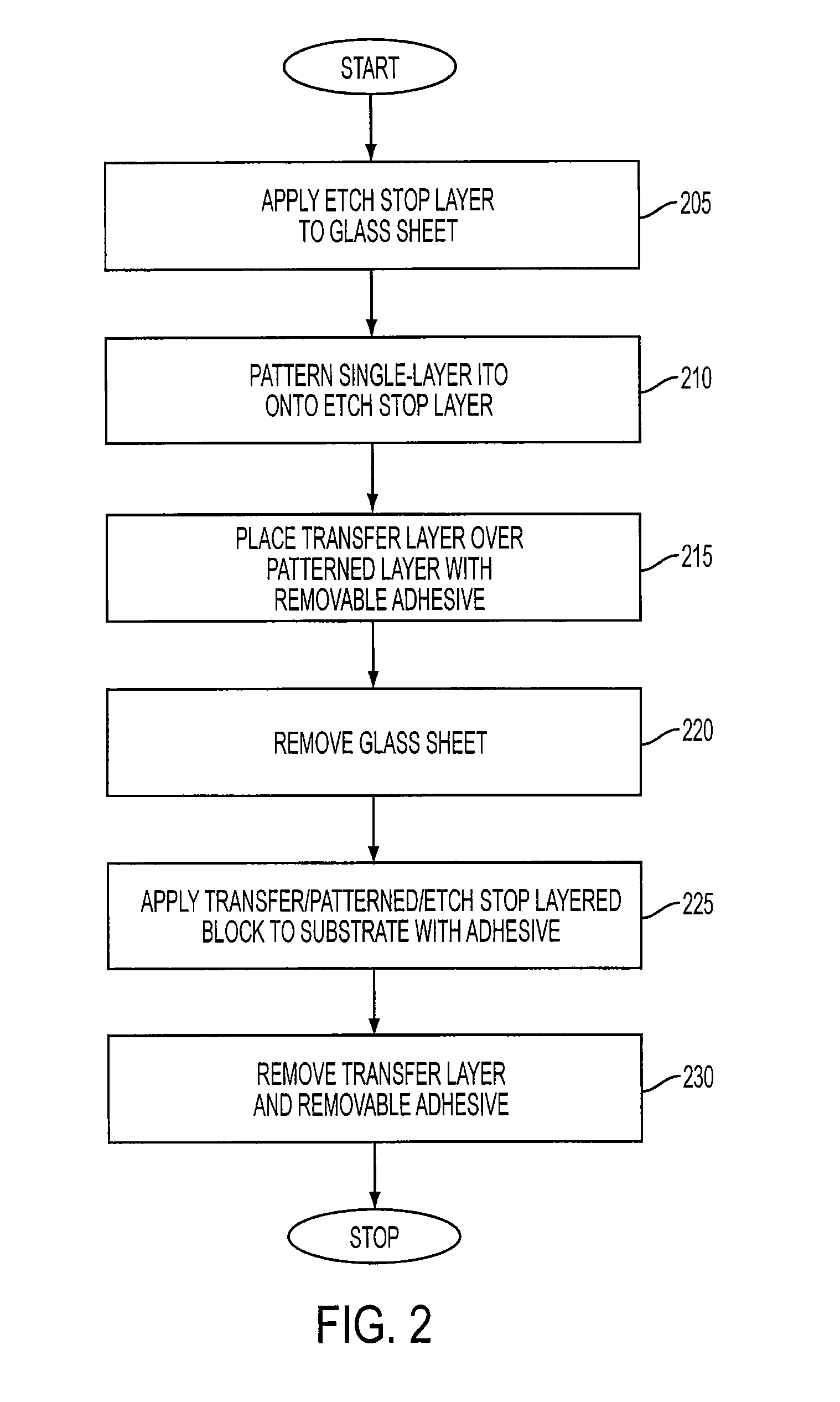

Method for Transferring Thin Film to Substrate

InactiveUS20100066683A1Synthetic resin layered productsLaminationConductive materialsOptoelectronics

Owner:APPLE INC

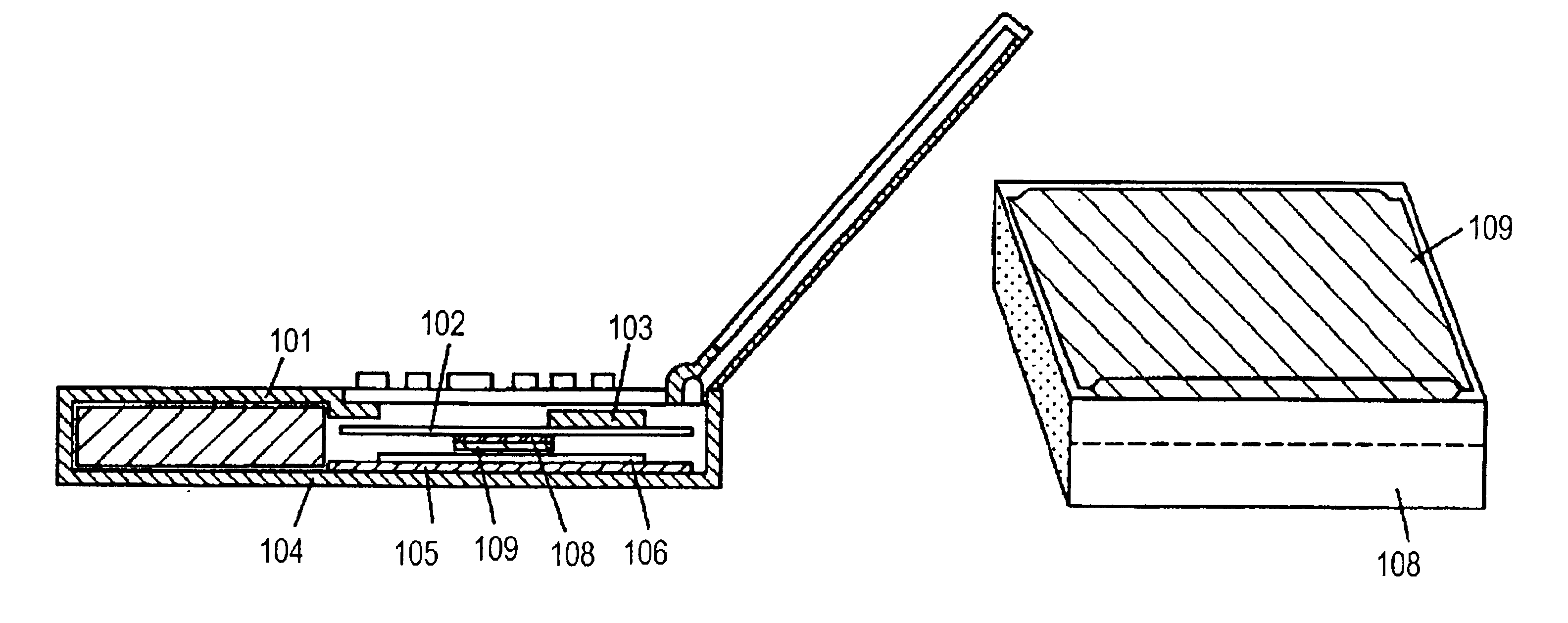

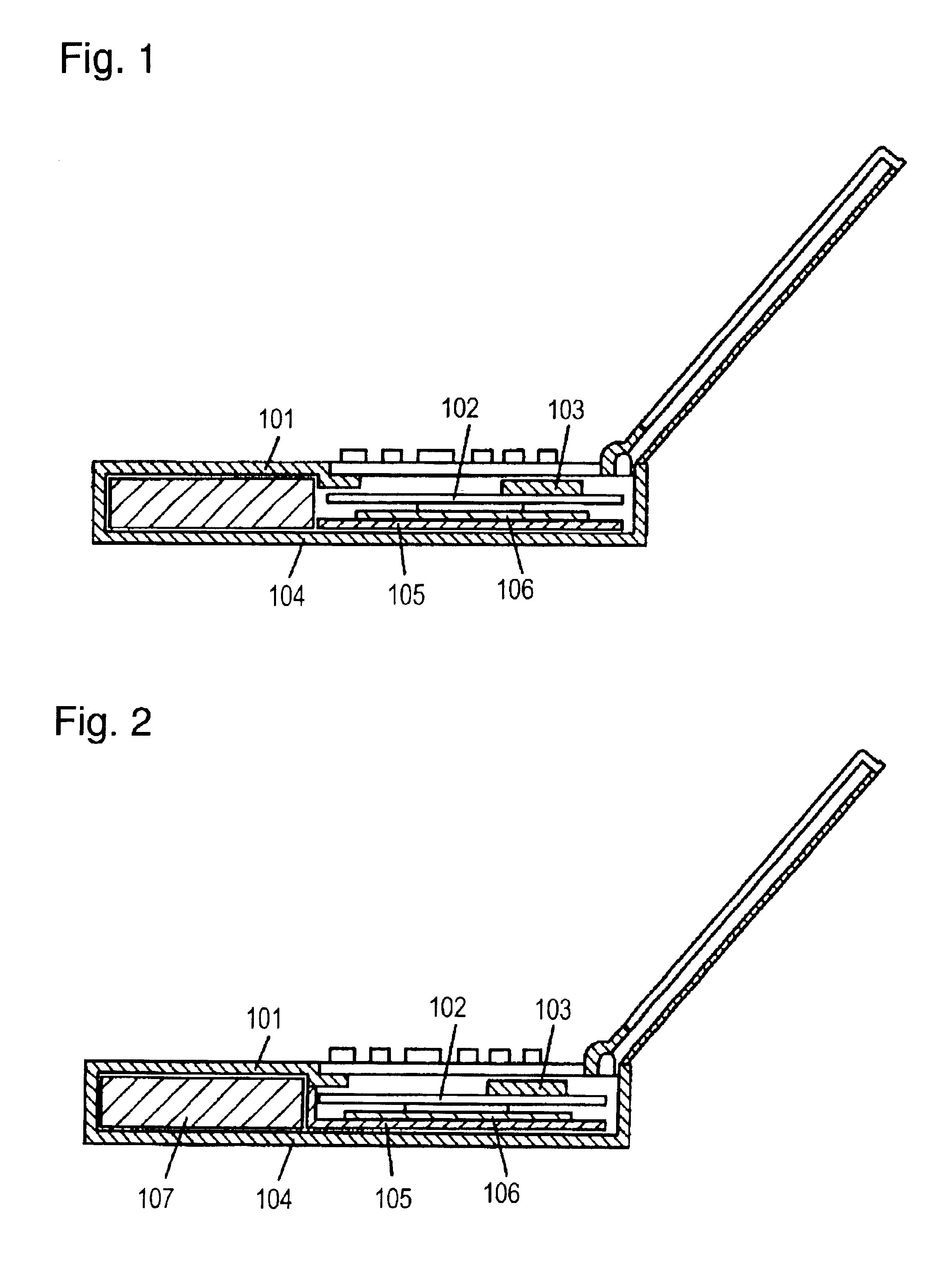

Portable information appliance

InactiveUS6859364B2Inhibit temperature riseNot to give uncomfortable feelingBiocideDomestic cooling apparatusFiberInformation device

A portable information device such as a notebook type computer is provided with a highly efficient thermal insulator capable of blocking transfer of heat between an internal heating component and a device enclosure, so as to reduce temperature rise on a surface of the device. The portable information device is also provided with a highly efficient thermal insulator to block transfer of heat between the heating component and an expansion unit mounting case, thereby reducing temperature rise and preventing malfunction of an external expansion unit. The information device includes the thermal insulator to separate between the internal heating component and the device enclosure, another thermal insulator to separate between the heating component and the expansion unit mounting case, and a heat sink. The thermal insulator is a vacuum thermal insulator including inorganic fiber as a core member.

Owner:PANASONIC CORP

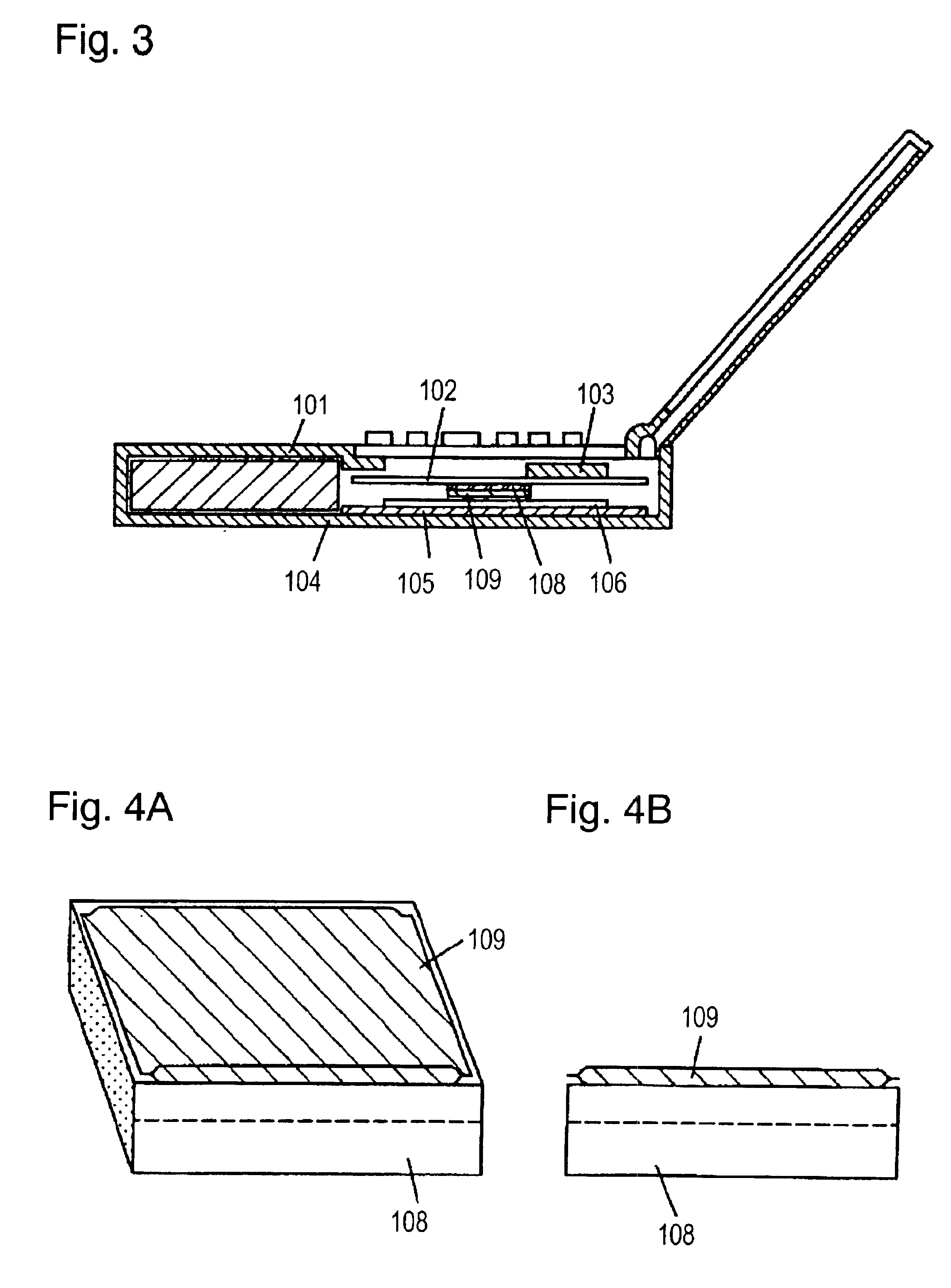

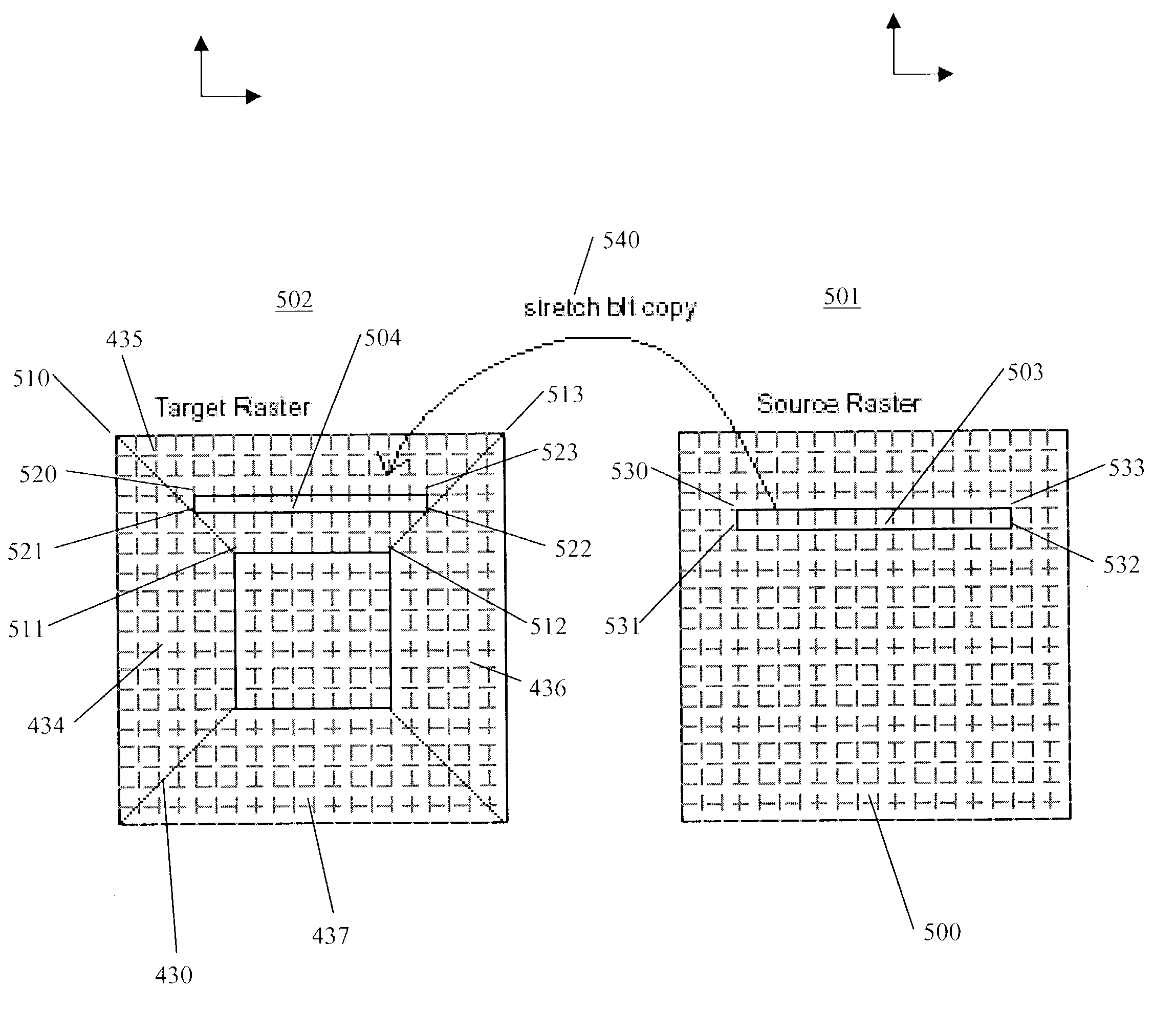

Fast rendering of pyramid lens distorted raster images

InactiveUS7667699B2Effective presentationDrawing from basic elementsGeometric image transformationViewpointsGrating

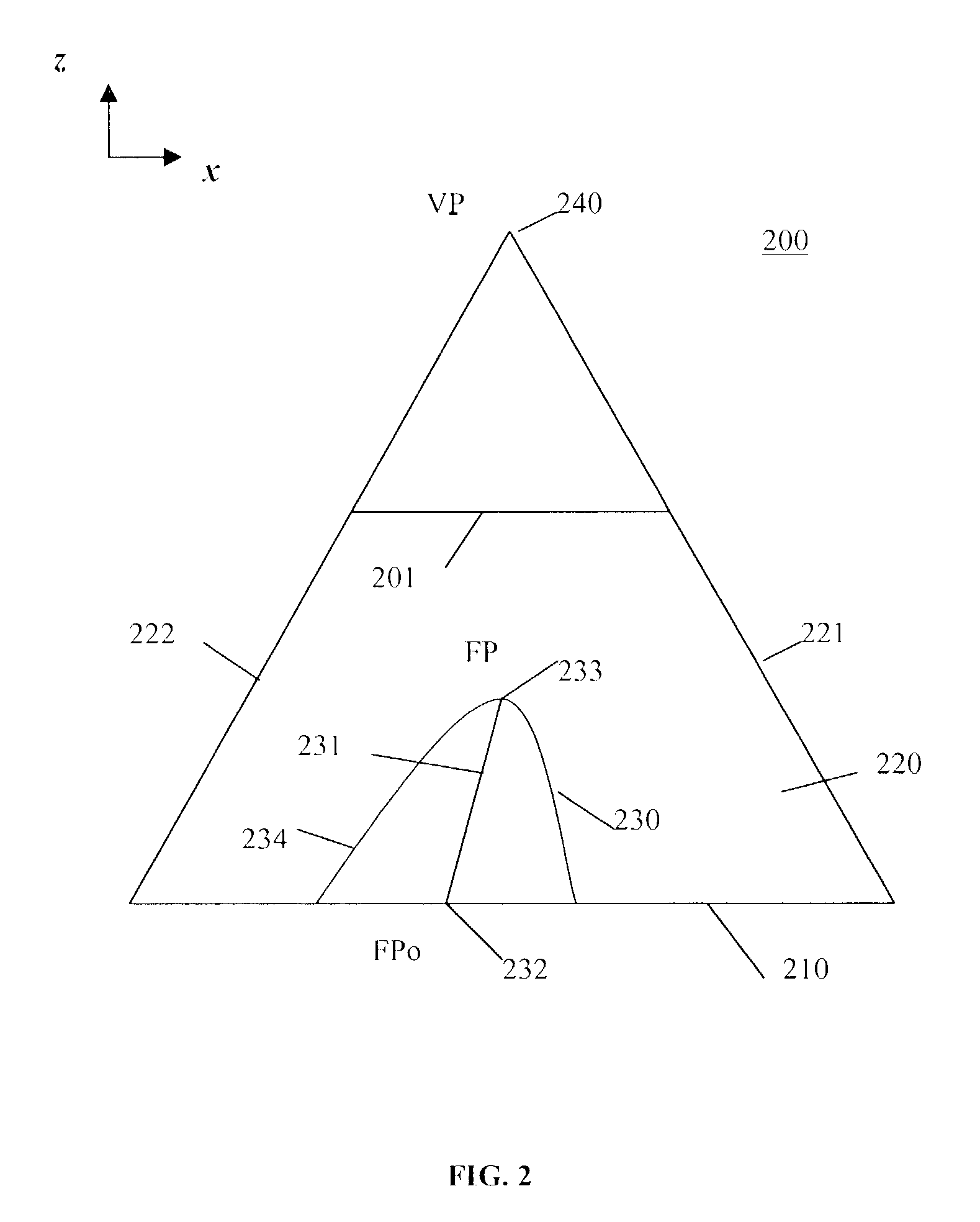

A method for generating a presentation of a region-of-interest in an information representation including the steps of: selecting a viewpoint for the region-of-interest; creating a lens surface for the region-of-interest; the lens surface having a focal region and a shoulder region surrounding the focal region; creating a transformed presentation by: determining boundaries in the representation for the focal region and the shoulder region; determining boundaries on the lens surface corresponding to the boundaries in the representation by applying a distortion function defining the lens surface to the boundaries in the representation; perspectively projecting the boundaries on the lens surface onto a plane spaced from the viewpoint; and, copying information in the representation lying within the boundaries in the representation onto the focal region and the shoulder region of the lens surface using respective focal region and shoulder region stretch bit-block transfer operations; and, displaying the transformed presentation on a display screen to generate the presentation of the region-of-interest.

Owner:INTELLECTUAL VENTURES ASSETS 186 LLC

Multi-processor, direct memory access controller, and serial data transmitting/receiving apparatus

InactiveUS20090259789A1Reduce memory capacityIncrease the length of timeMemory systemsInput/output processes for data processingDirect memory accessManagement unit

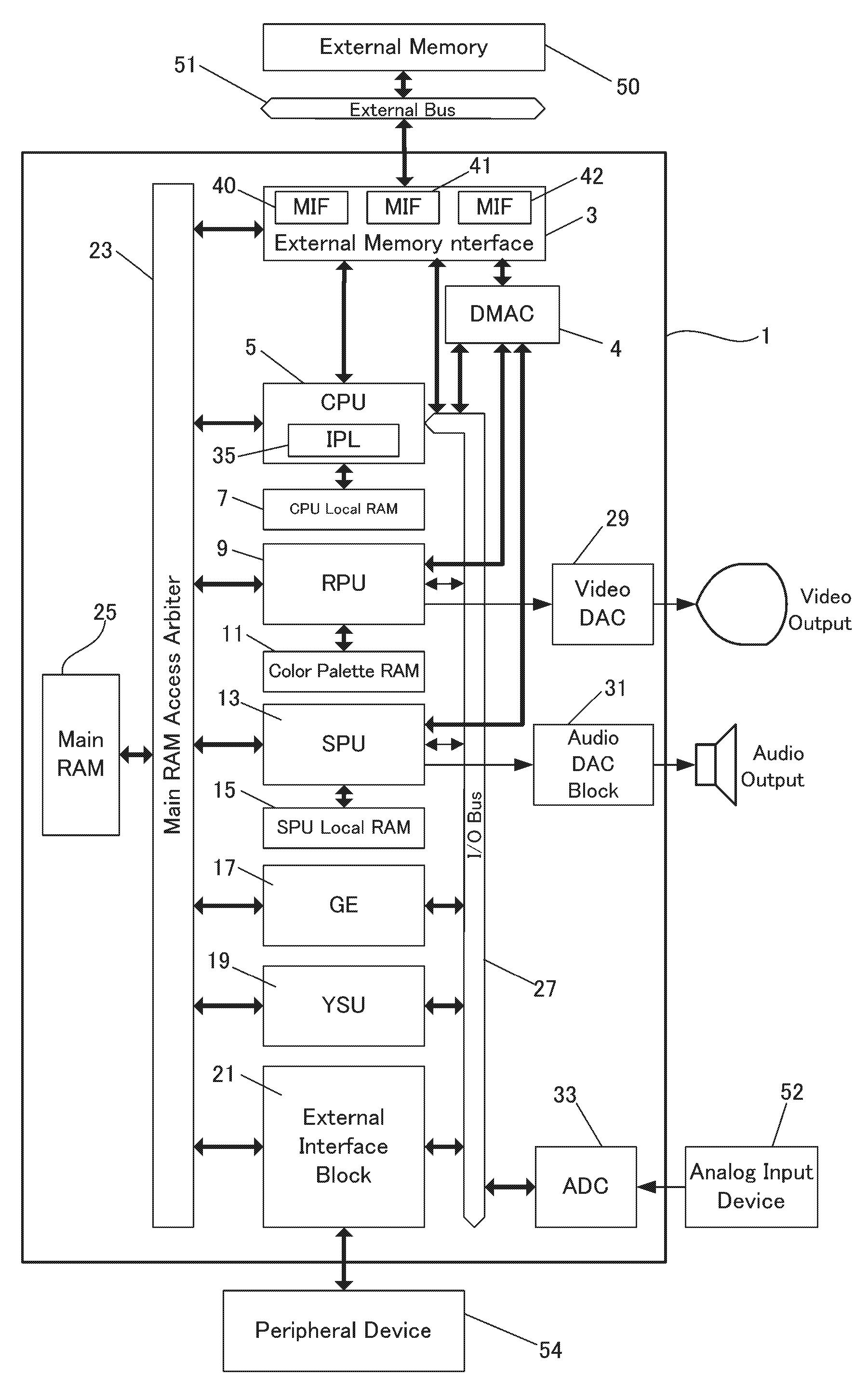

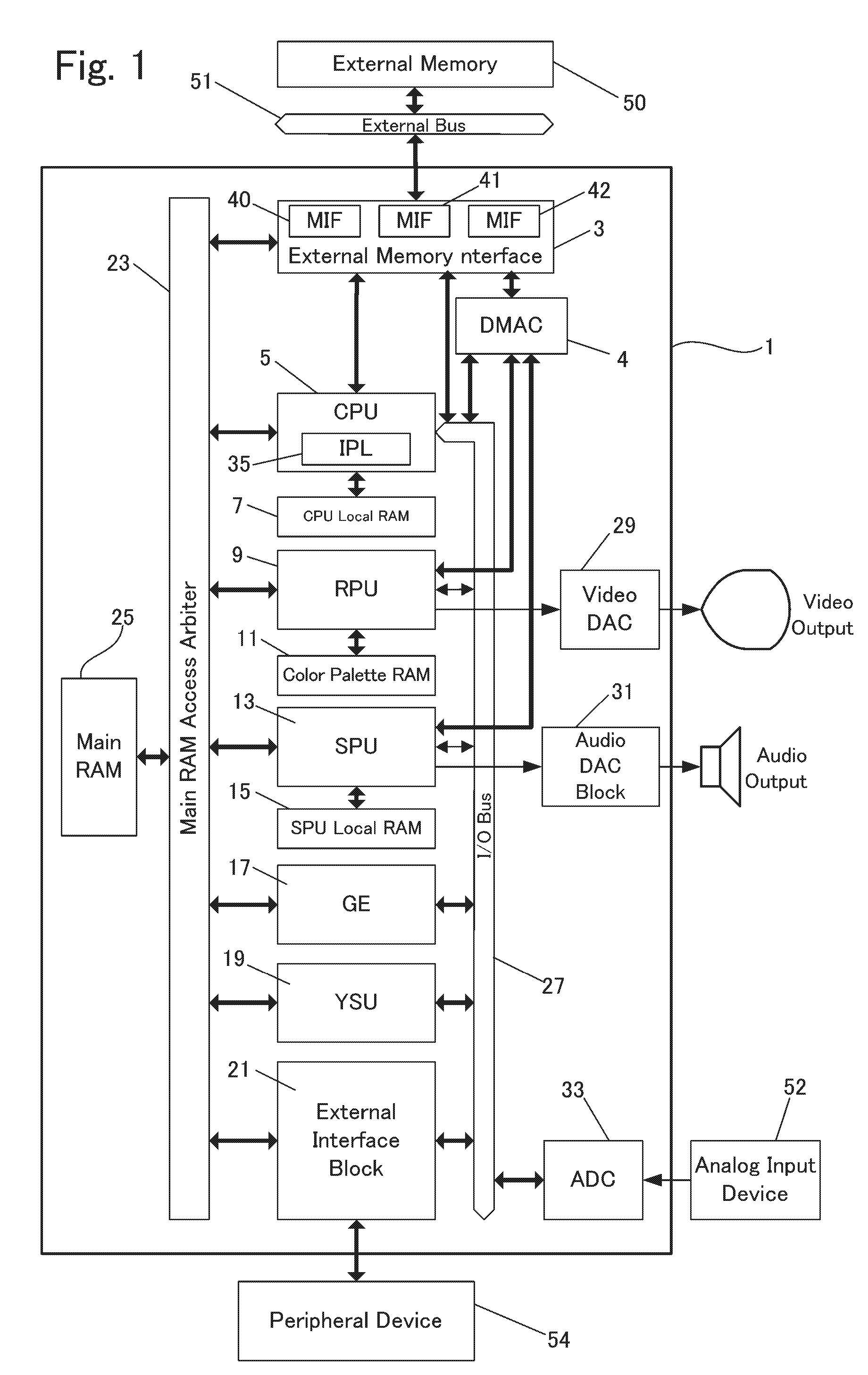

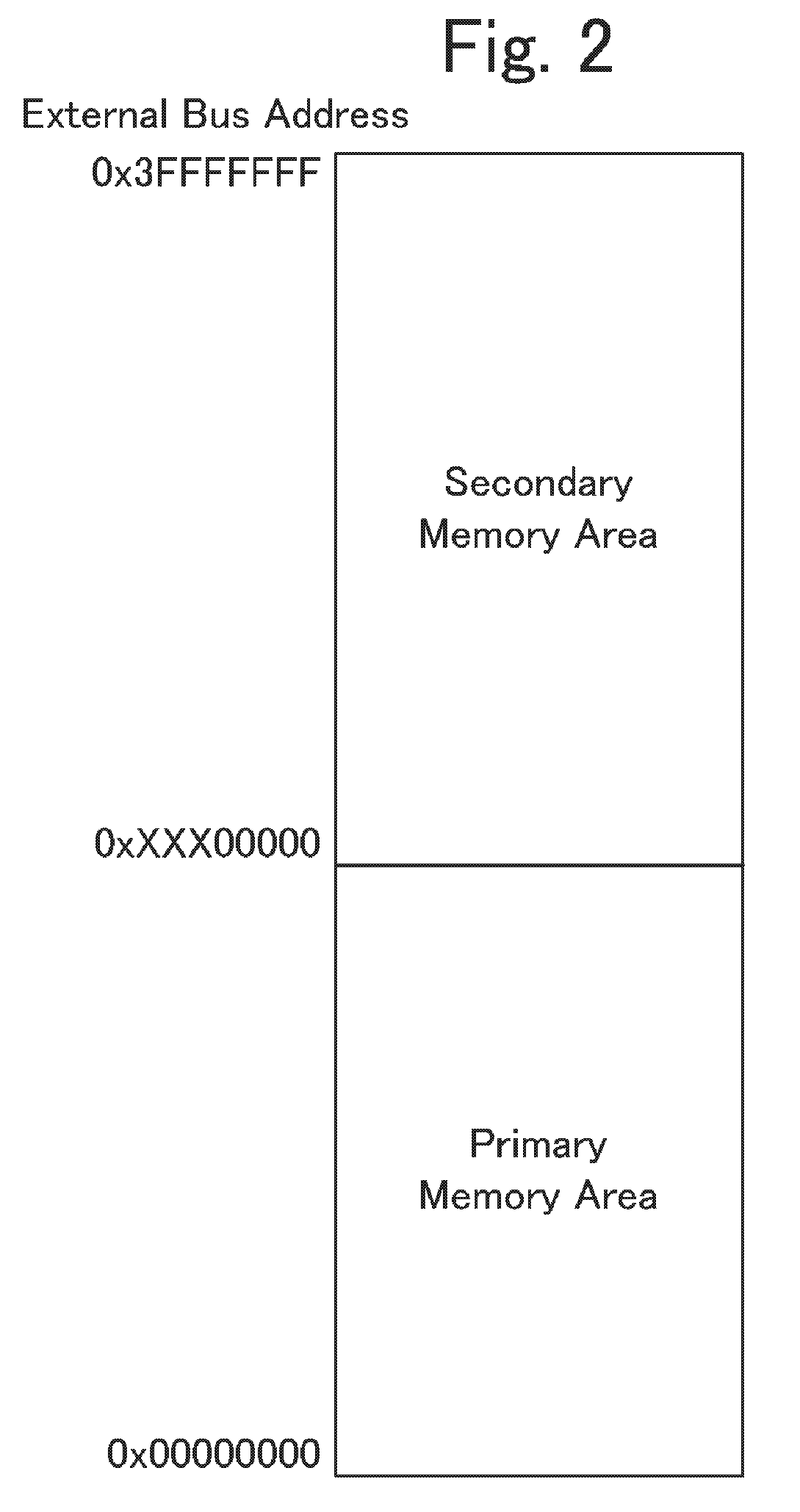

A CPU 5 is provided with both the functionality of issuing an external bus access request directly to an external memory interface 3 and the functionality of issuing a DMA transfer request to a DMAC 4. Accordingly, in the case where data is randomly accessed at discrete addresses, an external bus access request is issued directly to the external memory interface 3, and in the case of data block transfer or page swapping as requested by a virtual memory management unit or the like, a DMA transfer request is issued to the DMAC 4, so that it is possible to effectively access the external memory 50.

Owner:SHINSEDAI KK

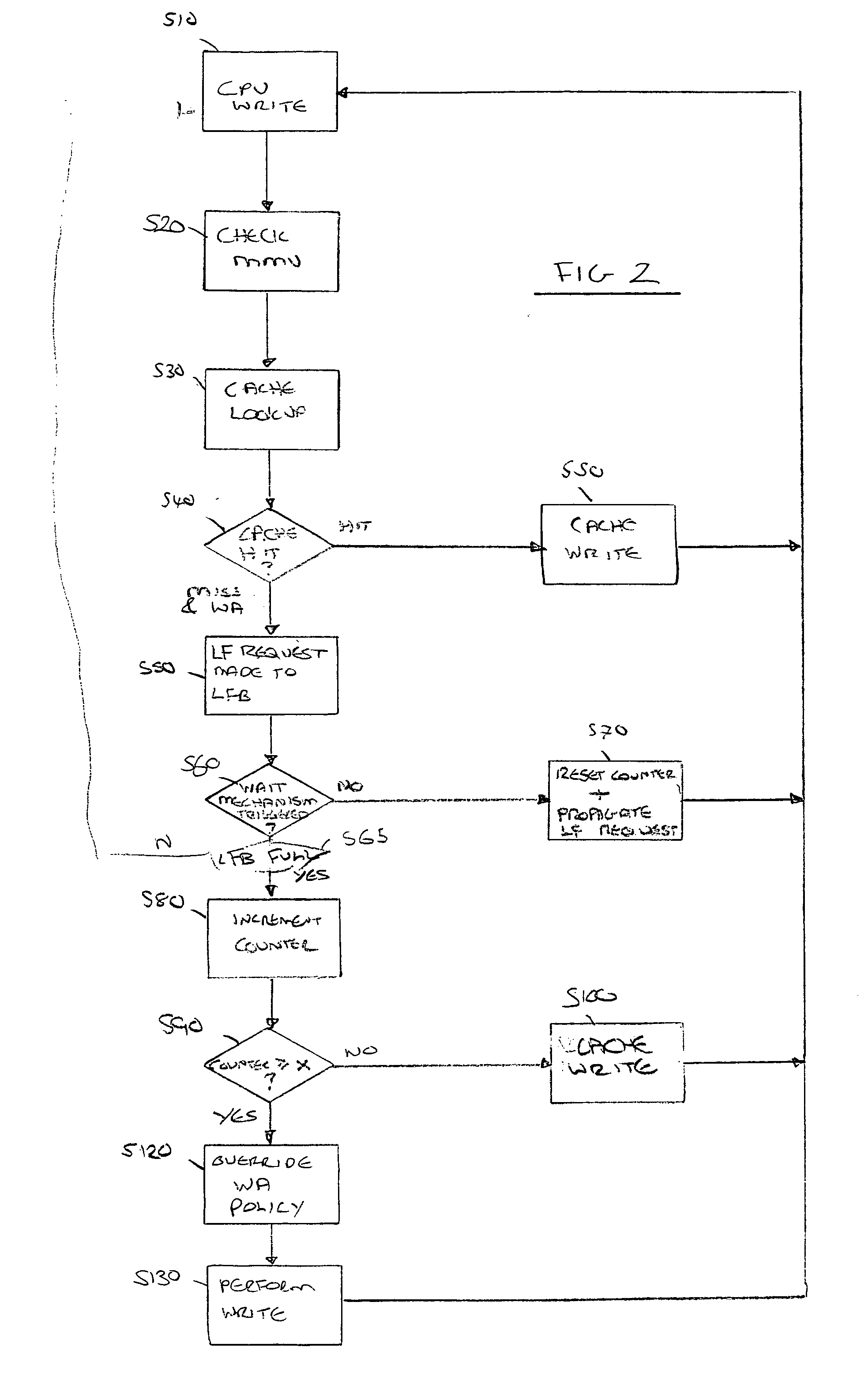

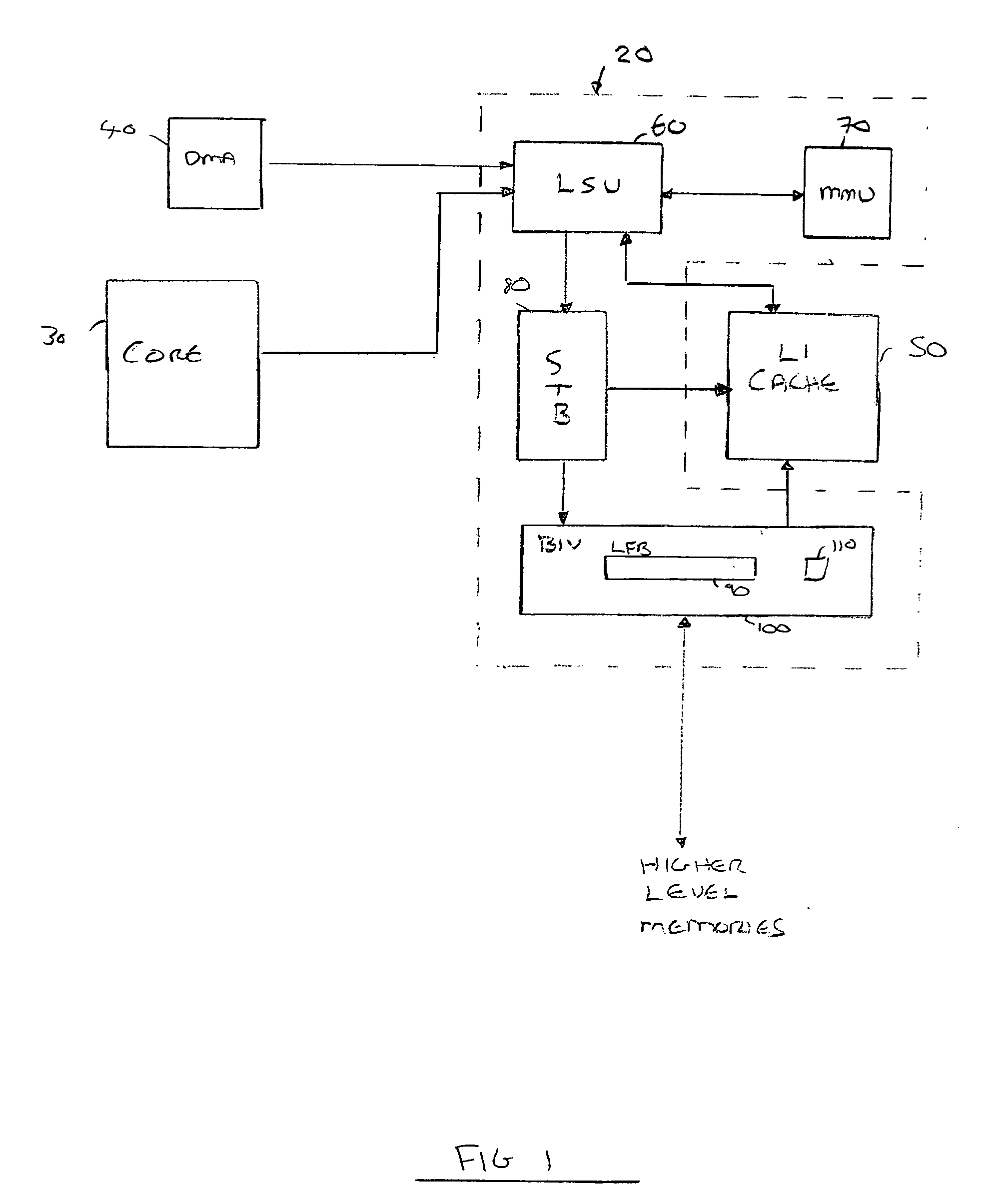

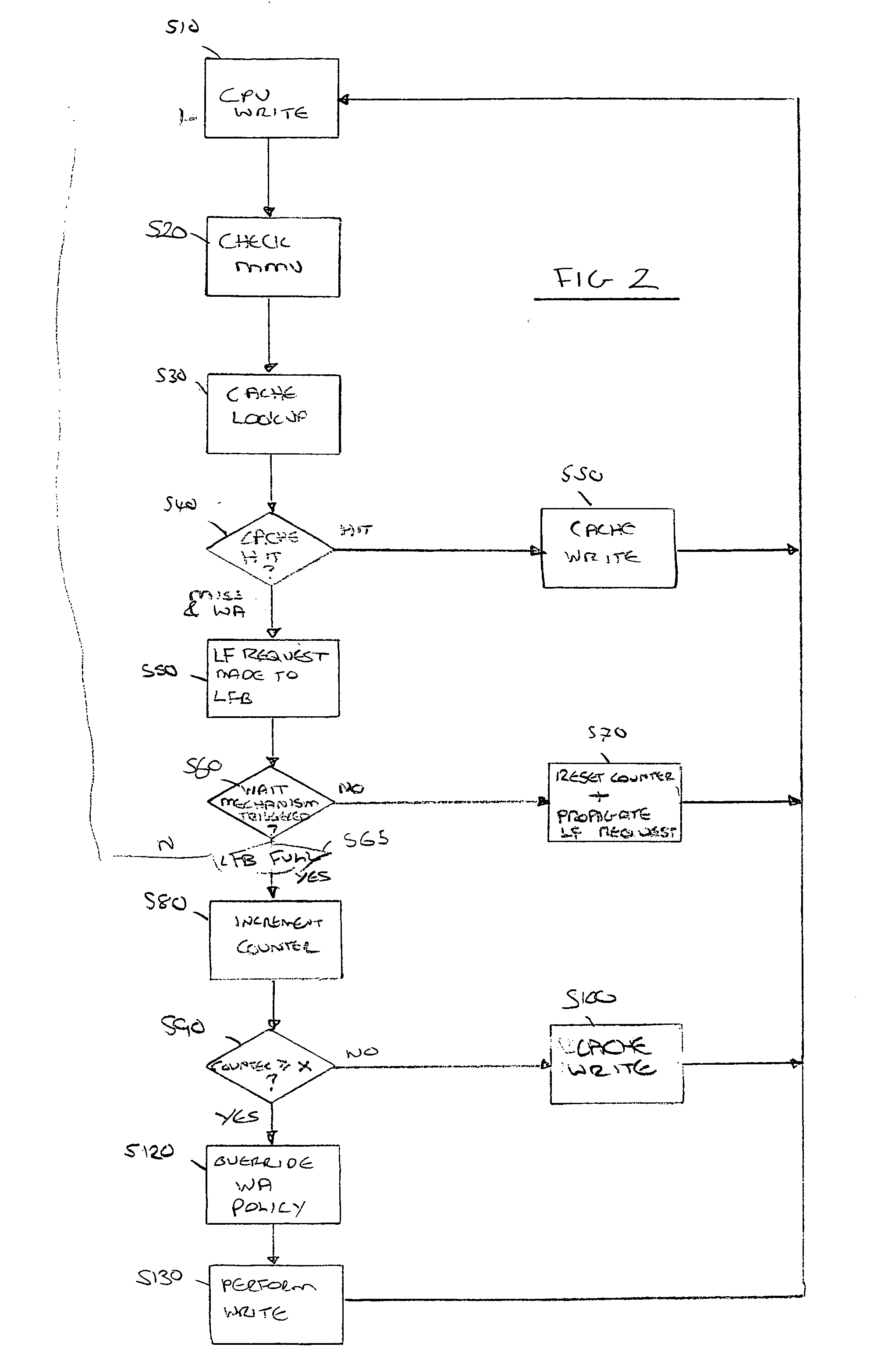

Cache controller

InactiveUS20070079070A1Adequate performance balanceUnlikely to resultMemory architecture accessing/allocationMemory systemsCache accessSequential data

A cache controller and a method is provided. The cache controller comprises: request reception logic operable to receive a write request from a data processing apparatus to write a data item to memory; and cache access logic operable to determine whether a caching policy associated with the write request is write allocate, whether the write request would cause a cache miss to occur, whether the write request is one of a number of write requests which together would cause greater than a predetermined number of sequential data items to be allocated in the cache and, if so, the cache access logic is further operable to override the caching policy associated with the write request to non-write allocate. In this way, in the event that the number of consecutive data items to be allocated within the cache exceeds the predefined number then the cache access logic will consider that it is highly likely that the write requests are associated with a block transfer operation and, accordingly, will override the write allocate caching policy. Accordingly, the write request will proceed but without the write allocate caching policy being applied. Hence, the pollution of the cache with these sequential data items is reduced.

Owner:ARM LTD

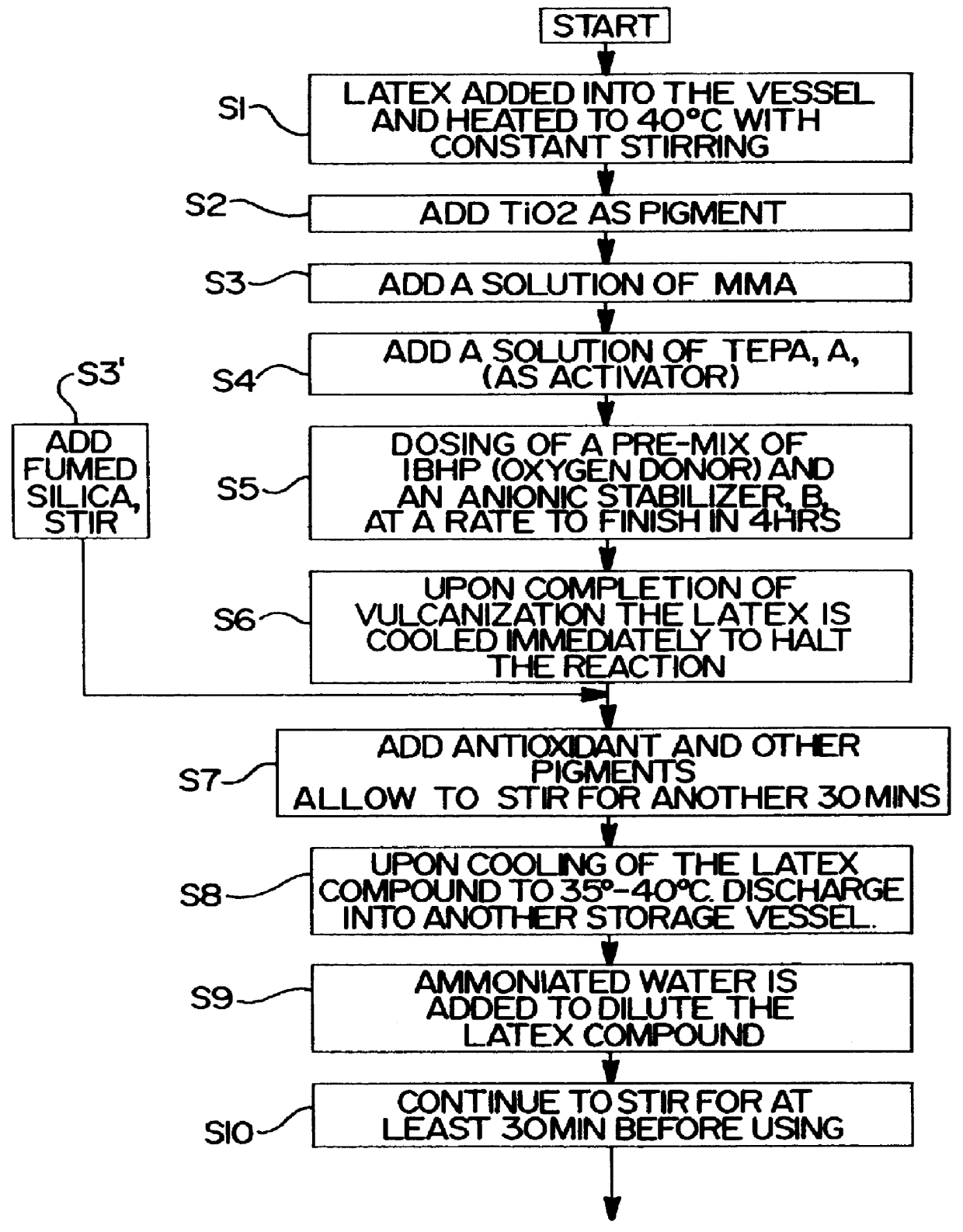

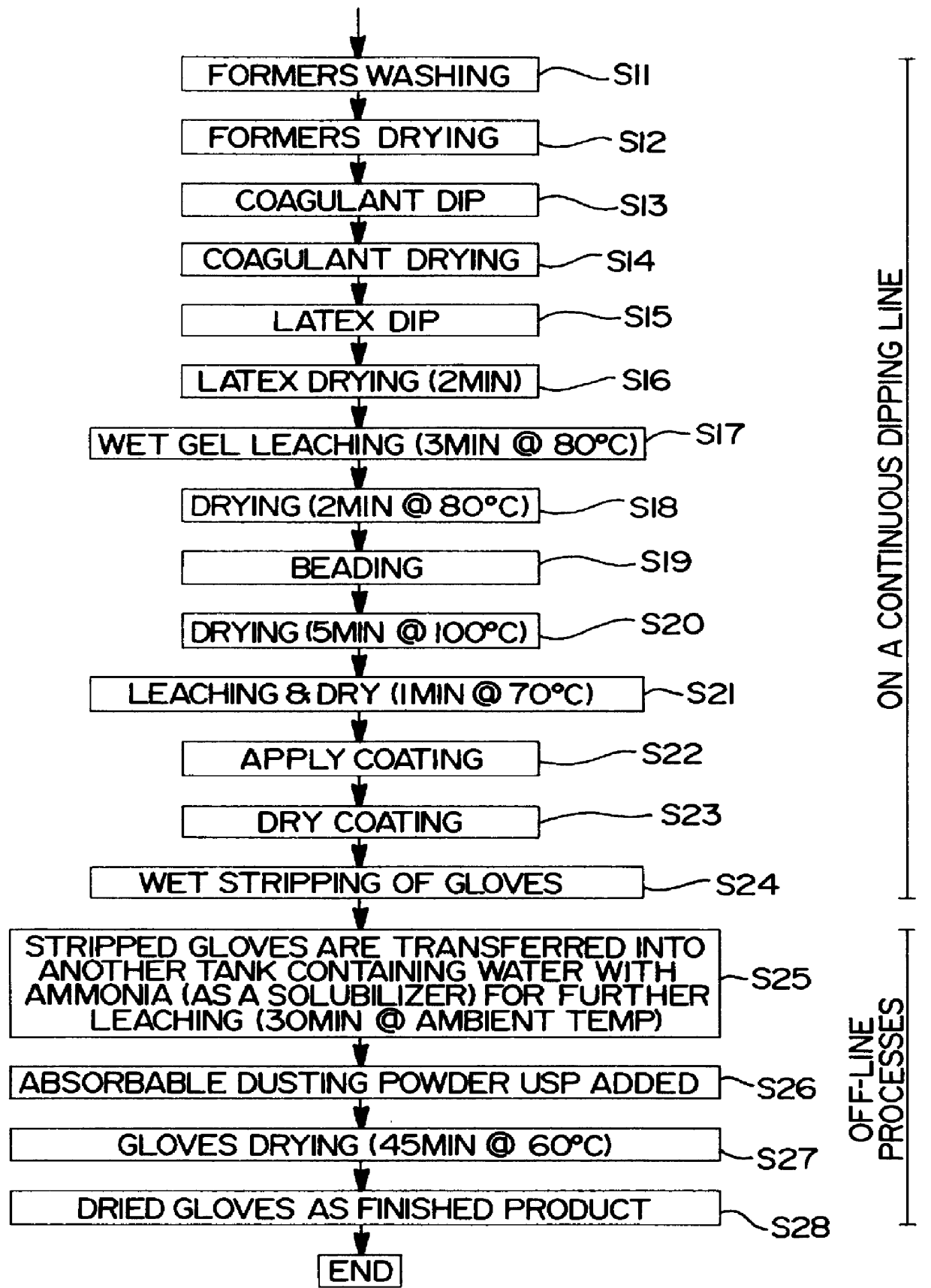

Thin-walled natural rubber latex material substantially free of sulfur and nitrosamines

InactiveUS6051320AEfficient processingEasy to useLayered productsGlovesMicrocrystalline waxGas phase

A thin walled natural rubber latex material is disclosed suitable for forming thin walled products including gloves, dental dams and shields, catheter tubing, penrose surgical drains, finger cots, coverings for body parts, and the like. The thin walled material is formed from a latex emulsion containing natural rubber, sulphur-free, oxygen-donating curing agents, and a strength enhancing agent which may be an inorganic substance such as fumed silica and / or an organic substance such as monomers and polymers of families of acrylics and esters. The emulsion also preferably includes microcrystaline wax as an oxygen barrier, and the material is also provided with a heat resistant and water resistant coating which blocks transfer of latex proteins from the material and enhances slip of the material.

Owner:HAU HO TEON +1

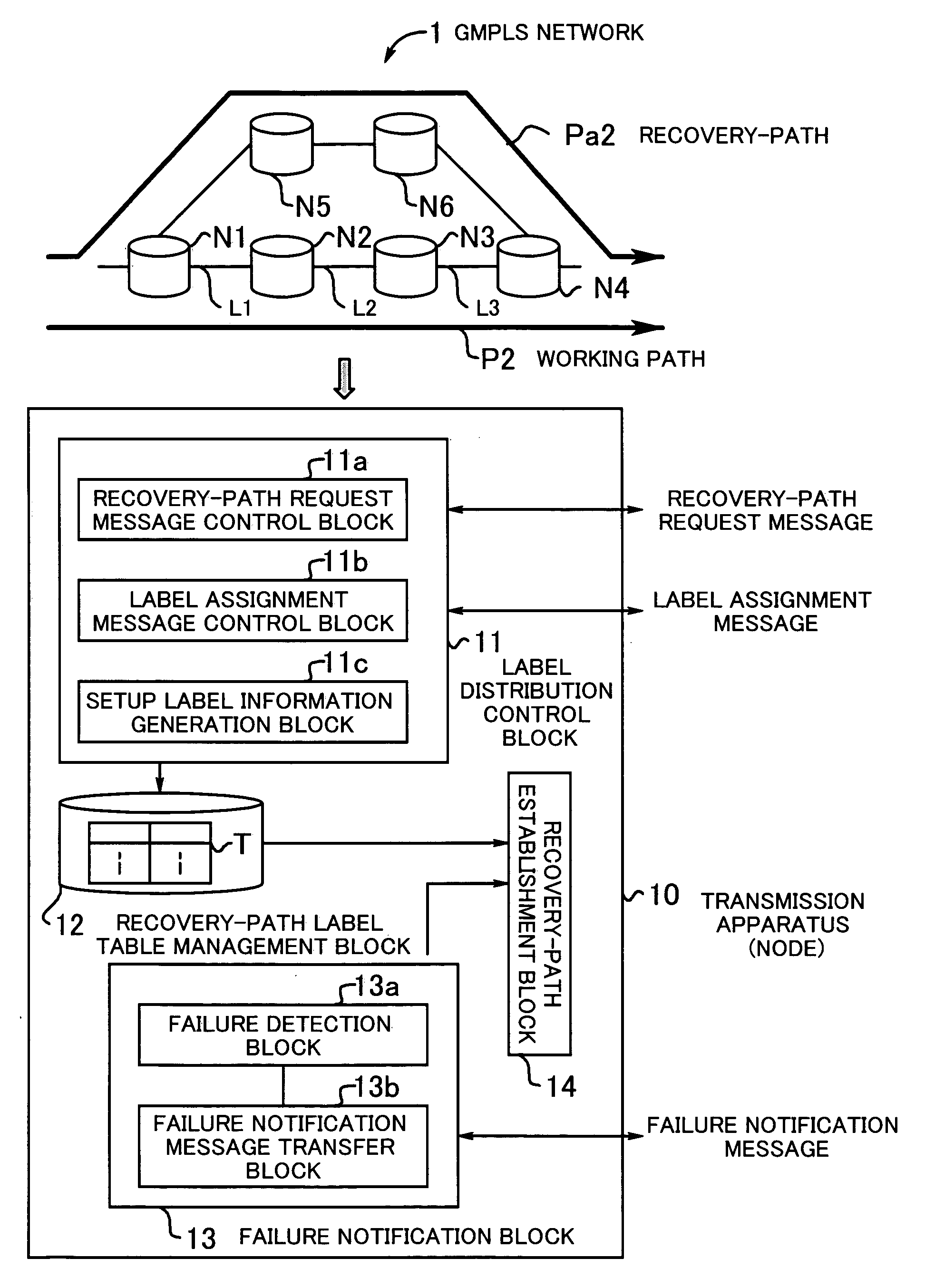

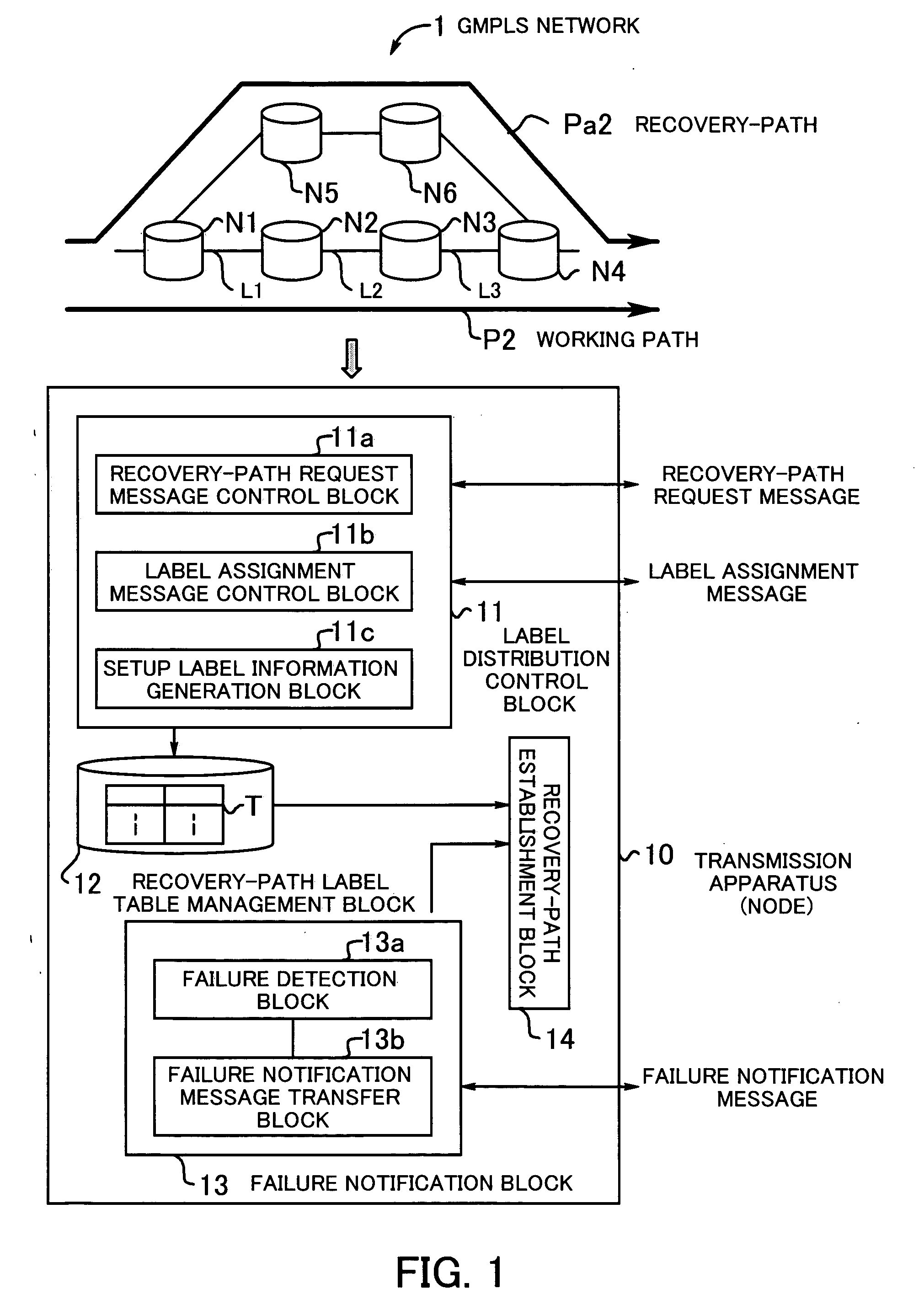

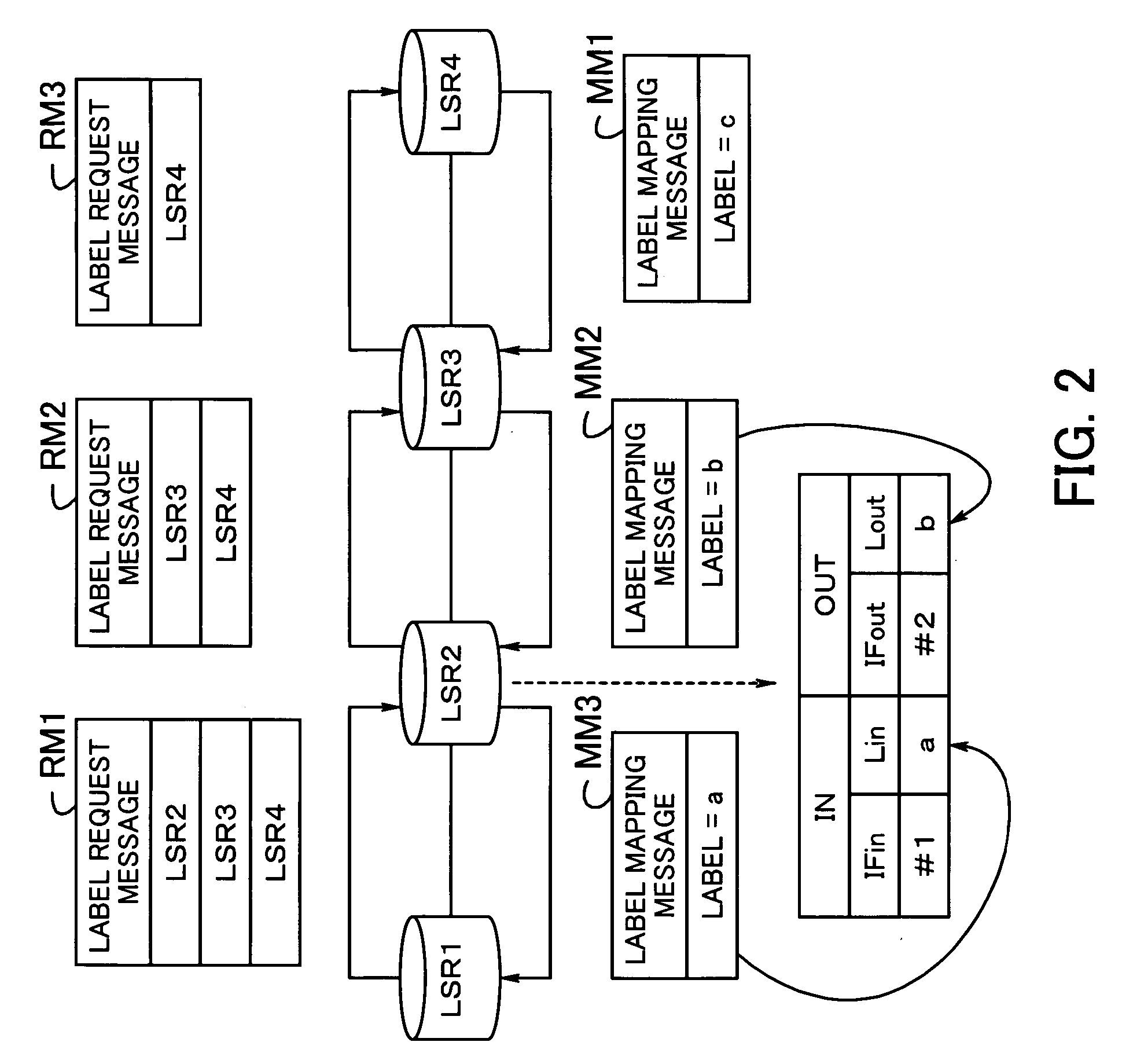

Transmission apparatus

InactiveUS20050237927A1Quality improvementImprove reliabilityError preventionTransmission systemsDependabilityTransmission quality

A transmission apparatus which can enhance the transmission quality and reliability by establishing a recovery-path efficiently at a high speed for failure circumvention. A recovery-path request message control block generates, sends, and receives a recovery-path request message containing failure location information and recovery-path setup information. A label assignment message control block generates, sends, and receives a label assignment message. A setup label information generation block generates setup label information. A recovery-path label table management block constructs and manages a recovery-path label table. A failure detection block detects the location of a failure. A failure notification message transfer block transfers a failure notification message containing failure location information. A recovery-path establishment block establishes a recovery-path by comparing failure location information contained in a failure notification message and failure location information contained in a recovery-path label table and by selecting setup label information corresponding to matching failure location information.

Owner:FUJITSU LTD

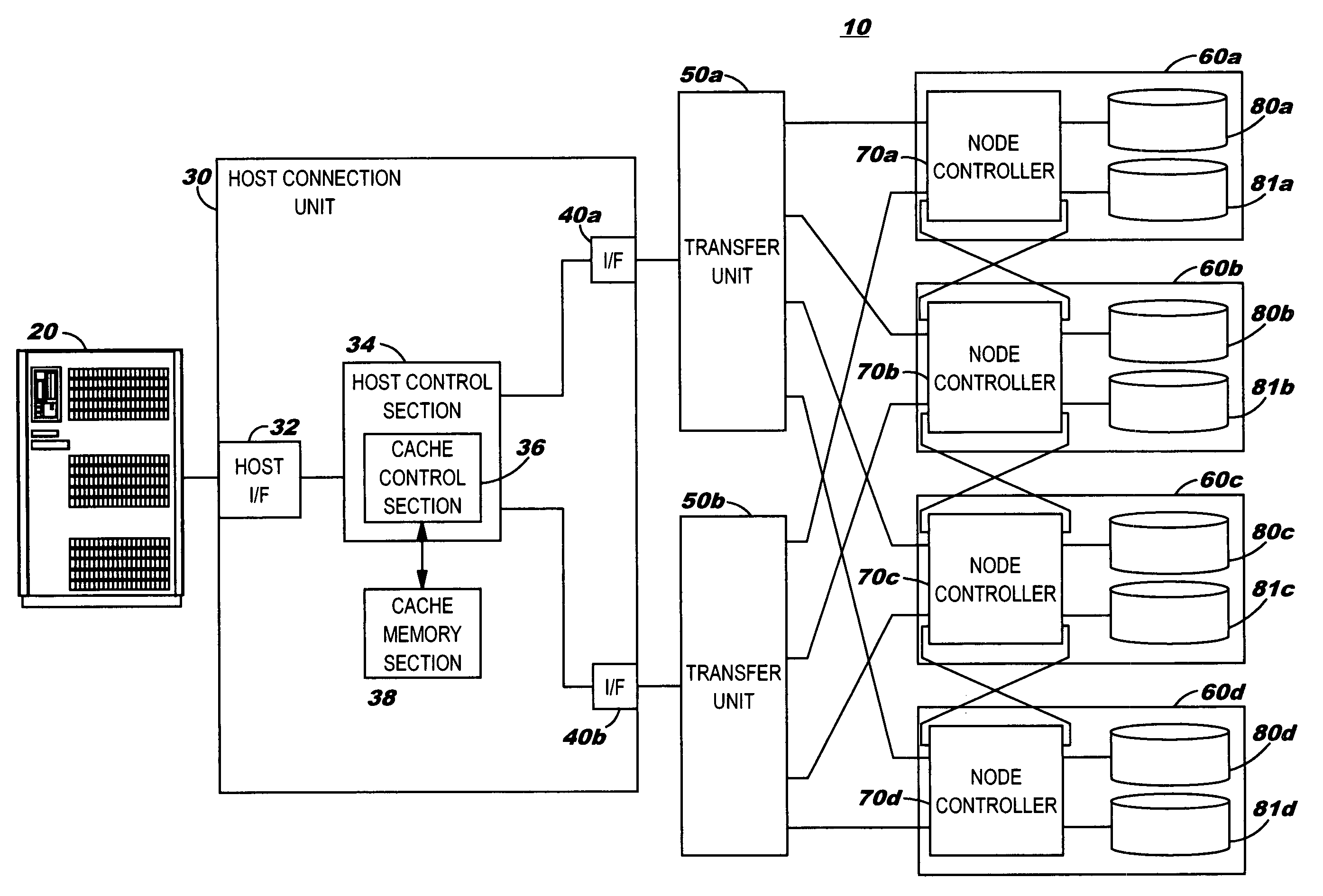

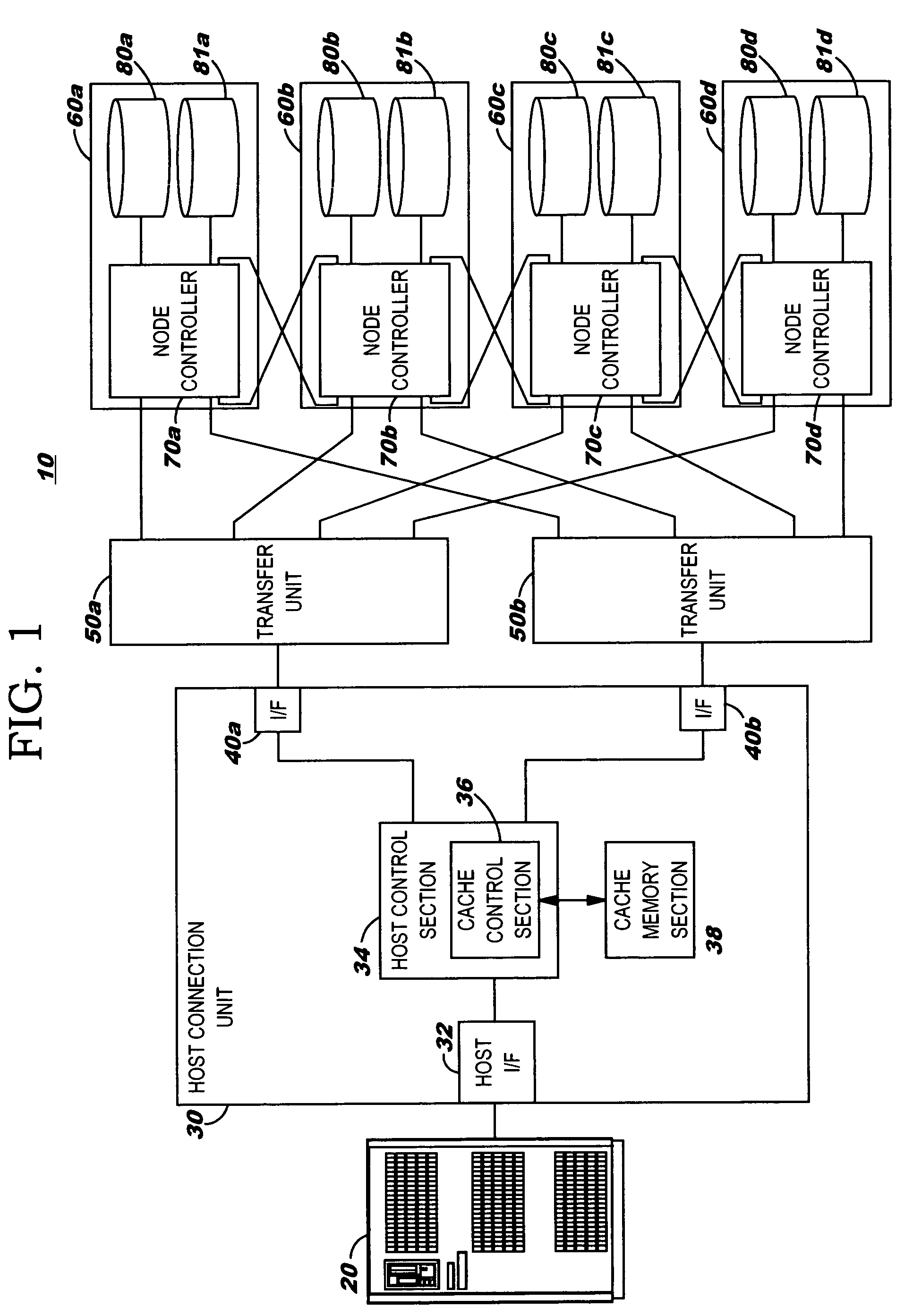

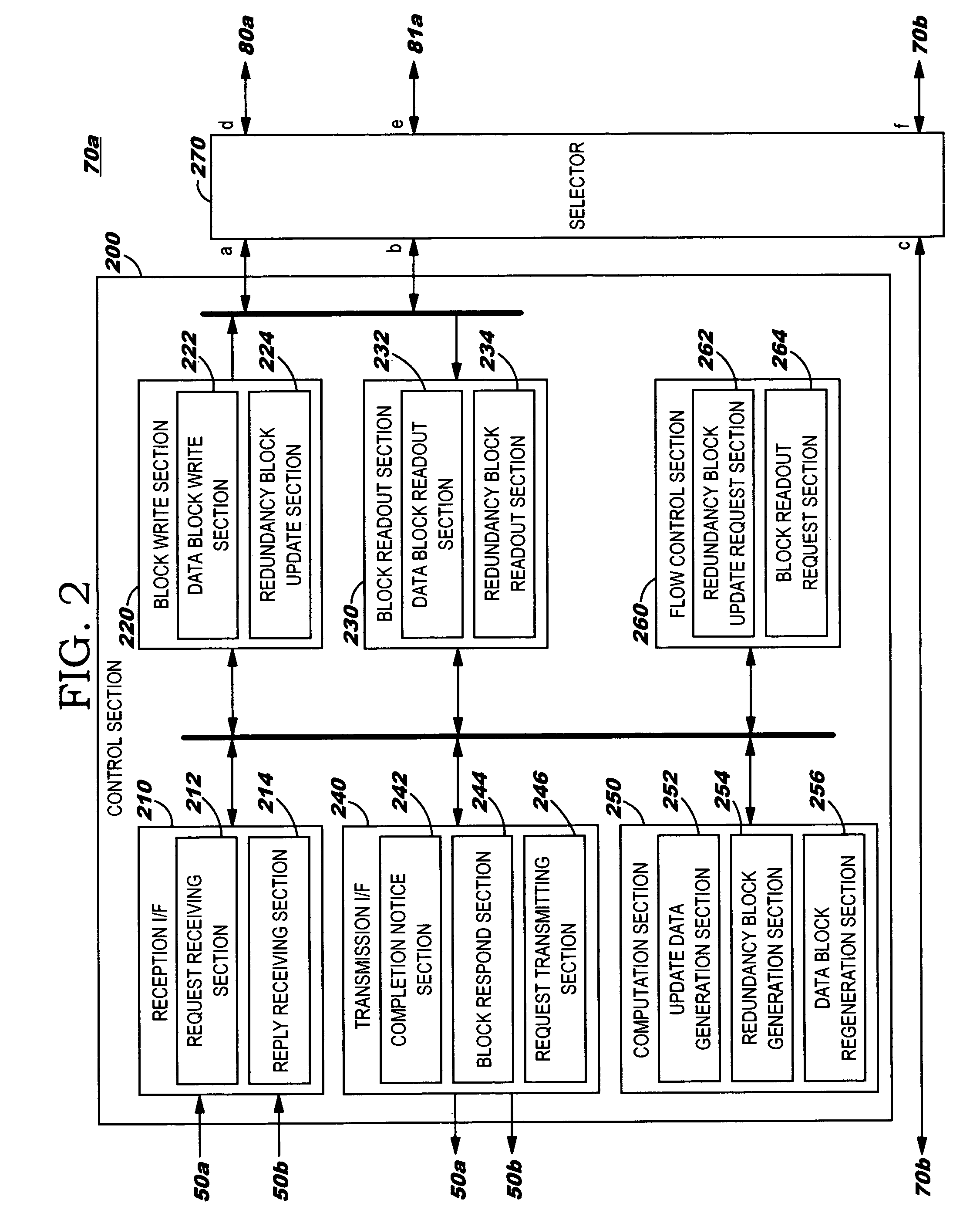

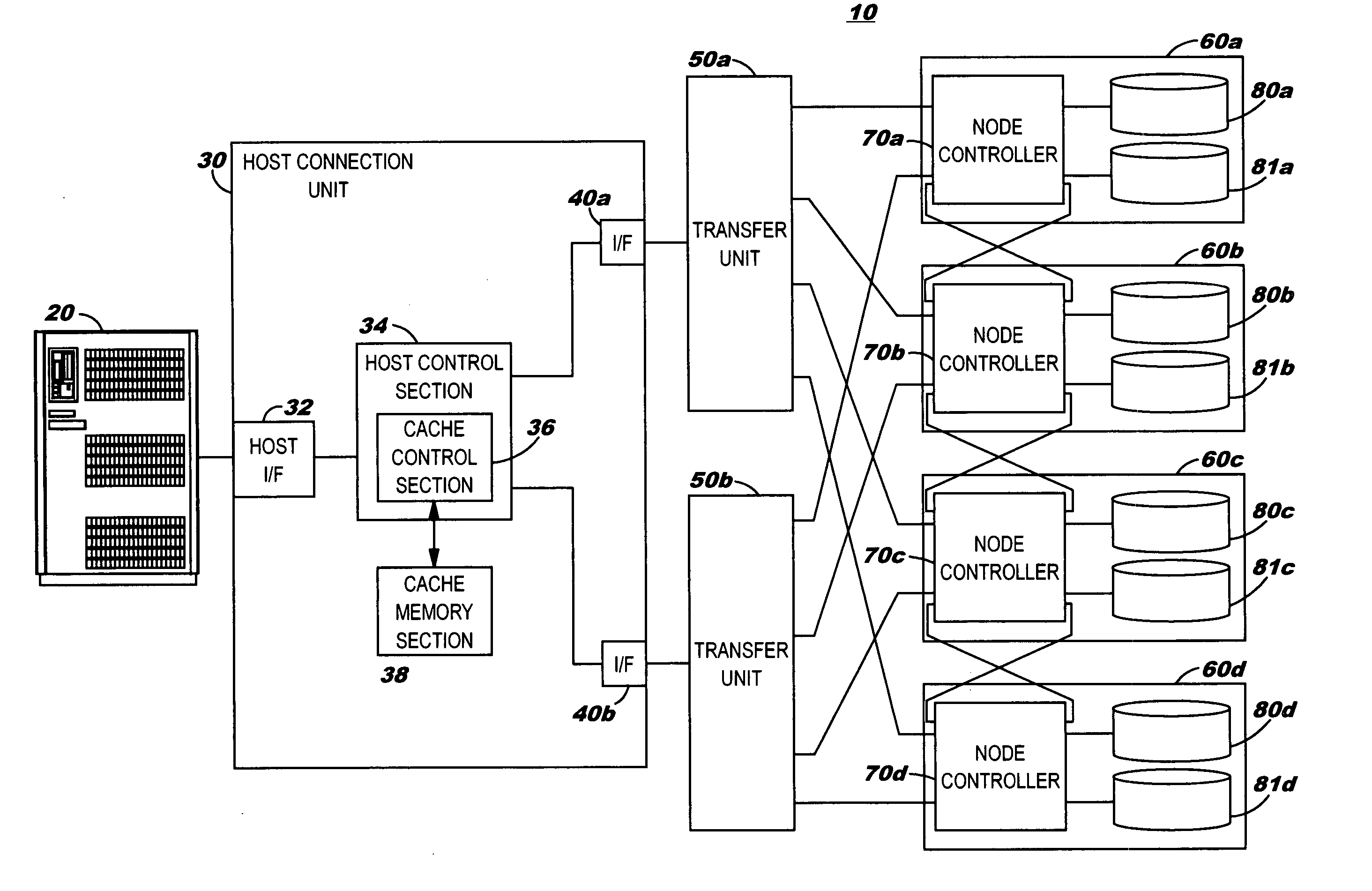

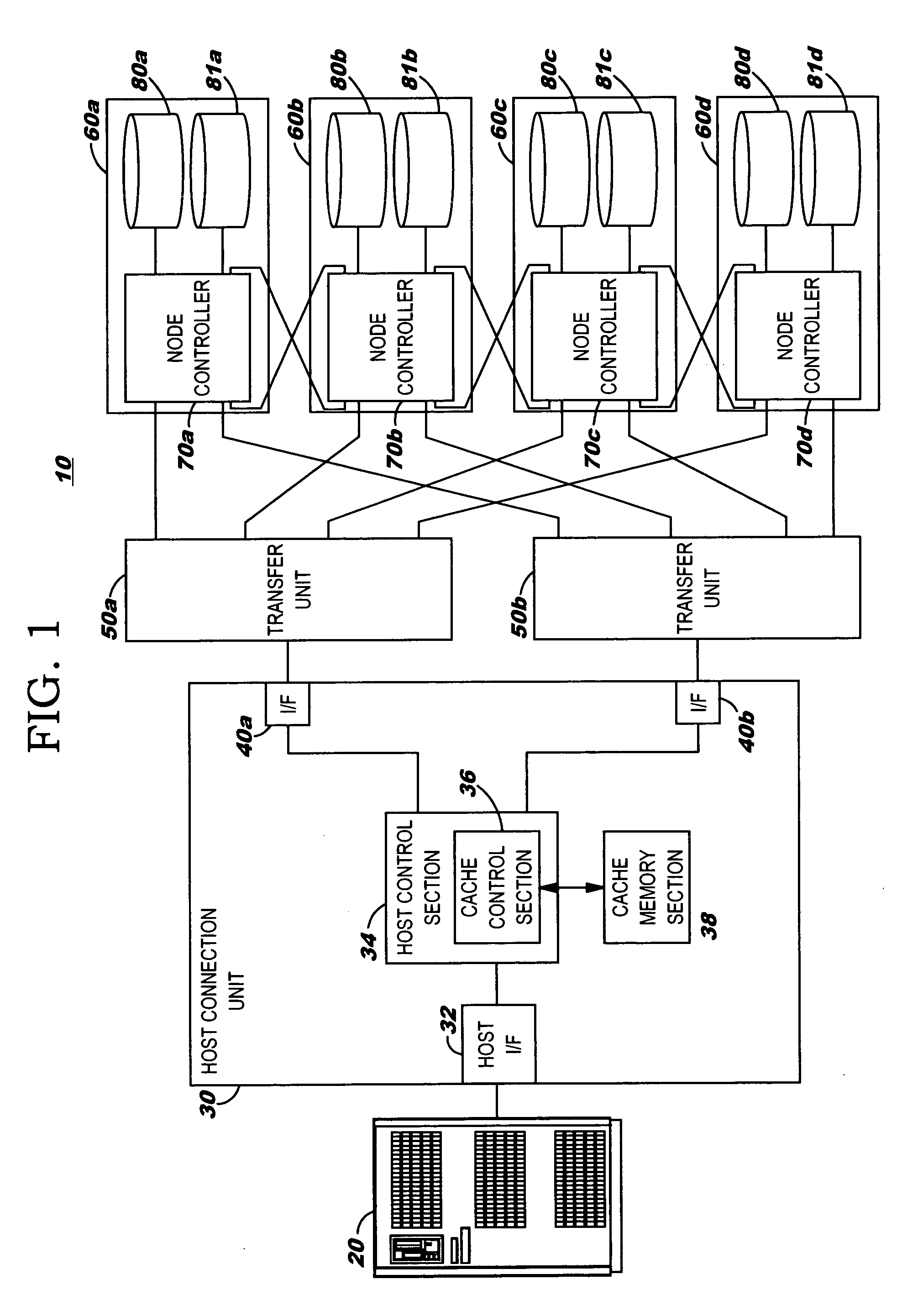

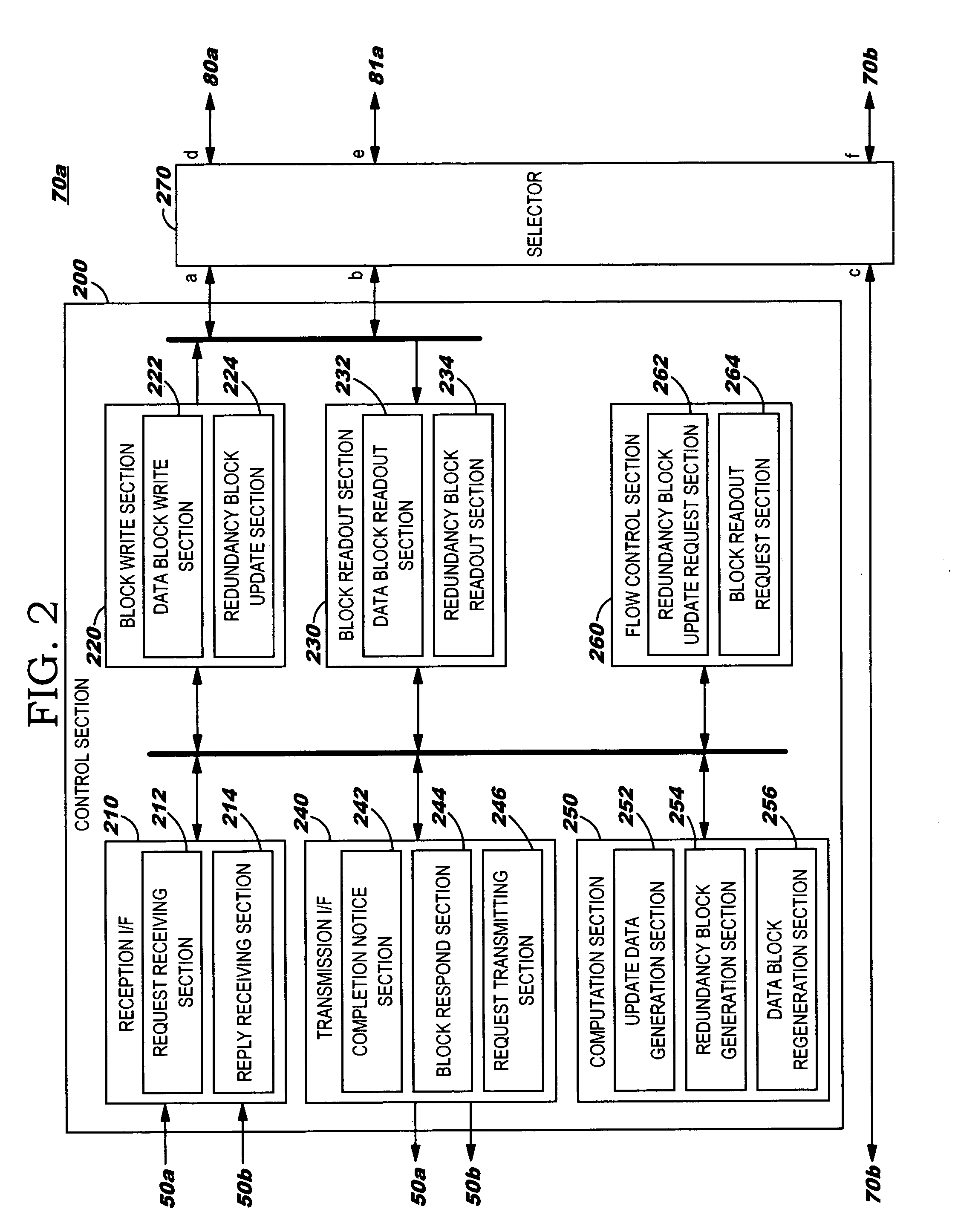

Storage system, controller, control method and program product therefor

InactiveUS7133967B2Input/output to record carriersMemory adressing/allocation/relocationOperating systemHost machine

A storage system in which a set of a data block and a redundancy block is stored has a plurality of control sections which respectively control a plurality of storages, a host connection unit which selects the control section controlling one of the storage in which a write data block which is a write-object block is to be stored, and a transfer unit which transfers the write data block to the control section. Each of the plurality of control sections includes a data block write section which writes the write data block transferred by a transfer unit to the storage in which the write data block is to be stored, a redundancy block update request section which requests the control section controlling the storage in which a redundancy block is to be stored to update the redundancy block, and a redundancy block update section which updates the redundancy block stored in the storage controlled by the control section when another of the control sections makes a request for updating the redundancy block.

Owner:INT BUSINESS MASCH CORP

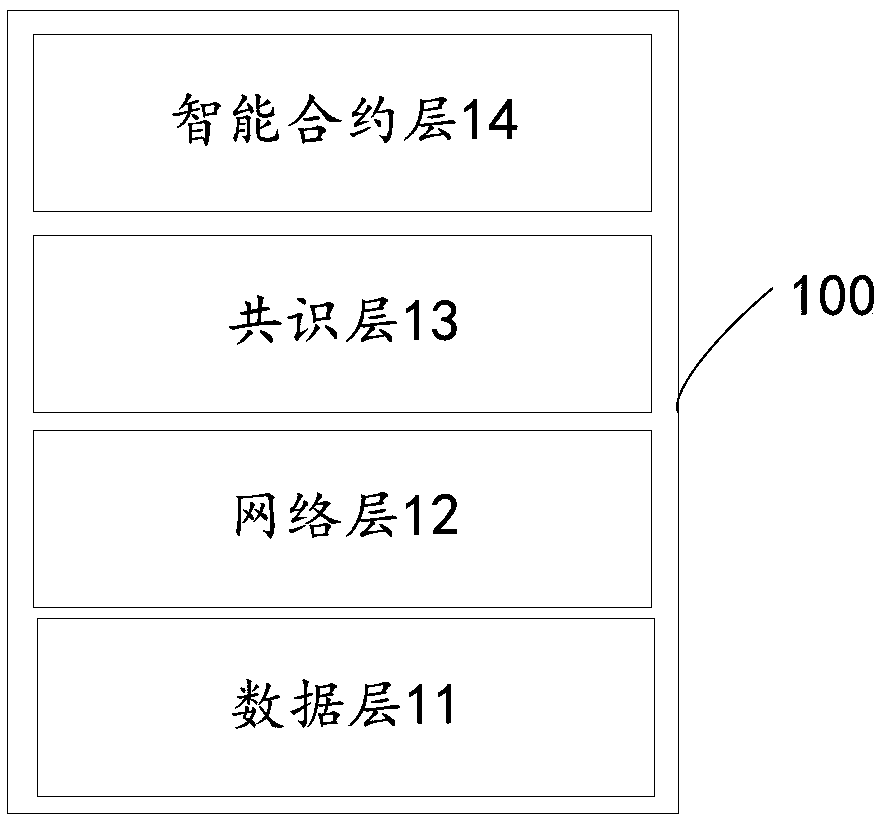

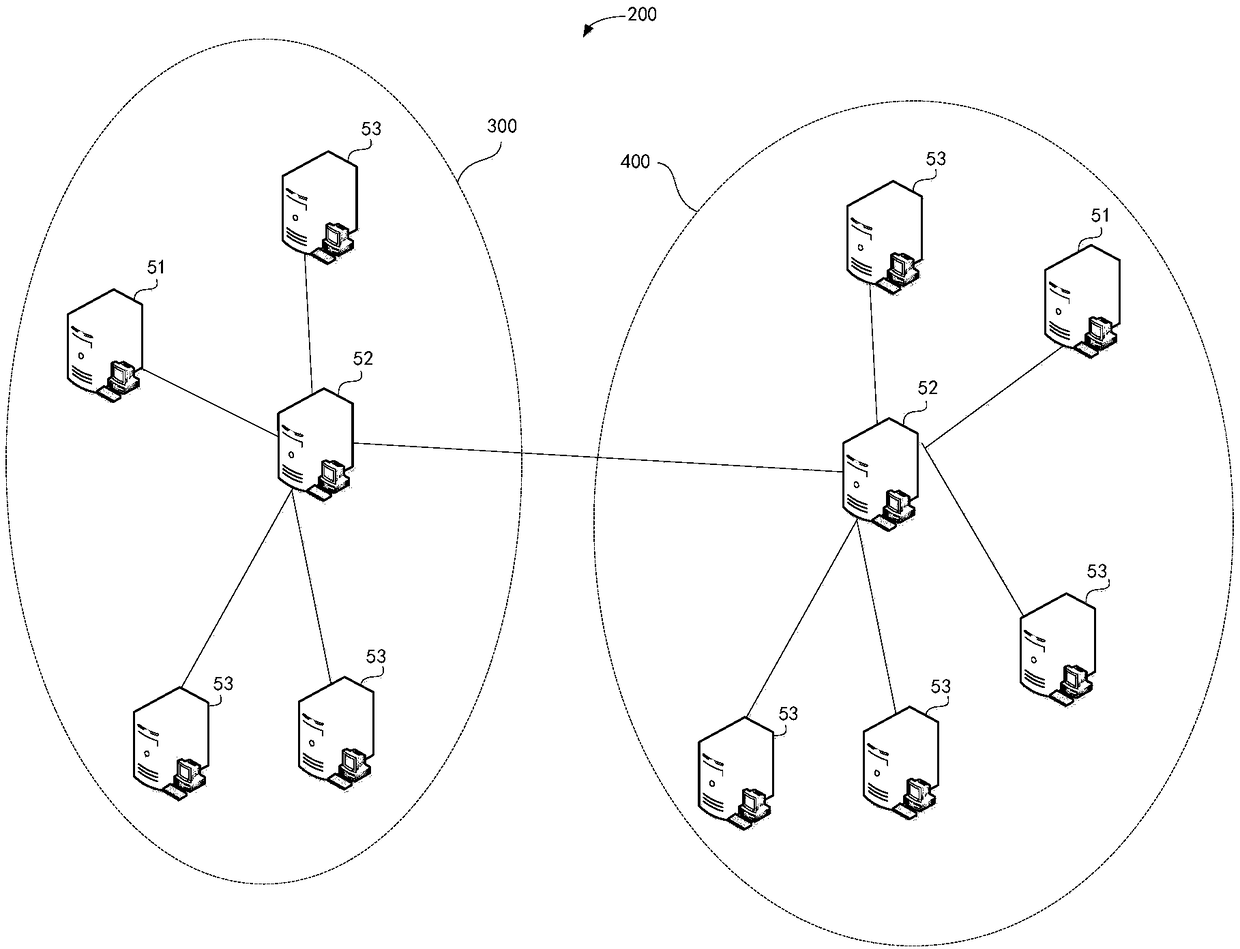

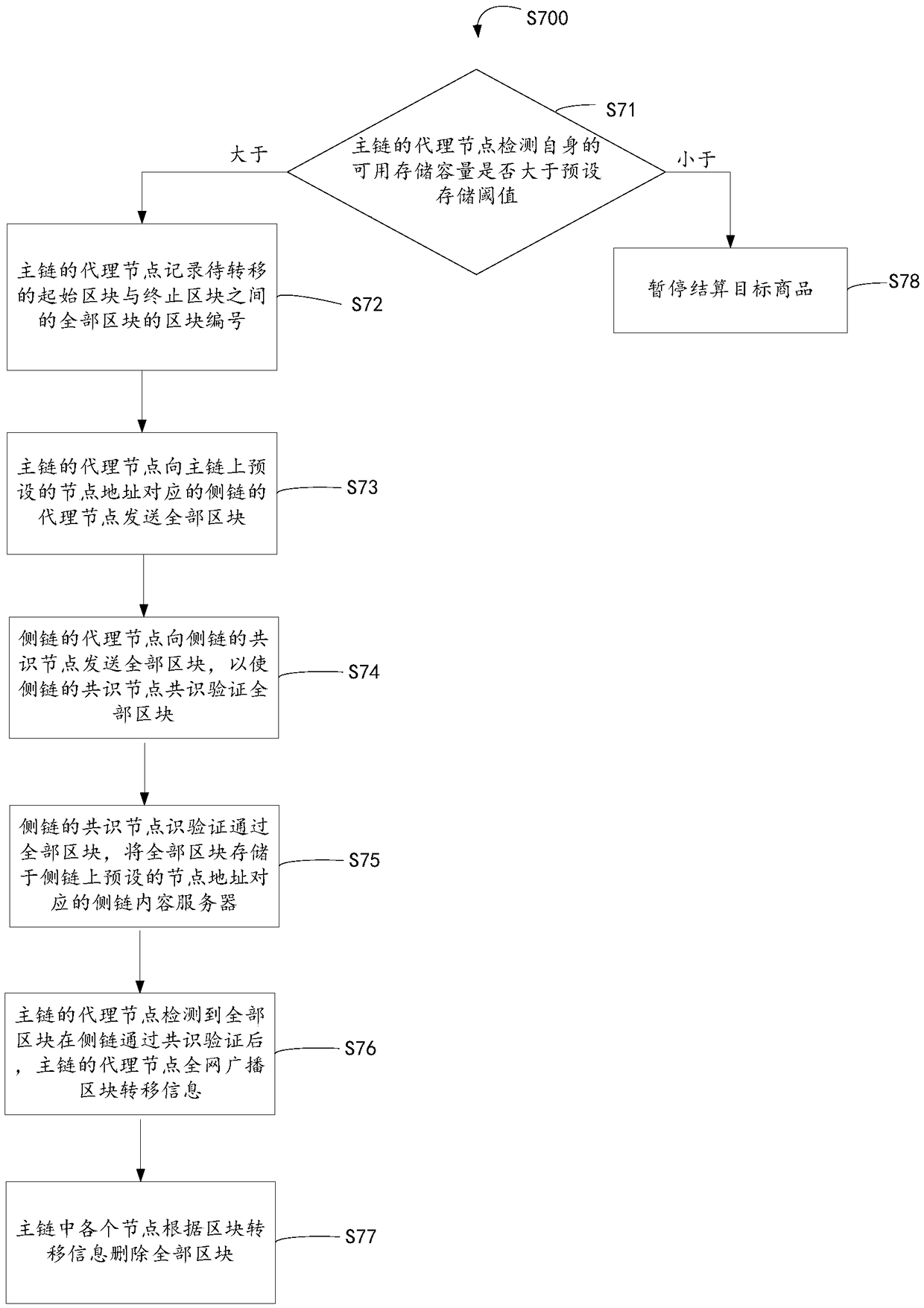

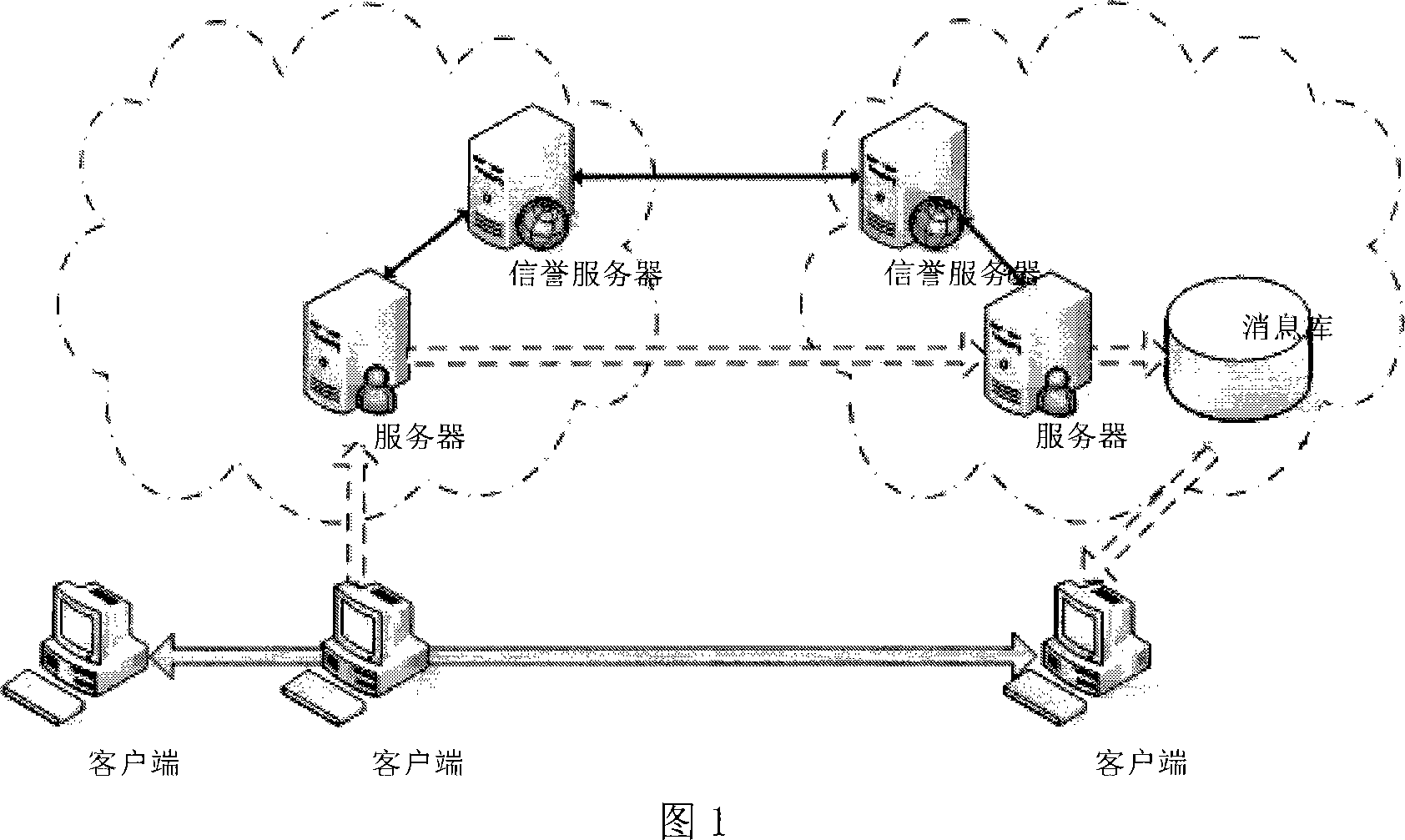

Data storage method and system based on block chain

ActiveCN109117097AHigh working reliabilitySafe storageInput/output to record carriersPayment protocolsSide chainOperating system

The invention relates to the technical field of block chain, in particular to a data storage method and a system based on the block chain. The method comprises the following steps: a proxy node of a main chain detects whether the available storage capacity of the proxy node is larger than a preset storage threshold; if it is larger than, the agent node of the main chain records the block numbers of all blocks between the starting block and the terminating block to be transferred. The proxy node of the side chain sends all the blocks to the consensus node of the side chain; the agent node of the main chain broadcasts the block transfer information to the whole network after detecting all the blocks in the side chain to pass the consensus verification. Each node in the main chain deletes allthe blocks according to the block transfer information. As the node in the main chain can transfer and store part or all of the blocks in the side chain when the available storage capacity is insufficient, each node in the main chain has more available storage capacity, so that each node in the main chain can store the block data more reliably, and the work reliability of the main chain is improved.

Owner:SHENZHEN GENUINE INNOVATIVE TECH CO LTD

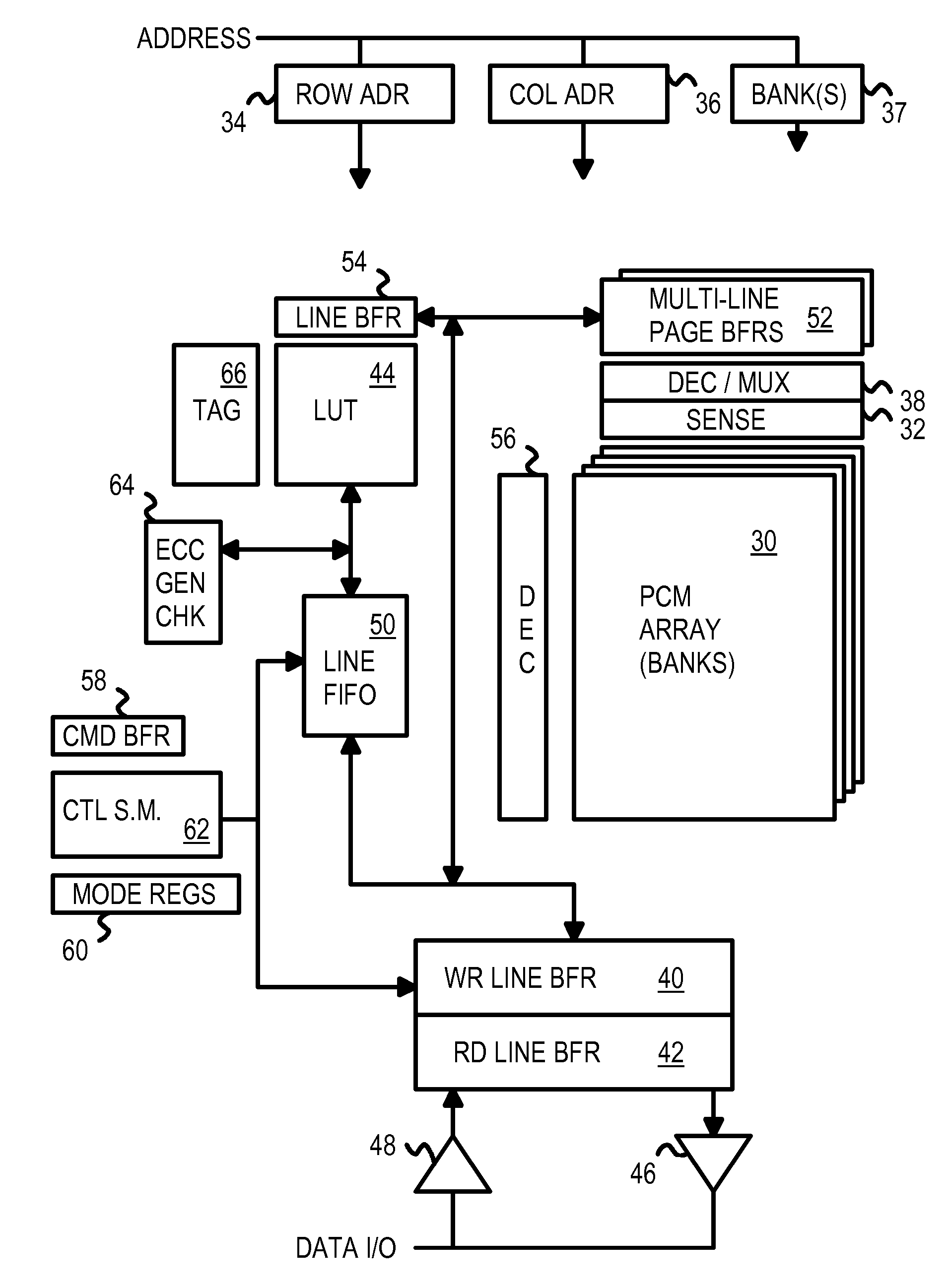

Synchronous page-mode phase-change memory with ECC and RAM cache

Owner:SUPER TALENT TECH CORP

Storage system, controller, control method and program product therefor

InactiveUS20040250019A1Improve performanceInput/output to record carriersMemory adressing/allocation/relocationOperating systemHost machine

A storage system in which a set of a data block and a redundancy block is stored has a plurality of control sections which respectively control a plurality of storages, a host connection unit which selects the control section controlling one of the storage in which a write data block which is a write-object block is to be stored, and a transfer unit which transfers the write data block to the control section. Each of the plurality of control sections includes a data block write section which writes the write data block transferred by a transfer unit to the storage in which the write data block is to be stored, a redundancy block update request section which requests the control section controlling the storage in which a redundancy block is to be stored to update the redundancy block, and a redundancy block update section which updates the redundancy block stored in the storage controlled by the control section when another of the control sections makes a request for updating the redundancy block.

Owner:IBM CORP

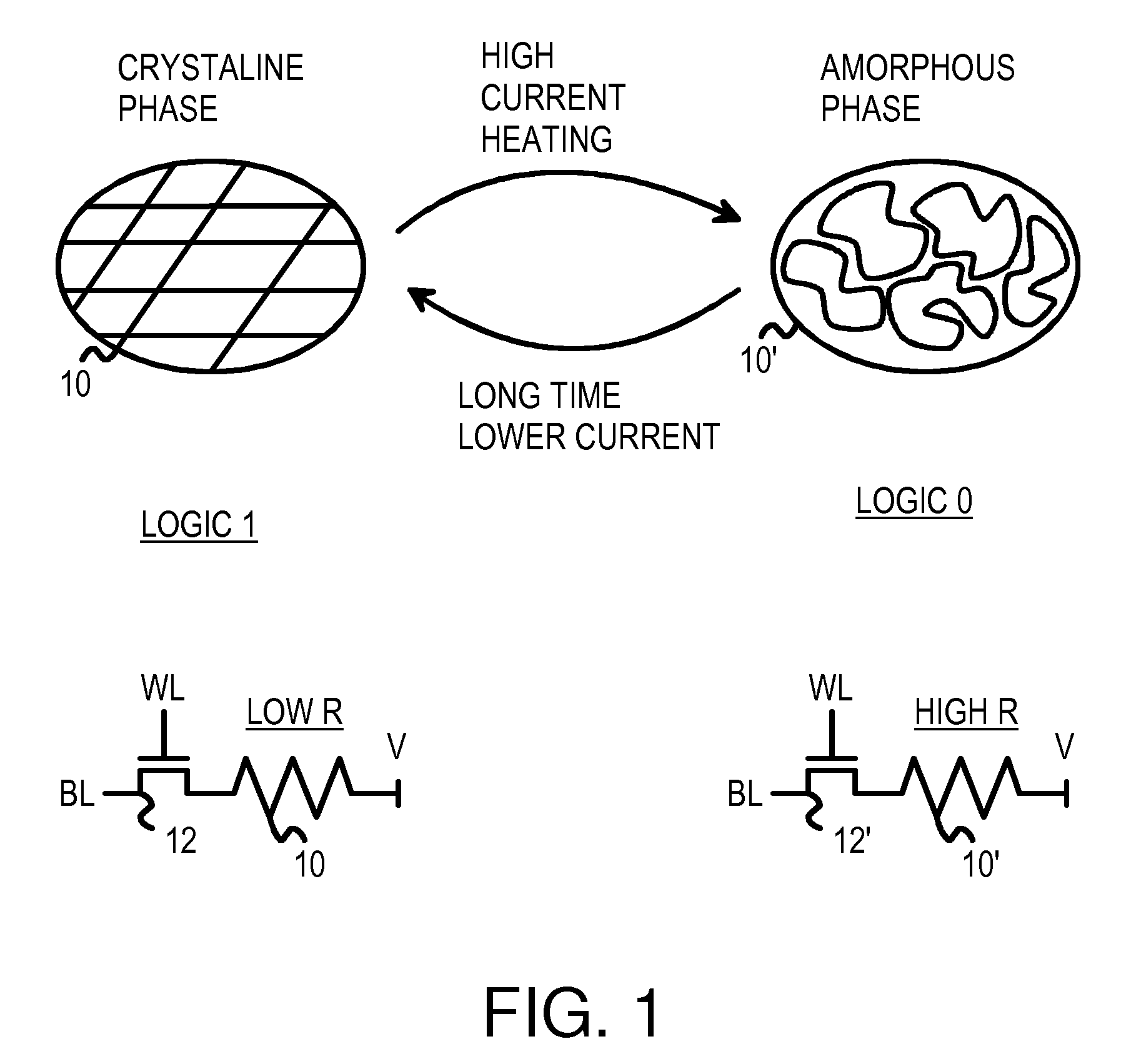

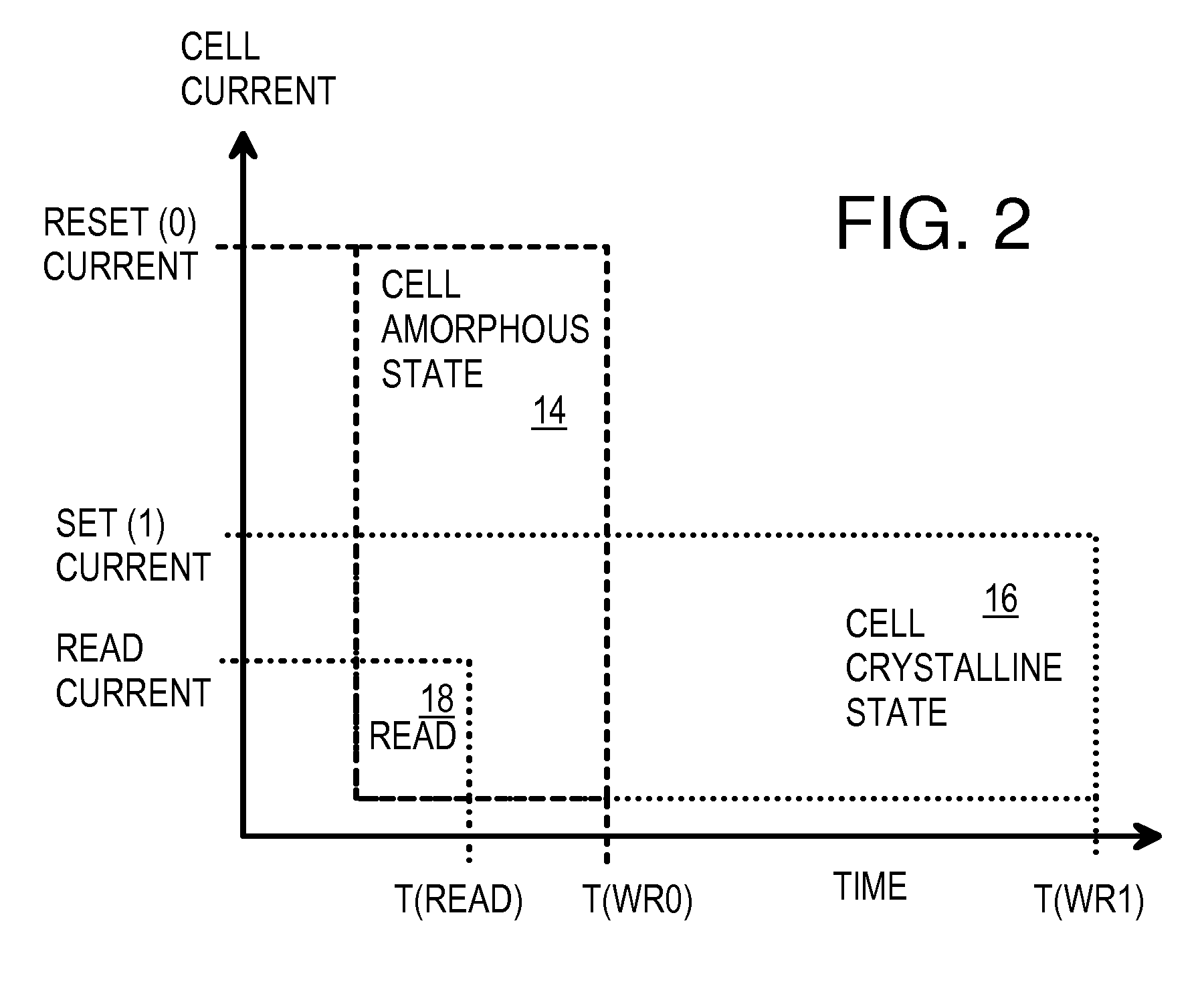

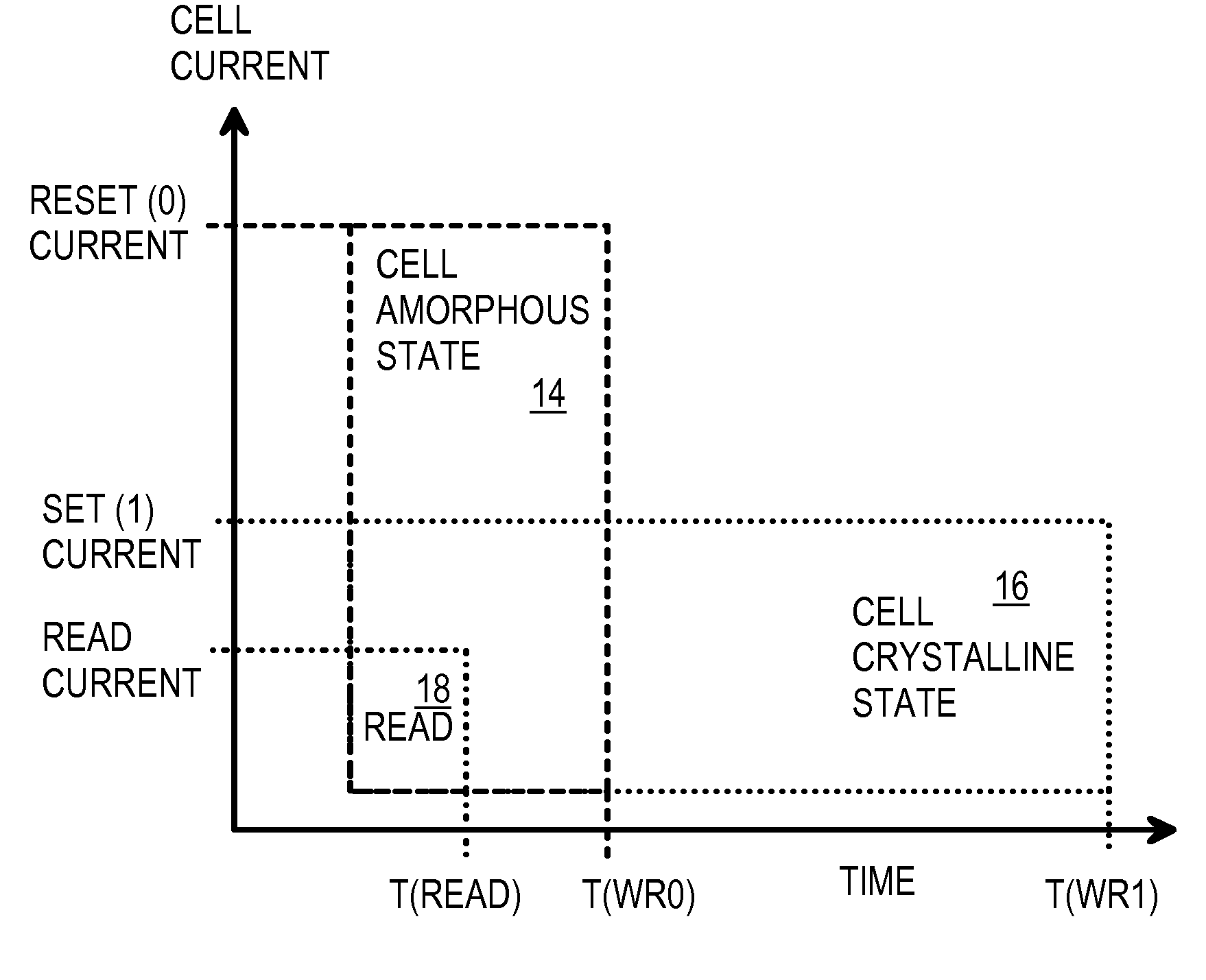

Synchronous Page-Mode Phase-Change Memory with ECC and RAM Cache

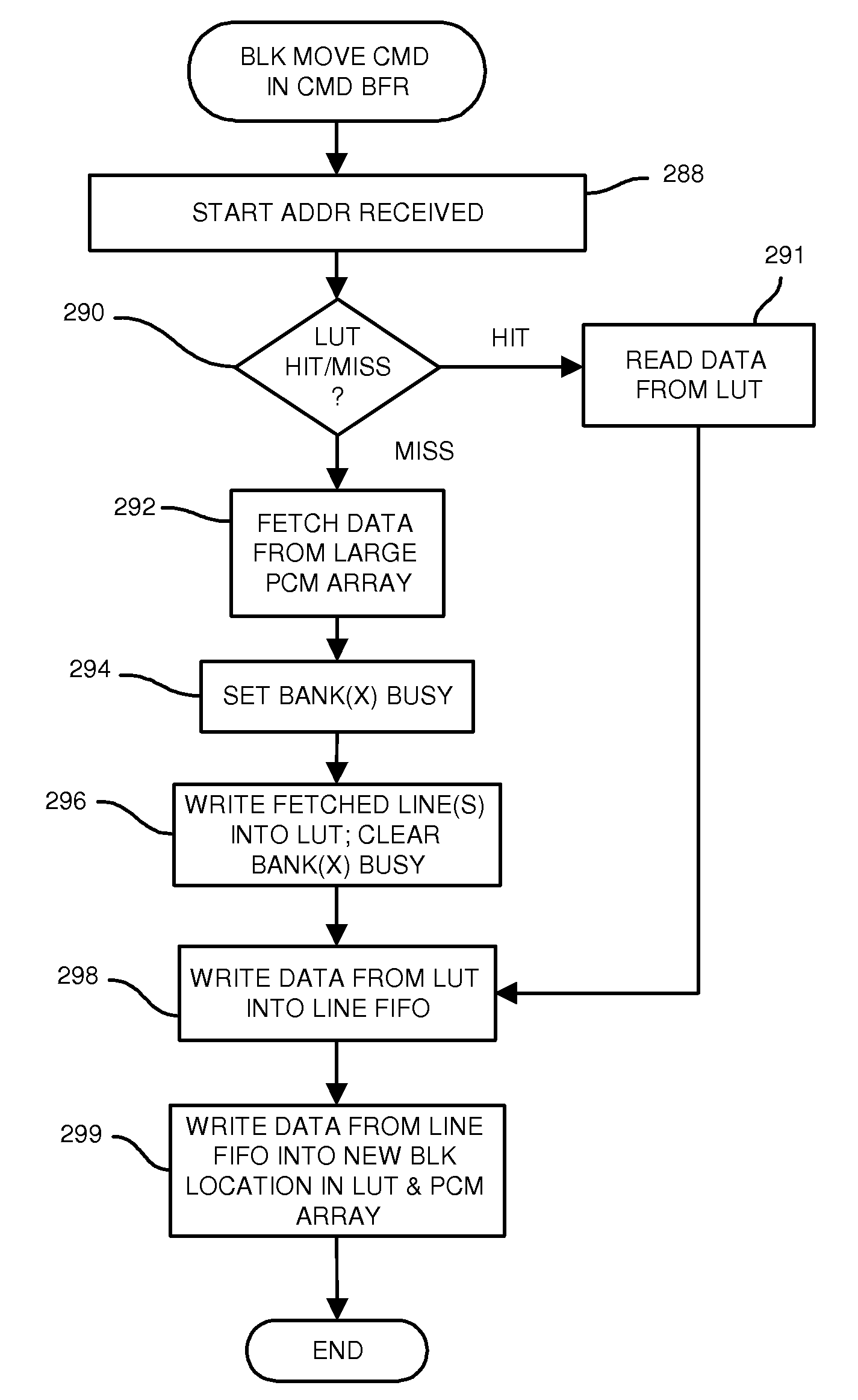

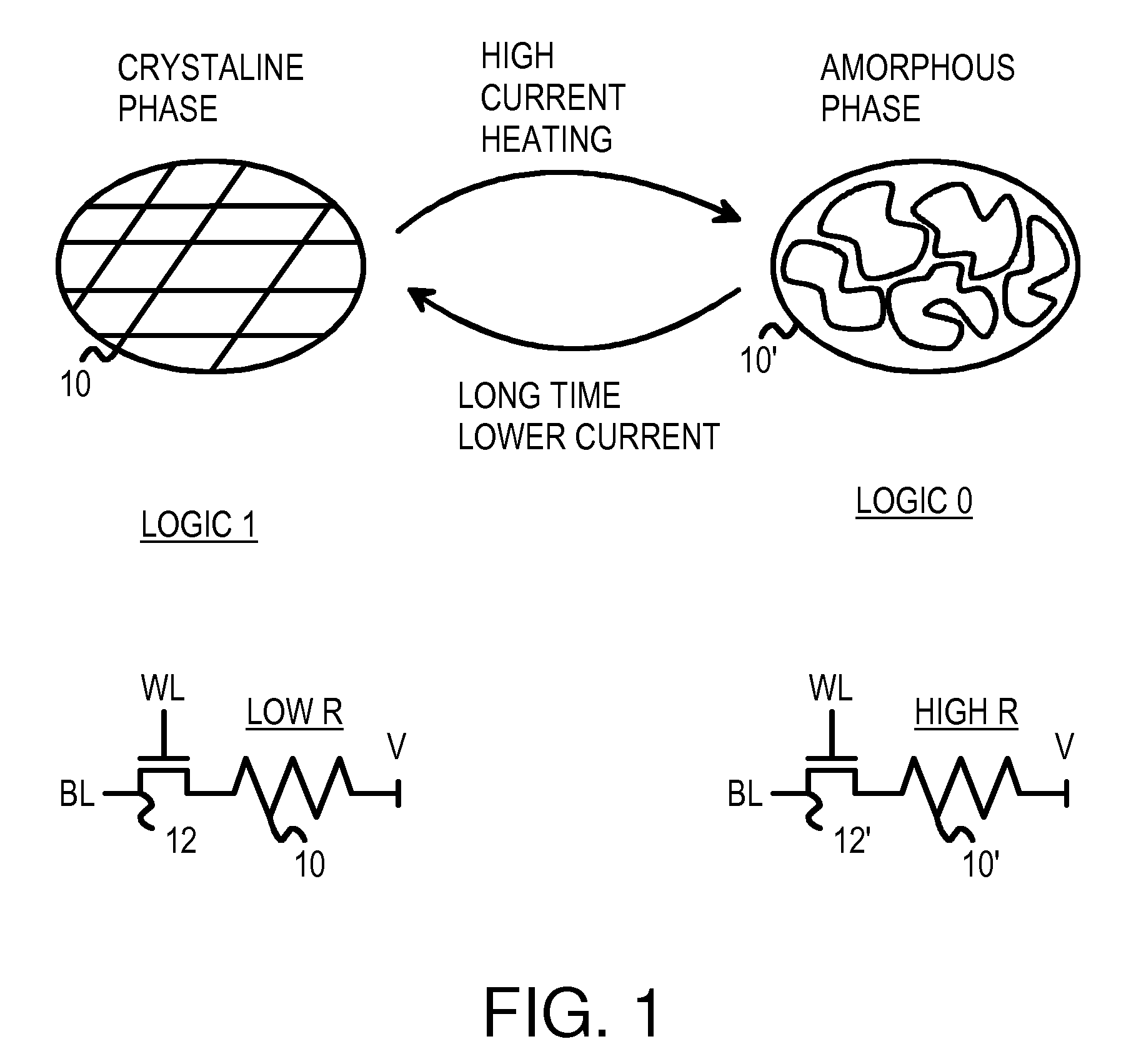

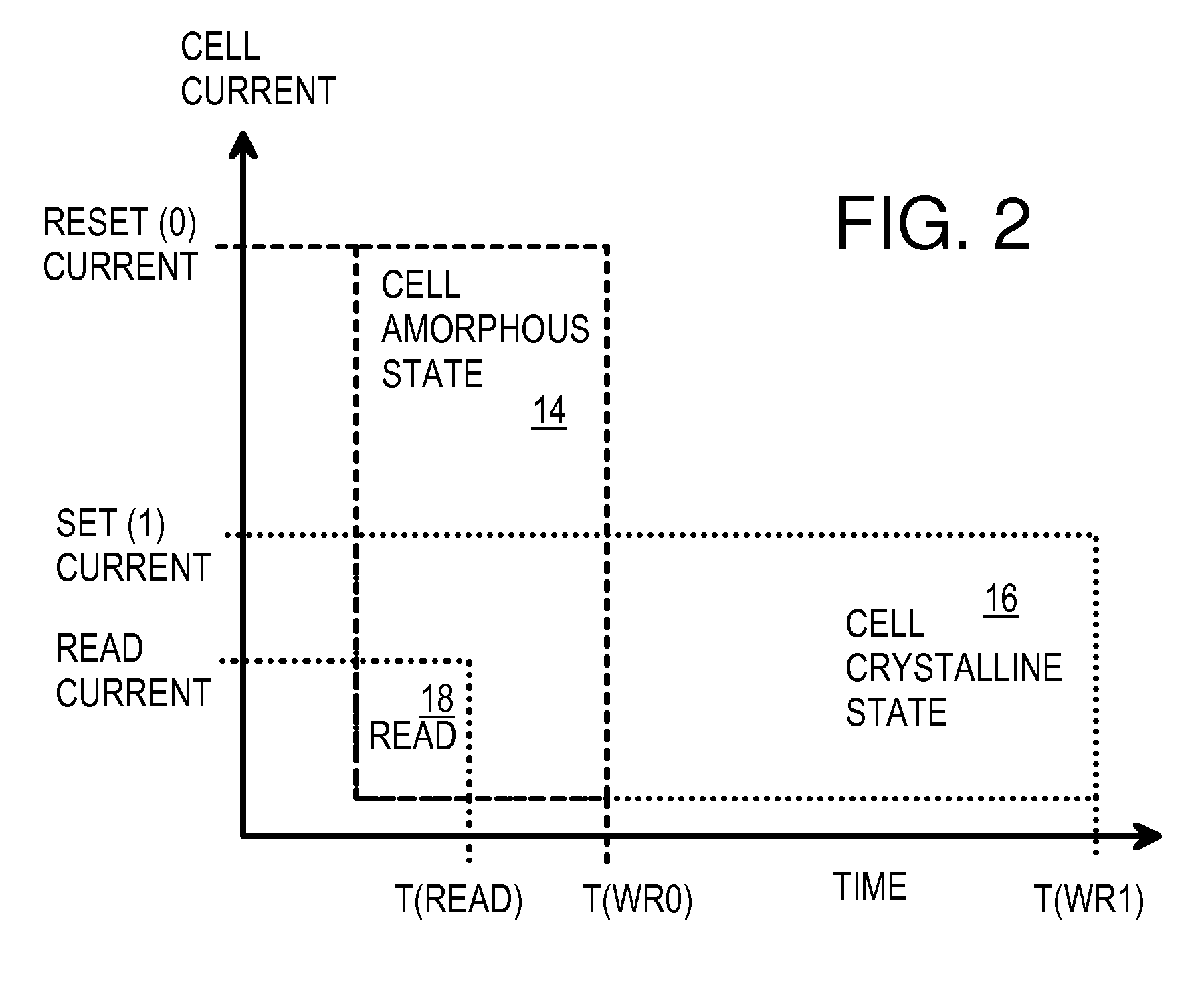

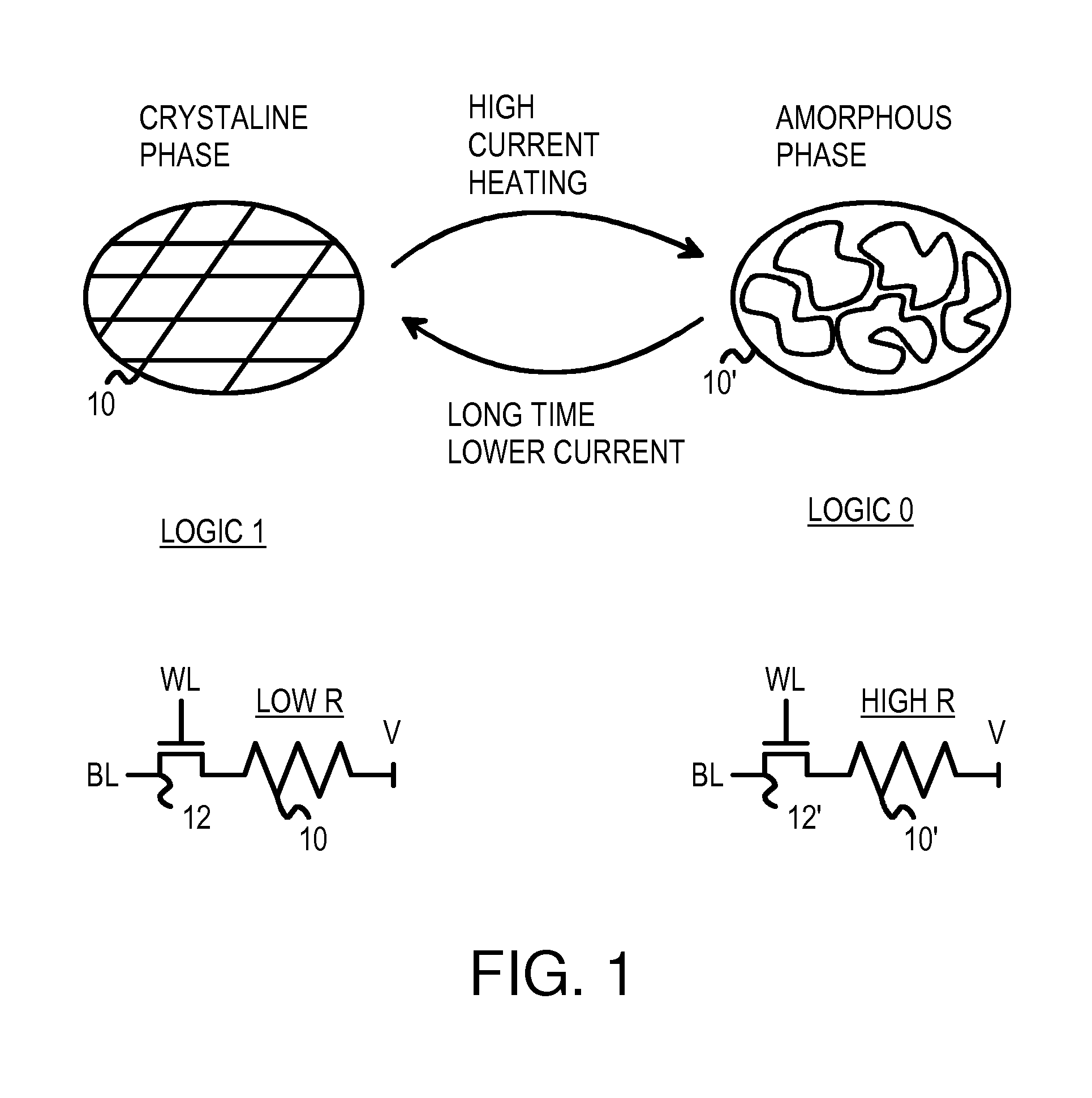

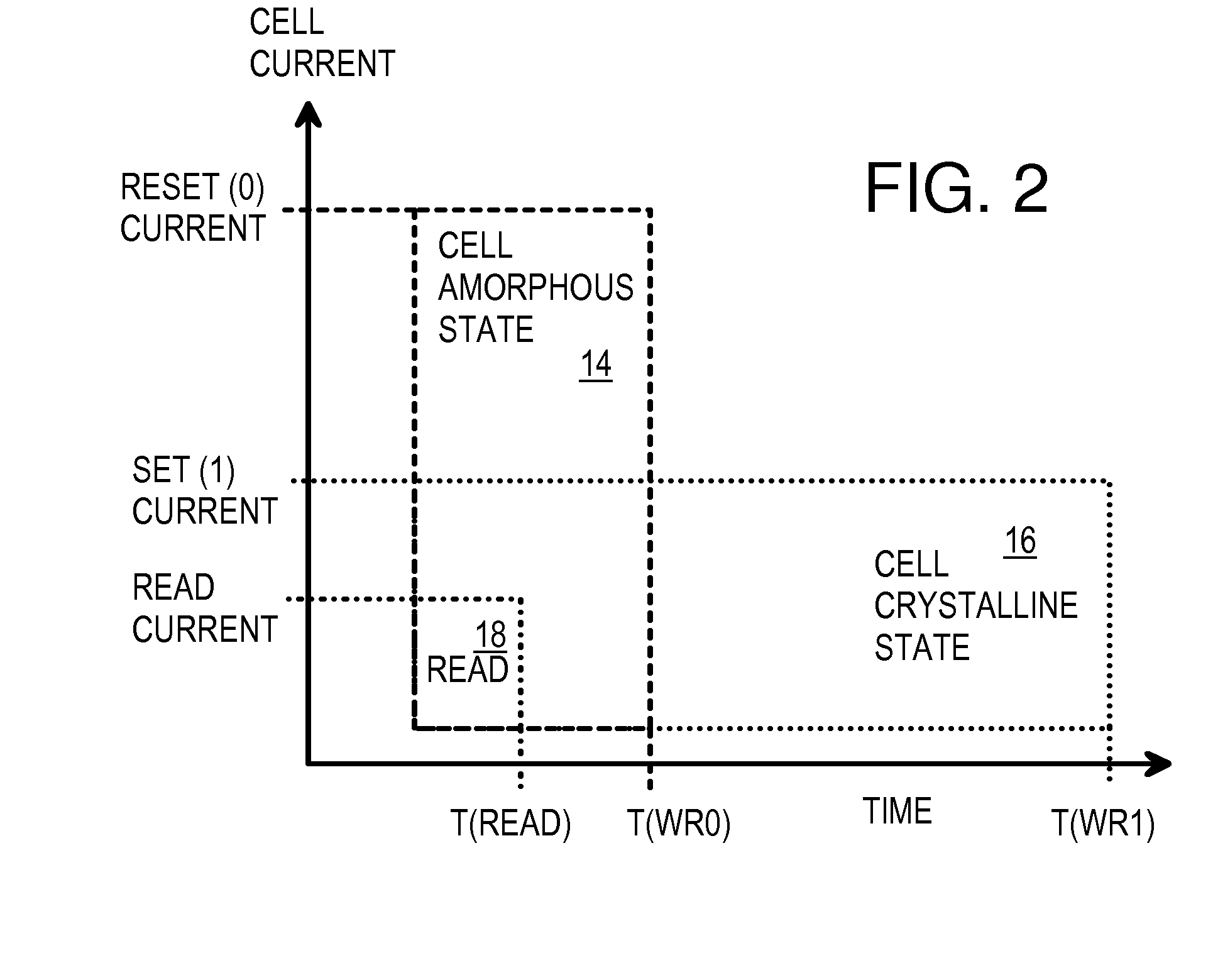

Phase-change memory (PCM) cells store data using alloy resistors in high-resistance amorphous and low-resistance crystalline states. The time of the memory cell's set-current pulse can be 100 ns, much longer than read or reset times. The write time thus depends on the write data and is relatively long. A page-mode caching PCM device has a lookup table (LUT) that caches write data that is later written to an array of PCM banks. Host data is latched into a line FIFO and written into the LUT, reducing write delays to the relatively slow PCM. Host read data can be supplied by the LUT or fetched from the PCM banks. A multi-line page buffer between the PCM banks and LUT allows for larger block transfers using the LUT. Error-correction code (ECC) checking and generation is performed for data in the LUT, hiding ECC delays for data writes into the PCM banks.

Owner:SUPER TALENT TECH CORP

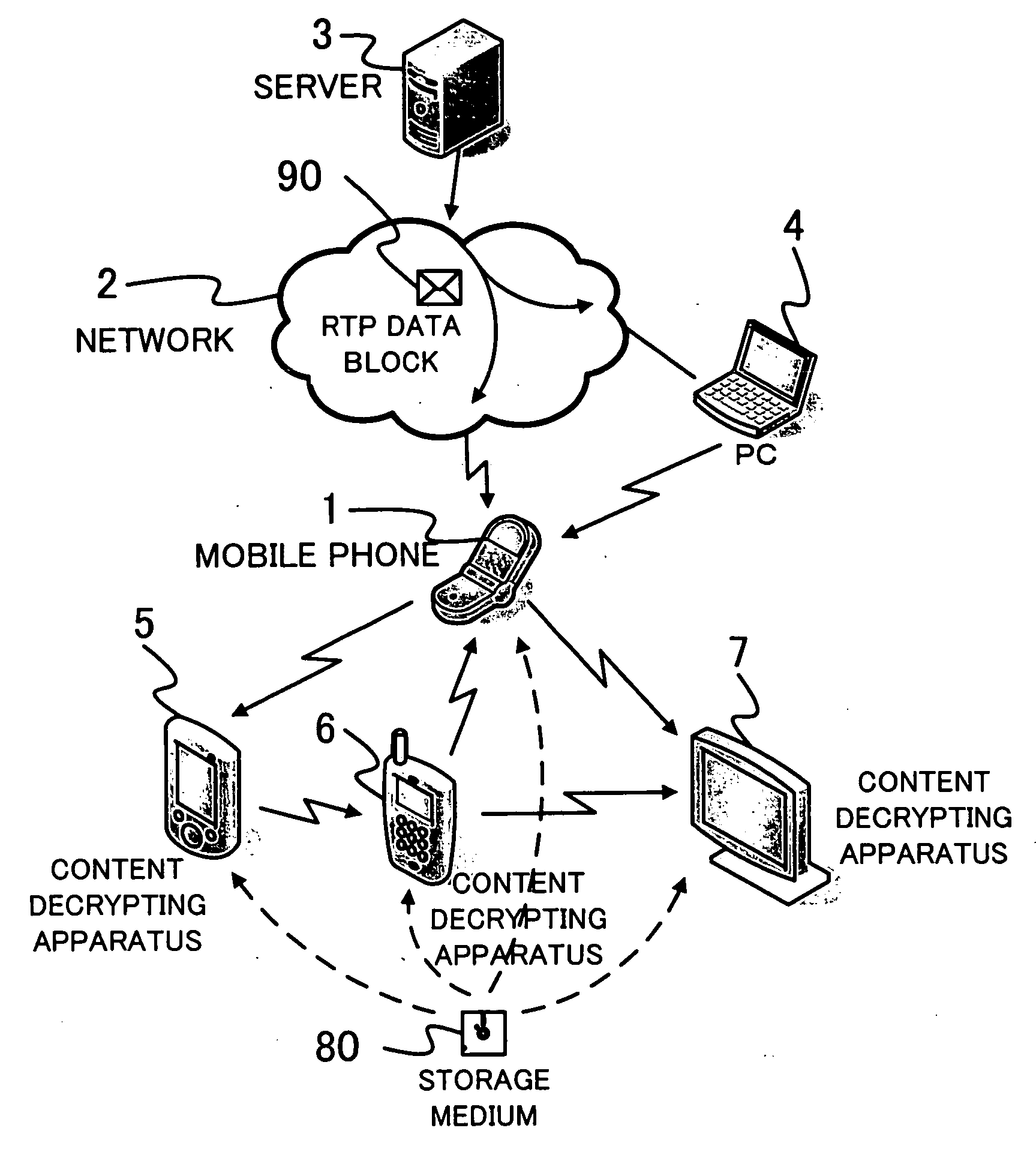

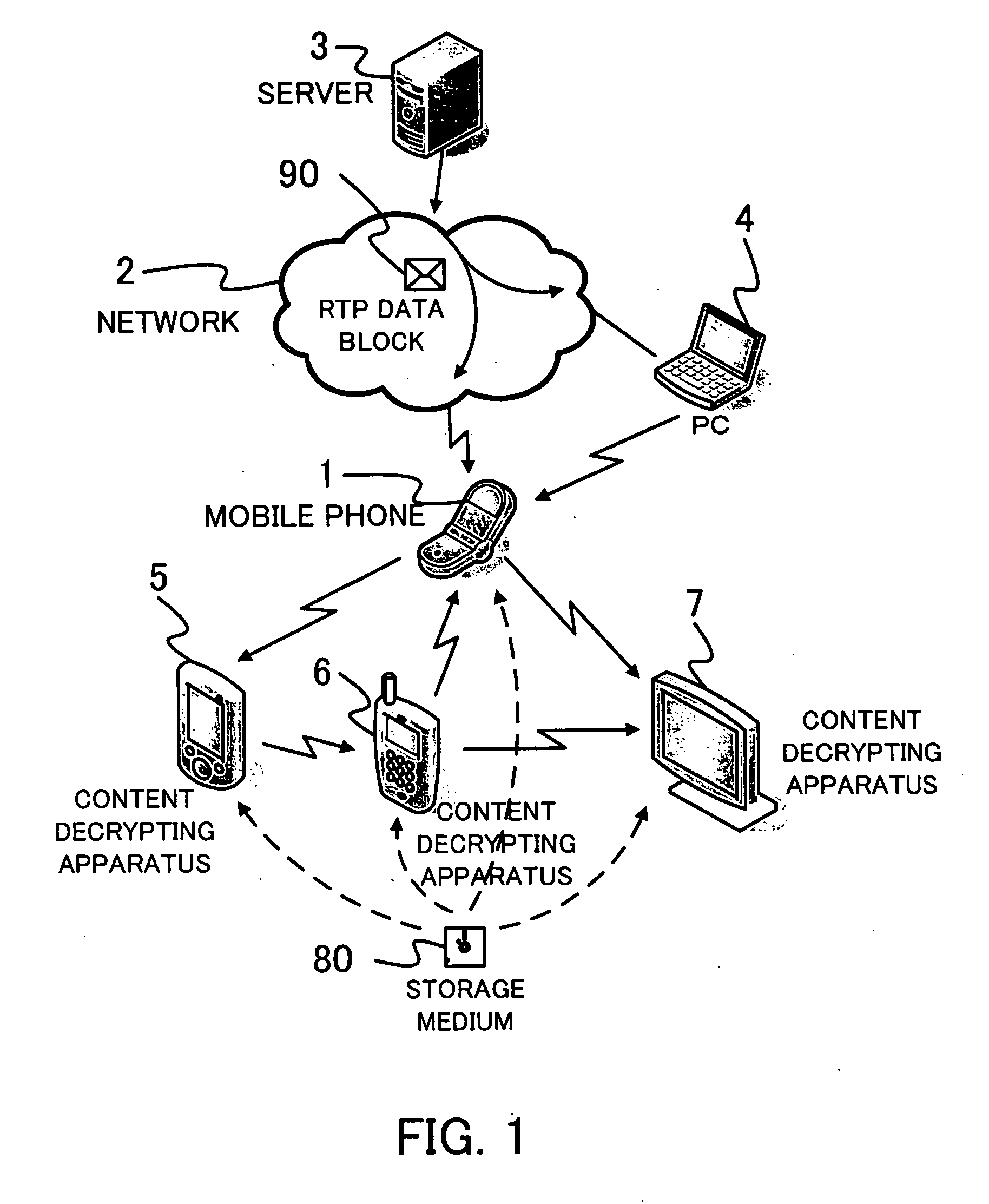

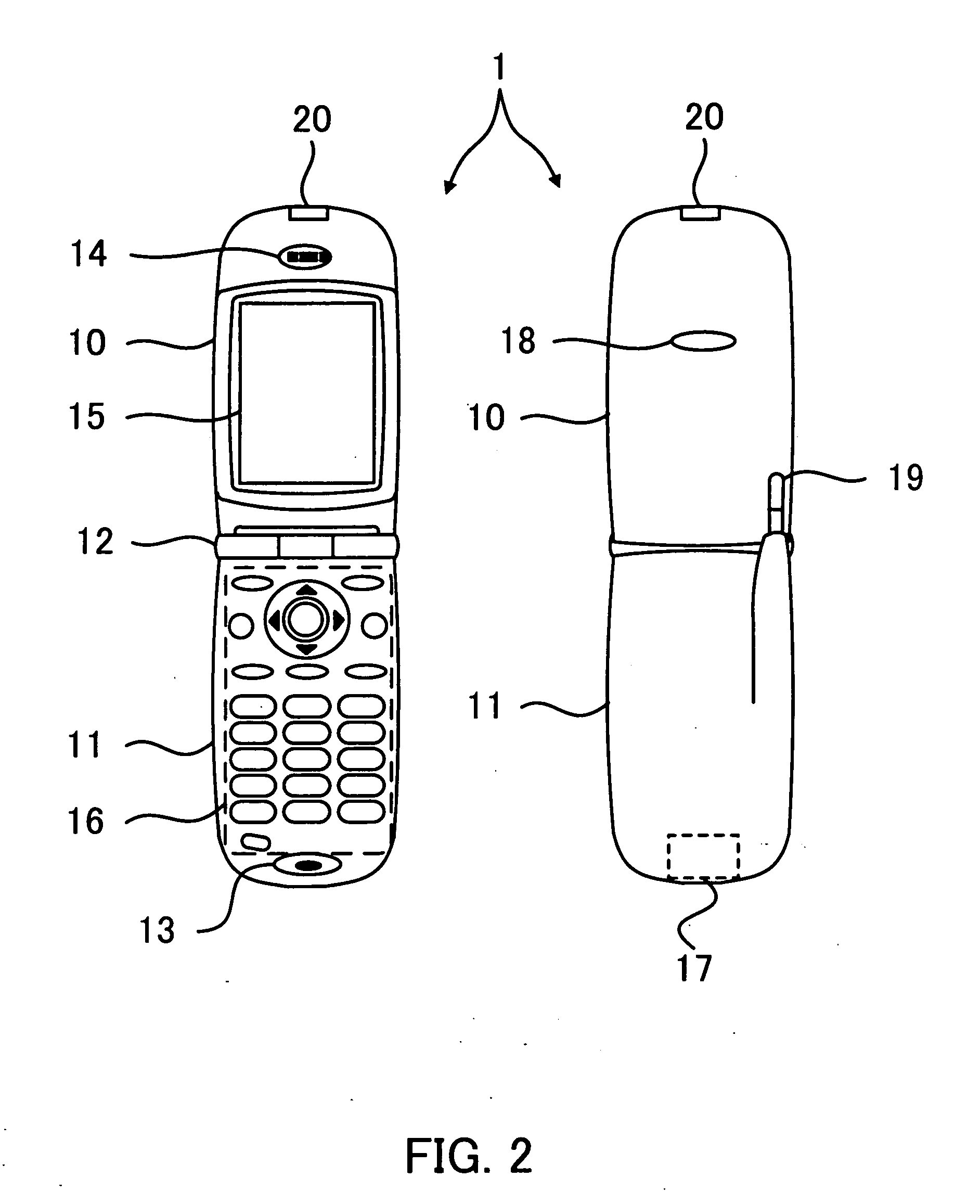

Apparatus and method for utilizing data block of right to decrypt content

Provided is a content decrypting apparatus given a bunch of secret keys and capable of decrypting a piece of content stored in a storage medium using a data block representing a right of decryption, including a communication circuit configured to request and receive the data block including a bunch of distributed keys and an allowed number of times of decryption, a first controller configured to decrypt a title key read from the storage medium with one of the distributed keys and one of the secret keys, and to decrypt the content with the decrypted title key, and a second controller configured, upon receiving a request for a data block transfer, to produce a secondary data block by copying the data block stored in the memory, and to move at least a portion of the allowed number of times of decryption to the secondary data block.

Owner:KK TOSHIBA

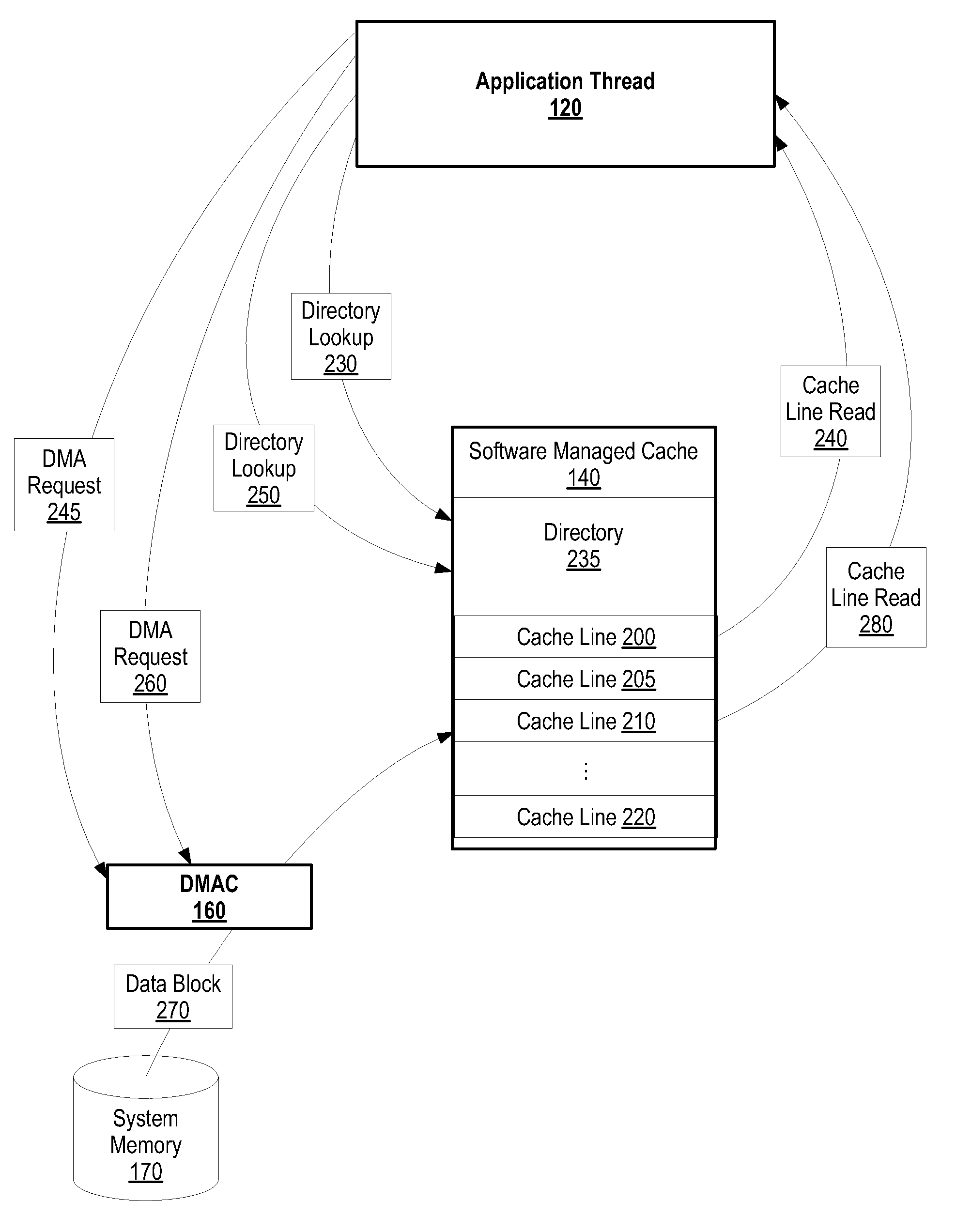

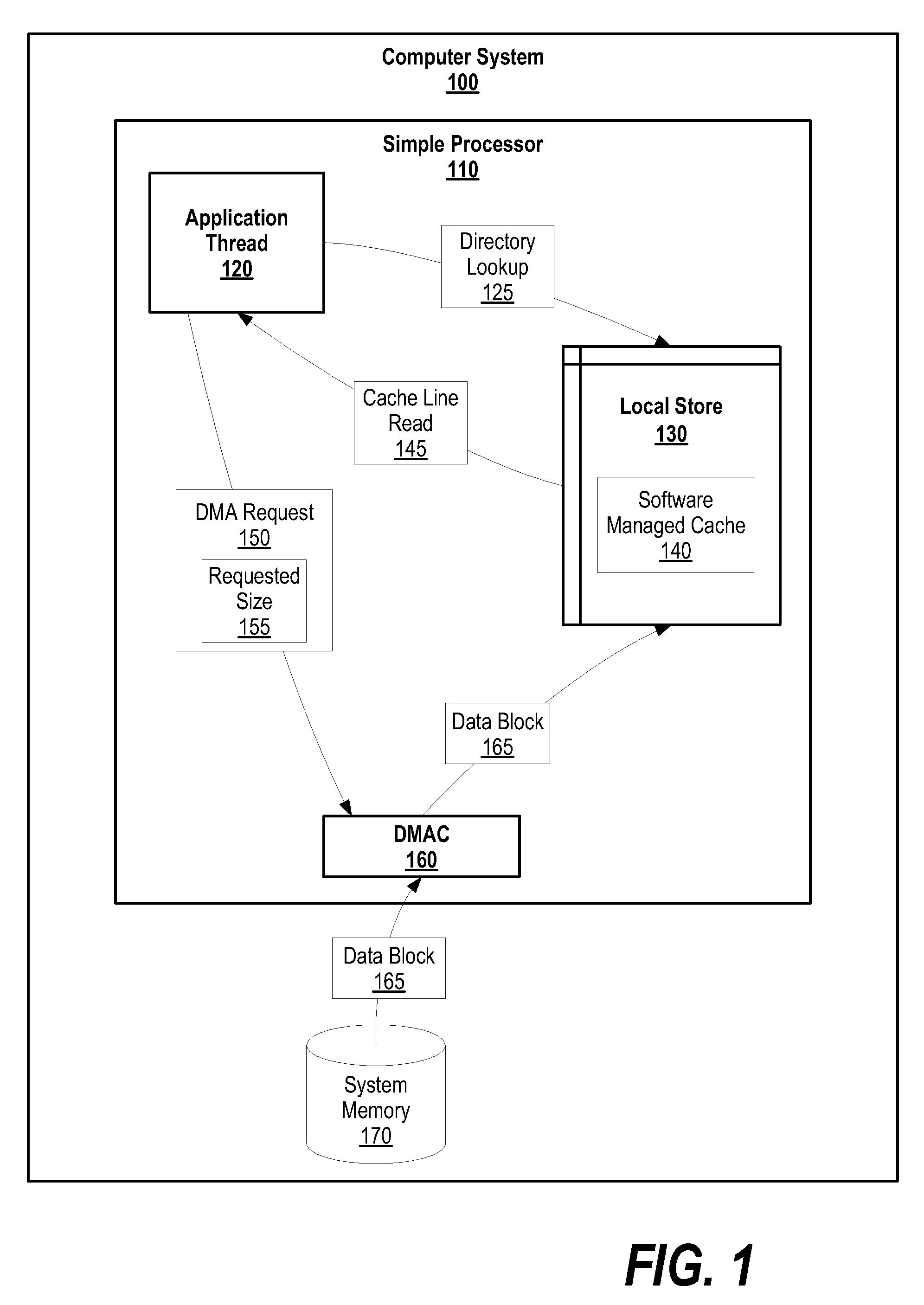

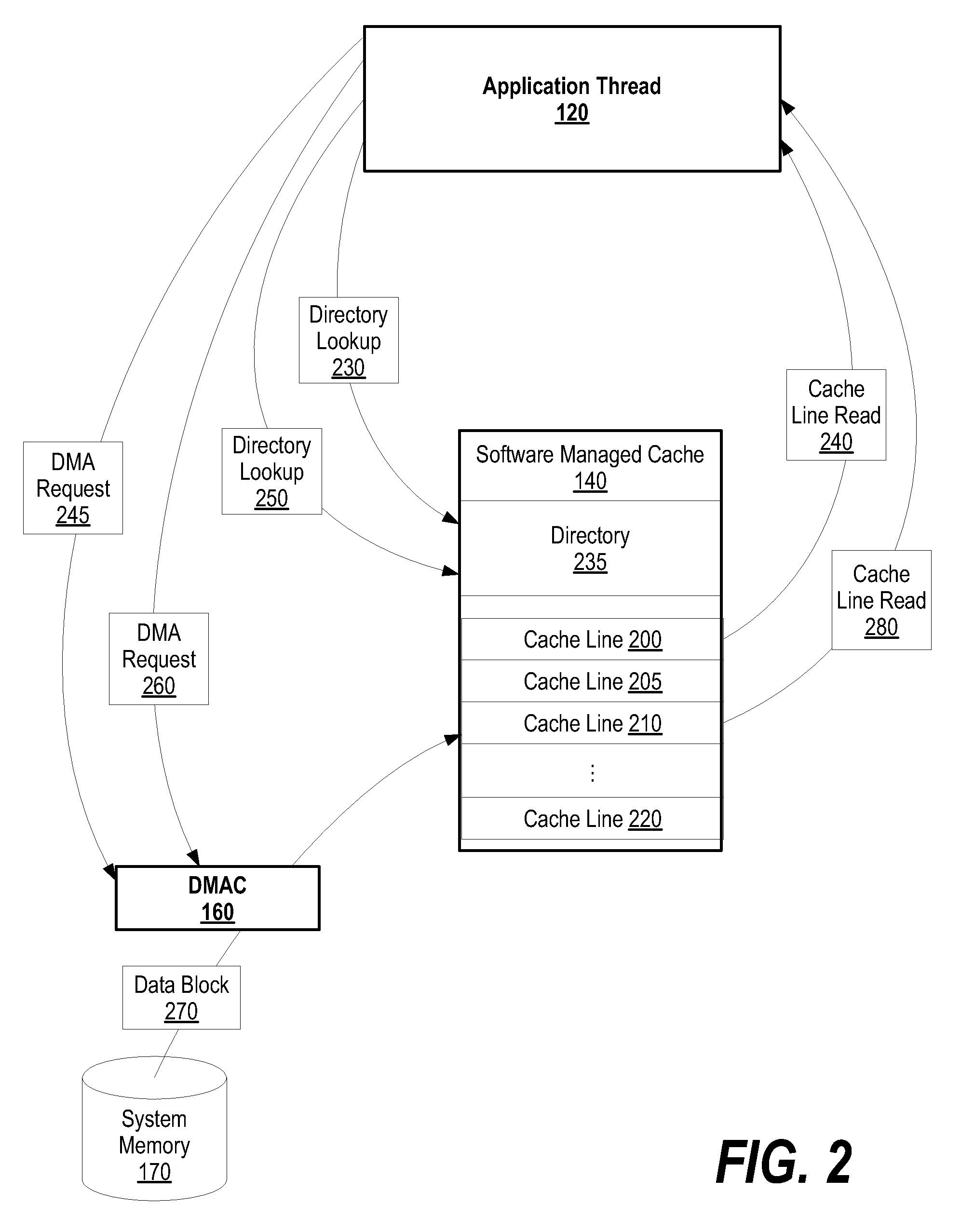

System and method for efficient implementation of software-managed cache

InactiveUS20080209127A1Memory adressing/allocation/relocationDigital computer detailsApplication softwareConditional branch

A system and method for an efficient implementation of a software-managed cache is presented. When an application thread executes on a simple processor, the application thread uses a conditional data select instruction for eliminating a conditional branch instruction when accessing a software-managed cache. An application thread issues a conditional data select instruction (DMA transfer) after a cache directory lookup, wherein the size of the requested data is dependent upon the outcome of the cache directory lookup. When the cache directory lookup results in a cache hit, the application thread requests a transfer of zero bits of data, which results in a DMA controller (DMAC) performing a no-op instruction. When the cache directory lookup results in a cache miss, the application thread requests a data block transfer the size of a corresponding cache line.

Owner:IBM CORP

Method for transferring thin film to substrate

Owner:APPLE INC

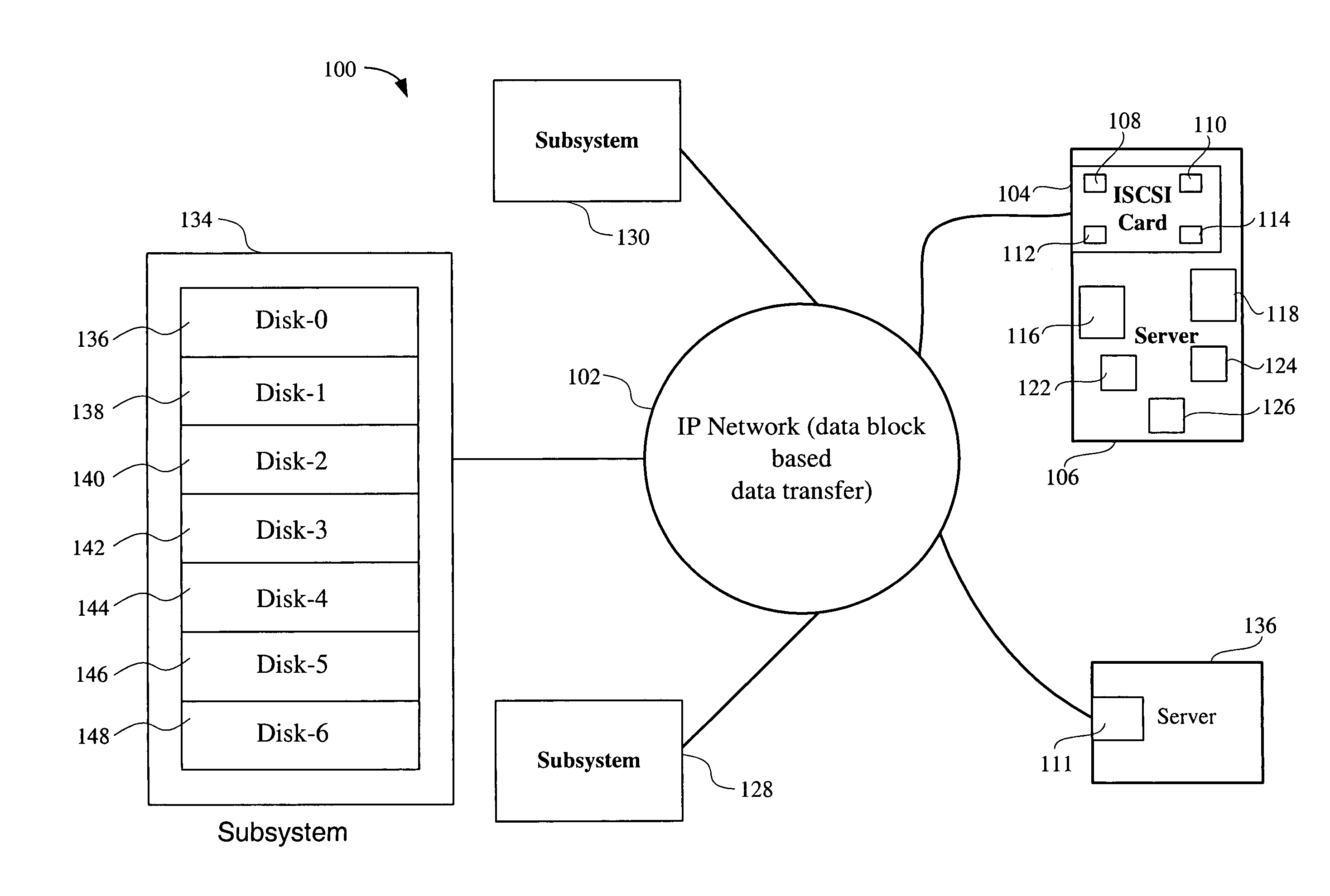

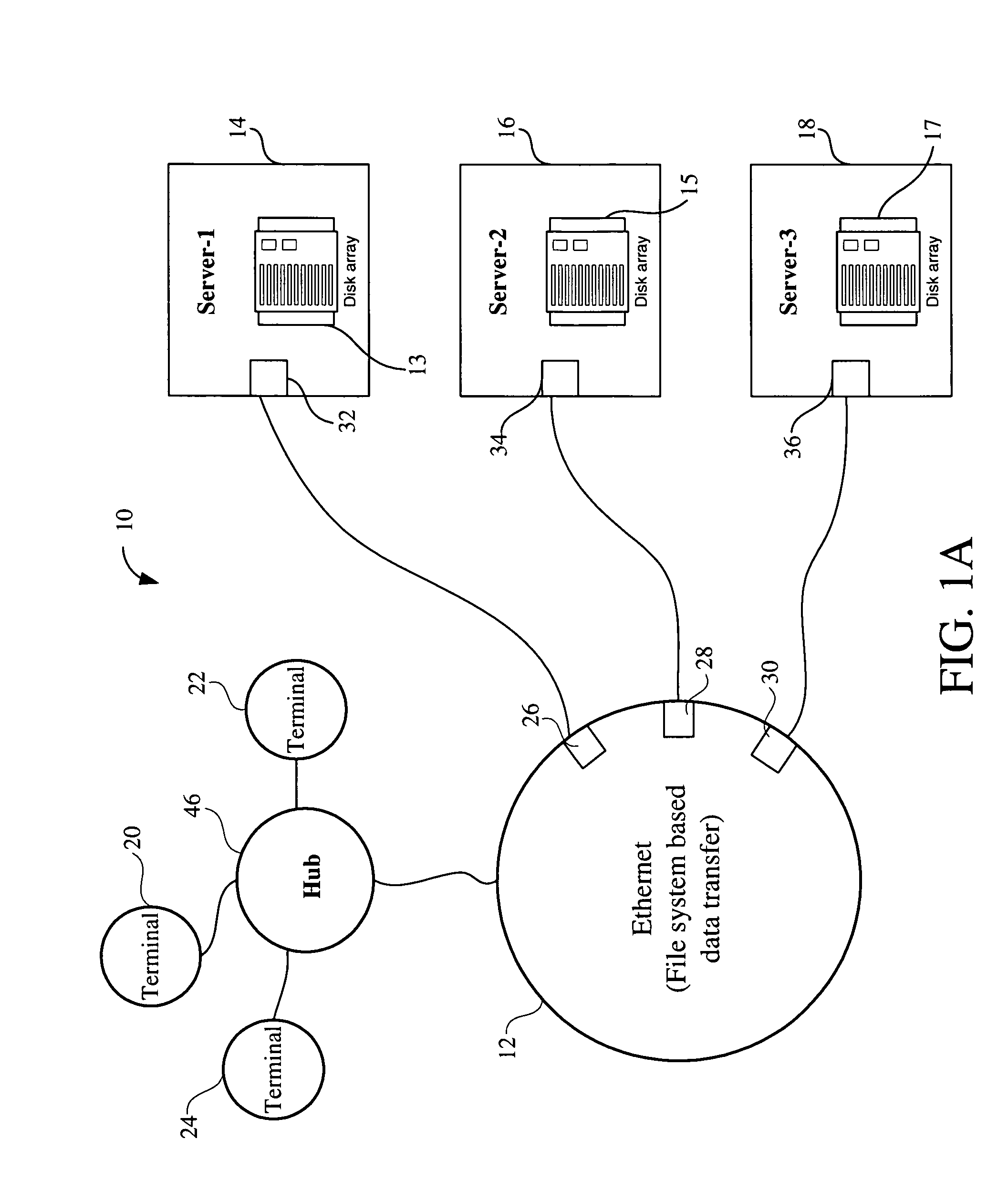

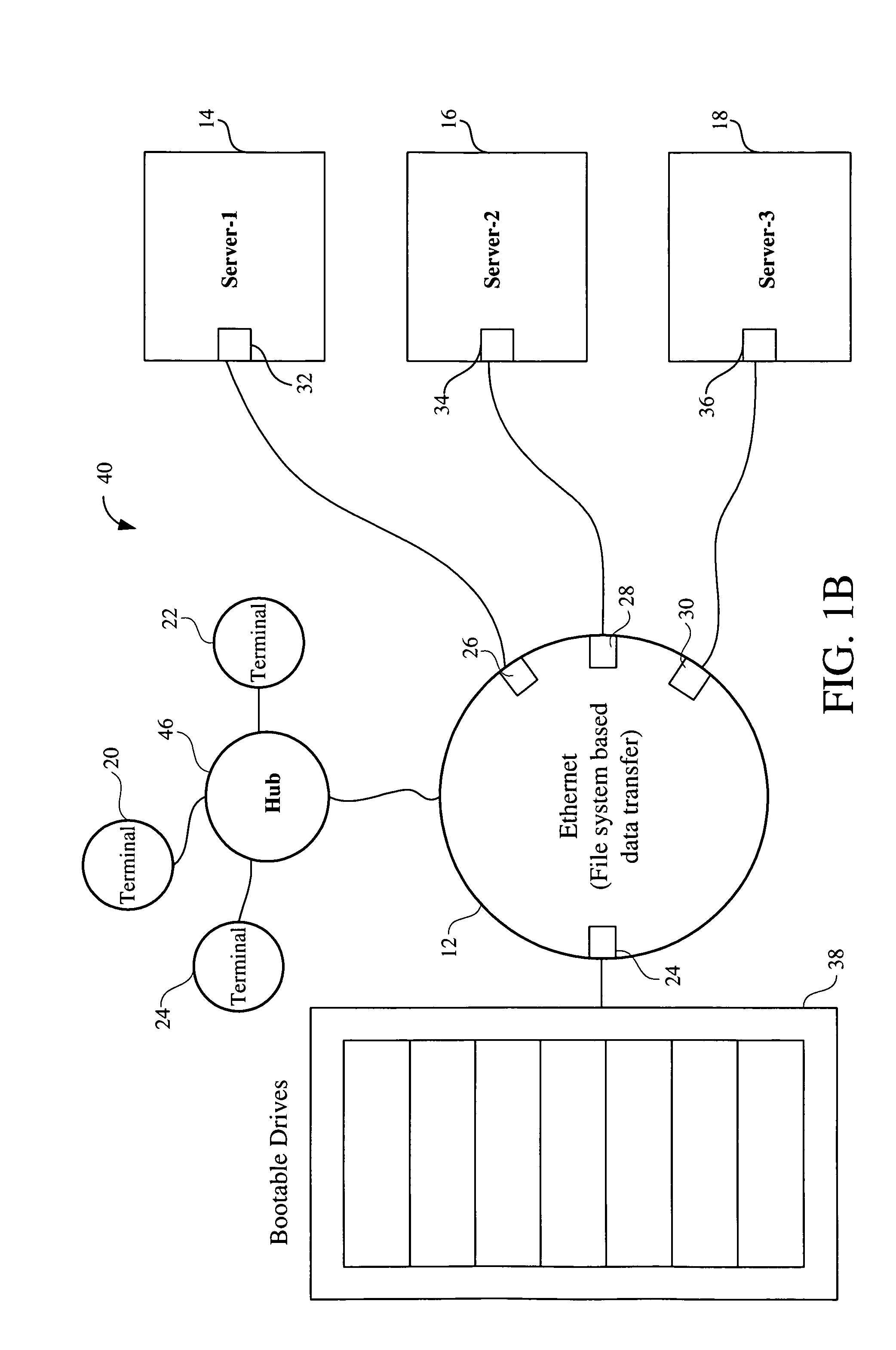

Methods for expansive netboot

ActiveUS7234053B1Easy to storeUser identity/authority verificationDigital computer detailsOperational systemIp address

A method to boot up a server using a target storage device over a network is provided. The method includes installing an operating system by storing the operating system and a dynamic configuration program in the target storage device on the network where the location of the target device is designated by an internet protocol (IP) address. The method also includes accessing the operating system on the target storage device using the IP address and the dynamic configuration program, the accessing occurring through data block transfers.

Owner:PMC-SIERRA

Synchronous Page-Mode Phase-Change Memory with ECC and RAM Cache

Phase-change memory (PCM) cells store data using alloy resistors in high-resistance amorphous and low-resistance crystalline states. The time of the memory cell's set-current pulse can be 100 ns, much longer than read or reset times. The write time thus depends on the write data and is relatively long. A page-mode caching PCM device has a lookup table (LUT) that caches write data that is later written to an array of PCM banks. Host data is latched into a line FIFO and written into the LUT, reducing write delays to the relatively slow PCM. Host read data can be supplied by the LUT or fetched from the PCM banks. A multi-line page buffer between the PCM banks and LUT allows for larger block transfers using the LUT. Error-correction code (ECC) checking and generation is performed for data in the LUT, hiding ECC delays for data writes into the PCM banks.

Owner:SUPER TALENT TECH CORP

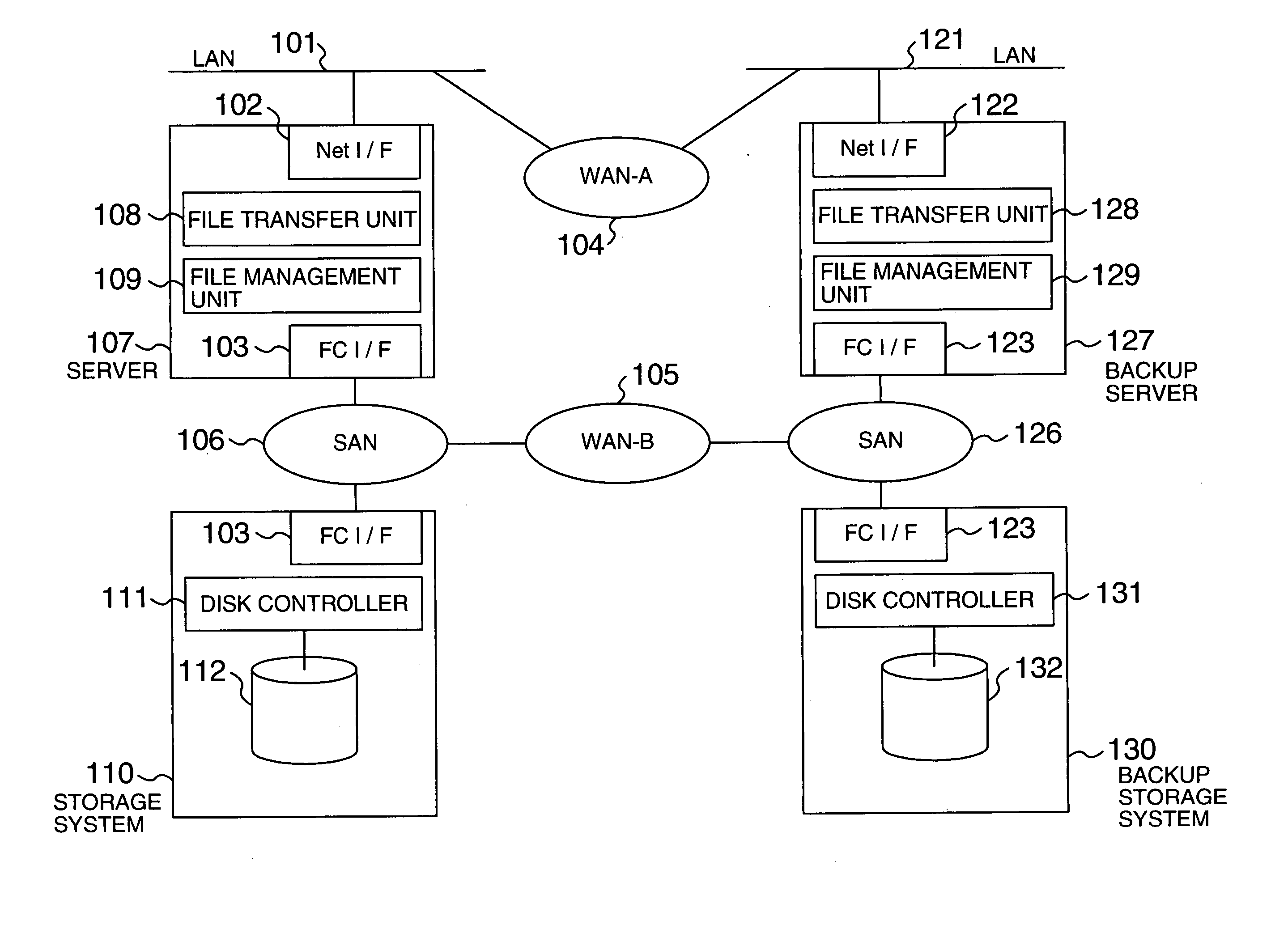

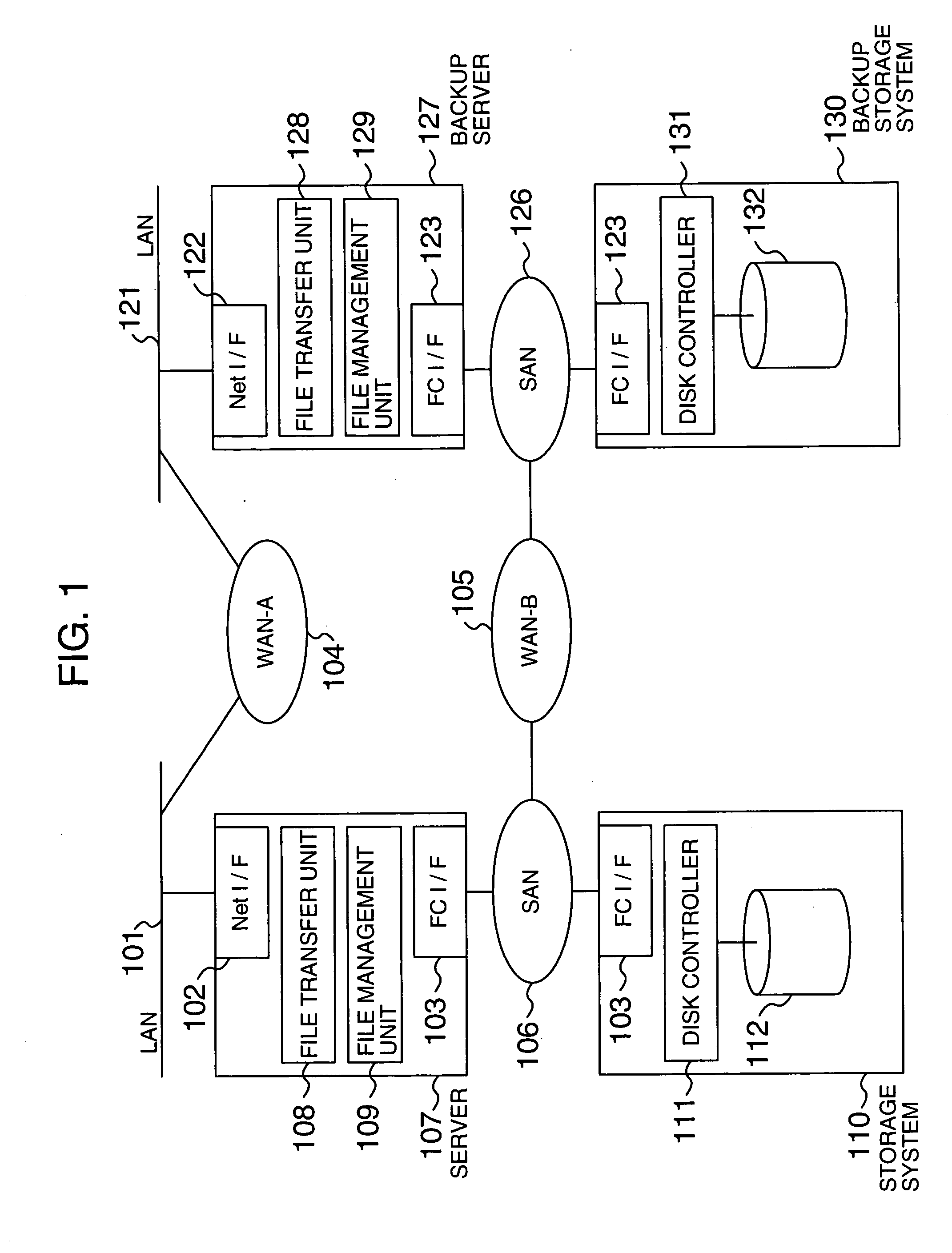

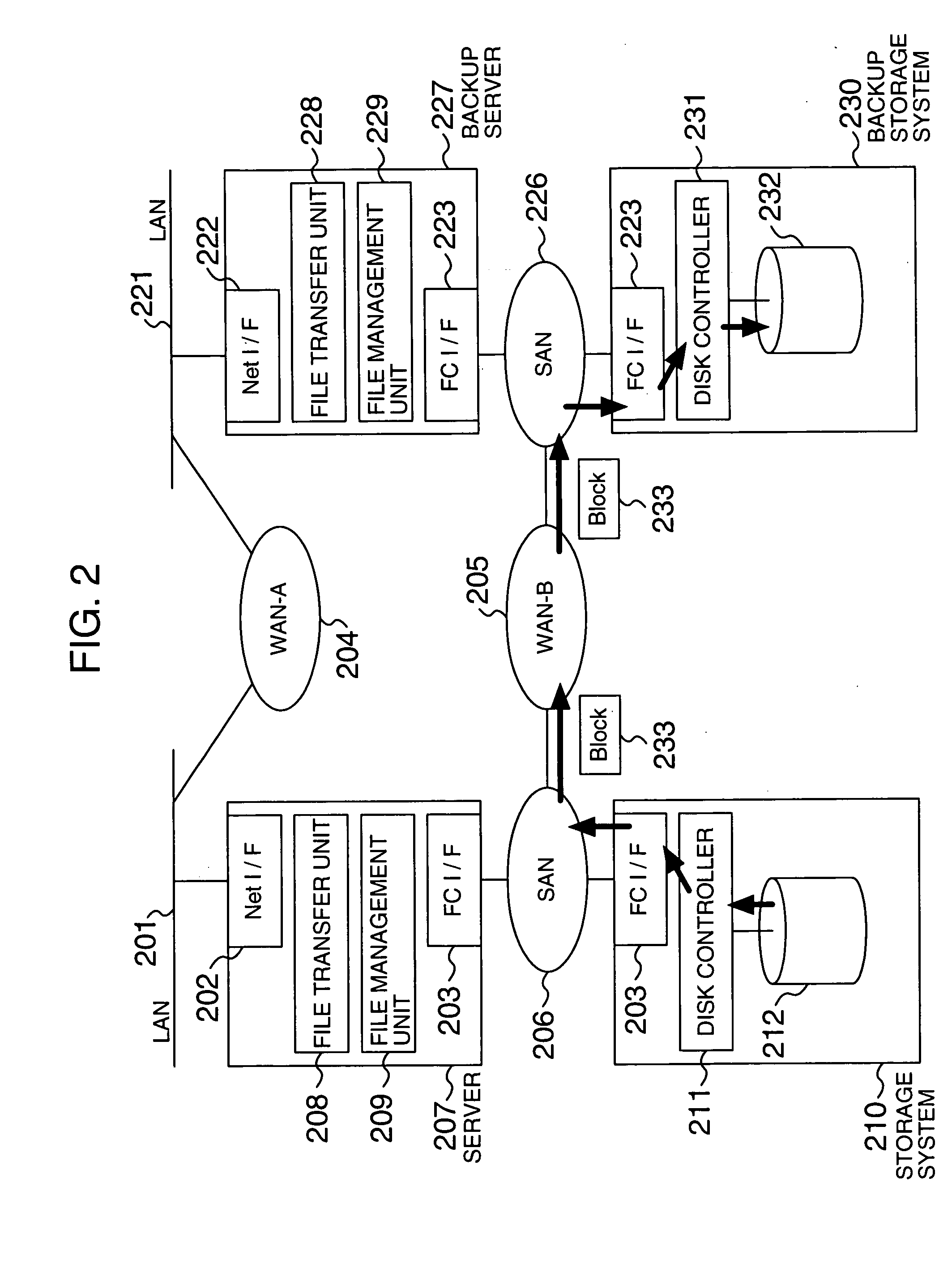

Data transfer method and system

InactiveUS20050144254A1Increase speedImprove reliabilityInput/output to record carriersMultiple digital computer combinationsTransmission protocolComputerized system

A computer system that transfers data from a first storage unit to a second storage unit via a network. The computer system includes a first controller that transfers data, stored in the first storage unit, to the second storage unit using a block transfer protocol; a table that associates a file composed of a plurality of blocks of data with blocks of data constituting the file; and a second controller that, in response to information that identifies a block from the first controller, identifies a file corresponding to the block using the table and transfers the identified file to the second storage unit using a file transfer protocol.

Owner:HITACHI LTD

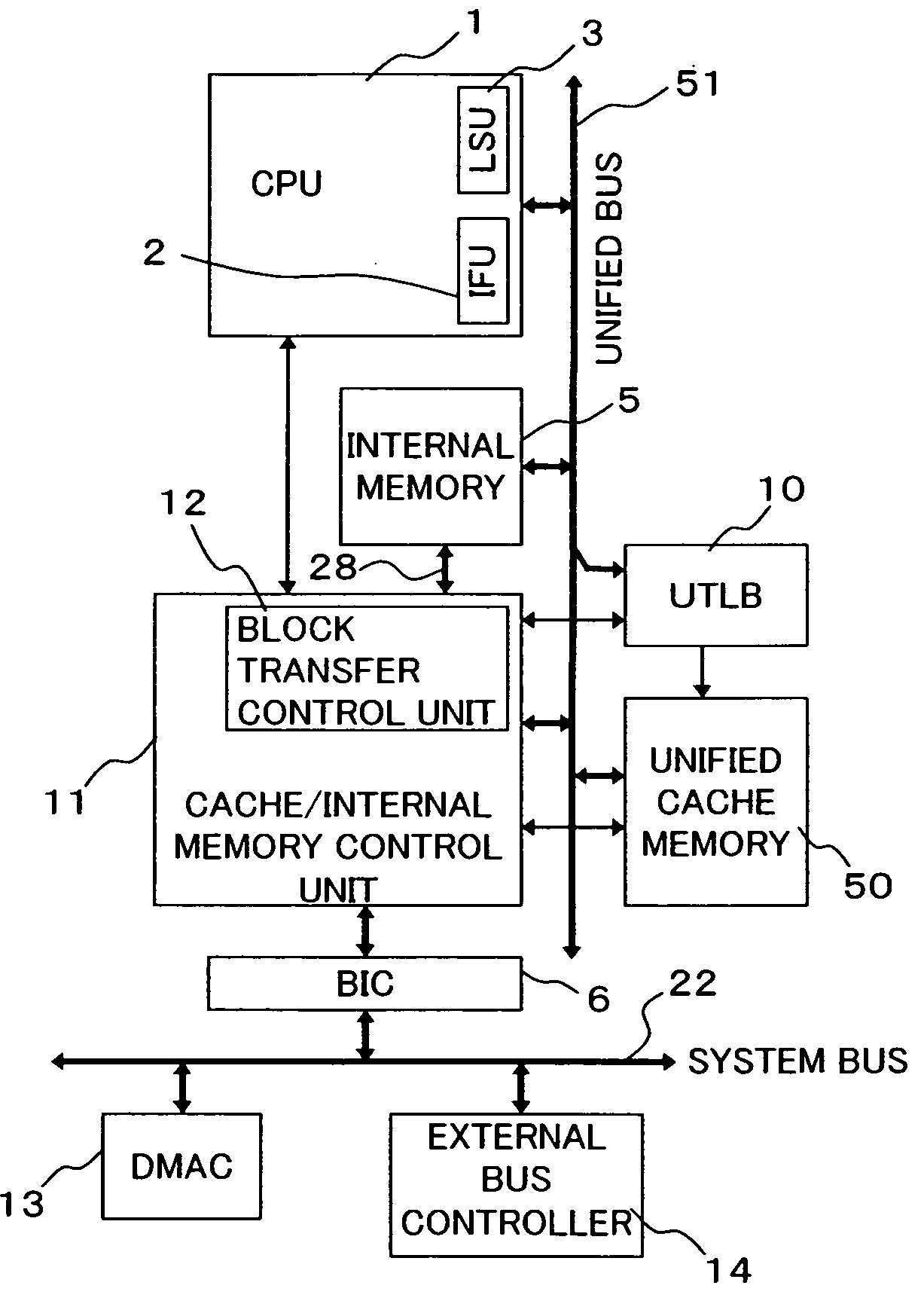

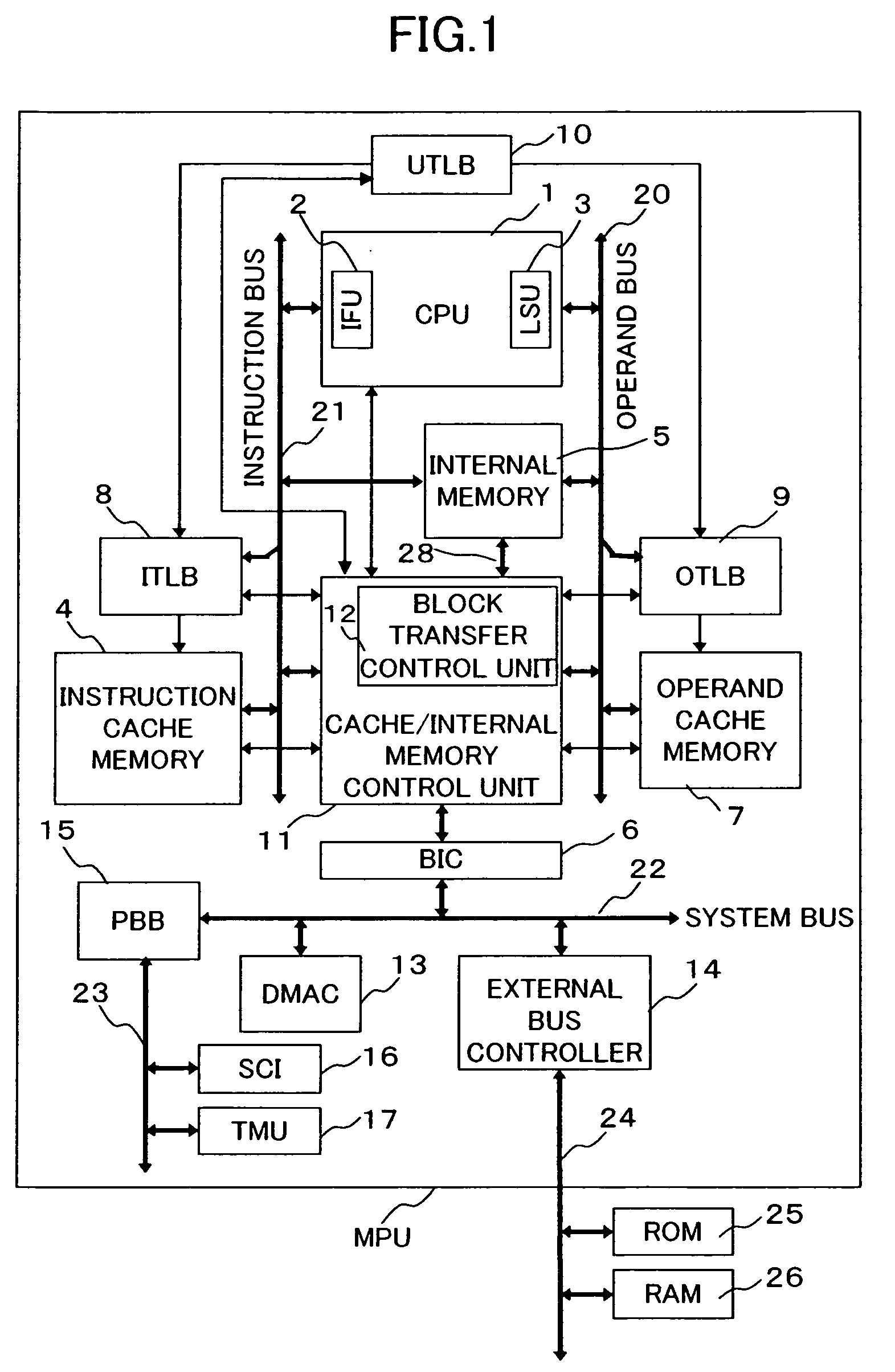

Data processor

InactiveUS20050172049A1Increase speedImprove efficiencyMemory adressing/allocation/relocationMachine execution arrangementsInternal memoryExternal storage

A data processor arranged so that a block transfer control unit (12) can initiate block transfer in response to the execution of a particular instruction by a CPU, in order to increase the speed and efficiency of the data transfer between a CPU-accessible internal memory (5) and an external memory (25,26). When an address specified by the addressing field coincides with an address mapped to the internal memory, the particular instruction sets a logical address as one of the transfer source or transfer destination addresses of the data block transfer. The internal memory is allotted to a part of virtual address space; the internal memory allotted so is associated with the physical address space, to which the external memory set as the other address is allotted, by a process in which a TLB is used when the MMU is in ON, and a given register is used when the MMU is in OFF.

Owner:RENESAS ELECTRONICS CORP

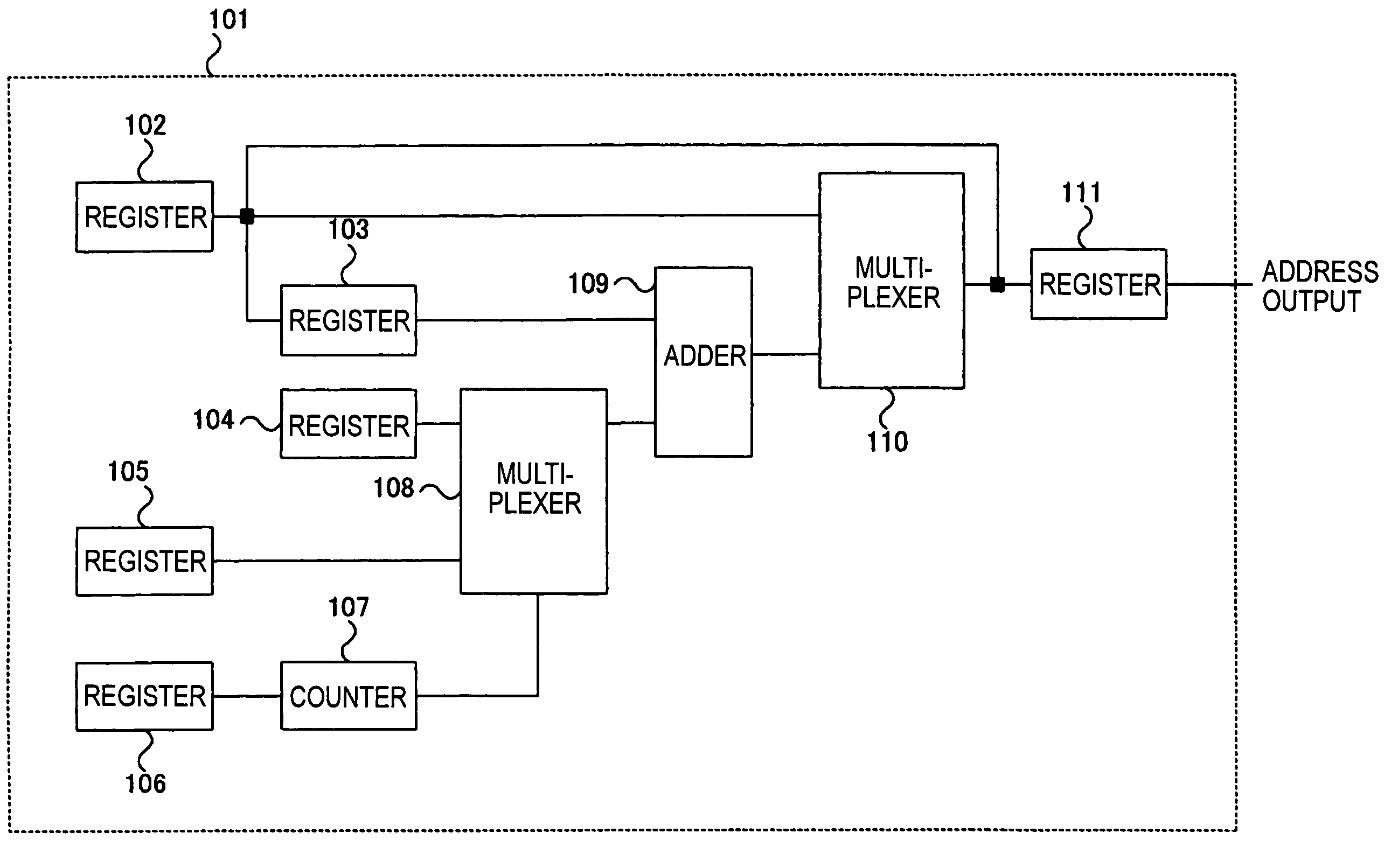

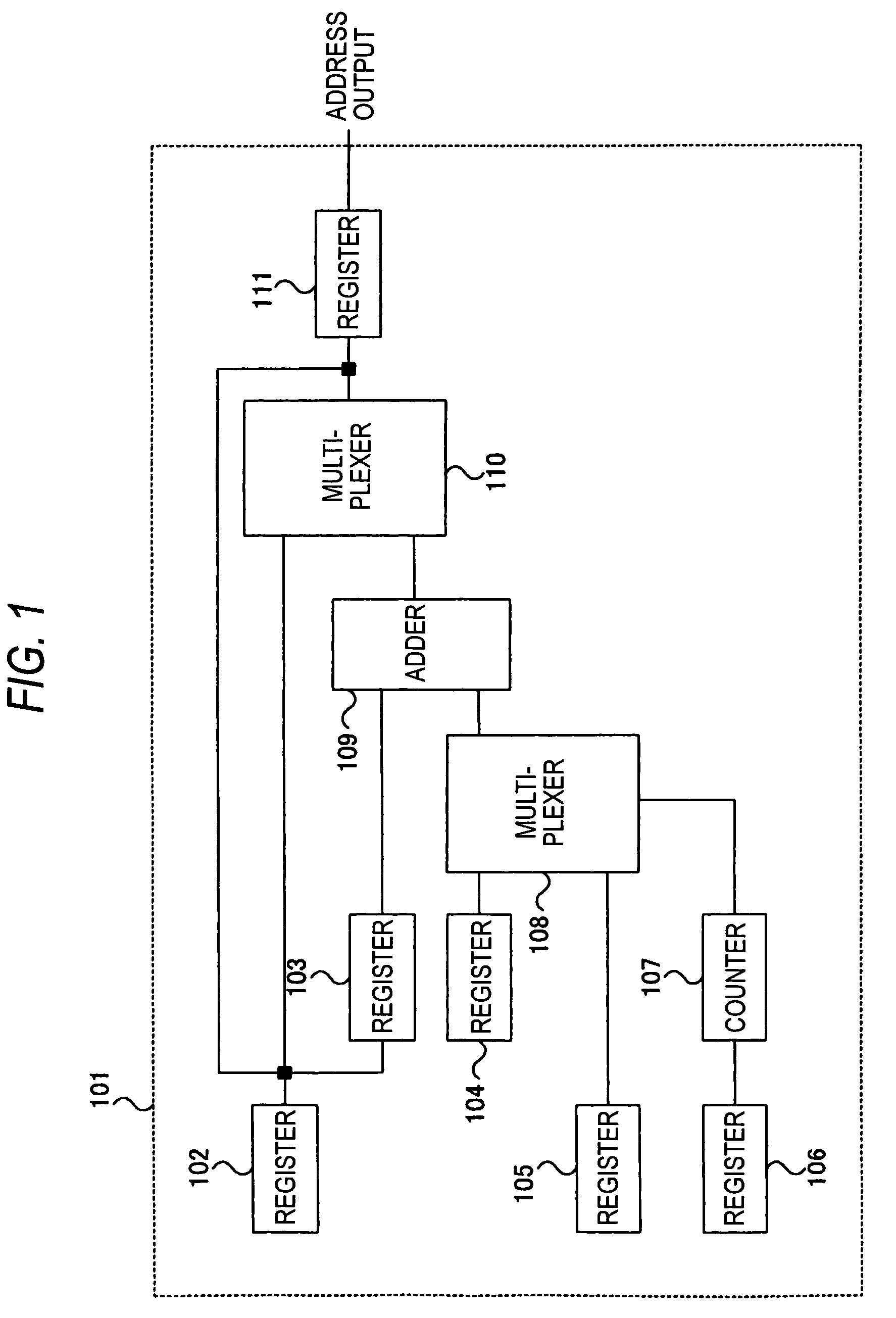

DMA controller providing for ring buffer and rectangular block transfers

ActiveUS7500028B2Reduce circuit sizeEliminate needInput/output processes for data processingData conversionComputer architectureProcessor register

Reducing the circuit scale by performing rectangular block transfer and ring buffer transfer in a same circuitThe inventive DMA controller includes a register for setting the start address of a ring buffer, a register for setting a current transfer address, a register for setting the number of DMA transfers from the start address to the end address, a register for setting the difference between the end address and the start address, and a counter for counting the number of DMA transfers set to the register for setting the number of DMA transfers from the start address to the end address. In the DMA transfer of a rectangular area, the number of DMA transfers in a contiguous area is set to the register for setting the number of DMA transfers from the start address to the end address and the address increment of a non-contiguous area to the register for setting the difference between the end address and the start address. At the end of counting by the counter 107, the value of the register 103 and the value of the register 105 are summed to provide a next address.

Owner:SOCIONEXT INC

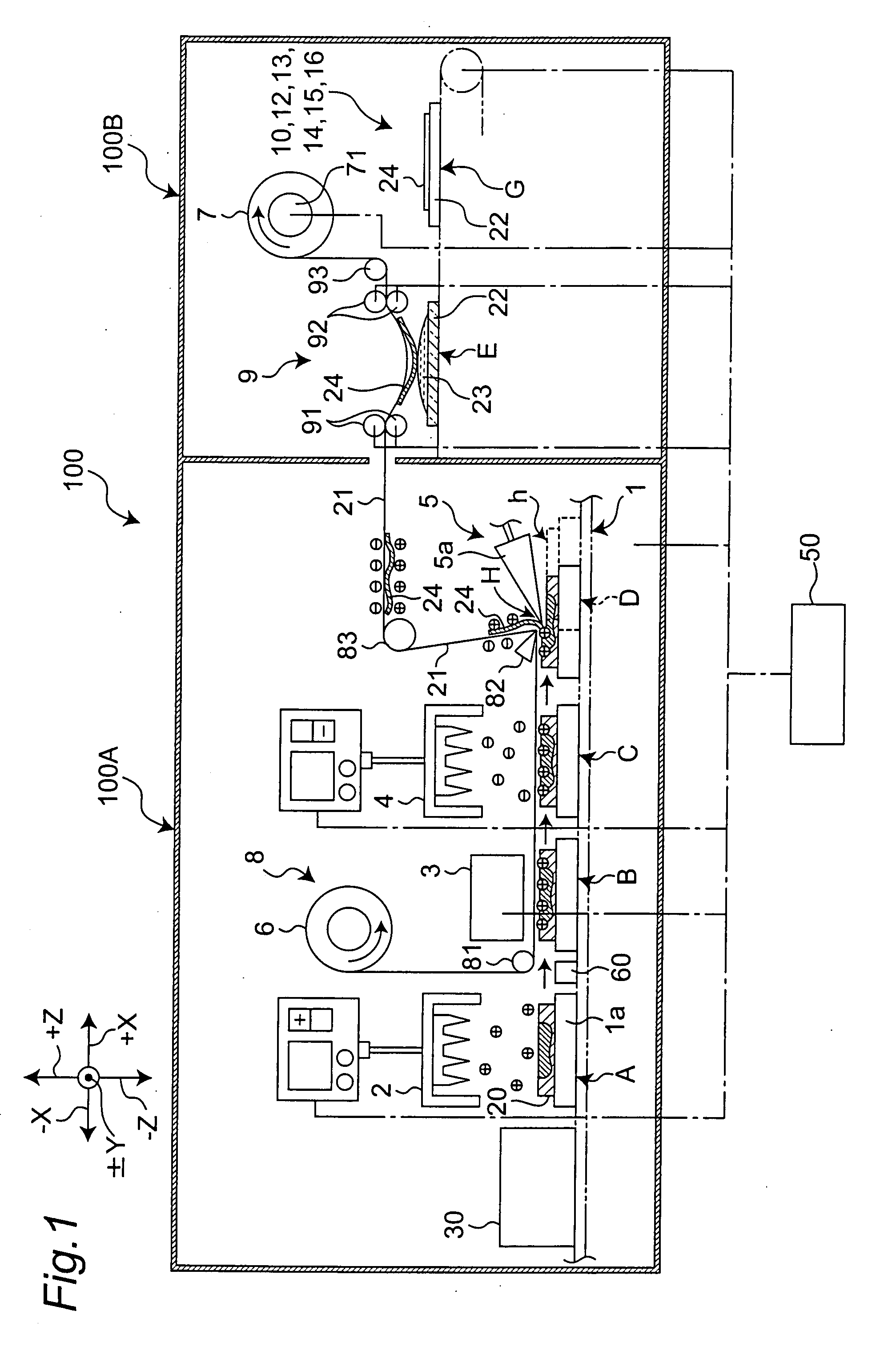

Apparatus and method for preparing sliced specimen

InactiveUS20080072723A1High precisionEasy to operateAnalysis using chemical indicatorsWithdrawing sample devicesEngineeringBlock transfer

Sliced specimens can be automatically and continuously prepared and burdens of an operator can be reduced while accuracy required for the sliced specimen is maintained. The sliced specimen is prepared by relatively moving a specimen block transfer section and a cutter, and when a slicing operation to adjust the height position of the specimen block is continuously performed so that the cutting surface of the specimen block is located at a sliceable position, the cutter is moved so that a contacting area of a blade edge of the cutter that firstly contacts the specimen block after the height position adjustment is sequentially changed, every time previously set number of times of slicing operation is completed. Thereafter, the height position of the blade edge of the cutter after the change is measured by a detector, and based on the measurement information of the detector, the sliceable position is corrected and the slicing operation is resumed.

Owner:KURASHIKI BOSEKI KK

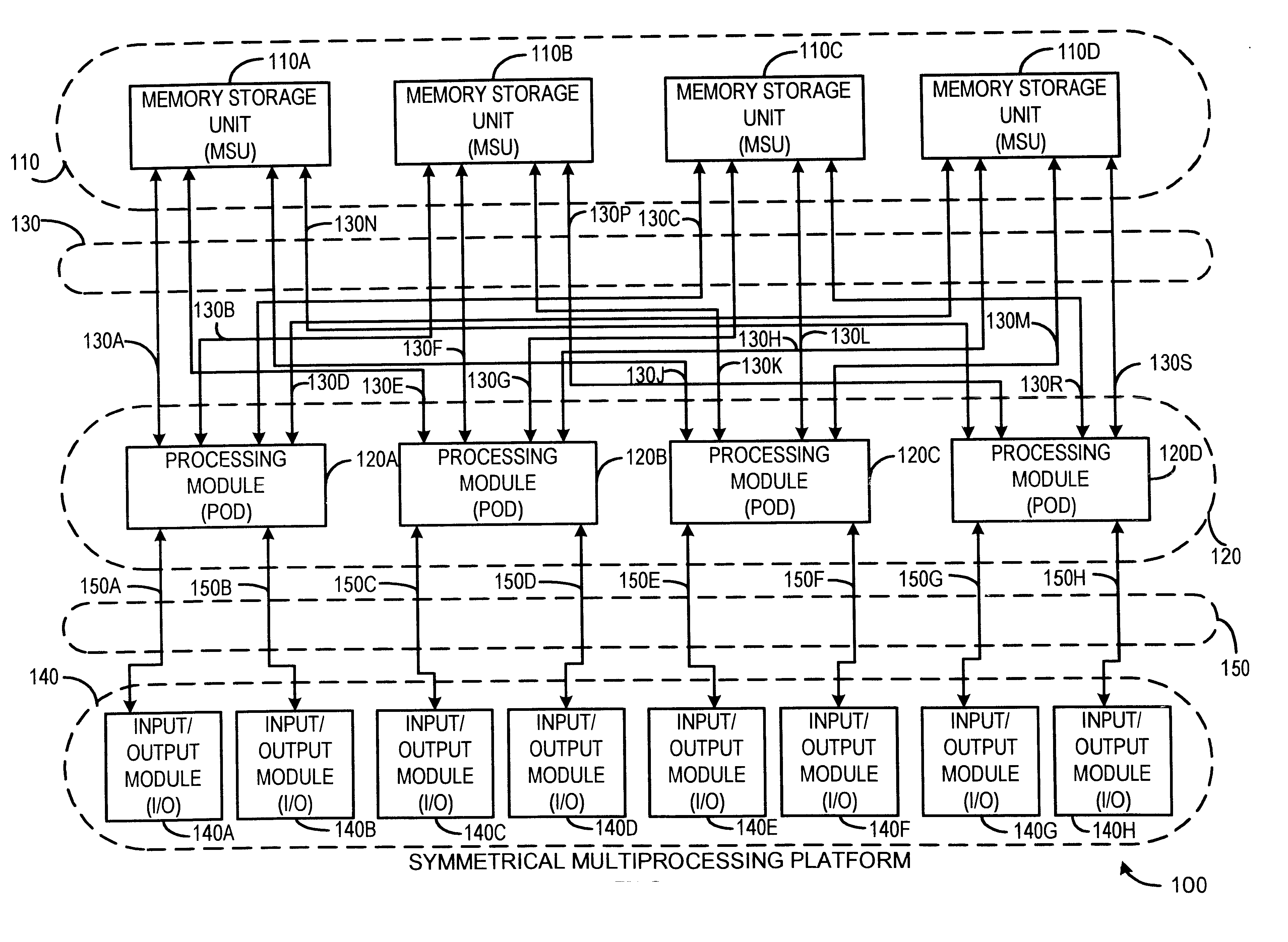

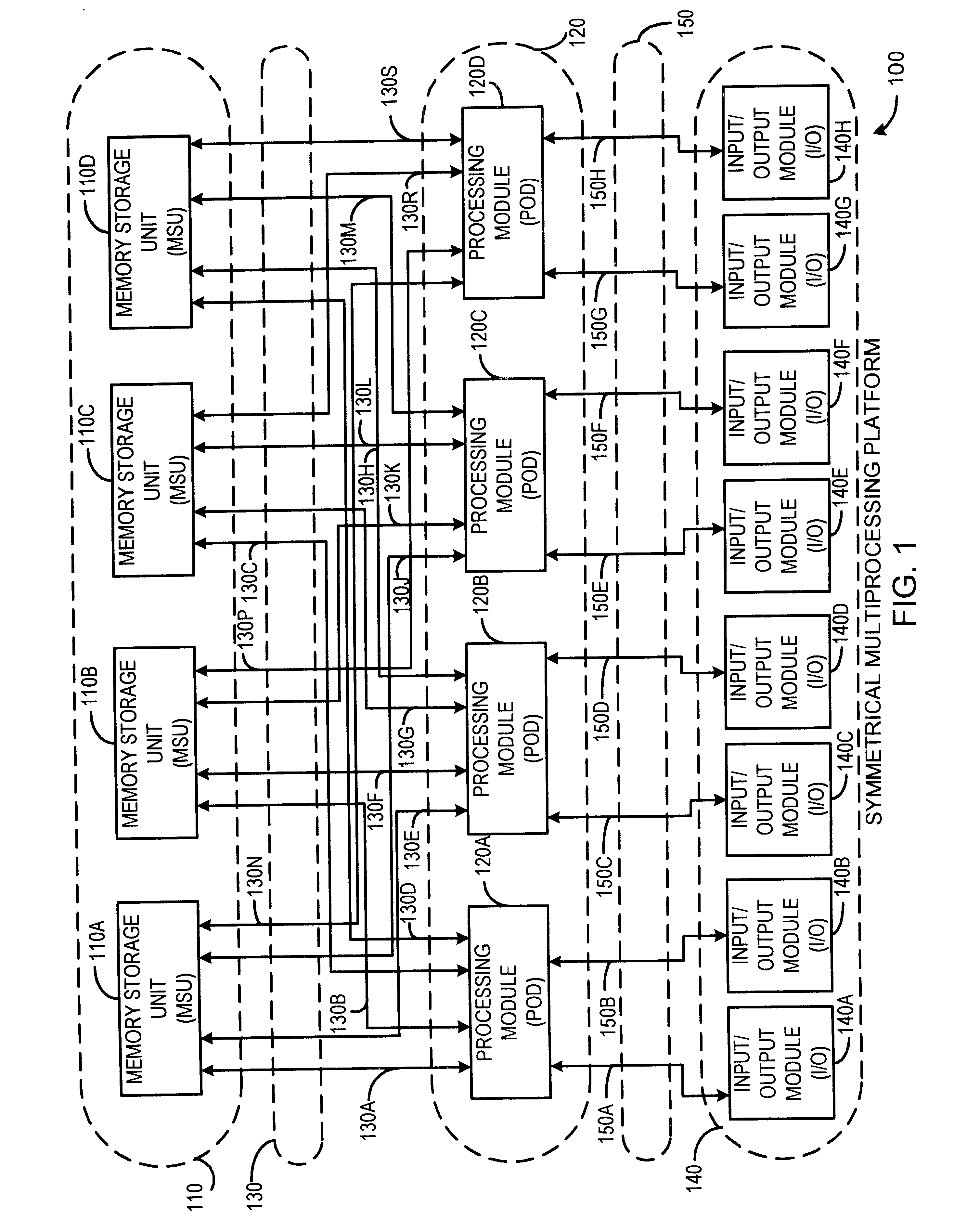

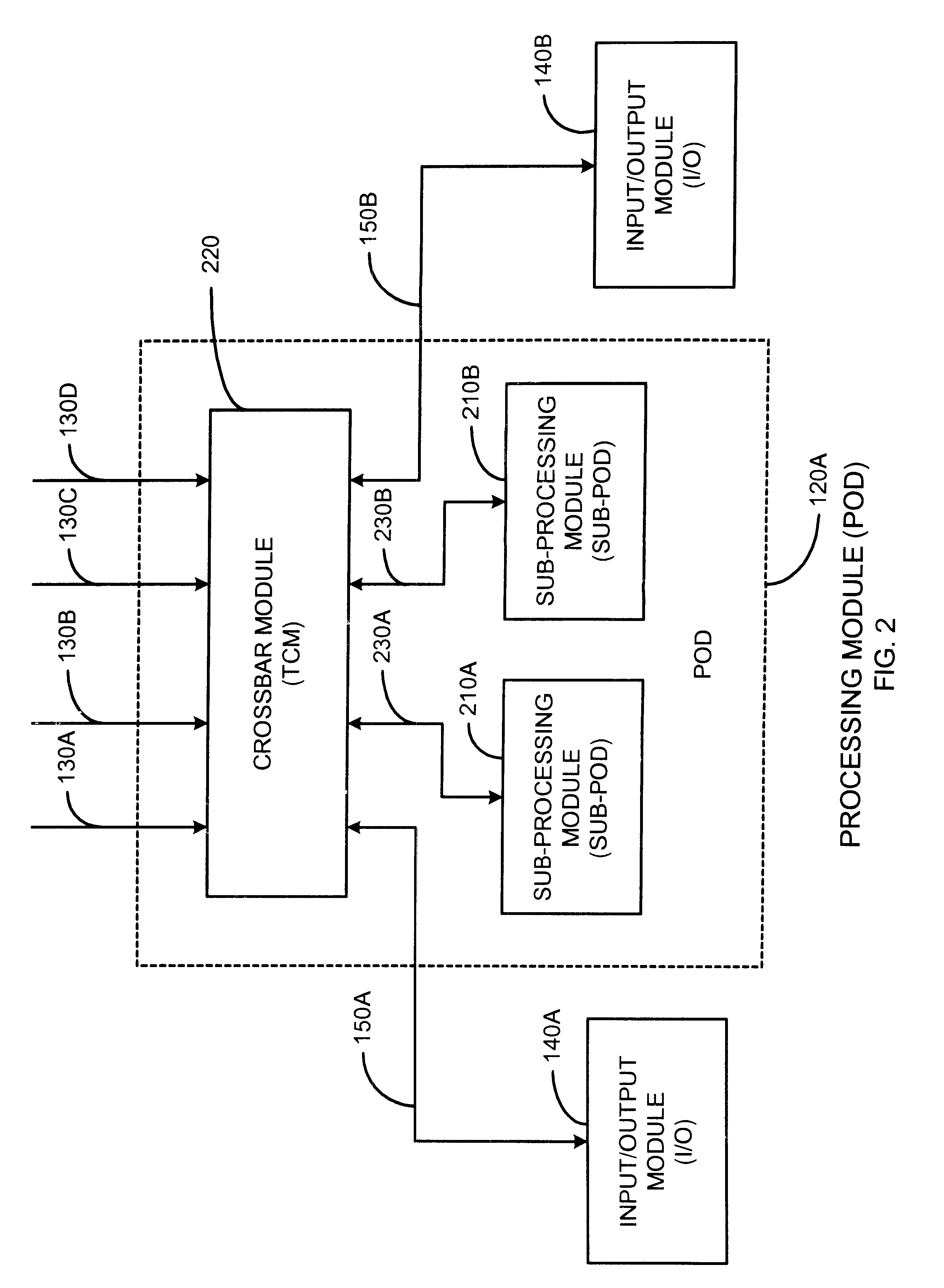

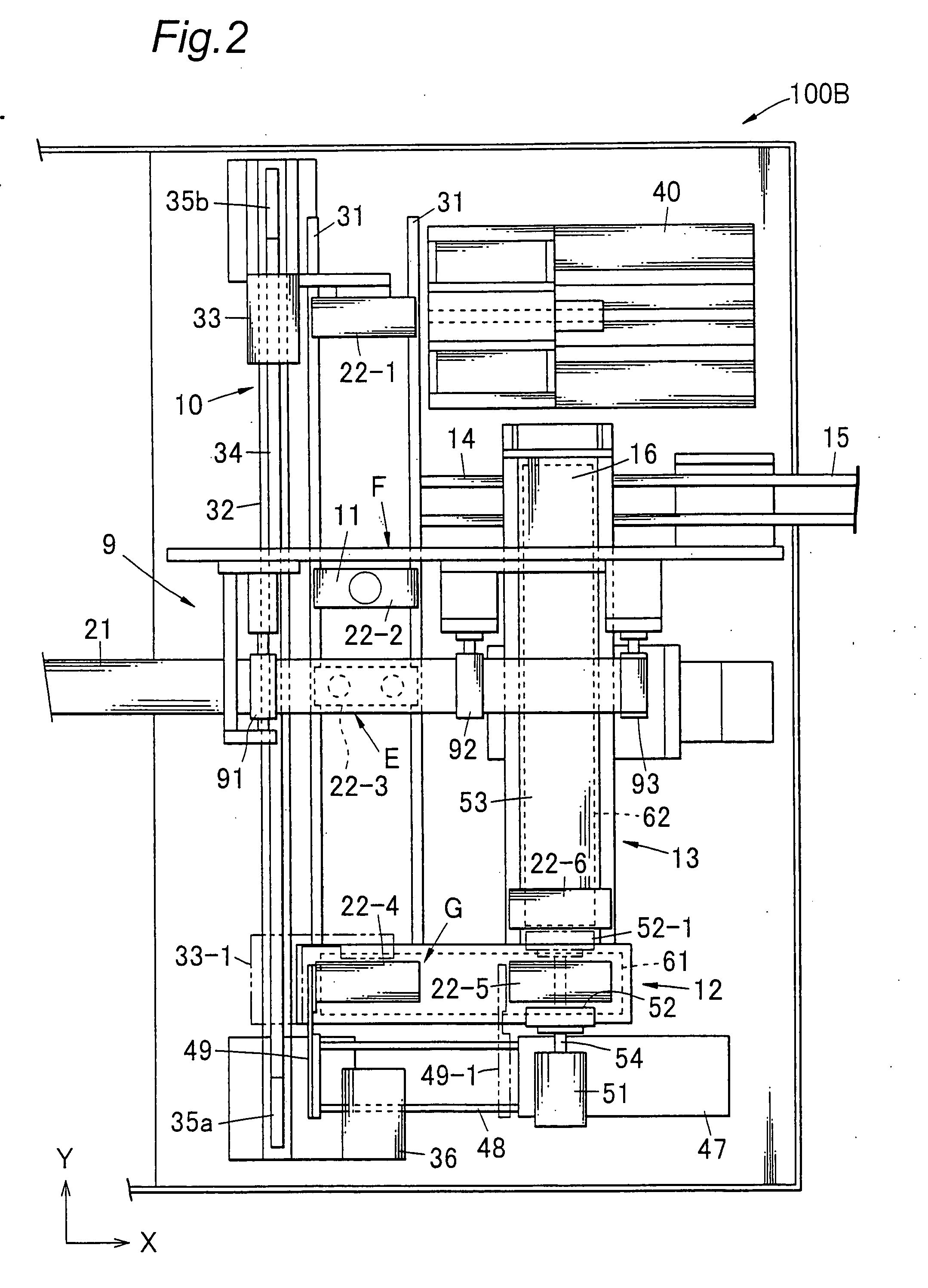

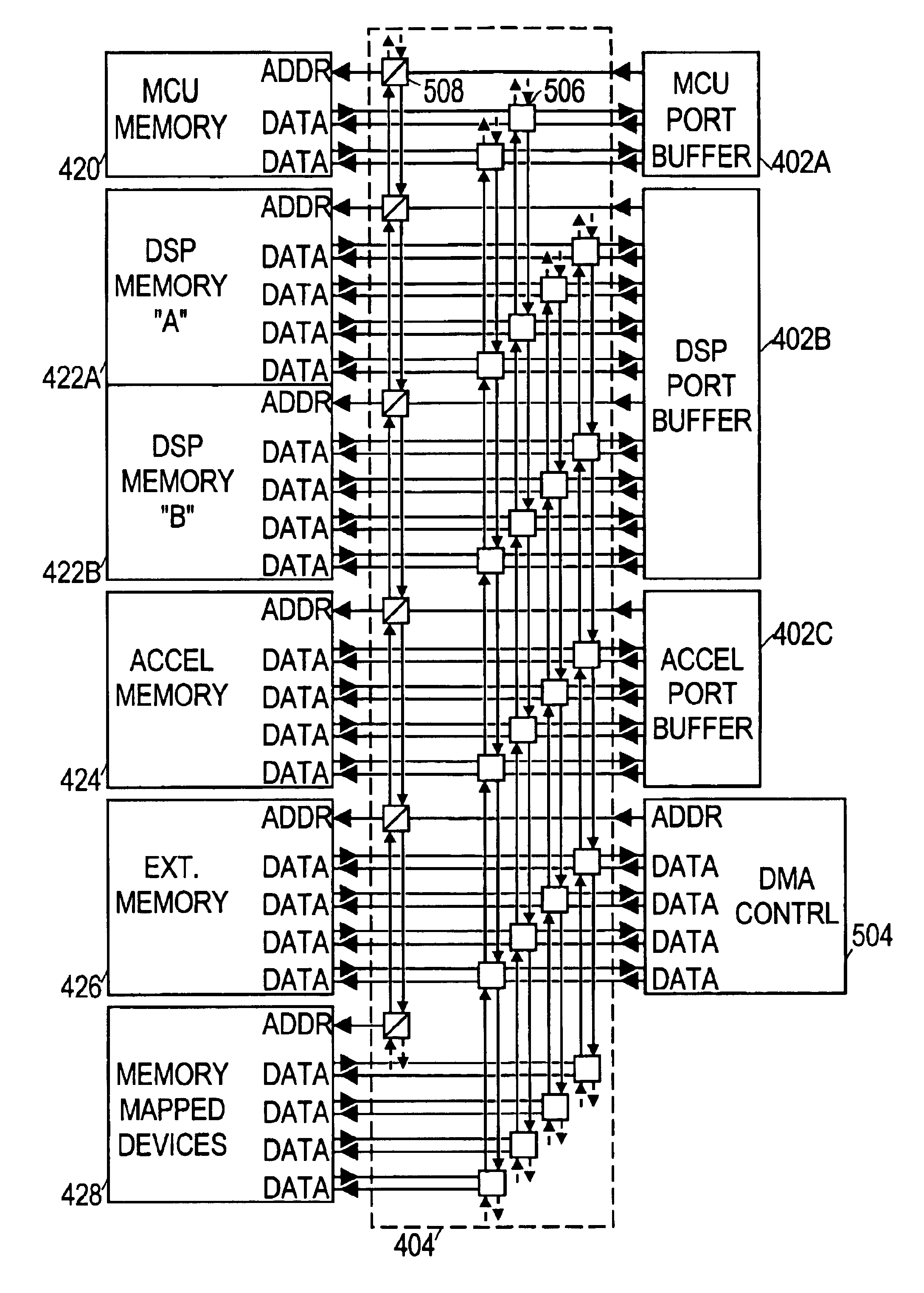

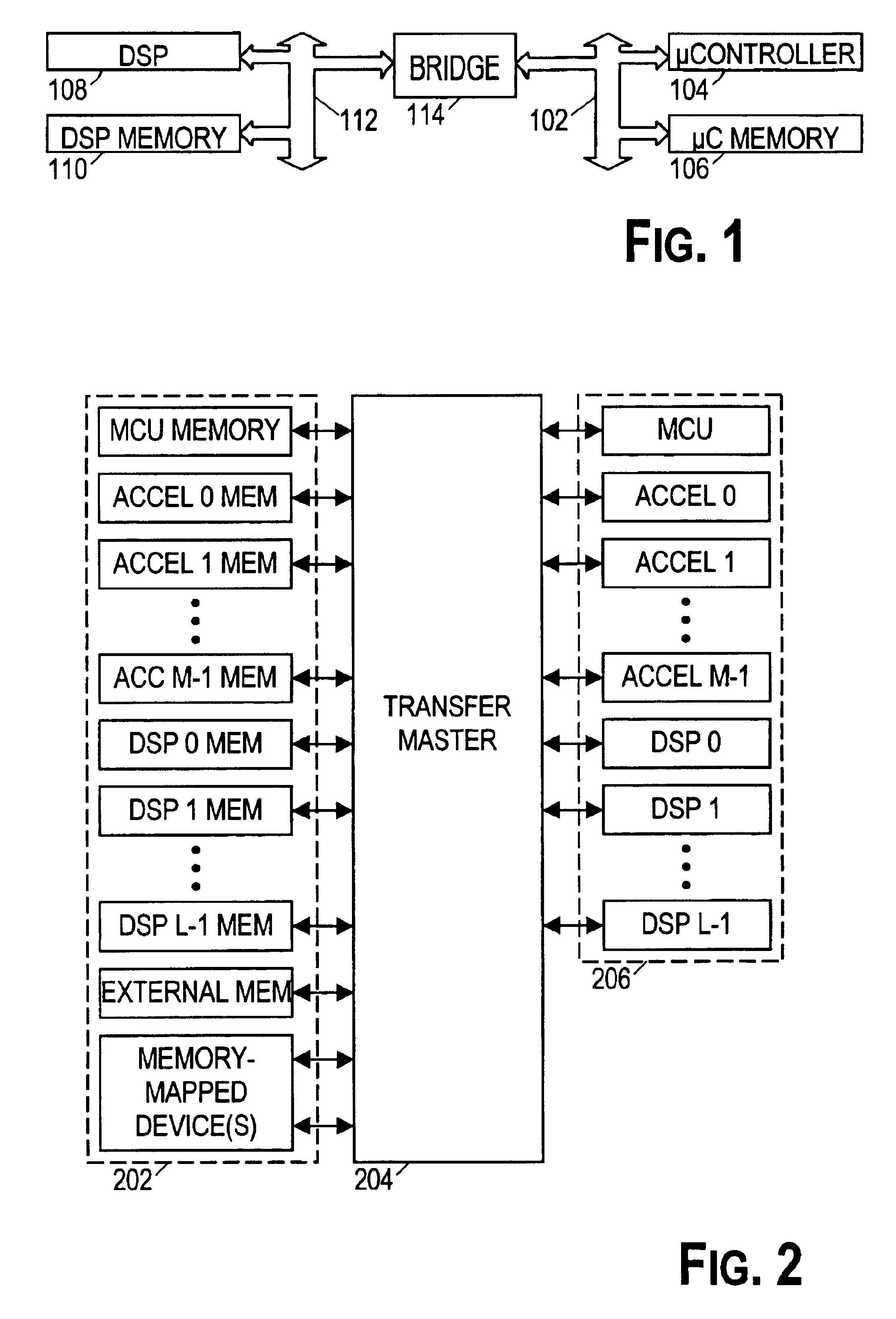

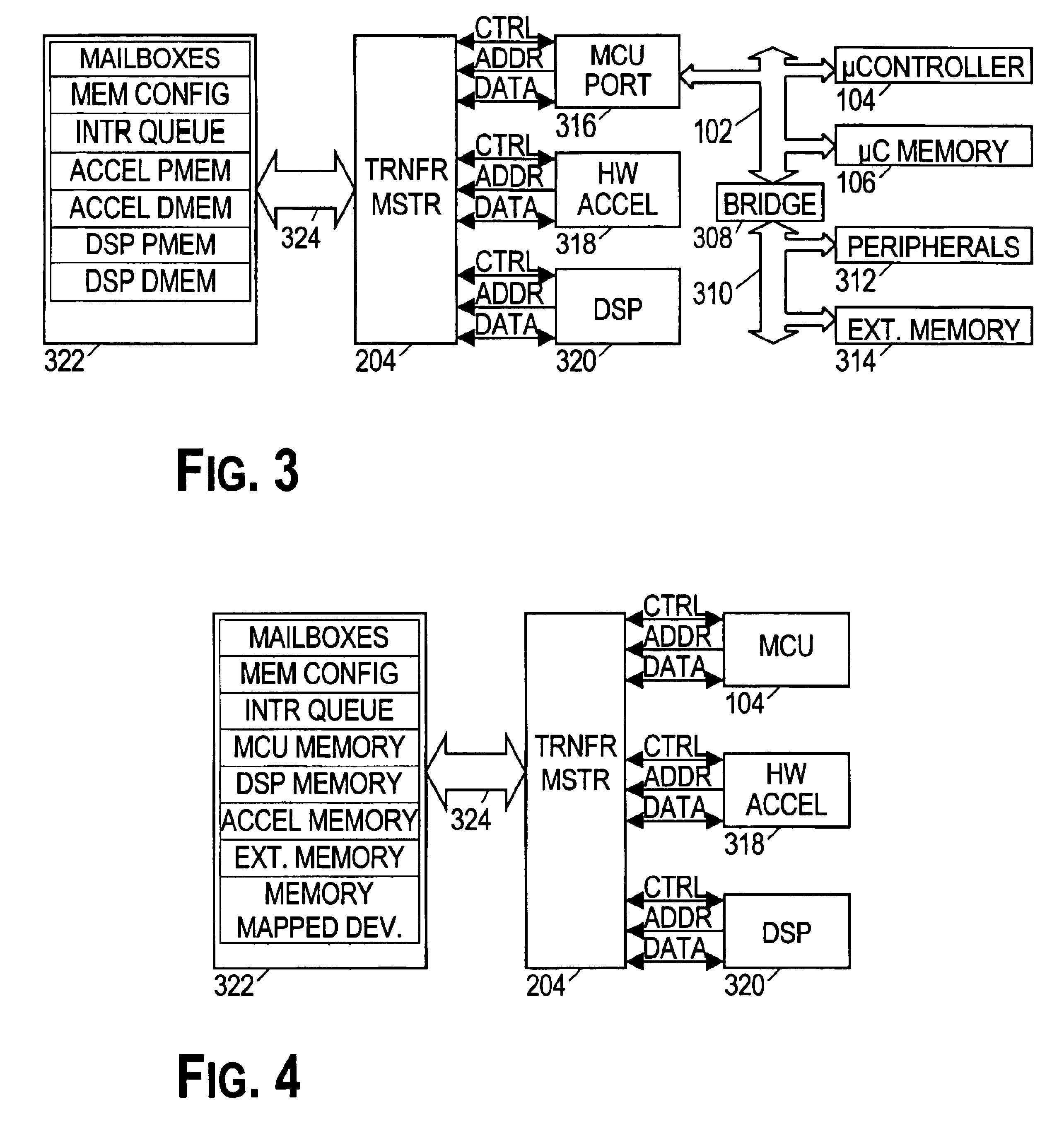

Modular and scalable system bus structure

InactiveUS6915369B1Improve process capabilitySingle instruction multiple data multiprocessorsCathode-ray tube indicatorsMicrocontrollerScalable system

A high-bandwidth data transfer apparatus that is suitable for modular and scalable processing systems is disclosed. In one embodiment, the data transfer apparatus includes a local bus between each of several processing devices and associated memory modules. The local busses are each coupled to a cross-bus through a bus bridge that consists of multiplexers to steer address and data signals from a local bus along the cross-bus to another local bus. The multiplexer structure of the bridges allows the cross-bus to be dynamically divided into segments in any suitable manner to support multiple concurrent links over the cross-bus. A controller is provided to set the multiplexers in accordance with transfer requests that it receives from the various processing devices. The transfer requests may be of various types such as: single transfer, block transfer, and / or message transfer. The controller may include a request queue for each type of transfer request. The controller may also include a direct memory access controller (DMA) for facilitating the block transfers, and may further include an interrupt controller for notifying the processing devices of various events such as: receipt of a message transfer request, completion of block transfer, and / or memory protection violation. The data transfer apparatus may include a processor interface port for each processor. The ports may be configured to enforce programmable memory protection settings. When applied to multimedia systems with a microcontroller, one or more digital signal processors, and one or more hardware accelerators, this data transfer apparatus is expected to provide a substantial increase in processing capabilities.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE +1

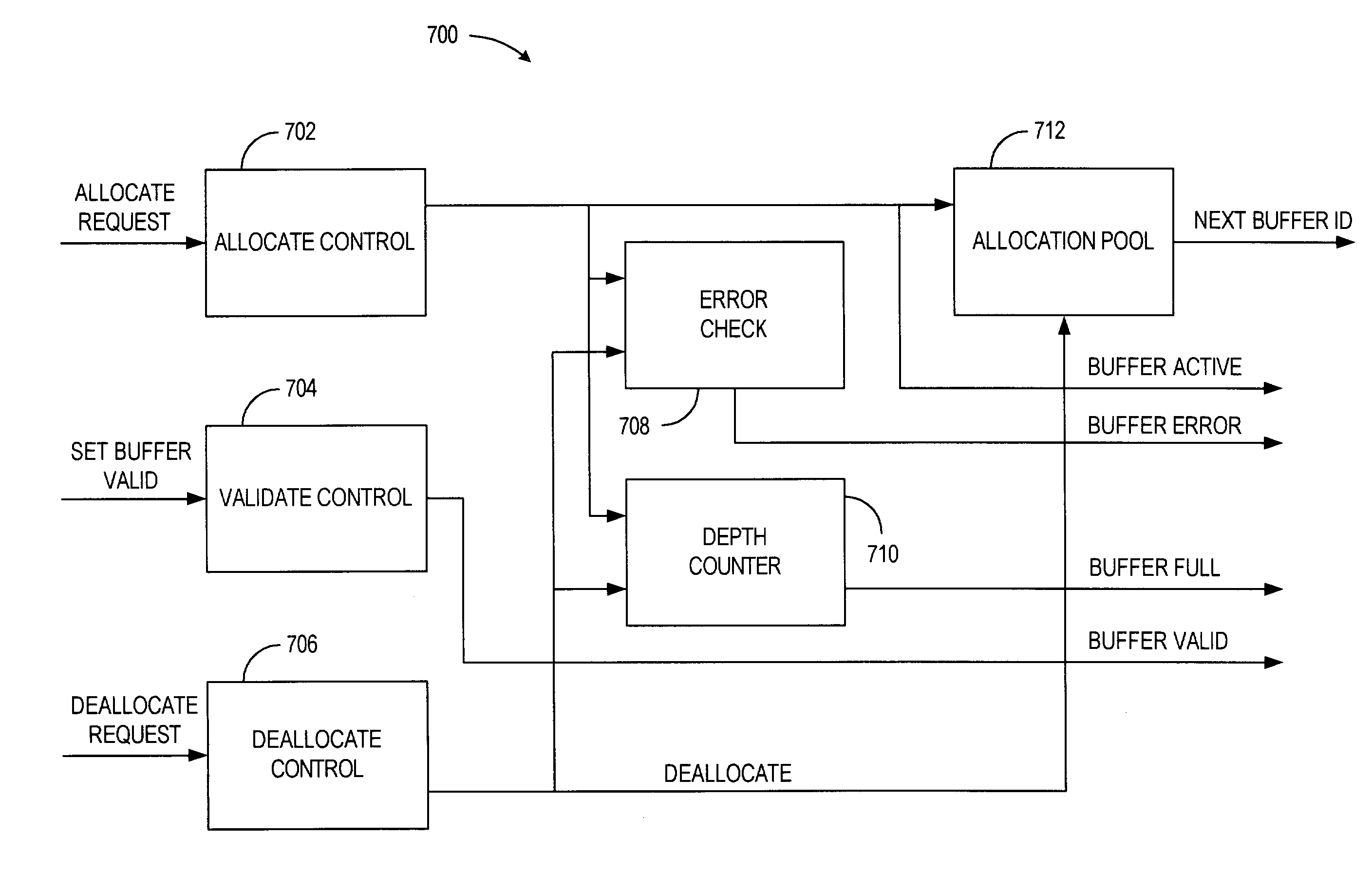

Buffered transfer of data blocks between memory and processors independent of the order of allocation of locations in the buffer

A data transfer system uses a data buffer and individual control of each storage location within the data buffer for improved control of data block transfers. The storage locations are assigned deallocate, active, or valid assignment bands to enable transfer control of the data blocks within the system. The deallocated storage locations are returned to an allocation pool for use as a future resource, where the active and valid assignment bands remain unavailable until deallocated. Error checking and depth control prohibit consecutive allocation or deallocation assignments as well as overflow.

Owner:UNISYS CORP

Patient transfer and transport bed

InactiveUS20060174405A1Prevent movementWheelchairs/patient conveyanceNursing bedsEngineeringTransfer mechanism

The present invention is a transfer and transport device and method for moving a patient from a bed to another location within a medical facility. The transport device includes an integral transfer mechanism for transferring a patient from a hospital bed to the device and back.

Owner:DANE INDS

Email transfer method for the online protocol and credit mechanism based on scalable message

ActiveCN101056281AAvoid aggressive behaviorReduce the burden onUser identity/authority verificationData switching networksTransfer procedureTransfer mode

Email sending method based on the scalable message online protocol and credit mechanism belongs to the network security area. Its features are as follows: this method utilizes the IM platform based on the XMPP protocol to effectively guarantee the true source identity. The 'pull mode' transmission mode is used in the Email sending. The IM platform is used to maintain the characteristics of the online status of the user and the block transfer mode is combined with the direct transfer mode between the sender and receiver in the message transfer. The method invents the distinct combination mechanism of the credit mechanism and blacklist policy and can real time prevent the rubbish message attack. The method can be deployed on the IM platform based on the XMPP protocol which is extensively used now. The method adopts the server forwarding and end-to-end direct message transfer solution, so it can alleviate the load of the old server and can not affect the performance of the old IM service.

Owner:TSINGHUA UNIV

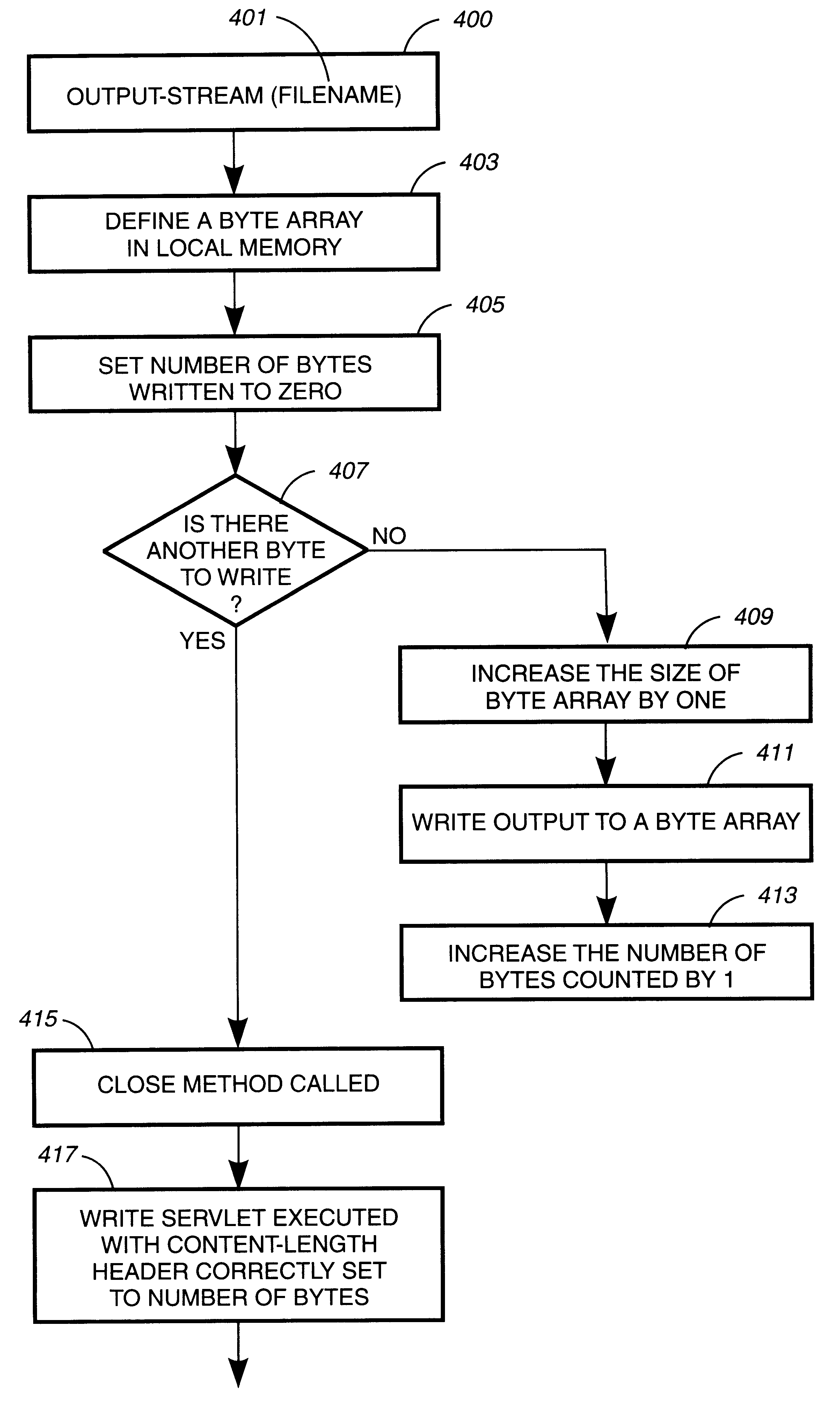

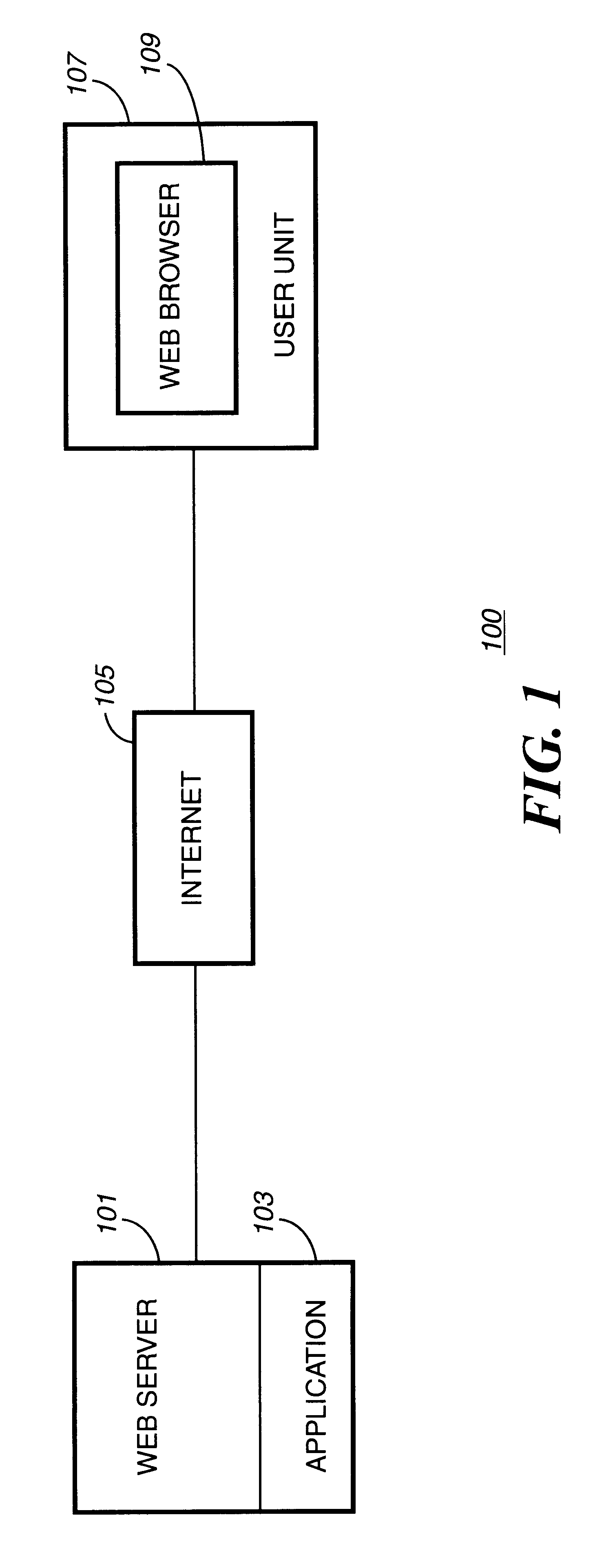

System for Java data block transfers of unknown length for applets and applications by determining length of data in local buffer and passing length of data combined with data out of program

InactiveUS6260083B1Multiprogramming arrangementsData switching by path configurationInformation processingApplication software

In an information processing system, a method to perform I / O (Input / Output) operations for an interpretative based program that is executing on an Interpretative Machine (IM). The method comprises the steps of: executing an interpretative based program on an Interpretative Machine (IM); receiving a request to pass data of unknown length out of the program; allocating a local buffer in the information processing unit to write the data of unknown length; writing the data of unknown length to the local buffer; determining the size of the data of unknown length in the local buffer; and passing the length of the data combined with the data in the buffer out of the program. In accordance with another aspect of the invention, a computer readable medium is described to carry out the above method.

Owner:IBM CORP