Patents

Literature

297 results about "Conditional branch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Conditional Branches. A conditional branch instruction branches to a new address only if a certain condition is true. Usually the condition is about the values in two registers.

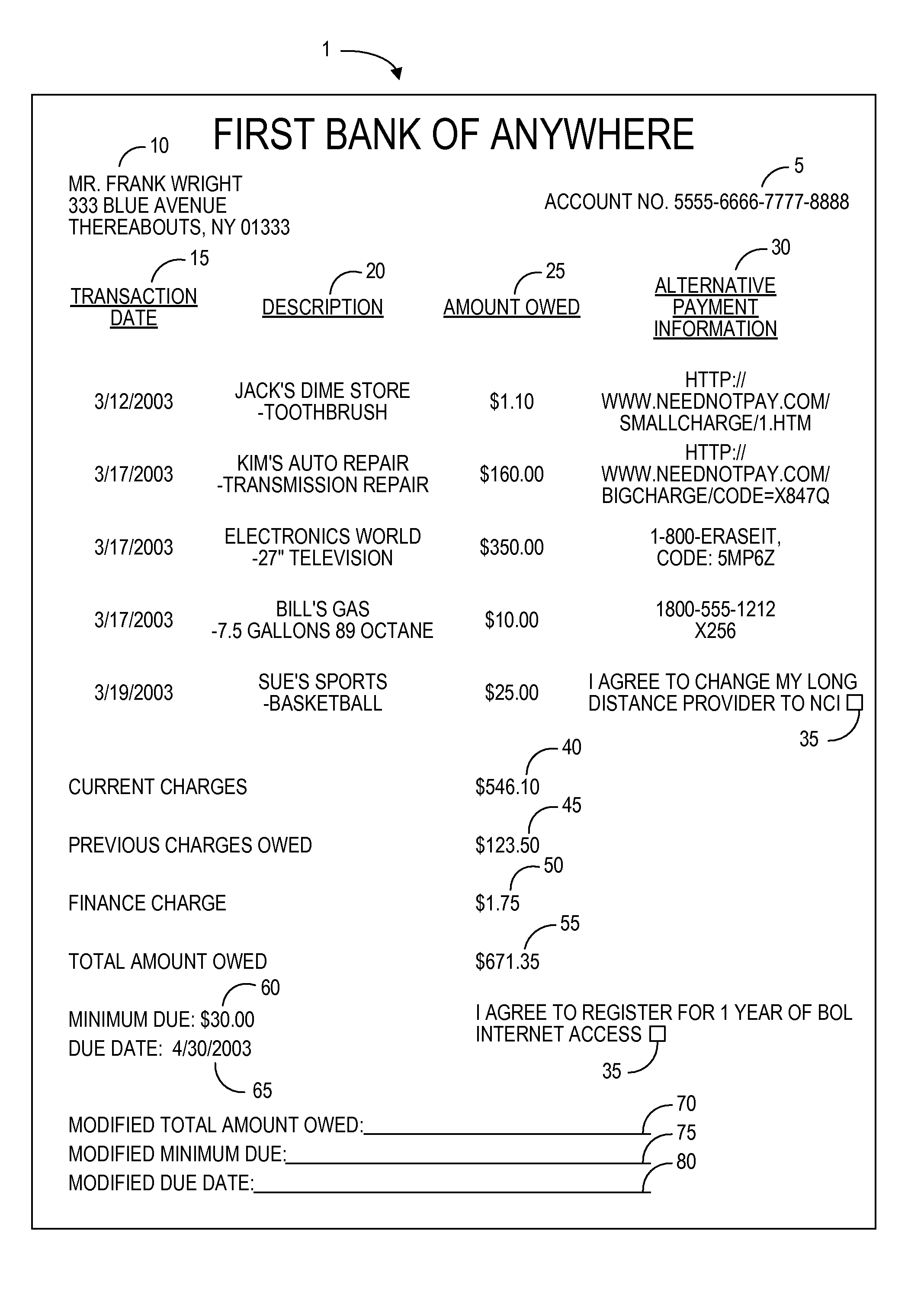

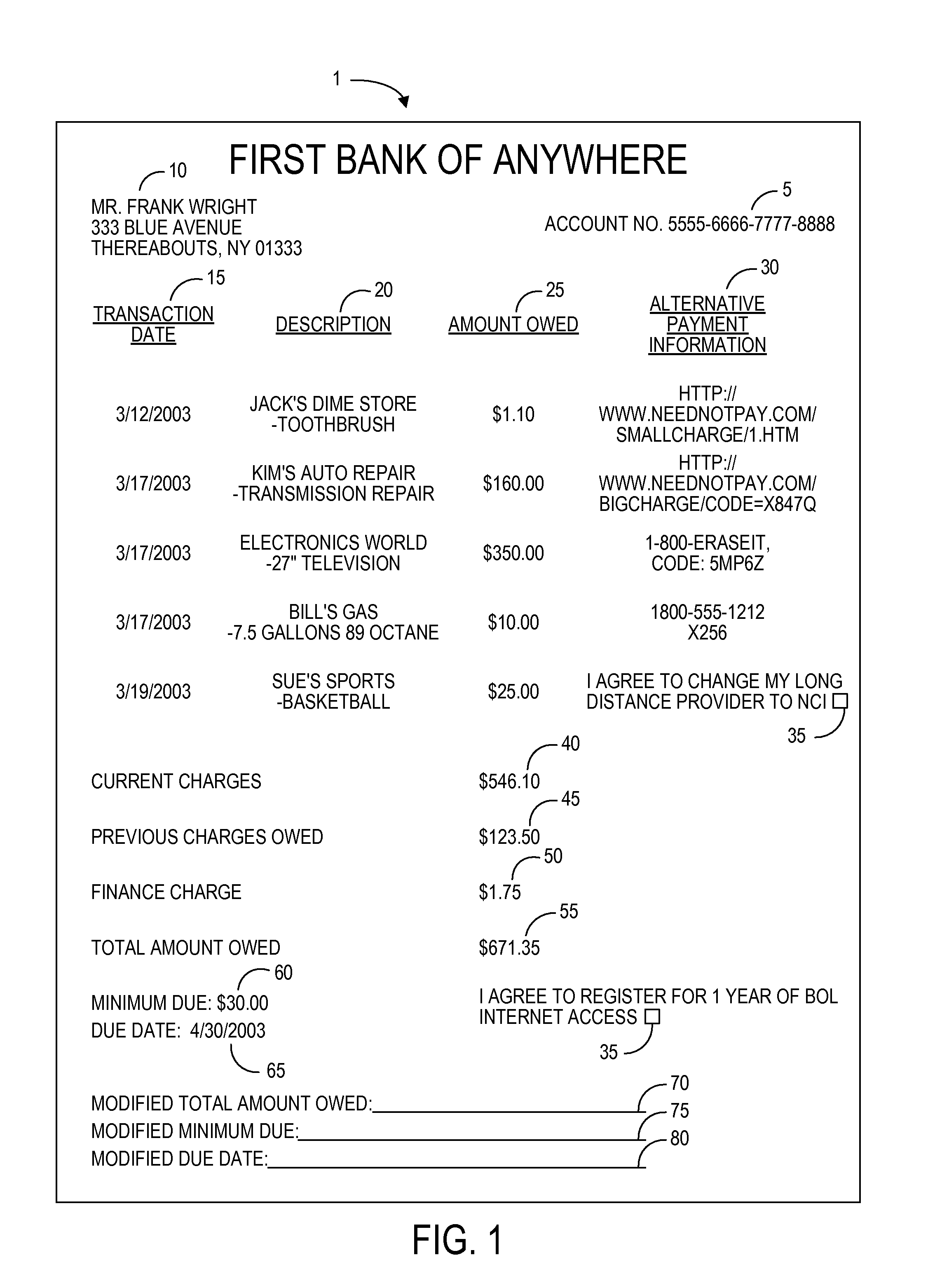

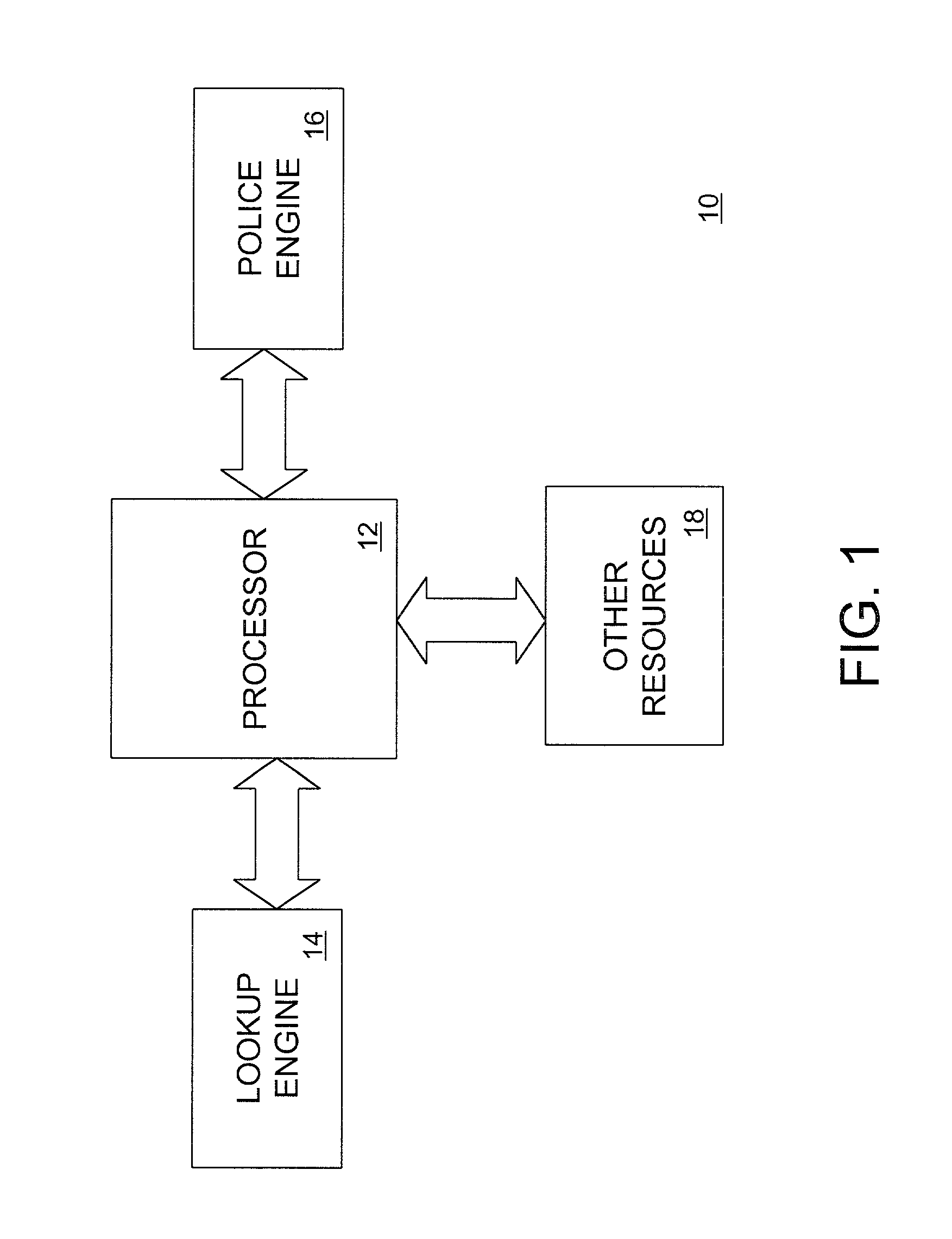

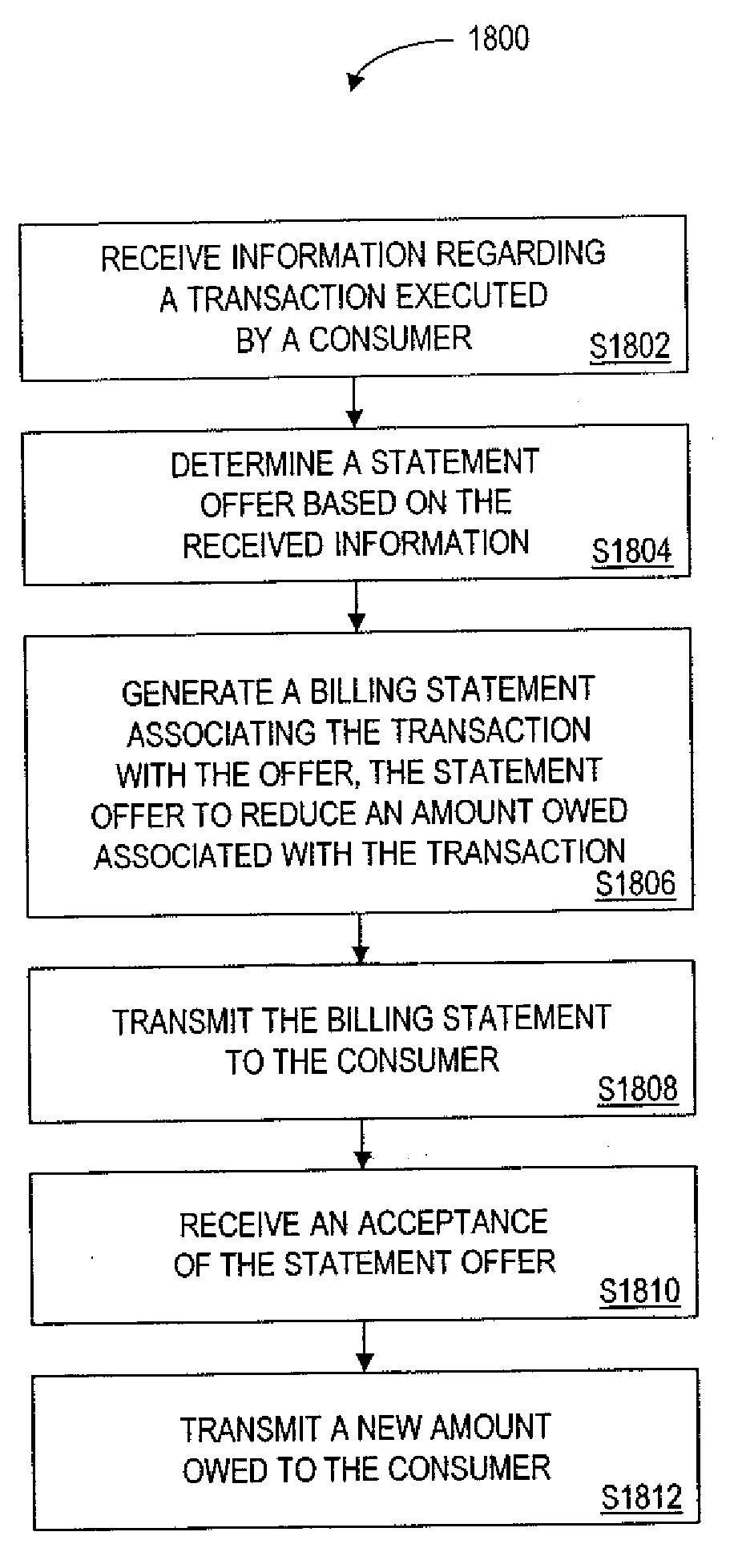

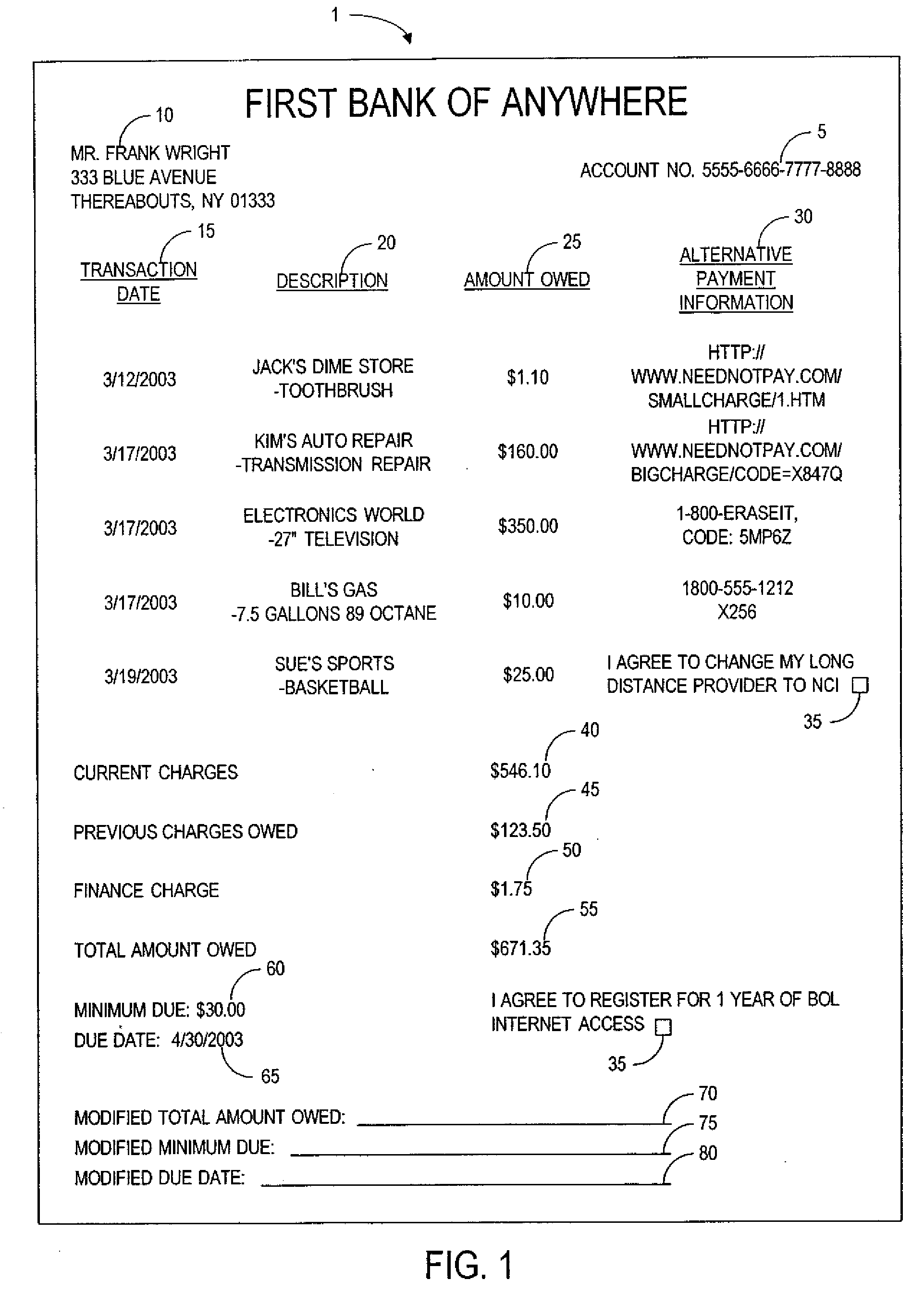

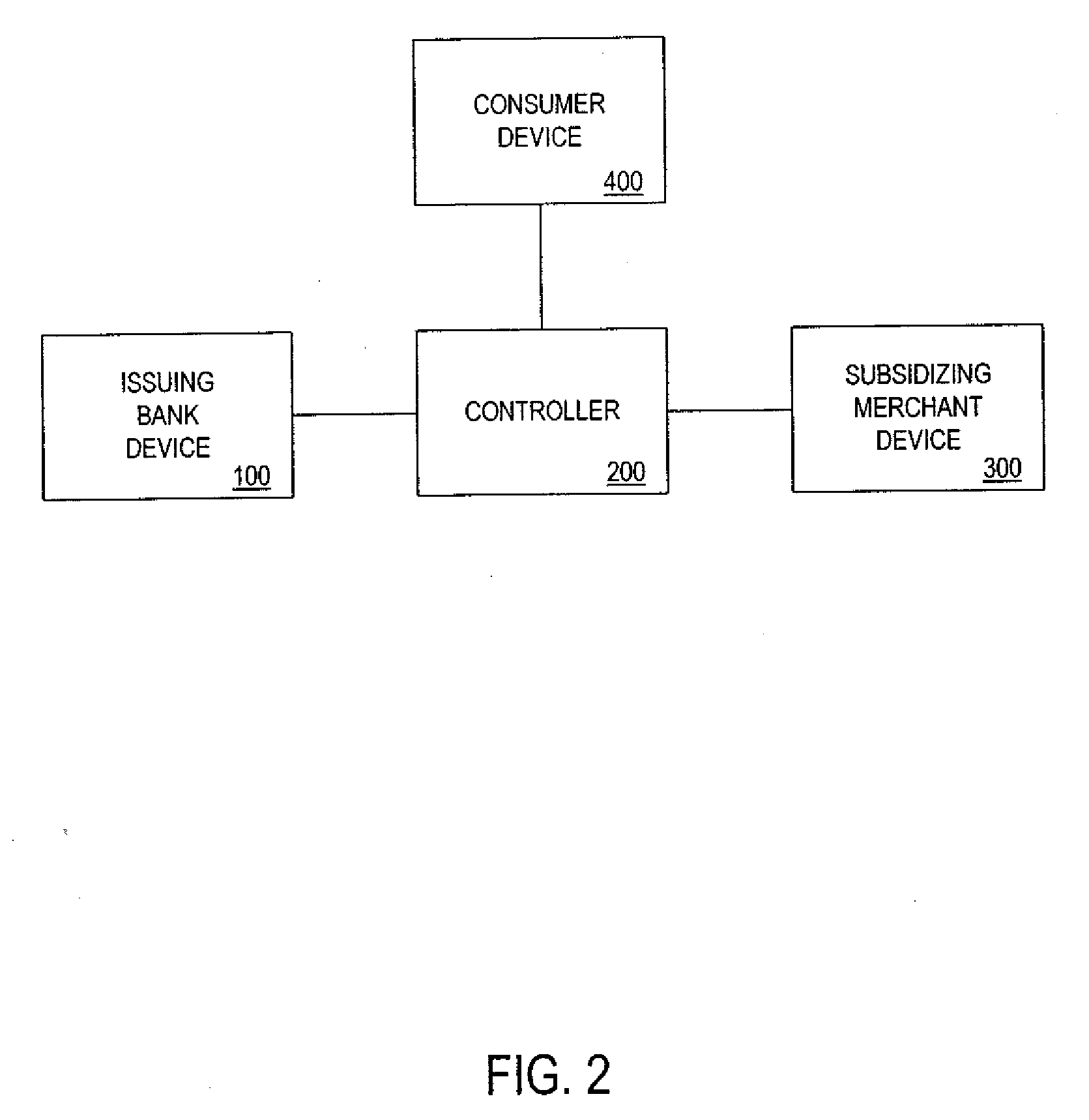

System for providing offers using a billing statement

A billing statement according to one aspect of the invention includes a description of a transaction and an offer pointer associated with the transaction, wherein the offer pointer includes information that may be used to review an offer. In one example of this aspect, the offer pointer is a telephone number printed adjacent to a description of a transaction on a credit card billing statement. The telephone number accesses a voice response system presenting conditional branches through which a consumer can navigate to review an offer. In another example, a hyperlink is positioned adjacent to a total amount owed listed on an electronically-displayed billing statement. The hyperlink may be selected to access a website presenting offers for review by the consumer. The offers reviewed in each of these examples may be customized based on details of the transaction such as the product purchased or the amount of the purchase, the identity of the consumer, and / or on other data.

Owner:PAYPAL INC

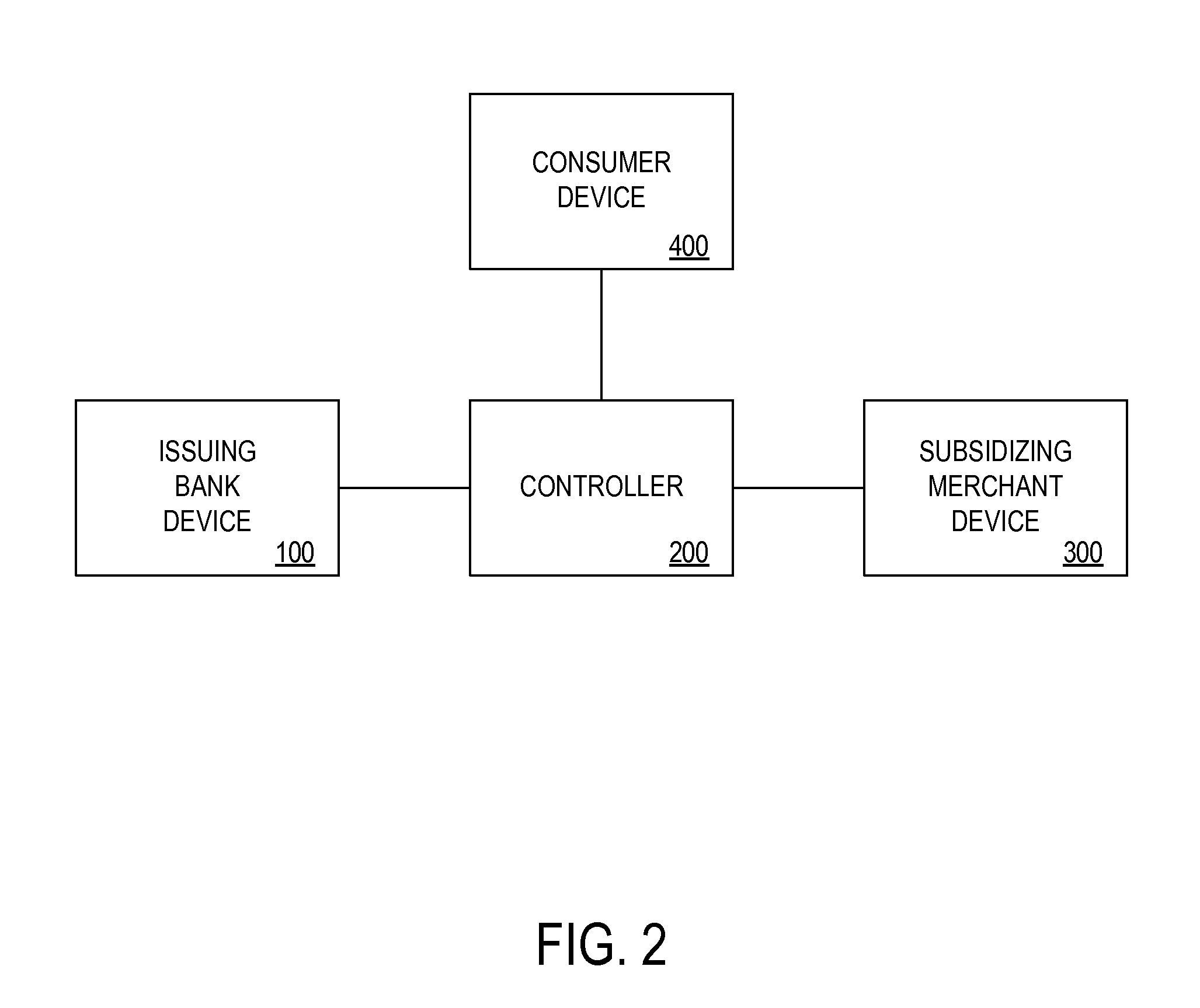

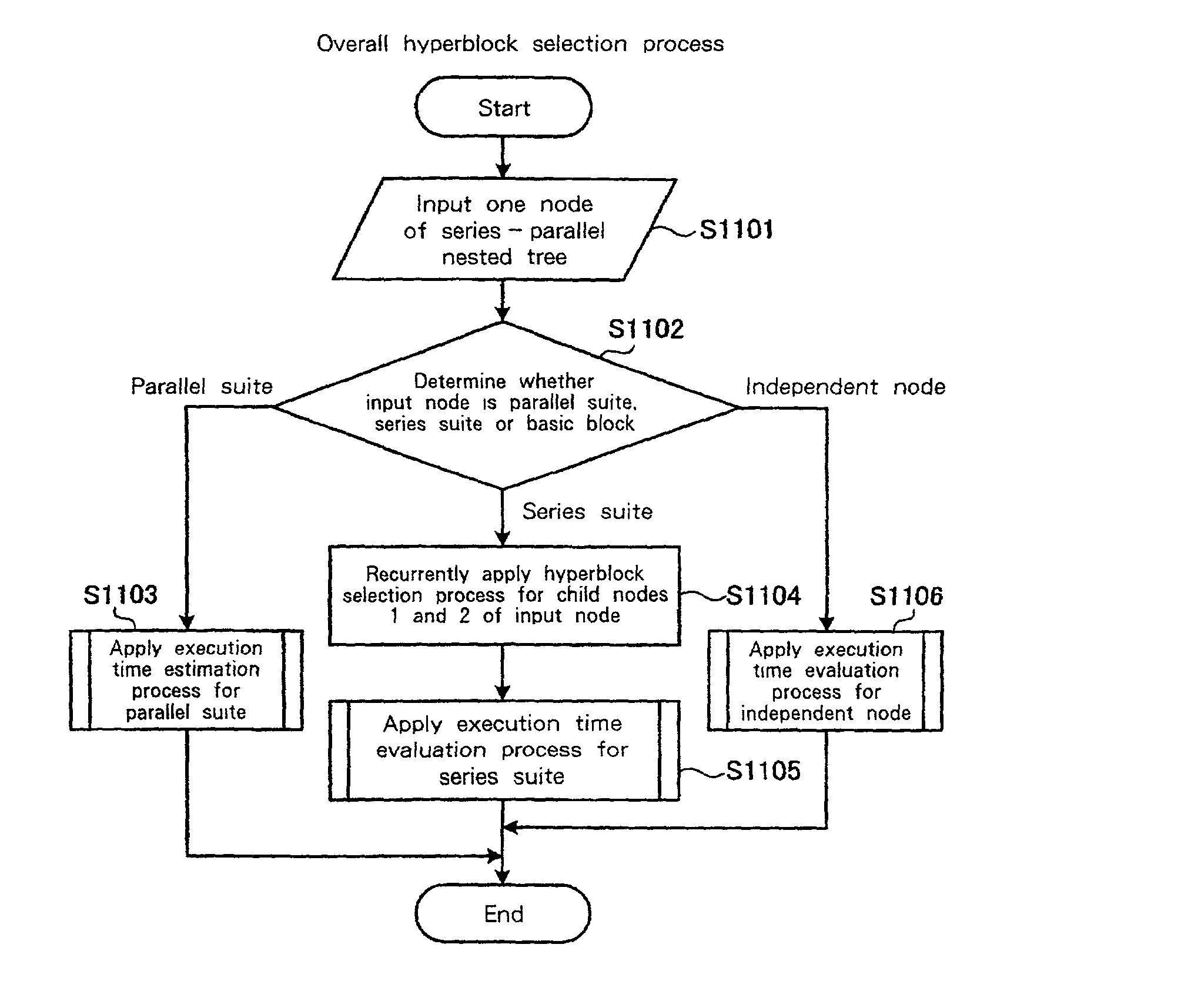

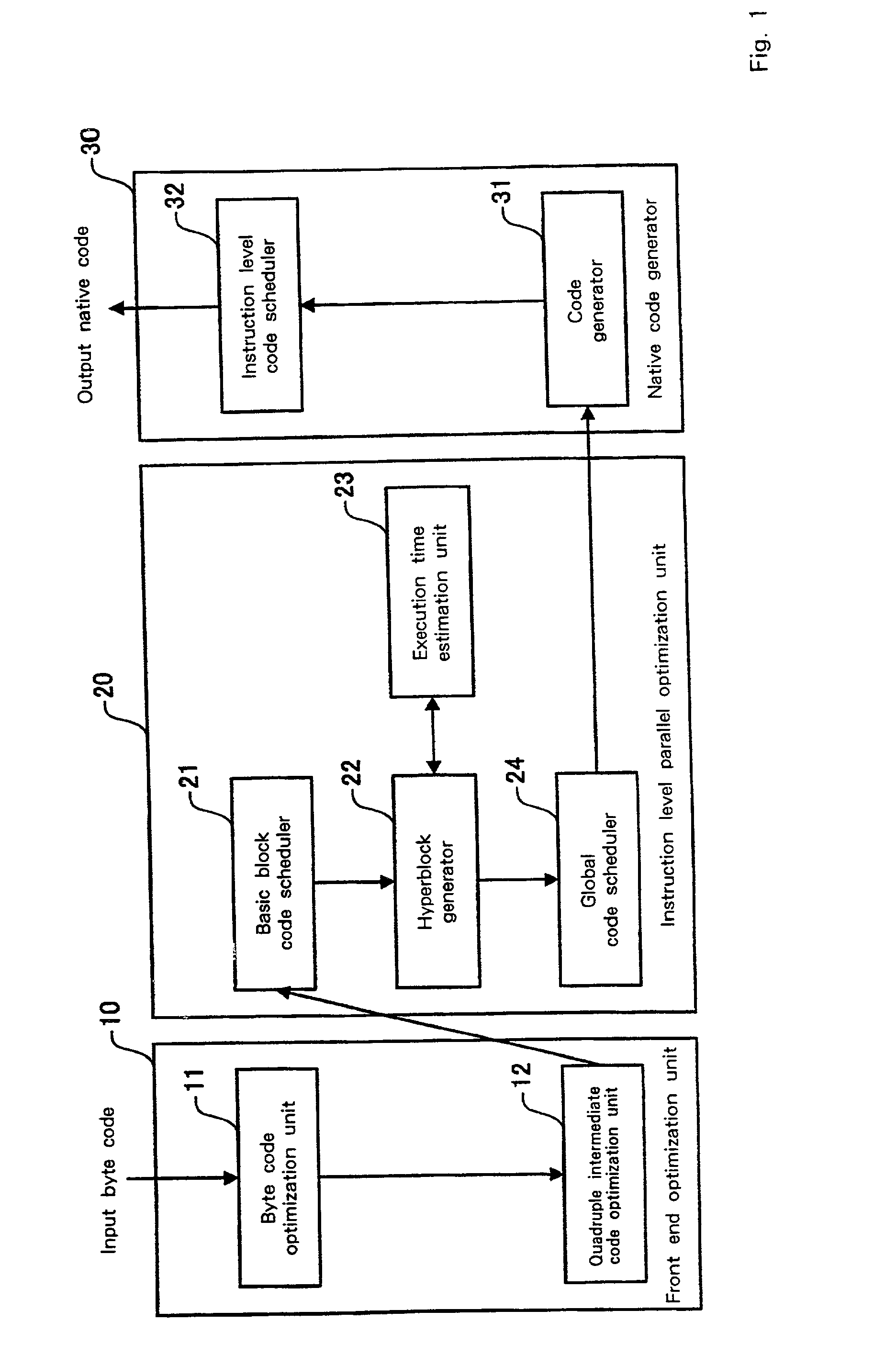

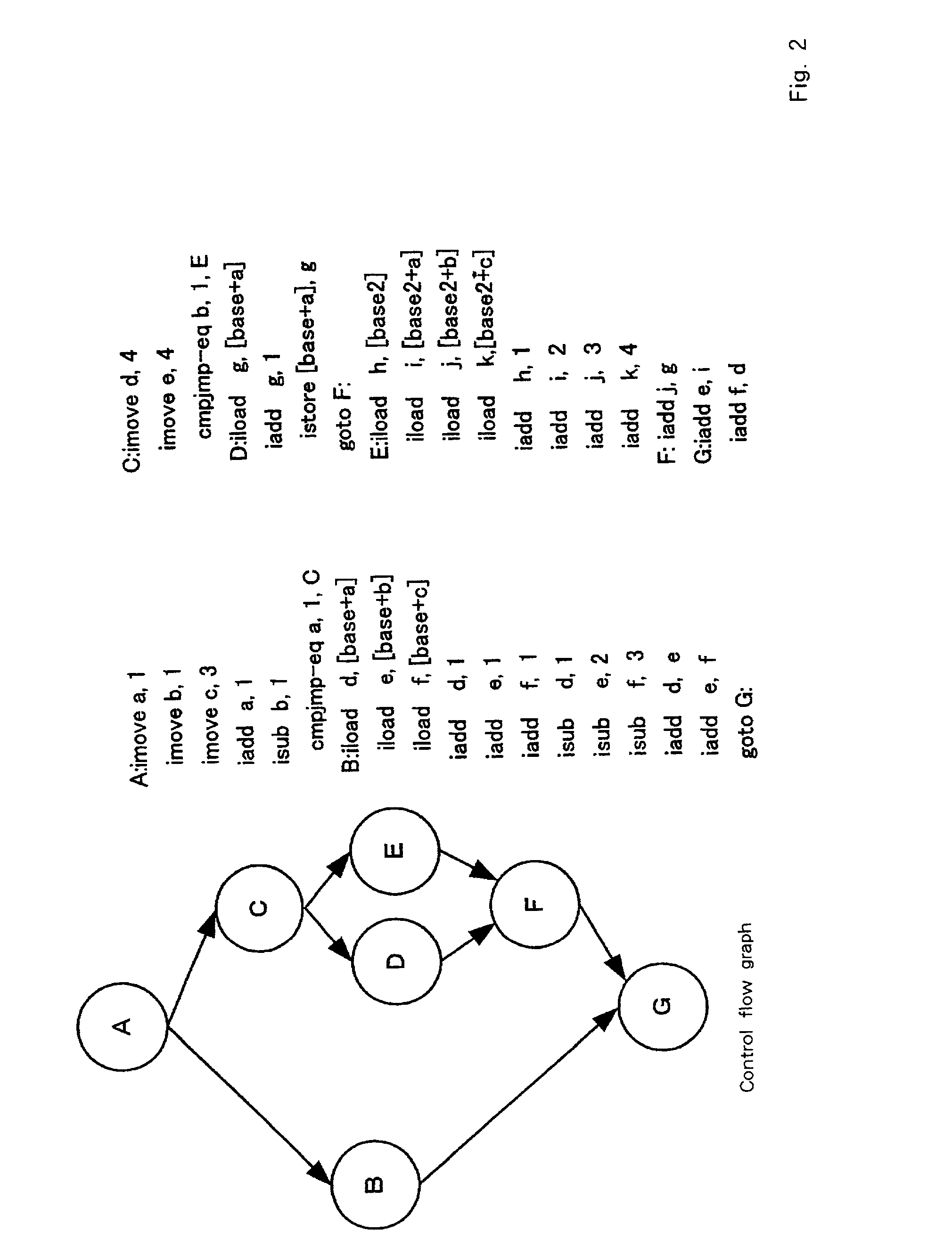

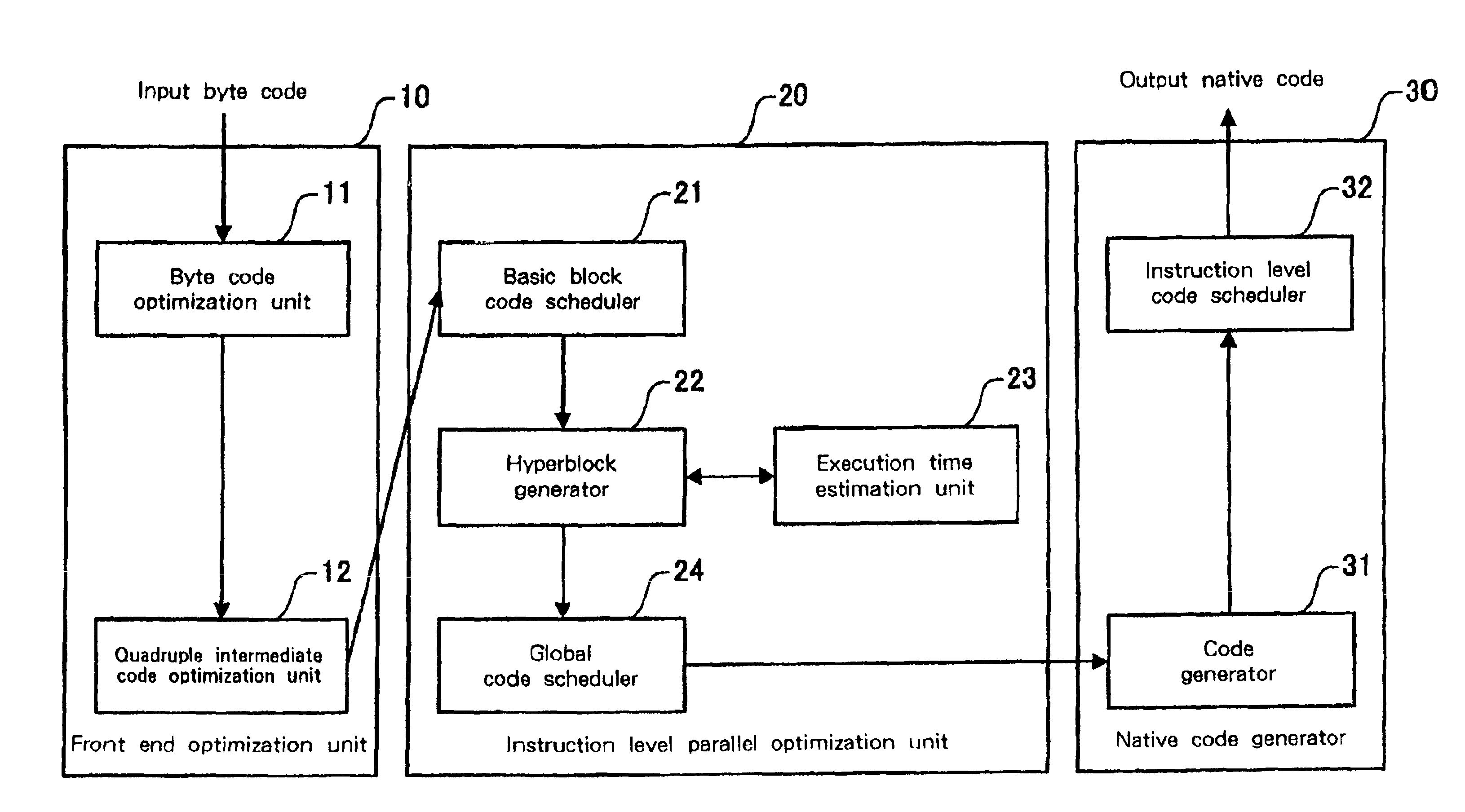

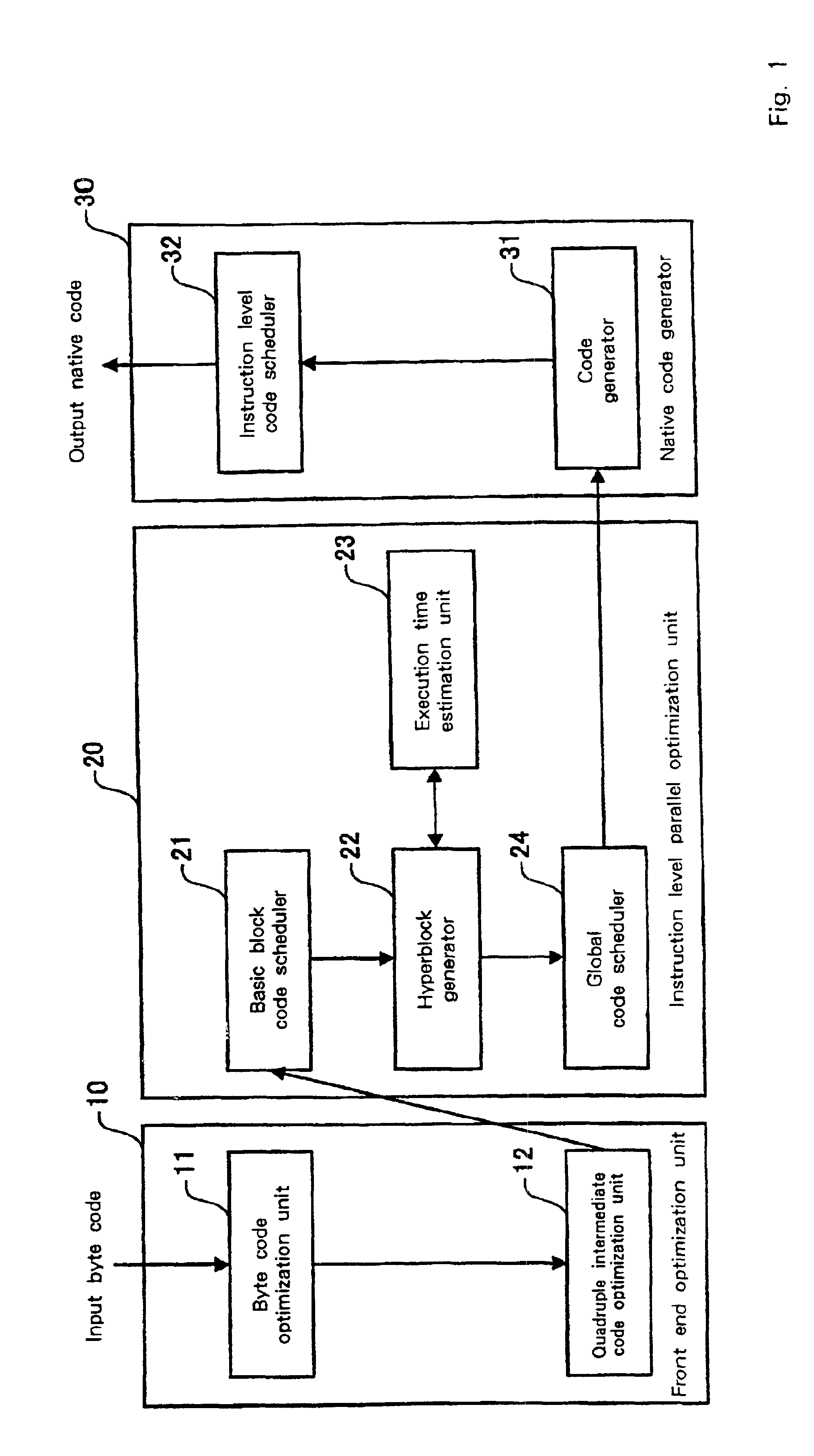

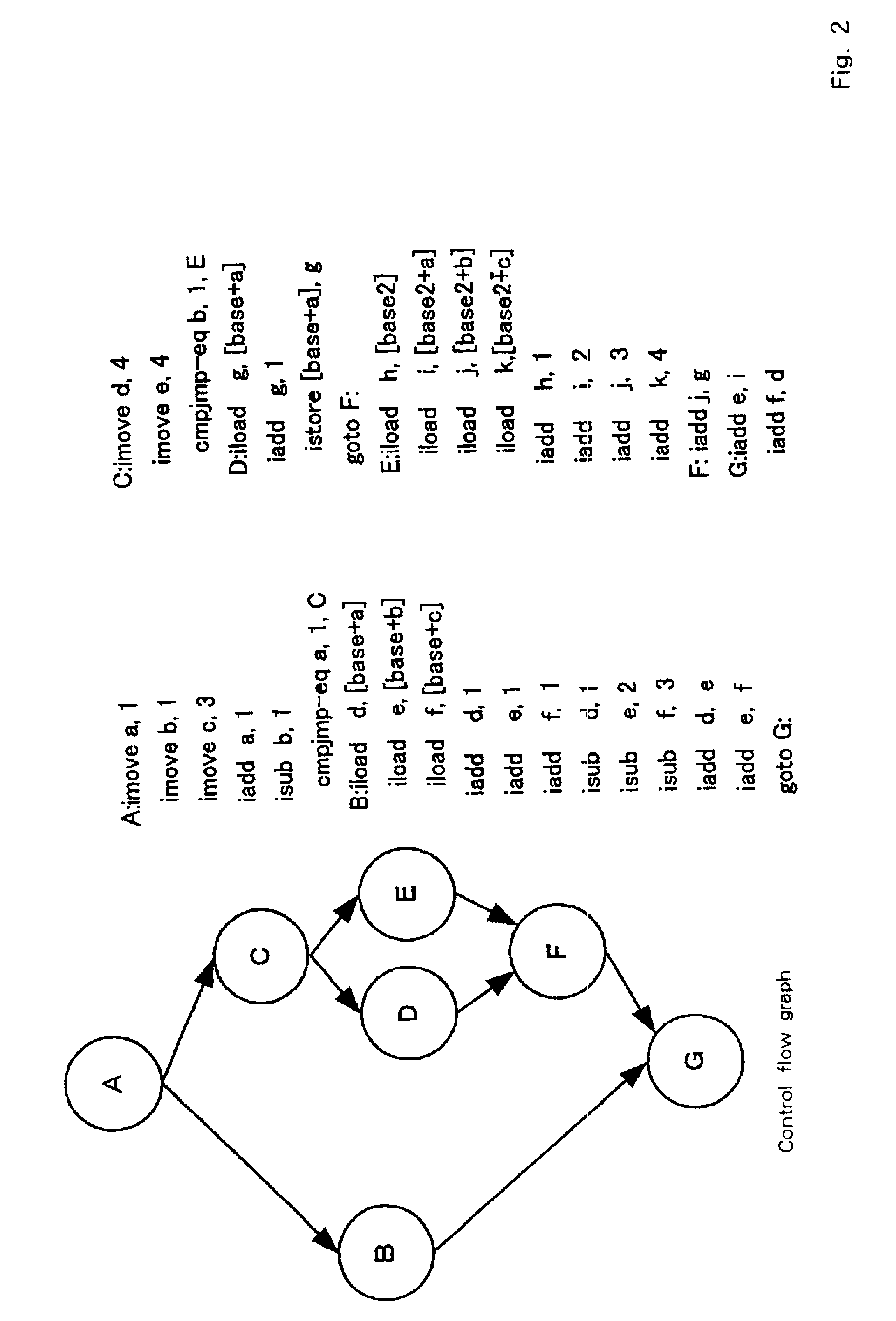

Program optimization method, and compiler using the same

InactiveUS20020095666A1Short processing timeEfficient executionSoftware engineeringDigital computer detailsSource codeBasic block

An optimization method and apparatus for converting source code for a program written in a programming language into machine language and for optimizing the program includes employing a basic block as a unit to estimate an execution time for the program to be processed, generating a nested tree that represents the connections of the basic blocks using a nesting structure, when a conditional branch is accompanied by a node in the nested tree, employing the execution time estimated by using the basic blocks as units to obtain an execution time at the node of the program when a conditional branching portion of a program is directly executed and when the conditional branching portion is executed in parallel, and defining the node as a parallel execution area group when the execution time required for the parallel execution is shorter or dividing multiple child nodes of the nodes into multiple parallel execution areas when the execution time for the conditional branching portion is shorter.

Owner:IBM CORP

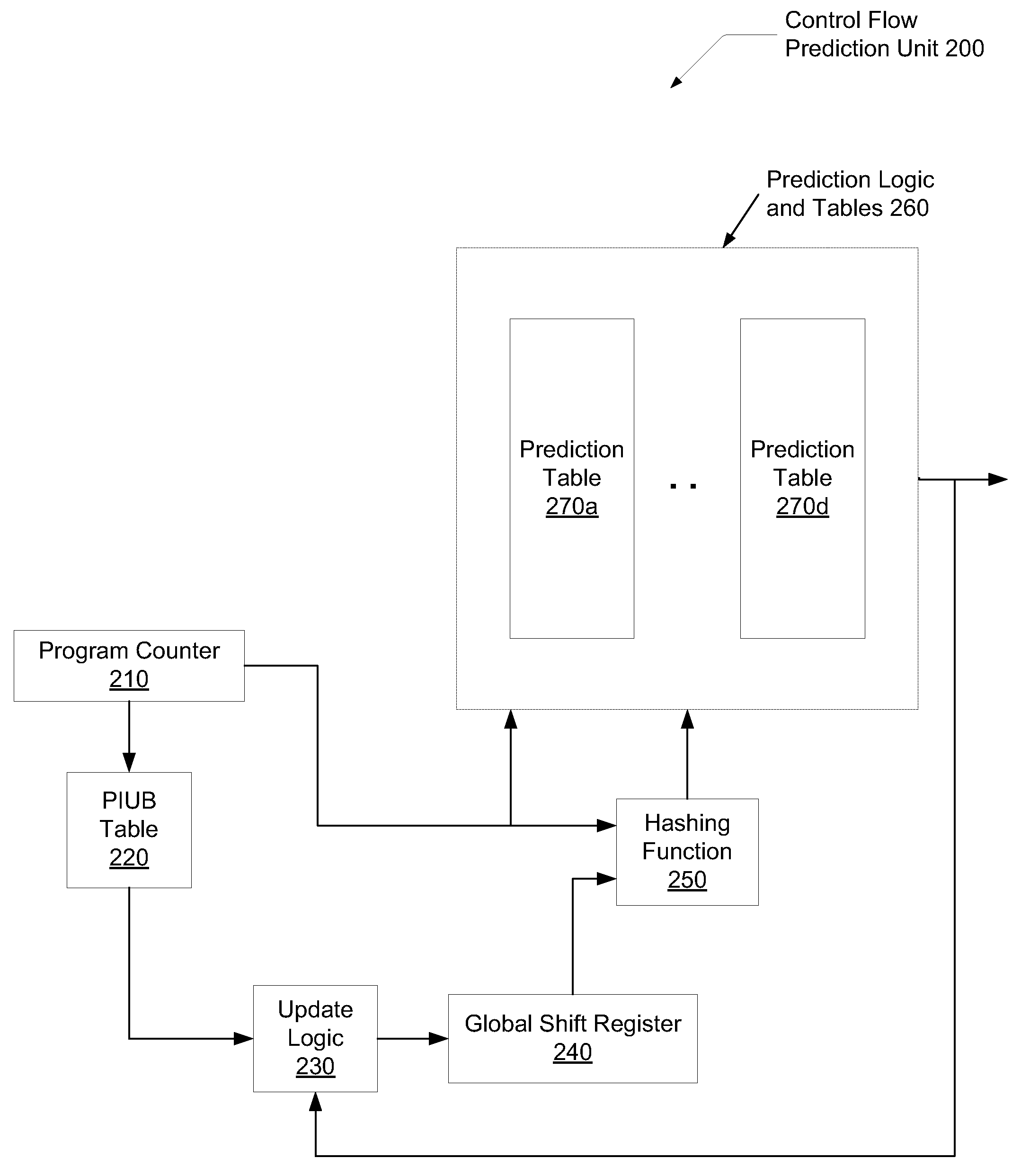

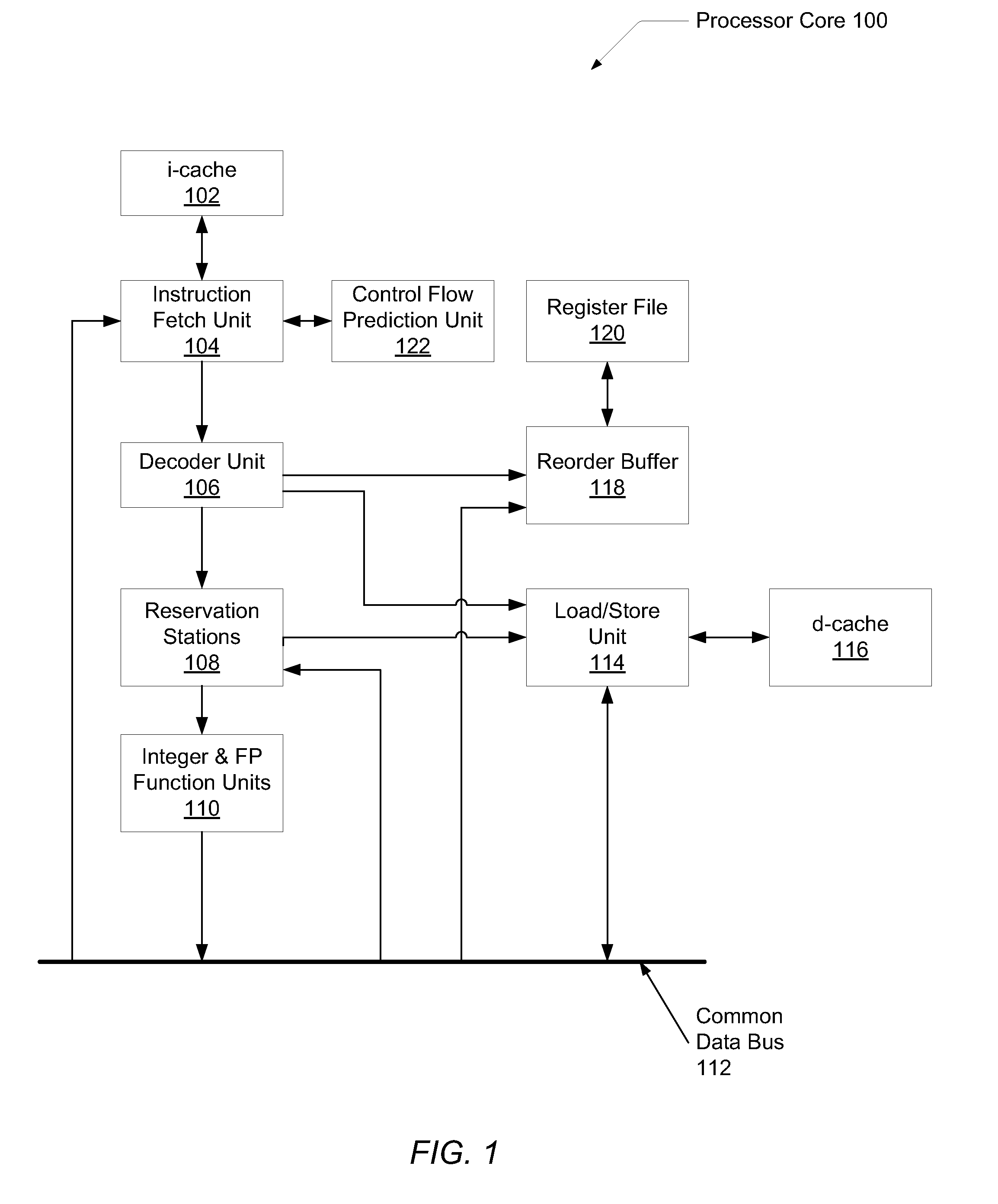

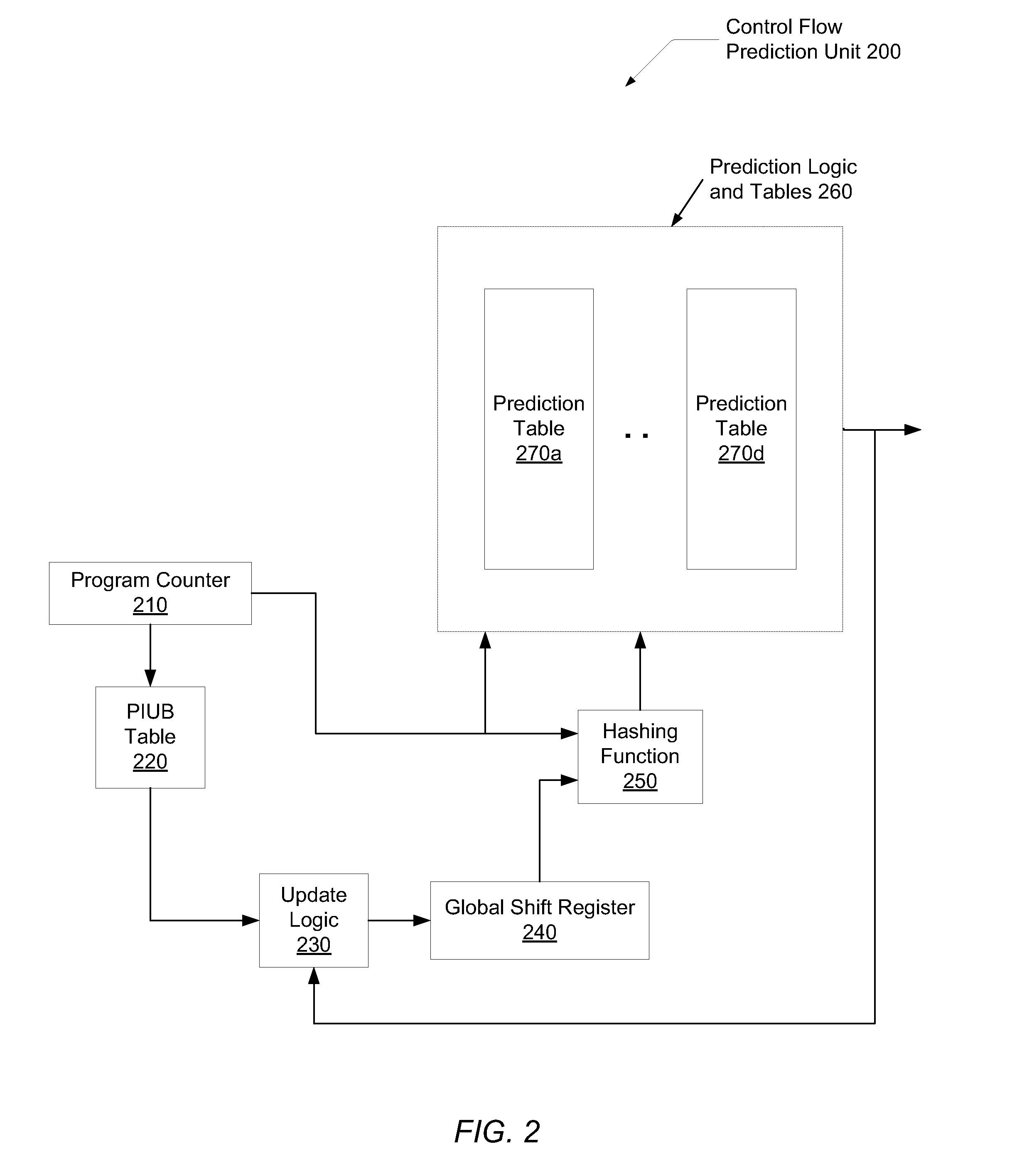

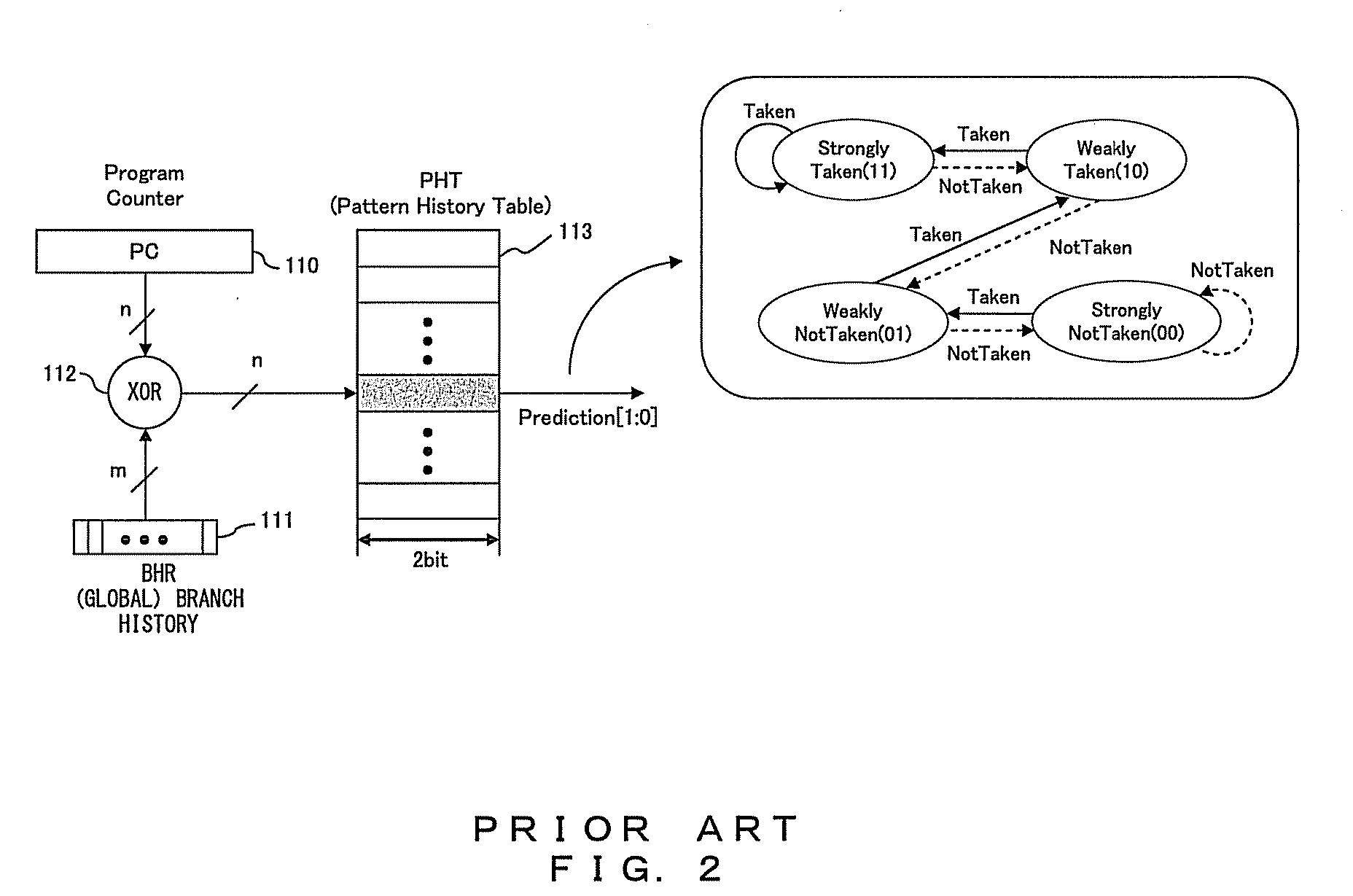

Branch history with polymorphic indirect branch information

ActiveUS20090164766A1Improve accuracyImprove forecast accuracyDigital computer detailsConcurrent instruction executionTarget arrayShift register

A system and method for efficient improvement of branch prediction in a microprocessor with negligible impact on die-area, power consumption, and clock cycle period. It is determined if a program counter (PC) register contains a polymorphic indirect unconditional branch (PIUB) instruction. One determination may be searching a table with a portion or all of a PC of past PIUB instructions. If a hit occurs in this table, the global shift register (GSR) is updated by shifting a portion of the branch target address into the GSR, rather than updating the GSR with a taken / not-taken prediction bit. The stored value in the GSR is input into a hashing function along with the PC in order to index prediction tables such as a pattern history table (PHT), a branch target buffer (BTB), an indirect target array, or other. The updated value due to the PIUB instruction improves the accuracy of the prediction tables.

Owner:ADVANCED MICRO DEVICES INC

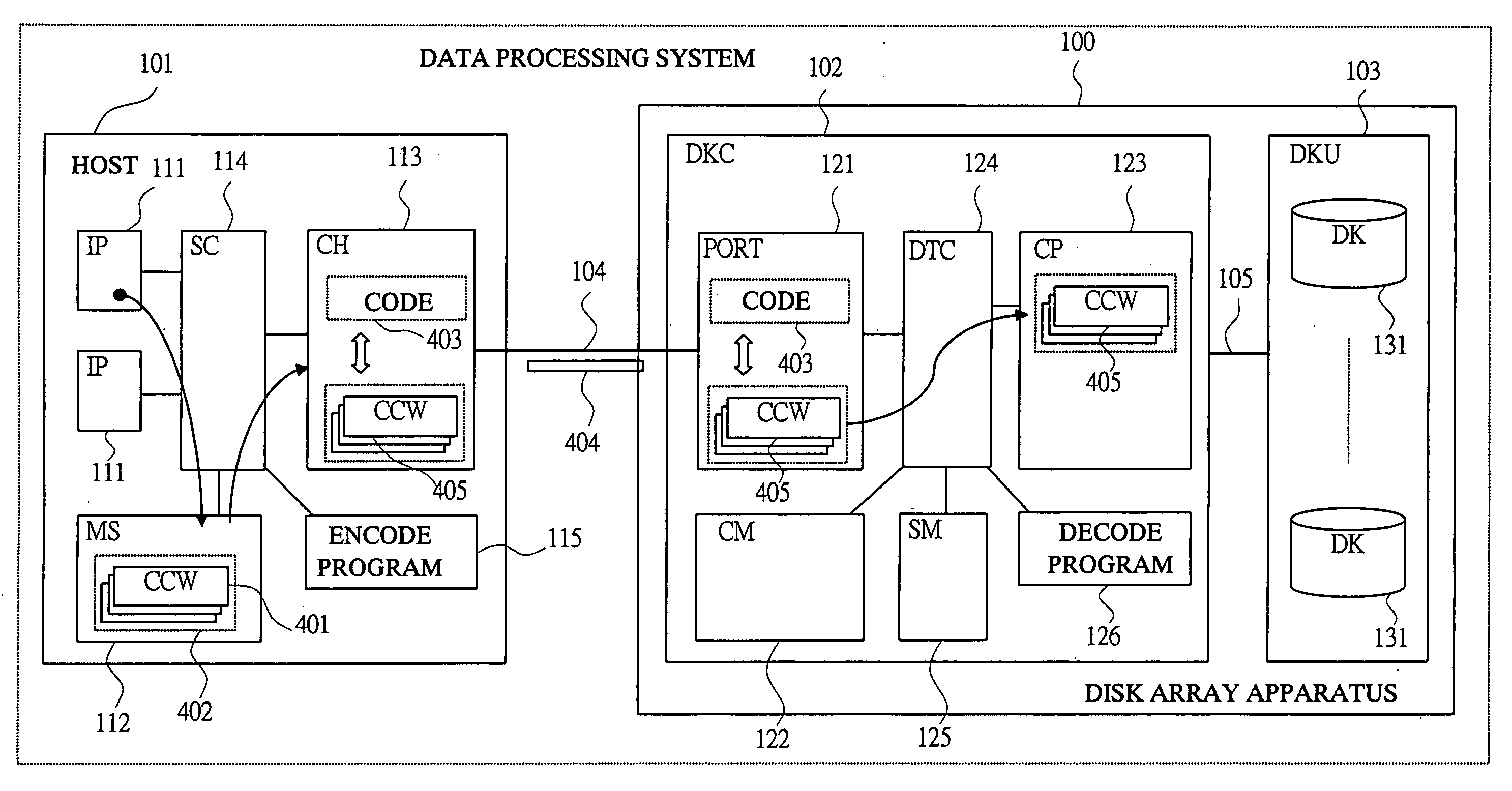

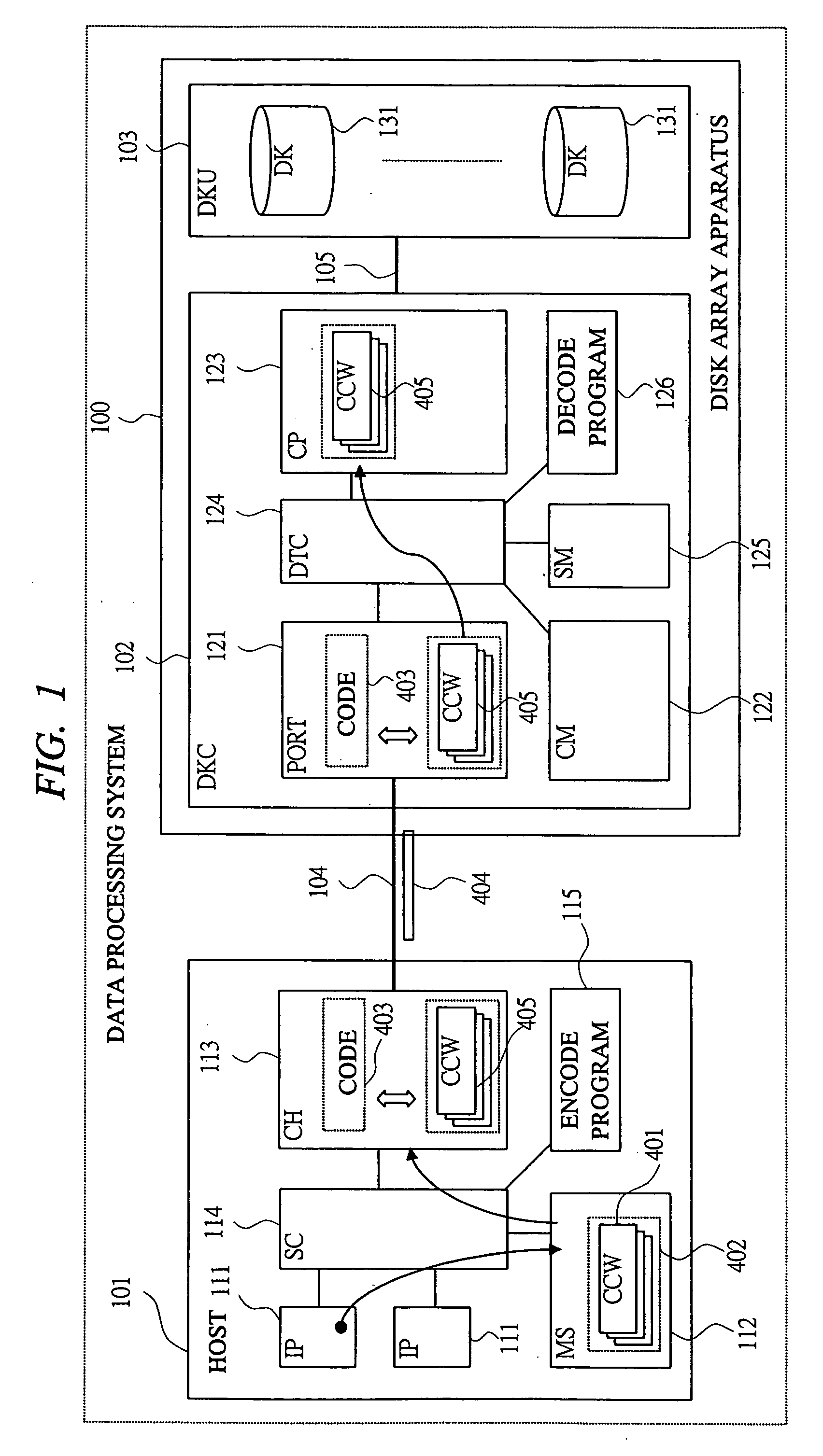

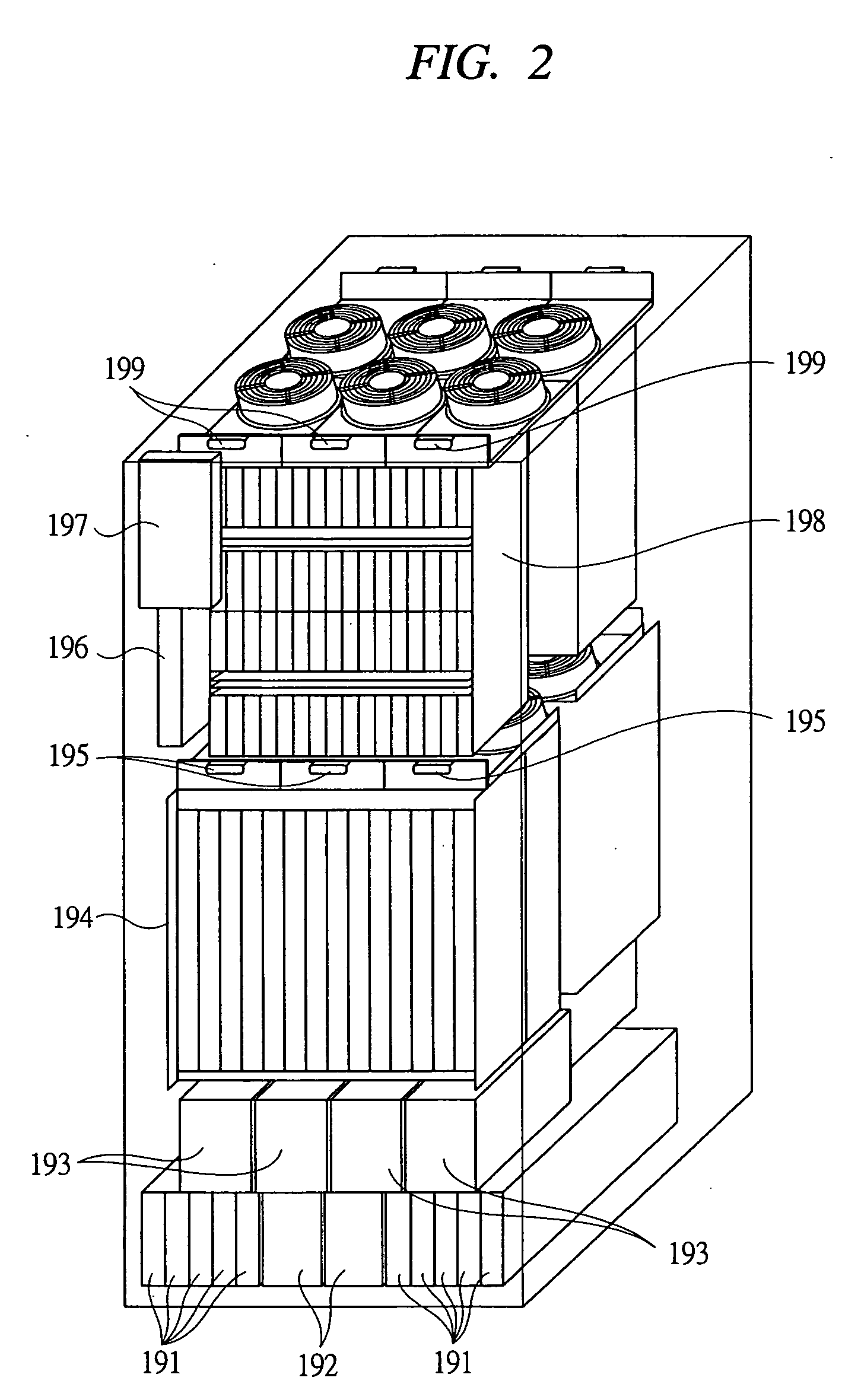

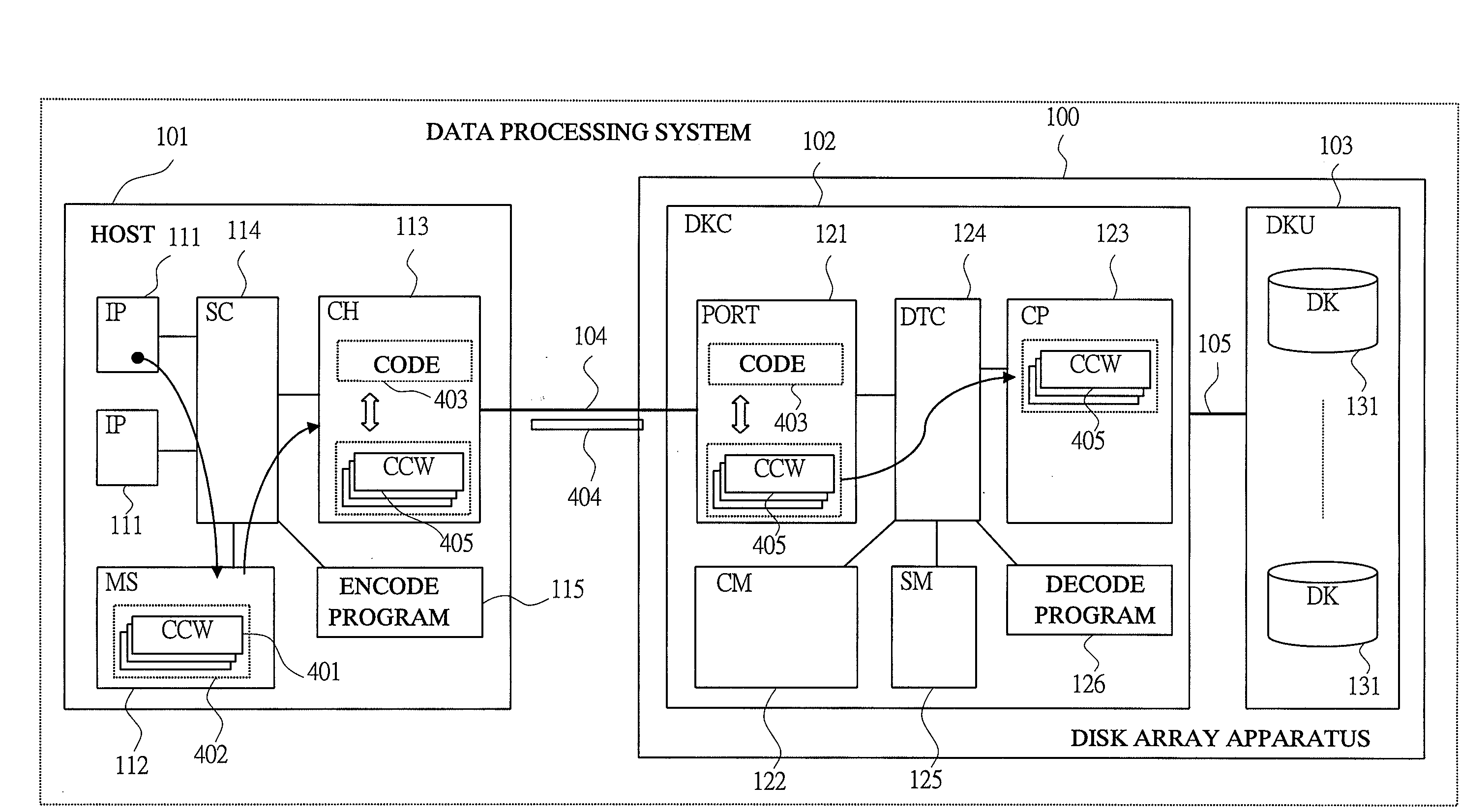

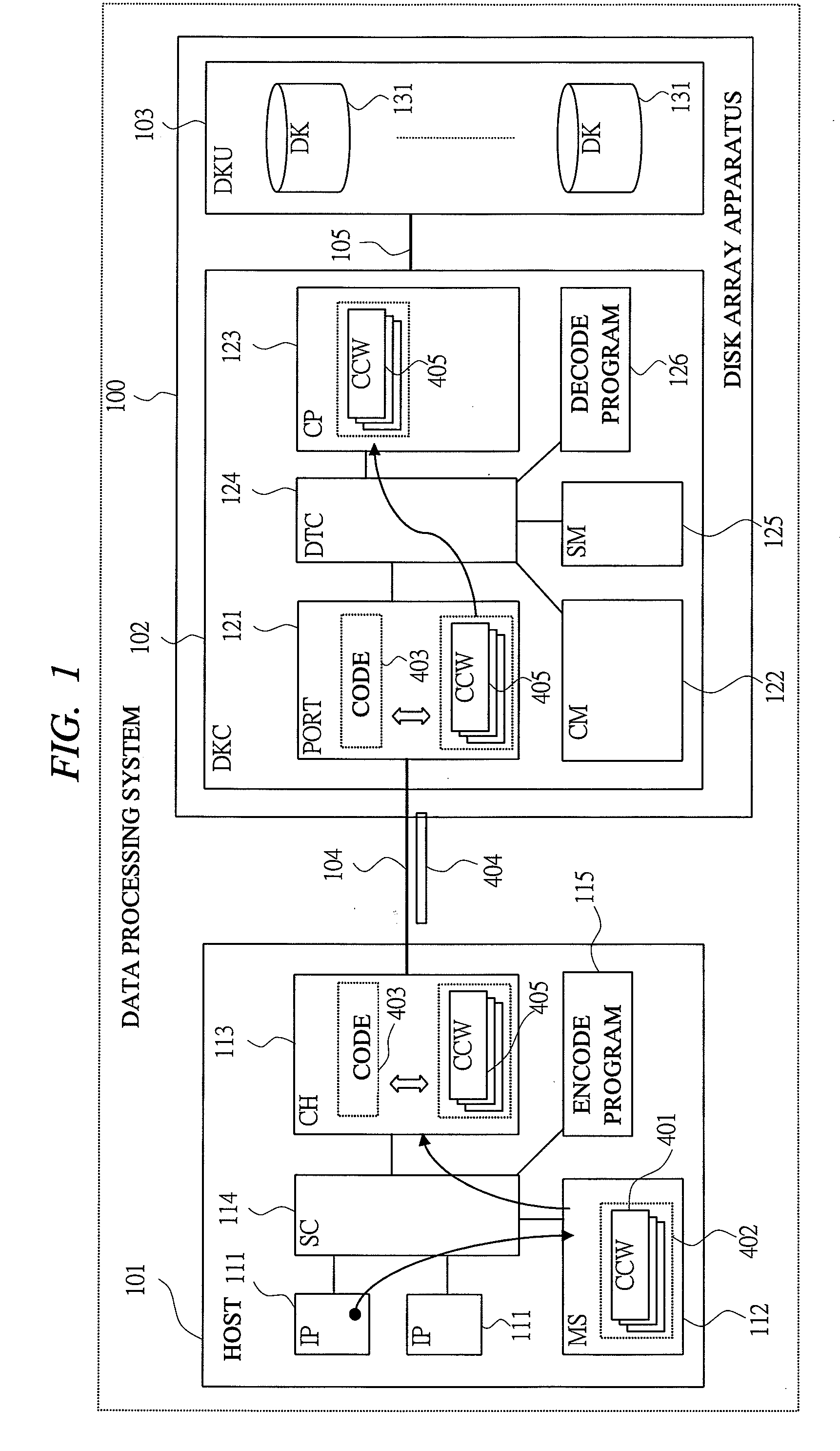

Data processing system, data processing method and program

InactiveUS20060224795A1Processing loadEasy to processElectric digital data processingData processing systemENCODE

In the host, an IP issues CCW, and a CH encodes the CCW and a CCW chain by the encode program to create a code including the description of controlling a conditional branch with the DKC and transmits the code to a PORT in the DKC. In the DKC, the PORT decodes the code by the decode program, and a CP sequentially processes each command obtained by the decoding and returns a return code representing the end state of the processing. The host receives the return code to recognize the end state of the processing.

Owner:HITACHI LTD

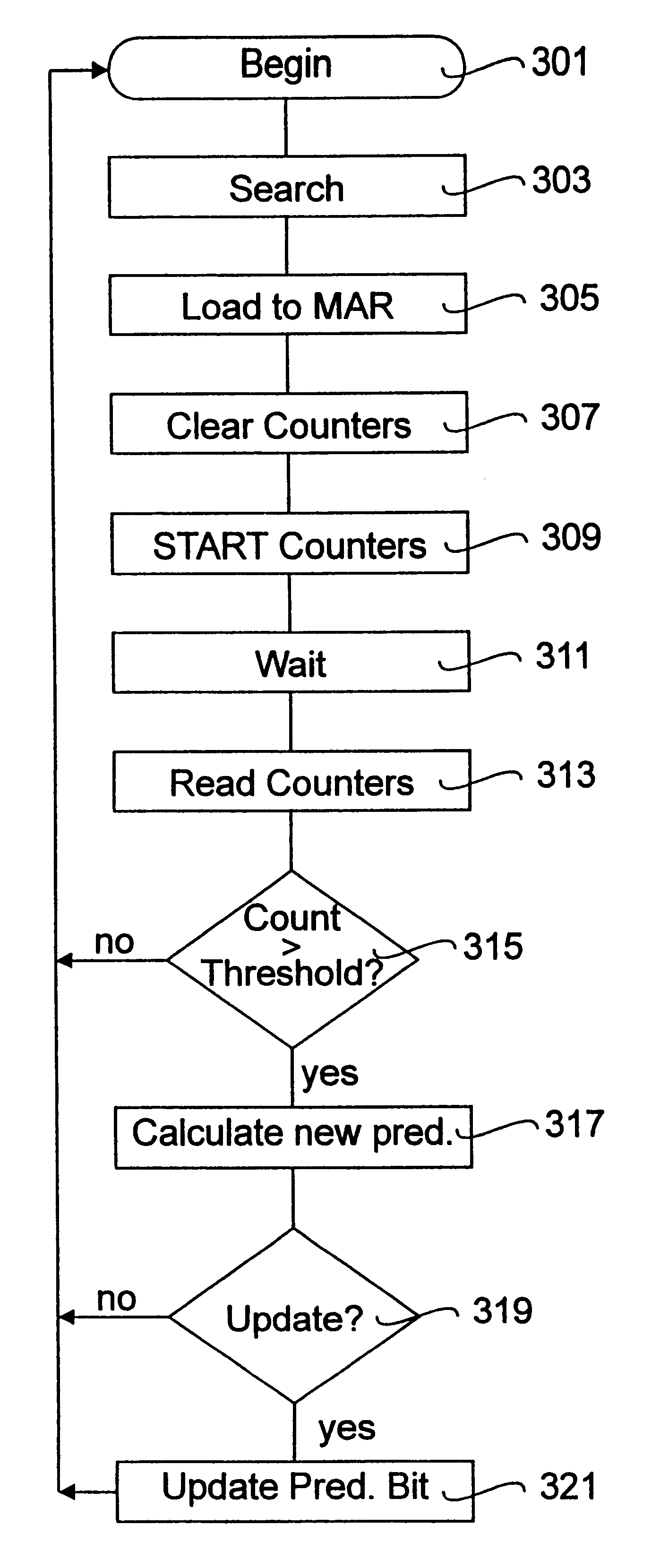

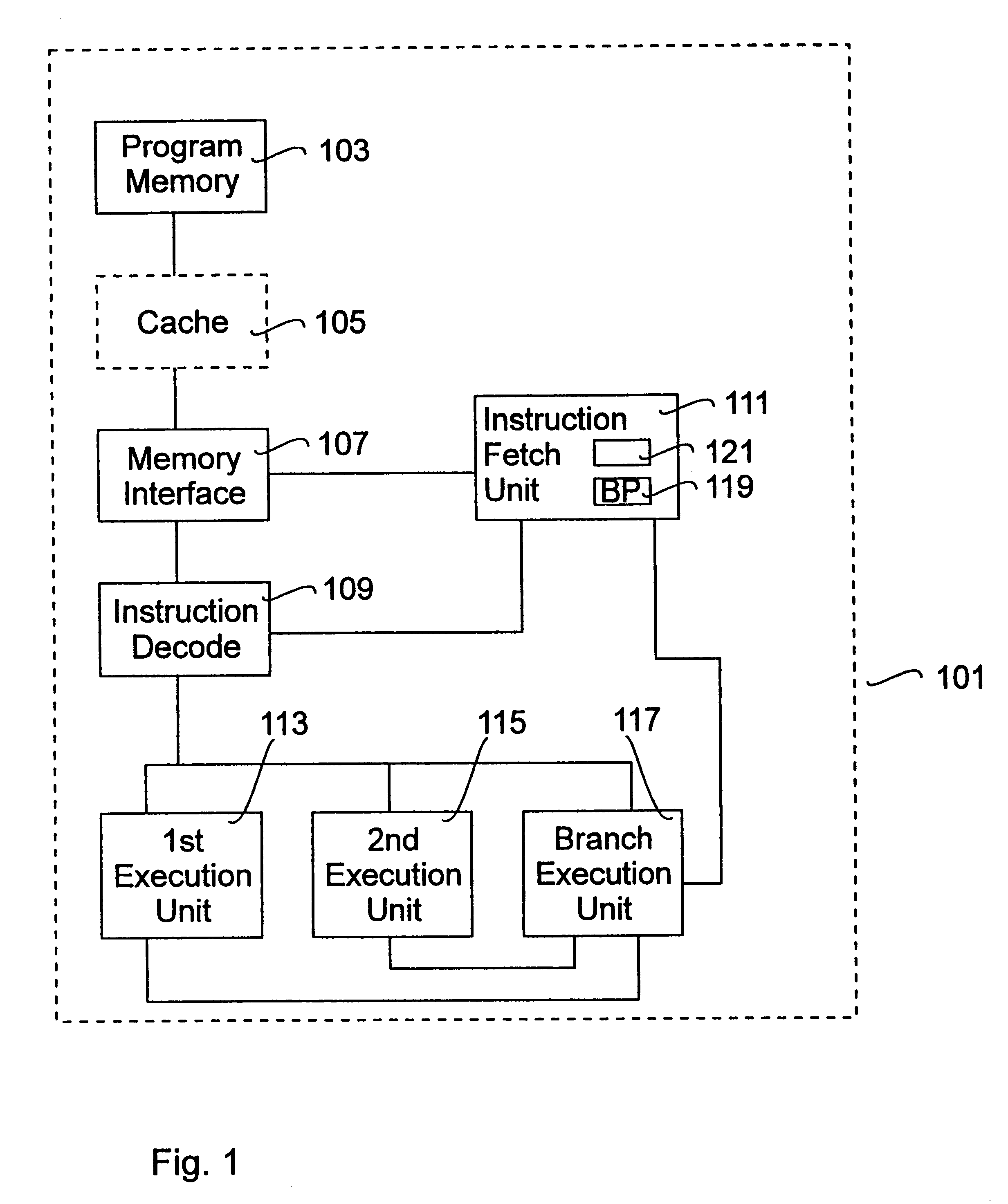

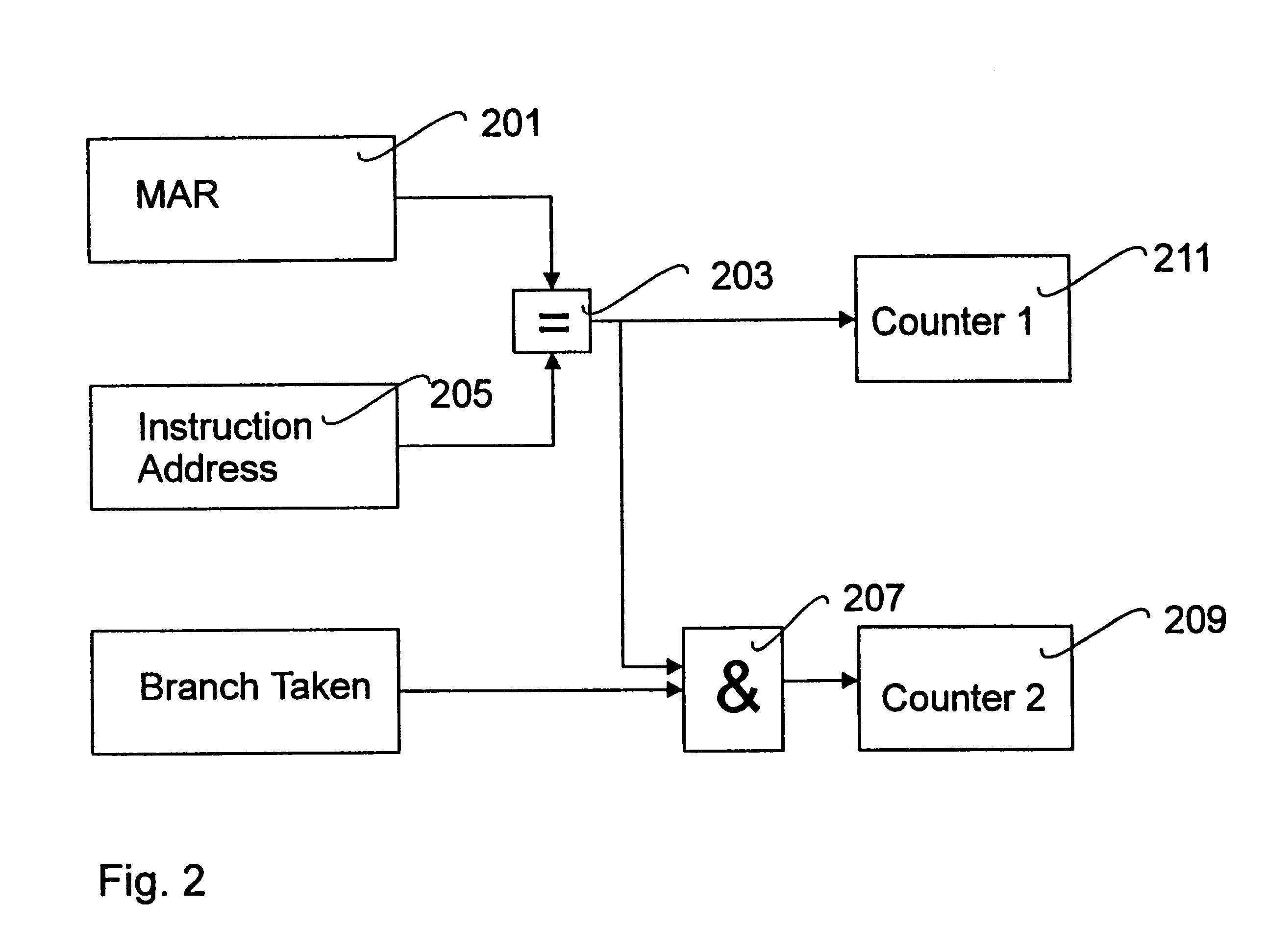

Method and system for branch prediction

InactiveUS6233679B1Digital computer detailsNext instruction address formationPrediction systemSystem usage

In a computer a system for branch prediction is arranged. The branch prediction system uses a scanning mechanism (303) for scanning the program memory for conditional branch instructions during the running of the program. When finding such an instruction the system records during a preset time interval (311) the statistics for that specific conditional branch instruction and sets a branch prediction but in the instruction accordingly (321). The system then starts to scan for the next conditional branch instruction in the program memory. The system can also be used for updating a BHT during the running of a program. The use of the system is particularly useful in applications when a program is run for a relatively long time such as a program used in a telephone switch. The use of the system also allows for changing branch predictions during the run of a program.

Owner:TELEFON AB LM ERICSSON (PUBL)

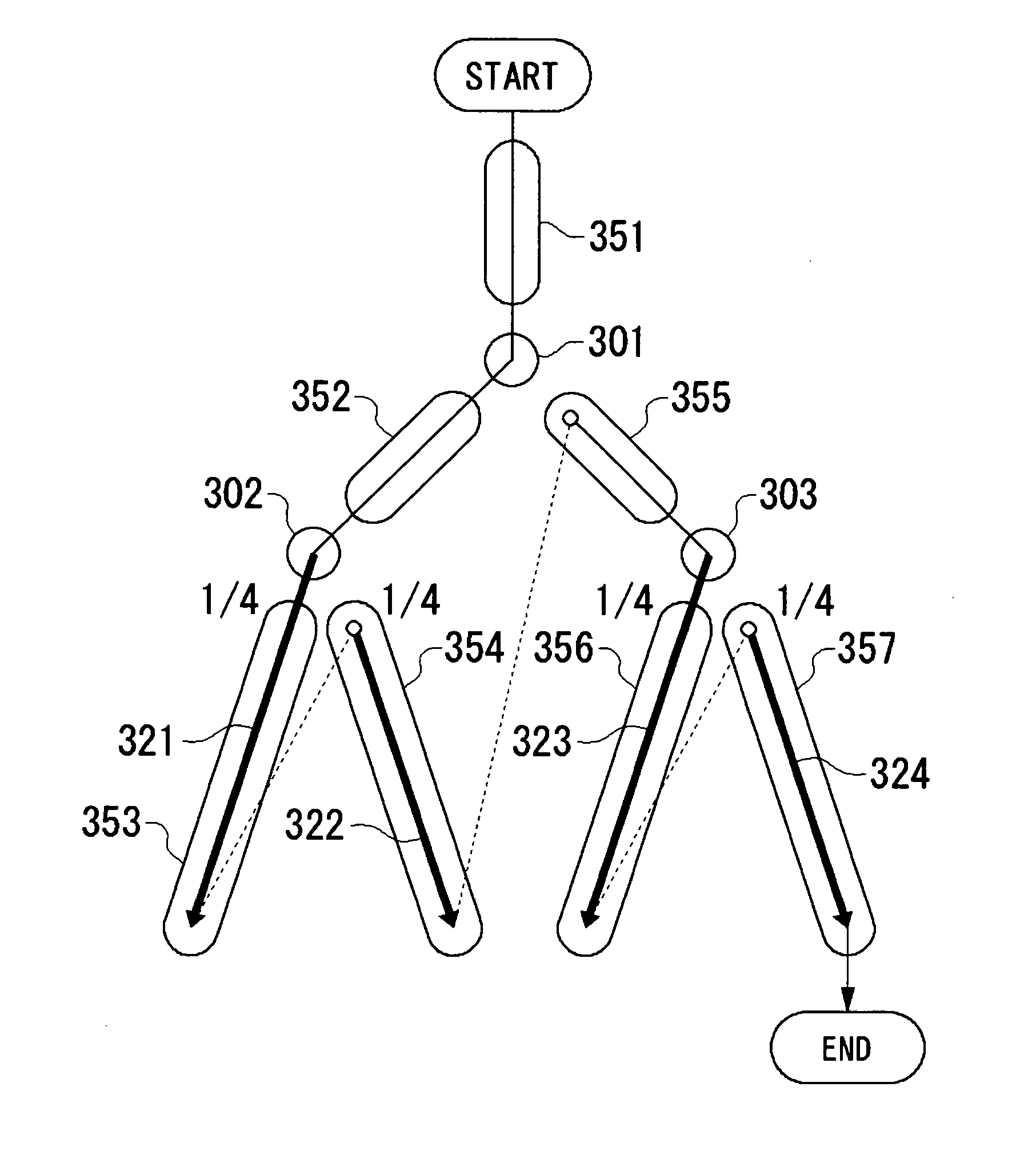

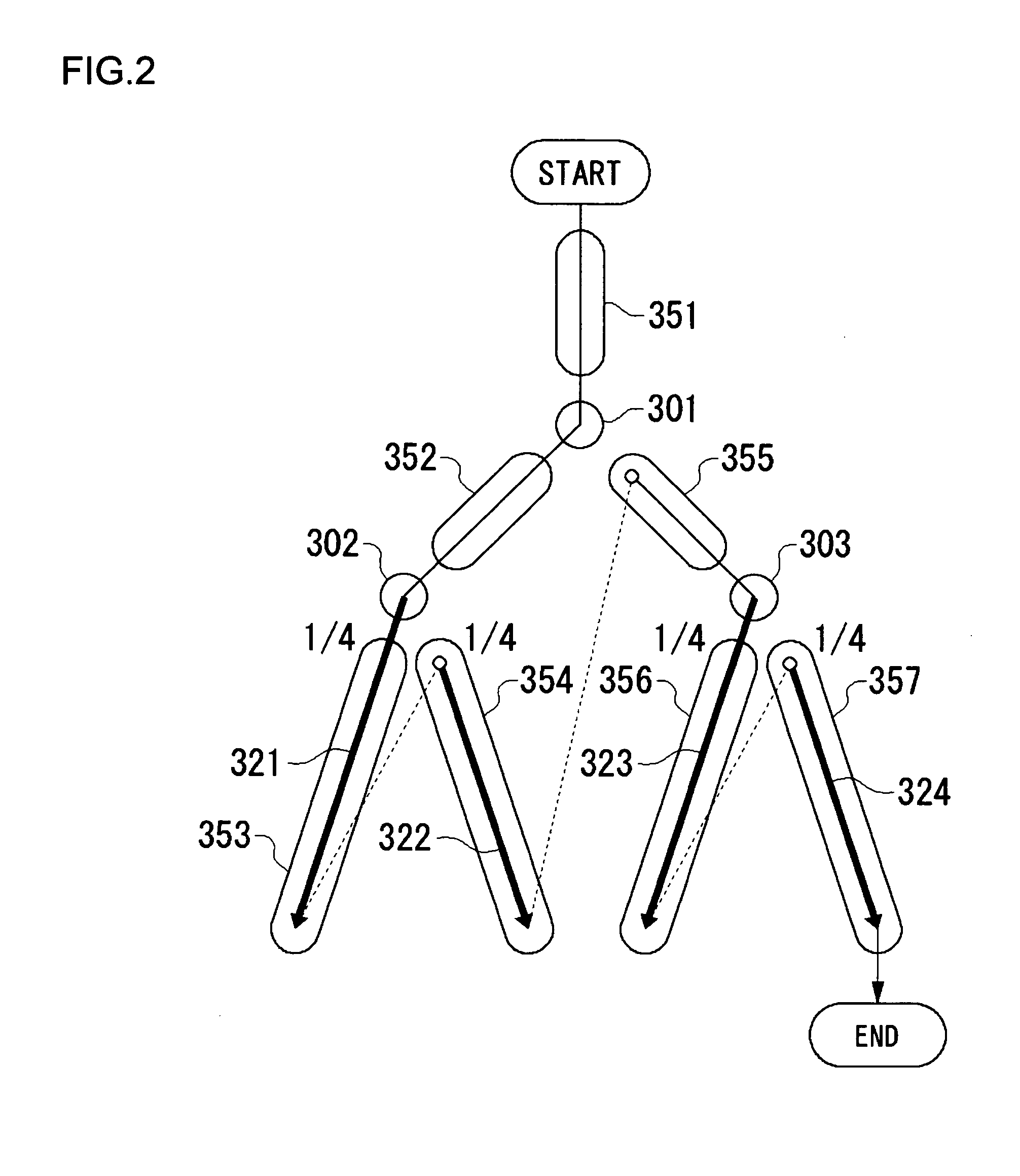

Program optimization method, and compiler using the same

InactiveUS6817013B2Short processing timeEfficient executionSoftware engineeringDigital computer detailsBasic blockSource code

An optimization method and apparatus for converting source code for a program written in a programming language into machine language. The program includes a basic block as a unit to estimate an execution time for the program to be processed, generating a nested tree that represents the connections of the basic blocks using a nesting structure, when a conditional branch is accompanied by a node in the nested tree, employing the execution time estimated by using the basic blocks as units to obtain an execution time at the node of the program when a conditional branching portion of a program is directly executed and when the conditional branching portion is executed in parallel, and defining the node as a parallel execution area group when the execution time required for the parallel execution is shorter or dividing multiple child nodes of the nodes into multiple parallel execution areas.

Owner:INT BUSINESS MASCH CORP

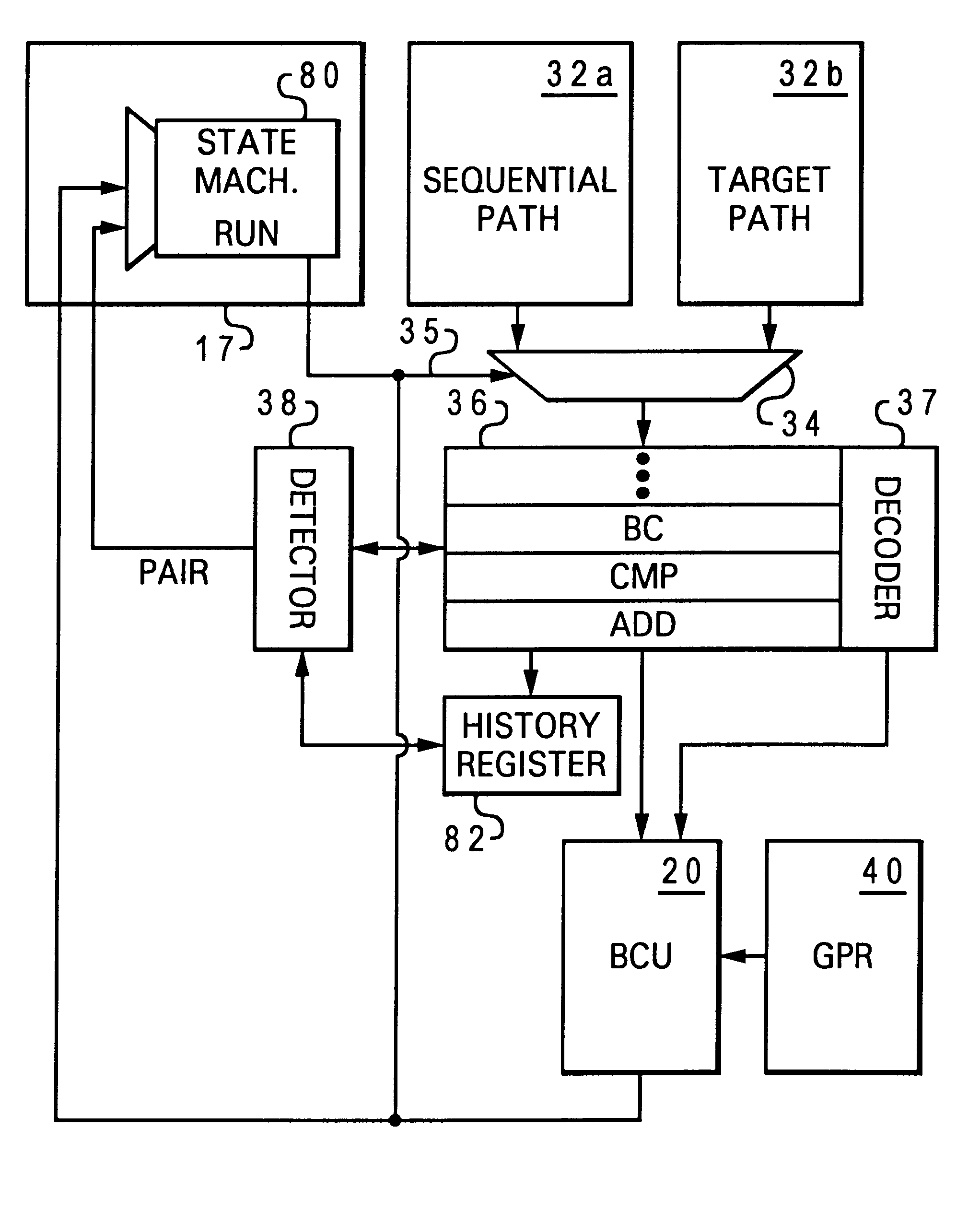

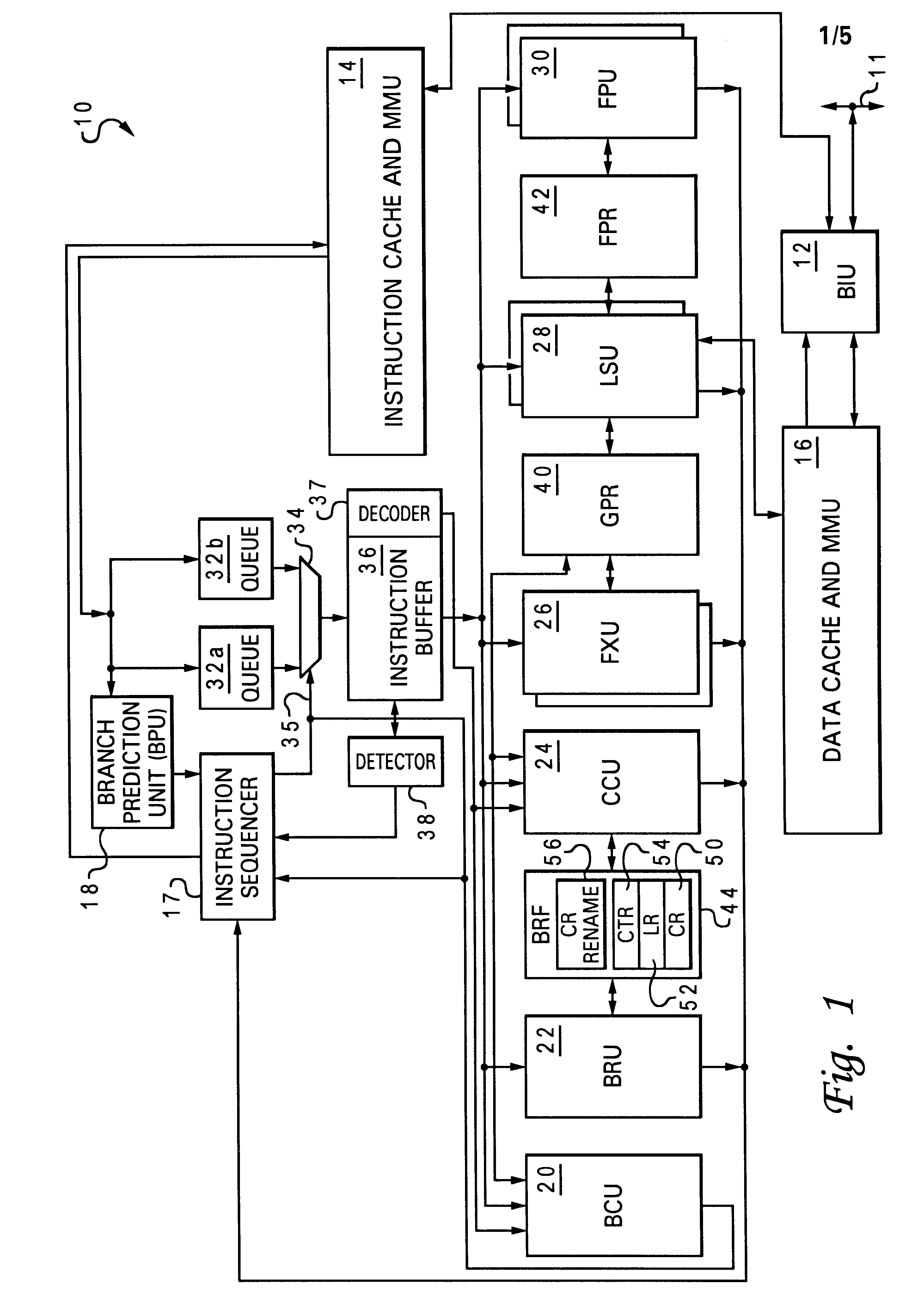

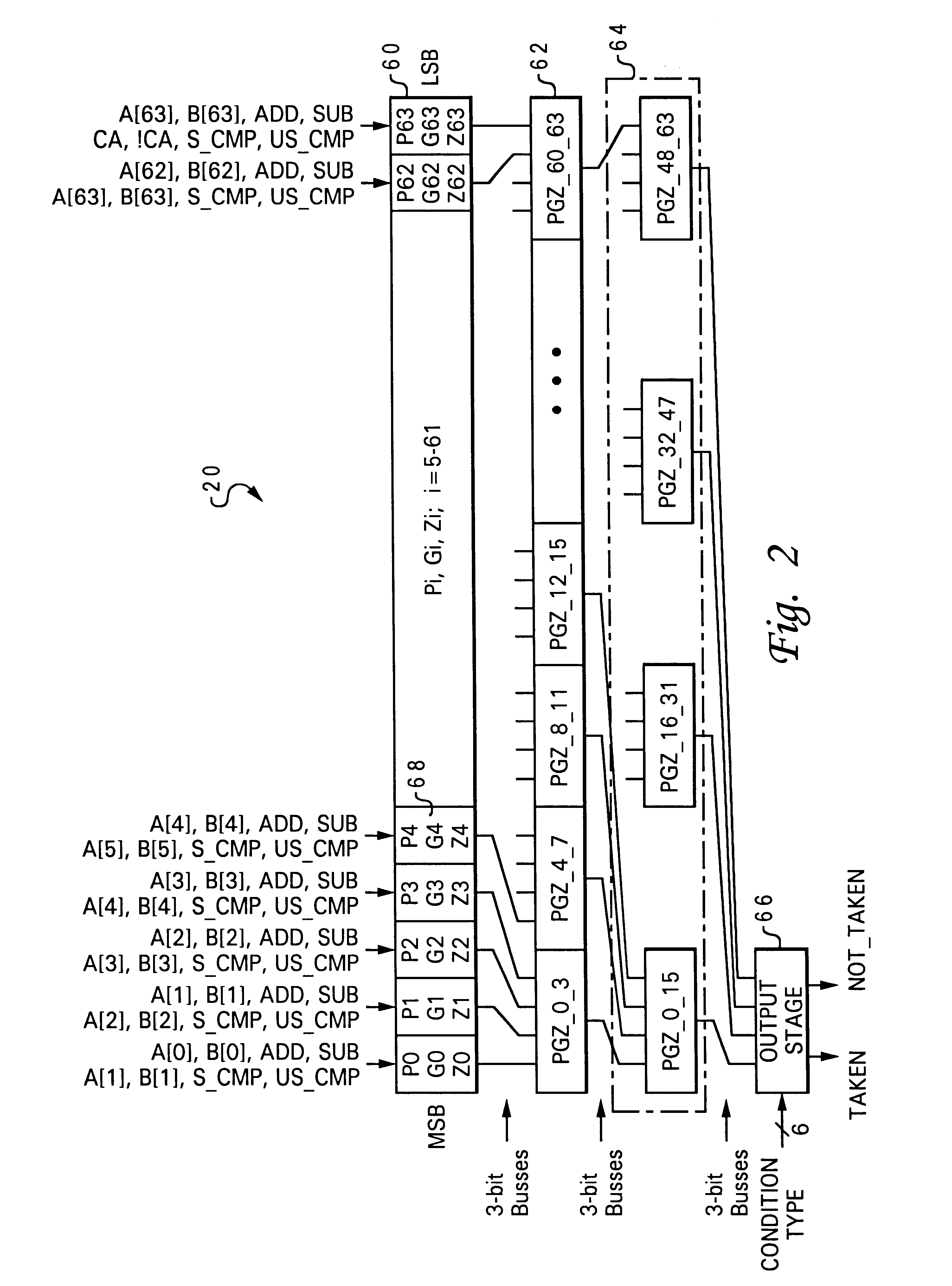

Processor and method that accelerate evaluation of pairs of condition-setting and branch instructions

InactiveUS6598153B1Conditional code generationDigital computer detailsImage resolutionExecution unit

A processor that promotes accelerated resolution of conditional branch instructions includes an instruction sequencer that fetches a plurality of instructions and a detector that detects, among the plurality of fetched instructions, a condition-setting instruction and a conditional branch instruction that depends upon the condition-setting instruction. The processor further includes a decoder that decodes the conditional branch instruction to produce a decoded condition type and an execution unit. In response to the detection of the condition-setting instruction and the conditional branch instruction, the execution unit resolves the conditional branch instruction by evaluating the condition-setting instruction and the decoded condition type in a single operation. Because the condition code bits are not computed or stored as an intermediate result as in prior art processors, branch resolution is accelerated.

Owner:GOOGLE LLC

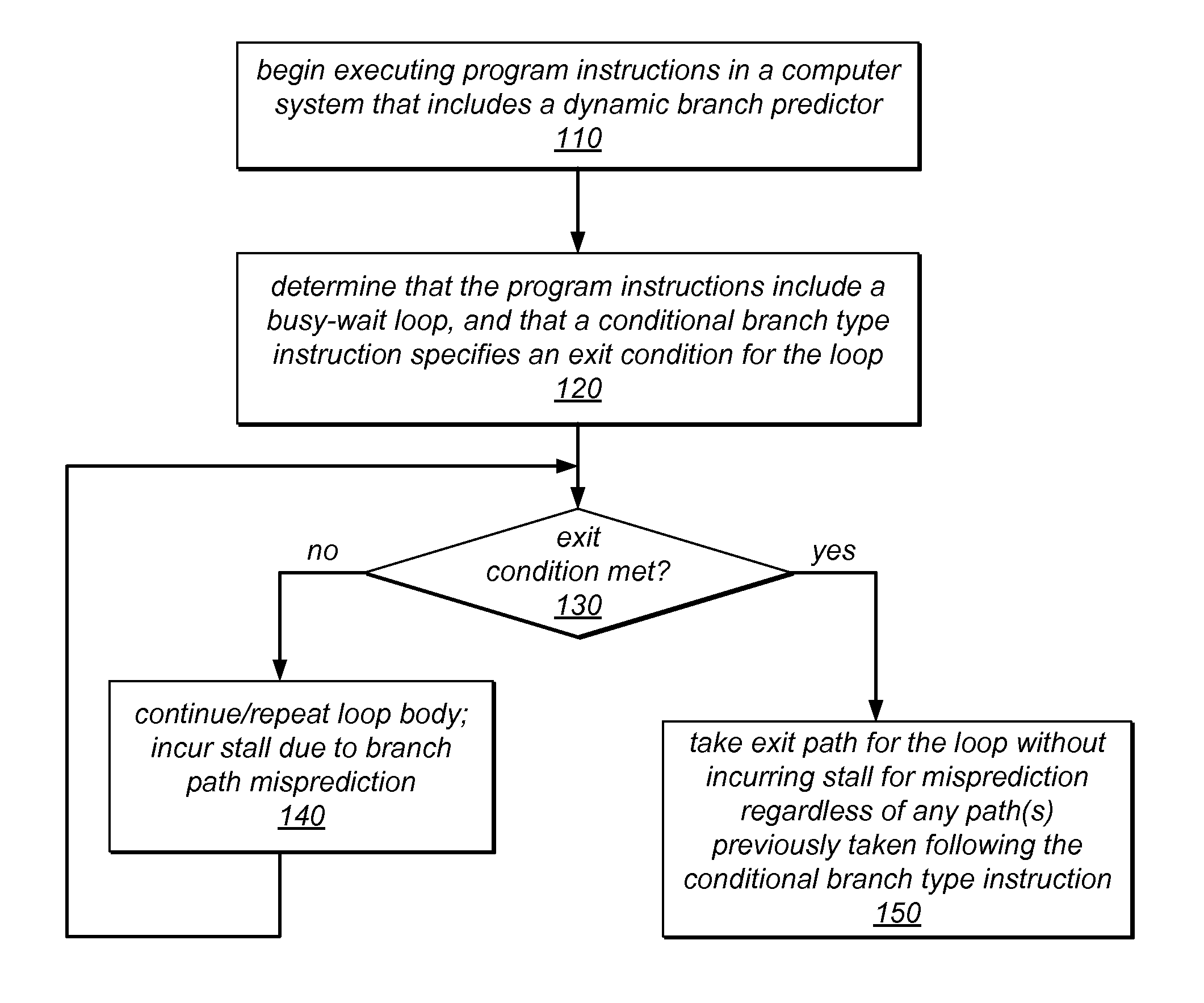

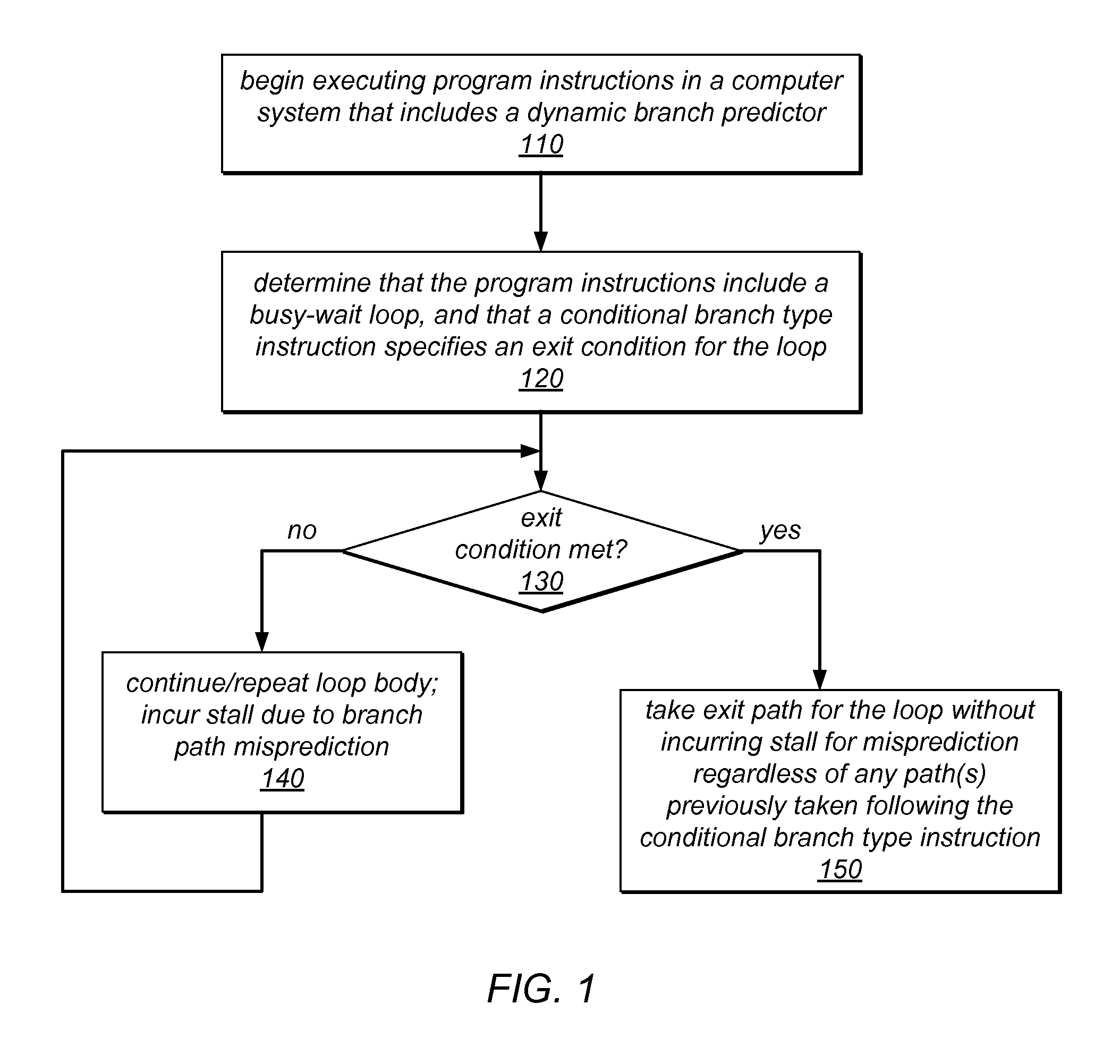

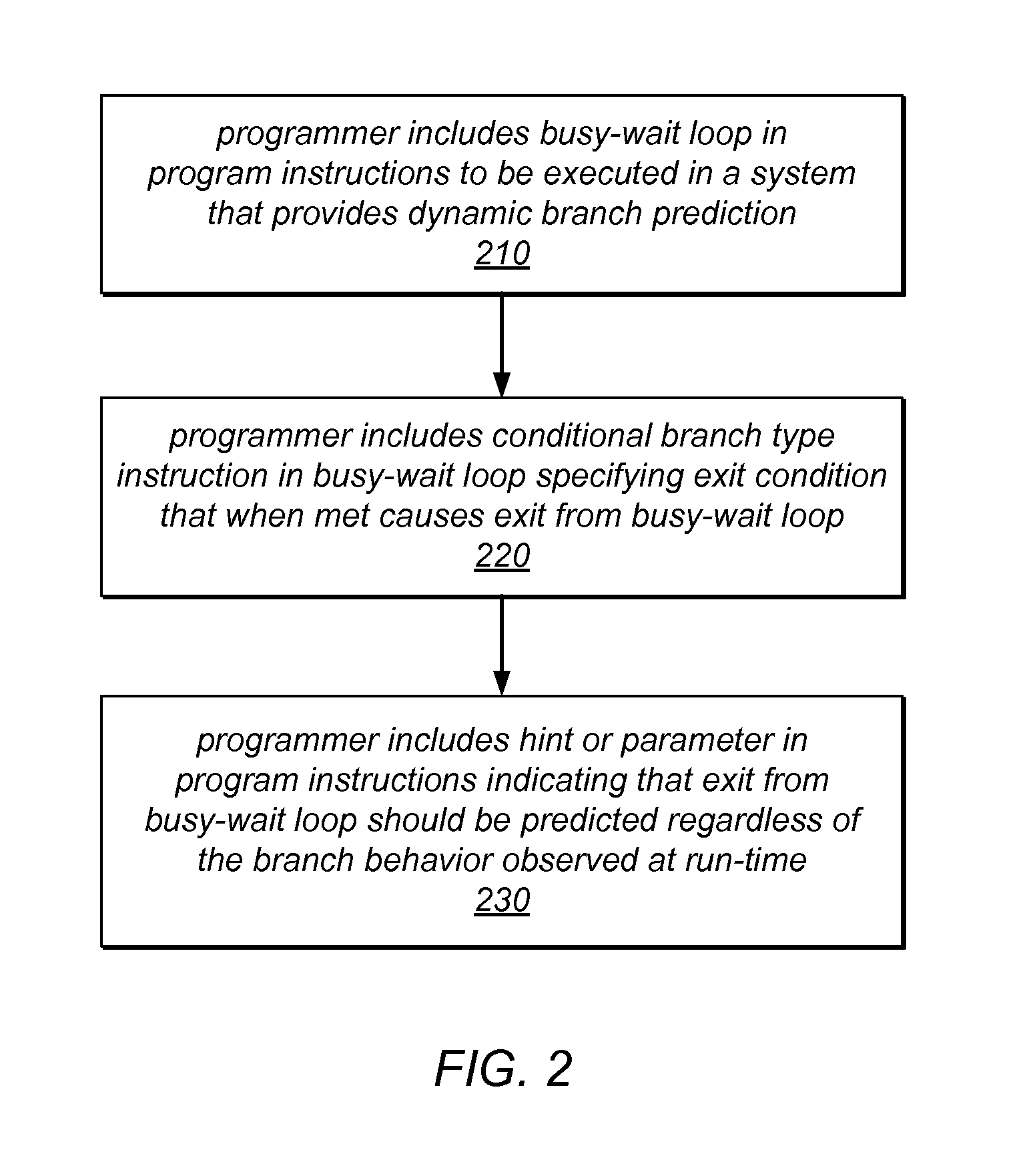

System and Method for Mitigating the Impact of Branch Misprediction When Exiting Spin Loops

ActiveUS20130198499A1None meet conditionsQuick responseDigital computer detailsConcurrent instruction executionProgram instructionComputerized system

A computer system may recognize a busy-wait loop in program instructions at compile time and / or may recognize busy-wait looping behavior during execution of program instructions. The system may recognize that an exit condition for a busy-wait loop is specified by a conditional branch type instruction in the program instructions. In response to identifying the loop and the conditional branch type instruction that specifies its exit condition, the system may influence or override a prediction made by a dynamic branch predictor, resulting in a prediction that the exit condition will be met and that the loop will be exited regardless of any observed branch behavior for the conditional branch type instruction. The looping instructions may implement waiting for an inter-thread communication event to occur or for a lock to become available. When the exit condition is met, the loop may be exited without incurring a misprediction delay.

Owner:ORACLE INT CORP

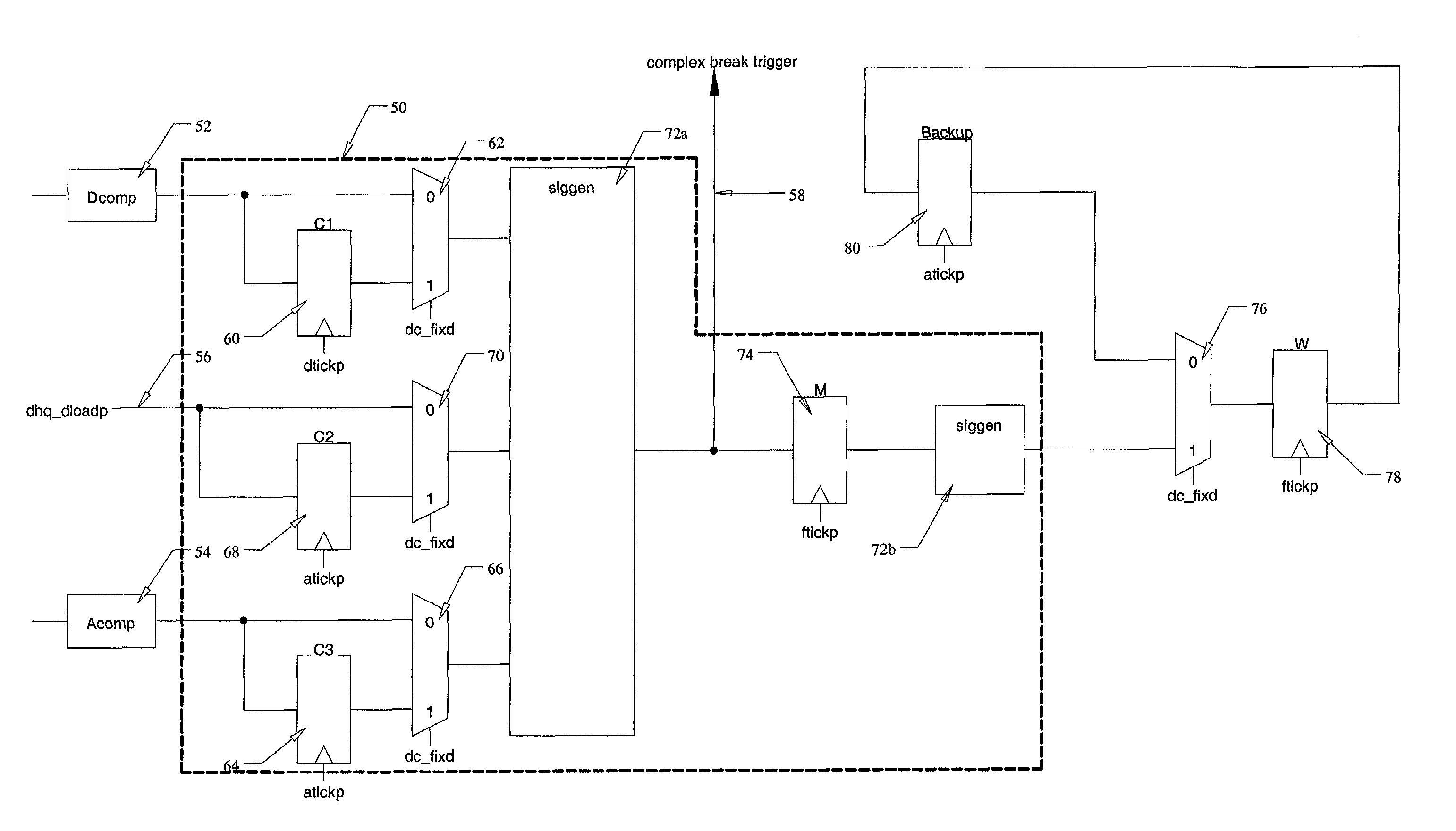

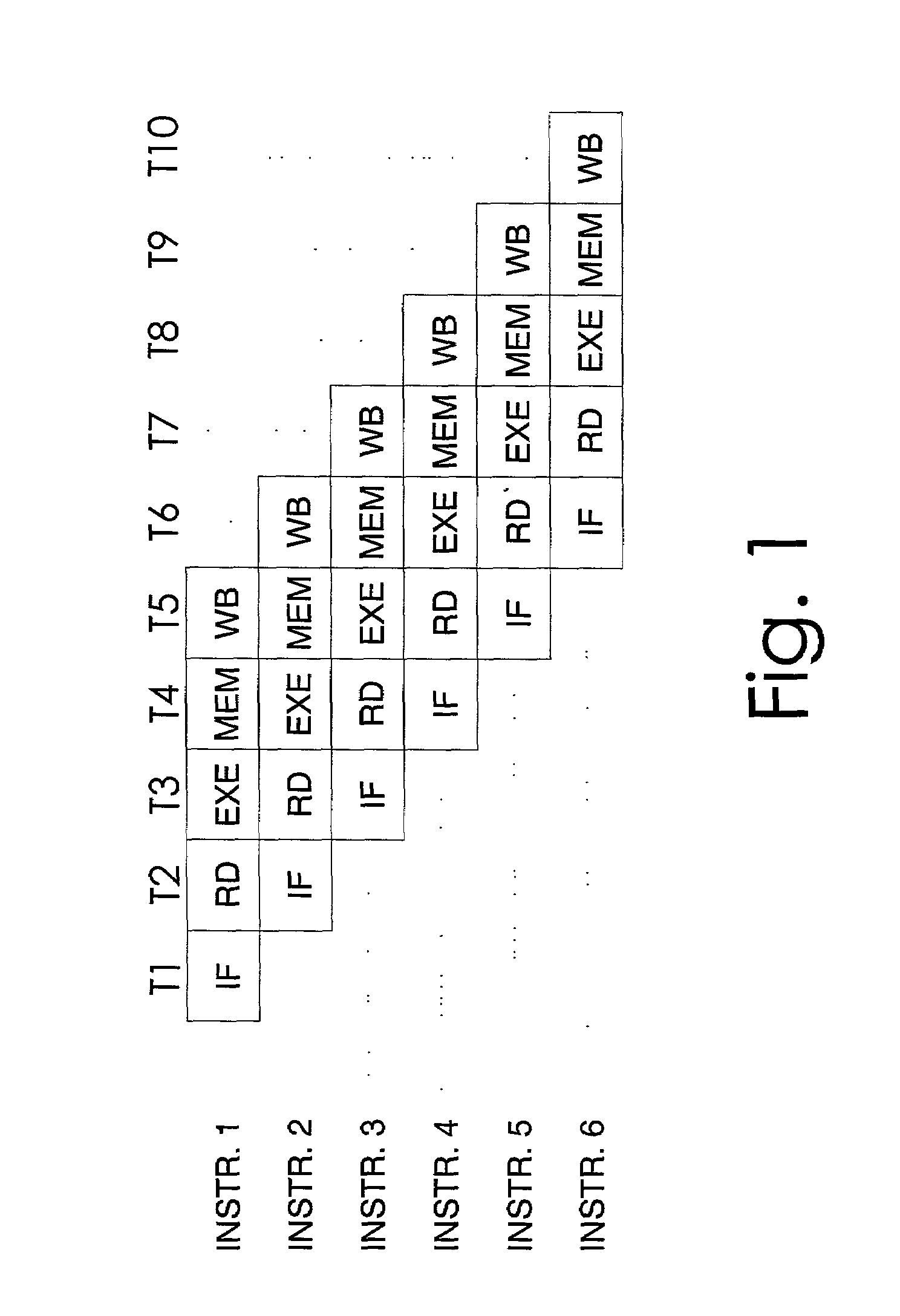

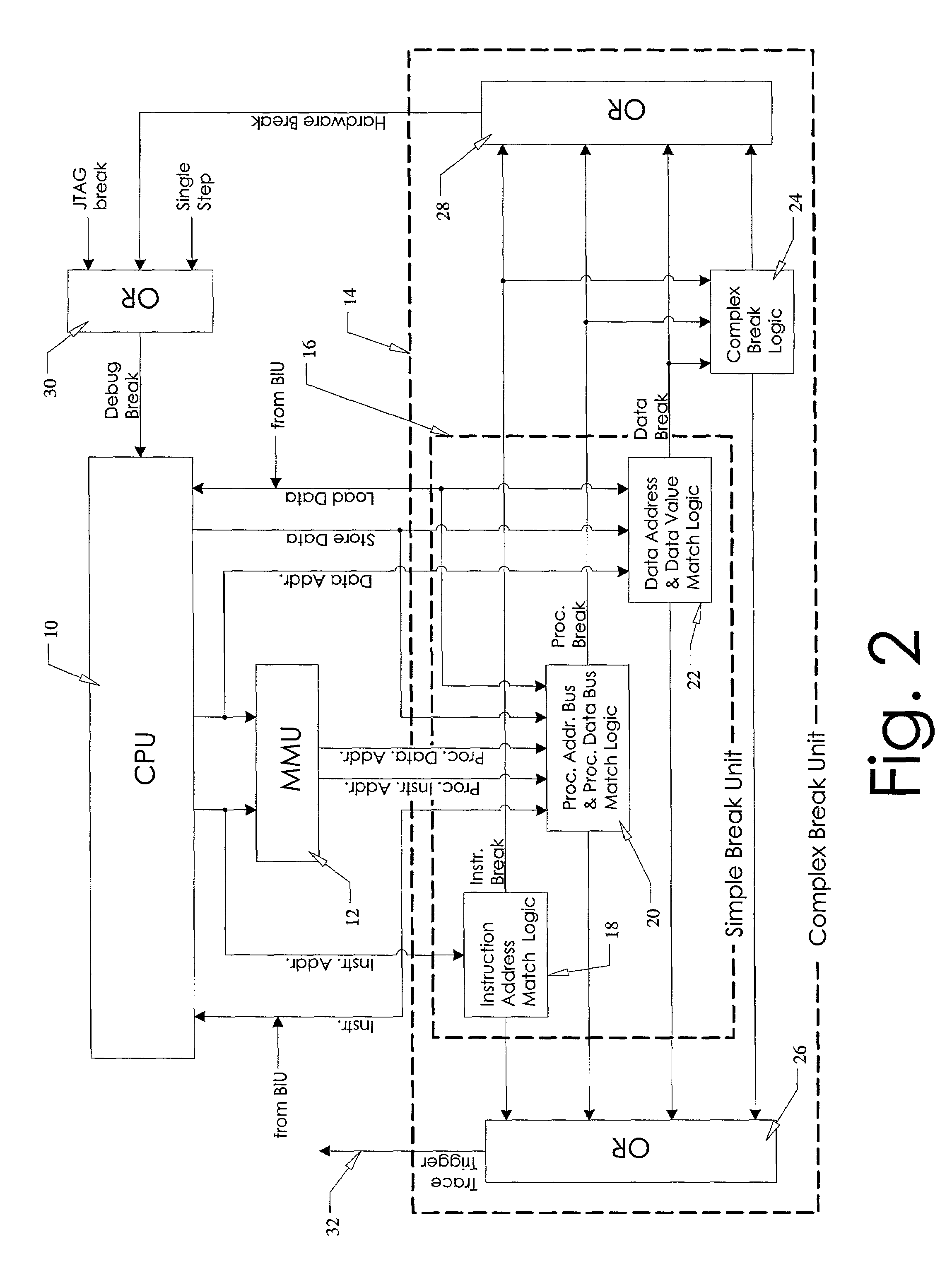

System and method for state restoration in a diagnostic module for a high-speed microprocessor

InactiveUS7043416B1Data processing applicationsAnalogue computers for electric apparatusProgram counterComputer science

A system and method are presented for saving and restoring the state of a diagnostic module in a microprocessor. The diagnostic module contains a complex break state machine, capable of halting the microprocessor at specified breakpoints. These breakpoints are based on combinations of instruction locations and / or data values, along with previous machine states. A problem occurs with prior art diagnostic modules when the processor returns from an exception occurring during a fix-up cycle inserted to handle a data load miss associated with an instruction located in a branch delay slot (the location immediately following a conditional branch instruction). Under these circumstances, the exception handler restores the program counter to the location of the branch instruction, causing the branch to be re-executed. The prior art state machine erroneously updates its internal state a second time when the branch is re-executed. According to the system and method disclosed herein, at each state change the previous machine state saved. Thus, when a branch instruction is re-executed, the complex break state machine of the present invention is restored to its previous state, thereby correcting the error.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Data processing system, data processing method and program

InactiveUS20080256264A1Load on the processing including CW transferEasy to processGeneral purpose stored program computerSpecific program execution arrangementsData processing systemENCODE

In the host, an IP issues CCW, and a CH encodes the CCW and a CCW chain by the encode program to create a code including the description of controlling a conditional branch with the DKC and transmits the code to a PORT in the DKC. In the DKC, the PORT decodes the code by the decode program, and a CP sequentially processes each command obtained by the decoding and returns a return code representing the end state of the processing. The host receives the return code to recognize the end state of the processing.

Owner:HITACHI LTD

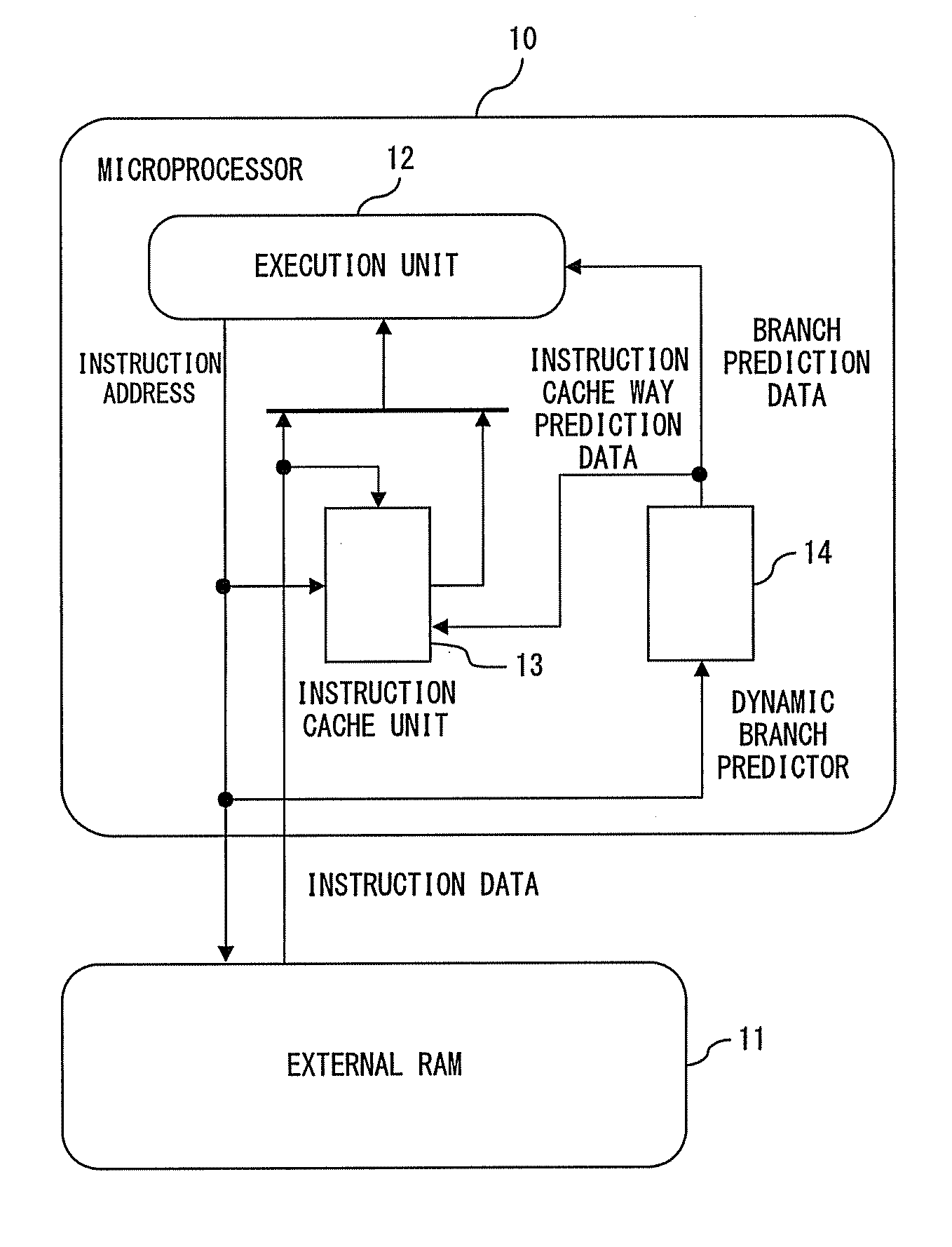

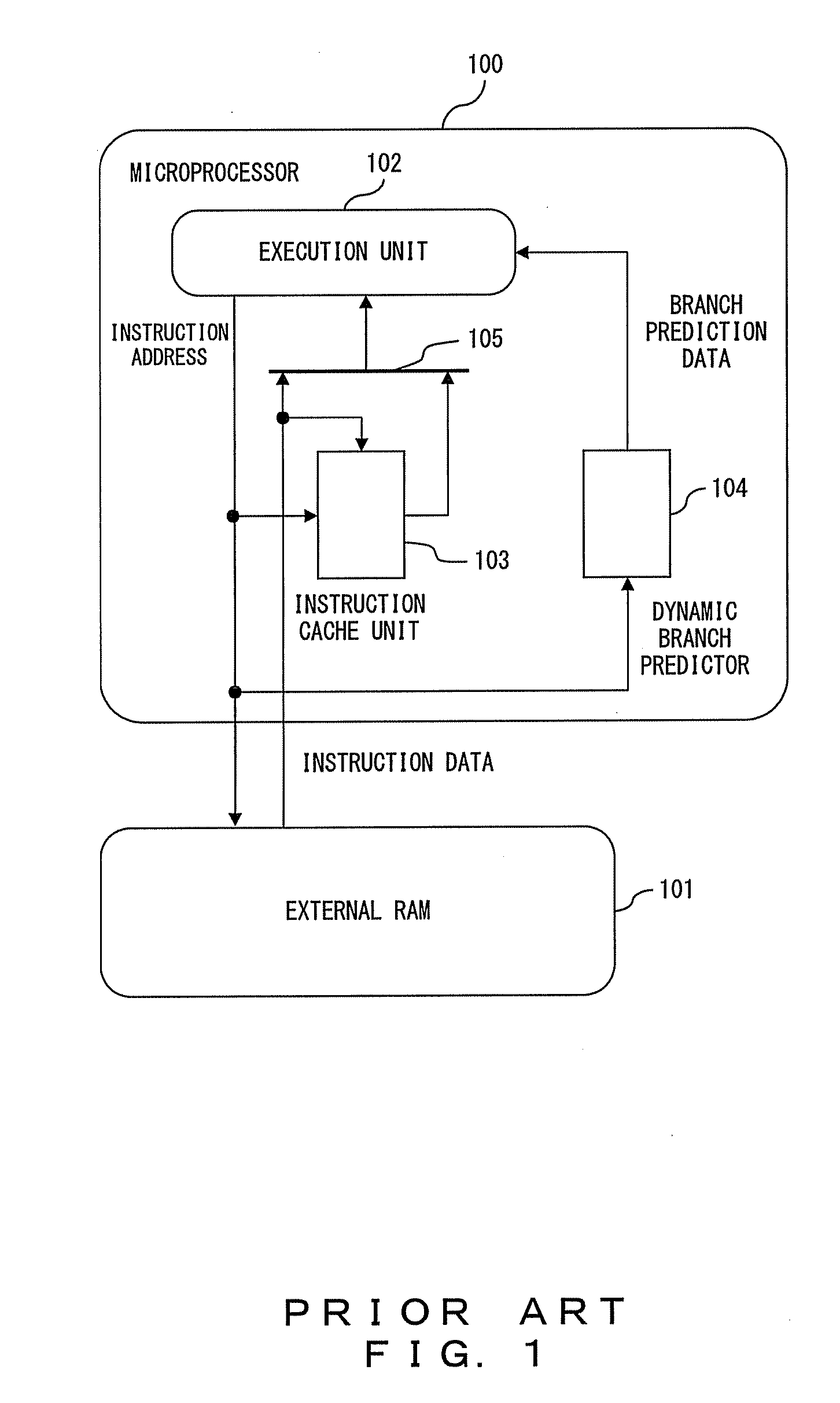

Data processor and memory read active control method

InactiveUS20080215865A1Memory architecture accessing/allocationEnergy efficient ICTControl signalConditional branch

Instruction cache memory having a plurality of memory (for example, cache WAY), means 3 for storing prediction data of a conditional branch of a branch instruction being taken or not taken and for storing prediction data of memory storing the branch instruction data of the plurality of memory when the prediction is the branch being taken, and means for, when an instruction to be executed is a branch instruction, outputting a read active control signal to the plurality of memories 1 by using two pieces of prediction data obtained from the means by an index corresponding to the branch instruction, are comprised.

Owner:SOCIONEXT INC

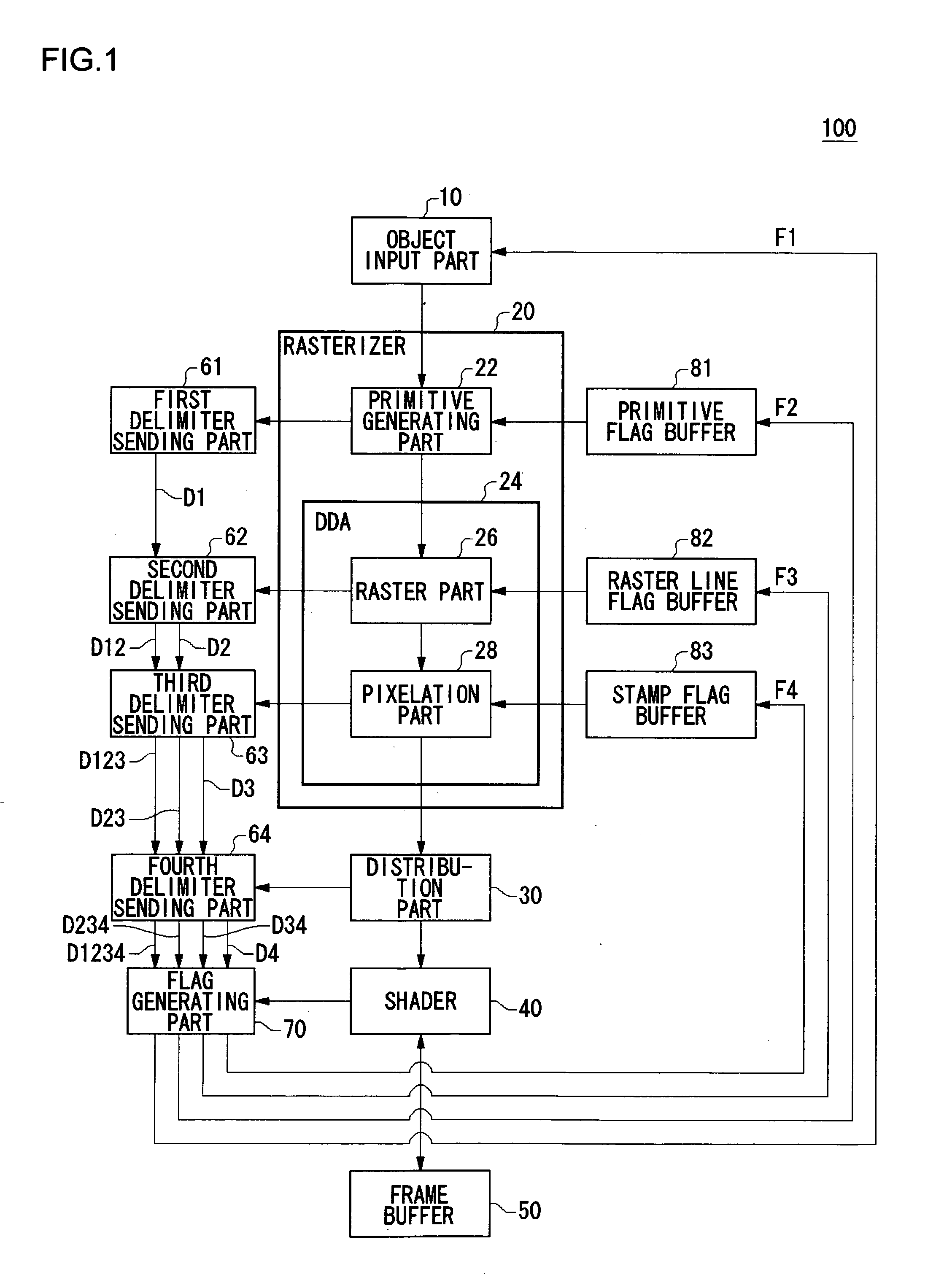

Drawing processing apparatus and drawing processing method for multipass rendering

ActiveUS20060267981A1Efficient executionMultiple digital computer combinationsProcessor architectures/configurationComputer graphics (images)Granularity

A drawing processing apparatus capable of executing a drawing processing program having conditional branches efficiently by multipass rendering. The drawing processing apparatus comprises arithmetic processing parts including an object input part, a primitive generating part, a raster part, a pixelation part, a distribution part, and a shader which constitute pipeline stages. The shader divides the program into and executes the same in a plurality of passes depending on conditional branches. The shader generates enable flags determining whether or not respective pixels satisfy branch conditions. The flag generating part generates bind enable flags which are the enable flags on the pixels bound into the processing granularities of the pipeline stages, and feeds back the same to the respective pipeline stages. The arithmetic processing parts in the individual pipeline stages refer to the bind enable flags and limit the submission of data not targeted for arithmetic processing in the branched passes.

Owner:SONY COMPUTER ENTERTAINMENT INC

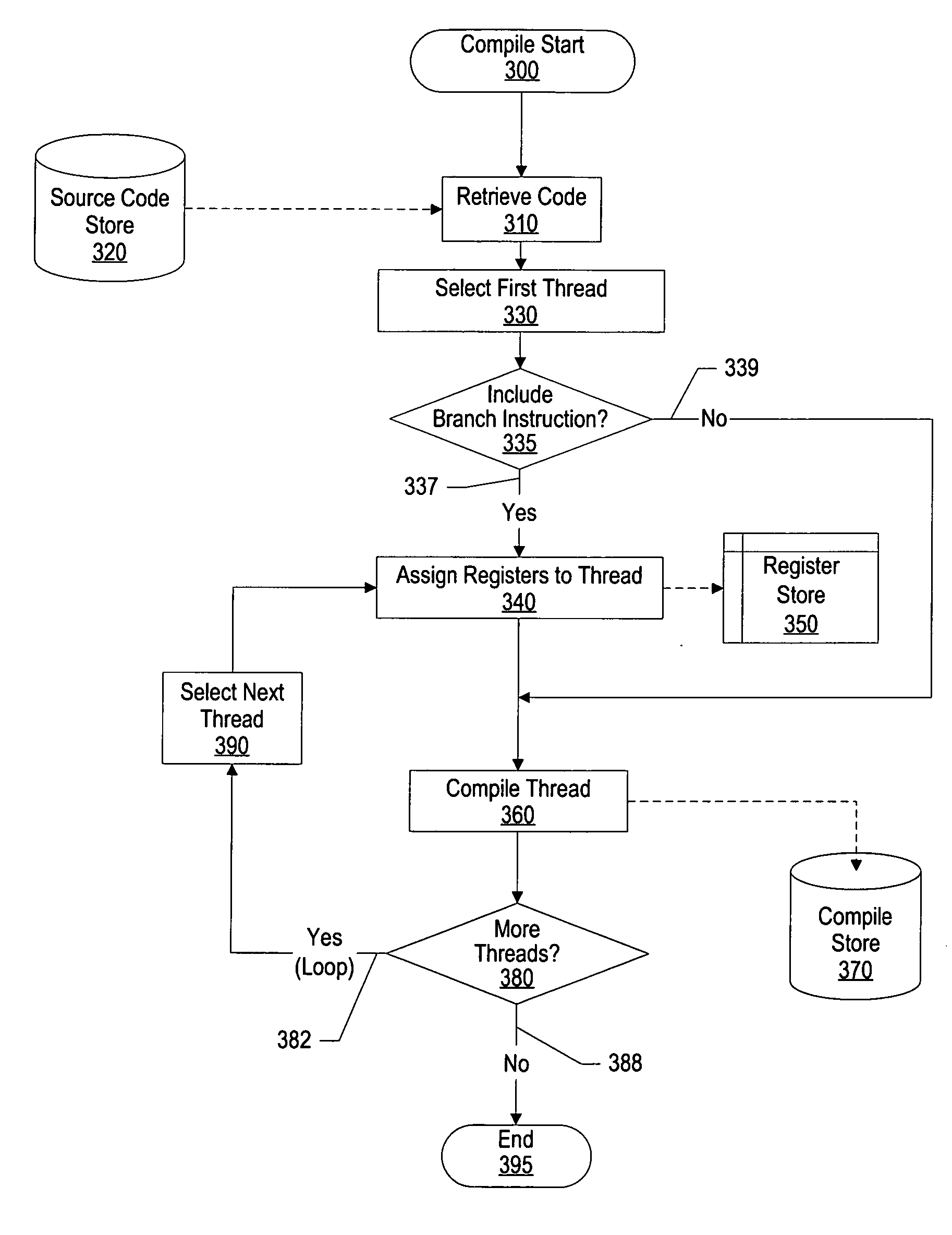

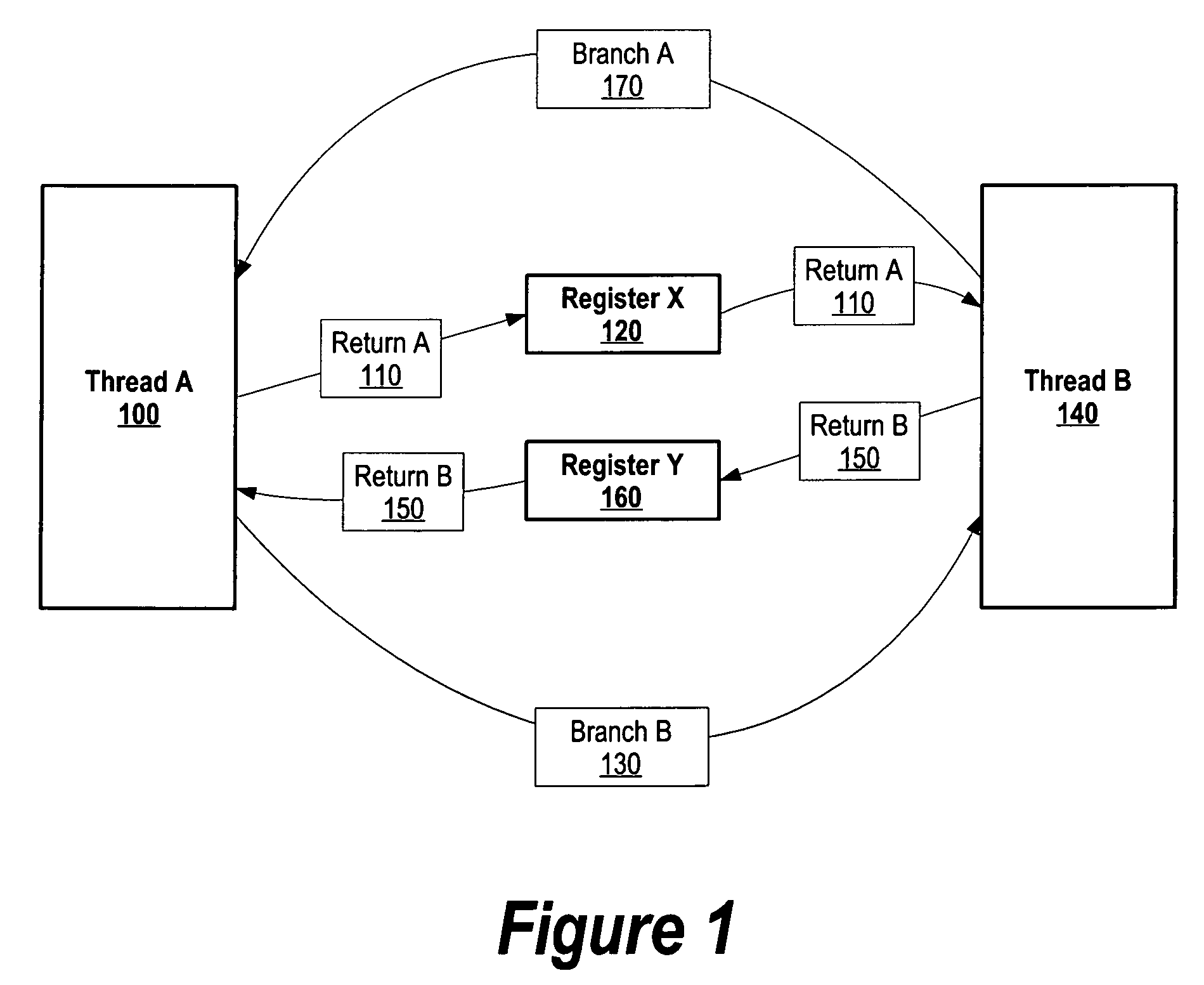

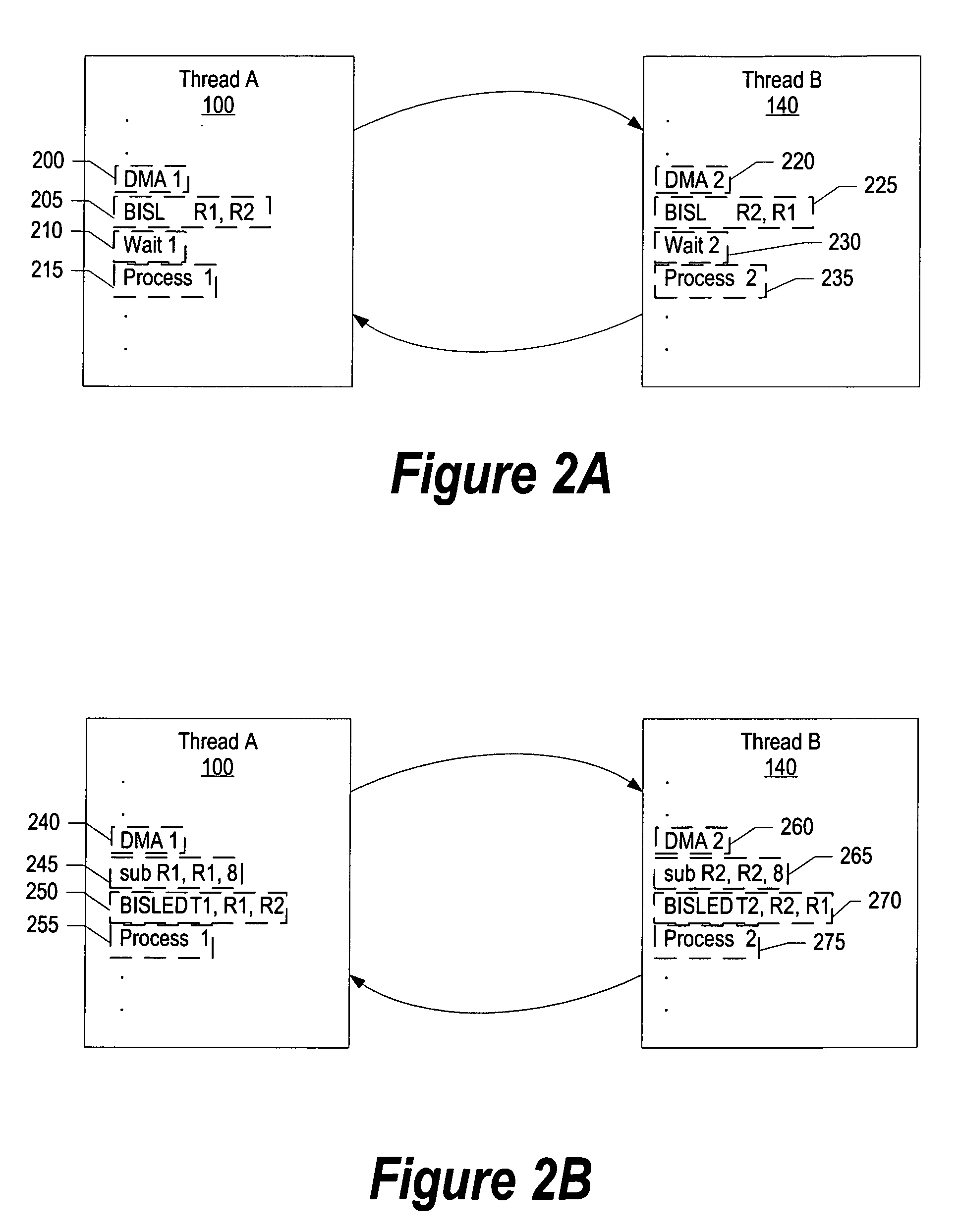

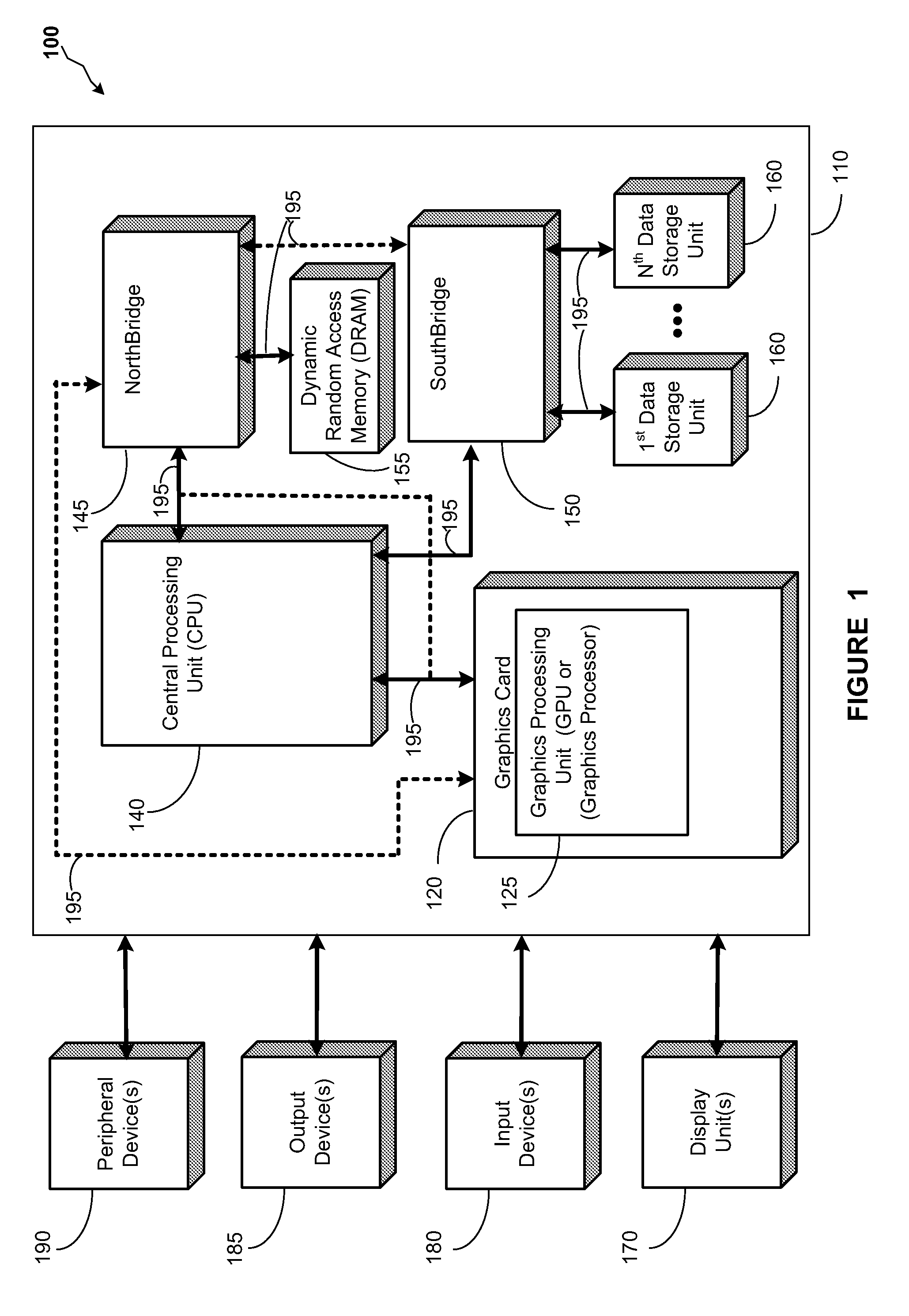

System and method for partitioning processor resources based on memory usage

A system and method for partitioning processor resources based on memory usage is provided. A compiler determines the extent to which a process is memory-bound and accordingly divides the process into a number of threads. When a first thread encounters a prolonged instruction, the compiler inserts a conditional branch to a second thread. When the second thread encounters a prolonged instruction, a conditional branch to a third thread is executed. This continues until the last thread conditionally branches back to the first thread. An indirect segmented register file is used so that the “return to” and “branch to” logical registers within each thread are the same (e.g., R1 and R2) for each thread. These logical registers are mapped to hardware registers that store actual addresses. The indirect mapping is altered to bypass completed threads. When the last thread completes it may signal an external process.

Owner:IBM CORP

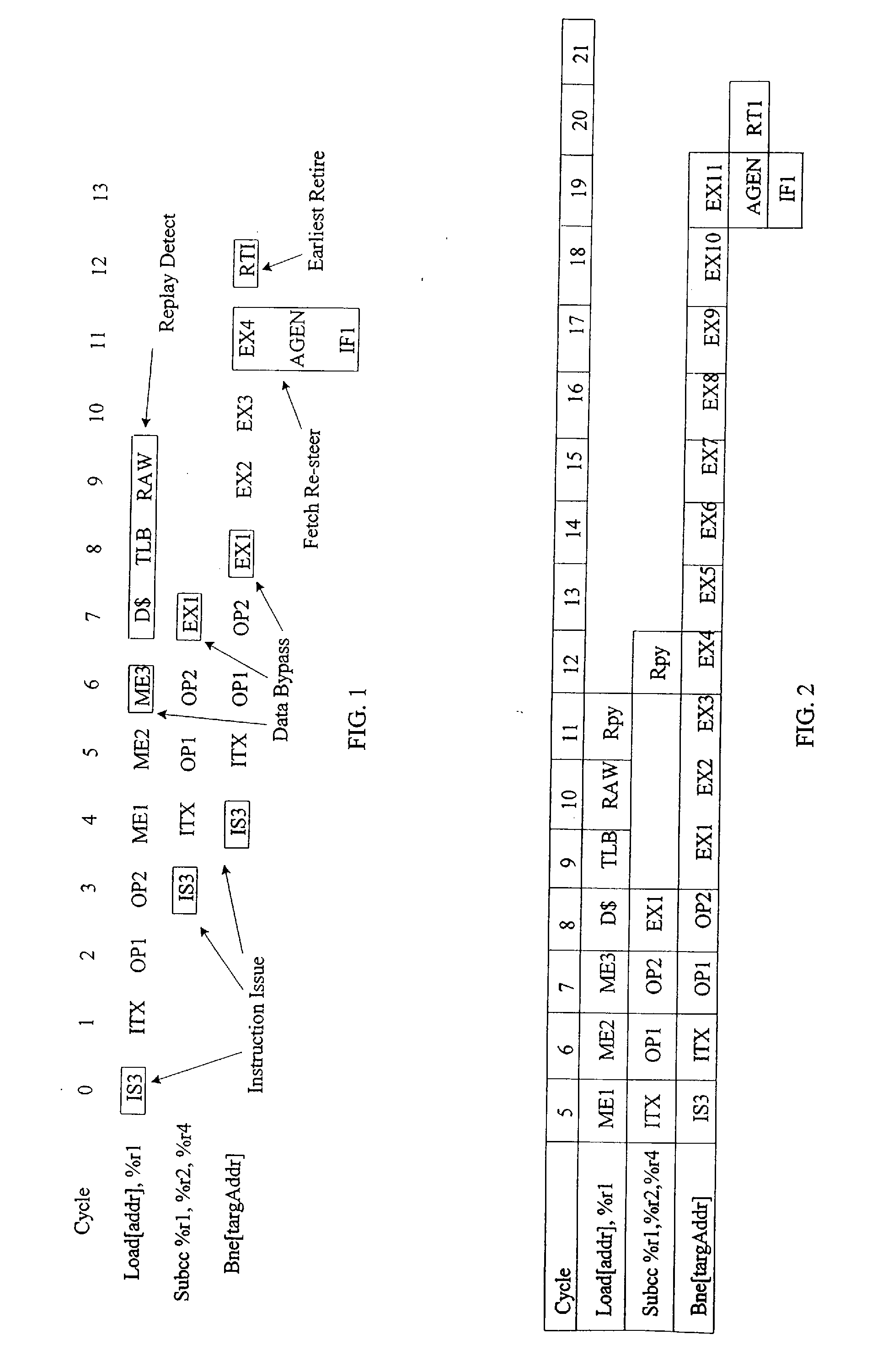

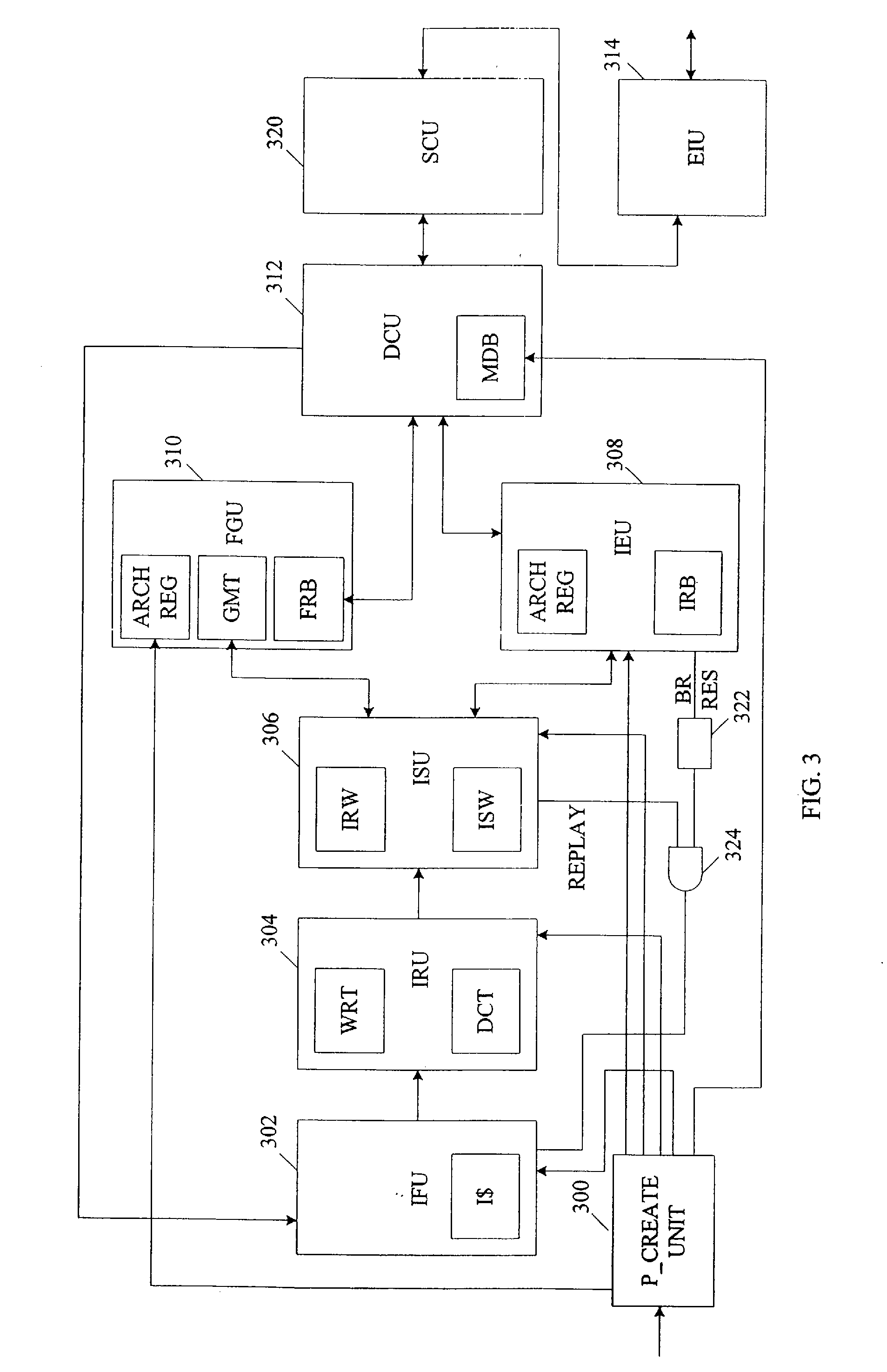

Validating branch resolution to avoid mis-steering instruction fetch

InactiveUS20060248319A1Avoids and eliminates repetitive replay conditionResolve delayDigital computer detailsSpecific program execution arrangementsLoad instructionImage resolution

A processor avoids or eliminates repetitive replay conditions and frequent instruction resteering through various techniques including resteering the fetch after the branch instruction retires, and delaying branch resolution. A processor resolves conditional branches and avoids repetitive resteering by delaying branch resolution. The processor has an instruction pipeline with inserted delay in branch condition and replay control pathways. For example, an instruction sequence that includes a load instruction followed by a subtract instruction then a conditional branch, delays branch resolution to allow time for analysis to determine whether the condition branch has resolved correctly. Eliminating incorrect branch resolutions prevents flushing of correctly predicted branches.

Owner:SUN MICROSYSTEMS INC

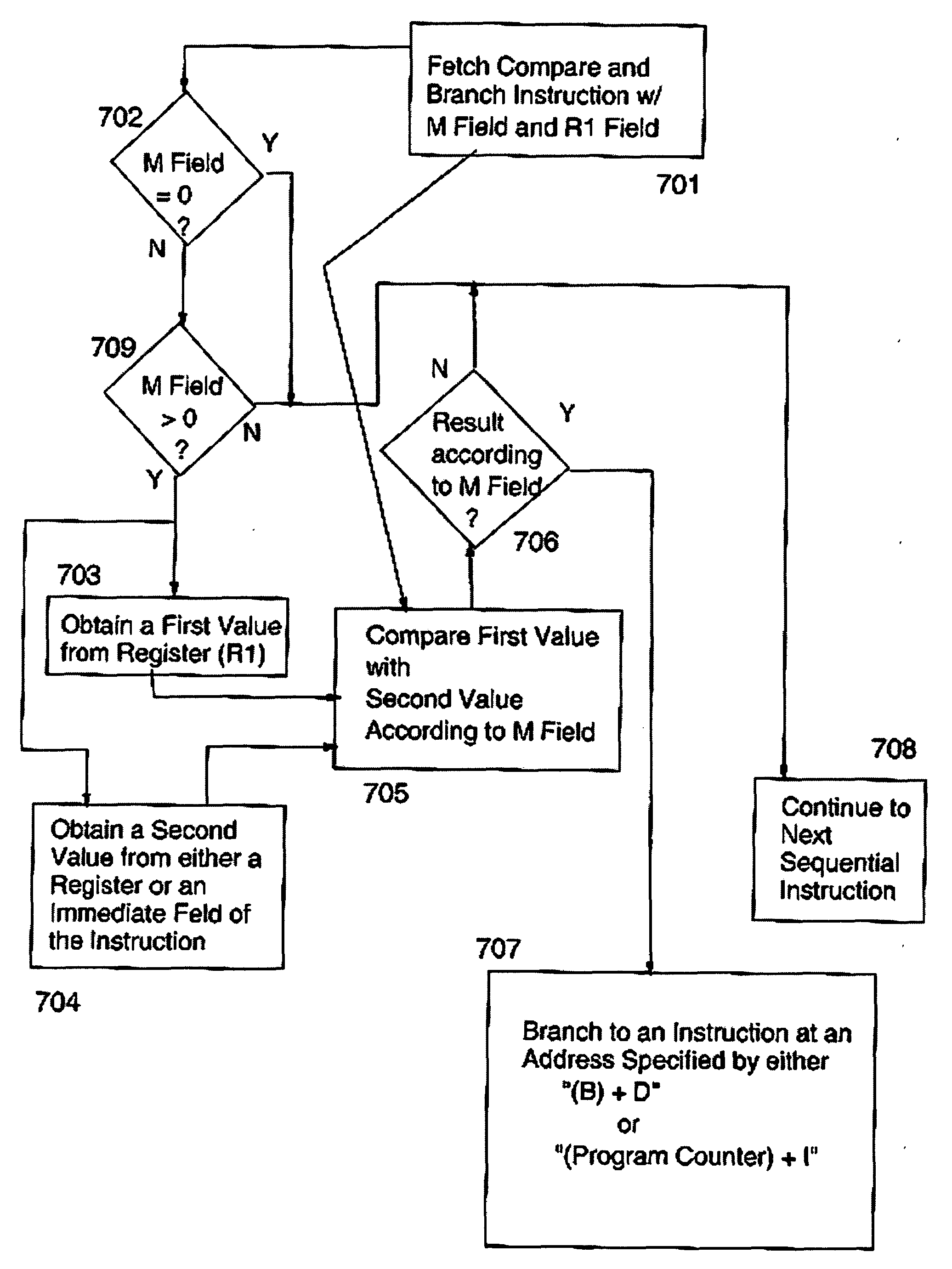

Compare and Branch Facility and Instruction Therefore

InactiveUS20090182983A1Conditional code generationDigital computer detailsCondition CodeConditional branch

An atomic compare and branch instruction is executed that combines the function of a compare instruction having an option field with a conditional branch or jump instruction such that condition codes are preserved rather than setting condition codes to a value representative of the compare results. One comparand is obtained from any one of a memory location or an immediate field and the other comparand is obtained from a register field.

Owner:IBM CORP

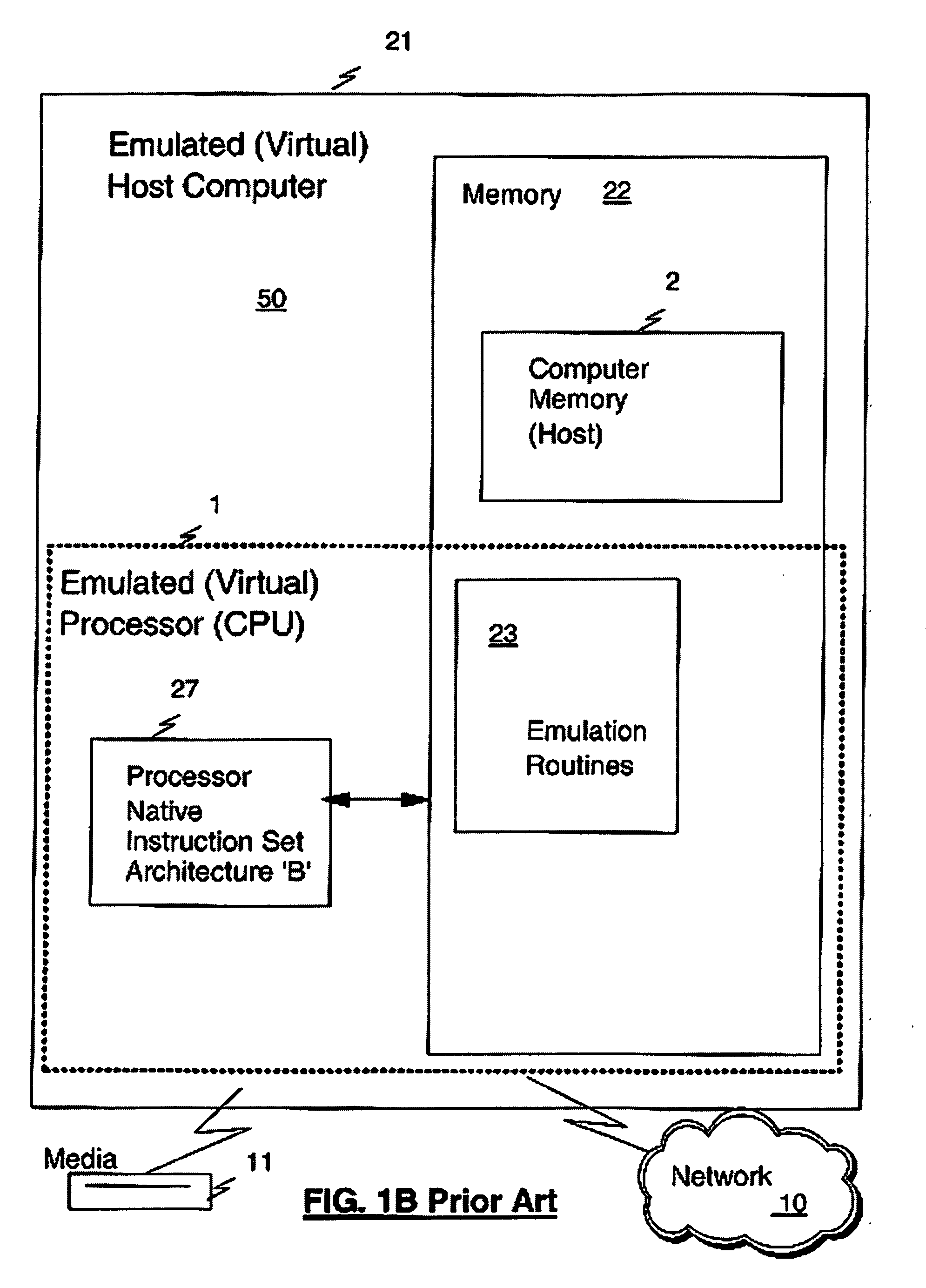

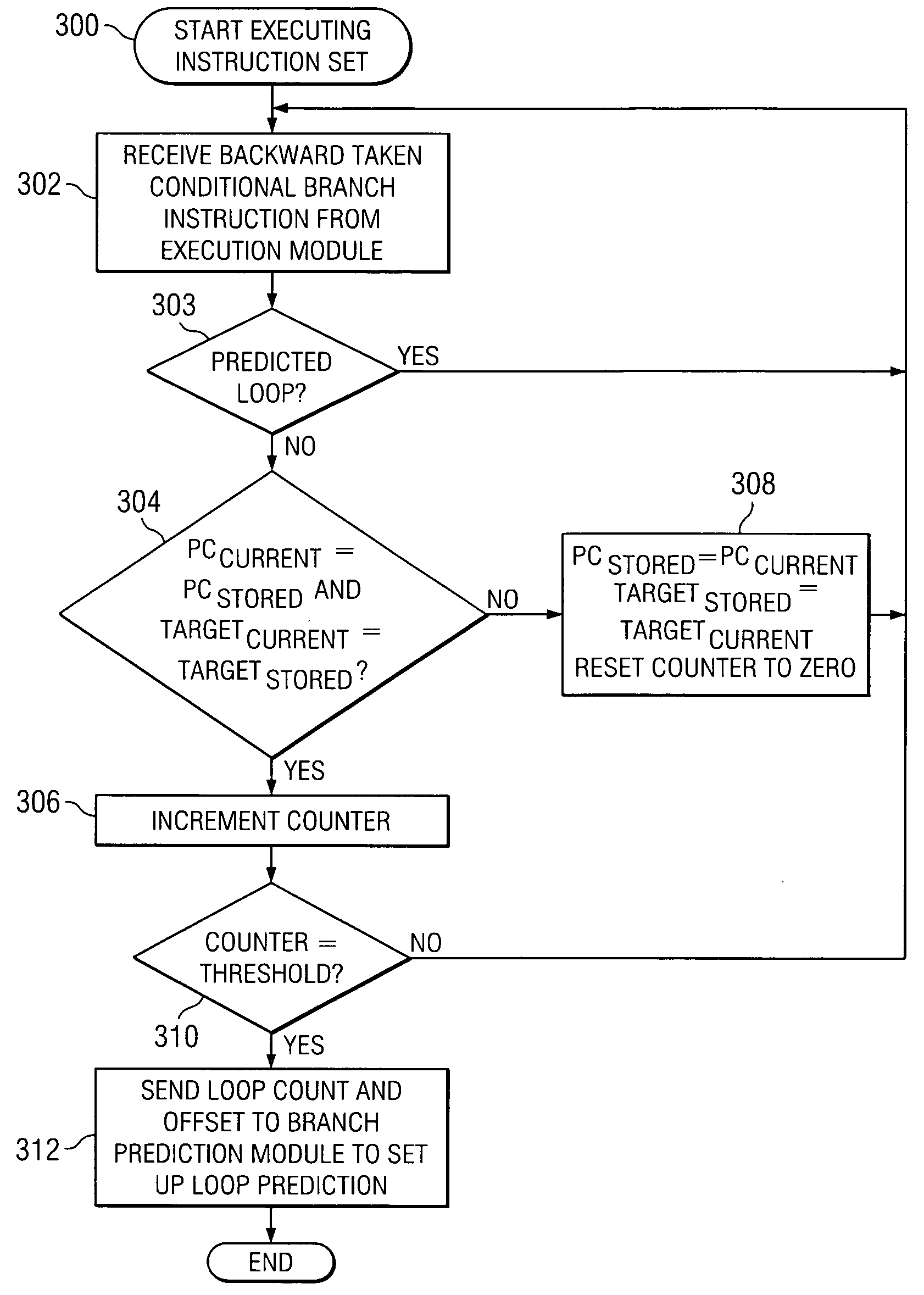

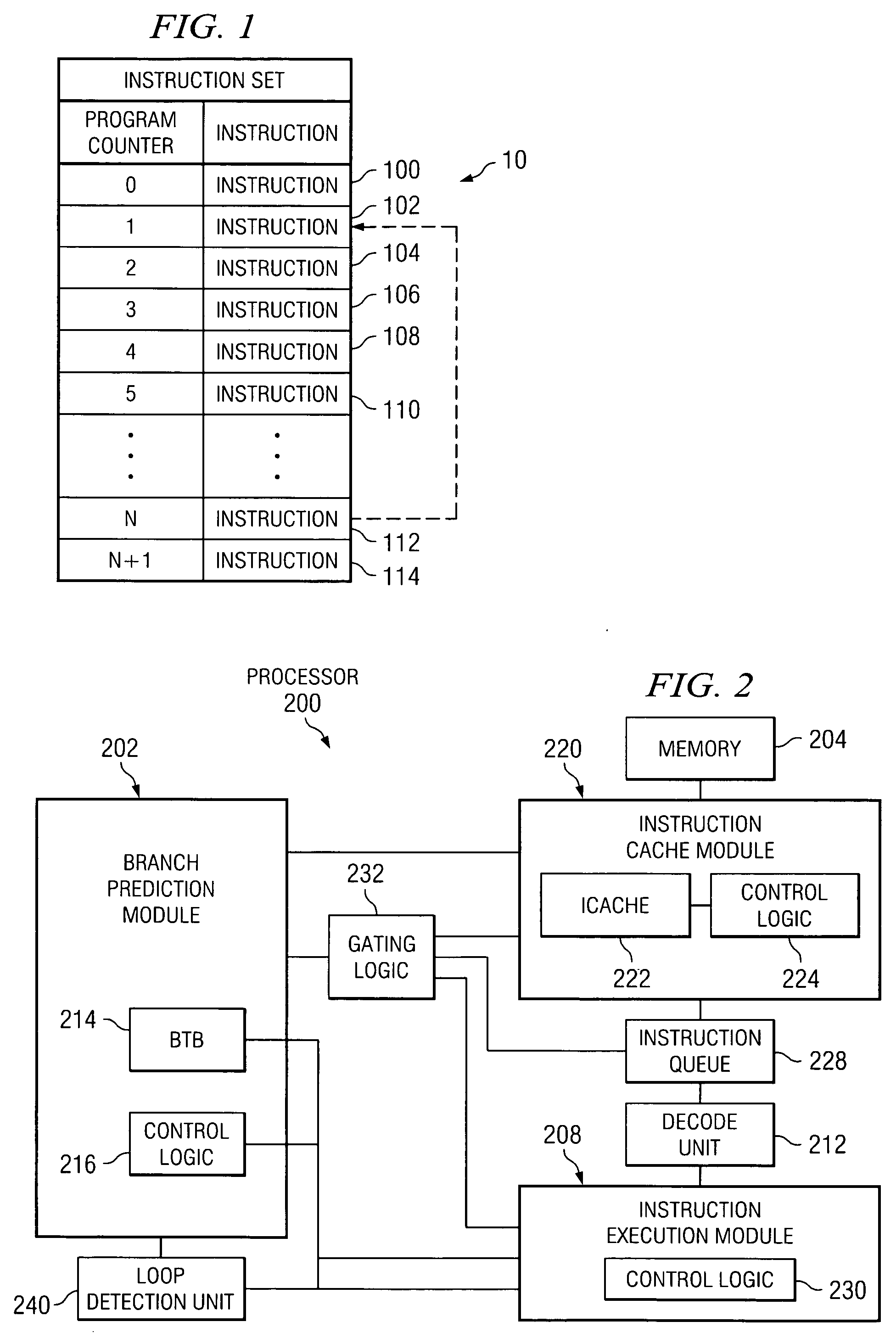

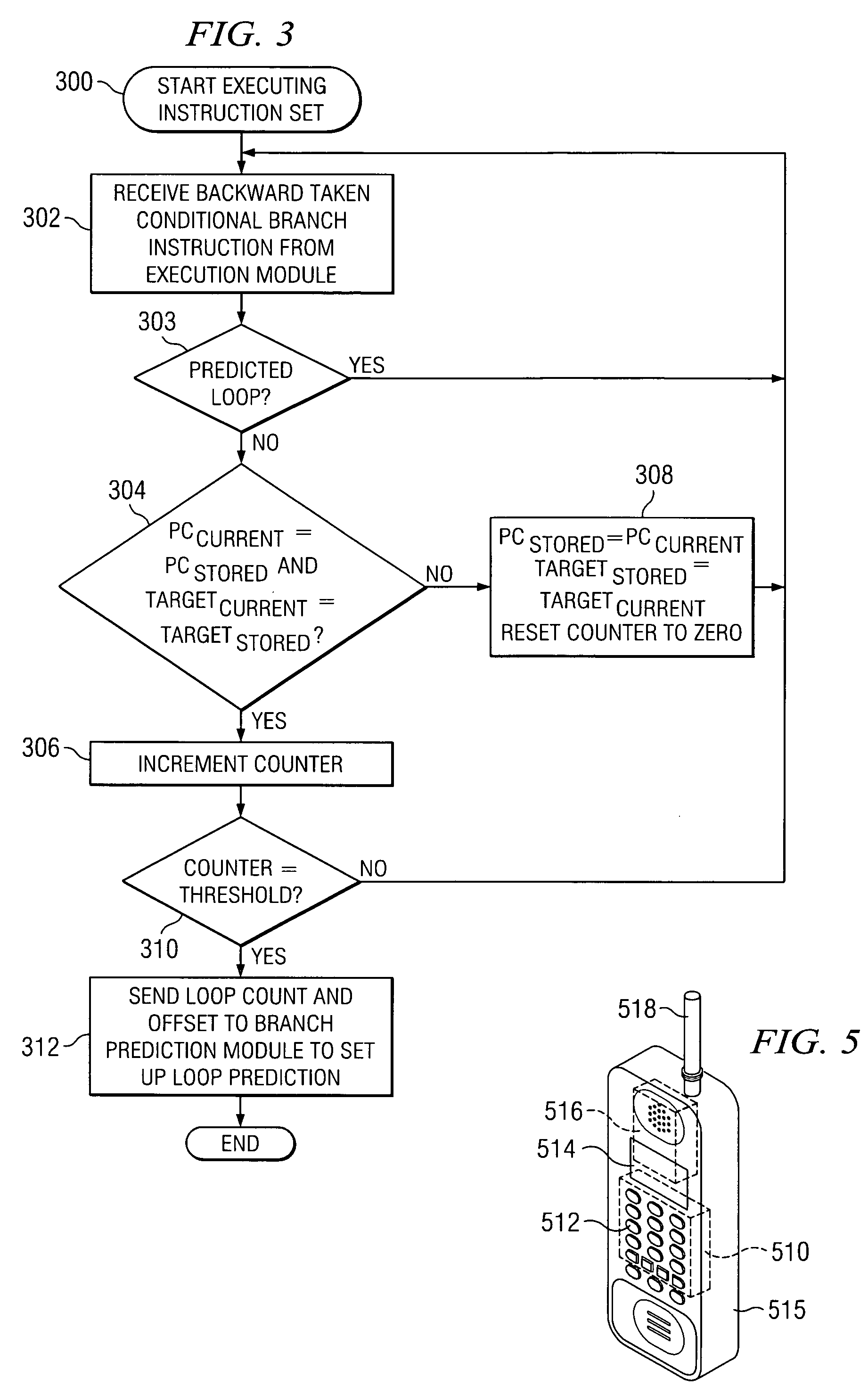

Loop detection and capture in the intstruction queue

ActiveUS20070113059A1Digital computer detailsSpecific program execution arrangementsProgram counterCycle detection

A system and a method to identify a conditional branch instruction having a program counter and a target address, and increment a loop count each time the program counter and the target address equal a stored program counter and a target address. The system and method additionally includes assignment of a start loop pointer and an end loop pointer, based on an offset, when the loop count is equal to a threshold value, and capturing instructions for a loop, as defined by the start loop pointer and the end loop pointer, in an instruction queue.

Owner:TEXAS INSTR INC

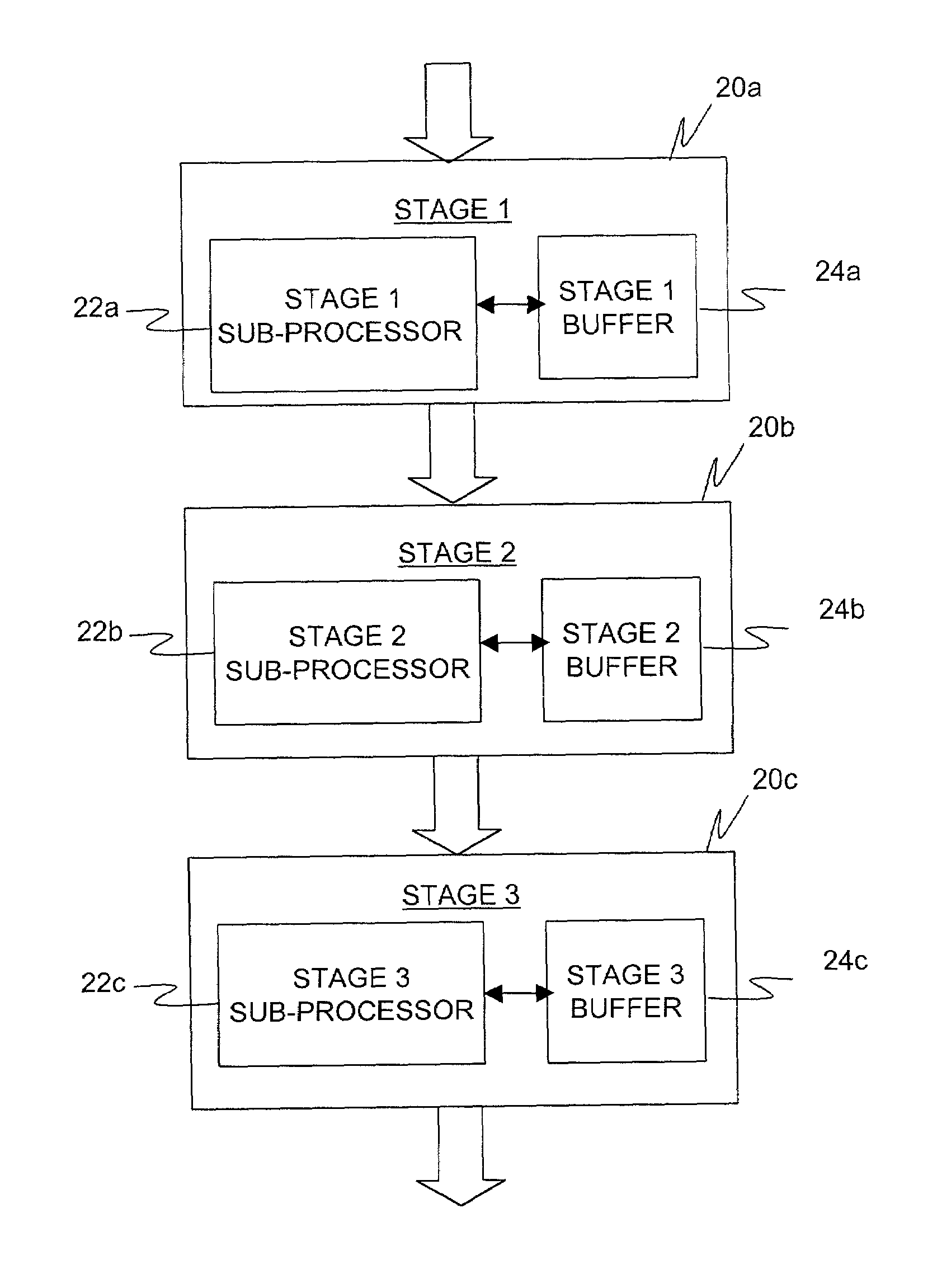

Methods and apparatus for fusing instructions to provide or-test and and-test functionality on multiple test sources

ActiveUS20140281389A1Binary to binaryConditional code generationJust-in-time compilationMicro-operation

Methods and apparatus are disclosed for fusing instructions to provide OR-test and AND-test functionality on multiple test sources. Some embodiments include fetching instructions, said instructions including a first instruction specifying a first operand destination, a second instruction specifying a second operand source, and a third instruction specifying a branch condition. A portion of the plurality of instructions are fused into a single micro-operation, the portion including both the first and second instructions if said first operand destination and said second operand source are the same, and said branch condition is dependent upon the second instruction. Some embodiments generate a novel test instruction dynamically by fusing one logical instruction with a prior-art test instruction. Other embodiments generate the novel test instruction through a just-in-time compiler. Some embodiments also fuse the novel test instruction with a subsequent conditional branch instruction, and perform a branch according to how the condition flag is set.

Owner:INTEL CORP

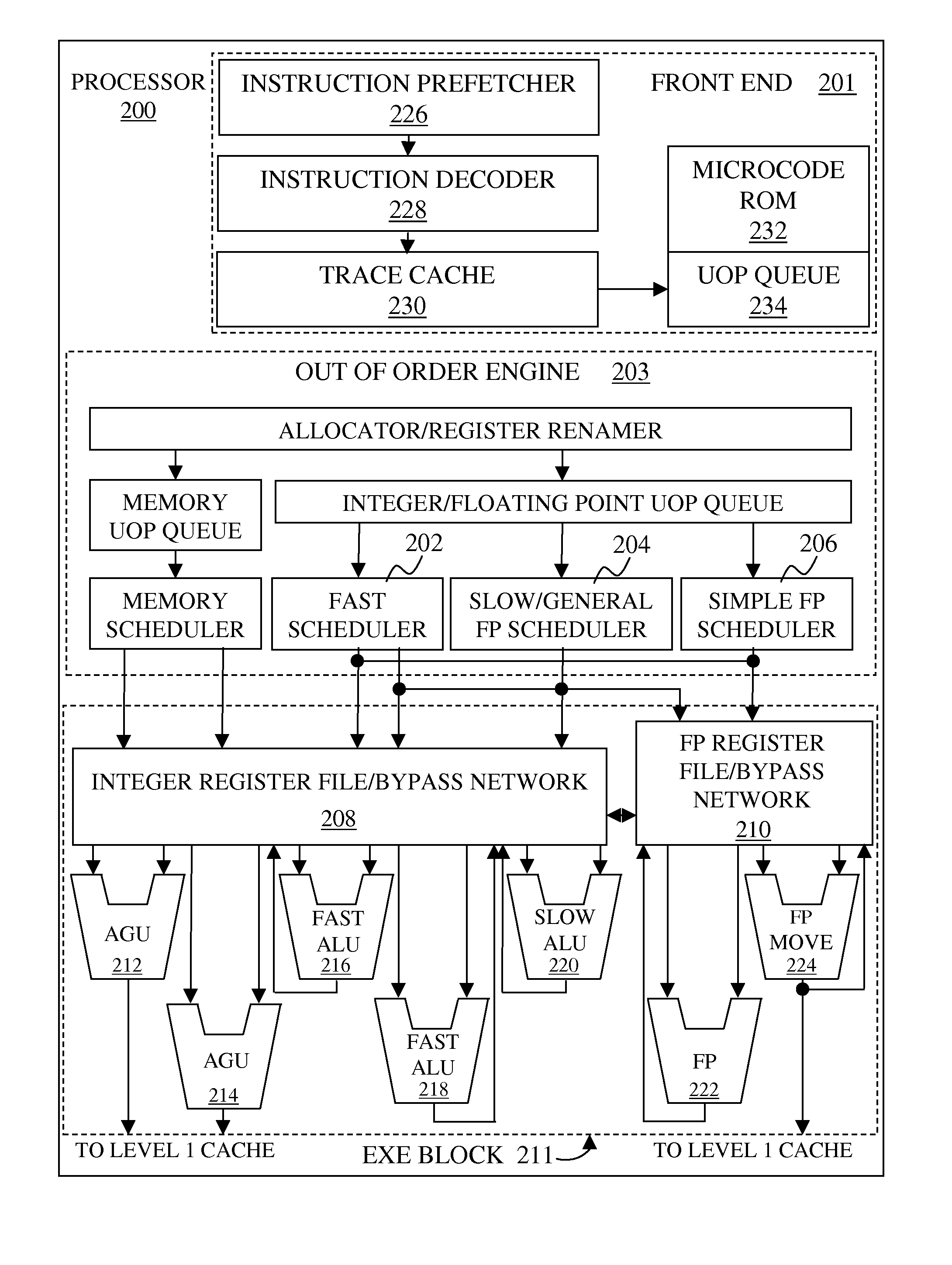

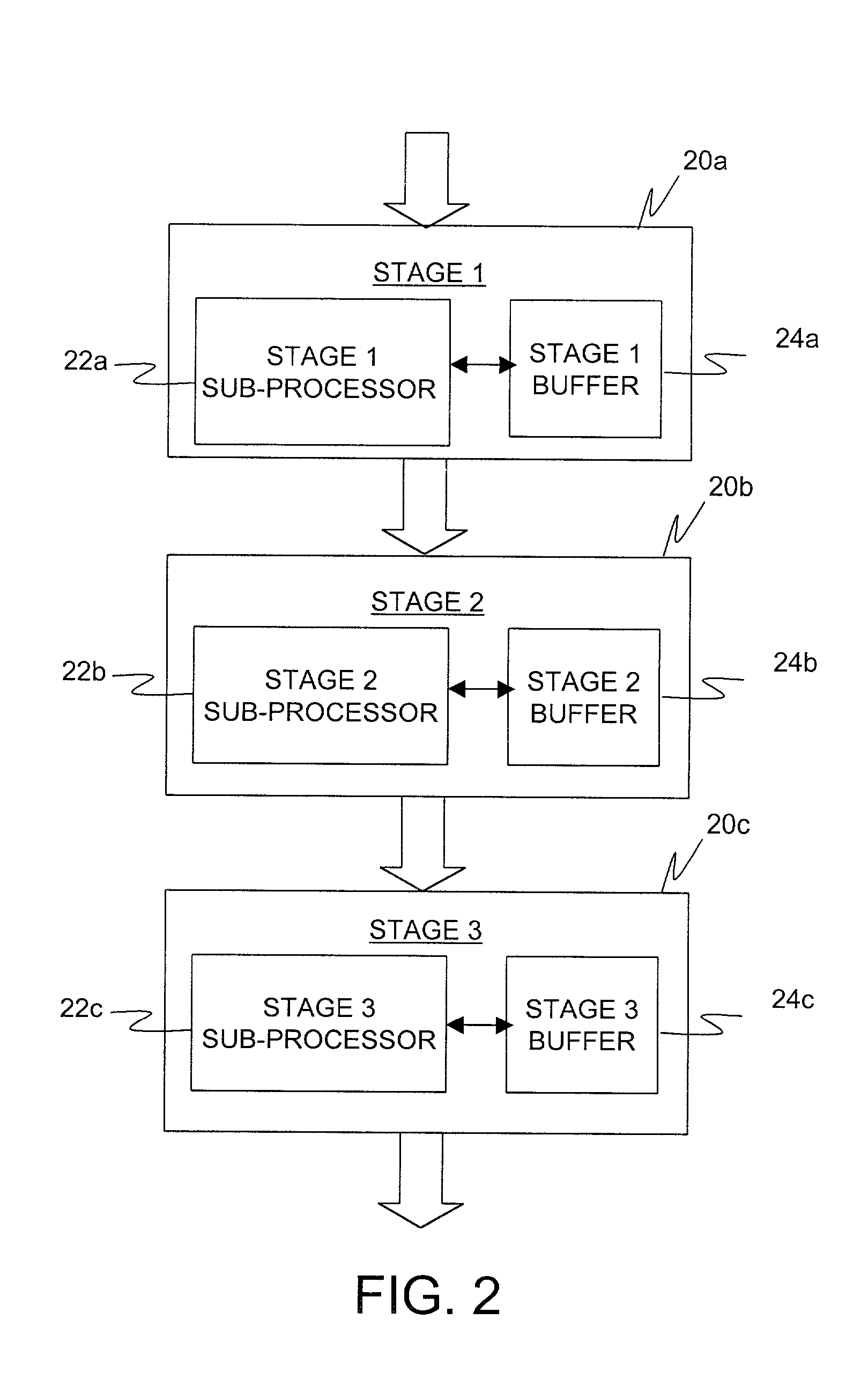

Non-blocking, multi-context pipelined processor

ActiveUS7080238B2Improve throughputImprove processing efficiencyData switching by path configurationConcurrent instruction executionWaste processingConditional branch

A packet processor whose processing capabilities are optimized by concurrently processing multiple packets within various pipelined stages. At each stage, multiple packets are processed via an internally pipelined sub-processor. In one embodiment, the packets are processed in a round robin fashion. When a particular packet is done processing at a particular stage, it may pass another packet whose processing is not complete, and move to a next stage. In another embodiment, a packet is processed until a conditional branch instruction or any other instruction causing a potential stall is encountered. If such an instruction is encountered, a next available packet is selected and processed instead of wasting processing cycles during the stall, or proceeding with the processing of the current packet based on a predicted result. The sub-processor resumes processing of the packet once the stall is over.

Owner:ALCATEL INTERNETWORKING PE

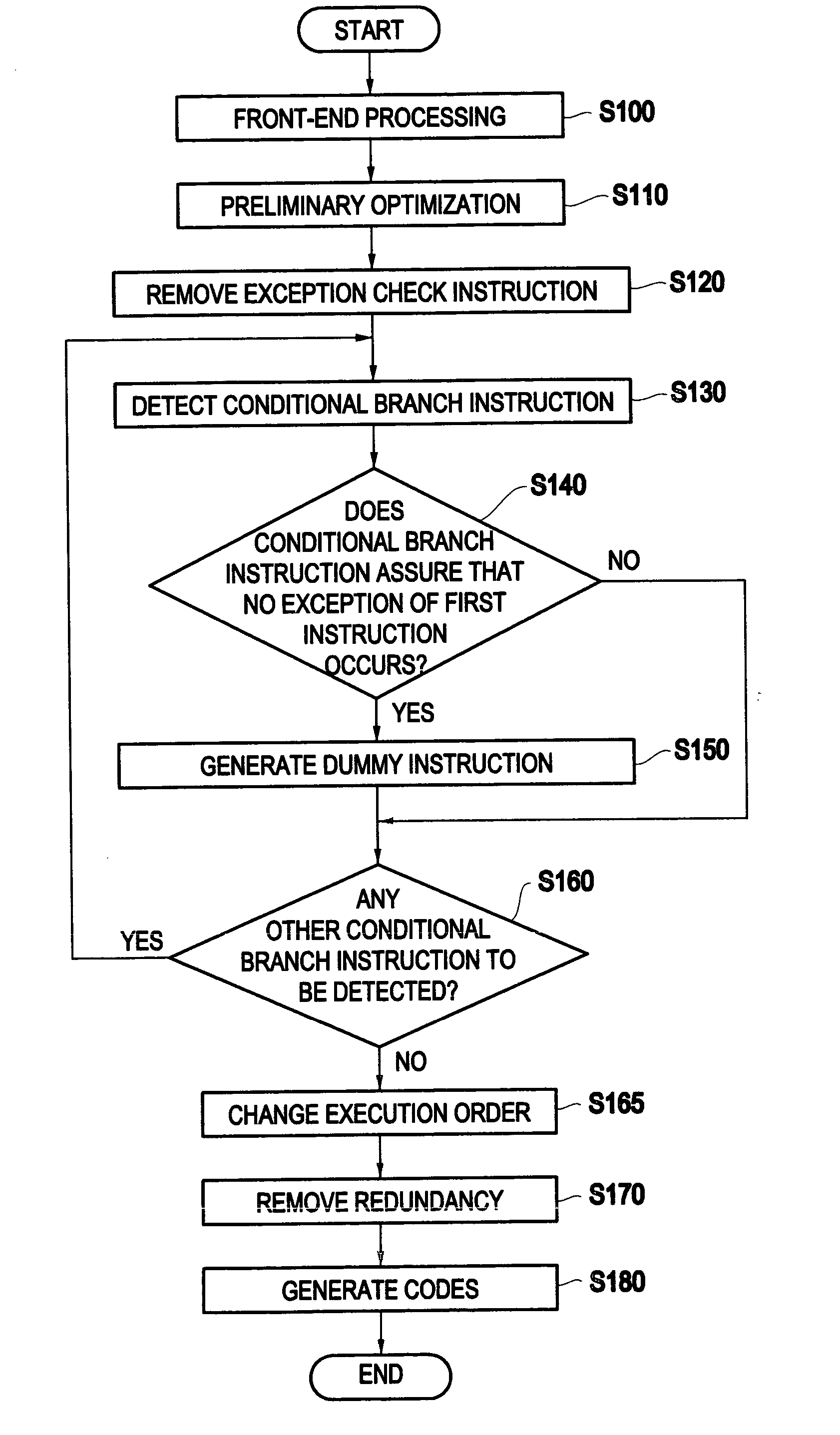

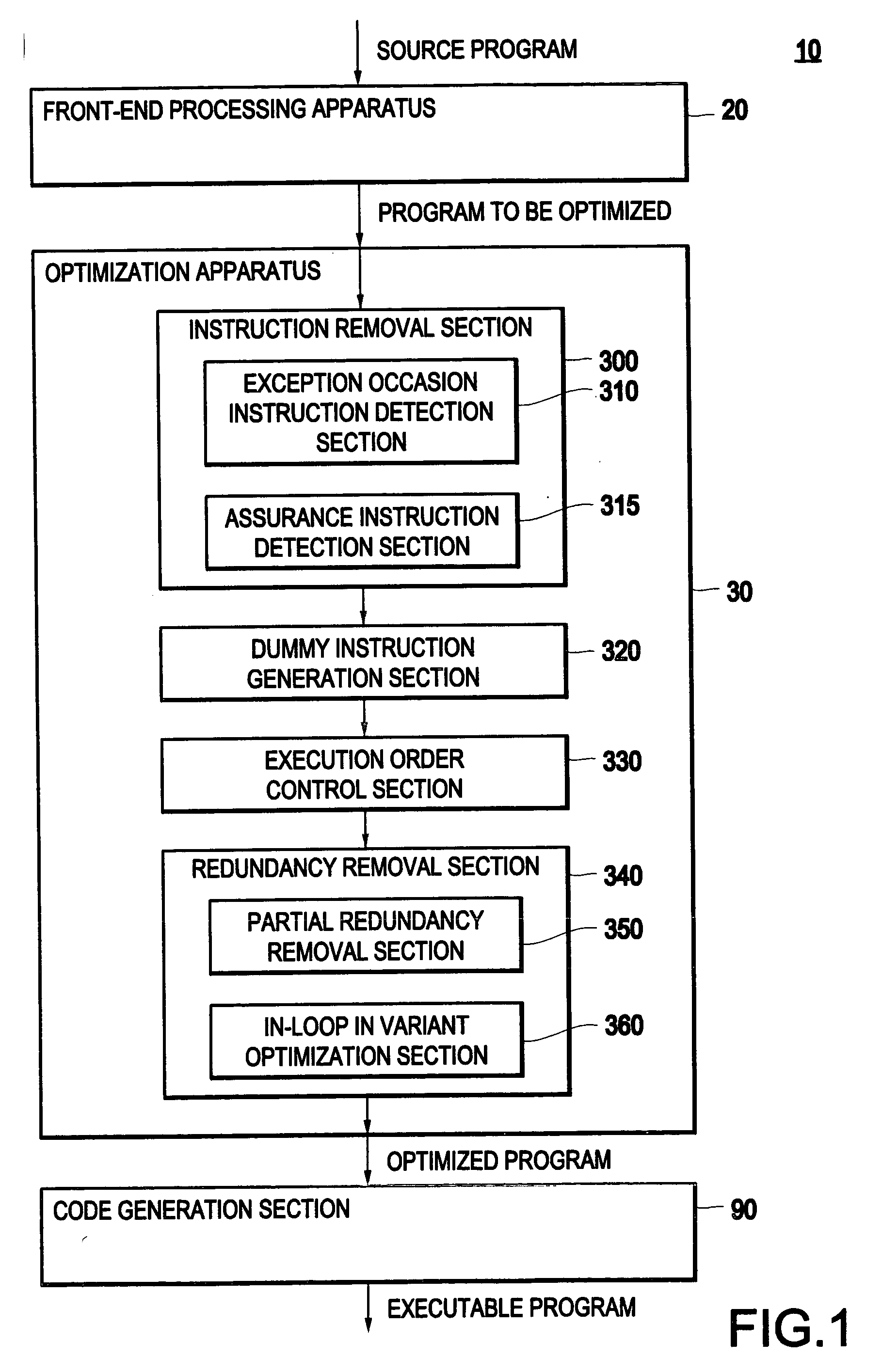

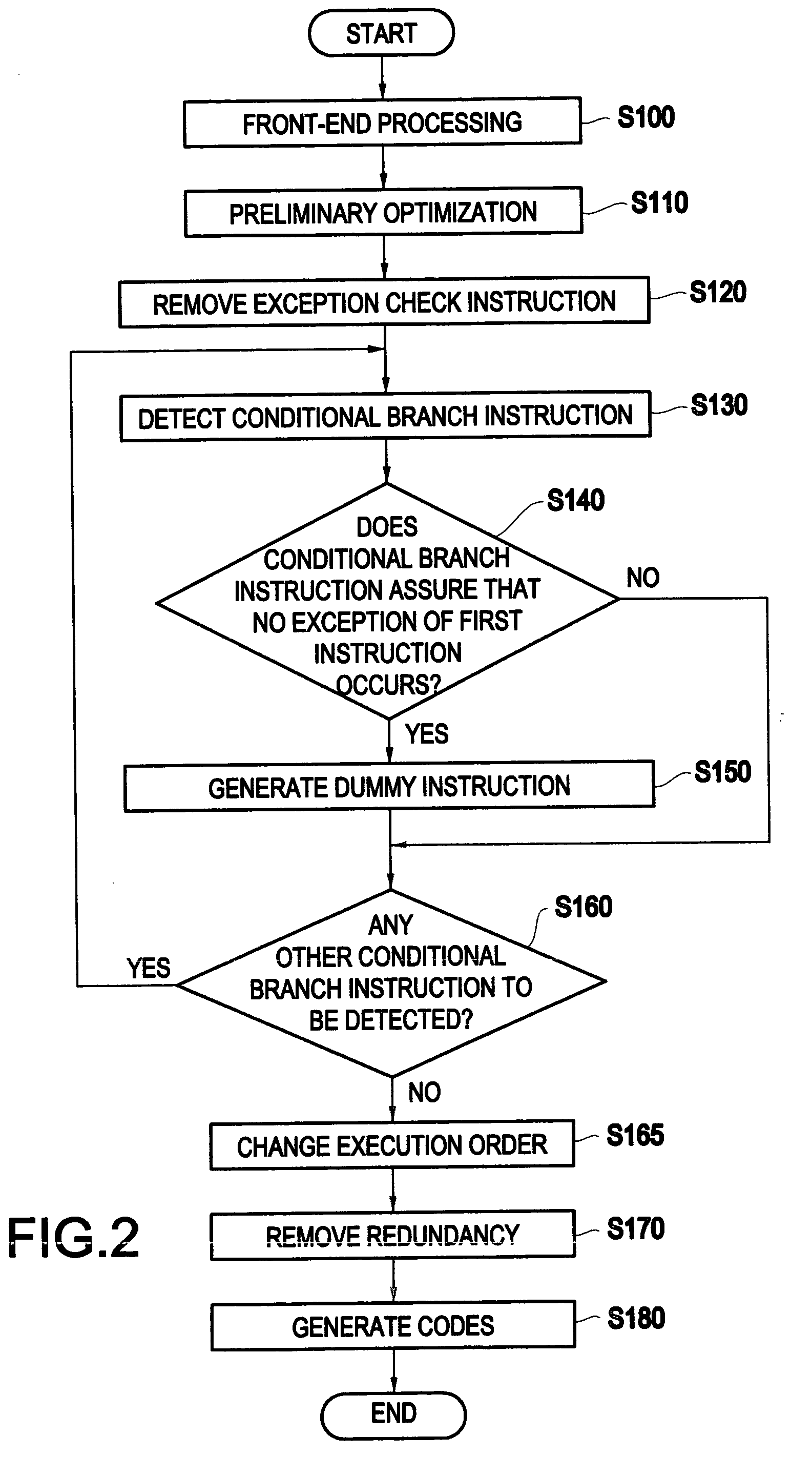

Optimization apparatus, compiler program, optimization method and recording medium

InactiveUS20040019770A1Control changesSoftware engineeringDigital computer detailsOrder controlConditional branch

An optimization apparatus (compiler program, method and recording medium) for changing the order of execution of instructions in a program to be optimized includes an exception occasion instruction detection section which detects a first instruction having a possibility to cause an exception, an assurance instruction detection section which detects a second instruction executed prior to the first instruction, the second instruction assuring that no exception of the first instruction occurs, and an execution order control section which changes the position of the first instruction in execution order so that the first instruction is executed before a conditional branch instruction for selectively executing the first instruction and after the second instruction.

Owner:IBM CORP

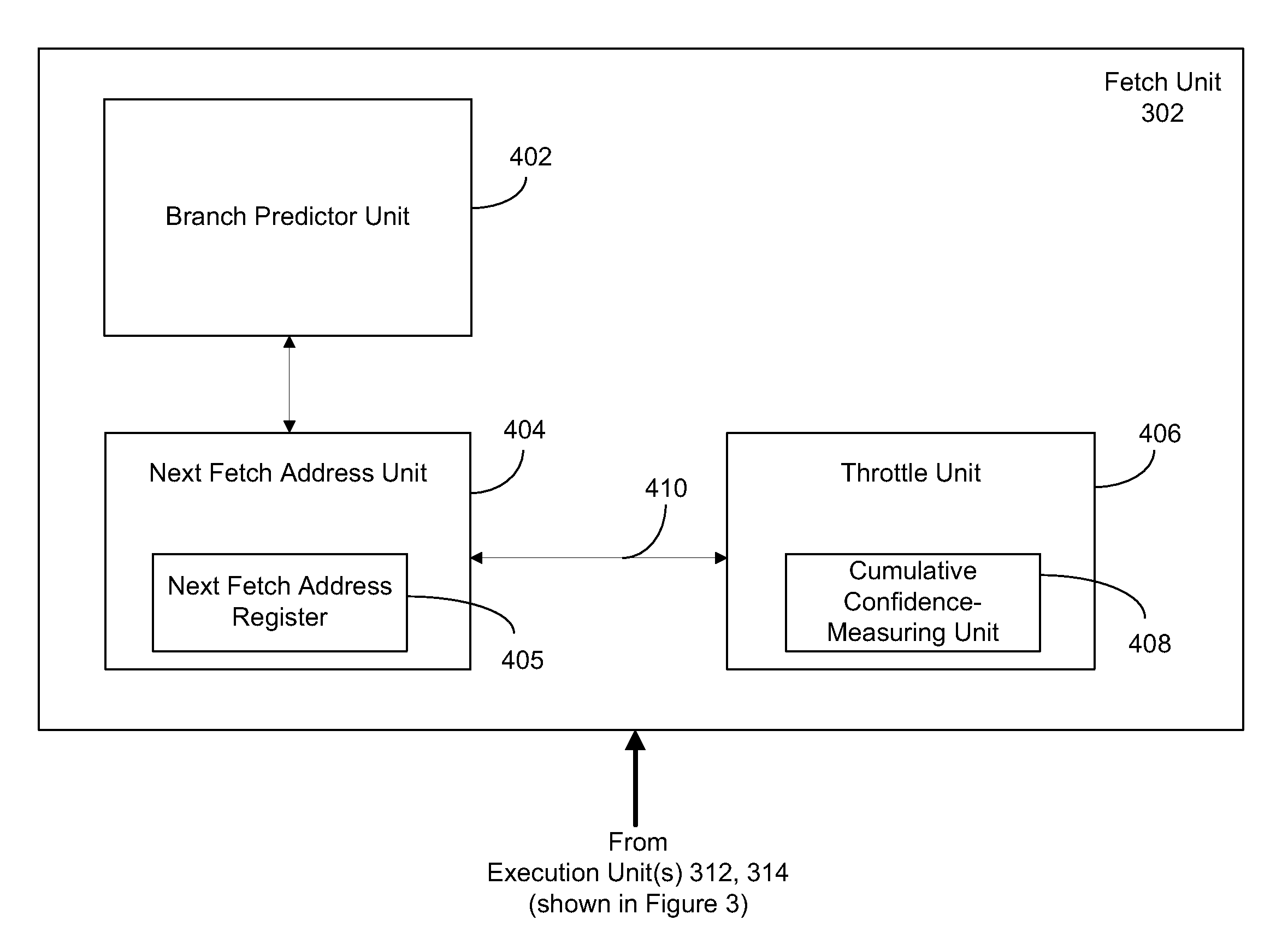

Cumulative confidence fetch throttling

ActiveUS20120124345A1Reducing prefetching operationReduce stepsDigital computer detailsConcurrent instruction executionSpeculative executionConfidence measures

A method and apparatus to utilize a fetching scheme for instructions in a processor to limit the expenditure of power caused by the speculative execution of branch instructions is provided. Also provided is a computer readable storage device encoded with data for adapting a manufacturing facility to create an apparatus. The method includes calculating a cumulative confidence measure based on one or more outstanding conditional branch instructions. The method also includes reducing prefetching operations in response to detecting that the cumulative confidence measure is below a first threshold level.

Owner:ADVANCED MICRO DEVICES INC

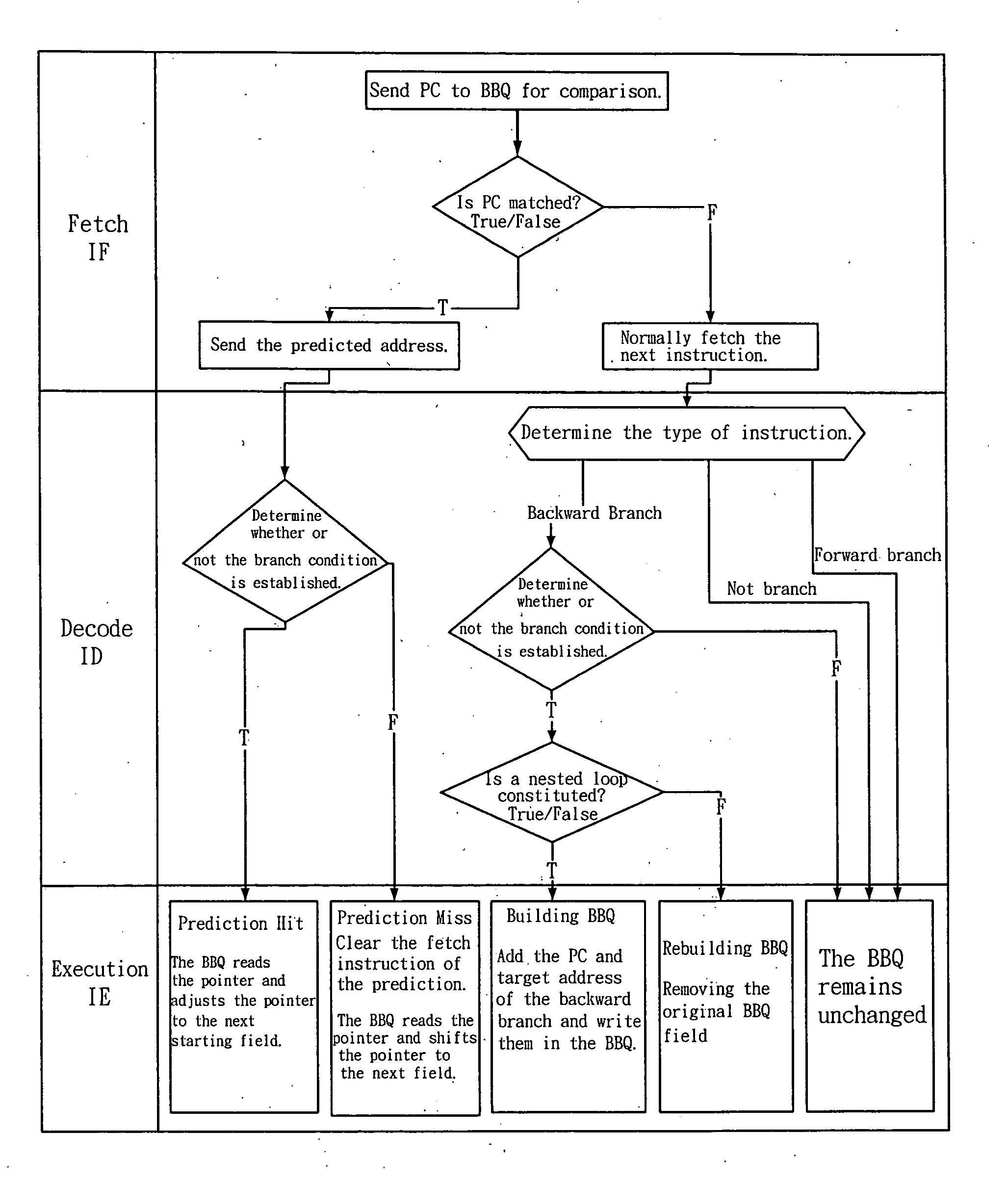

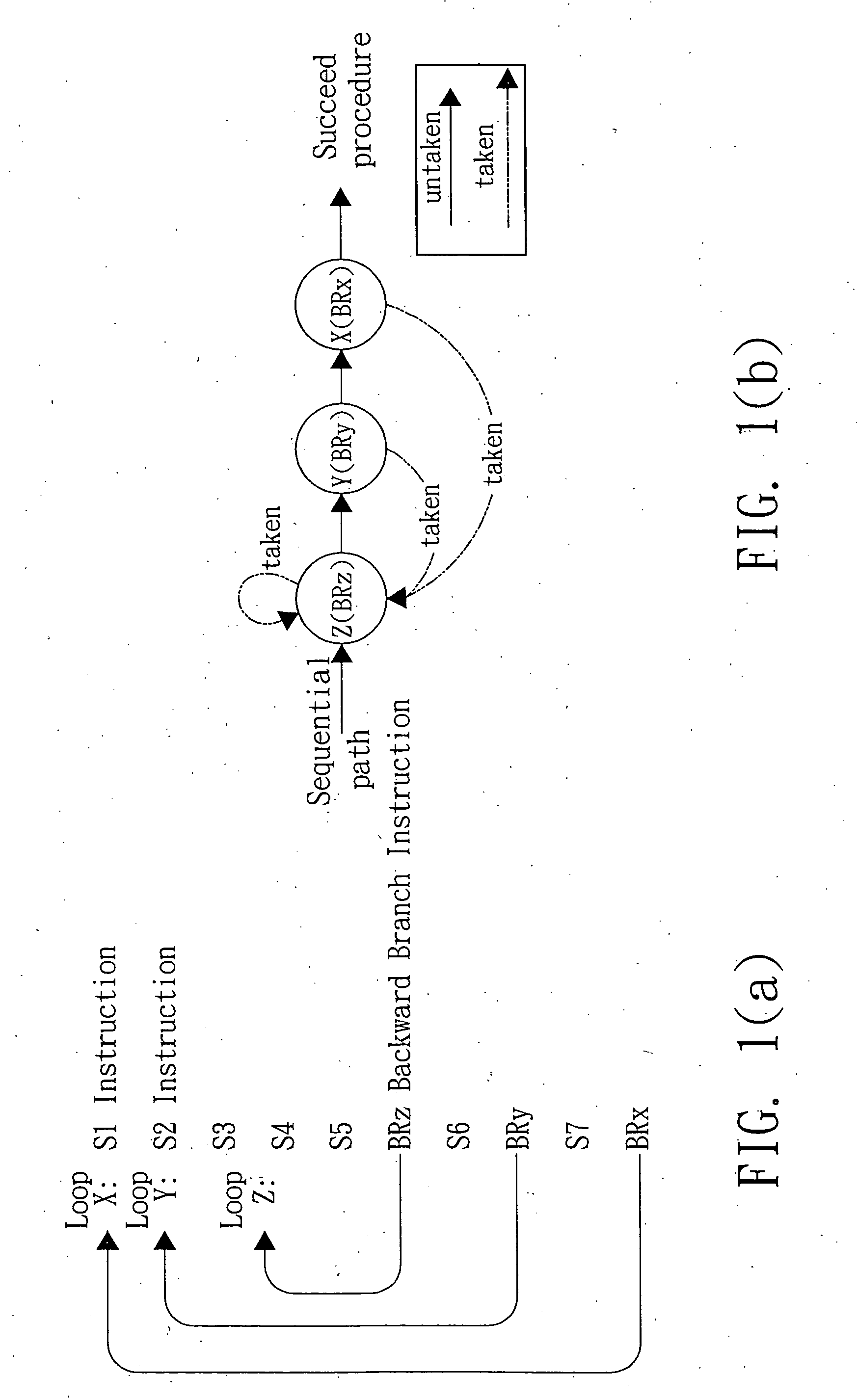

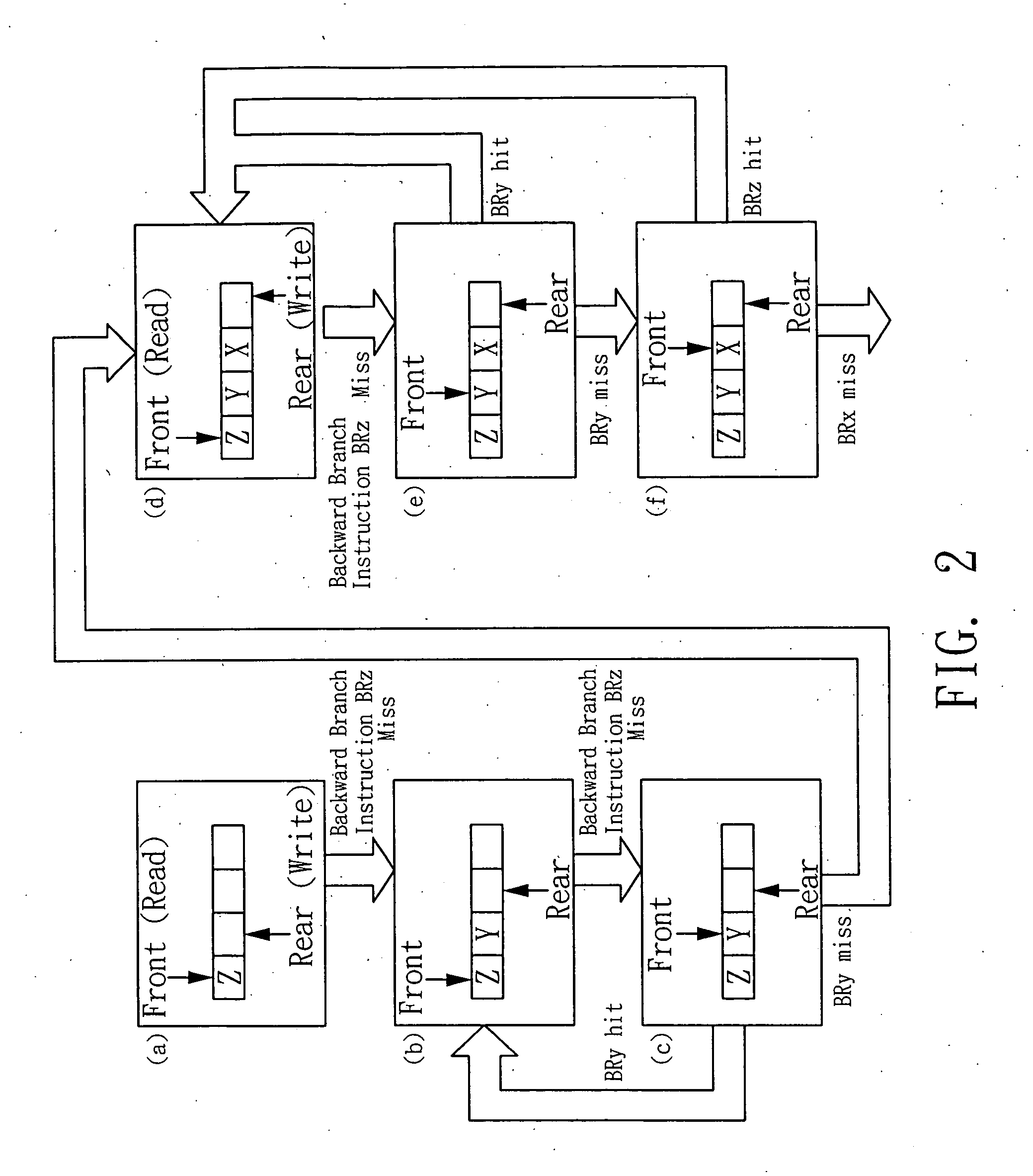

Programmable backward jump instruction prediction mechanism

InactiveUS20070239975A1Maximization of executionLower levelDigital computer detailsSpecific program execution arrangementsRound complexityInner loop

A programmable backward jump instruction prediction mechanism includes a backward branch prediction queues (BBQ) for assisting an embedded processor to overcome an inevitable control hazard caused in a pipeline execution for a conditional branch instruction. A large percentage of nested loops exists in an application program executed by the embedded processor, and thus when the backward branch encounters a nested loop, the behavior of branch of a nested loop is similar to a queue that will automatically restore its original status; the whole nested loop iterates at a center and repeats the execution of innermost loops (Queue Front) and leaves the prediction miss to the next backward branch (an outer loop, Queue Next); once if an outer loop hits a branchy, the inner loop will repeat the branch ( and returns to the innermost loop Queue Front). Since the program counter (PC) and the branch address of the queue can be used for determining whether or not the program execution is still in a nested loop or whether or not a jump is from a backward branch by the target address of the branch instruction. It is only necessary to predict an execution and compare a specific branch address in the queue for each time, and thus the queue structure needs not to store too many instructions or quickly compare a large number of data by the associative memory technique. The hardware is very simple, but the effect is excellent. According to the simulation analysis of the application program, it is discovered that the average prediction accuracy is up to 82% and some applications may even have an accuracy of 99%. The hardware mechansim of the invention features a low cost and a low level of complexity, and thus fully satifying the requirements for low cost, low power consumption, and high performance / cost ratio of an embedded processor.

Owner:FENG CHIA UNIVERSITY

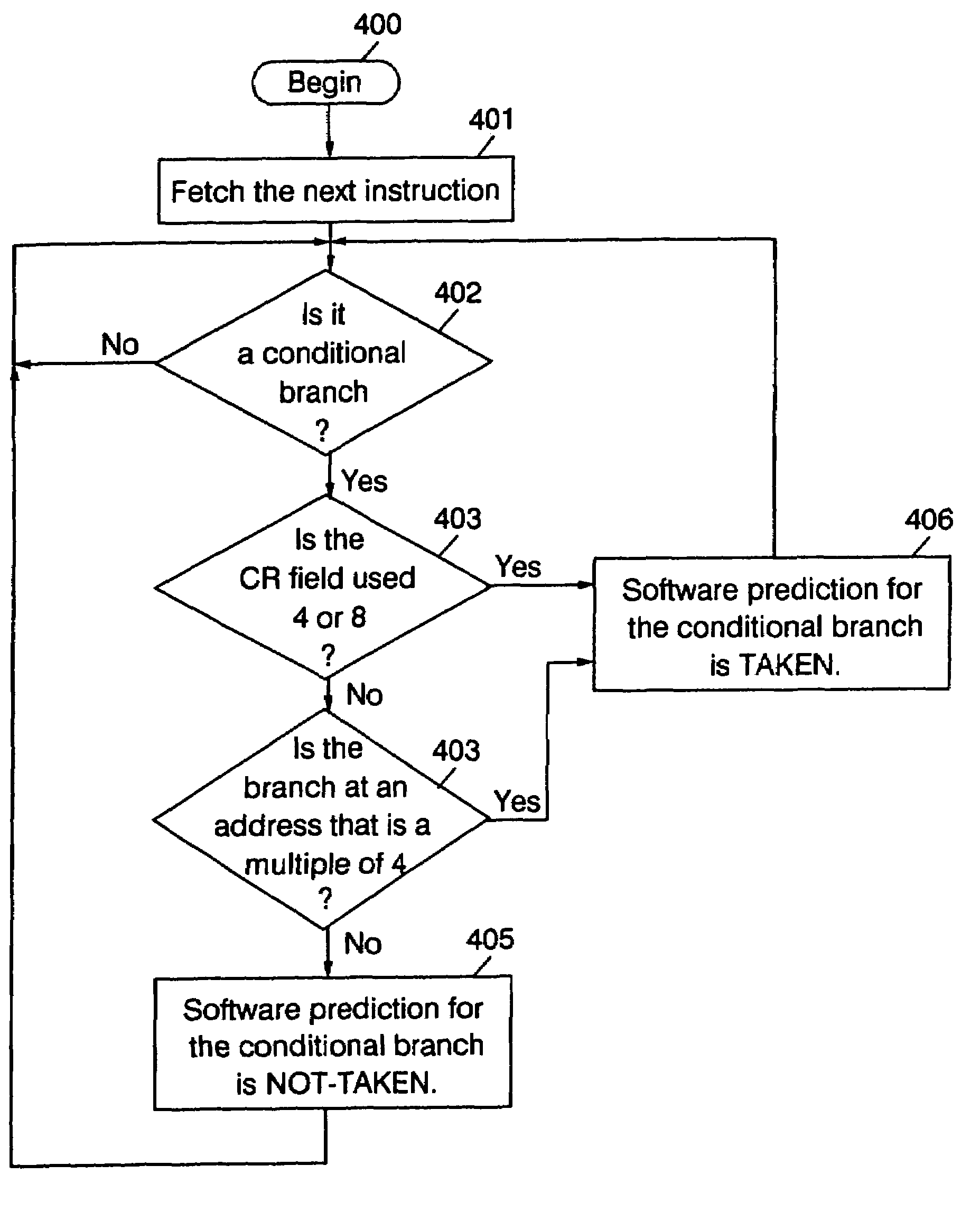

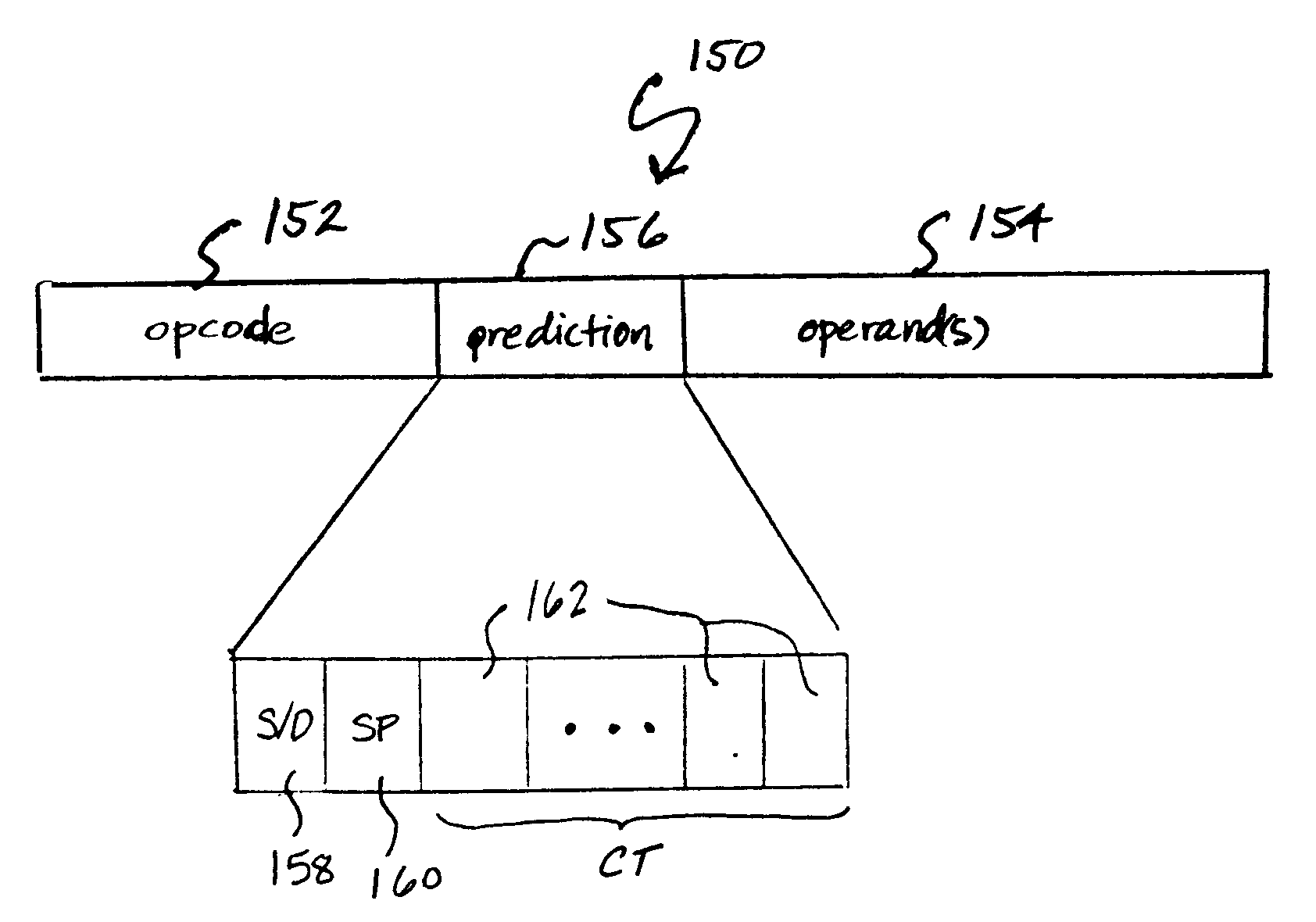

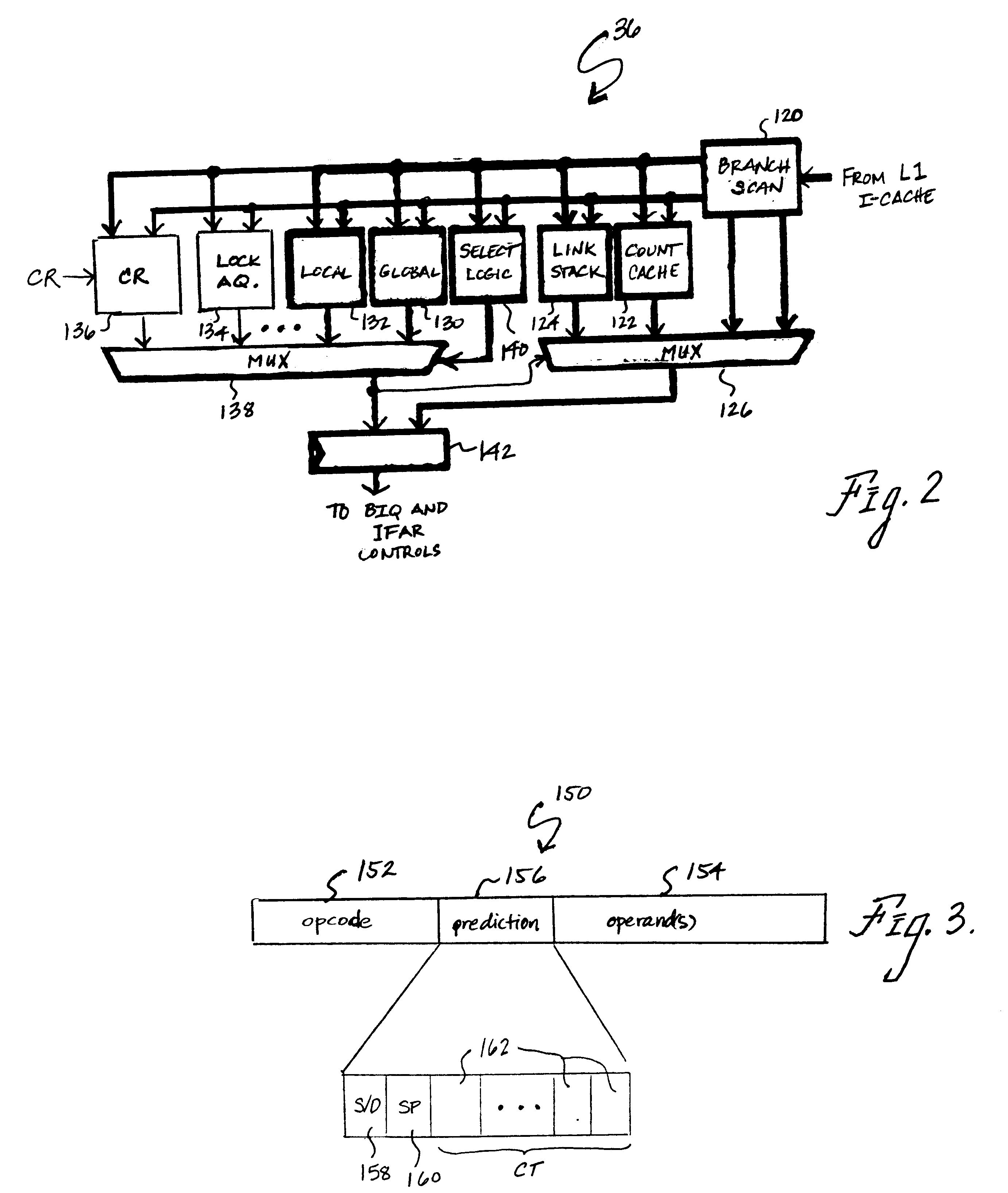

Use of software hint for branch prediction in the absence of hint bit in the branch instruction

InactiveUS6971000B1Need be addressSoftware engineeringDigital computer detailsConditional branchSoftware

In a processor, when a conditional branch instruction is encountered, a software prediction for the conditional branch is made as a function of the specific condition register field used to store the branch condition for the conditional branch instruction. If a specified condition register field is not used, the software prediction may be made dependent upon the specific address at which the branch instruction is located.

Owner:IBM CORP

Processor and method that predict condition register-dependent conditional branch instructions utilizing a potentially stale condition register value

InactiveUS6766442B1Conditional code generationDigital computer detailsProcessor registerExecution unit

A processor having improved branch prediction accuracy includes at least one execution unit that executes sequential instructions, a condition register, and a branch prediction circuit that predicts a condition register-dependent branch instruction by reference to a potentially stale condition register value to produce a speculative instruction fetch address. In a preferred embodiment, the processor includes branch execution circuitry that subsequently determines if the speculative instruction fetch address is correct by reference to a non-stale value of the condition register.

Owner:IBM CORP

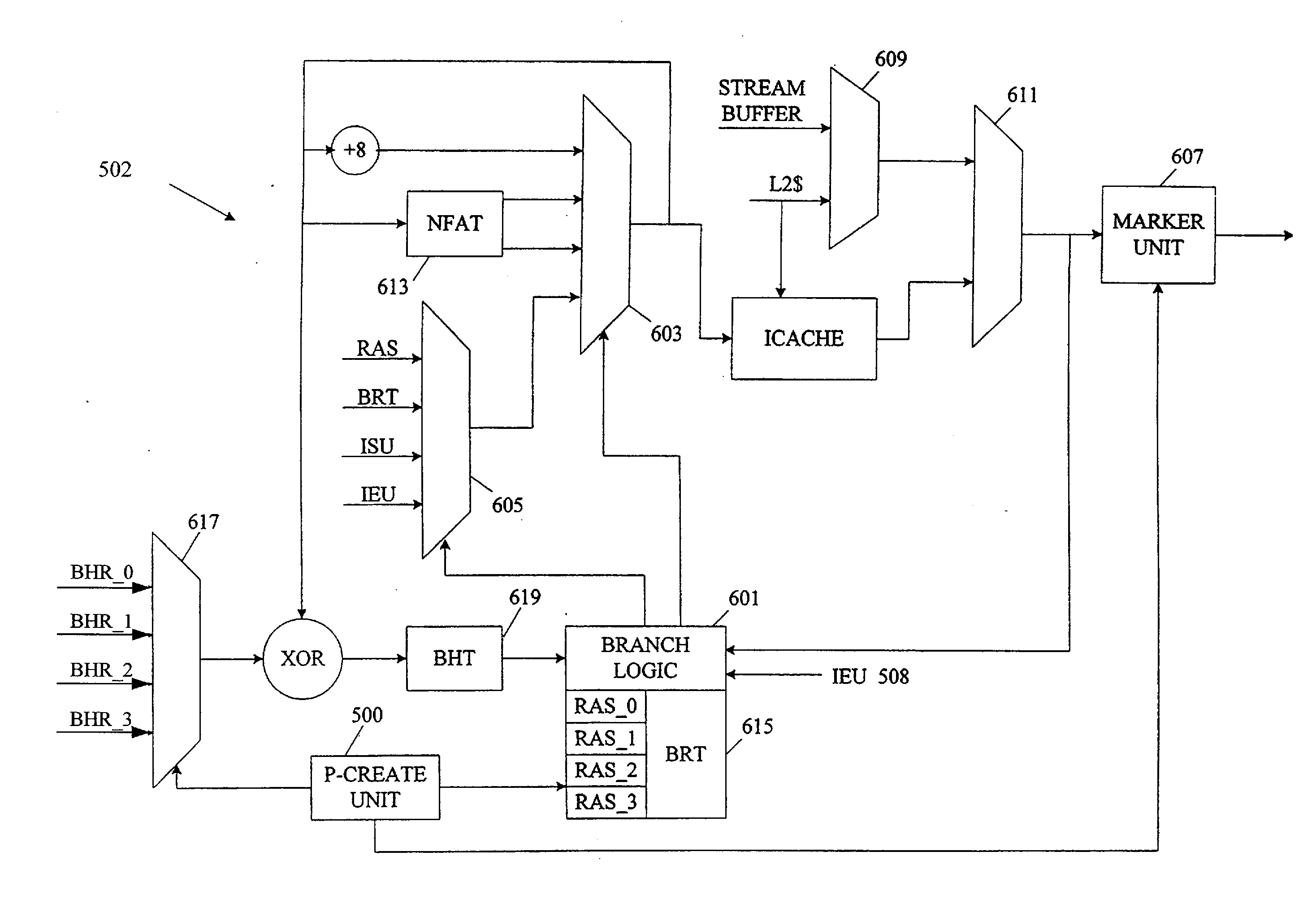

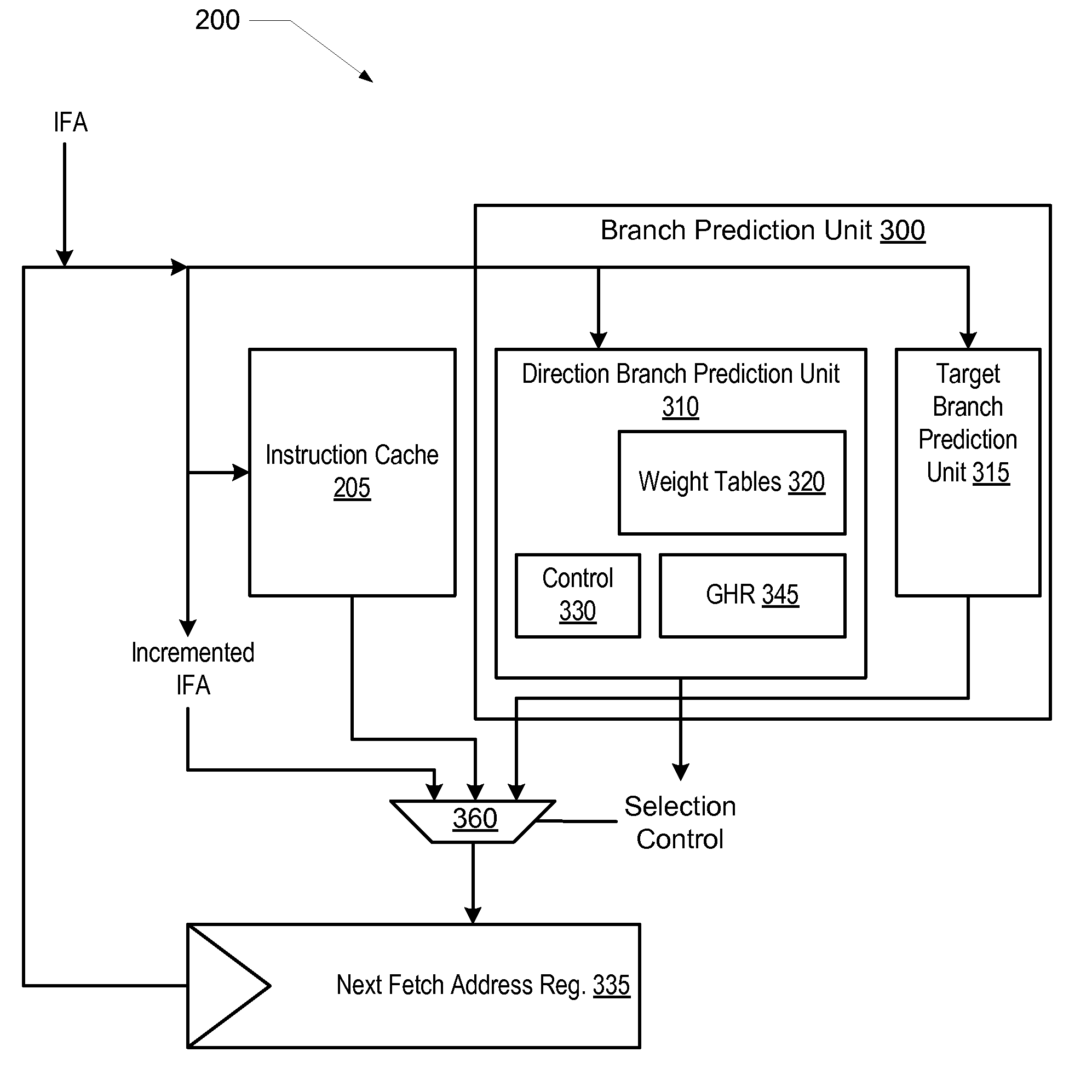

Perceptron-based branch prediction mechanism for predicting conditional branch instructions on a multithreaded processor

ActiveUS20110087866A1Digital computer detailsConcurrent instruction executionConditional branchPerceptron

A multithreaded microprocessor includes an instruction fetch unit including a perceptron-based conditional branch prediction unit configured to provide, for each of one or more concurrently executing threads, a direction branch prediction. The conditional branch prediction unit includes a plurality of storages each including a plurality of entries. Each entry may be configured to store one or more prediction values. Each prediction value of a given storage may correspond to at least one conditional branch instruction in a cache line. The conditional branch prediction unit may generate a separate index value for accessing each storage by generating a first index value for accessing a first storage by combining one or more portions of a received instruction fetch address, and generating each other index value for accessing the other storages by combining the first index value with a different portion of direction branch history information.

Owner:SUN MICROSYSTEMS INC

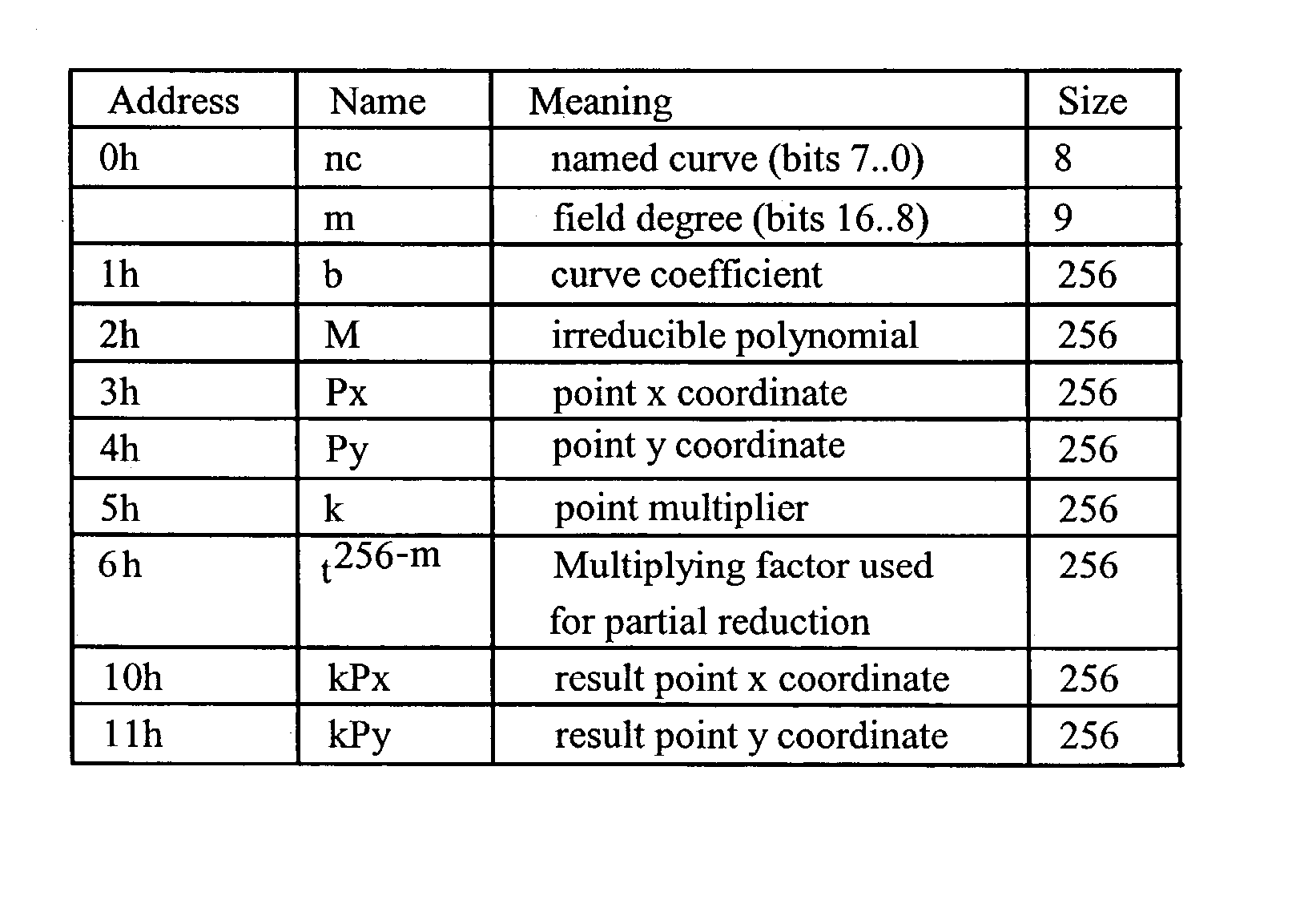

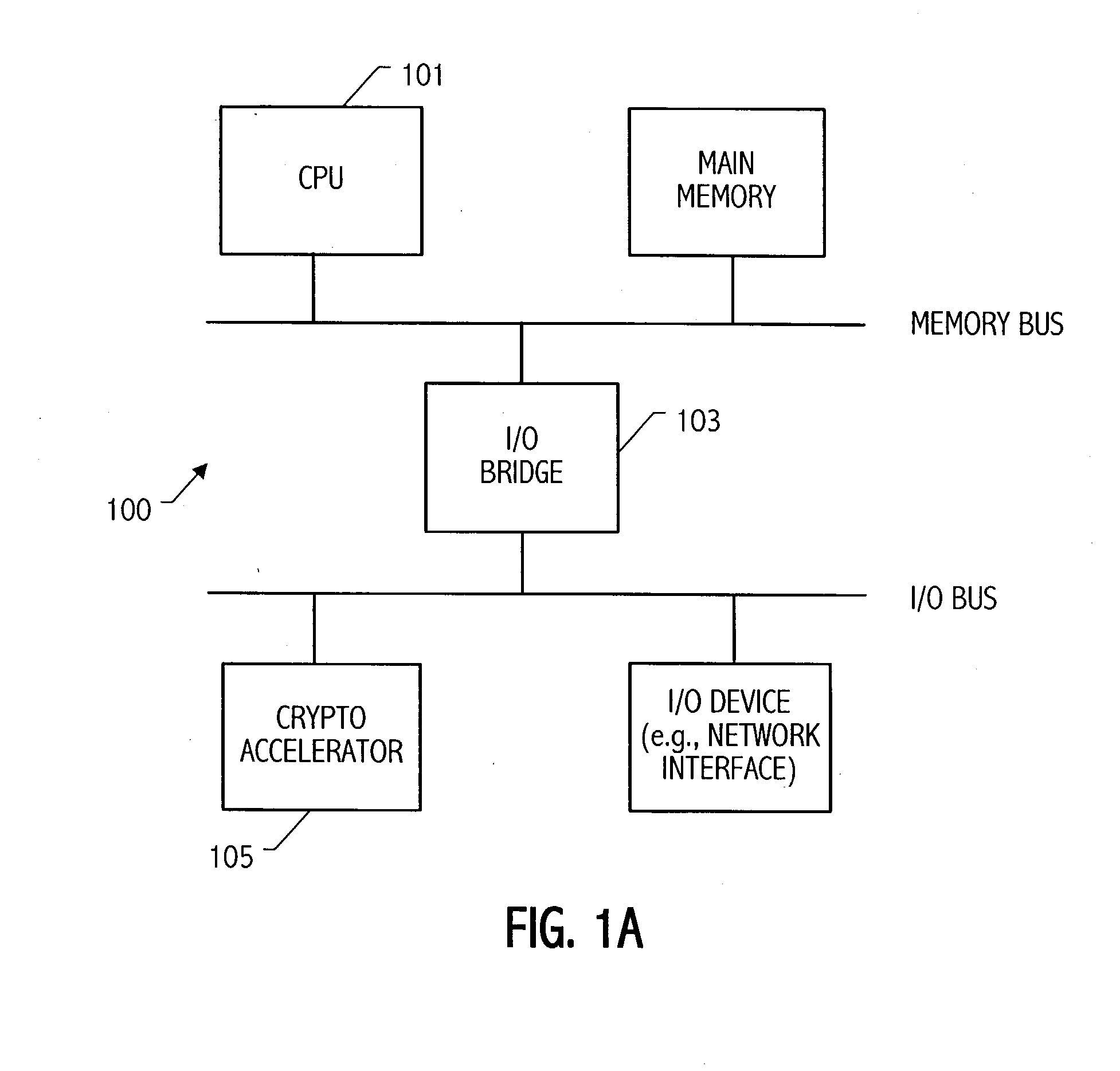

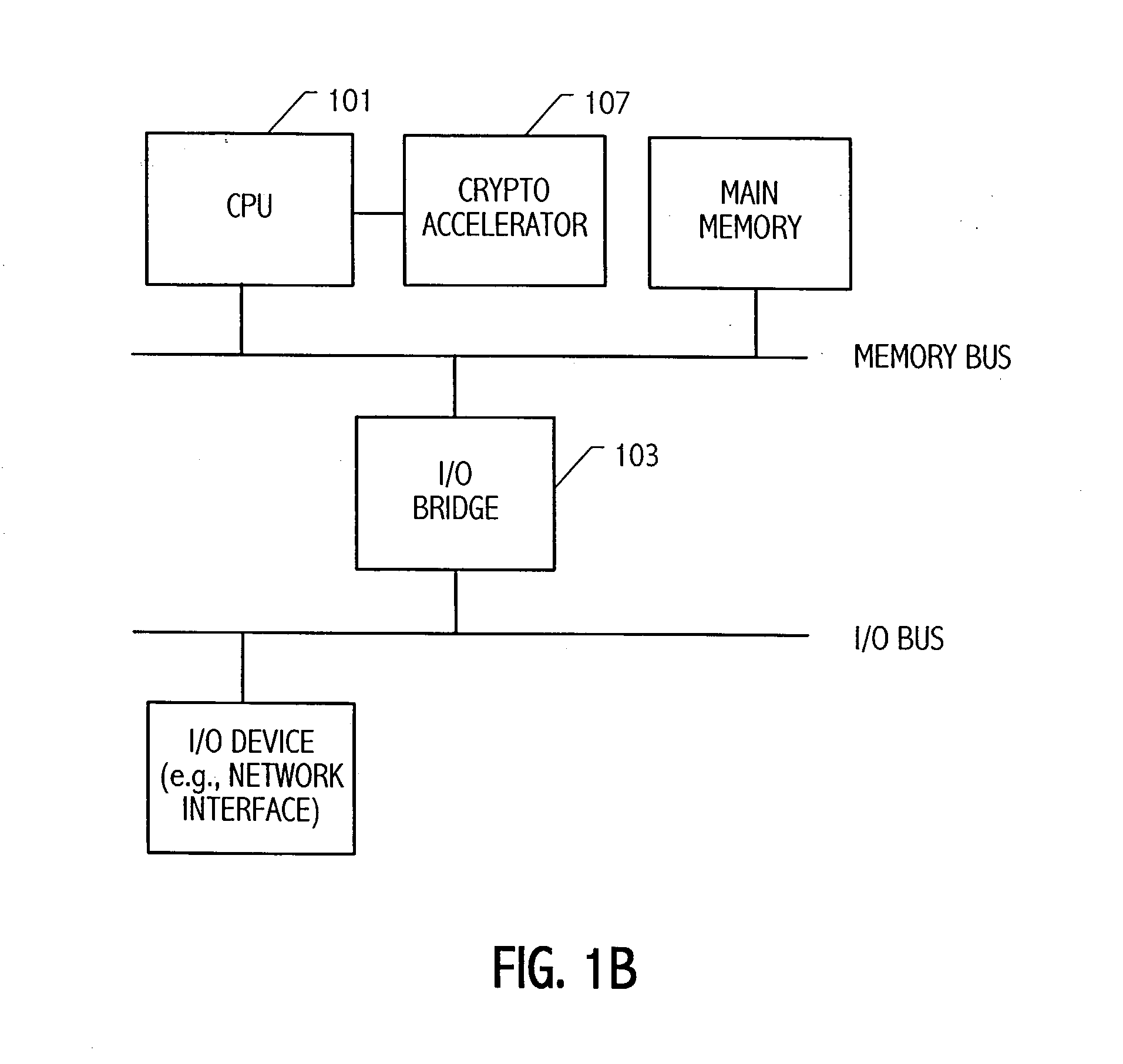

Hardware accelerator for elliptic curve cryptography

ActiveUS20030206629A1Public key for secure communicationDigital computer detailsEllipseElliptic curve cryptography

An elliptic curve processing apparatus that performs operations on elliptic curves specified over binary polynomial fields includes a functional unit that has a digit serial multiplier with a digit size of at least two bits. The elliptic curve processing apparatus performs reduction for respective generic curves using arbitrary irreducible polynomials, which correspond to respective ones of the generic curves. The elliptic curve processing apparatus may include hardwired reduction circuits in the functional unit for use with respective named curves. A storage location in the elliptic curve processing apparatus may be used to specify whether an operation is for one of the named curves or for one of the generic curves. The elliptic curve processing apparatus responds to an arithmetic instruction to utilize a respective one of the hardwired reduction circuits for reduction for respective named curves and a multiplier circuit for reduction for a plurality of generic curves, the multiplier coupled to perform reduction for respective generic curves using arbitrary irreducible polynomials, the arbitrary irreducible polynomials corresponding to respective ones of the generic curves. The elliptic curve processing apparatus operable on elliptic curves specified over binary polynomial fields performs a conditional branch according to whether a curve being processed is a generic curve or a named curve.

Owner:SUN MICROSYSTEMS INC

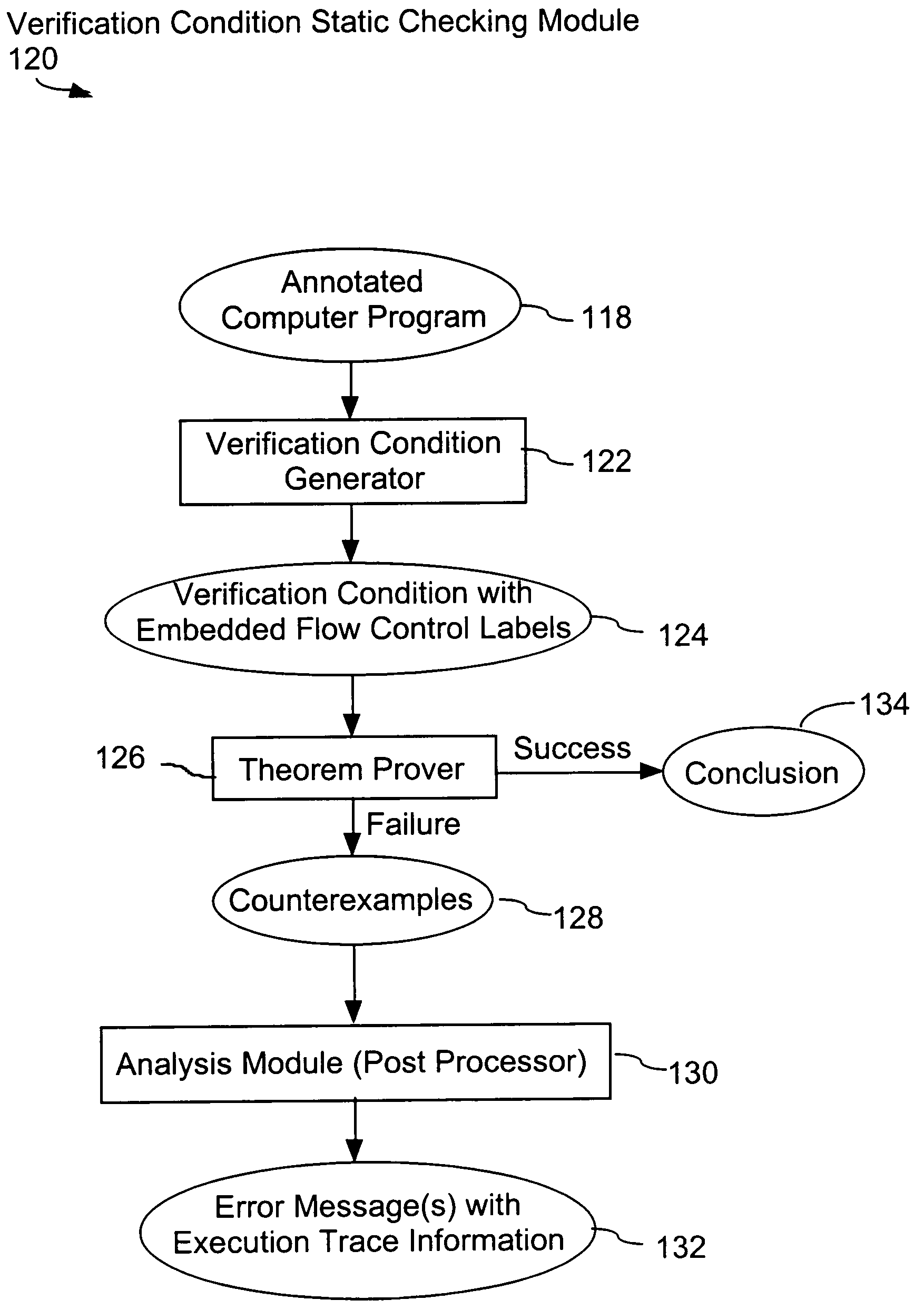

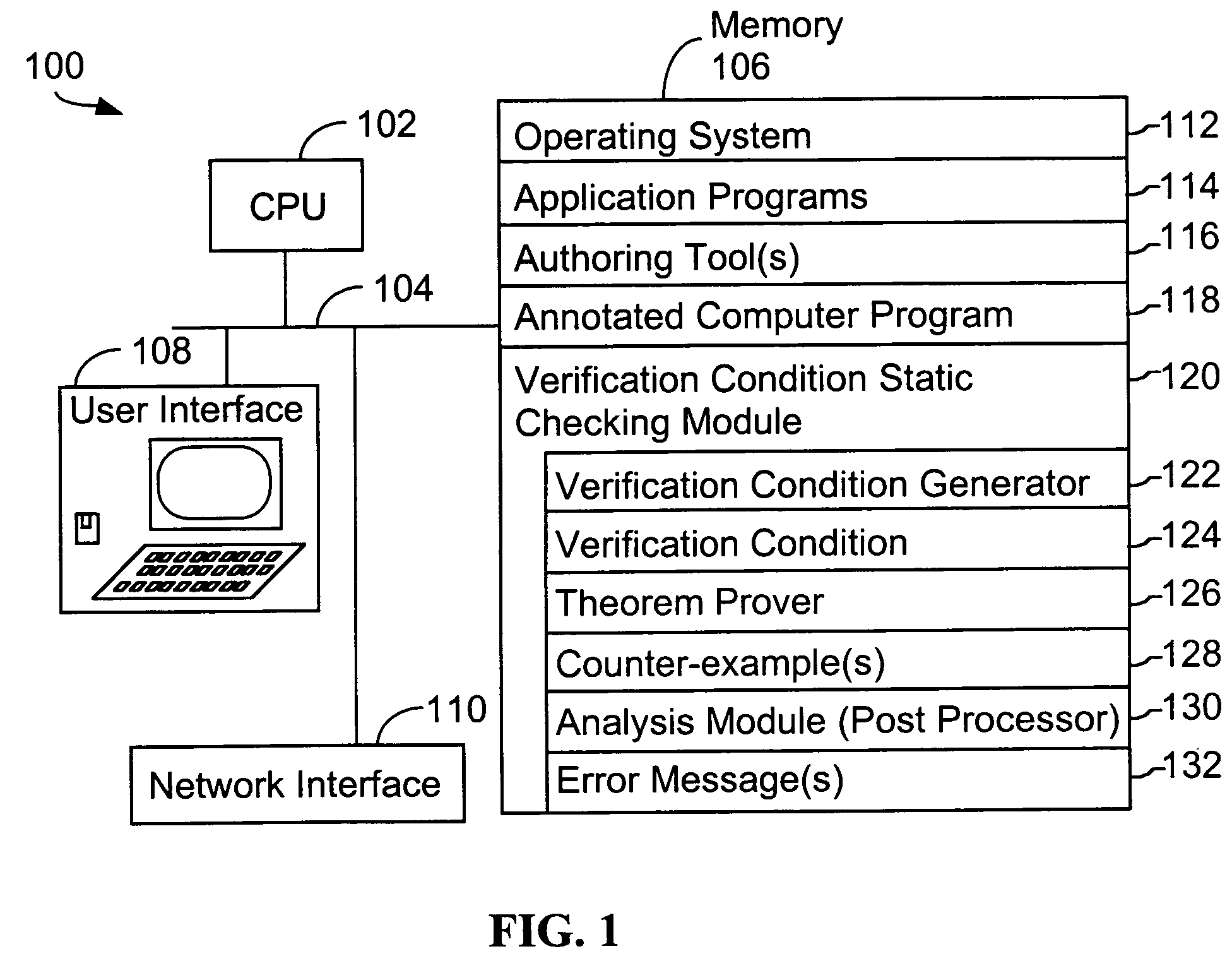

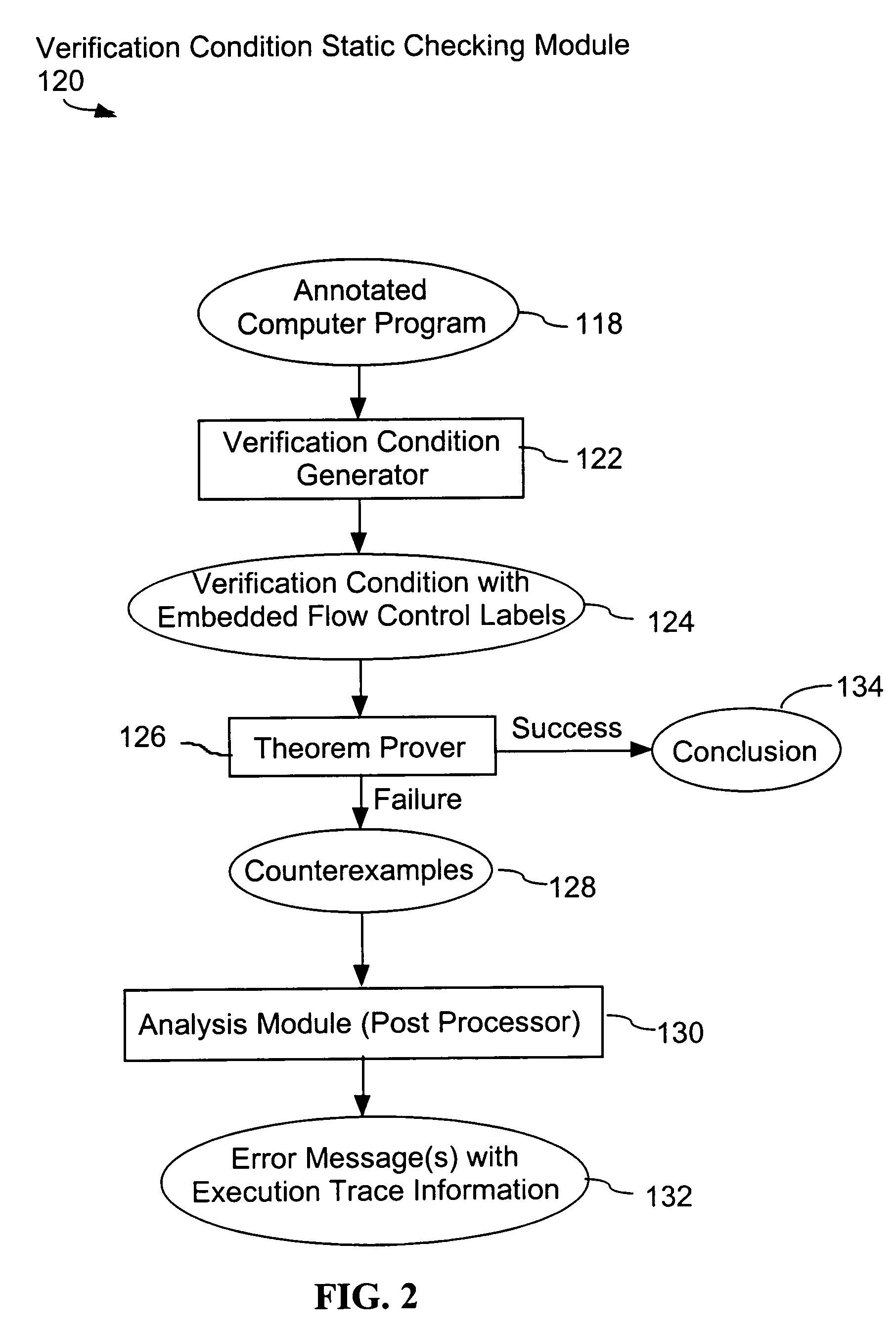

System and method for verifying computer program correctness and providing recoverable execution trace information

In a system for statically analyzing a specified computer, a verification condition generator converts the program into a logical equation, called a verification condition, and inserts program flow control labels into the sub-equations of the verification condition. The flow control labels identify conditional branch points in the specified computer program. A theorem prover is applied to the logical equation to determine truth of the logical equation, and when the truth of the logical equation cannot be proved, the theorem prover generates at least one counter-example identifying one of the conditions, one or more variable values inconsistent with that condition, and any of the flow control labels for conditional branch points of the program associated with the identified variable values. A post processing module converts each counter-example into an error message that includes a program trace when the counter-example identifies one or more of the flow control labels.

Owner:HEWLETT PACKARD DEV CO LP

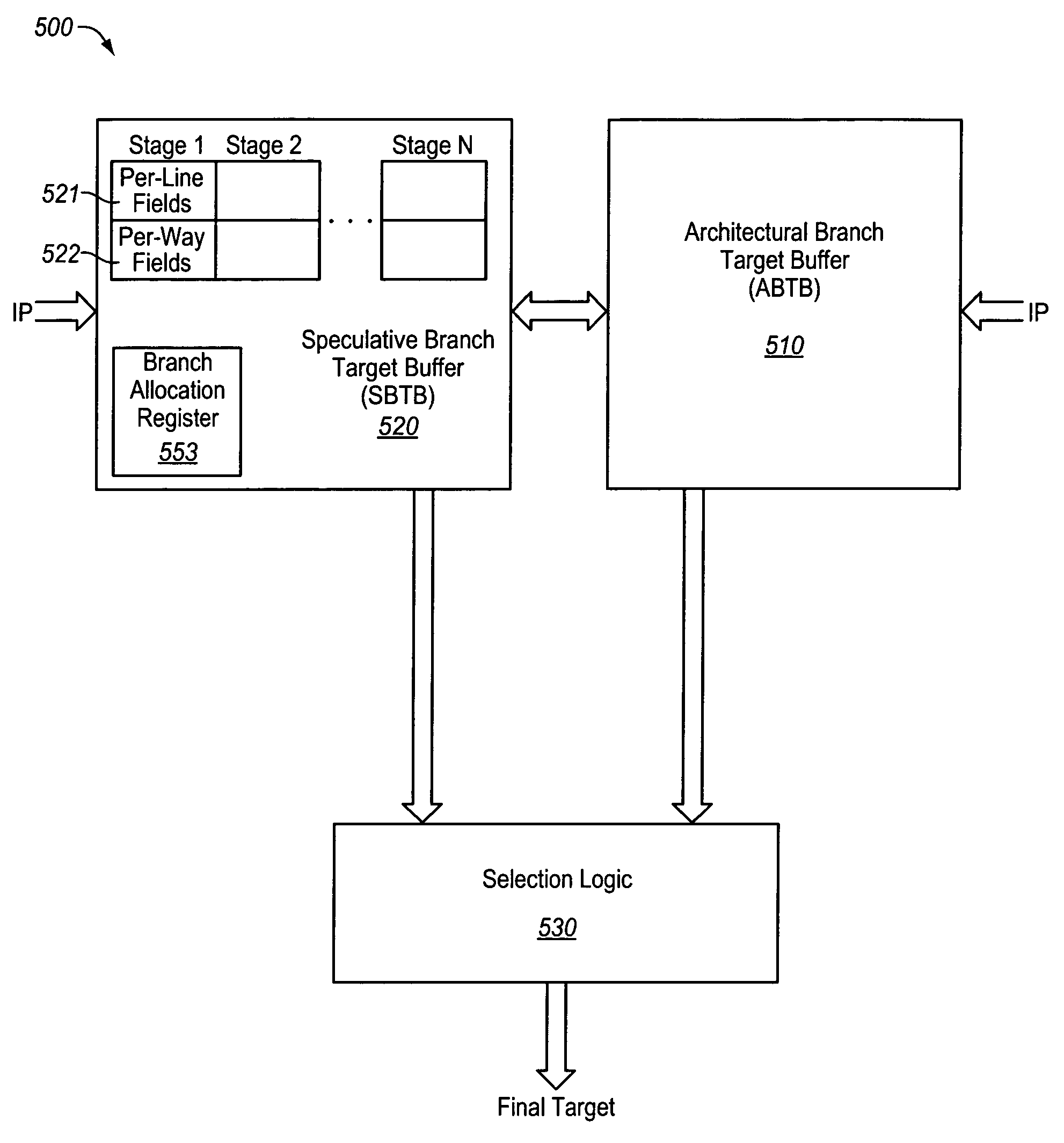

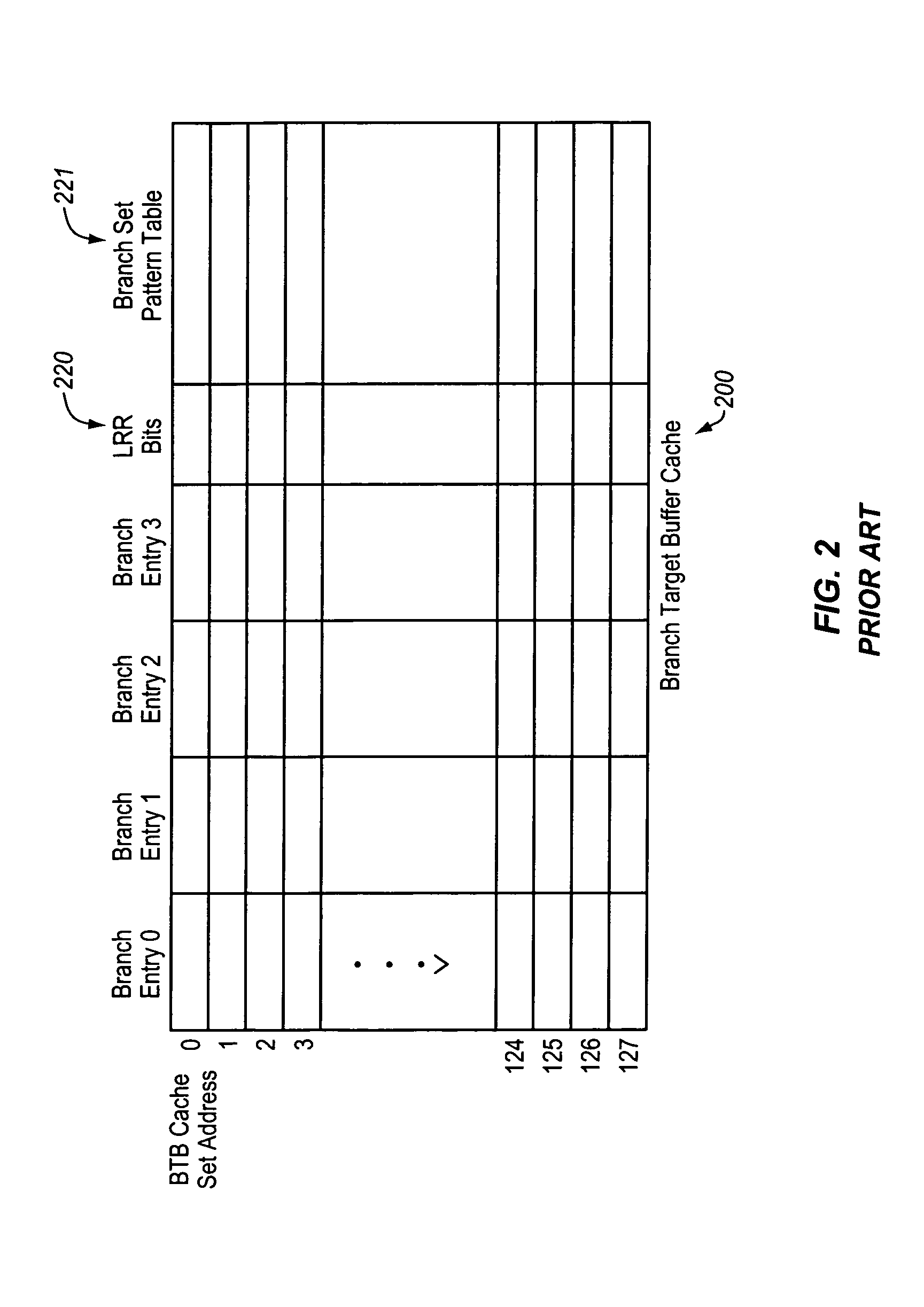

Branch target buffer (BTB) including a speculative BTB (SBTB) and an architectural BTB (ABTB)

InactiveUS7107437B1Digital computer detailsSpecific program execution arrangementsConditional branchSubroutine

A method and apparatus are provided for improving the performance of branch prediction using a combination of a speculative branch target buffer (SBTB) and an architectural branch target buffer (ABTB). According to one embodiment, speculative branch data is maintained for in-flight branches (i.e., those that have been fetched but not yet retired). A branch entry is speculatively allocated in a line of the SBTB after decoding an instruction containing a branch, such as a conditional branch, a return from a subroutine, a call to a subroutine, or an unconditional branch. Subsequently, the branch data associated with the branch entry is speculatively updated after branch prediction has been completed for the branch. Finally, the branch data is corrected after the branch has been executed. According to another embodiment, a novel branch prediction circuit includes both a speculative branch target buffer (SBTB) cache and an architectural branch target buffer (ABTB) cache. The SBTB cache contains multiple branch entries to maintain speculative branch data associated with in-flight branches. The speculative branch data includes a speculative history of taken / not-taken outcomes associated with the in-flight branches. The ABTB cache is coupled to the SBTB cache. The ABTB cache also includes multiple branch entries, however, they are for maintaining architectural branch data including the actual taken / not-taken outcomes associated with retired conditional branches.

Owner:INTEL CORP

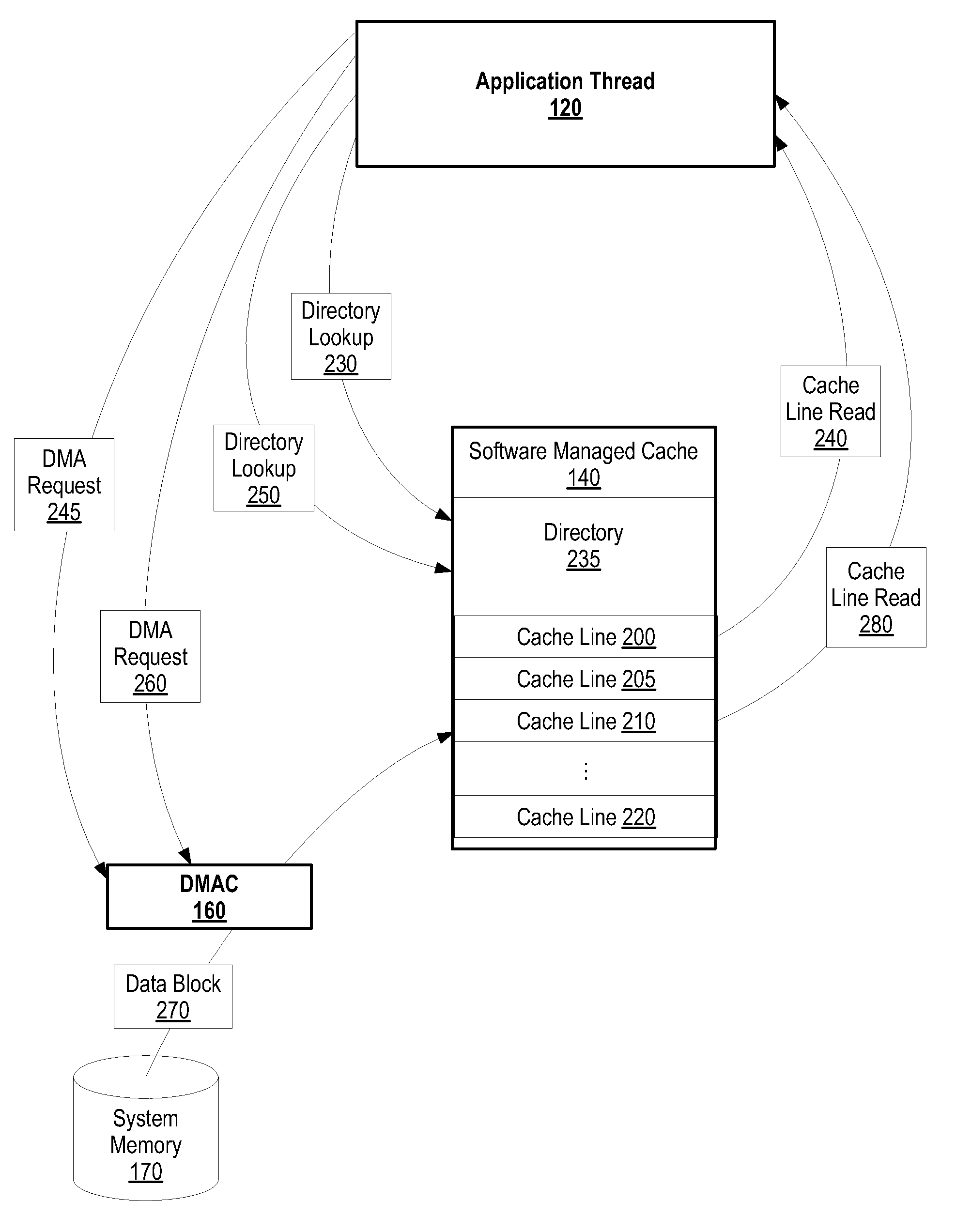

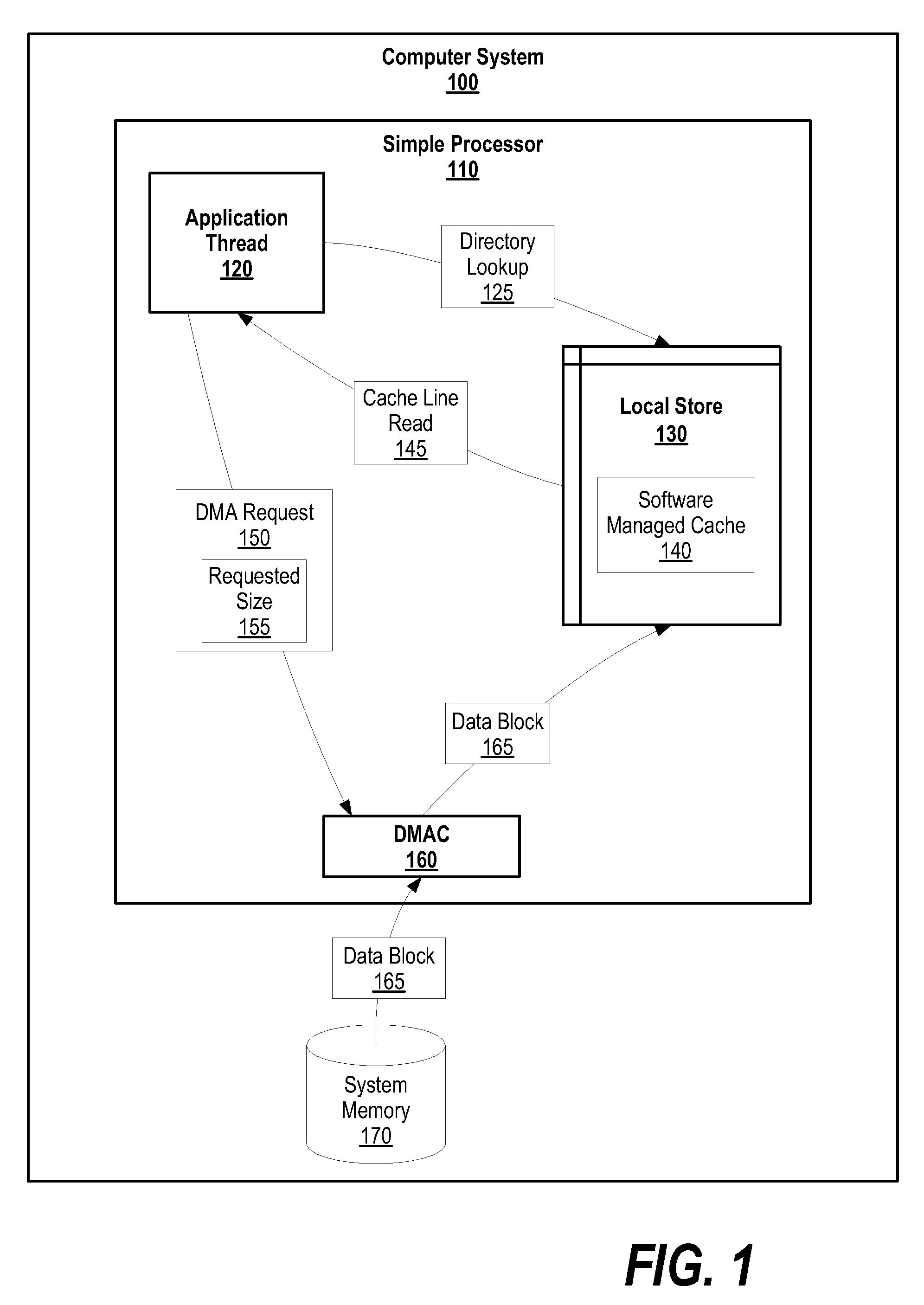

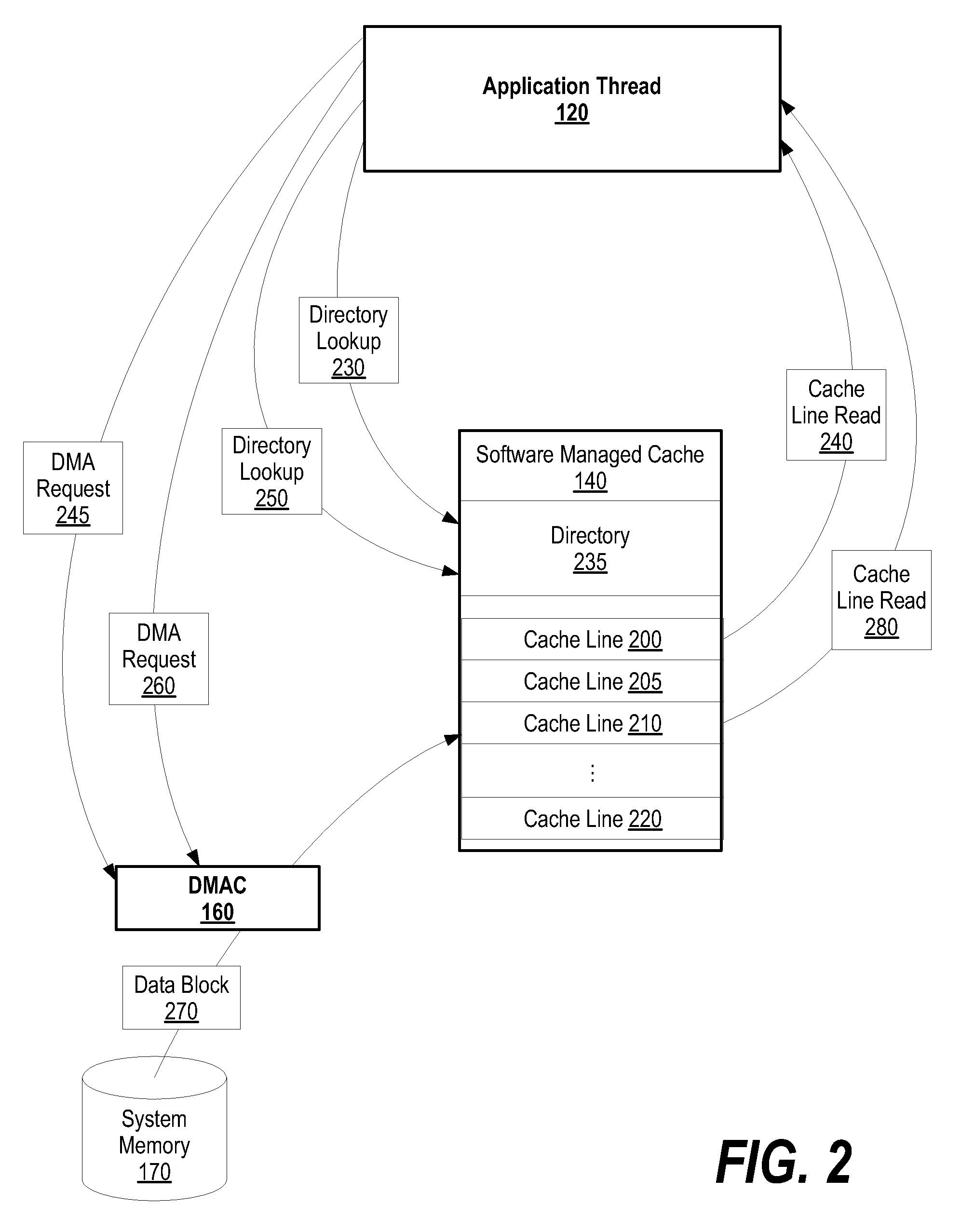

System and method for efficient implementation of software-managed cache

InactiveUS20080209127A1Memory adressing/allocation/relocationDigital computer detailsApplication softwareConditional branch

A system and method for an efficient implementation of a software-managed cache is presented. When an application thread executes on a simple processor, the application thread uses a conditional data select instruction for eliminating a conditional branch instruction when accessing a software-managed cache. An application thread issues a conditional data select instruction (DMA transfer) after a cache directory lookup, wherein the size of the requested data is dependent upon the outcome of the cache directory lookup. When the cache directory lookup results in a cache hit, the application thread requests a transfer of zero bits of data, which results in a DMA controller (DMAC) performing a no-op instruction. When the cache directory lookup results in a cache miss, the application thread requests a data block transfer the size of a corresponding cache line.

Owner:IBM CORP

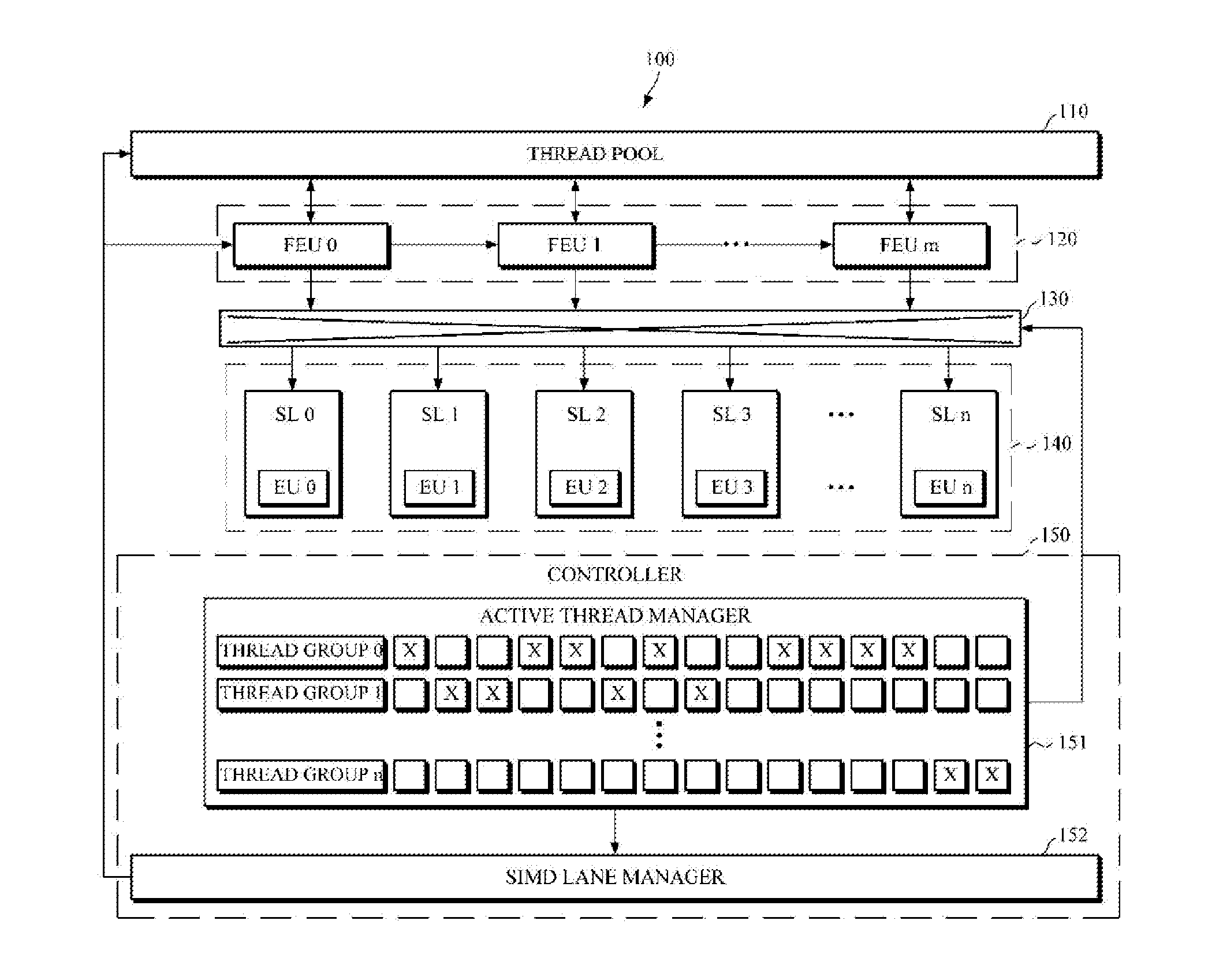

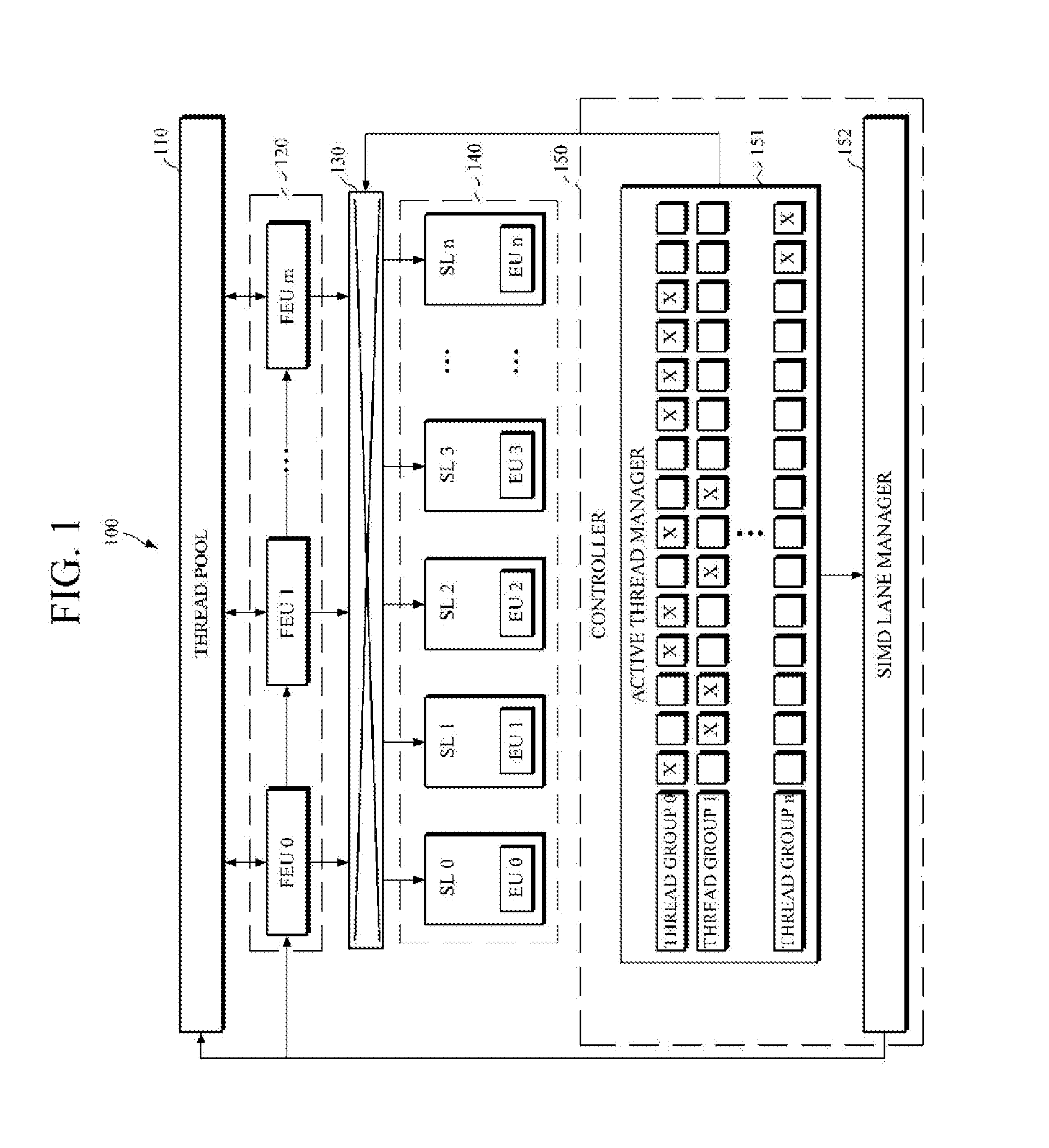

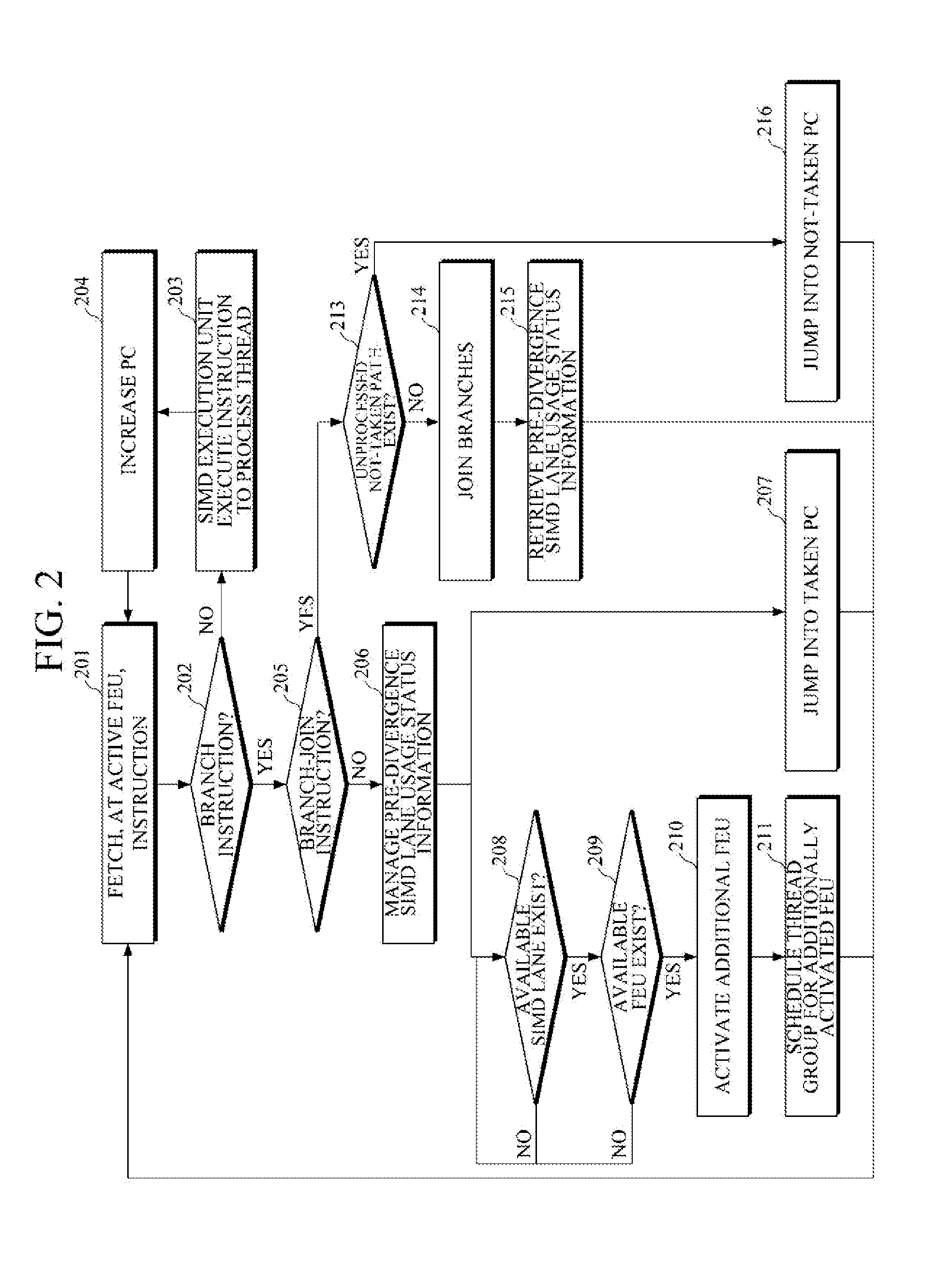

Device and method for managing simd architecture based thread divergence

ActiveUS20160132338A1Minimize idle SIMD laneImprove performanceInstruction analysisDigital computer detailsExecution controlConditional branch

Provided are an apparatus and a method for effectively managing threads diverged by a conditional branch based on Single Instruction Multiple-based Data (SIMD). The apparatus includes: a plurality of Front End Units (FEUs) configured to fetch, for execution by SIMD lanes, instructions of thread groups of a program flow; and a controller configured to schedule a thread group based on SIMD lane availability information, activate an FEU of the plurality of FEUs, and control the activated FEU to fetch an instruction for processing the scheduled thread group.

Owner:SAMSUNG ELECTRONICS CO LTD

System for providing offers using a billing statement

A billing statement according to one aspect of the invention includes a description of a transaction and an offer pointer associated with the transaction, wherein the offer pointer includes information that may be used to review an offer. In one example of this aspect, the offer pointer is a telephone number printed adjacent to a description of a transaction on a credit card billing statement. The telephone number accesses a voice response system presenting conditional branches through which a consumer can navigate to review an offer. In another example, a hyperlink is positioned adjacent to a total amount owed listed on an electronically-displayed billing statement. The hyperlink may be selected to access a website presenting offers for review by the consumer. The offers reviewed in each of these examples may be customized based on details of the transaction such as the product purchased or the amount of the purchase, the identity of the consumer, and / or on other data.

Owner:PAYPAL INC