Patents

Literature

1470 results about "Register file" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A register file is an array of processor registers in a central processing unit (CPU). Modern integrated circuit-based register files are usually implemented by way of fast static RAMs with multiple ports. Such RAMs are distinguished by having dedicated read and write ports, whereas ordinary multiported SRAMs will usually read and write through the same ports.

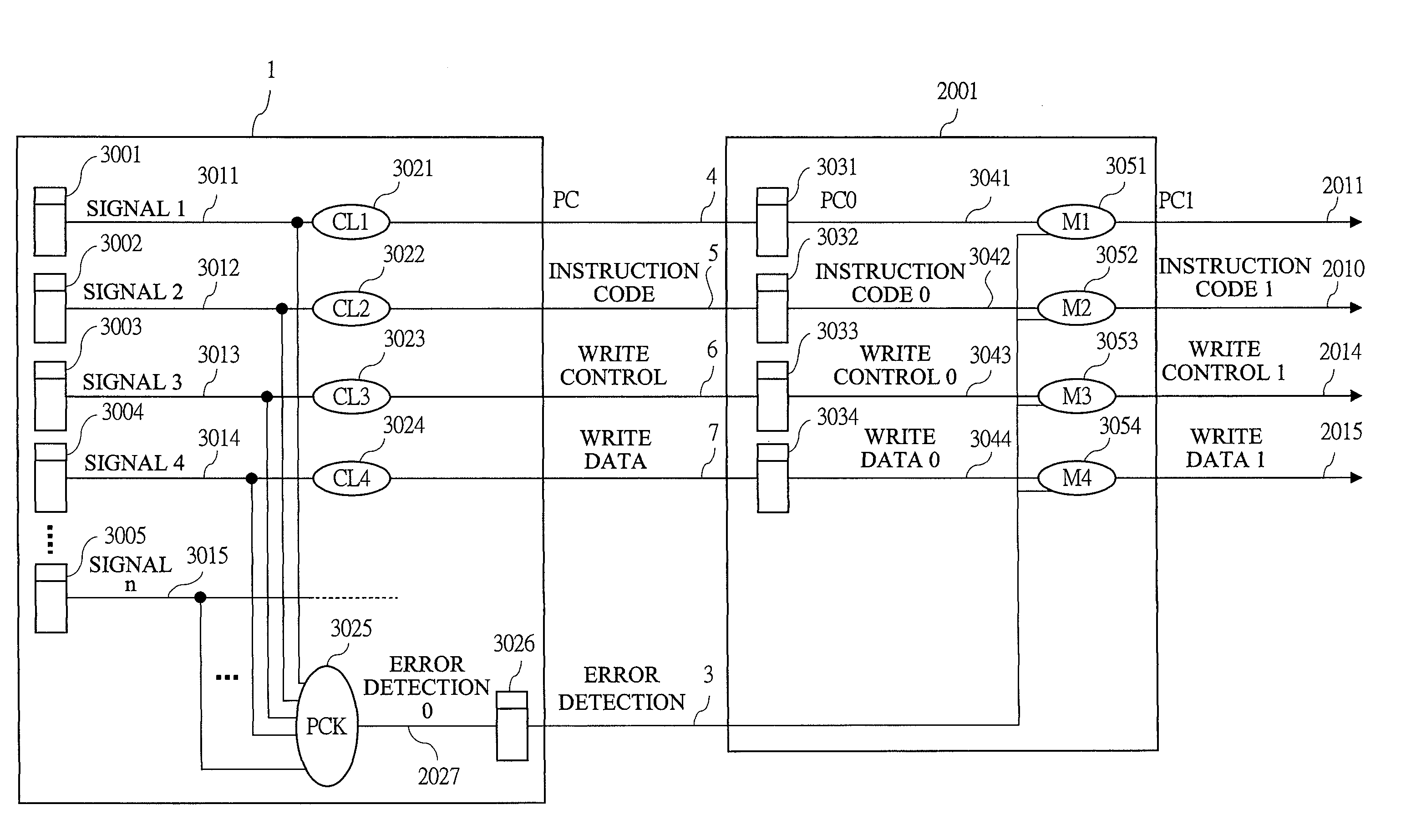

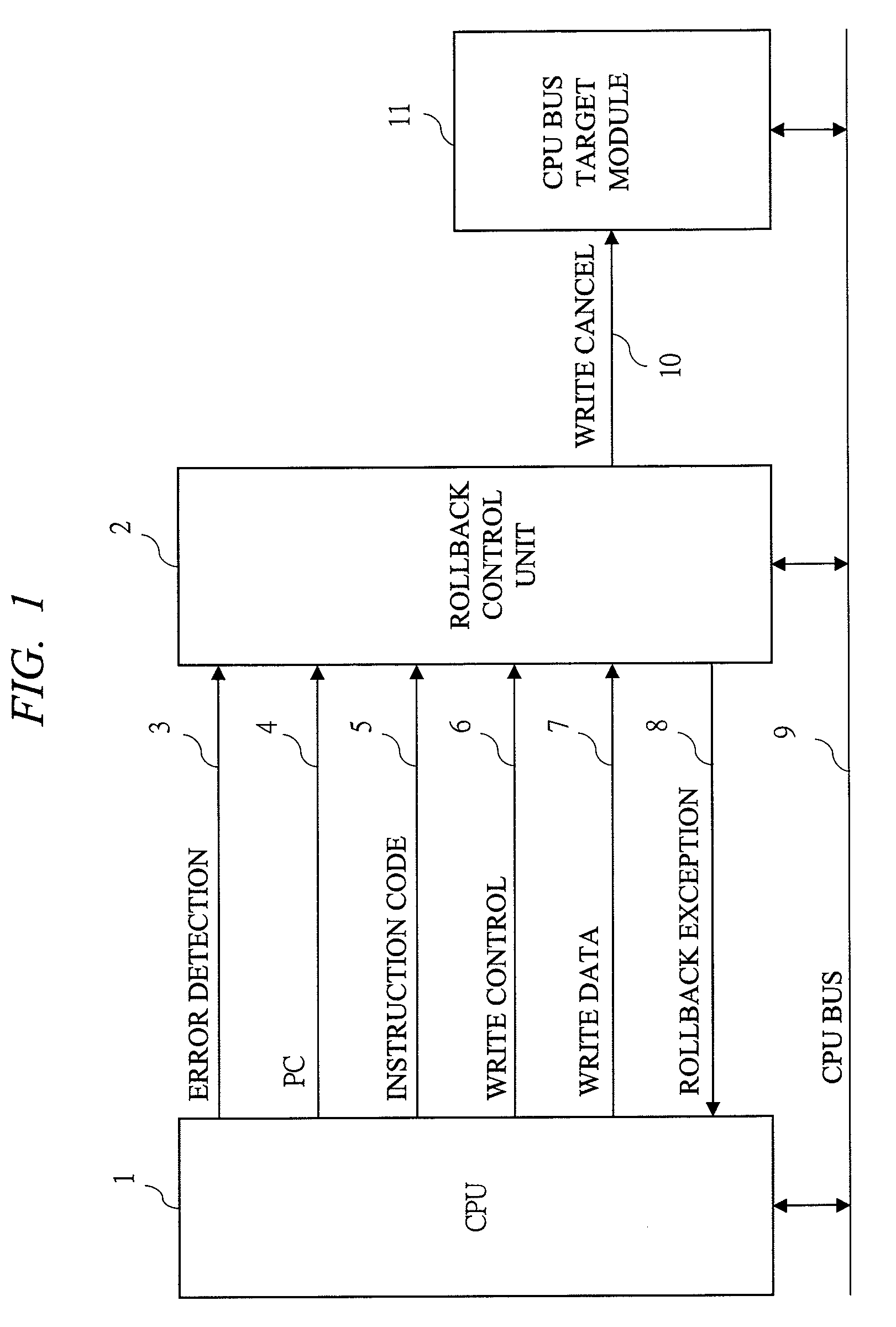

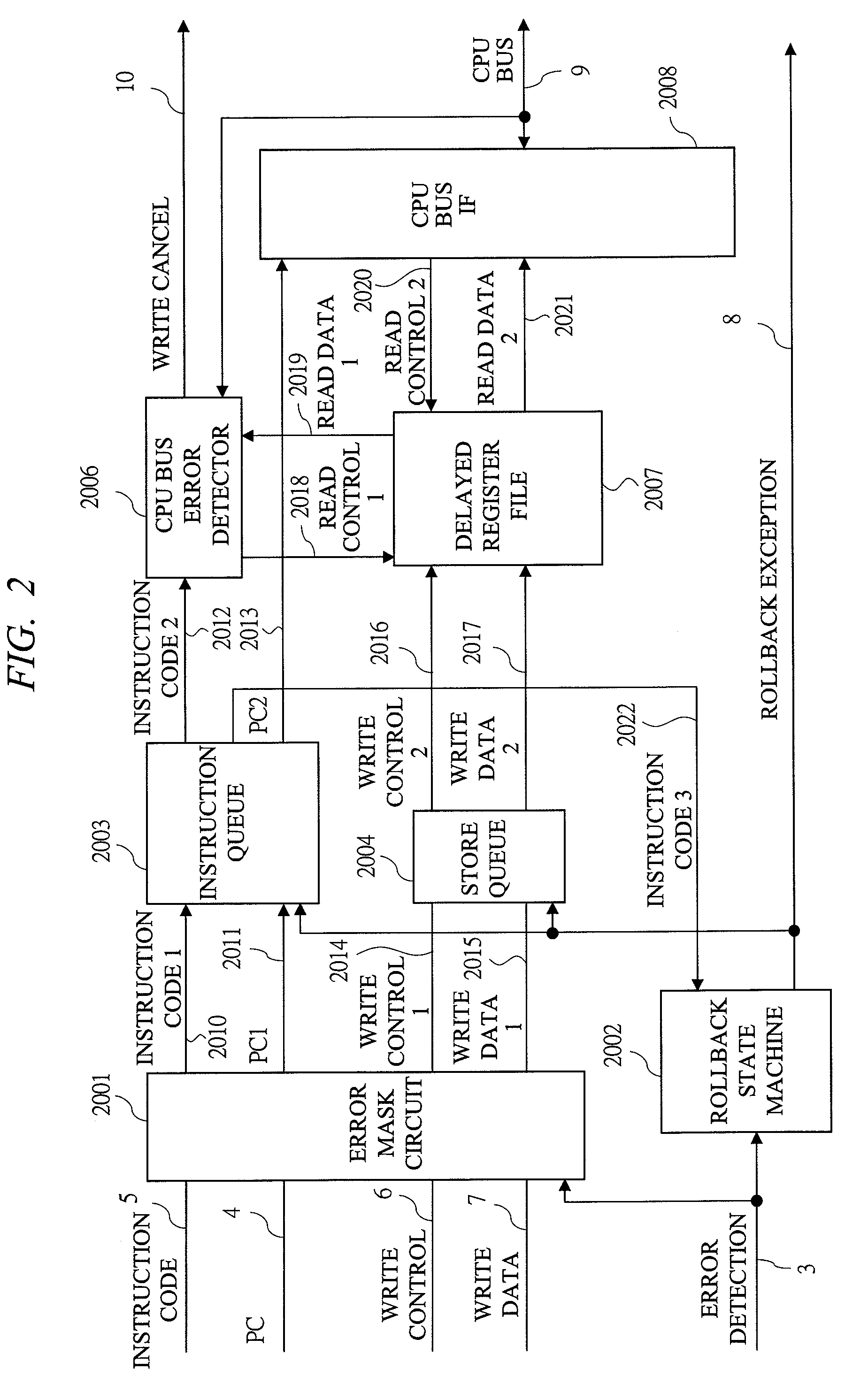

Error correction method with instruction level rollback

This method is an error correction method such that, when an error is detected in a CPU with pipeline structure, a content of a register file is restored by a delayed register file which holds an execute completion state of an [Instruction N] correctly executed before this error, and a rollback control that re-executes an instruction from the [Instruction N+1] which is the next instruction of the [Instruction N] is performed. The method collects a parity check result of arbitrary Flip-Flops existing inside the CPU, and detects an error. As a result, the content of the register file is restored into the instruction execute completion state preceding to the instruction range likely to malfunction by the error, and the instruction can be roll backed from the beginning of the instruction range likely having malfunctioned by the error.

Owner:RENESAS ELECTRONICS CORP

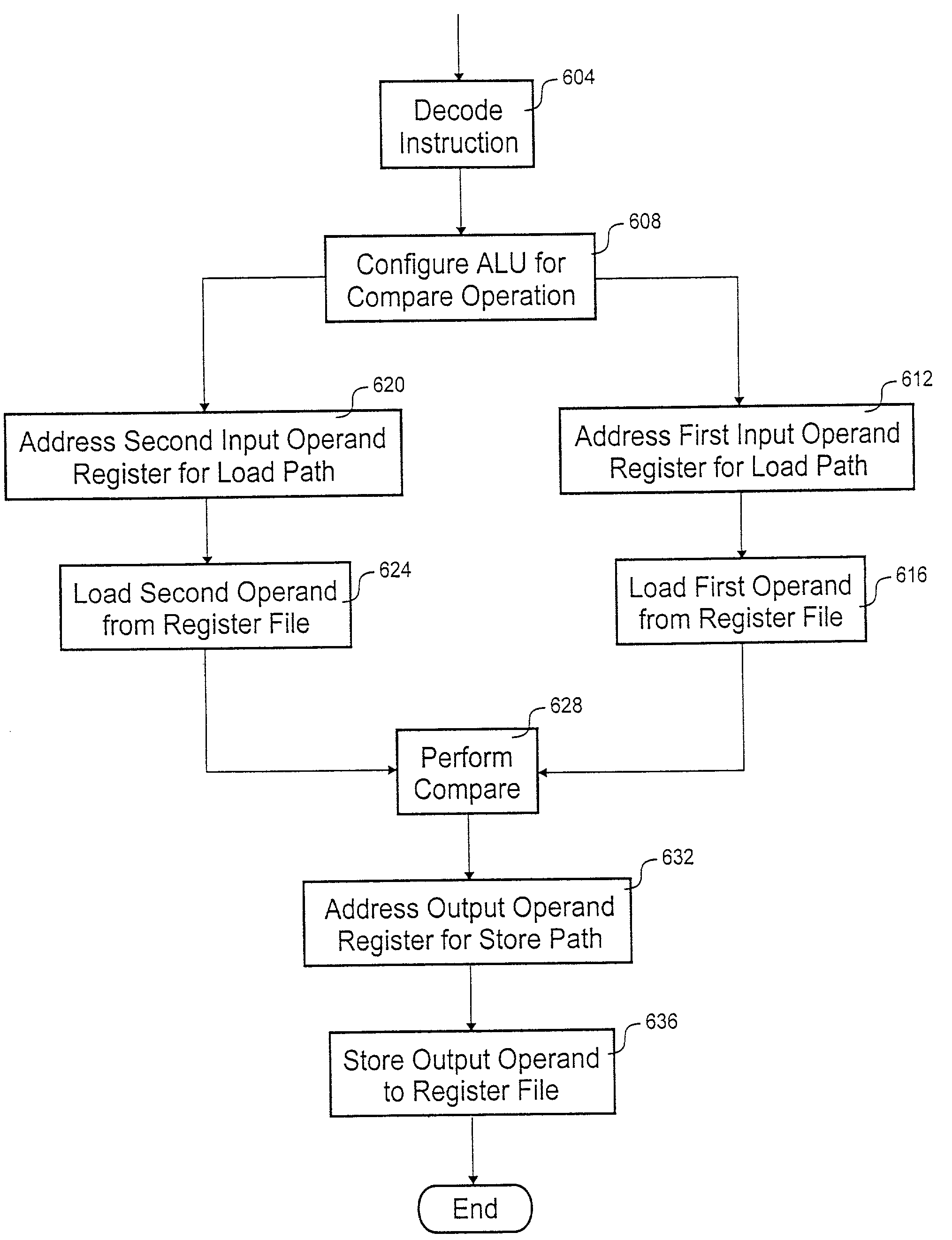

Processing architecture having a compare capability

According to the invention, a processing core that executes a compare instruction is disclosed. The processing core includes a register file, comparison logic, decode logic, and a store path. Included in the register file are a number of general-purpose registers. The general-purpose registers include a first input operand register, a second input operand register and an output operand register. Comparison logic is coupled to the register file. The comparison logic tests for at least two of the following relationships: less than, equal to, greater than and no valid relationship. The decode logic selects the output operand register from the plurality of general-purpose registers. The store path extends between the comparison logic and the selected output operand register.

Owner:ORACLE INT CORP

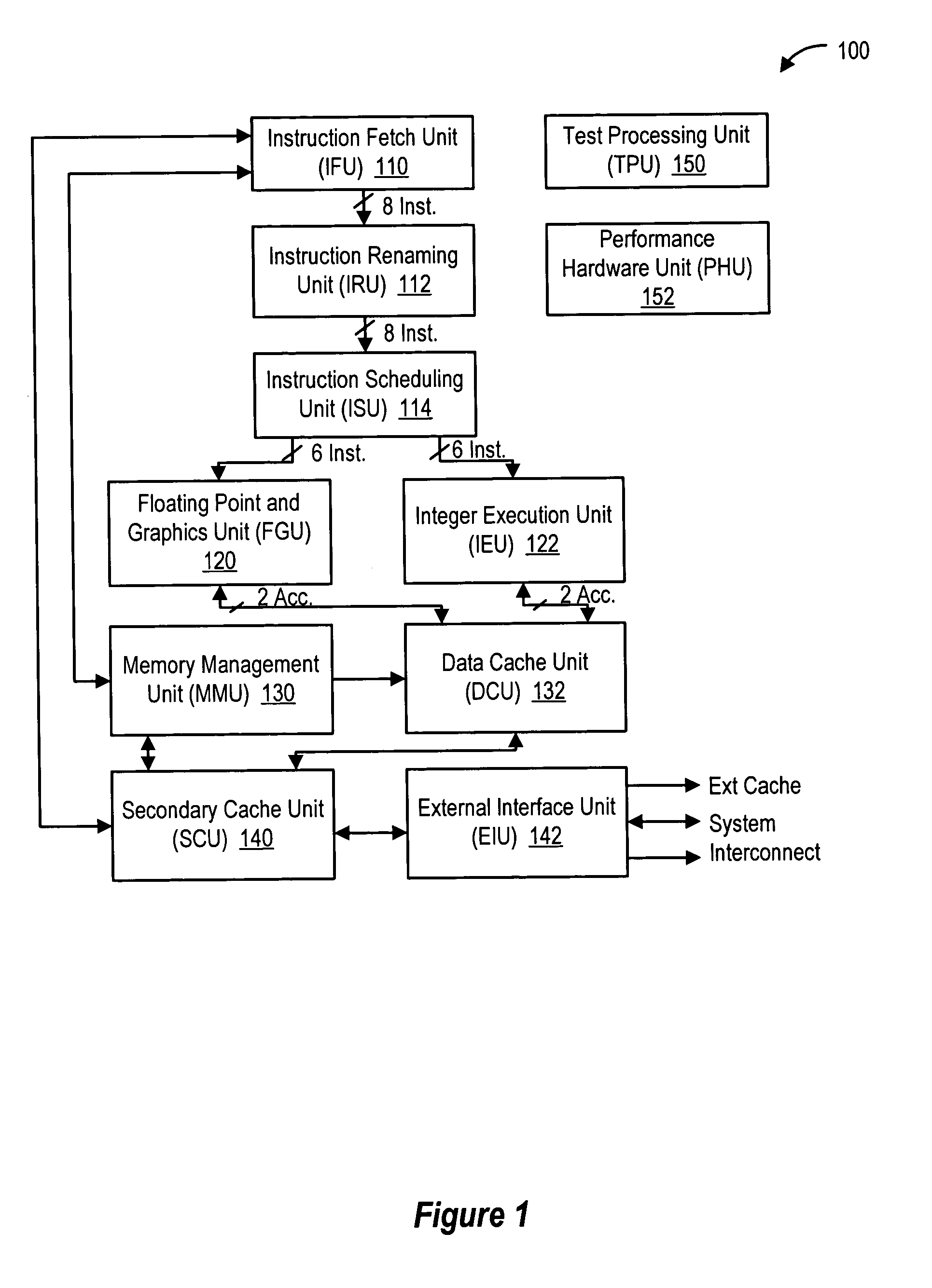

SIMD datapath coupled to scalar/vector/address/conditional data register file with selective subpath scalar processing mode

InactiveUS6839828B2Not compromise SIMD data processing performanceReduce consumptionRegister arrangementsDigital data processing detailsProcessor registerOperation mode

There is provided a processor designed to operate in a plurality of modes for processing vector and scalar instructions. Register files are each for storing scalar and vector data and address information. A parallel vector unit, coupled to the register files, includes functional units configurable to operate in a vector operation mode and a scalar operation mode. The vector unit includes an apparatus for tightly coupling the functional units to perform an operation specified by a current instruction. Under a vector operation mode, the vector unit performs, in parallel, a single vector operation on a plurality of data elements. The operations performed on the plurality of data elements are each performed by a different functional unit of the vector unit. Under a scalar operation mode, the vector unit performs a scalar operation on a data element received from the register files in a functional unit within the vector unit.

Owner:INTEL CORP

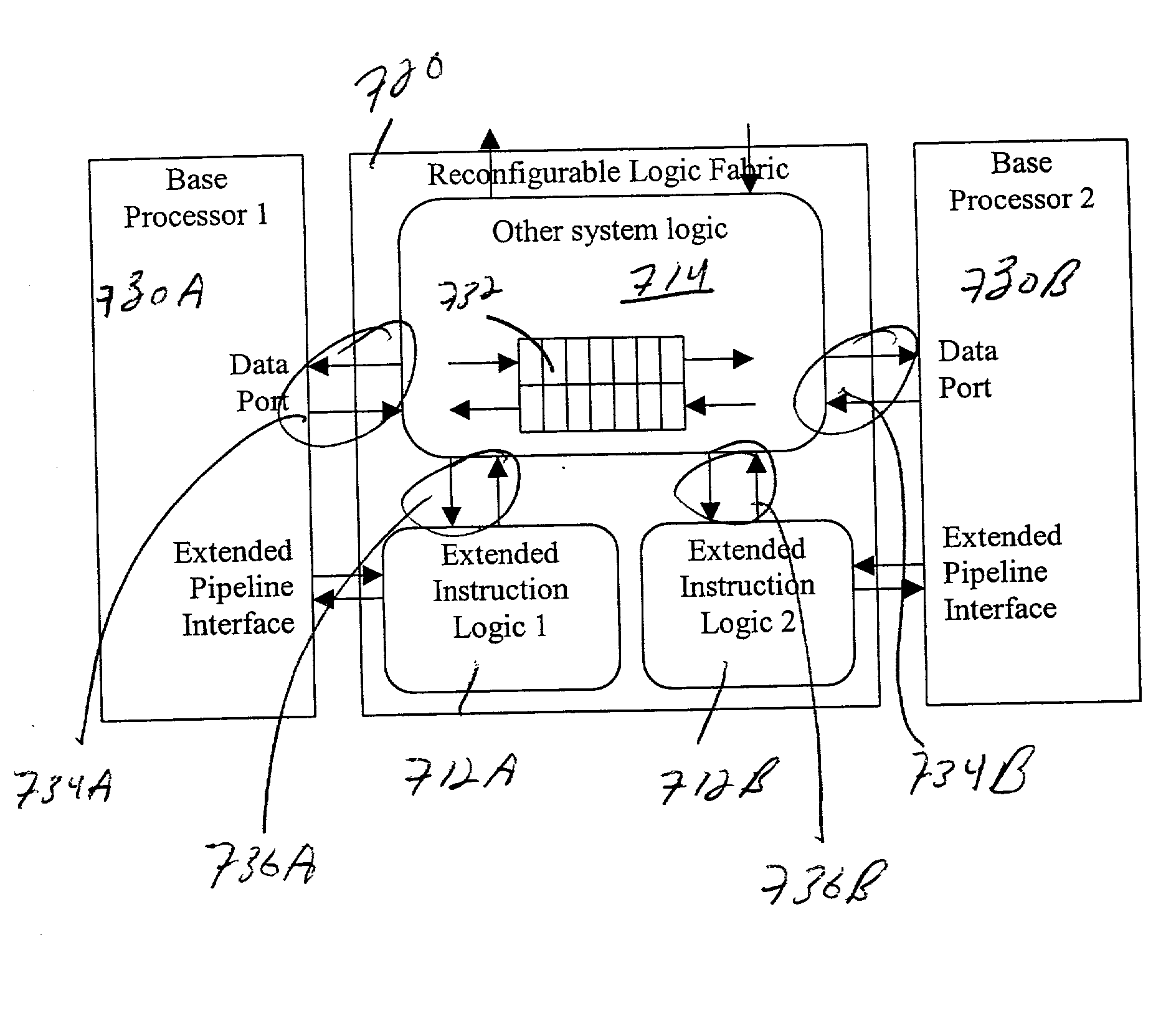

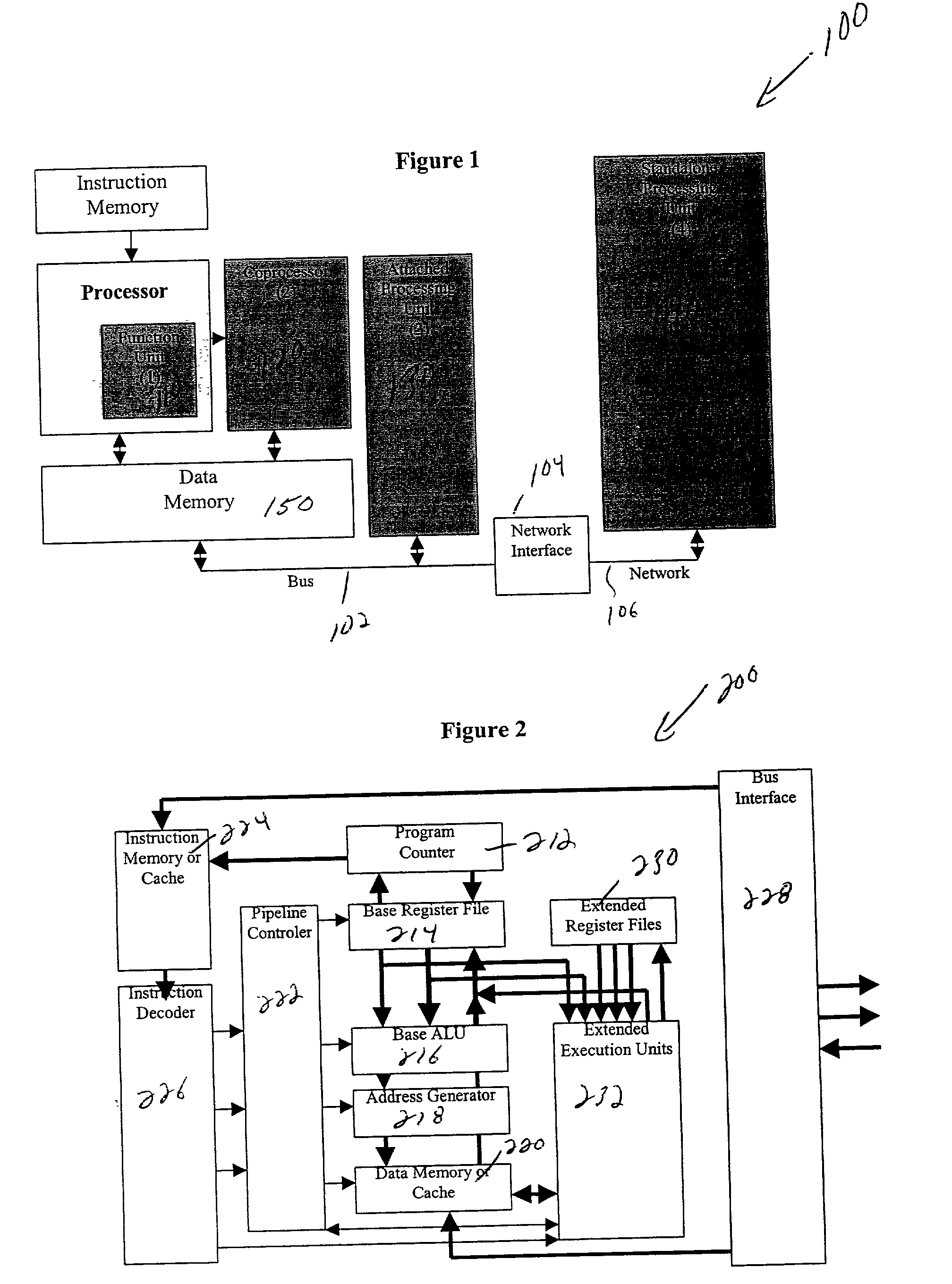

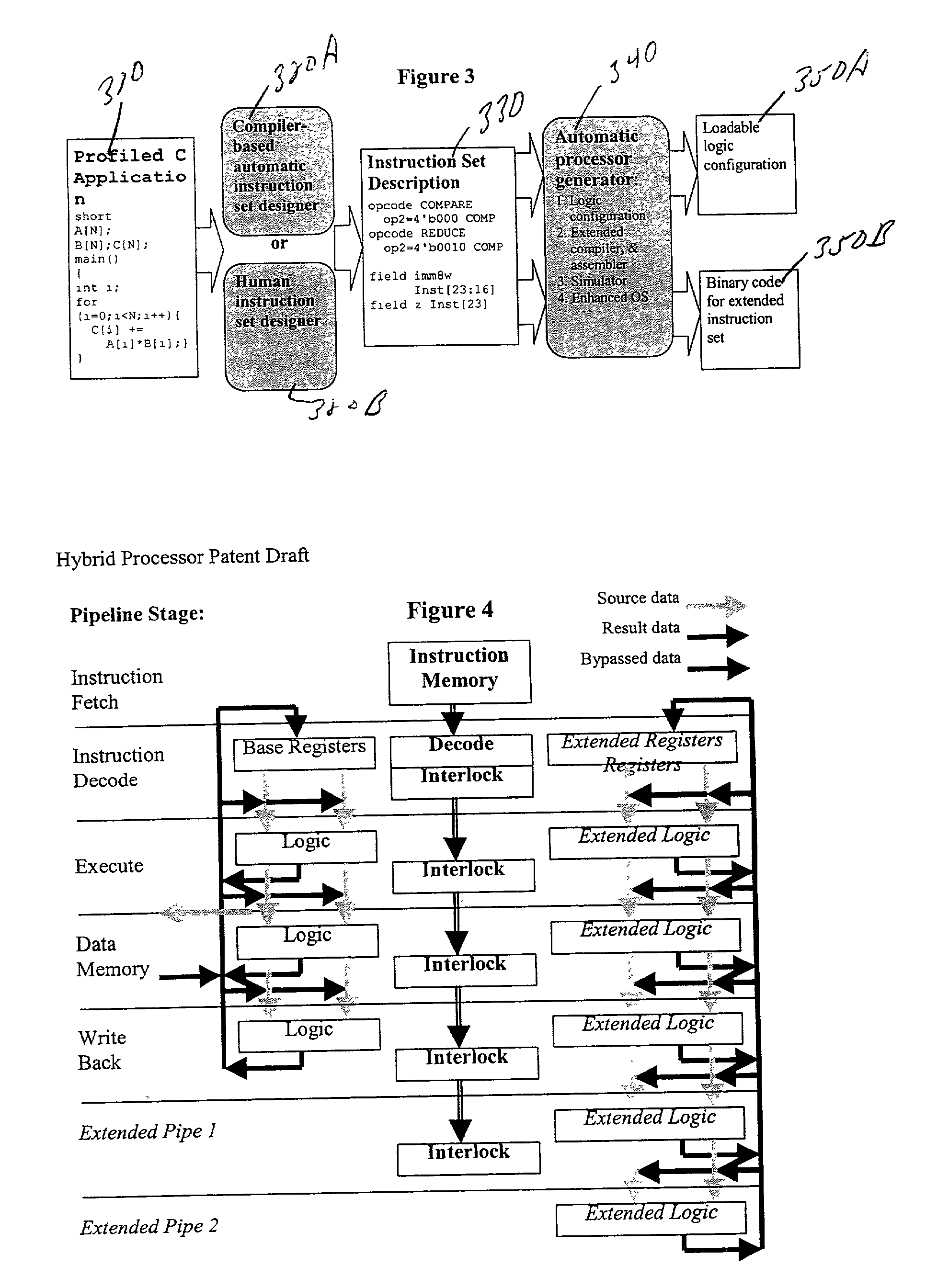

High-performance hybrid processor with configurable execution units

InactiveUS20050166038A1High bandwidthFlexibilityInstruction analysisConcurrent instruction executionHigh bandwidthLatency (engineering)

A new general method for building hybrid processors achieves higher performance in applications by allowing more powerful, tightly-coupled instruction set extensions to be implemented in reconfigurable logic. New instructions set configurations can be discovered and designed by automatic and semi-automatic methods. Improved reconfigurable execution units support deep pipelining, addition of additional registers and register files, compound instructions with many source and destination registers and wide data paths. New interface methods allow lower latency, higher bandwidth connections between hybrid processors and other logic.

Owner:TENSILICA

Apparatus and Method for Processing Complex Instruction Formats in a Multi-Threaded Architecture Supporting Various Context Switch Modes and Virtualization Schemes

ActiveUS20100161948A1Efficient context switchingEfficient switchingInstruction analysisDigital computer detailsVirtualizationProcessor register

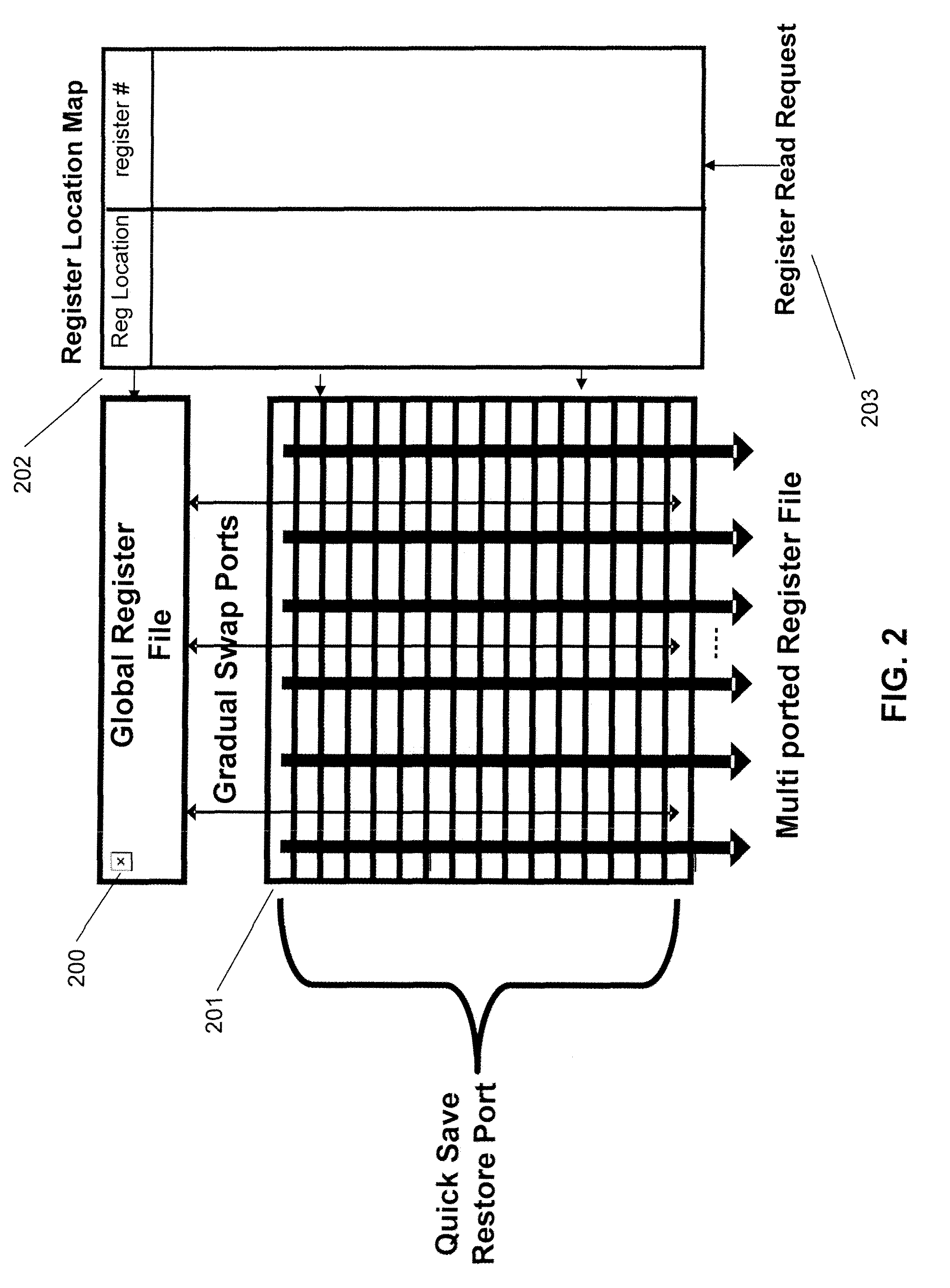

A unified architecture for dynamic generation, execution, synchronization and parallelization of complex instructions formats includes a virtual register file, register cache and register file hierarchy. A self-generating and synchronizing dynamic and static threading architecture provides efficient context switching.

Owner:INTEL CORP

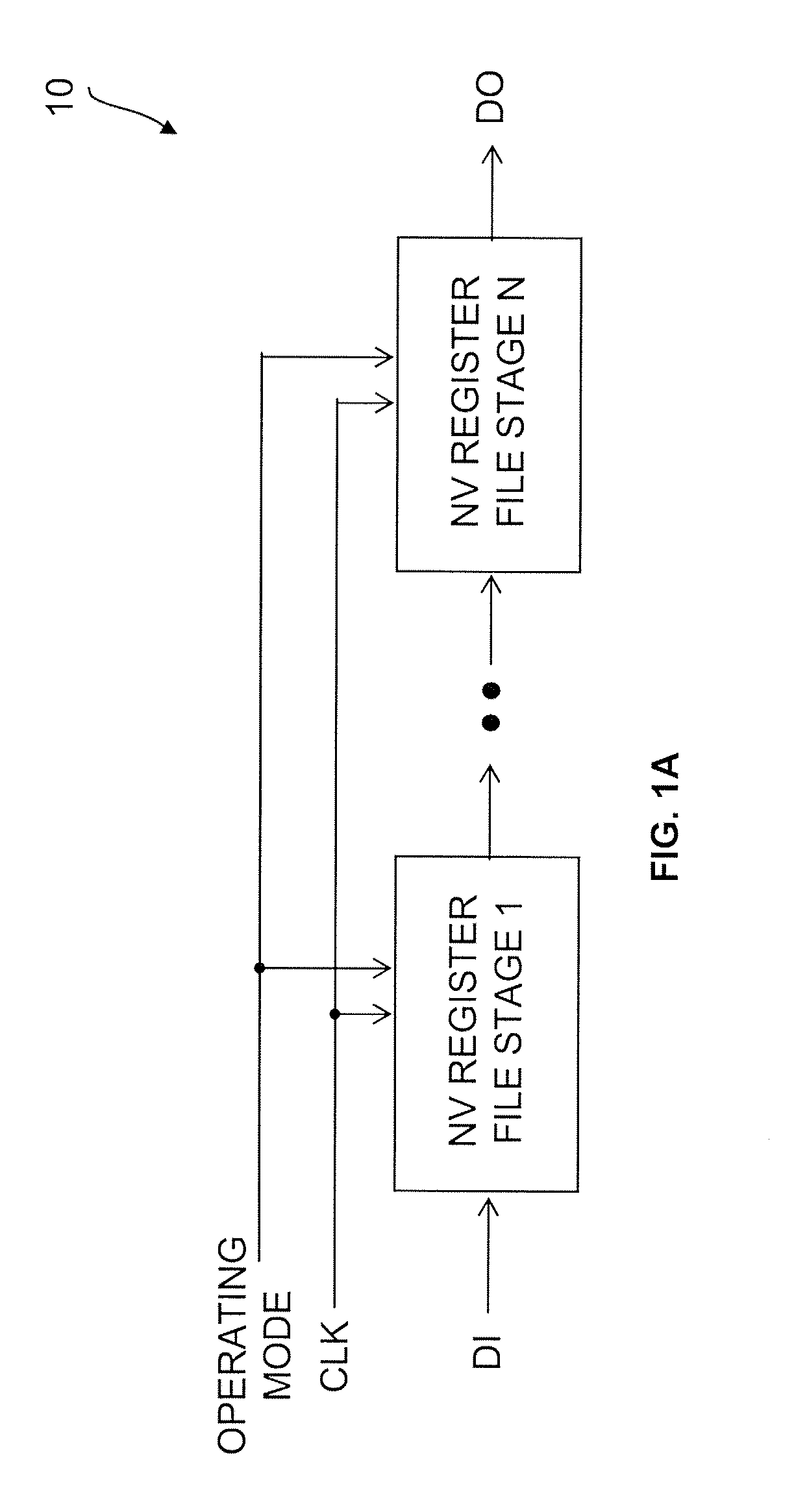

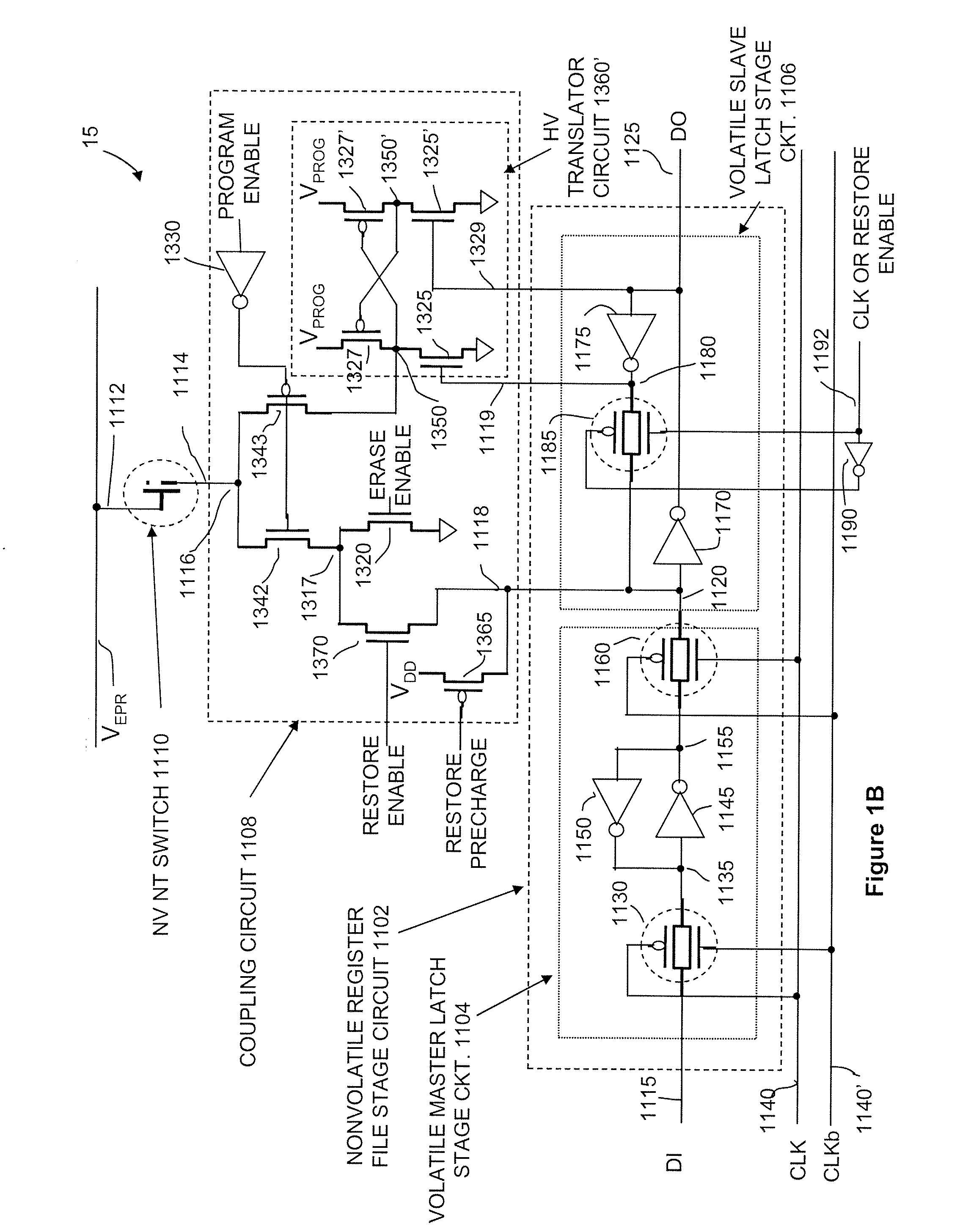

Latch circuits and operation circuits having scalable nonvolatile nanotube switches as electronic fuse replacement elements

ActiveUS20080159042A1TransistorSemiconductor/solid-state device detailsProcessor registerHemt circuits

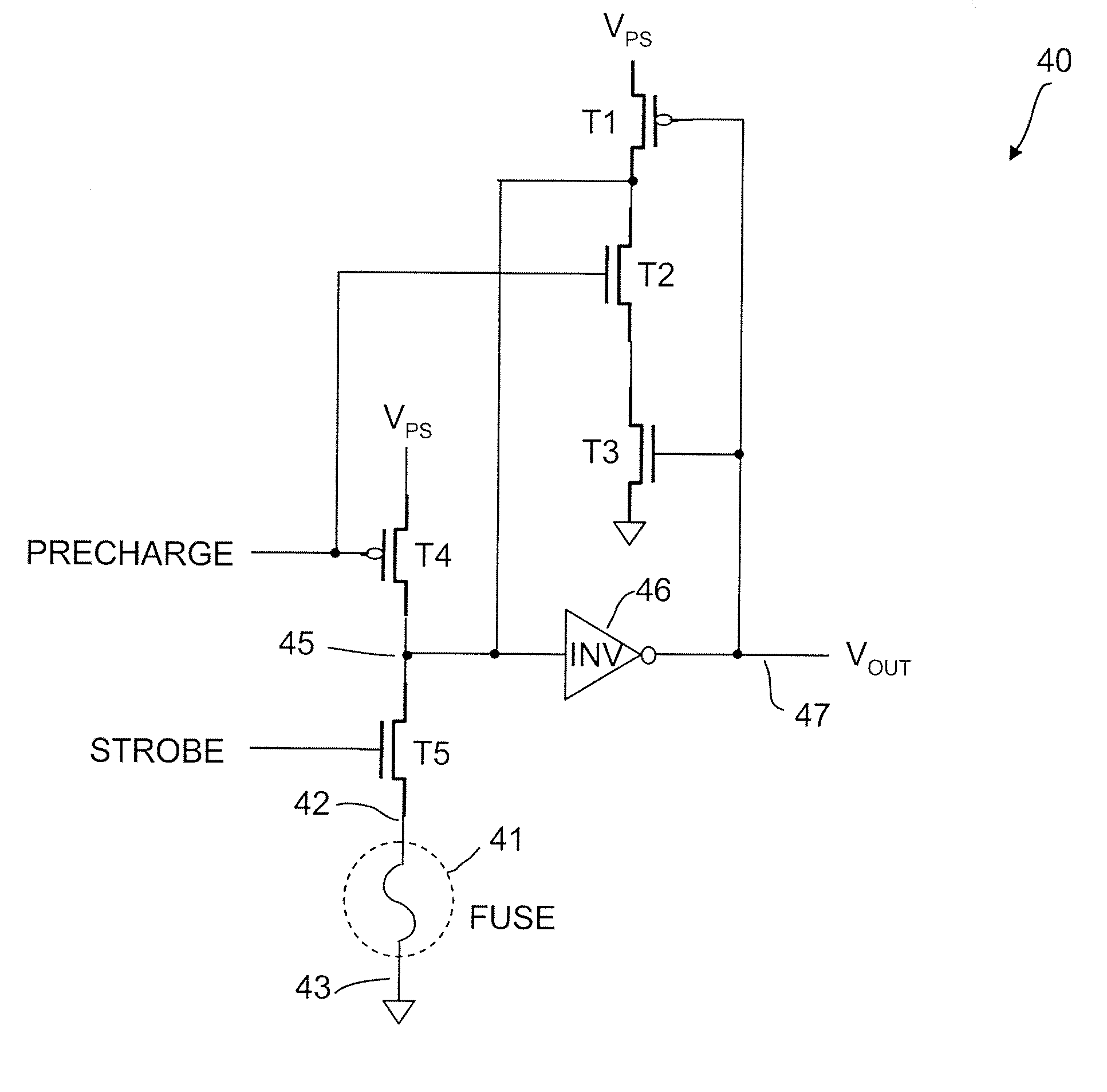

A non-volatile latch circuit is provided. The non-volatile latch circuit includes a nanotube switching element capable of switching between resistance states and non-volatilely retaining the resistance state. The non-volatile latch circuit includes a volatile latch circuit is capable of receiving and volatilely storing a logic state. When the nanotube switching element is a resistance state, the volatile latch circuit retains a corresponding logic state and outputs that corresponding logic state at an output terminal. A non-volatile register file configuration circuit for use with a plurality of non-volatile register files is also provided. The non-volatile register file configuration circuit includes a selection circuitry and a plurality of nanotube fuse elements, each in electrical communication with one of a plurality of non-volatile register files. The selection circuitry is capable of applying electrical stimulus to each of the selected nanotube fuse elements to selectively bypass the corresponding register file.

Owner:NANTERO

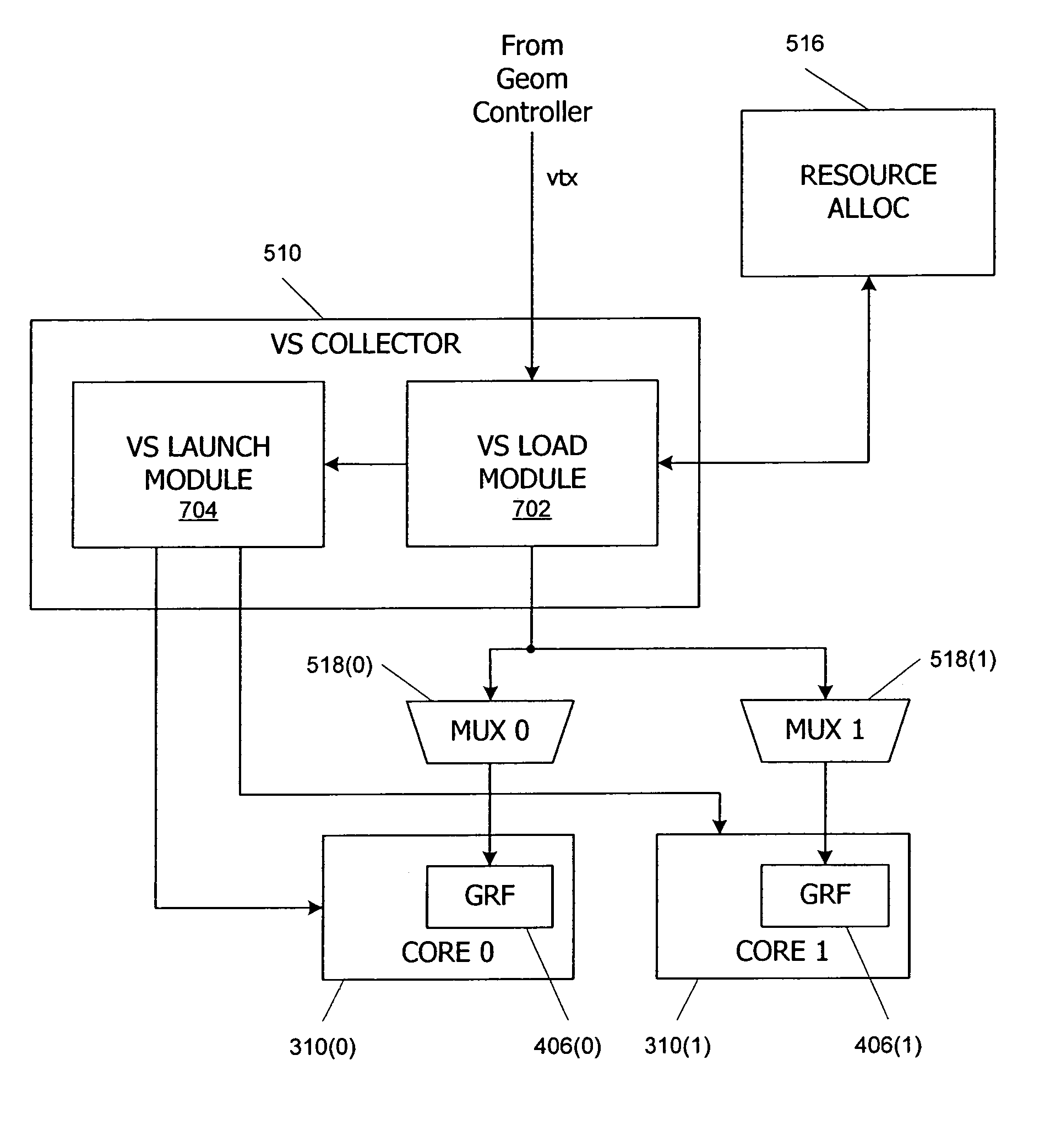

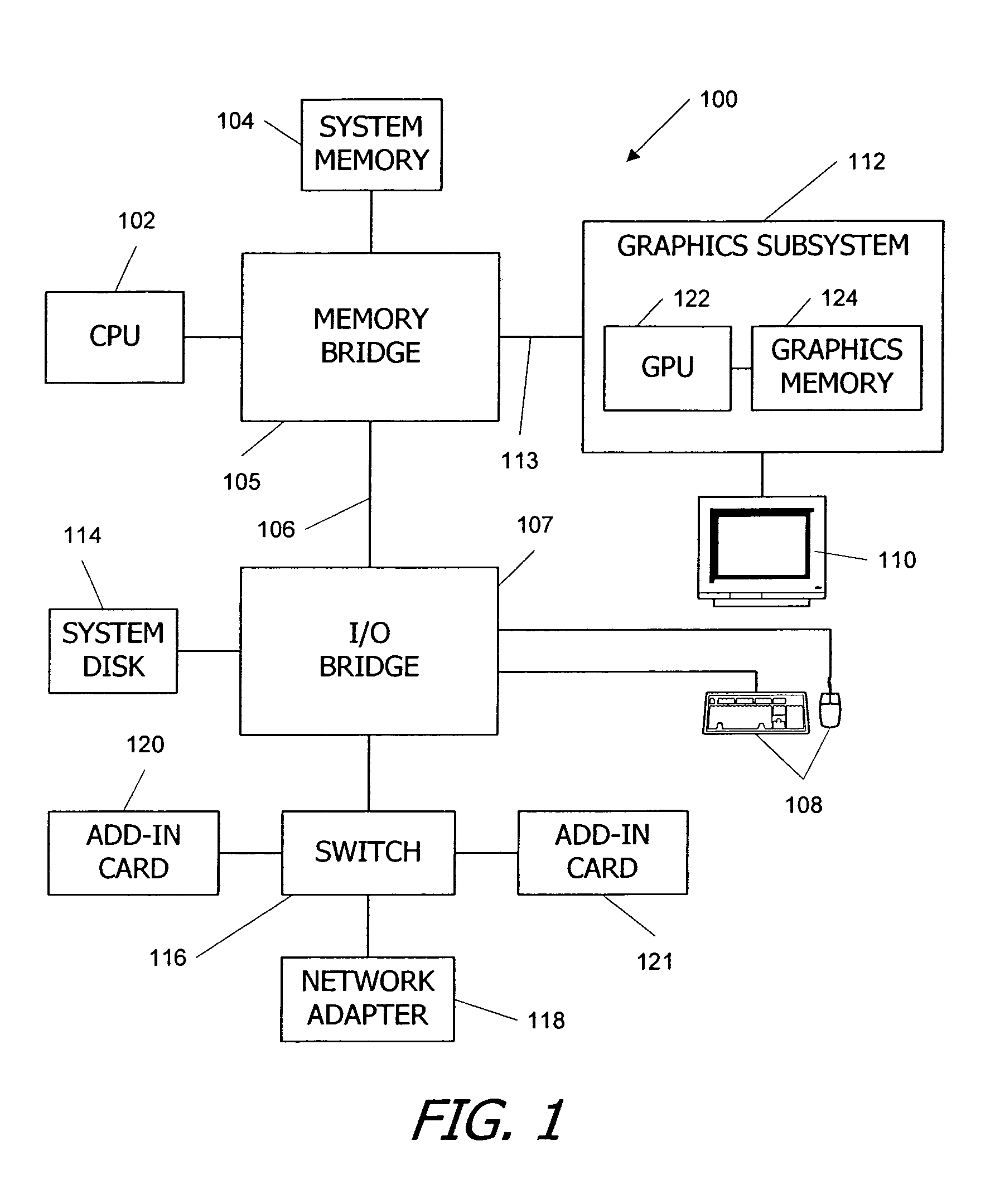

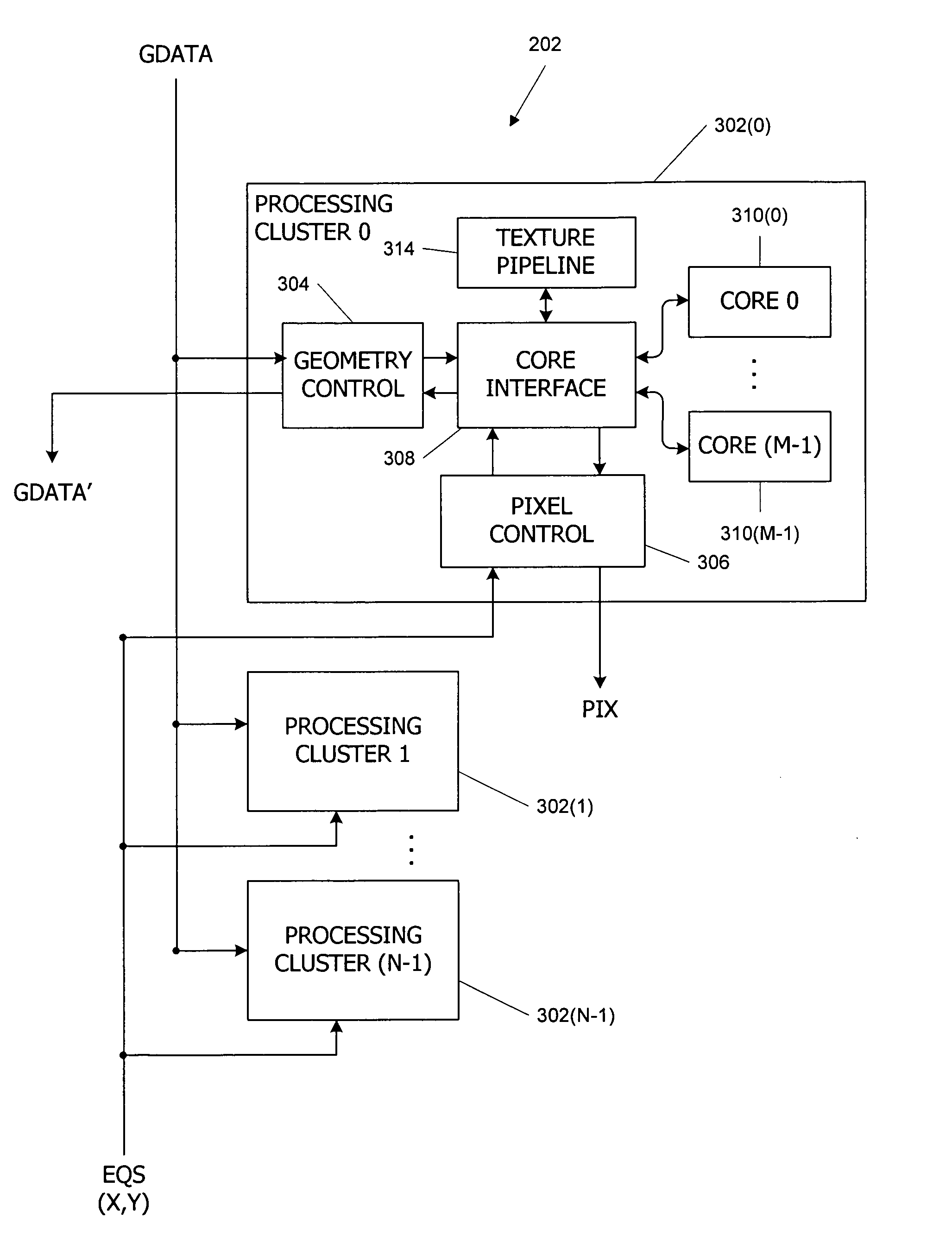

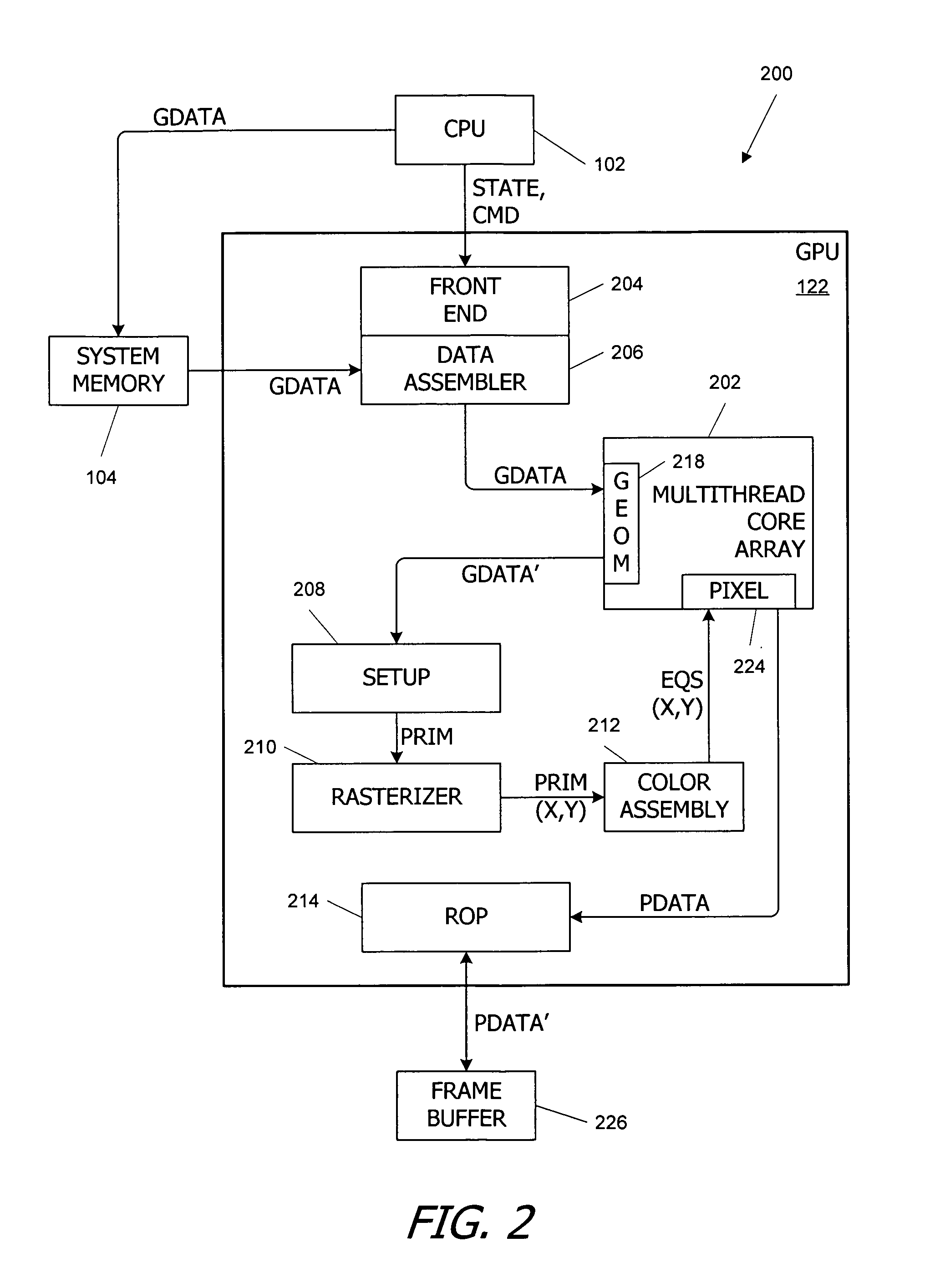

Multithreaded SIMD parallel processor with loading of groups of threads

ActiveUS7447873B1Management loadRegister arrangementsGeneral purpose stored program computerProcessing coreProcessor register

In a multithreaded processing core, groups of threads are executed using single instruction, multiple data (SIMD) parallelism by a set of parallel processing engines. Input data defining objects to be processed received as a stream of input data blocks, and the input data blocks are loaded into a local register file in the core such that all of the data for one of the input objects is accessible to one of the processing engines. The input data can be loaded directly into the local register file, or the data can be accumulated in a buffer and loaded after accumulation, for instance during a launch operation for a SIMD group. Shared input data can also be loaded into a shared memory in the processing core.

Owner:NVIDIA CORP

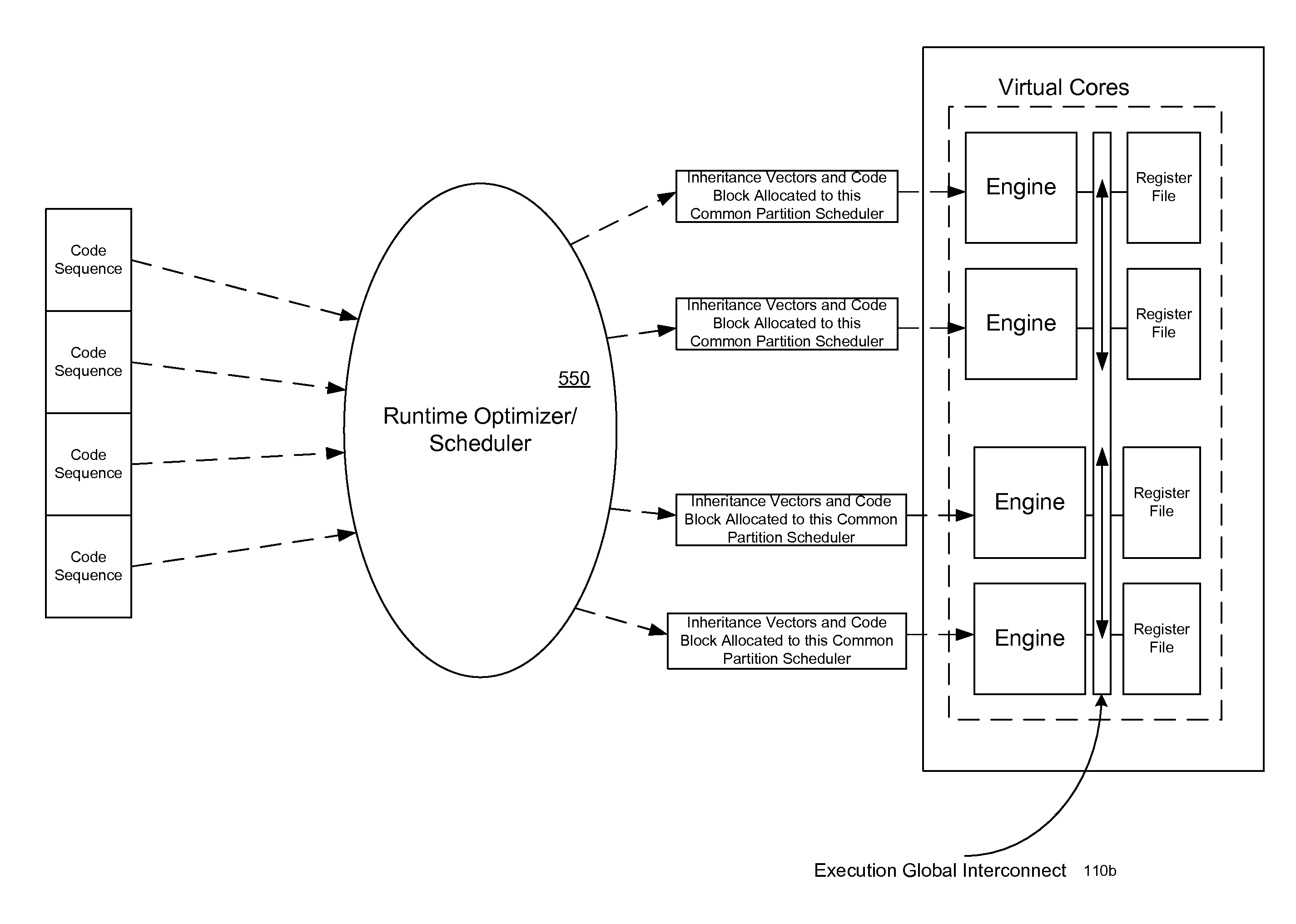

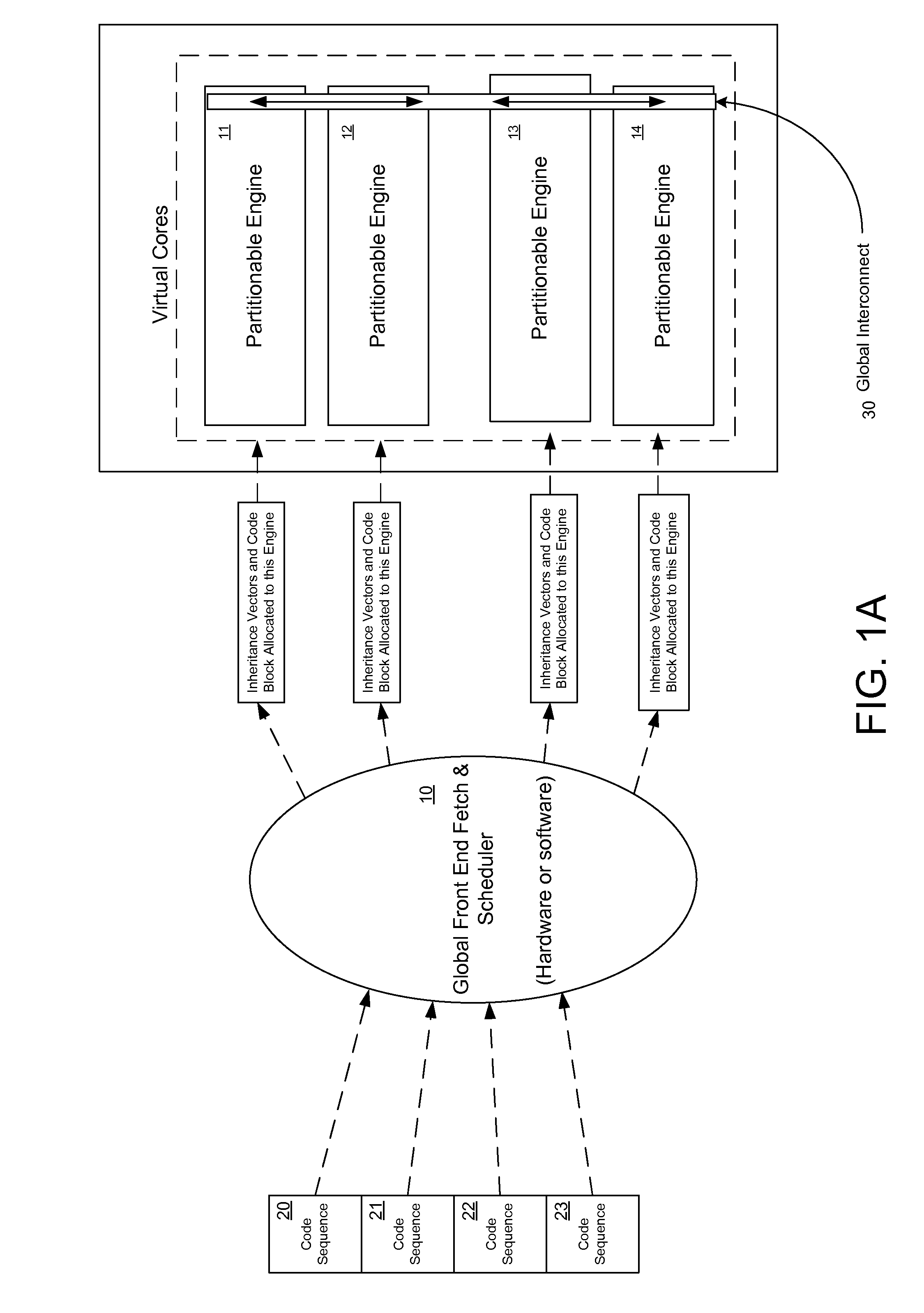

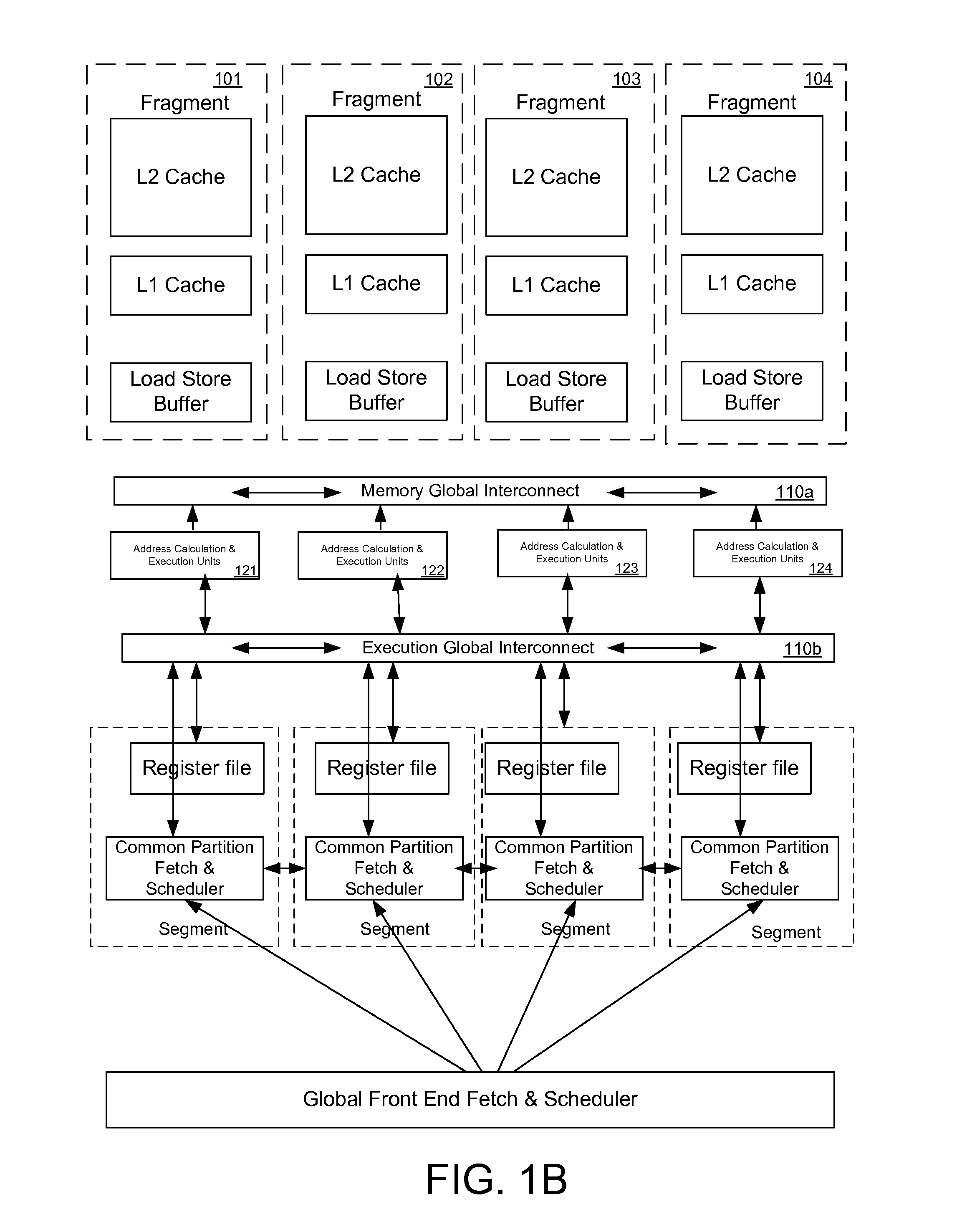

Register file segments for supporting code block execution by using virtual cores instantiated by partitionable engines

ActiveUS20120246450A1ScalingMemory architecture accessing/allocationProgram control using stored programsCoding blockProcessor register

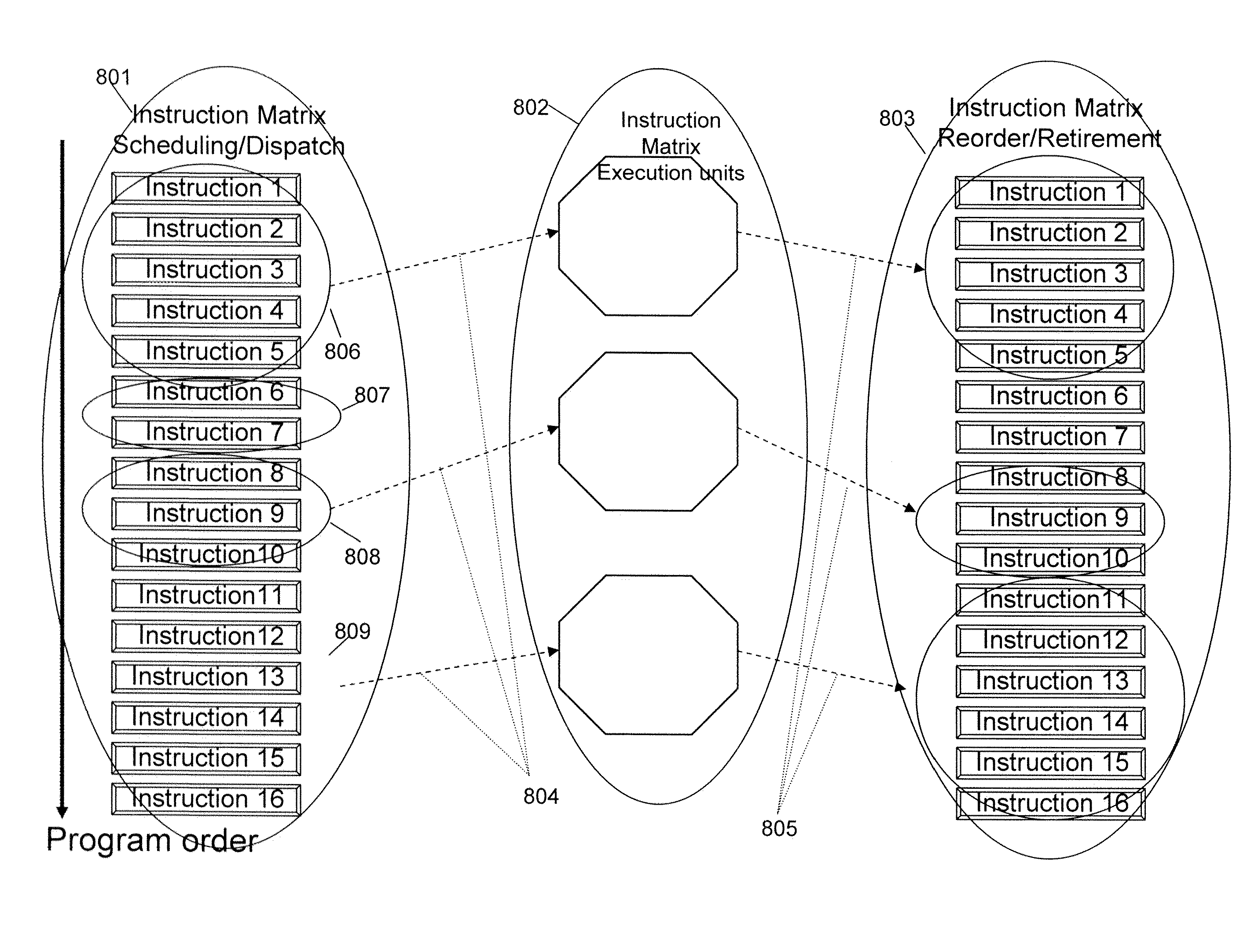

A system for executing instructions using a plurality of register file segments for a processor. The system includes a global front end scheduler for receiving an incoming instruction sequence, wherein the global front end scheduler partitions the incoming instruction sequence into a plurality of code blocks of instructions and generates a plurality of inheritance vectors describing interdependencies between instructions of the code blocks. The system further includes a plurality of virtual cores of the processor coupled to receive code blocks allocated by the global front end scheduler, wherein each virtual core comprises a respective subset of resources of a plurality of partitionable engines, wherein the code blocks are executed by using the partitionable engines in accordance with a virtual core mode and in accordance with the respective inheritance vectors. A plurality register file segments are coupled to the partitionable engines for providing data storage.

Owner:INTEL CORP

System and method for performing compound vector operations

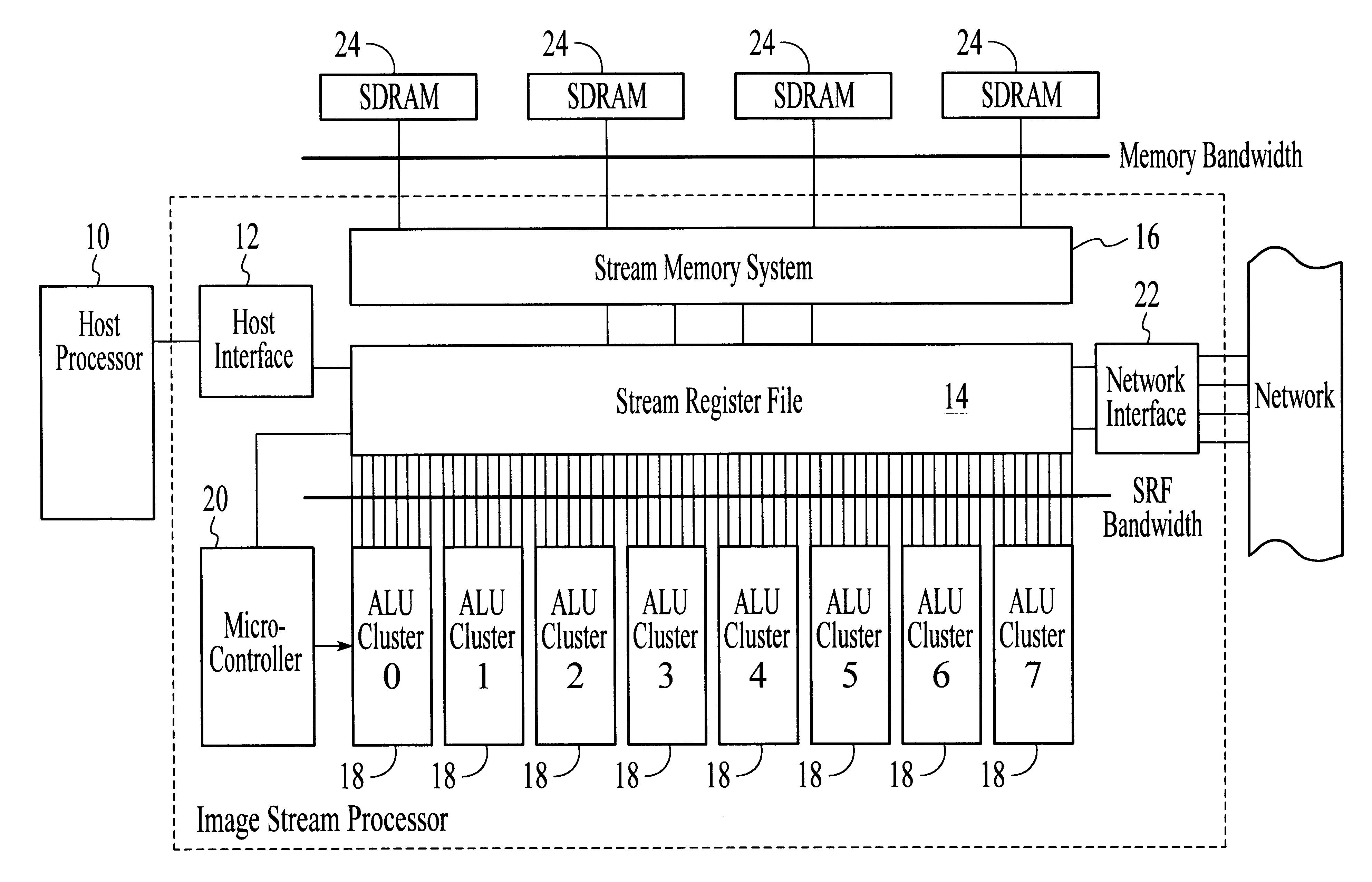

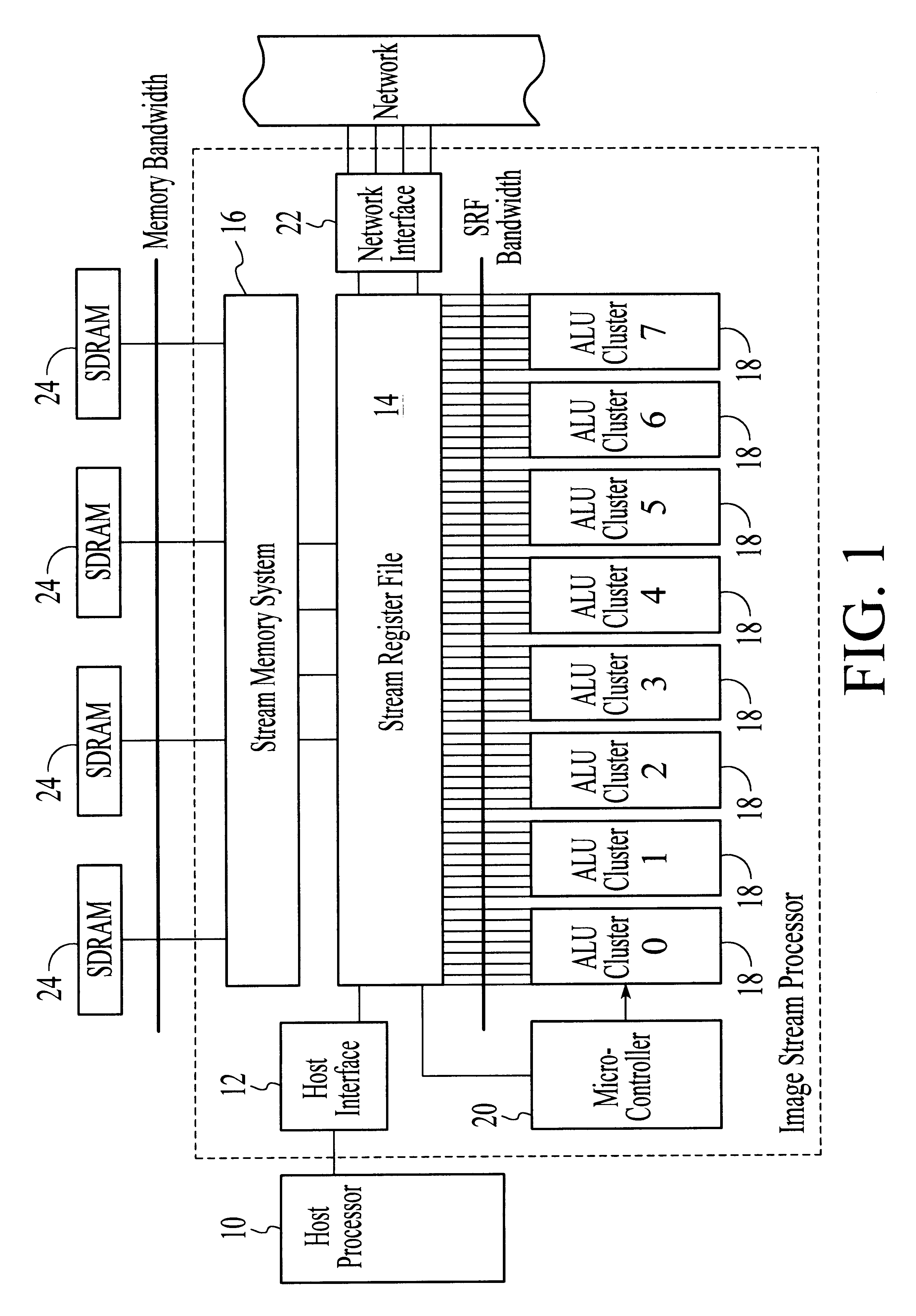

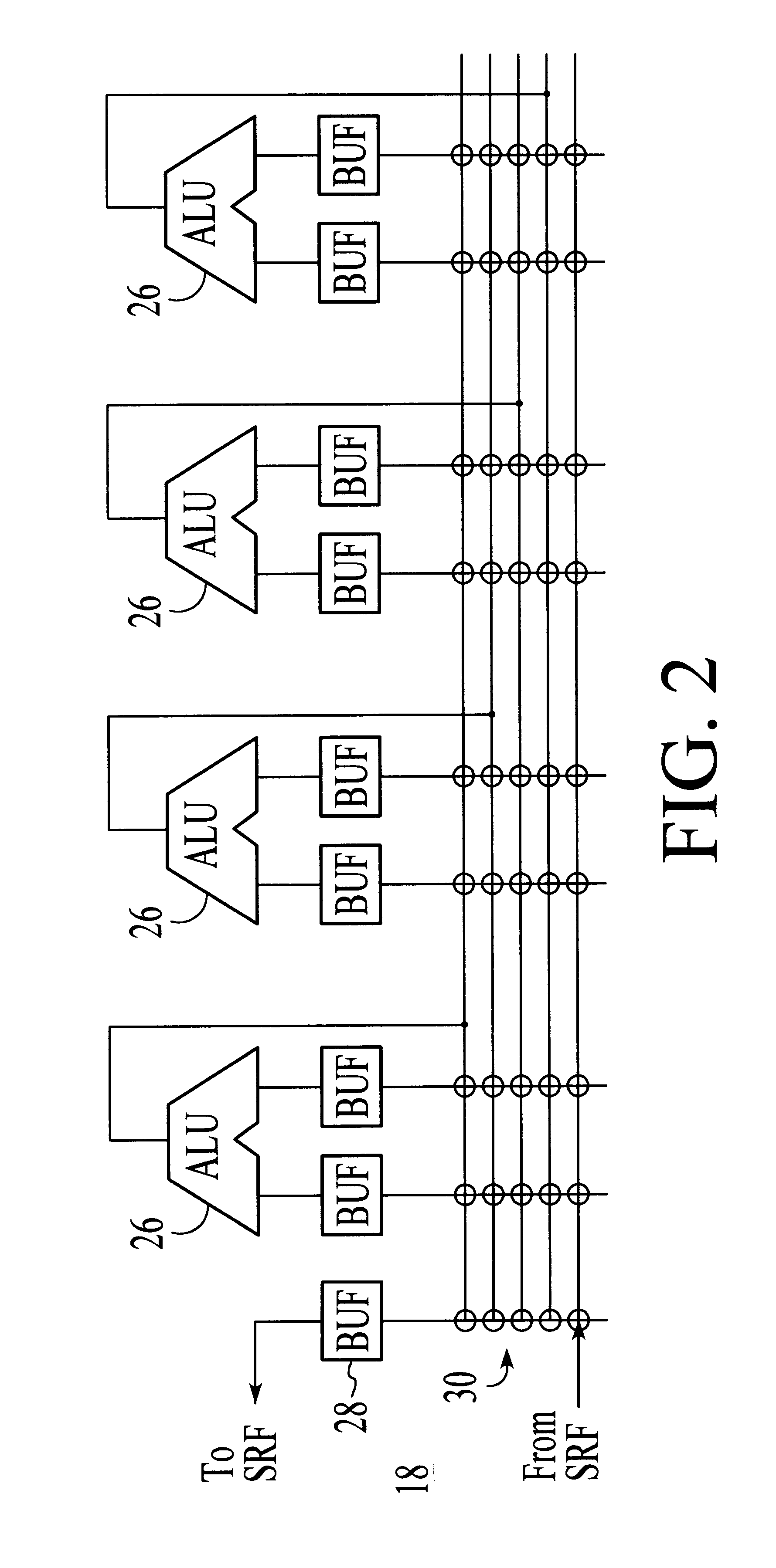

InactiveUS6192384B1Reduce bandwidth requirementsMinimize the numberOperational speed enhancementRegister arrangementsOperating instructionImaging processing

A processor particularly useful in multimedia applications such as image processing is based on a stream programming model and has a tiered storage architecture to minimize global bandwidth requirements. The processor has a stream register file through which the processor's functional units transfer streams to execute processor operations. Load and store instructions transfer streams between the stream register file and a stream memory; send and receive instructions transfer streams between stream register files of different processors; and operate instructions pass streams between the stream register file and computational kernels. Each of the computational kernels is capable of performing compound vector operations. A compound vector operation performs a sequence of arithmetic operations on data read from the stream register file, i.e., a global storage resource, and generates a result that is written back to the stream register file. Each function or compound vector operation is specified by an instruction sequence that specifies the arithmetic operations and data movements that are performed each cycle to carry out the compound operation. This sequence can, for example, be specified using microcode.

Owner:THE BOARD OF TRUSTEES OF THE LELAND +1

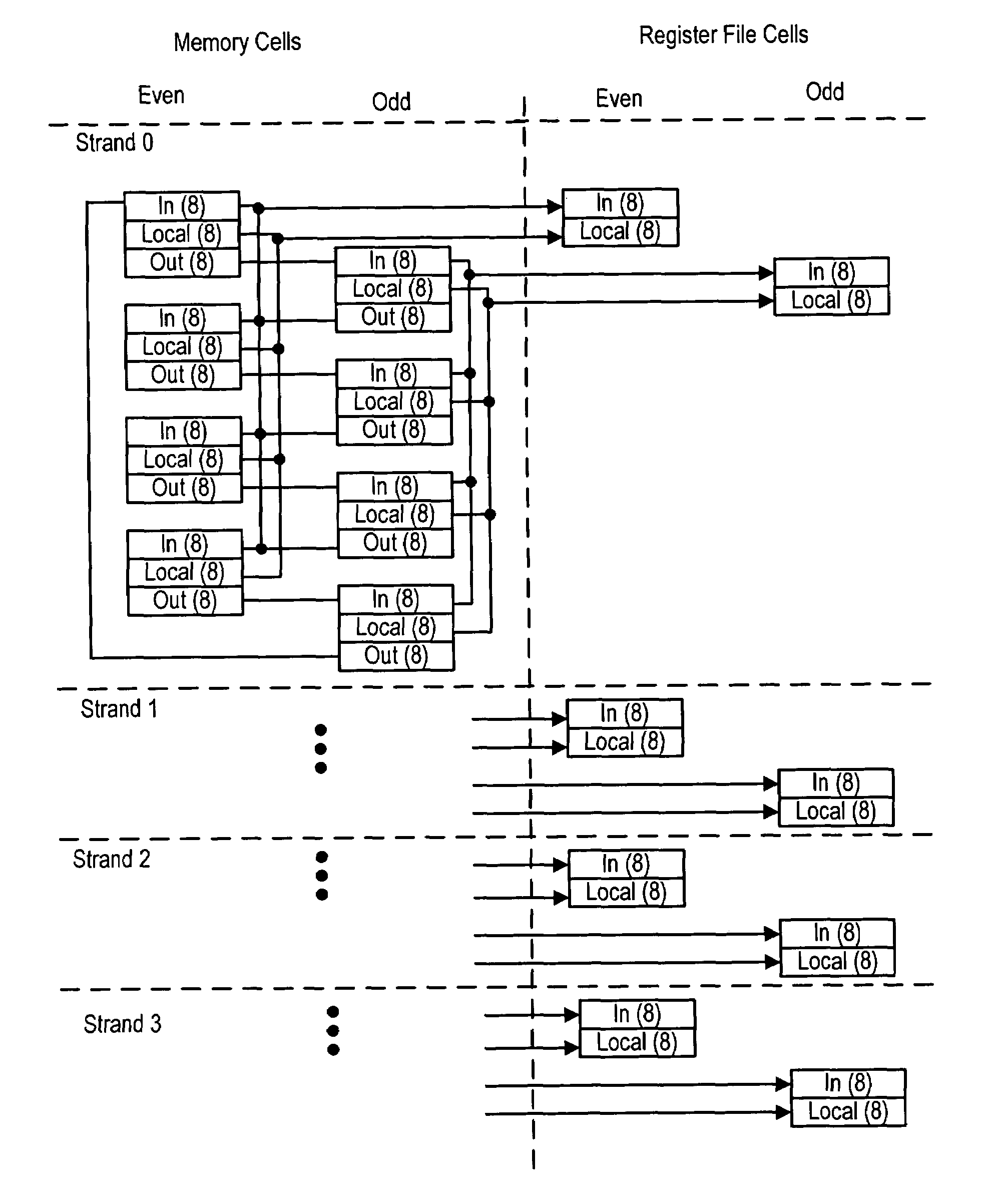

Programmable processor with group floating-point operations

InactiveUS7216217B2Reduce in quantityImprove performanceInstruction analysisMemory adressing/allocation/relocationComputer architectureEngineering

A programmable processor that comprises a general purpose processor architecture, capable of operation independent of another host processor, having a virtual memory addressing unit, an instruction path and a data path; an external interface; a cache operable to retain data communicated between the external interface and the data path; at least one register file configurable to receive and store data from the data path and to communicate the stored data to the data path; and a multi-precision execution unit coupled to the data path. The multi-precision execution unit is configurable to dynamically partition data received from the data path to account for an elemental width of the data and is capable of performing group floating-point operations on multiple operands in partitioned fields of operand registers and returning catenated results. In other embodiments the multi-precision execution unit is additionally configurable to execute group integer and / or group data handling operations.

Owner:MICROUNITY

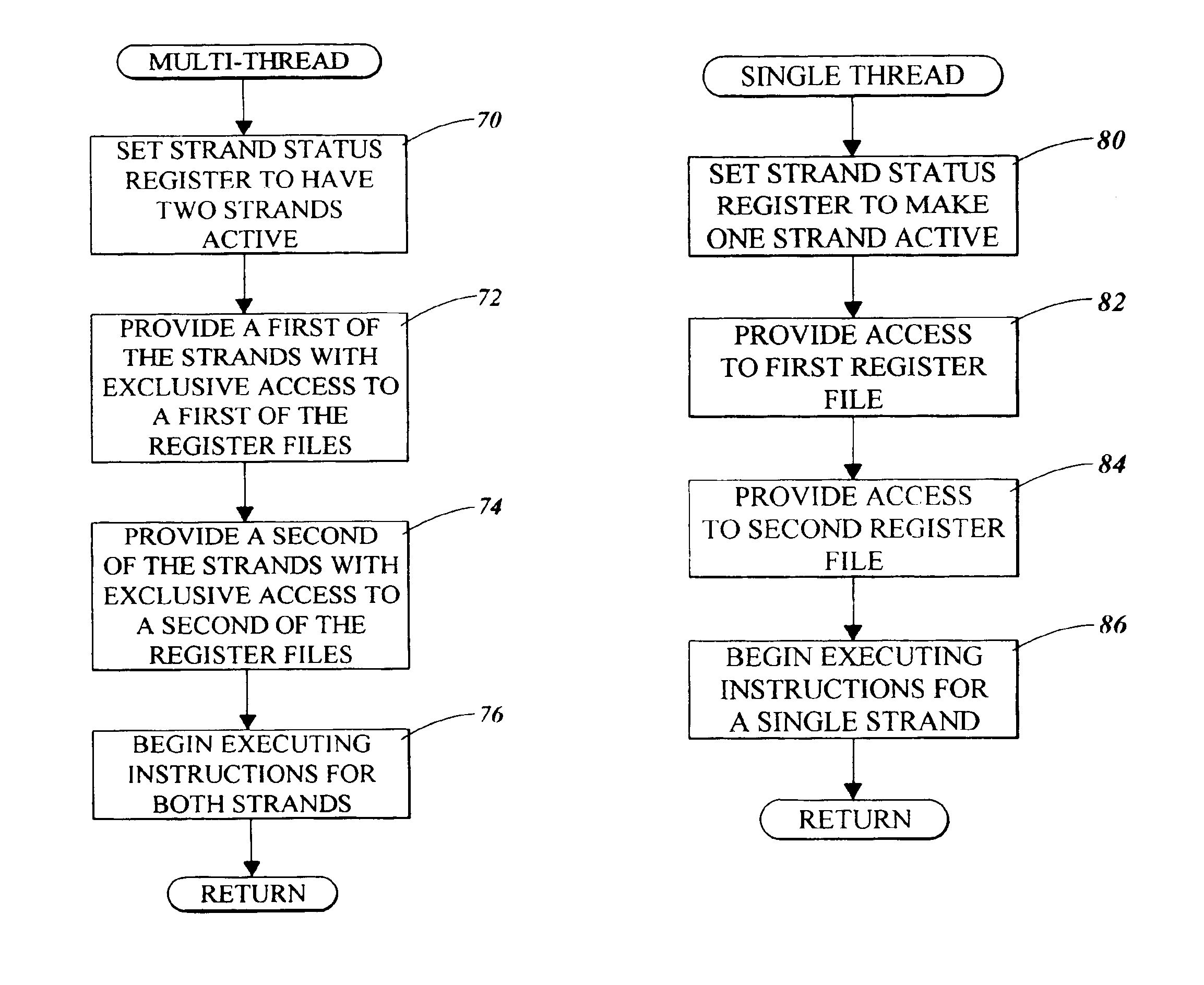

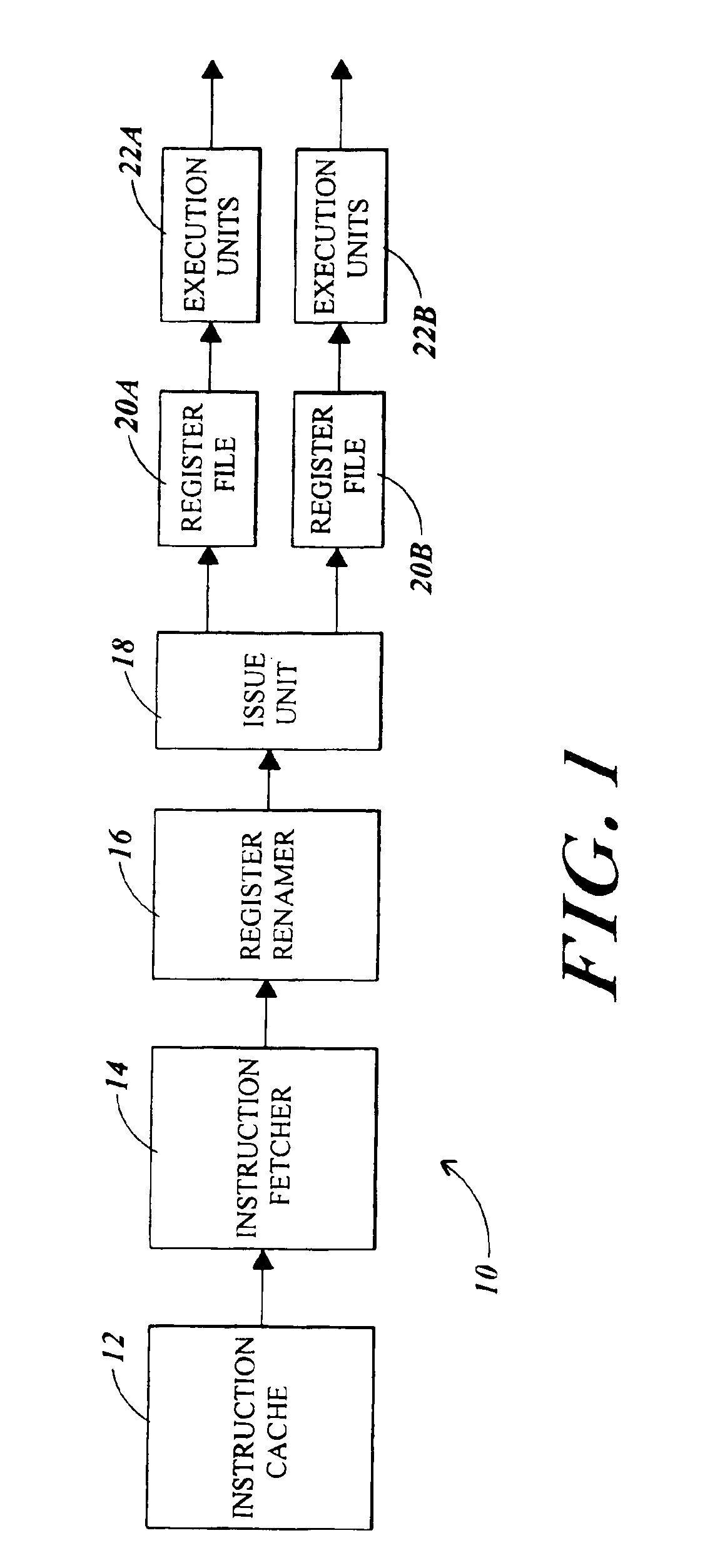

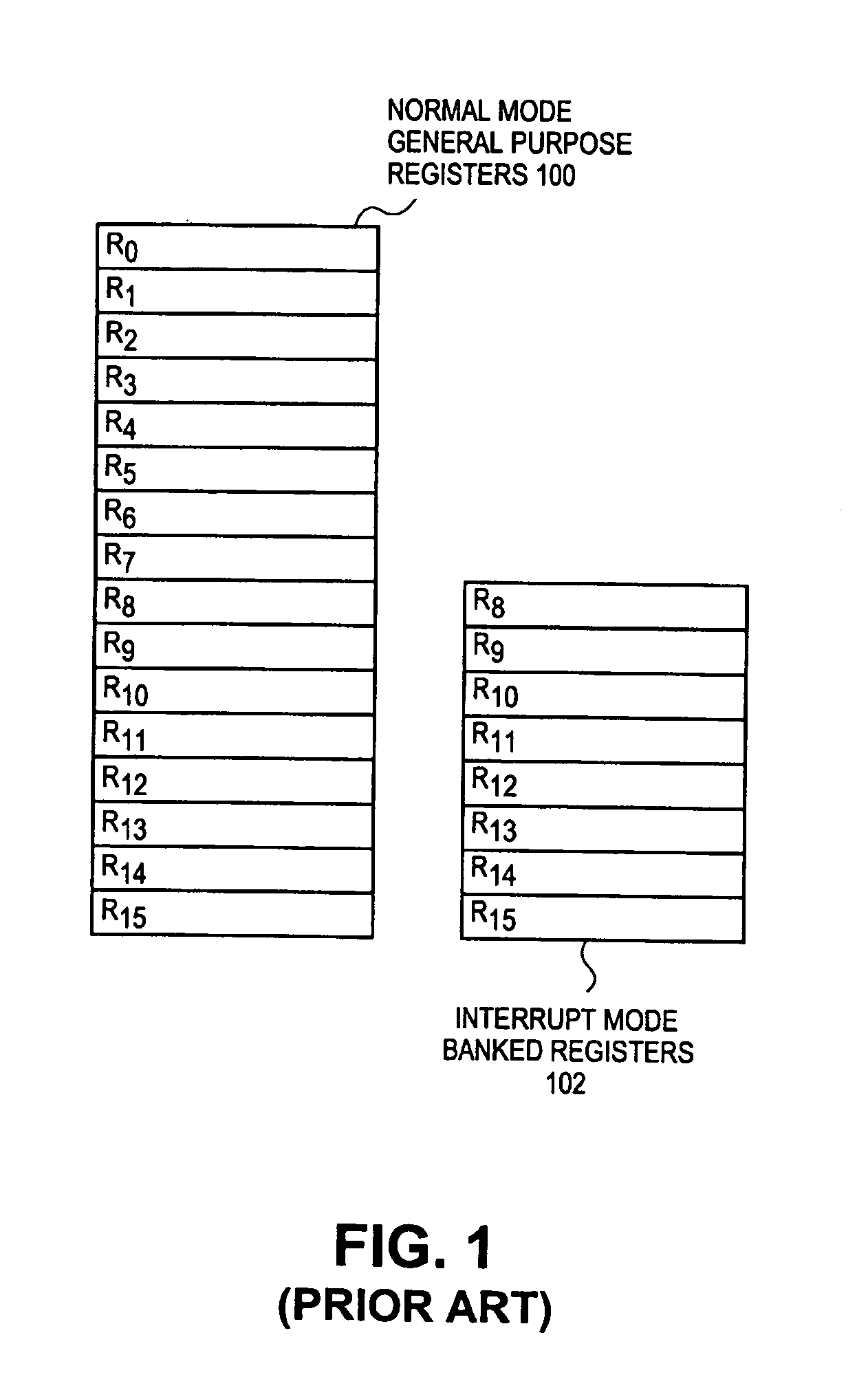

Microprocessor and method for giving each thread exclusive access to one register file in a multi-threading mode and for giving an active thread access to multiple register files in a single thread mode

InactiveUS6954846B2Maximize issue rateRegister arrangementsUnauthorized memory use protectionMicroprocessorExclusive access

A microprocessor includes multiple register files. In a single thread mode, the microprocessor allows a single thread to have access to multiple ones of the register files. In a multi-thread mode, each thread has access to respective ones of the register files. In the multi-thread mode, multiple threads are simultaneously executing. Circuitry and hardware are provided to facilitate the respective modes and to facilitate transitions between the modes.

Owner:ORACLE INT CORP

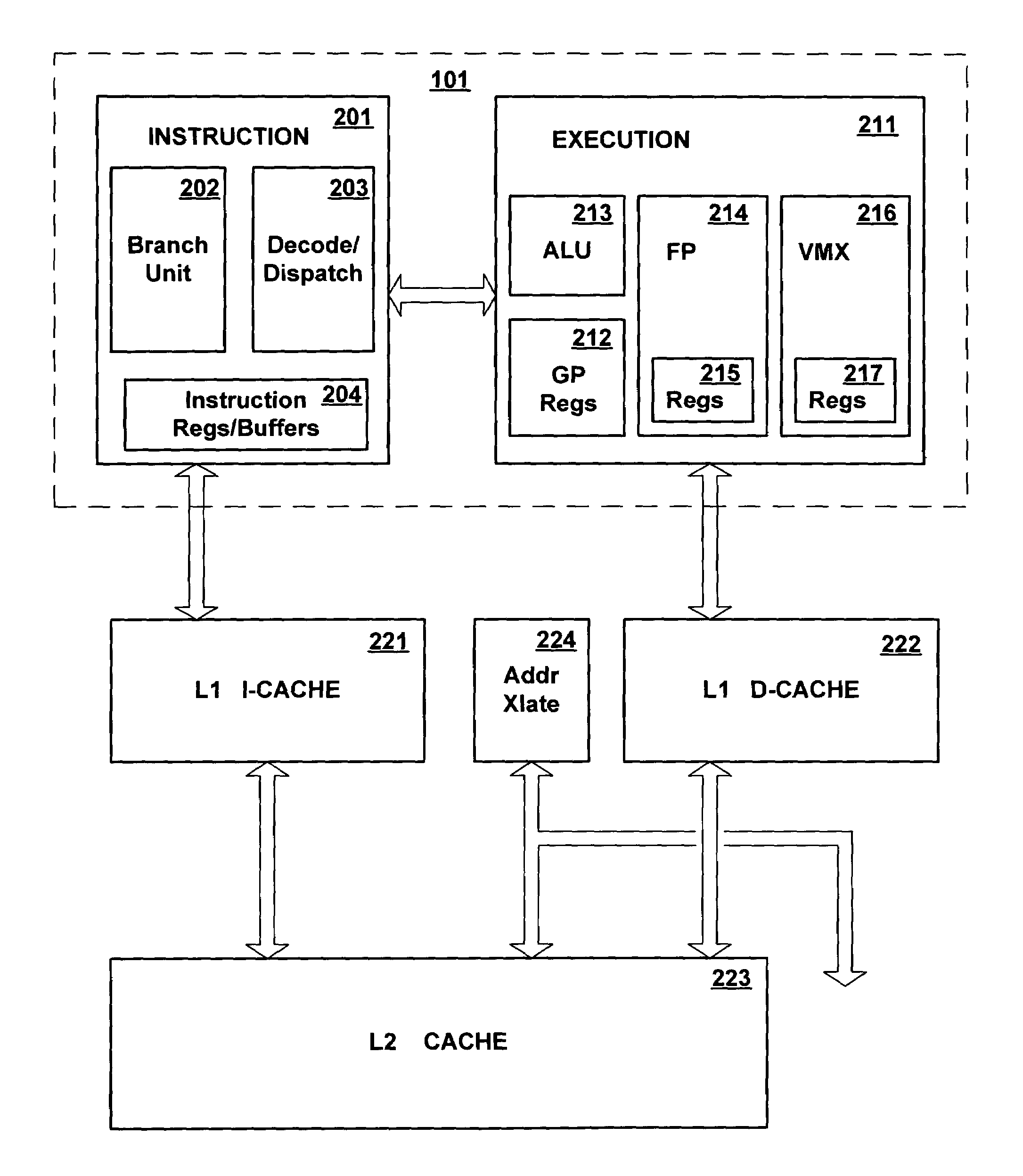

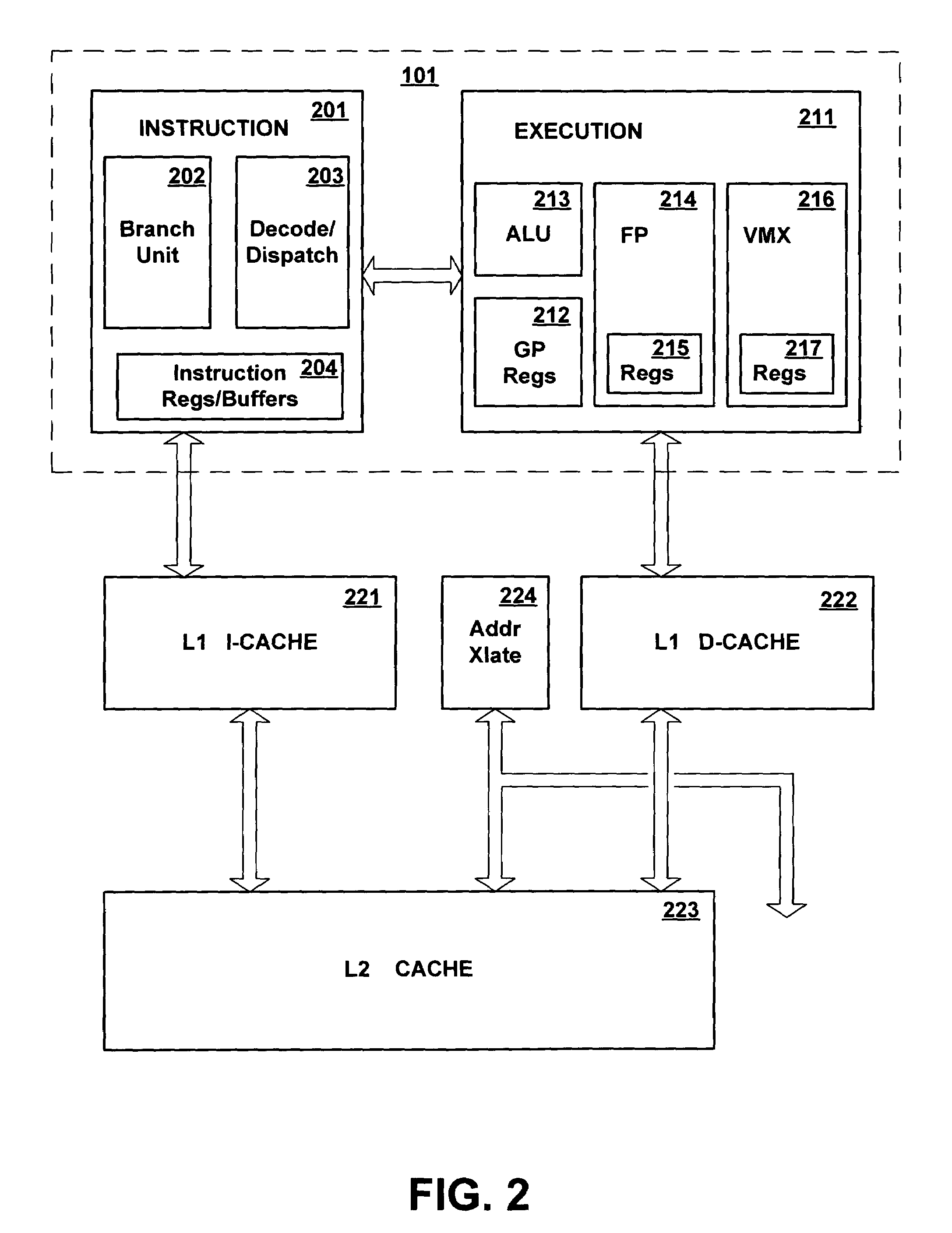

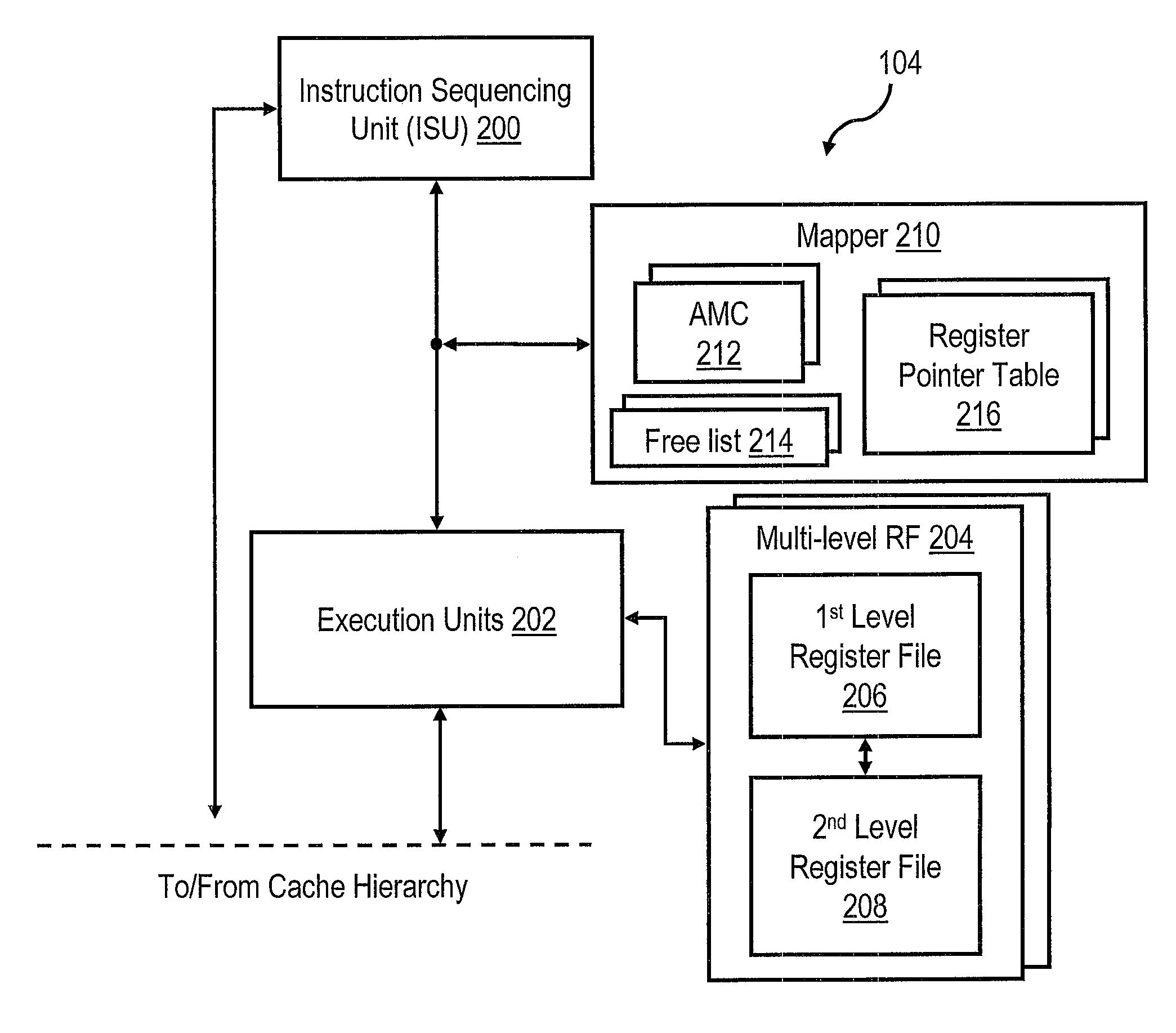

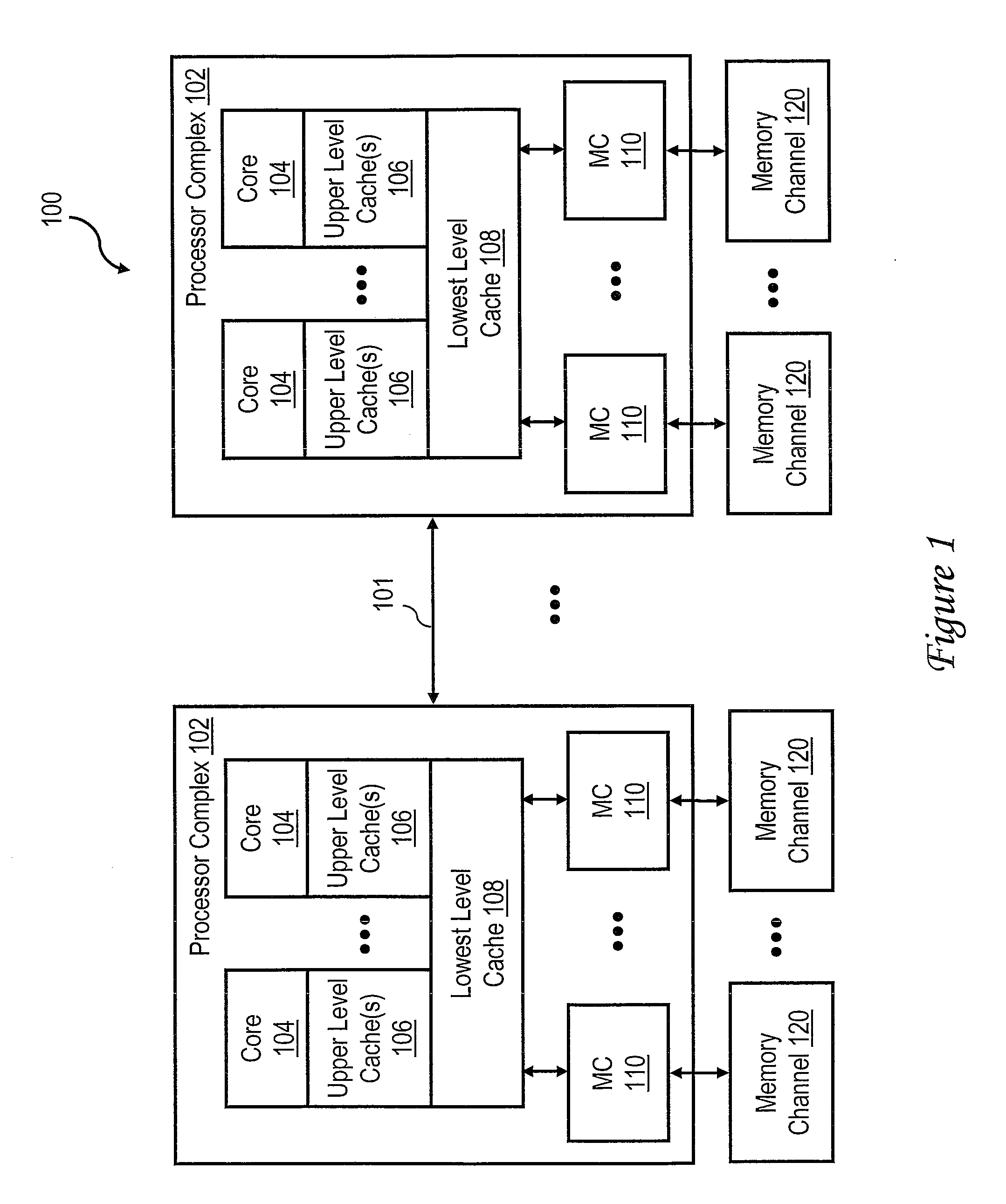

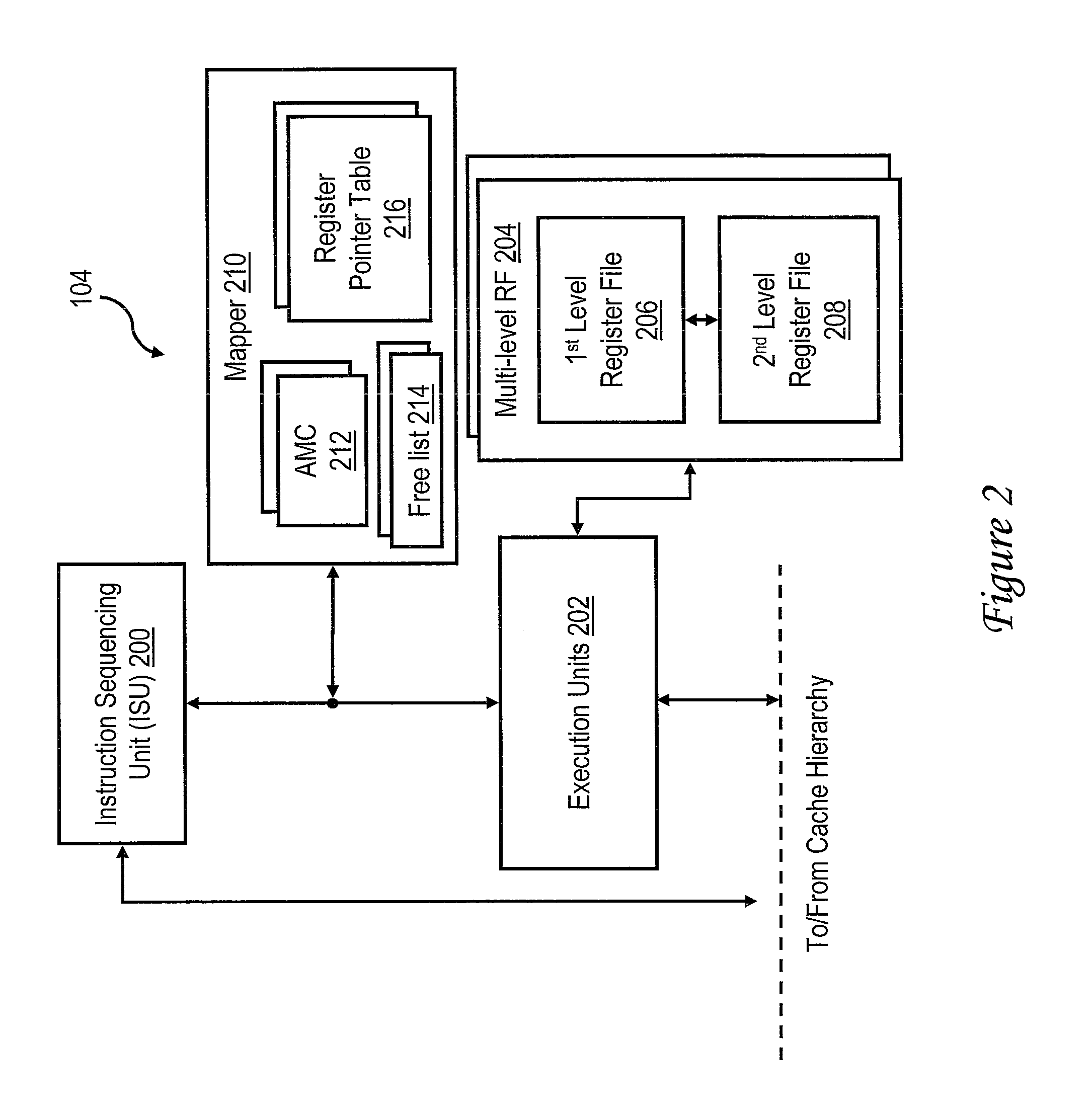

Digital data processing apparatus having multi-level register file

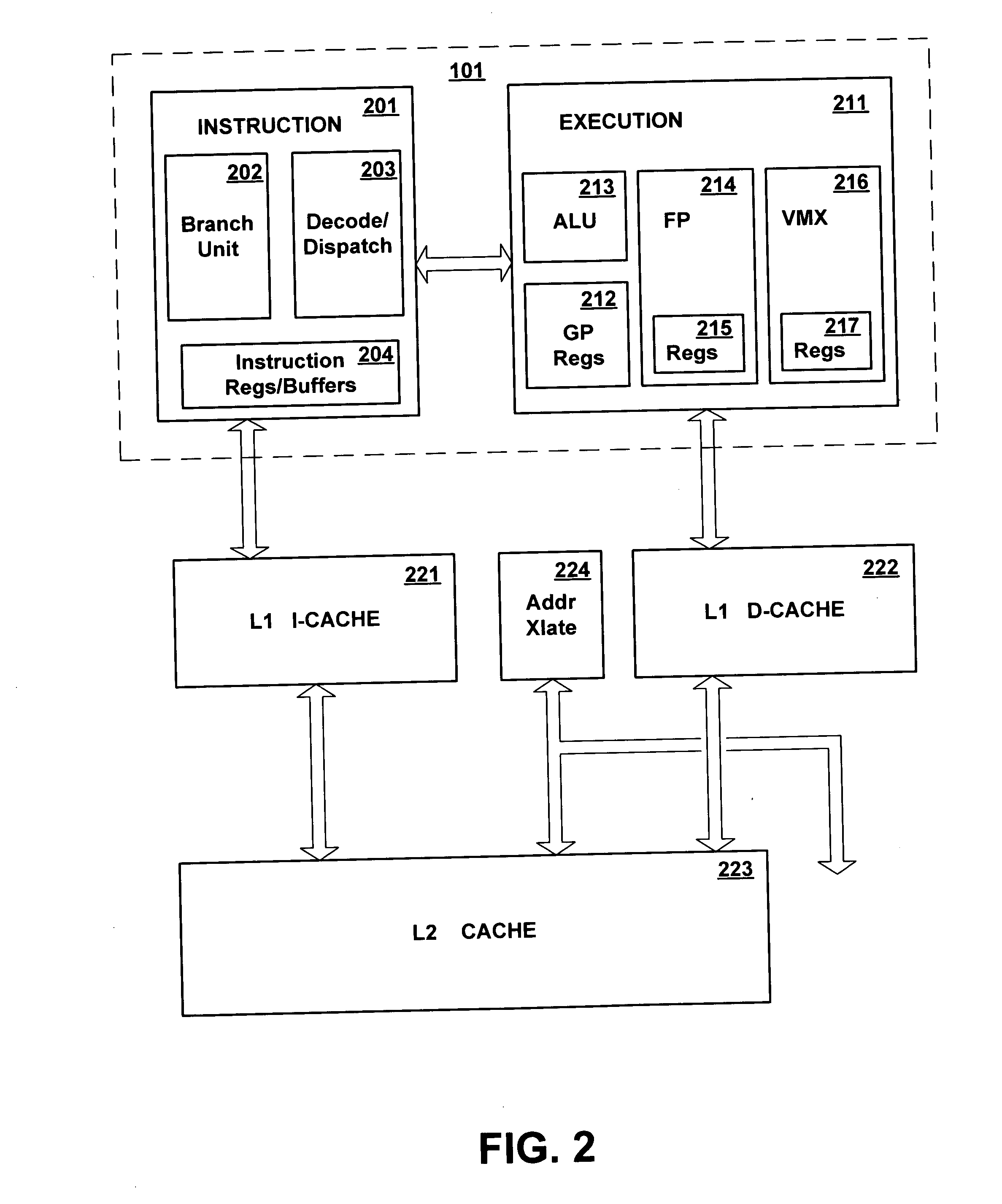

InactiveUS20050289299A1Faster access latency timeSlow access latency timeRegister arrangementsMemory adressing/allocation/relocationDigital dataMemory bank

A processor contains multiple levels of registers having different access latency. A relatively smaller set of registers is contained in a relatively faster higher level register bank, and a larger, more complete set of the registers is contained in a relatively slower lower level register bank. Physically, the higher level register bank is placed closer to functional logic which receives inputs from the registers. Preferably, the lower level bank includes a complete set of all processor registers, and the higher level bank includes a smaller subset of the registers, duplicating information in the lower level bank. The higher level bank is preferably accessible in a single clock cycle.

Owner:IBM CORP

Scalar hardware for performing SIMD operations

InactiveUS6292886B1Digital computer detailsConcurrent instruction executionProcessor registerExecution unit

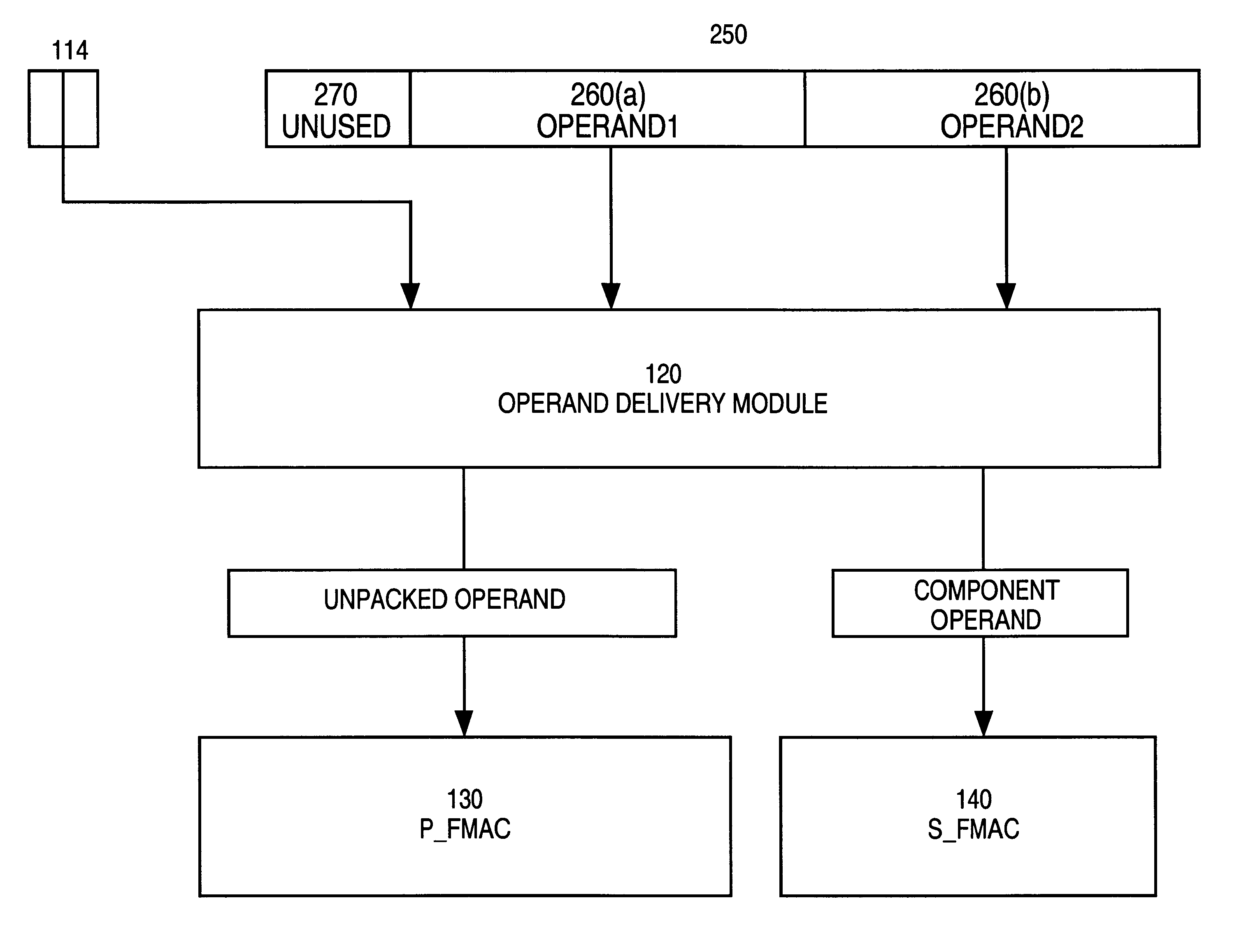

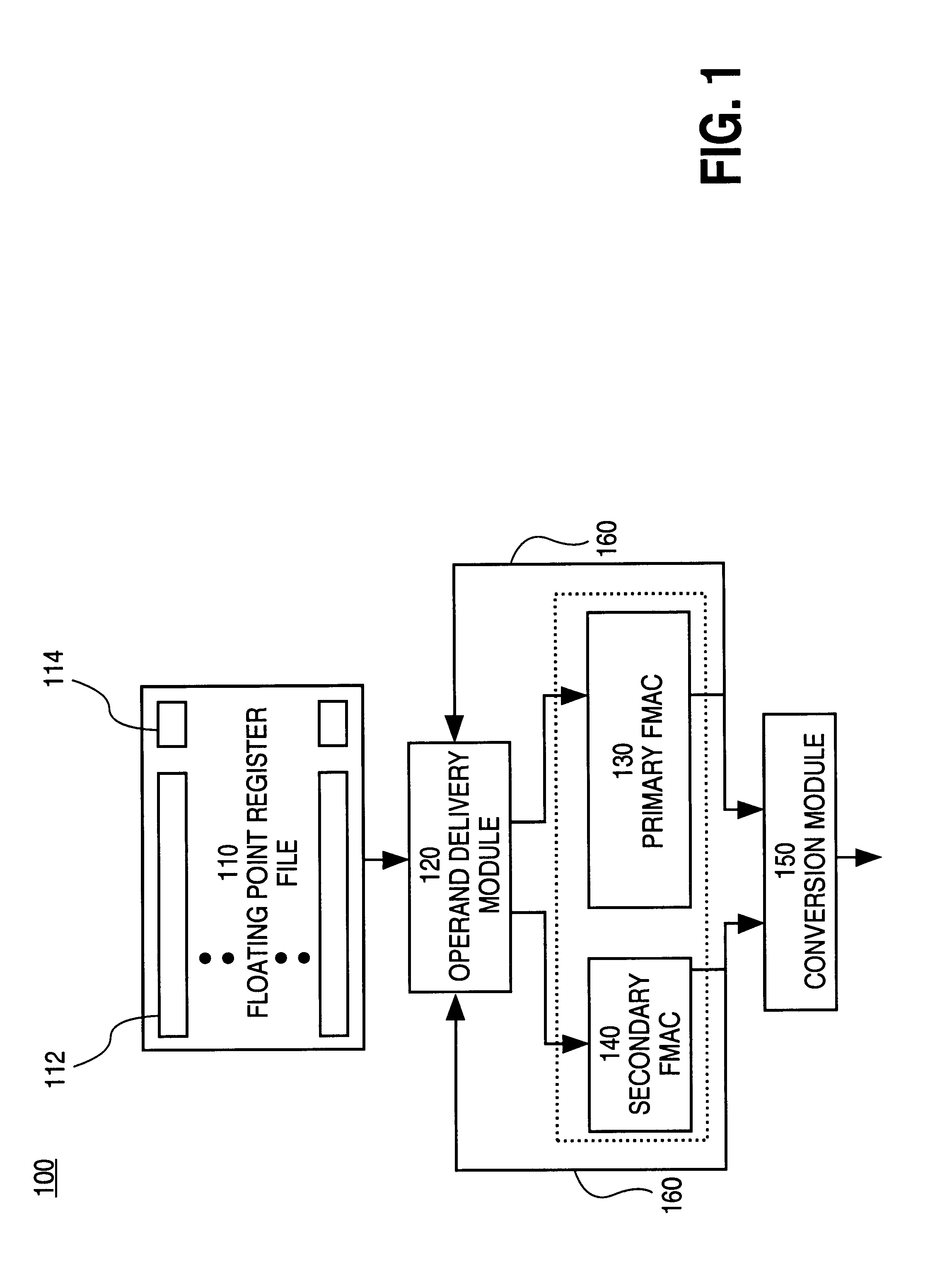

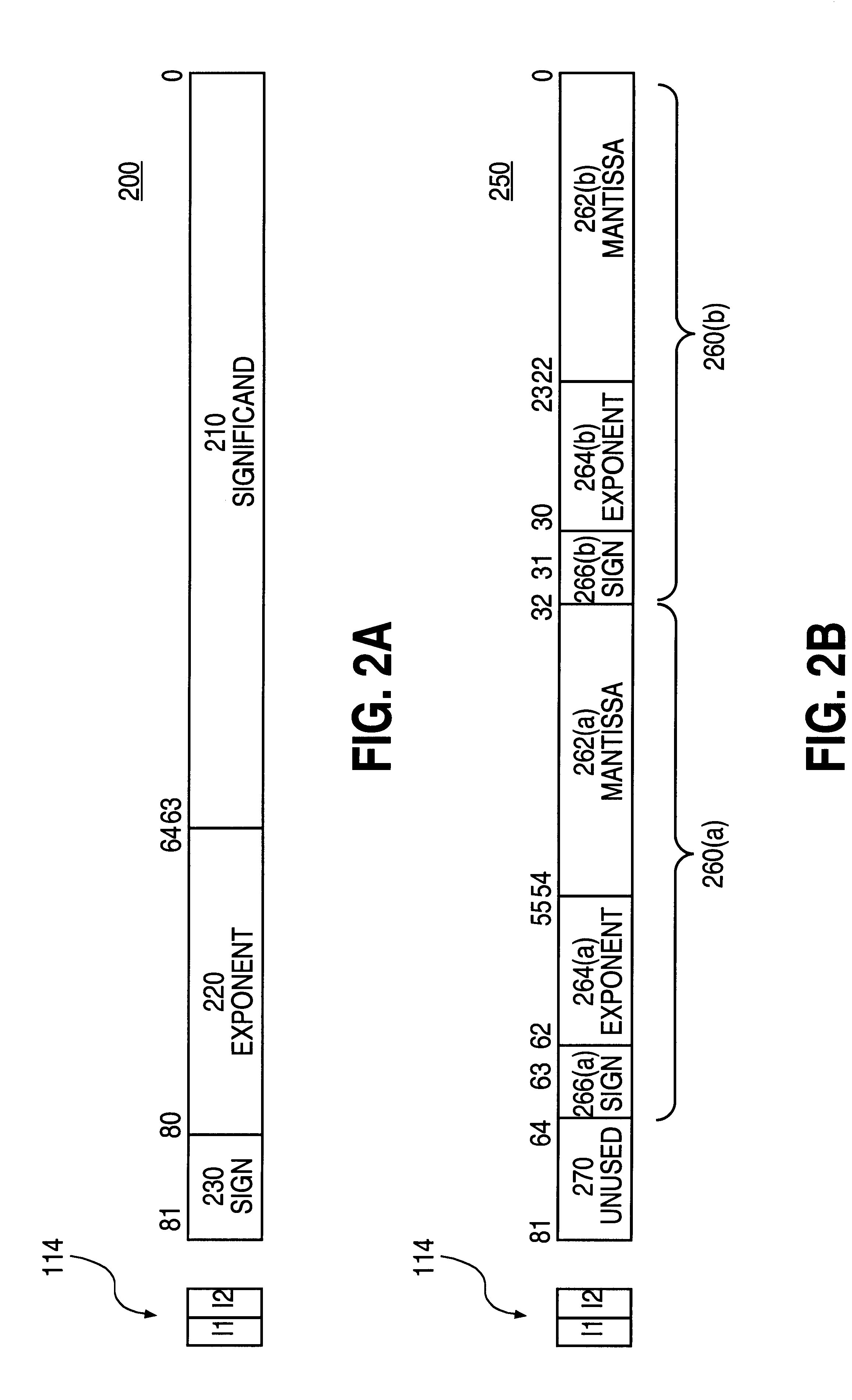

A system for processing SIMD operands in a packed data format includes a scalar FMAC and a vector FMAC coupled to a register file through an operand delivery module. For vector operations, the operand delivery module bit steers a SIMD operand of the packed operand into an unpacked operand for processing by the first execution unit. Another SIMD operand is processed by the vector execution unit.

Owner:INTEL CORP

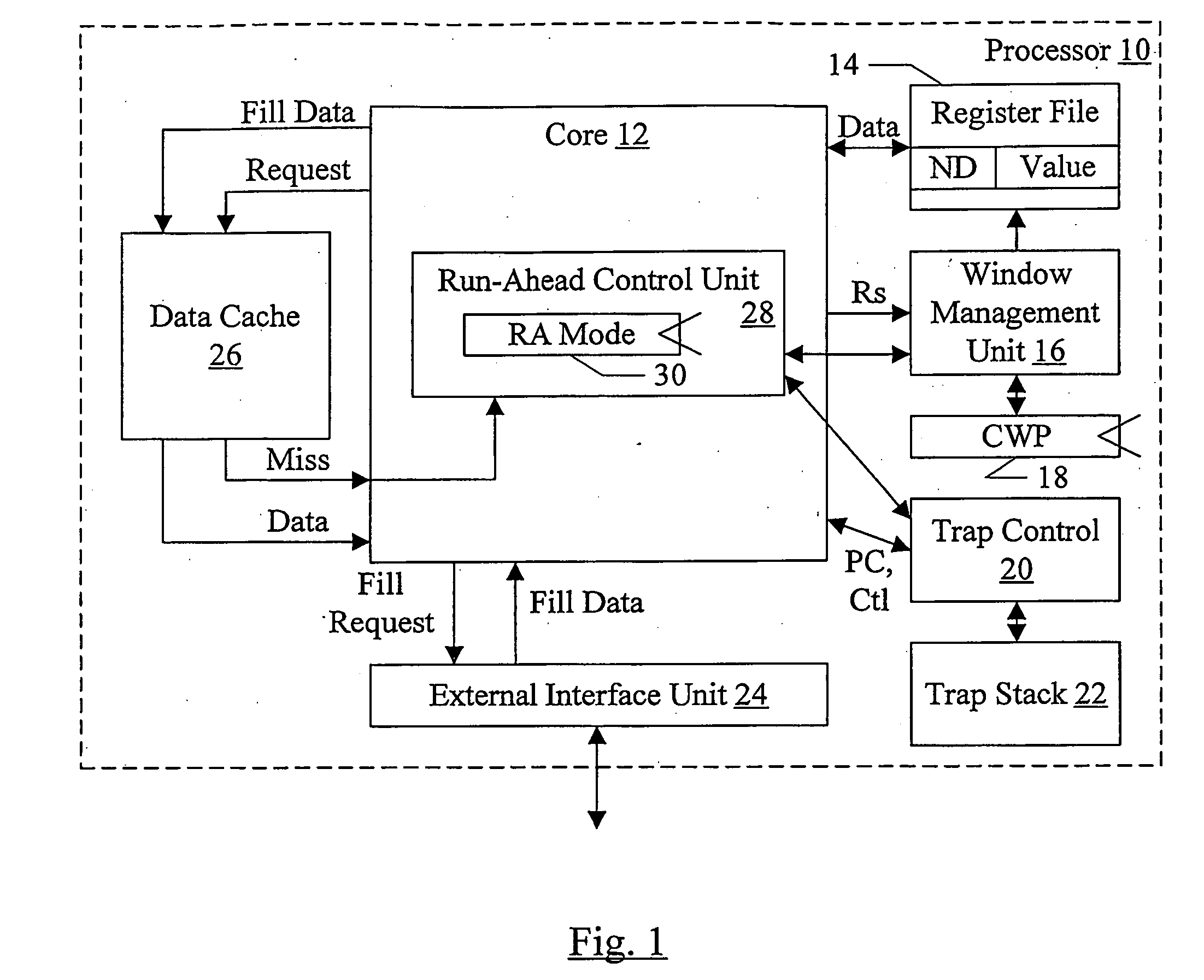

Using windowed register file to checkpoint register state

InactiveUS20080016325A1Register arrangementsDigital computer detailsSpeculative executionManagement unit

In one embodiment, a processor comprises a core configured to execute instructions; a register file comprising a plurality of storage locations; and a window management unit. The window management unit is configured to operate the plurality of storage locations as a plurality of windows, wherein register addresses encoded into the instructions identify storage locations among a subset of the plurality of storage locations that are within a current window. Additionally, the window management unit is configured to allocate a second window in response to a predetermined event. One of the current window and the second window serves as a checkpoint of register state, and the other one of the current window and the second window is updated in response to instructions processed subsequent to the checkpoint. The checkpoint may be restored if the speculative execution results are discarded.

Owner:SUN MICROSYSTEMS INC

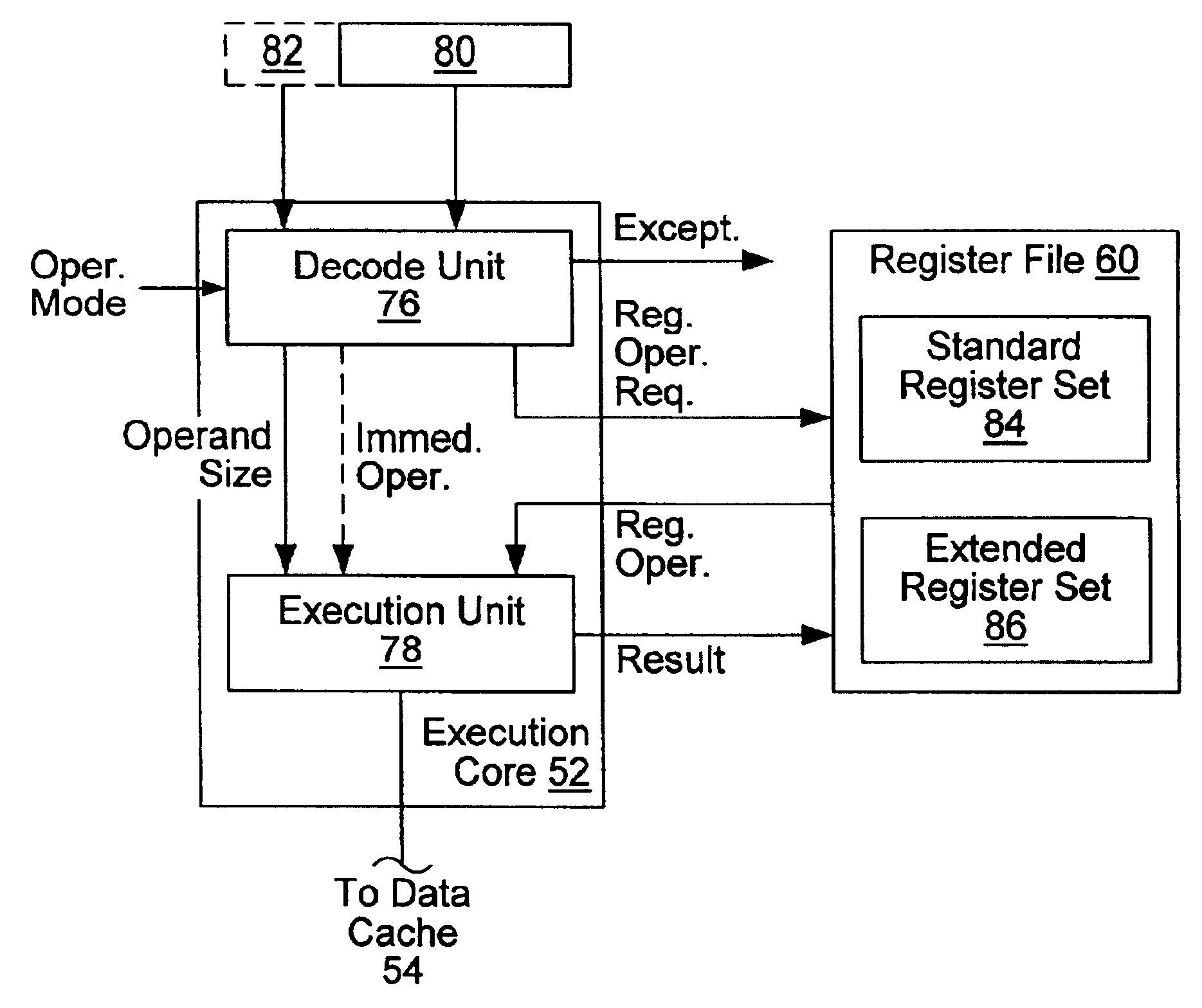

Central processing unit (CPU) accessing an extended register set in an extended register mode

InactiveUS6877084B1Resource allocationMemory adressing/allocation/relocationGeneral purposeComputer architecture

A central processing unit (CPU) is described including a register file and an execution core coupled to the register file. The register file includes a standard register set and an extended register set. The standard register set includes multiple standard registers, and the extended register set include multiple extended registers. The execution core fetches and executes instructions, and receives a signal indicating an operating mode of the CPU. The execution core responds to an instruction by accessing at least one extended register if the signal indicates the CPU is operating in an extended register mode and the instruction includes a prefix portion including information needed to access the at least one extended register. The standard registers may be general purpose registers of a CPU architecture associated with the instruction. The number of extended registers may be greater than the number of general purpose registers defined by the CPU architecture. In this case, the additional register identification information in the prefix portion is needed to identify a selected one of the extended registers. A width of the extended registers may also be greater than a width of the standard registers. In this case, the prefix portion may also include an indication that the entire contents of the least one extended register is to be accessed. In this way, instruction operand sizes may selectively be increased when the CPU is operating in the extended register mode. A computer system including the CPU is also described.

Owner:GLOBALFOUNDRIES INC

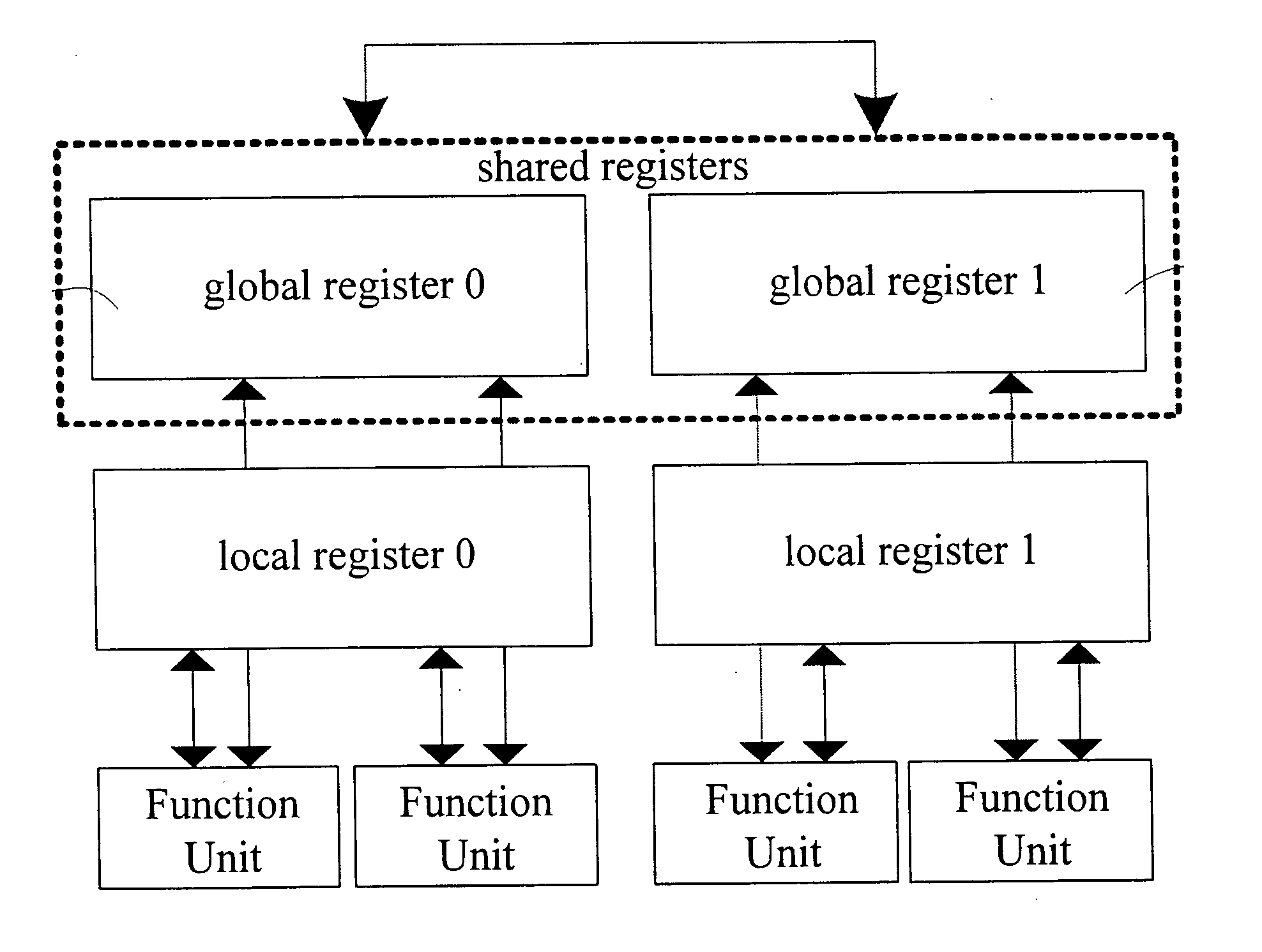

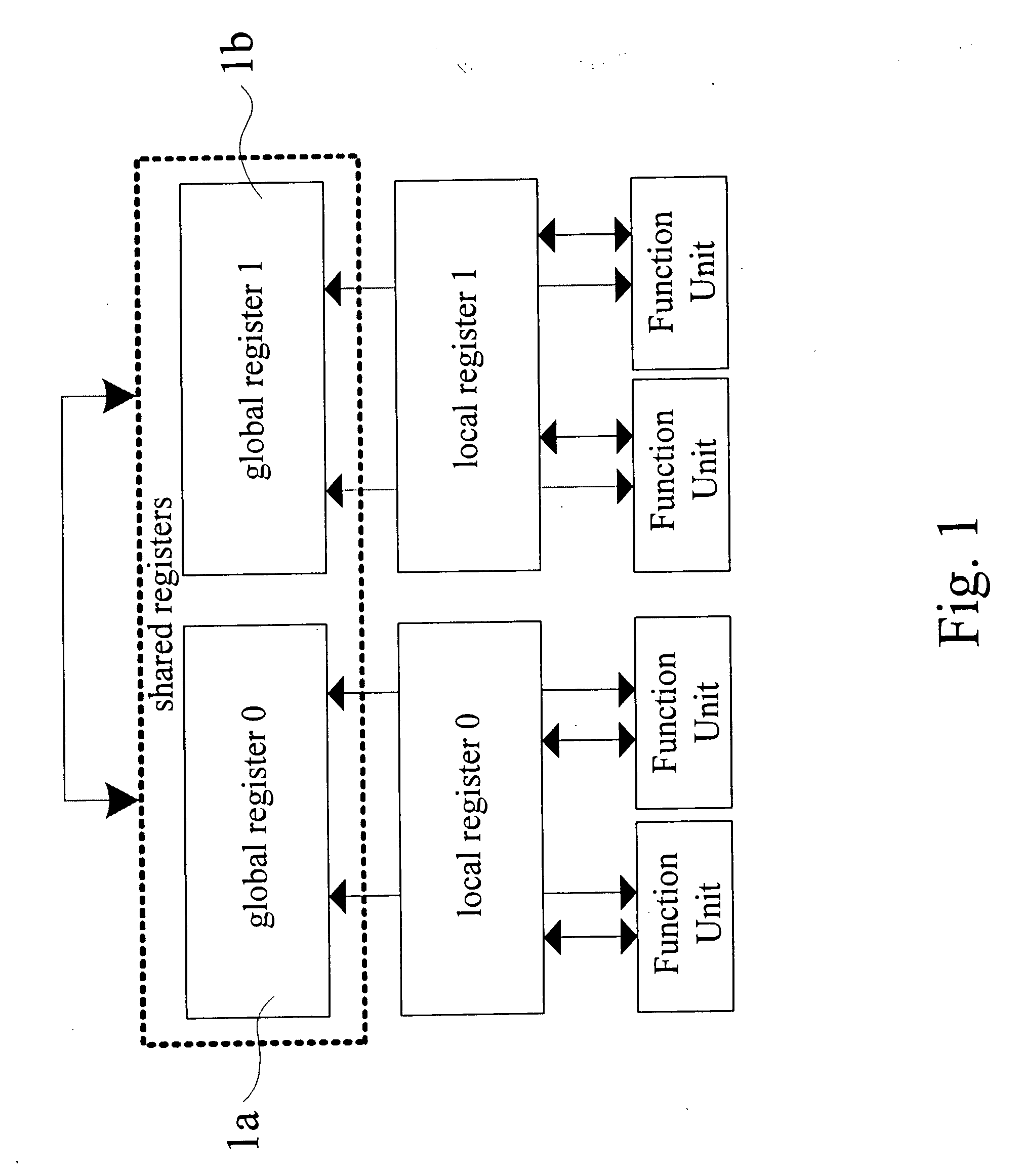

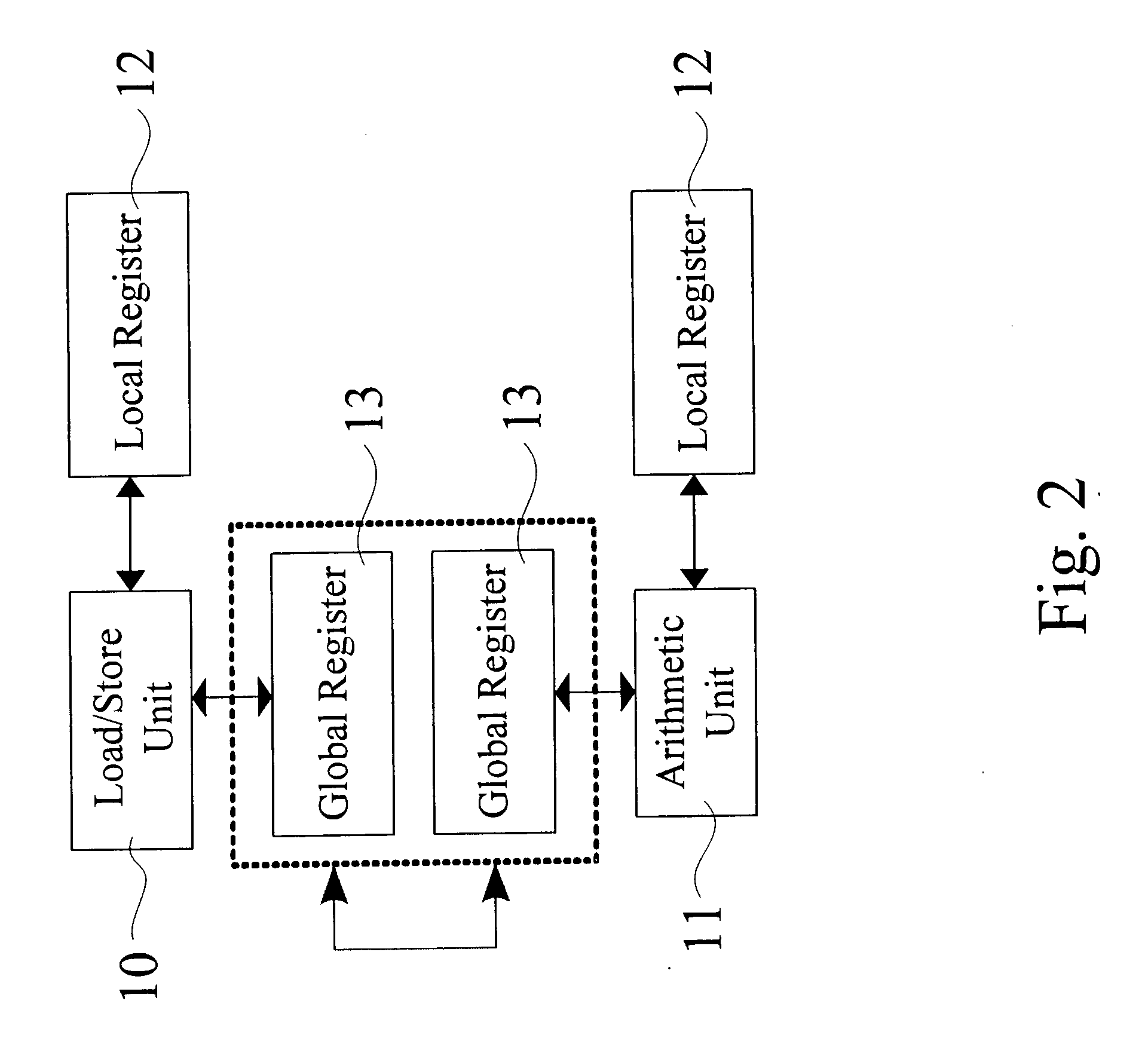

Local and global register partitioning in a vliw processor

InactiveUS20010042190A1Register arrangementsDigital computer detailsProcessor registerVery long instruction word

A Very Long Instruction Word (VLIW) processor having a plurality of functional units includes a multi-ported register file that is divided into a plurality of separate register file segments, each of the register file segments being associated to one of the plurality of functional units. The register file segments are partitioned into local registers and global registers. The global registers are read and written by all functional units. The local registers are read and written only by a functional unit associated with a particular register file segment. The local registers and global registers are addressed using register addresses in an address space that is separately defined for a register file segment / functional unit pair. The global registers are addressed within a selected global register range using the same register addresses for the plurality of register file segment / functional unit pairs. The local registers in a register file segment are addressed using register addresses in a local register range outside the global register range that are assigned within a single register file segment / functional unit pair. Register addresses in the local register range are the same for the plurality of register file segment / functional unit pairs and address registers locally within a register file segment / functional unit pair.

Owner:ORACLE INT CORP

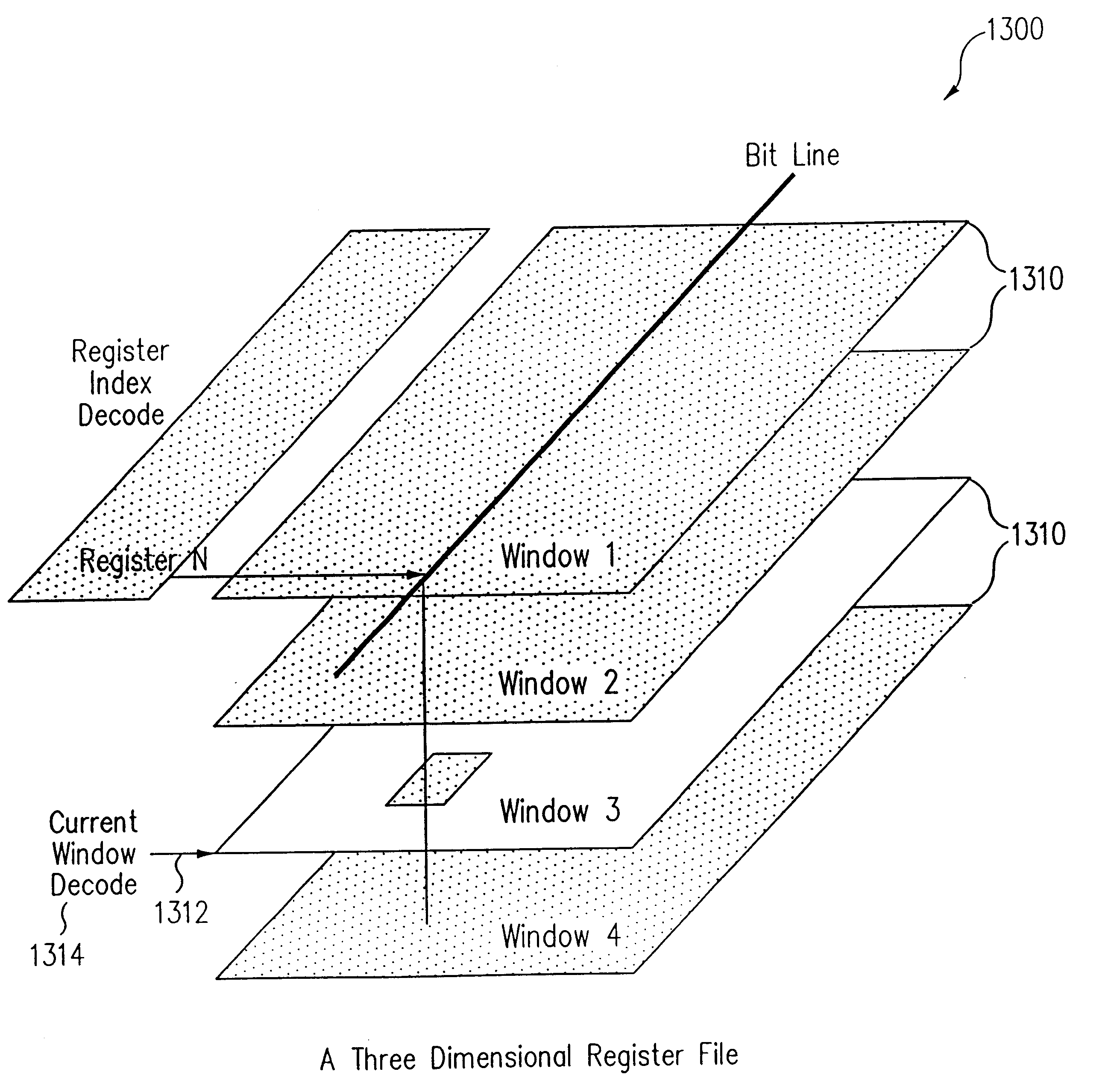

Vertically and horizontally threaded processor with multidimensional storage for storing thread data

InactiveUS6351808B1Register arrangementsDigital computer detailsMultidimensional scalingProcessor register

A processor includes a "four-dimensional" register structure in which register file structures are replicated by N for vertical threading in combination with a three-dimensional storage circuit. The multi-dimensional storage is formed by constructing a storage, such as a register file or memory, as a plurality of two-dimensional storage planes.

Owner:ORACLE INT CORP

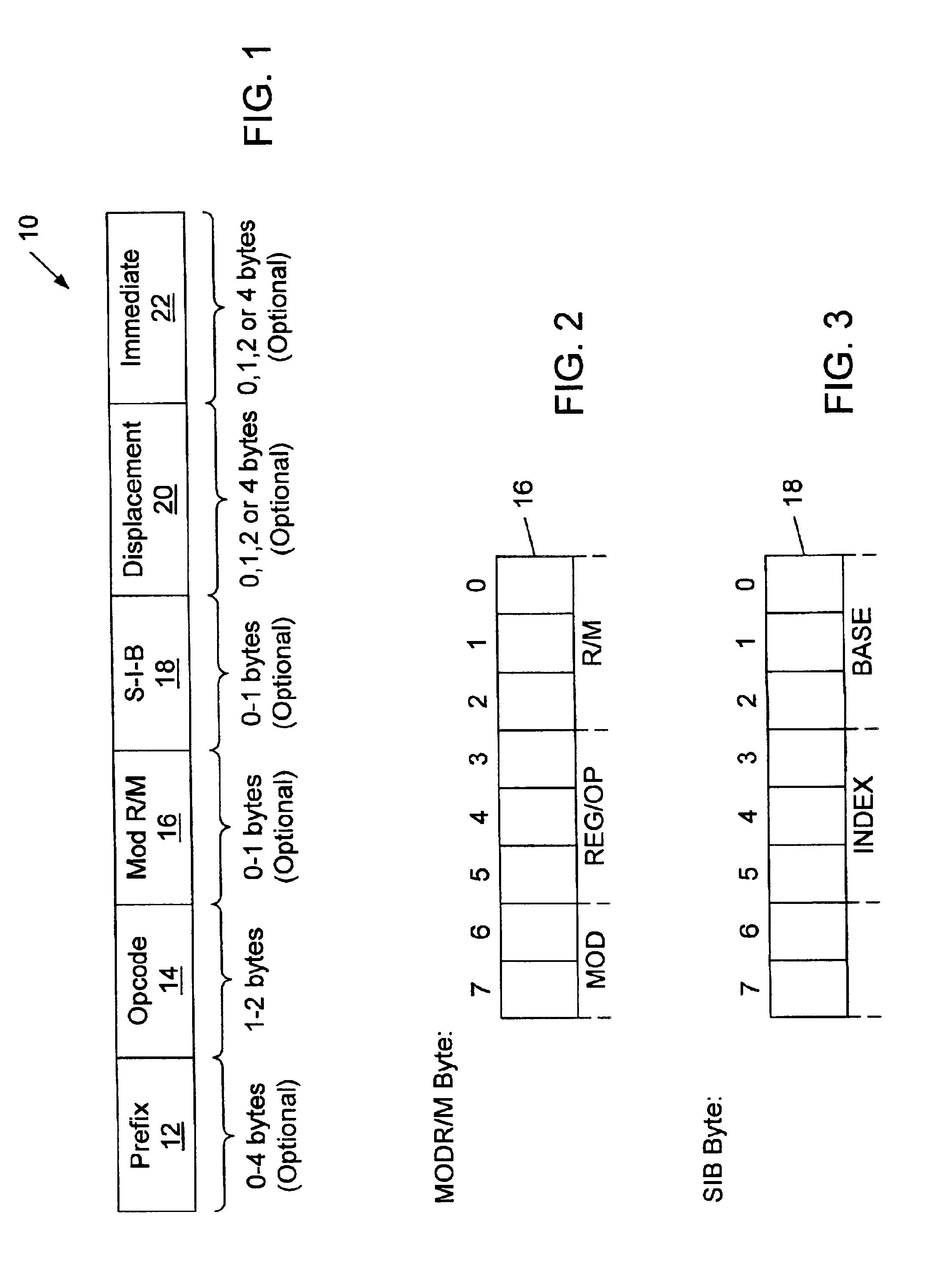

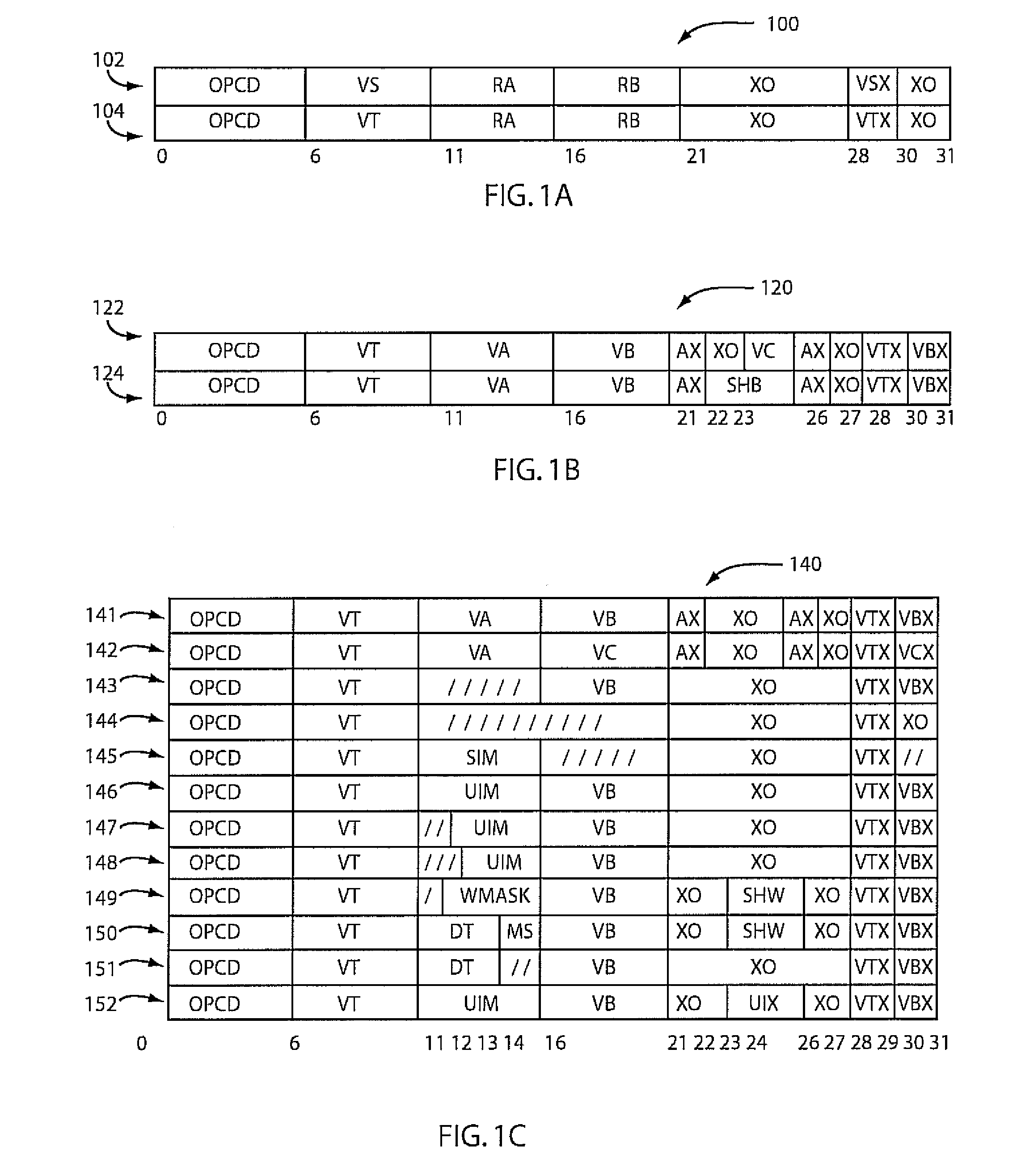

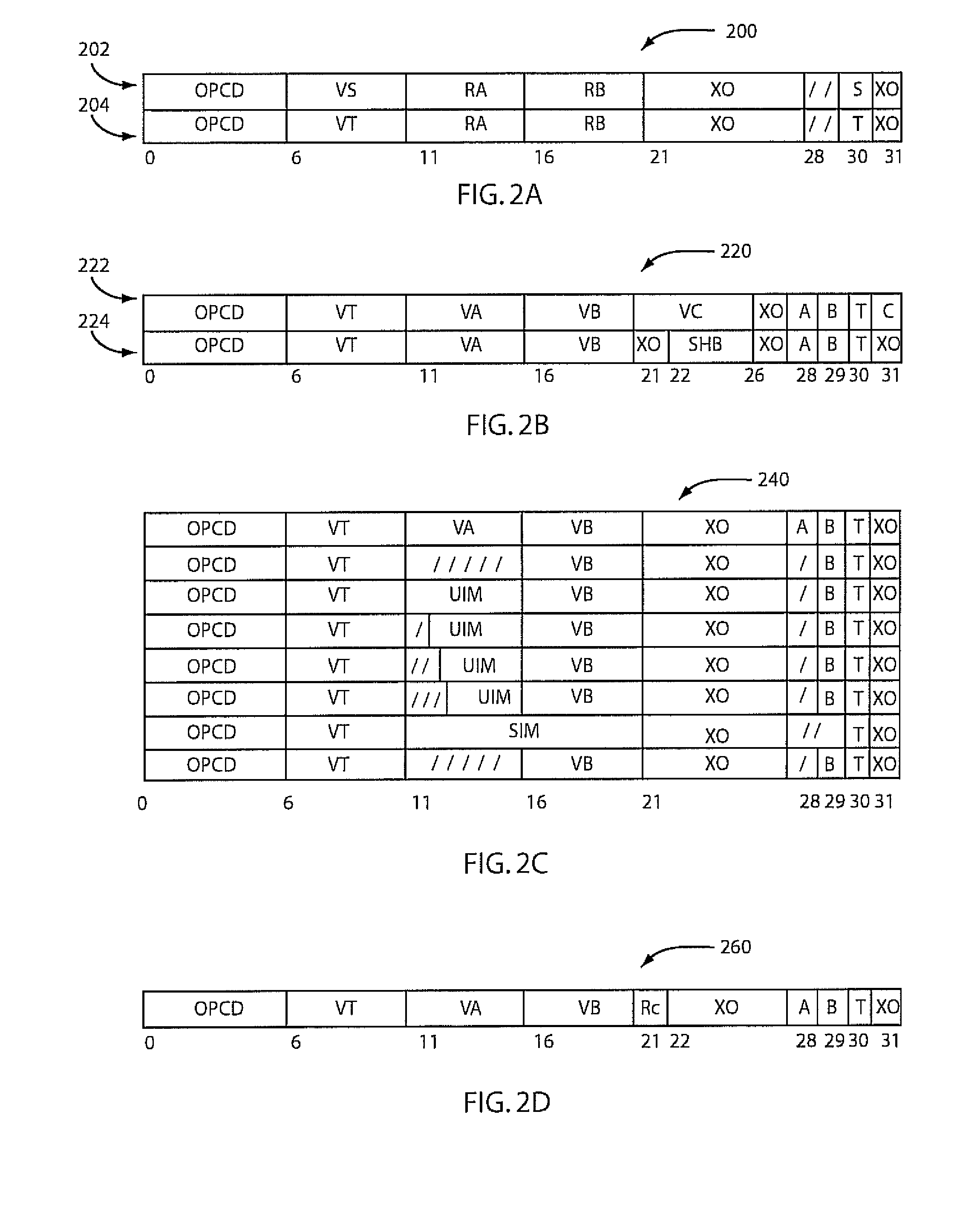

Implementing instruction set architectures with non-contiguous register file specifiers

ActiveUS20080189519A1Register arrangementsInstruction analysisProcessing InstructionProcessor register

There are provided methods and computer program products for implementing instruction set architectures with non-contiguous register file specifiers. A method for processing instruction code includes processing a fixed-width instruction of a fixed-width instruction set using a non-contiguous register specifier of a non-contiguous register specification. The fixed-width instruction includes the non-contiguous register specifier.

Owner:INT BUSINESS MASCH CORP

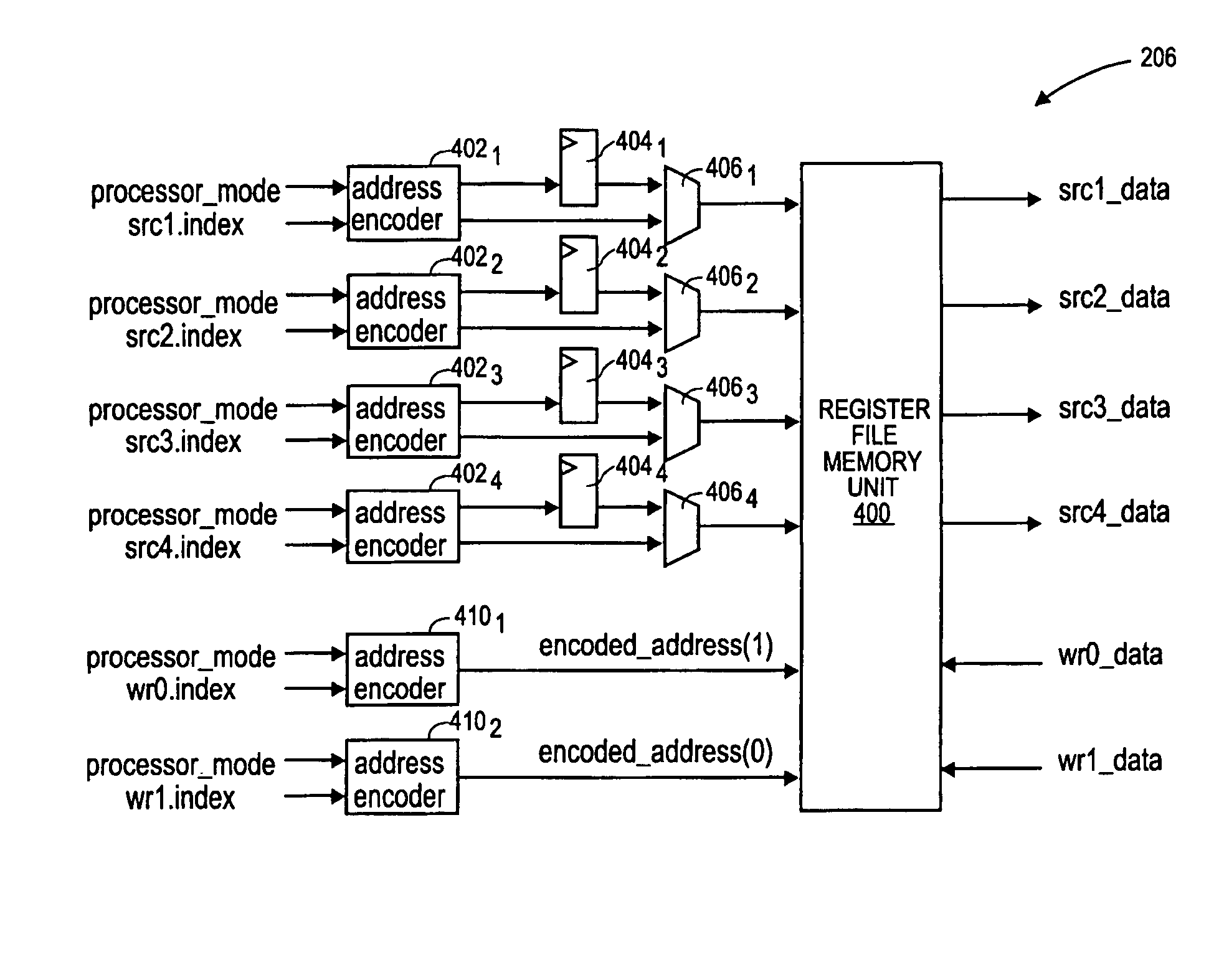

Memory mapped register file and method for accessing the same

InactiveUS7558942B1Register arrangementsGeneral purpose stored program computerData processing systemProcessing Instruction

A data processing system comprises a processor to process instructions. A plurality of pipeline stages to execute instructions including a register file. The register file includes a memory unit having a plurality of memory locations, each memory location being addressable by an encoded address. The encoded address corresponds to at least one register and processing mode. Input ports receive inputs for addressing at least one of the memory locations using an encoded address. Output ports to output data from at least one of the memory locations using an encoded address.

Owner:MARVELL ASIA PTE LTD

Residue number system based pre-computation and dual-pass arithmetic modular operation approach to implement encryption protocols efficiently in electronic integrated circuits

InactiveUS7027598B1Computations using contact-making devicesComputation using non-contact making devicesProcessor registerModularity

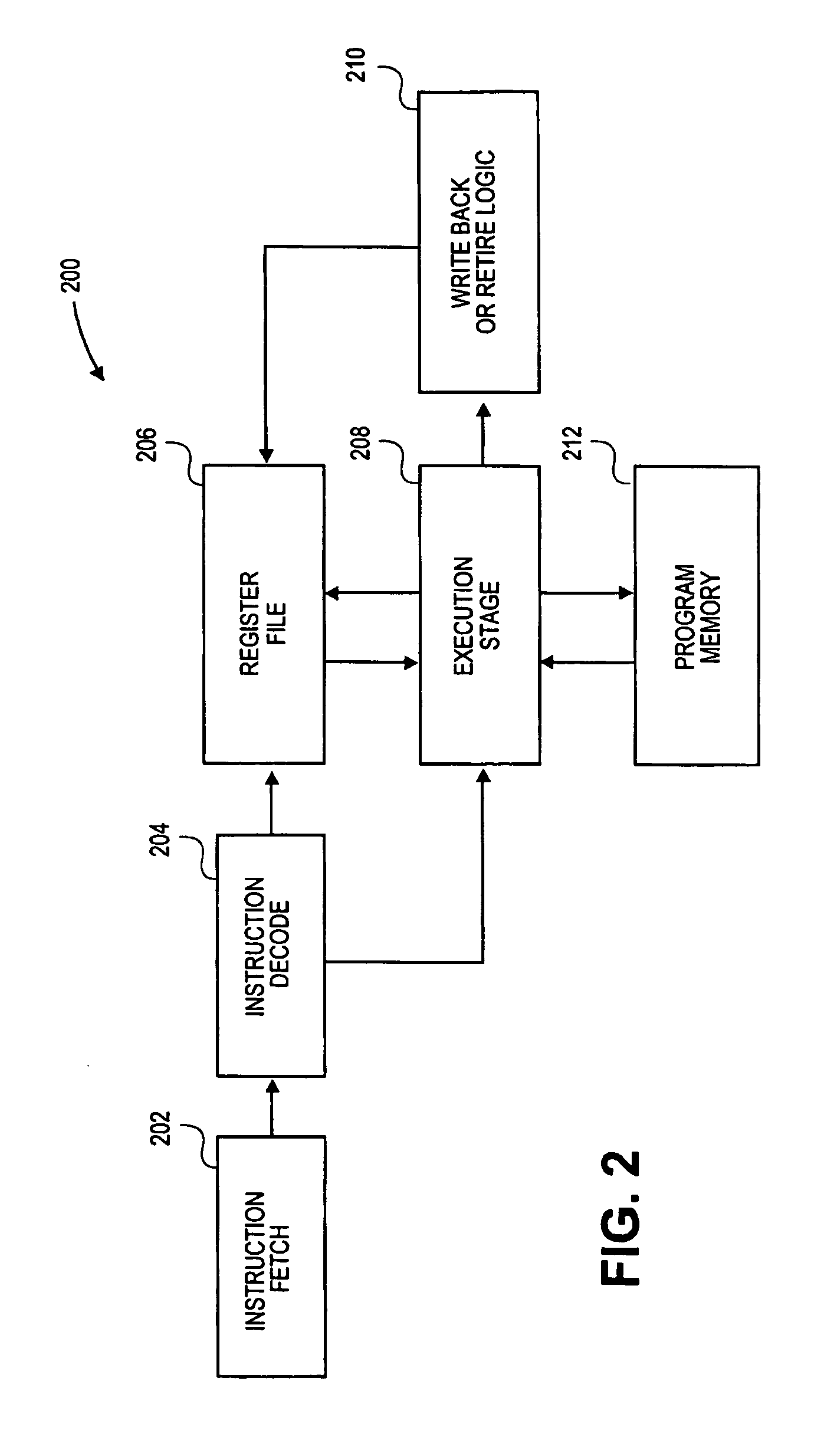

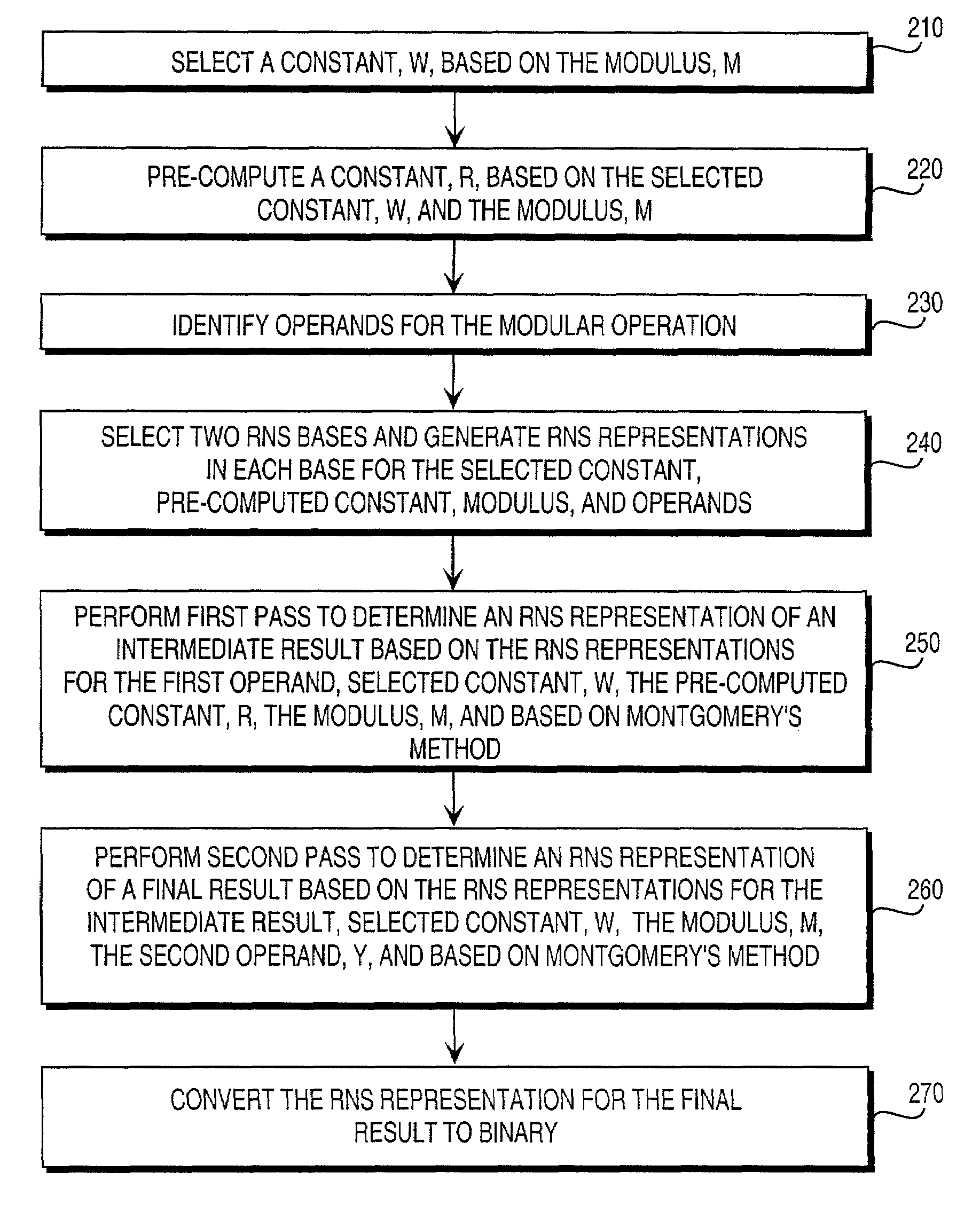

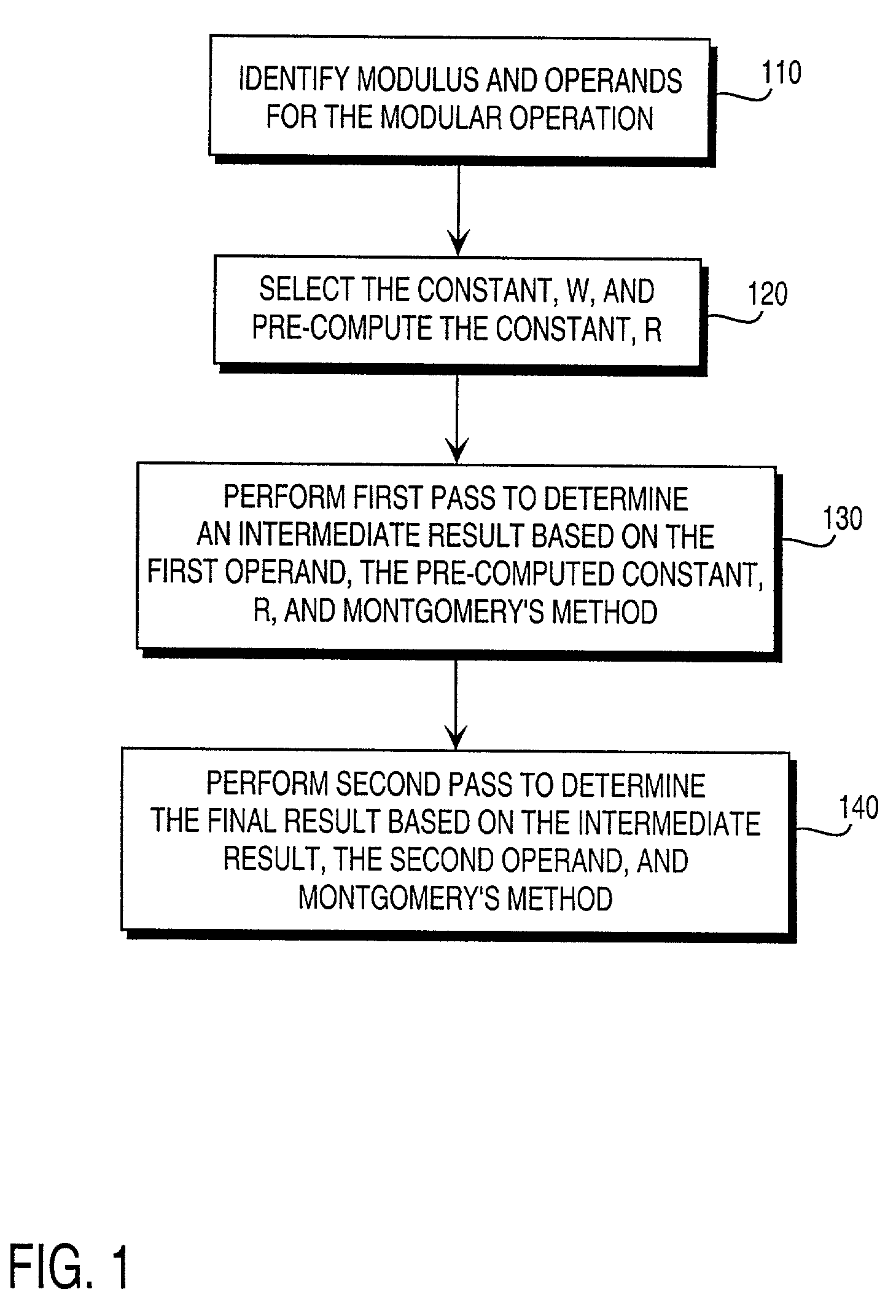

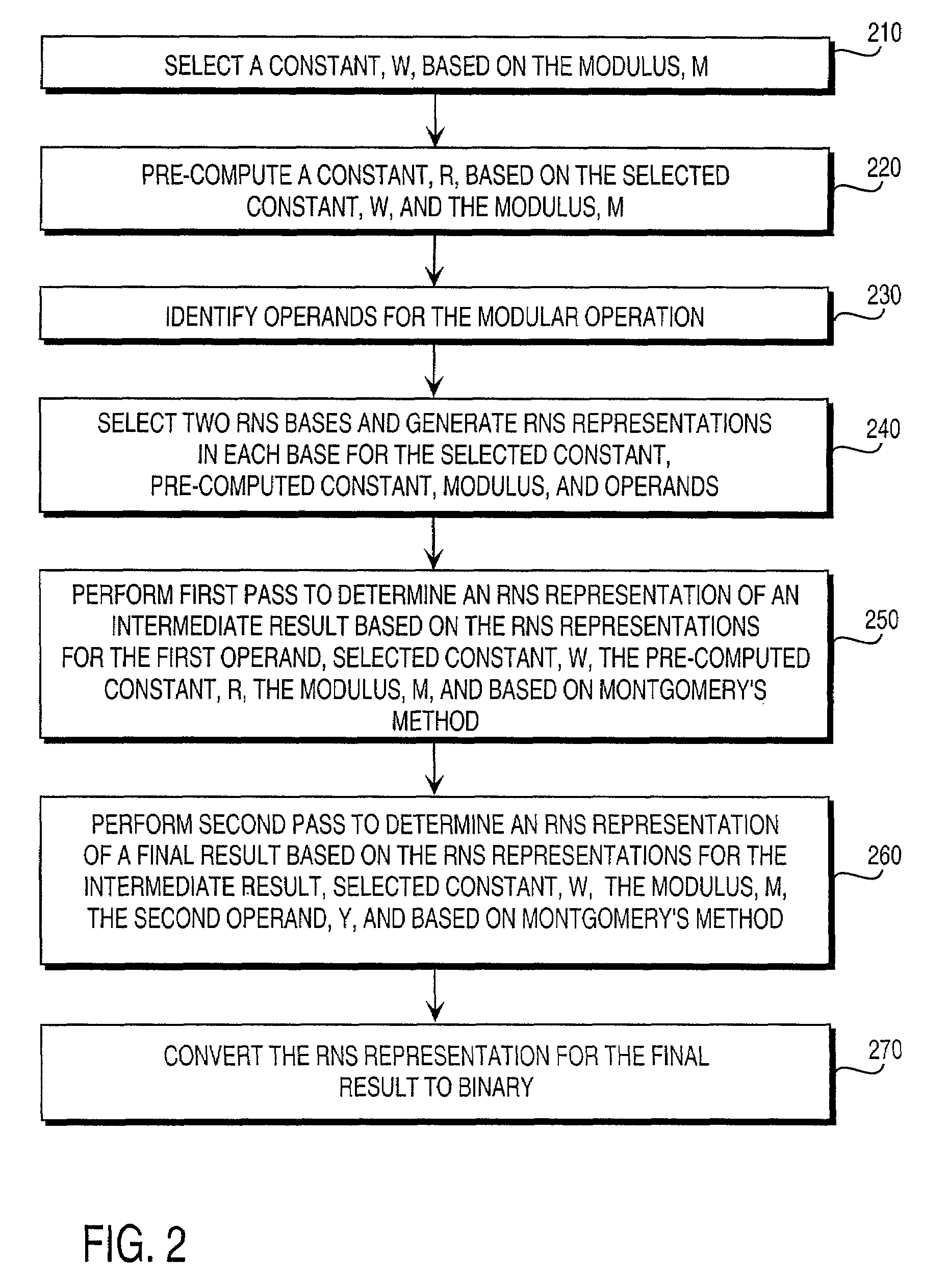

A pre-computation and dual-pass modular operation approach to implement encryption protocols efficiently in electronic integrated circuits is disclosed. An encrypted electronic message is received and another electronic message generated based on the encryption protocol. Two passes of Montgomery's method are used for a modular operation that is associated with the encryption protocol along with pre-computation of a constant based on a modulus. The modular operation may be a modular multiplication or a modular exponentiation. Modular arithmetic may be performed using the residue number system (RNS) and two RNS bases with conversions between the two RNS bases. A minimal number of register files are used for the computations along with an array of multiplier circuits and an array of modular reduction circuits. The approach described allows for high throughput for large encryption keys with a relatively small number of logical gates.

Owner:CISCO TECH INC

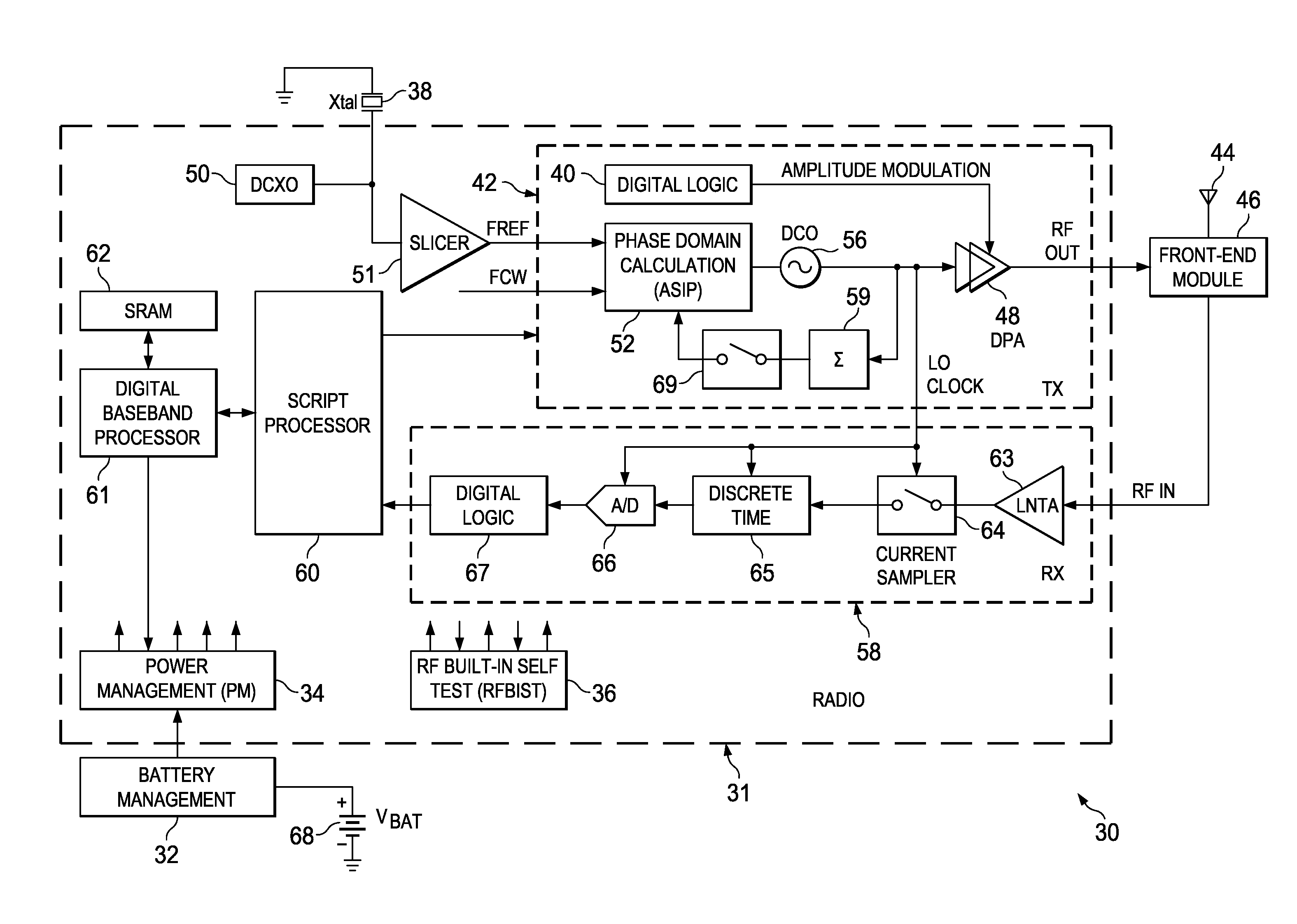

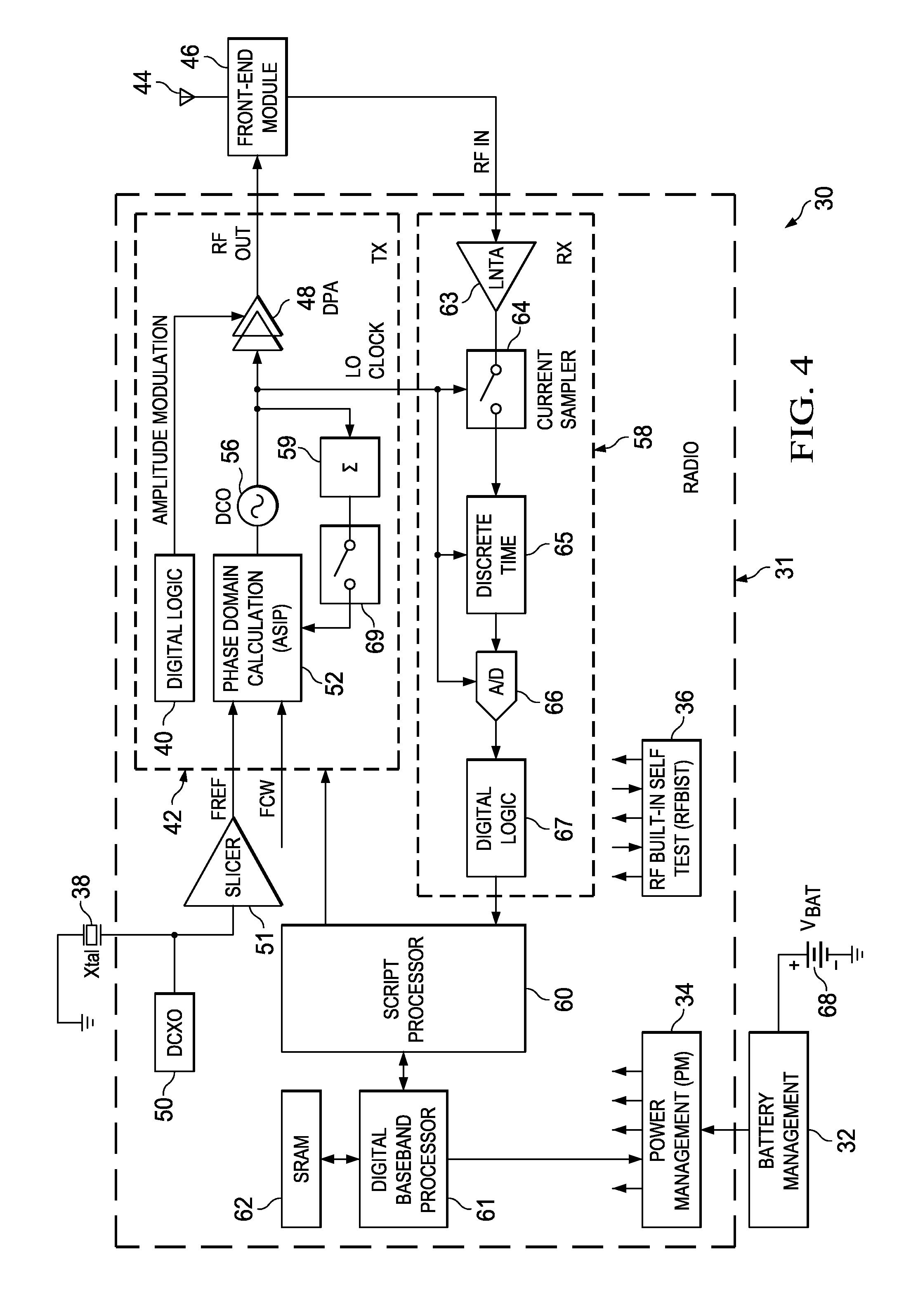

Computation parallelization in software reconfigurable all digital phase lock loop

ActiveUS20090070568A1Easy to reconfigureReduce per cycle current transientPulse automatic controlGeneral purpose stored program computerData stream processingTime-sharing

Owner:TEXAS INSTR INC

Processor implementation having unified scalar and SIMD datapath

InactiveUS20030037221A1Register arrangementsConcurrent instruction executionProcessor registerDatapath

An improved processor implementation is described in which scalar and vector processing components are merged to reduce complexity. In particular, the implementation includes a scalar-vector register file for storing scalar and vector instructions, as well as a parallel vector unit comprising functional units that can process vector or scalar instructions as required. A further aspect of the invention provides the ability to disable unused functional units in the parallel vector unit, such as during a scalar operation, to achieve significant power savings.

Owner:INTEL CORP

Multithreaded SIMD parallel processor with launching of groups of threads

ActiveUS7594095B1General purpose stored program computerProgram controlProcessing coreProcessor register

In a multithreaded processing core, groups of threads are launched in parallel for single-instruction, multiple-data (SIMD) execution by a set of parallel processing engines. Thread-specific input data for threads in a new SIMD group can be loaded directly into the local register files used by the parallel processing engines, or the data can be accumulated in a buffer until a launch condition is satisfied. When the launch condition is satisfied, the entire group is launched. Various launch conditions can be defined, including but not limited to full population of the SIMD group, a change in data processing conditions, or a timeout.

Owner:NVIDIA CORP

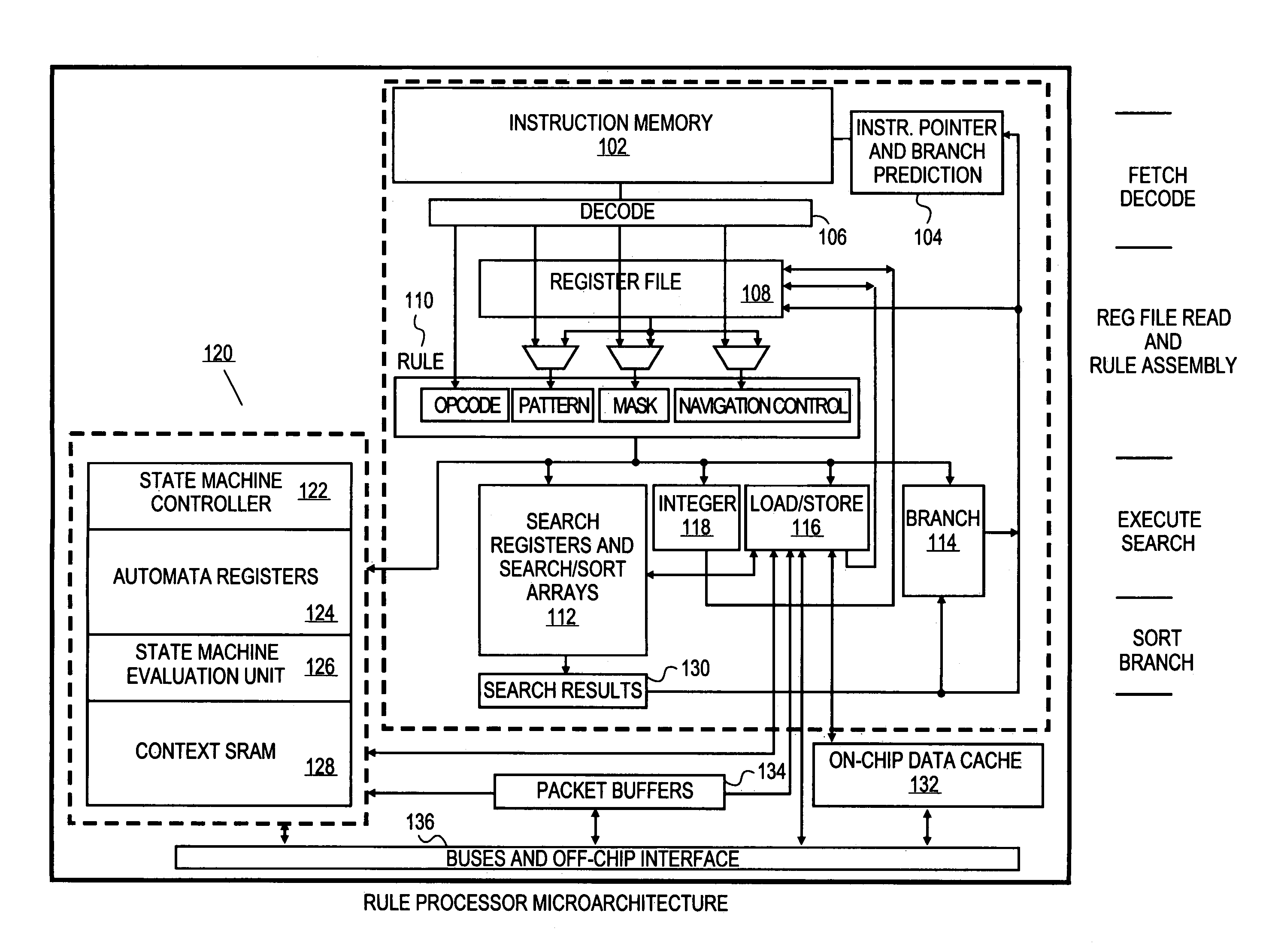

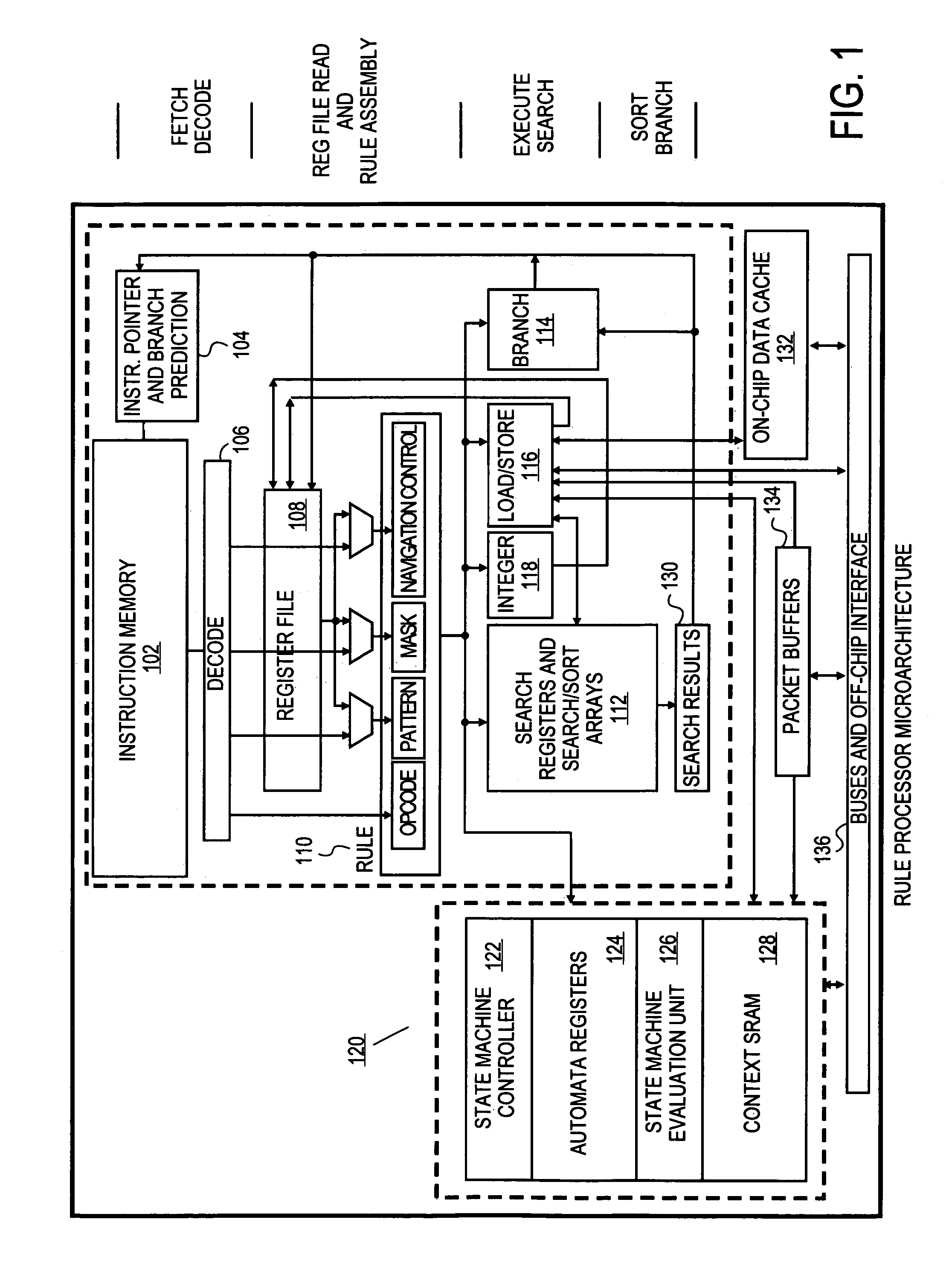

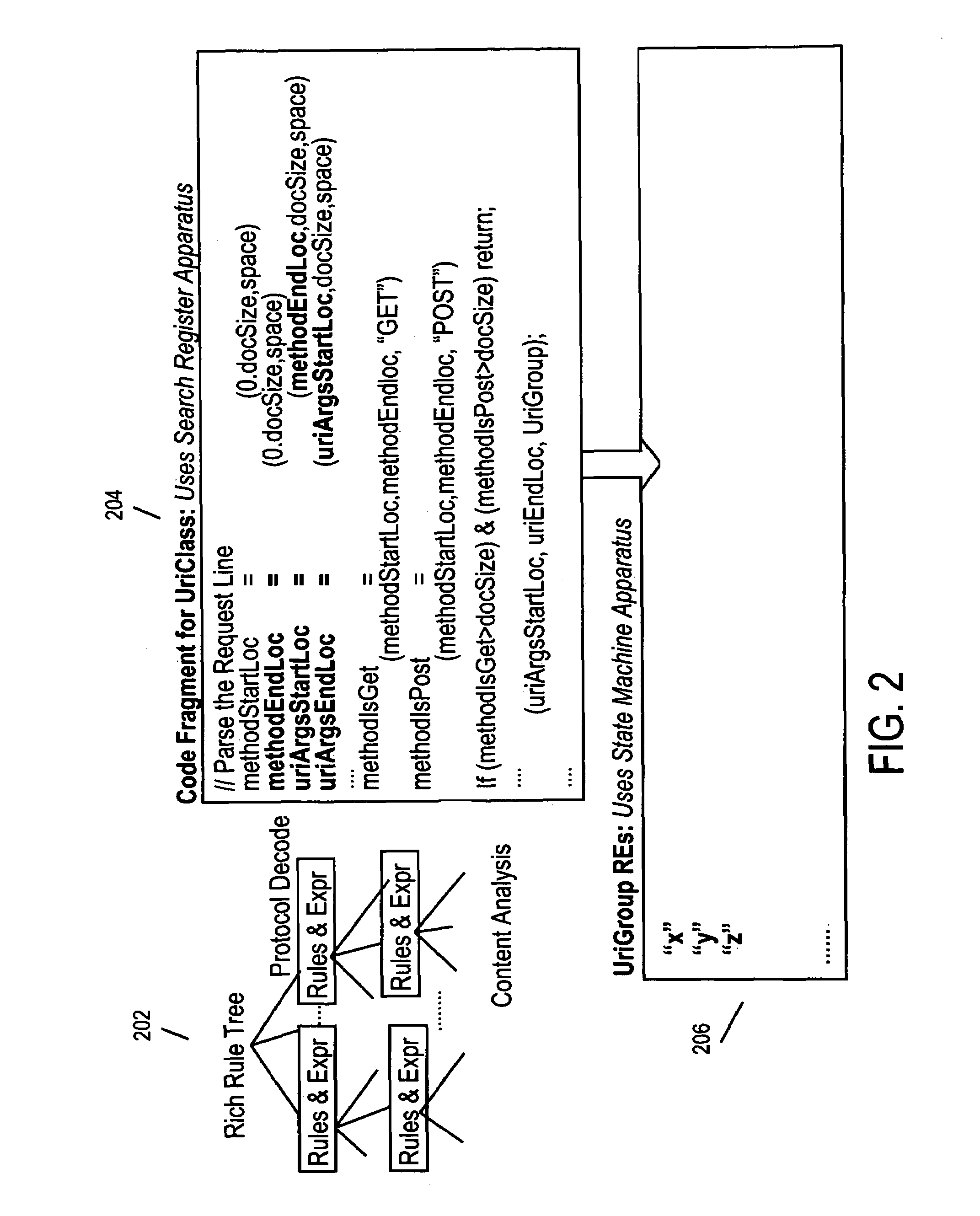

Programmable processor apparatus integrating dedicated search registers and dedicated state machine registers with associated execution hardware to support rapid application of rulesets to data

InactiveUS7464254B2Programme controlDigital data information retrievalGeneral purposeProcessor register

A rule processor and method for using the same are disclosed. In one embodiment, the rule processor comprises a general purpose register file, an instruction sequencer to provide instructions, a decoder coupled to the general purpose register file to decode a set of instructions specified by the instruction sequencer, and a state machine unit coupled to the decoder and having state machine registers to store one or more state machines and state machine execution hardware coupled to the state machine registers to evaluate the one or more state machines in response to executing one or more of the set of instructions and based on information from one or both of the decoder and the general purpose register file.

Owner:CISCO TECH INC

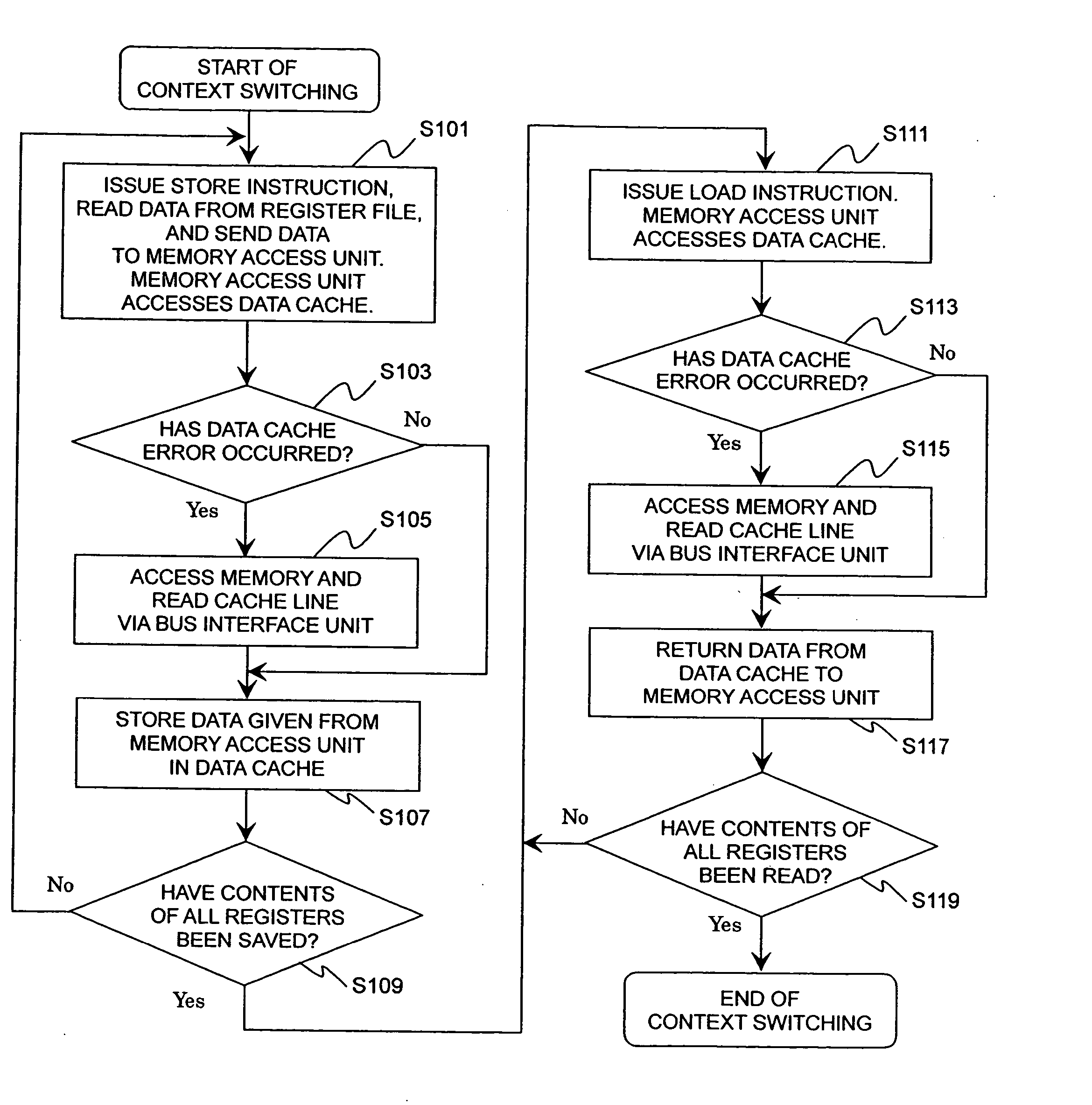

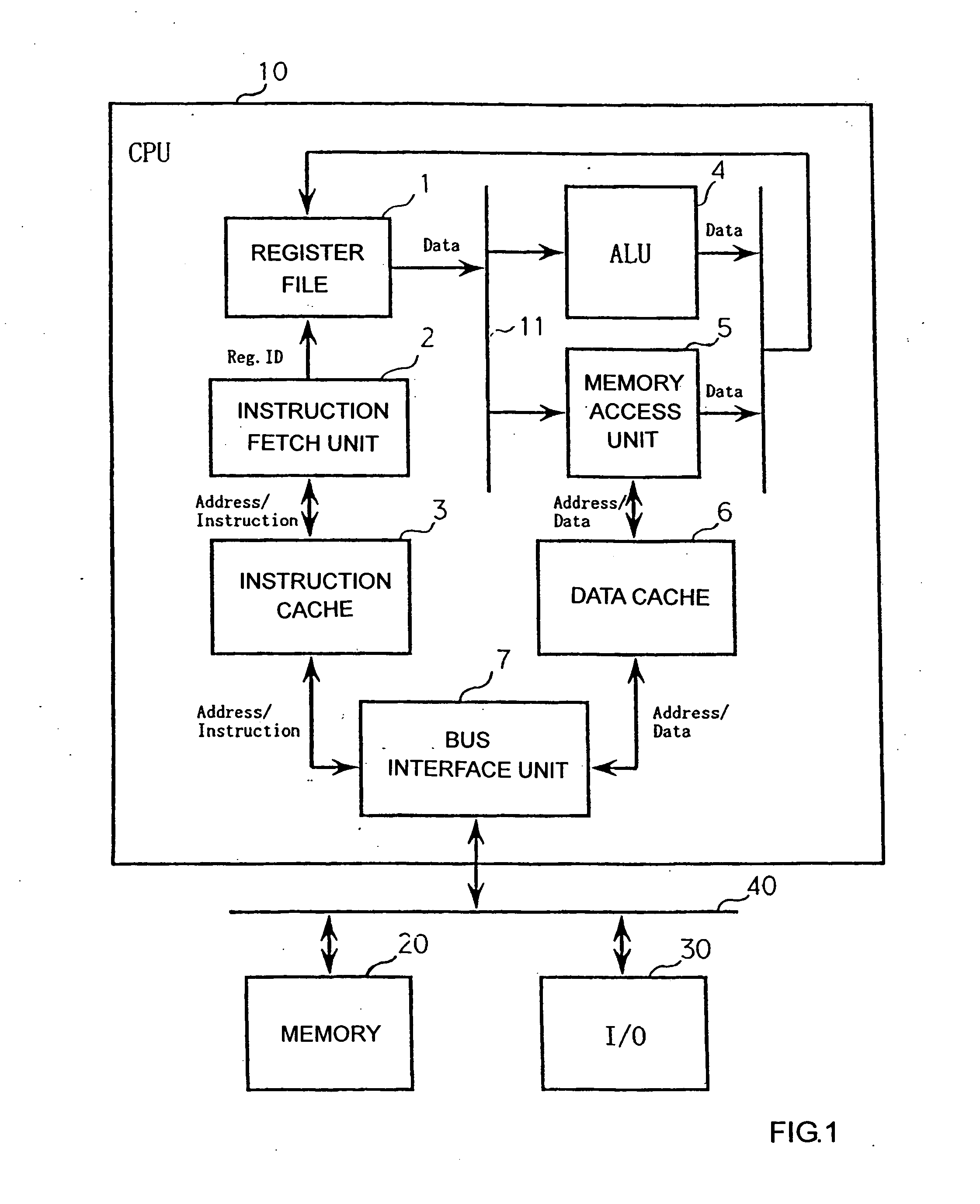

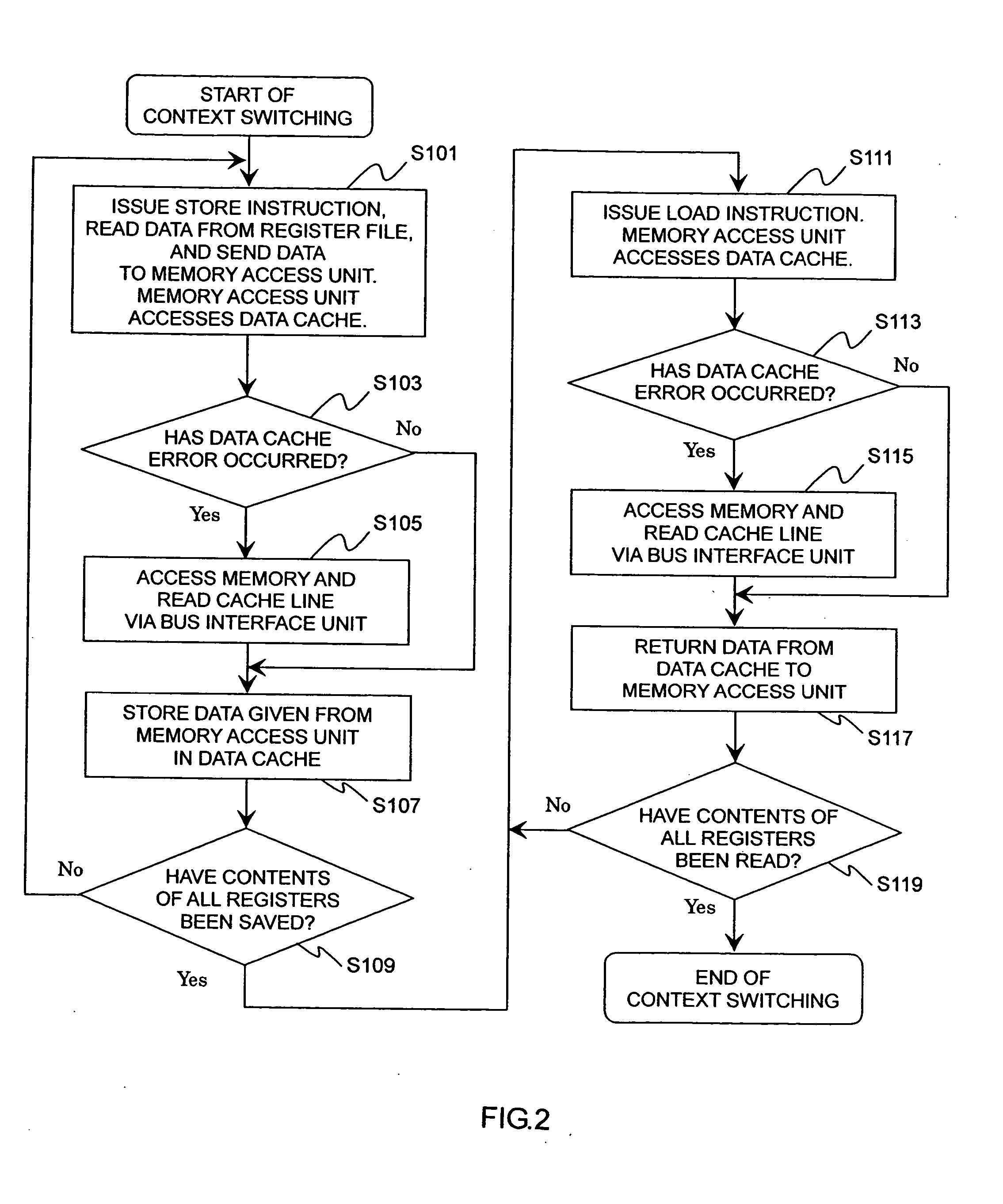

Context switching method, device, program, recording medium, and central processing unit

ActiveUS20070022428A1Reduce overheadMinimize time quantumProgram initiation/switchingDigital computer detailsOperational systemProcessor register

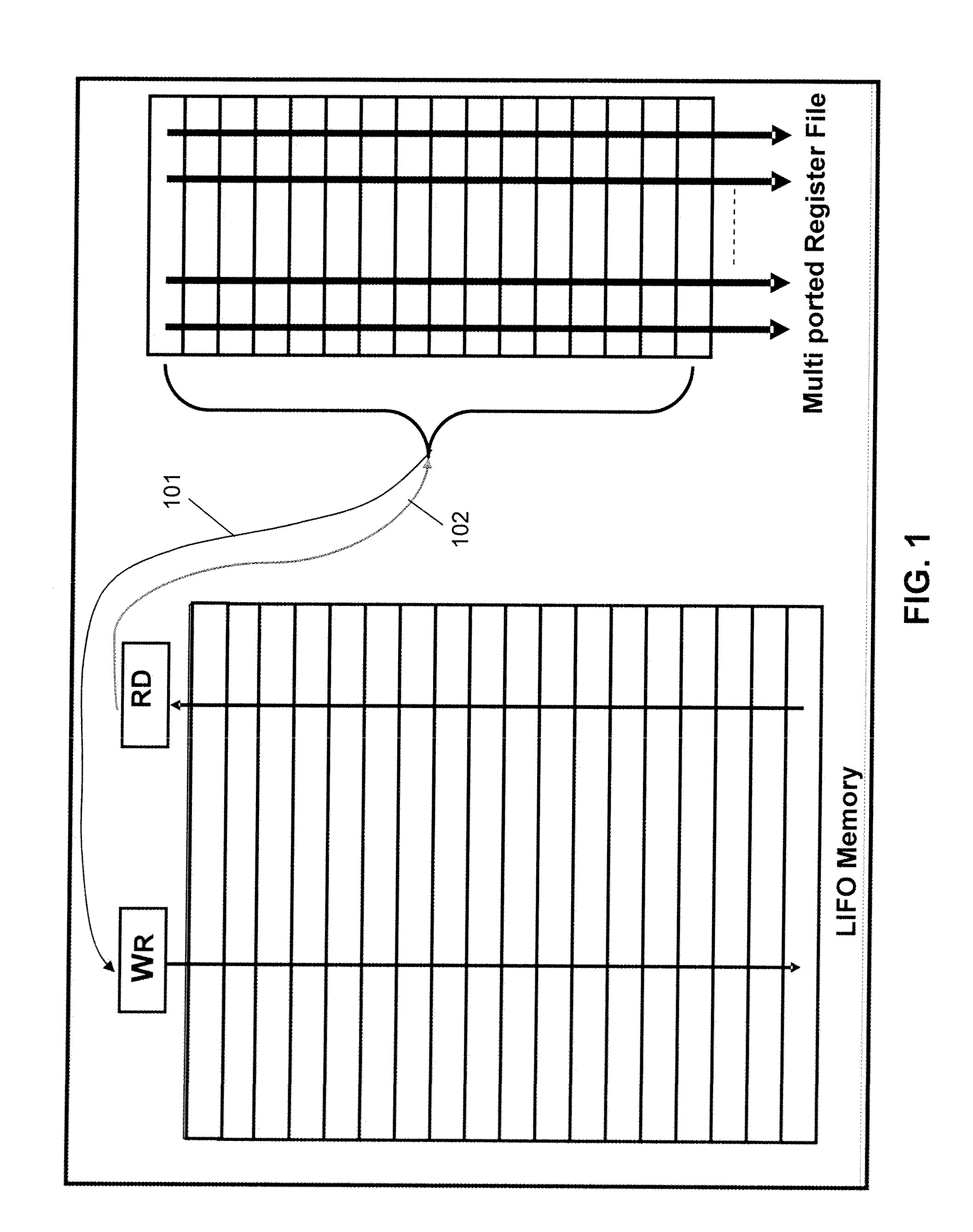

In an application in which context switching often occurs such as in a real time OS, it is possible to significantly reduce the overhead caused by the context switching. The OS issues a Swap instruction and a context switch starts. The Swap instruction is issued together with a thread (i.e., context) ID to be replaced, to a thread control unit (9). The thread ID is used to uniquely identify threads stored in a context cache (8). The thread control unit (9) saves data from a register file (1) to the context cache (8) via a context-dedicated bus (12) and transmits data of a new thread from the context cache (8) to the register file (1). According to the thread ID received, the thread control unit (9) automatically interchanges the necessary number of data in the register file (1) and the data in the context cache (8).

Owner:JAPAN SCI & TECH CORP

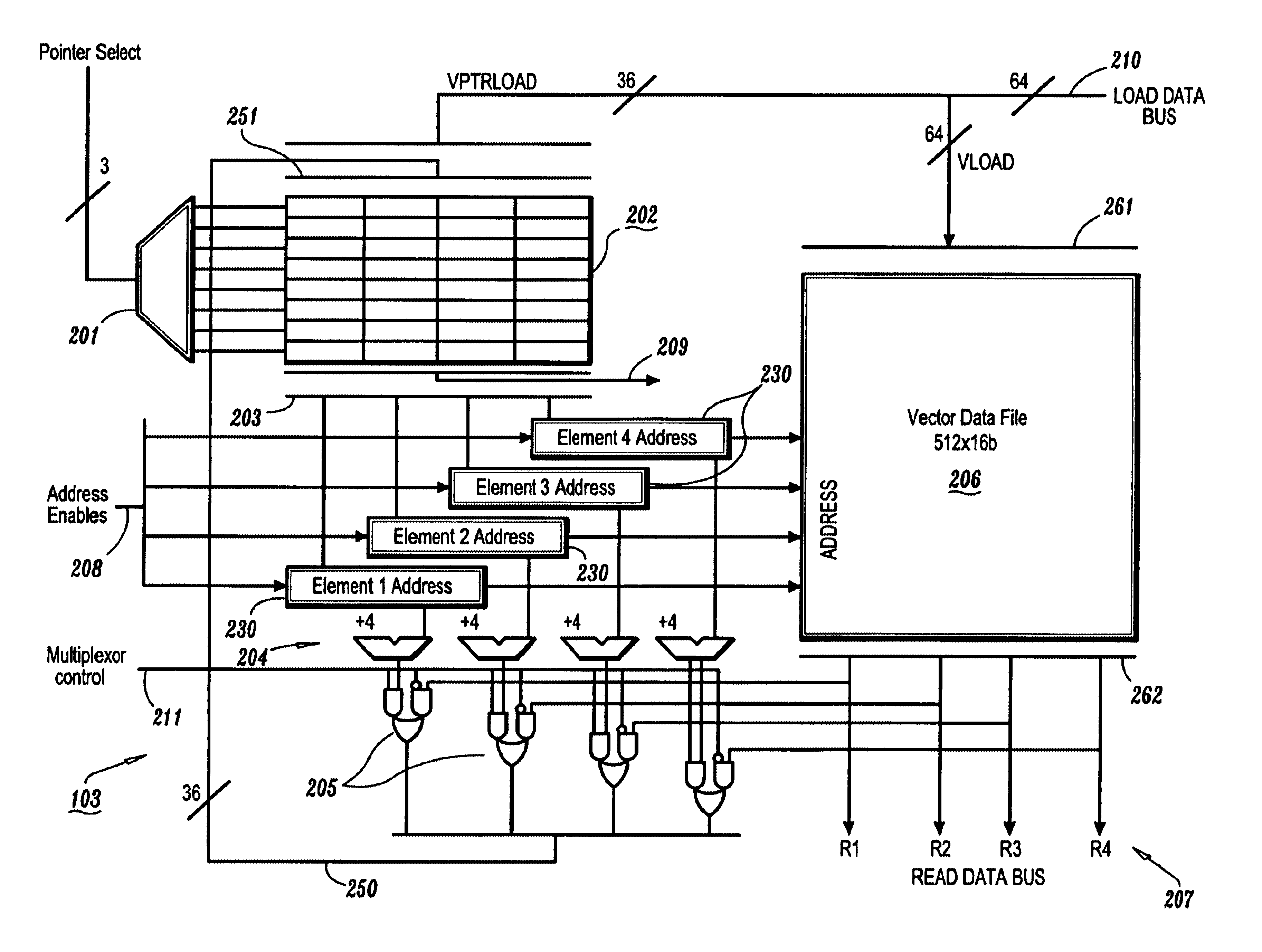

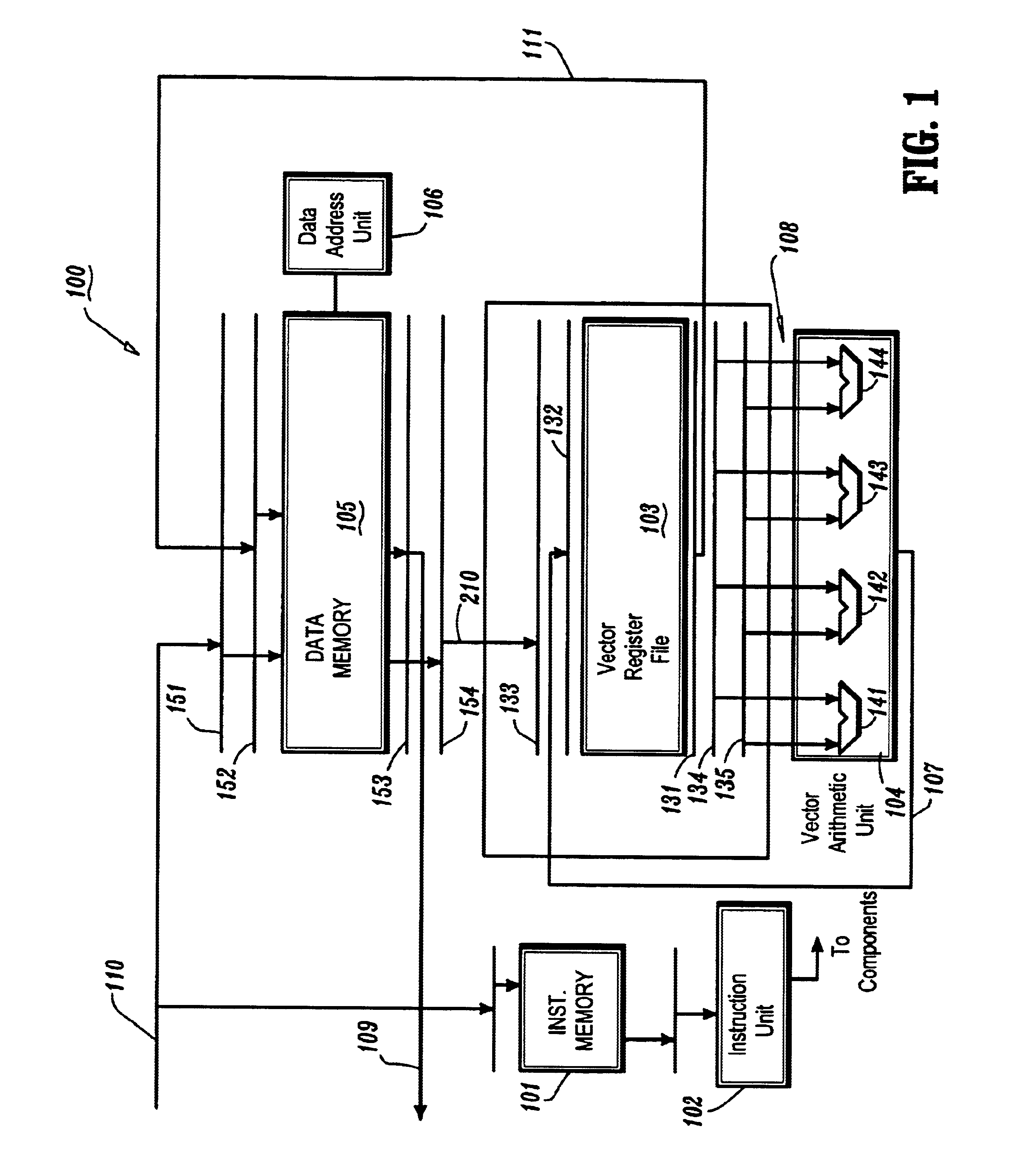

Vector register file with arbitrary vector addressing

InactiveUS6665790B1Register arrangementsArchitecture with single central processing unitData fileData element

A system and method for processing operations that use data vectors each comprising a plurality of data elements, in accordance with the present invention, includes a vector data file comprising a plurality of storage elements for storing data elements of the data vectors. A pointer array is coupled by a bus to the vector data file. The pointer array includes a plurality of entries wherein each entry identifies at least one storage element in the vector data file. The at least one storage element stores at least one data element of the data vectors, wherein for at least one particular entry in the pointer array, the at least one storage element identified by the particular entry has an arbitrary starting address in the vector data file.

Owner:IBM CORP

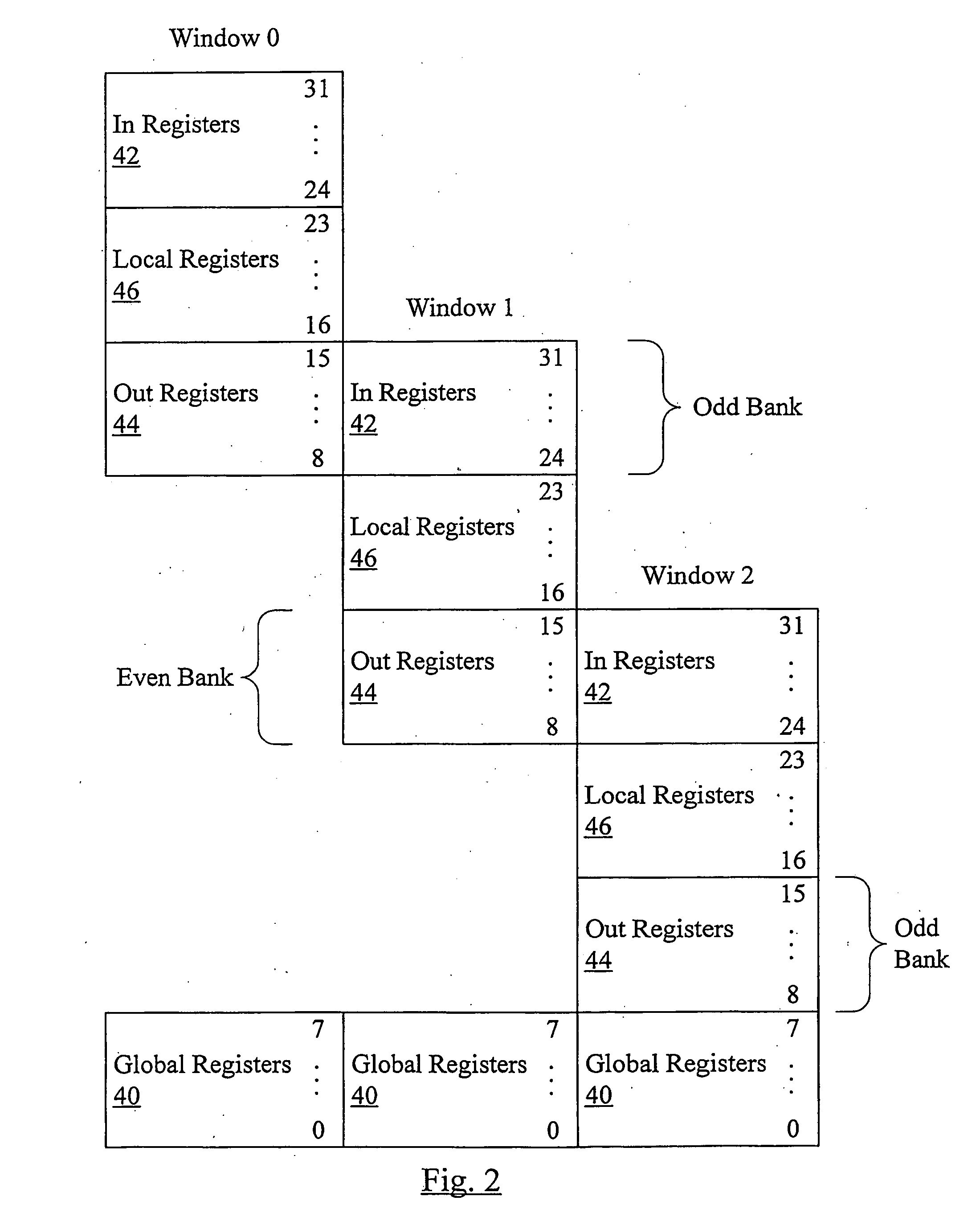

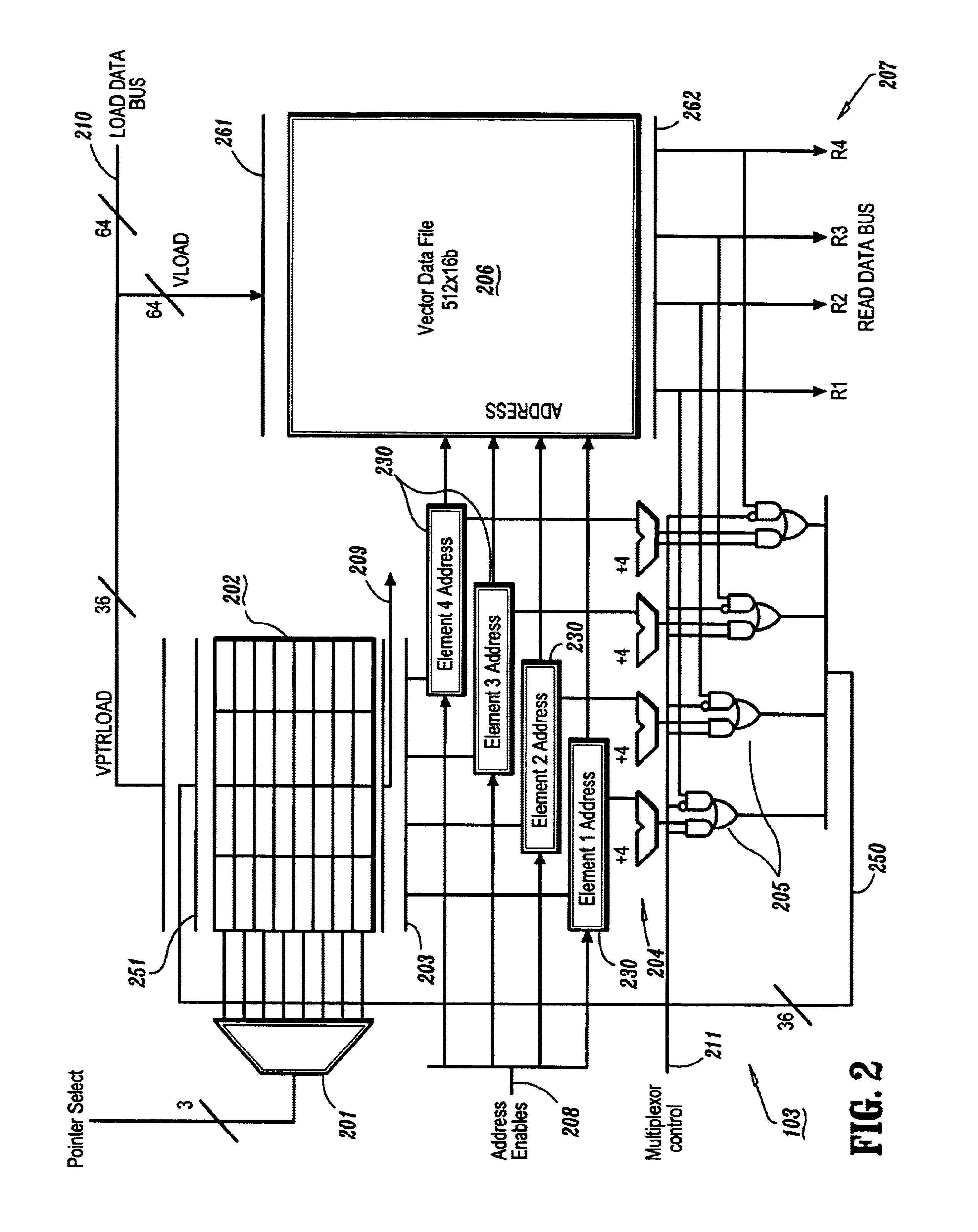

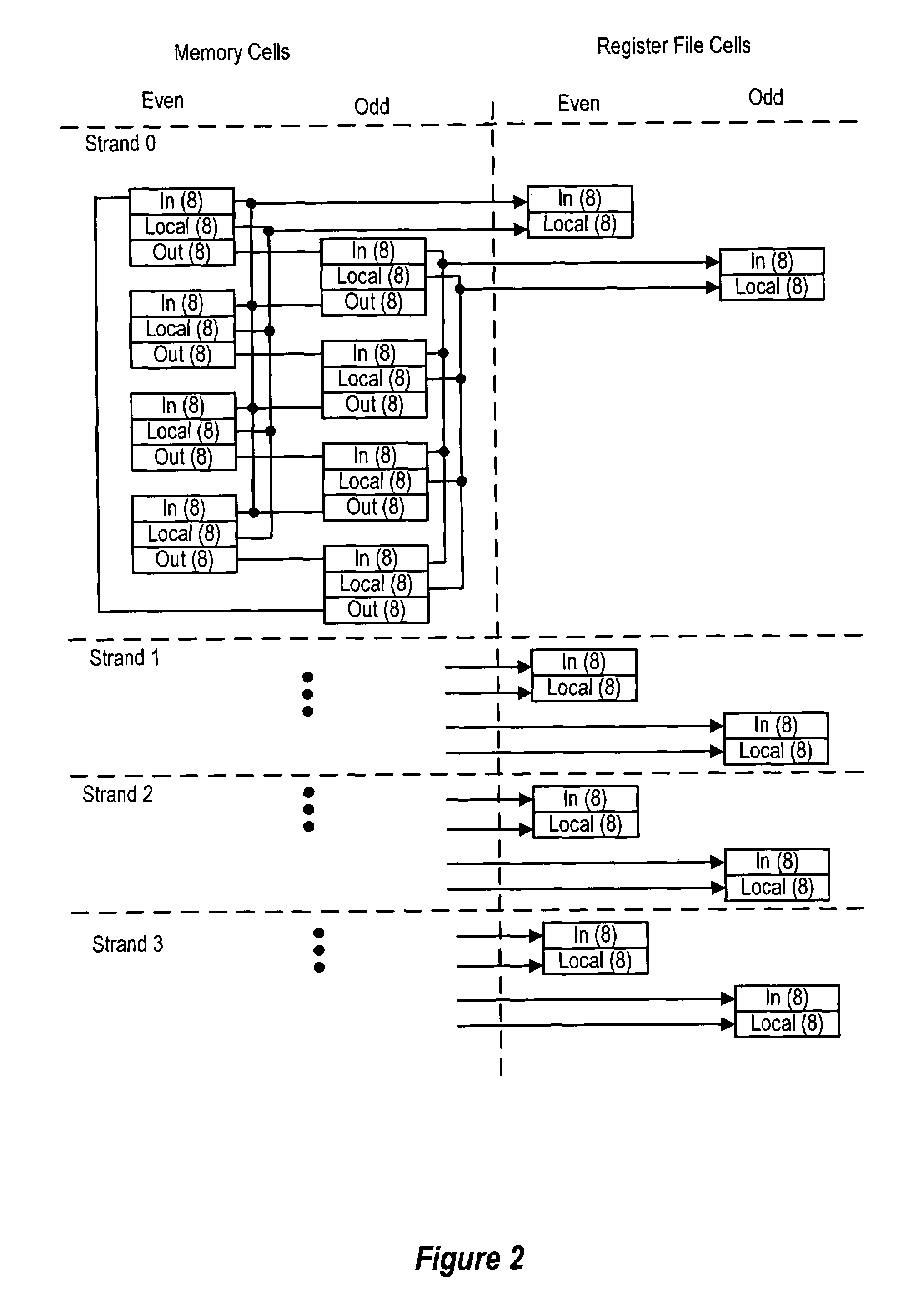

Versatile register file design for a multi-threaded processor utilizing different modes and register windows

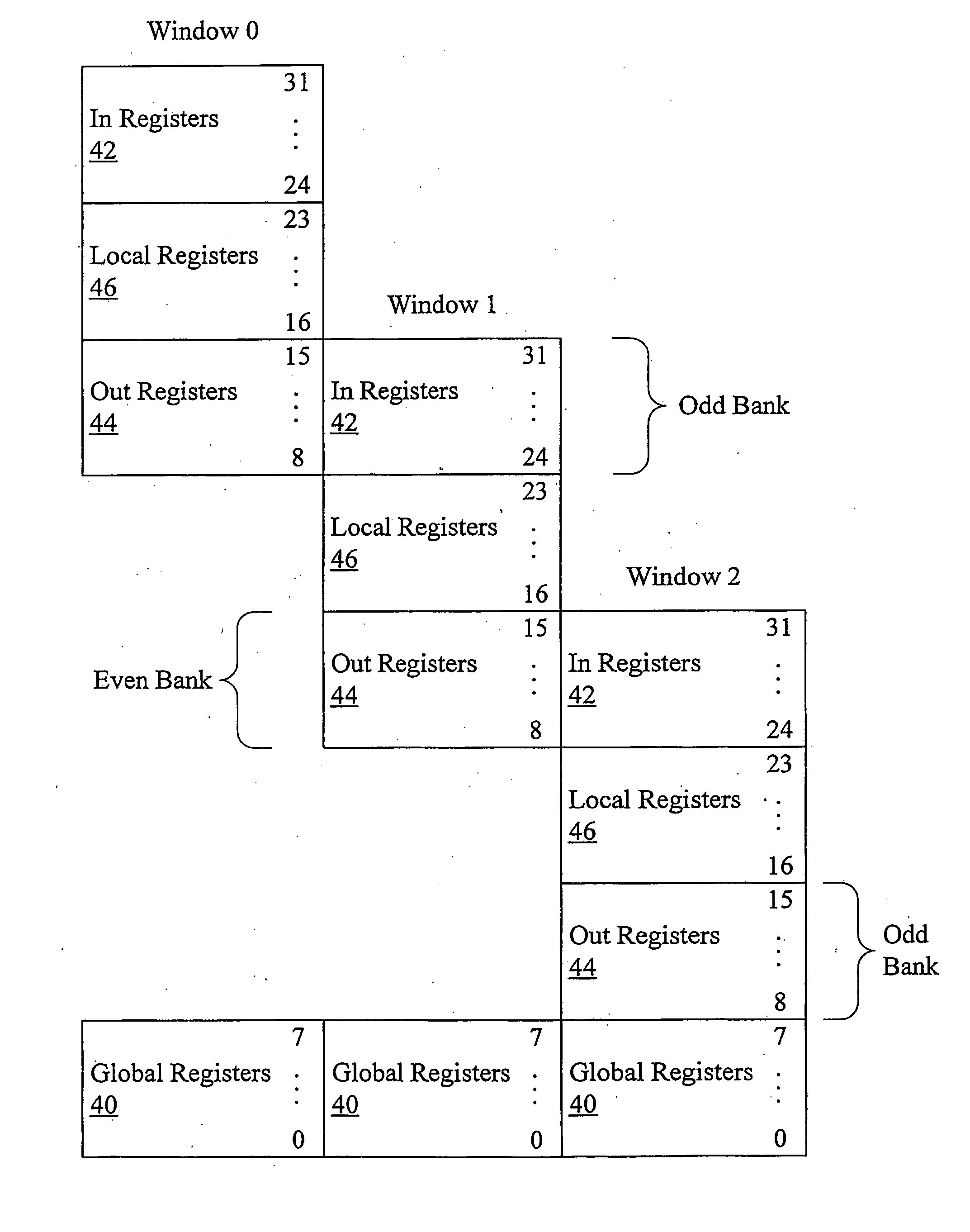

ActiveUS7418582B1Improve performanceRegister arrangementsDigital computer detailsFile designRegister window

A method for optimizing a register file hierarchy in a multithreaded processor. The method includes providing a register file hierarchy with a plurality of register file cells, associating the plurality of register file cells with respective threads when the processor is operating in a multithreaded mode and flattening the plurality of register file cells with a single thread when the processor is operating in a single threaded mode. The register file cells correspond to threads of the multithreaded processor.

Owner:ORACLE INT CORP

Digital data processing apparatus having multi-level register file

InactiveUS7284092B2Faster access latency timeShorten the timeRegister arrangementsMemory adressing/allocation/relocationProcessor registerElectronic data processing

A processor contains multiple levels of registers having different access latency. A relatively smaller set of registers is contained in a relatively faster higher level register bank, and a larger, more complete set of the registers is contained in a relatively slower lower level register bank. Physically, the higher level register bank is placed closer to functional logic which receives inputs from the registers. Preferably, the lower level bank includes a complete set of all processor registers, and the higher level bank includes a smaller subset of the registers, duplicating information in the lower level bank. The higher level bank is preferably accessible in a single clock cycle.

Owner:IBM CORP

Register file supporting transactional processing

InactiveUS20110283096A1Digital computer detailsMicrocontrol arrangementsProcessor registerExecution unit

A processor includes an instruction sequencing unit, execution unit, and multi-level register file including a first level register file having a lower access latency and a second level register file having a higher access latency. Responsive to the processor processing a second instruction in a transactional code section to obtain as an execution result a second register value of the logical register, the mapper moves a first register value of the logical register to the second level register file, places the second register value in the first level register file, marks the second register value as speculative, and replaces a first mapping for the logical register with a second mapping. Responsive to unsuccessful termination of the transactional code section, the mapper designates the second register value in the first level register file as invalid so that the first register value in the second level register file becomes the working value.

Owner:IBM CORP

Method for inter-cluster communication that employs register permutation

InactiveUS20050204118A1Increase data bandwidthReduce power consumptionRegister arrangementsDigital computer detailsAccess timeComputer science

The present invention is a method for inter-cluster communication that employs register permutation by dynamically mapping the registers to the functional units. Because only the mapping between registers and functional units is changed and no actual data movement occurs, the present invention greatly diminishes the power consumption. Owing to the inter-cluster communication mechanism, a centralized register file can be replaced with small register sub-blocks, where the silicon area is greatly reduced, and the access time and the power consumption are also diminished.

Owner:NAT CHIAO TUNG UNIV