Patents

Literature

476results about "Microcontrol arrangements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

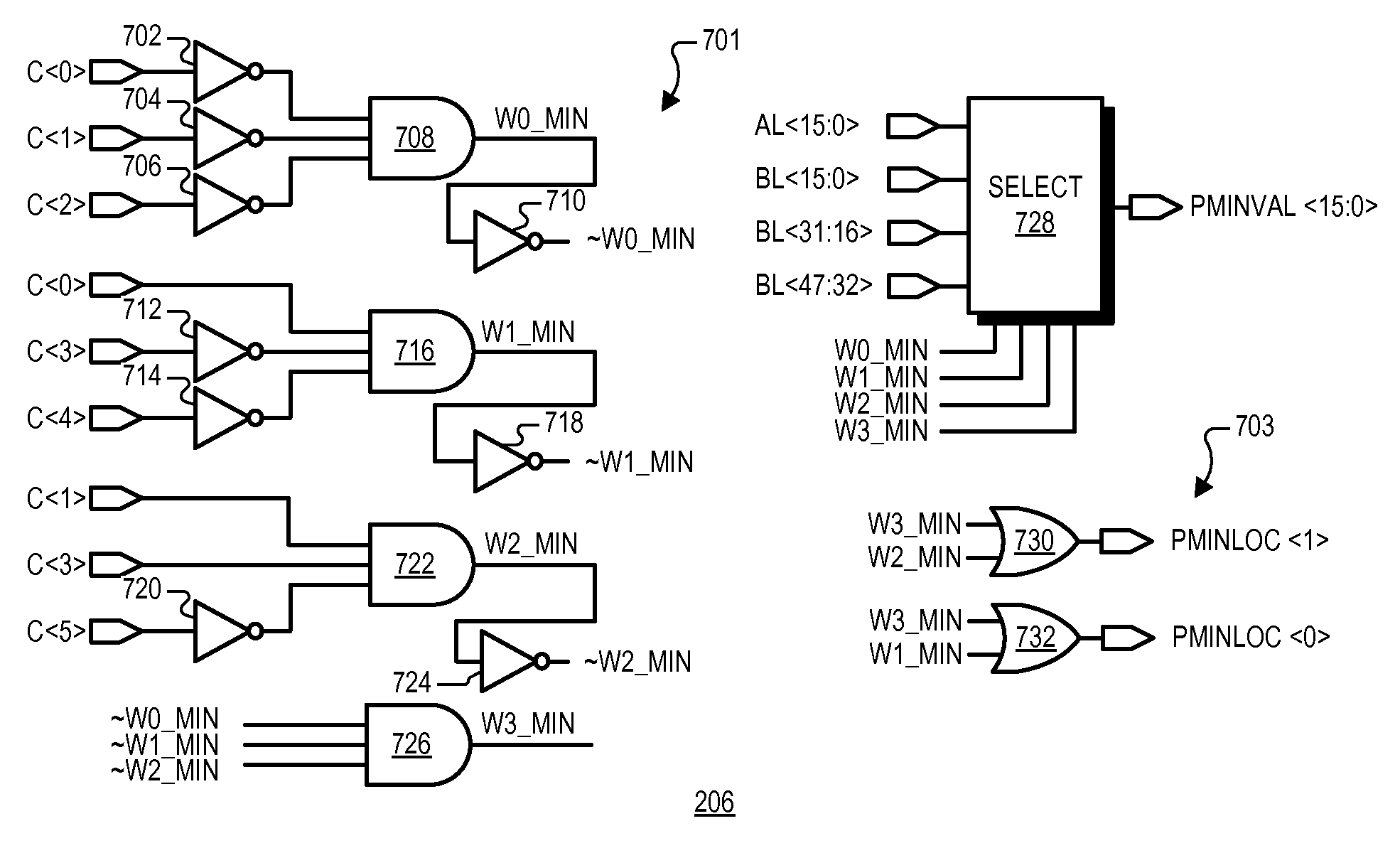

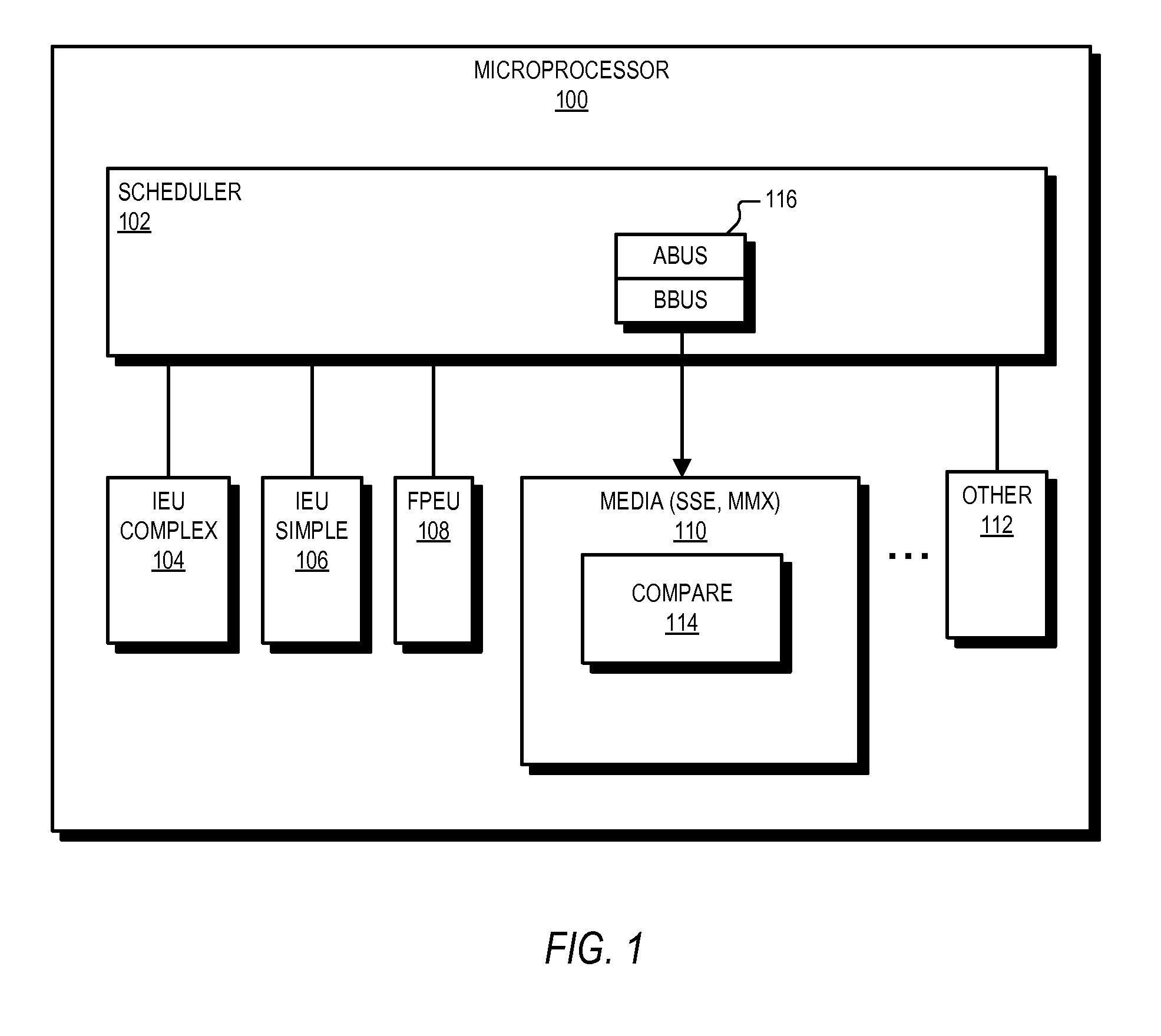

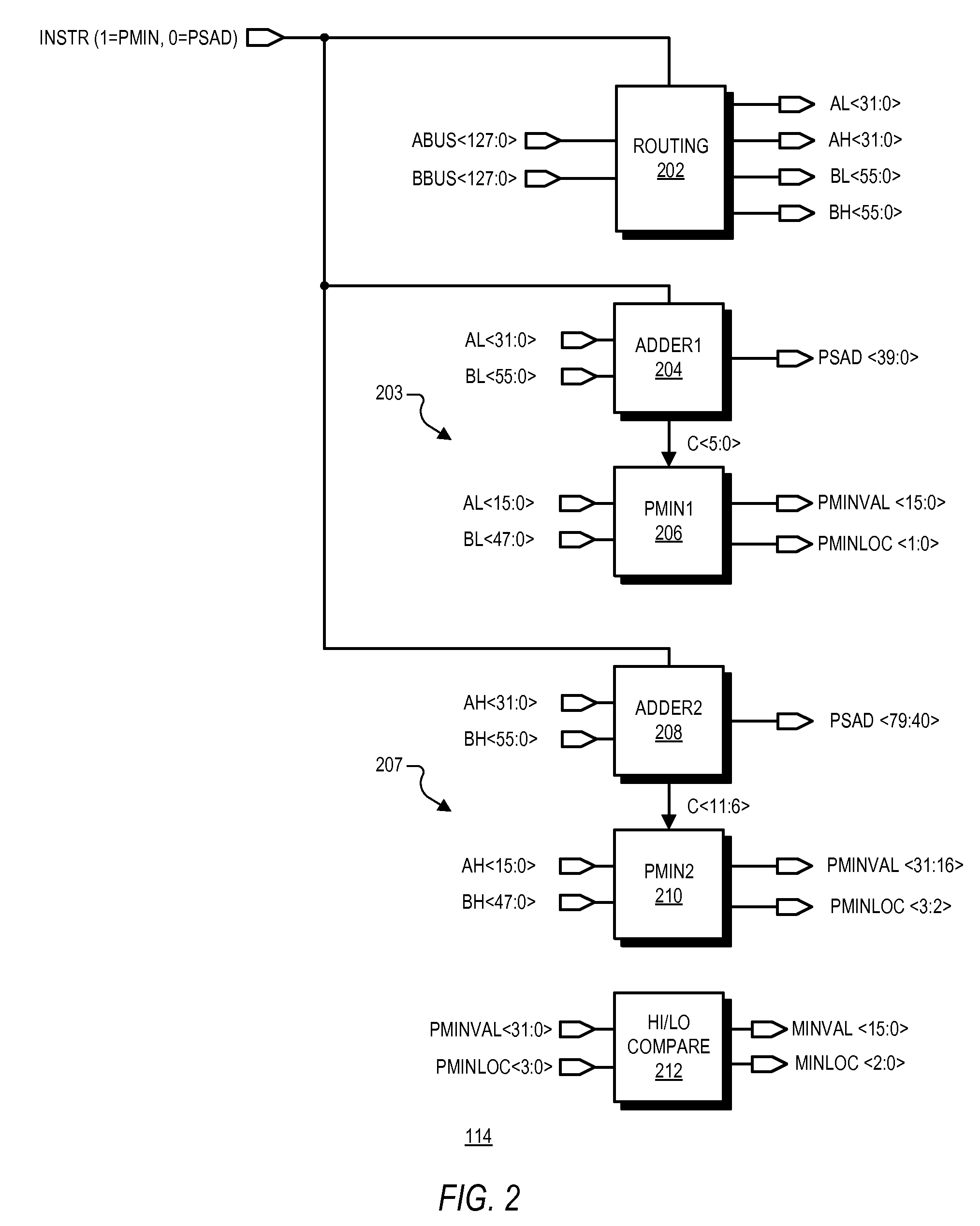

System and method for determination of a horizontal minimum of digital values

ActiveUS8650232B2Logic circuits characterised by logic functionComputation using non-contact making devicesComputer science

A system for fast determination of a horizontal minimum of multiple digital values including a difference circuit and a compare circuit. The difference circuit may include first and second adders in which the first adder compares upper bits of a first digital value with upper bits of a second digital value and provides a first carry output and a propagate output. The second adder compares lower bits of the first digital value with lower bits of the second digital value and provides a second carry output. The compare circuit determines whether the first digital value is greater than the second digital value based on the carry and propagate outputs. Multiple difference circuits may be used to compare each of multiple digital values with every other digital value to provide corresponding compare bits, which are then used to determine a minimum one of the digital values and its corresponding location.

Owner:VIA TECH INC

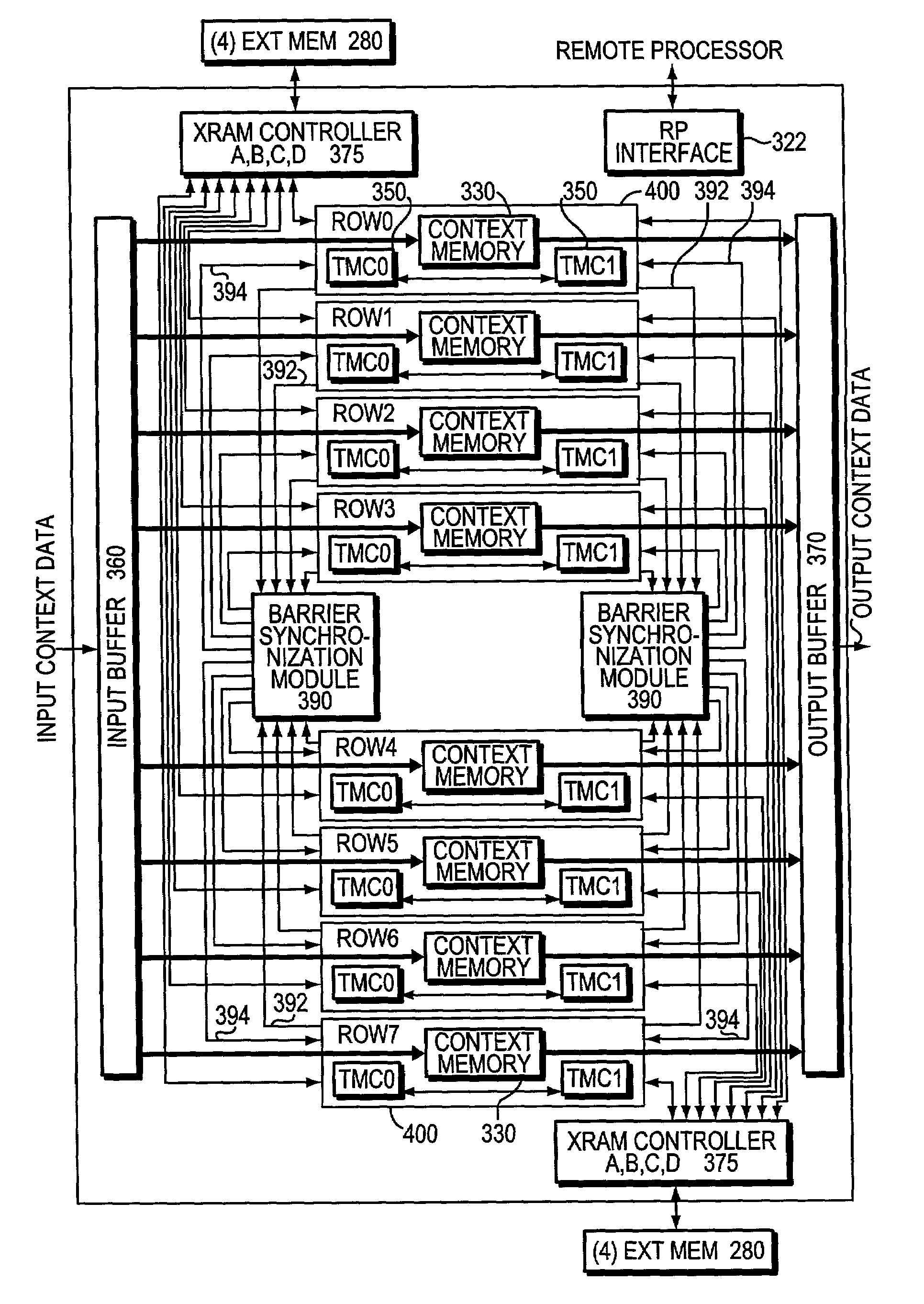

Barrier synchronization mechanism for processors of a systolic array

InactiveUS7100021B1Without consuming substantial memory resourceImprove latencyProgram synchronisationGeneral purpose stored program computerSystolic arrayCommon point

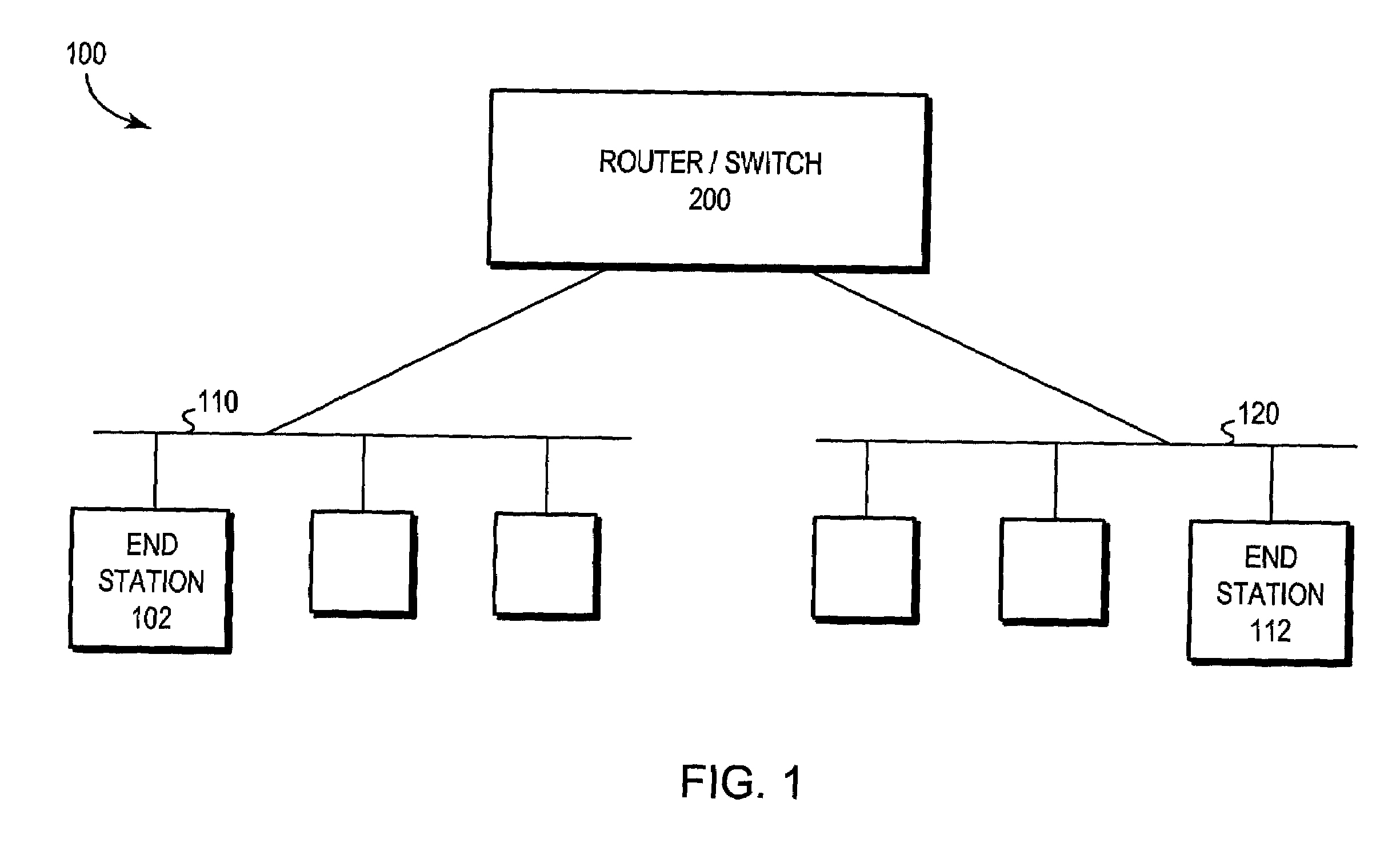

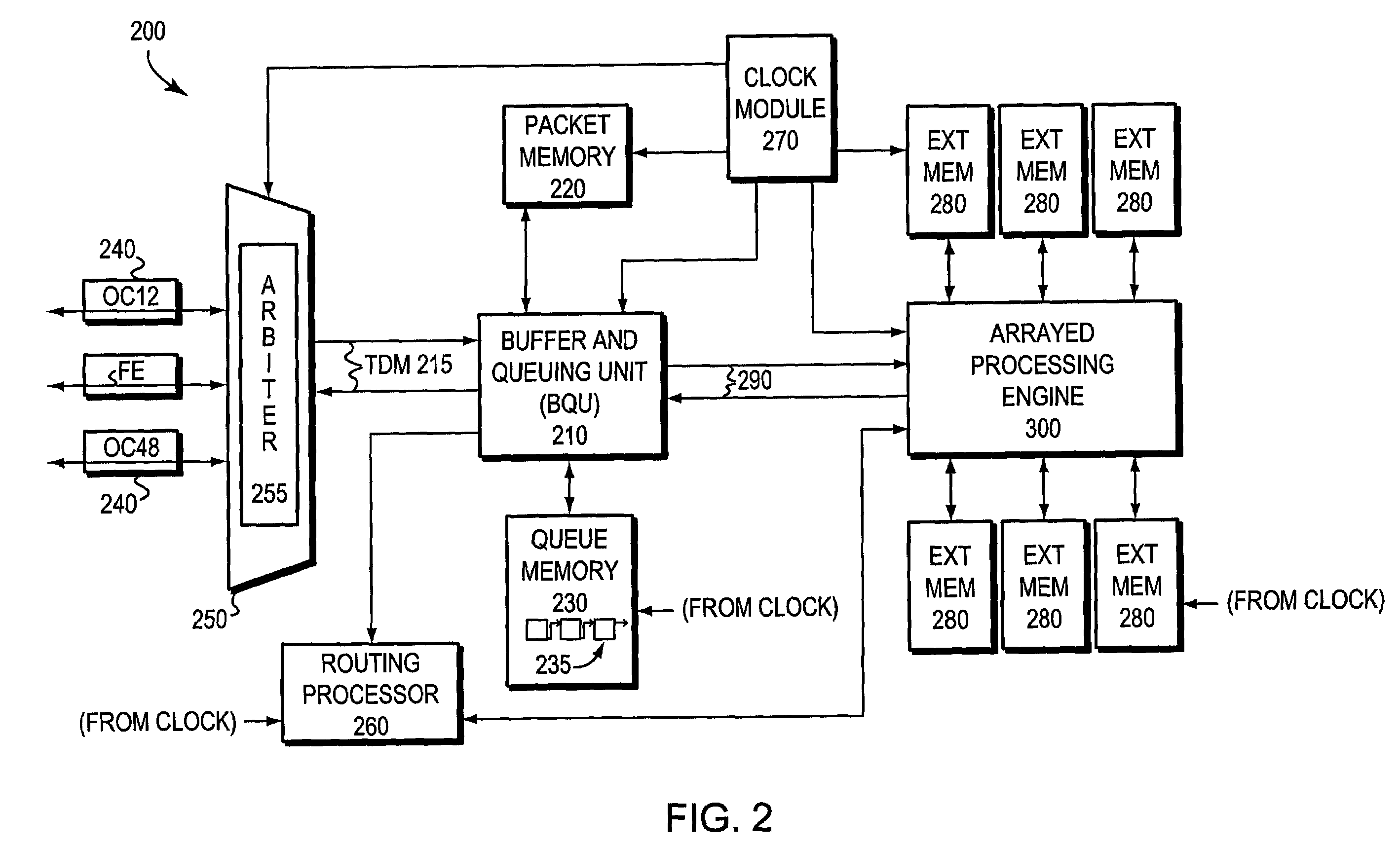

A mechanism synchronizes among processors of a processing engine in an intermediate network station. The processing engine is configured as a systolic array having a plurality of processors arrayed as rows and columns. The mechanism comprises a barrier synchronization mechanism that enables synchronization among processors of a column (i.e., different rows) of the systolic array. That is, the barrier synchronization function allows all participating processors within a column to reach a common point within their instruction code sequences before any of the processors proceed.

Owner:CISCO TECH INC

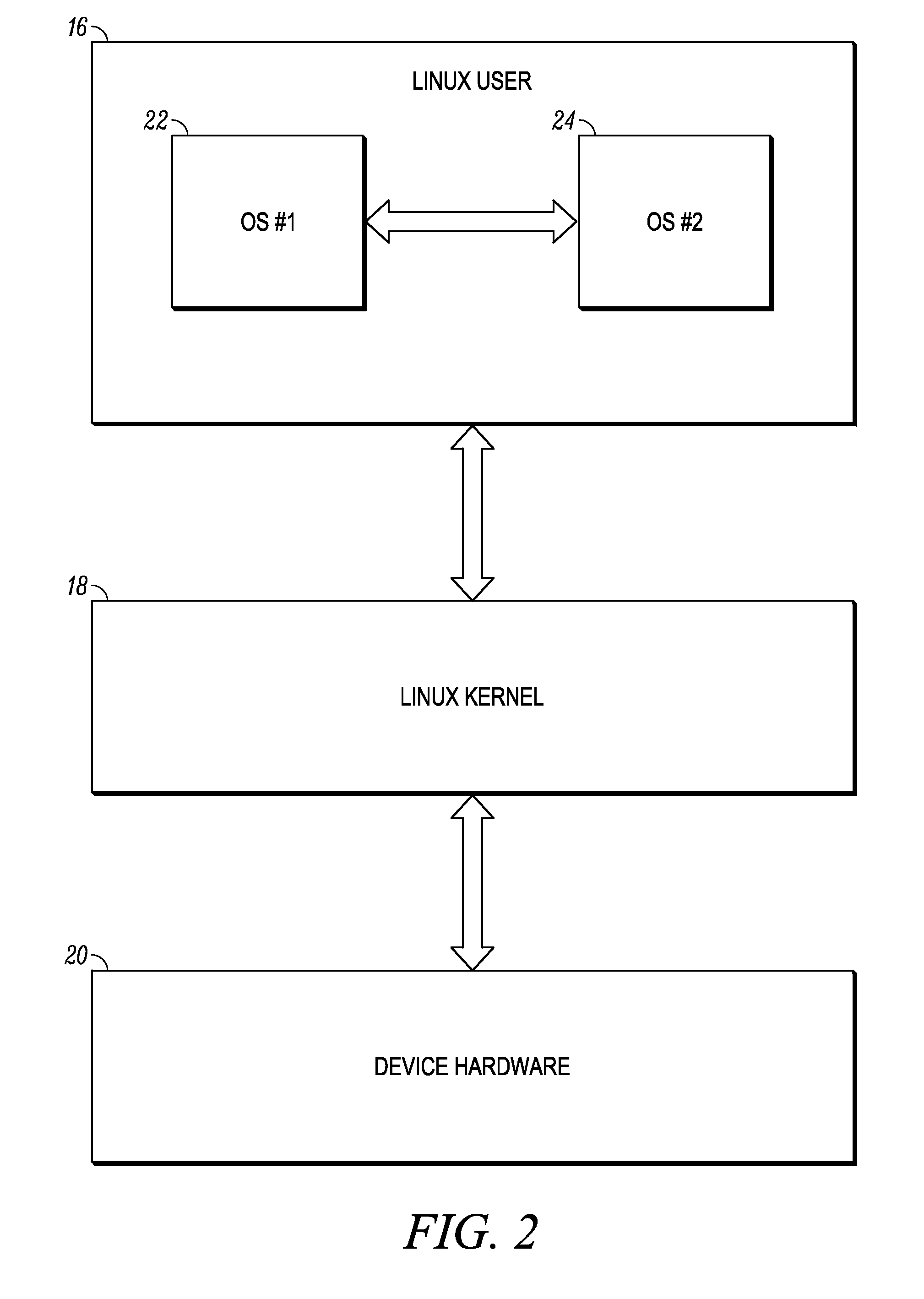

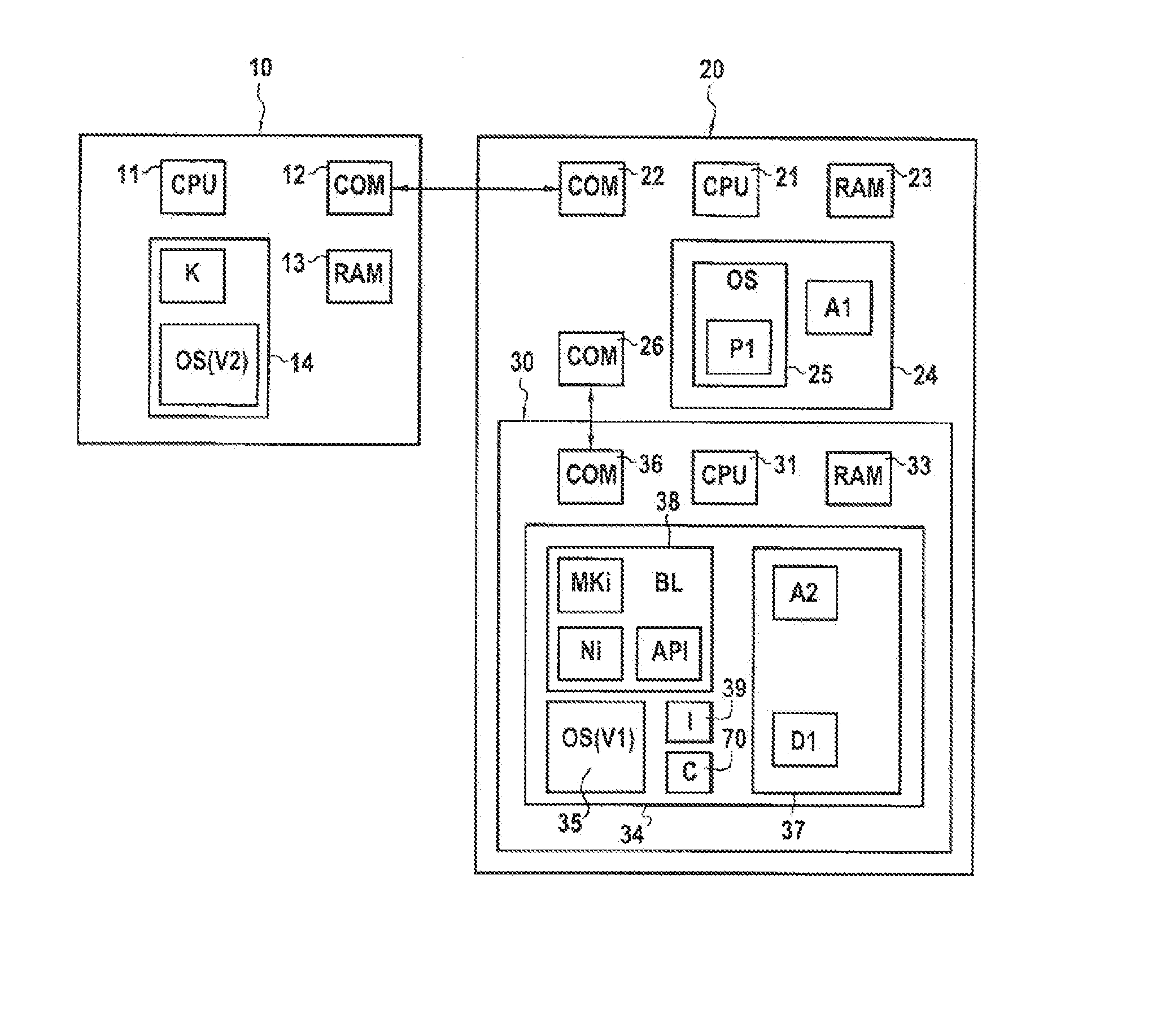

System and method for switching between environments in a multi-environment operating system

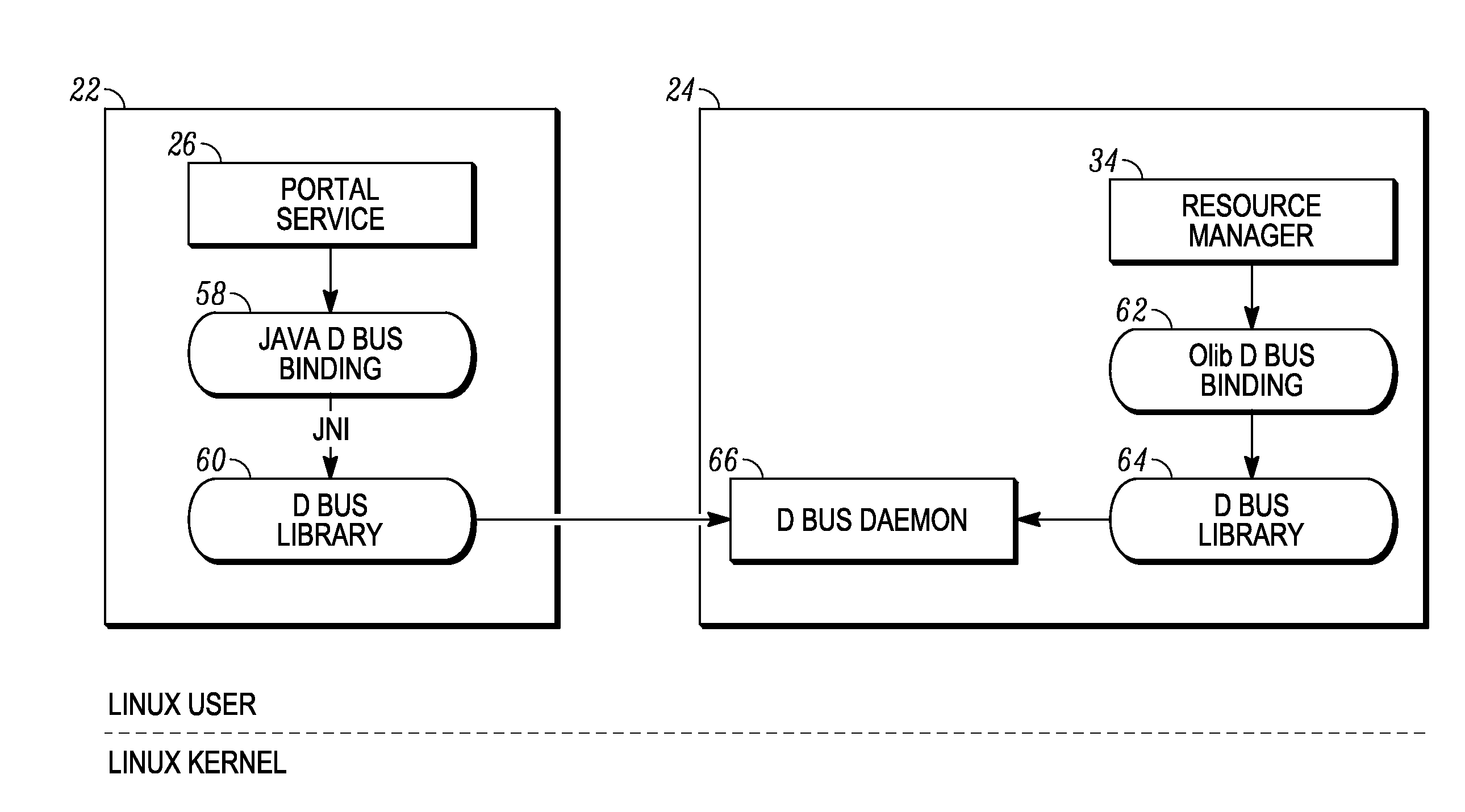

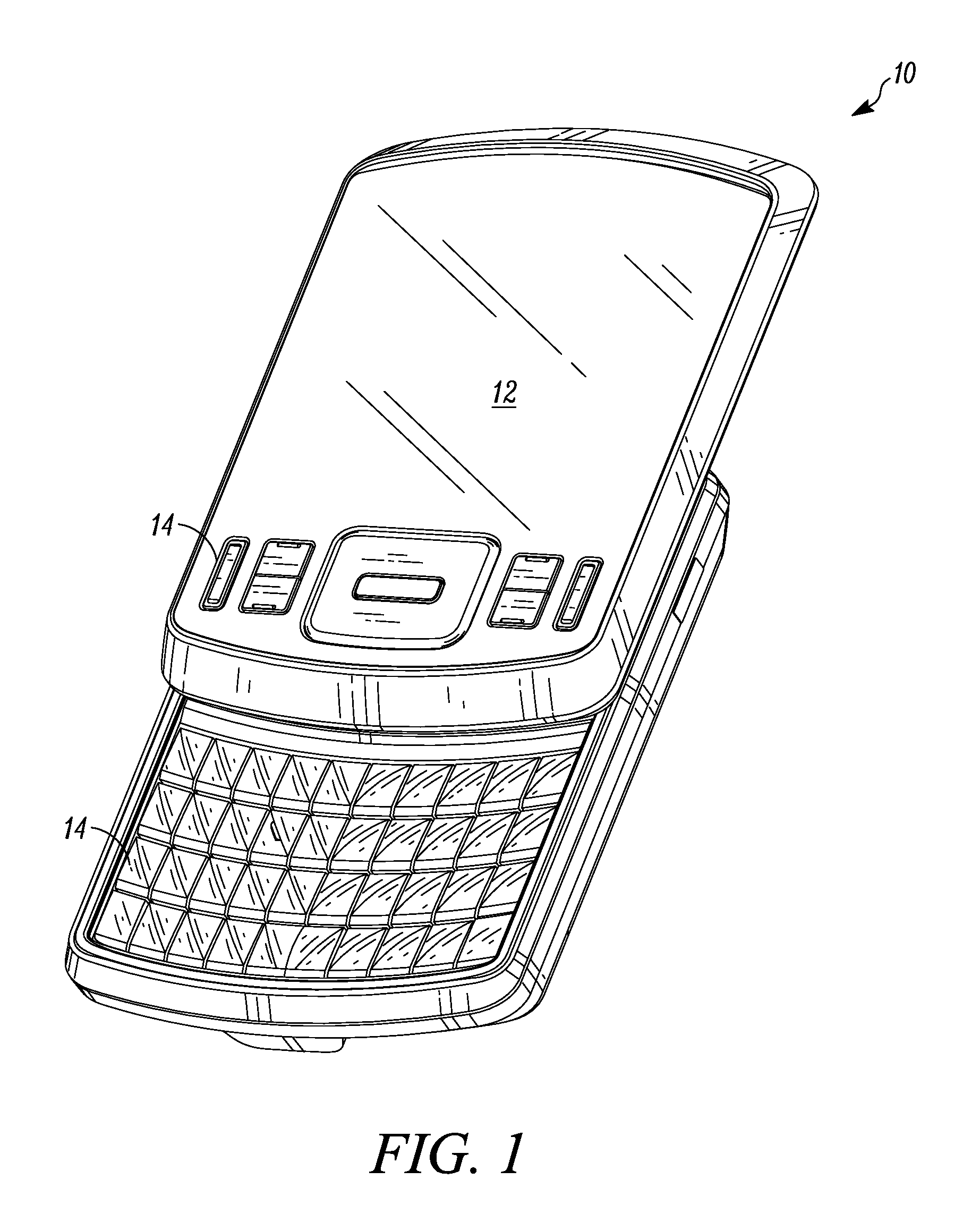

Various embodiments of the present invention provide a mobile computing device that operates multiple, co-existing and independent operating system environments on a common kernel. A booting process for initiating a multiple operating system environment is also provided. Additionally, various embodiments of the present invention include processes for managing a switch between one operating system environment to a second operating system environment.

Owner:GOOGLE TECH HLDG LLC

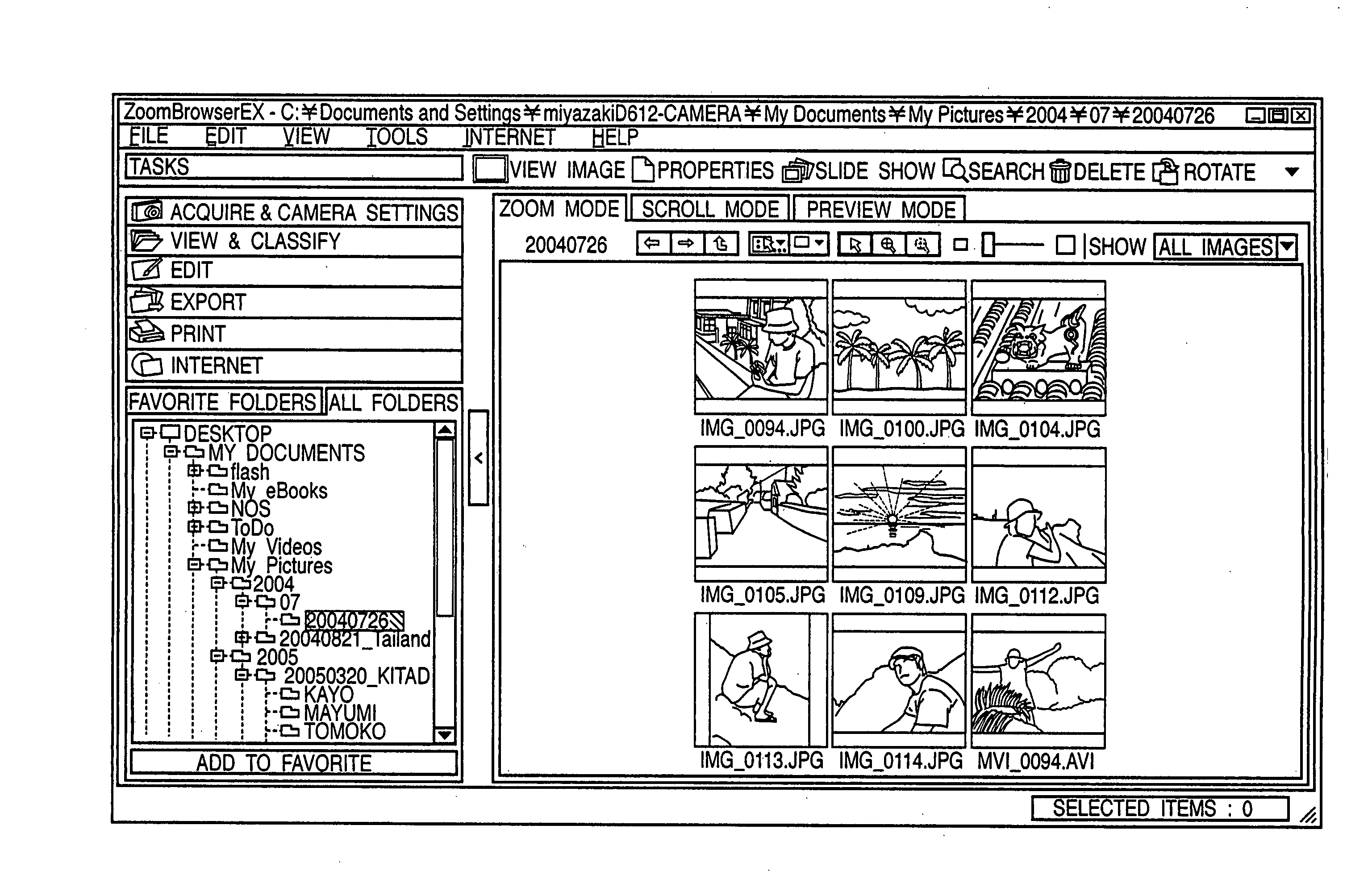

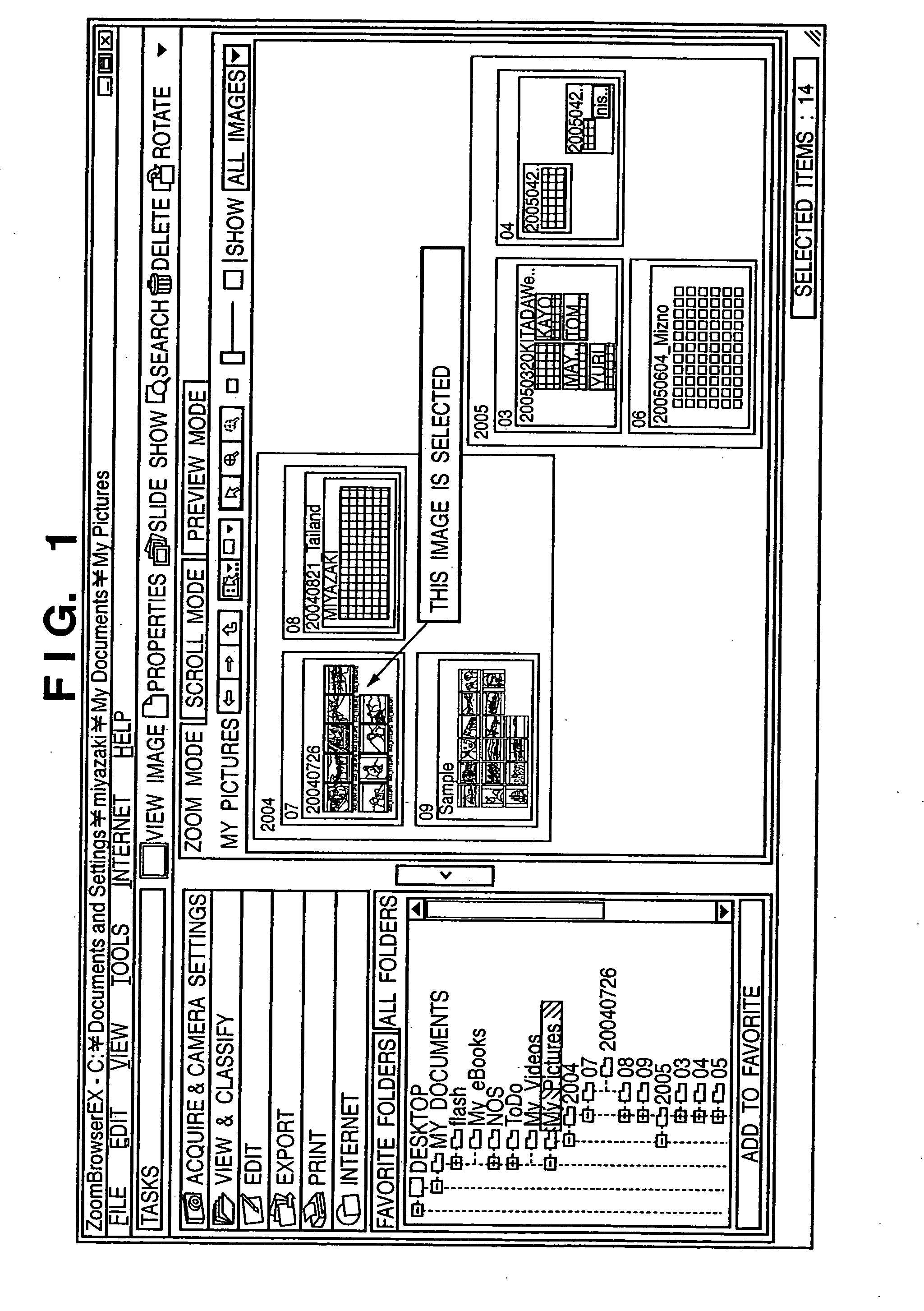

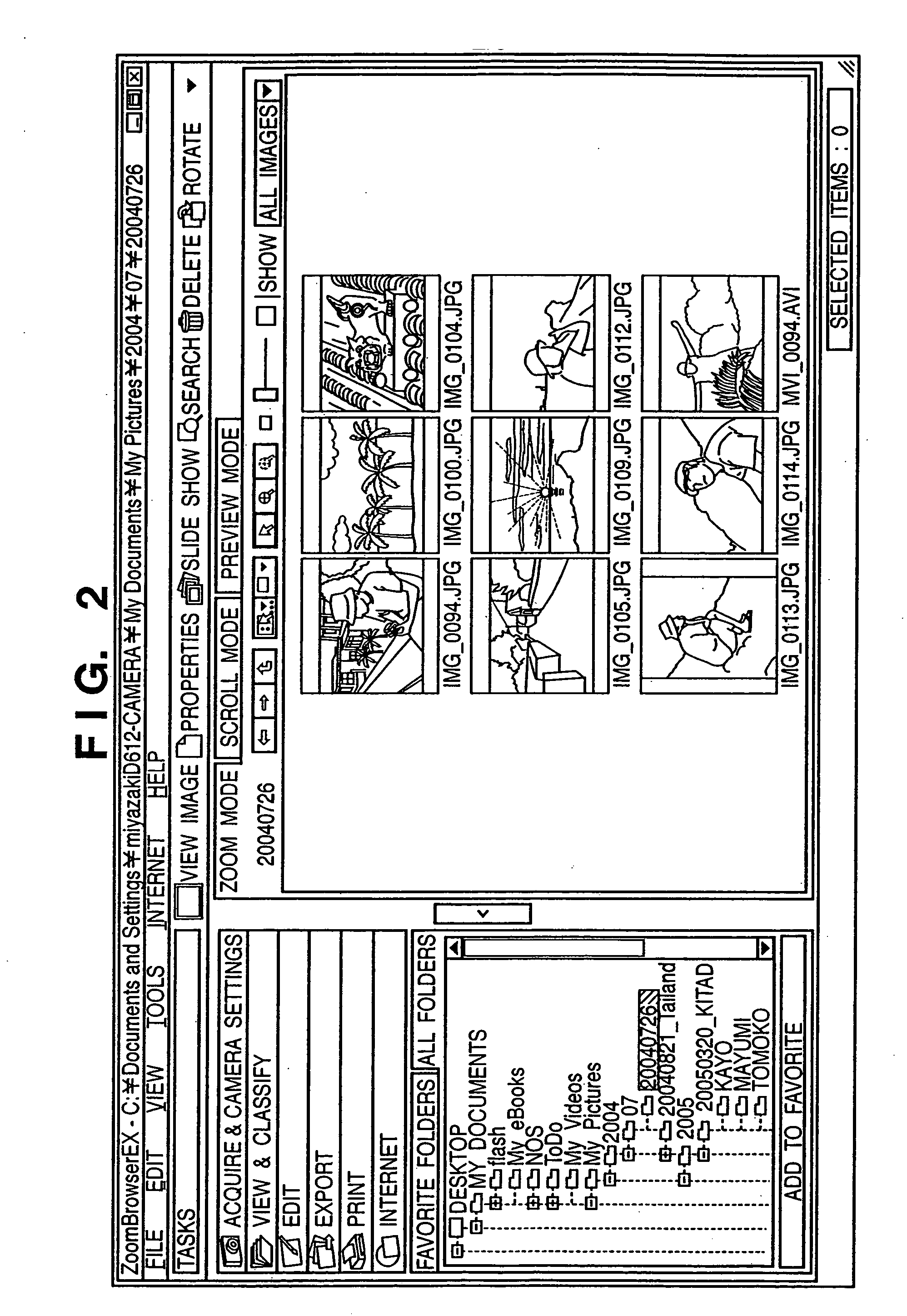

Image file management apparatus and method, program, and storage medium

ActiveUS20060044416A1Easy to identifyTelevision system detailsData processing applicationsComputer graphics (images)File transfer

An object of this invention is to easily identify an image file transferred from an image input apparatus and saved in an image file management apparatus. In an image file management method of saving an image file transferred from an image input apparatus in a folder created in accordance with the photographing date information of the image file, when transferred image files include one kind of photographing date, one kind of folder to save the image files is displayed on a screen as a current folder. When a plurality of kinds of photographing dates are present, a folder of an upper hierarchy which includes a plurality of folders created in correspondence with the plurality of kinds of photographing dates is displayed on the screen as the current folder.

Owner:CANON KK

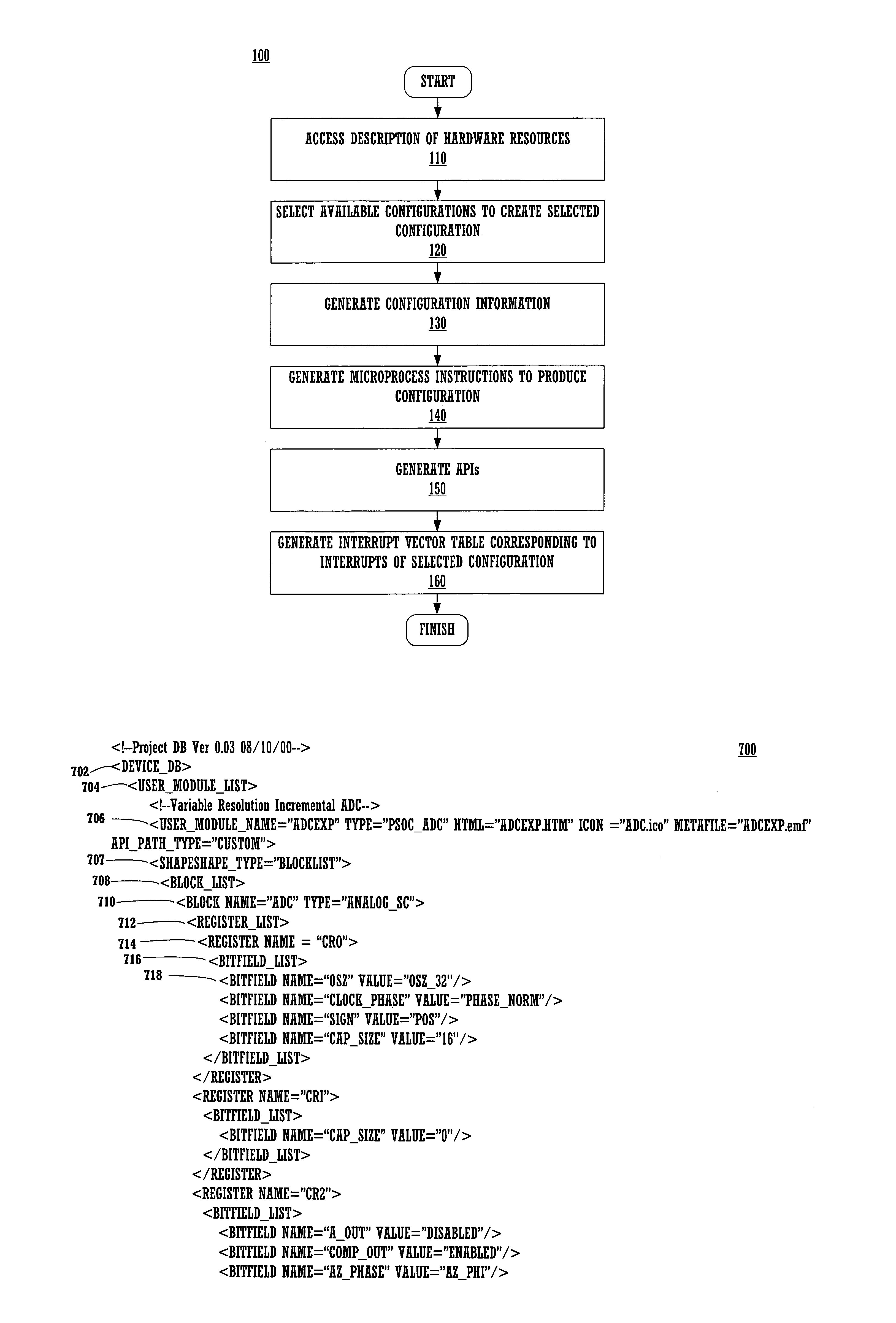

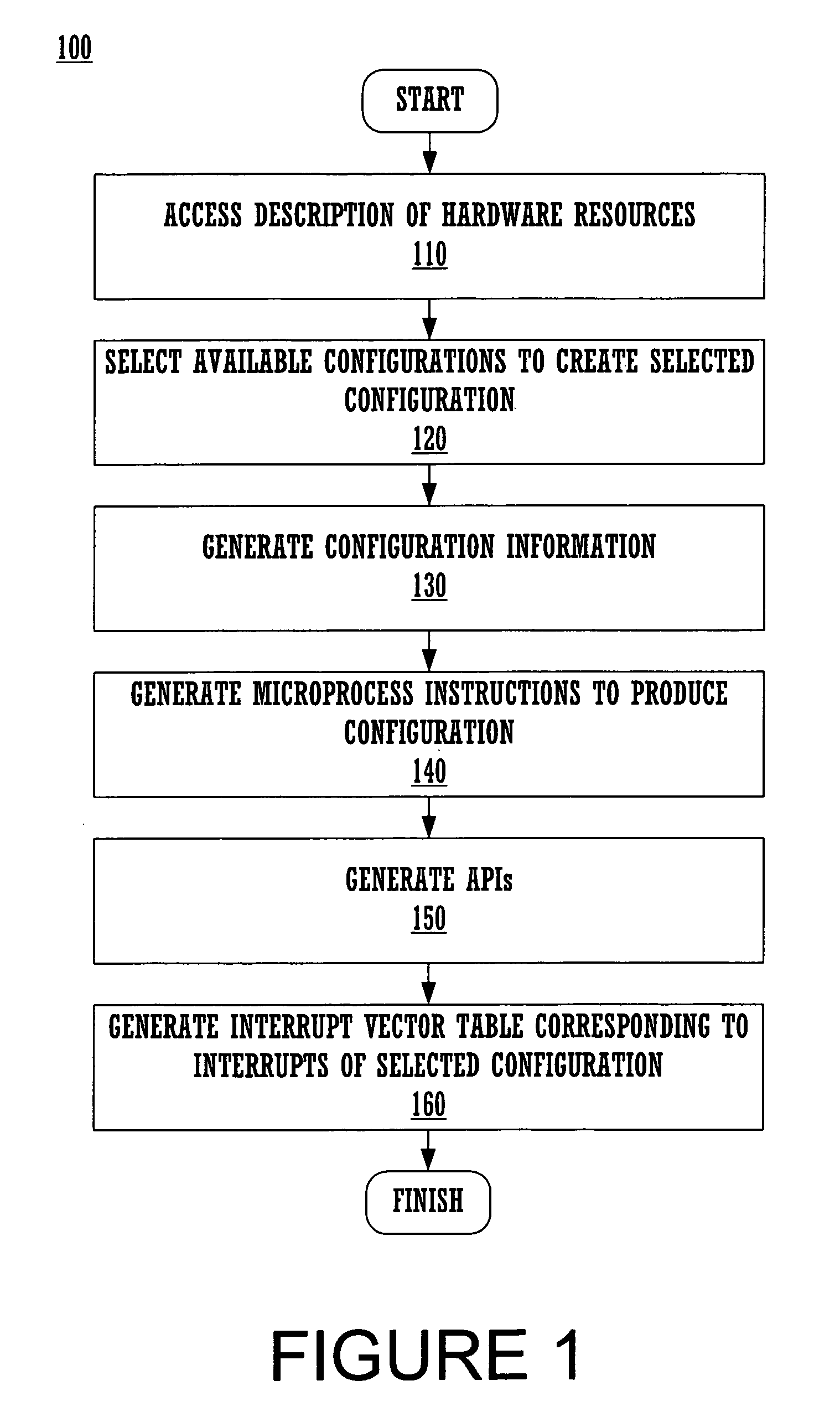

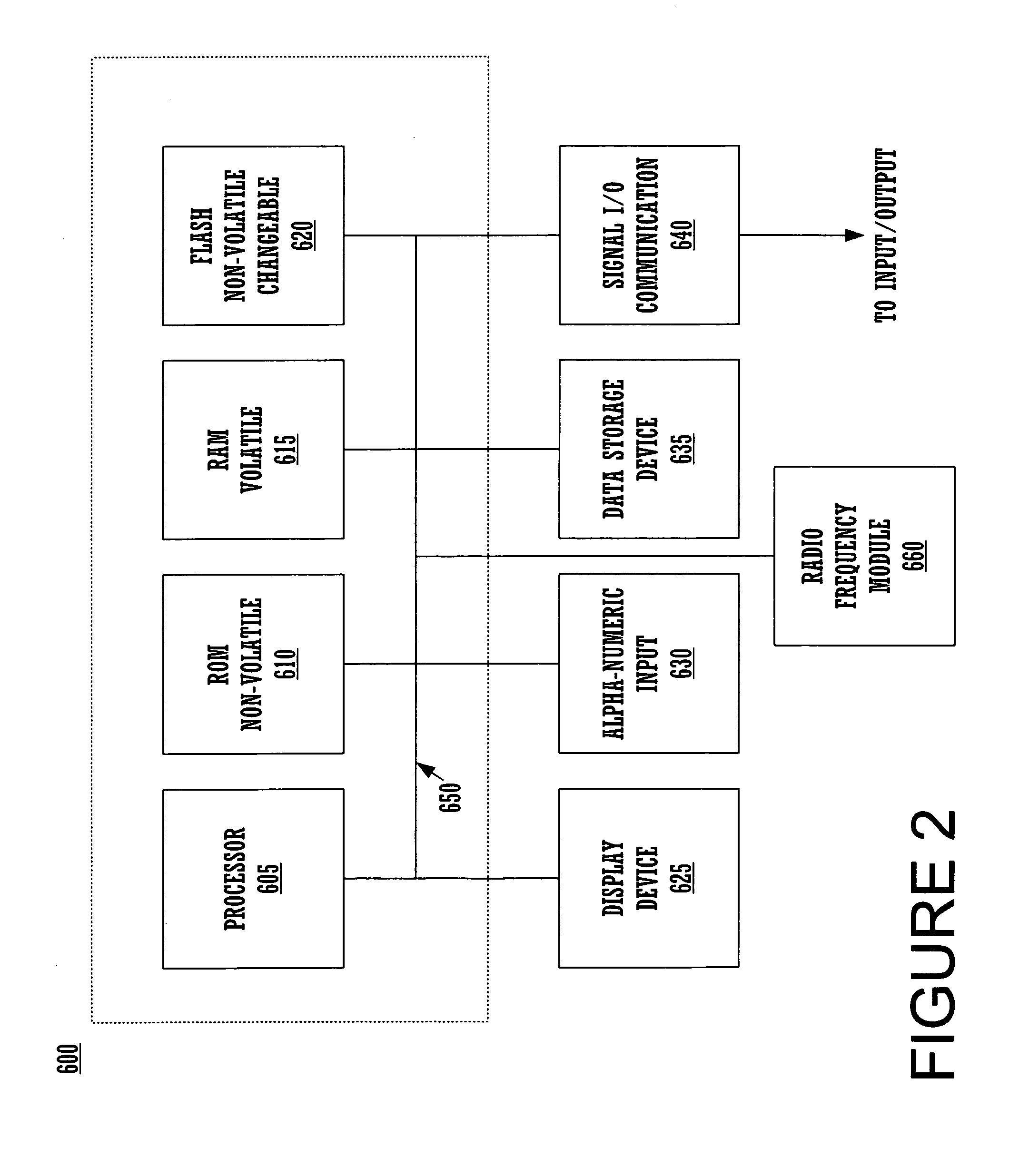

Method and apparatus for generating microcontroller configuration information

ActiveUS7406674B1Improve usabilityIncreased complexityCAD circuit designVisual/graphical programmingMicrocontrollerApplication programming interface

A method and apparatus for configuring a microcontroller. An XML description of the microcontroller's hardware resources may be accessed. A user may select from available hardware resources and pre-defined user modules to select a configuration. Configuration information, which may include register bit patterns and microprocessor instructions, may be automatically generated. Additionally, application programming interface calls and structure, as well as interrupt vector tables may be automatically generated. Embodiments of the present invention provide improved ease of use and the ability to manage greater complexity in the configuration of configurable microcontrollers.

Owner:CYPRESS SEMICON CORP

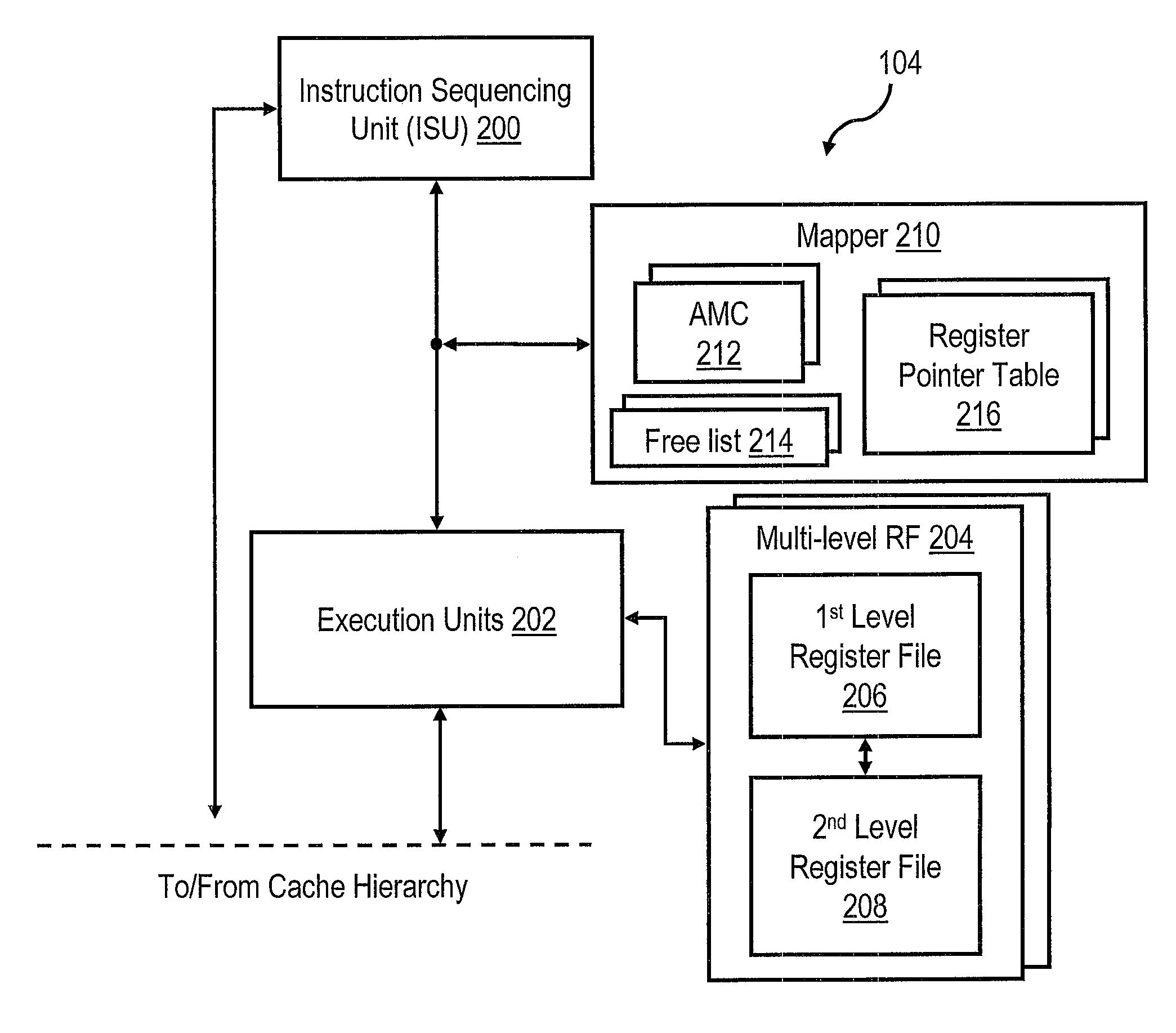

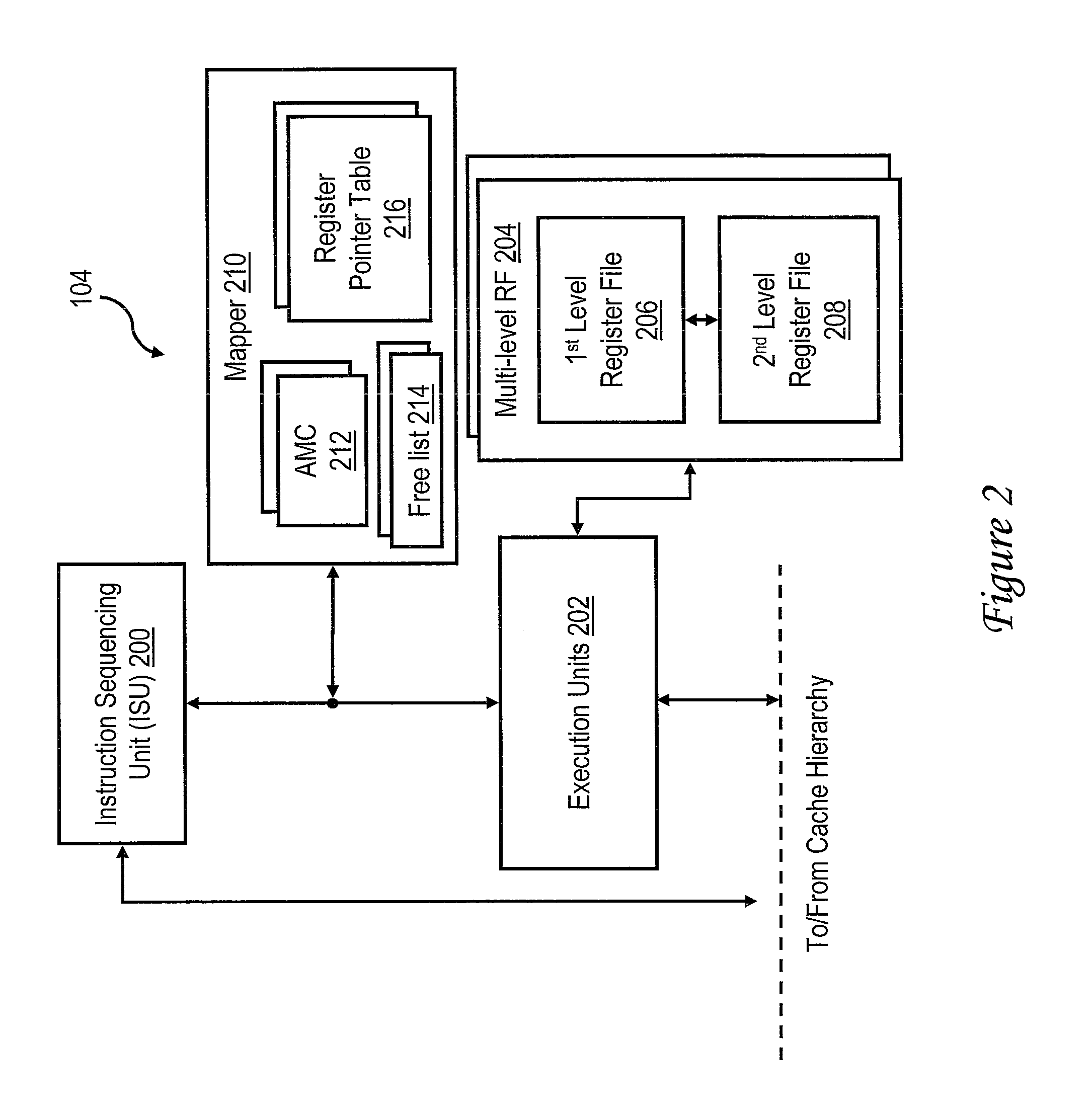

Register file supporting transactional processing

InactiveUS20110283096A1Digital computer detailsMicrocontrol arrangementsProcessor registerExecution unit

A processor includes an instruction sequencing unit, execution unit, and multi-level register file including a first level register file having a lower access latency and a second level register file having a higher access latency. Responsive to the processor processing a second instruction in a transactional code section to obtain as an execution result a second register value of the logical register, the mapper moves a first register value of the logical register to the second level register file, places the second register value in the first level register file, marks the second register value as speculative, and replaces a first mapping for the logical register with a second mapping. Responsive to unsuccessful termination of the transactional code section, the mapper designates the second register value in the first level register file as invalid so that the first register value in the second level register file becomes the working value.

Owner:IBM CORP

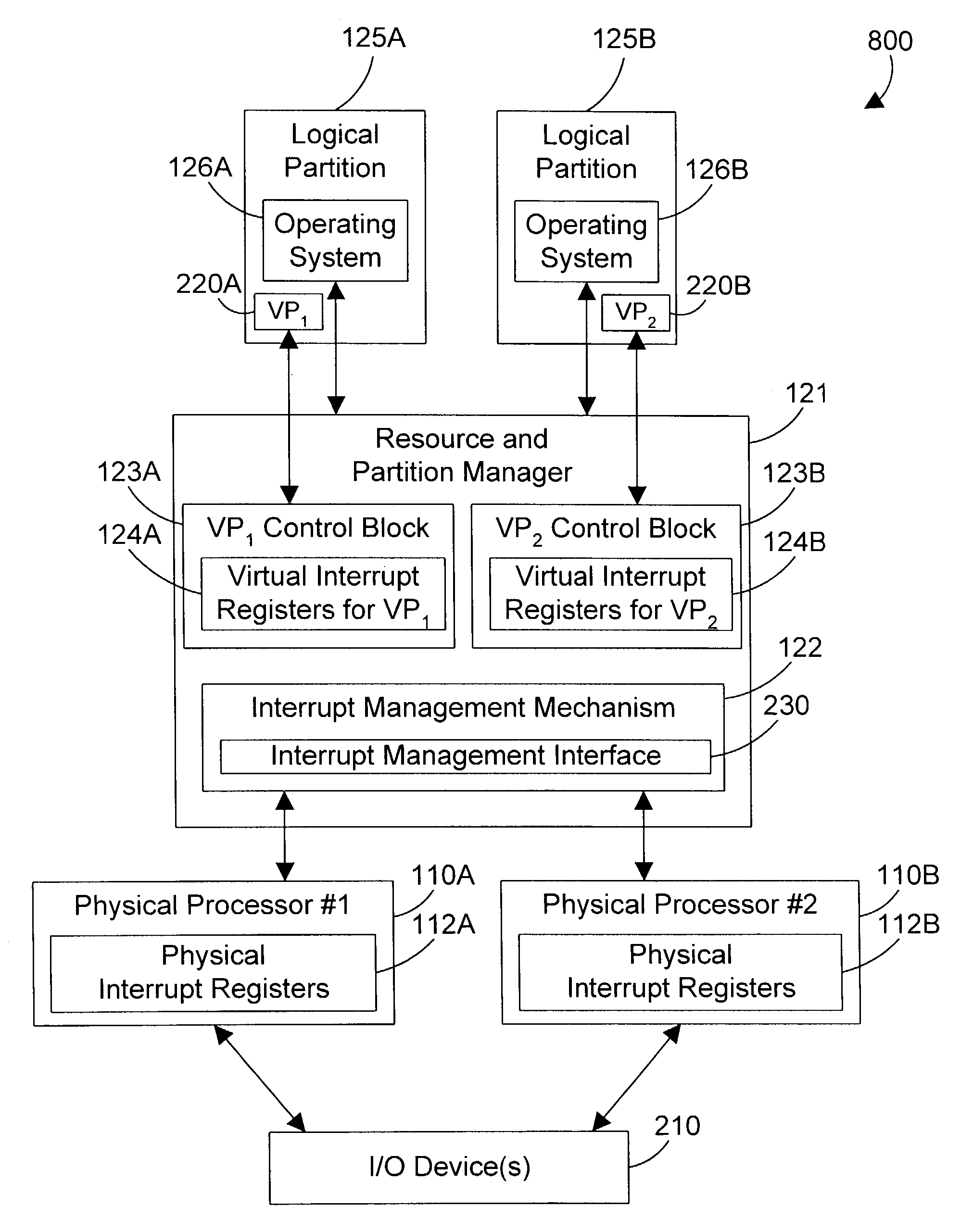

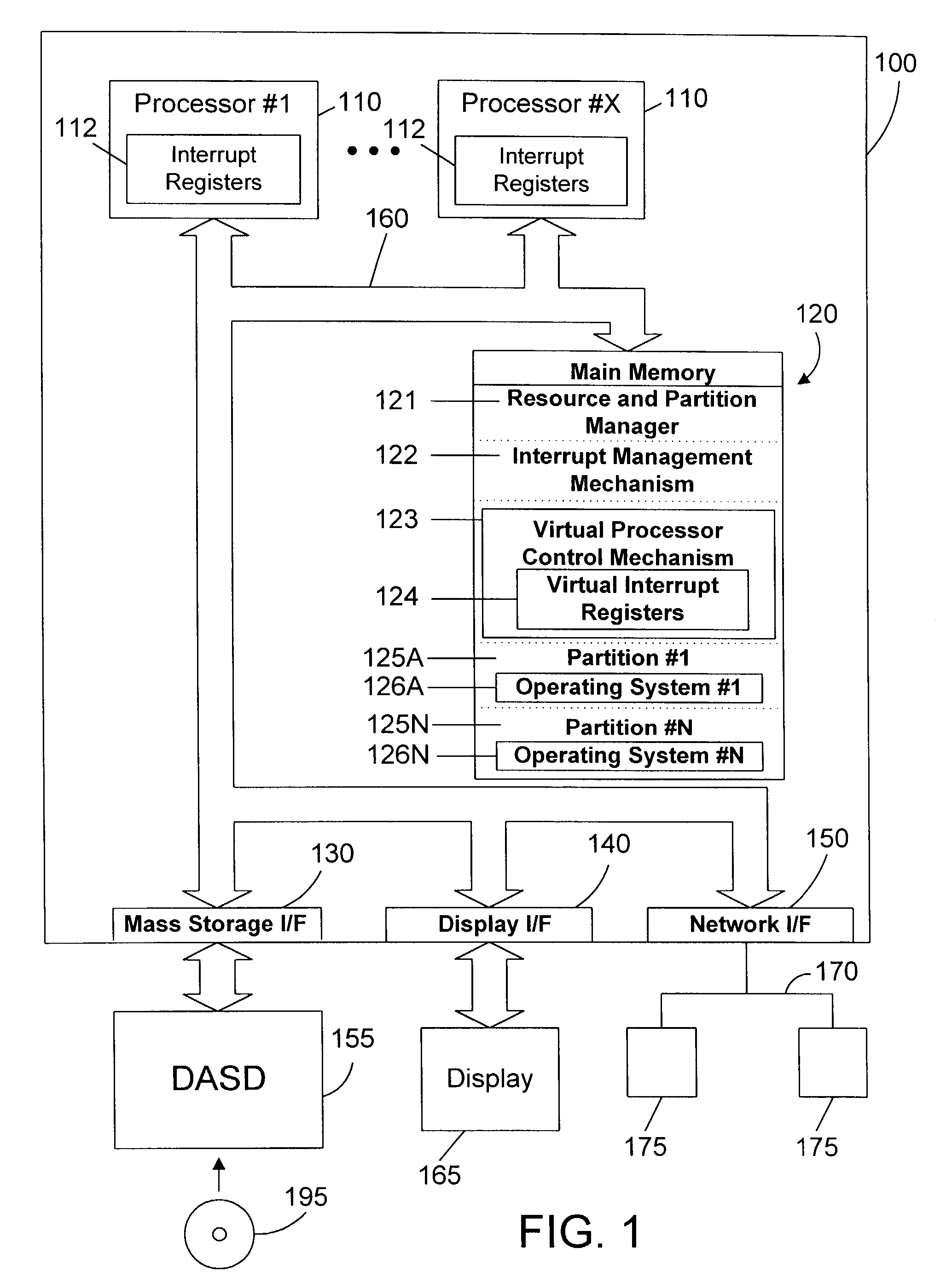

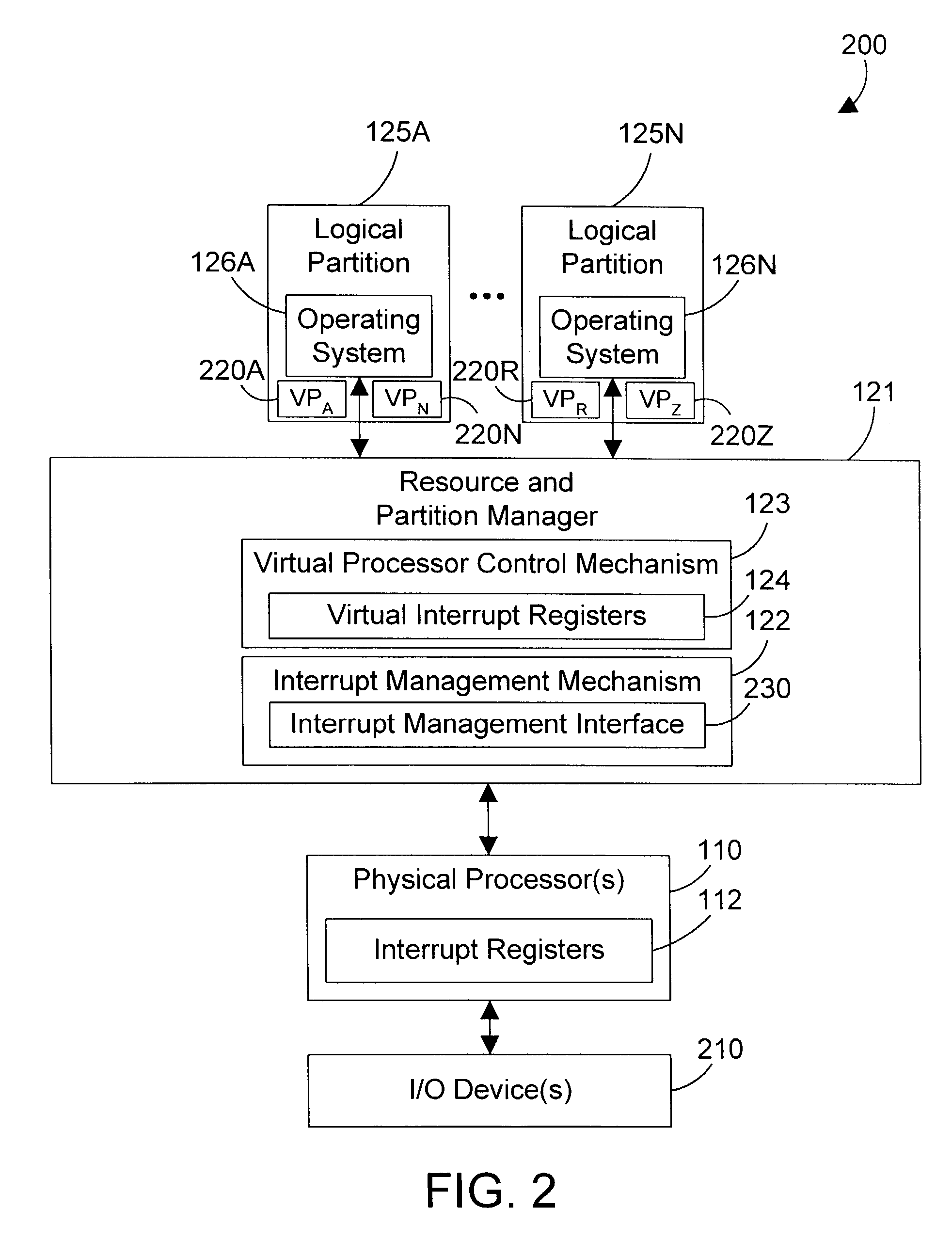

Apparatus and method for virtualizing interrupts in a logically partitioned computer system

A resource and partition manager virtualizes interrupts without using any additional hardware in a way that does not disturb the interrupt processing model of operating systems running on a logical partition. In other words, the resource and partition manager supports virtual interrupts in a logically partitioned computer system that may include share processors with no changes to a logical partition's operating system. A set of virtual interrupt registers is created for each virtual processor in the system. The resource and partition manager uses the virtual interrupt registers to process interrupts for the corresponding virtual processor. In this manner, from the point of view of the operating system, the interrupt processing when the operating system is running in a logical partition that may contain shared processors and virtual interrupts is no different that the interrupt processing when the operating system is running in computer system that only contains dedicated processor partitions.

Owner:IBM CORP

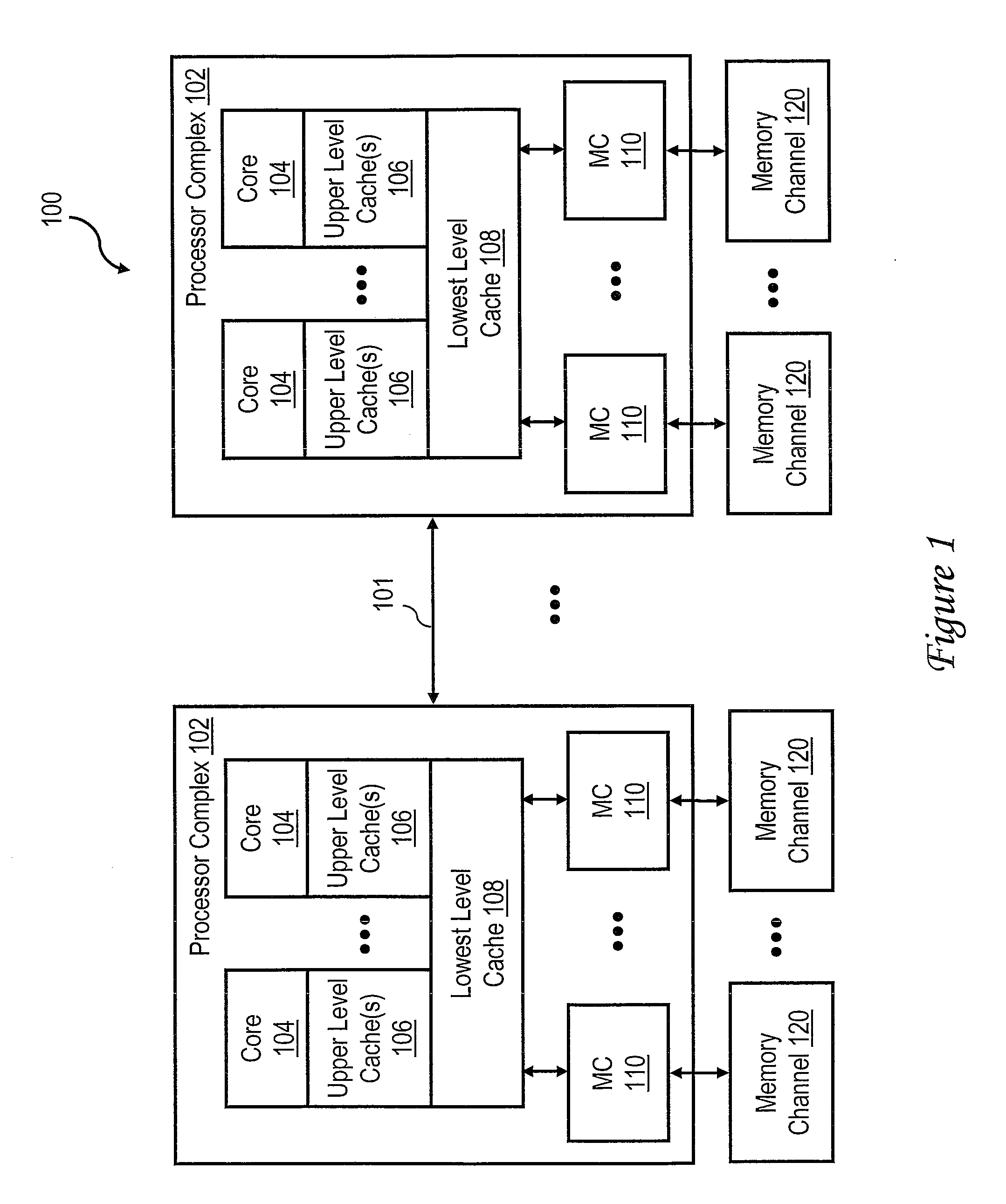

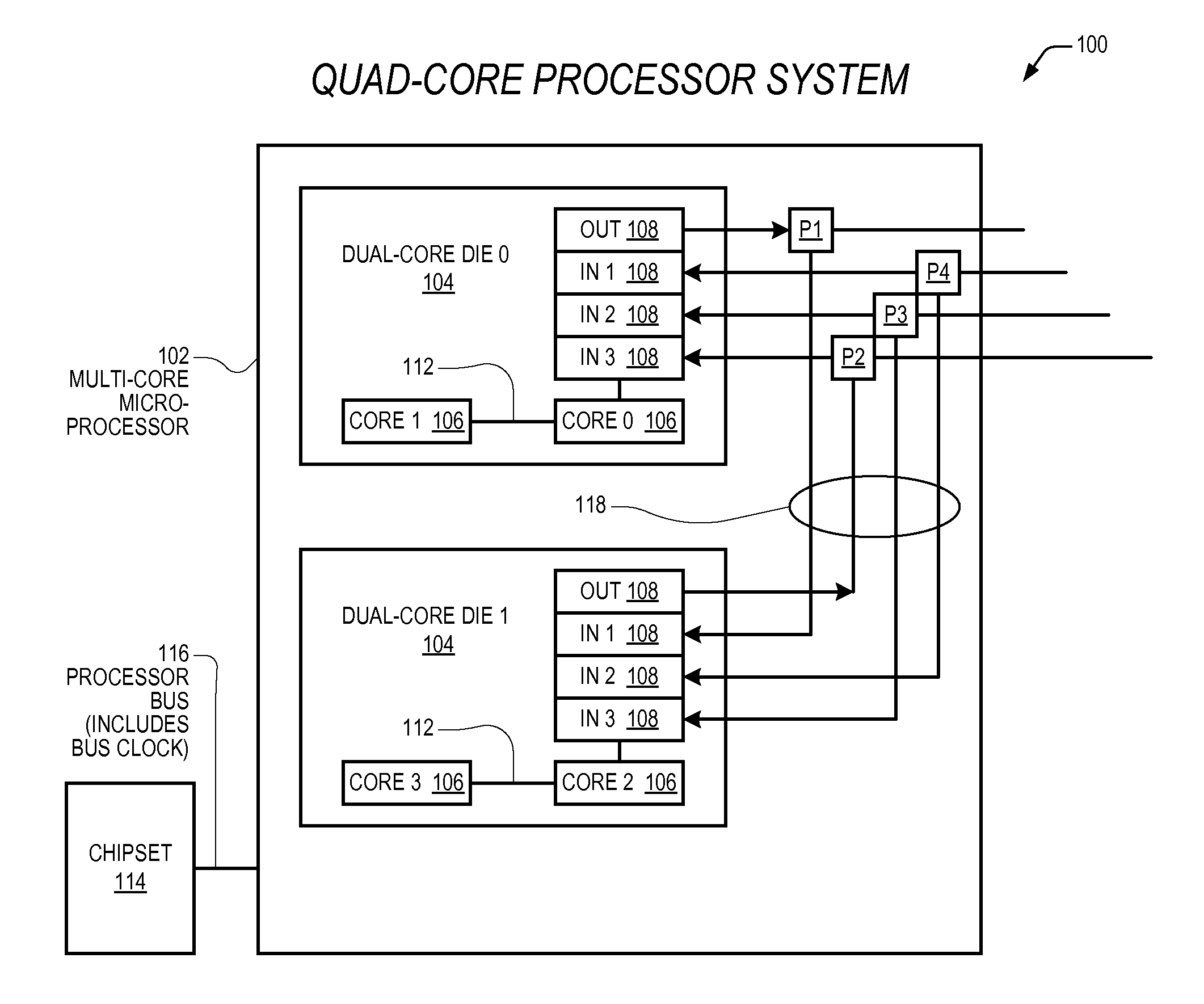

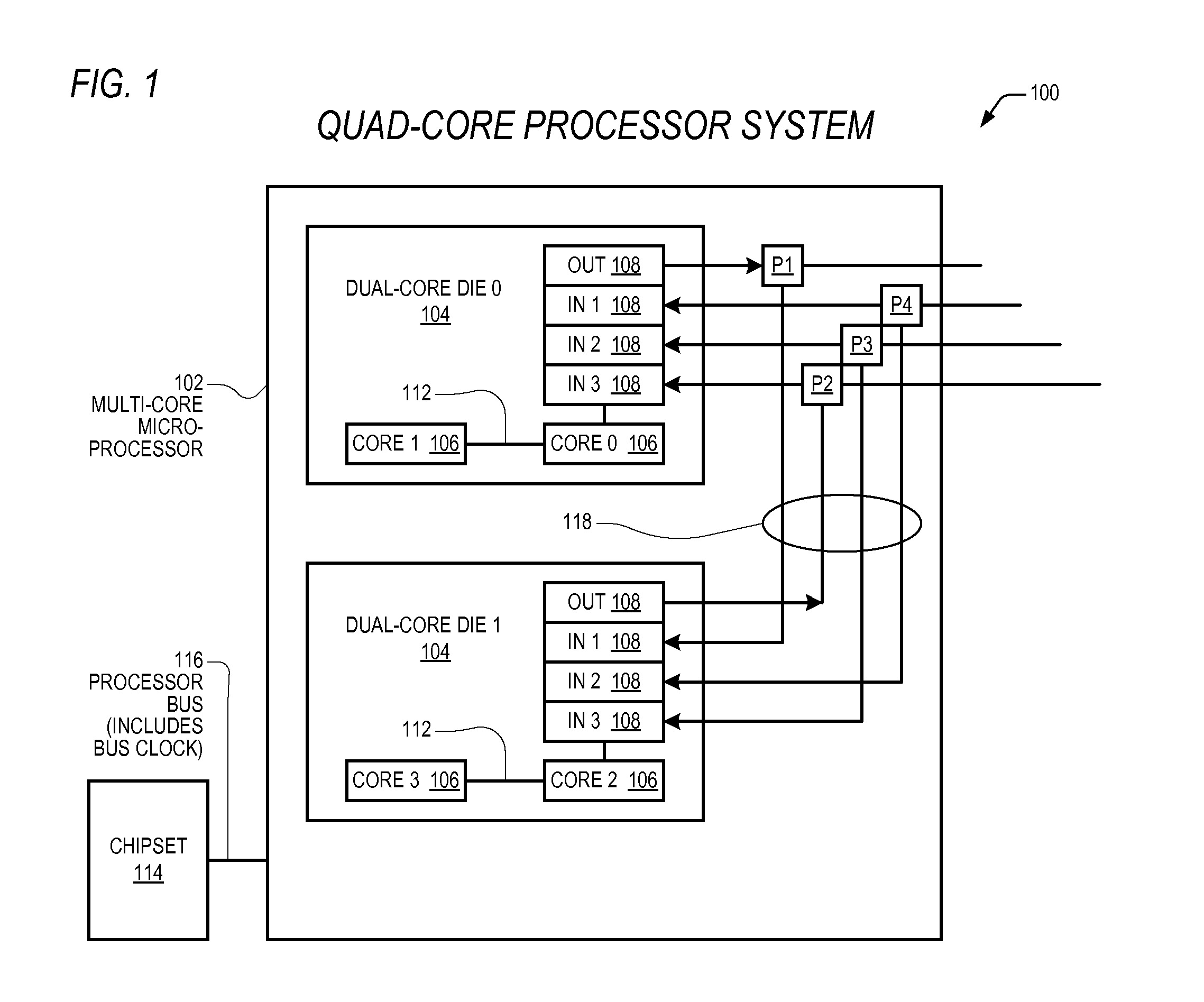

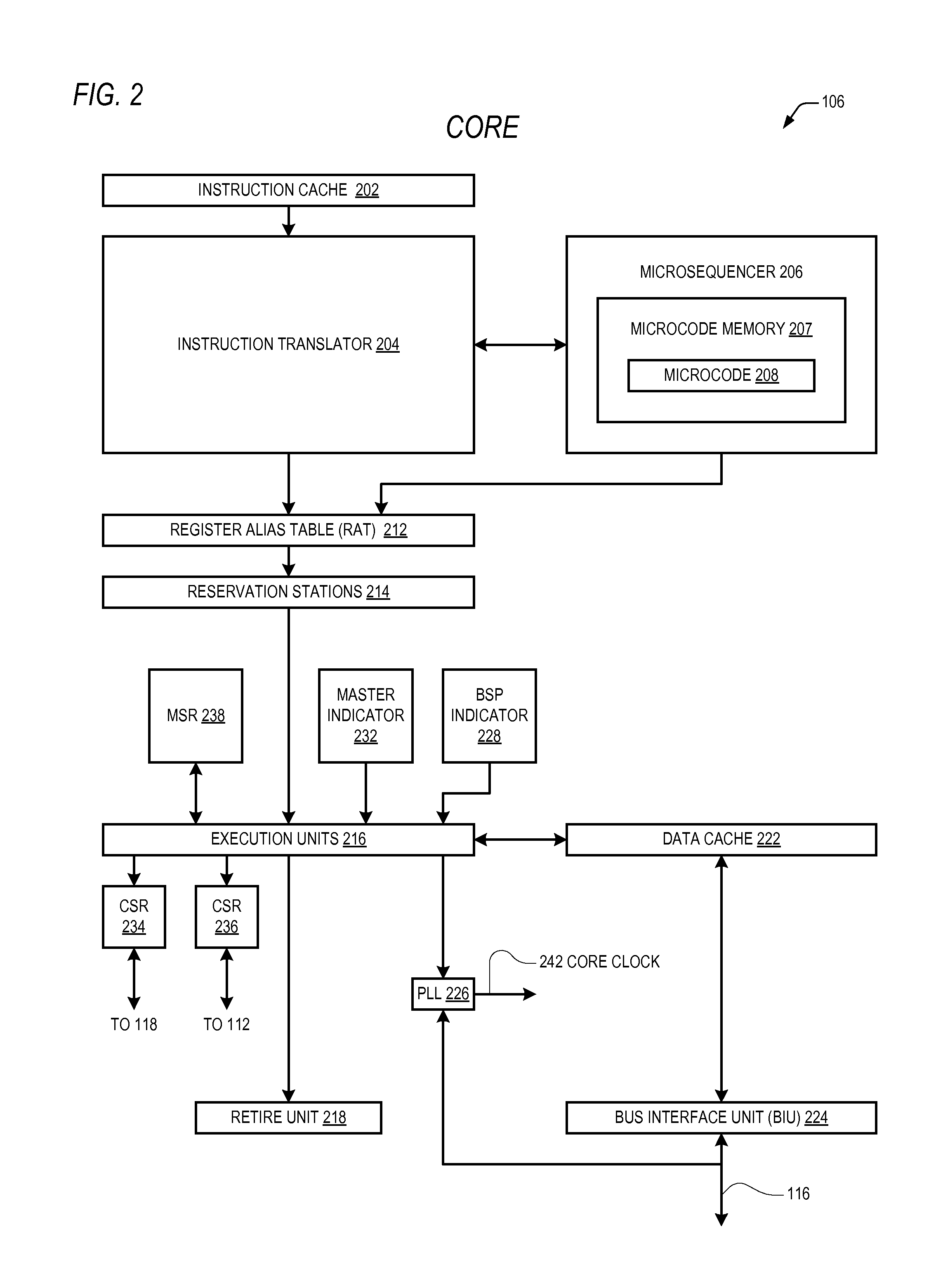

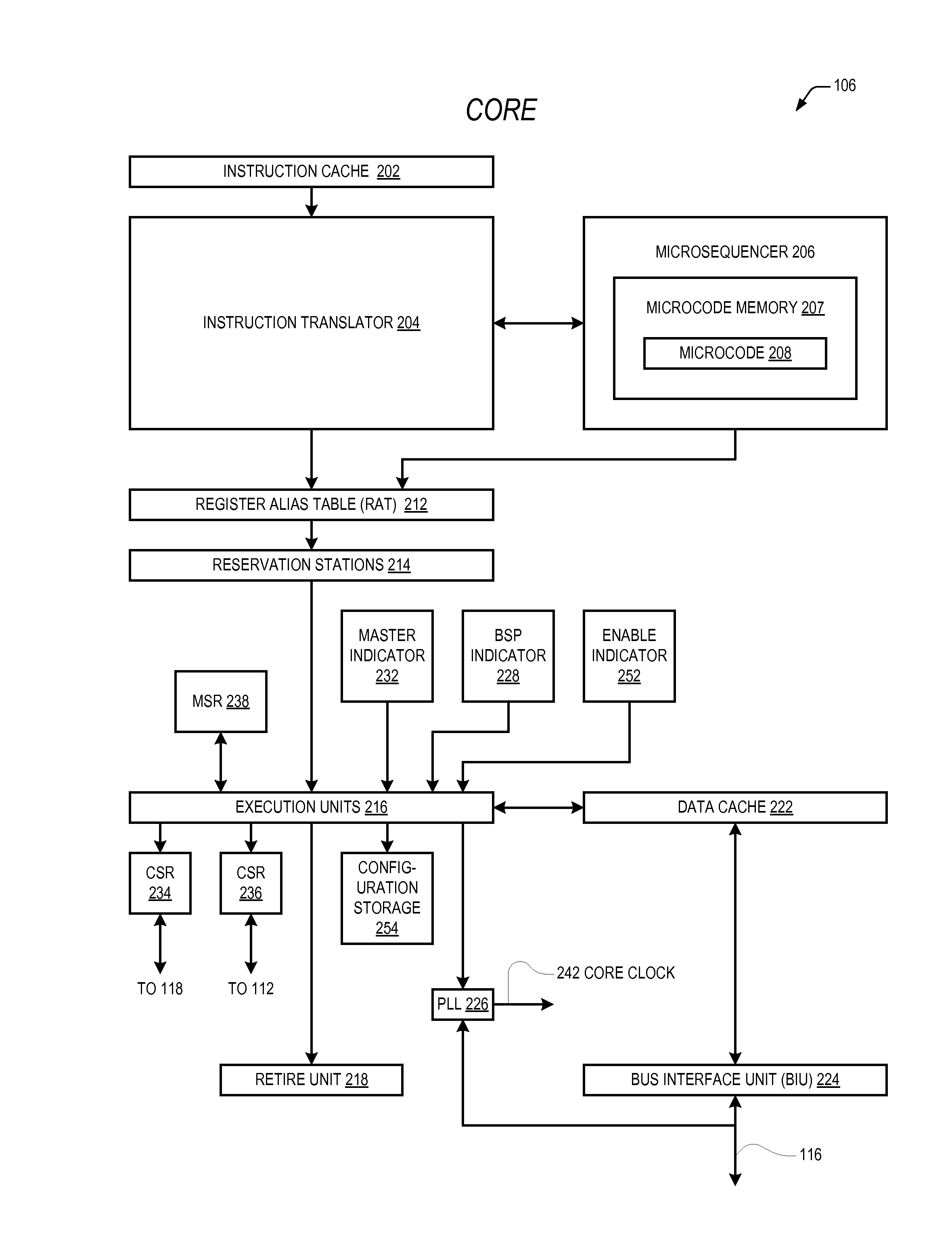

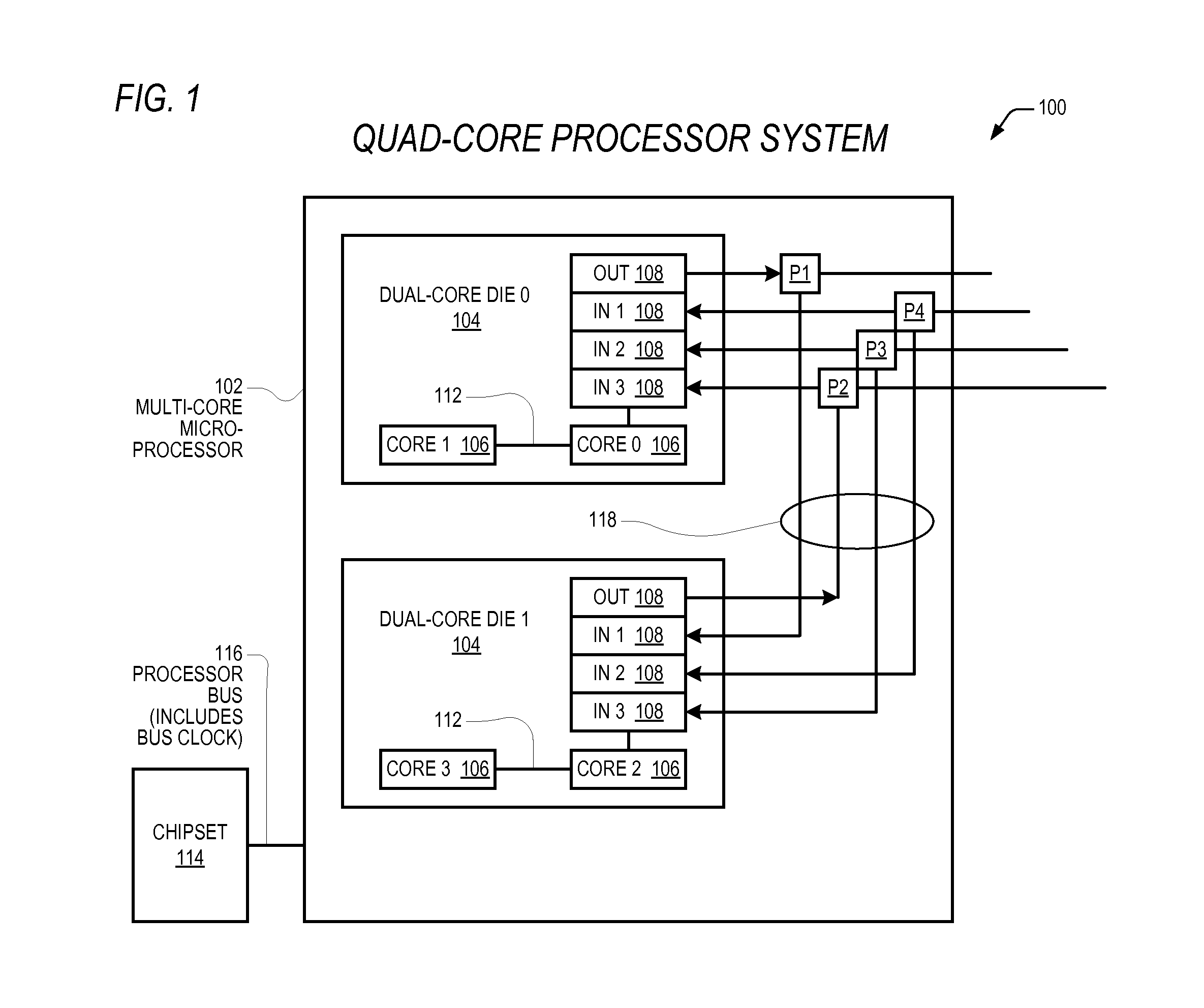

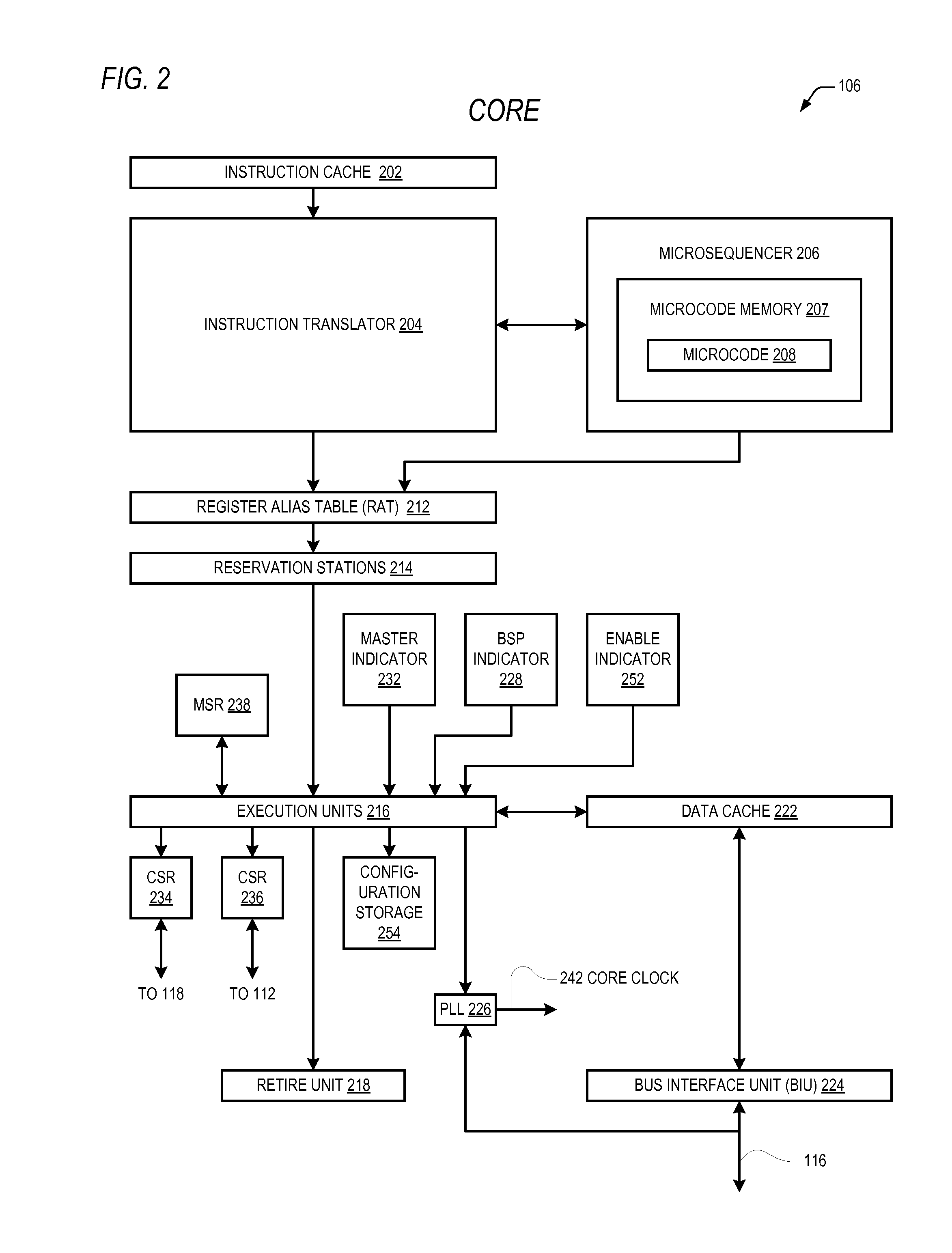

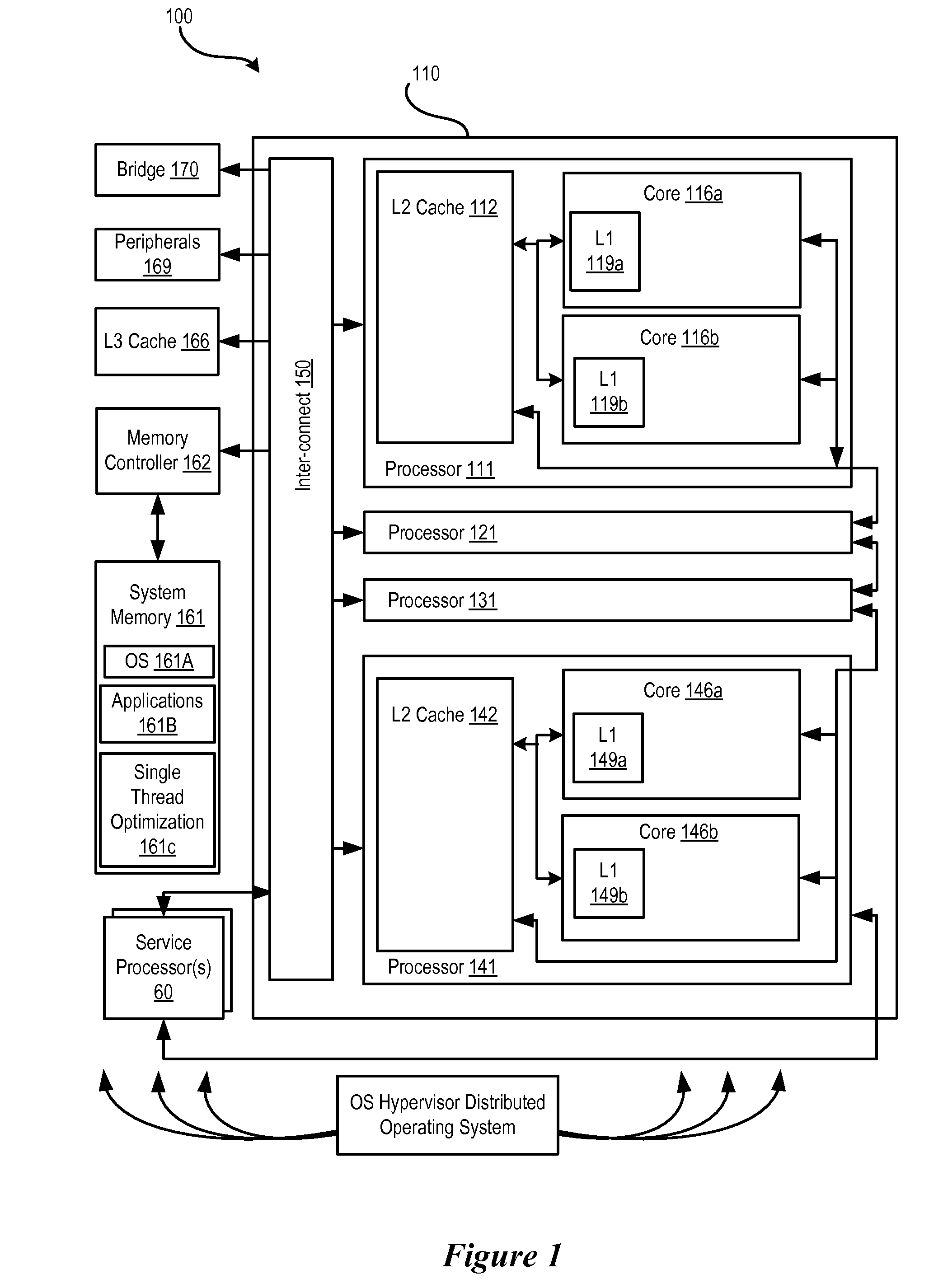

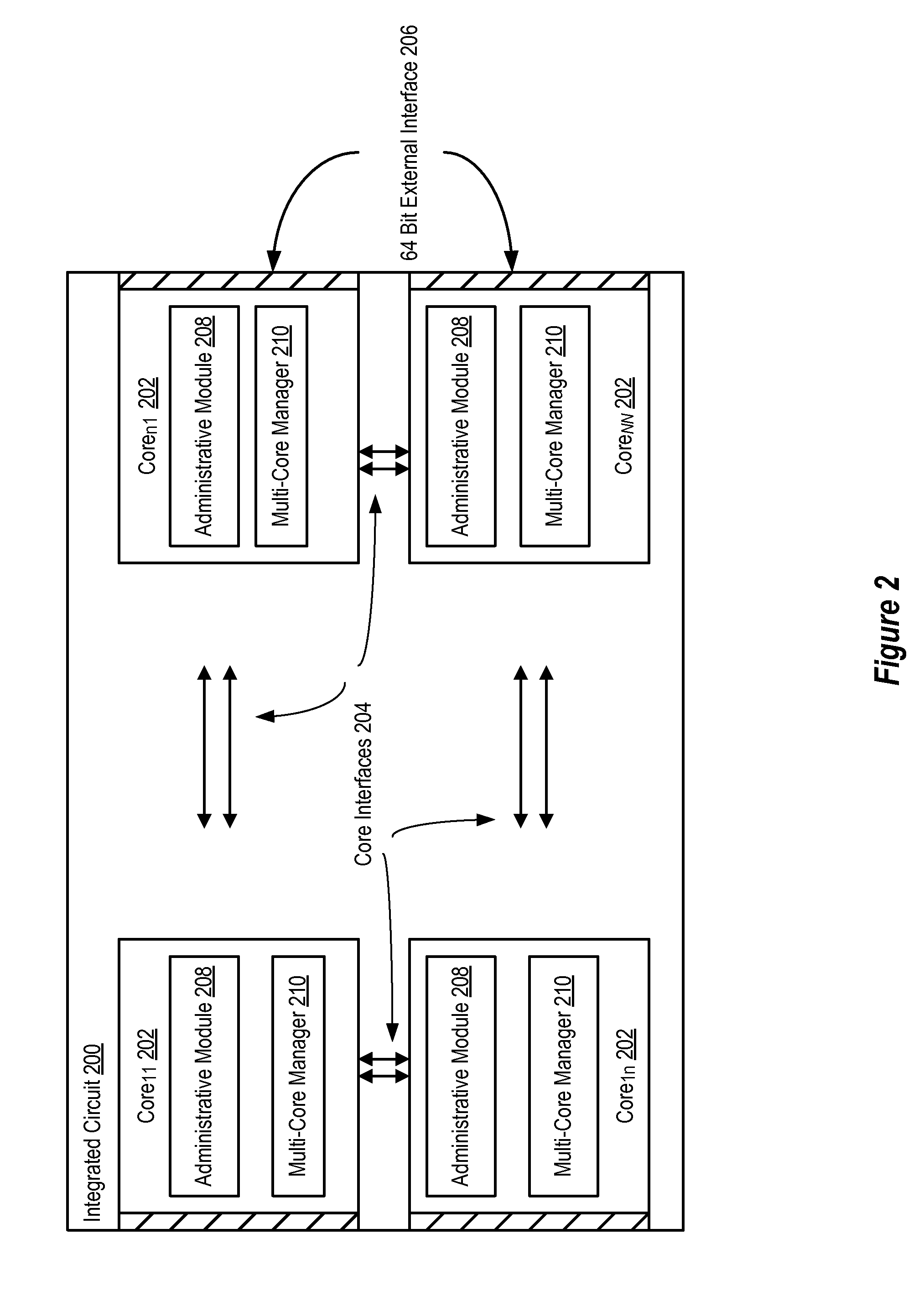

Power state synchronization in a multi-core processor

ActiveUS20120166845A1Energy efficient ICTVolume/mass flow measurementComputer architectureStructure of Management Information

A multi-core processor includes microcode distributed in each core enabling each core to participate in a de-centralized inter-core state discovery process. In a related microcode-implemented method, states of a multi-core processor are discovered by at least two cores participating in a de-centralized inter-core state discovery process. The inter-core state discovery process is carried out through a combination of microcode executing on each participating core and signals exchanged between the cores through sideband non-system-bus communication wires. The discovery process is unmediated by any centralized non-core logic. Applicable discoverable states include target and composite power states, whether and how many cores are enabled, the availability and distribution of various resources, and hierarchical structures and coordination systems for the cores. The inter-core state discovery process may be carried out in accordance with various hierarchical coordination systems involving chained inter-core communications.

Owner:VIA TECH INC

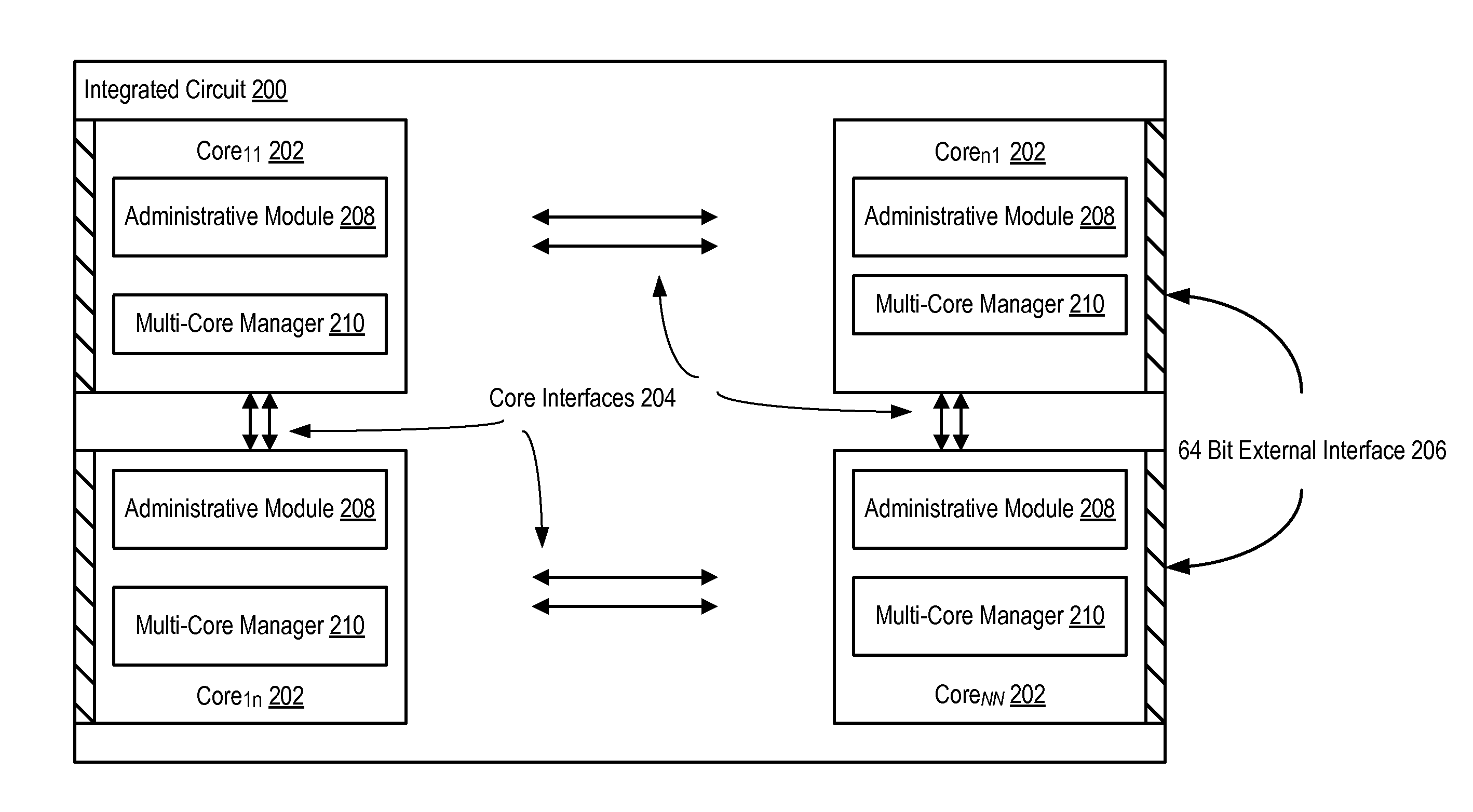

Dynamic multi-core microprocessor configuration discovery

ActiveUS20120166763A1Digital data processing detailsGeneral purpose stored program computerState managementVoltage source

A core configuration discovery method and corresponding microprocessor are provided that does not rely on off-core logic or queries by system BIOS. Reset microcode is provided in the microprocessor's cores. Upon reset, the microcode queries and / or receives from other cores configuration-revealing information and collects the configuration-revealing information to determine a composite core configuration for the microprocessor. The composite core configuration may reveal the number of enabled cores, identify the enabled cores, reveal a hierarchical coordination system of the multi-core processor, such as a nodal map of the cores for certain inter-core communication processes or restricted activities, identify various domains and domain masters within such a system, and / or identify resources, such as voltage sources, clock sources, and caches, shared by various domains of the microprocessor. The composite core configuration may be used for power state management, reconfiguration, and other purposes.

Owner:VIA TECH INC

Multicore Processor And Method Of Use That Configures Core Functions Based On Executing Instructions

InactiveUS20100153700A1Improve efficiencyReduce designProgram control using stored programsGeneral purpose stored program computerCore functionParallel computing

A processor having multiple cores coordinates functions performed on the cores to automatically, dynamically and repeatedly reconfigure the cores for optimal performance based on characteristics of currently executing software. A core running a thread detects a multi-core characteristic of the thread and assigns one or more other cores to the thread to dynamically combine the cores into what functionally amounts to a common core for more efficient execution of the thread.

Owner:IBM CORP

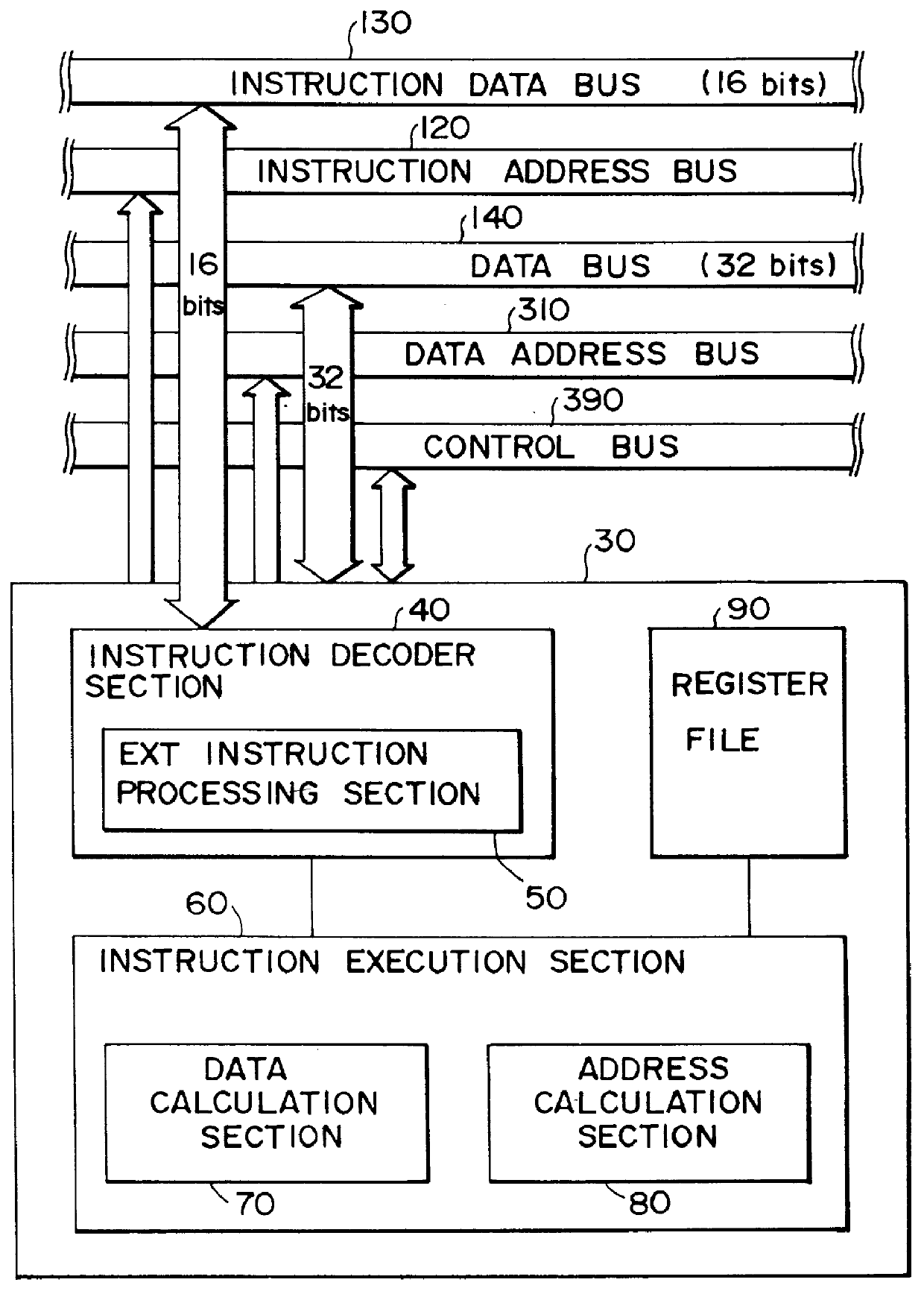

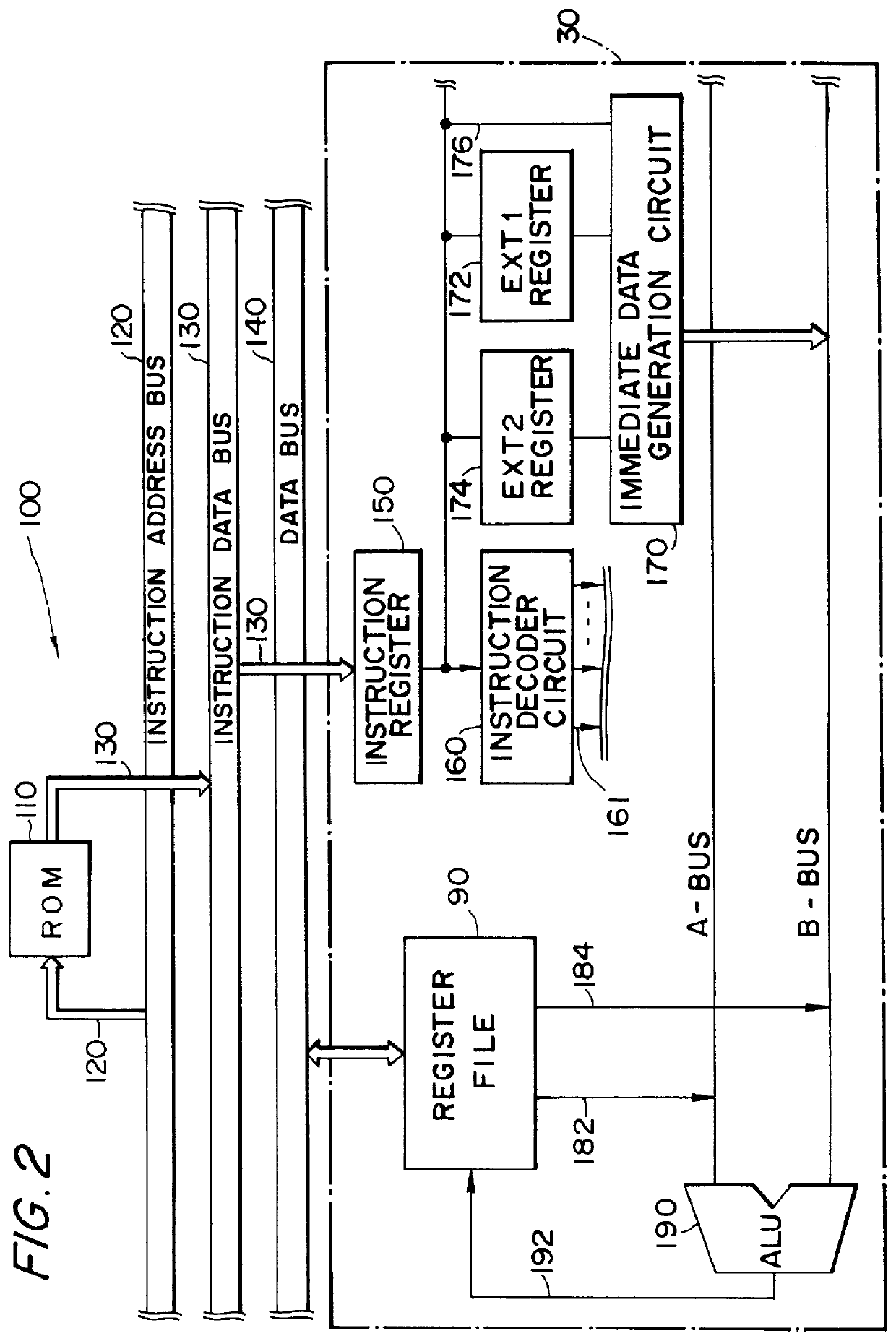

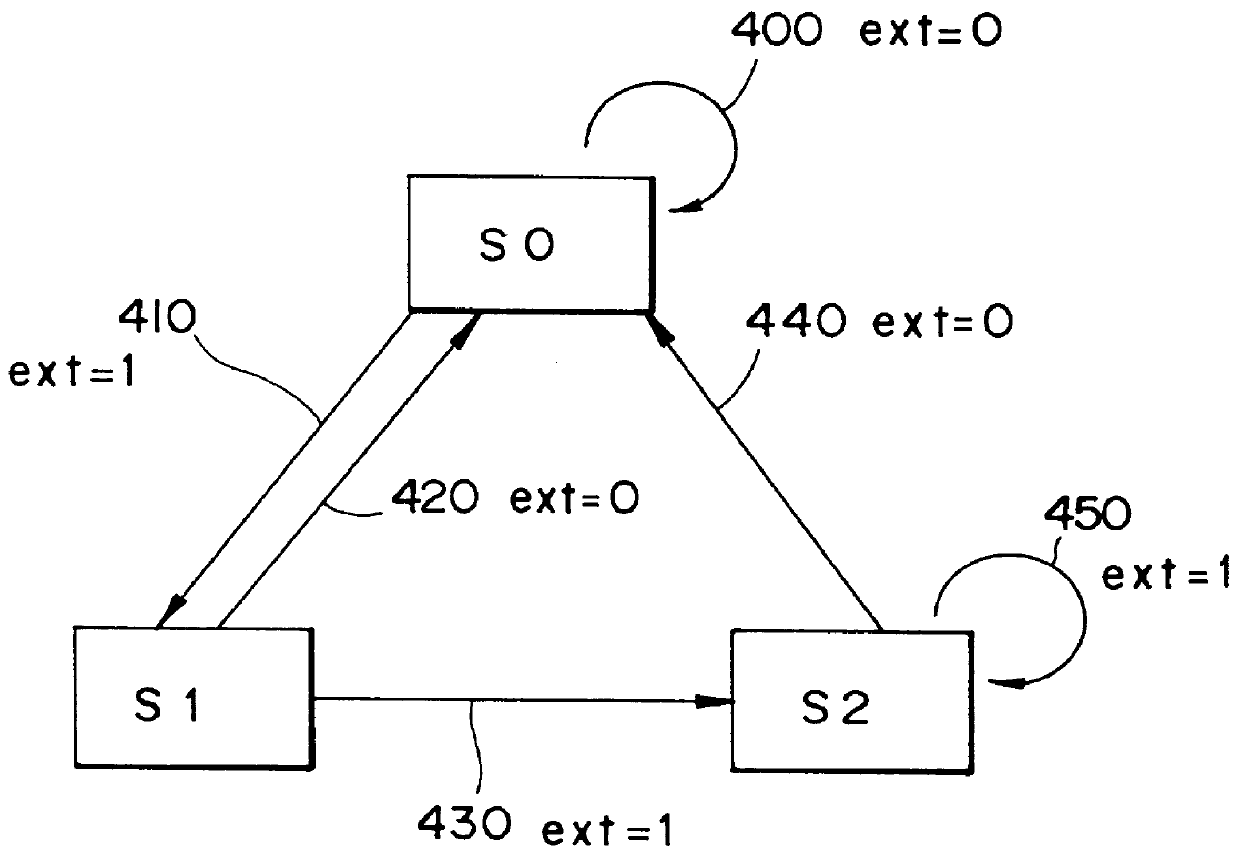

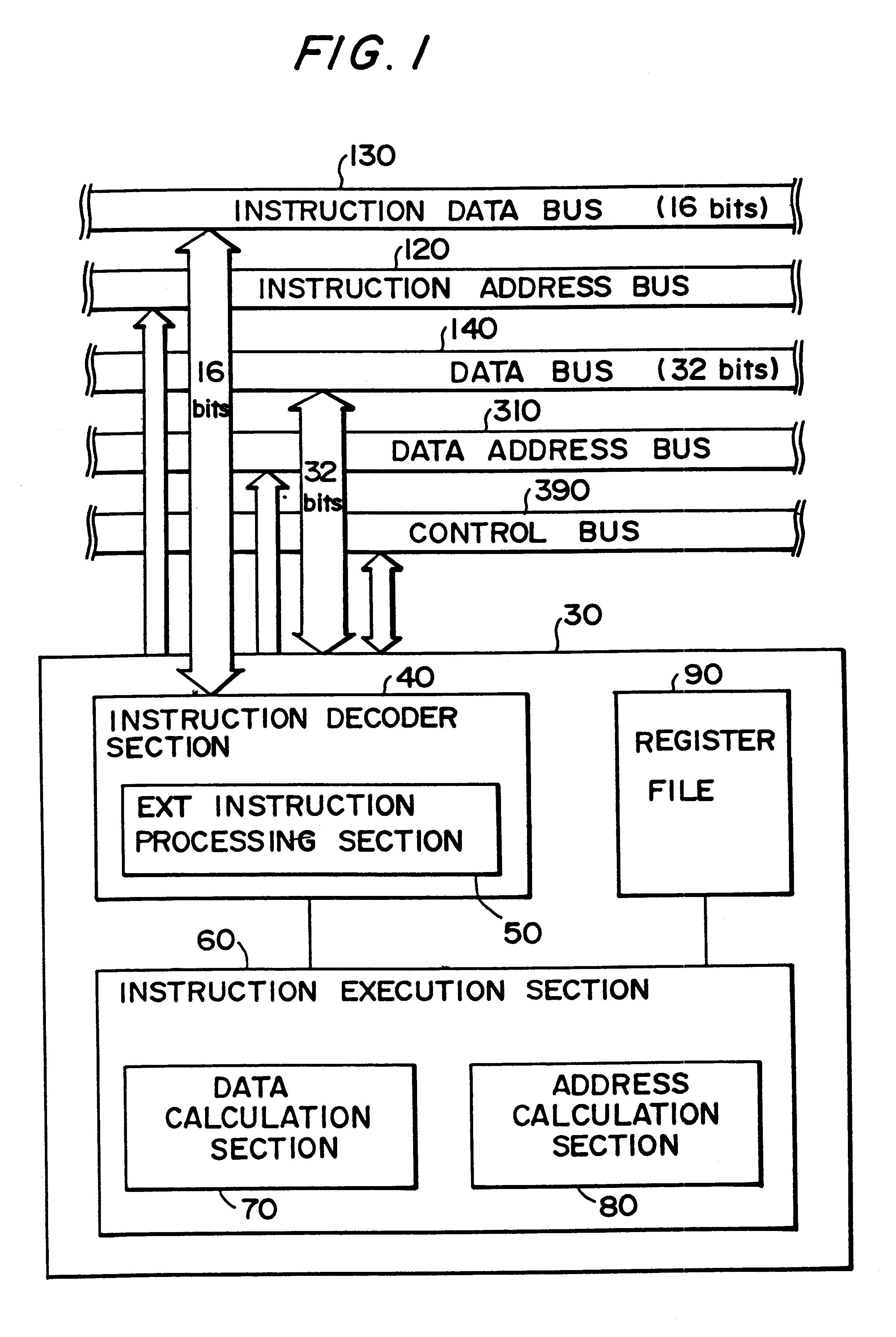

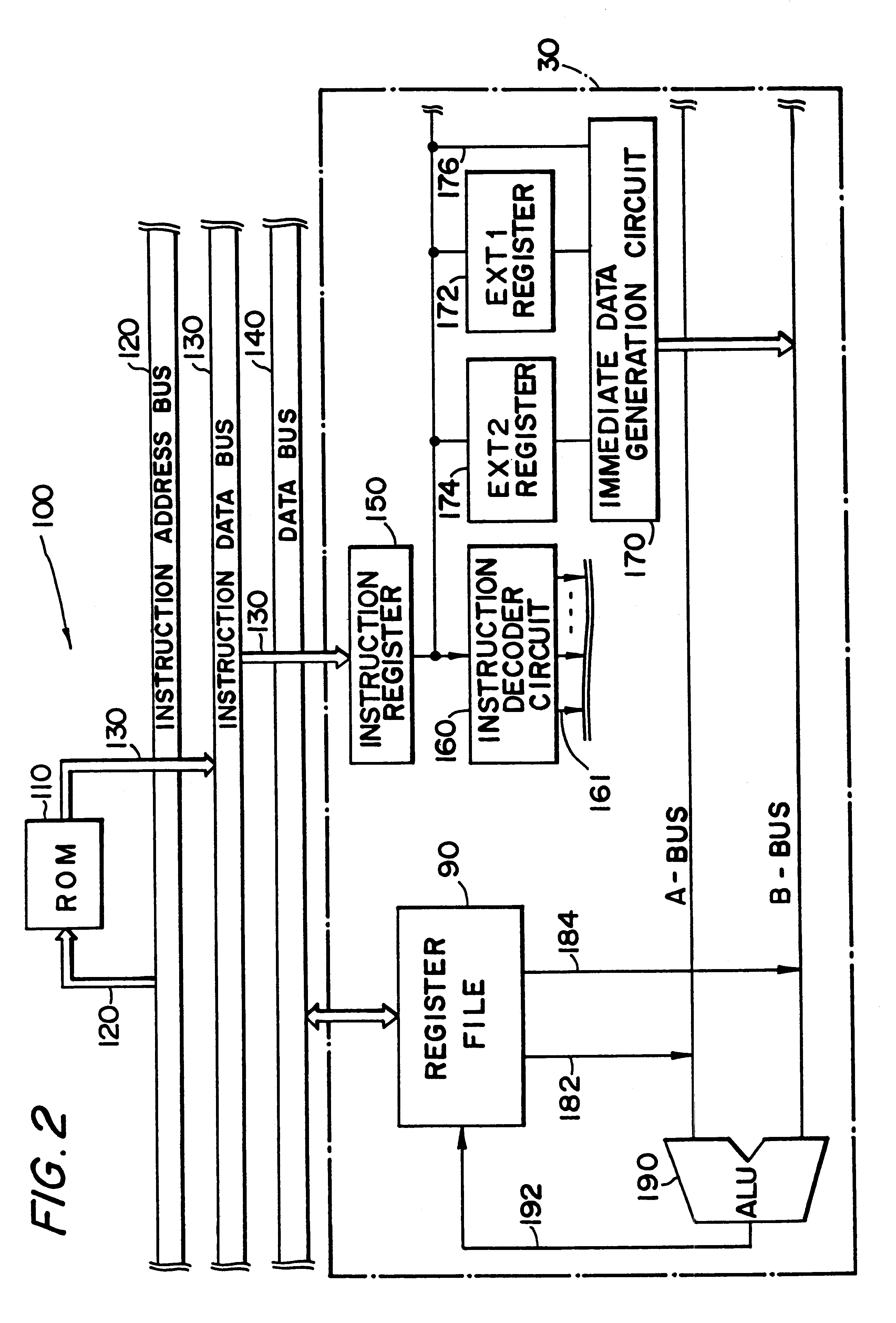

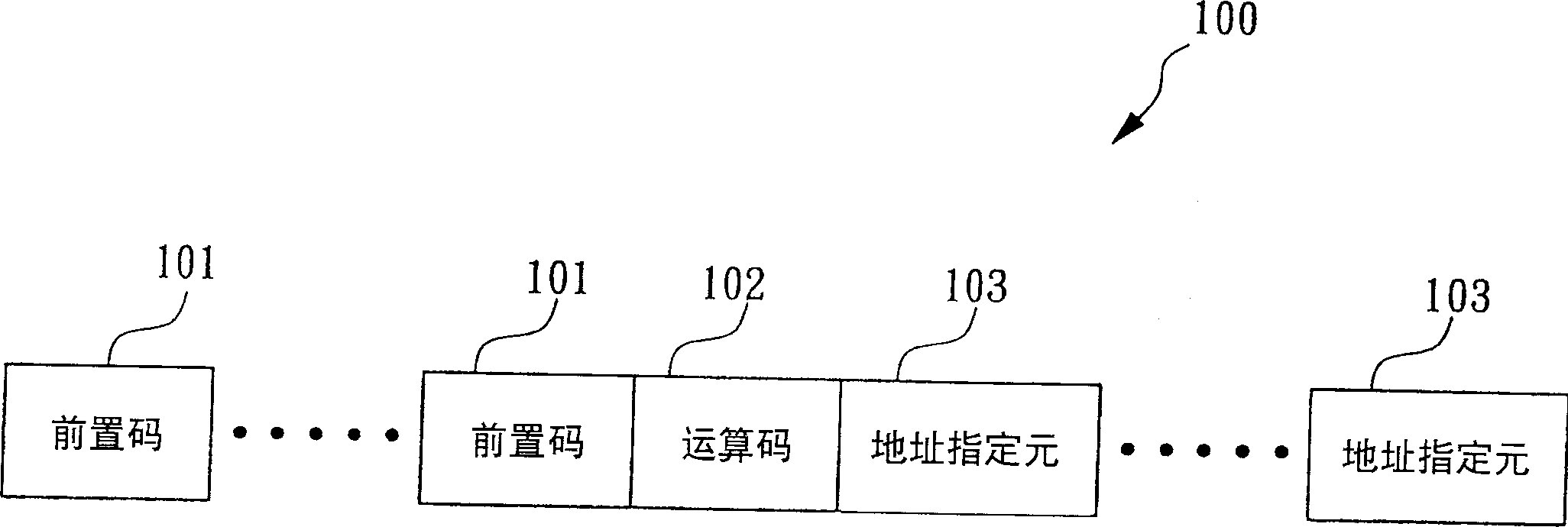

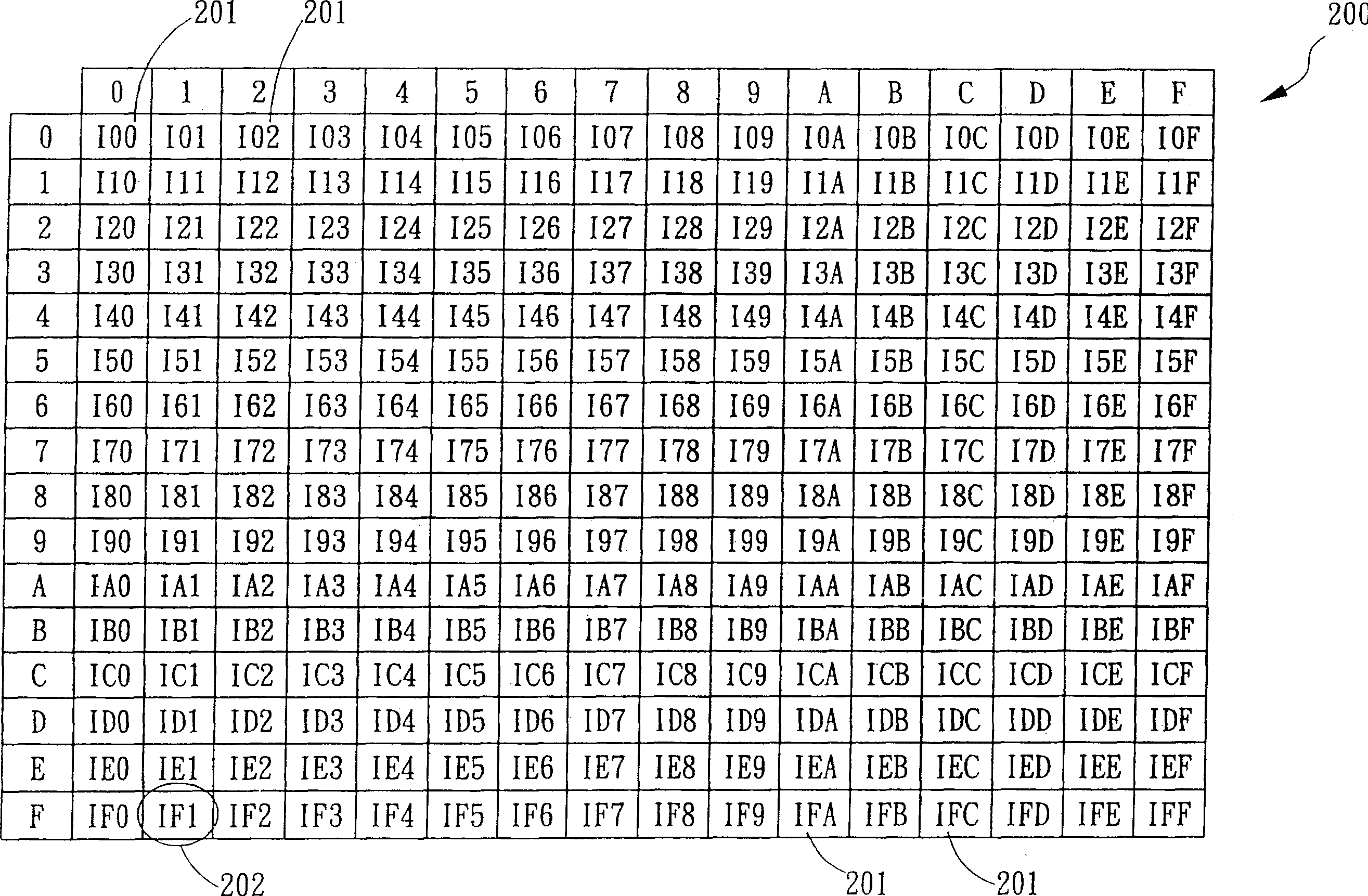

Data processing circuit with target instruction and prefix instruction

InactiveUS6167505AEasy to operateSimple structureInstruction analysisDigital computer detailsRegister fileInstruction code

A certain target instruction and a prefix instruction for expanding the function of that target instruction are input to the present data processing circuit. The data processing circuit analyzes the thus-input instruction code and performs the processing necessary for the execution of that instruction. The data processing circuit comprises an instruction decoder section, a register file, and an instruction execution section that executes the instruction based on operational details of the instruction analyzed by the instruction decoder section. The instruction decoder section comprises an ext instruction processing section that processed the expansion of immediate data from the prefix instruction.

Owner:SEIKO EPSON CORP

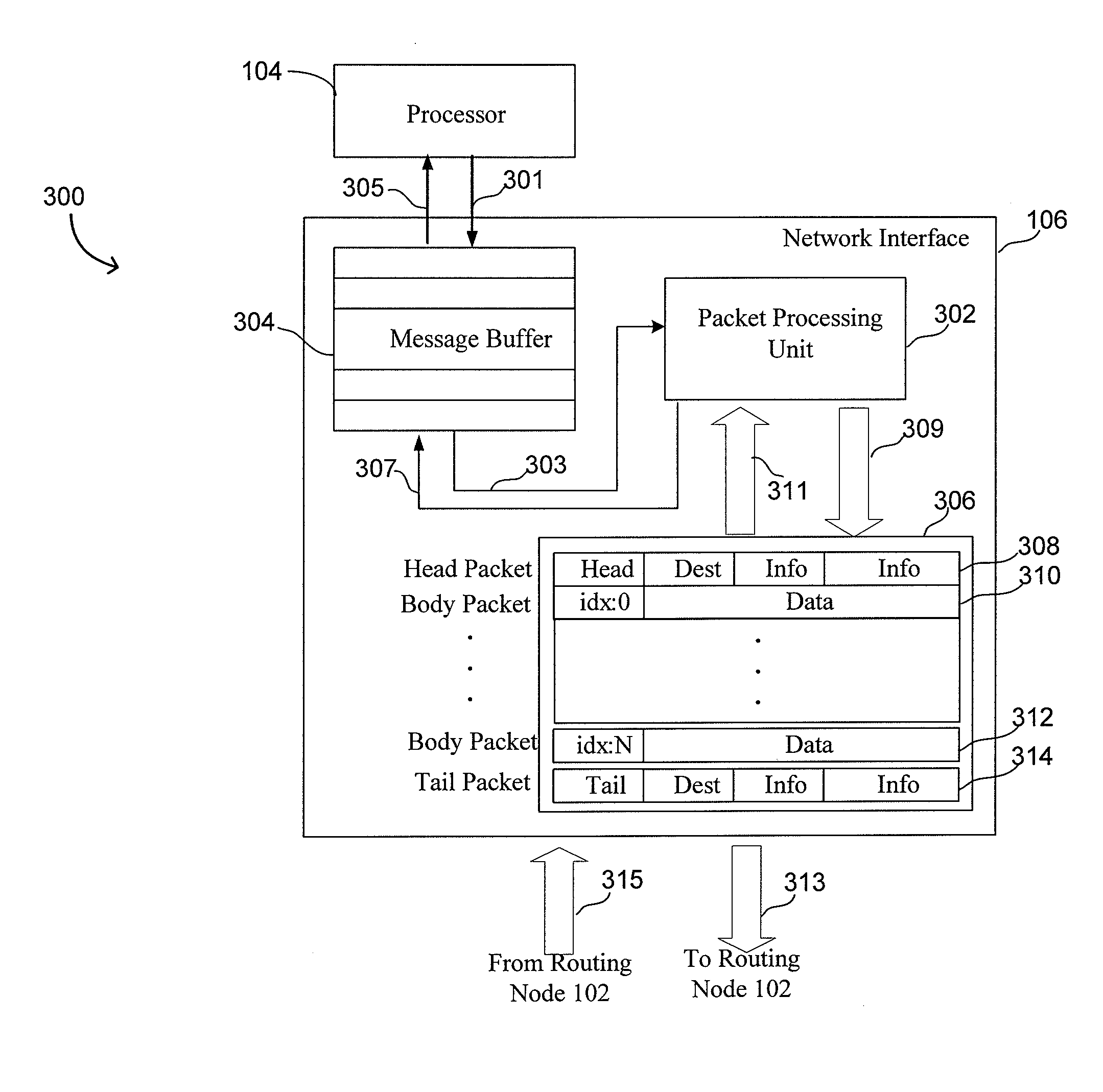

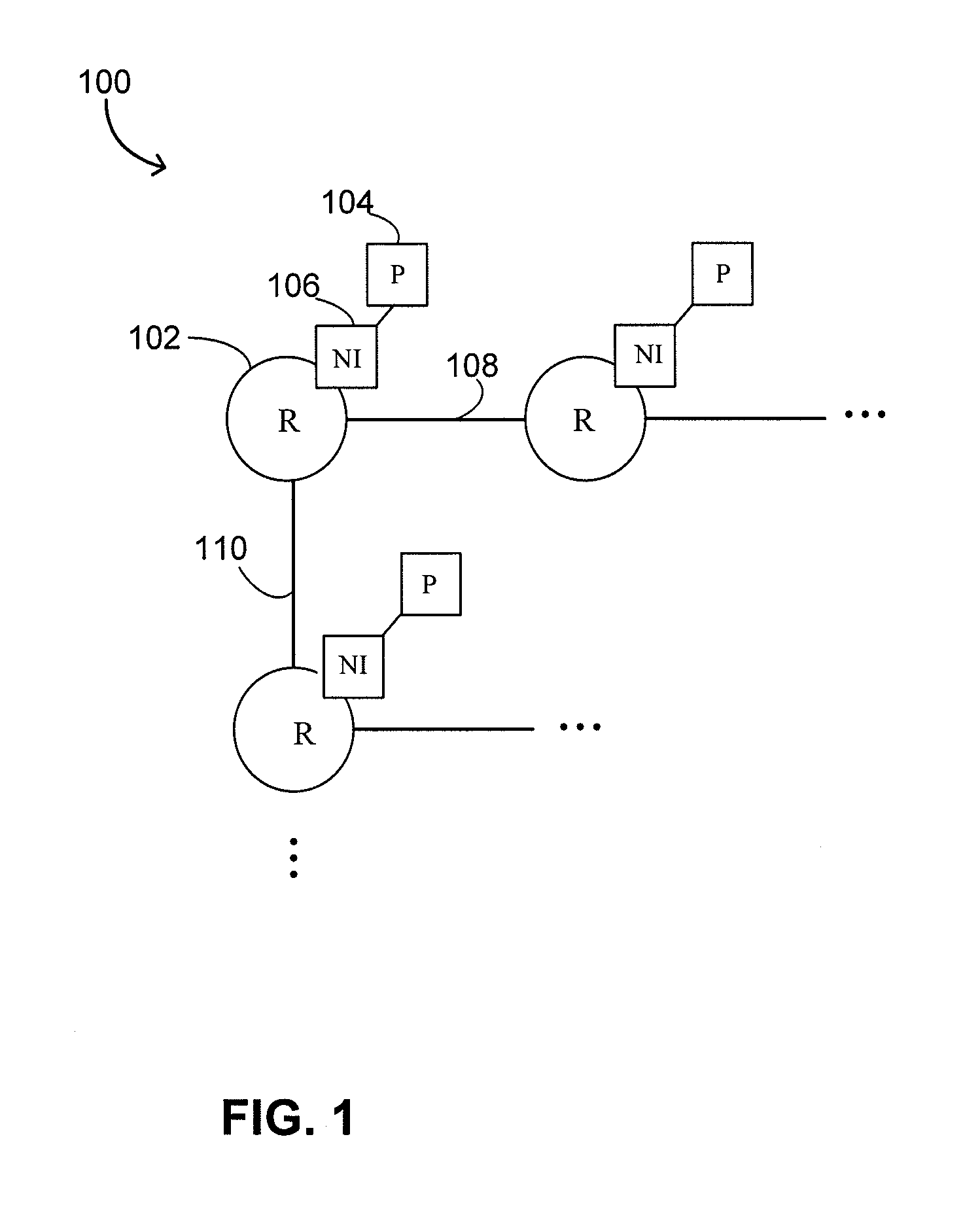

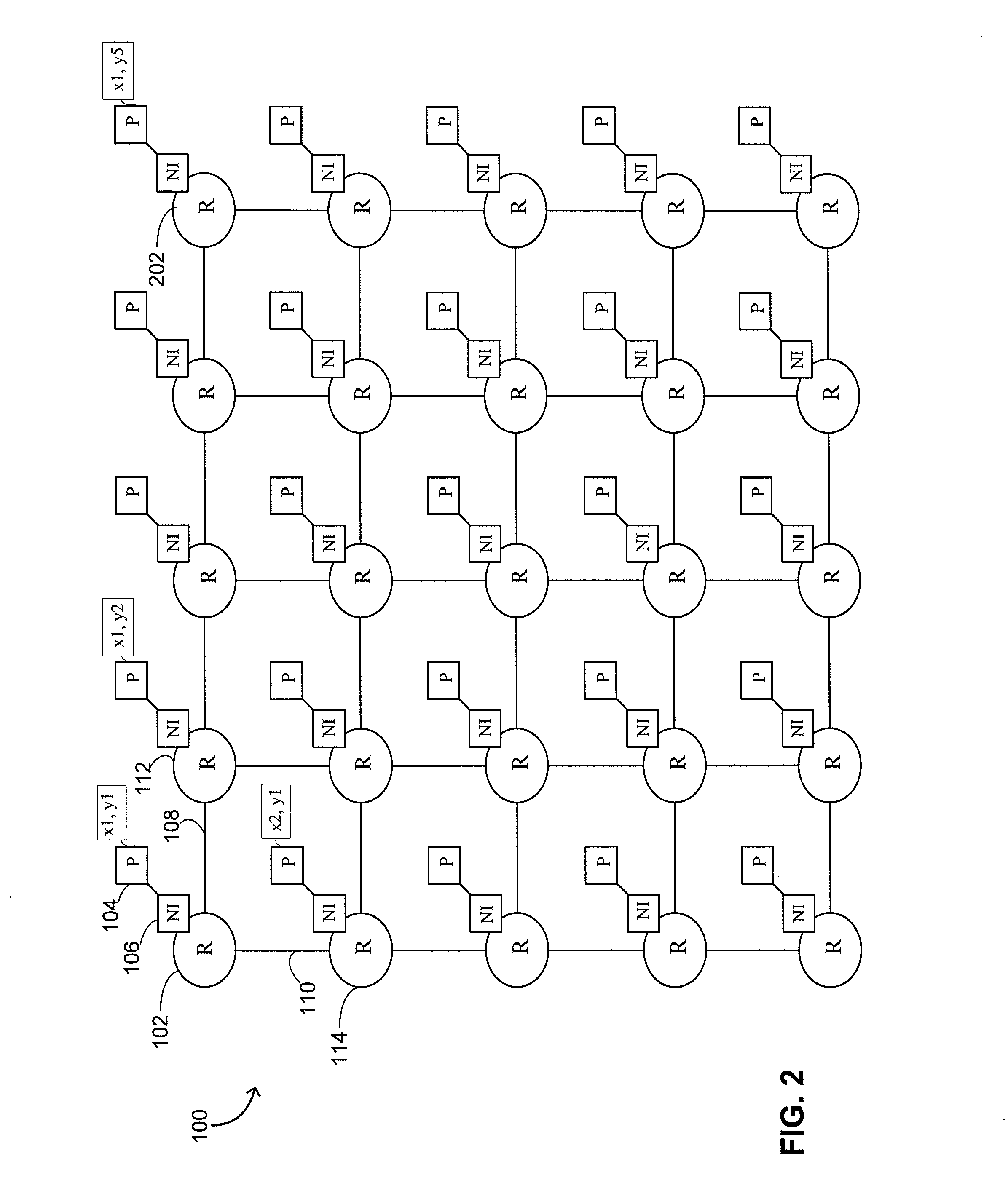

Method to reduce the energy cost of network-on-chip systems

InactiveUS20120173846A1General purpose stored program computerPower supply for data processingByteNetworks on chip

In a network-on-chip (NoC) system, multiple data messages may be transferred among modules of the system. Power consumption due to the transfer of the messages may affect a cost and overall performance of the system. A described technique provides a way to reduce a volume of data transferred in the NoC system by exploiting redundancy of data messages. Thus, if a data message to be sent from a source in the NoC includes so-called “zero” bytes that are bytes including only bits set to “0,” such zero bytes may not be transmitted in the NoC. Information on whether each byte of the data message is a zero byte may be recorded in a storage such as a data structure. This information, together with non-zero bytes of the data message, may form a compressed version of the data message. The information may then be used to uncompress the compressed data message at a destination.

Owner:STMICROELECTRONICS BEIJING R& D

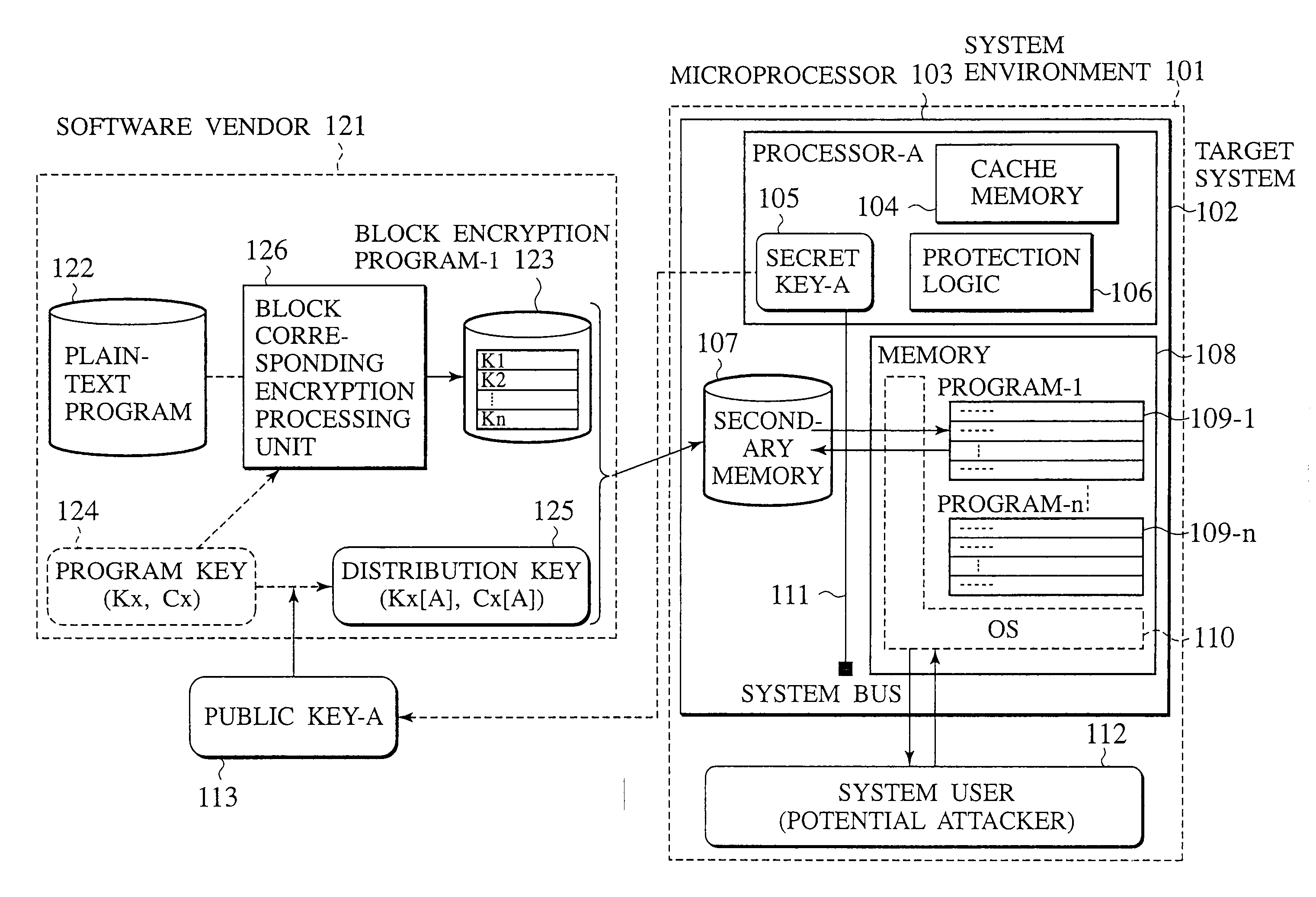

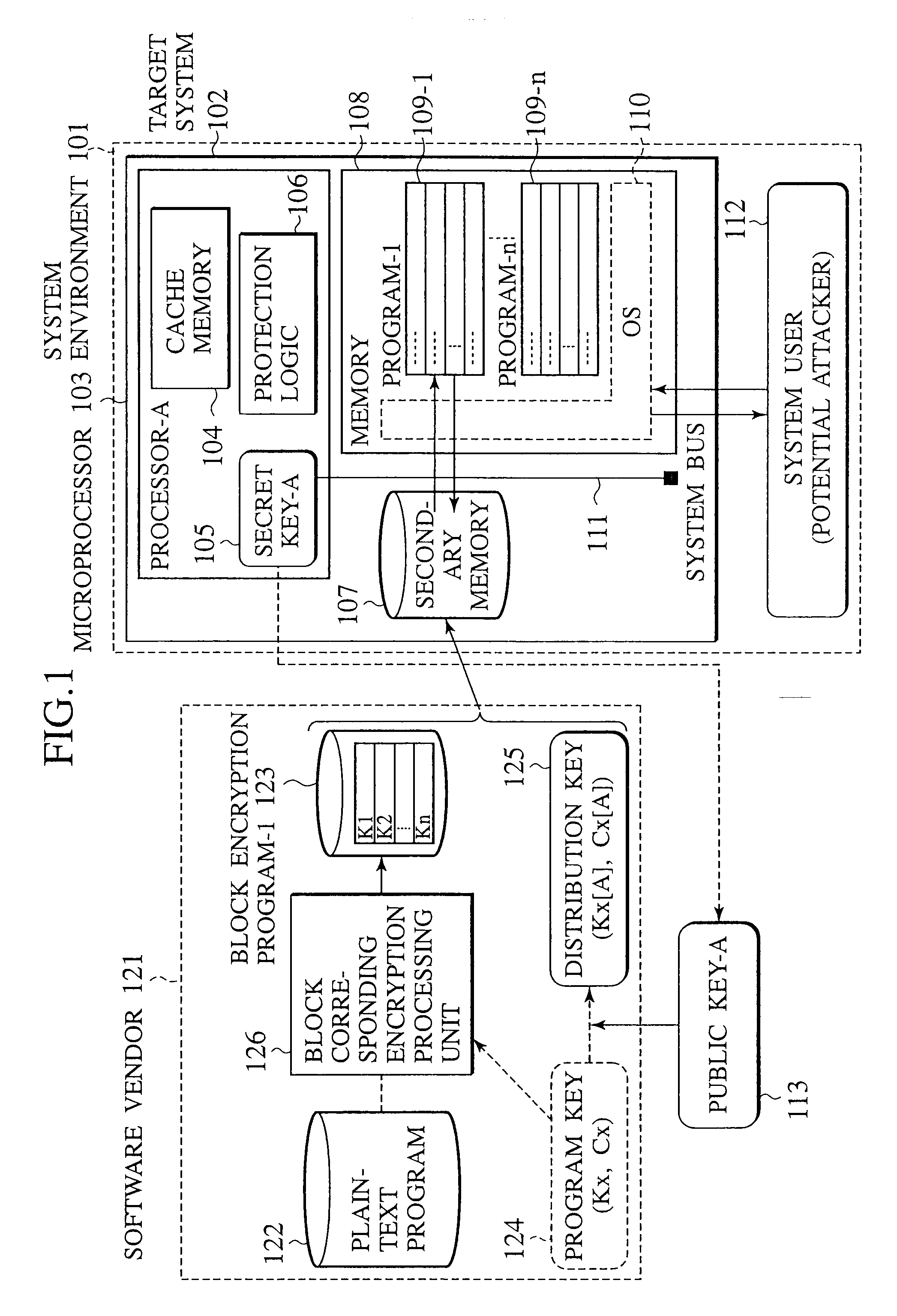

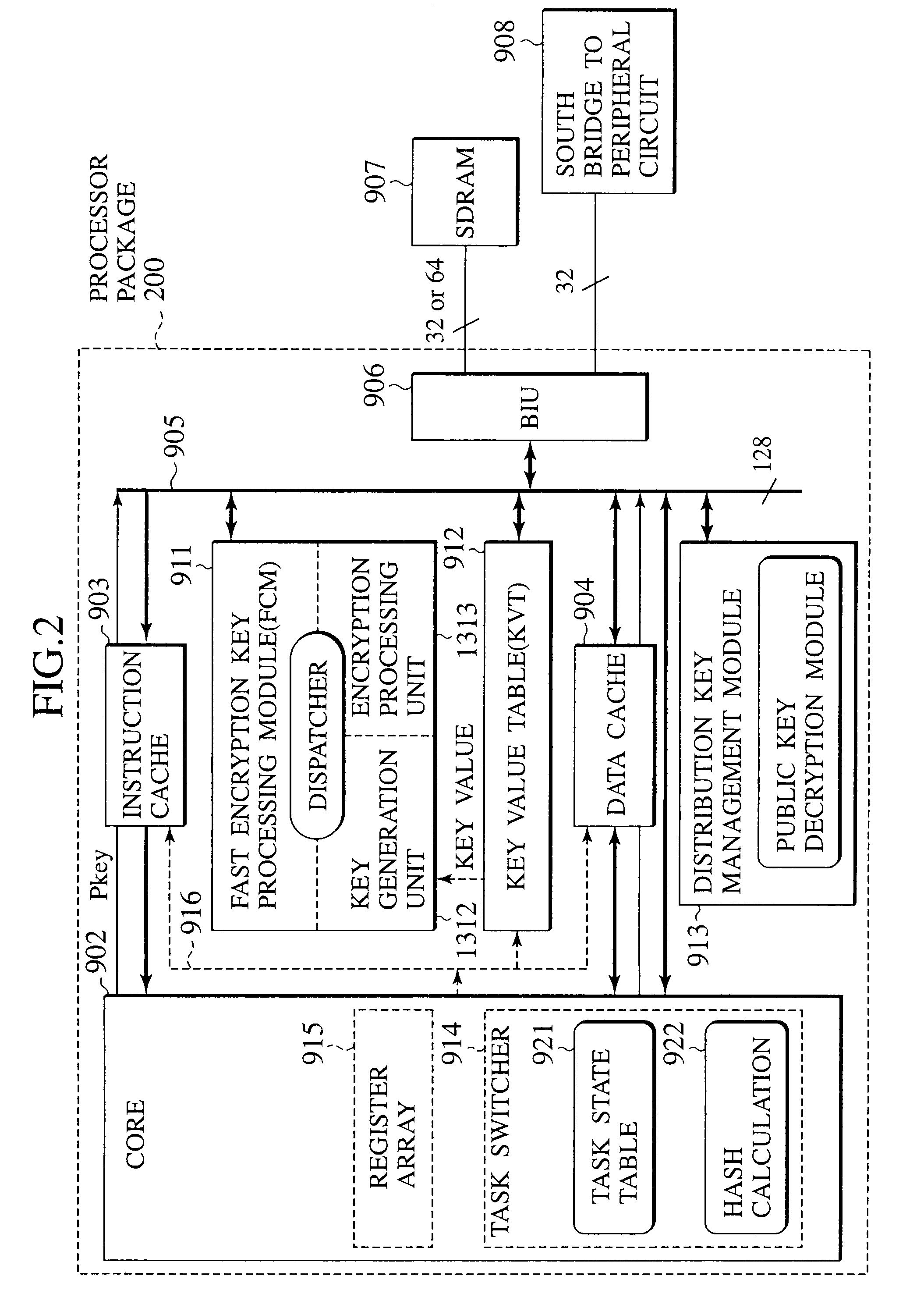

Microprocessor with improved task management and table management mechanism

InactiveUS20090006864A1Key distribution for secure communicationUser identity/authority verificationExternal storageProcessor register

A tamper resistant microprocessor has a task state table for assigning a task identifier to a task that can take a plurality of states, and storing a state of the task in correspondence to the task identifier; a task register for storing the task identifier of a currently executed task; an interface for reading a program stored in a form encrypted by using a program key at an external memory, in units of cache lines, when a request for the task is made; an encryption processing unit for generating decryption keys that are different for different cache lines, according to the program key, and decrypt a content read by the interface; a cache memory formed by a plurality of cache lines each having a tag, for storing the task identifier corresponding to a decryption key used in decrypting each cache line in the tag of each cache line; and an access check unit for comparing the task identifier stored in the tag of each cache line with a value of the task register, and discarding a content of each cache line when the task identifier in the tag and the value of the task register do not coincide.

Owner:KK TOSHIBA

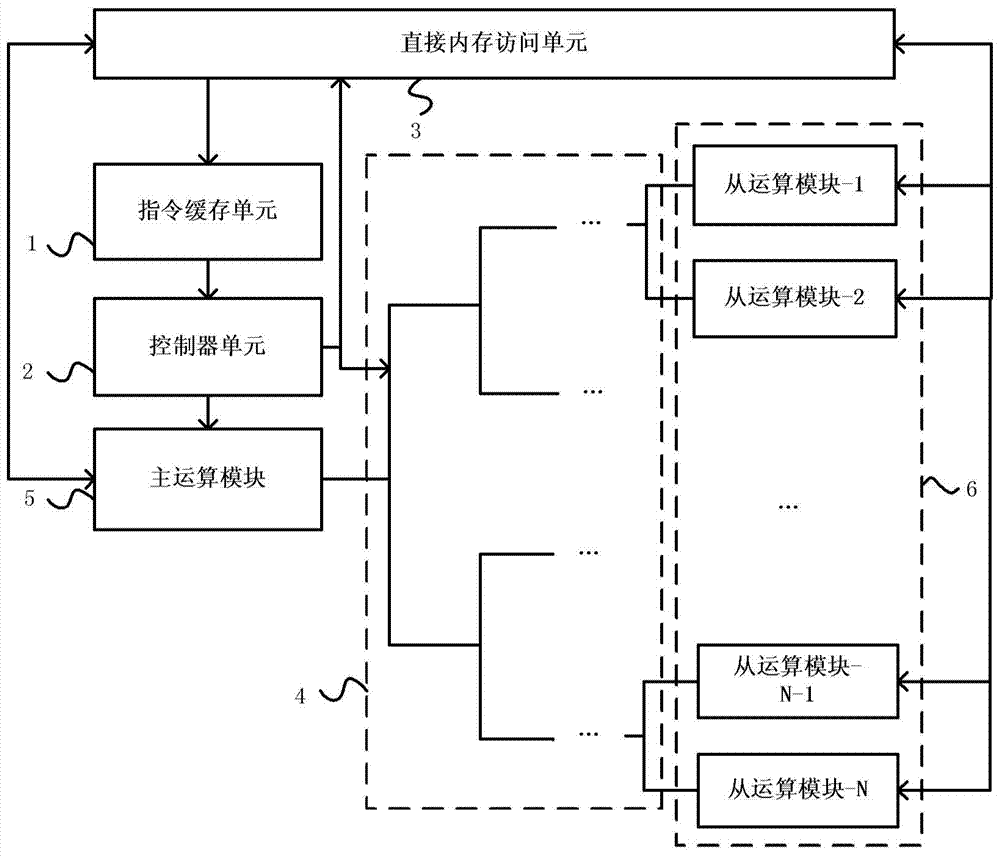

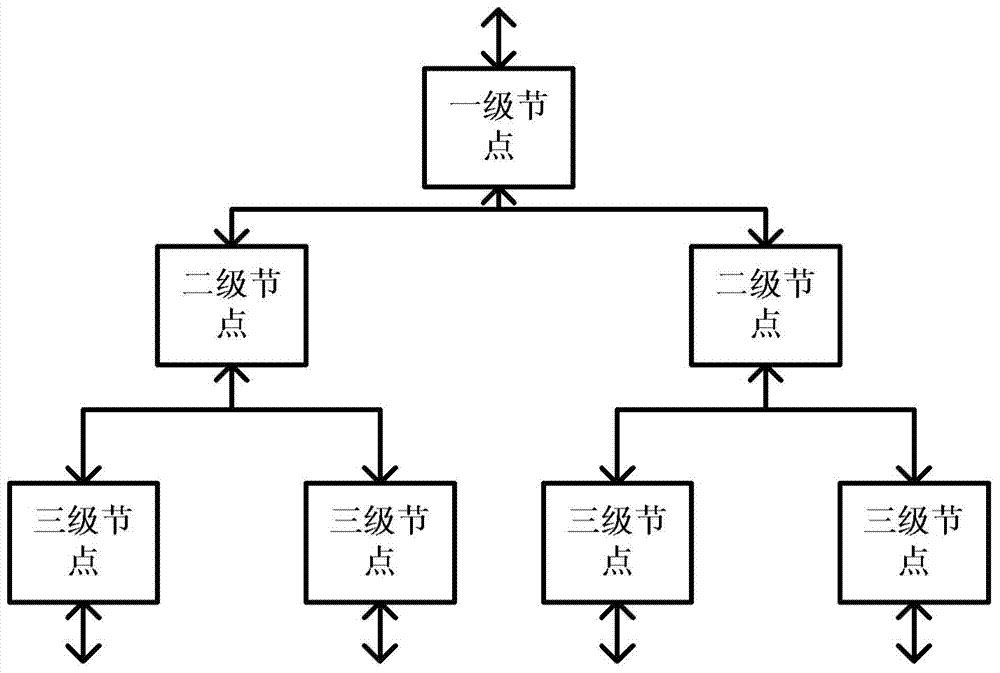

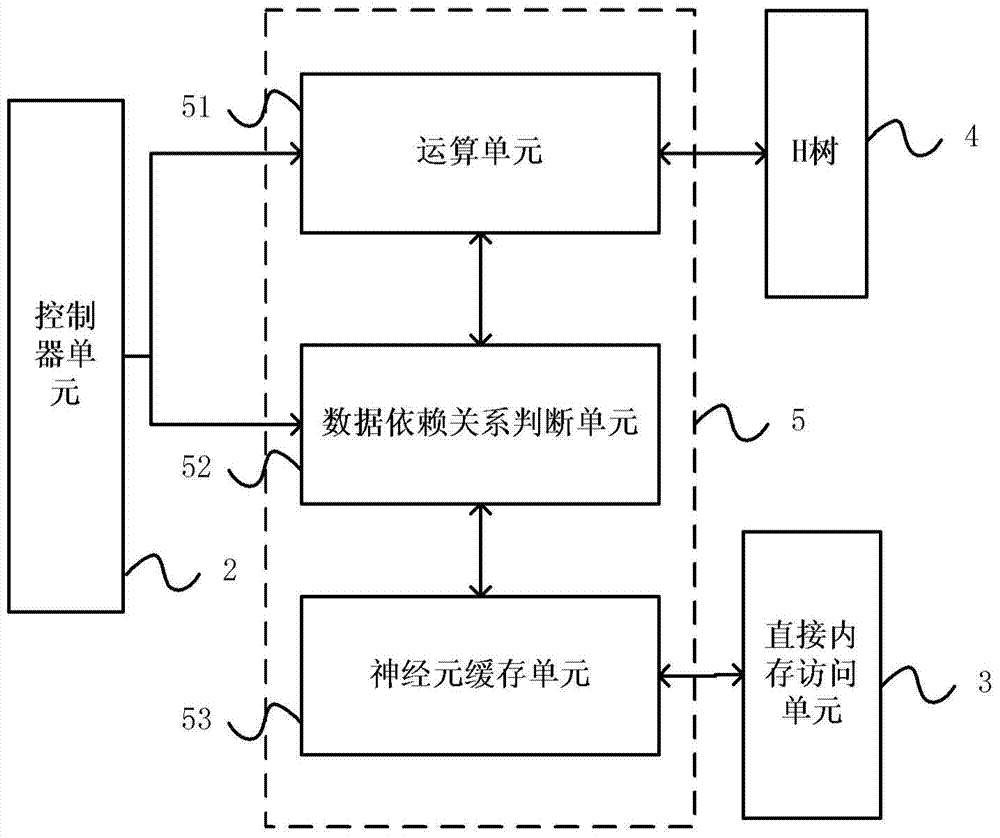

Device and method for executing reverse training of artificial neural network

The invention provides a device for executing reverse training of an artificial neural network. The device comprises an instruction buffer memory unit, a controller unit, a direct memory accessing unit, an H-tree module, a main operation module and a plurality of auxiliary operation modules. The device can realize reverse training of a multilayer artificial neural network. For each layer, weighted summation is performed on an input gradient vector and an output gradient vector of the layer is calculated. An input gradient vector of a next layer can be obtained through multiplying the output gradient vector by a derivative value of an excited function in forward operation. The gradient of the weight at this layer is obtained through multiplying the input gradient vector by an input neuron in forward operation. Then the weight of this layer can be updated according to the gradient of the weight at this layer.

Owner:CAMBRICON TECH CO LTD

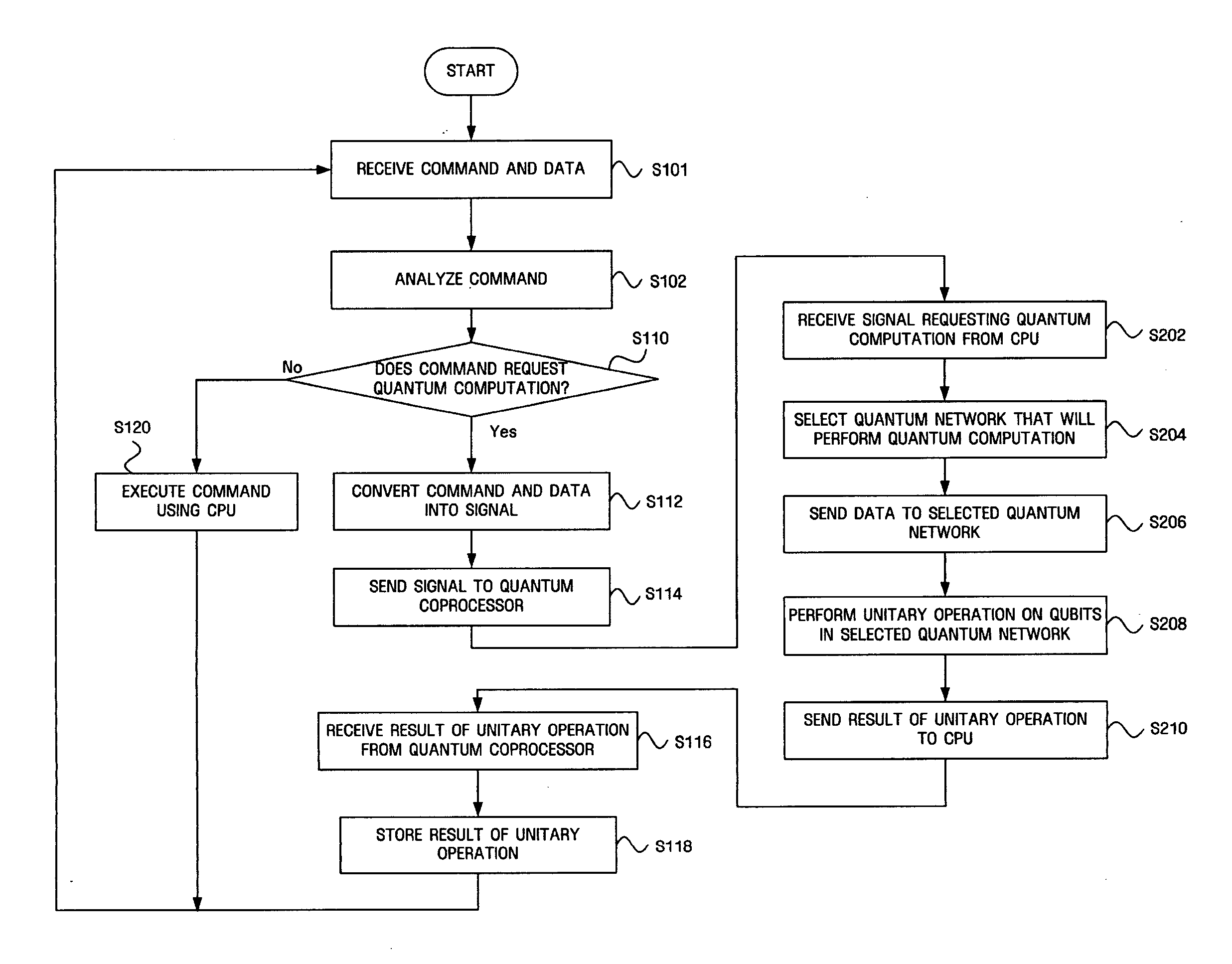

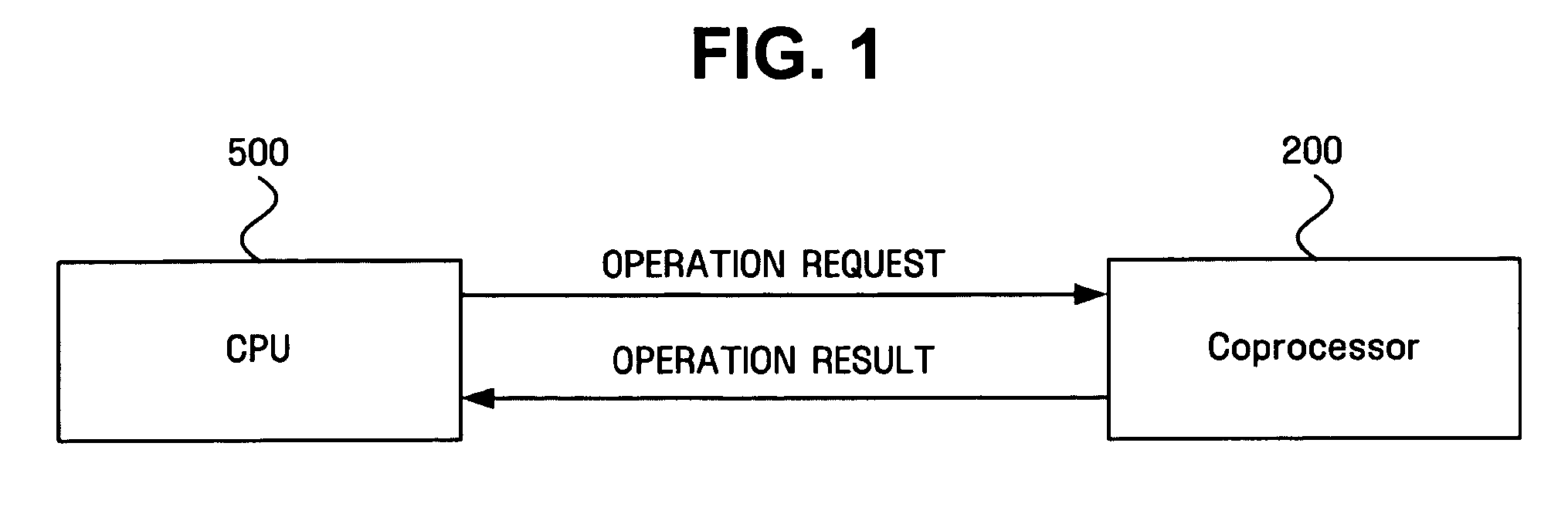

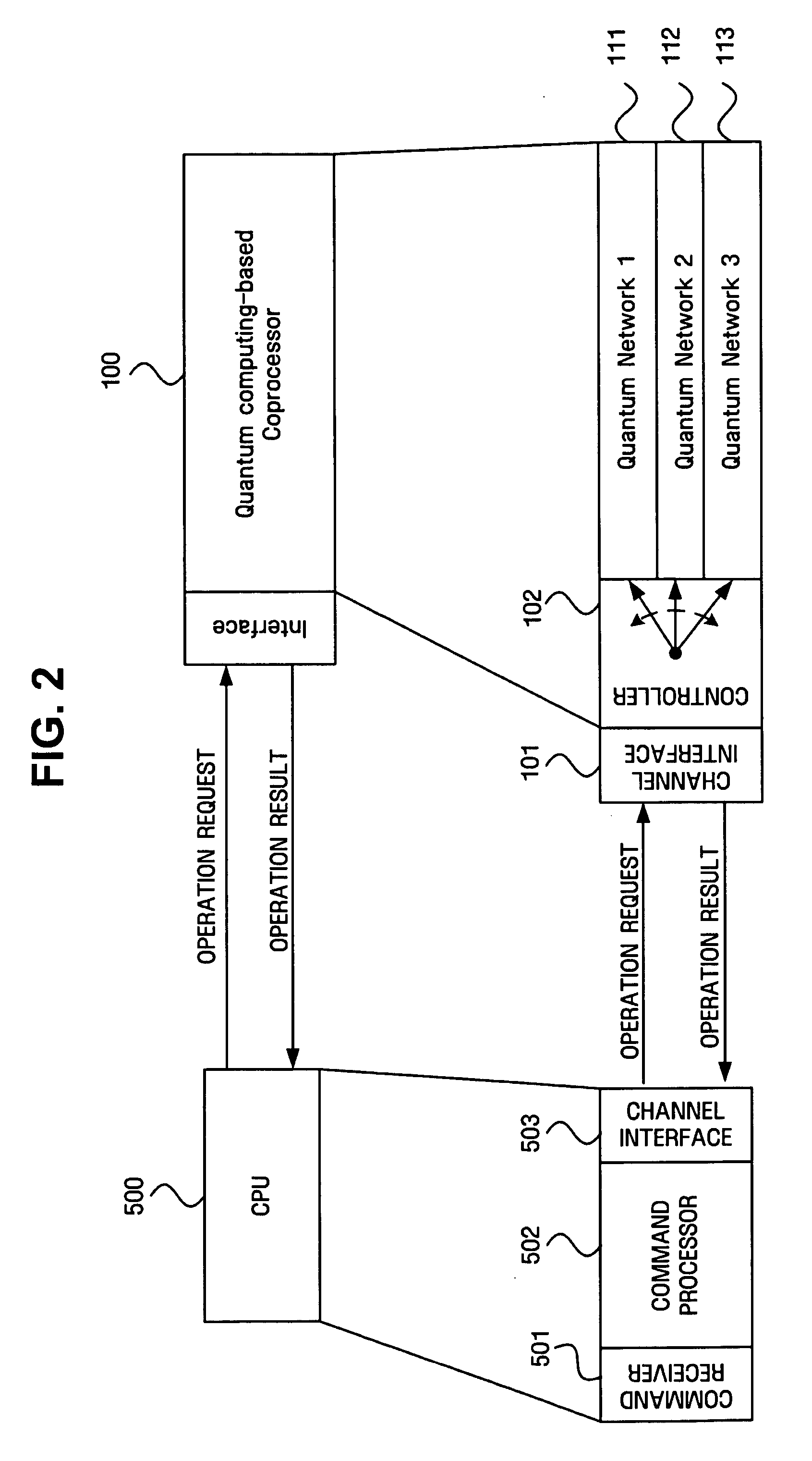

Method and apparatus for increasing processing speed using quantum coprocessor

InactiveUS20060101236A1Improve processing speedQuantum computersNanoinformaticsCoprocessorComputer science

A method and apparatus for increasing a processing speed using a quantum coprocessor are provided. The method includes receiving a command and data for performing a predetermined task, converting the command and the data into a signal having a format that the quantum coprocessor can receive if the command requests a quantum computation, sending the signal to the quantum coprocessor, receiving a processing result from the quantum coprocessor, and storing the processing result as a result of the command.

Owner:SAMSUNG ELECTRONICS CO LTD

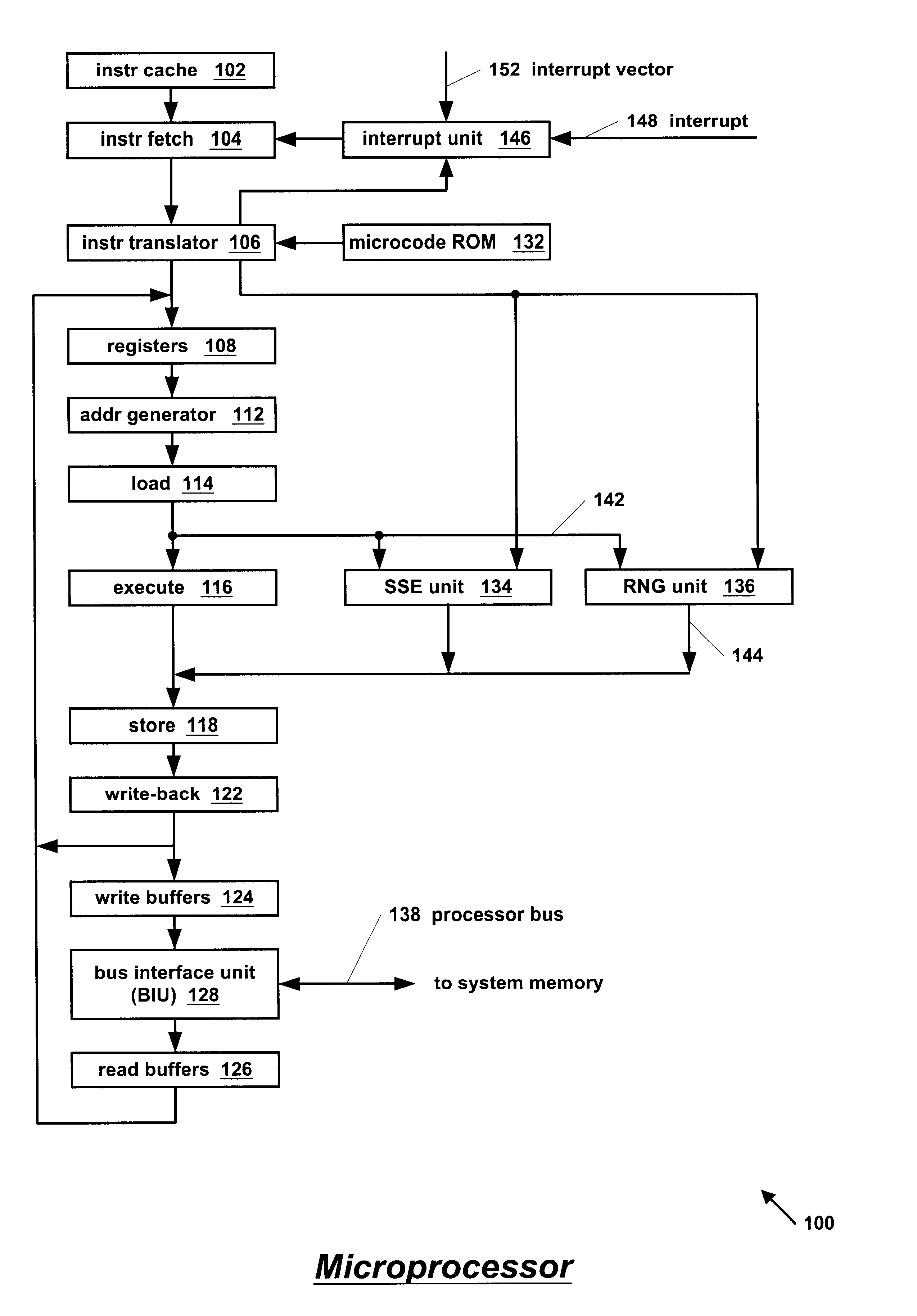

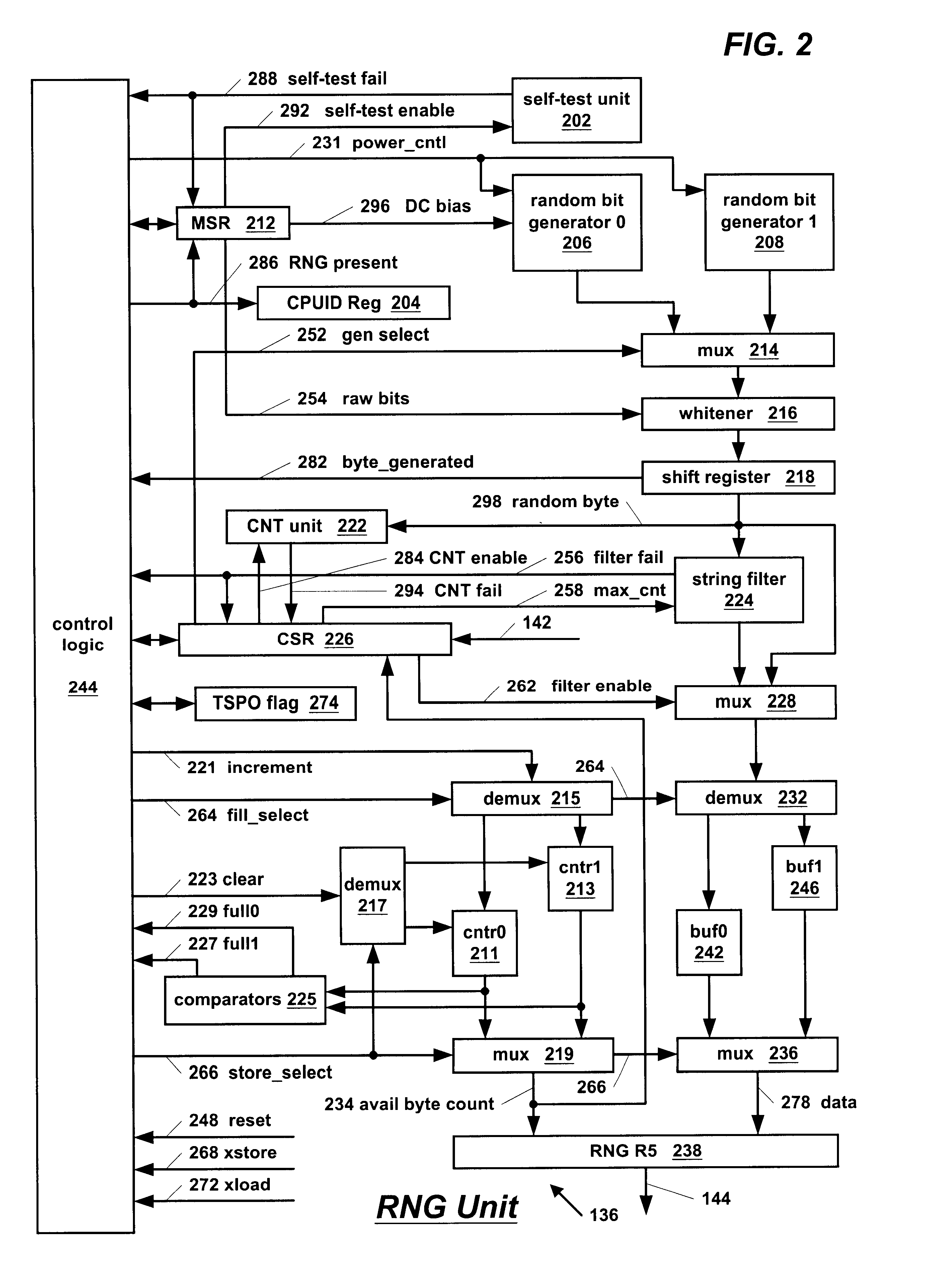

Continuous multi-buffering random number generator

InactiveUS6871206B2Improve performanceRaise the possibilityRandom number generatorsRuntime instruction translationNumber generatorByte

A multi-buffering apparatus in a random number generator. A microprocessor includes a random number generator that employs multiple buffers for buffering random data bytes generated by the generator. The apparatus maintains a first selector for selecting one of the buffers as the current buffer for filling with generated bytes. When the current fill buffer becomes full, the apparatus updates the first selector to a different buffer and continues the process until all buffers are full. The apparatus maintains a second selector for selecting one of the buffers as the current buffer for supplying random data bytes to an application. When the current supply buffer becomes empty, the apparatus updates the second selector to a different buffer and continues the process until all buffers are empty. The apparatus can concurrently fill the buffer selected by the fill selector and supply data from the buffer selected by the supply selector.

Owner:IP FIRST

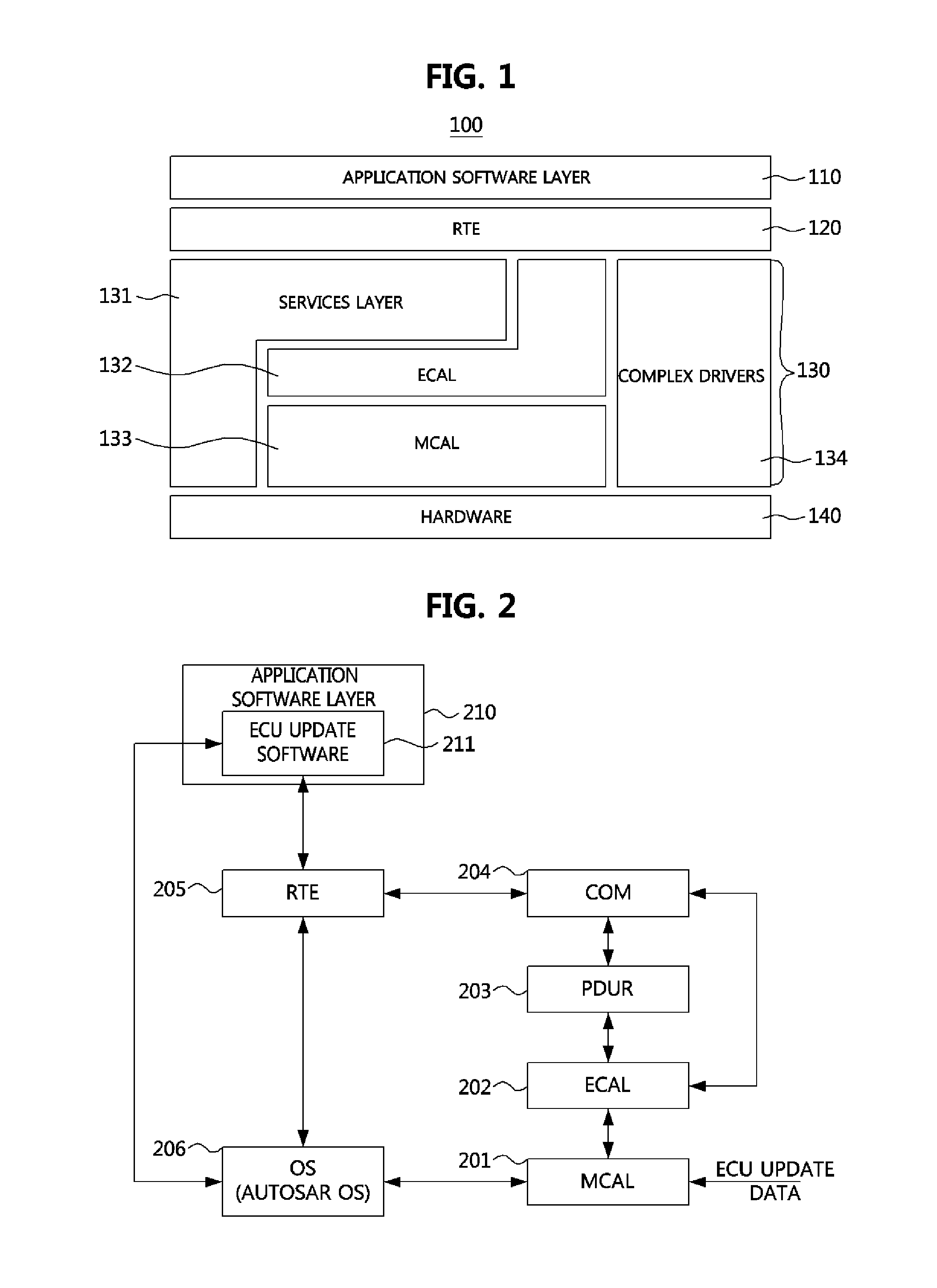

Method and apparatus for updating electronic control unit in system based on automotive open system architecture

InactiveUS20140082599A1Reduce time spentMinimizes of functionProgram loading/initiatingMicrocontrol arrangementsOpen systems architectureAUTOSAR

Disclosed are an ECU update method and apparatus of an AUTOSAR-based system. In the ECU update method, an MCAL driver layer receives ECU update data, and an ECAL driver layer receives the ECU update data from the MCAL driver layer and directly transfers the ECU update data to ECU update software. Therefore, the ECU update method minimizes unnecessary operations in updating an ECU while performing an operation conforming to the AUTOSAR standard, thus quickly updating the ECU.

Owner:ELECTRONICS & TELECOMM RES INST

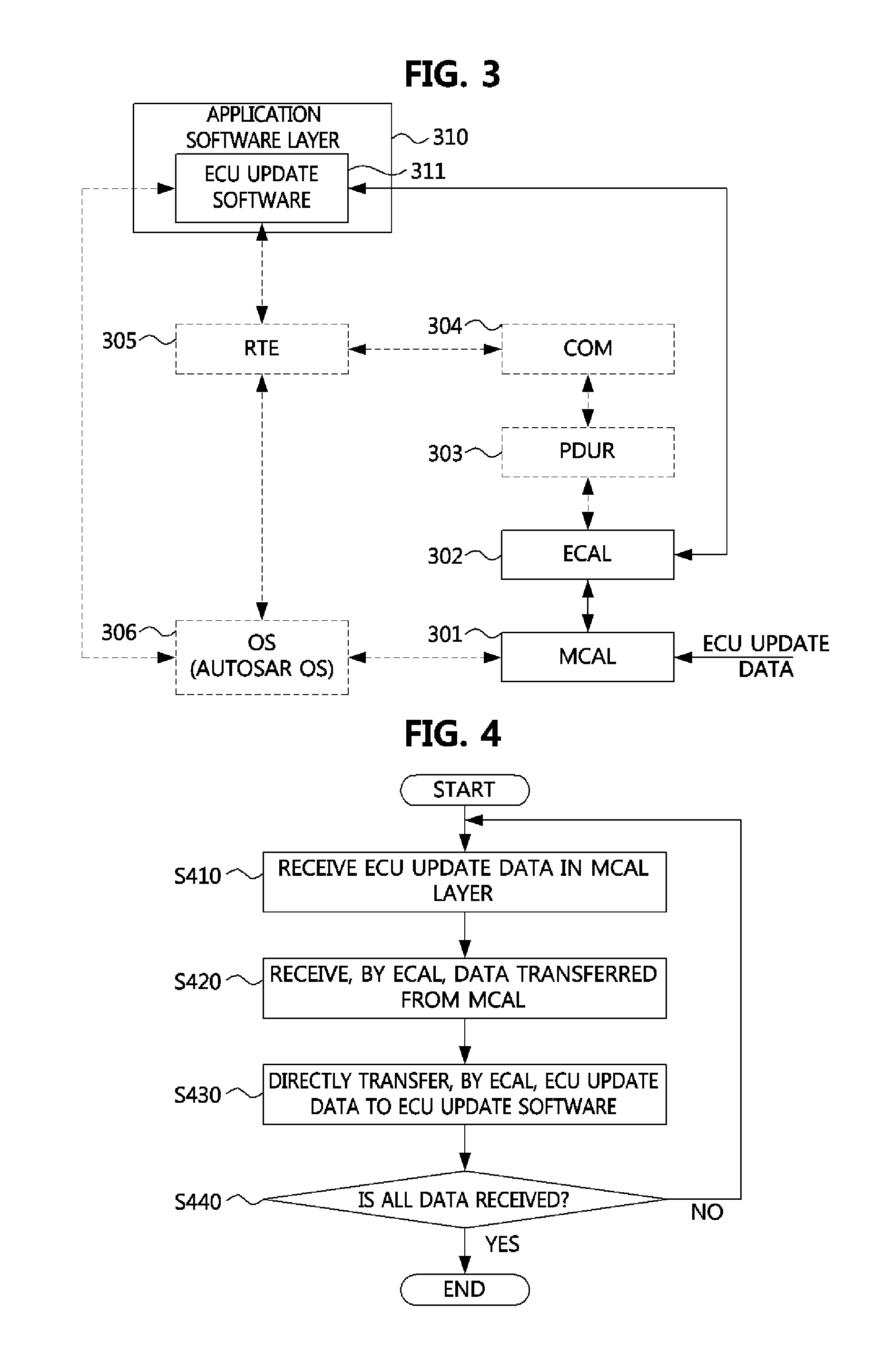

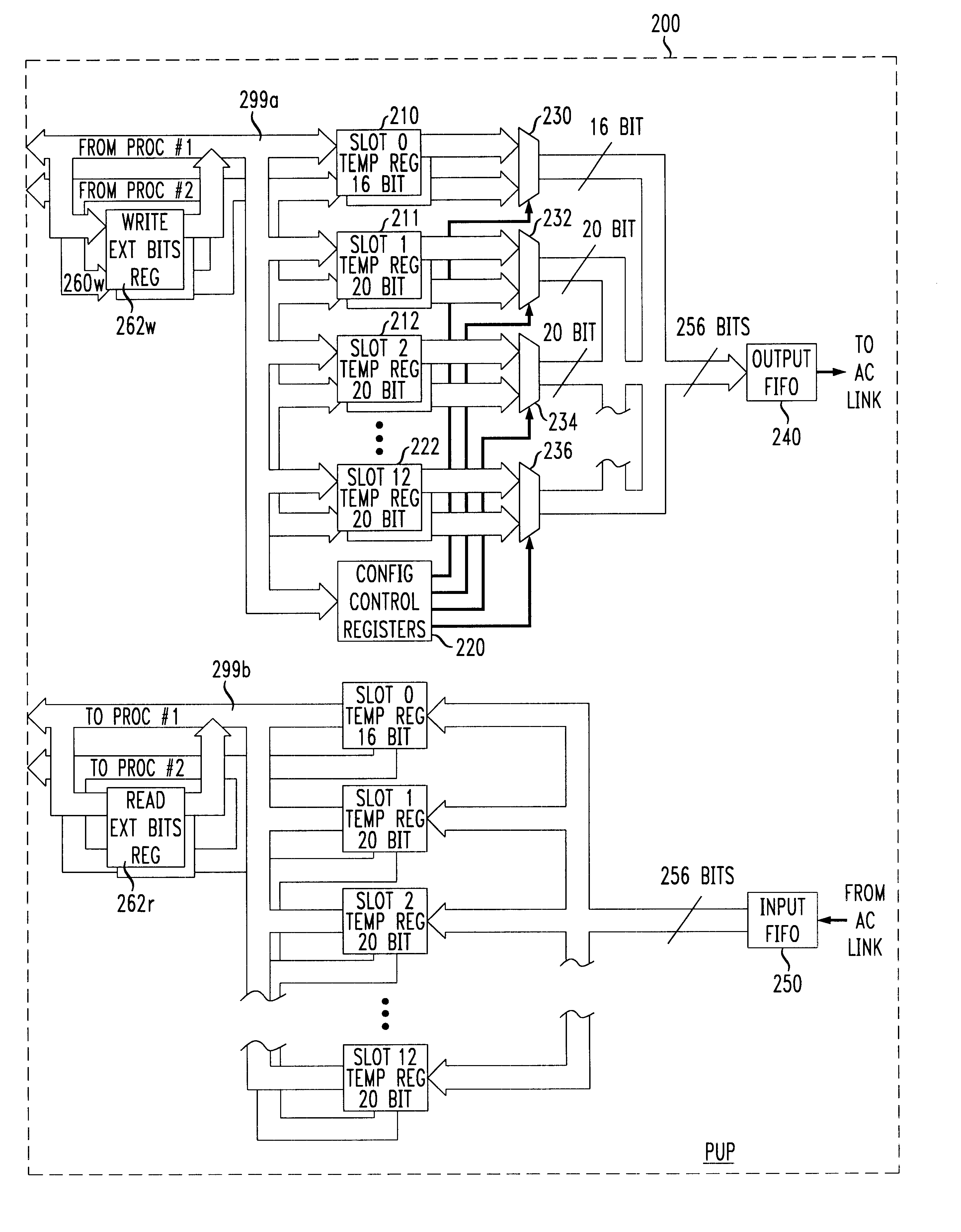

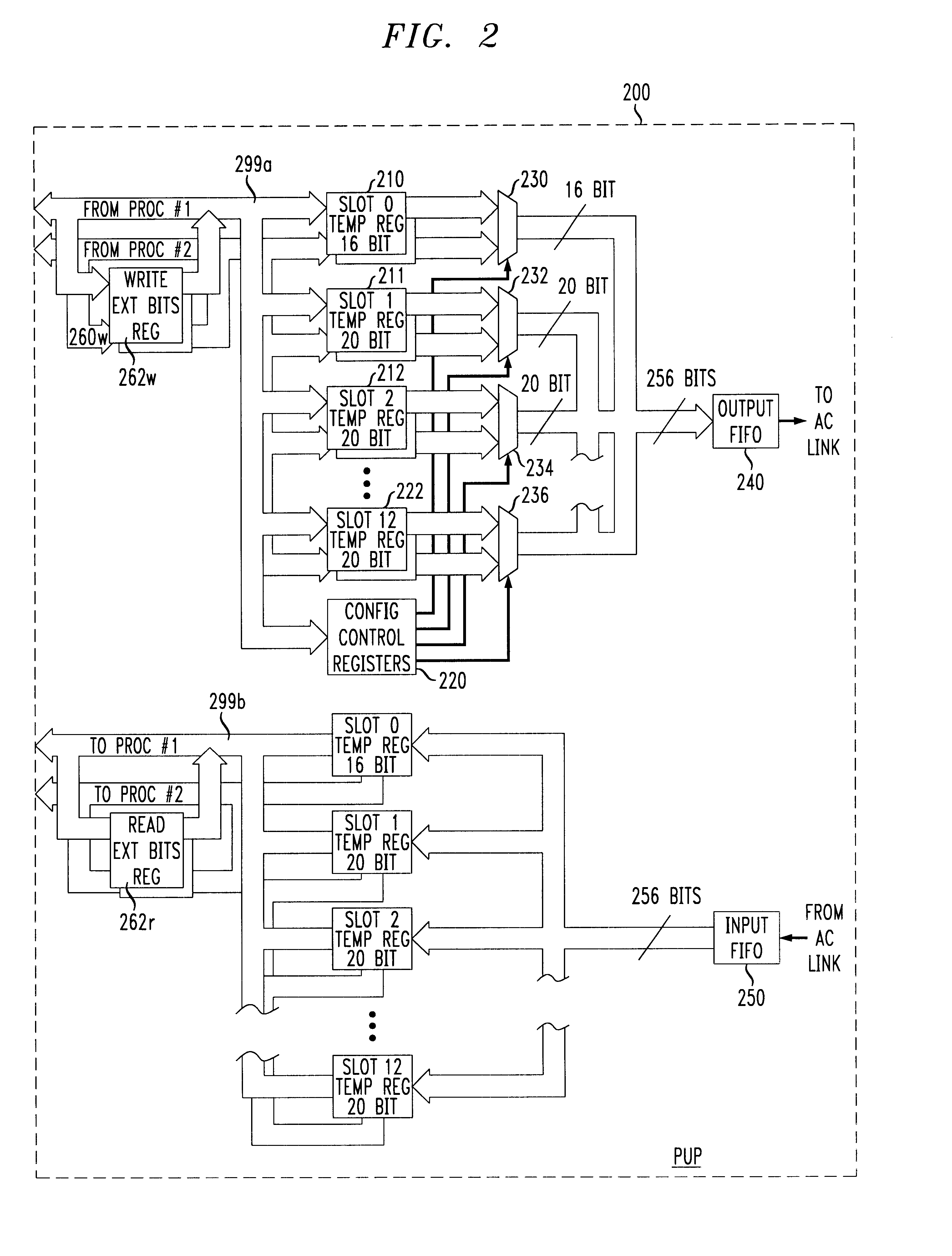

Multiple device access to serial data stream

One aspect of the present invention provides a packer-unpacker (PUP) for a digital serial interface which allows a plurality of processors to access time slot registers of a serial data stream relating to the digital serial interface. A configuration register is maintained either by one of the plurality of processors or by each of the processors to arbitrate access to the individual time slot registers. Another aspect of the invention allows one or more processors to efficiently access and / or write more bits to a resource such as a time slot register than the width of the processor's respective data bus allows. Extra bits registers are maintained for at least one of the read and write direction data busses. The extra bits correspond to the least significant bits conventionally ignored in changing from a data bus of one width to a data bus of a narrower width. The extra bits in the write direction are accessed, e.g., by a write to a write direction extra bits register addressable through a specific input / output (I / O) location. The extra bits are tacked on to a subsequent write cycle in the digital serial interface, e.g., in the AC '97 link, to write an excess length data word. In the read direction, each read cycle places excess bits in a read direction extra bits register for reading in a subsequent read cycle. Another aspect of the invention provides an automatic status register which provides, e.g., automatic creation of a TAG Phase in time slot 0 of an AC '97 link using, e.g., a write enable signal to various resources in the digital serial interface, e.g., write enable signals to time slot registers.

Owner:AGERE SYST INC

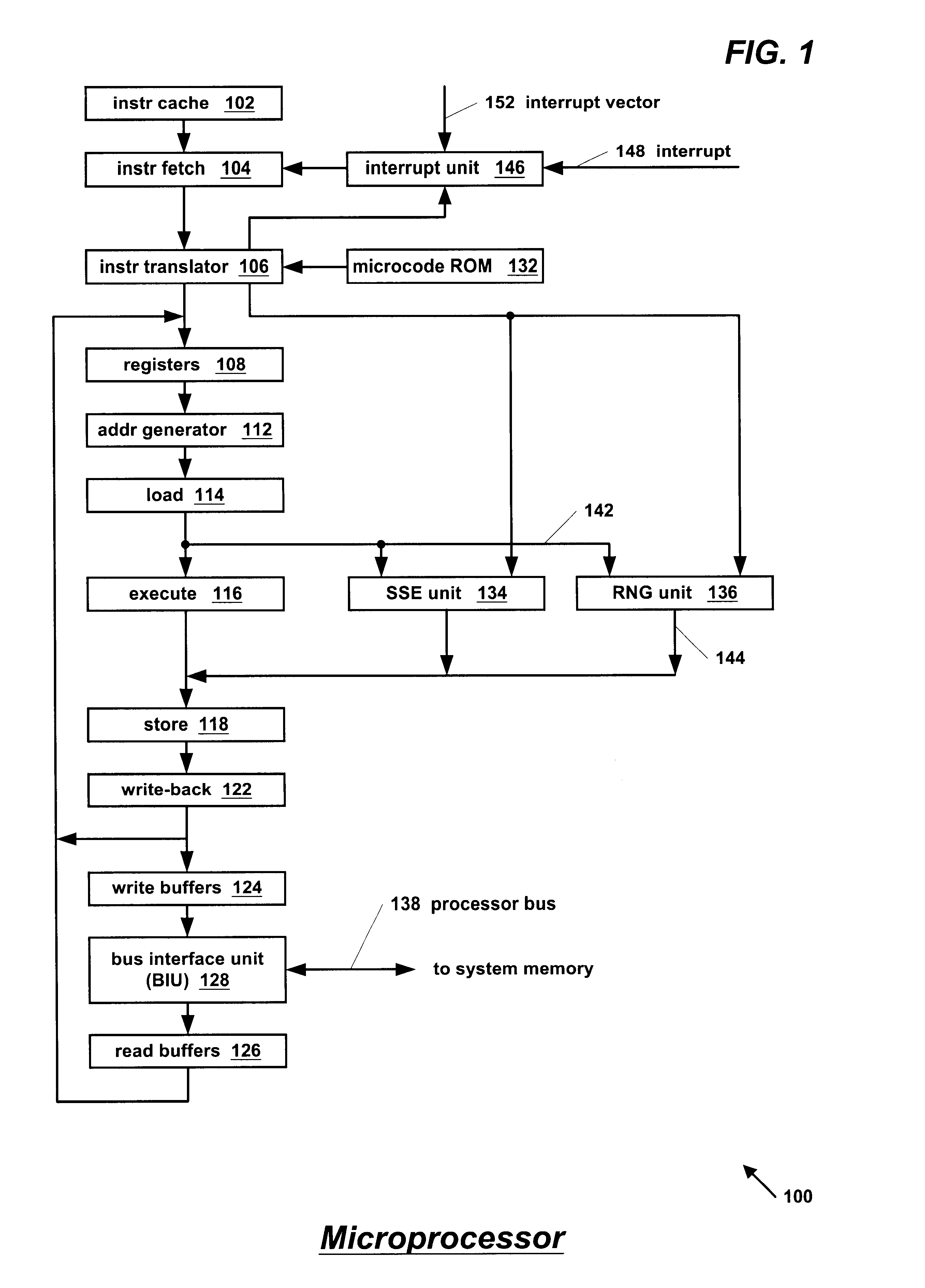

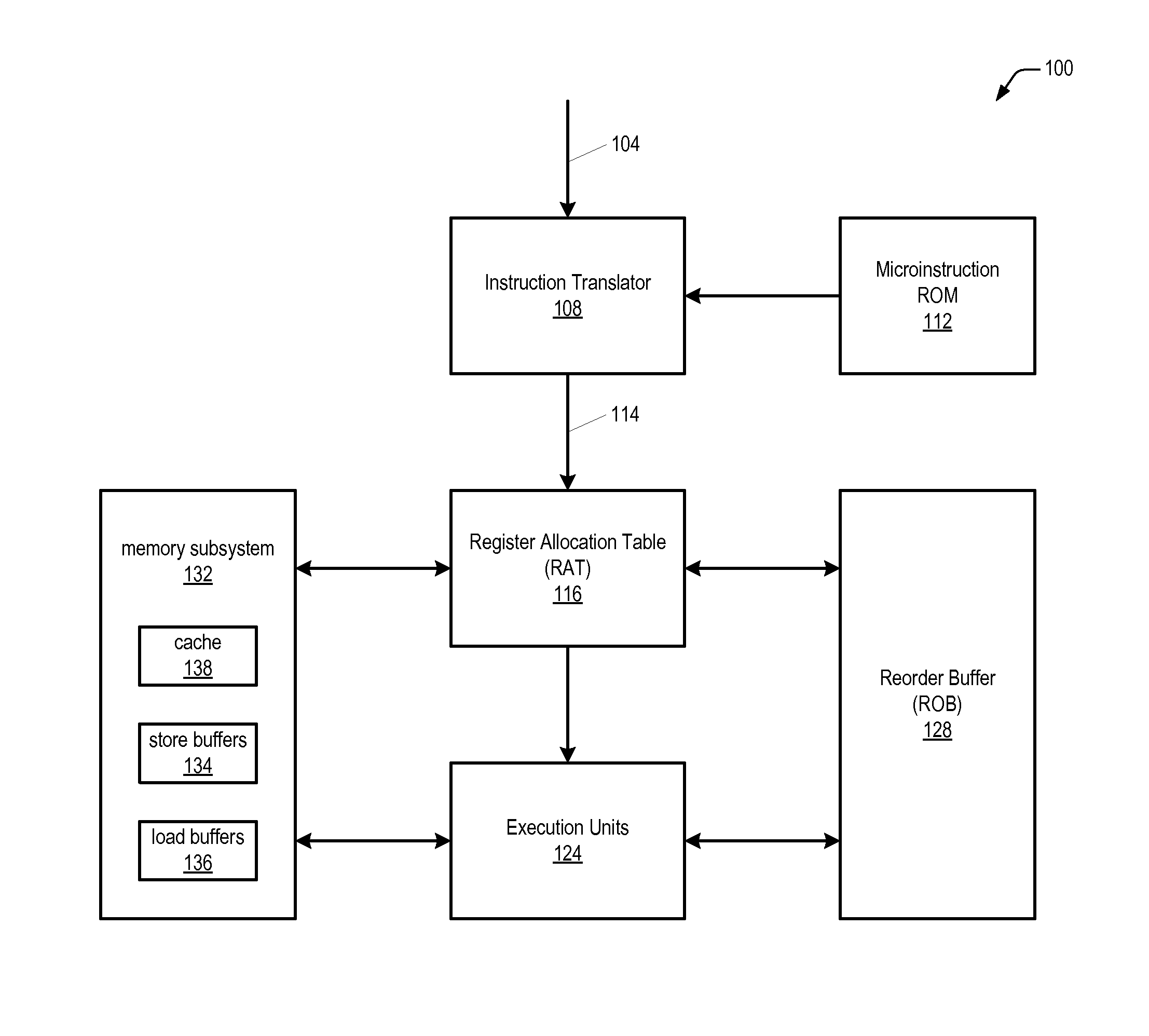

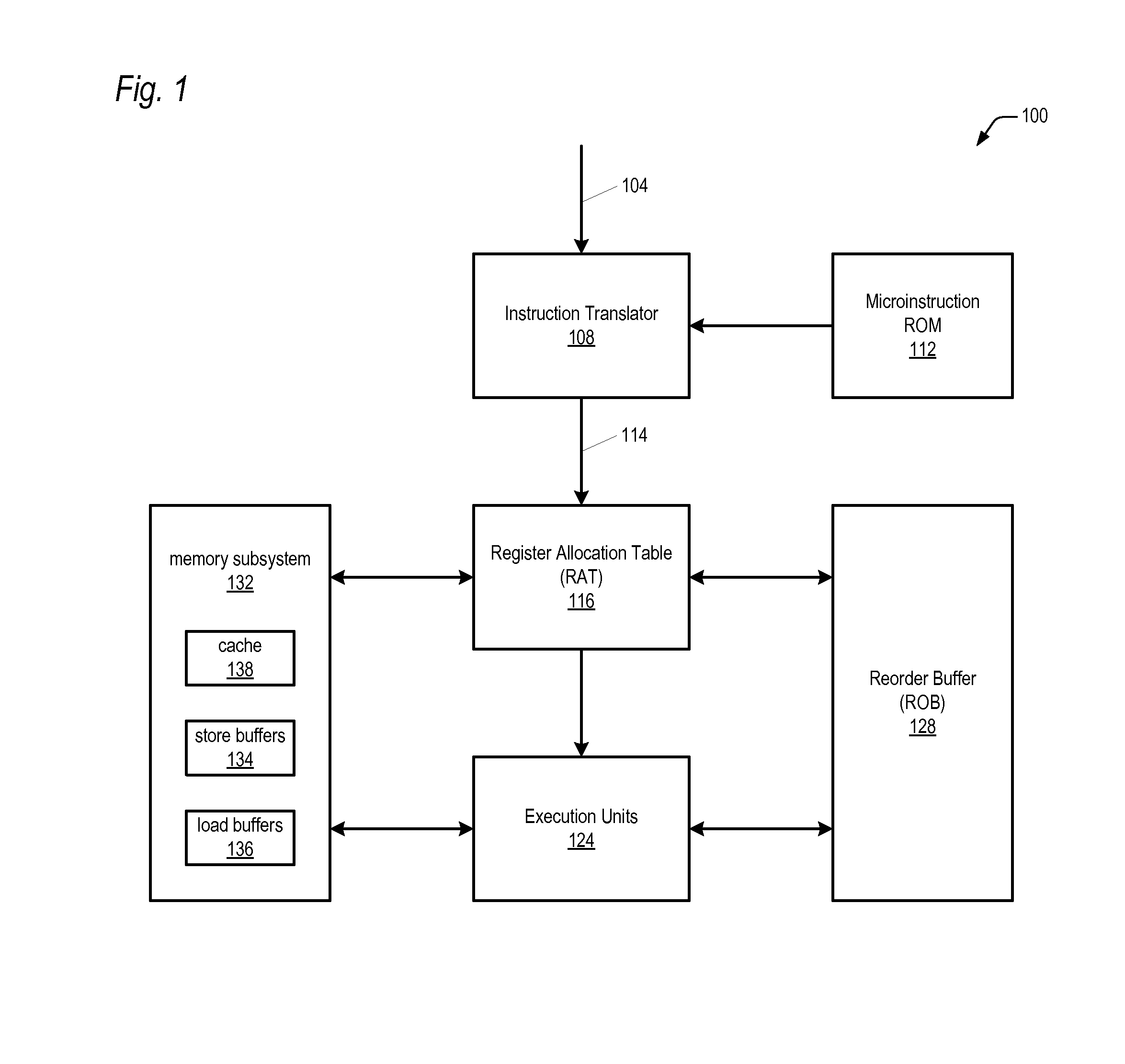

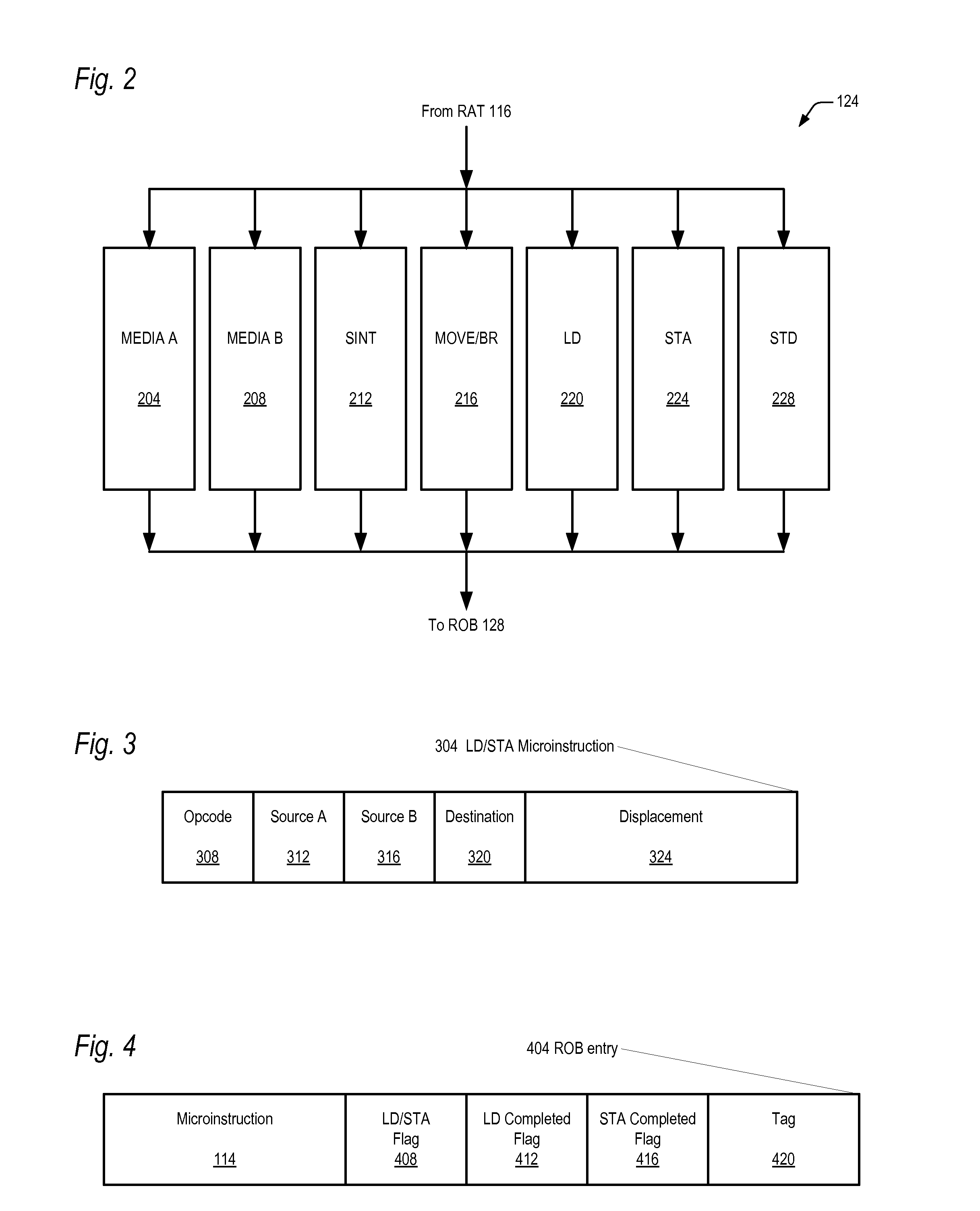

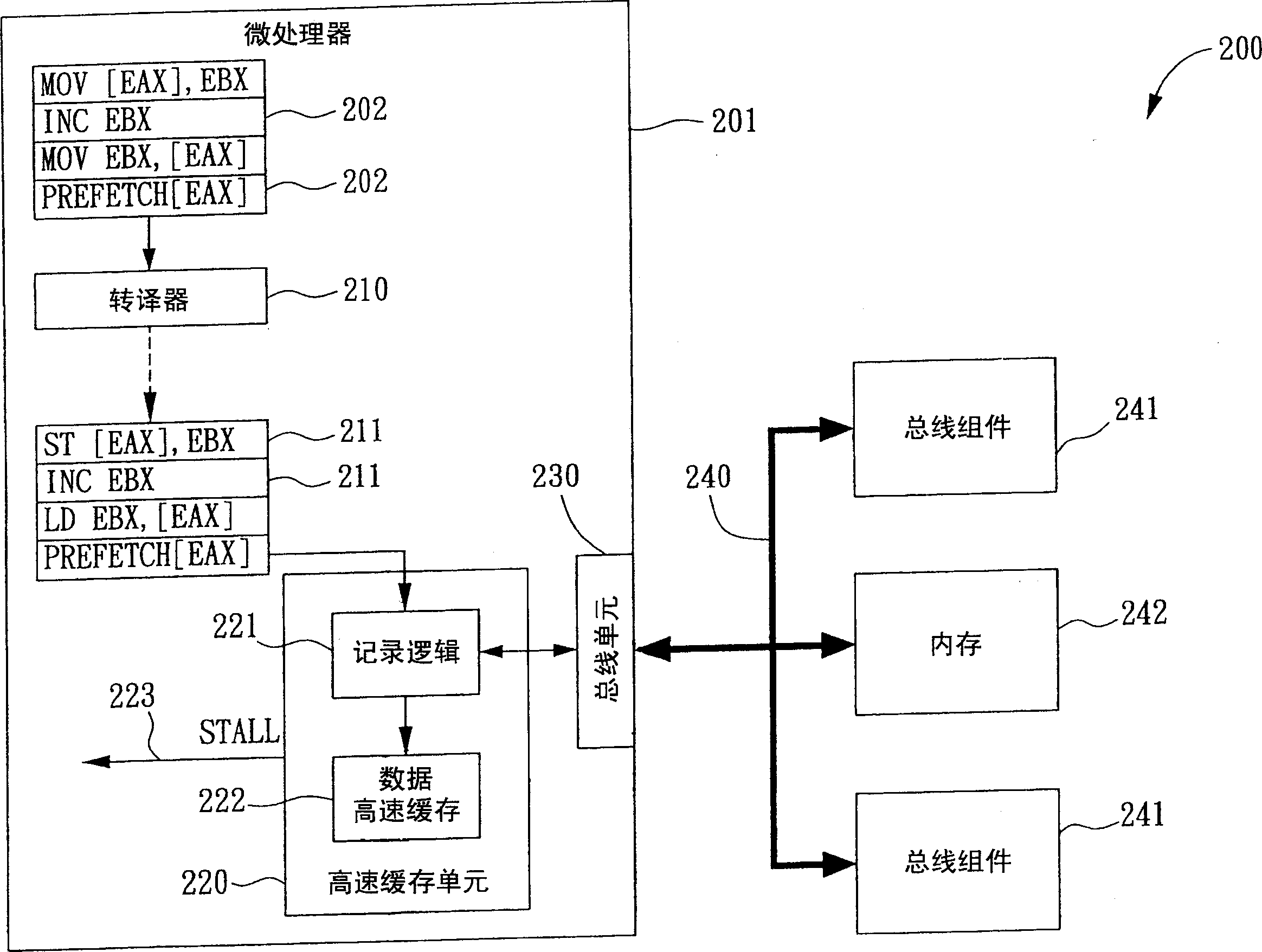

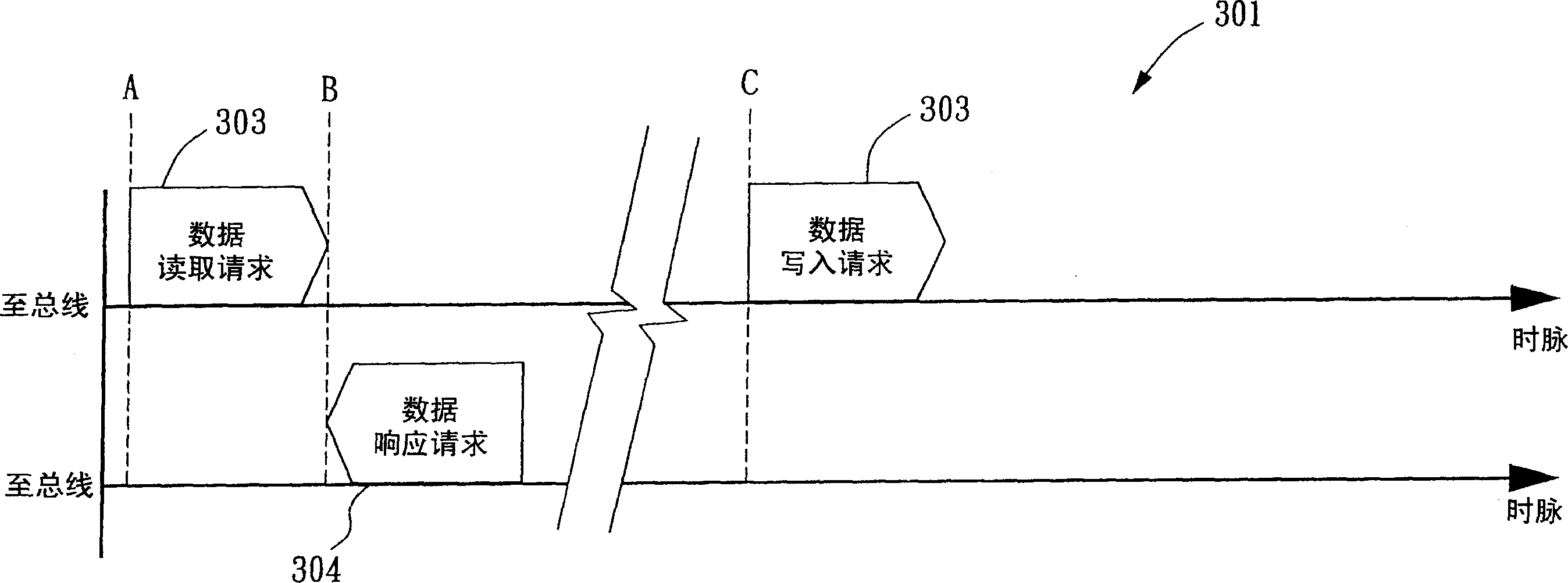

Microprocessor with microarchitecture for efficiently executing read/modify/write memory operand instructions

ActiveUS20090204800A1Reduce power consumptionImprove bindingRuntime instruction translationDigital computer detailsLogical operationsOperand

The microprocessor includes an instruction translator that translates a macroinstruction of a macroinstruction set in its macroarchitecture into exactly three microinstructions to perform a read / modify / write operation on a memory operand. The first microinstruction instructs the microprocessor to load the memory operand into the microprocessor from a memory location and to calculate a destination address of the memory location. The second microinstruction instructs the microprocessor to perform an arithmetic or logical operation on the loaded memory operand to generate a result. The third microinstruction instructs the microprocessor to write the result to the memory location whose destination address is calculated by the first microinstruction. A first execution unit receives the first microinstruction and responsively loads the memory operand into the microprocessor from the memory location, and a second distinct execution unit also receives the first microinstruction and responsively calculates the destination address of the memory location.

Owner:VIA TECH INC

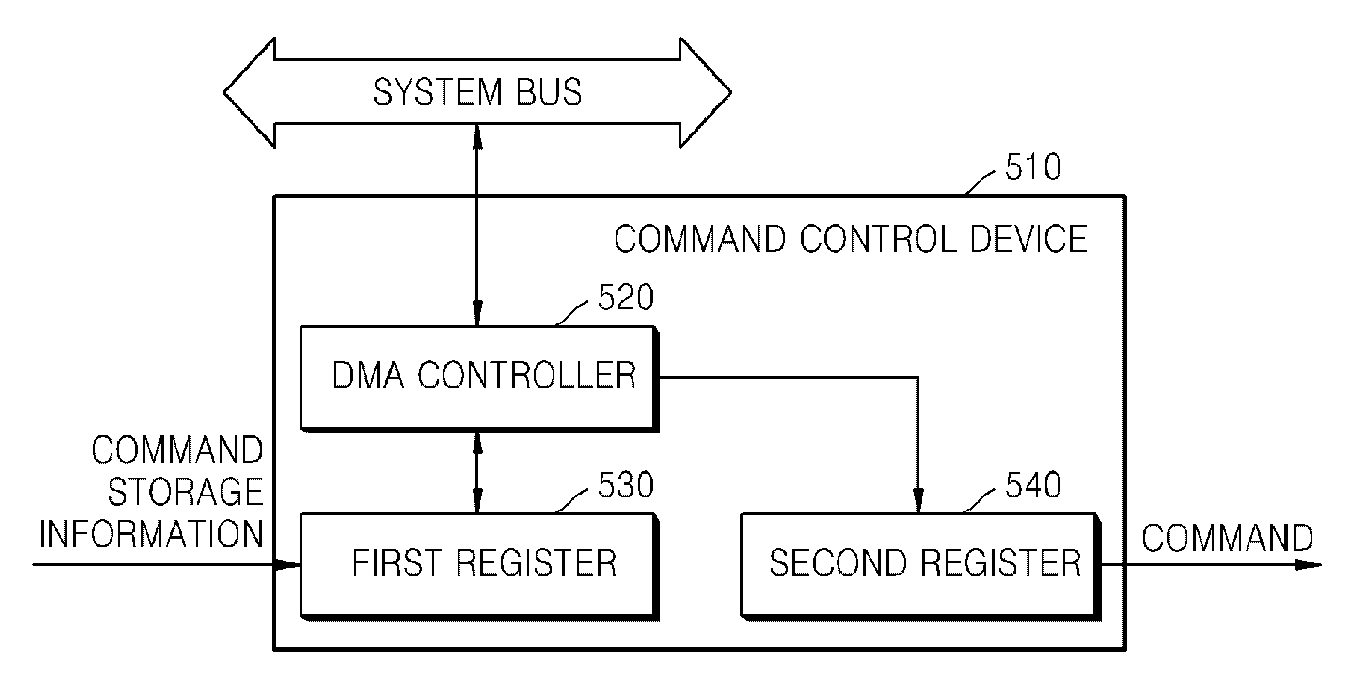

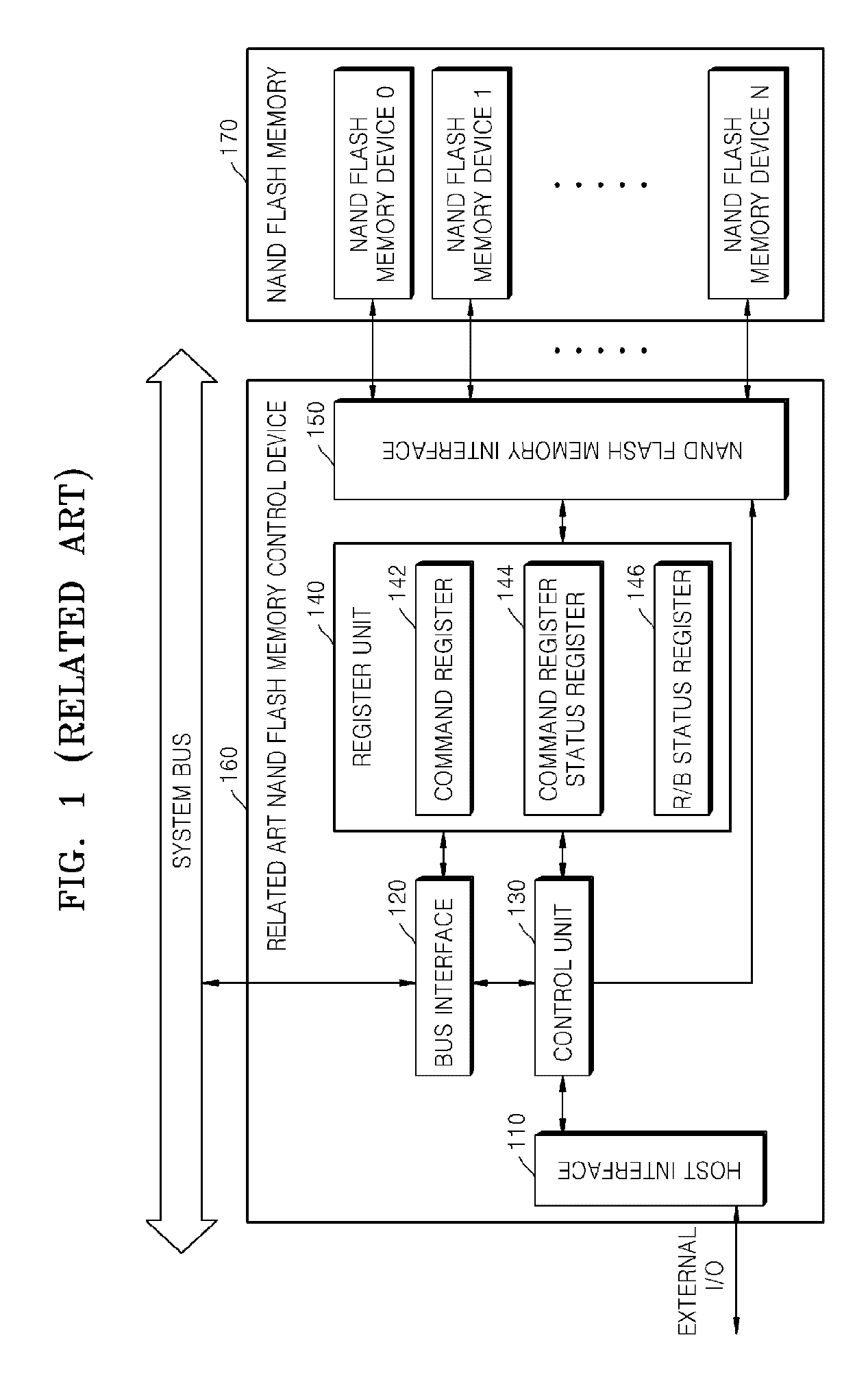

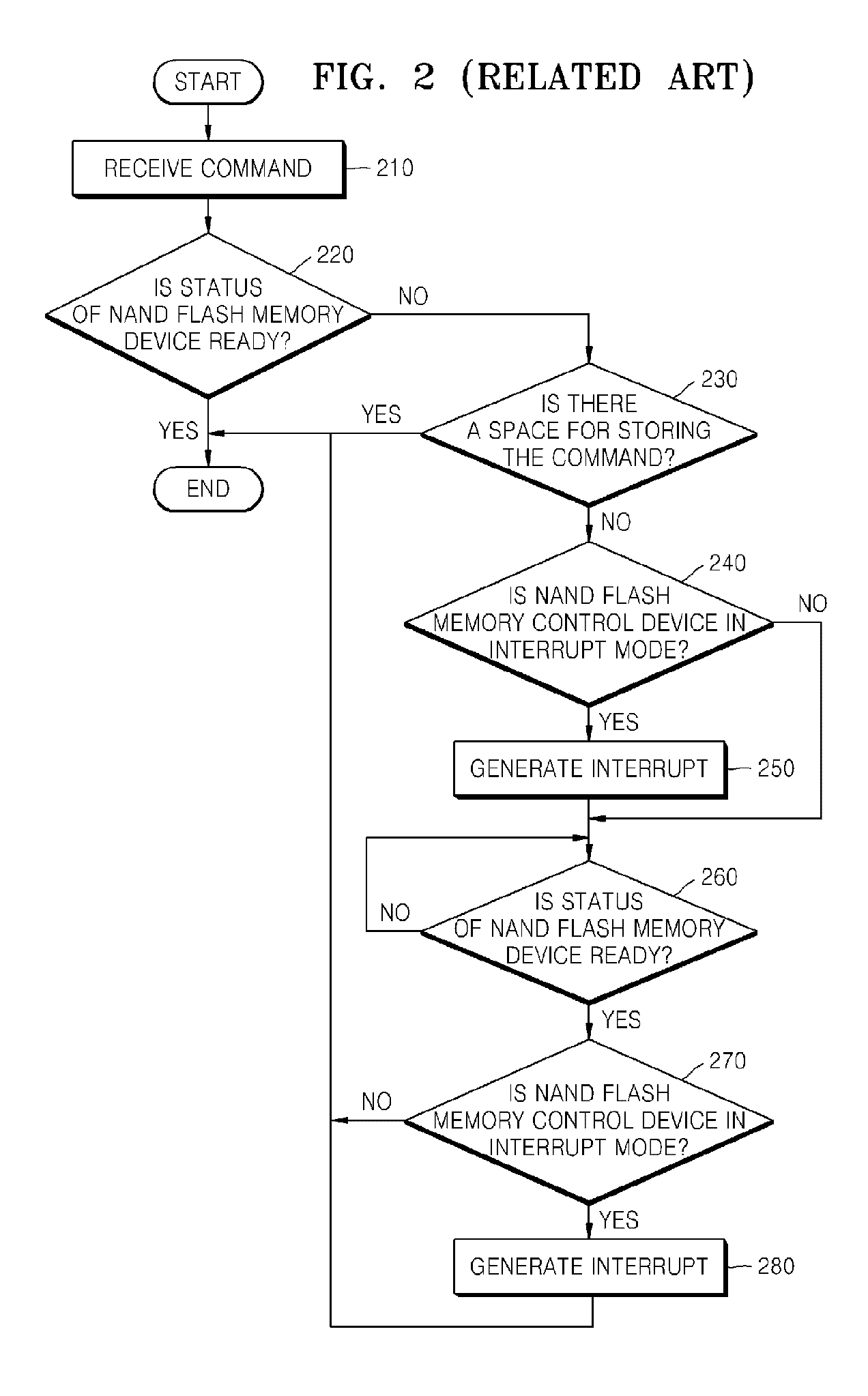

Device and method for controlling commands used for flash memory

InactiveUS20080301381A1Program control using stored programsMicrocontrol arrangementsFlash memoryCentral processing unit

A method and device for controlling commands used for a flash memory are provided. The method includes, substantially reducing usage of a central processing unit (CPU) and a bus, when controlling the flash memory, by receiving information on at least one command currently stored in a system memory, receiving a command represented by the received information from the system memory, and generating an interrupt representing that all the commands are received, when receiving of substantially all the commands represented by the received information is completed.

Owner:SAMSUNG ELECTRONICS CO LTD

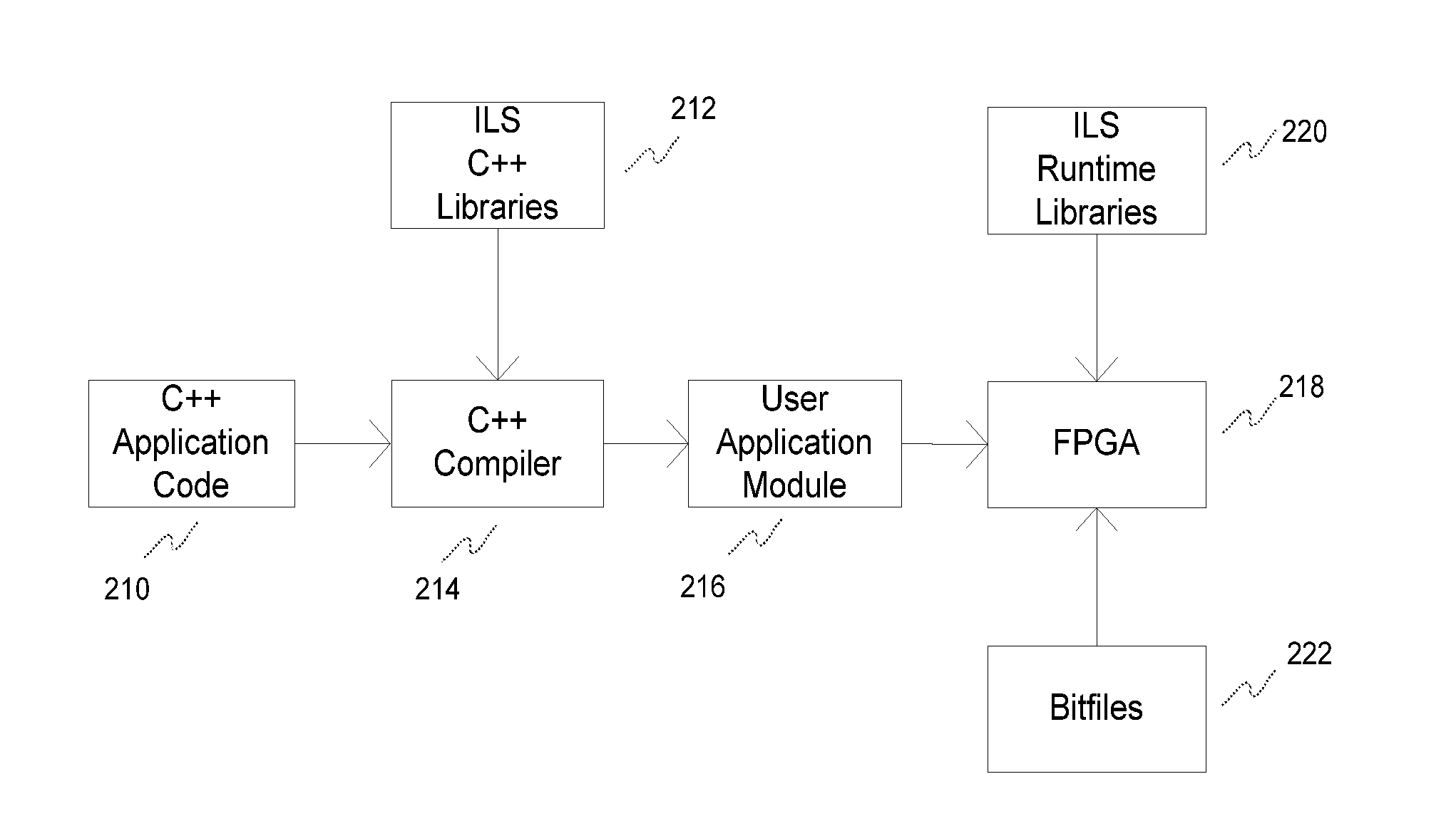

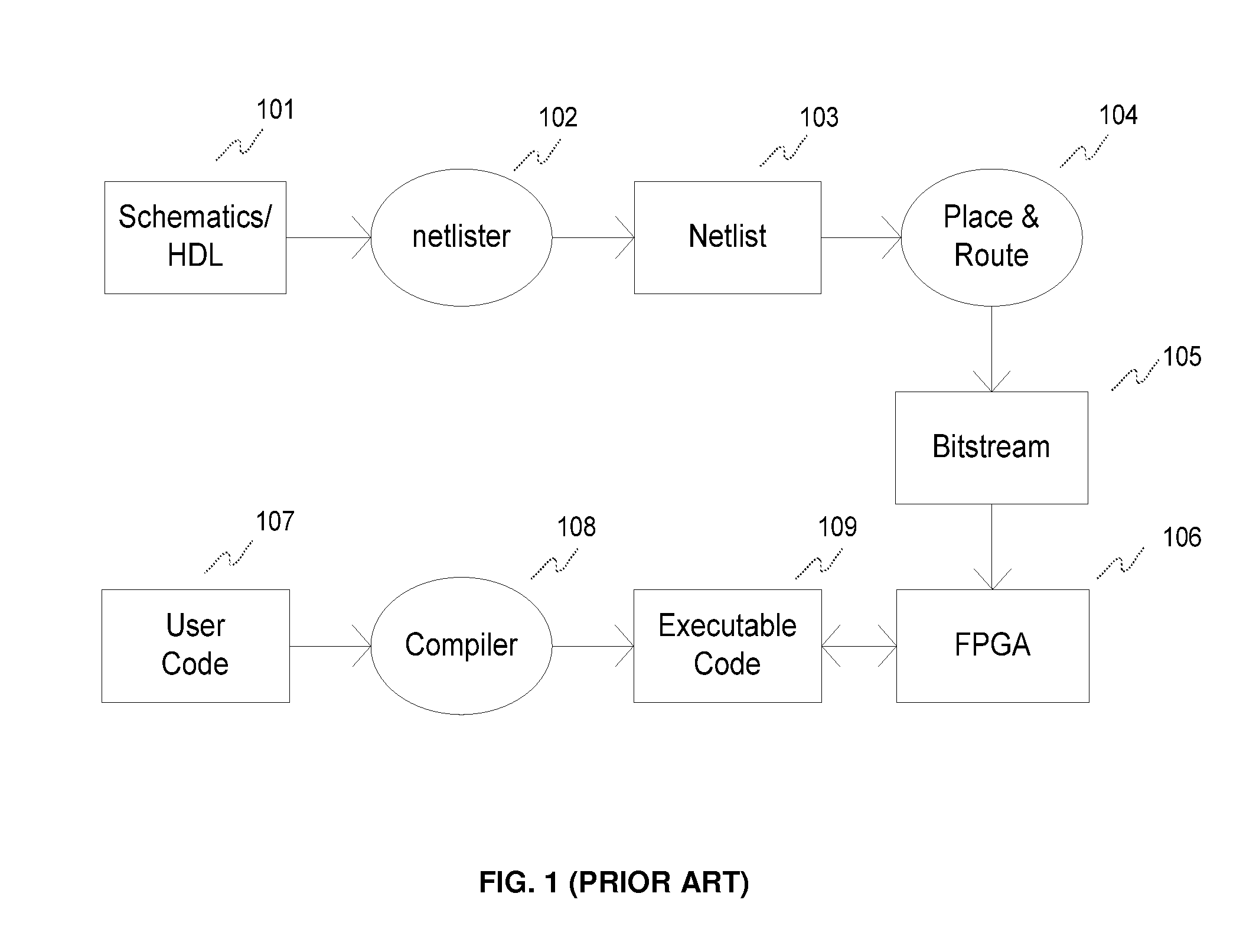

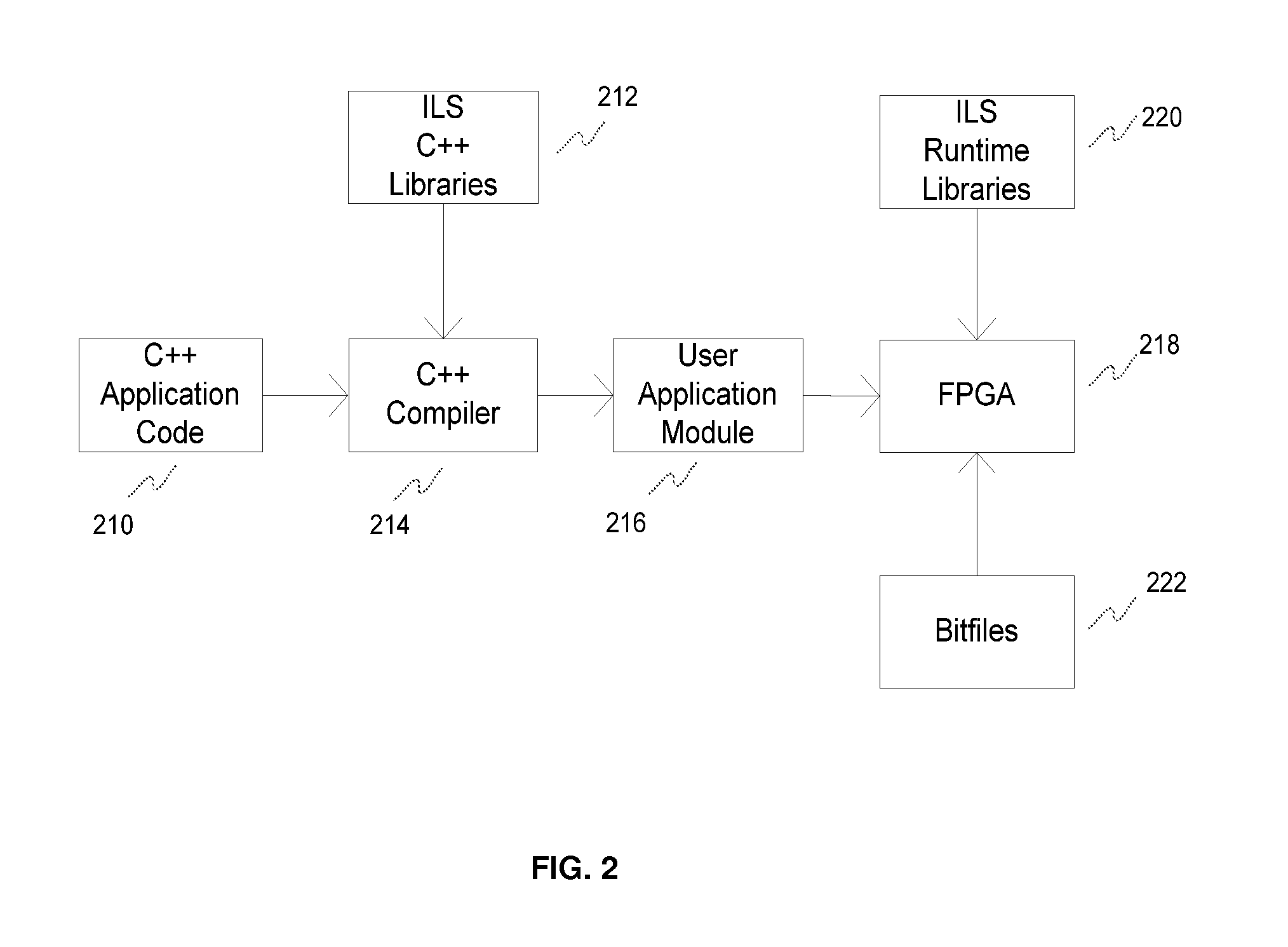

Reconfigurable computing system and method of developing application for deployment on the same

A method of developing an application for deployment on a computing system. The computing system includes a processor and a reconfigurable logic in communication with the processor for configuration thereby. The method includes programming the processor with hardware-neutral instructions in a high-level software programming language. The instructions are representative of an application configured to execute at least partially on the reconfigurable logic. The method further includes instantiating elements from a library of elements compatible with the high-level programming language; and constructing programmatically a generic data graph representative of the application to be mapped at least partially onto the reconfigurable logic. The generic data graph is expressed as streams of records flowing between operators. A computing system is also disclosed. By presenting an instruction level streaming data processing model that expresses an application as operators and data flows, the invention provide several advantages such as design portability.

Owner:ISHEBABI HAROLD

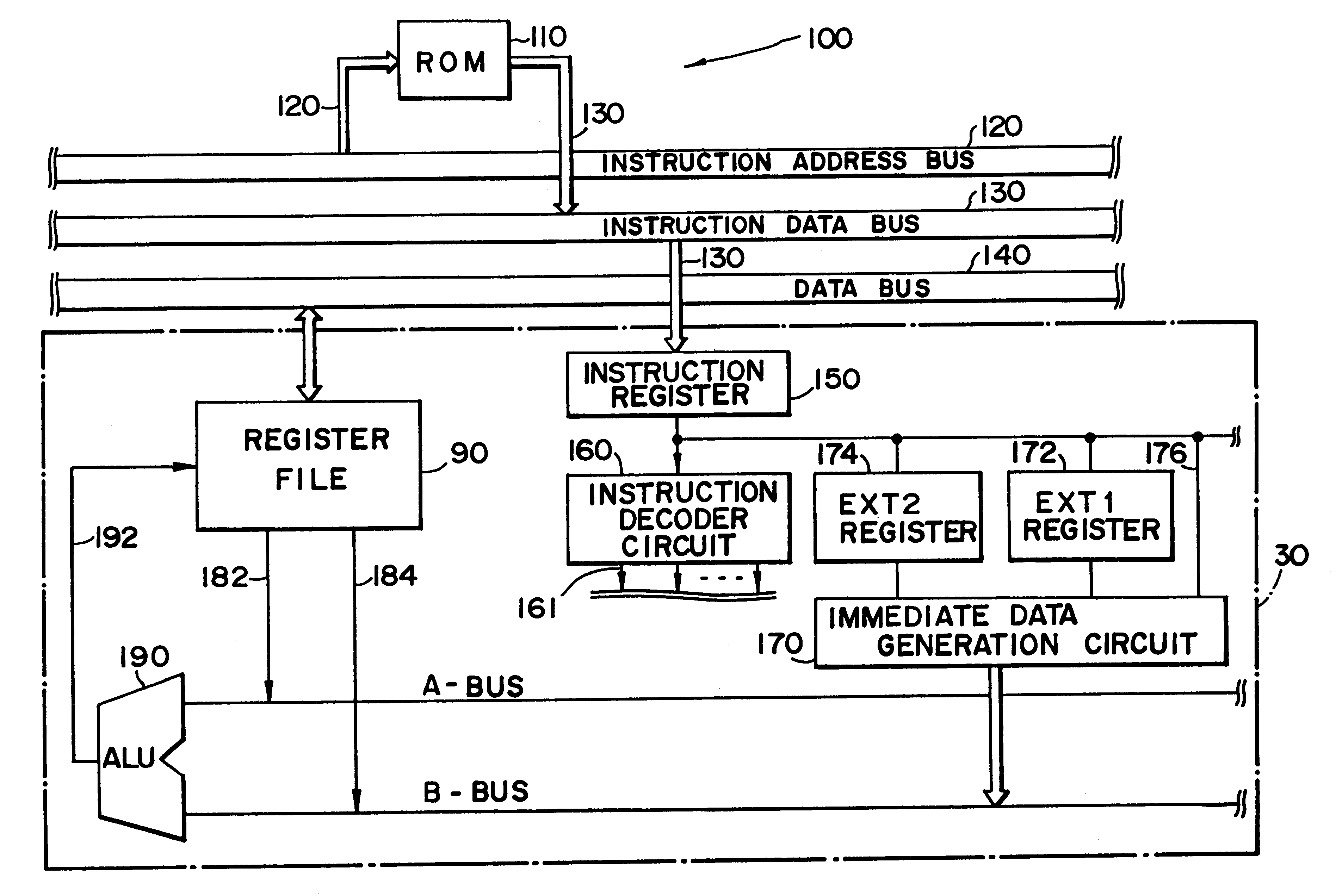

Data processing circuit with target instruction and prefix instruction

InactiveUS6308258B1Simple structureUses memory efficientlyInstruction analysisDigital computer detailsRegister fileInstruction decoder

A certain target instruction and a prefix instruction for expanding the function of that target instruction are input to the present data processing circuit. The data processing circuit analyses the thus-input instruction code and performs the processing necessary for the execution of that instruction. The data processing circuit comprises an instruction decoder section, a register file, and an instruction execution section that executes the instruction based on operational details of the instruction analyzed by the instruction decoder section. The instruction decoder section comprises an ext instruction processing section that processed the expansion of immediate data from the prefix instruction.

Owner:SEIKO EPSON CORP

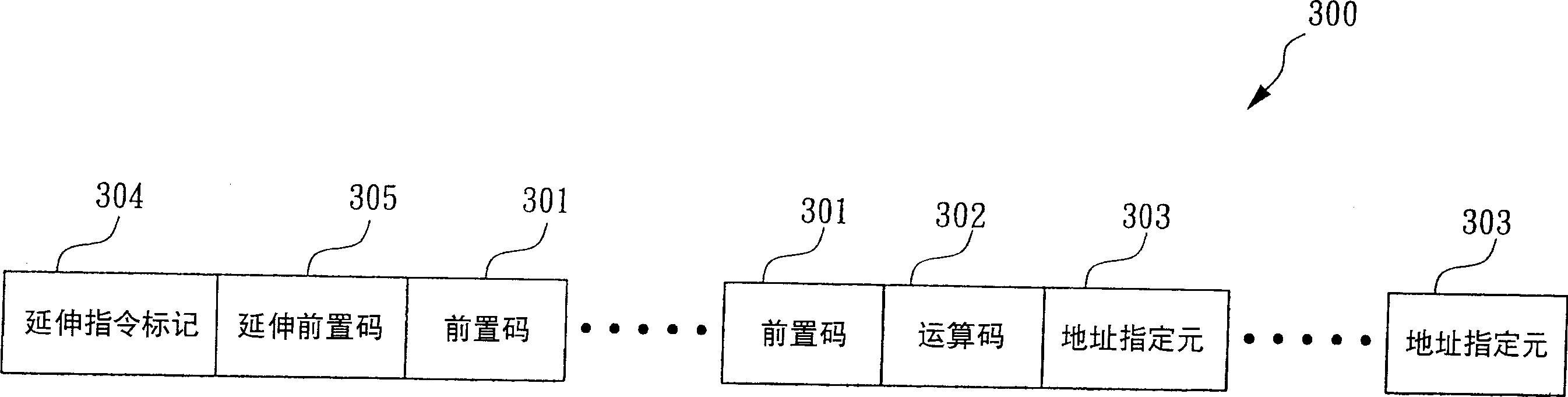

Appts. and method of extending microprocessor data mode

An apparatus and method are provided for extending a microprocessor instruction set beyond its current capabilities to allow for extended size operands specifiable by programmable instructions in the microprocessor instruction set. The apparatus includes translation logic and extended execution logic. The translation logic translates an extended instruction into corresponding micro instructions for execution by the microprocessor. The extended instruction has an extended prefix and an extended prefix tag. The extended prefix specifies an extended operand size for an operand corresponding to a prescribed operation, where the extended operand size cannot be specified by an existing instruction set. The extended prefix tag indicates the extended prefix, where the extended prefix tag is an otherwise architecturally specified opcode within the existing instruction set. The extended execution logic is coupled to the translation logic. The extended execution logic receives the corresponding micro instructions and performs the prescribed operation using the operand.

Owner:IP FIRST

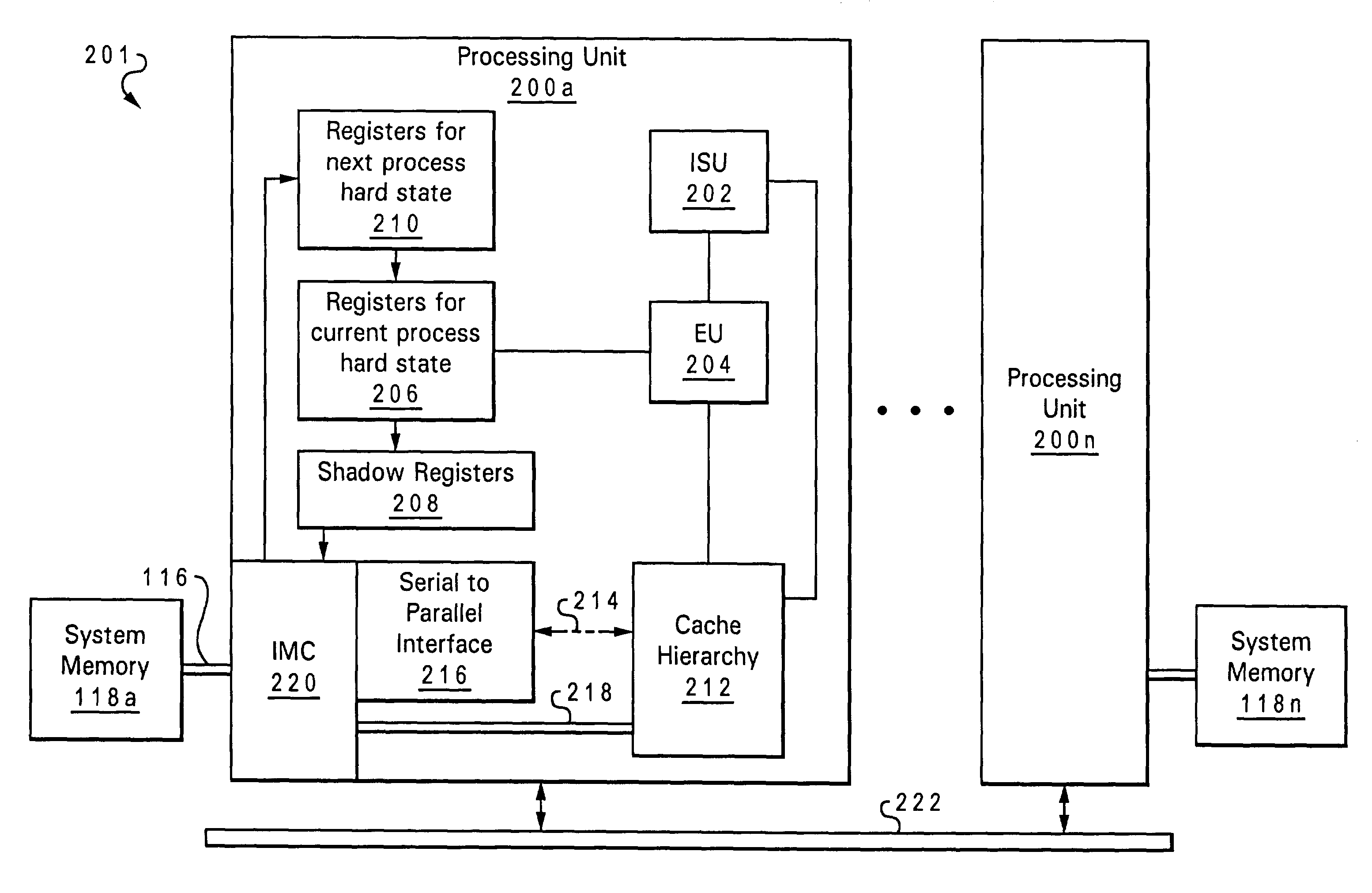

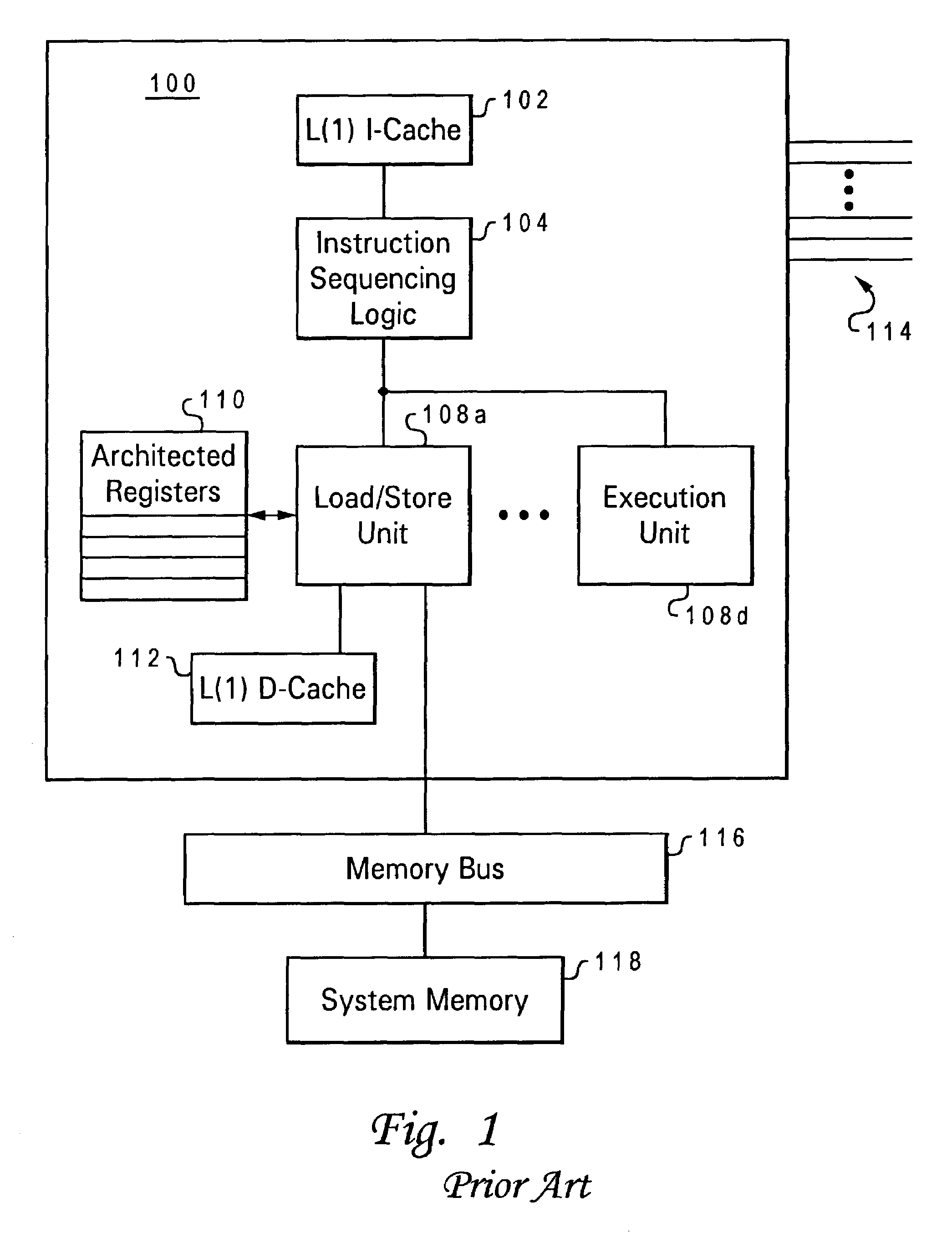

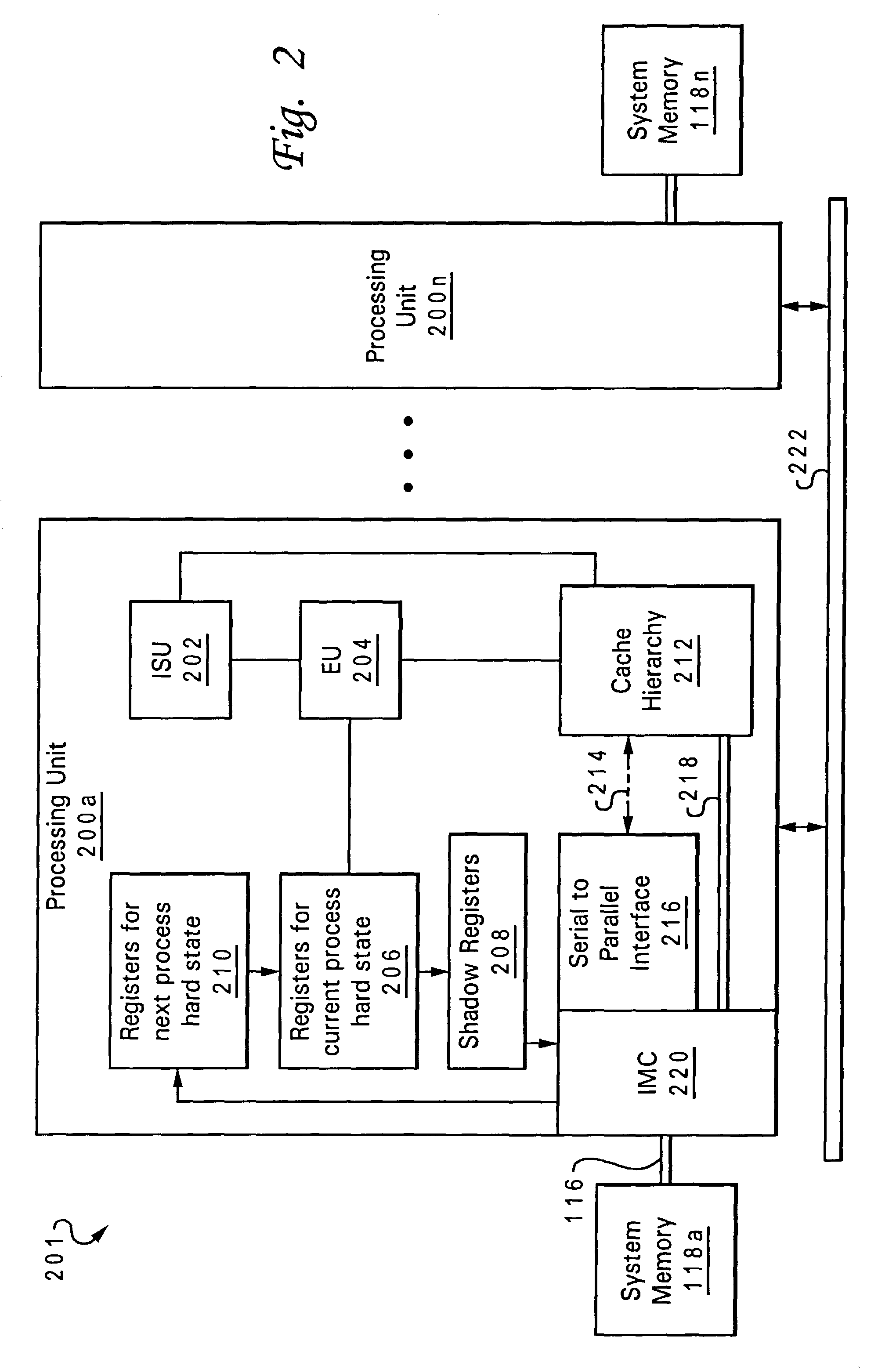

Processor virtualization mechanism via an enhanced restoration of hard architected states

InactiveUS6981083B2Rapidly begin executionIncrease savingsGeneral purpose stored program computerConcurrent instruction executionOperating systemProcessor virtualization

A method and system are disclosed for pre-loading a hard architected state of a next process from a pool of idle processes awaiting execution. When an executing process is interrupted on the processor, a hard architected state, which has been pre-stored in the processor, of a next process is loaded into architected storage locations in the processor. The next process to be executed, and thus its corresponding hard architected state that is pre-stored in the processor, are determined based on priorities assigned to the waiting processes.

Owner:IBM CORP

Apparatus and method for injected spin echo in a quantum processor

Apparatus and method for injected spin echo sequences in a quantum processor. For example, one embodiment of a processor comprises a decoder to decode quantum instructions to generate quantum microoperations (uops) and non-quantum instructions to generate non-quantum uops; execution circuitry to execute the quantum uops and non-quantum uops; a corrective sequence data structure to identify and / or store corrective sets of uops for one or more of the quantum instructions; wherein the decoder is to query the corrective sequence data structure upon receiving a first quantum instruction to determine if one or more corrective uops exist and if the one or more corrective uops exist, then to submit the one or more corrective uops for execution by the execution circuitry.

Owner:INTEL CORP

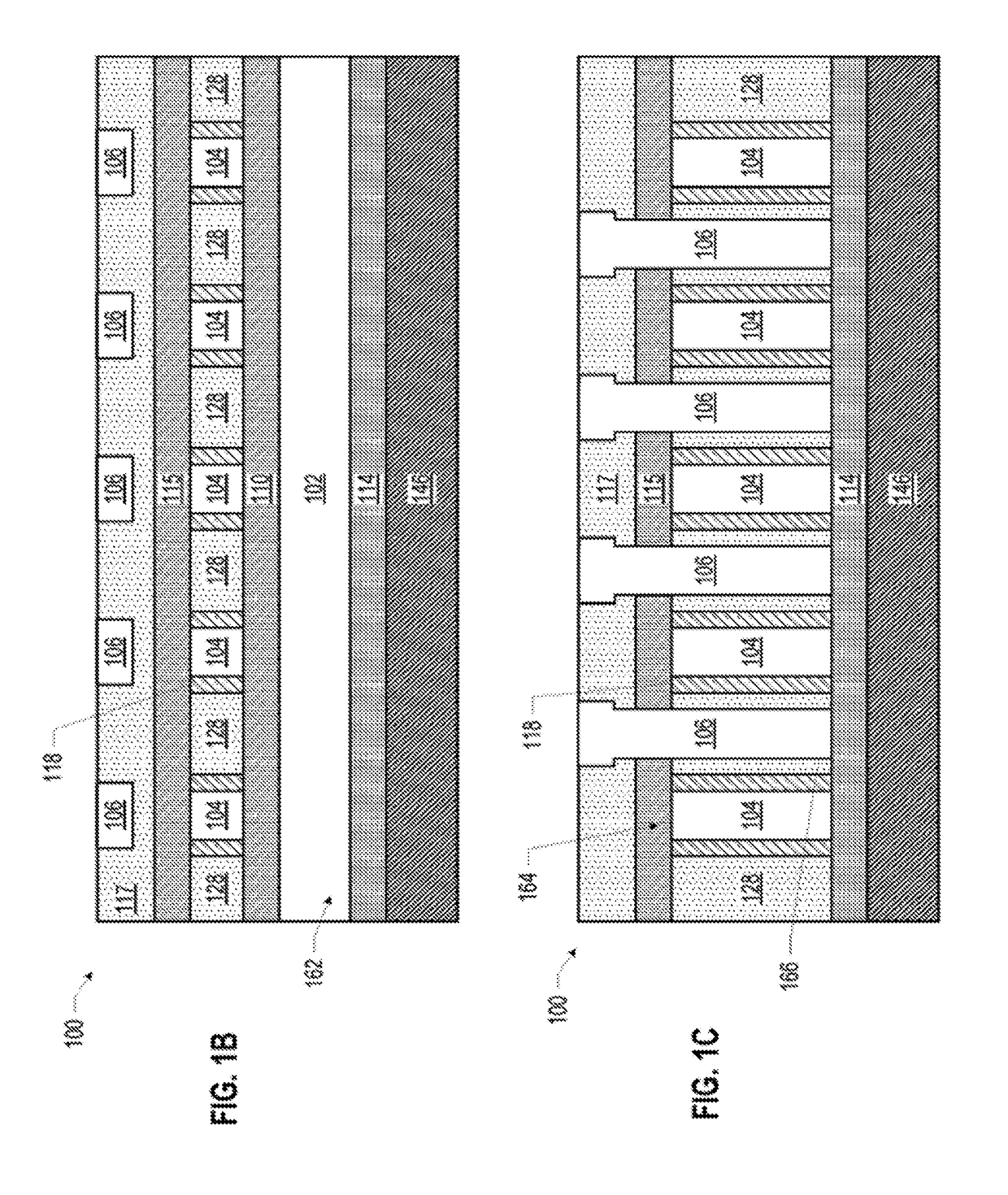

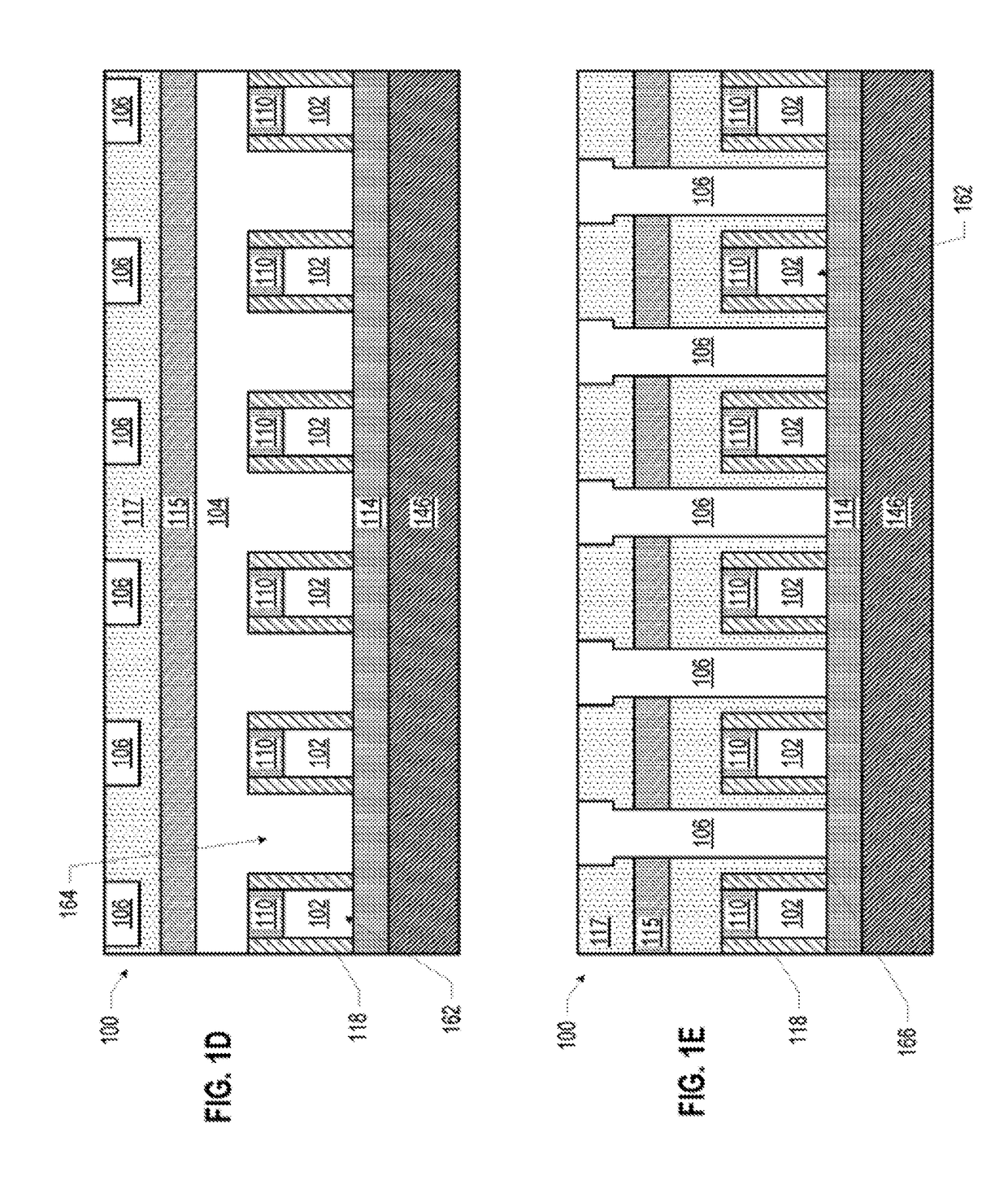

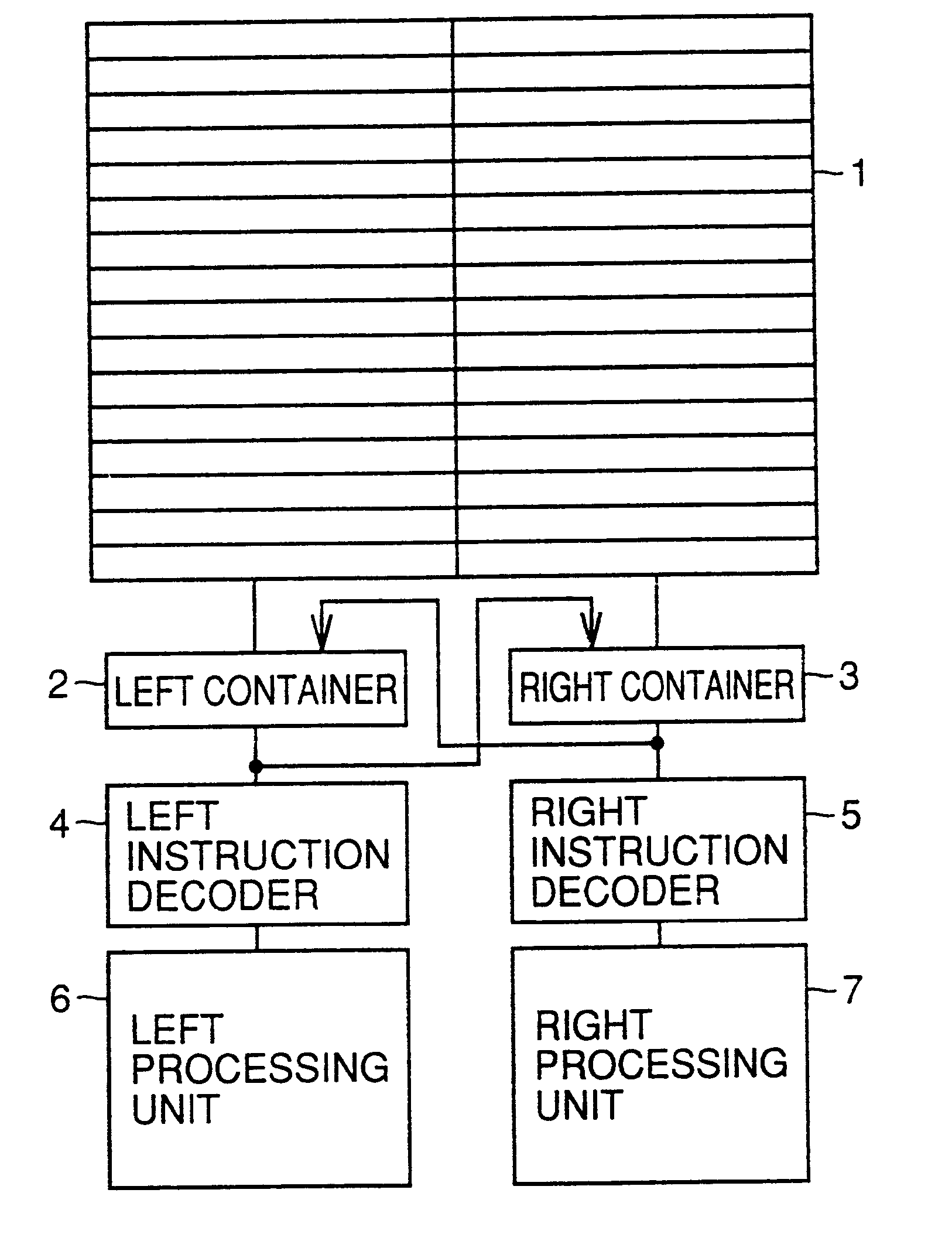

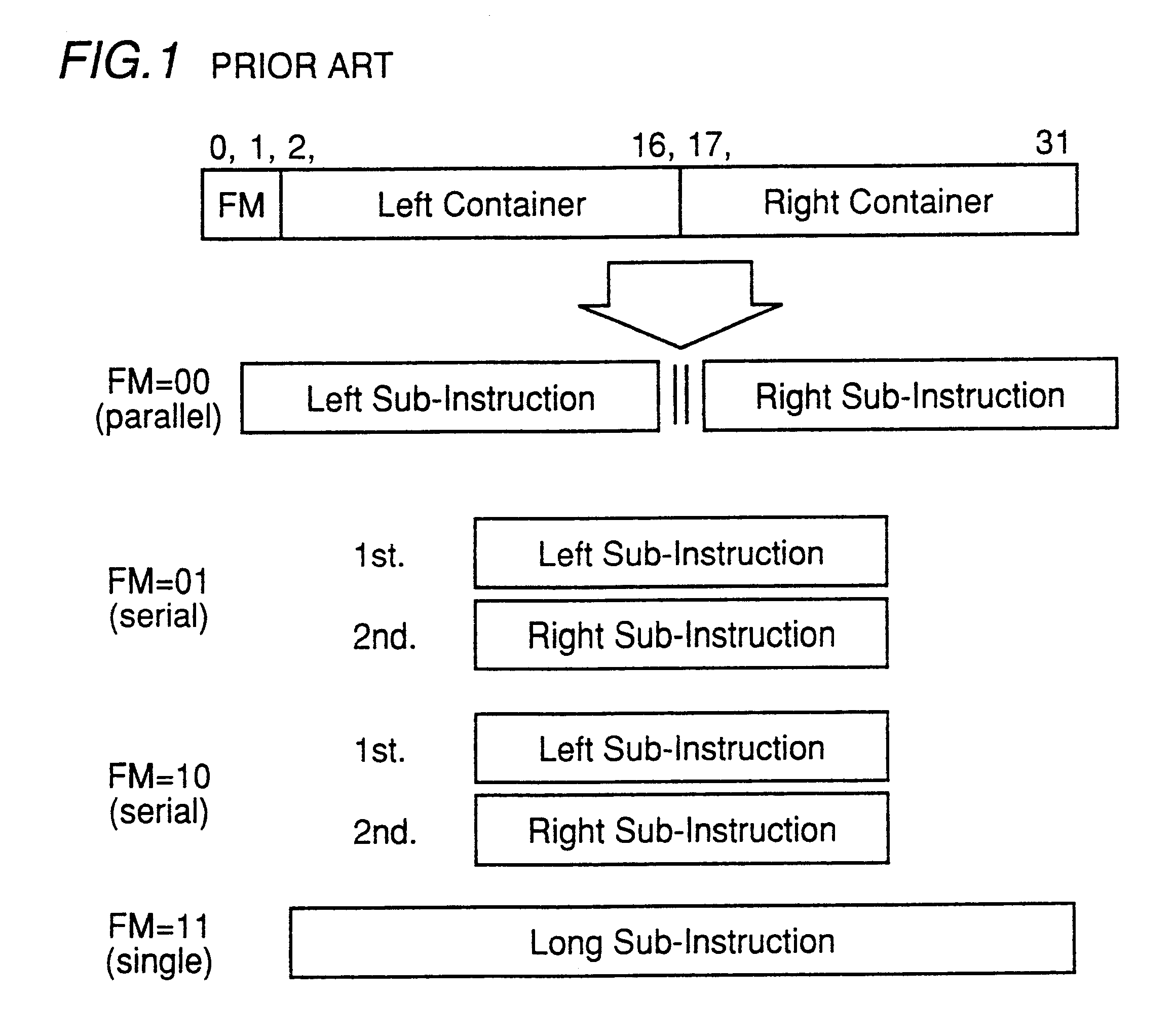

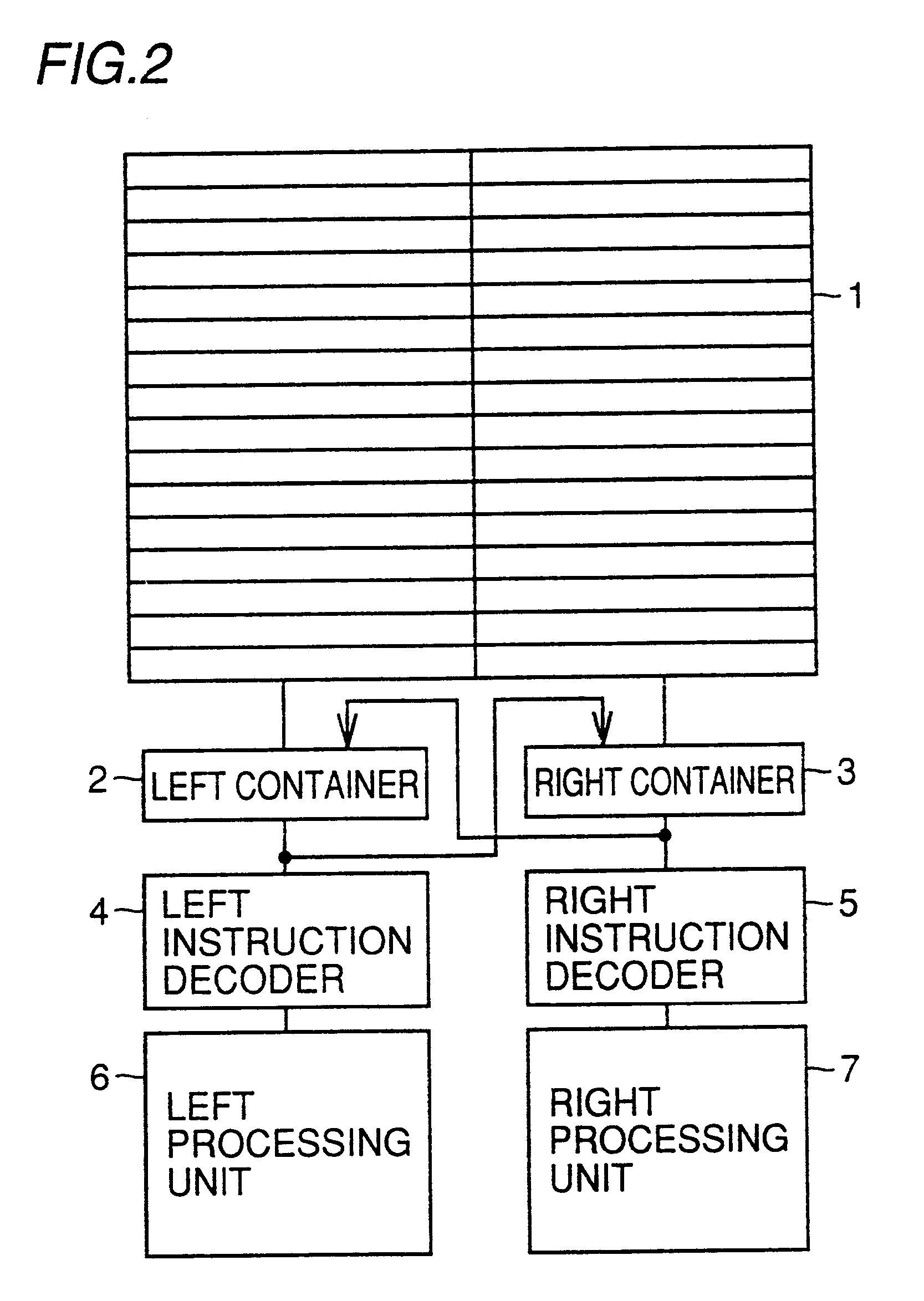

VLIW processor for exchanging and inputting sub-instructions to containers, and code compression device and method for compressing program code

InactiveUS6499096B1General purpose stored program computerConcurrent instruction executionCompression deviceCode compaction

A VLIW processor includes a plurality of containers holding a plurality of sub-instructions in a VLIW instruction, an exchanging portion exchanging the plurality of sub-instructions held in the plurality of containers and inputting the instructions to the plurality of containers, a plurality of decoders decoding the sub-instructions held in the plurality of containers, and a plurality of processing units executing the sub-instructions decoded by the plurality of decoders. Since the exchanging portion exchanges a plurality of sub-instructions held in the plurality of containers and inputs the instructions to the plurality of containers, a compressed code can be executed in such an execution sequence that is taken prior to compression.

Owner:MITSUBISHI ELECTRIC CORP

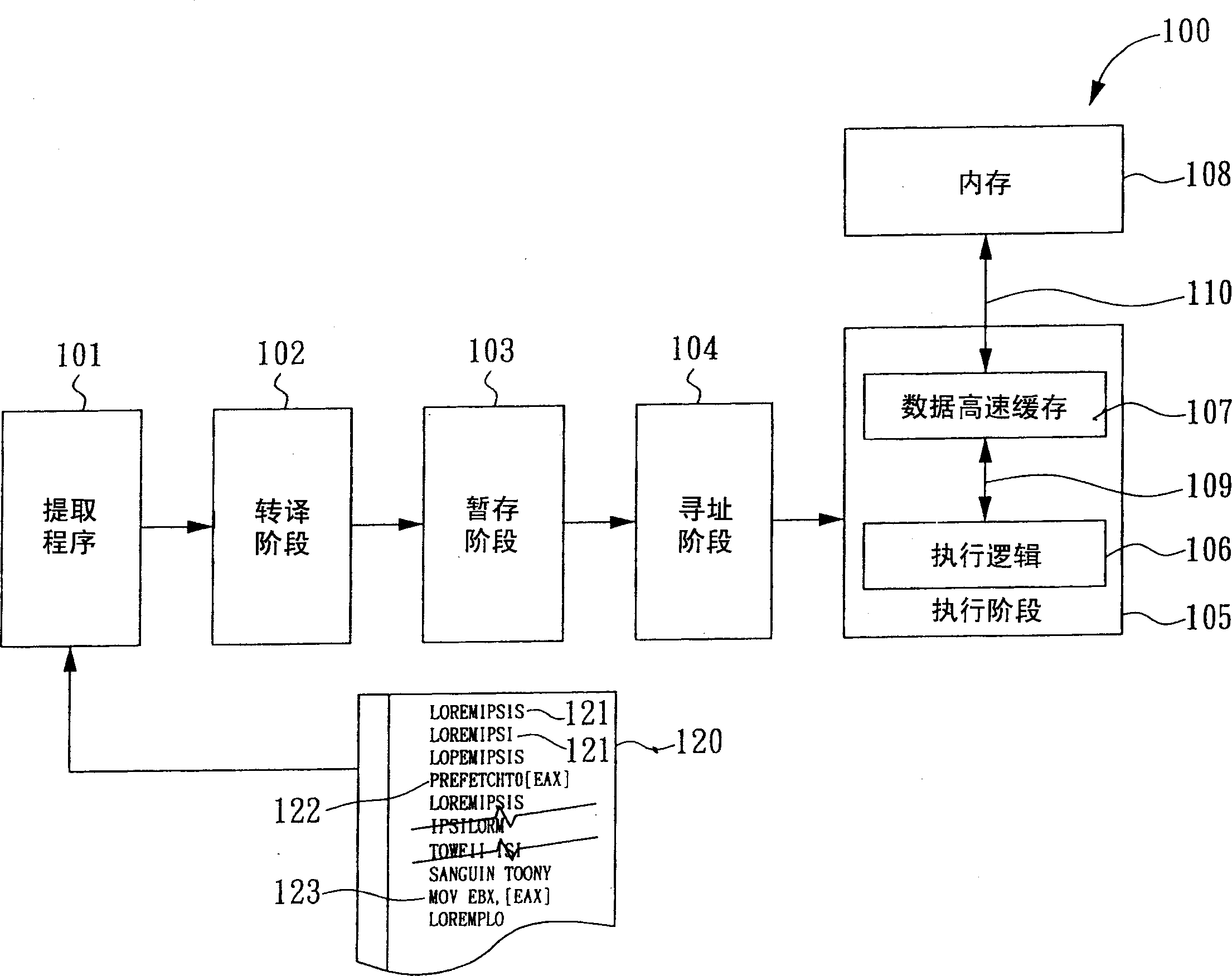

Allocation of cache memory data section and initial mechanism

InactiveCN1487409AMemory architecture accessing/allocationRuntime instruction translationMemory busParallel computing

A microprocessor apparatus is provided that enables exclusive prefetch and initialization of a block of cache lines from memory. The apparatus includes translation logic and execution logic. The translation logic translates a block allocate and initialize instruction into a micro instruction sequence that directs a microprocessor to prefetch a block of cache lines in an exclusive state and to initialize the block of cache lines to a specified value. The execution logic is coupled to the translation logic. The execution logic receives the micro instruction sequence, and issues transactions over a memory bus that requests the block of cache lines in the exclusive state. Upon receipt, the execution logic initializes the block of cache lines to the specified value.

Owner:IP FIRST

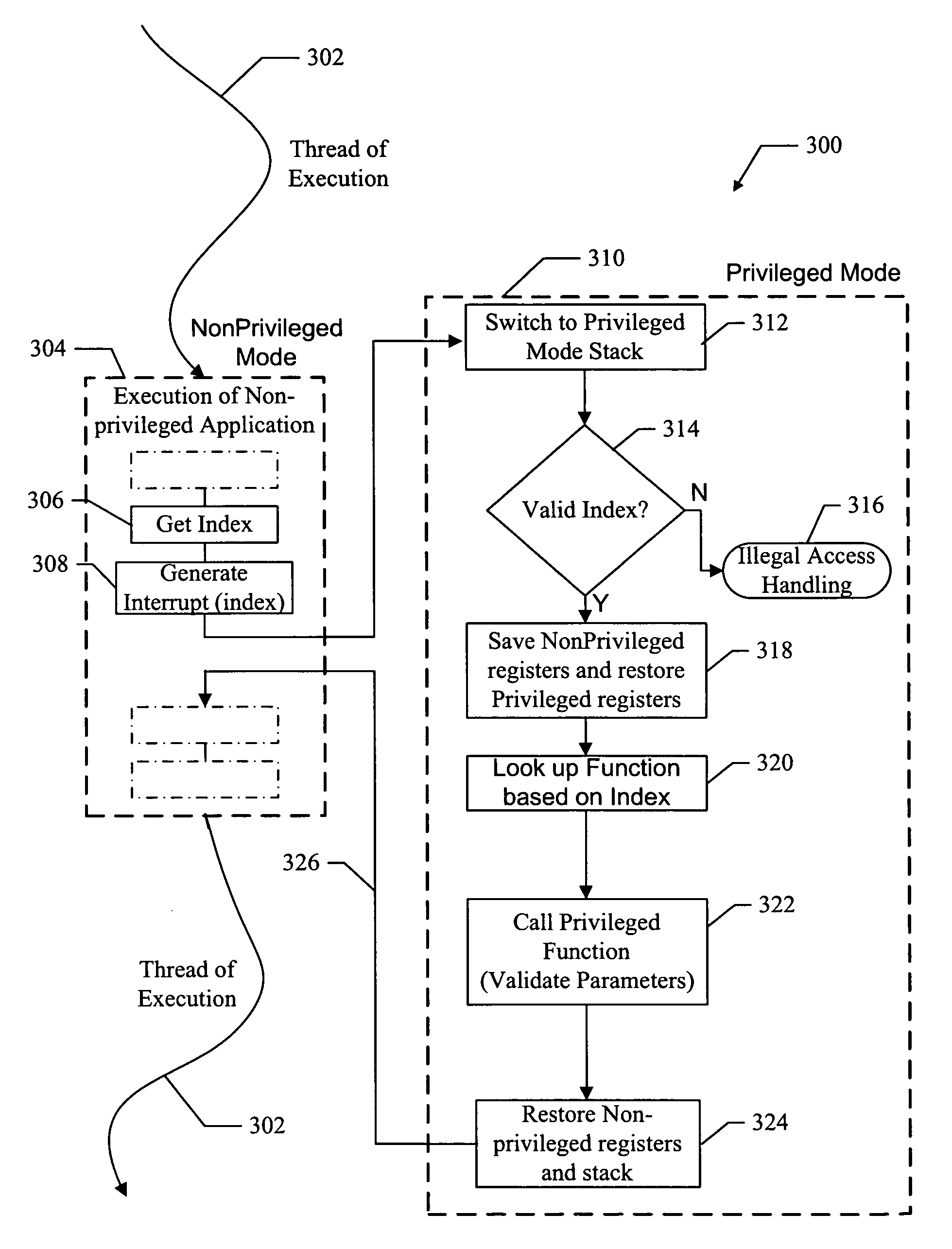

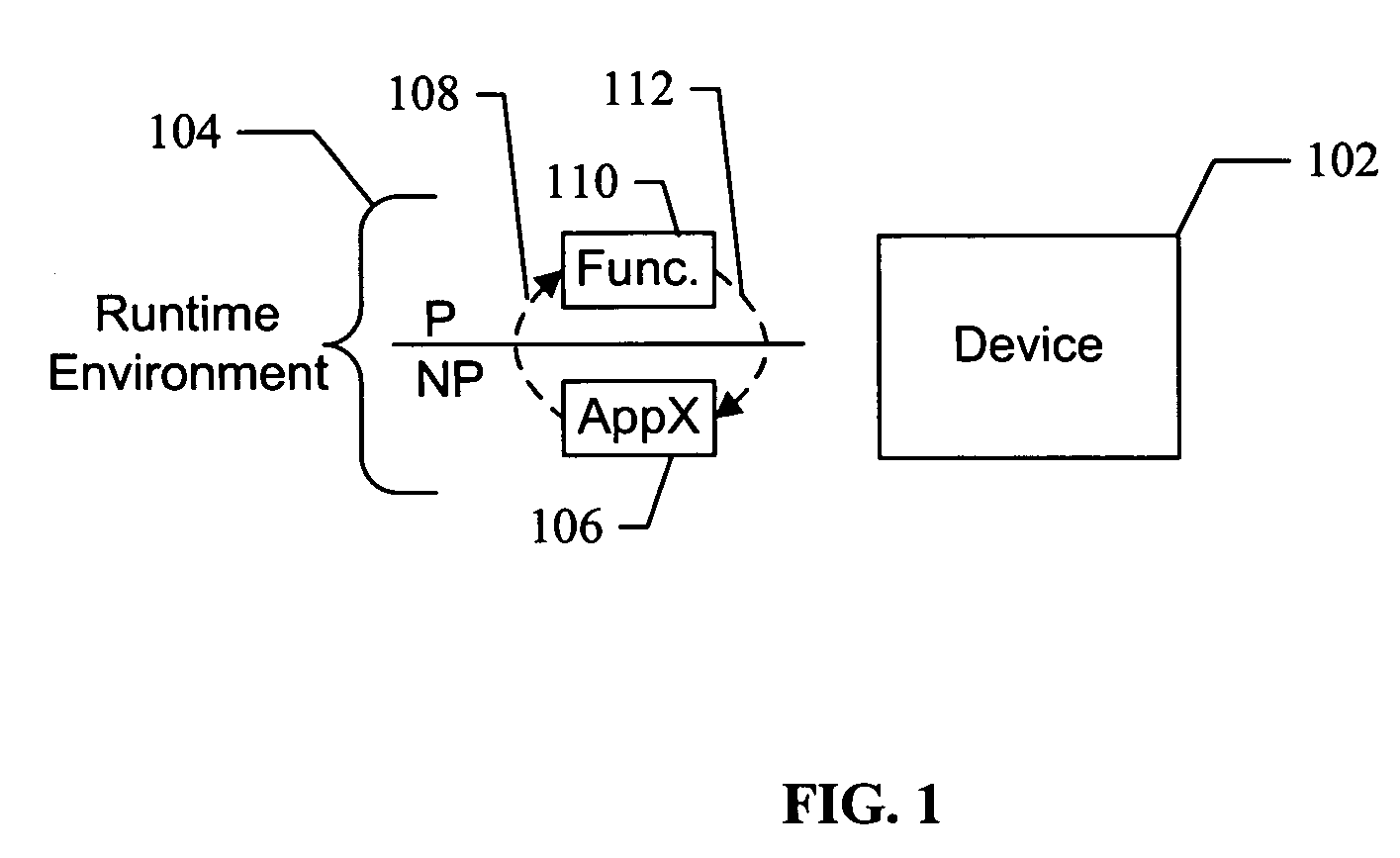

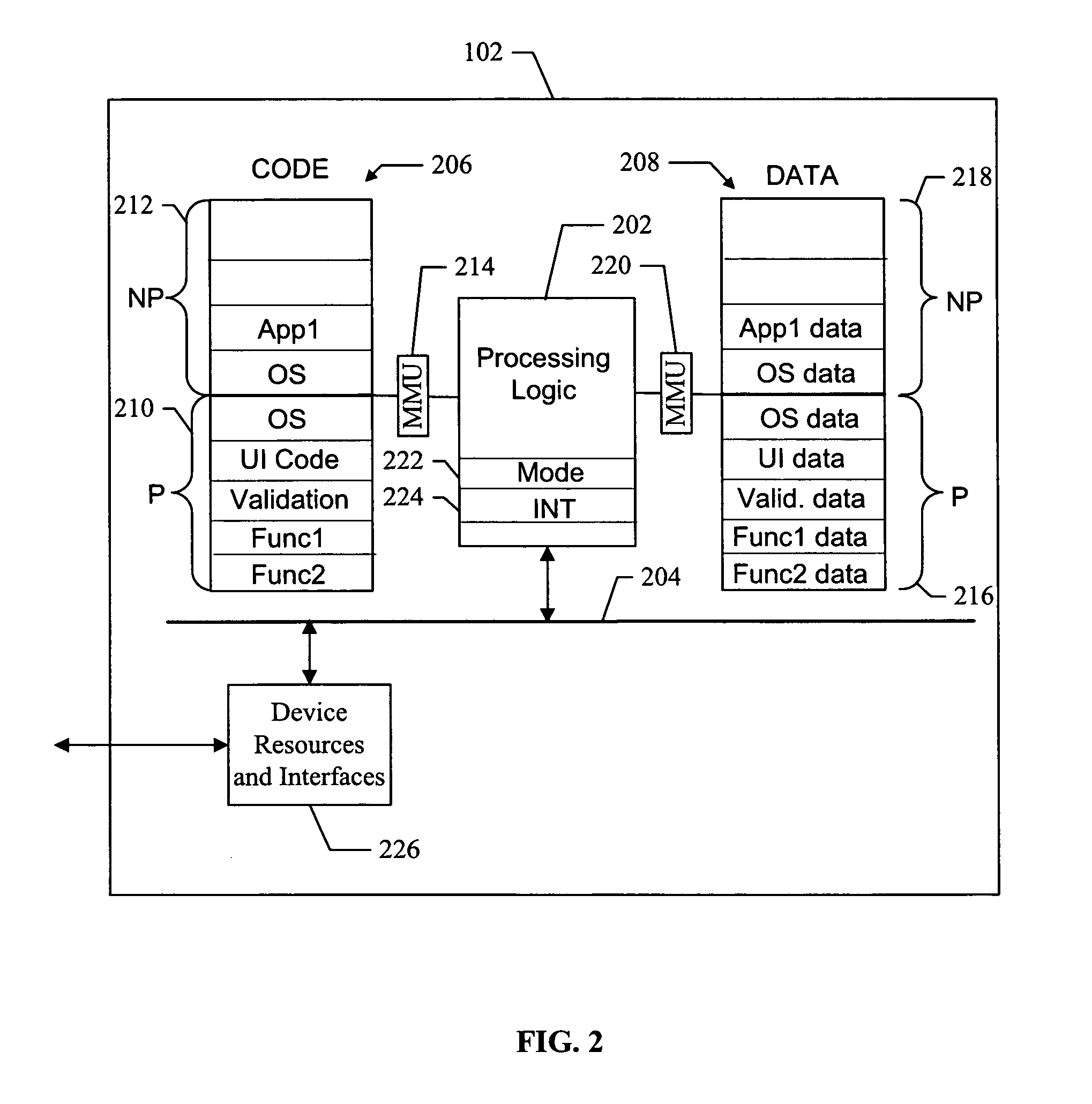

System for providing transitions between operating modes of a device

ActiveUS7076637B2Avoid creatingAvoiding latencySpecific access rightsProgram initiation/switchingOperation modeApplication software

System for providing transitions between operating modes of a device. The system includes a method for providing transitions between a privileged and a non-privileged operating mode. The method comprises executing an application in the non-privileged mode, generating an interrupt to request the services of a privileged function, and transitioning to the privileged mode to execute the privileged function, wherein the privileged function is executed as part of the same thread of execution as the application.

Owner:QUALCOMM INC

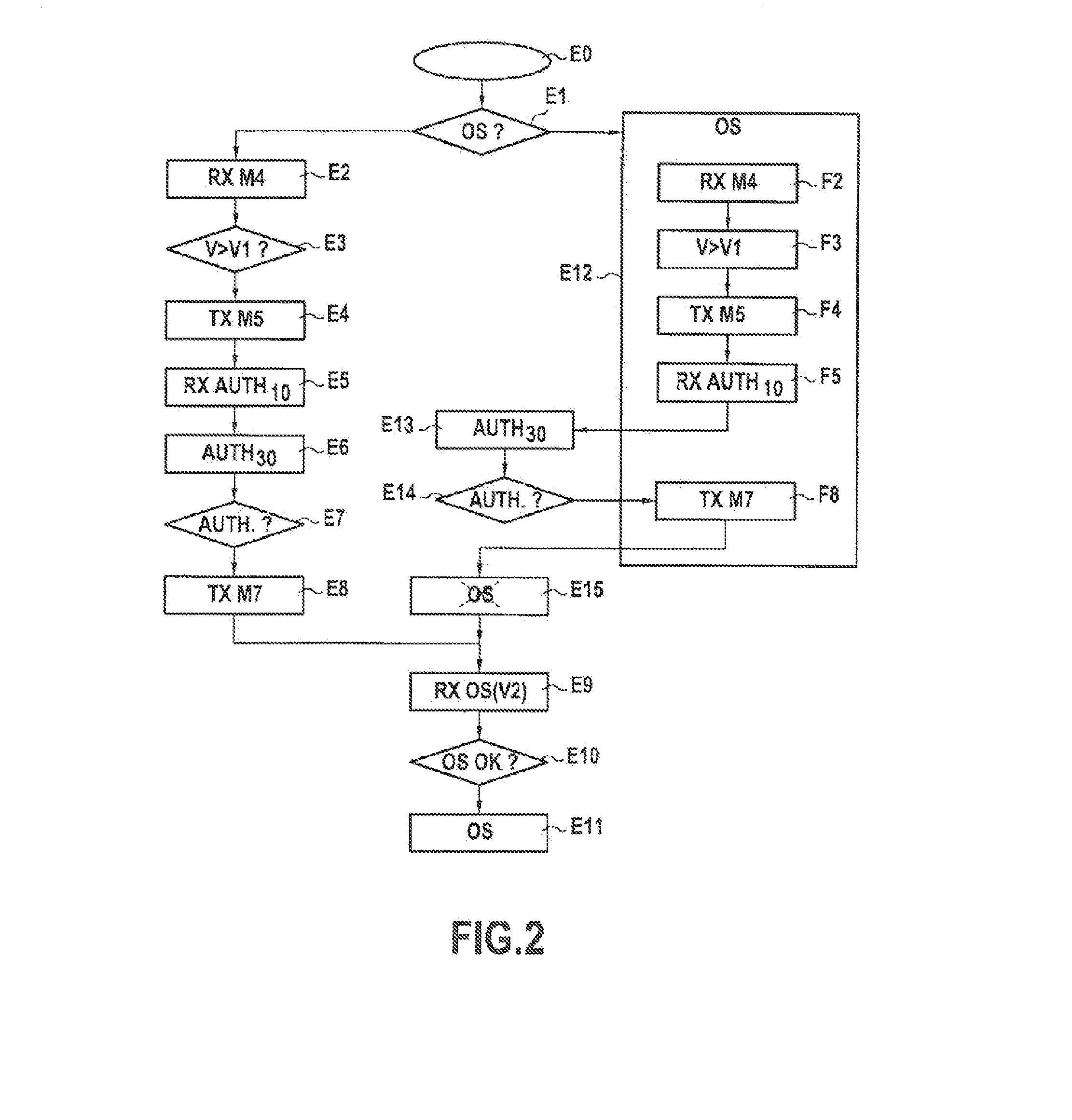

Updating an operating system for secure element

A secure element includes a boot program comprises instructions for the execution a startup step to determine if a non-volatile memory stores an active operating system, and, in the affirmative, to launch execution of the operating system, an authentication step of a updater device, as a function of first authentication data determined by a secure element and second authentication data received from the updater device, and, in response to the authentication step, a storage step of a new operating system received from the update, device in the non-volatile memory and an activation step of the new operating system, when said instructions are executed by a microprocessor.

Owner:IDEMIA FRANCE

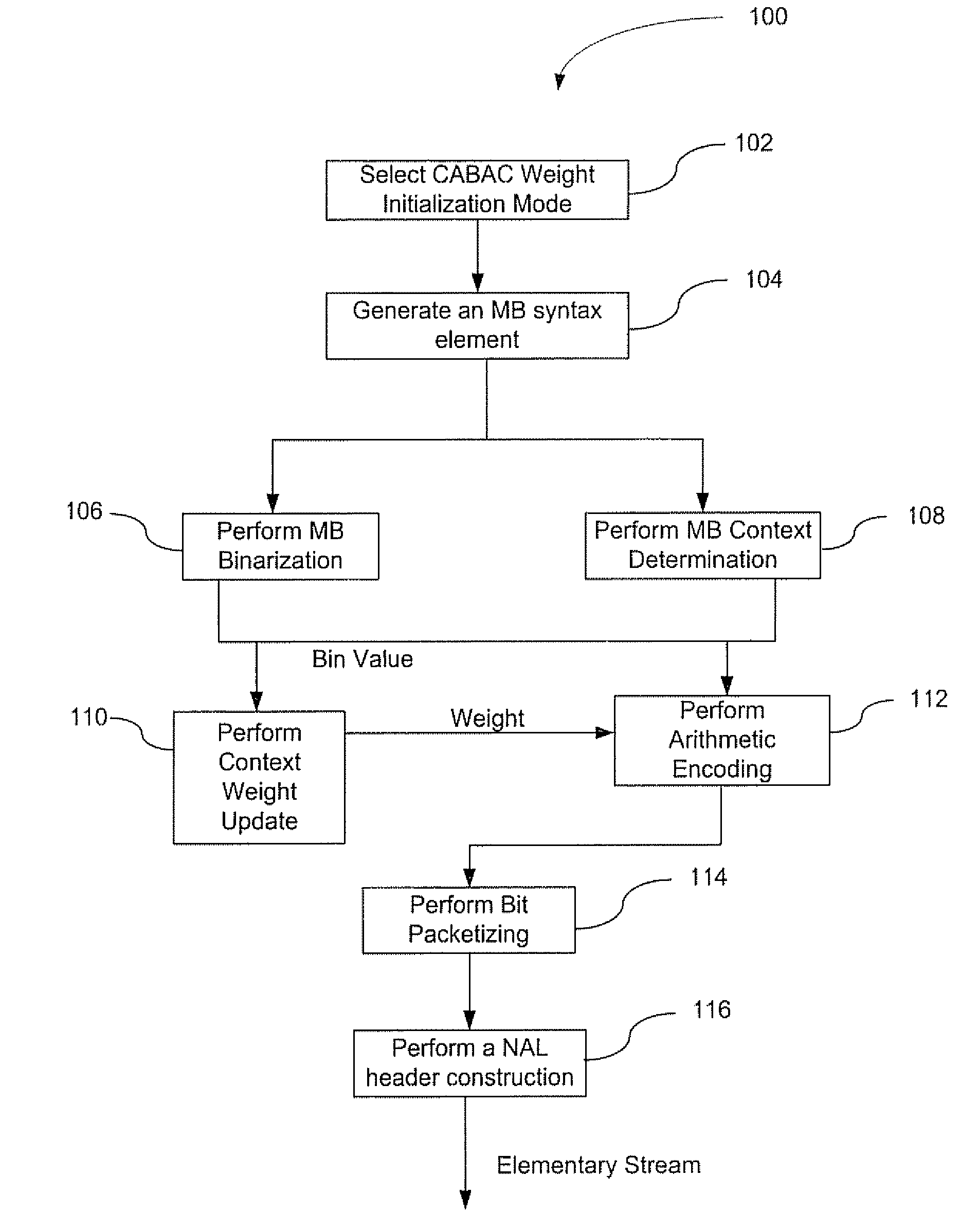

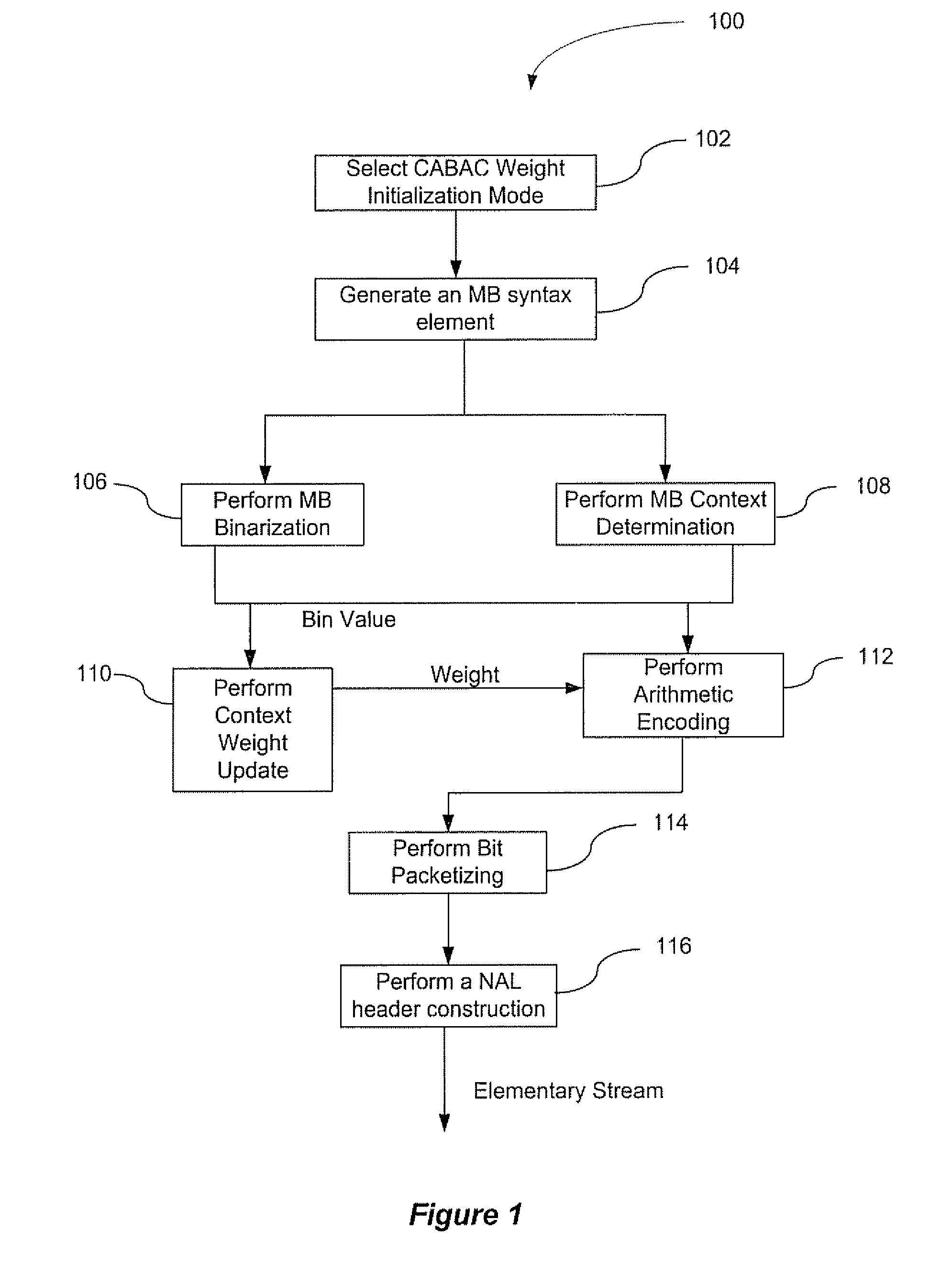

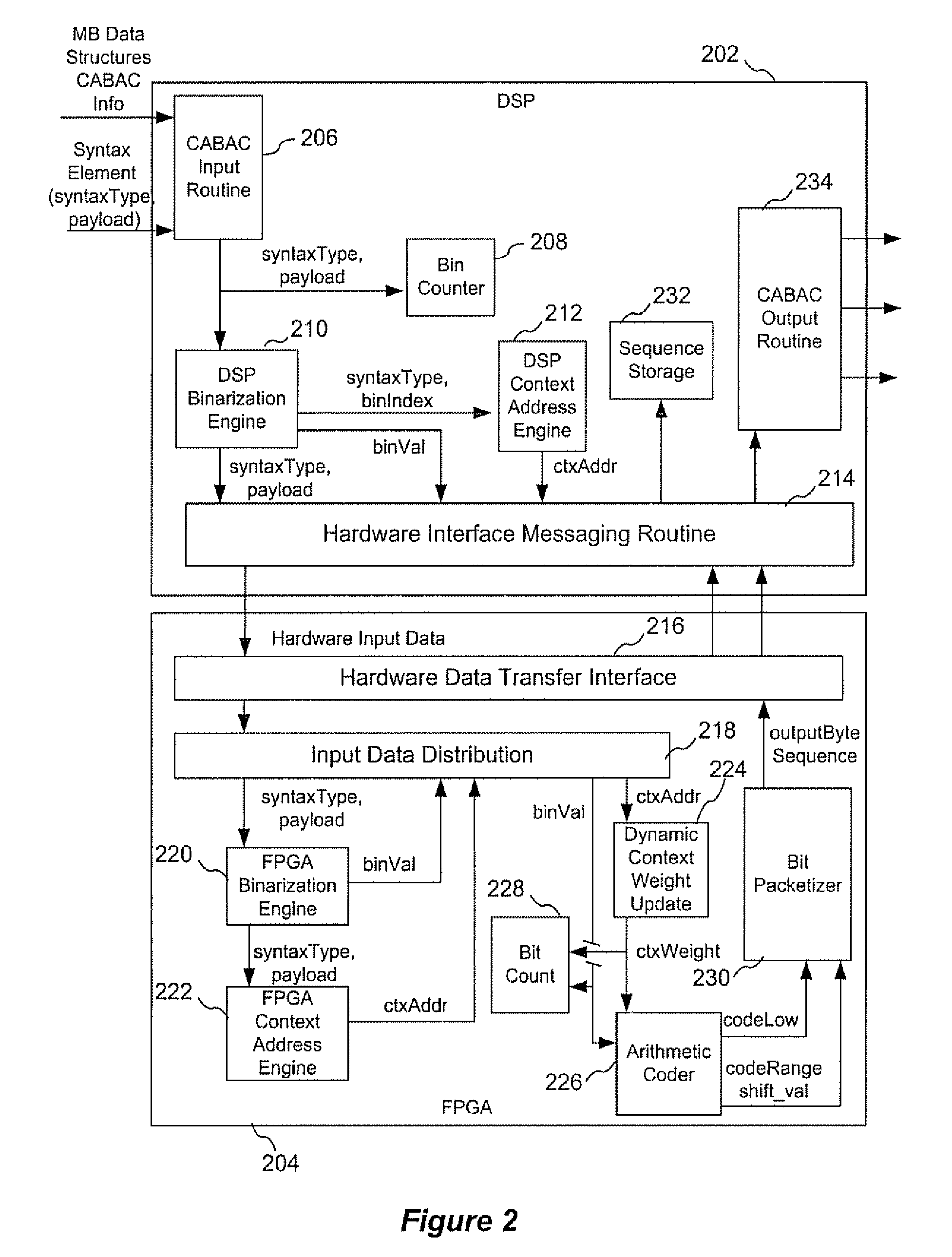

Method and Apparatus for Context Address Generation for Motion Vectors and Coefficients

ActiveUS20080276078A1Picture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningDigital signal processingMotion vector

A method for high / low usage is provided. The method receives a macroblock data structure and a syntax element at a digital signal processing engine. Further, the method classifies the syntax element as high use or low use. In addition, the method sends the syntax element from the digital signal processing engine to a logic unit, distinct from the digital processing engine, for binarization if the syntax element is high use.

Owner:ARRIS ENTERPRISES LLC