Patents

Literature

312results about "Receiver initialisation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Receiver for robust data extension for 8VSB signaling

InactiveUS7194047B2Robust of serviceImprove performanceData representation error detection/correctionBroadcast specific applicationsDigital televisionCarrier recovery

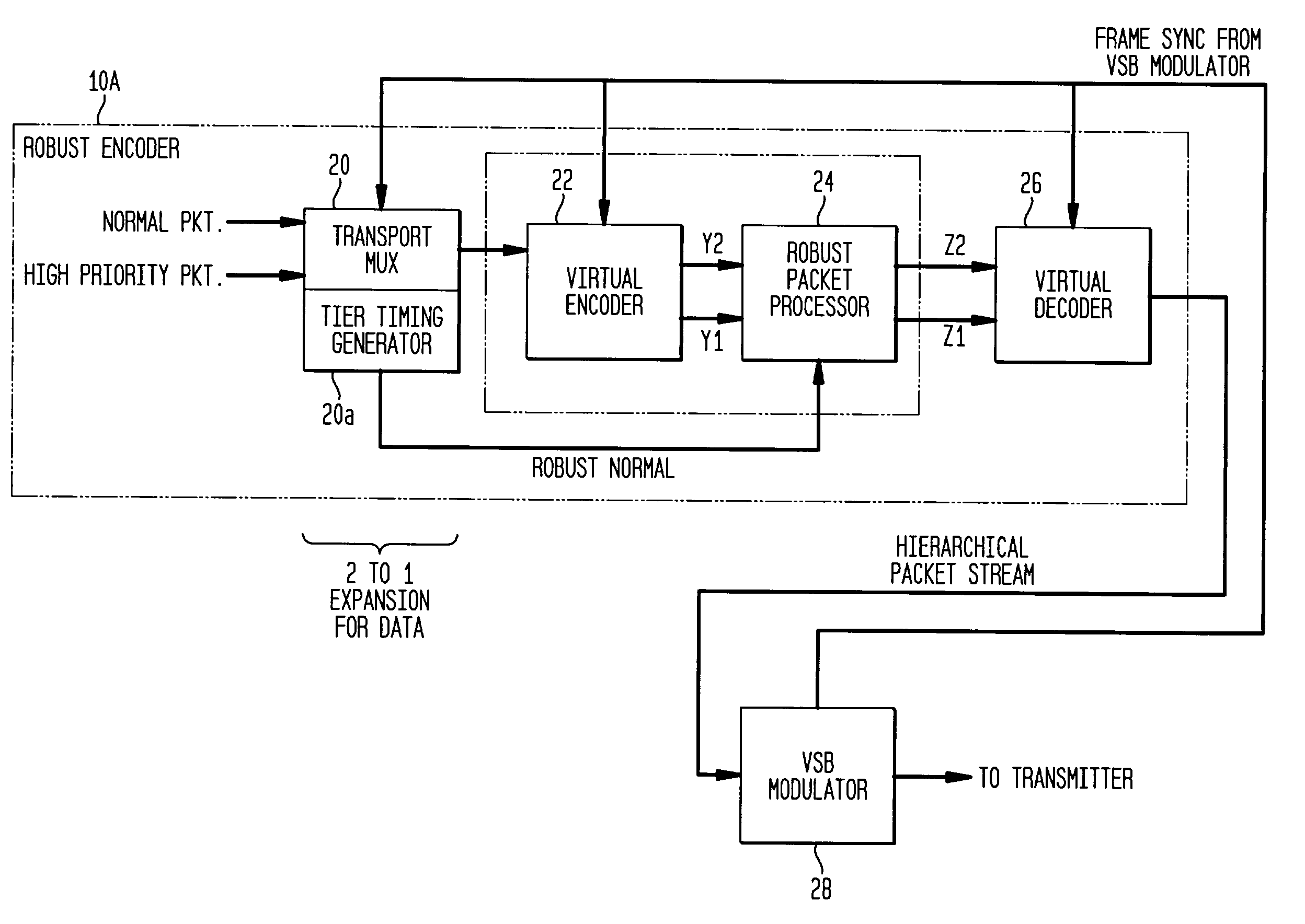

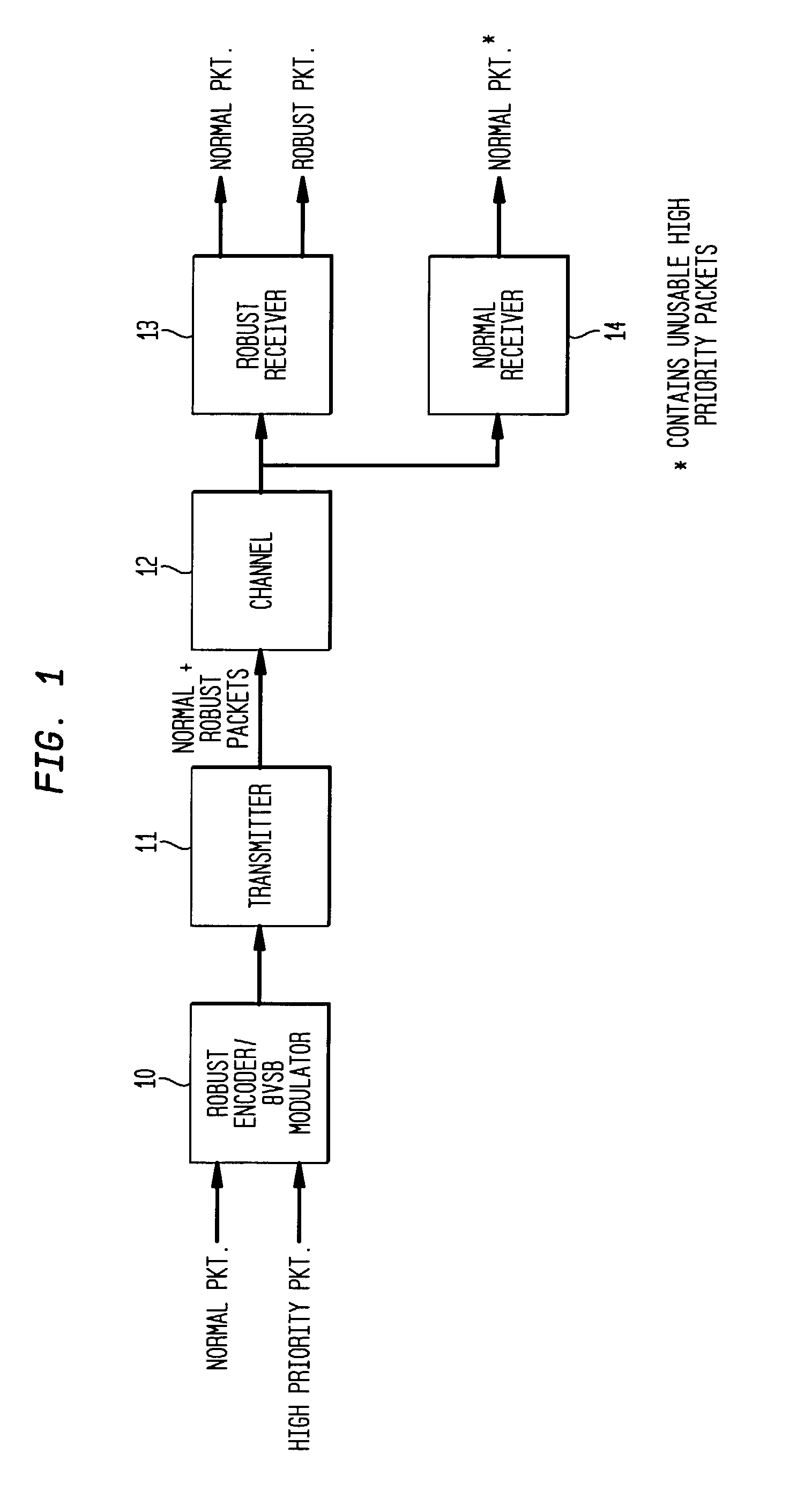

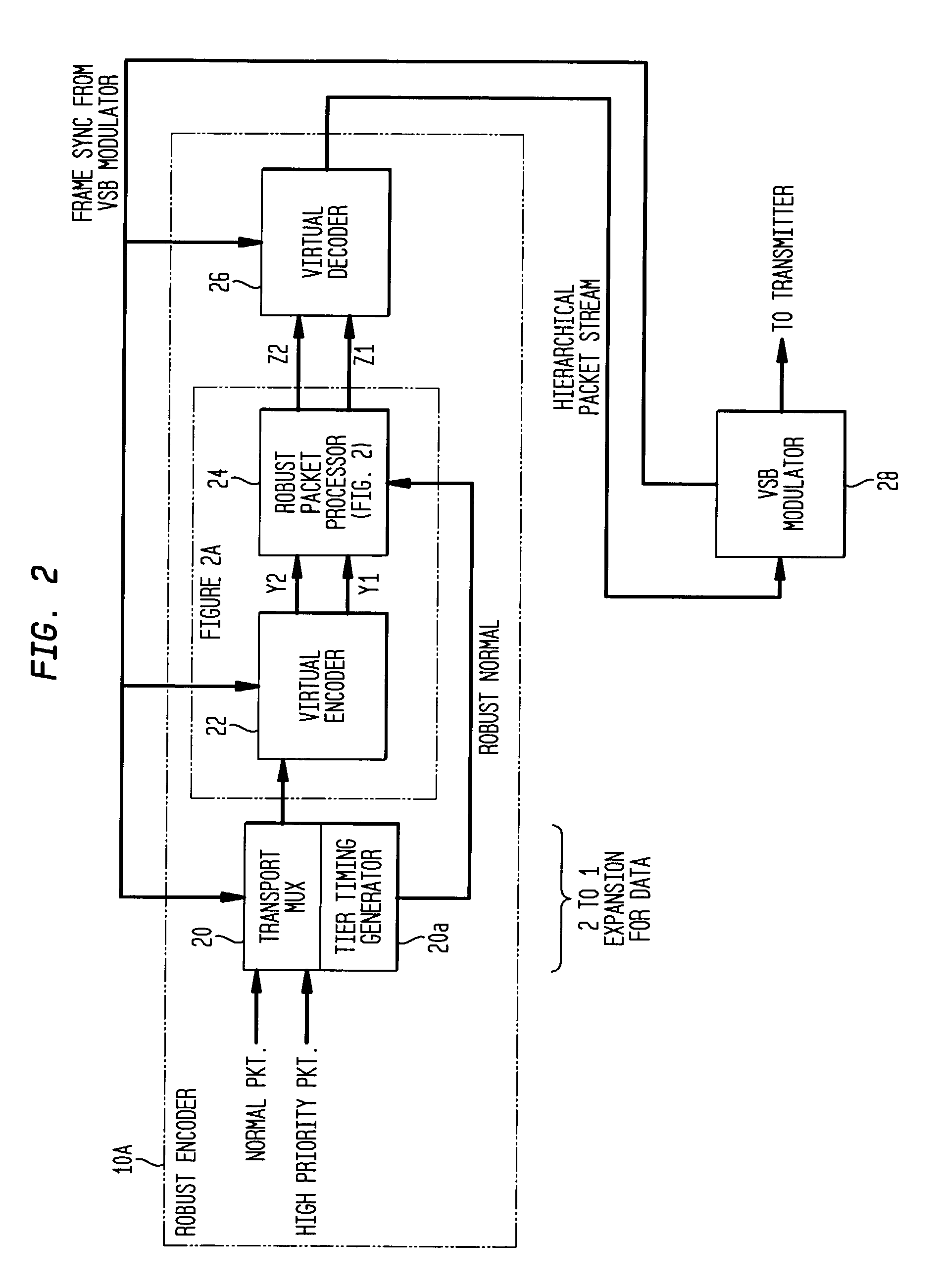

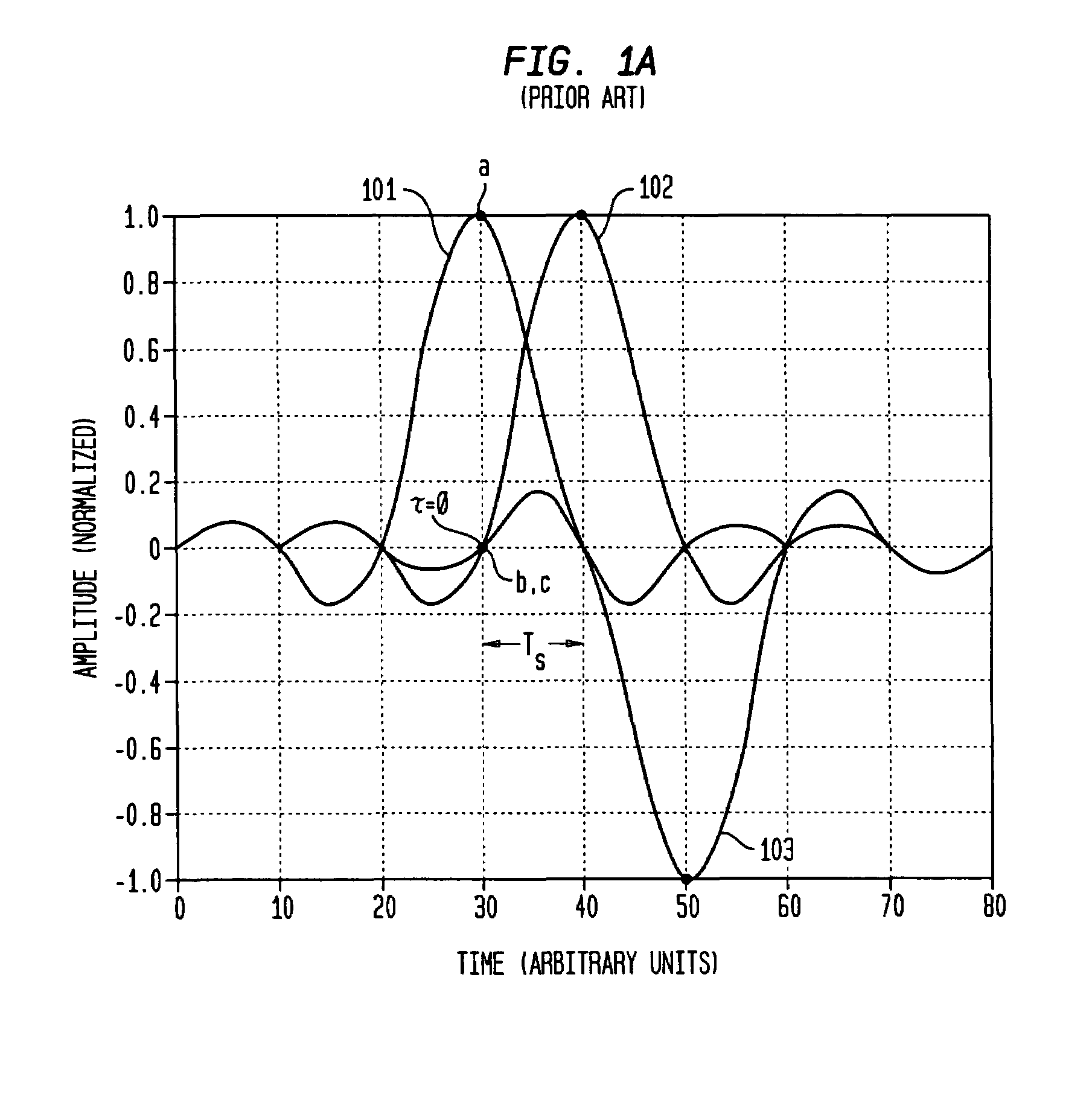

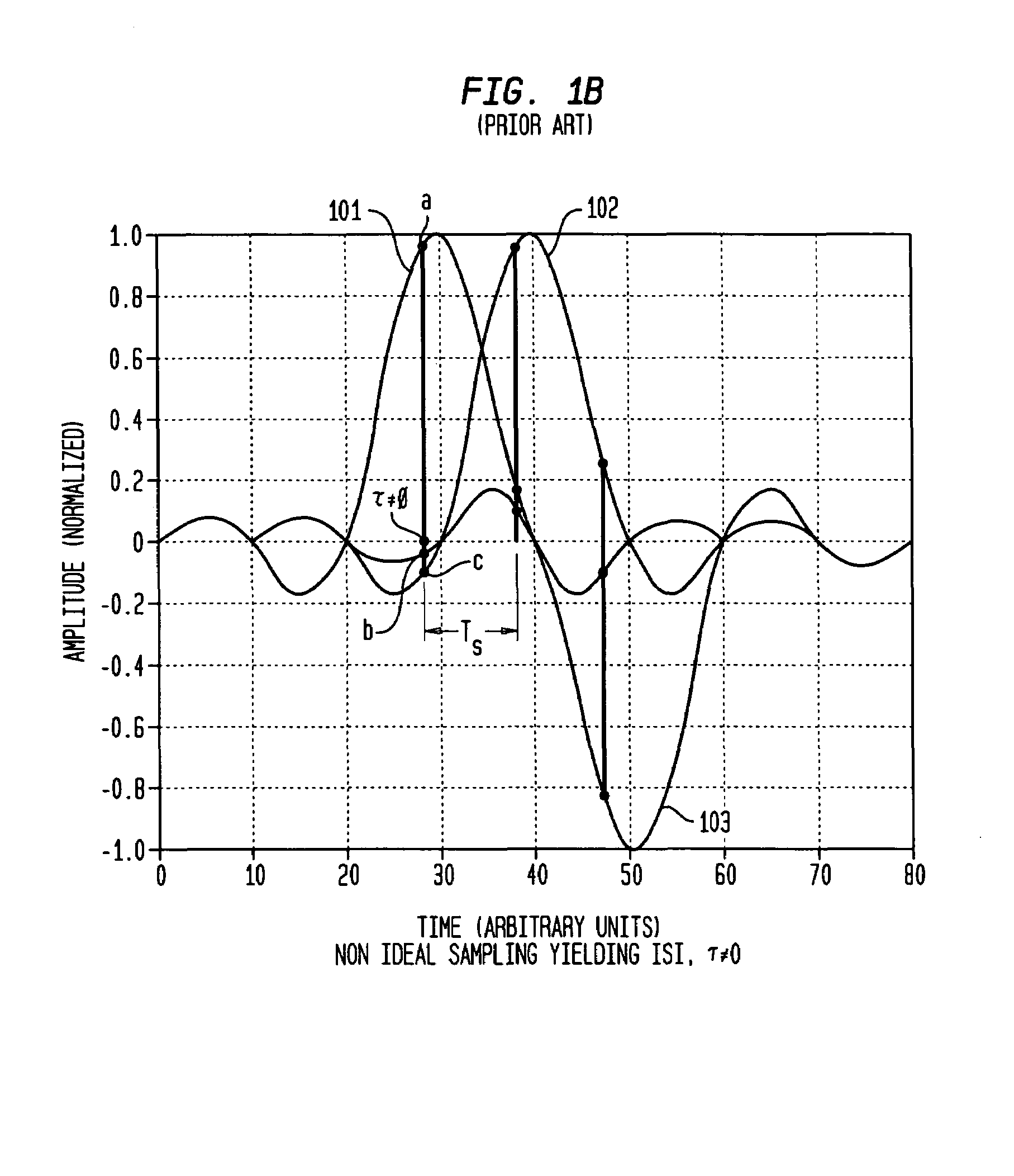

A robust data extension, added to a standard 8VSB digital television signal, is used to improve the performance of a digital television receiver. Robust data packets are encoded at a 1 / 3-trellis rate as compared to normal data packets that are encoded at a 2 / 3-trellis rate. In addition to delivery of robust data for mobile applications, the redundant robust data packets also improve the performance of the receiver in the normal tier of service. In particular, the robust data packets improve the performance of the receiver equalizer filter in the presence of rapidly changing transient channel conditions such as dynamic multipath for both robust data packets and normal data packets. The robust data packets improve the performance of the carrier recovery loop and the symbol timing recovery loop. Backward compatibility with existing receivers is maintained for 1) 8VSB signaling, 2) trellis encoding and decoding, 3) Reed Solomon encoding and decoding, and 4) MPEG compatibility.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

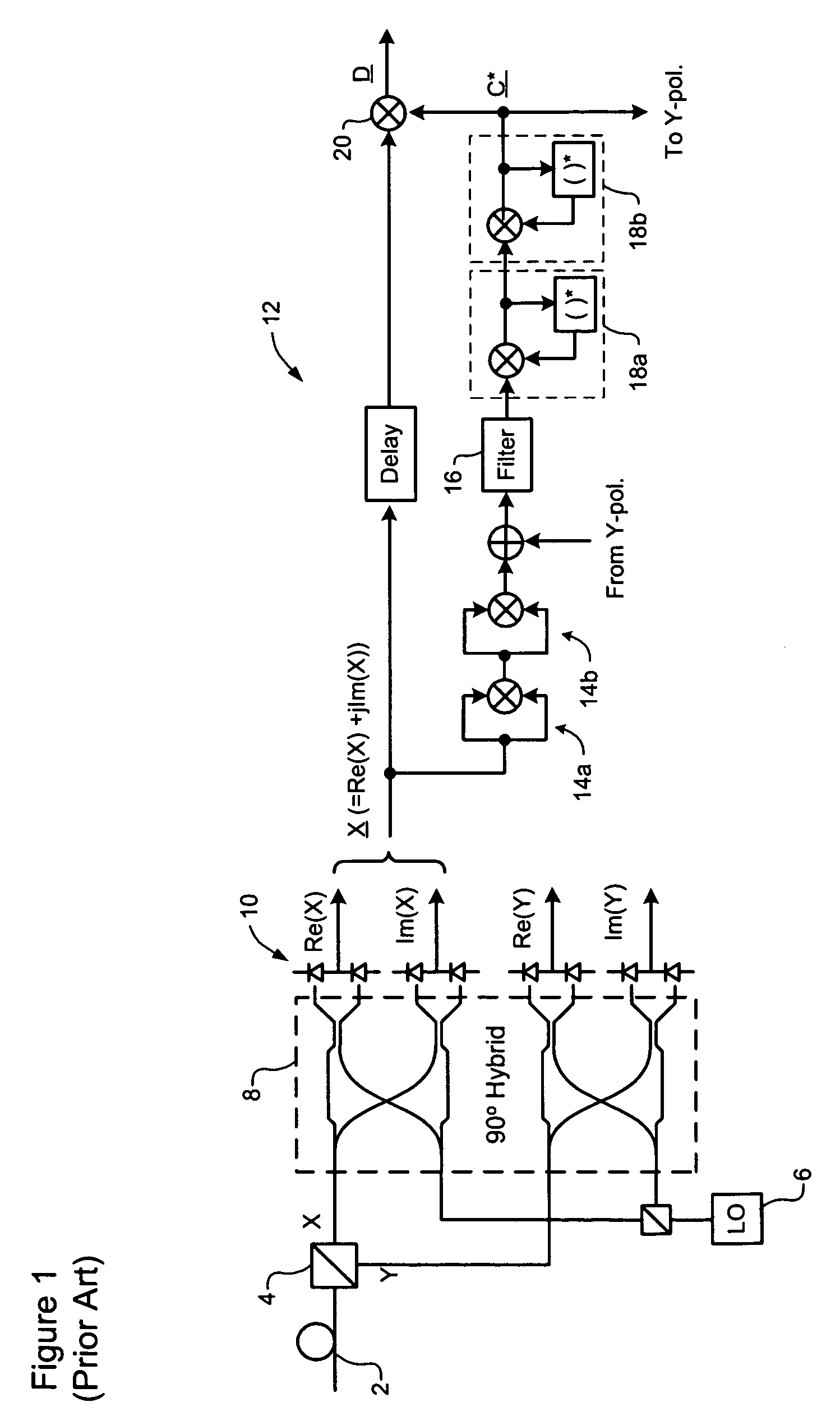

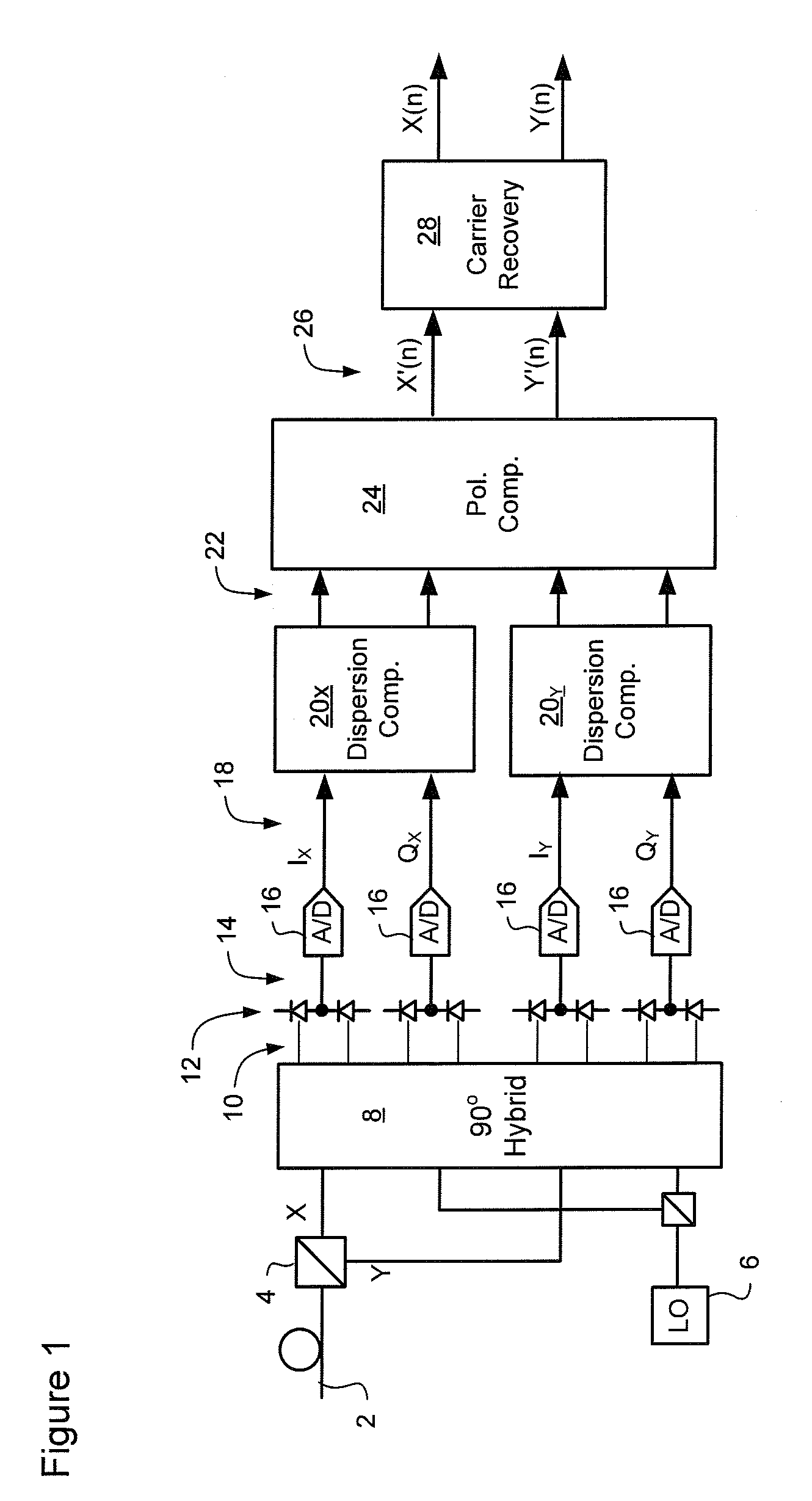

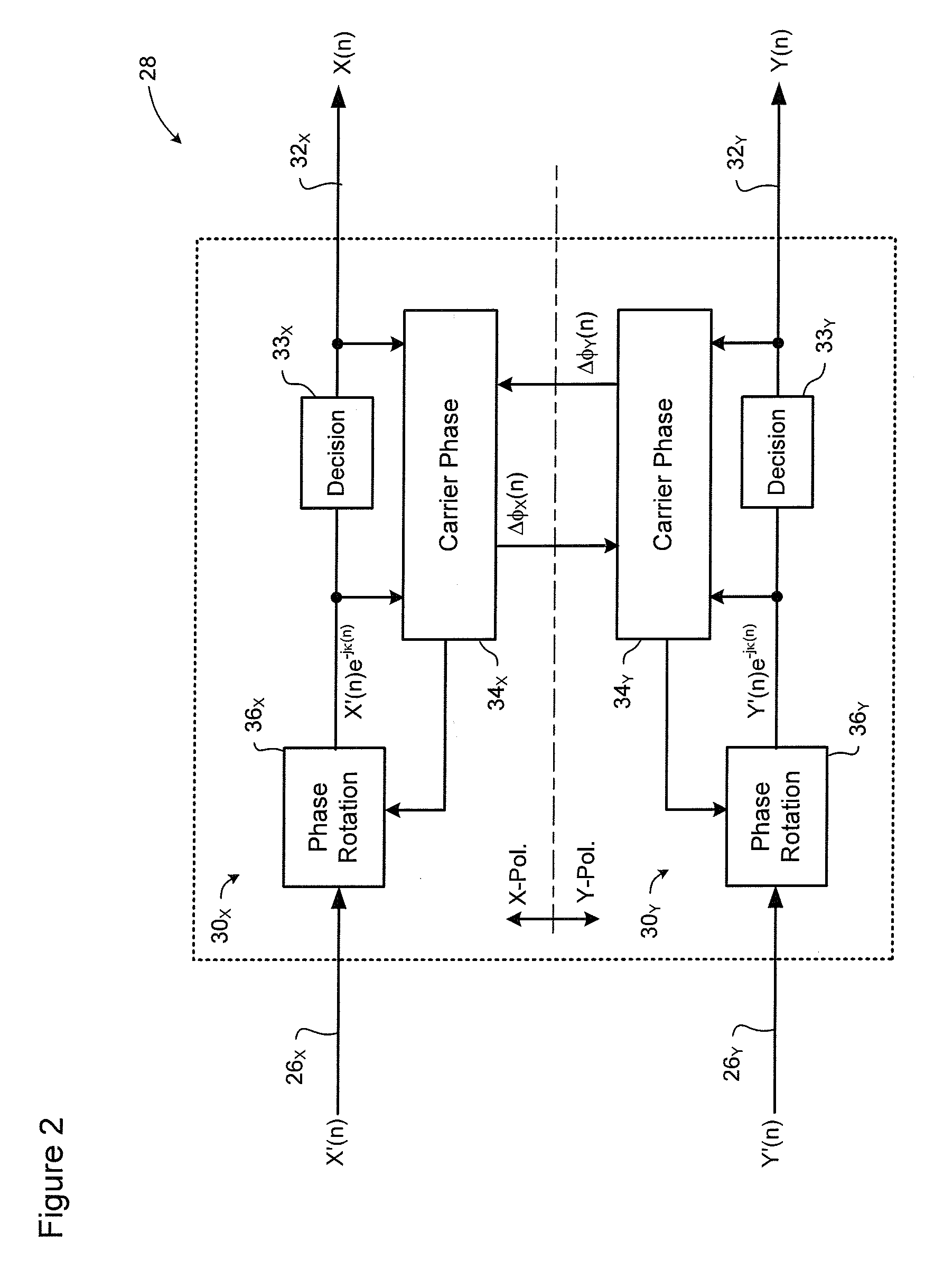

Carrier recovery in a coherent optical receiver

ActiveUS7606498B1Receiver initialisationSynchronisation by photonic/optical meansCarrier recoveryOptical receivers

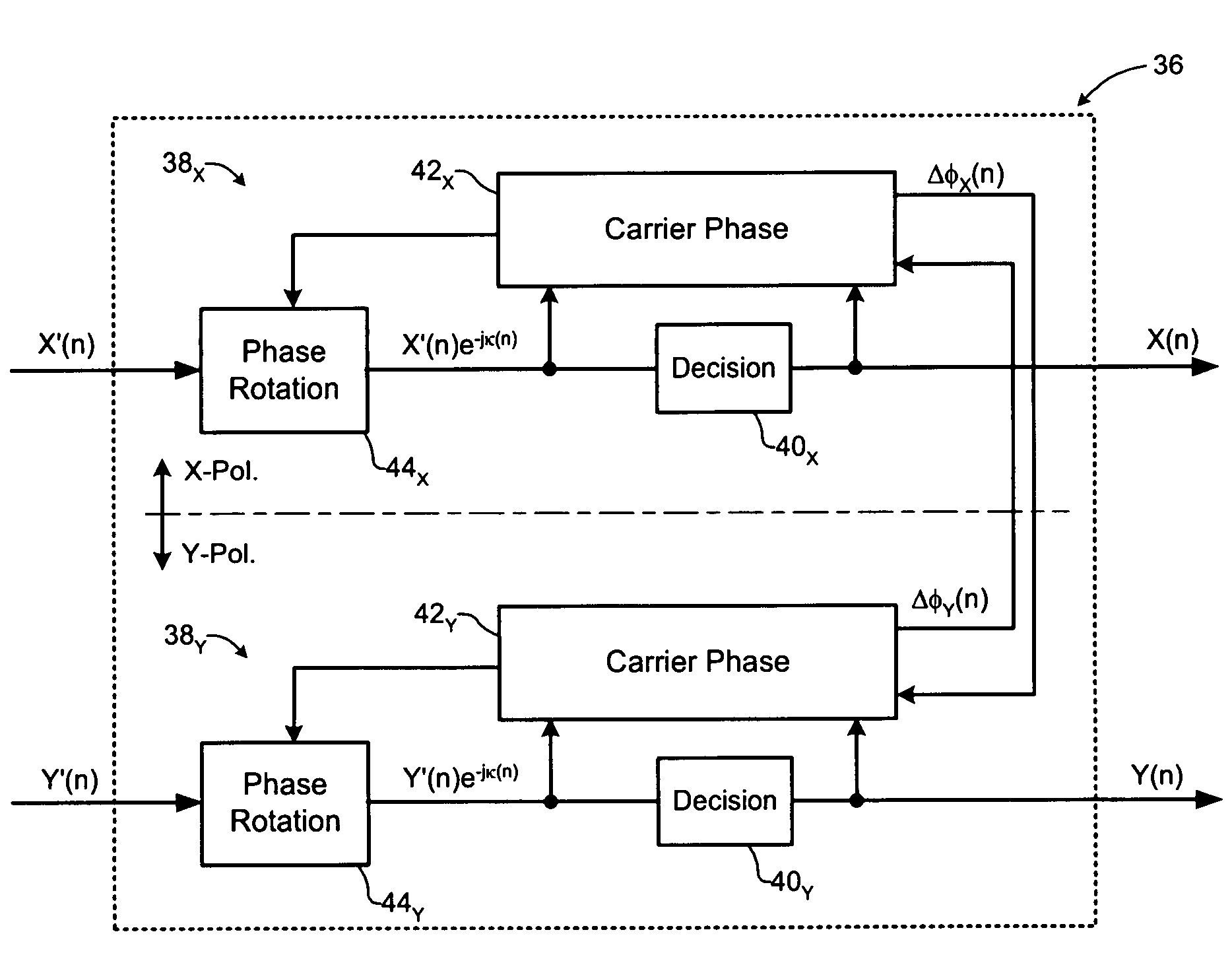

A method of carrier recovery from a high speed optical signal received through an optical communications network. A stream of multi-bit digital samples of the optical signal is processed to generate a multi-bit estimate X′(n) of each one of a plurality of transmitted symbols. A phase of each symbol estimate X′(n) is rotated, and a respective symbol phase error Δφ(n) of the rotated symbol estimate determined.

Owner:CIENA

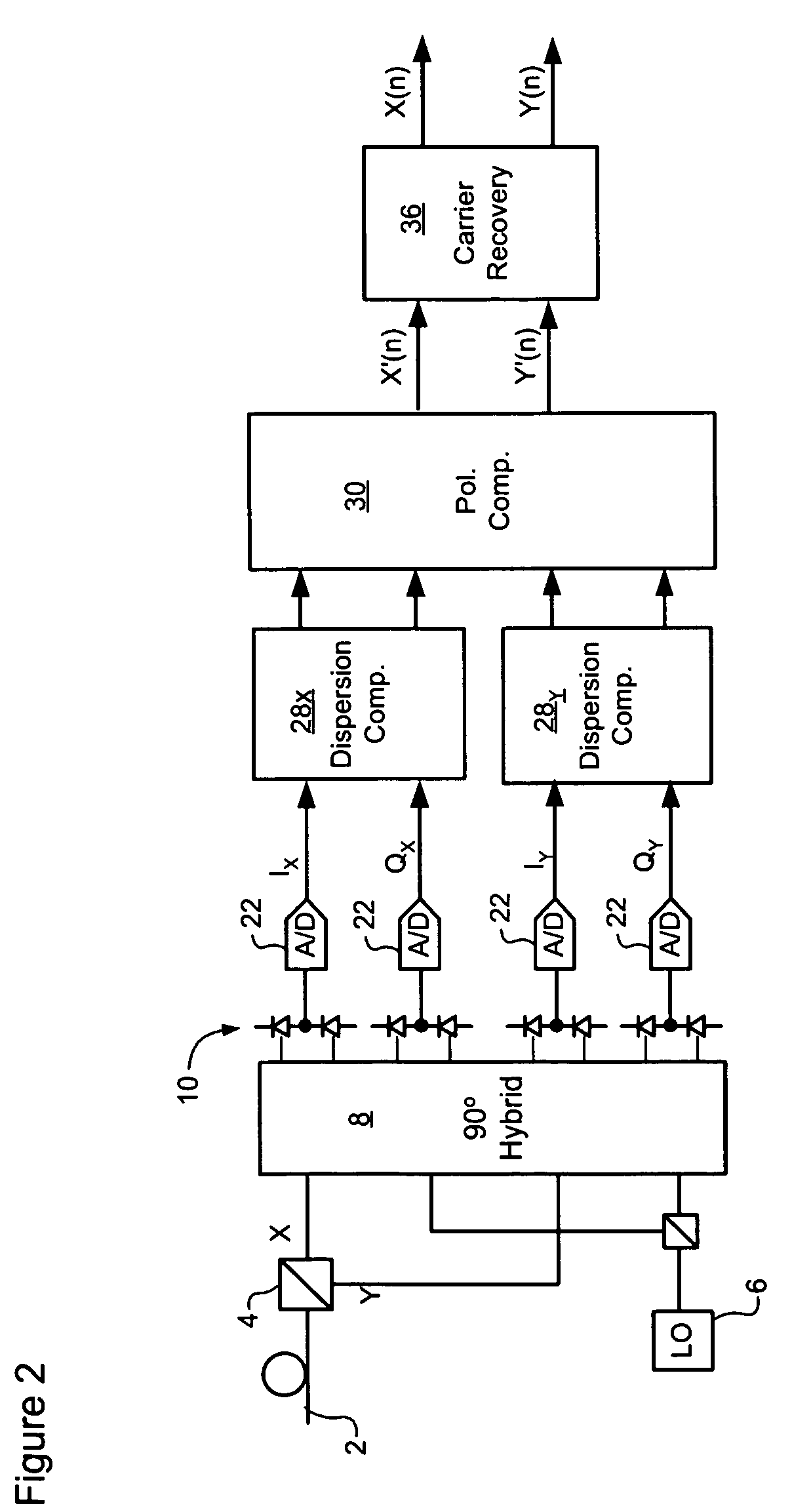

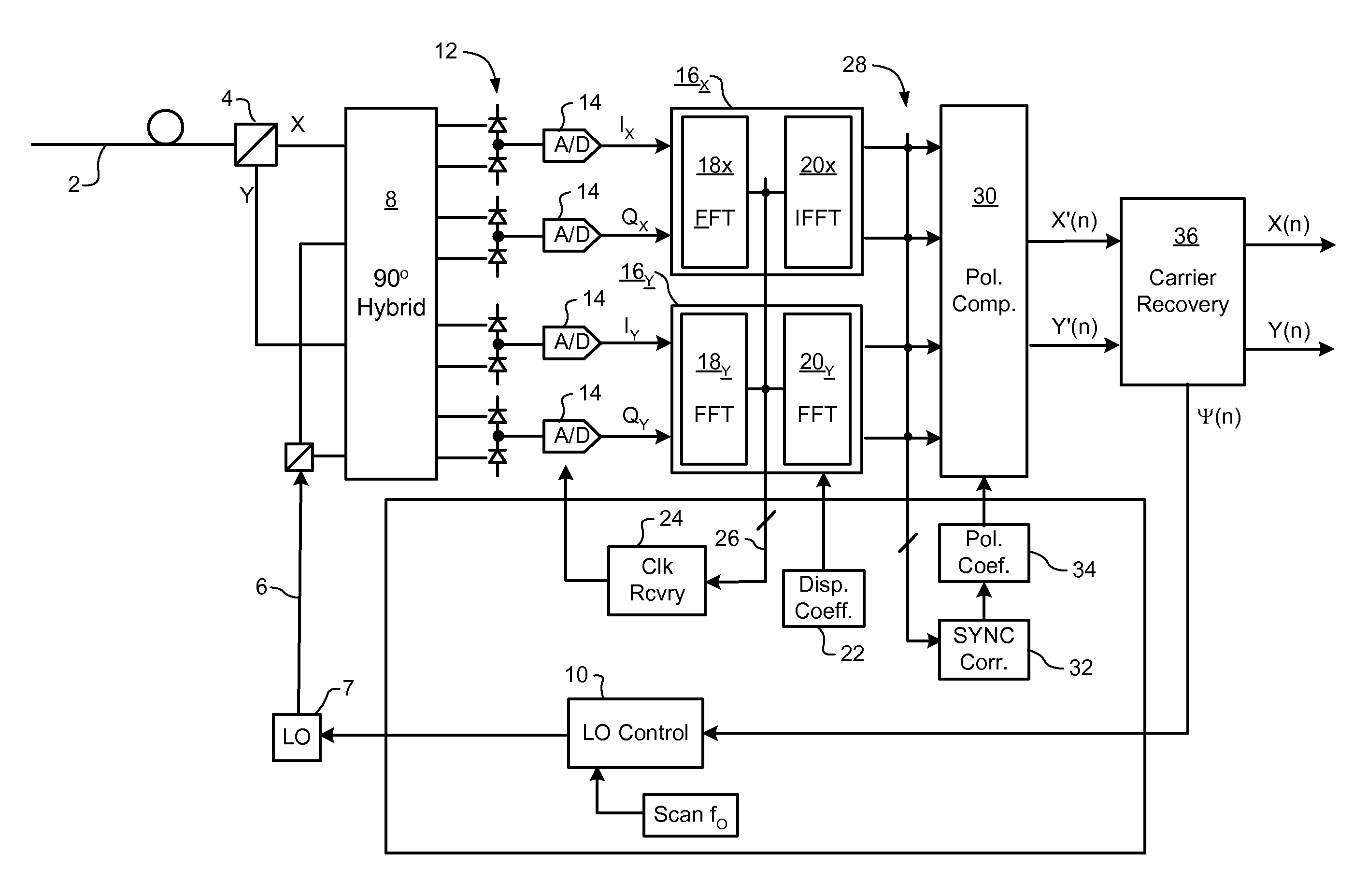

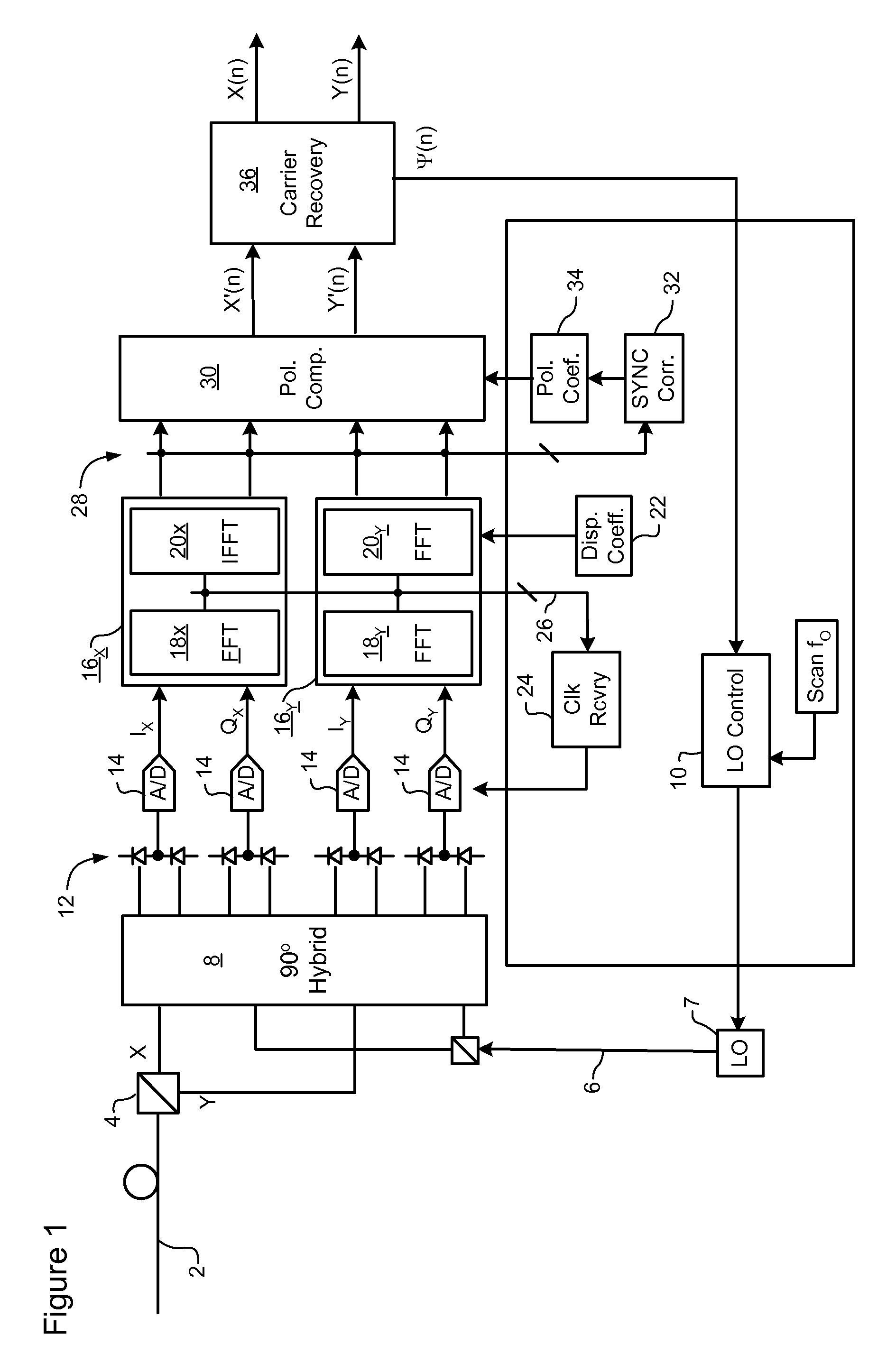

Signal acquisition in a coherent optical receiver

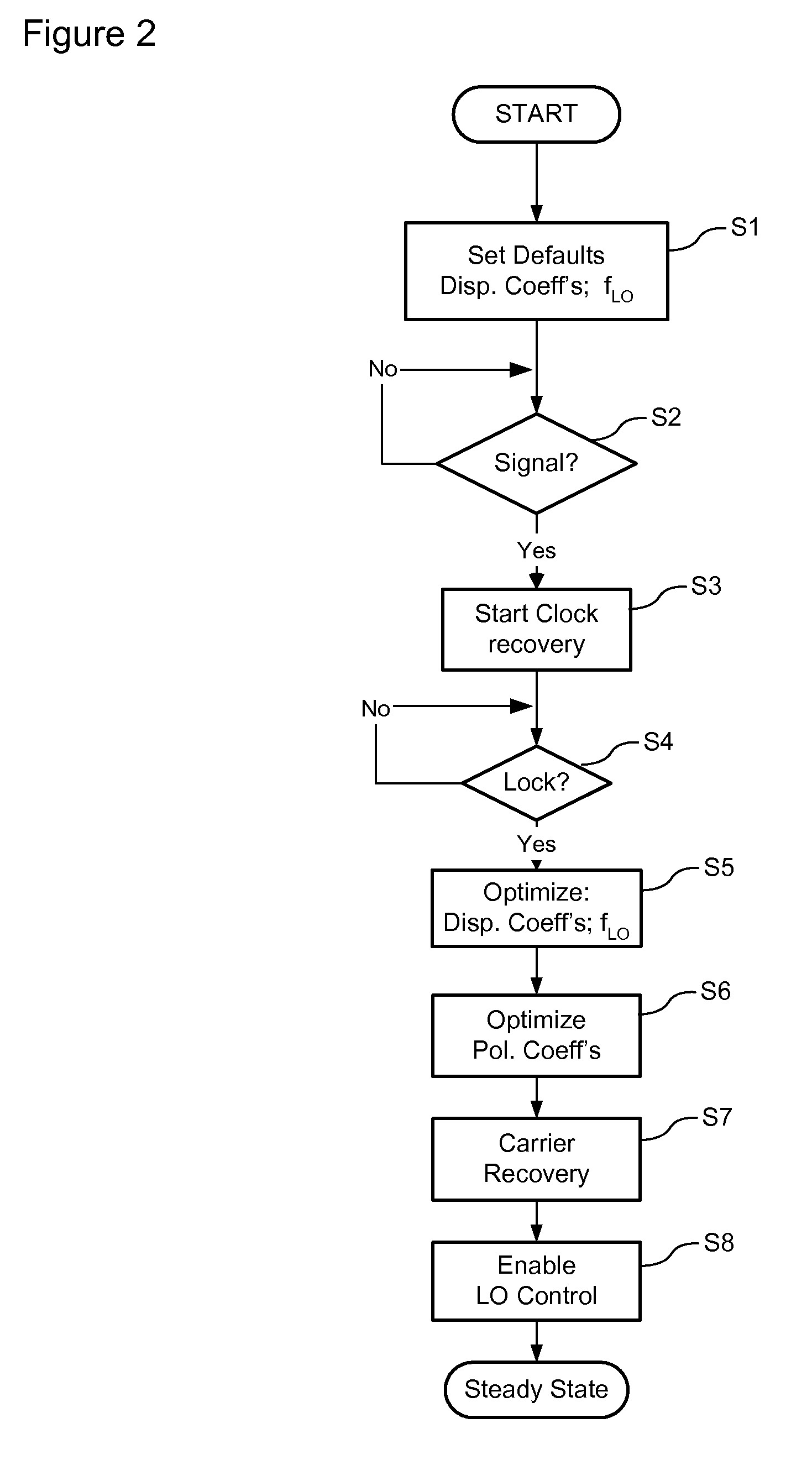

ActiveUS7636525B1Reliably acquire signalSteady-state operationReceiver initialisationSynchronisation by photonic/optical meansClock recoveryEngineering

A method and system for initializing a coherent optical receiver. Upon detection of an optical signal, a multi-bit digital sample stream of the optical signal is digitally processed to initialize each one of a plurality of adaptive control blocks of the coherent optical receiver. The adaptive control blocks include at least a dispersion compensation block and a clock recovery block. The dispersion compensation block is initialized before initializing the clock recovery block.

Owner:CIENA

Multimode system for calibrating a data strobe delay for a memory read operation

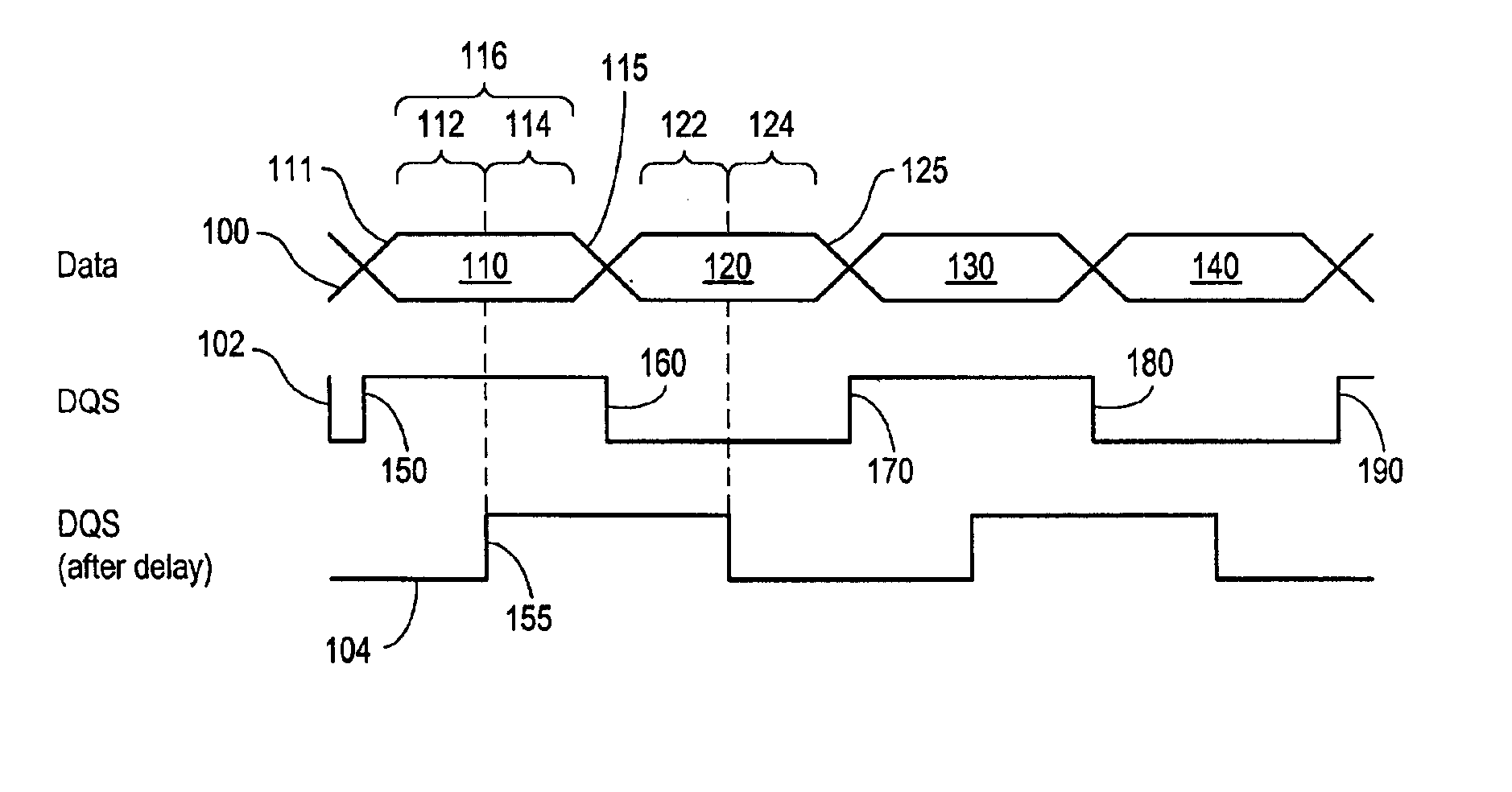

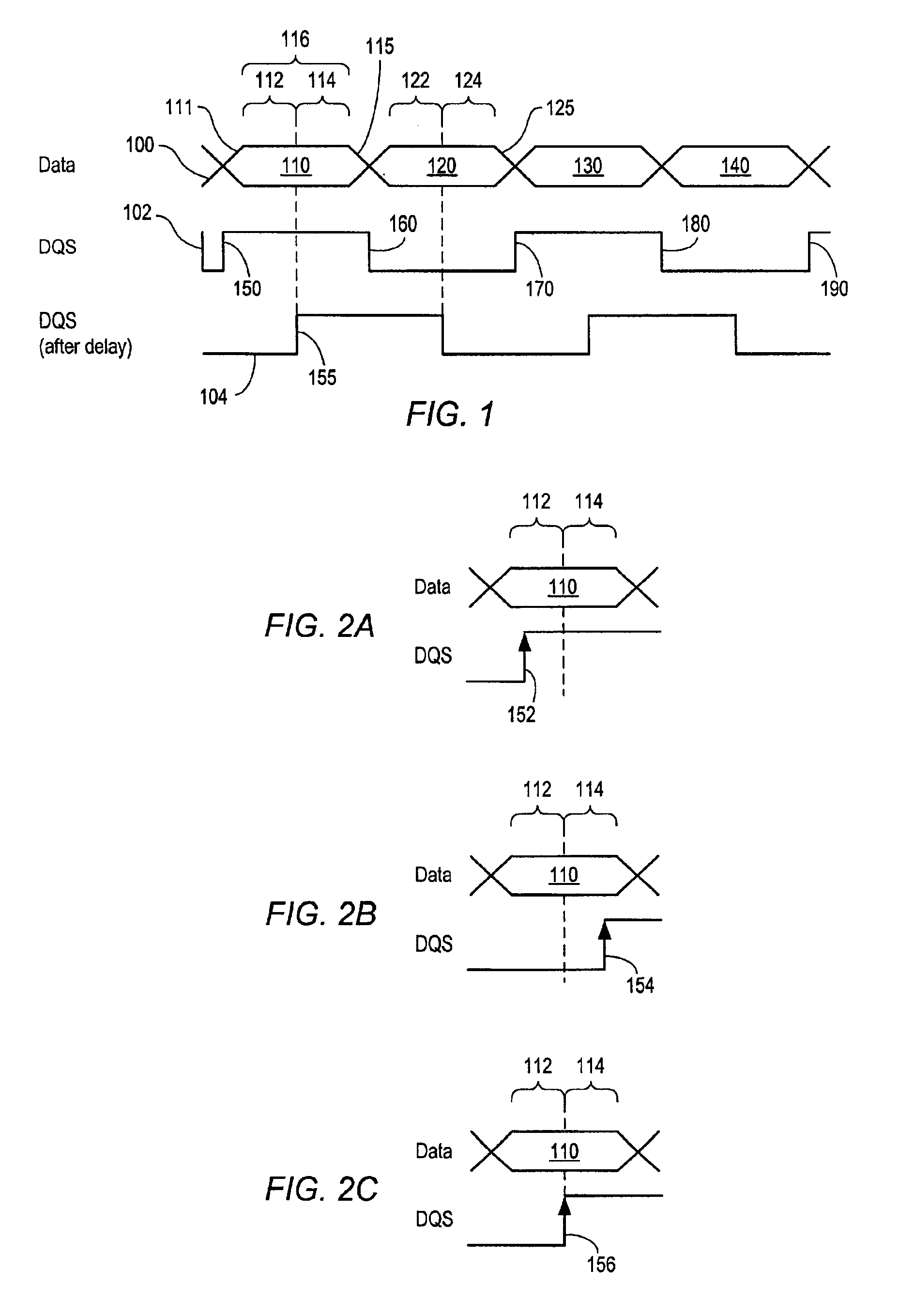

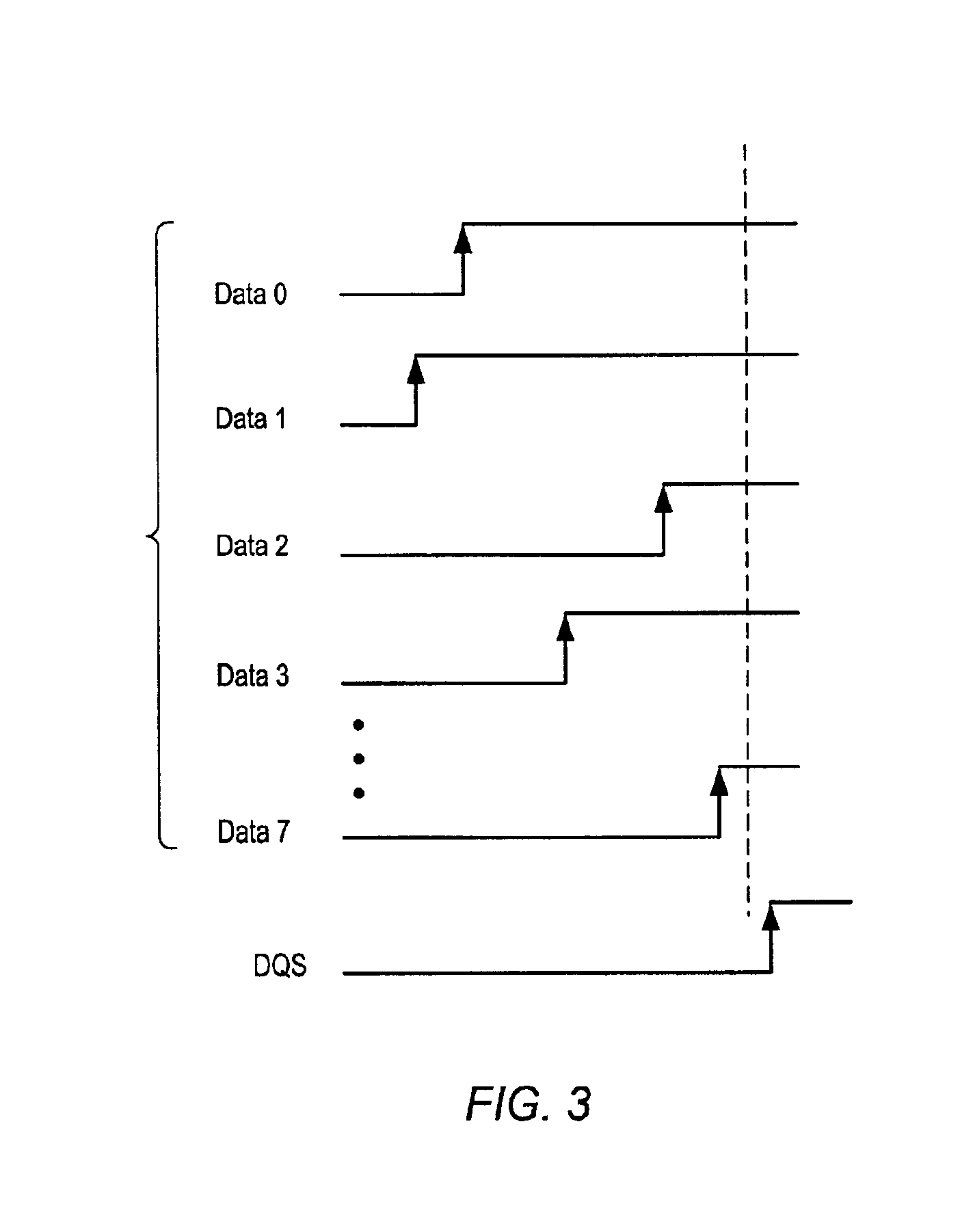

InactiveUS6889334B1Allow in applicationAllow in useElectronic circuit testingCode conversionComputer moduleMemory controller

A system for coordinating the timing of a data strobe with data supplied by a memory module to the memory controller read data FIFO of a processor-based system, providing multiple calibration modes. A calibration PDL (programmable delay line) is used to reiteratively test the time taken for a test data strobe to traverse a portion of the memory controller circuit, and to generate a calibration value based upon the time taken. The calibration procedure may be initiated in any one of several modes, including: according to a predetermined schedule; implemented in software; in response to changes in environmental factors such as temperature or voltages sampled at one or more locations; in response to a software-driven trigger; or in response to a user-initiated trigger, communicated to a system of the invention either by input via a user interface to the processor-based system or by a software command.

Owner:ADVANCED MICRO DEVICES INC

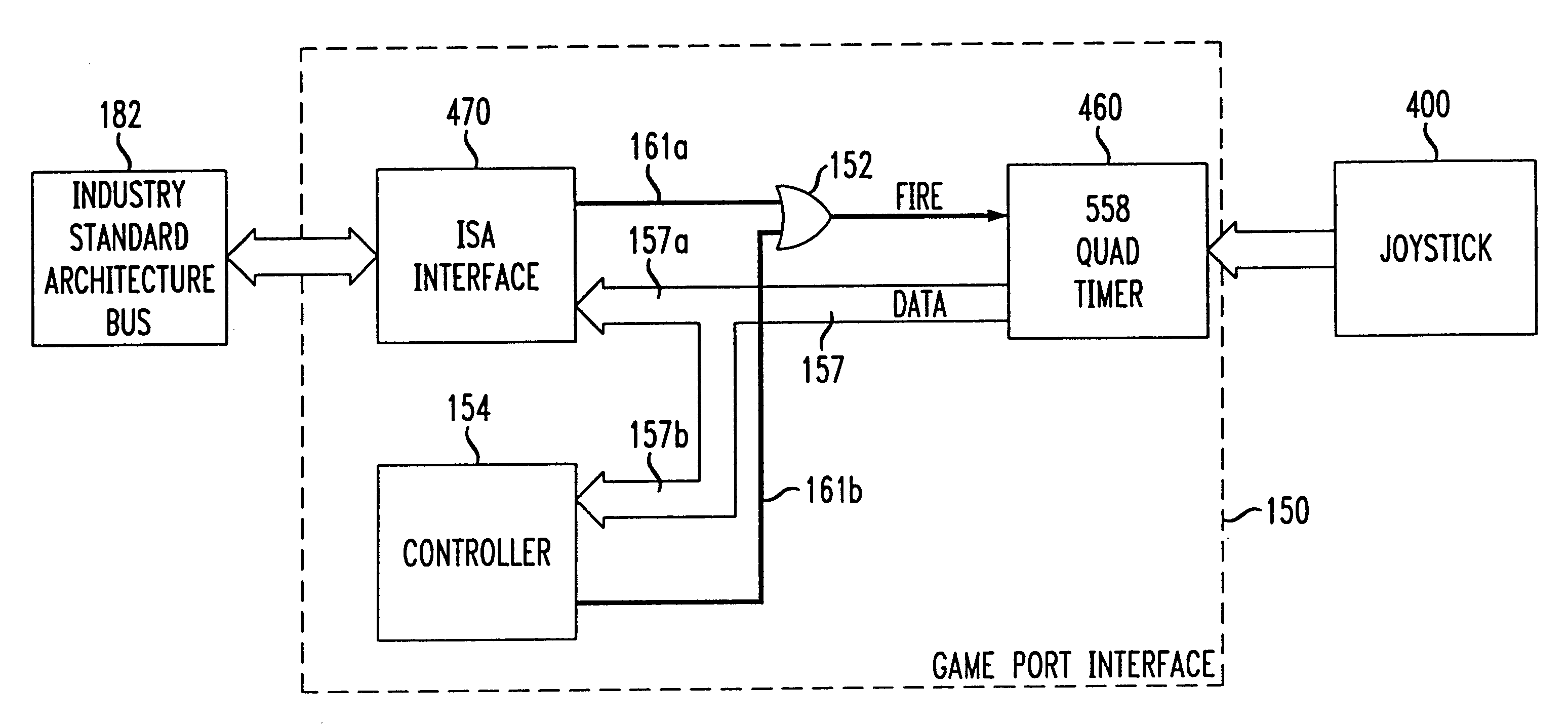

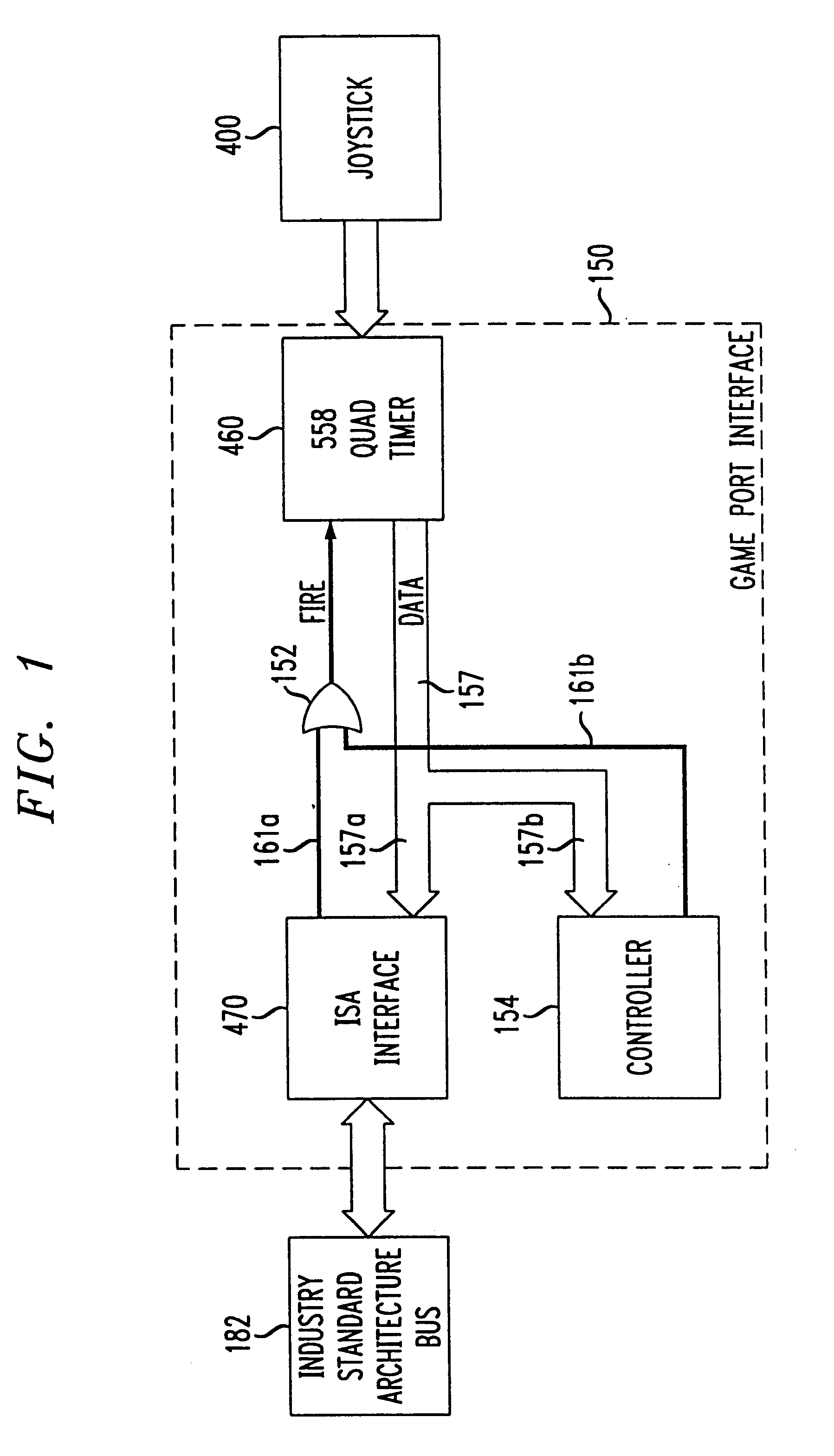

System wake-up based on joystick movement

The present invention provides a game port interface having a second processor interface in addition to an otherwise conventional first processor interface such that a second processor may directly poll the game port interface to detect movement of a joystick device while a first, host processor is in a low power mode. Thus, the second processor may identify movement in the joystick and initiate a wake up sequence in the first, host processor via a communication path between the two processor interfaces. The additional processor interface allows the second processor to poll the joystick without interfering with the normal operation of the joystick. The present invention provides the power savings benefits of maintaining a host processor in a low power mode while at the same allowing another processor which may or may not be in a reduced power mode to detect movement of the joystick and initiate a wake up sequence in the host processor in response thereto.

Owner:WSOU INVESTMENTS LLC +1

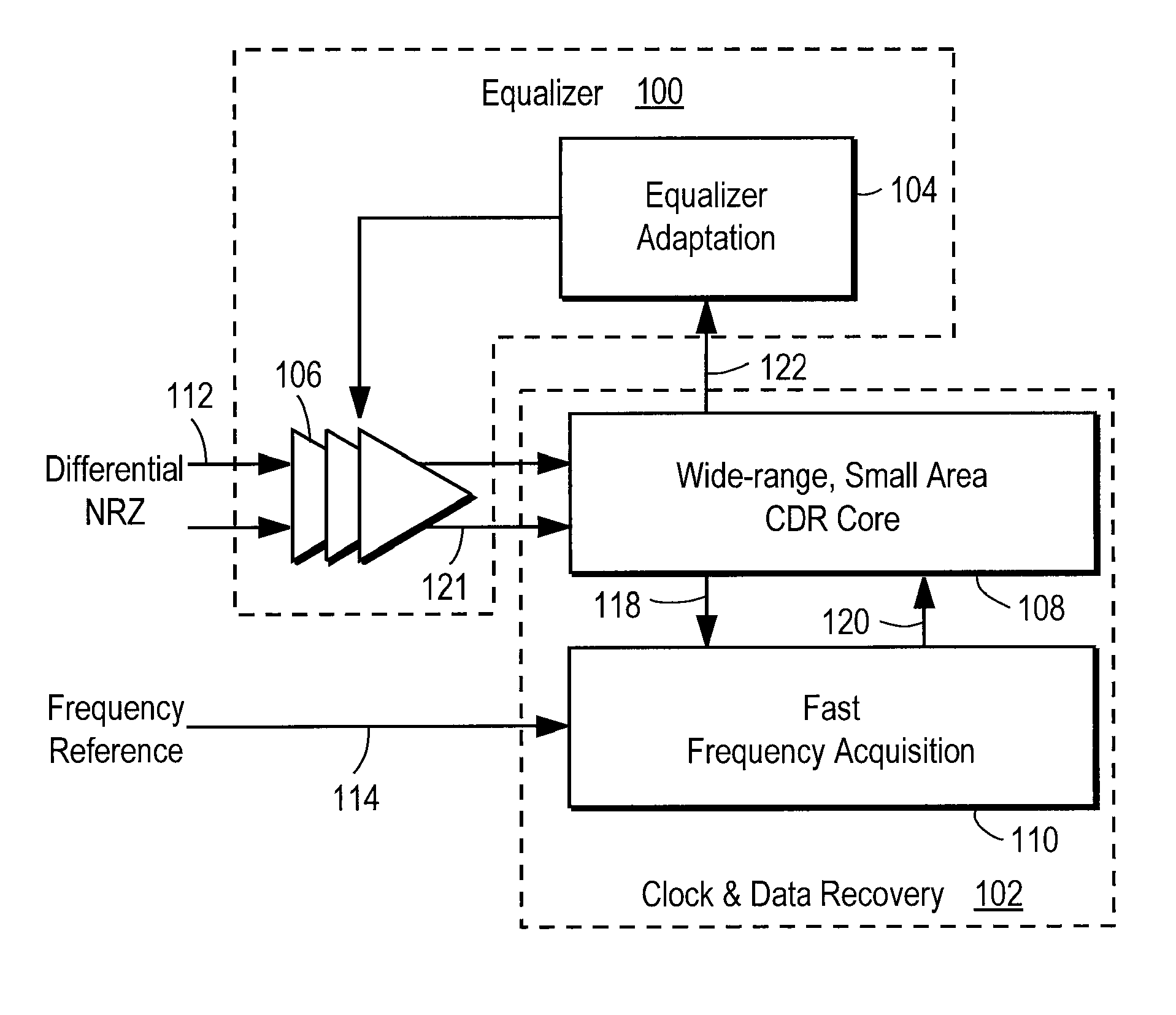

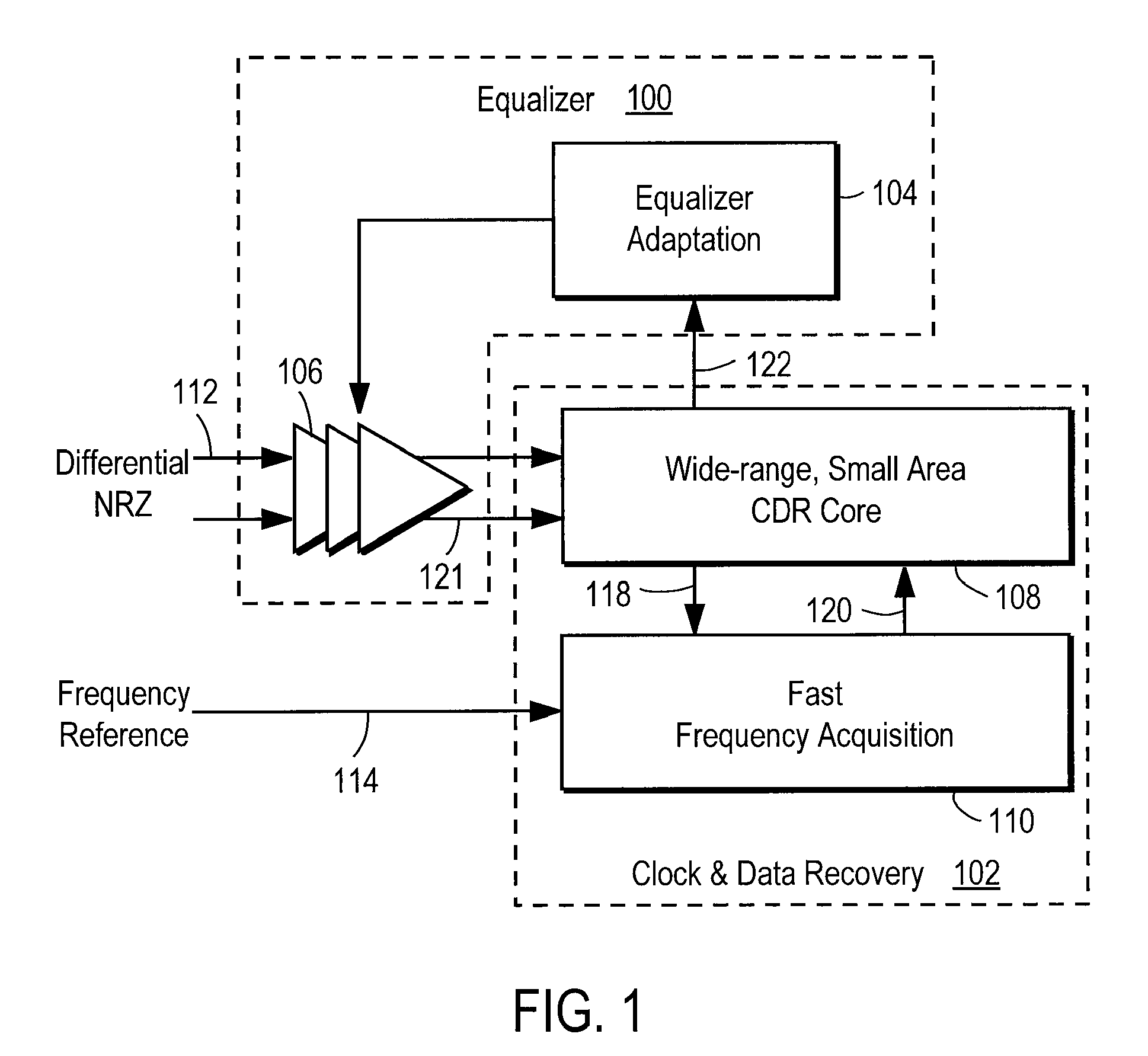

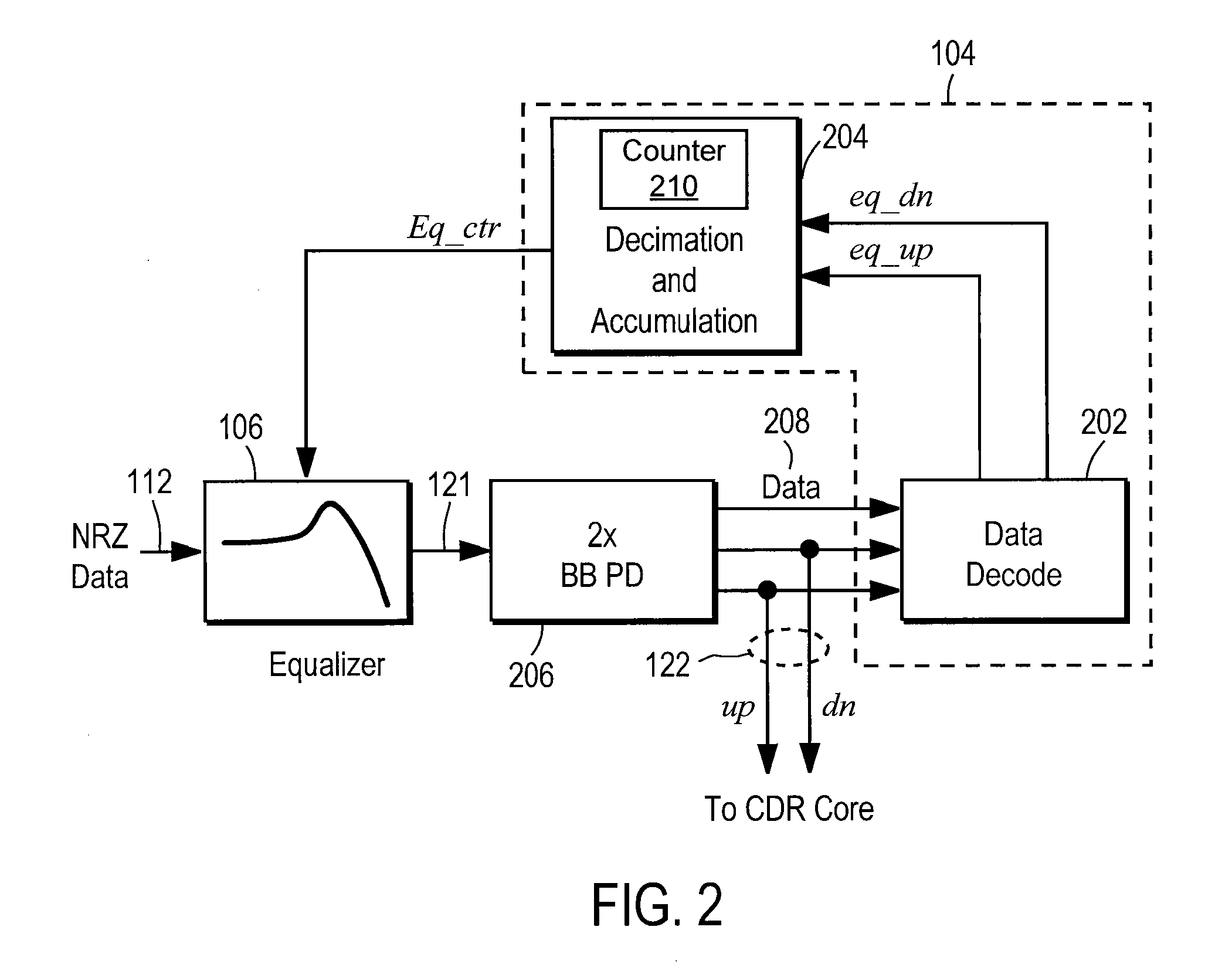

Adaptive equalizer for use with clock and data recovery circuit of serial communication link

ActiveUS20080247452A1Low costEffort-saving designMultiple-port networksReceiver initialisationPhase detectorTime information

An adaptive equalizer system for use in a serial communication link uses timing information generated by a phase detector of a clock and data recovery circuit of the serial communication link and a frequency pattern of the recovered data to determine whether the data received over the serial communication link is over-equalized or under-equalized. The equalizer strength of the adaptive equalizer system is adjusted based on such determination.

Owner:SILICON IMAGE INC

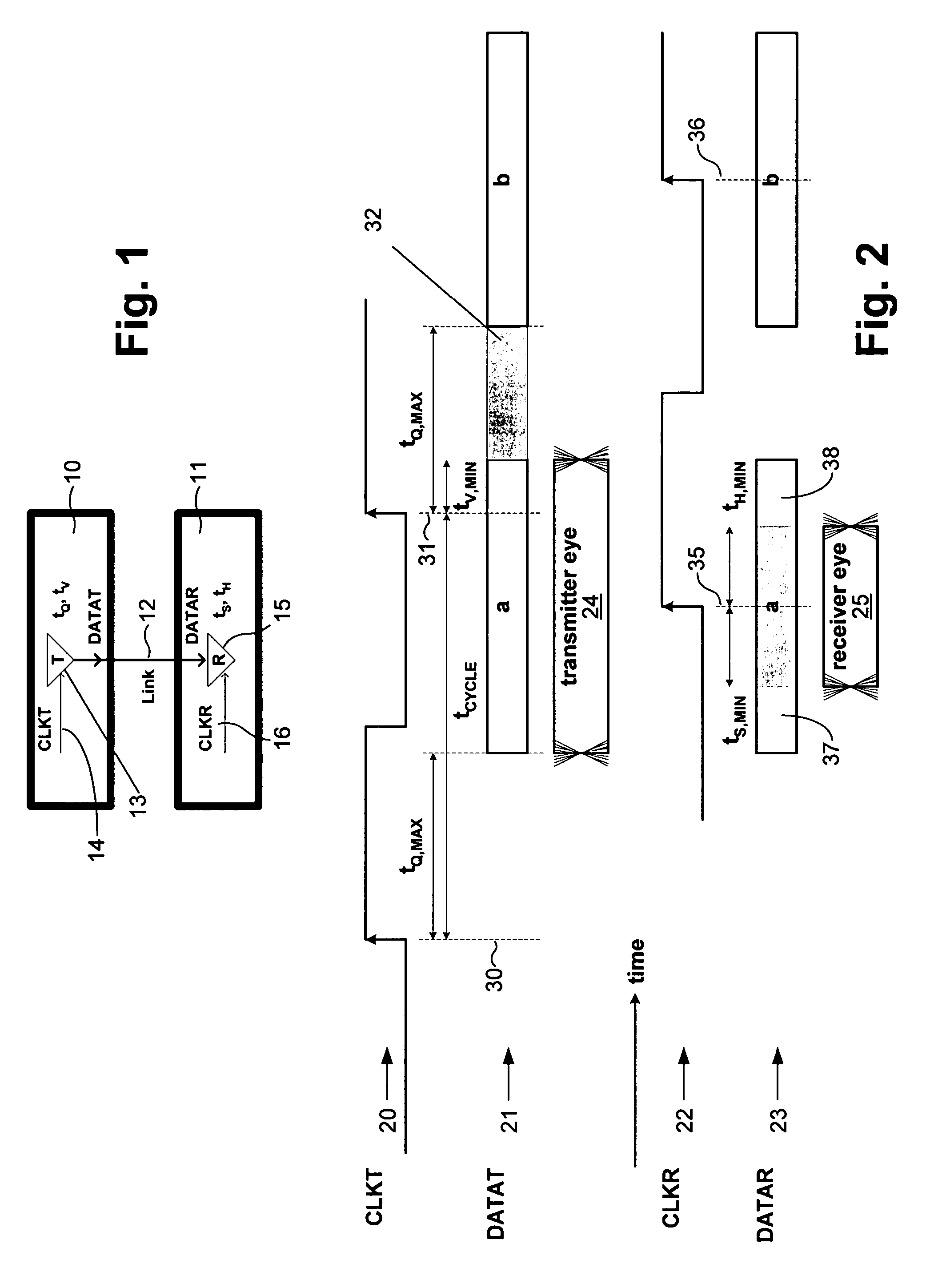

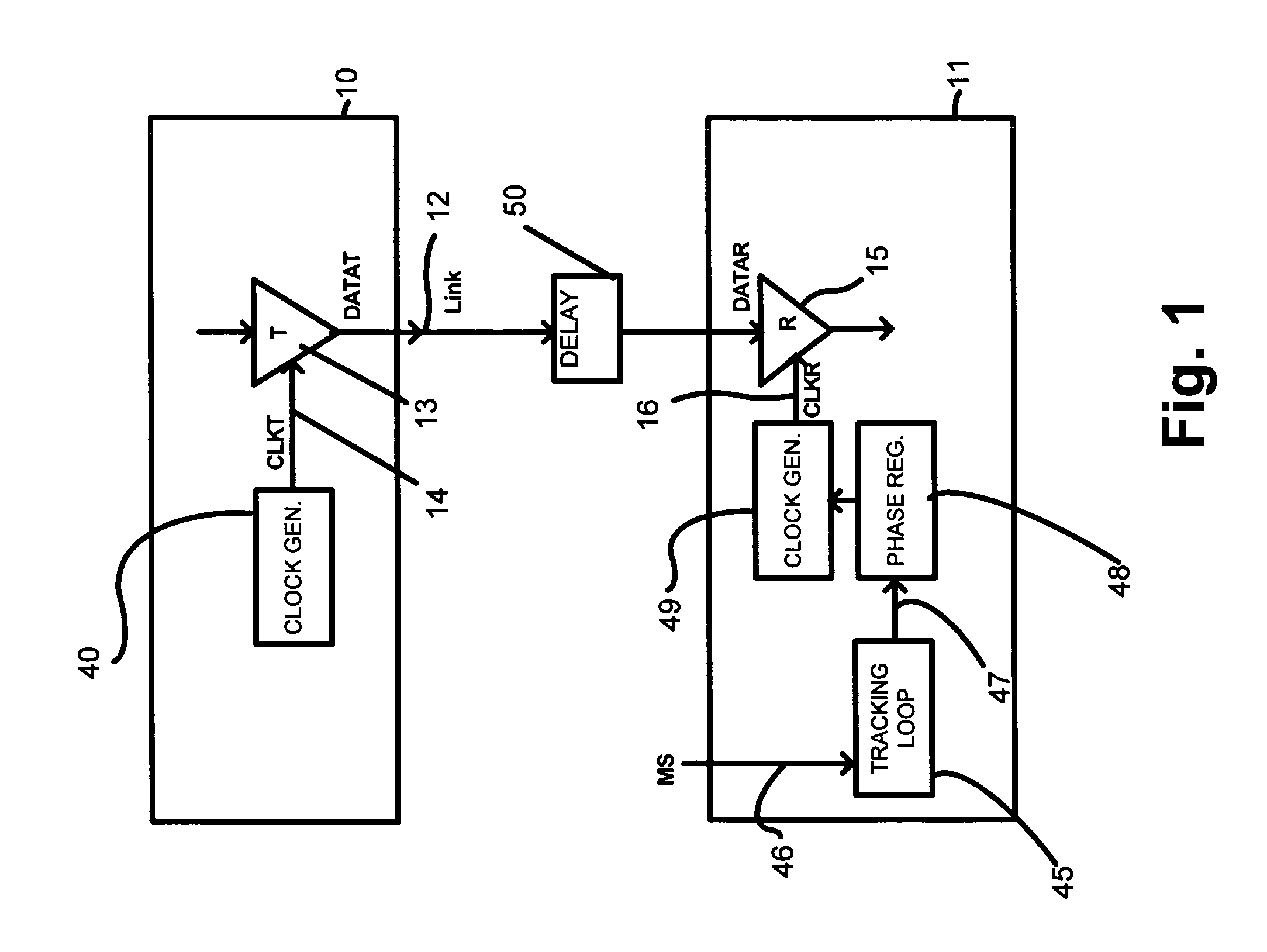

Periodic calibration for communication channels by drift tracking

ActiveUS20050163202A1Simplify sequenceEffectively accountedReceiver initialisationTransmitters monitoringByte

A method and system that provides for execution of a first calibration sequence, such as upon initialization of a system, to establish an operation value, which utilizes an algorithm intended to be exhaustive, and executing a second calibration sequence from time to time, to measure drift in the parameter, and to update the operation value in response to the measured drift. The second calibration sequence utilizes less resources of the communication channel than does the first calibration sequence. In one embodiment, the first calibration sequence for measurement and convergence on the operation value utilizes long calibration patterns, such as codes that are greater than 30 bytes, or pseudorandom bit sequences having lengths of 2N−1 bits, where N is equal to or greater than 7, while the second calibration sequence utilizes short calibration patterns, such as fixed codes less than 16 bytes, and for example as short as 2 bytes long.

Owner:RAMBUS INC

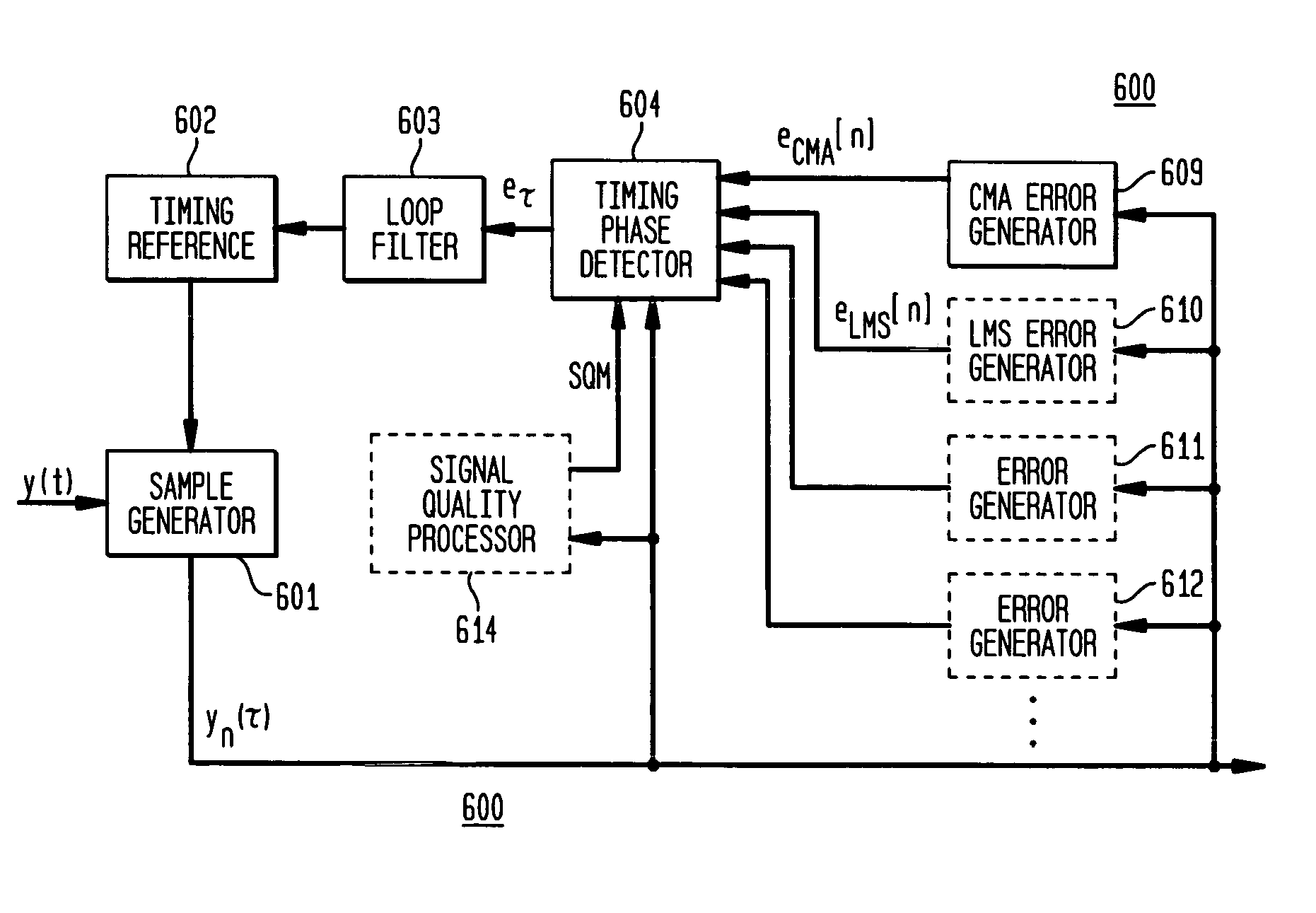

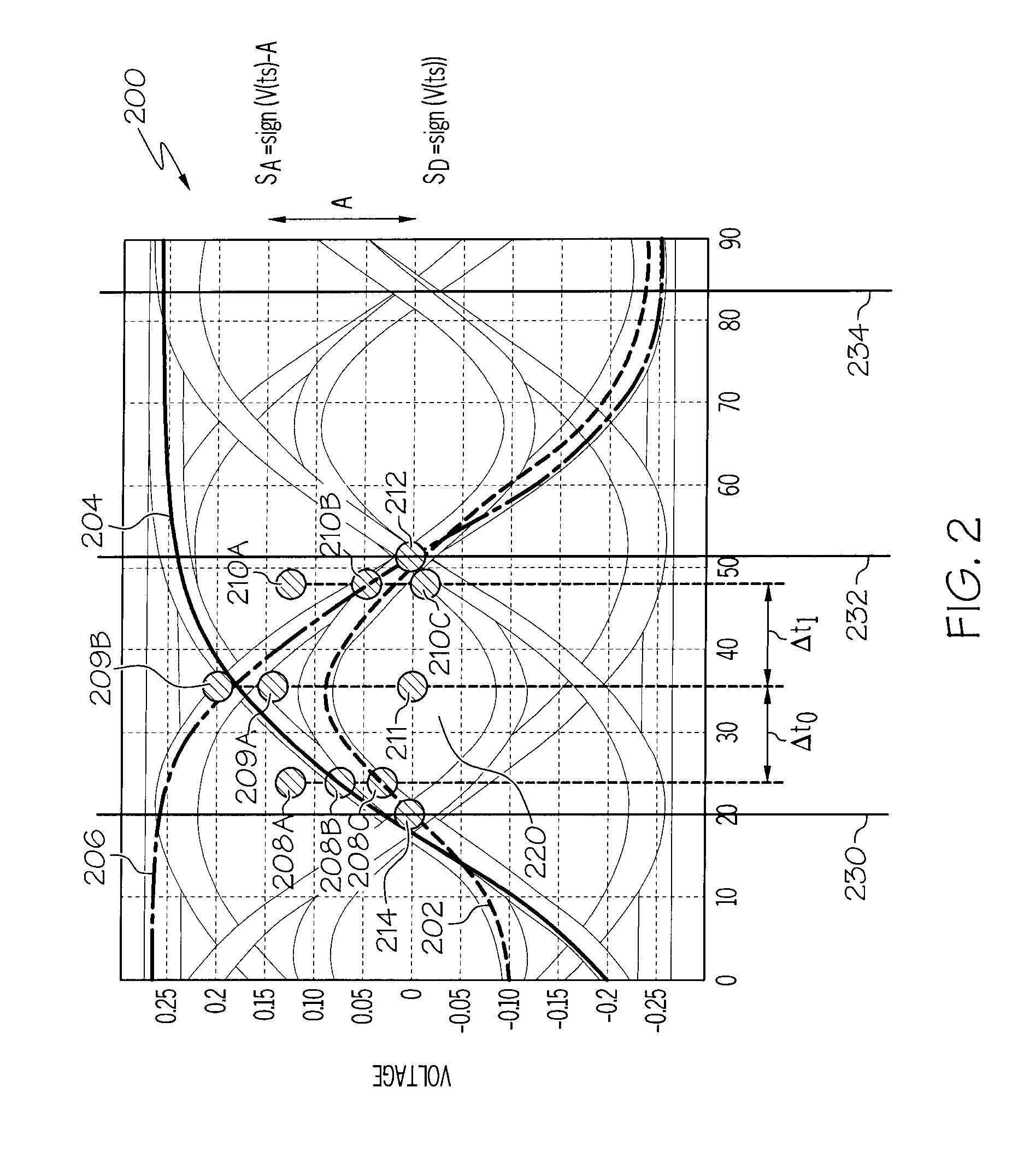

Blind cost criterion timing recovery

Symbol timing recovery employs a blind cost criterion from the Bussgang class of functions, and its stochastic gradient, to generate a timing phase error used to adjust sampling of received symbols. For one implementation, the estimate is derived in accordance with the Constant Modulus (CM) criterion and its gradient via the CM algorithm (CMA), and the estimate is calculated from a sequence of samples. This estimate is then used to adjust the period and phase of the sample sequence toward the period and phase of the transmitted symbols, driving the timing phase error to zero. The values used may be either i) samples themselves, ii) processed (e.g., interpolated) samples, or iii) equalized and processed samples. In addition, timing phase error estimates for other cost criteria, including the least mean squares algorithm, may be generated. These timing phase error estimates are selected either alone or in combination for deriving the timing phase error used to adjust the period and phase of the sample sequence.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

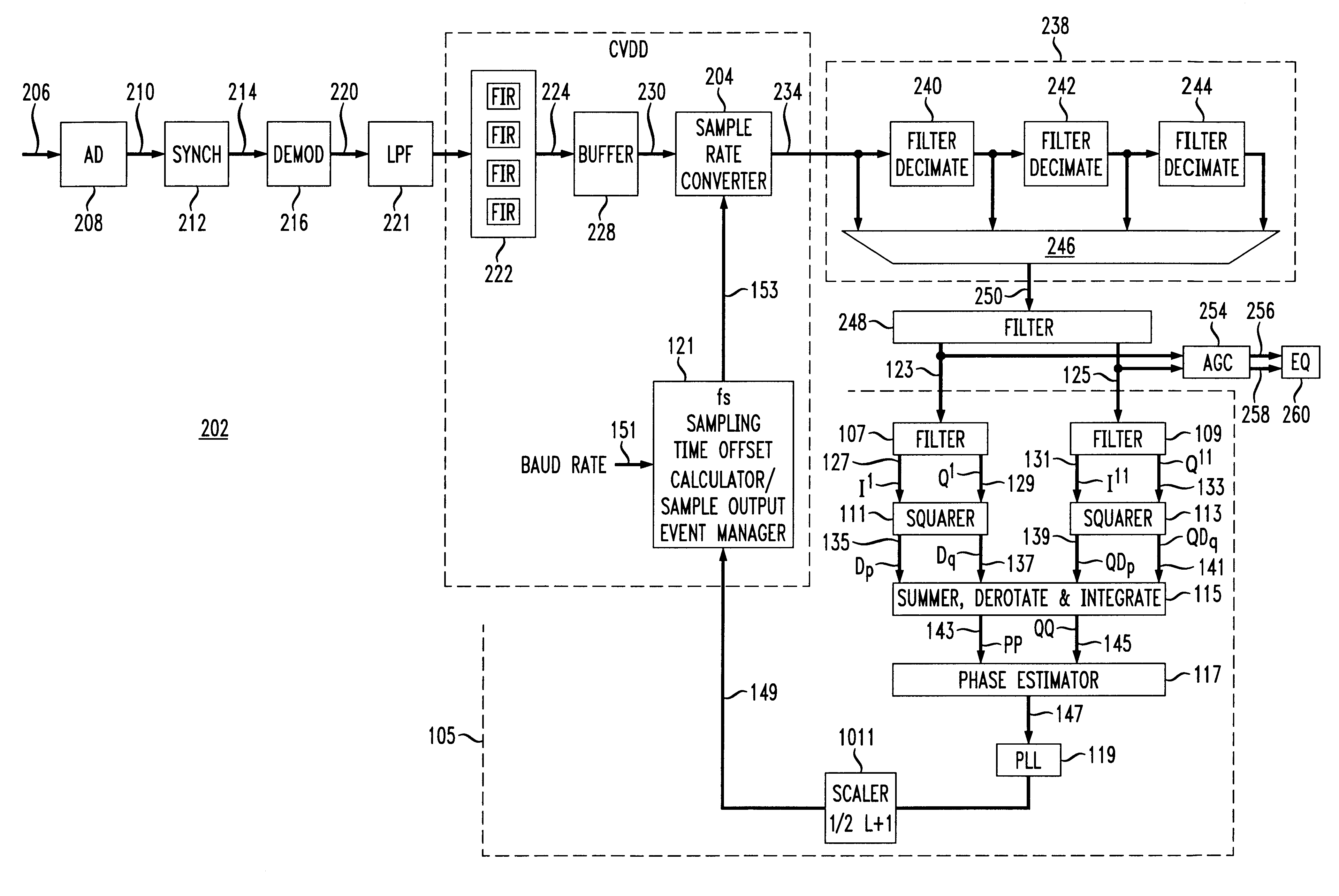

Fixed clock based arbitrary symbol rate timing recovery loop

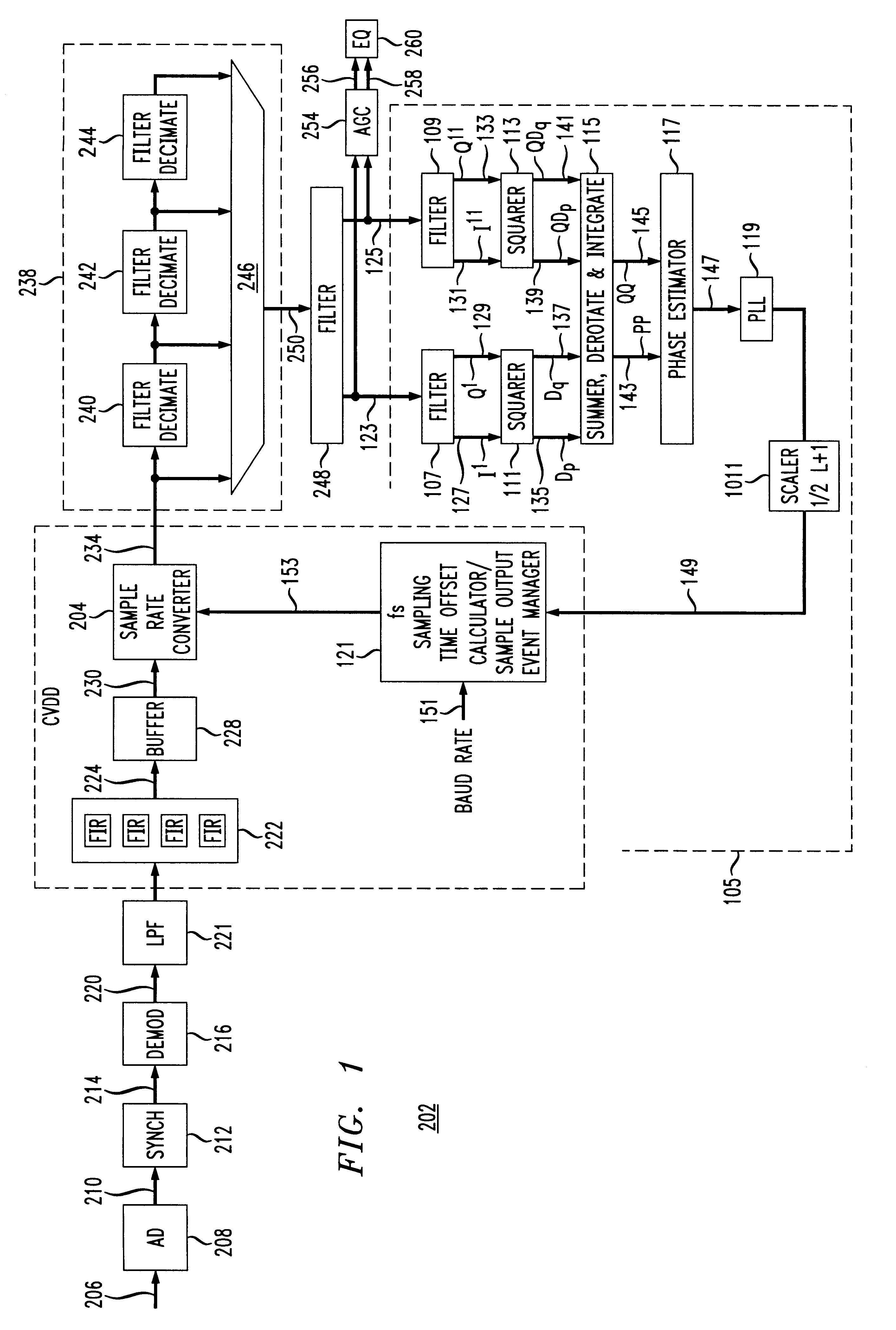

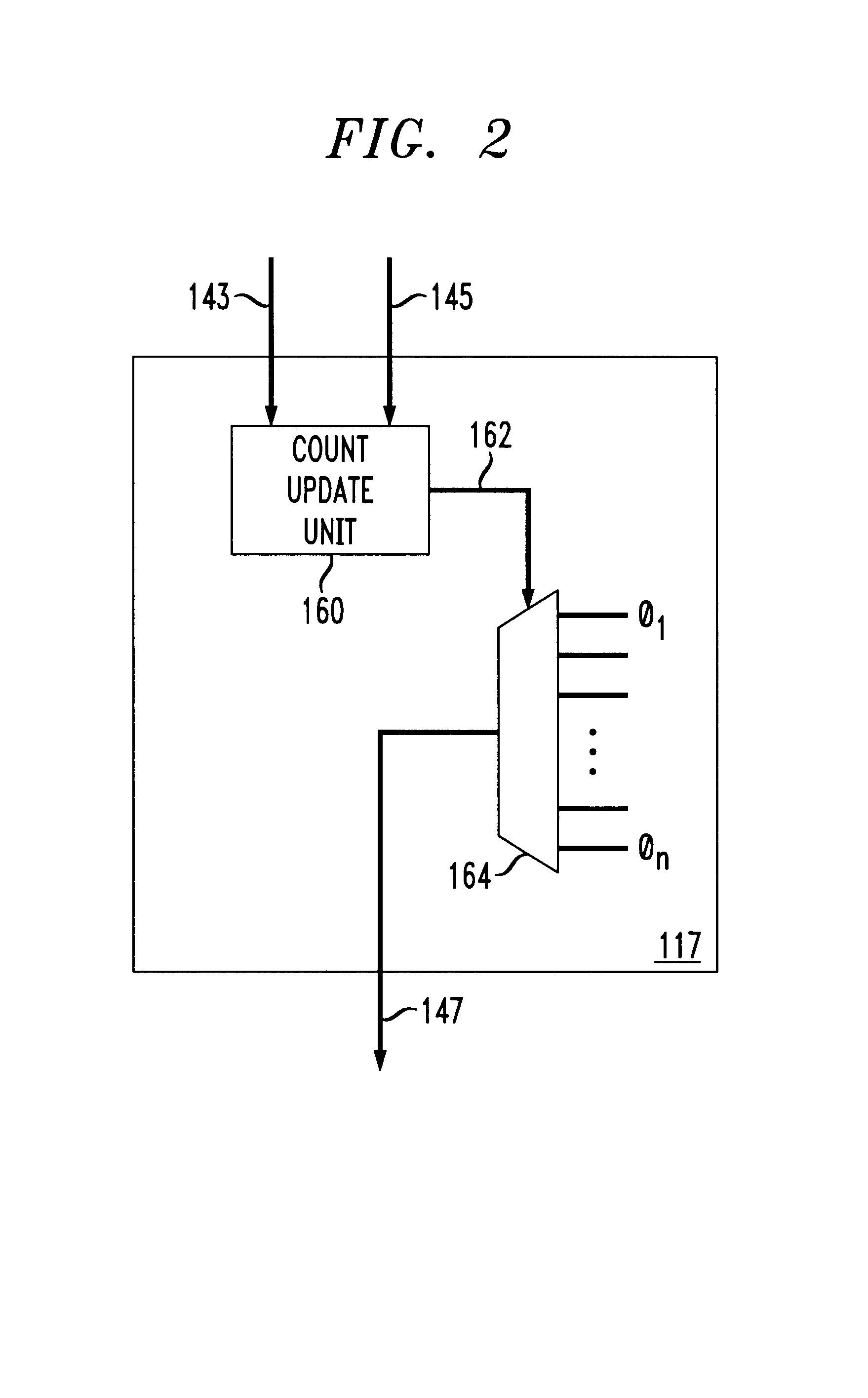

InactiveUS6295325B1Receiver initialisationAngle demodulation by phase difference detectionData signalSymbol rate

A QAM data signal timing recovery loop feedback element provides a fixed sampling time offset adjustment to two continuously variable digital rate interpolators / decimators to produce a quadrature output stream at a programmed rational rate multiple of the actual baud rate of the received data signal. The continuously variable digital rate interpolators / decimators are configured at startup so as to produce output streams at the same programmed rational rate multiple of the nominal baud rate of the anticipated received data signal, assuming the fs sample timing offset adjustment stream provided by the timing recovery feedback element to be identically 0. The "nominal" fixed sampling rate fs of the received analog input signal need not be rationally related to the nominal baud rate of the anticipated received data signal.

Owner:LUCENT TECH INC

Timing recovery circuit

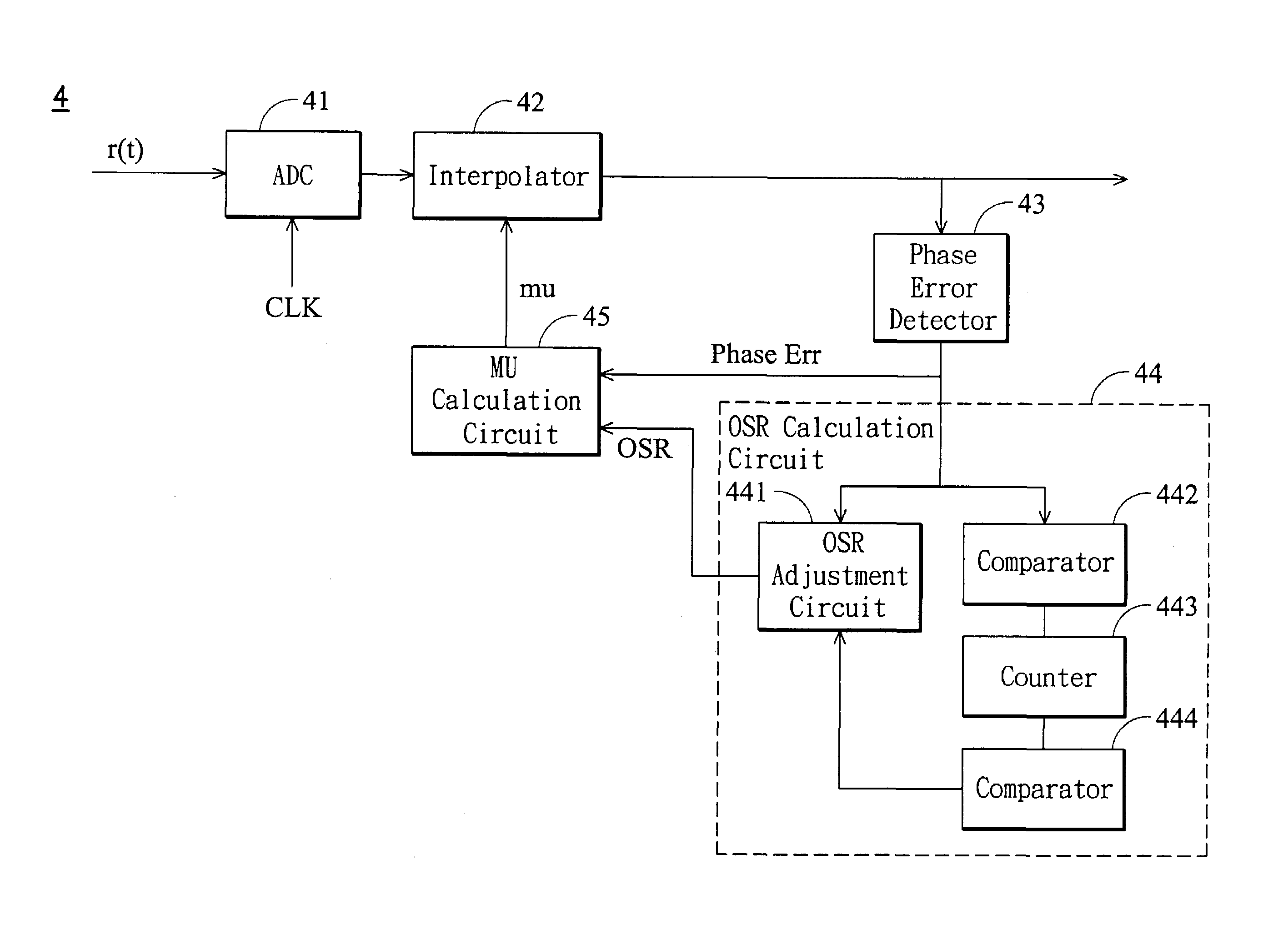

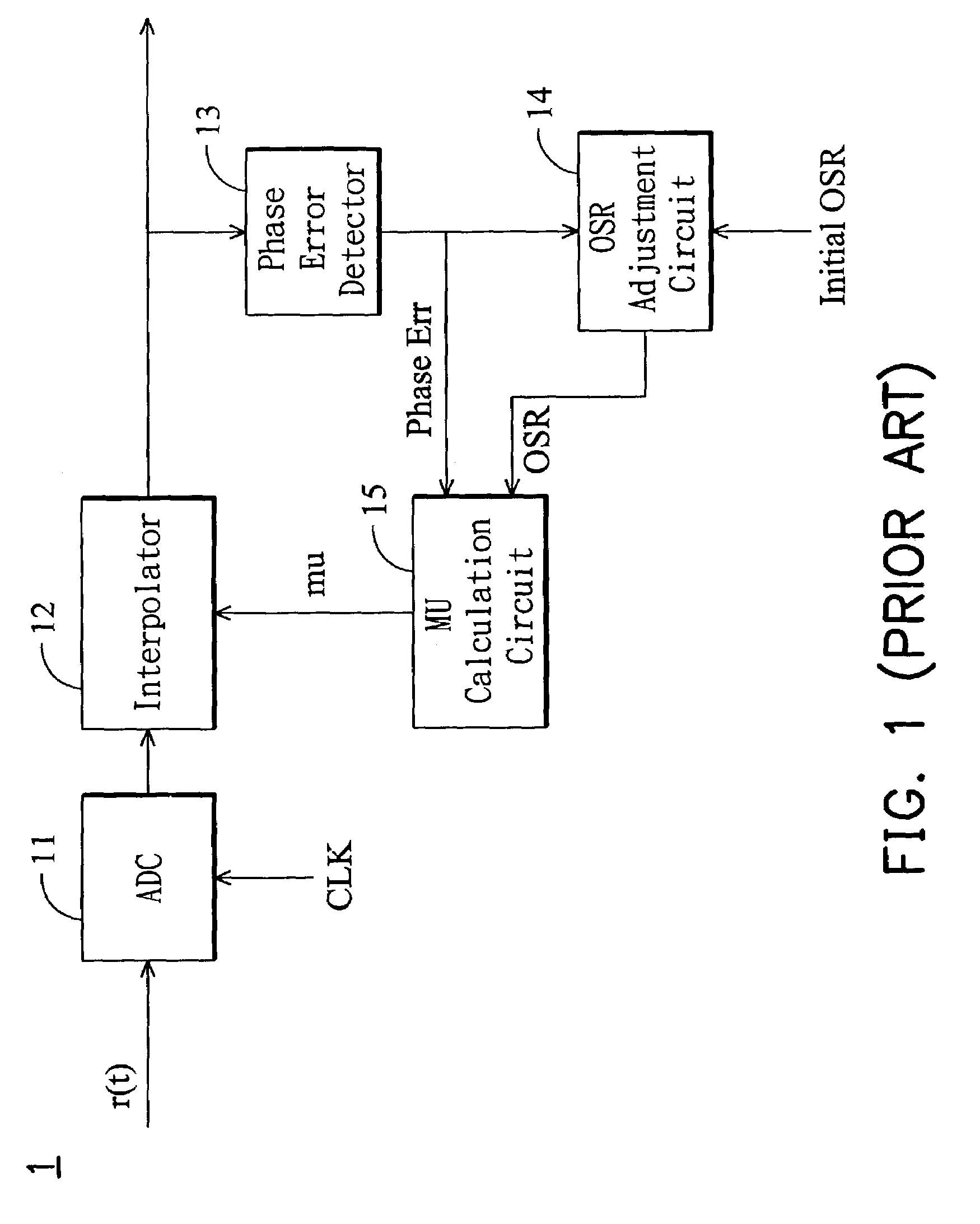

ActiveUS7187739B2Avoids steady errorError stableReceiver initialisationPhase detectorOver sampling ratio

A timing recovery circuit and related method is disclosed. The timing recovery circuit encompasses a converter, an interpolator, a phase error detector, an adjustment circuit, and a calculation circuit. The converter samples an input signal to generate an intermediate signal carrying samples of the input signal, while the interpolator inserts an interpolating sample into the intermediate signal in response to a control value to generate an output signal. The phase error detector outputs a phase error of the output signal. The adjustment circuit updates an over-sampling ratio according to a pair of first and second thresholds, and a counting value adjusted in response to the phase error and a median reference value. Finally, the calculation circuit derives the control value from the updated over-sampling ratio, and transferring the control value to the interpolator.

Owner:VIA TECH INC

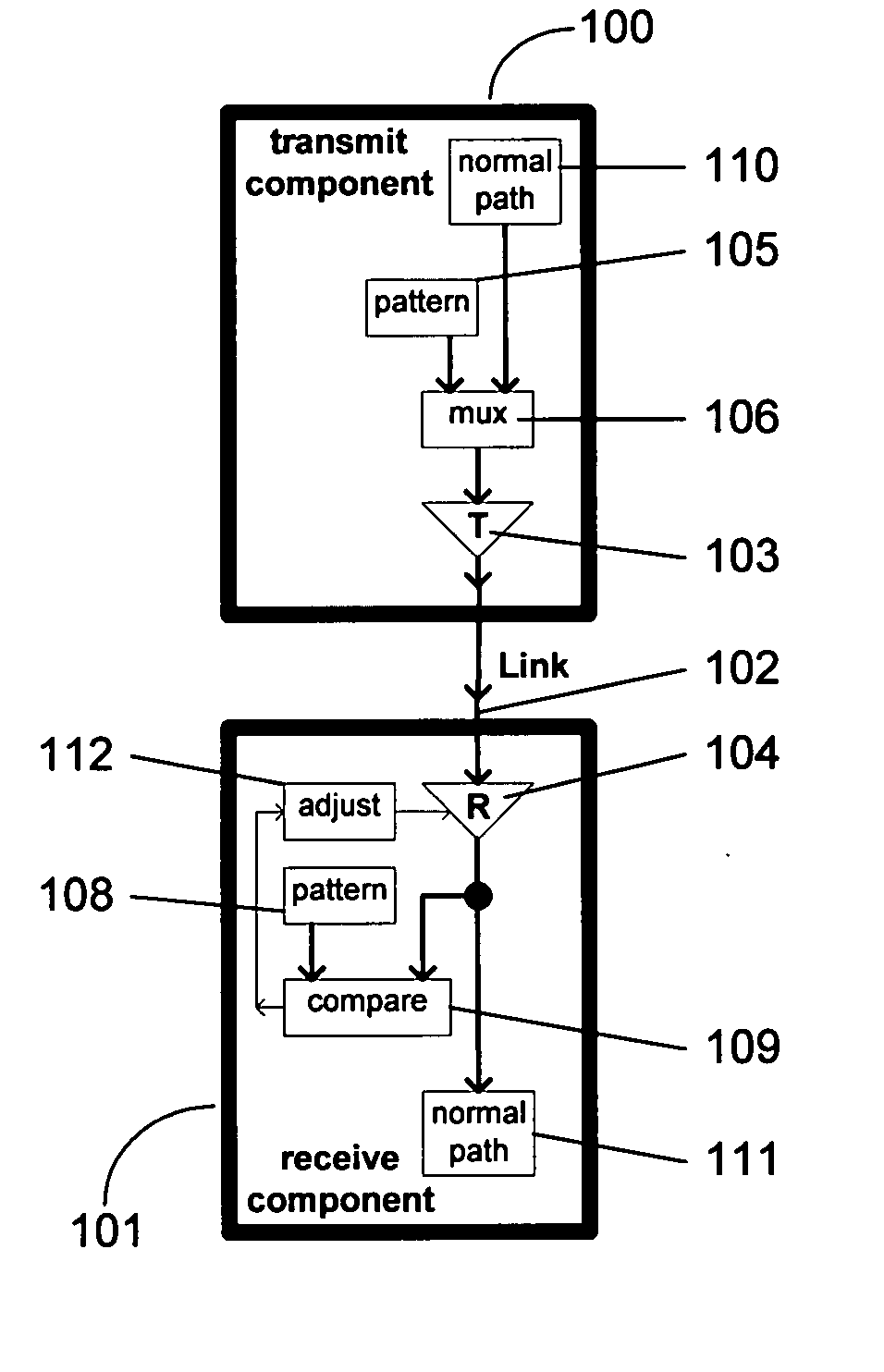

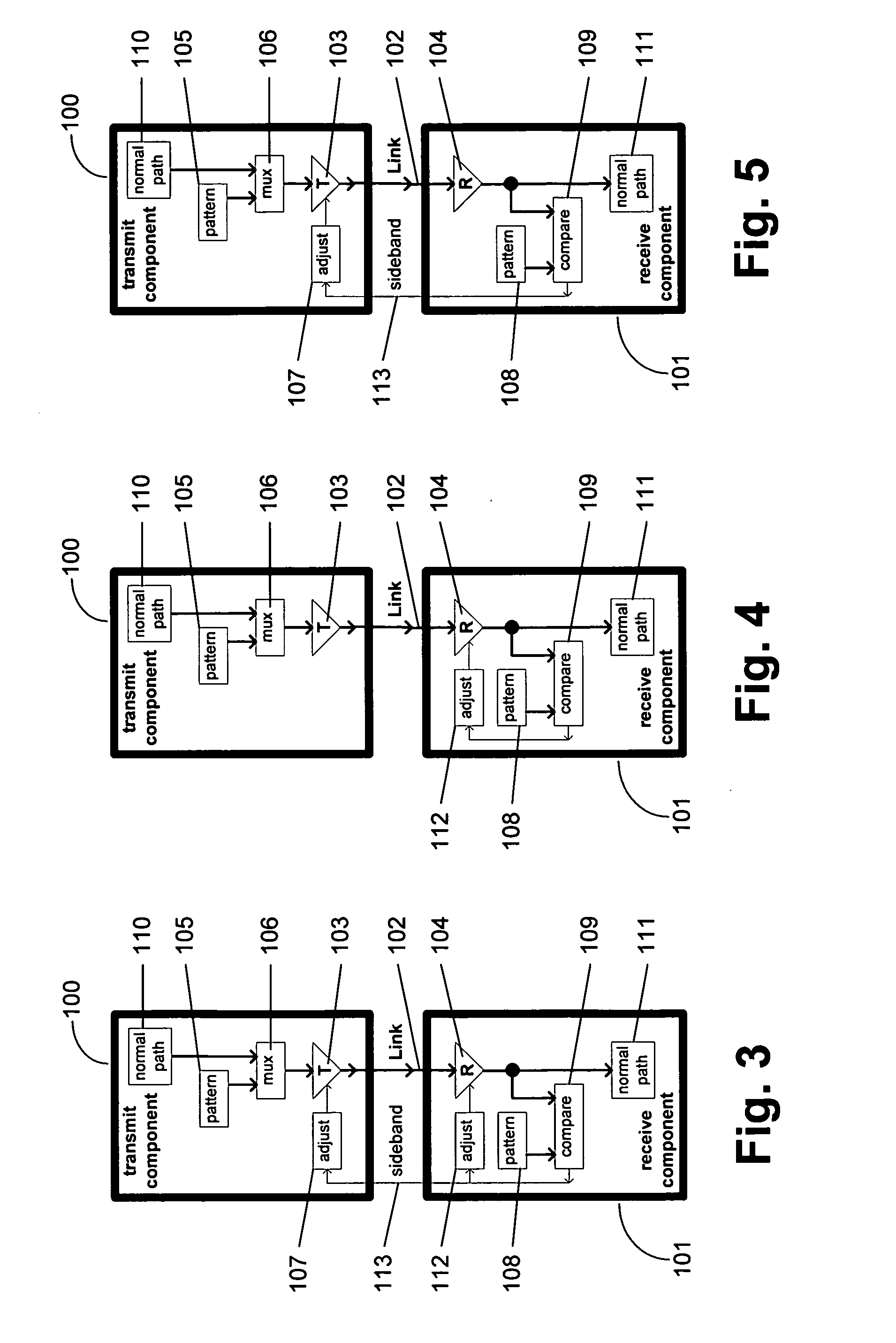

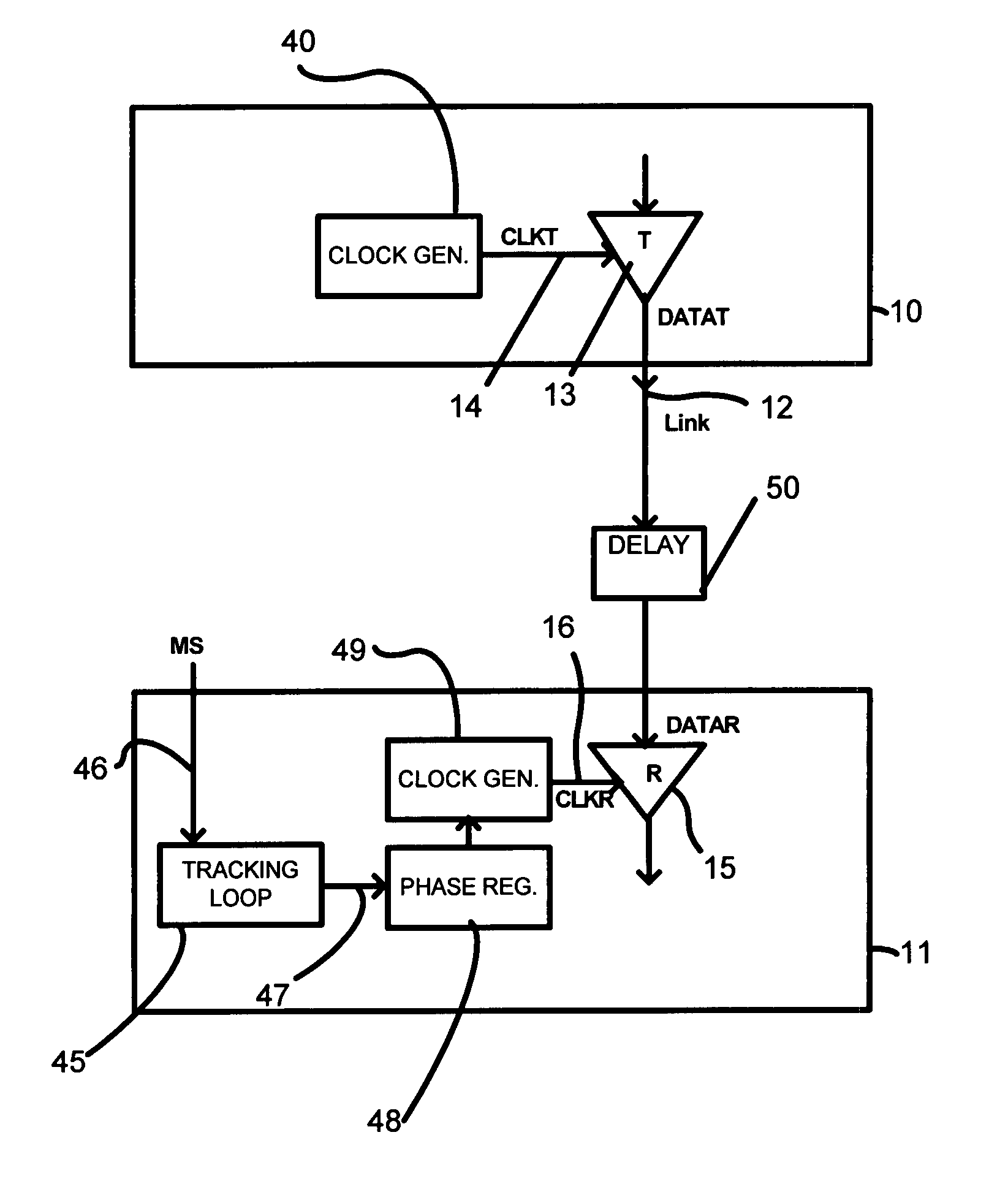

Drift tracking feedback for communication channels

ActiveUS6961862B2Efficiently tracking drift of property of channelReceiver initialisationChannel dividing arrangementsTelecommunications linkCommunication link

A communication channel includes a first component having a transmitter coupled to a normal signal source, and a second component having a receiver coupled to a normal signal destination. A communication link couples the first and second components. Calibration logic provides for setting an operation value for a parameter of the communication channel, such as by executing an exhaustive calibration sequence at initialization of the link. A tracking circuit, including a monitoring function, tracks drift in the parameter by monitoring a feedback signal that has a characteristic that correlates with drift in the communication channel, and updates, or indicates the need for updating of, the operation value of the parameter in response to the monitoring function.

Owner:RAMBUS INC

Information read device and read signal processing circuit

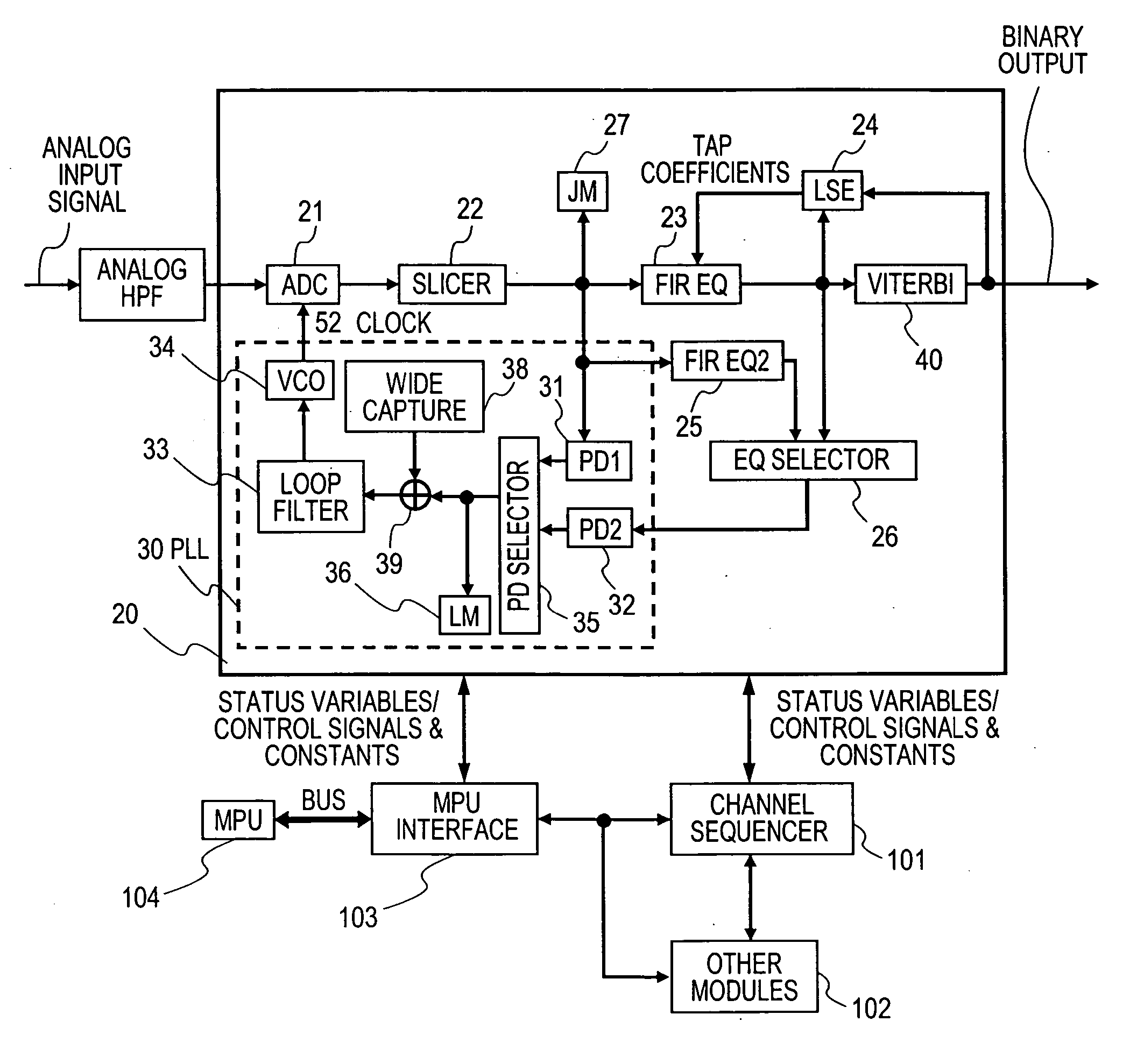

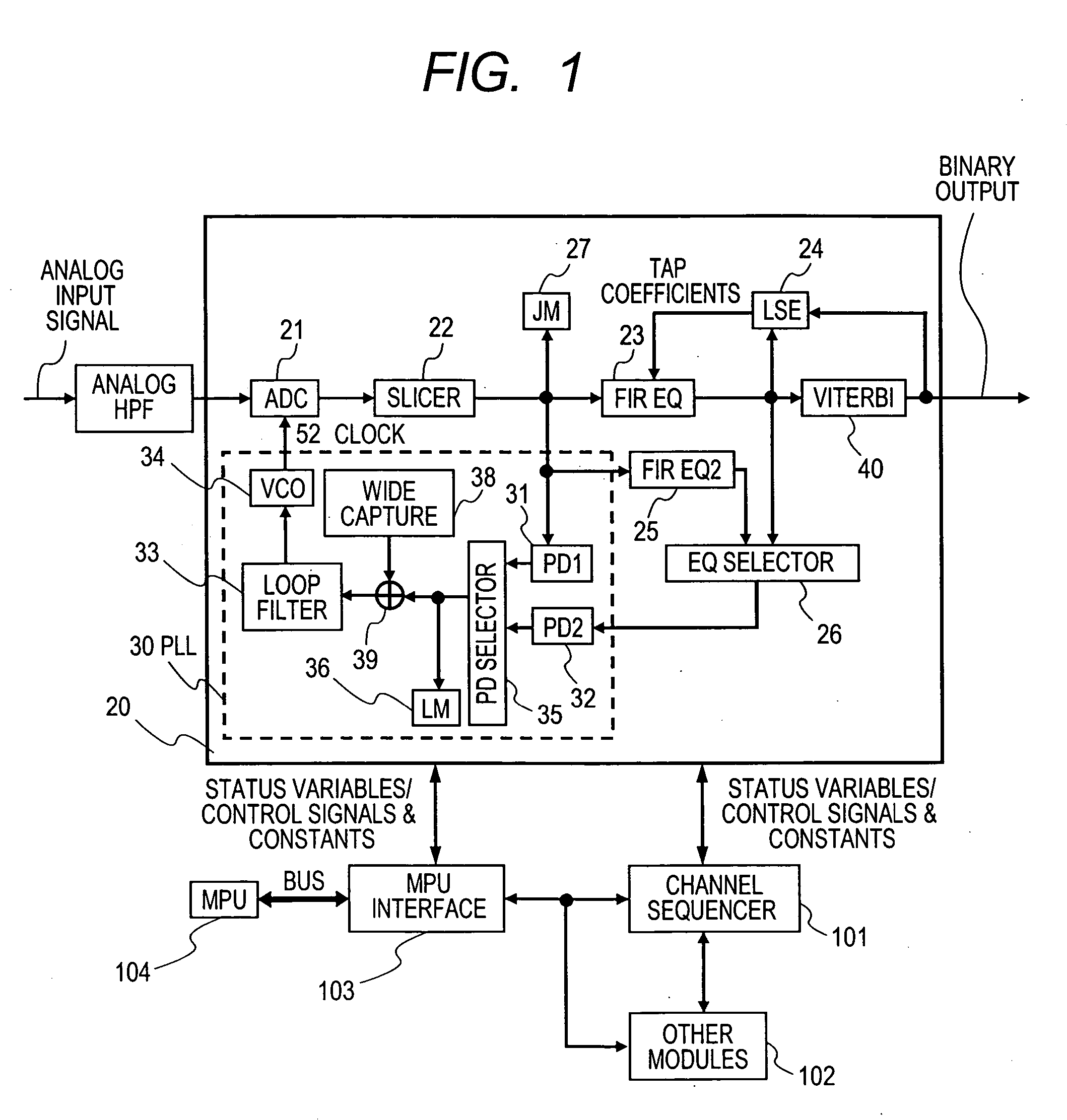

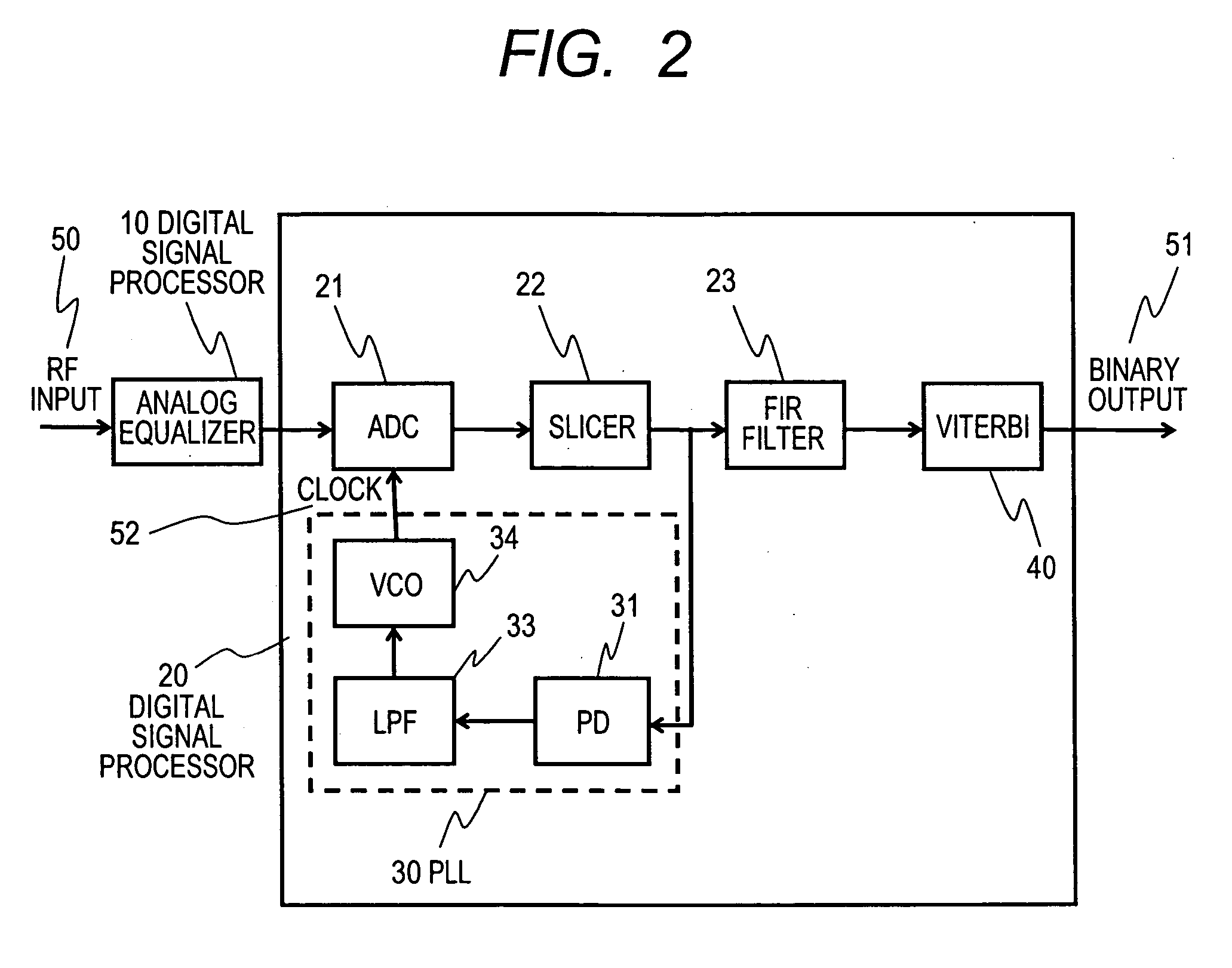

ActiveUS20060280240A1High error rateSatisfied with the effectMultiple-port networksFilamentary/web record carriersSignal processing circuitsSignal-to-noise ratio (imaging)

An optical disk read signal processing system for Blu-ray disc systems to ensure stable phase-locked locked operation even with a low signal-to-noise ratio. This system changes a loop configuration of a phase lock loop circuit according to the operating state, and utilizes a FIR equalizer for phase detection. This system attains a low error rate even when the signal-to-noise ratio of an input signal is low, and avoids pulse edges with low phase detection accuracy or signal pulse streams with a high possibility of being mistakenly detected as an edge in conventional methods, and also supports diverse types of input signals.

Owner:HITACHI CONSUMER ELECTRONICS CORP

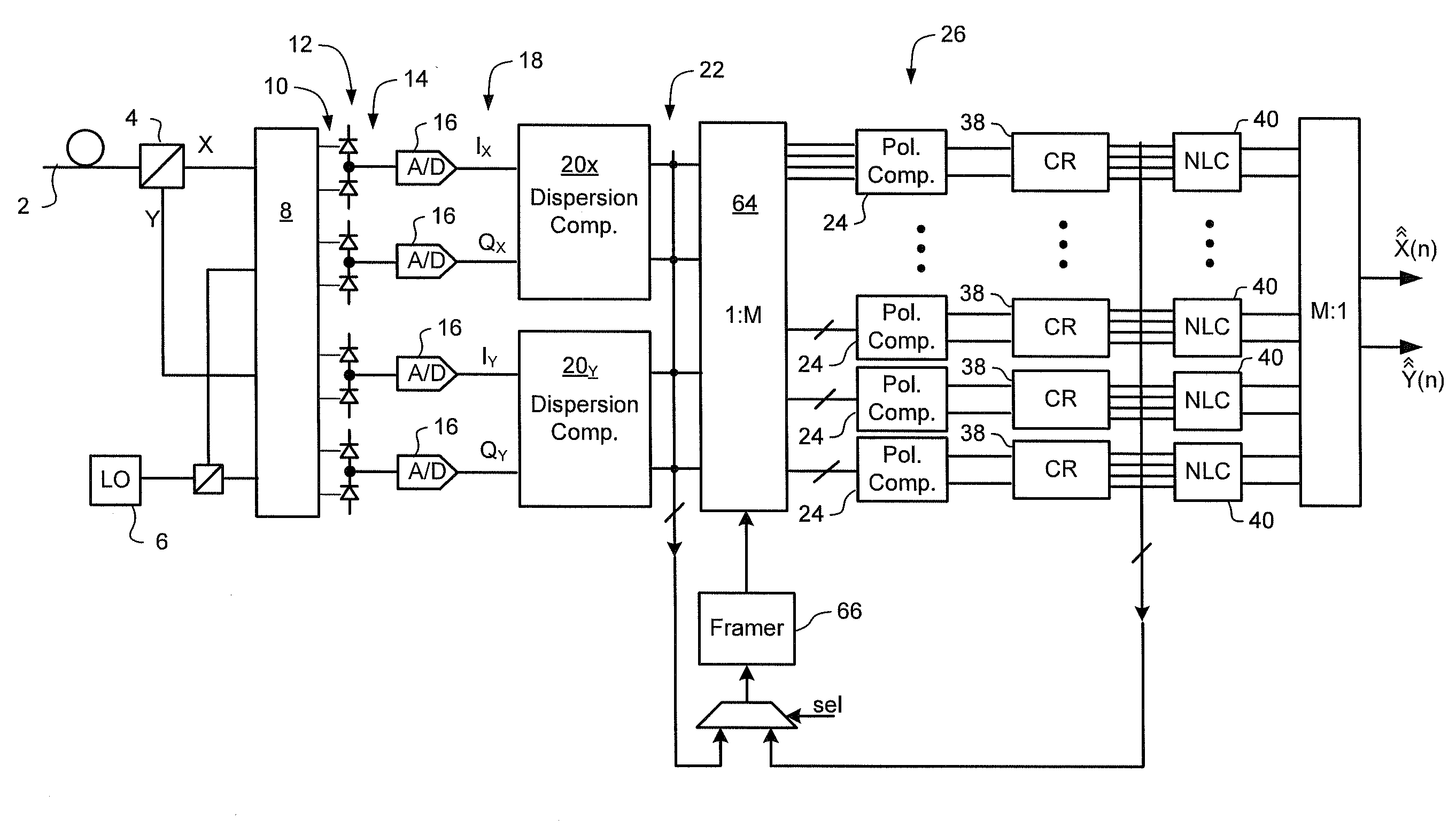

Non-linear equalizer in a coherent optical receiver

ActiveUS7684712B1Receiver initialisationSynchronisation by photonic/optical meansSignal restorationComputer science

A method of recovering a most likely value of each symbol transmitted through an optical communications network using a high speed optical signal. A stream of multi-bit digital samples of the optical signal is processed to generate a respective multi-bit estimate X′(n) of each transmitted symbol. A first function is applied to each symbol estimate X′(n) to generate a corresponding soft decision value {tilde over (X)}(n). Each soft decision value {tilde over (X)}(n) is processed to generate a corresponding hard decision value. {circumflex over (X)}(n) having an ideal amplitude and phase. A plurality of successive soft decision values and hard decision values are processed to determine a second function, which is applied to each soft decision value {tilde over (X)}(n) to generate a most likely symbol value {circumflex over ({circumflex over (X)}(n).

Owner:CIENA CORP

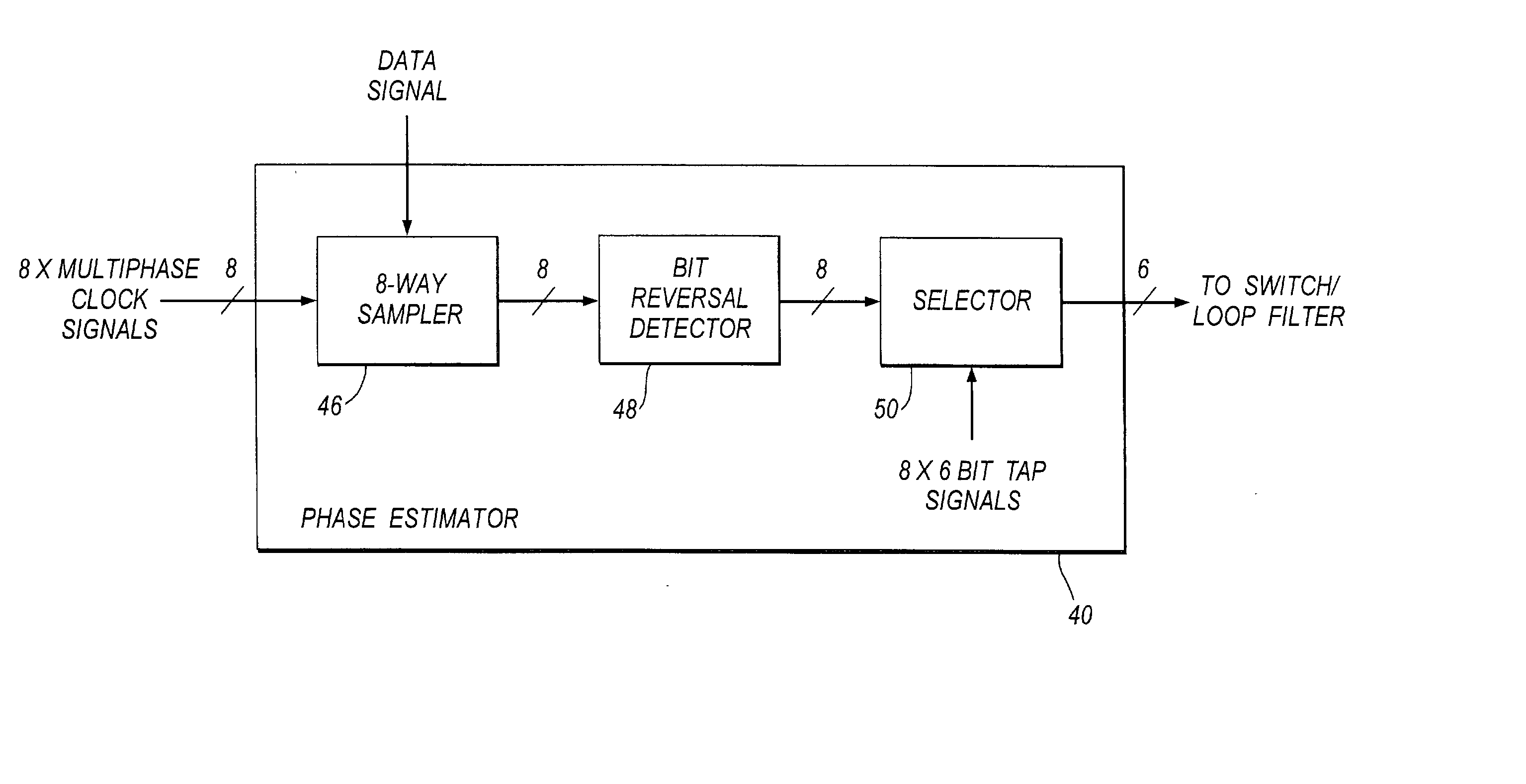

Clock recovery circuitry

Clock recovery circuitry for recovering a clock signal from a data signal is disclosed. The clock recovery circuitry comprises sampling means (46) for sampling the data signal at a plurality of sampling points, bit reversal detecting means (48) for determining a sampling point at which the data signal changes state, selecting means (50) for selecting a phase from amongst a plurality of candidate phases based on a sampling point at which the data signal is determined to change state, and phase setting means (38) for setting the phase of the clock signal in dependence on the selected phase. The circuitry may be used to produce an estimate of a desired phase of the clock signal for supply to a phase locked loop. This can allow the phase locked loop to be brought quickly into lock.

Owner:SOCIONEXT INC

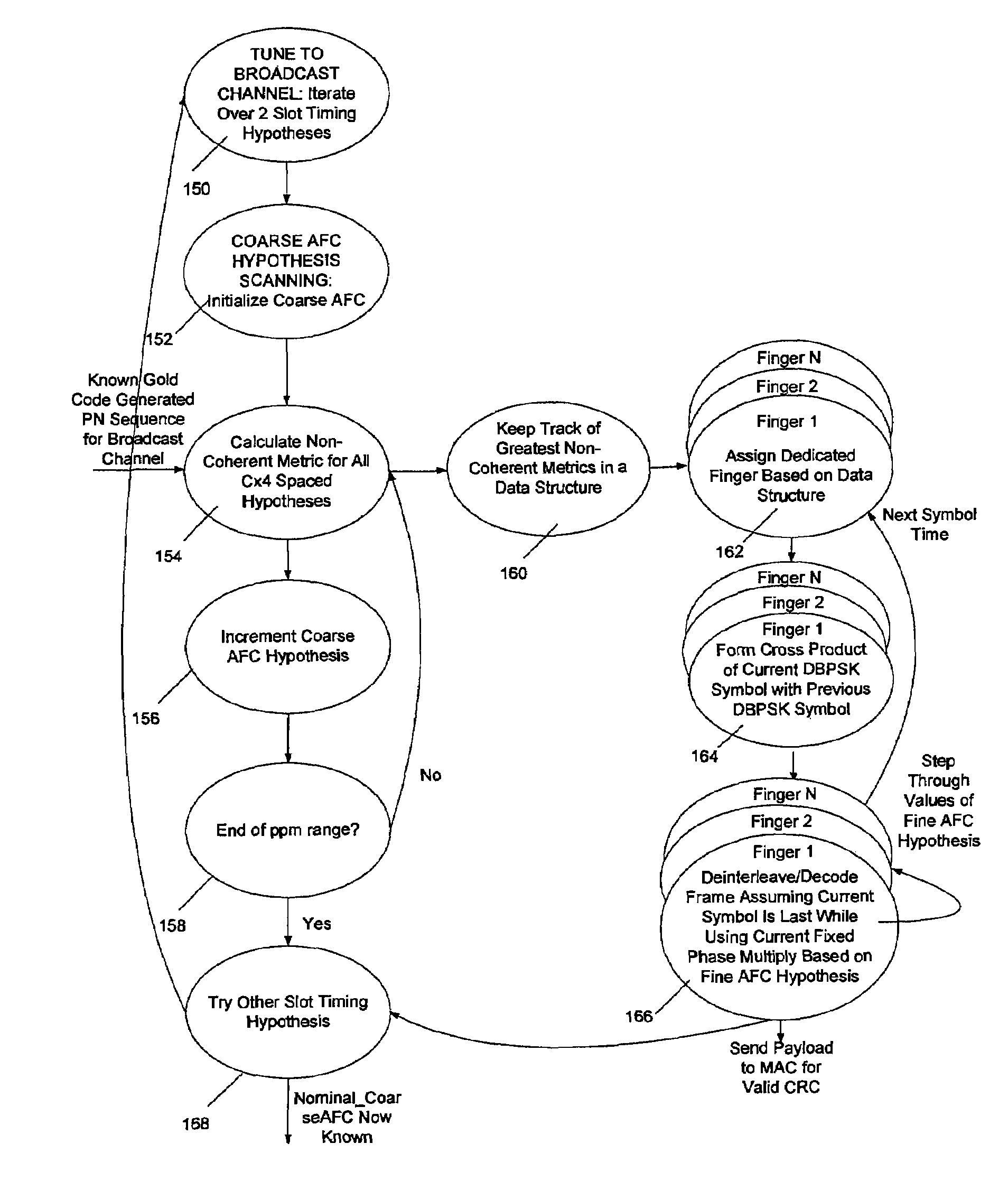

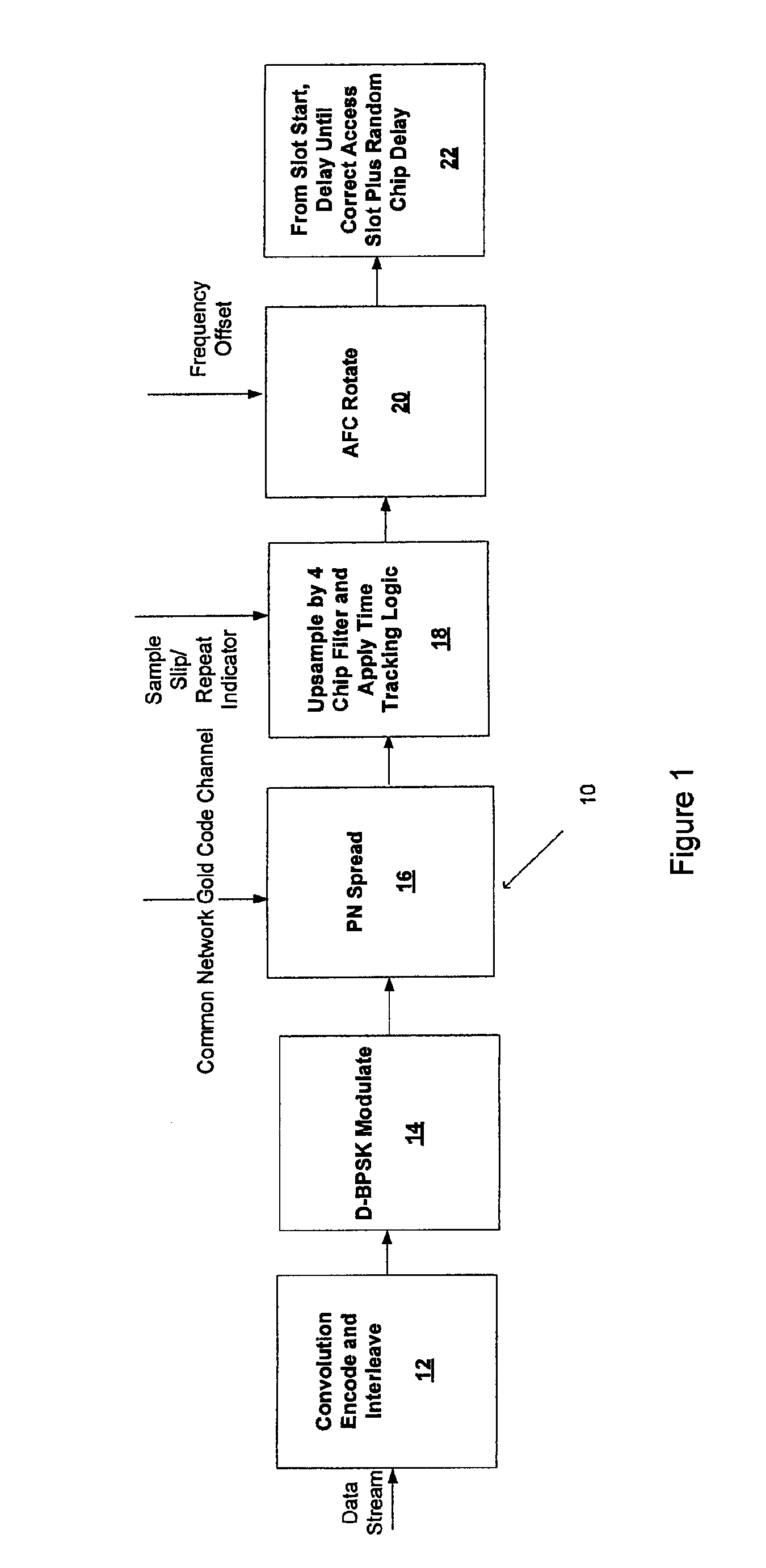

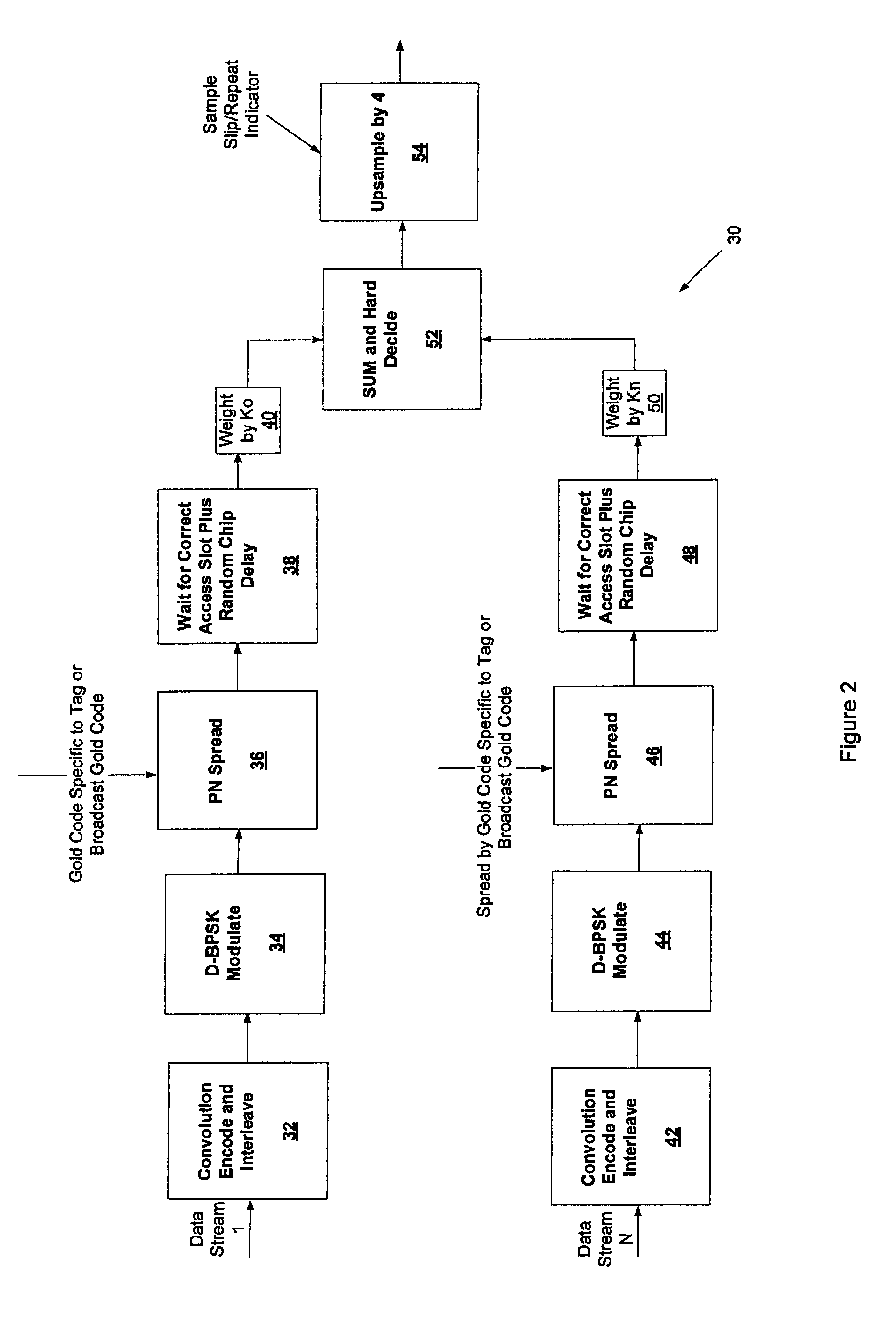

Tag communications with access point

ActiveUS7526013B1Easy accessProvide securityReceiver initialisationError prevention/detection by using return channelData streamCheque

A method of establishing communication at a tag includes calculating a metric for each of a plurality of automatic frequency control (AFC) hypotheses where the plurality of AFC hypotheses correspond to a timing used by an access point; based on the calculated metrics, identifying one or more relevant AFC hypotheses; performing a check on a demodulated data stream identified using the one or more relevant AFC hypotheses; identifying a valid AFC hypothesis based at least in part on the check; and determining where a frame starts based at least in part on the check.

Owner:INGENU INC

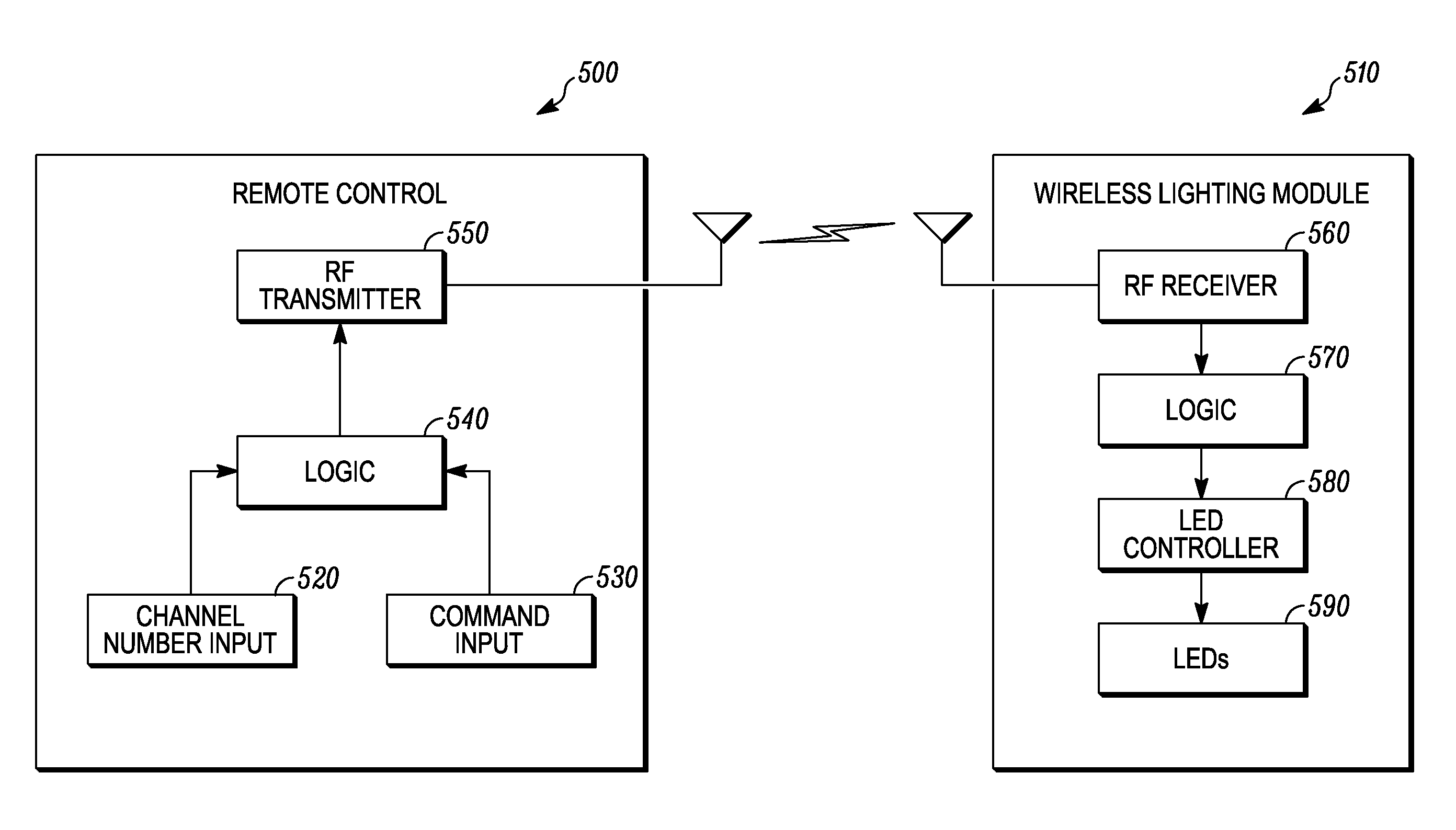

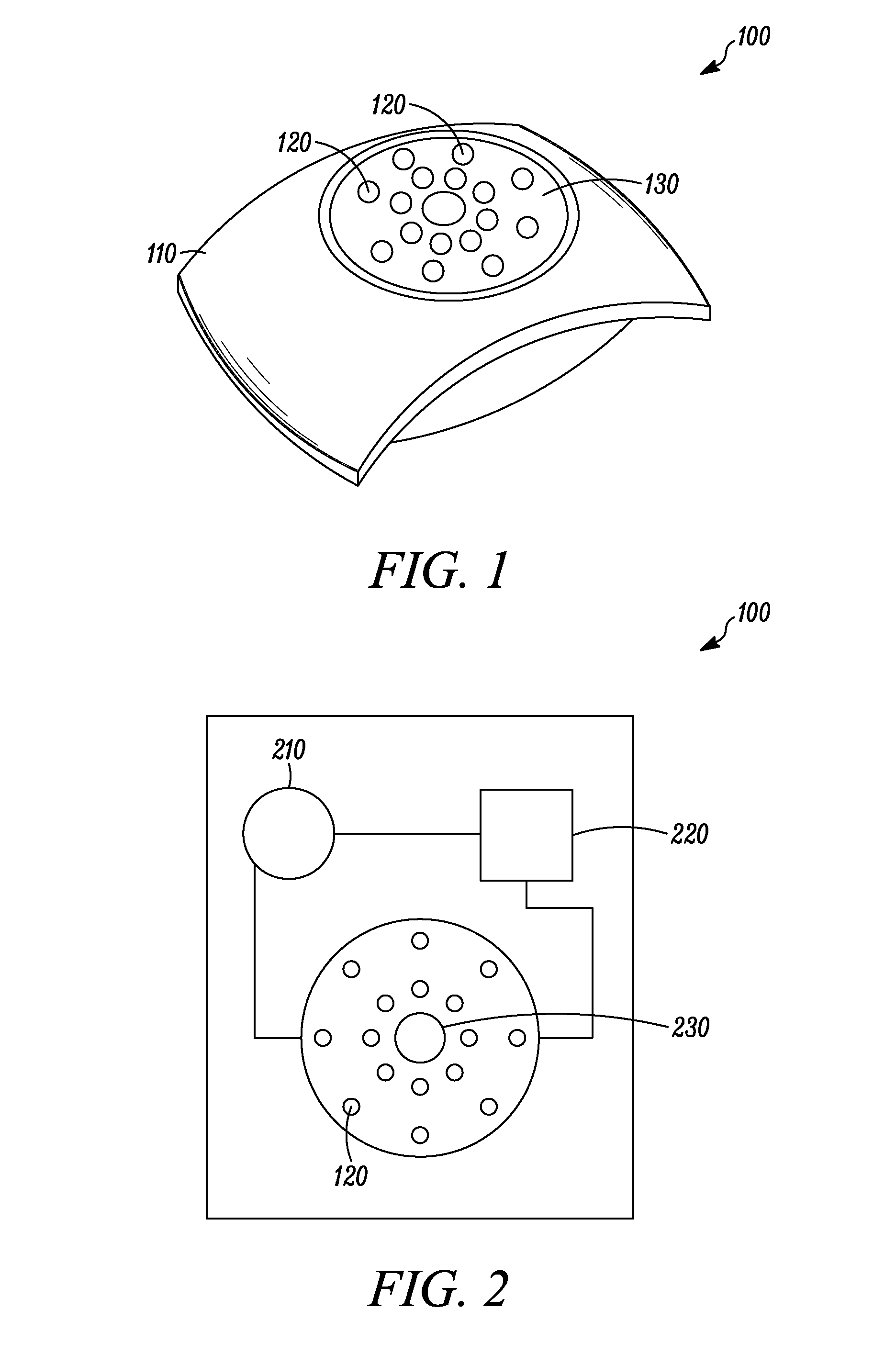

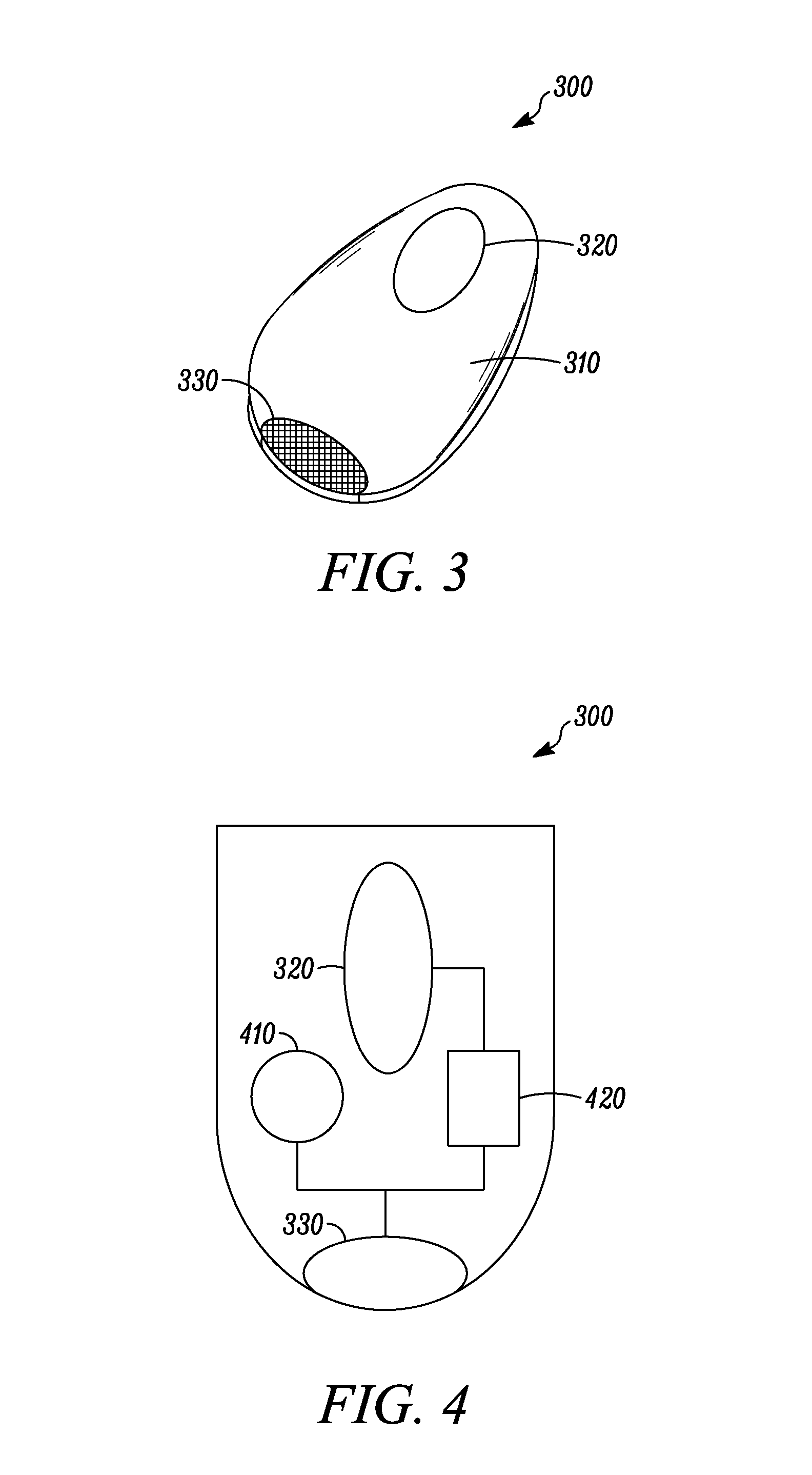

Integrated power outage lighting system controller

InactiveUS20130285558A1Advantage in easeLow costReceiver initialisationElectroluminescent light sourcesTransmitted powerEngineering

In embodiments of the present invention improved capabilities are described for systems and methods that provide for a power outage lighting management within an environment, comprising a power outage detection device adapted to detect a power outage condition and to wirelessly transmit power outage indication data to a plurality of lighting systems within the environment, where at least one of the plurality of lighting systems include an LED light source that is powered by an internal power source.

Owner:RING LLC

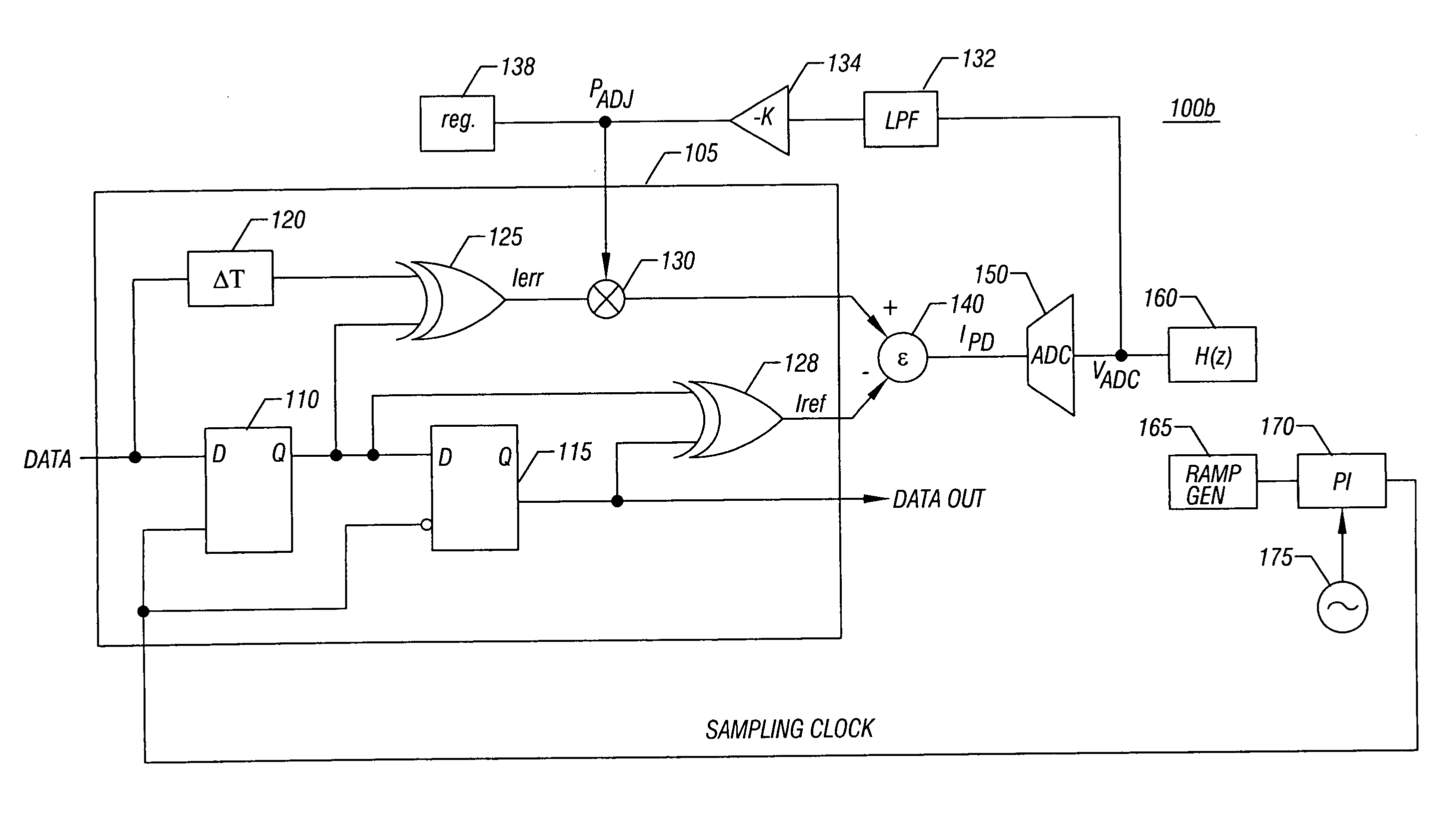

Calibrating a phase detector and analog-to-digital converter offset and gain

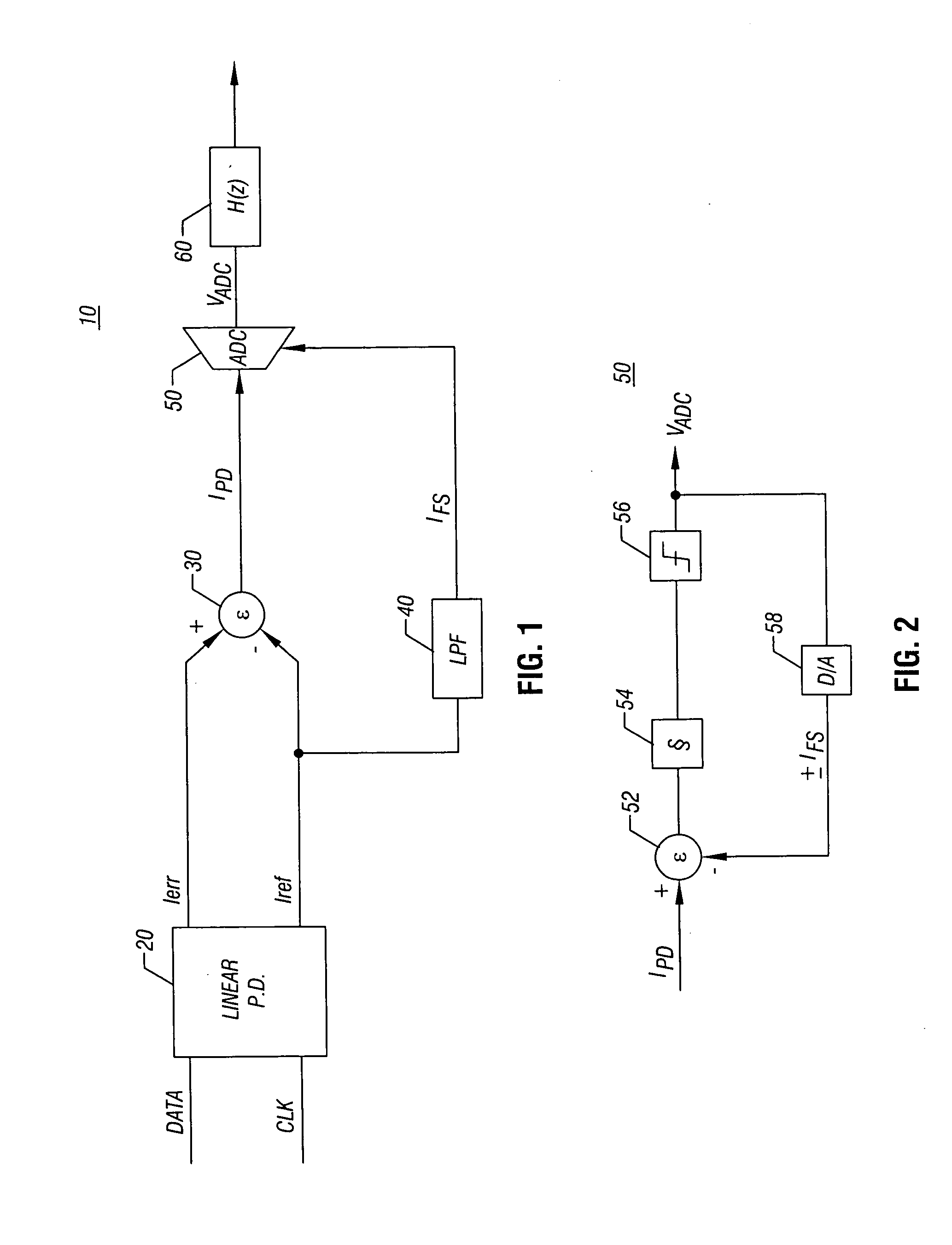

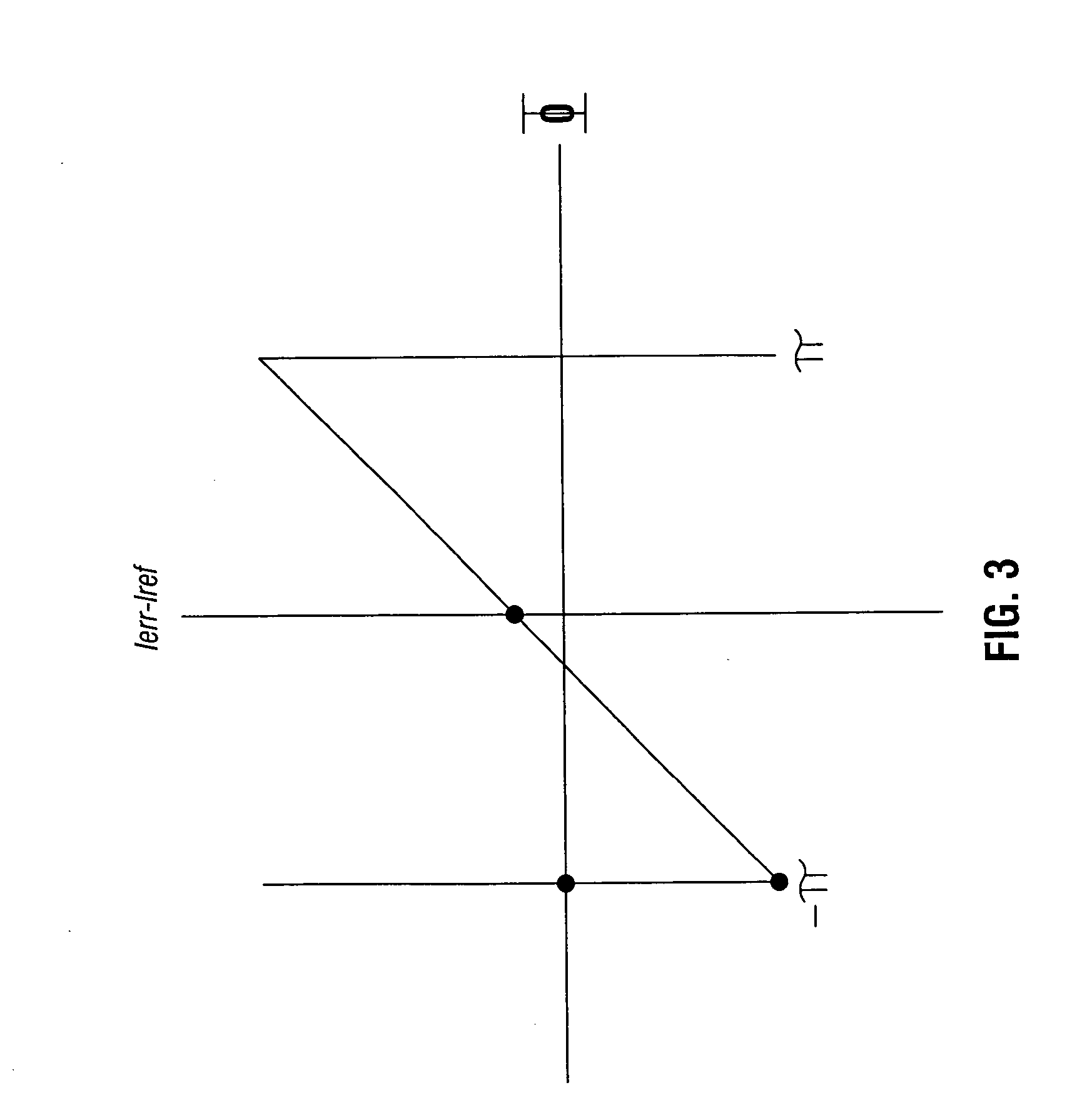

ActiveUS20060140319A1Reducing and eliminating offsetImprove errorReceiver initialisationAngle demodulation by phase difference detectionPhase detectorA d converter

The present invention includes apparatus and methods to calibrate a phase detector and an analog-to-digital converter (ADC) offset and gain. In one such embodiment, an apparatus includes a phase detector to generate an error pulse and a reference pulse, a combiner to combine the pulses, and an ADC to receive the combined pulses, where the ADC has a full scale set by an average of the reference pulse. Still further, a calibration loop may be coupled between the output of the ADC and the phase detector to generate and provide a phase adjust signal to reduce or eliminate phase offsets. Other embodiments are described and claimed.

Owner:SKYWORKS SOLUTIONS INC

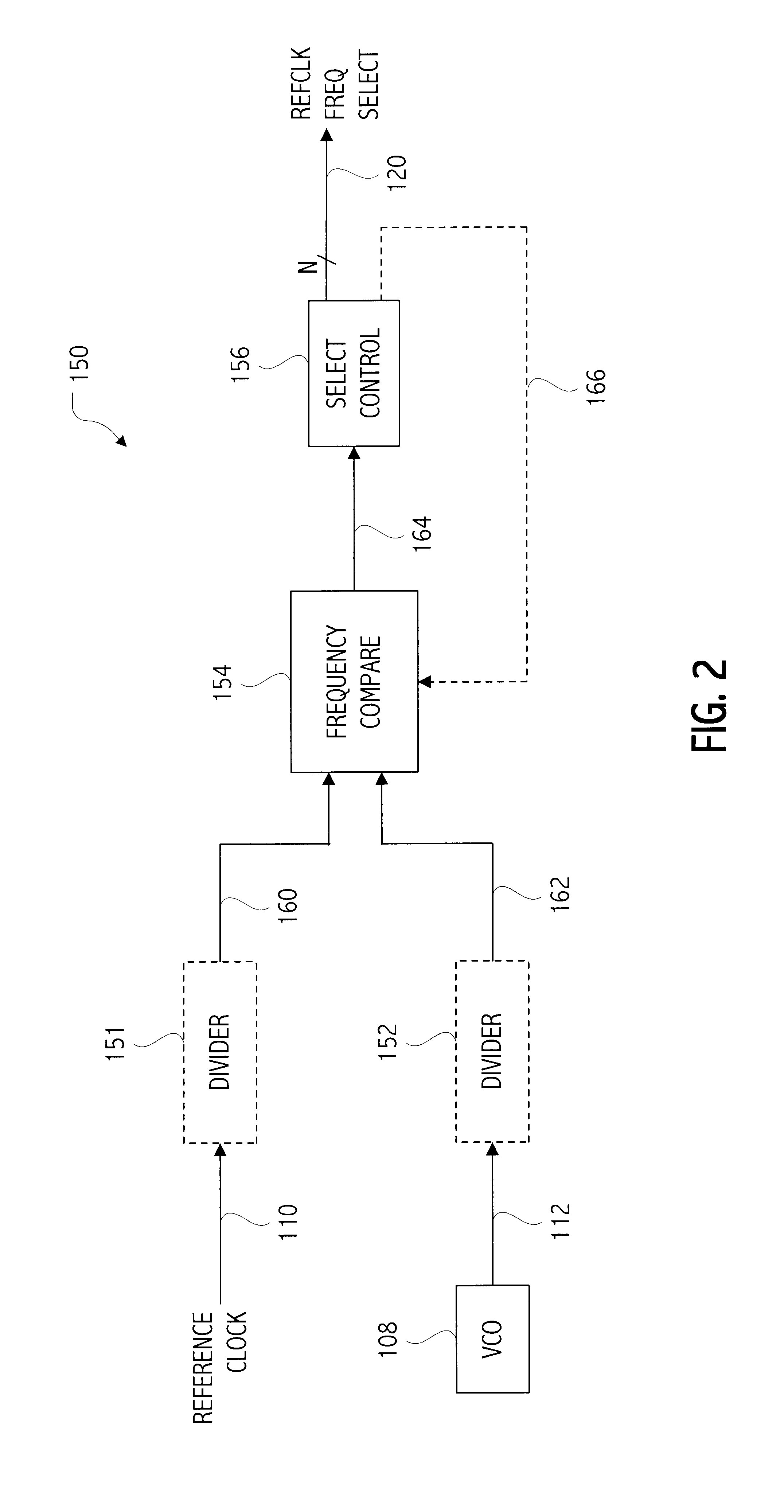

Auto-detection between referenceless and reference clock mode of operation

An internal frequency reference, such as a VCO used in a PLL, having a free-running frequency fairly well controlled within a predictable range, is used to determine which of two possible modes of operation, a referenceless or reference clock mode of operation, is used based on a detected frequency of an externally-provided frequency reference signal. The frequency is detected without any additional externally provided signal to indicate the mode of operation or the frequency of the reference clock. If the frequency detection circuit detects a frequency below a predetermined threshold, referenceless mode of operation is indicated. Otherwise, reference clock mode of operation is indicated. In referenceless mode of operation such operations as frequency acquisition and lock detect are performed without the use of a reference clock. In reference clock mode the reference clock is used for such operations as frequency acquisition and lock detect.

Owner:SKYWORKS SOLUTIONS INC

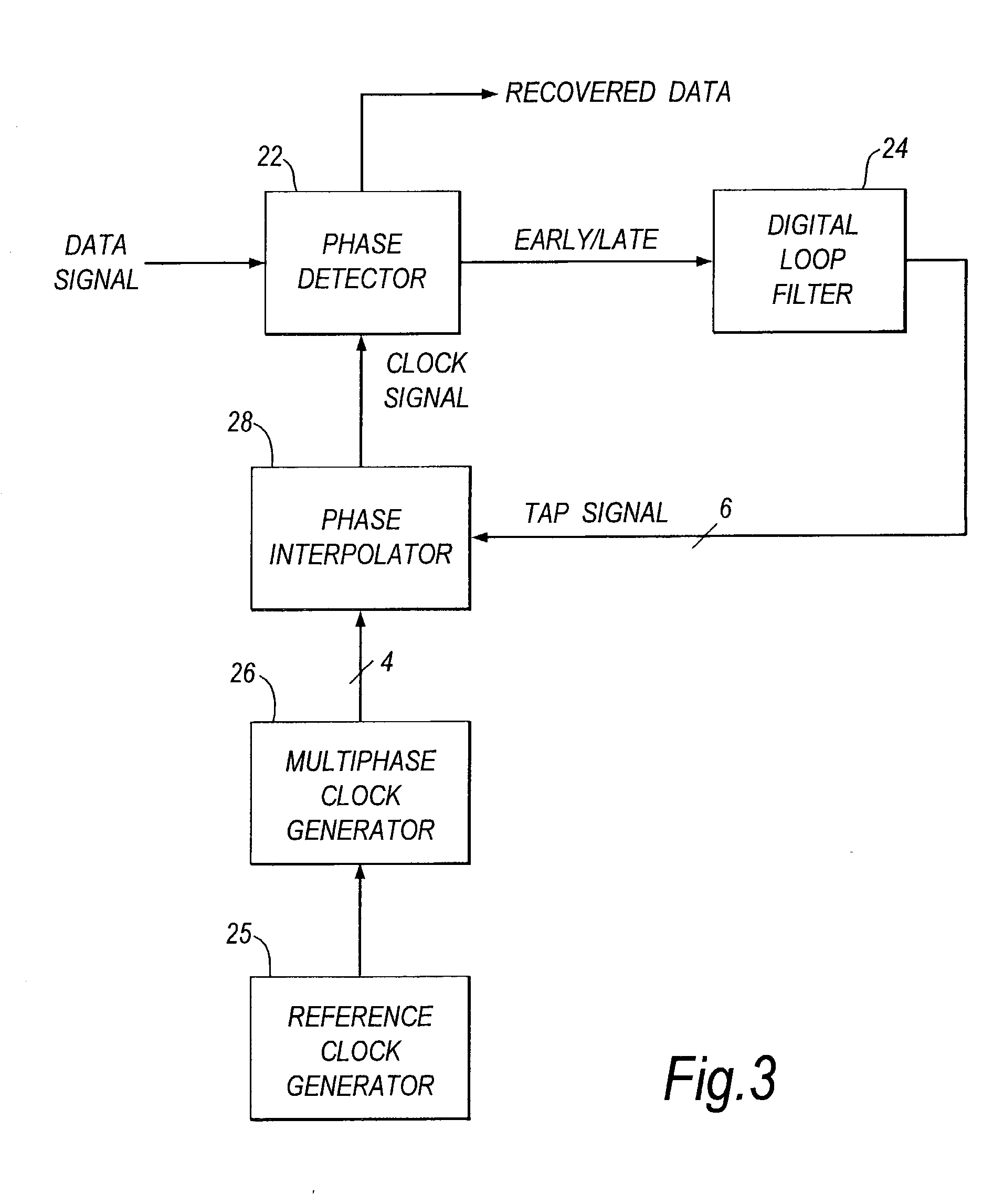

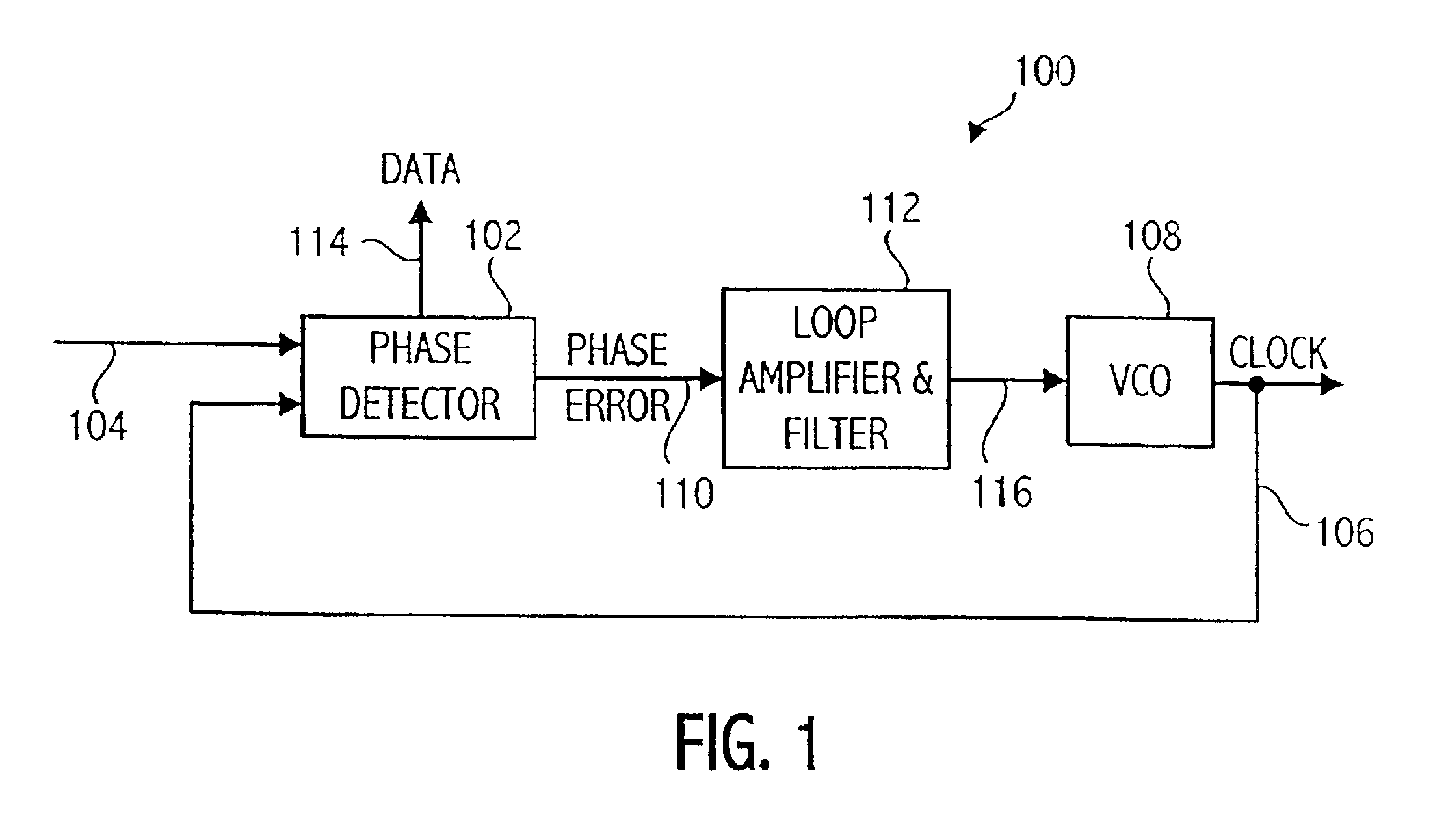

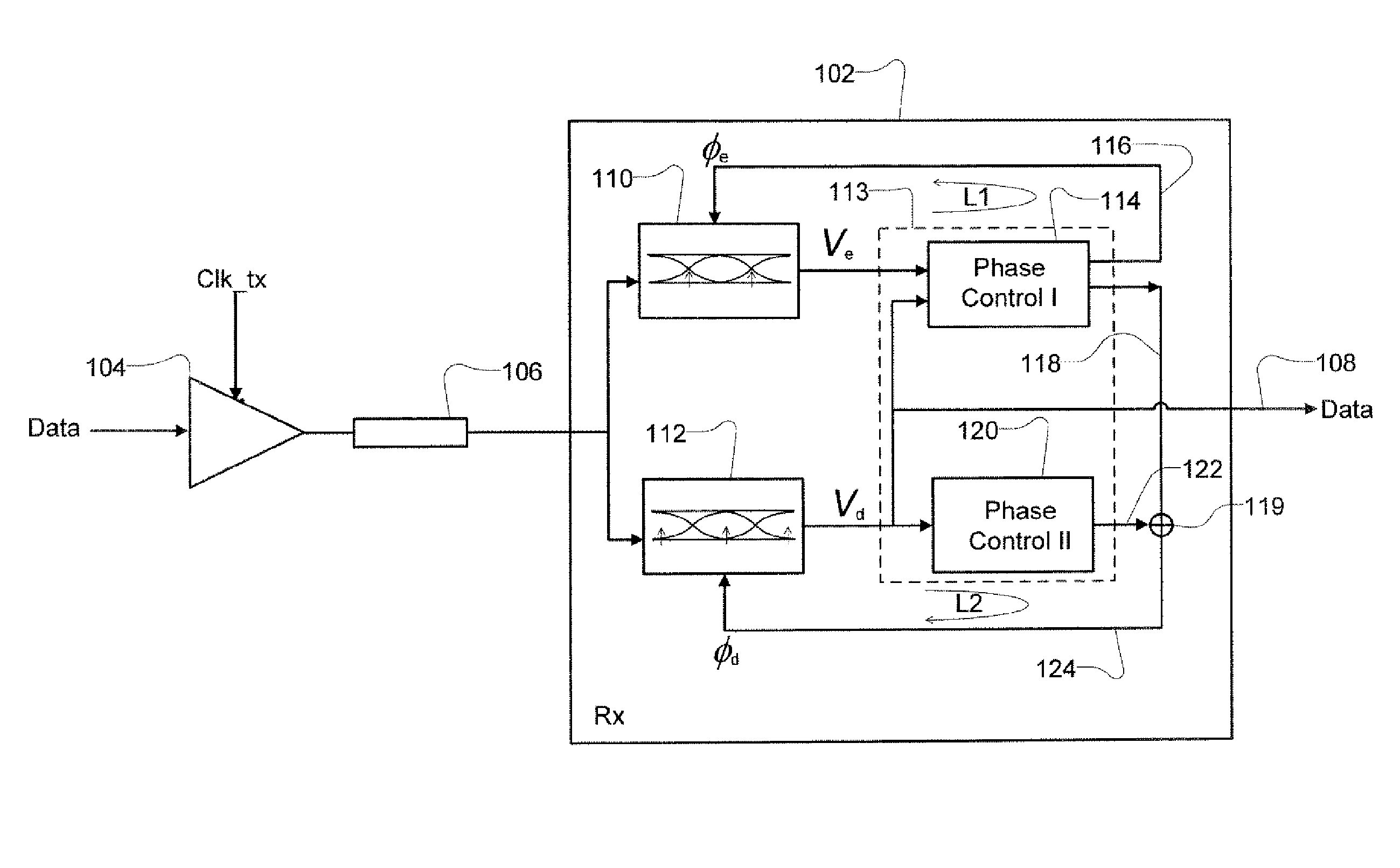

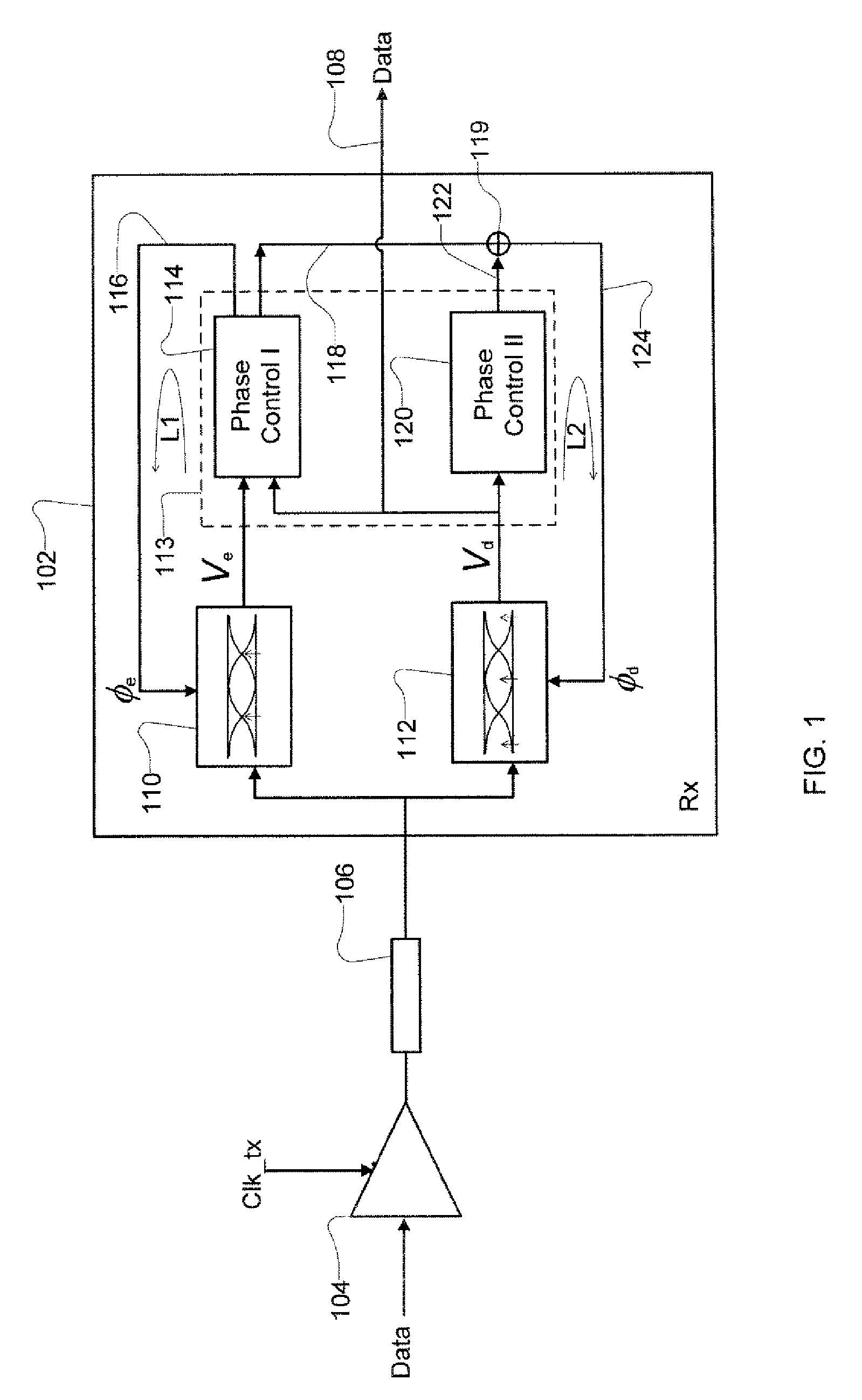

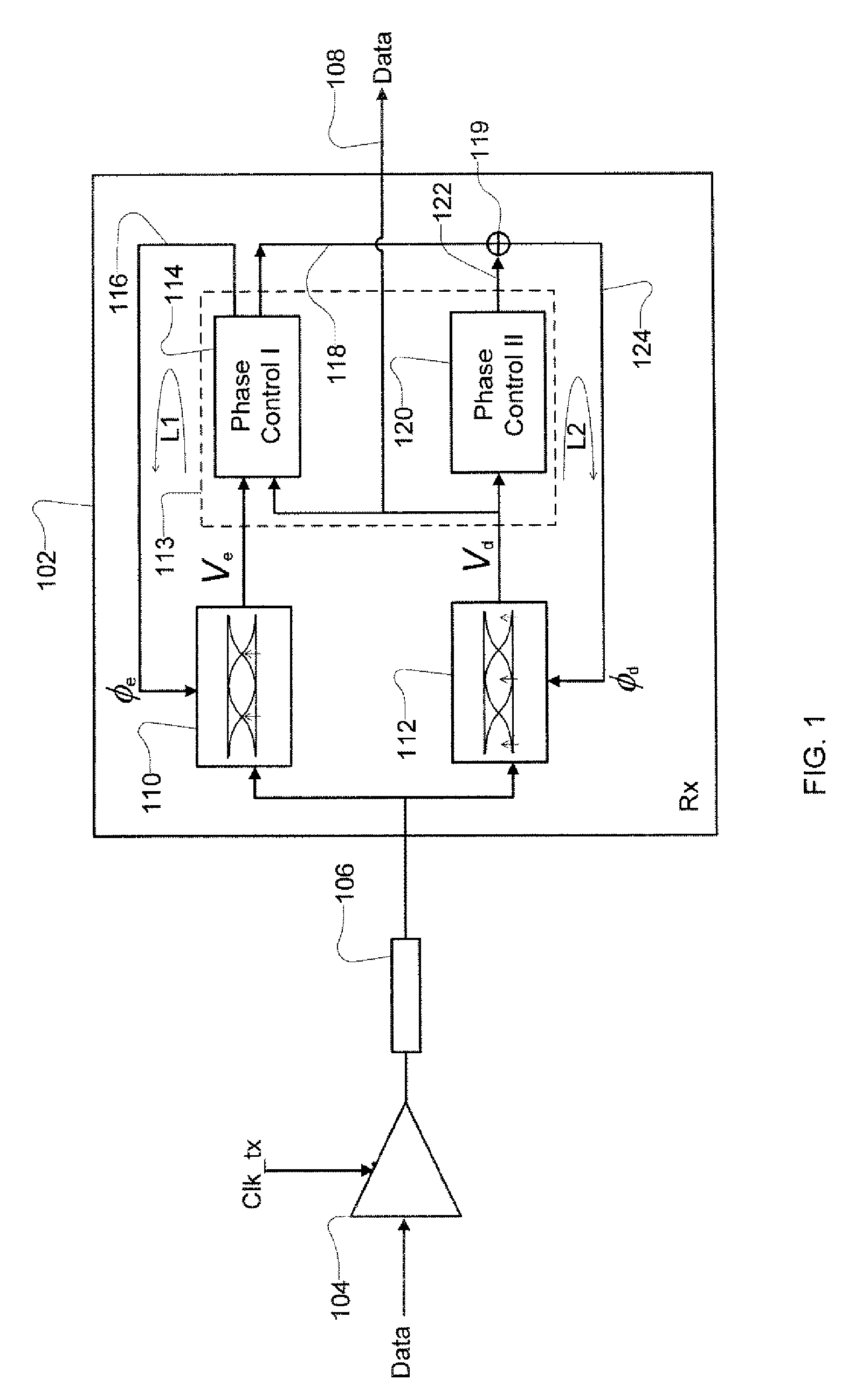

Receiver with enhanced clock and data recovery

ActiveUS8929496B2Receiver initialisationSynchronisation error correctionData transformationBang bang phase detector

A receiver device implements enhanced data reception with edge-based clock and data recovery such as with a flash analog-to-digital converter architecture. In an example embodiment, the device implements a first phase adjustment control loop, with for example, a bang-bang phase detector, that detects data transitions for adjusting sampling at an optimal edge time with an edge sampler by adjusting a phase of an edge clock of the sampler. This loop may further adjust sampling in received data intervals for optimal data reception by adjusting the phase of a data clock of a data sampler such a flash ADC. The device may also implement a second phase adjustment control loop with, for example, a baud-rate phase detector, that detects data intervals for further adjusting sampling at an optimal data time with the data sampler.

Owner:RAMBUS INC

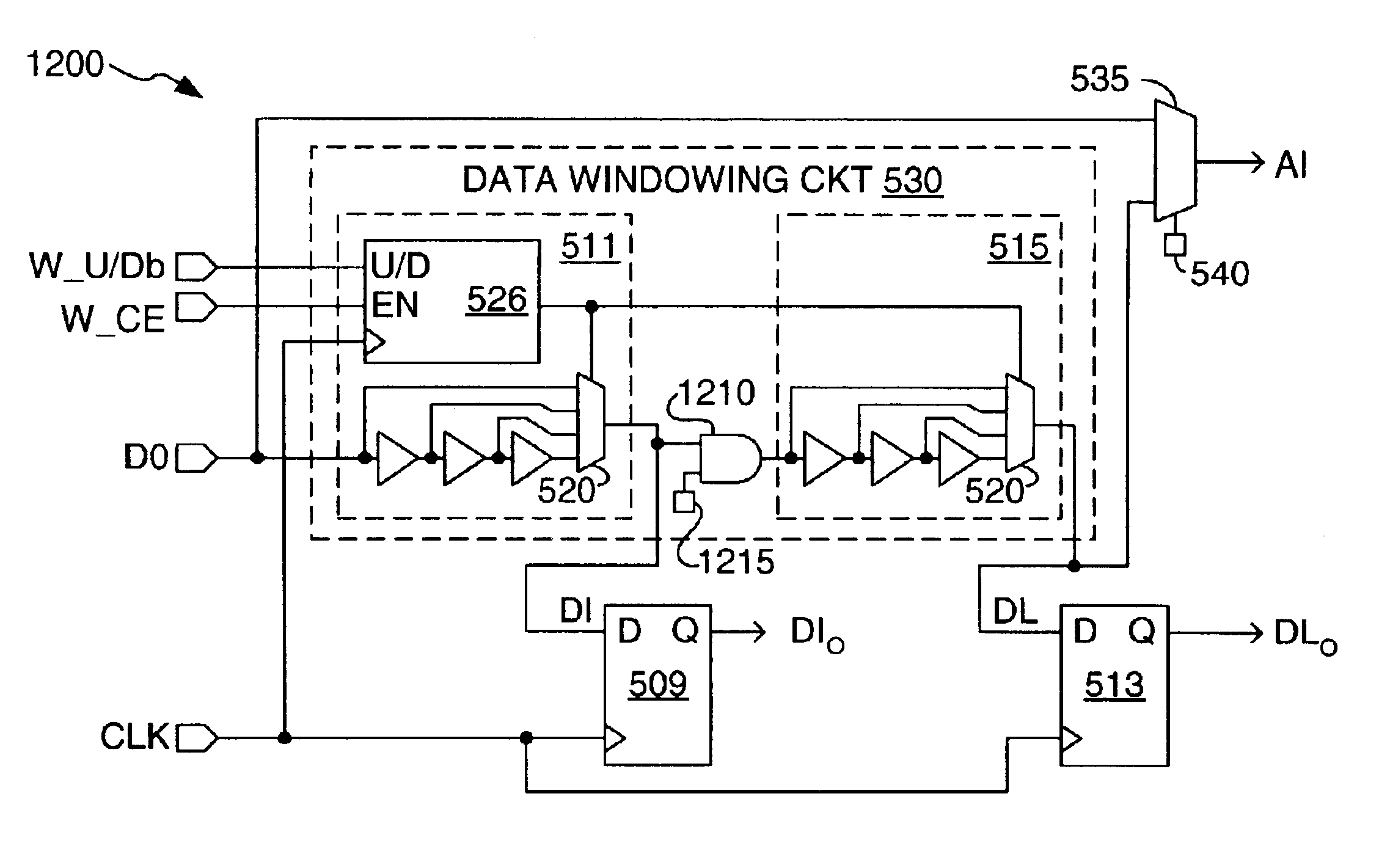

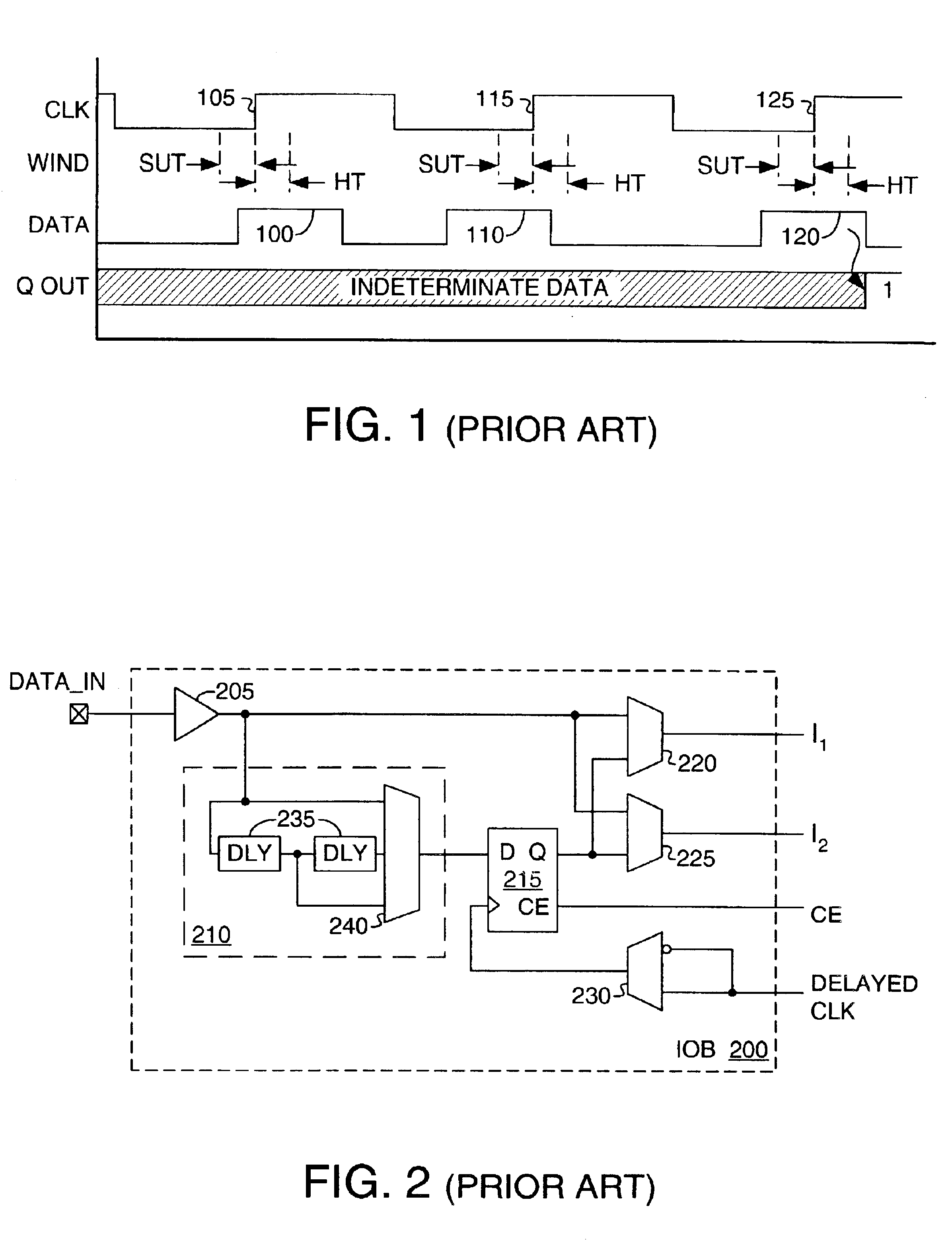

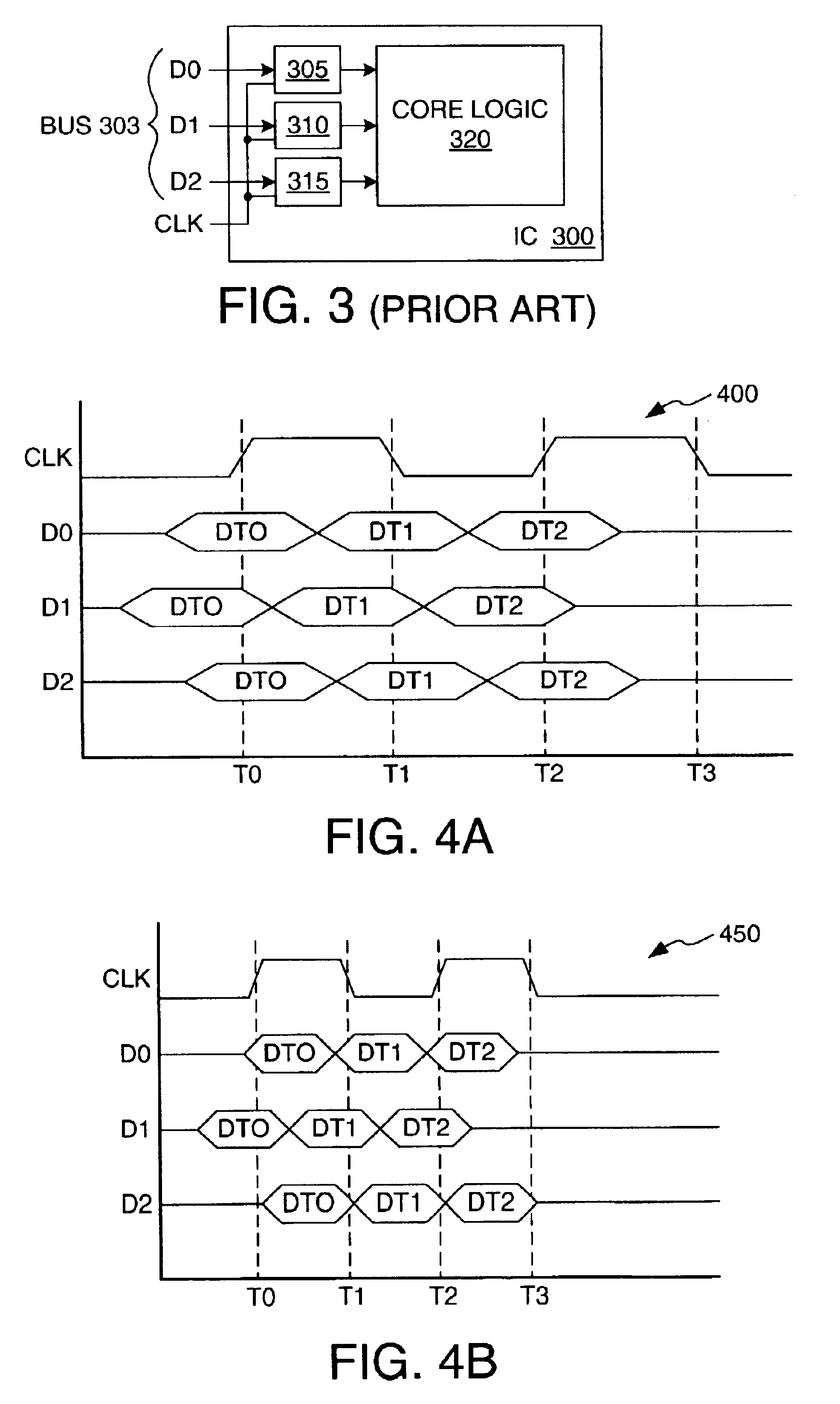

Windowing circuit for aligning data and clock signals

Described are circuits and methods for aligning data and clock signals. Circuits in accordance with some embodiments separate incoming data into three differently timed data signals: an early signal, an intermediate signal, and a late signal. The timing of the three data signals can be collectively moved with respect to the clock signal. In addition, the temporal spacing between the three signals can be adjusted so that the early and late signals define a window encompassing the intermediate signal. The three signals are aligned with respect to the clock edge to center the intermediate data signal on the clock edge. The early and late signals can be monitored to identify changes in the relative timing of the clock and data signals. Some embodiments automatically alter the timing of the data and / or clock signals to keep the intermediate data signal centered on the clock edge.

Owner:XILINX INC

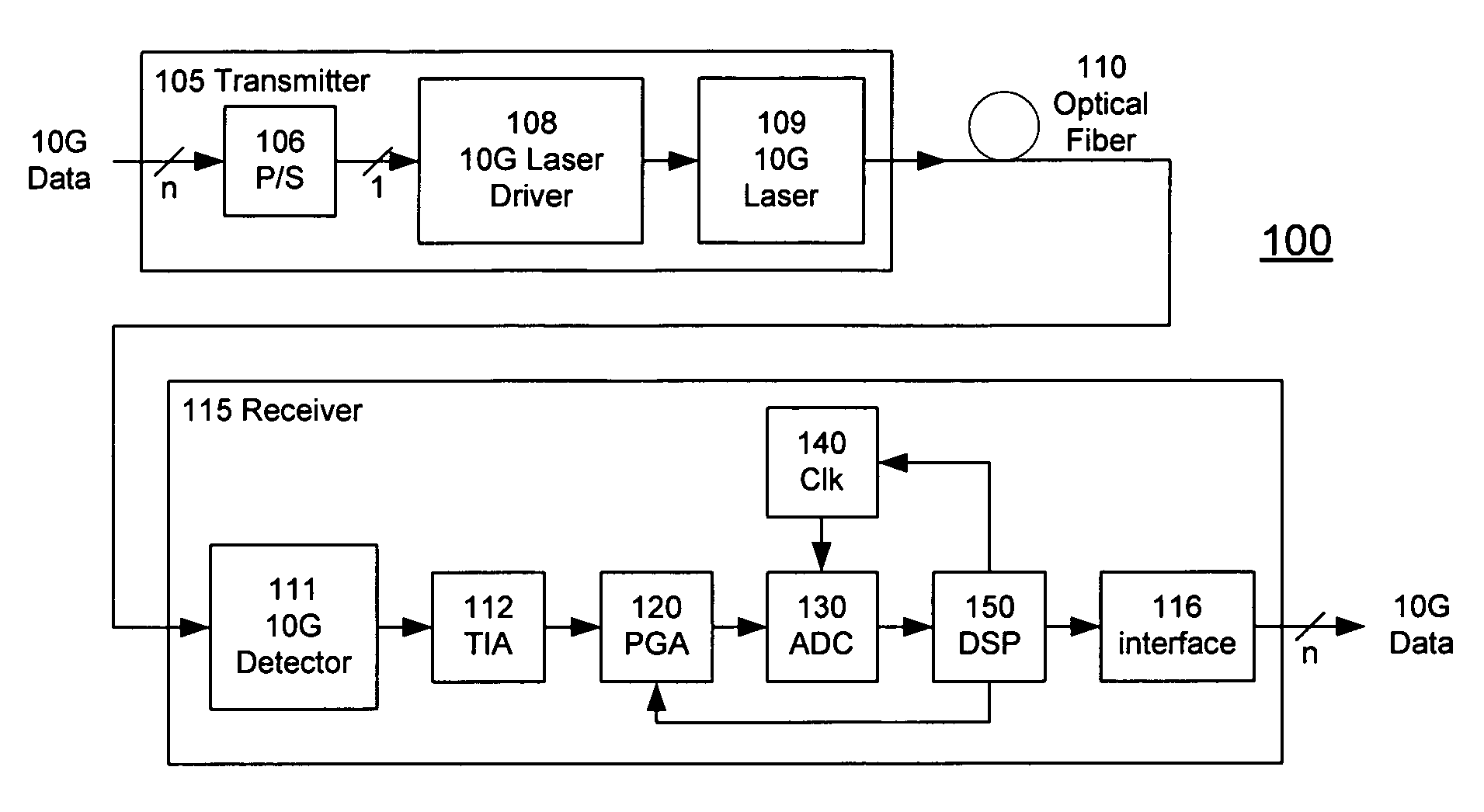

High-Speed Receiver Architecture

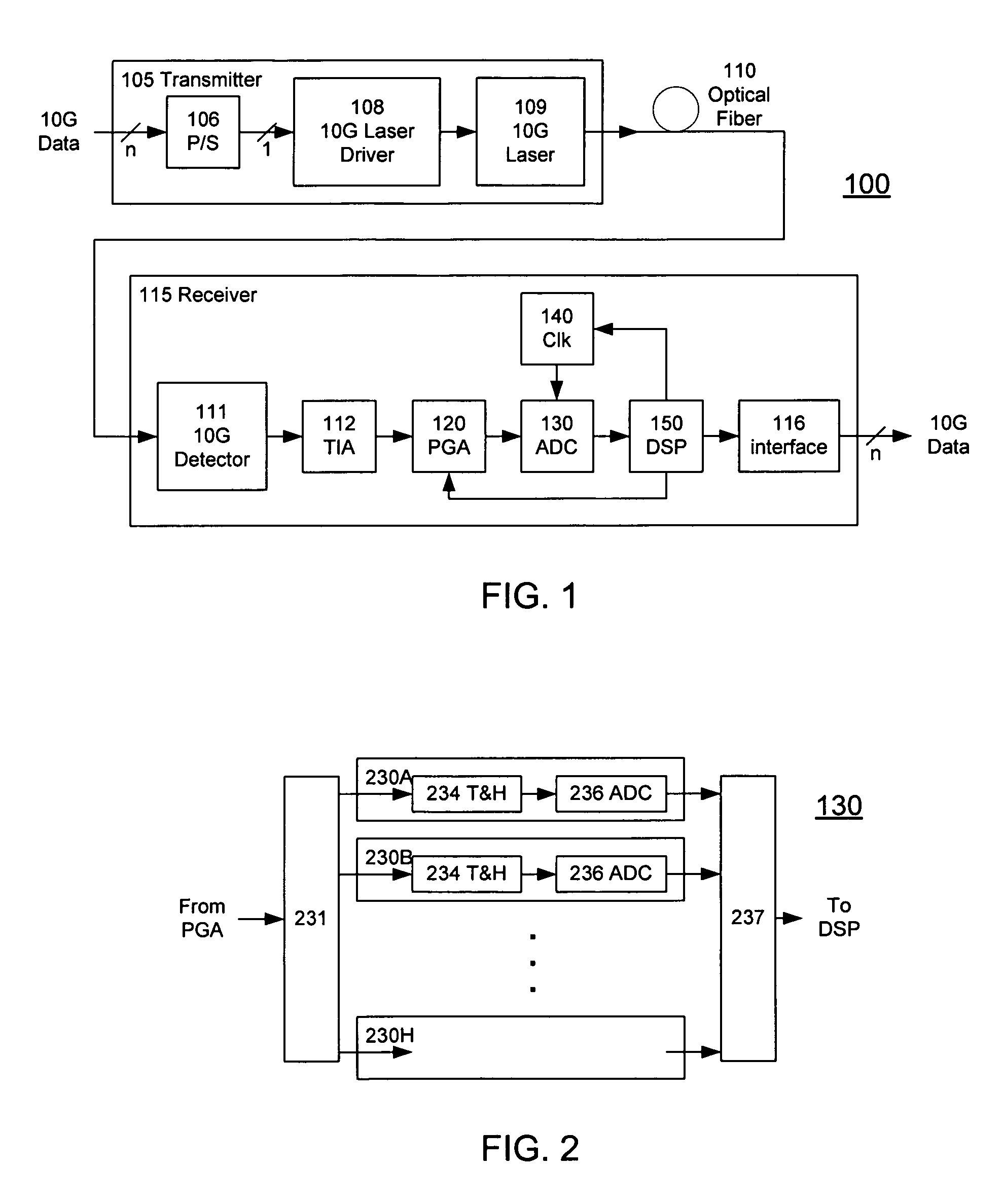

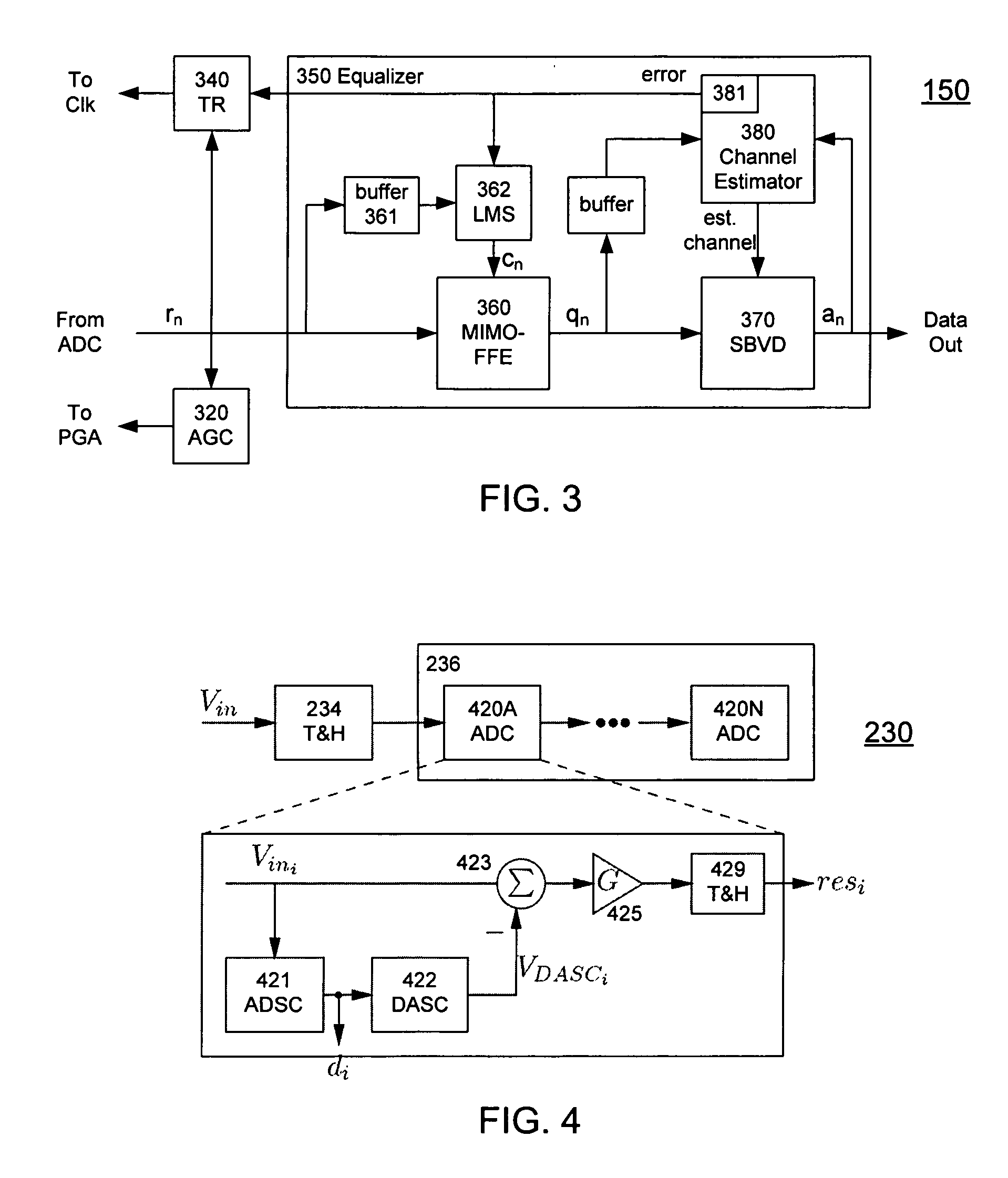

ActiveUS20080240325A1Overcome limitationsLower latencyAnalogue/digital conversionReceiver initialisationViterbi decoderTelecommunications link

A receiver (e.g., for a 10 G fiber communications link) includes an interleaved ADC coupled to a multi-channel equalizer that can provide different equalization for different ADC channels within the interleaved ADC. That is, the multi-channel equalizer can compensate for channel-dependent impairments. In one approach, the multi-channel equalizer is a feedforward equalizer (FFE) coupled to a Viterbi decoder, for example a sliding block Viterbi decoder (SBVD); and the FFE and / or the channel estimator for the Viterbi decoder are adapted using the LMS algorithm.

Owner:MARVELL ASIA PTE LTD

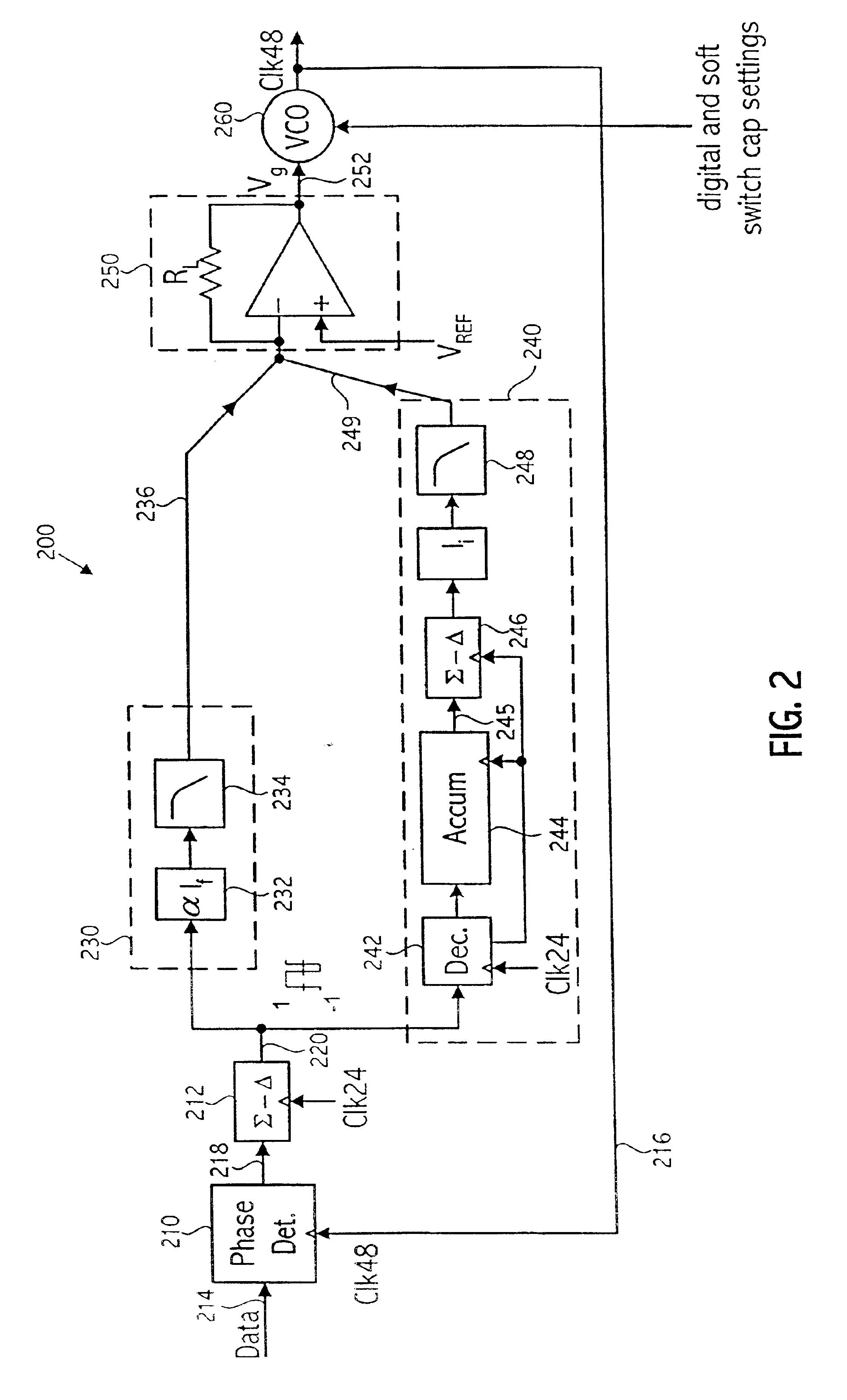

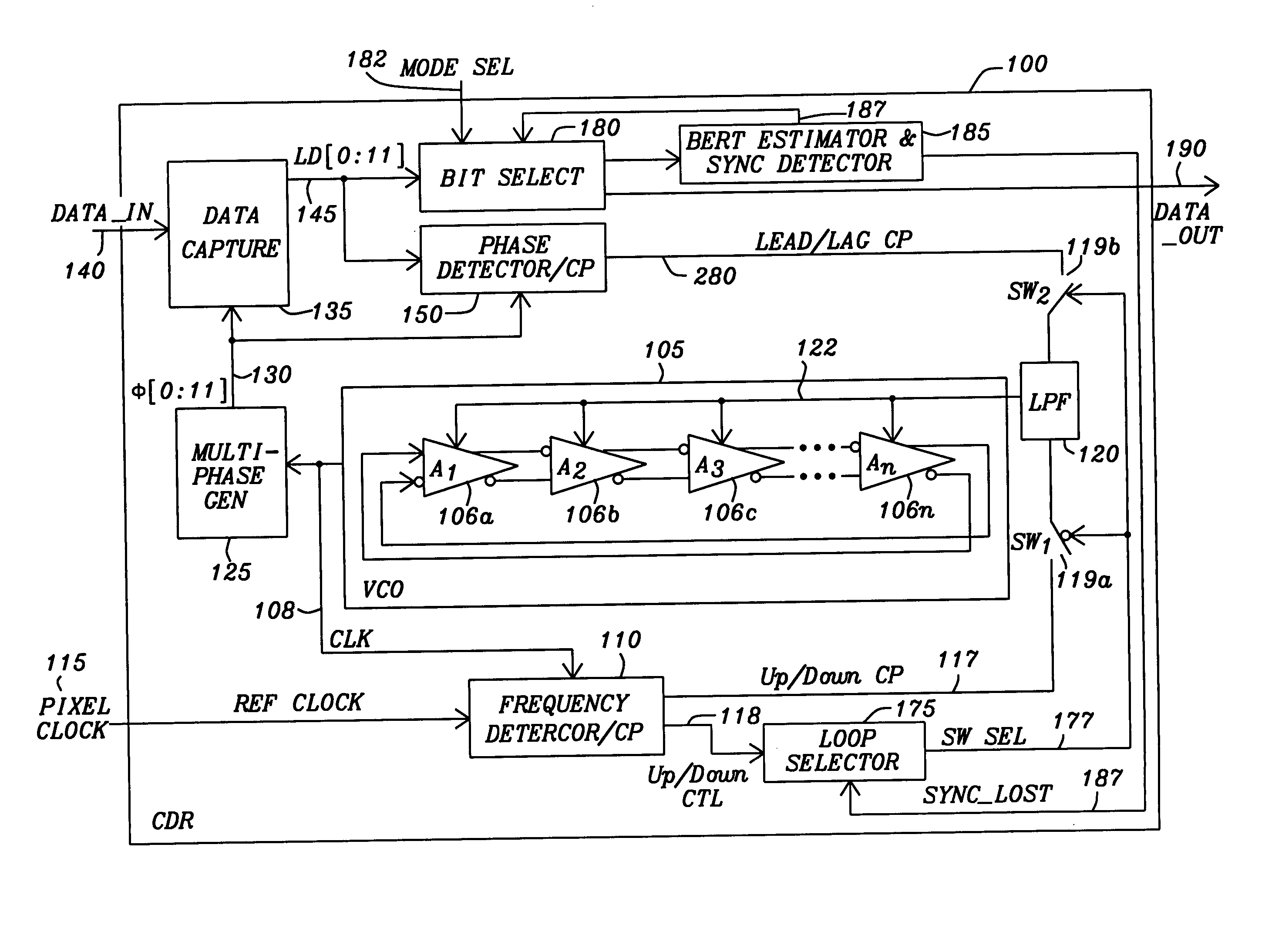

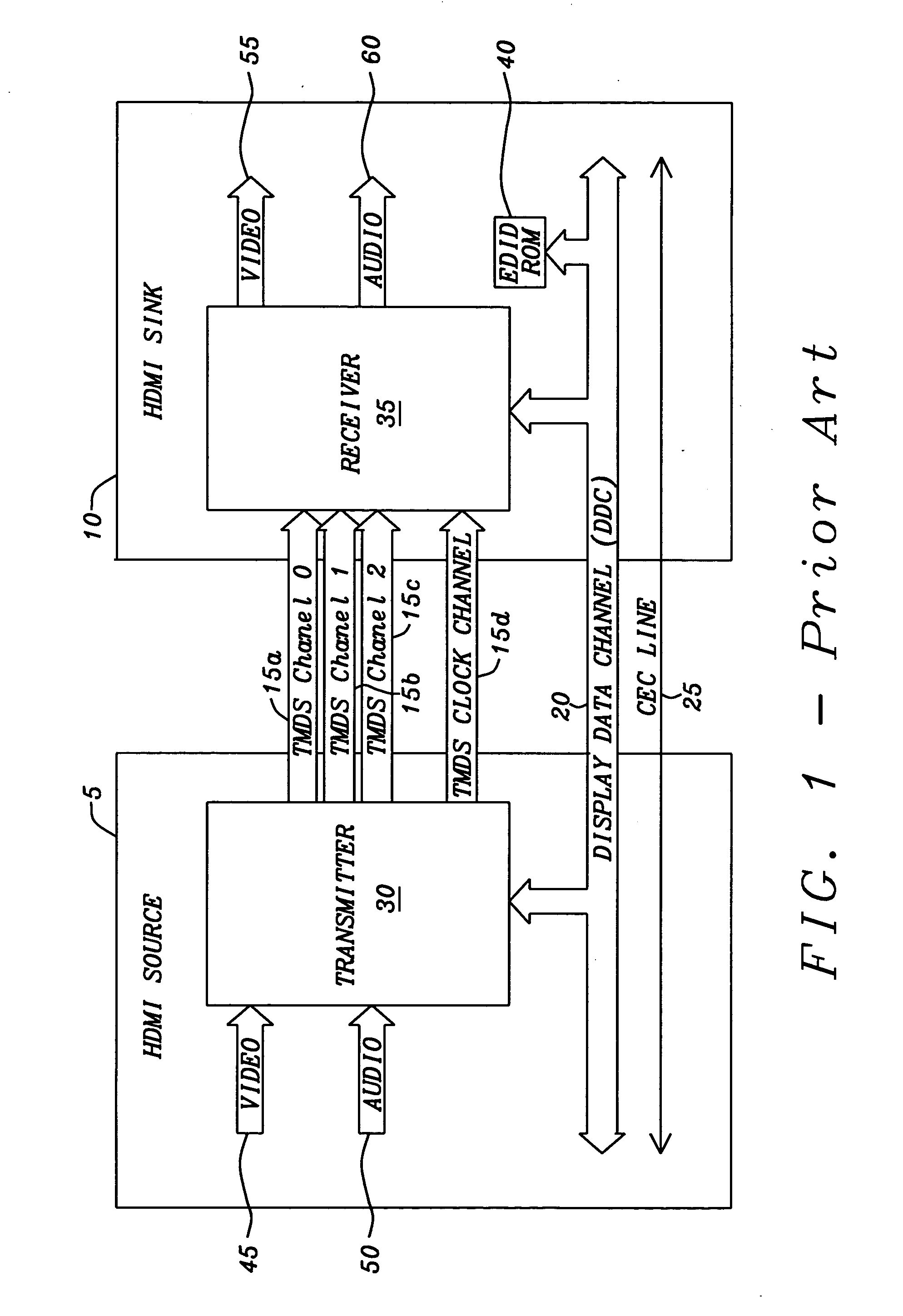

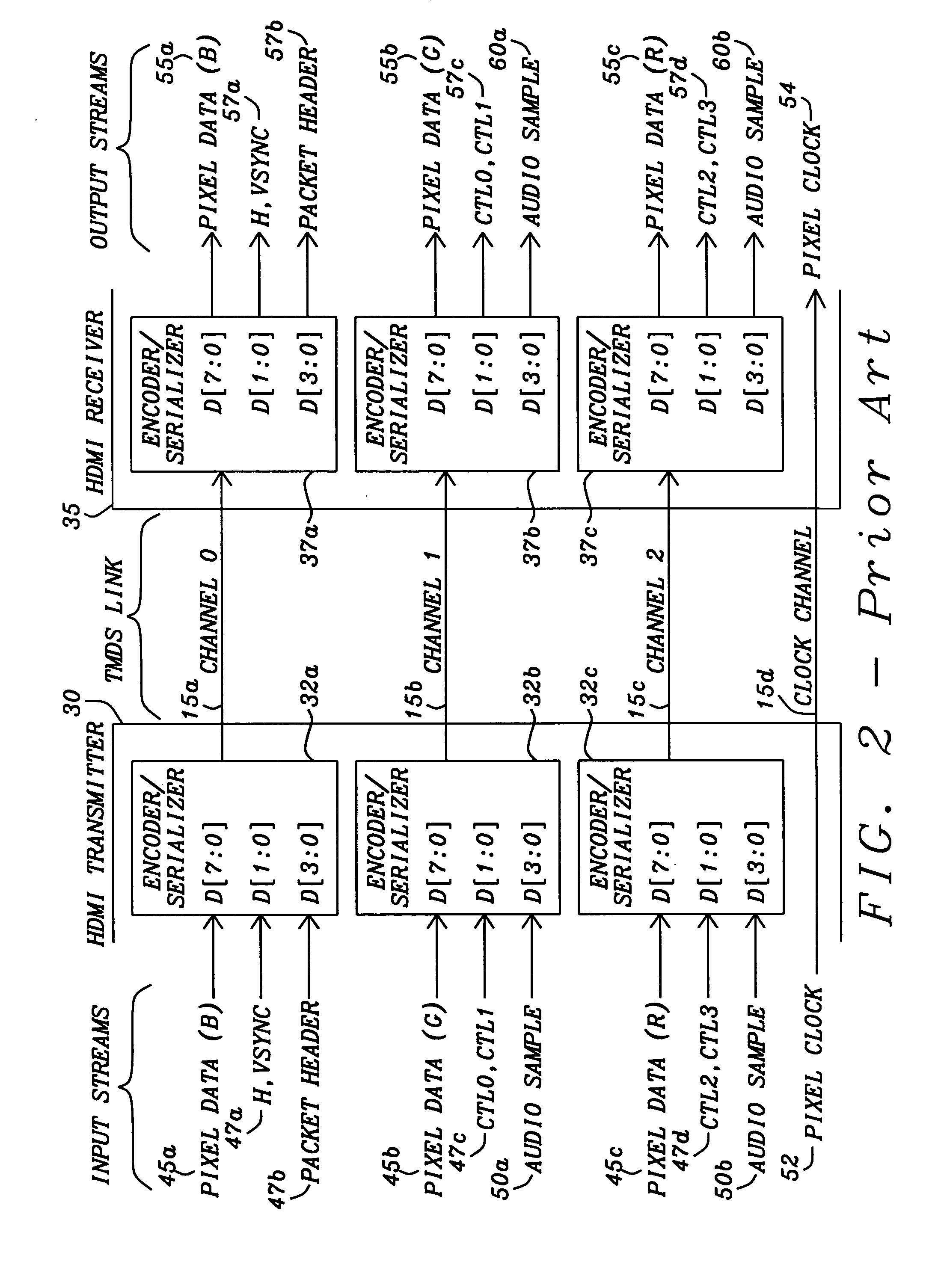

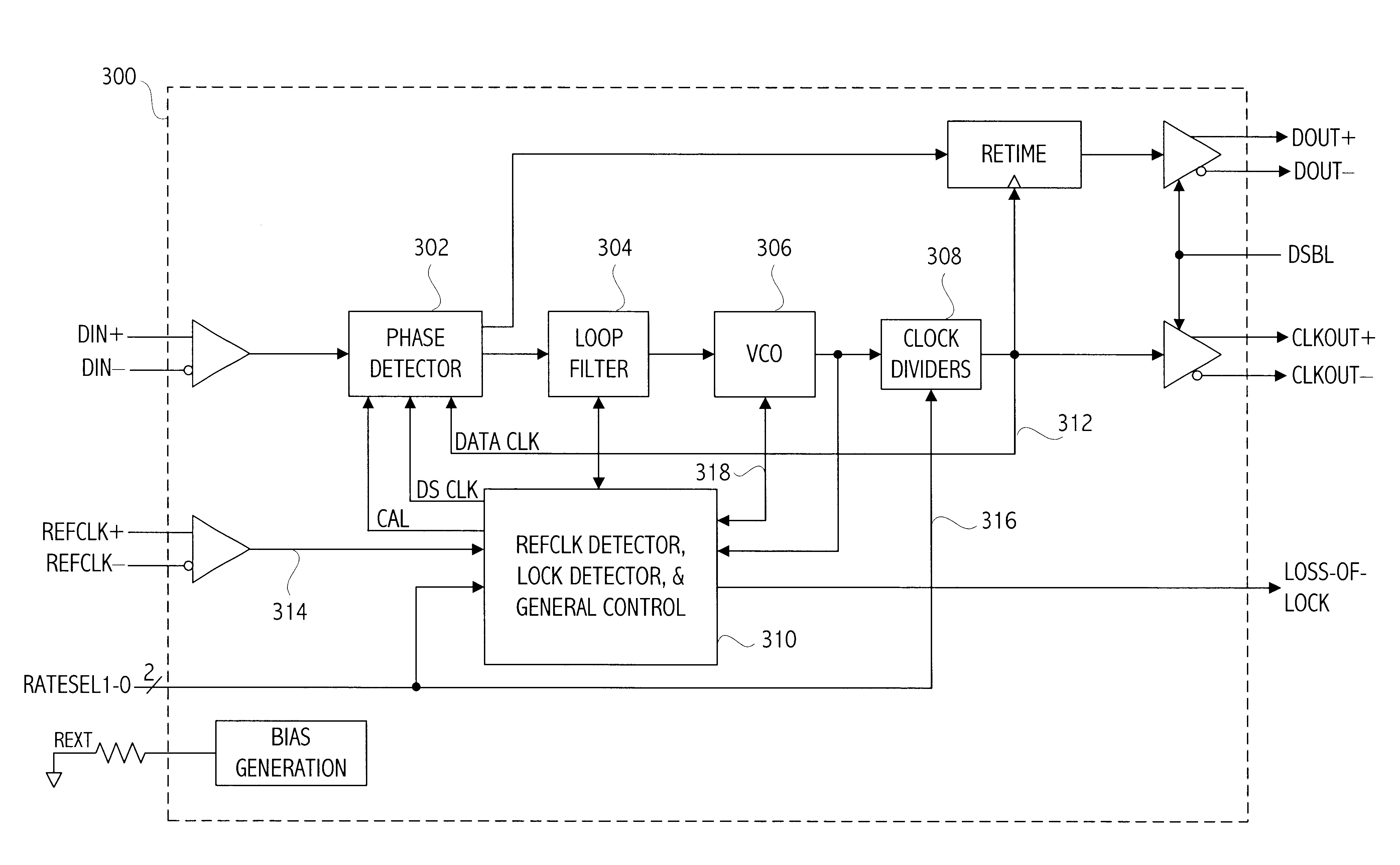

Single-VCO CDR for TMDS data at gigabit rate

InactiveUS20060256909A1Improve toleranceReceiver initialisationSynchronisation information channelsPhase detectorMultiplexer

A clock and data recovery circuit has a voltage controlled oscillator that provides a clocking signal synchronized to a received serialized data. A multiple phase generator converts the clocking signal to a plurality of multiple phased clocking signals. A data capture device acquires the serialized data with each of the plurality of multiple phased clocking signals to create multiple phased data signals. A phase detector determines if the clocking signal is in phase with the recovered serialized data and providing a lead signal and a lag signal indicating whether the clocking signal is in phase with the recovered serialized data. A frequency initializing device assists acquisition of lock of the voltage controlled oscillator to a reference clock signal. A recovered data selector selects which of the multiple phased data signals are to be transferred to external circuitry for further processing.

Owner:KARMIC DESIGN USA

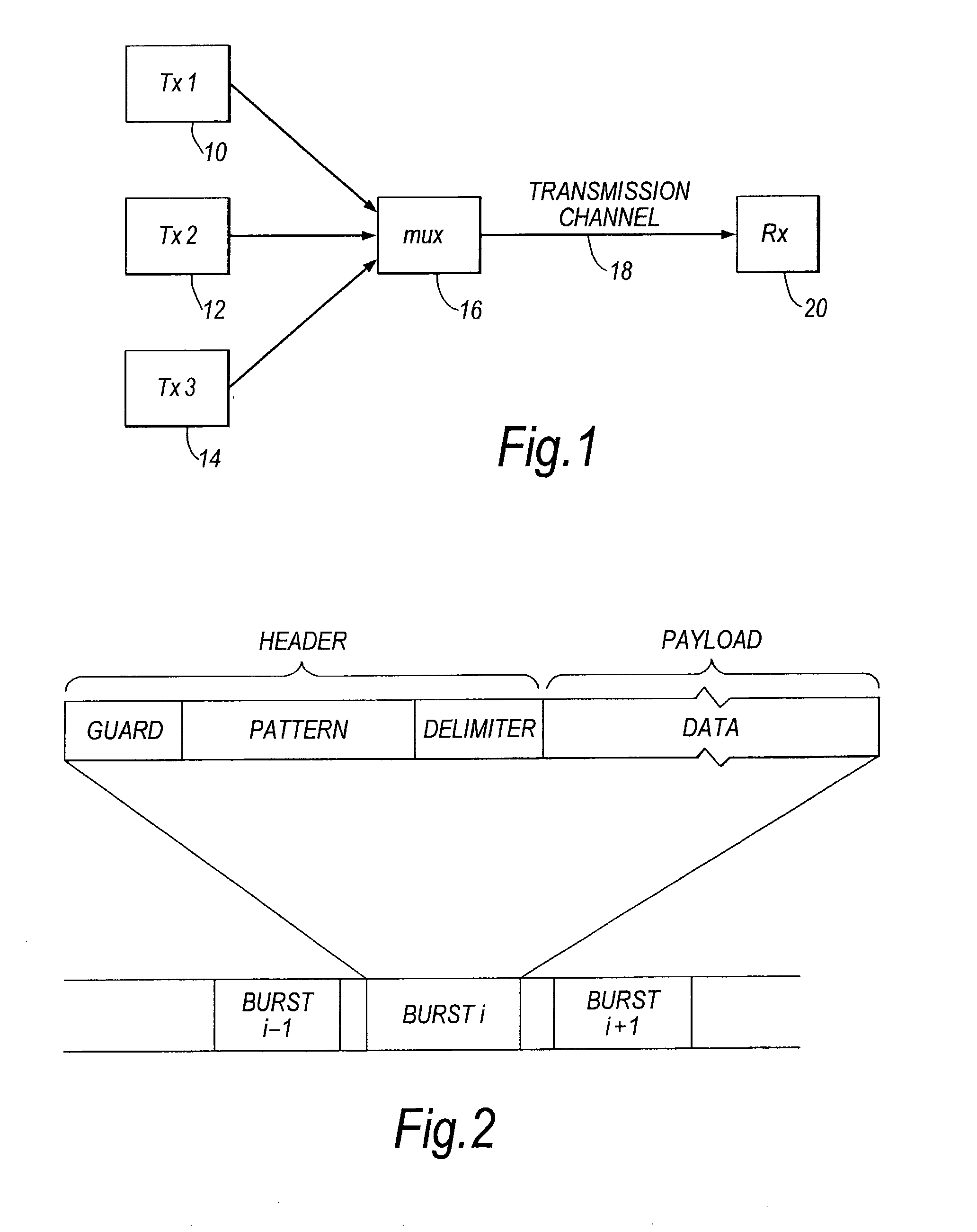

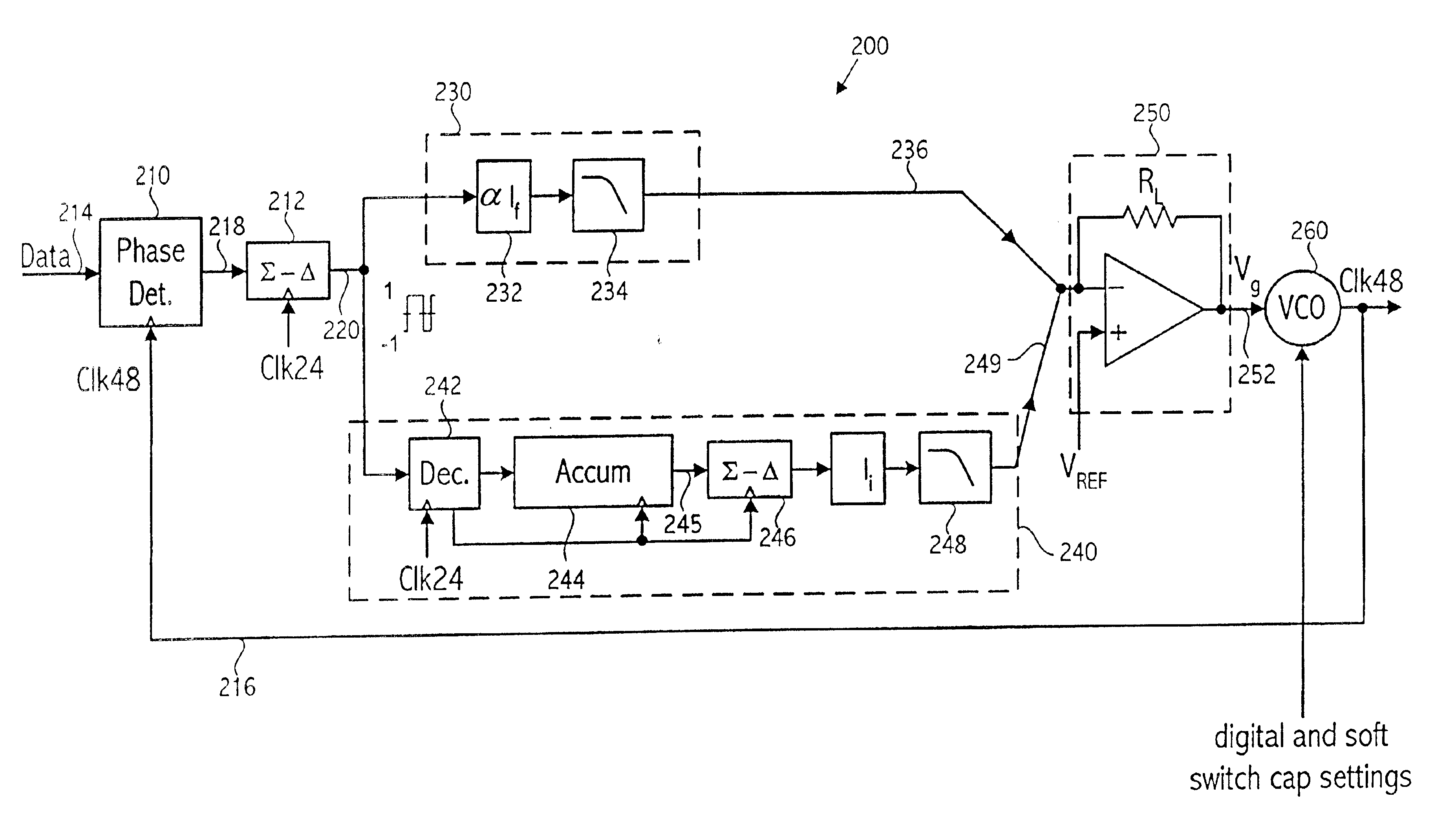

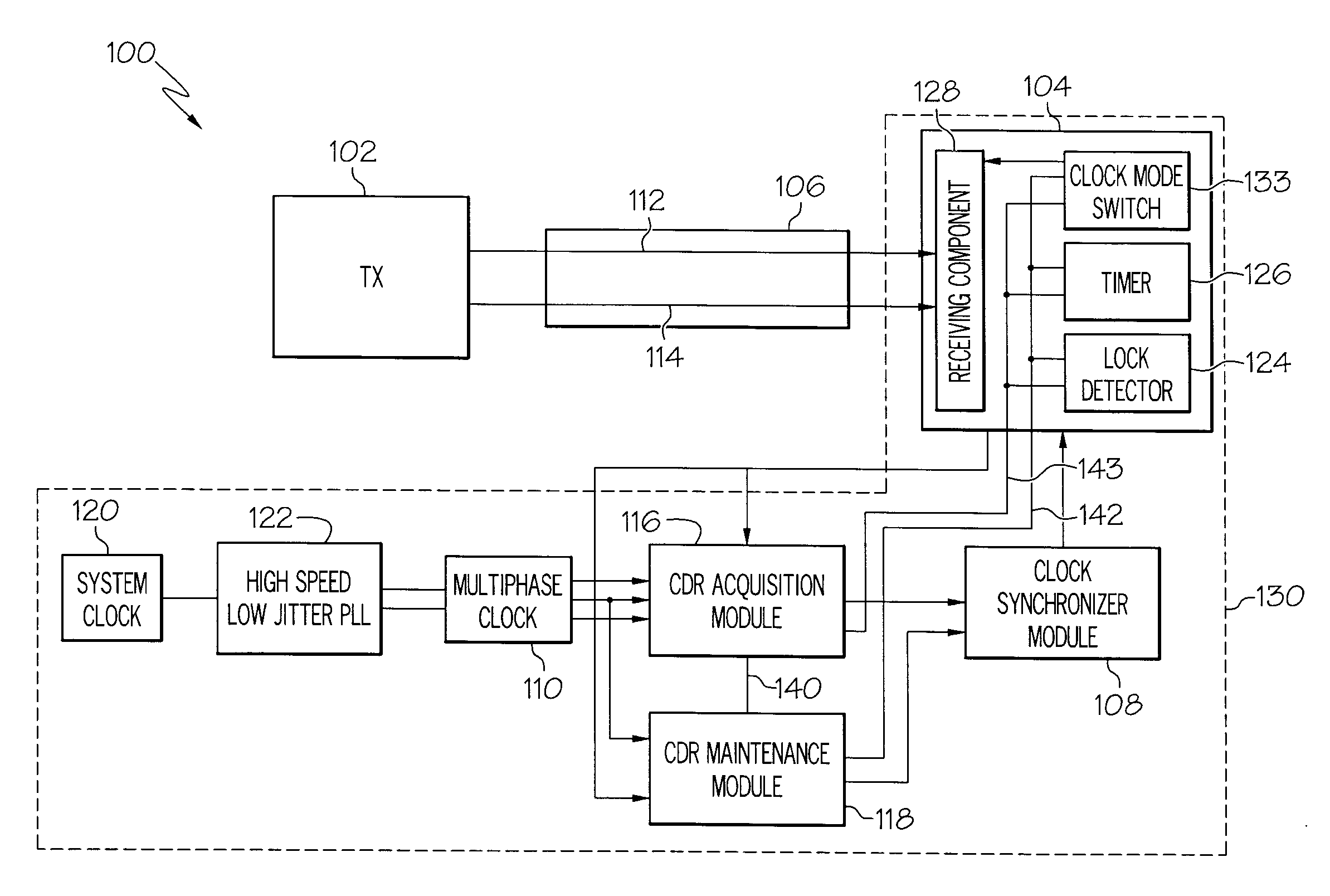

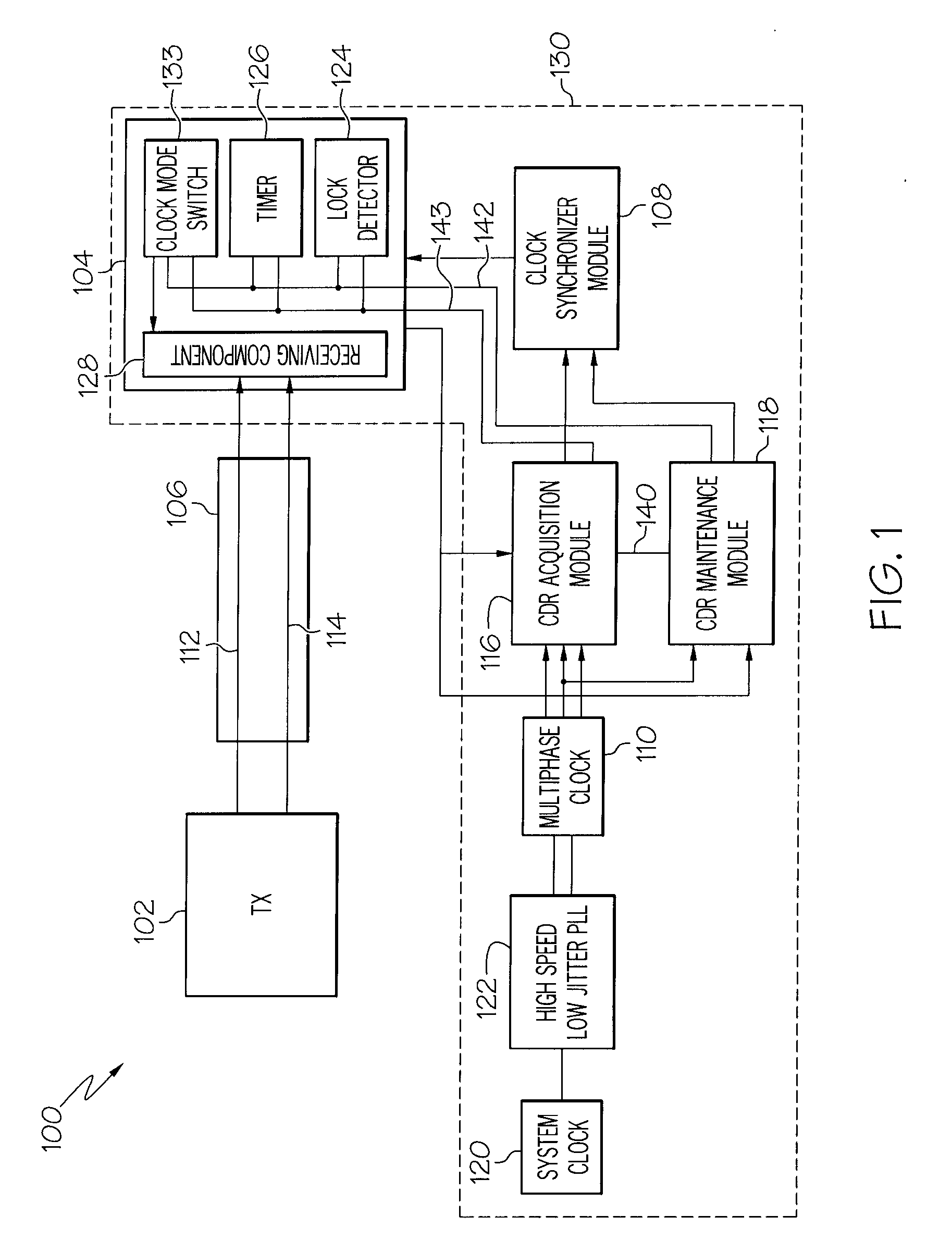

Systems and Arrangements for Clock and Data Recovery in Communications

InactiveUS20080137790A1Low power operationError rateReceiver initialisationTime-division multiplexData streamDual mode

A dual mode clock and data recovery (CDR) system is disclosed. A fast locking, oversampling CDR acquisition module can begin the process to quickly create a data acquisition clock signal in start up data acquisition conditions. When at least some data can be extracted from the incoming data stream, the DRR system can indicate such stability and switch to accept control from a low power CDR maintenance module. The low power CDR maintenance module can then fine tune and maintain the timing of the data acquisition signal. If the quality of the data lock under CDR maintenance module control degrades to a sufficient degree, the high power CDR acquisition module can be re-enables and re-assert control from the low power module until such time as the lock quality is again sufficient for the low power module to be used.

Owner:GLOBALFOUNDRIES INC

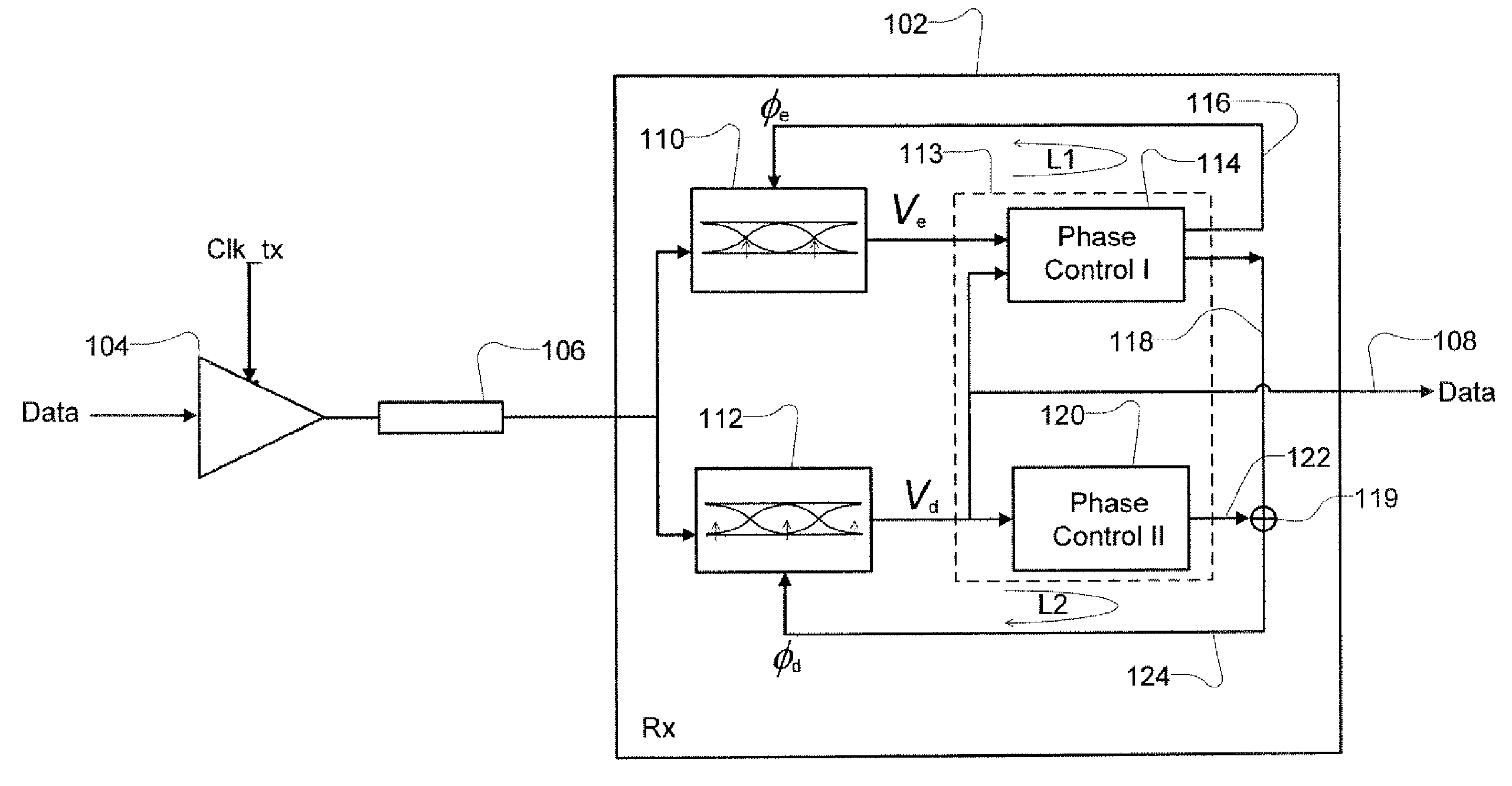

Receiver With Enhanced Clock And Data Recovery

ActiveUS20100289544A1Receiver initialisationSynchronisation error correctionBaudAnalog-to-digital converter

A receiver device implements enhanced data reception with edge-based clock and data recovery such as with a flash analog-to-digital converter architecture. In an example embodiment, the device implements a first phase adjustment control loop, with for example, a bang-bang phase detector, that detects data transitions for adjusting sampling at an optimal edge time with an edge sampler by adjusting a phase of an edge clock of the sampler. This loop may further adjust sampling in received data intervals for optimal data reception by adjusting the phase of a data clock of a data sampler such a flash ADC. The device may also implement a second phase adjustment control loop with, for example, a baud-rate phase detector, that detects data intervals for further adjusting sampling at an optimal data time with the data sampler.

Owner:RAMBUS INC

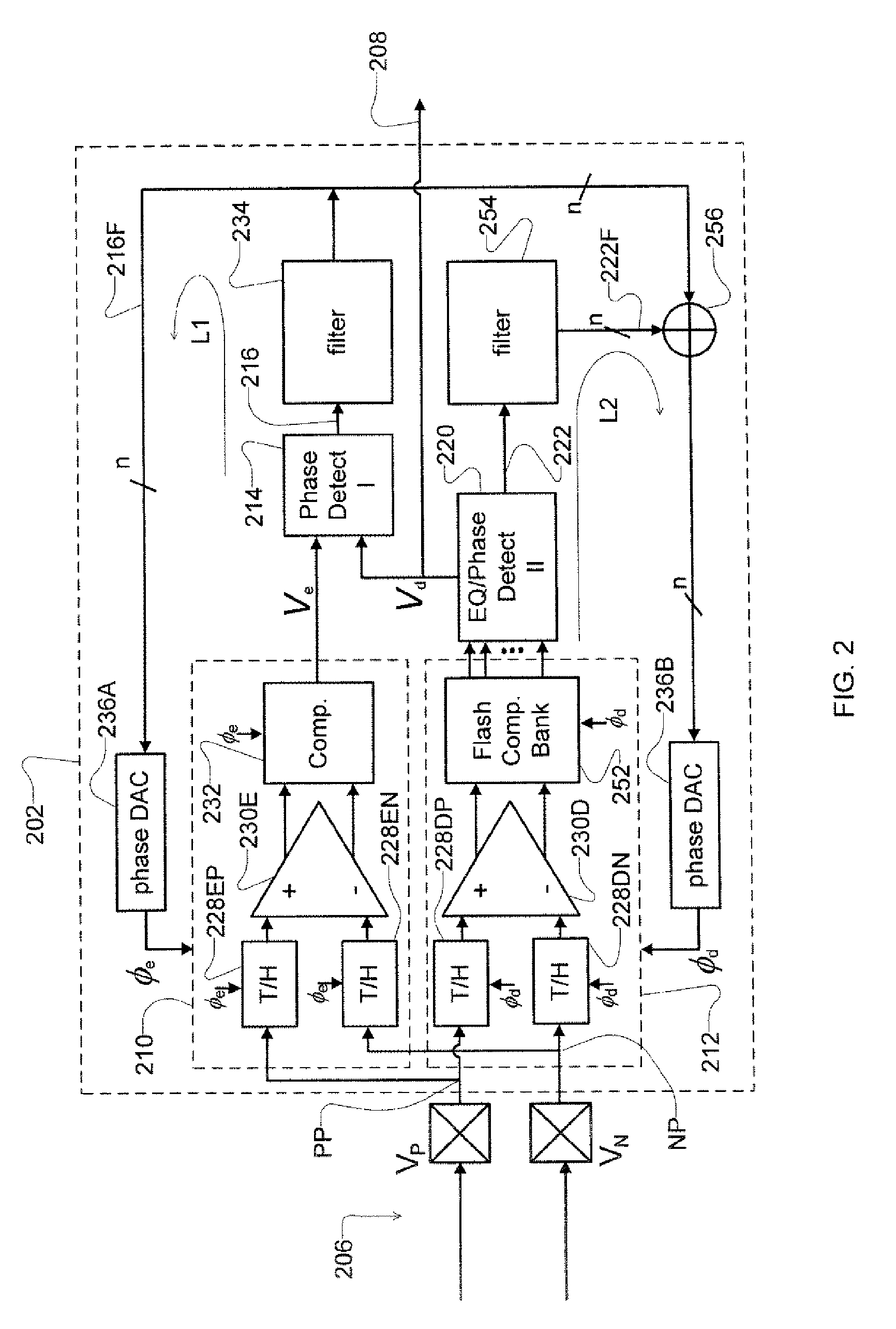

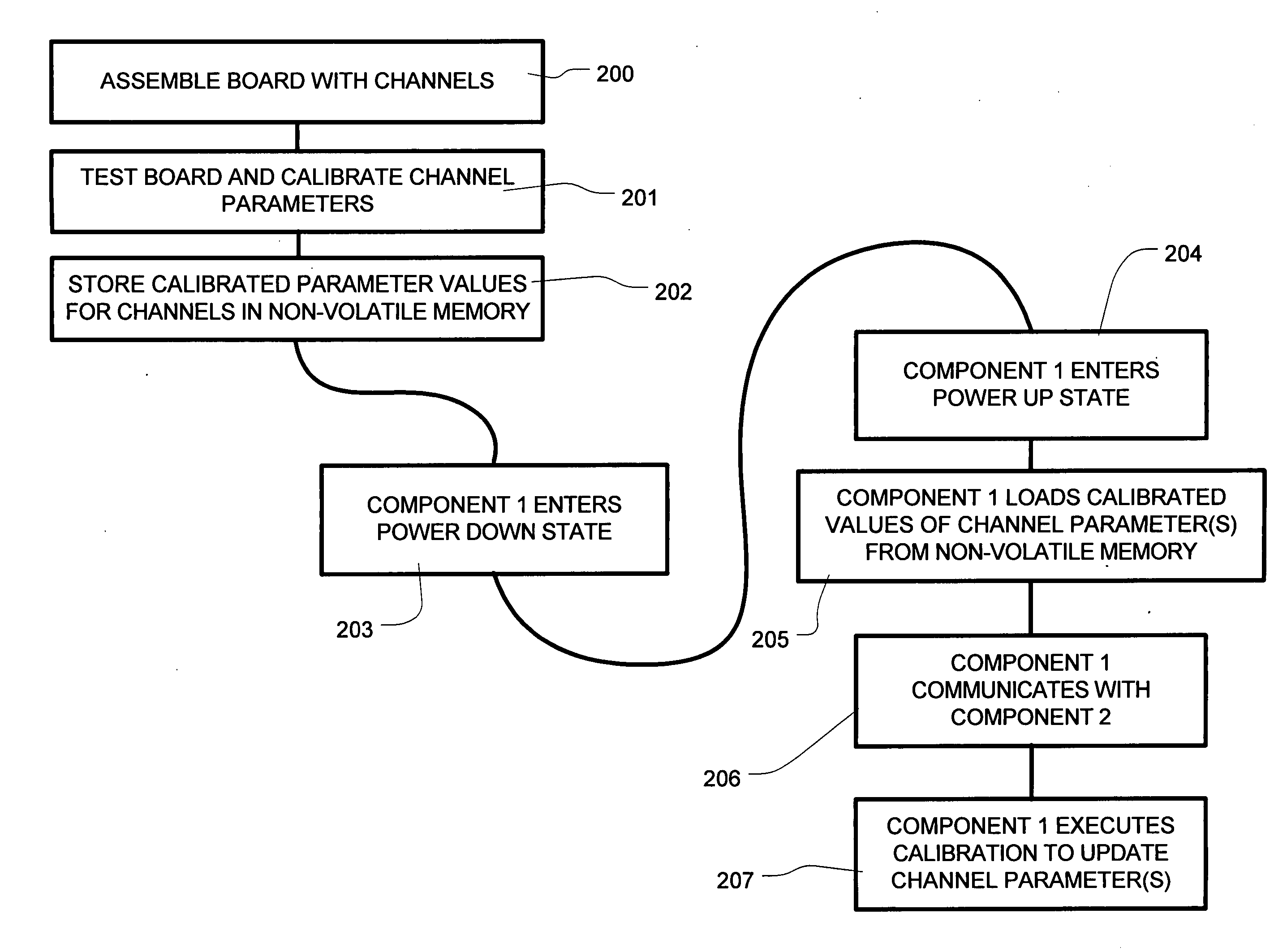

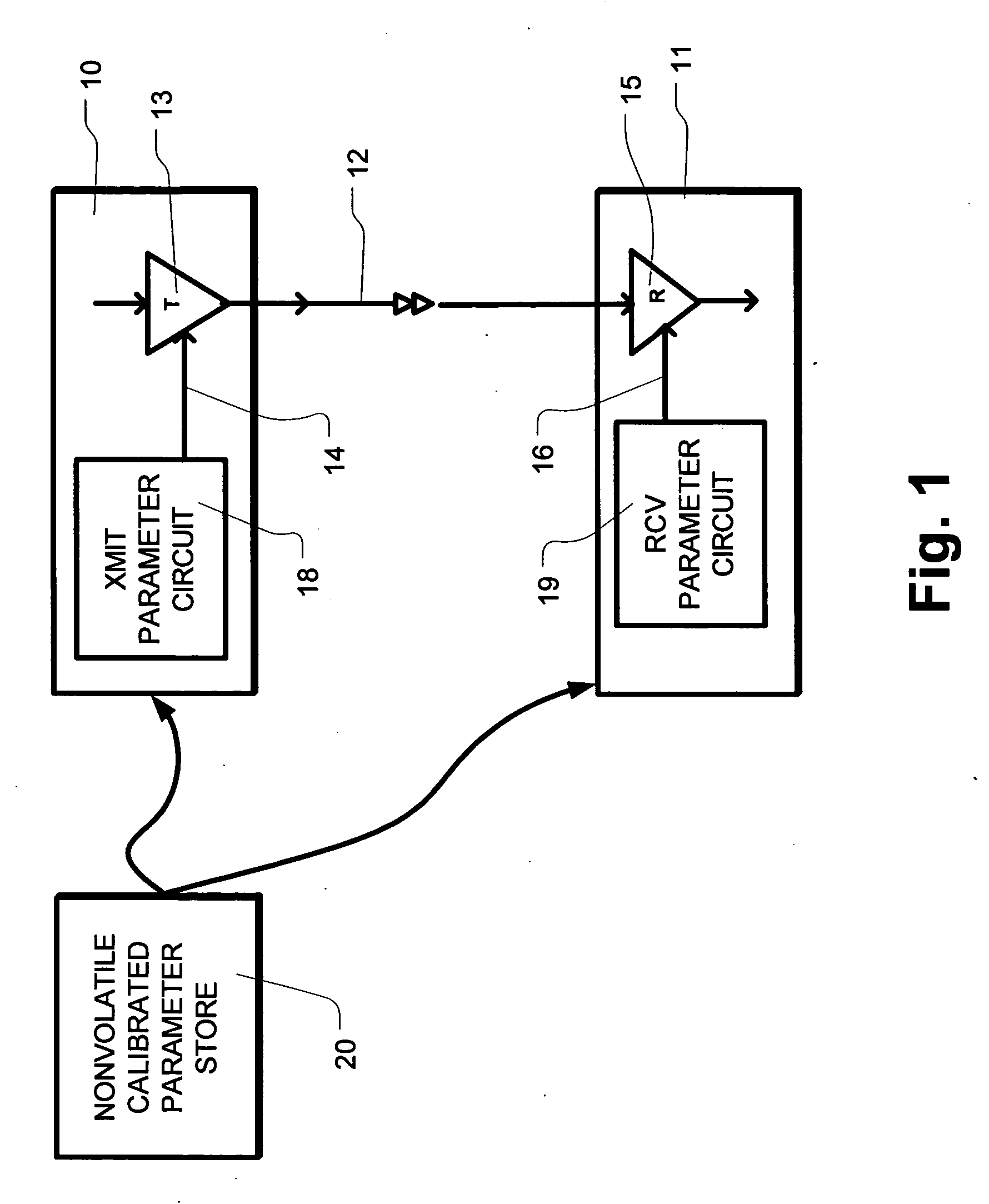

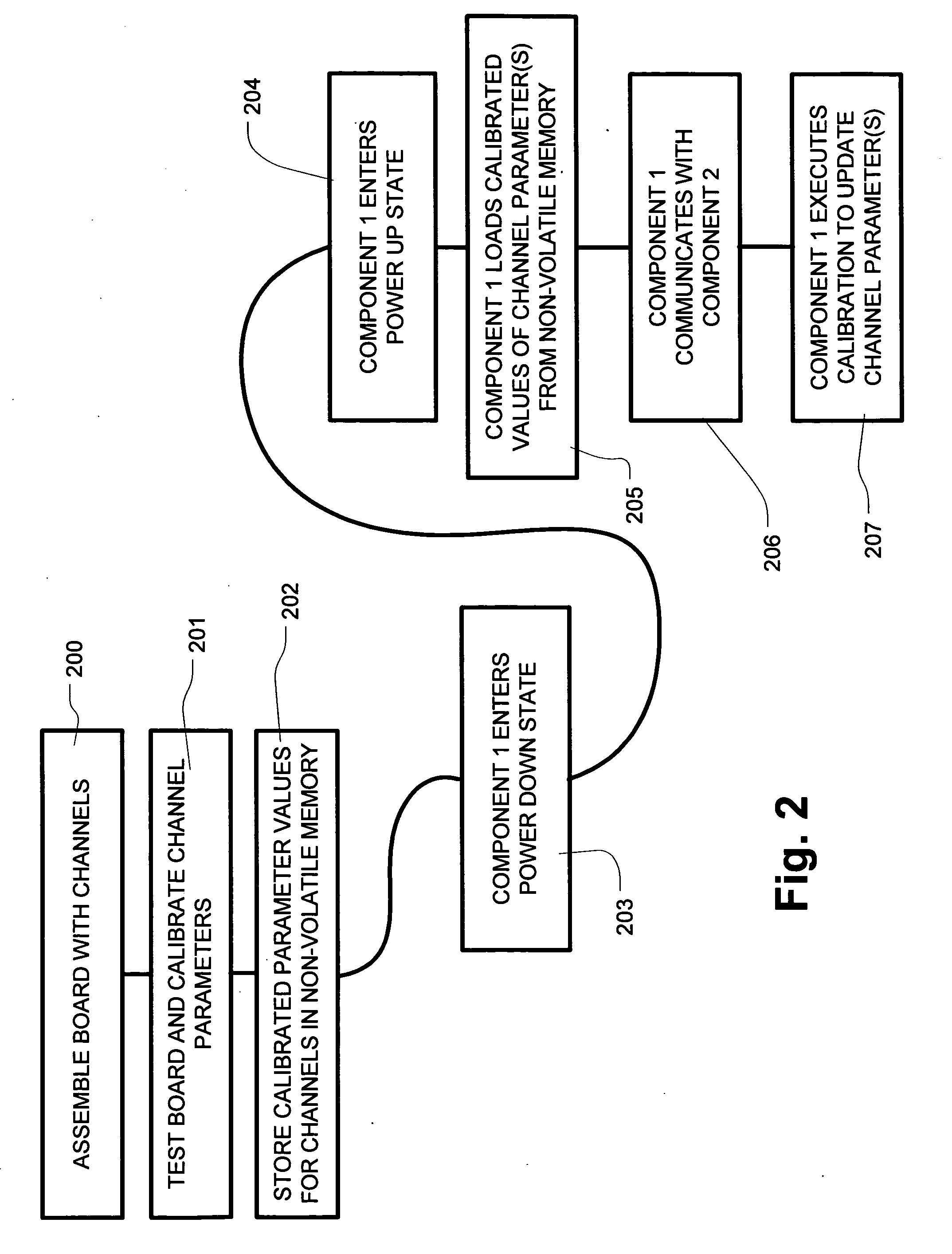

Communication channel calibration with nonvolatile parameter store for recovery

ActiveUS20050265437A1Communicating data very quicklyFast communicationThermometer detailsThermometers using material expansion/contactionComputer scienceStart up

A communication channel is operated by storing a calibrated parameter value in nonvolatile memory during manufacturing, testing, or during a first operation of the device. Upon starting operation of the communication channel in the field, the calibrated parameter value is obtained from the nonvolatile memory, and used in applying an operating parameter of the communication channel. After applying the operating parameter, communication is initiated on a communication channel. The operating parameter can be adjusted to account for drift immediately after starting up, or periodically. The process of starting operation in the field includes power up events after a power management operation. In embodiments where one component includes memory, steps can be taken prior to a power management operation using the communication channel, such as transferring calibration patterns to be used in calibration procedures.

Owner:RAMBUS INC

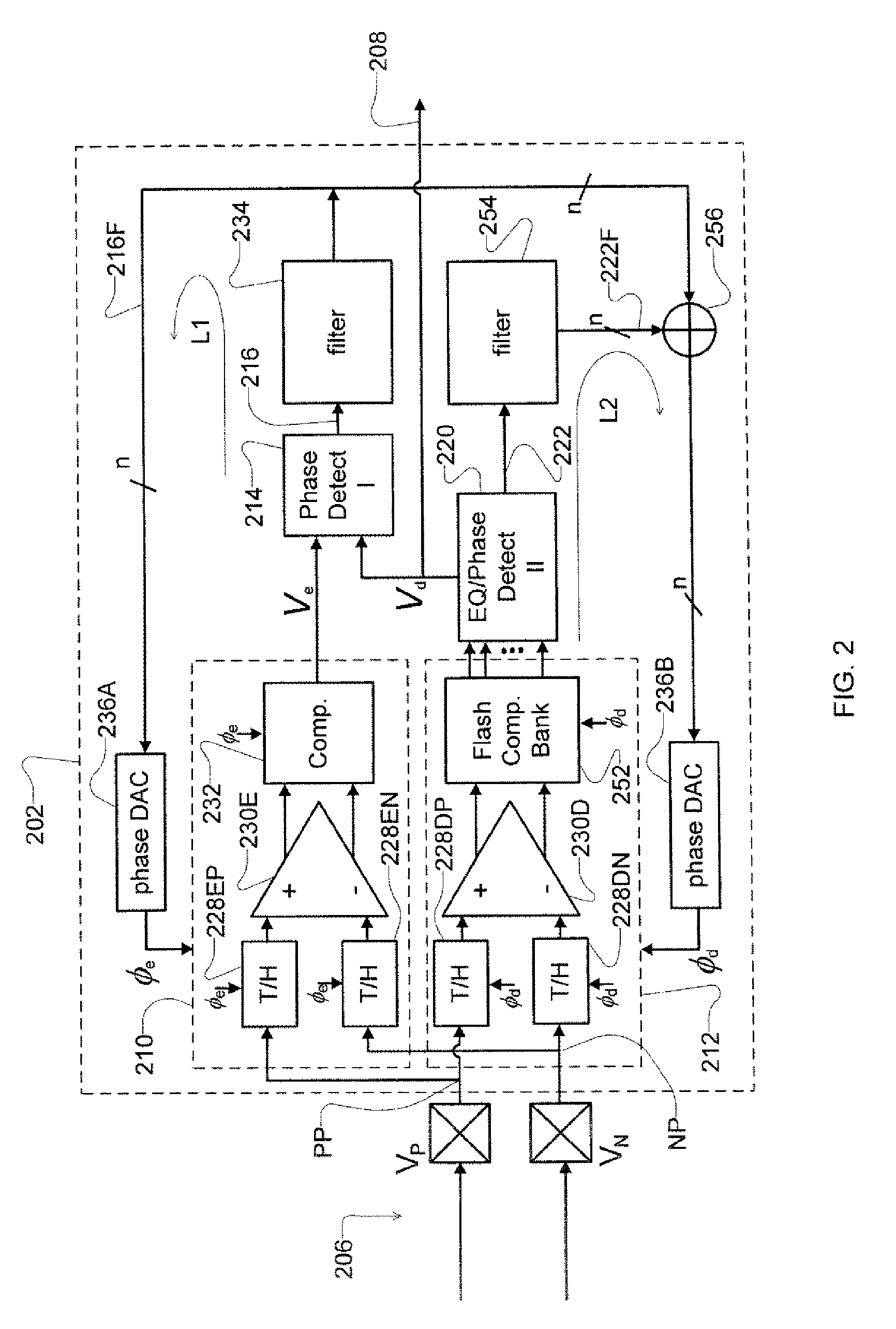

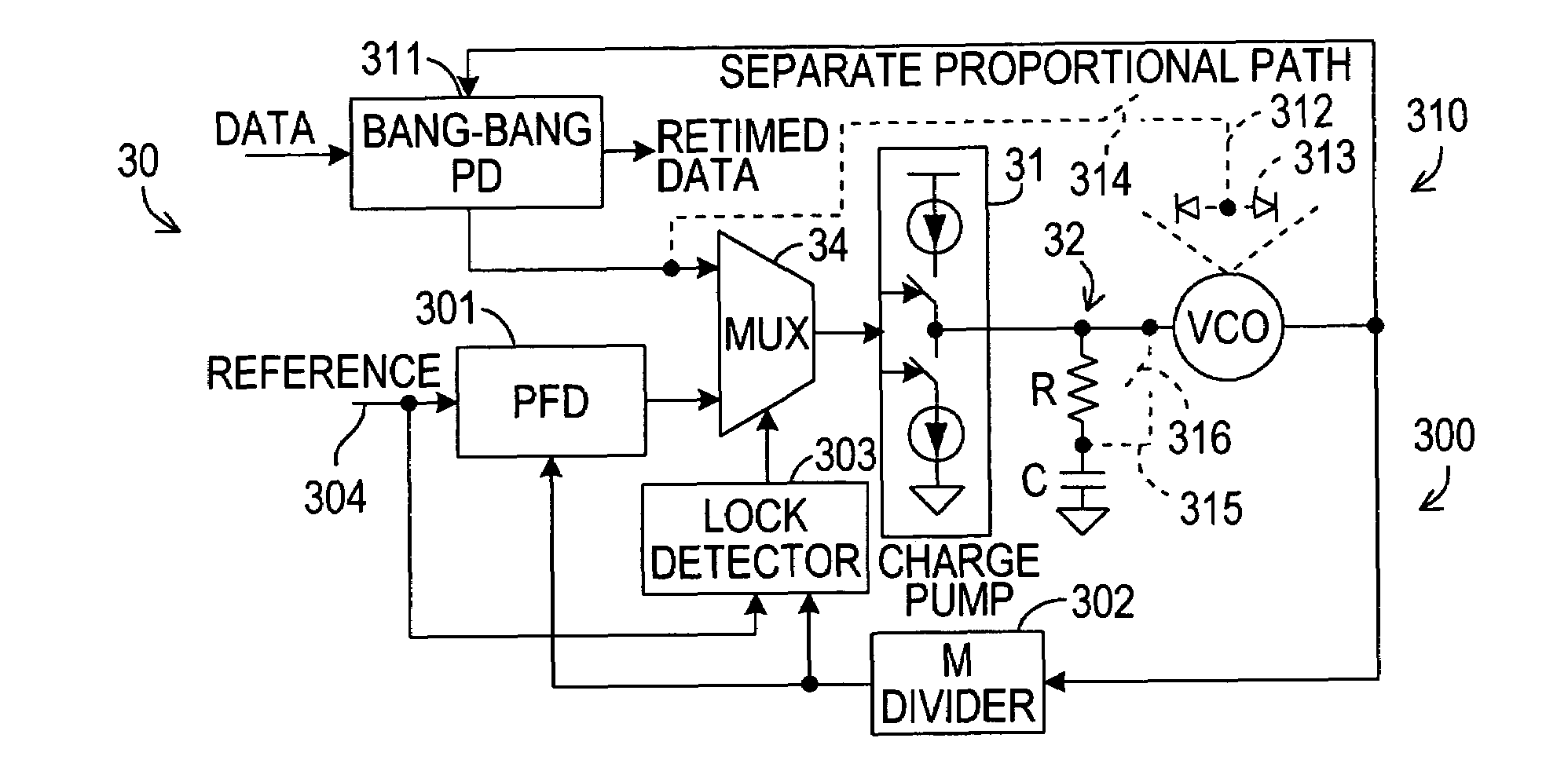

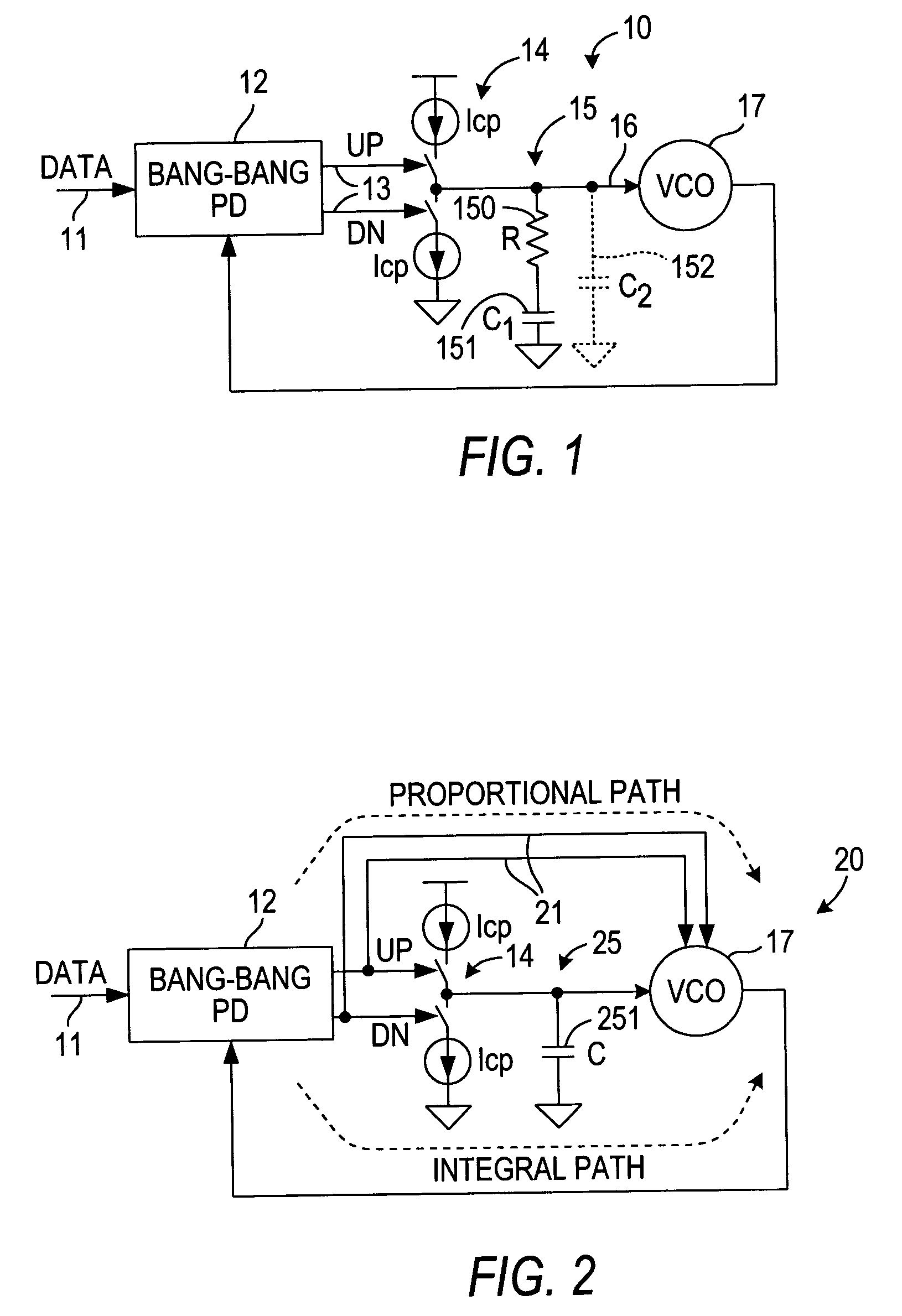

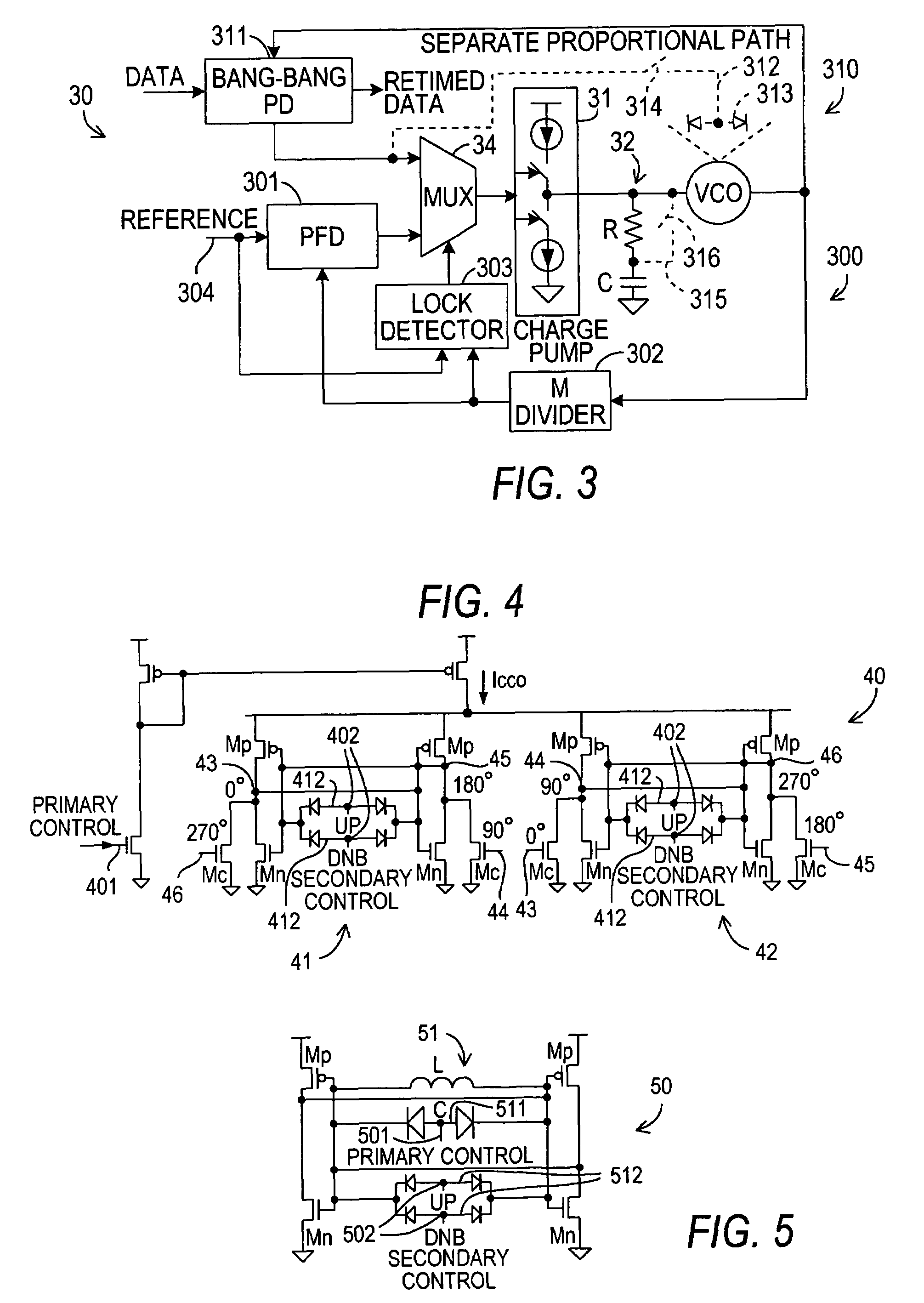

Clock data recovery loop with separate proportional path

InactiveUS7580497B2Improve stabilityLittle effectReceiver initialisationModulated-carrier systemsPhase detectorLoop filter

A clock data recovery loop that can be used over a wide range of data rates and maintain second-order behavior includes a nonlinear (e.g., Bang-Bang) phase detector, a charge pump, an RC loop filter, and signal generator (e.g., a voltage controlled oscillator (VCO)). At low data rates, the loop may be operated with the charge pump and loop filter with stable second-order behavior, with the resistor R of the loop filter serving as a proportional path. A separate proportional path is also provided that provides phase detector output directly to a control input of the VCO, while the resistor R of the loop filter is also bypassed. As increasing data rates give rise to third-order effects, the separate proportional path may be activated to maintain second-order behavior.

Owner:ALTERA CORP

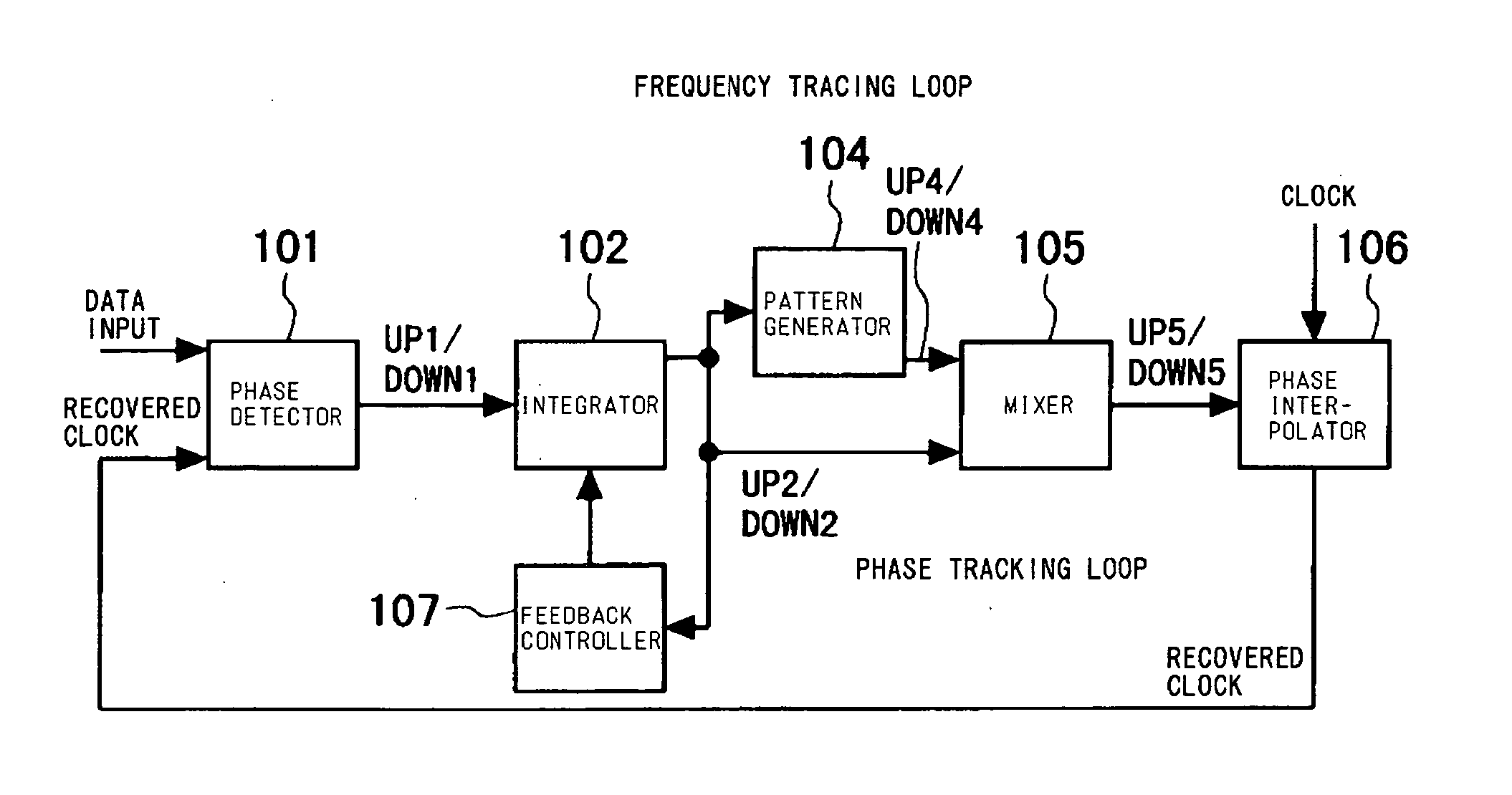

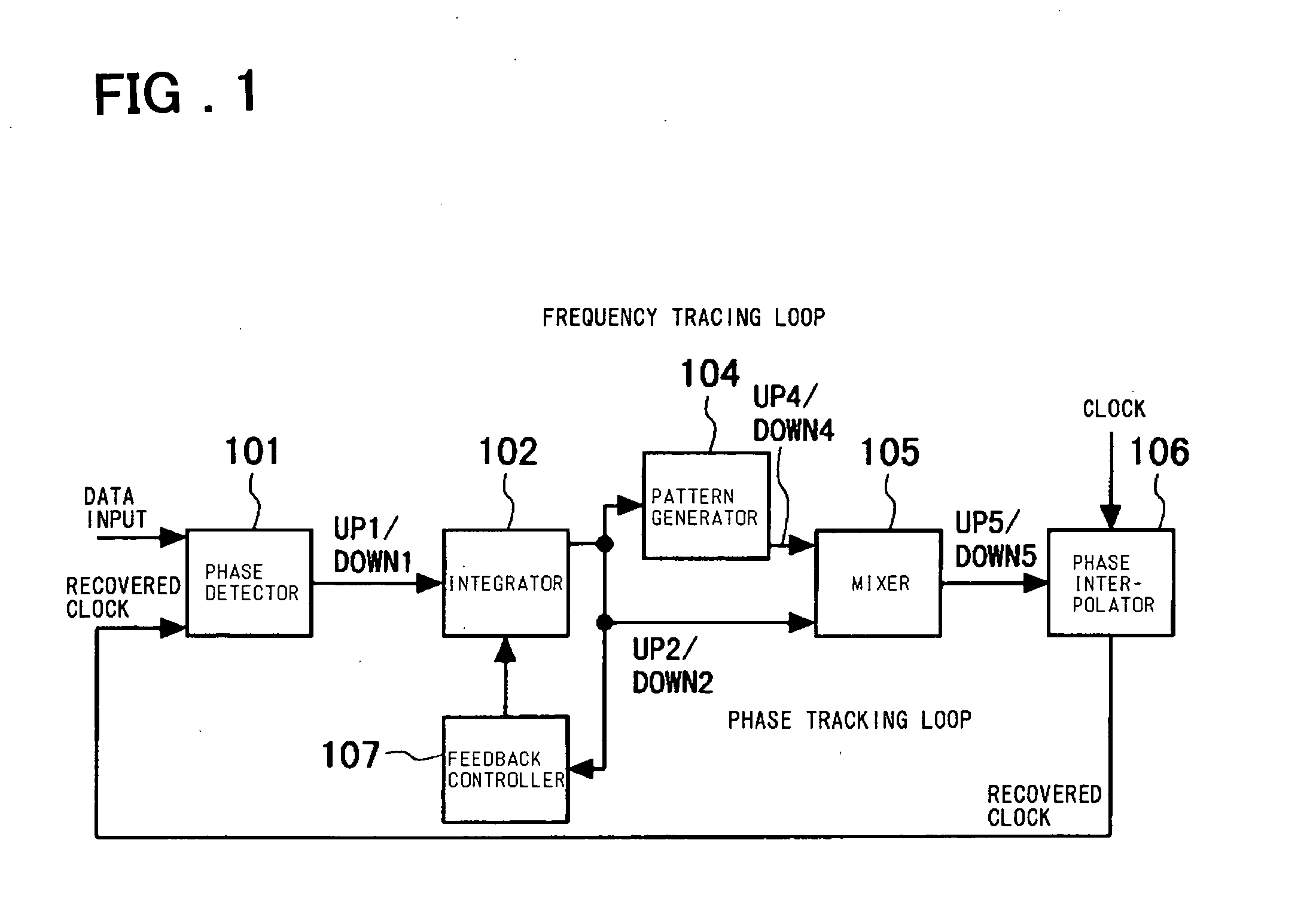

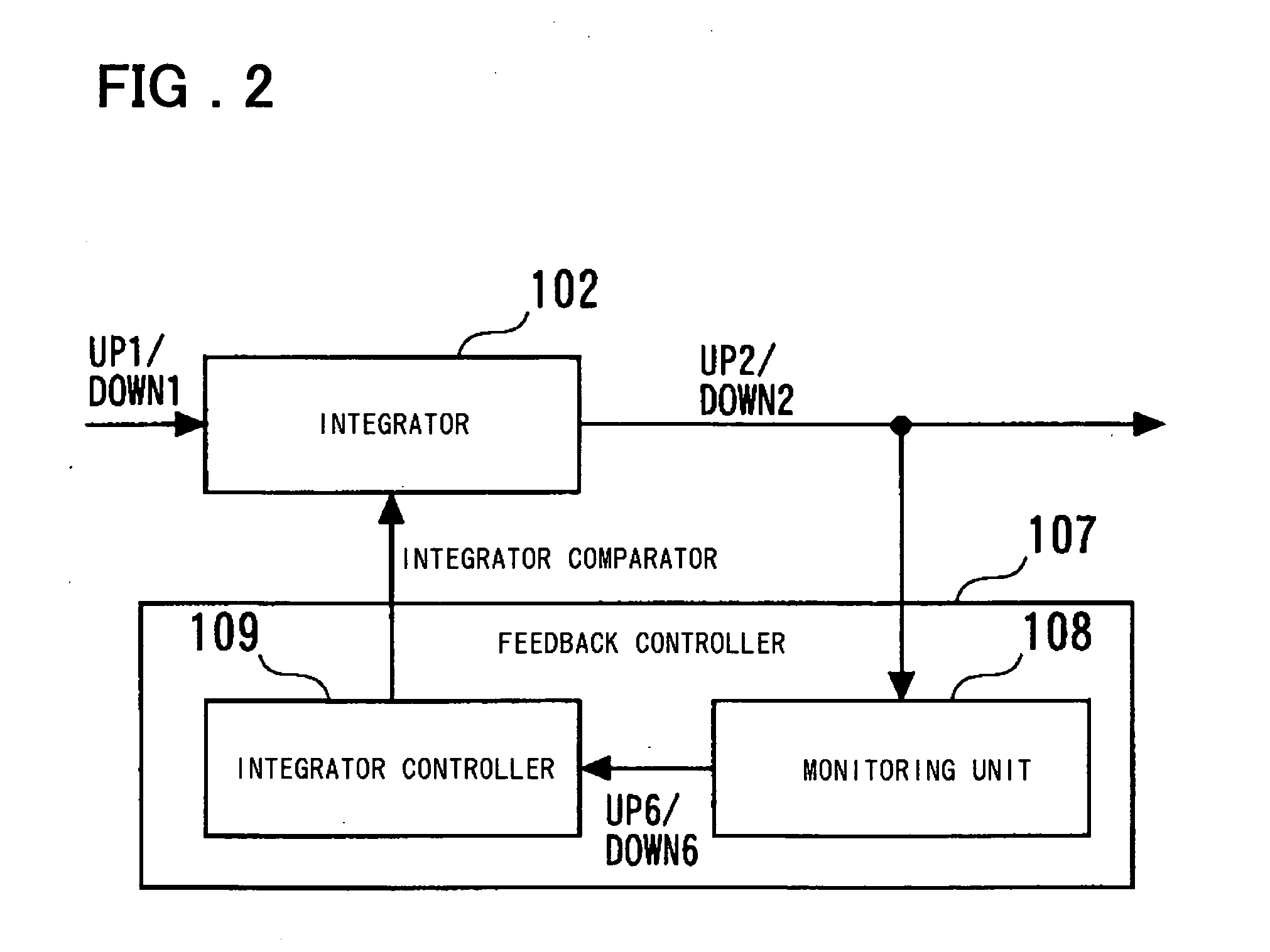

Clock and data recovery circuit

InactiveUS20060056564A1Excellent jitter tolerance characteristicImprove jitter tolerance characteristicReceiver initialisationPulse automatic controlIntegratorFeedback controller

A clock and data recovery circuit that tracks the frequency and phase fluctuation of serial data includes a feedback controller for monitoring tracking speed of an extraction clock with respect to the frequency and phase fluctuation of the serial data and applying feedback control to an integrator adaptively and moment to moment, thereby raising the tracking speed of the recovered clock and improving the jitter tolerance characteristic.

Owner:RENESAS ELECTRONICS CORP

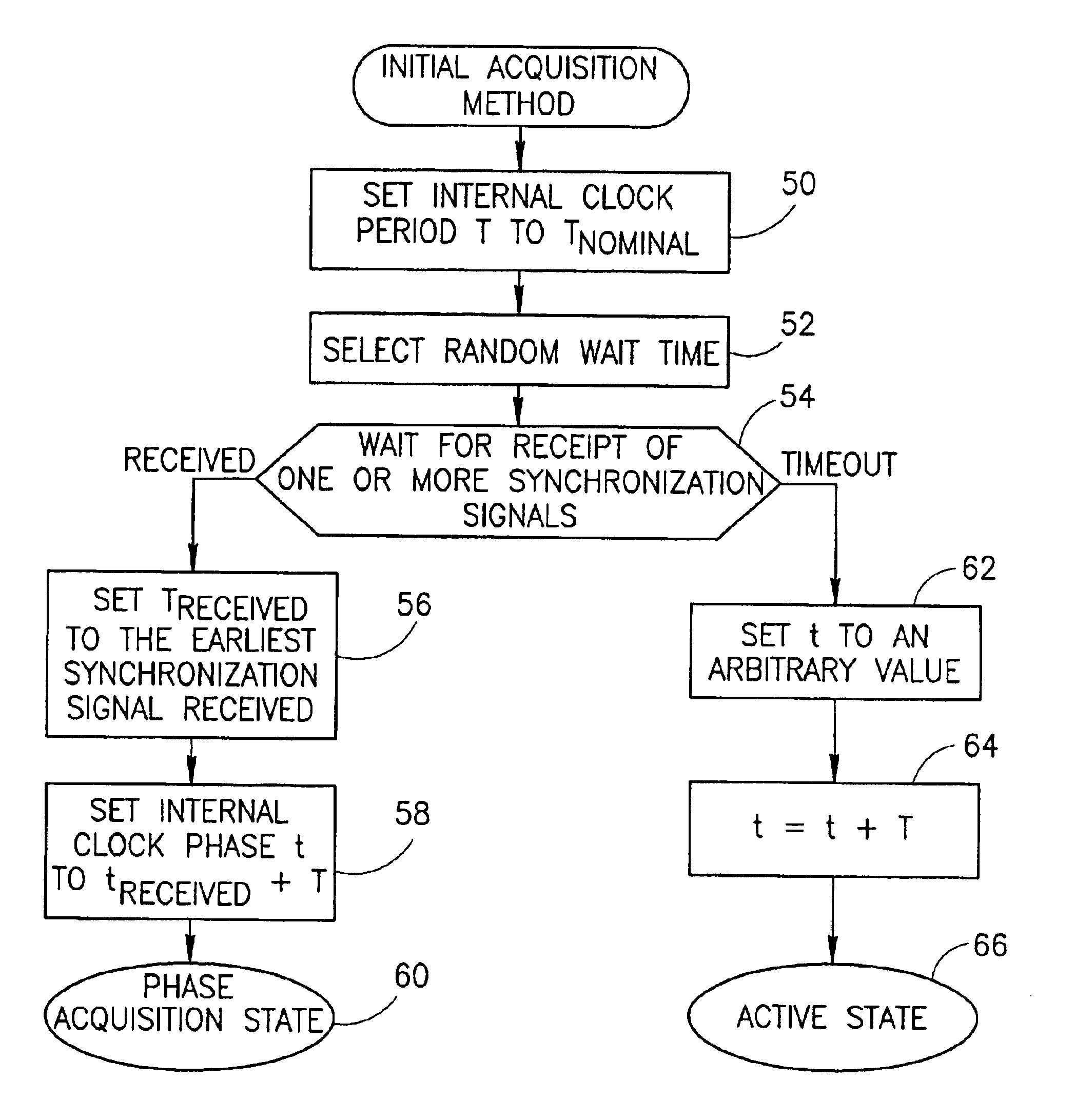

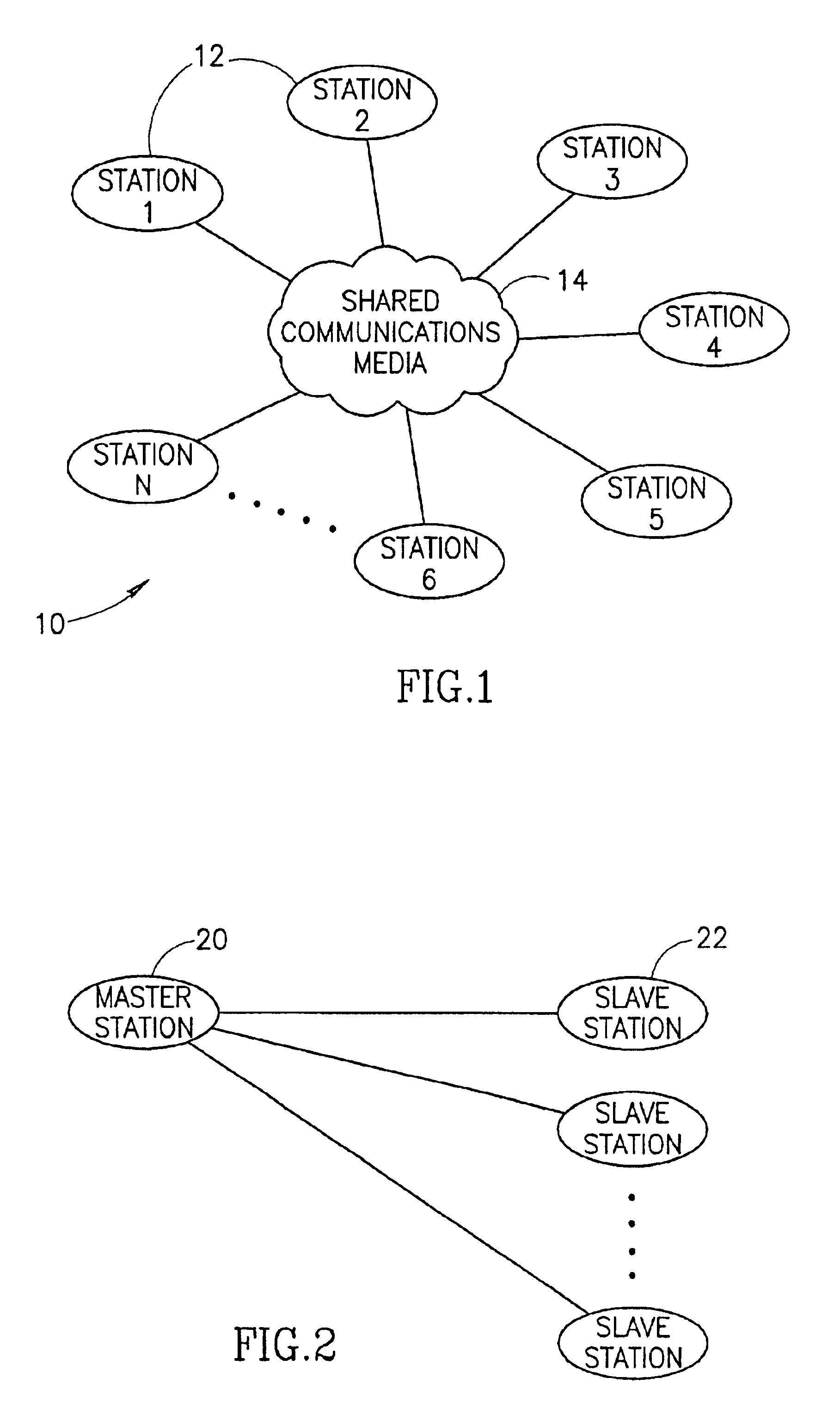

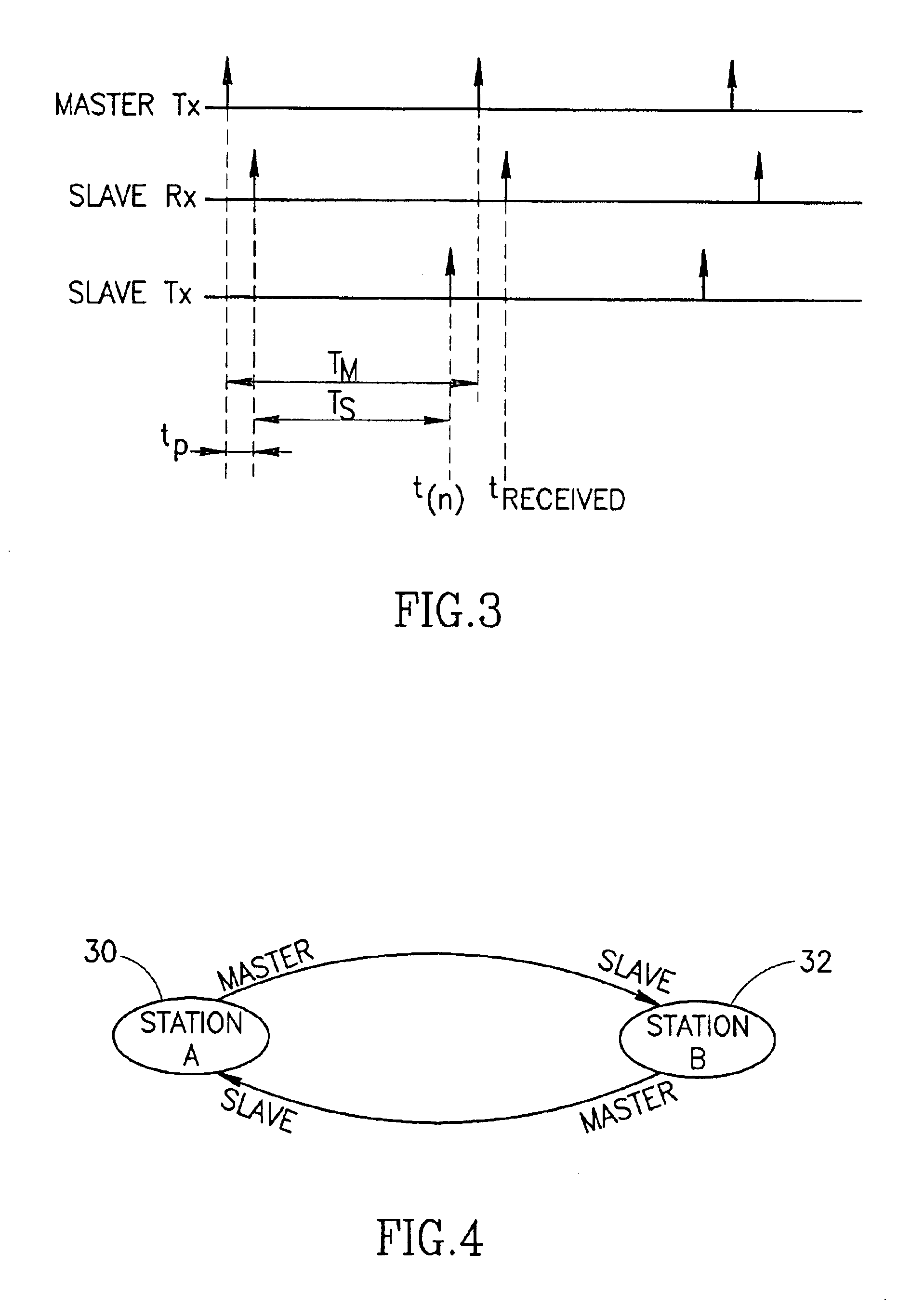

Distributed synchronization mechanism for shared communications media based networks

InactiveUS6907472B2Optimization mechanismEfficient workReceiver initialisationTransmission/receiving by adding signal to waveComputer scienceCommunications media

A novel and useful distributed synchronization mechanism. The synchronization loop of each station on the shared media based network considers only synchronization signals received having a time phase earlier than the time phase of its internal clock. From among the plurality of synchronization signals received by a given station having a time phase earlier than that of its internal clock, only the earliest of the received synchronization signals is considered. This allows the use of a second order synchronization tracking loop wherein both the phase and rate of the internal clock are tracked and adjusted. The station with the fastest internal clock effectively functions as an ad-hoc synchronization master for all stations in a given maximum connected group.

Owner:ITRAN COMM

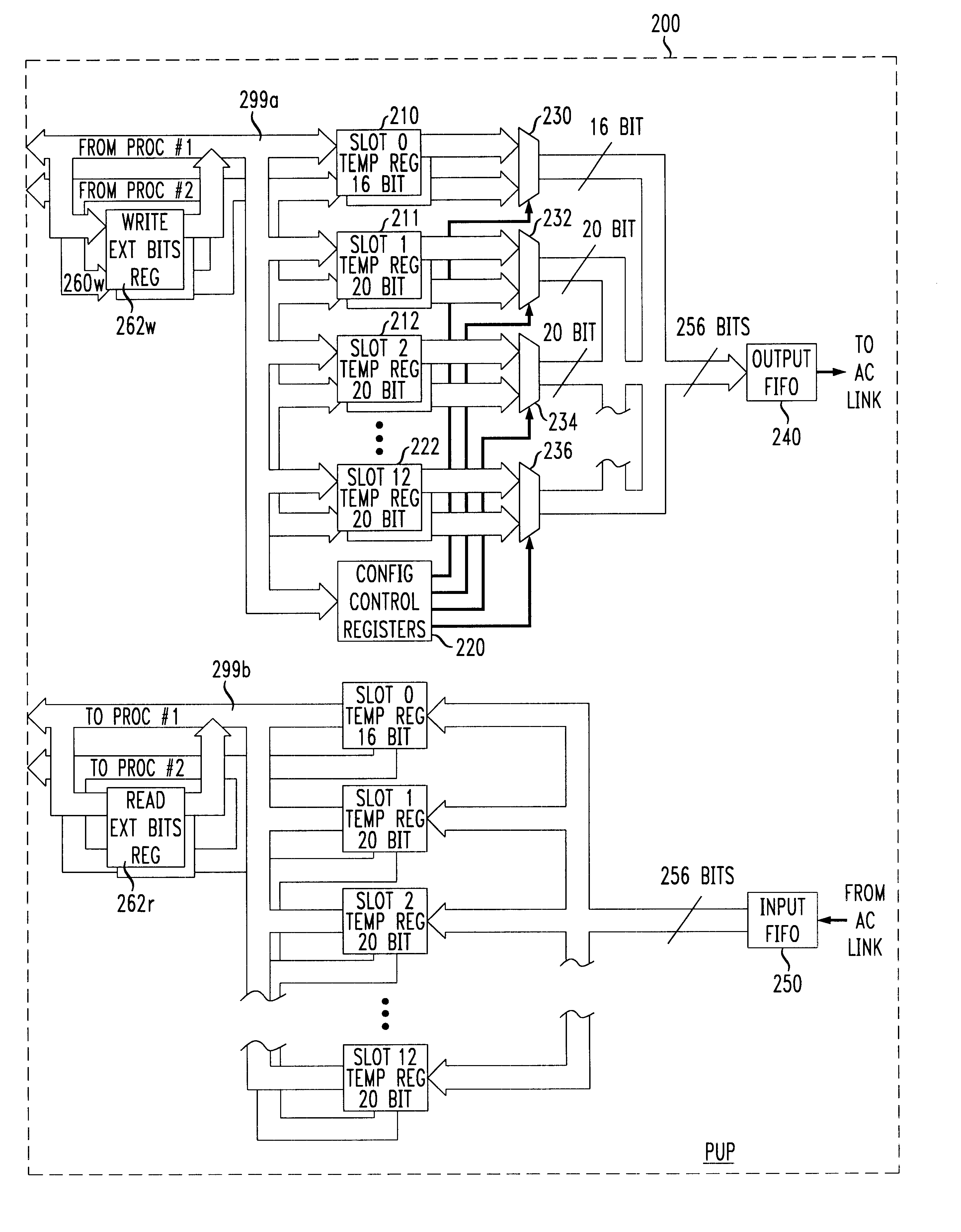

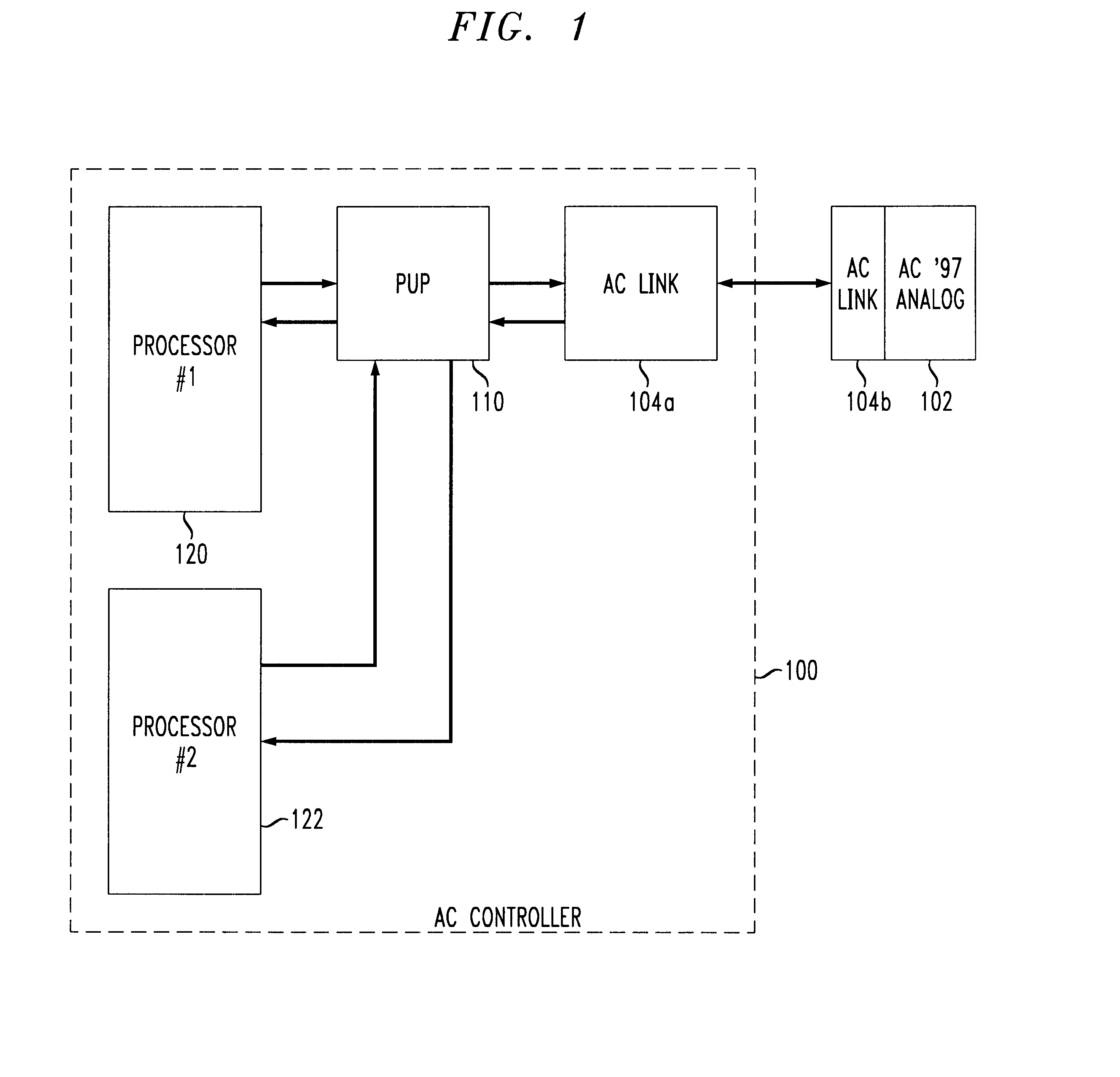

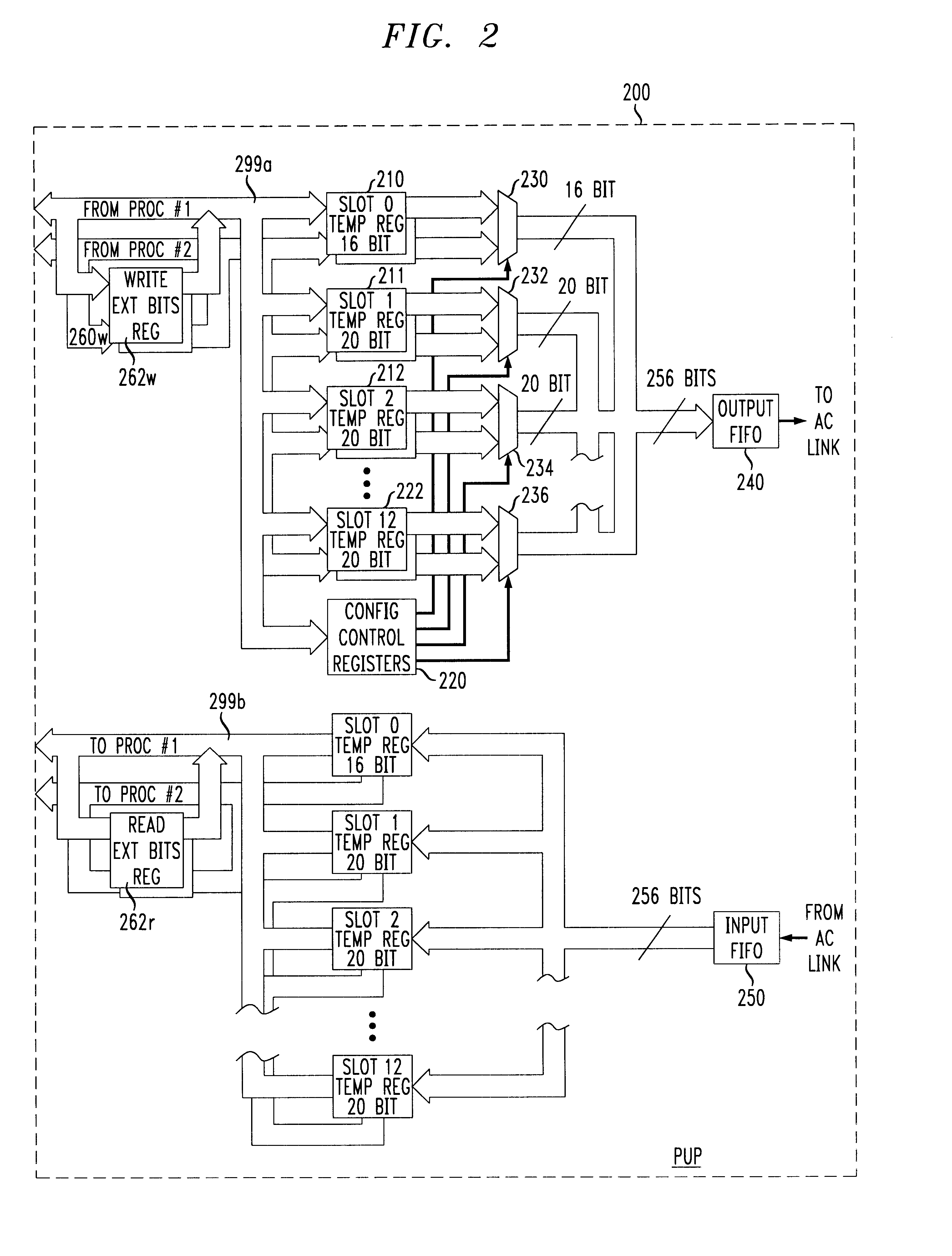

Multiple device access to serial data stream

One aspect of the present invention provides a packer-unpacker (PUP) for a digital serial interface which allows a plurality of processors to access time slot registers of a serial data stream relating to the digital serial interface. A configuration register is maintained either by one of the plurality of processors or by each of the processors to arbitrate access to the individual time slot registers. Another aspect of the invention allows one or more processors to efficiently access and / or write more bits to a resource such as a time slot register than the width of the processor's respective data bus allows. Extra bits registers are maintained for at least one of the read and write direction data busses. The extra bits correspond to the least significant bits conventionally ignored in changing from a data bus of one width to a data bus of a narrower width. The extra bits in the write direction are accessed, e.g., by a write to a write direction extra bits register addressable through a specific input / output (I / O) location. The extra bits are tacked on to a subsequent write cycle in the digital serial interface, e.g., in the AC '97 link, to write an excess length data word. In the read direction, each read cycle places excess bits in a read direction extra bits register for reading in a subsequent read cycle. Another aspect of the invention provides an automatic status register which provides, e.g., automatic creation of a TAG Phase in time slot 0 of an AC '97 link using, e.g., a write enable signal to various resources in the digital serial interface, e.g., write enable signals to time slot registers.

Owner:AGERE SYST INC

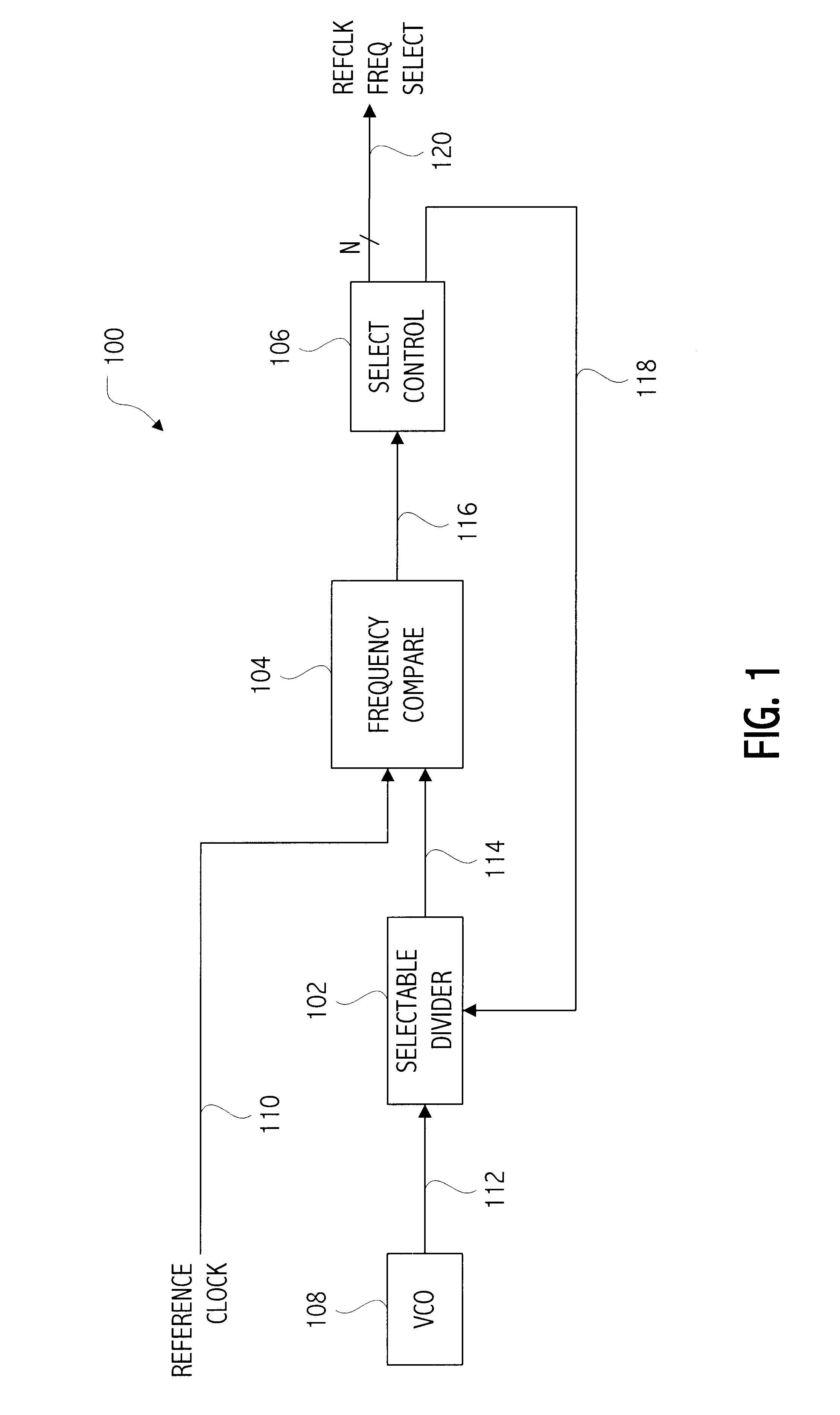

Integrated circuit incorporating circuitry for determining which of at least two possible frequencies is present on an externally provided reference signal and method therefor

An internal frequency reference, such as a VCO used in a PLL, having a free-running frequency fairly well controlled within a predictable range, is used as a rough frequency reference to determine, for an externally-provided frequency reference signal, which of a finite number of discrete frequencies is currently received. The VCO has a frequency range which varies less, as a percentage, than the ratio between possible reference frequency values. Consequently, the VCO is used as a frequency reference to measure the frequency reference signal. An internal signal is generated to indicate to remaining circuitry which of the possible reference frequencies is actually being provided, without requiring use of any dedicated input pins to receive a select signal. An integrated circuit device may be configured for different modes of operation as a function of which reference frequency is provided to the device. Moreover, if one of the available reference clock frequencies is chosen to correspond to an internal test mode, the device may be placed in a test mode without requiring any additional dedicated input pins for that purpose, either.

Owner:SKYWORKS SOLUTIONS INC

Popular searches

Modulation with suppressed carrier Plural information simultaneous broadcast Transmitter/receiver shaping networks Signal channels Local circuits Amplitude demodulation by homodyne/synchrodyne circuits Carrier regulation Amplitude-modulated carrier systems Forward error control use Electromagnetic receivers