Patents

Literature

406results about "Synchronisation error detection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

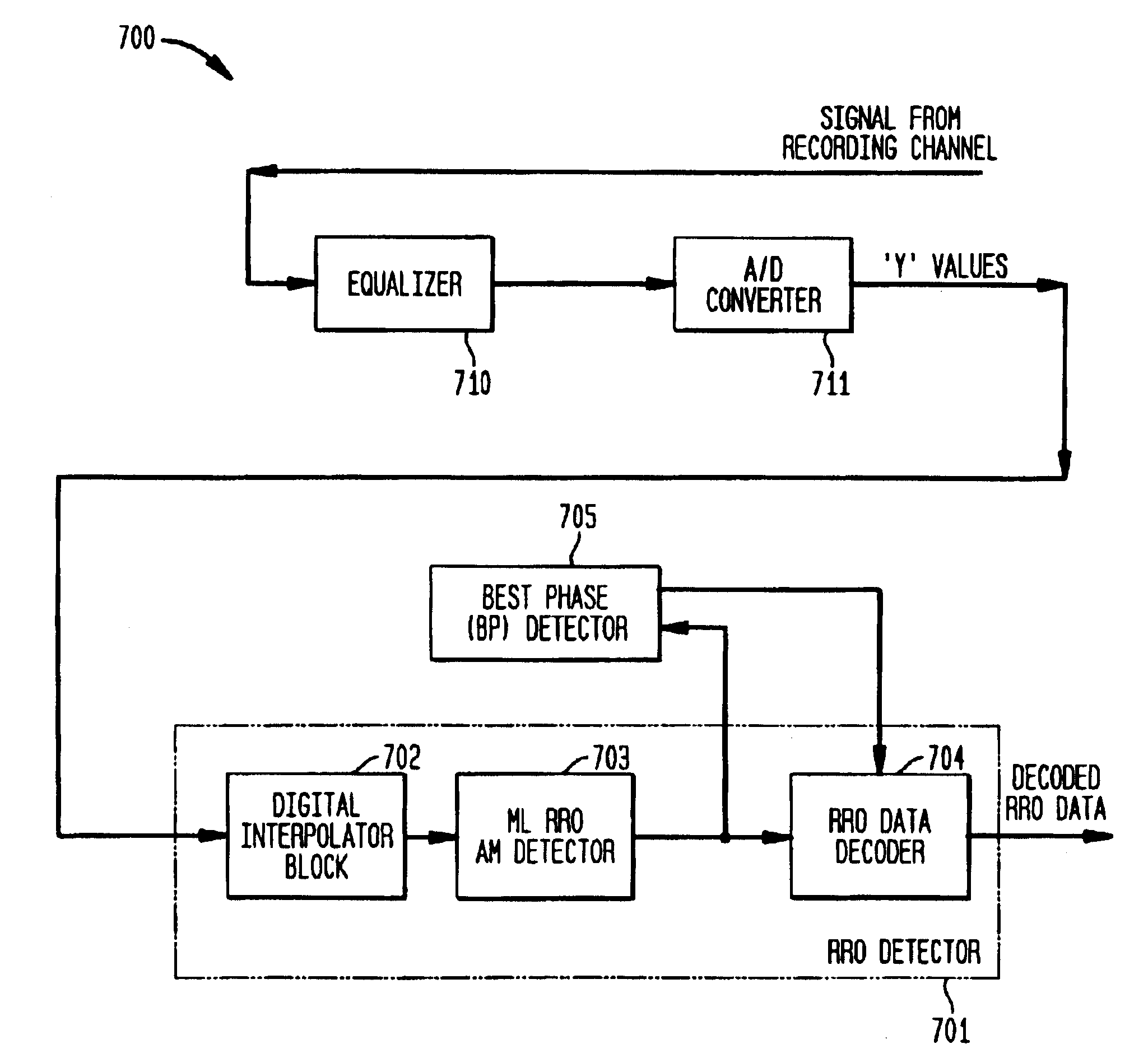

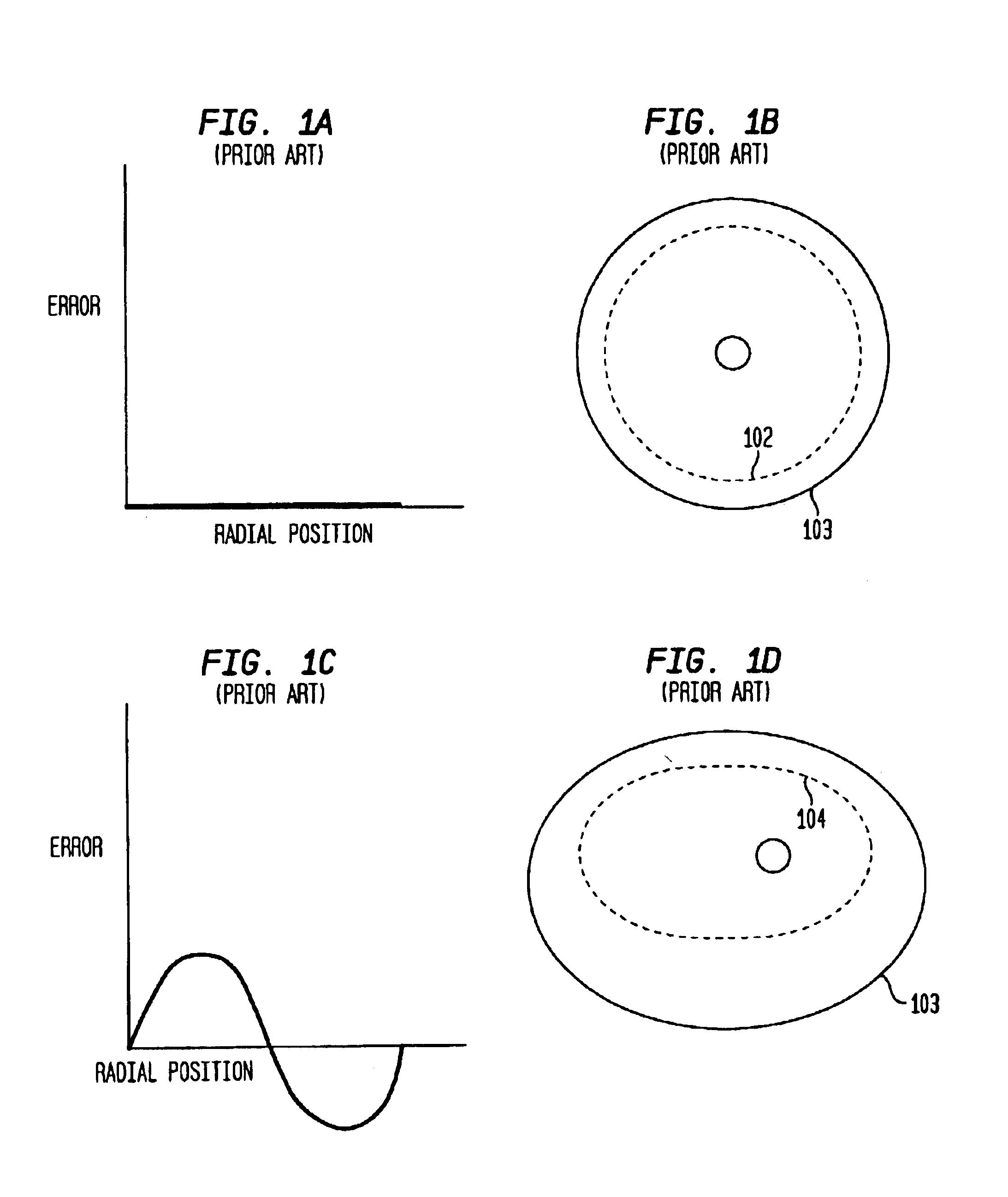

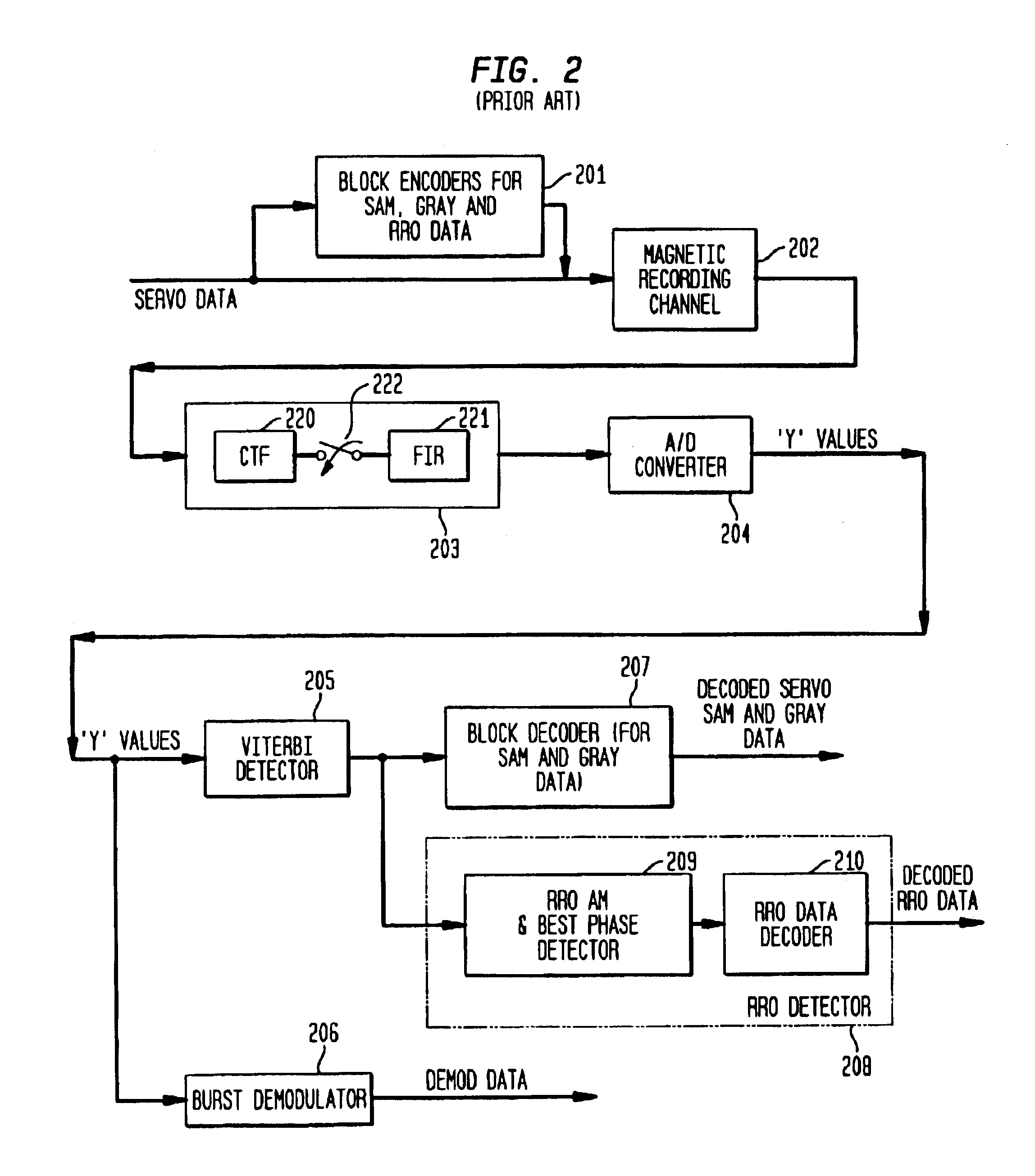

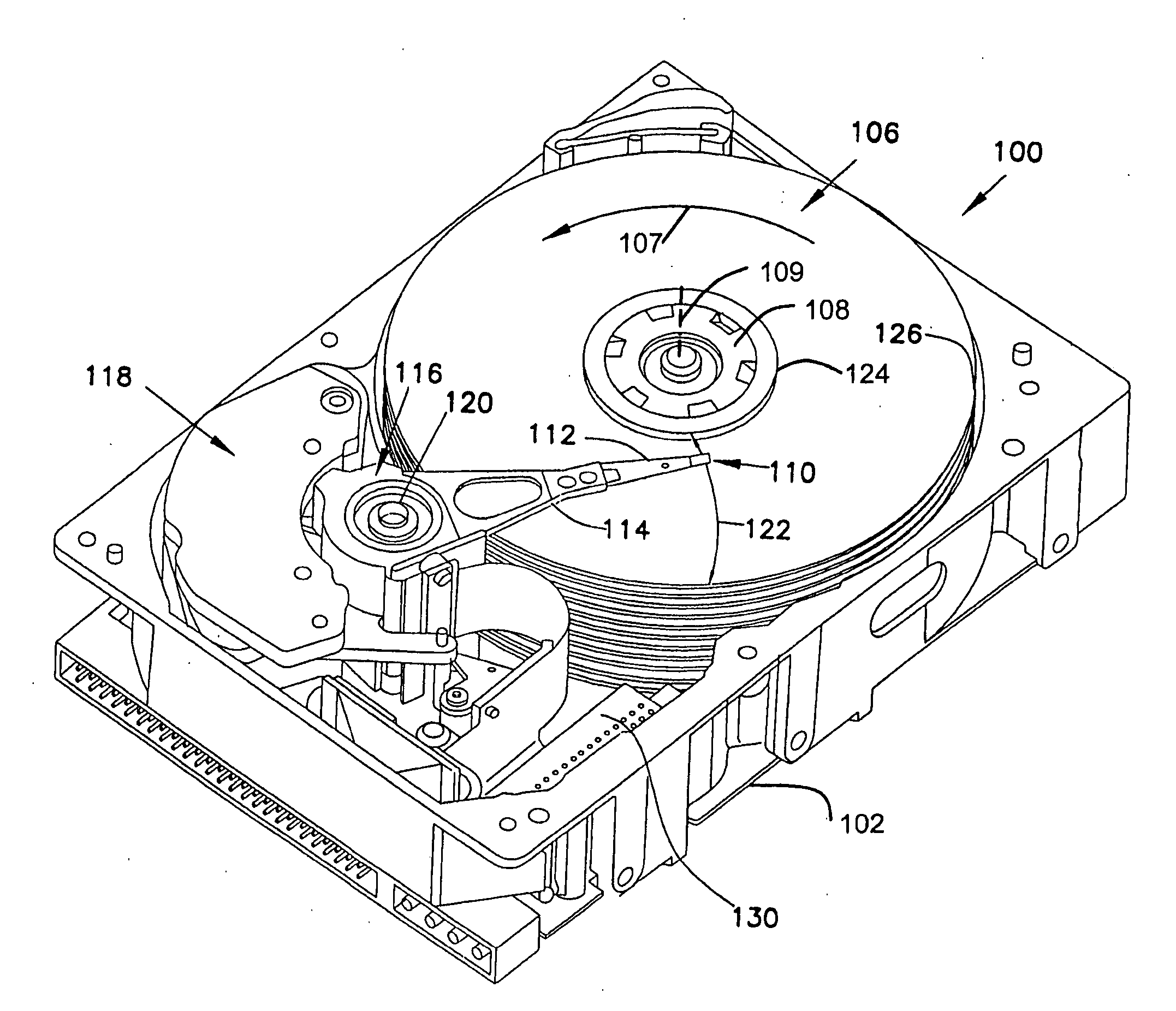

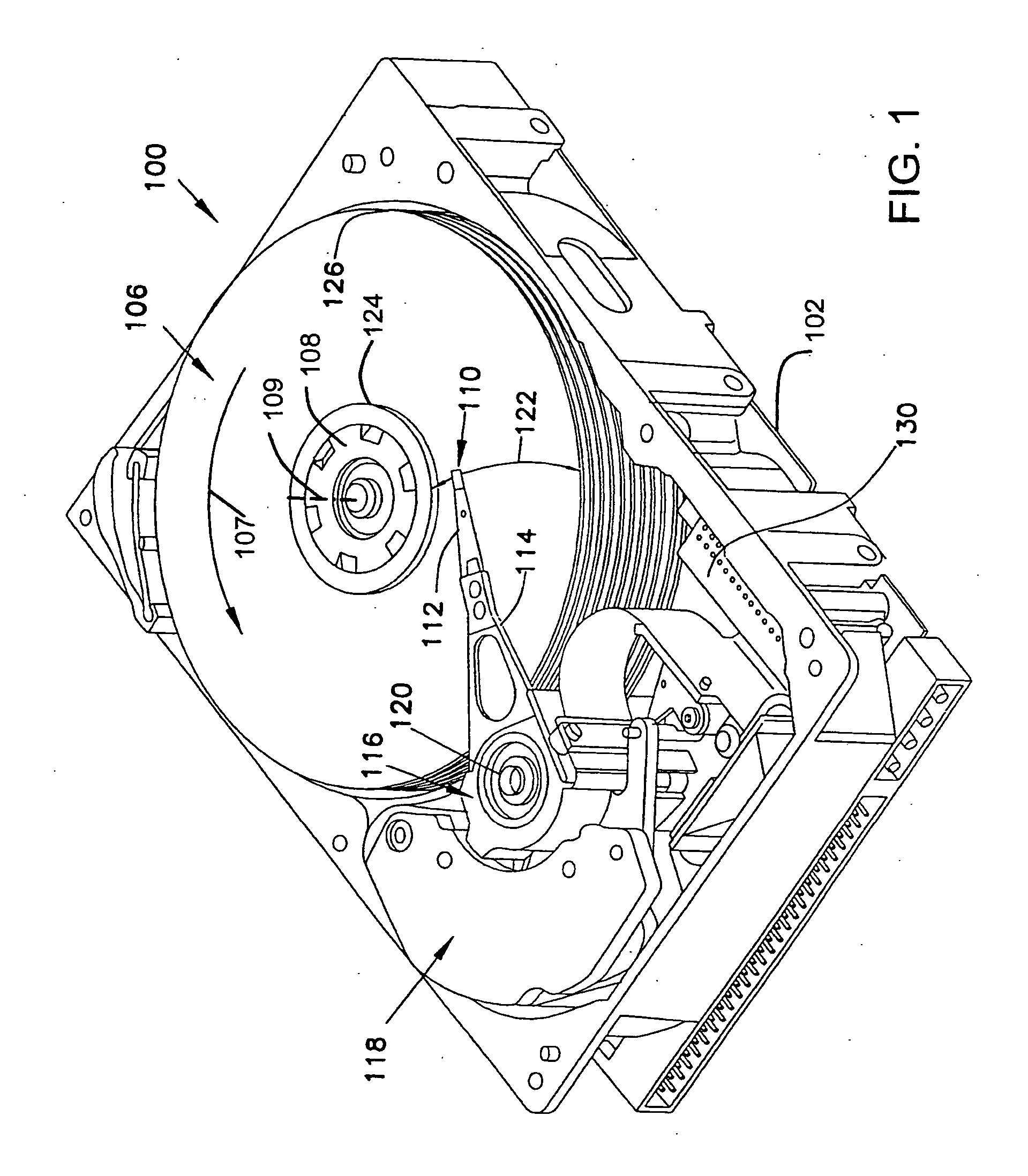

Maximum likelihood detection of asynchronous servo data employing interpolation

ActiveUS6912099B2Modification of read/write signalsSynchronisation error detectionSample sequenceMaximum likelihood detection

A repeatable run-out (RRO) detector employs one or more digital interpolators to interpolate asynchronous sample values representing an RRO address mark (AM) and RRO data, an asynchronous maximum-likelihood (AML) detector to detect the RRO AM, and a RRO data decoder to decode the RRO data. The AML detector employs an AML algorithm, such as a Viterbi algorithm, to detect the series of peaks of the RRO AM based on detection of the entire sequence of observed peaks. AML detection selects one of either the asynchronous or interpolated sample sequences that are closest in distance to the ideal RRO AM sample sequence. Once the RRO AM is detected, the AML detector provides a RRO AM found signal as well as the selected one of the sample sequences having the best phase for detecting and decoding the RRO data.

Owner:AVAGO TECH INT SALES PTE LTD

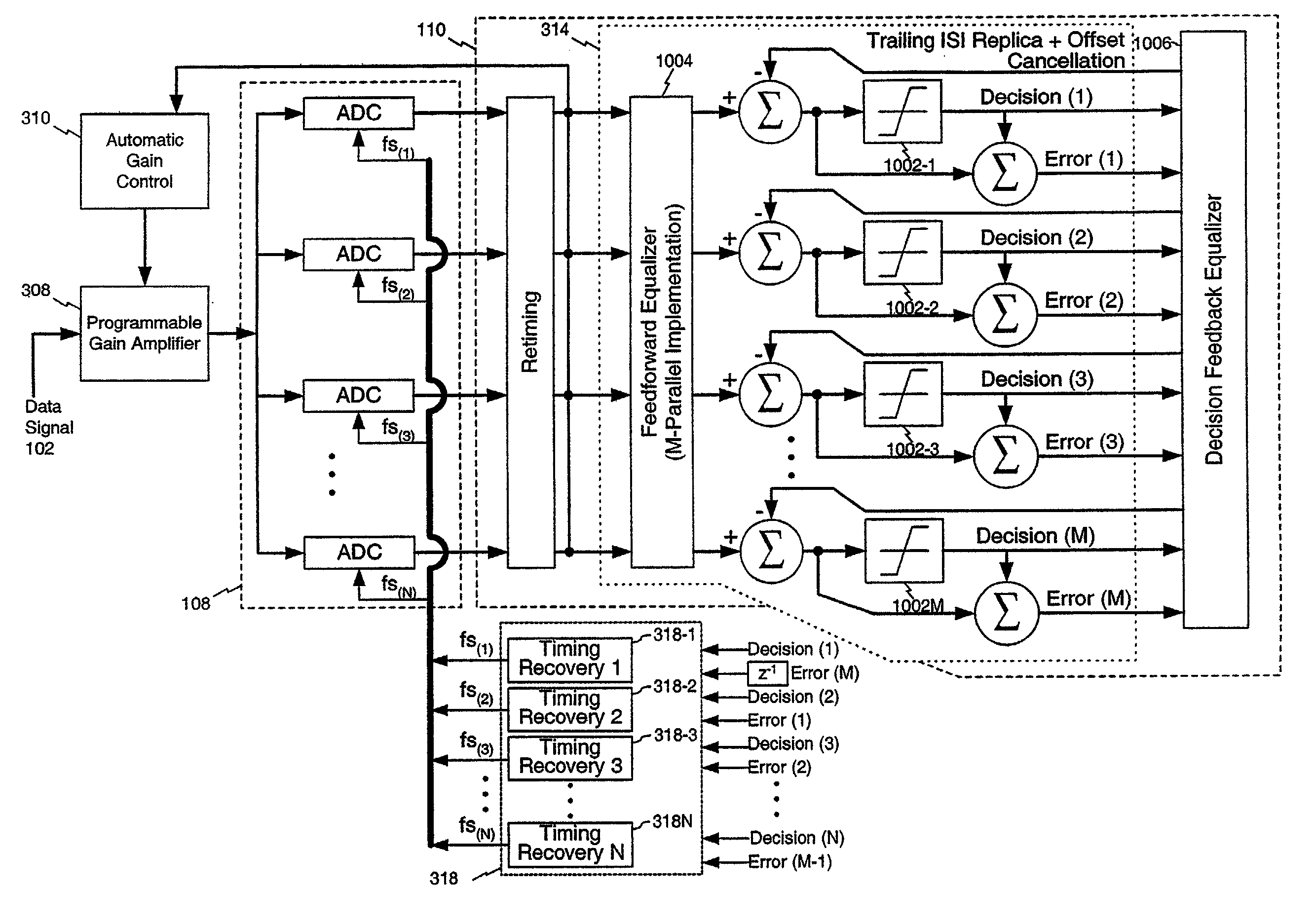

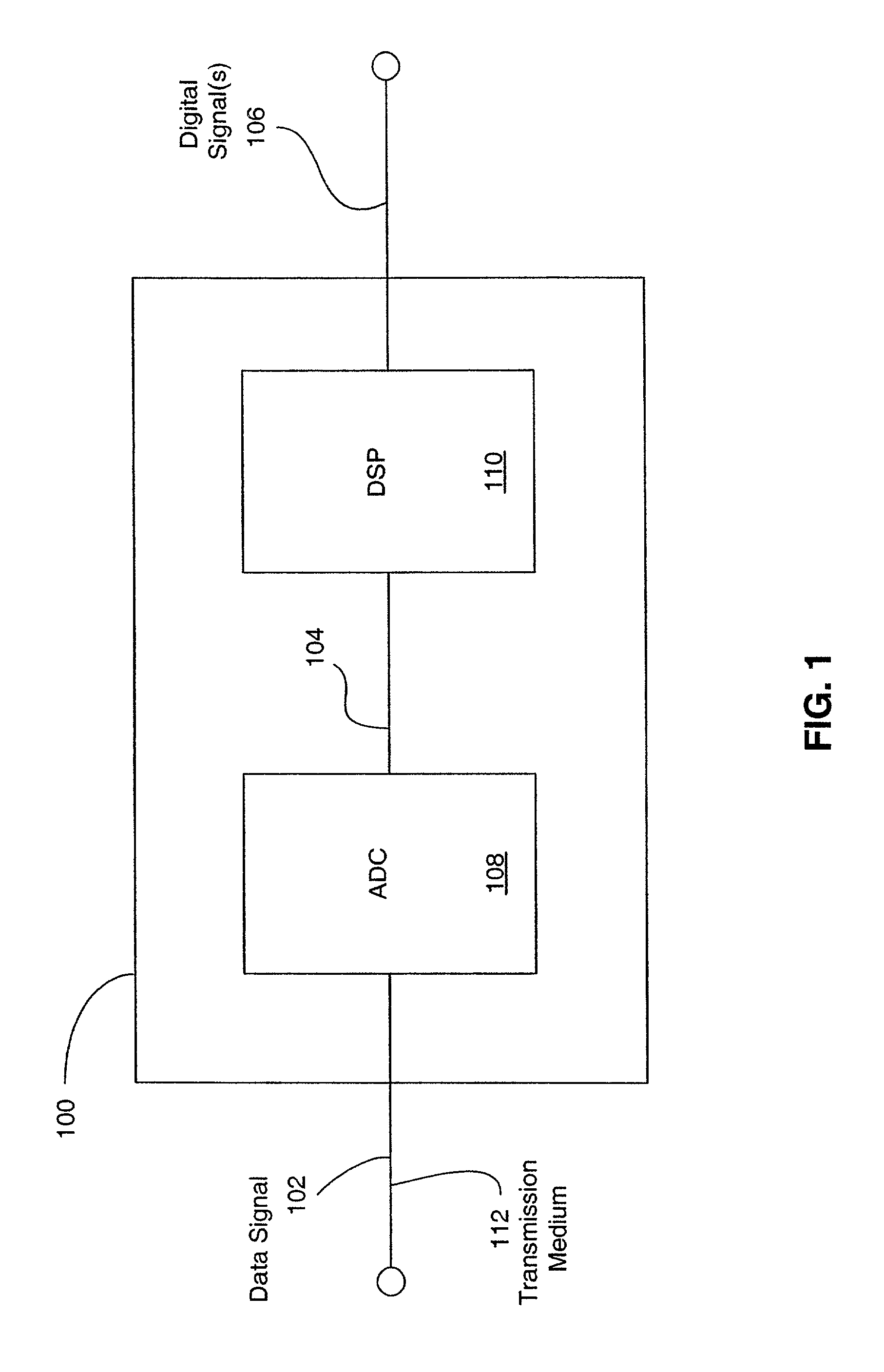

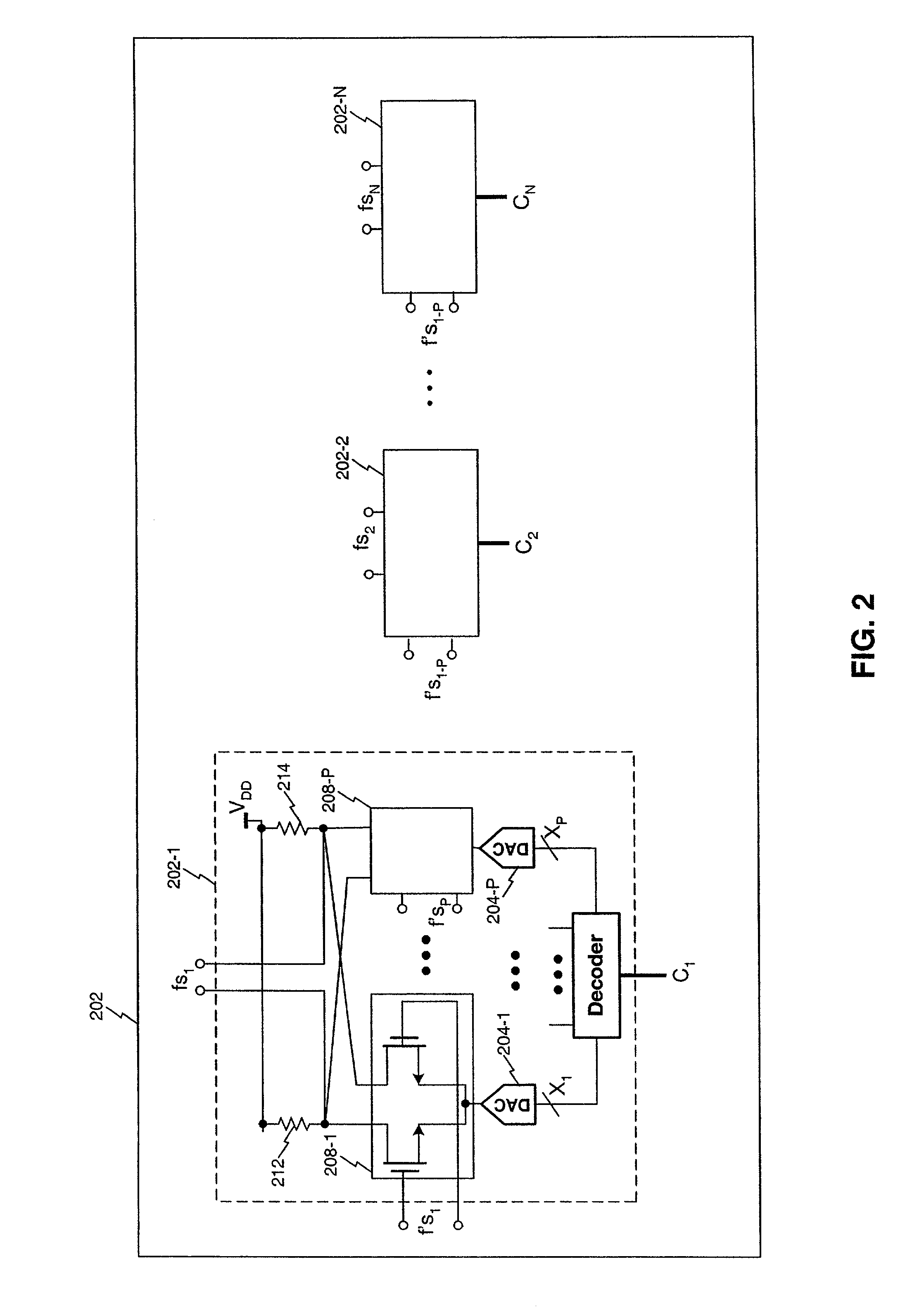

Methods and systems for DSP-based receivers

InactiveUS7245638B2Synchronisation error detectionTime-division multiplexDigital signal processingData signal

Digital signal processing based methods and systems for receiving data signals include parallel receivers, multi-channel receivers, timing recovery schemes, and, without limitation, equalization schemes. The present invention is implemented as a multi-path parallel receiver in which an analog-to-digital converter (“ADC”) and / or a digital signal processor (“DSP”) are implemented with parallel paths that operate at lower rates than the received data signal. In an embodiment, a parallel DSP-based receiver in accordance with the invention includes a separate timing recovery loop for each ADC path. In an embodiment, a parallel DSP-based receiver includes a separate automatic gain control (AGC) loop for each ADC path. In an embodiment, a parallel DSP-based receiver includes a separate offset compensation loop for each ADC path. In an embodiment the present invention is implemented as a multi-channel receiver that receives a plurality of data signals.

Owner:AVAGO TECH INT SALES PTE LTD

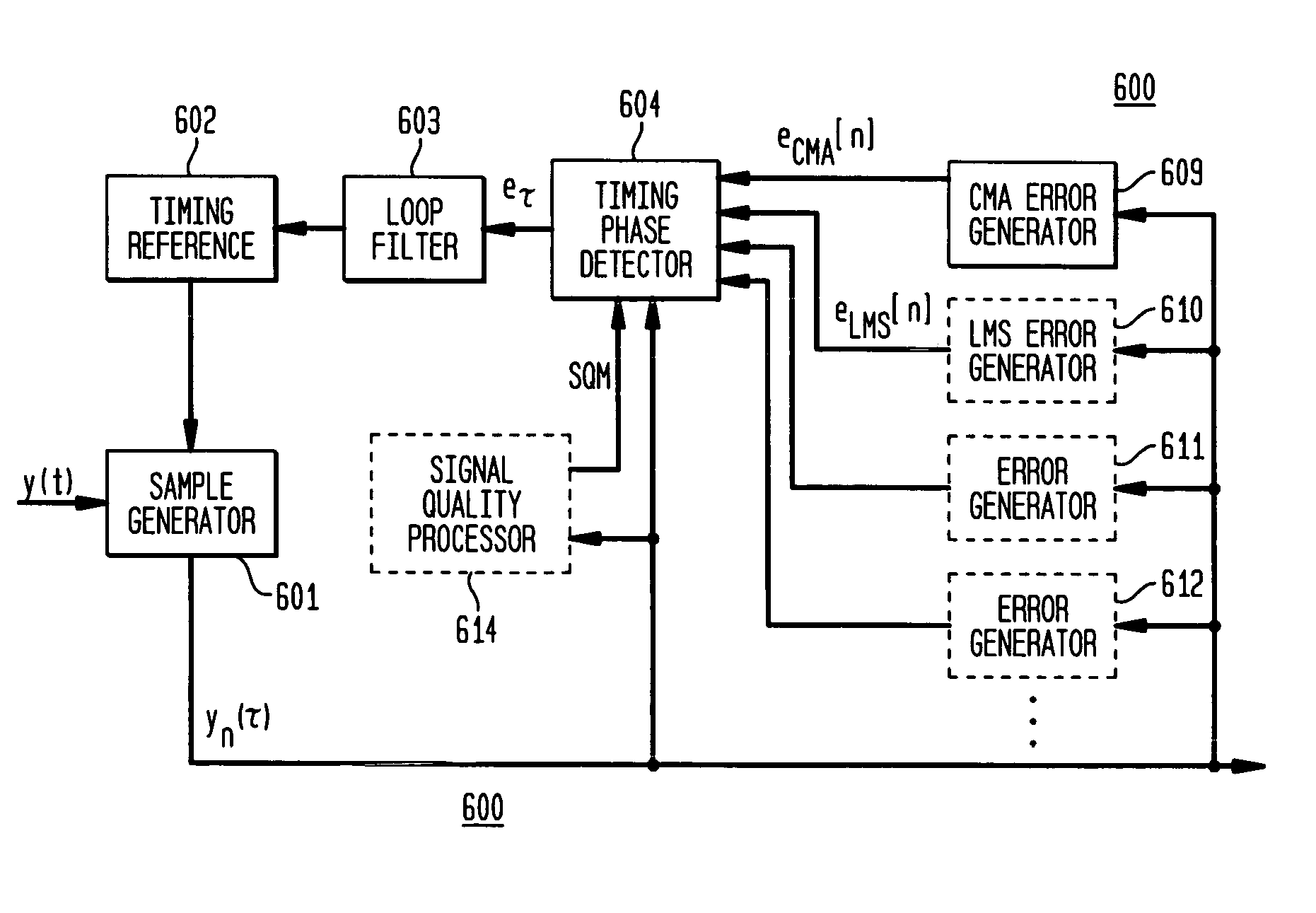

Blind cost criterion timing recovery

Symbol timing recovery employs a blind cost criterion from the Bussgang class of functions, and its stochastic gradient, to generate a timing phase error used to adjust sampling of received symbols. For one implementation, the estimate is derived in accordance with the Constant Modulus (CM) criterion and its gradient via the CM algorithm (CMA), and the estimate is calculated from a sequence of samples. This estimate is then used to adjust the period and phase of the sample sequence toward the period and phase of the transmitted symbols, driving the timing phase error to zero. The values used may be either i) samples themselves, ii) processed (e.g., interpolated) samples, or iii) equalized and processed samples. In addition, timing phase error estimates for other cost criteria, including the least mean squares algorithm, may be generated. These timing phase error estimates are selected either alone or in combination for deriving the timing phase error used to adjust the period and phase of the sample sequence.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Method and apparatus for coding information

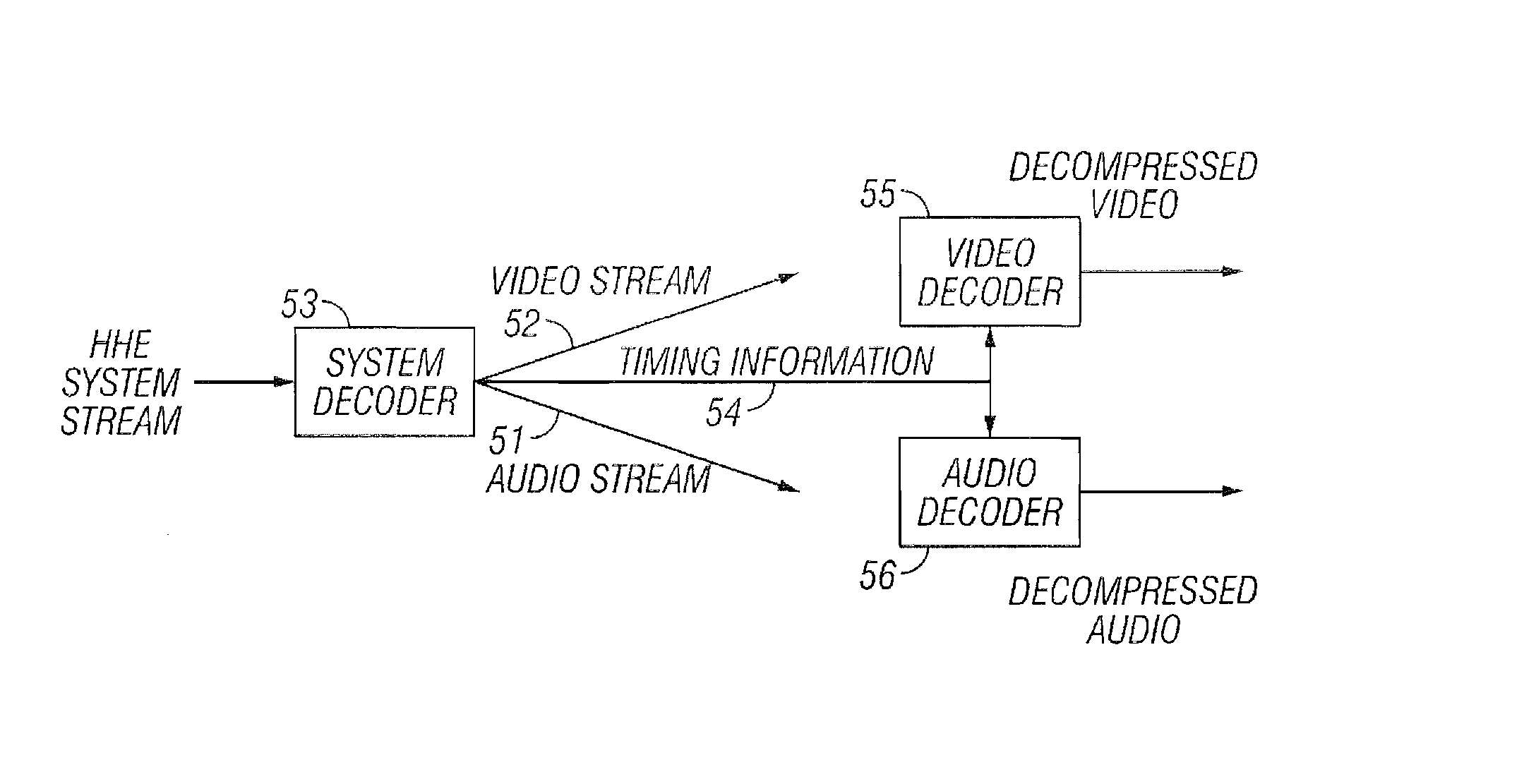

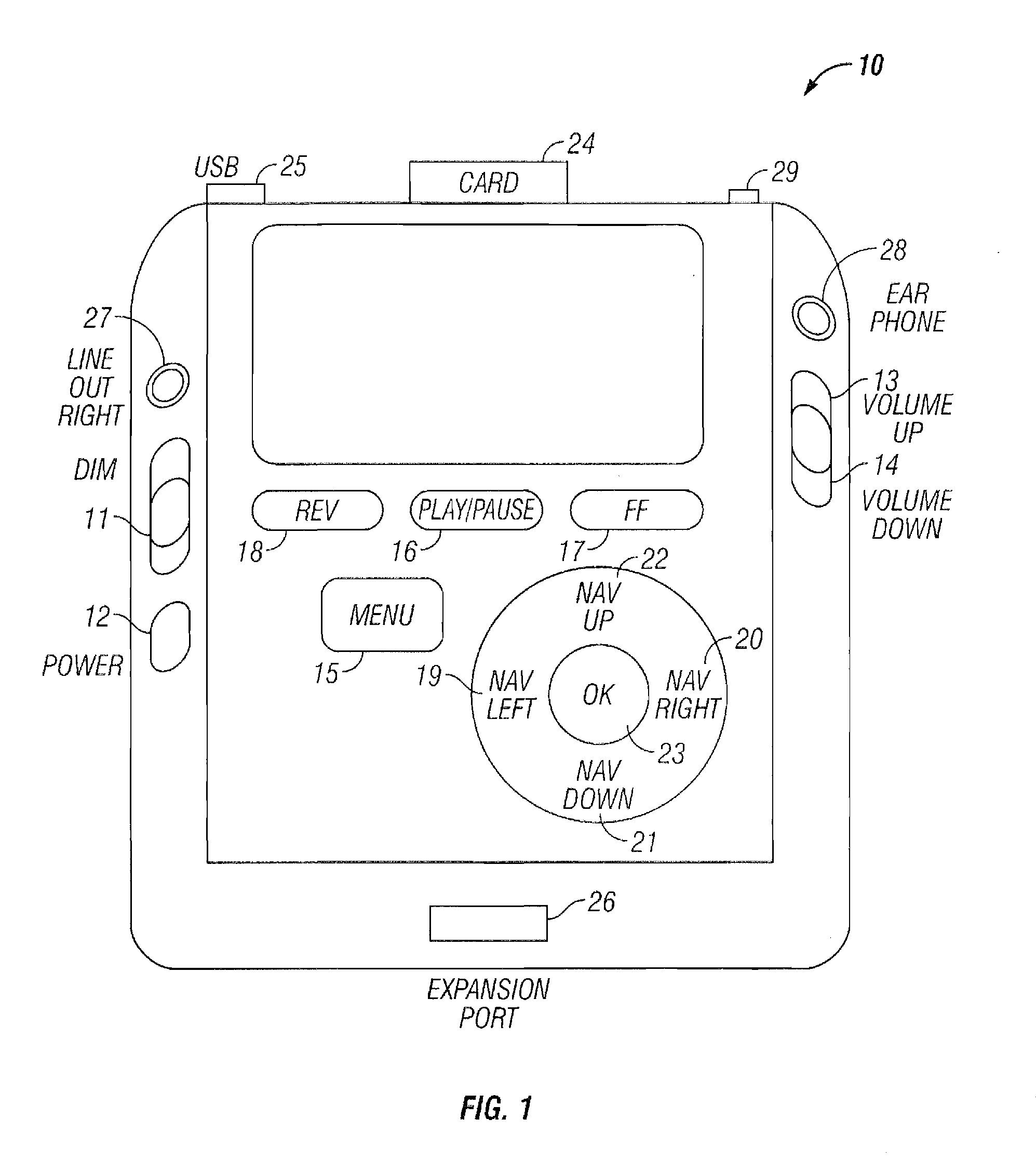

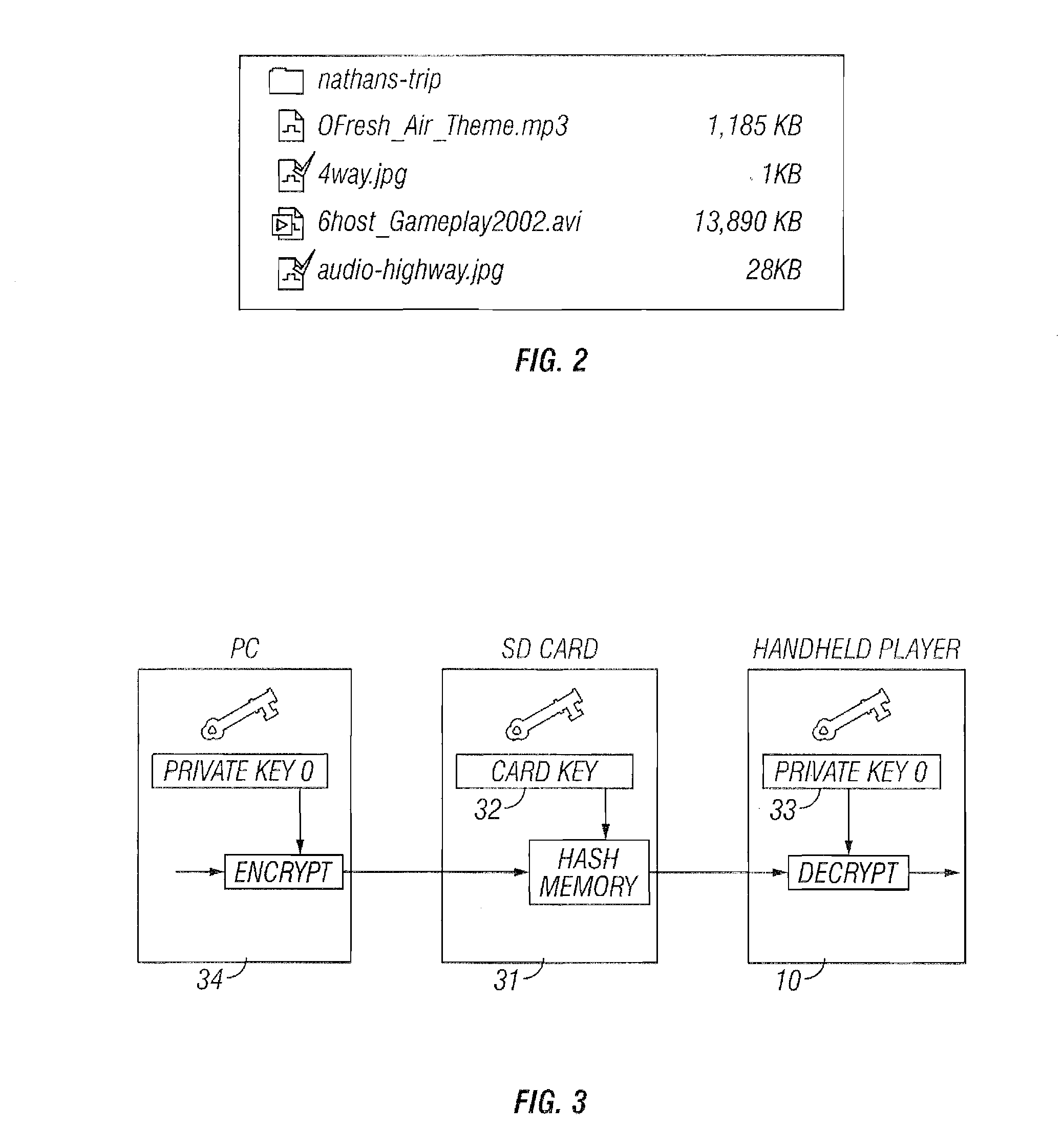

InactiveUS20060274835A1Reduce complexityTelevision system detailsPicture reproducers using cathode ray tubesVideo playerComputer graphics (images)

The invention provides a method and apparatus for coding information that is specifically adapted for smaller presentation formats, such as in a hand held video player. The invention addresses, inter alia, reducing the complexity of video decoding, implementation of an MP3 decoder using fixed point arithmetic, fast YcbCr to RGB conversion, encapsulation of a video stream and an MP3 audio stream into an AVI file, storing menu navigation and DVD subpicture information on a memory card, synchronization of audio and video streams, encryption of keys that are used for decryption of multimedia data, and very user interface (Ul) adaptations for a hand held video player that implements the improved coding invention herein disclosed.

Owner:INTERNET ENTERTAINMENT LLC

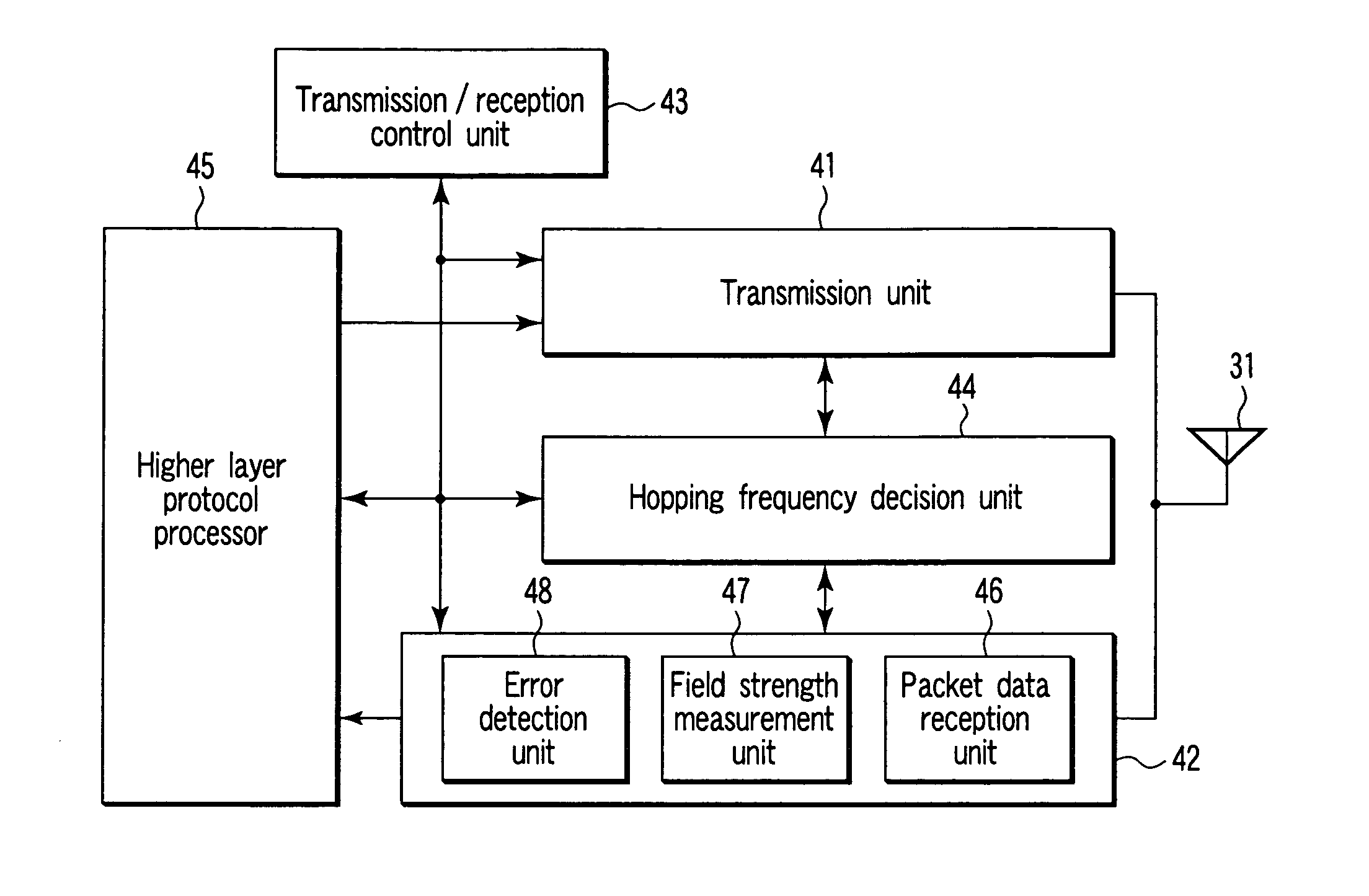

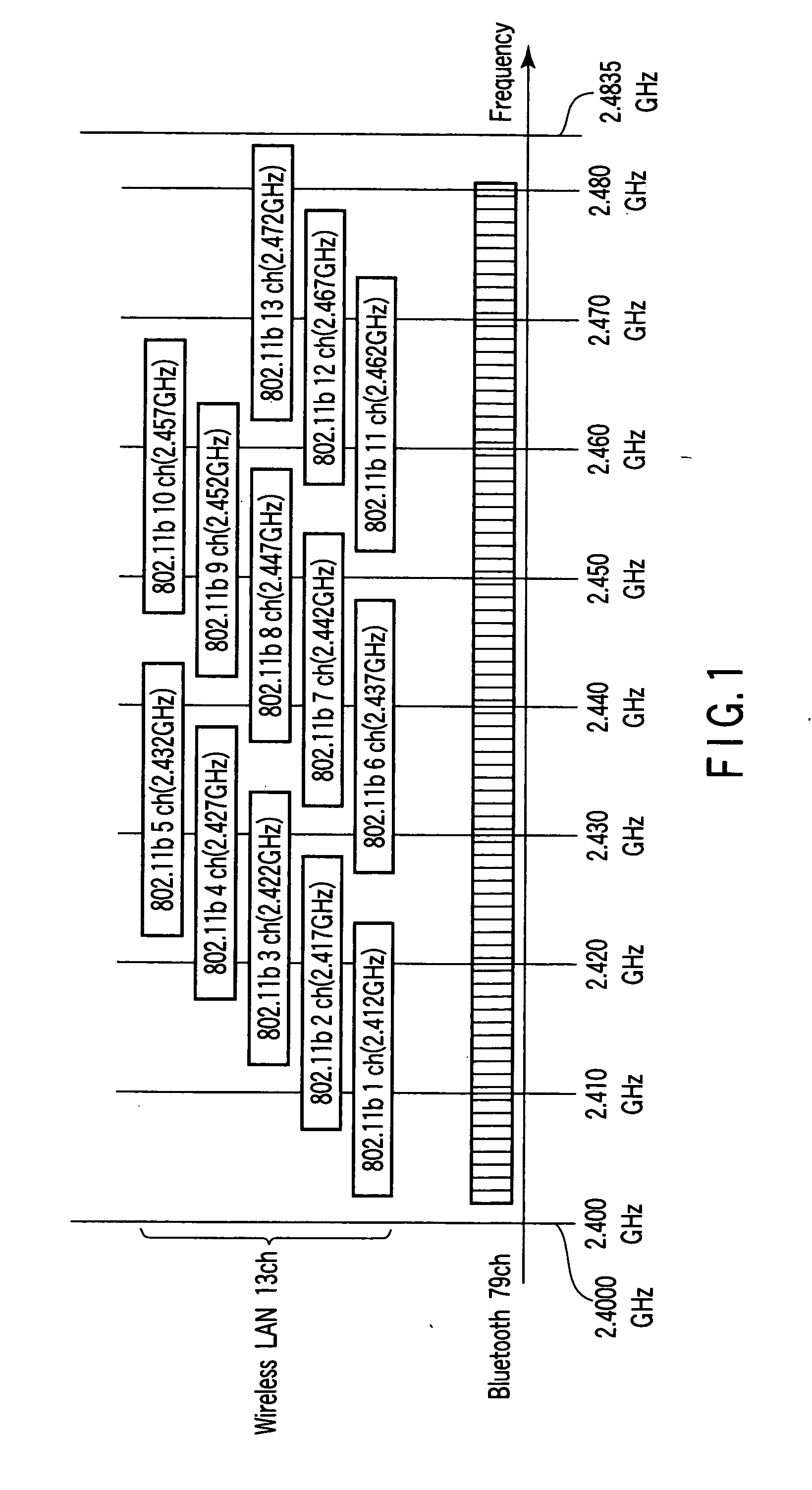

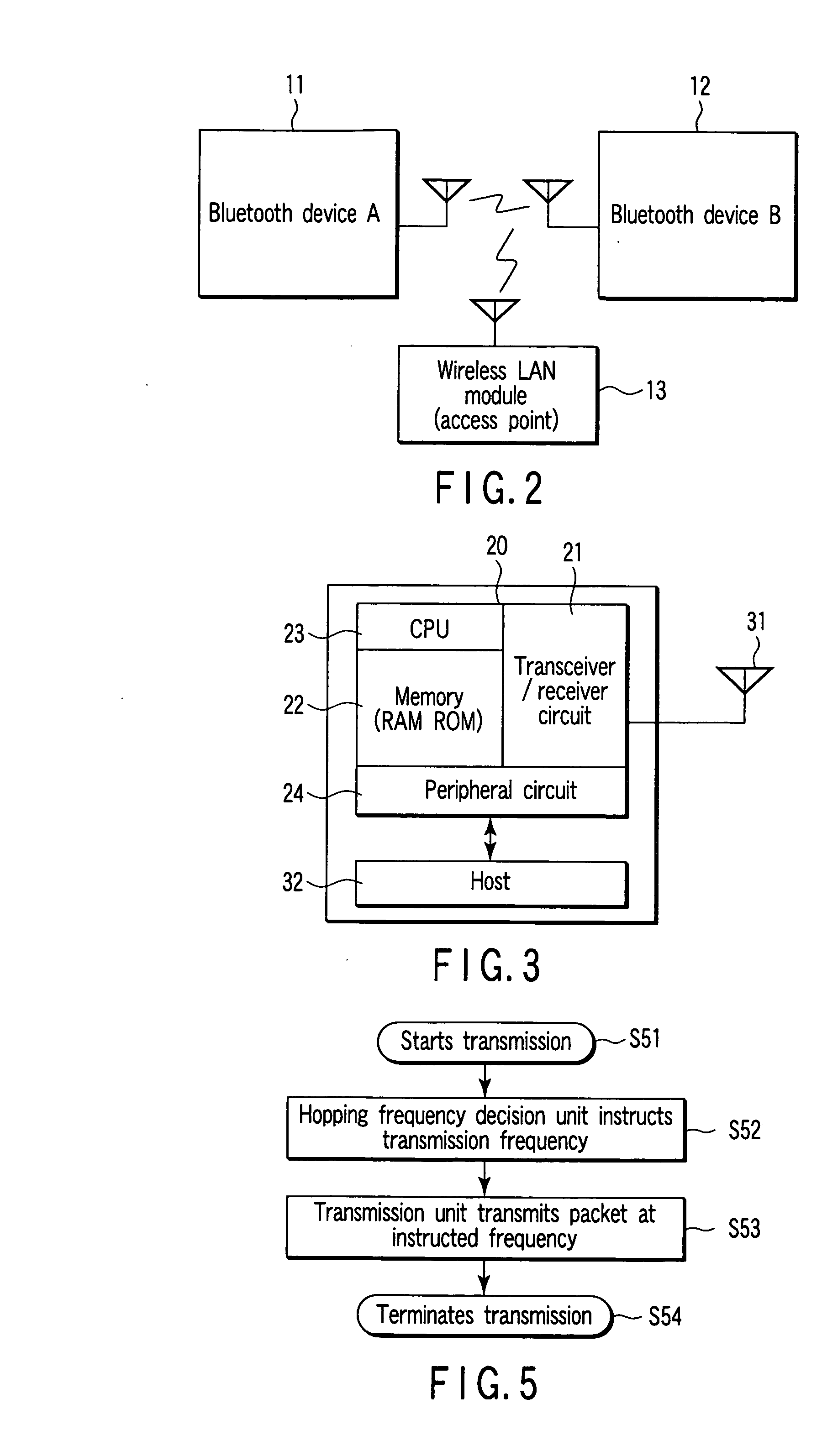

Radio communication device and semiconductor integrated circuit device used for the same

A semiconductor integrated circuit for a radio communication terminal sequentially uses a plurality of frequency channels by instructions from a hopping frequency decision unit to receive packet data by a reception unit. When the integrated circuit cannot detect the head of the packet data in reception operations, the integrated circuit cannot receive packet data should be received originally then assumes that the received packet data is a packet error. And the integrated circuit calculates packet error rates for each frequency channel on the basis of the number of times of reception operations performed for each frequency channel and of the number of times of packet errors to estimate channel qualities by using the packet error rates.

Owner:KK TOSHIBA

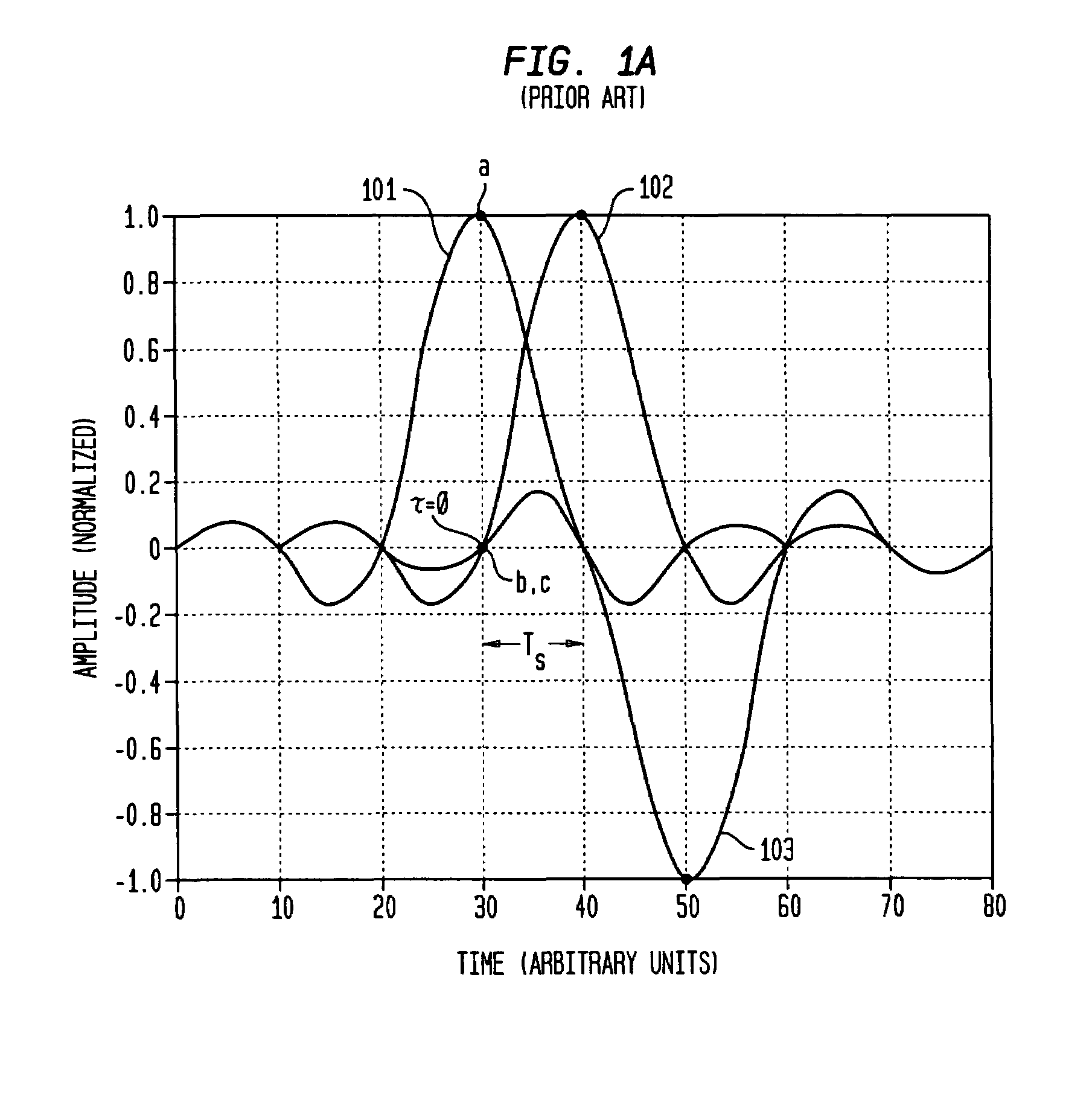

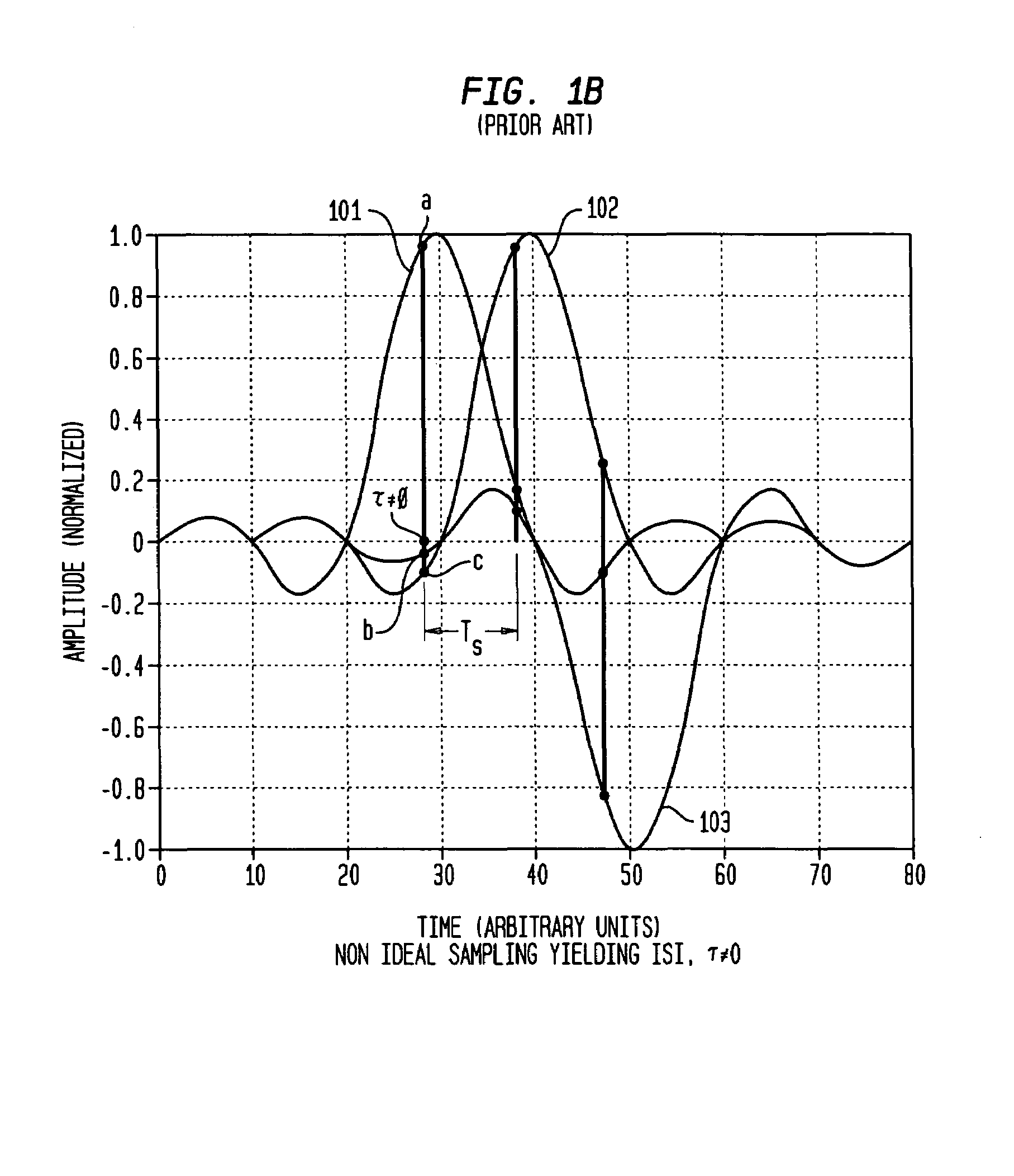

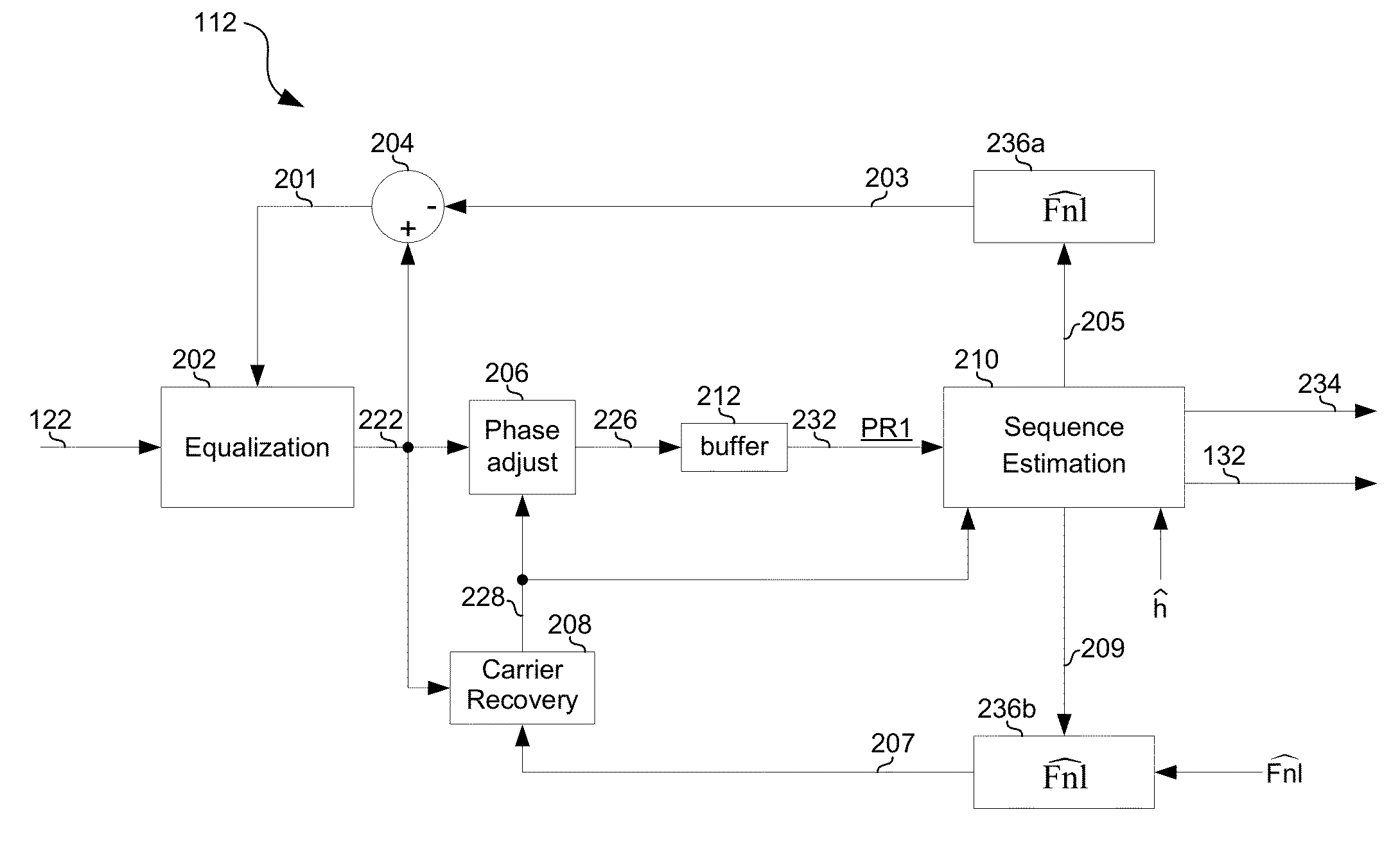

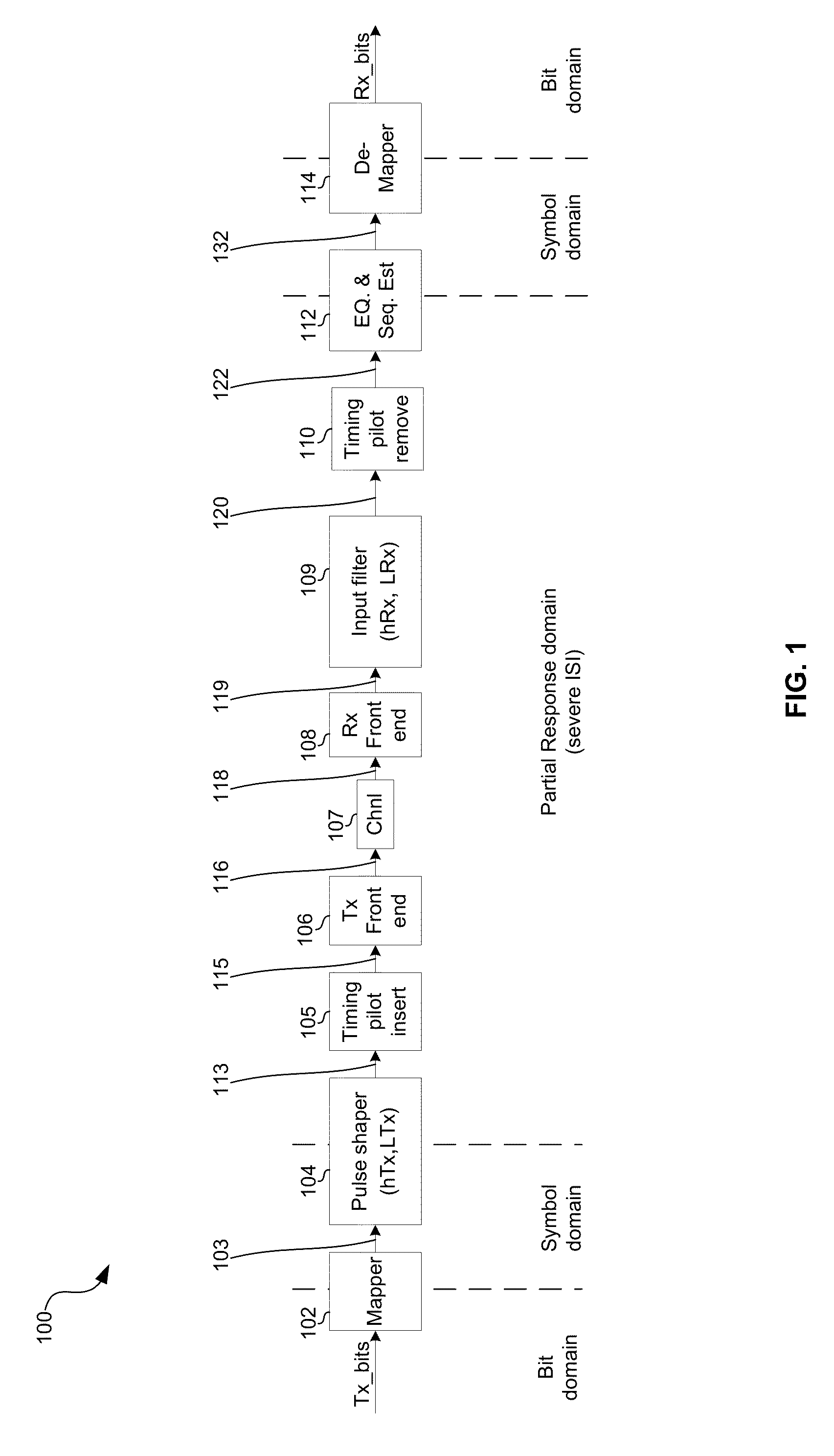

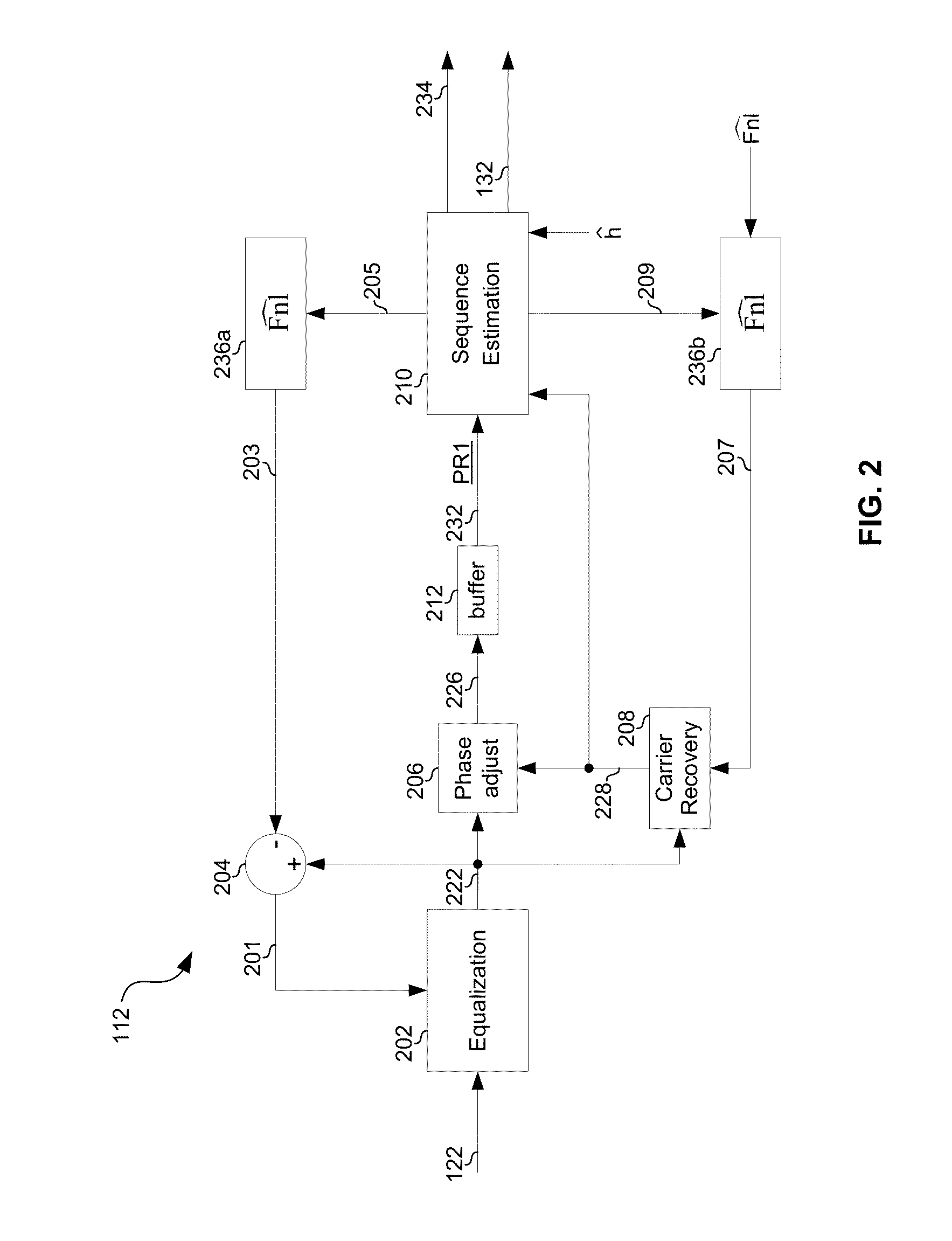

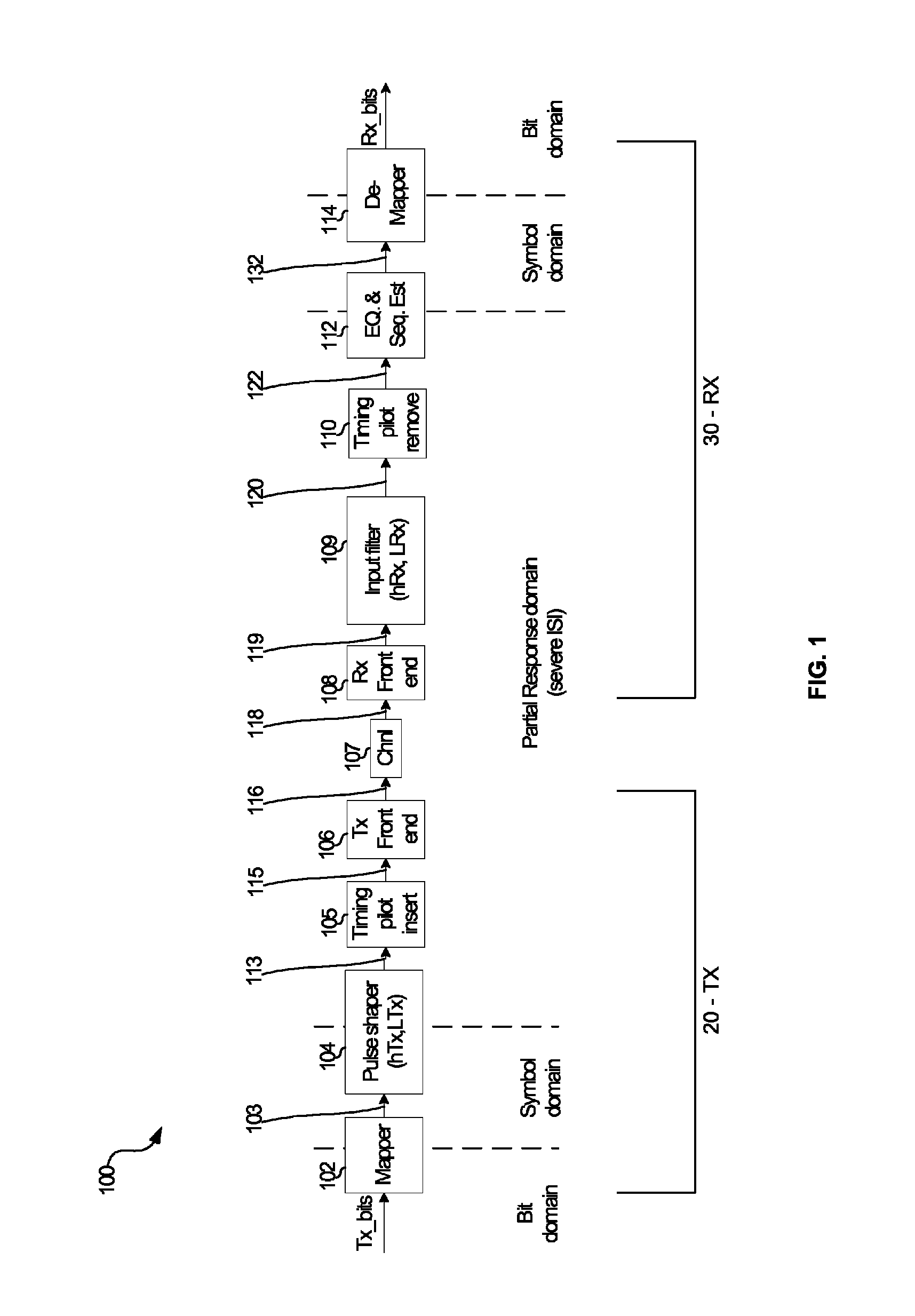

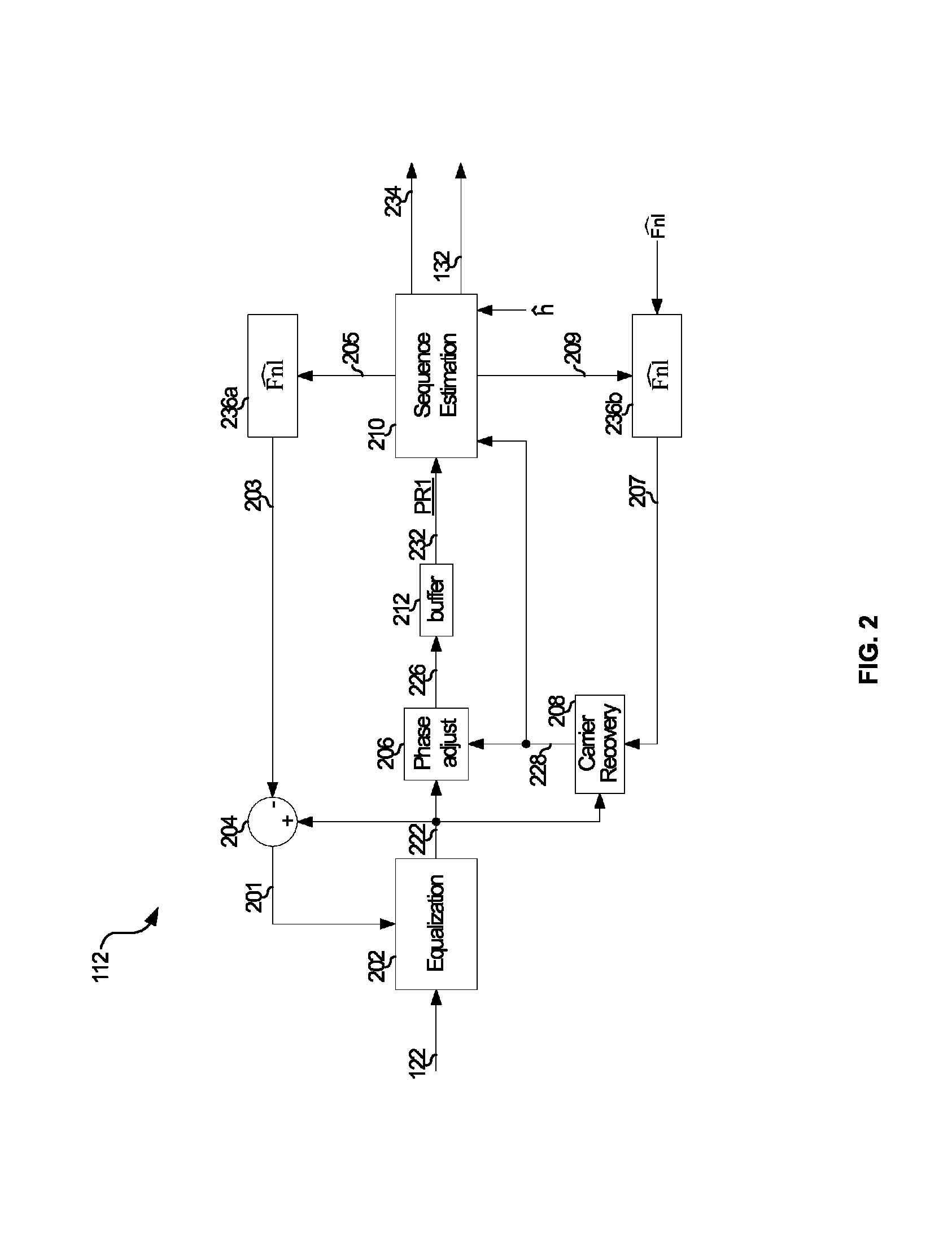

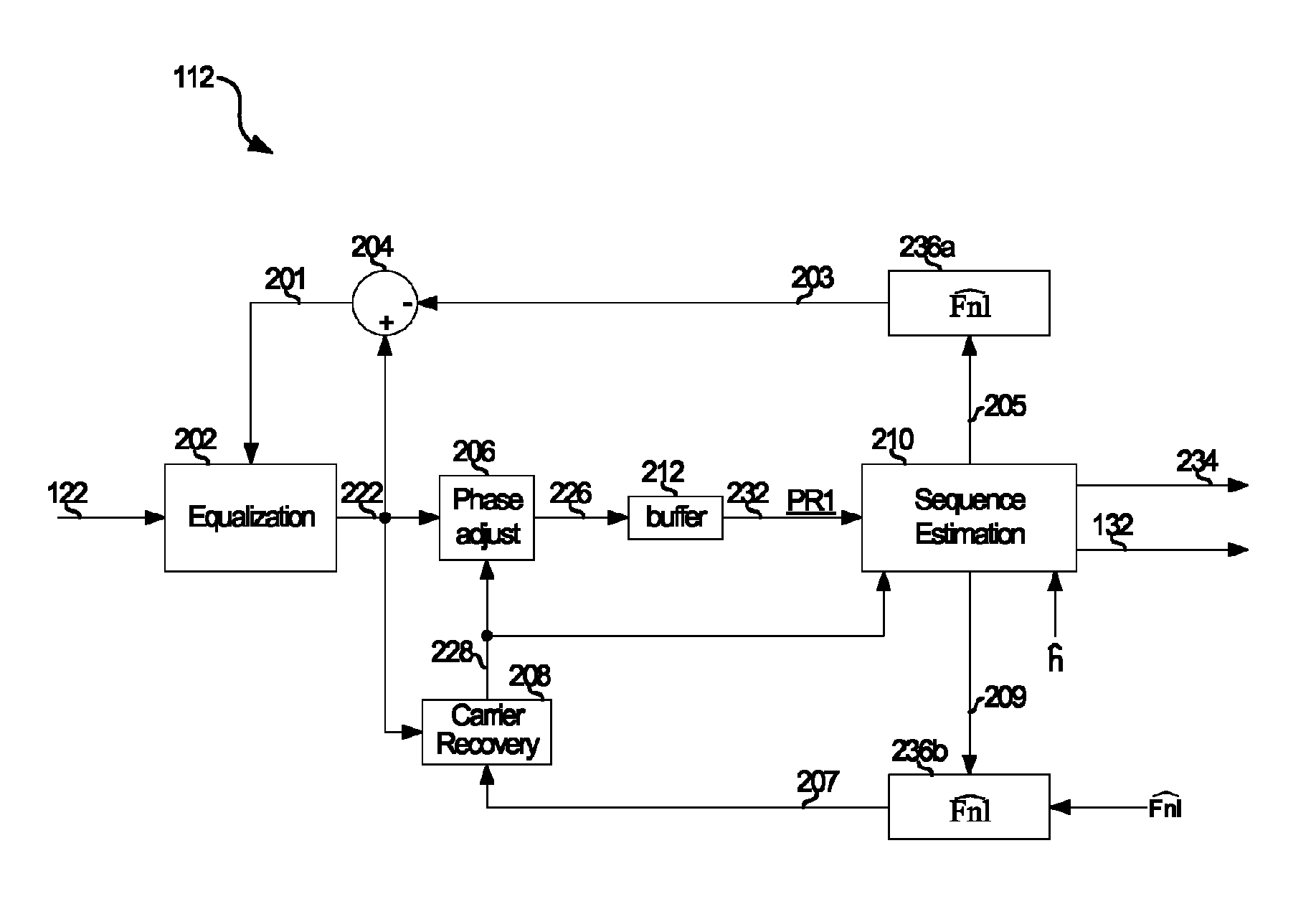

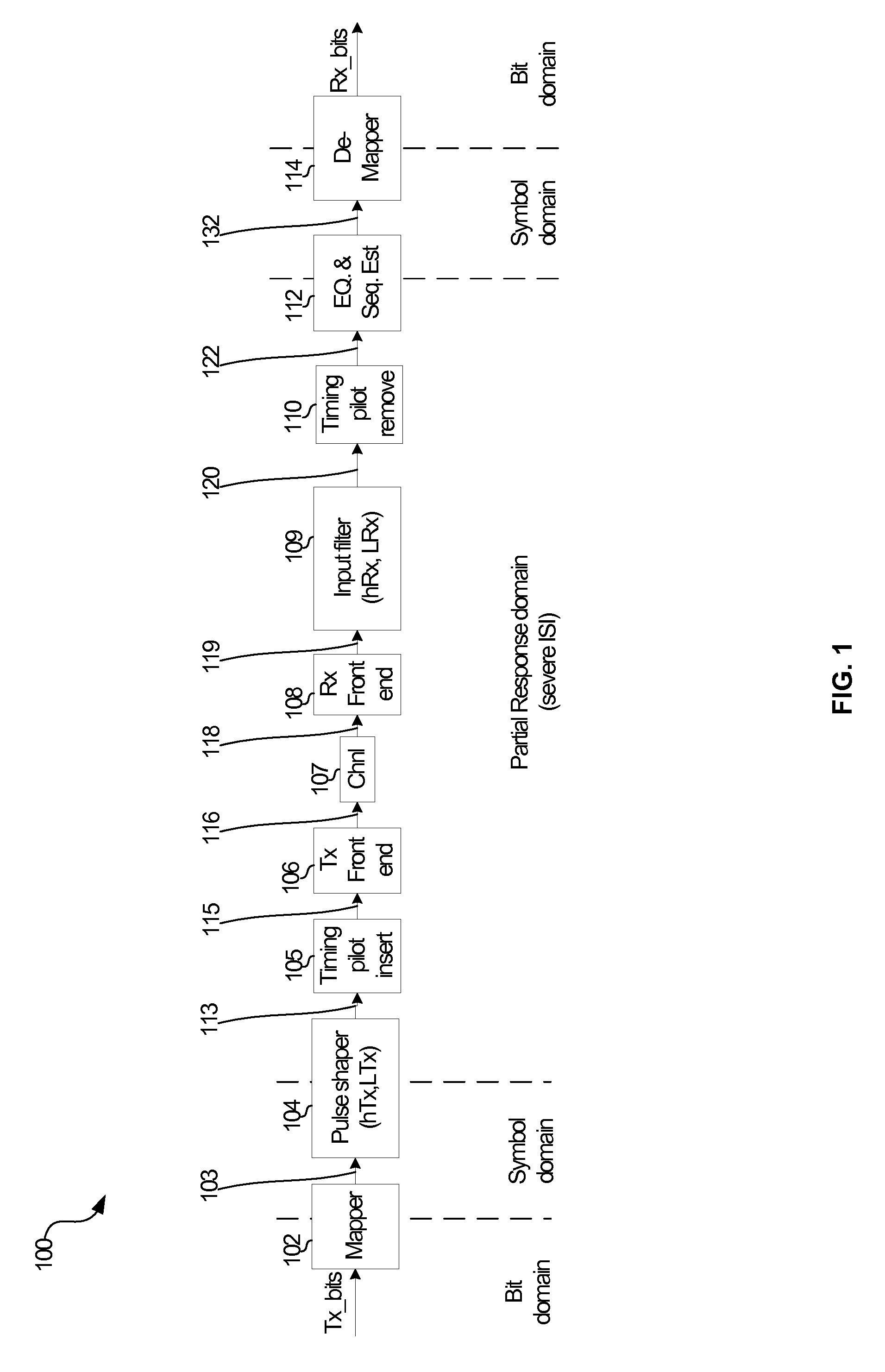

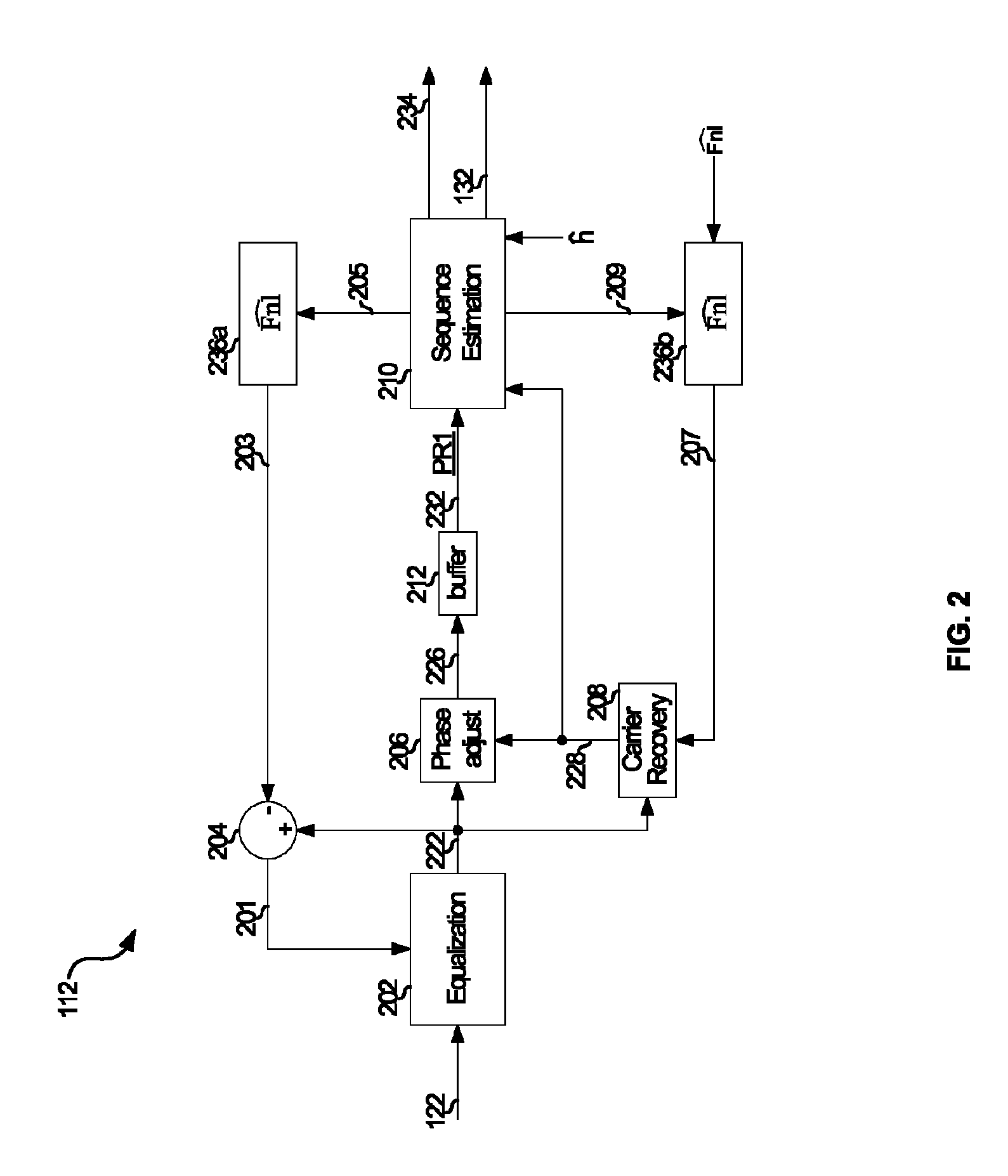

Highly-spectrally-efficient receiver

InactiveUS8526523B1Transmitters monitoringReceivers monitoringSignal-to-noise ratio (imaging)Pulse shaping

A receiver may be operable to receive a QAM-based, inter-symbol correlated (ISC) signal at a signal-to-noise ratio of between 29 dB and 31 dB and process the QAM-based, ISC signal to output estimated symbols at a symbol error rate of between 2×10−1 and 1×10−3. The QAM-based, ISC signal may be a partial response signal generated by passing a first signal through a partial response pulse shaping filter. The partial response pulse shaping filter may provide greater capacity than a capacity achieved by passing the first signal through a root-raised-cosine-based pulse shaping filter. The receiver may comprises an input filter, and the processing of the QAM-based, ISC signal may comprises filtering the QAM-based, ISC signal via a filter configured to achieve a desired total partial response in combination with the partial response pulse shaping filter.

Owner:AVAGO TECH INT SALES PTE LTD

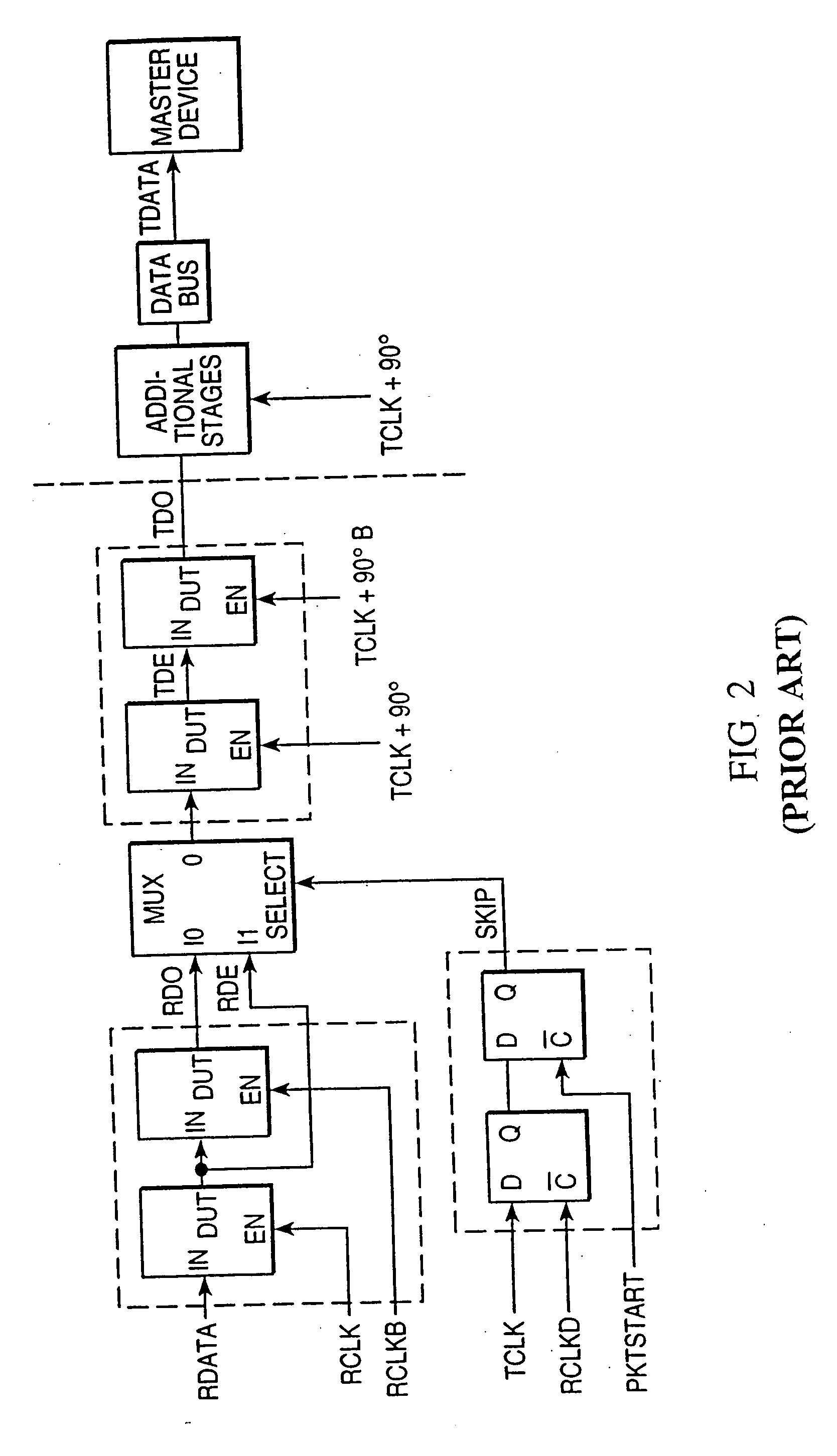

Method and apparatus for fail-safe resynchronization with minimum latency

InactiveUS20060022724A1Guaranteed uptimeMinimizes shiftingSynchronisation information channelsPulse automatic controlData latencyVoltage shift

Owner:RAMBUS INC

Method and apparatus for sampled optical signal monitoring

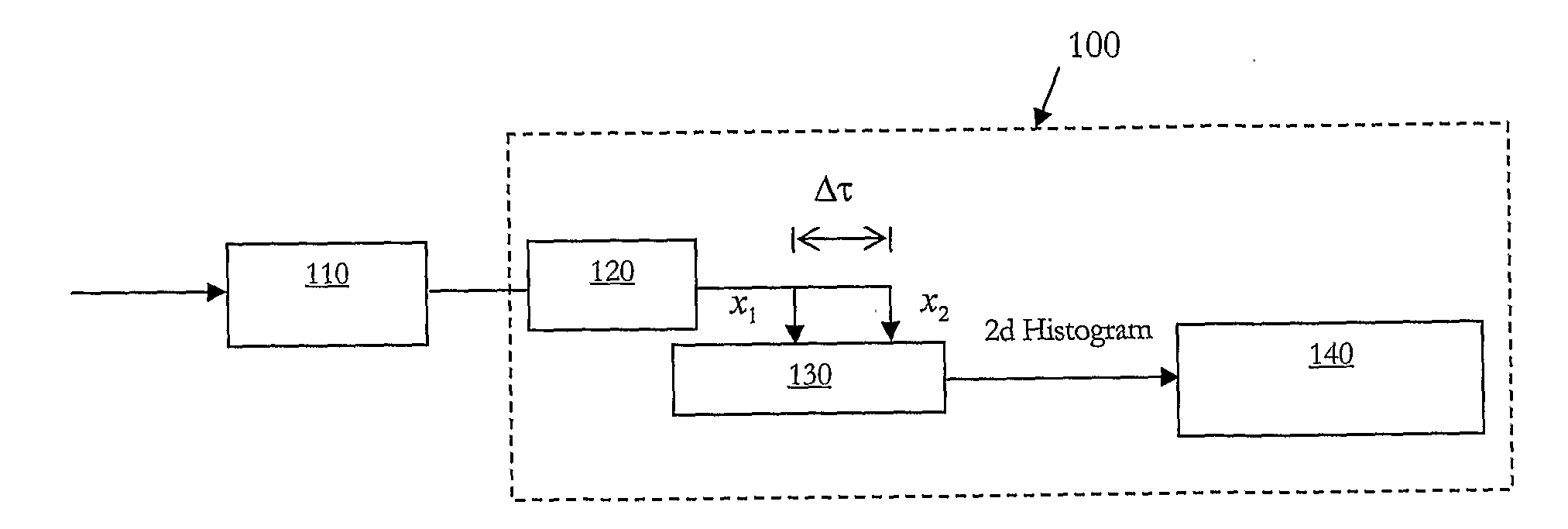

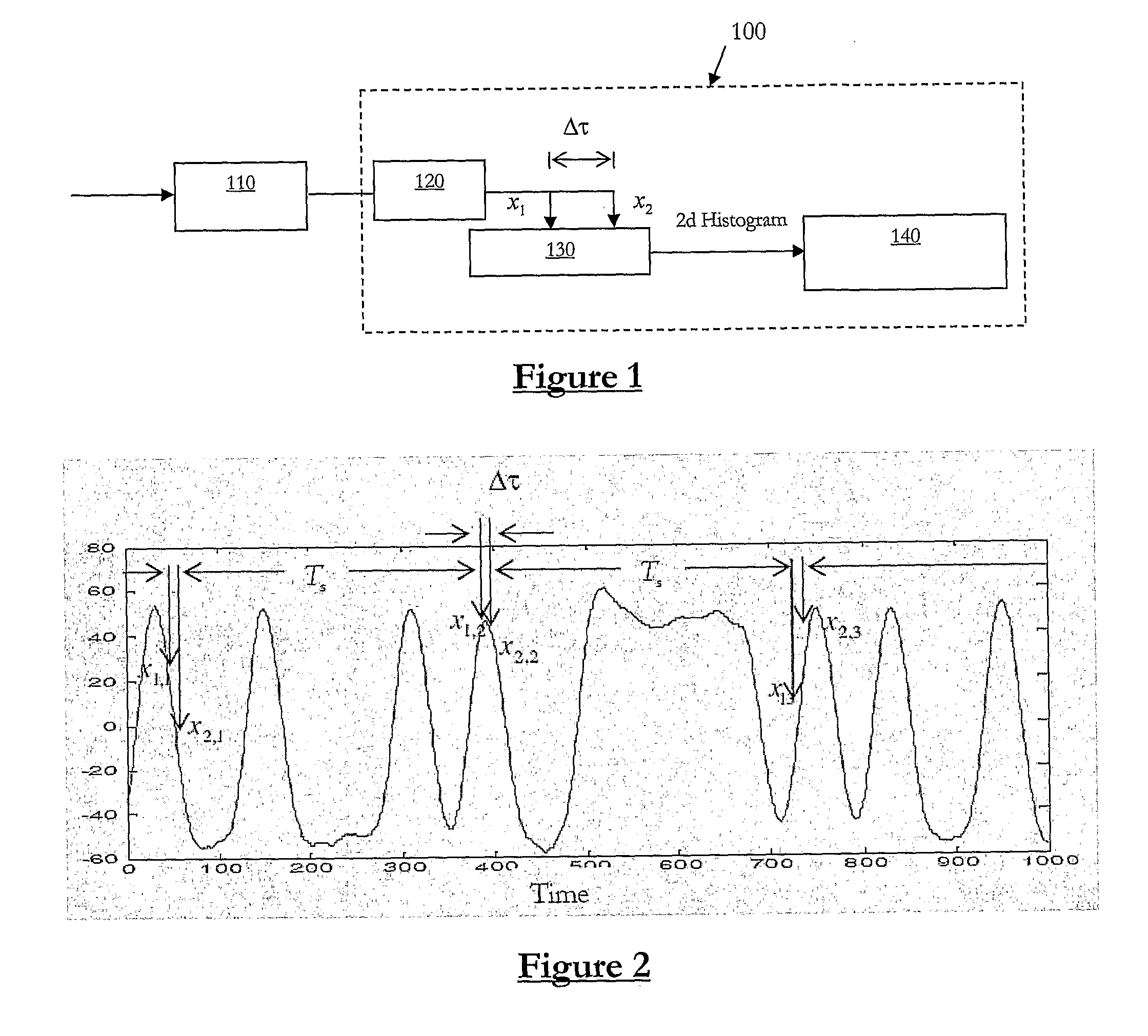

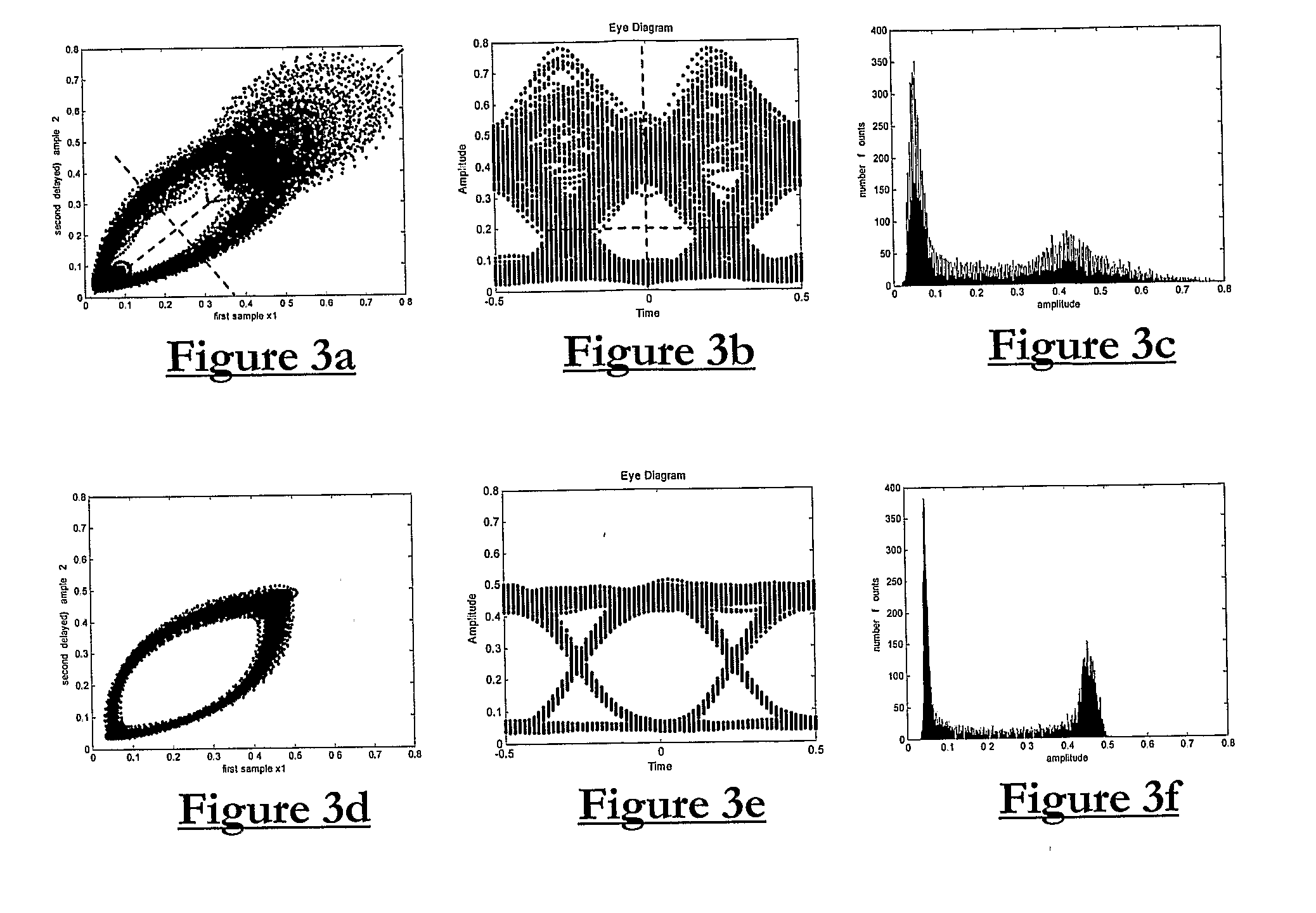

InactiveUS20090028554A1High receiver bandwidthLow costSynchronisation error detectionDigital computer detailsSignal qualityTime delays

Monitoring an optical signal comprises sampling the optical signal from two or more distinct tap points to retrieve a sample set. Multiple such sample sets are obtained over time. A joint probability distribution or phase portrait of the sample sets is assessed for indications of optical signal quality. The tap distinction can be polarisation, for example to determine OSNR, or frequency. The tap distinction can be a time delay, which can enable diagnostic differentiation between multiple impairments, such as OSNR, dispersion, PMD, jitter, Q, and the like. Machine learning algorithms are particularly suitable for such diagnosis, particularly when provided a two dimensional histogram of sample density in the phase portrait.

Owner:NICTA IPR

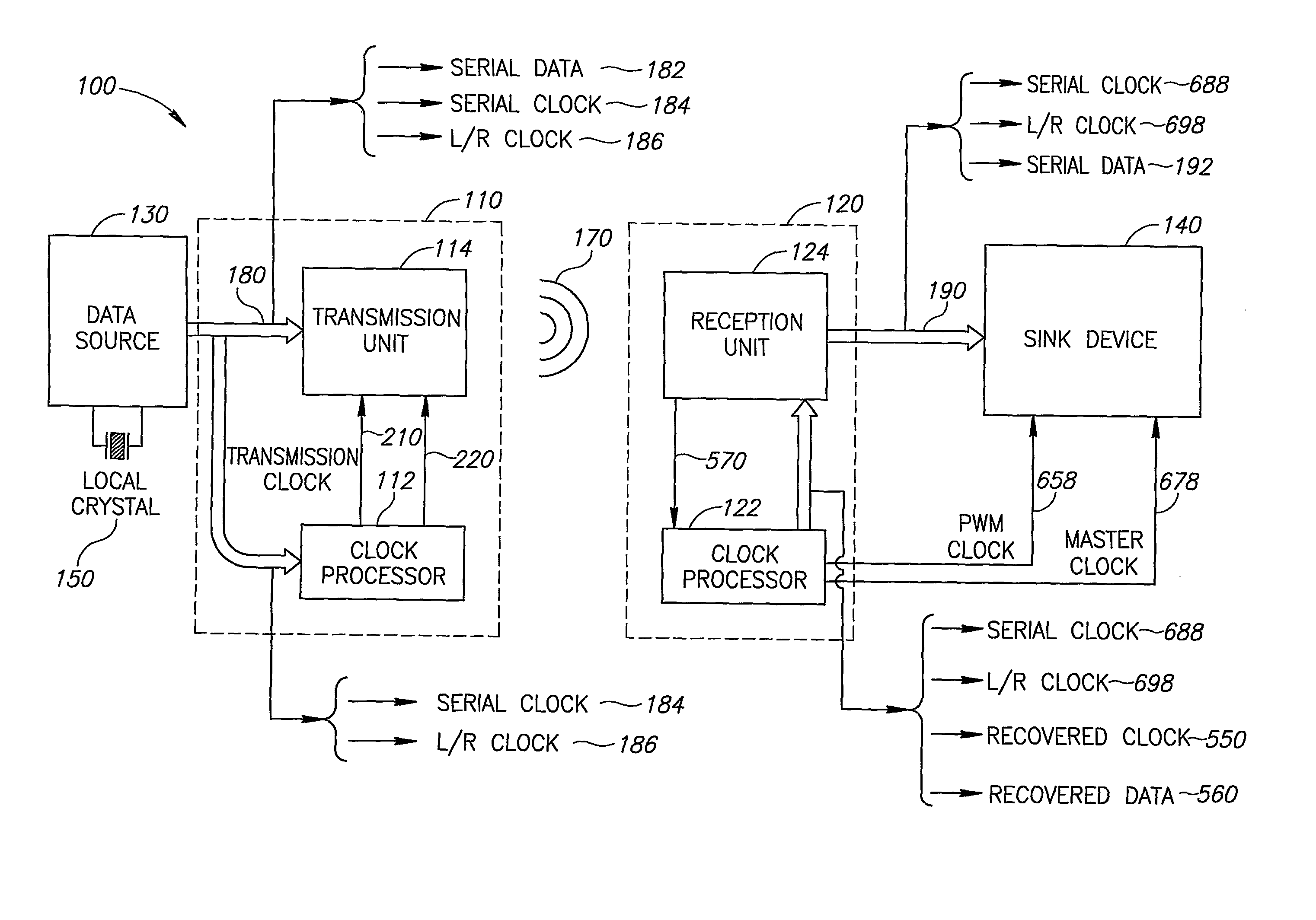

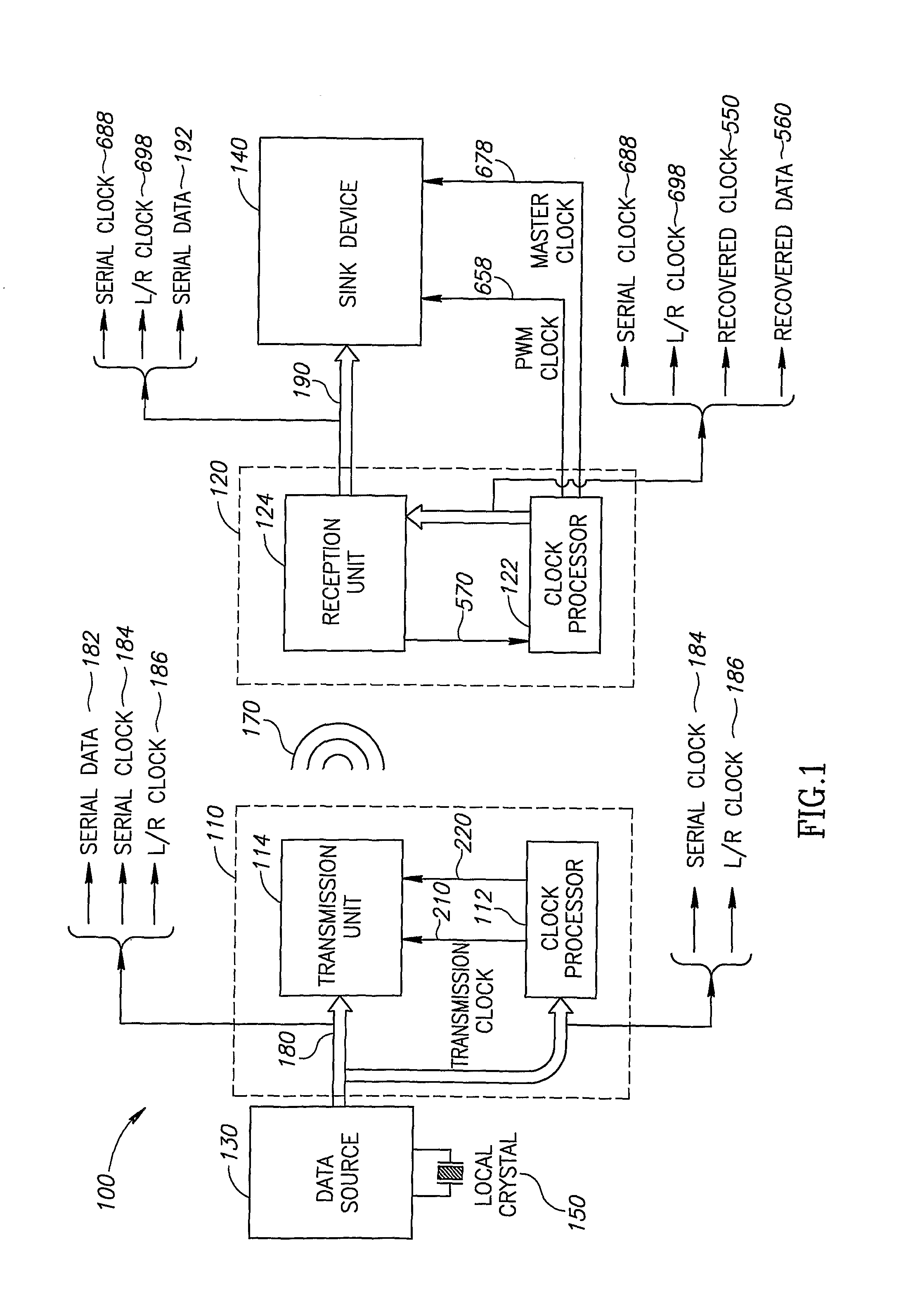

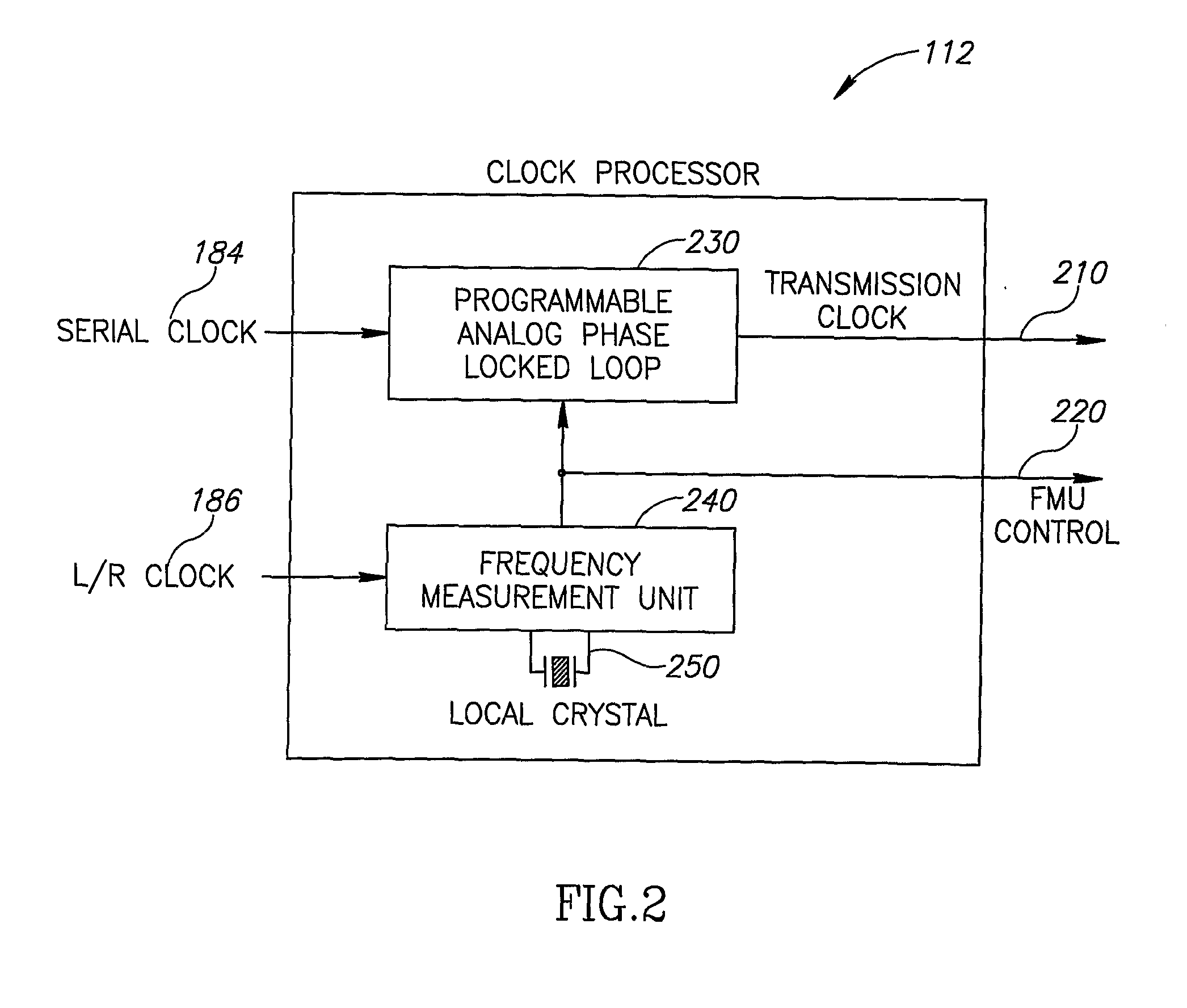

Low Jitter Clock Recovery from a Digital Baseband Data Signal Transmitted Over a Wireless Medium

InactiveUS20080212729A1Synchronisation error detectionCarrier regulationData streamWireless transmission

A system and method of transmitting a data stream from a data source over a baseband wireless communication system to one or more receivers. The receivers simultaneously recover the data and clock signals of the original data stream from the wireless transmitted data so that the data stream can be provided by the receivers to a data sink at the same rate as the original data stream, with low jitter performance.

Owner:INFRA

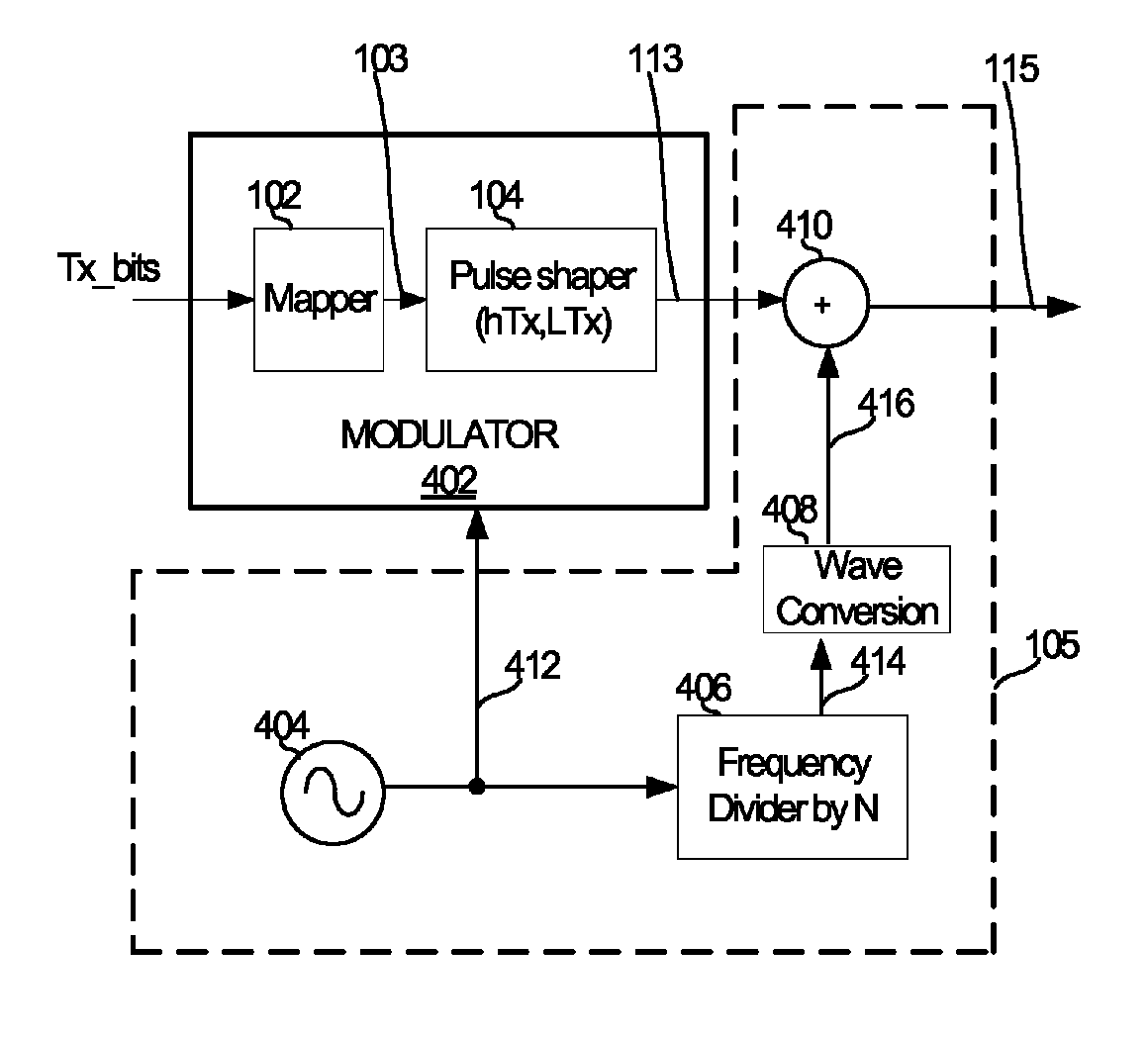

Timing pilot generation for highly-spectrally-efficient communications

Methods and systems are provided for timing synchronization for reception of highly-spectrally efficient communications. An example method may include, mapping, in a transmitter, a plurality of transmit bits to a plurality of symbols at a symbol rate that is based on an oscillator signal. The plurality of symbols may be processed via a filter. The processing may result in an inter-symbol correlated (ISC) signal. The oscillator signal may be frequency divided to generate one or more pilot signals having a frequency that is a sub-harmonic of a frequency of the oscillator signal. The pilot signal may be injected into the ISC signal. The injecting may result in an ISC signal with timing carrier. The ISC signal with timing carrier may be transmitted. Gain of the one or more pilot signals may be adjusted based on a spectral mask value associated with the transmitting.

Owner:AVAGO TECH INT SALES PTE LTD

Coarse phase estimation for highly-spectrally-efficient communications

Owner:AVAGO TECH INT SALES PTE LTD

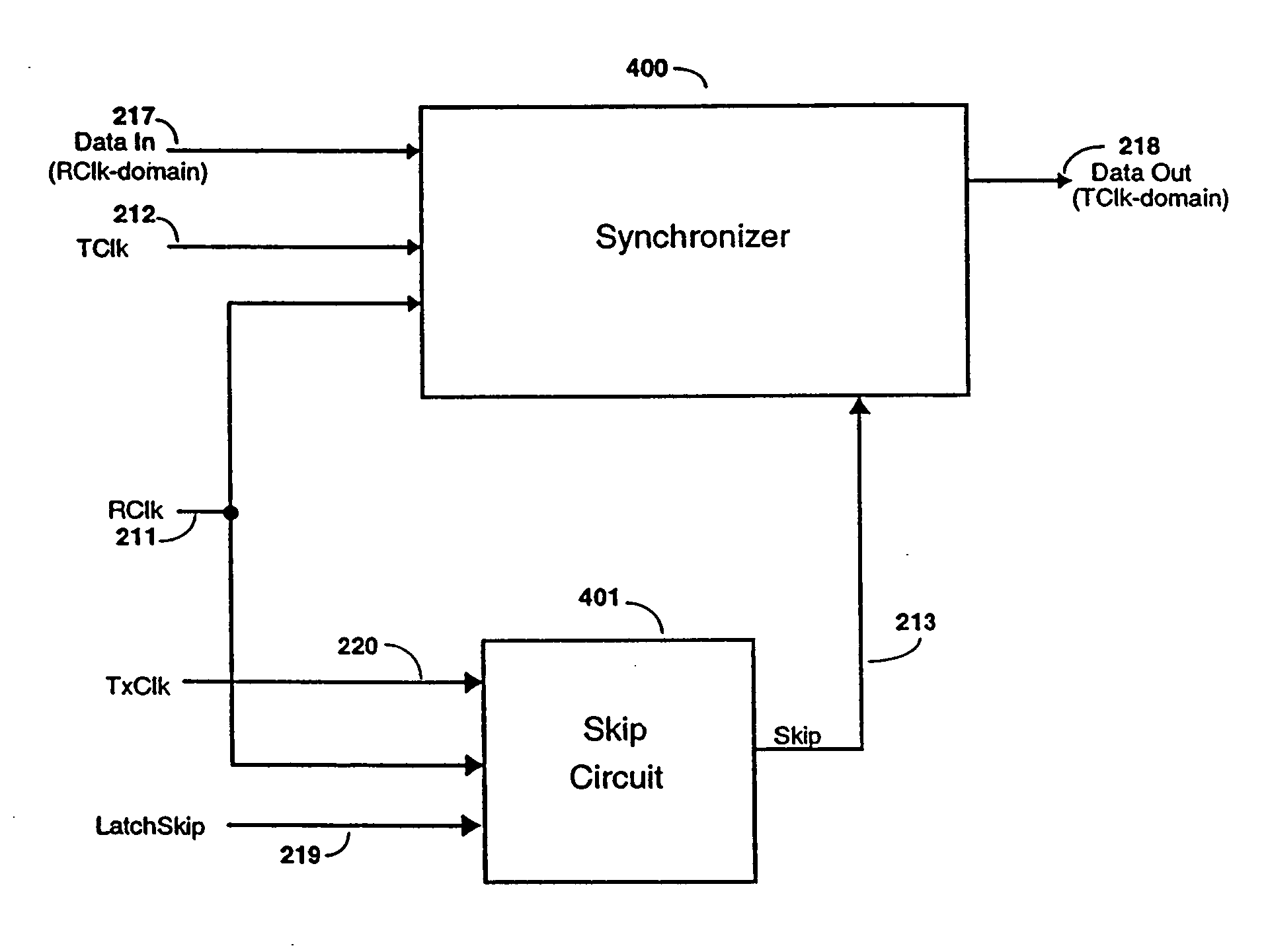

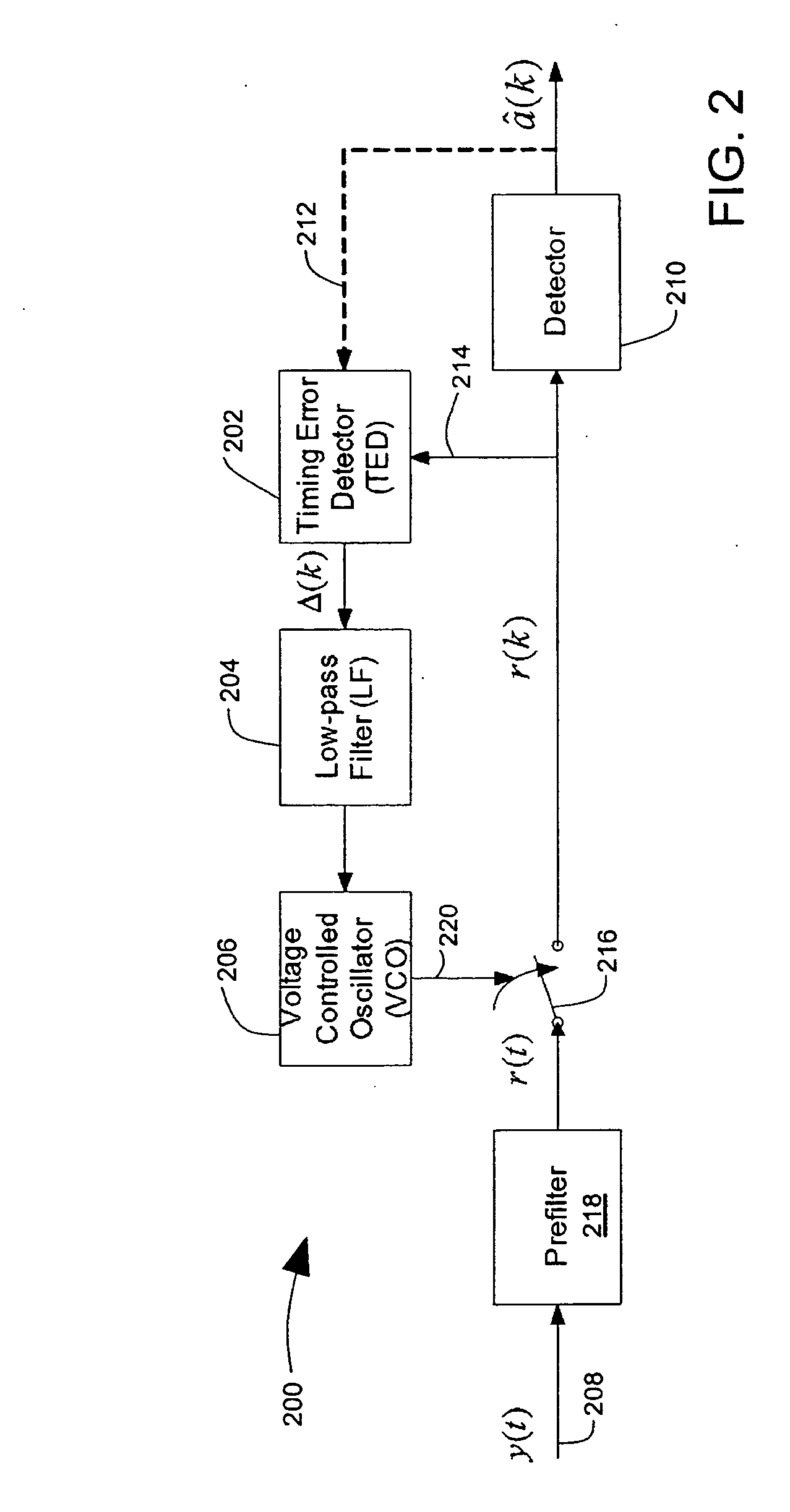

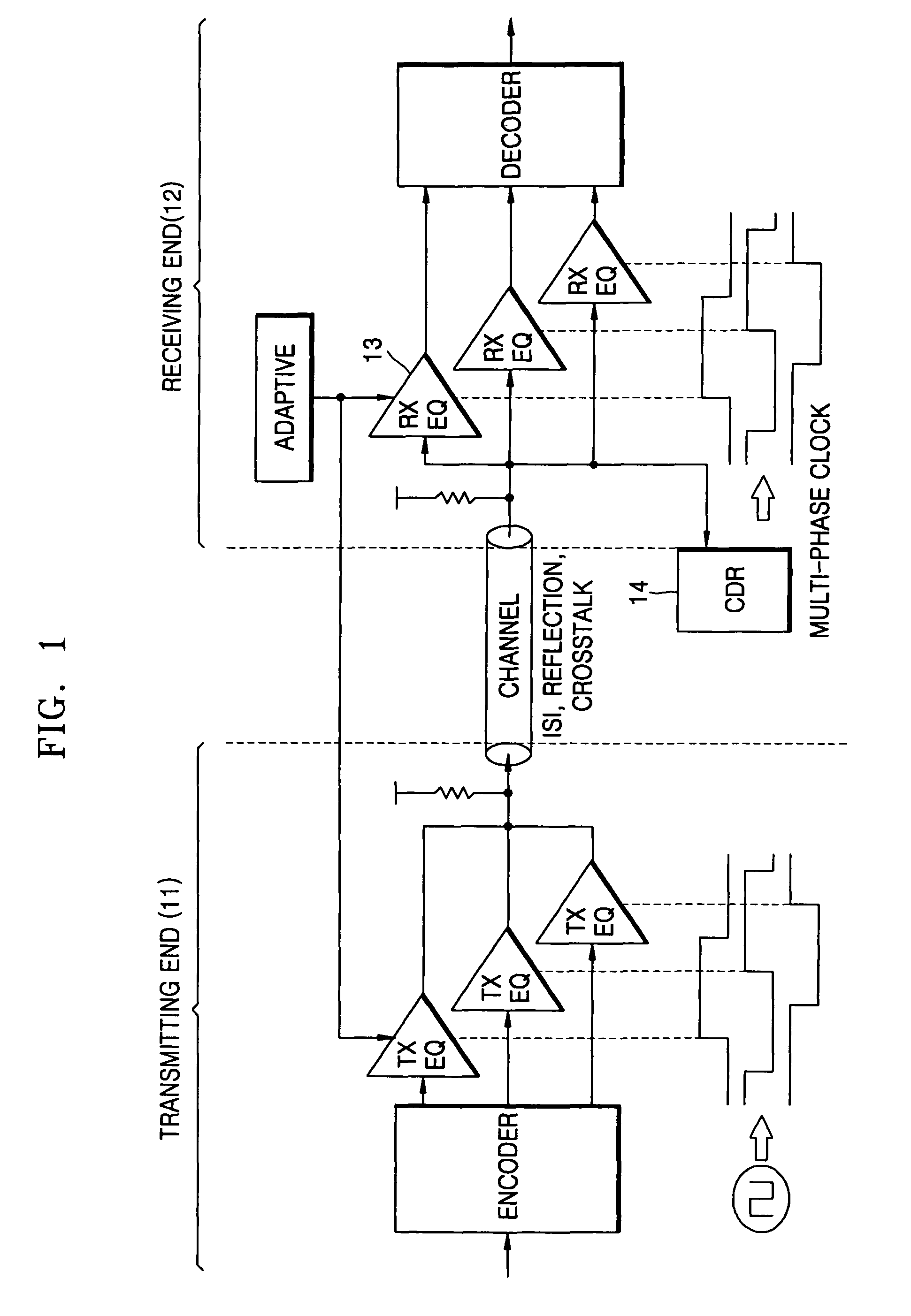

Timing recovery in a parallel channel communication system

ActiveUS20060210002A1Modification of read/write signalsSynchronisation error detectionCommunications systemDiscrete-time signal

A parallel channel timing recovery circuit. The parallel timing recovery circuit comprises multiple prefilters receiving parallel channel outputs and providing prefilter outputs. Multiple sampling filters receive the prefilter outputs and provide multiple discrete time signal samples. A self-timing circuit has multiple inputs receiving the multiple discrete time signal samples. The self-timing circuit provides a sampling control output to the sampling filters. The sampling control output is based on a composite of the multiple discrete time signal samples. Each of the sampling filters generates a discrete time signal sample based on the sampling control output and the prefilter outputs.

Owner:SEAGATE TECH LLC

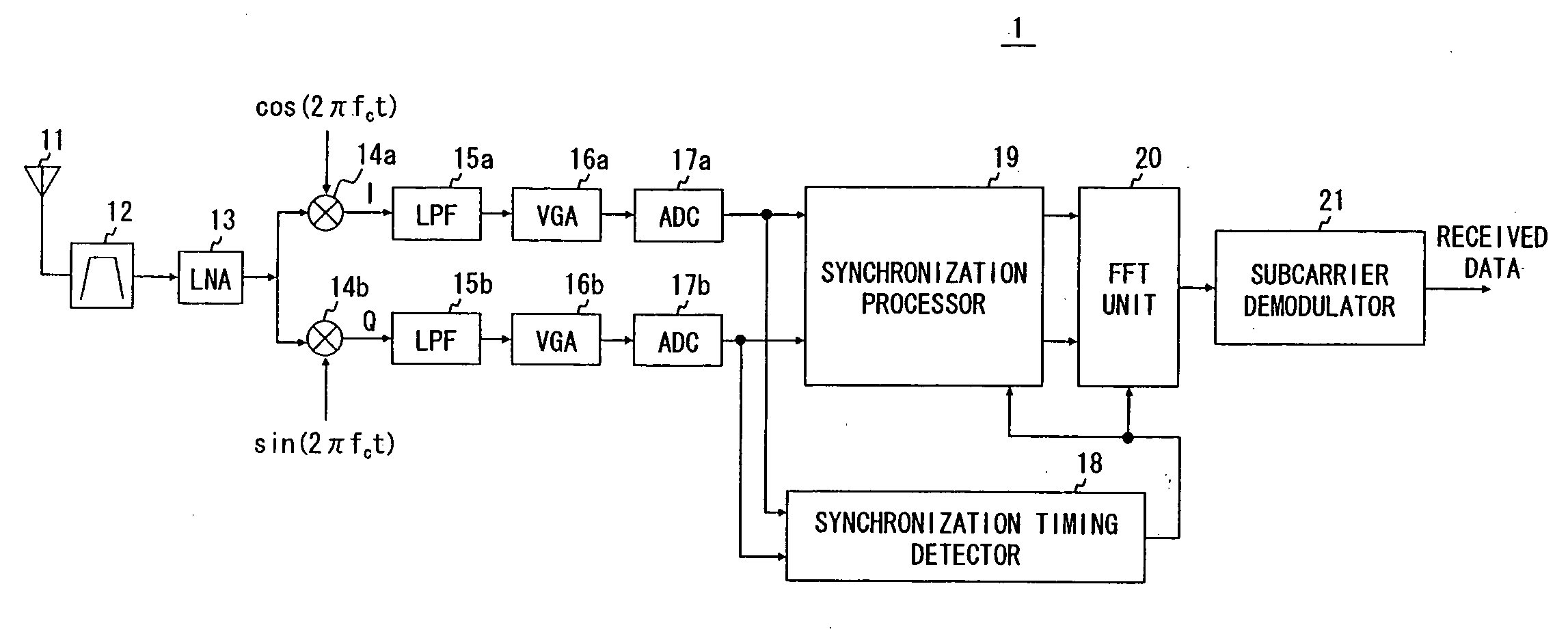

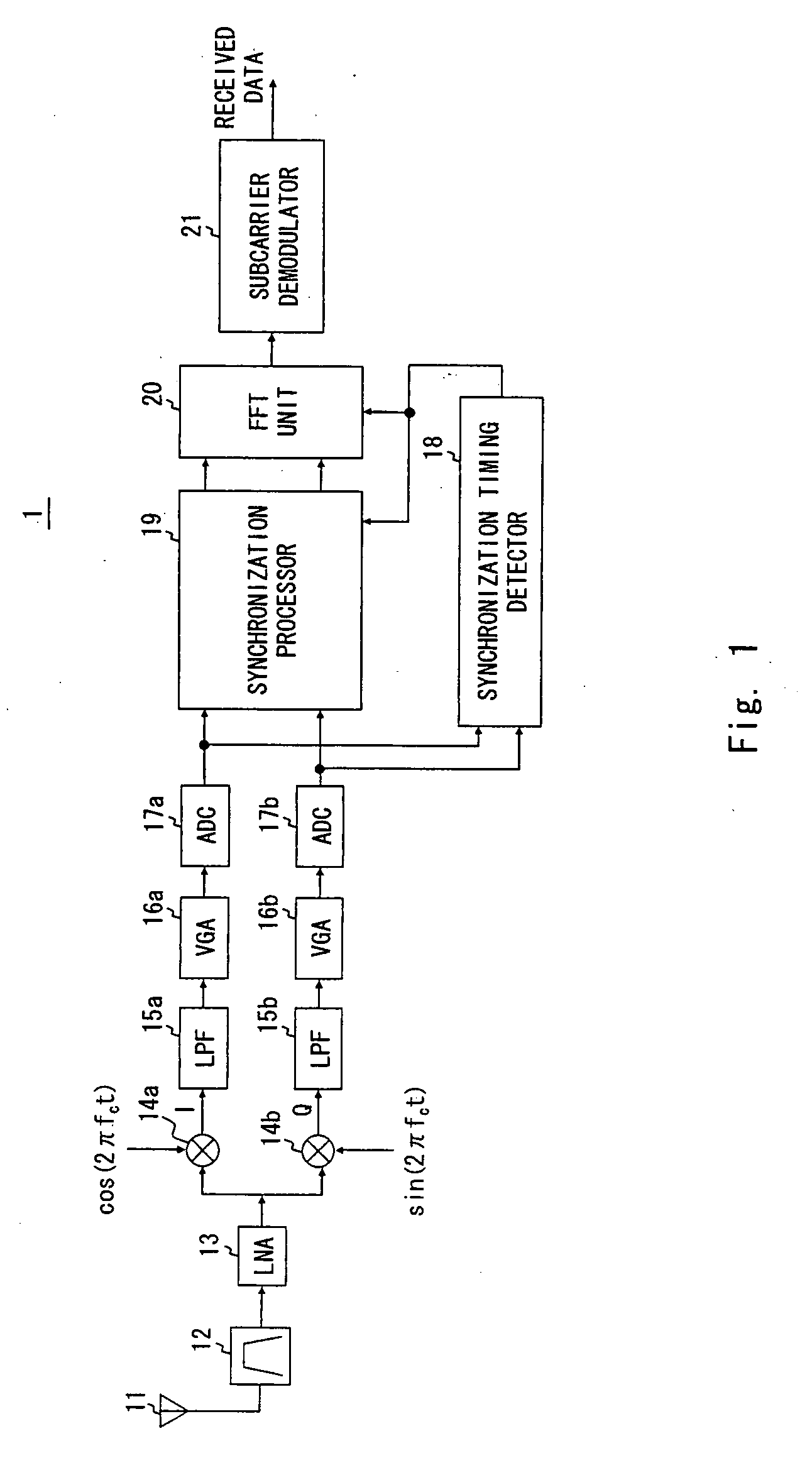

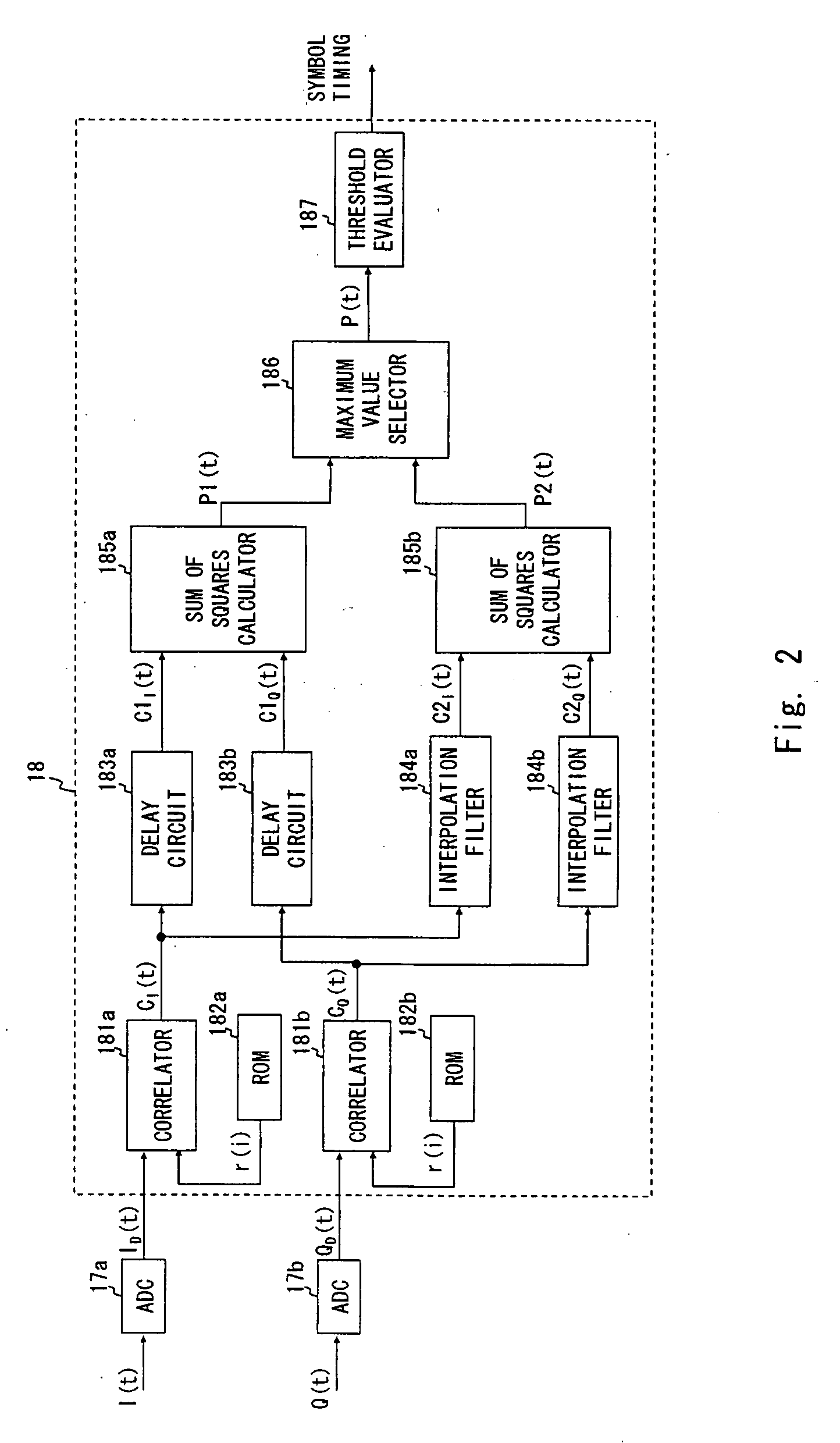

Synchronization timing detecting apparatus, receiving apparatus, and synchronization timing detecting method

InactiveUS20070211835A1Reduced sampling rate requirementsMaintain accuracySynchronisation error detectionTime-division multiplexSelf correlationComputer science

A synchronization timing detecting apparatus includes a correlation calculator configured to generate a first correlation value by calculating a cross-correlation between an input signal being sampled and a reference signal or an auto-correlation of the sampled input signal, an interpolation processor configured to generate a second correlation value interpolating a plurality of the first correlation values having a different combination of sampling points of the input signal, and a detector to detect a synchronization timing based on the first and the second correlation values.

Owner:RENESAS ELECTRONICS CORP

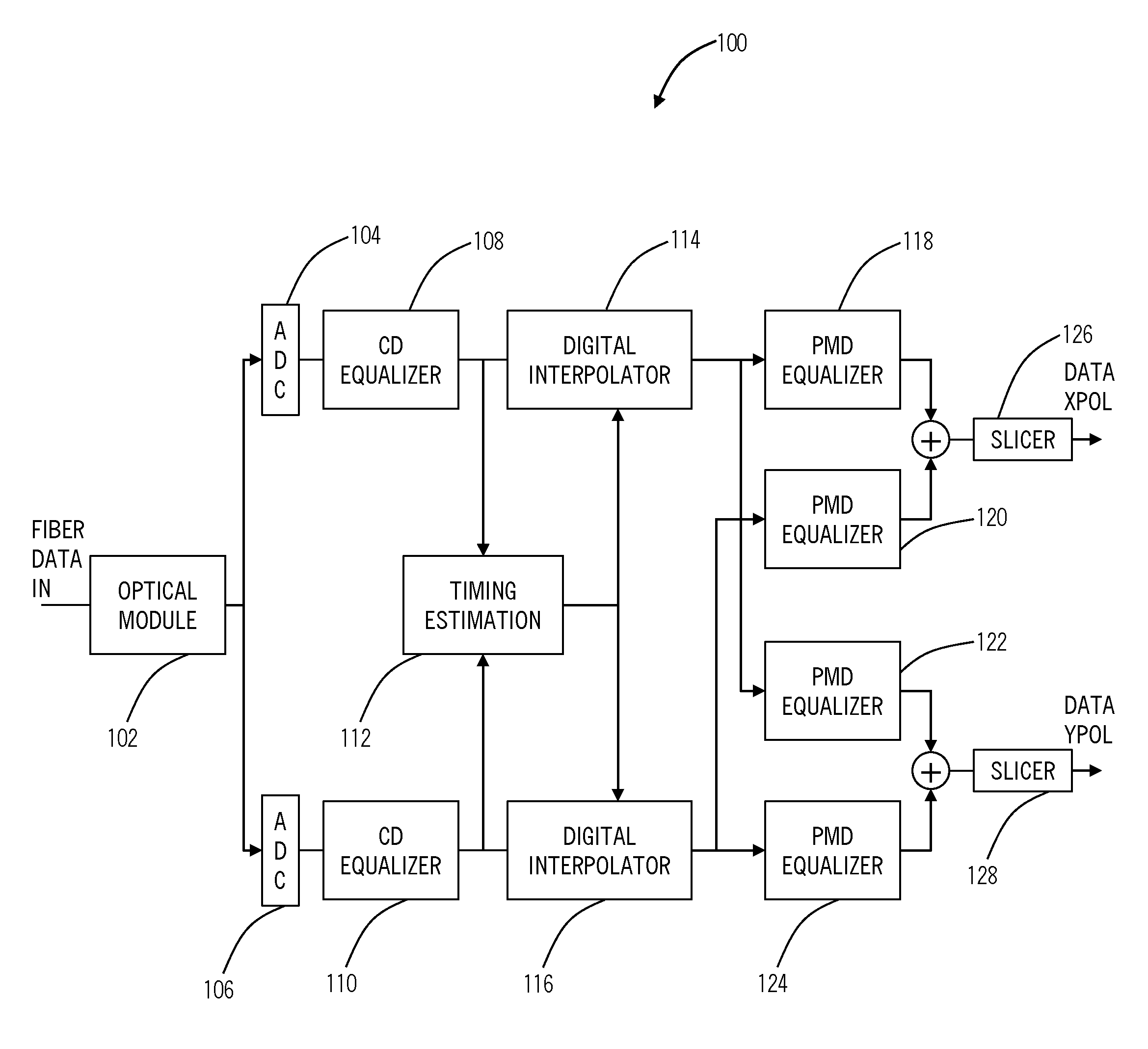

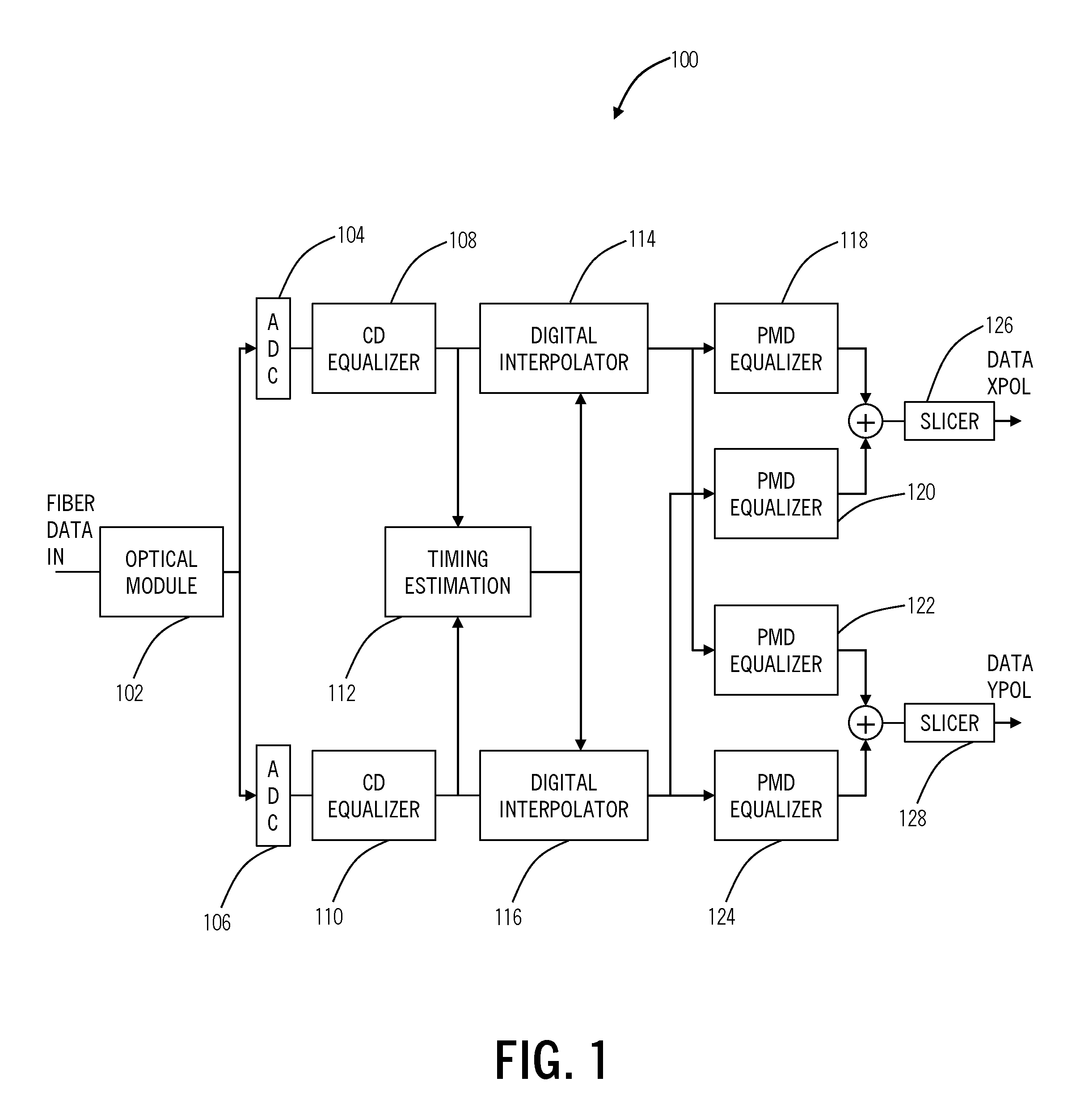

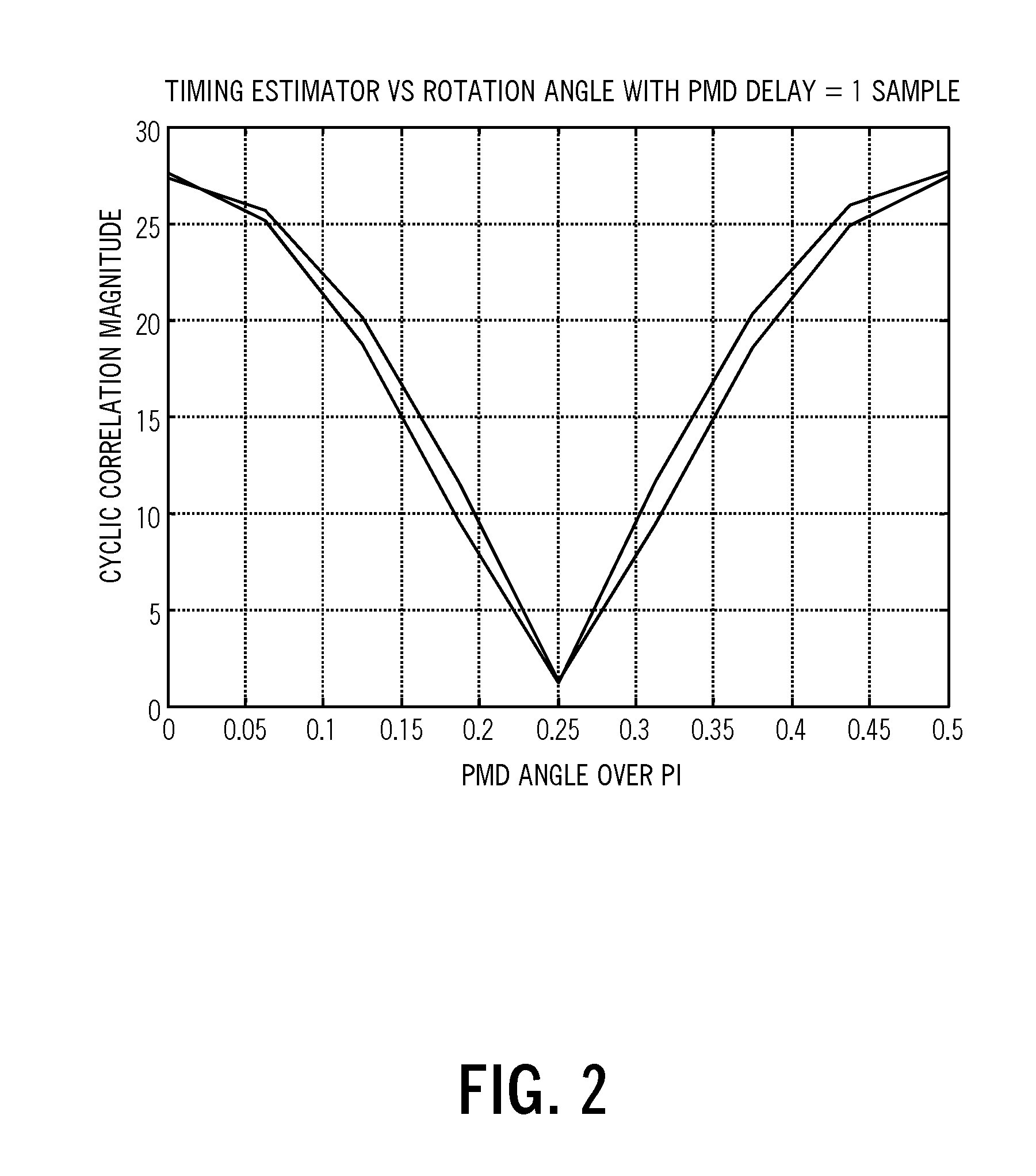

Timing recovery in presence of optical impairments and optimization of equalization based on timing recovery moment strengths

ActiveUS20110268459A1Minimizing hardwarePolarisation multiplex systemsSynchronisation error detectionTransceiverEngineering

The present disclosure provides timing recovery in optical systems in the presence of chromatic dispersion (CD), polarization mode dispersion (PMD), and polarization dependent loss (PDL) and to optimization of equalization settings based upon timing recovery moment strengths. A stable timing point may be determined in the presence of PMD and PDL impairments, even when the direct estimate of timing becomes unreliable. This determination may be performed entirely in the digital domain providing precise, predictable performance. Also, the present invention utilizes a monotonic relationship between the timing metric and CD setting error to provide directed search in setting the CD equalizer thereby reducing significantly the overall search effort in optimizing CD equalizer settings. This utilizes computations already performed by the transceiver for timing recovery function yielding a computational advantage over competing methods.

Owner:CIENA

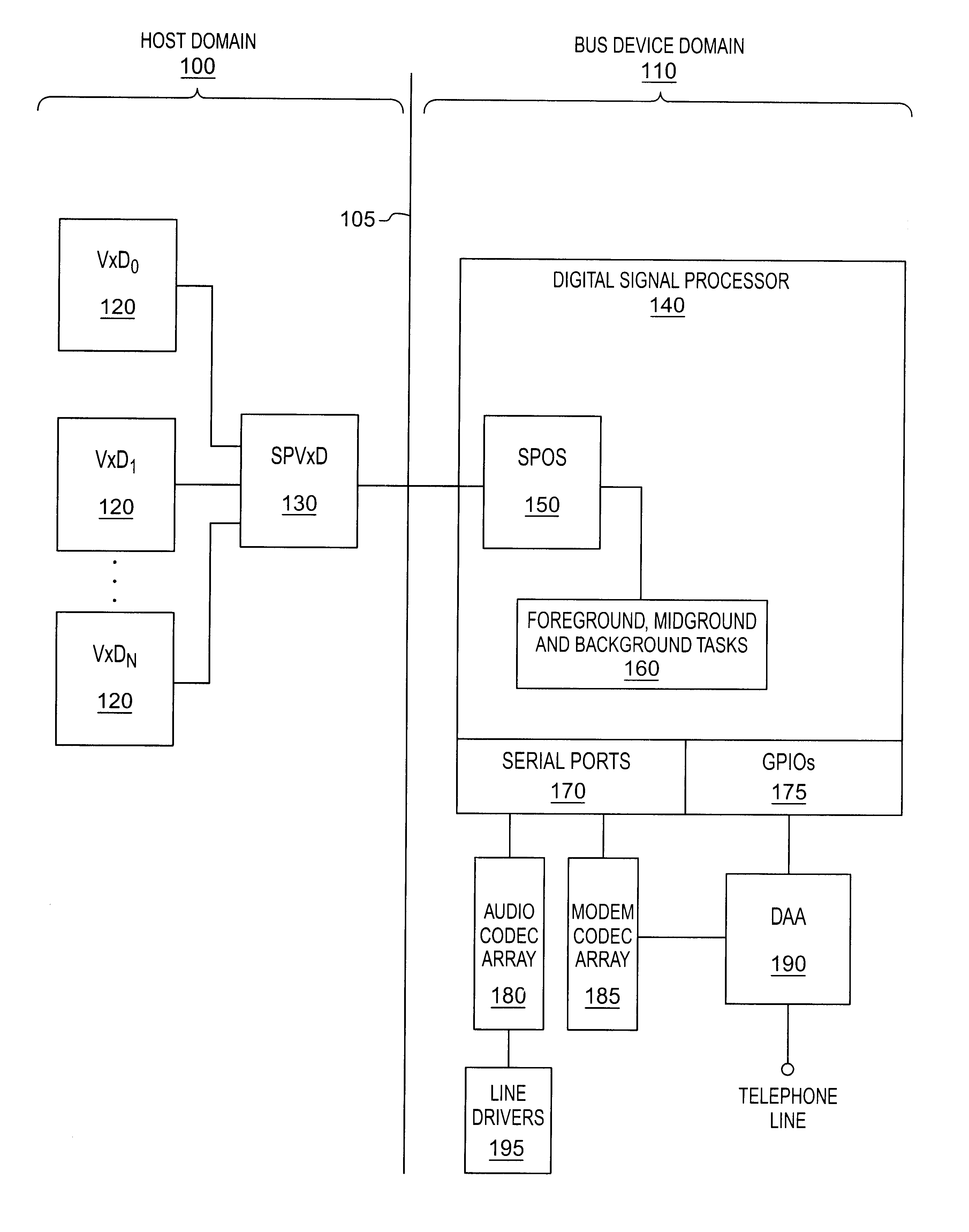

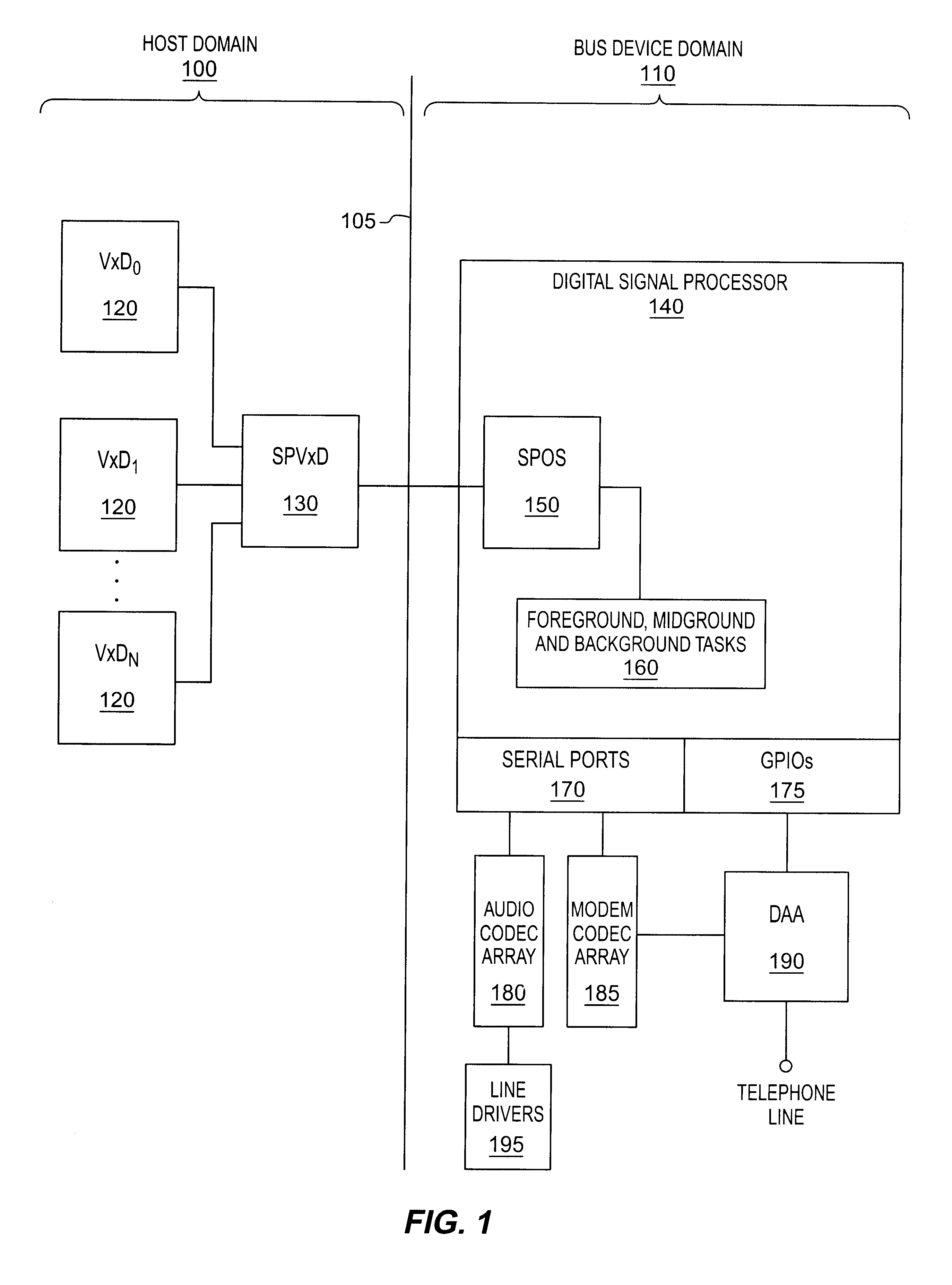

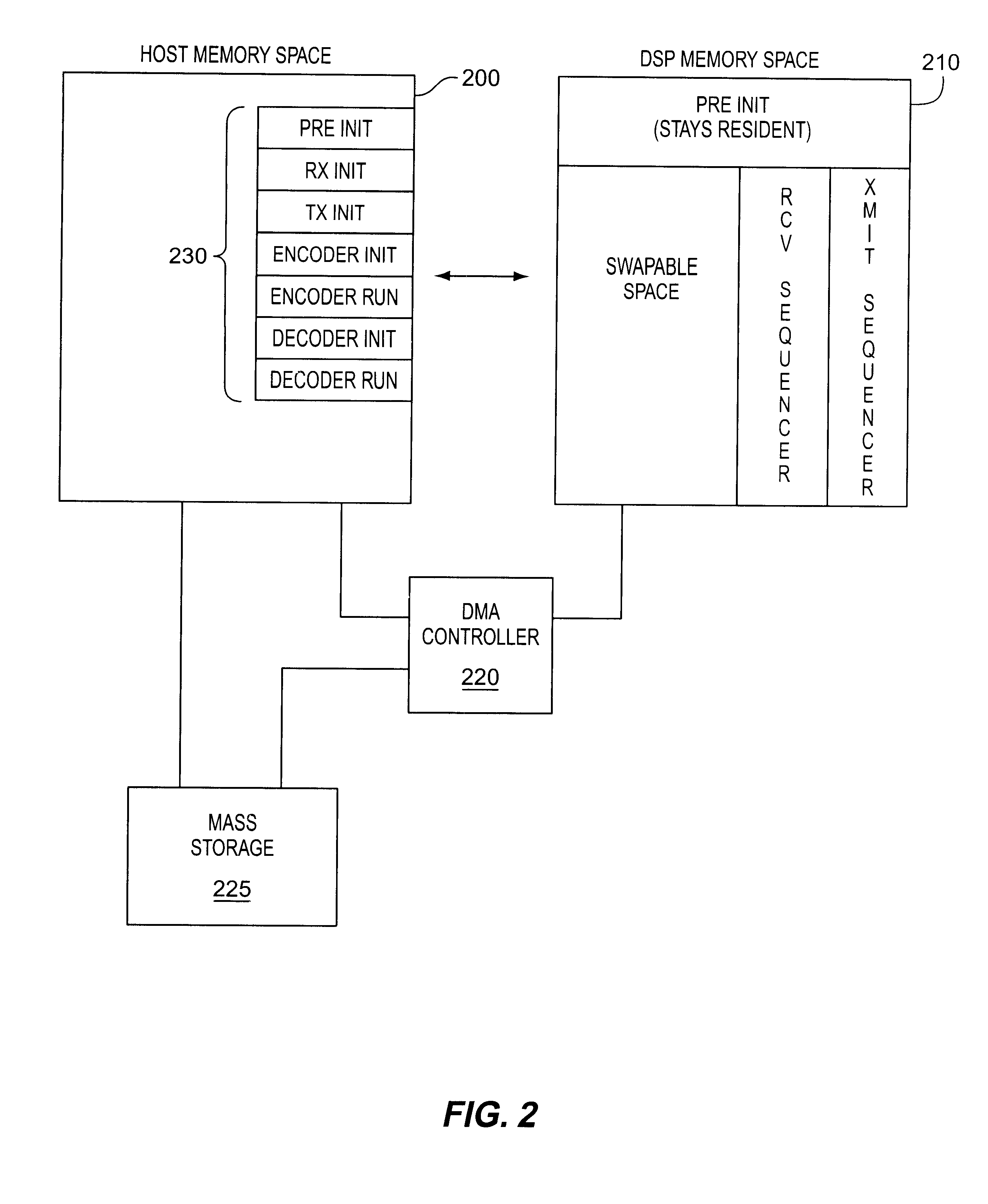

System for dedicating a host processor to running one of a plurality of modem programs and dedicating a DSP to running another one of the modem programs

InactiveUS6374312B1Multiple modulation transmitter/receiver arrangementsSynchronisation error detectionModem deviceDigital signal processor

A plurality of modems or modem types can run on a host processor, a digital signal processor or both, either concurrently or selectively. Modules of more than one modem program can be swapped in and out of DSP memory space. Common modem code can be run on either a host processor or on a DSP using respective command libraries.

Owner:INTEL CORP

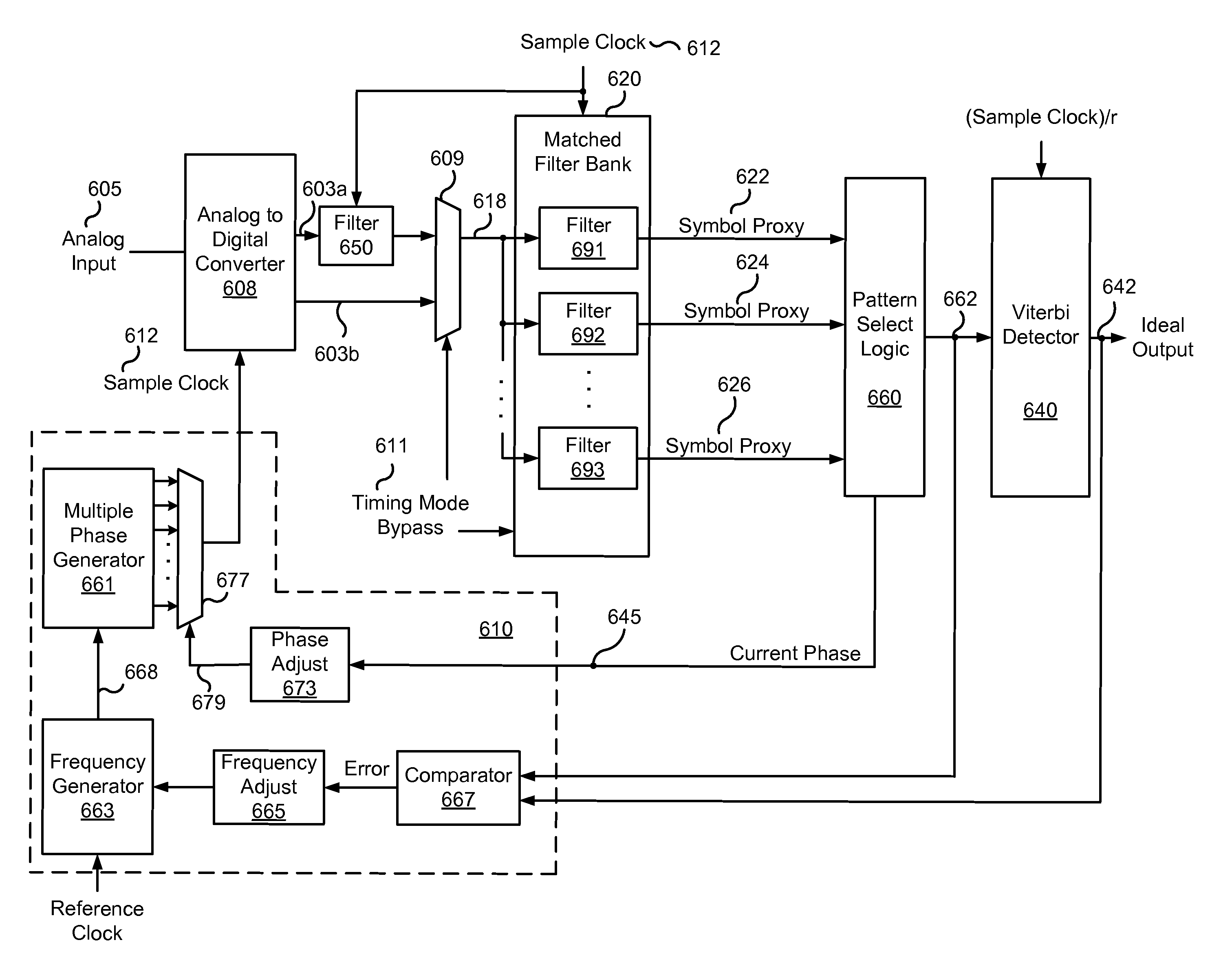

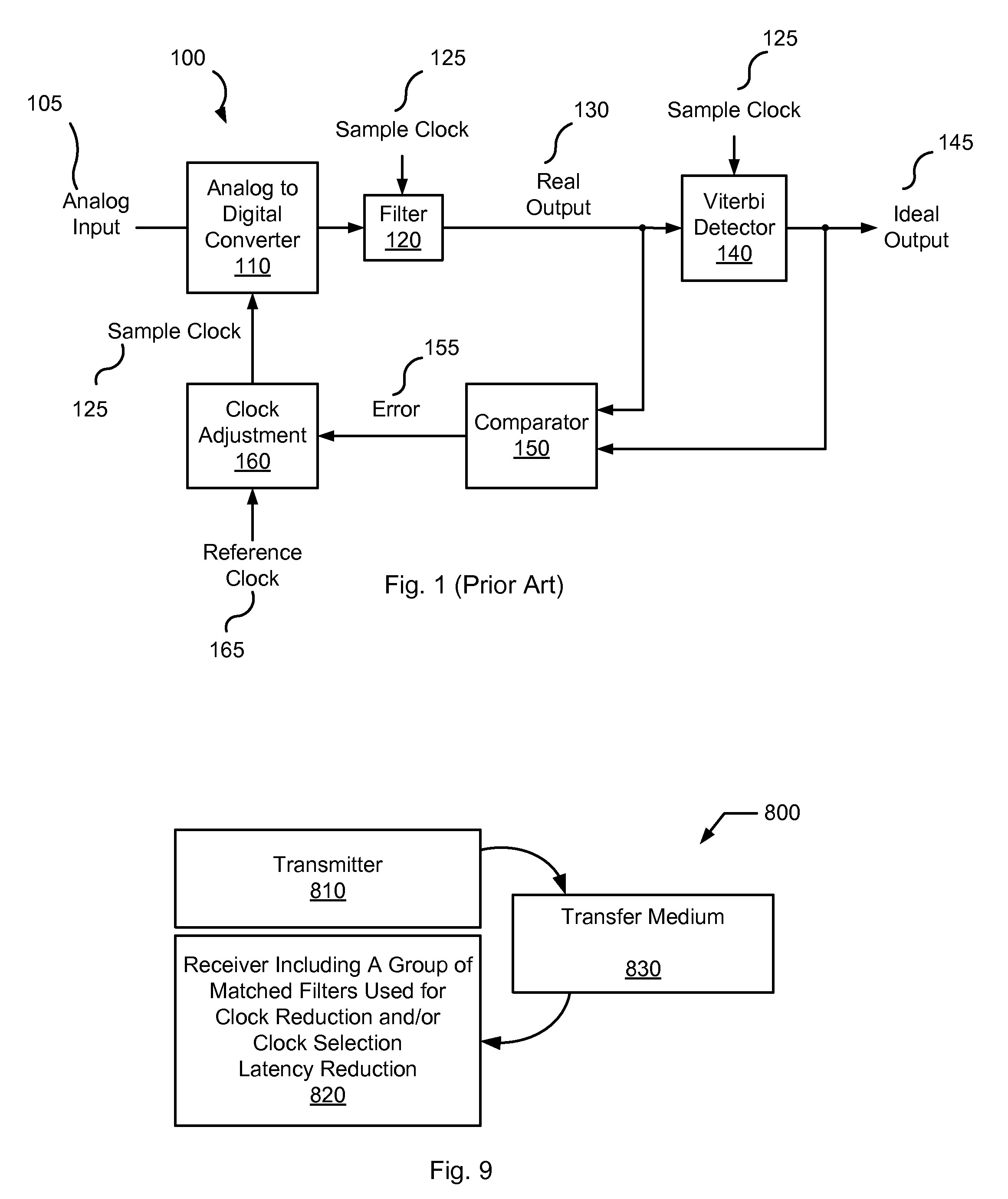

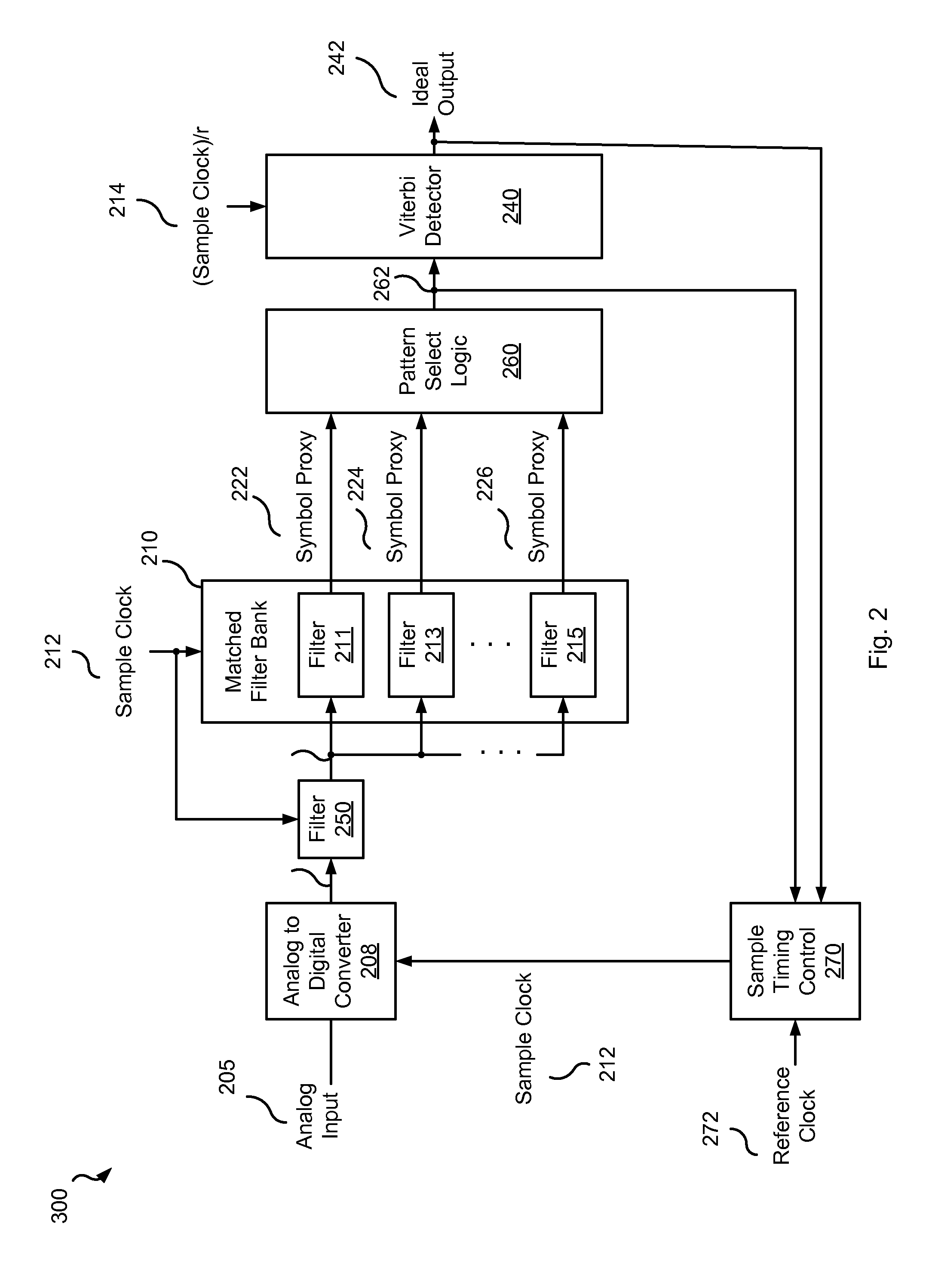

Timing Phase Detection Using a Matched Filter Set

ActiveUS20100061490A1Lower latencyError preventionSynchronisation error detectionData processing systemData treatment

Various embodiments of the present invention provide systems and methods for phase identification in data processing systems. As one example, a circuit is disclosed that includes a bank of matched filters with two or more matched filters tuned to detect patterns corresponding to a timing pattern sampled using different phases of a sample clock. In particular, the bank of matched filters includes at least a first matched filter tuned to detect a first pattern corresponding to the timing pattern sampled using a first phase of a sample clock, and a second matched filter tuned to detect a second pattern corresponding to the timing pattern sampled using a second phase of the sample clock. The circuits further include a logic circuit operable to determine whether the sample clock is closer to the first phase or the second phase based on an output of the first matched filter and an output of the second matched filter.

Owner:AVAGO TECH INT SALES PTE LTD

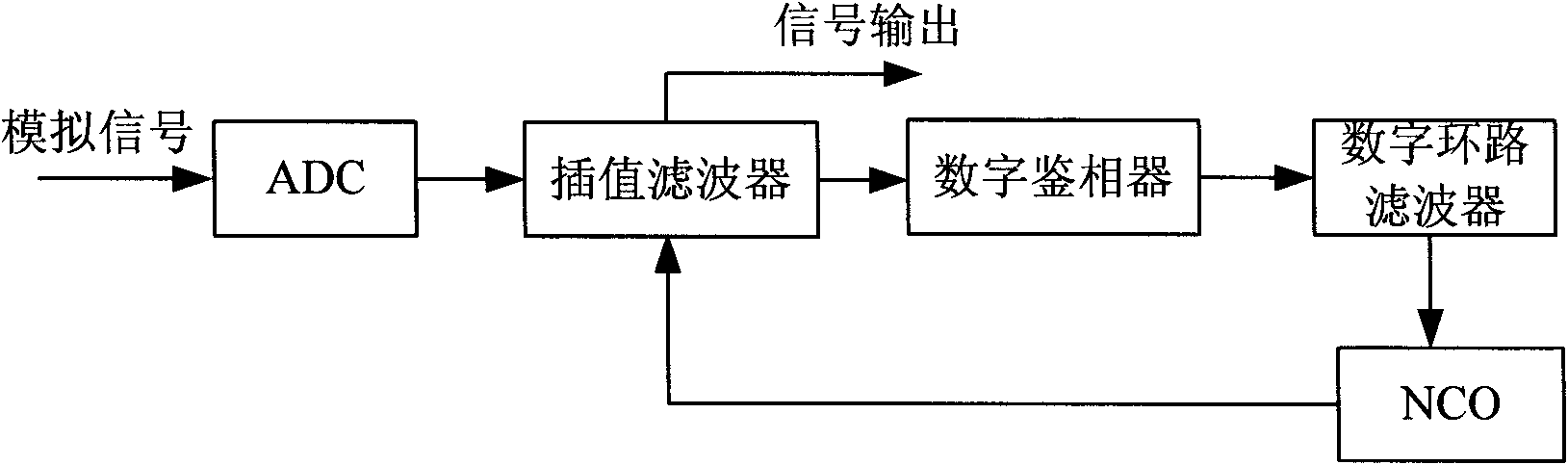

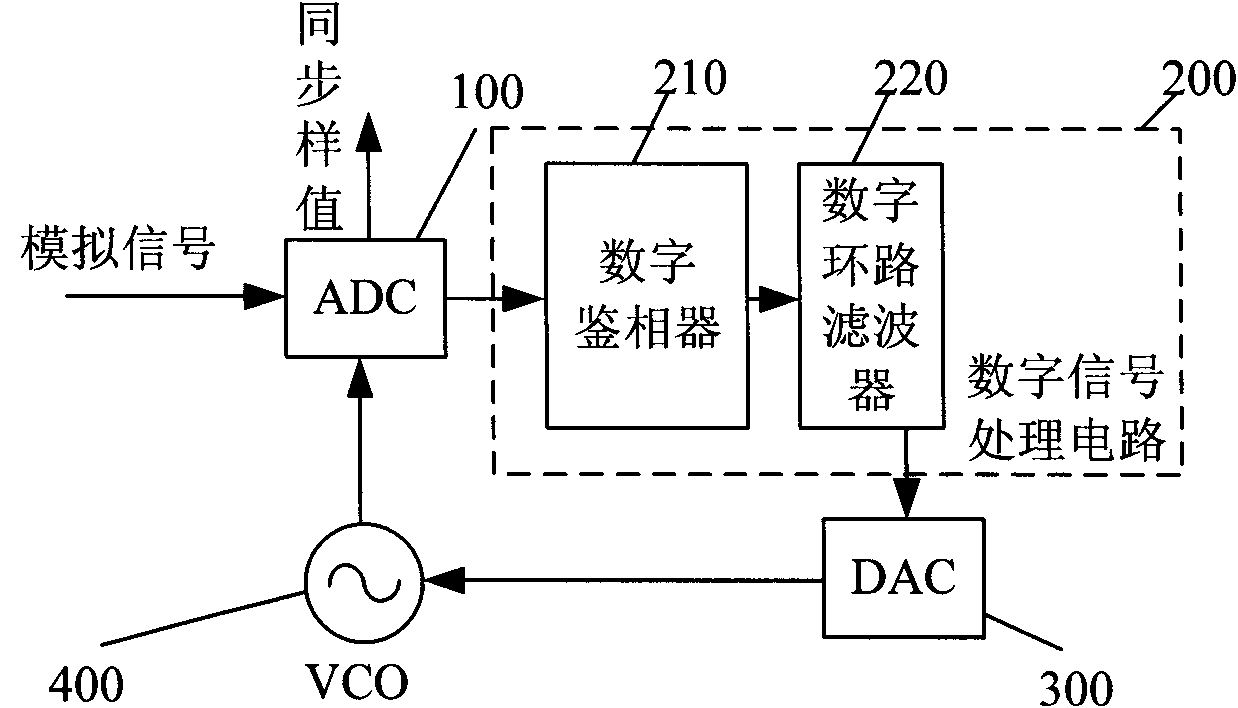

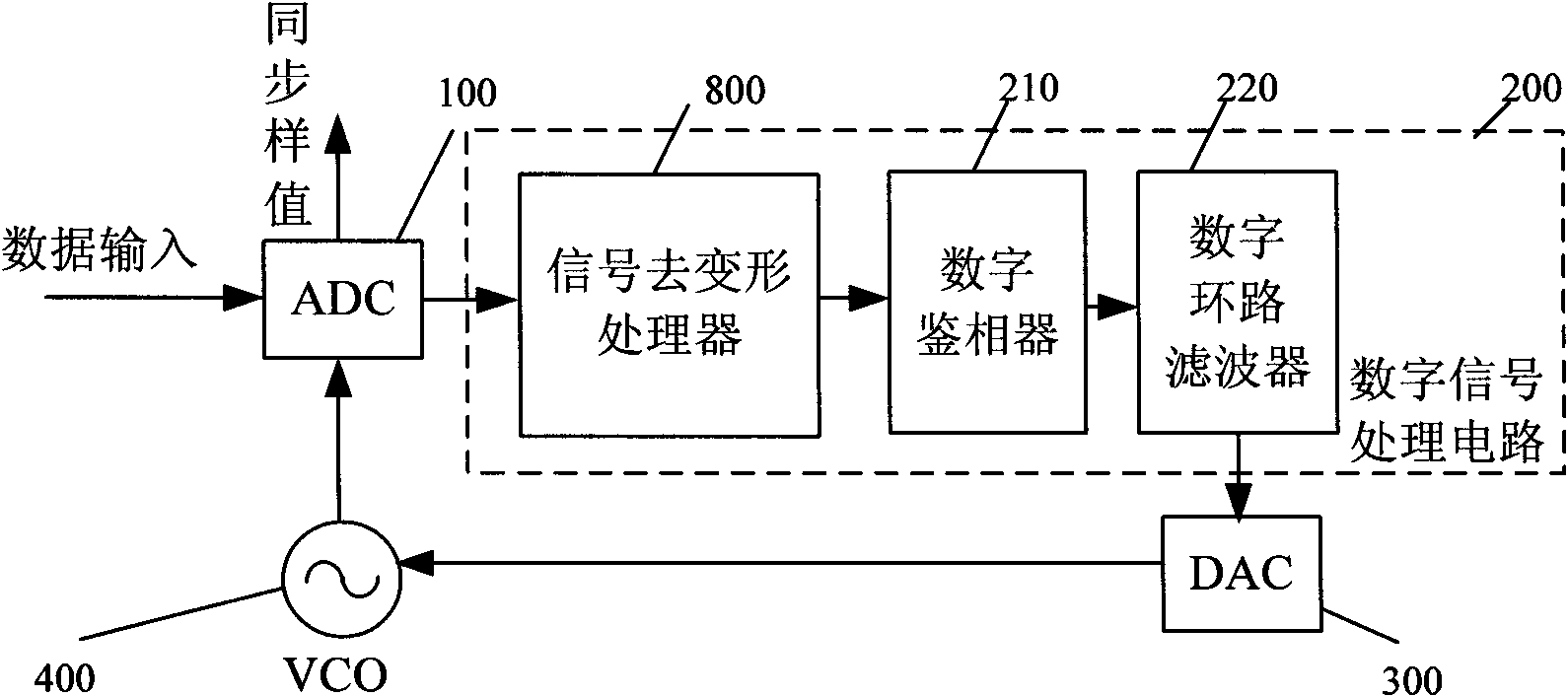

Clock recovery device and method

InactiveCN101820340AModulated-carrier systemsSynchronisation error detectionDigital signal processingEngineering

The invention discloses a clock recovery device and a clock recovery method. The clock recovery device comprises an analog-to-digital converter, a digital signal processing circuit, a digital-to-analog converter and a voltage-controlled oscillator which are connected in turn, wherein the voltage-controlled oscillator is connected with the analog-to-digital converter; the analog-to-digital converter is used for converting received analog signals into digital signals, and sending the digital signals to the digital signal processing circuit; the digital signal processing circuit is used for carrying out phase demodulation and filtering processing on the received digital signals so as to obtain digital clock error signals, and sending the digital clock error signals to the digital-to-analog converter; the digital-to-analog converter is used for converting the received digital clock error signals into control voltage signals, and sending the control voltage signals to the voltage-controlled oscillator; and the voltage-controlled oscillator is used for generating a synchronous clock according to the received control voltage signals, and outputting the synchronous clock to the analog-to-digital converter. The invention can provide a reference clock for chips in a digital circuit.

Owner:ZTE CORP +1

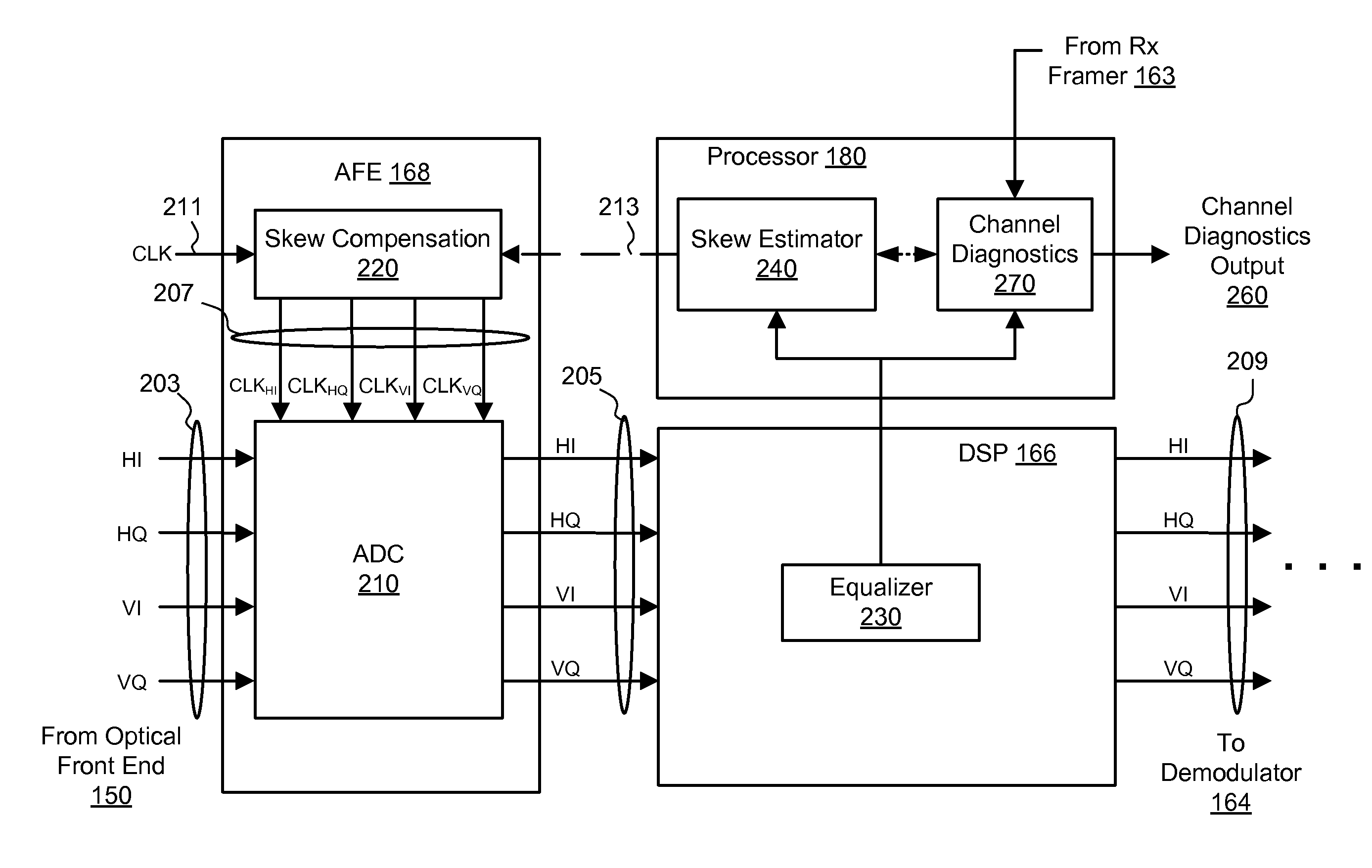

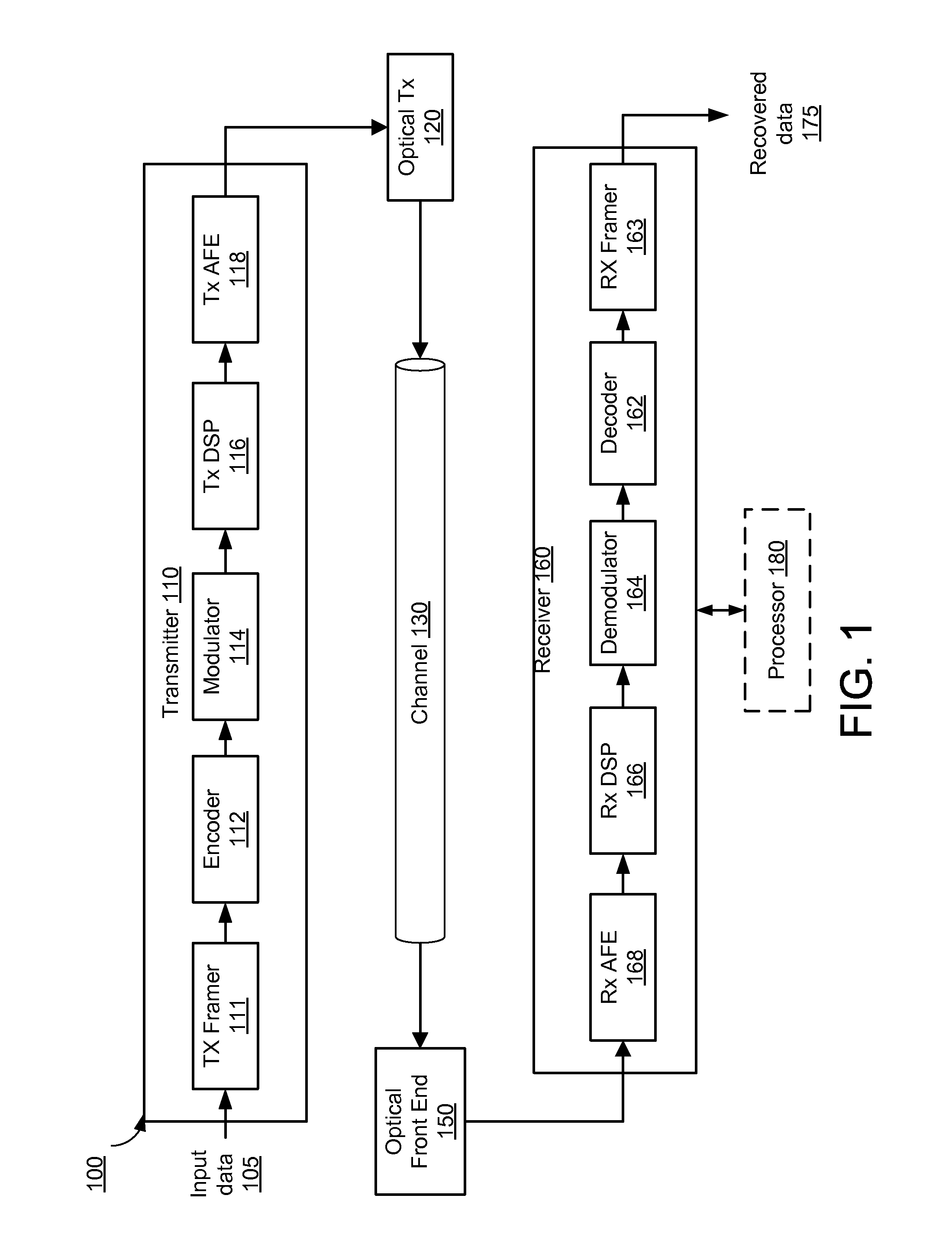

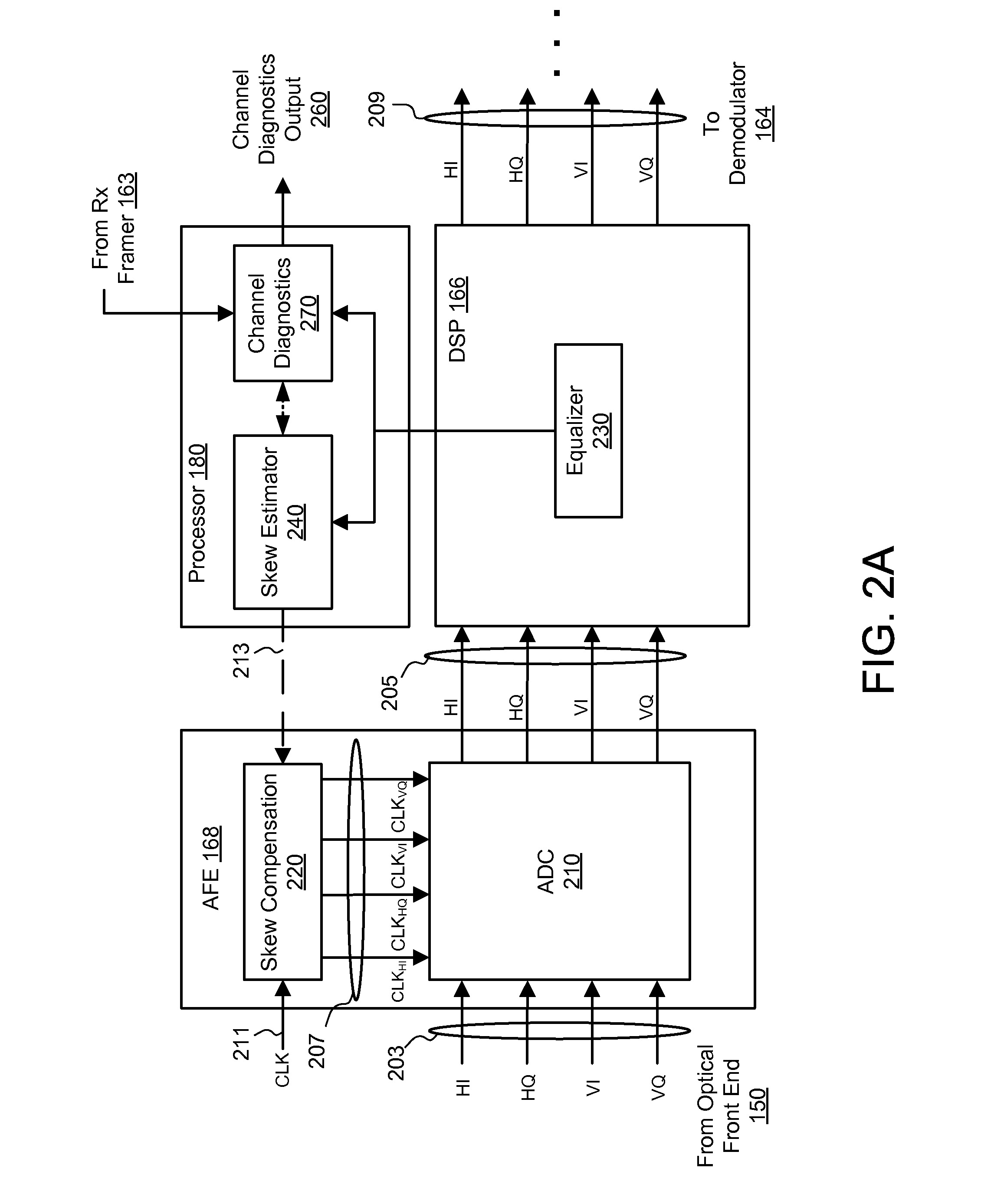

Skew compensation based on equalizer coefficients

ActiveUS9036751B1Multiple-port networksTelevision system detailsChannel state informationDiagnostic information

A receiver applies a calibration method to compensate for skew between input channels. The receiver skew is estimated by observing the coefficients of an adaptive equalizer which adjusts the coefficients based on time-varying properties of the multi-channel input signal. The receiver skew is compensated by programming the phase of the sampling clocks for the different channels. Furthermore, during real-time operation of the receiver, channel diagnostics is performed to automatically estimate differential group delay and / or other channel characteristics based on the equalizer coefficients using a frequency averaging or polarization averaging approach. Framer information can furthermore be utilized to estimate differential group delay that is an integer multiple of the symbol rate. Additionally, a DSP reset may be performed when substantial signal degradation is detected based on the channel diagnostics information.

Owner:MARVELL ASIA PTE LTD

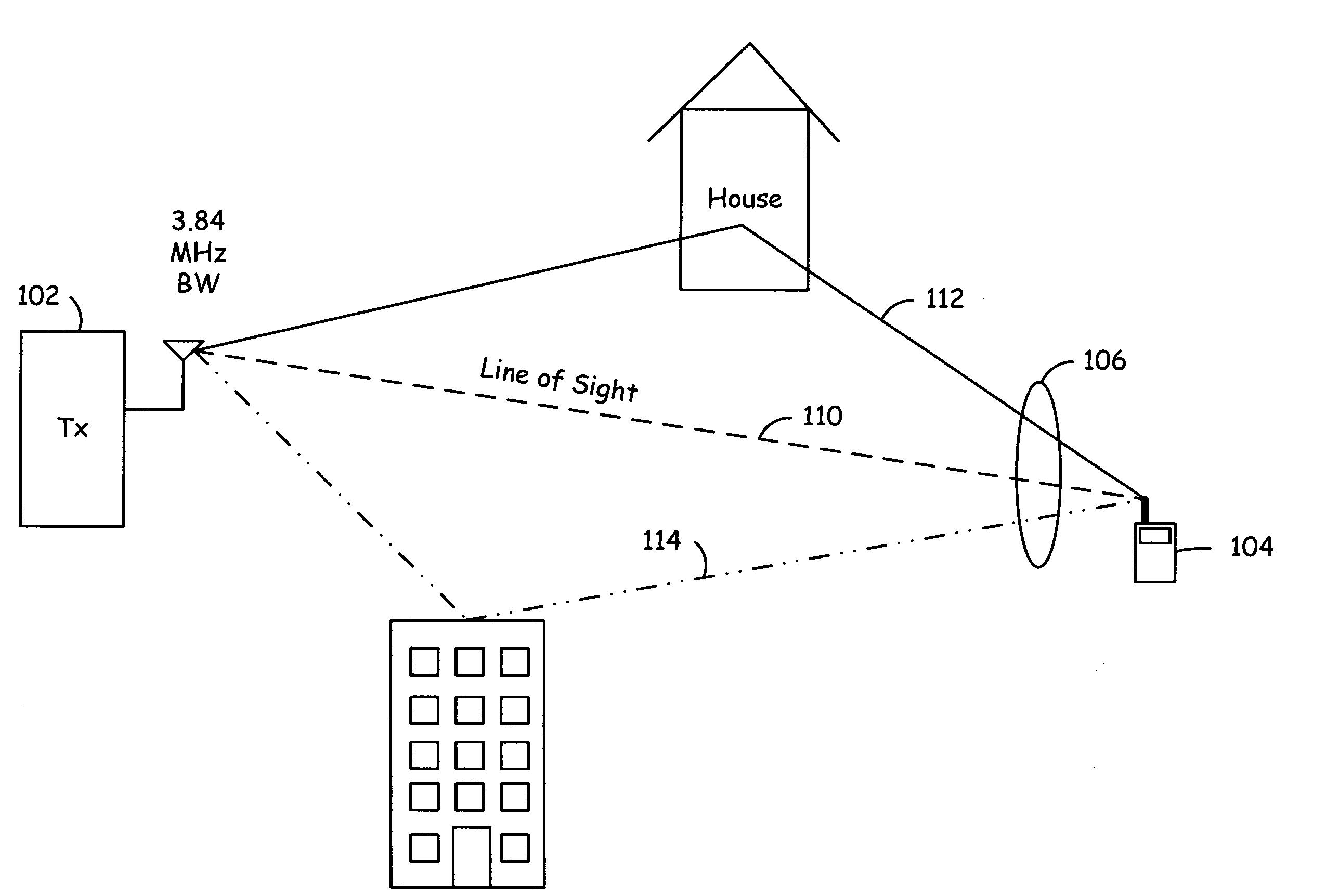

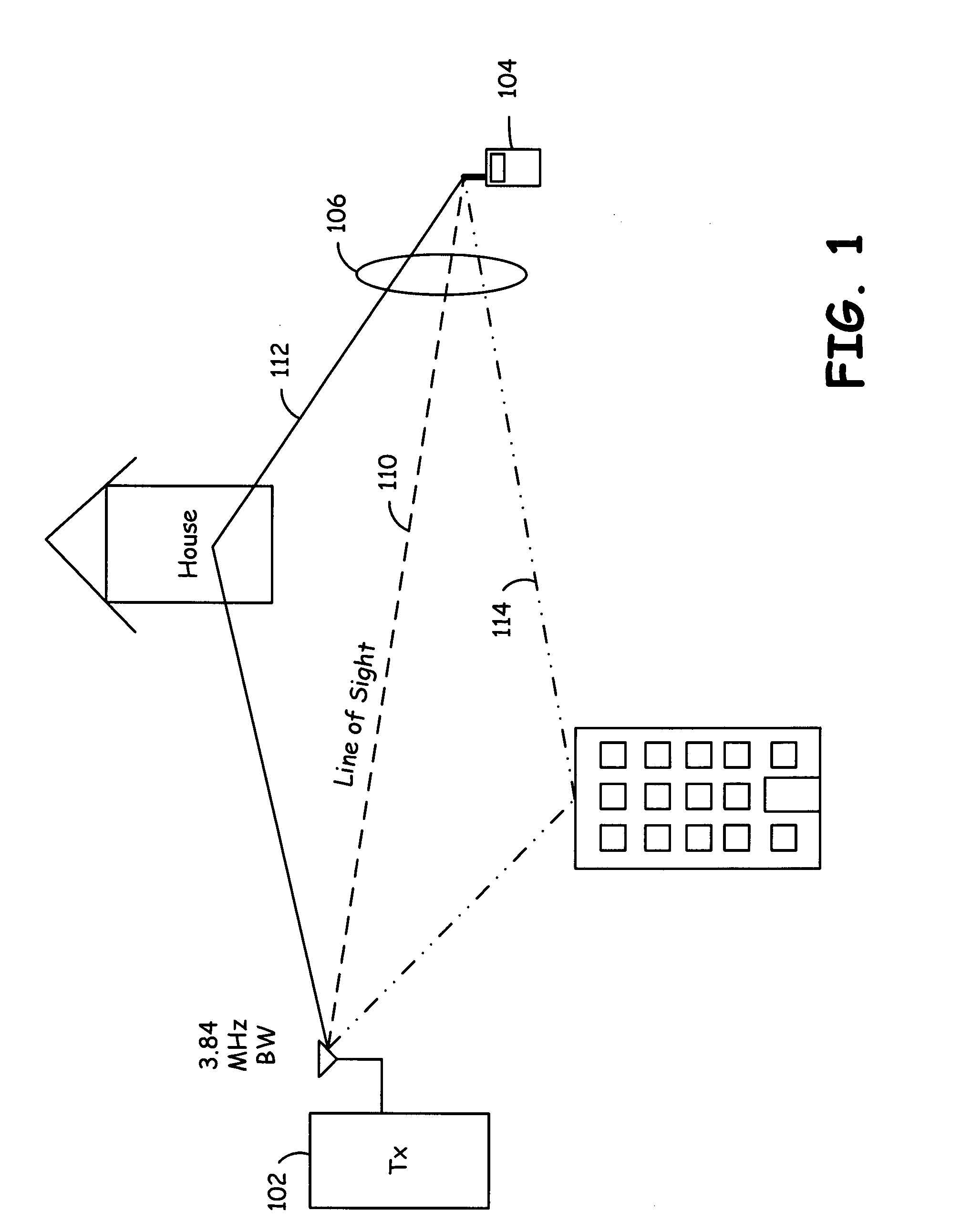

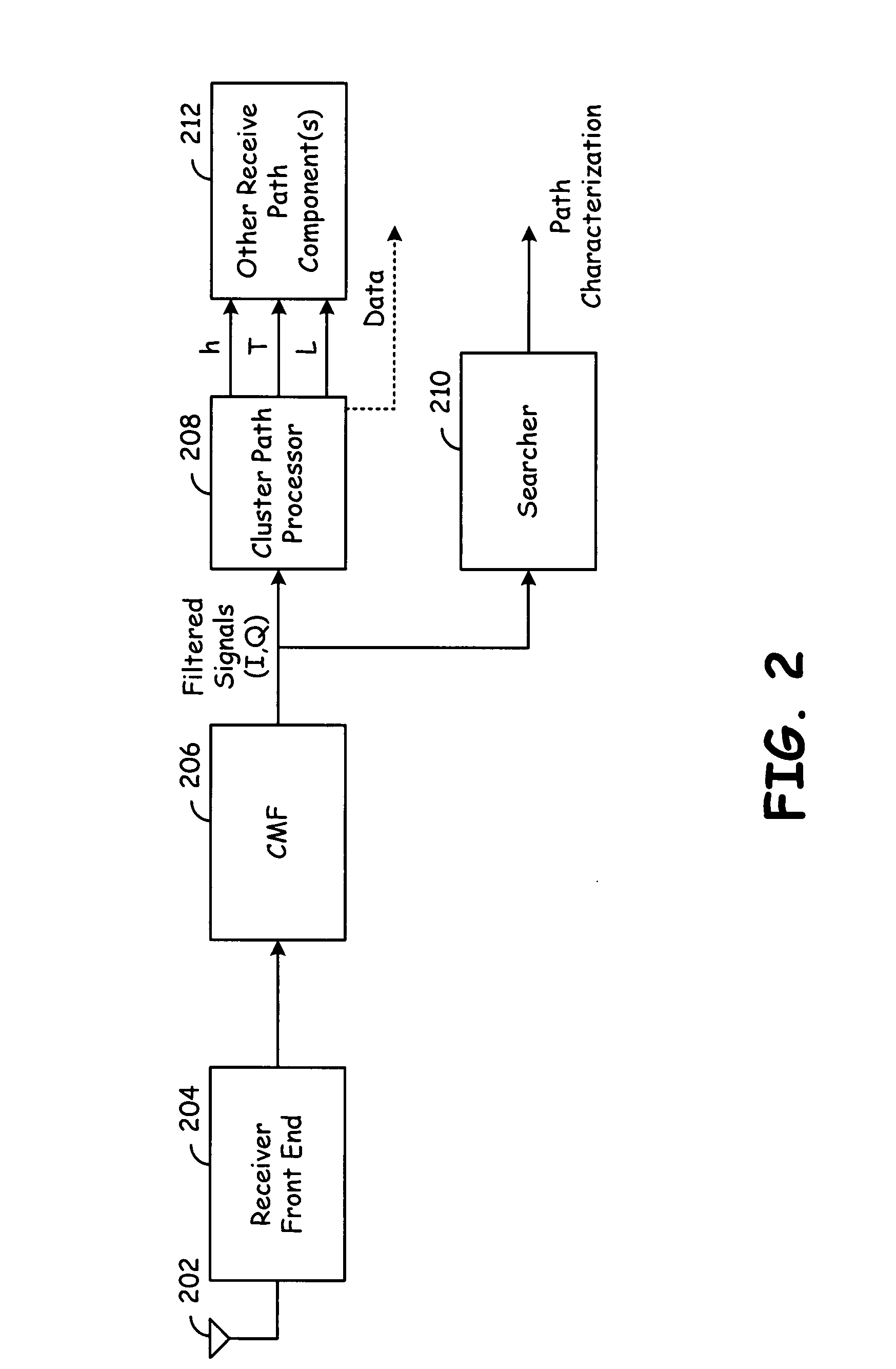

Cluster path processor time alignment for signal suppression/separation in a wireless device

ActiveUS20080075216A1Polarisation/directional diversitySynchronisation error detectionDelay spreadSignal Repression

A system for processing radio frequency (RF) signals includes a searcher and a plurality of Cluster Path Processor (CPPs). The searcher detects a maximum signal energy level and position of at least one of a plurality of individual distinct path signals in a signal cluster of a first information signal, wherein at least a portion of the plurality of individual distinct path signals is received within a duration of a corresponding delay spread. The sampling position is used as a starting sampling location by the plurality of CPPs, including a first information signal CPP and a second information signal CPP. Fine sampling positions of the plurality of CPPs are based upon channel energy estimates for the plurality of individual distinct path signals. CPP outputs are employed to produce channel estimates, which are themselves used in subsequent equalization operations. Sampling positions may change over time in order to satisfy alignment criteria.

Owner:AVAGO TECH INT SALES PTE LTD

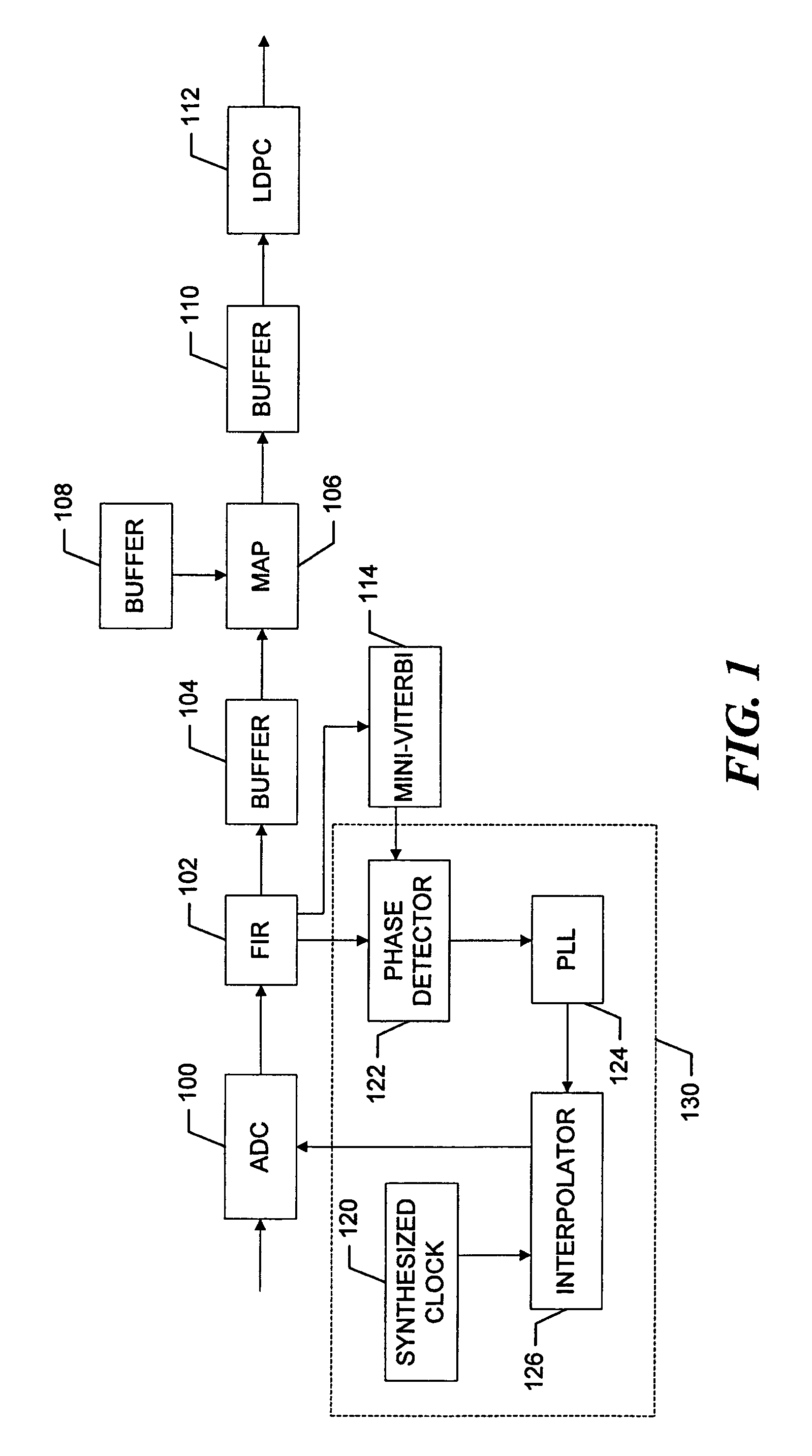

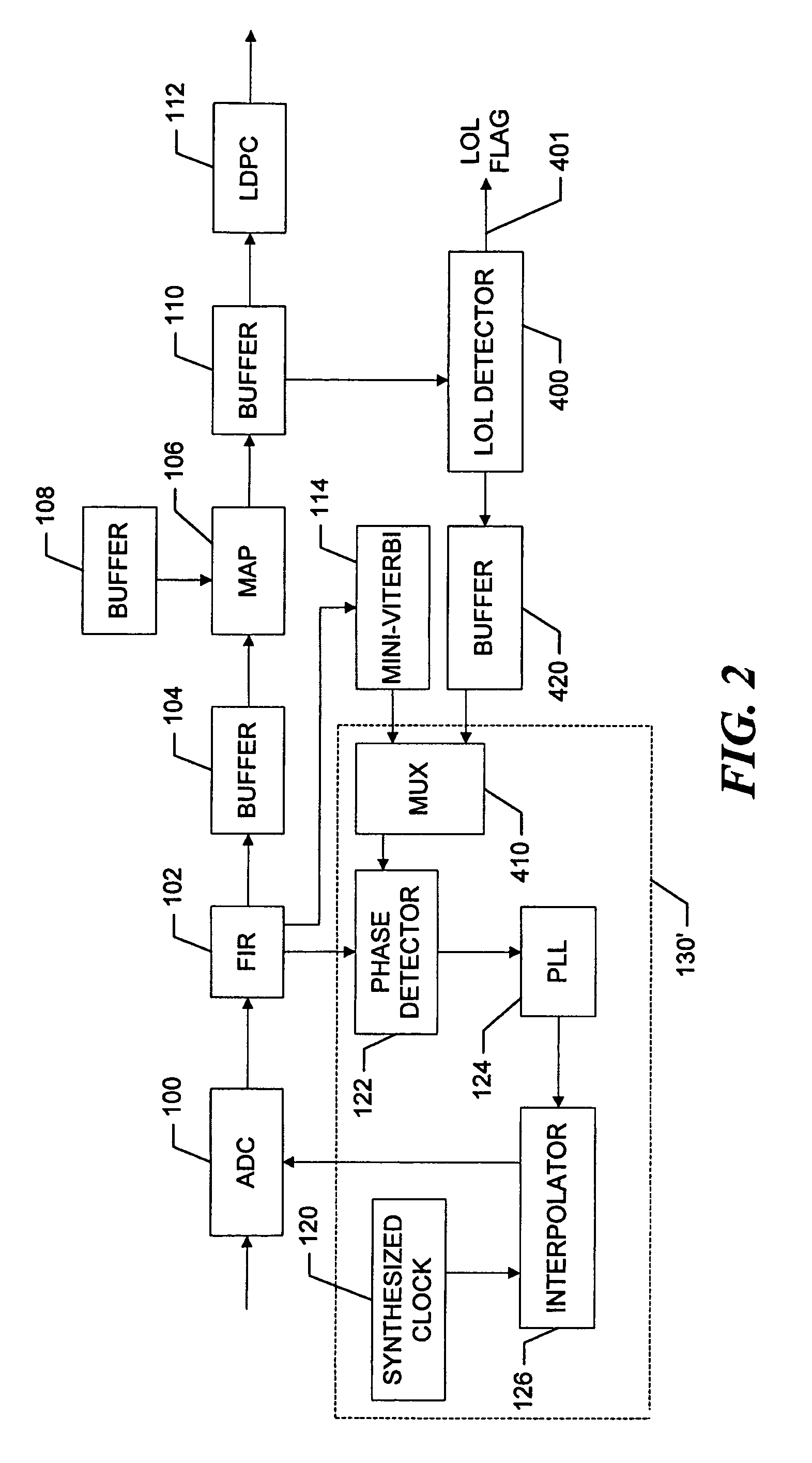

Timing recovery in error recovery for iterative detection

InactiveUS7596196B1Raw bit error rateAccurate signal valueModification of read/write signalsSynchronisation error detectionNormal modeOperation mode

A decoding system includes a timing loop for use in error recovery mode operations, in which “fast decode” bit values that are used for timing recovery purposes in the normal modes of operation are replaced, at an appropriate iteration in the error recovery mode, with detected bit values from an iterative detector. The replacement occurs after a reread operation in which the timing loop maintains lock.

Owner:SEAGATE TECH LLC

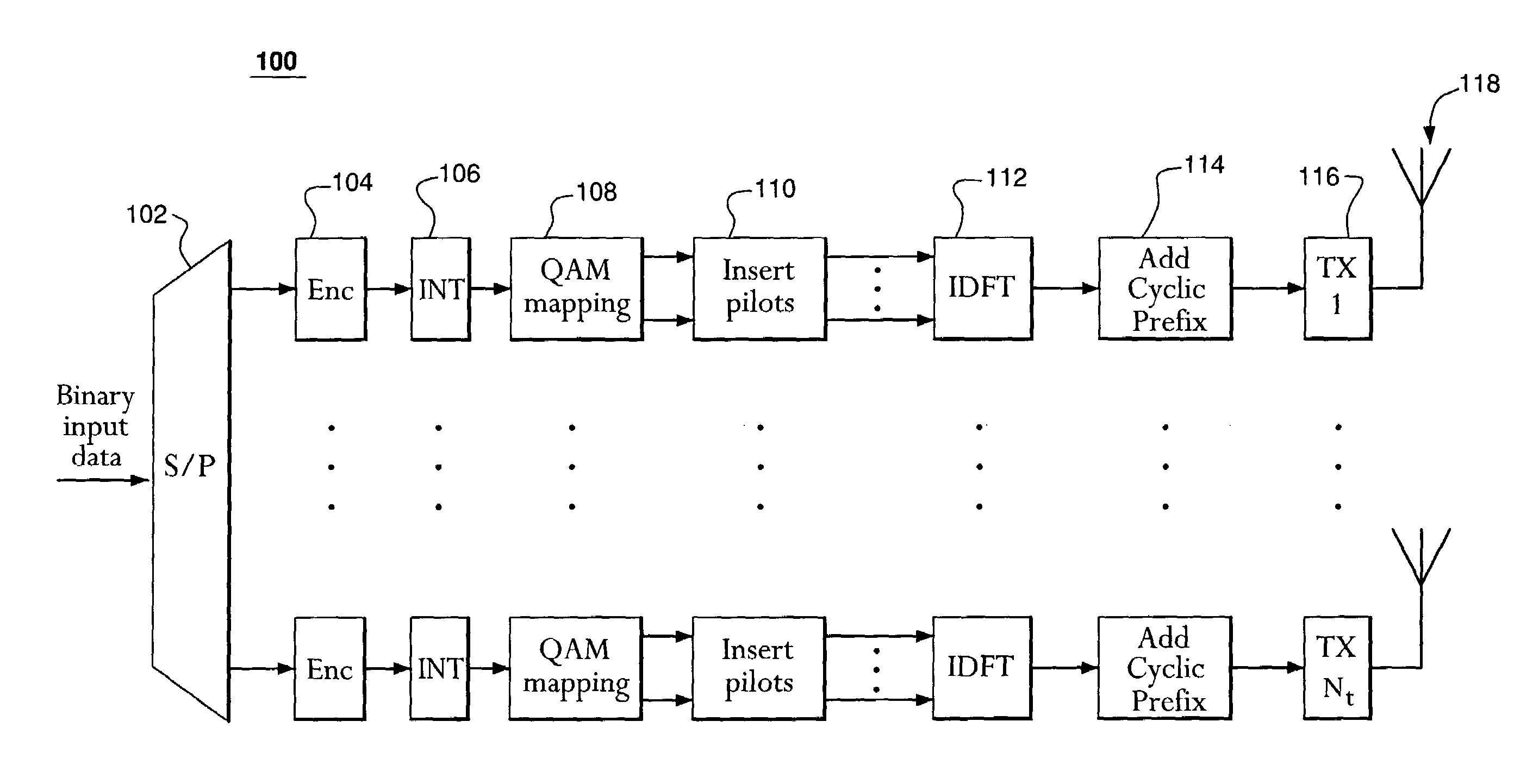

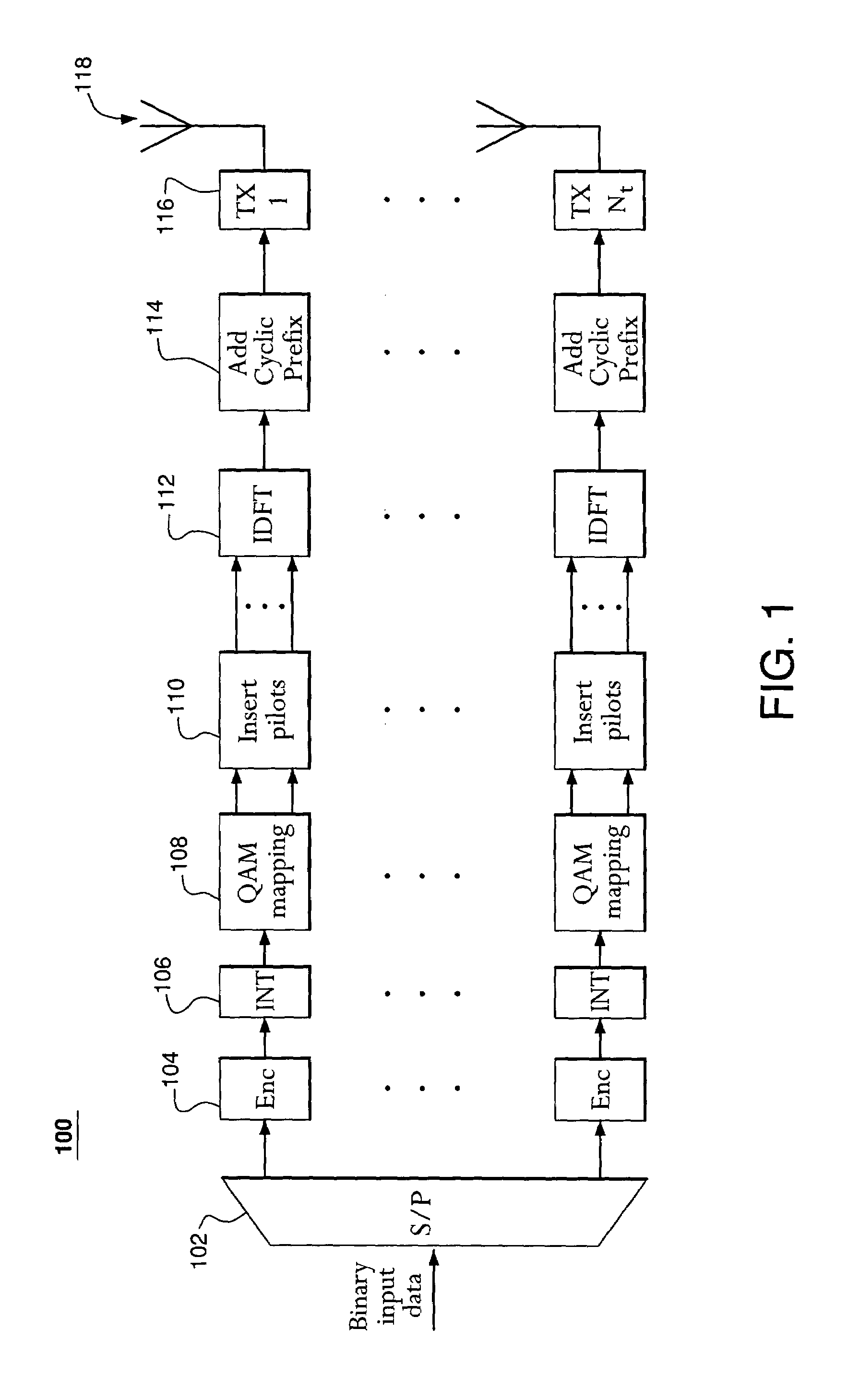

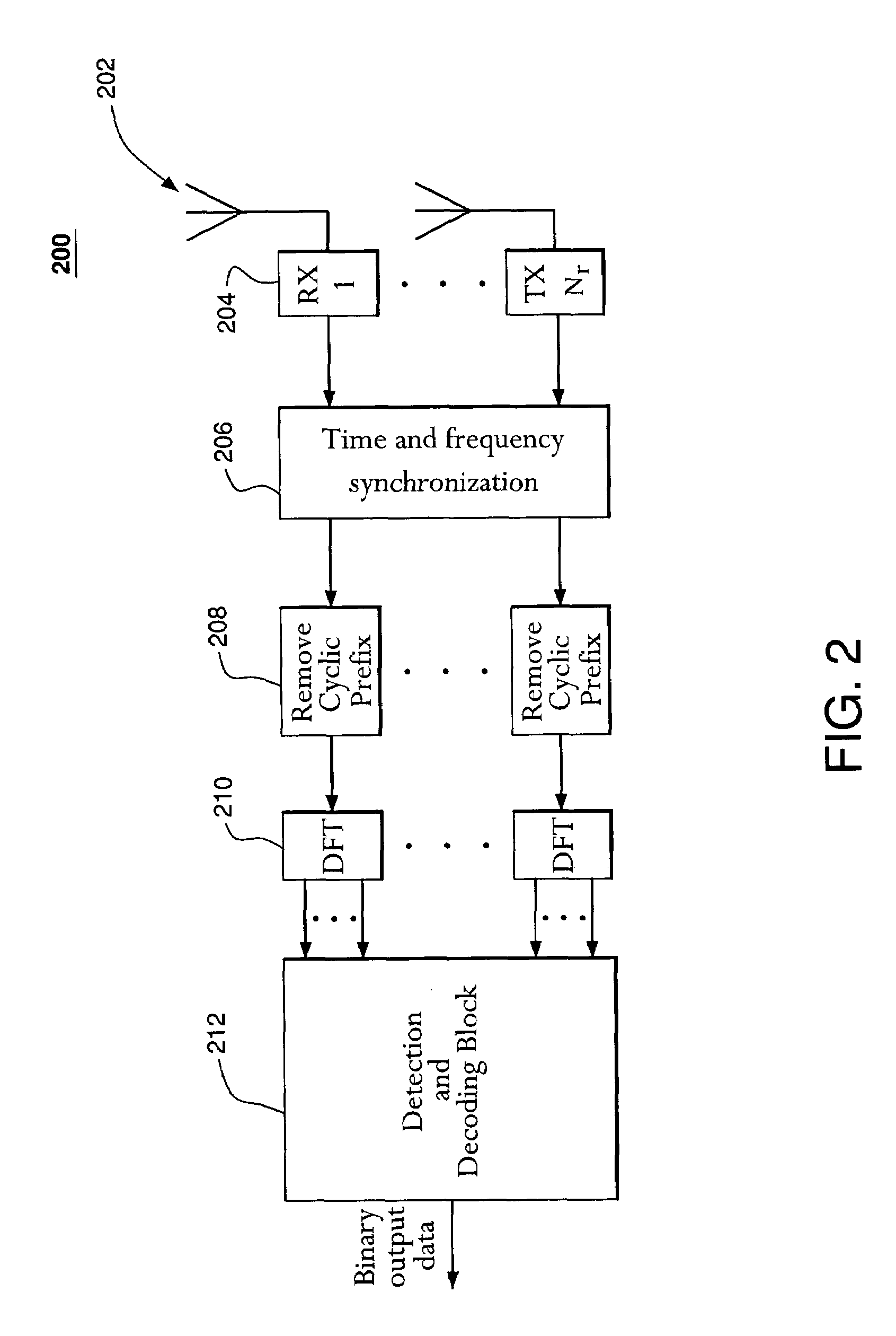

Symbol timing for MIMO OFDM and other wireless communication systems

InactiveUS7254196B2Easy to spreadError ratePolarisation/directional diversitySynchronisation error detectionChannel impulse responseCommunications system

Symbol timing for a wireless communication system, such as a multiple-input multiple-output (MIMO) orthogonal frequency division multiplexing (OFDM) wireless LAN system, is determined by summing the powers for an appropriate set of channel impulse responses, integrating this power summation over an appropriate window (e.g., equivalent to the guard interval), and identifying the time at which the maximum integration occurs. Depending on the implementation, symbol timing can be determined for each receiver branch individually or for all receiver branches jointly. In either case, the determined symbol timing(s) can minimize the amount of inter-symbol and inter-channel interferences that are invoked in the system.

Owner:AVAGO TECH INT SALES PTE LTD

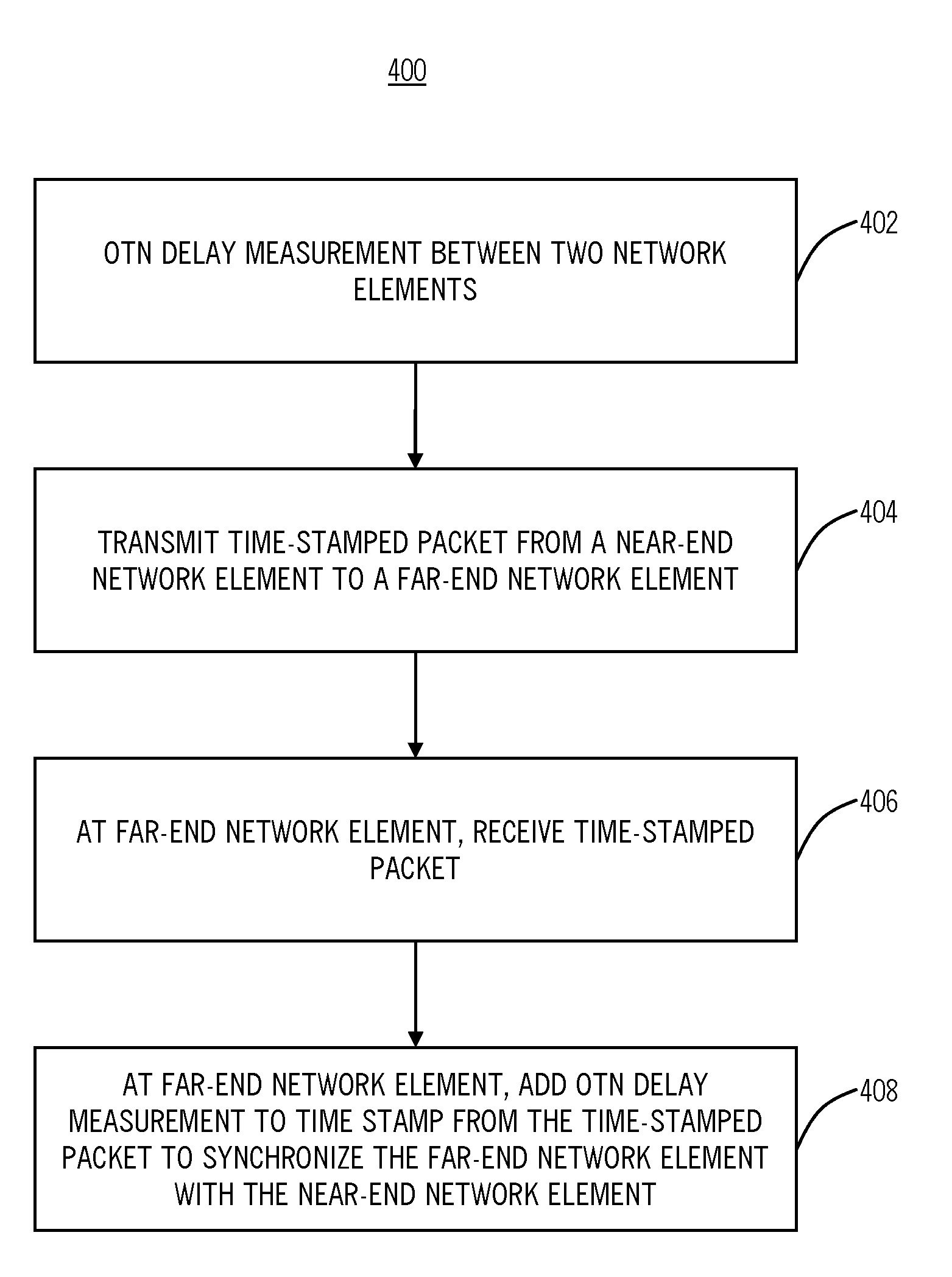

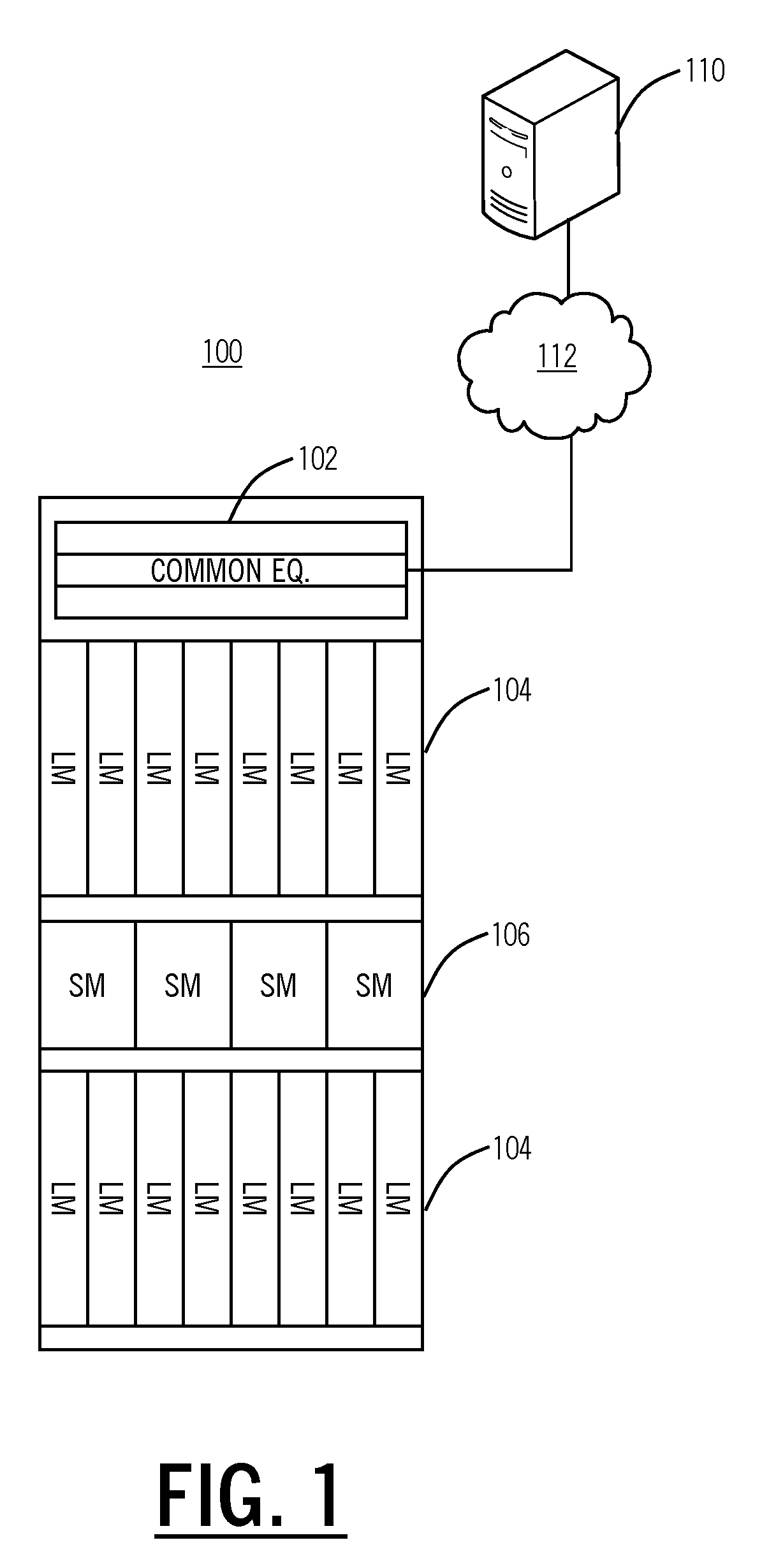

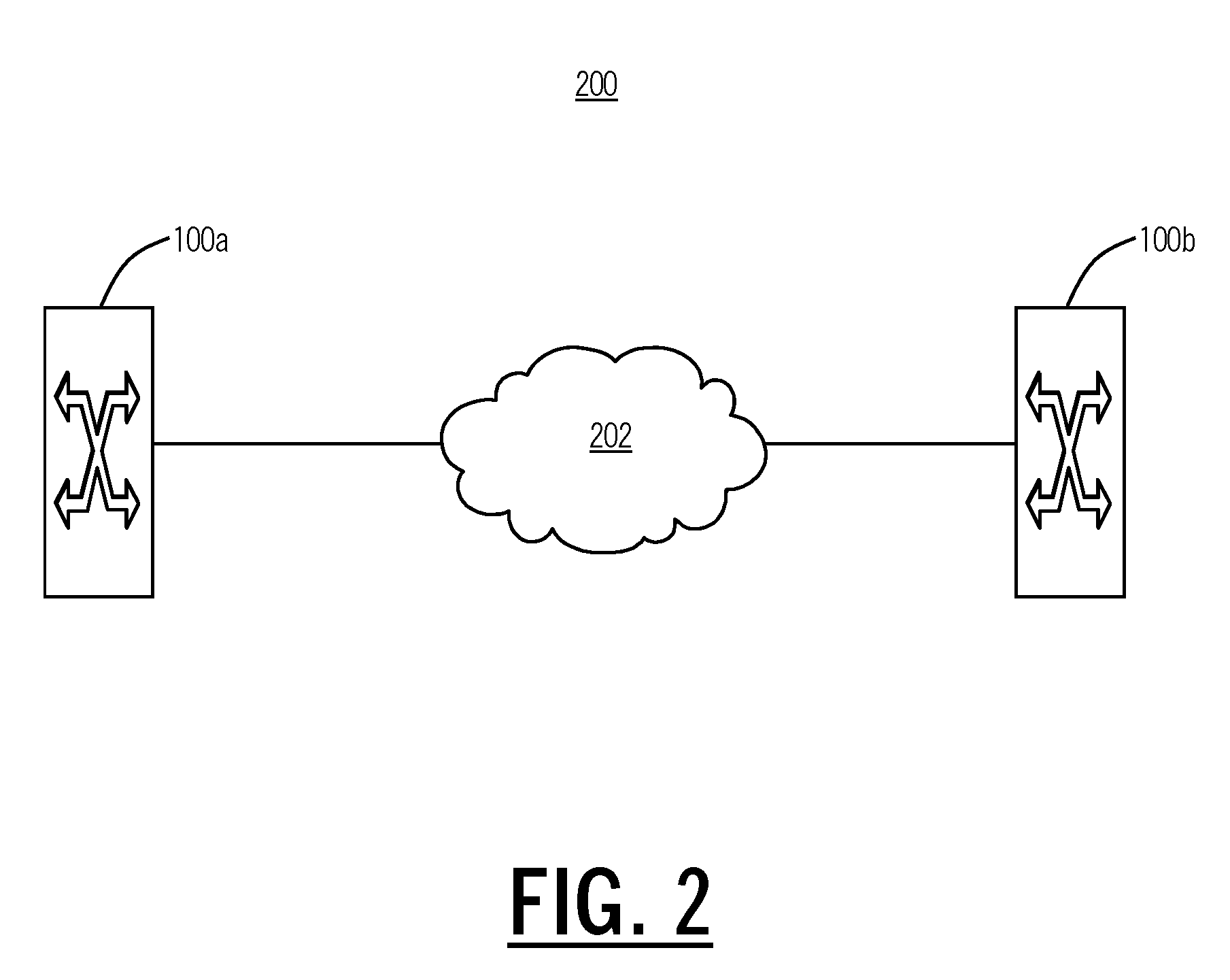

Network element clock synchronization systems and methods using optical transport network delay measurement

ActiveUS20120213508A1Synchronising transmission/receiving encryption devicesModulated-carrier systemsFiberOptical Transport Network

The present disclosure provides Network Element (NE) clock synchronization using Optical Transport Network (OTN) delay measurement systems and methods such as described in ITU-T G.709 (12 / 2009) “Interfaces for the Optical Transport Network (OTN)” and G.798 (10 / 2010) “Characteristics of optical transport network hierarchy equipment functional blocks”. OTN provides a Delay Measurement (DM) function to measure fiber path latency between two network elements to within microsecond accuracy. The convergence of packet switching and OTN transport into the same network element allows the sharing of this information between the two applications. The OTN delay measurement value can be used to synchronize two network element clocks to within microsecond accuracy without the need for a costly GPS synchronization solution or reduced accuracy NTP solutions.

Owner:CIENA

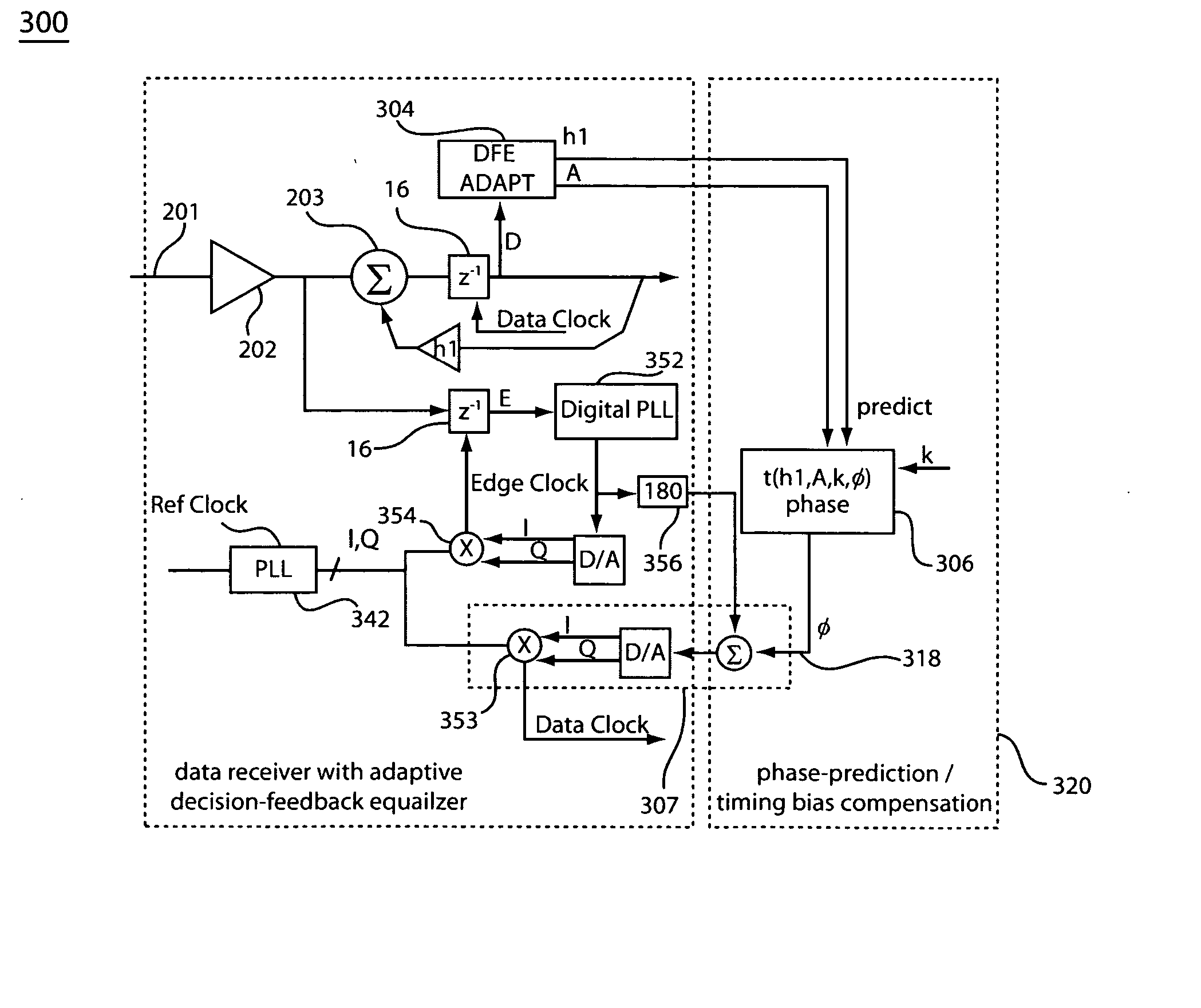

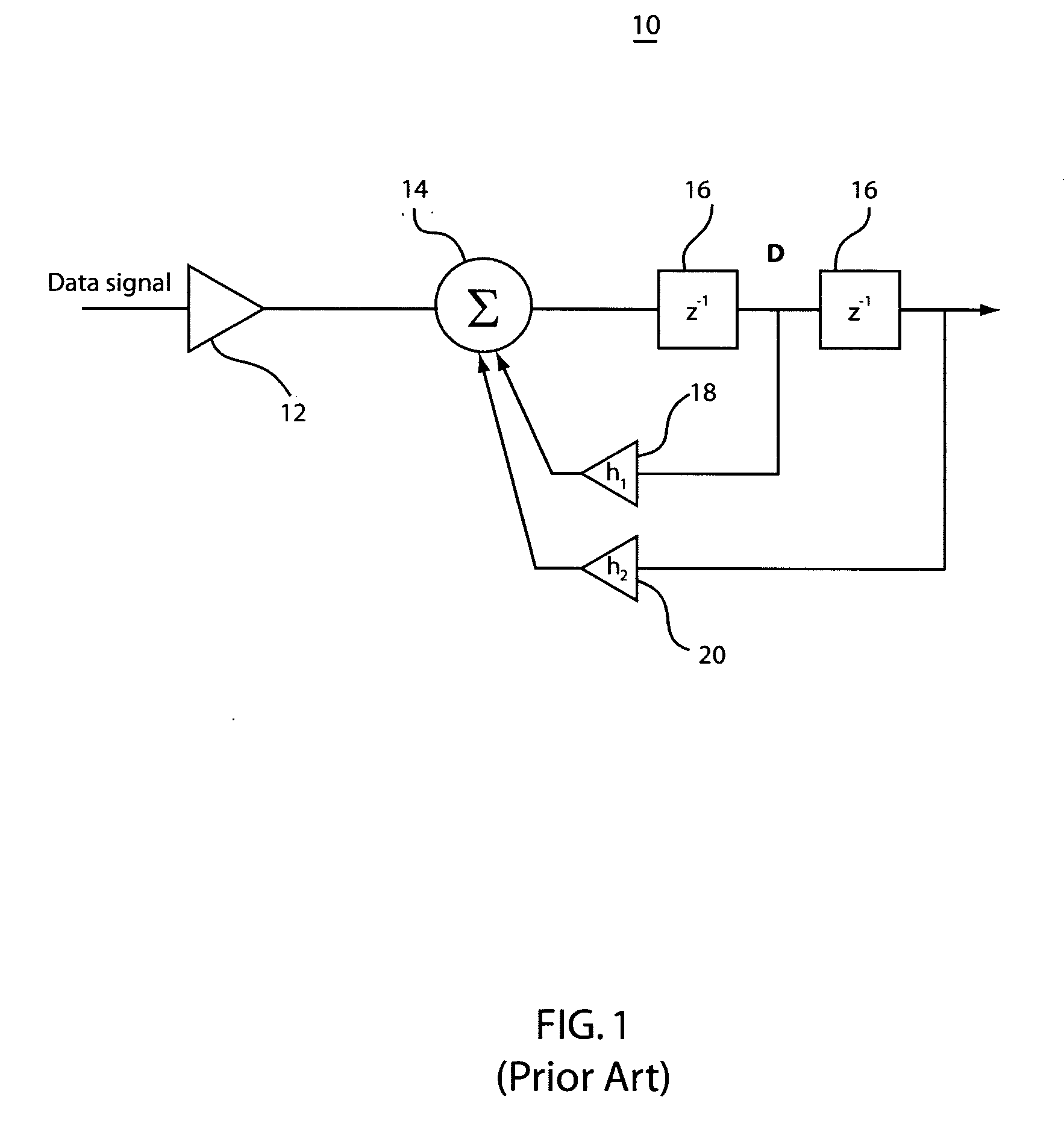

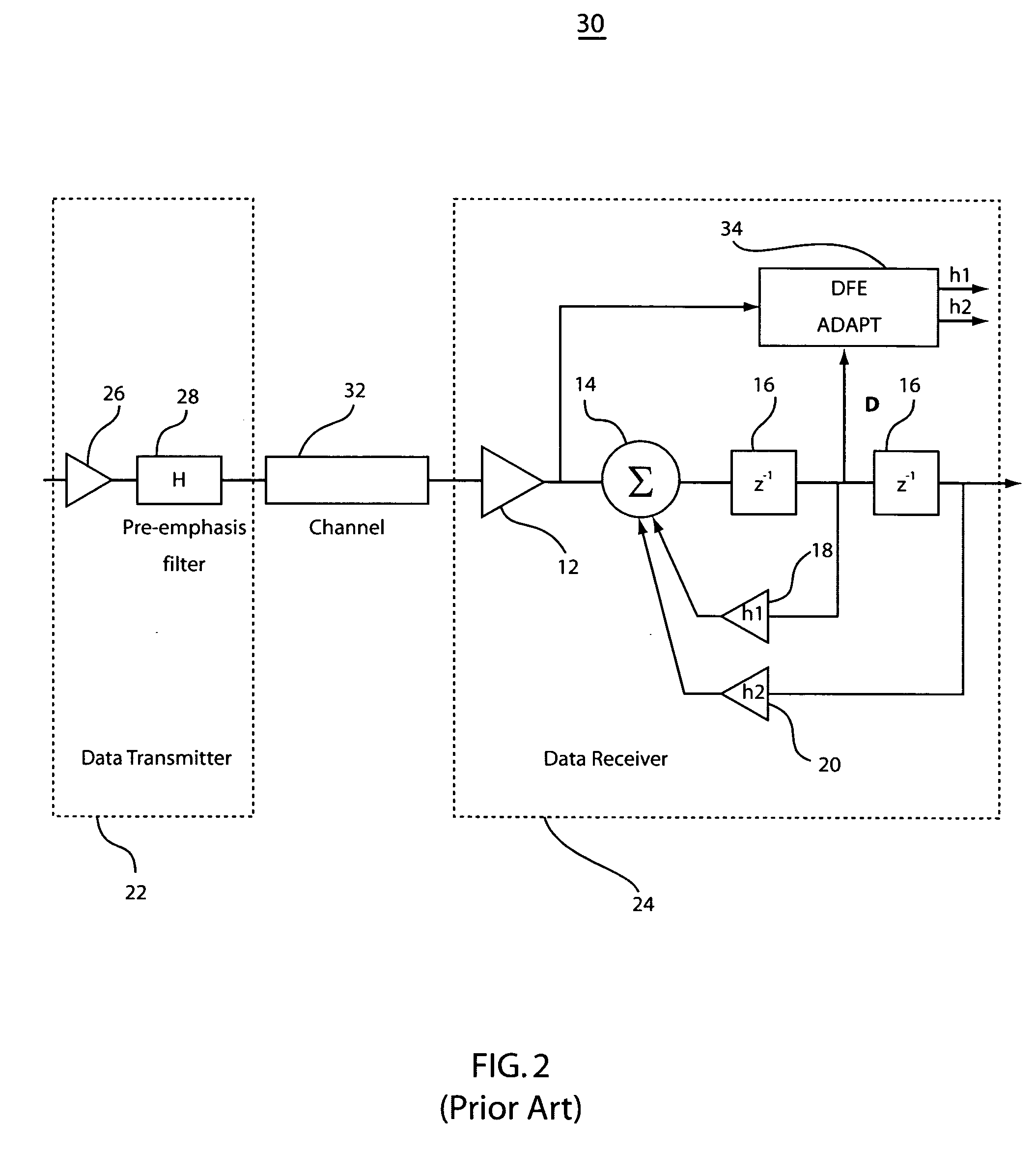

Timing bias compensation for a data receiver with decision-feedback equalizer

InactiveUS20060109940A1Improves jitter toleranceDegradation of bit-error rateSynchronisation error detectionBaseband systemsPhase adjustmentReceiver system

Owner:GLOBALFOUNDRIES INC

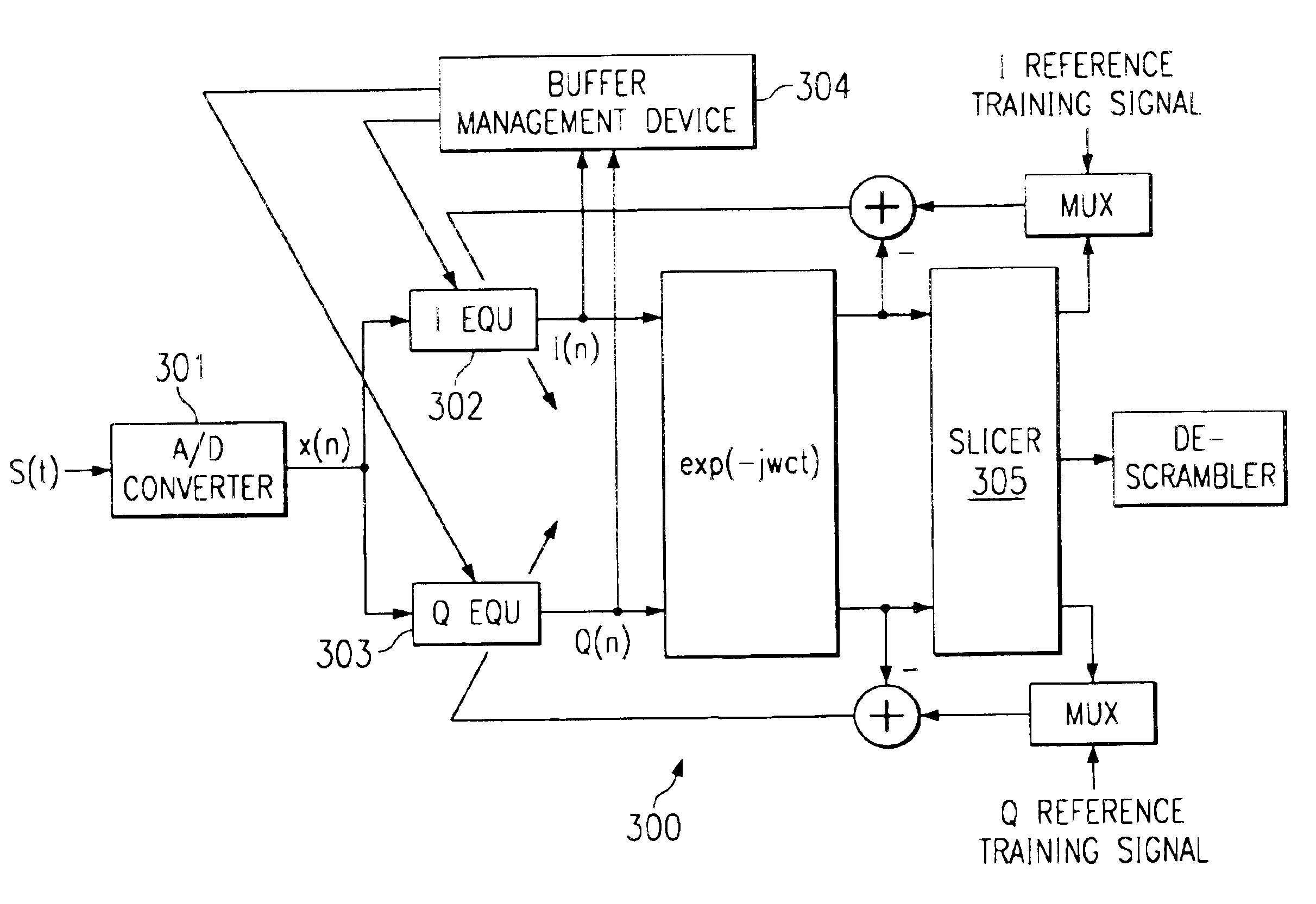

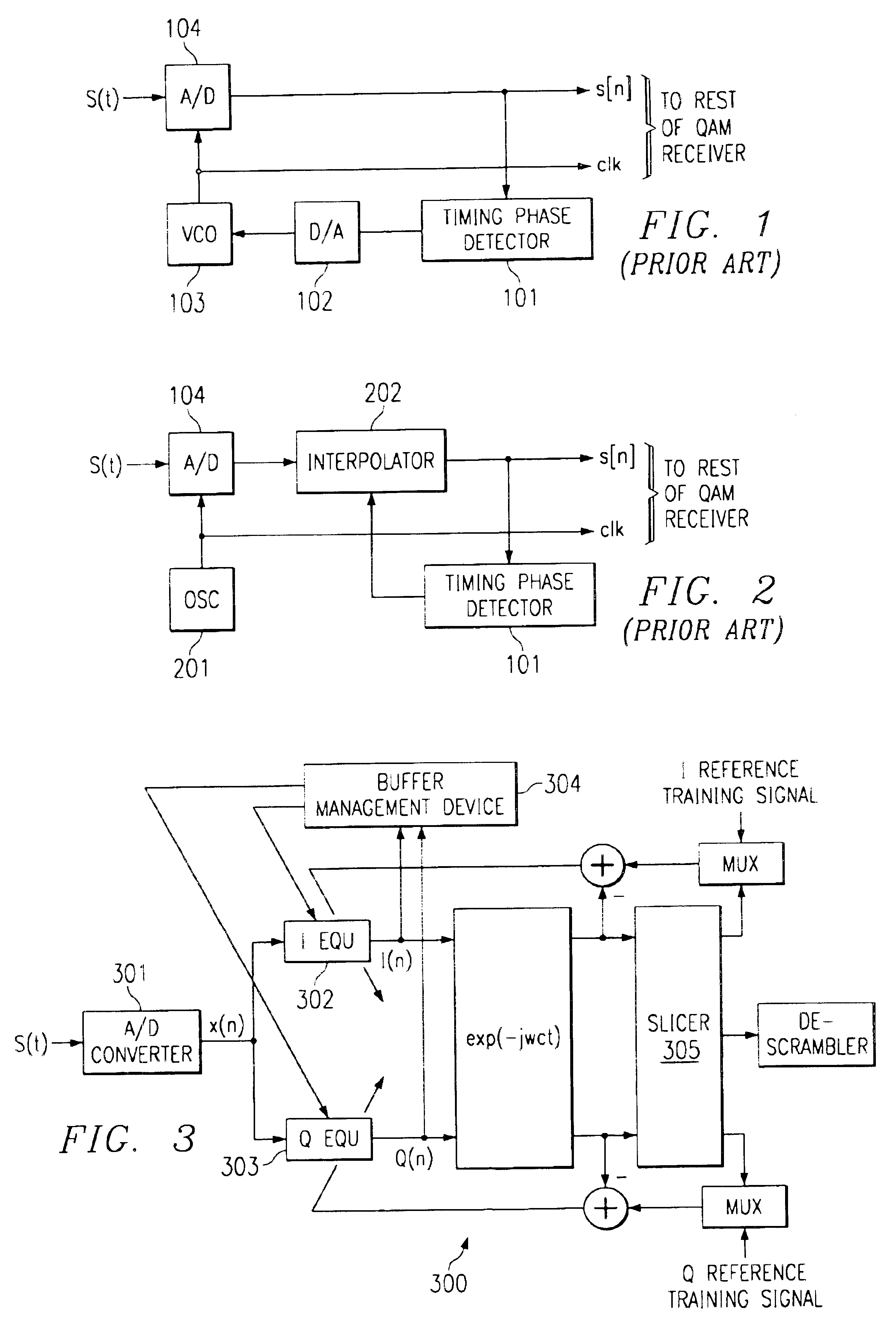

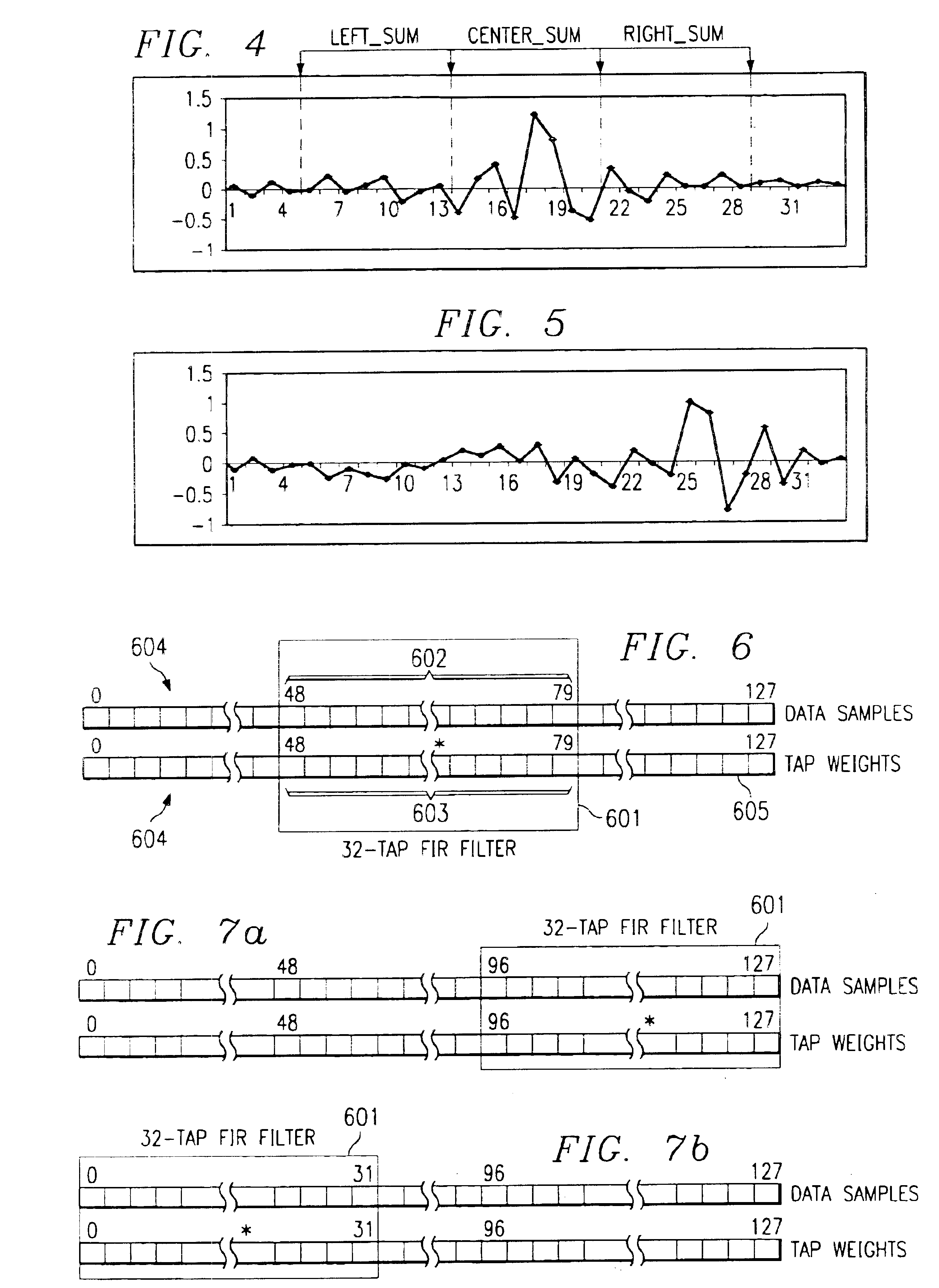

Timing recovery device and method for telecommunications systems

InactiveUS6856655B1Avoid driftingModulated-carrier systemsSynchronisation error detectionQam modulationComputer science

A timing recovery device for CAP / QAM modems includes an equalizer filter designed to monitor the movement of the filter coefficients within a memory buffer and to adjust the relative position of the filter coefficients within the memory buffer so that the coefficients remain substantially centered within the buffer.

Owner:TEXAS INSTR INC

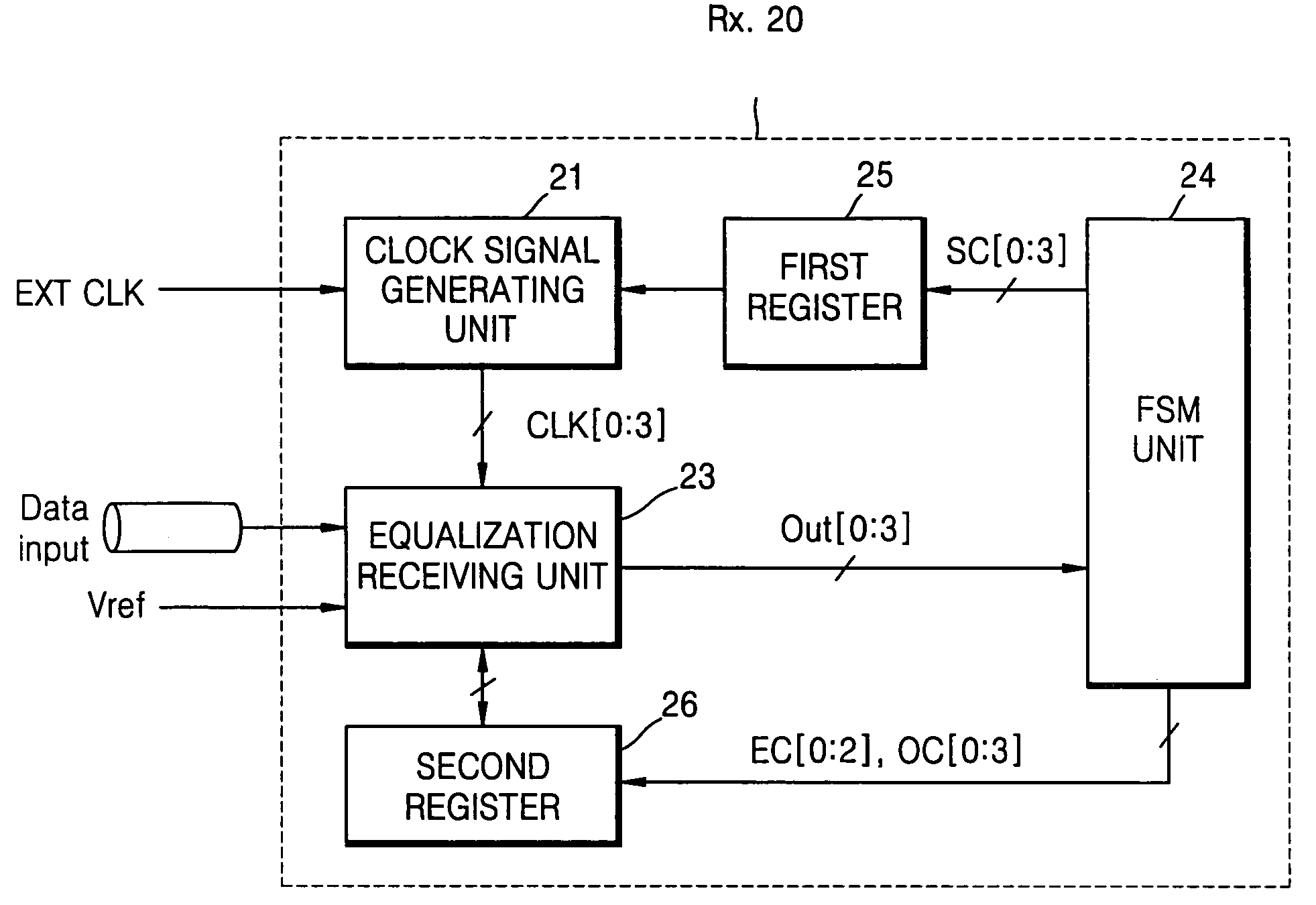

Receiving apparatus and method thereof

ActiveUS7822111B2Reduce power consumptionReduce chip areaMultiple-port networksError preventionData signalEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

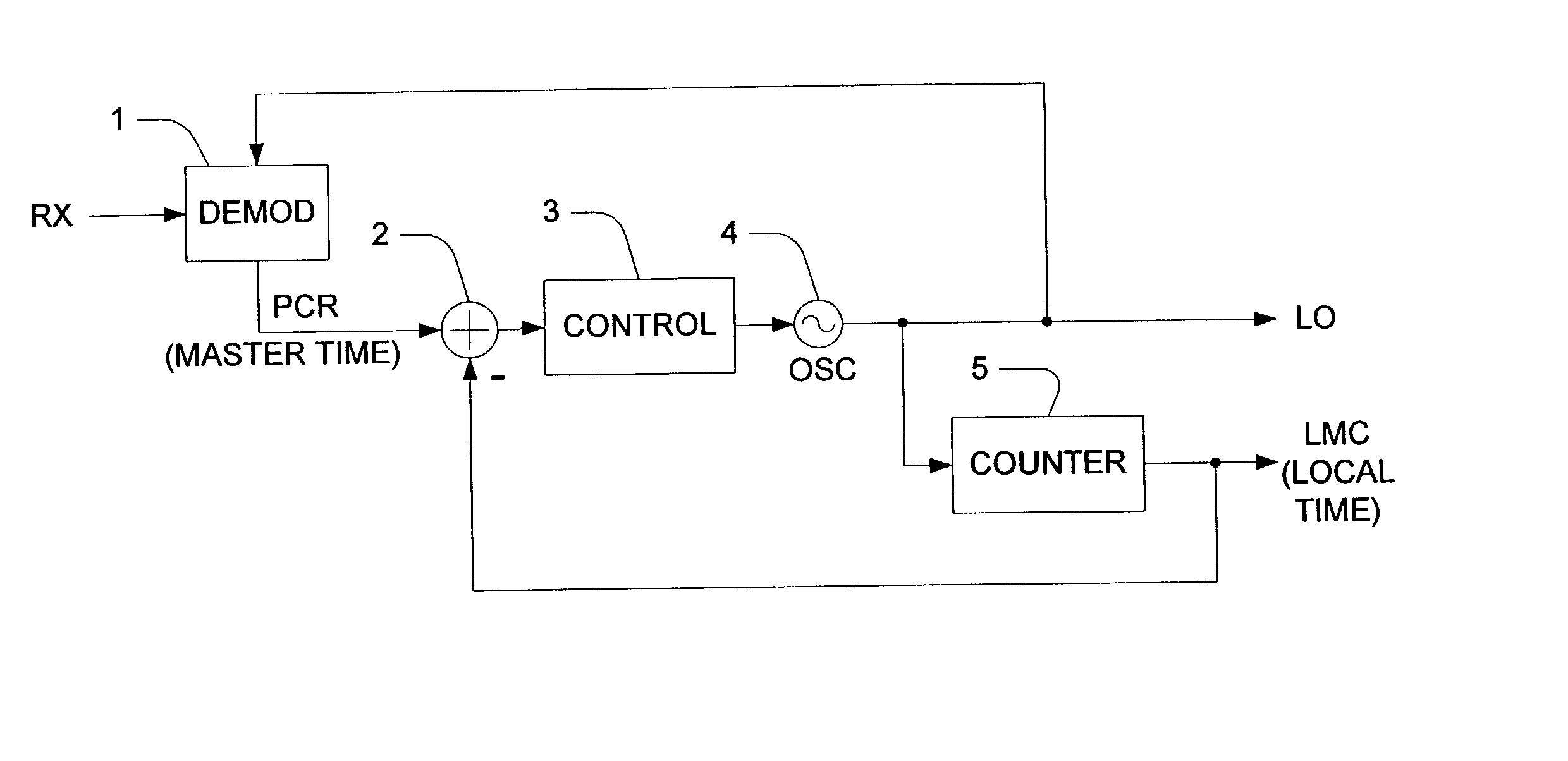

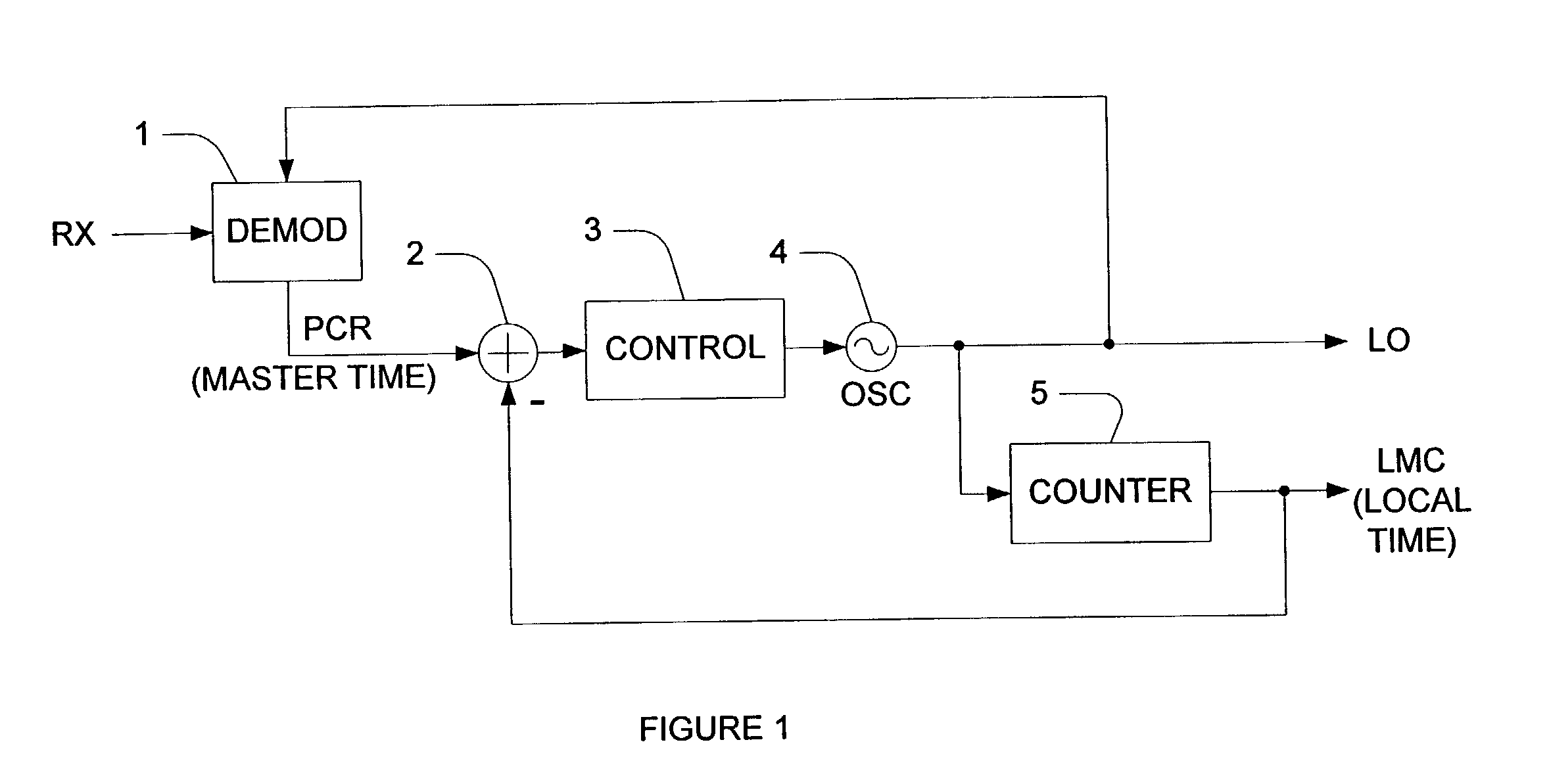

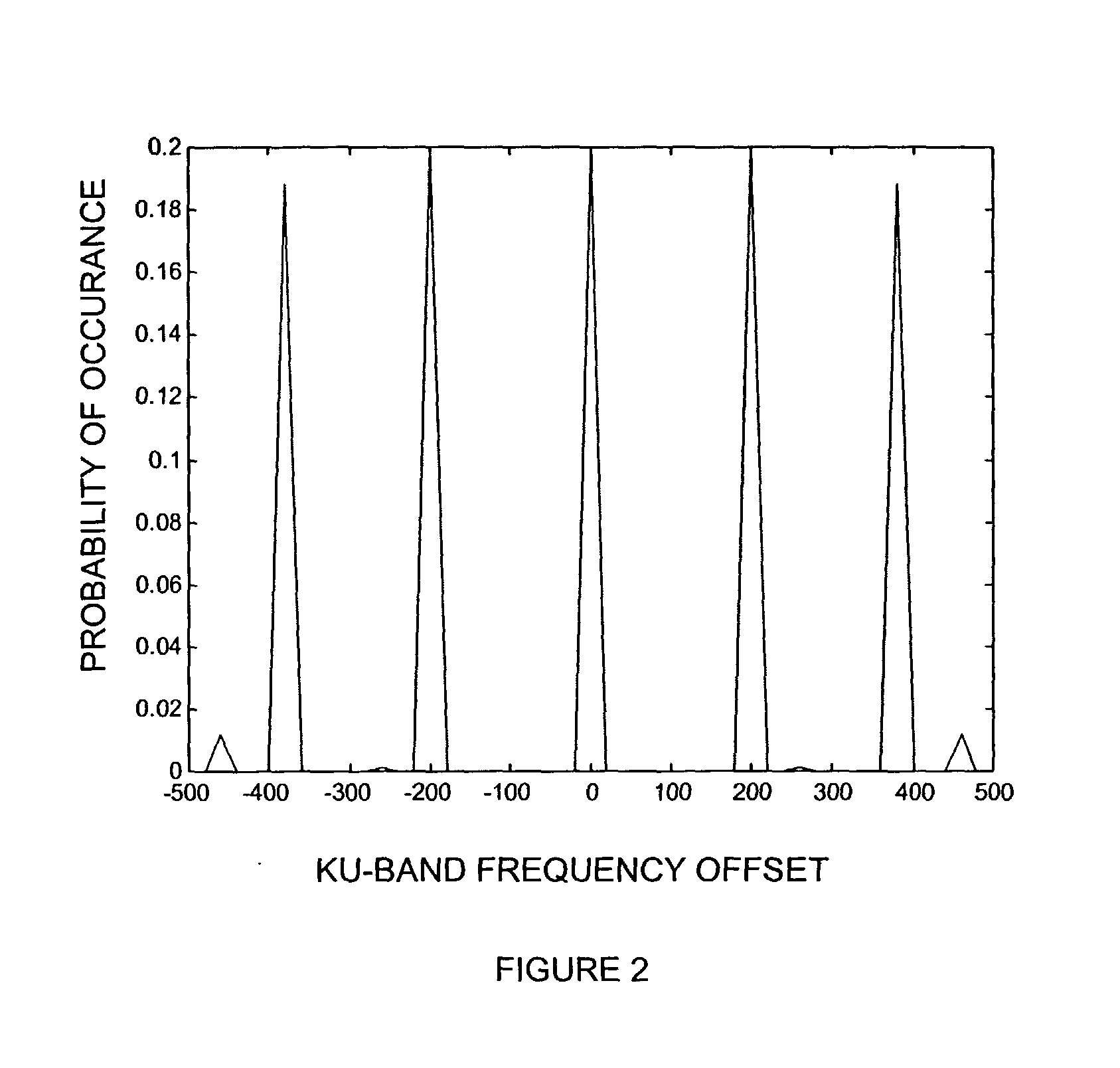

System and method of timing and frequency control in TDM/TDMA networks

ActiveUS20030147426A1Broadcast information characterisationSynchronisation error detectionProgram clock referenceLoop filter

A method and system of synchronizing two nodes of a network uses a demodulated output signal of a time division multiplex (TDM) demodulator to perform frequency and timing synchronization independently. Frequency synchronization is performed without using a program clock reference, by detecting a symbol timing loop error of the TDM demodulator. The error is filtered by an oscillator control loop filter if the error is within a predetermined range. Thus, an output voltage of a digital to analog converter that receives the filtered output controls an oscillator. In the timing synchronizer, an error between a program clock reference (PCR) and a value of a counter in the terminal is computed if the PCR is a not a first PCR, and the error is filtered with a timing loop control filter. A processor then adjusts a value of the counter in the terminal based on the filtered output.

Owner:VIASAT INC

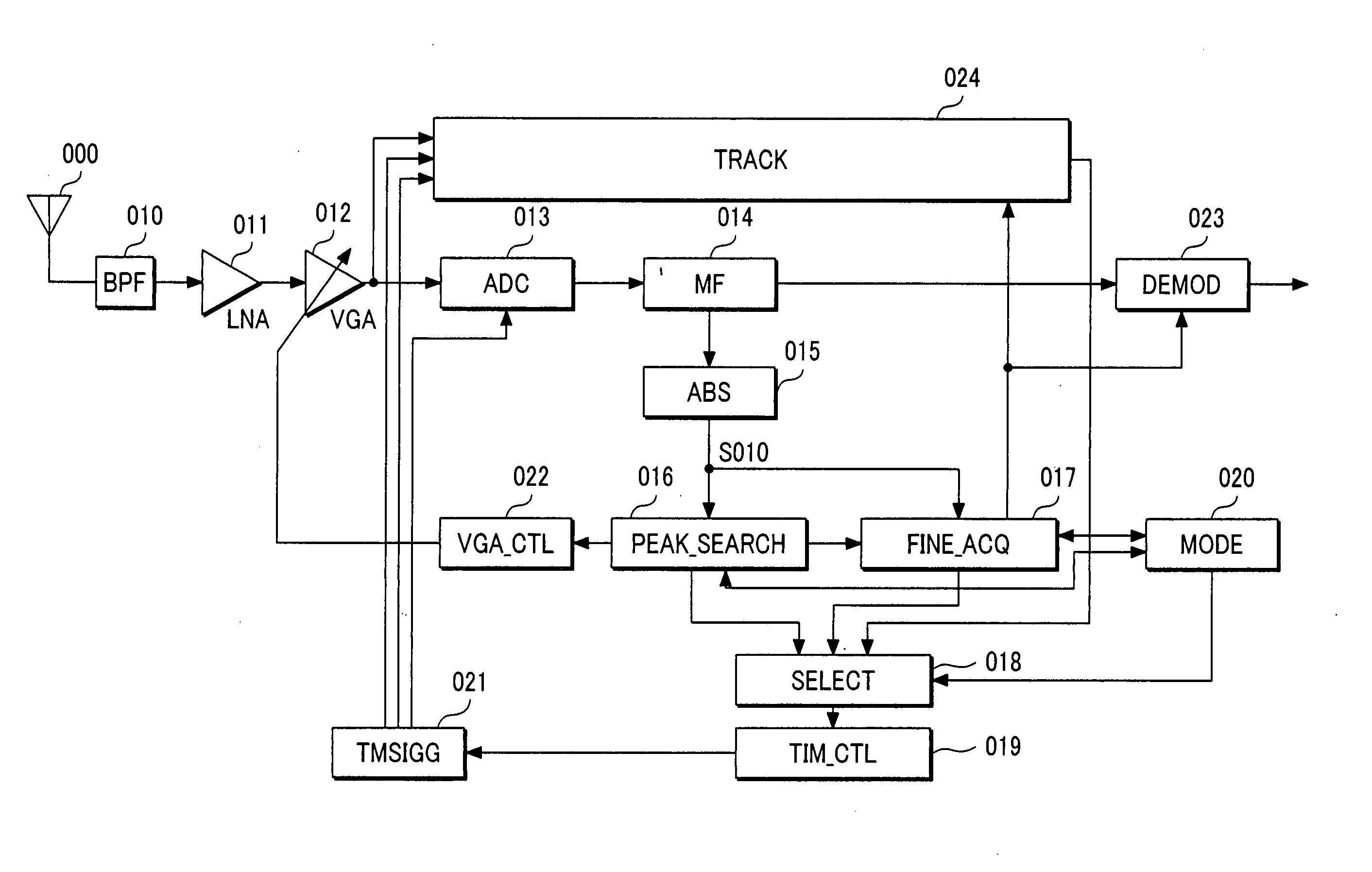

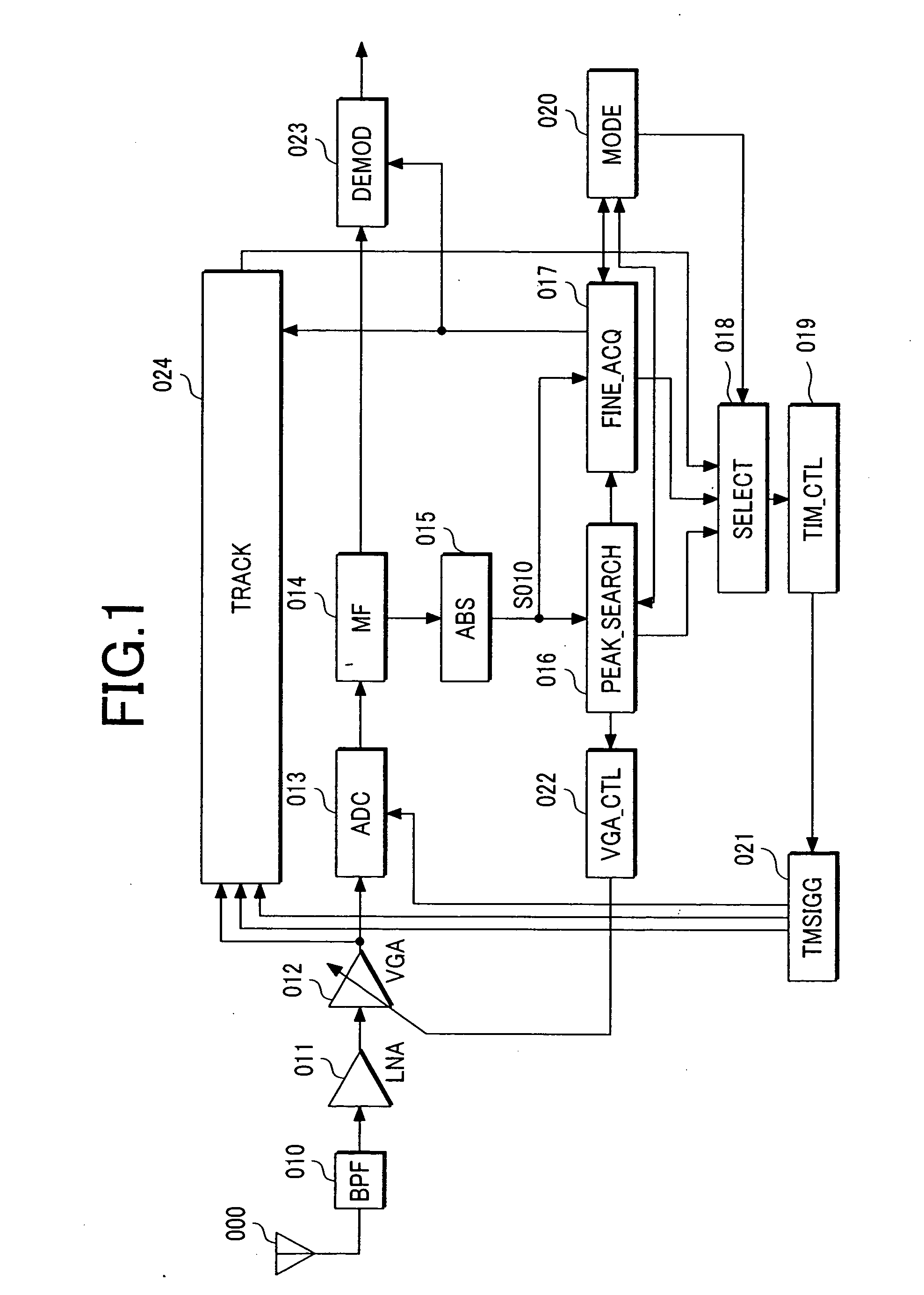

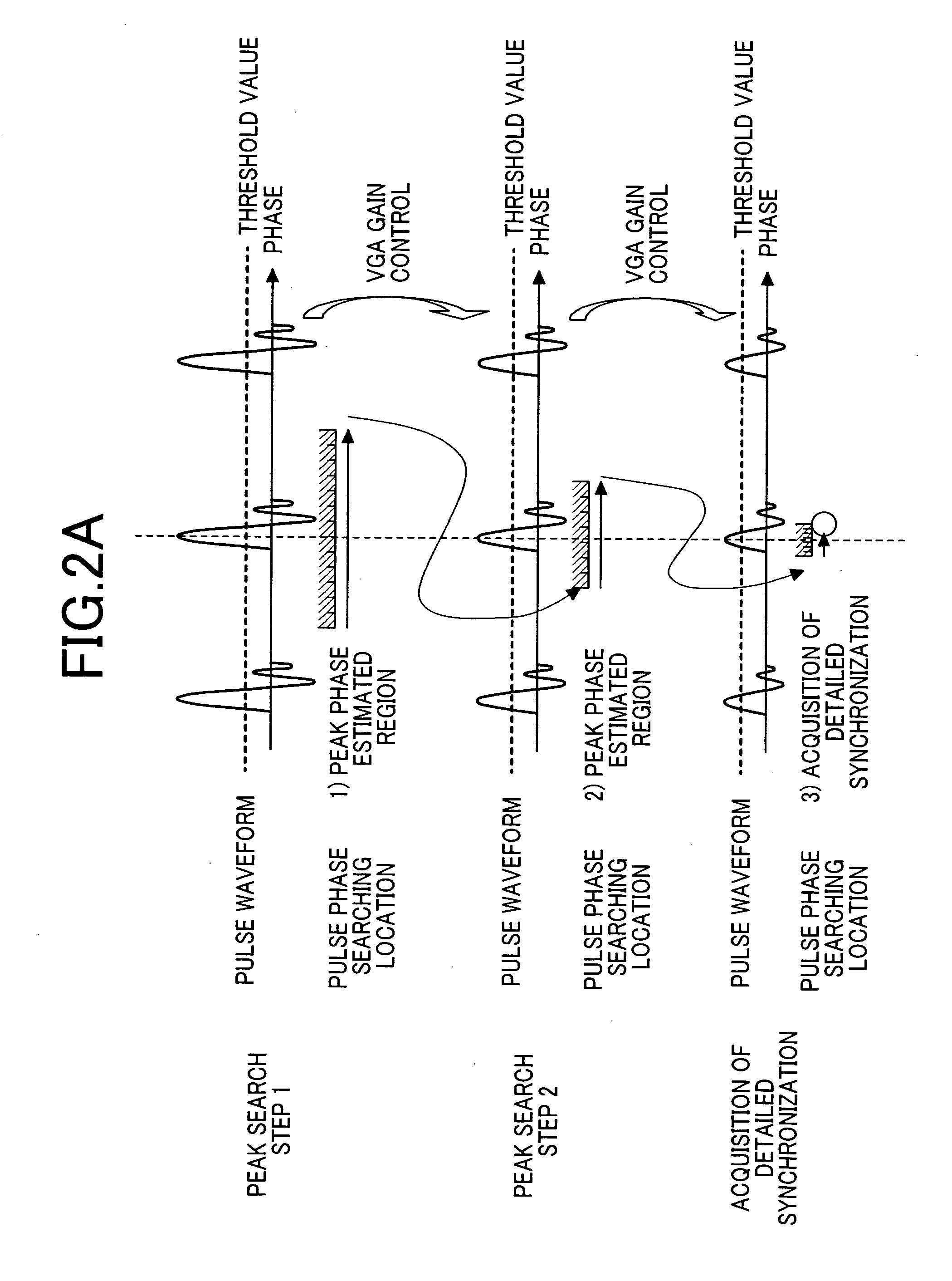

Receiving apparatus, communication apparatus and control apparatus using the same

ActiveUS20070116104A1Guaranteed normal transmissionSimple structureSynchronisation error detectionAmplitude-modulated carrier systemsUltra-widebandImage resolution

The present invention conducts the initial synchronization acquisition of the rapid and high precision ultra-wideband signal without complicatedness of hardware and increase in power consumption. For this purpose, a communication apparatus for exchanging information with an intermittent pulse train signal searches all phases among the pulses in the predetermined search resolution in the process to acquire initial synchronization of the input pulse, estimates the region where the peak phase of the largest output value exists, narrows the region where the peak phase exists up to the predetermined range by repeating the search for all phases in the estimated region in the next step, and conducts acquisition of detailed synchronization in the estimated region. In every step, the threshold value for judging existence of signal or a gain in the analog circuit is controlled for each step. Moreover, the search resolution is set coarse for estimation of the peak phase and set fine for acquisition of detailed synchronization.

Owner:RENESAS ELECTRONICS CORP

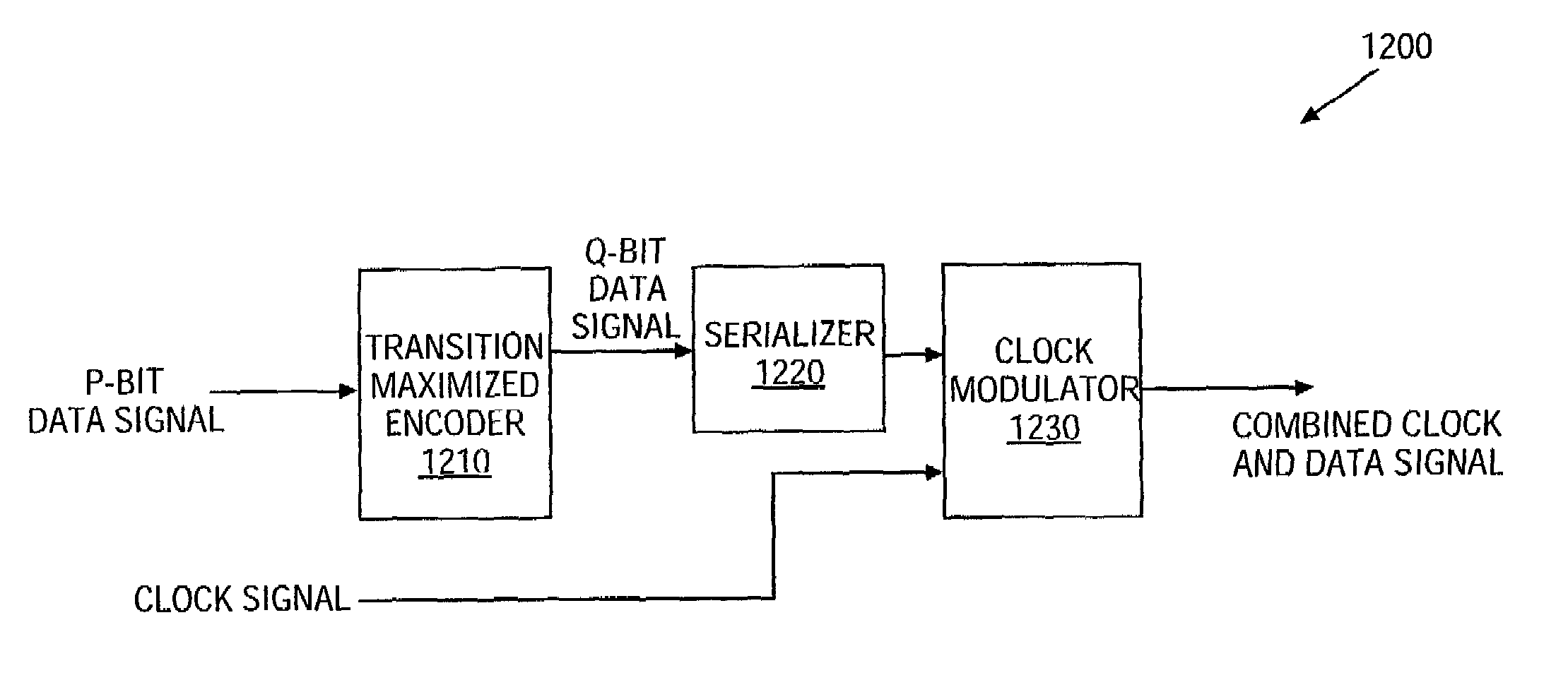

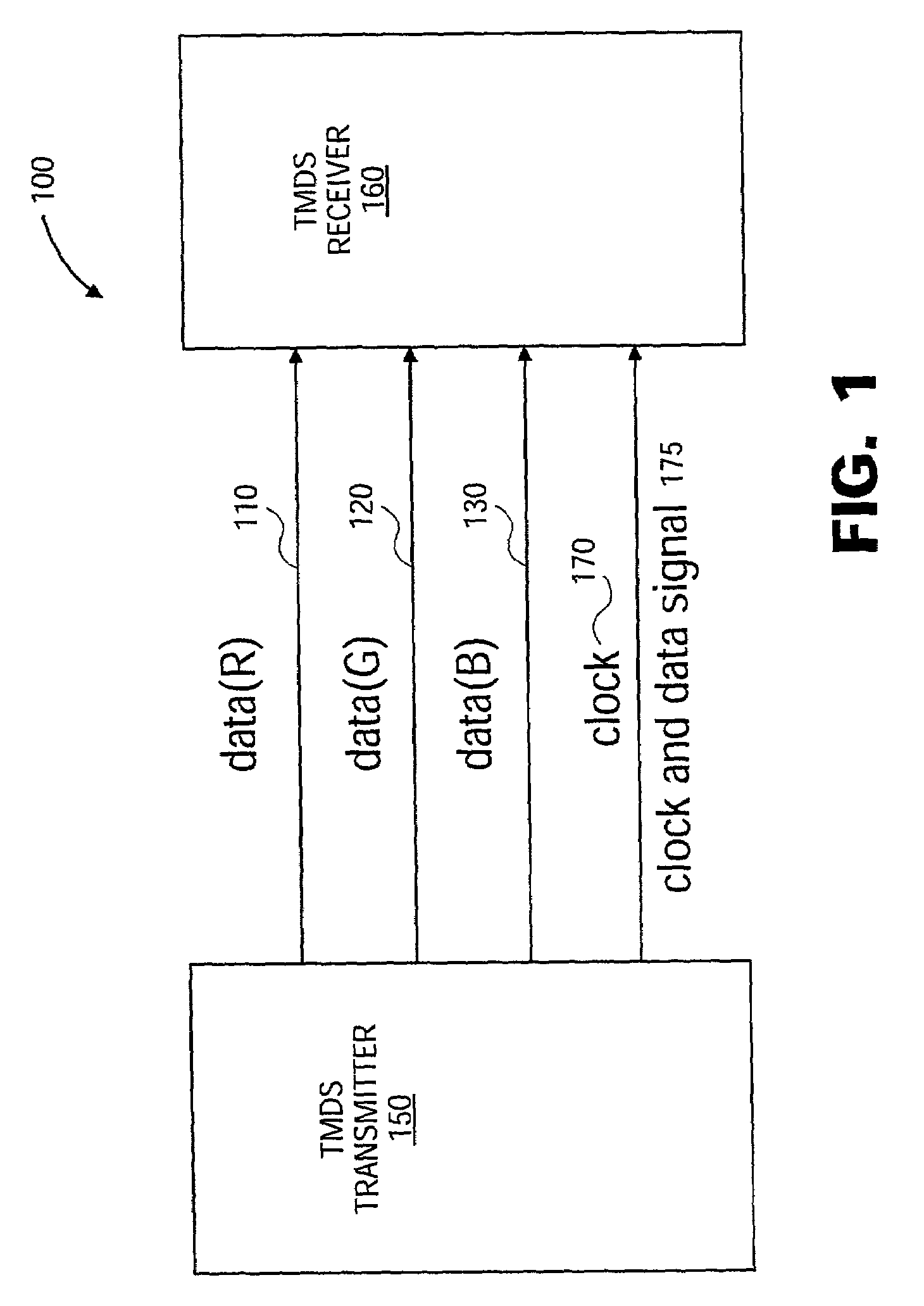

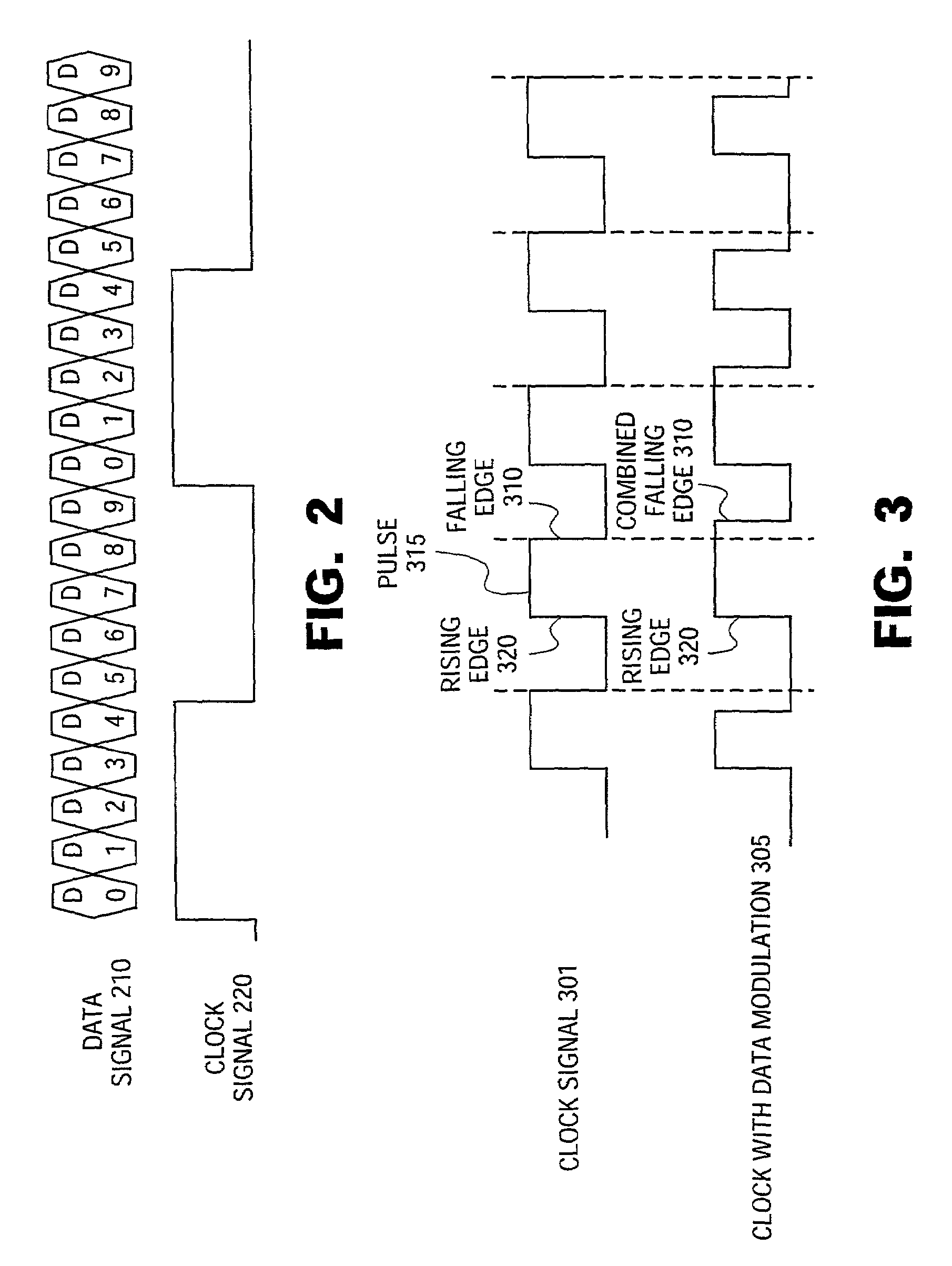

Combining a clock signal and a data signal

A method of transmitting data in a system including at least one data channel and a separate clock channel is disclosed. The method involves combining a clock signal to be transmitted on the clock channel with a data signal to generate a combined clock and data signal. In one embodiment, the data signal has been generated from data words using an encoding scheme that shifts an energy spectrum of the data signal away from an energy spectrum of the clock signal. In another embodiment, the clock signal has a plurality of pulses each having a front edge and a back edge, and the data signal is modulated onto the clock signal by moving at least one edge (i.e. front or back or both) of the plurality of pulses, thereby to create a combined clock and data signal.

Owner:SILICON IMAGE INC

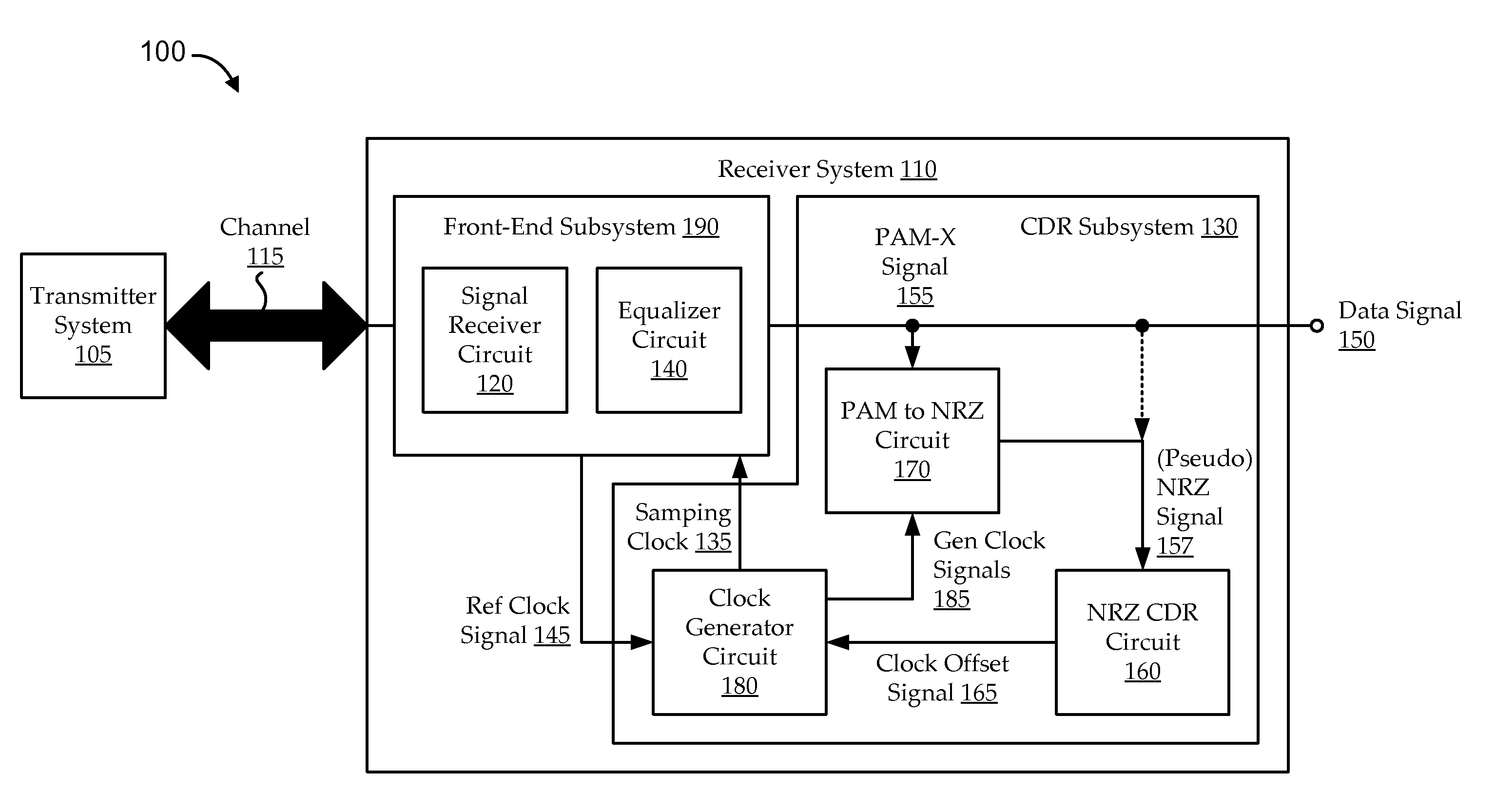

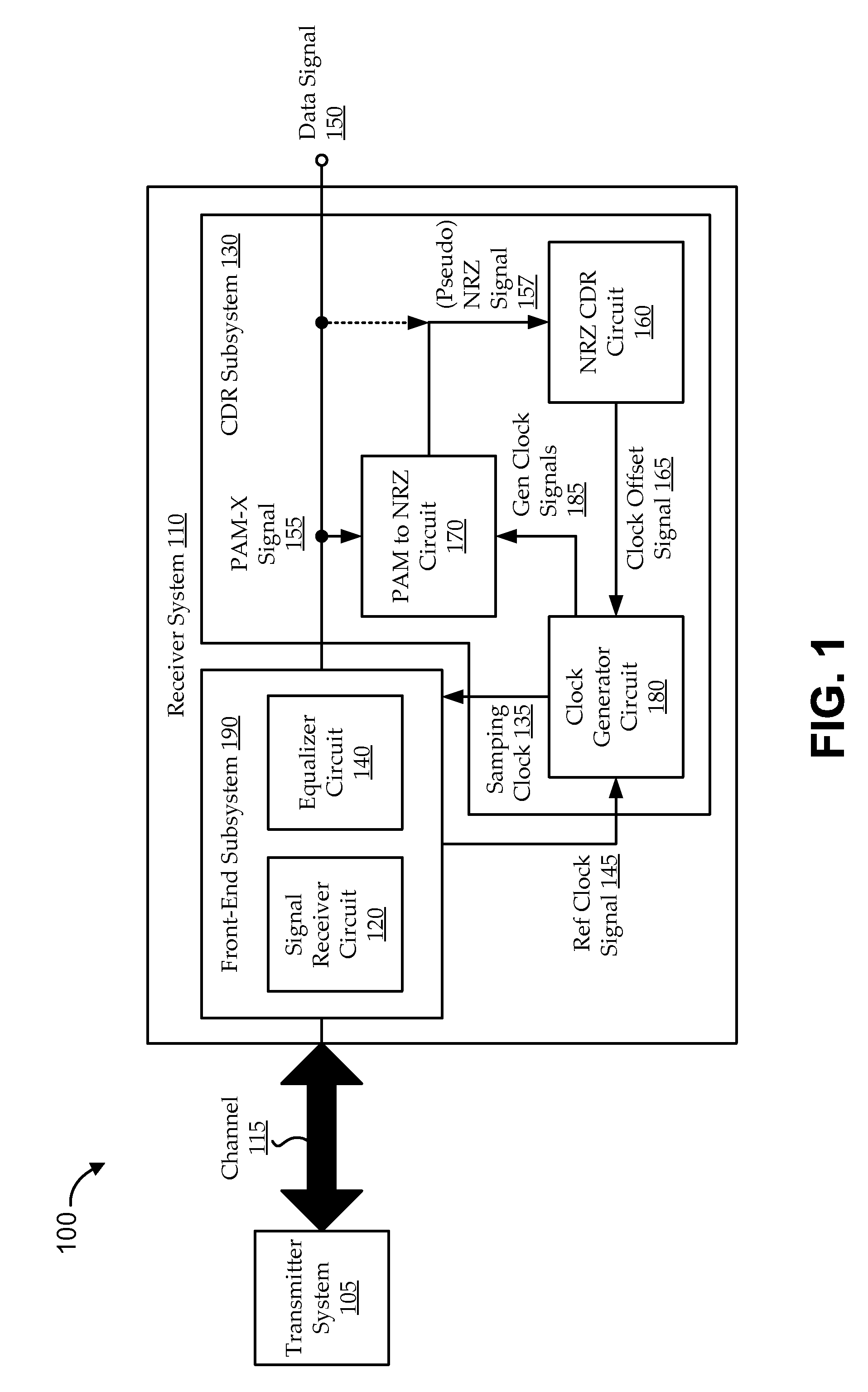

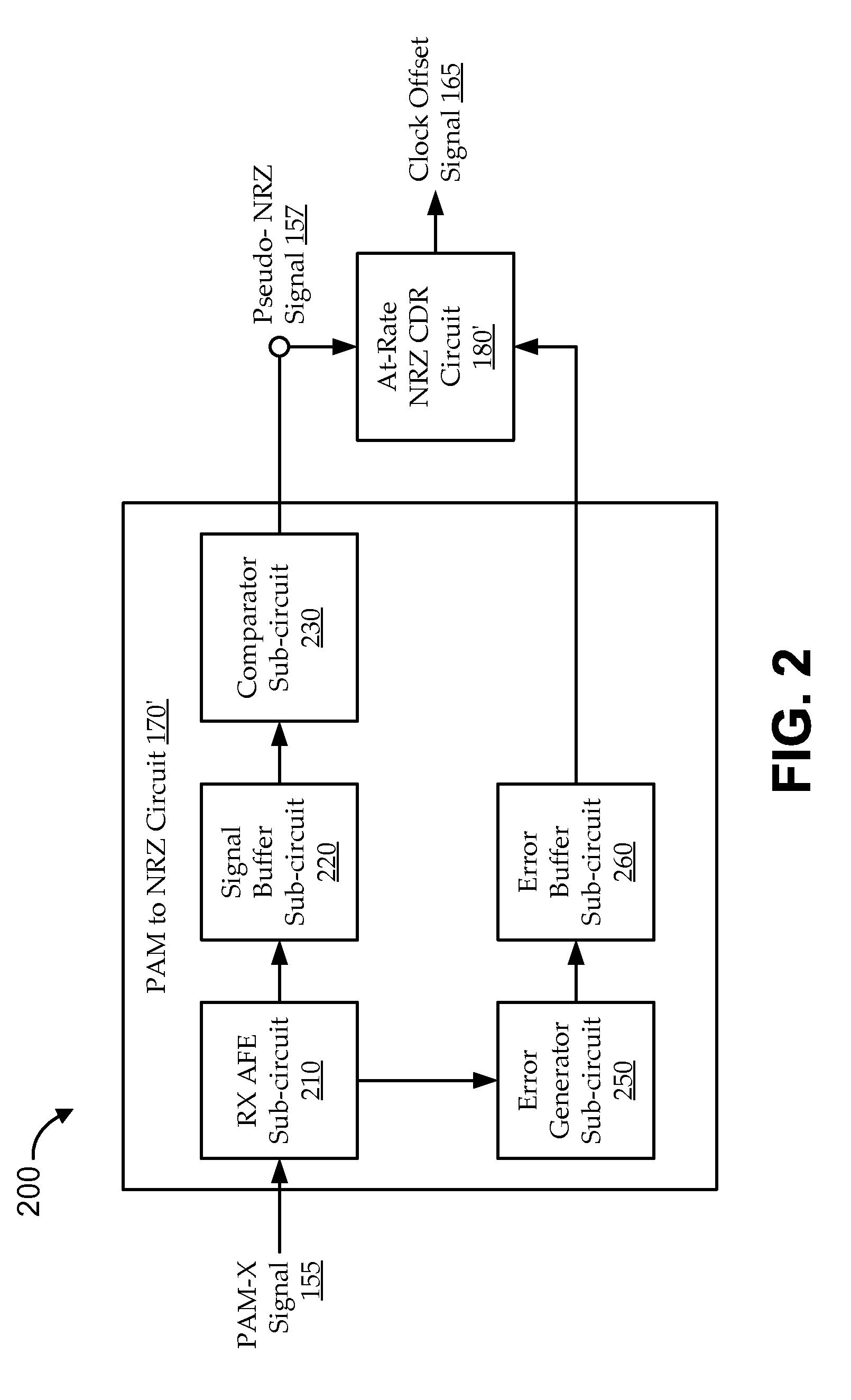

Configurable pulse amplitude modulation clock data recovery

ActiveUS9184906B1Facilitate dual-mode signalingReduce workloadSynchronisation error correctionSynchronisation error detectionReturn-to-zeroDual mode

Embodiments include systems and methods for using generalized pulse amplitude modulation (PAM-X) signaling with an at-rate not-return-to-zero (NRZ) clock data recovery (CDR) system. Some implementations include dual-mode signaling for an at-rate CDR (e.g., using standard NRZ signaling at lower operating frequencies and pseudo-NRZ signaling derived from PAM-X signaling at higher operating frequencies. Embodiments derive an apparent direction of signal transition from PAM-X signaling. The direction can be used to calculate pseudo-NRZ values. For example, when the PAM-X signal transitions in an upward direction, a pseudo-current NRZ value and a pseudo-previous NRZ value of ‘−1’ and ‘+1’ can be generated, respectively. An at-rate NRZ CDR can use the pseudo-NRZ values and a derived error value to make an offset determination. The offset determination can then be used to offset a generated clock signal in the CDR system.

Owner:ORACLE INT CORP

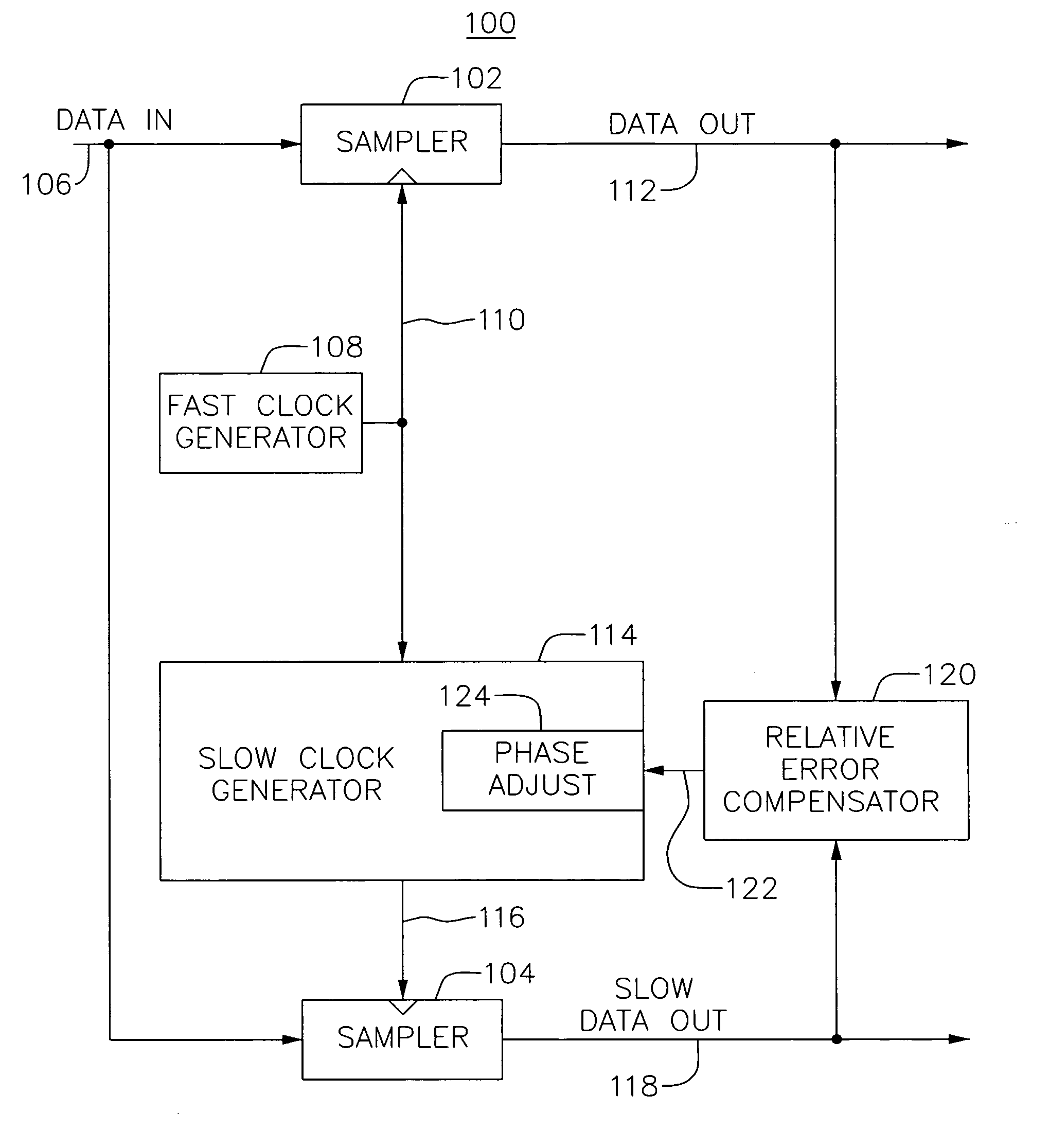

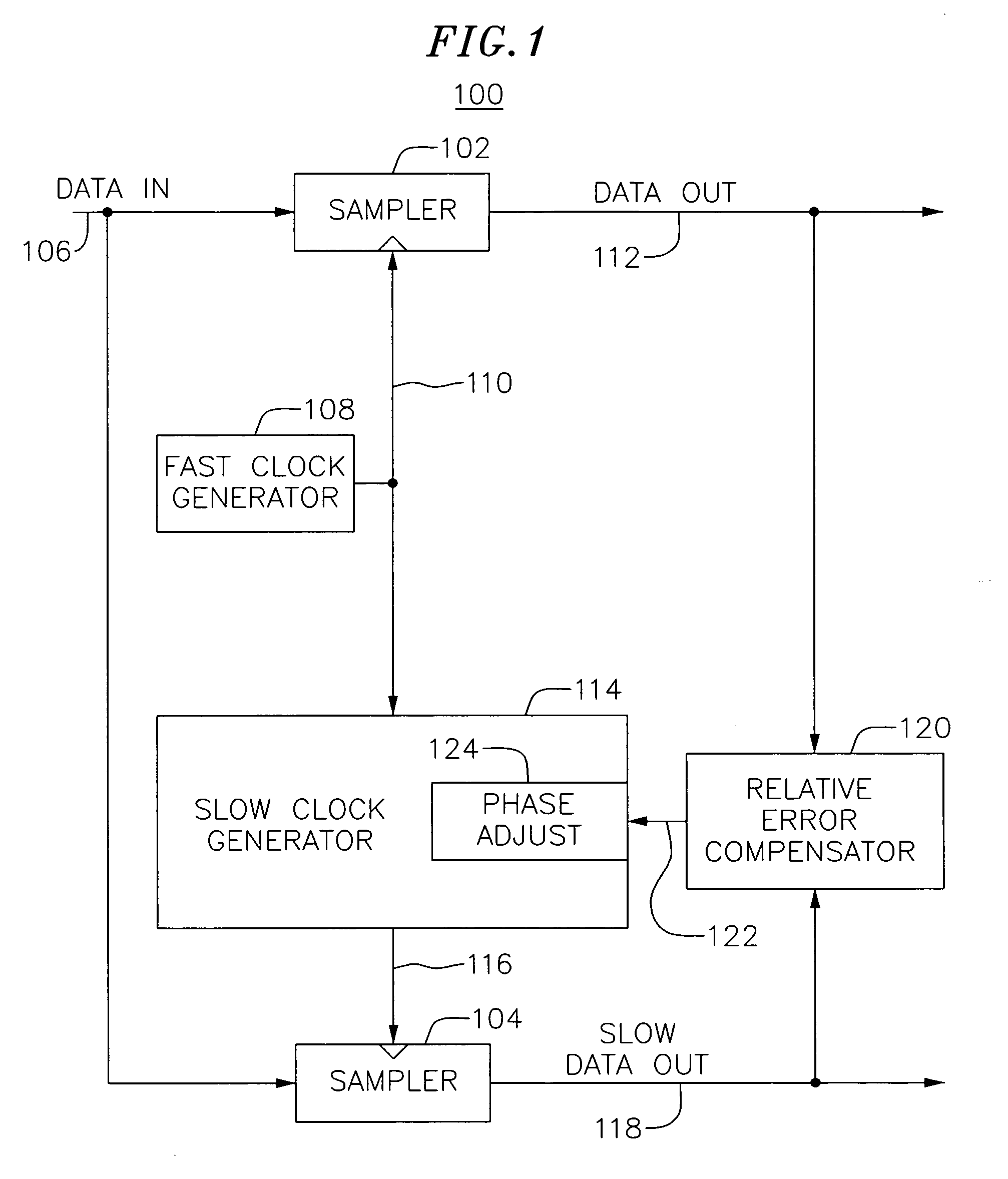

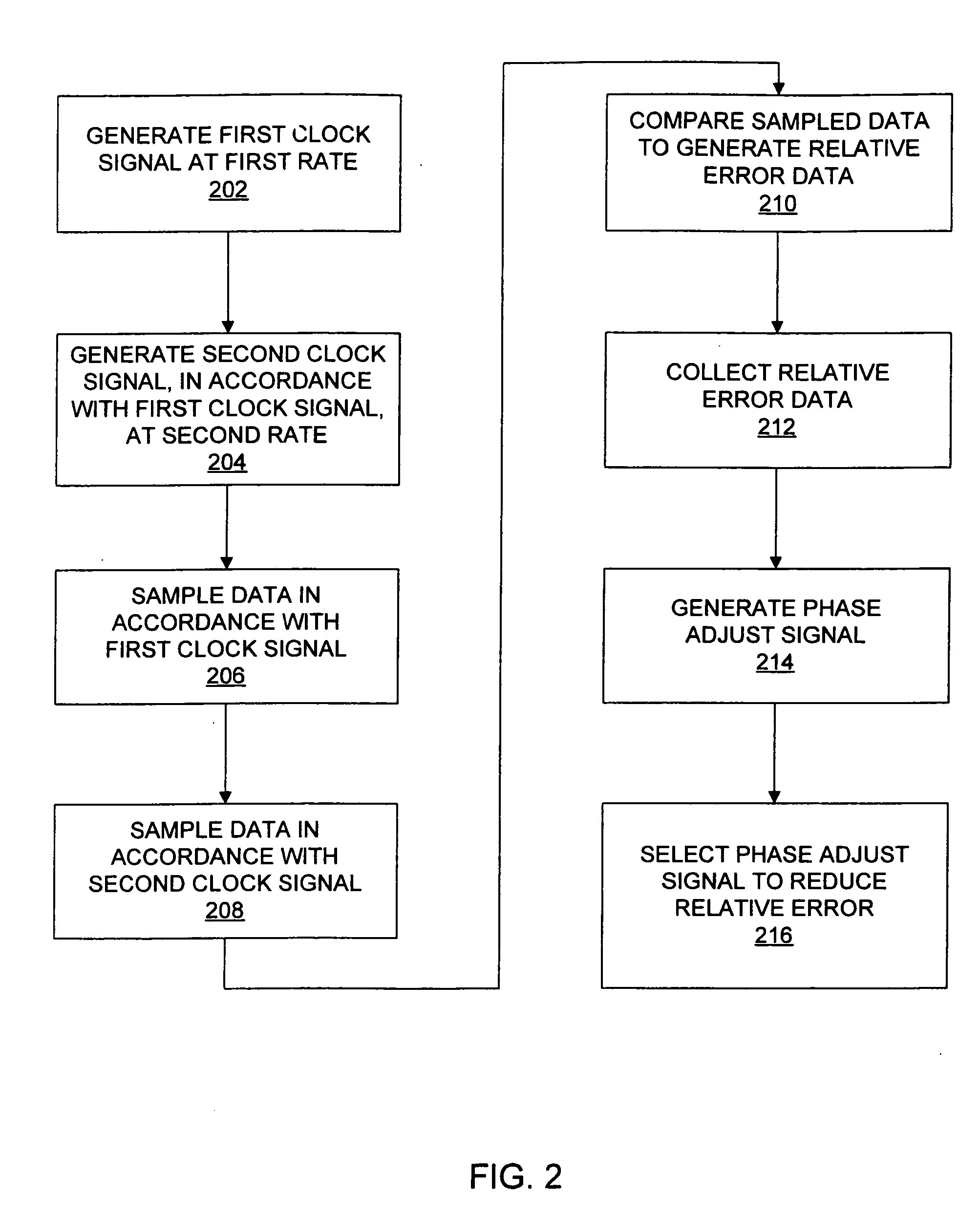

Phase adjust using relative error

InactiveUS20060253746A1Analogue/digital conversionPulse automatic controlDigital down converterLow data rate

A system may adjust the times at which data is sampled by separate sampling mechanisms. Here, it may be desirable to ensure that one sampler samples data at substantially the same time as the other sampler. For example, output data from a high speed sampler that samples received data may be compared with an output of an analog to digital converter that samples the received data at a lower data rate. This difference or relative error may be accumulated over a period of time for given values of delay applied to the clock for the analog to digital converter. In this way, a delay value that minimizes the relative error may be selected as a desired delay value.

Owner:AVAGO TECH INT SALES PTE LTD

Popular searches

Record information storage Alignment for track following on disks Digital recording Synchronisation signal speed/phase control Transmitter/receiver shaping networks Digital signal error detection/correction Analogue-digital converters Electromagnetic transmission Angle demodulation by phase difference detection Physical parameters compensation/prevention