Patents

Literature

3115results about "Physical parameters compensation/prevention" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

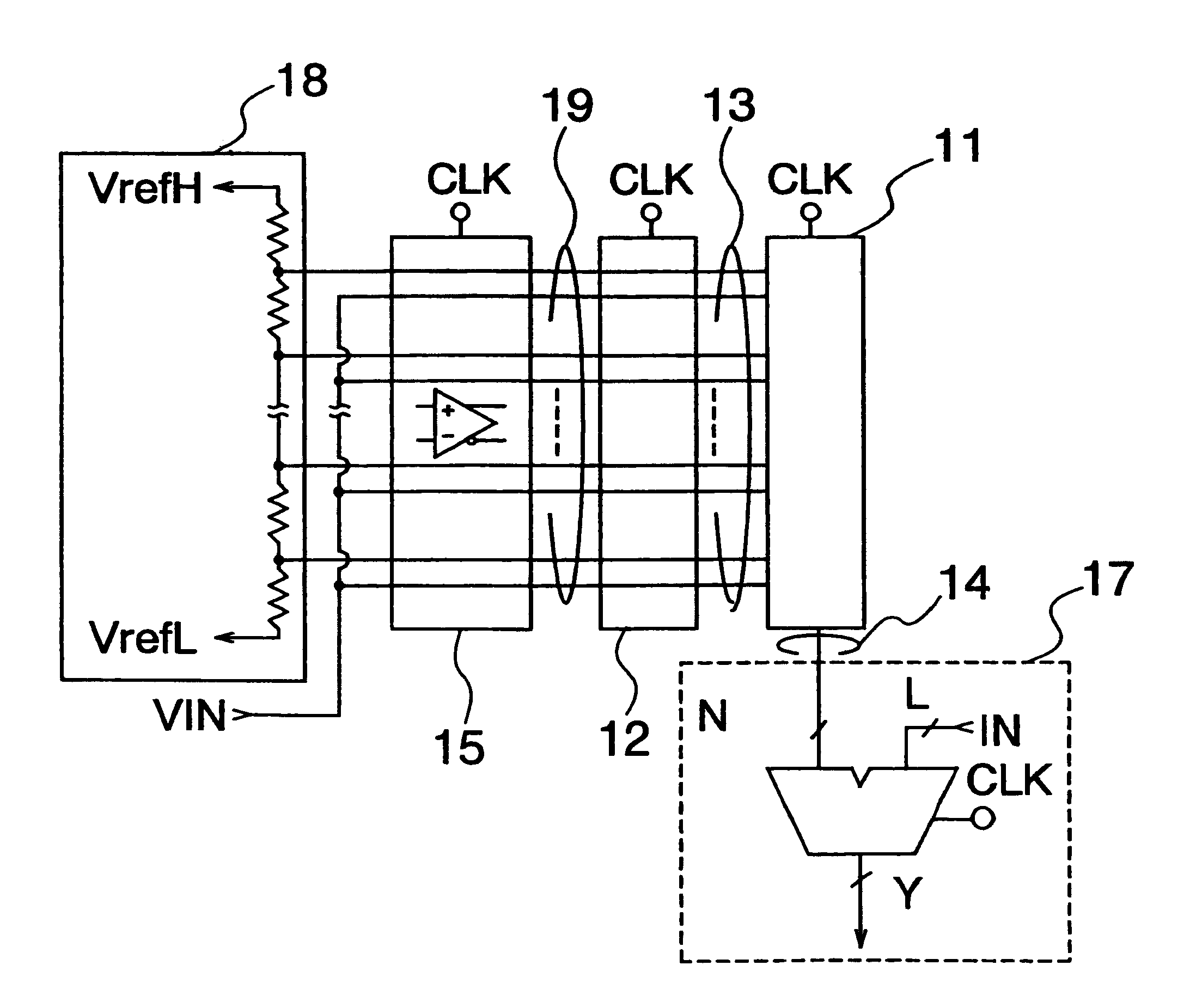

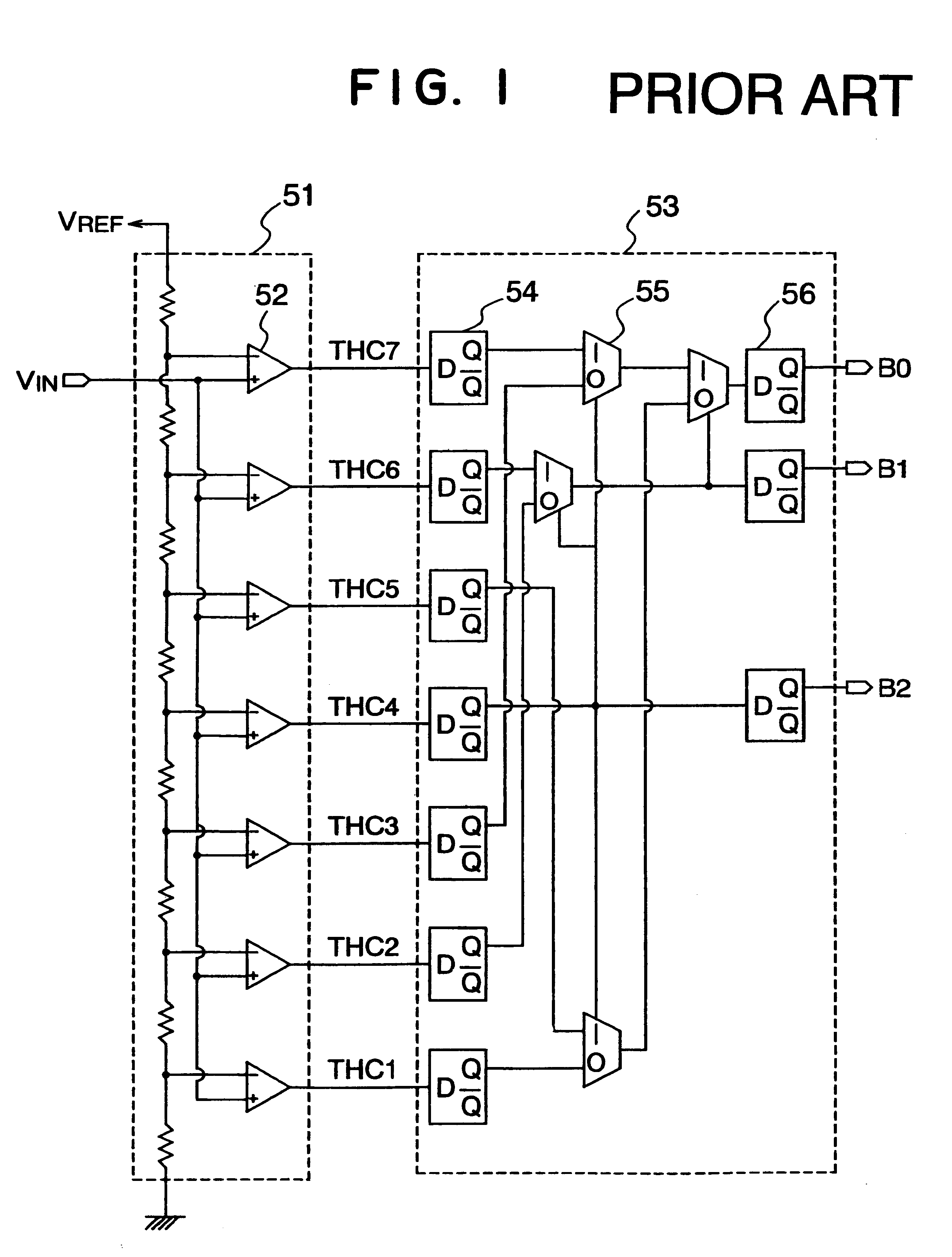

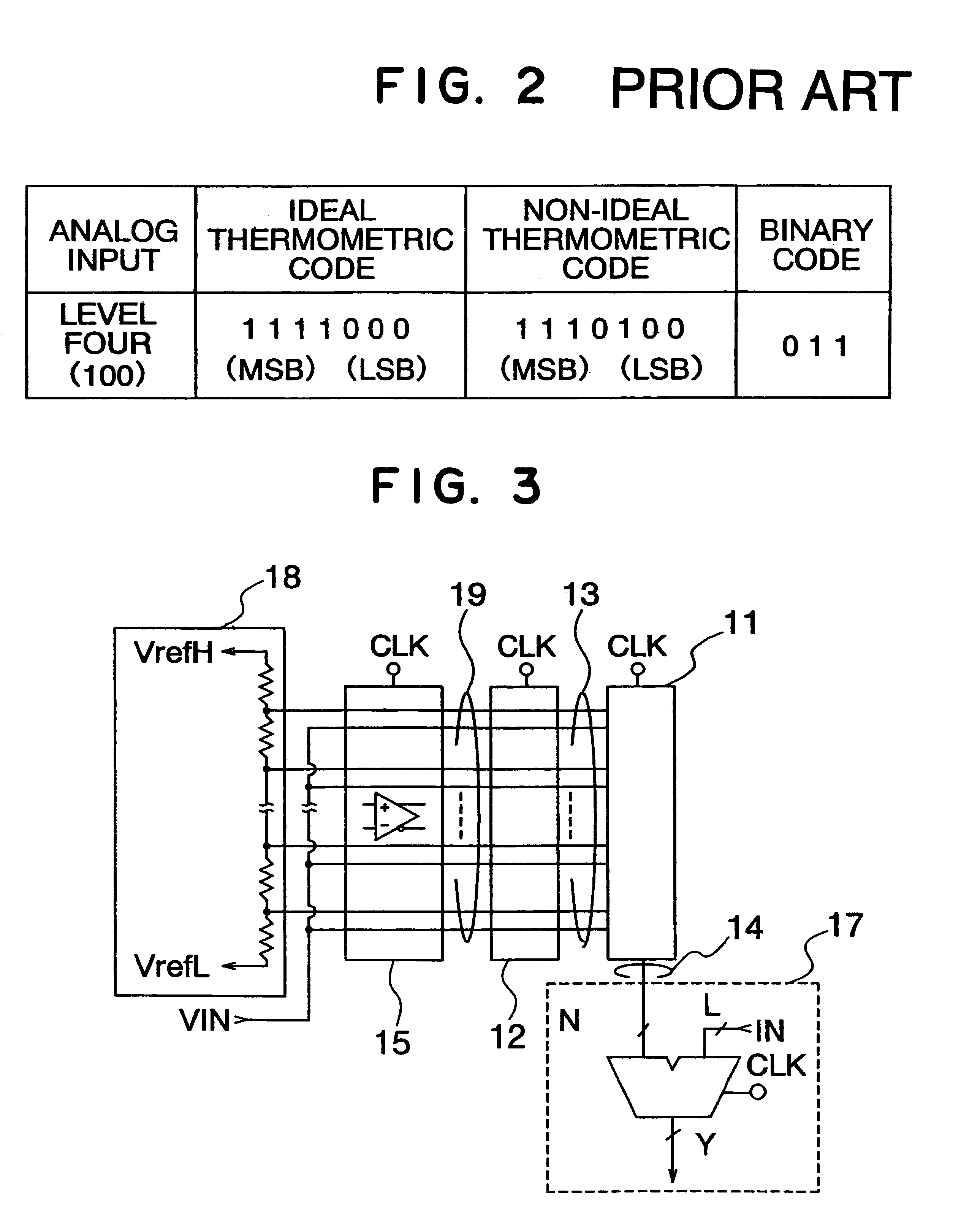

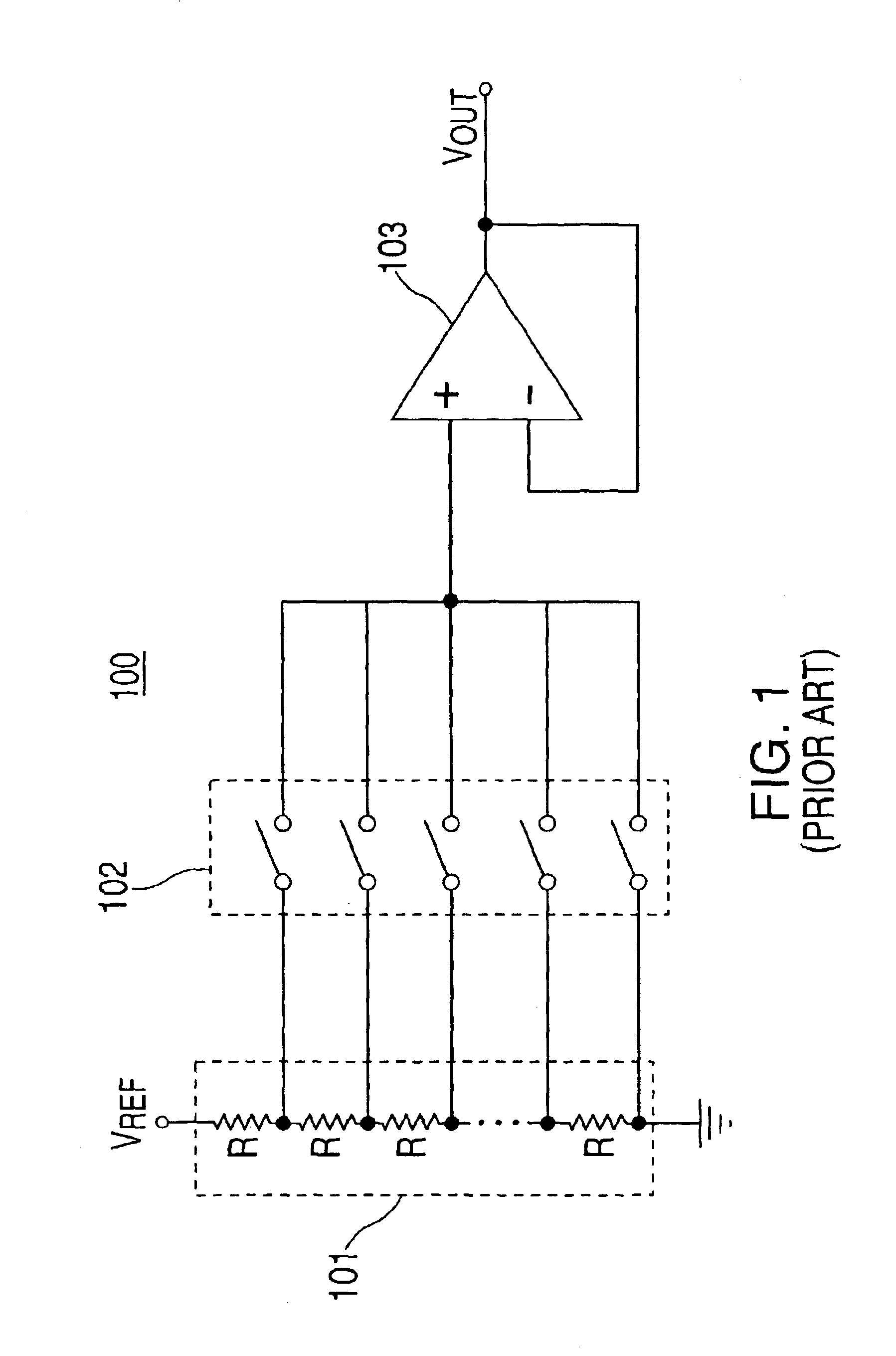

A/D converter having a dynamic encoder

InactiveUS6232908B1Increase speedReduce circuit sizeElectric signal transmission systemsAnalogue-digital convertersBuck converterA d converter

An A / D converter includes a resistor ladder for generating a plurality of reference potentials, a comparing section for comparing each of the reference potentials against an input analog signal to output a thermometric code, and a dynamic encoder composed of a combinational circuit to encode the thermometric code to a binary code by responding a clock signal. The A / D conversion is finished in a single clock cycle at a high speed, with a reduced number of elements and reduced power dissipation.

Owner:NEC ELECTRONICS CORP

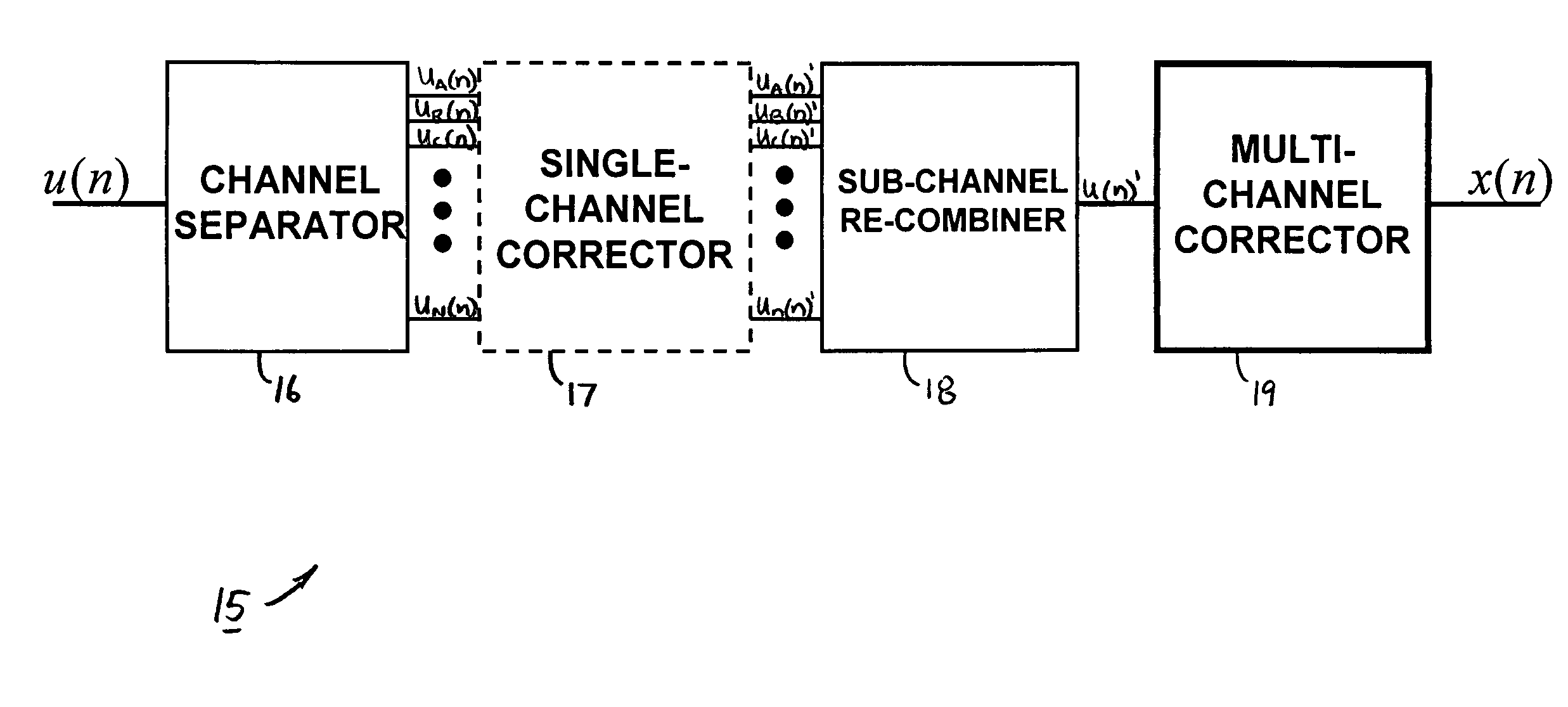

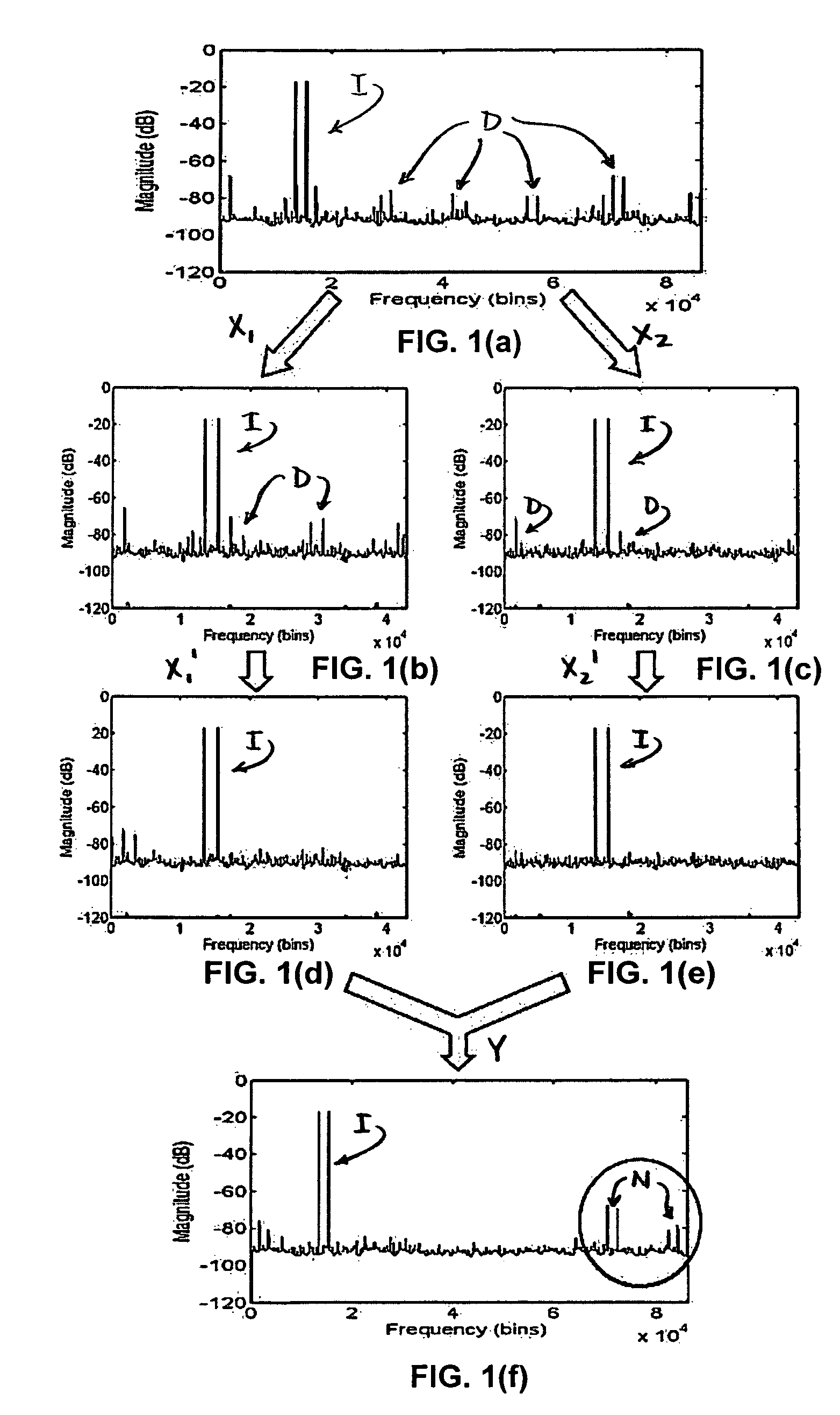

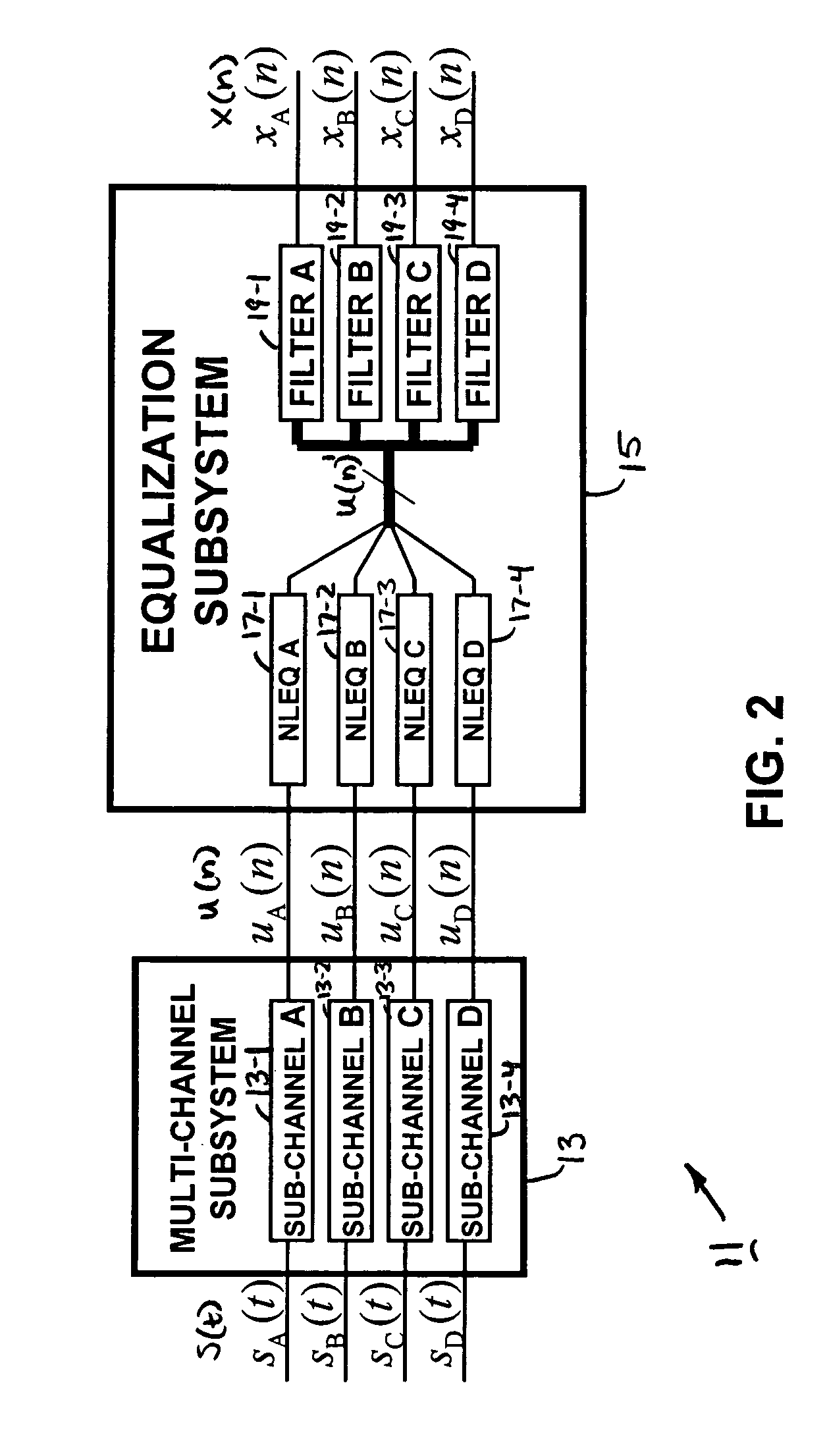

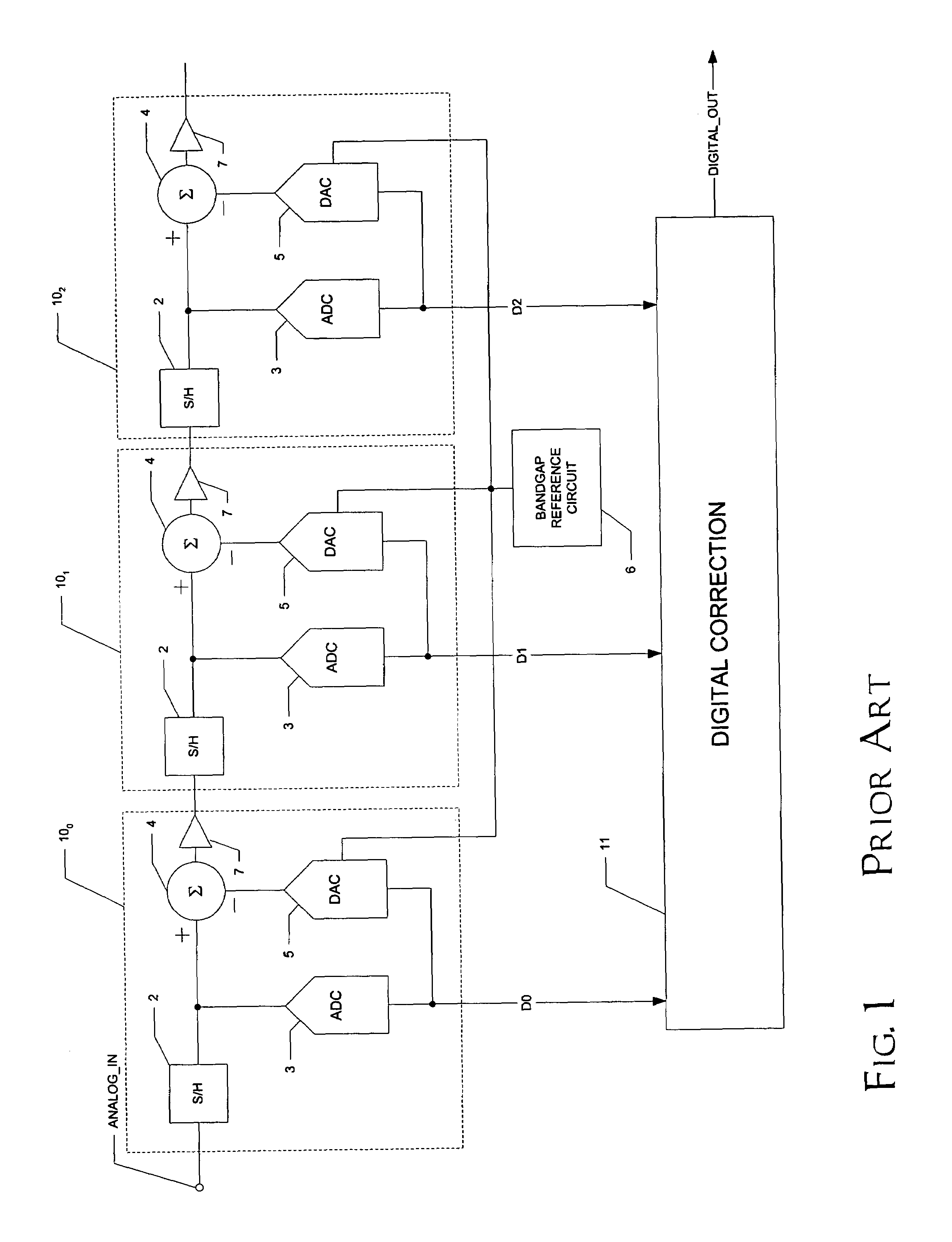

System and method of multi-channel signal calibration

InactiveUS7796068B2Electric signal transmission systemsPhysical parameters compensation/preventionSignal processingDistortion

A signal processing system for reducing calibration-related distortions in a complete-channel signal generated by a multi-channel subsystem, such as an interleaved ADC, includes a channel separator for separating the distorted digital signal into its various sub-channels and a single-channel corrector for independently processing each sub-channel to reduce distortion products present therein. The system additionally includes a subchannel re-combiner for combining the plurality of sub-channels processed by the single-channel corrector and a multi-channel corrector for calibrating each of plurality of sub-channels relative to one another to yield an equalized, complete-channel output signal. The multi-channel corrector includes a bank of optimized filters, each filter being assigned to a corresponding sub-channel of the complete-channel signal. In one embodiment, one of the plurality of sub-channels is selected as an ideal reference signal and the filters assigned to the remaining sub-channels are optimized to yield outputs which match the ideal reference signal.

Owner:RAZ GIL M

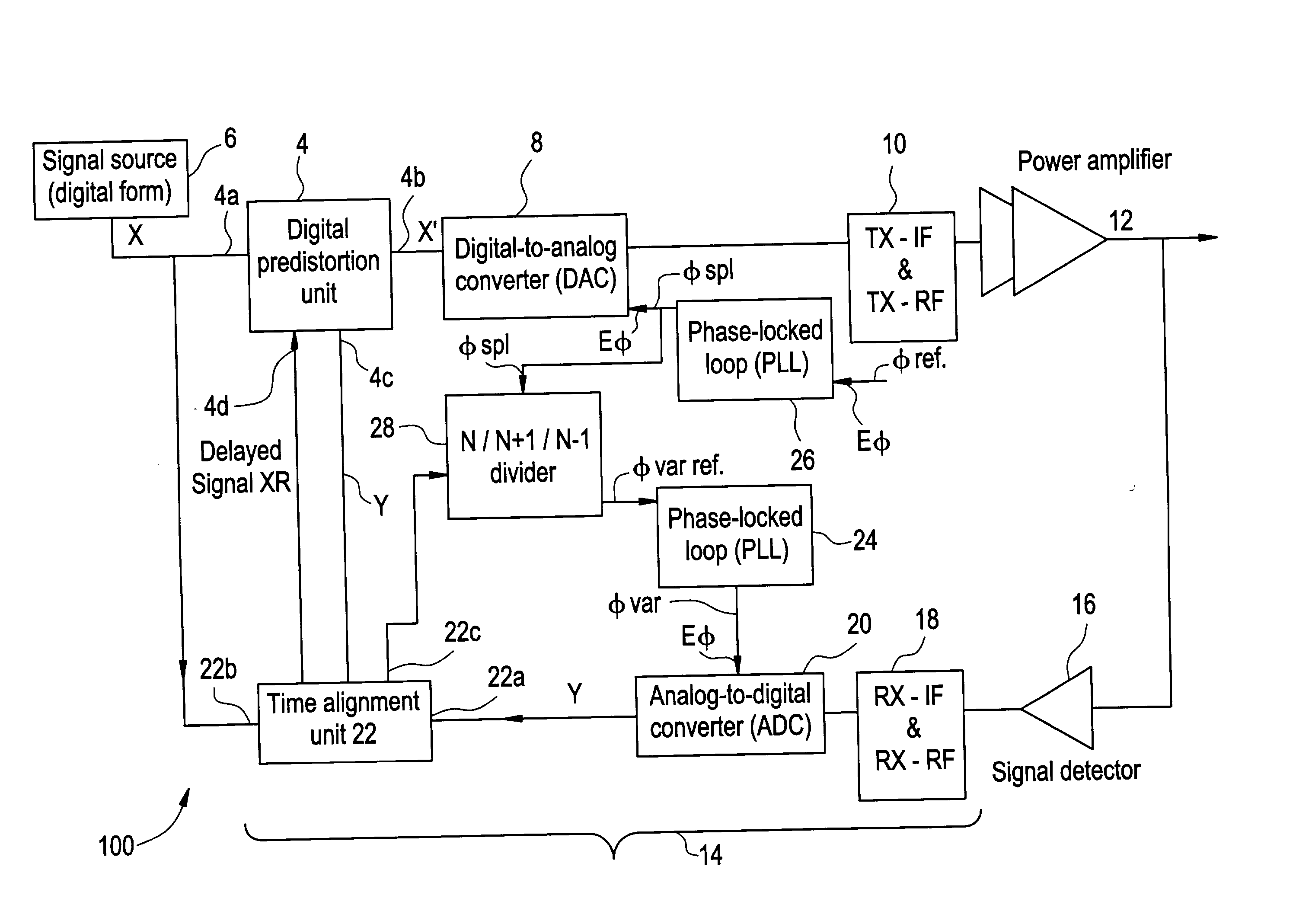

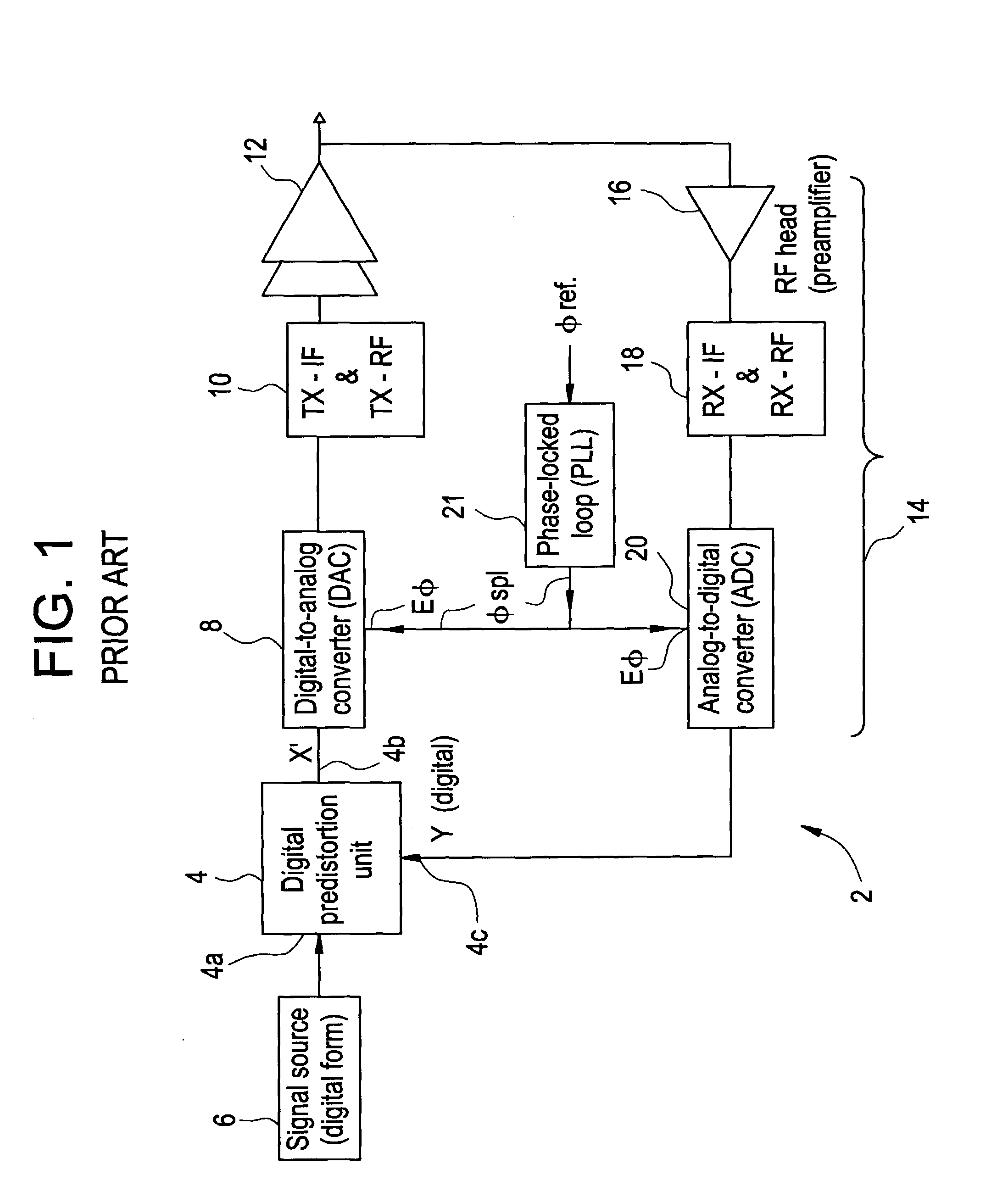

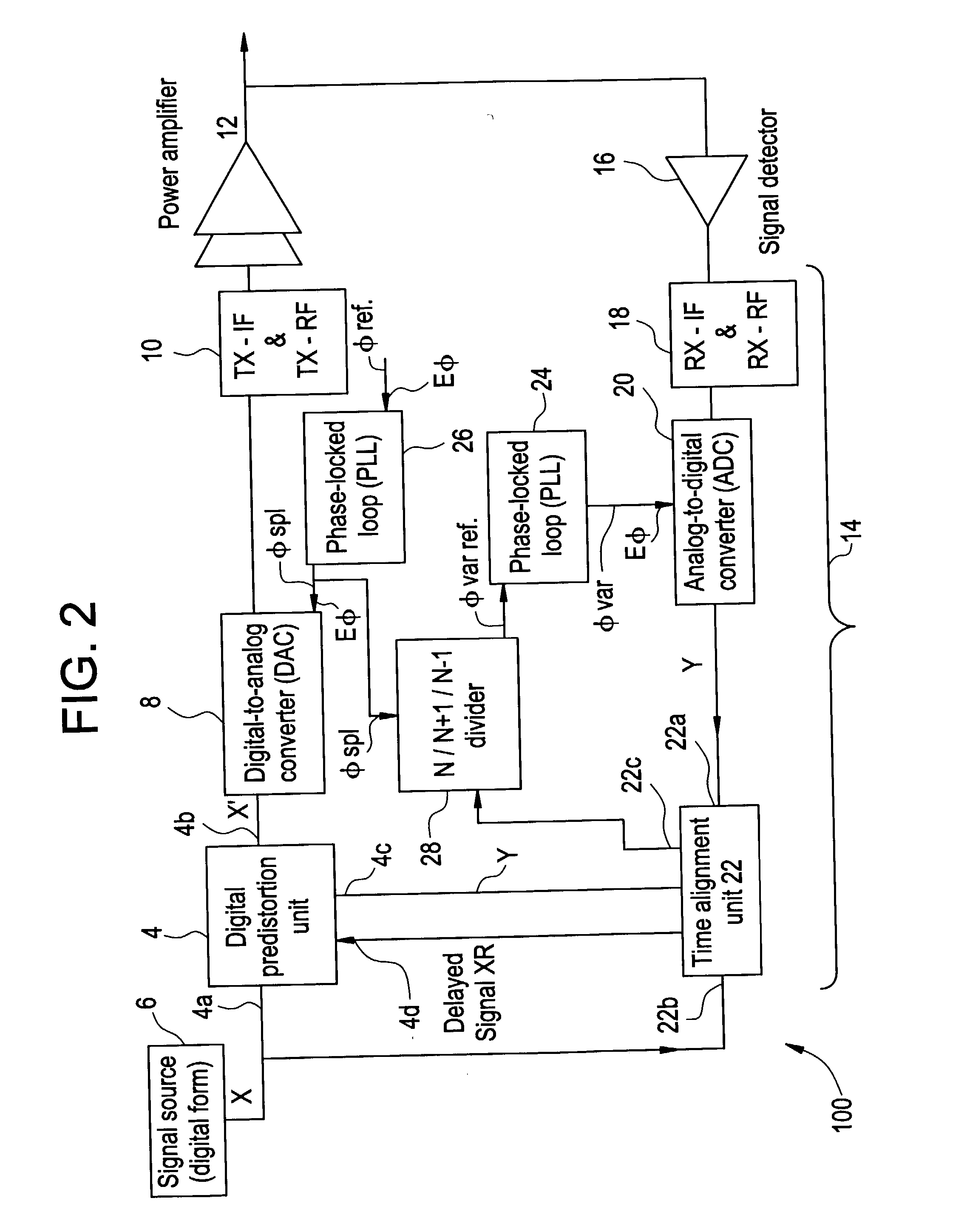

Method and apparatus for preparing signals to be compared to establish predistortion at the input of an amplifier

InactiveUS20030156658A1Improve electricity efficiencyImprove performance efficiencyAmplifier modifications to reduce non-linear distortionElectric signal transmission systemsAudio power amplifierUnit of time

The invention relates to a method of preparing signals (X and Y) to be compared to establish predistortion at the input of an amplifier (12), the signals comprising a signal (X) before amplification and a signal (Y) after amplification by said amplifier. Preparation includes time aligning (22) the signal before amplification (X) with the signal after amplification (Y) before using them to establish said predistortion. The invention preferably operates in two stages, namely a stage of coarse time alignment, in which the signal before amplification (X) is subjected to a time delay comprising an integer number of first time units, and a stage of fine time alignment, in which a delay or advance value of a fraction of the first time unit is determined.

Owner:EVOLIUM

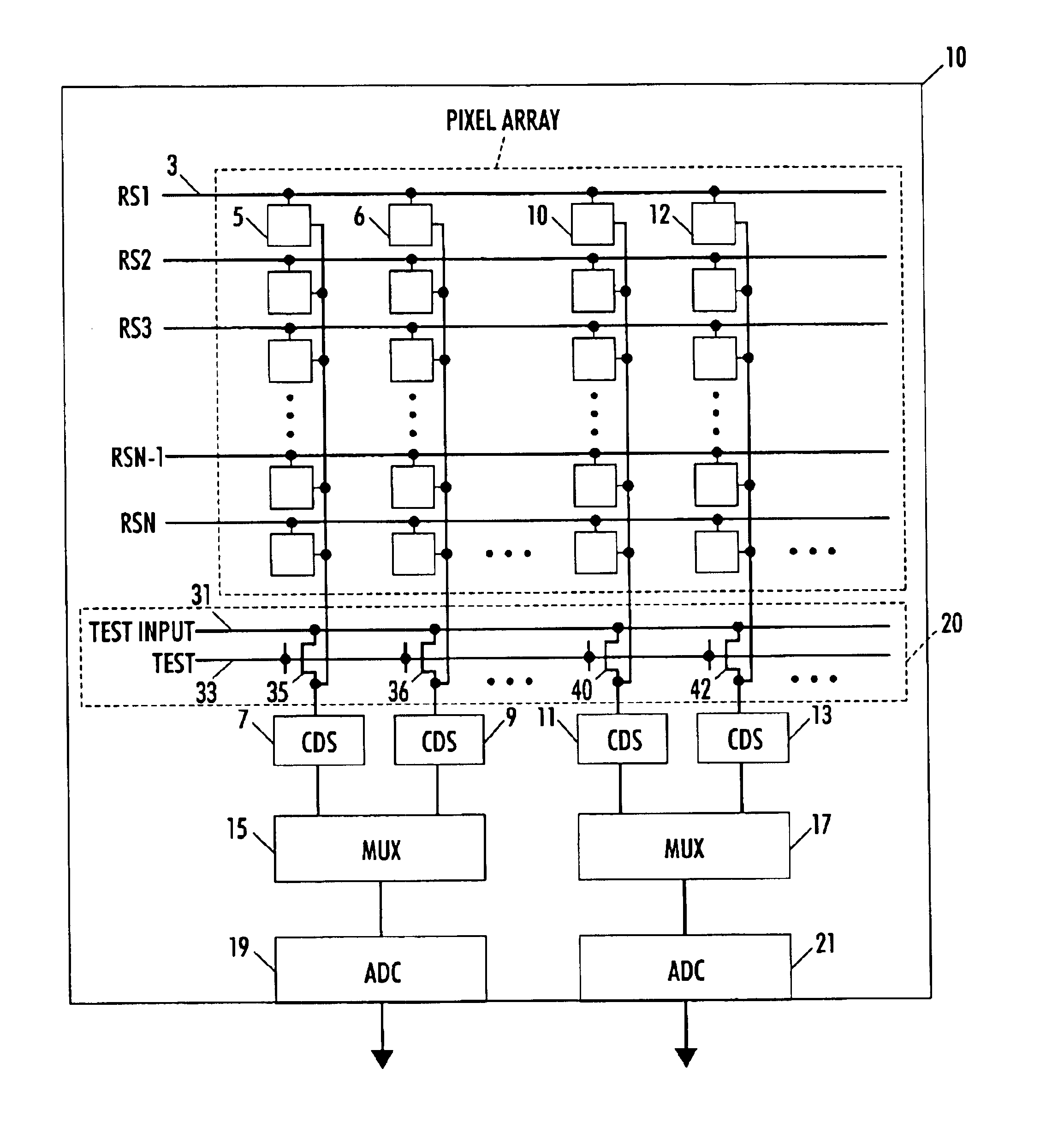

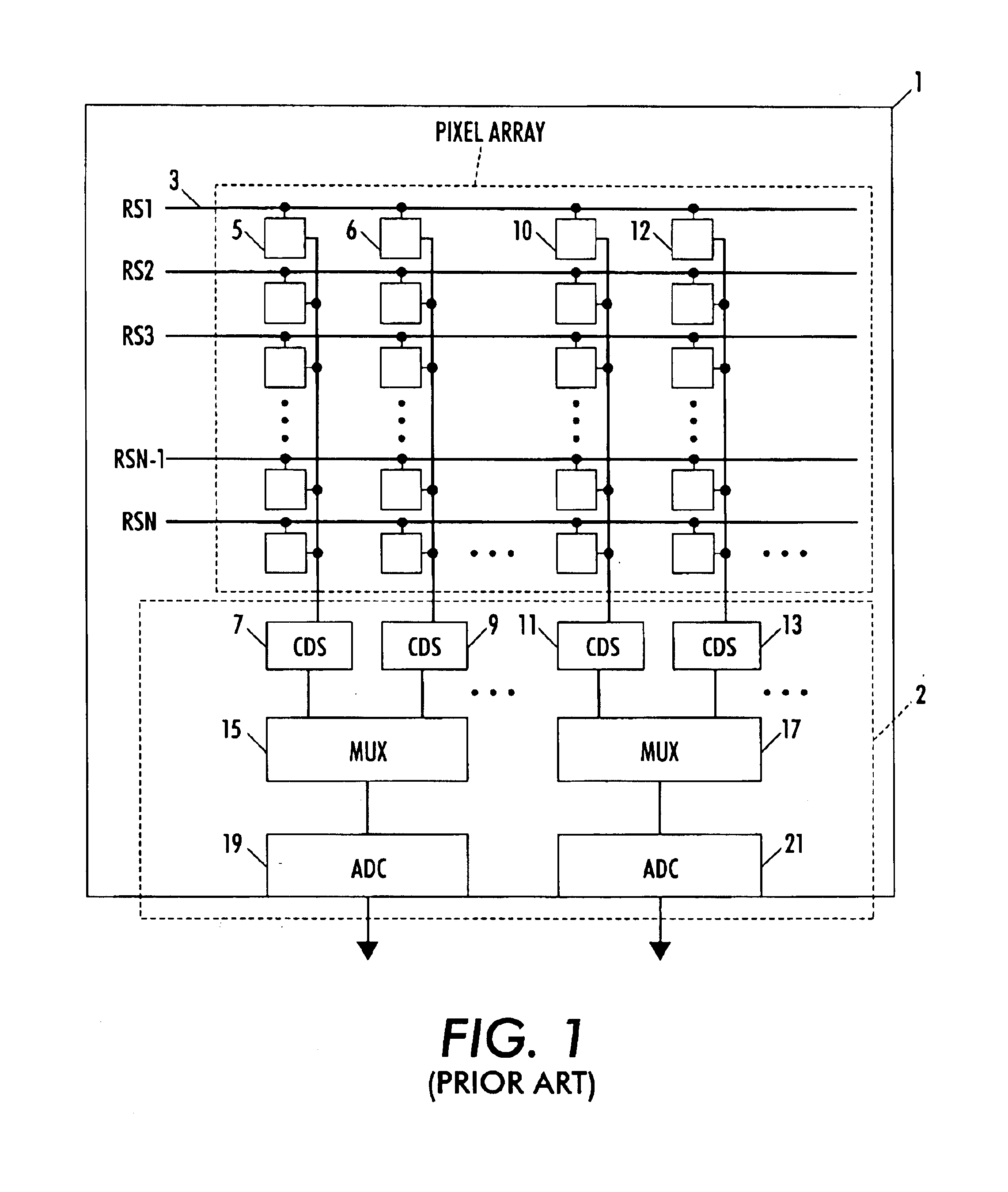

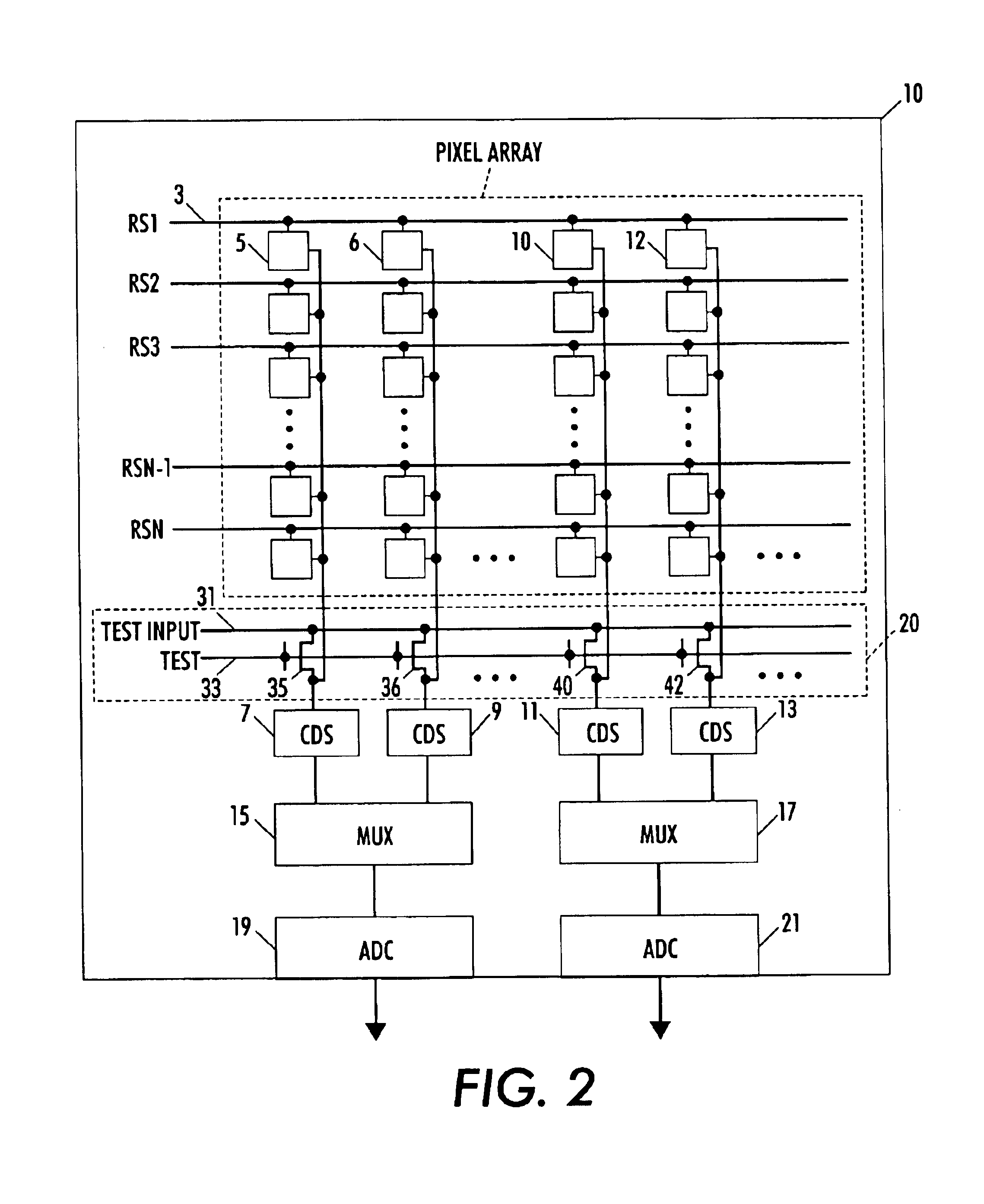

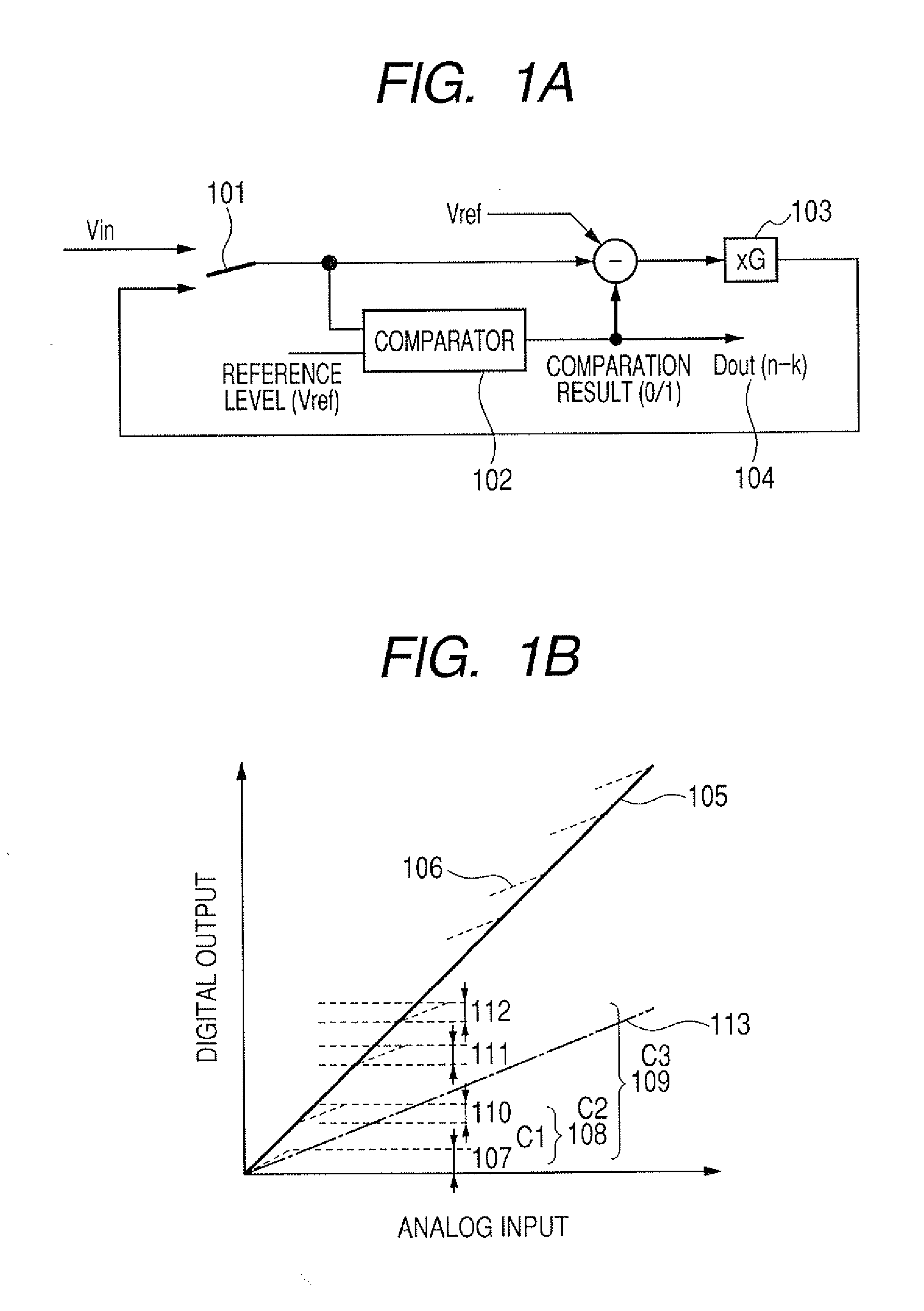

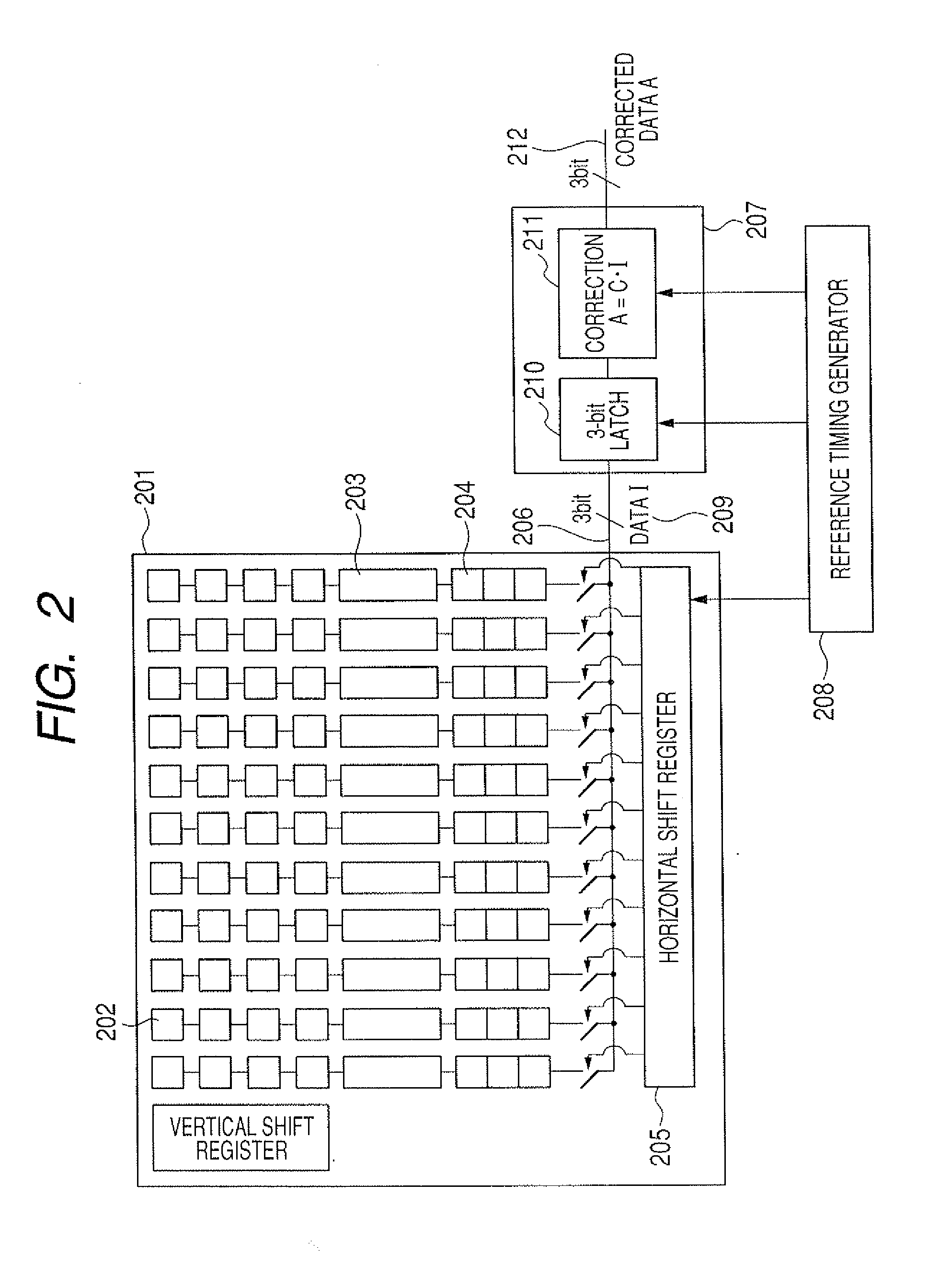

Circuit and method for cancellation of column pattern noise in CMOS imagers

ActiveUS6903670B1Corrects non-linearityCompensating for such errorTelevision system detailsElectric signal transmission systemsSignal processing circuitsAudio power amplifier

A circuit and method measure the output voltage of a CMOS pixel in a manner that substantially reduces all columnar pattern noise due to mismatches in the signal processing circuits including the correlated double sampling amplifiers and A / D converters. The circuit includes a test switch, operatively connected between a reference voltage source and a correlated double sampling amplifier, for applying a test voltage from the reference voltage source when the state of the test switch is ON to the correlated double sampling amplifier. The reference voltage source produces a voltage corresponding to a full-scale voltage level to enable the determination of a gain error in the correlated double sampling amplifier and / or A / D converter; a voltage corresponding to ground to enable the determination of an offset error in the correlated double sampling amplifier and / or A / D converter; and a plurality of analog voltages ranging from analog ground to a full-scale voltage level to enable the determination of non-linearity errors in the A / D converter.

Owner:SMAL CAMERA TECH

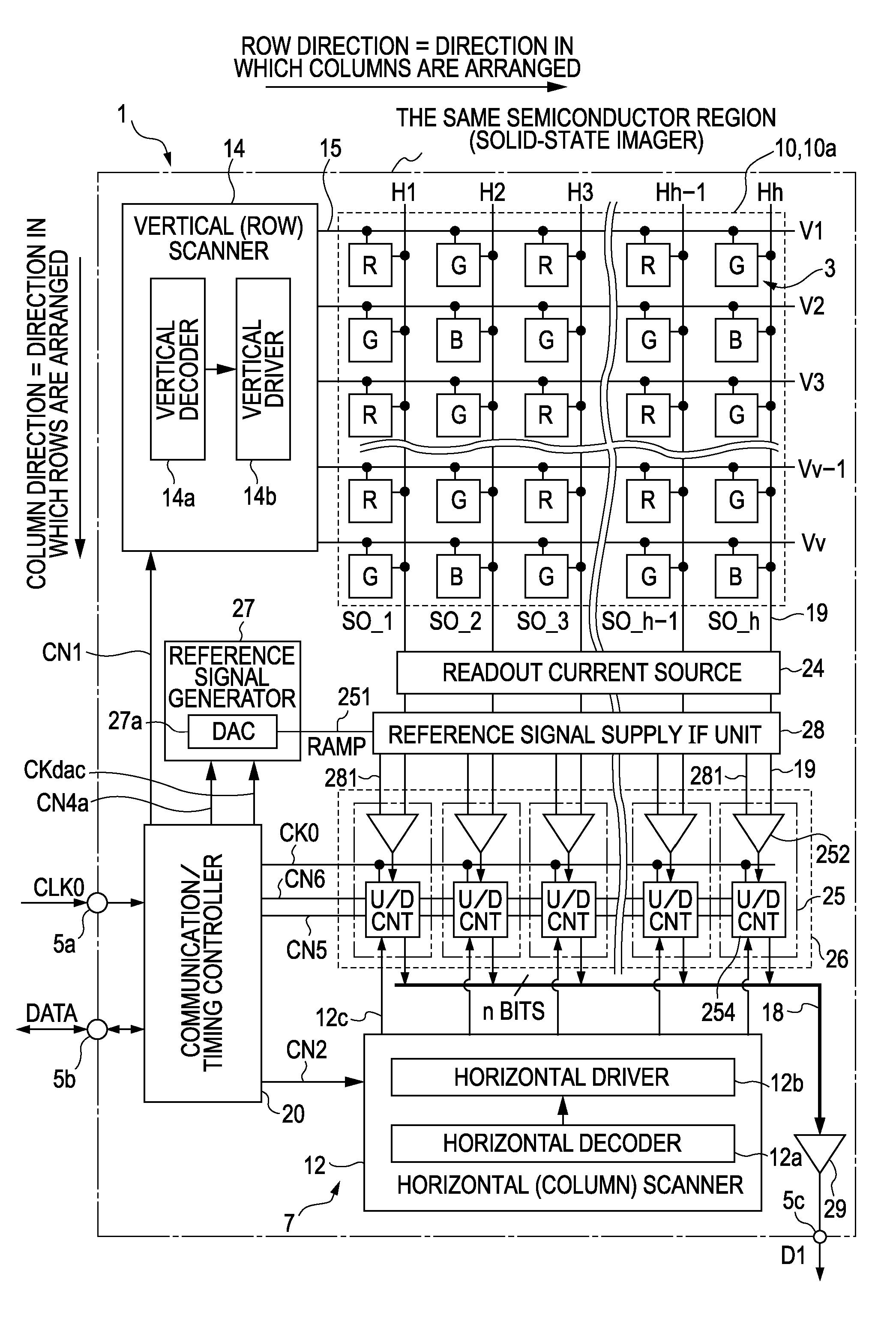

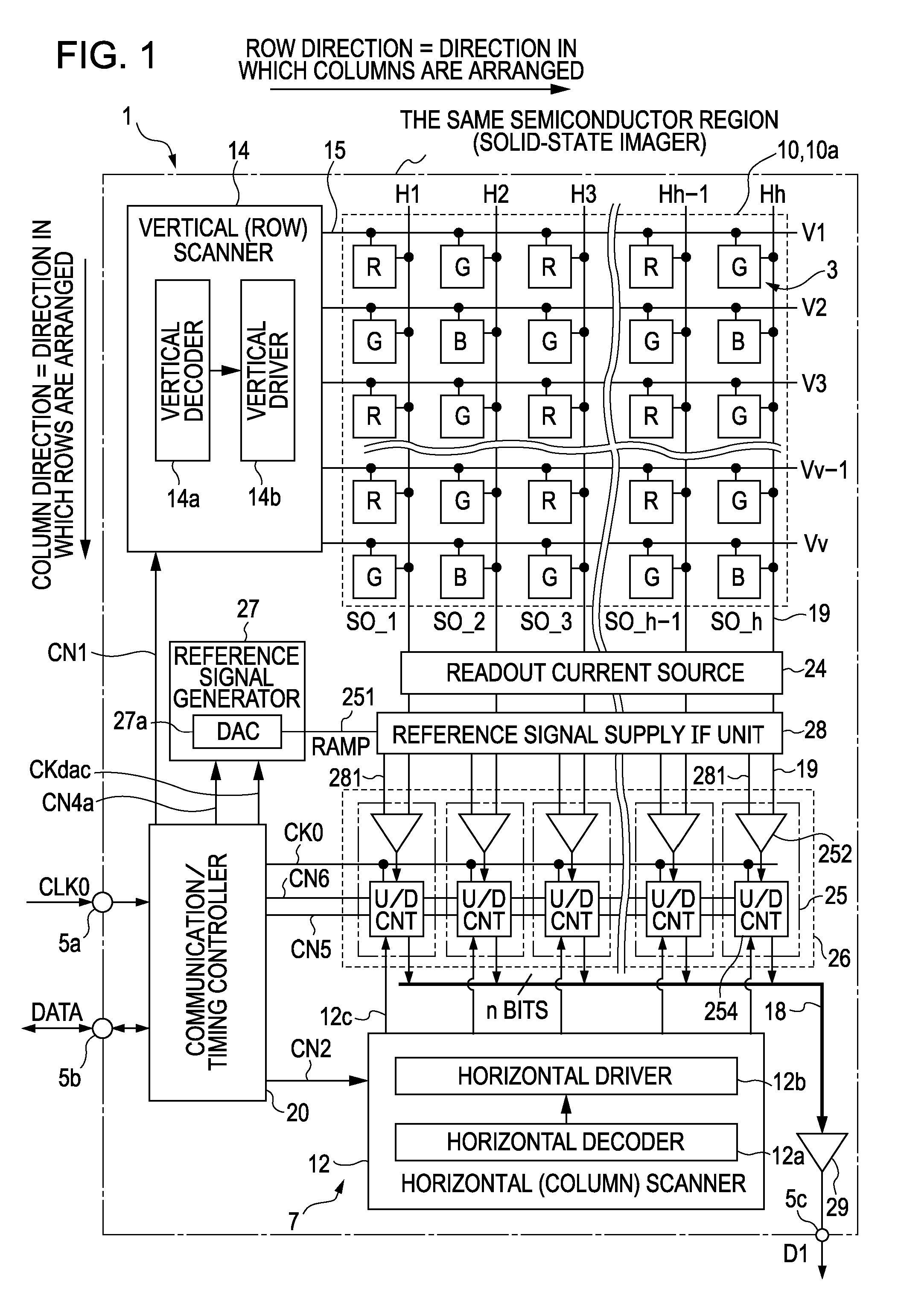

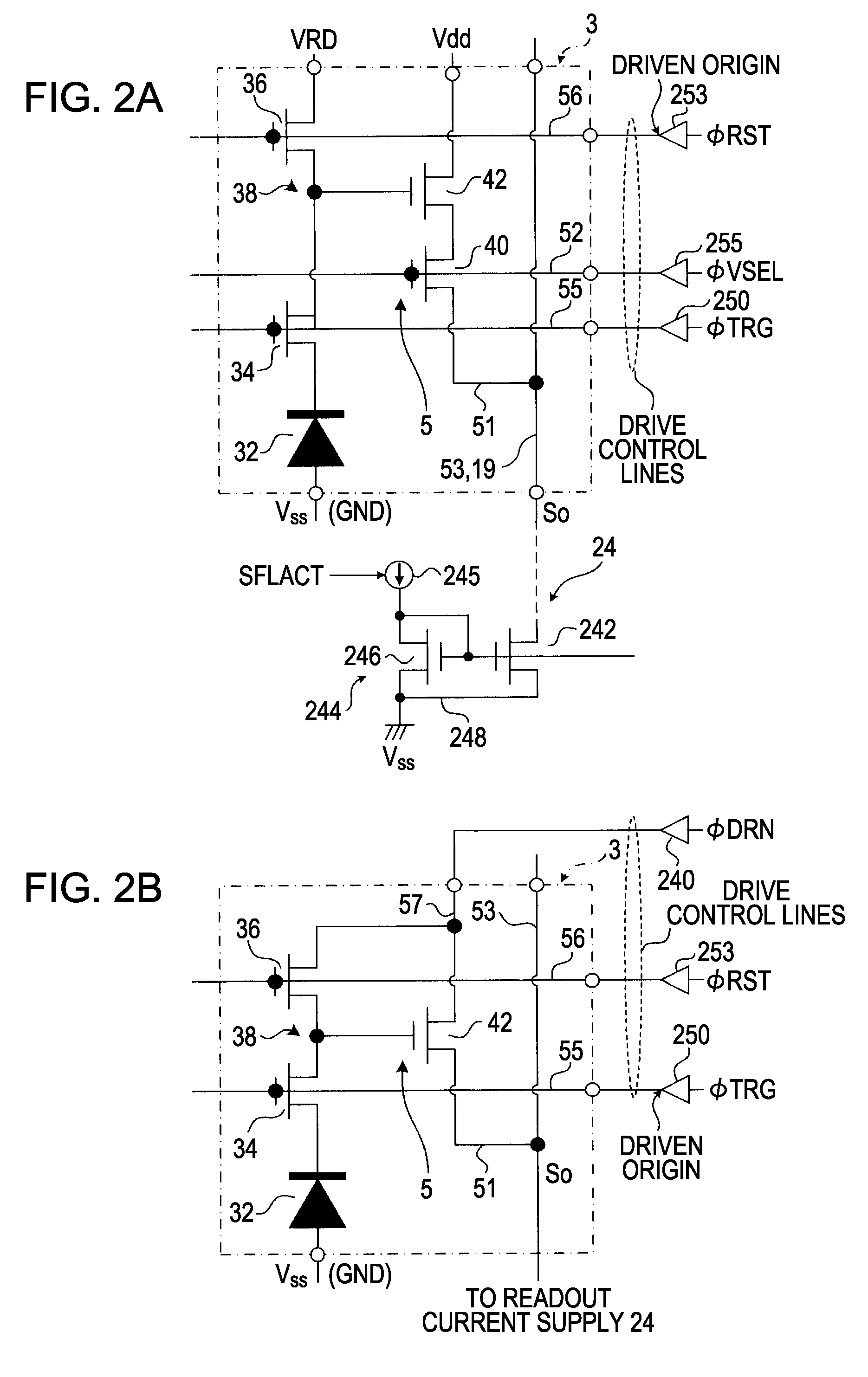

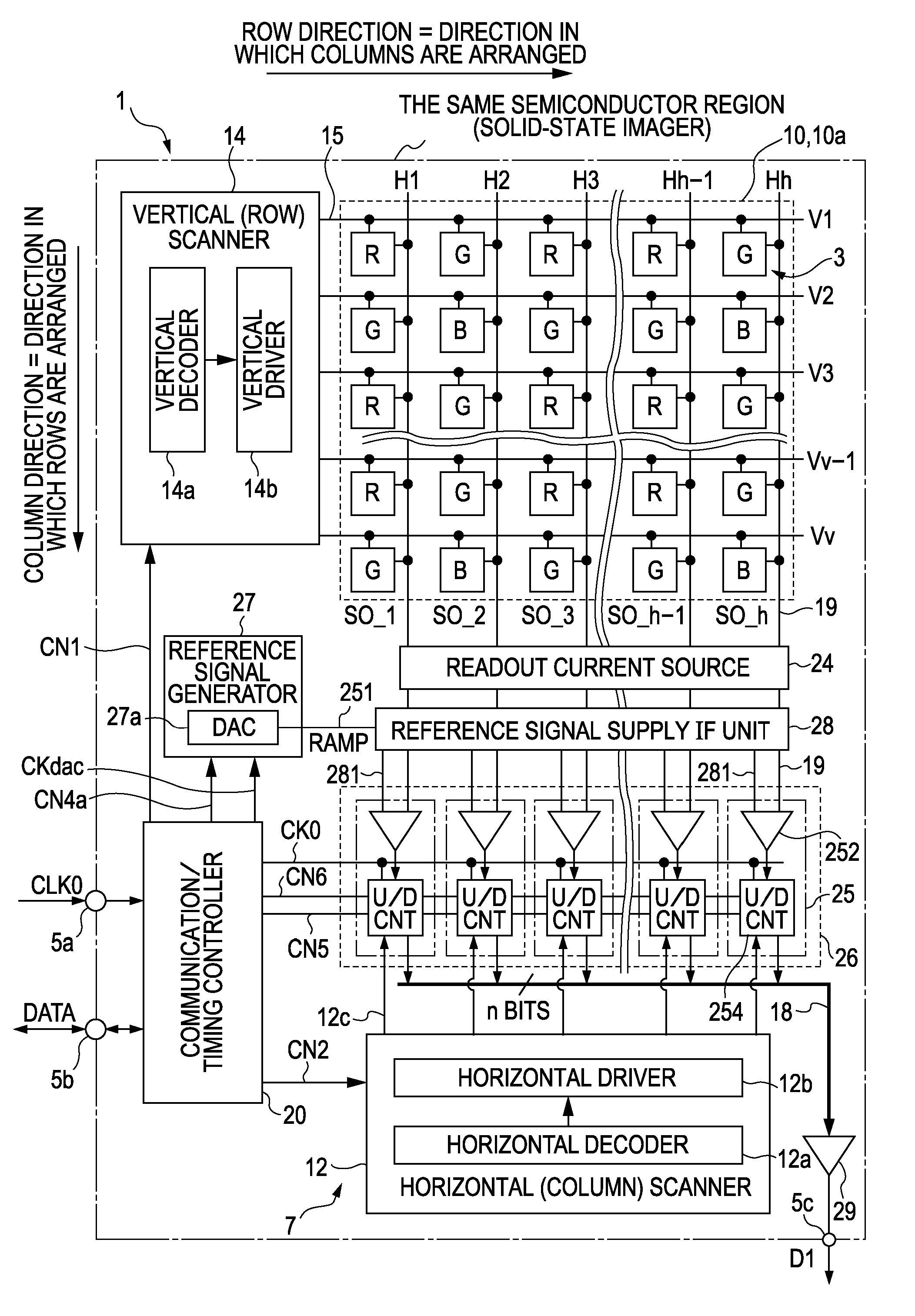

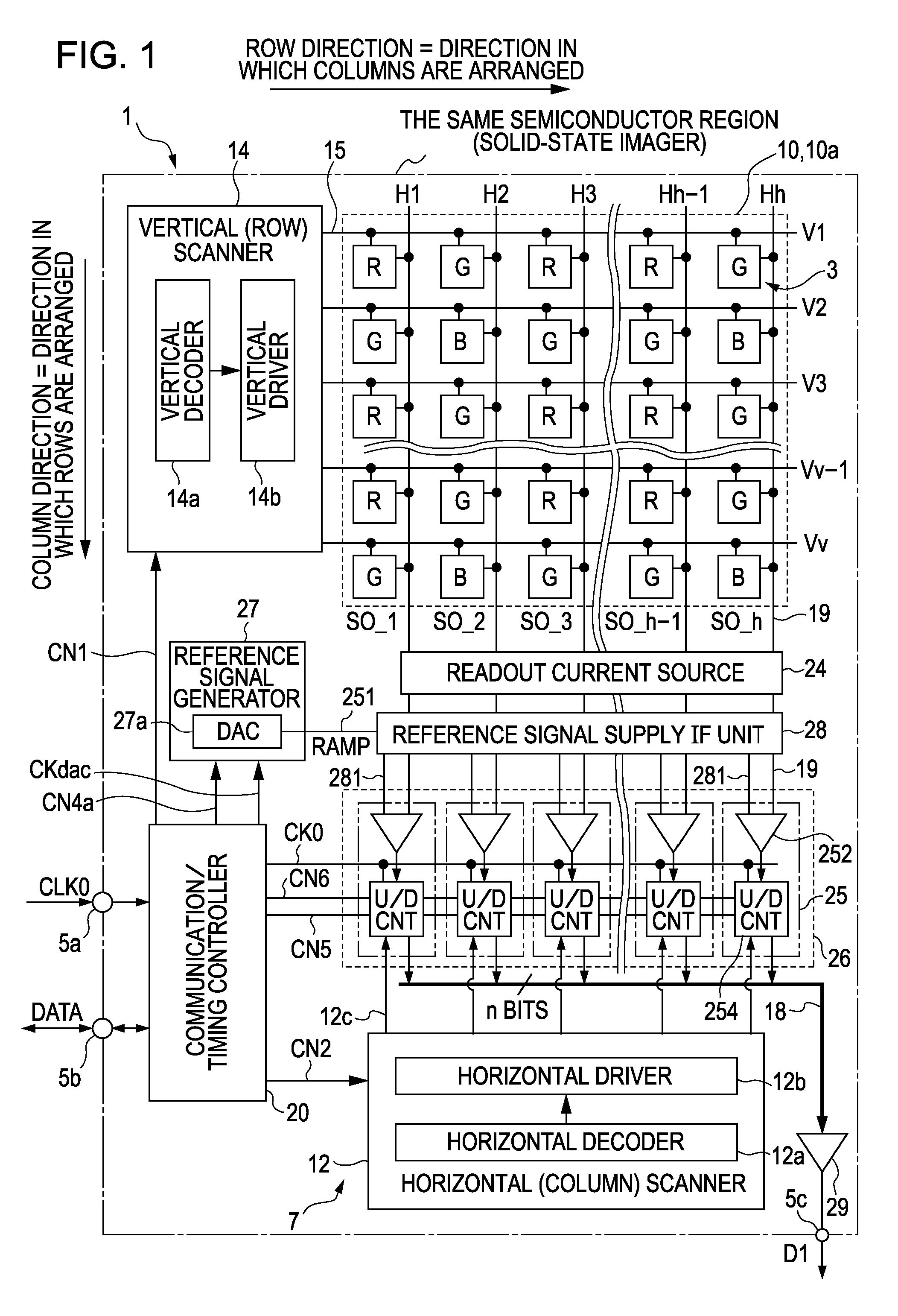

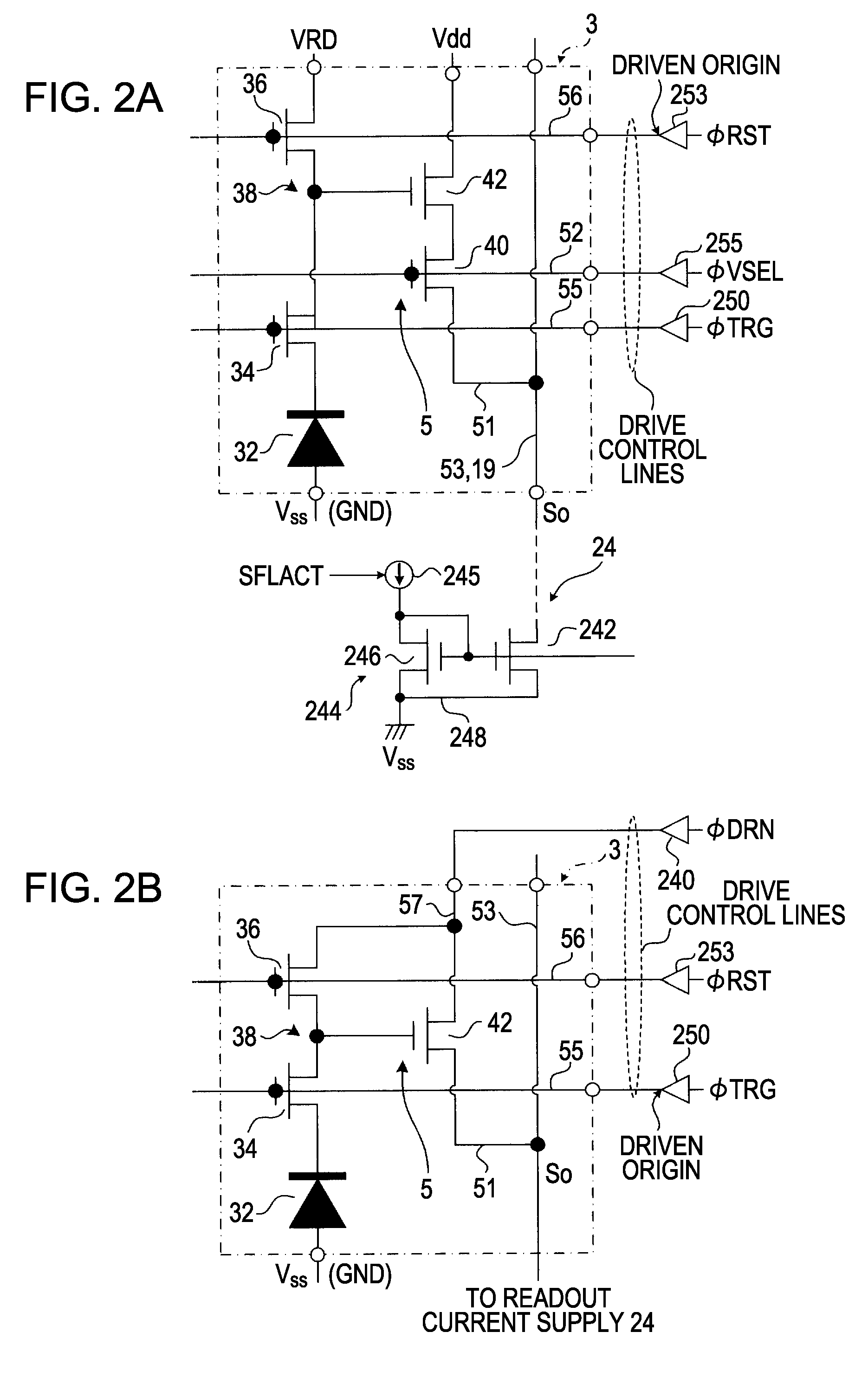

Analog-to-digital converter and semiconductor device

ActiveUS7321329B2Reduce adverse effectsTelevision system detailsElectric signal transmission systemsCMOSDigital down converter

An electronic apparatus includes a CMOS image sensor and a signal processor operable to process an output signal from the CMOS image sensor. The CMOS image sensor includes the following elements: an imaging region; a reference signal generator operable to generate a reference signal; a comparator operable to compare the reference signal generated by the reference signal generator with a signal transmitted from the imaging region; a counter operable to count, in parallel with comparison performed by the comparator, a predetermined count clock and to hold a count value at the time of completion of comparison performed by the comparator; and a reference signal supply interface unit operable to supply the reference signal generated by the reference signal generator to a plurality of comparators via different signal lines, respectively.

Owner:SONY CORP

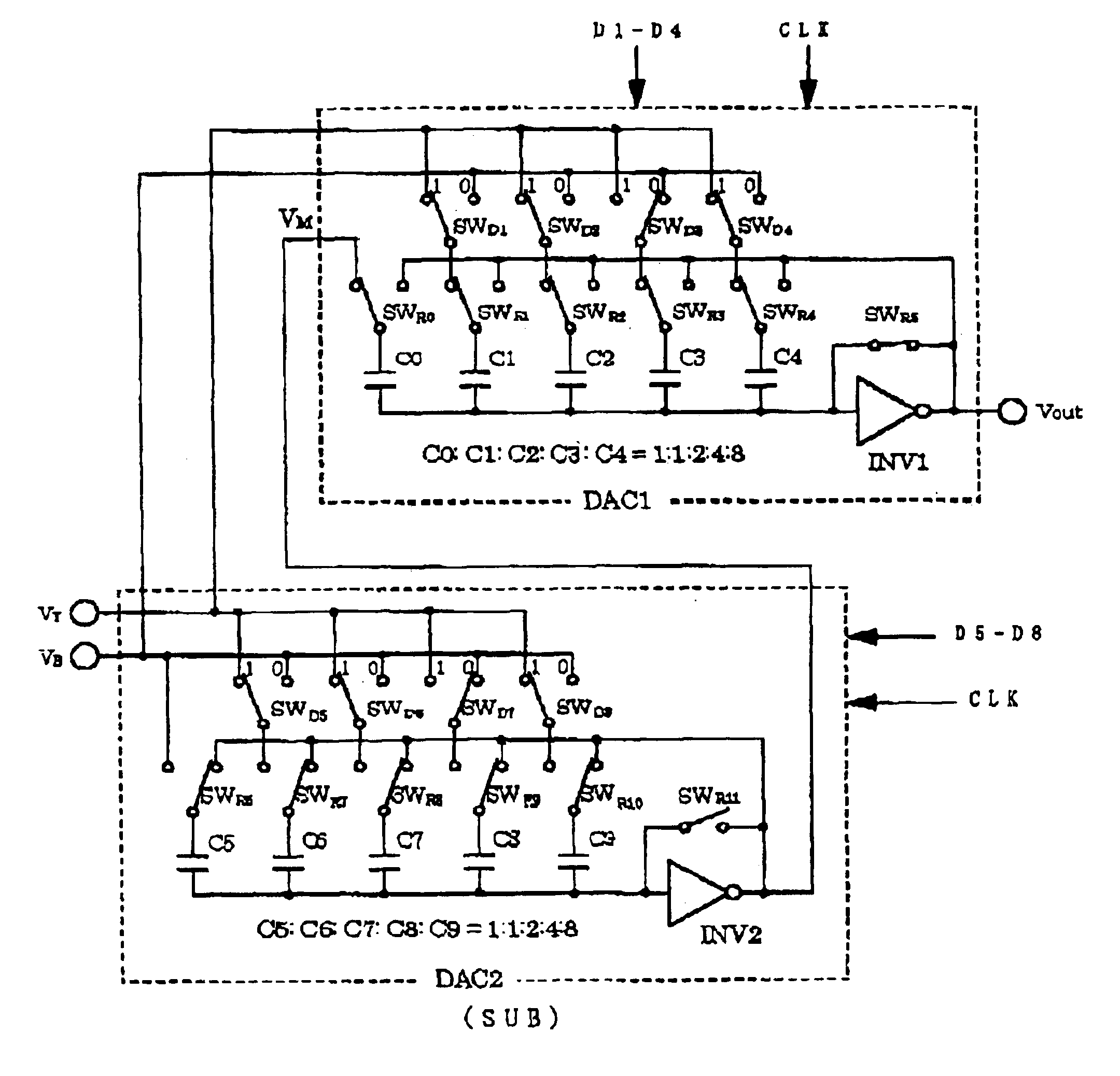

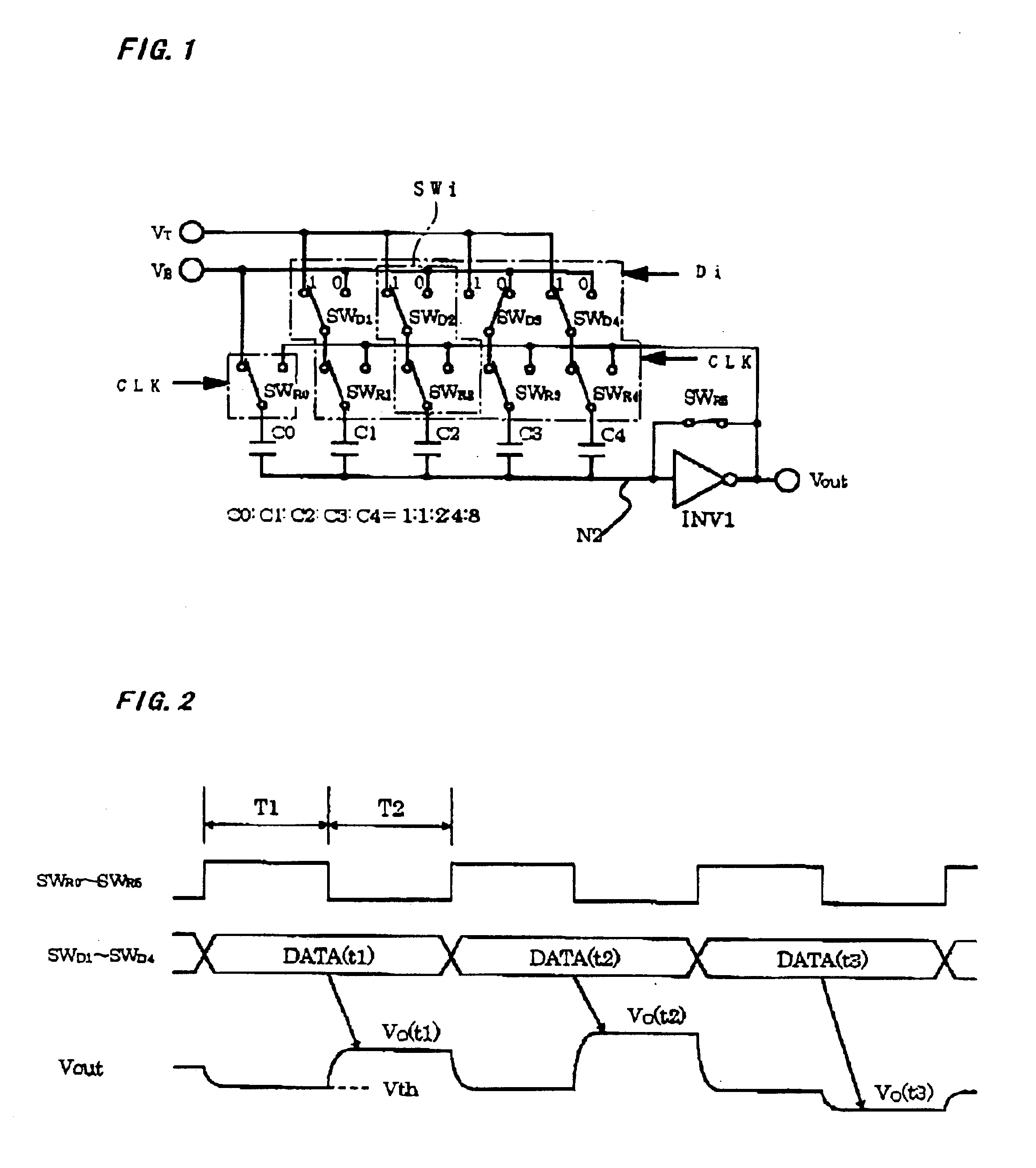

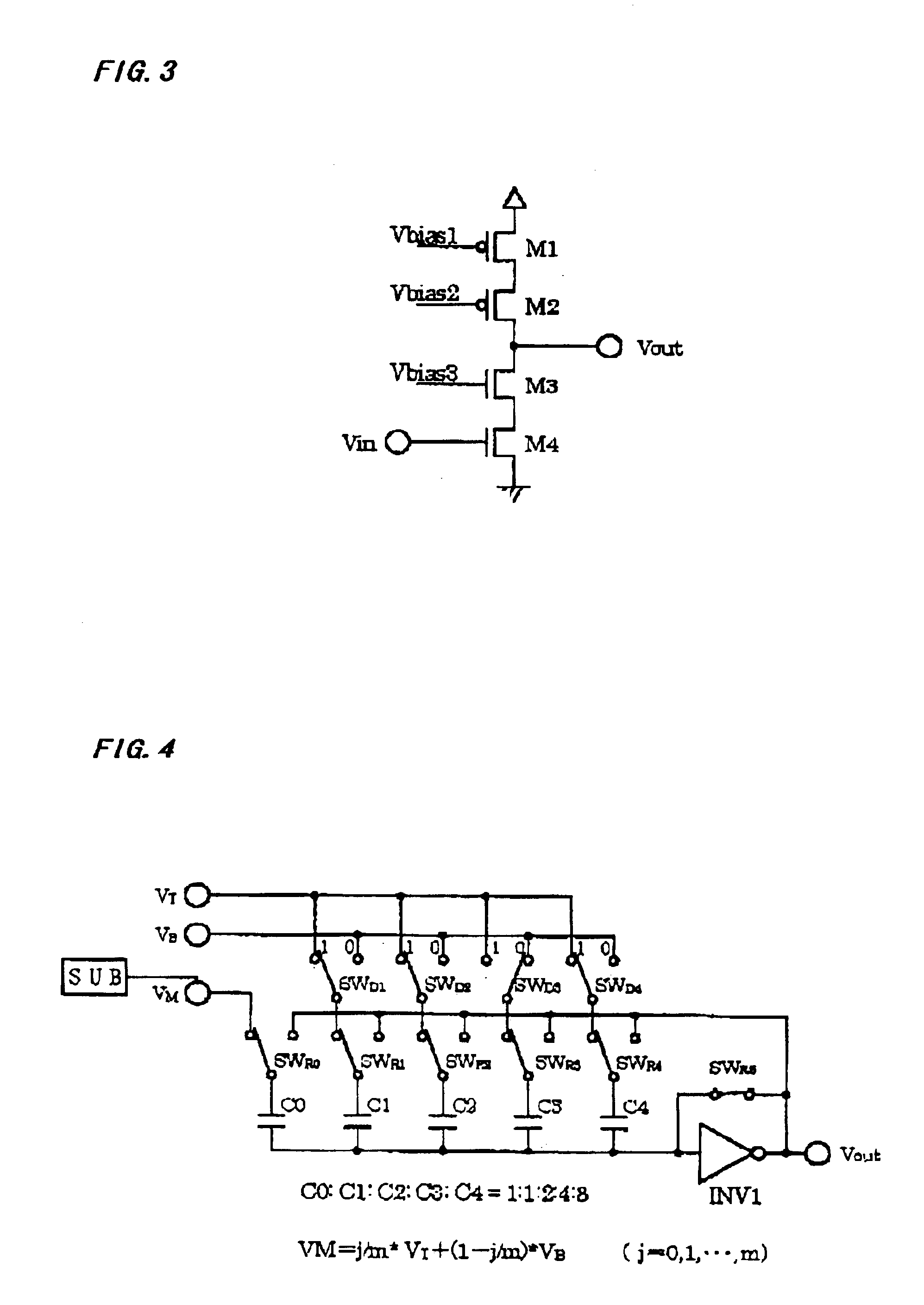

Digital to analog converter with a weighted capacitive circuit

InactiveUS6906653B2Reduce areaImprove accuracyElectric signal transmission systemsComputing operations for addition/subtractionDigital dataVoltage reference

D / A converter of this invention including n+1 capacitors in total consisting of one terminating capacitor (C0) and n binary-weighted capacitors (C1-4) that are subjected to binary weighting ratio of 1:2:4: . . . :2(n−1), and, an inverting amplifier (INV1), further comprising: a feedback switching means (SWR5) provided between the input and output of the inverting amplifier (INV1); a switching means for terminating operation (SWR0) supplies one of two main reference voltages (VB,VT) to the terminating capacitor (C0), and then, makes connection of the terminating capacitor (C0) to the output of the inverting amplifier (INV1); a plurality of switching means for input operation (SWD1-4,SWR1-4) makes selection of one of the two main reference voltages (VB,VT) to be provided for the n binary-weighted capacitors (C1-4) depending on digital data (D1-4), and then, makes connection of the second terminal side of the n binary-weighted capacitors (C1-4) to the output of the inverting amplifier (INV1).

Owner:LINEAR CELL DESIGN COJ

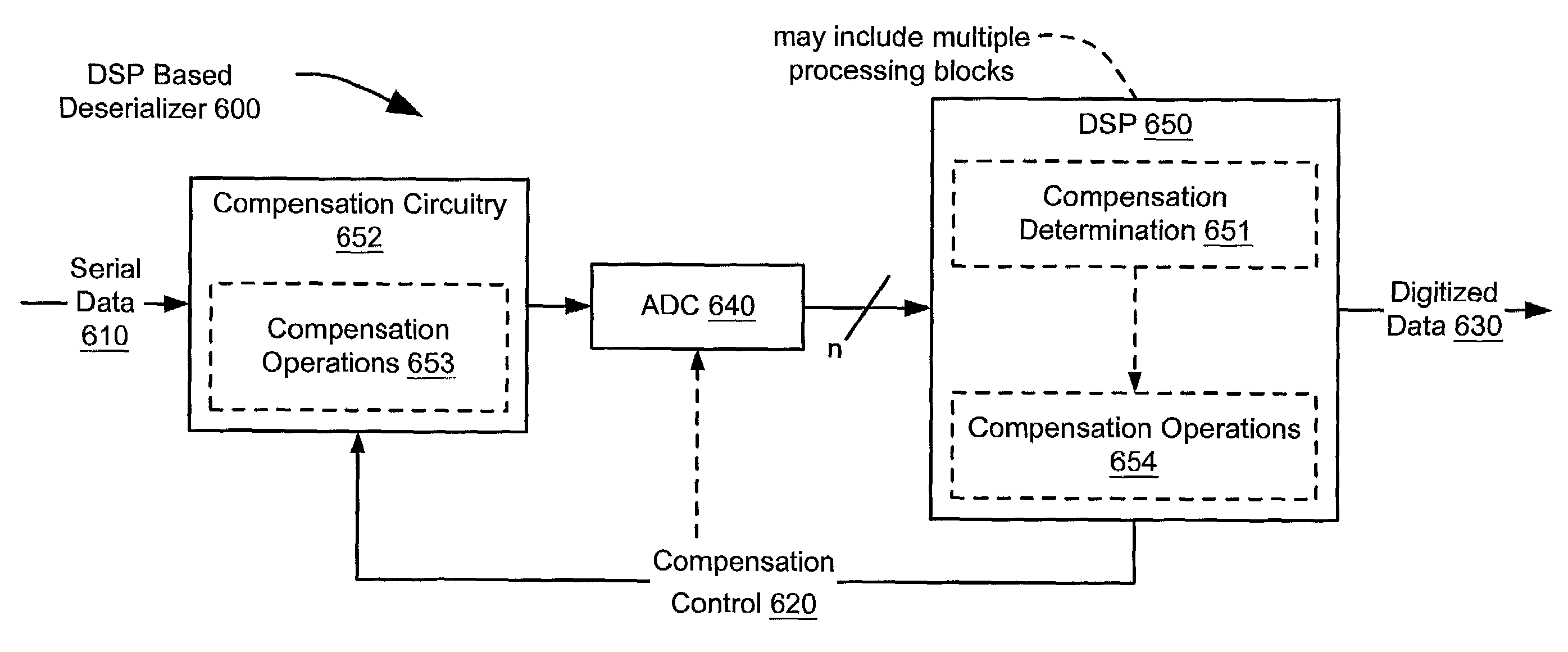

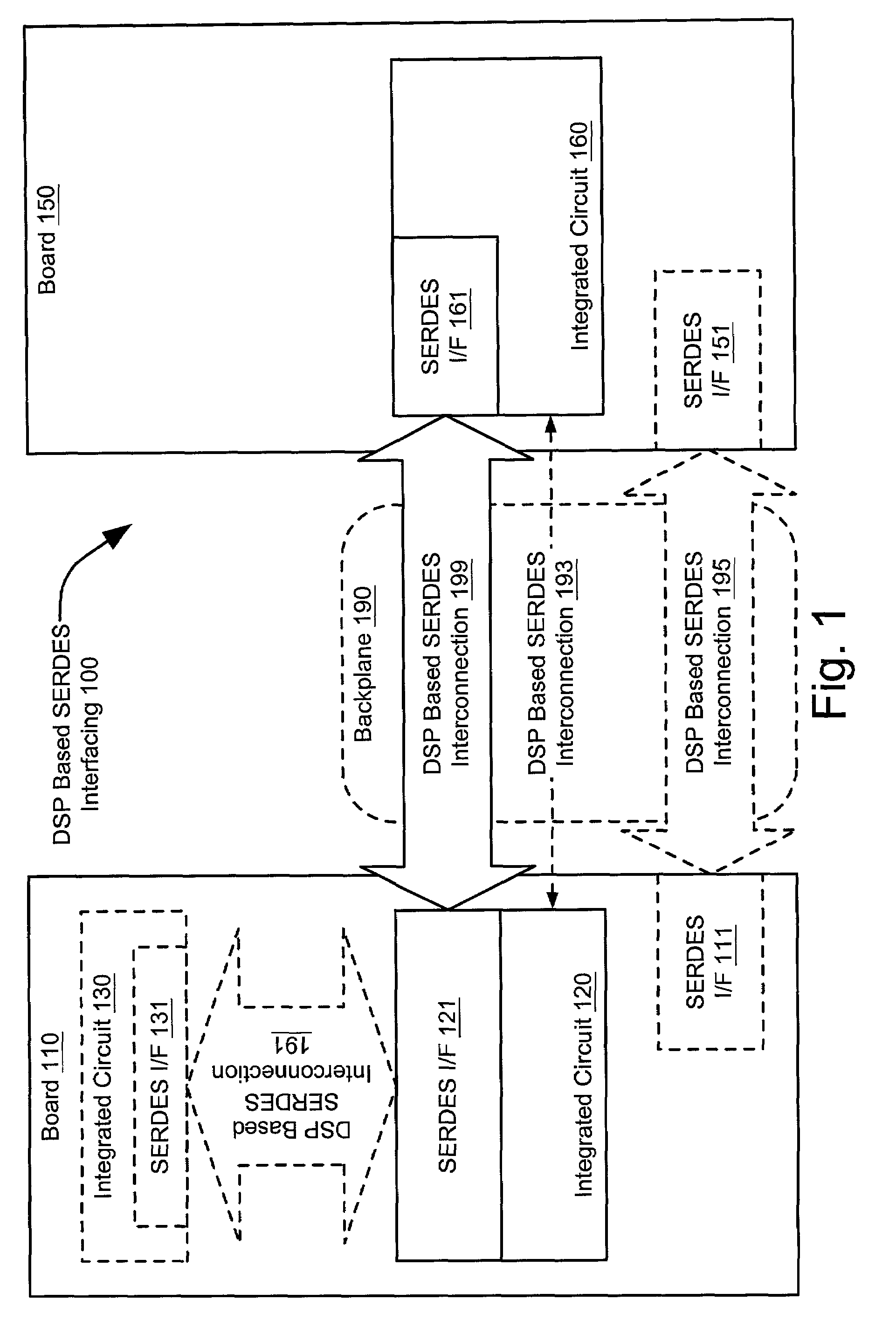

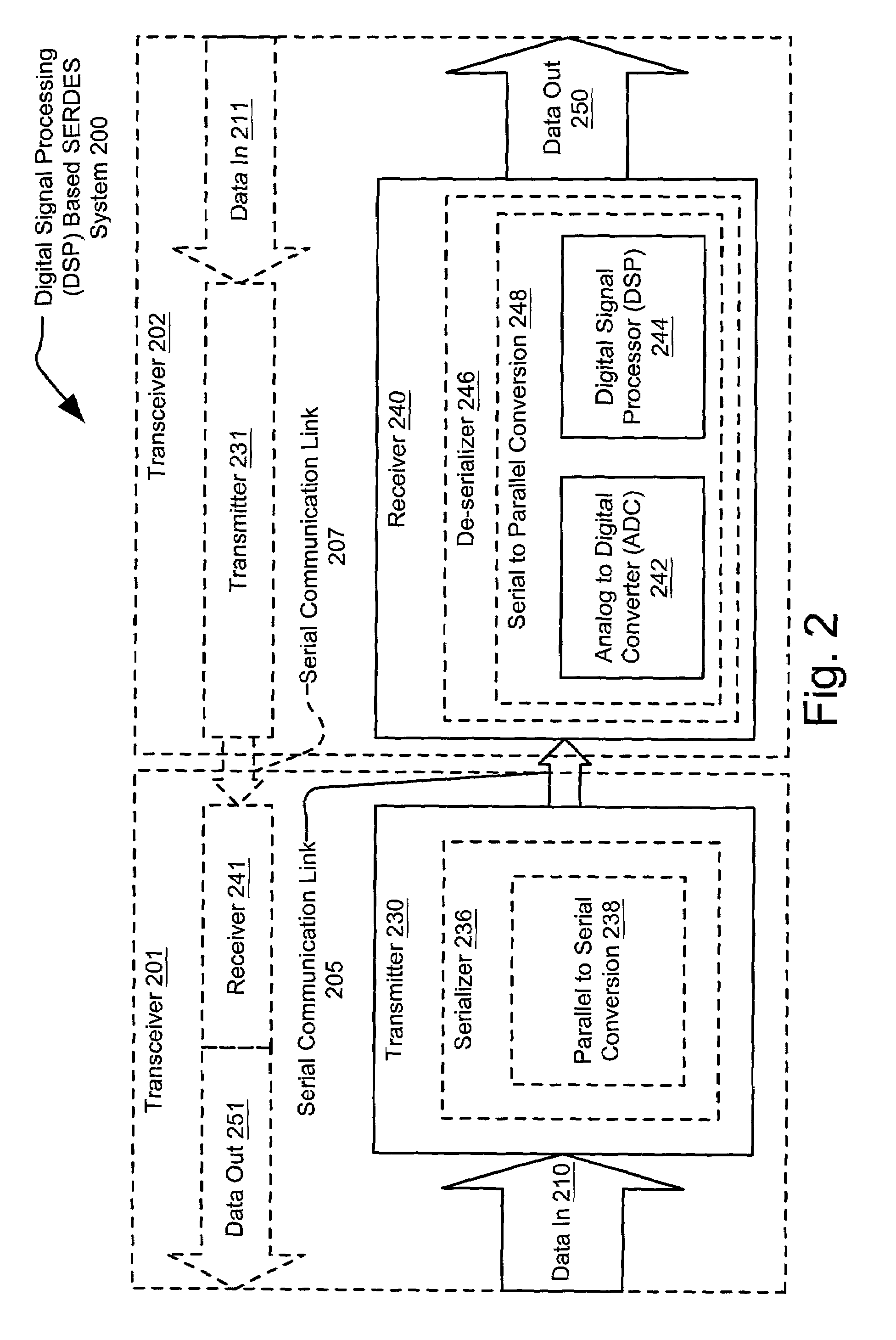

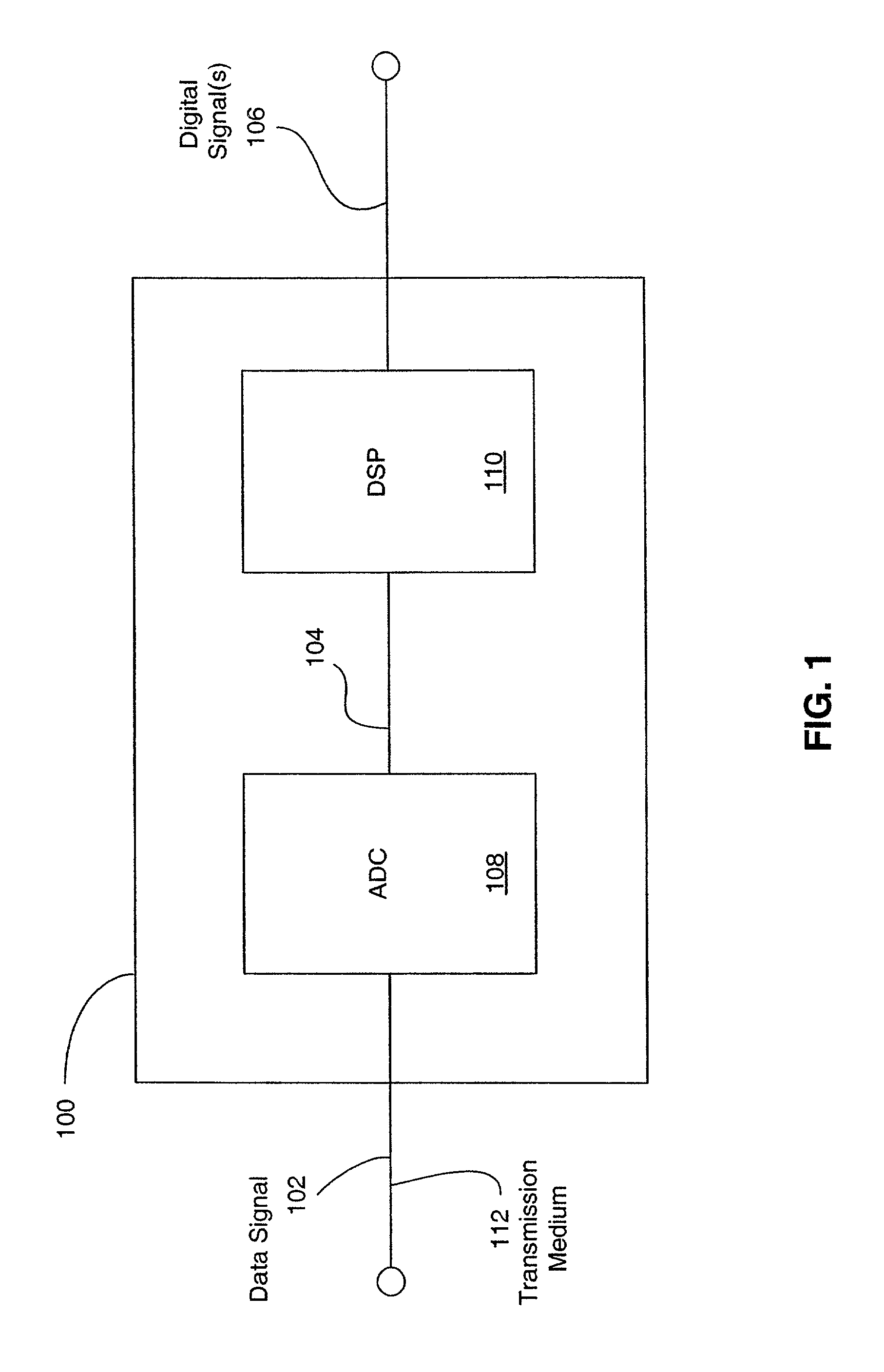

Digital signal processing based de-serializer

ActiveUS7336729B2Lower performance requirementsSolve problemsElectric signal transmission systemsAmplitude-modulated carrier systemsDigital signal processingSerialization

A DSP based SERDES performs compensation operations to support high speed de-serialization. A receiver section of the DSP based SERDES includes one or more ADCs and DSPs. The ADC operates to sample (modulated) analog serial data and to produce digitized serial data (digital representation of the modulated analog serial data). The DSP communicatively couples to the ADC and receives the digitized serial data. Based upon the known characteristics of the digitized serial data and the digitized serial data itself, the DSP determines compensation operations to be performed upon the serial data to compensate for inadequacies of the receiver and / or channel response. These compensation operations may be (1) performed on the analog serial data before digitization by the ADC; (2) applied to the ADC to modify the operation of the ADC; and / or (3) performed on the digitized serial data by the DSP or another device.

Owner:AVAGO TECH INT SALES PTE LTD

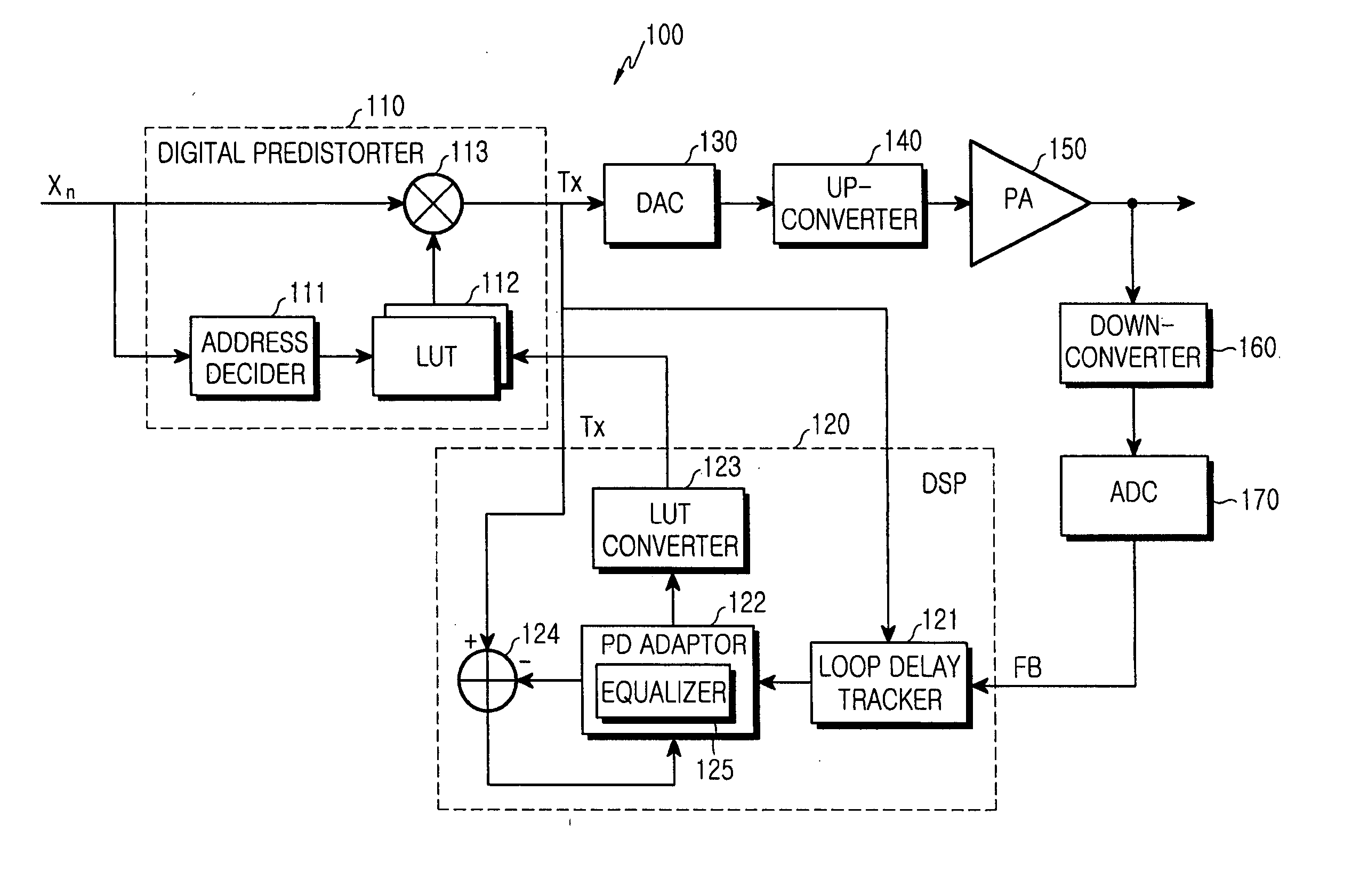

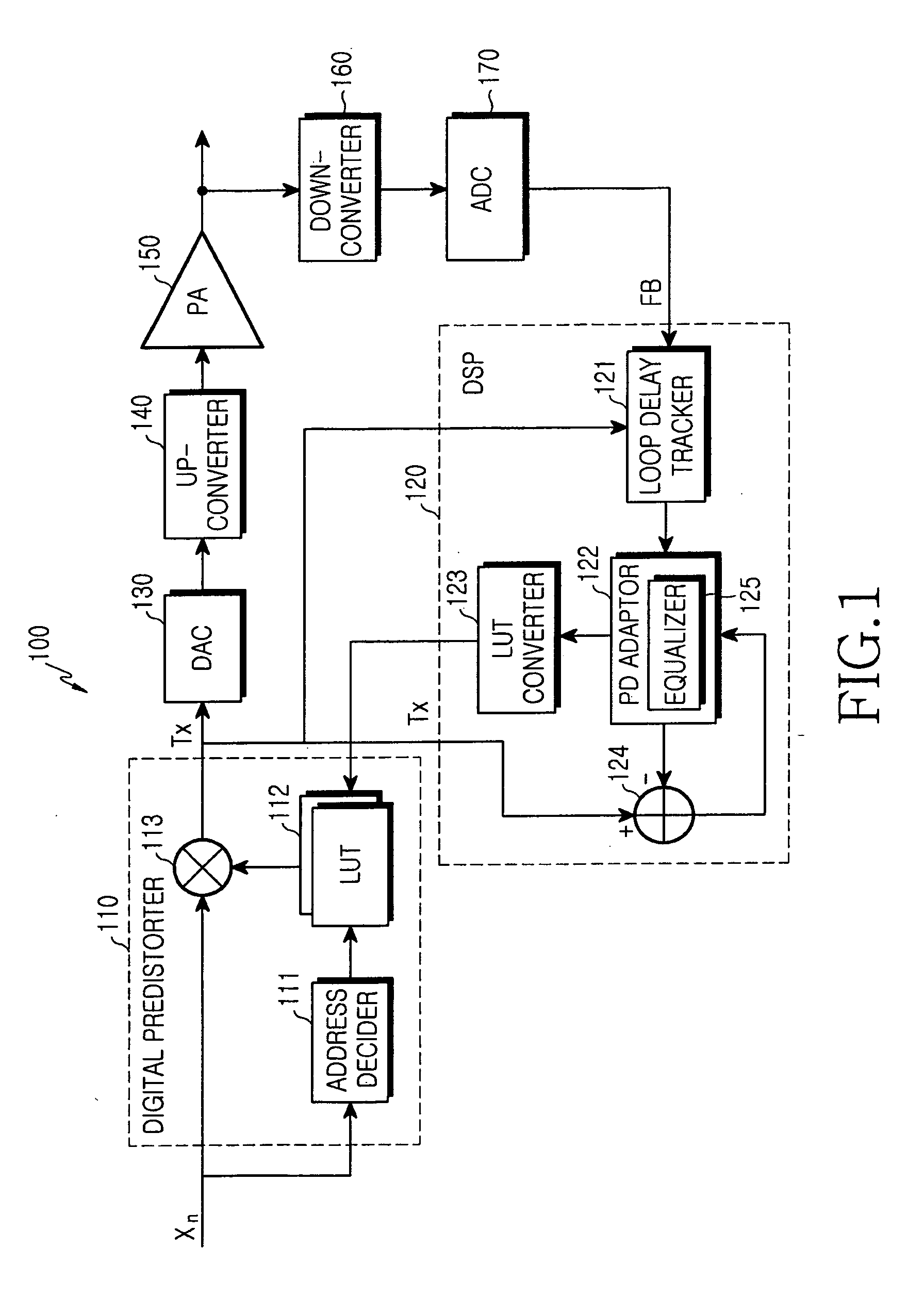

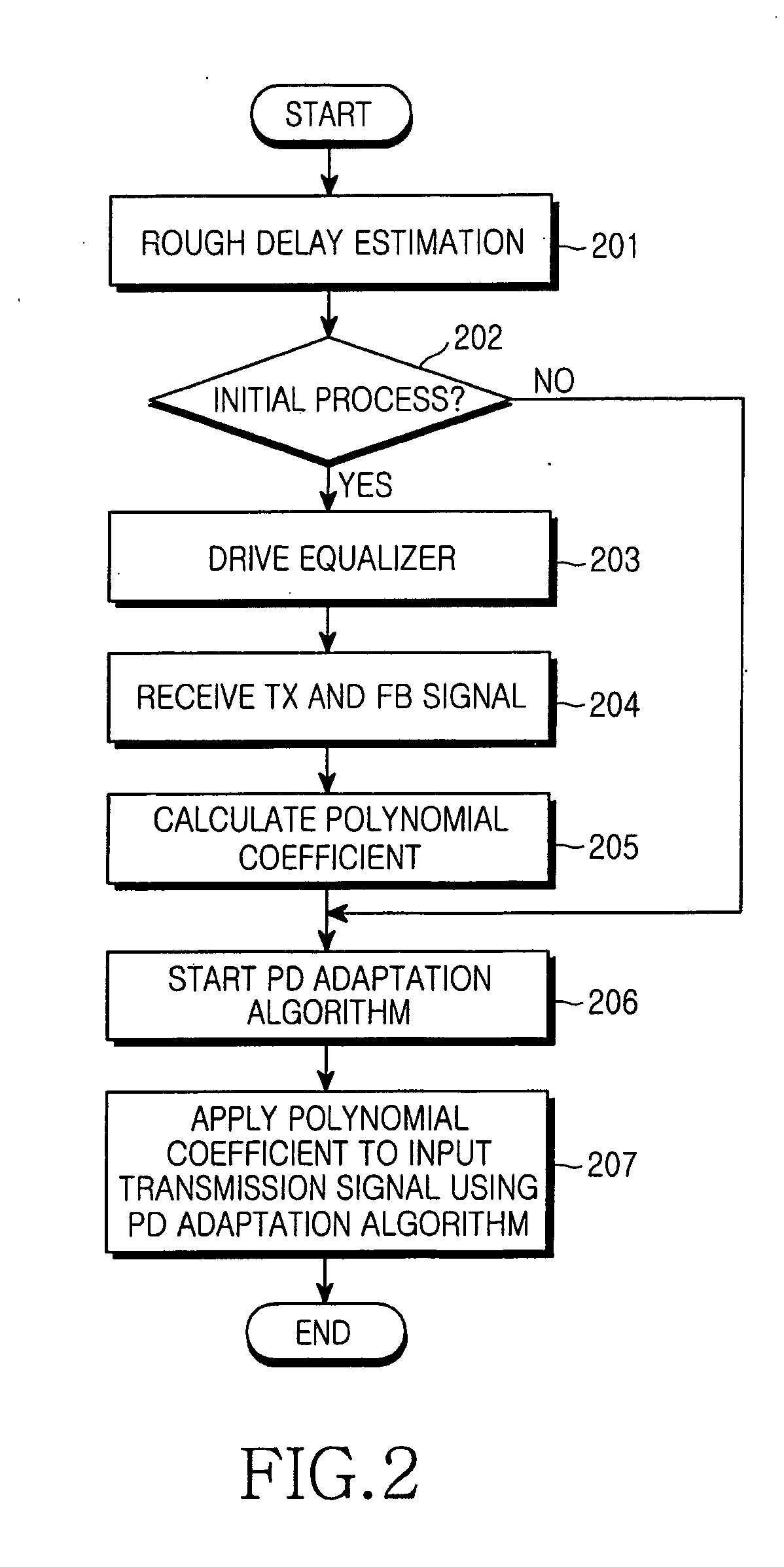

Digital predistortion apparatus and method for a wideband power amplifier

InactiveUS20050253745A1Performance maximizationShorten convergence timeAmplifier modifications to reduce non-linear distortionElectric signal transmission systemsCommunications systemAudio power amplifier

A method and apparatus compensate for a non-linear characteristic of a wideband power amplifier in a transmitter for a communication system, which has the wideband power amplifier for amplifying a digital input signal. The method involves the steps of (a) generating an address based on the digital input signal, reading a distortion control value corresponding to the address from a look-up table, and applying the read distortion control value to the digital input signal to predistort the digital input signal; (b) frequency up-converting the predistorted signal and amplifying the frequency up-converted signal; (c) frequency down-converting the amplified signal and compensating for a delay of the frequency down-converted signal; and (d) updating a predetermined distortion control value in the look-up table to compensate for an error value generated in the power amplifier and an analog path occurring in steps (b) and (c) based on the compensated signal.

Owner:SAMSUNG ELECTRONICS CO LTD

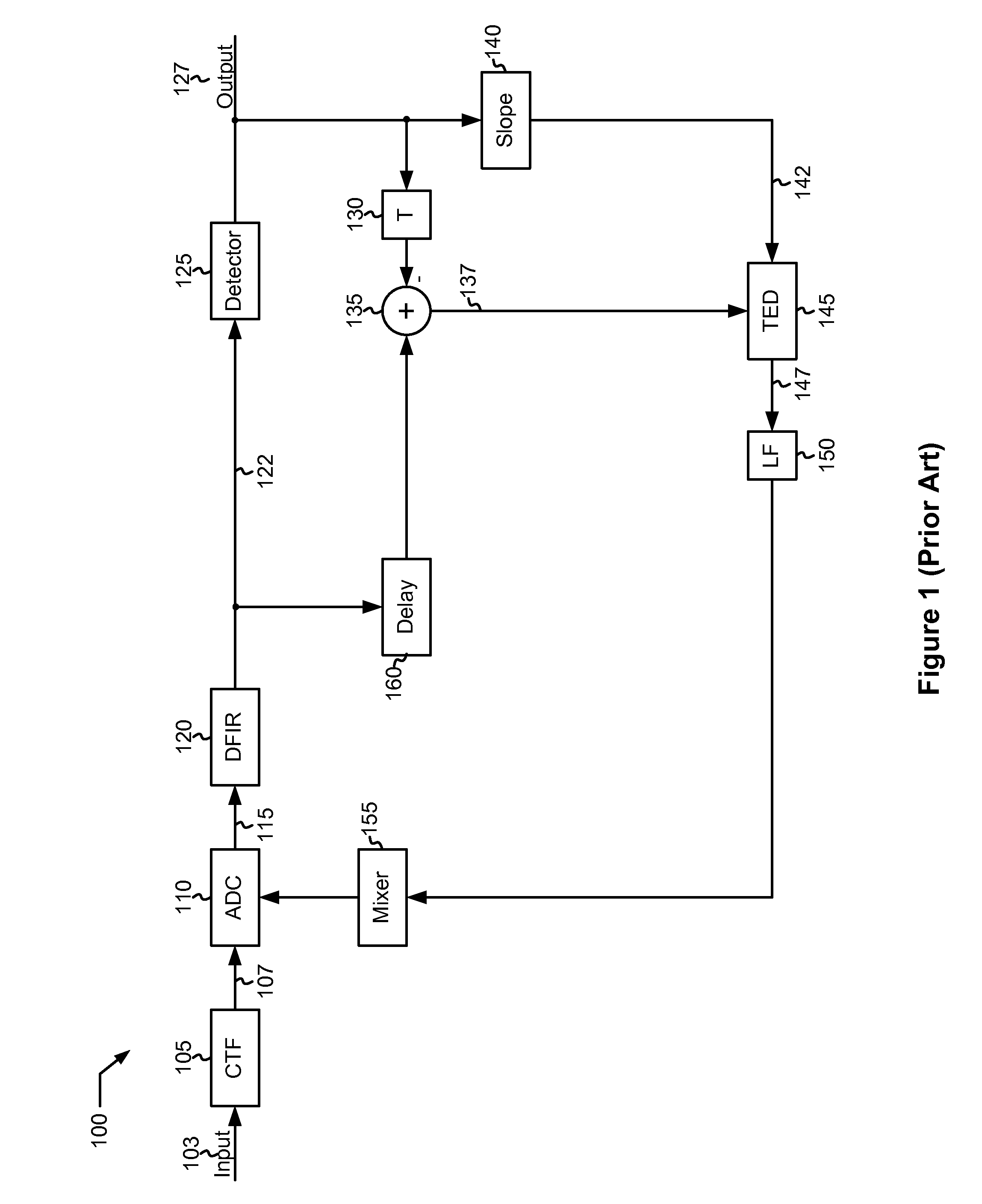

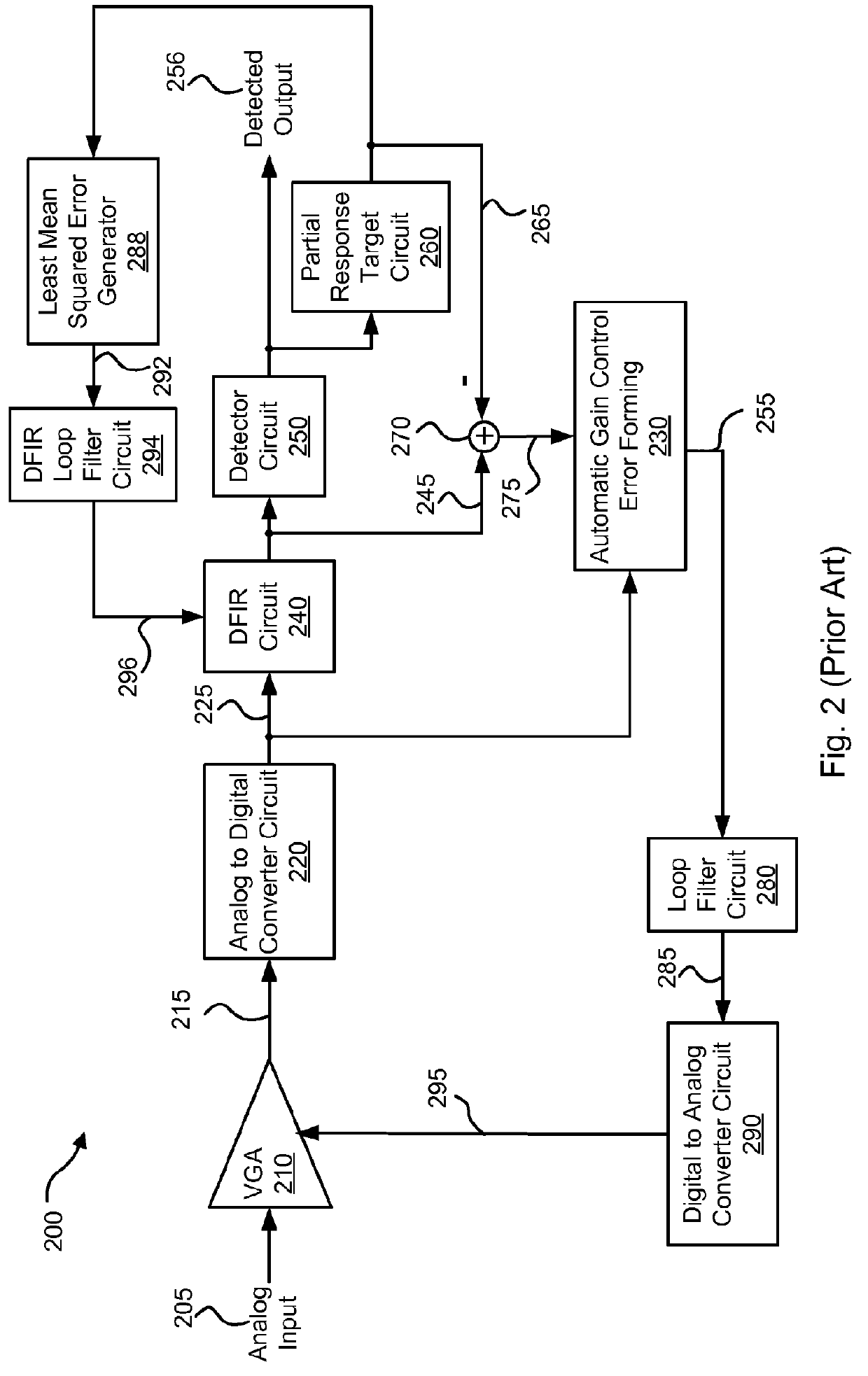

Systems and methods for mitigating latency in a data detector feedback loop

InactiveUS8018360B2Reduce latency impactLower latencyModification of read/write signalsElectric signal transmission systemsSampling instantData retrieval

Methods and systems for mitigating latency in a data detector feedback loop are included. For example, a method for reducing latency in an error corrected data retrieval system is included. The method includes performing an analog to digital conversion at a sampling instant to create a digital sample, and performing a data detection on the digital sample to create a detected output. The detected output is compared with the digital sample to determine a phase error. During an interim period, the digital sample is adjusted to reflect the phase error to create an adjusted digital sample. After the interim period, the sampling instant is adjusted to reflect the phase error.

Owner:LSI CORP +1

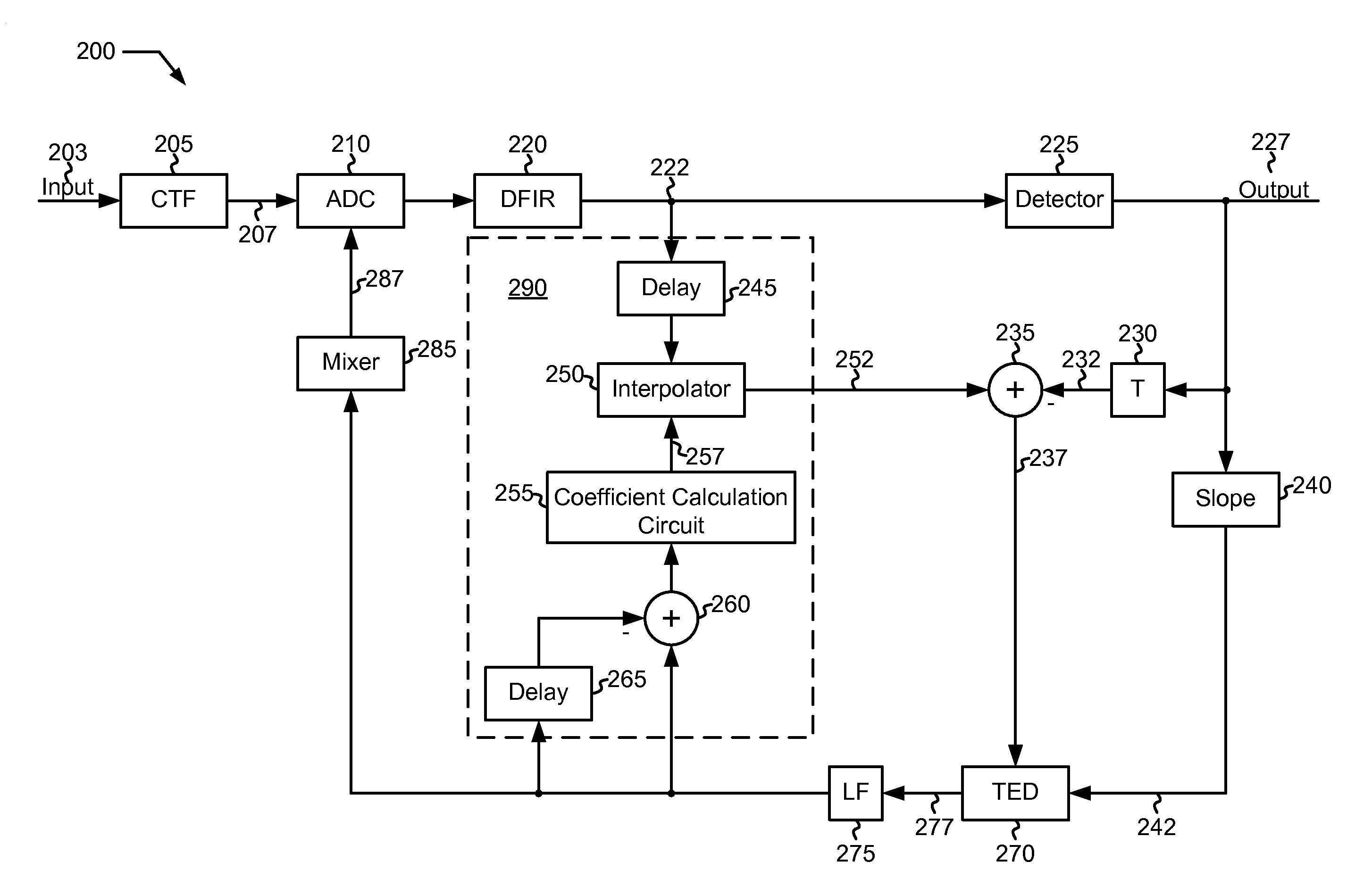

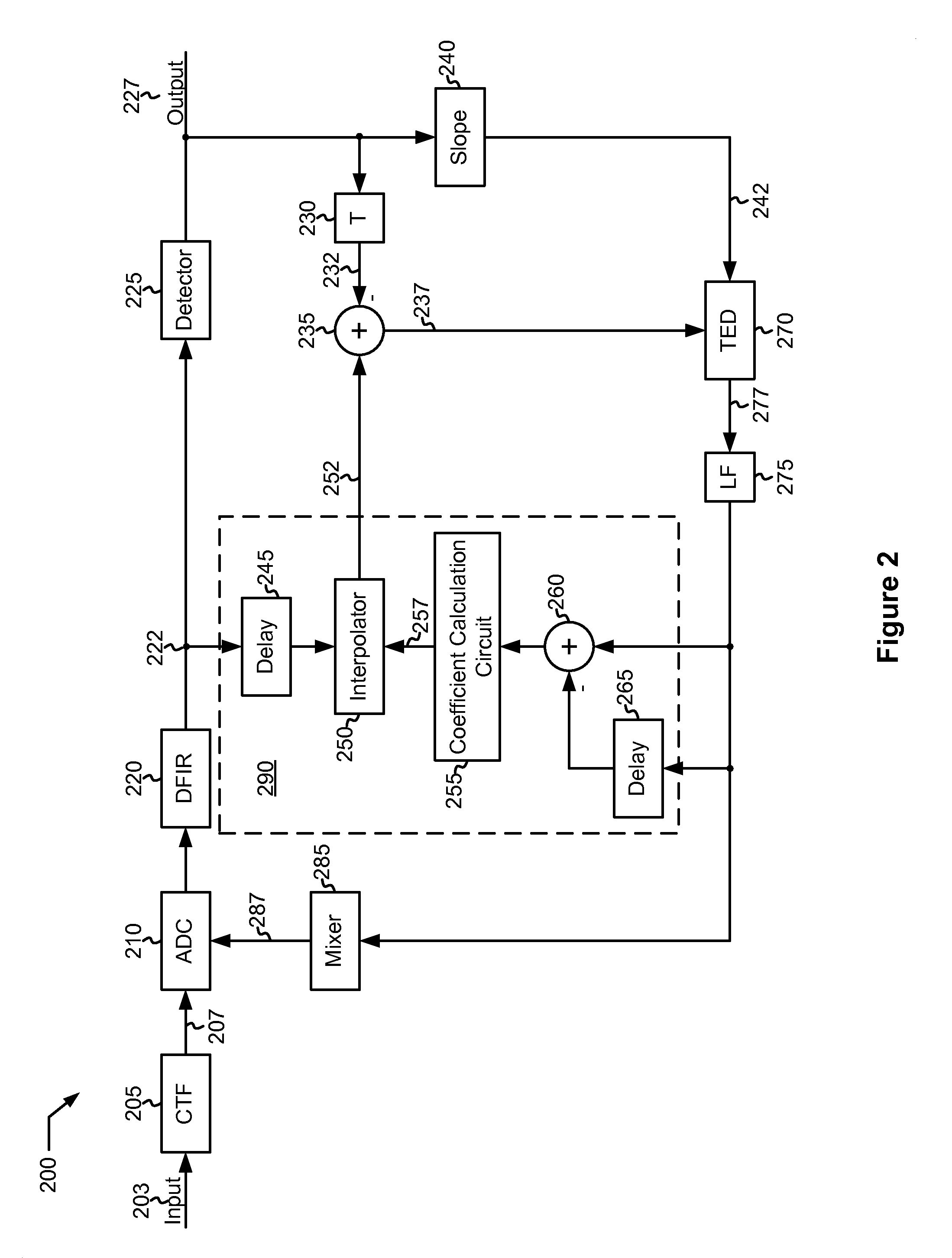

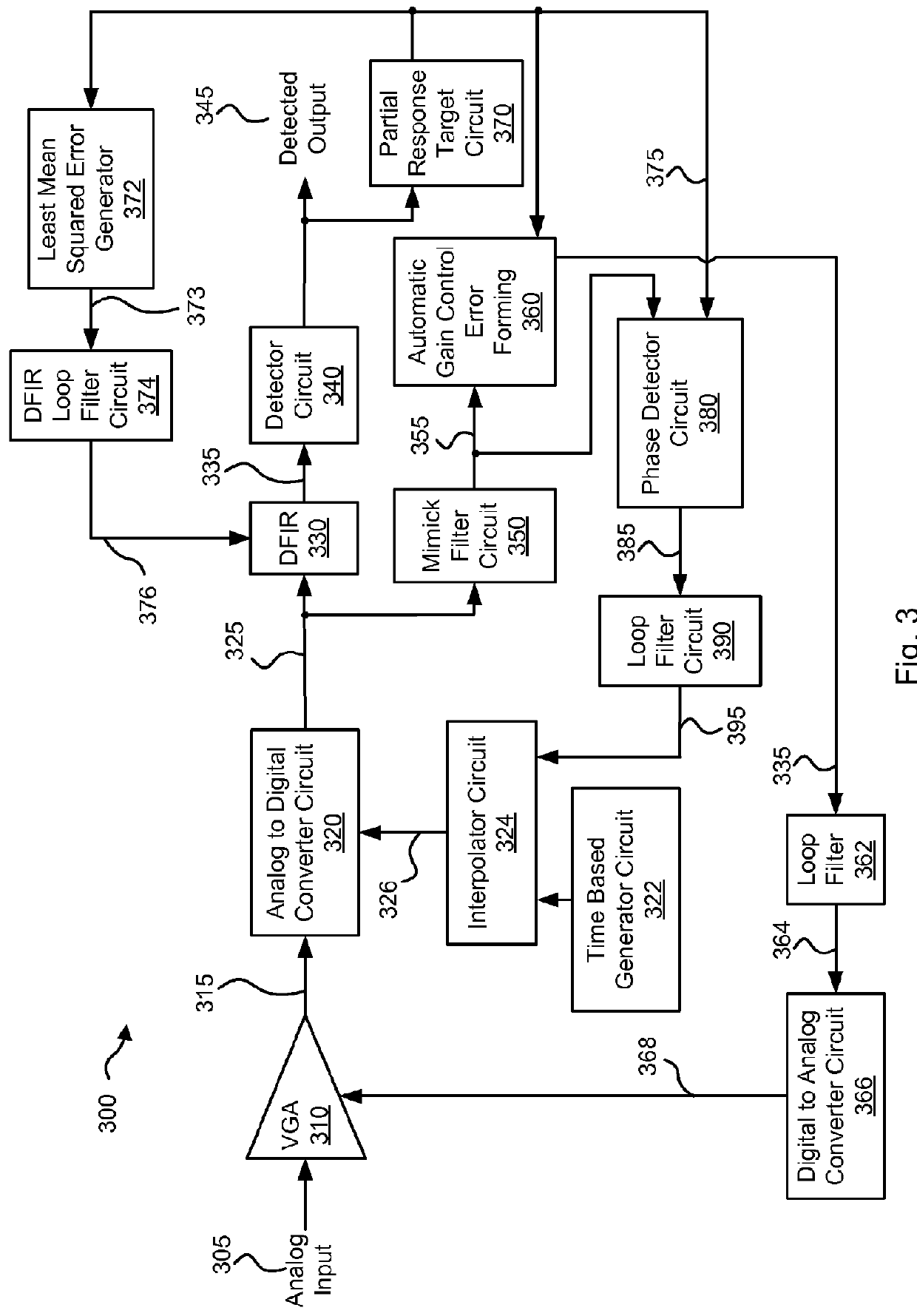

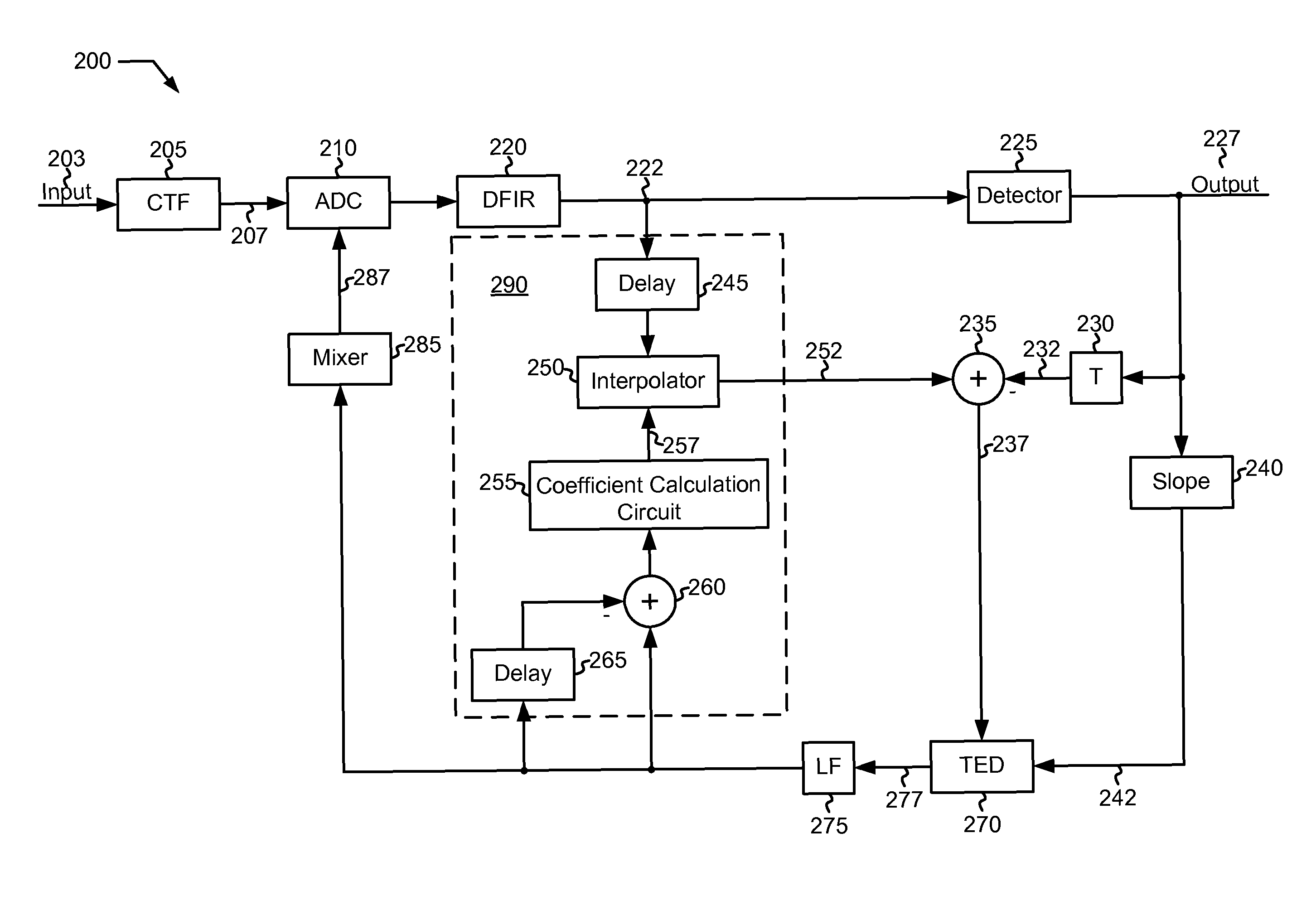

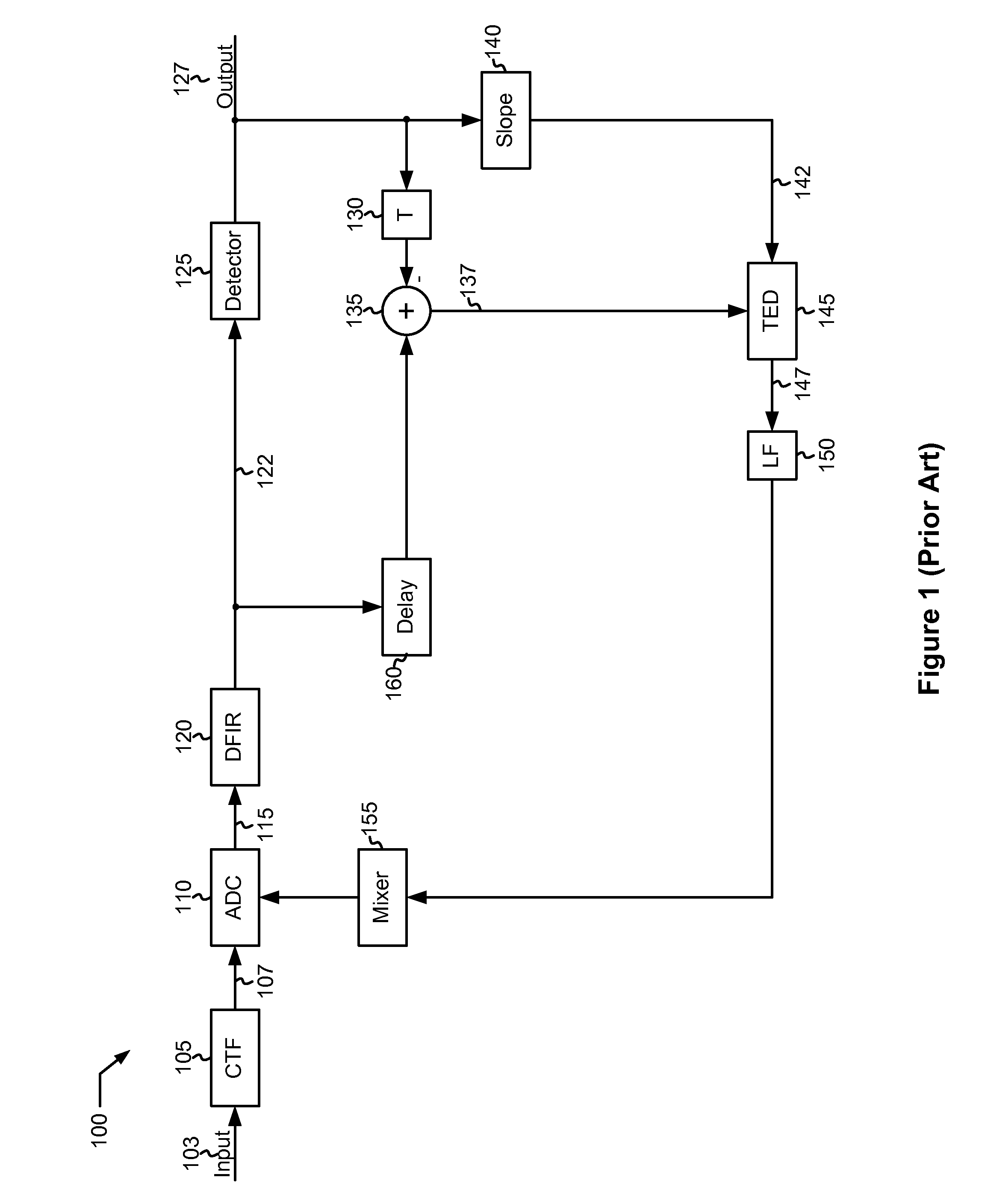

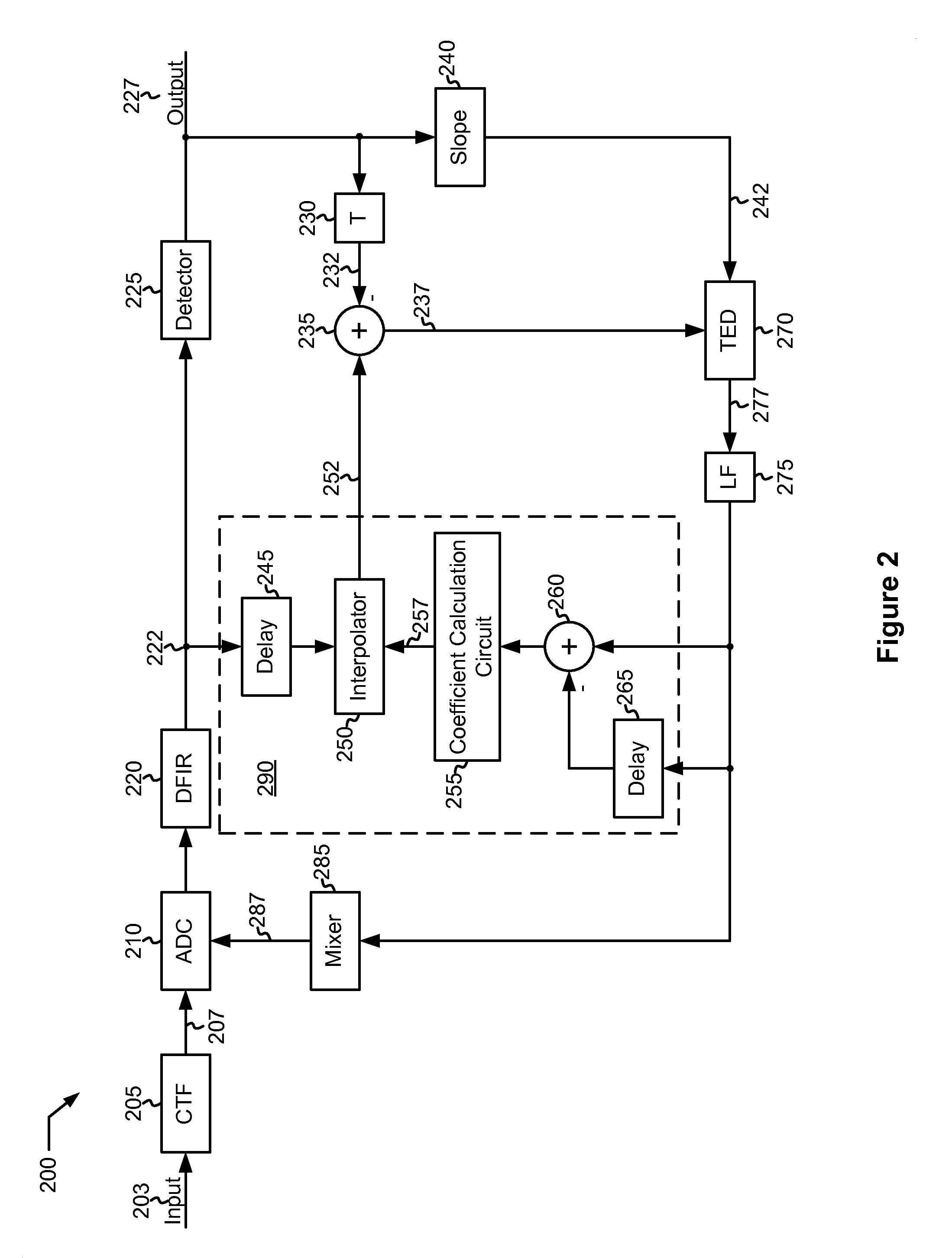

Systems and methods for semi-independent loop processing

InactiveUS8237597B2Electric signal transmission systemsRecord information storageDetector circuitsAnalog-to-digital converter

Various embodiments of the present invention provide systems and methods for data processing. For example, a data processing circuit is discussed that includes an analog to digital converter circuit, a digital filter circuit, a data detector circuit, a mimic filter circuit, and a sample clock generation circuit. The analog to digital converter circuit is operable to receive a data input and to provide corresponding digital samples. The digital filter circuit is operable to receive the digital samples and to provide a filtered output. The data detector circuit is operable to perform a data detection process on the filtered output to yield a detected output. The mimic filter circuit is operable to receive the digital samples and to provide a mimicked output. The sample clock generation circuit is operable to provide a sample clock based at least in part on the detected output and the mimicked output.

Owner:AVAGO TECH INT SALES PTE LTD

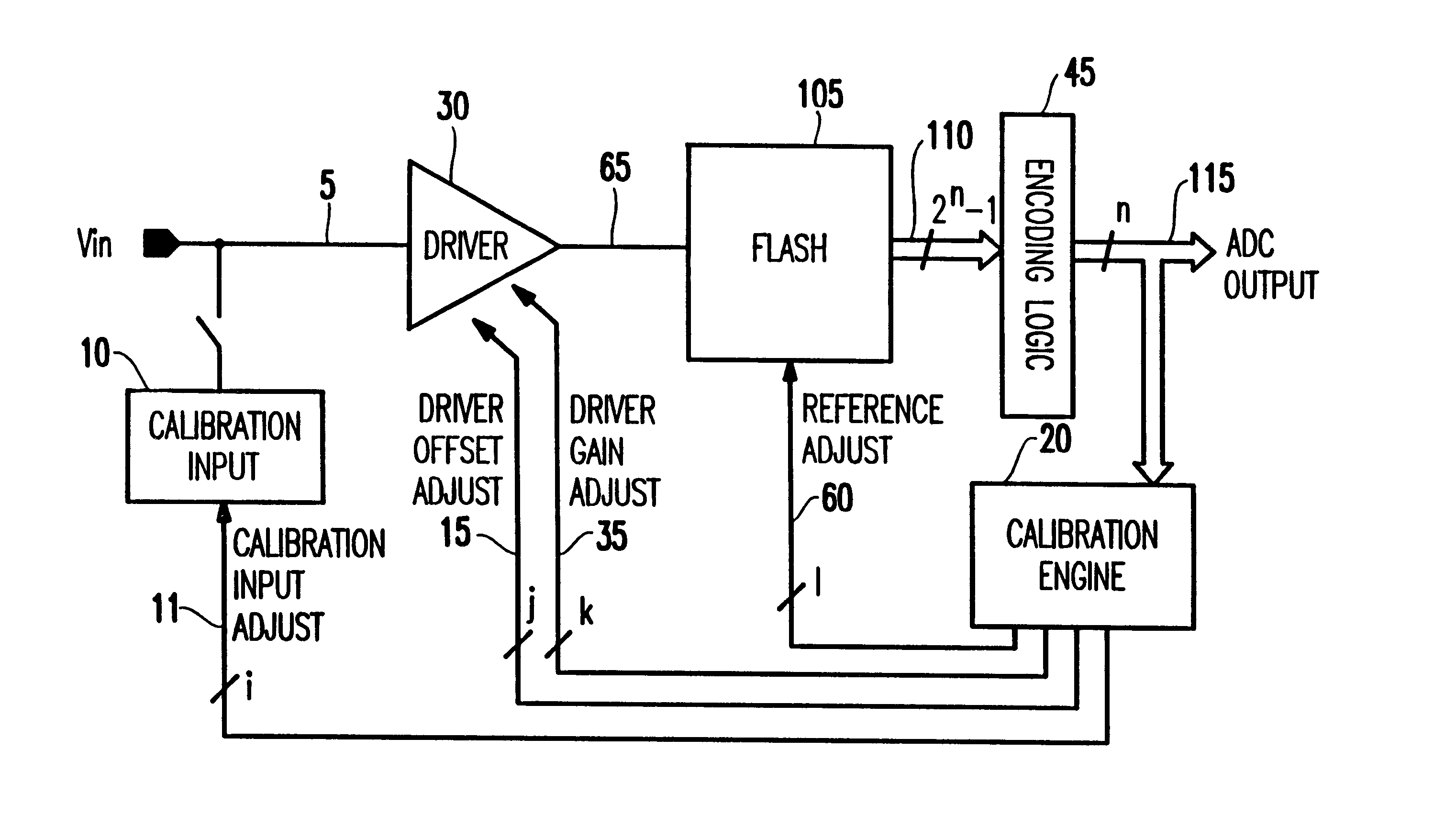

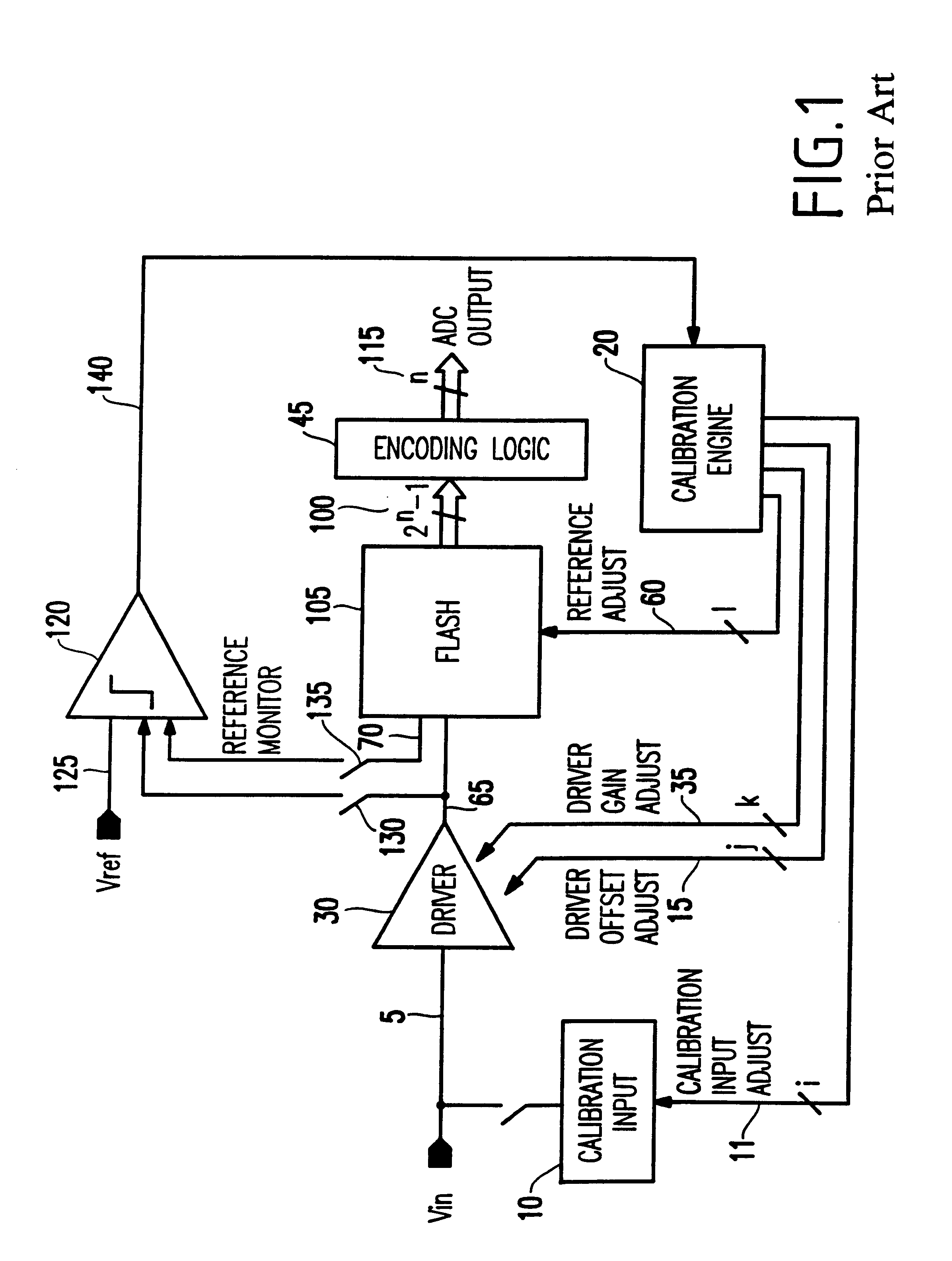

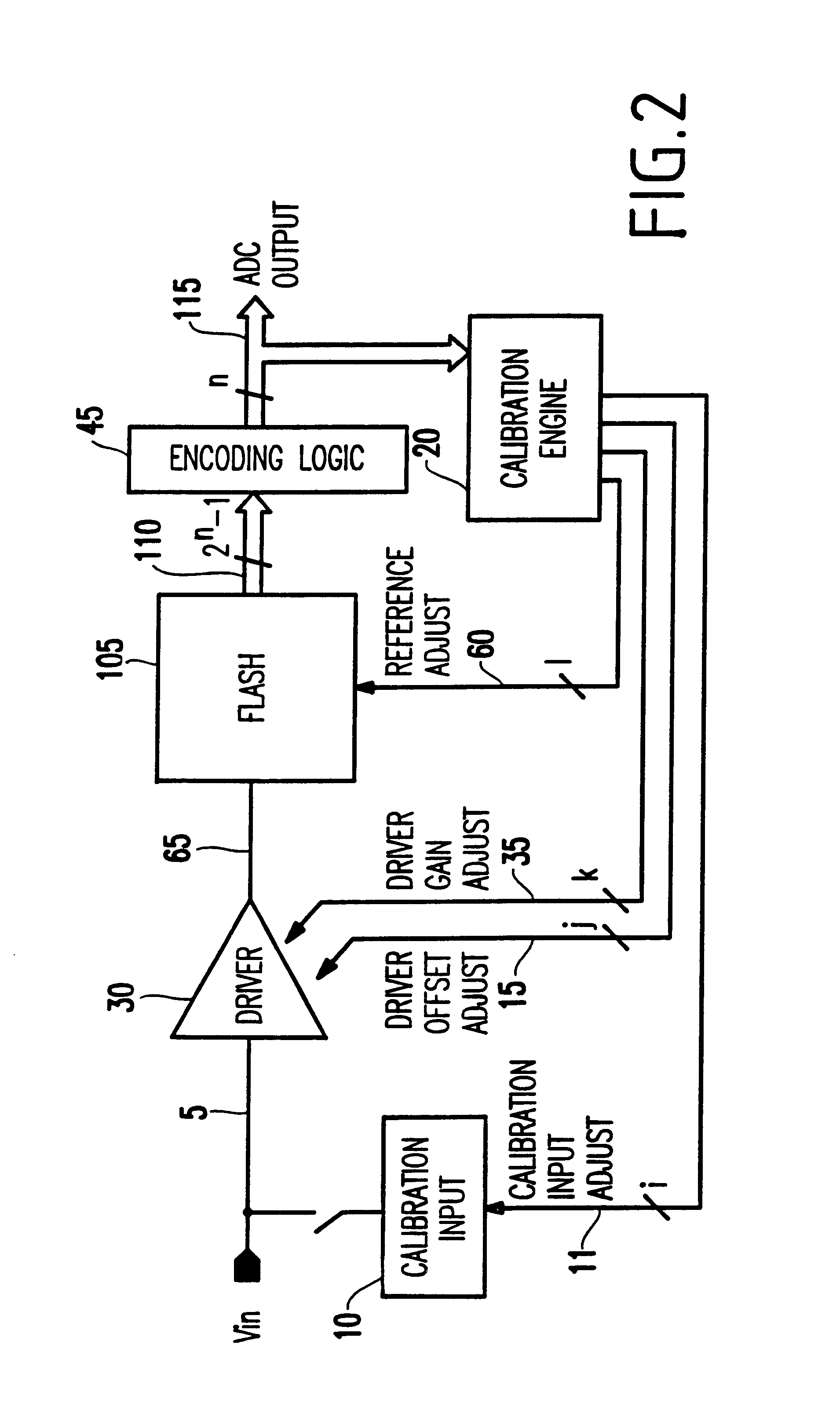

Method and circuit for dynamic calibration of flash analog to digital converters

InactiveUS6603416B2Electric signal transmission systemsAnalogue-digital convertersEngineeringAnalog-to-digital converter

A method and structure for calibrating an analog to digital converter comprises an input signal; a driver receiving the input signal, wherein the driver outputs a driver output signal; a flash circuit receiving the driver output signal, wherein the flash circuit outputs a comparison result equaling 2n-1 digital outputs; an encoding logic unit encoding the comparison result into n digital bits as an output signal; a calibration engine outputting a calibration input adjust signal, a reference adjust signal, a driver gain adjust signal, a driver offset adjust signal; and a calibration input circuit receiving the calibration input adjust signal, wherein the driver receives the driver gain adjust signal and the driver offset adjust signal, wherein the flash circuit receives the reference adjust signal, wherein the calibration engine receives n digital bits, and controls an operation of the driver or flash circuit based on the output signal.

Owner:IBM CORP

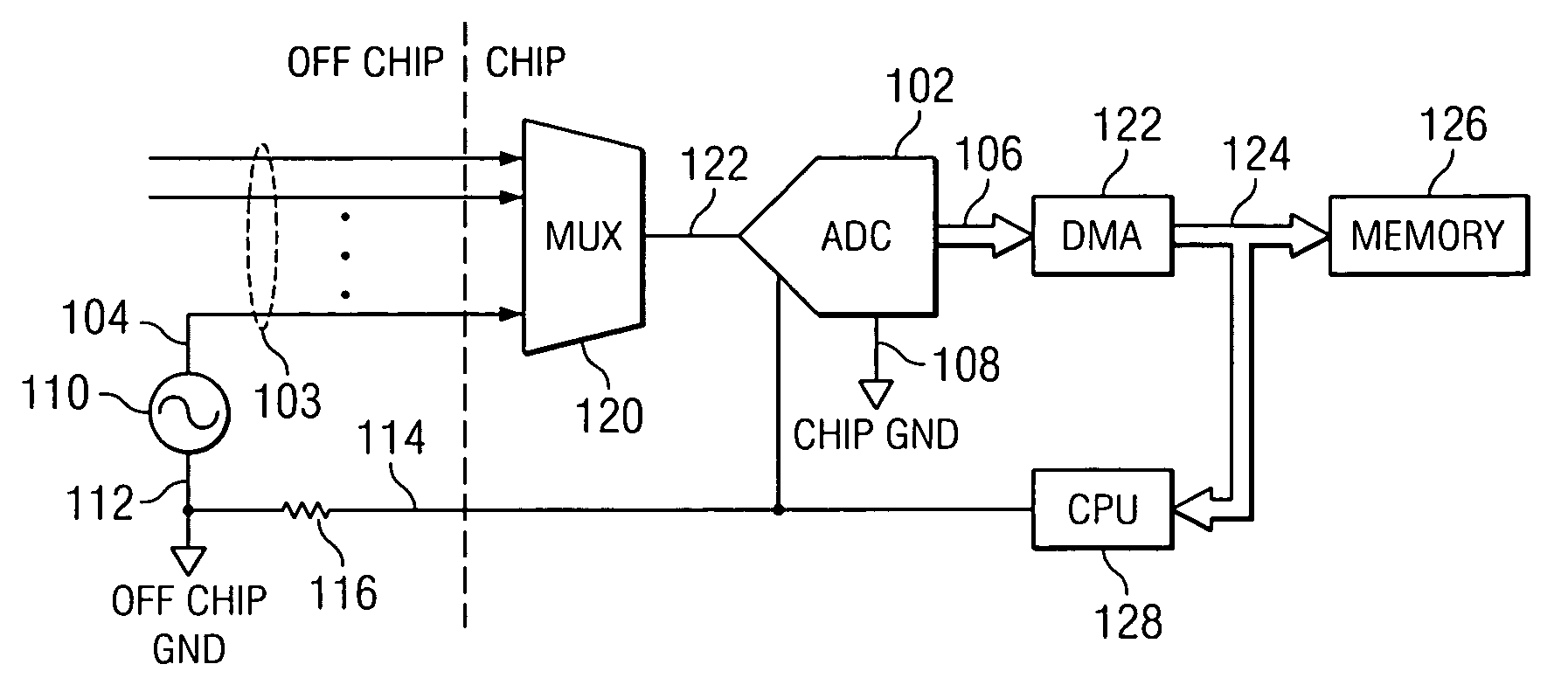

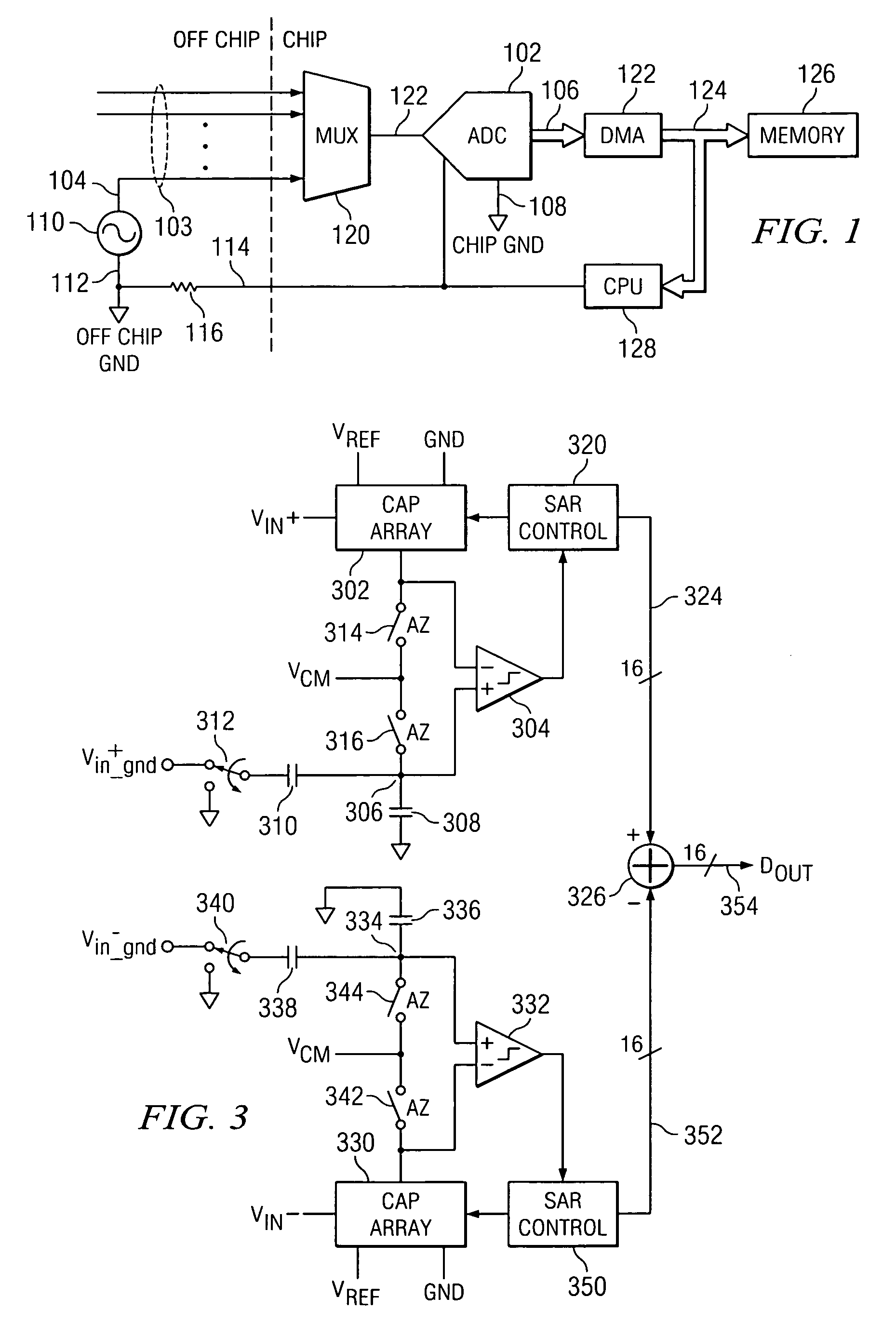

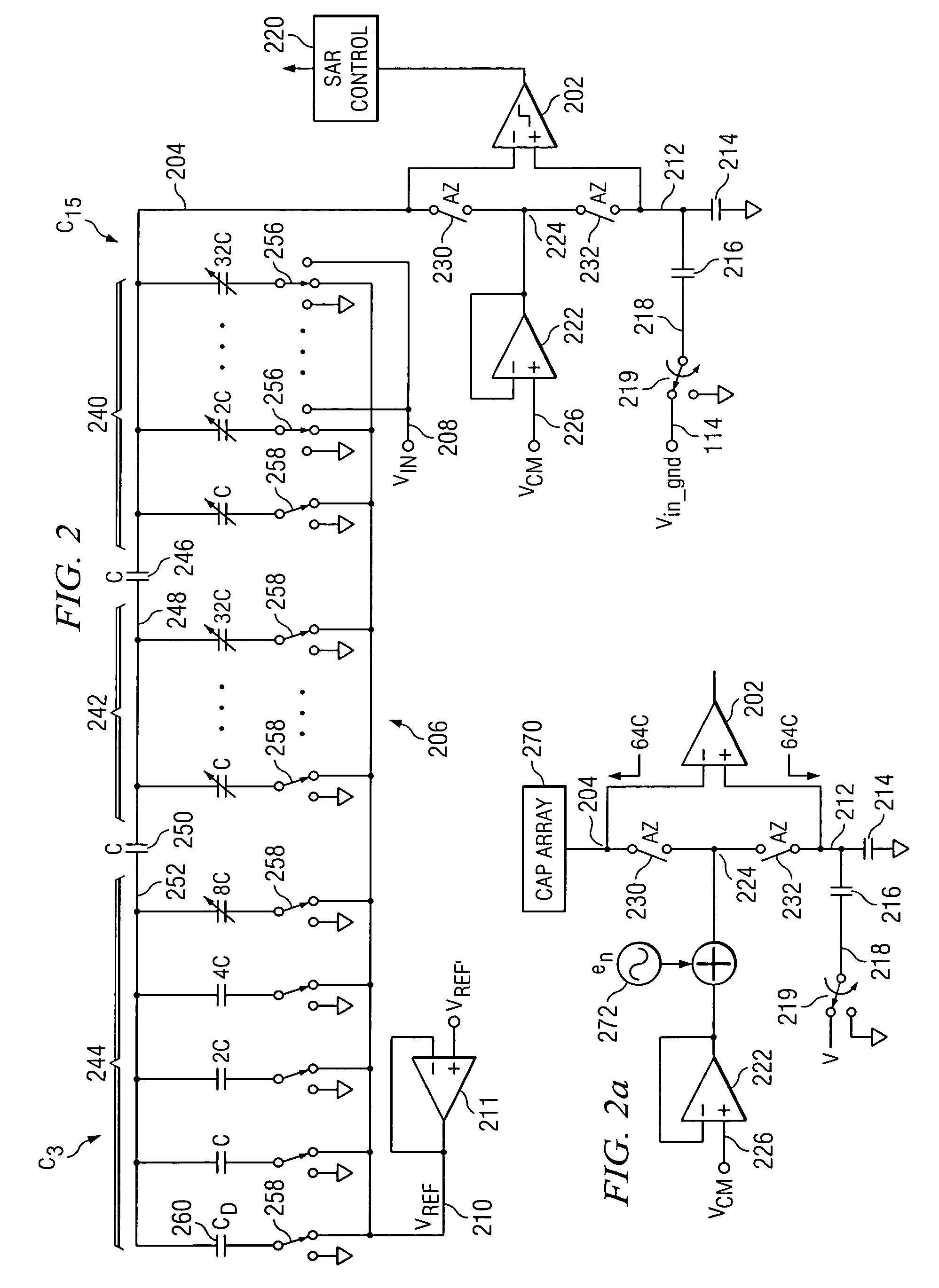

DMA controller that restricts ADC from memory without interrupting generation of digital words when CPU accesses memory

InactiveUS7188199B2Electric signal transmission systemsResistors with plural resistive elementsControl dataMixed-signal integrated circuit

DMA controller for mixed signal device. A mixed signal integrated circuit with memory control is disclosed. A data conversion circuit is provided that is operable to receive an analog input signal and convert discrete samples thereof at a predetermined sampling rate to a digital representations thereof as a plurality of digital words. A memory stores the digital words generated by the data conversion circuit. A processor is included on the integrated circuit and operable to access the memory to output select ones of the digital words for processing thereof in accordance with a predetermined processing algorithm. A memory access controller controls access to the memory by the data conversion circuit and the processor. The memory access controller is operable to restrict access to the memory by the data conversion circuit without interrupting the generation of digital words therefrom when the processor is accessing the memory, and allowing access to the memory by the data conversion circuitry when the processor is not accessing the memory, such that the data conversion circuit can transfer currently generated digital words and previously generated and non stored digital words for storage in said memory upon gaining access thereto.

Owner:SILICON LAB INC

Analog-to-digital converter and semiconductor device

ActiveUS20070008206A1Reduce adverse effectsTelevision system detailsElectric signal transmission systemsCMOSDevice material

An electronic apparatus includes a CMOS image sensor and a signal processor operable to process an output signal from the CMOS image sensor. The CMOS image sensor includes the following elements: an imaging region; a reference signal generator operable to generate a reference signal; a comparator operable to compare the reference signal generated by the reference signal generator with a signal transmitted from the imaging region; a counter operable to count, in parallel with comparison performed by the comparator, a predetermined count clock and to hold a count value at the time of completion of comparison performed by the comparator; and a reference signal supply interface unit operable to supply the reference signal generated by the reference signal generator to a plurality of comparators via different signal lines, respectively.

Owner:SONY CORP

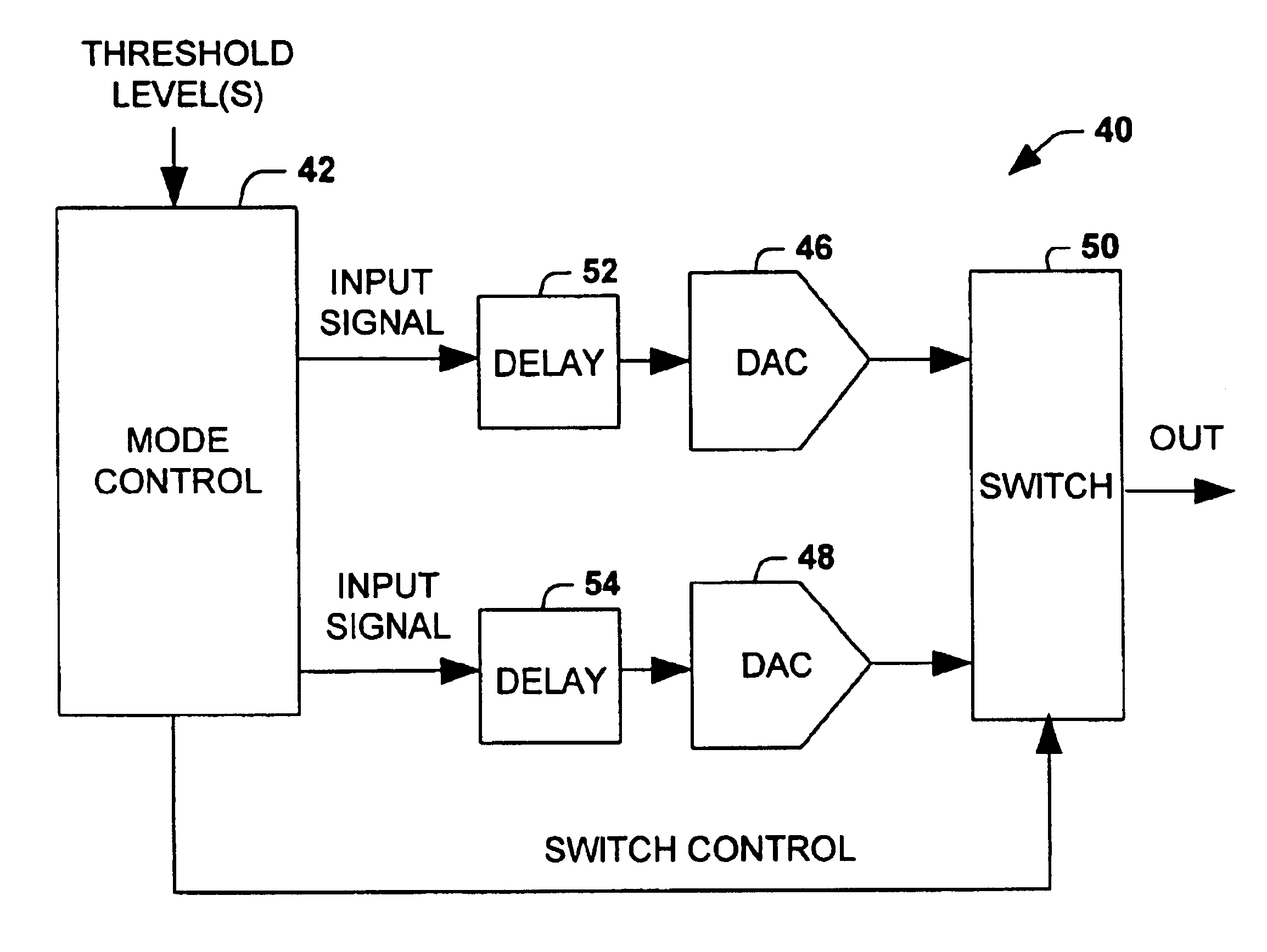

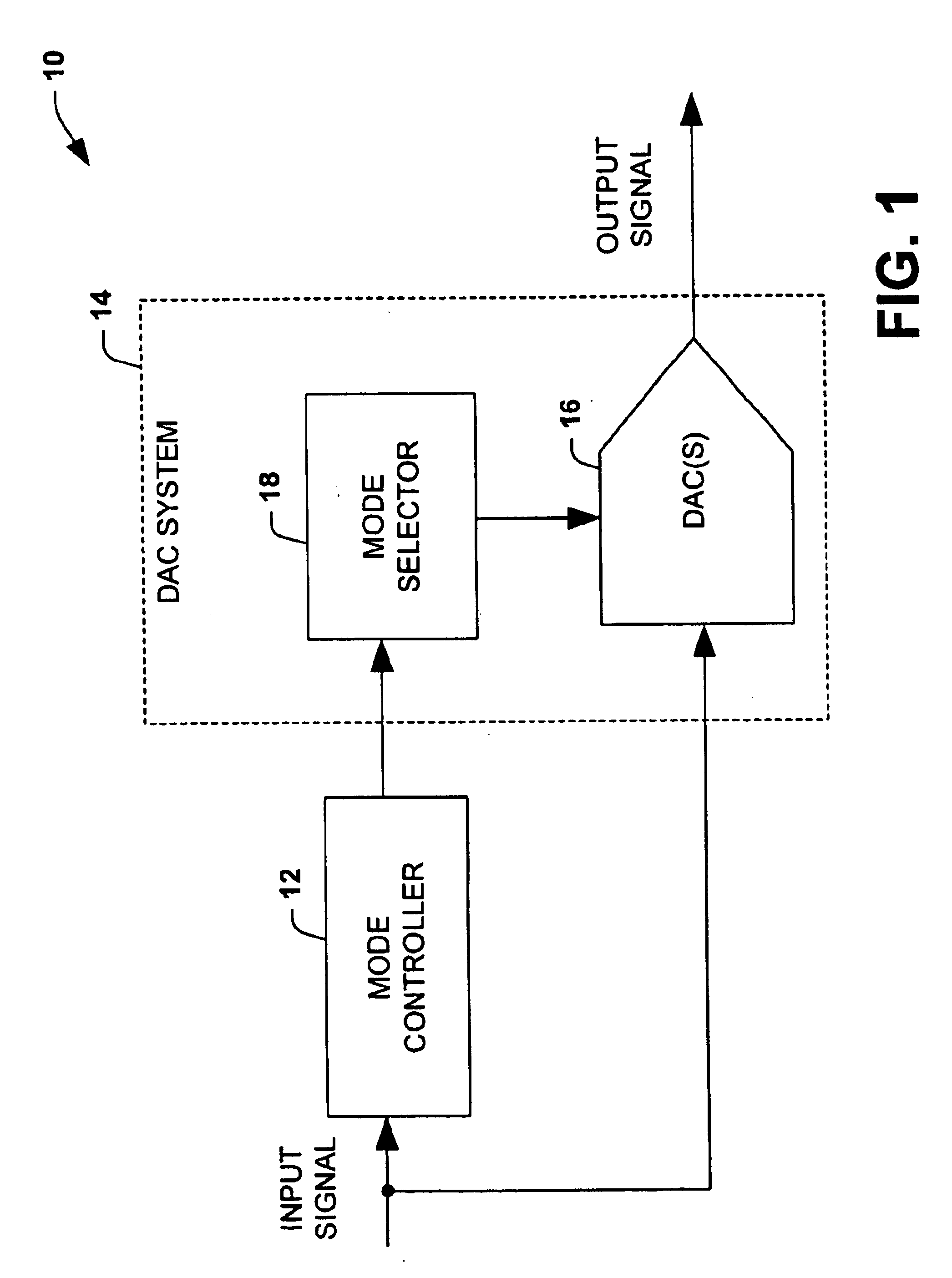

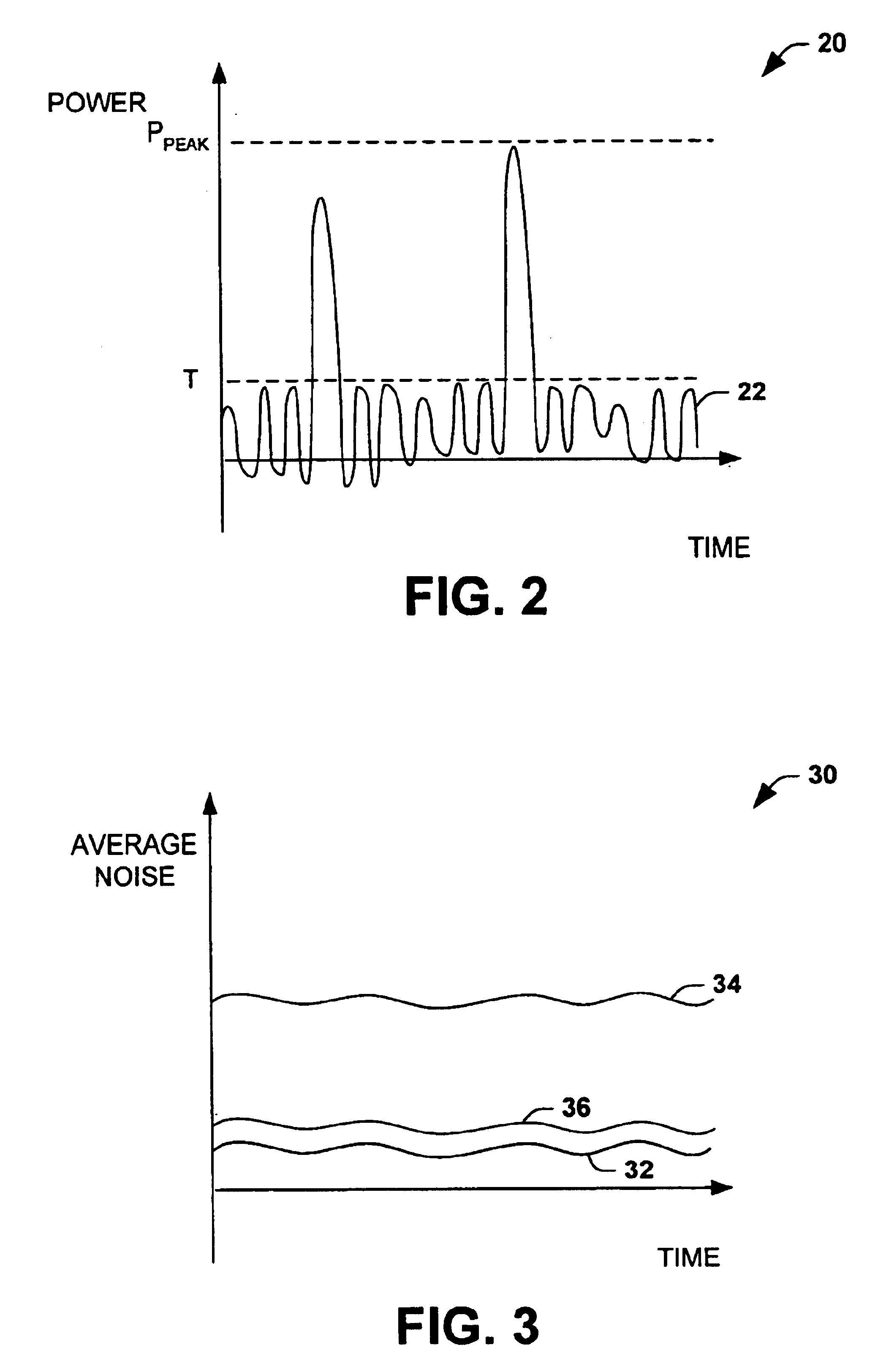

Extended range digital-to-analog conversion

InactiveUS6822595B1Reduce quantization noiseElectric signal transmission systemsAnalogue conversionDigital analog converterNoise level

A conversion system converts an input signal from a digital signal to an analog signal over an extended dynamic range. The system includes a DAC system and a mode selector. The mode selector selects a mode of operation for the digital-to-analog converter system from a plurality of modes. The mode selector selects a mode according to a characteristic of the input signal. Each of the modes is associated with an instantaneous dynamic range and quantization noise level of the DAC system. The ensemble of modes provides an improvement in total or effective dynamic range compared to any DAC component within the DAC system.

Owner:NORTHROP GRUMMAN SYST CORP

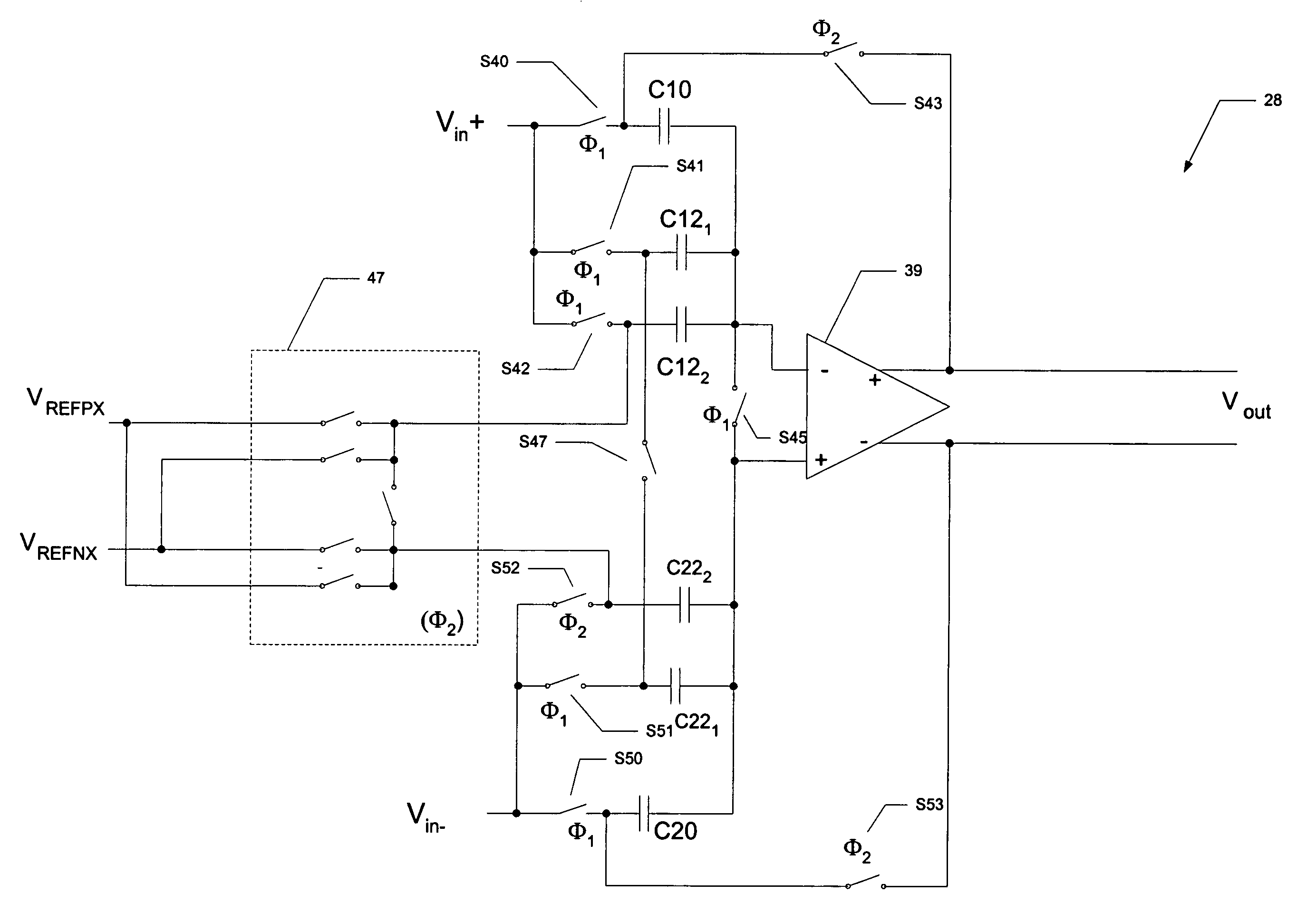

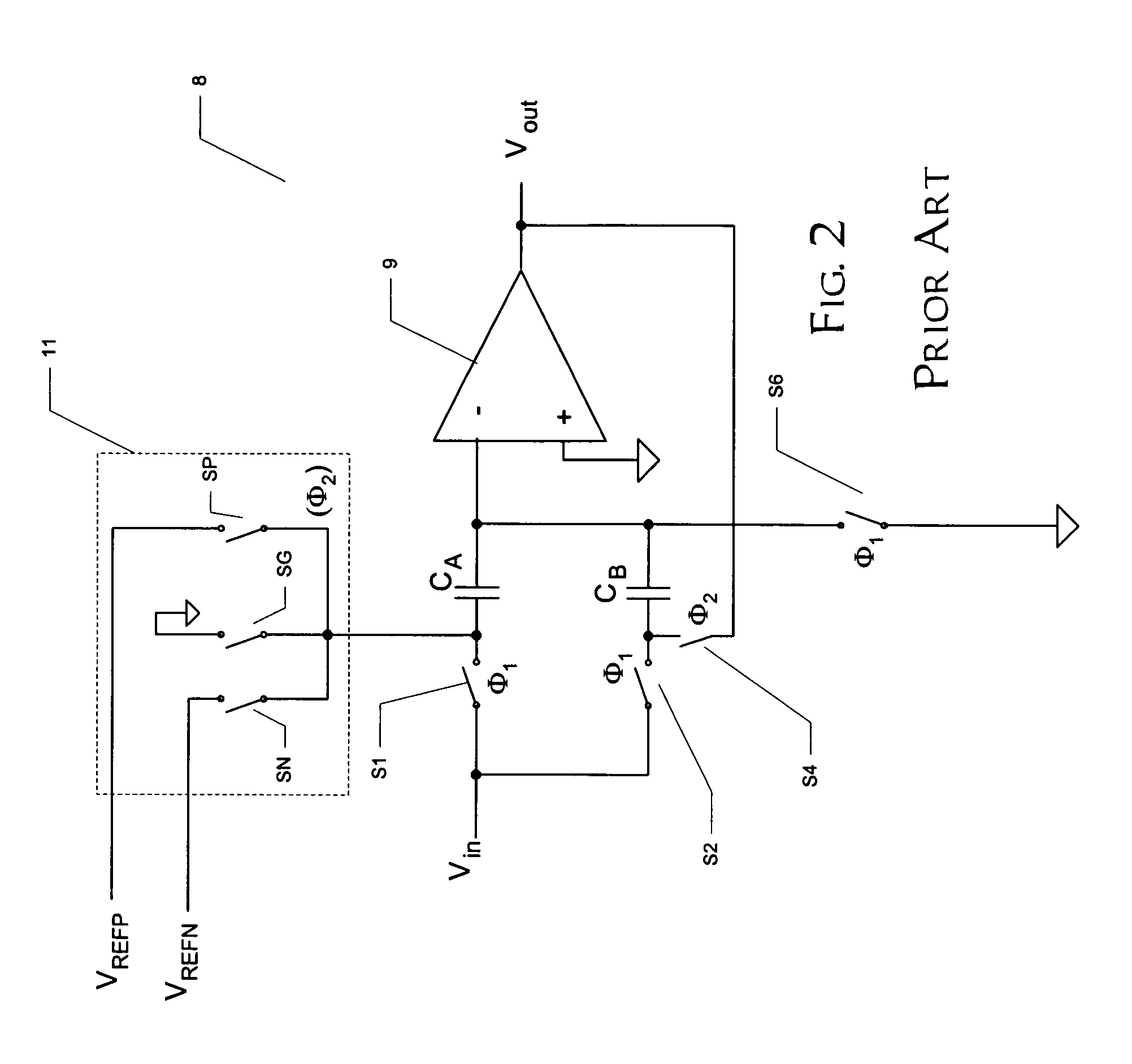

Switched-capacitor circuit with scaled reference voltage

ActiveUS7009549B1Improve precisionImprove stabilityElectric signal transmission systemsAnalogue-digital convertersCapacitanceAudio power amplifier

A pipelined analog-to-digital converter (ADC) (30) with improved precision is disclosed. The pipelined ADC (30) includes a sequence of stages (20), each of which includes a sample-and-hold circuit (22), an analog-to-digital converter (23), and the functions of a digital-to-analog converter (DAC) (25), an adder (24), and a gain stage (27) at which a residue signal (RES) is generated for application to the next stage (20) in the sequence. A multiplying DAC (28) performs the functions of the DAC (25), adder (24), and gain stage (27) in the stage (20), and is based on an operational amplifier (29). Sample capacitors (C10, C20) and reference capacitors (C122, C222) receive the analog input from the sample-and-hold circuit (22) in a sample phase; parallel capacitors (C121, C221) are provided to maintain constant circuit gain. Extended reference voltages (VREFPX, VREFNX) at levels that exceed the output range (V0+, V0−) of the operational amplifier (29) are applied to the reference capacitors, in response to the digital output of the analog-to-digital converter (23) in its stage (20). The reference capacitors (C12, C22) are scaled according to the extent to which the extended reference voltages (VREFPX, VREFNX) exceed the op amp output levels (V0+, V0−). The effects of noise on the reference voltages (VREFPX, VREFNX) on the residue signal (RES) are thus greatly reduced.

Owner:TEXAS INSTR INC

Systems and Methods for Mitigating Latency in a Data Detector Feedback Loop

ActiveUS20100164764A1Reduce latency impactLower latencyModification of read/write signalsElectric signal transmission systemsSampling instantData retrieval

Various embodiments of the present invention provide systems and methods for mitigating latency in a data detector feedback loop. For example, a method for reducing latency in an error corrected data retrieval system is disclosed. The method includes performing an analog to digital conversion at a sampling instant to create a digital sample, and performing a data detection on the digital sample to create a detected output. The detected output is compared with the digital sample to determine a phase error. During an interim period, the digital sample is adjusted to reflect the phase error to create an adjusted digital sample. After the interim period, the sampling instant is adjusted to reflect the phase error.

Owner:LSI CORPORATION +1

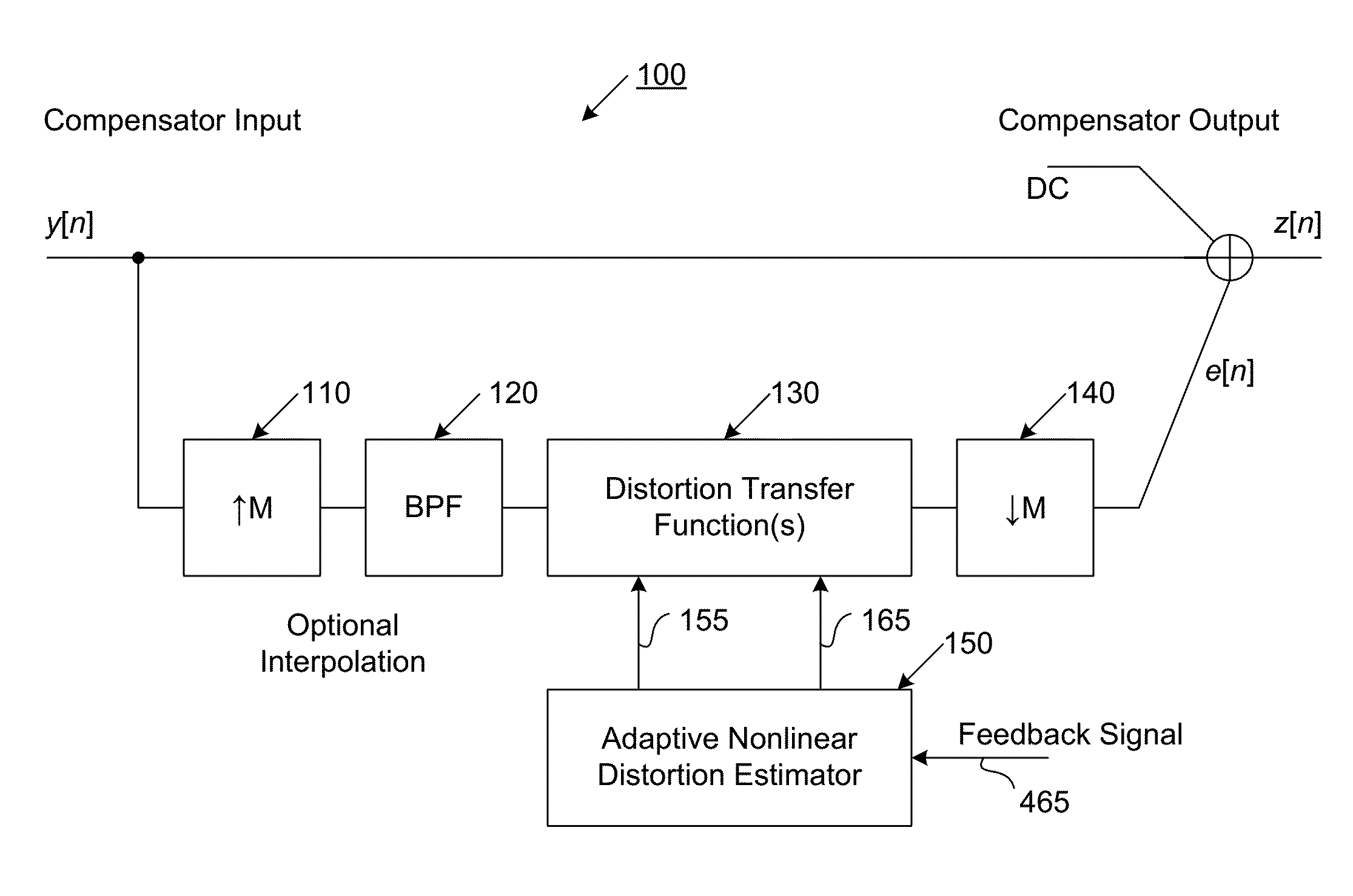

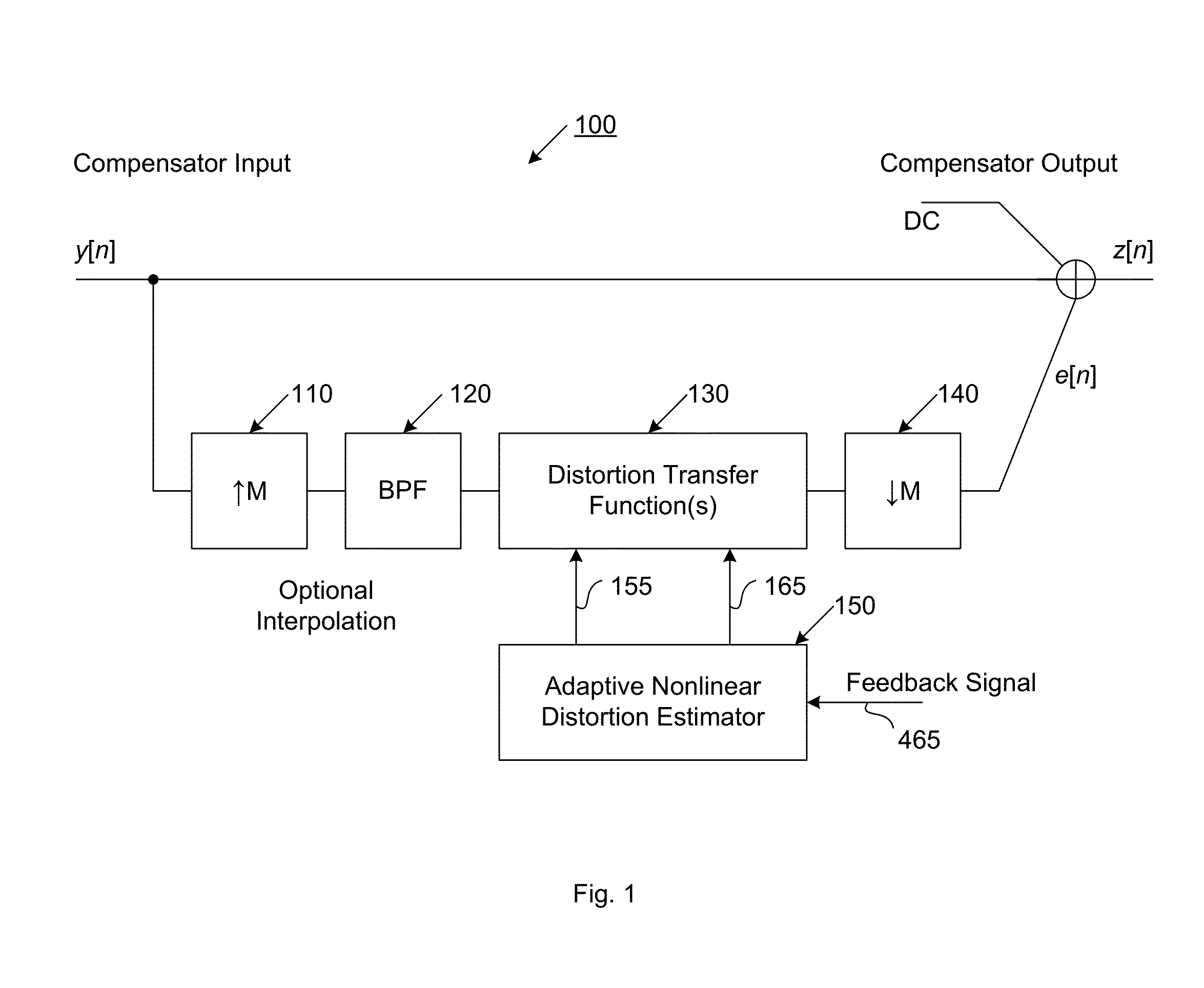

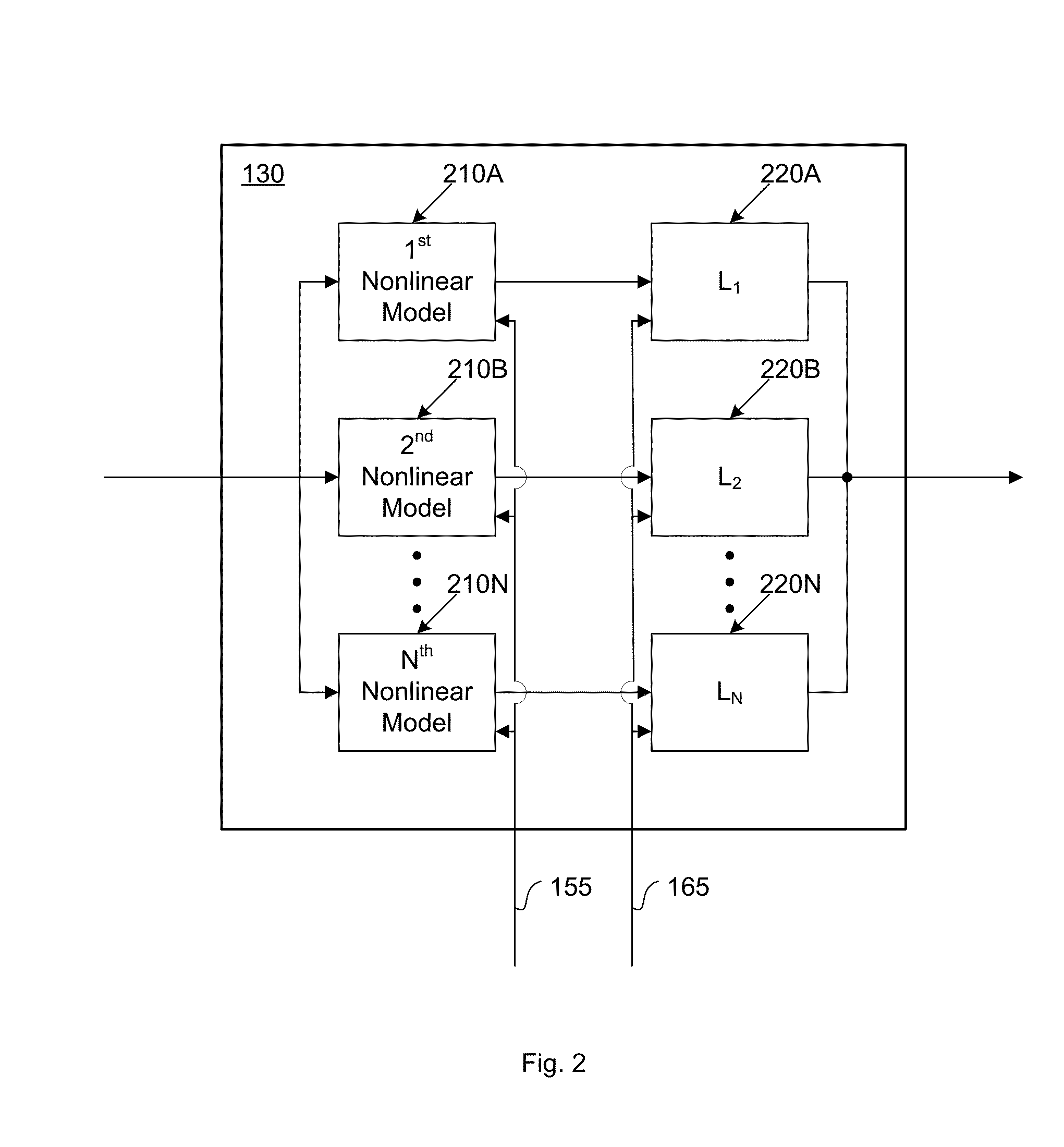

Compensator for removing nonlinear distortion

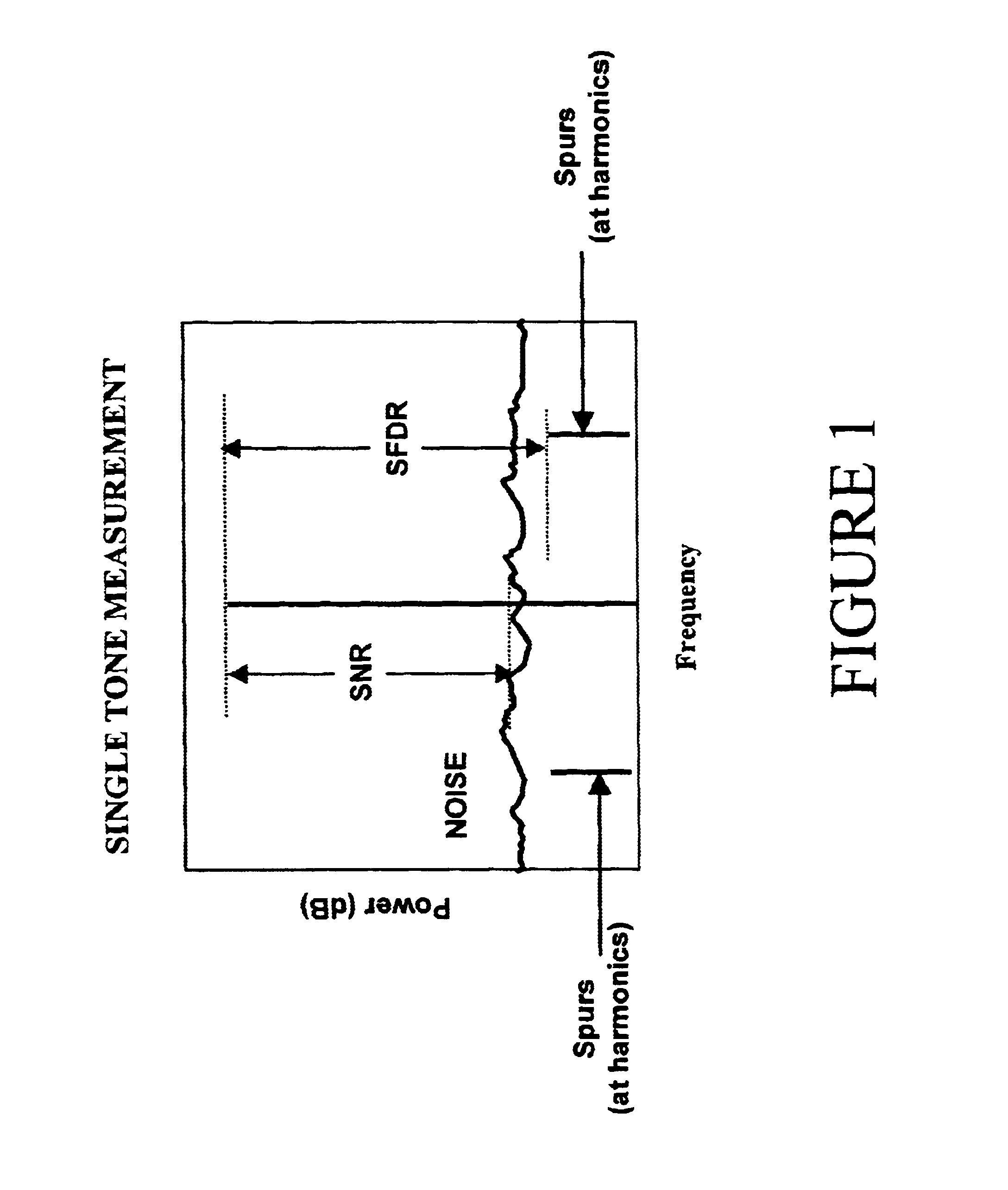

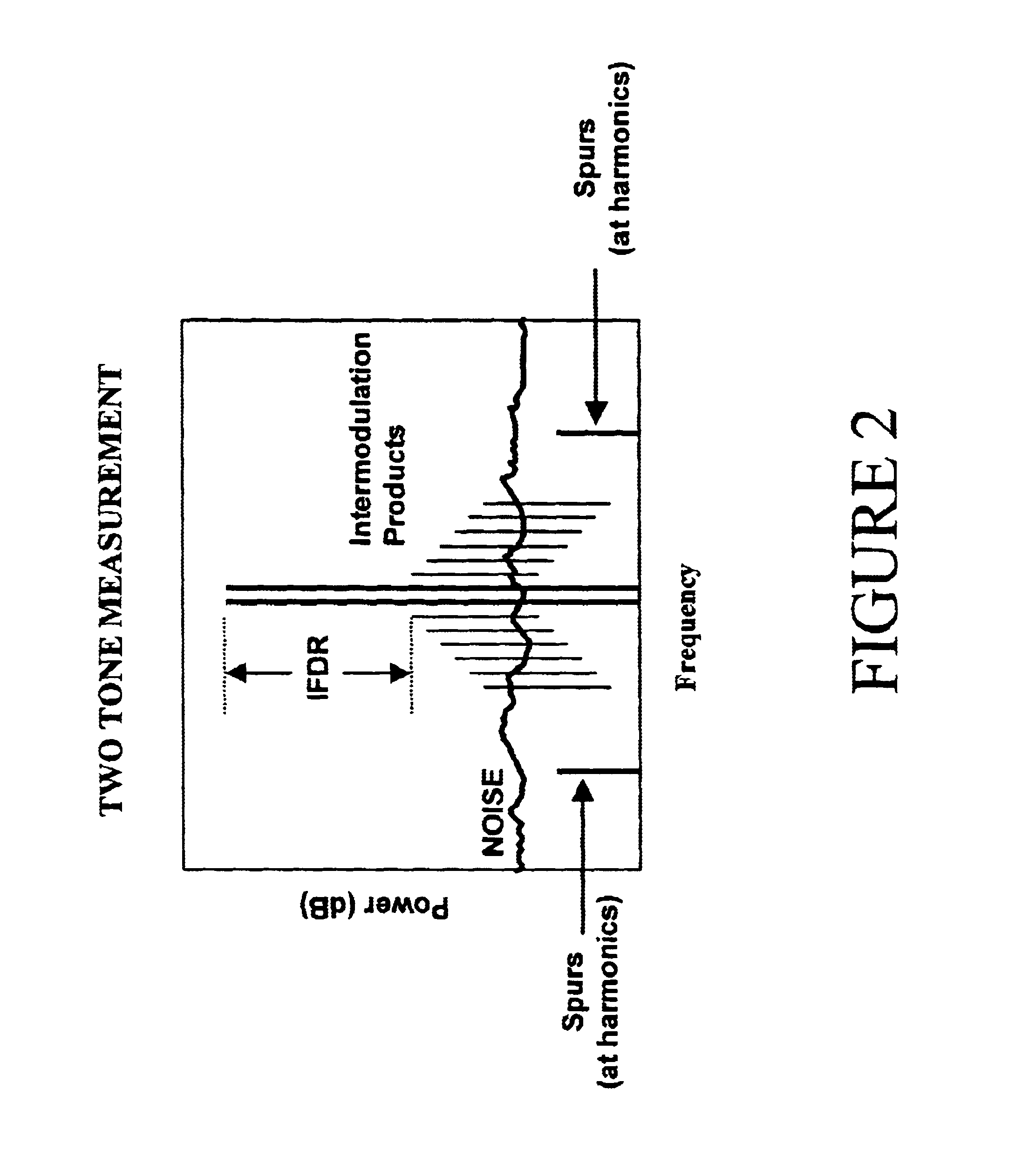

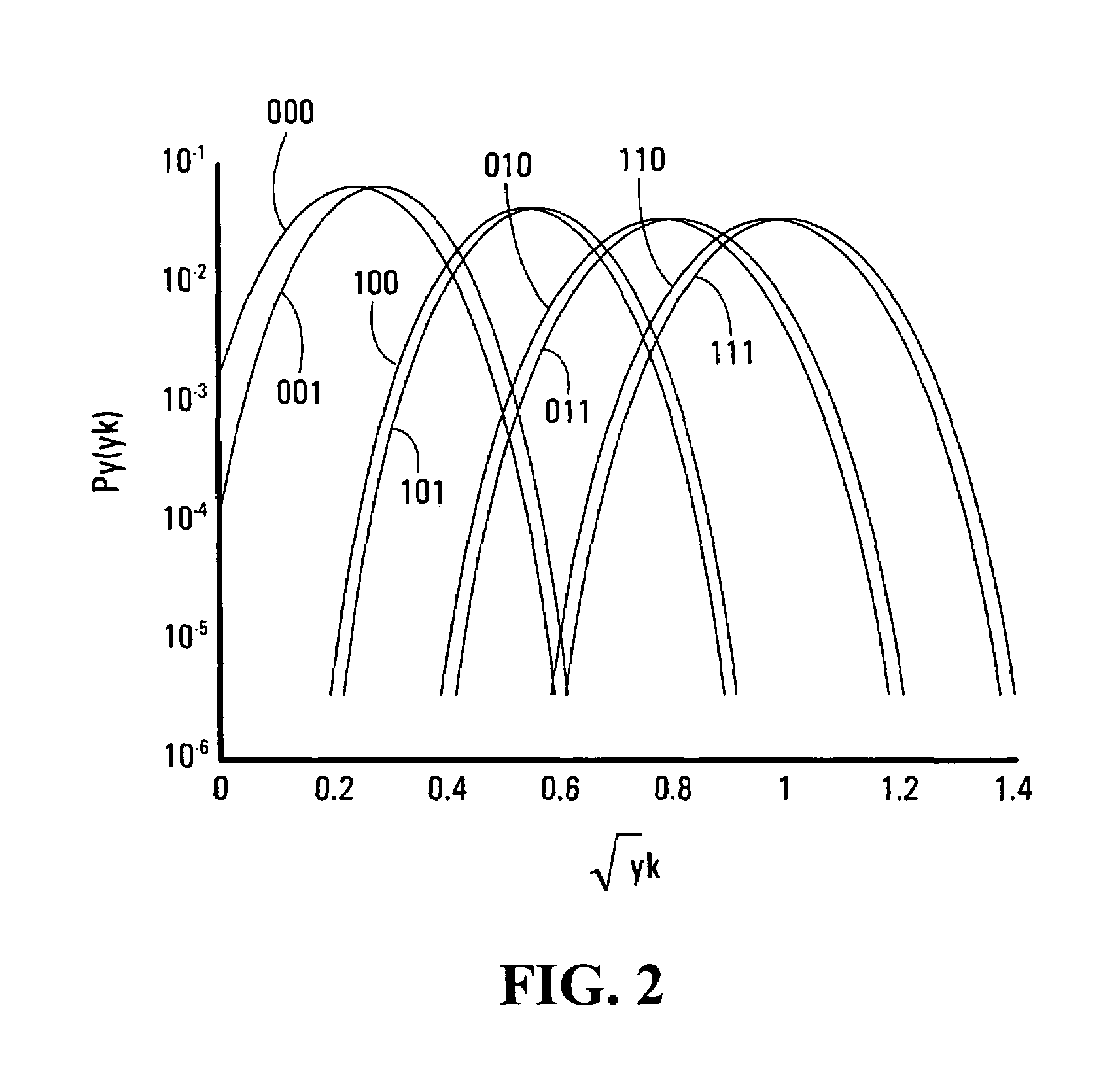

ActiveUS20160191020A1Easy to processReduce complexityChannel dividing arrangementsElectric signal transmission systemsNonlinear distortionComputation complexity

The present invention is a computationally-efficient compensator for removing nonlinear distortion. The compensator operates in a digital post-compensation configuration for linearization of devices or systems such as analog-to-digital converters and RF receiver electronics. The compensator also operates in a digital pre-compensation configuration for linearization of devices or systems such as digital-to-analog converters, RF power amplifiers, and RF transmitter electronics. The compensator effectively removes nonlinear distortion in these systems in a computationally efficient hardware or software implementation by using one or more factored multi-rate Volterra filters. Volterra filters are efficiently factored into parallel FIR filters and only the filters with energy above a prescribed threshold are actually implemented, which significantly reduces the complexity while still providing accurate results. For extremely wideband applications, the multi-rate Volterra filters are implemented in a demultiplexed polyphase configuration which performs the filtering in parallel at a significantly reduced data rate. The compensator is calibrated with an algorithm that iteratively subtracts an error signal to converge to an effective compensation signal. The algorithm is repeated for a multiplicity of calibration signals, and the results are used with harmonic probing to accurately estimate the Volterra filter kernels. The compensator improves linearization processing performance while significantly reducing the computational complexity compared to a traditional nonlinear compensator.

Owner:LINEARITY LLC

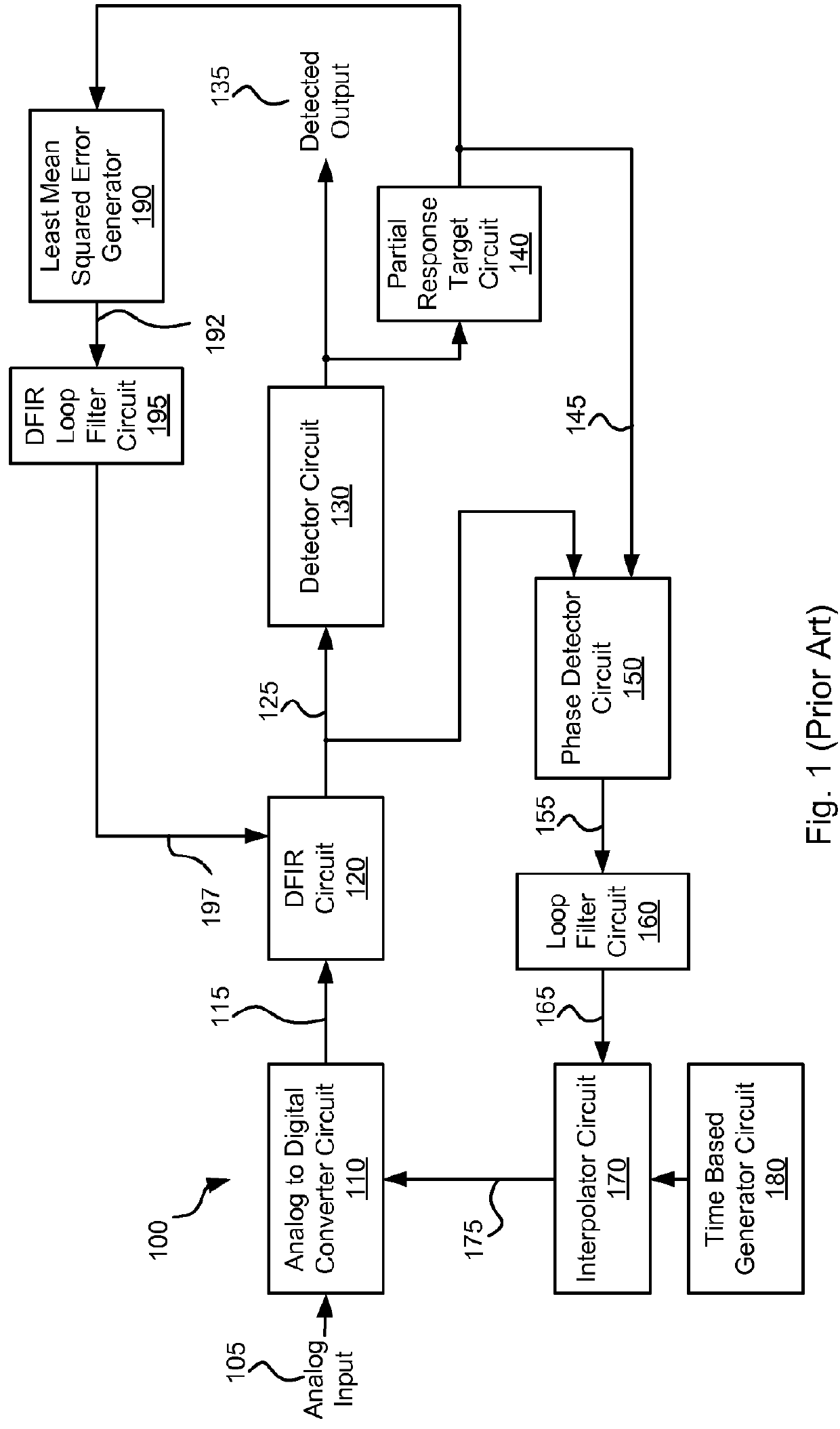

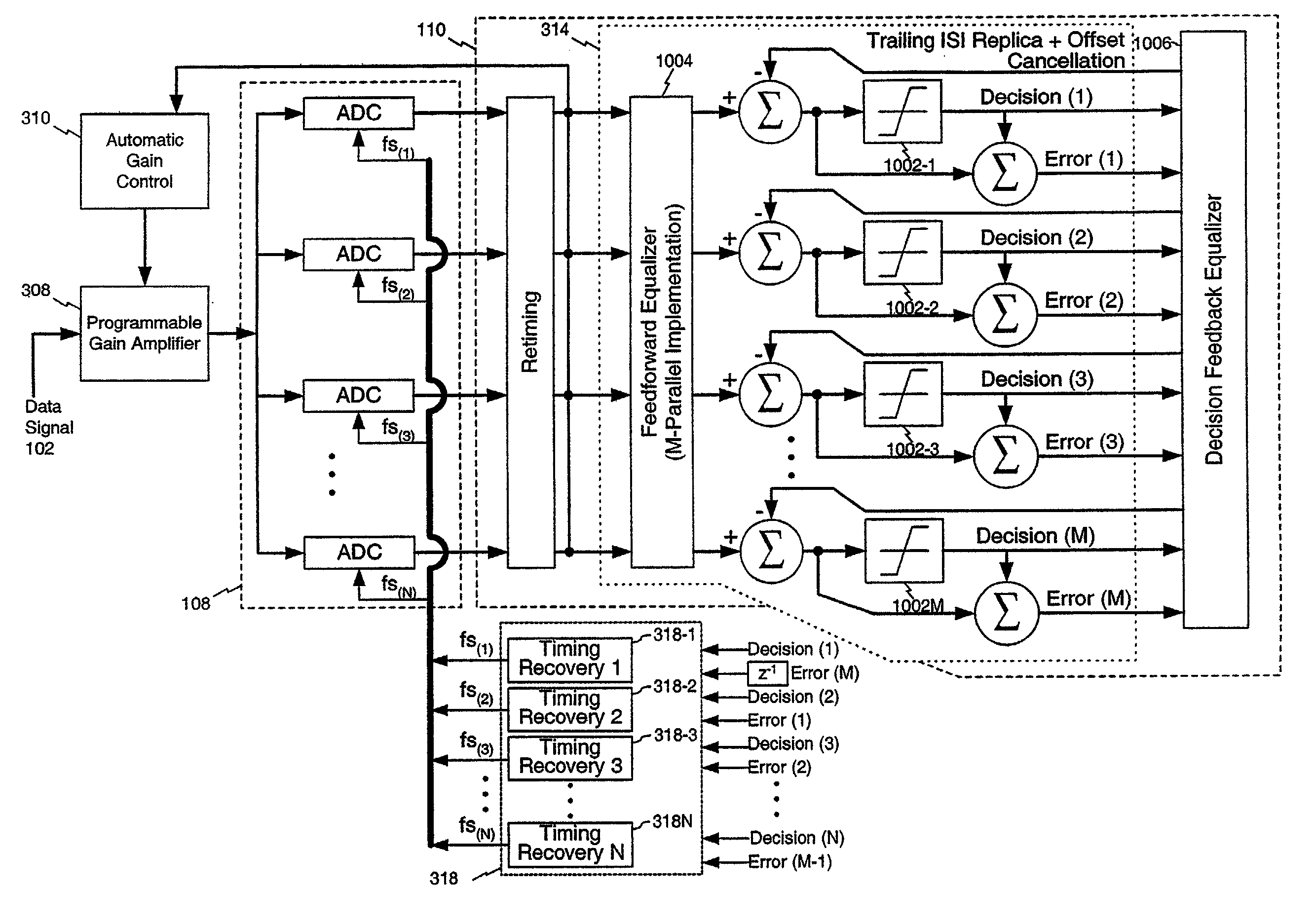

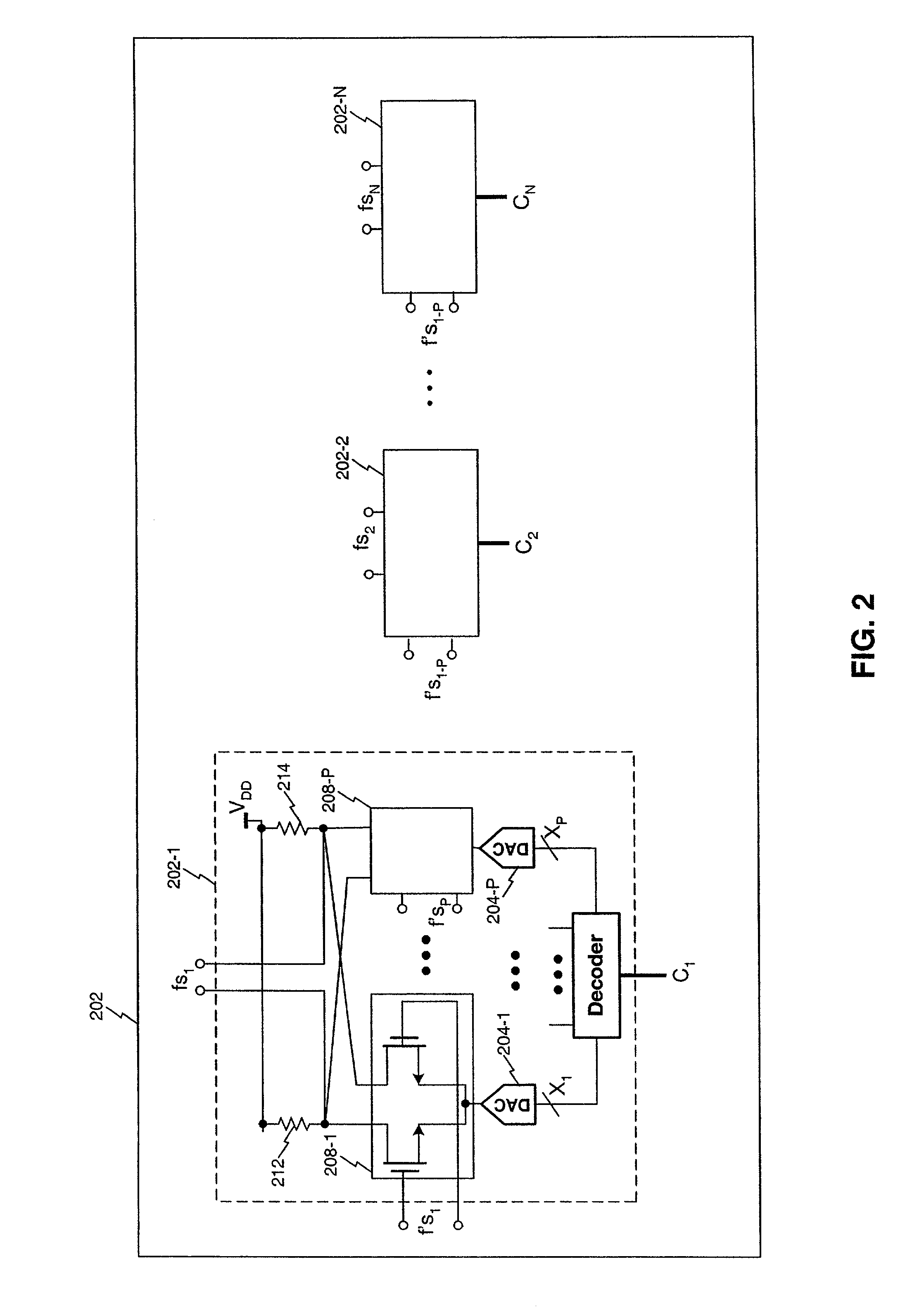

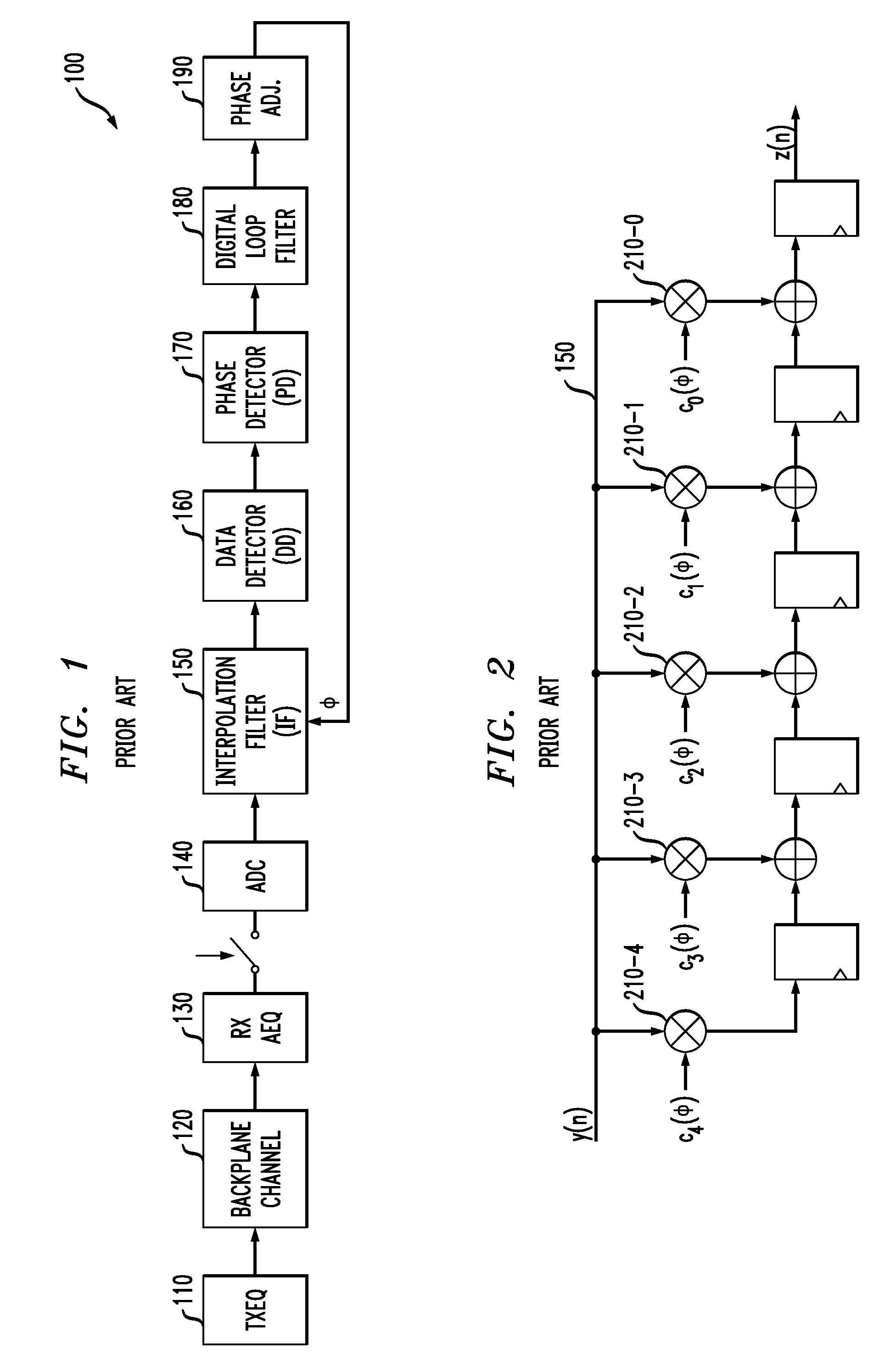

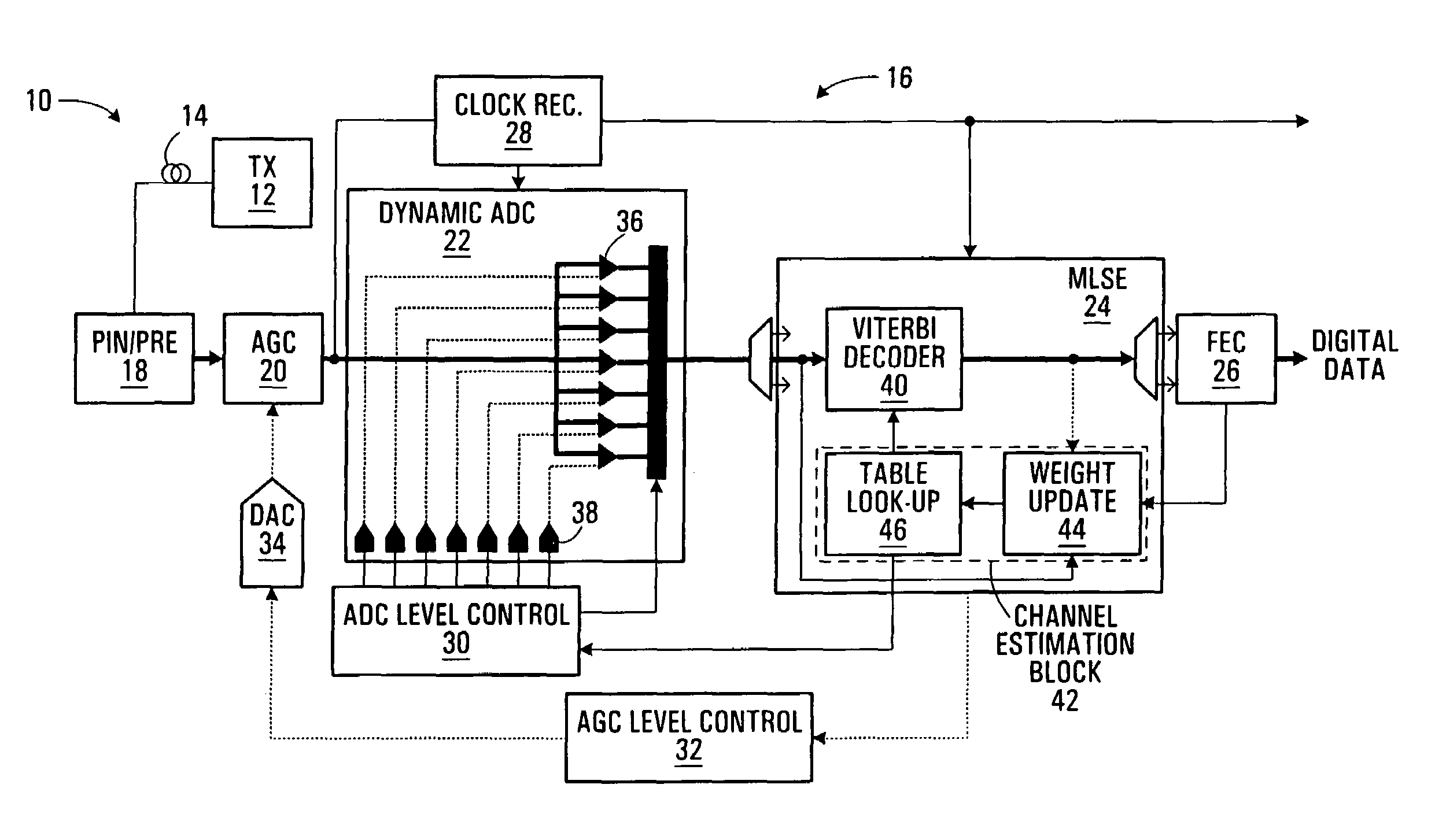

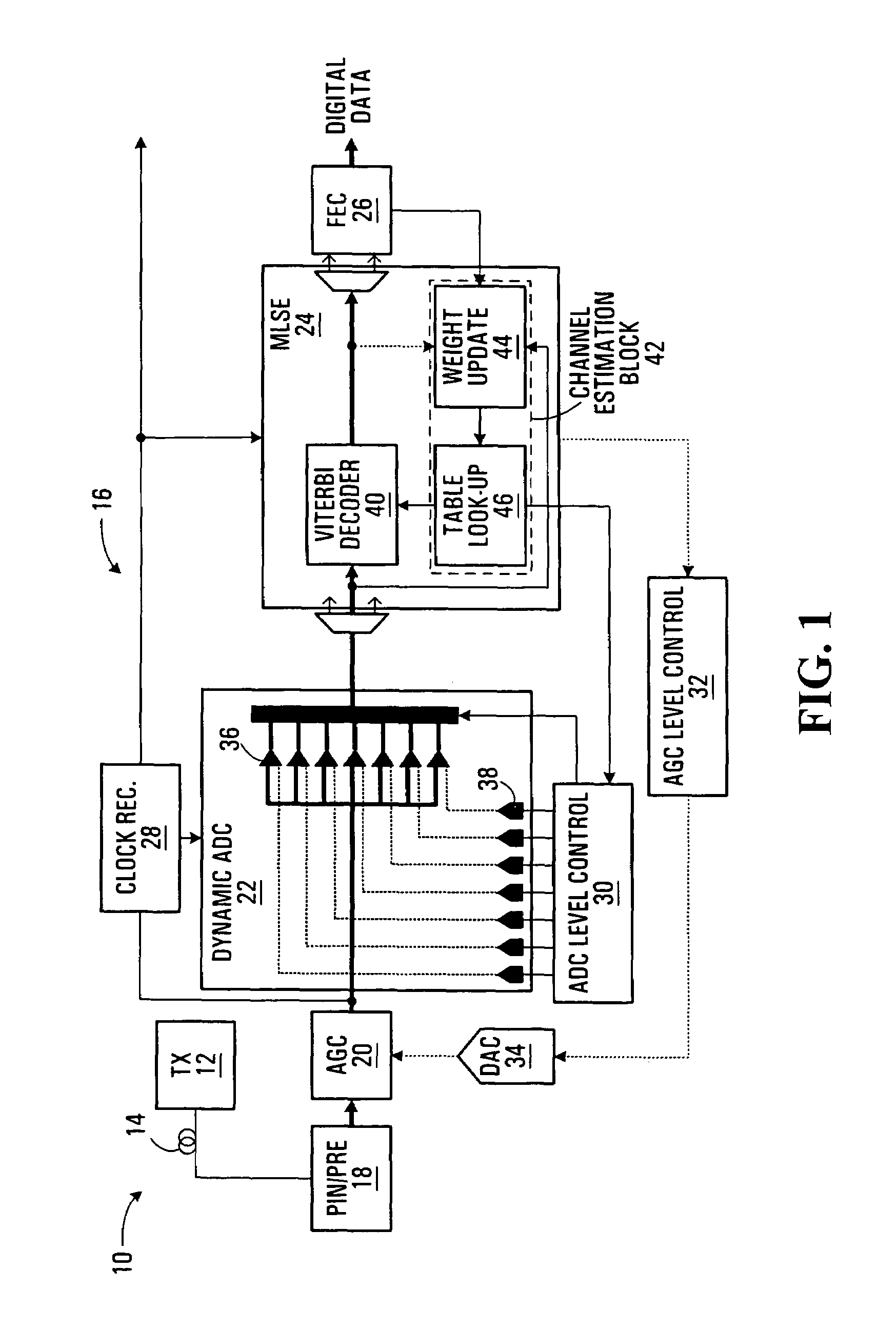

Methods and systems for DSP-based receivers

InactiveUS7245638B2Synchronisation error detectionTime-division multiplexDigital signal processingData signal

Digital signal processing based methods and systems for receiving data signals include parallel receivers, multi-channel receivers, timing recovery schemes, and, without limitation, equalization schemes. The present invention is implemented as a multi-path parallel receiver in which an analog-to-digital converter (“ADC”) and / or a digital signal processor (“DSP”) are implemented with parallel paths that operate at lower rates than the received data signal. In an embodiment, a parallel DSP-based receiver in accordance with the invention includes a separate timing recovery loop for each ADC path. In an embodiment, a parallel DSP-based receiver includes a separate automatic gain control (AGC) loop for each ADC path. In an embodiment, a parallel DSP-based receiver includes a separate offset compensation loop for each ADC path. In an embodiment the present invention is implemented as a multi-channel receiver that receives a plurality of data signals.

Owner:AVAGO TECH INT SALES PTE LTD

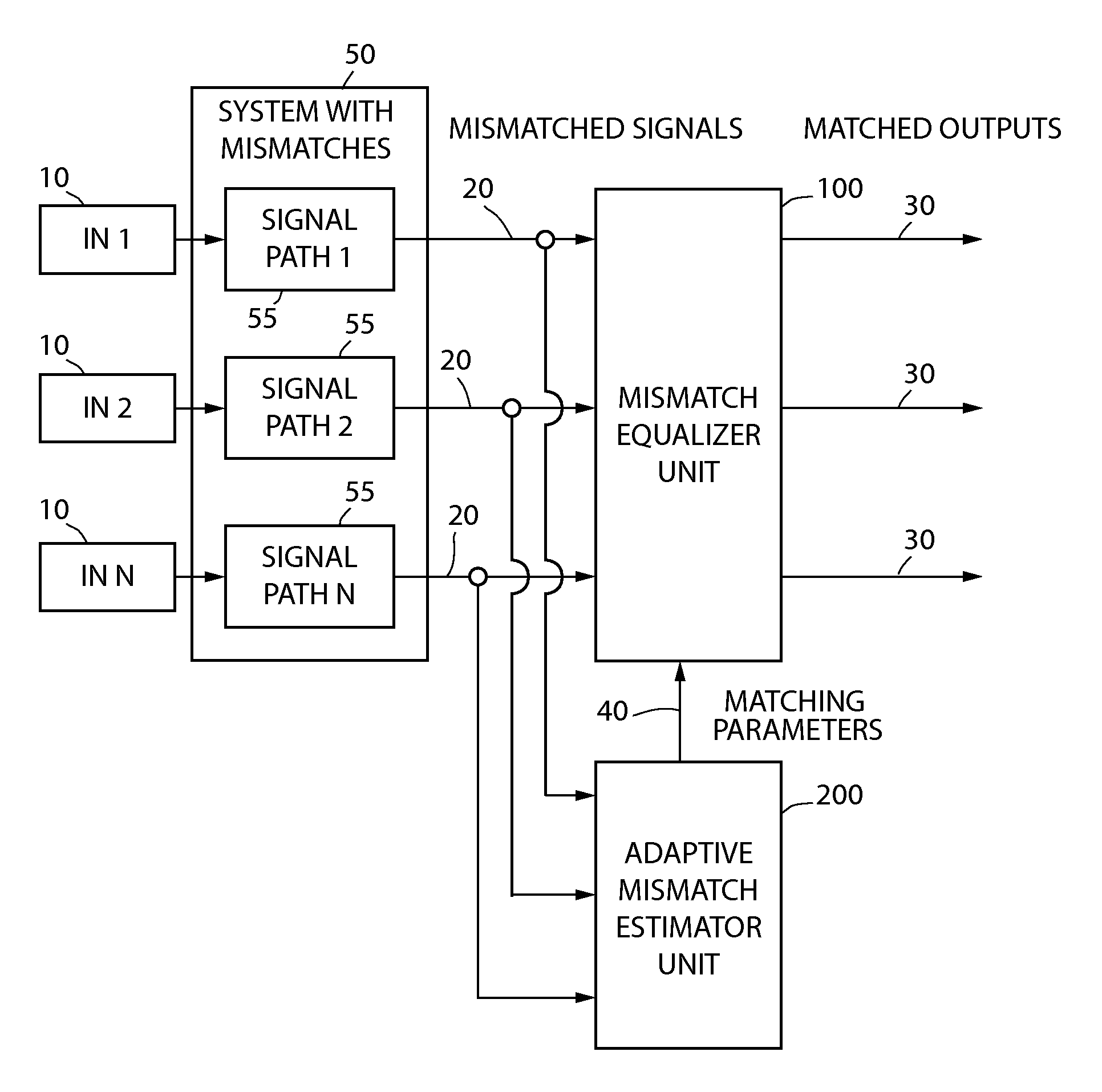

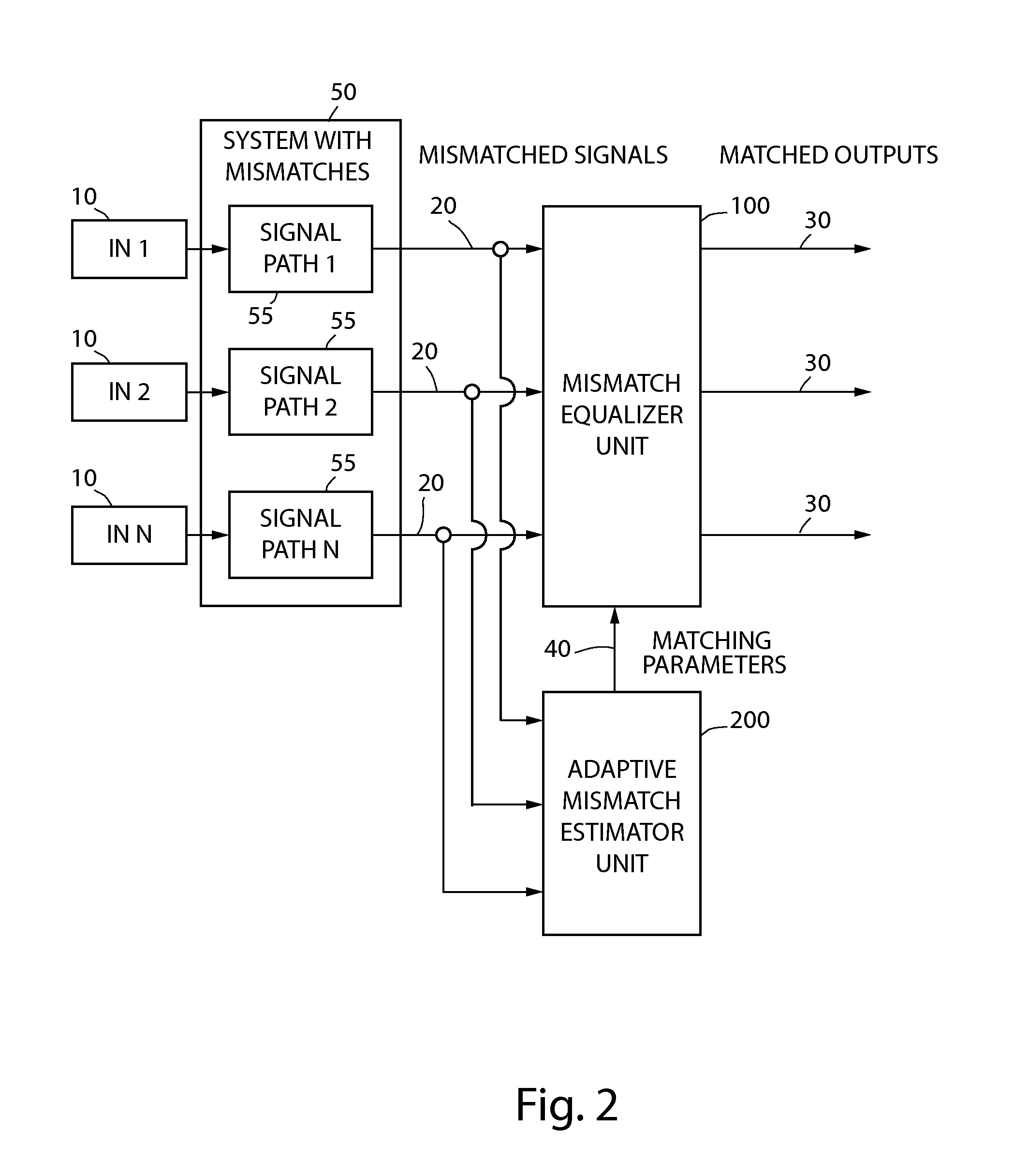

Adaptive mismatch compensators and methods for mismatch compensation

ActiveUS7782235B1Control performanceSimplify and eliminate needElectric signal transmission systemsWave based measurement systemsMonitoring systemEngineering

In a compensator for compensating mismatches, and in methods for such compensation, the compensator compensates for mismatches in output signals of a system with mismatches during normal operation of the system with mismatches. The compensator comprises: a mismatch estimator that monitors at least two mismatched signals output by the system with mismatches during normal operation and that generates matching parameters indicating an amount of mismatch between the at least two mismatched signals, the mismatch estimator updating the matching parameters during normal operation of the system with mismatches, and a mismatch equalizer that compensates mismatches in the mismatched signals output by the system with mismatches during normal operation of the system with mismatches in response to the matching parameters.

Owner:LINEARITY LLC

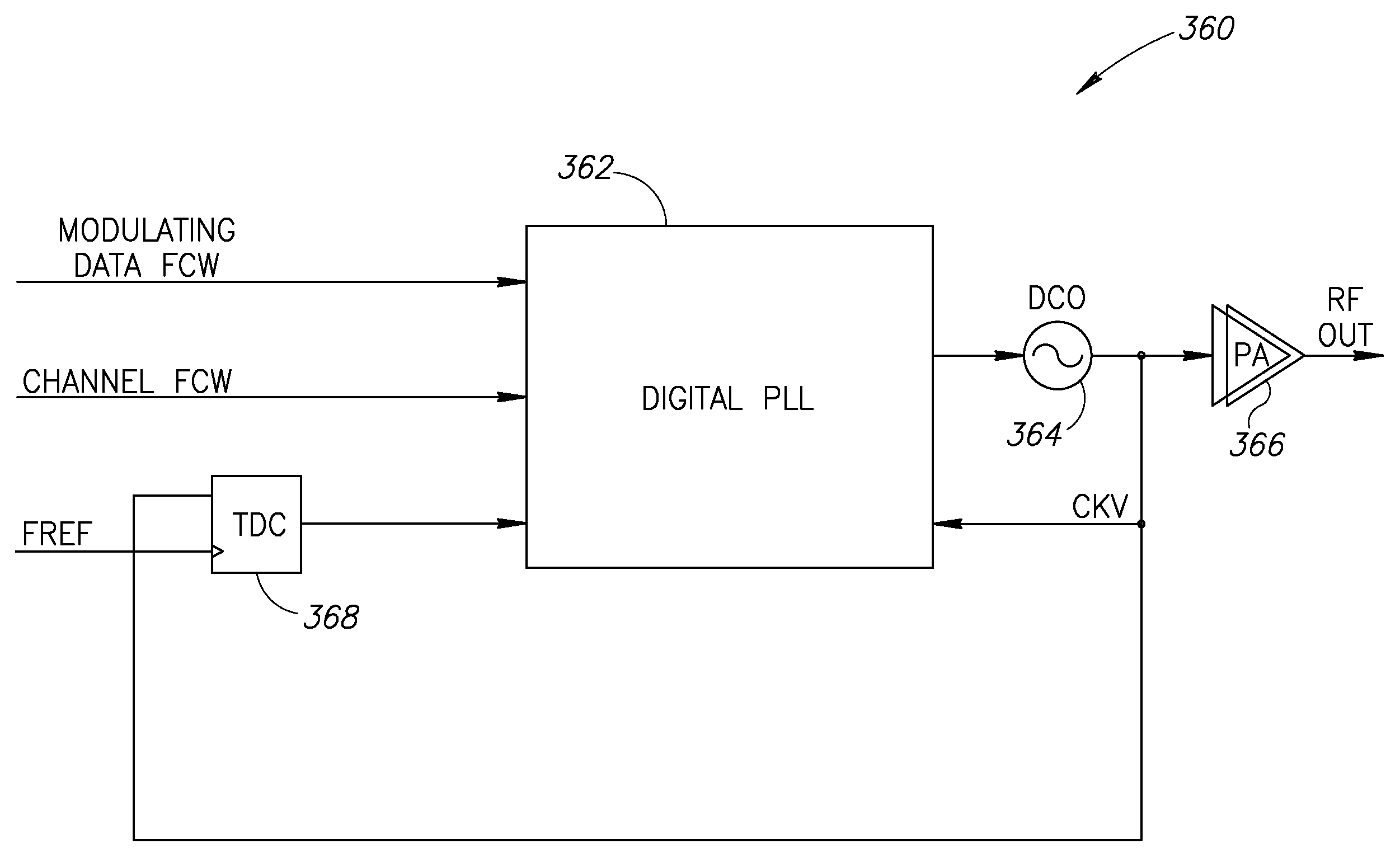

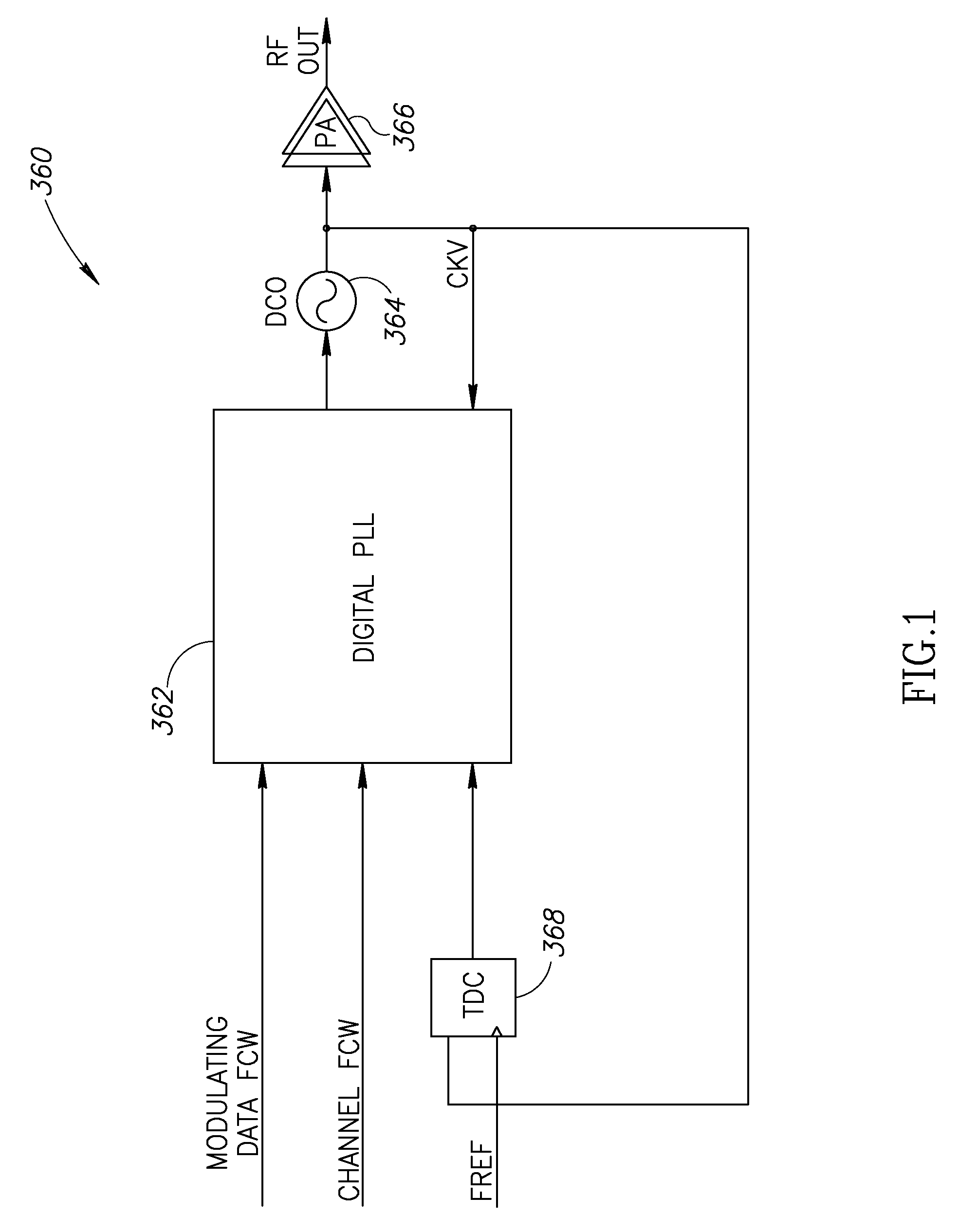

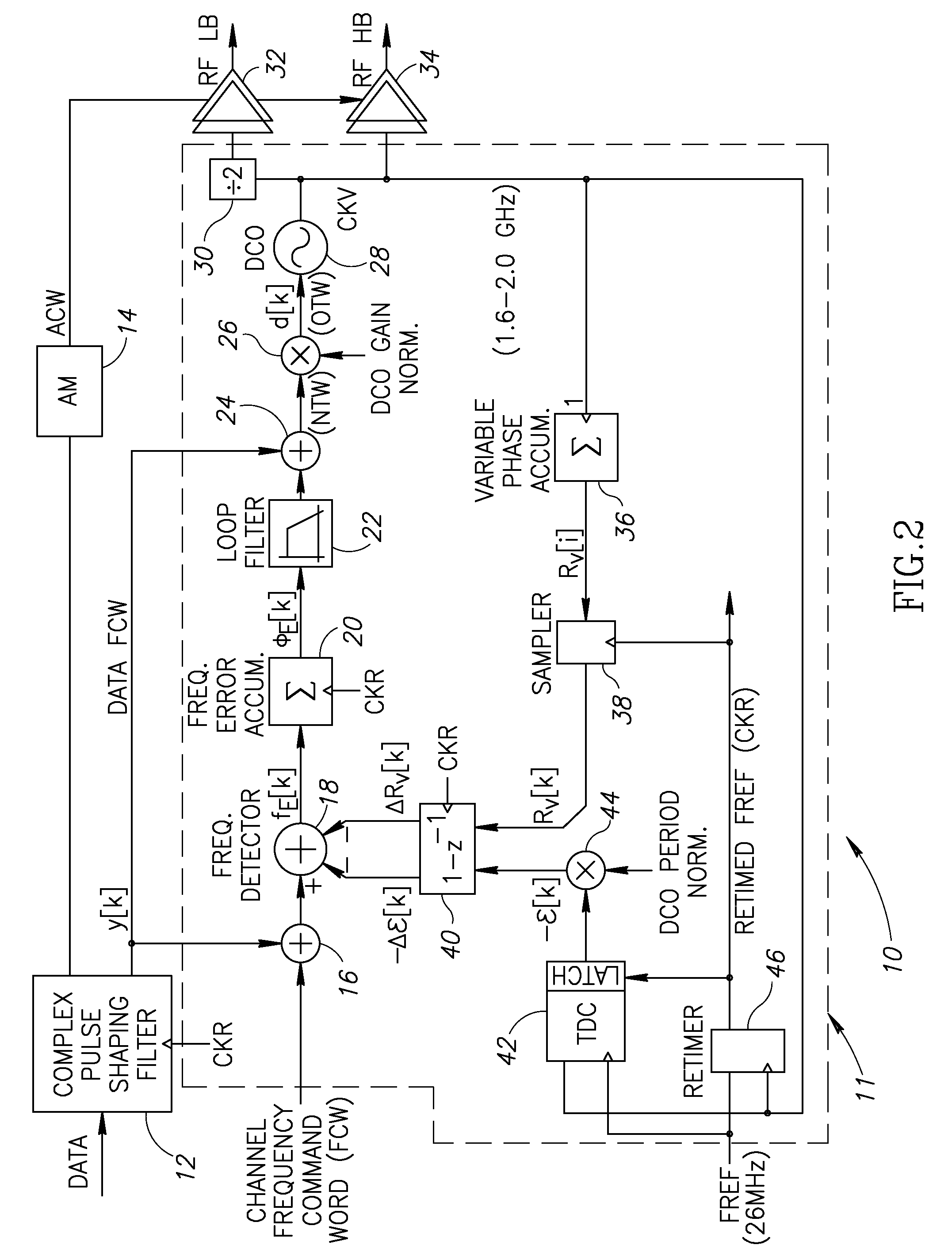

Adaptive spectral noise shaping to improve time to digital converter quantization resolution using dithering

ActiveUS20080068236A1High resolutionHigh frequency noiseElectric signal transmission systemsAnalogue conversionFrequency spectrumNoise shaping

A novel and useful apparatus for and method of improving the quantization resolution of a time to digital converter in a digital PLL using noise shaping. The TDC quantization noise shaping scheme is effective to reduce the TDC quantization noise to acceptable levels especially in the case of integer-N channel operation. The mechanism monitors the output of the TDC circuit and adaptively generates a dither (i.e. delay) sequence based on the output. The dither sequence is applied to the frequency reference clock used in the TDC which adjusts the timing alignment between the edges of the frequency reference clock and the RF oscillator clock. The dynamic alignment changes effectively shape the quantization noise of the TDC. By shaping the quantization noise, a much finer in-band TDC resolution is achieved resulting in the quantization noise being pushed out to high frequencies where the PLL low pass characteristic effectively filters it out.

Owner:TEXAS INSTR INC

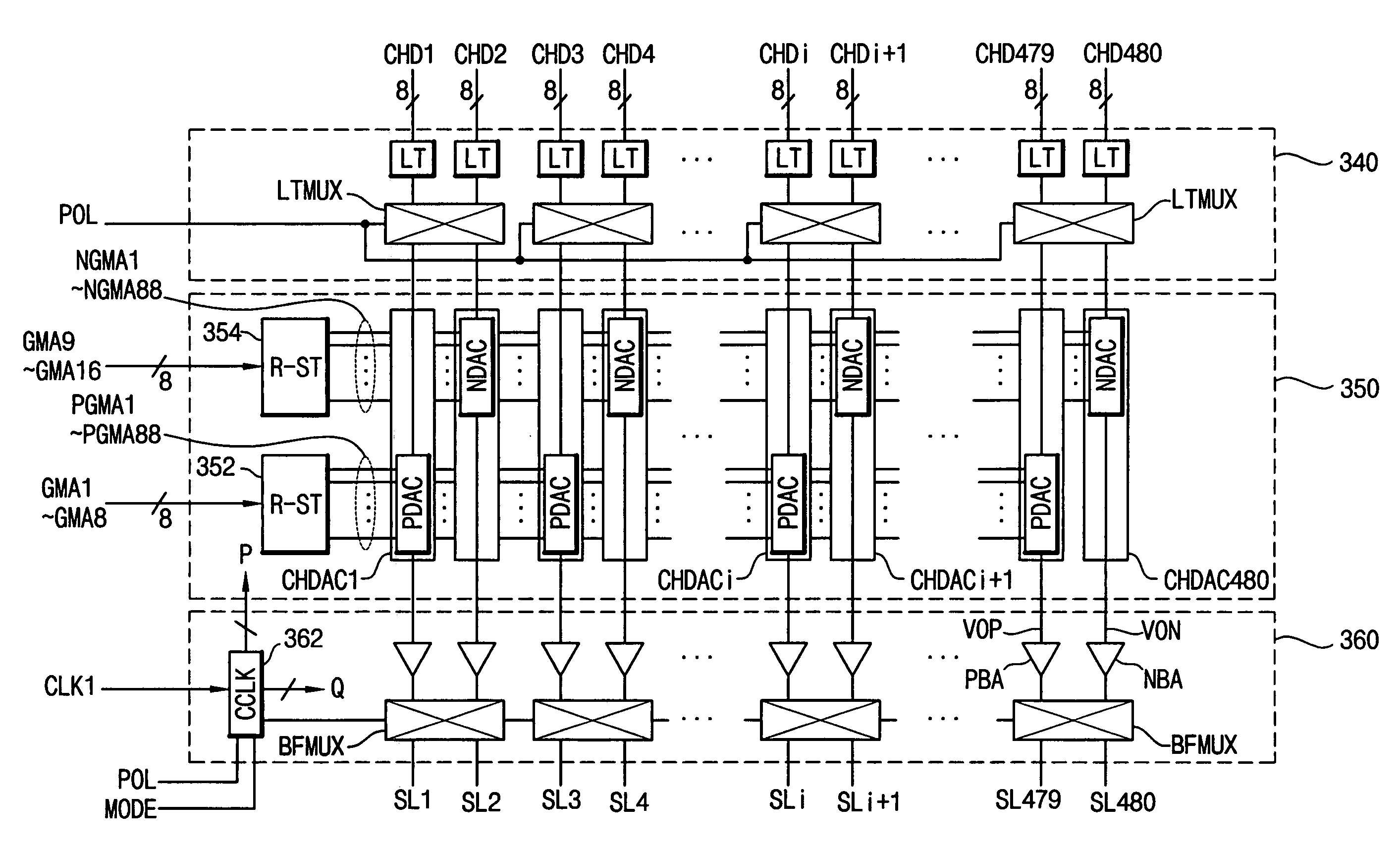

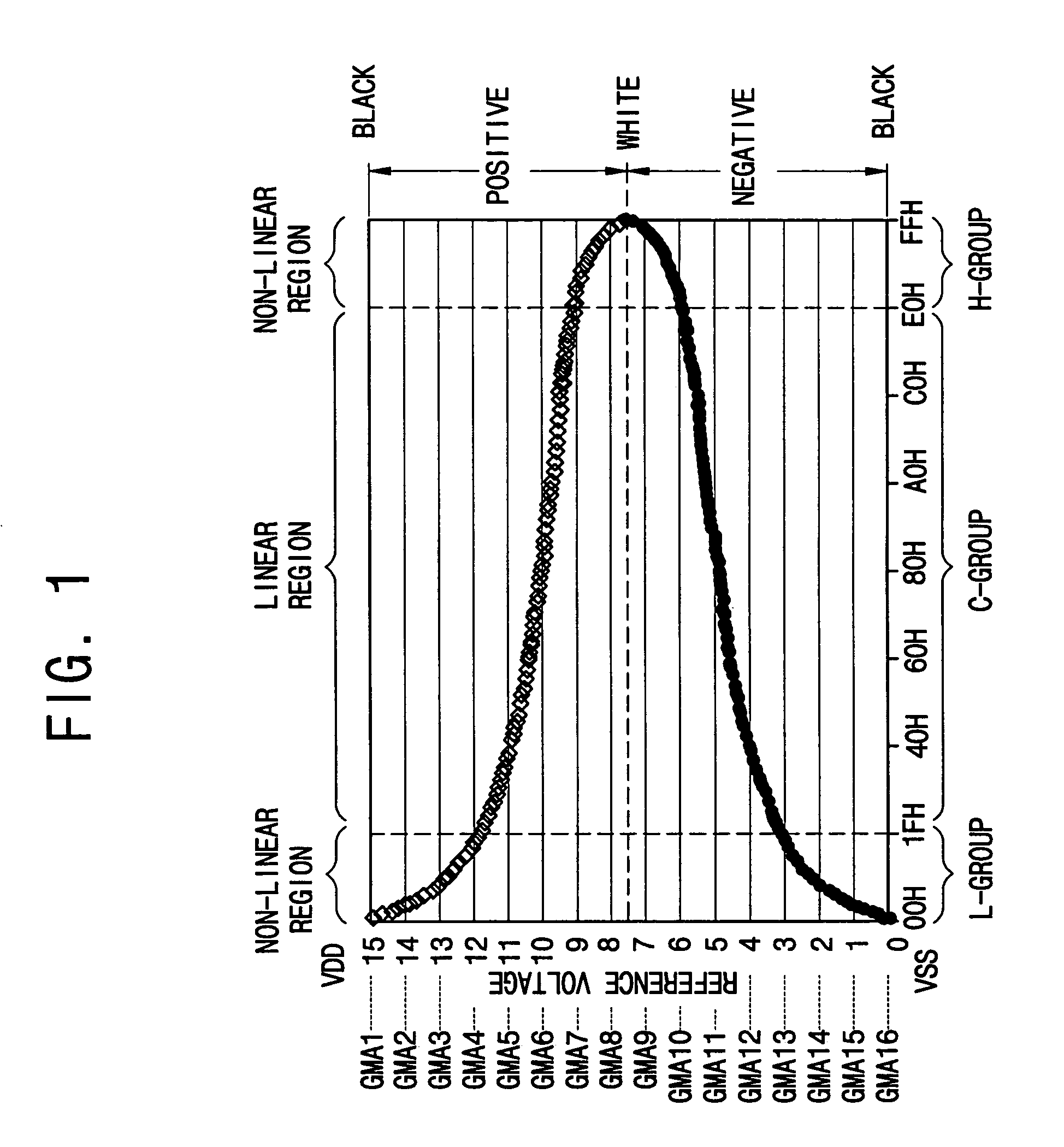

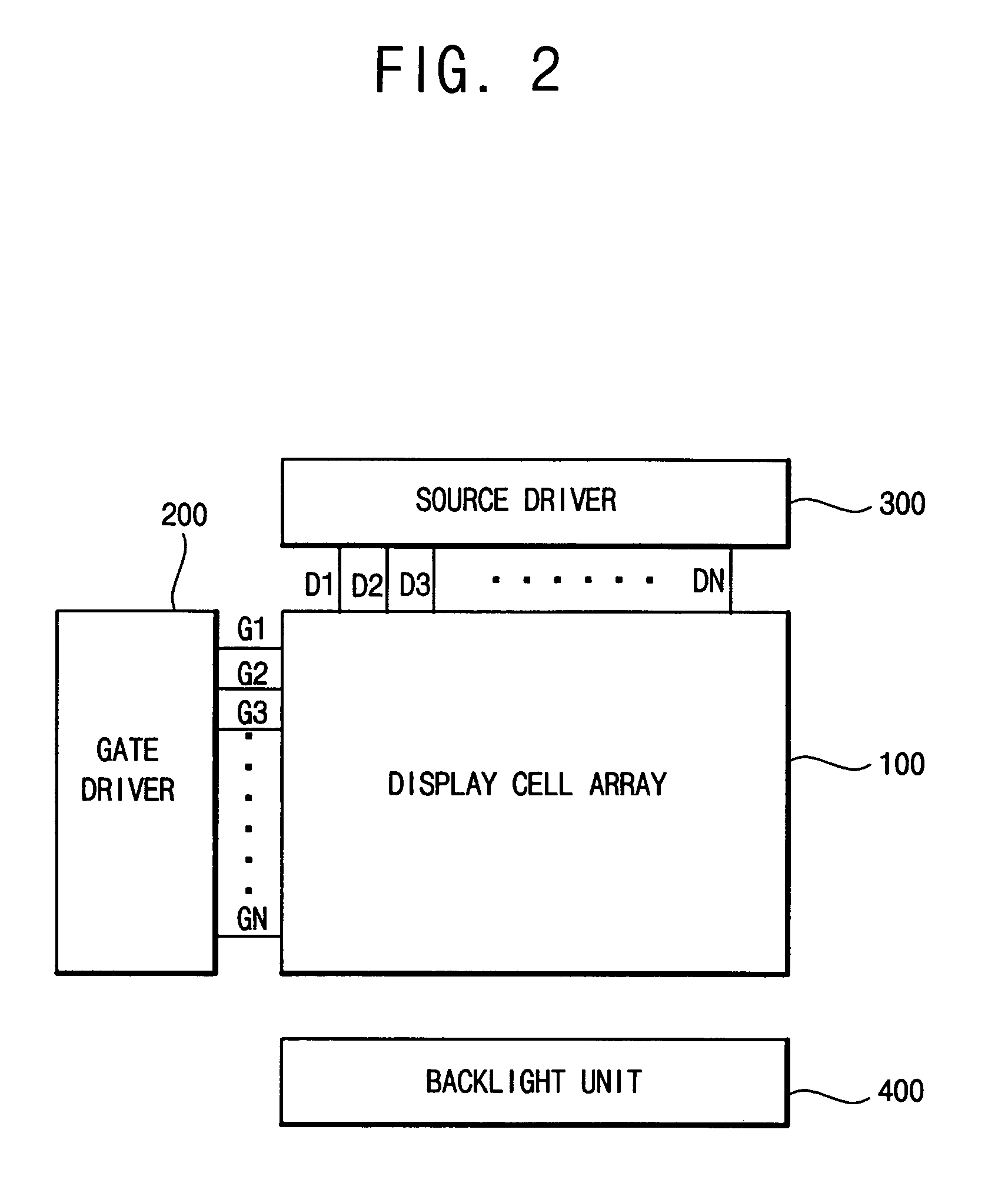

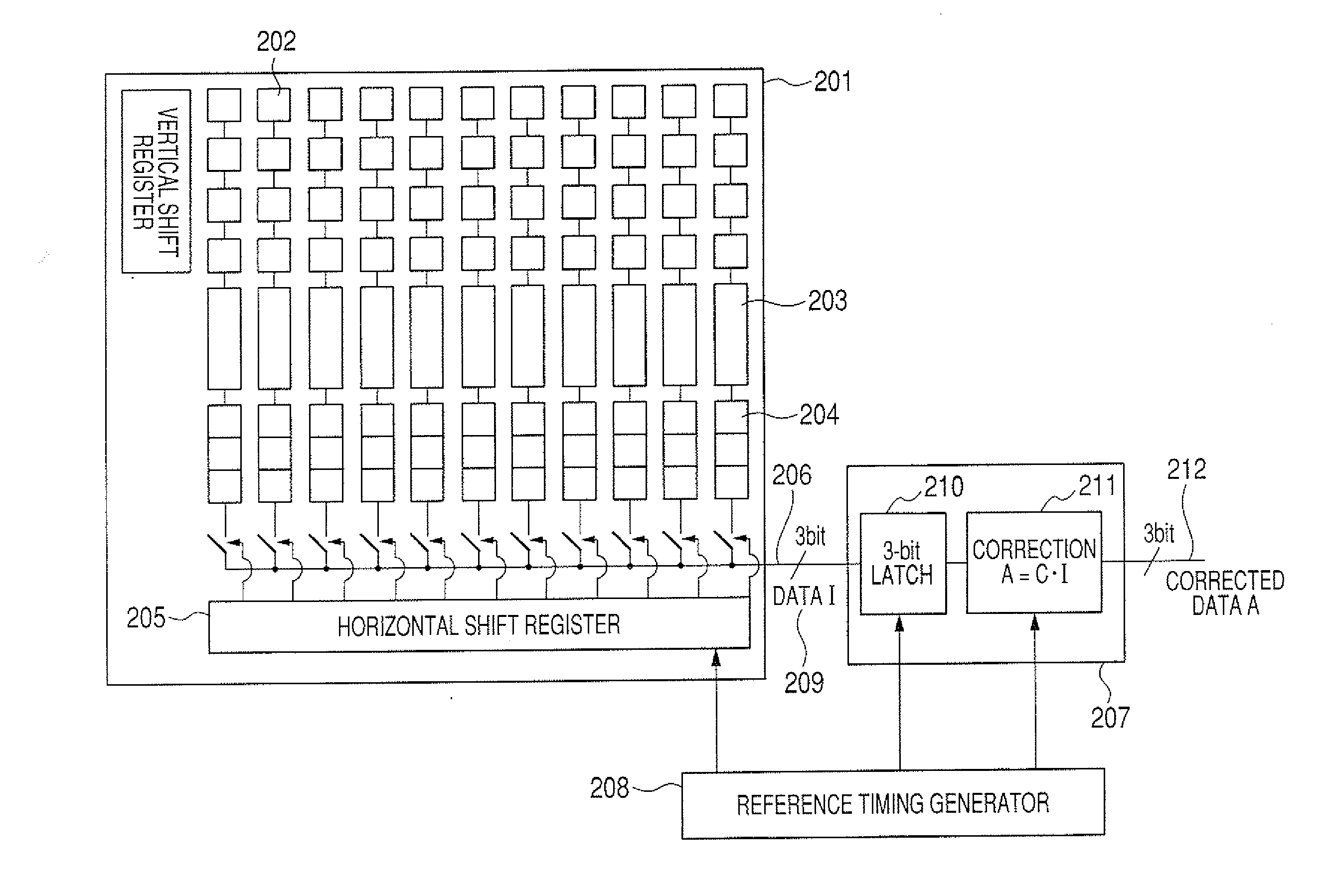

Gamma correction D/A converter, source driver integrated circuit and display having the same and D/A converting method using gamma correction

InactiveUS6950045B2Small sizeAccurate operationElectric signal transmission systemsStatic indicating devicesDisplay deviceVoltage reference

In a gamma correction digital-to-analog converter, one of first gamma correction reference voltage signals is selected as a first corresponding gray scale signal based on lower m+n bits of a k bit digital input signal when upper l bits of the k bit input signal correspond to an upper or lower code set, where k=l+m+n, and where k, l, m and n are integers. A pair of adjacent second gamma correction reference voltage signals is selected from second gamma correction reference voltage signals based on upper l+m bits when the upper l bits correspond to a middle code set, and one is selected from the pair of second gamma correction reference voltage signals and 2n−1 divided signals as a second corresponding gray scale signal, the divided signals being obtained by dividing an interval between the selected pair into 2n levels. The first or second gray scale signal is selected to be output.

Owner:SAMSUNG ELECTRONICS CO LTD

Image pickup device and signal processing method thereof

InactiveUS20090244328A1Television system detailsElectric signal transmission systemsDigital down converterDigital converter

Owner:CANON KK

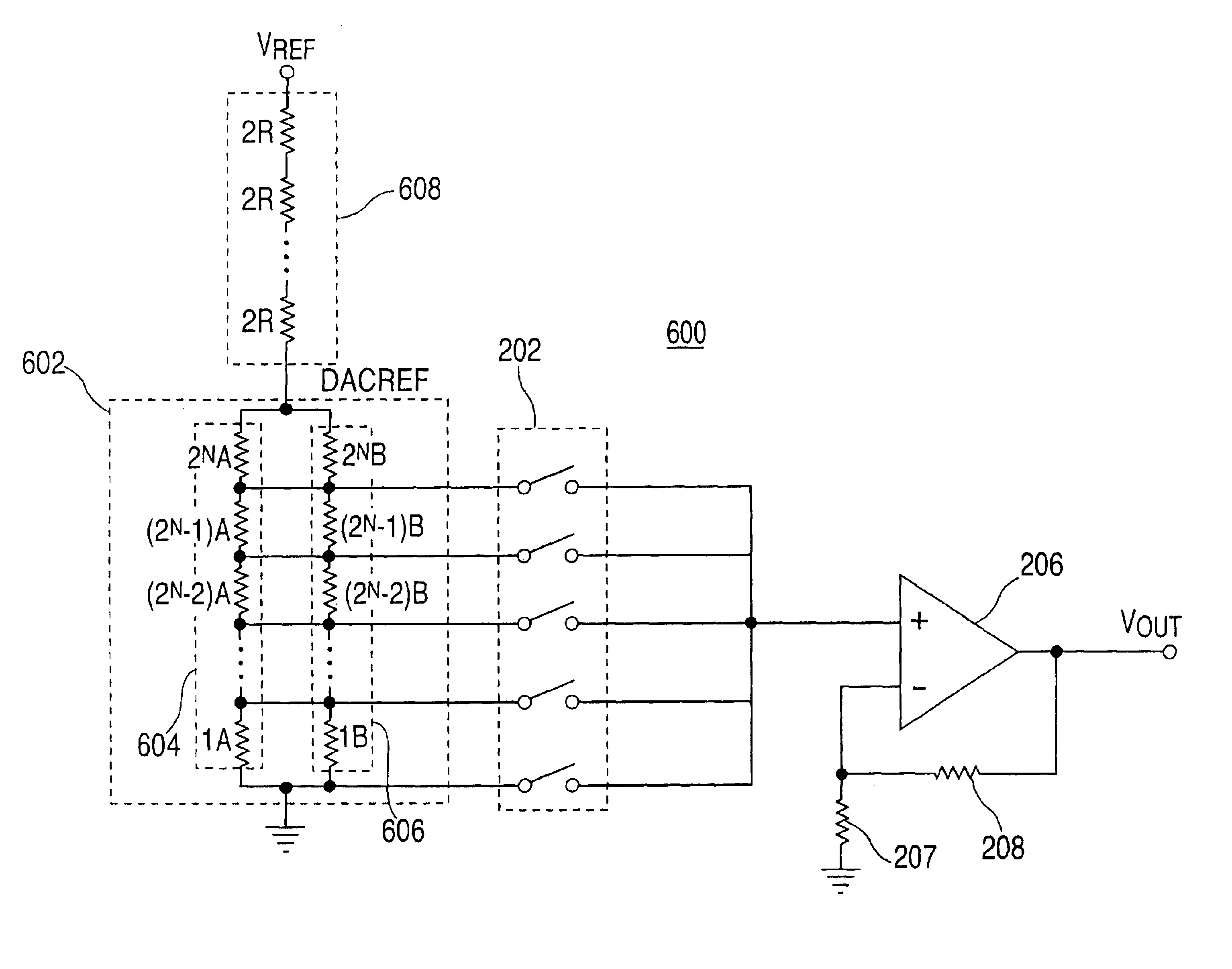

Gradient insensitive split-core digital to analog converter

InactiveUS6937178B1Offsetting effectCancellation effectElectric signal transmission systemsDigital-analogue convertorsElectrical resistance and conductanceDigital analog converter

Digital to analog converter circuits and methods are provided for producing an analog output voltage indicative of a digital input signal with at least partial insensitivity to error gradients. Described are split-core resistive elements, which include a plurality of one-dimensional or multi-dimensional resistive strings, that may be used to reduce or substantially eliminate the effects that error gradients have on the linearity of the analog output voltages of a resistive string or interpolating amplifier DACs. The resistor strings that make up the split-core resistive elements are configured in such a manner that combining respective output voltages from each of the resistor strings results in an analog output voltage that is at least partially insensitive to the effects of error gradients.

Owner:ANALOG DEVICES INT UNLTD

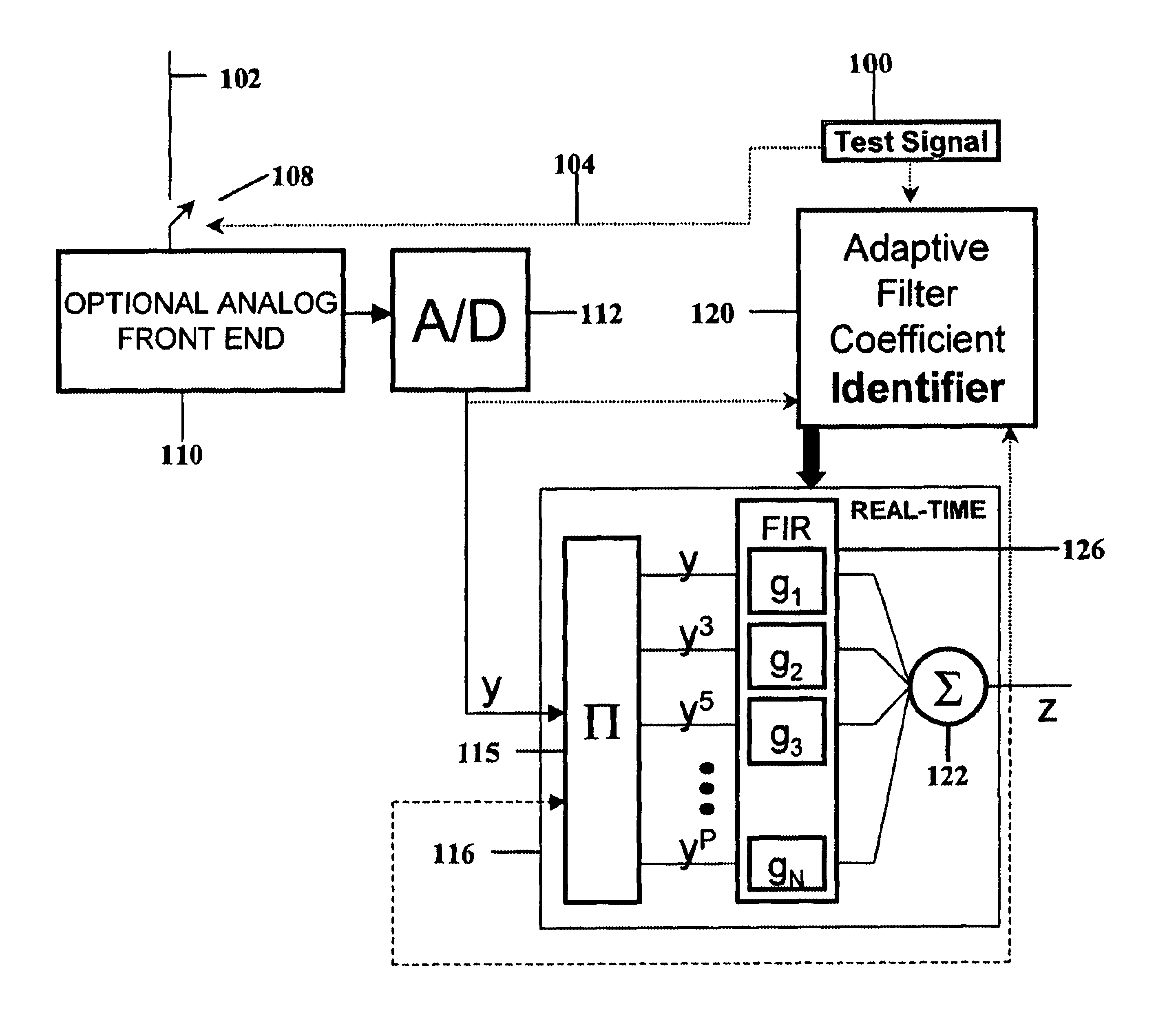

Highly linear analog-to-digital conversion system and method thereof

InactiveUS6639537B1Reduce nonlinear distortionMinimizes non-linear distortionElectric signal transmission systemsAnalogue conversionFinite impulse responseNonlinear distortion

A highly linear analog-to-digital (ADC) conversion system has an analog front-end device in cascade with a standard ADC converter, and a tunable digital non-linear equalizer. The equalizer corrects the quantization distortion, deviations from ideal response, and additive noises generated by the analog front-end device and ADC converter. The equalizer is formed by three main parts: Generate Function Streams Unit, Finite Impulse Response FIR filters and a summer. The equalizer receives the unequalized output from the ADC converter and generates a plurality of monomial streams in a systolic fashion. Each of the monomial streams is passed through a corresponding linear finite impulse response FIR filter. A convolution sum of all outputs from the FIR filters produces a unique equalized output with the non-linear distortion reduced to a satisfactory level. The FIR filter coefficients are determined by an Identity Equalizer Coefficient Unit, and a Test Signal Generator with different types of test signals. The FIR filter coefficients are set to minimize an error function.

Owner:MASSACHUSETTS INST OF TECH

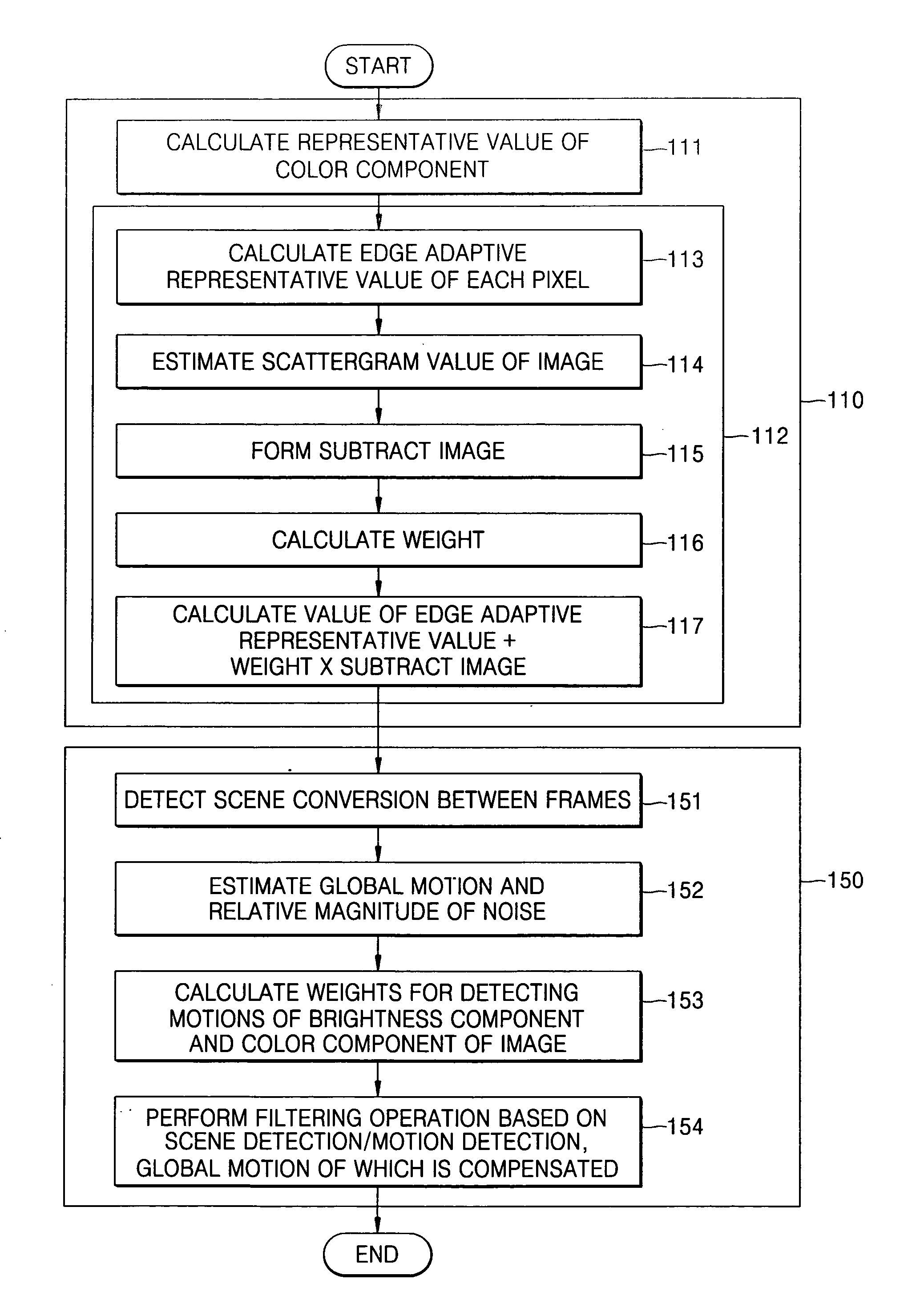

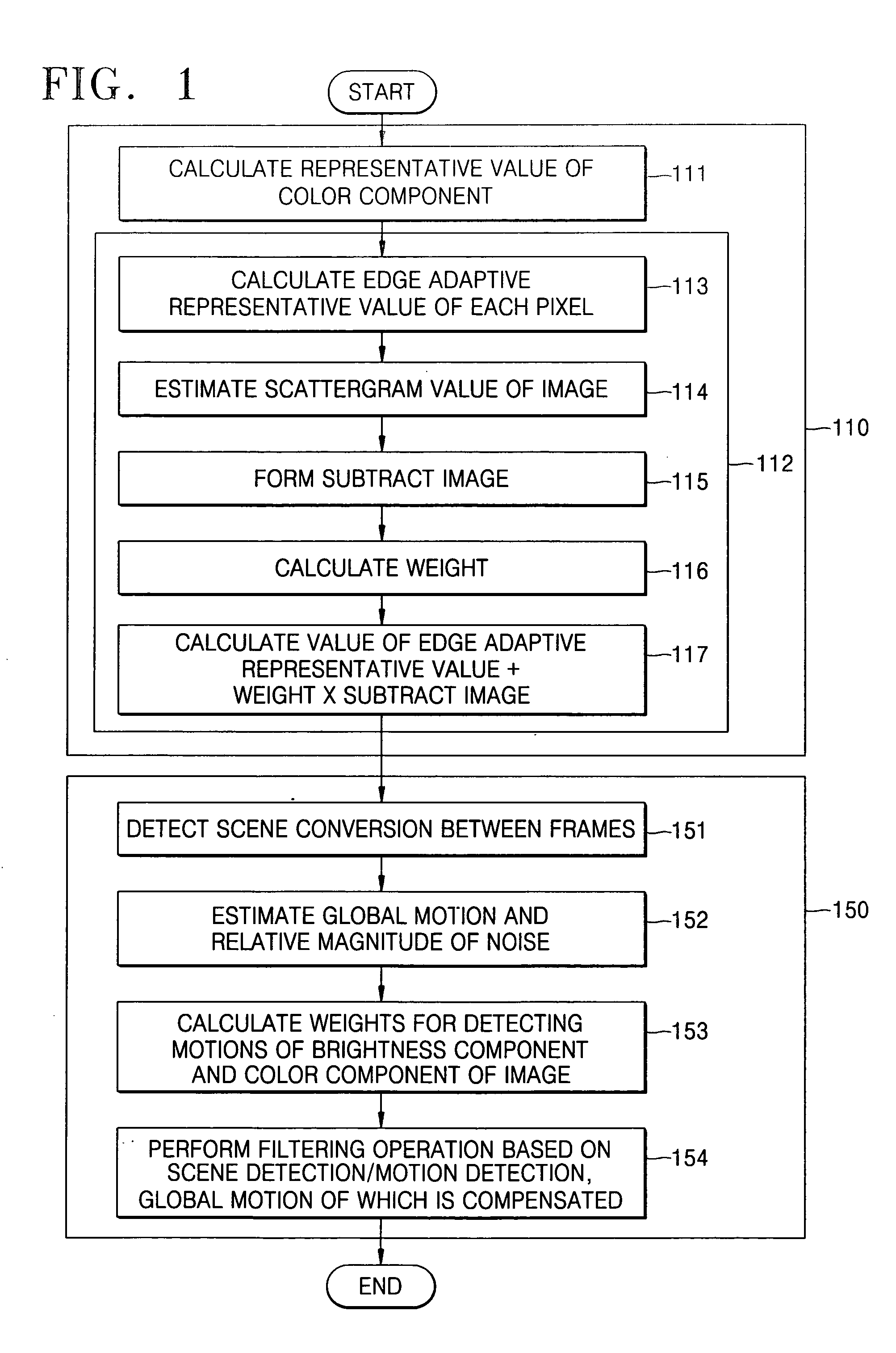

Method of removing noise from digital moving picture data

ActiveUS20050128355A1Cancel noiseMinimize the numberImage enhancementTelevision system detailsPattern recognitionYcbcr color space

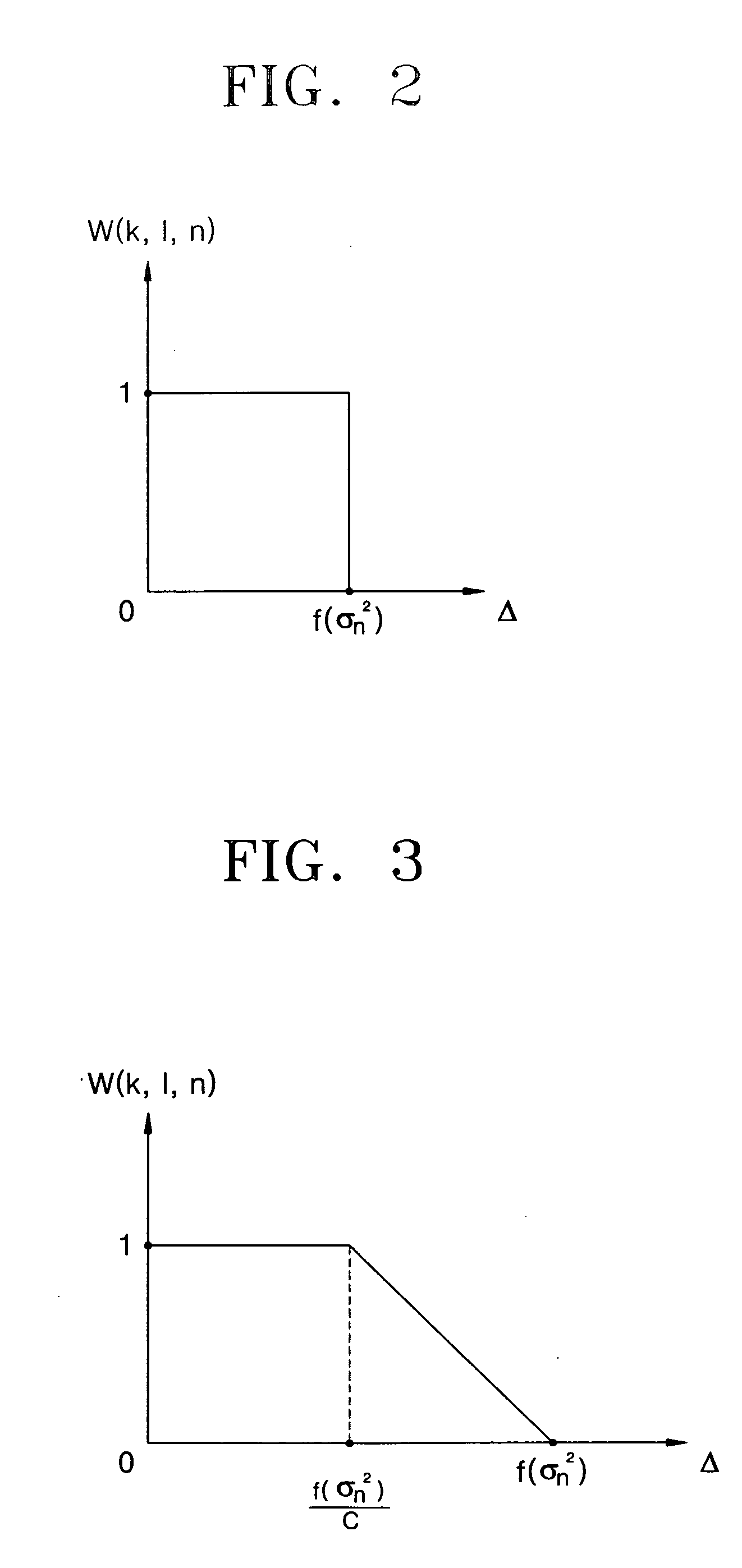

Provided is a method of removing noise from digital moving picture data reducing the number of frames used in a temporal filtering operation and able to detect motion between frames easily. The method comprises a method of spatial filtering, a method of temporal filtering, and a method of performing the spatial filtering and the temporal filtering sequentially. The spatial filtering method applies a spatial filtering in a YCbCr color space, preserving a contour / edge in the image in the spatial domain, and generating a weight that is adaptive to the noise for discriminating the contour / edge in the temporal filtering operation. The temporal filtering method applies temporal filtering based on motion detection and scene change detection, compensating for global motion, the motion detection considering the brightness difference and color difference of the pixels compared between frames in the temporal filtering operation, and a weight that is adaptive to the noise for detecting the motion in the temporal filtering operation. The spatial filtering method is preferably performed first, and the temporal filtering method is performed with the result of the spatial filtering.

Owner:SAMSUNG ELECTRONICS CO LTD +1

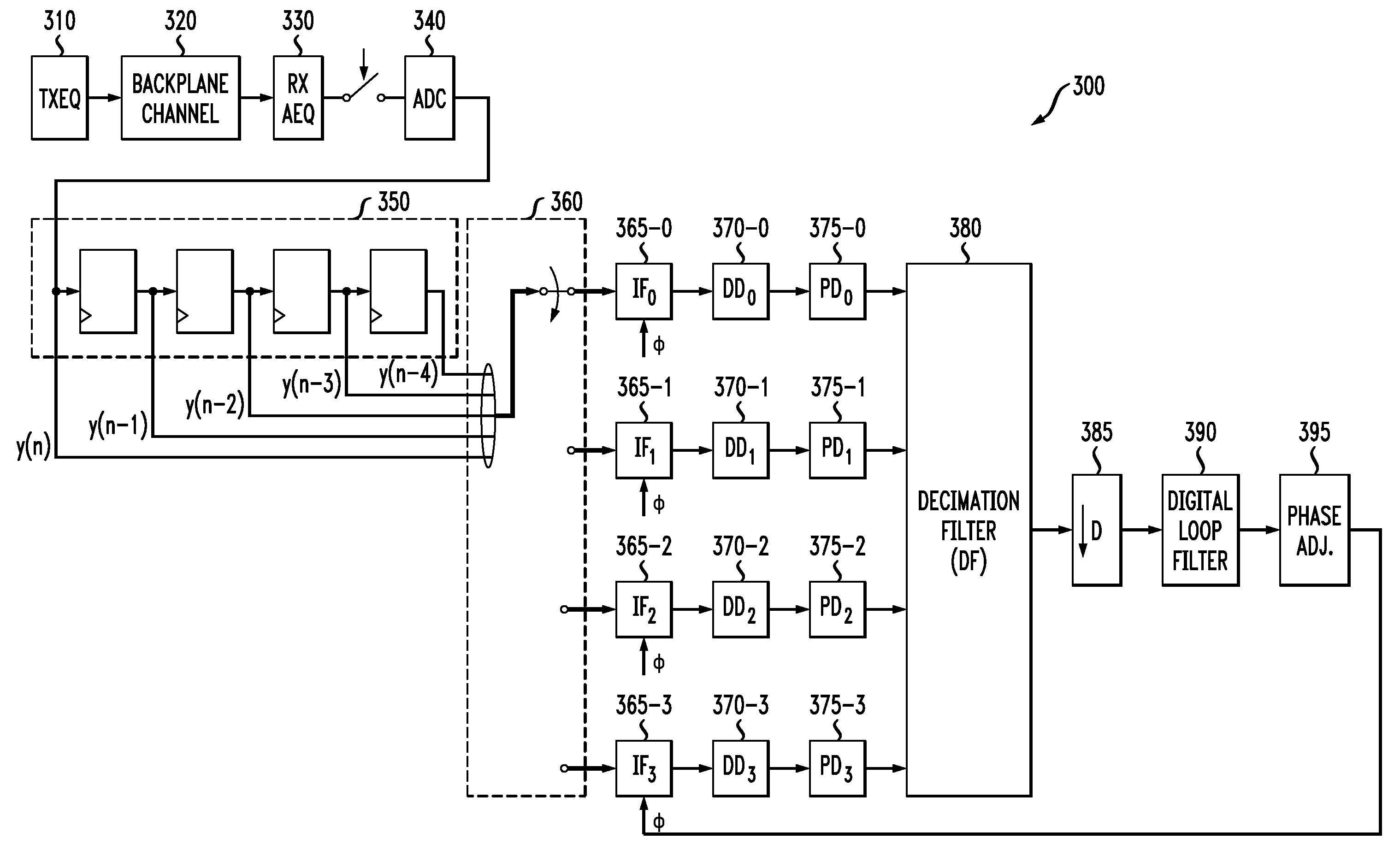

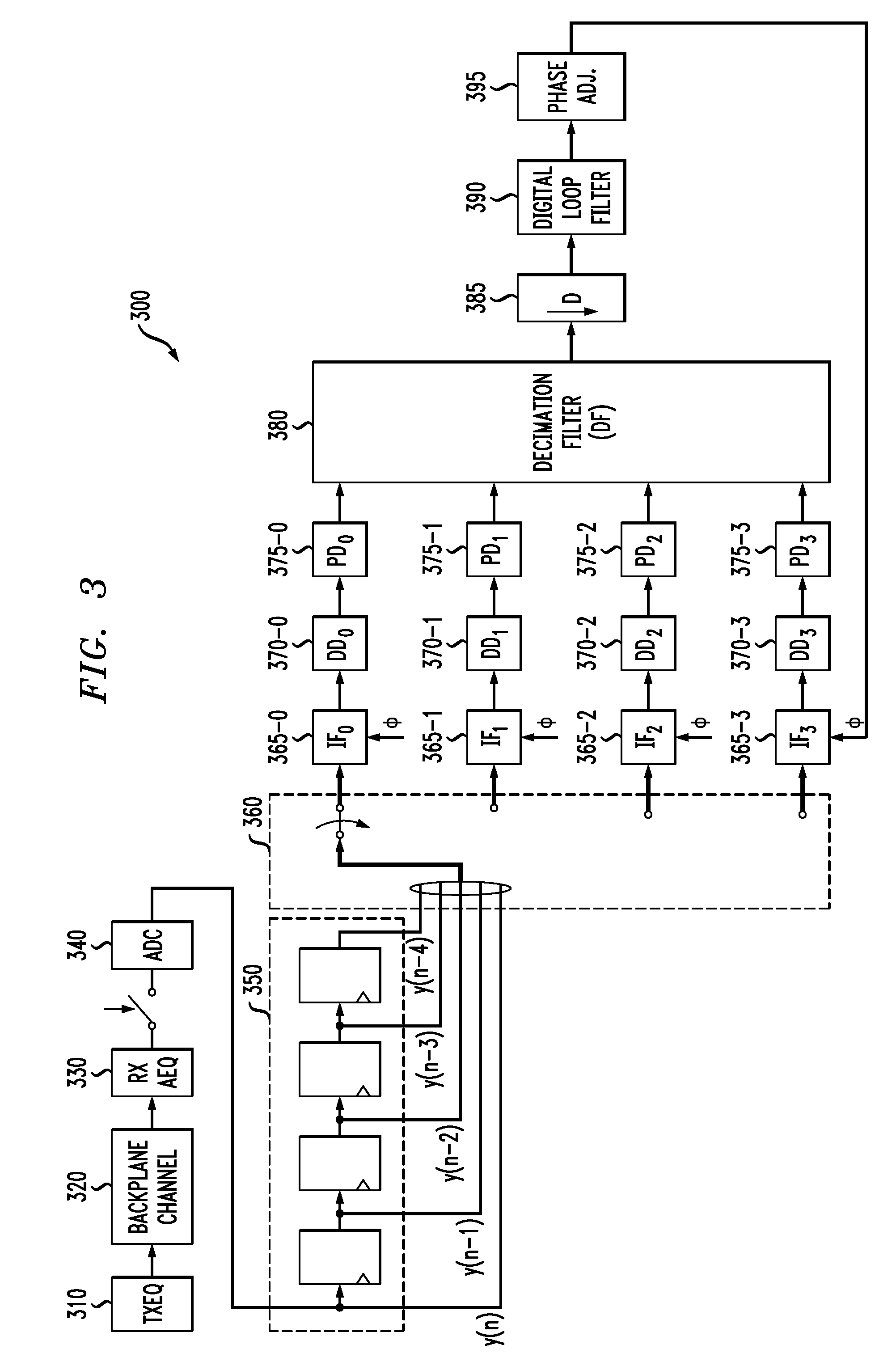

Methods and apparatus for asynchronous sampling of a received signal at a downsampled rate

InactiveUS7411531B2Electric signal transmission systemsPhysical parameters compensation/preventionDigital dataComputer science

Methods and apparatus are provided for decimated interpolated clock / data recovery (ICDR) to perform asynchronous sampling of a received signal. A received signal is converted to a plurality of digital samples at a downsampled rate that is lower than a rate of the received signal. The plurality of digital samples are interpolated using a plurality of parallel interpolation filters operating at the downsampled rate. An output of each parallel interpolation filter is applied to a corresponding data detector operating at the downsampled rate to generate digital data. An estimate of a timing error is generated based on the digital data. The timing error values are processed to generate an interpolation phase value that is applied to the parallel interpolation filters. A recovered clock is optionally generated, having edges corresponding to a desired synchronous sampling period.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

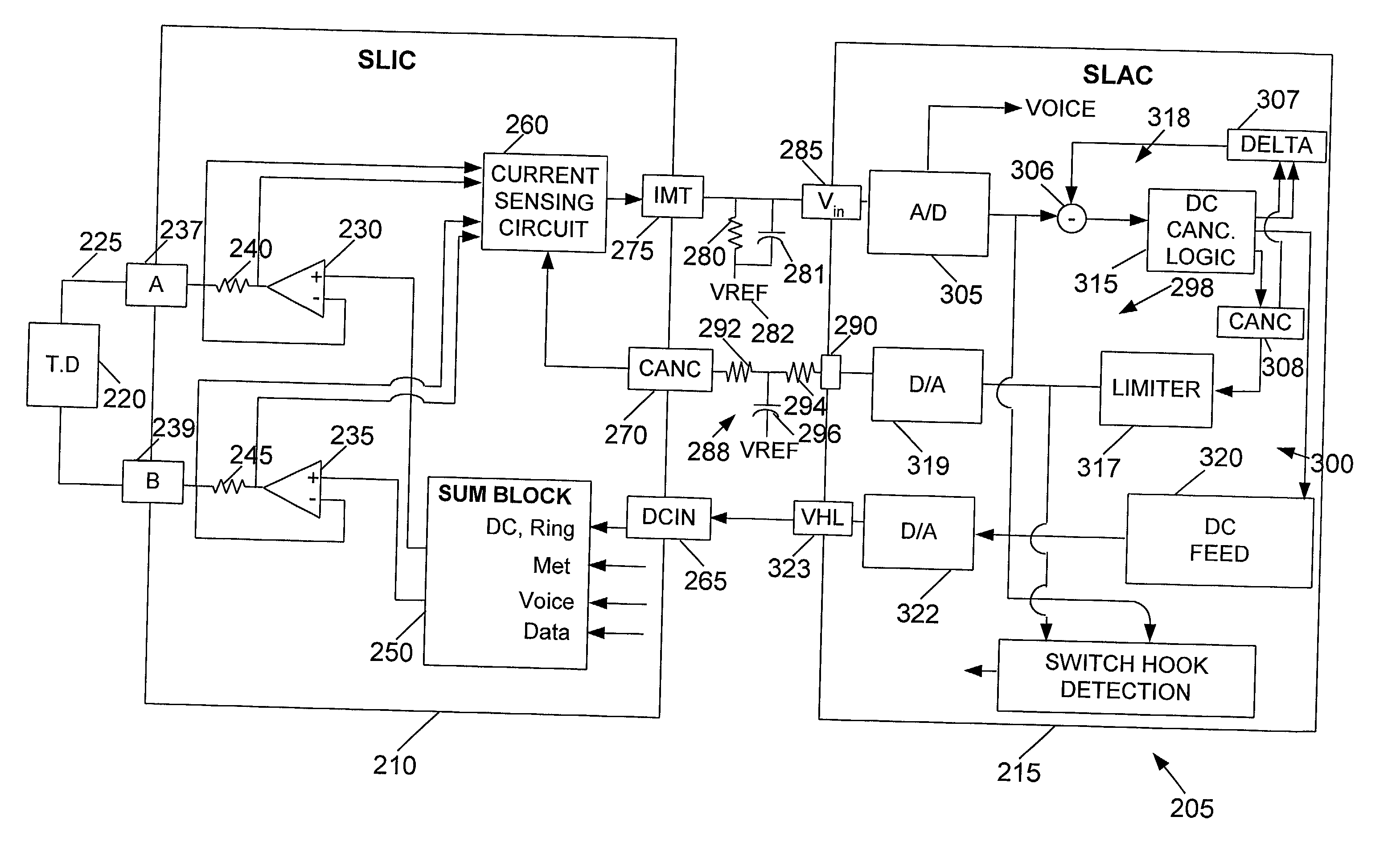

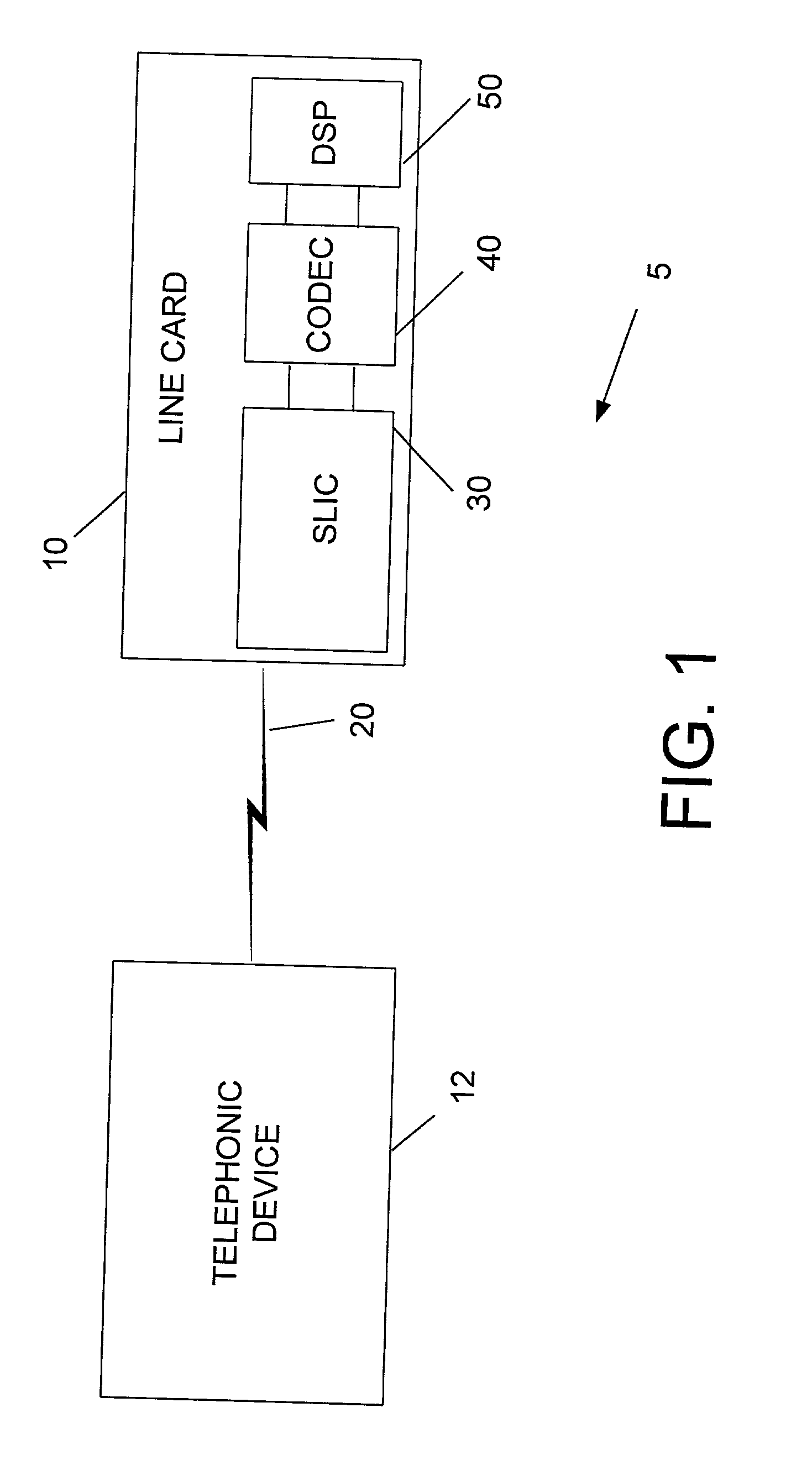

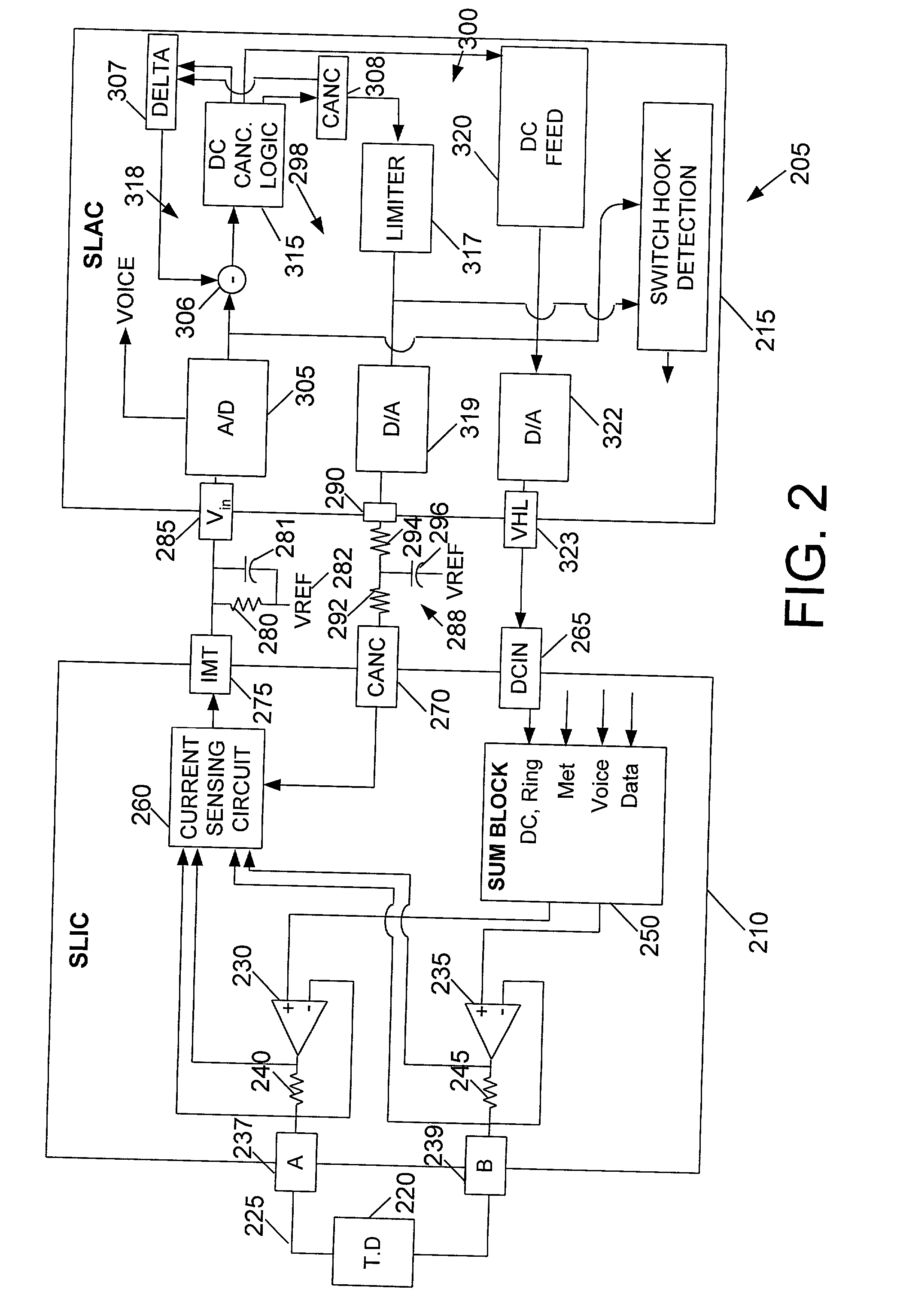

Method and apparatus for adaptive DC level control

ActiveUS20020084923A1Cordless telephonesElectric signal transmission systemsDigital analog converterDigital input

A method and apparatus is provided for DC level control in a line card. The method includes receiving a digital input signal, determining a first DC component value of the digital input signal at a first preselected time, and determining a second DC component value of the digital input signal at a second preselected time. The method further includes determining a difference between the first DC component value and the second DC component value. The method includes providing the first DC component value to a digital-to-analog converter in response to determining that the difference is less than a first preselected value. The apparatus includes a digital-to-analog converter and logic. The logic is coupled to the digital-to-analog converter, wherein the logic is capable of receiving a digital input signal, determining a first DC component value of the digital input signal at a first preselected time, and determining a second DC component value of the digital input signal at a second preselected time. The logic is farther capable of determining a difference between the first DC component value and the second DC component value, and providing the first DC component value to the digital-to-analog converter in response to determining that the difference is less than a first preselected value.

Owner:MICROSEMI SEMICON U S

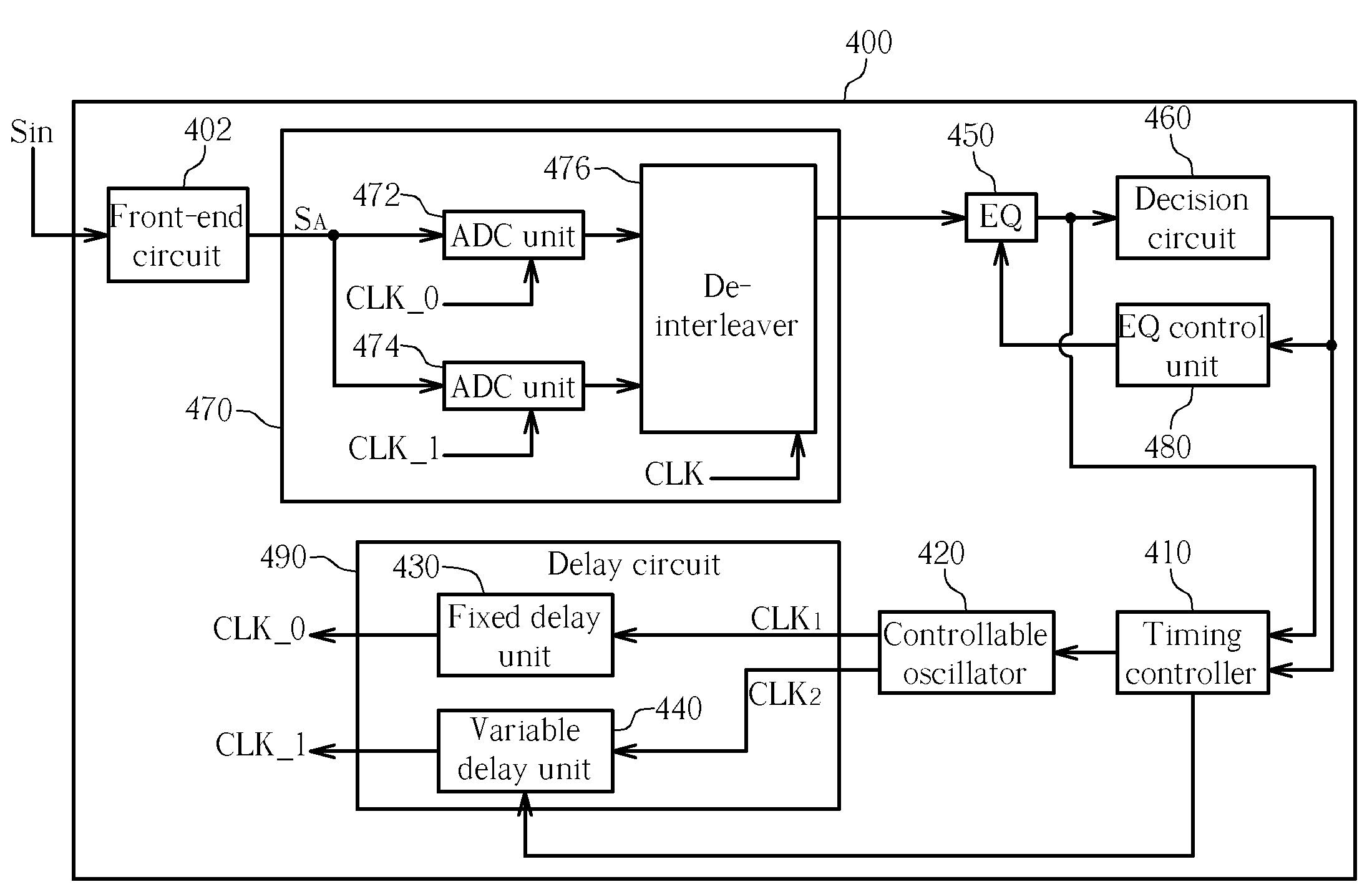

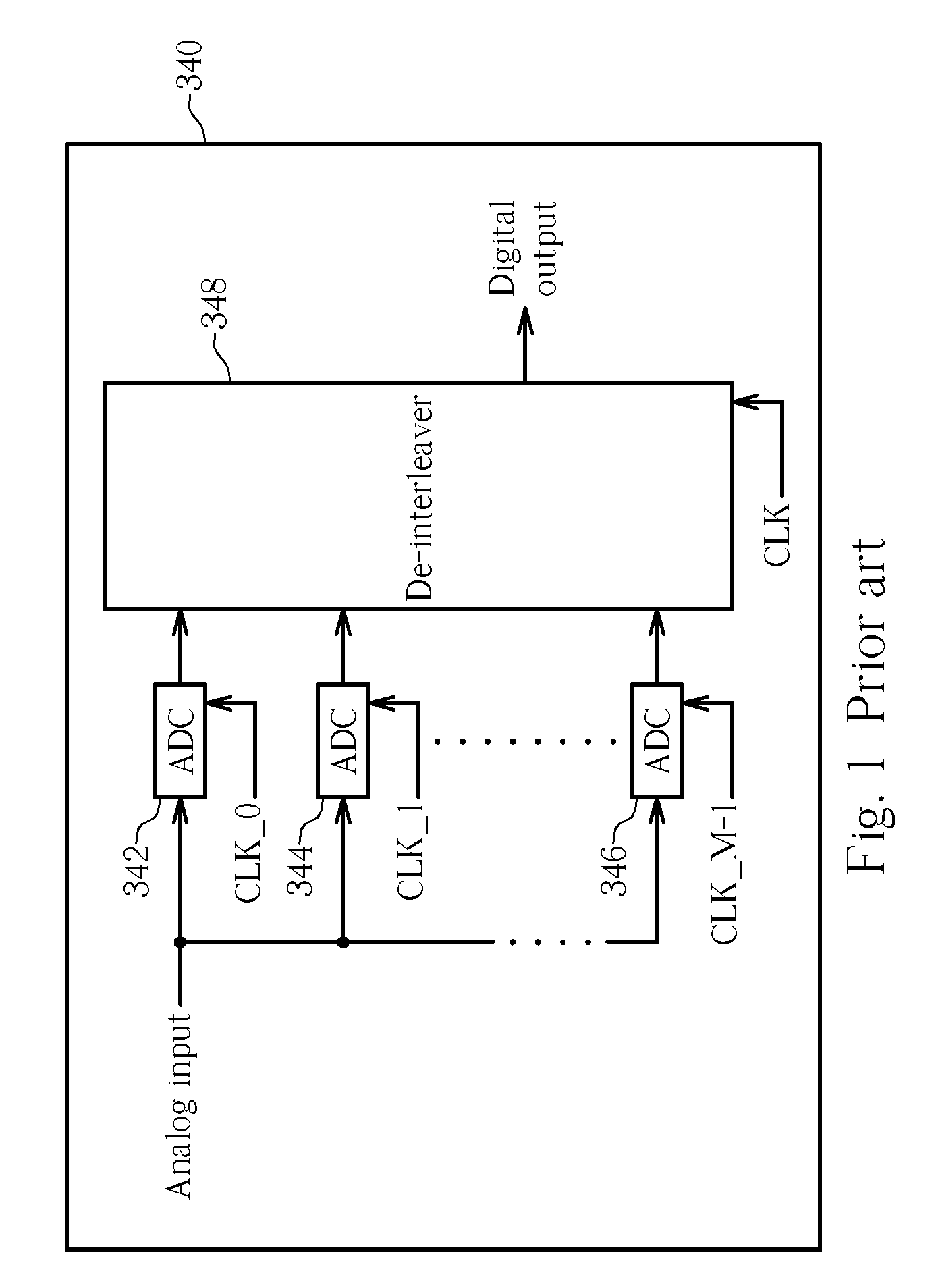

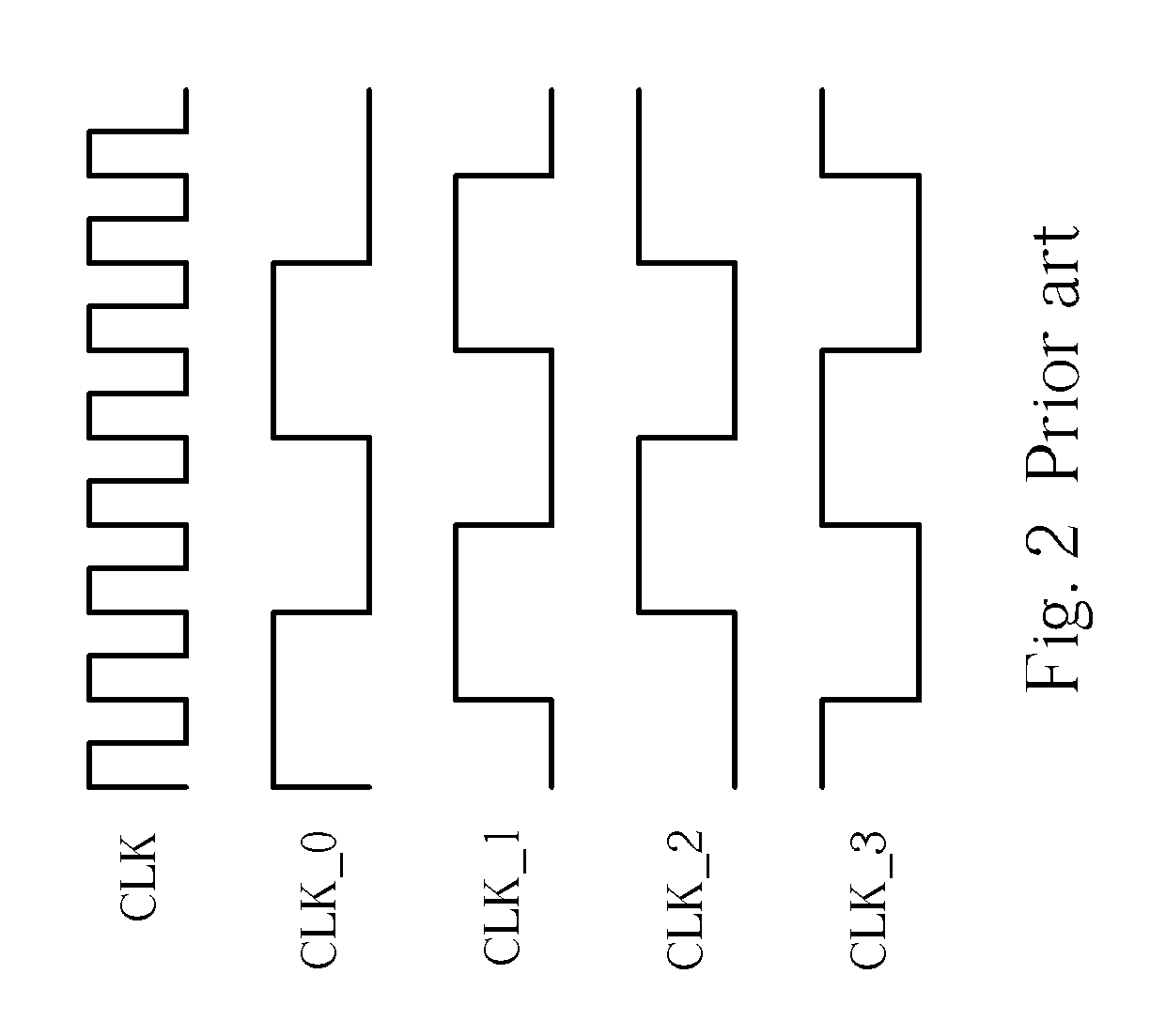

Receiver capable of correcting mismatch of time-interleaved parallel ADC and method thereof

ActiveUS7233270B2Electric signal transmission systemsPhysical parameters compensation/preventionTime interleavedAnalog-to-digital converter

A compensation method for a receiver is disclosed, the method includes: receiving and processing an incoming signal to generate an analog input signal; utilizing a time-interleaved parallel analog-to-digital converter (ADC) for converting the analog input signal to a digital input signal according to a plurality of clock signals of different phases; equalizing the digital input signal to generate a plurality of soft decision values; generating a plurality of hard decision values according to the soft decision values; calculating a plurality of error values according to the hard decision values and the soft decision values; and compensating the receiver according to at least part of the error values.

Owner:REALTEK SEMICON CORP

Flash ADC receiver with reduced errors

ActiveUS6980140B1Improve link qualityData representation error detection/correctionElectric signal transmission systemsSymbol decodingVoltage reference

Symbol decoding errors at a receiver utilising a flash analog to digital converter (ADC) can be reduced by adjusting a reference voltage level of the ADC where a decoding error rate at the reference voltage level exceeds a threshold.

Owner:CIENA

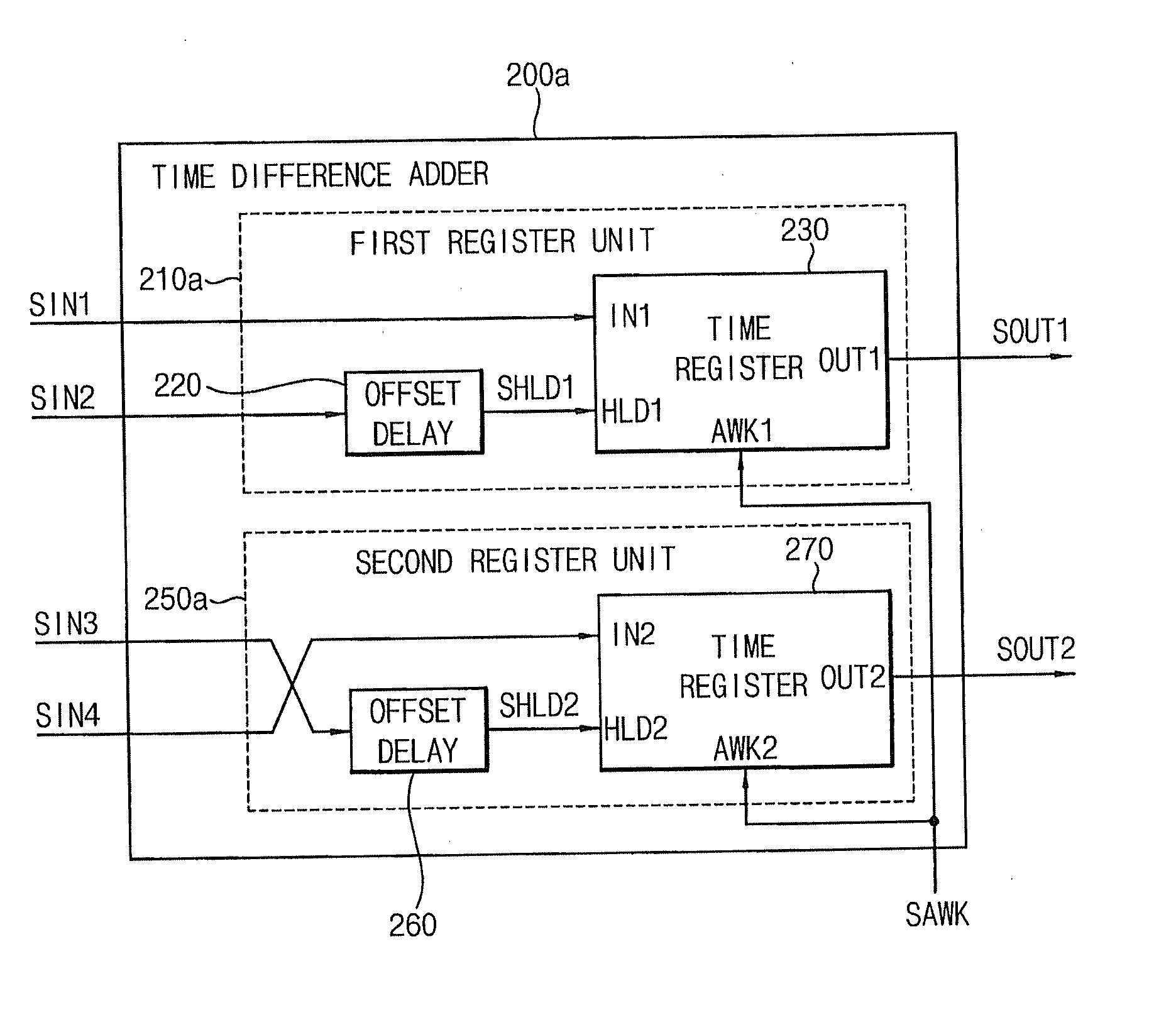

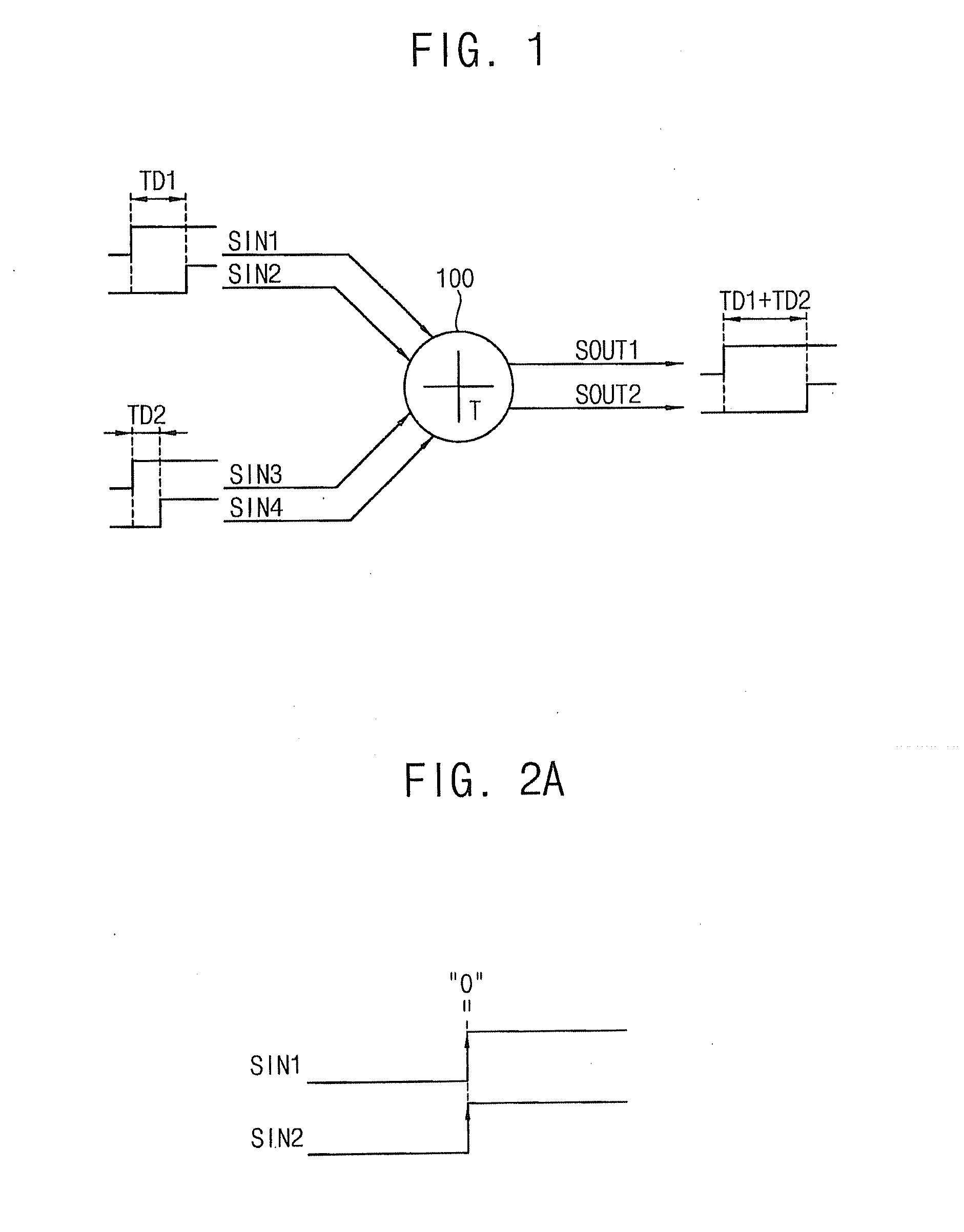

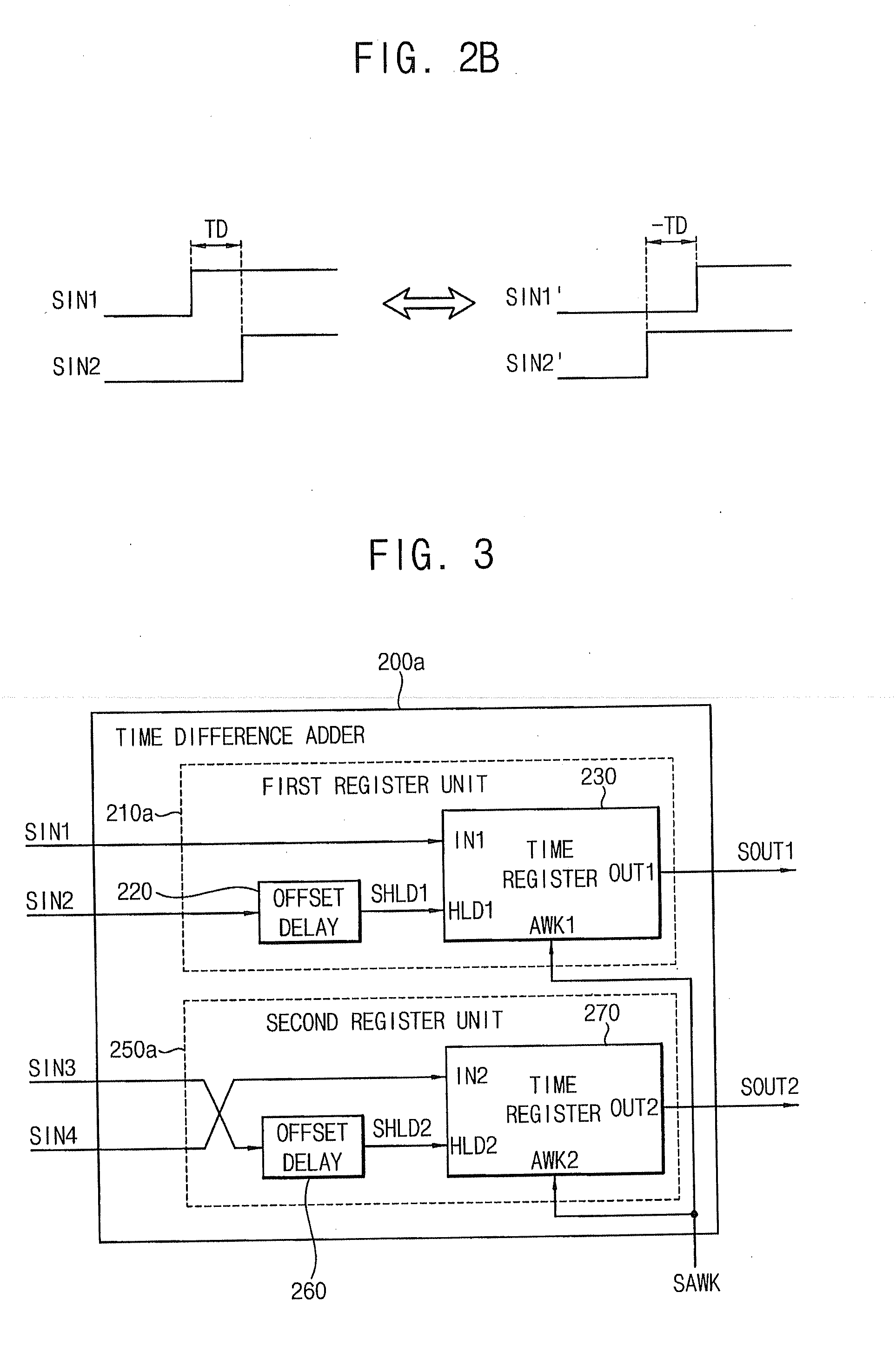

Time difference adders, time difference accumulators, sigma-delta time-to-digital converters, digital phase locked loops and temperature sensors

ActiveUS20120306553A1Computations using contact-making devicesPulse automatic controlDigital down converterProcessor register

A time difference adder included in a system-on-chip (SOC) includes a first register unit and a second register unit. The first register unit is configured to receive first and second input signals having a first time difference, and generate a first output signal in response to a first signal. The second register unit is configured to receive third and fourth input signals having a second time difference, and generate a second output signal having a third time difference with respect to the first output signal in response to the first signal. The third time difference corresponds to a sum of the first time difference and the second time difference.

Owner:SAMSUNG ELECTRONICS CO LTD

Popular searches

Input/output processes for data processing Analogue/digital conversion calibration/testing Secret communication Transmitter/receiver shaping networks Synchronous/start-stop systems Television system scanning details Color television details Color signal processing circuits Electromagnetic receivers Synchronising arrangement