Patents

Literature

186results about "Resistors with plural resistive elements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

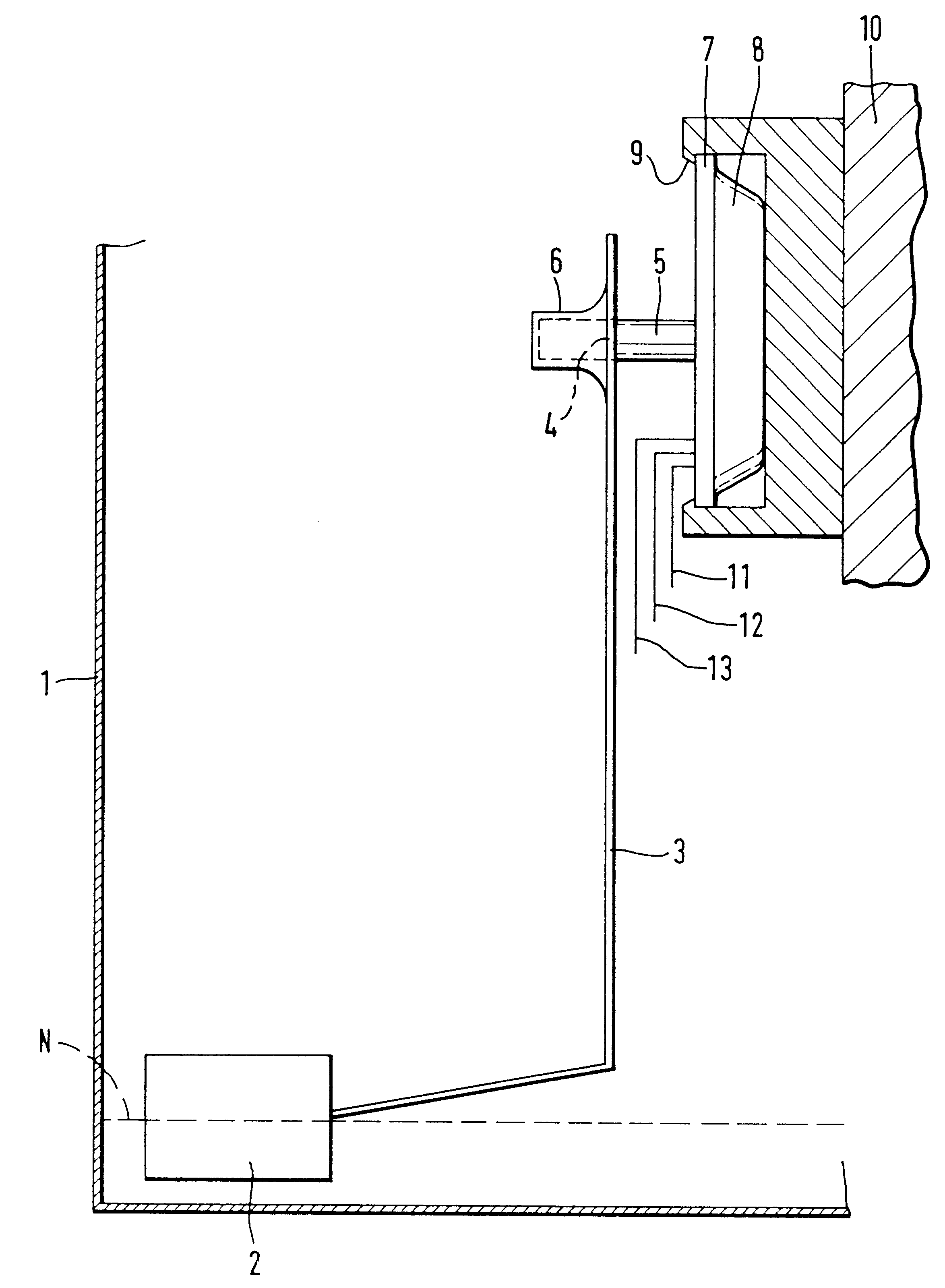

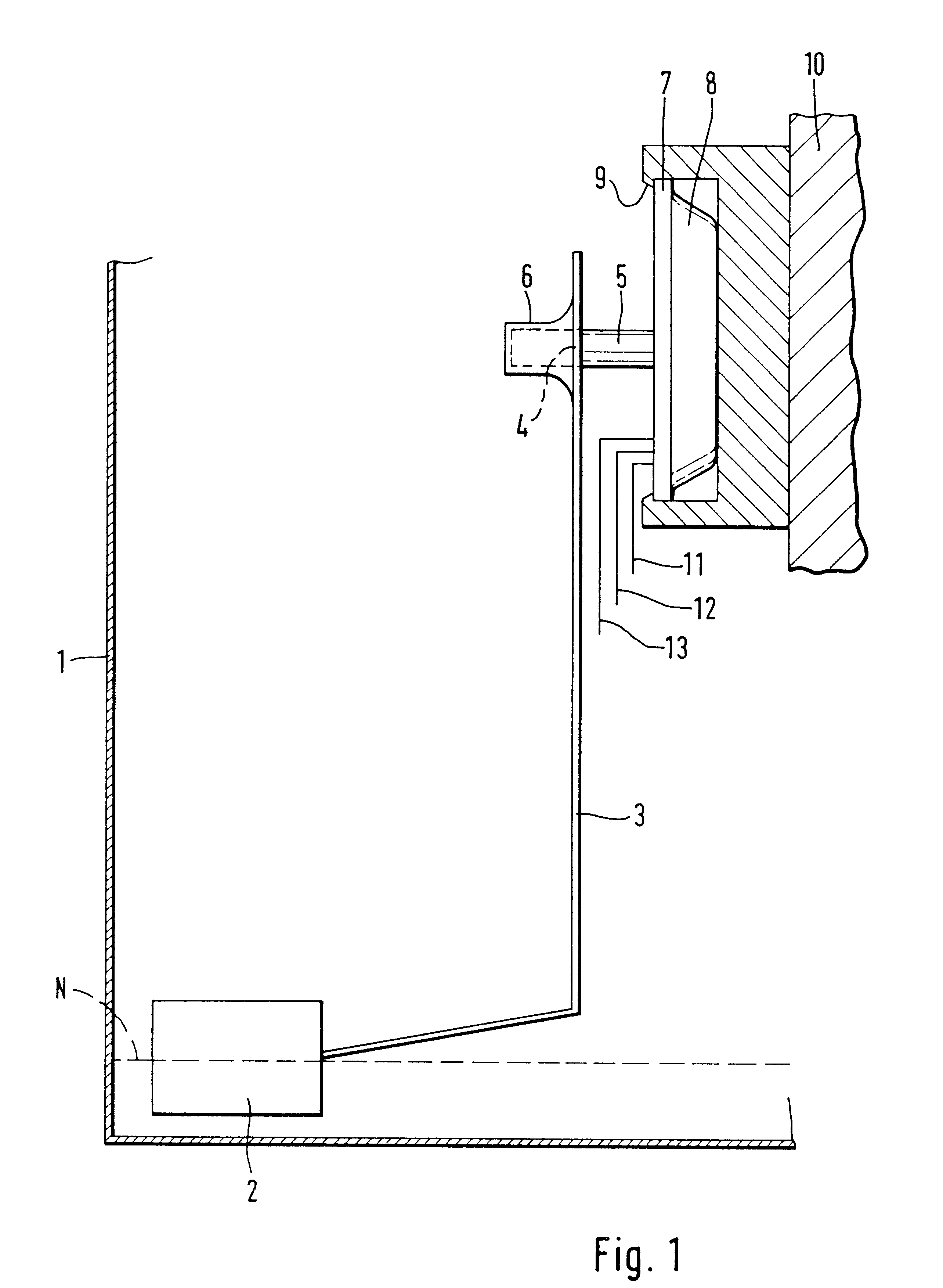

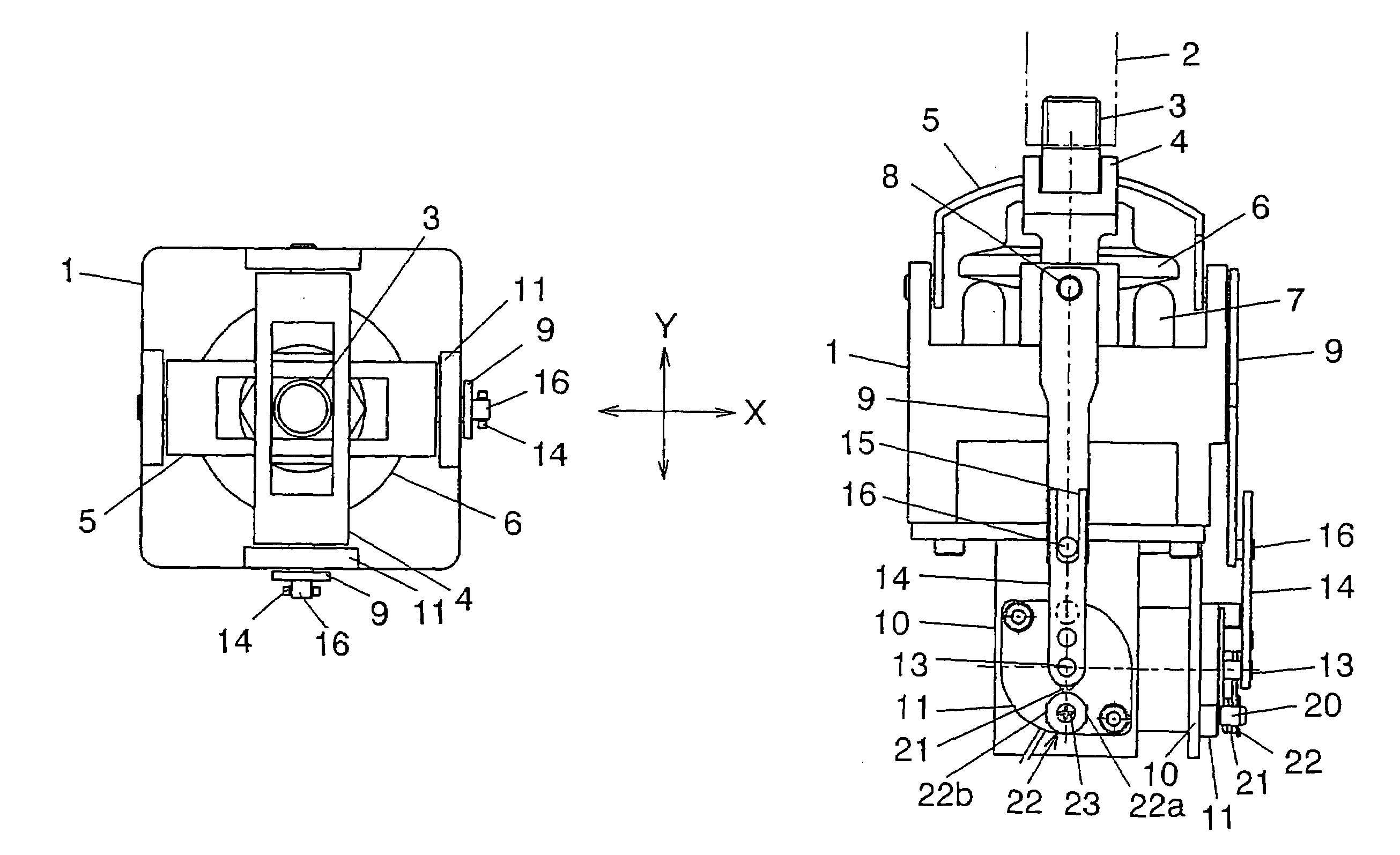

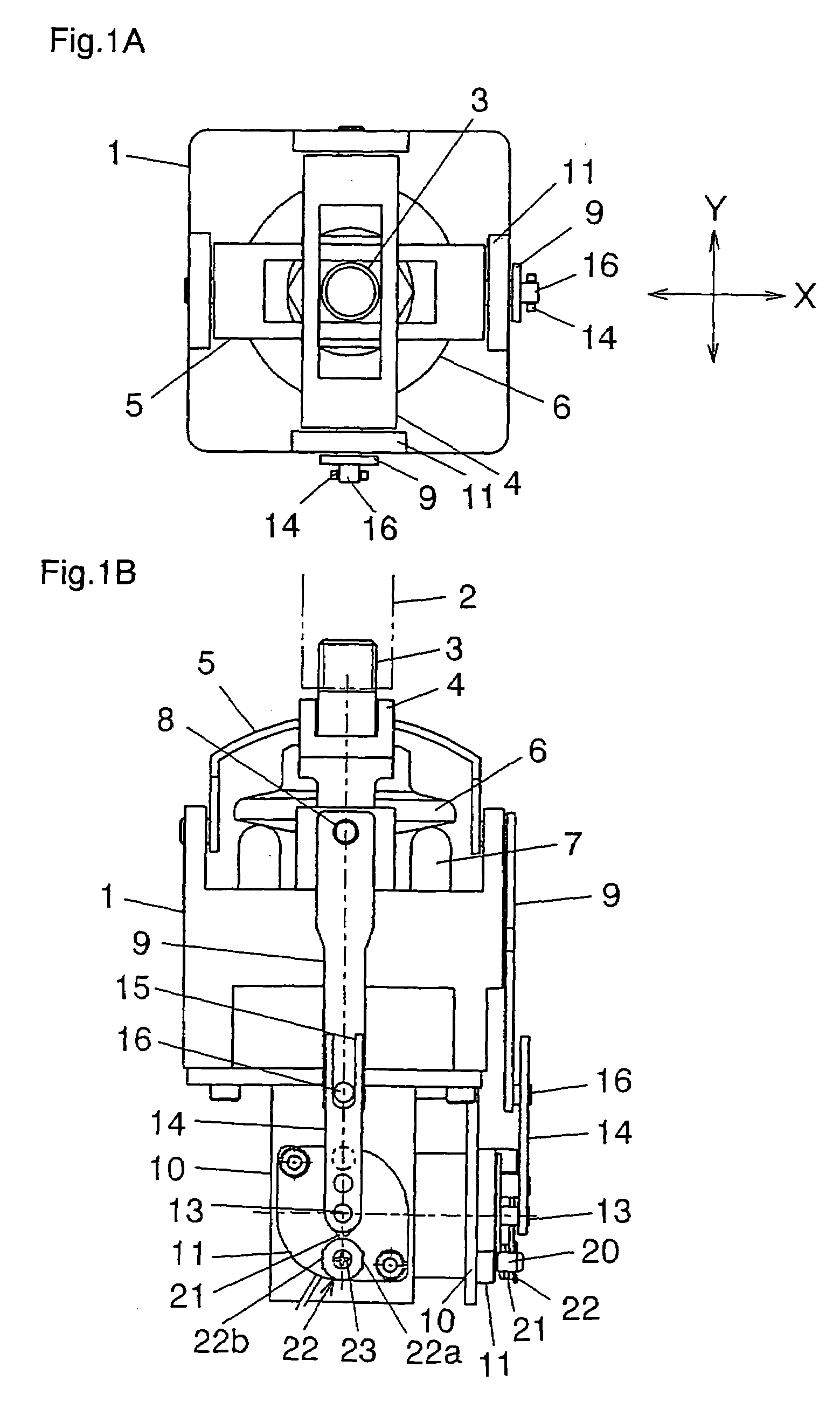

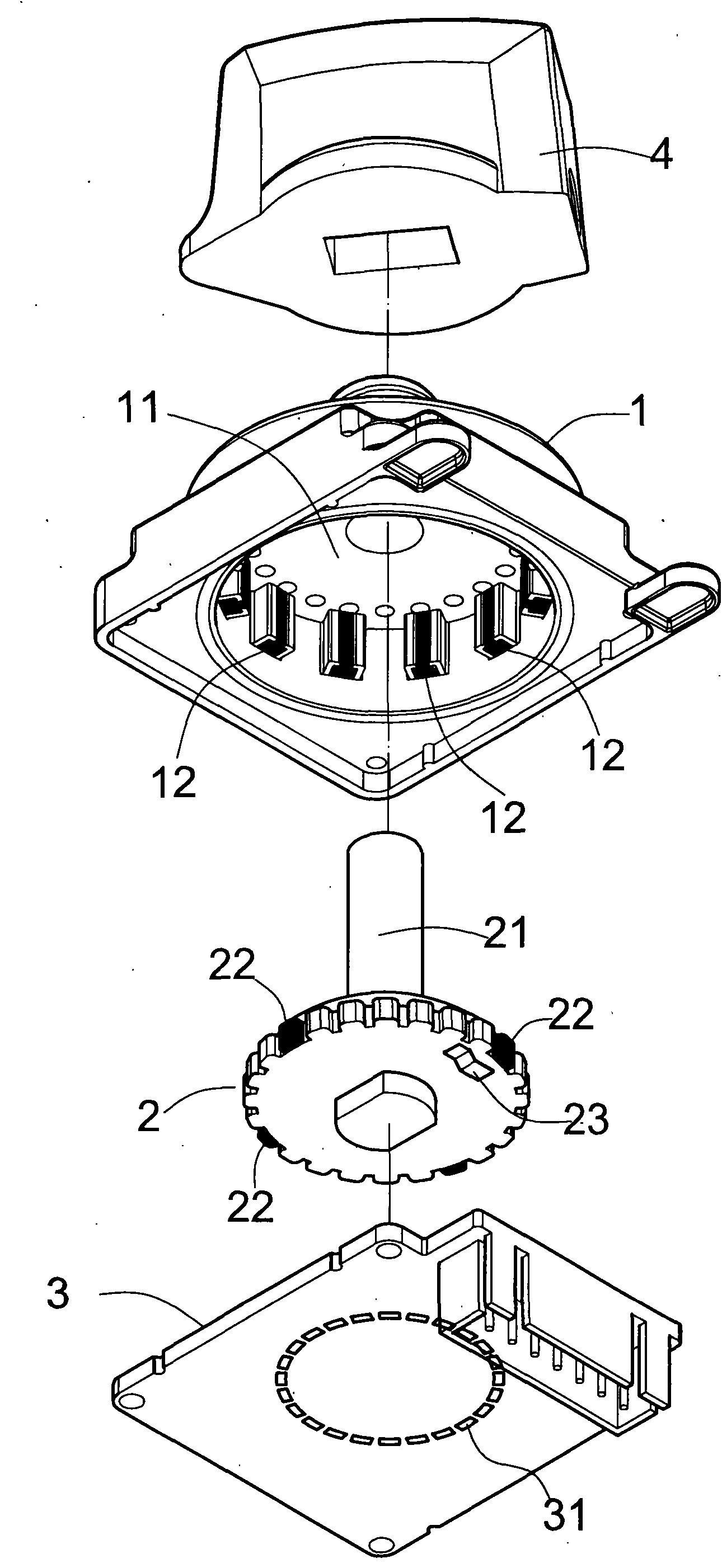

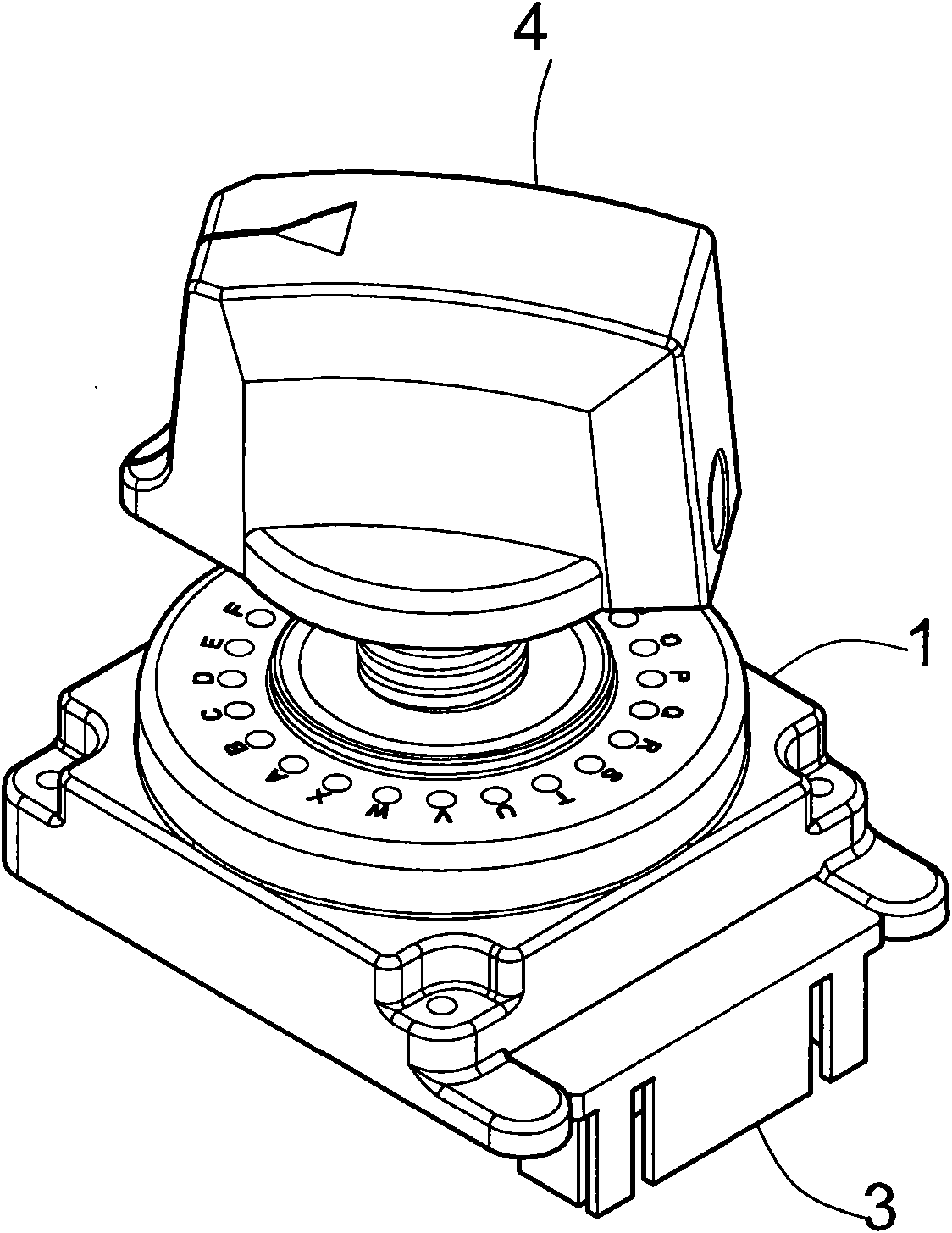

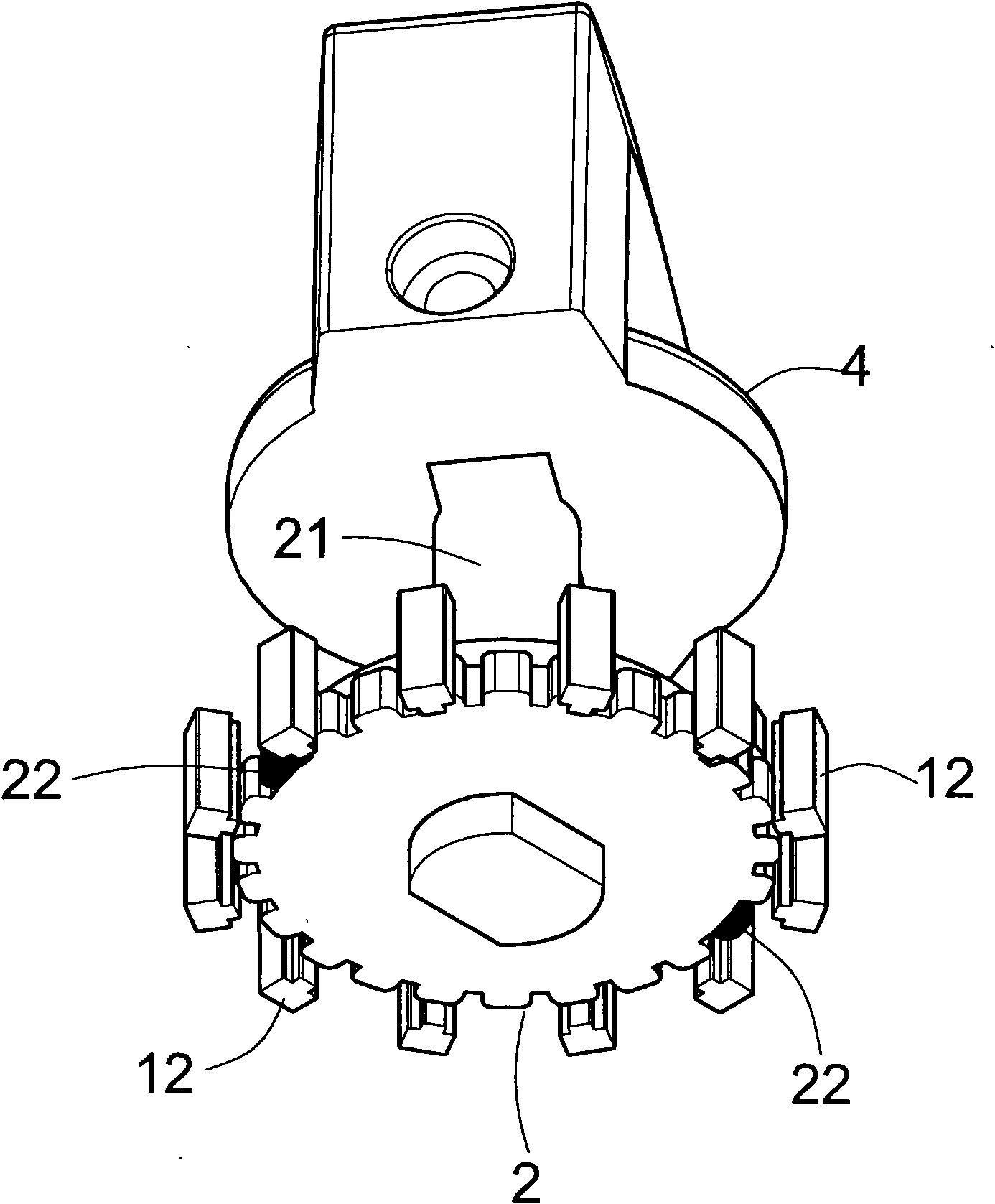

Ball joint with integrated angle sensor

InactiveUS6879240B2Improve accuracyDetect any spatial positionBearing assemblyShaftsTransducerEngineering

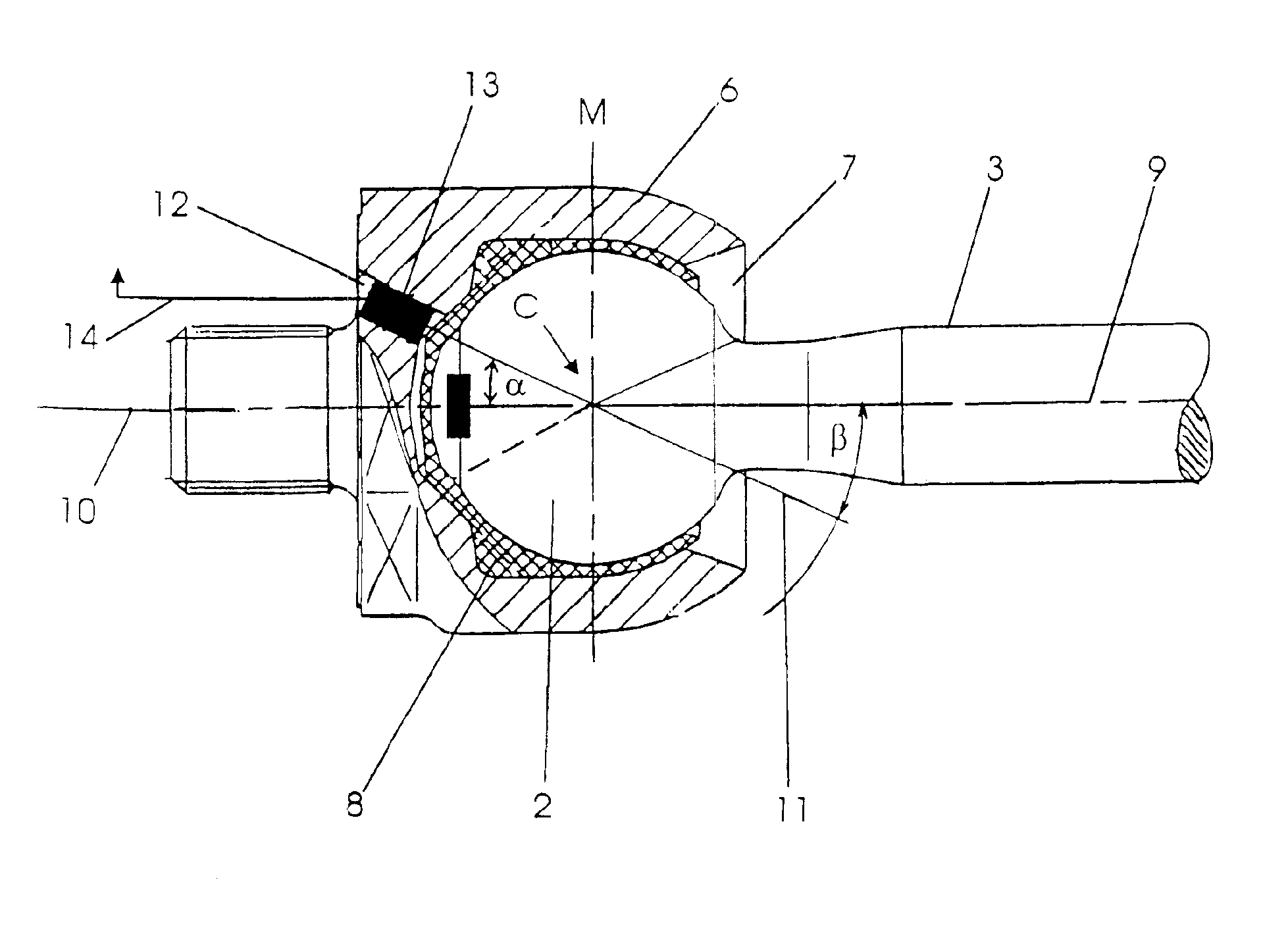

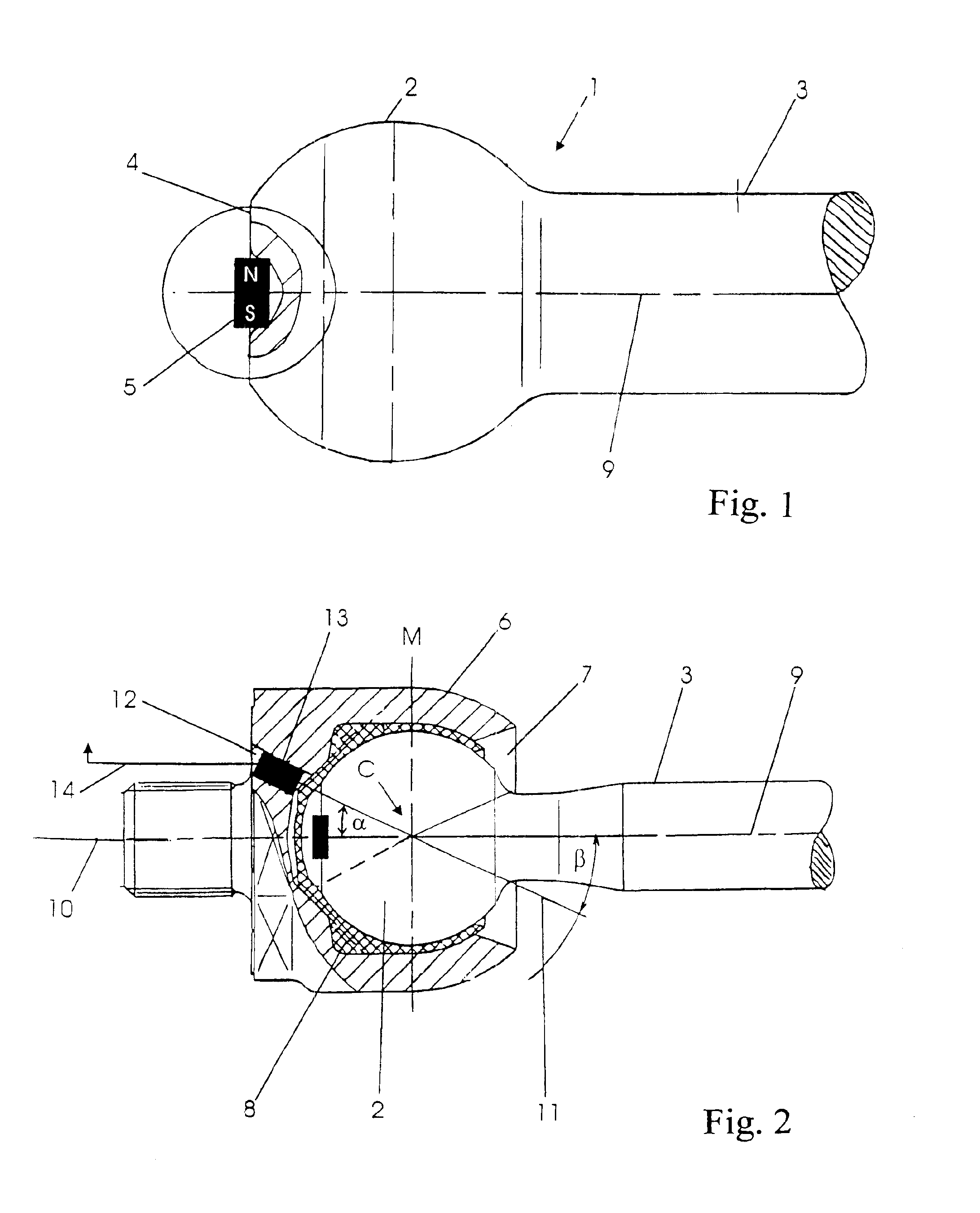

A ball-and-socket joint with integrated angle sensor for a motor vehicle, especially for the chassis of the motor vehicle is created. The ball-and-socket joint has a ball-and-socket joint housing (6) provided with a joint opening (7), a ball pivot (1) having a joint ball (2) and a pin (3), which is mounted, with its joint ball (2), rotatably and pivotably in a hollow-ball-shaped bearing surface in the ball-and-socket joint housing (6), and projects, with its pin (3), through the joint opening (7) out of the ball-and-socket joint housing (6). A two-pole field transducer (5) is provided at the end of the joint ball (2) facing away from the pin (3). The poles of the field transducer (5) are arranged on the ball surface. In this case, at least two field sensors (13) are arranged at a distance from one another with respect to the meridian plane defined by the large circle on the hollow-ball-shaped bearing surface running at right angles to the bearing longitudinal axis in the area or on the ball-and-socket joint housing (6) facing away from the joint opening, and interact with the field produced by the field transducer (5).

Owner:ZF LEMFOERDER METALLWAREN AG

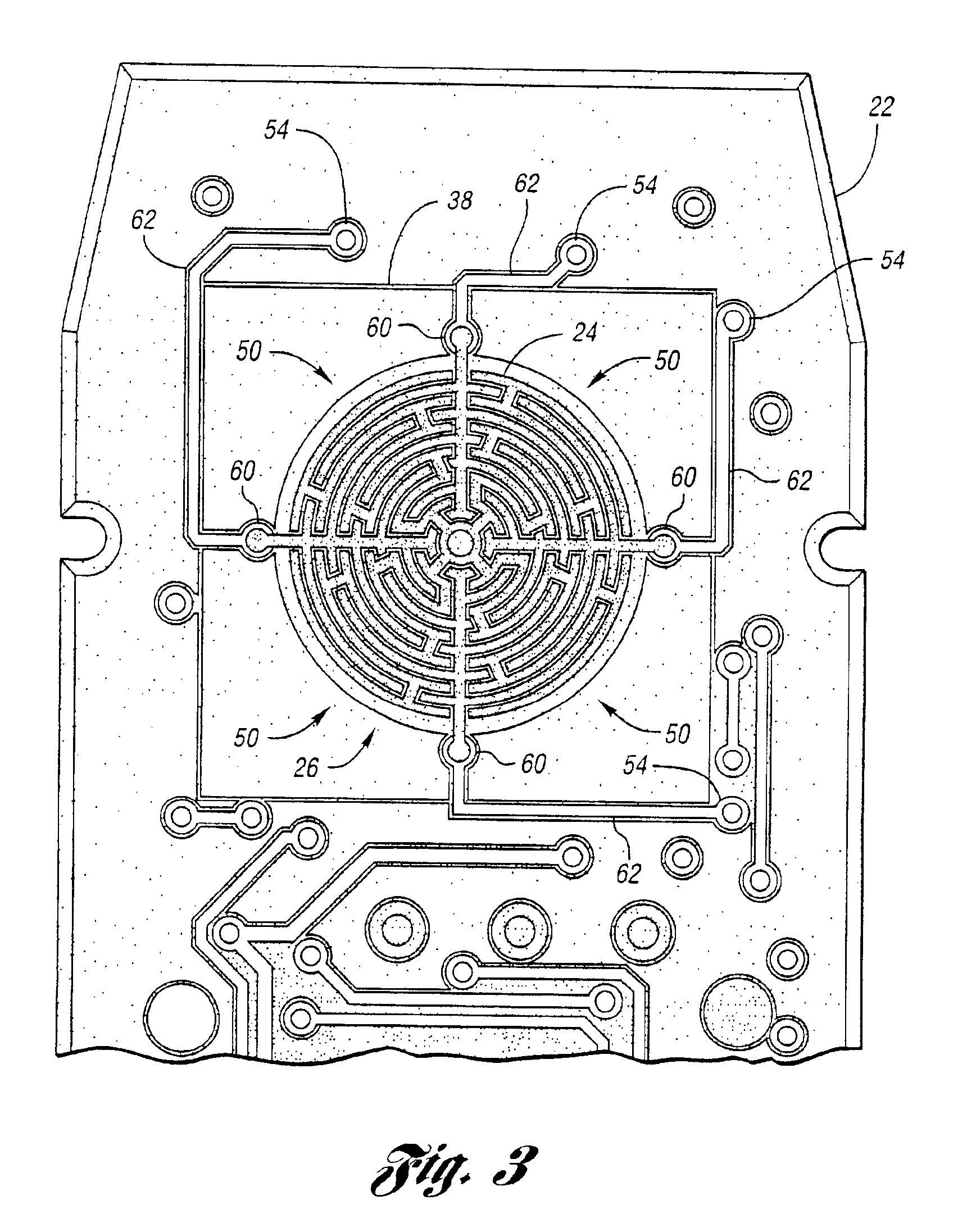

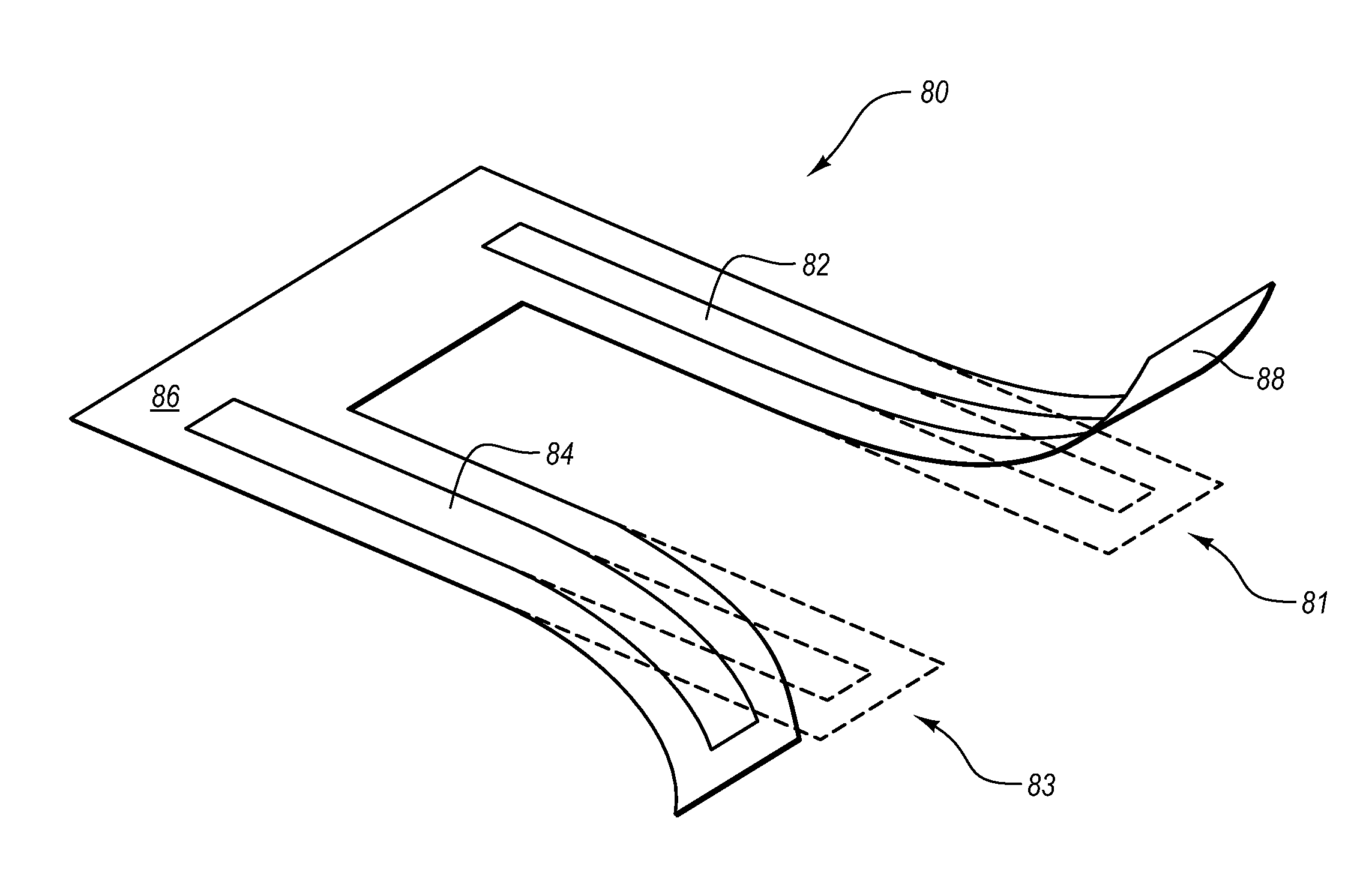

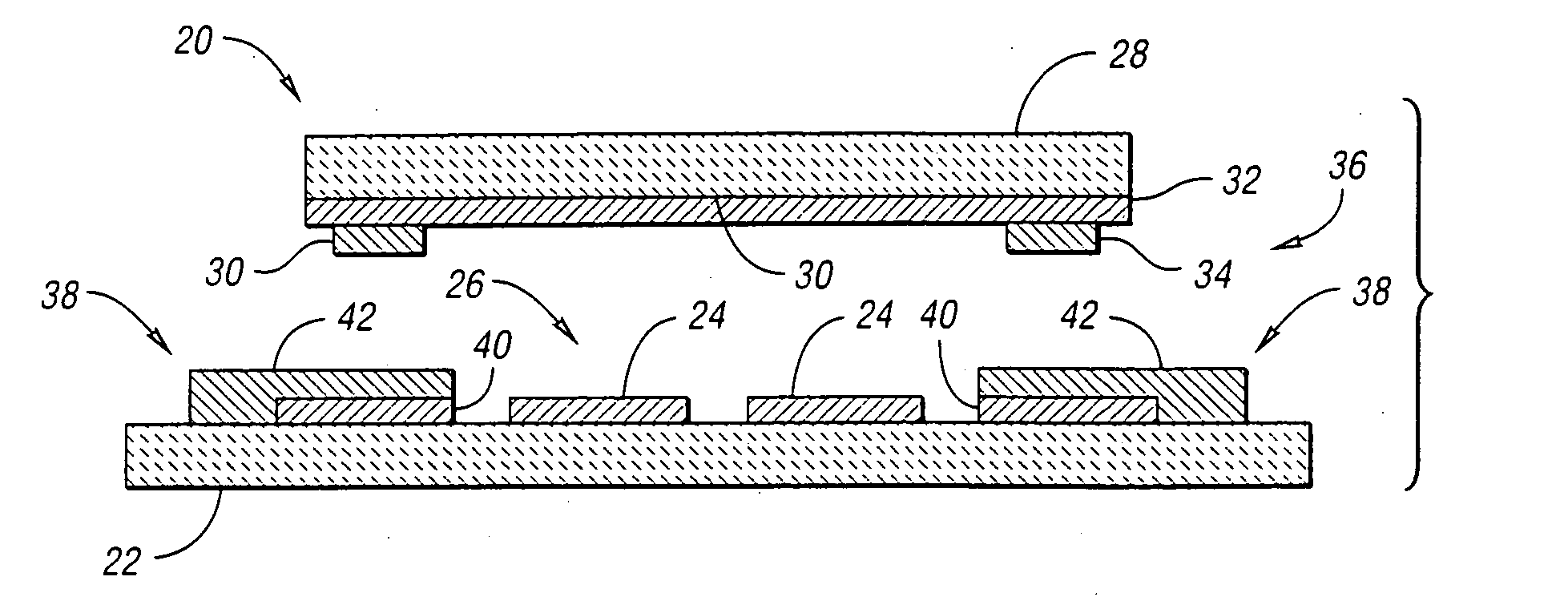

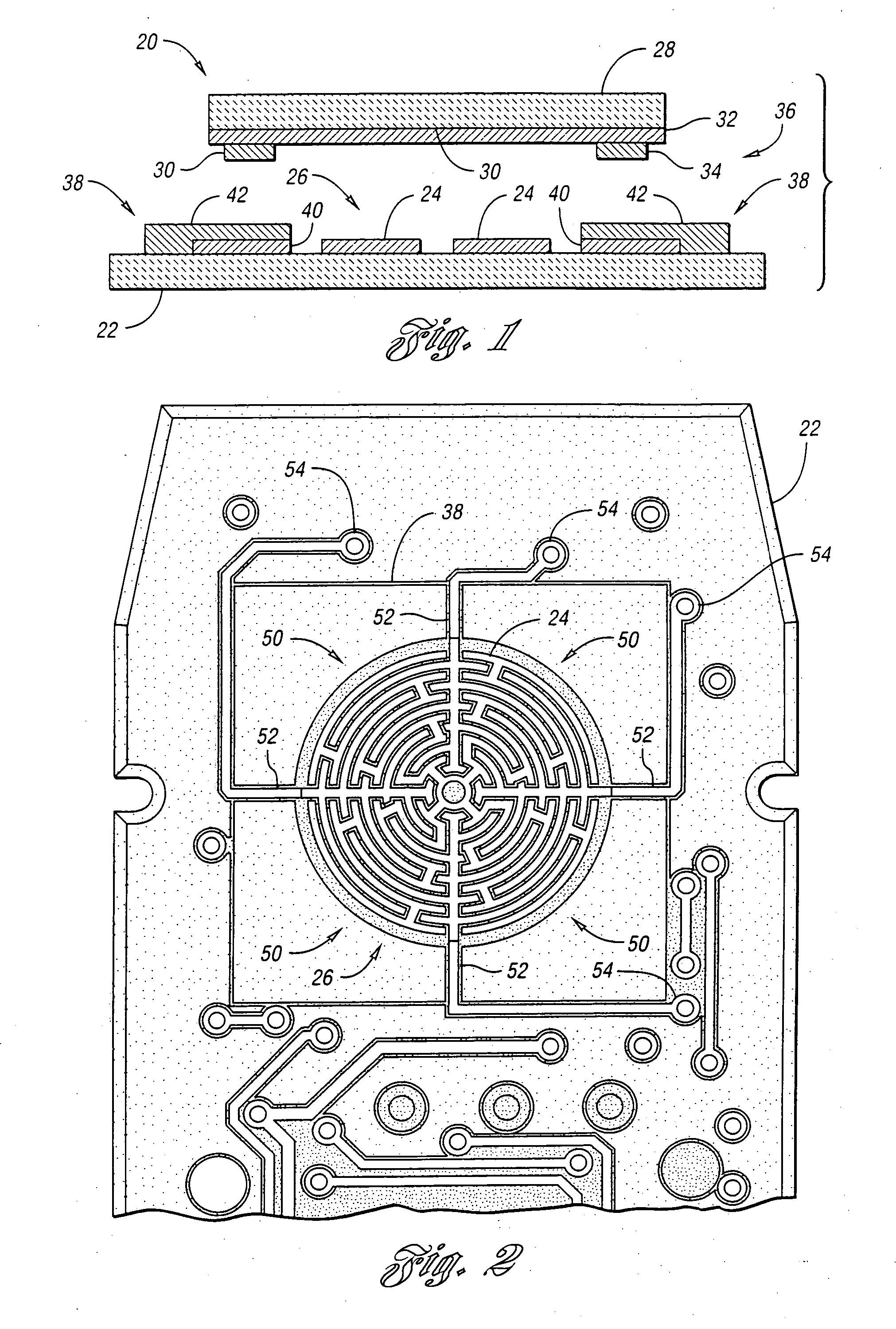

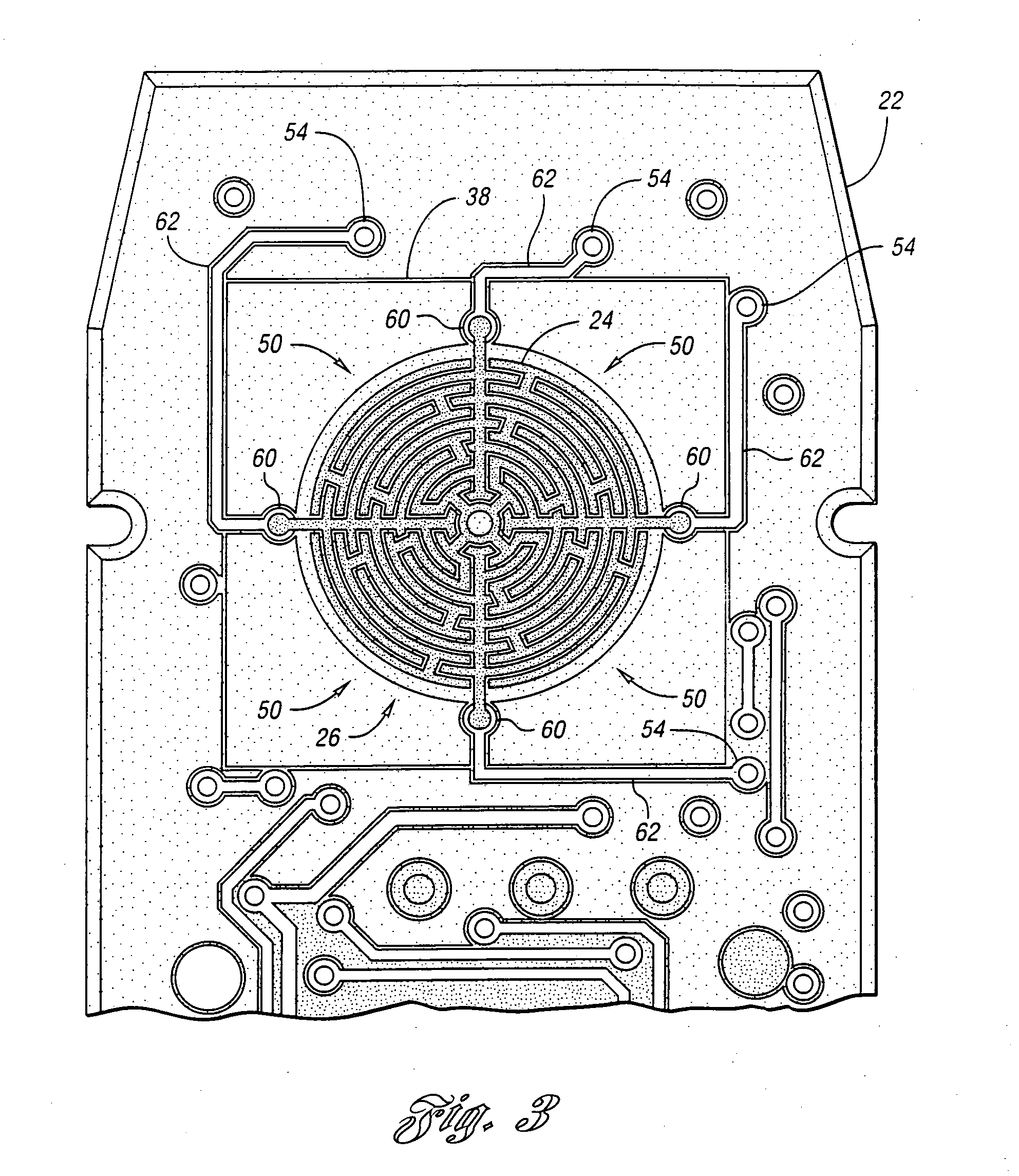

Electronic pressure sensitive transducer apparatus and method for manufacturing same

InactiveUS6909354B2Low costReduce complexityPrinted circuit assemblingPrinted circuit aspectsTransducerEngineering

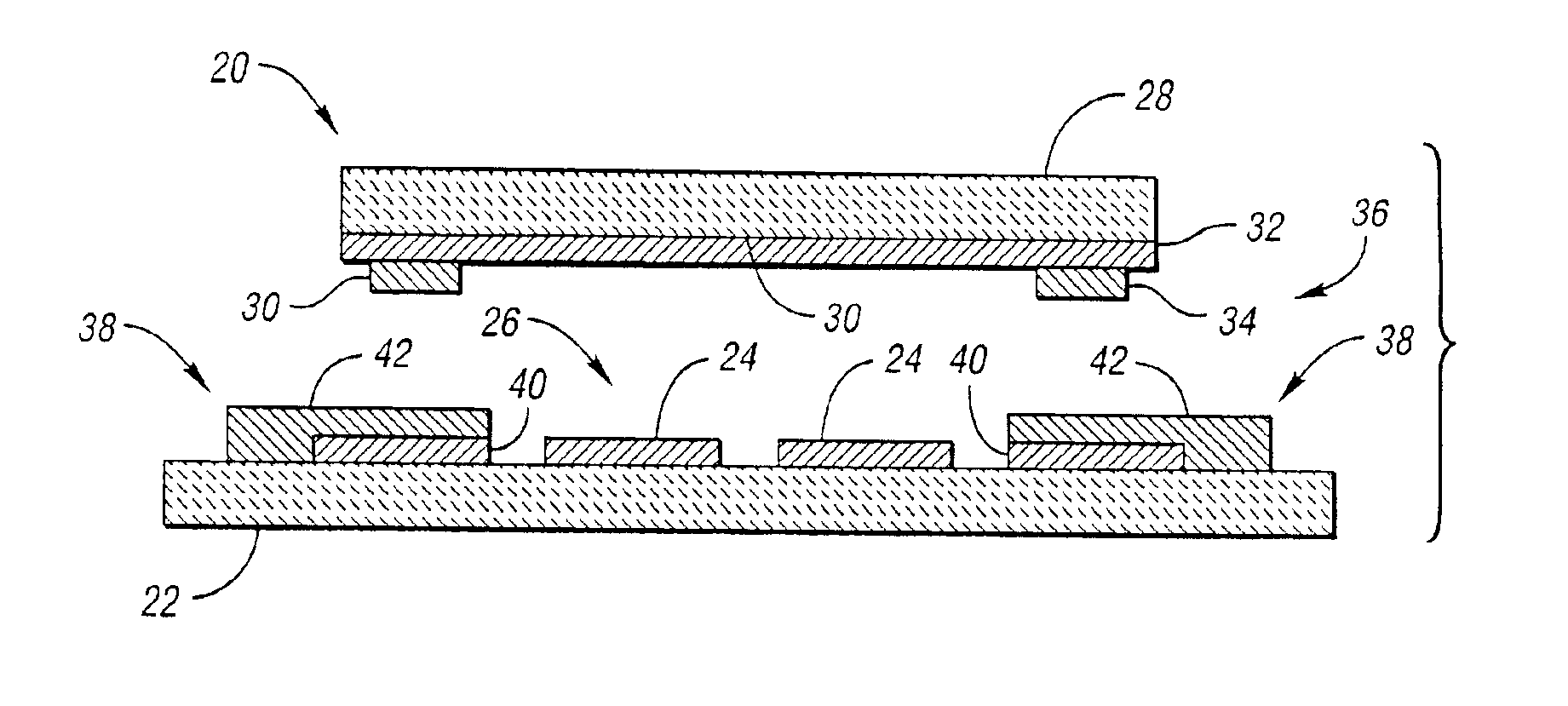

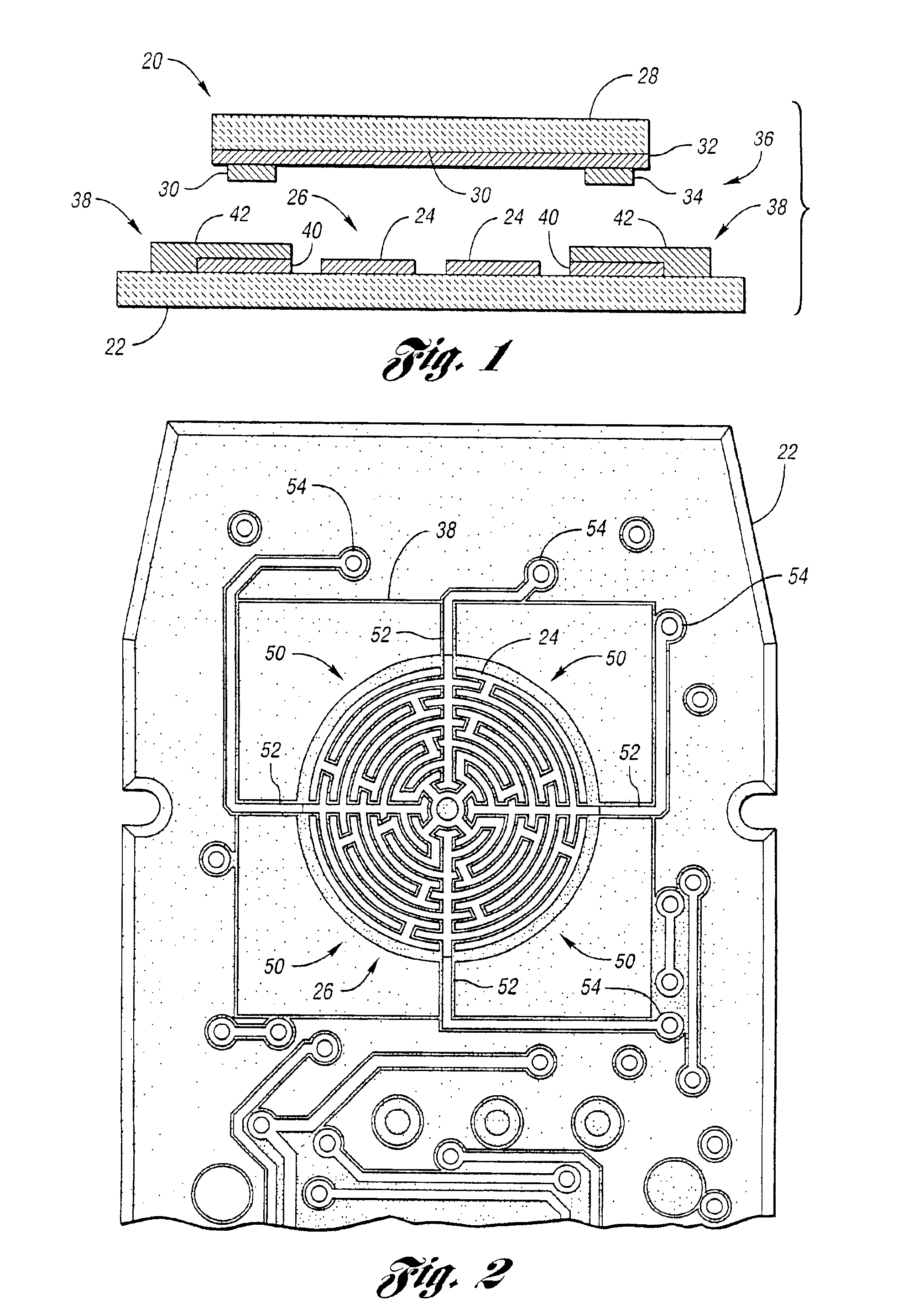

The cost and complexity of an electronic pressure sensitive transducer are decreased by constructing such a transducer directly on a printed circuit board containing support electronics. Conductive traces are formed on the printed circuit board to define a contact area. A flexible substrate having an inner surface is positioned over the contact area. An adhesive spacer, substantially surrounding the contact area, attaches the flexible substrate to the printed circuit board. At least one resistive layer is deposited on the flexible substrate inner surface. In use, the resistive layer contacts at least two conductive traces in response to pressure applied to the flexible substrate to produce an electrical signal indicative of applied pressure.

Owner:INTERLINK ELECTRONICS

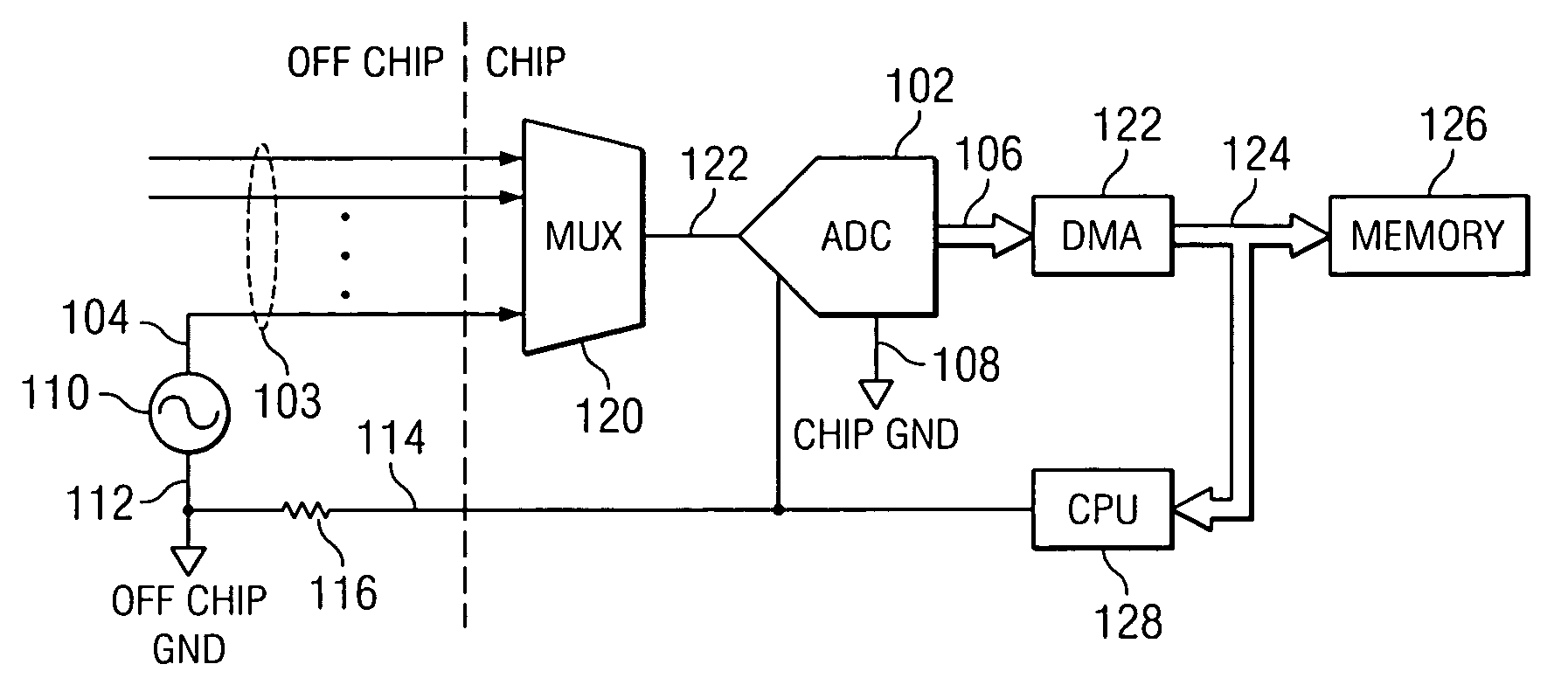

DMA controller that restricts ADC from memory without interrupting generation of digital words when CPU accesses memory

InactiveUS7188199B2Electric signal transmission systemsResistors with plural resistive elementsControl dataMixed-signal integrated circuit

DMA controller for mixed signal device. A mixed signal integrated circuit with memory control is disclosed. A data conversion circuit is provided that is operable to receive an analog input signal and convert discrete samples thereof at a predetermined sampling rate to a digital representations thereof as a plurality of digital words. A memory stores the digital words generated by the data conversion circuit. A processor is included on the integrated circuit and operable to access the memory to output select ones of the digital words for processing thereof in accordance with a predetermined processing algorithm. A memory access controller controls access to the memory by the data conversion circuit and the processor. The memory access controller is operable to restrict access to the memory by the data conversion circuit without interrupting the generation of digital words therefrom when the processor is accessing the memory, and allowing access to the memory by the data conversion circuitry when the processor is not accessing the memory, such that the data conversion circuit can transfer currently generated digital words and previously generated and non stored digital words for storage in said memory upon gaining access thereto.

Owner:SILICON LAB INC

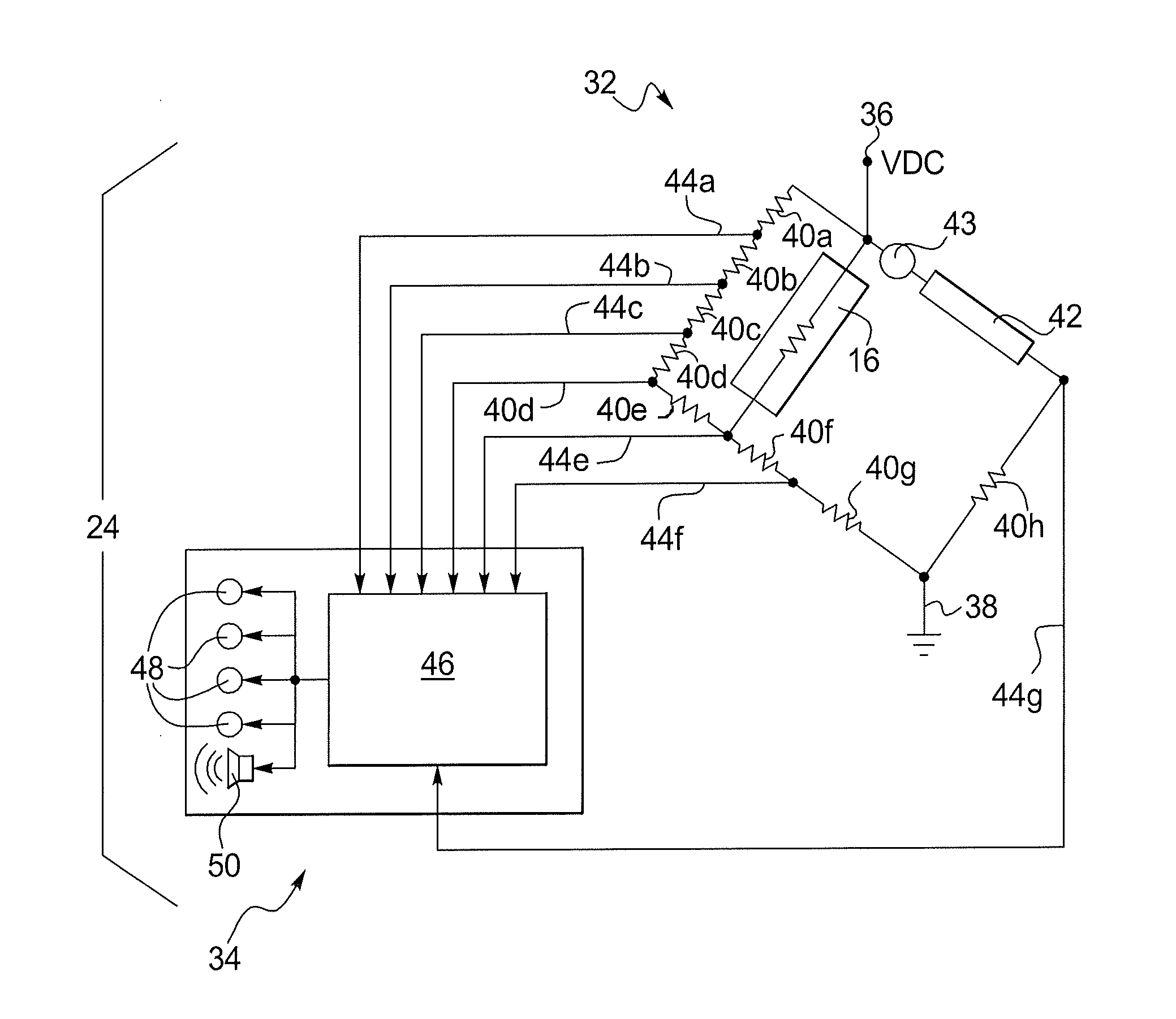

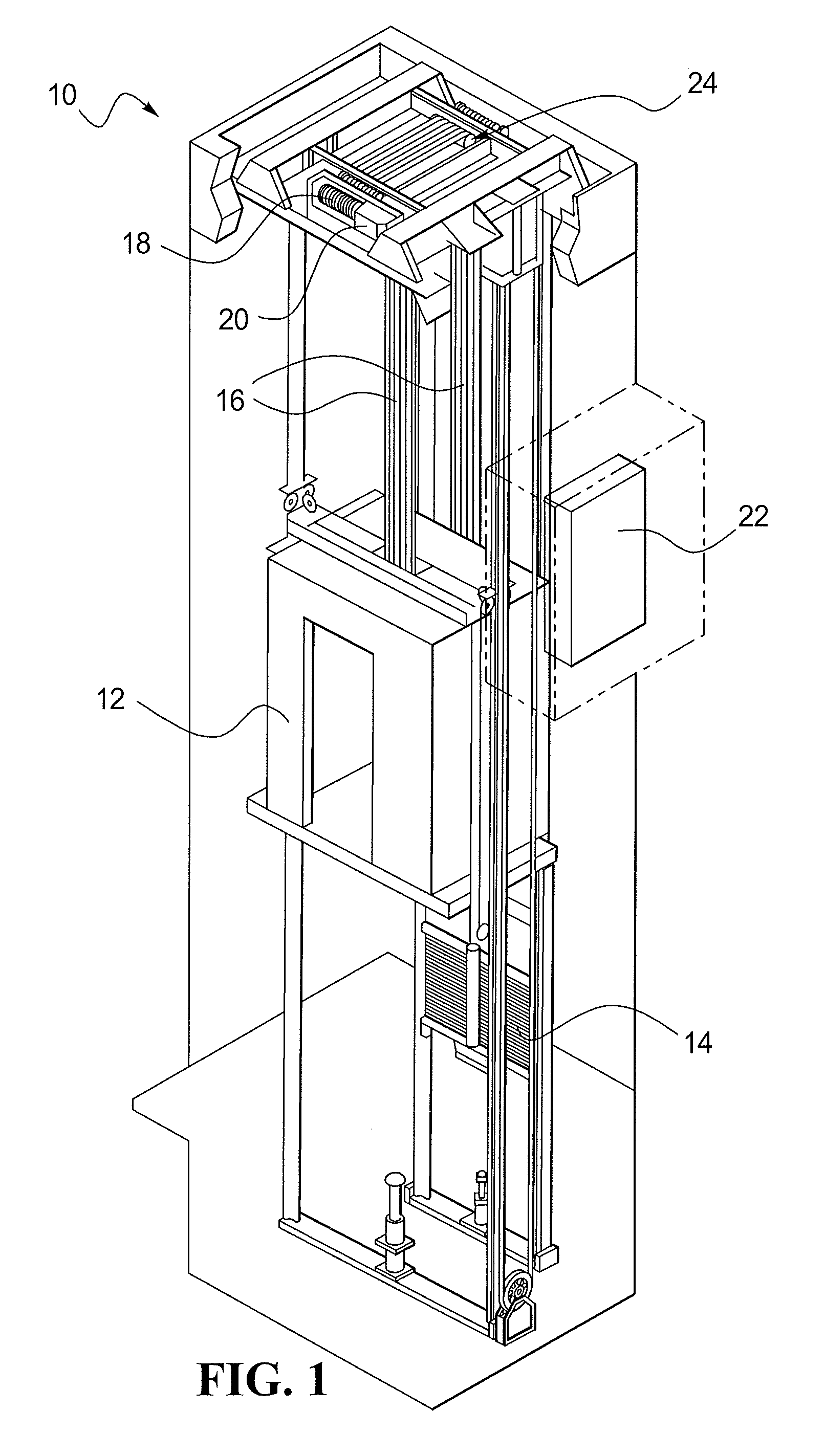

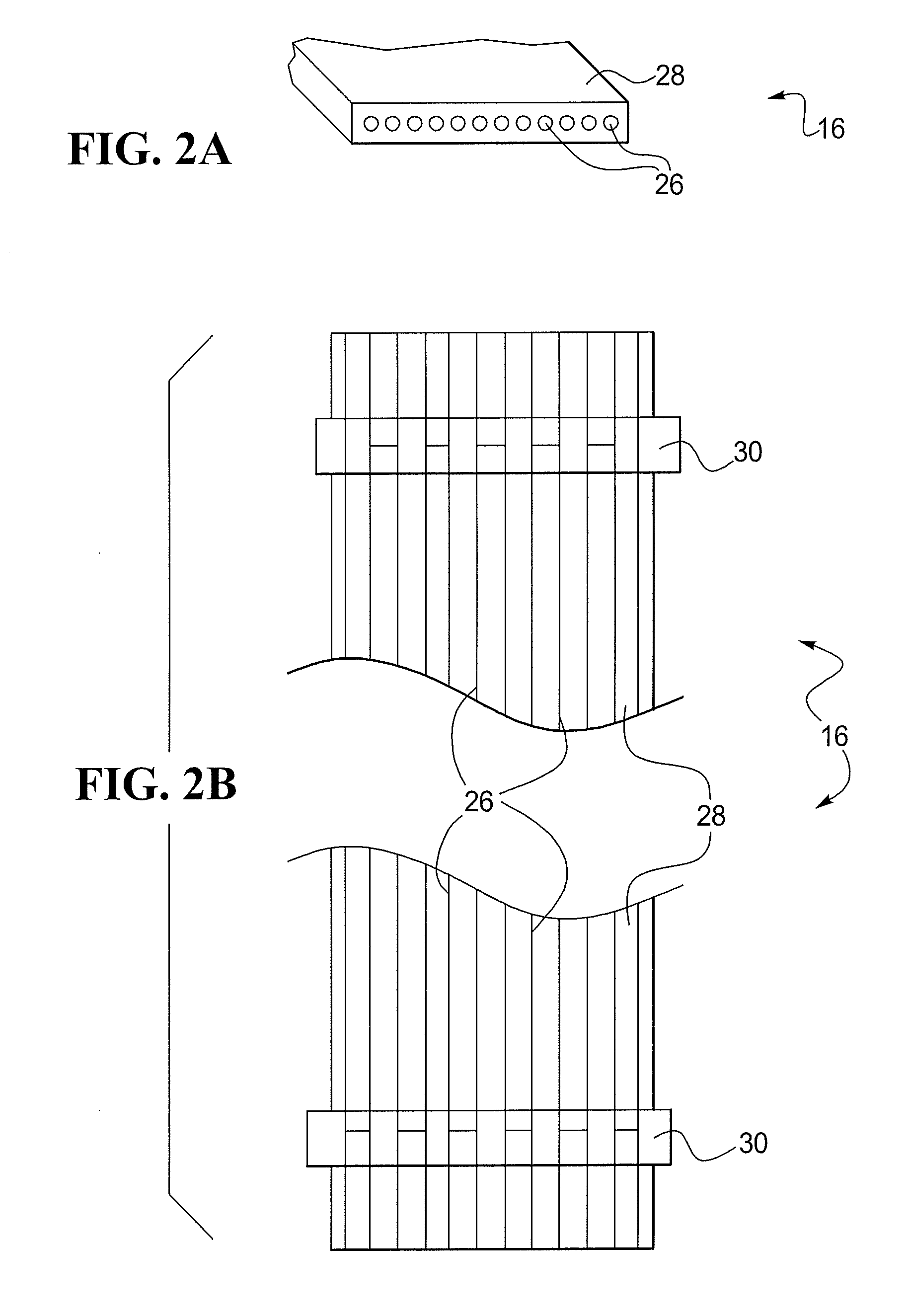

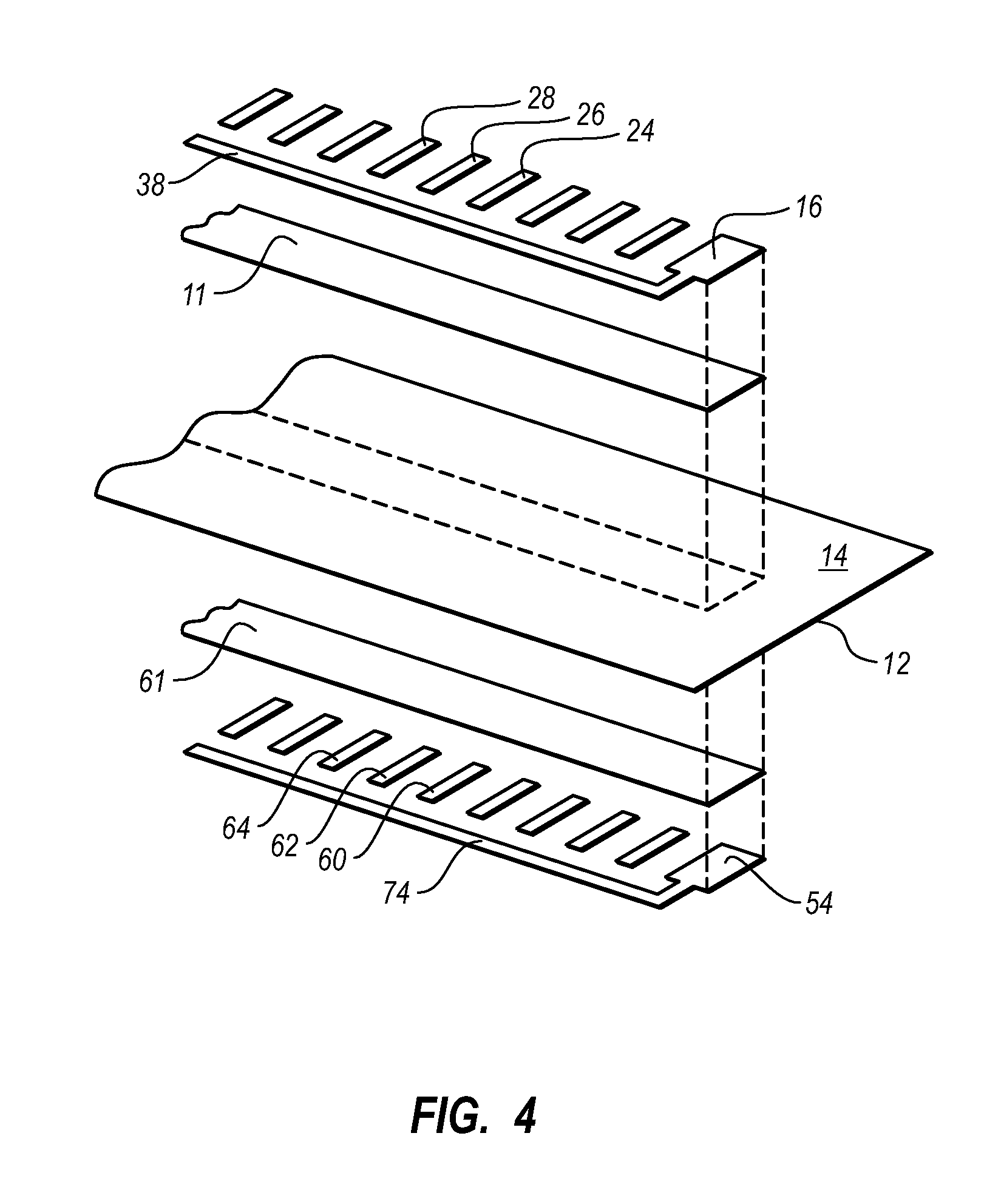

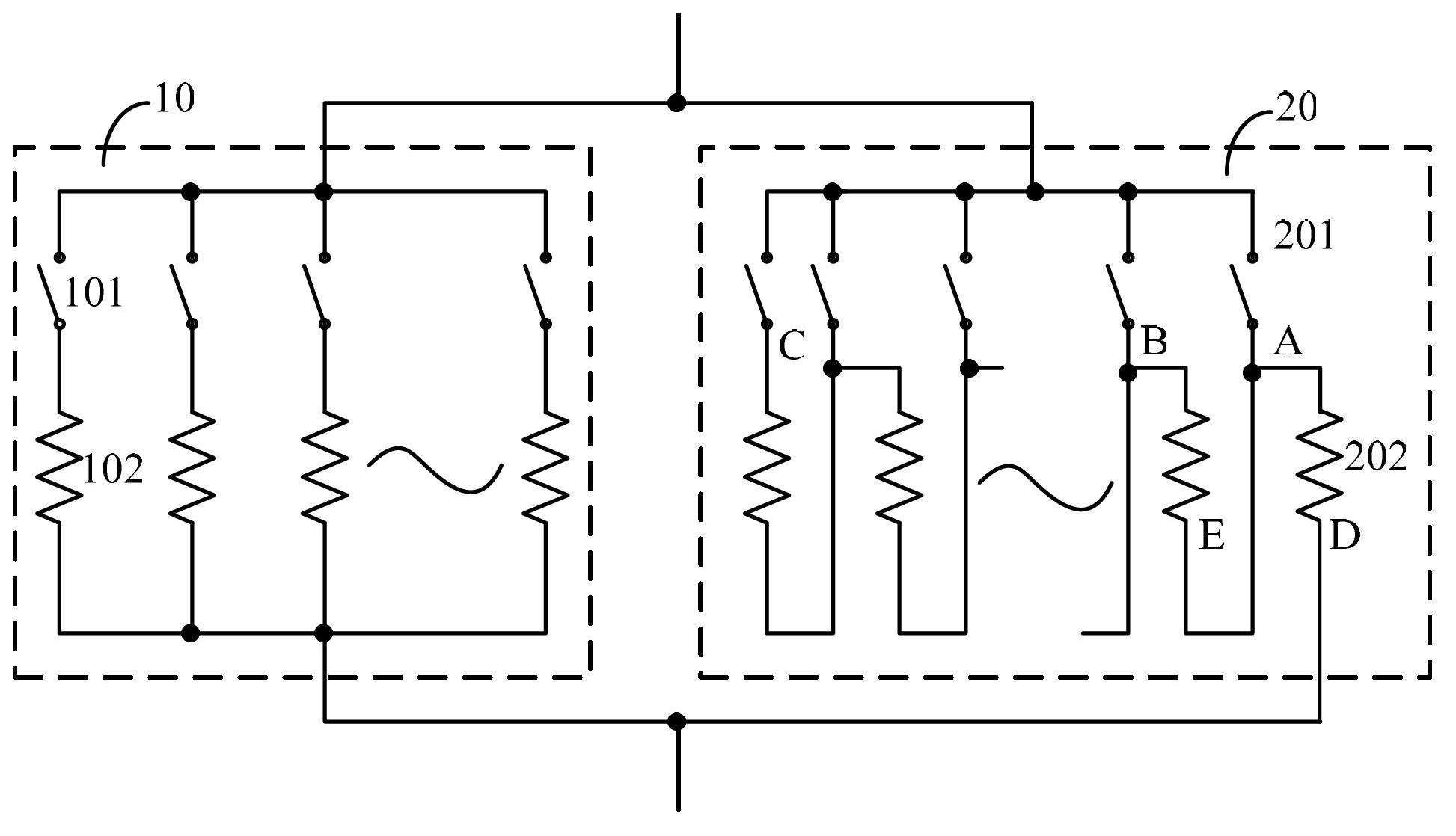

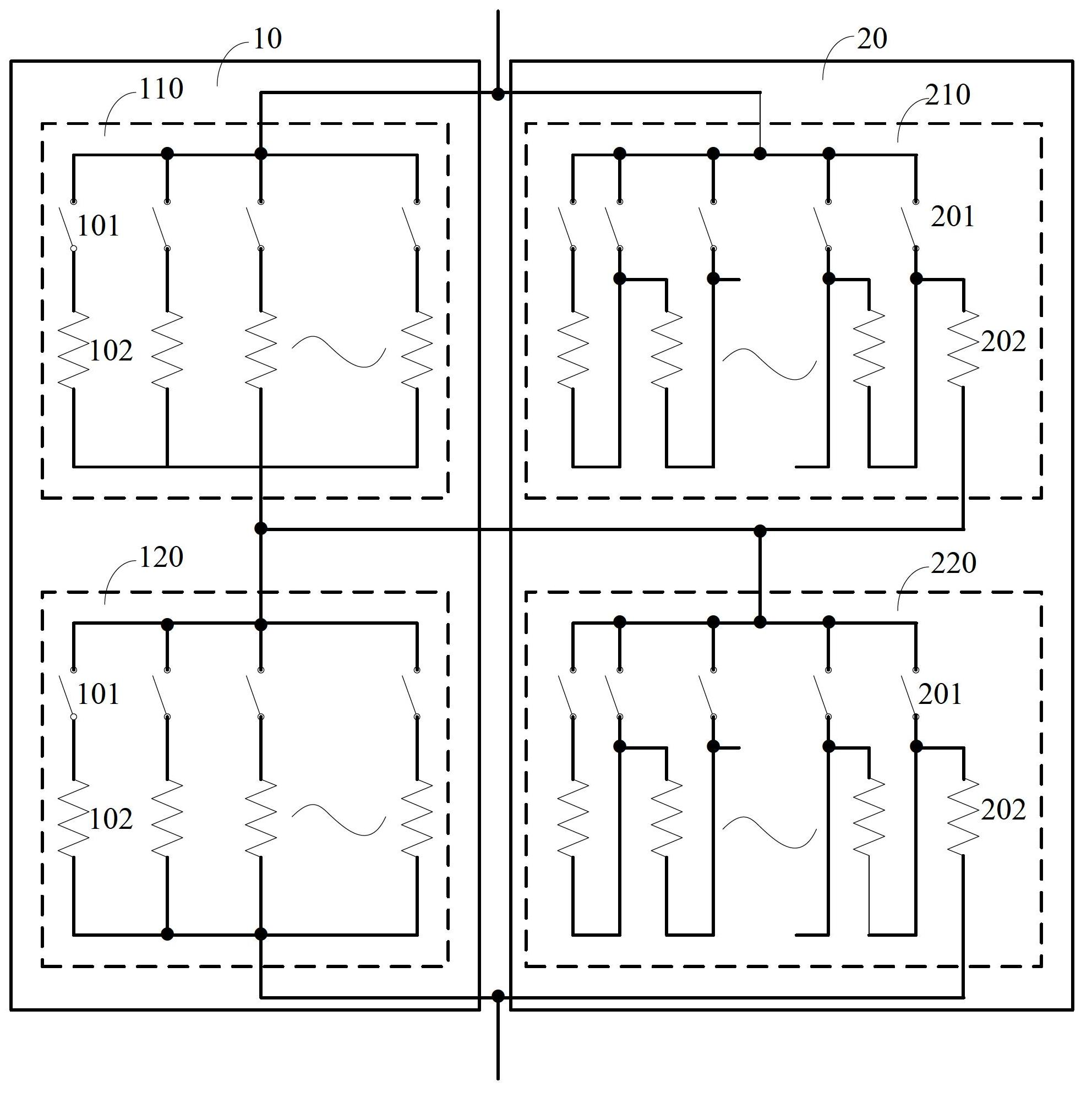

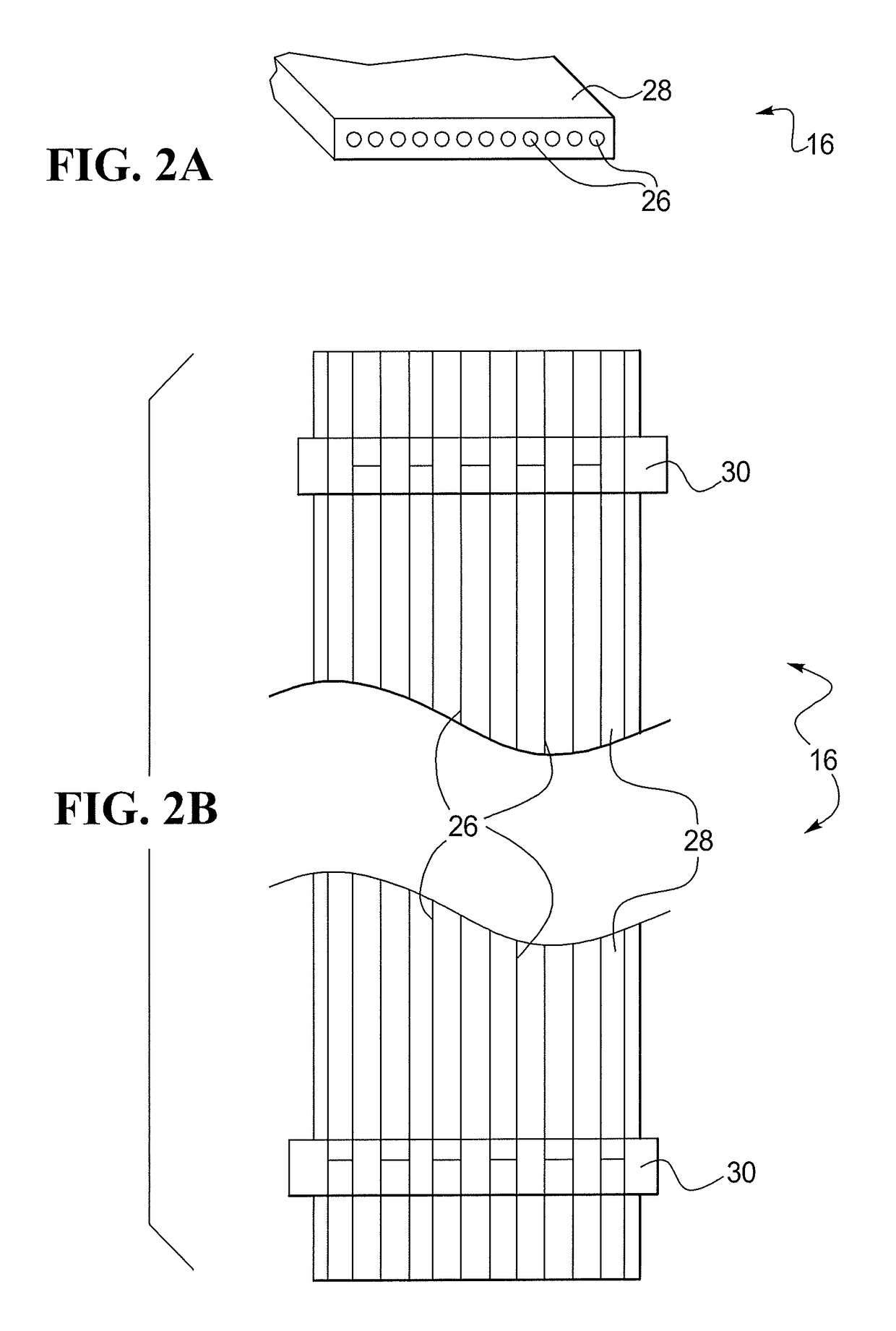

Simplified Resistance Based Belt Inspection

ActiveUS20130207668A1Other resistor networksResistance/reactance/impedenceElectrical resistance and conductanceResistor

A resistance circuit for monitoring a support structure is provided. The resistance circuit may include a first set of resistors disposed at a belt-side and a second set of resistors disposed at a monitor-side. The first set of resistors may be configured to indicate one or more voltages thereacross corresponding to an effective resistance of the support structure. The first set of resistors may include at least one temperature-dependent resistor. The second set of resistors may be configured to indicate one or more voltages thereacross corresponding to an initial effective resistance of the support structure. The second set of resistors may include at least one switched resistor having an adjustable resistance capable of selectively approximating the initial effective resistance.

Owner:OTIS ELEVATOR CO

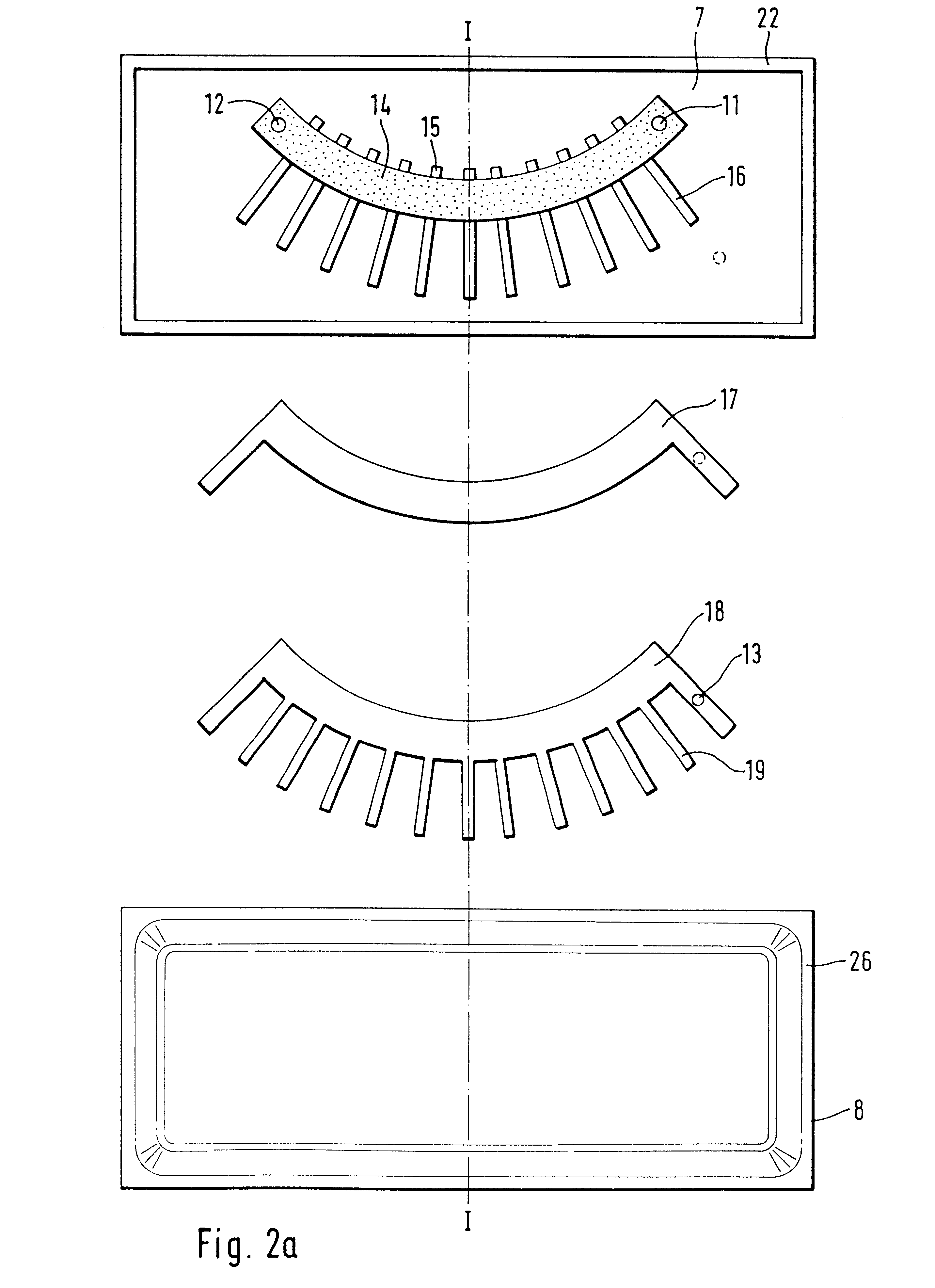

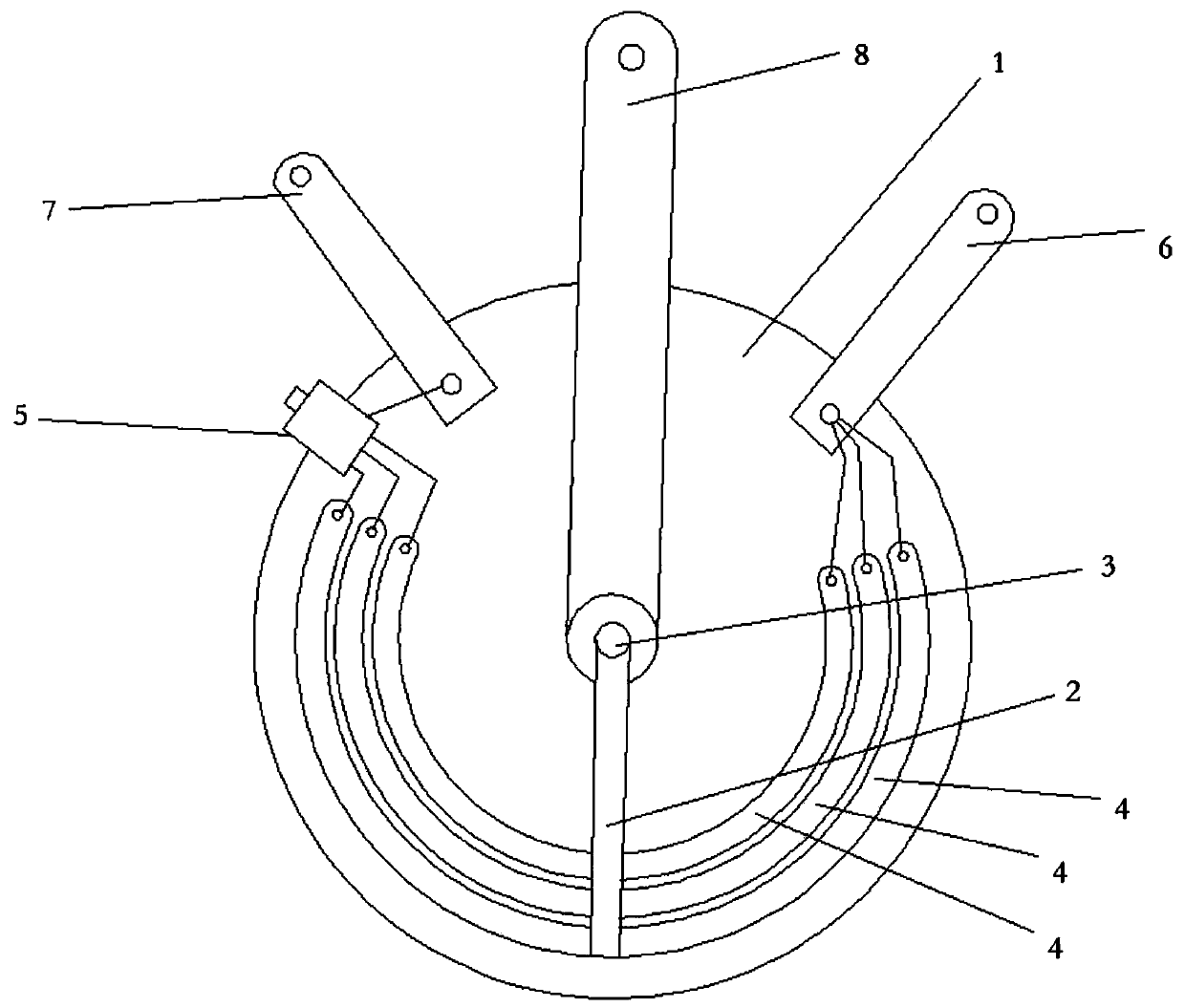

Level indicator

A fluid level sensor that is particularly useful in fluid fuel tanks of motor vehicles wherein a resistor network is arranged on a fixed support and it is possible to generate an output signal from the resistor network which corresponds to the position of a float member. The level sensor has particularly low wear and is inexpensive to produce with a contact structure for the resistor network that operates through interaction of a magnetic member is moved by the float and can be deflected such that an electrical connection is dependent on the position of the float.

Owner:CONTINENTAL AUTOMOTIVE GMBH

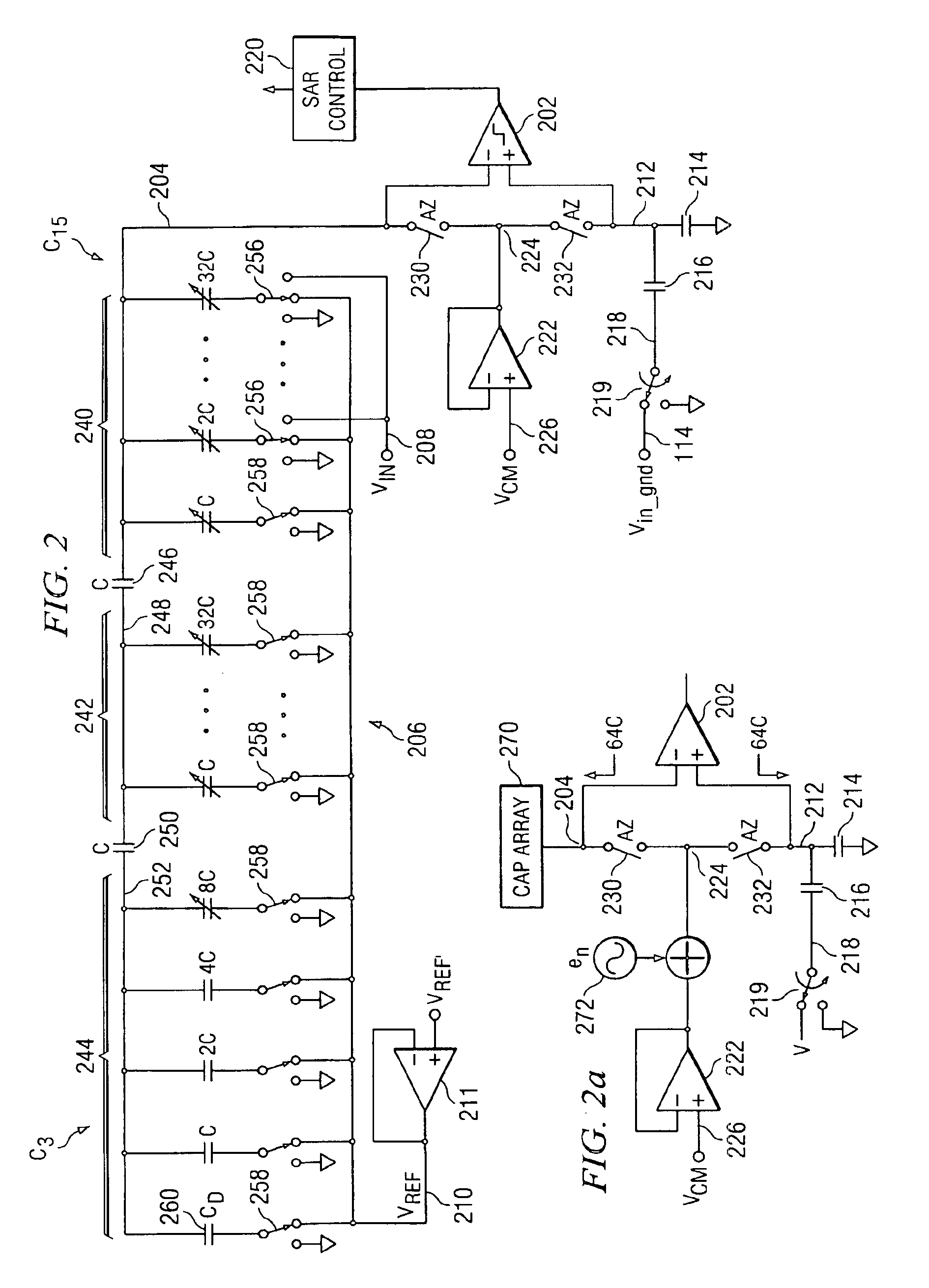

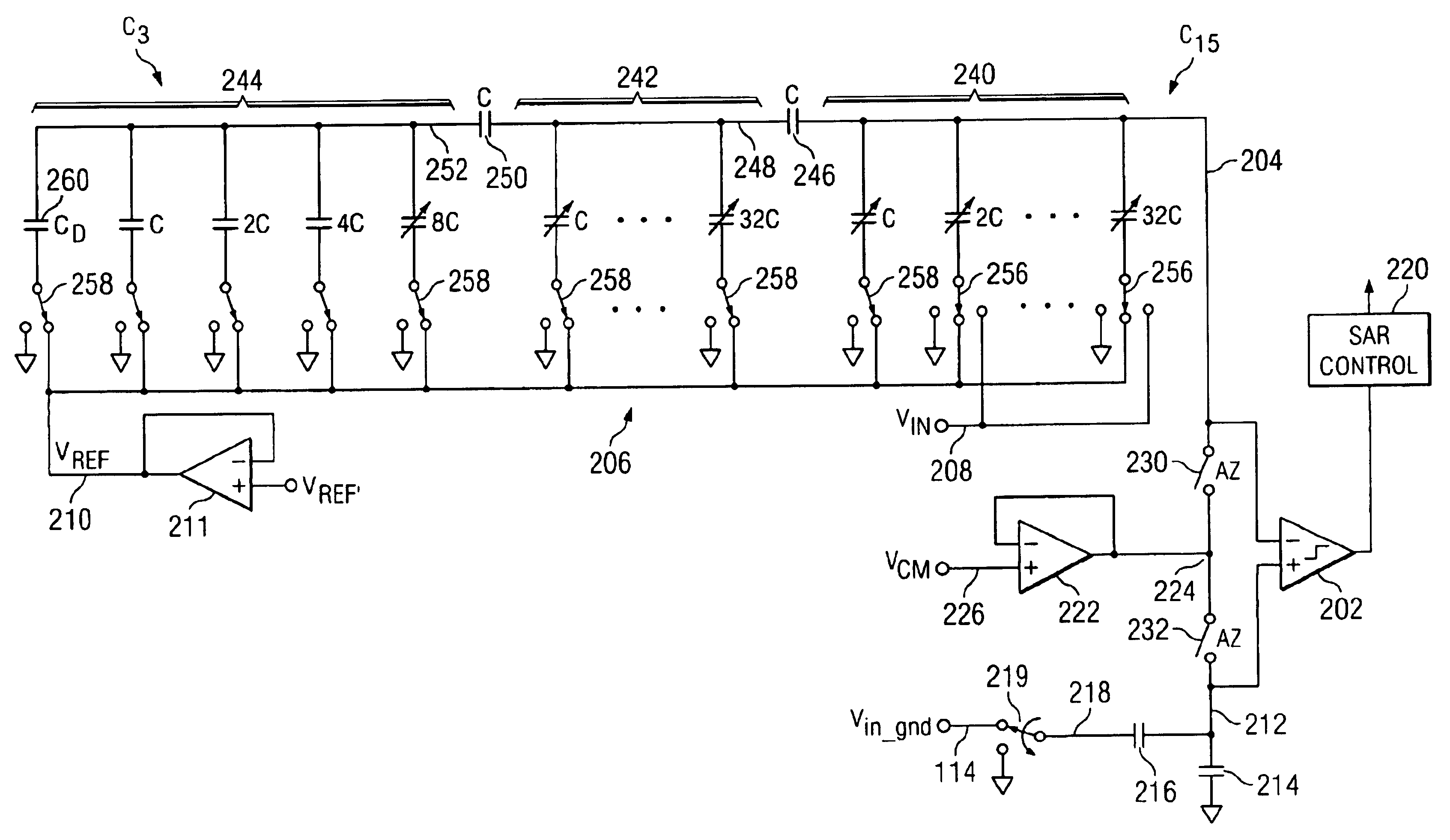

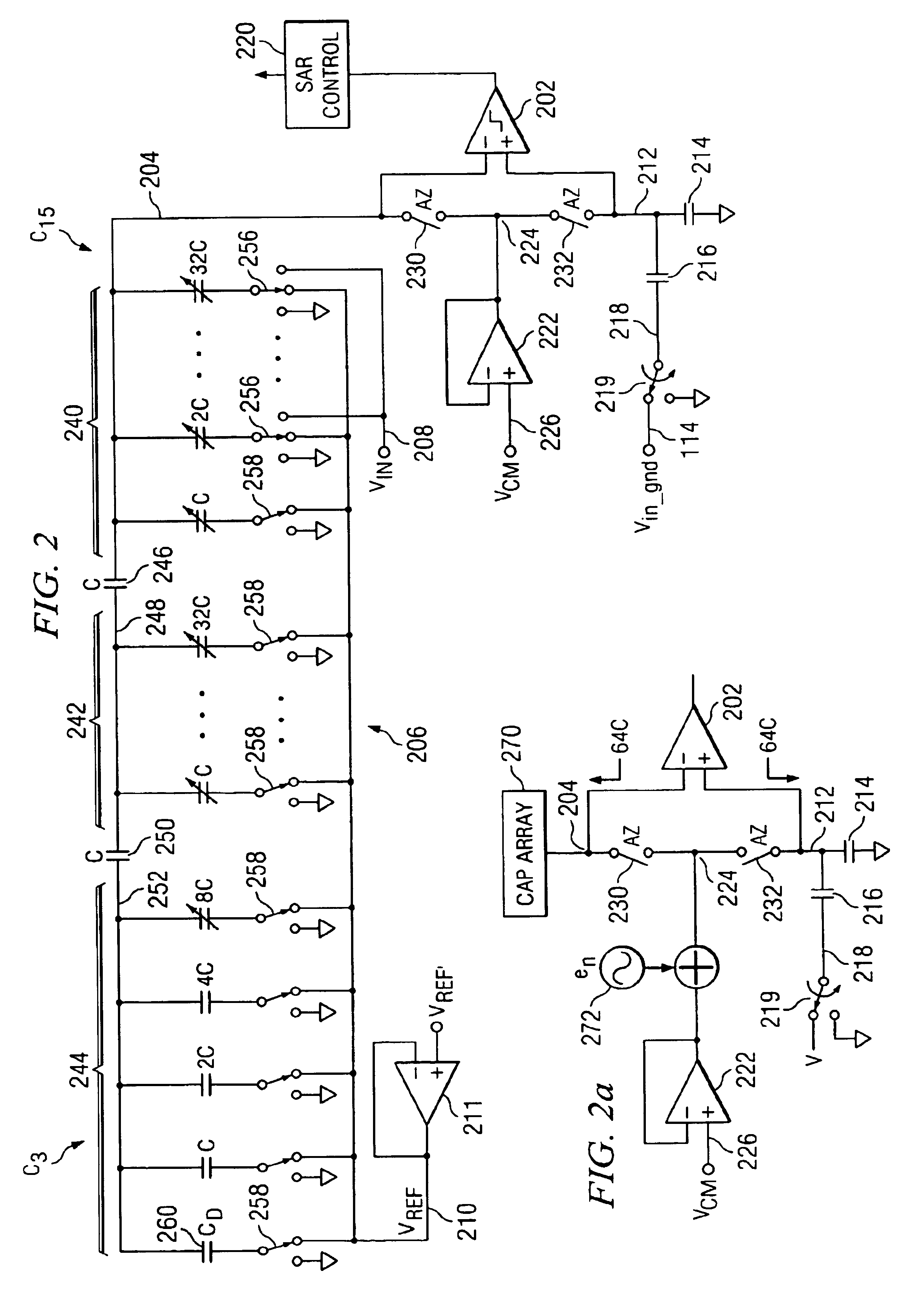

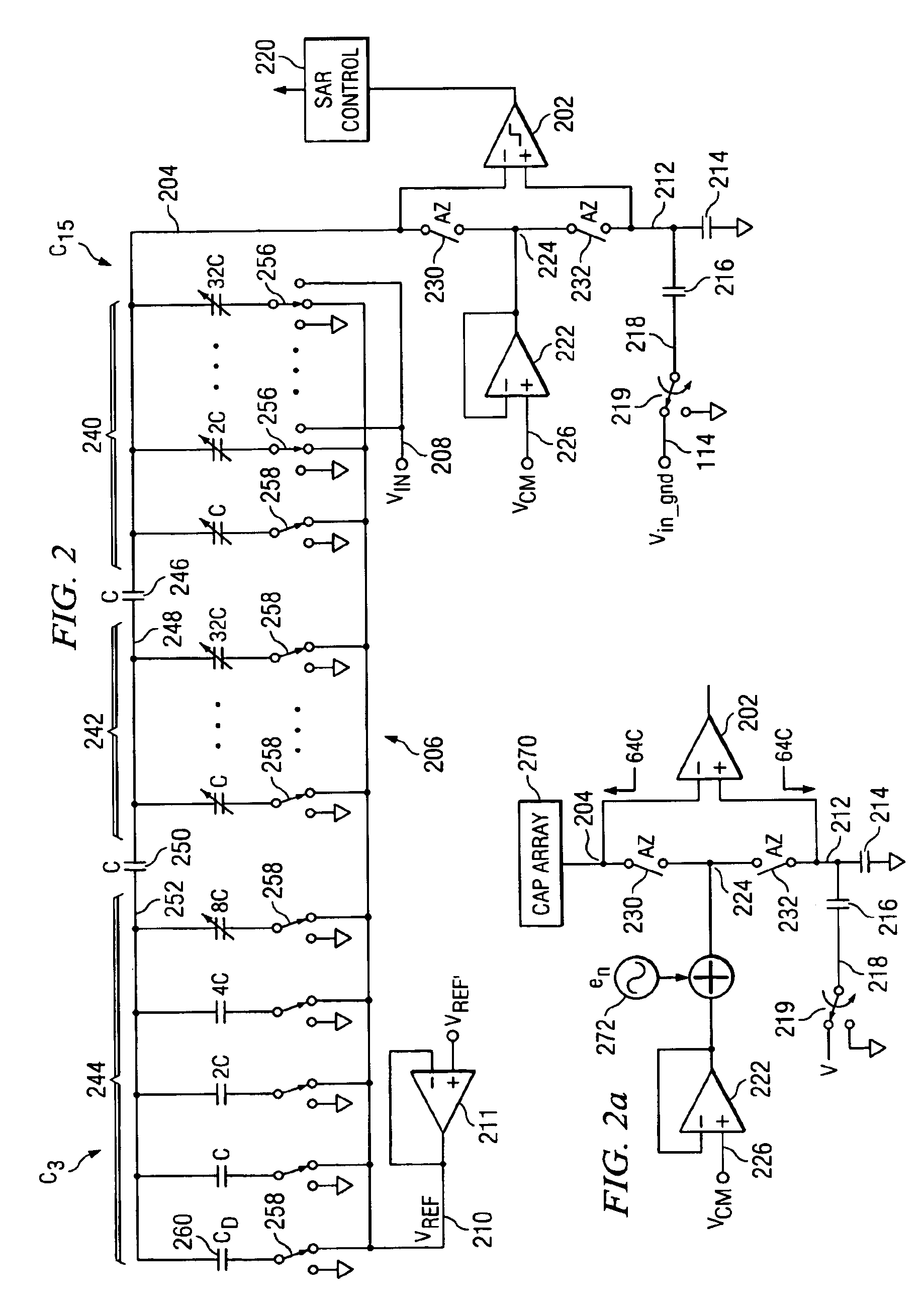

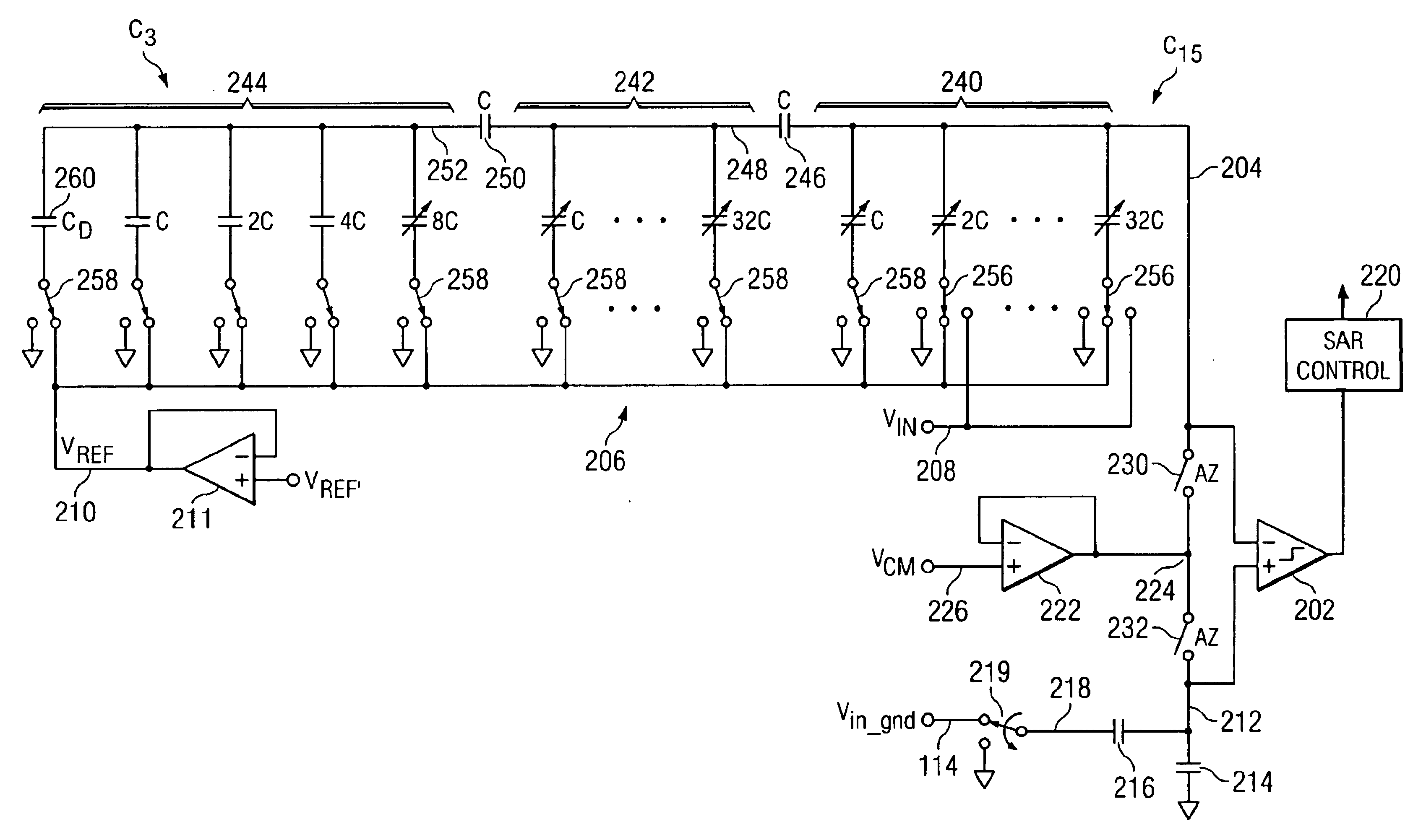

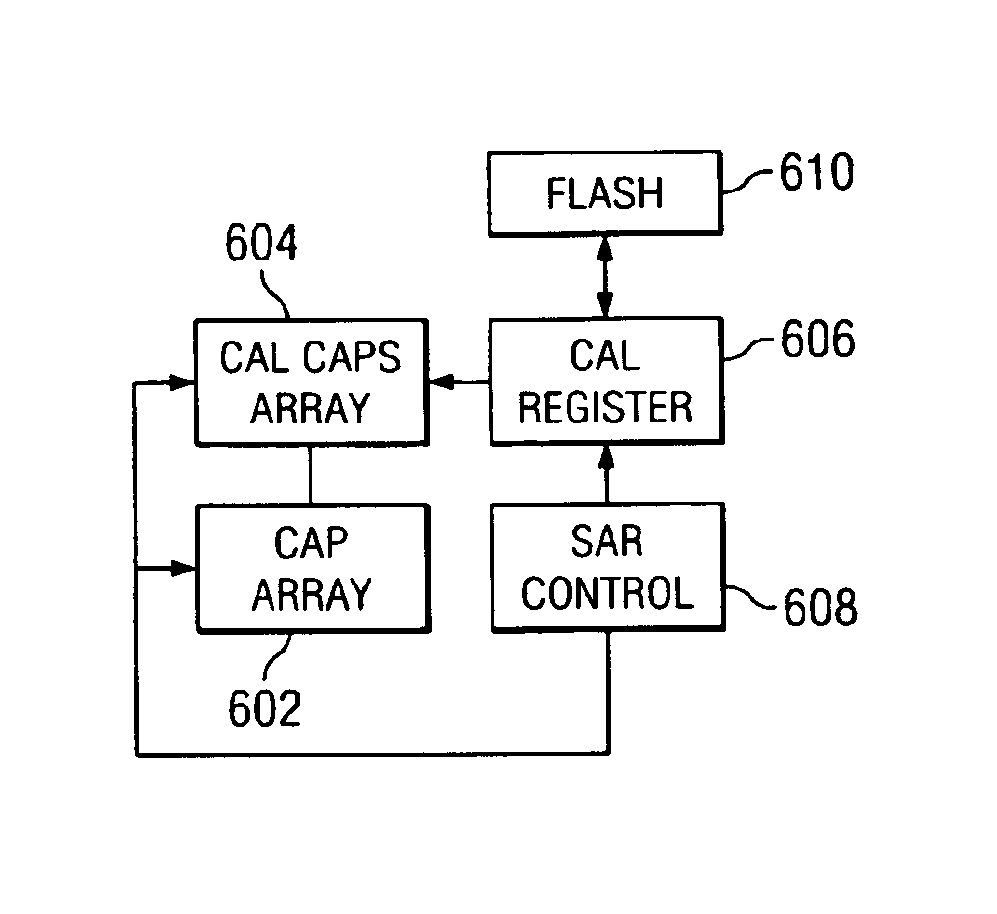

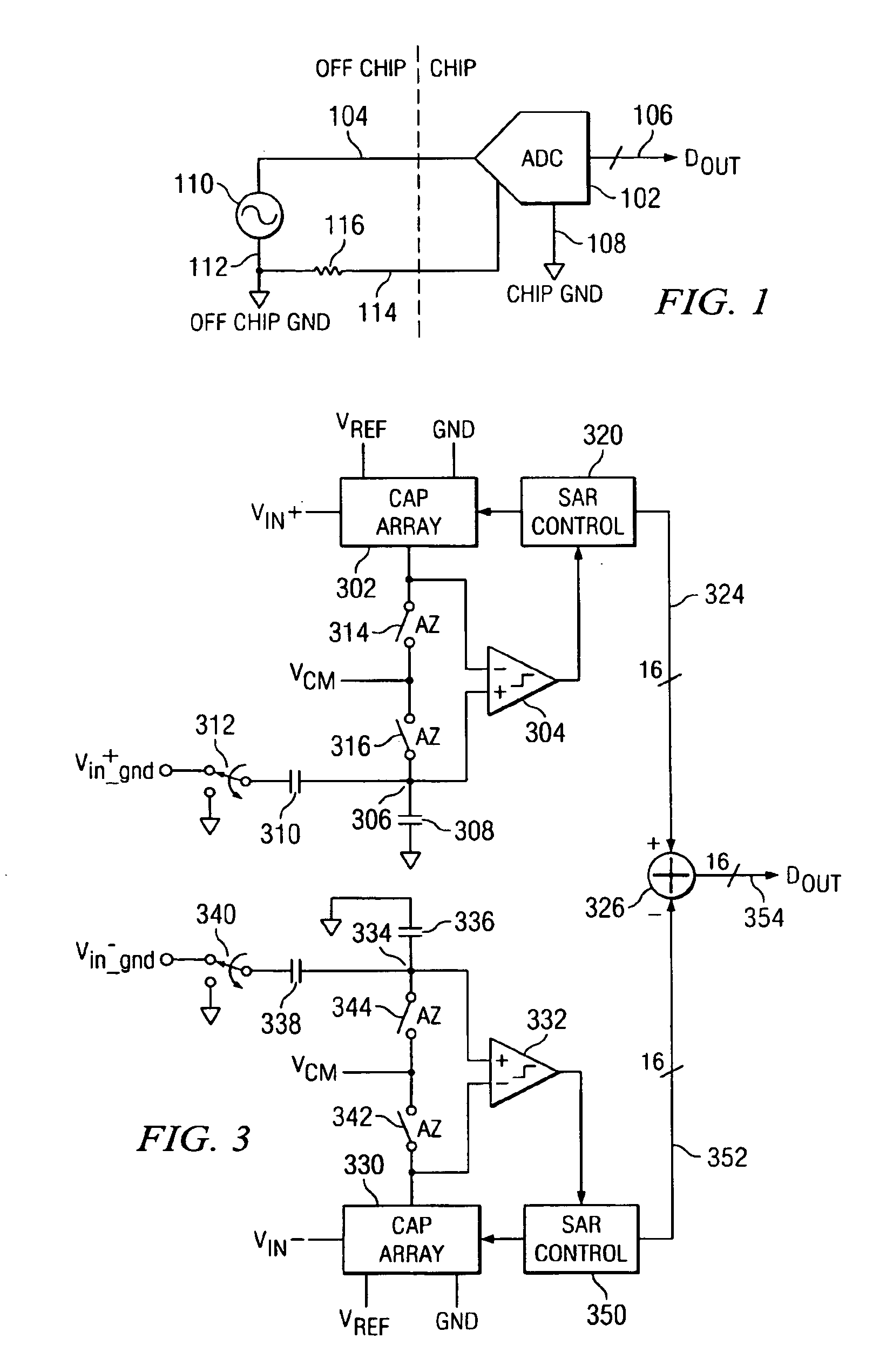

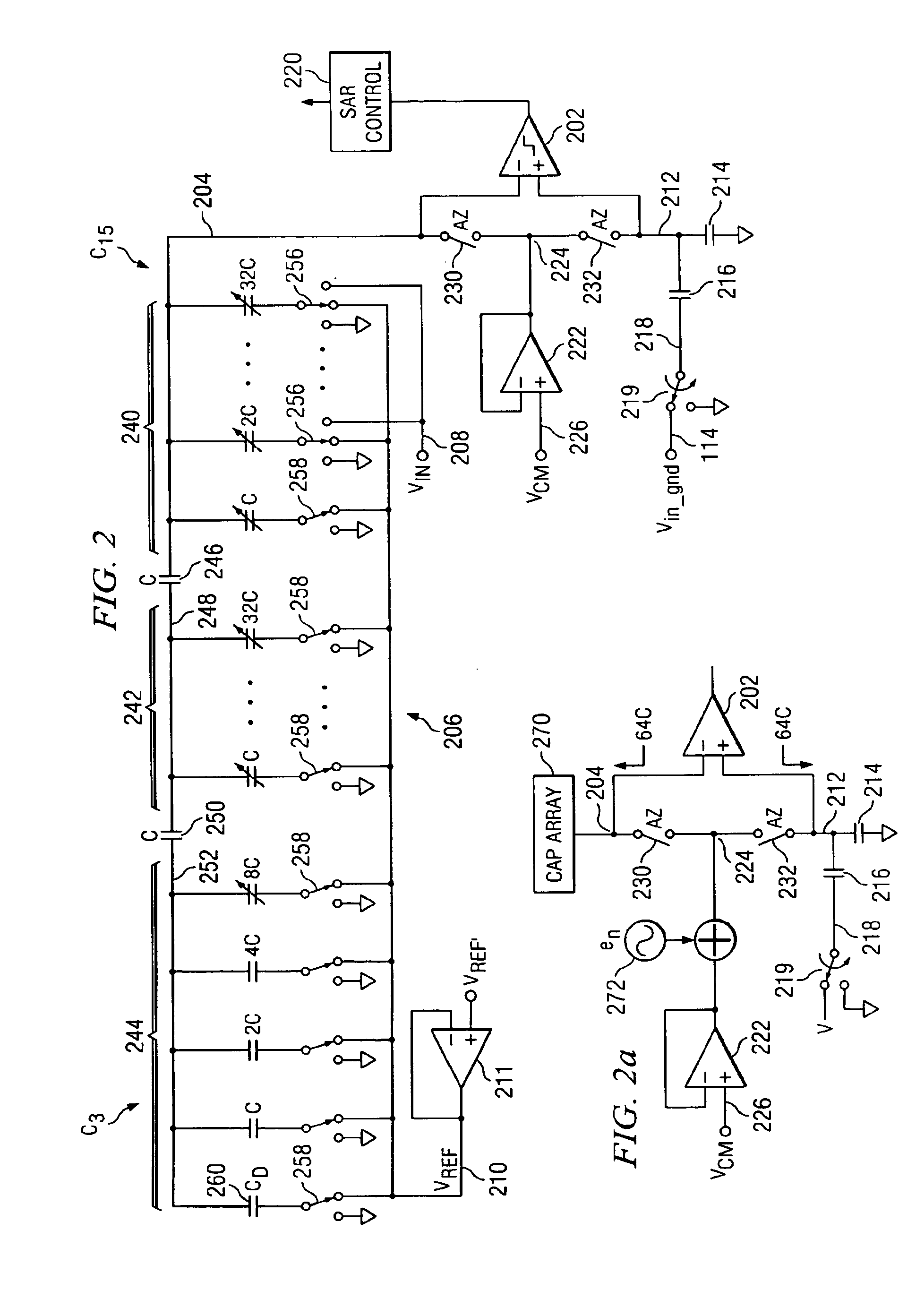

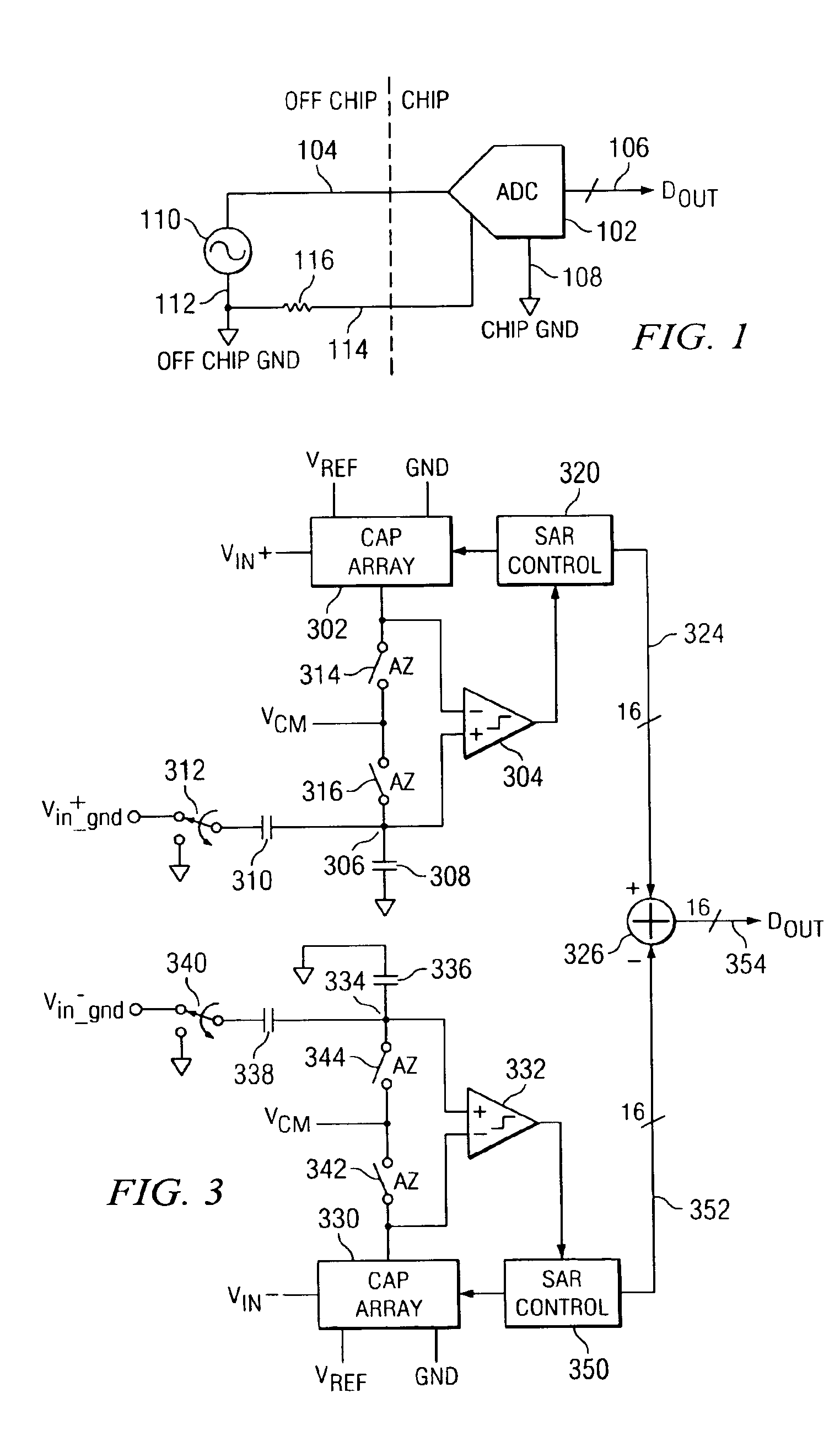

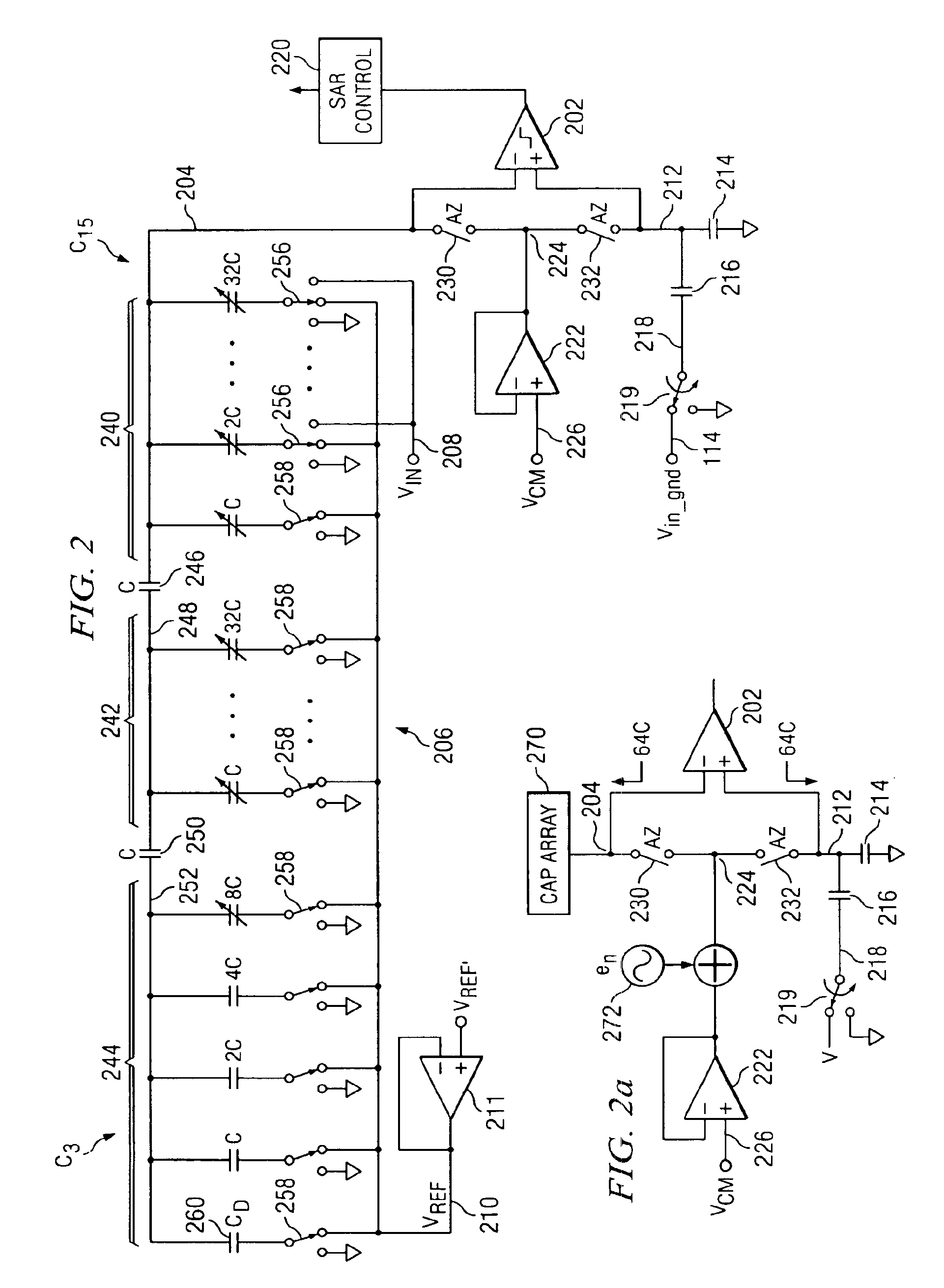

Capacitor calibration in SAR converter

InactiveUS6891487B2Electric signal transmission systemsResistors with plural resistive elementsVoltage referenceSwitched capacitor

Capacitor calibration in SAR converter. A method for calibrating a switched capacitor array in a SAR data converter is disclosed, which array includes a plurality of primary capacitors having a common node plate interfaced to a common node and a switched plate interfaced to a switch that is operable to be switched between first and second reference voltages. A comparator having an input connected to the common node and a reference input connected to a comparator reference node receives a comparator reference voltage. In a first calibration step for calibrating one of the primary capacitors, a reference capacitor is provided and then, the switched plate of the select primary capacitor is connected to the first reference voltage, the switched plate of the other capacitors and the reference capacitor are connected to the second reference voltage, and the common node and the comparator reference node are driven with a driver to dispose a first voltage thereon. In a second calibration step, the common node is allowed to float, the switched plate of the select primary capacitor is connected to the second reference voltage, the switched plate of the reference capacitor is connected to the first reference voltage, and the voltage on the common node is compared to the first voltage on the comparator reference node. A determination is then made as to whether the voltage on the common node is greater than the first voltage. A plurality of trim capacitors are provided and, if in the second calibration step, the voltage on the common node was determined to be greater than the first voltage, then one of the trim capacitors is disposed in parallel with the select one of the primary capacitors and then the first and second calibrating steps are repeated.

Owner:SILICON LAB INC

High speed comparator with blocking switches for SAR convertor

InactiveUS6985101B2Electric signal transmission systemsResistors with plural resistive elementsCapacitanceVoltage reference

Open loop common mode driver for switched capacitor input to SAR. A method for controlling the operation of a SAR conversion cycle. The method includes the steps of first initiating the SAR conversion cycle by connecting one side of a plurality of capacitors in a capacitor array to a first capacitor reference voltage and the other side of the plurality of capacitors to the input of a comparator. This is followed by the step of sequentially switching in a plurality of compare cycles the one side of a select one or ones of the capacitors to a second capacitor reference voltage to change the voltage on the input of the comparator. Then, a compare operation is initiated after initiation of each compare cycle to compare the value on the input of the comparator with a compare reference voltage after a predetermined settling time has elapsed from the beginning of the initiation of each compare cycle. During the compare cycle, transients due to voltage variations on the input of the comparator are reduced as a result of the step of sequentially switching, the reduction operating for a predetermined portion of the associated compare cycle.

Owner:SILICON LAB INC

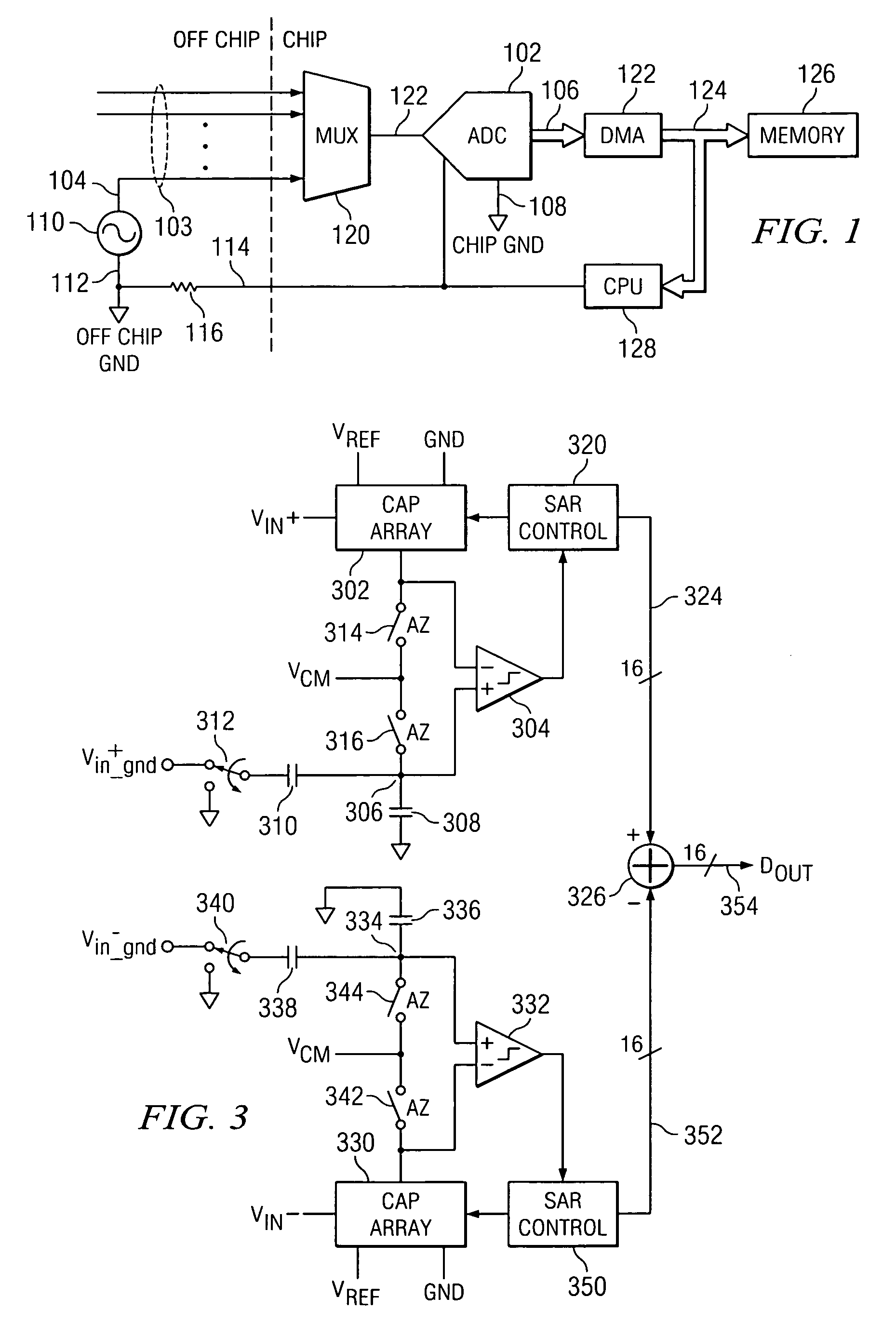

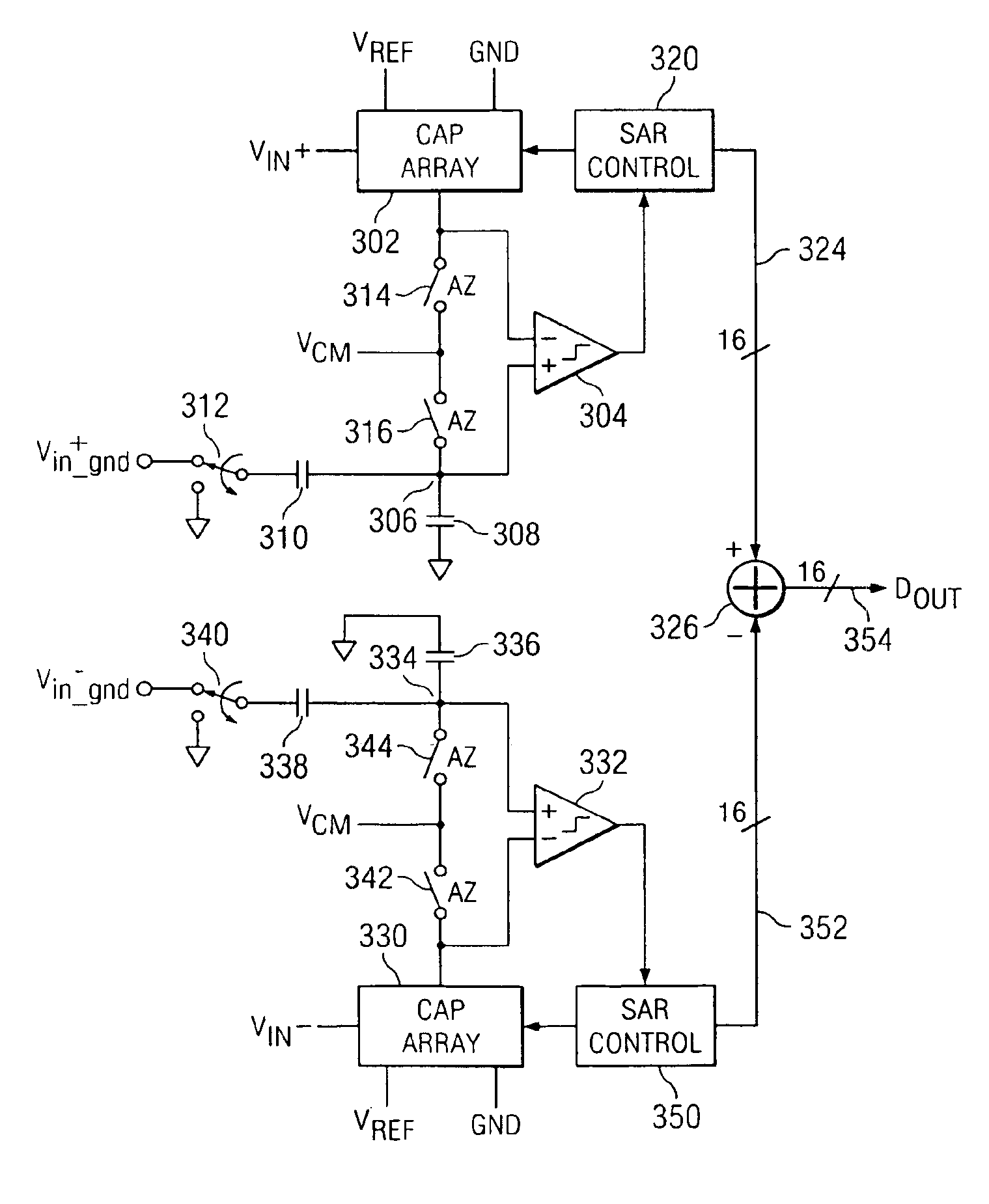

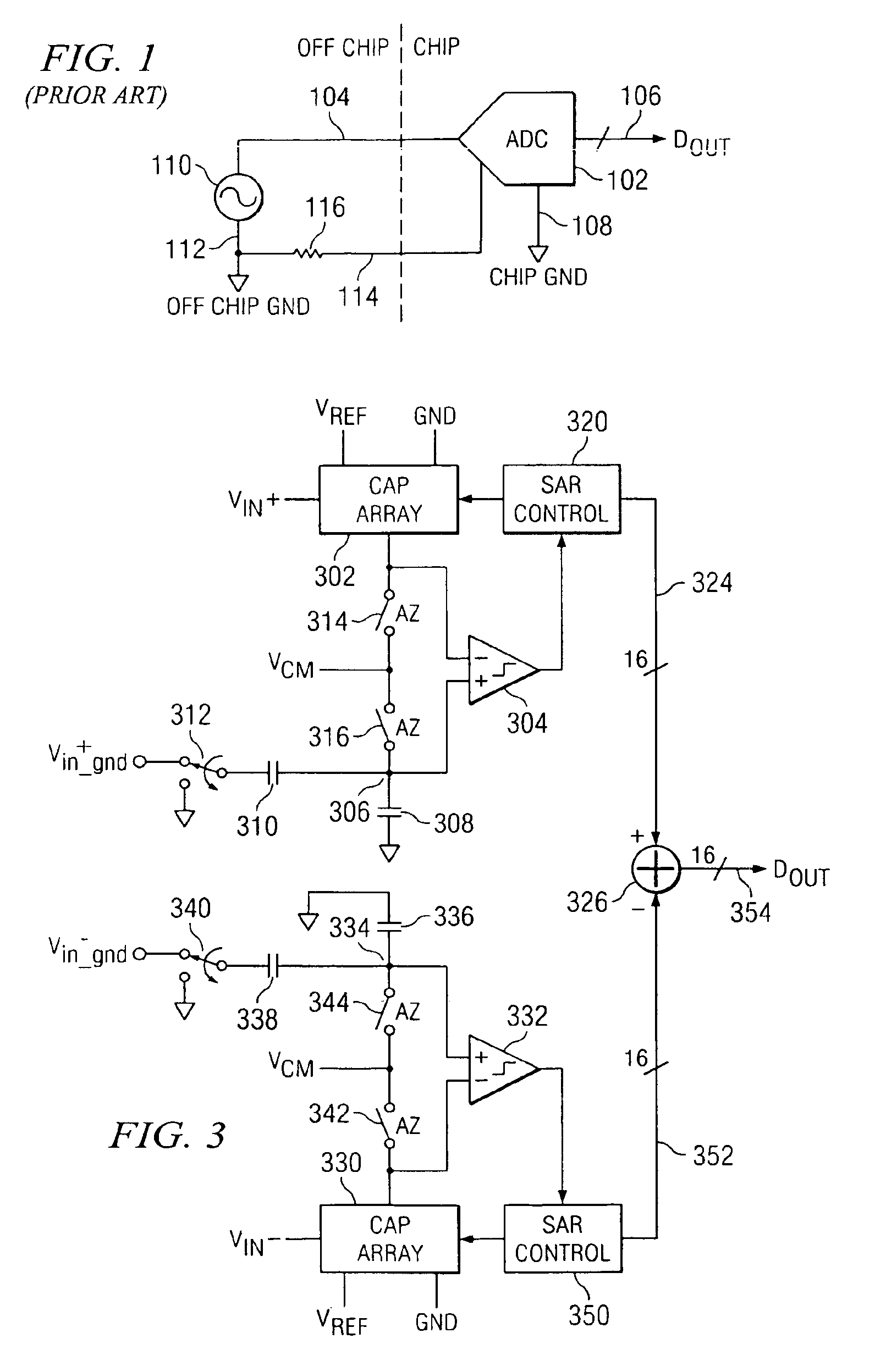

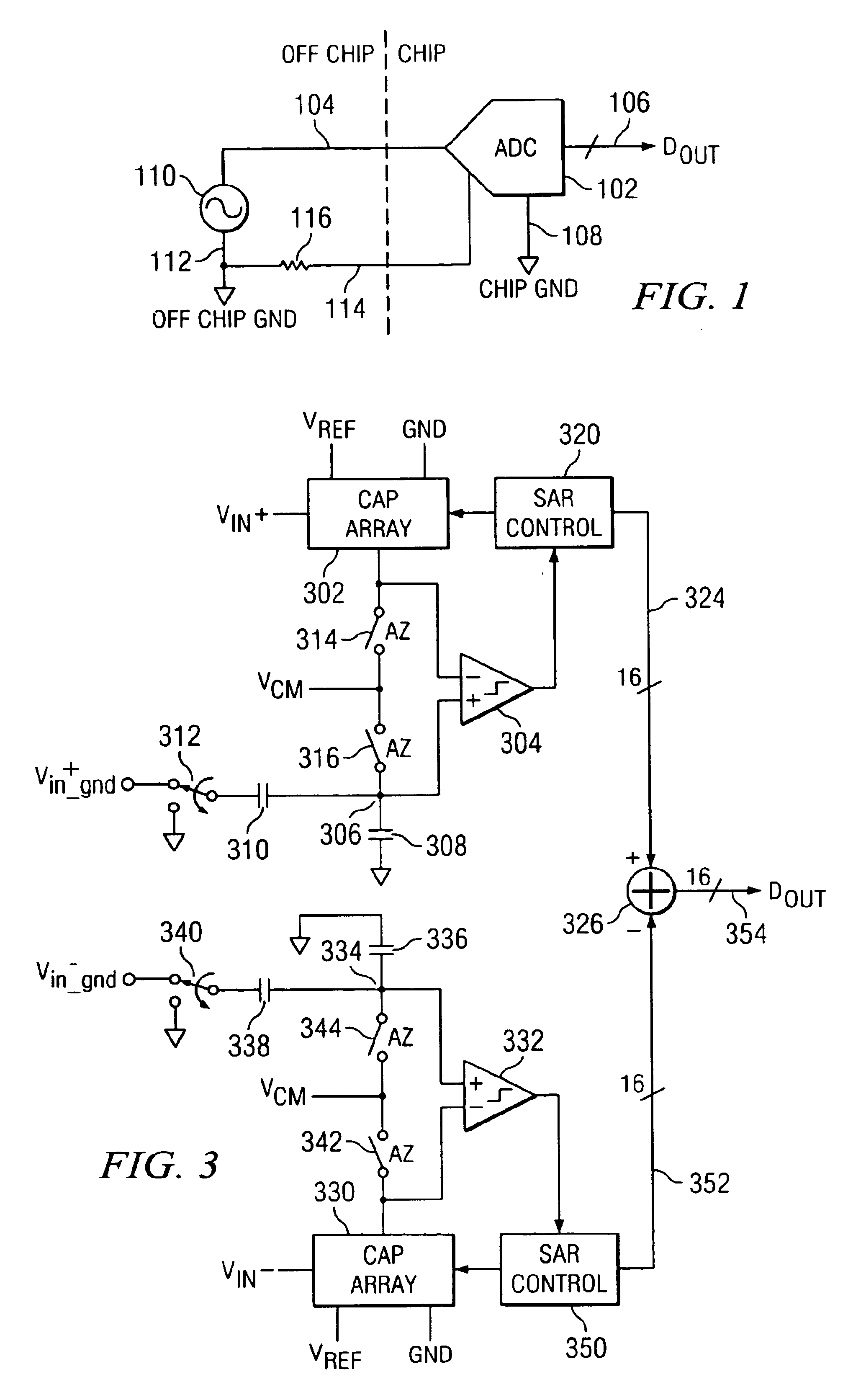

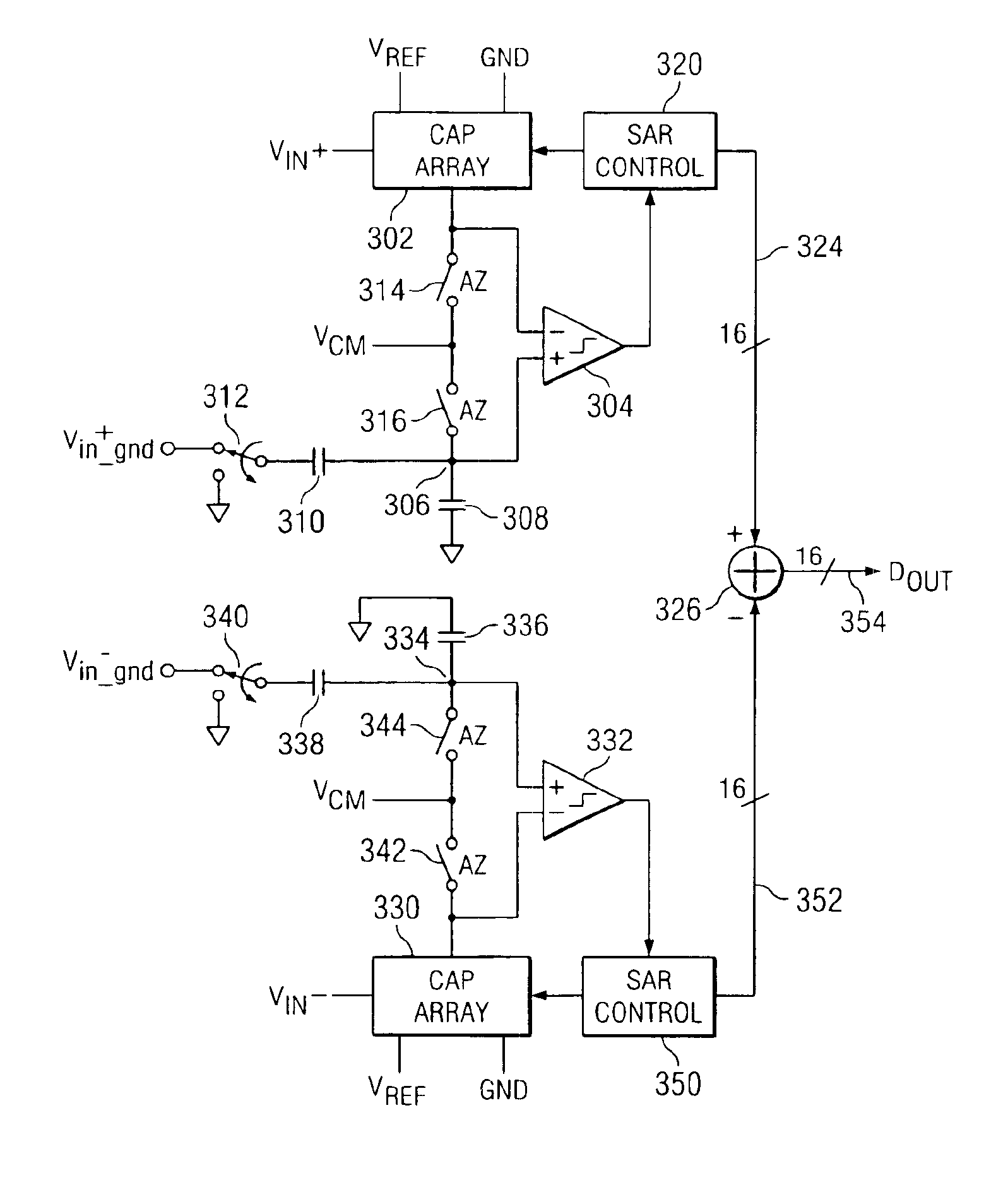

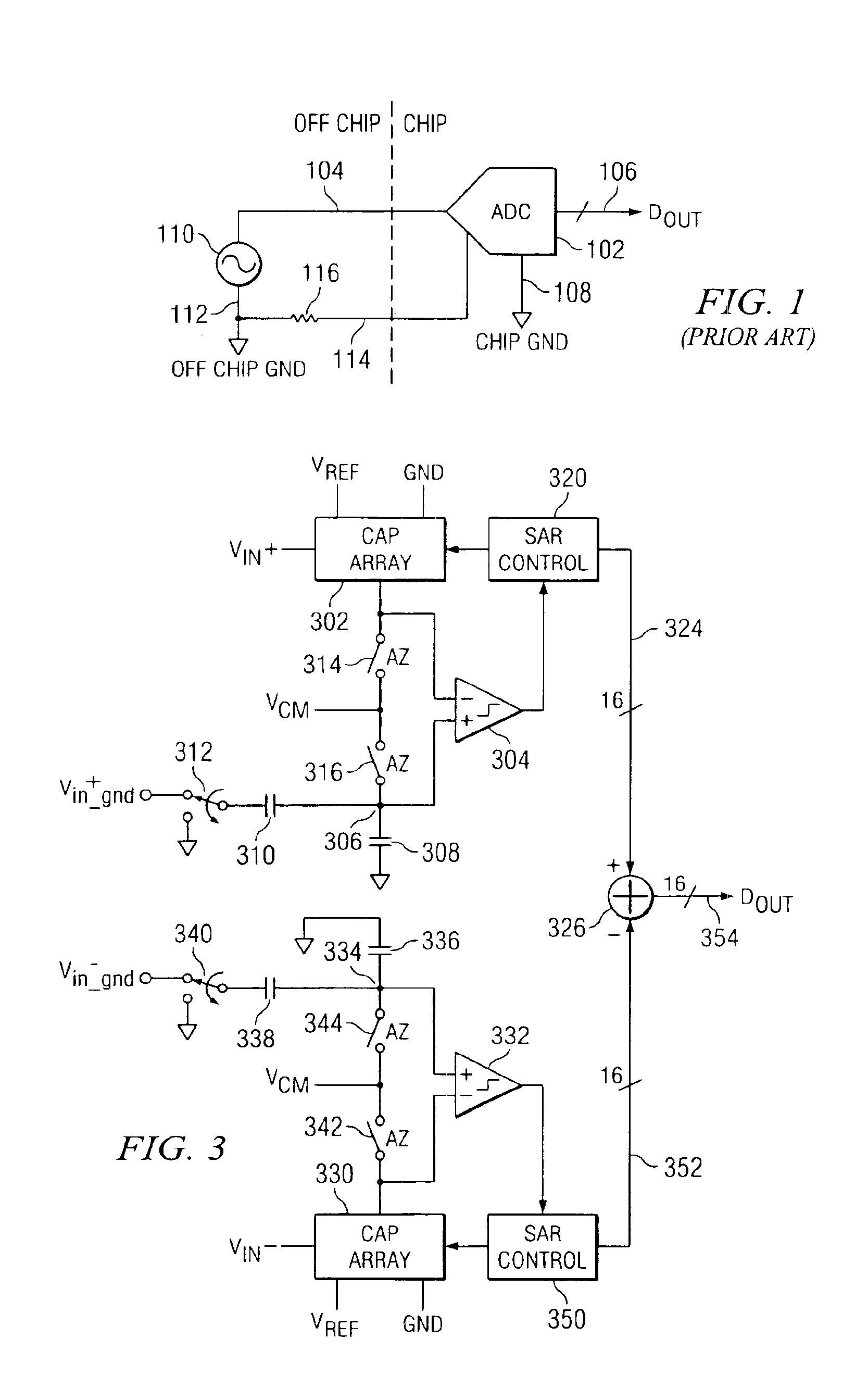

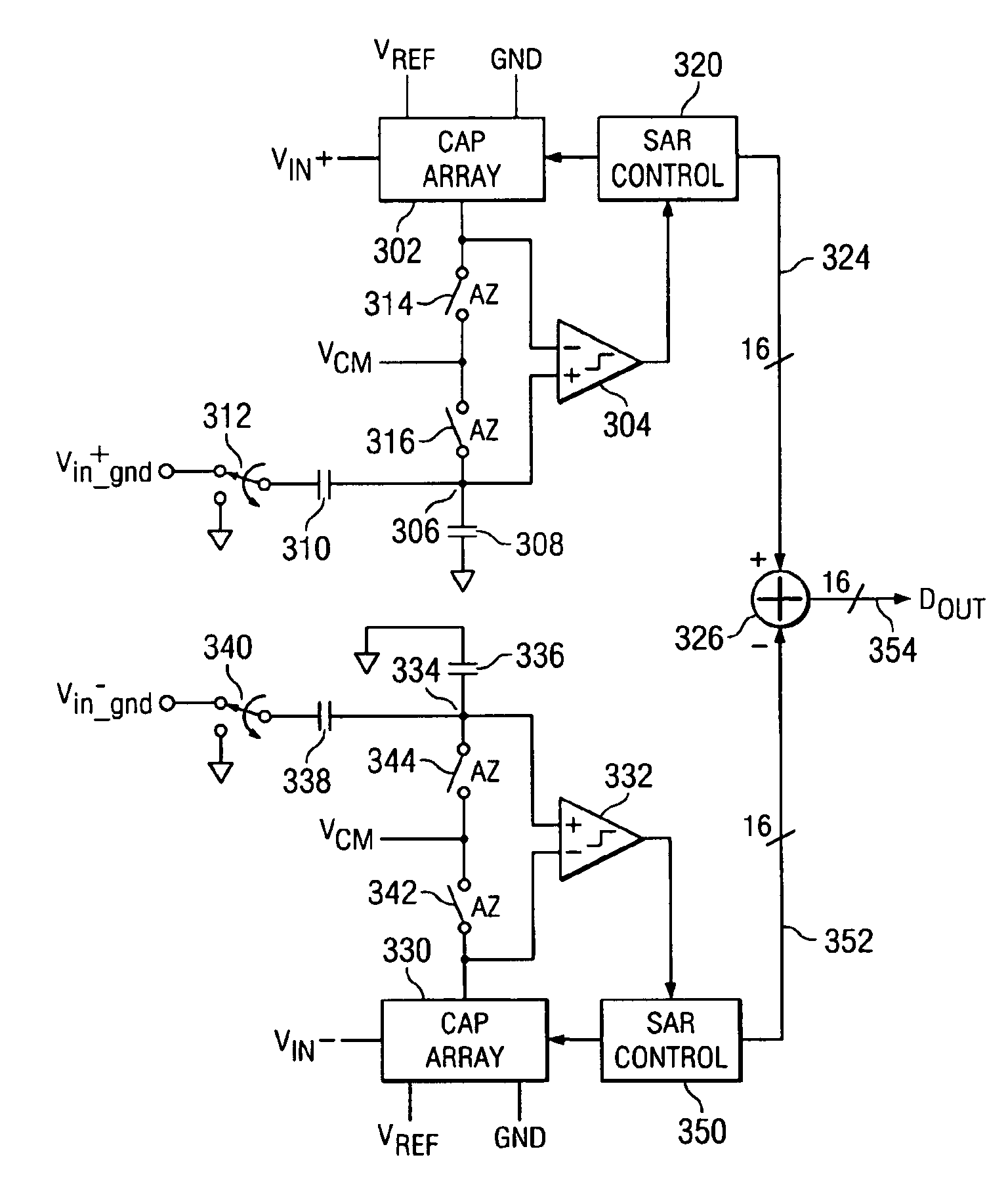

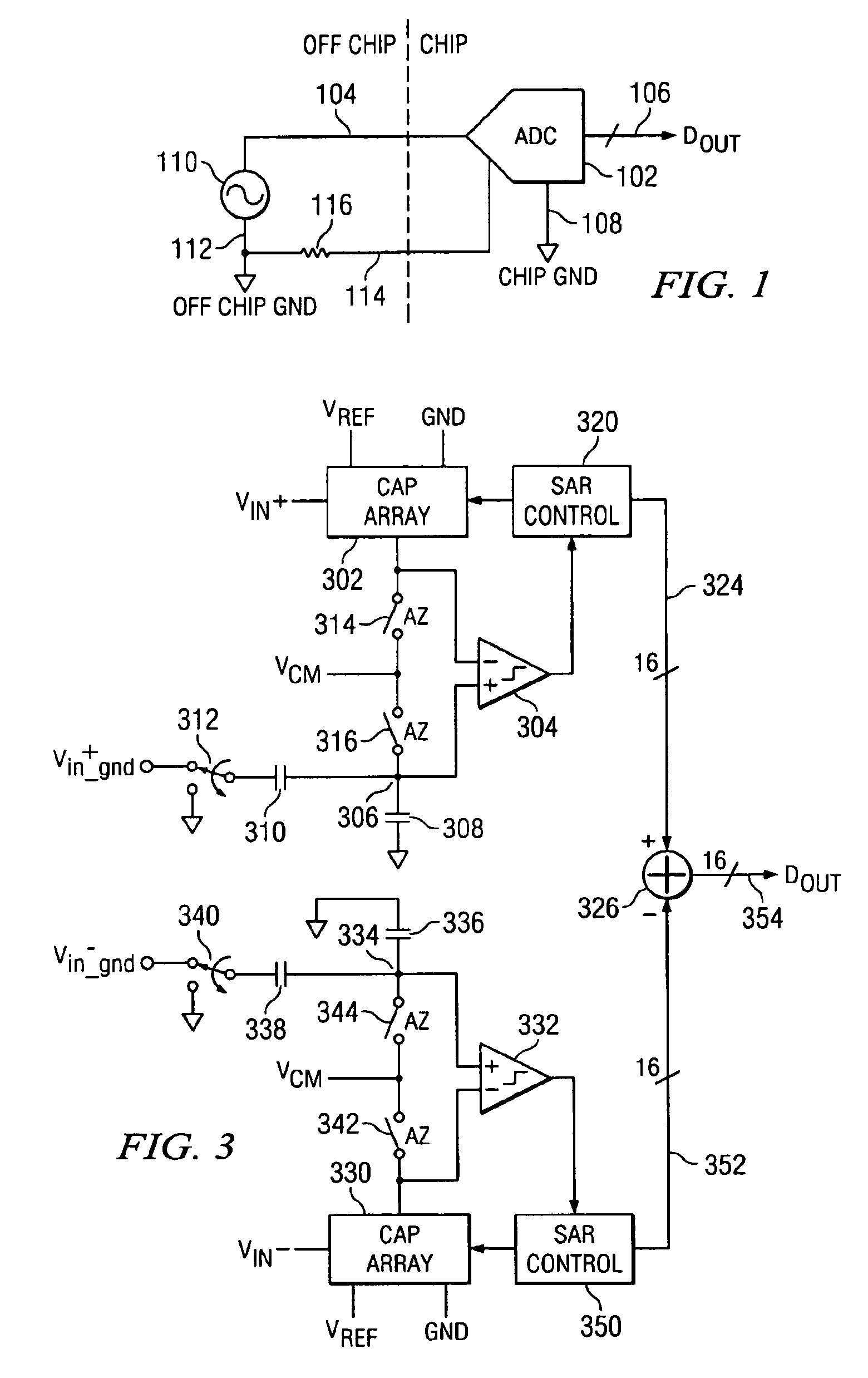

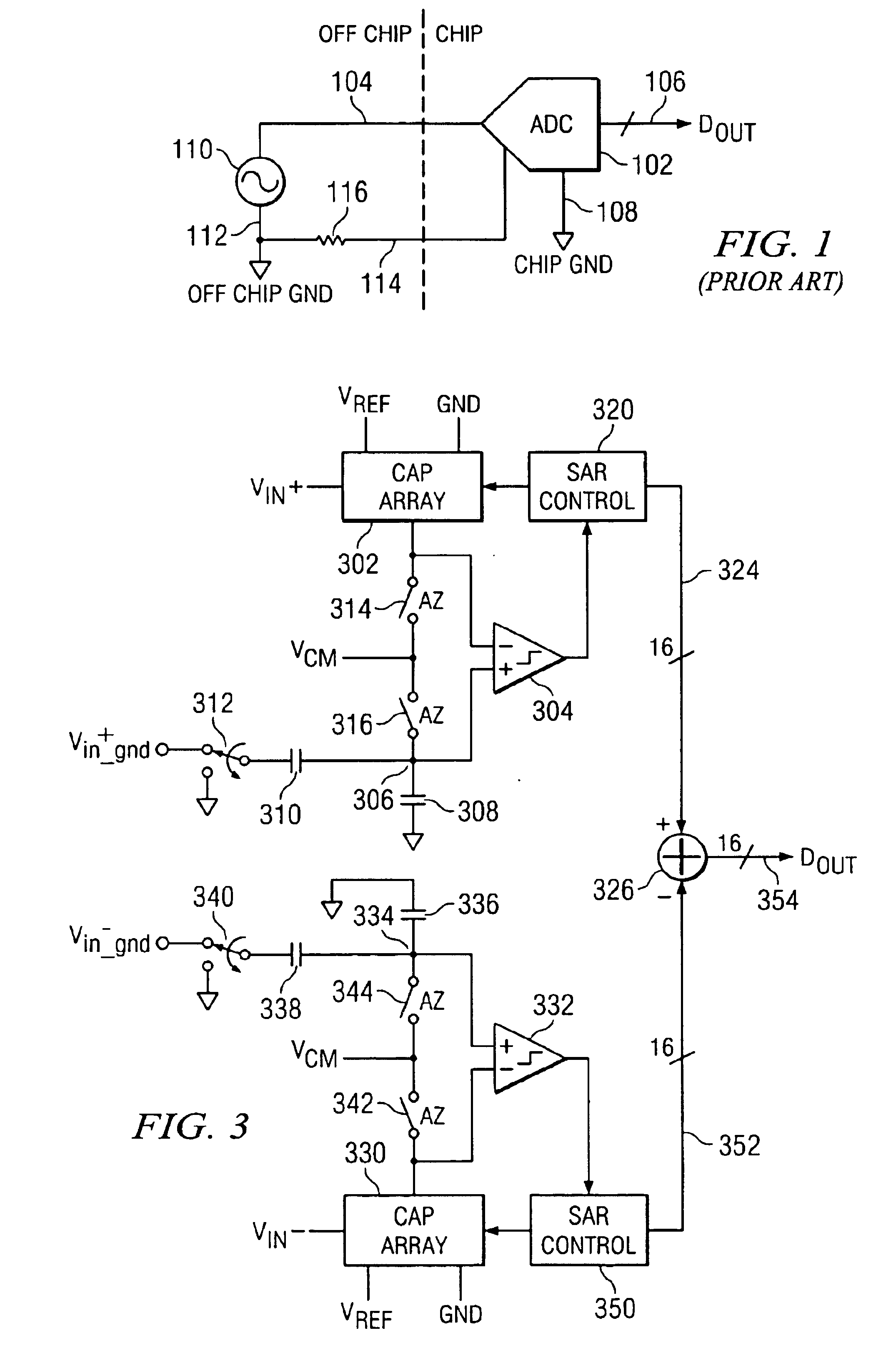

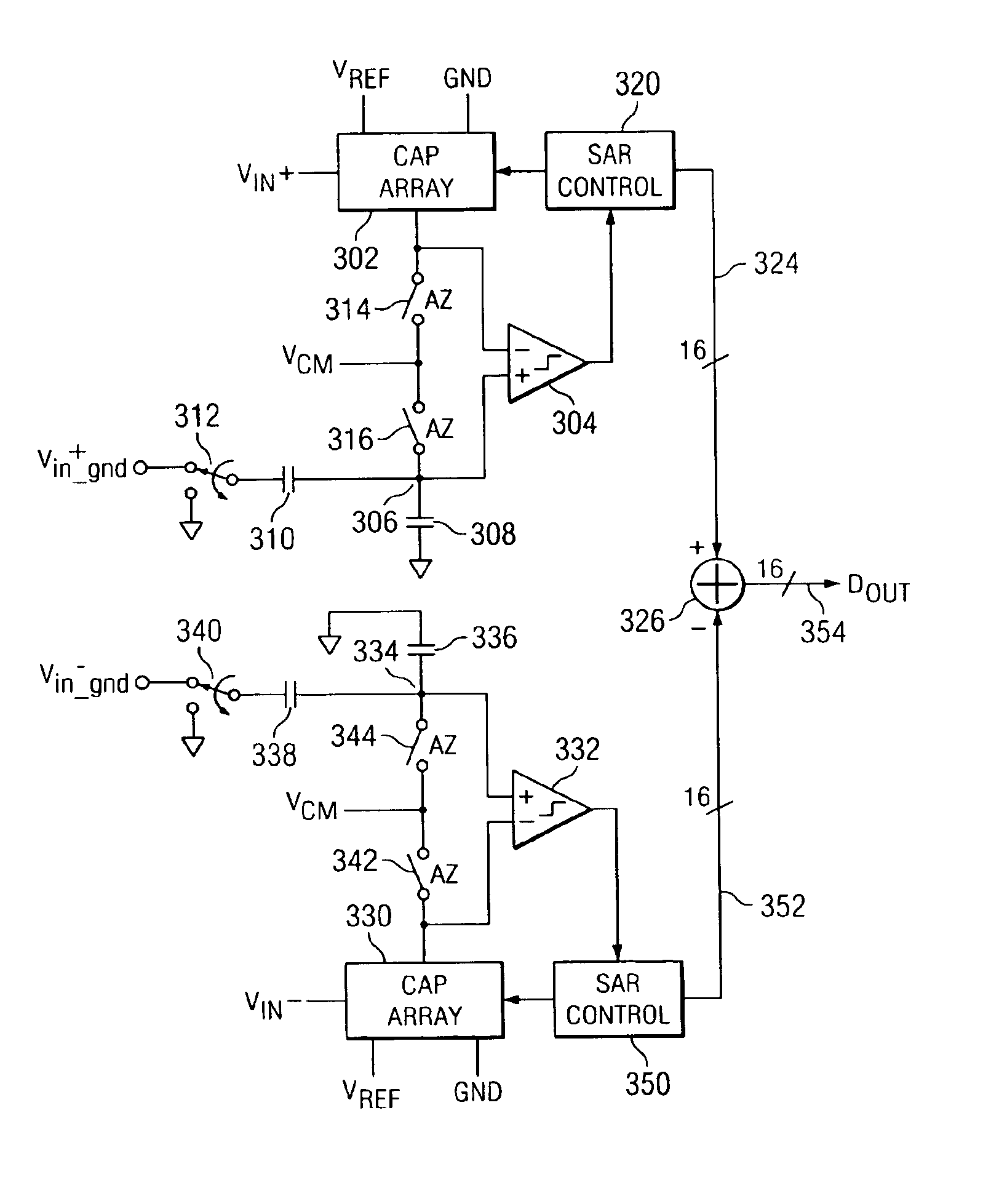

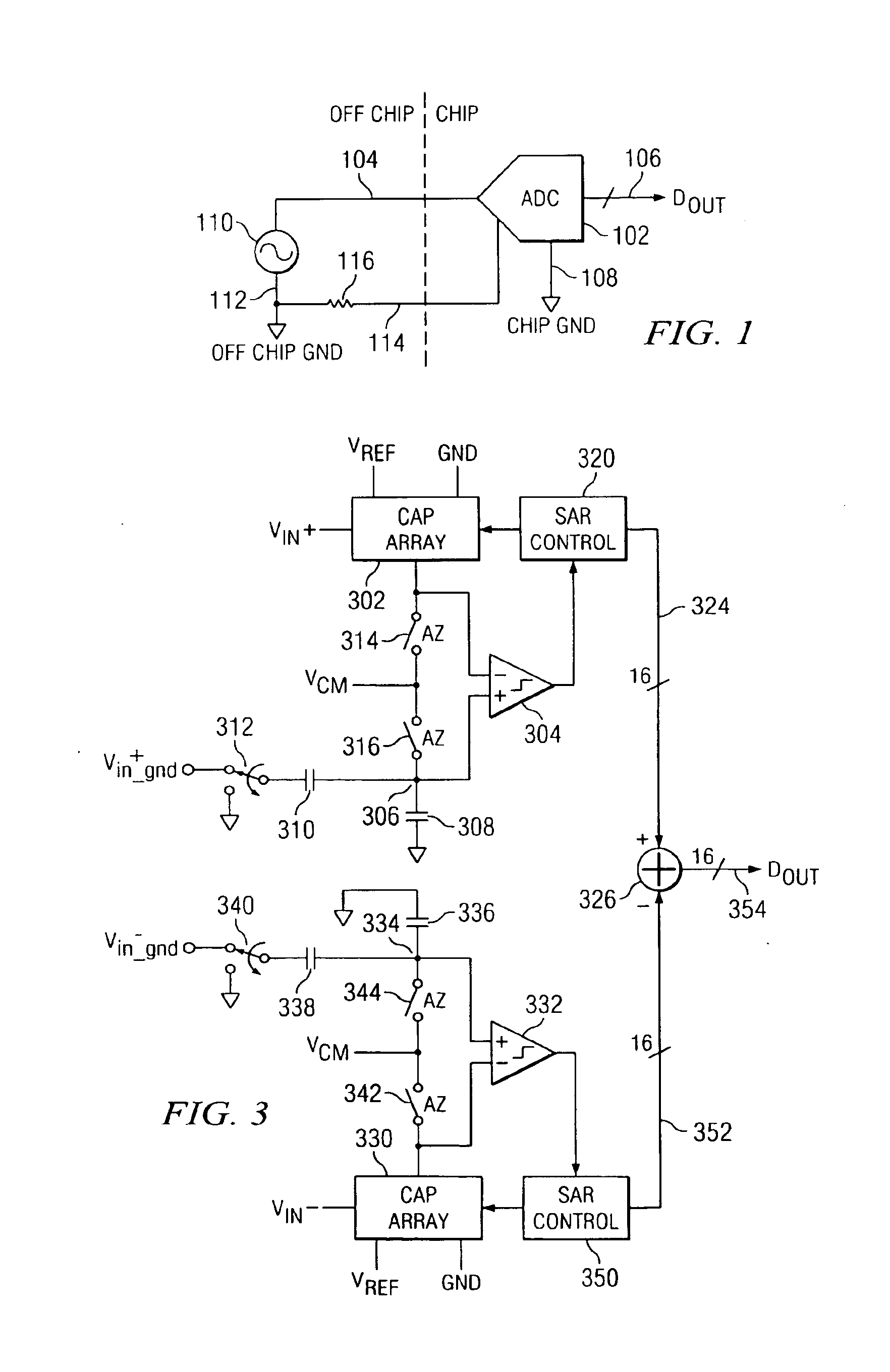

SAR analog-to-digital converter with two single ended inputs

InactiveUS6882298B2Electric signal transmission systemsResistors with plural resistive elementsDigital dataDigital down converter

Self calibrating SAR analog-to-digital converter. A data converter for converting analog data on a differential data input having a positive analog input terminal and a negative analog input terminal to digital data. The data converter includes a first single ended successive approximation register (SAR) analog-to-digital converter for converting the analog signal on the positive analog input terminal to a first digital signal and a second single ended successive approximation register (SAR) analog-to-digital converter for converting the analog signal on the negative analog input terminal to a second digital signal. A circuit for combining the first and second digital signals as a digital output signal for the data converter that represents the difference between the analog signals on the positive and negative analog input terminals.

Owner:SILICON LAB INC

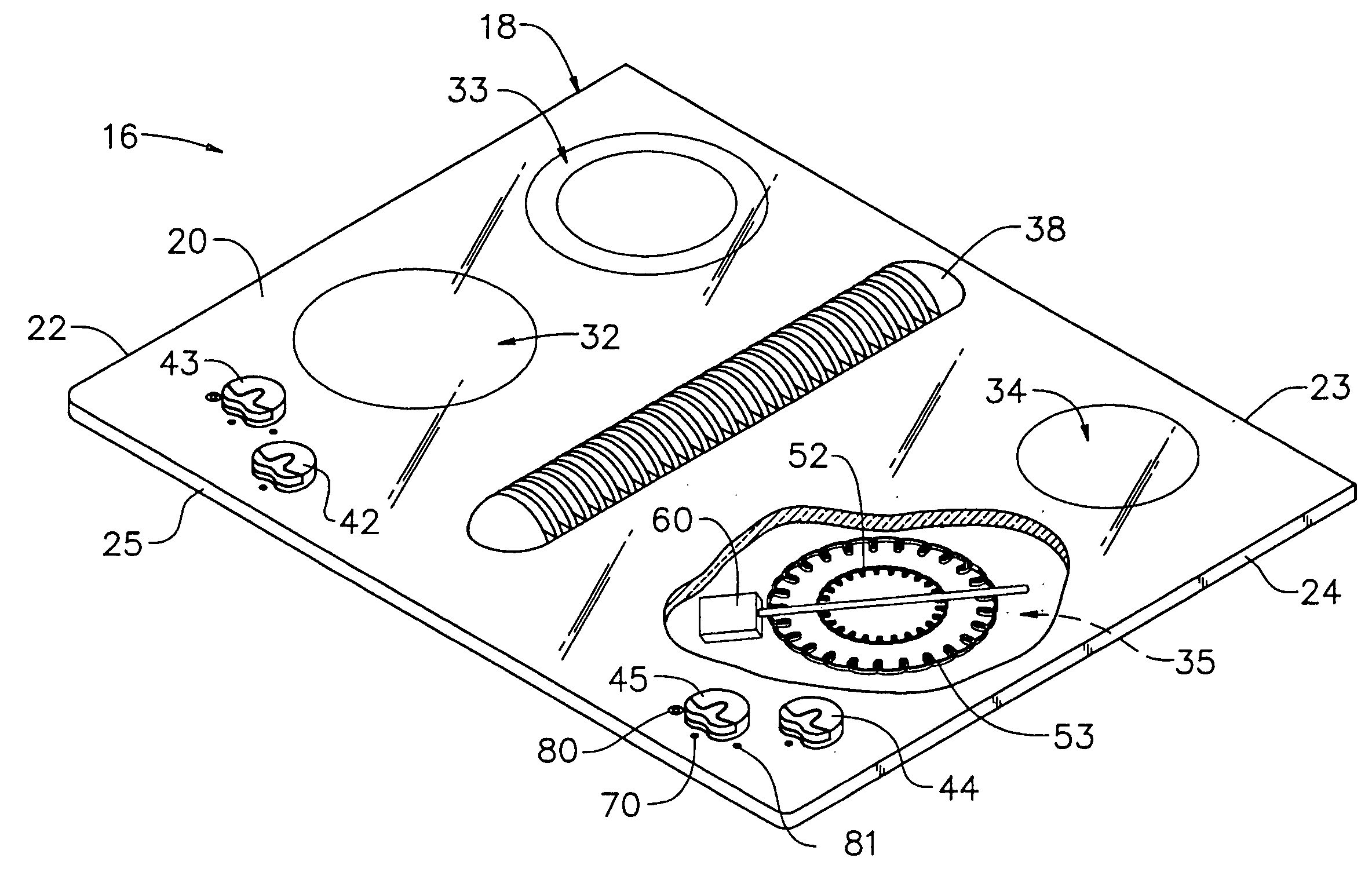

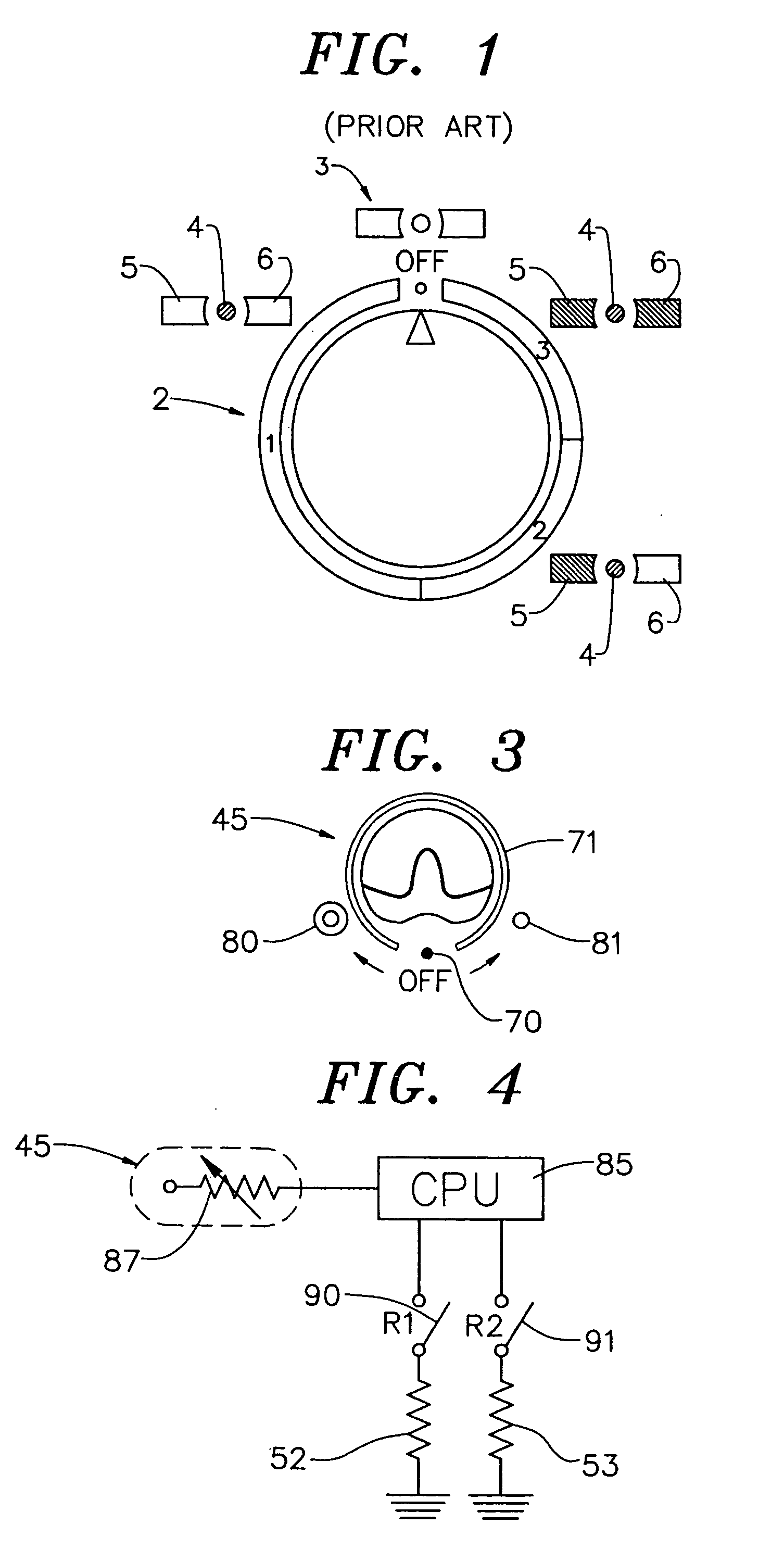

Infinite temperature control for heating element of a cooking appliance

ActiveUS20050184046A1Readily apparentDomestic stoves or rangesLighting and heating apparatusTemperature controlElectrical resistance and conductance

A cooking appliance includes a cooktop having at least one heating zone having first and second heating elements and a control element for setting a desired cooking temperature for the heating zone. When the control element is rotated in a first direction, only the first heating element will be activated and, when rotated in a second direction, both the first and second heating elements are activated. The control element includes a variable resistor that changes resistance as the control element is rotated through nearly 360° to alter the operational state of the heating element(s). A controller senses the change in resistance and determines in which direction the control element is rotated so as to activate the appropriate heating element(s).

Owner:MAYTAG

Bi-directional deflectable resistor

ActiveUS7277004B2Improve the immunityResistance/reactance/impedenceCurrent responsive resistorsElectrical resistance and conductanceEngineering

A system and method for a bi-directional deflectable resistor. The bi-directional deflectable resistor has a first layer of conductive material on a top surface of a substrate and a second layer of conductive material on a bottom surface of a substrate, each layer having a resistance that changes predictably when an electrical signal is applied thereto. The change of resistance of either the first layer of conductive material or the second layer of conductive material reflects an amount of deflection of the respective layer. Having two layers of conductive material allows for the measurement of deflection in all directions.

Owner:SENSITRON INC

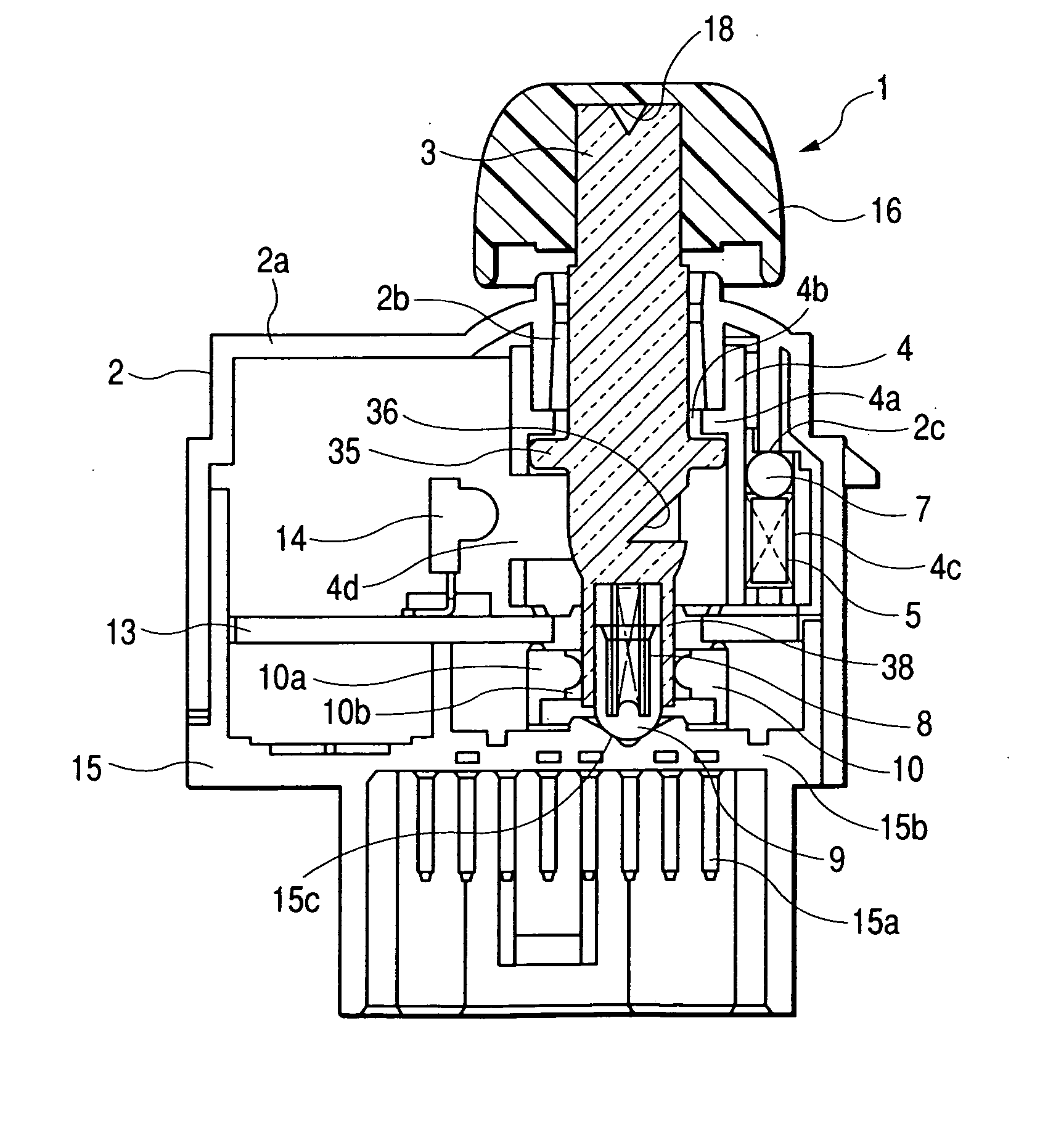

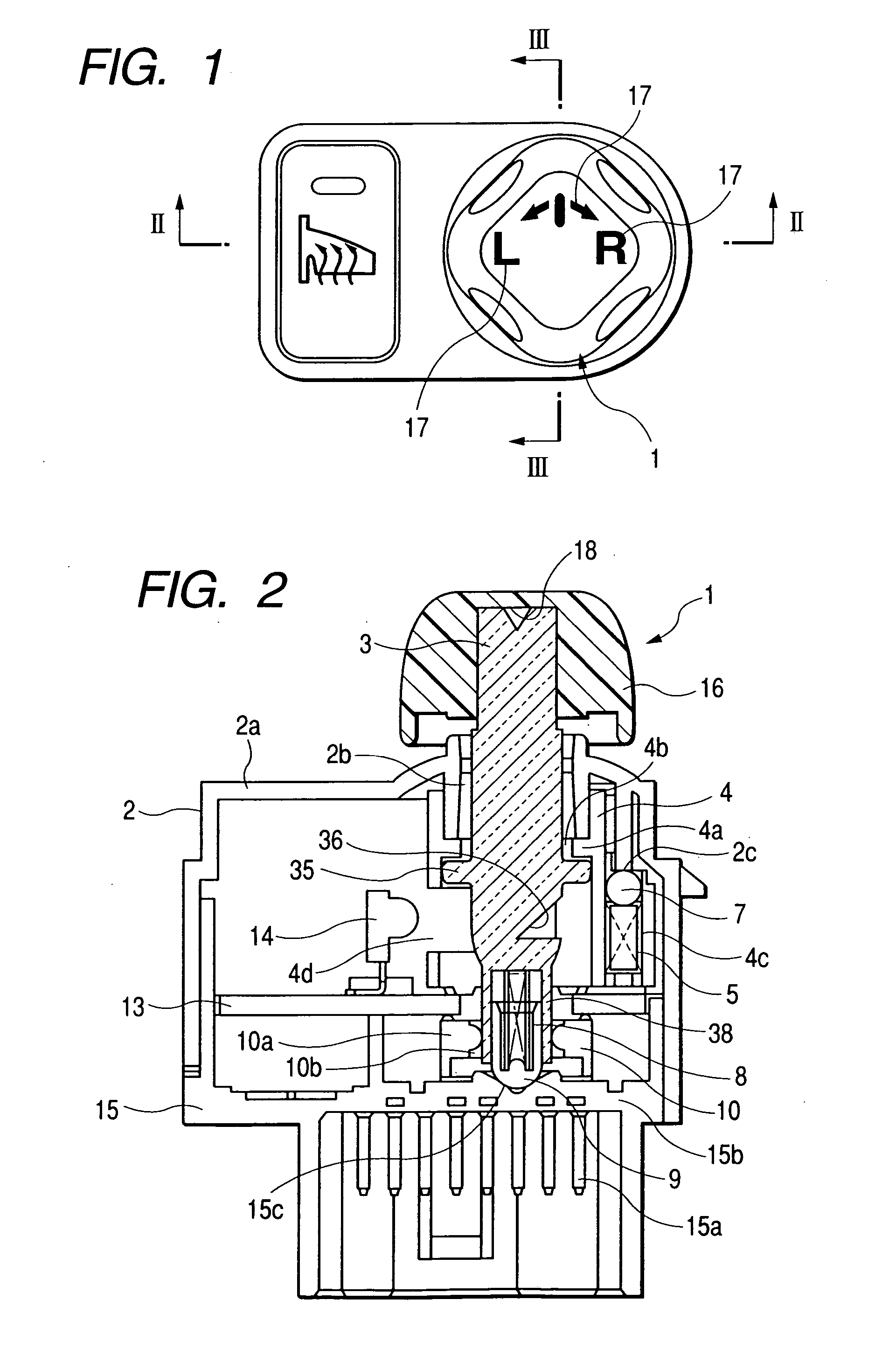

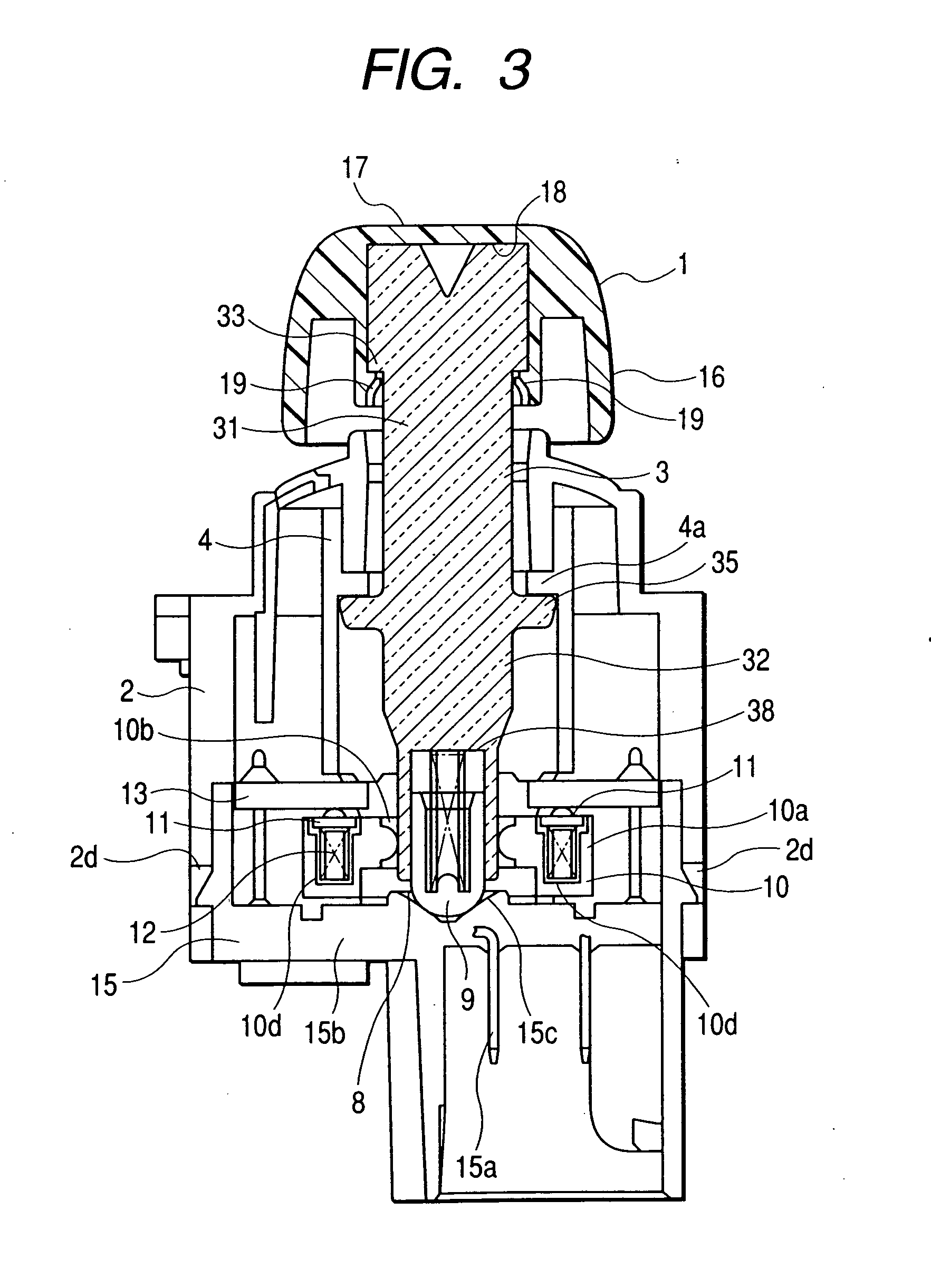

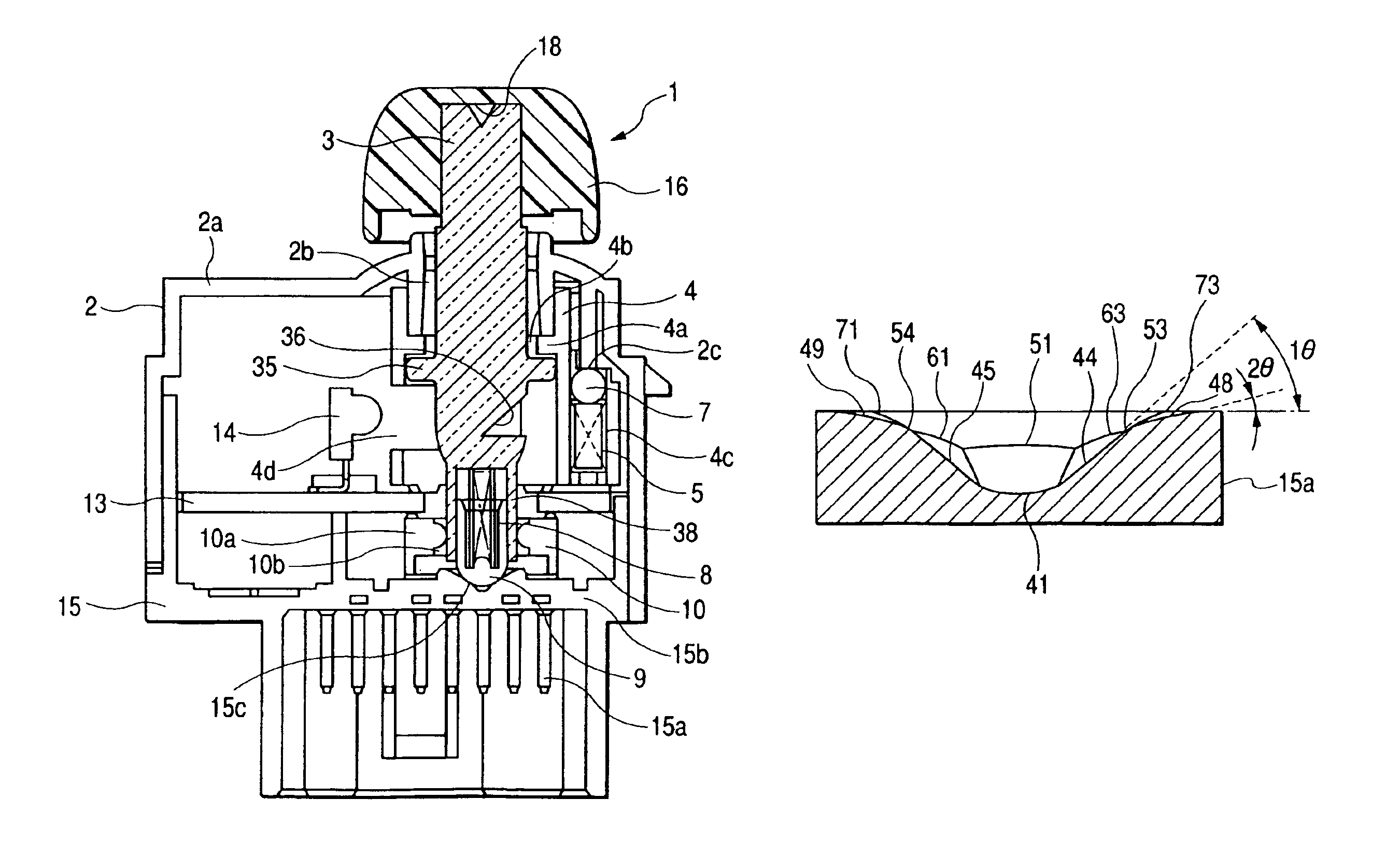

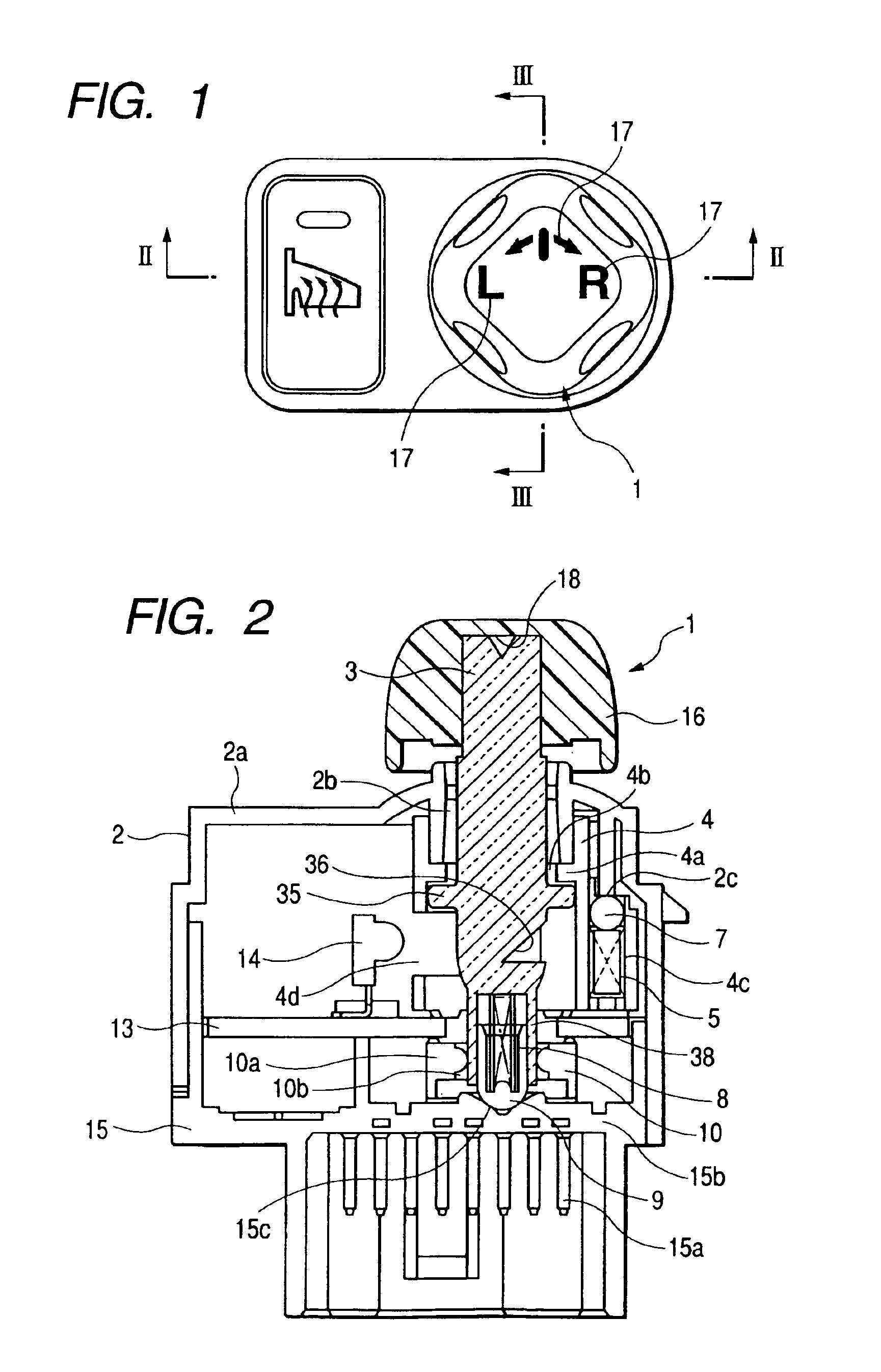

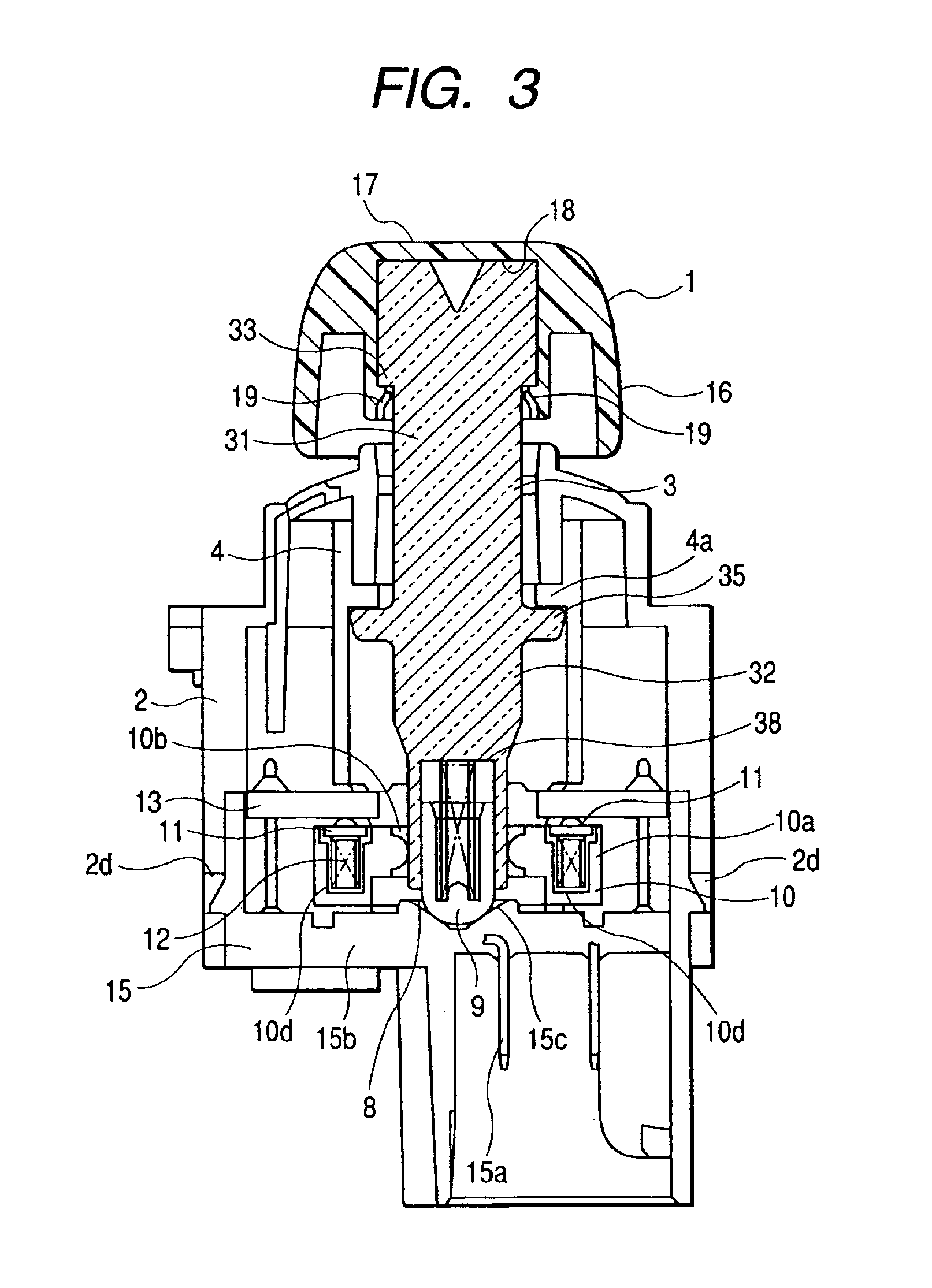

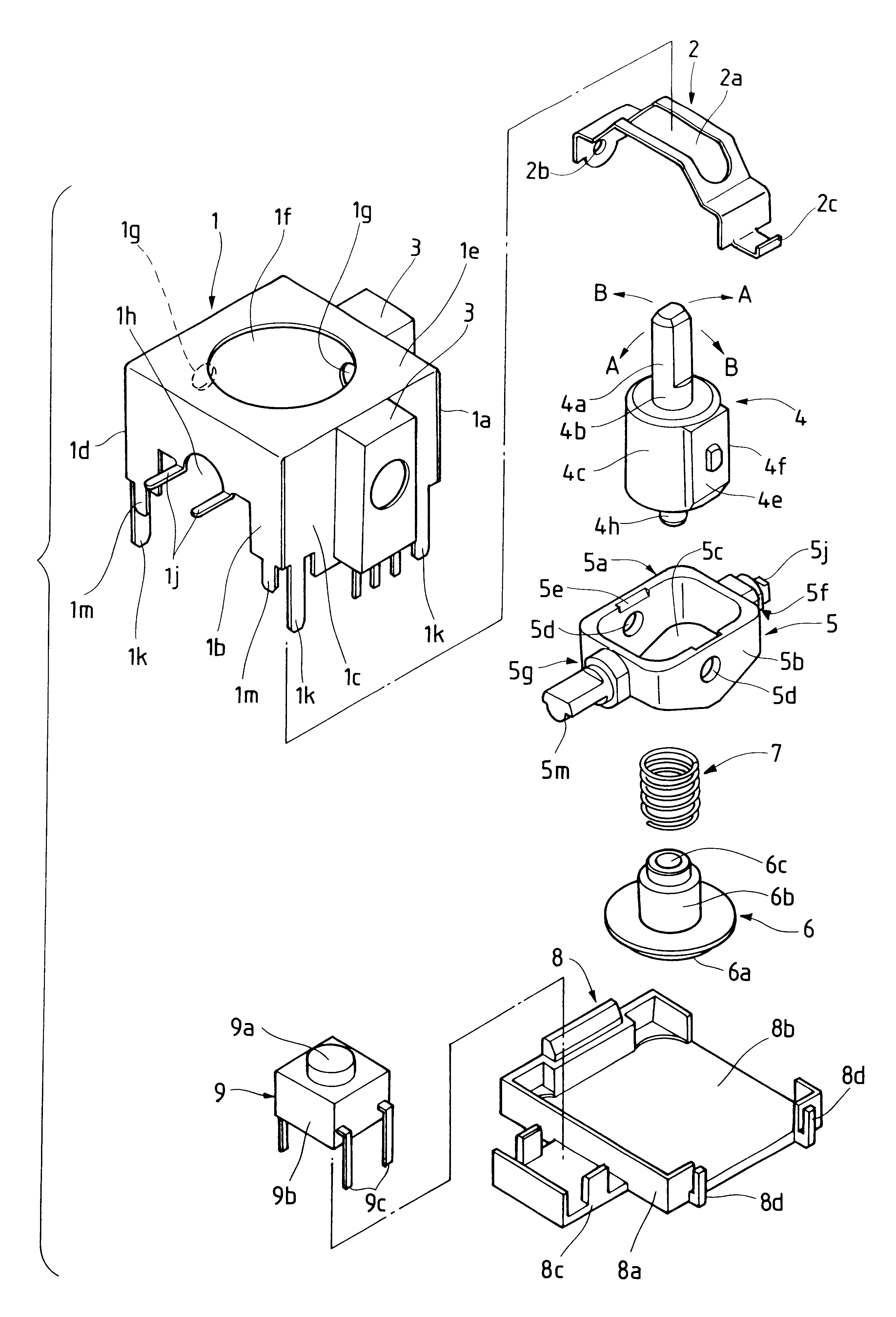

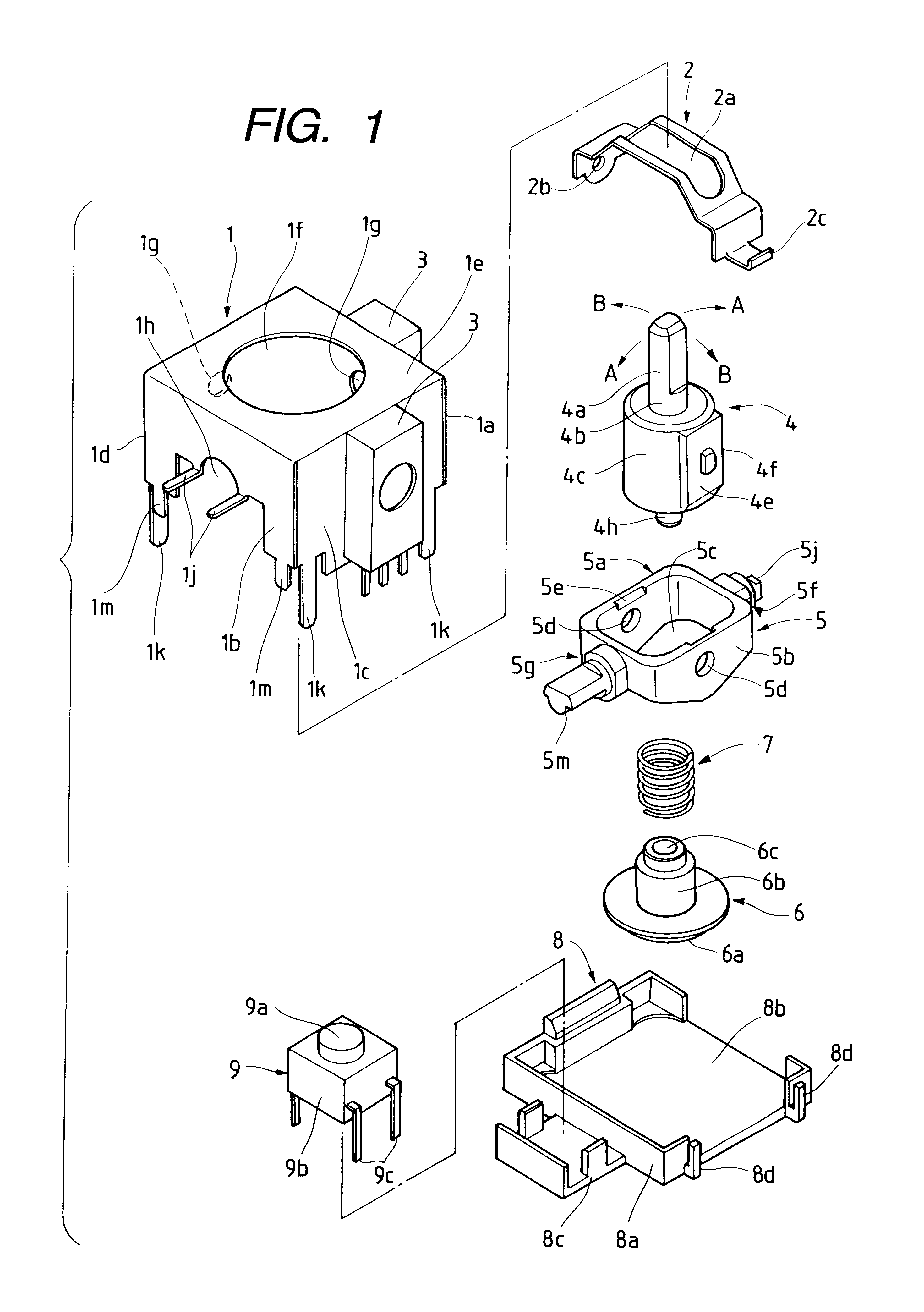

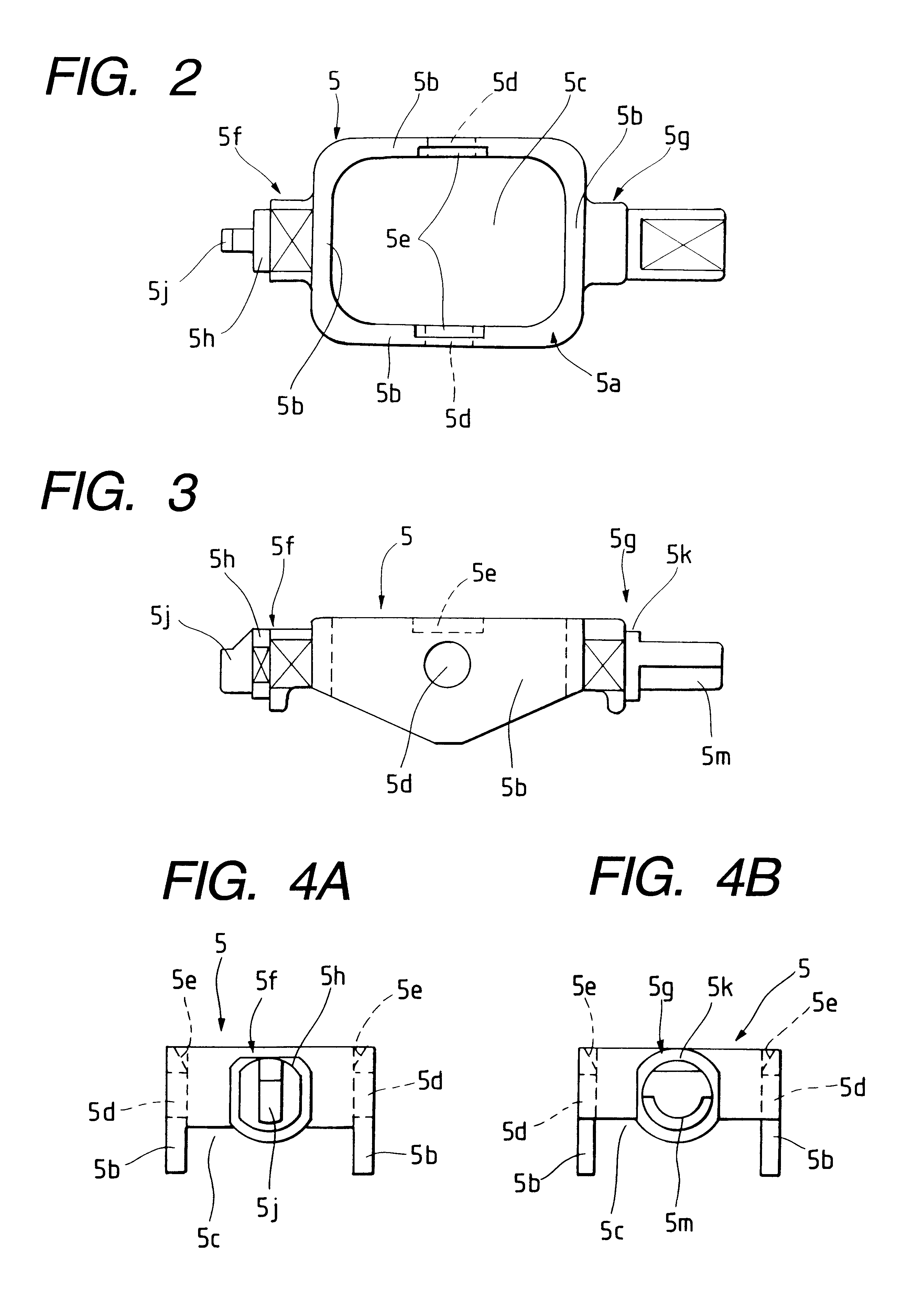

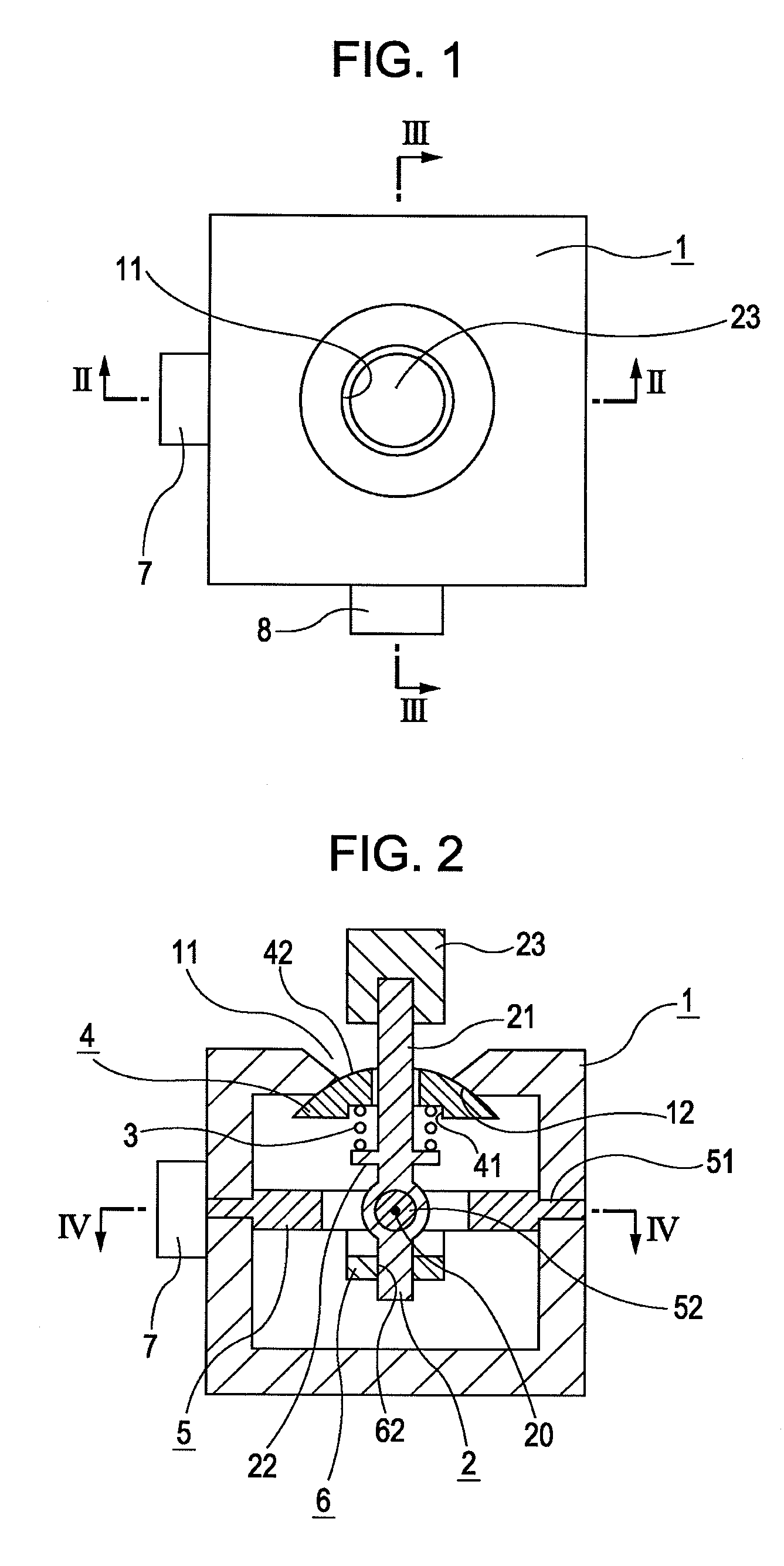

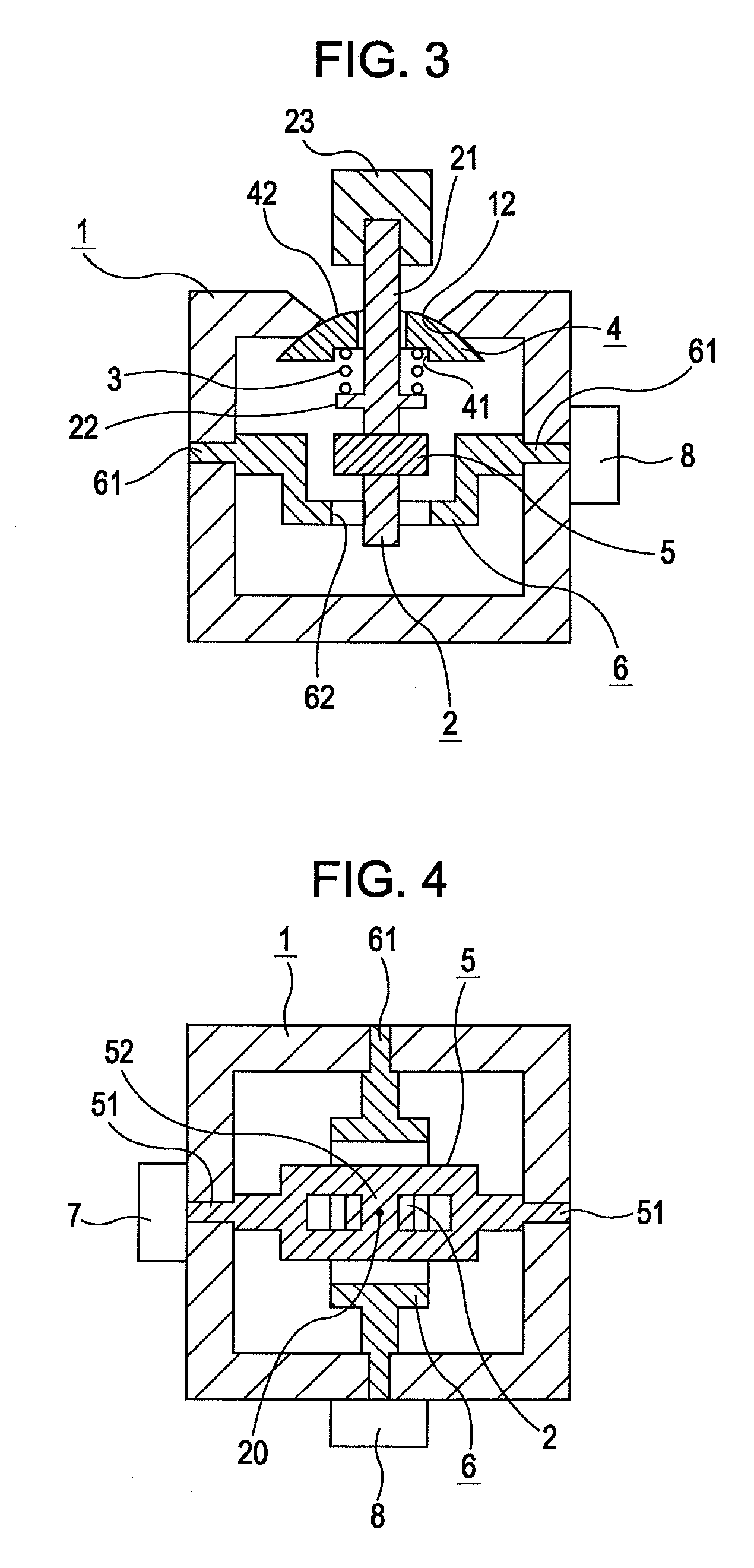

Multi-directional switch

ActiveUS20050040018A1Easy to operateLow priceControlling membersDashboard fitting arrangementsEngineeringMechanical engineering

A multi-directional switch contains a bearing 4, an operating shaft 3 supported rockably by the bearing 4, and a cam 15c for giving a required feeling of operation to a rocking operation of the operating shaft 3. In the cam 15c, a spherical surface-shaped bottom portion 41 for holeing the operating shaft 3 in a non-operation position, first inclined surfaces 42, 43, 44 and 45 formed in a radial shape at an outer circumference of the bottom portion 41, and second inclined surfaces 46, 47, 48 and 49 formed in a radial shape at an outer circumference of the first inclined surfaces, are formed, and at the boundaries between the first inclined surfaces and the second inclined surfaces, swelled step portions 50, 51, 52 and 53 are formed, respectively.

Owner:ALPS ALPINE CO LTD

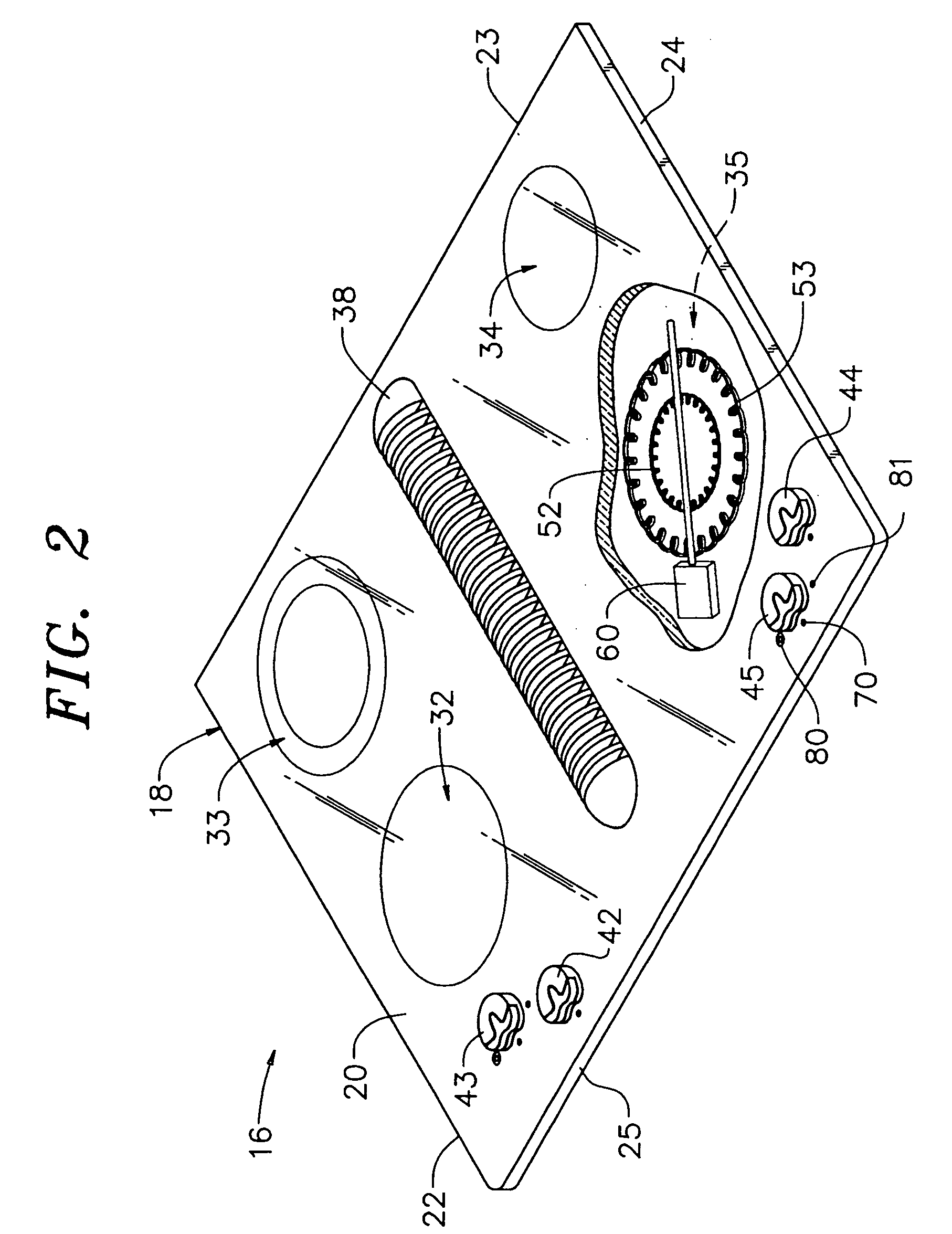

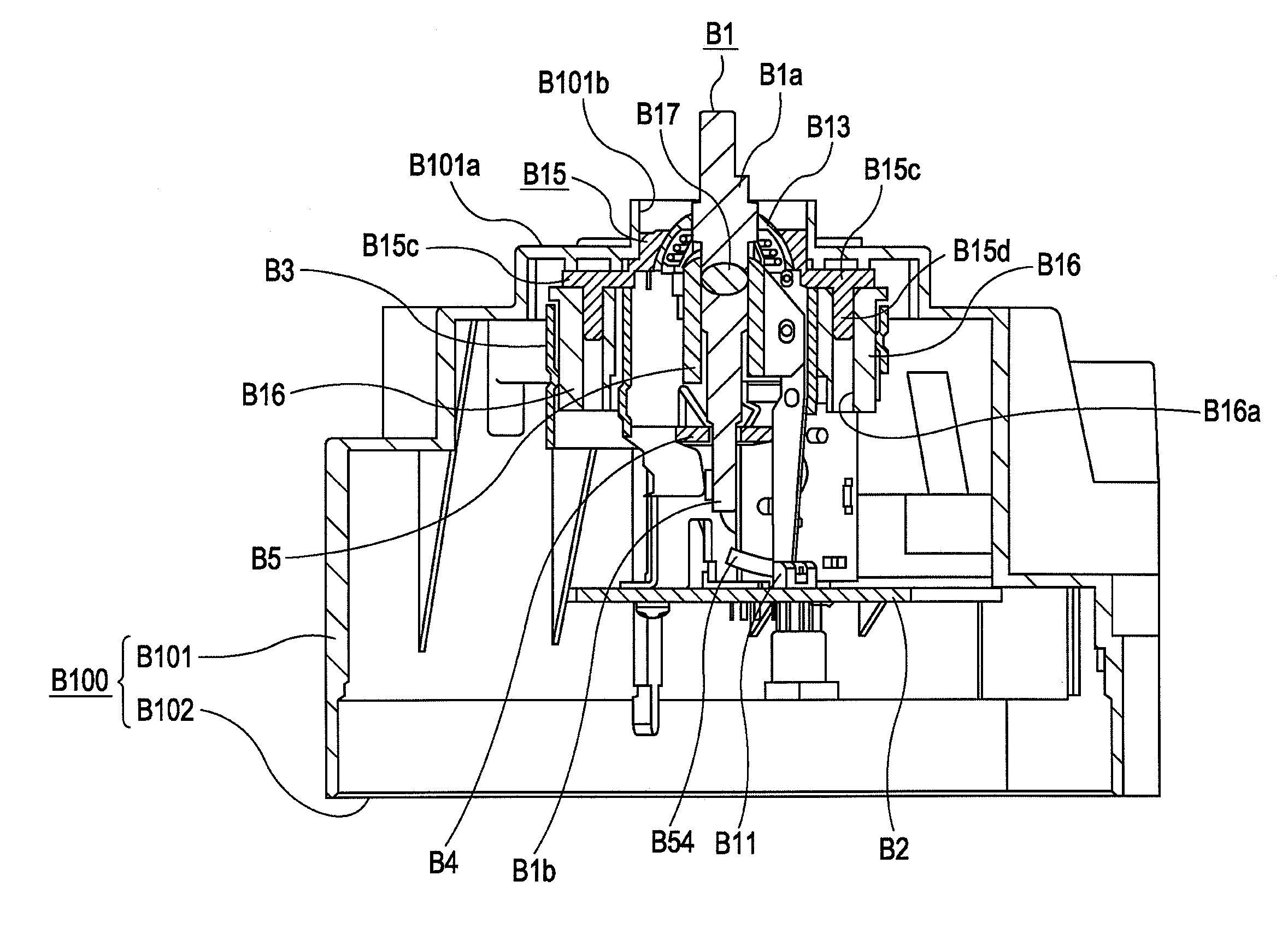

Joystick for electro-hydraulic control system

ActiveUS7265304B2Easy to manufactureLarge displacementManual control with multiple controlled membersServomotor componentsJoystickControl system

A joystick for an electro-hydraulic control system is provided with a rotary potentiometer having a pivotable arm. This pivotable arm is integrally arranged on a rotary shaft and pivots responsive to pivotal control of a joystick in a predetermined direction or a direction opposite to the predetermined direction. The joystick is also provided with a torsion coil spring for normally holding the pivotable arm in a neutral position, a pin arranged on the pivotable arm and capable of expanding the torsion coil spring upon pivotal movement of the pivotable arm, a holding pin for holding the torsion coil spring at its coil portion, and a cover member having a pair of guide portions for limiting movements of the coil portion of the torsion coil spring in the predetermined direction and the opposition direction when the torsion coil spring is in its neutral position.

Owner:NIHON KENKI CO LTD

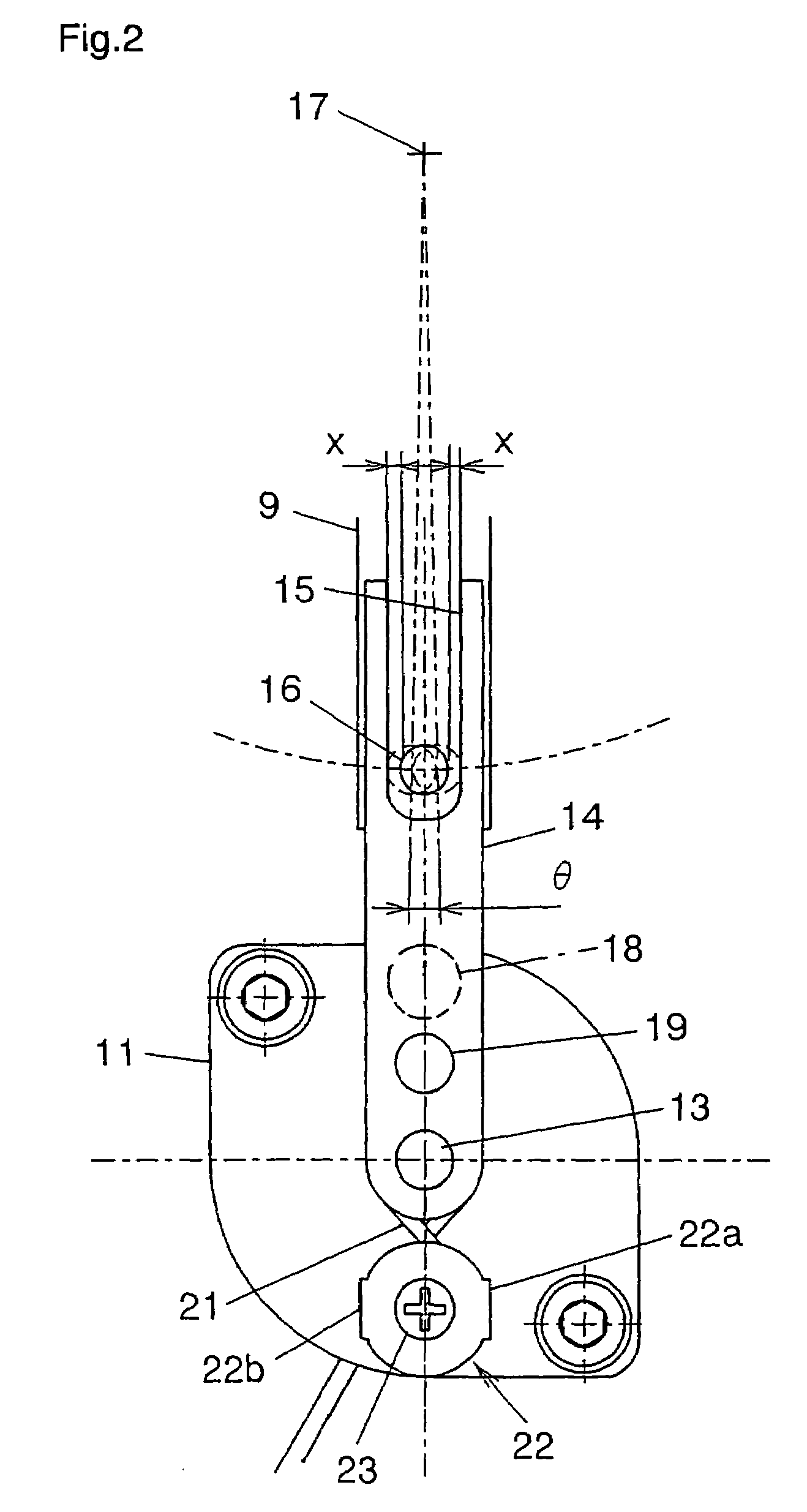

Digital adjustable resistor and adjusting method thereof

ActiveCN102693796AEasy to adjustHigh precisionResistors with plural resistive elementsElectrical resistance and conductanceResistor

Disclosed are a digital adjustable resistor and an adjusting method thereof. The digital adjustable resistor comprises a controlled resistor string and an adjustable resistor string which are connected in parallel, an approximate value of required resistance can be obtained via the controlled resistance string by means of adjusting the quantity of first resistors connected in parallel, the adjustable resistor string is connected with the controlled resistor string, the resistance of the digital adjustable resistor is adjusted by means of adjusting the quantity of second resistors connected in serial, and accordingly the required resistance is obtained. The adjusting method includes connecting a plurality of first resistors in parallel to obtain the approximate value of the required resistance; connecting a plurality of second resistors in series according to the required resistance and the approximate value of the required resistance so that the resistance of the digital adjustable resistor is adjusted; and connecting the first parallelly-connected resistors with the second serially-connected resistors in parallel to obtain the required resistance. The digital adjustable resistor and the adjusting method for the digital adjustable resistor have the advantage that small-step and high-precision adjustment of the resistor is realized.

Owner:ZHEJIANG JUEXIN MICROELECTRONICS CO LTD

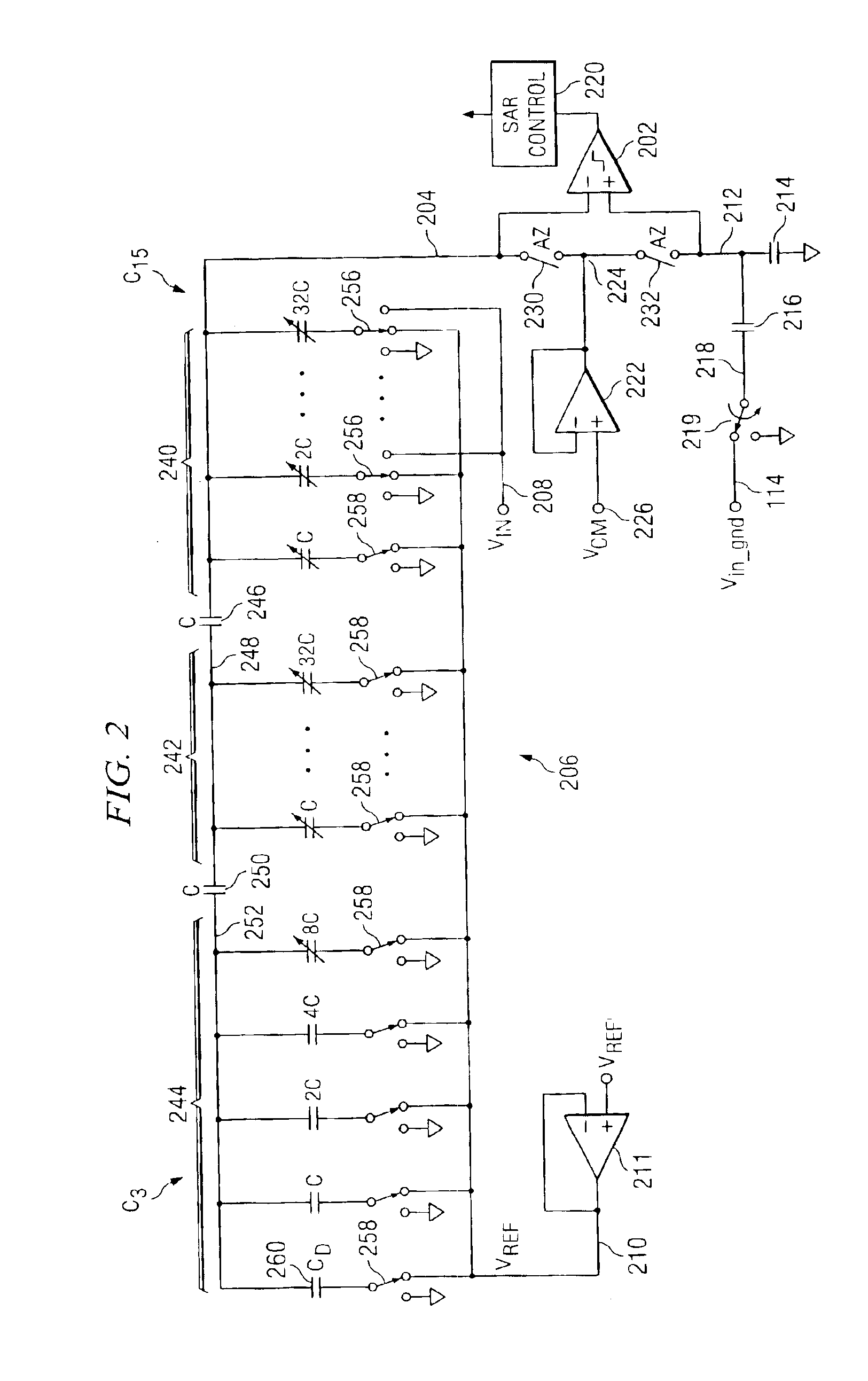

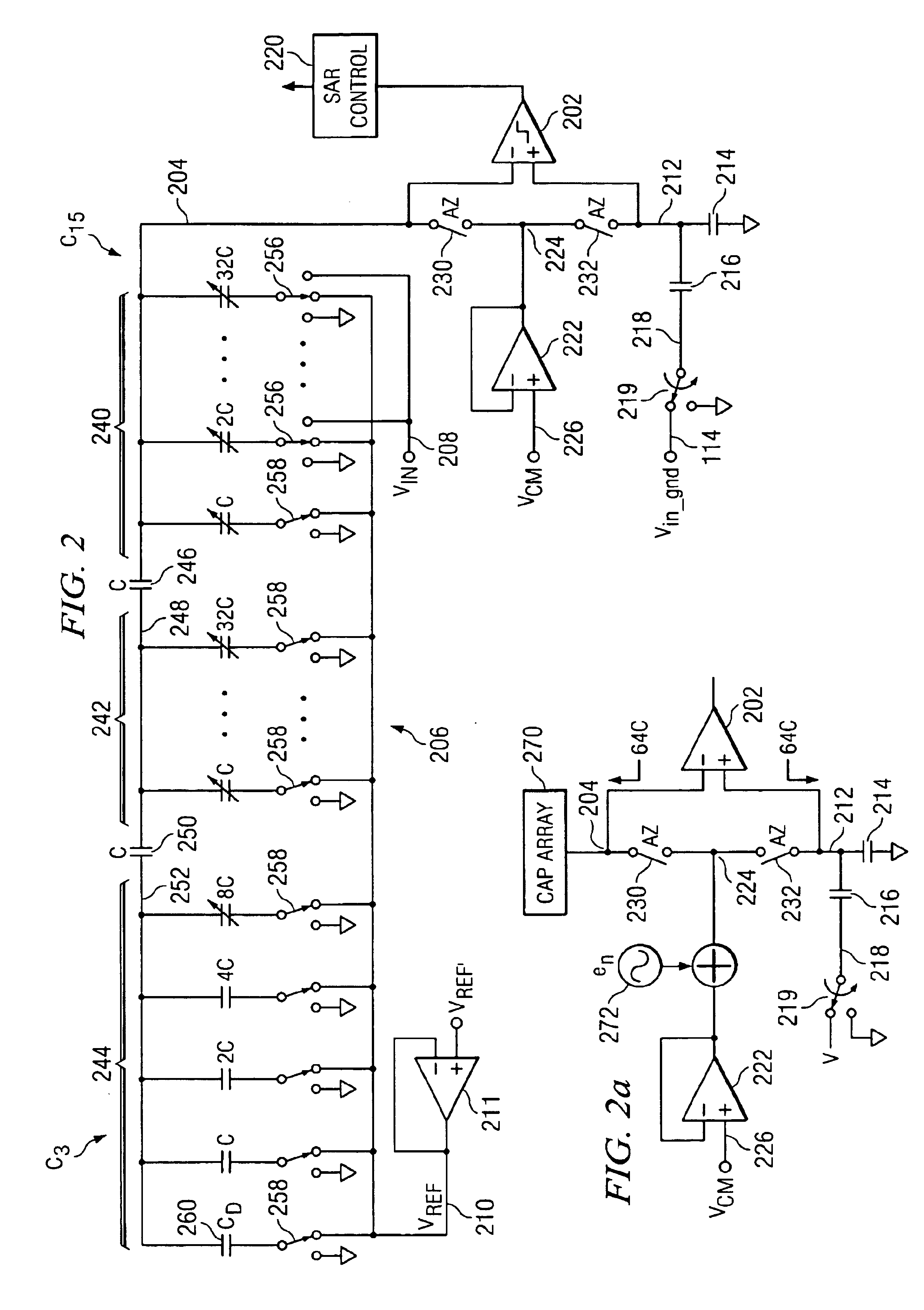

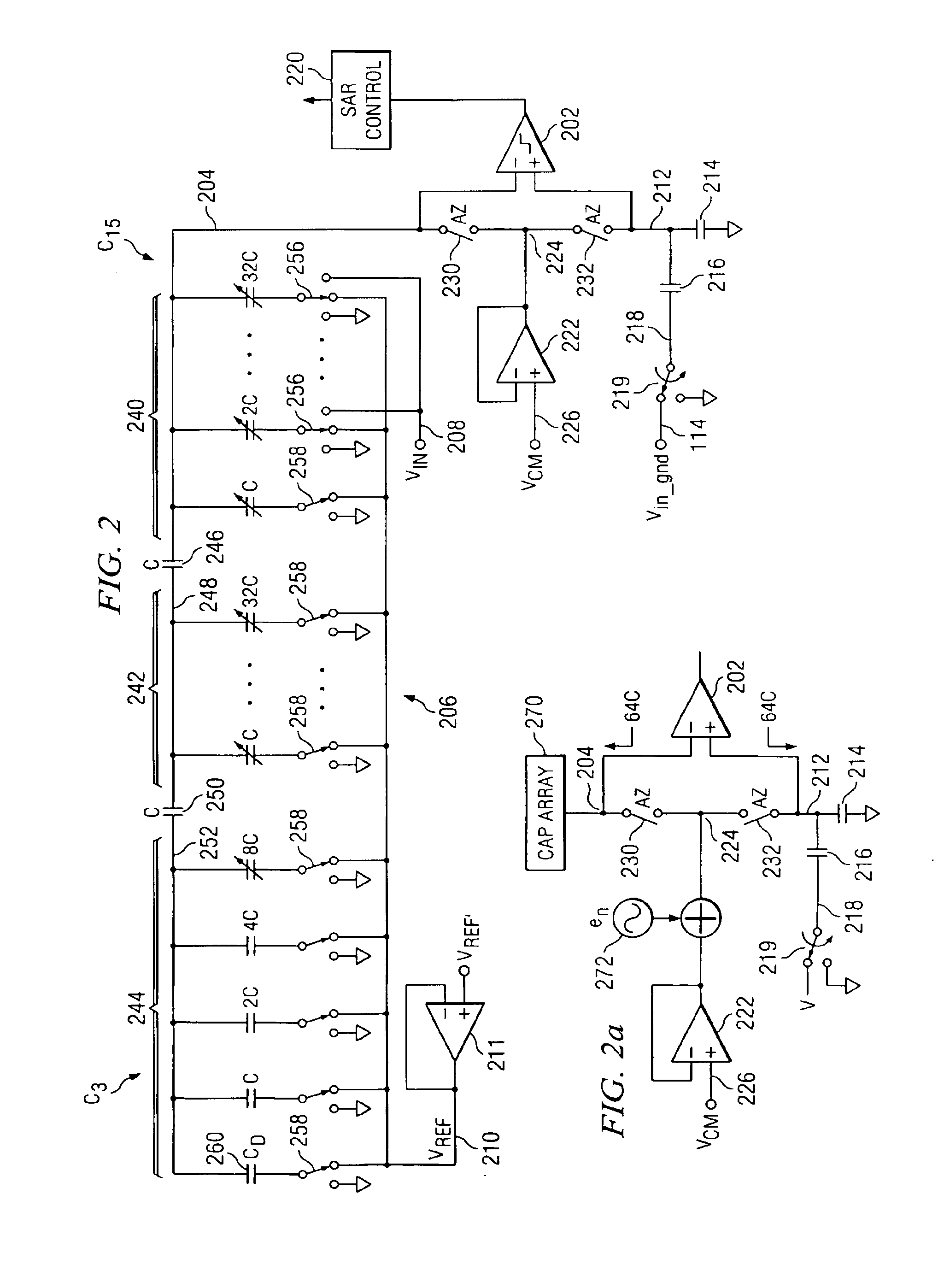

SAR with partial capacitor sampling to reduce parasitic capacitance

InactiveUS6977607B2Reduce parasitic capacitanceElectric signal transmission systemsResistors with plural resistive elementsParasitic capacitanceVoltage reference

SAR with partial capacitor sampling to reduce parasitic capacitance. An analog-to-digital convertor is disclosed with reduced parasitic capacitance on the input during a sampling operation. A charge-redistribution, binary-weighted switched-capacitor array is included having a plurality of array capacitors that each have a commonly connected plate interfaced to a first common node and a switched plate, the switched plate operable to be switched between first and second reference voltages during a redistribution phase and select ones of the capacitors additionally operable to be switched to the input during a sampling phase. Each of the array capacitors has a parasitic capacitance associated therewith. A compensation capacitor having a common plate is connected to the first common node and a switched plate, the compensation capacitor operable to be switched to the input during the sampling phase and to the first reference voltage during the redistribution phase. The compensation capacitor has a parasitic capacitance less than the parasitic capacitance of the combination of all of the non select ones of the array capacitors. A comparator compares the voltage on the first common node to a compare reference voltage during the redistribution phase. A successive approximation controller is provided for switching the switched plate of the array capacitors between the first and second reference voltages in accordance with a successive approximation algorithm during the redistribution phase.

Owner:SILICON LAB INC

Multi-directional switch

ActiveUS6884948B2Easy to operateLow priceControlling membersDashboard fitting arrangementsEngineeringMechanical engineering

Owner:ALPS ALPINE CO LTD

High speed comparator for a SAR converter with resistor loading and resistor bias to control common mode bias

InactiveUS6882295B2Electric signal transmission systemsResistors with plural resistive elementsDriving currentElectrical polarity

High speed comparator for a SAR converter with resistor loading and resistor bias to control common mode bias. A differential comparator having positive and negative inputs and positive and negative outputs is disclosed. The comparator includes a current source for driving current from a supply to a common node. A differential pair of transistors is disposed such that one side of the source / drain paths are tied together and to the common node, with the other side of the source / drain paths thereof for each of the transistors in the differential pair interfaced to the positive and negative outputs, respectively for applying drive thereto. A first resistor load is disposed between the positive output and a supply reference opposite in polarity to the supply. A second resistor is disposed between the negative output and the supply reference. The gate of the one of the transistors in the pair associated with the positive output is connected to the negative input and the gate of the other of the transistors in the pair is connected to the positive input. The current through the current source defines the common mode bias. A ratiometric bias circuit having associated therewith a bias resistor with a current driven there through is provided that controls the current through the current source, such that it is a ratio of the current through the bias resistor.

Owner:SILICON LAB INC

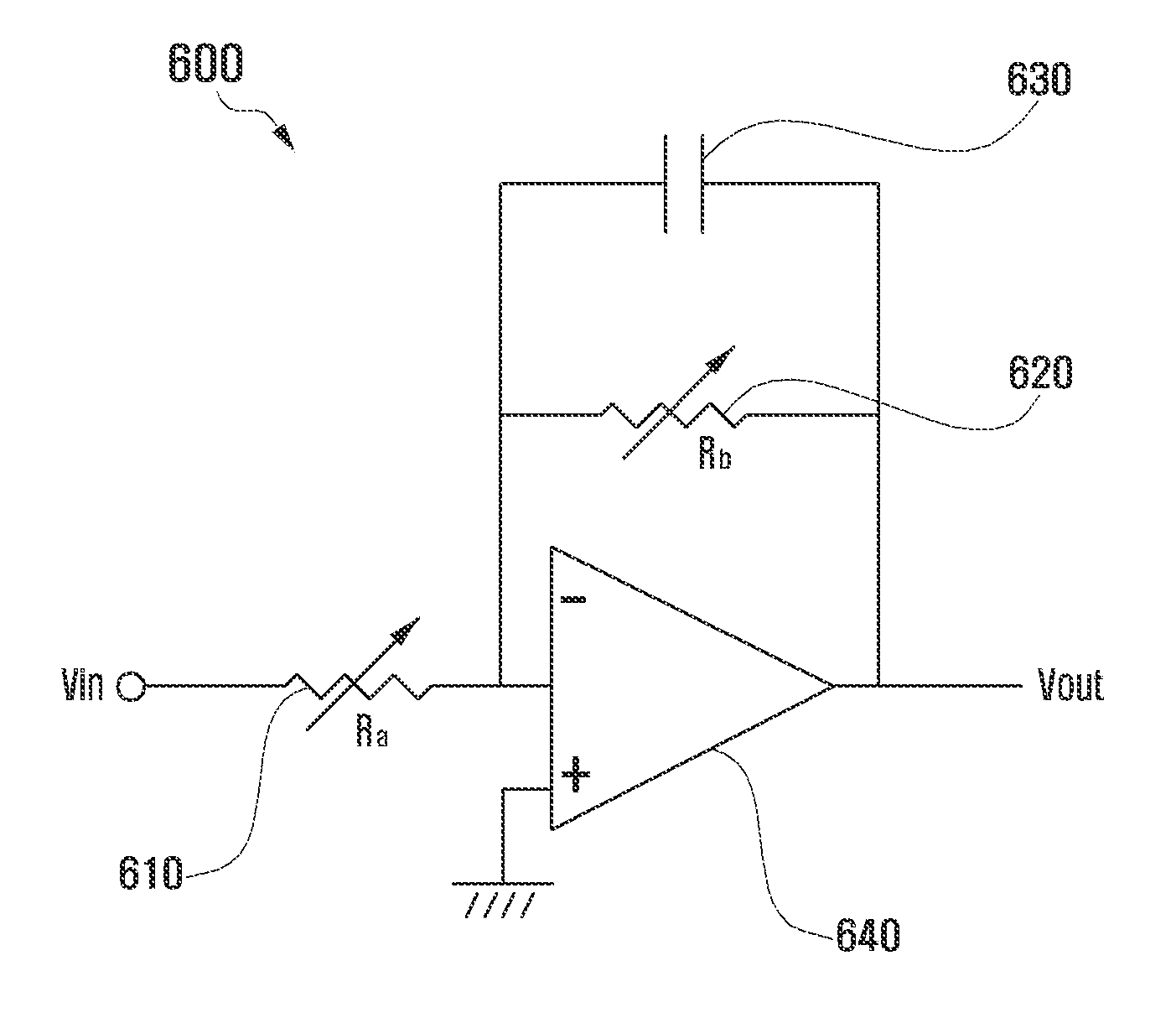

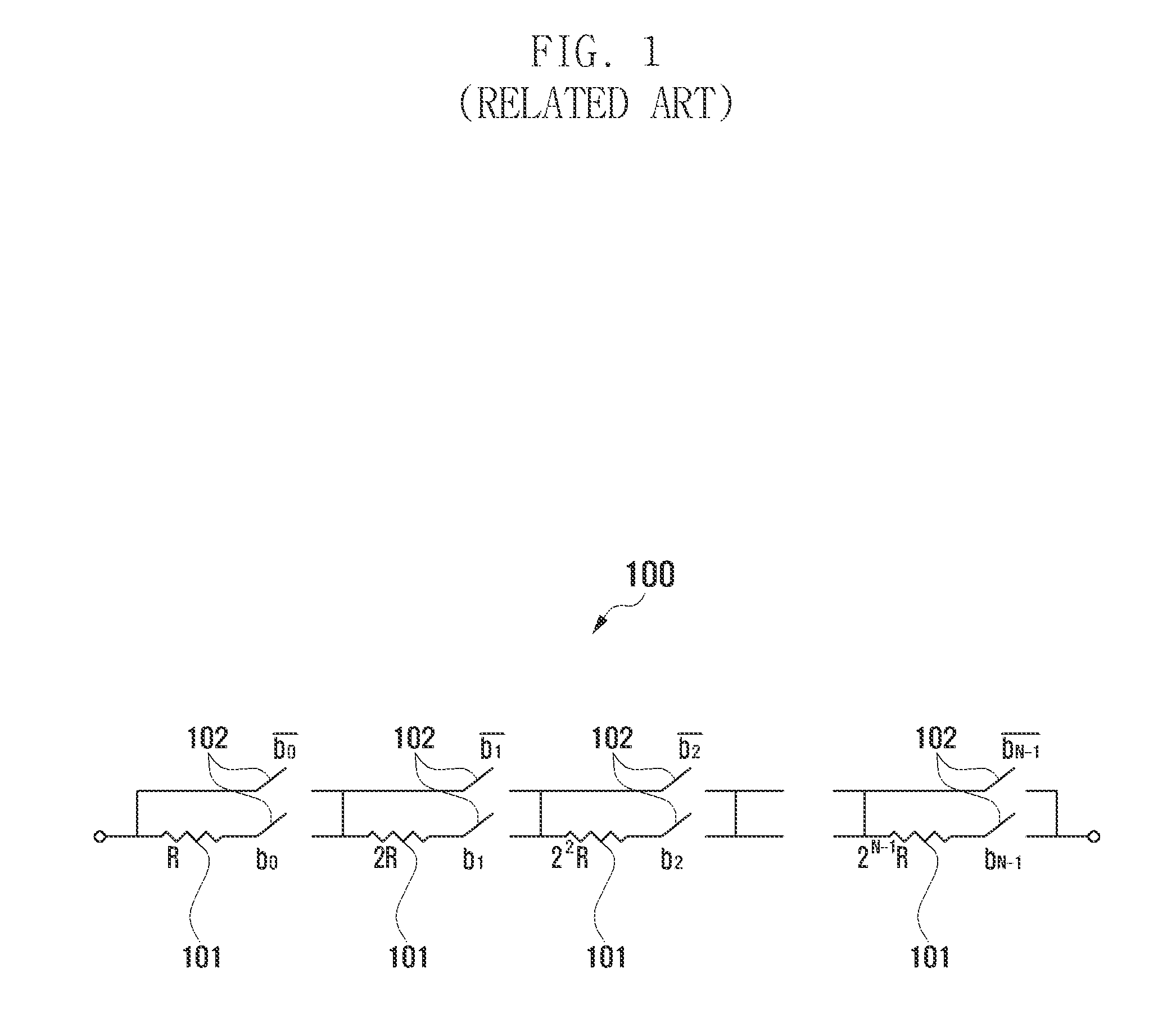

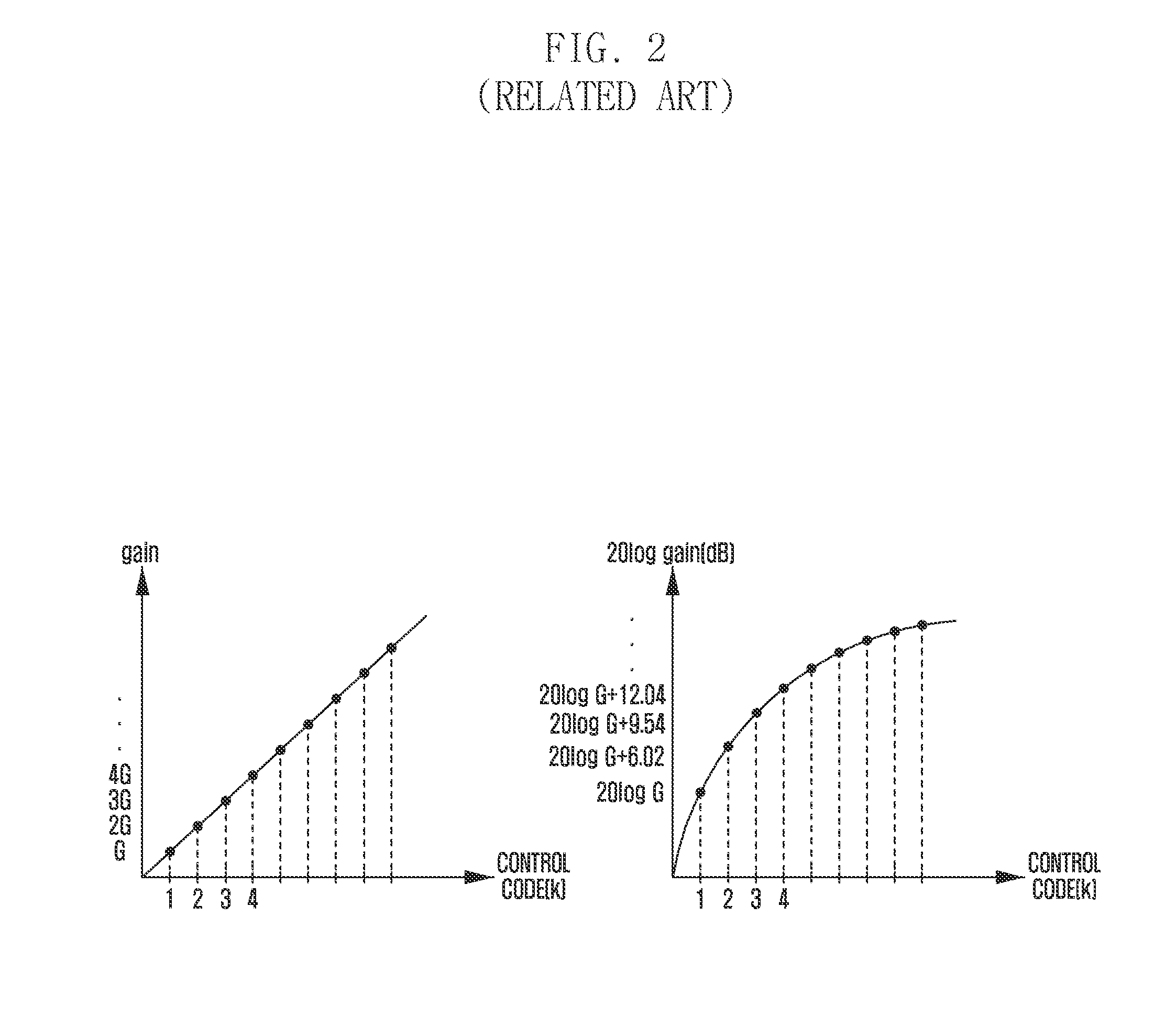

Variable resister having resistance varying geometrically ratio and control method thereof

ActiveUS20120019318A1Error minimizationMultiple-port networksNegative-feedback-circuit arrangementsAudio power amplifierVariable-gain amplifier

Provided is an analog amplifier for amplifying an analog signal and an analog filter, and in particular, an apparatus and method for controlling gain and cutoff frequency of the variable gain amplifier and the variable cutoff frequency filter that is capable of changing the gain and cutoff frequency. The variable resister includes a plurality of resister segments in the variable resister and, when a plurality of resistance candidates for the variable resister are arranged in order of size, the resistance candidates form a geometric series.

Owner:SAMSUNG ELECTRONICS CO LTD

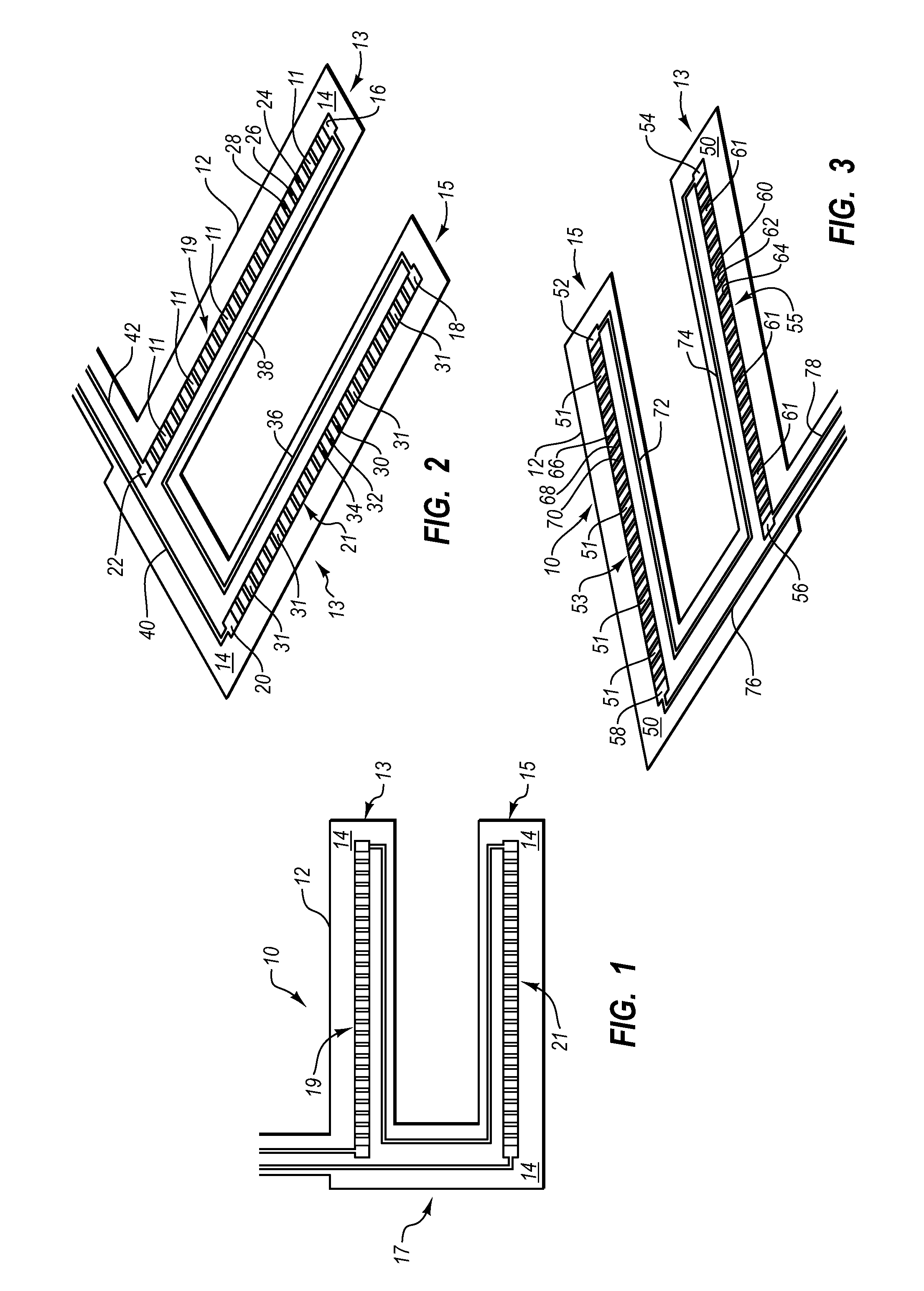

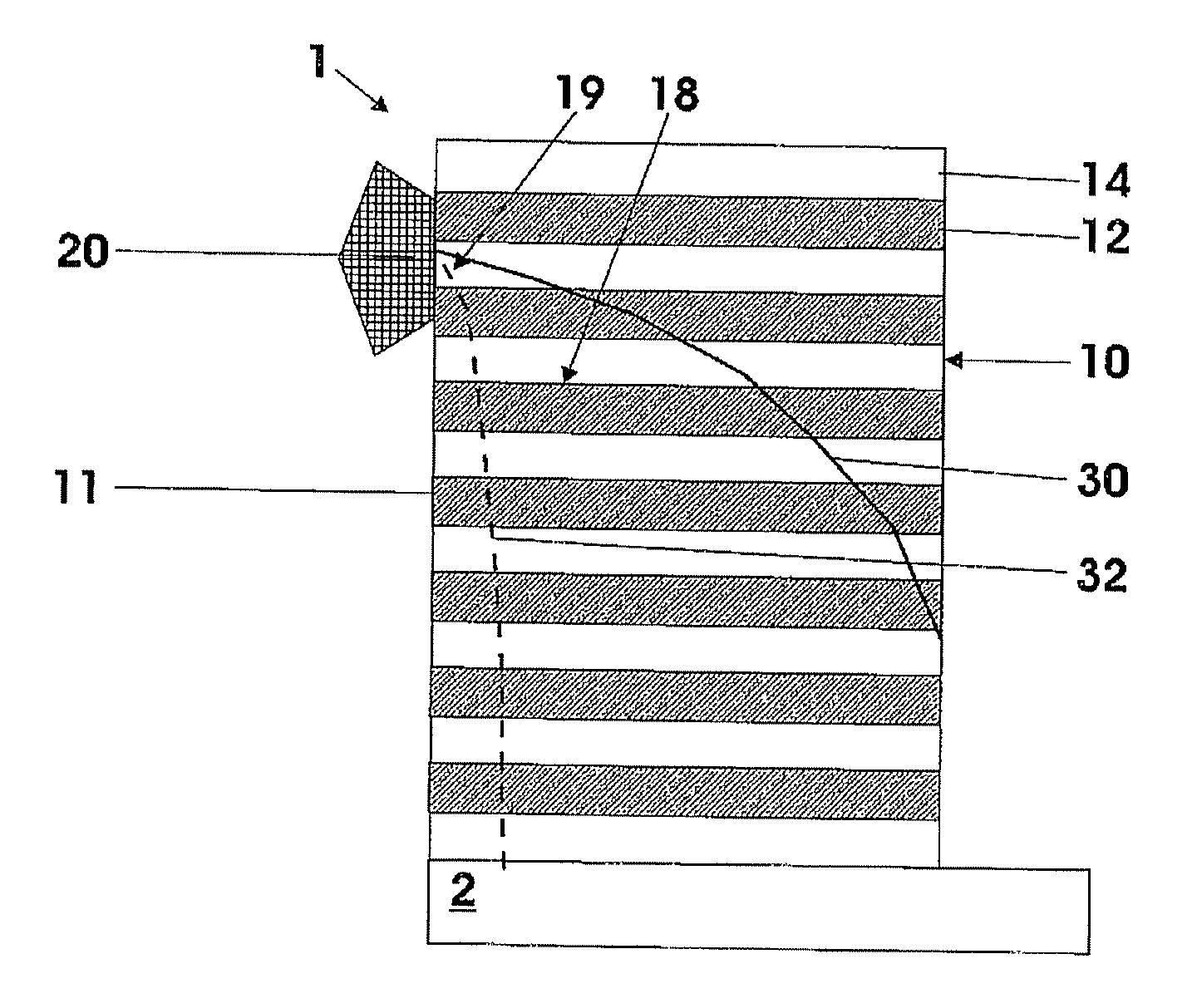

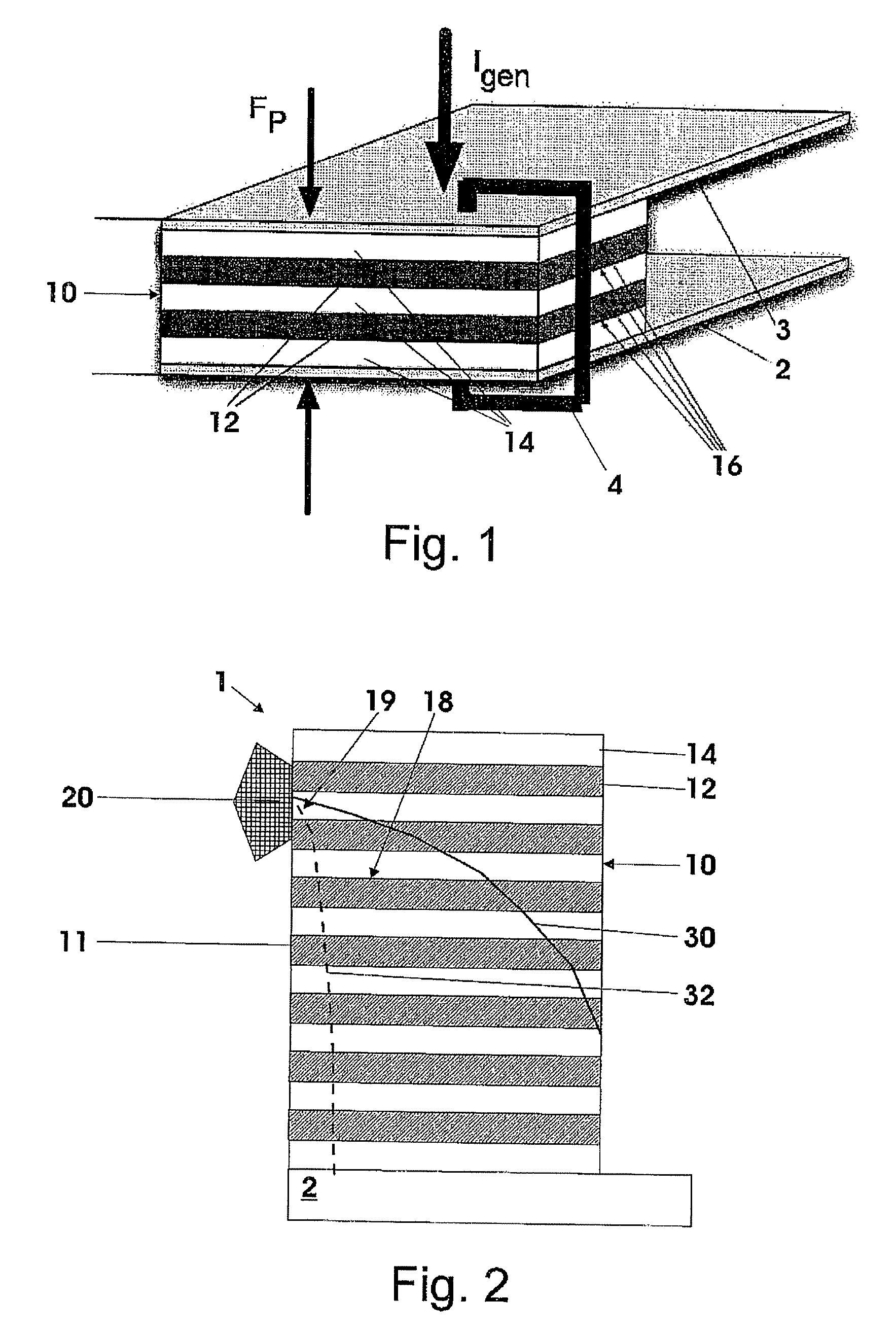

Layered electrically conductive material

An electrical resistor has an electrically conductive stack, which includes a plurality of metal first layers and second layers. The stack allows to produce a highly anisotropic resistor, in which the resistance in the direction perpendicular to the layers is much higher than in the plane of the layers. The anisotropy allows the current flowing through the stack to be made homogenous, e.g., to be distributed over the entire stack surface, even if the current is input into the stack in an inhomogenous manner.

Owner:ABB RES LTD

Multi-gear potentiometer

InactiveCN103440945AResisitors with sliding contactResistors with plural resistive elementsRotational axisElectrical resistance and conductance

The invention discloses a multi-gear potentiometer. The multi-gear potentiometer comprises an insulation substrate, a rotating shaft, a conductive rotating arm, at least two resistor bodies, a gear switch, a stator plate pin A, a stator plate pin B and a rotor plate pin, wherein the resistor bodies are arranged on the insulation substrate, the head part of each resistor body is connected with the stator plate pin A through a conducting wire, the tail part of each resistor body is connected into the gear switch through a conducting wire, the gear switch is connected with the stator plate pin B through a conducting wire, the rotating shaft is fixed at the central position of the insulation substrate, one end of the conductive rotating arm is connected with the rotating shaft, and the other end is contacted with the resistor bodies Through the matching of multiple resistor bodies and the gear switch, the potential can be adjusted by the potentiometer through different amplitudes, so that more flexibility and convenience can be realized.

Owner:KUNSHAN FAVORSTAR ELECTRONICS

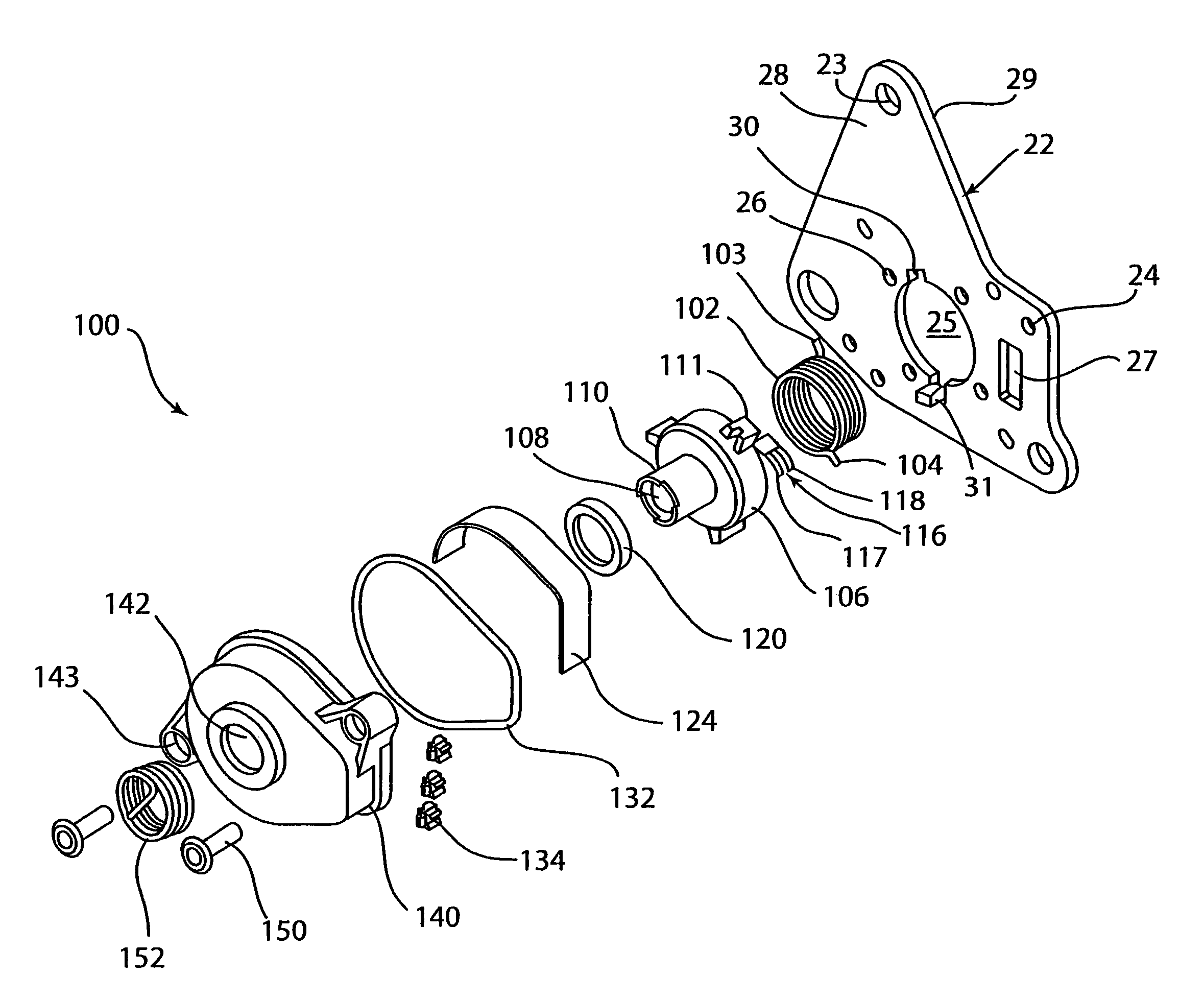

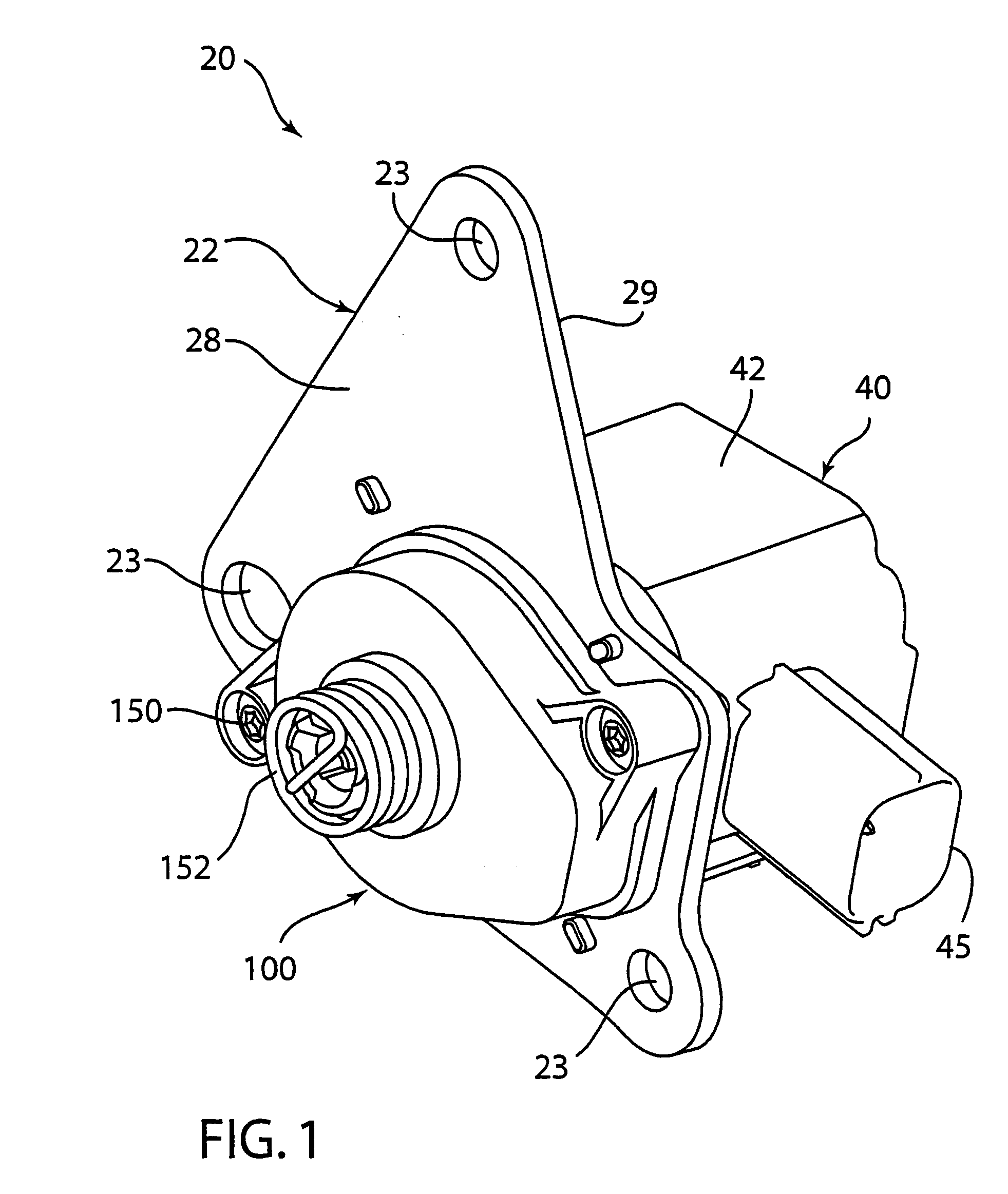

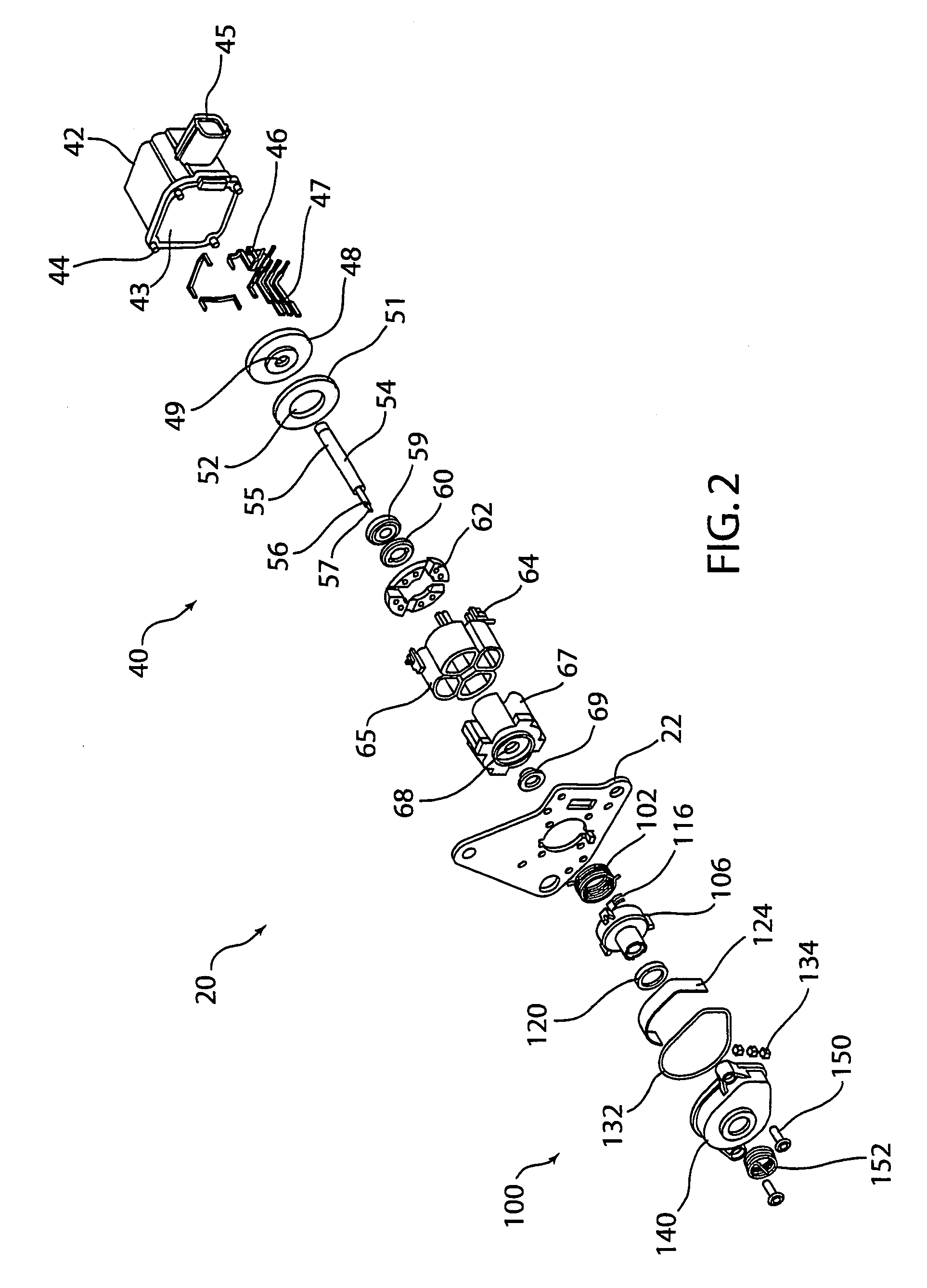

Actuator with integral position sensor

InactiveUS7116210B2Improve reliabilityResisitors with sliding contactEngine controllersDrive shaftControl theory

An actuator and integral position sensor has increased reliability with a fail-safe mode. The actuator and sensor assembly includes a rotary actuator that has a driving shaft. A sensor rotor has the driving shaft mounted in a bore. A contactor is mounted to an outer edge of the rotor. The contactor is engaged with a resistor film as the rotor rotates. A driven shaft is mounted to the rotor in another bore. The rotor couples the driving shaft and the driven shaft together.

Owner:CTS CORP ELKHART

Multi-way input device

InactiveUS6445377B1Manual control with multiple controlled membersControlling membersEngineeringMechanical engineering

In the multi-way input device, an operating shaft is formed with a cylindrical potion which receives a return spring therein, and pivot shaft portions of a convex shape are formed on part of an outer wall of the cylindrical portion, the pivot shaft portions being engaged by snap-fitting with engaging portions of a concave shape formed in side walls of a second interlocking member which define a slot. The return spring is received in a receptacle space formed within the cylindrical portion.

Owner:ALPS ALPINE CO LTD

SAR data converter with unequal clock pulses for MSBS to allow for settling

InactiveUS6956520B2Electric signal transmission systemsResistors with plural resistive elementsCapacitanceVoltage reference

Open loop common mode driver for switched capacitor input to SAR. A method for selectively switching capacitors in a SAR capacitor array that have a common plate thereof interfaced to the input of a comparator. The method includes the step of first initiating a SAR compare cycle. Then. the other plates the capacitors switched such that they are disposed at either a first capacitor reference voltage or a second capacitor reference voltage in a combination and sequence of switching operations defined by a successive approximation search algorithm. Each switching operation in the sequence requires, after the step of switching, a comparison of the voltage input to the comparator with a compare reference voltage after a predetermined settling time from the time the capacitor combination for the switching operation has been switched. The duration of the settling time is controlled for each of the switching operations in the sequence such that at least two of the durations are different.

Owner:SILICON LAB INC

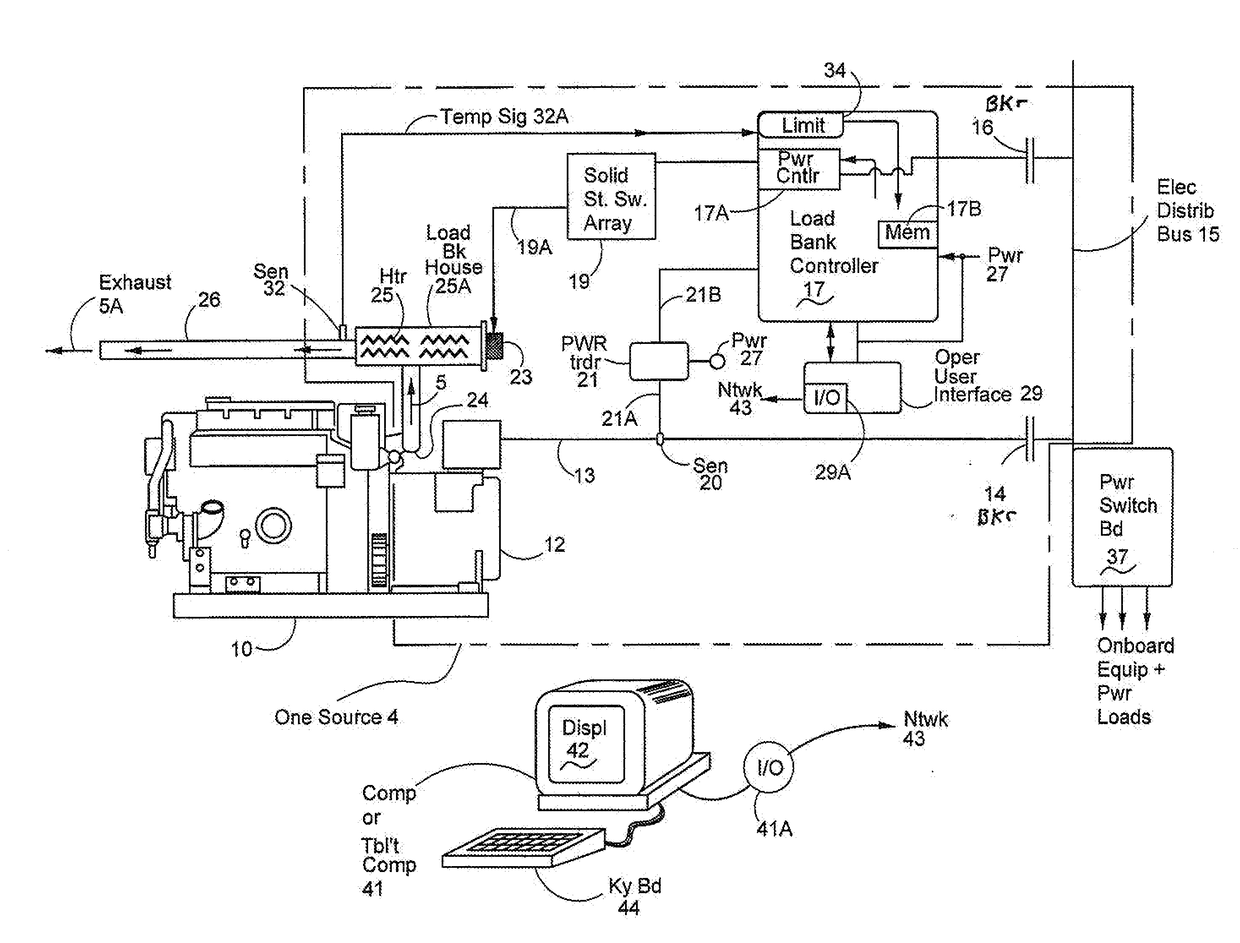

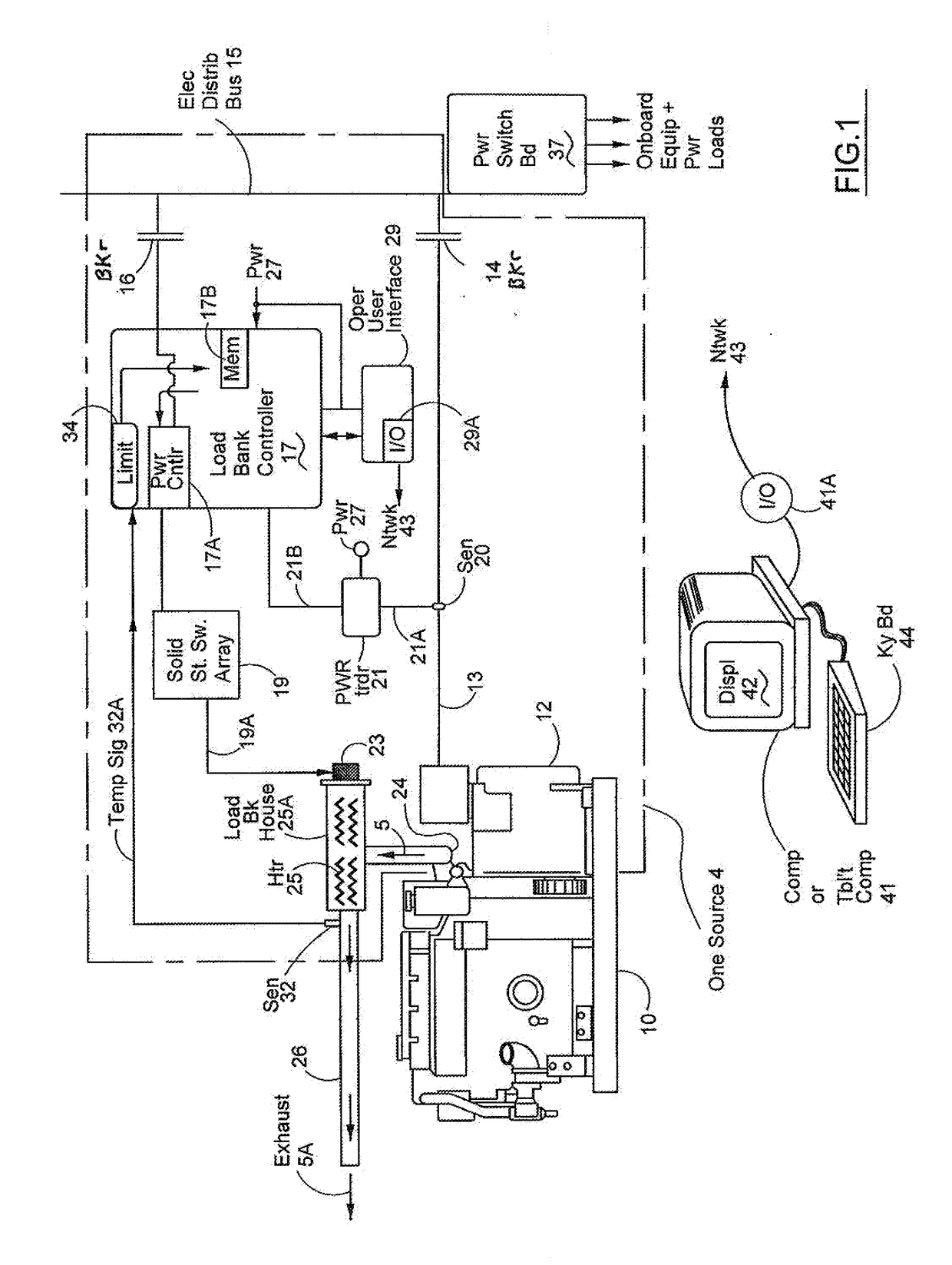

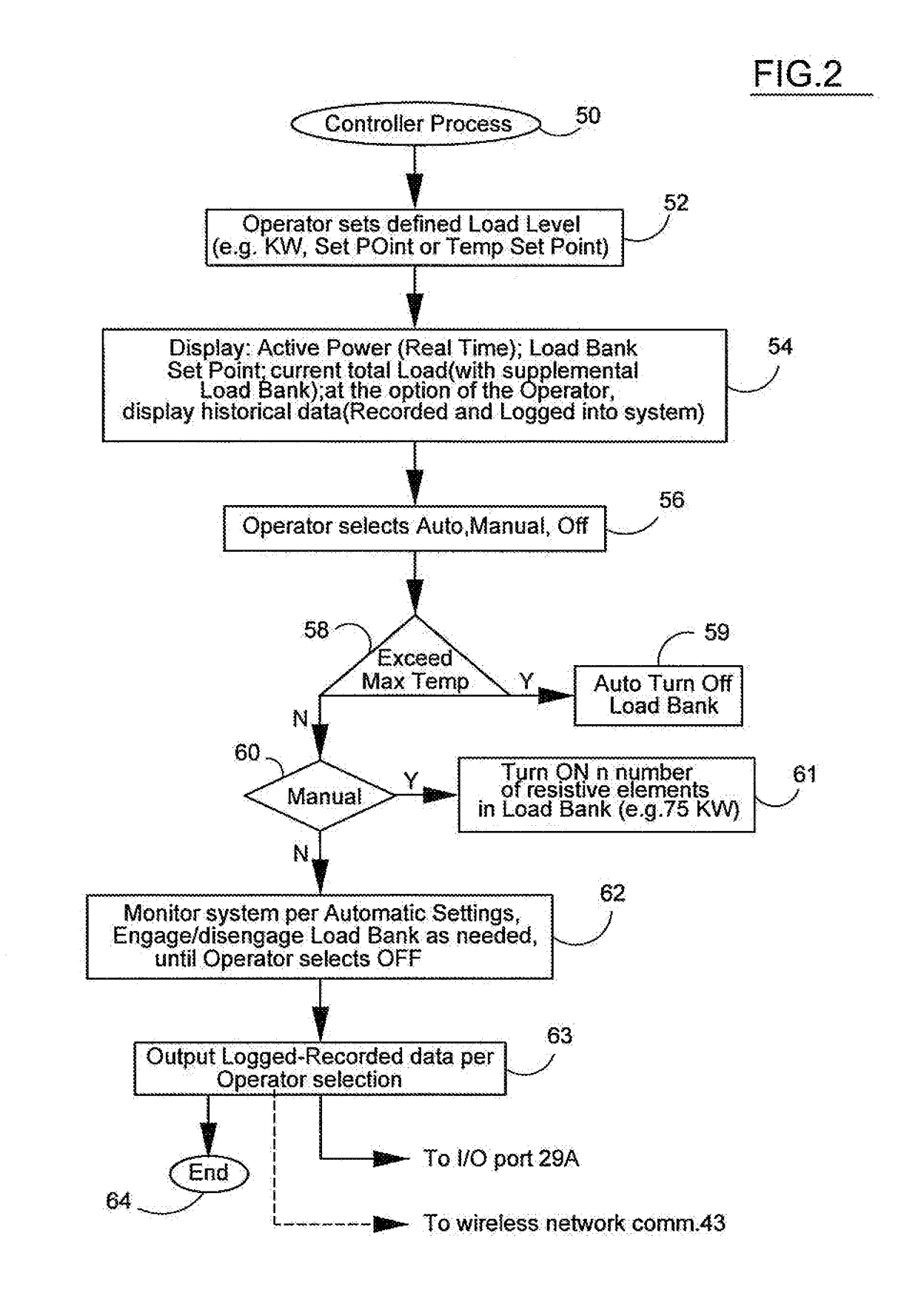

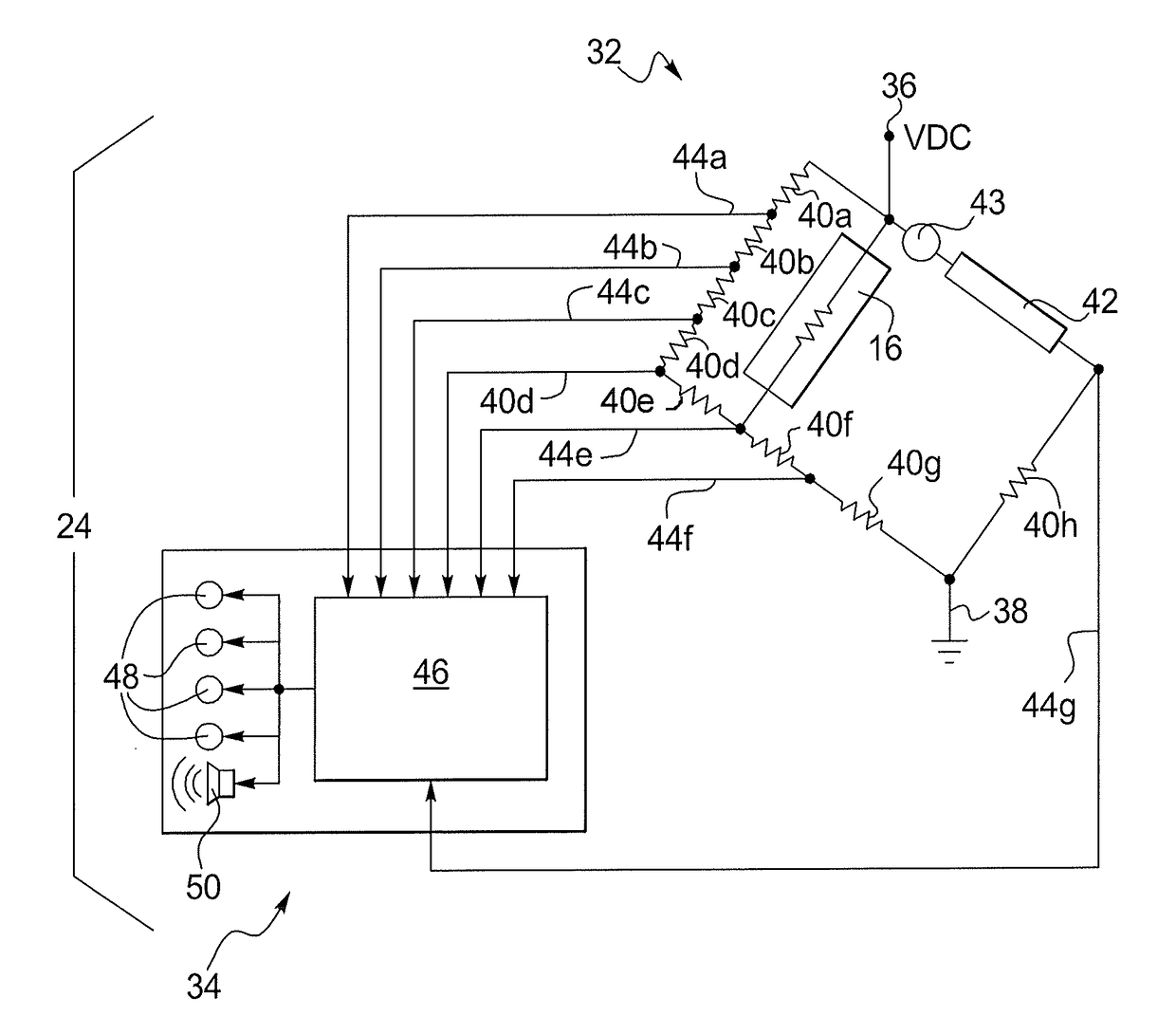

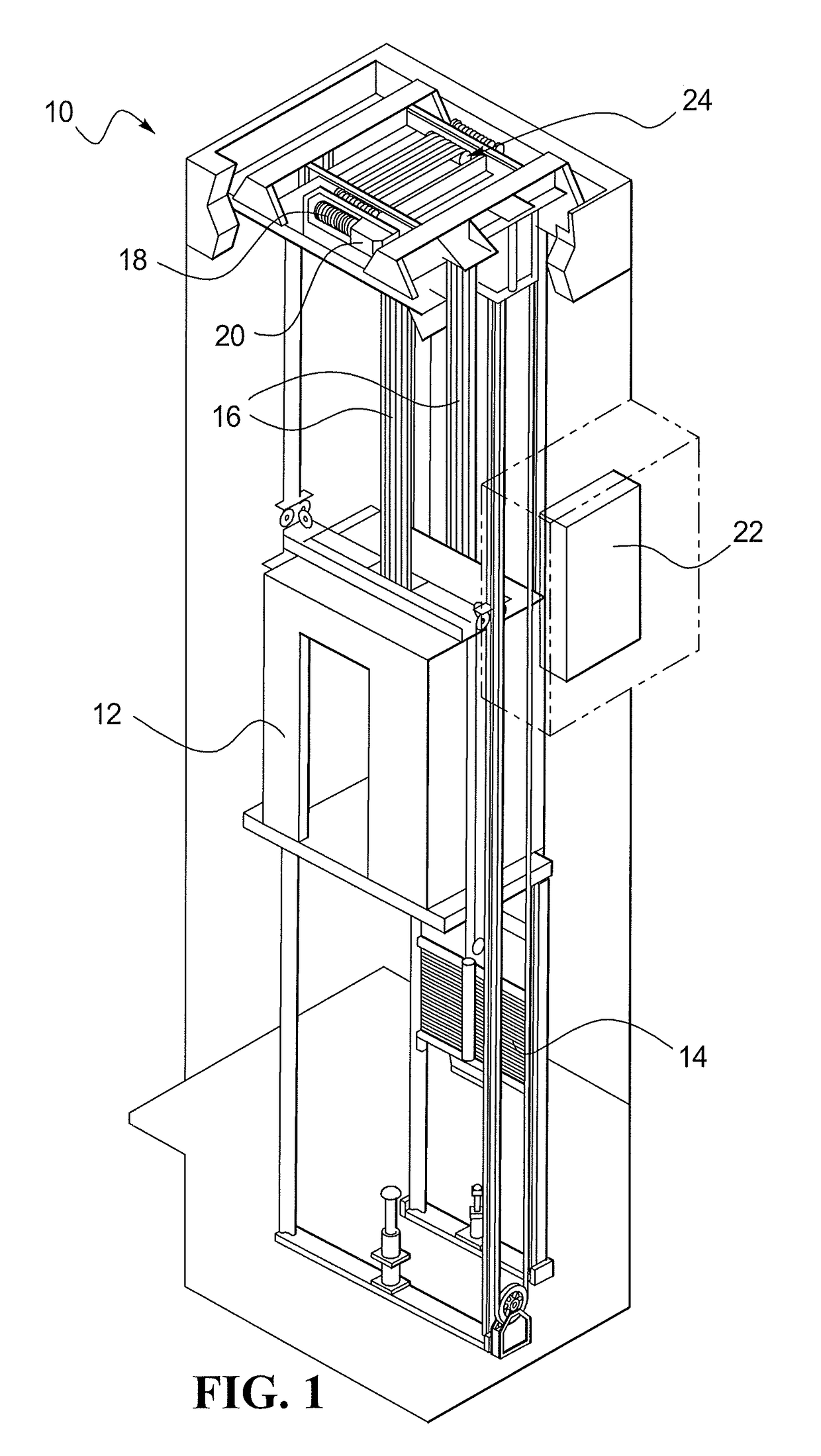

Diesel Electric Generator Load Bank System Cooled by Exhaust Gas and Method Therefor

InactiveUS20180142630A1Minimal loadingEasy to operateElectrical controlCoolant flow controlElectric powerLoad following power plant

A 3-phase driven resistor load bank, electrically connected to an engine-generator-set is controlled to maintain a minimum generator load by turning ON and OFF load-bank heaters for optimal operation of the engine. An operator selects KW power output that best meets electrical load conditions and the load bank converts surplus electrical energy to heat, then cooled by the exhaust gas. The exhaust-gas-cooled resistive heater load bank, mounted in gas flow path, provides a dummy load to the gen-set which allows gen-set to operate at operator defined load level to enhance engine performance and reduce maintenance costs. The gas flow cools the inline resistive heater elements. The 3-phase AC power to the resistor load bank is only switched ON / OFF at zero-crossing points to eliminate electrical noise.

Owner:BOGGS RICHARD

Simplified resistance based belt inspection

ActiveUS9599582B2Other resistor networksResistance/reactance/impedenceElectrical resistance and conductanceResistor

A resistance circuit for monitoring a support structure is provided. The resistance circuit may include a first set of resistors disposed at a belt-side and a second set of resistors disposed at a monitor-side. The first set of resistors may be configured to indicate one or more voltages thereacross corresponding to an effective resistance of the support structure. The first set of resistors may include at least one temperature-dependent resistor. The second set of resistors may be configured to indicate one or more voltages thereacross corresponding to an initial effective resistance of the support structure. The second set of resistors may include at least one switched resistor having an adjustable resistance capable of selectively approximating the initial effective resistance.

Owner:OTIS ELEVATOR CO

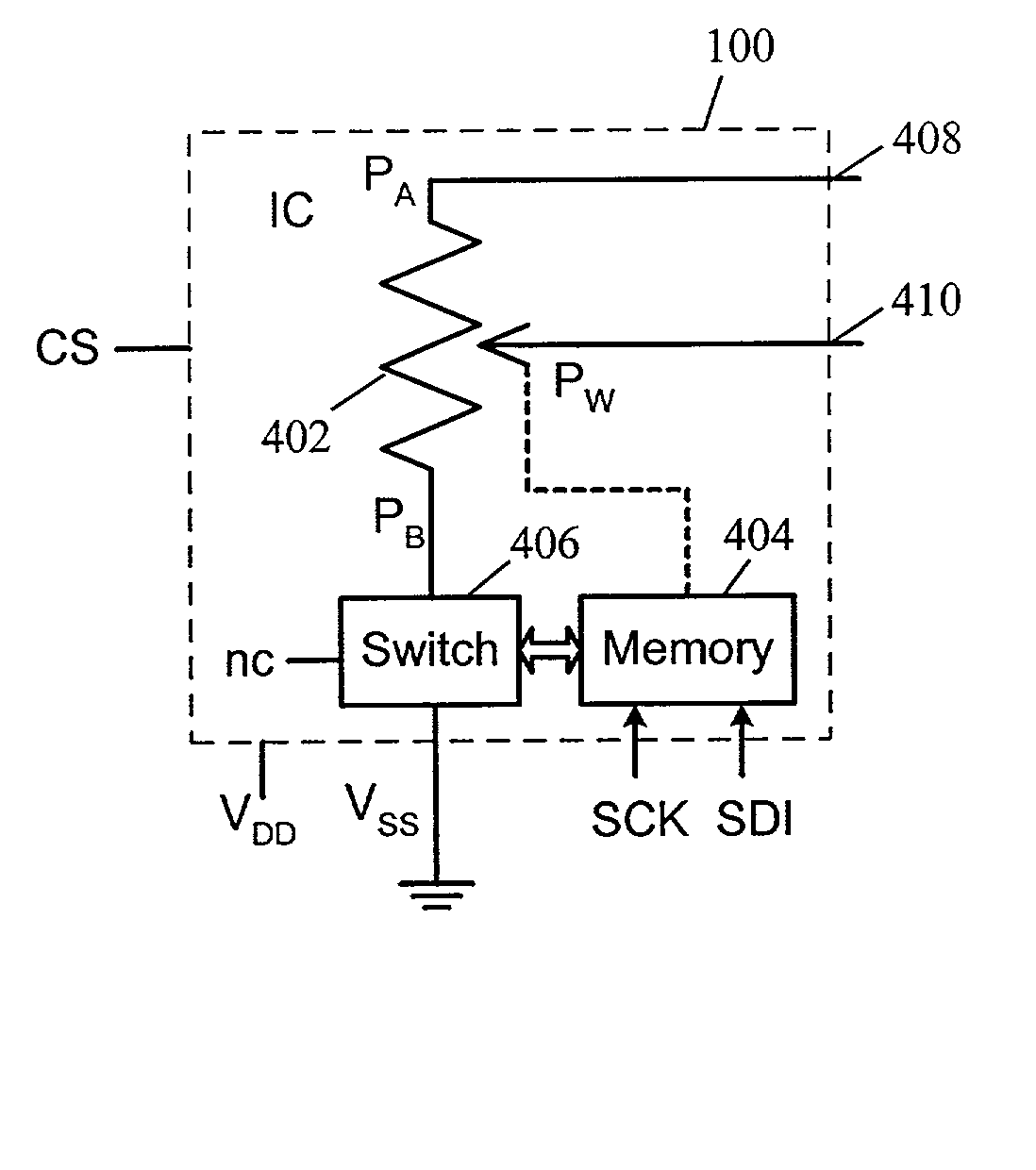

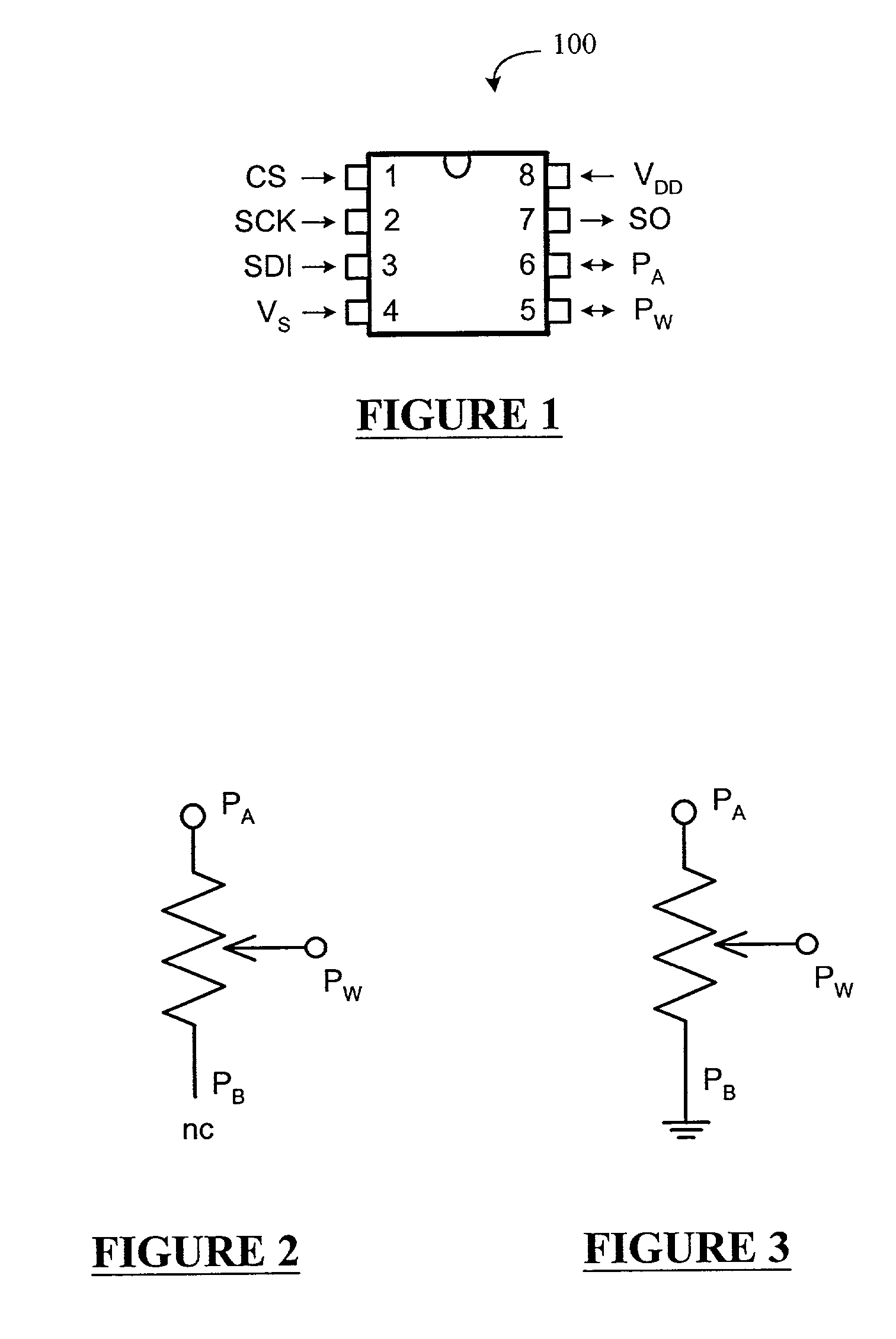

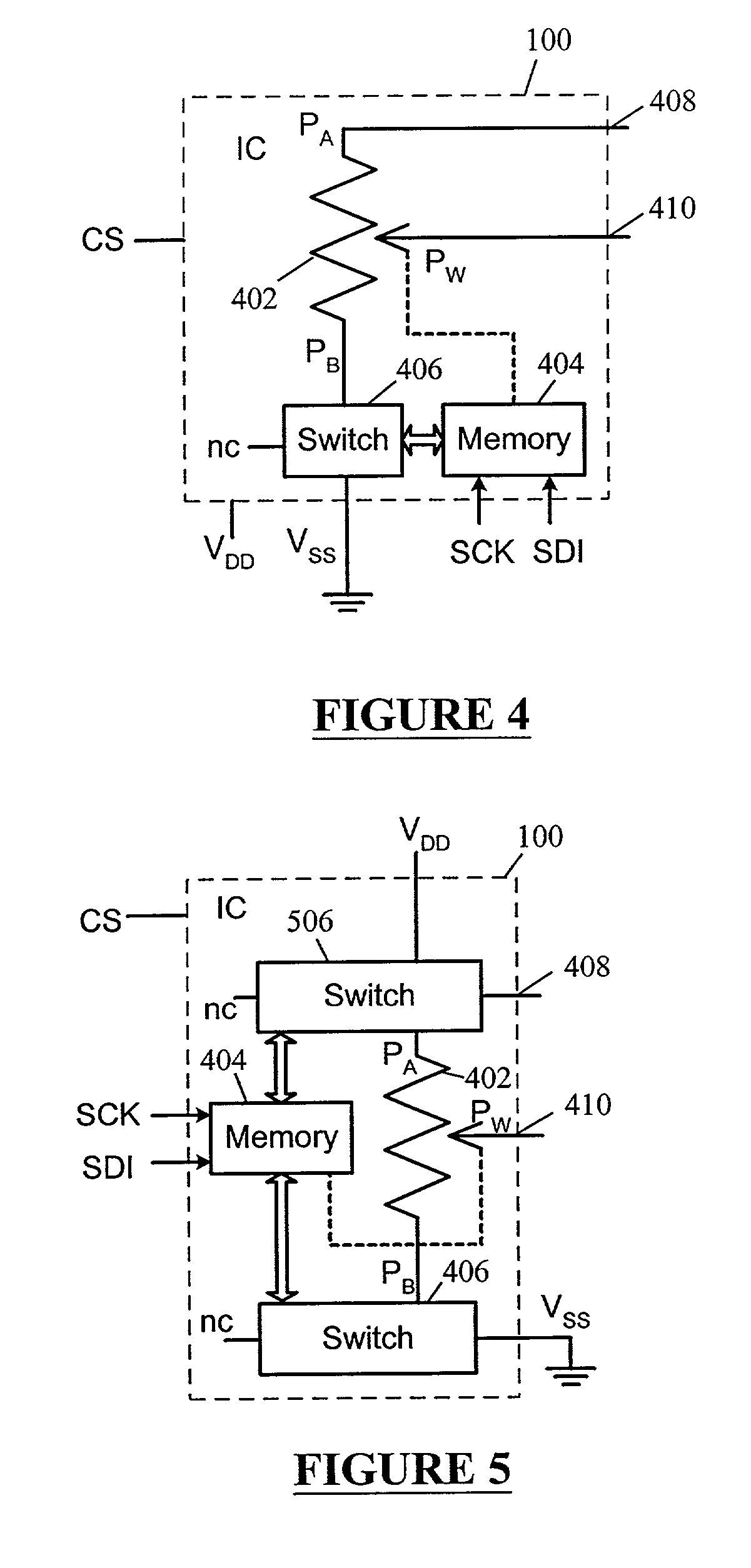

Apparatus and method for a two terminal implementation of rheostat and potentiometer modes in an integrated circuit

InactiveUS20030011464A1Analogue/digital conversionElectric signal transmission systemsHemt circuitsControl theory

A digitally adjustable rheostat and / or potentiometer in a low cost integrated circuit package having a minimum number of connection pins is configurable with a memory and switch included in the integrated circuit. The switch is coupled to one or both ends of the potentiometer and configures the digitally adjustable rheostat and / or potentiometer so that a minimum number of integrated circuit package pins are required for external circuit connection to the rheostat and / or potentiometer.

Owner:MICROCHIP TECH INC

Open loop common mode driver for switched capacitor input to SAR

InactiveUS6954170B2Electric signal transmission systemsResistors with plural resistive elementsCapacitancePhase shifted

Open loop common mode driver for switched capacitor input to SAR. A unity gain driver amplifier is disclosed for driving an output node that is connected to a capacitive load. The amplifier includes a first stage amplifier for driving an intermediate node, a positive voltage input node for being connected to an input voltage and a negative input node for receiving a feedback signal. A complimentary output stage is provided having an input connected to the intermediate node and an output connected to the output node, a voltage representative of the voltage on the output node fed back to the negative input of said first stage amplifier. Isolation circuitry then isolates the output node from the negative input node of the first stage amplifier as to phase shift due to large values of the capacitive loading during operation of the driver amplifier.

Owner:SILICON LAB INC

Range switch

InactiveCN101673637AReduce dirtResistors with plural resistive elementsContactsEngineeringElectronic component

The invention provides a range switch composed of a main body, a rotating part and a bottom cover. The main body is provided with a holding area, and magnetic substances are arranged around the innercircumference of the main body; the rotating part is arranged on the main body by a transmission axis, and the side edge of the rotating part is provided with at least one magnetic substance, and thebottom surface is fixedly provided with contact chips; the bottom cover is used for covering the holding area of the main body and comprises at least one electronic component which can contact the contact chips of the rotating part; moreover, the electronic component is provided with resistor elements with different coefficients. After the rotating part is rotated, the rotating part and the magnetic substances arranged around the main body can attract mutually, thereby achieving the goal of providing no-contact fine-tuning output.

Owner:LNC TECH CO LTD

Electronic pressure sensitive transducer apparatus and method for manufacturing same

InactiveUS20050156705A1Low costReduce complexityWave amplification devicesForce measurementTransducerPrinted circuit board

The cost and complexity of an electronic pressure sensitive transducer are decreased by constructing such a transducer directly on a printed circuit board containing support electronics. Conductive traces are formed on the printed circuit board to define a contact area. A flexible substrate having an inner surface is positioned over the contact area. An adhesive spacer, substantially surrounding the contact area, attaches the flexible substrate to the printed circuit board. At least one resistive layer is deposited on the flexible substrate inner surface. In use, the resistive layer contacts at least two conductive traces in response to pressure applied to the flexible substrate to produce an electrical signal indicative of applied pressure.

Owner:INTERLINK ELECTRONICS

Multi-directional input apparatus

ActiveUS8400333B2Facilitates size reduction and assemblyEasy to assembleManual control with multiple controlled membersElectronic switchingCoil springRubbing

A multi-directional input apparatus includes an operating member including a shaft portion which extends to the outside, a housing having an opening through which the shaft portion extends and configured to support the operating member in a tiltable manner, interlocking members moved by the operating member when the shaft portion is tilted, and detectors which detect changes in the positions of the interlocking members. A sliding member is externally fitted to the shaft portion such that the sliding member is movable in an axial direction, and a coil spring is disposed between a flange provided on the shaft portion and the sliding member. A rubbing surface of the sliding member is in elastic contact with a receiving surface on an inner wall of an annular edge portion surrounding the opening. The rubbing surface and the receiving surface are spherical surfaces centered on a tilting center of the shaft portion.

Owner:ALPS ALPINE CO LTD

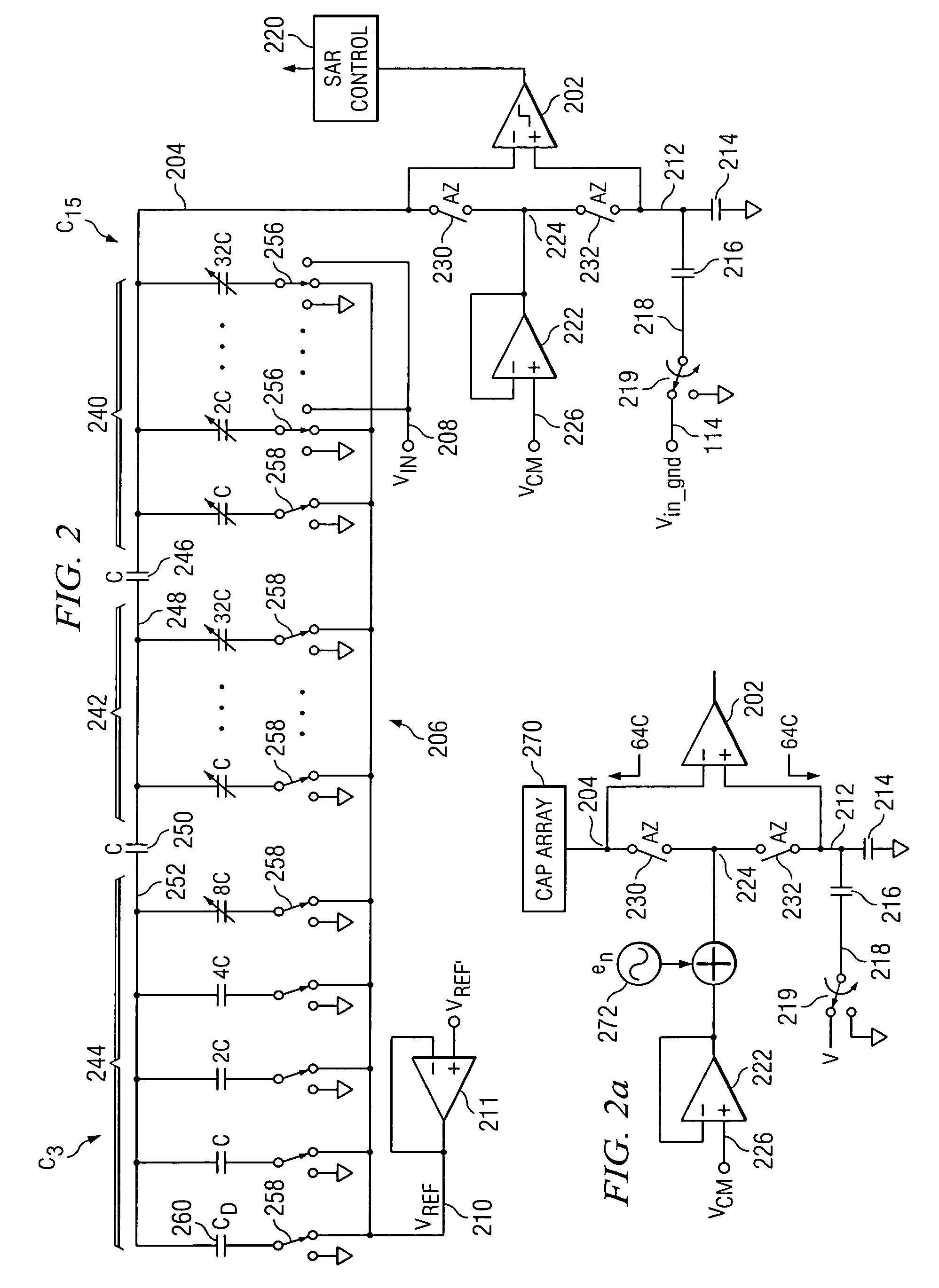

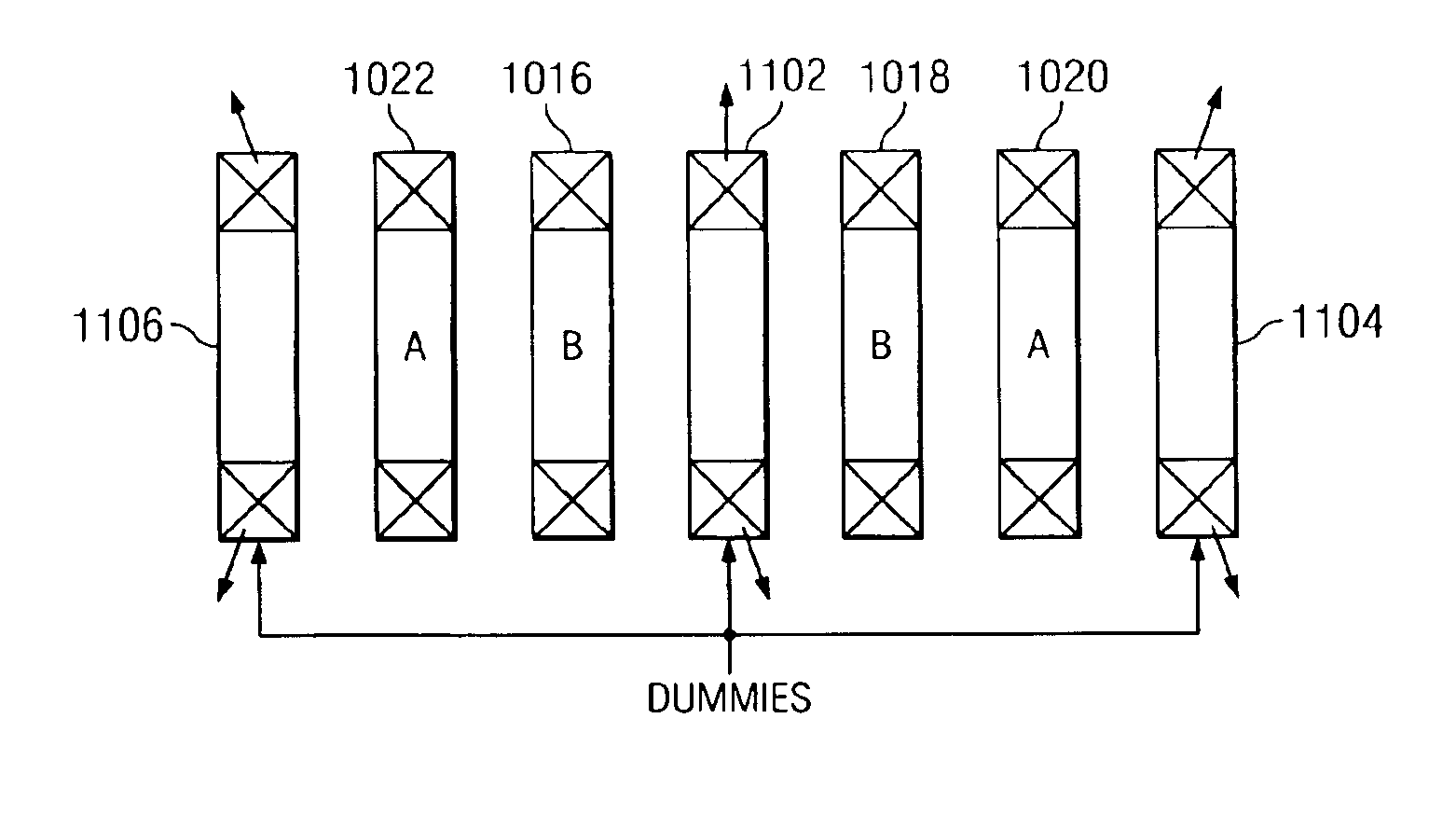

Common centroid layout for parallel resistors in an amplifier with matched AC performance

InactiveUS6954167B2Electric signal transmission systemsResistor terminals/electrodesAudio power amplifierEngineering

Common centroid layout for parallel resistors in an amplifier with matched AC performance. An amplifier is disclosed that is formed on a silicon substrate that includes first and second differential legs, each driving first and second resistive loads. The first resistive load comprises first and second parallel resistive loads connected on one side thereof to one end of the first differential leg and the other side of each of the first and second parallel resistive loads separately connected to a first reference voltage. The second resistive load comprises third and fourth resistive loads each connected on one side thereof to one end of the second differential leg and the other side of each of the third and fourth parallel resistive loads connected separately to the first reference voltage. Each of the first, second, third and fourth resistive loads is fabricated of a strip of resistive material disposed on the surface of the substrate and having a finite resistivity, length, width and thickness. The first parallel resistive load is disposed adjacent to a first dummy resistive strip on one side thereof, and disposed adjacent the third parallel resistive load on the opposite side thereof. The third parallel resistive load is disposed adjacent a second dummy resistive strip disposed on the diametrically opposite side thereof from the first parallel resistive load. The fourth parallel resistive load is disposed adjacent the second dummy resistive strip on the diametrically opposite side thereof from the third parallel resistive load. The second resistive load is disposed adjacent the fourth parallel resistive load and capacitively coupled thereto on the side diametrically opposite to the second dummy resistive strip. The second parallel resistive load is disposed adjacent a third dummy resistive strip on the side thereof diametrically opposite to the fourth parallel resistive load and capacitively coupled thereto. The first, second and third dummy resistive strips are connected to a second reference voltage.

Owner:SILICON LAB INC