Patents

Literature

110 results about "Mixed-signal integrated circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

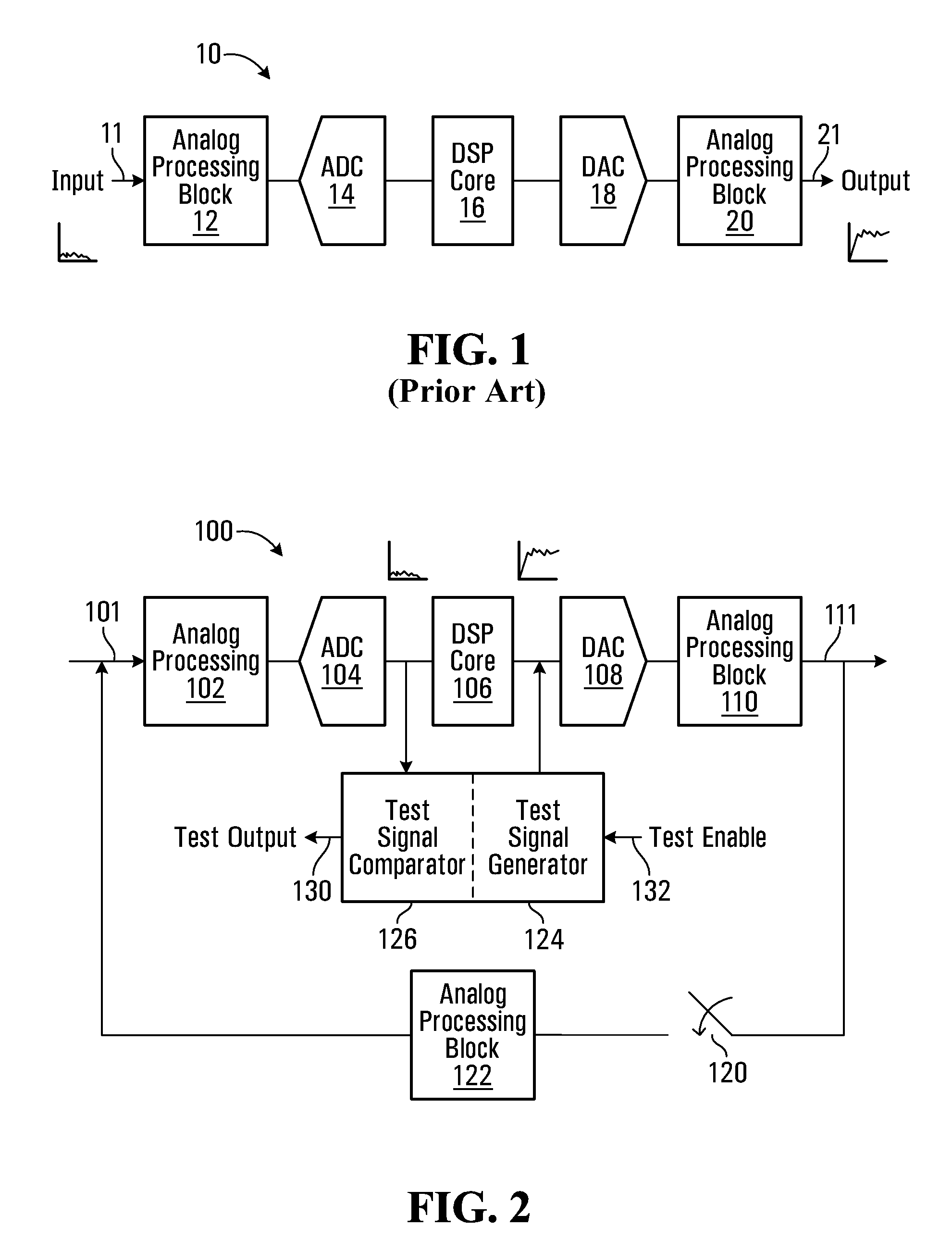

A mixed-signal integrated circuit is any integrated circuit that has both analog circuits and digital circuits on a single semiconductor die. In real-life applications mixed-signal designs are everywhere, for example, smart mobile phones. Mixed-signal ICs also process both analog and digital signals together. For example, an analog-to-digital converter is a mixed-signal circuit. Mixed-signal circuits or systems are typically cost-effective solutions for building any modern consumer electronics applications.

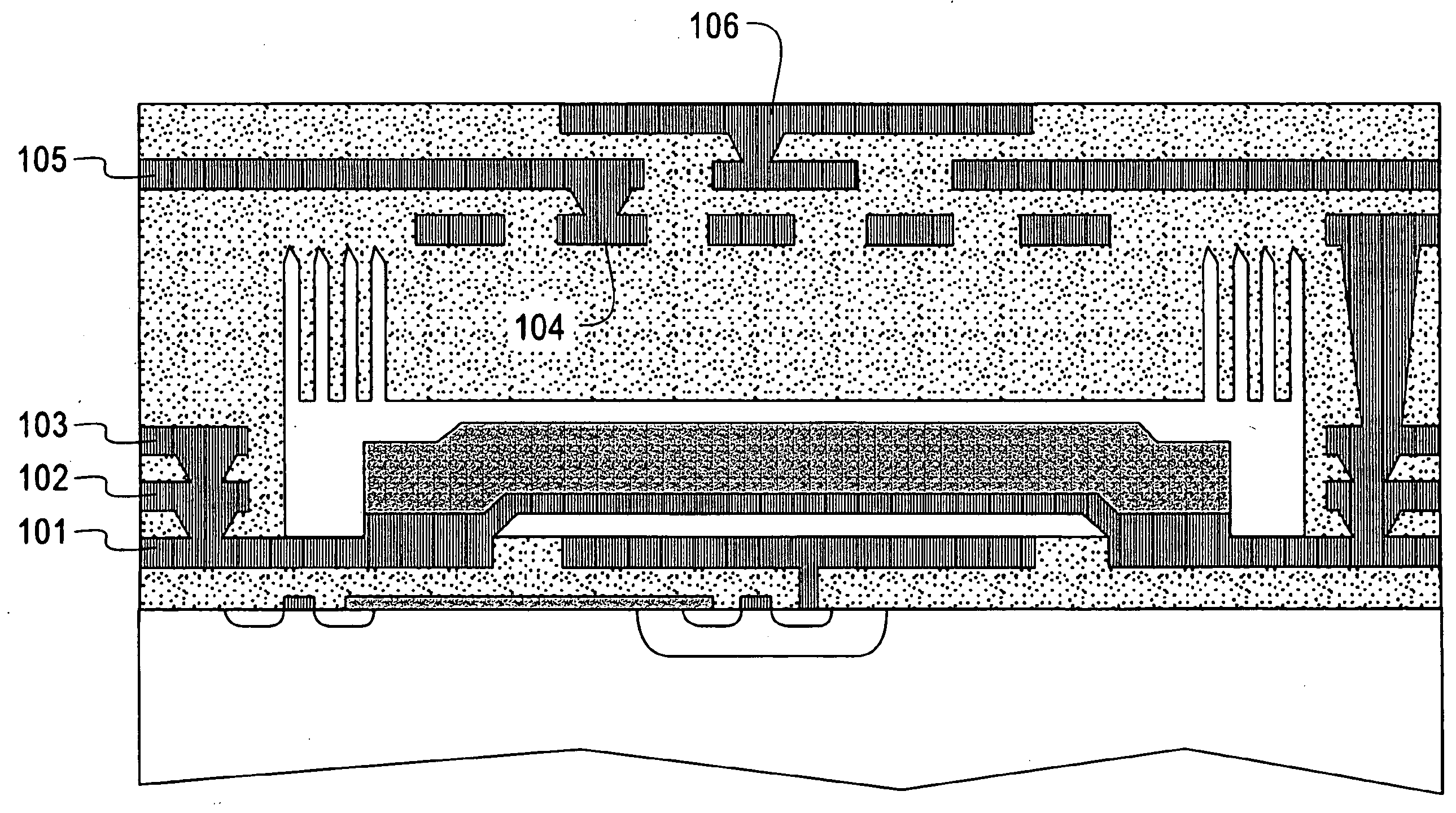

Low temperature bi-CMOS compatible process for MEMS RF resonators and filters

InactiveUS20090108381A1Impedence networksSemiconductor/solid-state device detailsMetal interconnectOxygen plasma

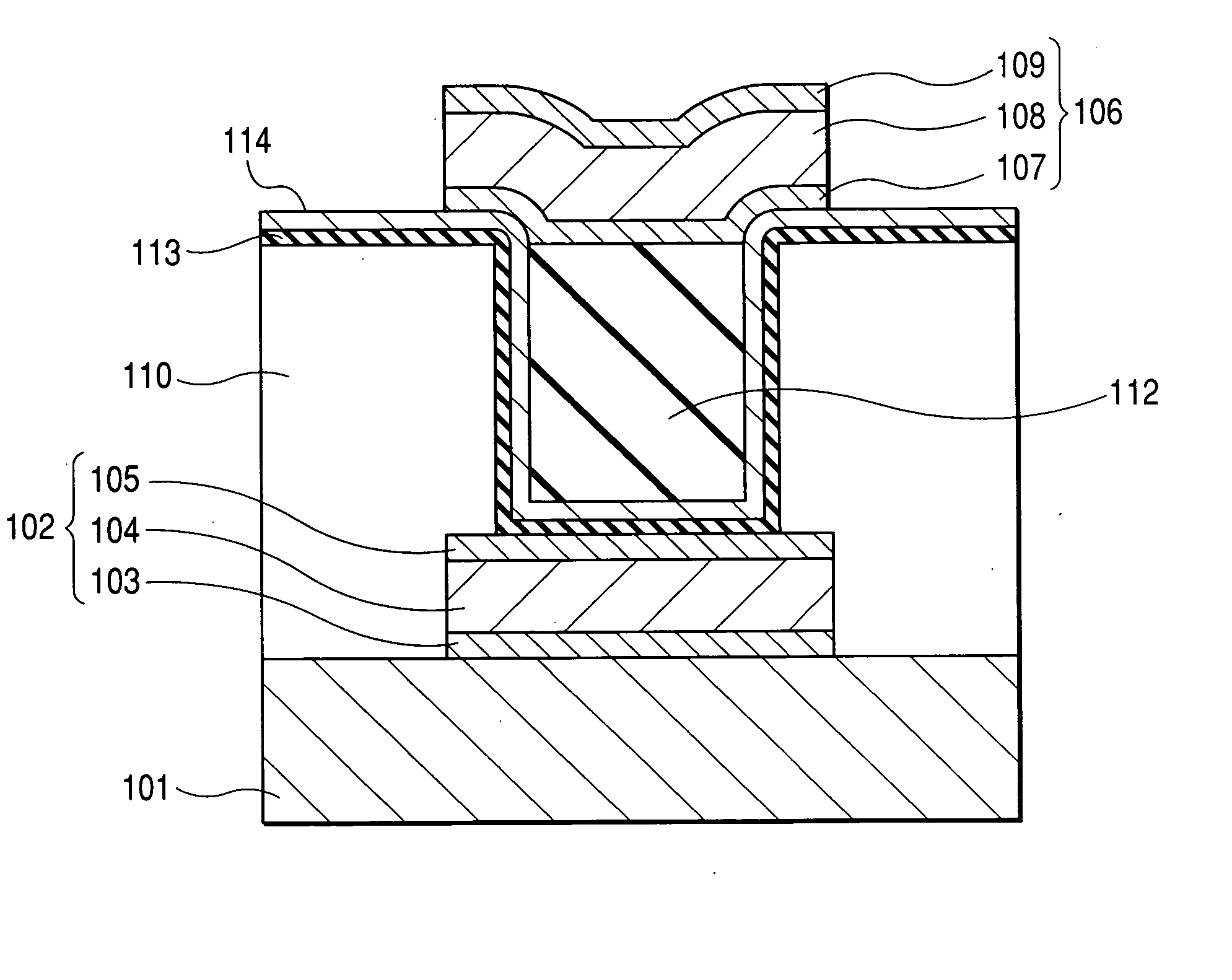

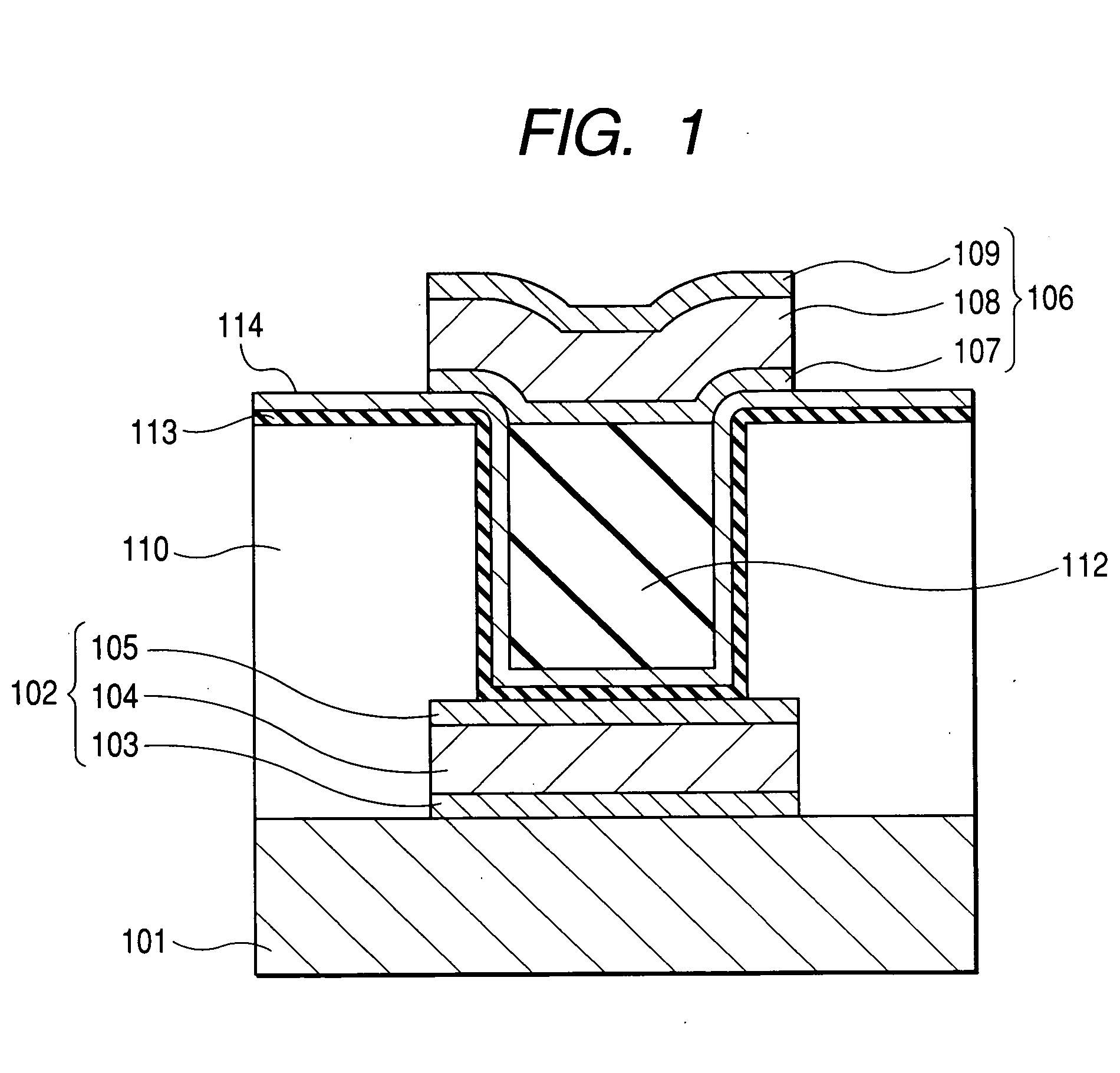

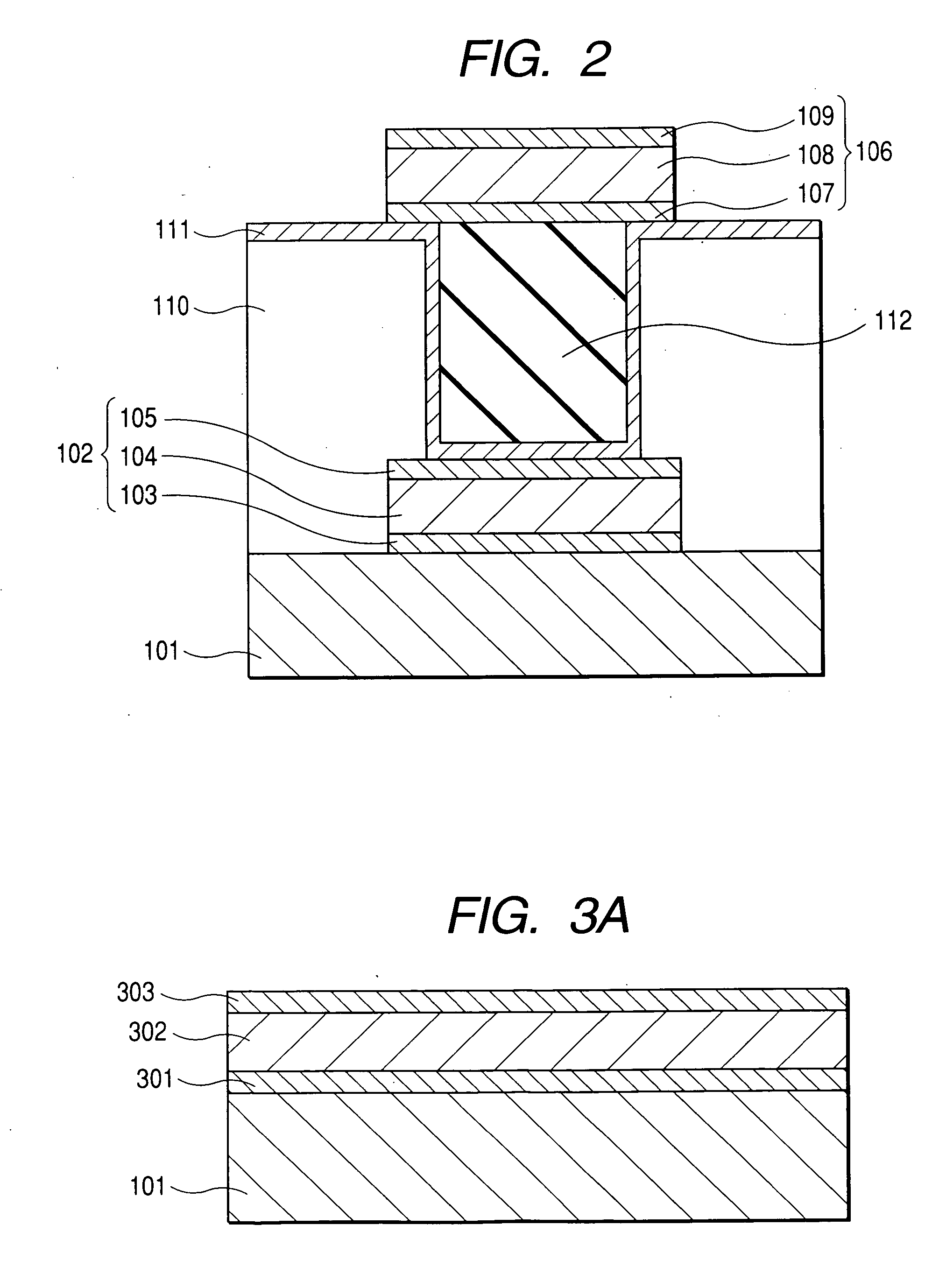

A method of formation of a microelectromechanical system (MEMS) resonator or filter which is compatible with integration with any analog, digital, or mixed-signal integrated circuit (IC) process, after or concurrently with the formation of the metal interconnect layers in those processes, by virtue of its materials of composition, processing steps, and temperature of fabrication is presented. The MEMS resonator or filter incorporates a lower metal level, which forms the electrodes of the MEMS resonator or filter, that may be shared with any or none of the existing metal interconnect levels on the IC. It further incorporates a resonating member that is comprised of at least one metal layer for electrical connection and electrostatic actuation, and at least one dielectric layer for structural purposes. The gap between the electrodes and the resonating member is created by the deposition and subsequent removal of a sacrificial layer comprised of a carbon-based material. The method of removal of the sacrificial material is by an oxygen plasma or an anneal in an oxygen containing ambient. A method of vacuum encapsulation of the MEMS resonator or filter is provided through means of a cavity containing the MEMS device, filled with additional sacrificial material, and sealed. Access vias are created through the membrane sealing the cavity; the sacrificial material is removed as stated previously, and the vias are re-sealed in a vacuum coating process.

Owner:IBM CORP

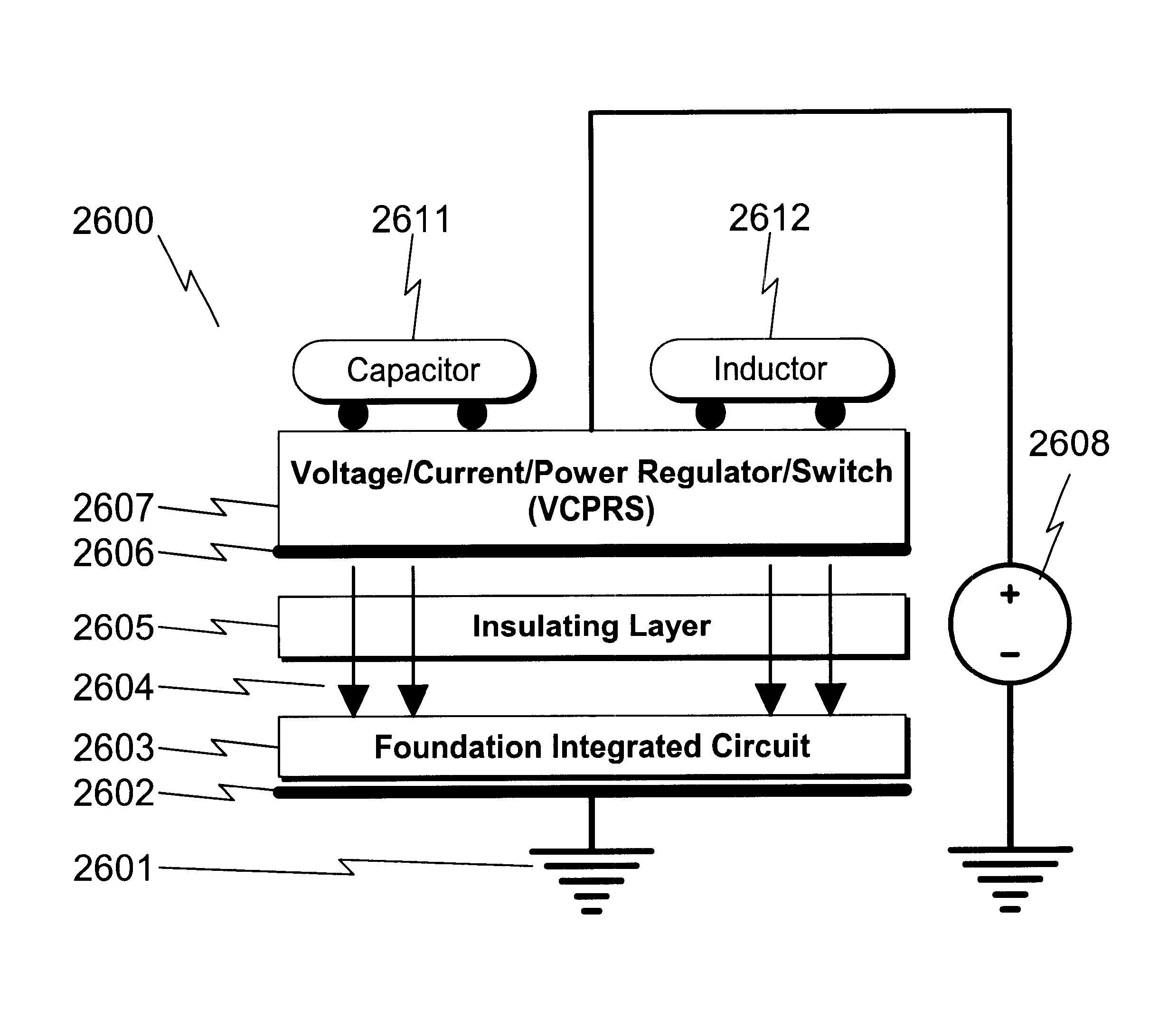

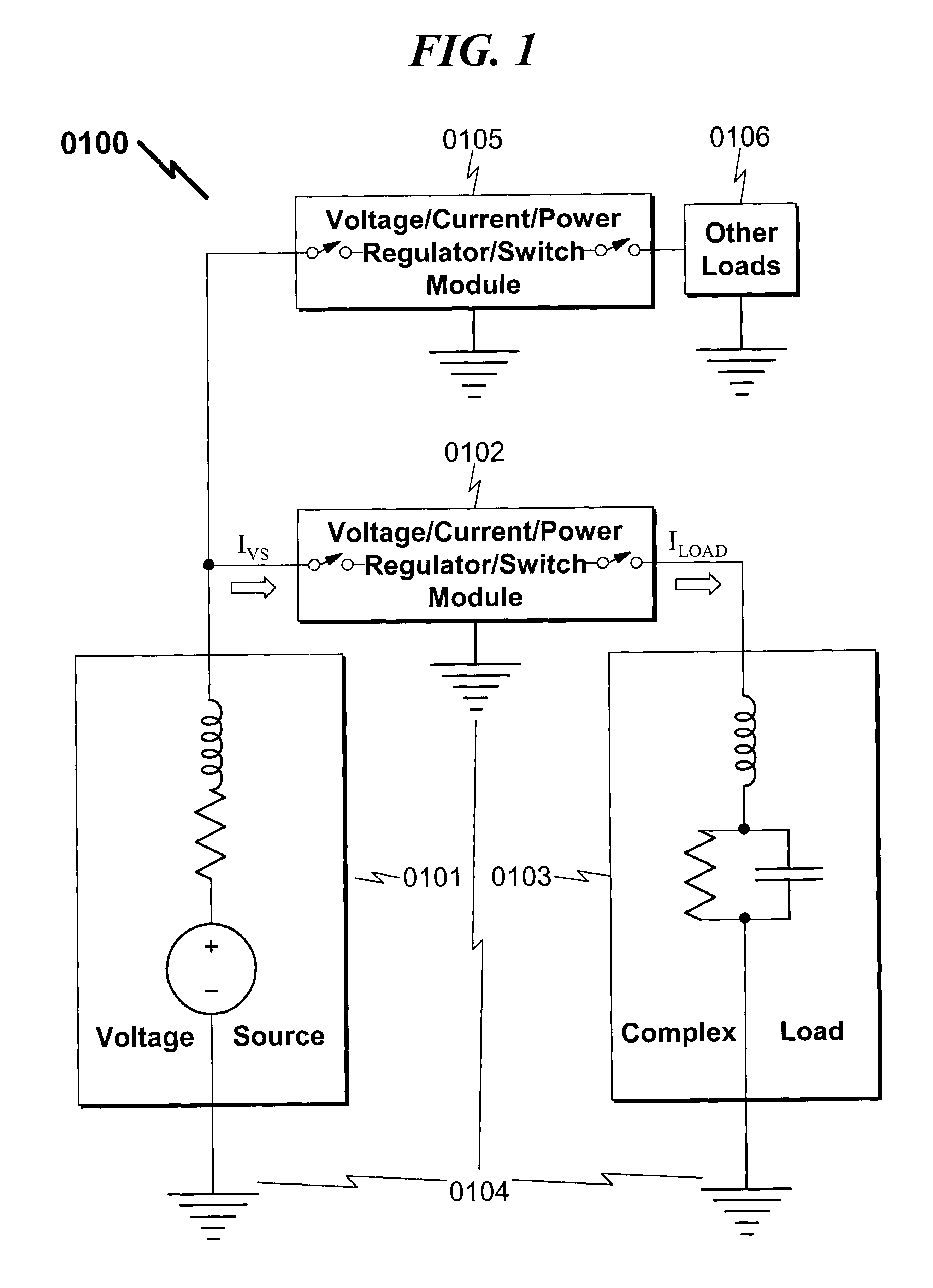

Integrated voltage/current/power regulator/switch system and method

InactiveUS6396137B1Minimal noiseGood PSRRSemiconductor/solid-state device detailsDc-dc conversionPower applicationPower capability

An integrated voltage / current / power regulator / switch (VCPRS) system and method are disclosed in which regulator / switch circuitry is vertically integrated on top of an existing integrated circuit. The present invention does not require additional integrated circuit chip area for the regulator pass device as is required in the prior art, and by virtue of its construction provides a significantly reduced on-resistance as compared to all prior art implementations. The present invention both stabilizes the power supply for large area integrated circuits and permits individual areas of the integrated circuit to have switched power capability, a highly desirable feature in low power and battery power applications. The present invention permits an increase in the power supply rejection ratio (PSRR) for digital, analog, and especially mixed-signal integrated circuit designs by permitting various circuit blocks to have localized power regulation that is obtained from a common power supply plane within the integrated circuit framework. Finally, the present invention appears to be the only economically practical method of addressing the power supply regulation requirements of modern and future integrated microprocessor designs.

Owner:KLUGHART KEVIN MARK

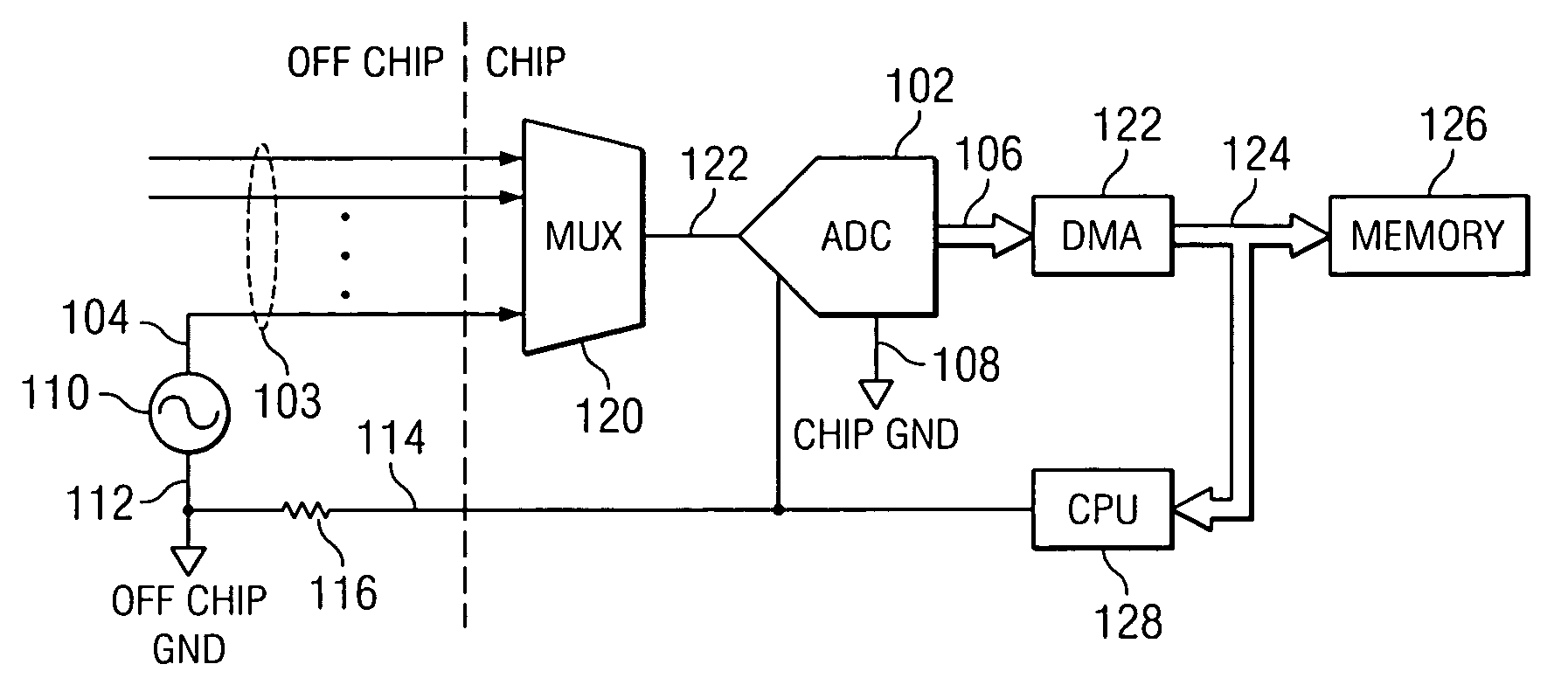

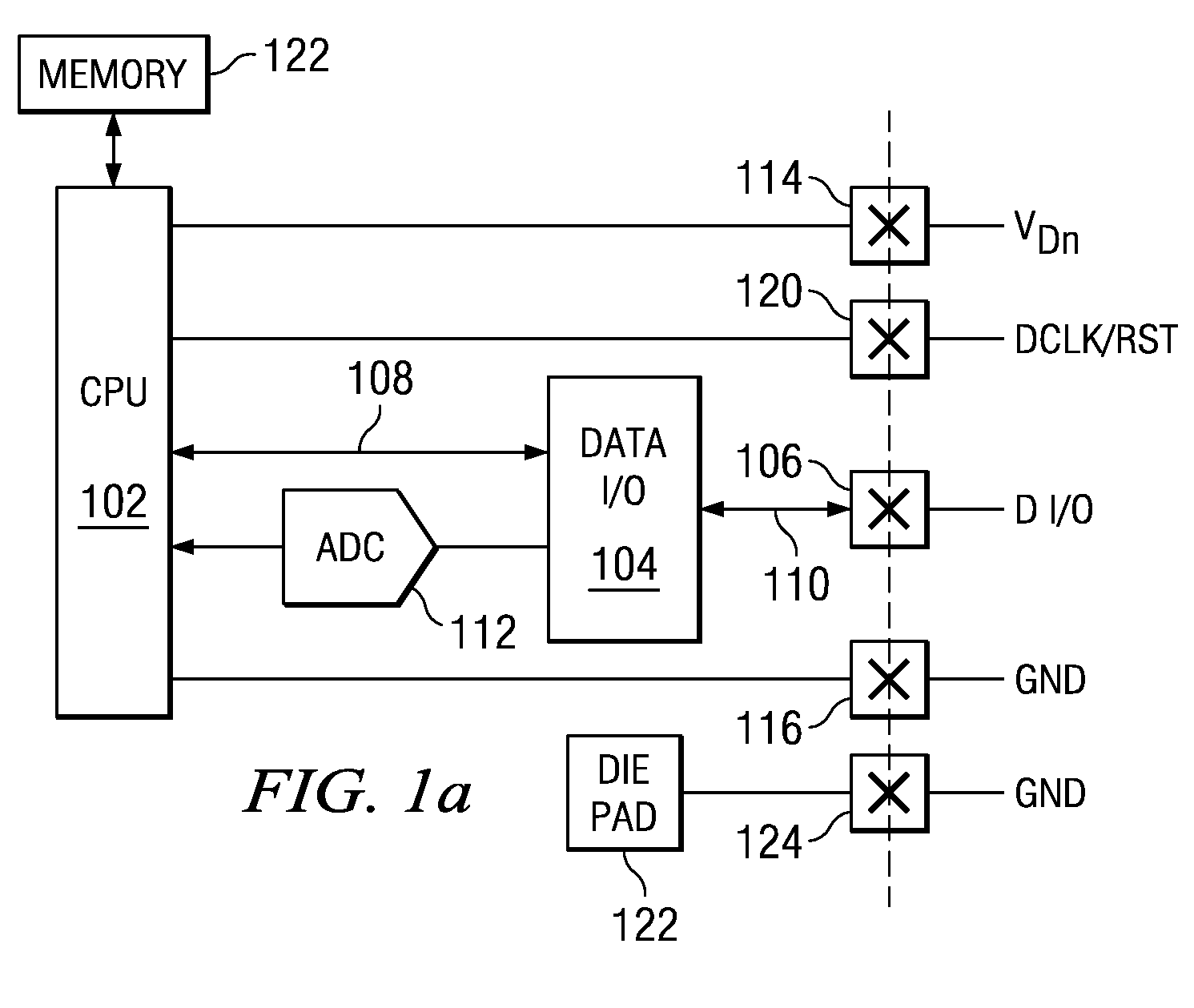

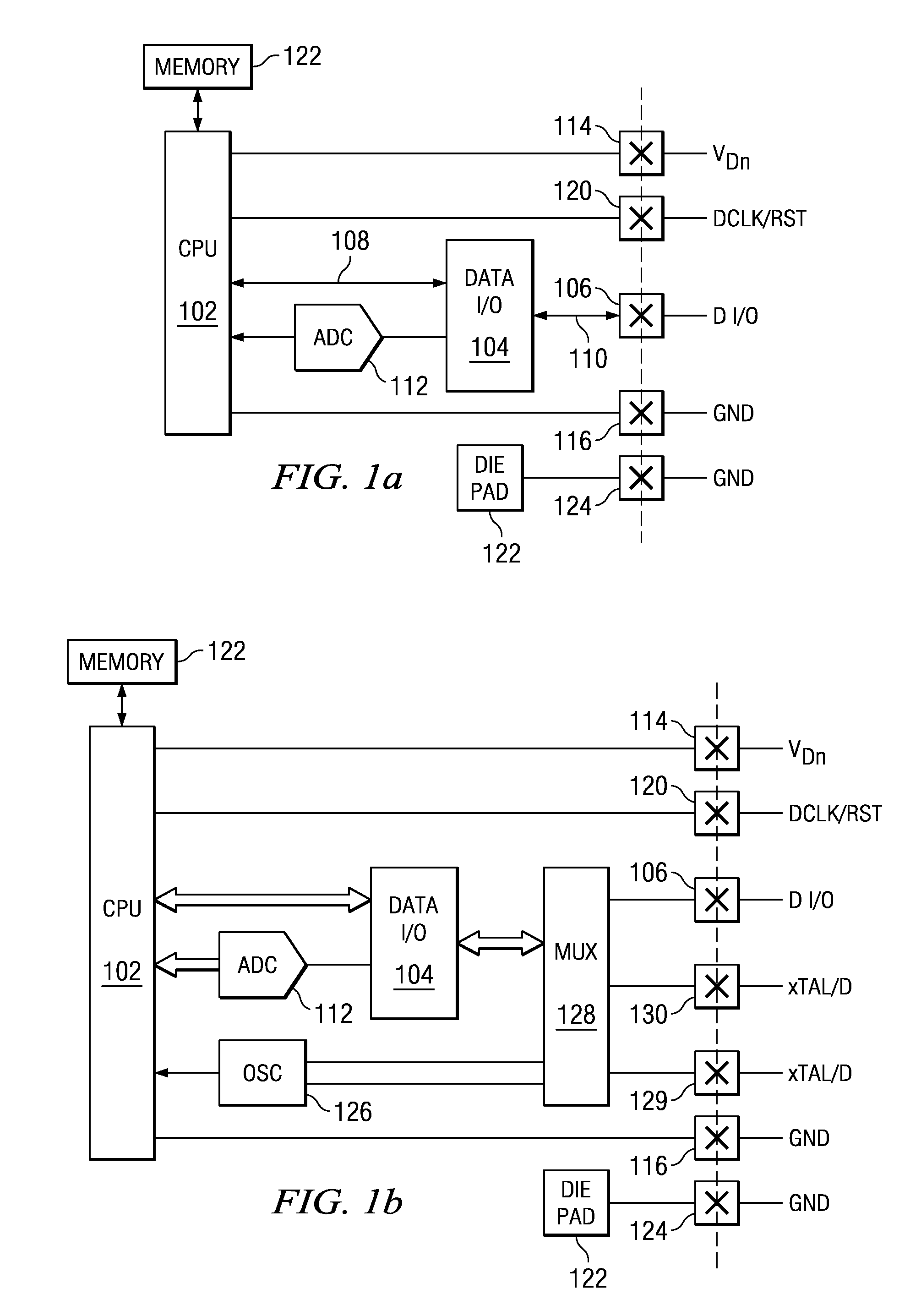

DMA controller that restricts ADC from memory without interrupting generation of digital words when CPU accesses memory

InactiveUS7188199B2Electric signal transmission systemsResistors with plural resistive elementsControl dataMixed-signal integrated circuit

DMA controller for mixed signal device. A mixed signal integrated circuit with memory control is disclosed. A data conversion circuit is provided that is operable to receive an analog input signal and convert discrete samples thereof at a predetermined sampling rate to a digital representations thereof as a plurality of digital words. A memory stores the digital words generated by the data conversion circuit. A processor is included on the integrated circuit and operable to access the memory to output select ones of the digital words for processing thereof in accordance with a predetermined processing algorithm. A memory access controller controls access to the memory by the data conversion circuit and the processor. The memory access controller is operable to restrict access to the memory by the data conversion circuit without interrupting the generation of digital words therefrom when the processor is accessing the memory, and allowing access to the memory by the data conversion circuitry when the processor is not accessing the memory, such that the data conversion circuit can transfer currently generated digital words and previously generated and non stored digital words for storage in said memory upon gaining access thereto.

Owner:SILICON LAB INC

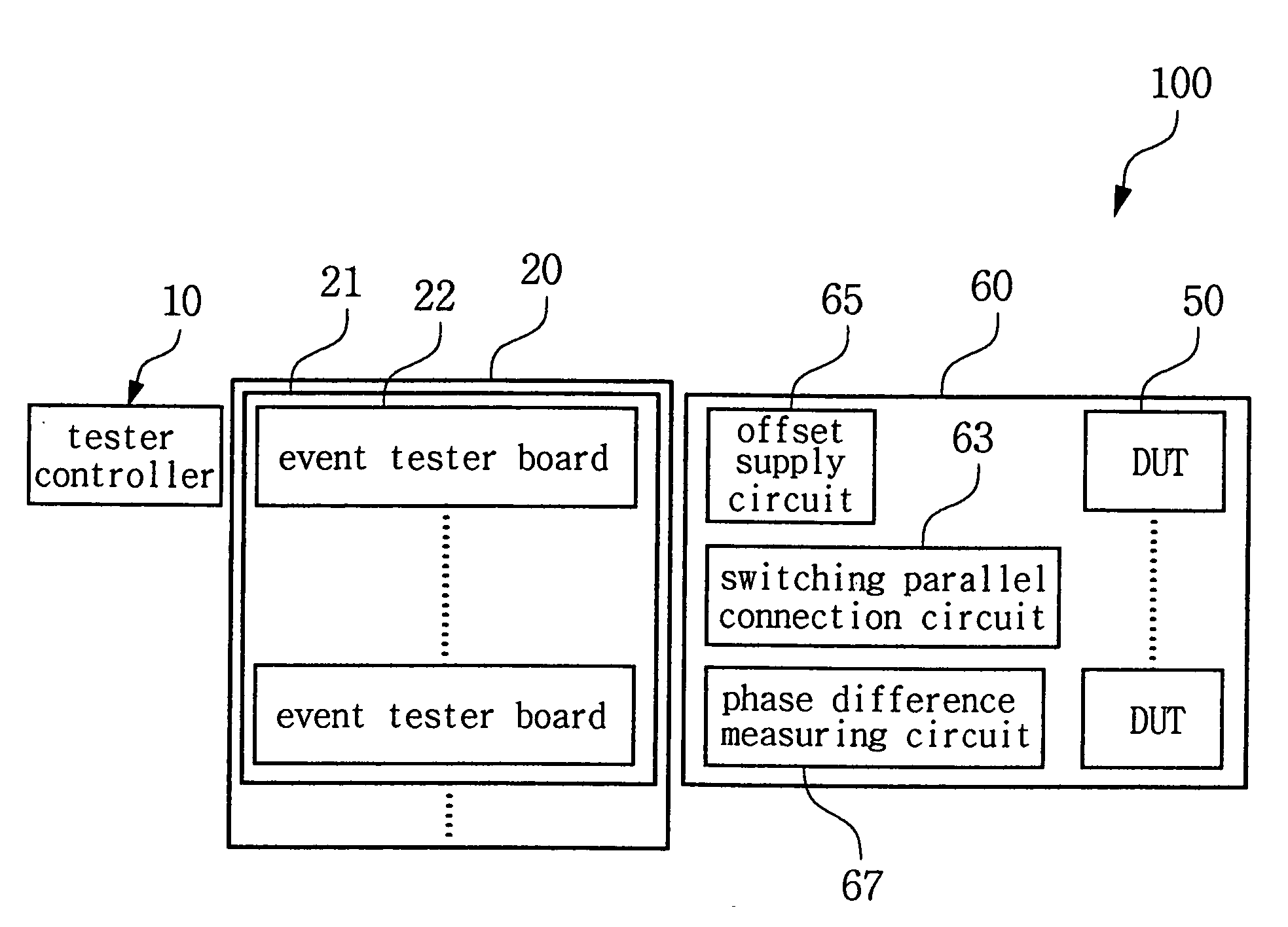

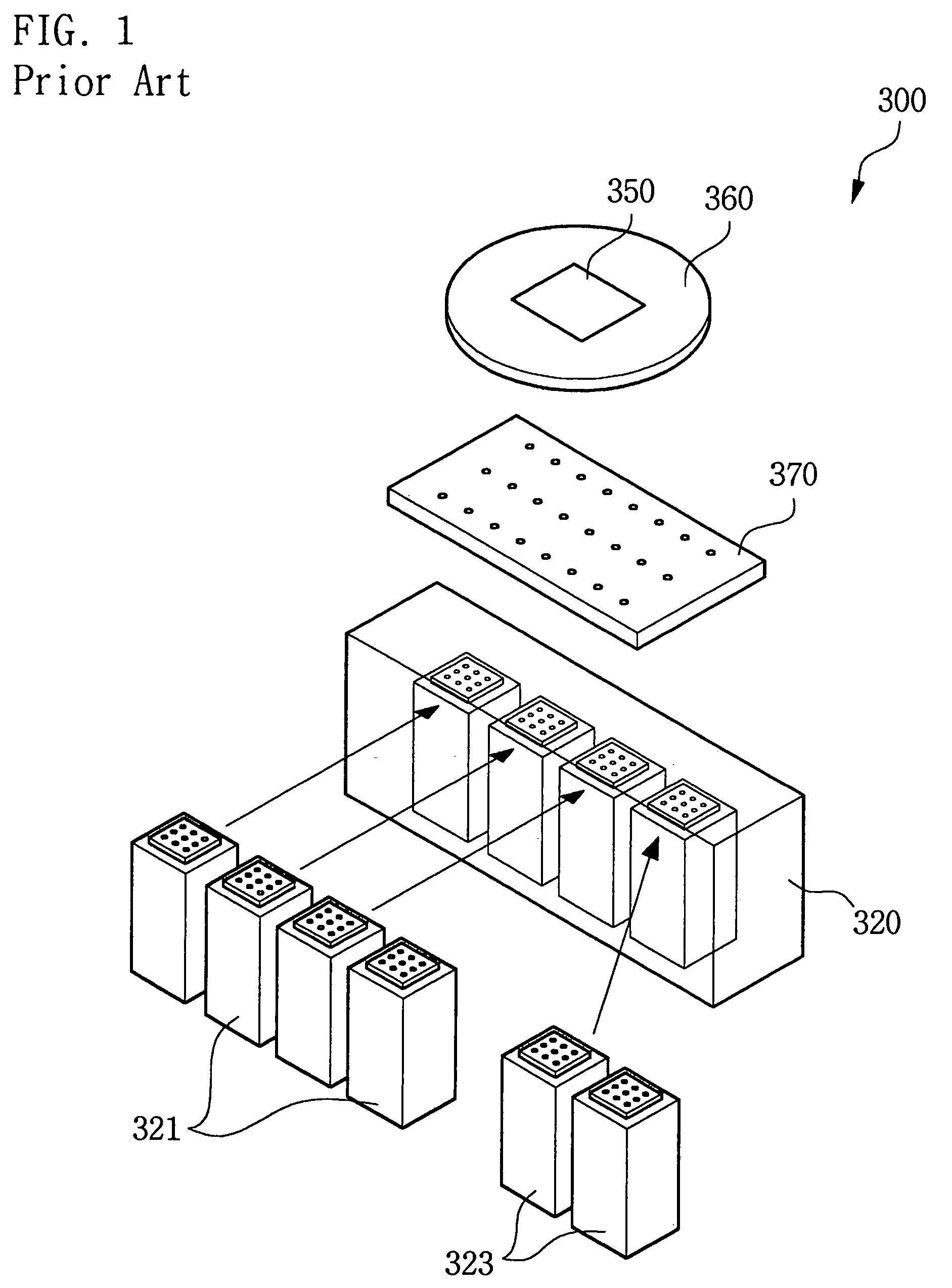

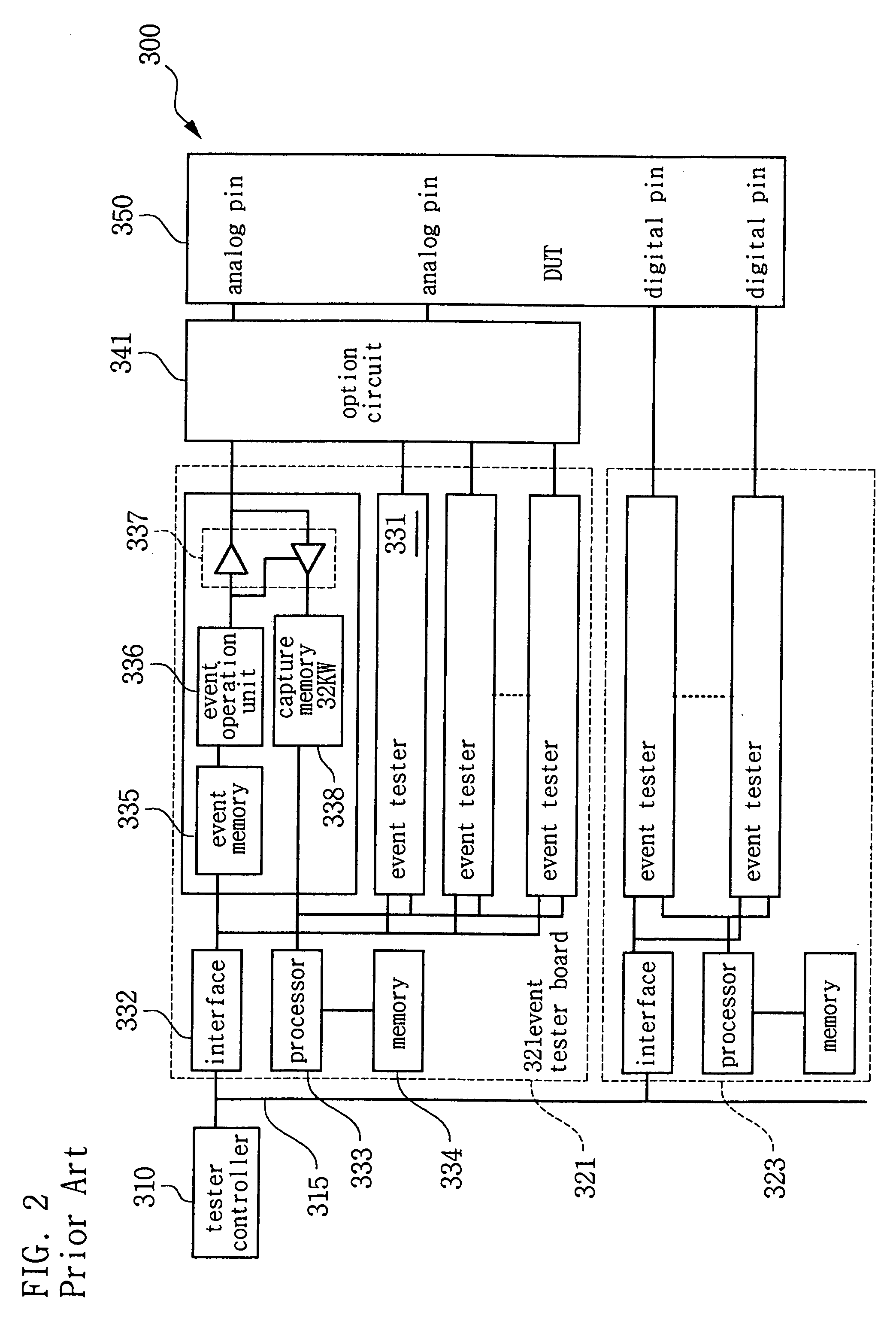

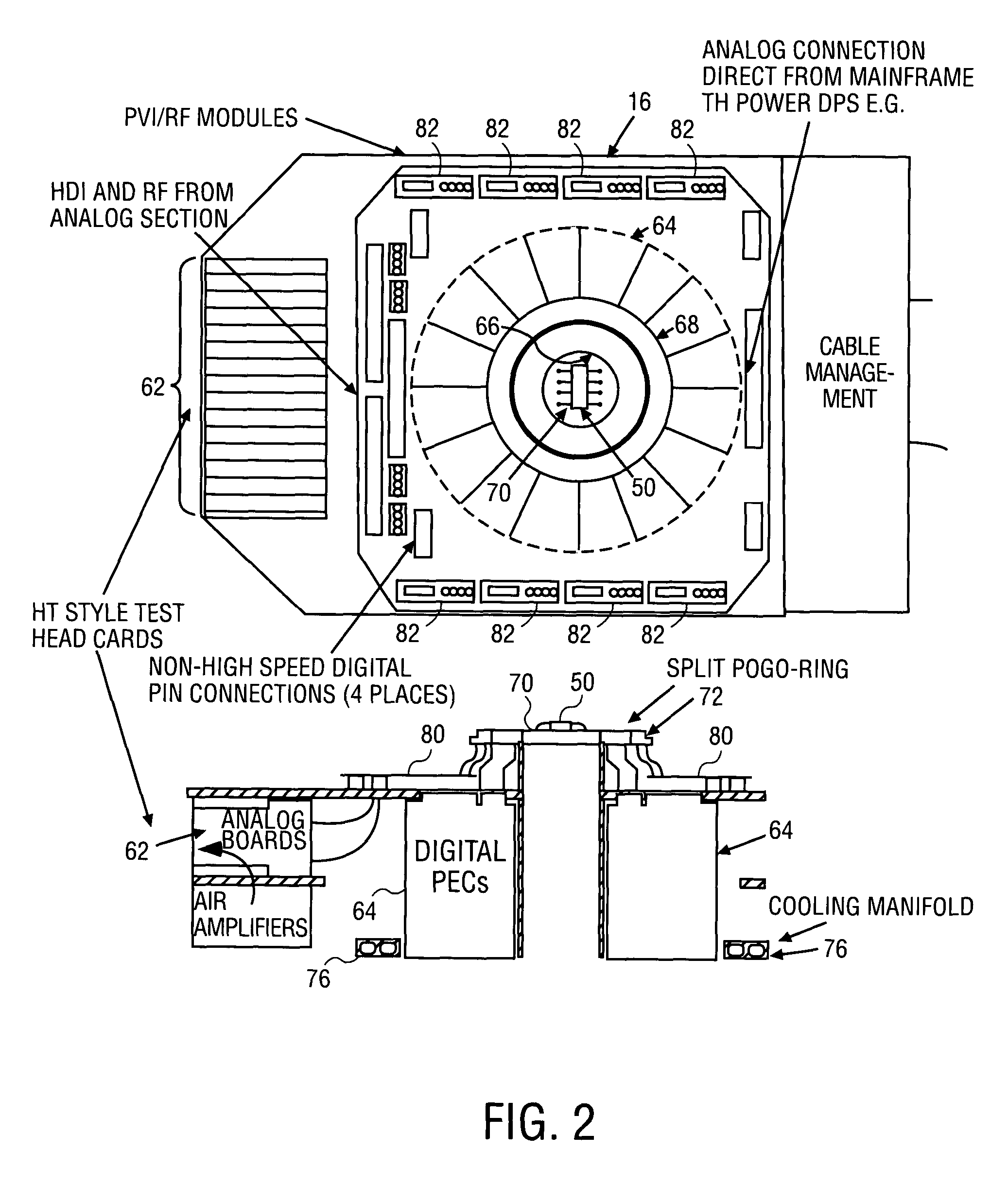

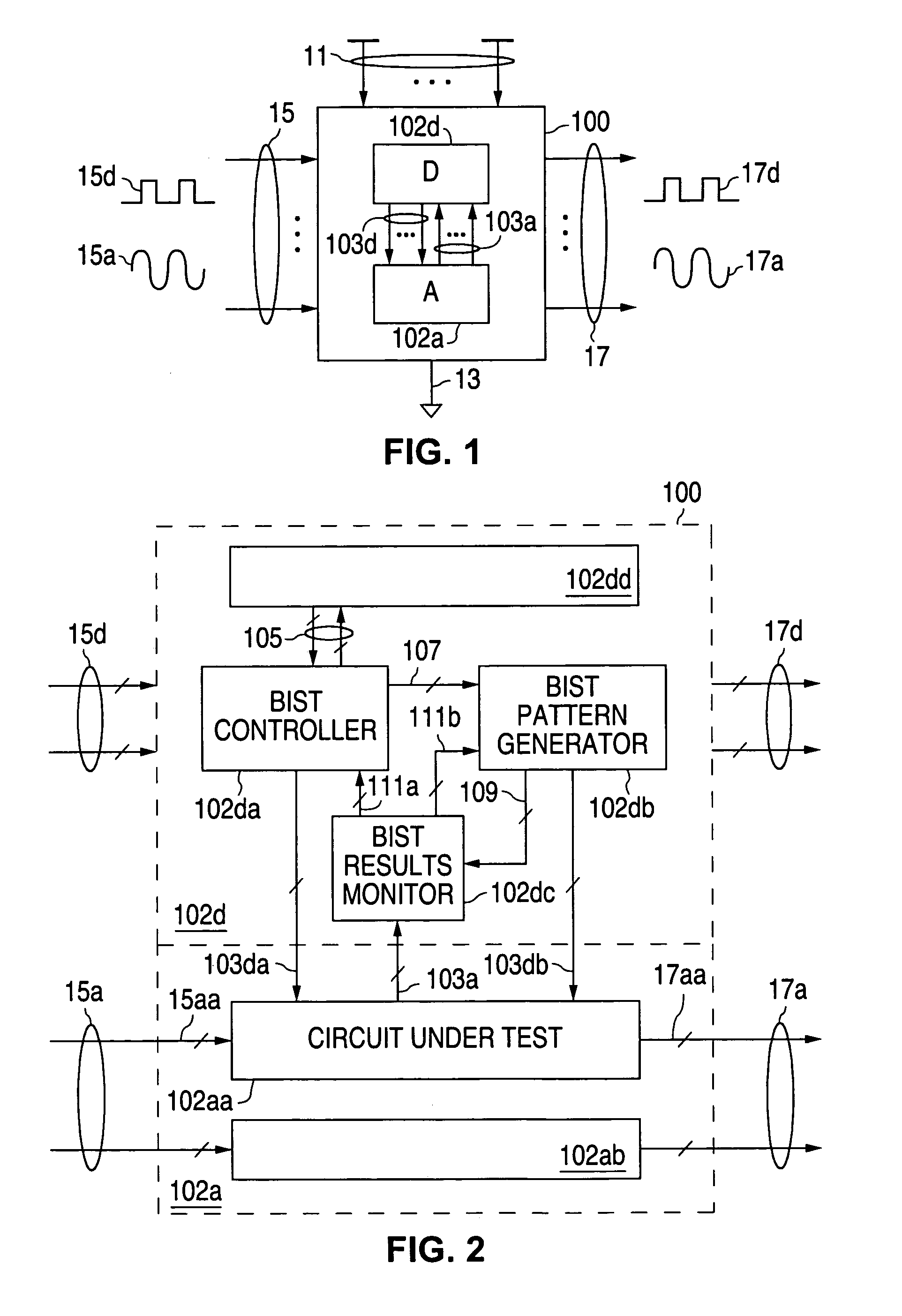

Test apparatus for mixed-signal semiconductor device

InactiveUS20060015785A1Increase the number ofElectronic circuit testingFunctional testingDevice materialTester device

A test apparatus for a mixed-signal semiconductor device that includes a plurality of event tester modules including analog and digital signal tester boards, a test head for event tester modules, a performance board including a socket for a DUT, a test fixture including a connection means, an option circuit for when the DUT is a mixed-signal integrated circuit including an analog and digital function blocks, a tester controller controlling the overall operation, and a switching parallel connection circuit sequentially connecting a single event tester board with a plurality of the DUTs. The event tester board and the DUTs are connected by a group unit. The number of parallel test is increased by an improved tester board or an improved performance board without the use of an extra event tester board for an analog signal test.

Owner:SAMSUNG ELECTRONICS CO LTD

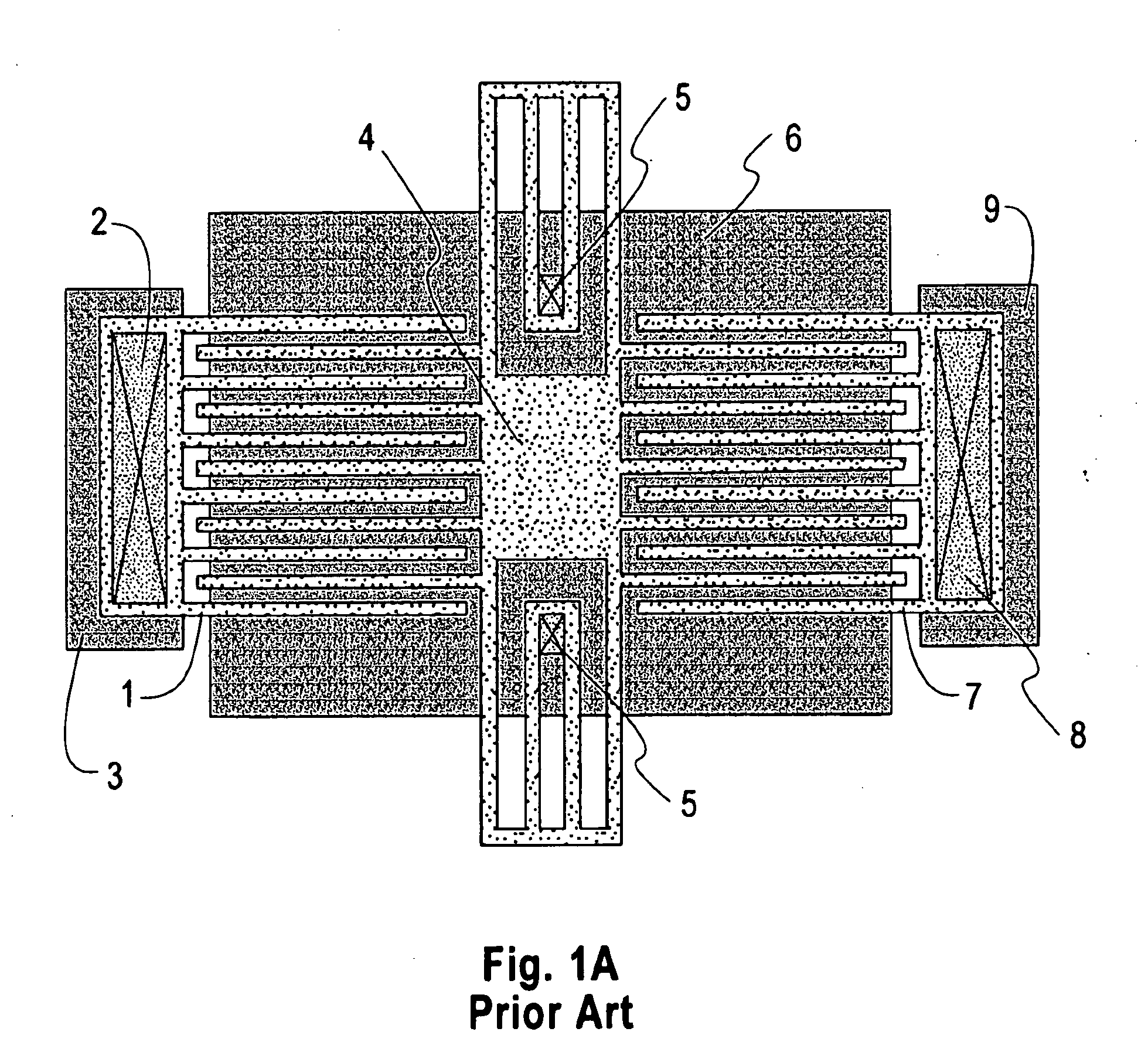

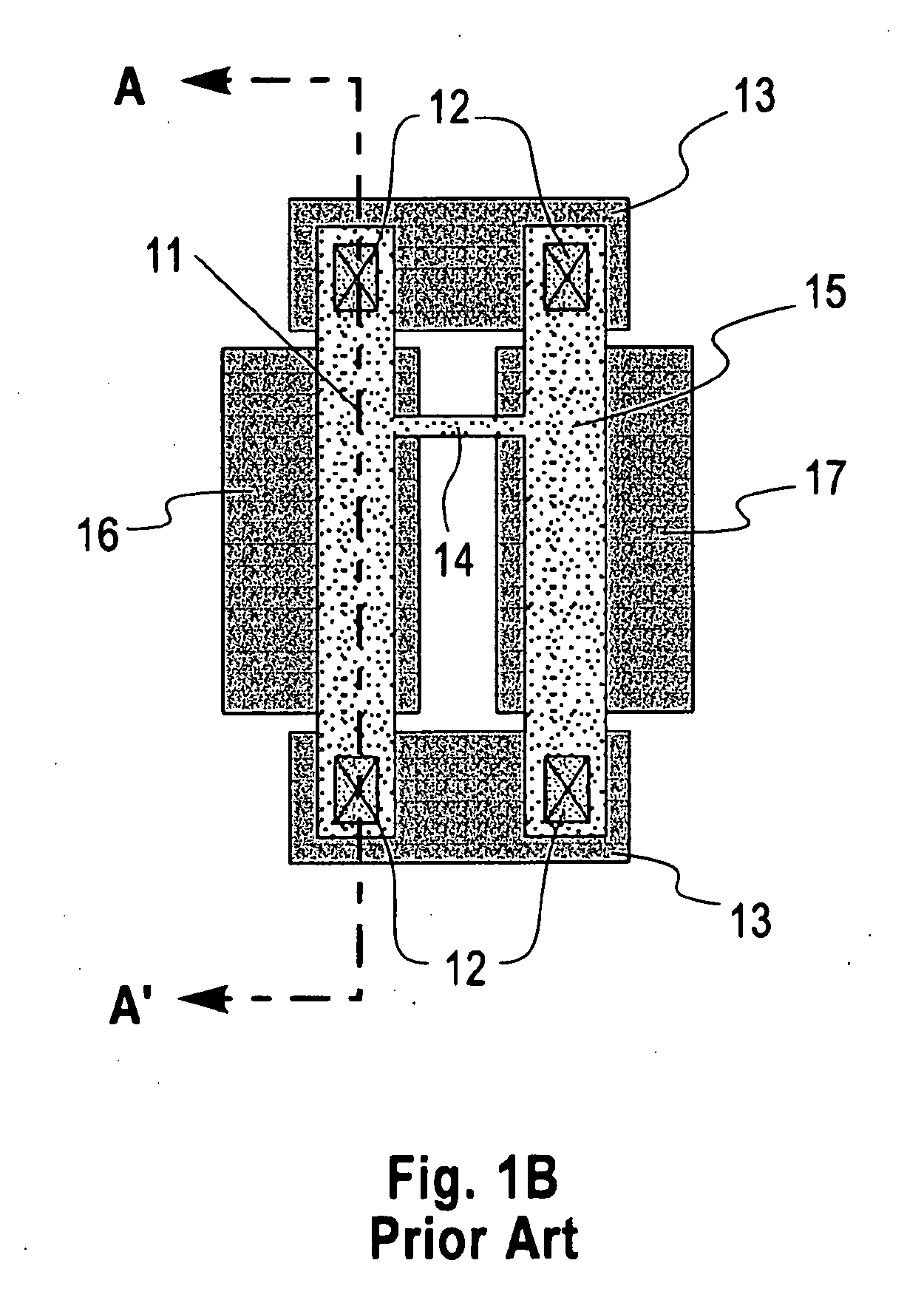

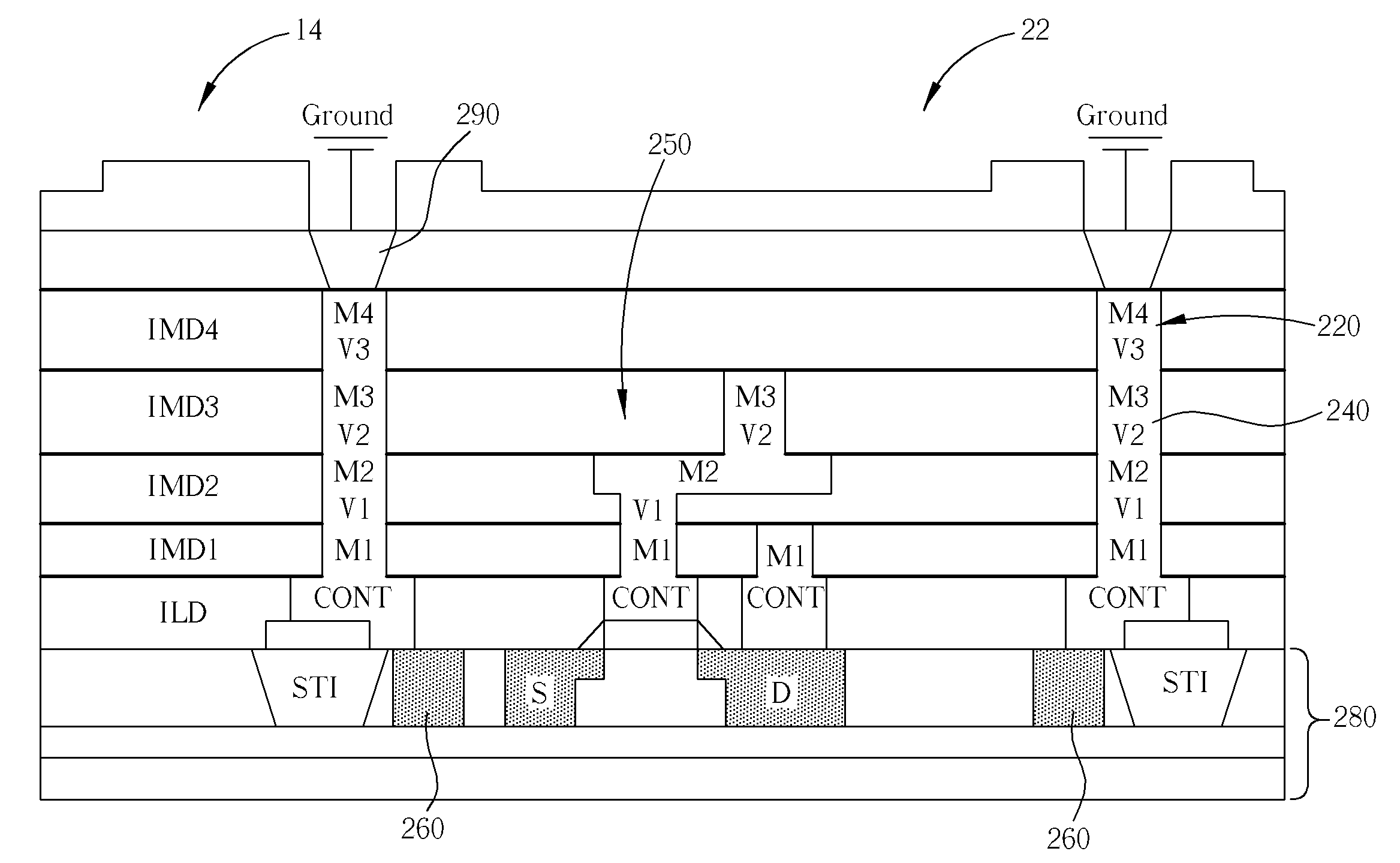

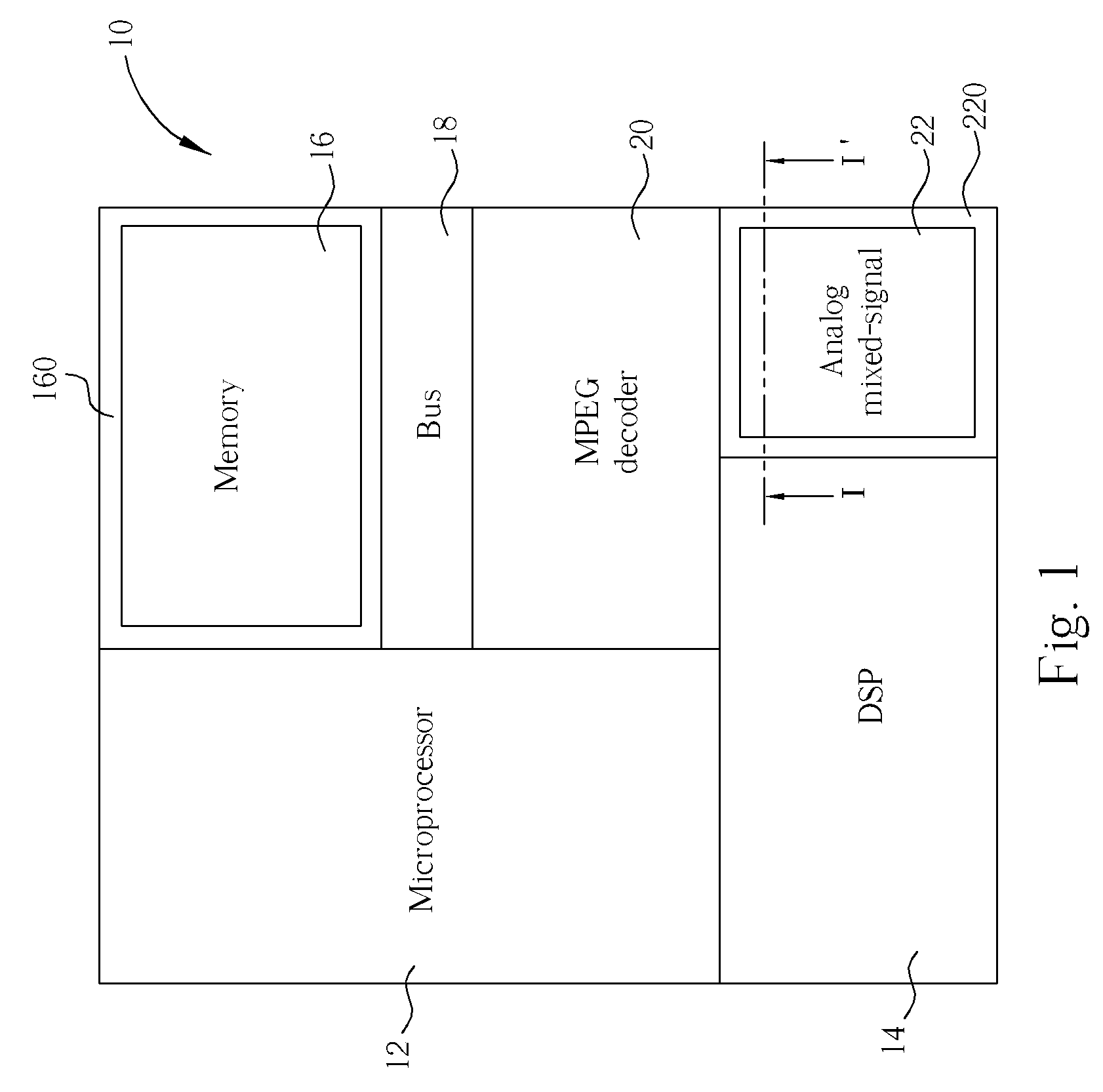

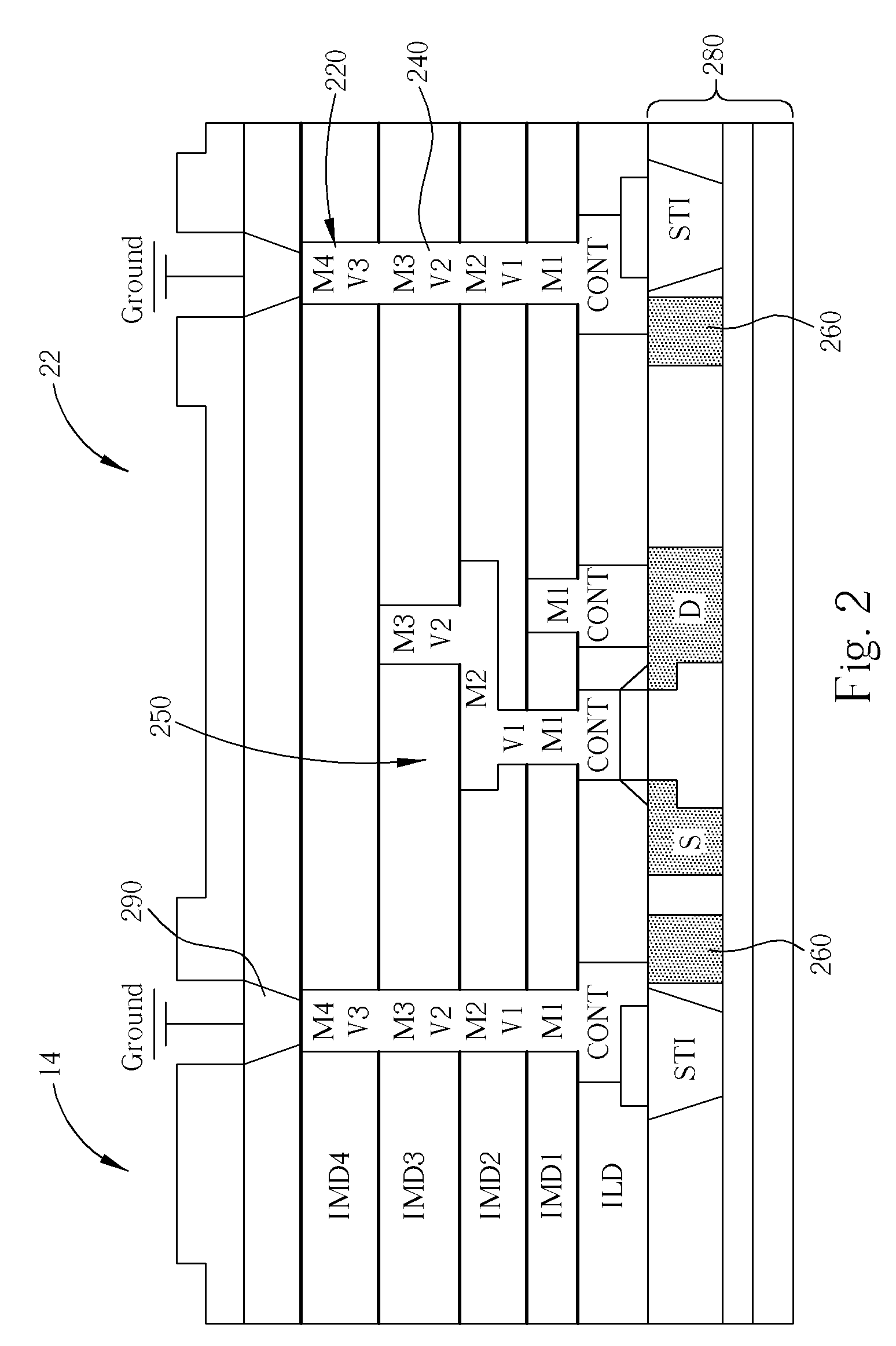

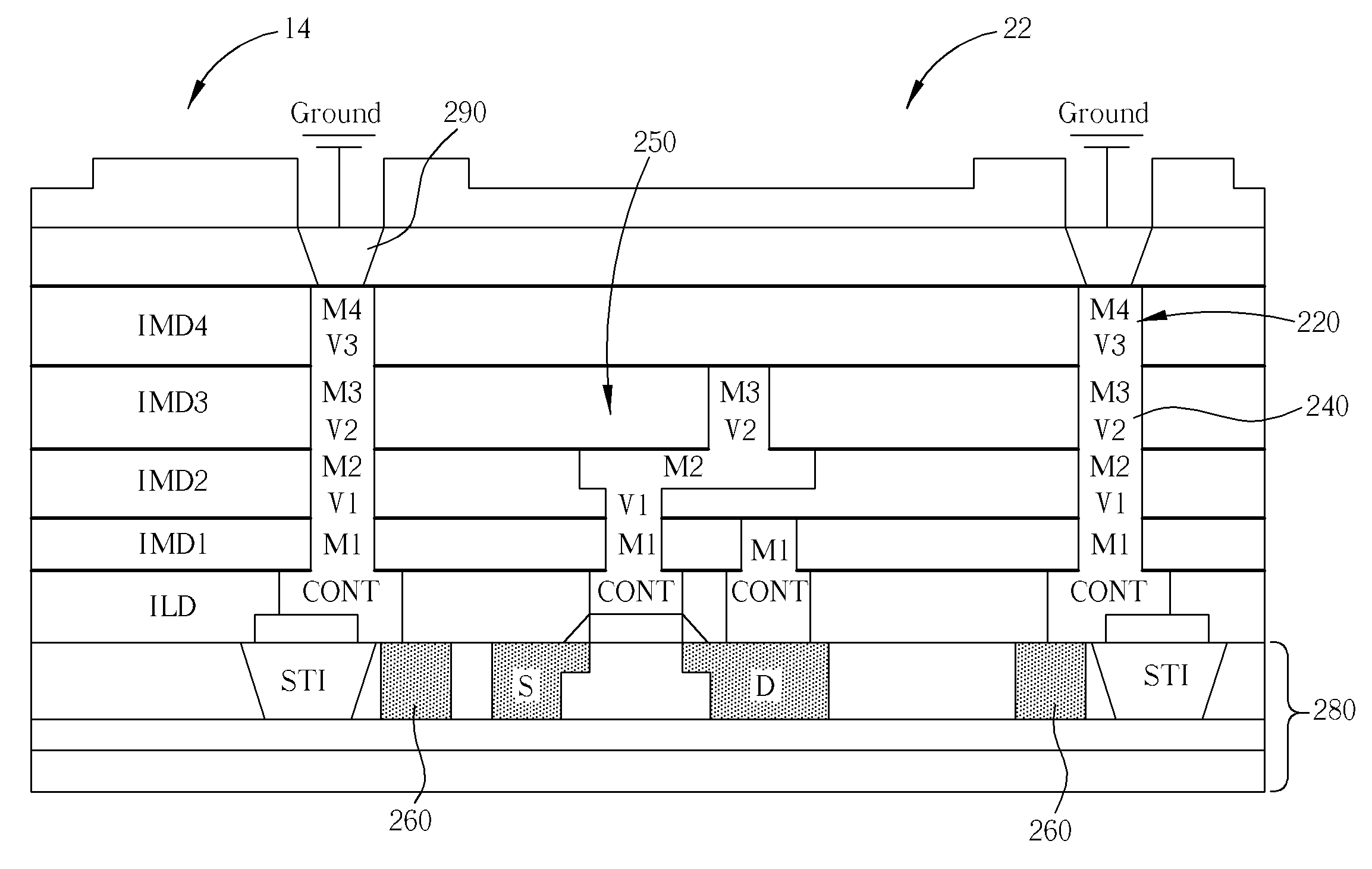

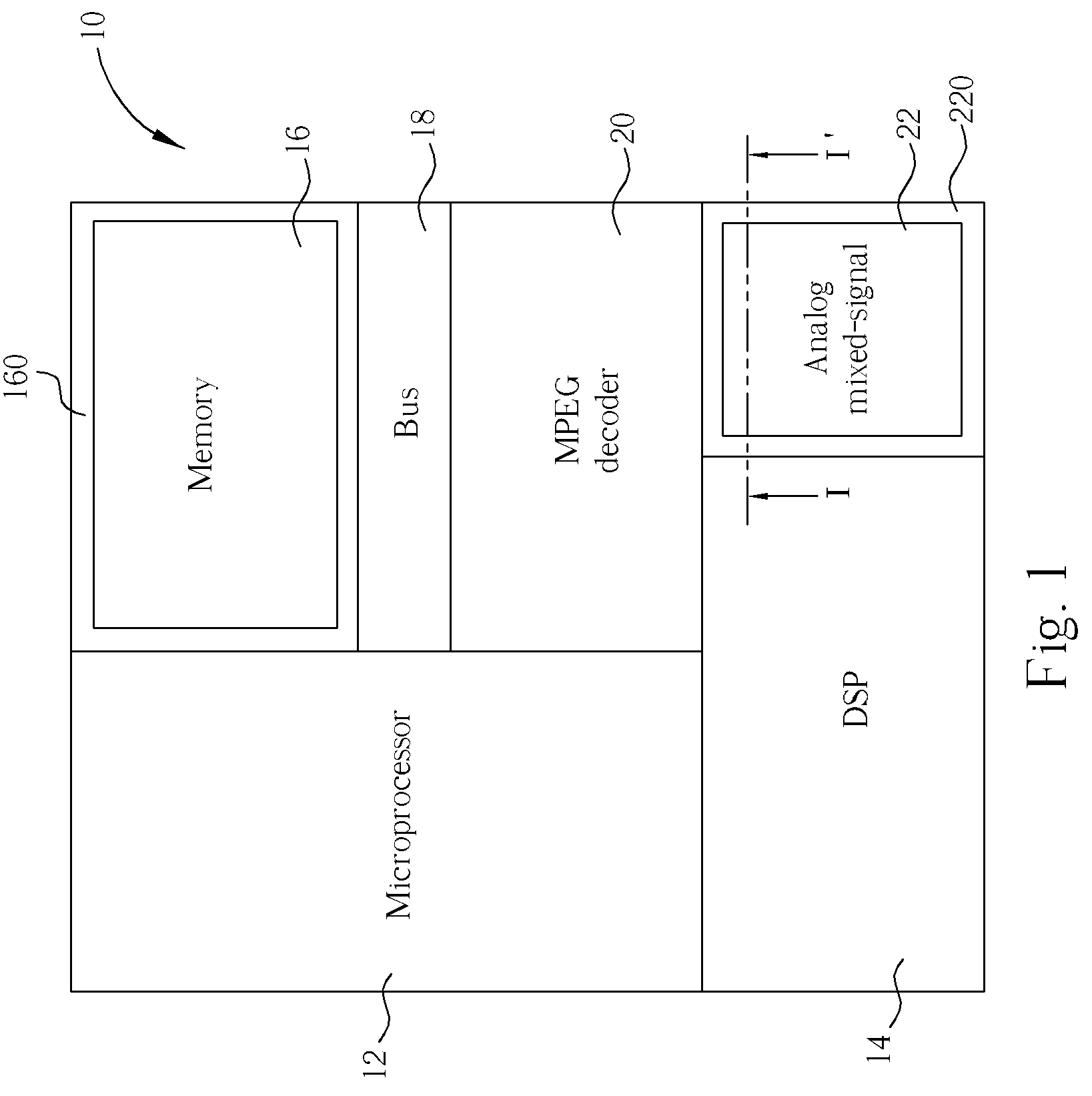

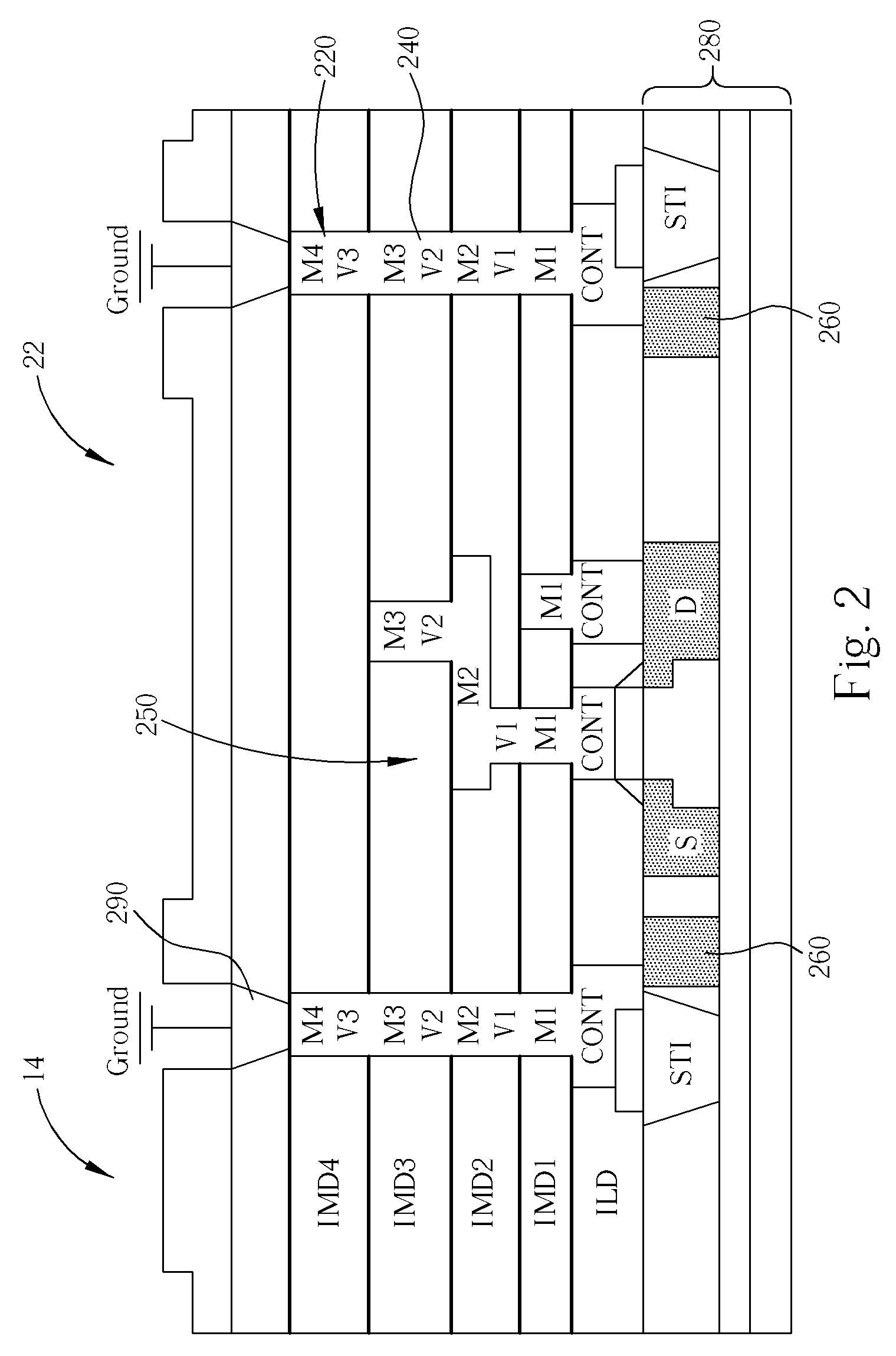

System-on-chip with shield rings for shielding functional blocks therein from electromagnetic interference

ActiveUS20060192265A1Semiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceBus interface

A system-on-chip (SoC) that is immune to electromagnetic interference has block shield rings fabricated therein. The SoC includes a microprocessor core; an on-chip bus interface; an embedded memory block; and an analog / mixed-signal integrated circuit shielded by an EMI shield ring encircling the analog / mixed-signal integrated circuit for protecting the analog / mixed-signal integrated circuit from electromagnetic interference. The EMI shield ring is grounded and includes a metal rampart consisting of multi-layer metals and vias. A pickup diffusion is connected to the metal rampart. In one embodiment, the memory block is also shielded.

Owner:MARLIN SEMICON LTD

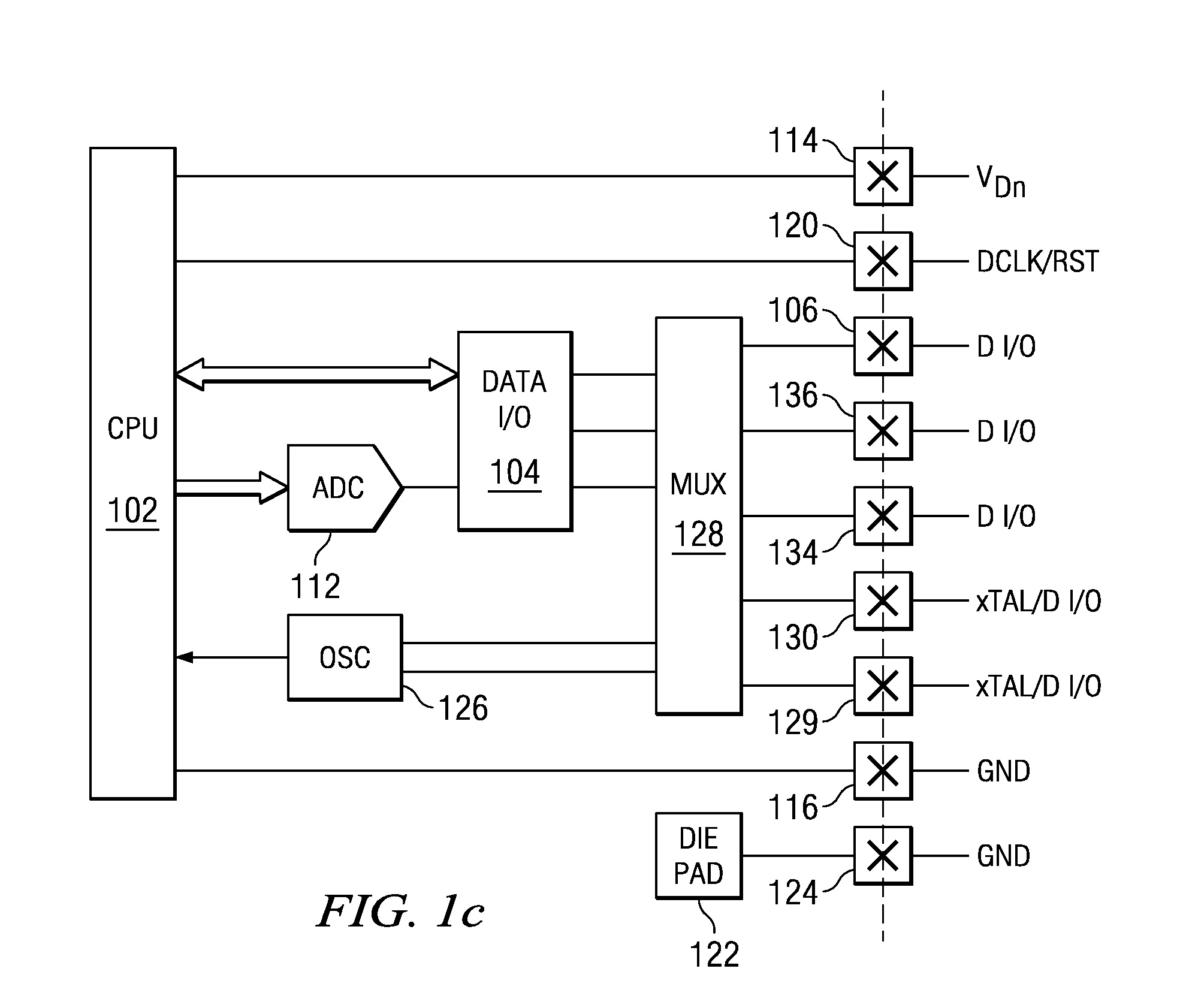

Package for mixed signal mcu with minimal pin count

InactiveUS20080079148A1Digital data processing detailsSemiconductor/solid-state device detailsSemiconductor chipMixed-signal integrated circuit

A minimal pin package for a mixed signal integrated circuit for a mixed signal processor based integrated circuit includes a semiconductor chip having a plurality of bond pads disposed thereon with a digital processor digitally interfaceable with at least one of the bond pads. An analog circuit block is provided and interfaceable with at least one of the bond pads. A die pad is provided on which the chip is mounted and N terminals on the package are interfaced to the exterior of the package, one of which is integral with the die pad. Bond wires interface select ones of the bond pads to a supply designated one of the terminals, a ground one of the terminals and the die pad associated with one of the terminals, the rest of the N-3 terminals interfaced to remaining functionality of the chip.

Owner:SILICON LAB INC

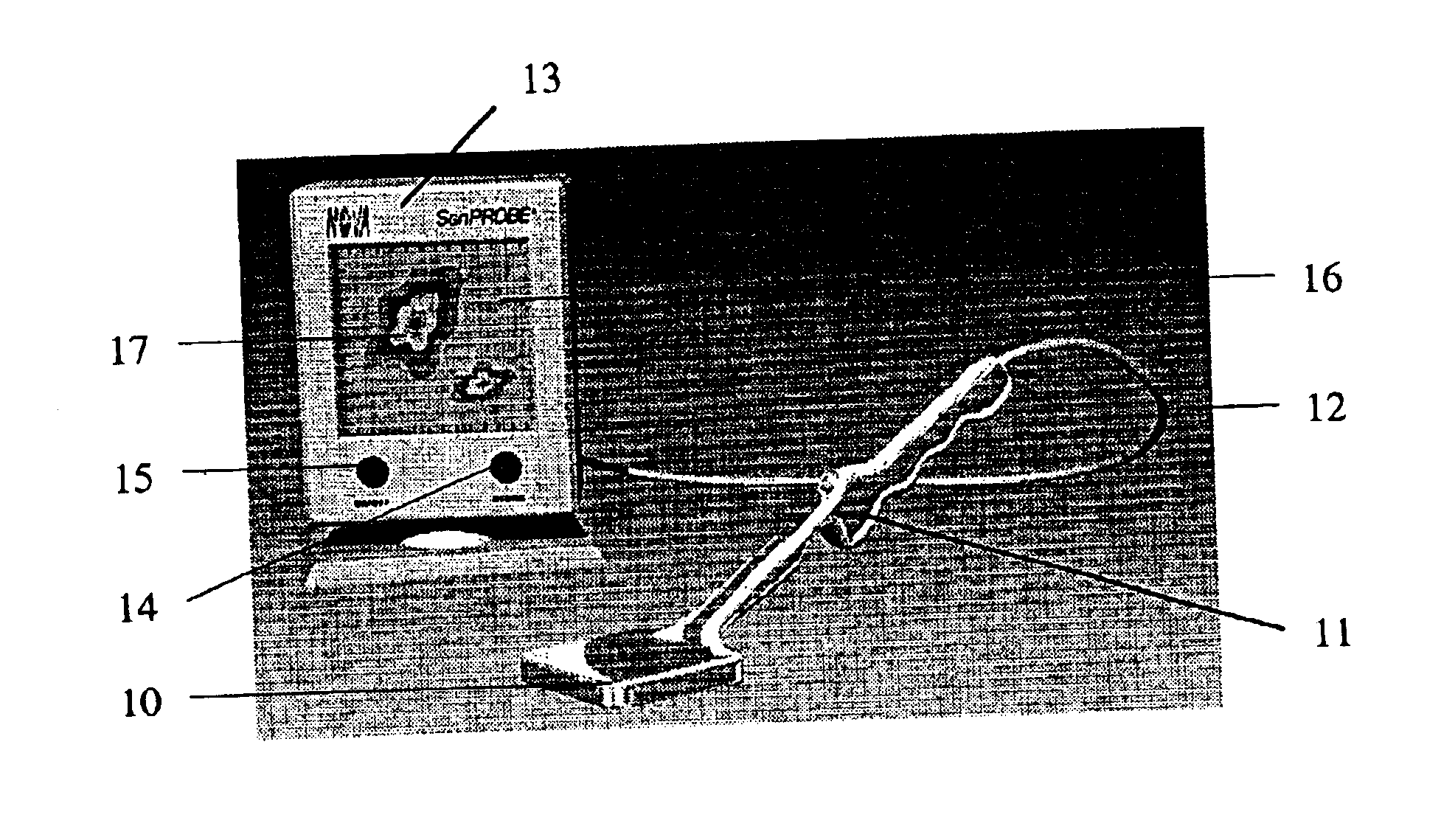

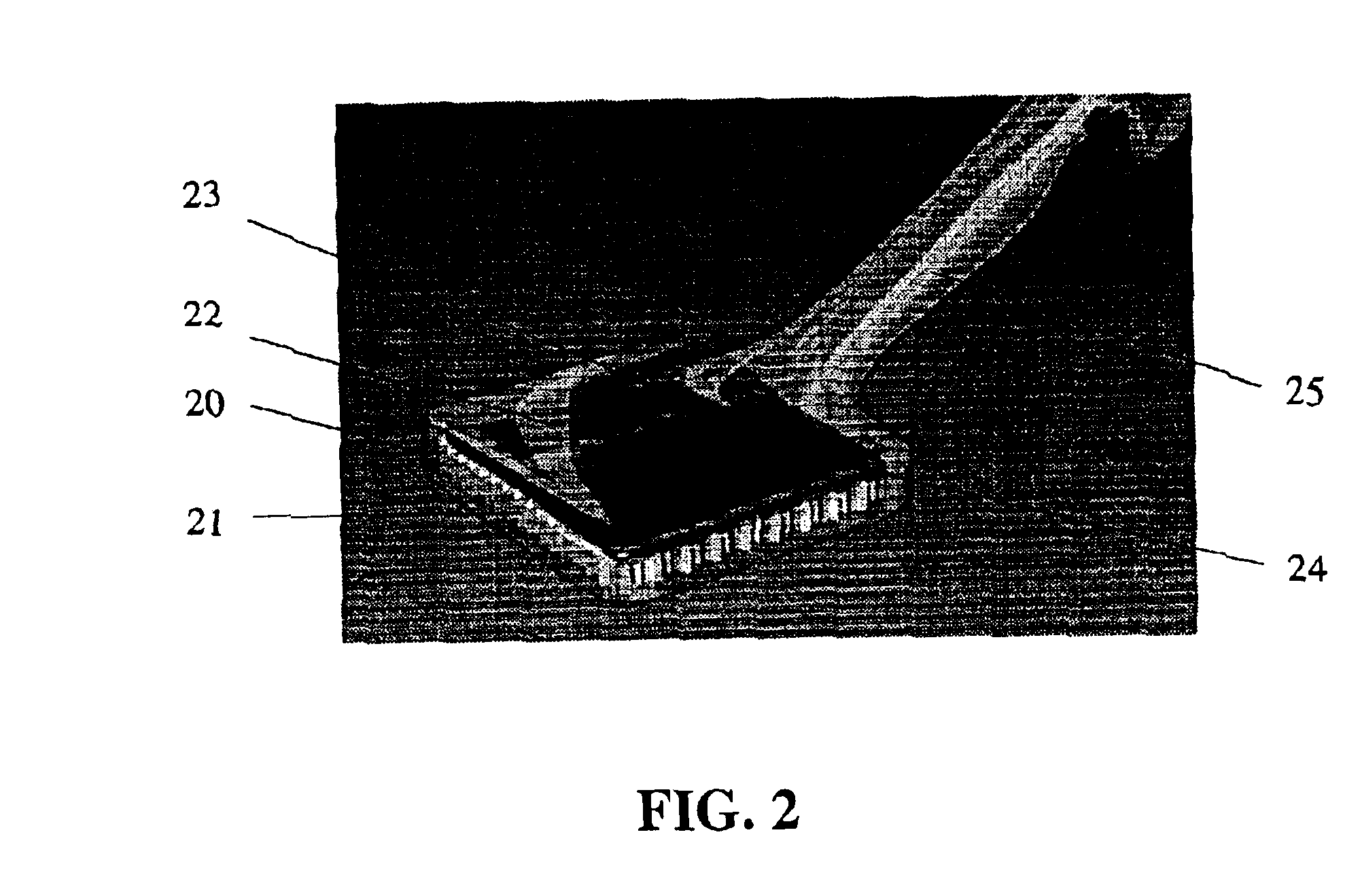

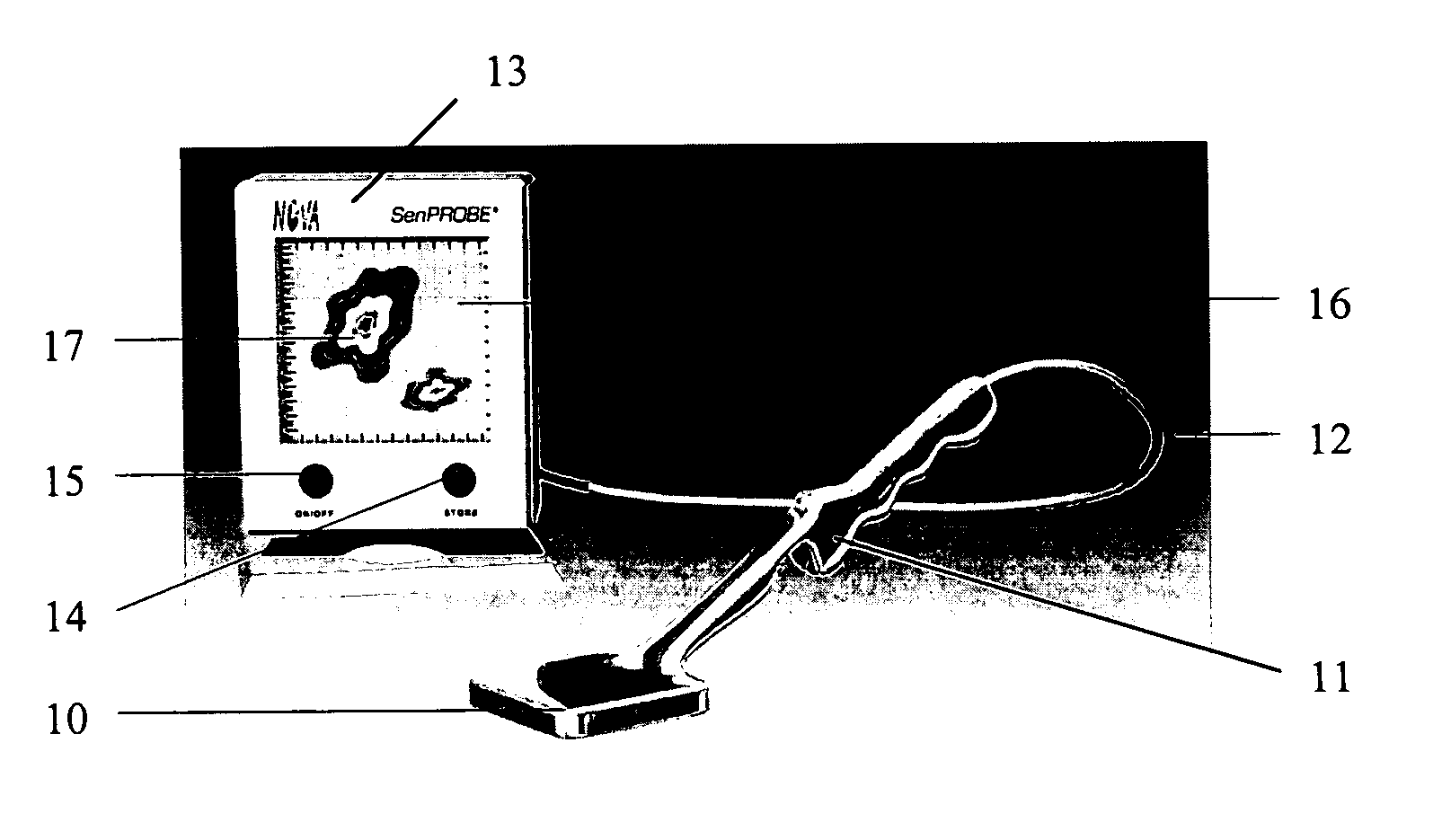

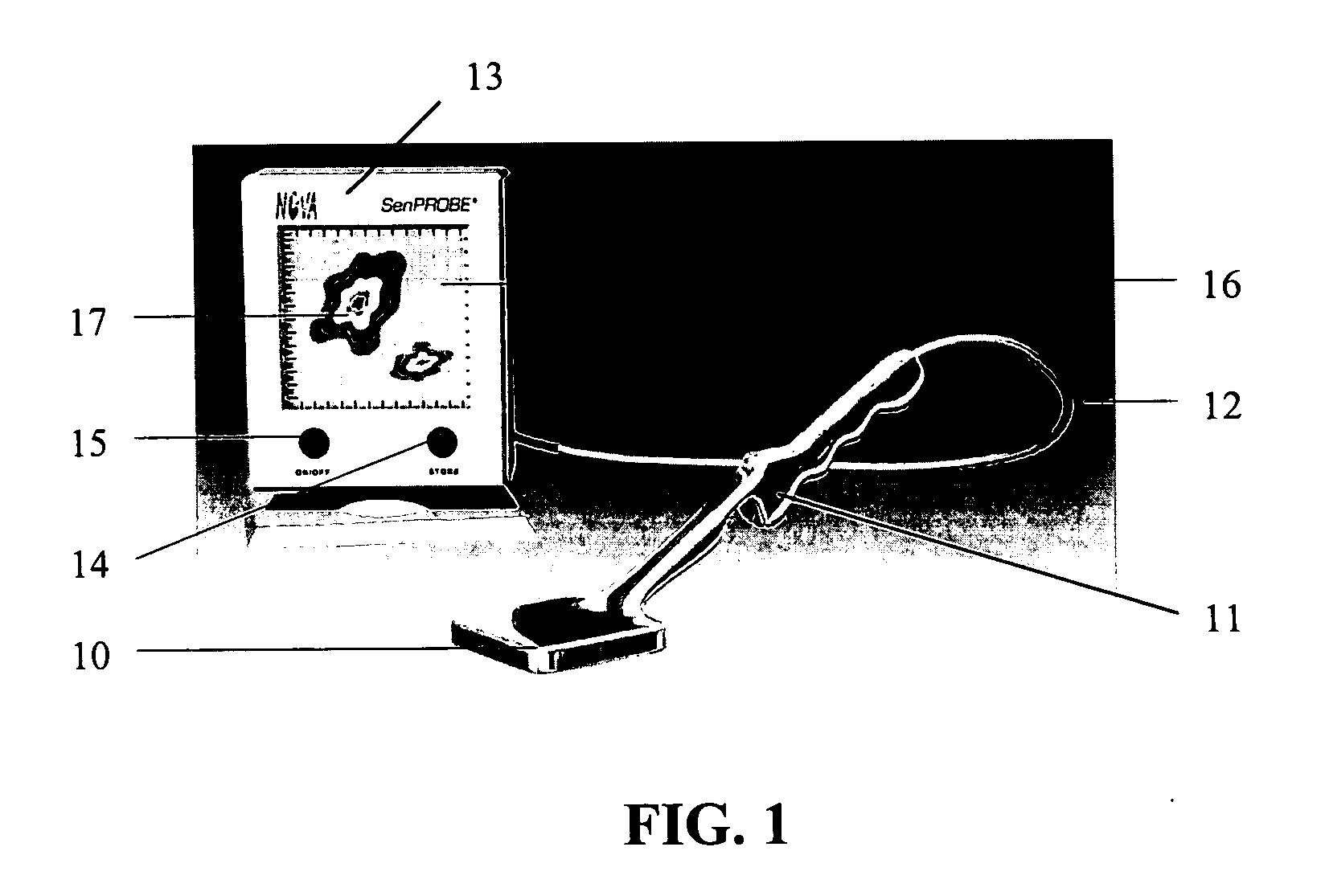

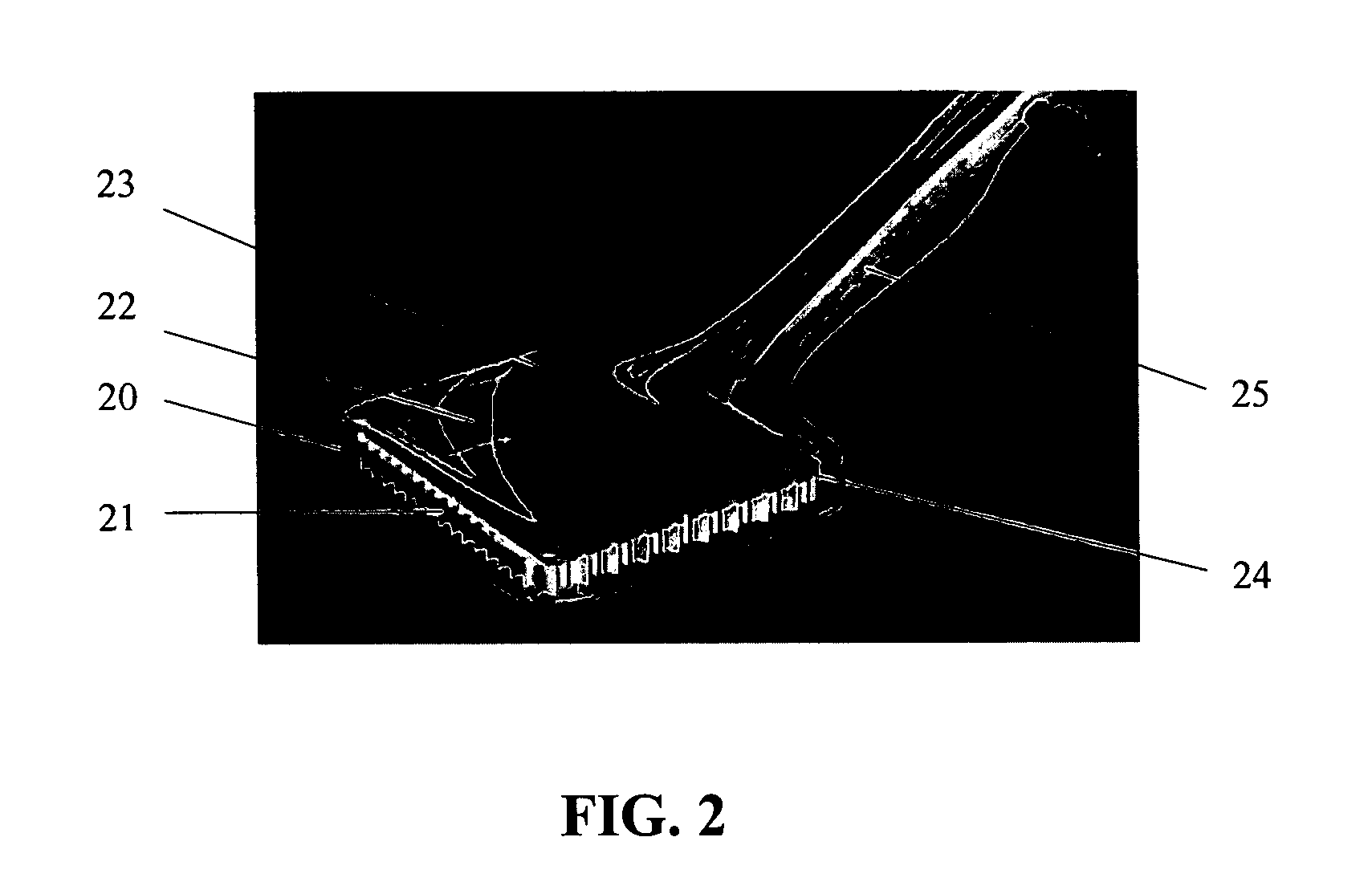

Imaging probe

InactiveUS6940070B2High sensitivityImprove quantum efficiencyMaterial analysis using wave/particle radiationRadiation/particle handlingLow noiseRadioactive agent

The design of a compact, handheld, solid-state and high-sensitivity imaging probe and a micro imager system is reported. These instruments can be used as a dedicated tool for detecting and locating sentinel lymph nodes and also for detecting and imaging radioactive material. The reported device will use solid state pixel detectors and custom low-noise frontend / readout integrated circuits. The detector will be designed to have excellent image quality and high spatial resolution. The imaging probes have two different embodiments, which are comprised of a pixelated detector array and a highly integrated readout system, which uses a custom multi-channel mixed signal integrated circuit. The instrument usually includes a collimator in front of the detector array so that the incident photons can be imaged. The data is transferred to an intelligent display system. A hyperspectral image can also be produced and displayed. These devices are designed to be portable for easy use.

Owner:NOVA R&D

Imaging probe

ActiveUS20060036157A1High sensitivityImprove quantum efficiencyDiagnostic recording/measuringSensorsRadioactive agentImaging quality

The design of a compact, handheld, solid-state and high-sensitivity imaging probe and a micro imager system is reported. These instruments can be used as a dedicated tool for detecting and locating sentinel lymph nodes and also for detecting and imaging radioactive material. The reported device will use solid state pixel detectors and custom low-noise frontend / readout integrated circuits. The detector will be designed to have excellent image quality and high spatial resolution. The imaging probes have two different embodiments, which are comprised of a pixelated detector array and a highly integrated readout system, which uses a custom multi-channel mixed signal integrated circuit. The instrument usually includes a collimator in front of the detector array so that the incident photons can be imaged. The data is transferred to an intelligent display system. A hyperspectral image can also be produced and displayed. These devices are designed to be portable for easy use.

Owner:NOVA R&D

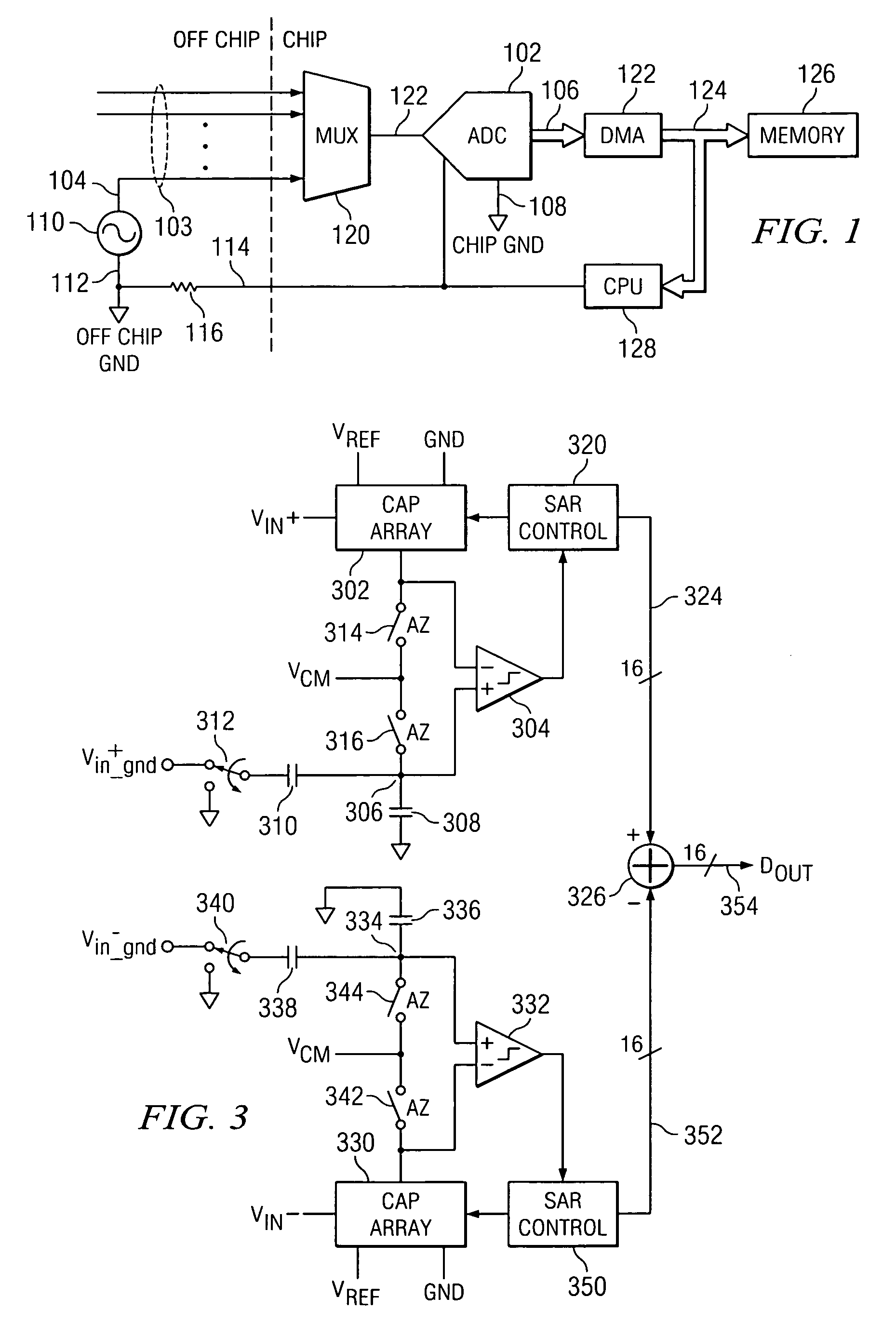

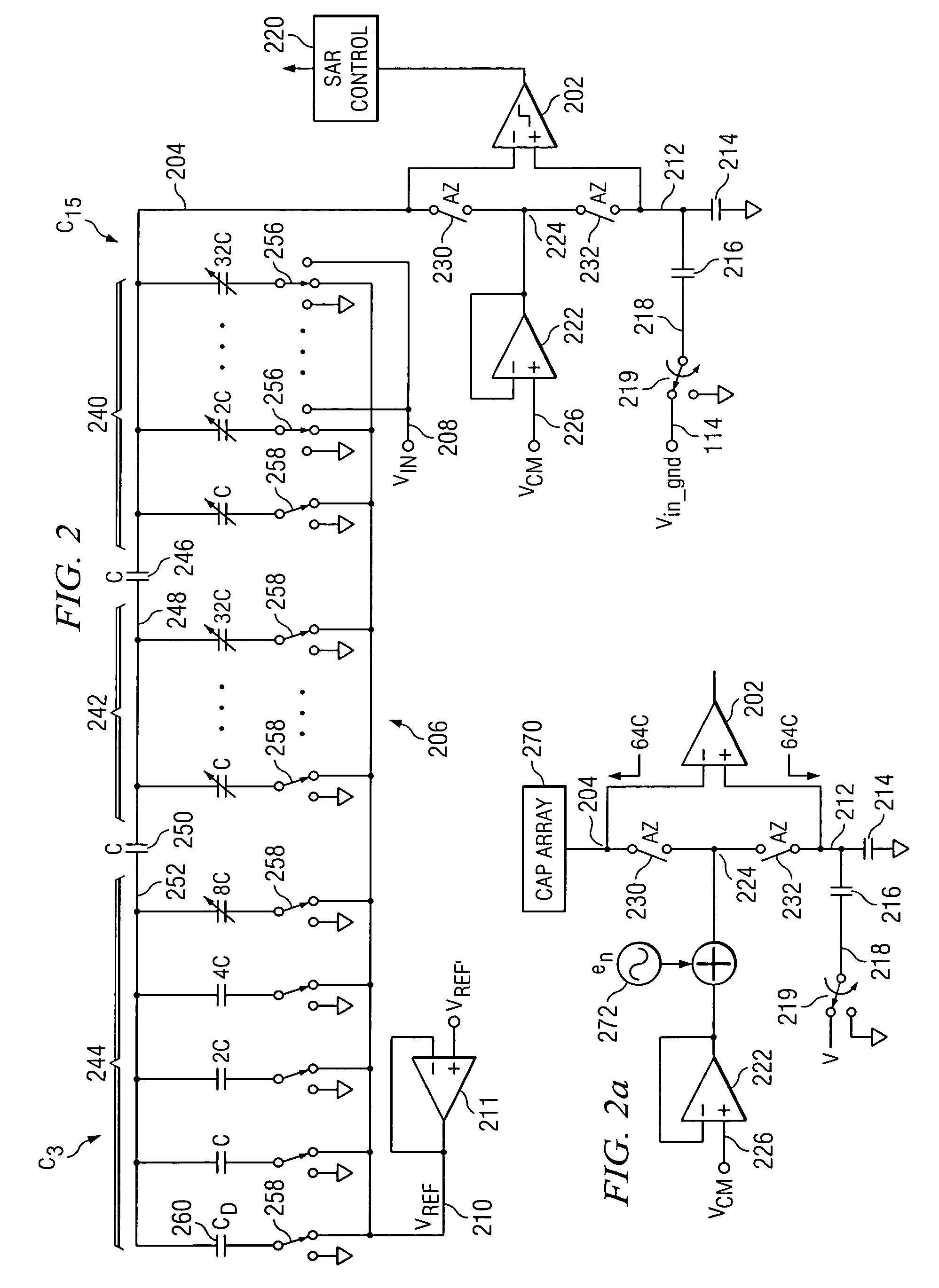

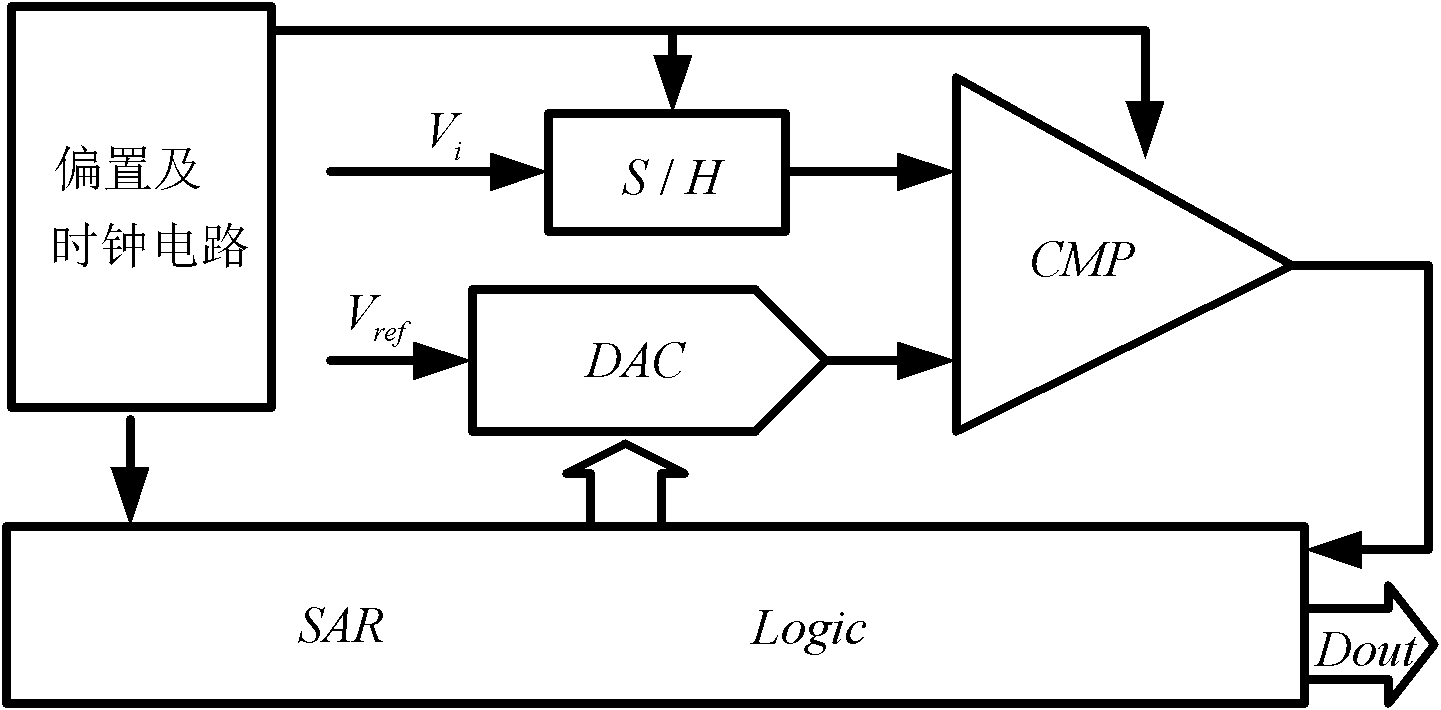

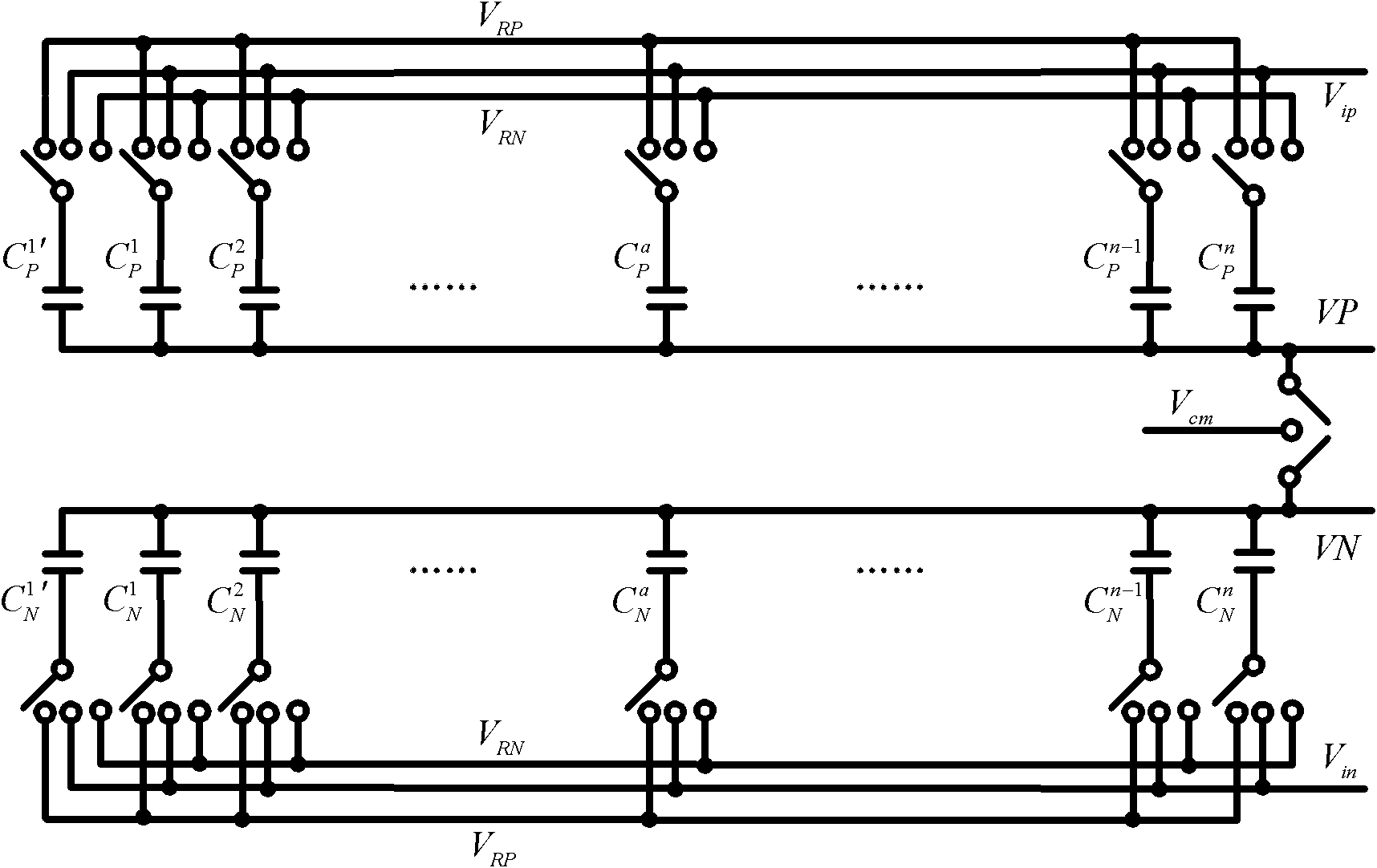

Device and method for calibrating capacitor array type successive-approximation analog-to-digital converter

ActiveCN102163973ASlew Rate AdvantageTo achieve the purpose of calibration outputAnalogue/digital conversion calibration/testingDigital down converterLogical operations

The invention relates to a device and method for calibrating a capacitor array type successive-approximation analog-to-digital converter, which belong to the field of mixed-signal integrated circuit design; the device comprises a capacitance measurement circuit, a static memory, a control circuit corresponding to the static memory, and a logical operation unit connected between the capacitance measurement circuit and the static memory; and the method comprises the following steps: measuring the true values of each pair of capacitors in a capacitor array to be calibrated by using the capacitance measurement circuit; according to the actual structure of the capacitor array, calculating the true weight values of each pair of capacitors according to the measured true values by using the logical operation unit, mapping the weight values into n-bit binary weight codes, and storing the binary weight codes into the static memory so as to form a final weight code table; and carrying out corresponding correction on the output codes of the analog-to-digital converter to be calibrated by using the final weight code table so as to obtain the finally-calibrated output codes. The device and method provided by the invention have the advantages in the aspects of hardware cost and conversion rate.

Owner:TSINGHUA UNIV

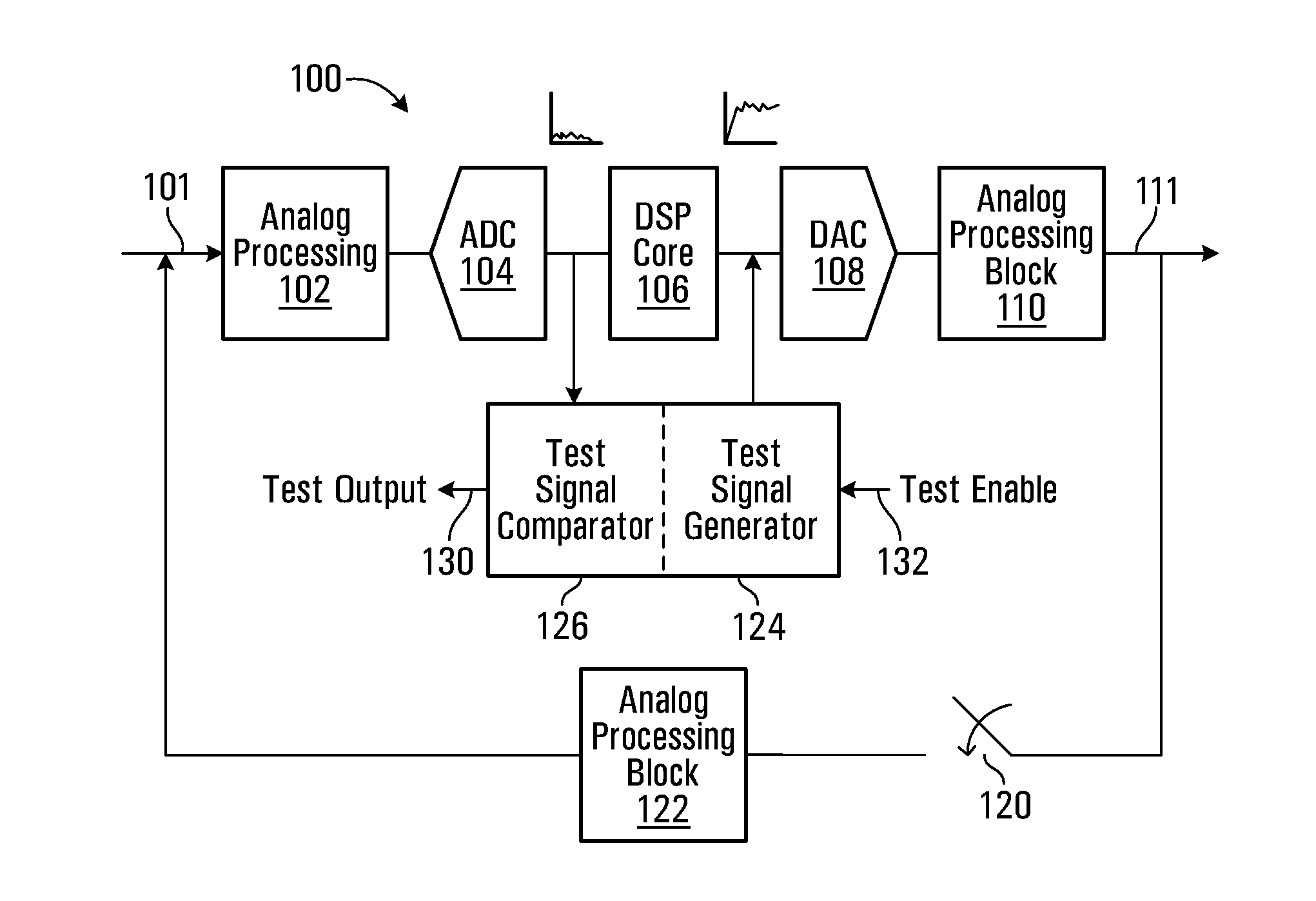

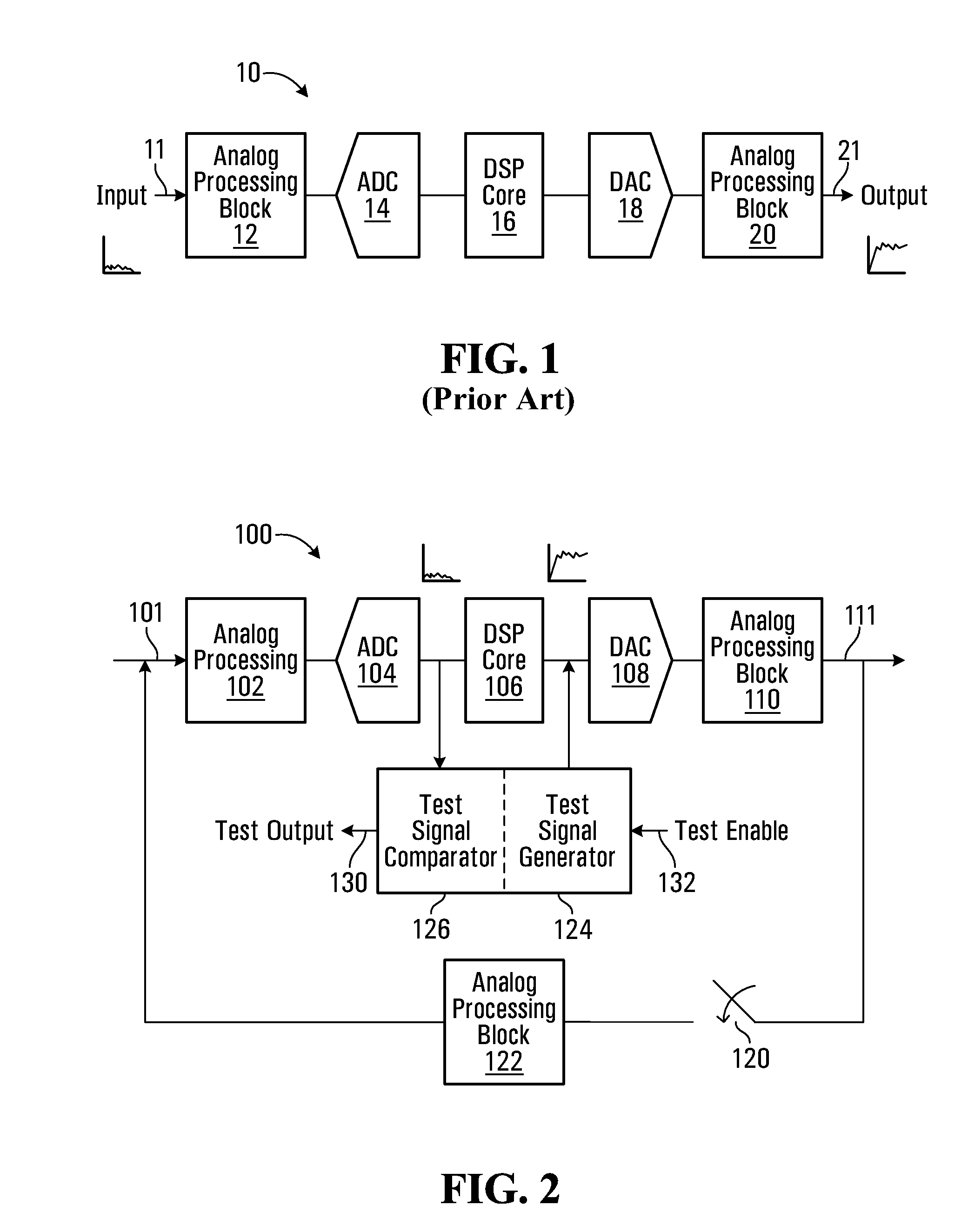

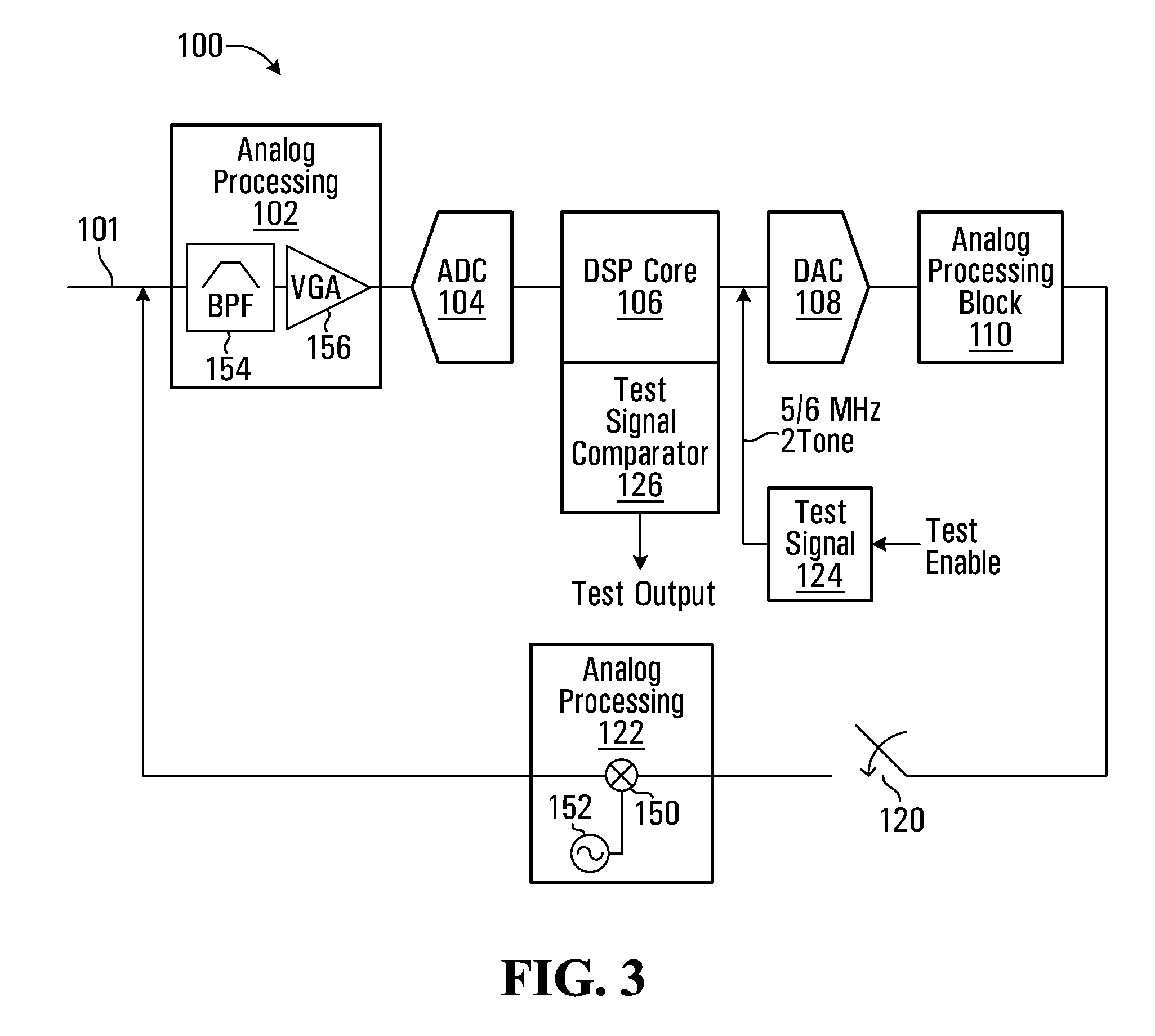

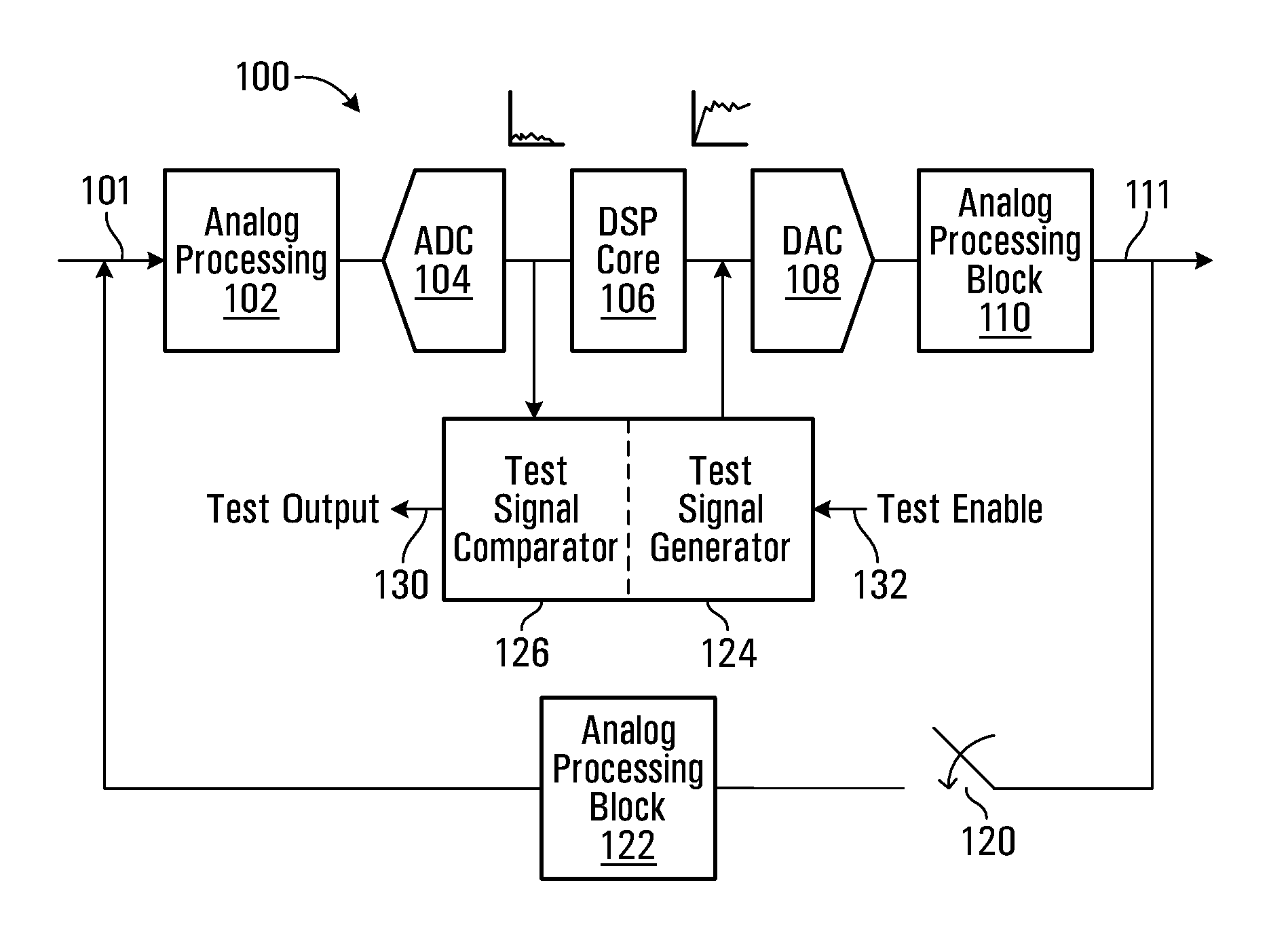

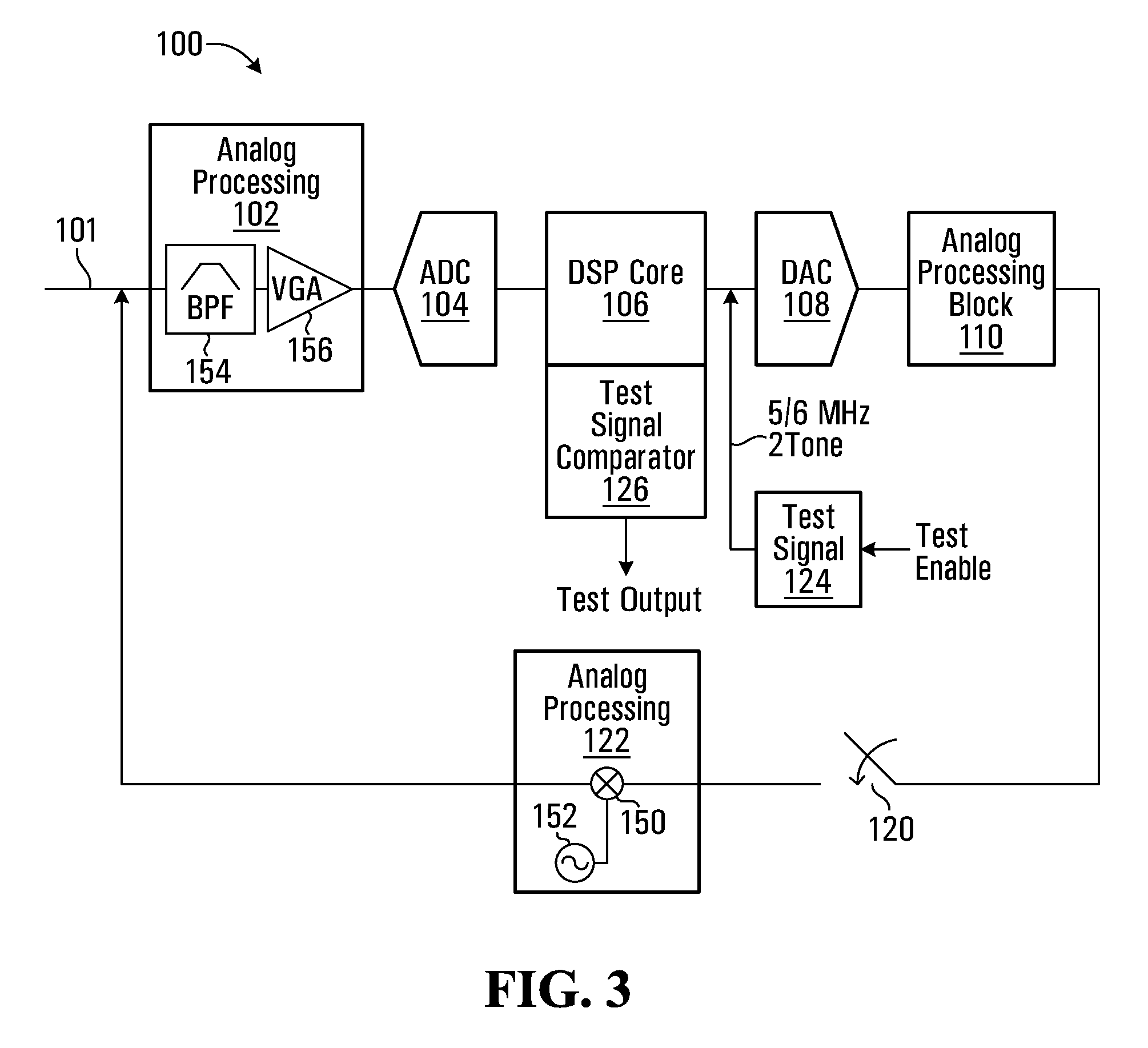

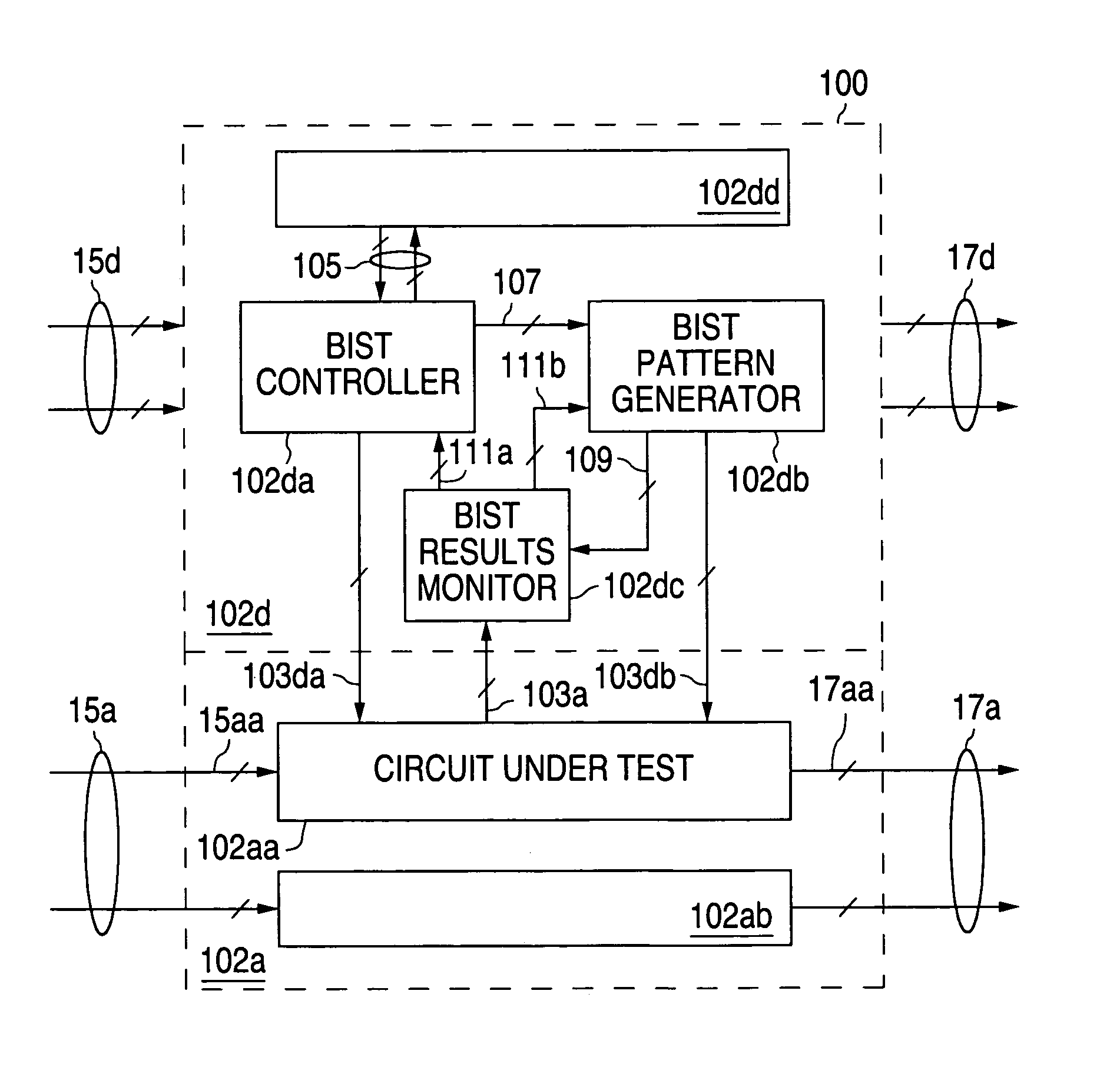

Mixed signal integrated circuit, with built in self test and method

A mixed signal integrated circuit includes a signal source to inject a test signal into the signal path of the mixed signal integrated circuit, a feedback loop and a signal comparator for determining characteristics of a resulting signal. Conveniently, the test signal may be a digital signal injected upstream of a digital to analog converter (DAC). By connecting the output to the input, the entirety of the signal path and the majority of the integrated circuit may be tested. The signal may be condition or manipulated in the feedback loop. By incorporating test signal generation and measurement into the mixed signal integrated circuit, the cost of test equipment and the test duration for each device under test may be reduced.

Owner:FRESCO MICROCHIP

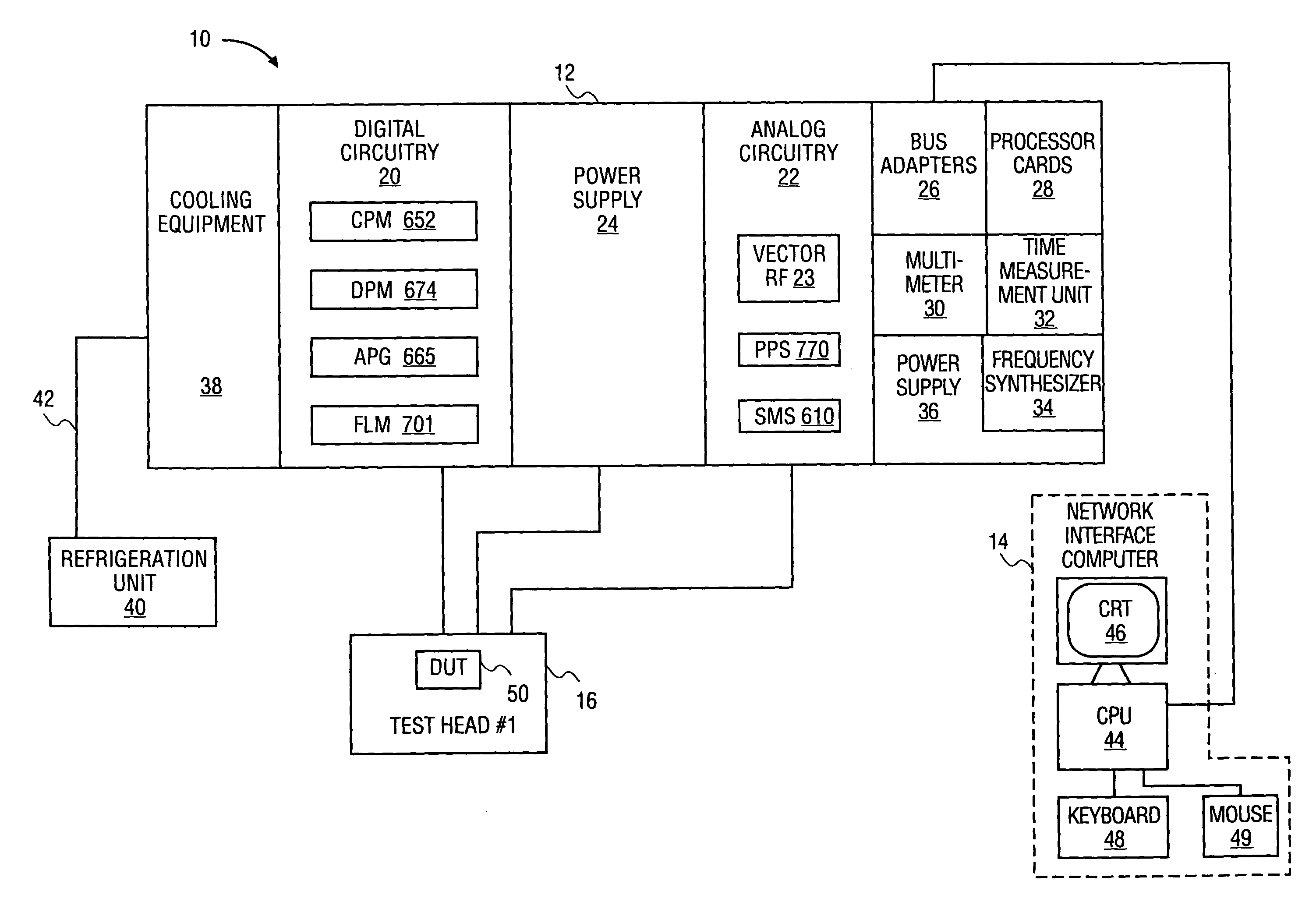

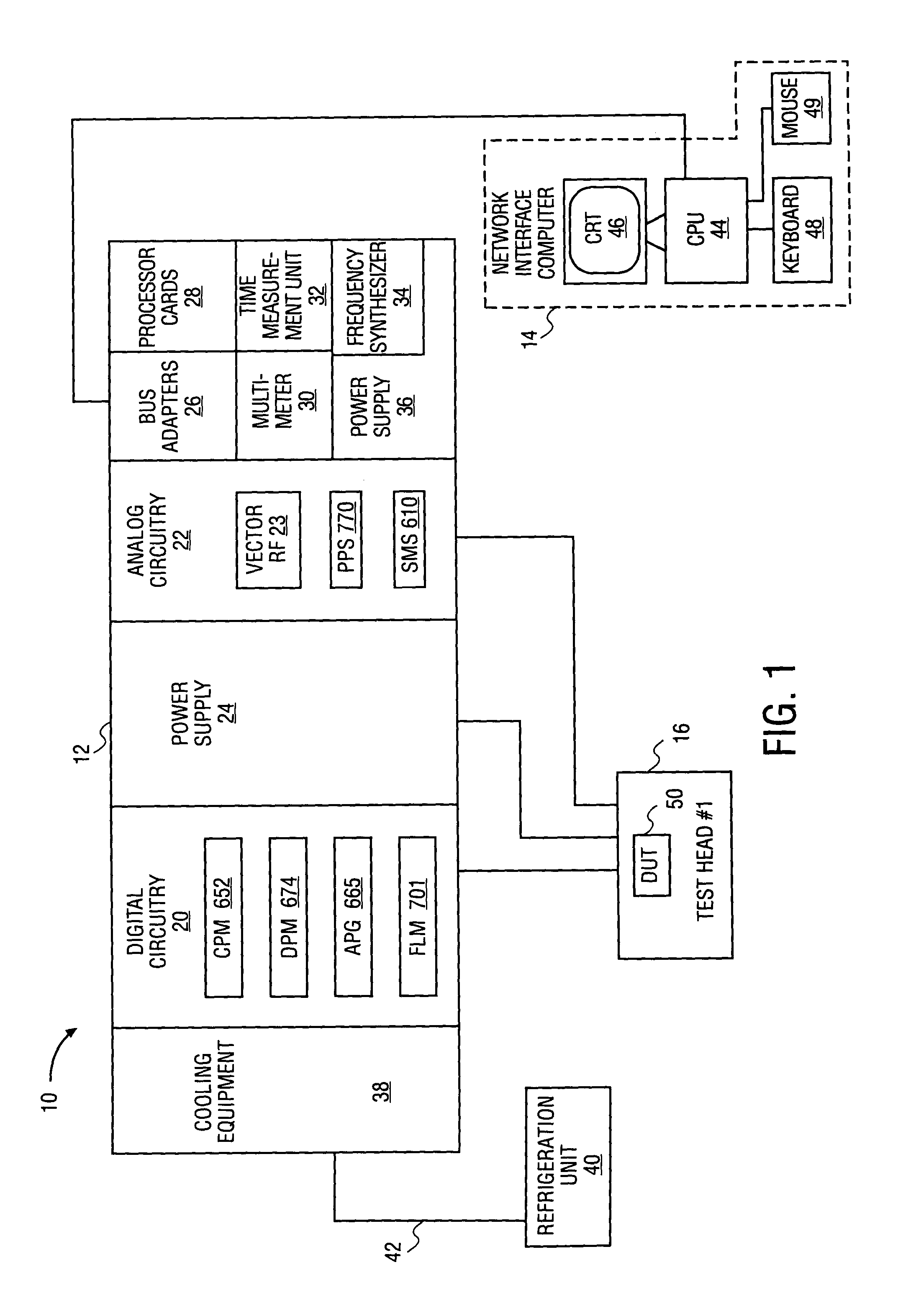

Single platform electronic tester

InactiveUS7092837B1Resistance/reactance/impedenceTesting/calibration of speed/acceleration/shock measurement devicesEquipment under testTester device

An electronic tester with digital, and analog, and memory test circuitry on a single platform. A test head is coupled to a device under test. The device under test can be a system-on-a-chip integrated circuit, a mixed signal integrated circuit, a digital integrated circuit, or an analog integrated circuit. Digital test circuitry applies digital test signals to the device under test coupled to the test head and receives digital outputs from the device under test in response to the digital test signals. Analog test circuitry applies analog test signals to the device under test coupled to the test head and receives analog outputs from the device under test in response to the analog test signals. Memory test circuitry applies memory test patterns to the device under test coupled to the test head and receives memory outputs from the device under test in response to the memory test patterns. A tester computer supervises the application of digital, analog, and memory test signals from the digital, analog, and memory test circuitry to the device under test such that signals applied to the device under test can be solely digital test signals, solely analog test signals, solely memory test signals, or mixed digital, analog, and memory test signals. The test head, the digital test circuitry, the analog test circuitry, the memory test circuitry, and the computer are operable as a single platform.

Owner:LTX CORP

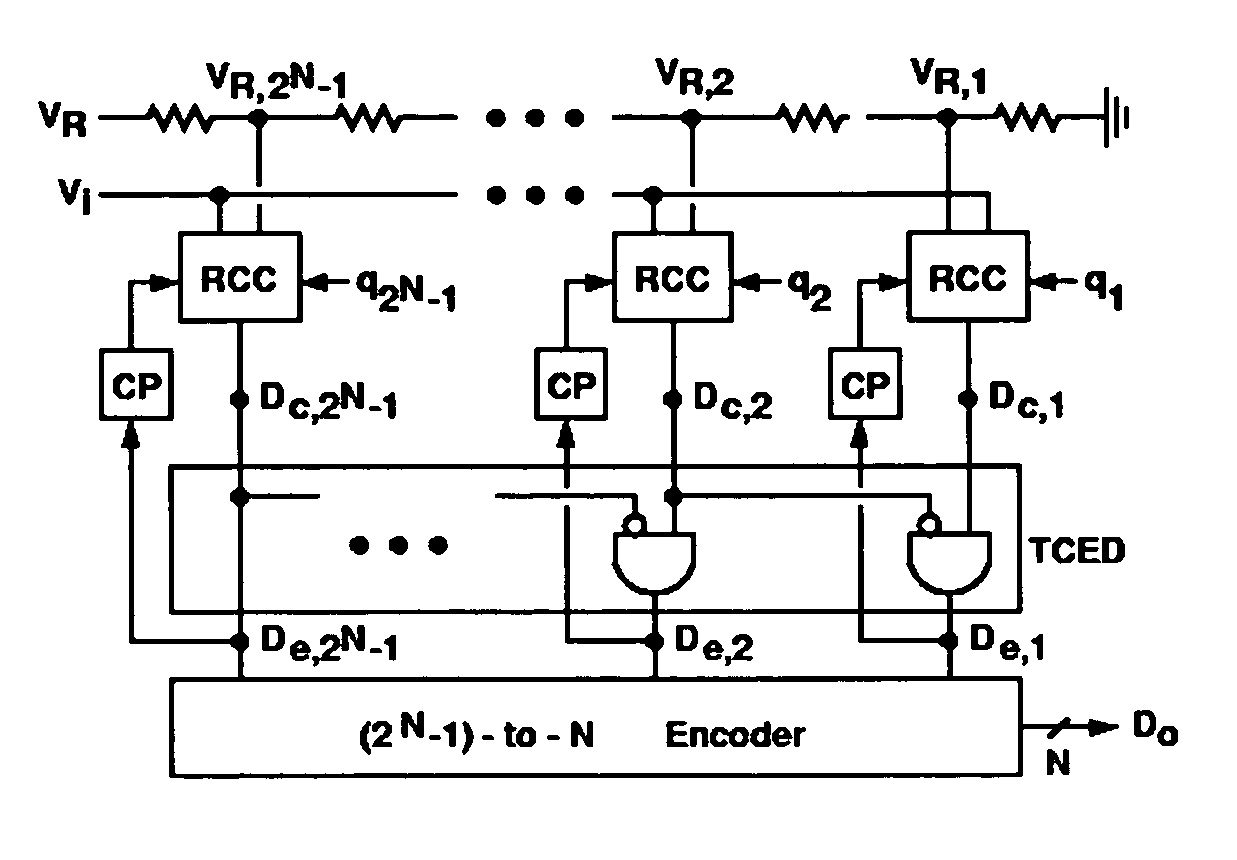

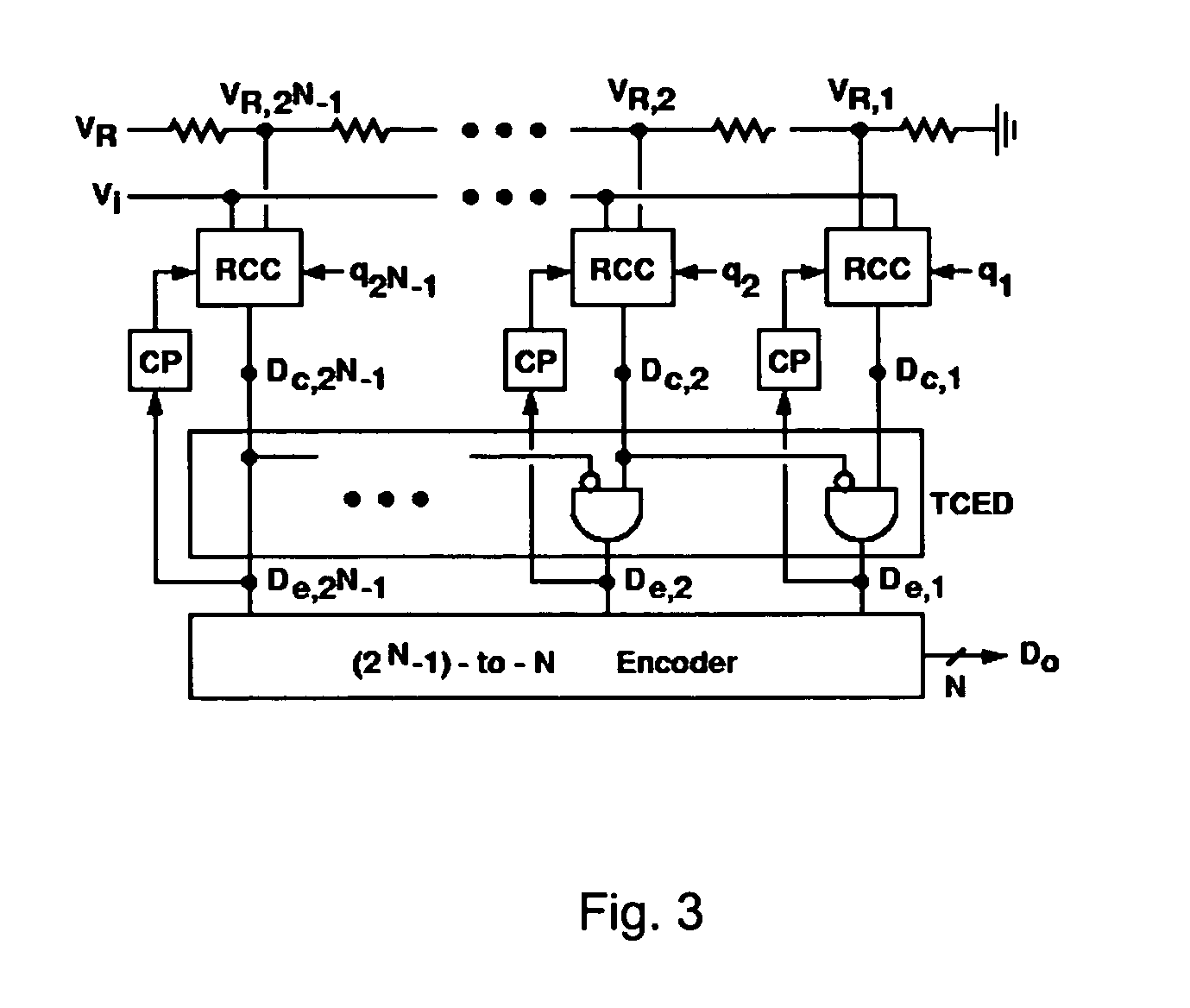

Background comparator offset calibration technique for flash analog-to-digital converters

InactiveUS7064693B1Suppress fluctuation noiseReduce the impactElectric signal transmission systemsAmplifier with semiconductor-devices/discharge-tubesDigital down converterEngineering

A background-calibrated comparator and a background-calibrated flash analog-to-digital converter are disclosed for using in mixed-signal integrated circuit design in particular on the high-speed analog-to-digital converter circuit. Without affecting the operation of the comparator, the disclosure is directed at reducing the unpredictable input offset voltage originated from the variation of process parameters and environmental factors. The background-calibrated comparator includes a random chopping comparator, a calibration processor, and a random sequence generator. The background-calibrated flash analog-to-digital converter (ADC) includes a background-calibrated comparator array together with a reference voltage generator, a thermometer code edge detector, and a set of digital encoders.

Owner:NAT CHIAO TUNG UNIV

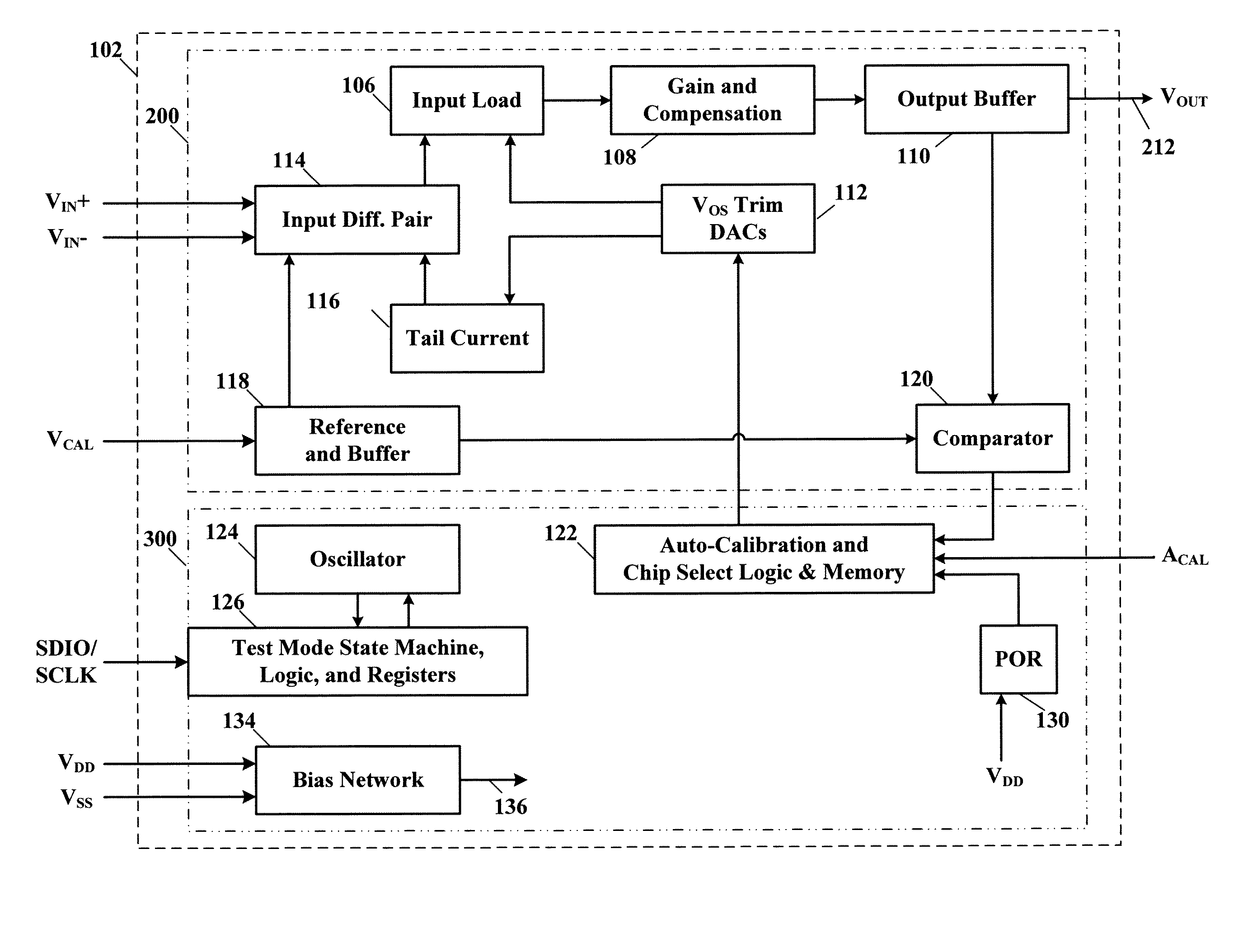

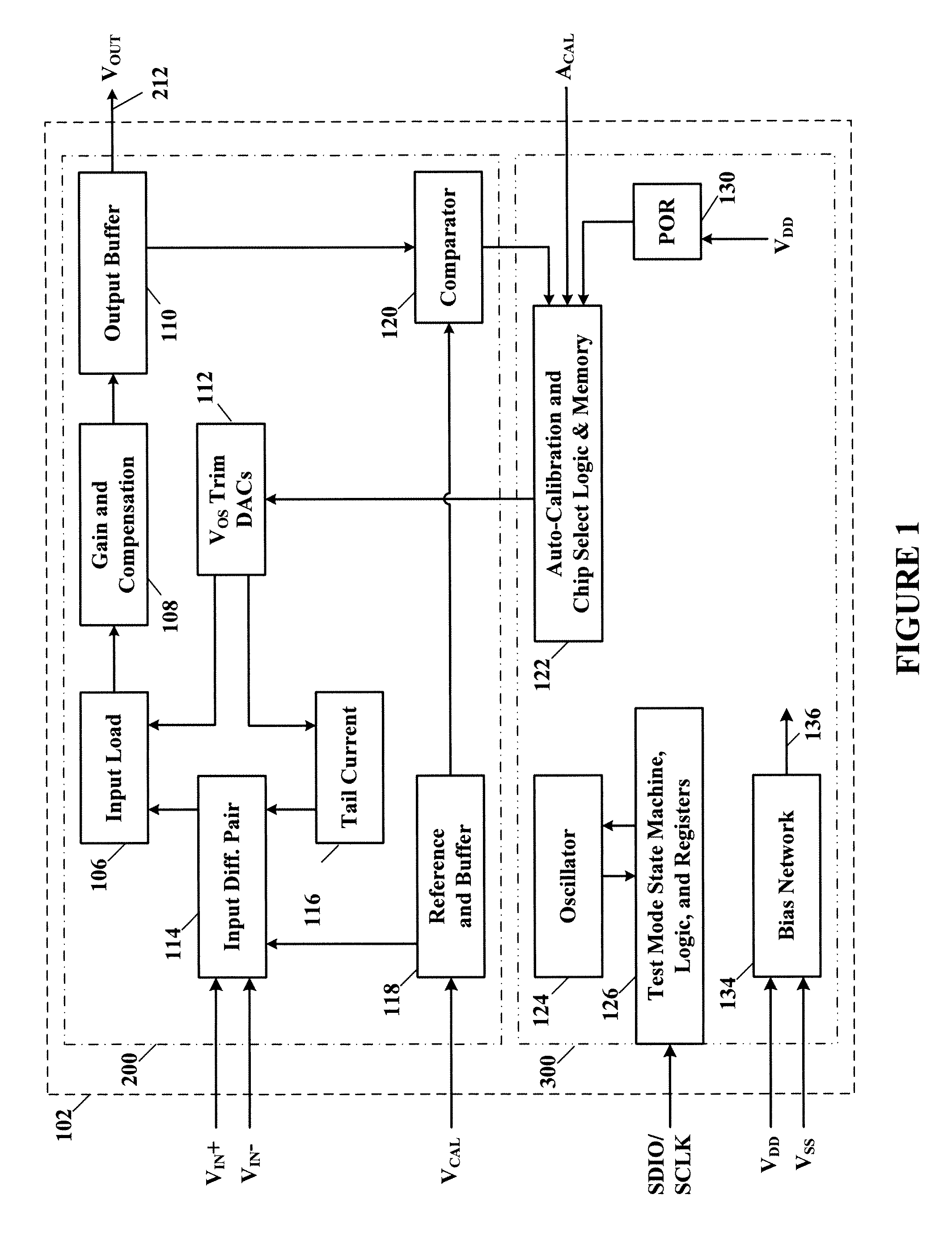

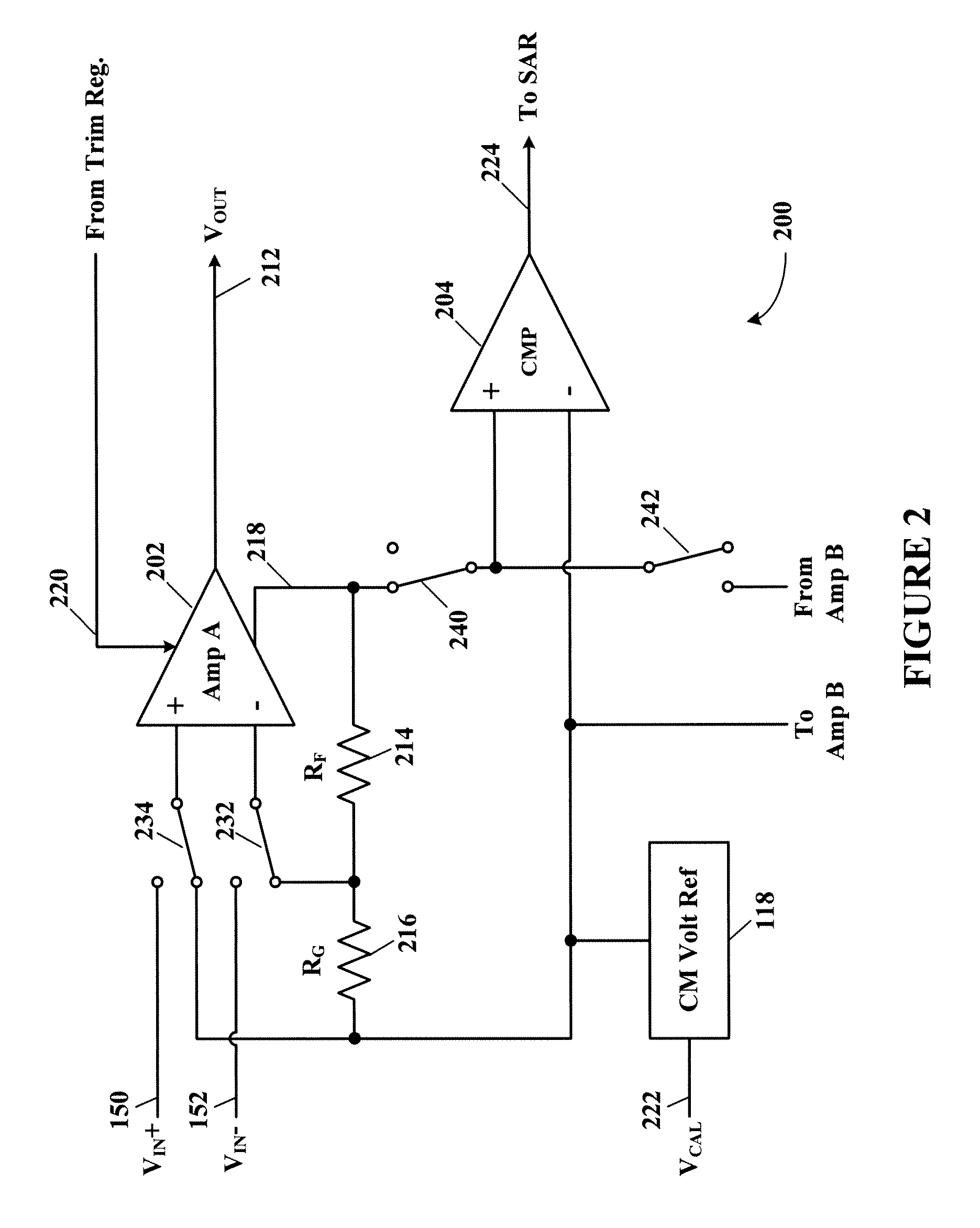

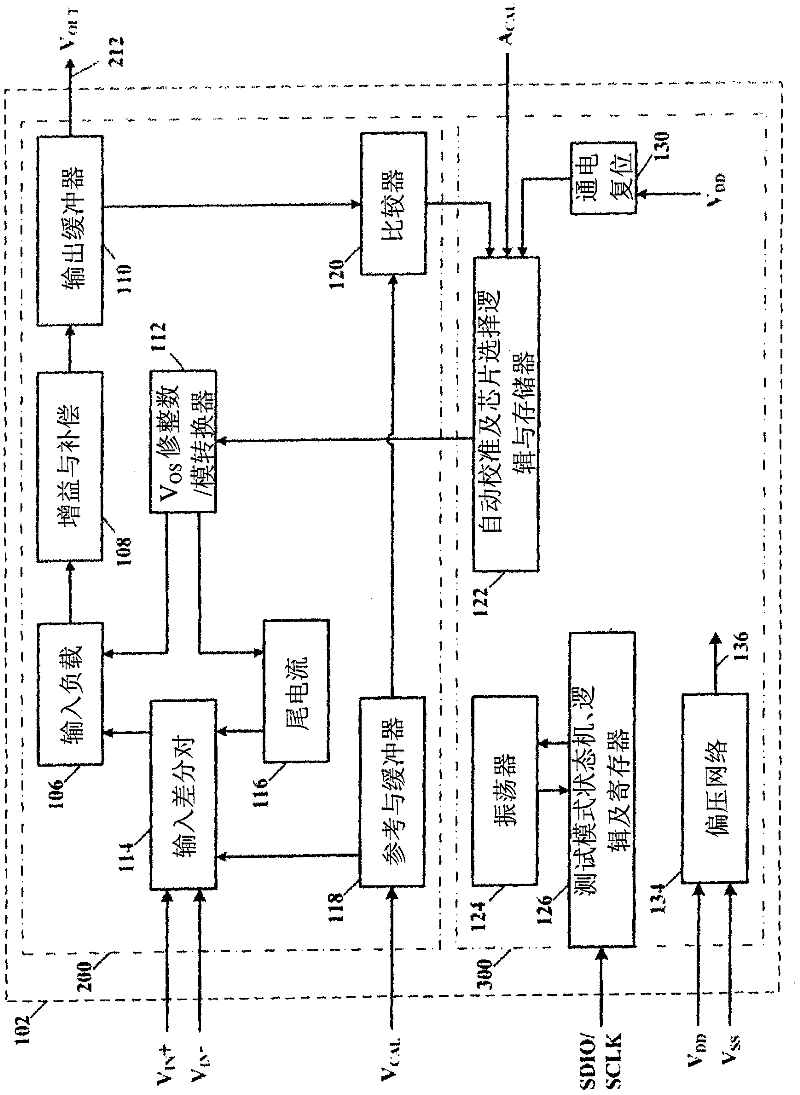

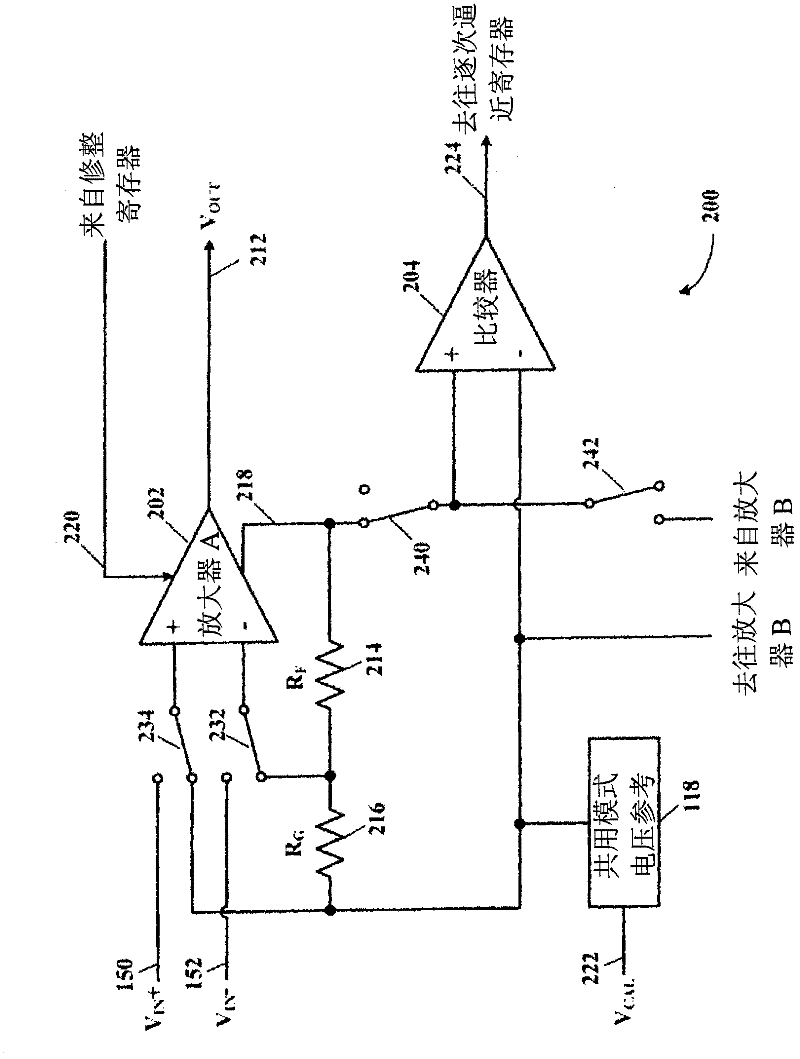

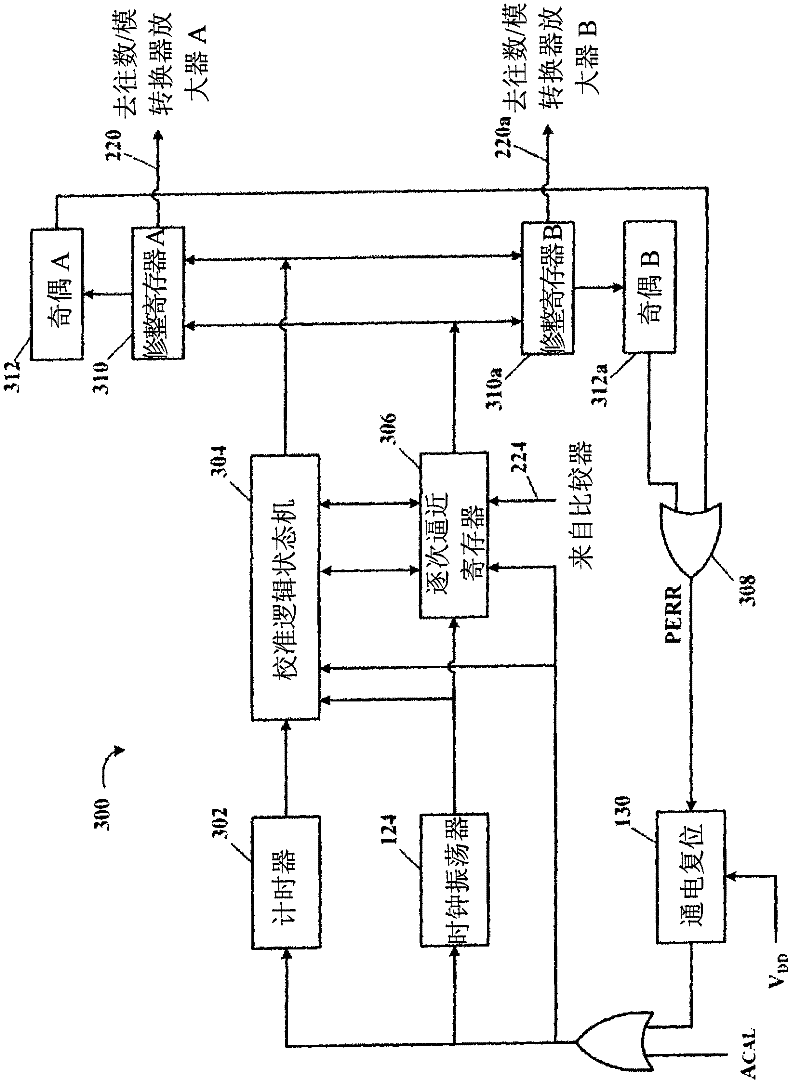

Self auto-calibration of analog circuits in a mixed signal integrated circuit device

ActiveUS7973684B2Minimizing input offset voltageMinimize voltageElectric signal transmission systemsPulse automatic controlDigital storageVoltage reference

Auto-calibration of the analog circuits occurs when requested by a user and / or the occurrence of an event(s). The user may invoke an auto-calibration on demand through an auto-calibration (ACAL) input to the mixed-signal integrated circuit. An external voltage calibration (VCAL) input may be used for auto-calibration of the mixed-signal integrated circuit to a user-supplied common-mode voltage reference. Auto-calibration of the mixed-signal integrated circuit may also be initiated upon the occurrence of any one or more of the following events: 1) detection of auto-calibration data corruption, e.g., parity checking of auto-calibration data values digitally stored in the mixed-signal integrated circuit; 2) an internal timer that causes a calibration request after a programmable timeout period, 3) change in the internal integrated circuit die temperature as determined by a temperature sensor, and 4) a change in the power supply and / or internal supply voltage(s).

Owner:MICROCHIP TECH INC

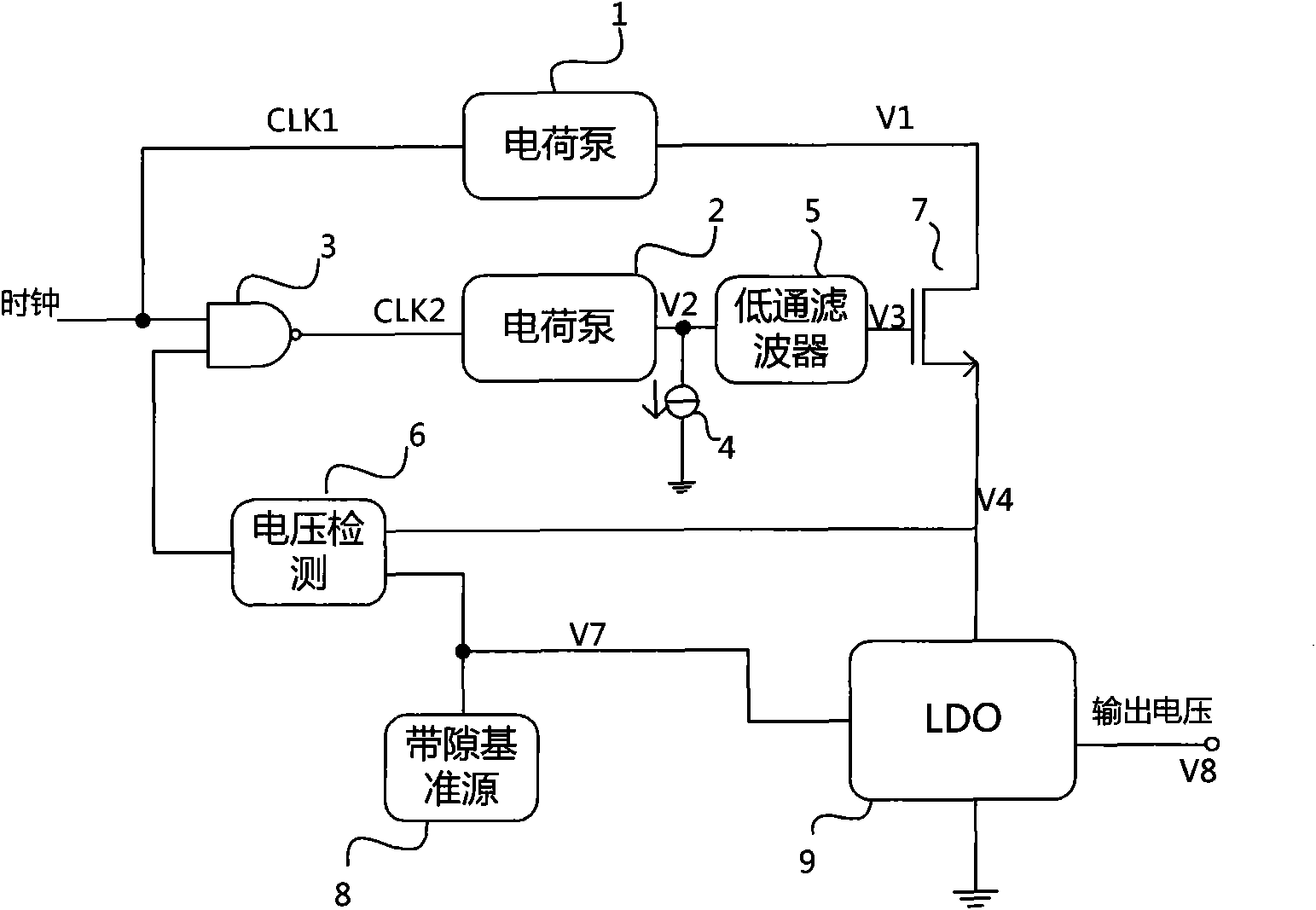

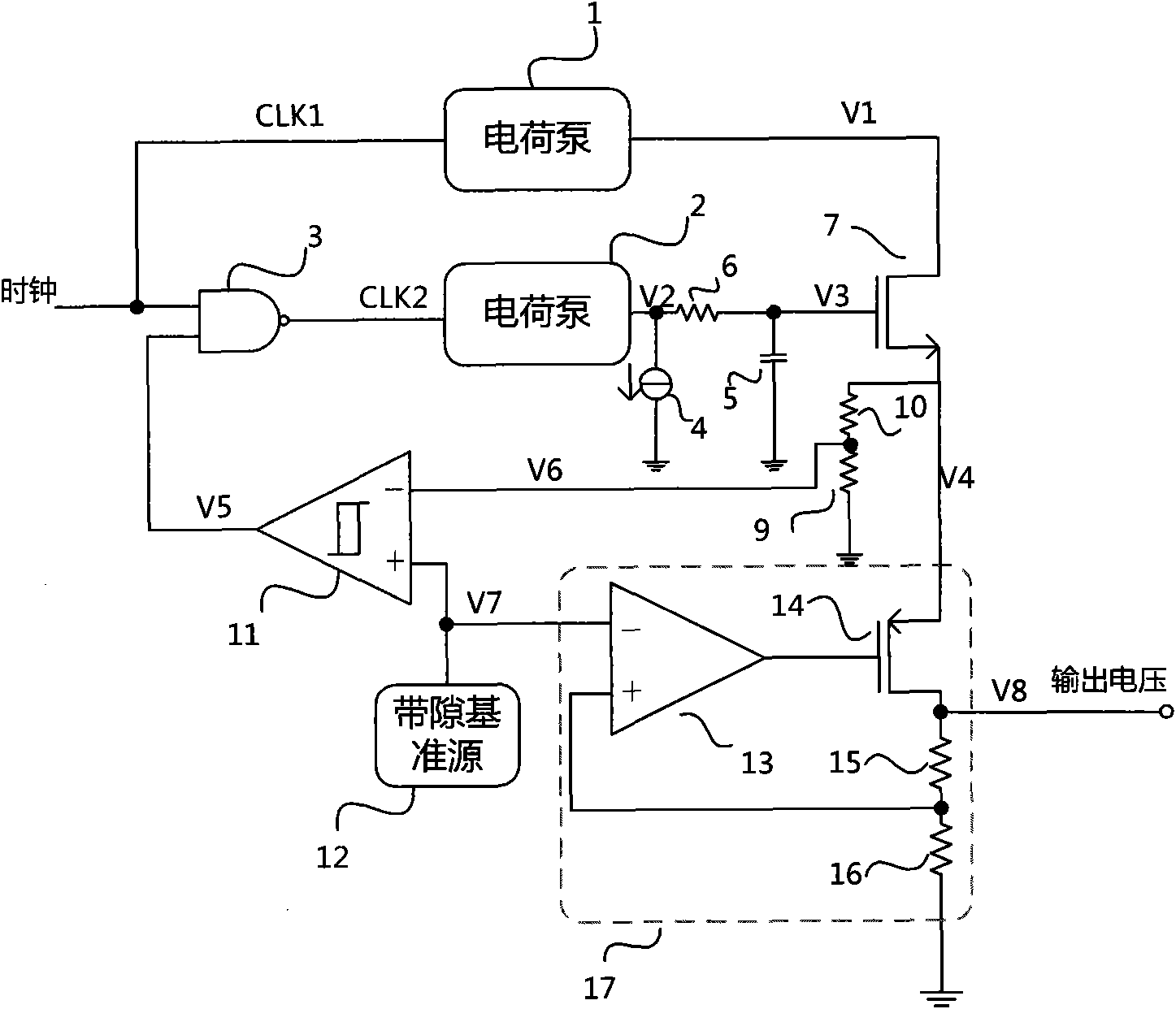

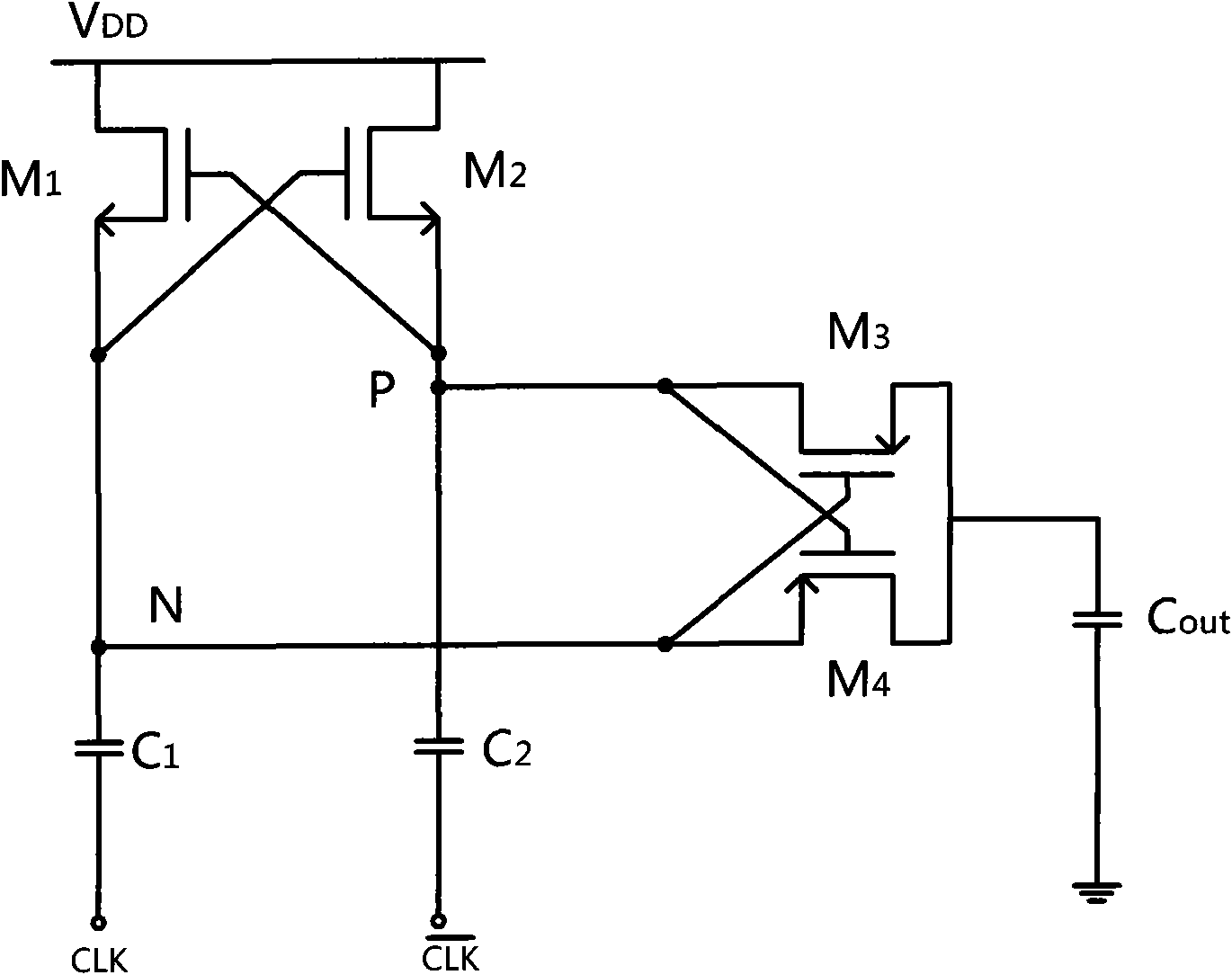

Voltage stabilizer on mixed signal integrated circuit chip

The invention relates to a voltage stabilizer on a mixed signal integrated circuit chip for providing a stable power supply to a sensitive analogue circuit. A charge pump generates a high voltage, while voltage generated by the other charge pump is connected to the grid electrode of an NMOS (N-channel Metal Oxide Semiconductor) source electrode follower after passing through a low pass filter. A current source is used as a load of the second charge pump. The drain electrode of the source electrode follower is connected to the output of the first charge pump and the stable voltage output is obtained at the source electrode after passing through a low dropout linear voltage stabilizer (LDO). The output voltage of a bandgap reference source is used as the reference voltage of the LDO. The clock of the second charge pump is generated by an NAND door and controlled by a voltage detection circuit.

Owner:BEIHANG UNIV

System-on-chip with shield rings for shielding functional blocks therein from electromagnetic interference

ActiveUS7170144B2Semiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceEngineering

A system-on-chip (SoC) that is immune to electromagnetic interference has block shield rings fabricated therein. The SoC includes a microprocessor core; an on-chip bus interface; an embedded memory block; and an analog / mixed-signal integrated circuit shielded by an EMI shield ring encircling the analog / mixed-signal integrated circuit for protecting the analog / mixed-signal integrated circuit from electromagnetic interference. The EMI shield ring is grounded and includes a metal rampart consisting of multi-layer metals and vias. A pickup diffusion is connected to the metal rampart. In one embodiment, the memory block is also shielded.

Owner:MARLIN SEMICON LTD

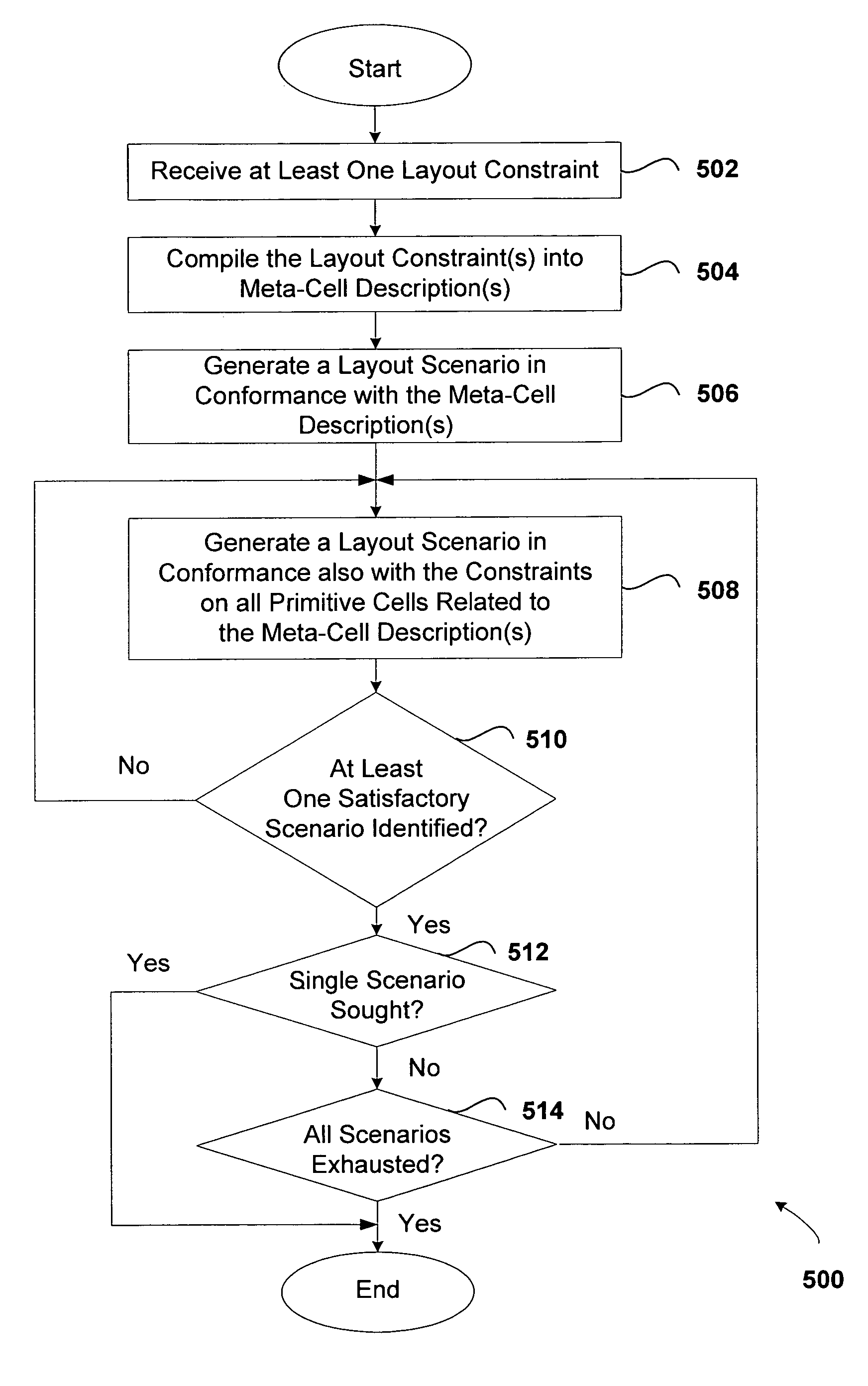

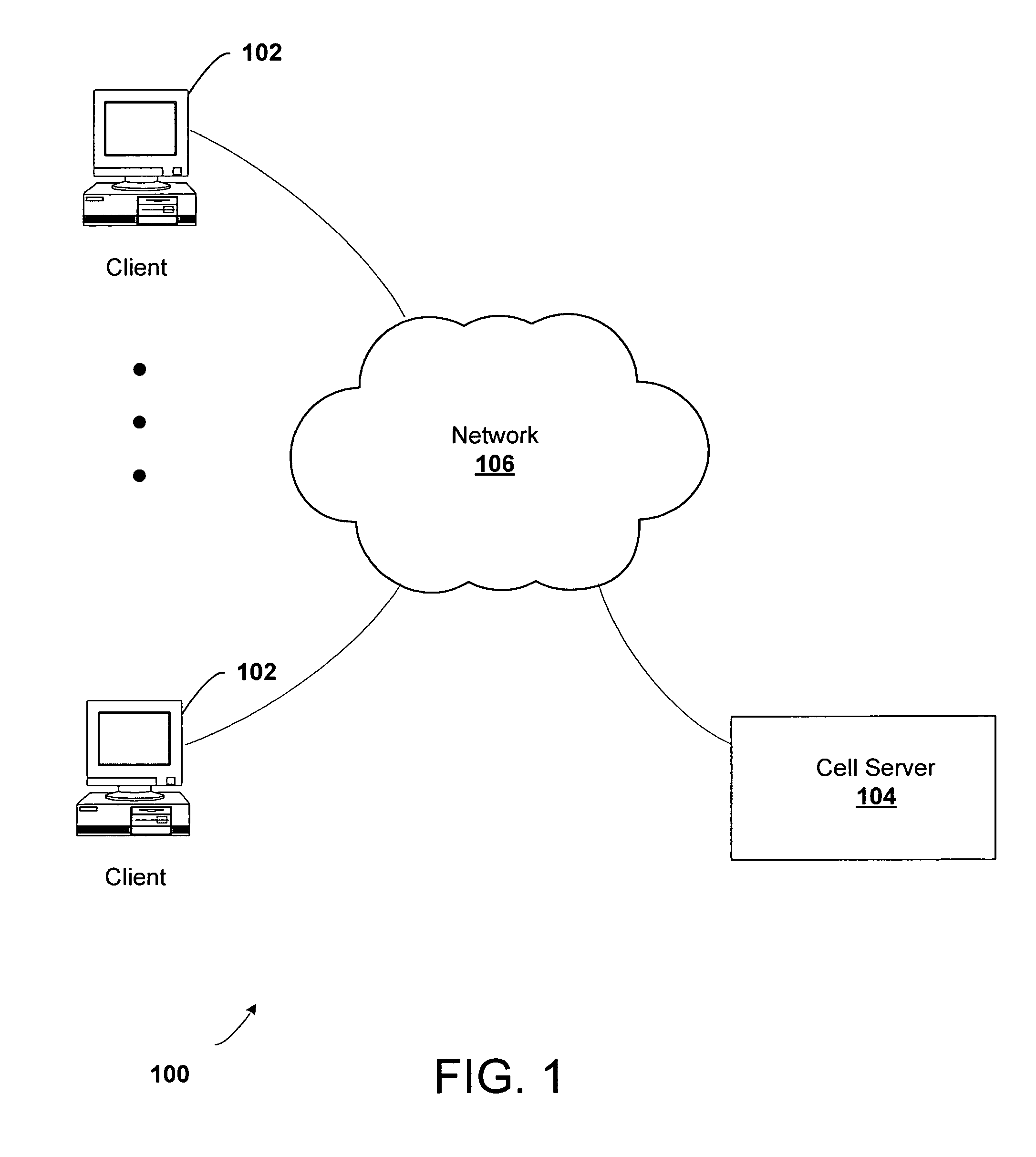

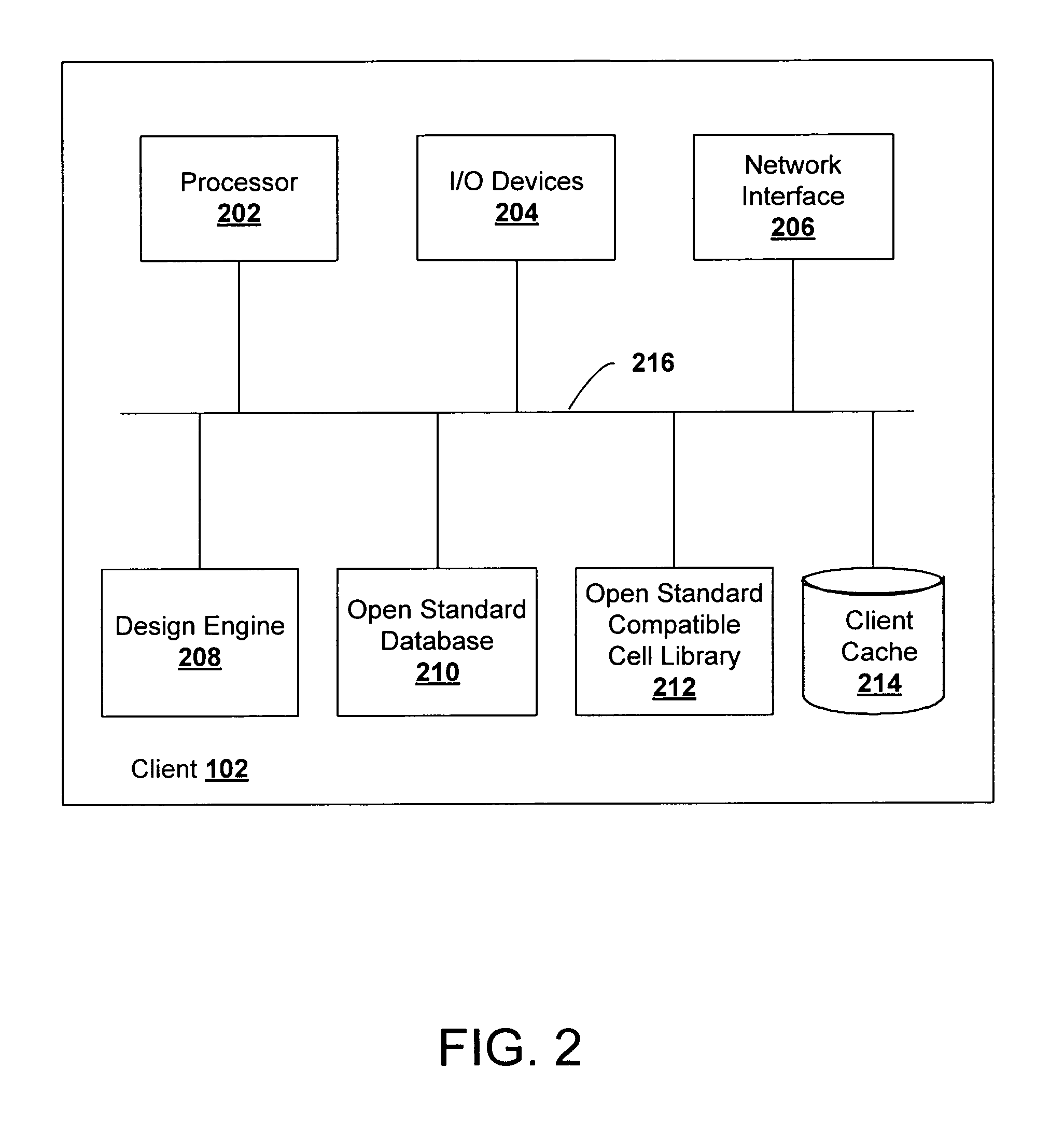

System and method for utilizing meta-cells

Exemplary systems and methods of laying out integrated circuits are disclosed. The systems include a layout application configured to place geometries in conformance with layout constraints transformed into composite cells. A composite cell defines a relationship between one or more cells, such as parameterized cells, and is independent of the physical topology of the cells. The exemplary systems are configured to use the composite cells to restrict a number of possible layout scenarios by generating a first layout scenario in conformance with the composite cell implementations, and to thereafter generate a second layout scenario in conformance with the constraints on all cells within the first layout scenario. Embodiments of the present invention are particularly suited to the layout of analog and mixed signal integrated circuits resulting in faster, more flexible, and more efficient layout as compared with conventional techniques which require the layout application to search through a much broader set of possible scenarios.

Owner:SYNOPSYS INC

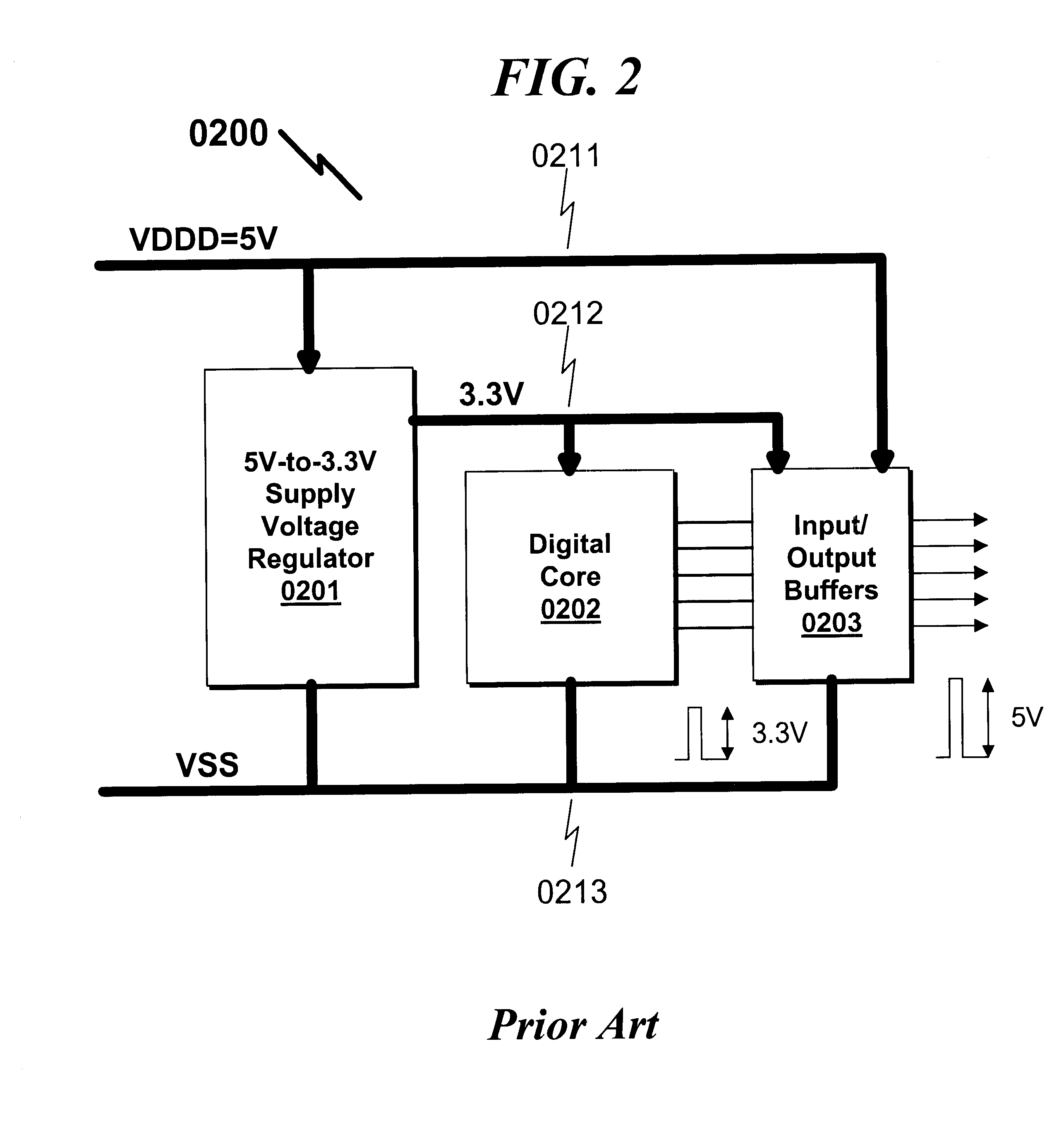

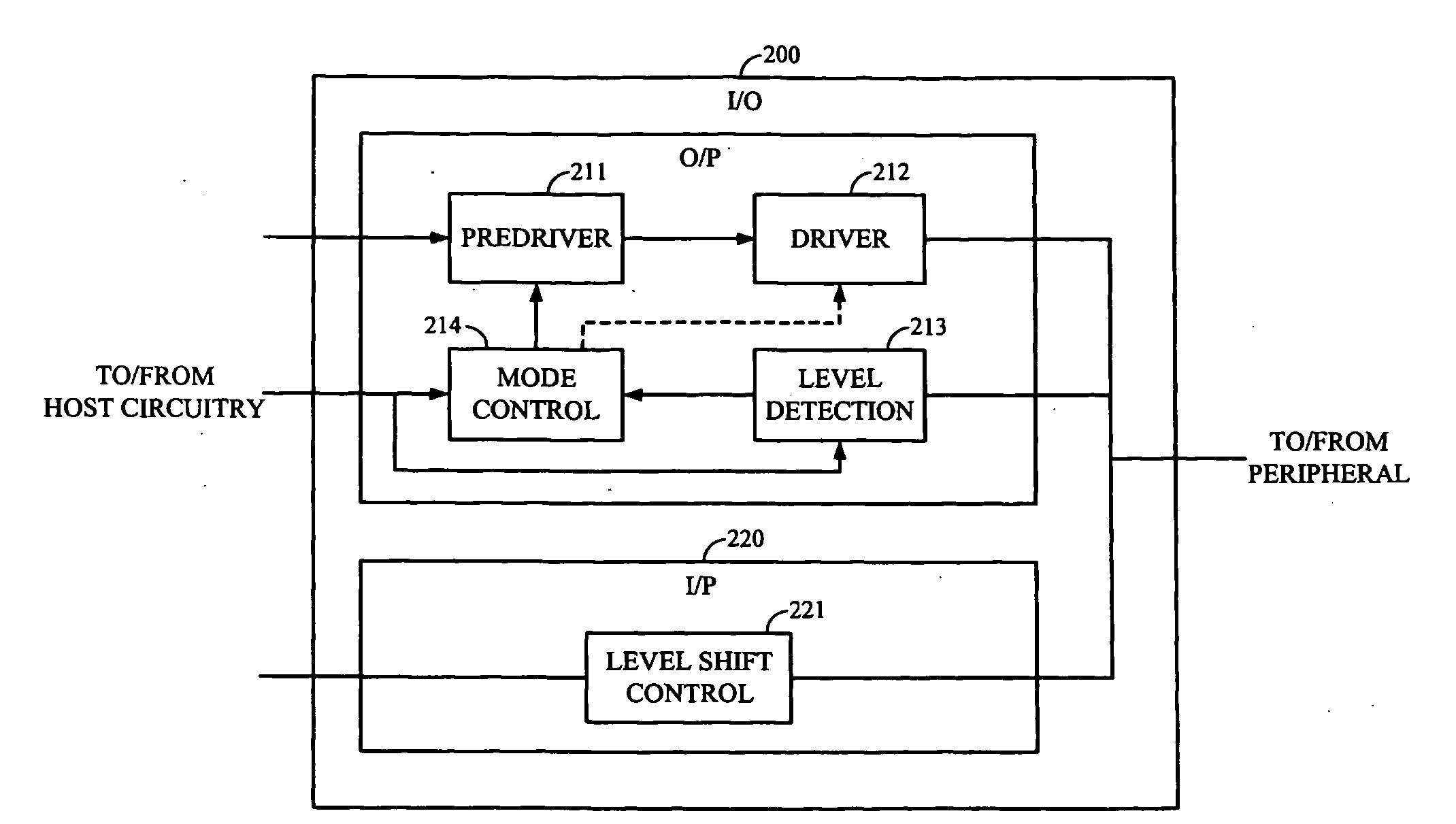

High signal level compliant input/output circuits

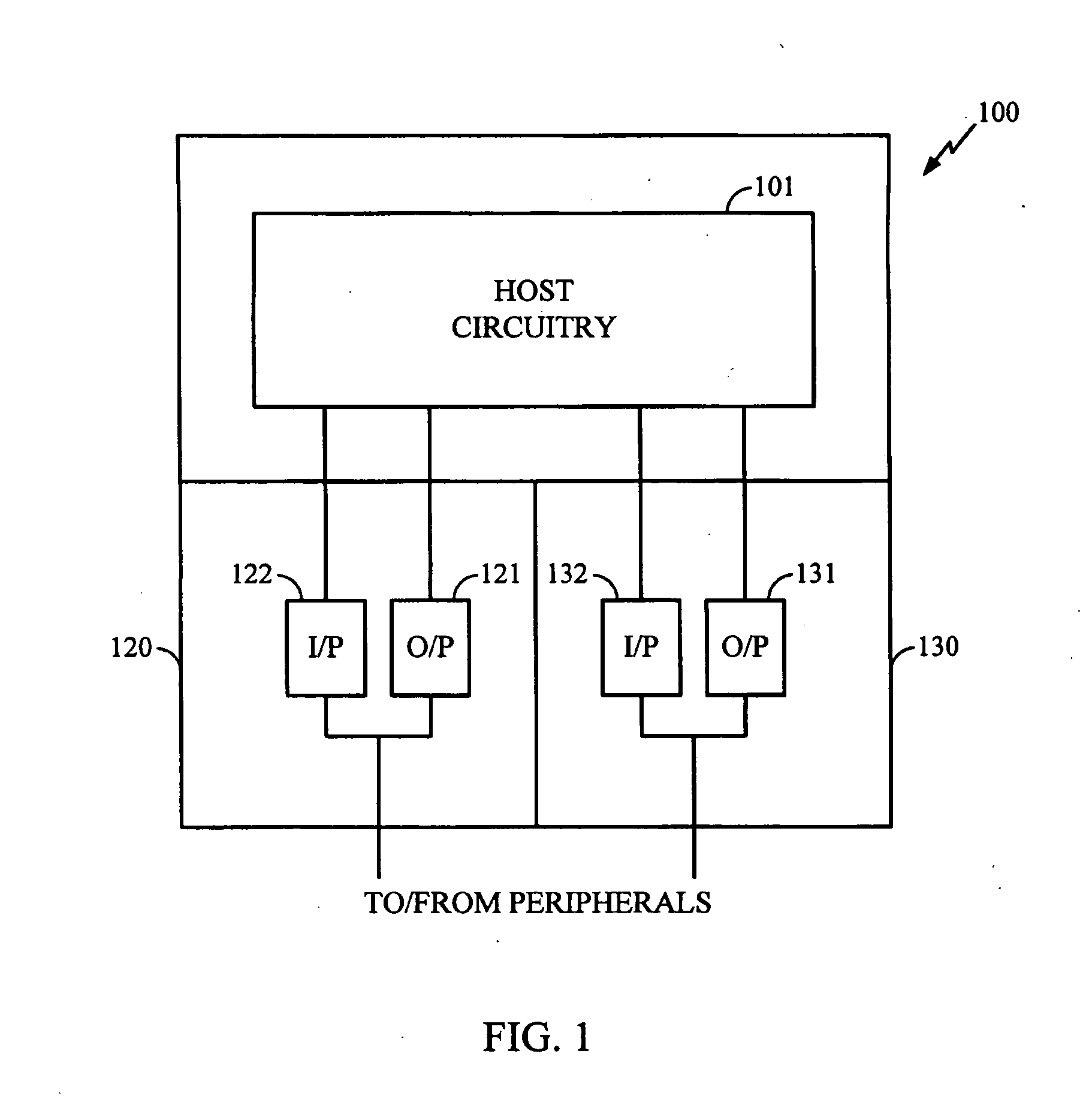

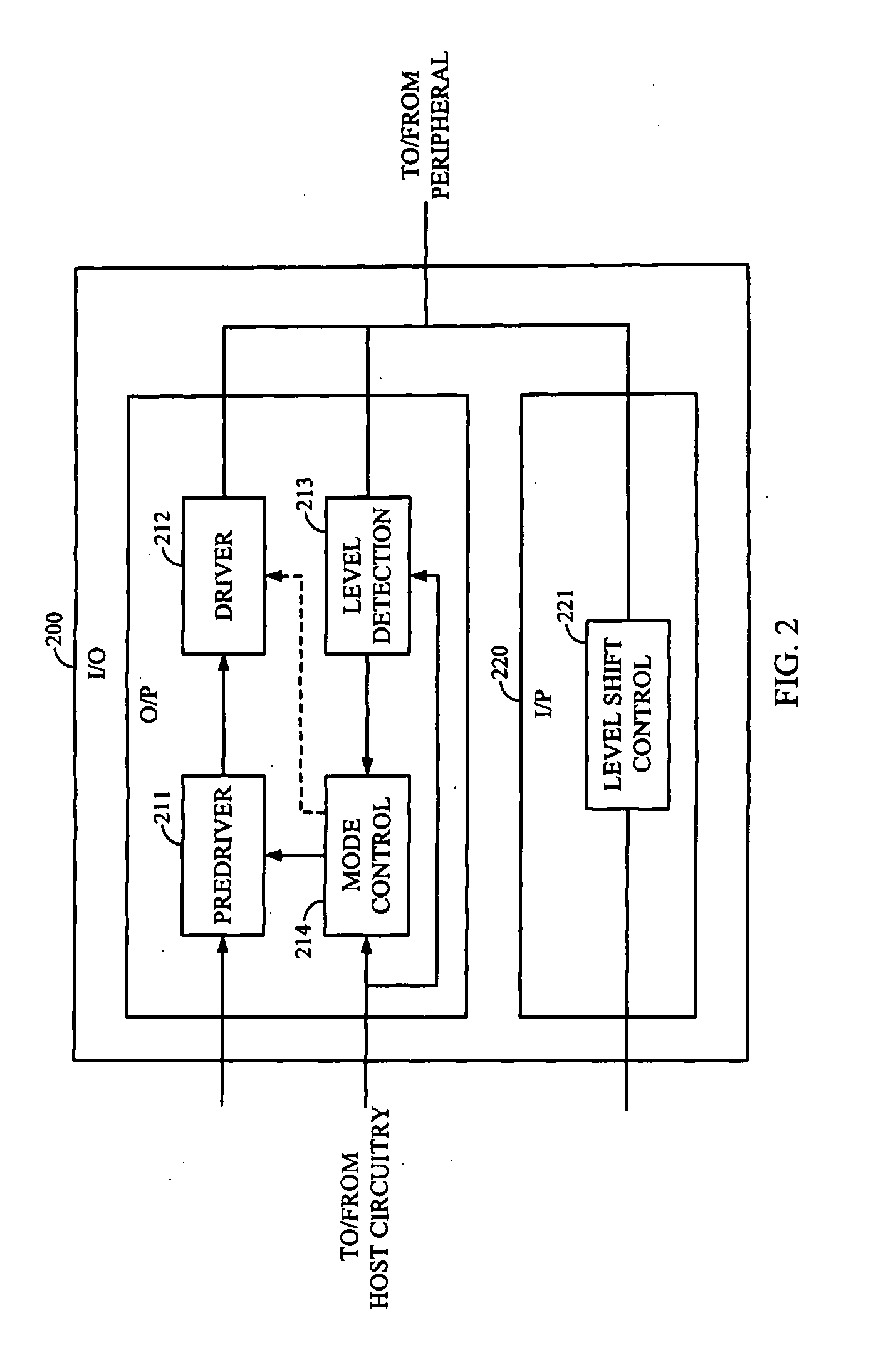

ActiveUS20100030924A1Less reliabilityInput/output processes for data processingLogic circuit coupling/interface arrangementsMixed-signal integrated circuitElectronic component

A signal interface circuit has a signal path for communicatively coupling host circuitry to peripheral circuitry of multiple peripherals. Communication signals in the signal path are of a peripheral signal level. The signal path has electronic components adapted for use in communicating signals between the host circuitry and the peripheral circuitry. The electronic components in the signal path have reliability limits less than the peripheral signal level. The configuration of the electronic components in the signal path allow communication of signals at the peripheral signal level.

Owner:QUALCOMM INC

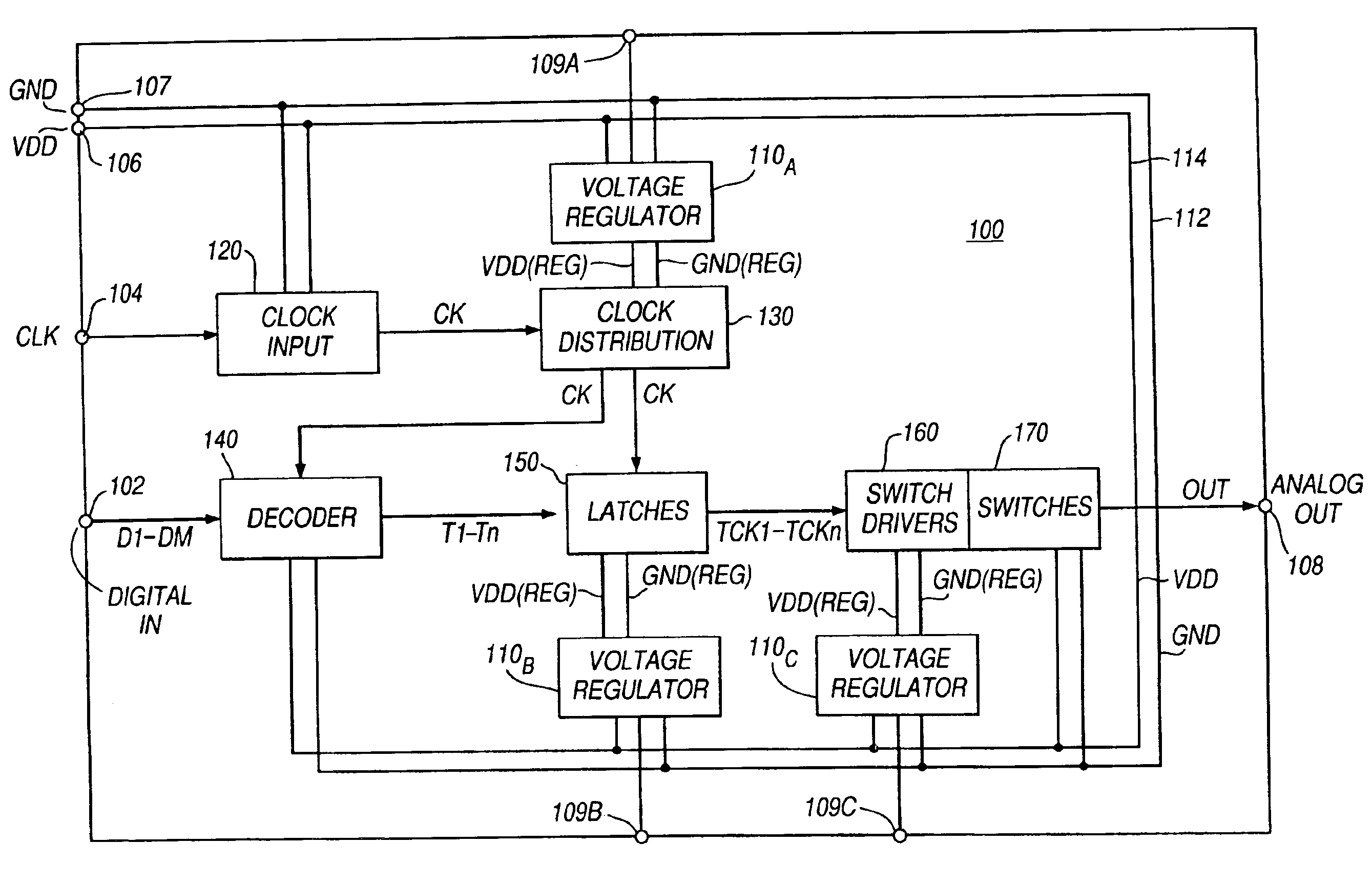

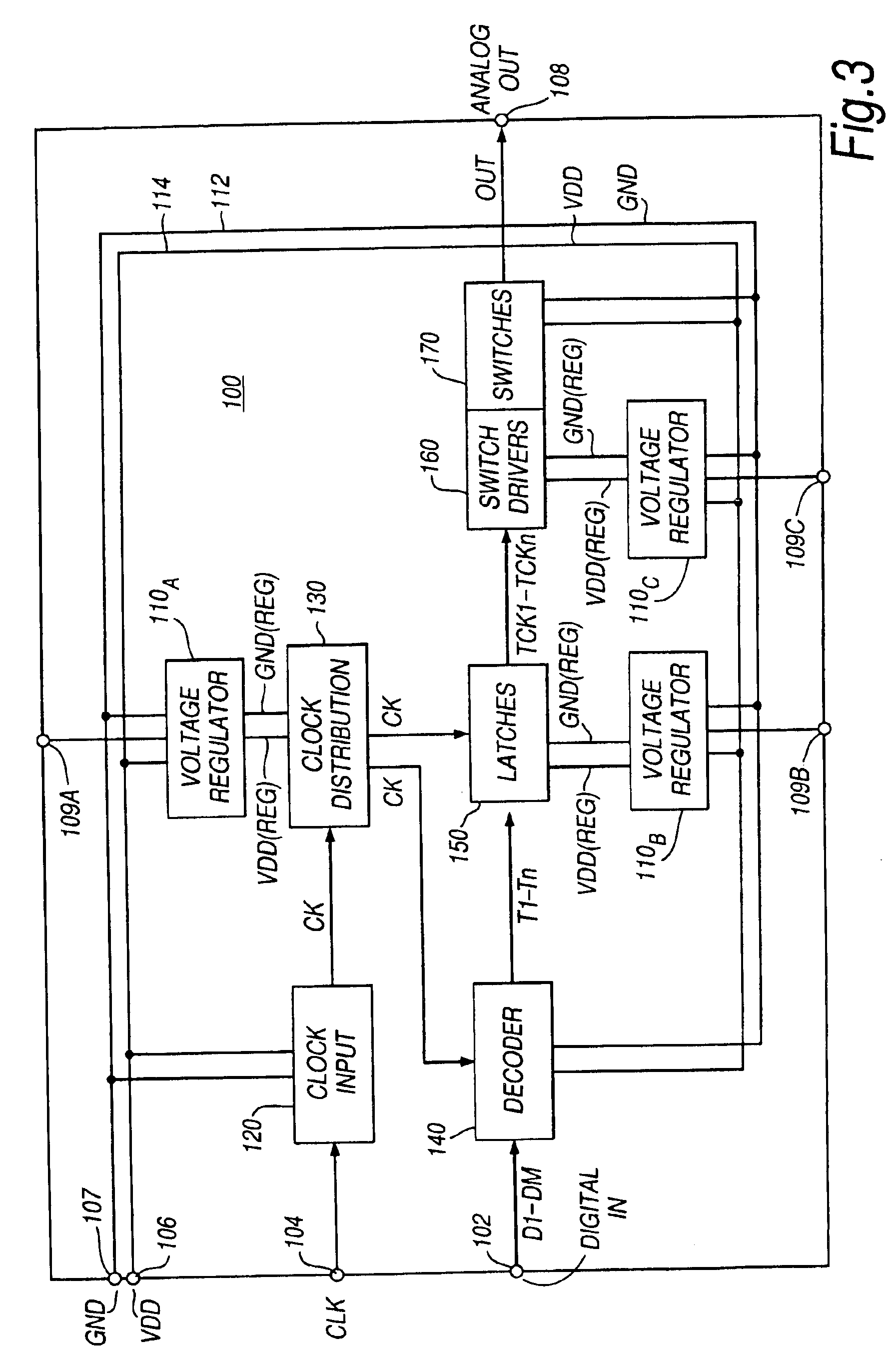

Reducing jitter in mixed-signal integrated circuit devices

InactiveUS6853322B2Reliability increasing modificationsElectric signal transmission systemsSignal processing circuitsDelayed time

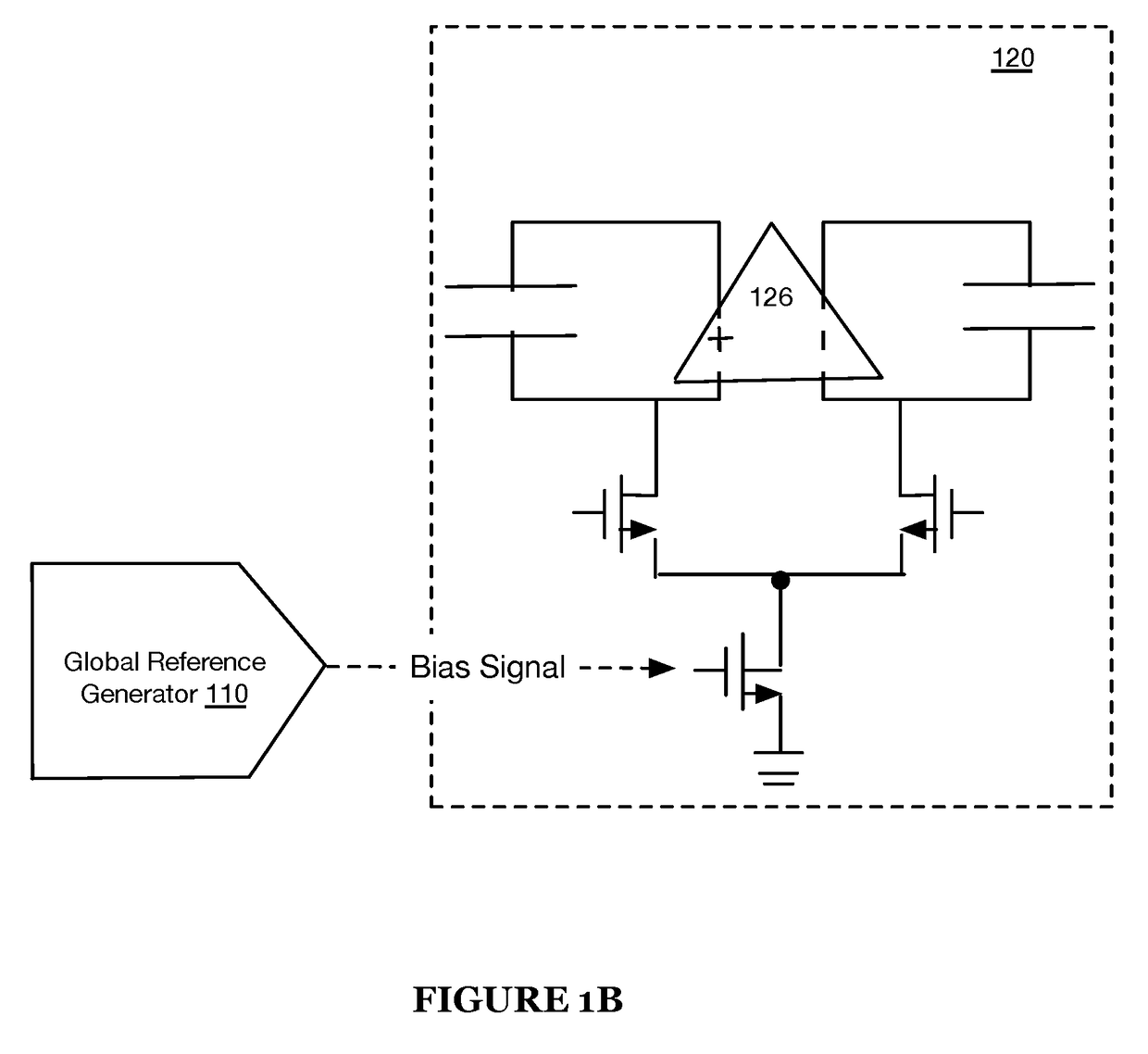

A data converter is implemented as an integrated circuit device (100). The converter comprises signal processing circuitry (120-170) which produces an output signal (OUT) in dependence upon a received input signal (D1-Dm). Production of the output signal (OUT) is initiated at a time determined by a timing signal (CLK) and is completed at a time which is delayed by a delay time with respect to the timing signal (CLK). A delay-contributing portion (130, 150, 160) makes a contribution to the delay time that is affected by variations in a power supply voltage (VDD) applied thereto. An internal supply voltage regulator (110) derives a regulated internal power supply voltage (VDD(REG)) from an external power source voltage (VDD), and applies this voltage to the delay-contributing portion (130, 150, 160) to fix its contribution to the delay time at some value independent of variations in the external power source voltage. At least one further circuitry portion (140, 170) within the integrated circuit device (100) is powered by a supply voltage (VDD) other than the regulated internal power supply voltage (VDD(REG)).

Owner:SOCIONEXT INC

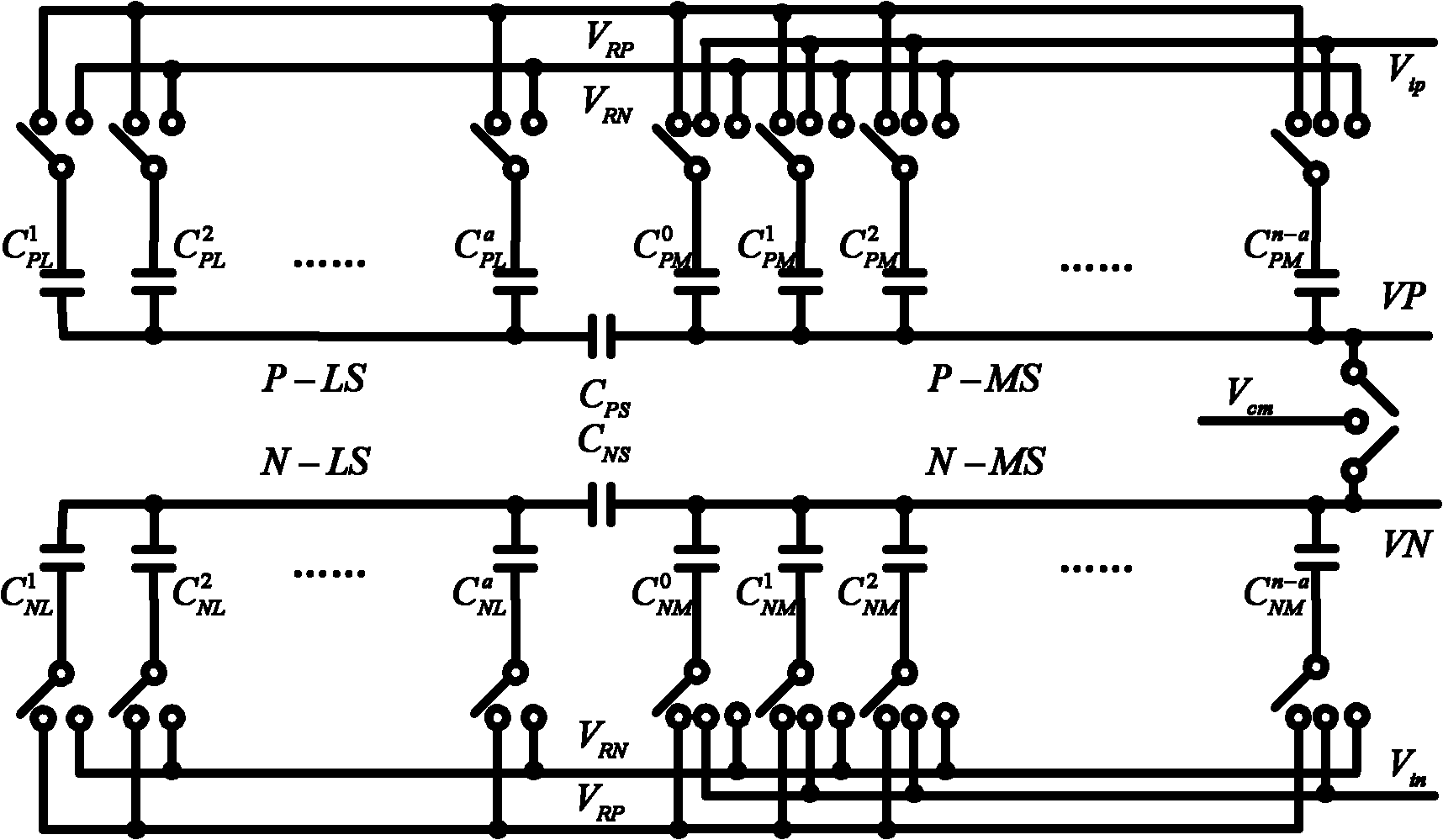

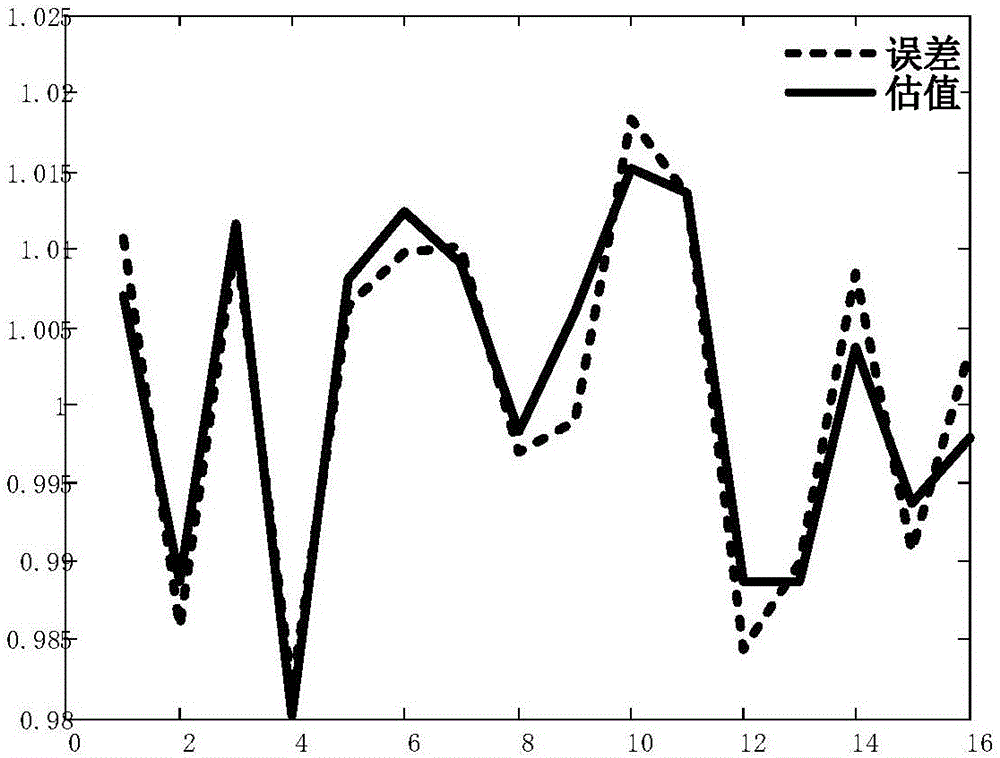

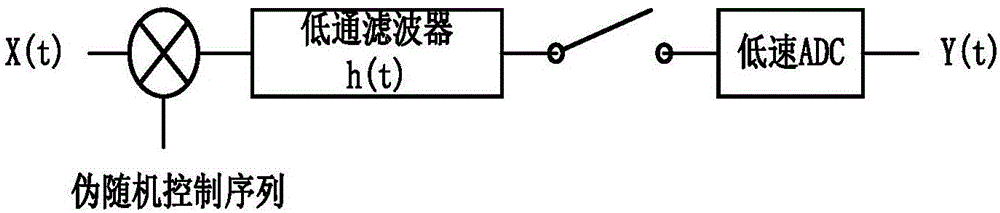

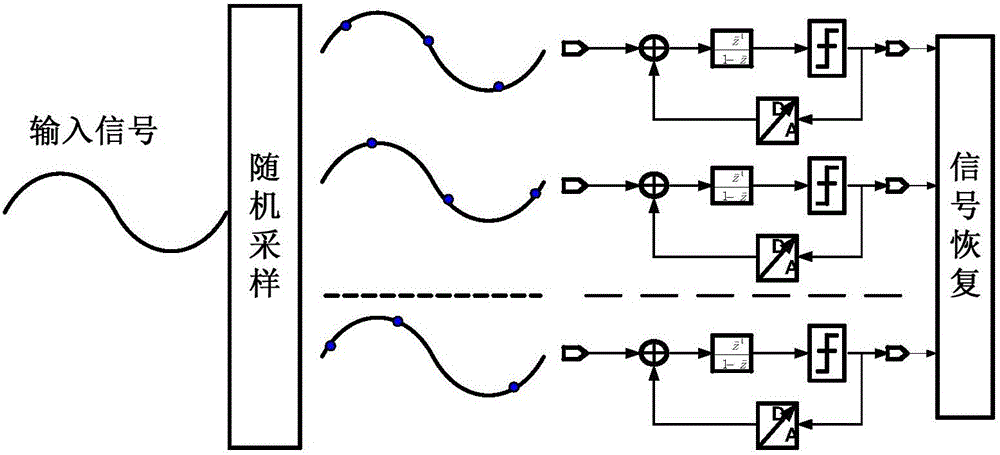

Compression sampling analog-to-digital converter using sampling and quantification circuit

ActiveCN105720987AReduce mismatchEliminate non-ideal factorsAnalogue/digital conversionElectric signal transmission systemsSignal restorationAnalog-to-digital converter

The invention provides a sampling and quantification circuit used for a compression sampling analog-to-digital converter and belongs to the field of mixed signal integration circuit design technology. According to the invention, a signal processing procedure including signal observation, error estimation, signal calibration and signal restoration for error correction and a sampling and quantification circuit realization structure with multi-way parallel sampling, simulation domain integration and signal quantization device quantification are provided. The sampling and quantification circuit realization structure successively inputs all simulation sampling and integration results into the same quantification device, so a mismatching problem in a multi-way quantification process is effectively reduced; complexity in realization of a compression sampling analog-to-digital converter system is reduced; and the sampling and quantification circuit is designed with modules, so independence and universality of designing of all modules are improved.

Owner:TSINGHUA UNIV

Integrated semiconductor device and method of manufacturing the same

InactiveUS20060125048A1Low temperature coefficientLow densitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

An integrated semiconductor device comprising an analog integrated circuit or mixed signal integrated circuit having a capacitor, wherein the dielectric film of the capacitor is a laminated film consisting of a first dielectric film essentially composed of aluminum oxide and a second dielectric film essentially composed of crystallized niobium oxide. This integrated semiconductor device is small in size and has a low temperature coefficient and high reliability. The niobium oxide is crystallized to increase its dielectric constant and reduce its loss. To reduce the temperature coefficient, the film thickness ratio of the aluminum oxide layer to the niobium oxide layer is set to 0.2 to 1, preferably 0.4 to 0.7.

Owner:HITACHI LTD

Mixed signal integrated circuit, with built in self test and method

Owner:FRESCO MICROCHIP

Mixed signal integrated circuits with self-test capability

ActiveUS7315177B1Individual semiconductor device testingDigital signal processingMixed-signal integrated circuit

A mixed signal integrated circuit with self test capability in which a portion of the digital circuitry, during substantially mutually exclusive time intervals, controls self test functions within the analog circuitry and performs digital signal processing functions in conjunction with the remaining portion of the digital circuitry.

Owner:NAT SEMICON CORP

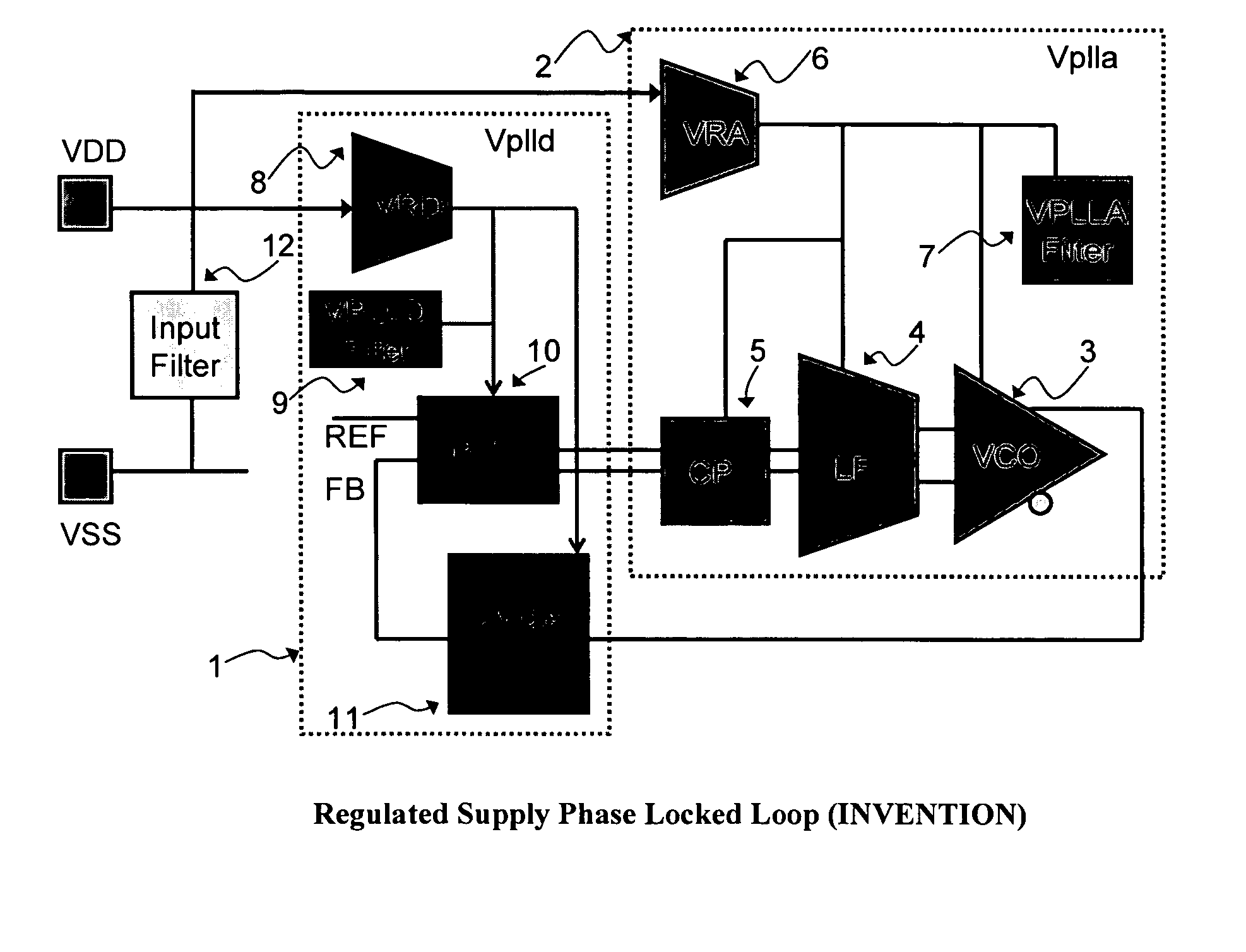

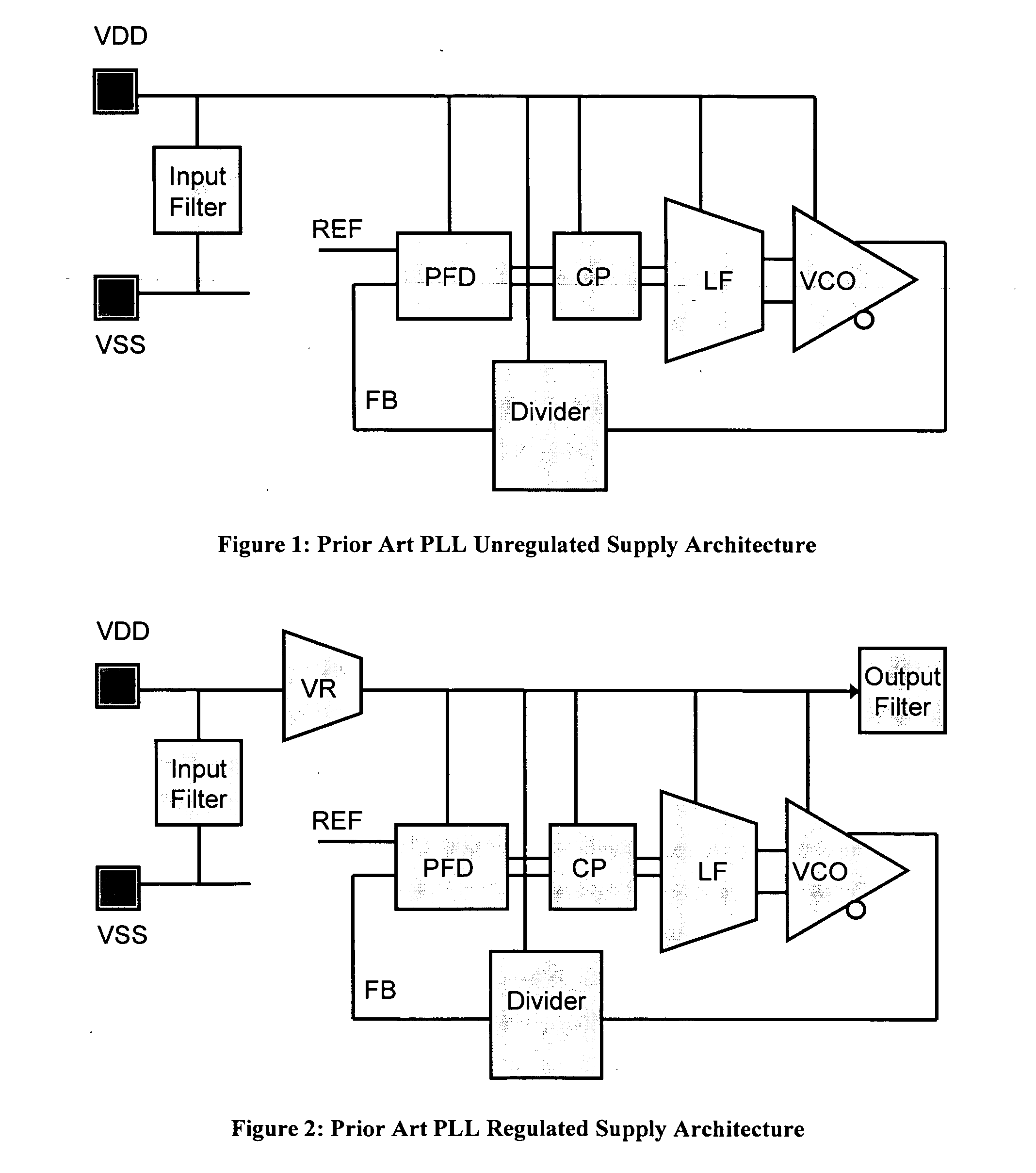

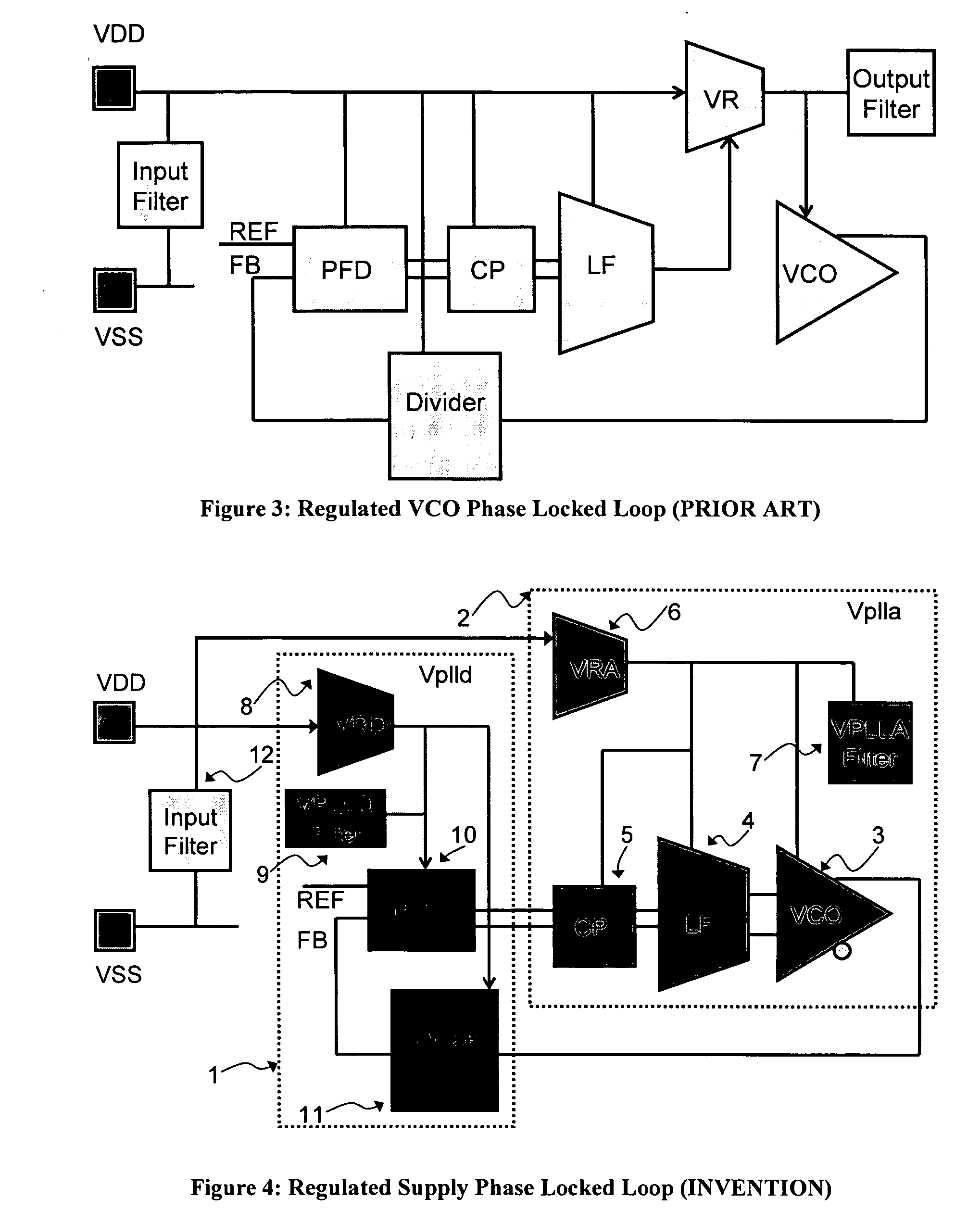

Regulated supply phase locked loop

A noise-minimizing supply regulation architecture enabling high-performance integrated mixed-signal circuit systems is disclosed. The architecture identifies noise-generating and noise-sensitive sub-components of a PLL or other complex mixed-signal circuit and isolates the noise-sensitive sub-components from the noise-generating sub-components through the use of separate, wideband, high-PSRR voltage regulators for the two isolated supply domains. This isolation is further enhanced through techniques that separate or isolate the substrate regions occupied by the two types of sub-components. Further, internally generated noise is minimized by the allocation of available decoupling capacitance area in proportion to the noise generated within the domains. This supply isolation architecture achieves very low noise operation of the critical components of the mixed-signal integrated circuit system, thereby improving output quality.

Owner:NAIR RAJENDRAN

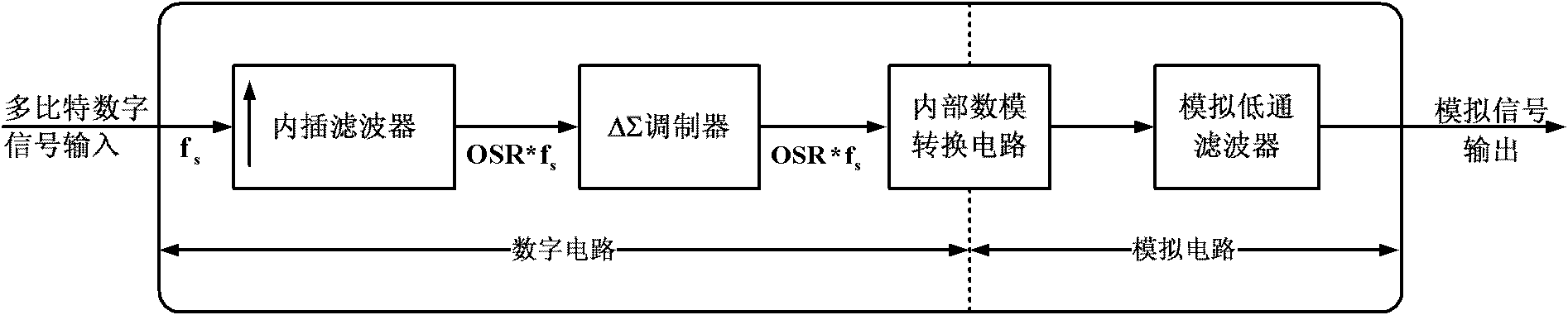

Digital-to-analog converter capable of optimizing power consumption and output signal-to-noise ratio

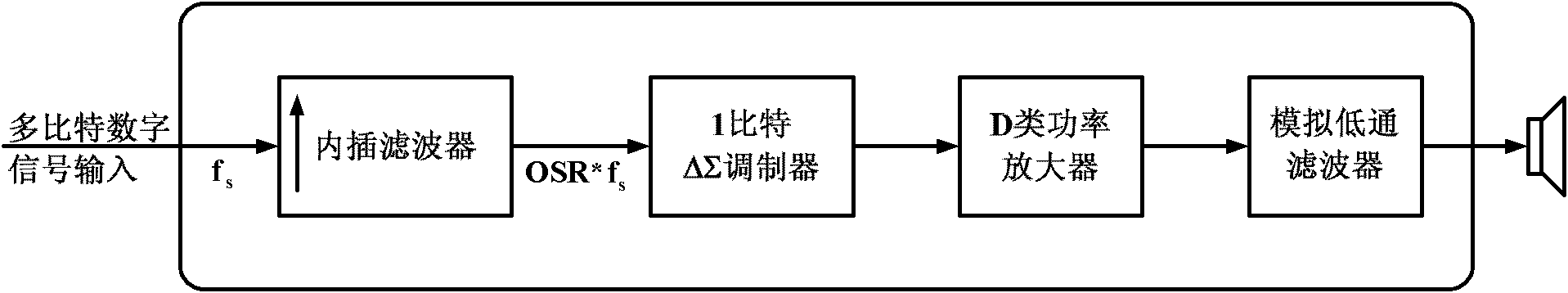

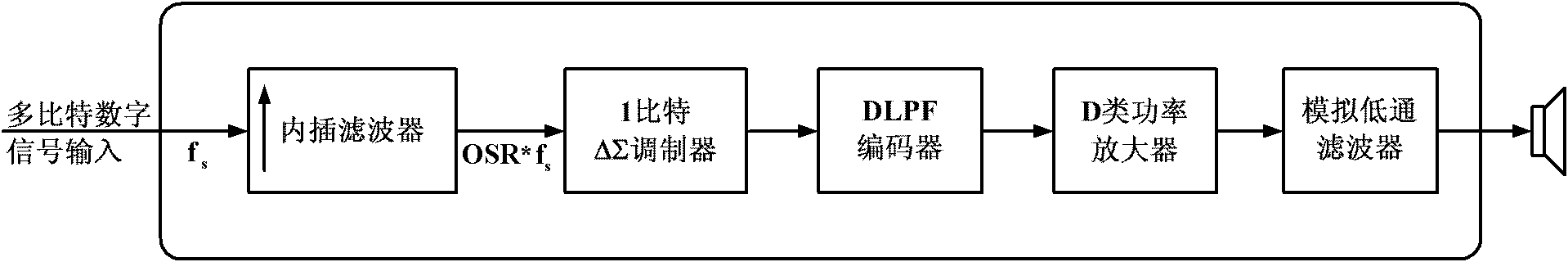

InactiveCN102055479AReduce switching frequencyReduce power consumptionDigital-analogue convertorsDigital analog converterSignal-to-noise ratio (imaging)

The invention relates to a digital-to-analog converter capable of optimizing power consumption and output signal-to-noise ratio, belonging to the design field of mixed signal integrated circuits. The digital-to-analog converter comprises an interpolation filter, a 1-bit delta-sigma modulator, a class-D power amplifier, an analog low pass filter and a DLPF (Digital Low Pass Filter) coder, wherein the interpolation filter, the 1-bit delta-sigma modulator, the class-D power amplifier and the analog low pass filter are sequentially connected; and the DLPF coder is connected between the 1-bit delta-sigma modulator and the class-D power amplifier. The input multi-bit digital signals firstly finish the up-sampling through the interpolation filter and then finish the noise shaping through the 1-bit delta-sigma modulator, 1-bit codes output by the modulator are coded by the DLPF coder, 2-bit codes output by the DLPF coder control the switching operation of the class-D power amplifier, and finally, the unnecessary out-of-band noise is filtered out through the analog low pass filter, thereby realizing digital-to-analog conversion and power amplification. The invention can lower the switching operation frequency of the class-D power amplifier, thereby lowering the power consumption of a delta-sigma digital-to-analog converter; and the invention also can improve the signal-to-noise ratio of output signals.

Owner:TSINGHUA UNIV

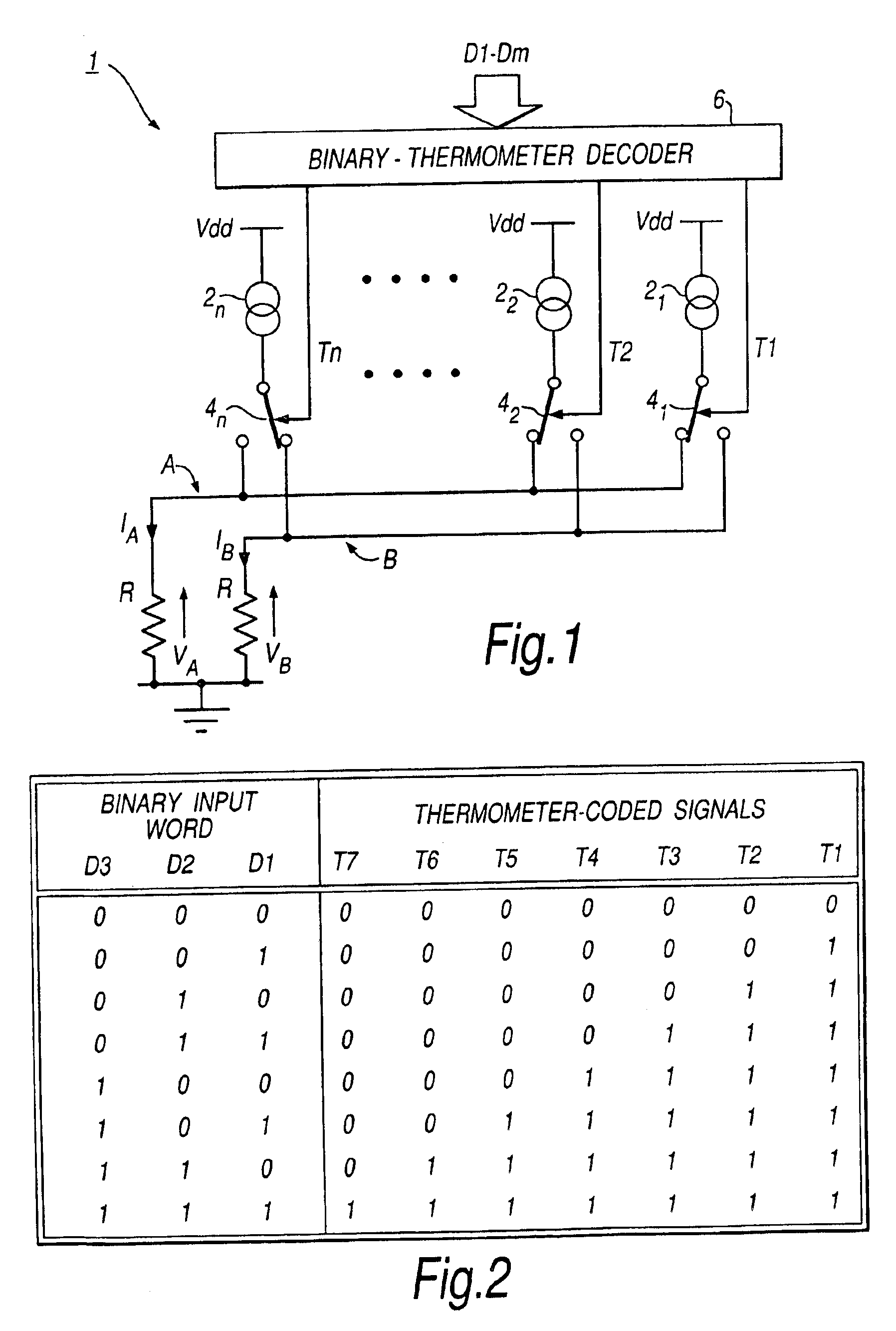

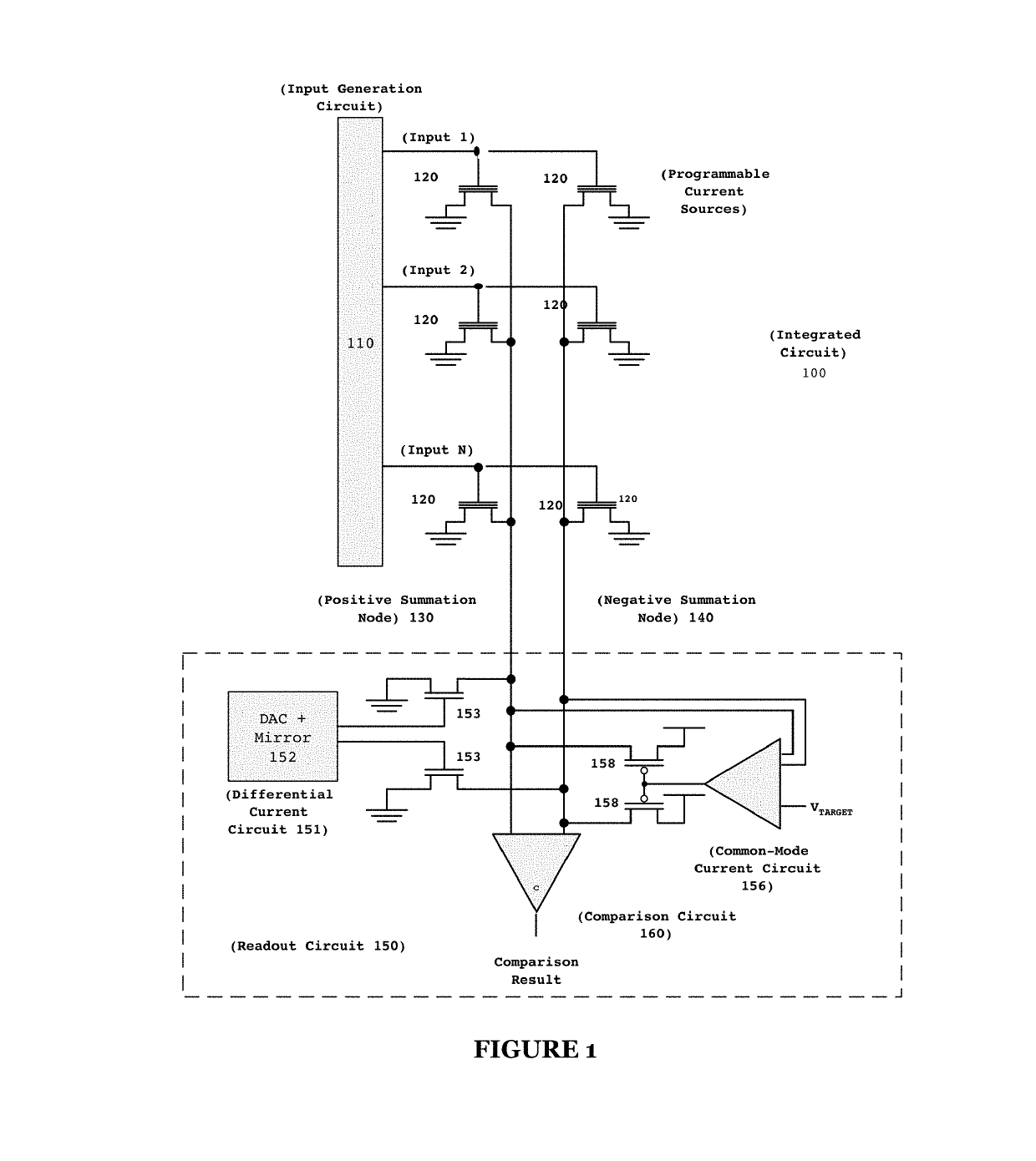

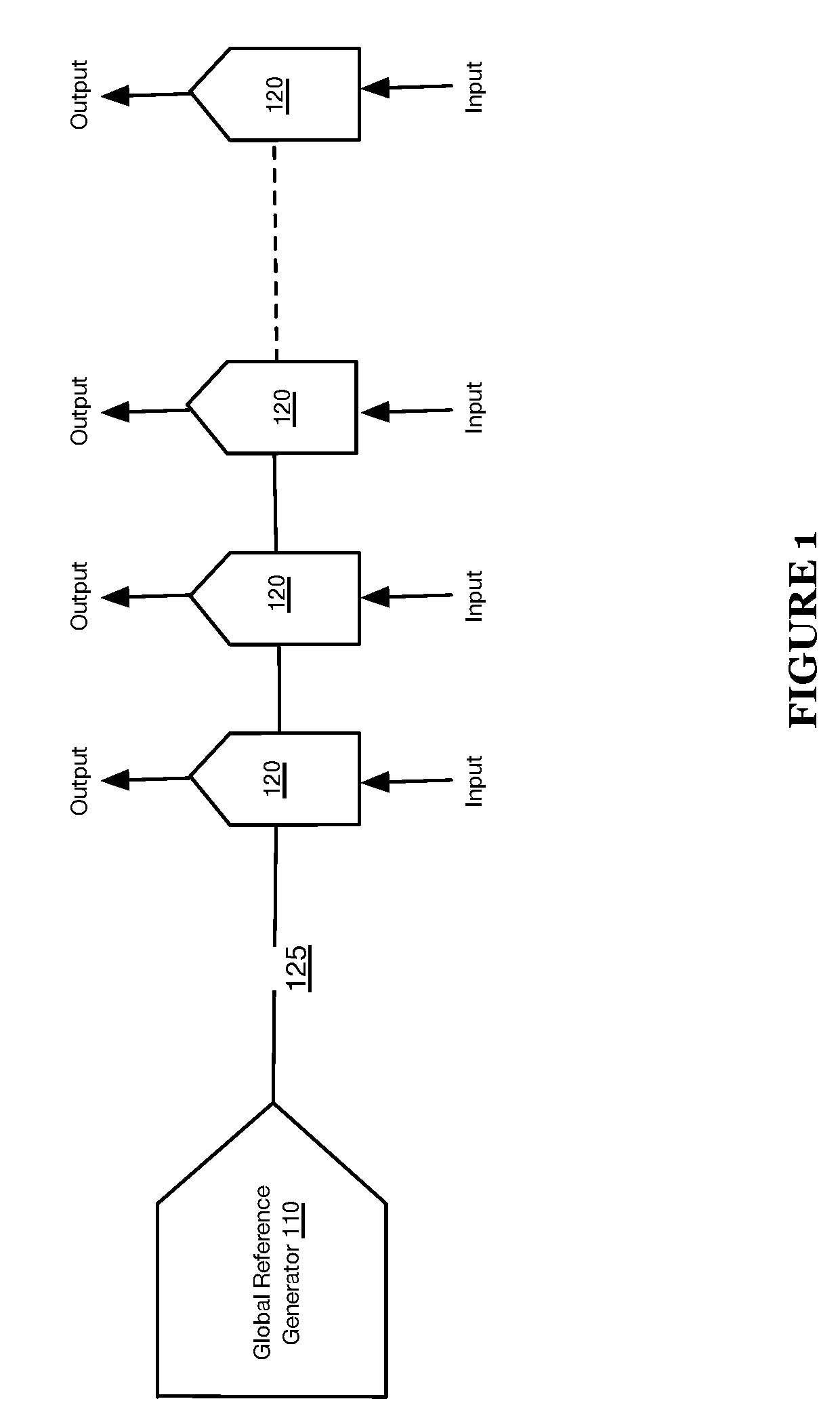

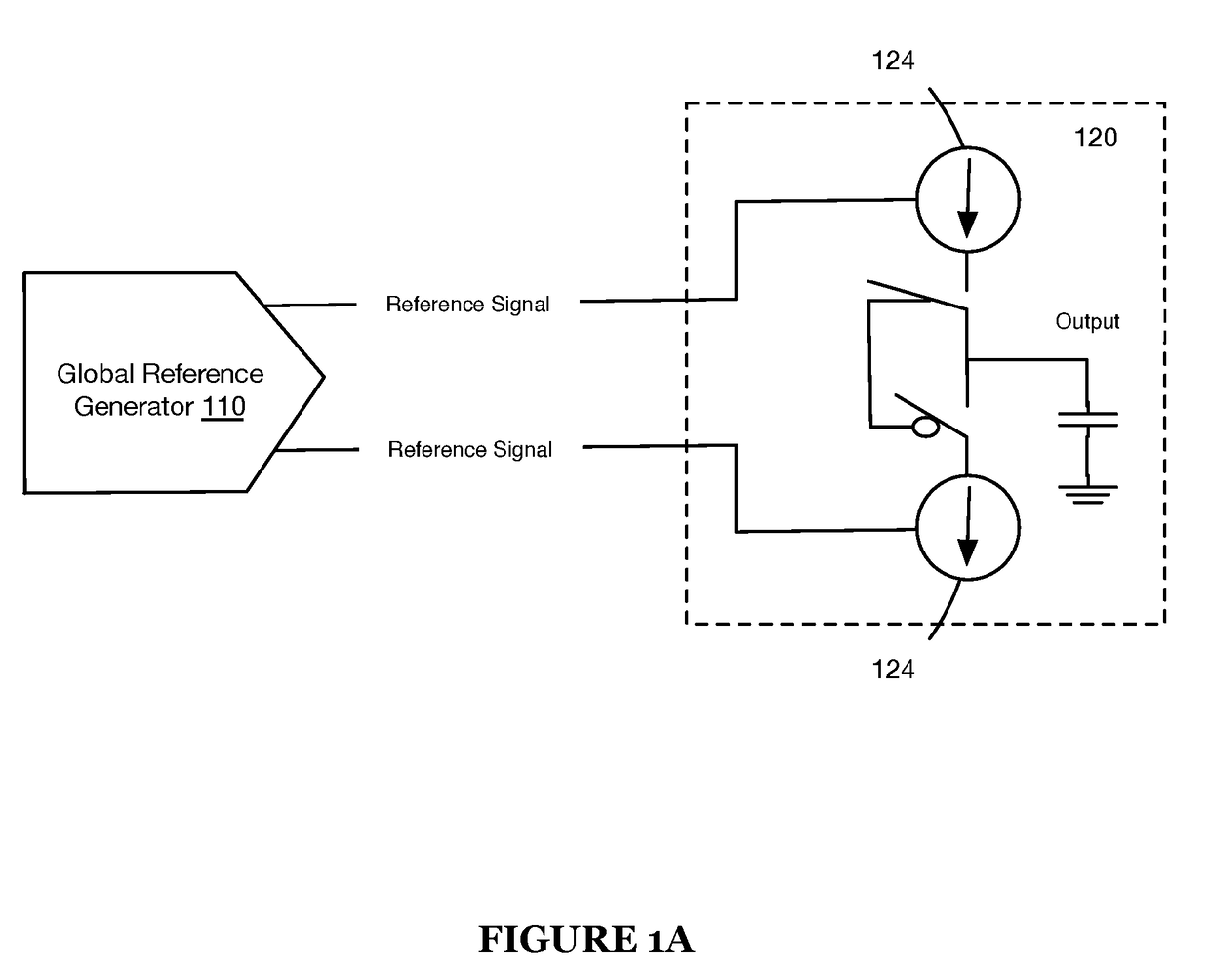

System and methods for mixed-signal computing

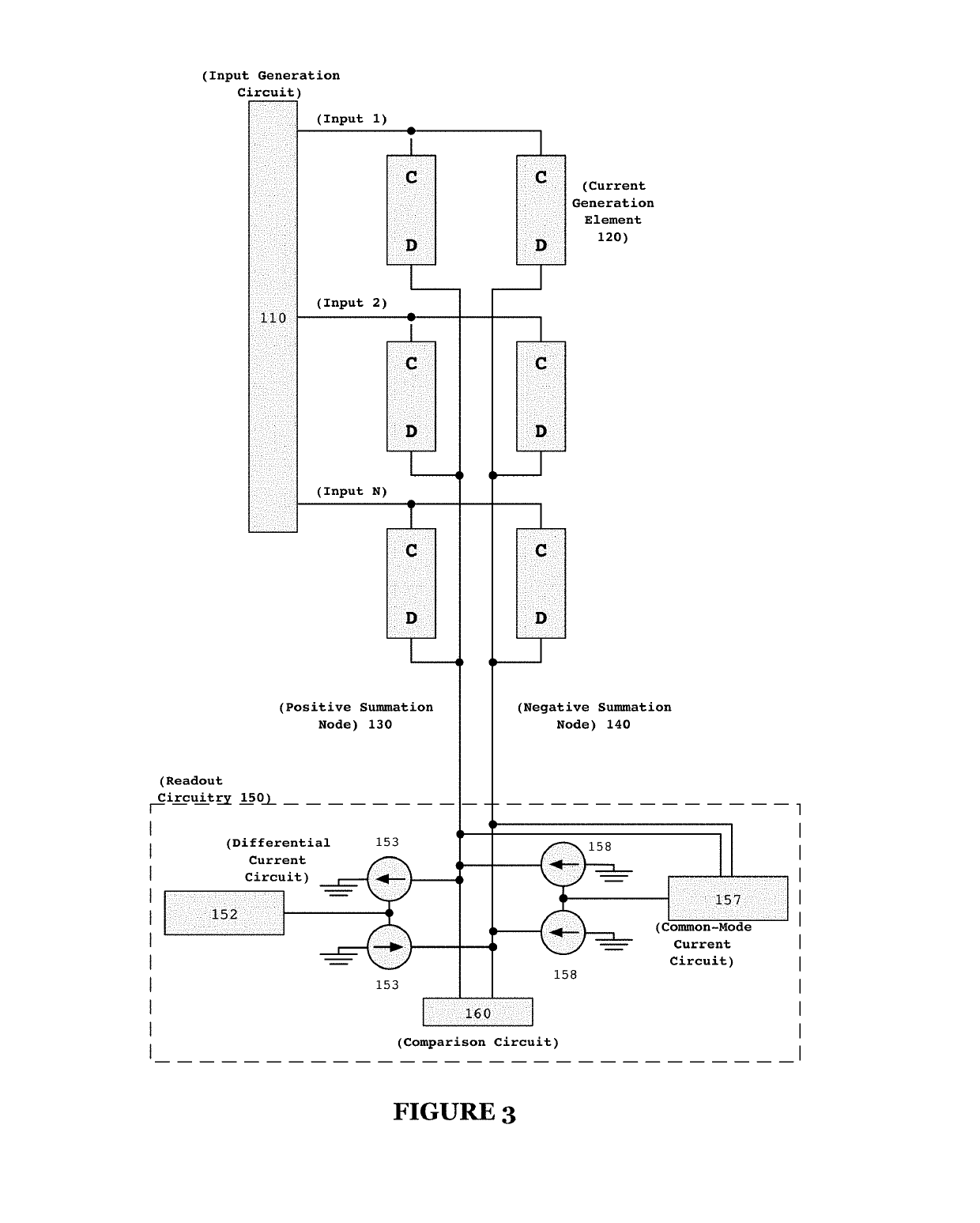

A mixed-signal integrated circuit that includes: a global reference signal source; a first summation node and a second summation node; a plurality of distinct pairs of current generating circuits arranged along the first summation node and the second summation node; a first current generating circuit of each of the plurality of distinct pairs that is arranged on the first summation node and a second current generating circuit of each of the plurality of distinct pairs is arranged on the second summation node; a common-mode current circuit that is arranged in electrical communication with each of the first and second summation nodes; where a local DAC adjusts a differential current between the first second summation nodes based on reference signals from the global reference source; and a comparator or a finite state machine that generates a binary output value current values obtained from the first and second summation nodes.

Owner:MYTHIC INC

Self auto-calibration of analog circuits in a mixed signal integrated circuit device

ActiveCN102187571ALower total production costRF amplifierAnalogue-digital convertersEngineeringVoltage reference

Auto-calibration of the analog circuits occurs when requested by a user and / or the occurrence of an event(s). The user may invoke an auto-calibration on demand through an auto-calibration (ACAL ) input to the mixed-signal integrated circuit. An external voltage calibration (VCAL ) input may be used for auto-calibration of the mixed-signal integrated circuit to a user-supplied common-mode voltage reference. Auto-calibration of the mixed- signal integrated circuit may also be initiated upon the occurrence of any one or more of the following events: 1 ) detection of auto-calibration data corruption, e.g., parity checking of auto-calibration data values digitally stored in the mixed-signal integrated circuit; 2) an internal timer that causes a calibration request after a programmable timeout period, 3) change in the internal integrated circuit die temperature as determined by a temperature sensor, and 4) a change in the power supply and / or internal supply voltage(s).

Owner:MICROCHIP TECH INC

Mixed signal integrated circuit with improved isolation

InactiveUS6909150B2Improve isolationReduce resistanceTransistorSolid-state devicesEngineeringVoltage reference

An integrated circuit having improved isolation includes a first circuit section formed in a substrate and a second circuit section formed in the substrate, the second circuit section being spaced laterally from the first circuit section. The integrated circuit further includes an isolation buried layer formed under at least a portion of the first circuit section, and a conductive layer formed on a surface of the substrate and electrically coupled to the buried layer and to a voltage reference, the conductive layer reducing an effective lateral resistance of the buried layer, whereby an isolation between the first and second circuit sections is increased. A second isolation buried layer can be formed under at least a portion of the second circuit section as well to provide further isolation between the first and second circuit sections.

Owner:BELL SEMICON LLC +1

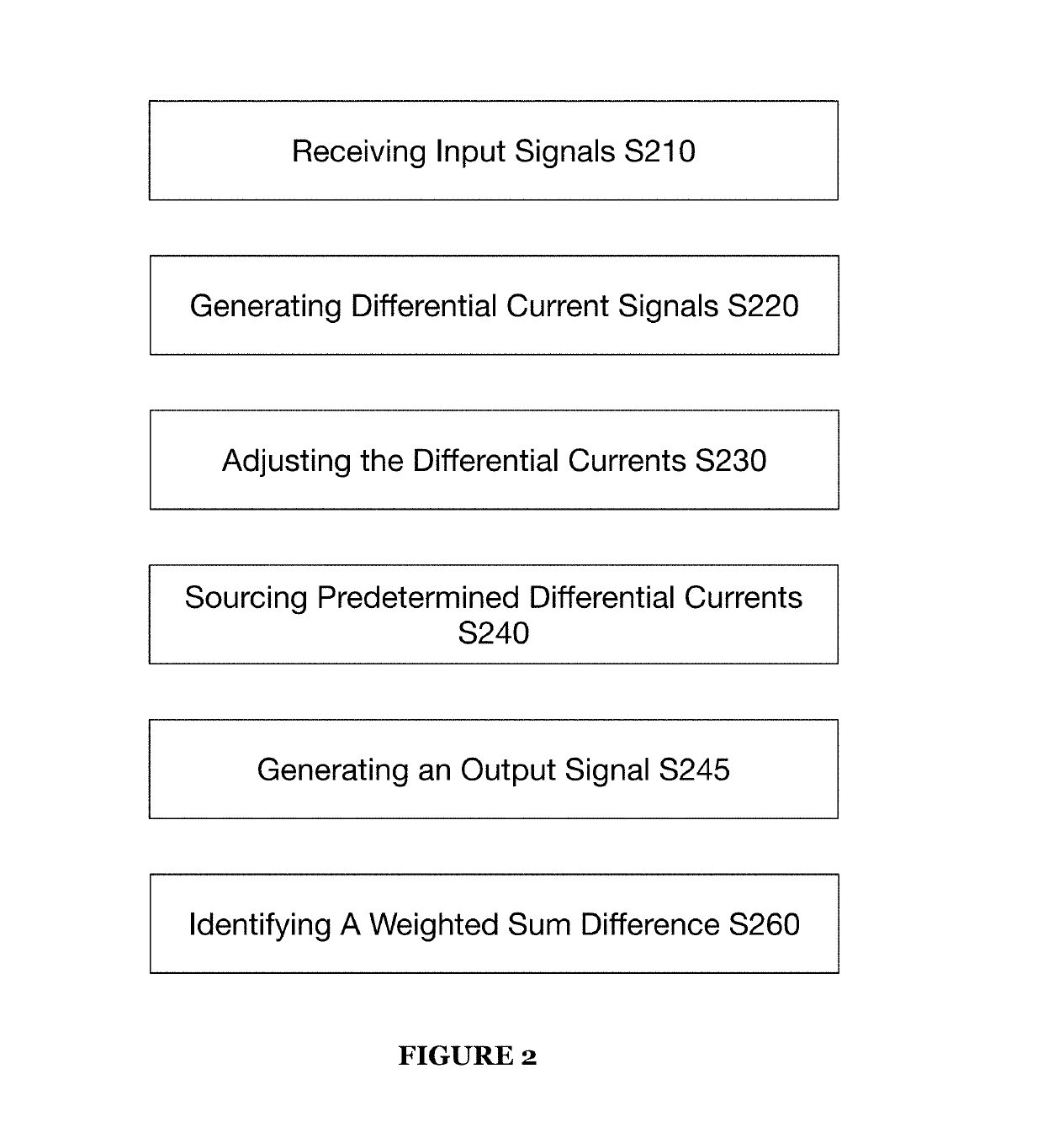

System and methods for mixed -signal computing

ActiveUS20190087356A1Program controlGenerating/distributing signalsEngineeringMixed-signal integrated circuit

Systems and methods of implementing a mixed-signal integrated circuit includes sourcing, by a reference signal source, a plurality of analog reference signals along a shared signal communication path to a plurality of local accumulators; producing an electrical charge, at each of the plurality of local accumulators, based on each of the plurality of analog reference signals; adding or subtracting, by each of the plurality of local accumulators, the electrical charge to an energy storage device of each of the plurality of local accumulators over a predetermined period; summing along the shared communication path the electrical charge from the energy storage device of each of the plurality of local accumulators at an end of the predetermined period; and generating an output based on a sum of the electrical charge from each of the plurality of local accumulators.

Owner:MYTHIC INC

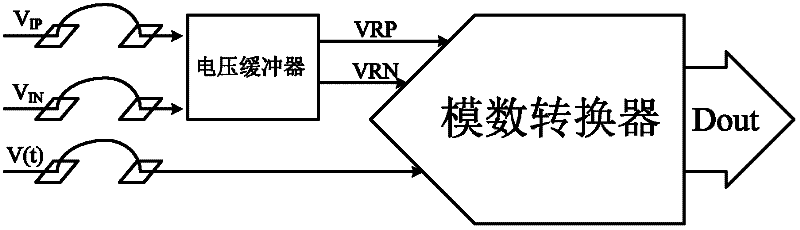

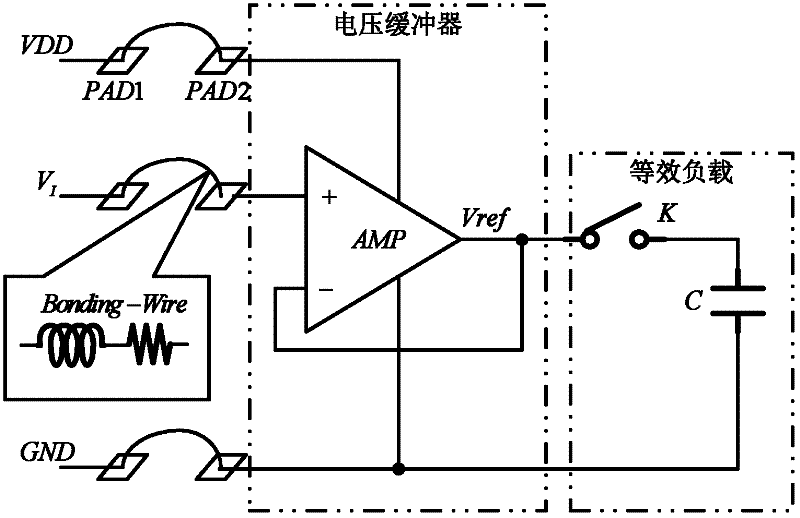

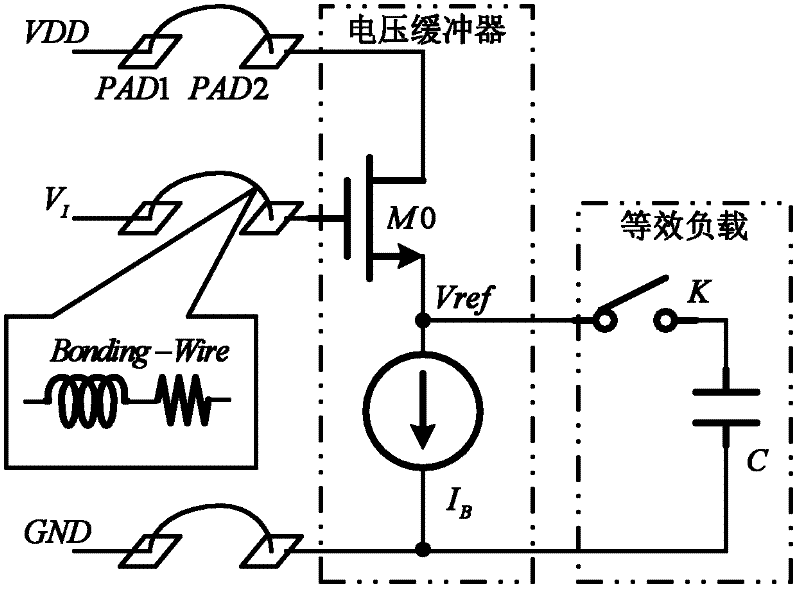

Voltage buffer applied to high-speed analogue-to-digital converter

ActiveCN102355261ASmall time constantFast chargingAnalogue-digital convertersPhysical parameters compensation/preventionA d converterVoltage reference

The invention relates to a voltage buffer applied to a high-speed analogue-to-digital converter, and belongs to the field of mixed signal integrated circuit designing. The voltage buffer comprises three P-channel metal oxide semiconductor (PMOS) transistor and three N-channel metal oxide semiconductor (NMOS) transistors. Connection relationships among the MOS transistors are that: the drain and gate of a first NMOS transistor are connected together and connected to the gate of the second PMOS transistor and the drain of the first PMOS transistor; a positive reference input voltage is connected to the gate of the first PMOS transistor after passing through a bonding wire; the source of the first PMOS transistor and the drain of the second PMOS transistor are connected together; the sources of the second and third PMOS transistors are connected together and finally connected to an external power potential after passing through the bonding wire; the drain and gate of the third PMOS transistor are connected together and connected to the gate of the third NMOS transistor and the drain of the second NMOS transistor; a negative reference input voltage is connected to the gate of the second NMOS transistor after passing through the bonding wire; the source of the second NMOS transistor and the drain of the third NMOS transistor are connected together; and the sources of the first and third NMOS transistors are connected together and finally connected to an external ground potential after passing through the bonding wire. The voltage buffer has the characteristics of higher charging speed and reference voltage capable of reaching rated accuracy faster.

Owner:TSINGHUA UNIV

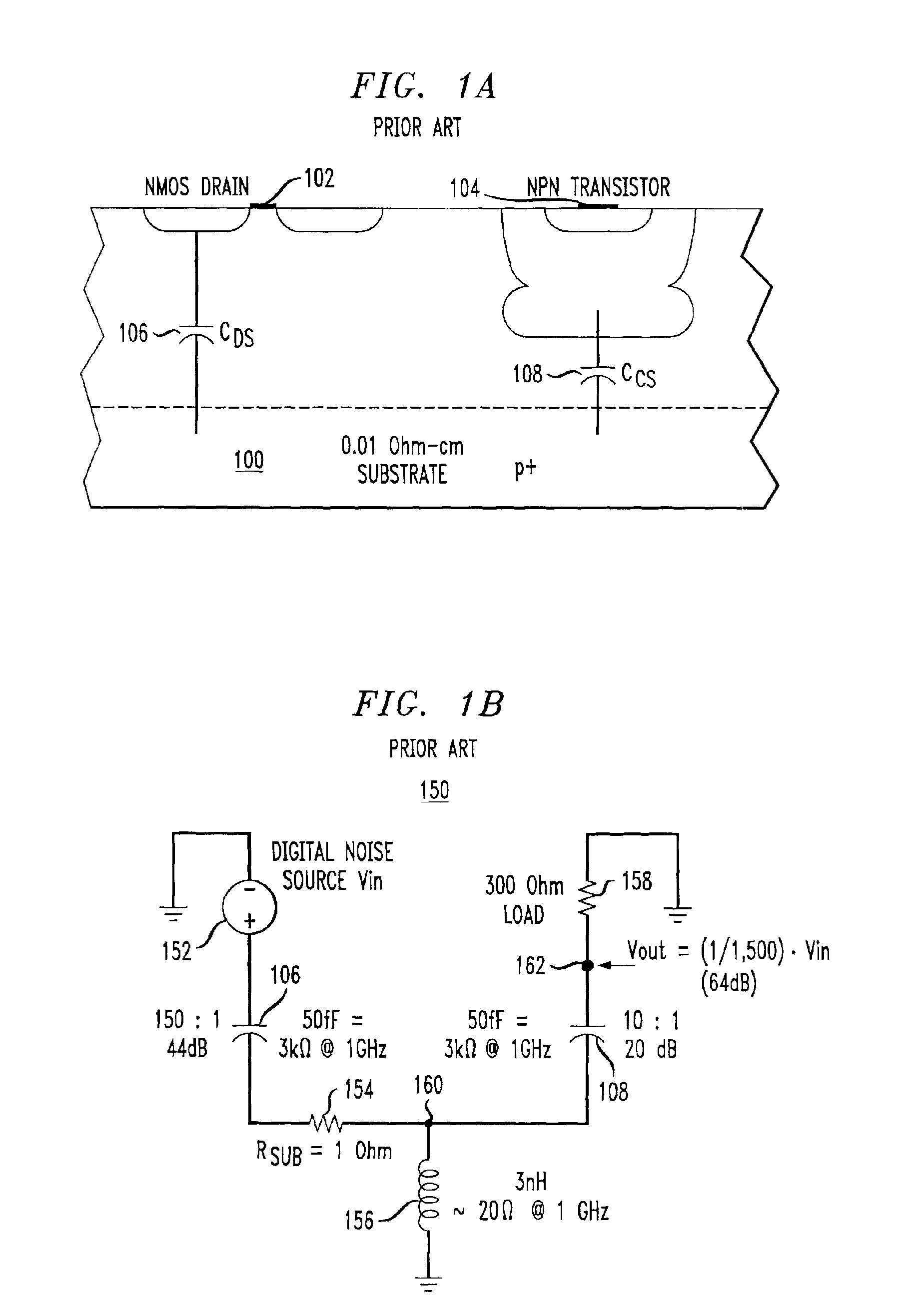

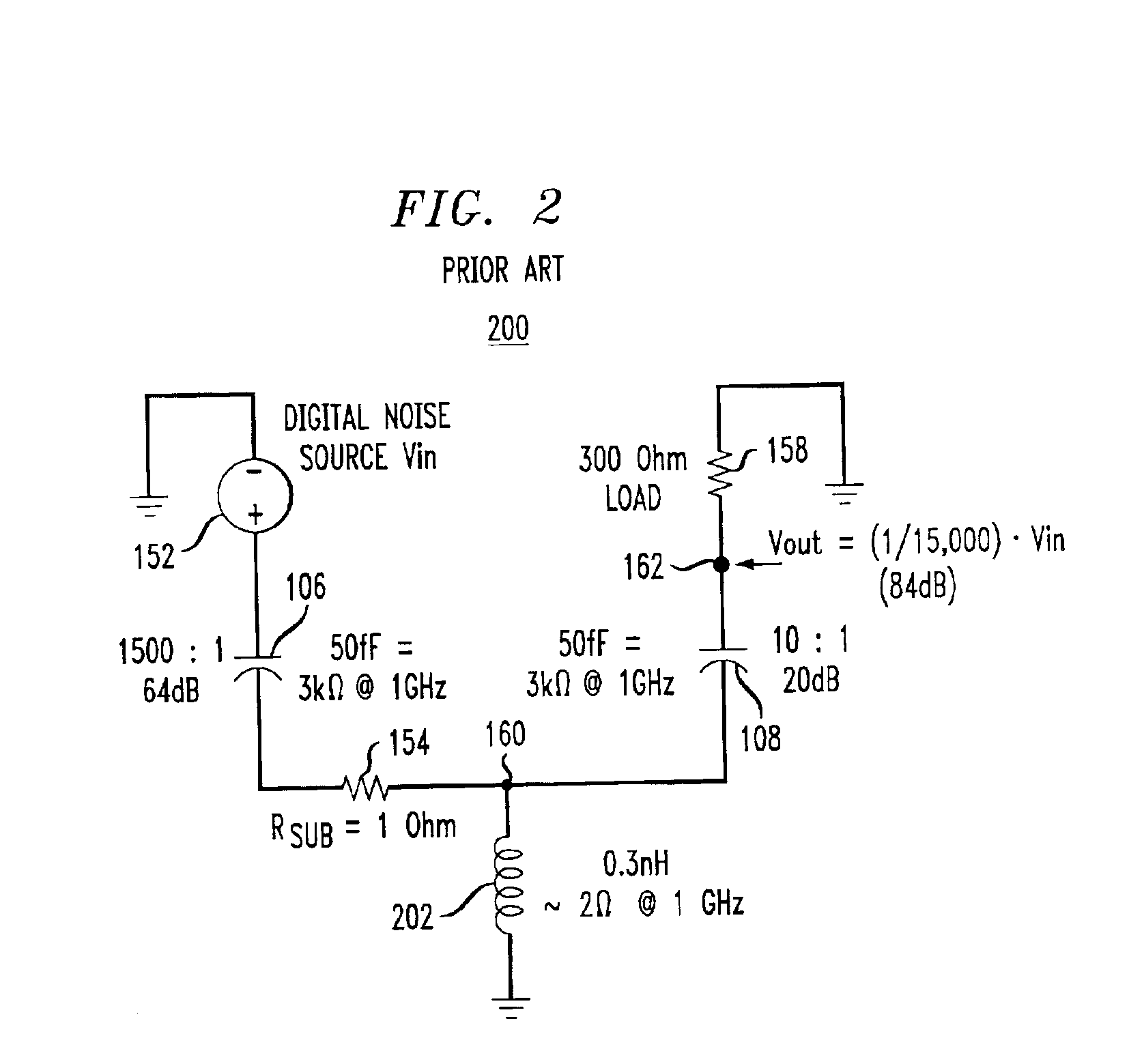

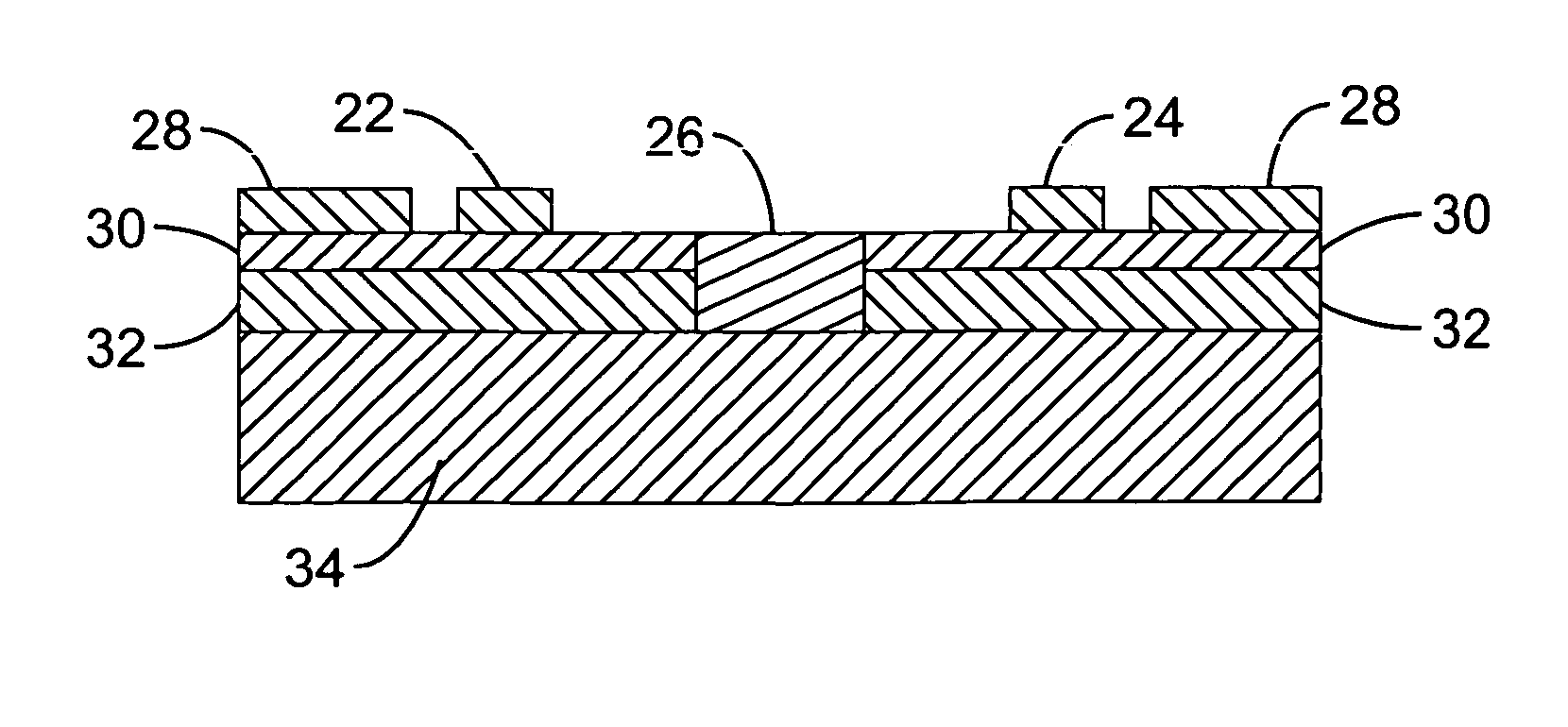

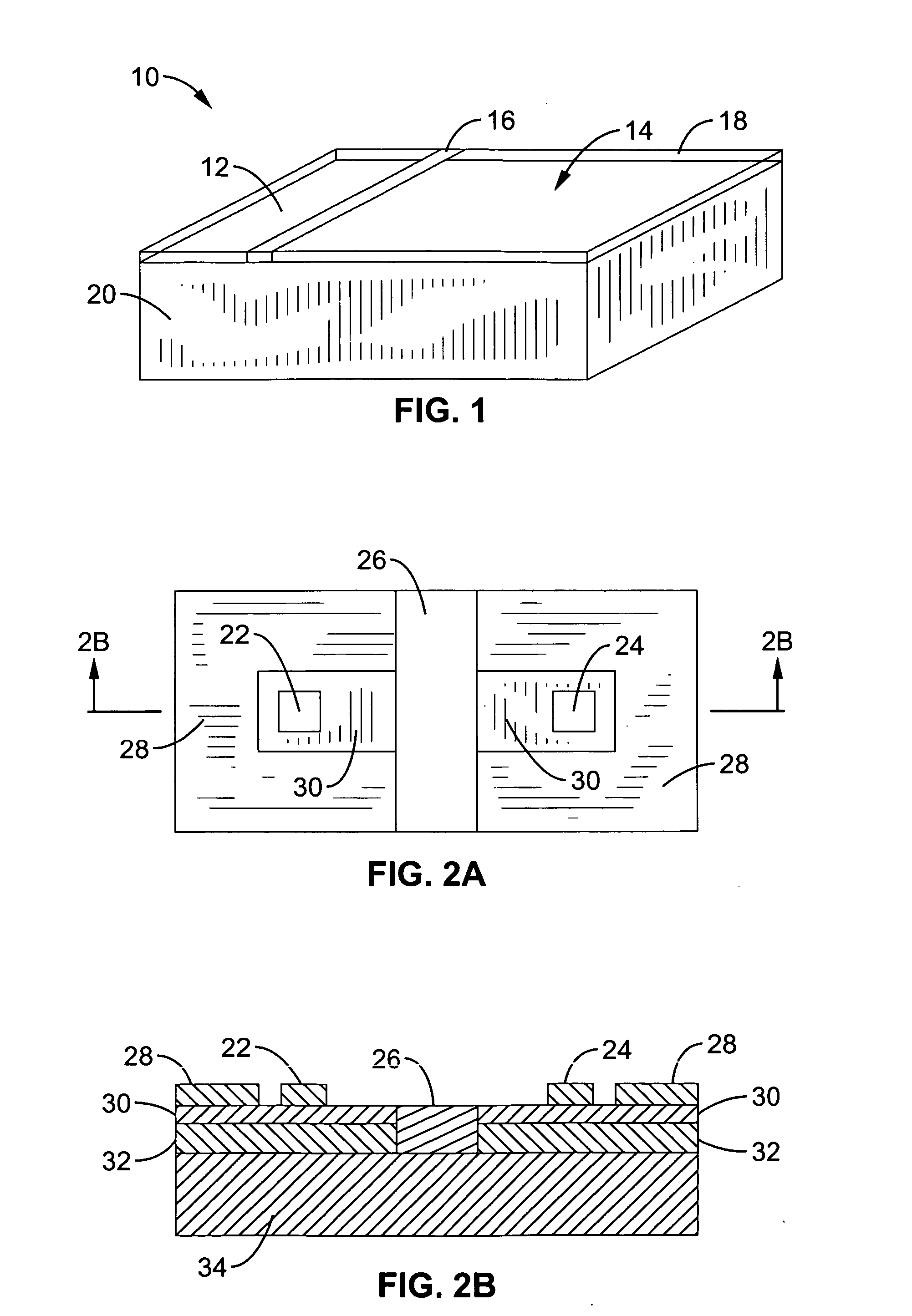

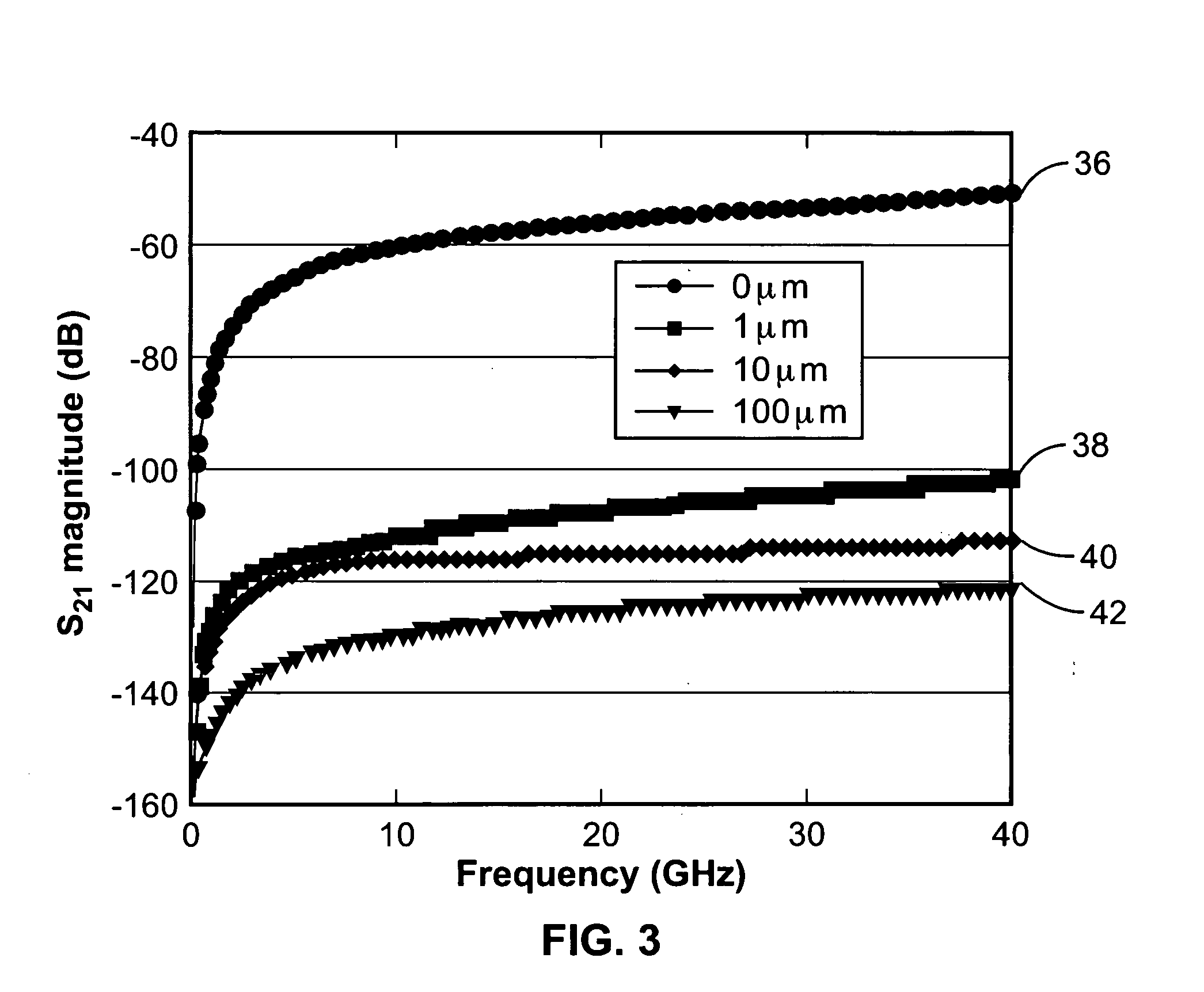

Low crosstalk substrate for mixed-signal integrated circuits

ActiveUS20060255425A1Improved crosstalk isolationImprove heat sinkSemiconductor/solid-state device detailsSolid-state devicesInsulation layerEngineering

An integrated circuit laminate with a metal substrate for use with high performance mixed signal integrated circuit applications. The metal substrate provides substantially improved crosstalk isolation, enhanced heat sinking and an easy access to a true low impedance ground. In one embodiment, the metal layer has regions with insulation filled channels or voids and a layer of insulator such as unoxidized porous silicon disposed between the metal substrate and a silicon integrated circuit layer. The laminate also has a plurality of metal walls or trenches mounted to the metal substrate and transacting the silicon and insulation layers thereby isolating noise sensitive elements from noise producing elements on the chip. In another embodiment, the laminate is mounted to a flexible base to limit the flexion of the chip.

Owner:RGT UNIV OF CALIFORNIA