Patents

Literature

1075 results about "Digital processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

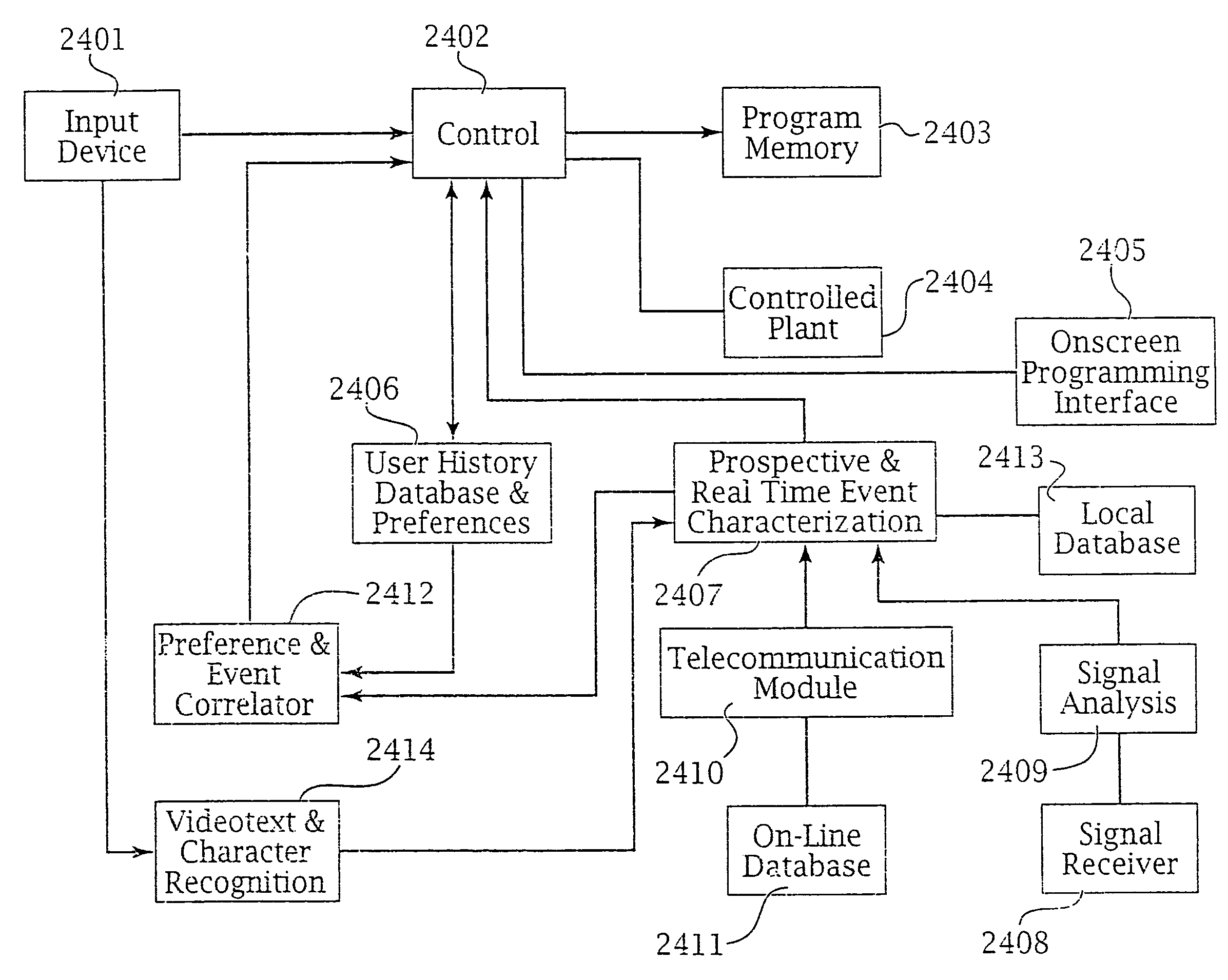

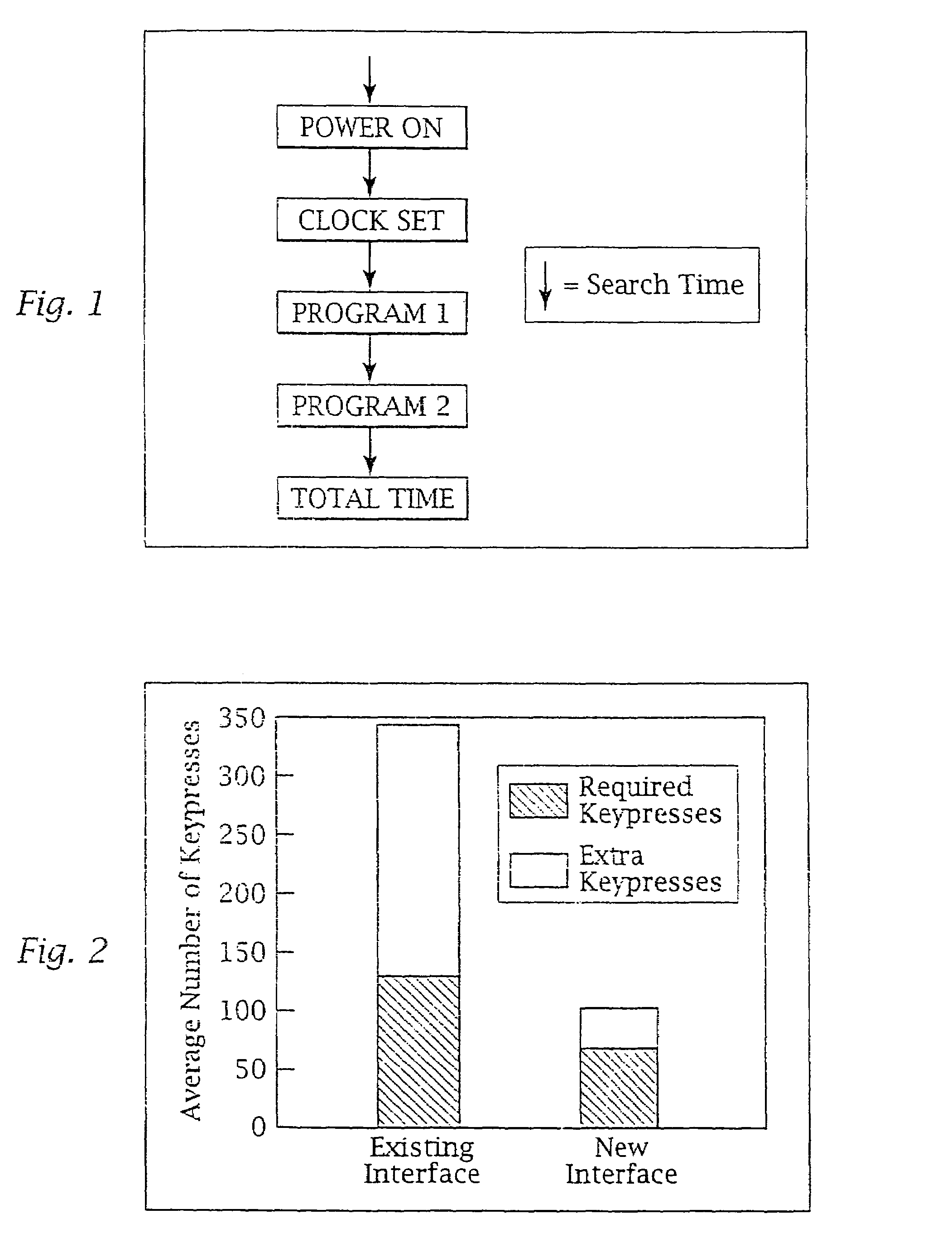

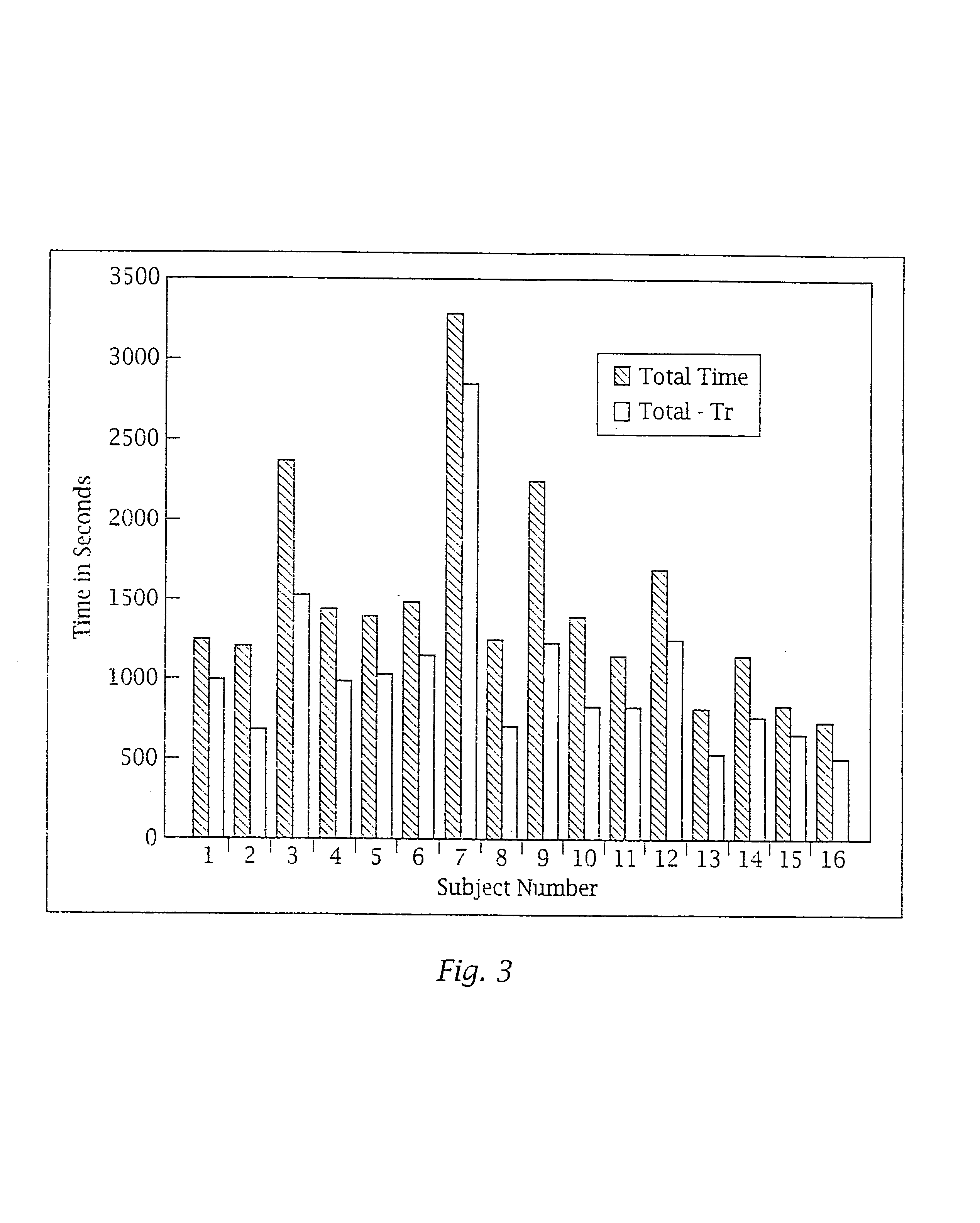

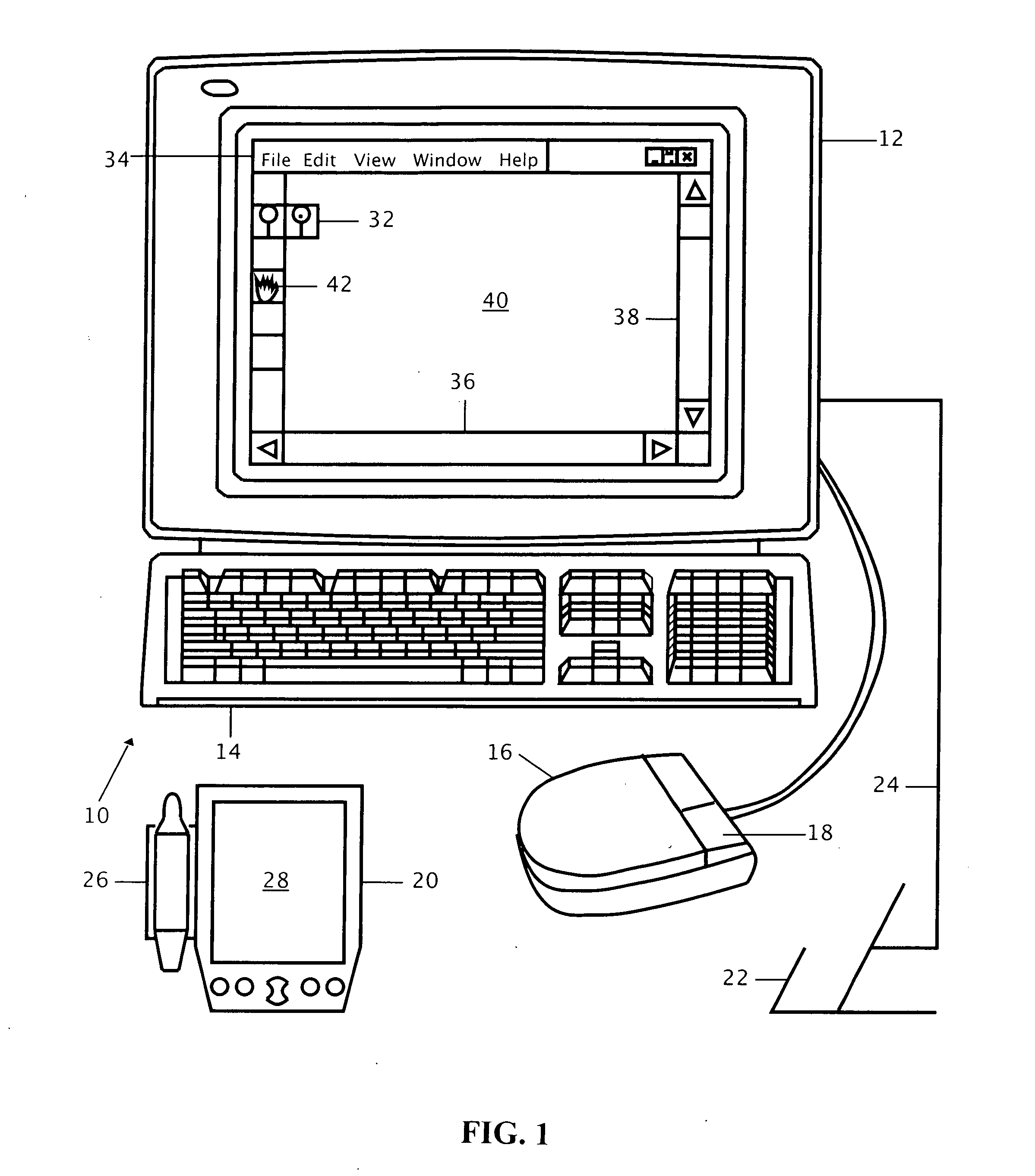

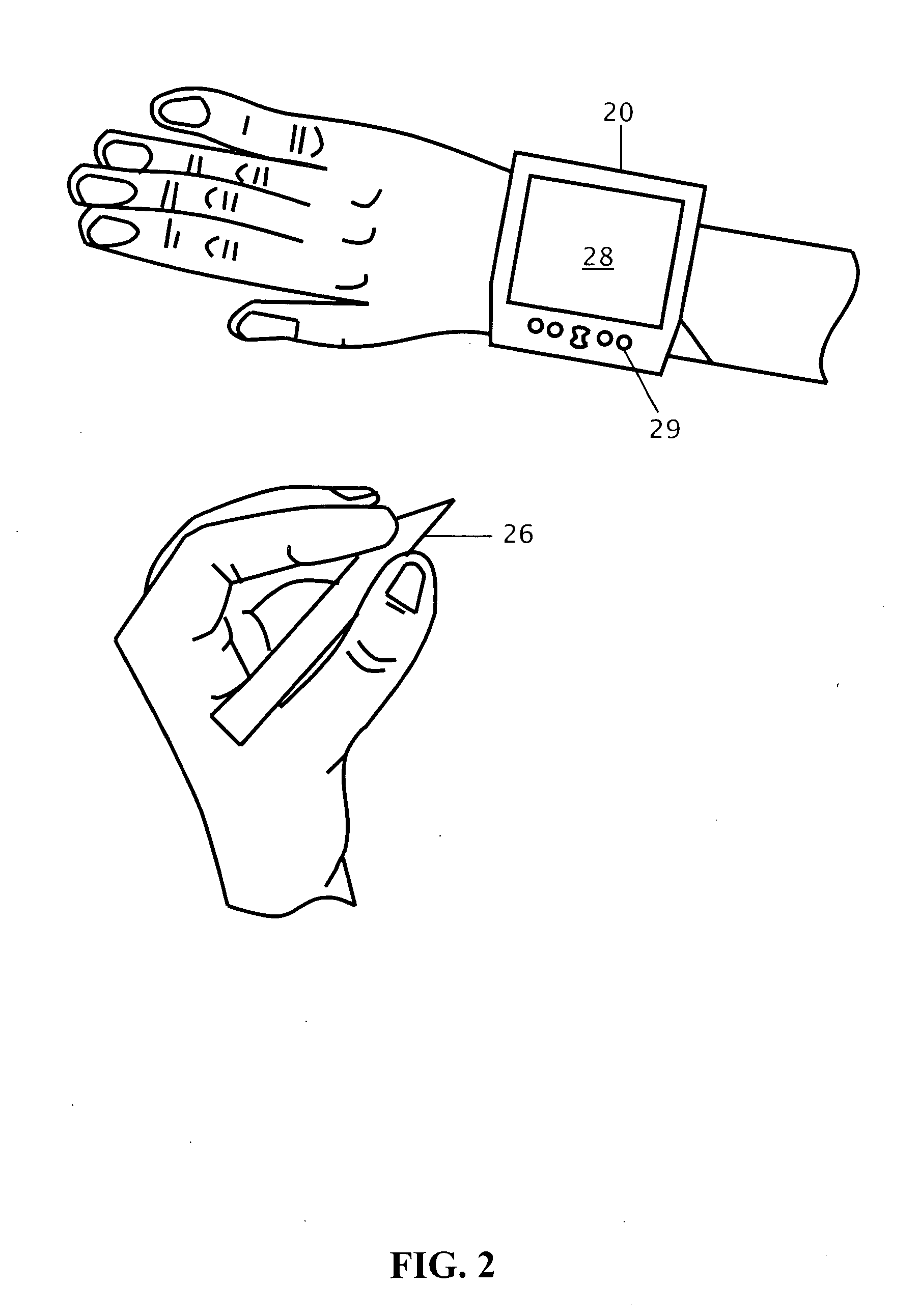

Media recording device with remote graphic user interface

InactiveUS7006881B1Minimize timeTelevision system detailsAnalogue secracy/subscription systemsGraphicsGraphical user interface

An apparatus for processing digital media signals, comprising a digital processor for controlling the apparatus; a graphic user interface, having a wireless remote control providing a command input to the processor; a network interface for transmitting digital information from the processor to a remote location over a communications network, the information identifying a digital media signal for desired reproduction based, at least in part, on an input received from the remote control; and an output, controlled by, and local to, the processor, for transferring the desired digital media signals for reproduction thereof.

Owner:BLANDING HOVENWEEP

Ladar sensor for a dense environment

ActiveUS20160003946A1Optical rangefindersElectromagnetic wave reradiationDiscriminatorFloating point

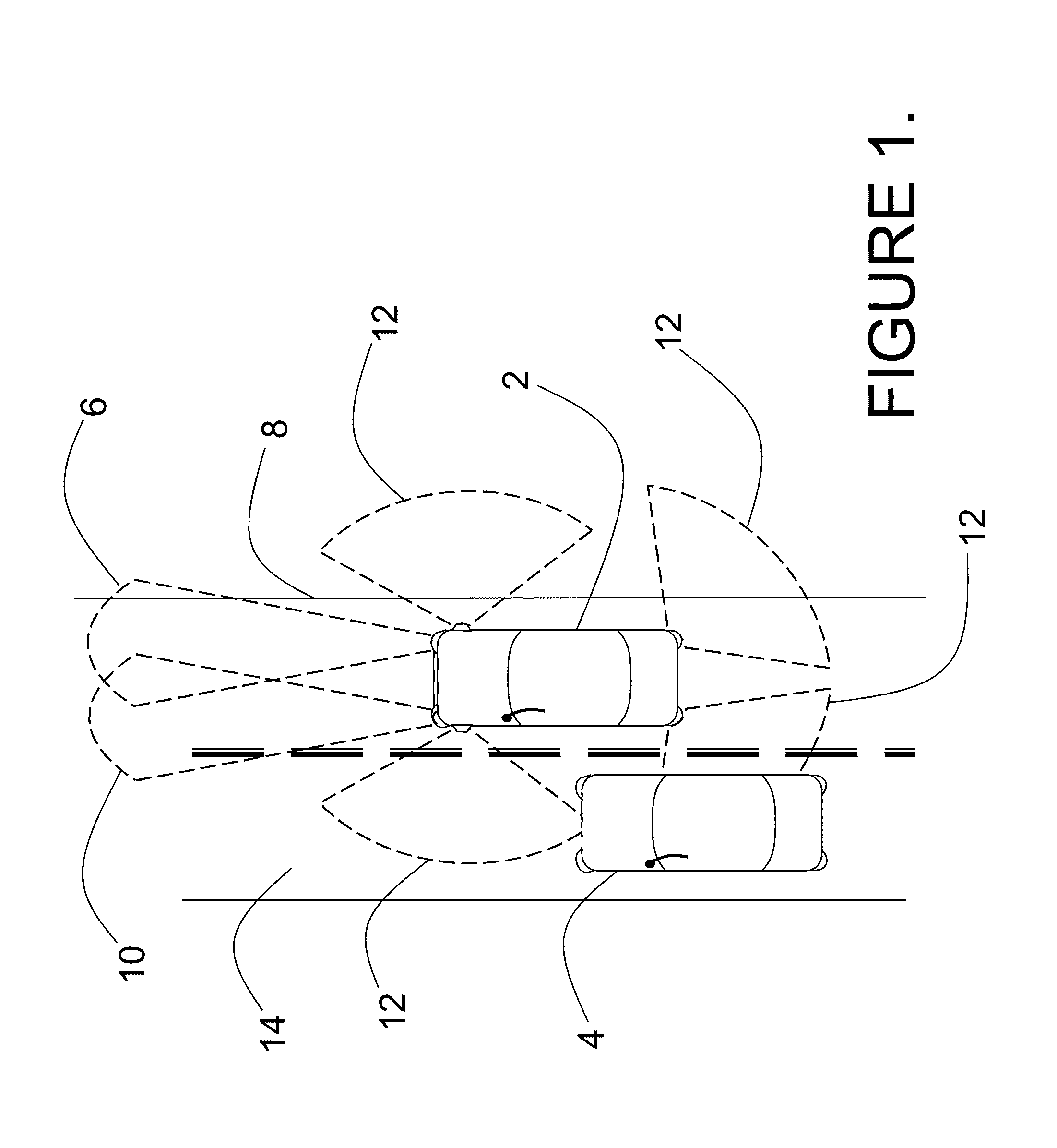

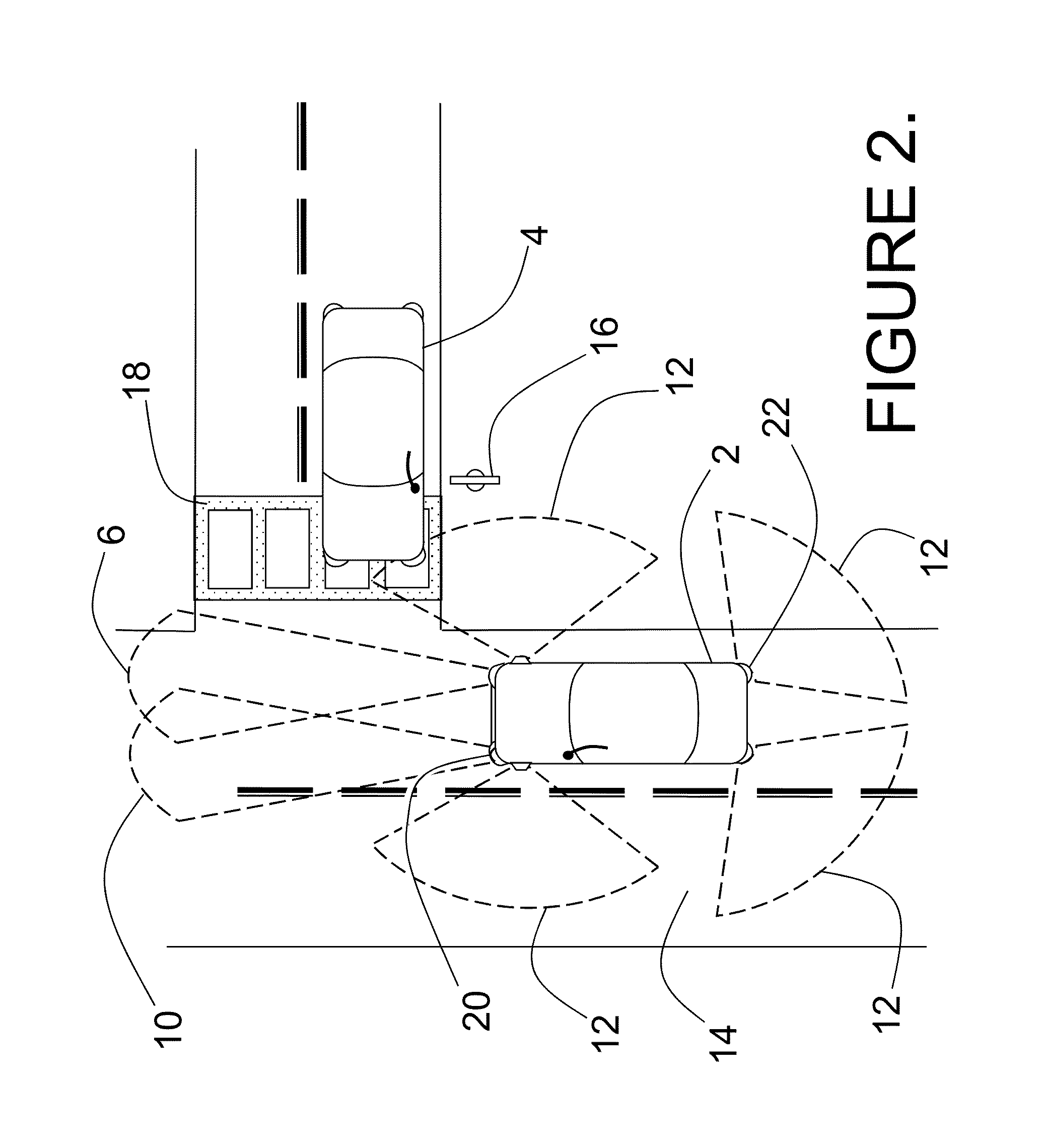

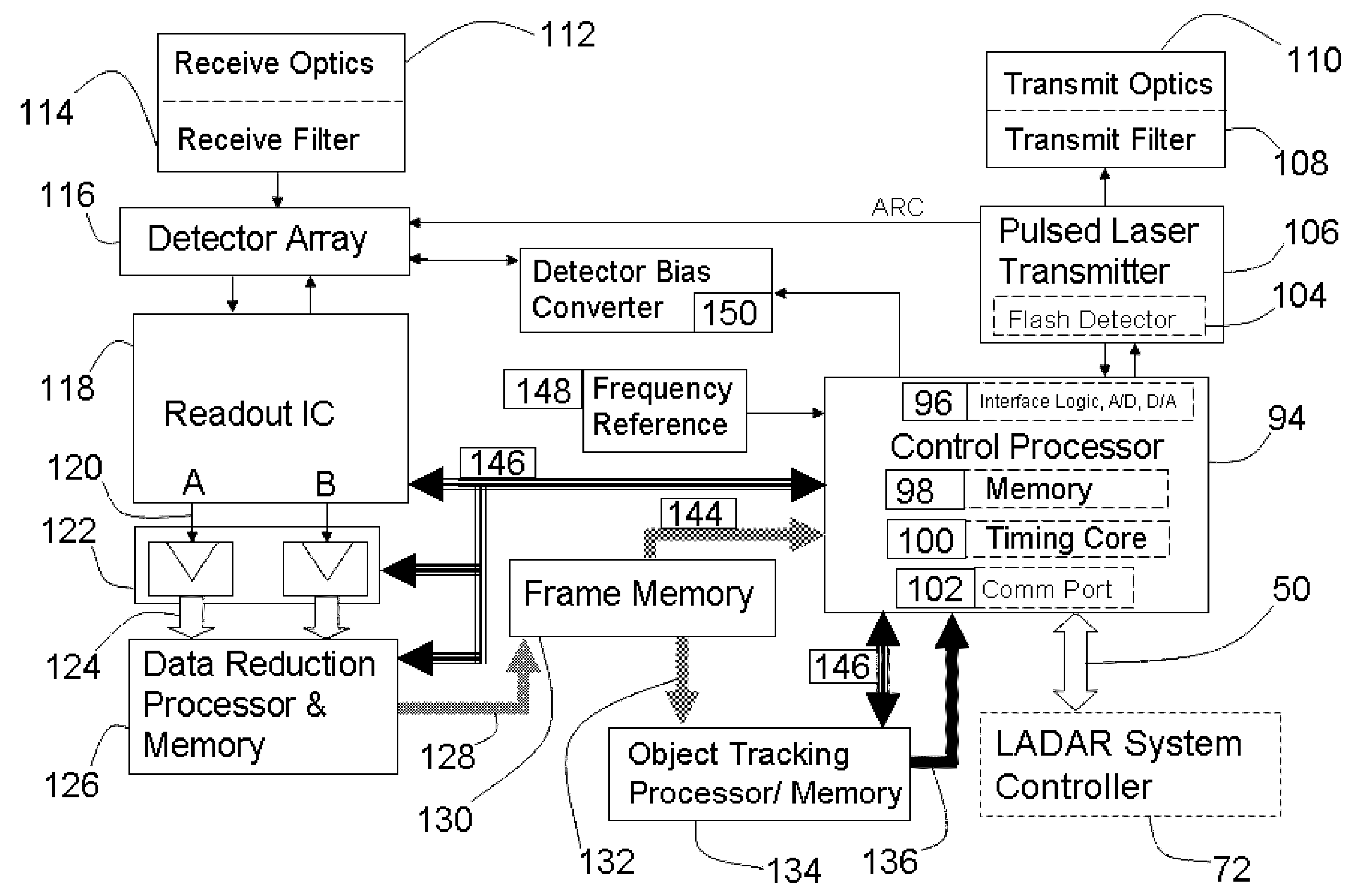

A multi-ladar sensor system is proposed for operating in dense environments where many ladar sensors are transmitting and receiving burst mode light in the same space, as may be typical of an automotive application. The system makes use of several techniques to reduce mutual interference between independently operating ladar sensors. In one embodiment, the individual ladar sensors are each assigned a wavelength of operation, and an optical receive filter for blocking the light transmitted at other wavelengths, an example of wavelength division multiplexing (WDM). Each ladar sensor, or platform, may also be assigned a pulse width selected from a list, and may use a pulse width discriminator circuit to separate pulses of interest from the clutter of other transmitters. Higher level coding, involving pulse sequences and code sequence correlation, may be implemented in a system of code division multiplexing, CDM. A digital processor optimized to execute mathematical operations is described which has a hardware implemented floating point divider, allowing for real time processing of received ladar pulses, and sequences of pulses.

Owner:CONTINENTAL AUTONOMOUS MOBILITY US LLC

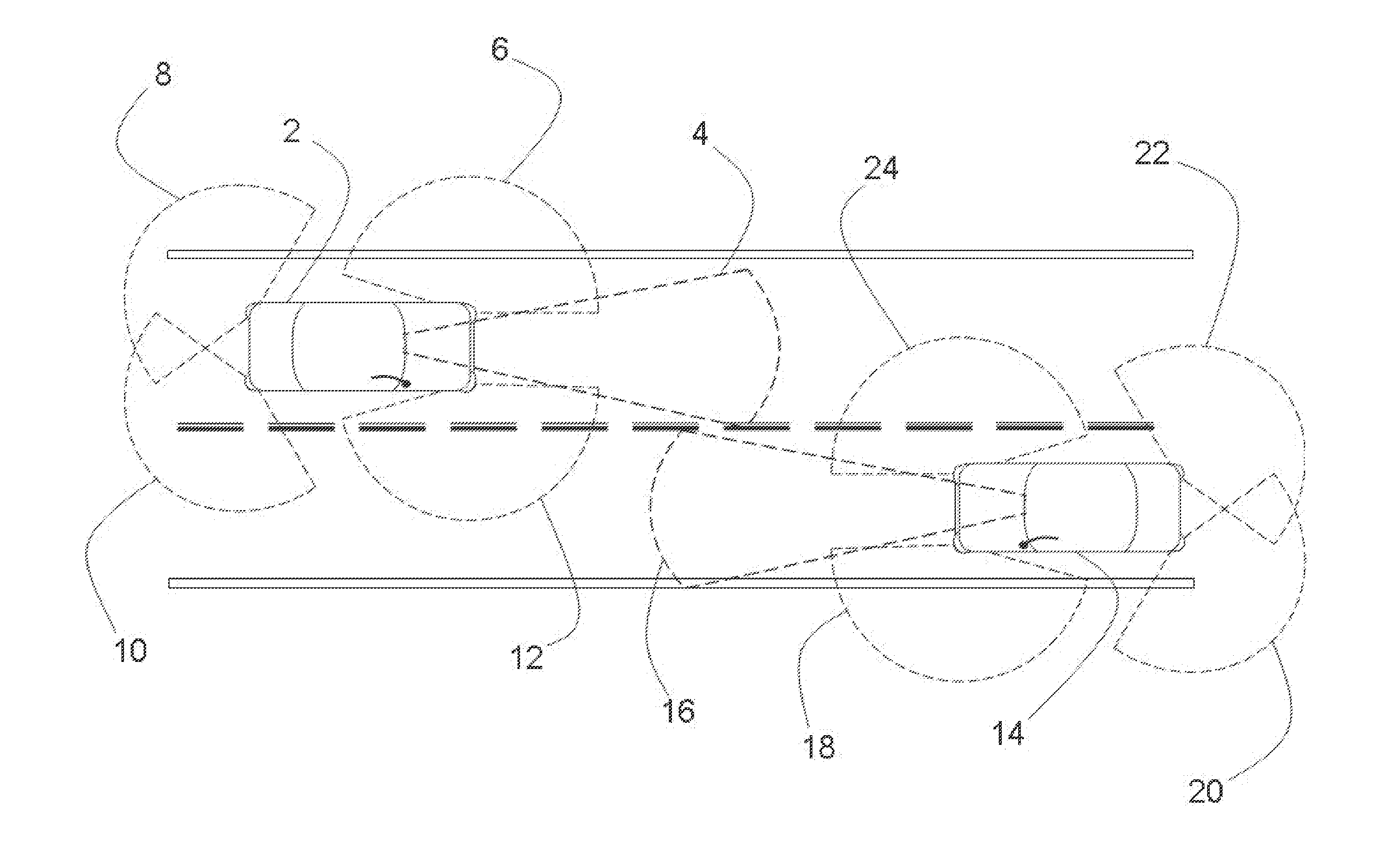

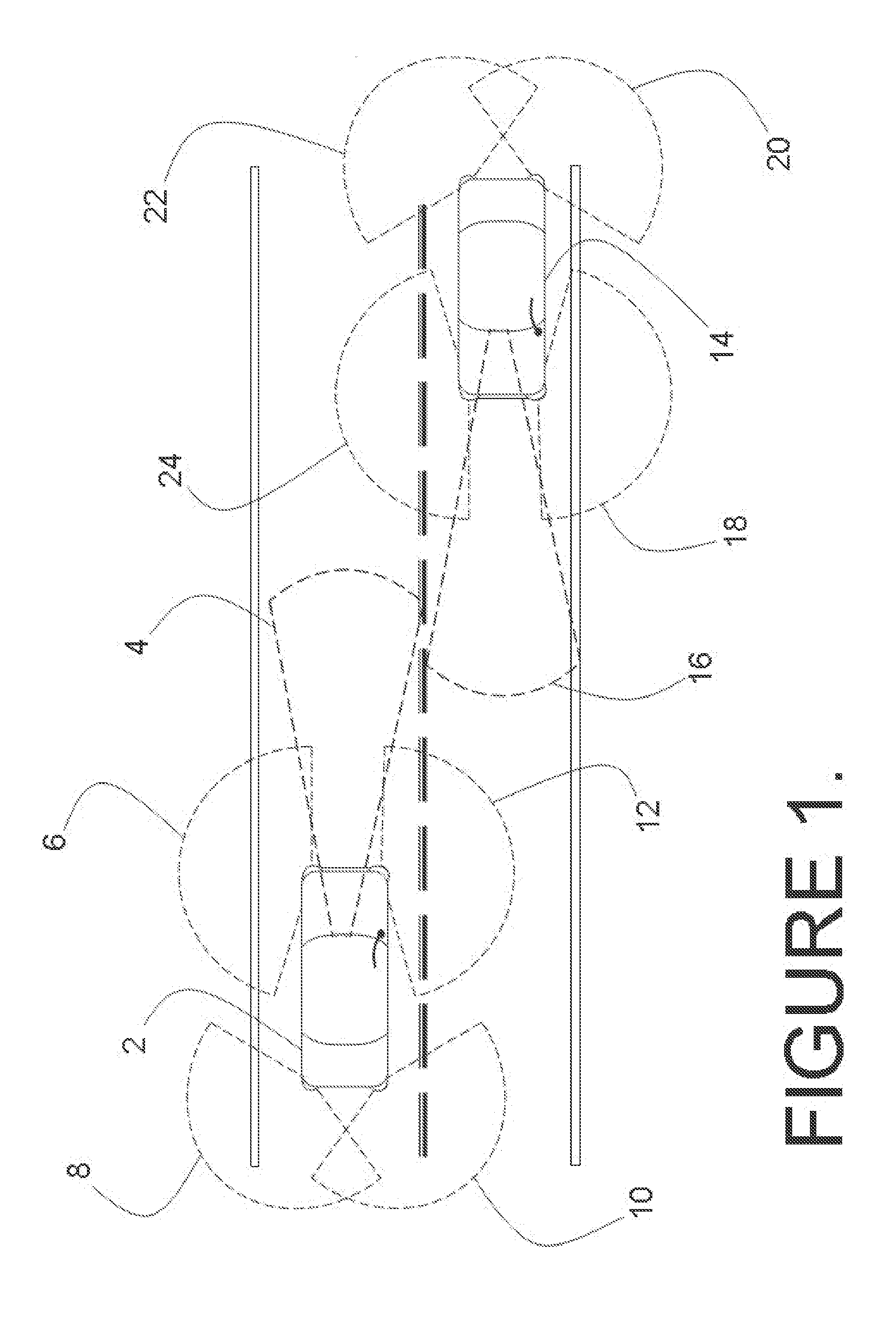

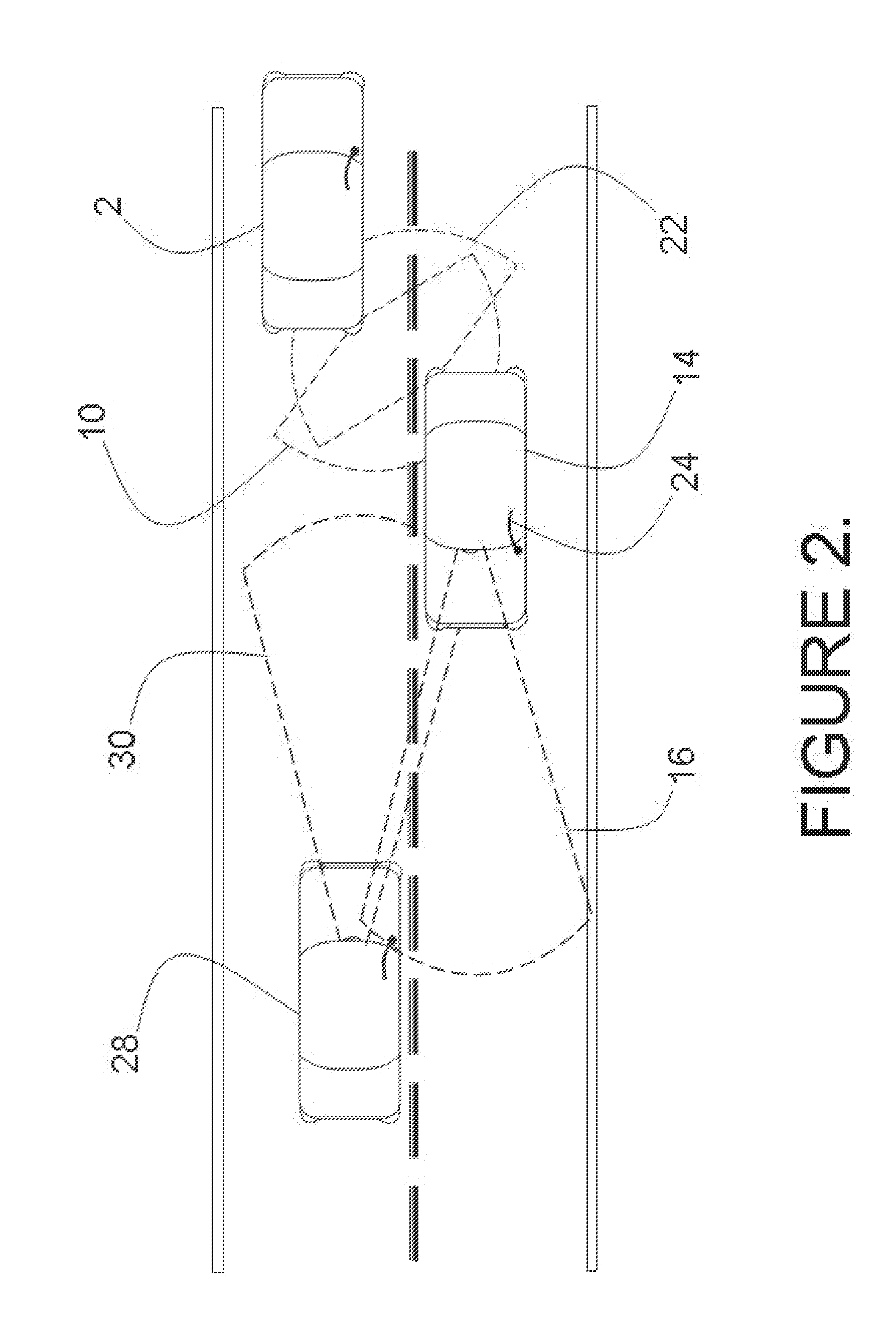

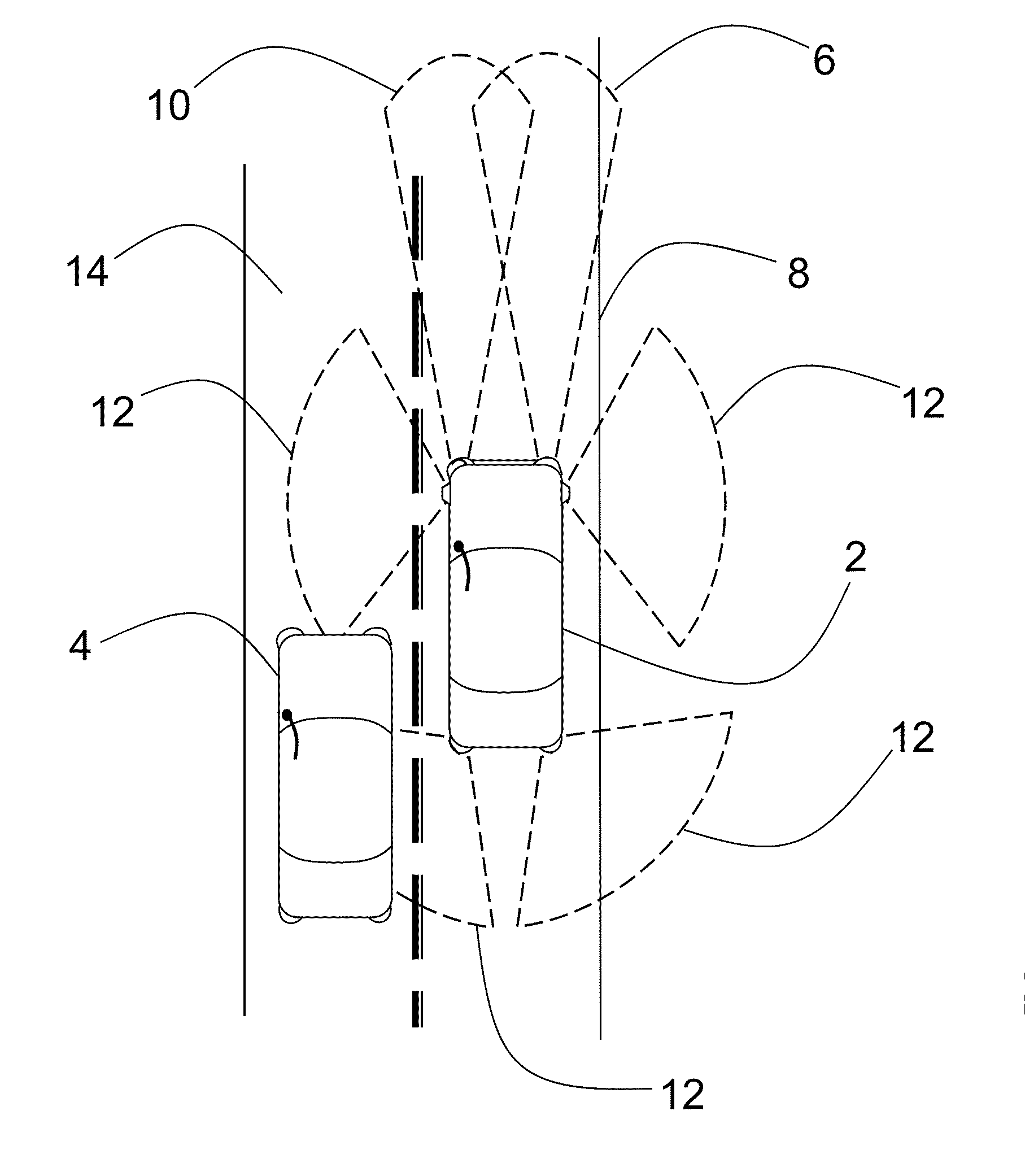

Automotive auxiliary ladar sensor

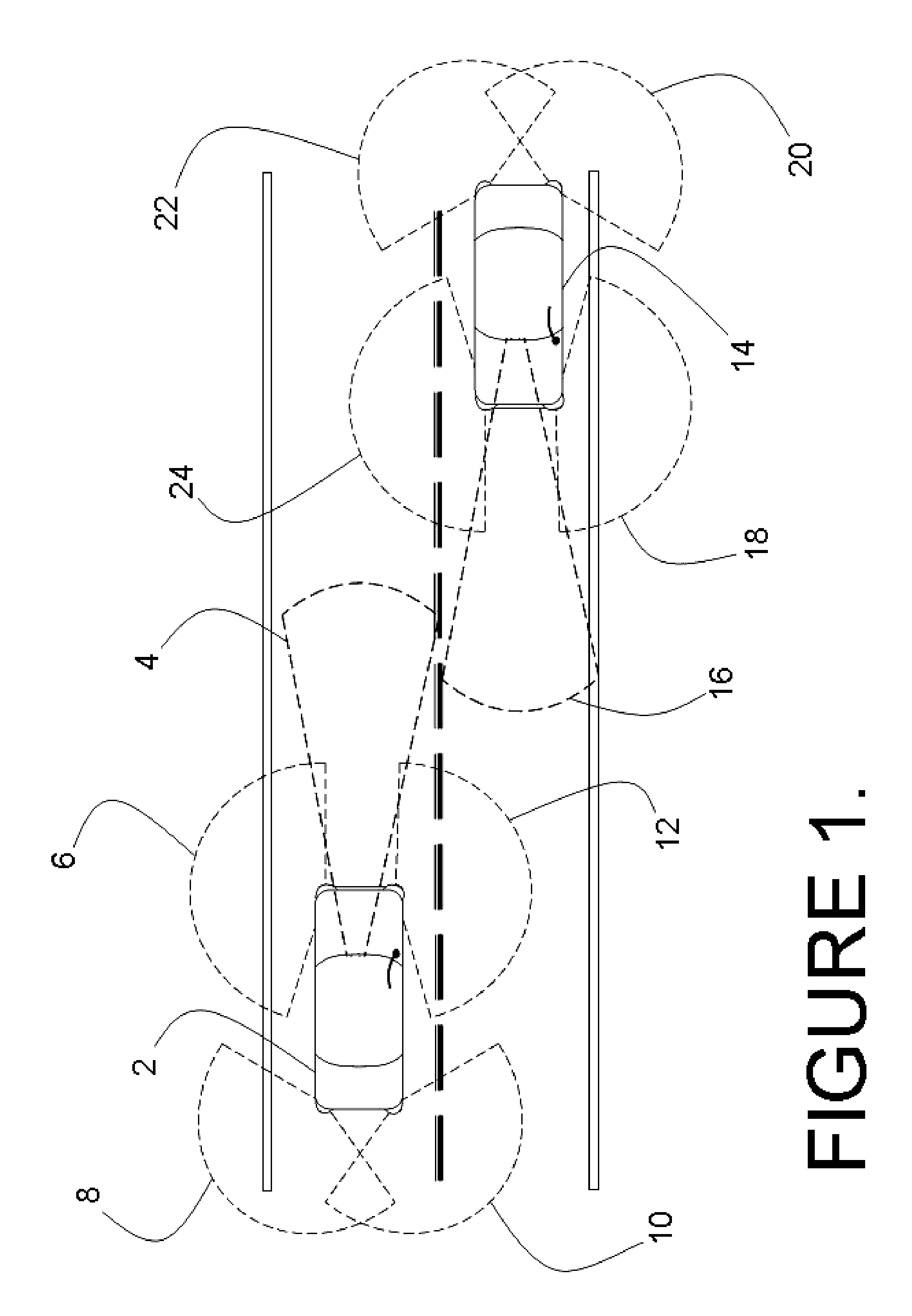

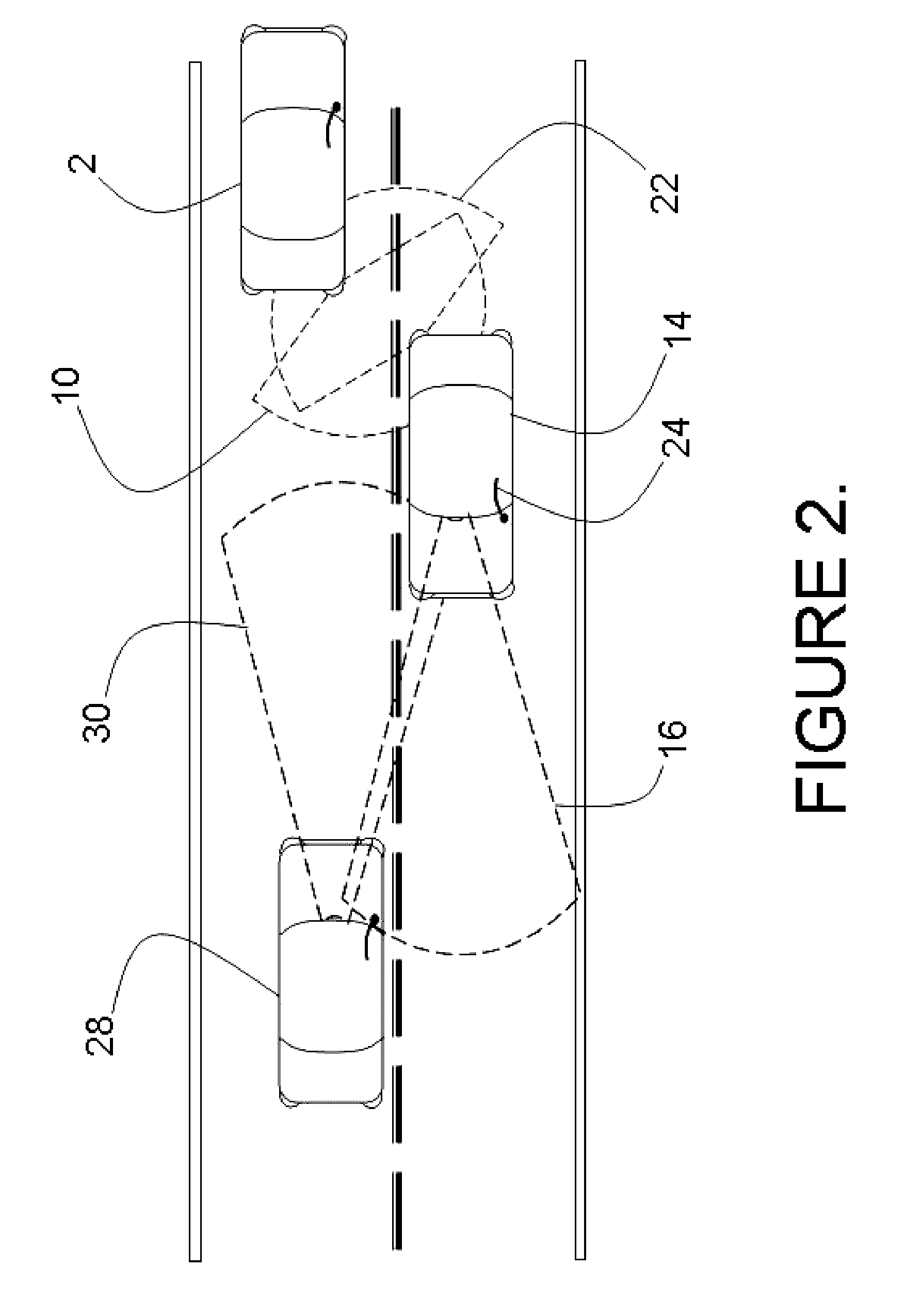

A vehicle and ladar sensor assembly system is proposed which makes use of forward mounted long range ladar sensors and short range ladar sensors mounted in auxiliary lamps to identify obstacles and to identify potential collisions with the vehicle. A low cost assembly is developed which can be easily mounted within a body panel cutout of a vehicle, and which connects to the vehicle electrical and computer systems through the vehicle wiring harness. The vehicle has a digital processor which interprets 3D data received from the ladar sensor assembly, and which is in control of the vehicle subsystems for steering, braking, acceleration, and suspension. The digital processor onboard the vehicle makes use of the 3D data and the vehicle control subsystems to avoid collisions and steer a best path.

Owner:CONTINENTAL AUTONOMOUS MOBILITY US LLC

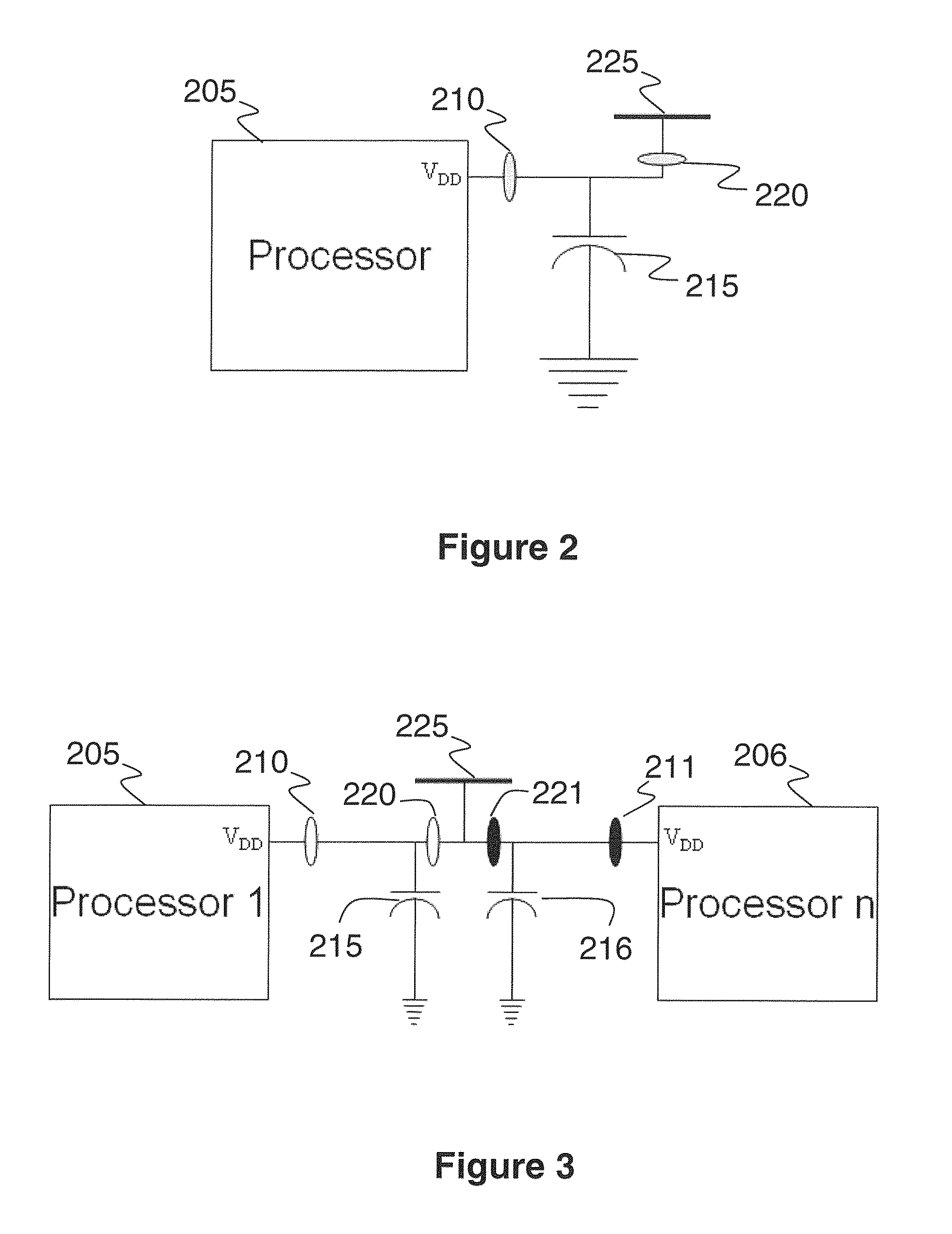

Heart monitors and processes with accelerometer motion artifact cancellation, and other electronic systems

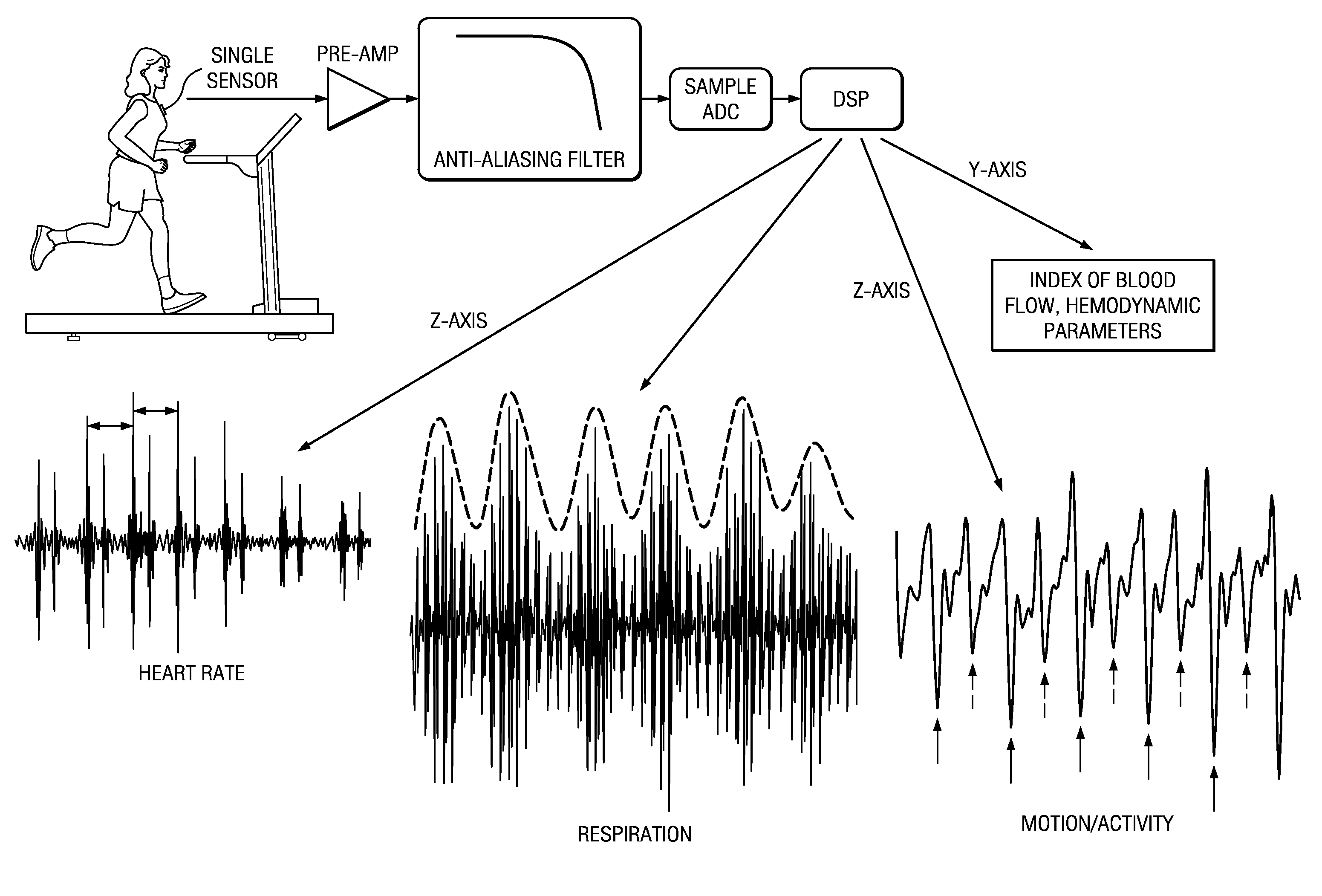

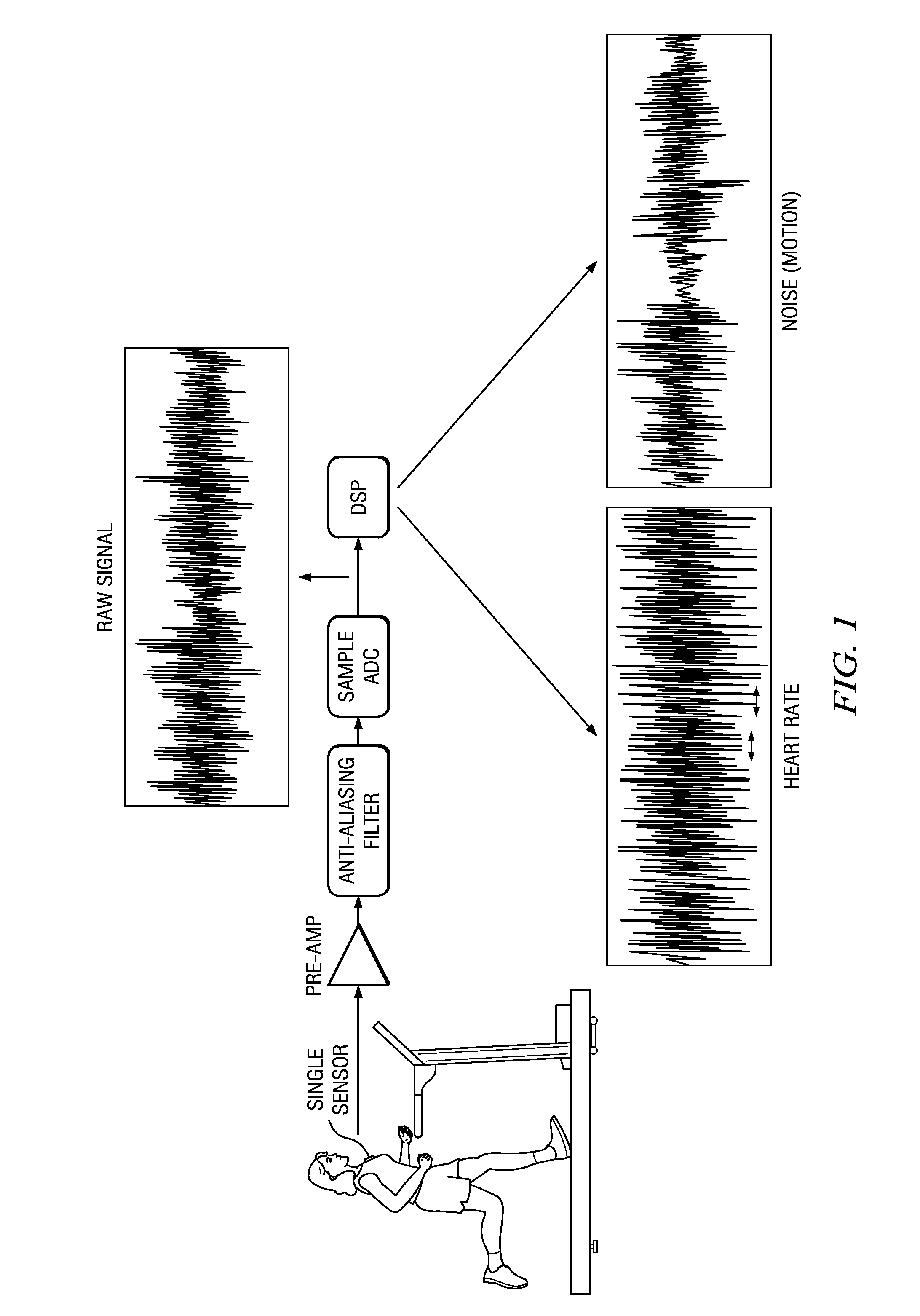

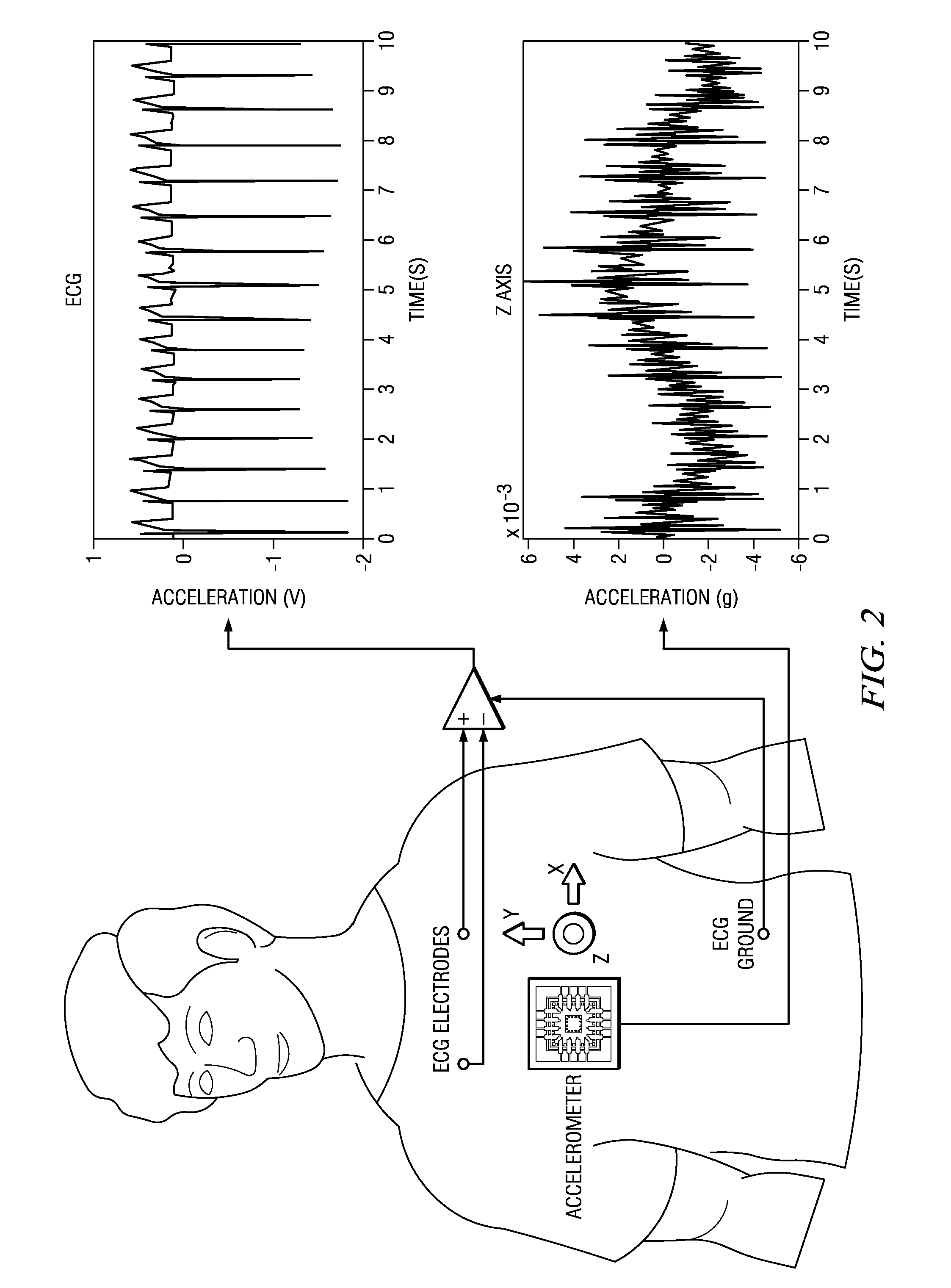

A heart monitor includes a single chest accelerometer (210), an analog signal conditioning and sampling section (215) responsive to said accelerometer to produce a digital signal substantially representing acceleration, and a digital processor (220) operable to filter the acceleration signal into a signal affected by body motion and to cancel the body motion signal from the acceleration signal, thereby to produce an acceleration-based cardiac-related signal. Other processes and electronic systems are also disclosed.

Owner:TEXAS INSTR INC

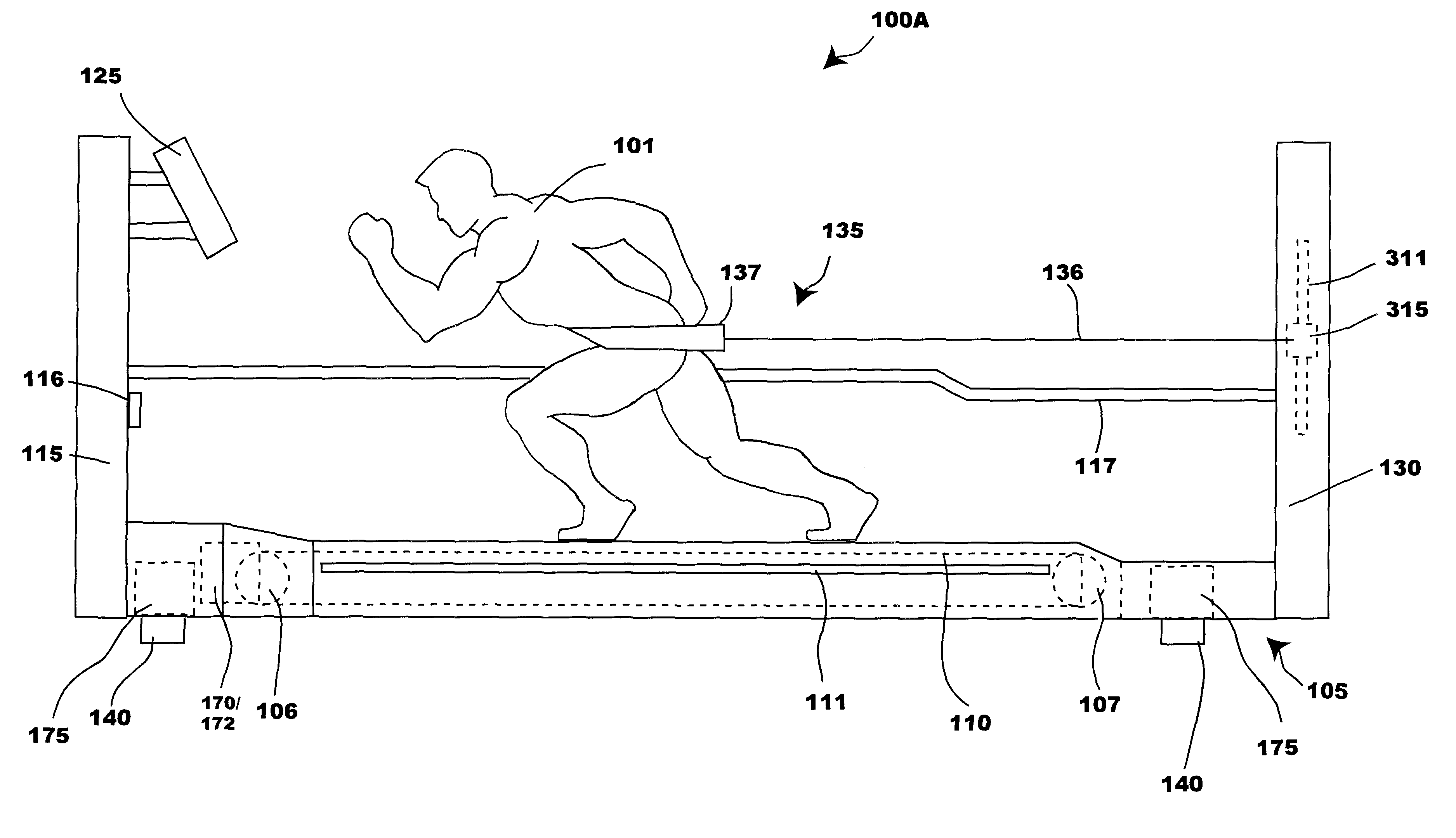

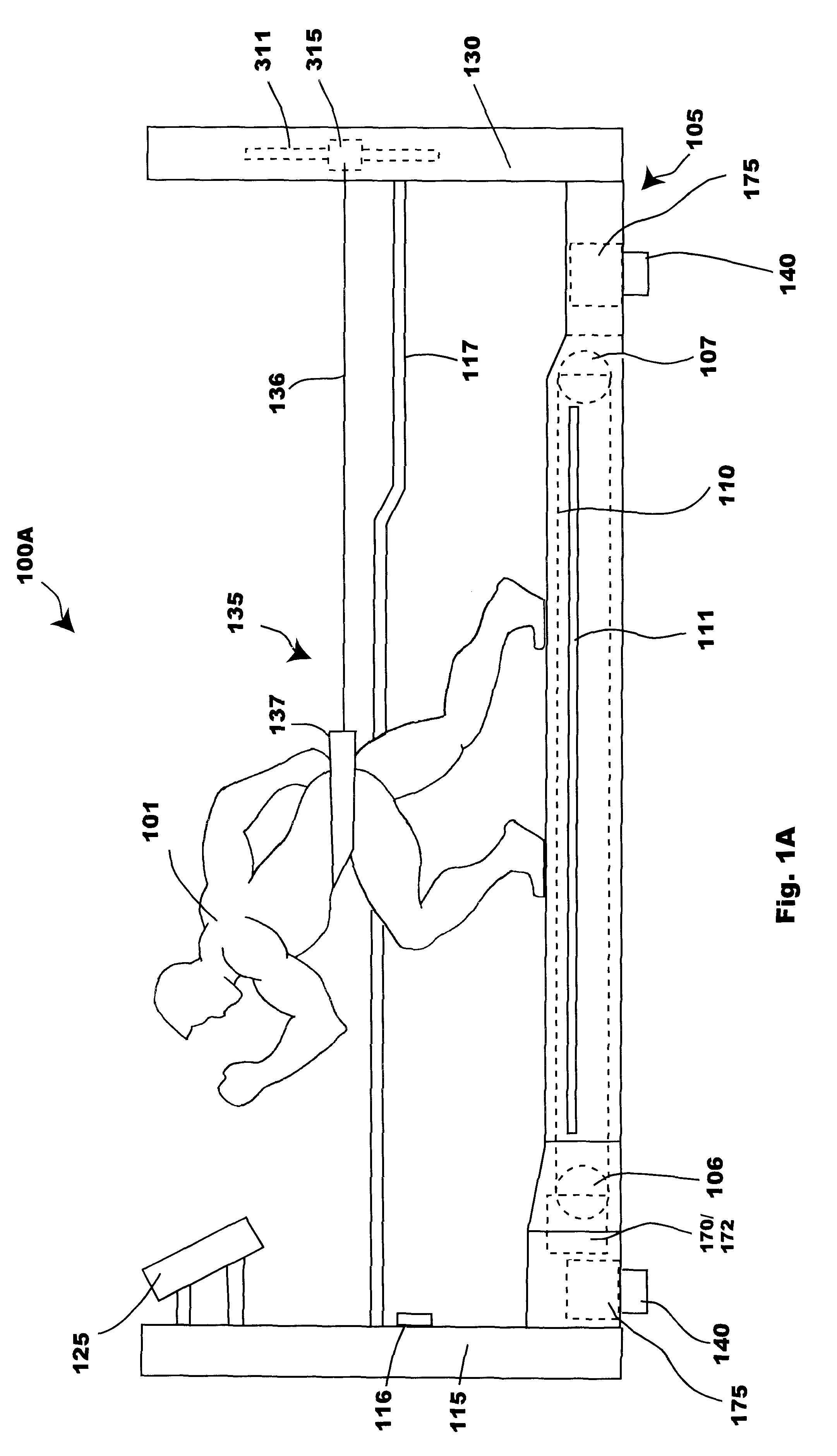

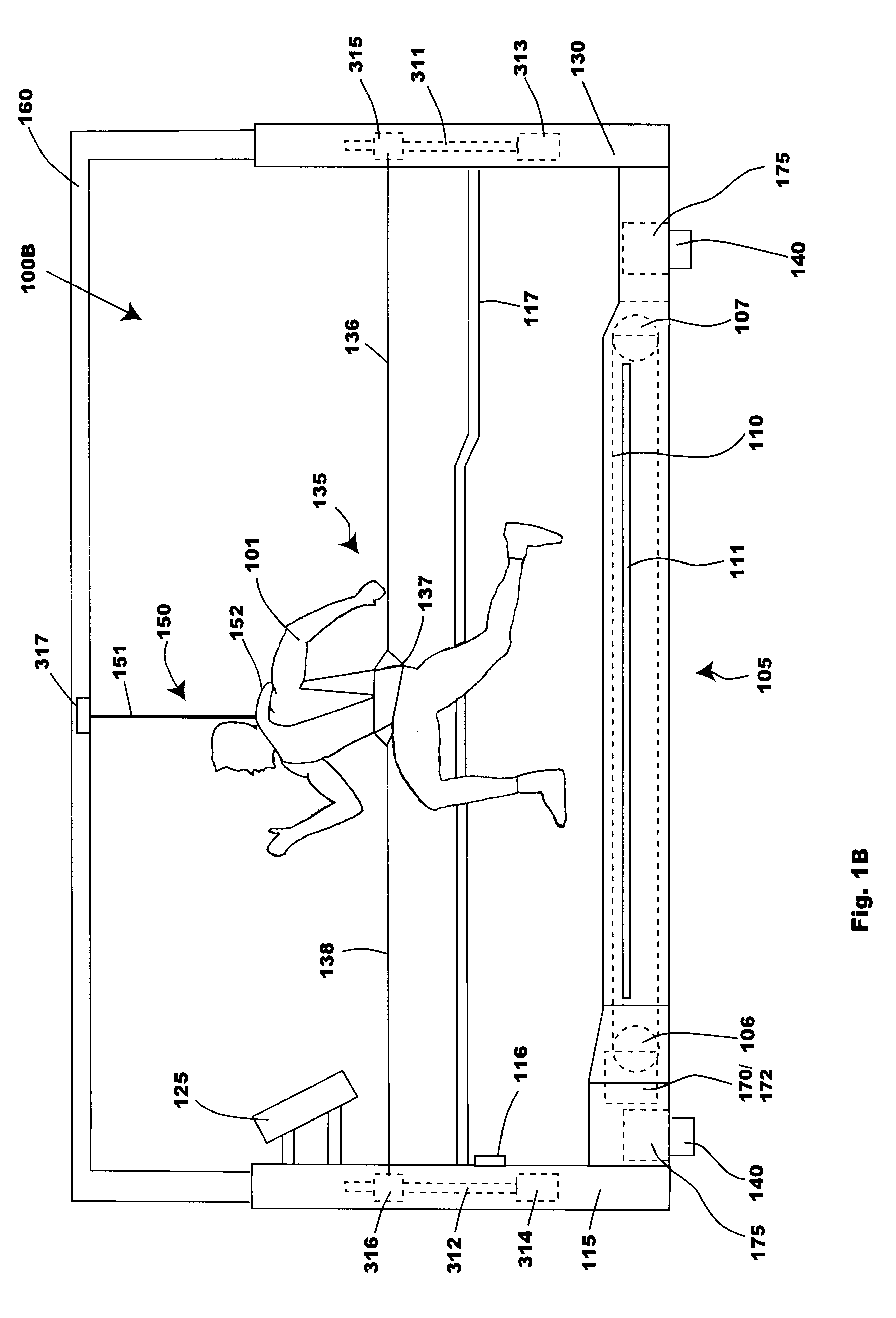

Bipedal locomotion training and performance evaluation device and method

InactiveUS6454679B1Effective mass reductionTherapy exerciseMovement coordination devicesExercise performanceForce velocity

A bipedal locomotion exercise and performance evaluation apparatus including a revolving belt, a harness for securing the position of a subject on the belt, a harness-force measuring means, and a belt volocity monitoring and controlling means. The harness may be secured on various points of a subject and includes push / pull engagement means. An overhead harness may be used to reduce effective body mass. The velocity of the belt may be controlled by a unidirectional or bidirectional motor / brake system. Velocity of the belt may also be controlled by a brake only. A digital processor may be used to control the motor and / or brake as a function of the forces applied allowing multiple operating modes. Recording of velocity and force as functions of time facilitates analysis of exercise performance. The apparatus allows exertions throughout the first quadrant of a force-velocity-duration space, and outside that first quadrant.

Owner:RADOW SCOTT BRIAN

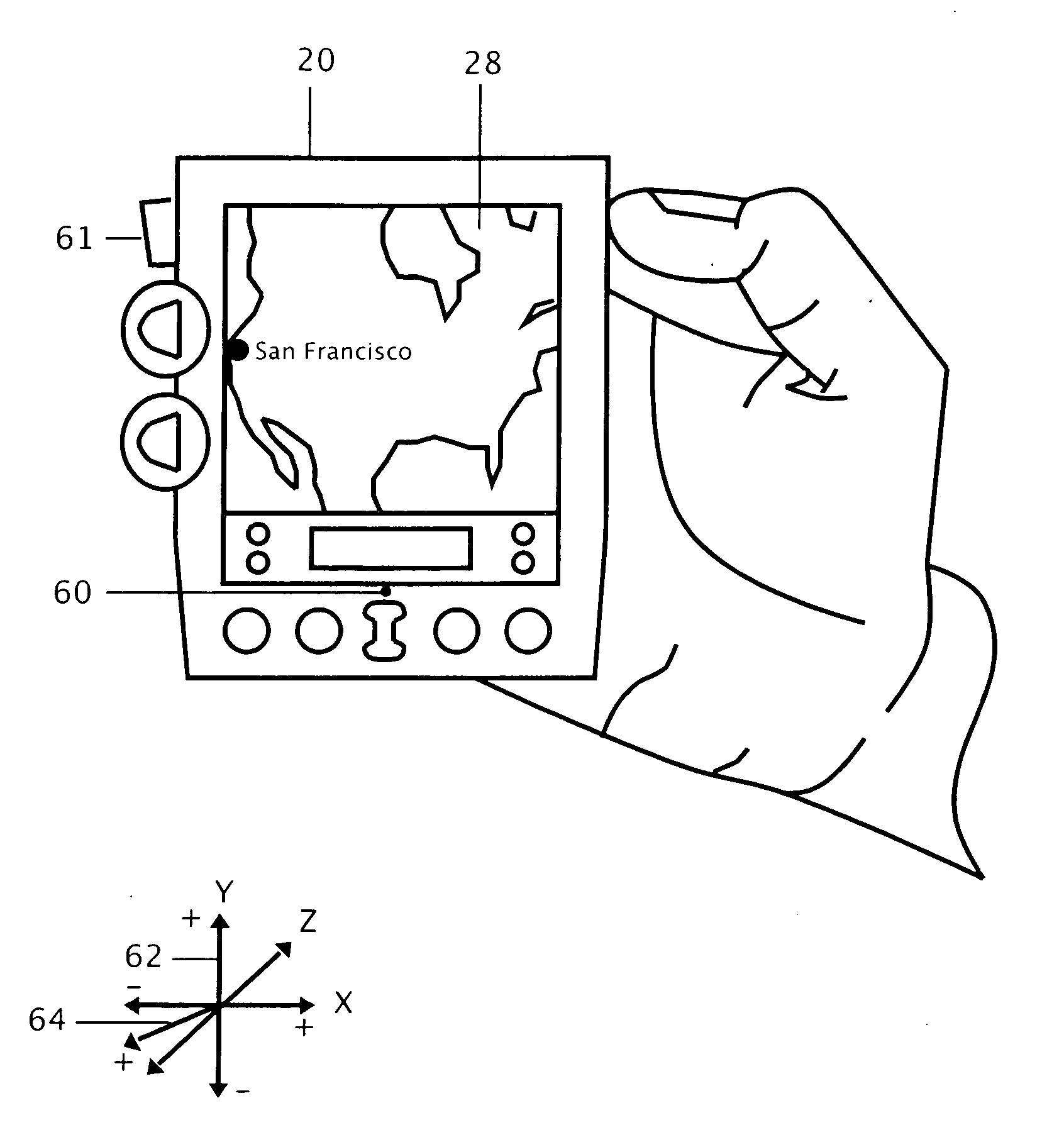

Motion detection and tracking system to control navigation and display of portable displays including on-chip gesture detection

InactiveUS20060061551A1Simple methodThrough simpleCathode-ray tube indicatorsDetails for portable computersComputer graphics (images)Display device

A computer program, system and method to track motion and control navigation and display of an object viewer. Information content generated by a digital processor is mapped into a virtual display space suitable for conveying the information to a user. A certain portion of the virtual display space is displayed using a display device coupled to the digital processor. An image capture device captures an image from which a reference navigation target is acquired. Tracked movement of a display device relative to the reference navigation target is used to update the displayed certain portion of the virtual display space in a manner related to the tracked movement.

Owner:REMBRANDT PORTABLE DISPLAY TECH LP

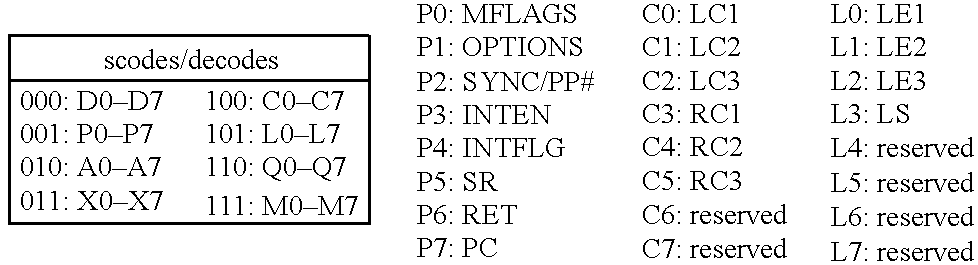

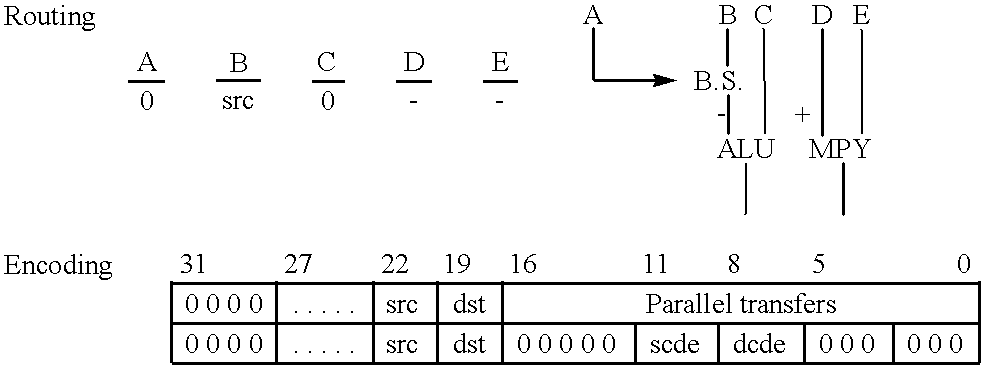

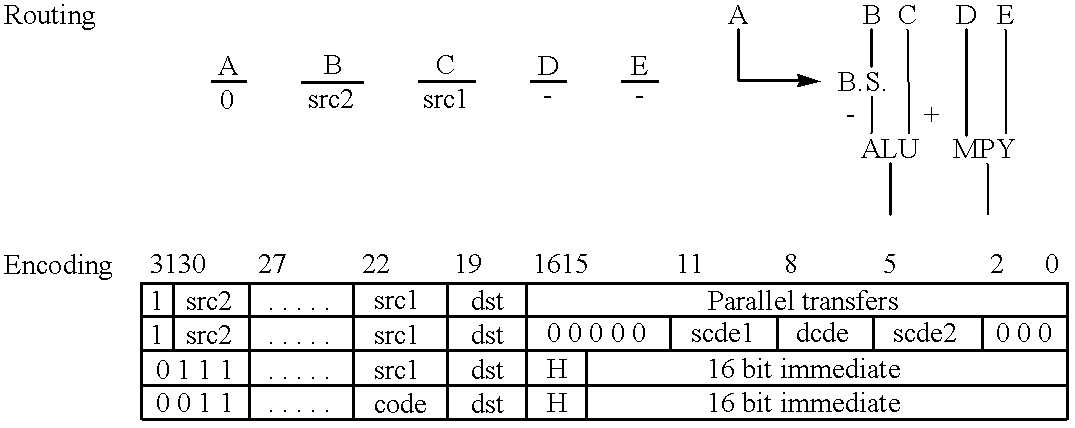

Single integrated circuit embodying a risc processor and a digital signal processor

InactiveUS6260088B1Save spaceImprove versatilityGeneral purpose stored program computerMultiple digital computer combinationsDigital signal processingComputer image

A single integrated circuit includes first and second data processors operating on different instruction sets independently operating on disjoint programs and data. The single integrated circuit preferably includes an external interface, a shared data transfer controller and shared memory divided into plural independently accessible memory banks. The two data processors are preferably a digital signal processor (DSP) and a reduced instruction set computer (RISC) processor. The DSP and RISC processors are suitably programmed to perform differing aspects of computer image processing.

Owner:TEXAS INSTR INC

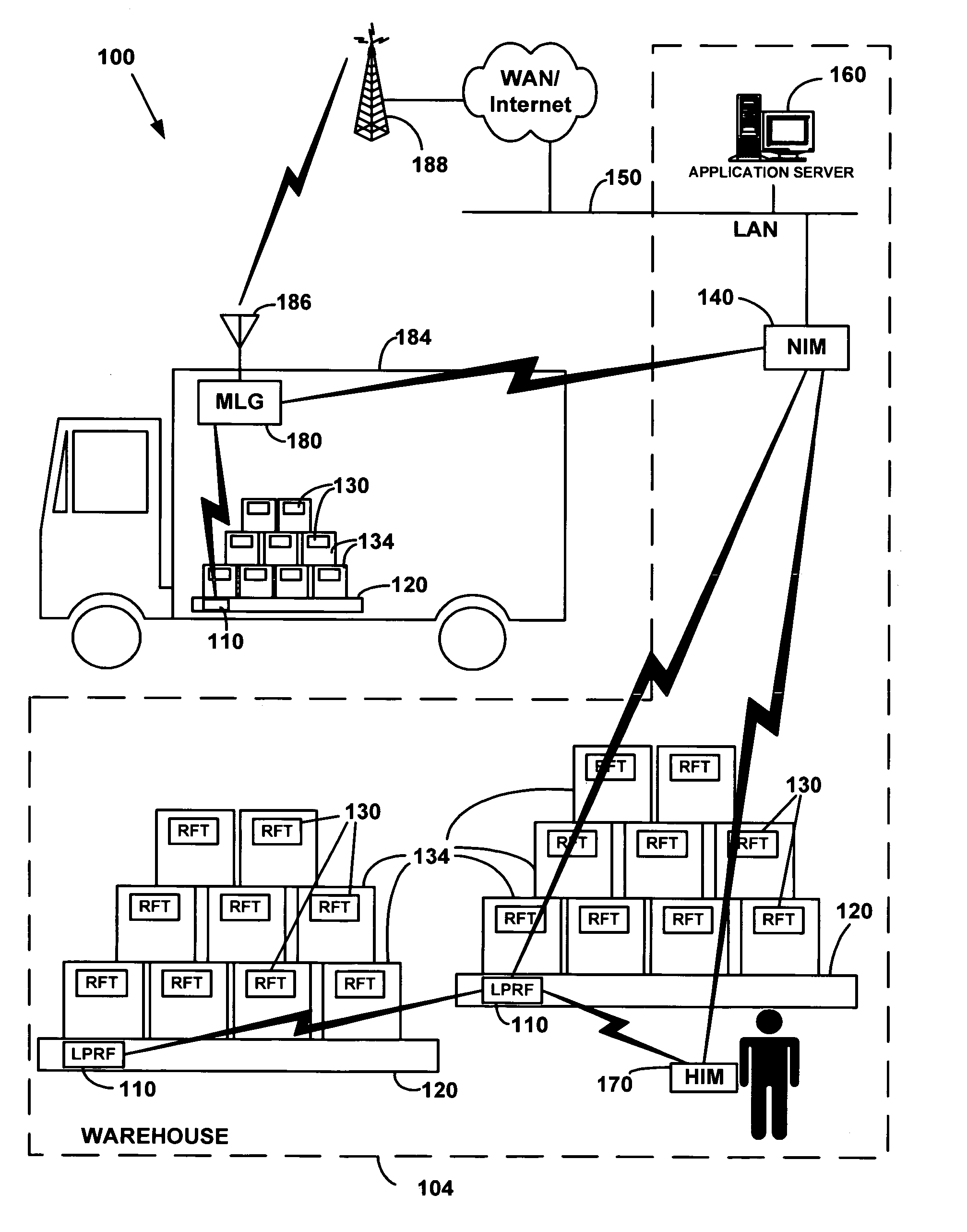

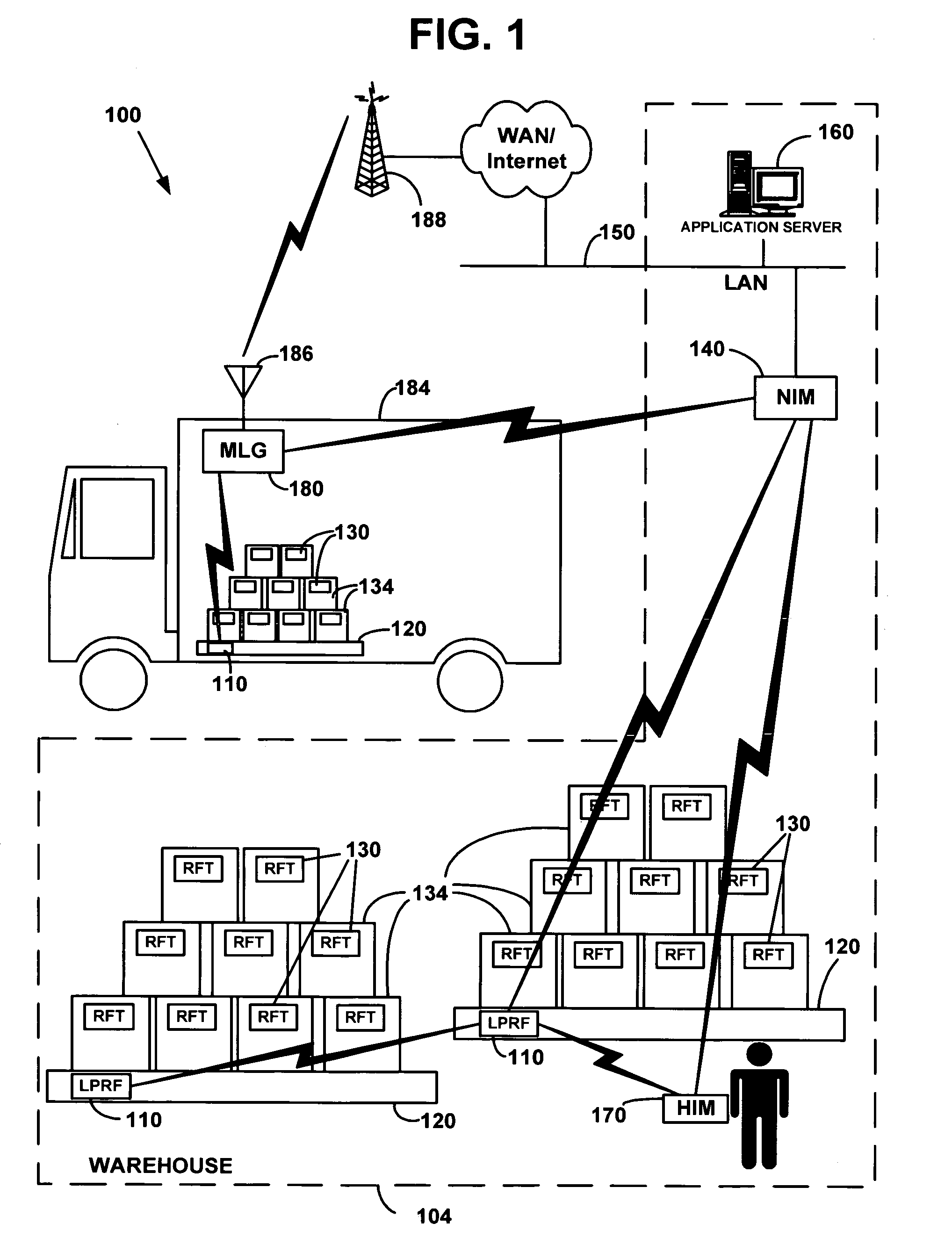

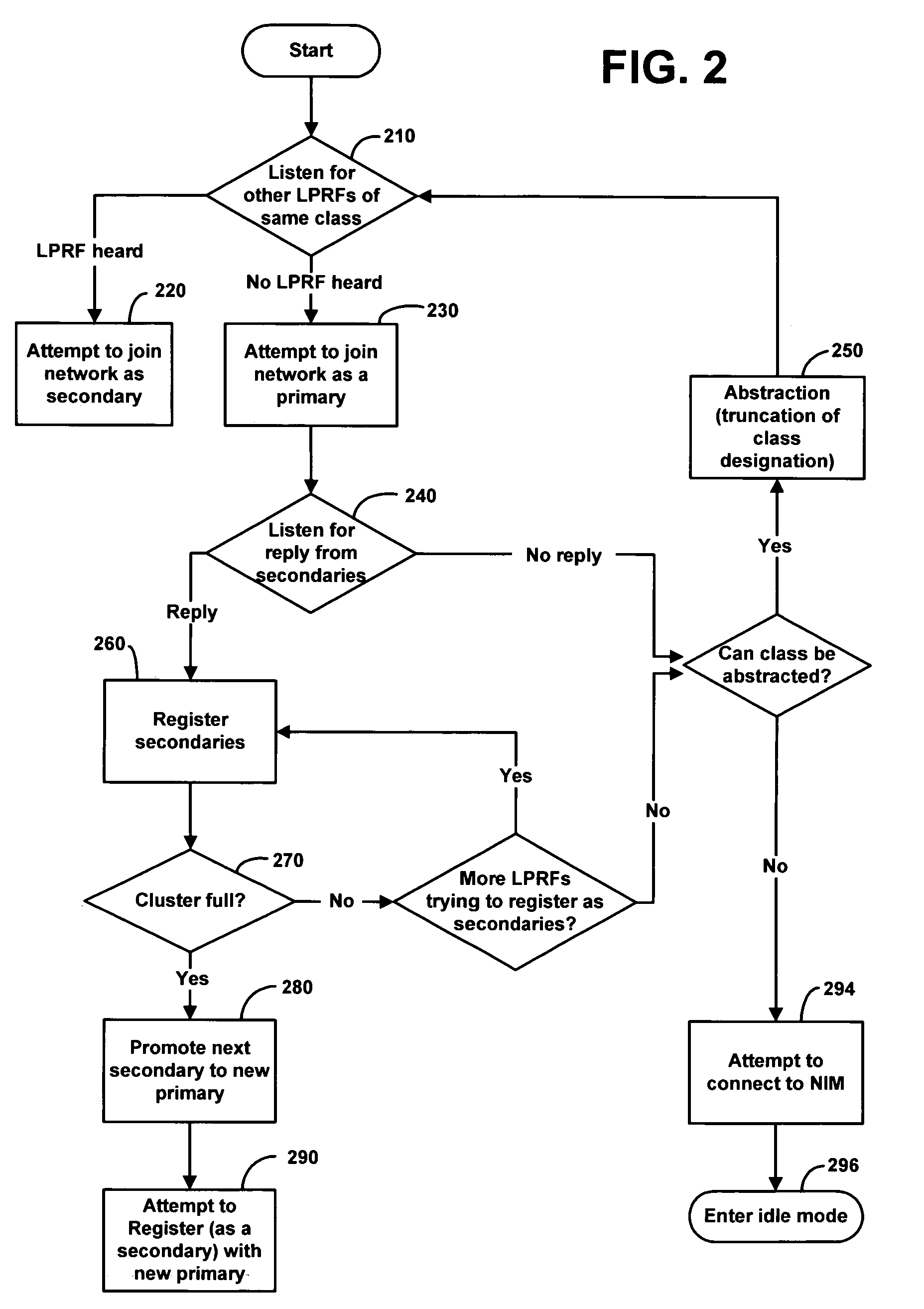

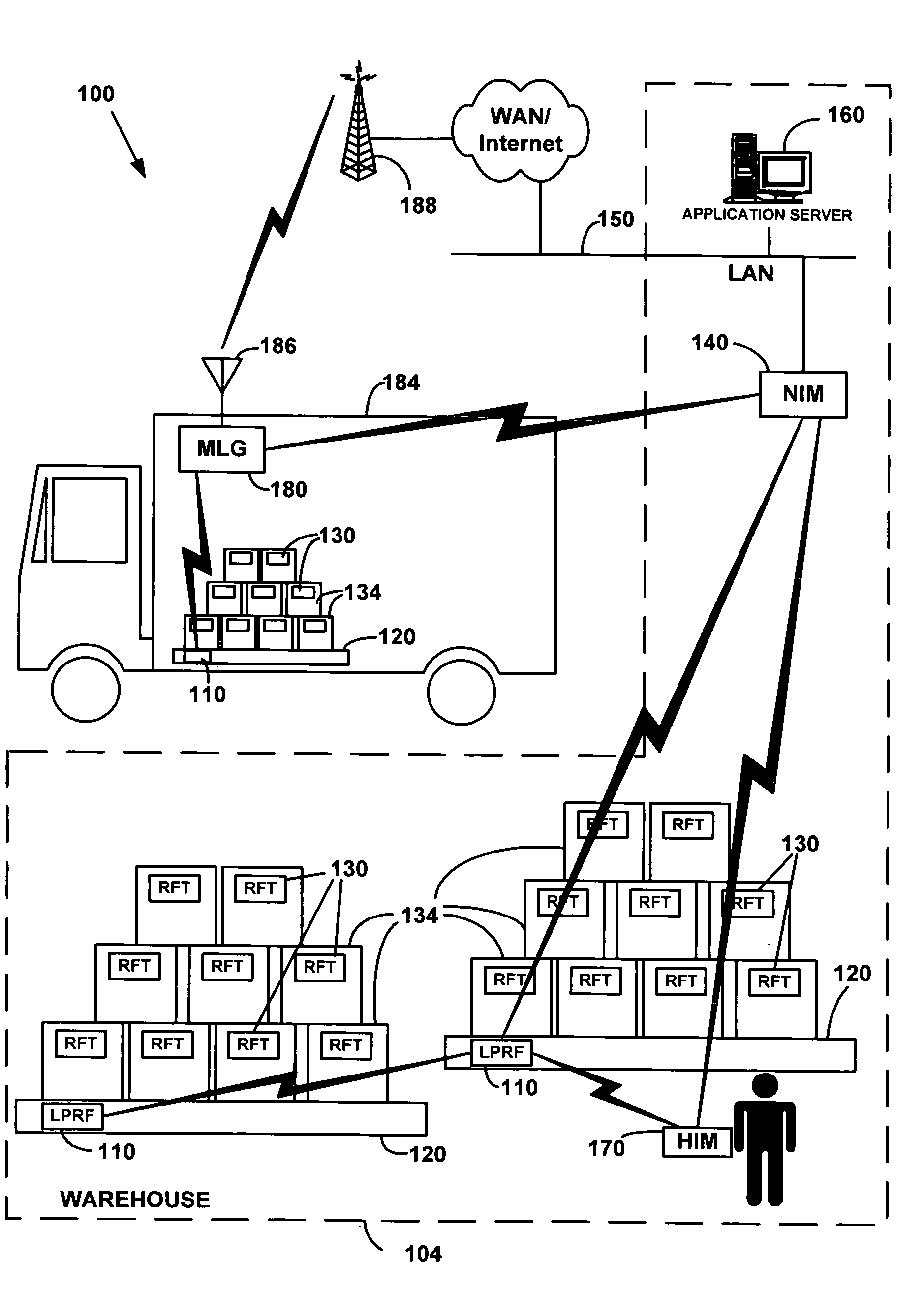

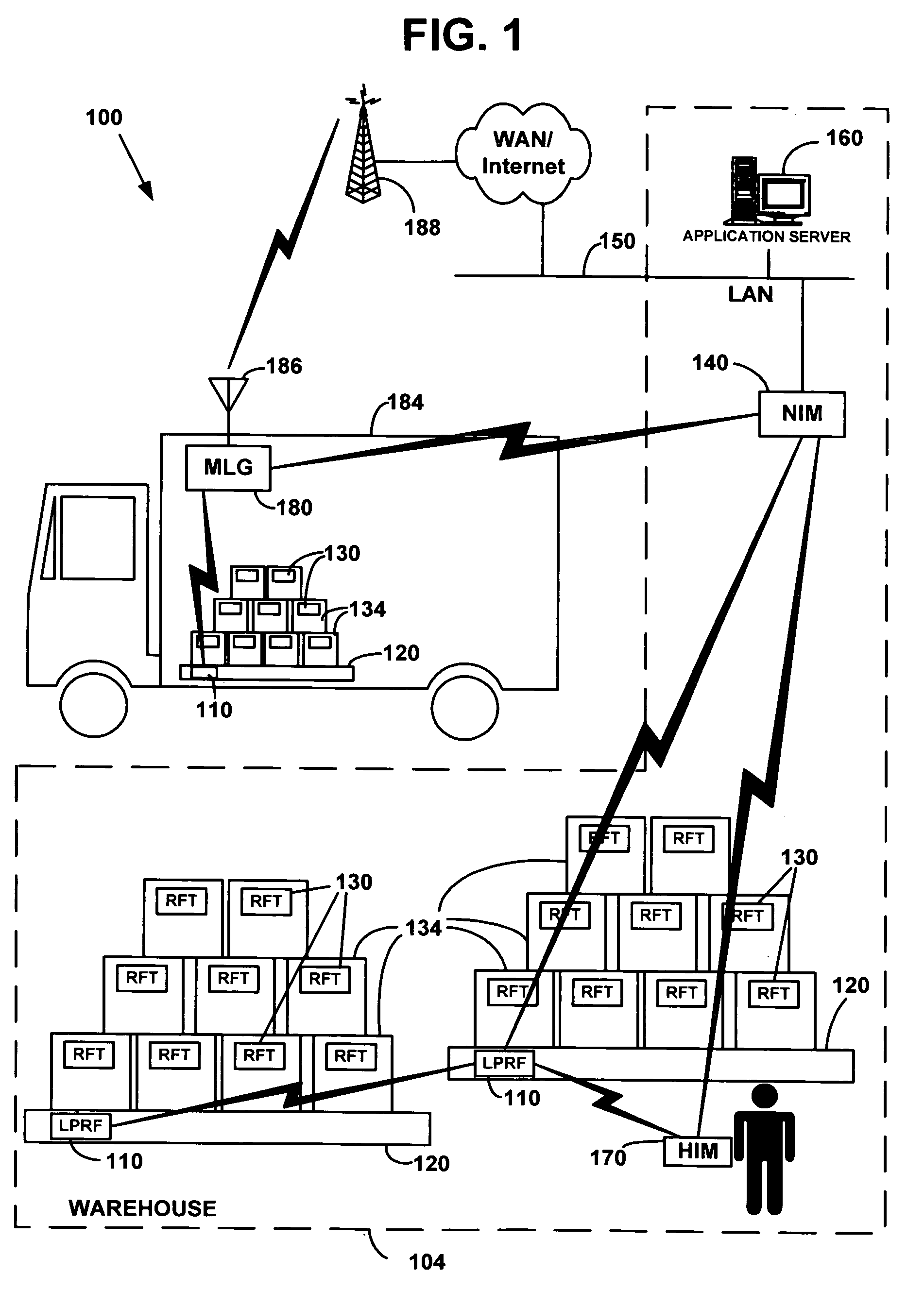

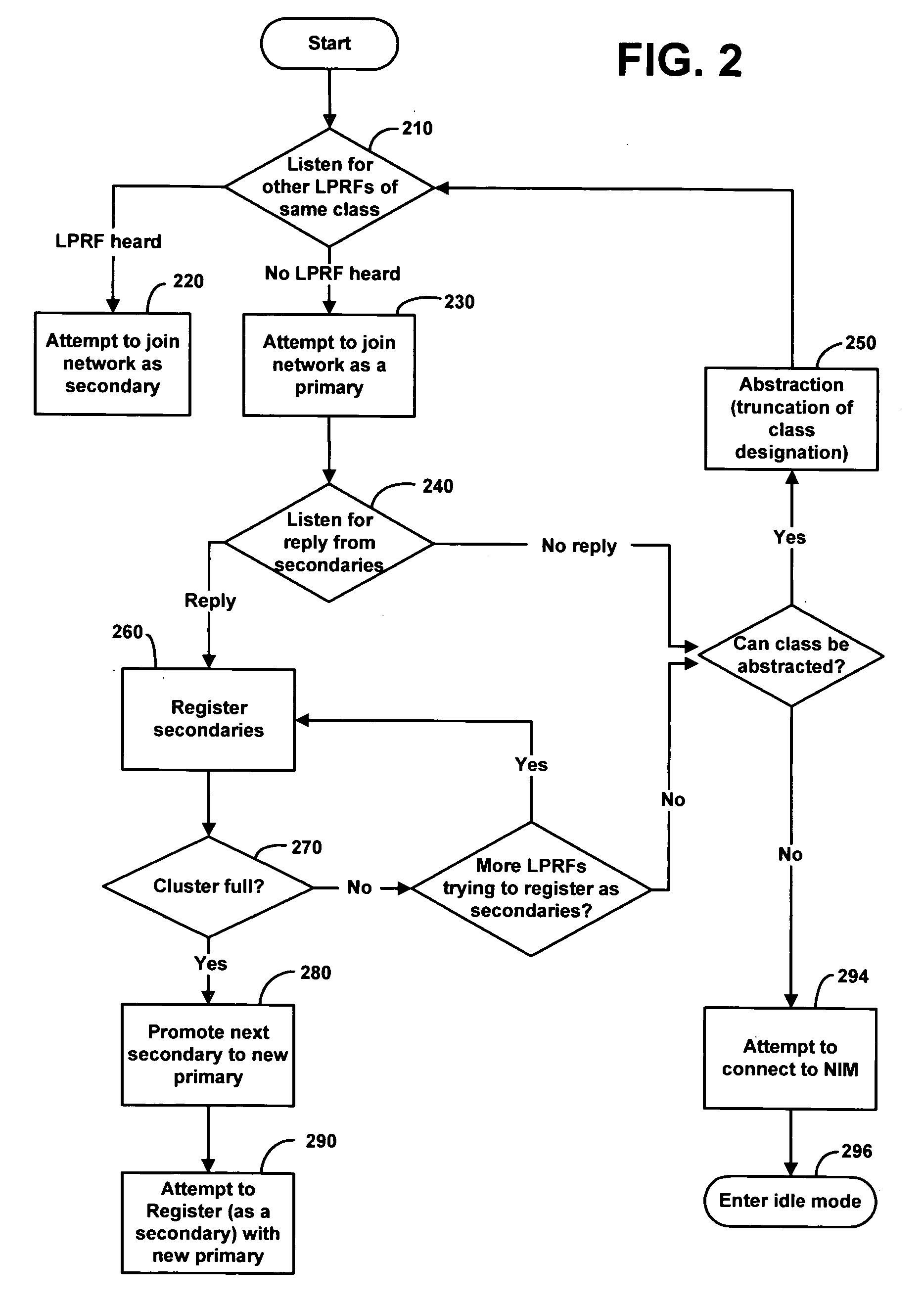

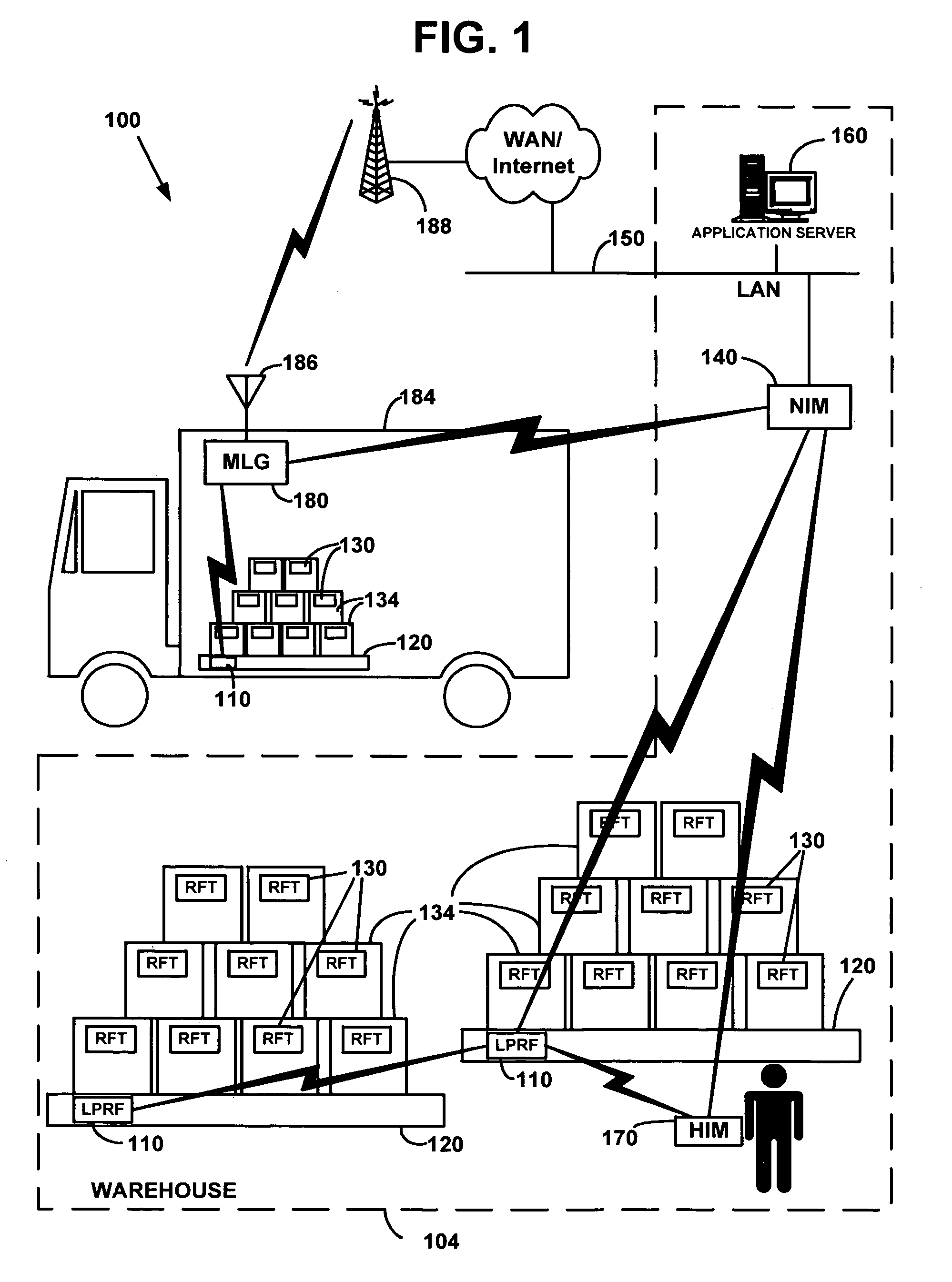

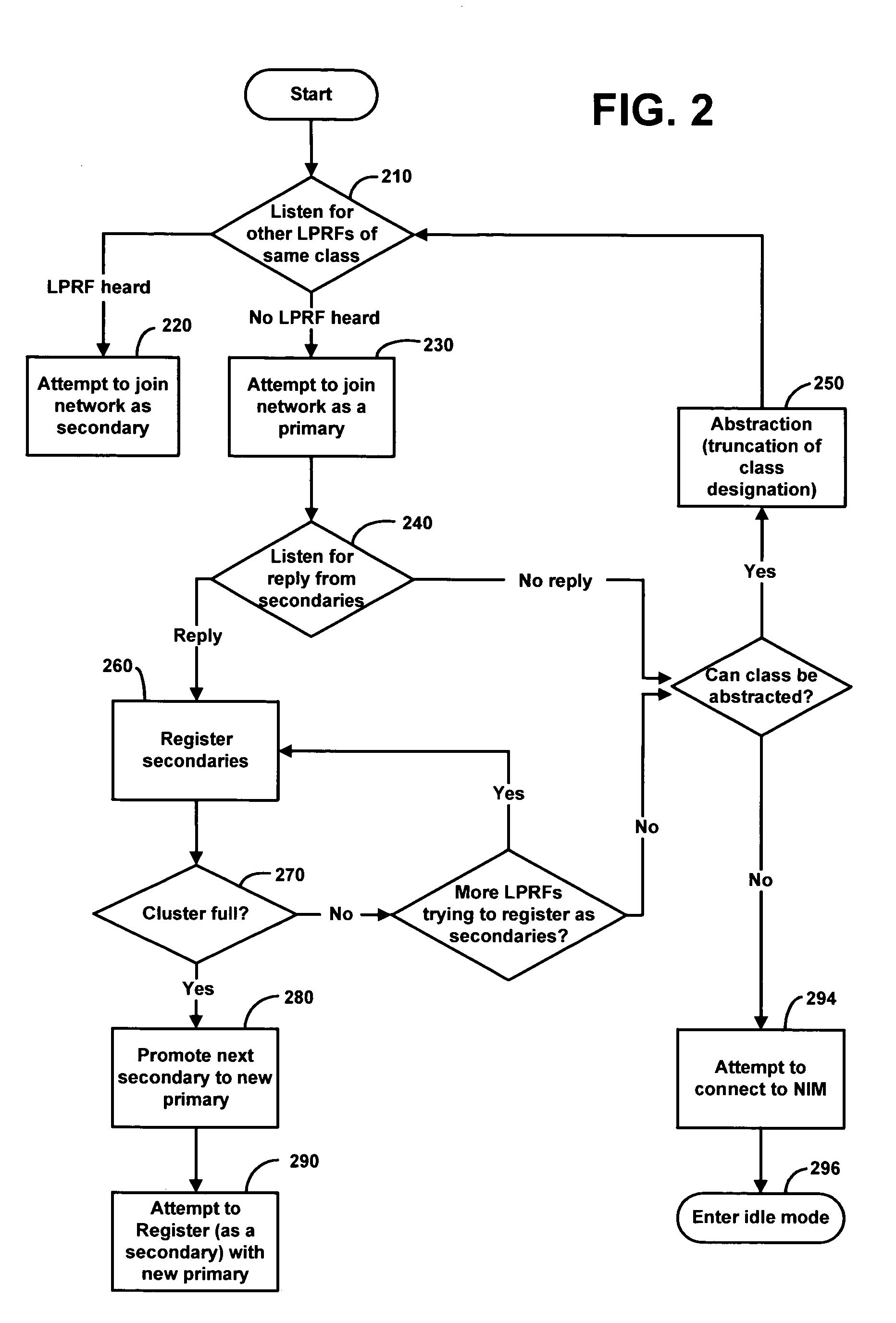

Communications within population of wireless transceivers based on common designation

InactiveUS7221668B2High sensitivityIncrease rangeEnergy efficient ICTPosition fixationWireless transceiverTransceiver

Owner:GOOGLE LLC

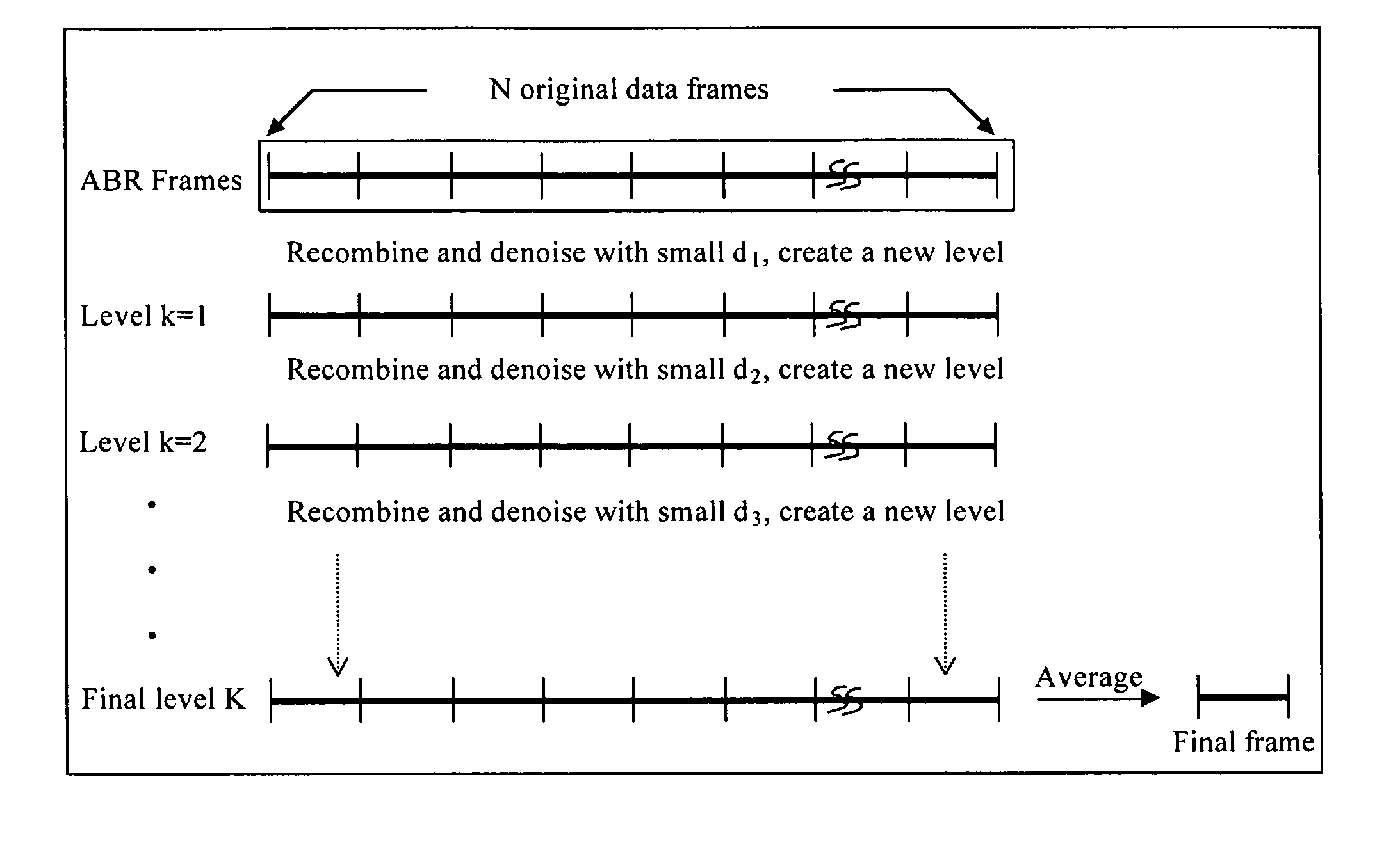

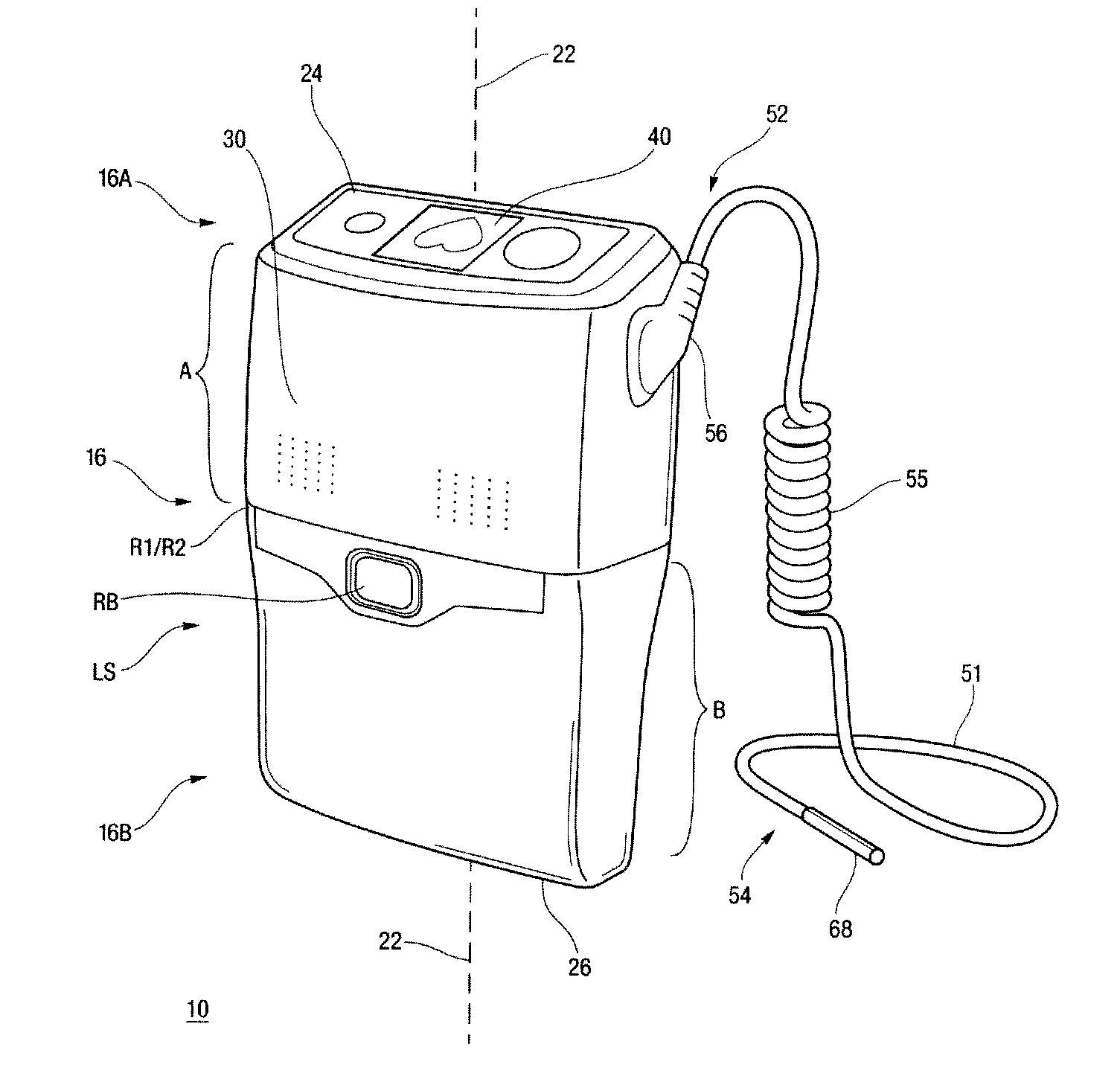

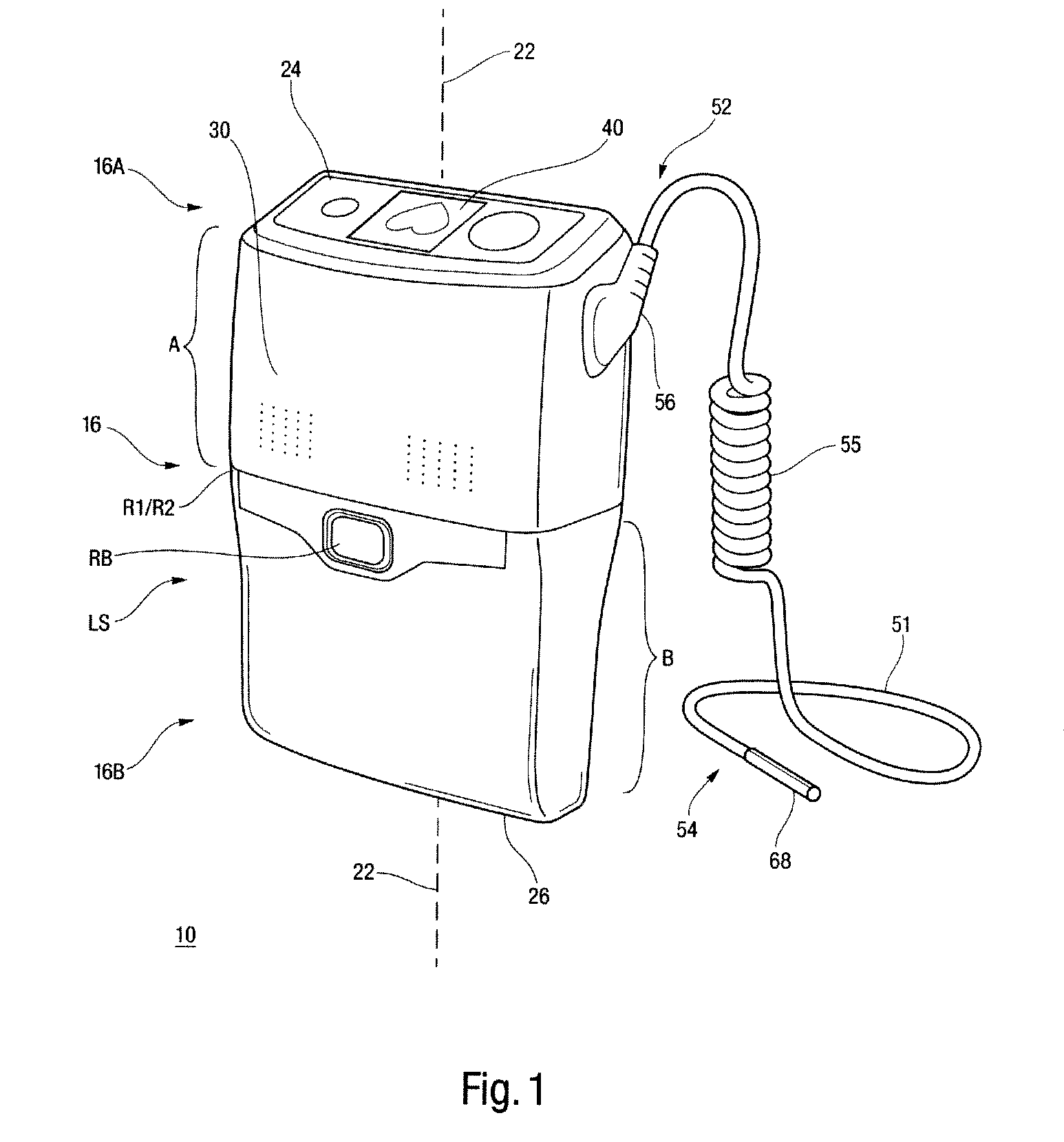

Fast estimation of weak bio-signals using novel algorithms for generating multiple additional data frames

InactiveUS7054453B2Improve signal qualityQuick estimateSpeech analysisAudiometeringData setComputer science

Owner:BRAINSCOPE SPV LLC

Fast wavelet estimation of weak bio-signals using novel algorithms for generating multiple additional data frames

InactiveUS7054454B2Improve signal qualityQuick estimateElectroencephalographySupply voltage controlData setSignal-to-noise ratio (imaging)

A method and apparatus for de-noising weak bio-signals having a relatively low signal to noise ratio utilizes an iterative process of wavelet de-noising a data set comprised of a new set of frames of wavelet coefficients partially generated through a cyclic shift algorithm. The method preferably operates on a data set having 2N frames, and the iteration is performed N−1 times. The resultant wavelet coefficients are then linearly averaged and an inverse discrete wavelet transform is performed to arrive at the de-noised original signal. The method is preferably carried out in a digital processor.

Owner:BRAINSCOPE SPV LLC +1

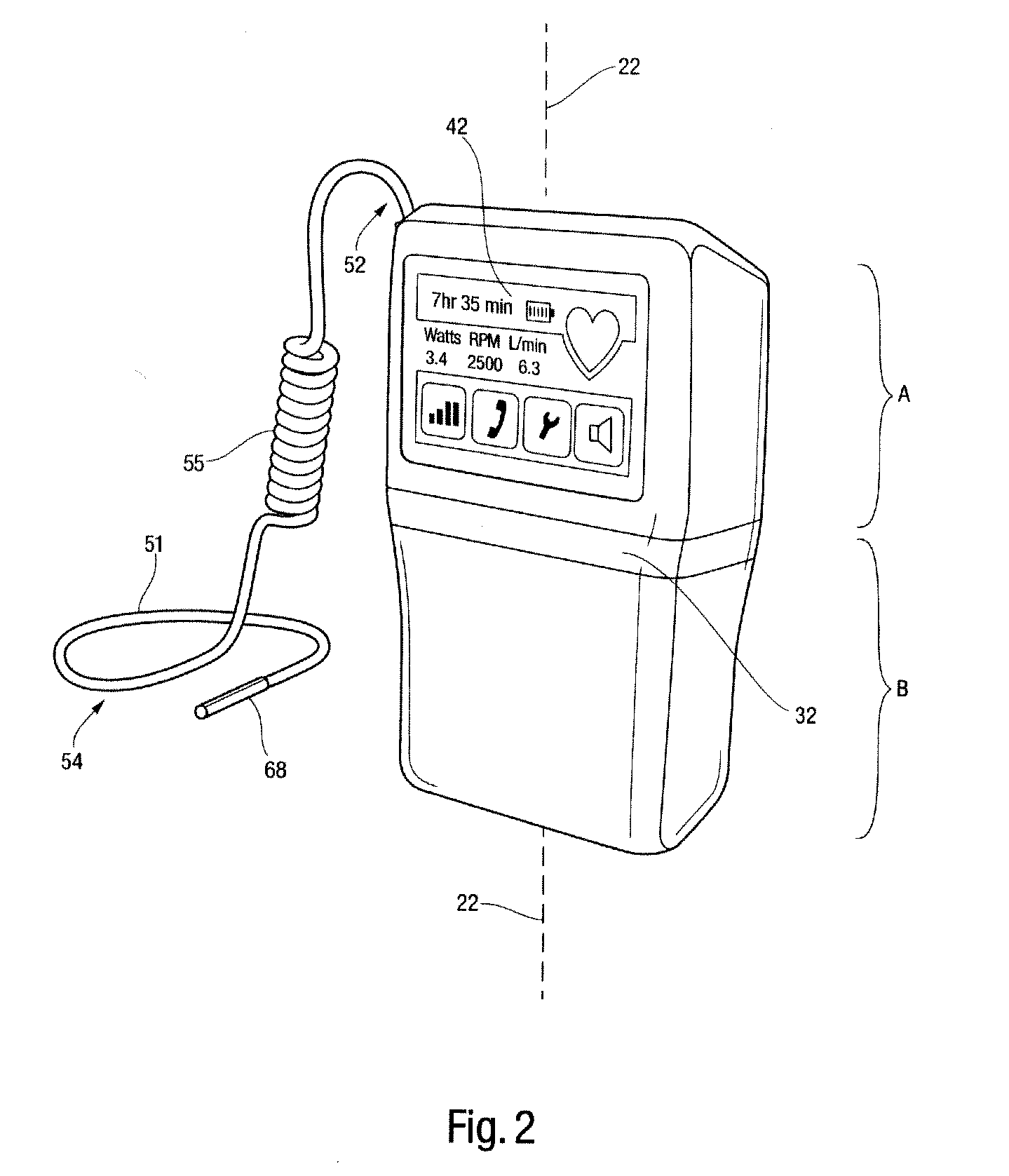

Controller and power source for implantable blood pump

Methods and apparatus for controlling the operation of, and providing power for and to, implantable ventricular assist devices which includes a pump employing a brushless DC motor-driven blood pump, are disclosed. In one embodiment, a control system for driving an implantable blood pump is provided. The digital processor is responsive to data associated with the operation of the pump received at the data transfer pump, and from program data stored in the memory, (i) to determine therefrom, the identity of the pump, (ii) to determine therefrom, electrical characteristics and features of the identified pump, and (iii) to adaptively generate and apply to the data port, control signals for driving the identified pump.

Owner:HEARTWARE INC

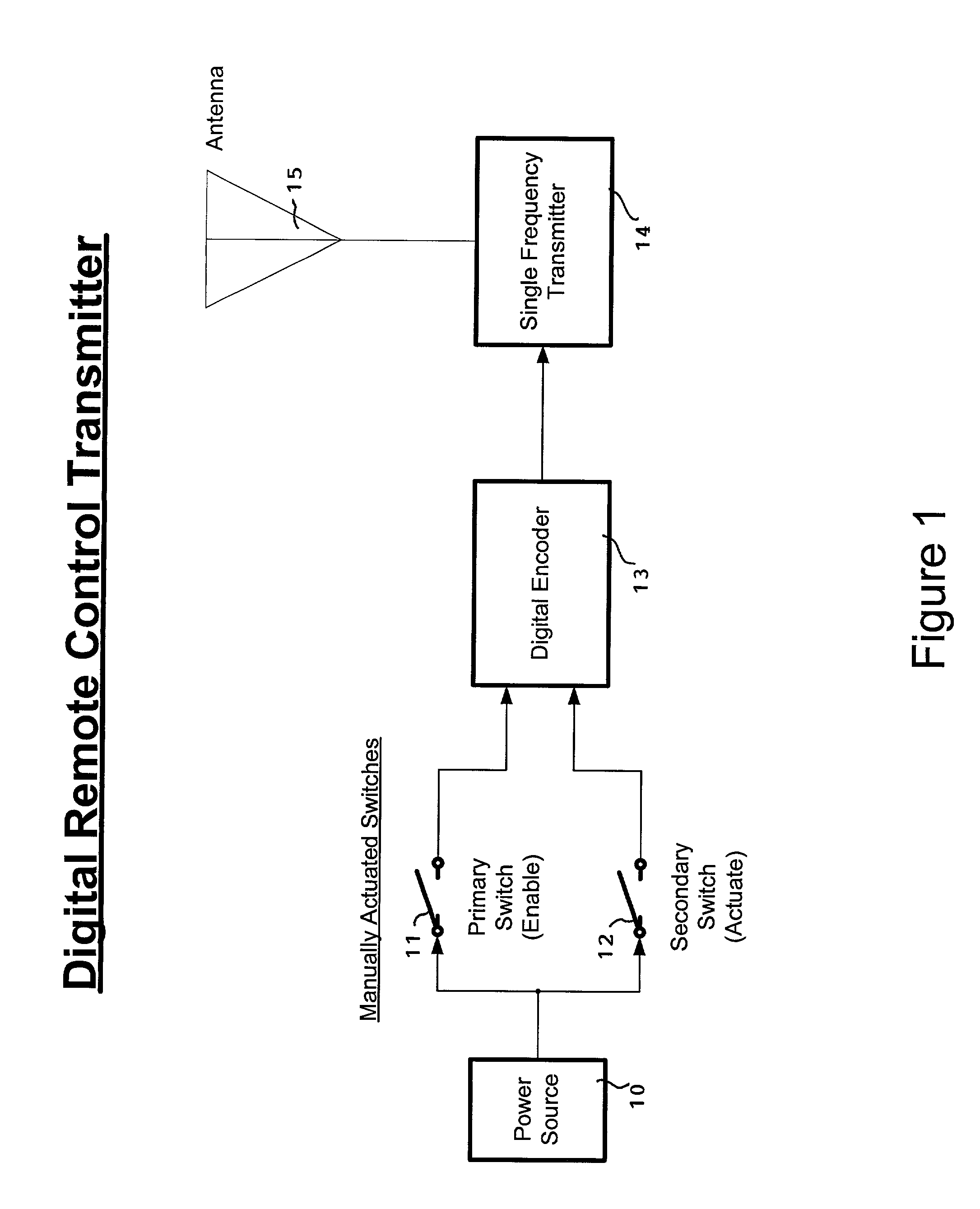

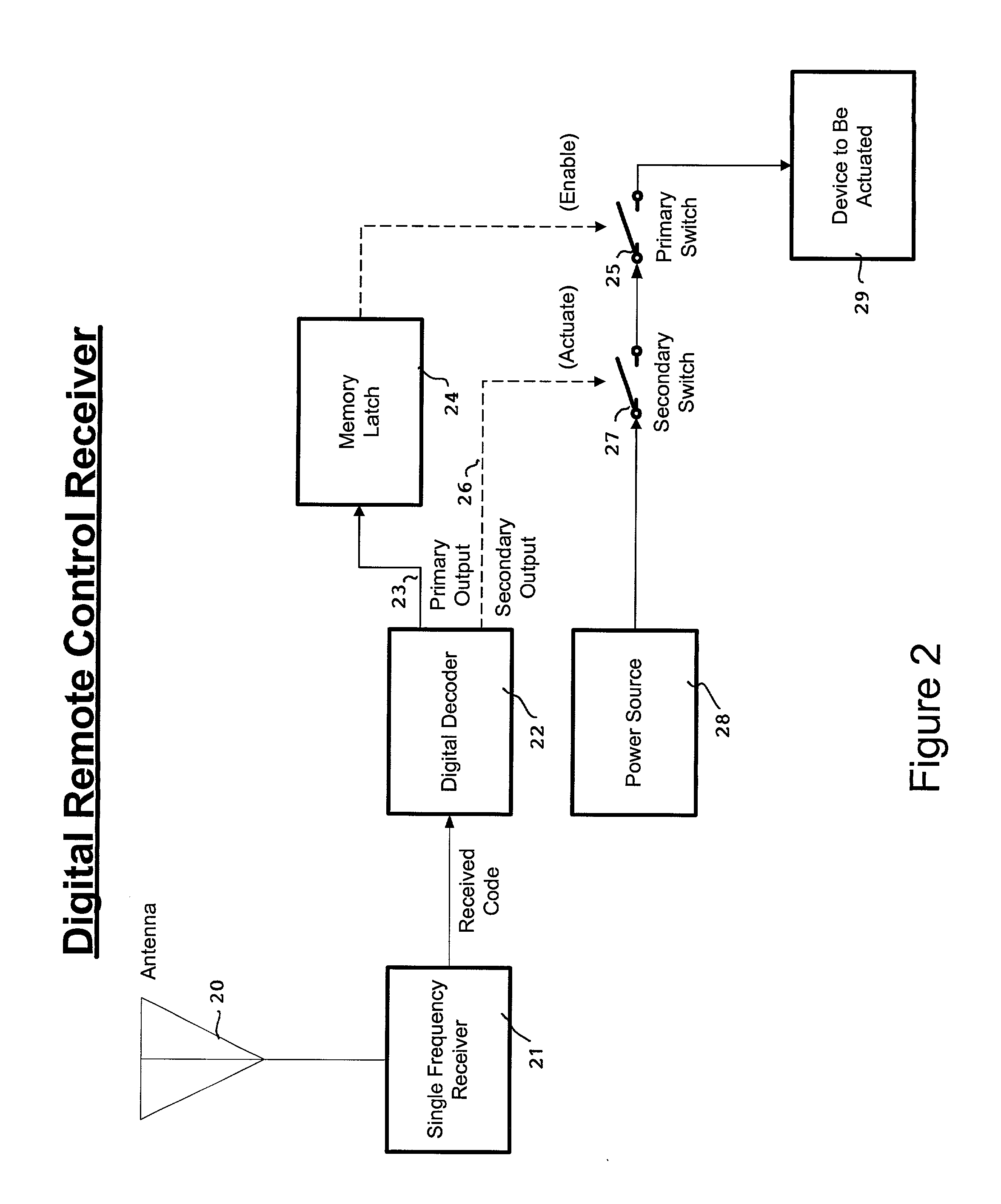

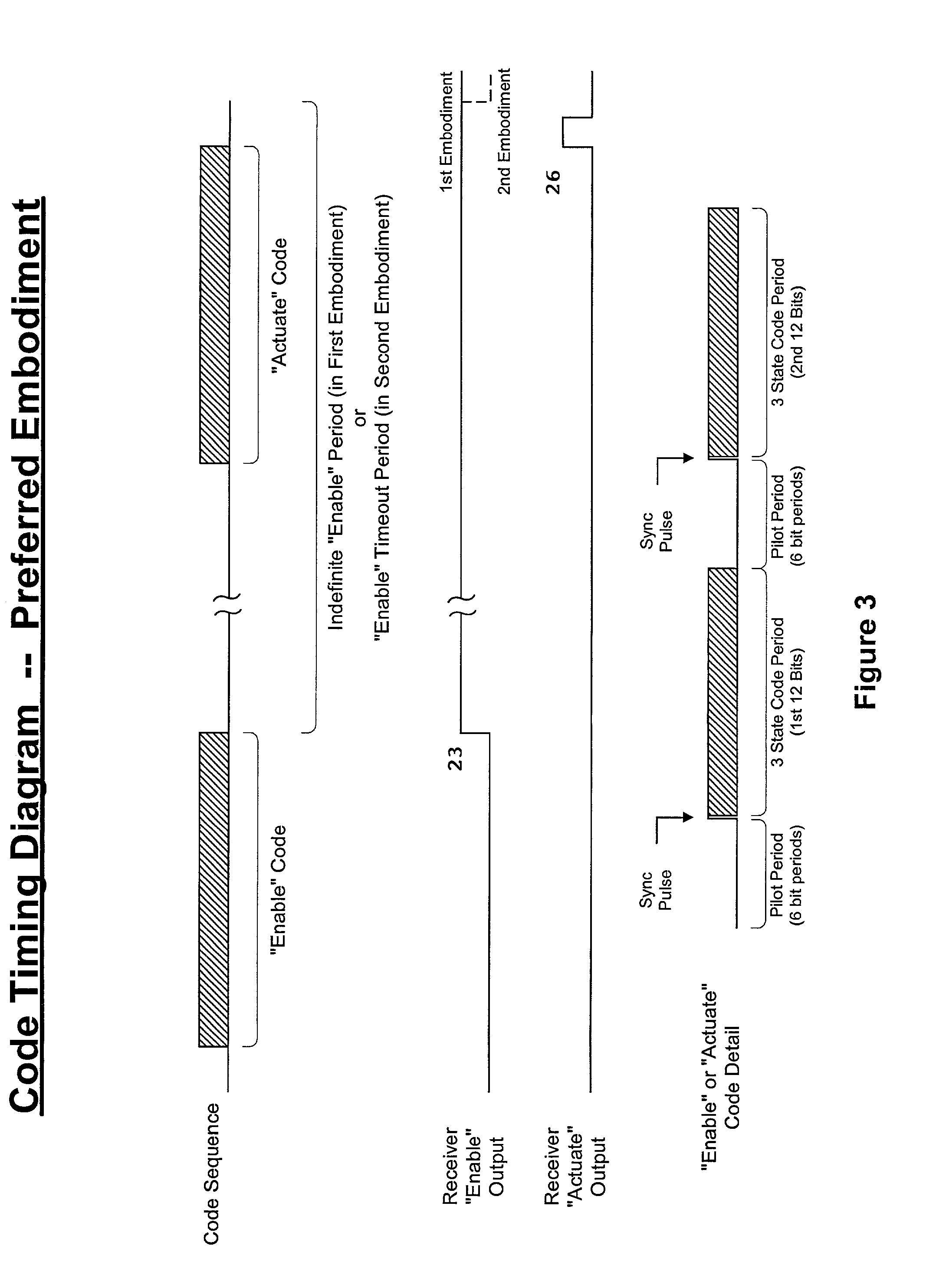

Wireless digital launch or firing system

InactiveUS20010045883A1Simple configurationSaving assemblyProgramme controlElectric signal transmission systemsComputer scienceTransmitter

A wireless digital launch or firing system has a transmitter unit that can transmit separate RF signals representing an "enable" code sequence and an "actuate" code sequence, and a receiver unit which decodes the "enable" code sequence to enable receipt of the "actuate" code sequence, and decodes the "actuate" code sequence to actuate launching or firing. A digital processor receives the code sequences from a receiver circuit and compares them to stored digital code sequences. A memory latch maintains a normally-off primary switch in an "on" condition when the "enable" signal is received. A normally-off secondary switch is set to an "on" condition when the "actuate" signal is received. Preferably, the RF signals are transmitted in pulse code form, and the code sequences include bits that are predetermined and stored in the hardware, bits that are selected for an individual code by the user, and bits that differentiate the "enable" from the "actuate" signal. The memory latch can be set to an indefinite "enable" period, for multiple launchings, or a timed "enable" period, for toys or single launch devices. A sequencer module can be coupled to the receiver unit for sequenced firings.

Owner:HOLDAWAY CHARLES R +1

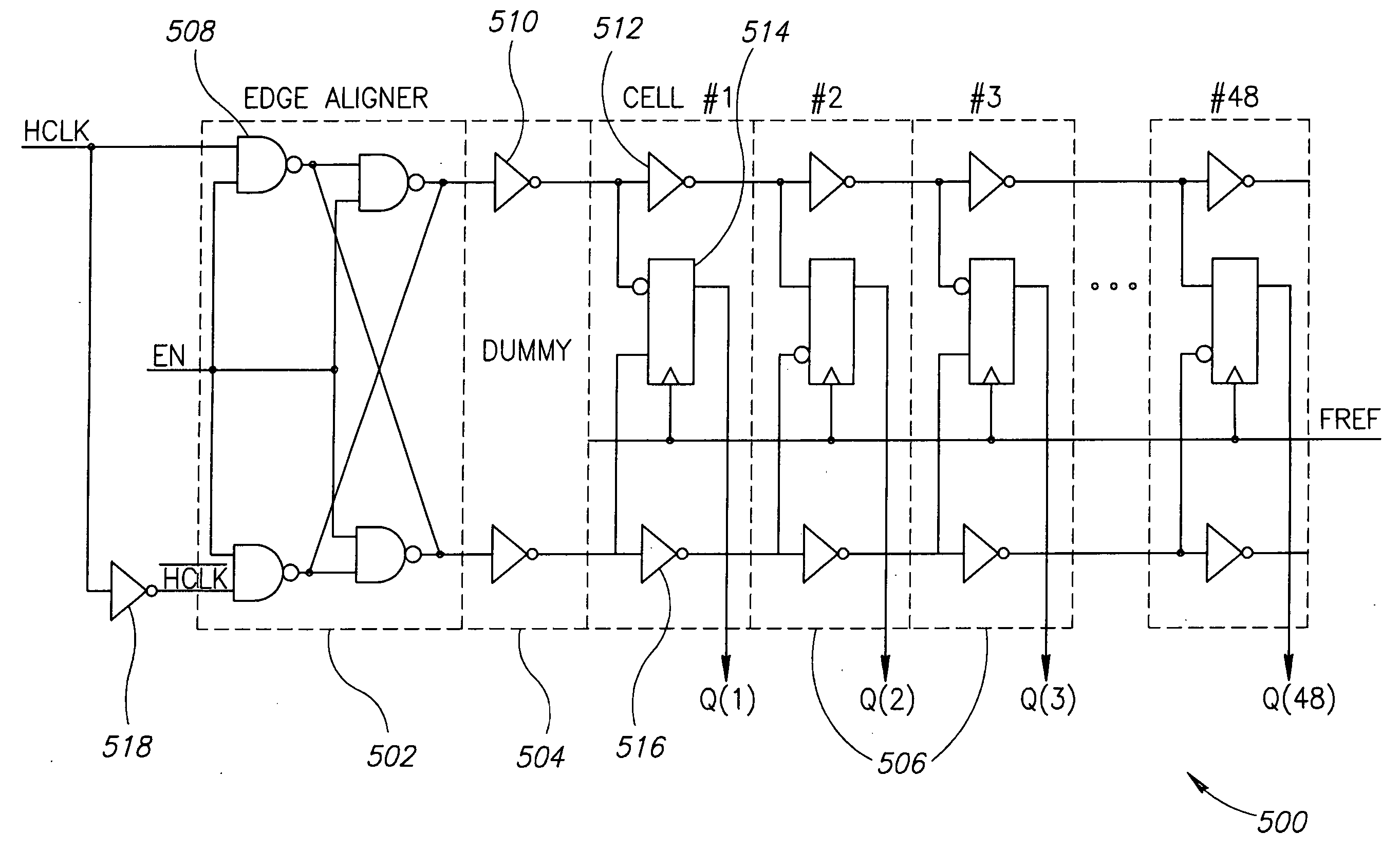

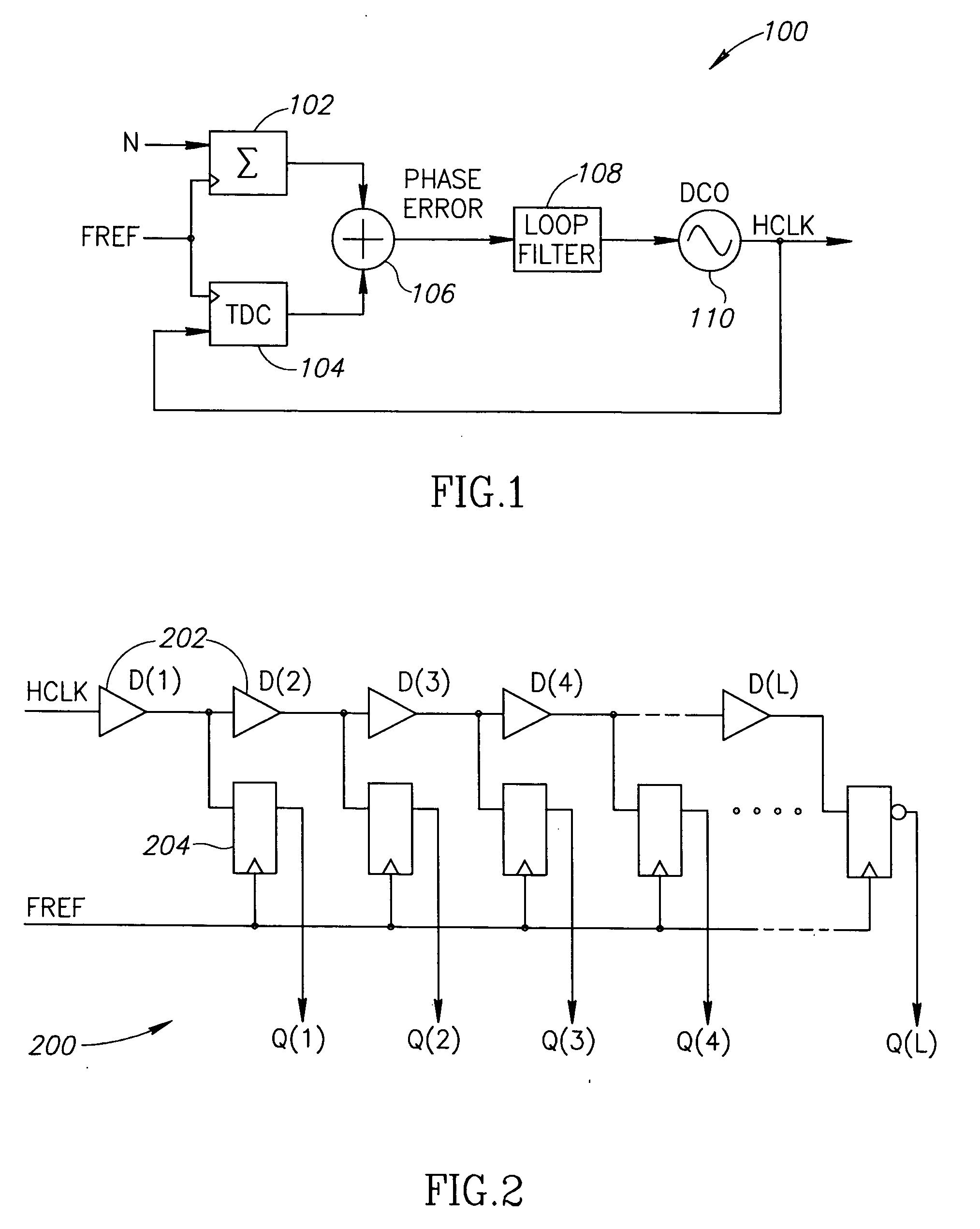

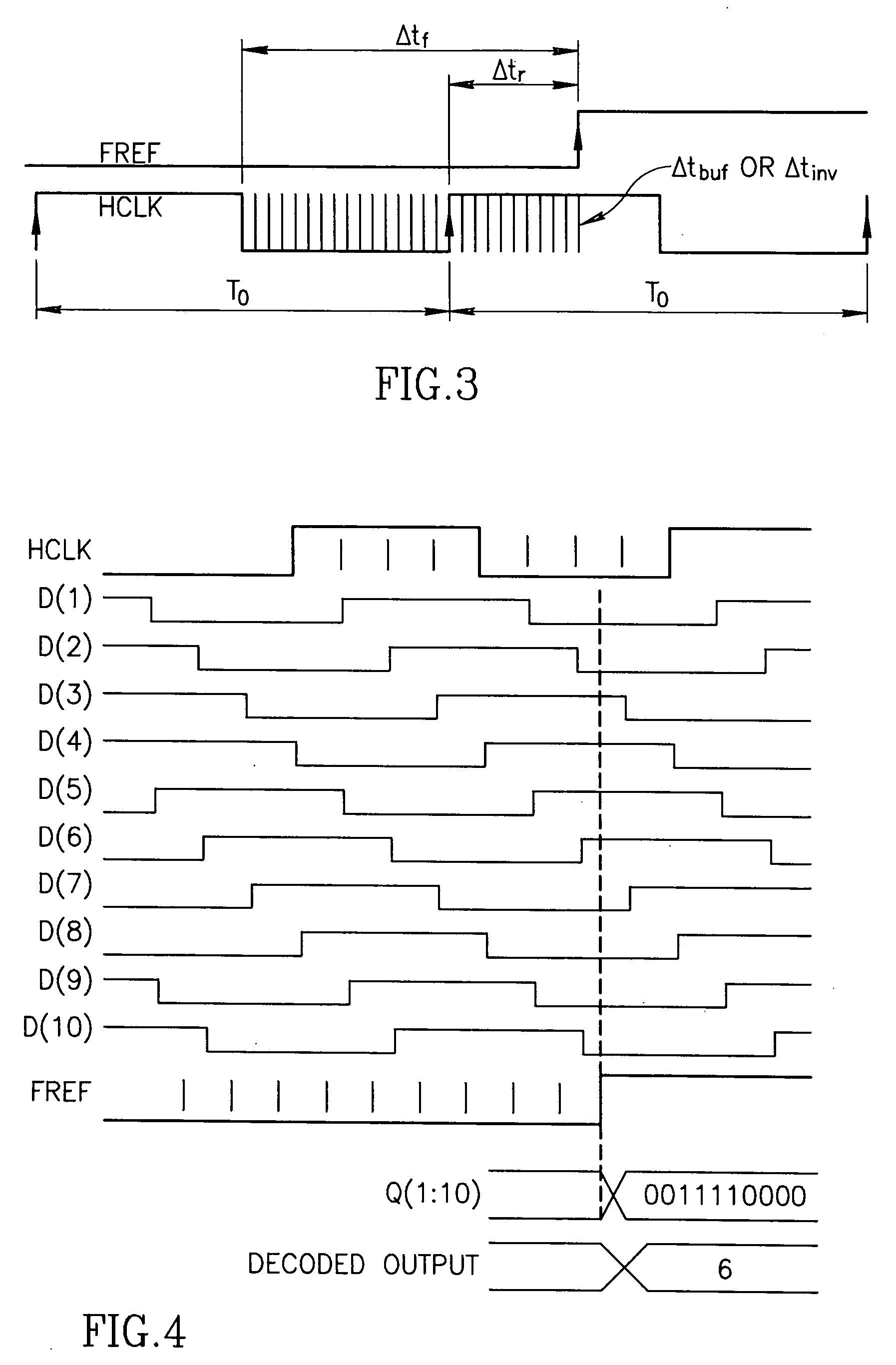

Circuit for high-resolution phase detection in a digital RF processor

ActiveUS20060103566A1Less sensitiveReduce power consumptionElectric signal transmission systemsPulse automatic controlEngineeringDigital converter

A novel time-to-digital converter (TDC) used as a phase / frequency detector and charge pump replacement in an all-digital PLL within a digital radio processor. The TDC core is based on a pseudo-differential digital architecture making it insensitive to NMOS and PMOS transistor mismatches. The time conversion resolution is equal to an inverter propagation delay, e.g., 20 ps, which is the finest logic-level regenerative timing in CMOS. The TDC is self calibrating with the estimation accuracy better than 1%. The TDC circuit can also serve as a CMOS process strength estimator for analog circuits in large SoC dies. The circuit also employs power management circuitry to reduce power consumption to a very low level.

Owner:TEXAS INSTR INC

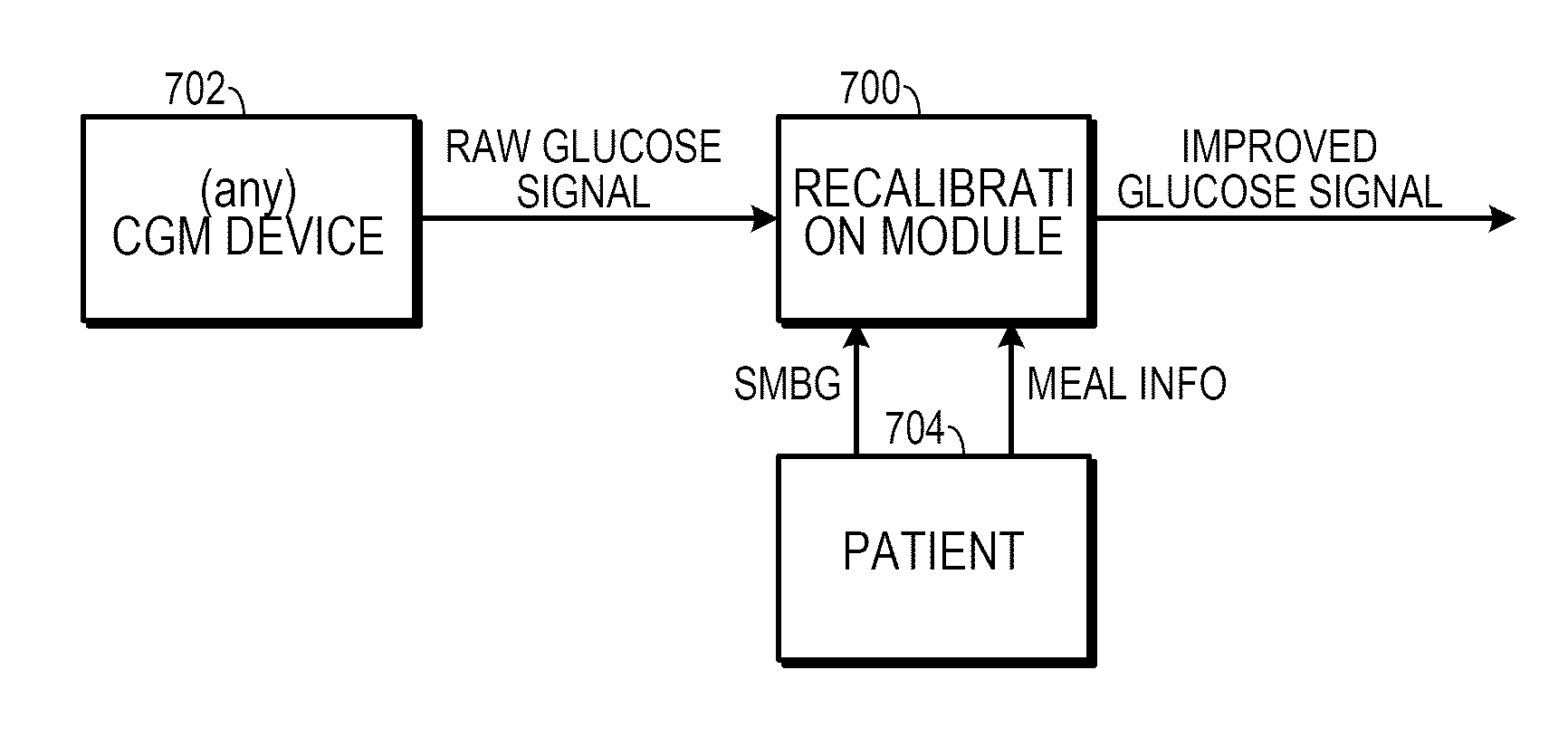

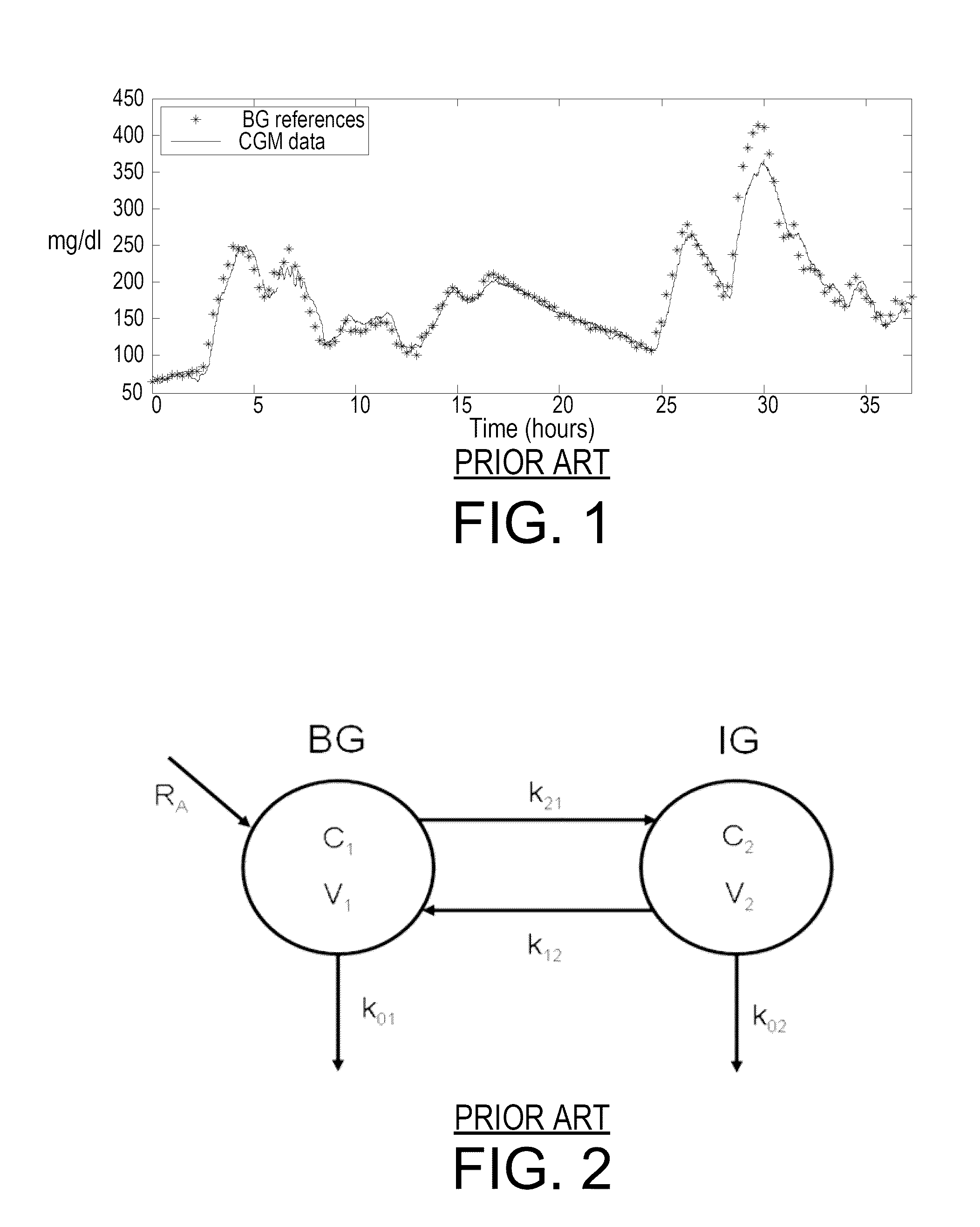

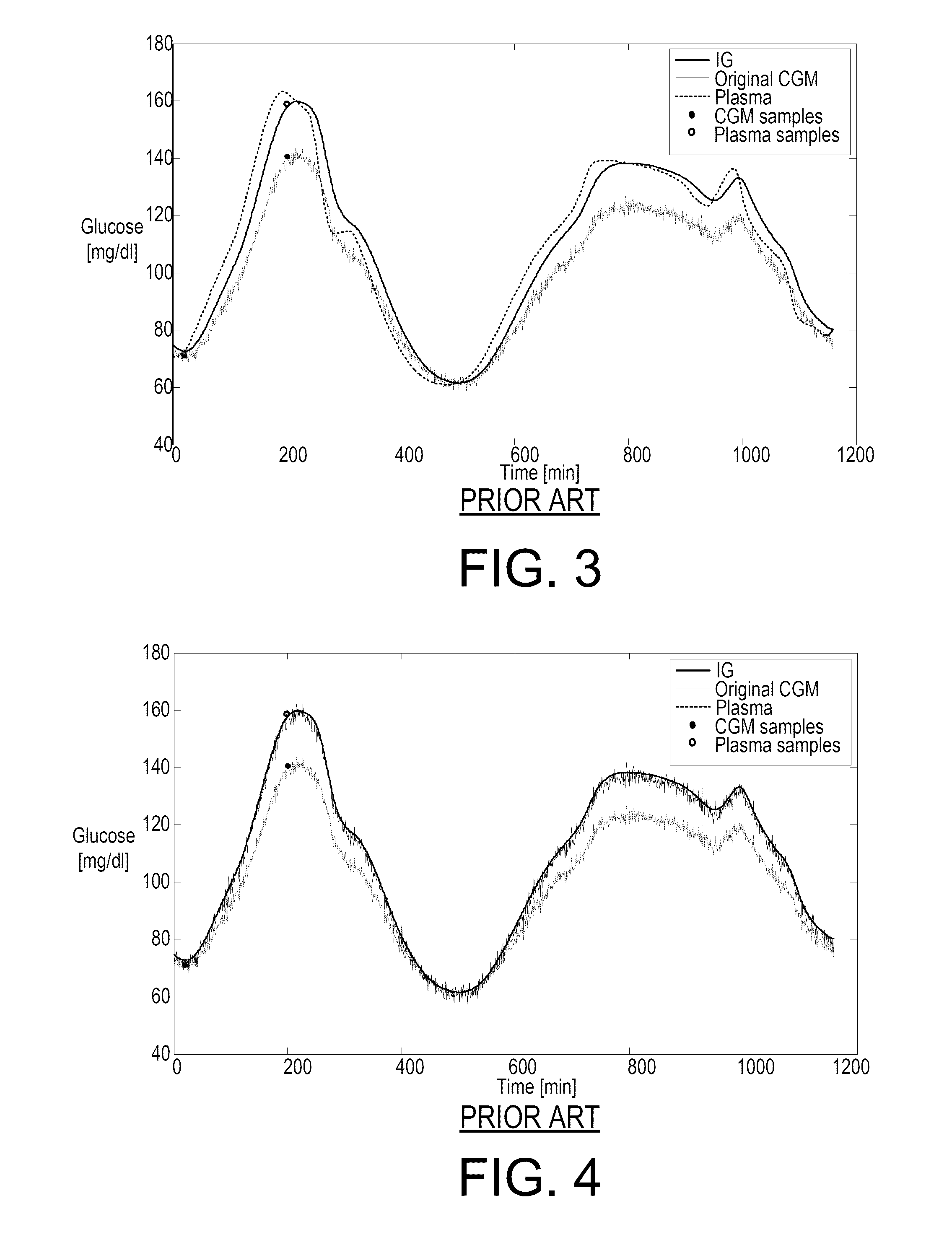

Method to recalibrate continuous glucose monitoring data on-line

ActiveUS20120215087A1Improve CGM recalibration algorithmMore physiology-awareLocal control/monitoringDiagnostic recording/measuringContinuous glucose monitoringLinear regression

In a method of recalibrating continuous glucose monitoring data from a user, operable on a digital processor, an indication from the user that the user has taken a meal is received (806). A self-monitored of blood glucose levels from the user (810) at two separate times during a day corresponding to when the user has taken a meal. A glucose signal is received from a continuous glucose monitoring sensor (818) at times corresponding to the two separate times that the user has taken a meal. Two reconstructed blood glucose values based on the glucose signal from the continuous monitoring sensor at times when the at least two self-monitored of blood glucose levels are received from the user. A linear regression is performed (822) using y=ax+b, wherein x corresponds to the two reconstructed blood glucose values and y corresponds to the two self-monitored of blood glucose levels thereby generating an estimation of a and b. A recalibration signal, including the estimation of a and b, is transmitted to the continuous glucose monitoring sensor (824) based on the linear regression.

Owner:UNIV DEGLI STUDI DI PADOVA

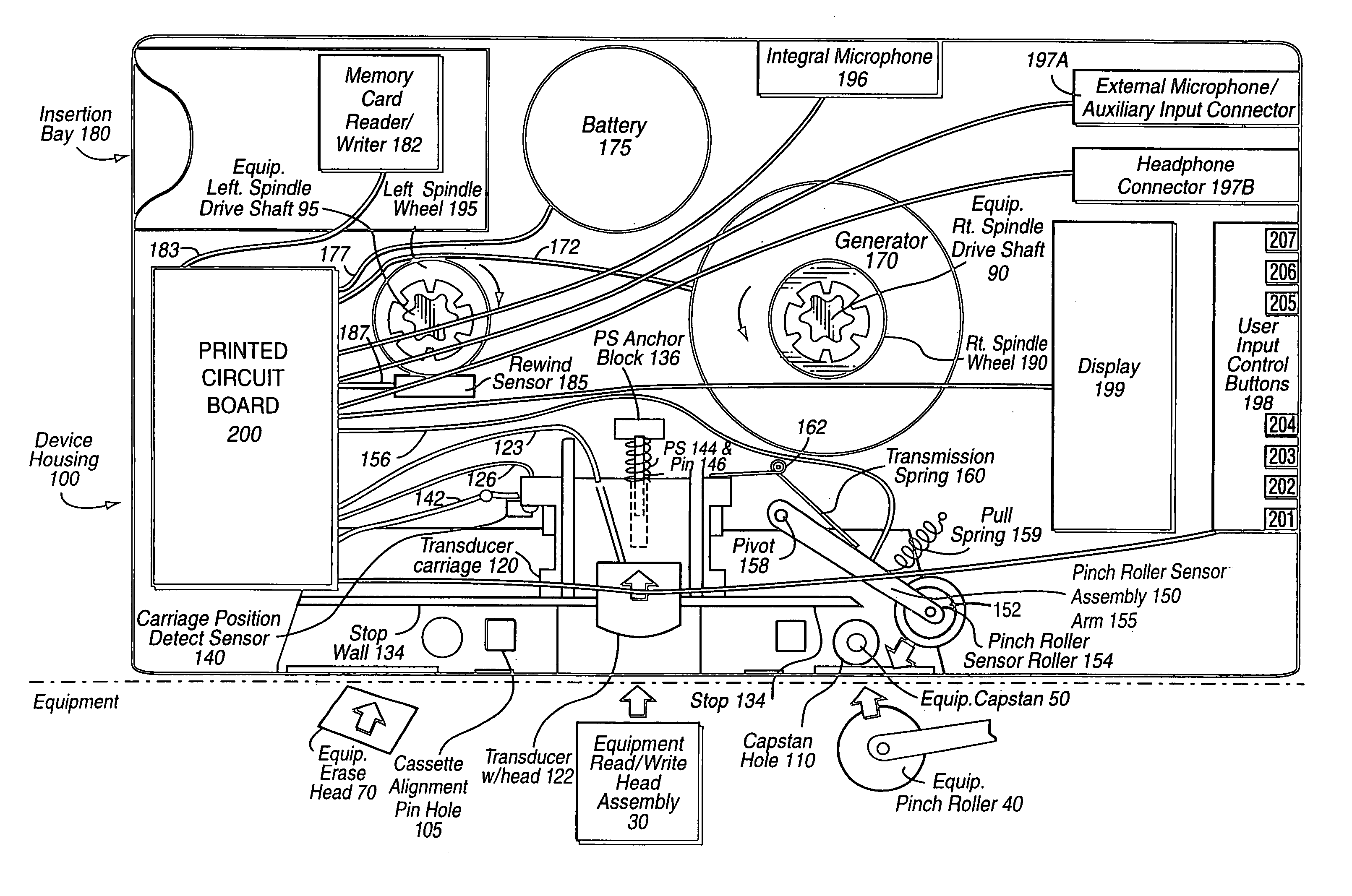

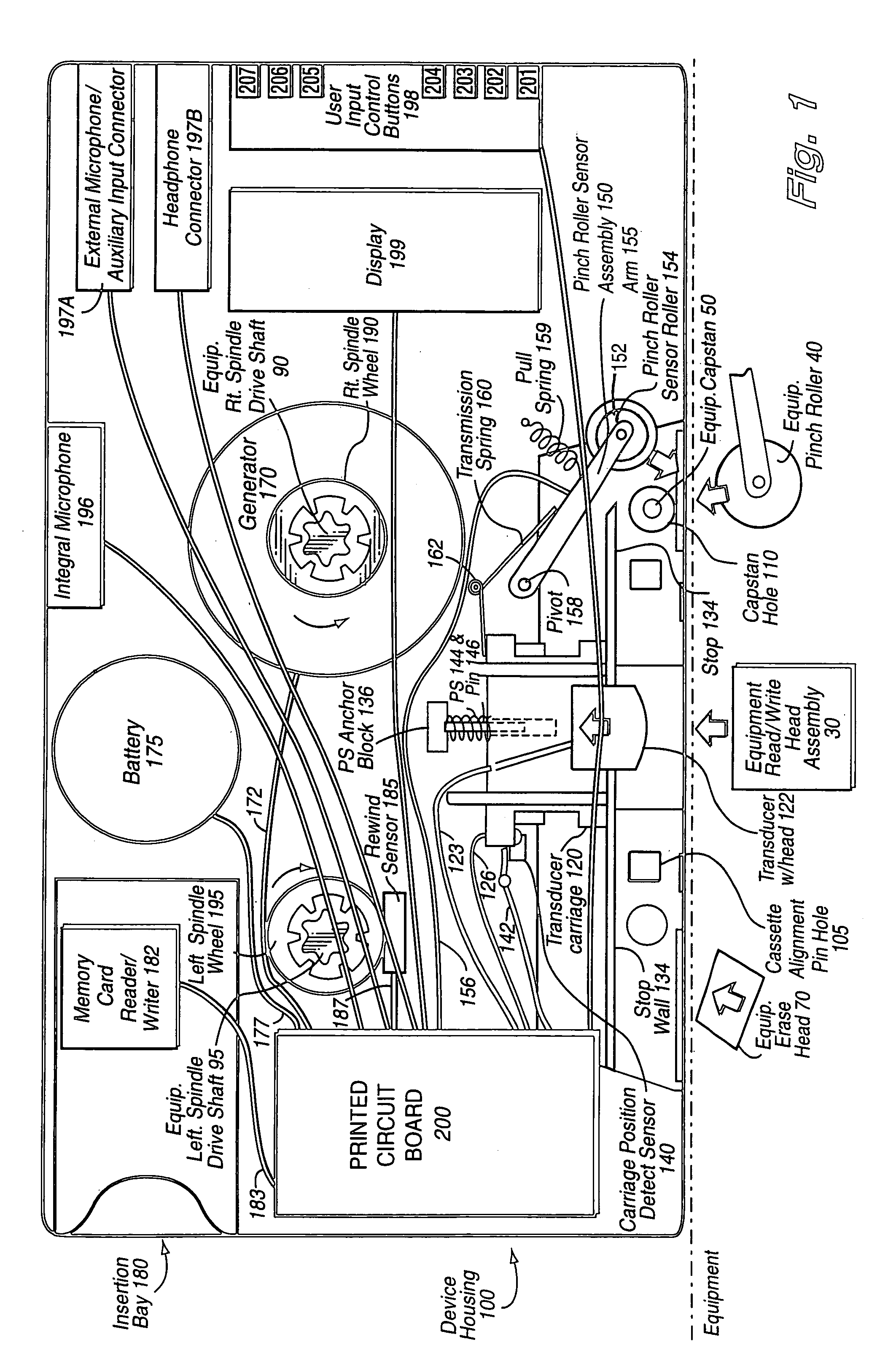

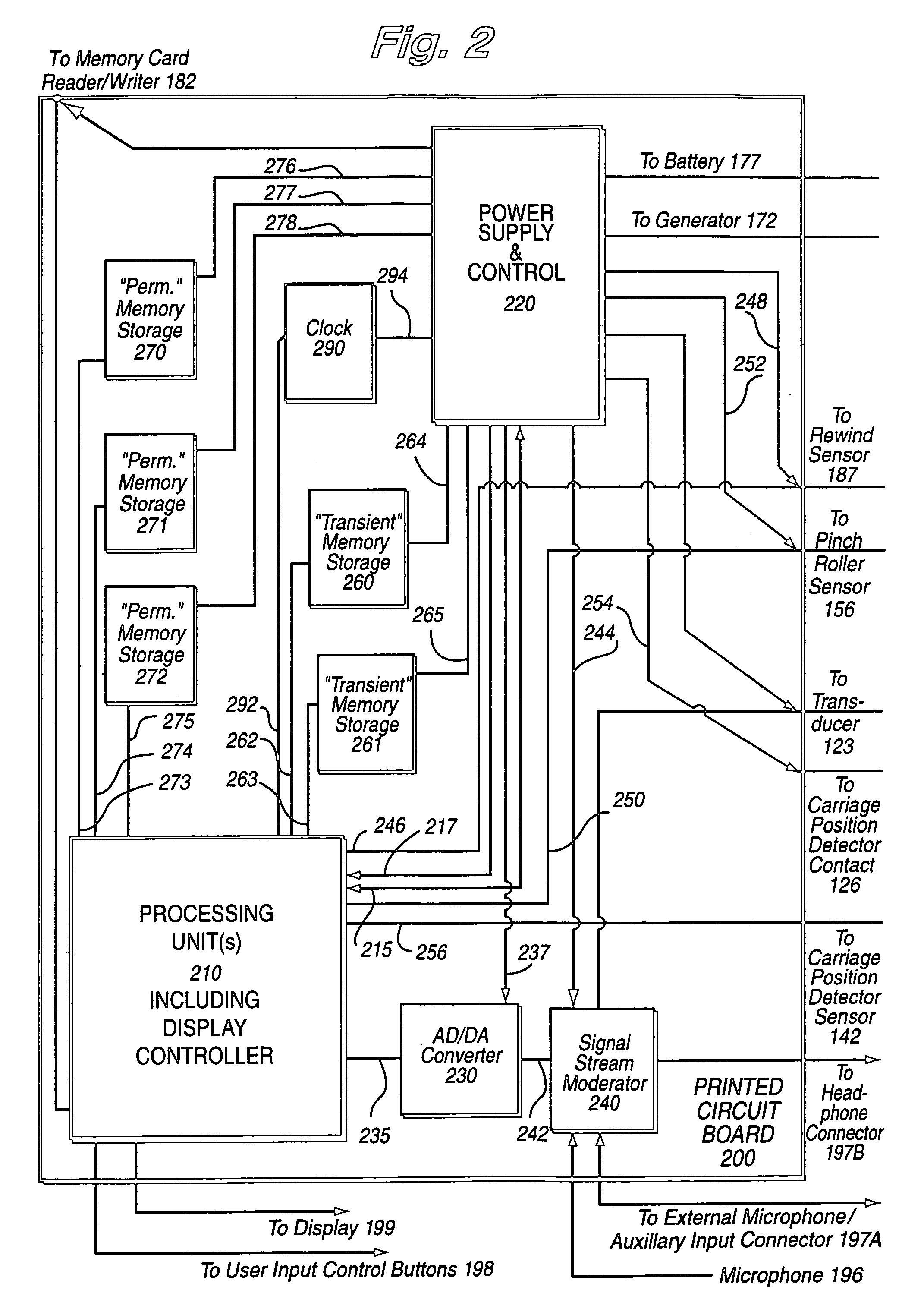

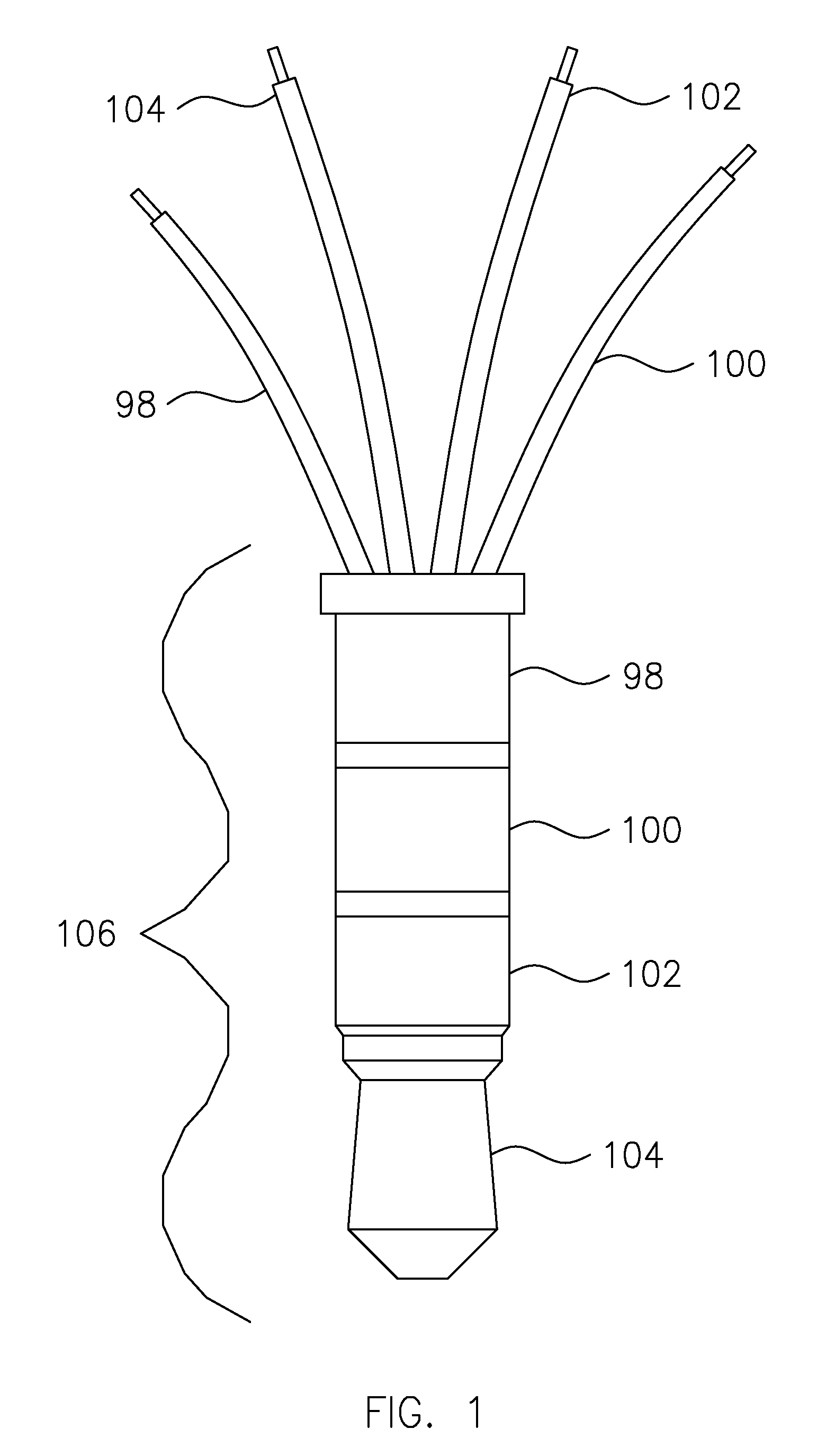

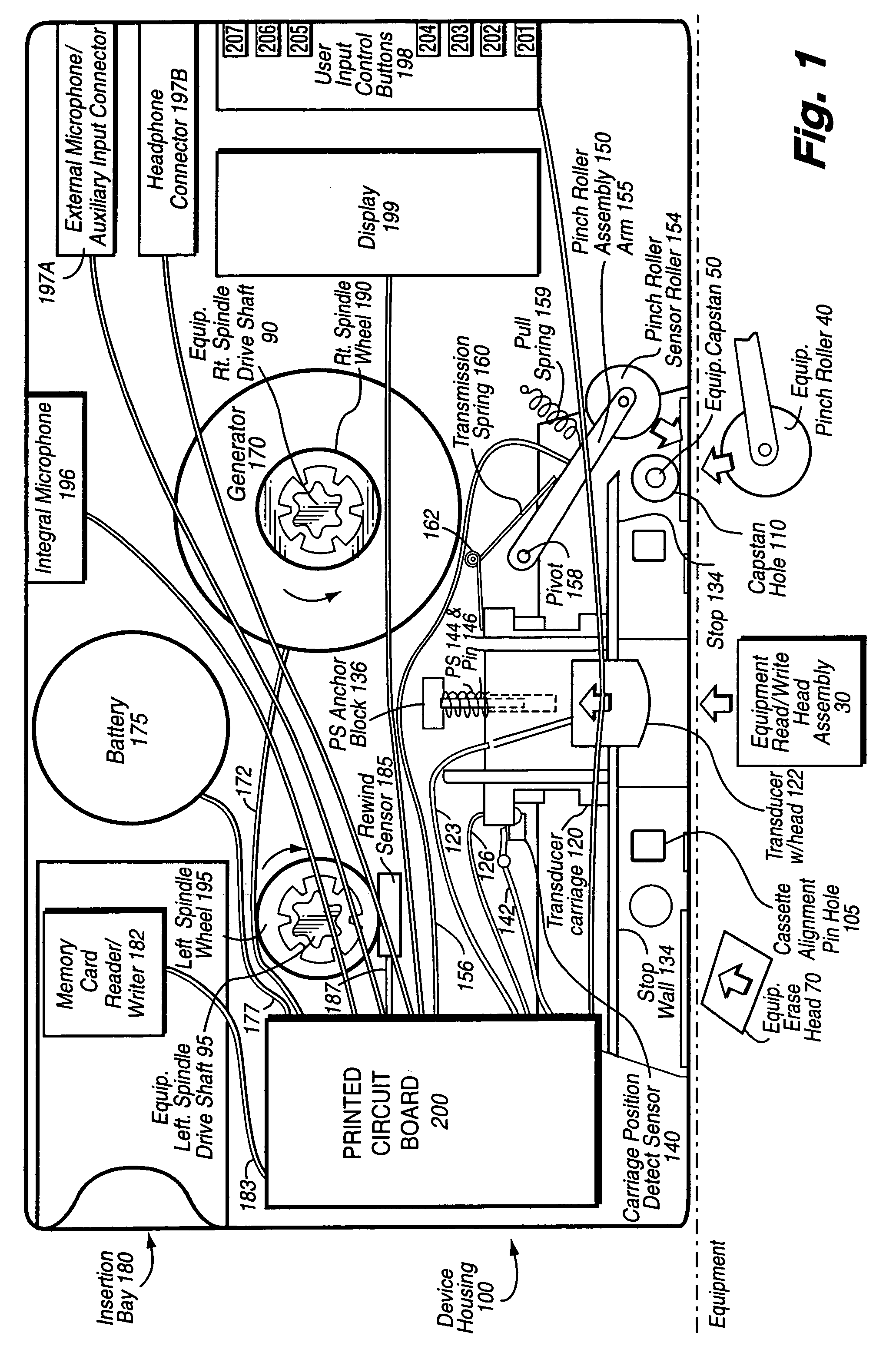

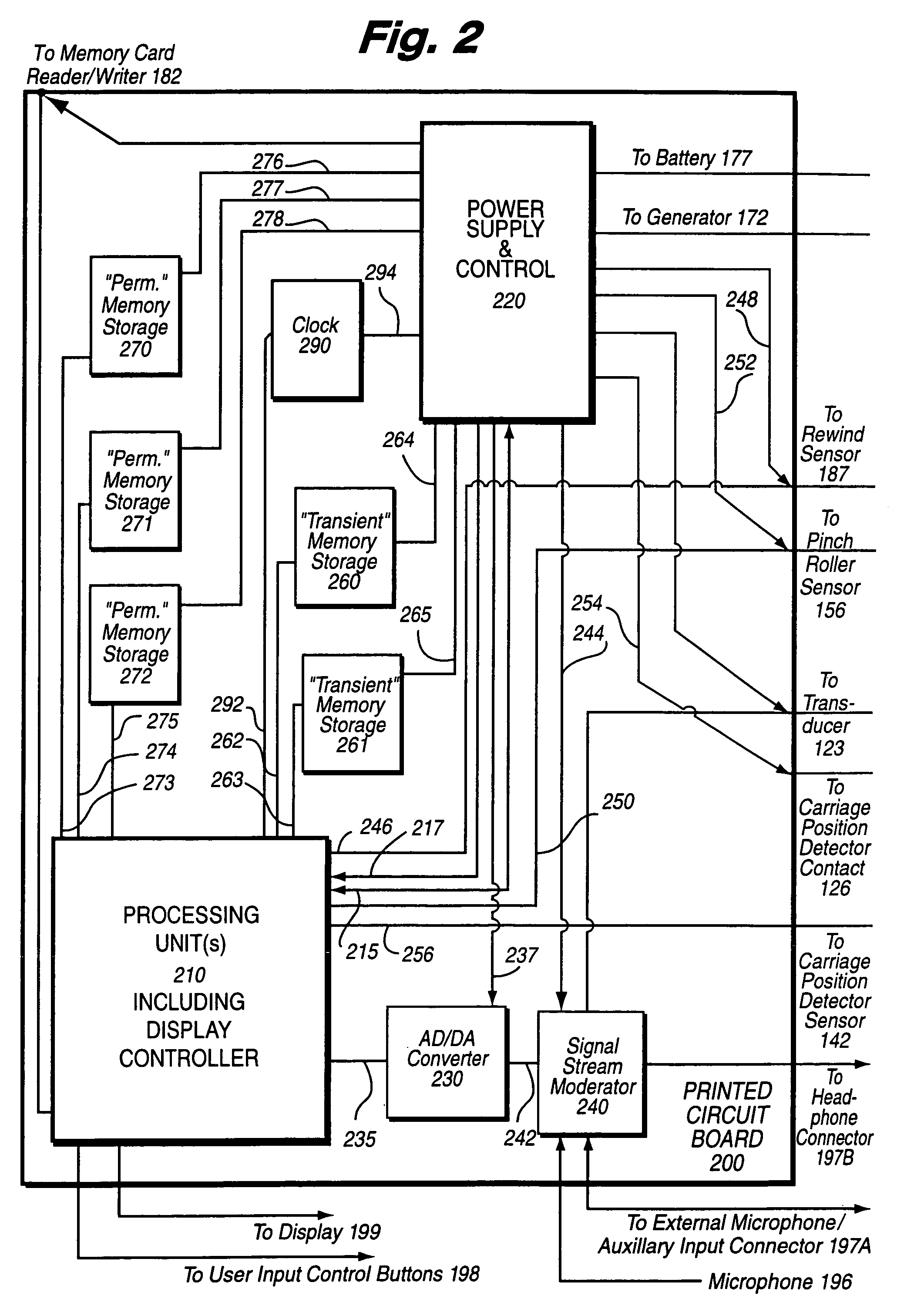

Audio cassette emulator

InactiveUS6941180B1Saving positionSaving stateApparatus for flat record carriersRecord information storageThe InternetMultiple sensor

A device of the same general physical size and shape as a standard audio cassette tape, but which accepts digital information from any of a variety of sources—including for example: Internet transmission, a digital computer, or memory cards (especially digital memory cards)—and plays this digital information through any, for example, standard audio tape cassette player. The device operates by converting the digital representation of the sound into magnetic signals which are presented to the read / write head of the cassette player equipment. The device allows the user of the cassette player to regulate the audio playback using conventional equipment controls such as: START, STOP, REWIND, FAST REWIND, FORWARD, FAST FORWARD, etc. In one exemplary implementation, the device has the same general physical dimensions of a standard audio cassette; at least one digital processor; and a slot into which electronic media such as, for example, memory cards, smart cards having a processor and a memory embodied thereon and other memory media may be inserted. Converter circuitry converts data stored in digital memory to an analog signal which is magnetically coupled to the read head of the equipment. Numerous sensors detect changes in at least one of the tape equipment mechanisms in the audio cassette emulator.

Owner:FISCHER ADDISON M

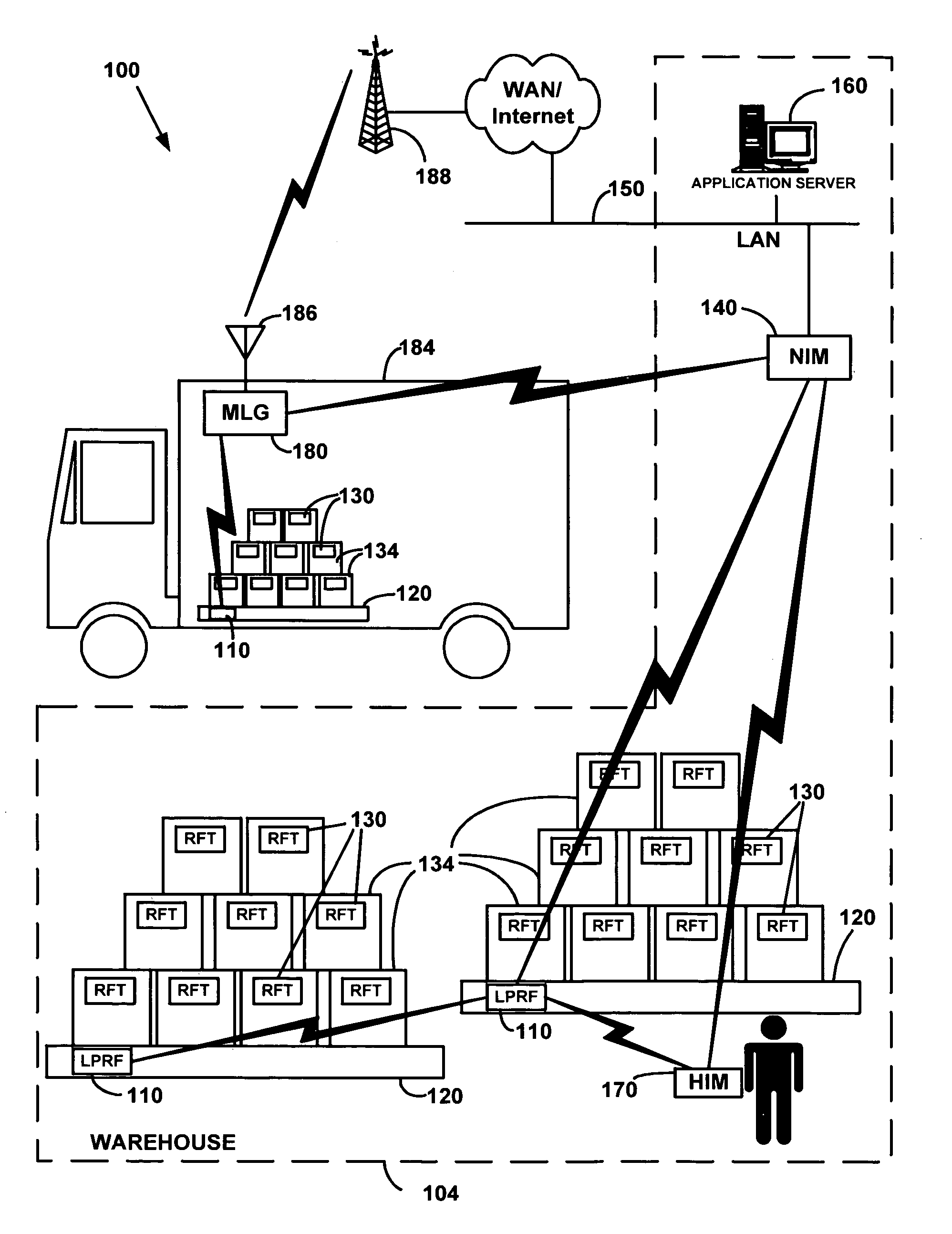

Forming ad hoc RSI networks among transceivers sharing common designation

InactiveUS7200132B2High sensitivityIncrease rangeEnergy efficient ICTPosition fixationWireless transceiverTransceiver

A method of forming ad hoc RSI hierarchical communication networks among pluralities of wireless transceivers includes assigning to each of the transceivers one or more common designations. A network organization routine of the transceivers operates to establish hierarchical networks based on the transceivers' common designations, resulting in a logical network organization that provides efficiencies for acquiring information from particular transceivers that share a common designation. Each transceiver's common designation is used by a digital processor of the transceiver to selectively receive data packets that are intended for receipt by transceivers sharing the particular common designation. Such a “common designation” network reduces power consumption and signal interference thereby increasing battery life. Each transceiver may include a sensor interface a query handling routine in communication with a memory of the transceiver for serving as a dynamic distributed hierarchical database system of information such as, for example, sensor-derived information and time-sensitive information.

Owner:GOOGLE LLC

LADAR sensor for a dense environment

A multi-ladar sensor system is proposed for operating in dense environments where many ladar sensors are transmitting and receiving burst mode light in the same space, as may be typical of an automotive application. The system makes use of several techniques to reduce mutual interference between independently operating ladar sensors. In one embodiment, the individual ladar sensors are each assigned a wavelength of operation, and an optical receive filter for blocking the light transmitted at other wavelengths, an example of wavelength division multiplexing (WDM). Each ladar sensor, or platform, may also be assigned a pulse width selected from a list, and may use a pulse width discriminator circuit to separate pulses of interest from the clutter of other transmitters. Higher level coding, involving pulse sequences and code sequence correlation, may be implemented in a system of code division multiplexing, CDM. A digital processor optimized to execute mathematical operations is described which has a hardware implemented floating point divider, allowing for real time processing of received ladar pulses, and sequences of pulses.

Owner:CONTINENTAL AUTONOMOUS MOBILITY US LLC

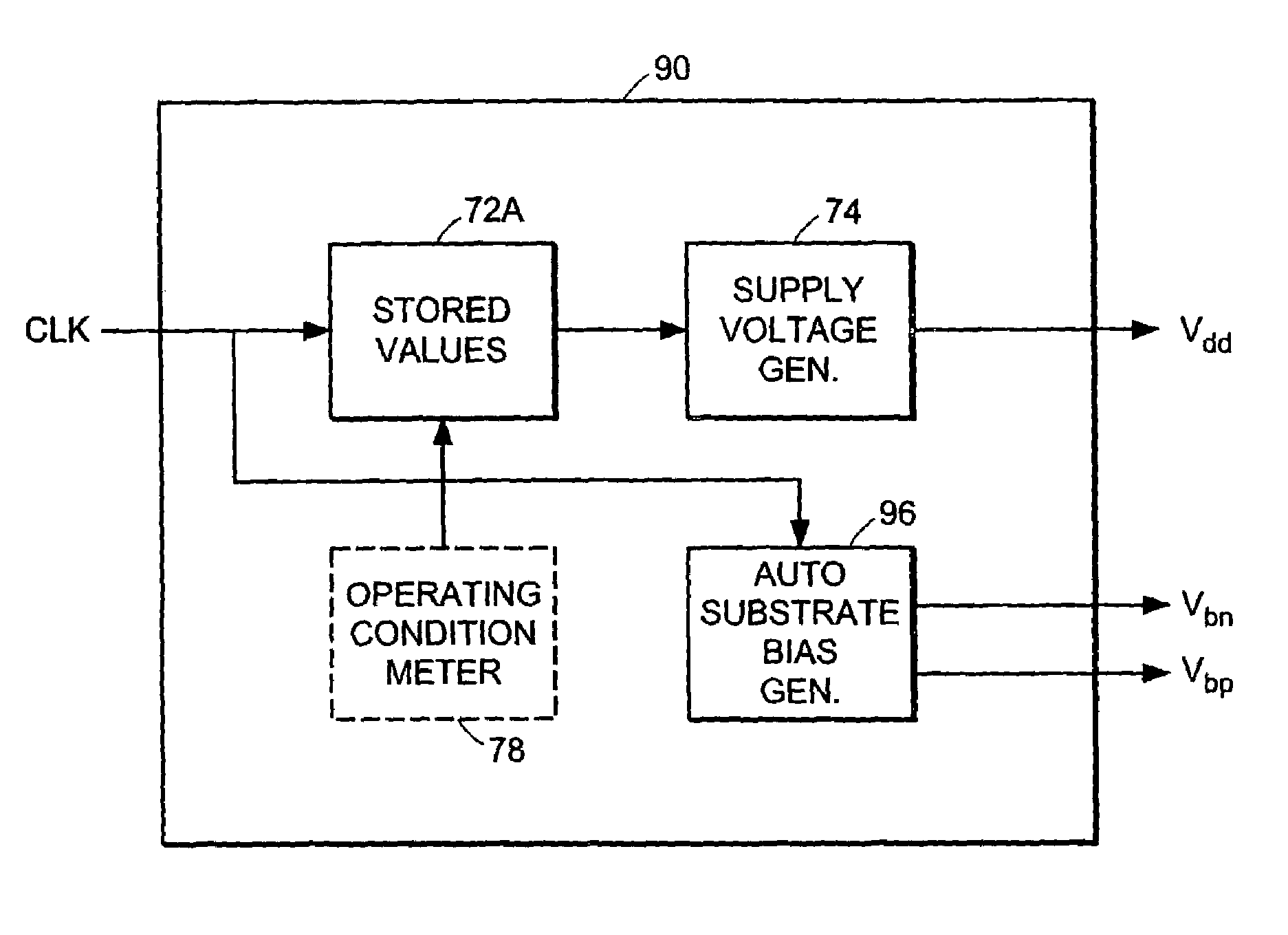

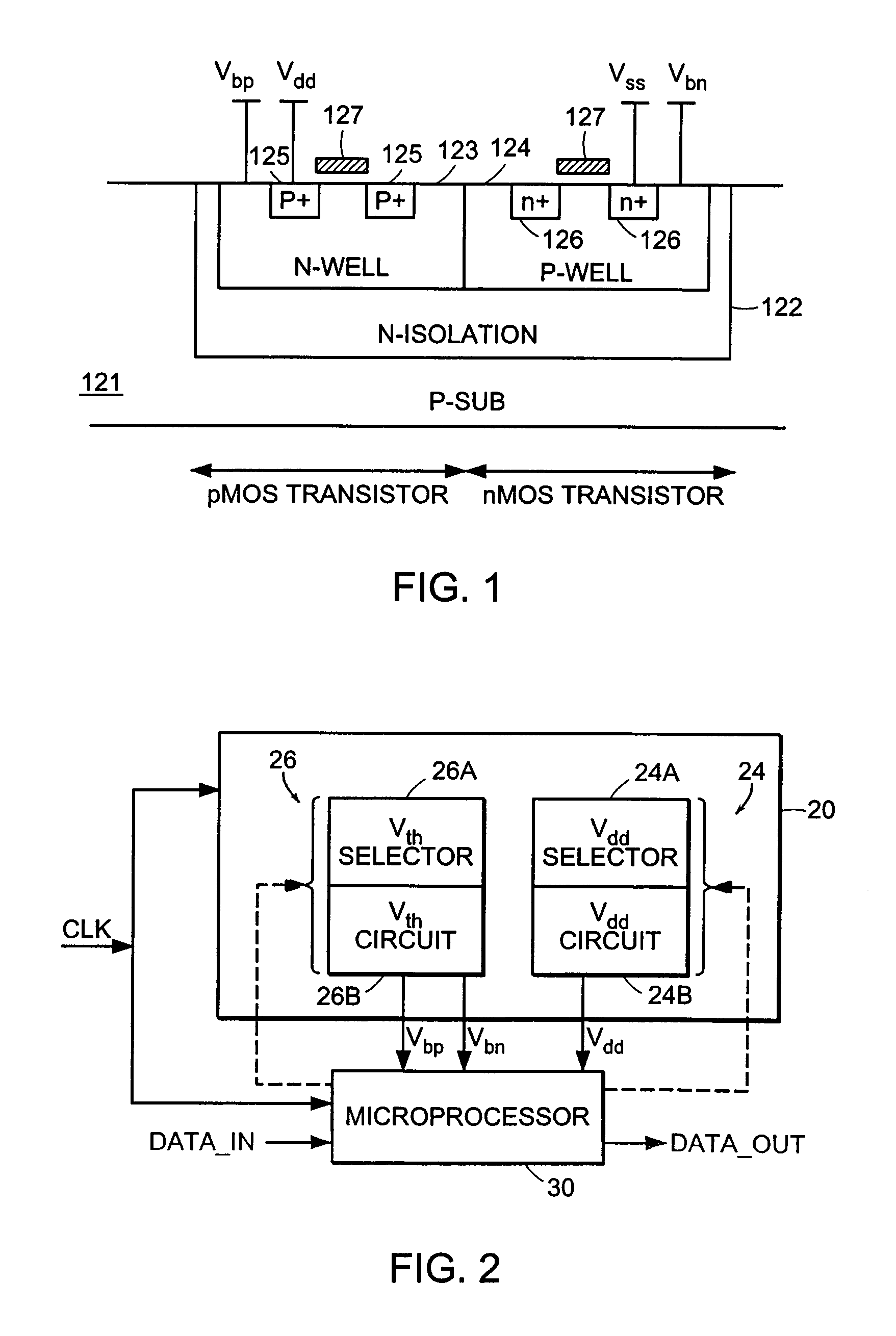

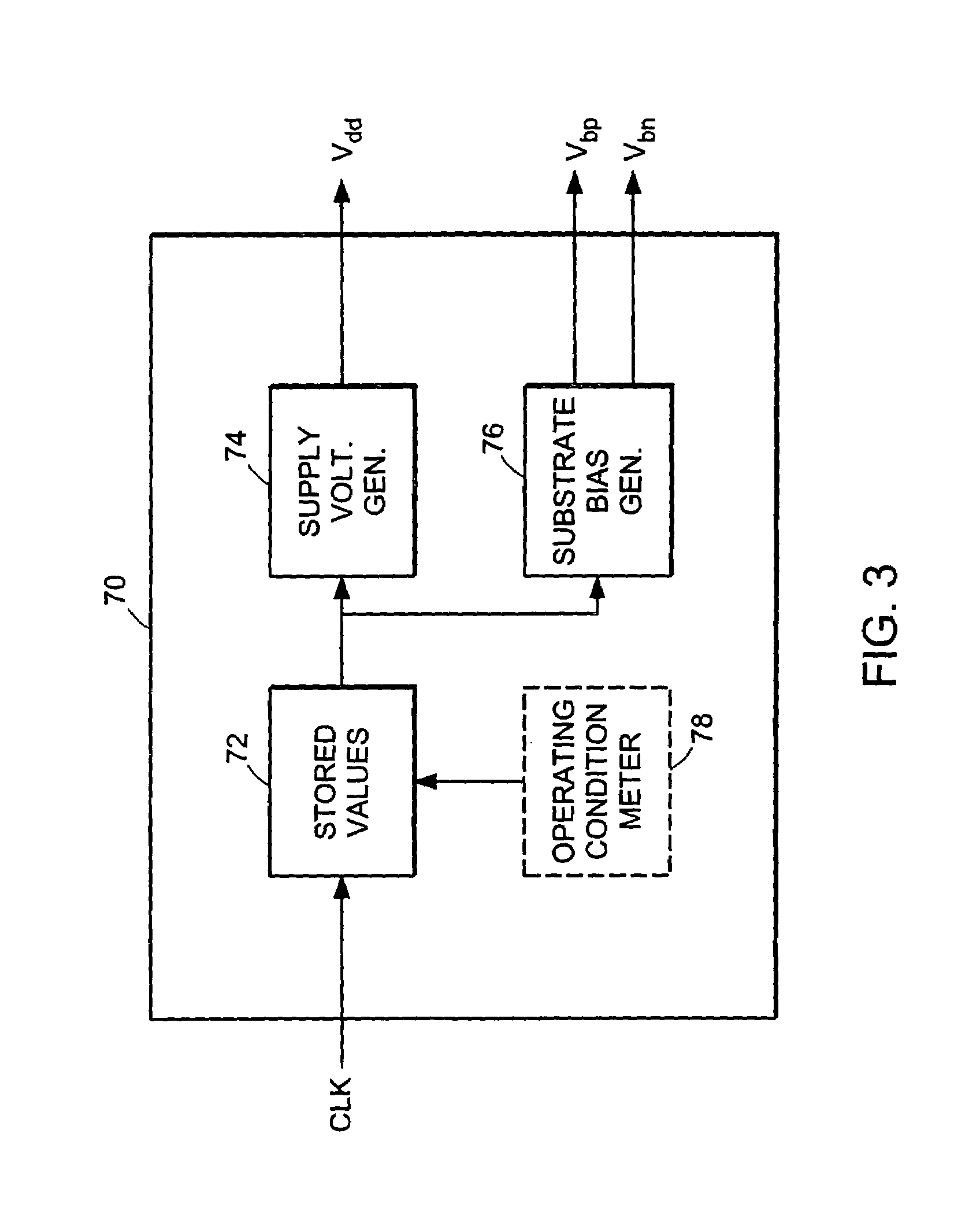

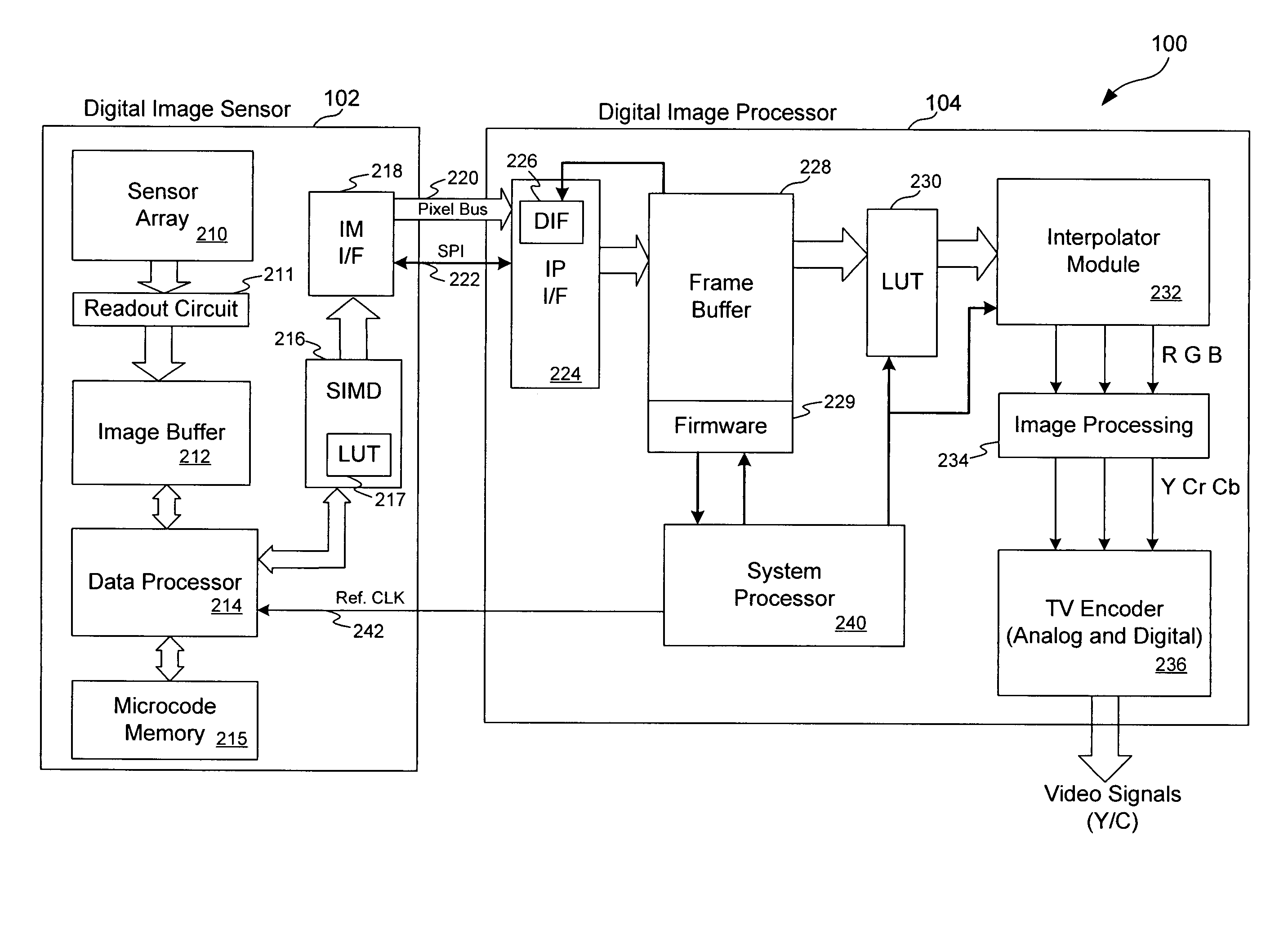

Adaptive power supply and substrate control for ultra low power digital processors using triple well control

InactiveUS6967522B2Improve power efficiencyMinimize power consumptionElectric pulse generator detailsElectric variable regulationEngineeringSelf adaptive

A system for improving the power efficiency of an electronic device includes a threshold voltage selector and a supply voltage selector. The threshold voltage selector selects a value of a threshold voltage for operation of the device in response to a present operating condition of the device. The supply voltage selector selects a value of a supply voltage to be applied to the device in response to the present operating condition of the device. The value of the threshold voltage and the value of the supply voltage control a power consumption of the device.

Owner:MASSACHUSETTS INST OF TECH

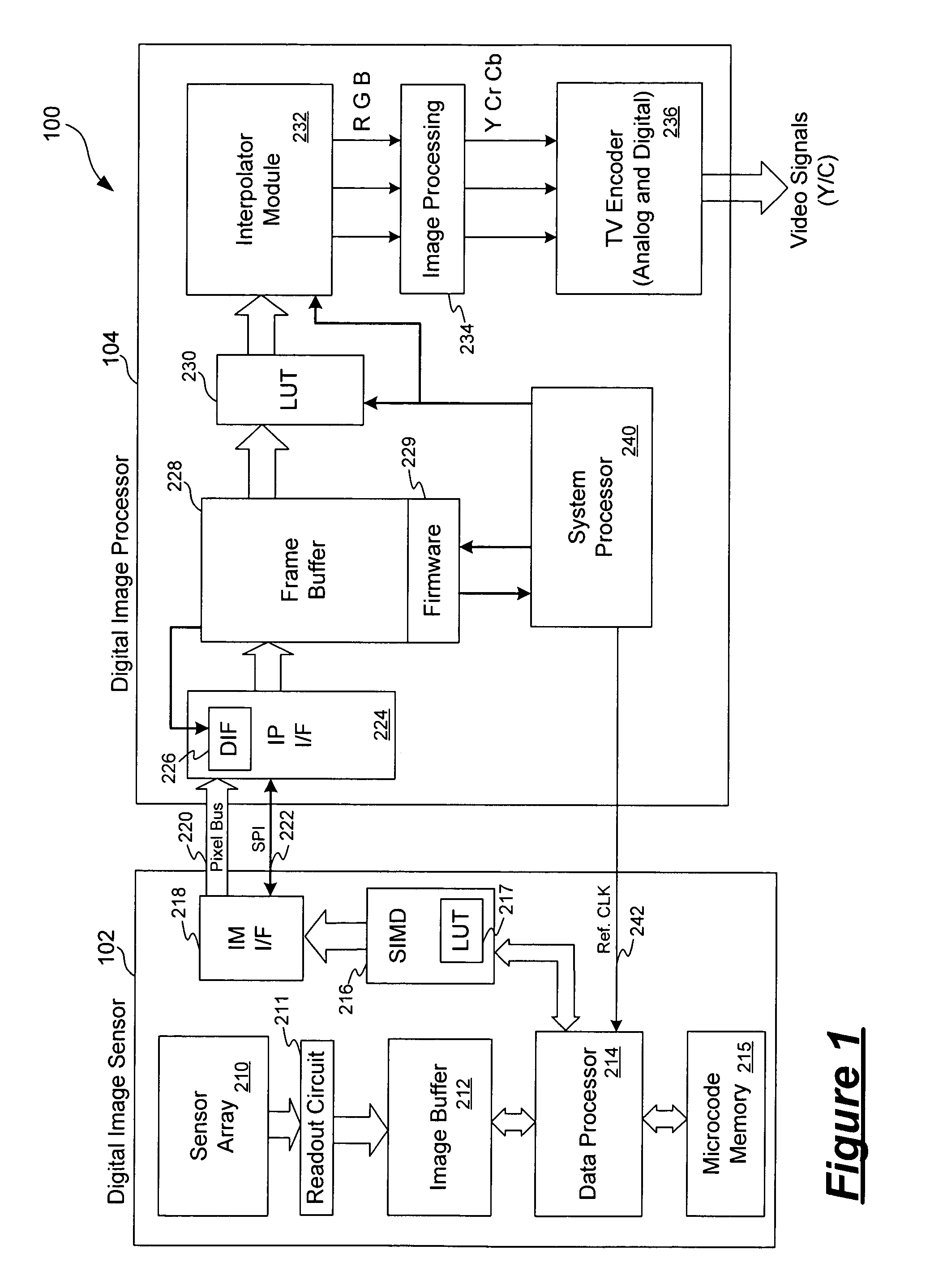

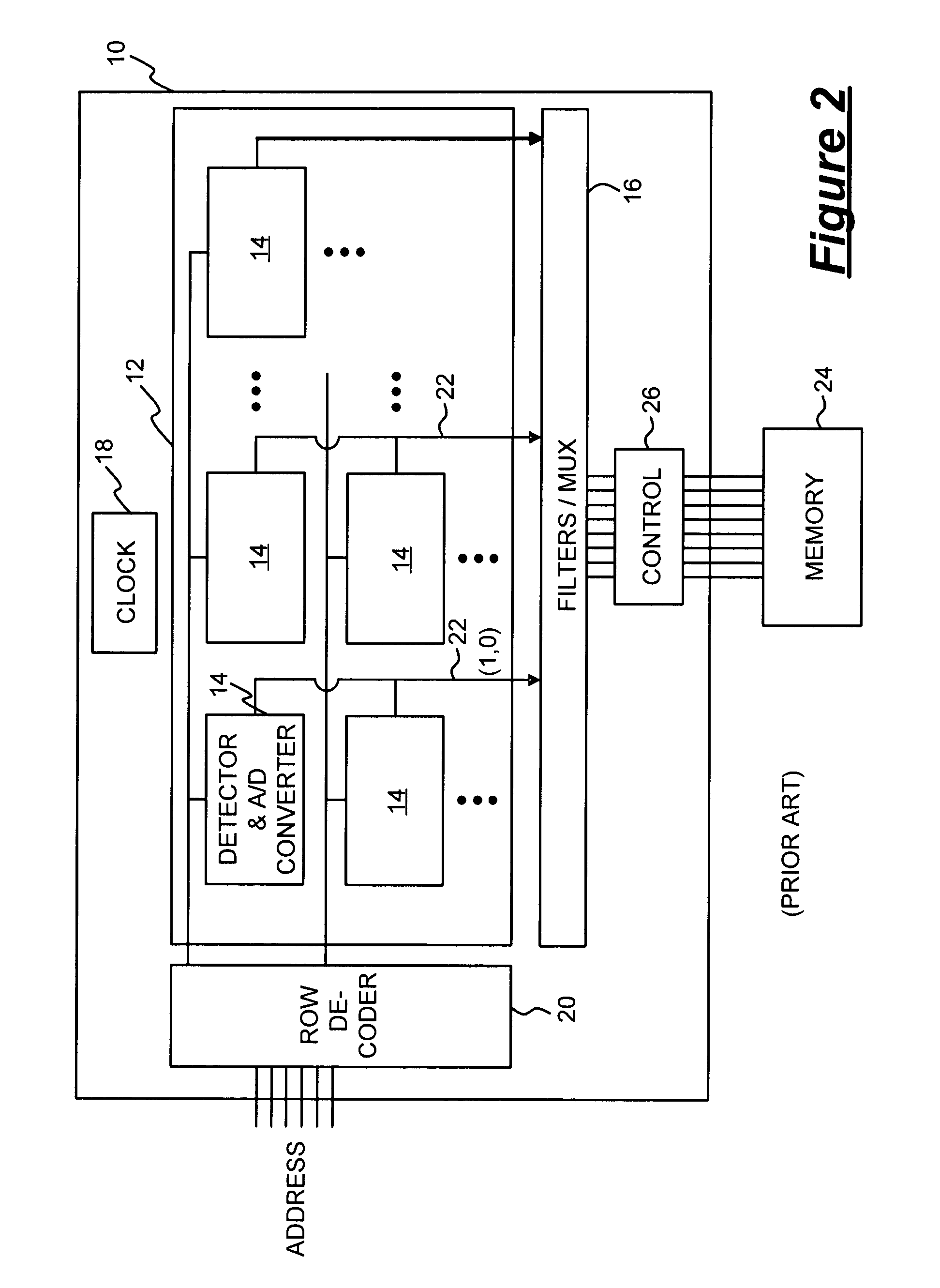

Video imaging system including a digital image sensor and a digital signal processor

ActiveUS7483058B1Reduce noiseRemove random noiseTelevision system detailsColor television detailsSensor arrayDigital signal processing

A video imaging system includes a digital image sensor for performing image capture operations and a digital image processor for performing image processing operations. The digital image sensor includes a sensor array outputting digital pixel data, an image buffer for storing the pixel data, a first processor and a first interface circuit for transferring the pixel data onto a pixel bus. The digital image processor includes a second interface circuit coupled to receive the pixel data from the pixel bus, a frame buffer coupled to store the pixel data, an image processing pipeline for processing the pixel data stored in the frame buffer into video data, and a second processor. The digital image sensor and the digital image processor transfer control information over a control interface bus and the digital image sensor performs the image capture operations independent of the image processing operations performed by the digital image processor.

Owner:PIXIM

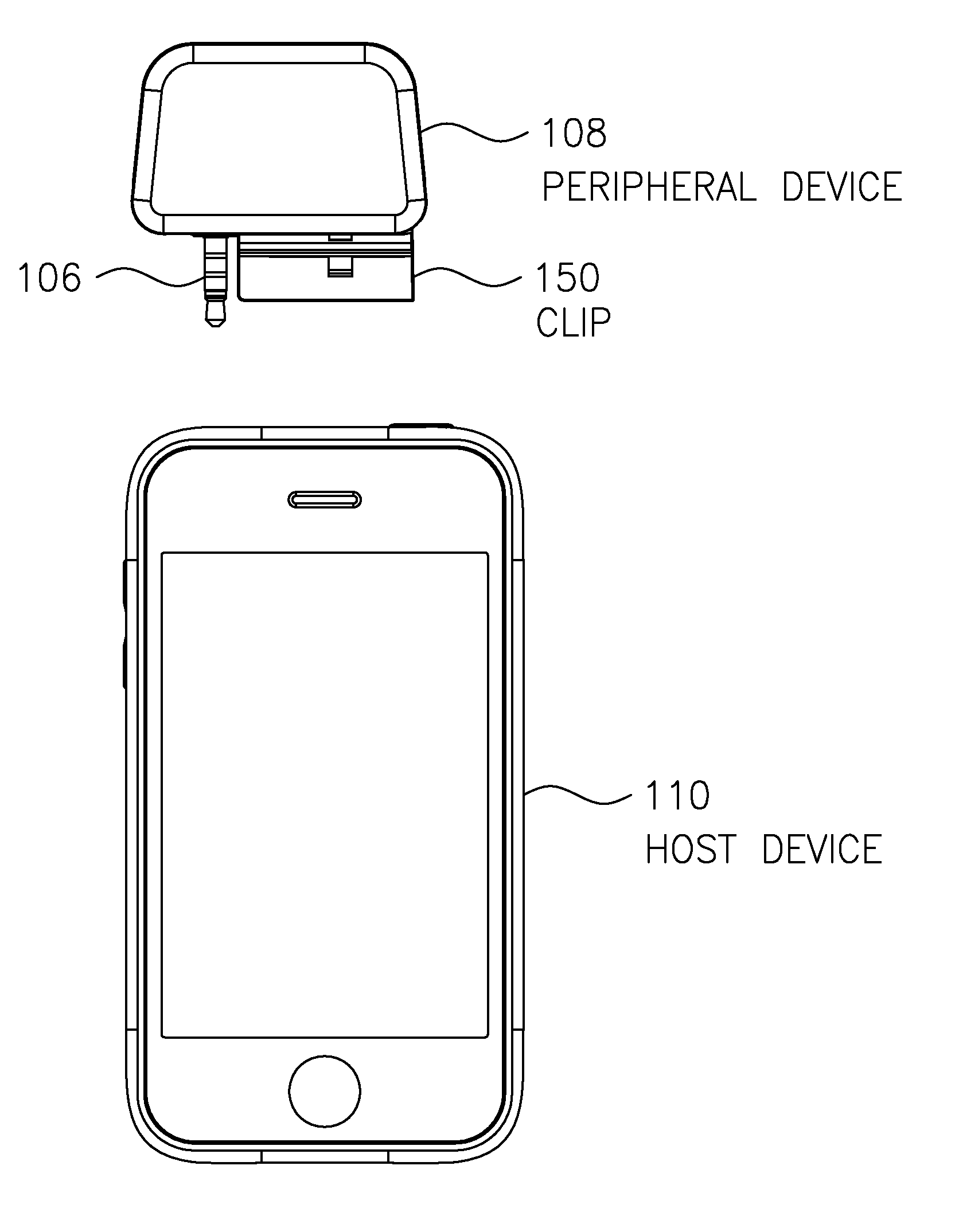

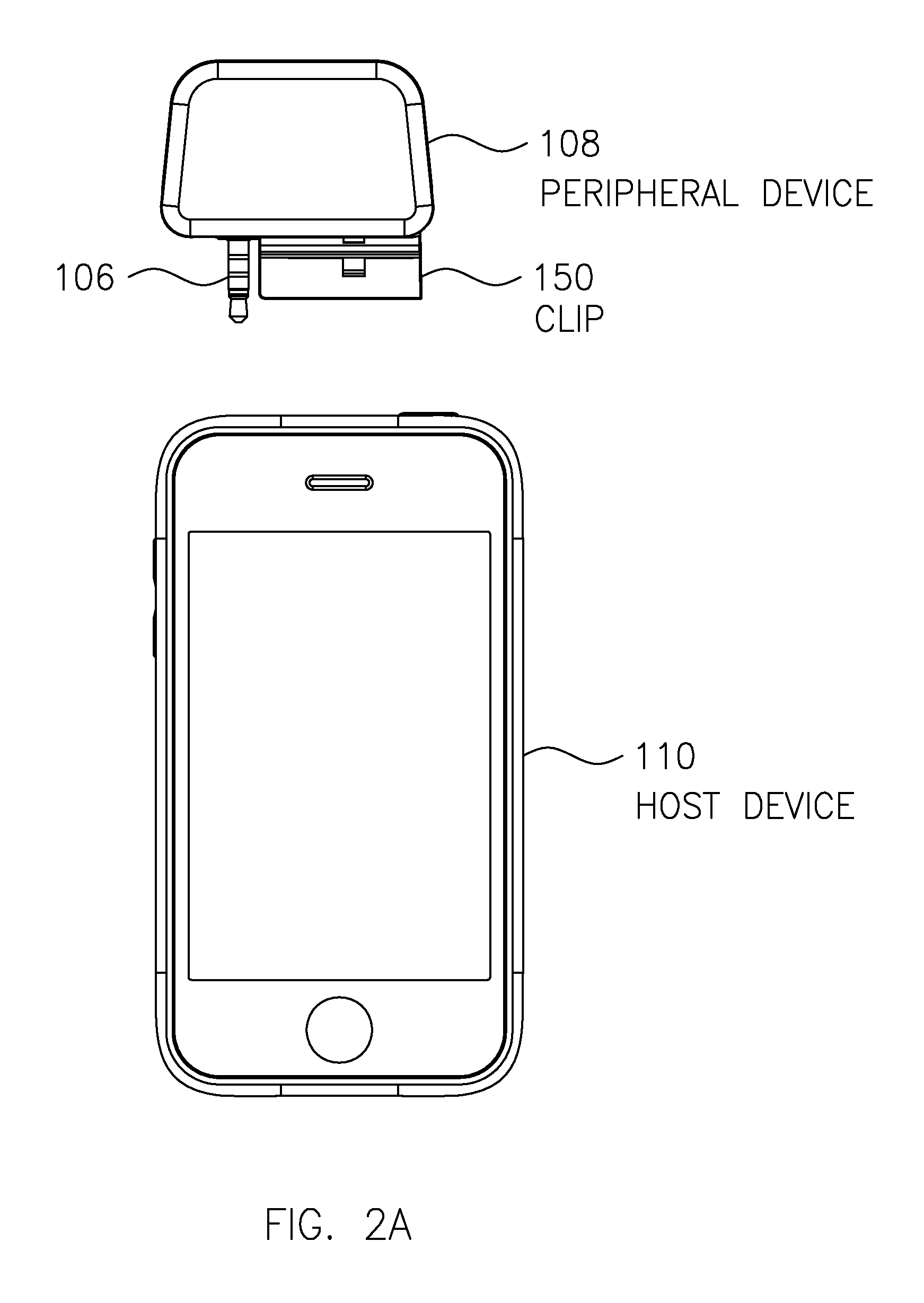

Audio port communication and power device

InactiveUS20120052910A1Facilitate communicationDevices with card reading facilitySubstation equipmentCard readerAudio frequency

Versions of the present invention have many advantages, including providing communication devices that can transact on a universal peripheral device with a host device that may have different serial interface connectors, proprietary communication protocols or mechanical shapes. Among the many other advantages include that the peripheral device does not need a power source aside from the power supplied to it by the host device.One embodiment is a communication device comprising a host device comprised of software and an audio connector input; a peripheral device comprised of an analog and digital processor, a card reader and an audio connector output; and an audio connector line connecting said audio connector output and said audio connector input.

Owner:ID TECK

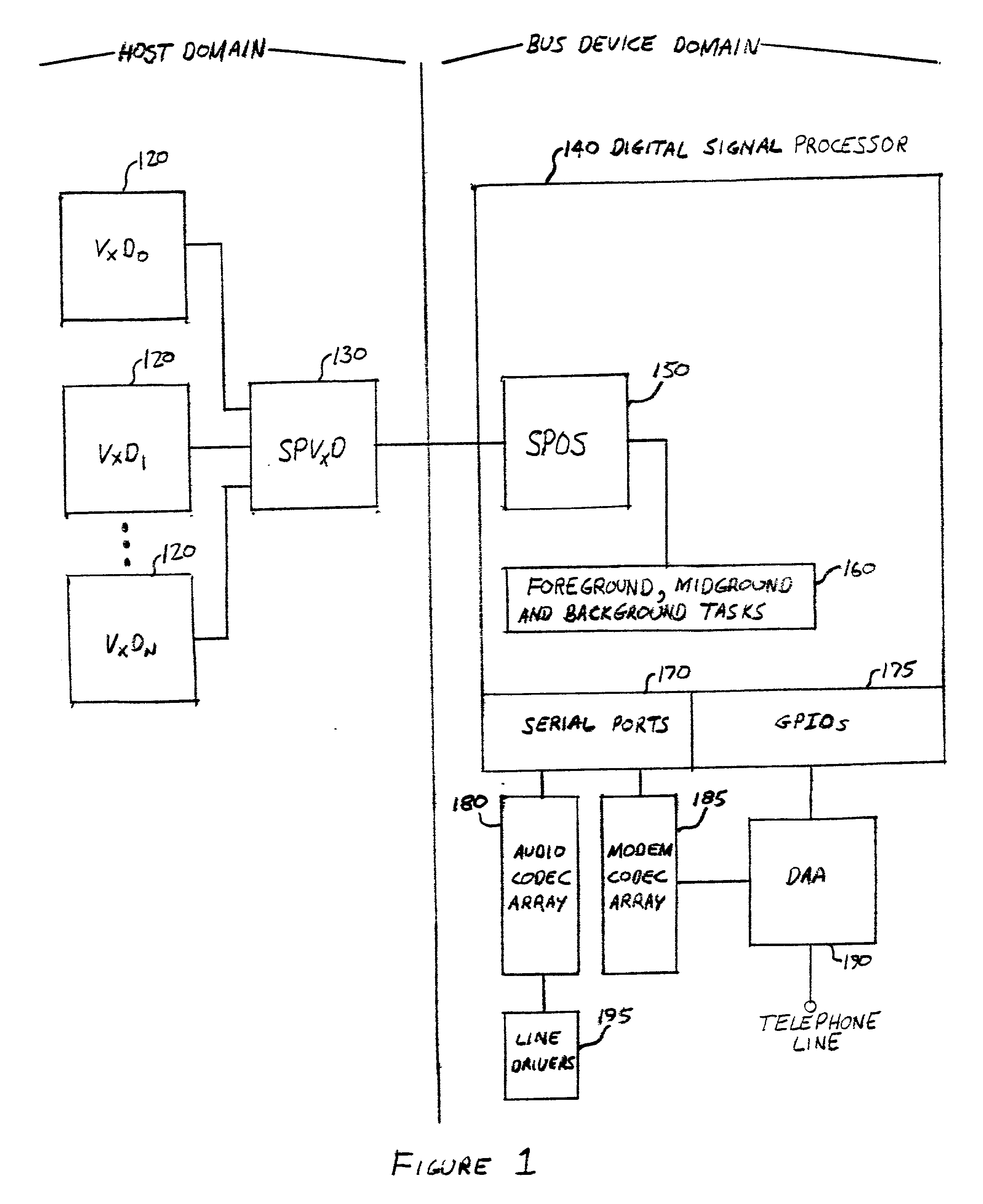

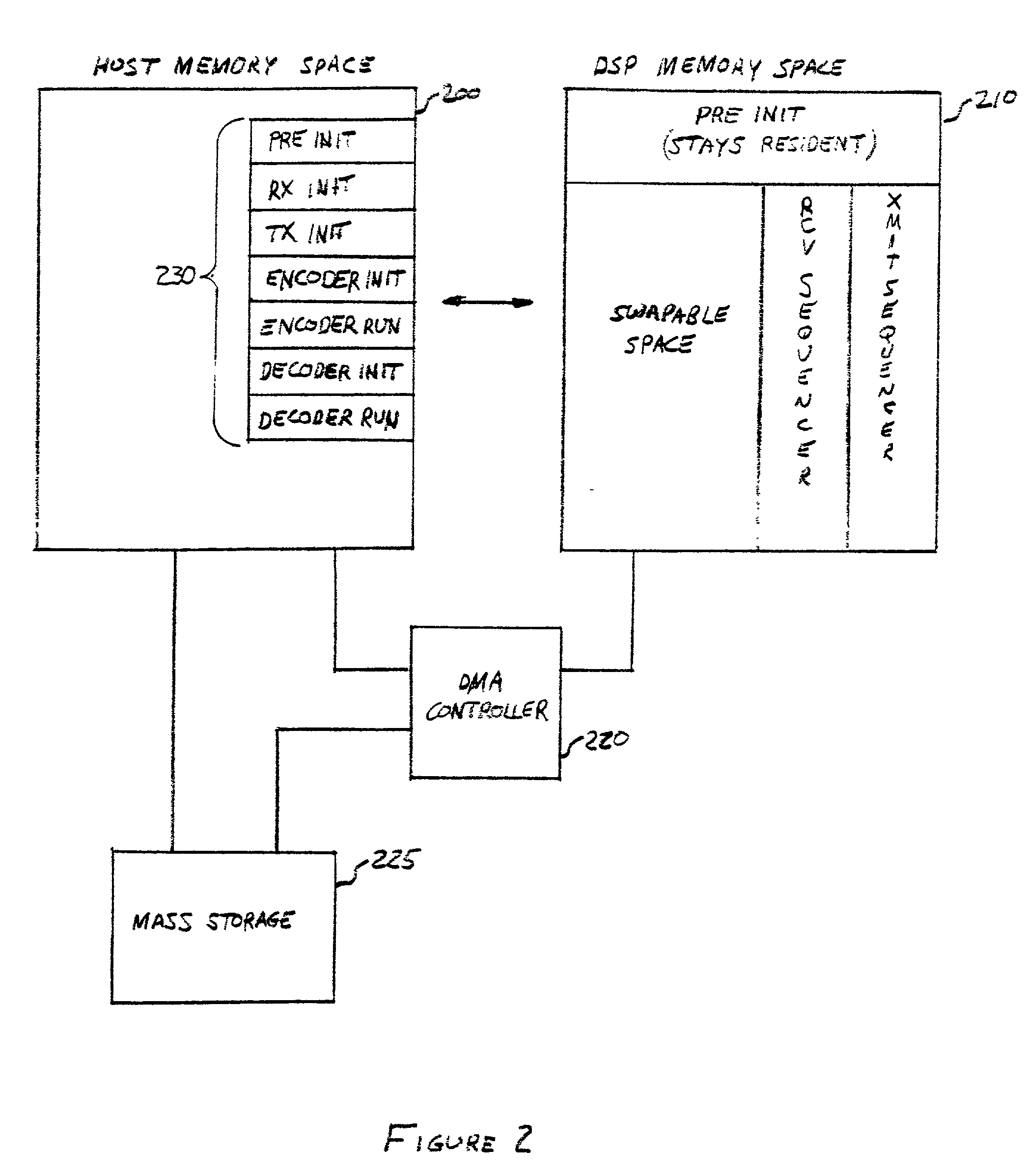

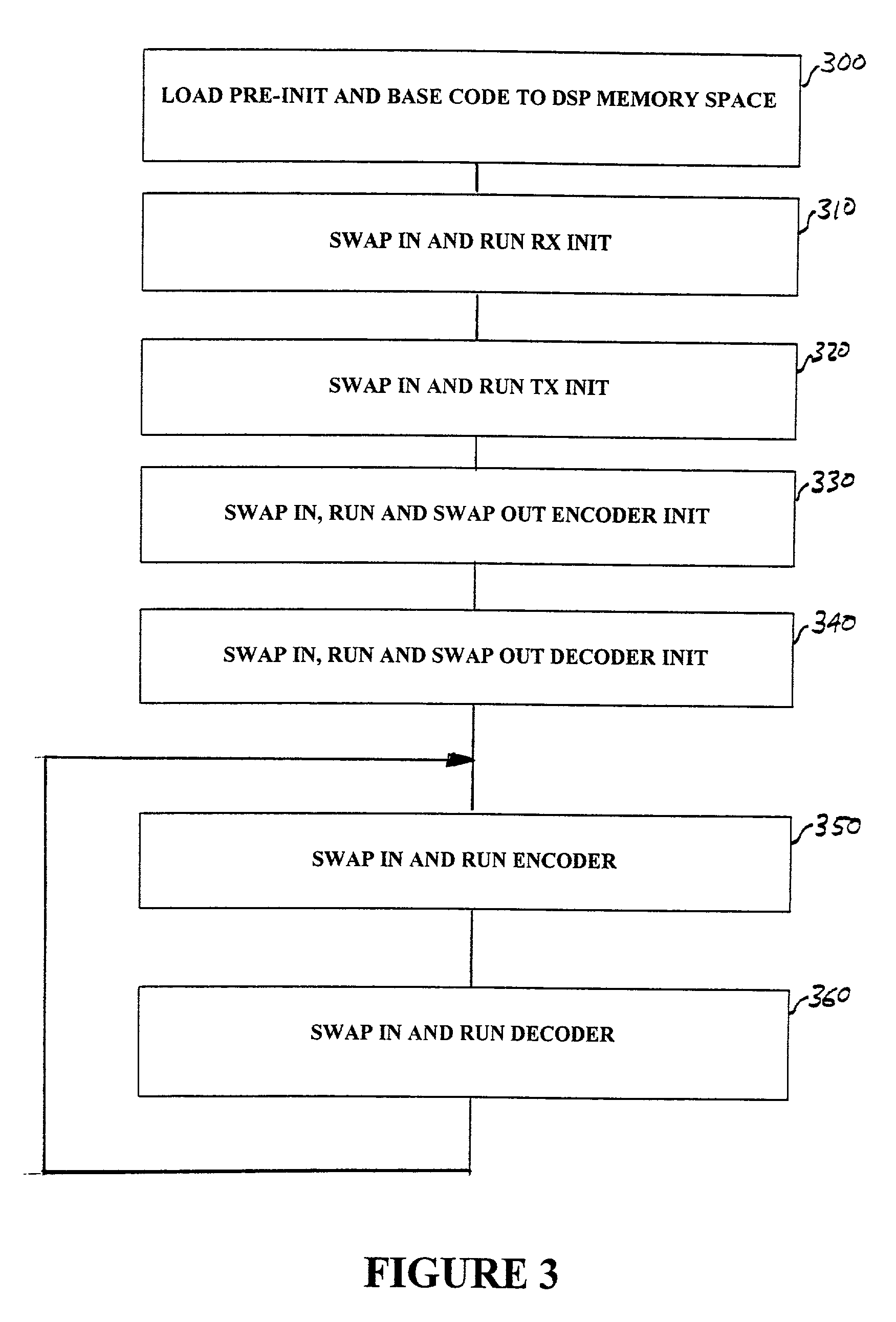

Modem using a digital signal processor and a signal based command set

InactiveUS20010011213A1Modulated-carrier systemsMultiprogramming arrangementsDigital signal processingModem device

Modems are implemented using a language made of instructions or commands which are based on the types of signals needed to be generated or processed by the modem. That is, the commands are individually tailored to specify the signals to be sent or processed. The modems can be implemented on a digital signal processor or on a host. The language permits a terseness of expression resulting in smaller code, makes it easy to express the needed manipulations required for modem functionality and permits faster execution.

Owner:INTEL CORP

Forming communication cluster of wireless AD HOC network based on common designation

InactiveUS7209468B2High sensitivityIncrease rangeEnergy efficient ICTPosition fixationWireless transceiverTransceiver

A method of forming an ad hoc hierarchical communication network among a plurality of wireless transceiver includes assigning to each of the transceivers one or more common designations. A network organization routine of the transceivers operates to establish hierarchical networks based on the transceivers' common designations, resulting in a logical network organization that provides efficiencies for acquiring information from particular transceivers that share a common designation. Each transceiver's common designation is used by a digital processor of the transceiver to selectively receive data packets that are intended for receipt by transceivers sharing the particular common designation. Such a “common designation” network reduces power consumption and signal interference, which increases battery life in the transceivers. The transceivers may include a query handling routine in communication with a memory of the transceiver for serving as a dynamic distributed hierarchical database system of information such as, for example, sensor-derived information and time-sensitive information.

Owner:GOOGLE LLC

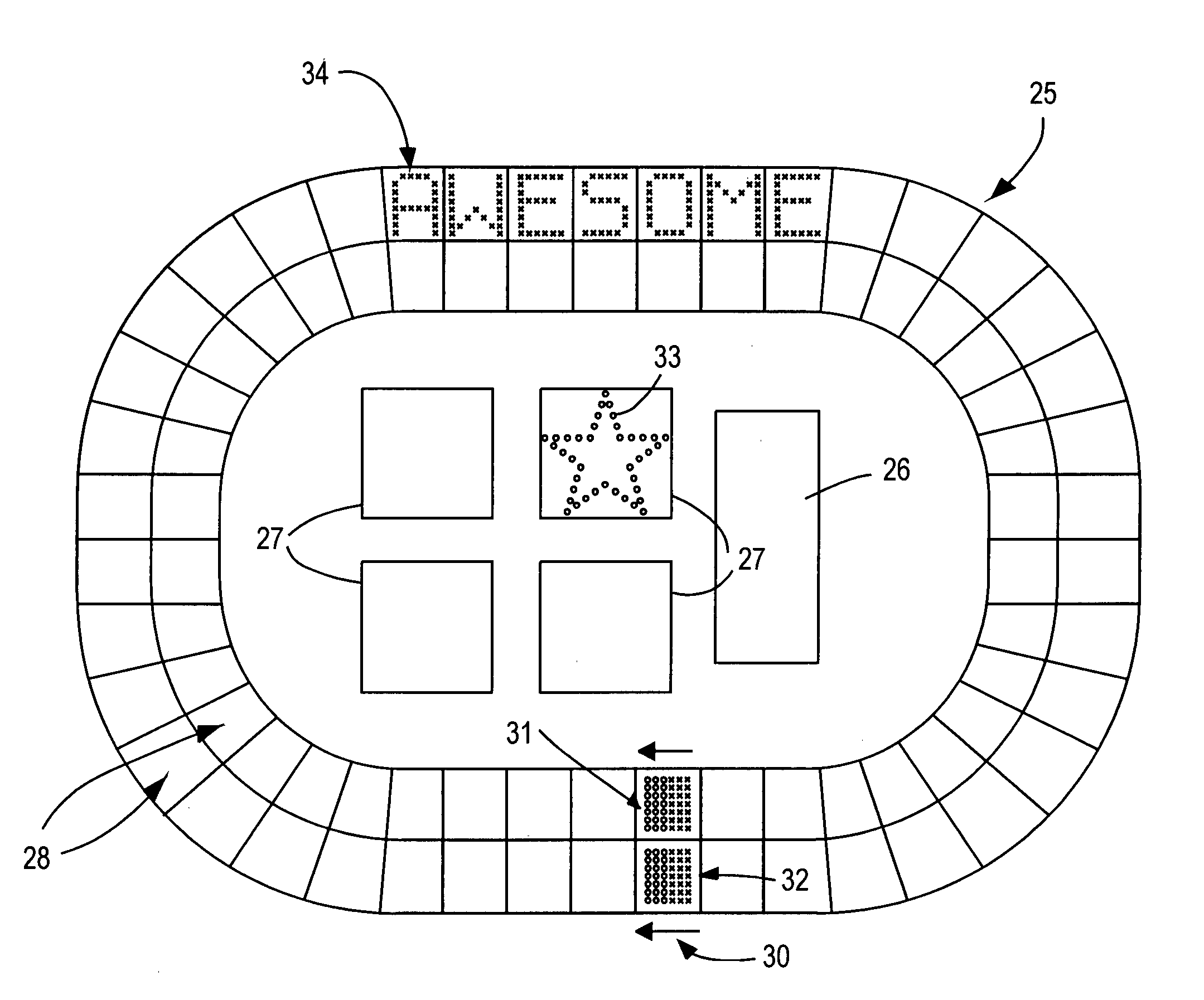

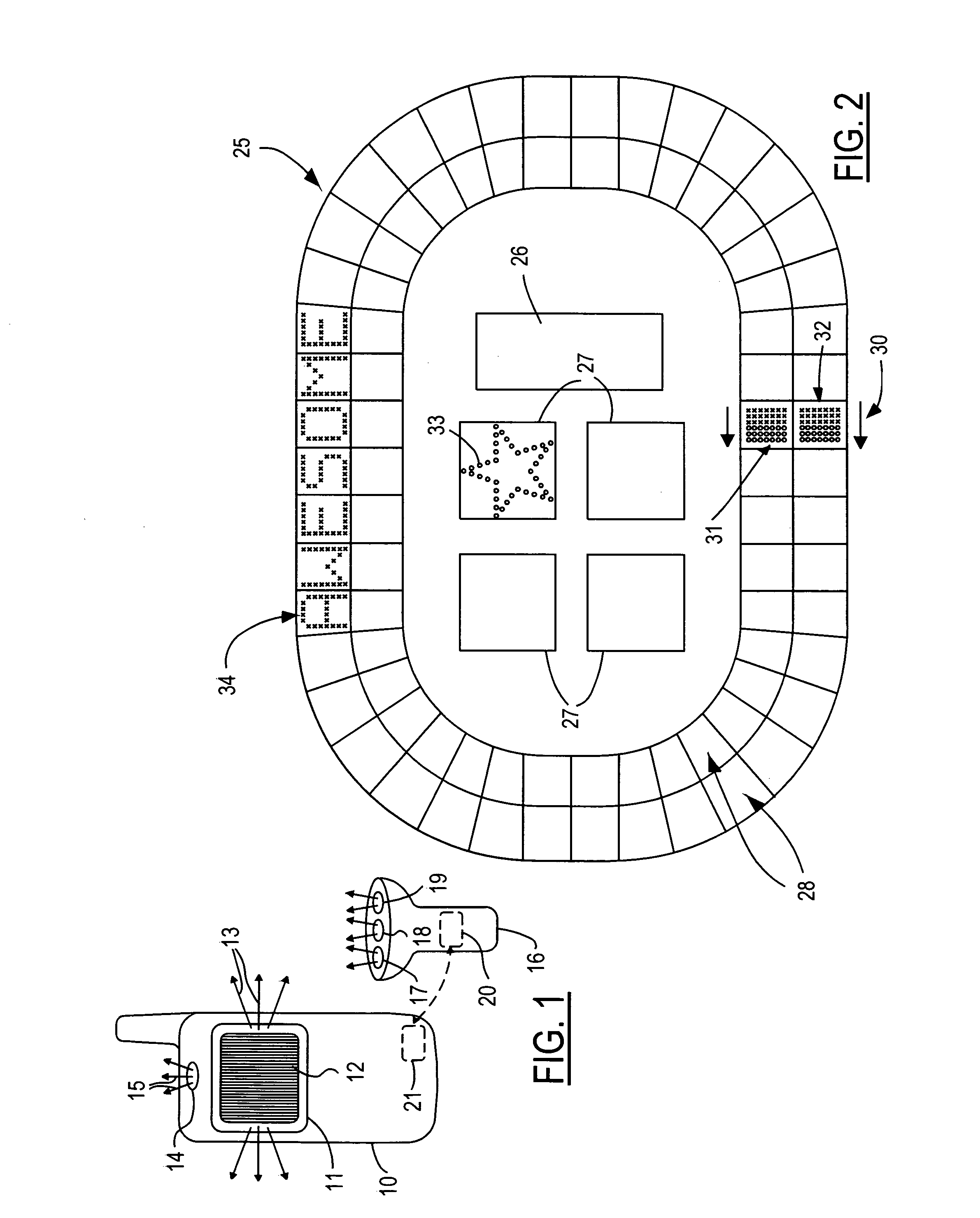

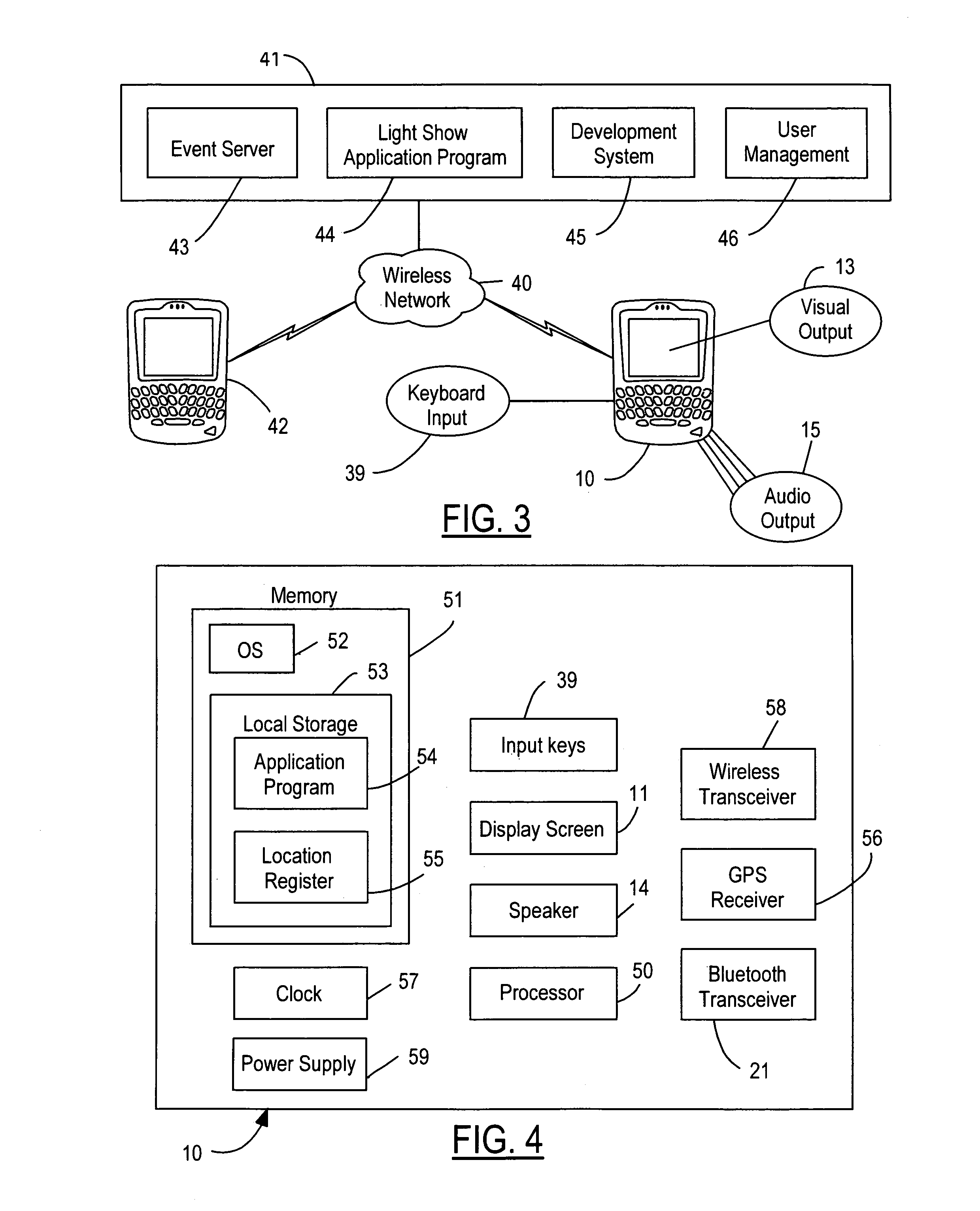

Synchronized light shows on cellular handsets of users at a gathering

InactiveUS7697925B1Improve abilitiesEffective synchronizationDevices with GPS signal receiverElectric light circuit arrangementBiological activationBluetooth

Light shows are produced by a plurality of individuals at a gathering using a plurality of personal wireless cellular devices wherein each device is carried by a respective individual and wherein each device has a programmable digital processor and a controllable light show illumination source. A light show application program resides on each personal wireless cellular device for providing coordinated control of the light show illumination sources. An event server stores at least one event sequence corresponding to a predetermined gathering and including at least one timed action. The event sequence is downloadable by the plurality of personal wireless cellular devices for activation of the controllable light show illumination sources in accordance with the event sequence. The system further includes a synchronizer in each device for initiating the timed action. The synchronizer may be a clock or a proximity detector (such as a Bluetooth connection with nearby users).

Owner:SPRINT CORPORATION

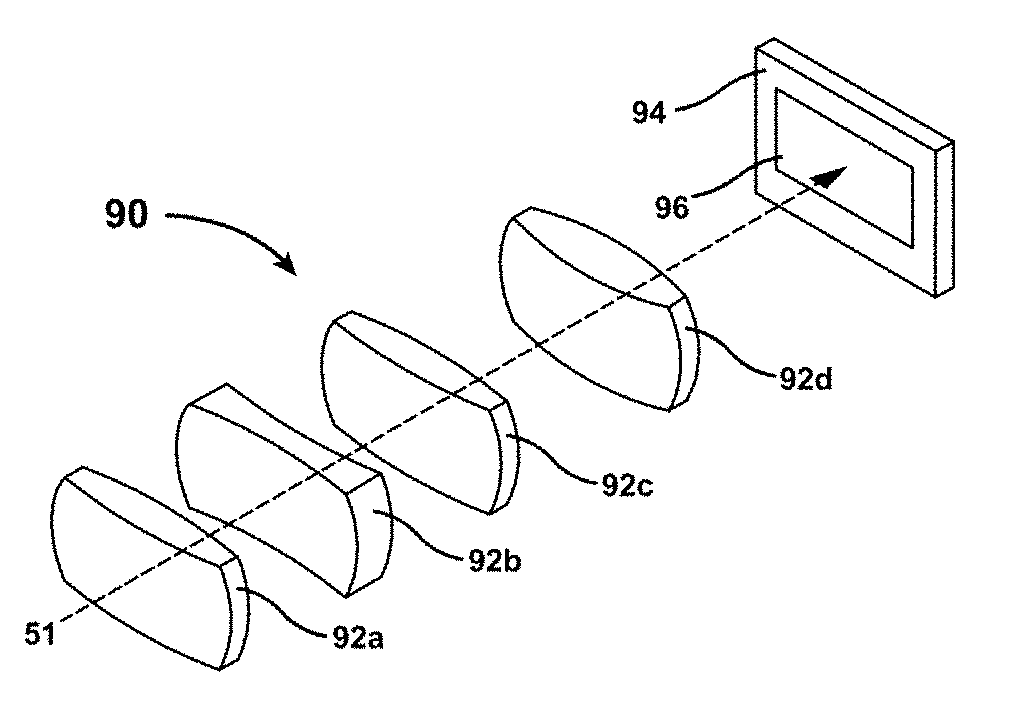

Thin optical system and camera

InactiveUS20170242225A1Improve scanning rateReduced Power RequirementsMountingsCamera lensScanning mirror

A camera module (170) includes a miniature scanning mirror (120), lens elements (163a to 163d) corresponding to thin lateral lens slices, and a short, wide imaging sensor (165). As the scanning mirror (120) pivots to scan a scene, the imaging sensor (165) captures successive image segments. Multiple image segments are stitched together by software running on a digital processor to provide a complete image. The assembly of lens elements (163a to 163d) may include moveable elements to allow variable focus, variable magnification and image stabilization, and may utilize refraction, reflection, diffraction and / or planar optical elements. The camera module (170) may be less than 5 millimeters thick while allowing long focal length lenses and increased light collecting area. Other embodiments include a switchable scan mirror with two apertures and a dual-camera system that provides binocular images and video.

Owner:FISKE ORLO JAMES

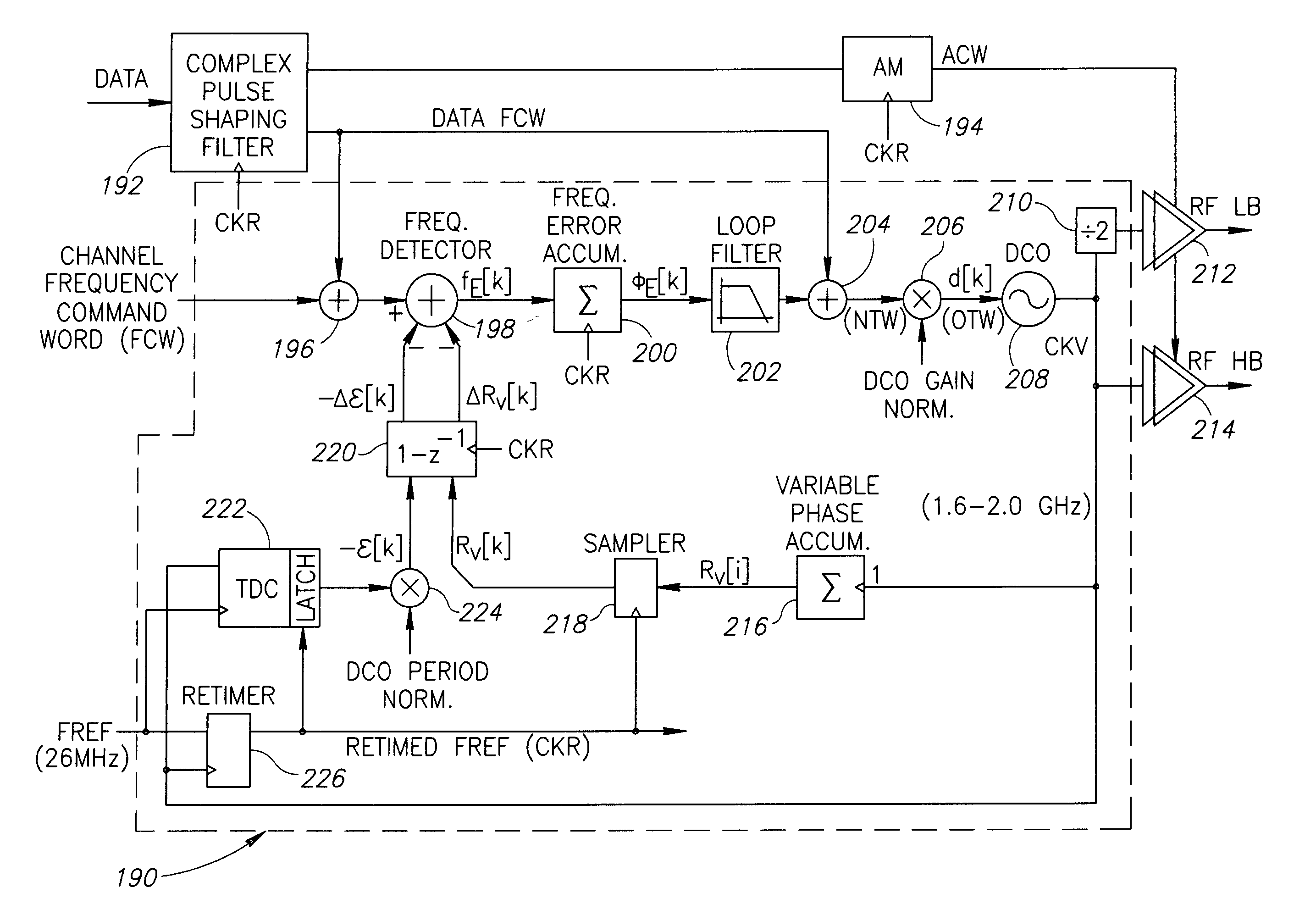

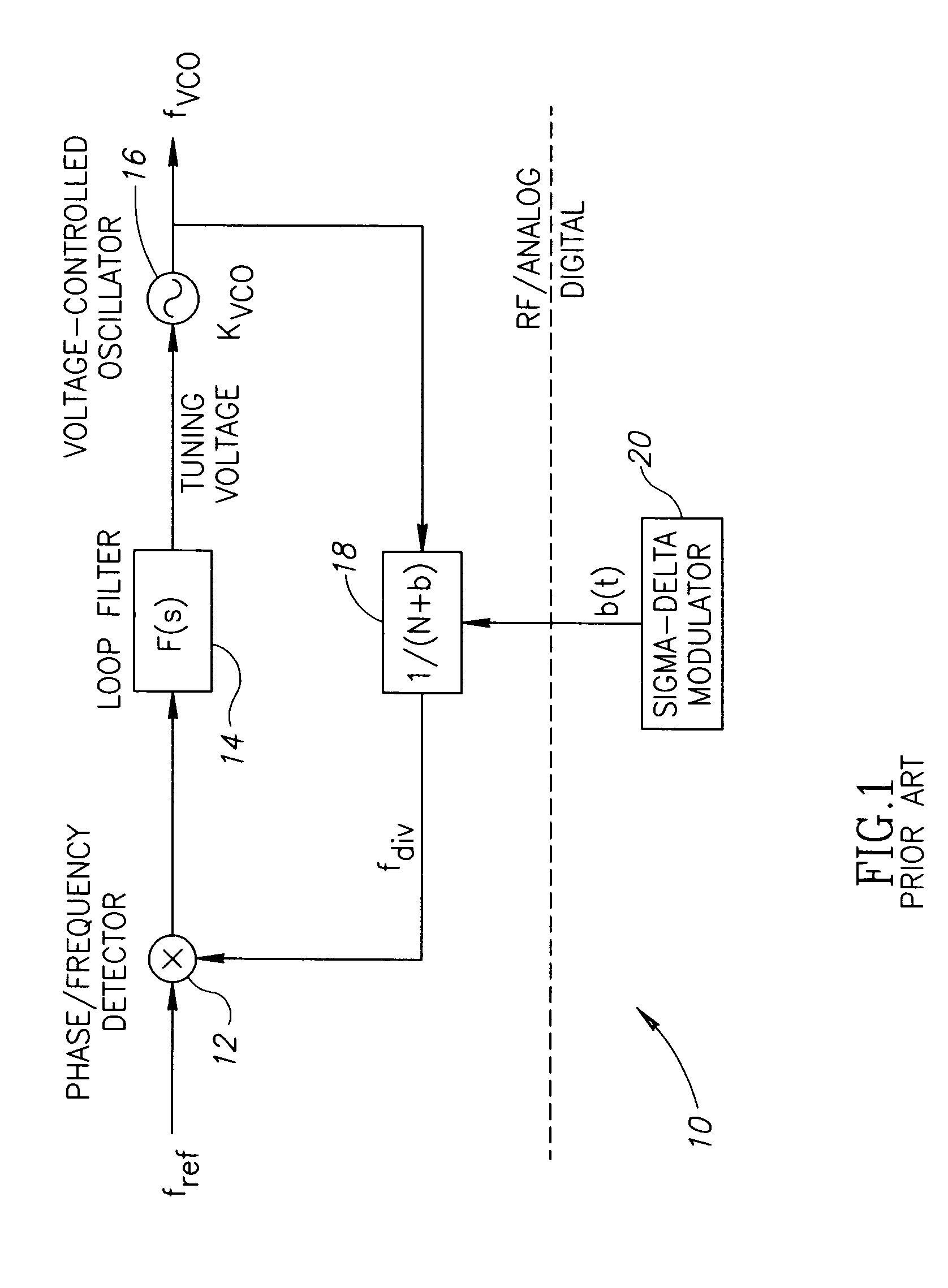

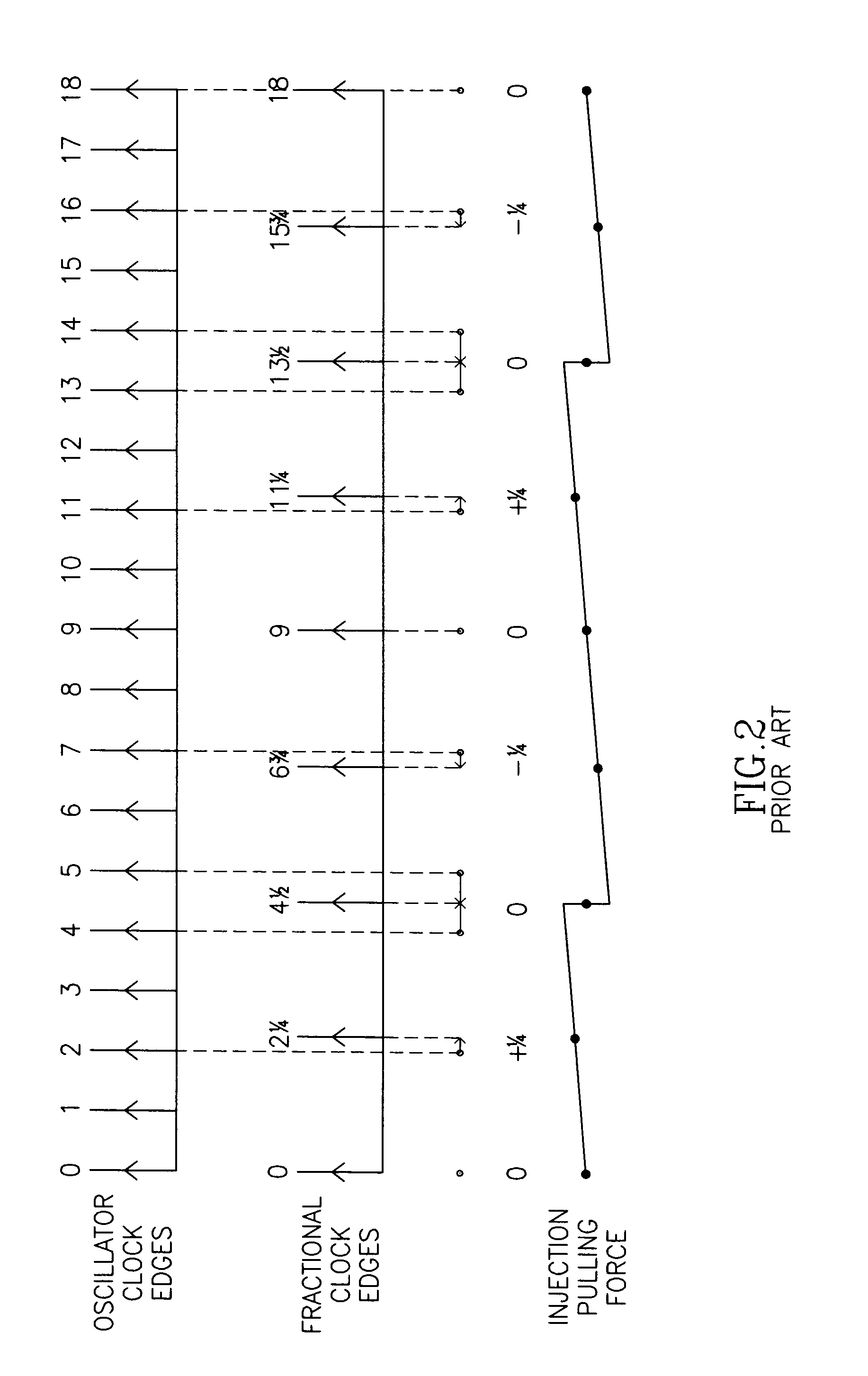

Apparatus for and method of noise suppression and dithering to improve resolution quality in a digital RF processor

InactiveUS20050186920A1Cancel noiseAvoid it happening againPulse automatic controlAngle modulationImage resolutionEngineering

A novel apparatus for and a method of noise and spurious tones suppression in a digital RF processor (DRP). The invention is well suited for use in highly integrated system on a chip (SoC) radio solutions that incorporate a very large amount of digital logic circuitry. The noise suppression scheme eliminates the noise caused by various on chip interference sources transmitted through electromagnetic, power, ground and substrate paths. The noise suppression scheme permits an all digital PLL (ADPLL) to operate in such a way to avoid generating the spurs that would normally be generated from the injection pulling effect of interfering sources on the chip. The frequency reference clock is retimed to be synchronous to the RF oscillator clock and used to drive the entire digital logic circuitry of the DRP. This ensures that the different clock edges throughout the system will not exhibit mutual drift. A method of improving the resolution quality of a time to digital converter within the ADPLL is also taught. The method dithers the reference clock by passing it through a delay circuit that is controlled by a sigma-delta modulator. The dithered reference clock reduces the affect on the phase noise at the output of the ADPLL due to ill-behaved quantization of the TDC timing estimation.

Owner:TEXAS INSTR INC

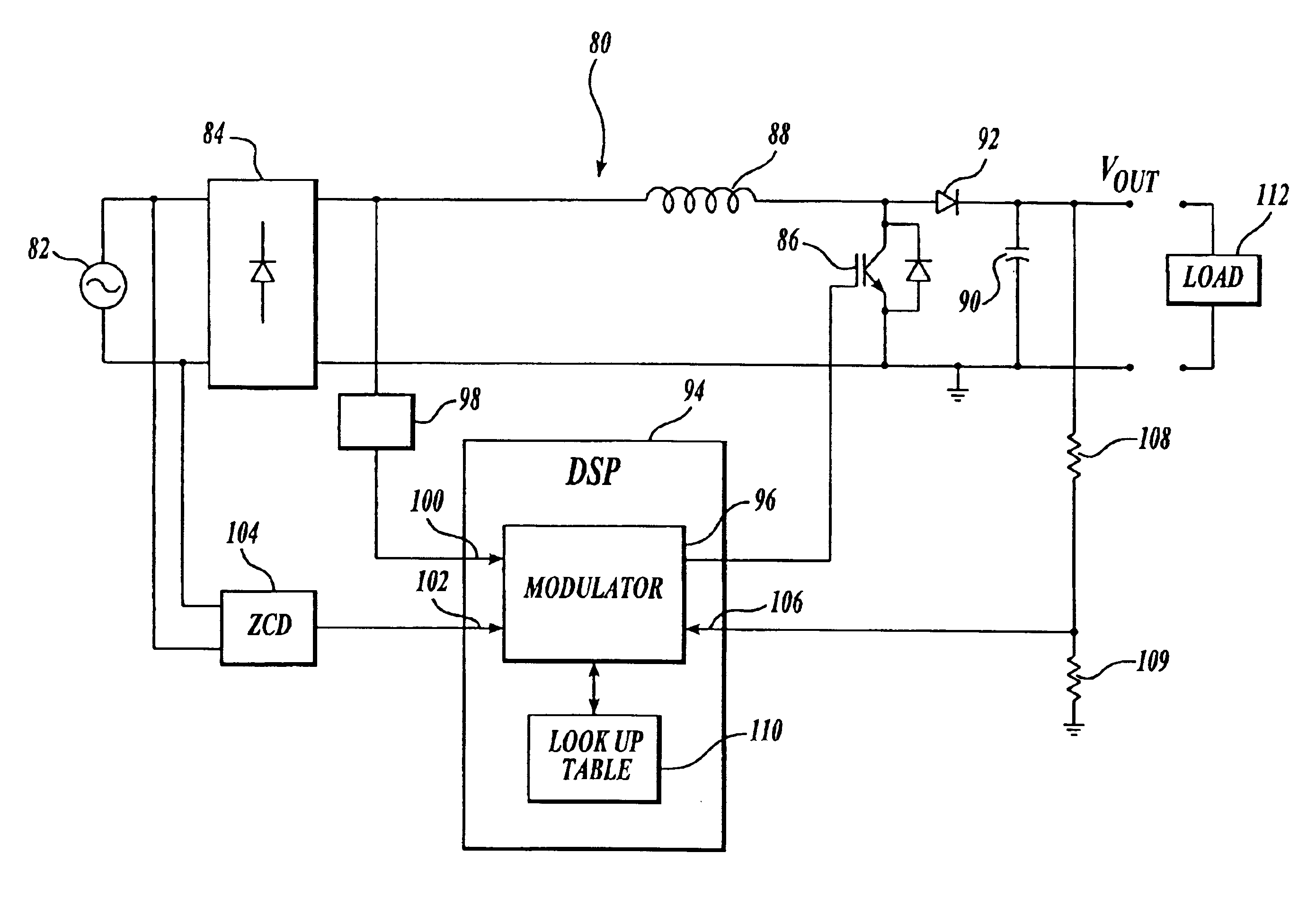

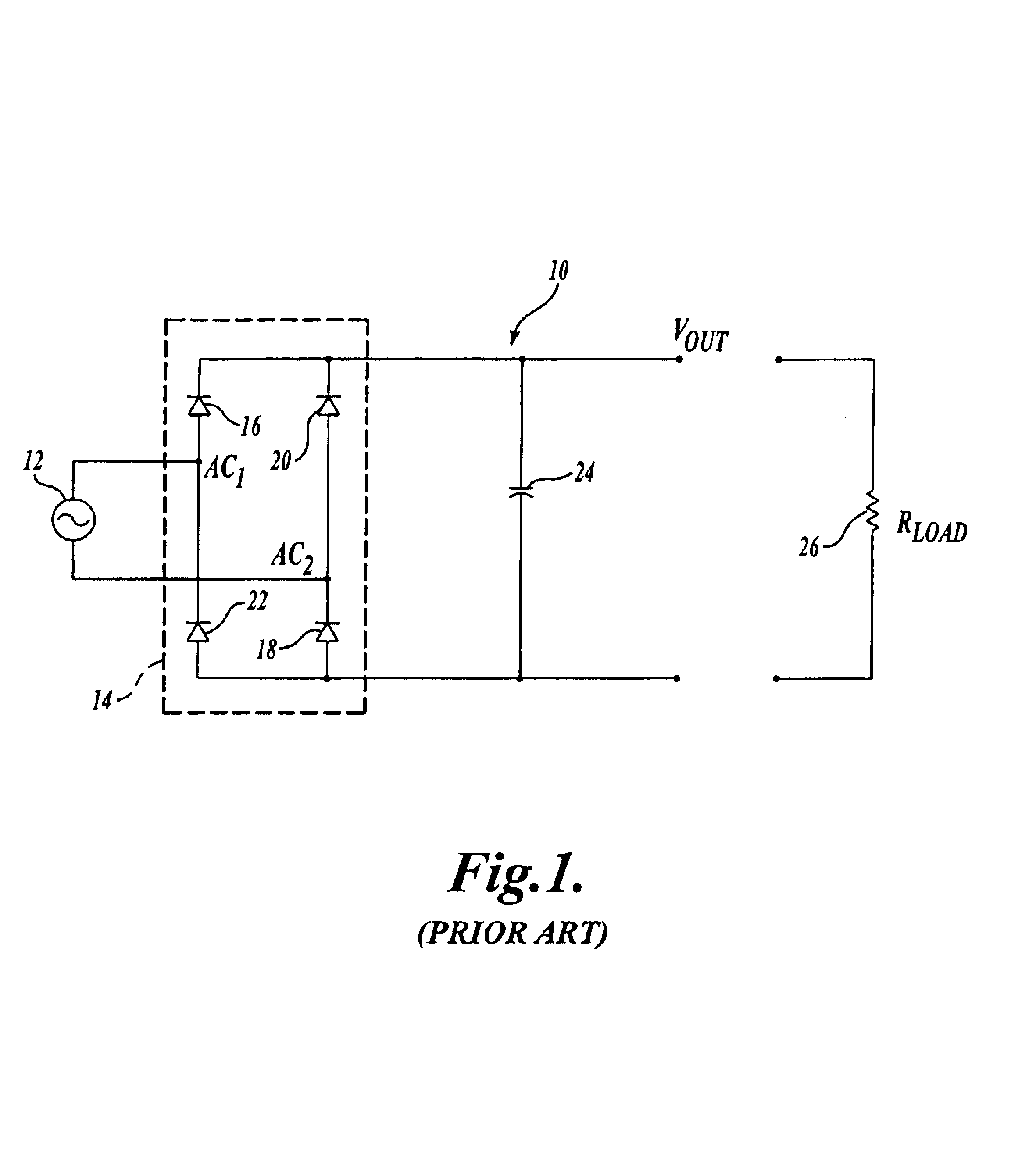

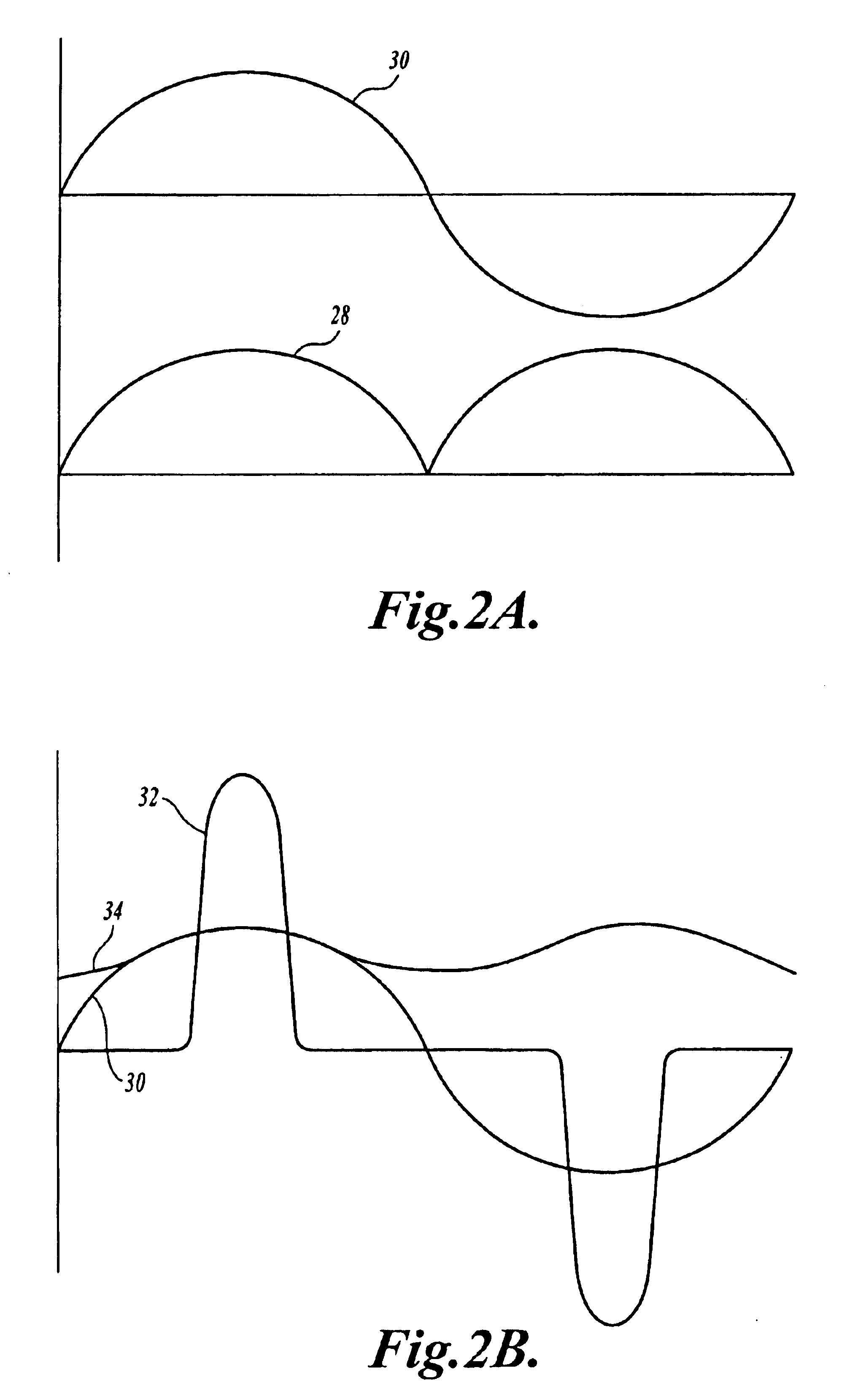

Power supply controller for exercise equipment drive motor

InactiveUS6906503B2Improve power factorRaise transfer toAc-dc conversion without reversalEfficient power electronics conversionPower controllerDrive motor

A combined power supply and driver control module includes rectifier circuitry, switching circuitry, and driver circuitry for providing output power to a load. Rectified output from an input power source is used to produce a DC power. The switching circuitry receives the DC power and modulates the input current drawn from the power source. An intelligent control module includes control circuitry, such as a digital processor, for controlling the switching circuitry. Power factor is improved by modulating the input current to be closer in phase with the voltage of the power source. Also disclosed is a power factor correction circuit in which a digital processor reads waveform values from a lookup table and modulates the input current waveform based on the values. A zero crossing detector connected to the input power source may direct the digital processor when to commence reading values from the lookup table.

Owner:PRECOR

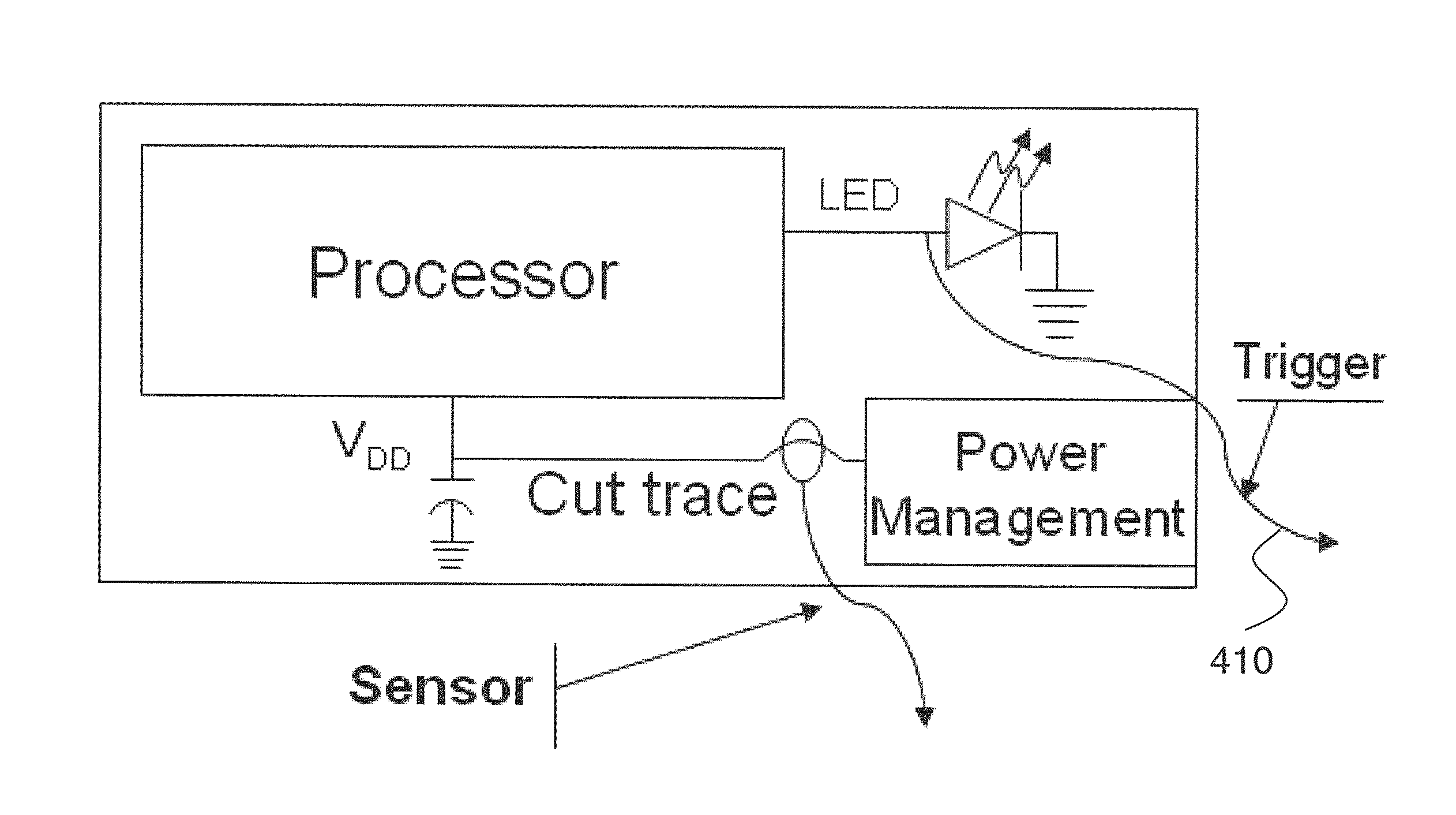

Using Power Fingerprinting (PFP) to Monitor the Integrity and Enhance Security of Computer Based Systems

ActiveUS20130318607A1Enhancing target system execution integrity assessmentImprove abilitiesMemory loss protectionDetecting faulty computer hardwareIntegrity assessmentComputerized system

Procedures are described for enhancing target system execution integrity determined by power fingerprinting (PFP): by integrating PFP into the detection phase of comprehensive defense-in-depth security; by deploying a network of PFP enabled nodes executing untrusted devices with predefined inputs forcing a specific state sequence and specific software execution; by embedding module identification information into synchronization signaling; by combining signals from different board elements; by using malware signatures to enhance PFP performance; by automatic characterization and signature extraction; by providing secure signature updates; by protecting against side-channel attacks; performing real-time integrity assessment in embedded platform by monitoring their dynamic power consumption and comparing it against signatures from trusted code, including pre-characterizing power consumption of the platform by concentrating on trace sections carrying the most information about the internal execution status; by using PFP from sequence of bit transitions to detect deviations from authorized execution of software in a digital processor.

Owner:VIRGINIA TECH INTPROP INC

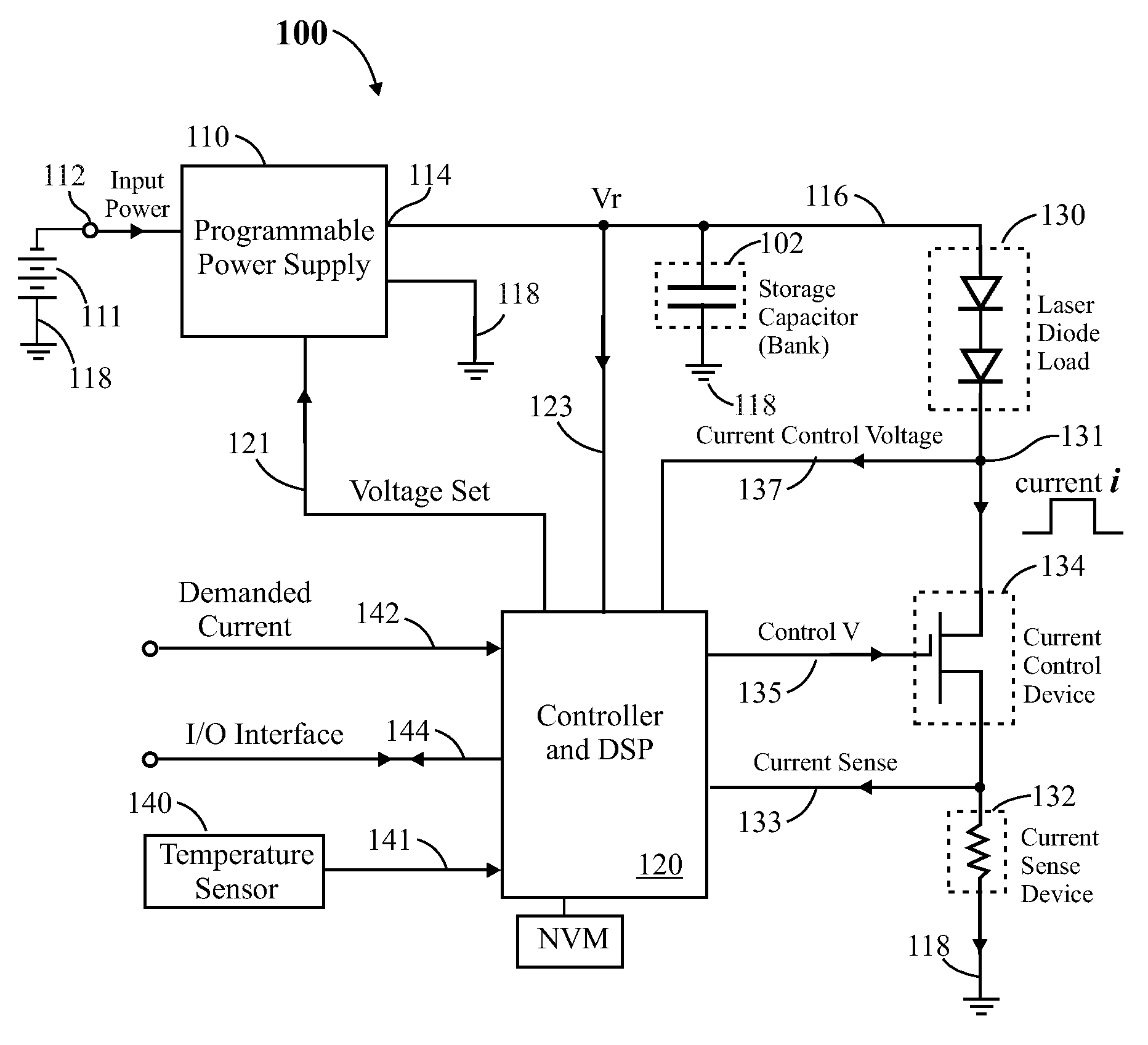

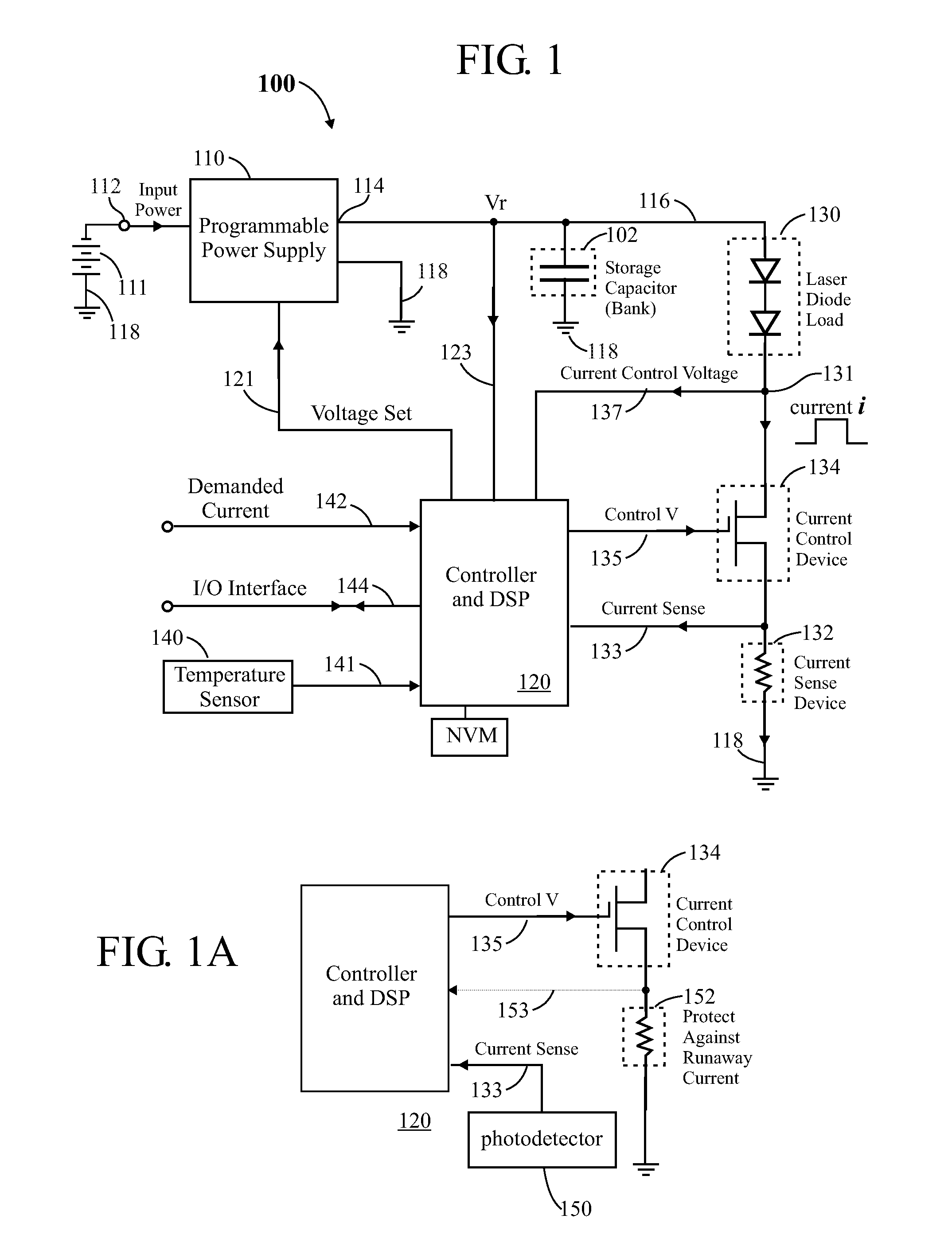

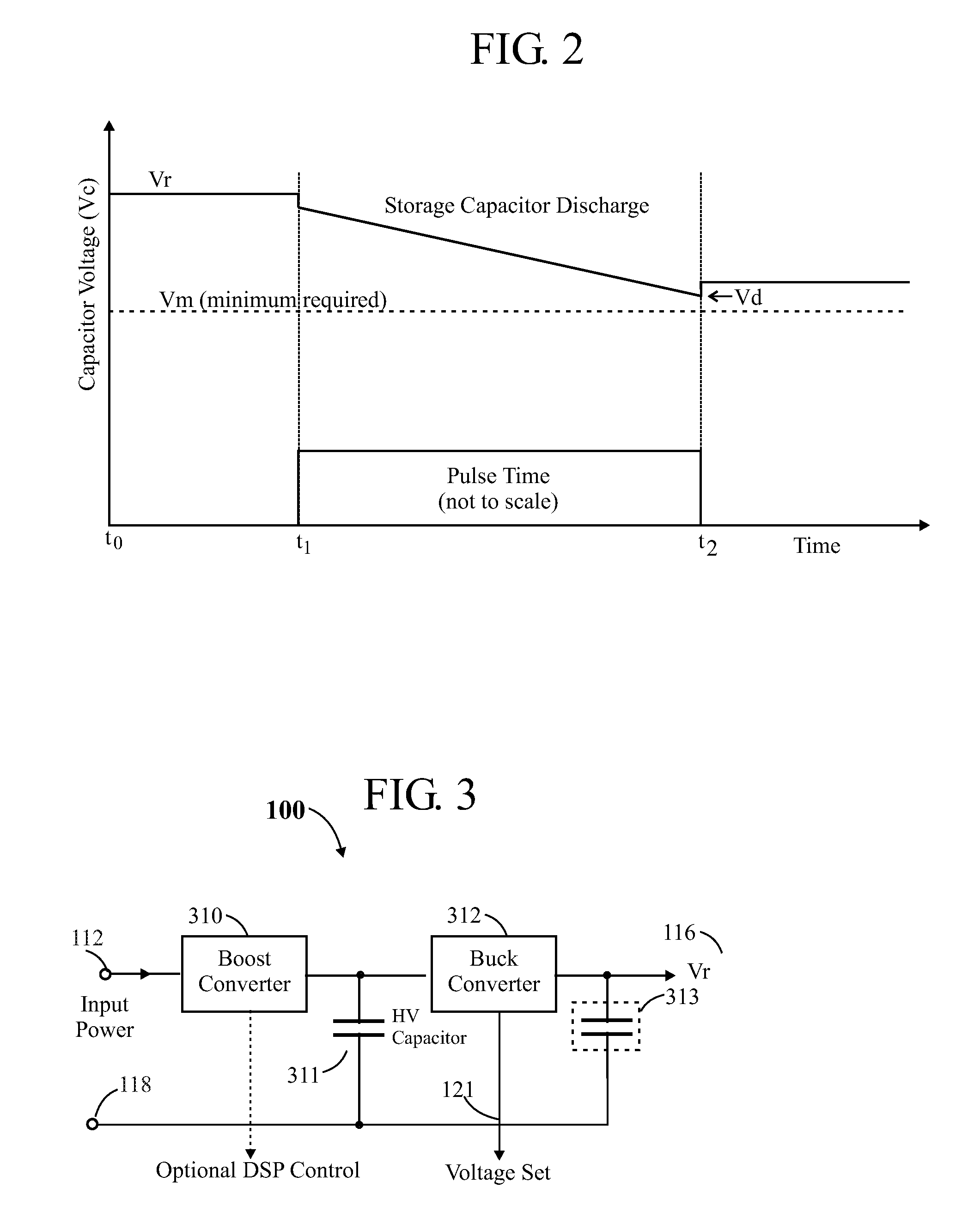

Smart linear pulsed laser diode driver, and method

ActiveUS20110085576A1Improve efficiencySmall sizeLaser detailsElectroluminescent light sourcesCapacitor voltageEngineering

In a pulsed laser diode driver an energy storage capacitor is continuously being charged to a supply voltage Vr. When a pulse is initiated, energy stored in the capacitor is delivered to the laser diode load. The capacitor voltage Vd at the end of a pulse is used to control Vr to ensure that Vd is maintained above a minimum voltage Vm required to ensure operation of a current control device (such as FET) just above saturation. Test pulses (such as with attenuated currents or reduced pulsewidth) may be fired to determine an initial optimum value for Vr. After a test pulse, a slightly high estimate for Vr may be used and may be iterated (incremented) down to an optimum value Vm during a firing burst. A digital processor may be used to calculate and store data to optimize the performance. Various embodiments are disclosed.

Owner:ANALOG MODULES

Audio cassette emulator with cryptographic media distribution control

InactiveUS7436957B1Saving positionSaving stateKey distribution for secure communicationDigital data processing detailsDistribution controlThe Internet

A device of the same general physical size and shape as a standard audio cassette tape, but which accepts digital information from any of a variety of sources—including for example: Internet transmission, a digital computer, or memory cards (especially digital memory cards)—and plays this digital information through any, for example, standard audio tape cassette player. The device operates by converting the digital representation of the sound into magnetic signals which are presented to the read / write head of the cassette player equipment. The device allows the user of the cassette player to regulate the audio playback using conventional equipment controls such as: START, STOP, REWIND, FAST REWIND, FORWARD, FAST FORWARD, etc. The device has the same general physical dimensions of a standard audio cassette; at least one digital processor; and a slot into which electronic media such as, for example, memory cards, smart cards having a processor and a memory embodied thereon and other memory media may be inserted. Numerous sensors detect changes in at least one of the tape equipment mechanisms in the audio cassette emulator. Various cryptographic techniques are described for protecting the unauthorized distribution of audio information.

Owner:FISCHER ADDISON M