Patents

Literature

8933 results about "Digital signal processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A digital signal processor (DSP) is a specialized microprocessor (or a SIP block), with its architecture optimized for the operational needs of digital signal processing. The goal of DSP is usually to measure, filter or compress continuous real-world analog signals. Most general-purpose microprocessors can also execute digital signal processing algorithms successfully, but may not be able to keep up with such processing continuously in real-time. Also, dedicated DSPs usually have better power efficiency, thus they are more suitable in portable devices such as mobile phones because of power consumption constraints. DSPs often use special memory architectures that are able to fetch multiple data or instructions at the same time.

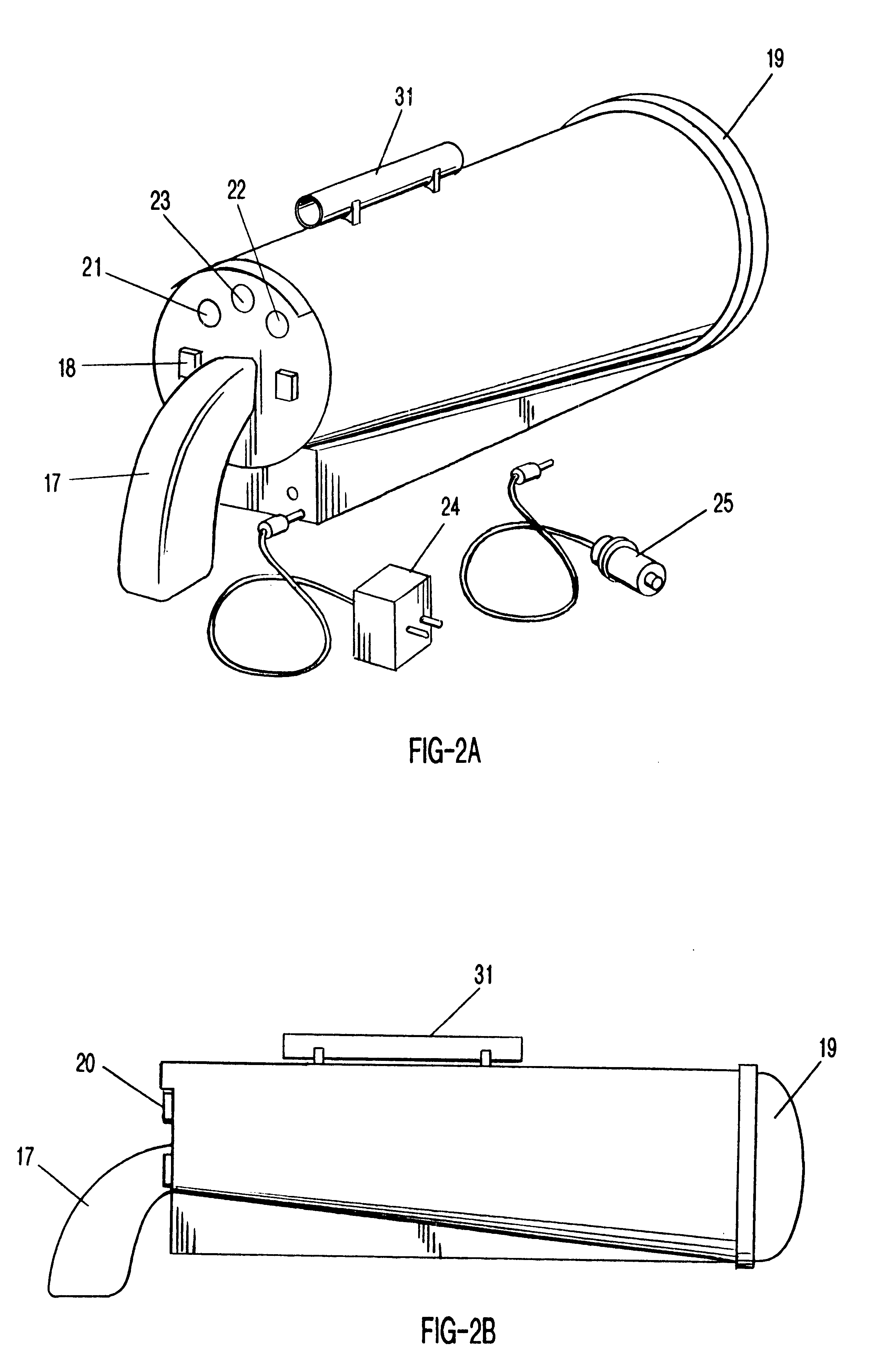

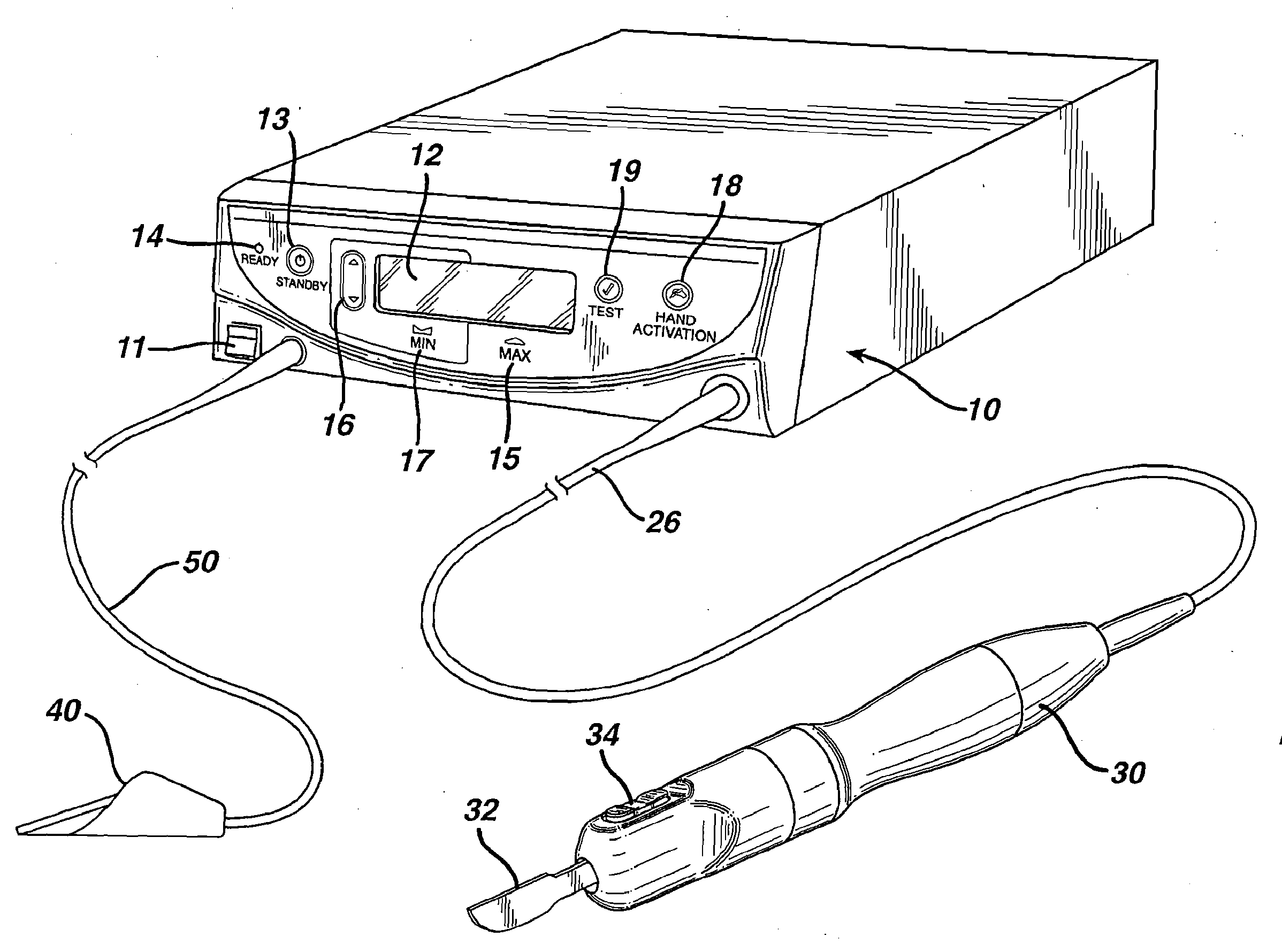

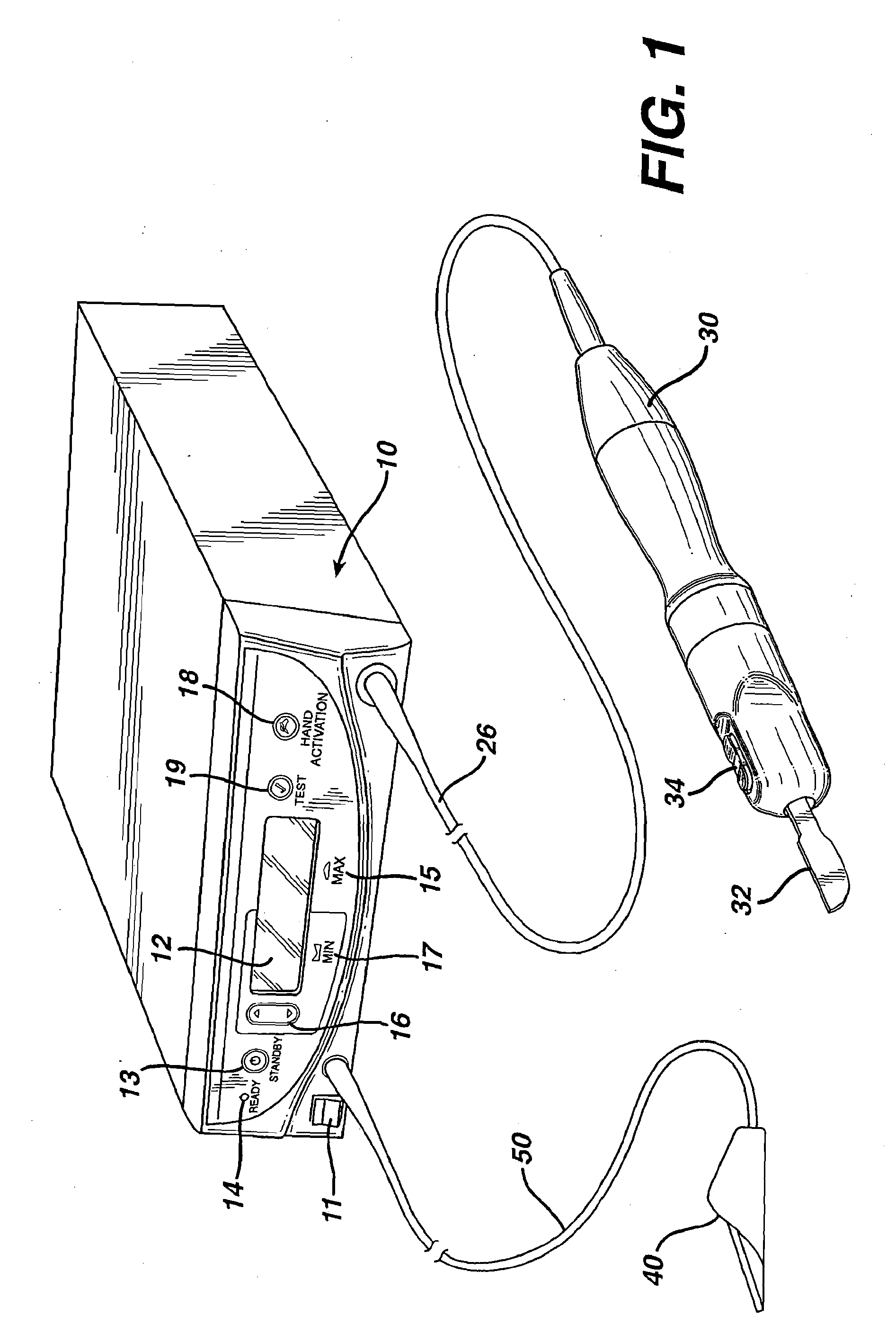

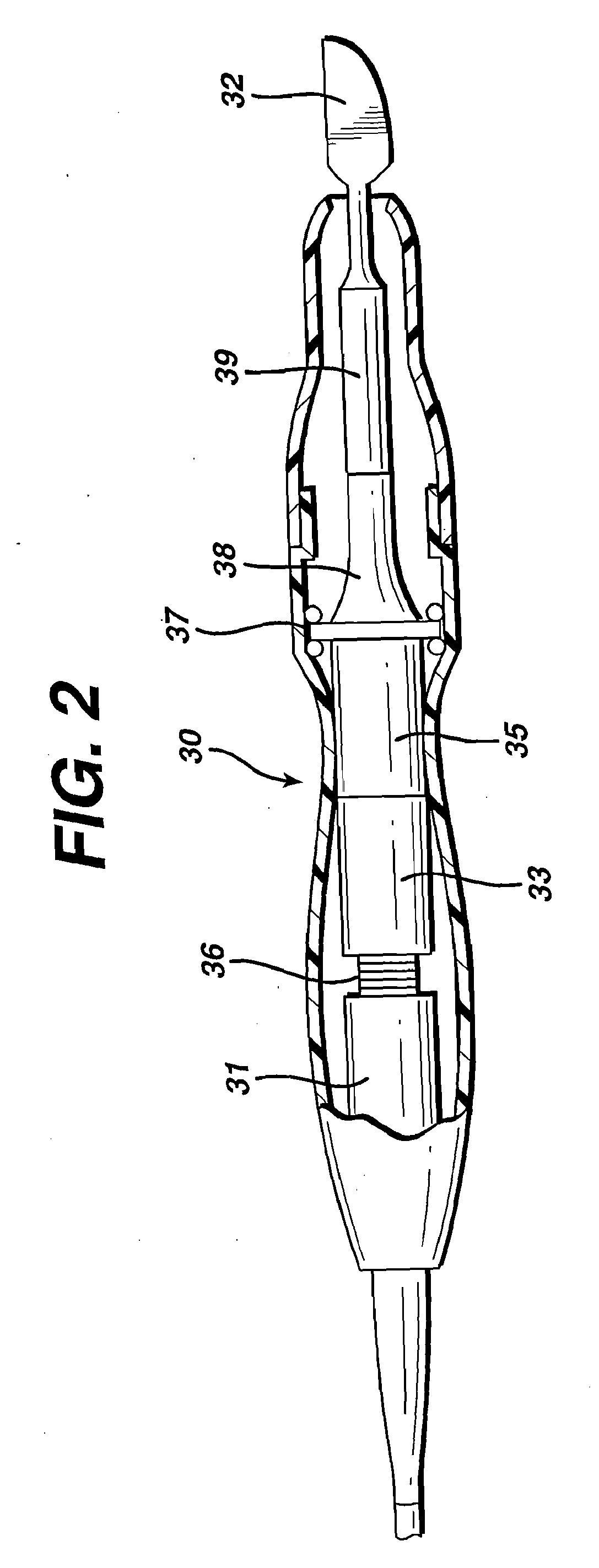

Apparatus and method for altering generator functions in an ultrasonic surgical system

InactiveUS6908472B2Avoid mistakesNew system functionalityIncision instrumentsDiagnosticsDriving currentElectricity

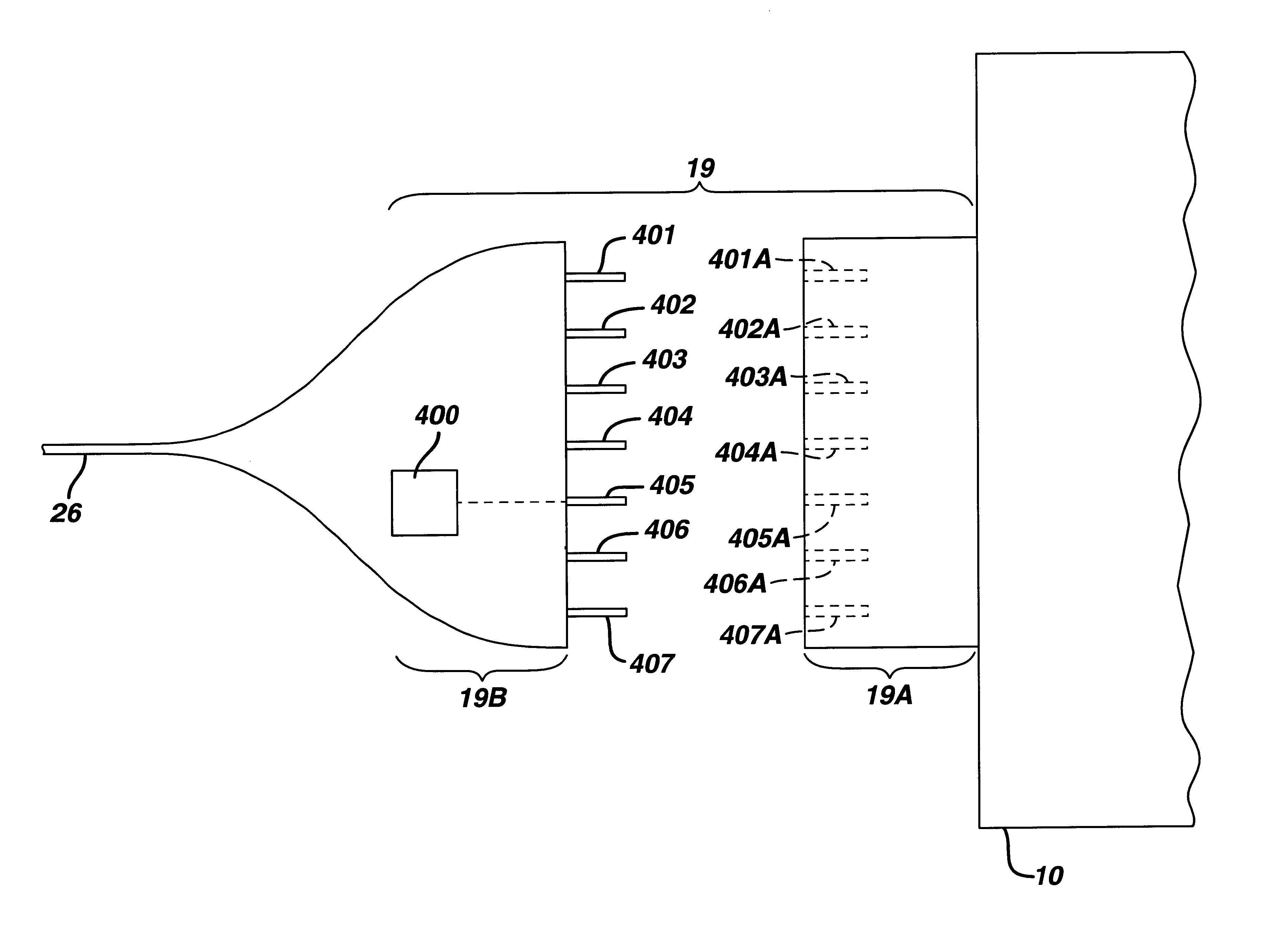

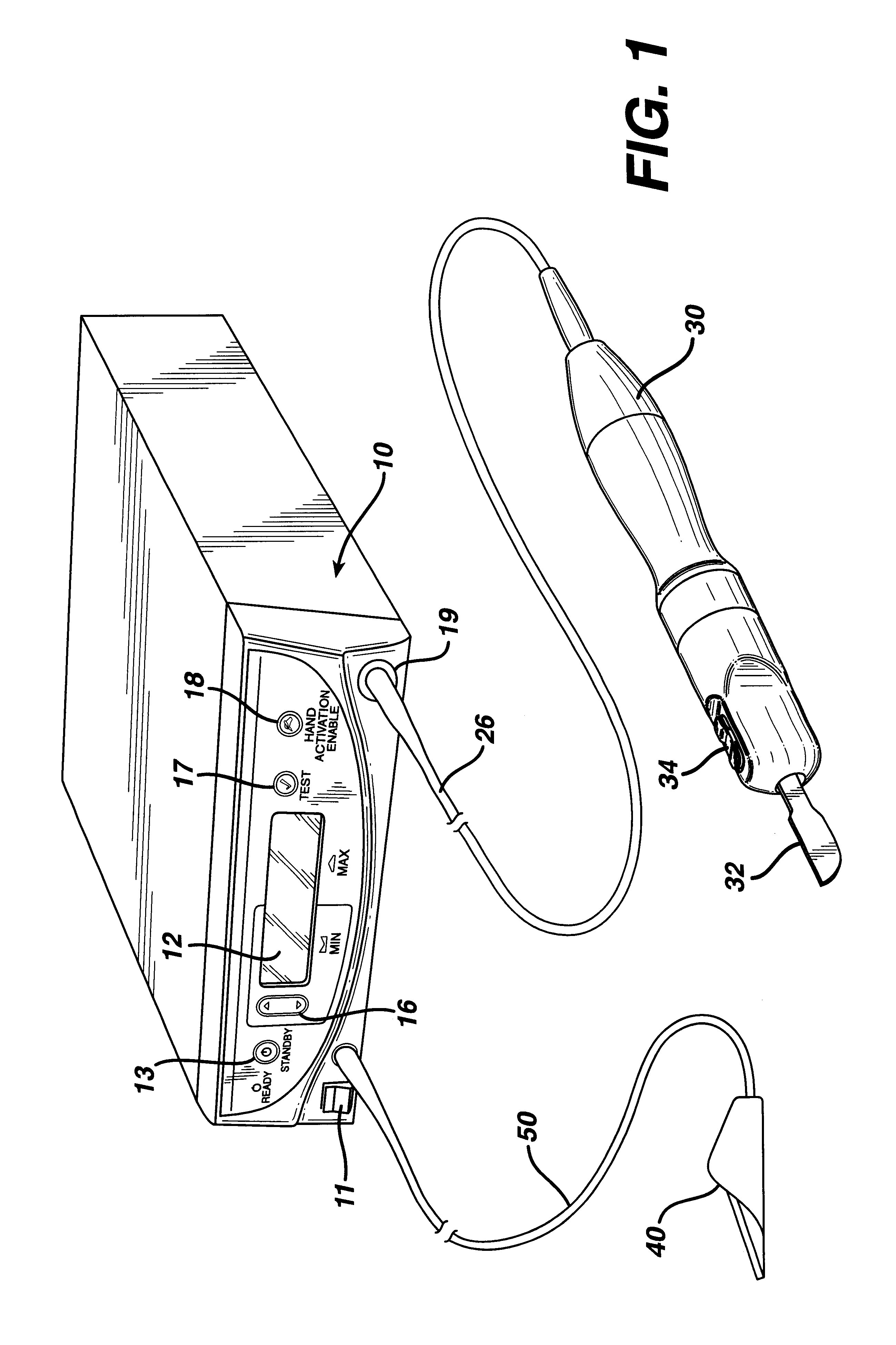

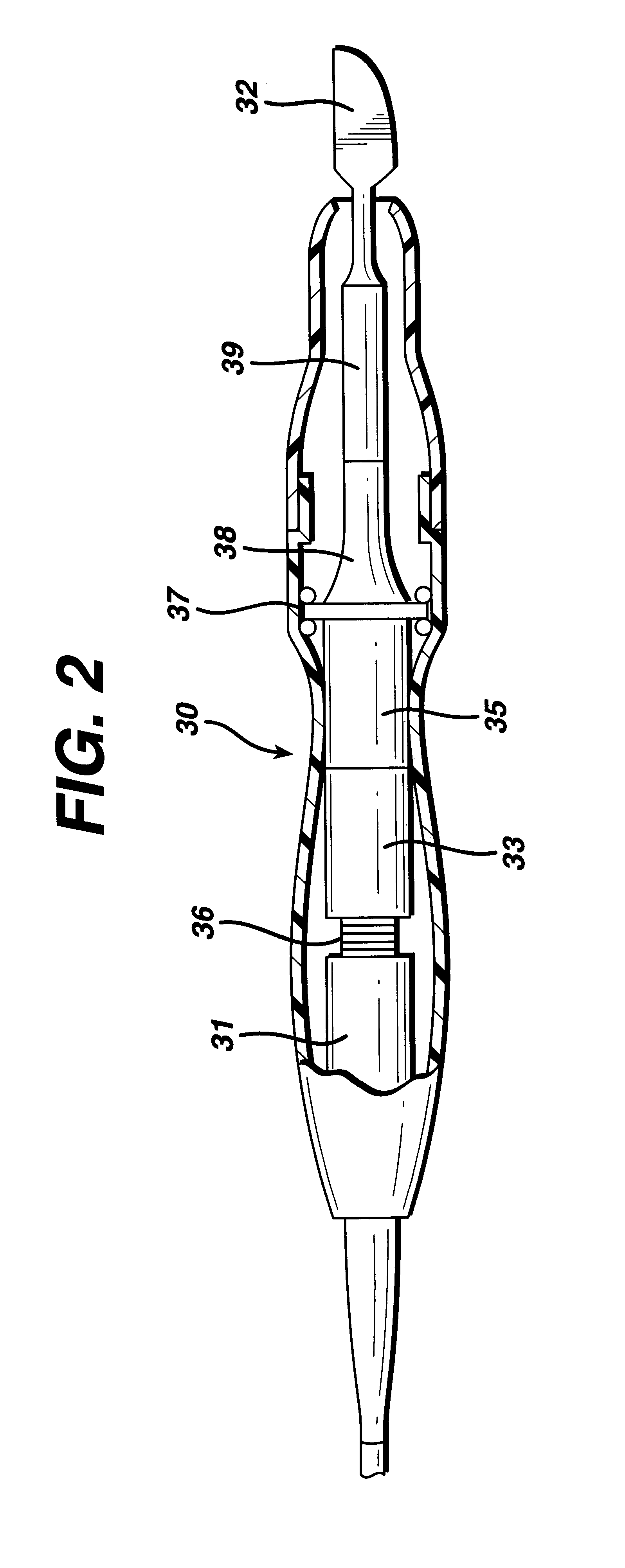

The present invention provides a system for implementing surgical procedures which includes an ultrasonic surgical hand piece having an end-effector, a console having a digital signal processor (DSP) for controlling the hand piece, an electrical connection connecting the hand piece and the console, and a memory, such as an EEPROM (Electrically Erasable Programmable Read Only Memory), disposed in the electrical connection. The console sends a drive current to drive the hand piece which imparts ultrasonic longitudinal movement to the blade. The console reads the memory and authenticates the hand piece for use with the console if particular or proprietary data are present in the memory. Moreover, to prevent errors in operating the hand piece, the memory can store certain diagnostic information which the console can utilize in determining whether the operation of the hand piece should be handicapped or disabled. Furthermore, the memory can be used to reprogram the console, if needed.

Owner:ETHICON ENDO SURGERY INC

Signal component processor

InactiveUS6850787B2Poor signal qualityImprove robustnessCatheterSensorsOxygen Saturation MeasurementPulse oximetry

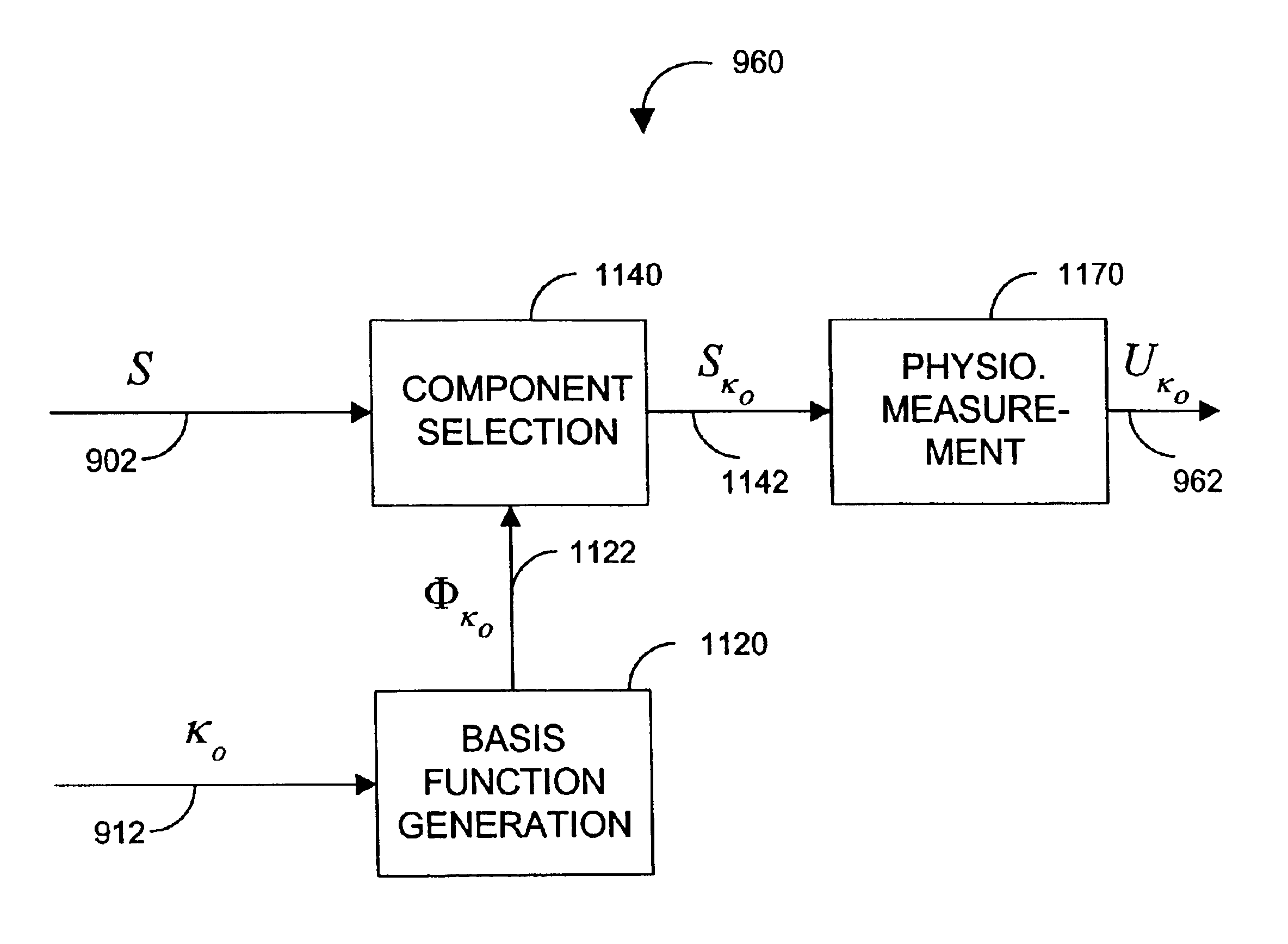

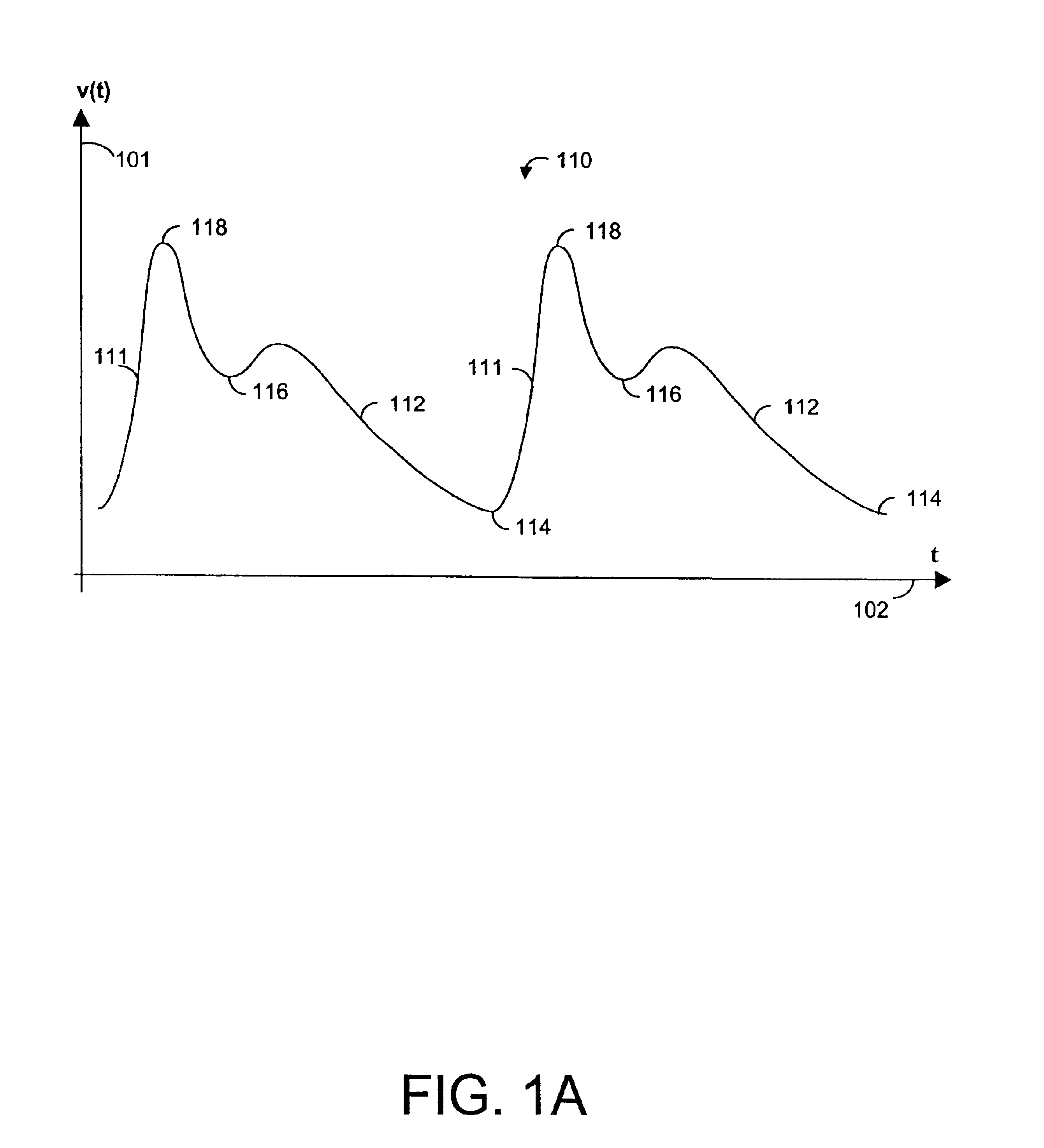

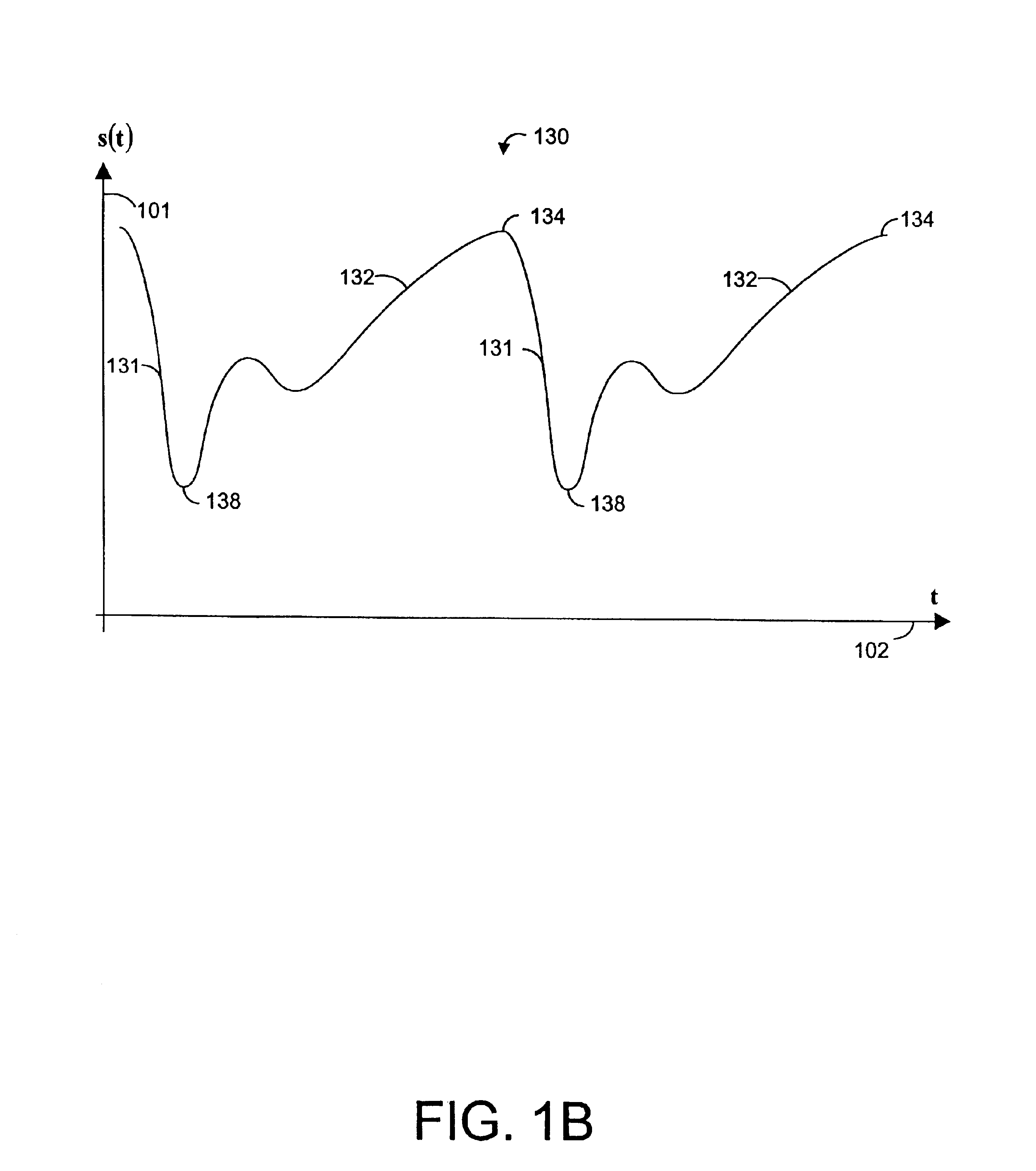

A signal processor generates basis functions and identifies at least one basis function component of a sensor signal in order to calculate a physiological measurement. The signal processor is advantageously applied to pulse oximetry so as to directly calculate oxygen saturation and so as to calculate a robust oxygen saturation measurement. In particular, a signal component transform may be calculated within a window around a derived pulse rate estimate. A signal component transform may also utilize sinusoidal basis functions, and an optimization of a signal component transform may occur at a particular frequency or a set of frequencies. A sinusoidal waveform or waveforms at that frequency or set of frequencies is generated to select associated red and infrared components of the sensor signal, and an oxygen saturation is calculated from a magnitude ratio of these components.

Owner:JPMORGAN CHASE BANK NA

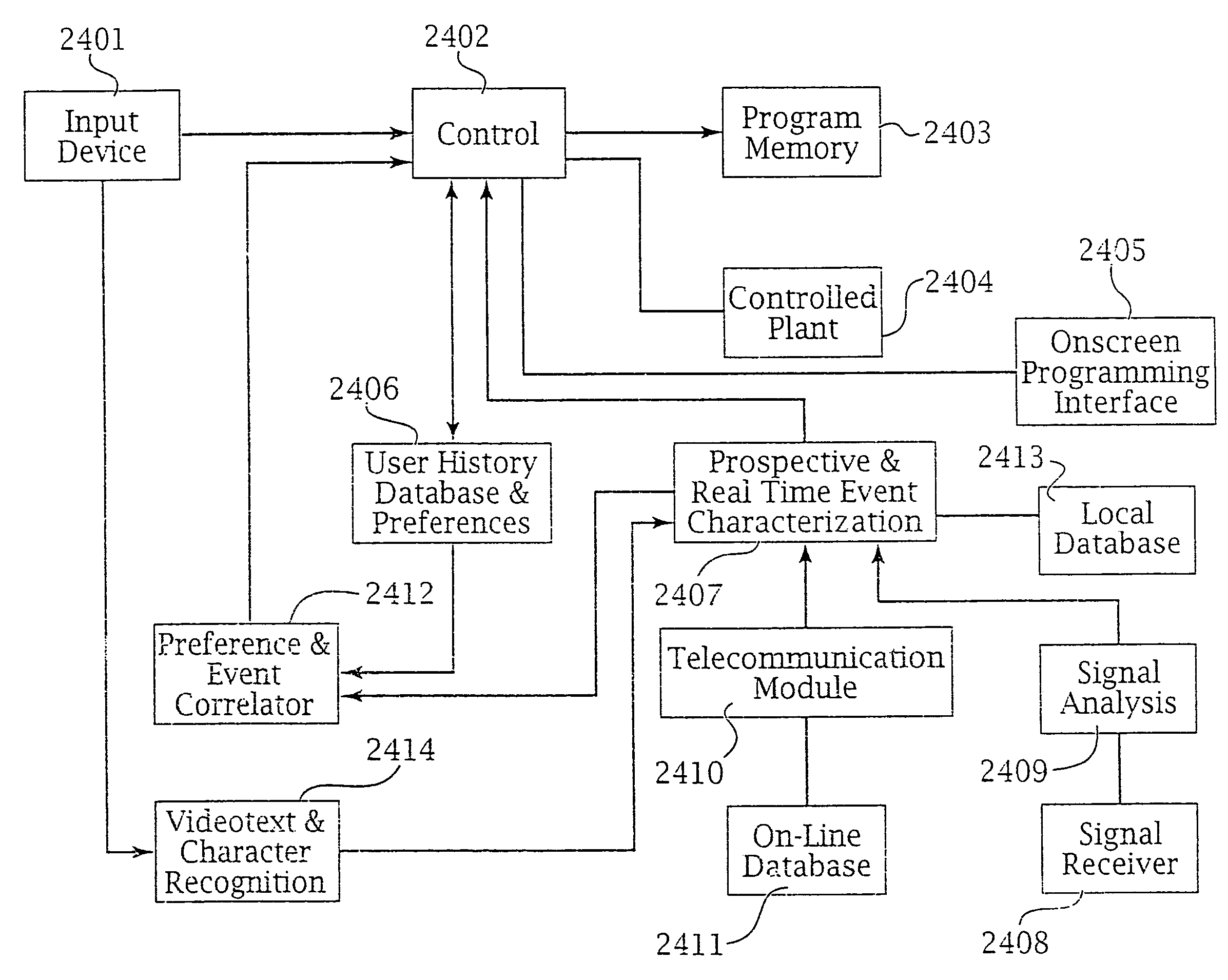

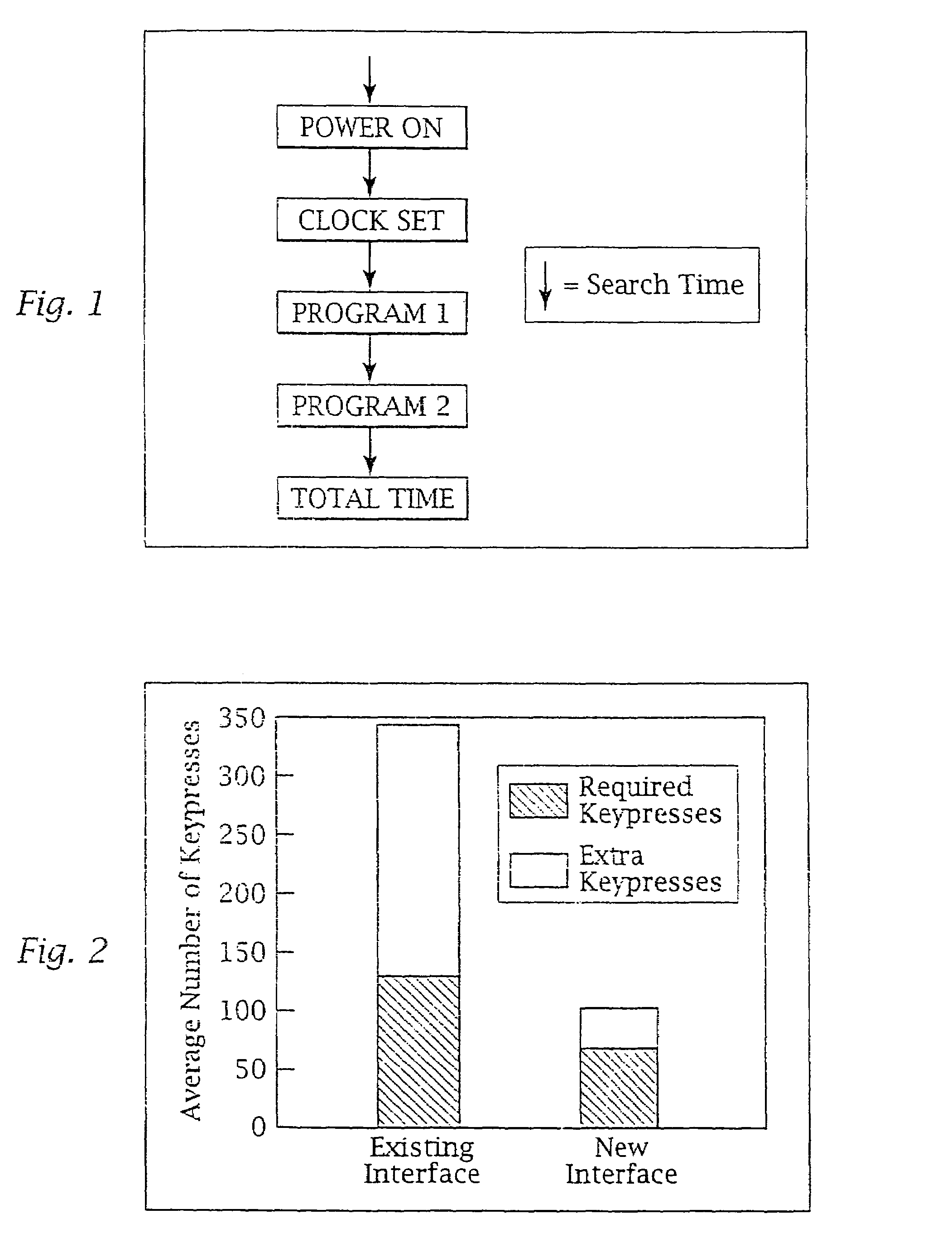

Media recording device with remote graphic user interface

InactiveUS7006881B1Minimize timeTelevision system detailsAnalogue secracy/subscription systemsGraphicsGraphical user interface

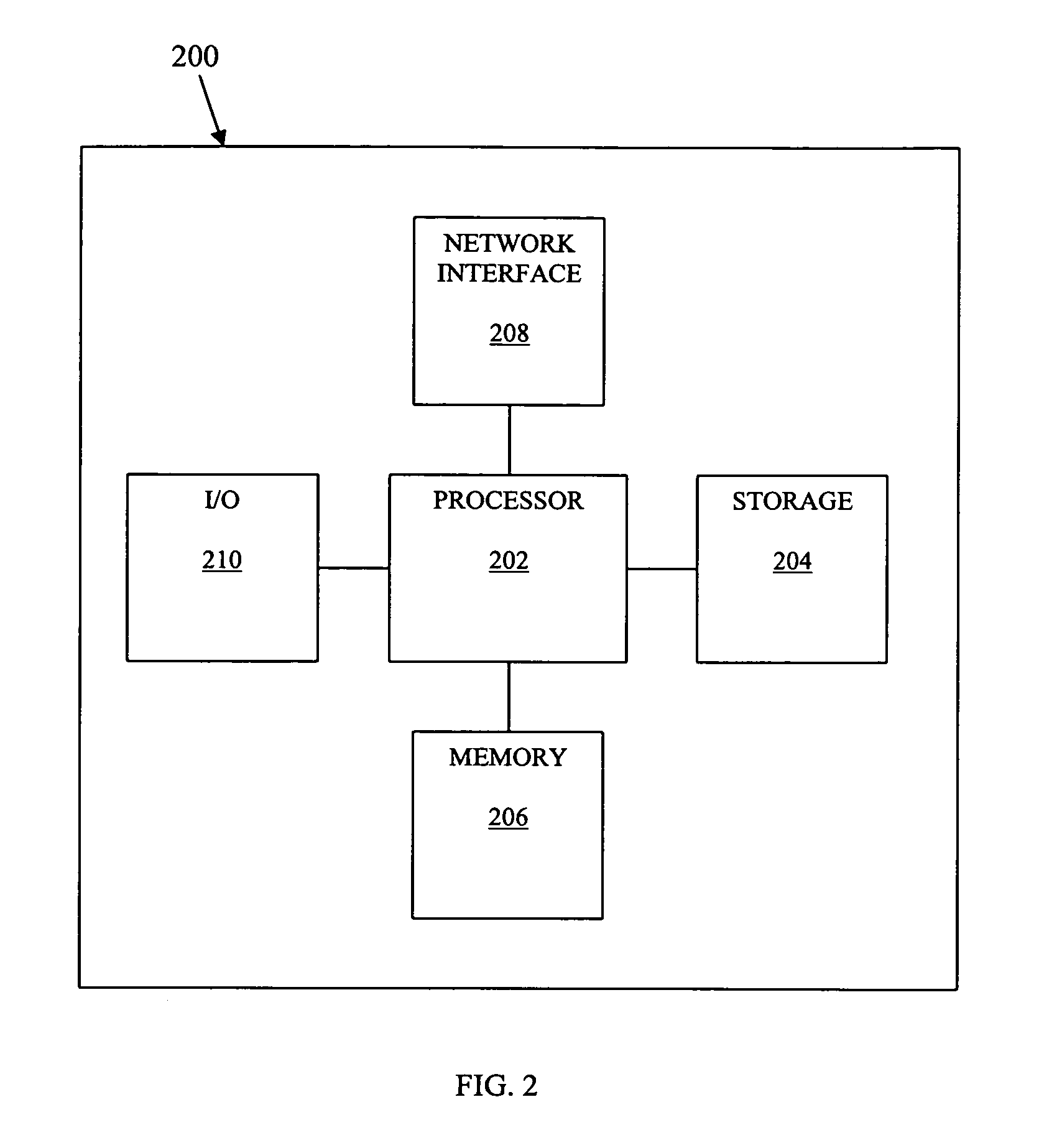

An apparatus for processing digital media signals, comprising a digital processor for controlling the apparatus; a graphic user interface, having a wireless remote control providing a command input to the processor; a network interface for transmitting digital information from the processor to a remote location over a communications network, the information identifying a digital media signal for desired reproduction based, at least in part, on an input received from the remote control; and an output, controlled by, and local to, the processor, for transferring the desired digital media signals for reproduction thereof.

Owner:BLANDING HOVENWEEP

System and method for highly phased power regulation using adaptive compensation control

InactiveUS7007176B2Improved power regulation systemAdd control functionVolume/mass flow measurementDc-dc conversionComputer moduleEngineering

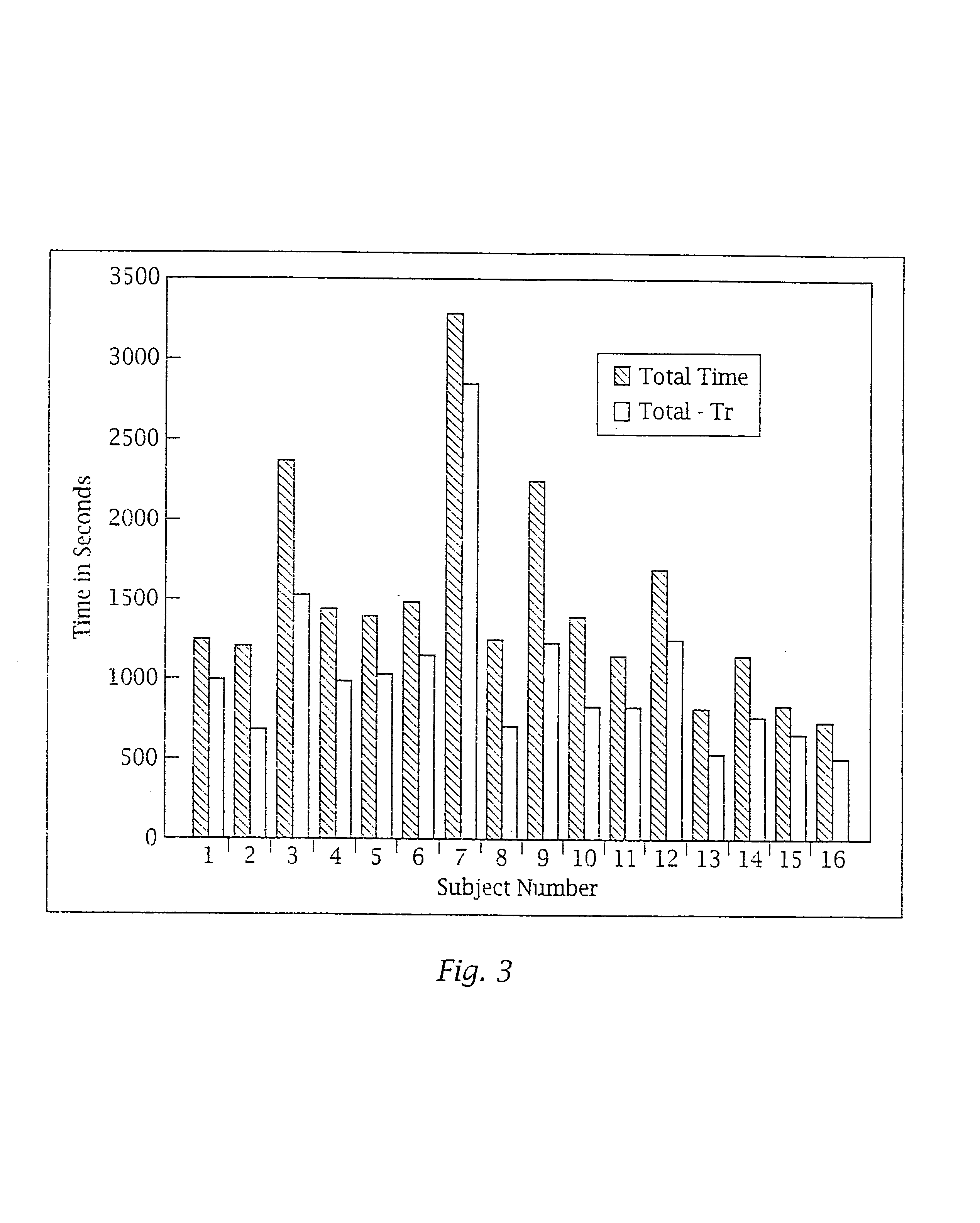

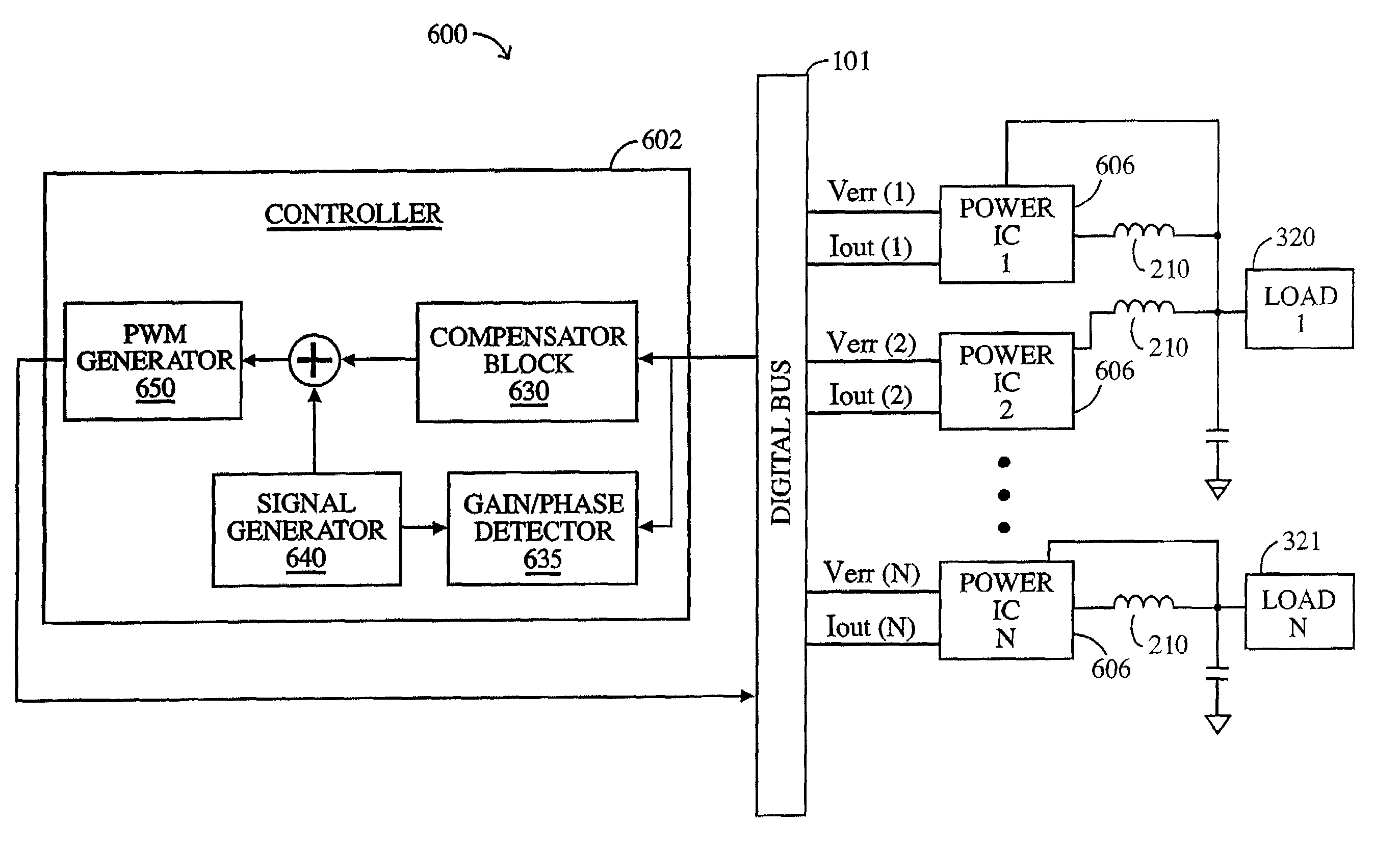

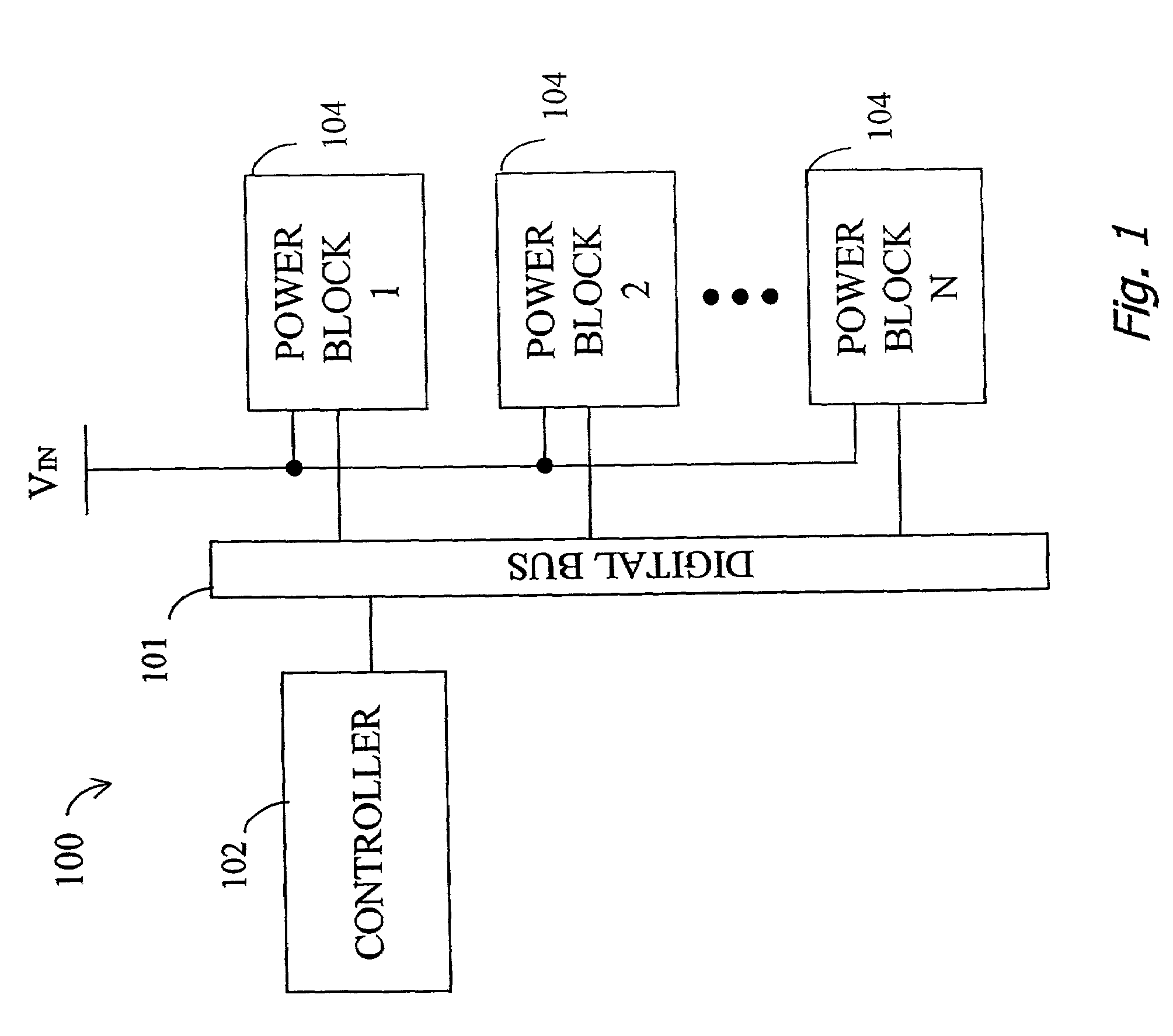

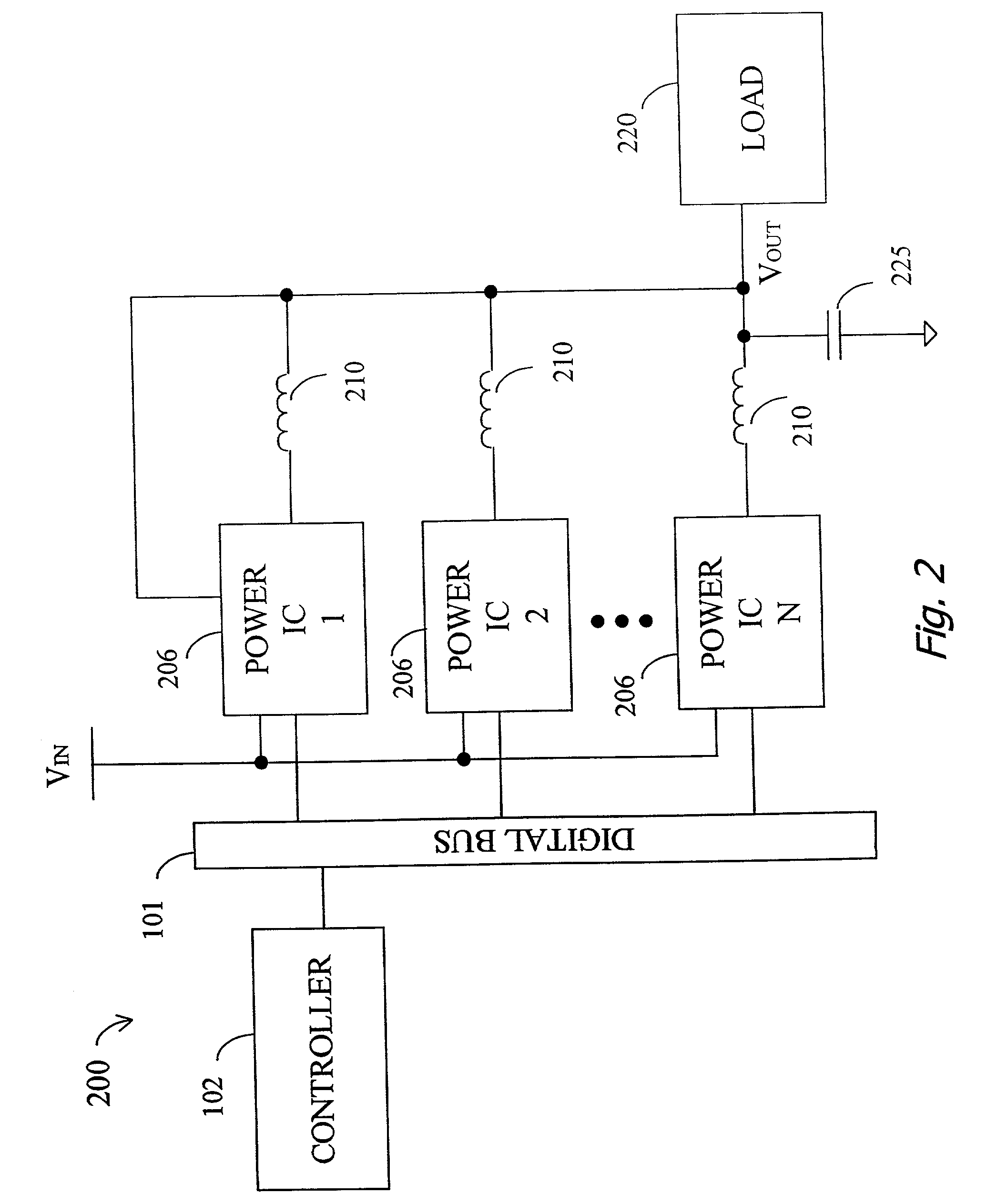

A highly phased power regulation (converter) system having an improved control feature is provided. A controller, such as a digital signal processor or microprocessor, receives digital information from a plurality of power conversion blocks and transmits control commands in response to the information. The controller is able to change the mode of operation of the system and / or re-phase the power blocks to accommodate a dynamic load requirement, occasions of high transient response or detection of a fault. A compensation block within the controller is used to regulate the output voltage and provide stability to the system. In one embodiment, the controller is implemented as a PID compensator controller. In another embodiment, a microprocessor is able to receive feedback on its own operation thus providing enabling the controller to anticipate and predict conditions by analyzing precursor data.

Owner:INFINEON TECH AUSTRIA AG

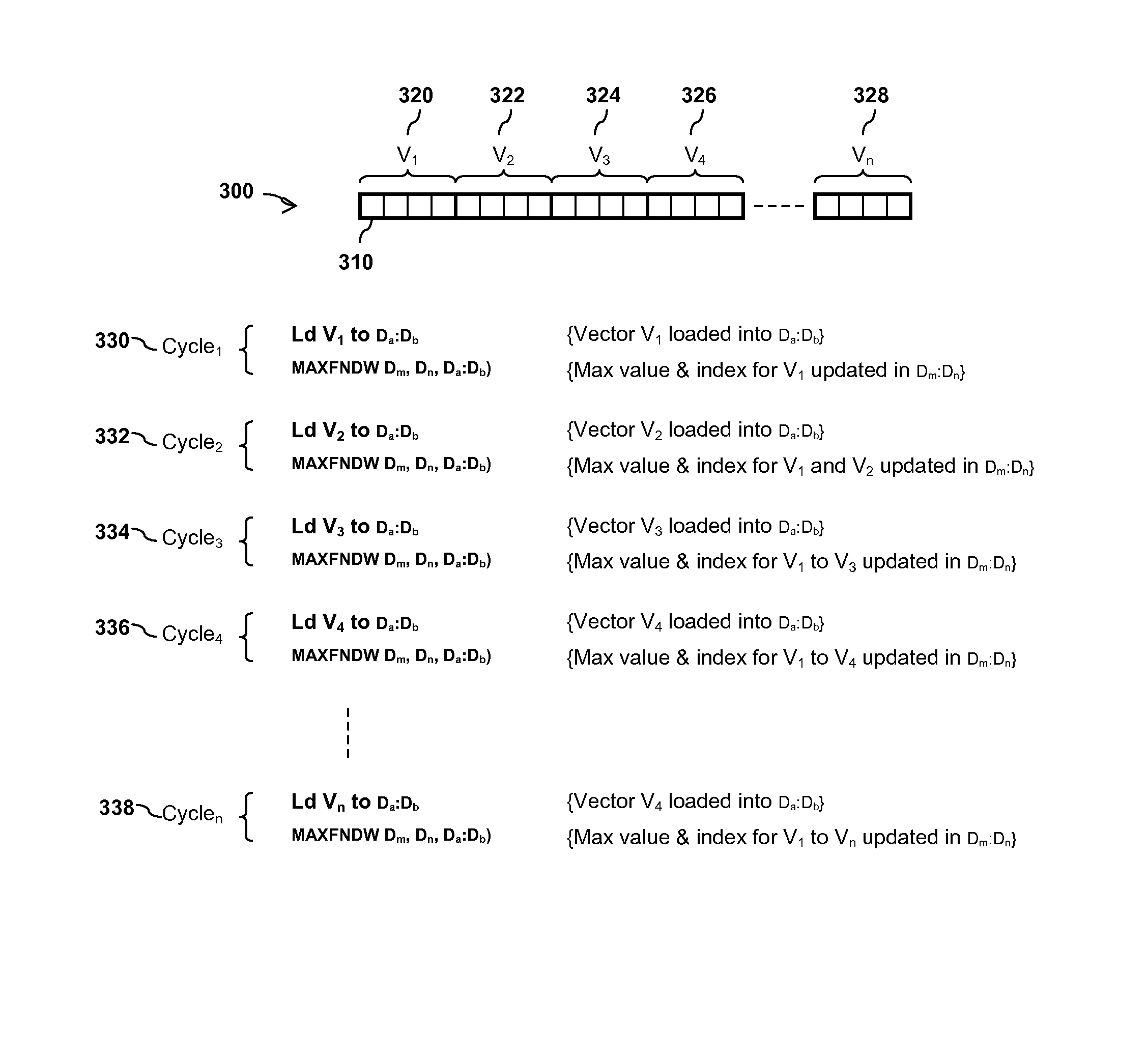

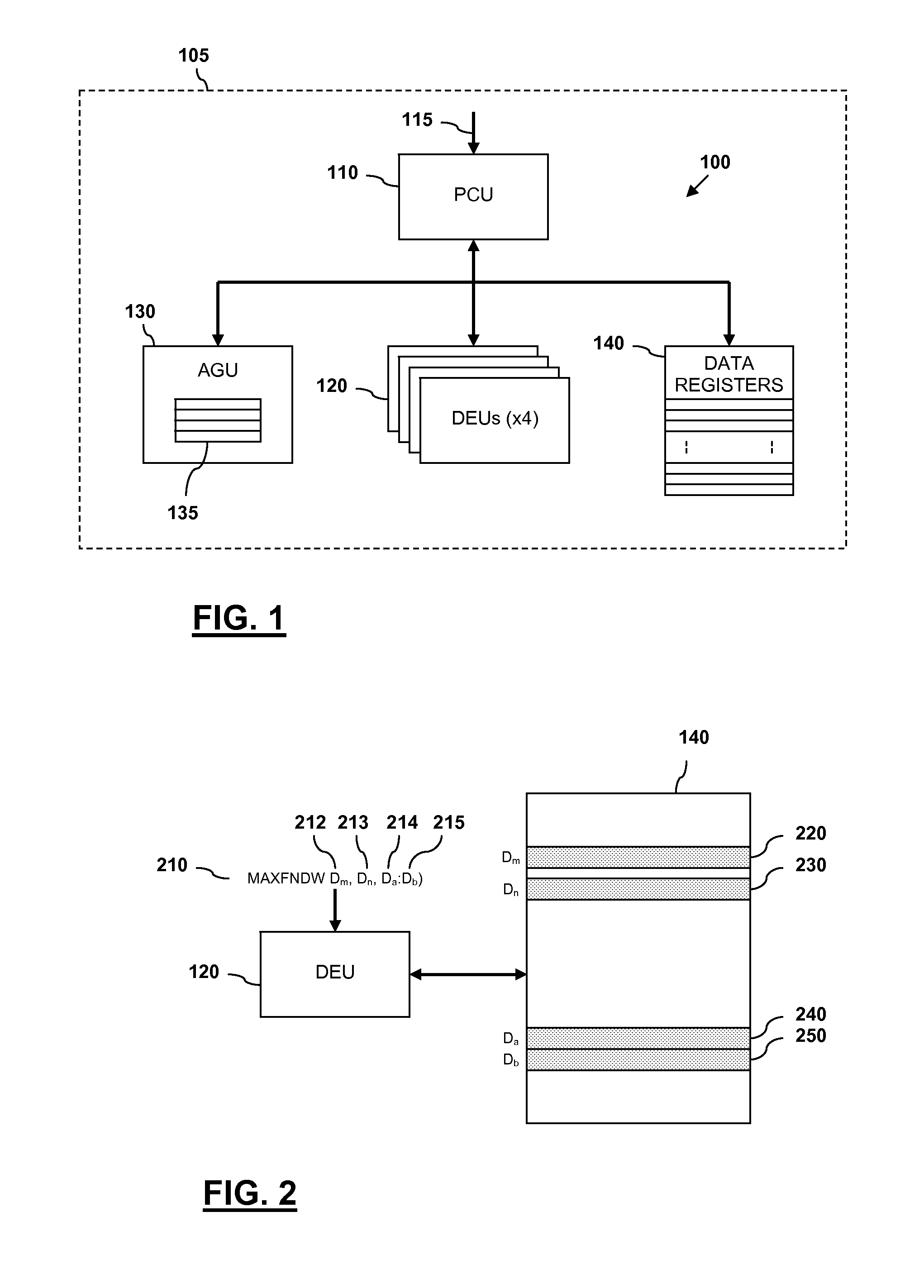

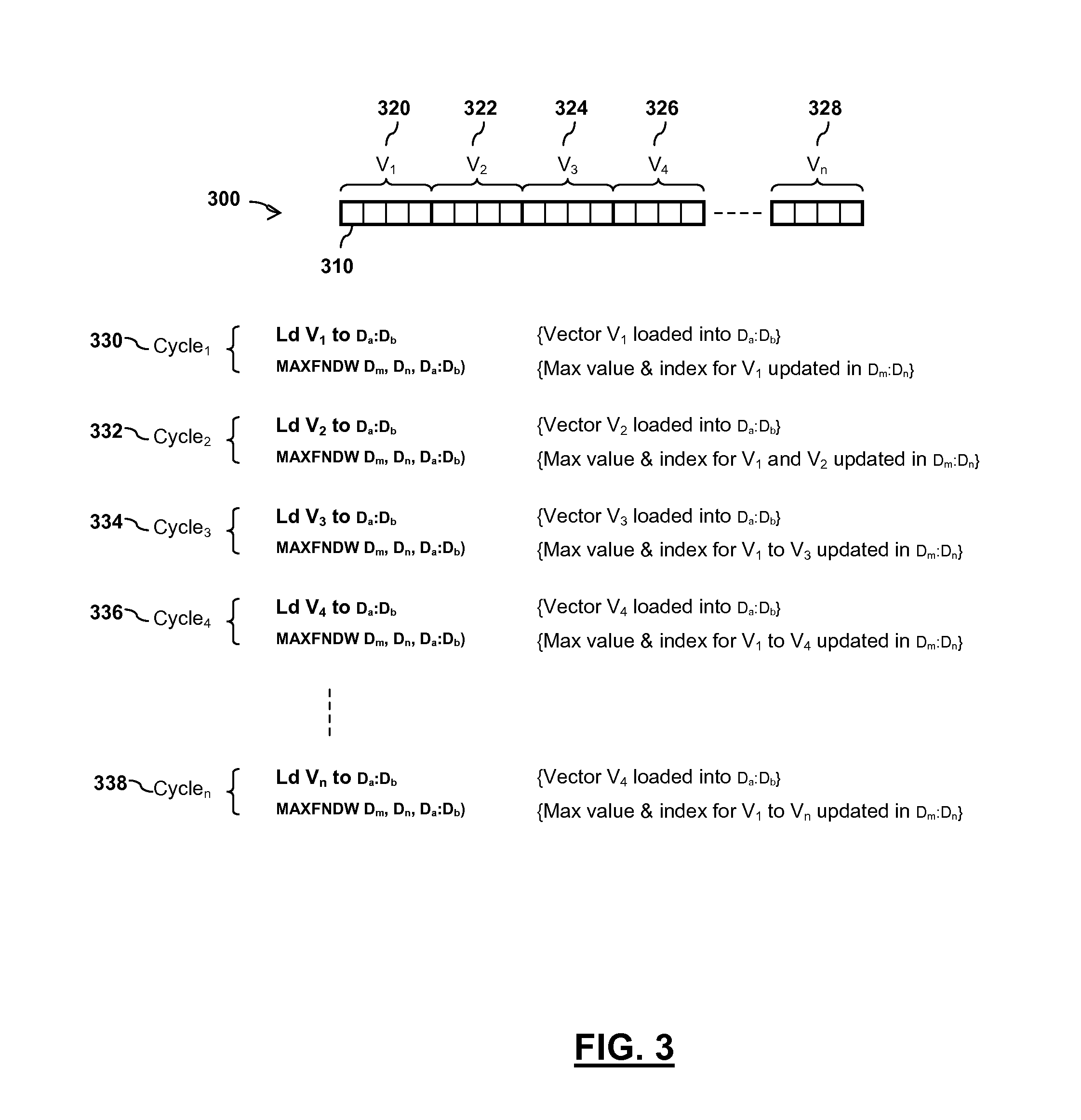

Integrated circuit device and method for determining an index of an extreme value within an array of values

InactiveUS9165023B2Digital data information retrievalDigital data processing detailsProcessor registerComputer module

An integrated circuit device comprises at least one digital signal processor, DSP, module, the at least one DSP module comprising a plurality of data registers and at least one data execution unit, DEU, module arranged to execute operations on data stored within the data registers. The at least one DEU module is arranged to, in response to receiving an extreme value index instruction, compare a previous extreme value located within a first data register set of the DSP module with at least one input vector data value located within a second data register set of the DSP module, and determine an extreme value thereof. The at least one DEU module is further arranged to, if the determined extreme value comprises an input vector data value located within the second data register set, store the determined extreme value in the first data register set, determine an index value for the determined extreme value, and store the determined index value in the first data register set.

Owner:NXP USA INC

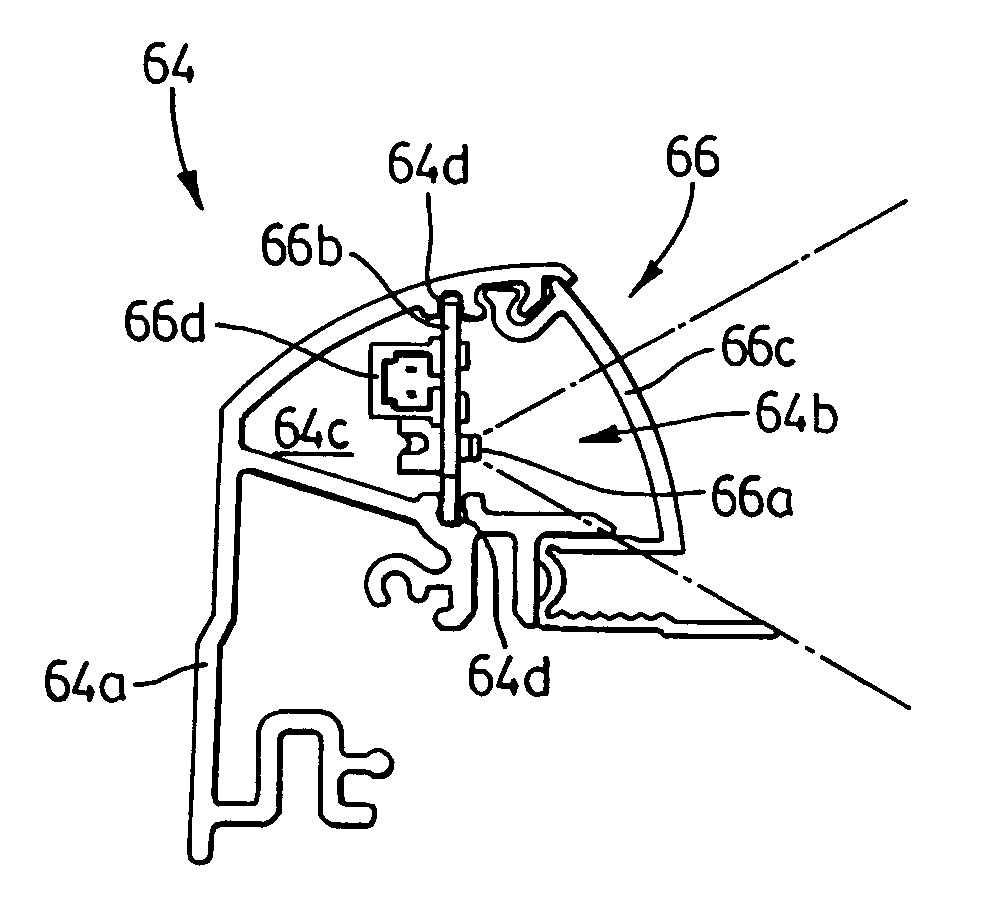

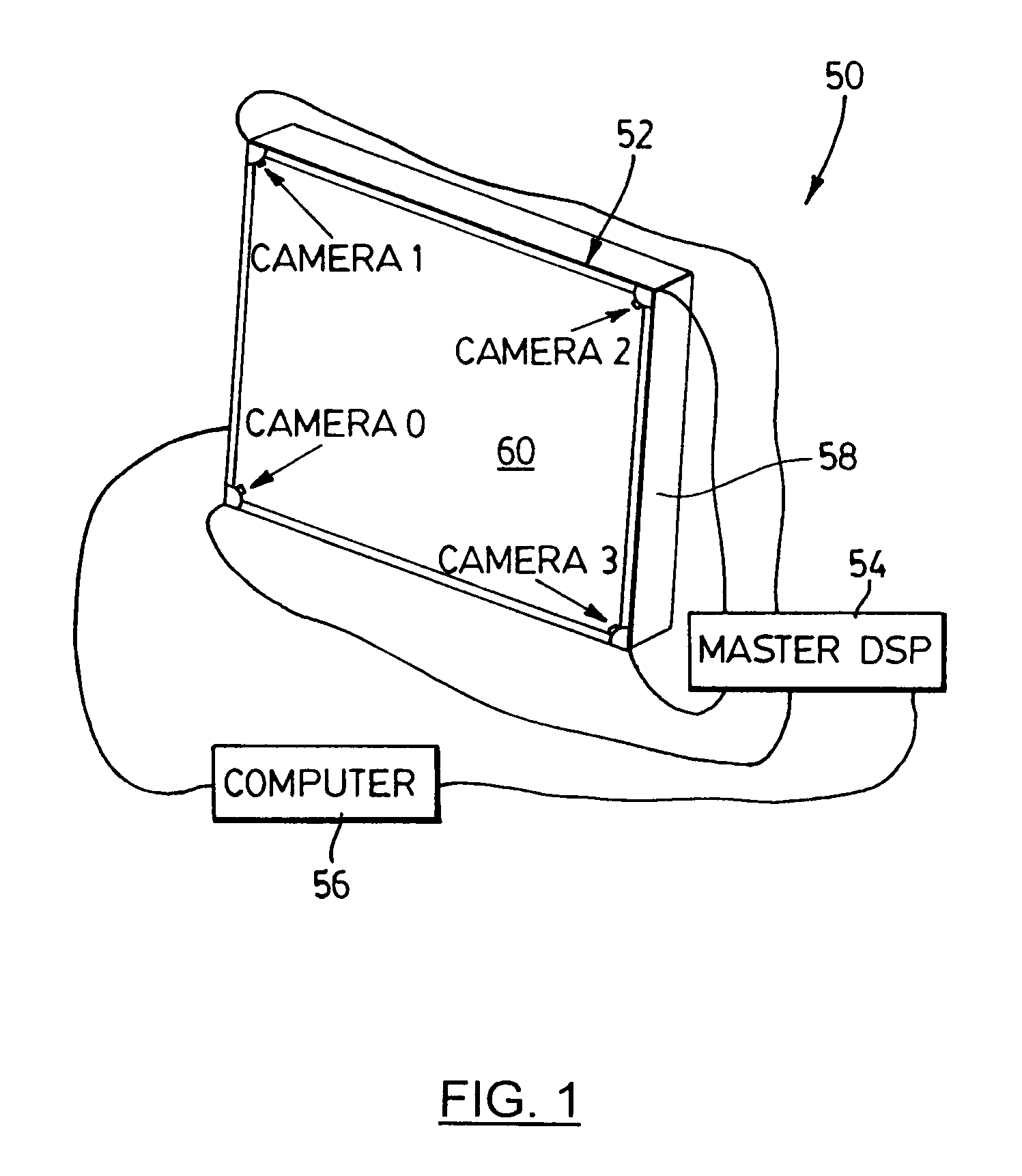

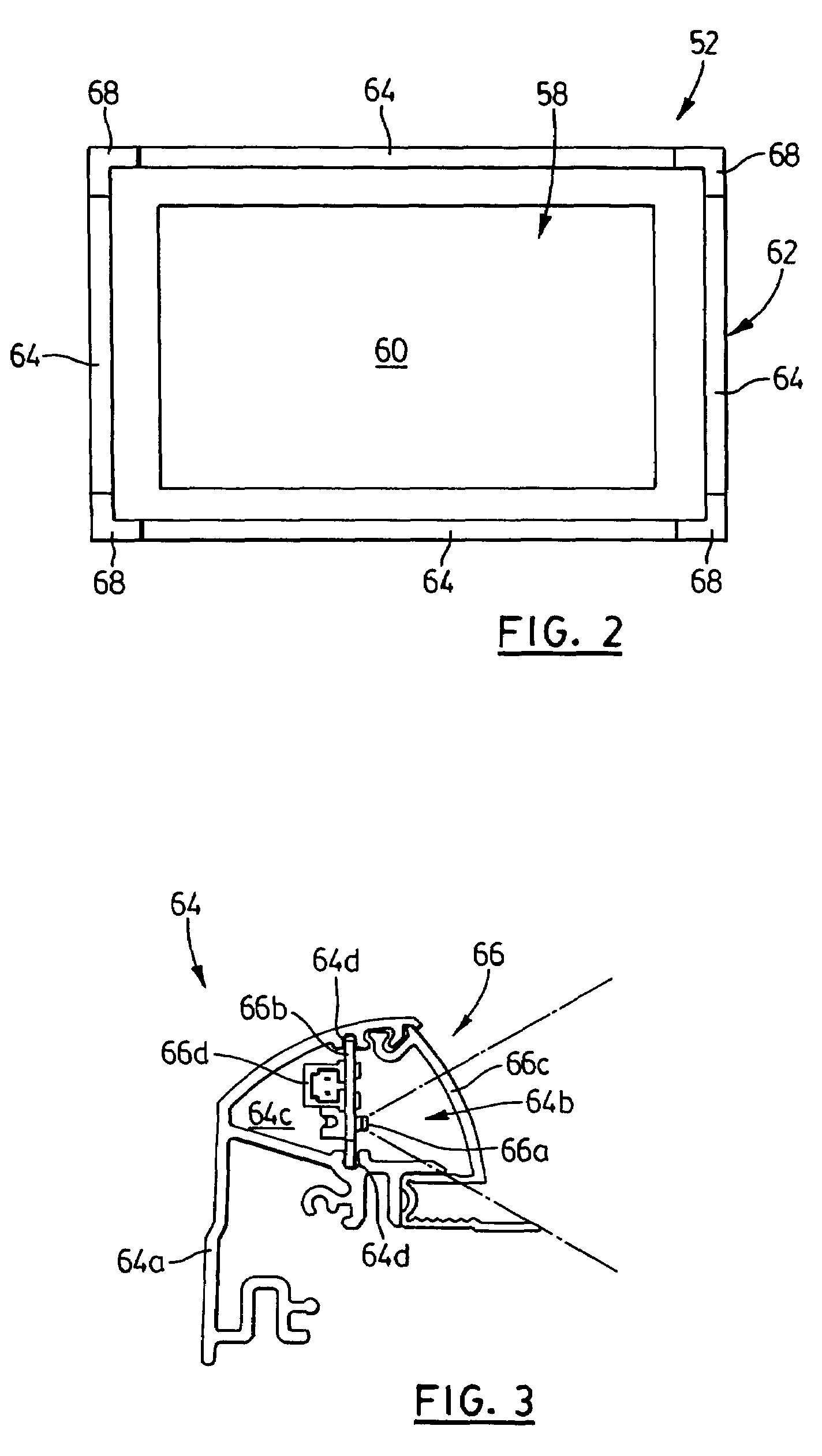

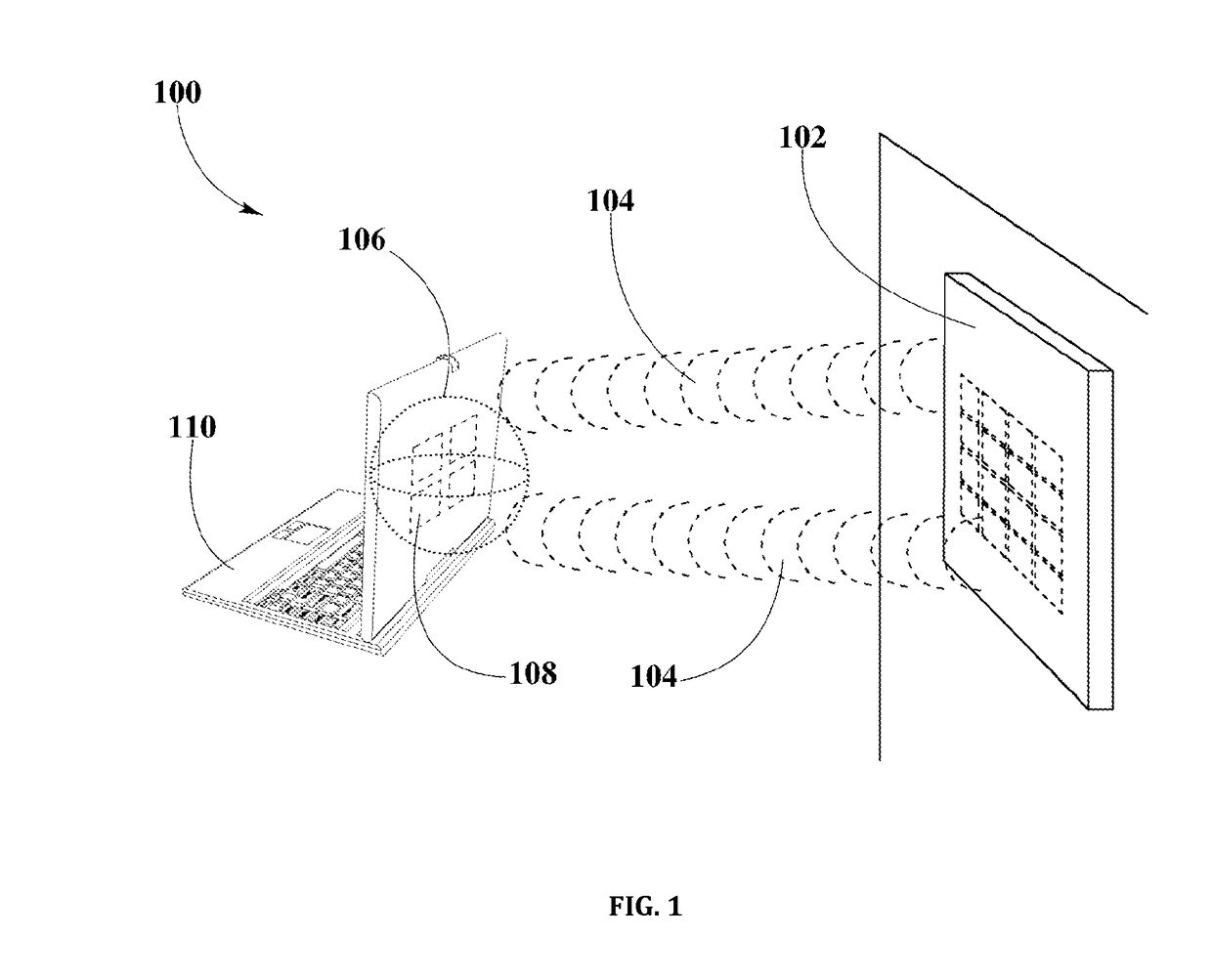

Illuminated bezel and touch system incorporating the same

ActiveUS6972401B2Good backlightHigh resolutionBeam/ray focussing/reflecting arrangementsLighting elementsComputer scienceDigital signal

A passive touch system includes a touch surface and at least one source of backlight illumination projecting backlighting across the touch surface. At least two image sensors are associated with the touch surface and acquire images of the touch surface from different locations. A digital signal processor is associated with each image sensor. The digital signal processors select pixel subsets of images acquired by the image sensors and process pixel data acquired by the selected pixel subsets to generate pointer characteristic data when a pointer exists in the acquired images. A master digital signal processor in communication with the digital signal processors triangulates the pointer characteristic data to determine the location of the pointer relative to the touch surface.

Owner:SMART TECH INC (CA)

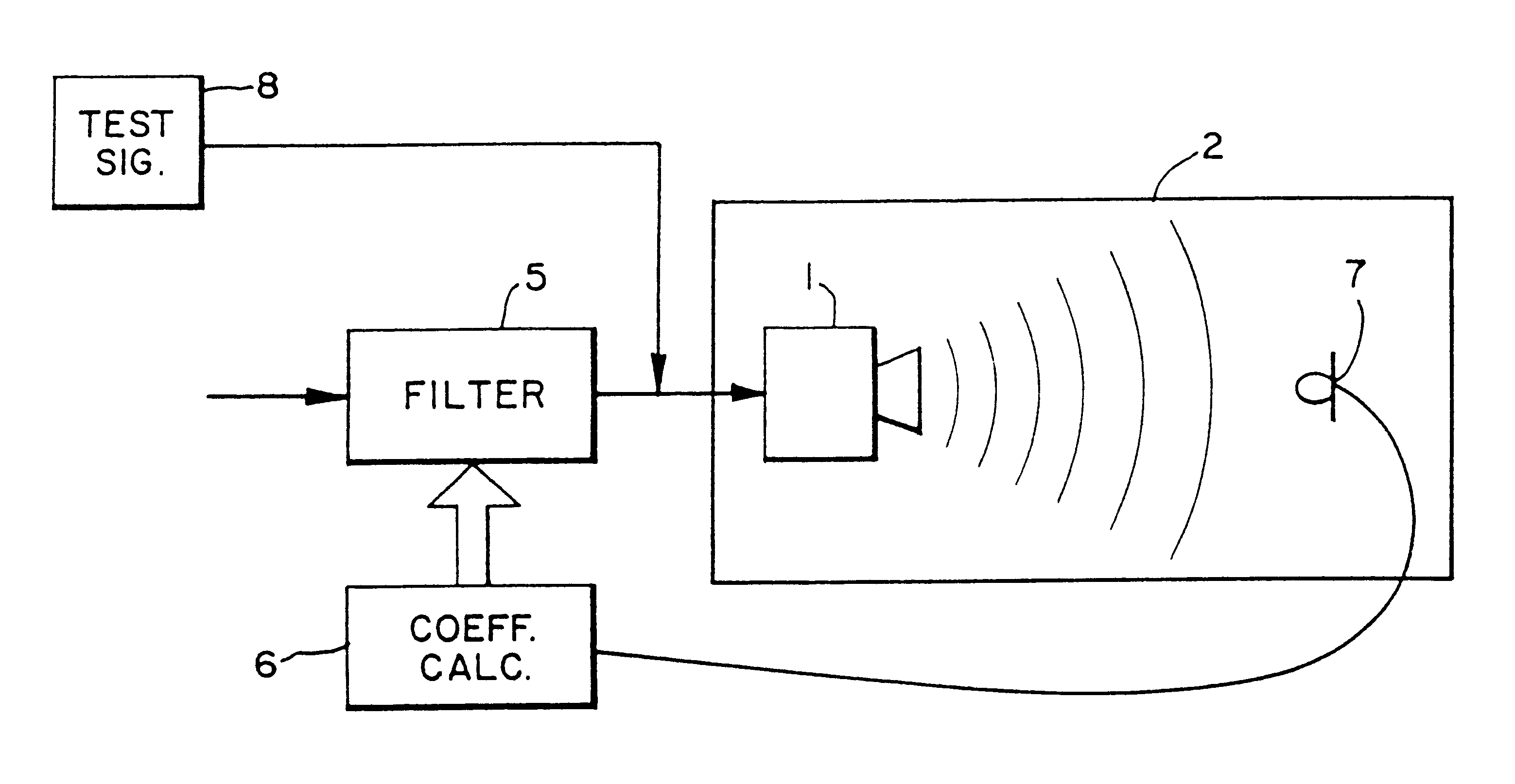

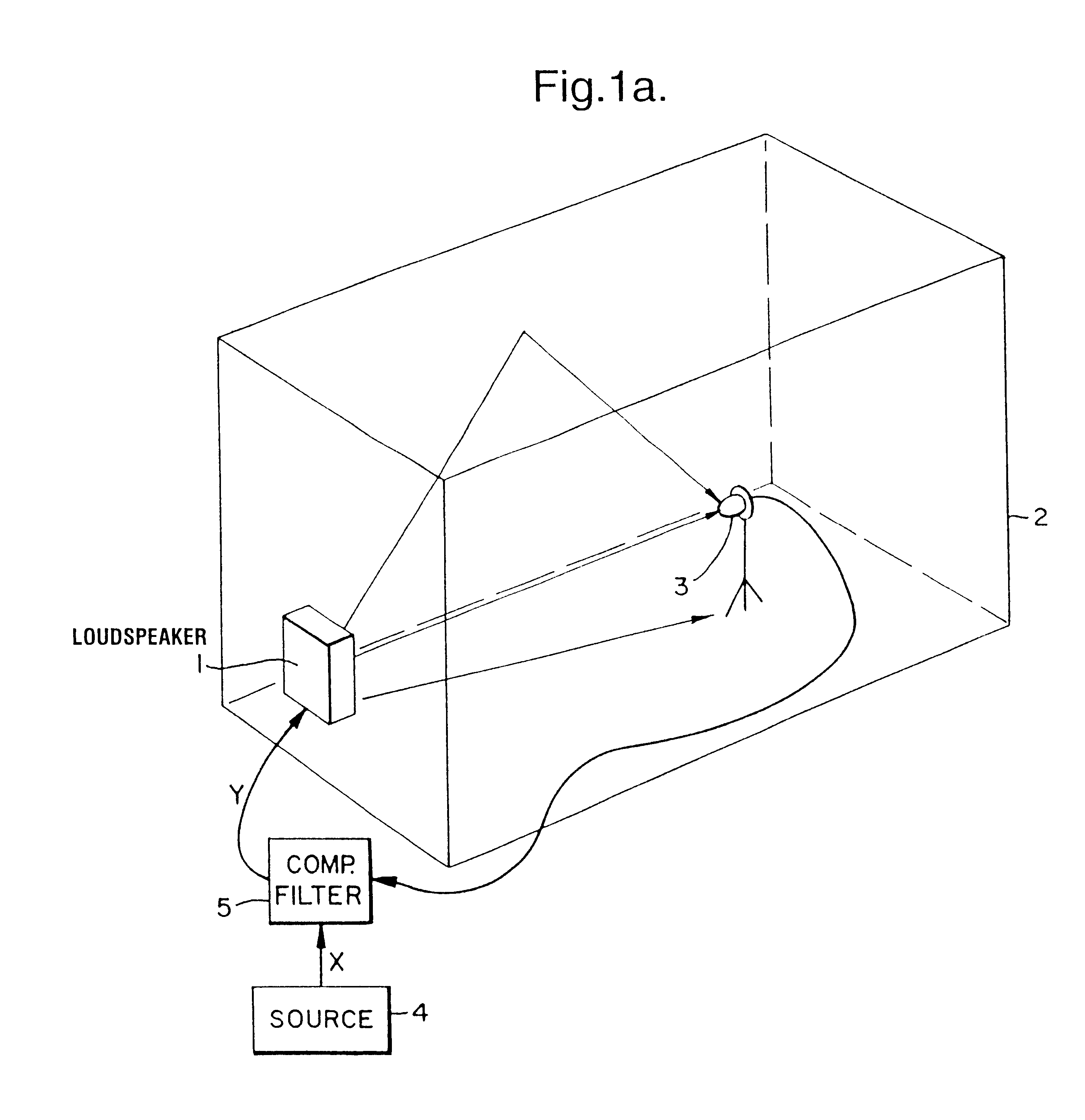

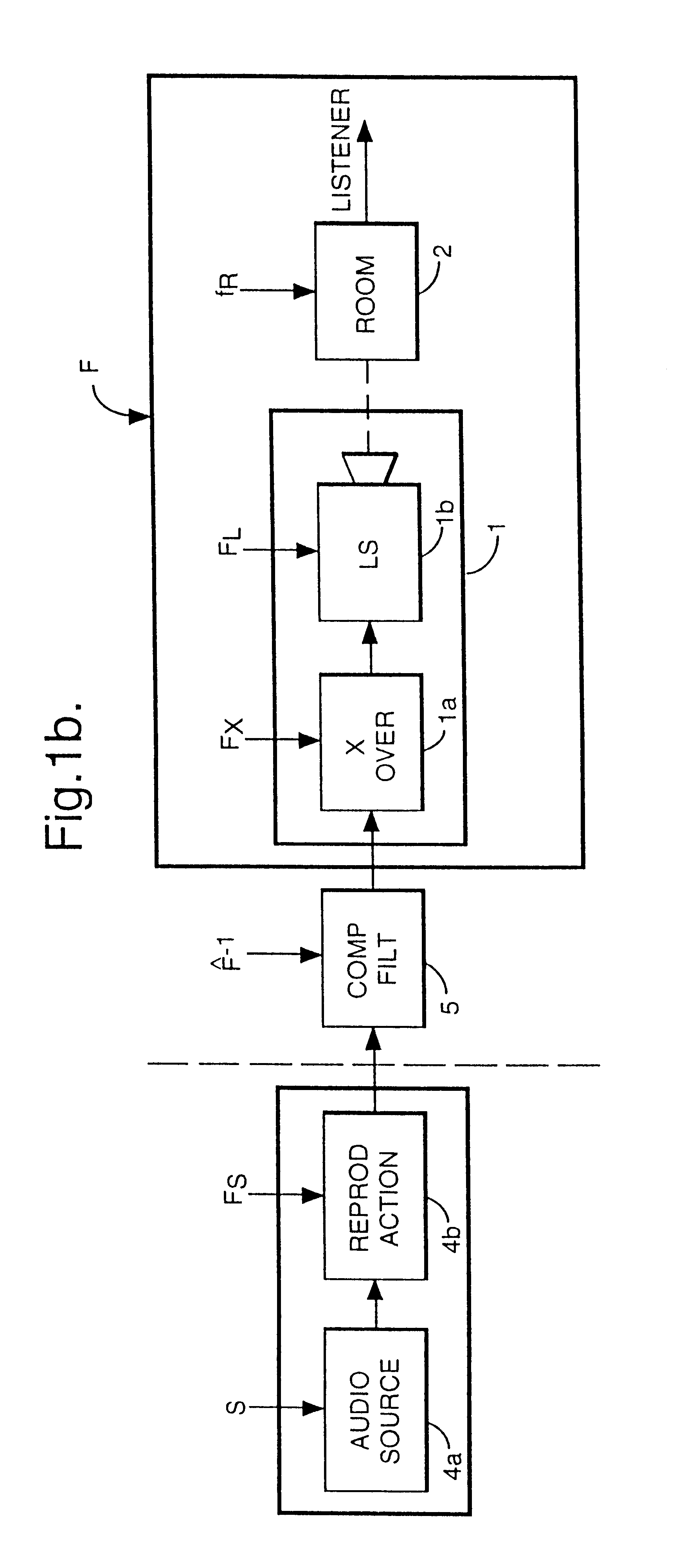

Compensating filters

InactiveUS6760451B1Eliminate phase distortionAdaptive networkAutomatic tone/bandwidth controlDigital signal processingAmplitude response

A prefilter (5) for an audio system comprising a loudspeaker (1) in a room (2), which corrects both amplitude and phase errors due to the loudspeaker (1) by a linear phase correction filter response and corrects the amplitude response of the room (2) whilst introducing the minimum possible amount of extra phase distortion by employing a minimum phase correction filter stage. A test signal generator (8) generates a signal comprising a periodic frequency sweep with a greater phase repetition period than the frequency repetition period. A microphone (7) positioned at various points in the room (2) measures the audio signal processed by the room (2) and loudspeaker (1), and a coefficient calculator (6) (e.g. a digital signal processor device) derives the signal response of the room and thereby a requisite minimum phase correction to be cascaded with the linear phase correction already calculated for the loudspeaker (1). Filter (5) may comprise the same digital signal processor as the coefficient calculator (6). Applications in high fidelity audio reproduction, and in car stereo reproduction.

Owner:CRAVEN PETER GRAHAM +1

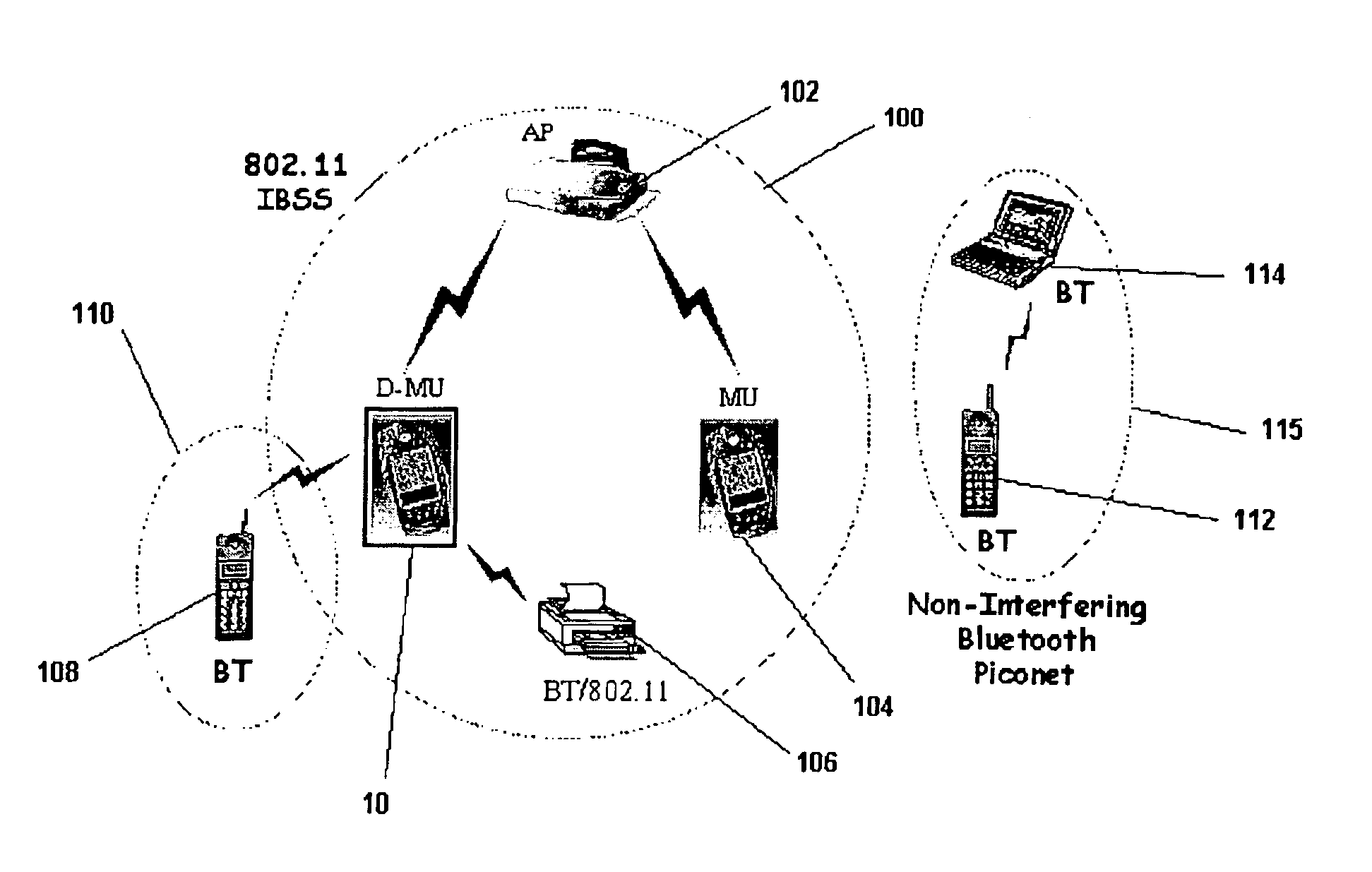

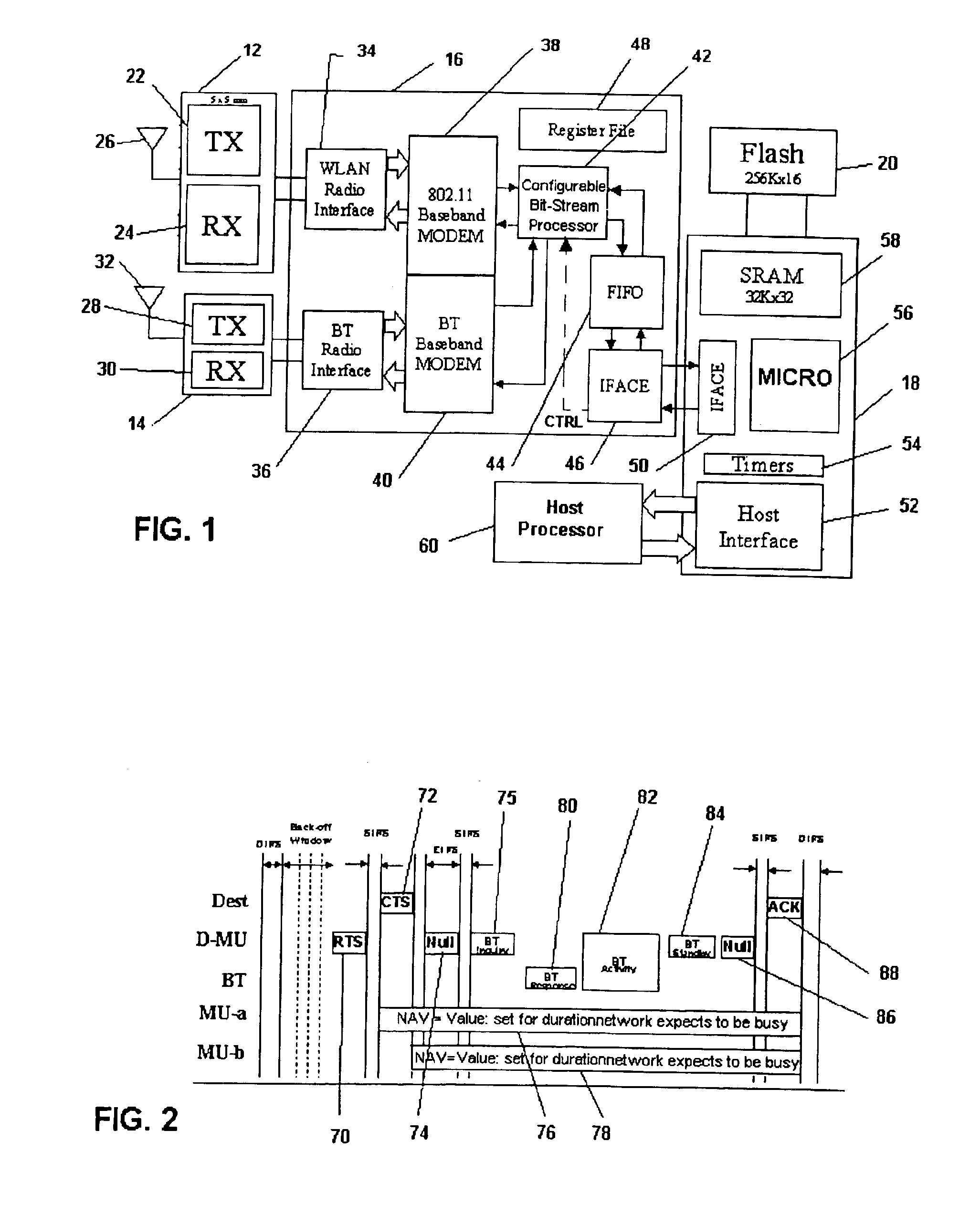

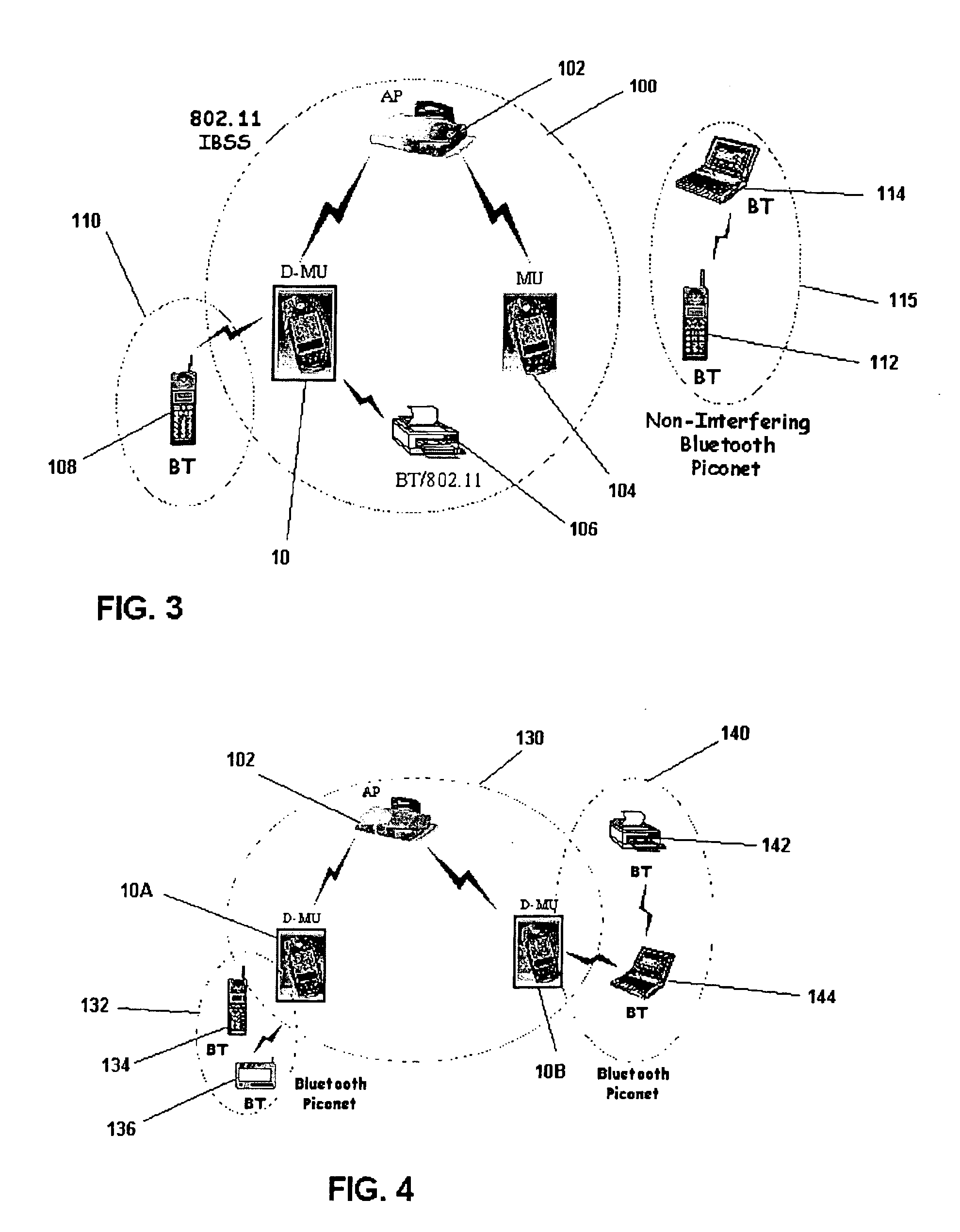

Dual mode wireless data communications

A dual mode mobile unit is arranged to communicate in either a first or second data communications standard, such as combined Bluetooth and 802.11 operation. An interface unit converts received Bluetooth or 802.11 format signals into 802.11 frame format data signals to be provided to a digital signal processor which is programmed to process signals in either standard. The dual mode mobile unit can operate in the 802.11 standard to reserve a time interval for Bluetooth activity during which other 802.11 units will avoid-transmissions to avoid interference.

Owner:SYMBOL TECH LLC

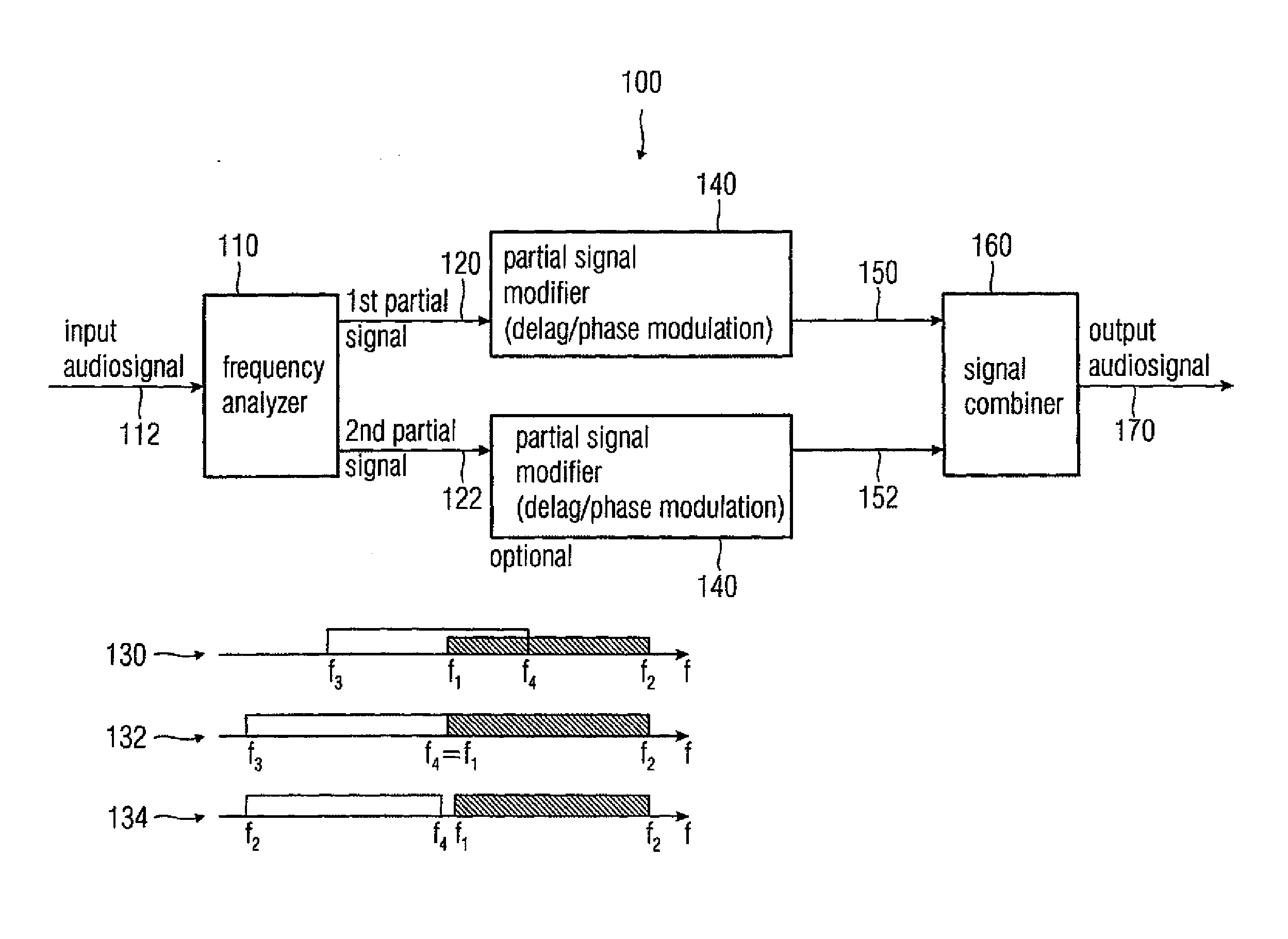

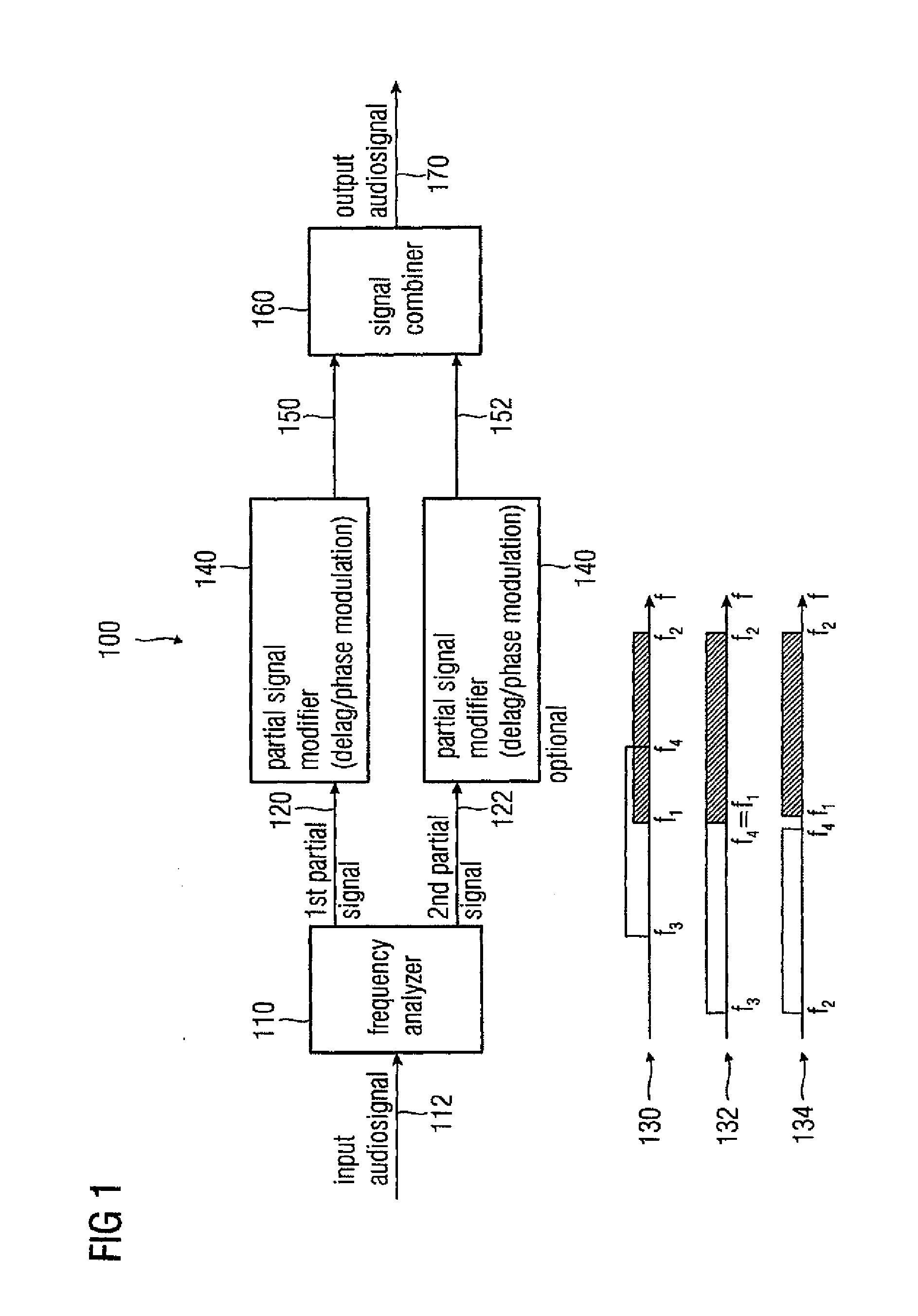

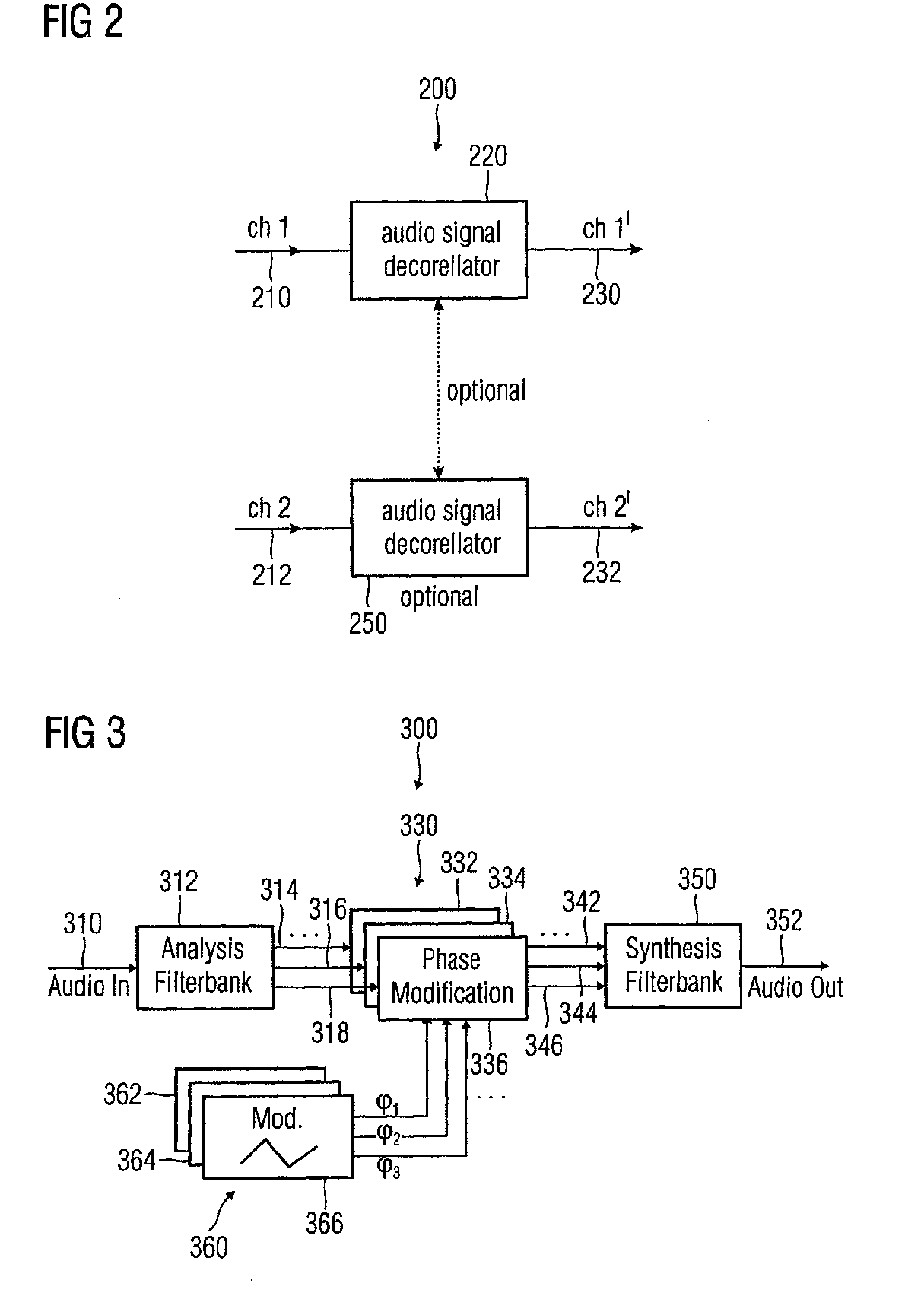

Audio signal decorrelator, multi channel audio signal processor, audio signal processor, method for deriving an output audio signal from an input audio signal and computer program

ActiveUS20090304198A1Simple designReducing and removing audio contentTwo-way loud-speaking telephone systemsSpeech analysisVIT signalsAudio signal

An audio signal decorrelator for deriving an output audio signal from an input audio signal has a frequency analyzer for extracting from the input audio signal a first partial signal descriptive of an audio content in a first audio frequency range and a second partial signal descriptive of an audio content in a second audio frequency range having higher frequencies compared to the second audio frequency range. A partial signal modifier for modifies the first and second partial signals, to obtain first and second processed partial signals, so that a modulation amplitude of a time variant phase shift or time variant delay applied to the first partial signal is higher than that applied to the second partial signal, or for modifying only the first partial signal. A signal combiner combines the first and second processed partial signals, or combines the first processed partial signal and the second partial signal, to obtain an output audio signal.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

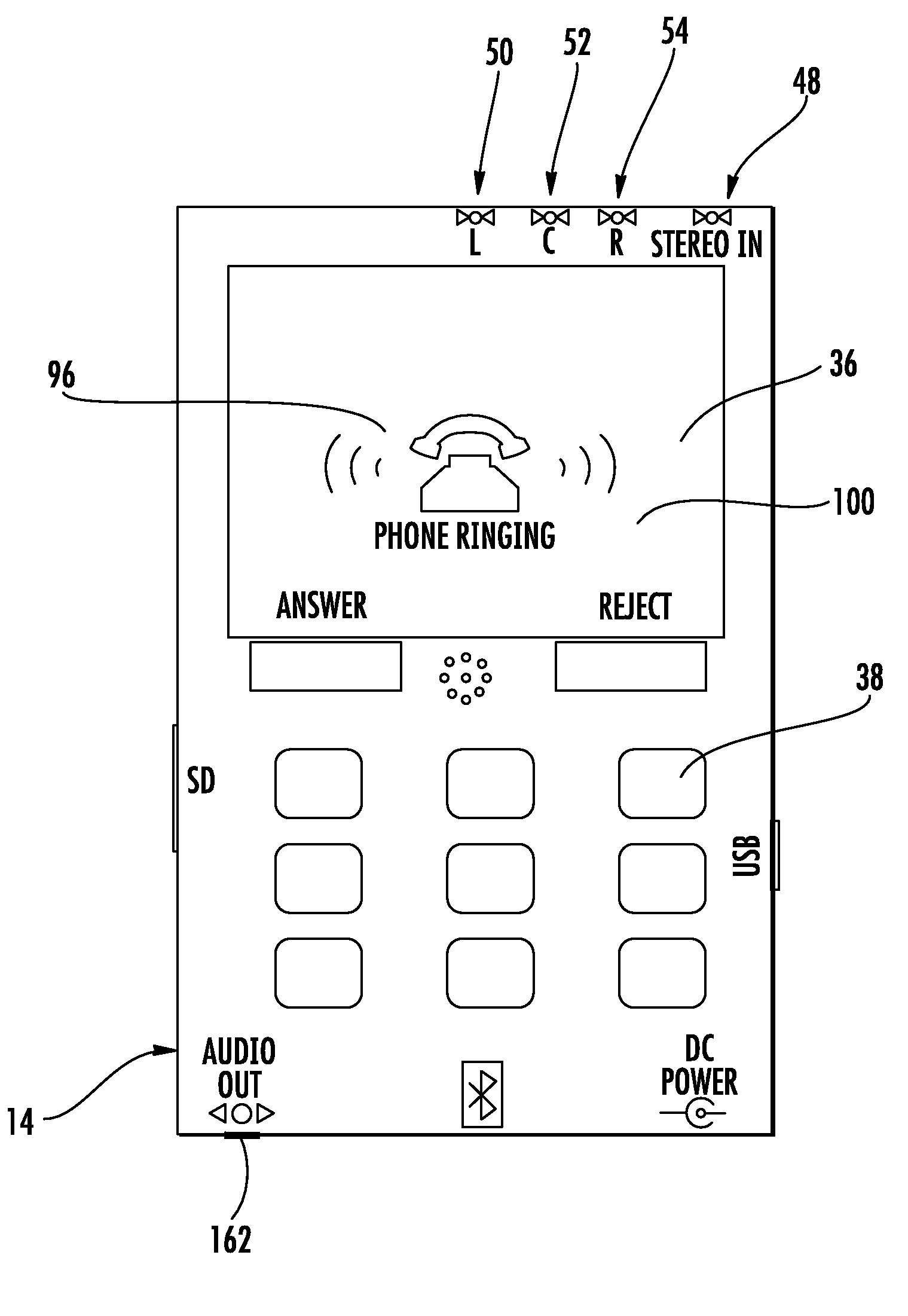

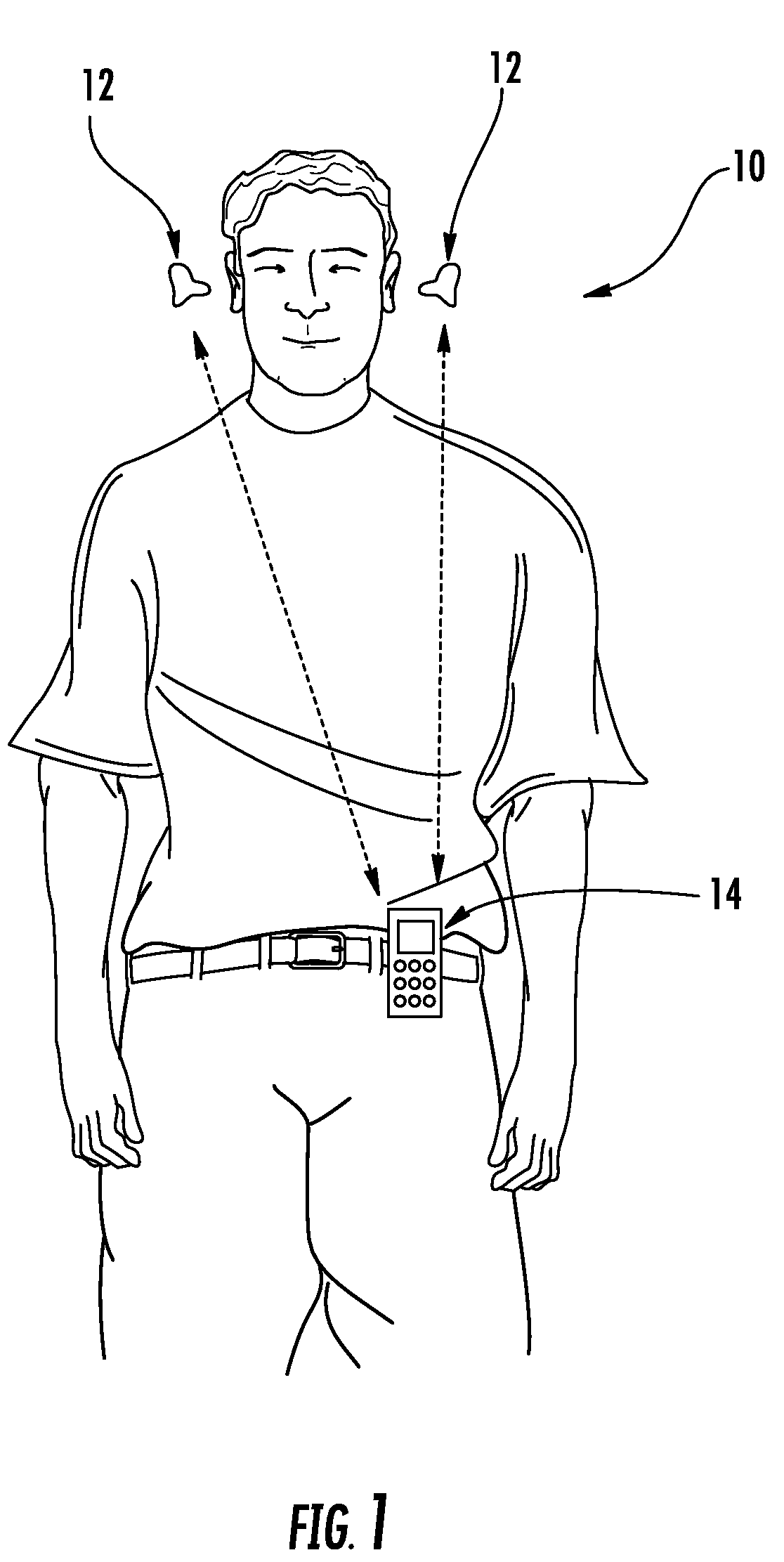

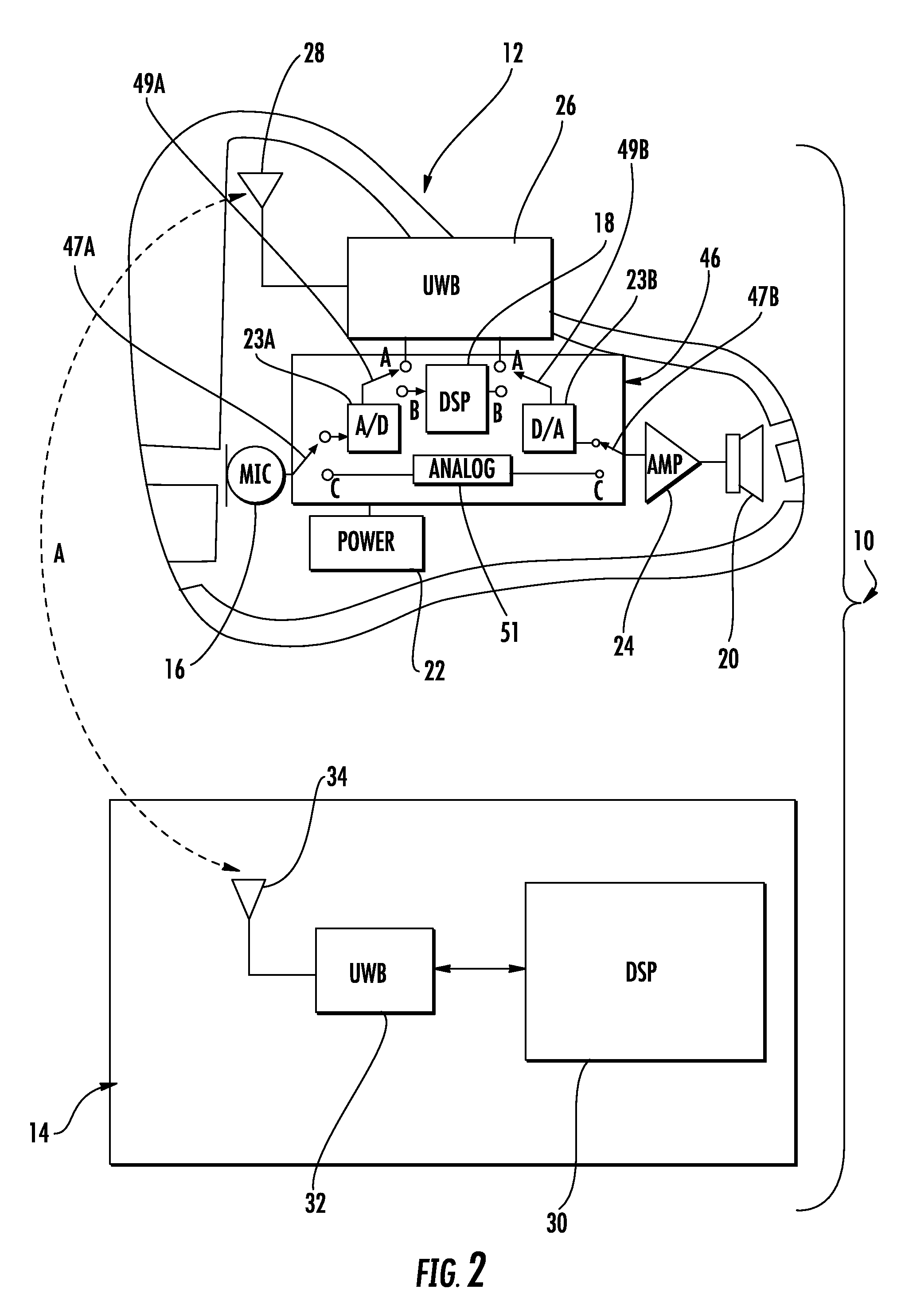

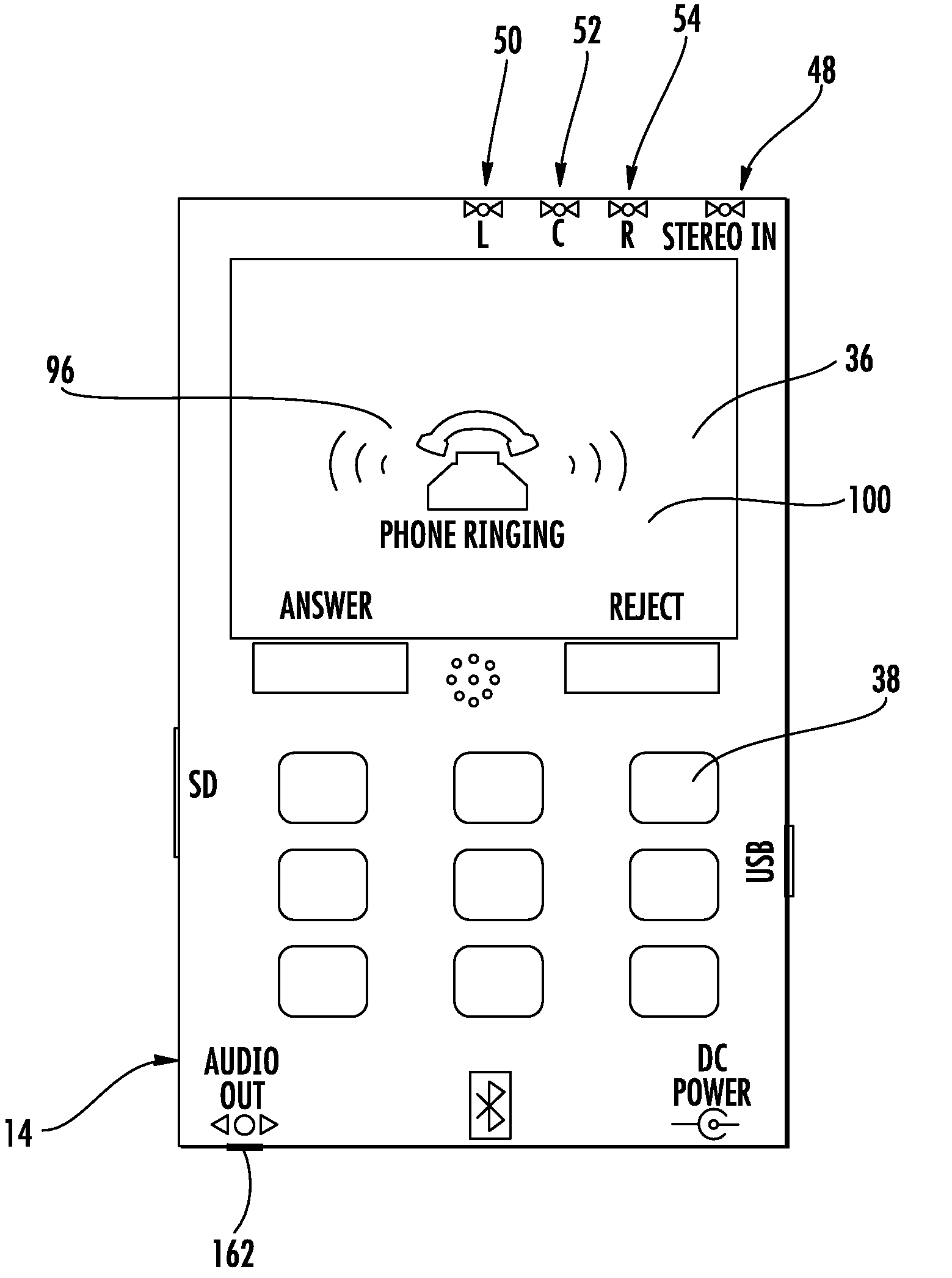

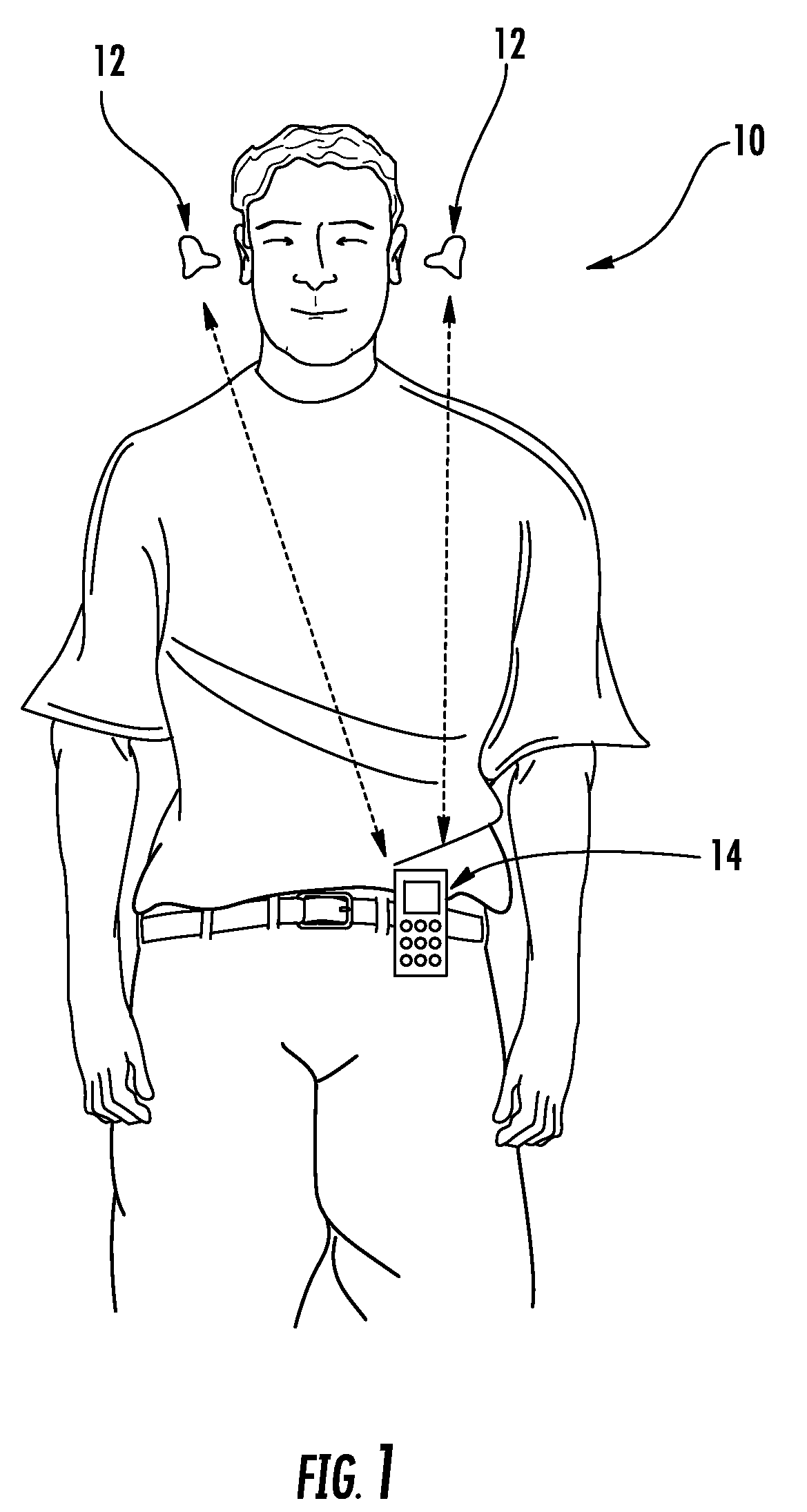

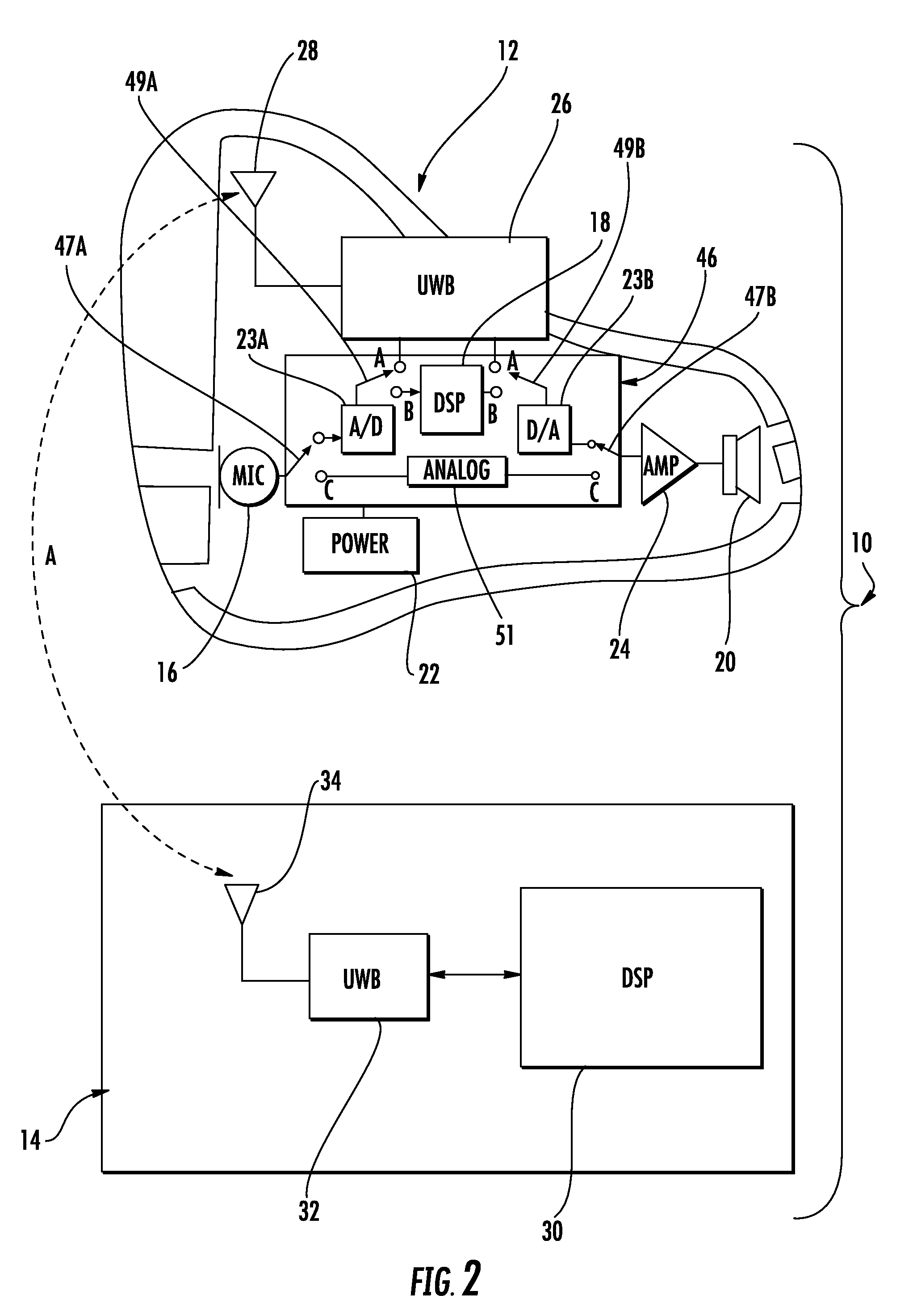

Method of enhancing sound for hearing impaired individuals

InactiveUS20090076825A1Improve functionalityImprove usabilitySpeech recognitionDeaf-aid setsDigital signal processingSound sources

A portable assistive listening system for enhancing sound for hearing impaired individuals includes a fully functional hearing aid and a separate handheld digital signal processing (DSP) device. The focus of the present invention is directed to the handheld DSP device and a unique method of processing incoming audio signals. The DSP device includes a programmable digital signal processor, a UWB transceiver for communicating with the hearing aid and / or other wireless audio sources, an LCD display, and a user input device (keypad). The handheld device is user programmable to apply different sound enhancement algorithms for enhancing sound signals received from the hearing aid and / or other audio source. The handheld device is capable of receiving audio signals from multiple sources, and gives the user control over selection of incoming sound sources and selective enhancement of sound. In the context of being user programmable, the digital signal processing device includes a software platform that provides for the ability of the user to select, or plug-in, desired enhancement algorithms for application to selected incoming audio signals. Specifically, the invention focuses on a method of buffering an incoming audio signal, and selectively replaying the buffered audio. The method further includes converting the replayed audio signal to text for display on the handheld DSP device.

Owner:BIONICA CORP

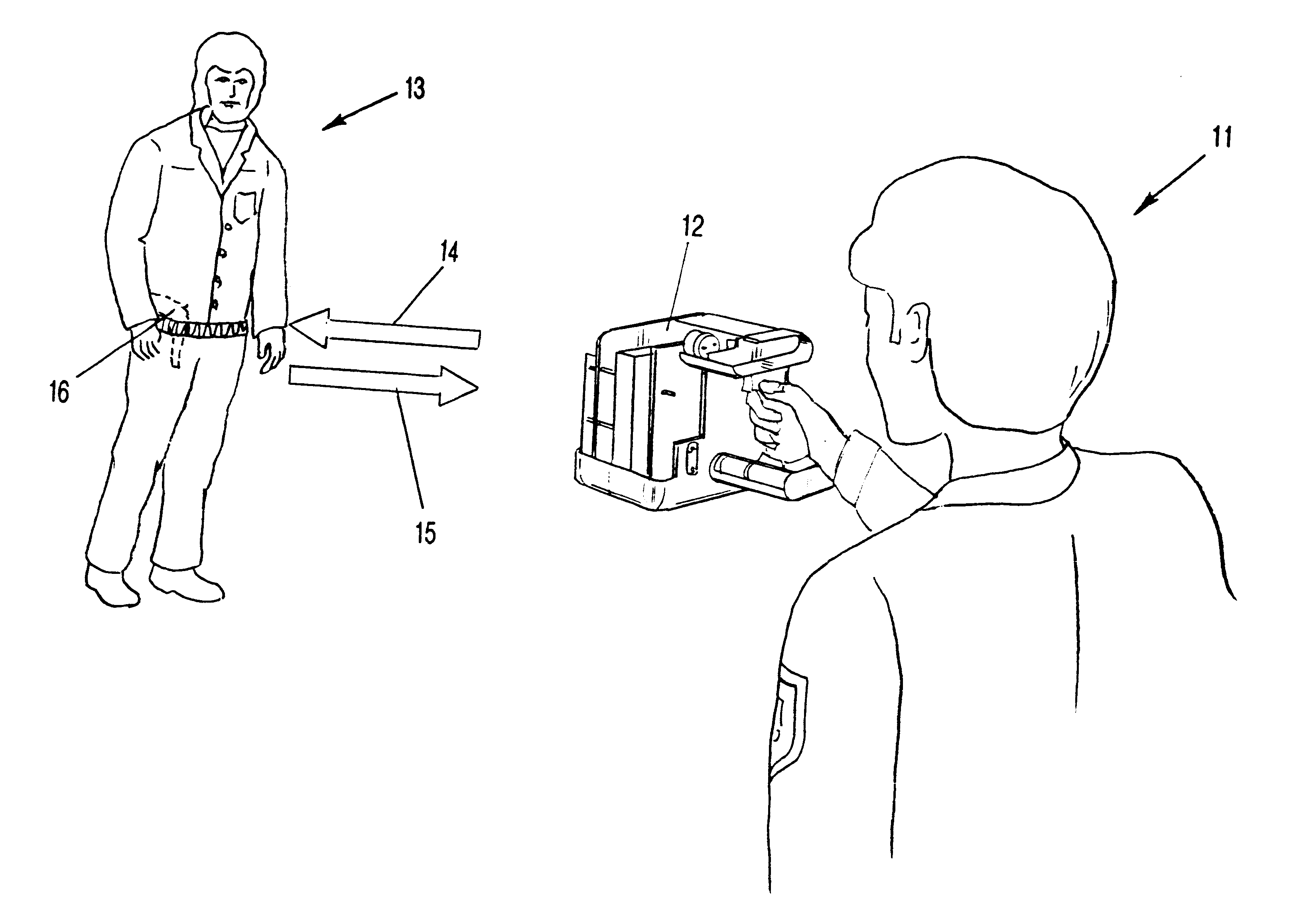

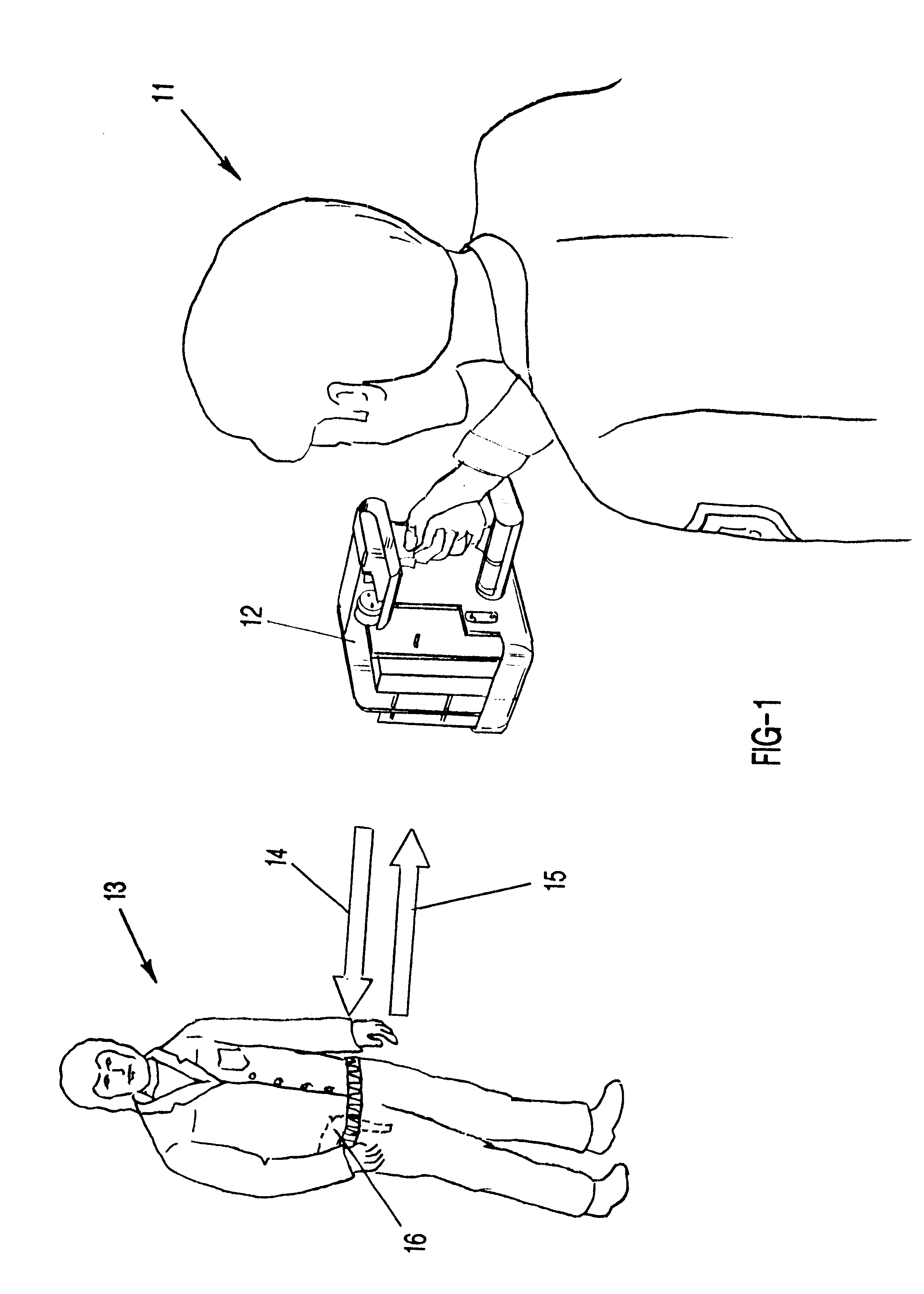

Concealed weapons detection system

InactiveUS6359582B1Detection using electromagnetic wavesRadio wave reradiation/reflectionRadarEngineering

A weapons detector (12) and method utilizing radar. The system comprises a transmitter (27) for producing an output (14) of frequencies of a set of self-resonant frequencies of weaponry; an antenna (28) directing the transmitter output toward locations potentially having weaponry and collecting backscattered signals (15); a receiver (29) receiving the backscattered signals (15) and operating over a range of the self-resonant frequencies; and a signal processor (30) for detecting the presence of a plurality of the self-resonant frequencies in the backscattered signals (15). Accuracies of greater than 98% can be obtained at distances, preferably between 4-15 yards. The weapons detector (12) is capable of detecting metal and non-metal weapons (16) on a human body (13) in purses, briefcases and under clothing; and discerning weapons (16) from objects such as belt buckles, coins, keys, calculators, cellular phones.

Owner:MACALEESE +1

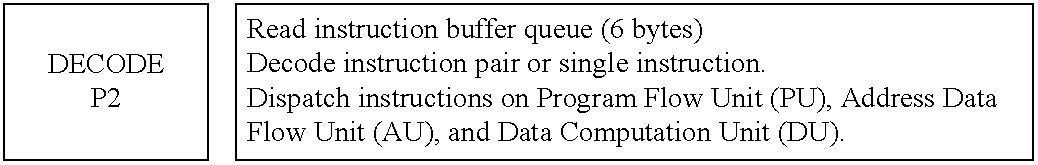

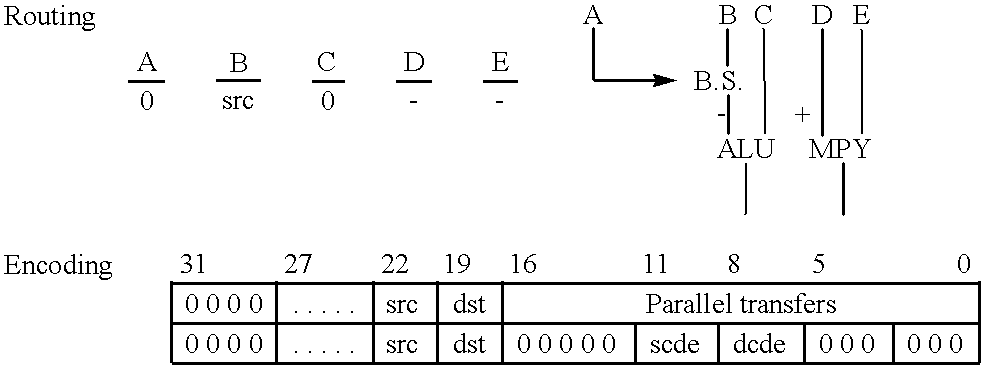

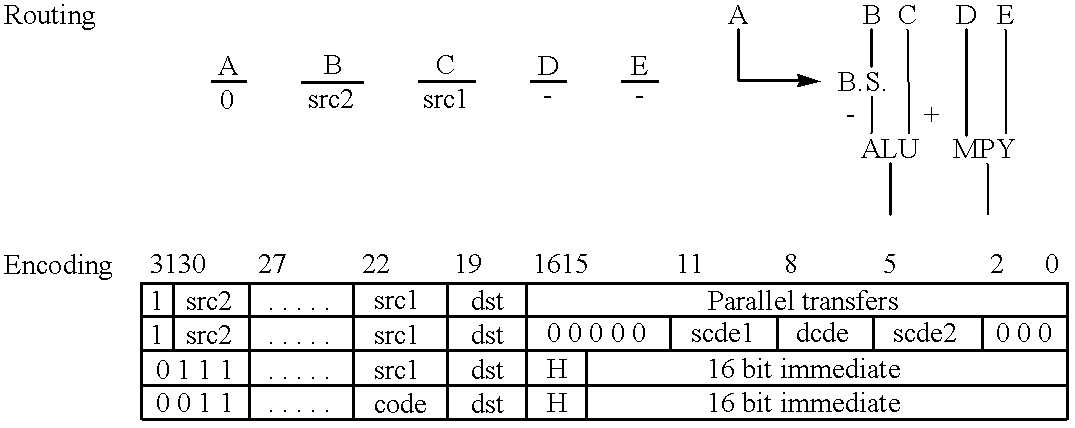

Microprocessors

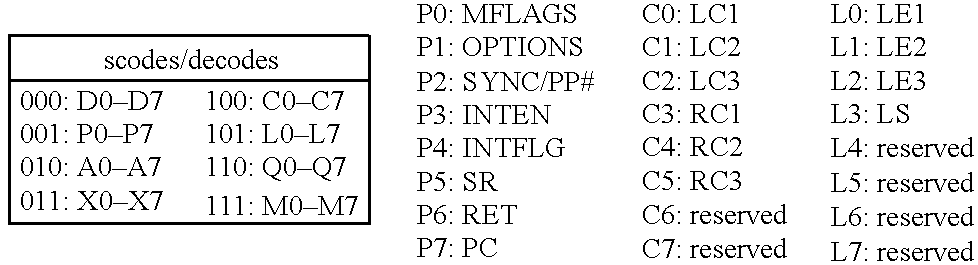

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

Assistive listening system with plug in enhancement platform and communication port to download user preferred processing algorithms

InactiveUS20090074214A1Improve functionalityImprove usabilityInput/output for user-computer interactionCathode-ray tube indicatorsDigital signal processingTransceiver

Owner:BIONICA CORP

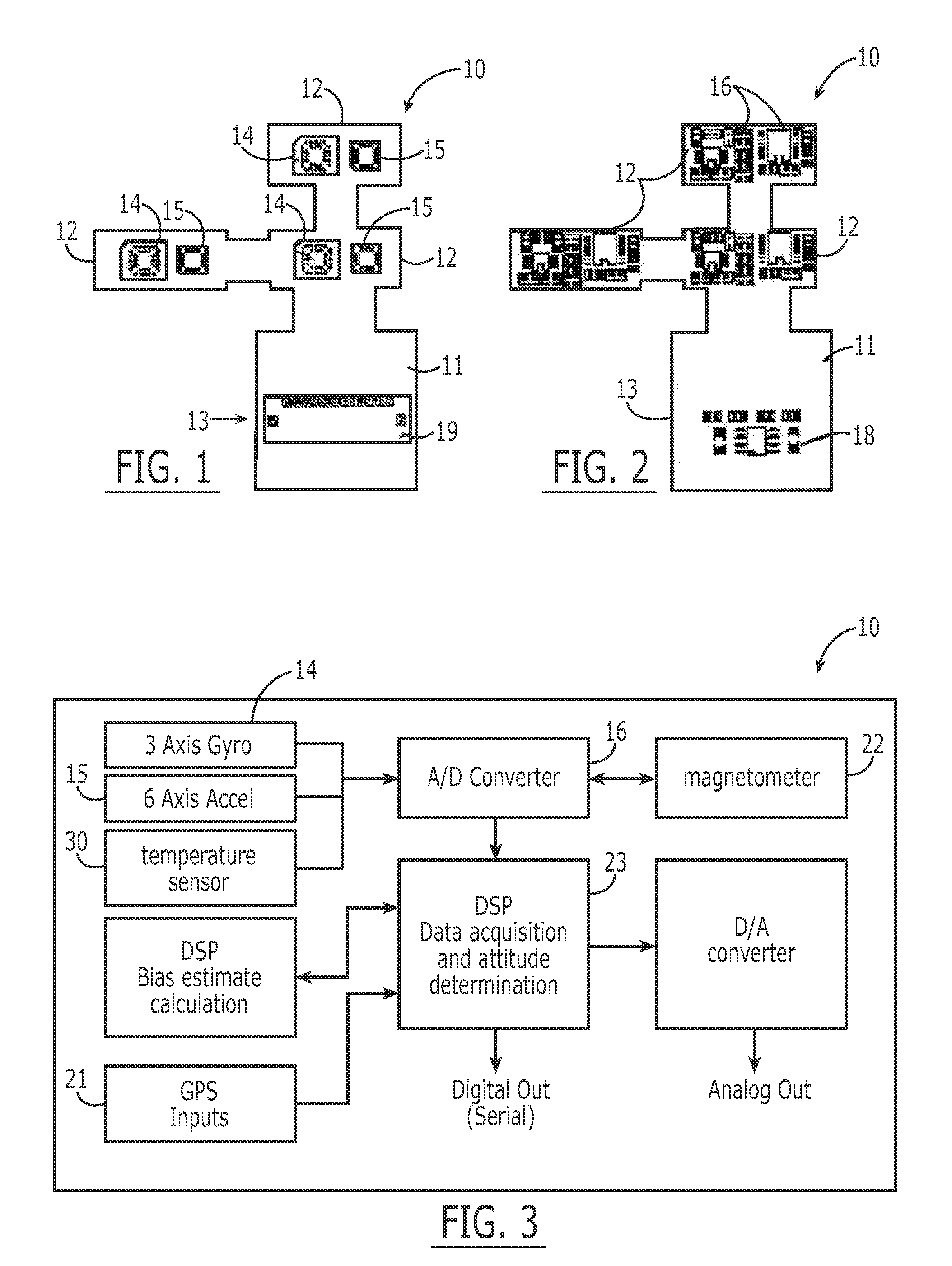

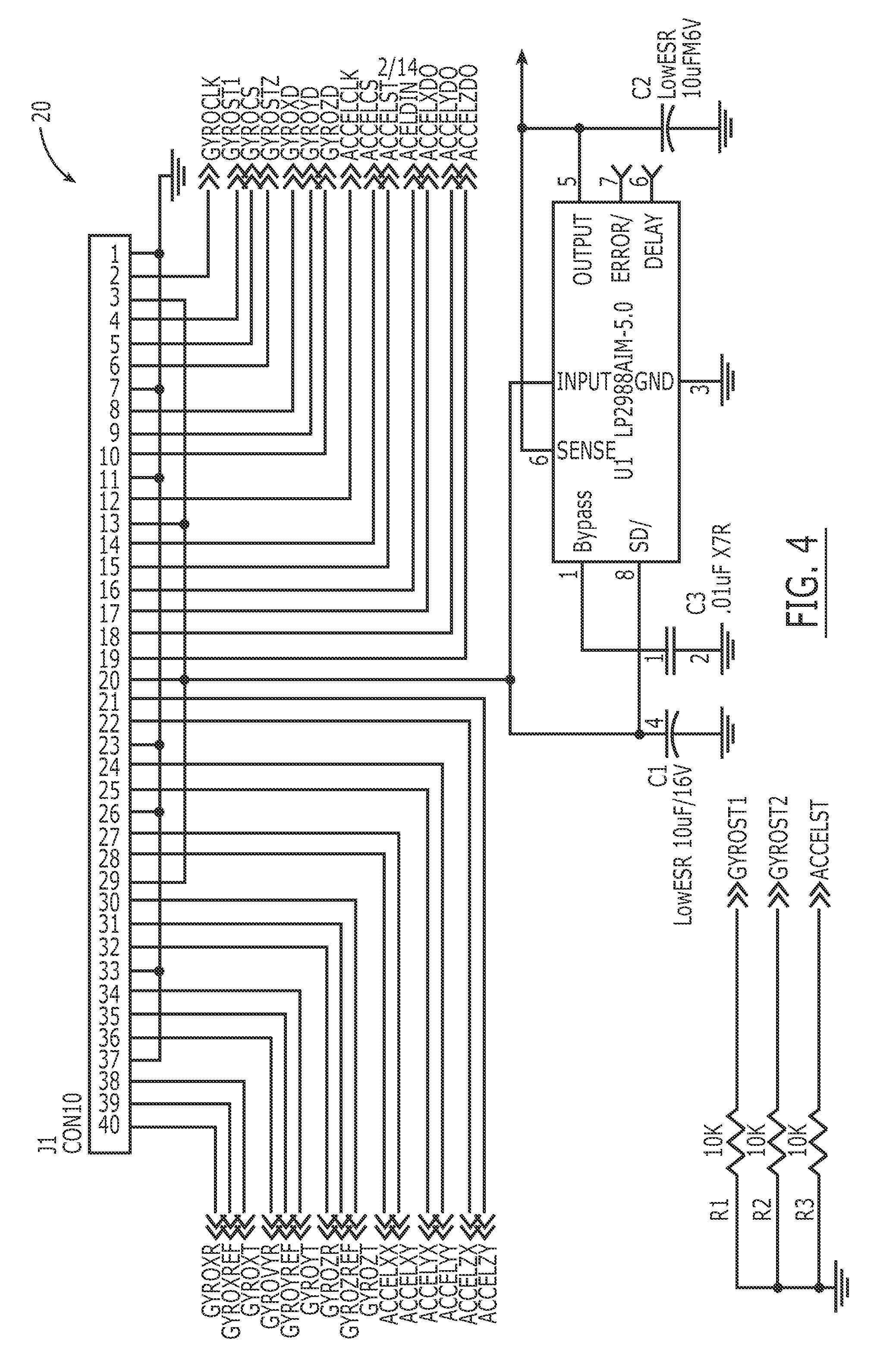

Miniaturized Inertial Measurement Unit and Associated Methods

InactiveUS20070032951A1Reduce noiseThe result is accurateNavigation by speed/acceleration measurementsDigital computer detailsDigital signal processingAccelerometer

A self-contained, integrated micro-cube-sized inertial measurement unit is provided wherein accuracy is achieved through the use of specifically oriented sensors, the orientation serving to substantially cancel noise and other first-order effects, and the use of a noise-reducing algorithm such as wavelet cascade denoising and an error correcting algorithm such as a Kalman filter embedded in a digital signal processor device. In a particular embodiment, a pair of three sets of angle rate sensors are orientable triaxially in opposite directions, wherein each set is mounted on a different sector of a base orientable normal to the other two and comprising N gyroscopes oriented at 360 / N-degree increments, where N≧2. At least one accelerometer is included to provide triaxial data. Signals are output from the angle rate sensors and accelerometer for calculating a change in attitude, position, angular rate, acceleration, and / or velocity of the unit.

Owner:JAYMART SENSORS

Apparatus and method for alerting generator functions in an ultrasonic surgical system

InactiveUS20090118751A1Avoid mistakesNew system functionalityIncision instrumentsSurgical instrument detailsDriving currentPower flow

Owner:WIENER EITAN T +3

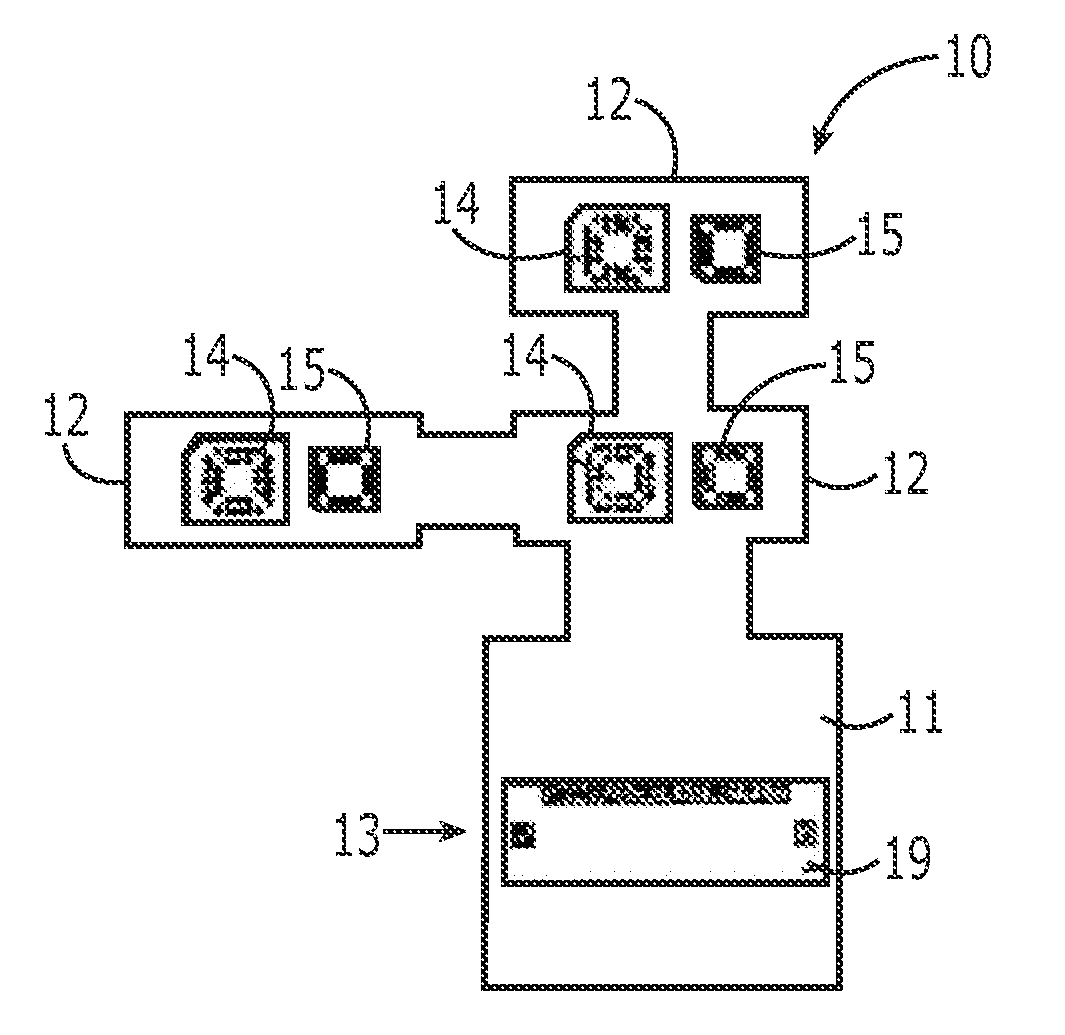

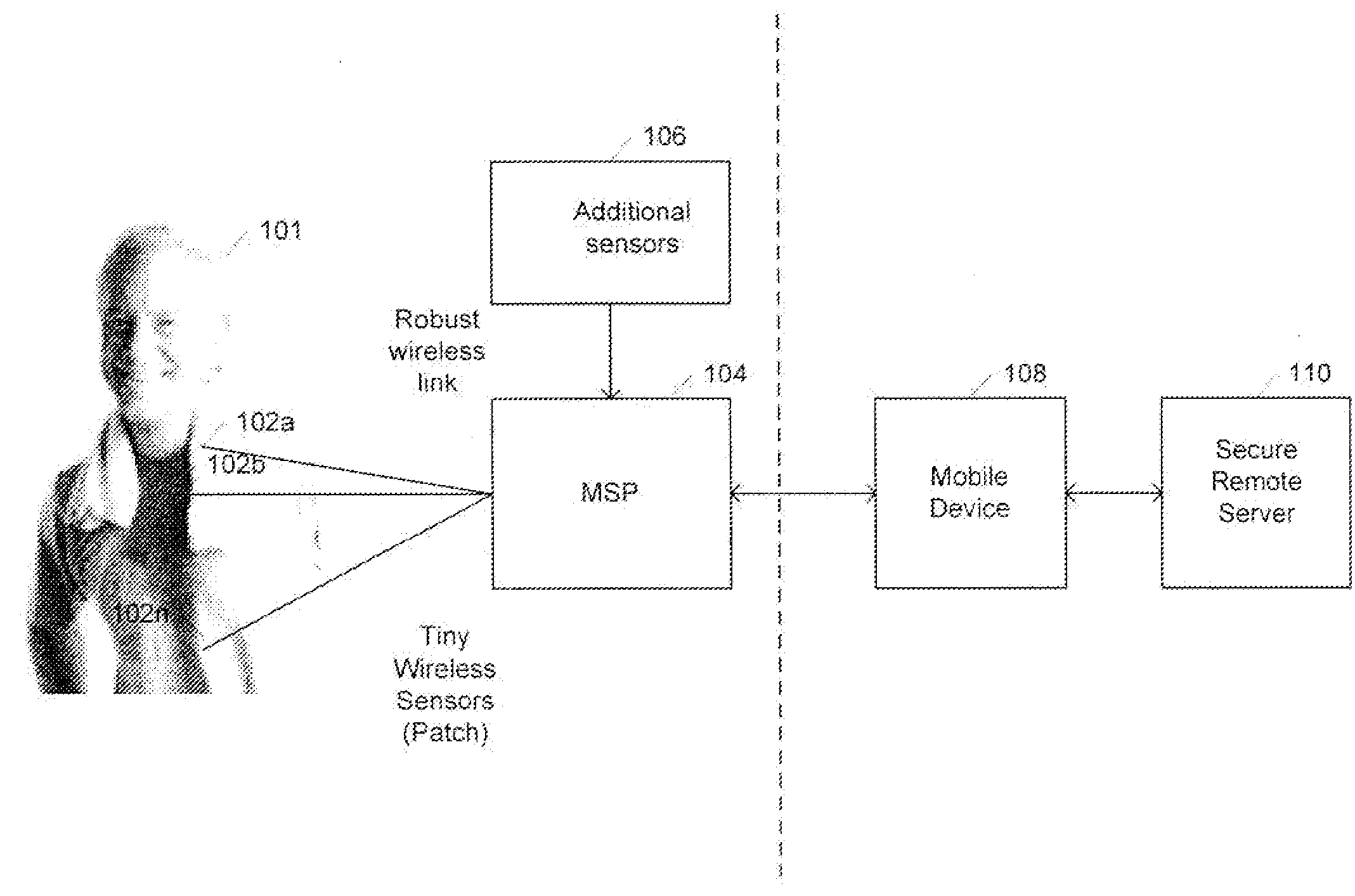

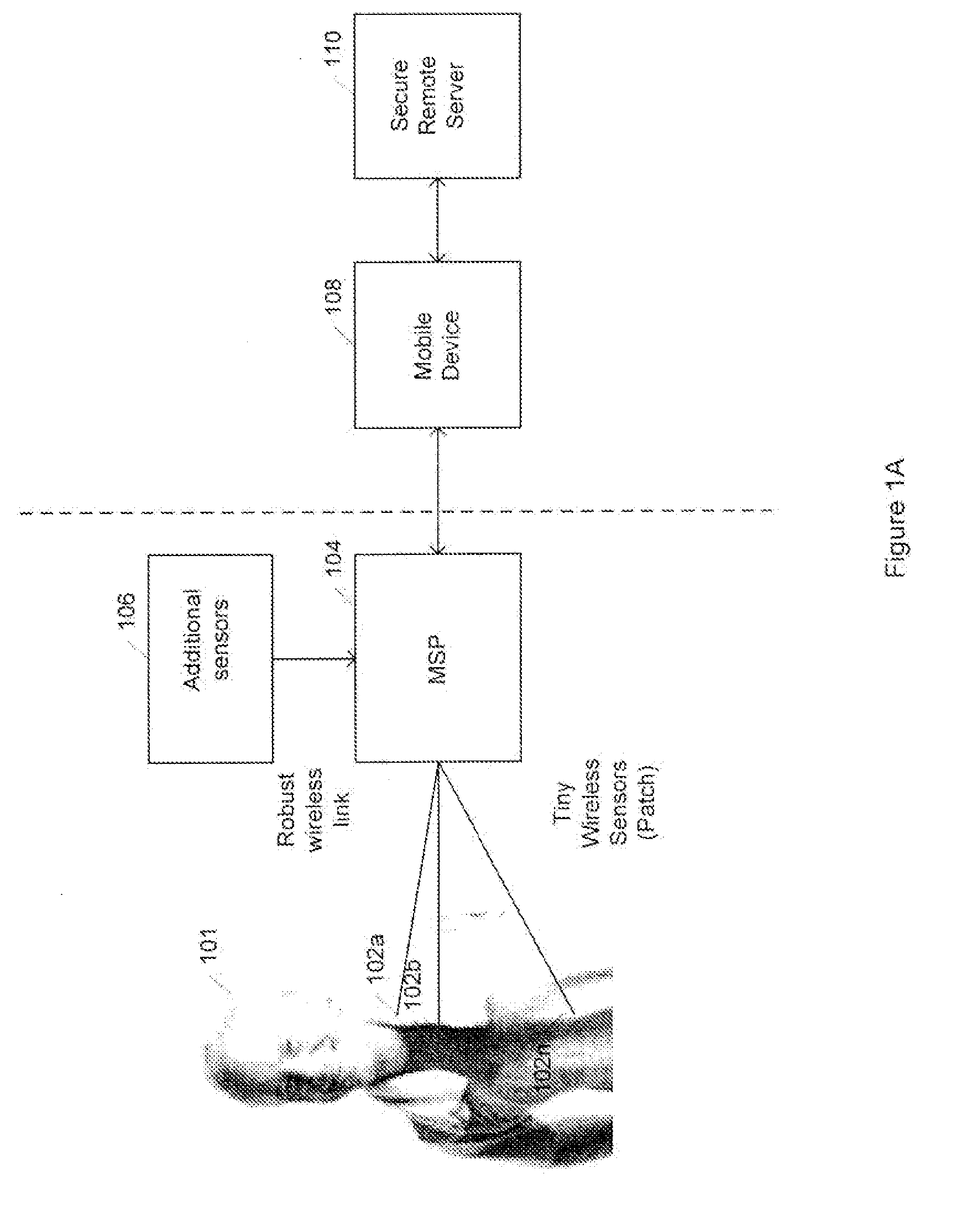

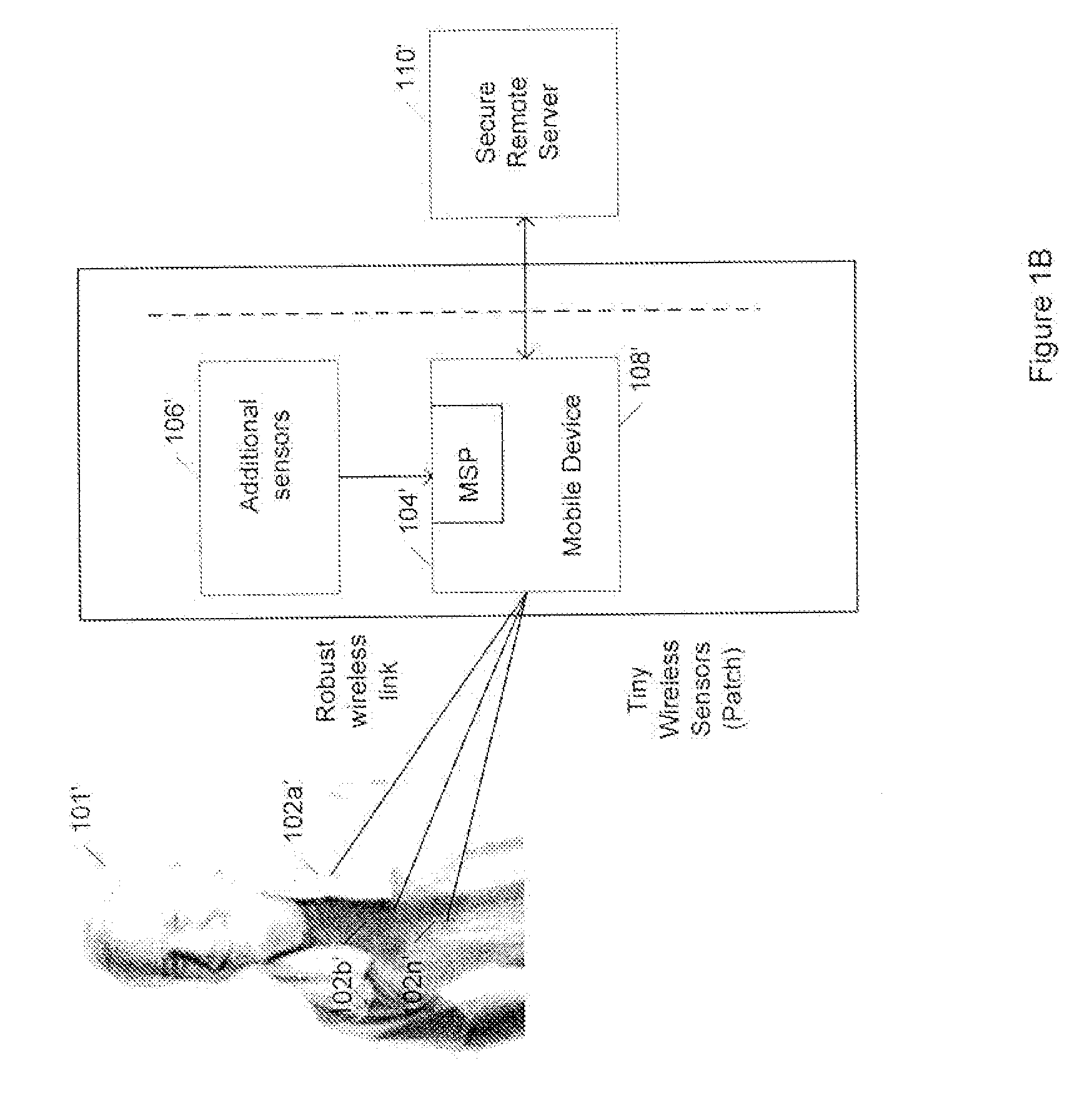

Medical signal processing system with distributed wireless sensors

InactiveUS20100049006A1High wireless link reliability/securityReduce power consumptionElectrocardiographyInertial sensorsDiseaseLine sensor

A wireless medical signal processing system for health monitoring is disclosed which achieves high wireless link reliability / security, low power dissipation, compactness, low cost and supports a variety of sensors for various physiological parameters. The system includes a medical signal processor which communicates with a wireless distributed sensor system as its peripheral for detecting physiological parameters of the person and for providing signals indicative thereof. The medical signal processor wirelessly receives the signals from the distributed wireless sensor system in a multiplexed fashion and processes the signals to provide an indication of the health of the person. The indication of health could relate to a disease state, general health or fitness level of a person. The system also includes a mobile device for receiving the indication of the health of the person to allow for a diagnosis or treatment of the person.

Owner:HMICRO

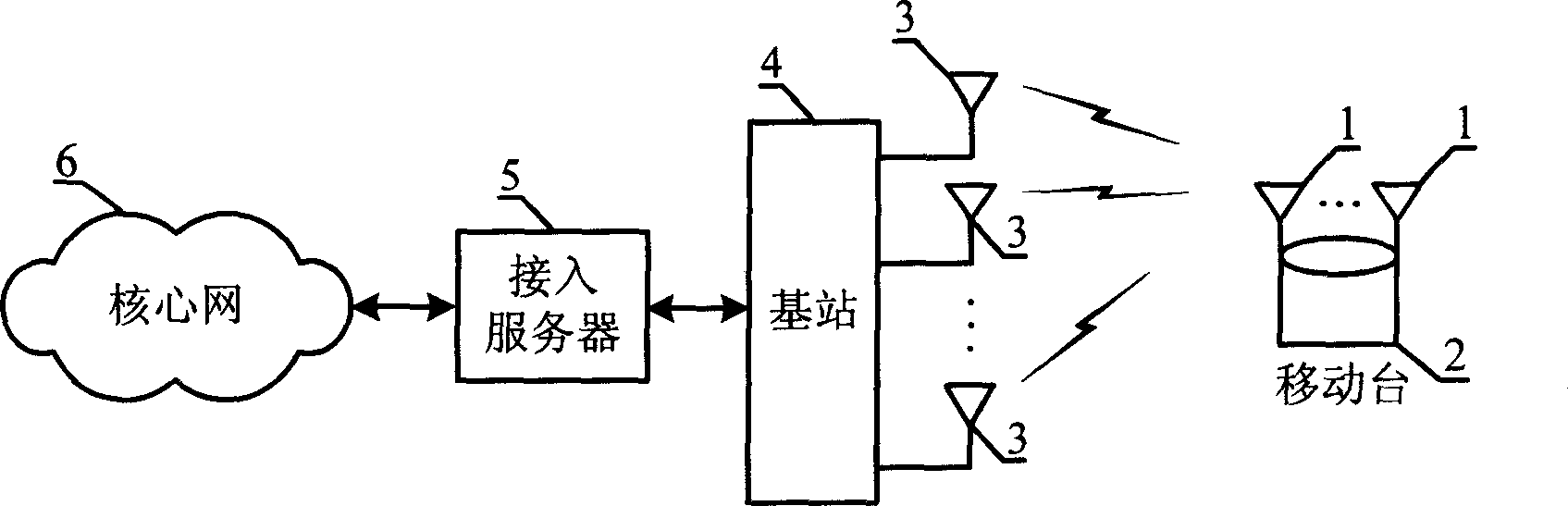

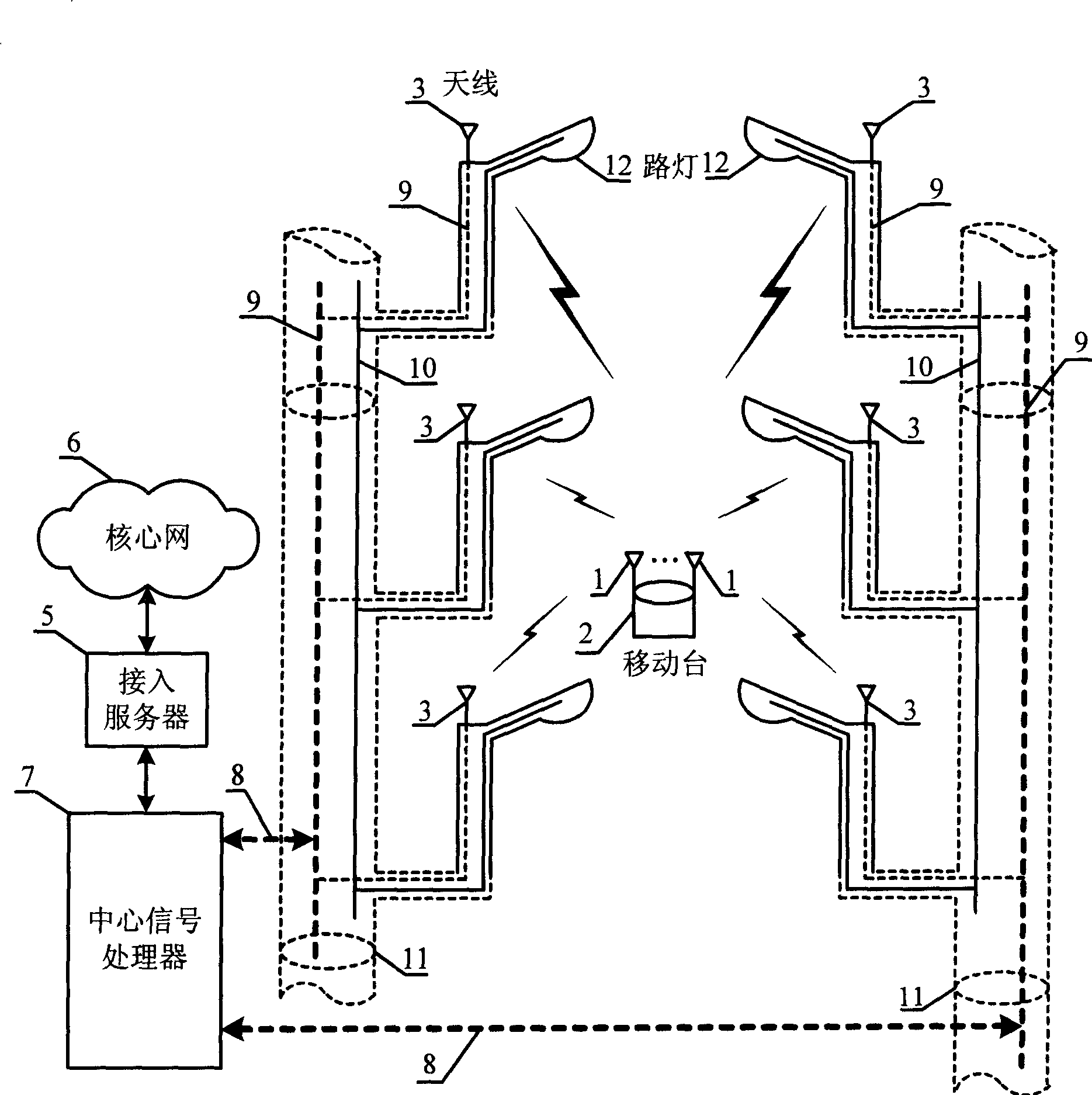

Distributed MIMO public mobile communication system

InactiveCN1885736AReduce spatial correlationIncrease independenceSpatial transmit diversityGeolocationCost Controls

The disclosed distributed MIMO public mobile communication system comprises: spanning antenna on street lamp to connect antenna to a central signal processor through current lamp cable, and accessing server to connect with a core network. This invention makes full use of current lamp system, reduces antenna space correlation, and improves system performance and capacity with low cost.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

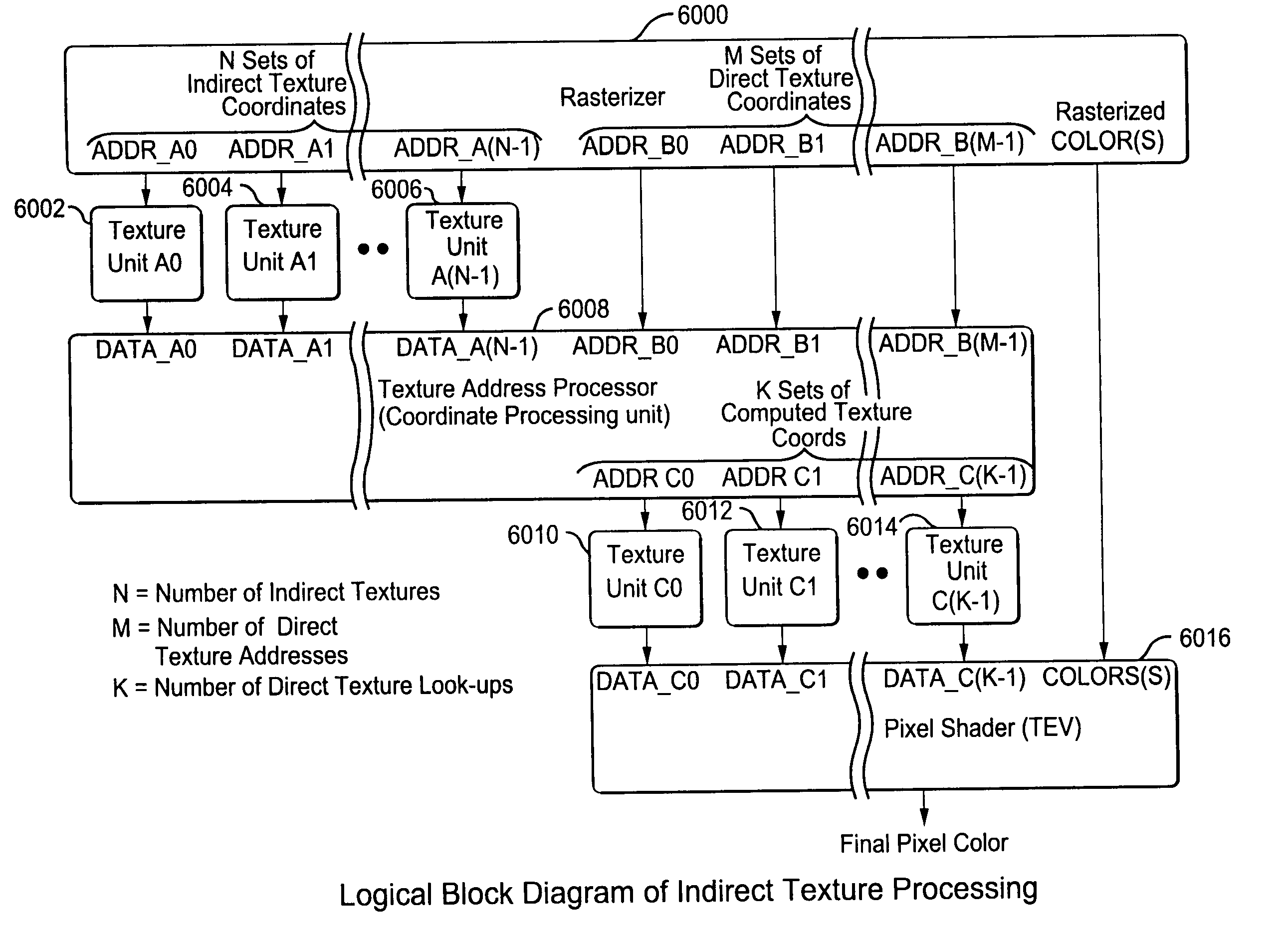

Method and apparatus for interleaved processing of direct and indirect texture coordinates in a graphics system

InactiveUS7002591B1Efficient implementationIncrease in texture mapping hardware complexityCathode-ray tube indicators3D-image renderingPattern recognitionProcessing

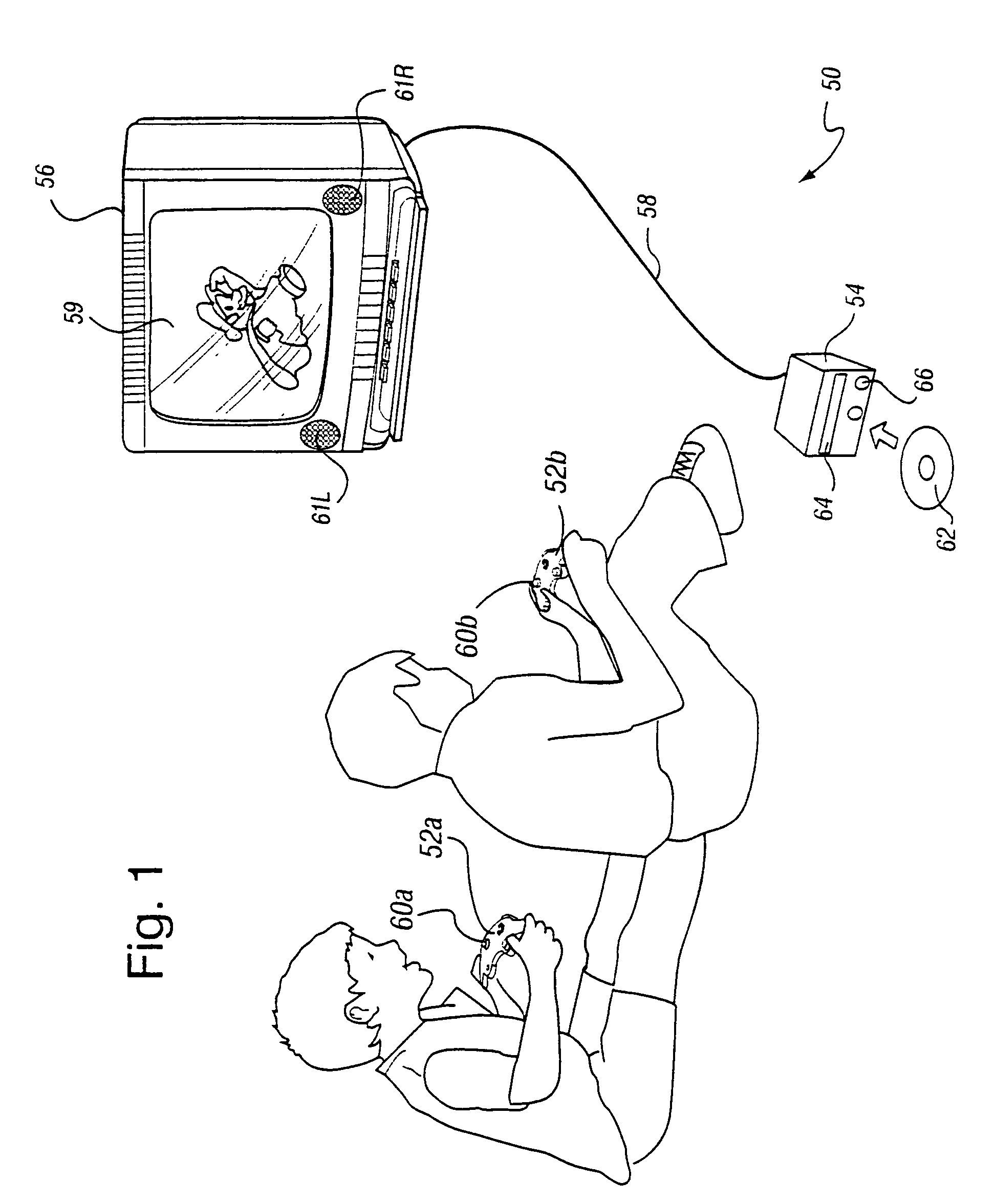

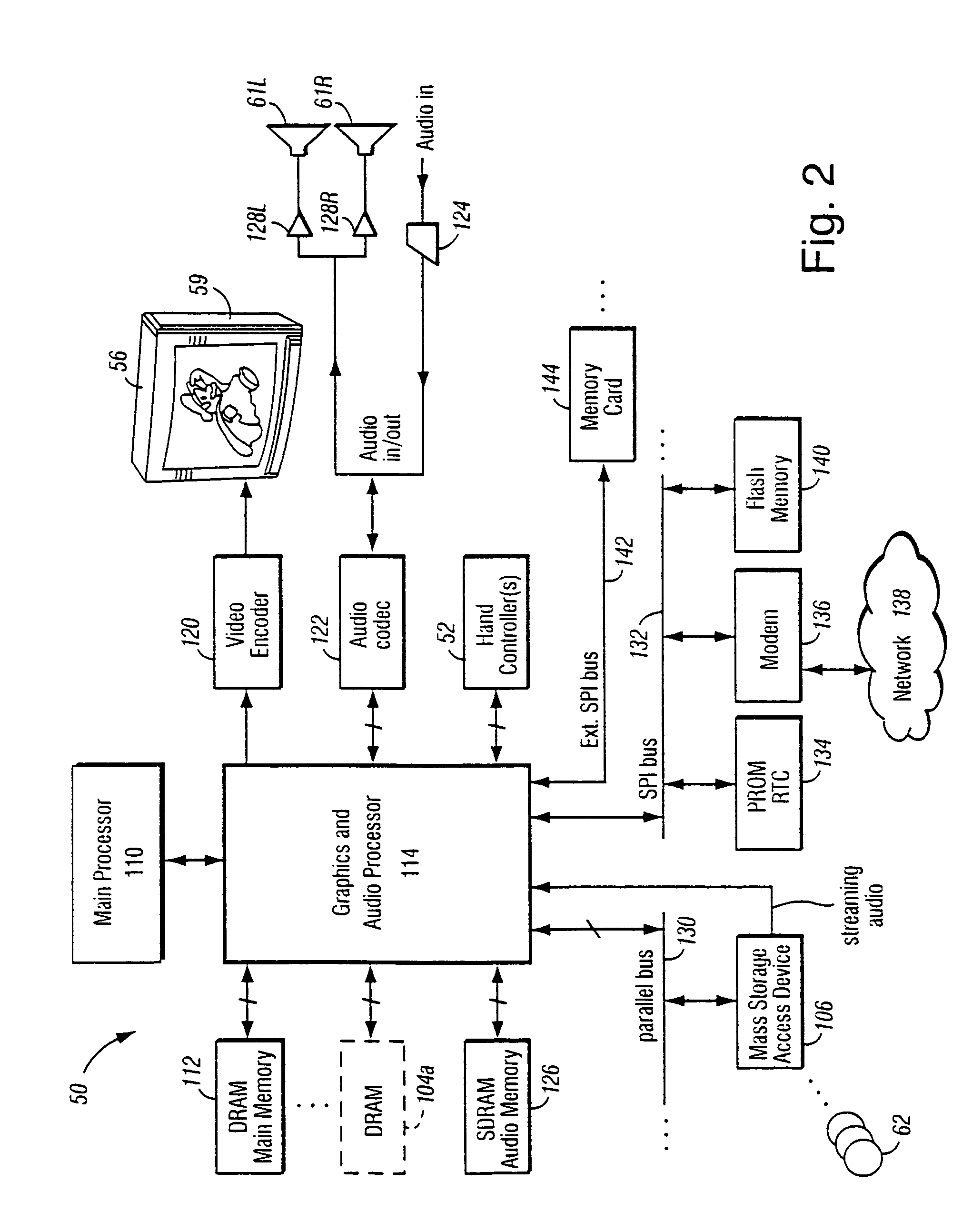

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. The graphics pipeline renders and prepares images for display at least in part in response to polygon vertex attribute data and texel color data stored as a texture images in an associated memory. An efficient texturing pipeline arrangement achieves a relatively low chip-footprint by utilizing a single texture coordinate / data processing unit that interleaves the processing of logical direct and indirect texture coordinate data and a texture lookup data feedback path for “recirculating” indirect texture lookup data retrieved from a single texture retrieval unit back to the texture coordinate / data processing unit. Versatile indirect texture referencing is achieved by using the same texture coordinate / data processing unit to transform the recirculated texture lookup data into offsets that may be added to the texture coordinates of a direct texture lookup. A generalized indirect texture API function is provided that supports defining at least four indirect texture referencing operations and allows for selectively associating one of at least eight different texture images with each indirect texture defined. Retrieved indirect texture lookup data is processed as multi-bit binary data triplets of three, four, five, or eight bits. The data triplets are multiplied by a 3×2 texture coordinate offset matrix before being optionally combined with regular non-indirect coordinate data or coordinate data from a previous cycle / stage of processing. Values of the offset matrix elements are variable and may be dynamically defined for each cycle / stage using selected constants. Two additional variable matrix configurations are also defined containing element values obtained from current direct texture coordinates. Circuitry for optionally biasing and scaling retrieved texture data is also provided.

Owner:NINTENDO CO LTD

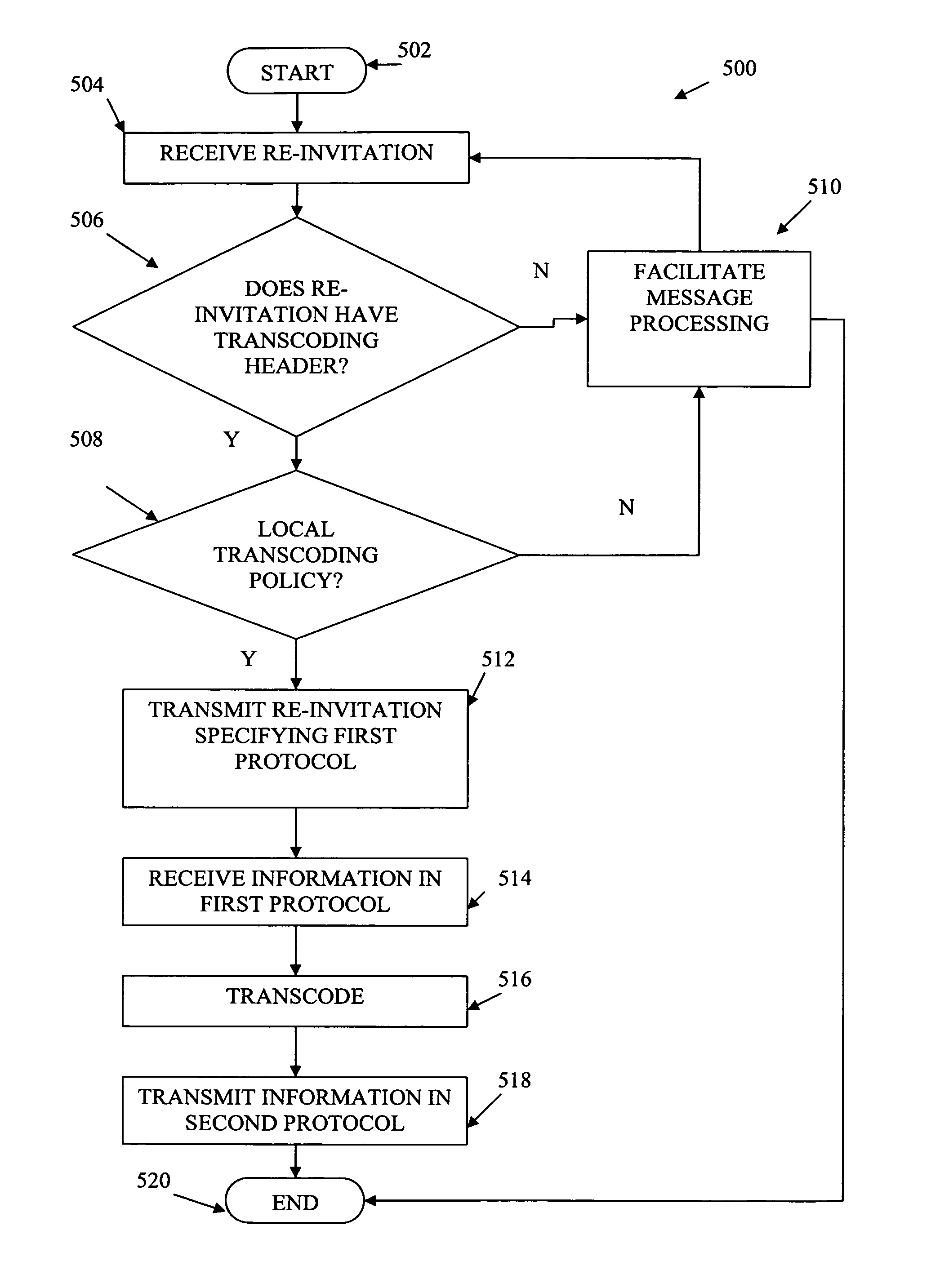

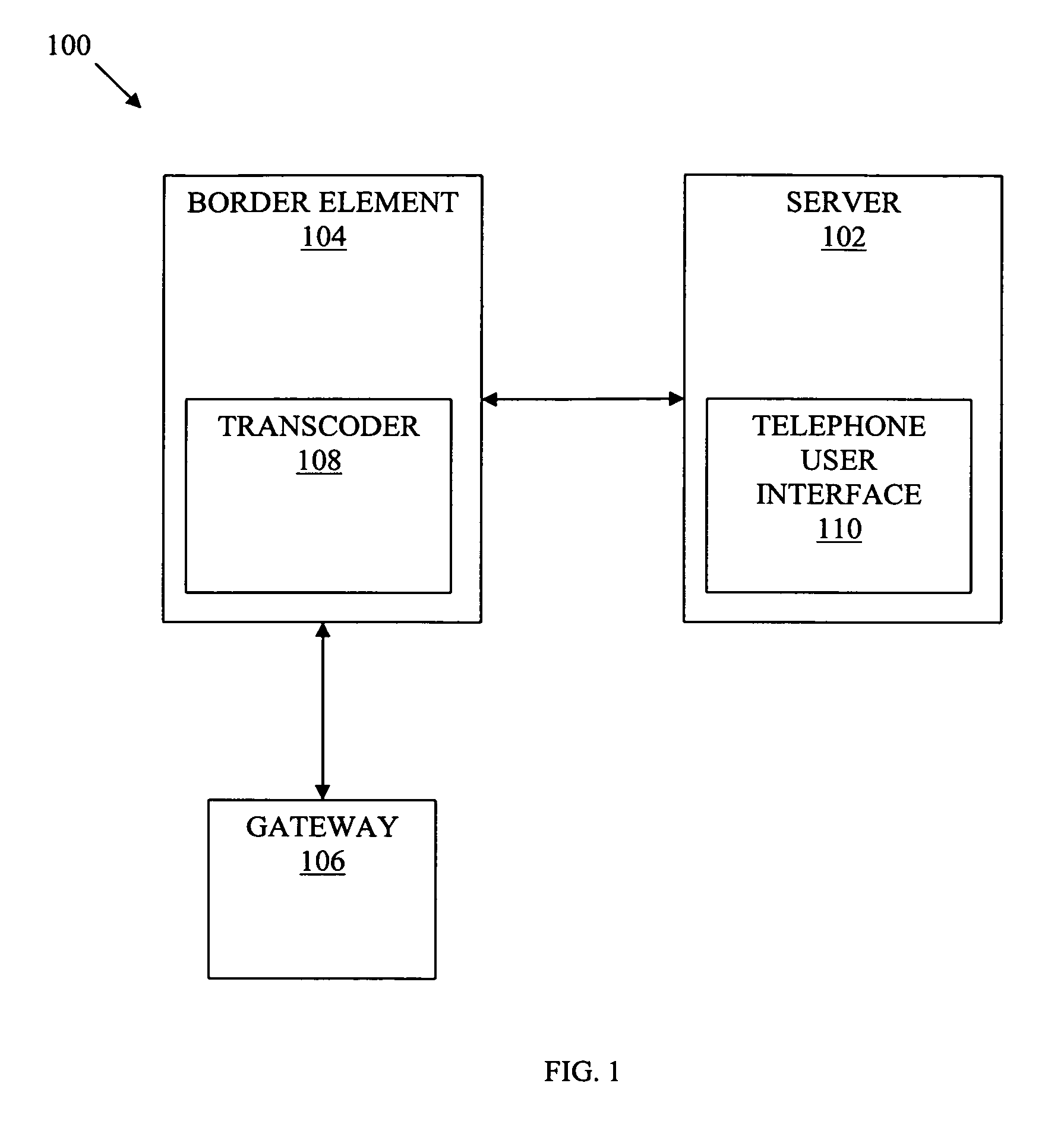

Dynamic facsimile transcoding in a unified messaging platform

Facsimile transcoding is dynamically invoked for devices that do not support T.38 fax protocol. In this way, a unified messaging platform can process facsimiles from endpoints that are not T.38 capable without using without digital signal processor resources. Dynamic fax transcoding can be performed at a session border controller, allowing transcoding resources to be engaged only for non-T.38 endpoints rather than for all calls on an interface.

Owner:AT&T INTPROP I L P

System and method for inspecting semiconductor wafers

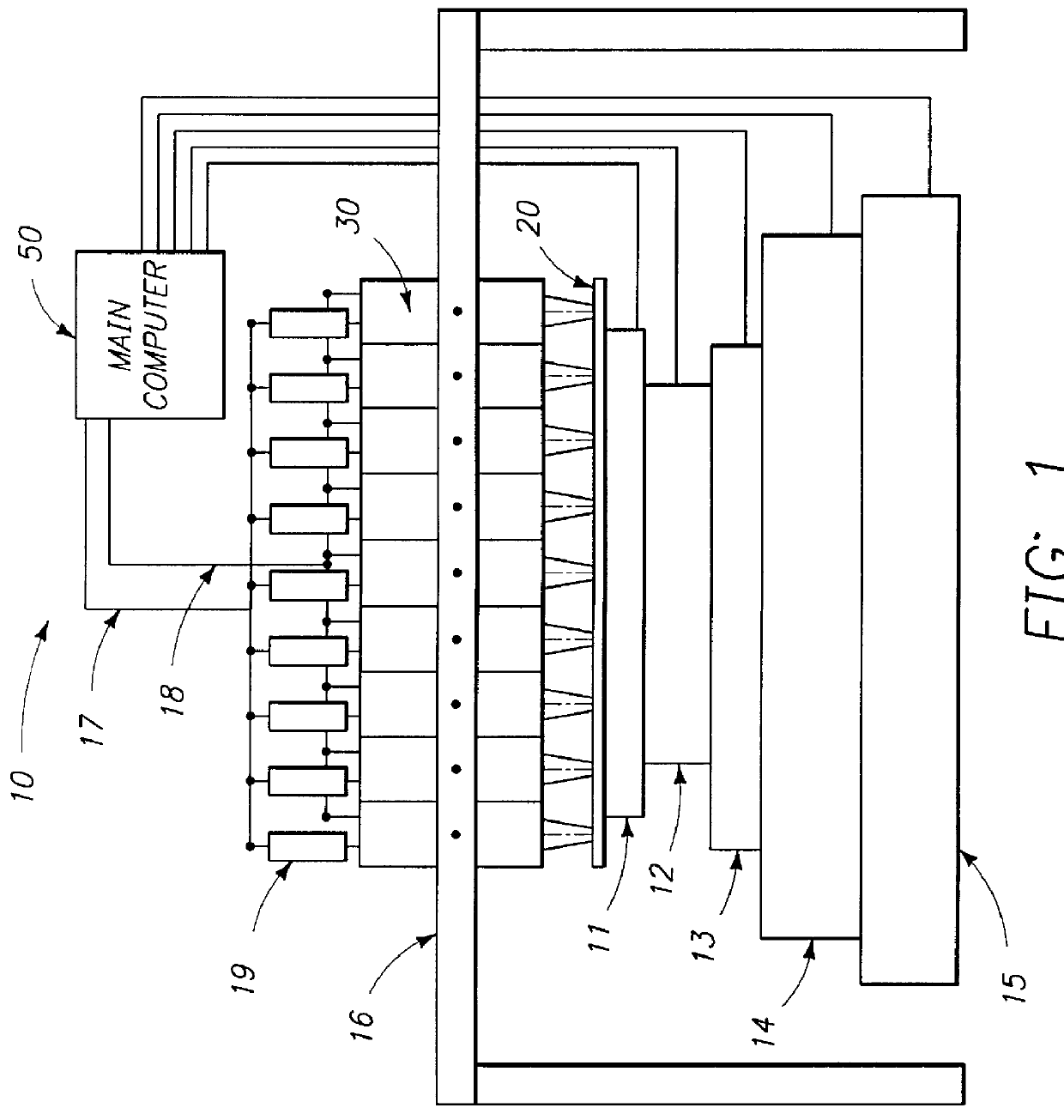

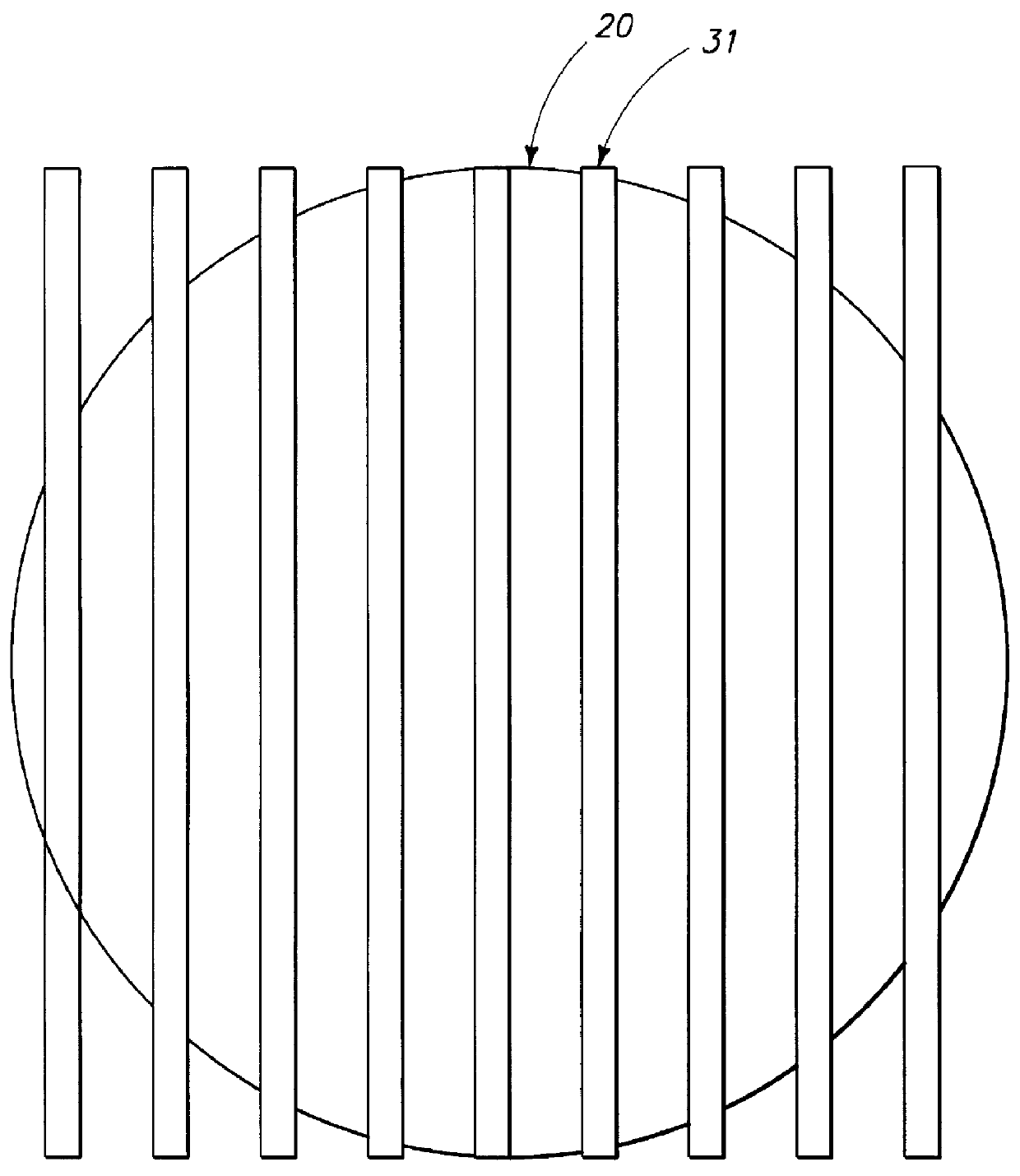

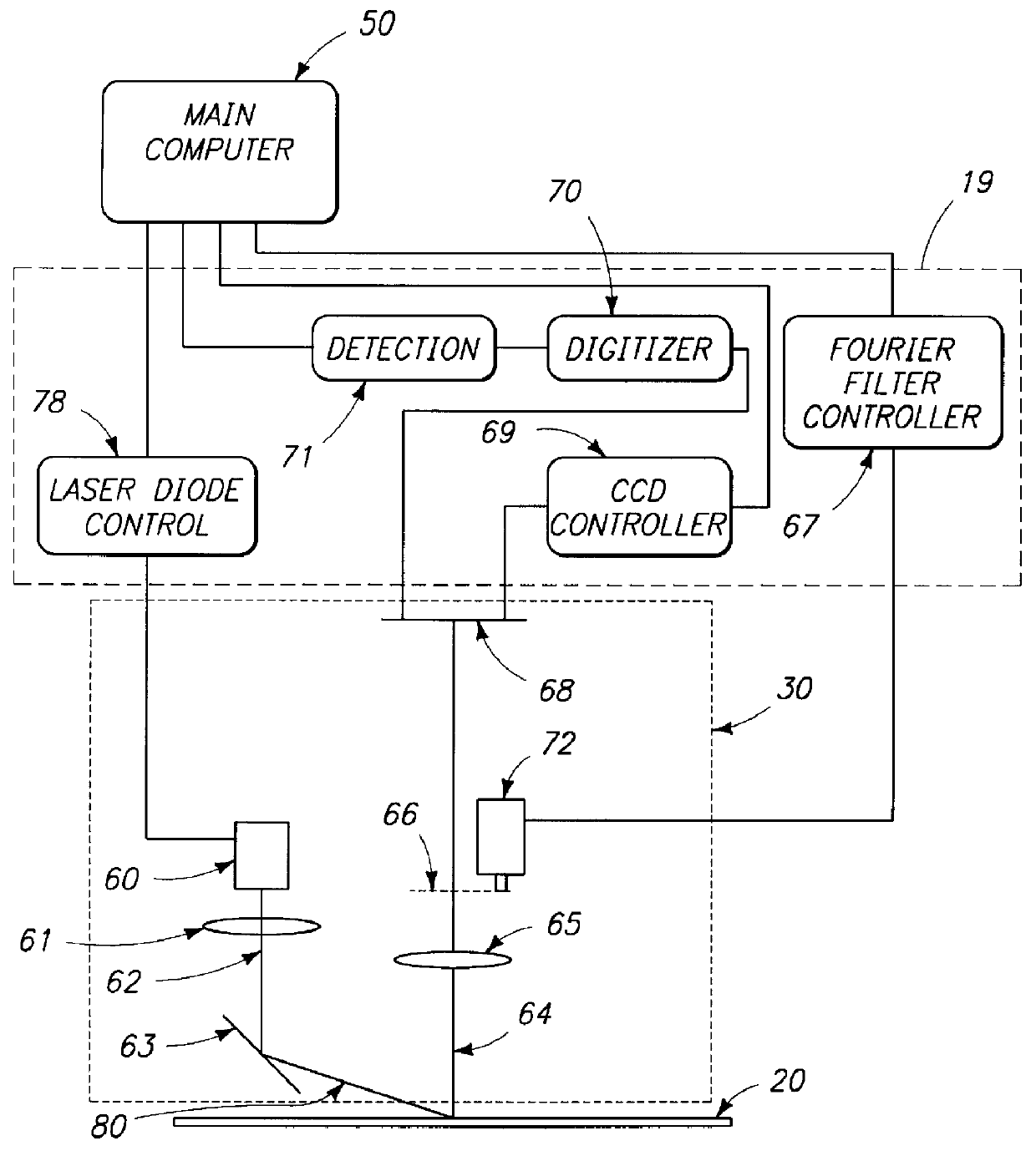

InactiveUS6020957ALow costFaster throughputSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingGratingImage subtraction

A method for inspecting semiconductor wafers is provided in which a plurality of independent, low-cost, optical-inspection subsystems are packaged and integrated to simultaneously perform parallel inspections of portions of the wafer, the wafer location relative to the inspection being controlled so that the entire wafer is imaged by the system of optical subsystems in a raster-scan mode. A monochromatic coherent-light source illuminates the wafer surface. A darkfield-optical system collects scattered light and filters patterns produced by valid periodic wafer structures using Fourier filtering. The filtered light is processed by general purpose digital-signal processors. Image subtraction methods are used to detect wafer defects, which are reported to a main computer to aid in statistical process control, particularly for manufacturing equipment.

Owner:KLA TENCOR CORP

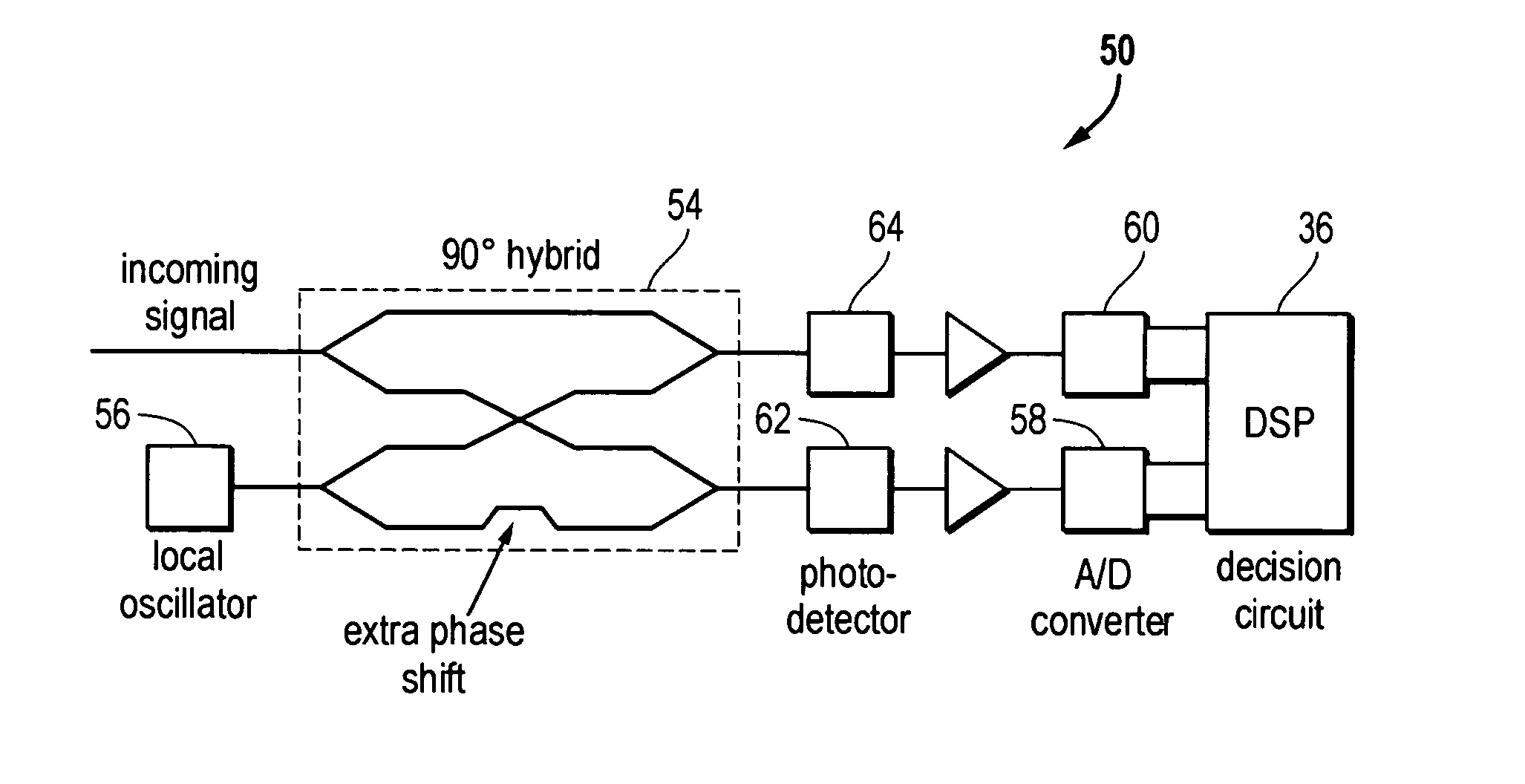

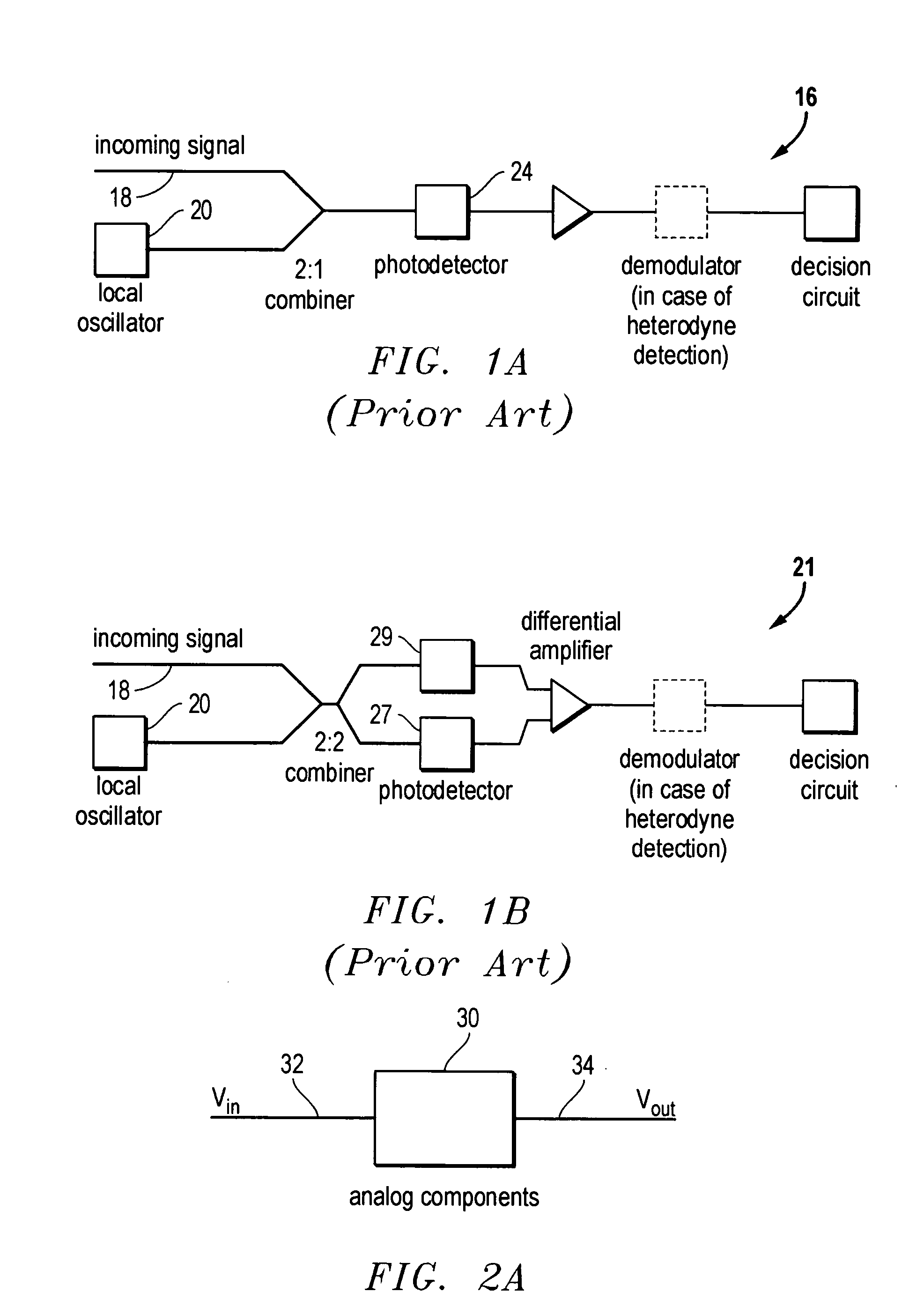

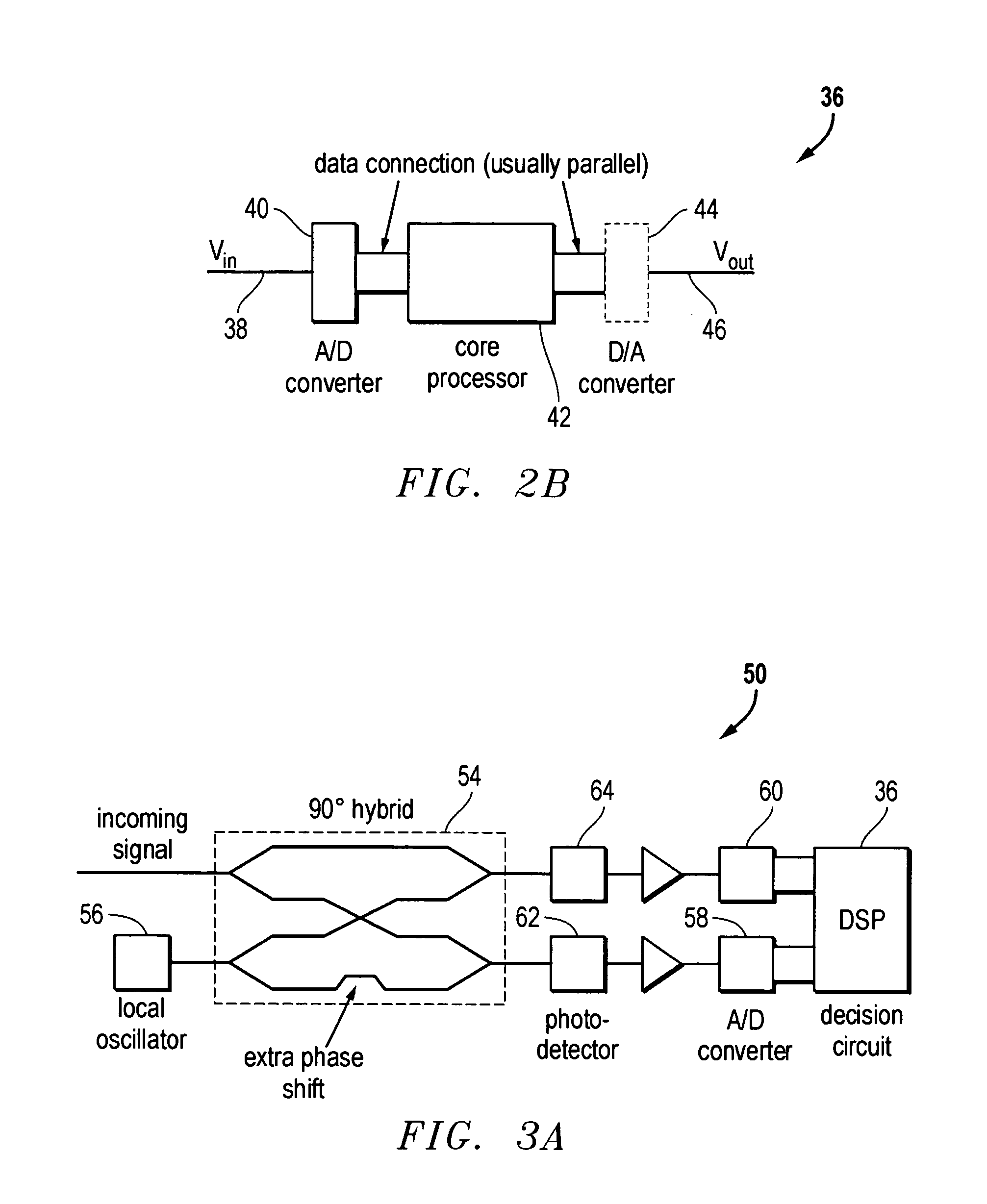

Coherent optical detection and signal processing method and system

A method and system of coherent detection of optical signals. The system utilizes a digital signal processor to recover an incoming optical signal. The system employs a local oscillator, which does not need to be phase locked to the signal. The signal may be consistently recovered, even when the polarization state varies over time. Additionally, the signal may be recovered when it comprises two channels of the same wavelength that are polarization multiplexed together. In addition, any impairment to the signal may be reversed or eliminated.

Owner:HUAWEI TECH CO LTD

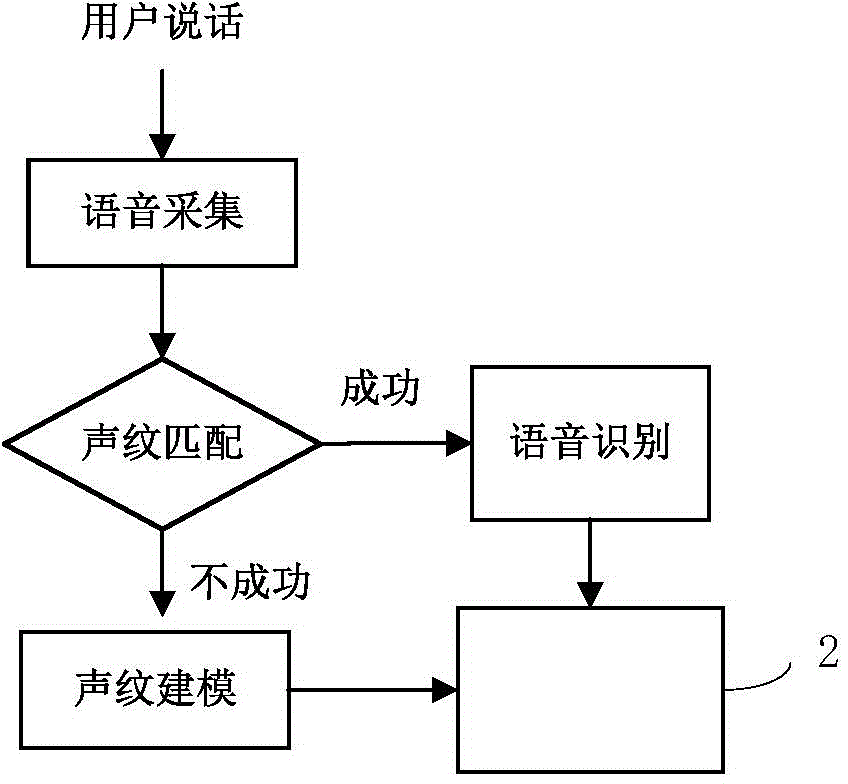

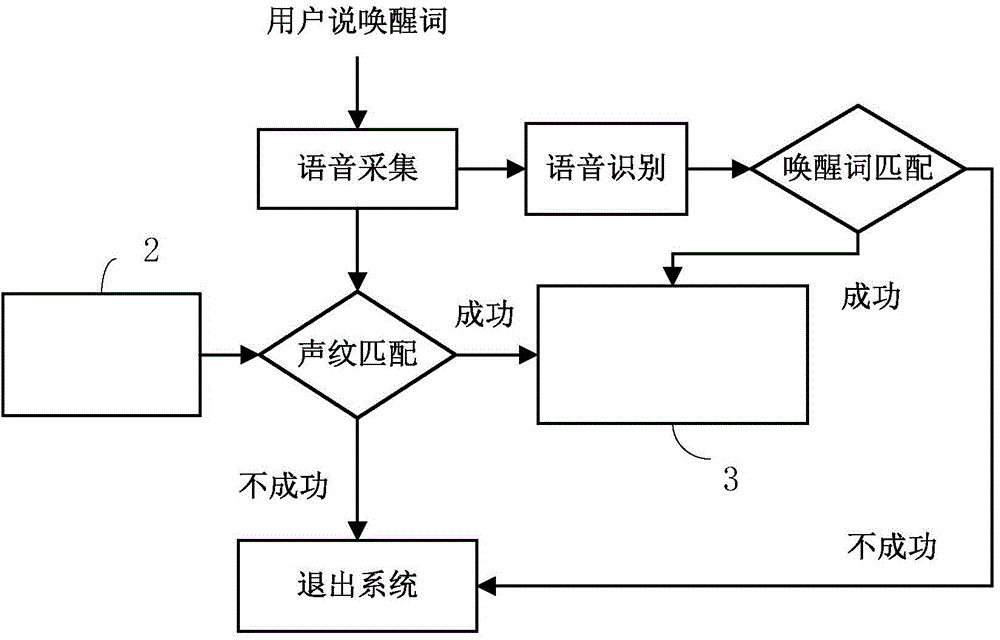

Method for personalized television voice wake-up by voiceprint and voice identification

InactiveCN104575504APersonalizedRealize TV voice wake-up functionSpeech recognitionSelective content distributionPersonalizationSpeech identification

The invention discloses a method for personalized television voice wake-up by voiceprint and voice identification, particularly a method for performing identity confirmation on a television user through voiceprint identification and controlling a television to perform personalized voice wake-up through confirmed identity and a voice identification result of user voice, and relates to voiceprint identification and voice identification technologies. A composition system comprises a voice control system (1), an information storage unit (2) and a television main controller (3) which are connected through electric signals. The method has the characteristics of short training time, very high voiceprint and voice identification speed and high identification rate. Voiceprint and voice identification can be finished by only offline training and testing, identification results do not need to be sent to a cloud server, use is convenient, and the safety of family information is guaranteed. The method also can be applied to user-personalized automatic voice channel change of the television, can be transplanted to a common high-speed DSP (digital signal processor) or chip for operation, and can be widely applied to the related fields of smart homes.

Owner:SHANGHAI NORMAL UNIVERSITY

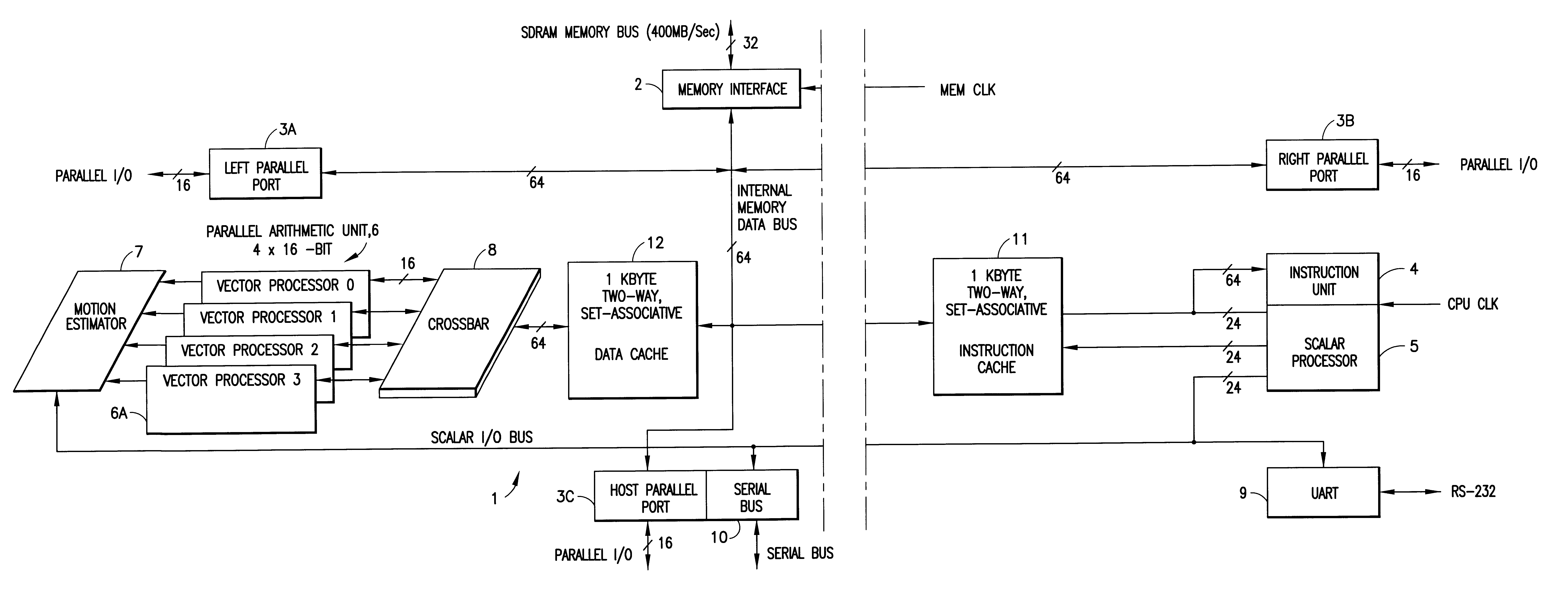

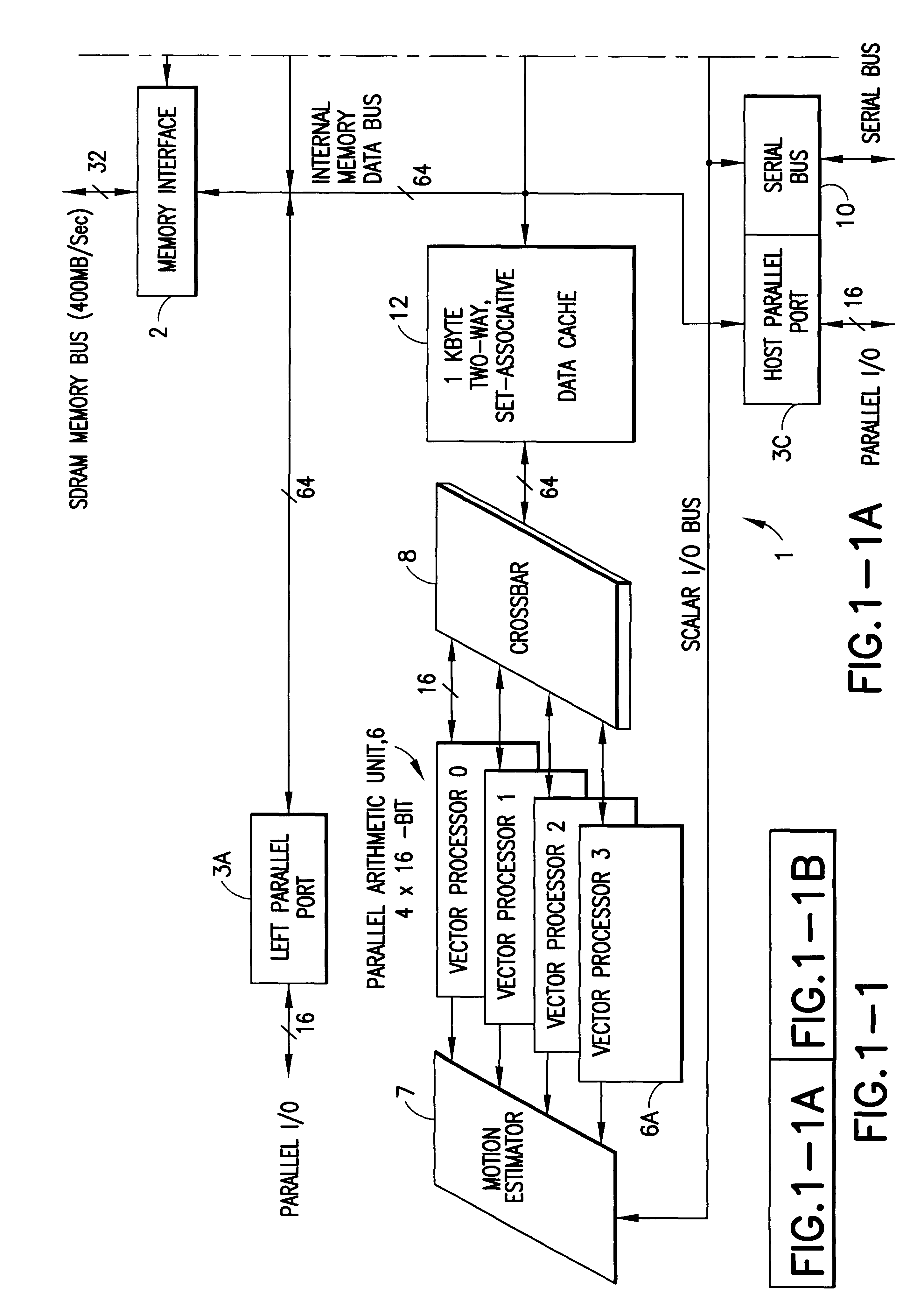

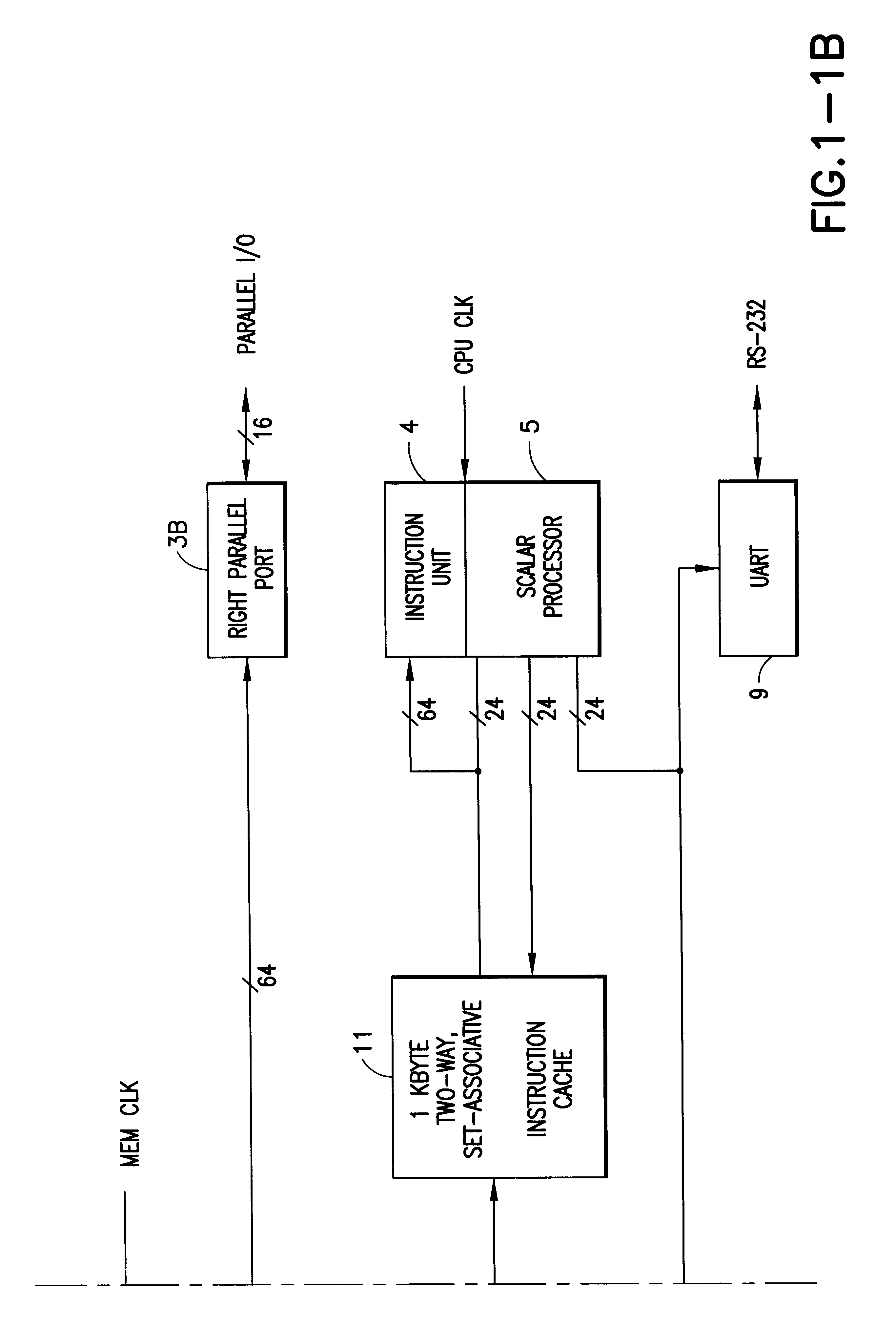

Digital signal processor containing scalar processor and a plurality of vector processors operating from a single instruction

InactiveUS6317819B1Register arrangementsMemory adressing/allocation/relocationCrossbar switchDigital data

A digital data processor integrated circuit (1) includes a plurality of functionally identical first processor elements (6A) and a second processor element (5). The first processor elements are bidirectionally coupled to a first cache (12) via a crossbar switch matrix (8). The second processor element is coupled to a second cache (11). Each of the first cache and the second cache contain a two-way, set-associative cache memory that uses a least-recently-used (LRU) replacement algorithm and that operates with a use-as-fill mode to minimize a number of wait states said processor elements need experience before continuing execution after a cache-miss. An operation of each of the first processor elements and an operation of the second processor element are locked together during an execution of a single instruction read from the second cache. The instruction specifies, in a first portion that is coupled in common to each of the plurality of first processor elements, the operation of each of the plurality of first processor elements in parallel. A second portion of the instruction specifies the operation of the second processor element. Also included is a motion estimator (7) and an internal data bus coupling together a first parallel port (3A), a second parallel port (3B), a third parallel port (3C), an external memory interface (2), and a data input / output of the first cache and the second cache.

Owner:CUFER ASSET LTD LLC

System and method for text-to-phoneme mapping with prior knowledge

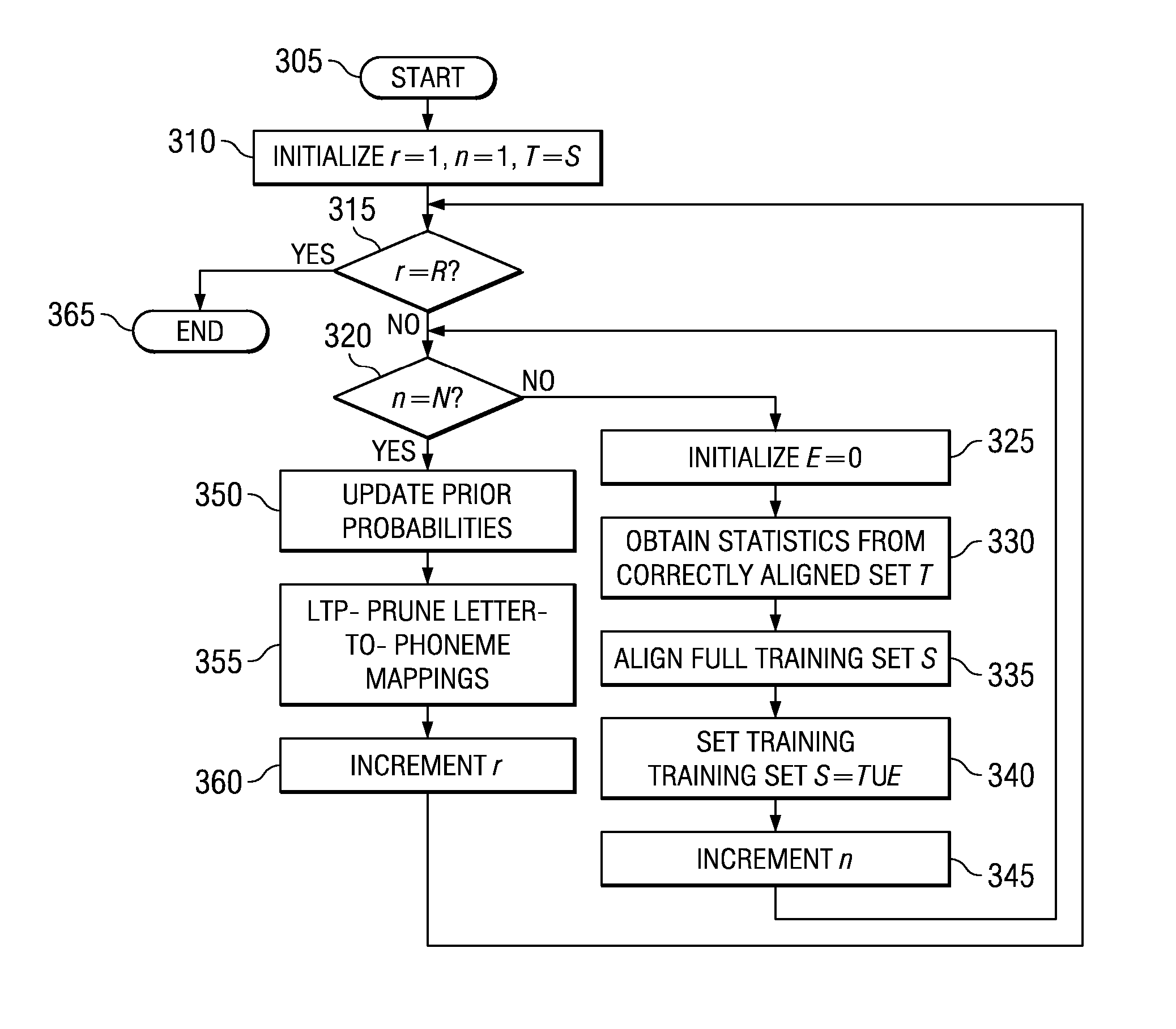

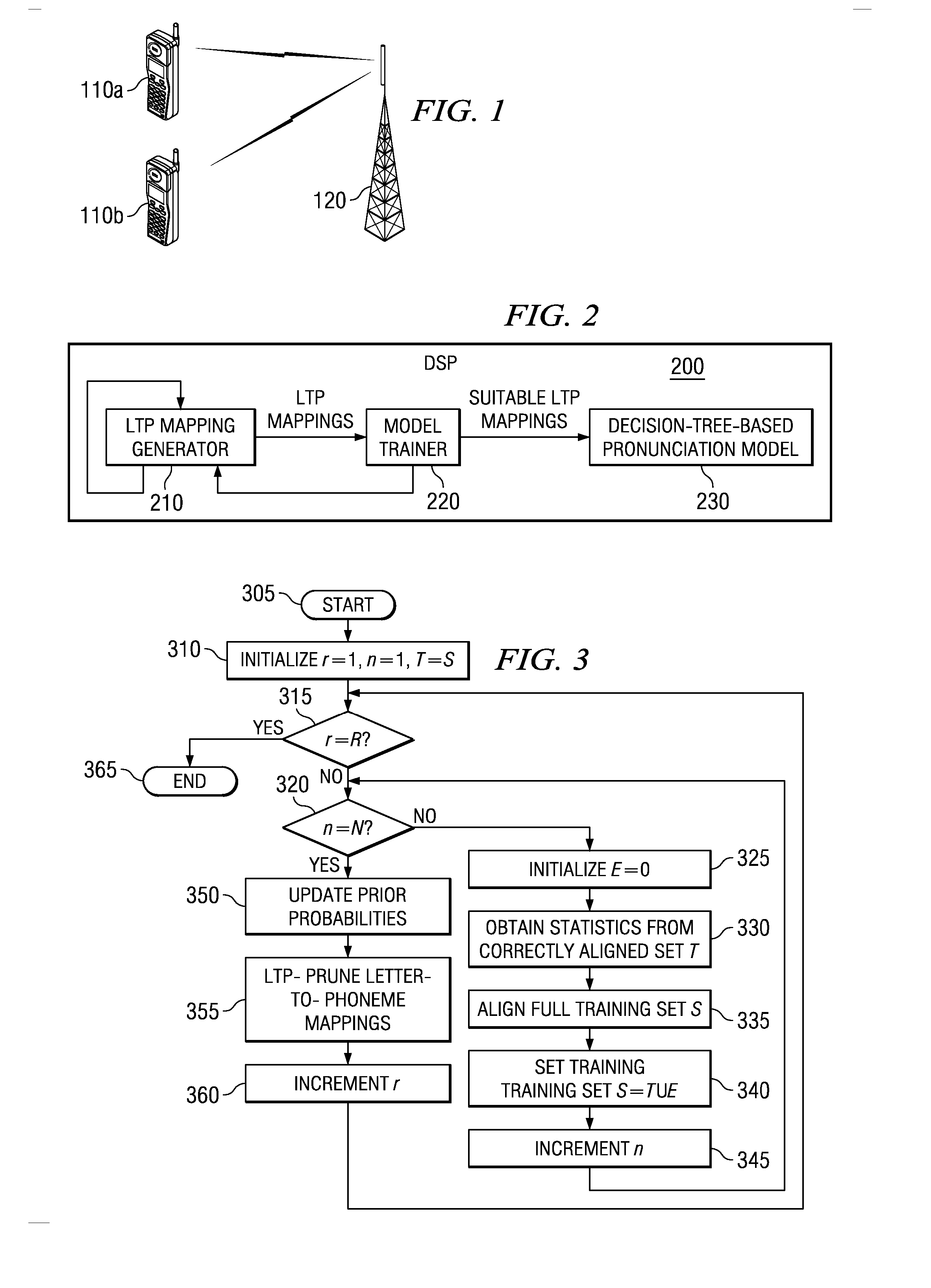

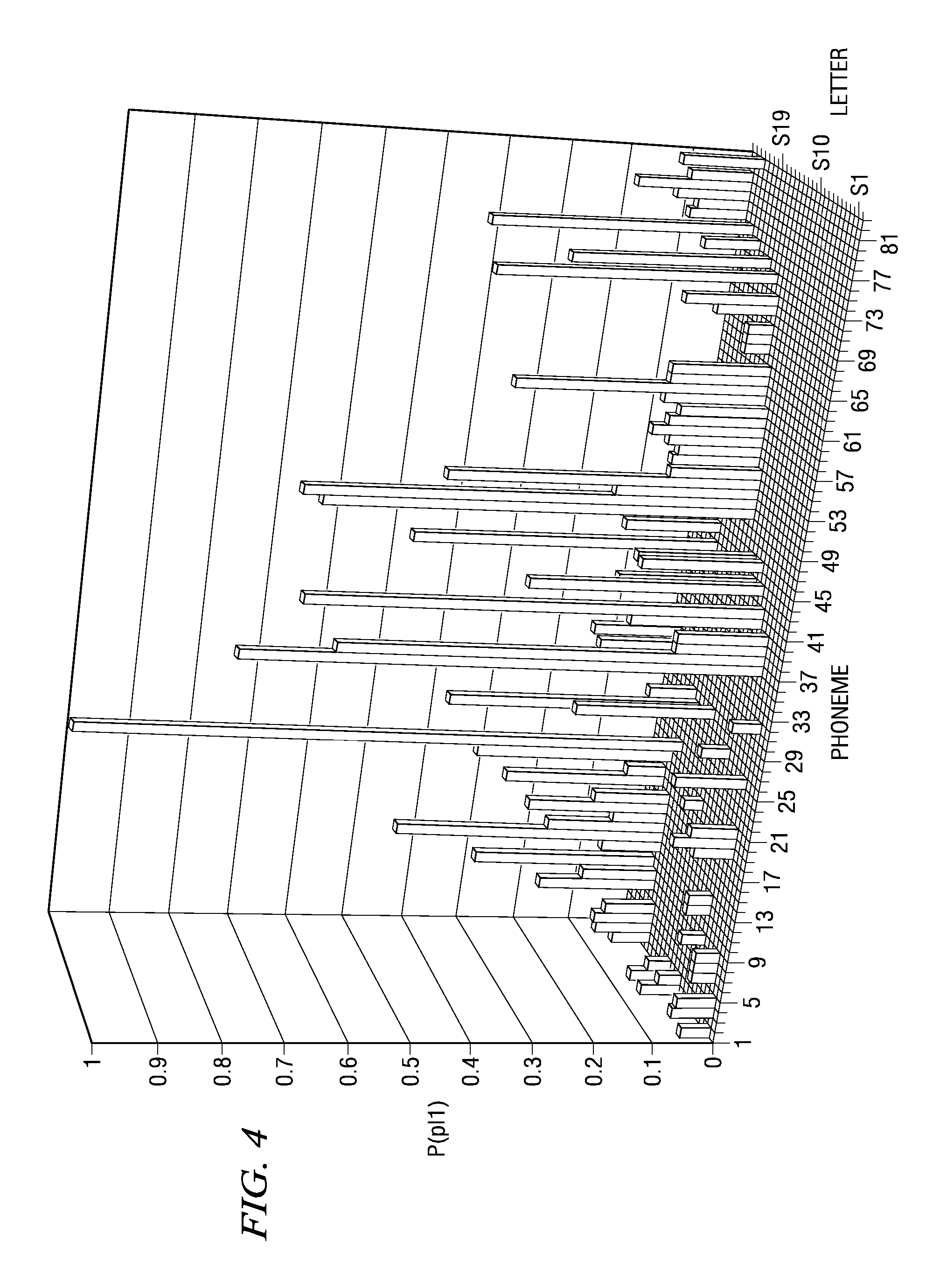

A system for, and method of, text-to-phoneme (TTP) mapping and a digital signal processor (DSP) incorporating the system or the method. In one embodiment, the system includes: (1) a letter-to-phoneme (LTP) mapping generator configured to generate an LTP mapping by iteratively aligning a full training set with a set of correctly aligned entries based on statistics of phonemes and letters from the set of correctly aligned entries and redefining the full training set as a union of the set of correctly aligned entries and a set of incorrectly aligned entries created during the aligning and (2) a model trainer configured to update prior probabilities of LTP mappings generated by the LTP generator and evaluate whether the LTP mappings are suitable for training a decision-tree-based pronunciation model (DTPM).

Owner:TEXAS INSTR INC

Single integrated circuit embodying a risc processor and a digital signal processor

InactiveUS6260088B1Save spaceImprove versatilityGeneral purpose stored program computerMultiple digital computer combinationsDigital signal processingComputer image

A single integrated circuit includes first and second data processors operating on different instruction sets independently operating on disjoint programs and data. The single integrated circuit preferably includes an external interface, a shared data transfer controller and shared memory divided into plural independently accessible memory banks. The two data processors are preferably a digital signal processor (DSP) and a reduced instruction set computer (RISC) processor. The DSP and RISC processors are suitably programmed to perform differing aspects of computer image processing.

Owner:TEXAS INSTR INC

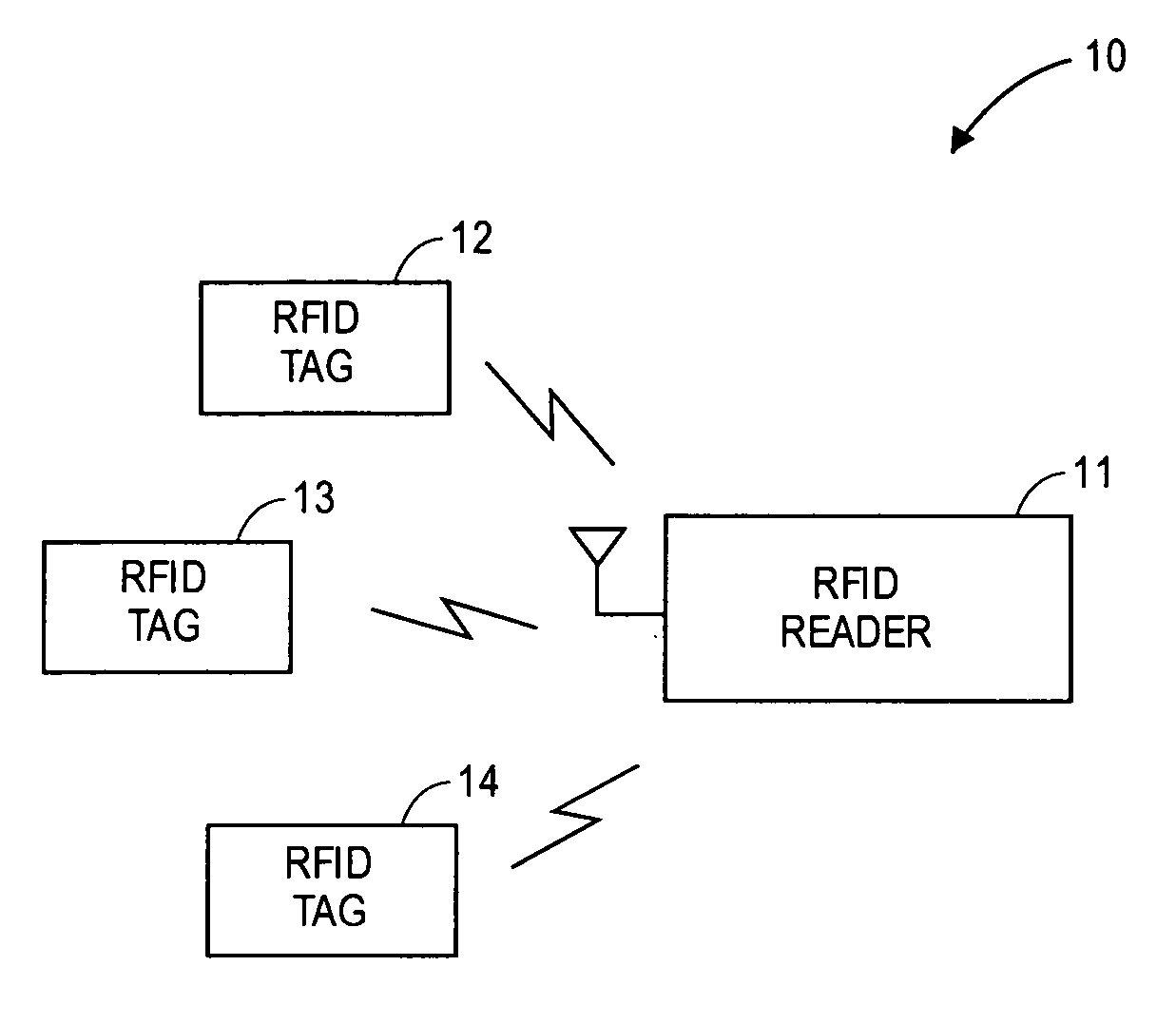

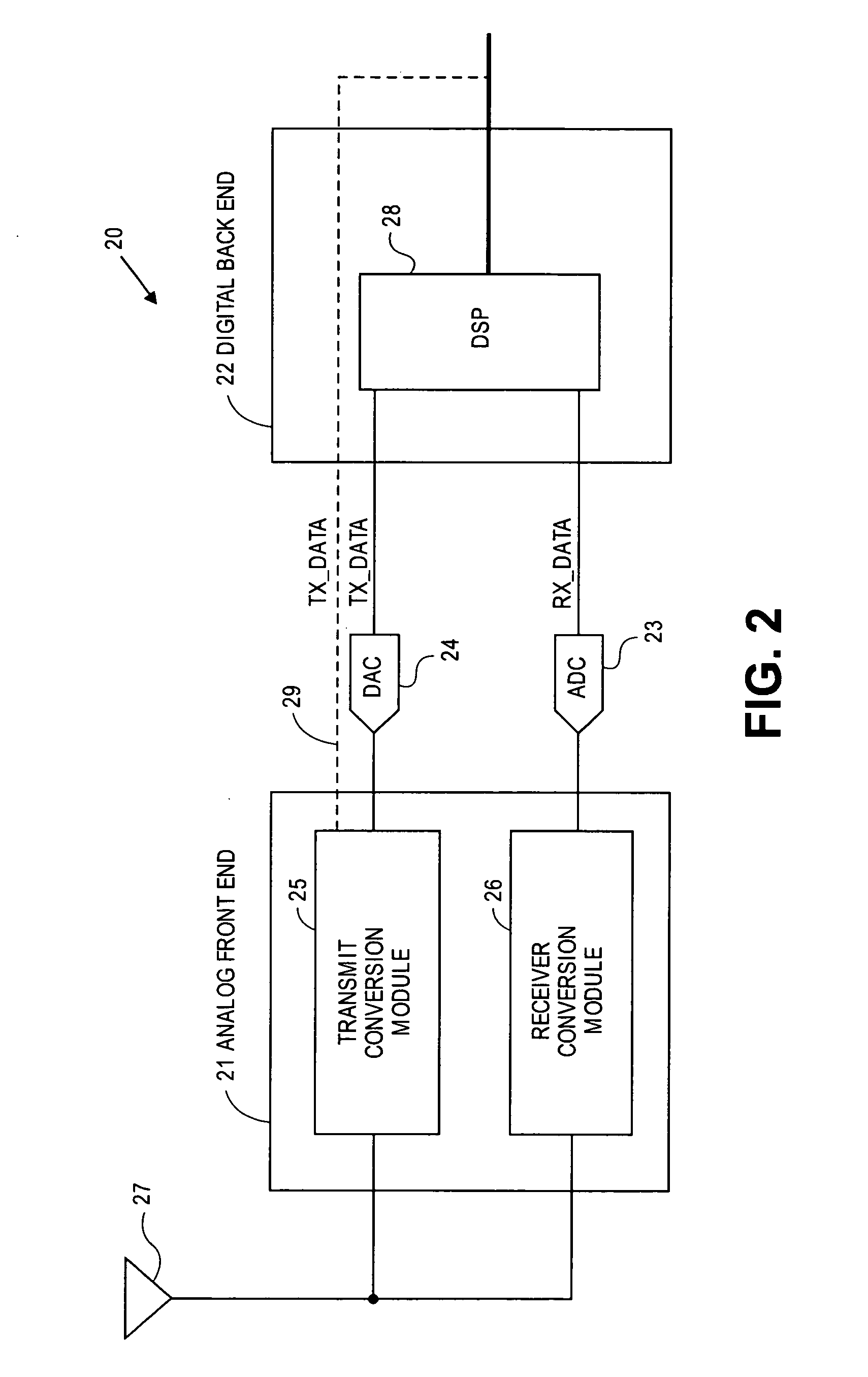

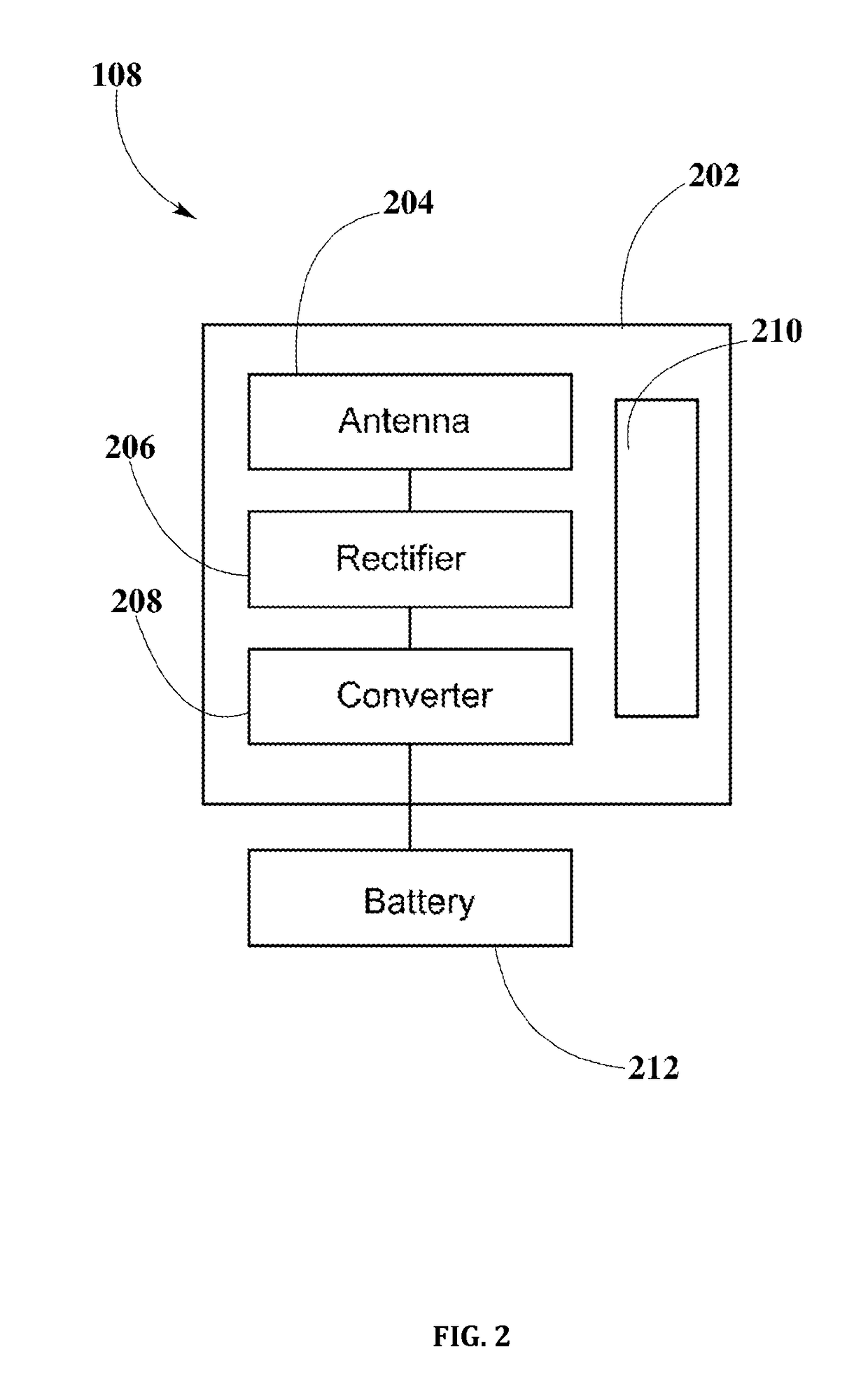

Multi-protocol radio frequency identification transponder transceiver

ActiveUS20060238301A1Memory record carrier reading problemsNear-field in RFIDTransceiverIn-phase and quadrature components

A transceiver for a RFID reader and a transceiver for a RFID transponder (tag) allow communication between the two devices. The RFID reader utilizes an analog front end and a digital backend. In the receiver portion of the transceiver, the front end of the RFID reader uses a pair of down-conversion mixers to demodulate a received signal into in-phase (I) and quadrature (Q) components and analog-to-digital converters (ADC) digitize the signal. A digital signal processor (DSP) in the back end processes the digital signal and uses a matched filter for data detection. The RFID tag receives an inductively coupled signal from the reader and the receiver portion of the tag uses a pulse / level detector that employs an analog comparator and a sample and hold circuit to detect the received signal. A digital decoder / controller is used to decode the incoming data and to establish a sampling clock for the pulse / level detector. An automatic gain control (AGC) circuit adjusts a receiver gain according to the received signal strength and controls tuning of magnetic coupling circuitry.

Owner:NXP USA INC

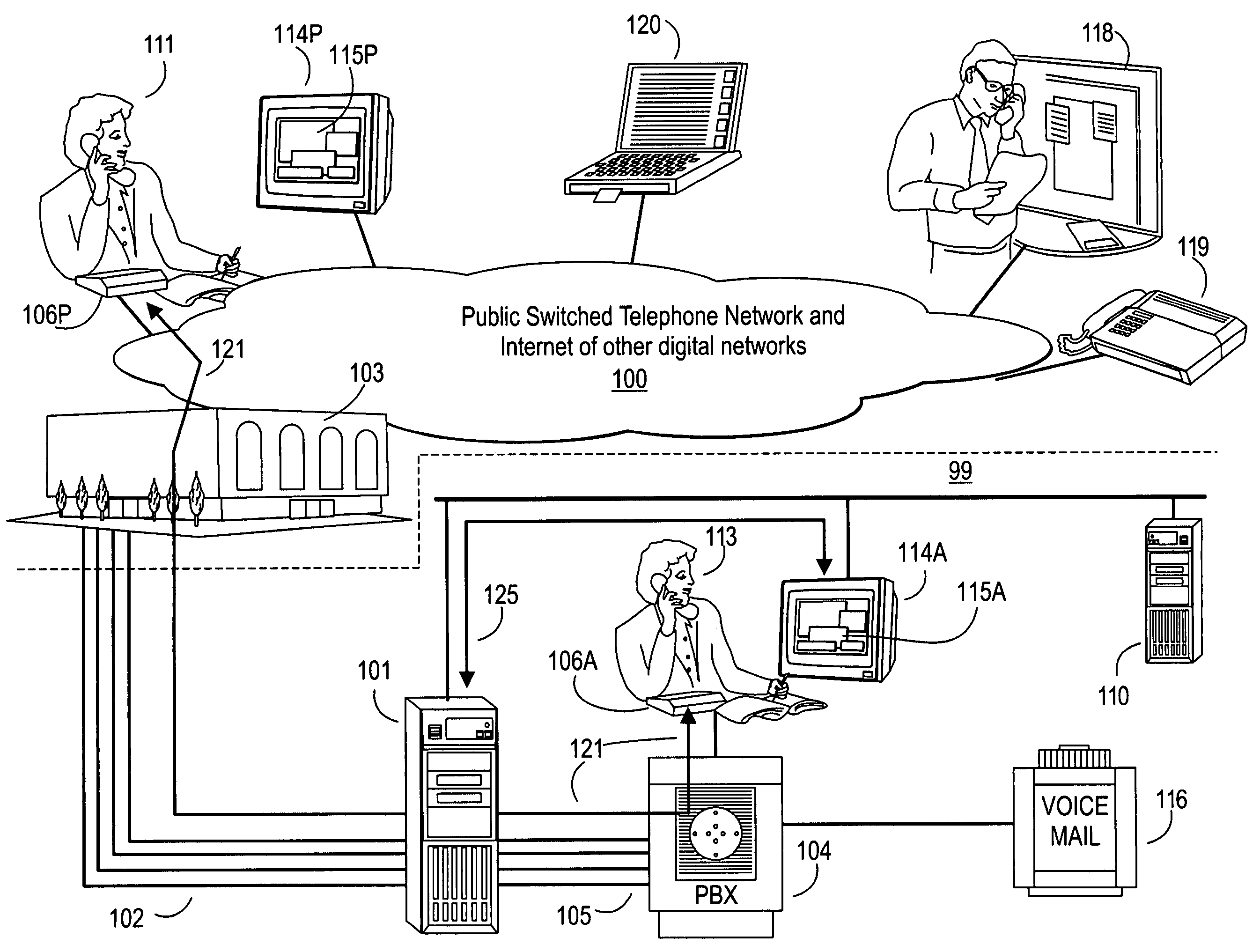

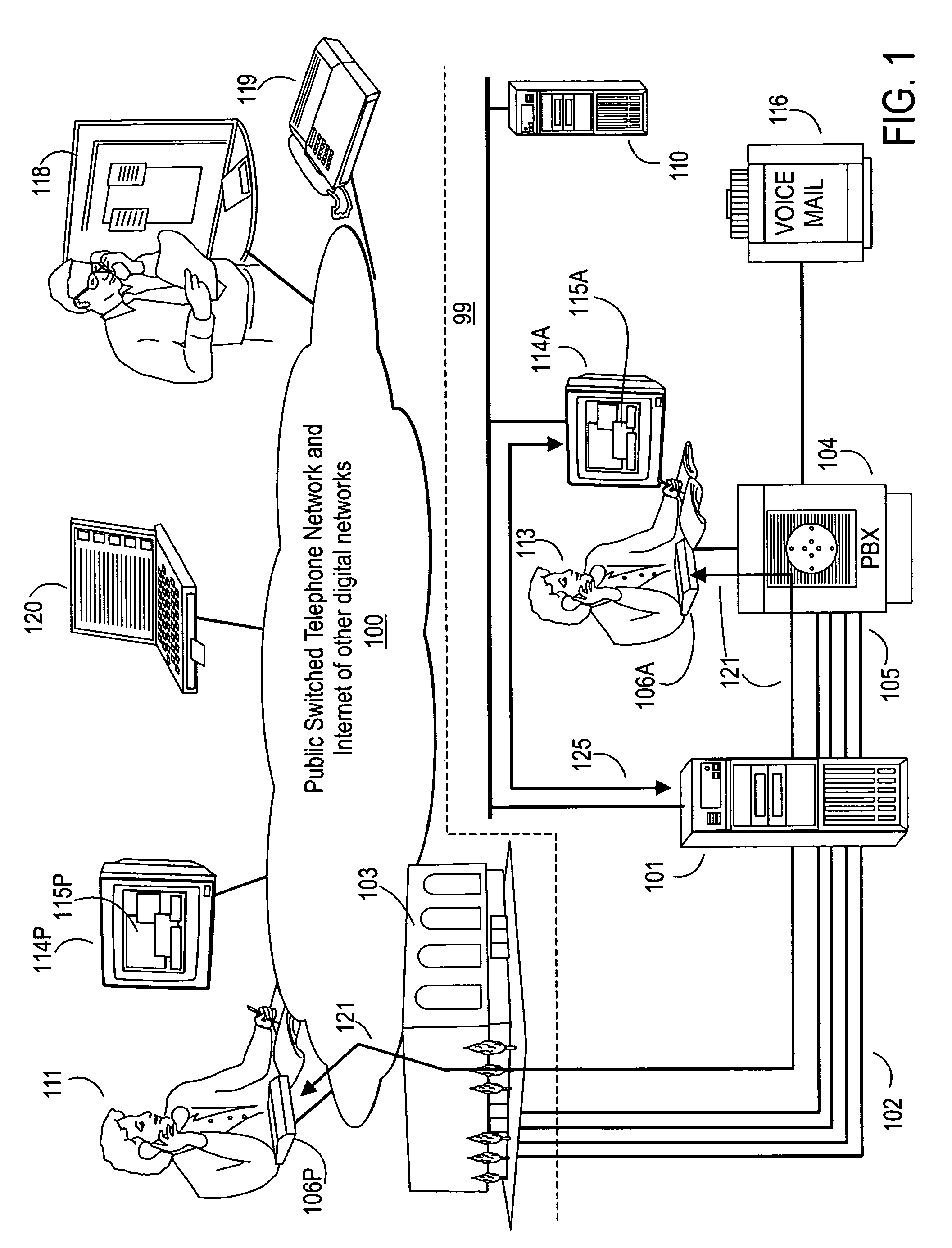

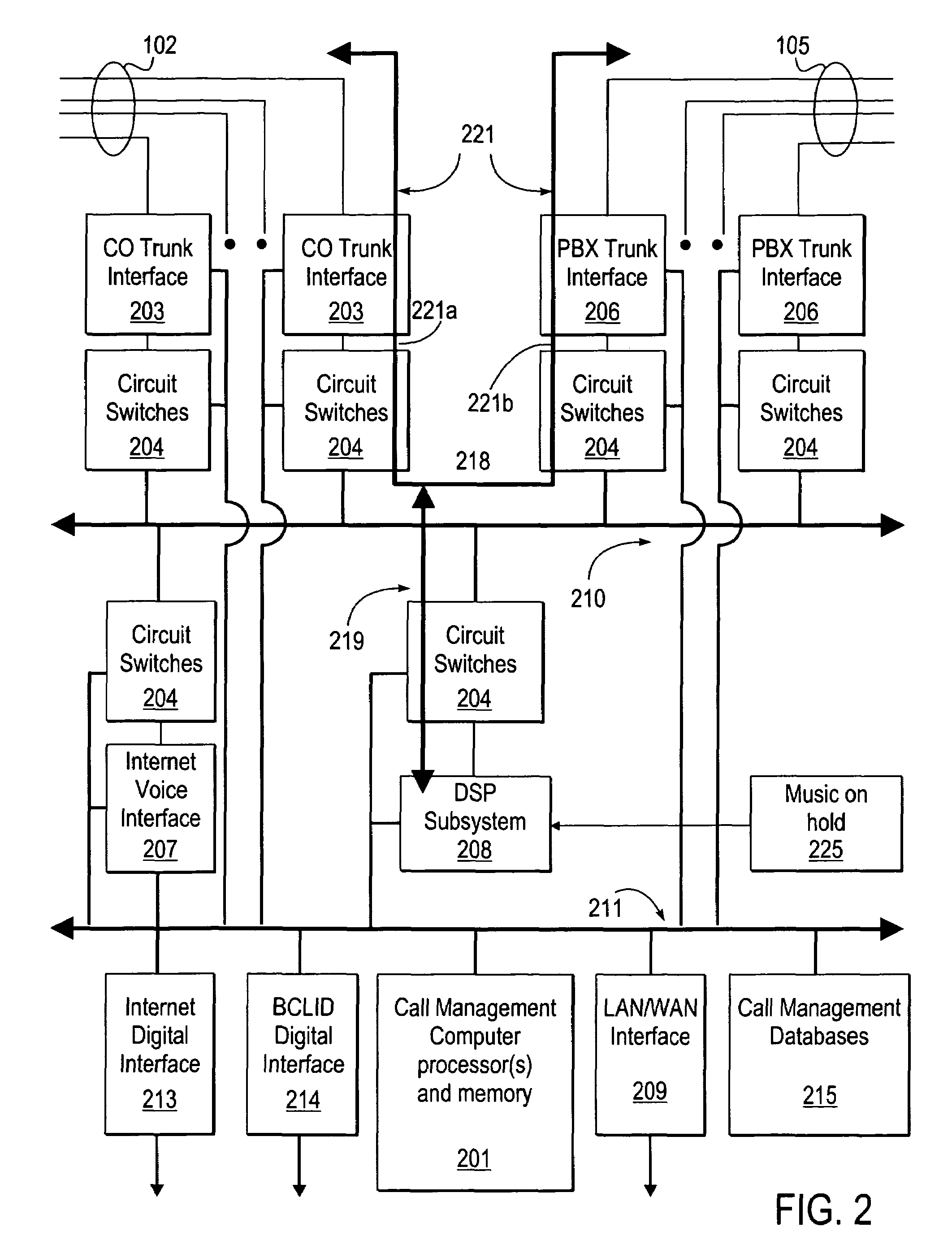

Call Management system with call control from user workstation computers

InactiveUS7136475B1Increase the itineraryImprove efficiencyInterconnection arrangementsSpecial service for subscribersDigital dataWorkstation

A Call Management System provides for management of calls directly by system users at their workstation computers via a digital data network such as a digital networks not controlled via the user's telephone instruments as in prior systems. A call management computer intercepts incoming calls and controls the handling of such calls according to instructions received from the users' workstations, which are accessed via the digital data network. Trunk circuits are monitored and controlled using digital signal processors to proactively identify the called party, the calling party and the call type (voice, Fax, data) and control and to monitor all calls. Each different type of call is managed differently and automatically through direct user workstation controls and / or user-generated rules to provide special treatment for designated callers. Multiple calls to user at the same time may be handled with no busy signals to callers. Only one number is needed for a user to receive voice Fax and data calls. Fax and data transmissions are automatically received.

Owner:WILMINGTON TRUST NAT ASSOC AS ADMINISTATIVE AGENT +1

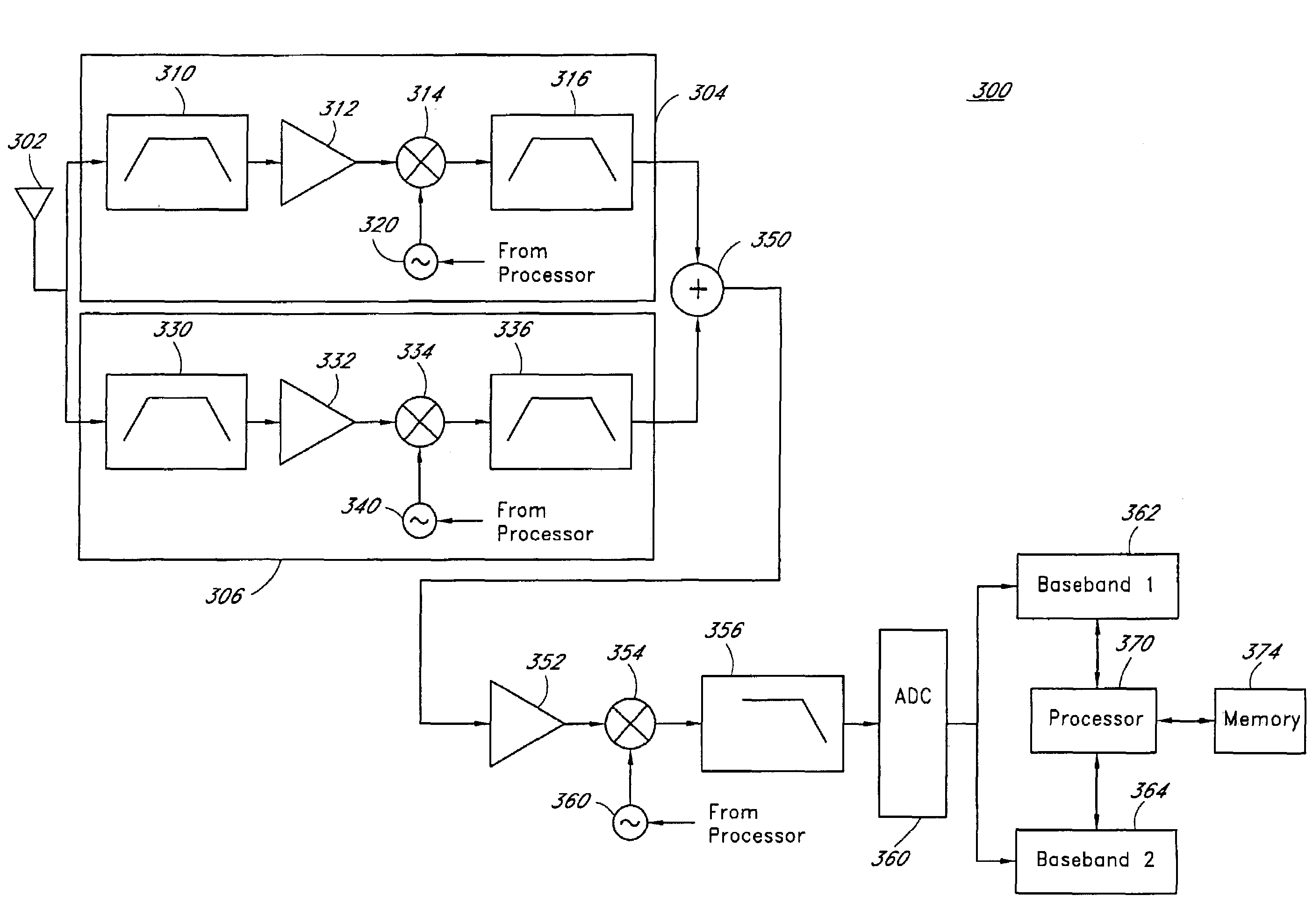

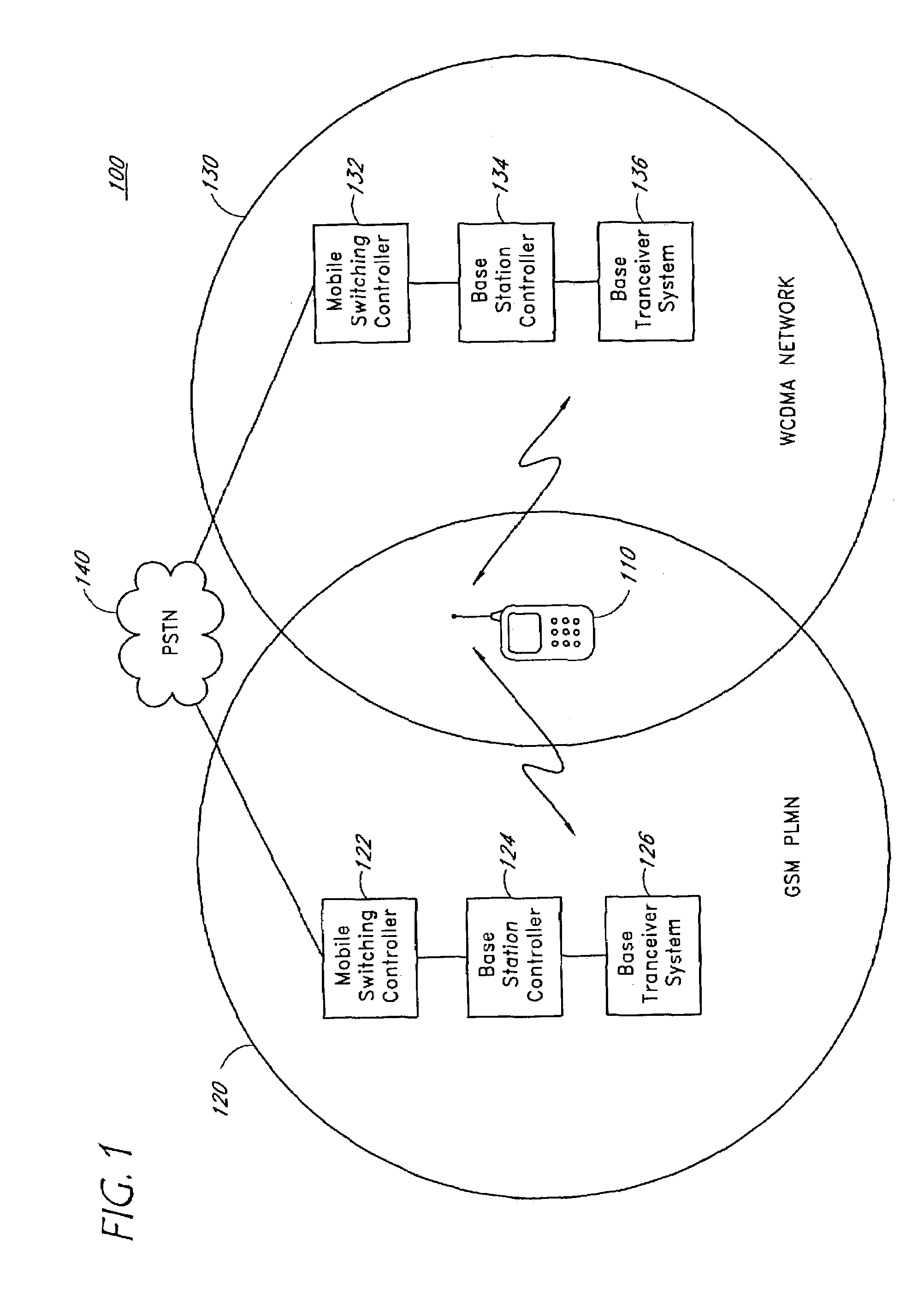

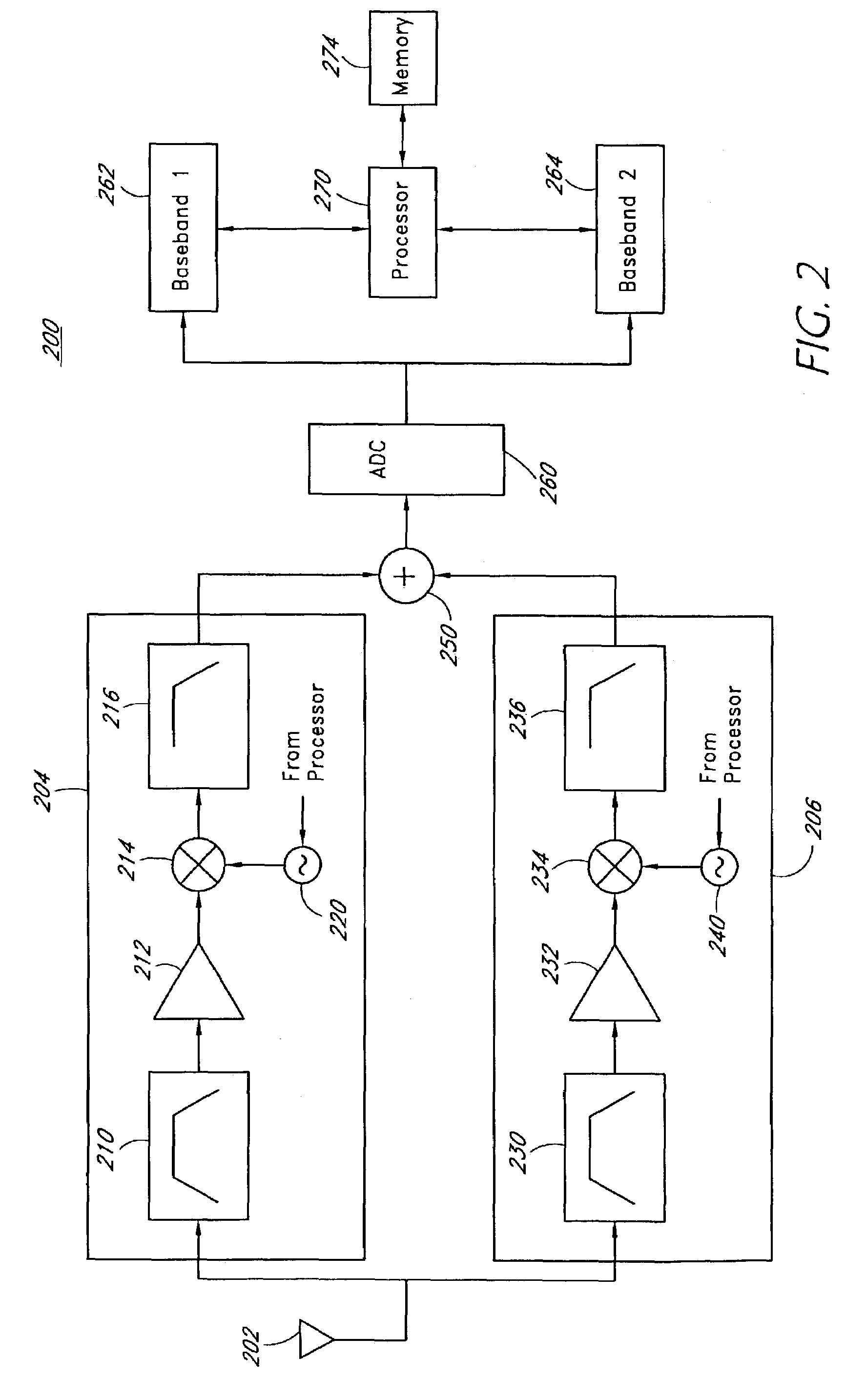

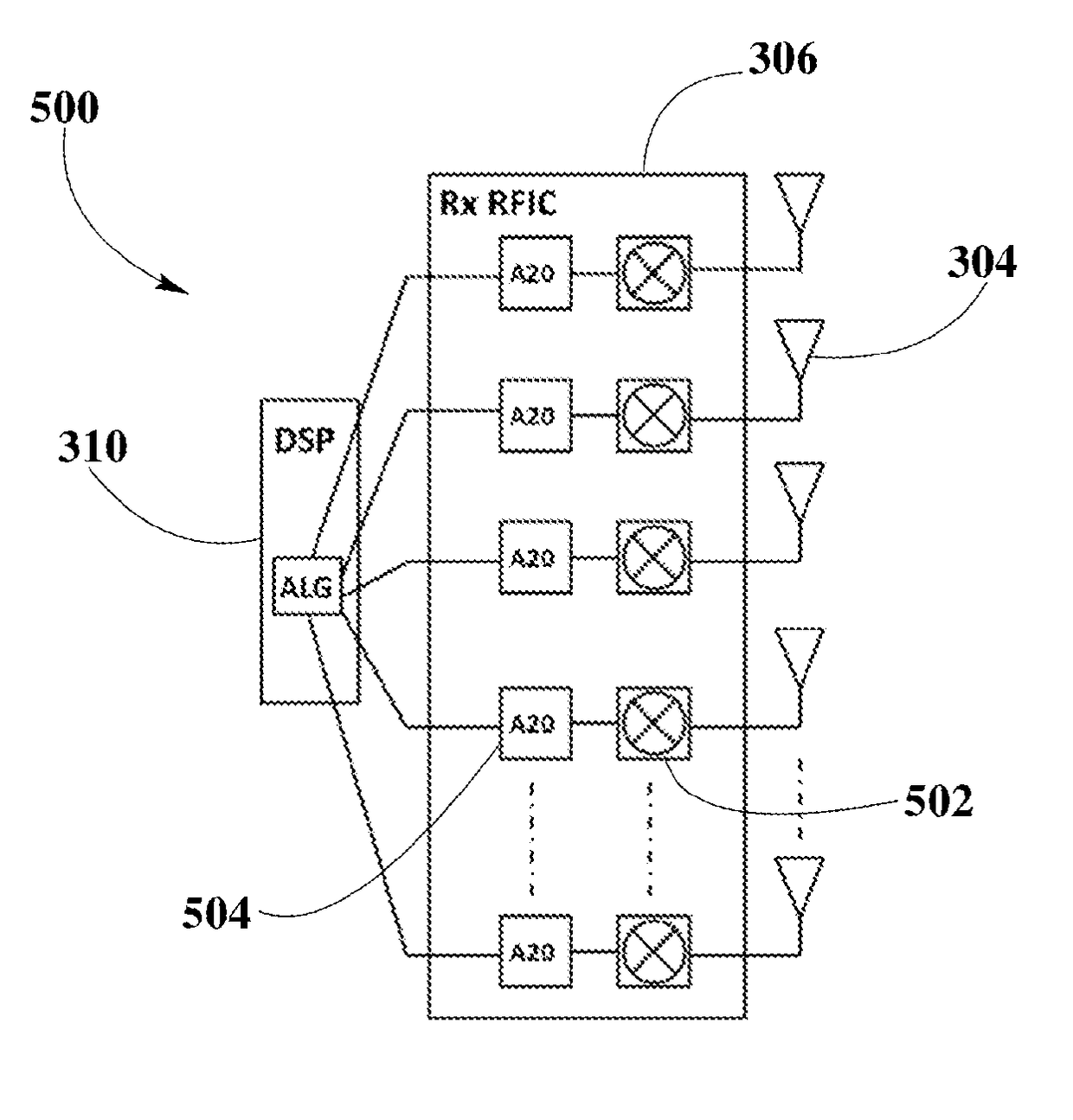

Shared receive path for simultaneous received signals

A method and apparatus are disclosed for a wireless communication device to simultaneously receive at least two signals. Two receiver portions are provided in the wireless communication device. A first receiver portion is configured to receive a first communication signal. A second receiver portion is configured to receive a second communication signal. The two receiver portions are configured to convert the first and second communication signals to a common frequency band. The common frequency band may be an intermediate frequency band or baseband frequency band. The converted first and second communication signals are combined in the common frequency band using an adder or other signal combiner. The combined signal is processed in a single signal processor. The communication device is able to resolve each of the received signals when the first communication signal is a narrowband signal and the second communication signal is a wideband signal, such as a spread spectrum signal.

Owner:QUALCOMM INC

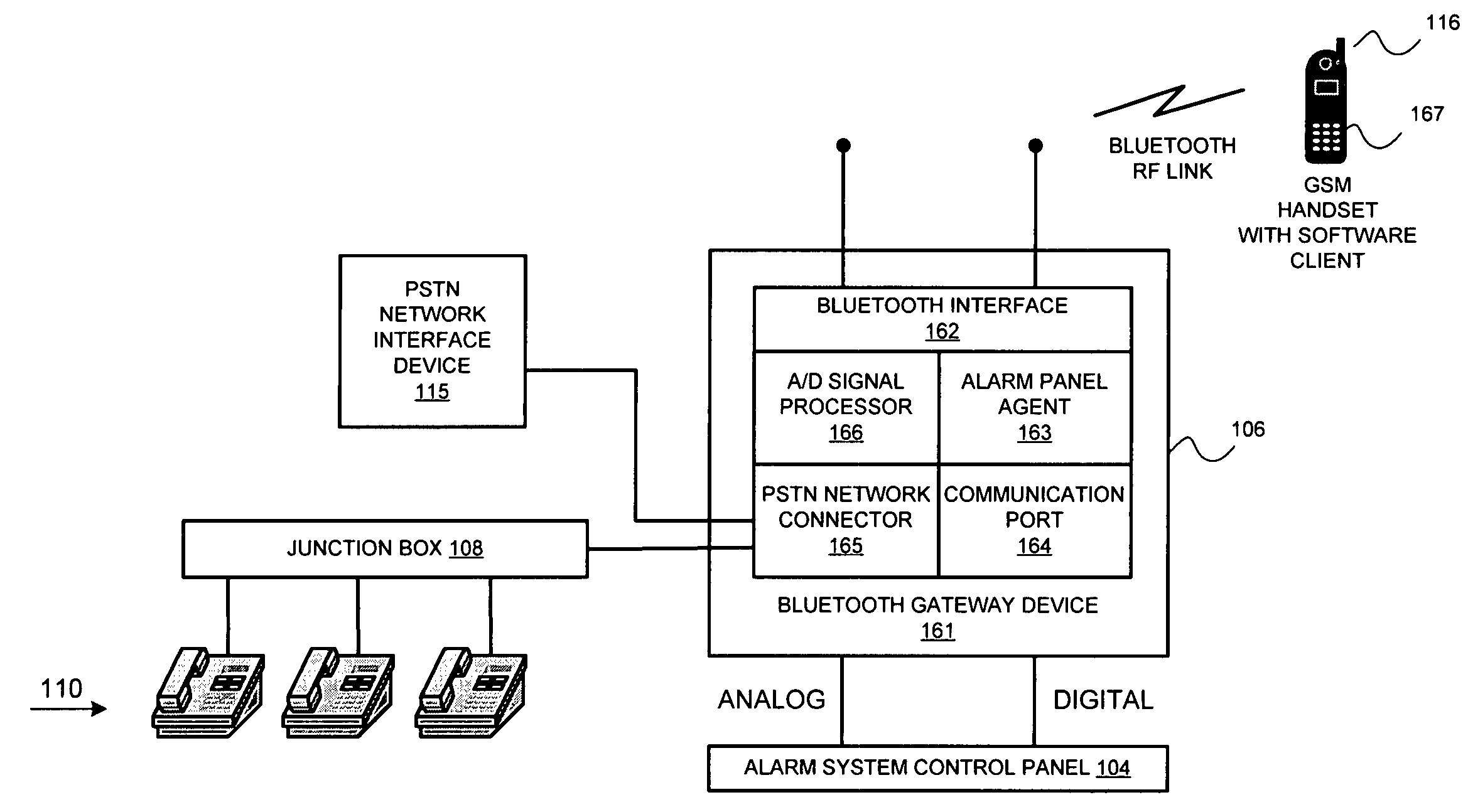

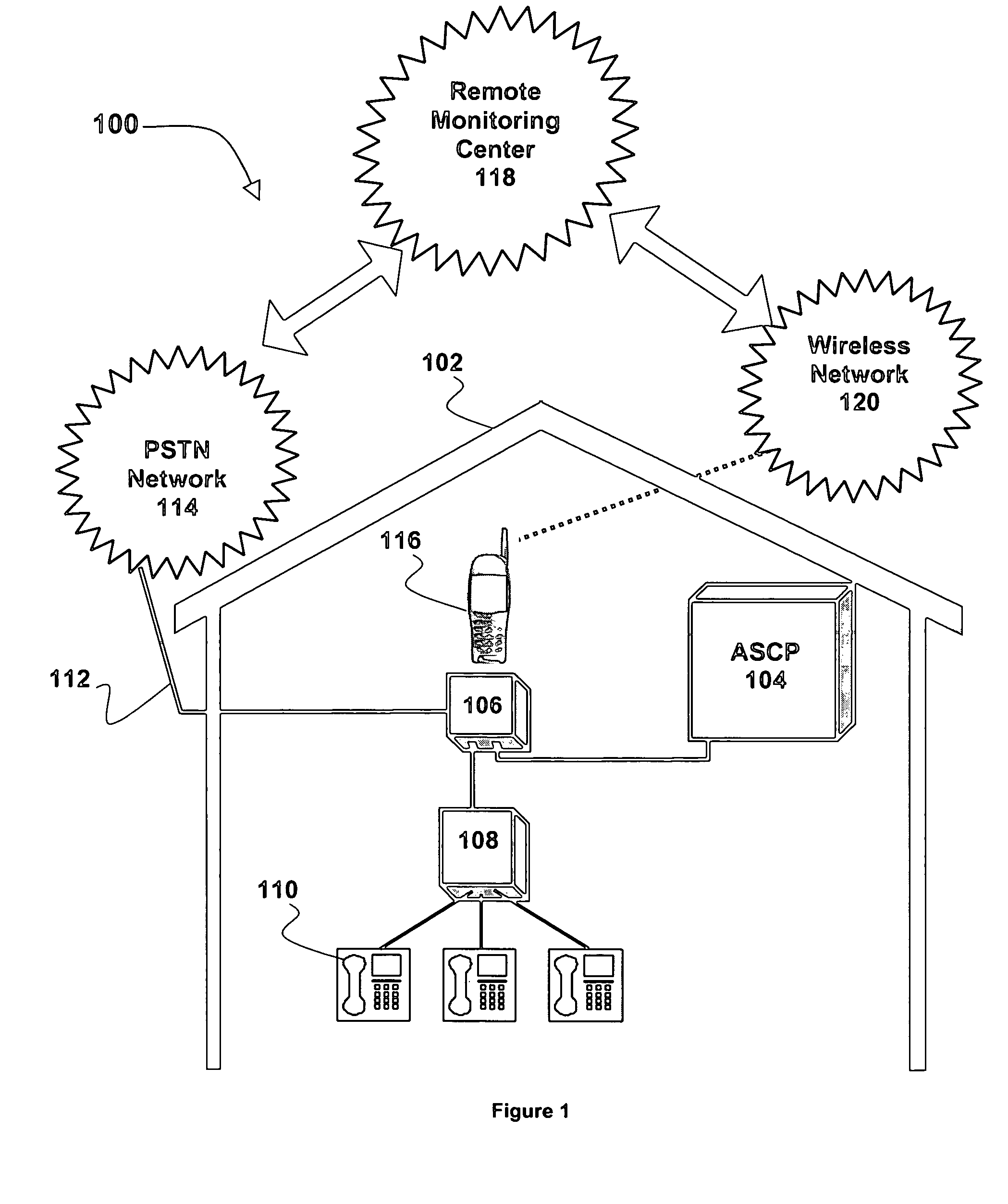

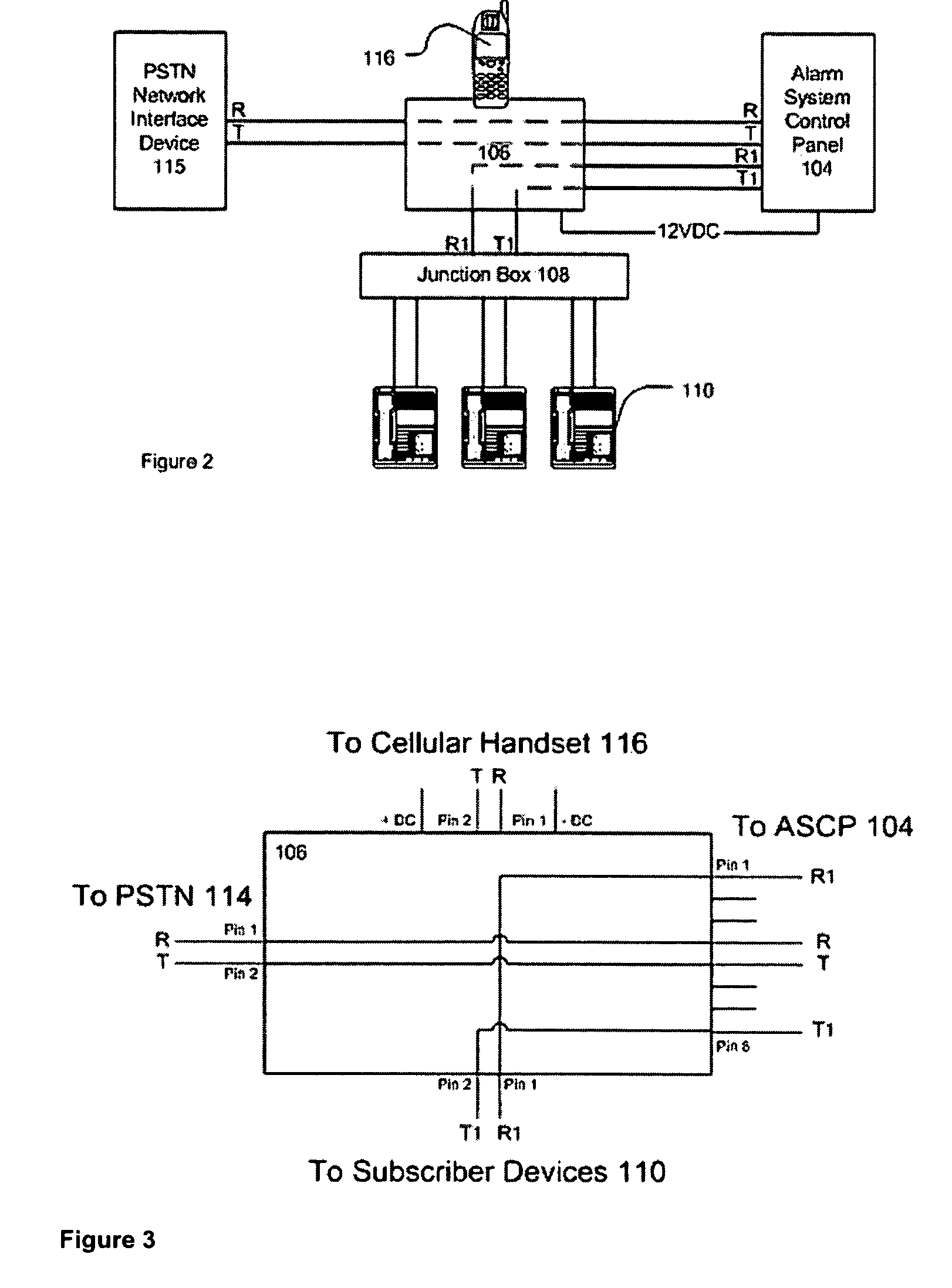

Systems and methods for providing non-dedicated wireless backup service for monitored security systems via Bluetooth

An interface provides a non-dedicated wireless communications path for reporting alarm events from a landline-based alarm system to a remote monitoring system via BLUETOOTH. The interface includes a BLUETOOTH receiver that communicates with a cellular handset, or other wireless device that has a BLUETOOTH transmitter, and a network connector (such as RJ31X jack) between an alarm control panel and the PSTN. When a wireless device is within range of the interface, the interface bypasses the landline and routes all security calls from the alarm control panel through an analog-to-digital signal processor and to the wireless device via BLUETOOTH, which places a call to the remote monitoring center.

Owner:CINGULAR WIRELESS LLC