Patents

Literature

1133 results about "Programmable read-only memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A programmable read-only memory (PROM) is a form of digital memory where the setting of each bit is locked by a fuse or antifuse. It is one type of ROM (read-only memory). The data in them is permanent and cannot be changed. PROMs are used in digital electronic devices to store permanent data, usually low level programs such as firmware or microcode. The key difference from a standard ROM is that the data is written into a ROM during manufacture, while with a PROM the data is programmed into them after manufacture. Thus, ROMs tend to be used only for large production runs with well-verified data, while PROMs are used to allow companies to test on a subset of the devices in an order before burning data into all of them.

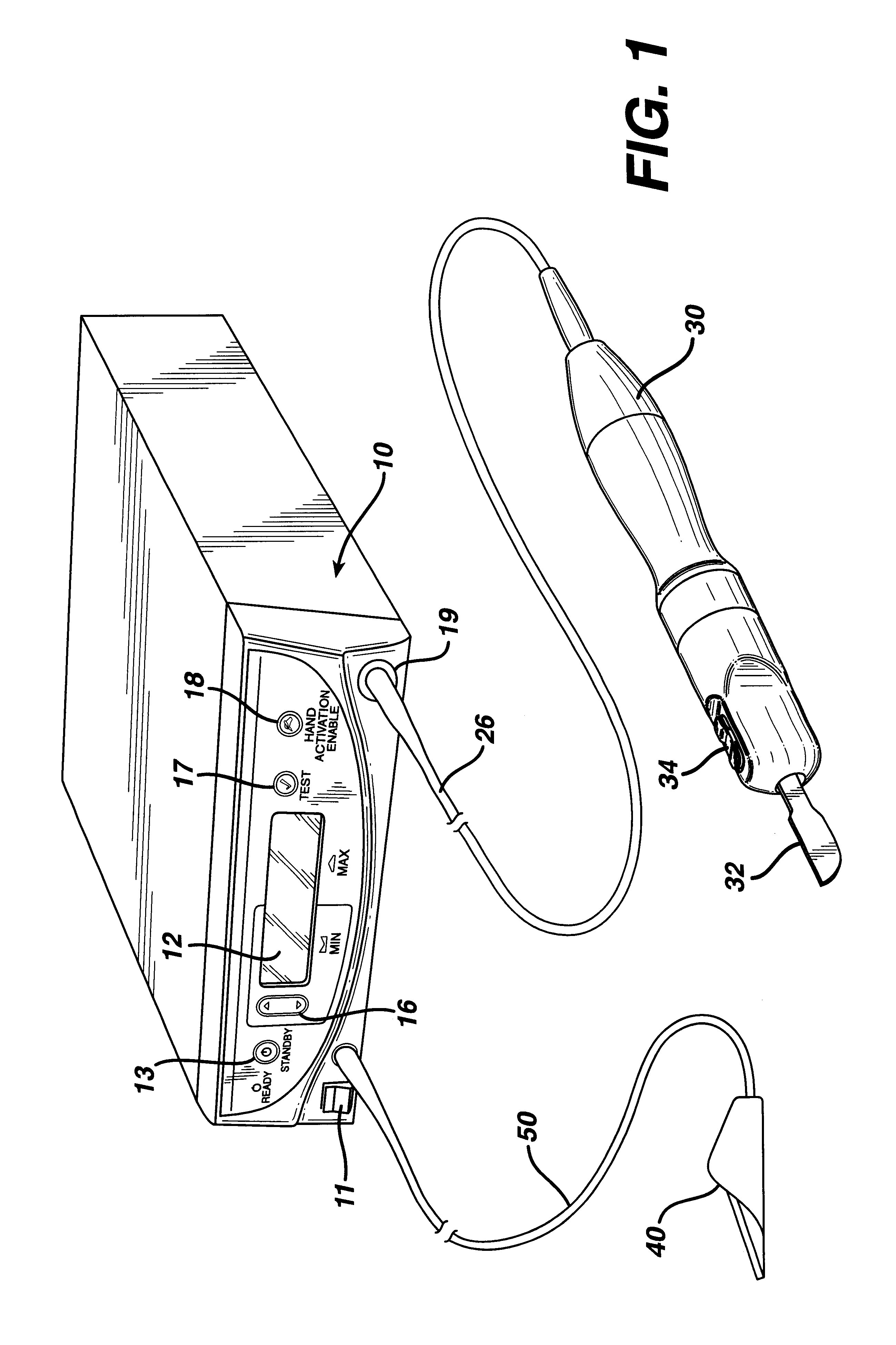

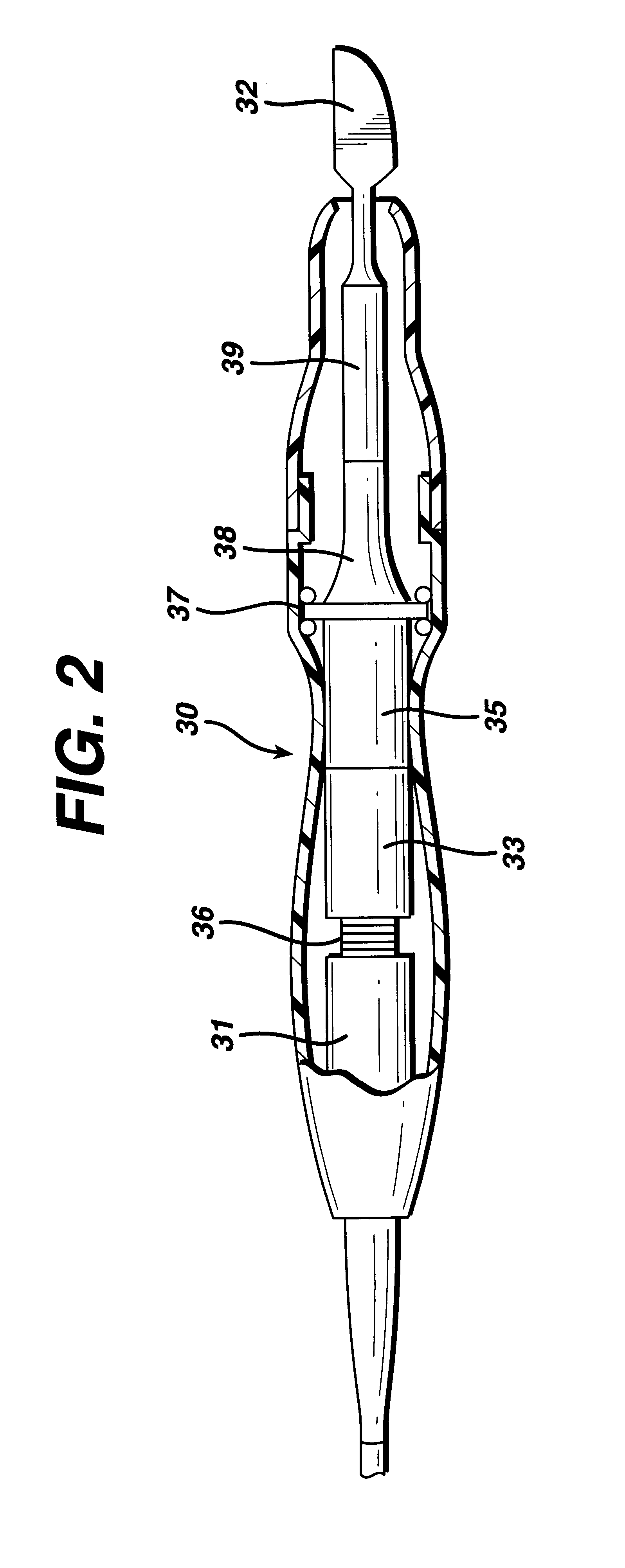

Apparatus and method for altering generator functions in an ultrasonic surgical system

InactiveUS6908472B2Avoid mistakesNew system functionalityIncision instrumentsDiagnosticsDriving currentElectricity

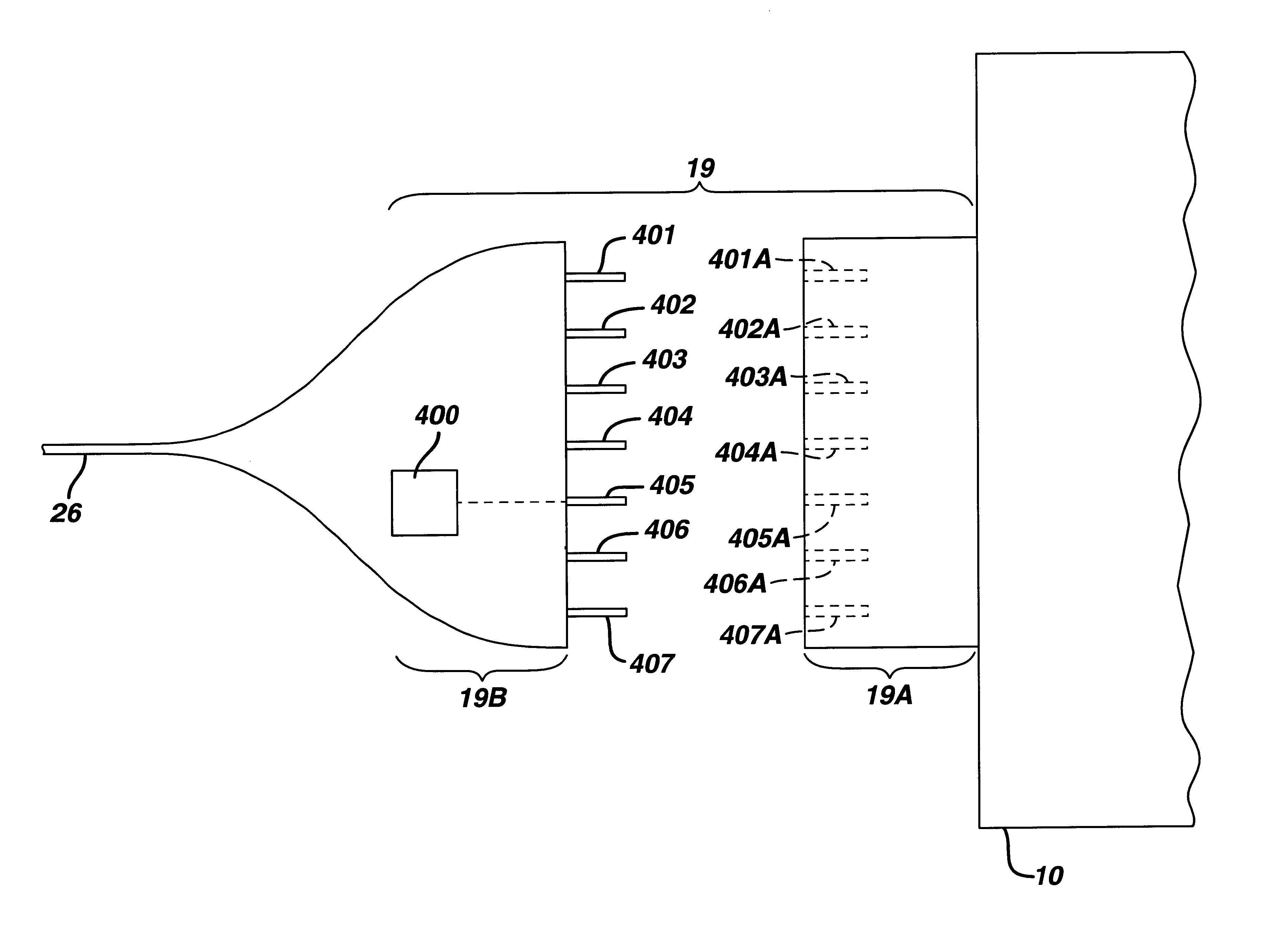

The present invention provides a system for implementing surgical procedures which includes an ultrasonic surgical hand piece having an end-effector, a console having a digital signal processor (DSP) for controlling the hand piece, an electrical connection connecting the hand piece and the console, and a memory, such as an EEPROM (Electrically Erasable Programmable Read Only Memory), disposed in the electrical connection. The console sends a drive current to drive the hand piece which imparts ultrasonic longitudinal movement to the blade. The console reads the memory and authenticates the hand piece for use with the console if particular or proprietary data are present in the memory. Moreover, to prevent errors in operating the hand piece, the memory can store certain diagnostic information which the console can utilize in determining whether the operation of the hand piece should be handicapped or disabled. Furthermore, the memory can be used to reprogram the console, if needed.

Owner:ETHICON ENDO SURGERY INC

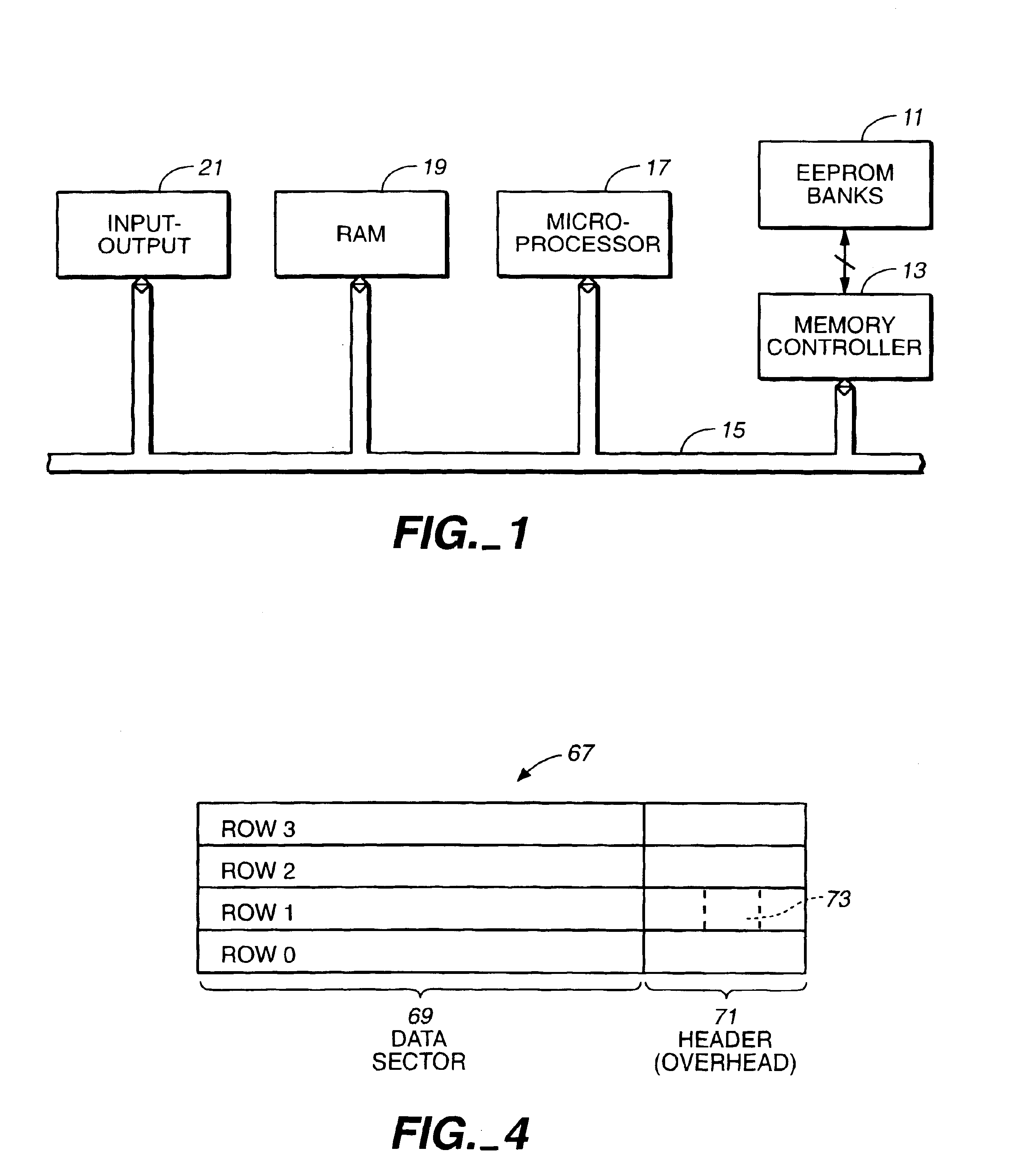

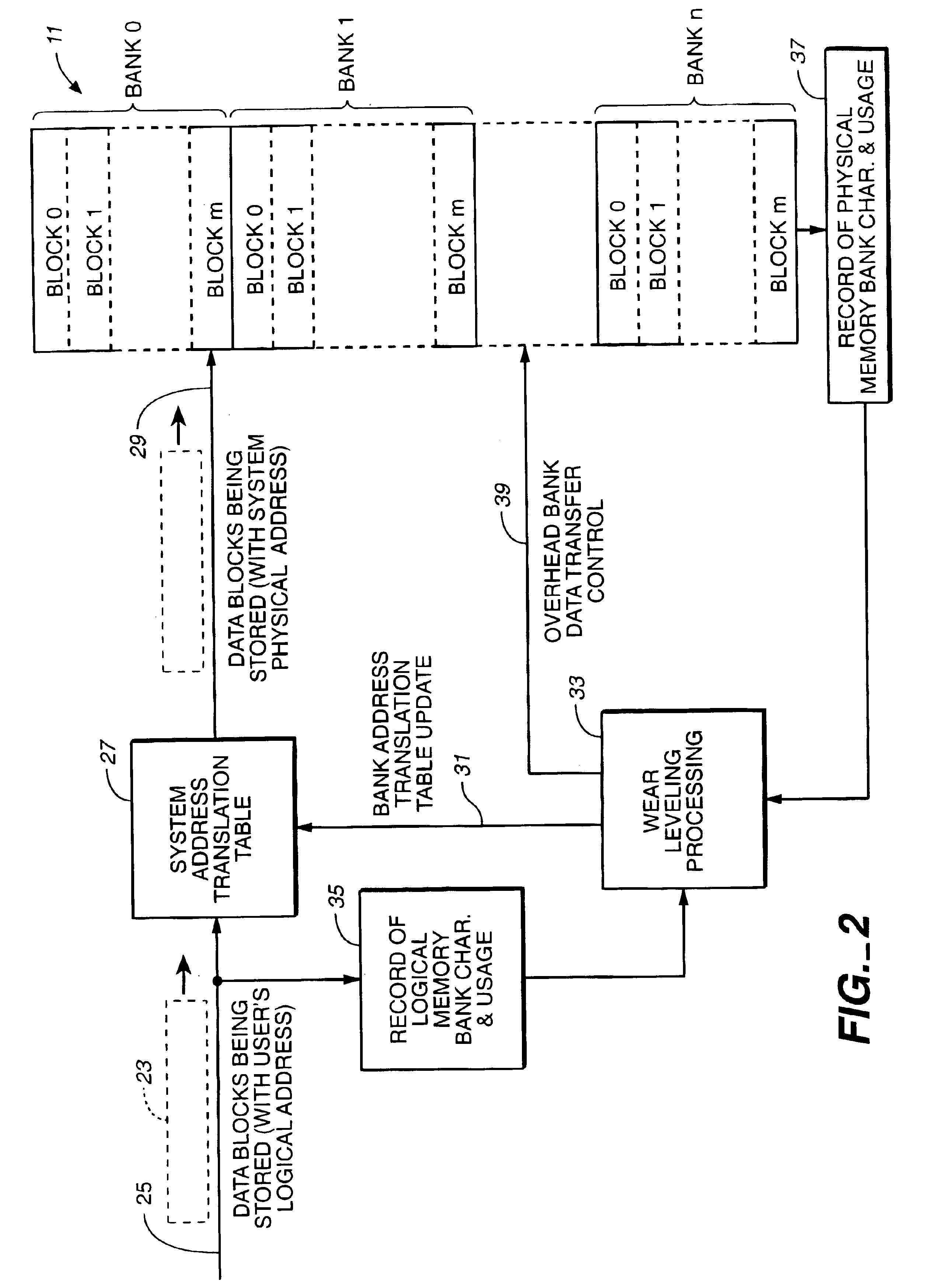

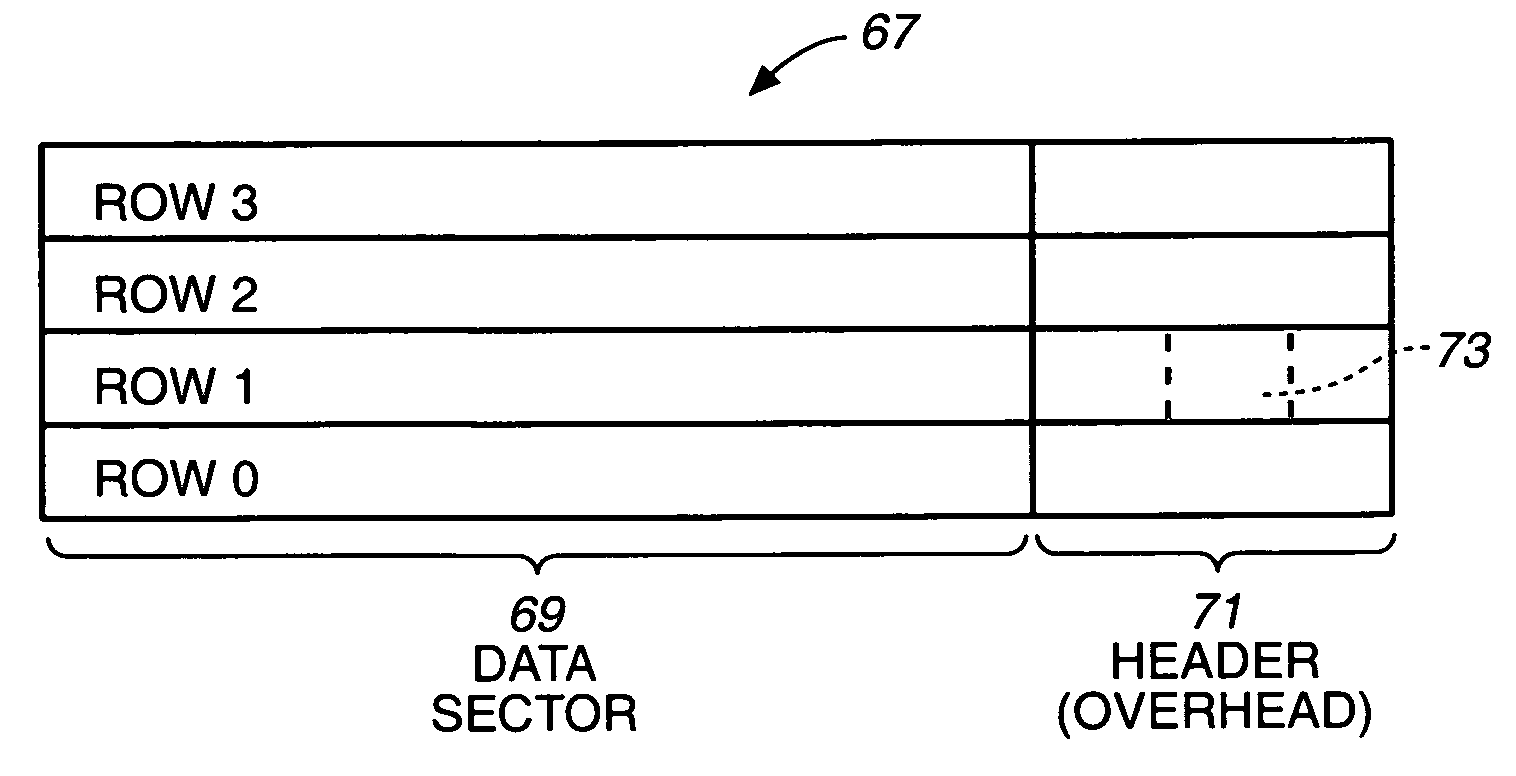

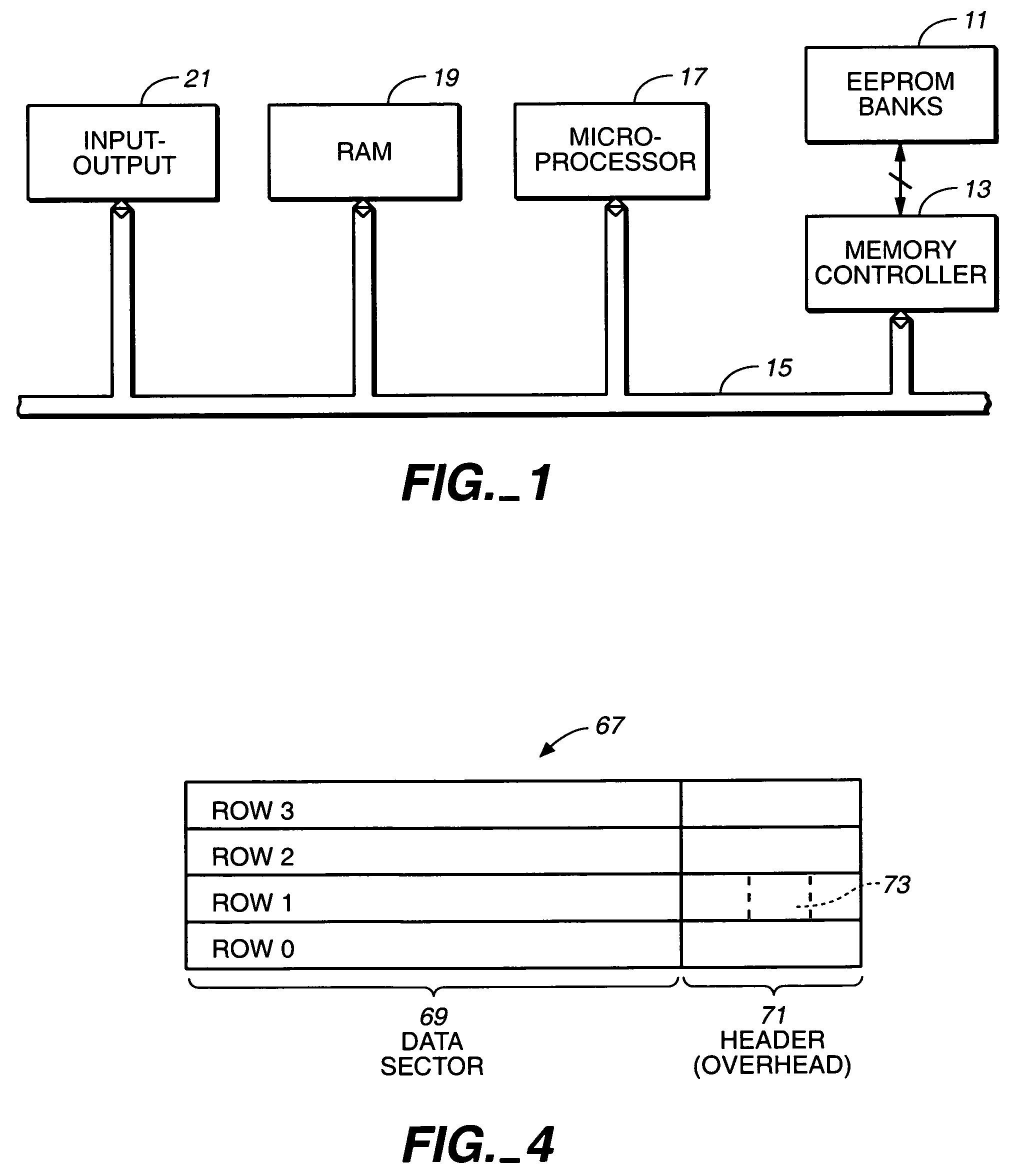

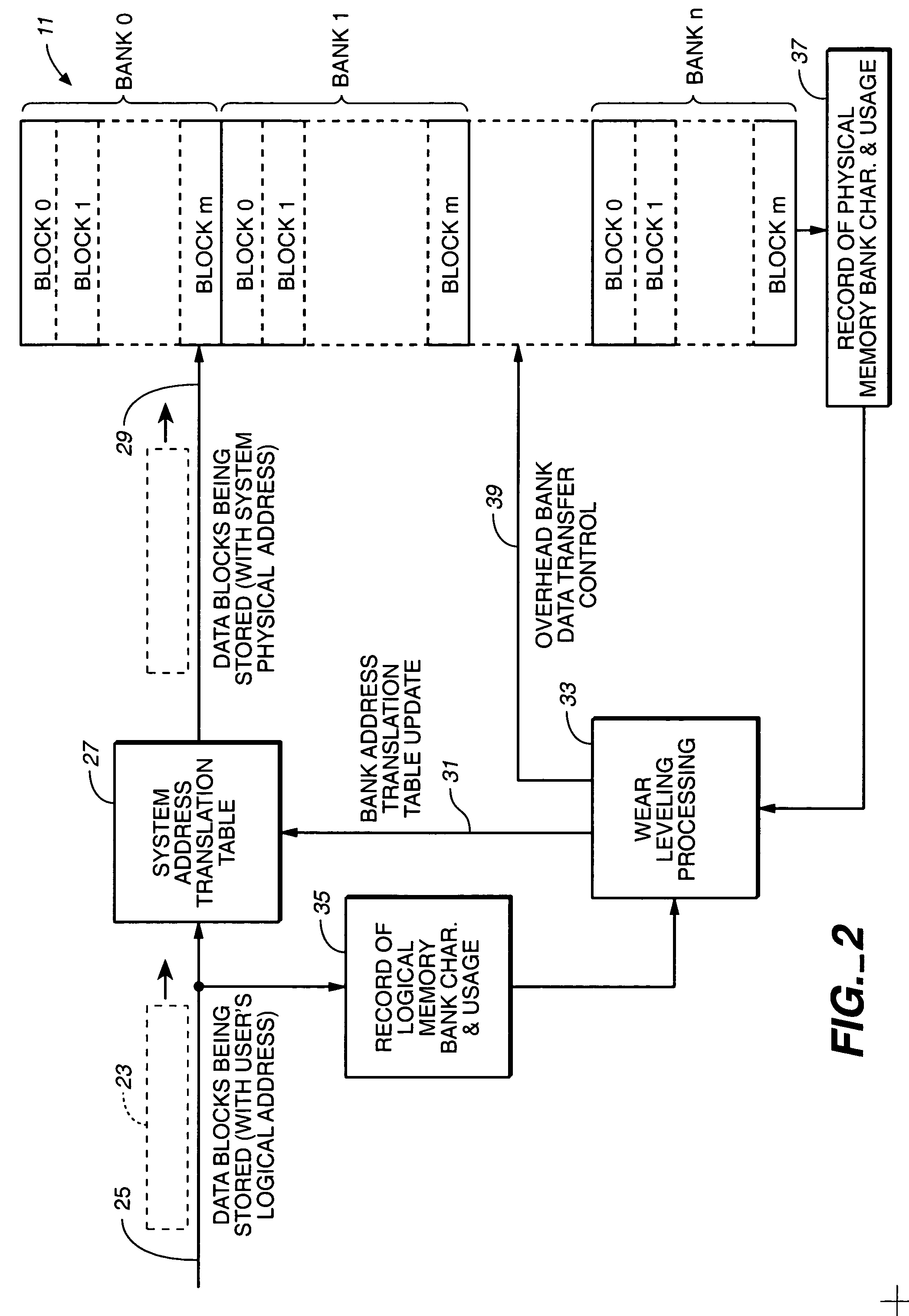

Wear leveling techniques for flash EEPROM systems

InactiveUS6850443B2Avoid uneven wearExtended service lifeMemory architecture accessing/allocationRead-only memoriesElectricityProgrammable read-only memory

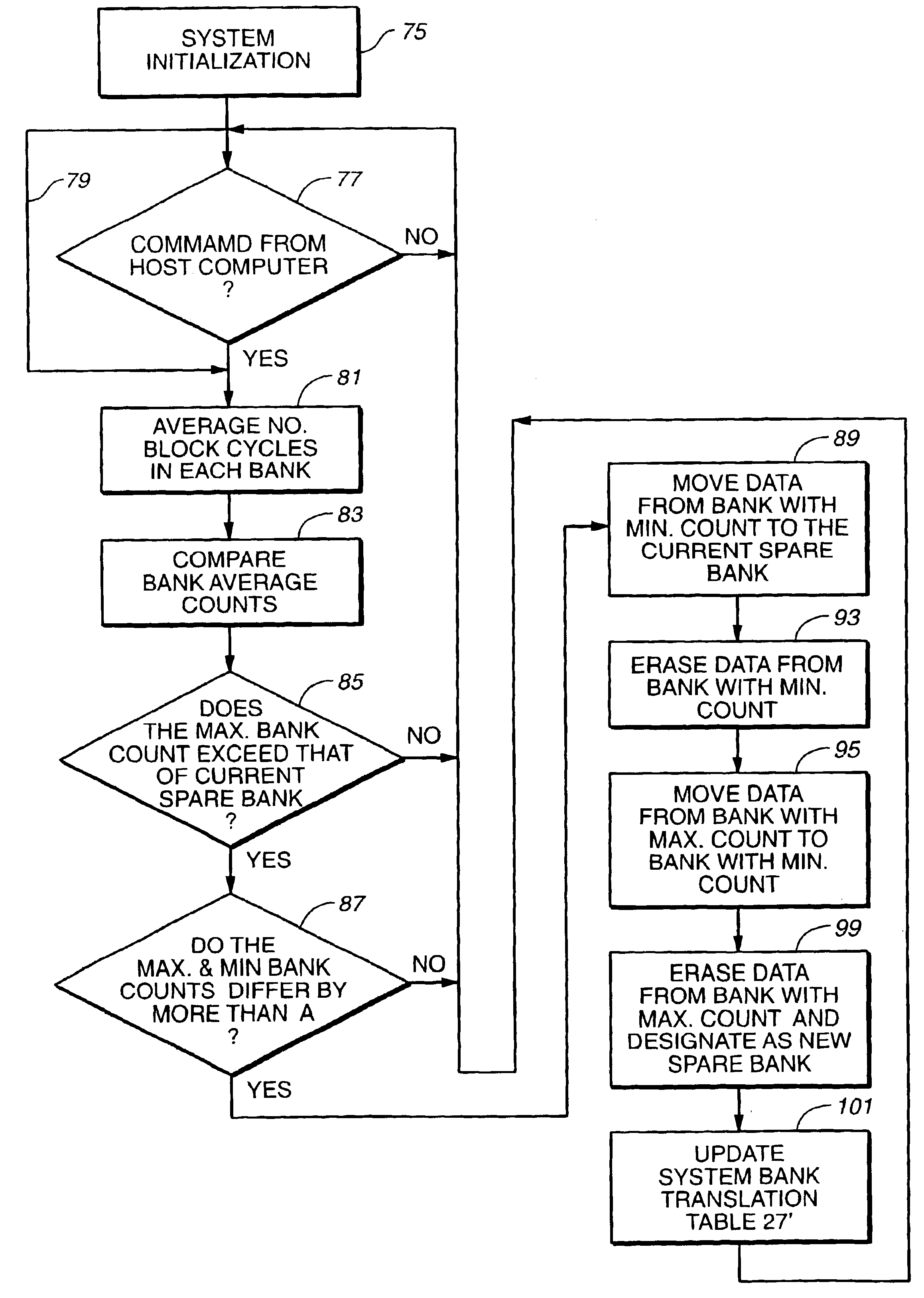

A mass storage system made of flash electrically erasable and programmable read only memory (“EEPROM”) cells organized into blocks, the blocks in turn being grouped into memory banks, is managed to even out the numbers of erase and rewrite cycles experienced by the memory banks in order to extend the service lifetime of the memory system. Since this type of memory cell becomes unusable after a finite number of erase and rewrite cycles, although in the tens of thousands of cycles, uneven use of the memory banks is avoided so that the entire memory does not become inoperative because one of its banks has reached its end of life while others of the banks are little used. Relative use of the memory banks is monitored and, in response to detection of uneven use, have their physical addresses periodically swapped for each other in order to even out their use over the lifetime of the memory.

Owner:SANDISK TECH LLC

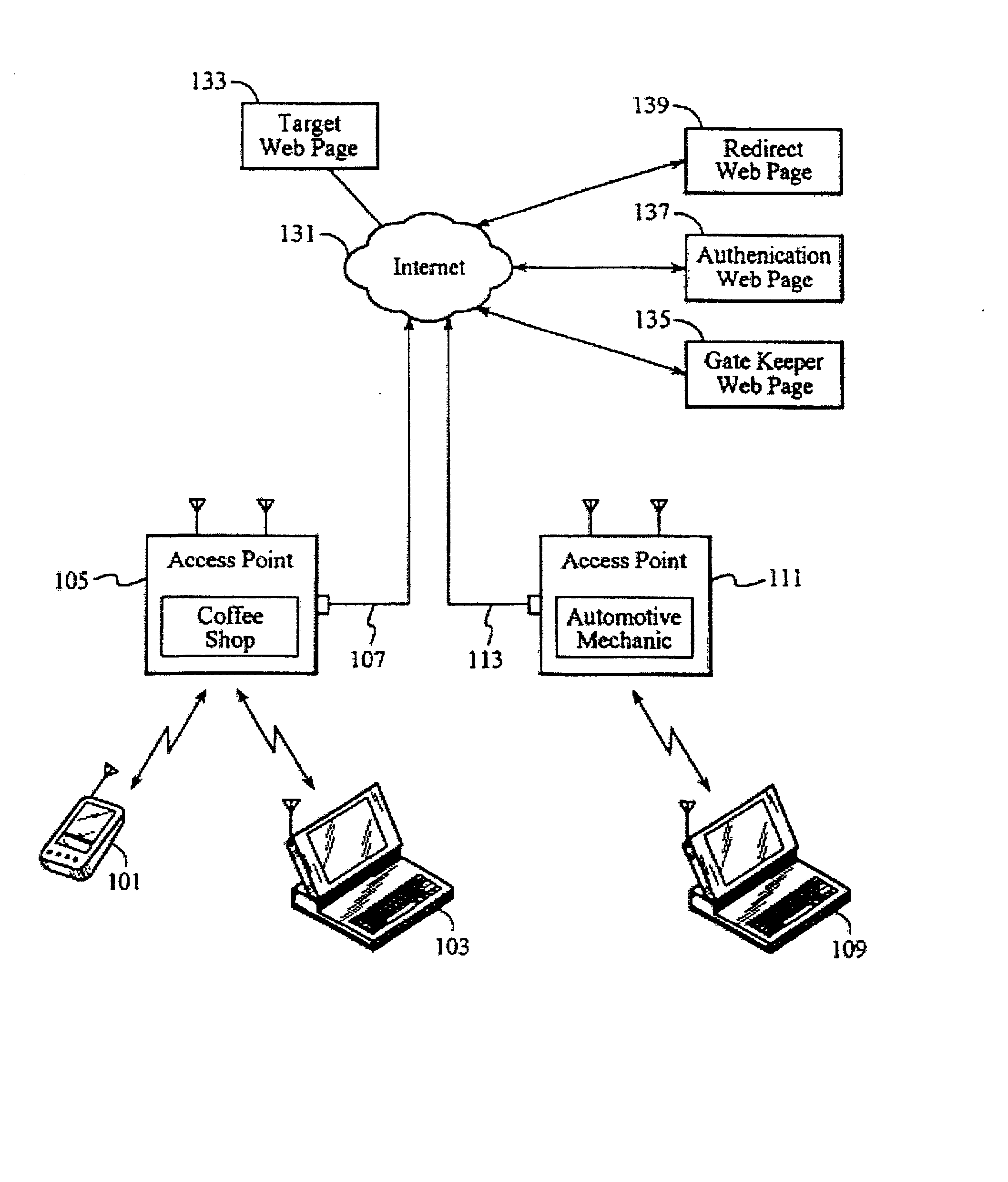

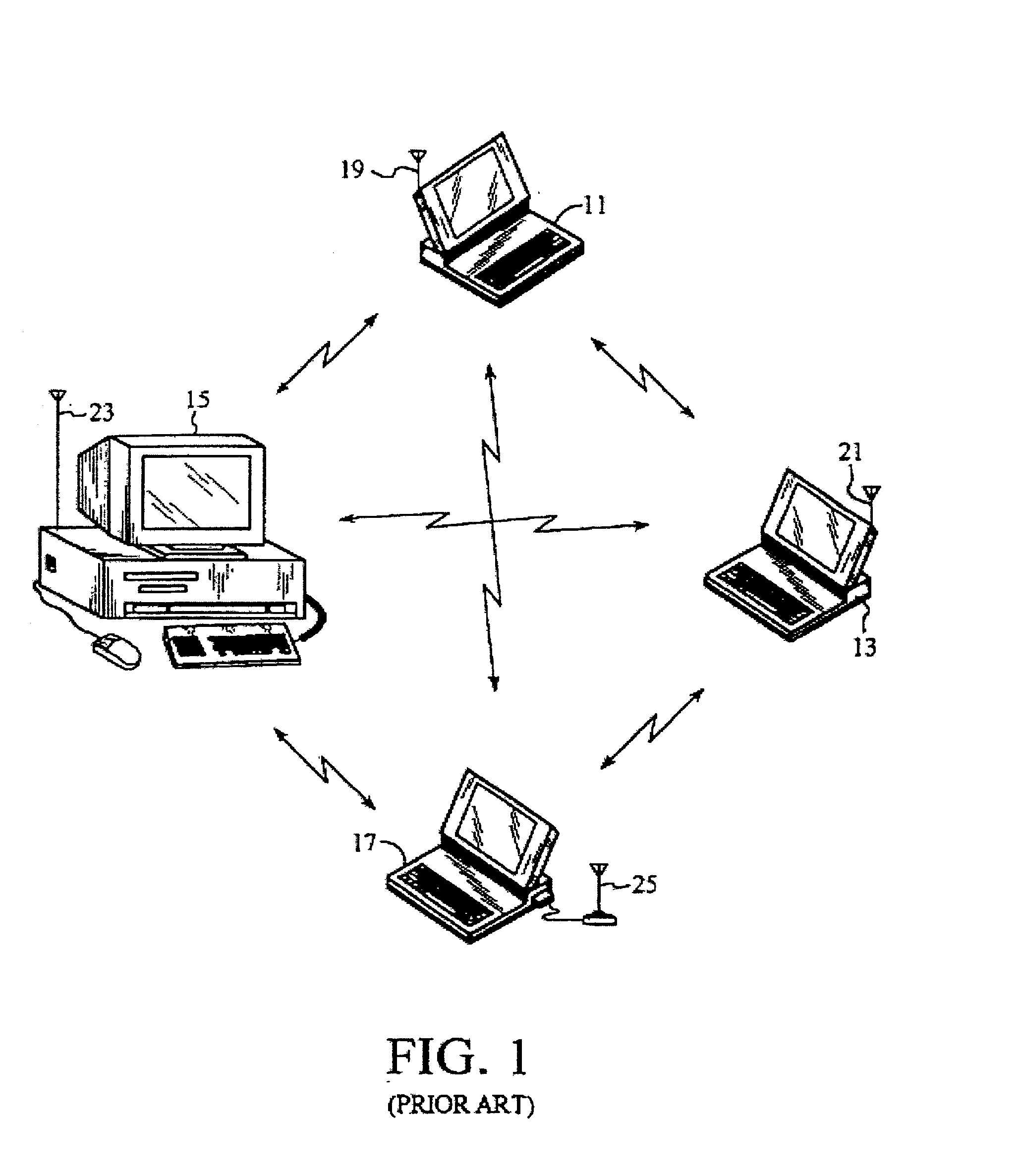

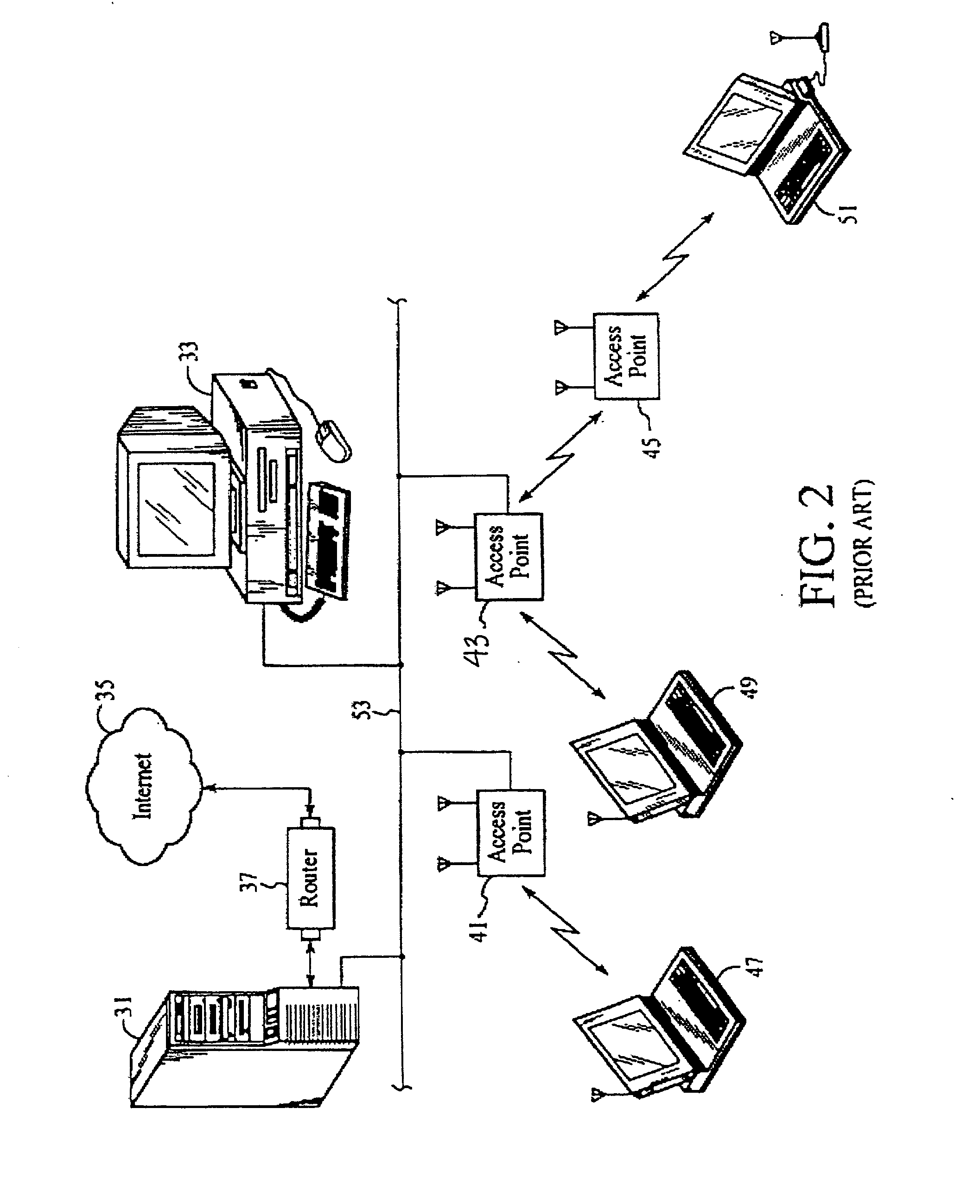

Automated updating of access points in a distributed network

InactiveUS20020157090A1Data switching by path configurationProgram loading/initiatingProgrammable read-only memoryRandom access memory

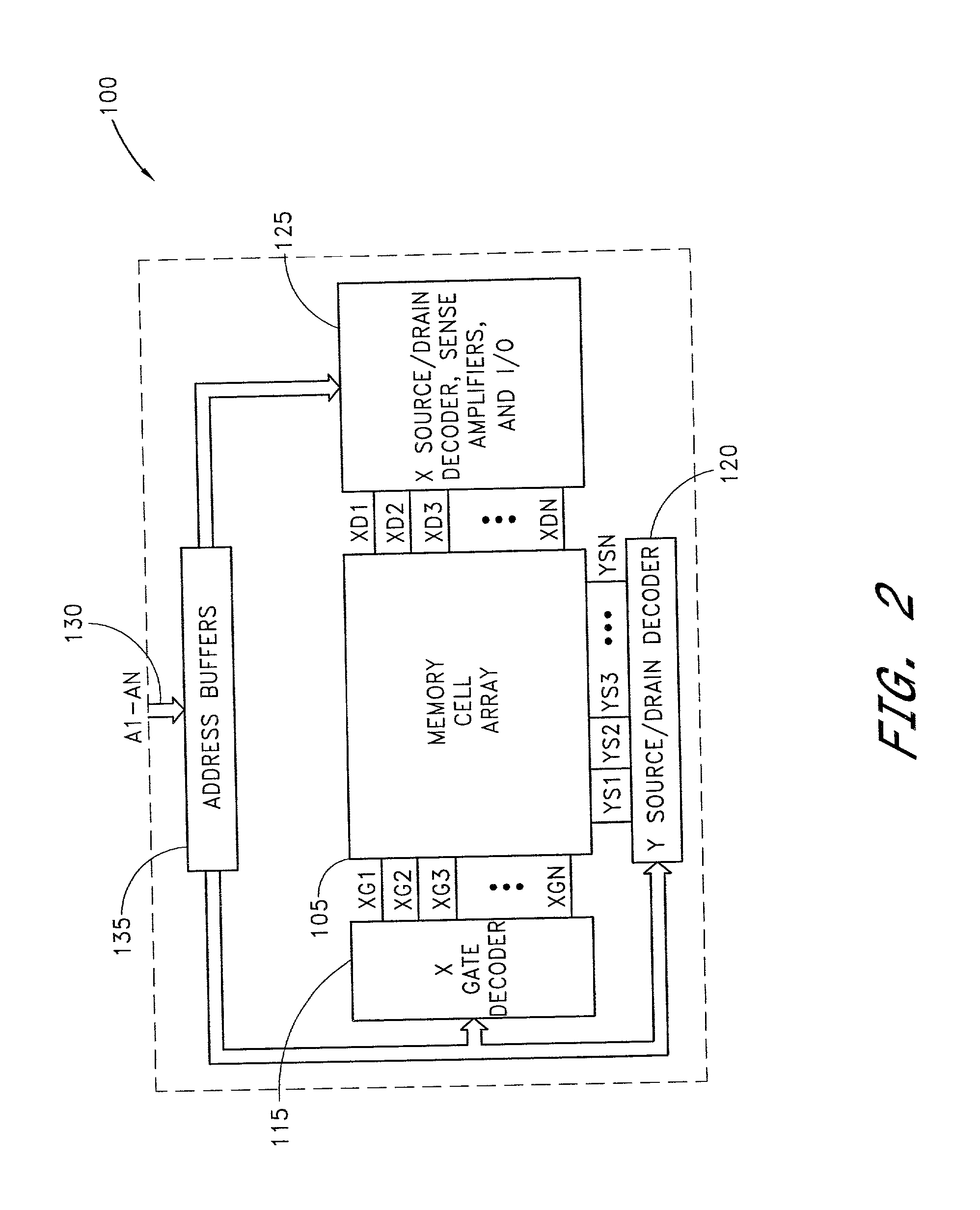

A method and system for maintaining network access point equipment including installing and upgrading software. The system includes a network server, and access point equipment including one or more access point devices, with each device equipped with a CPU including a random access memory (RAM) and a programmable read only memory (PROM). The server is configured for receiving software for maintaining the programming of access point devices. Both the access point devices and the server are programmed with authentication software for identifying each other prior to transmission of maintenance data. The access point devices are further programmed to periodically do a software check with the server. If the current software version in the device is the same as that stored in the server, no action is taken. If the version in the server is different, then the server and device automatically load the current software version into the device.

Owner:HEREUARE COMMUNICATIOINS

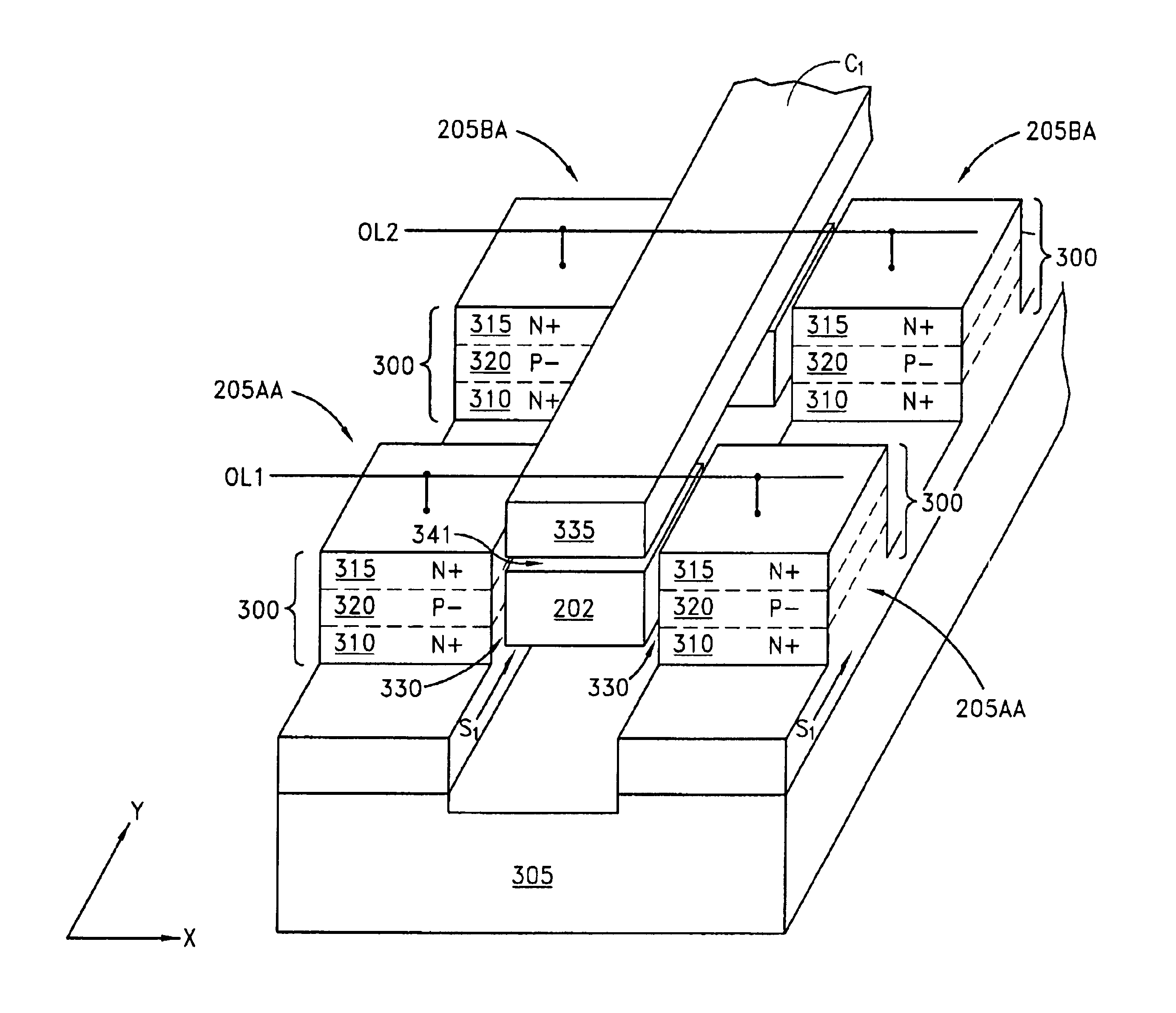

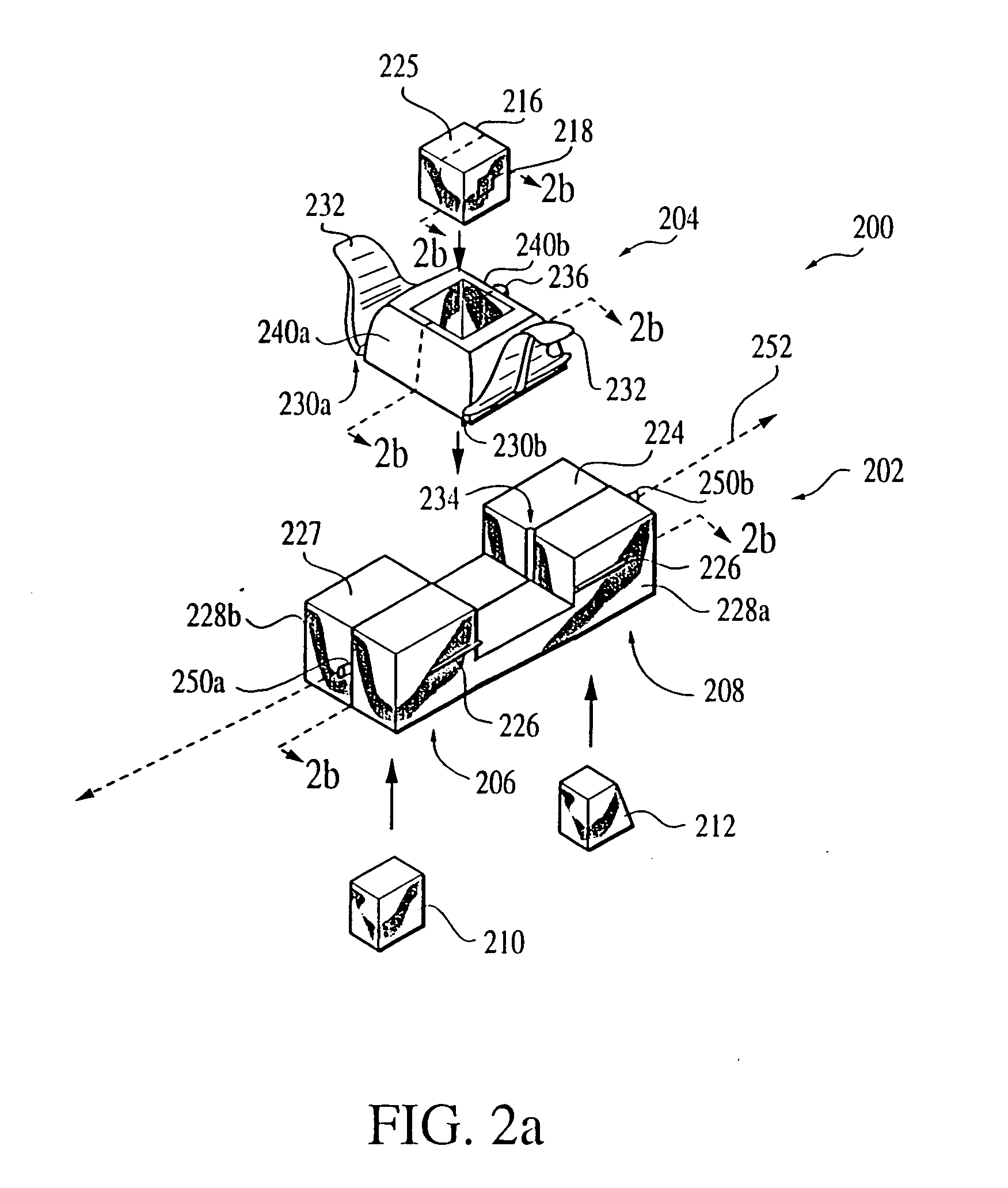

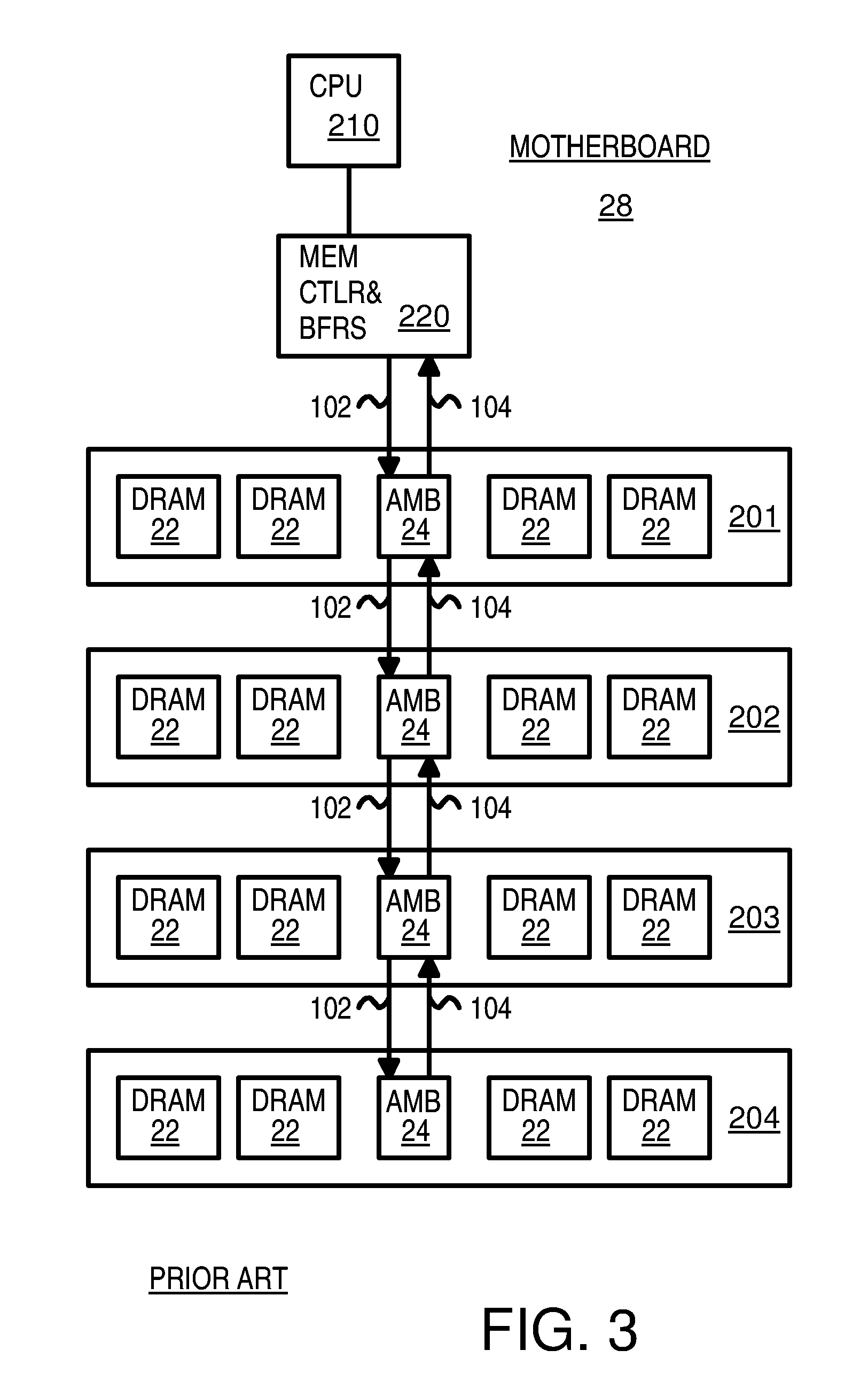

Floating gate transistor with horizontal gate layers stacked next to vertical body

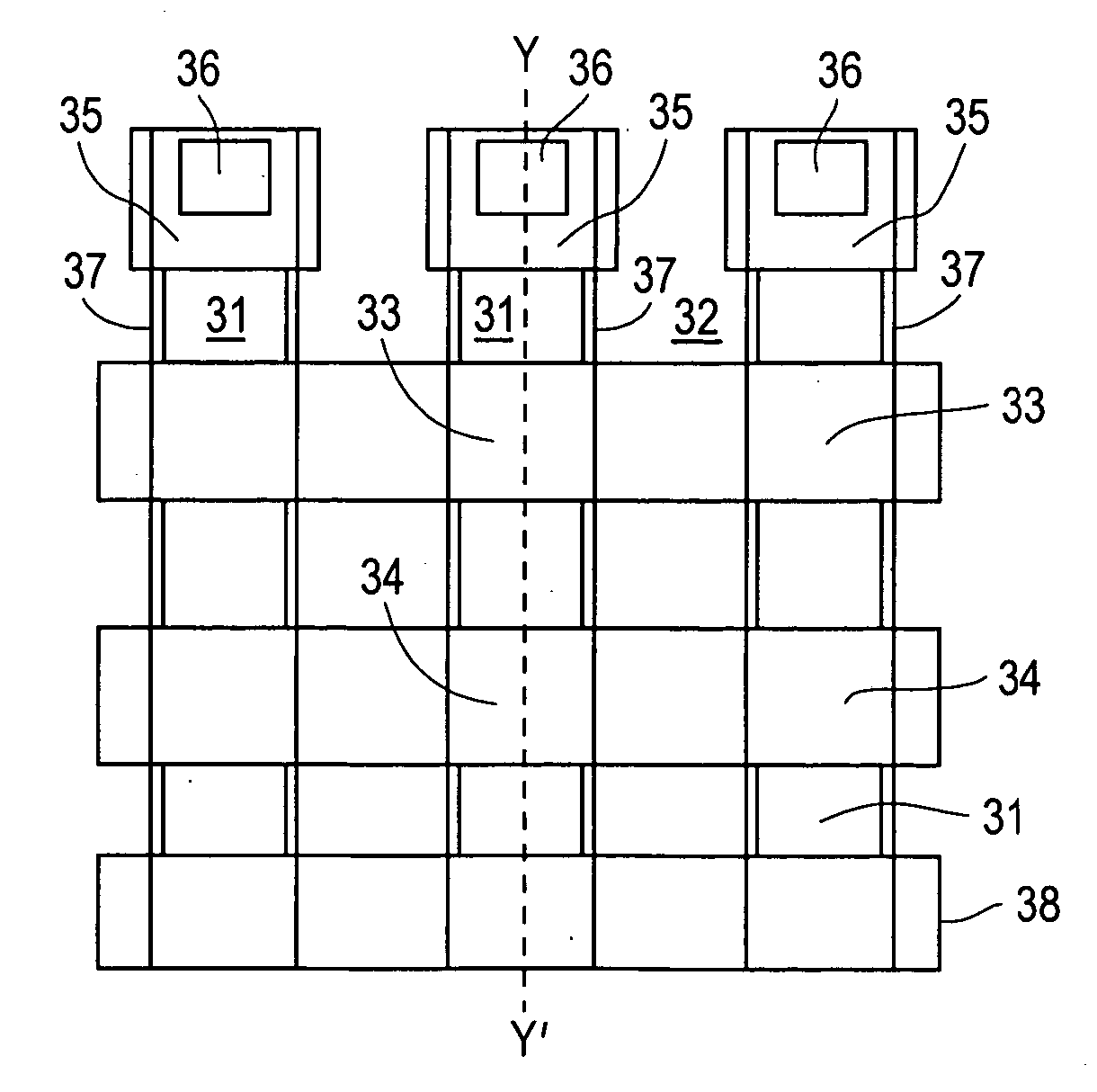

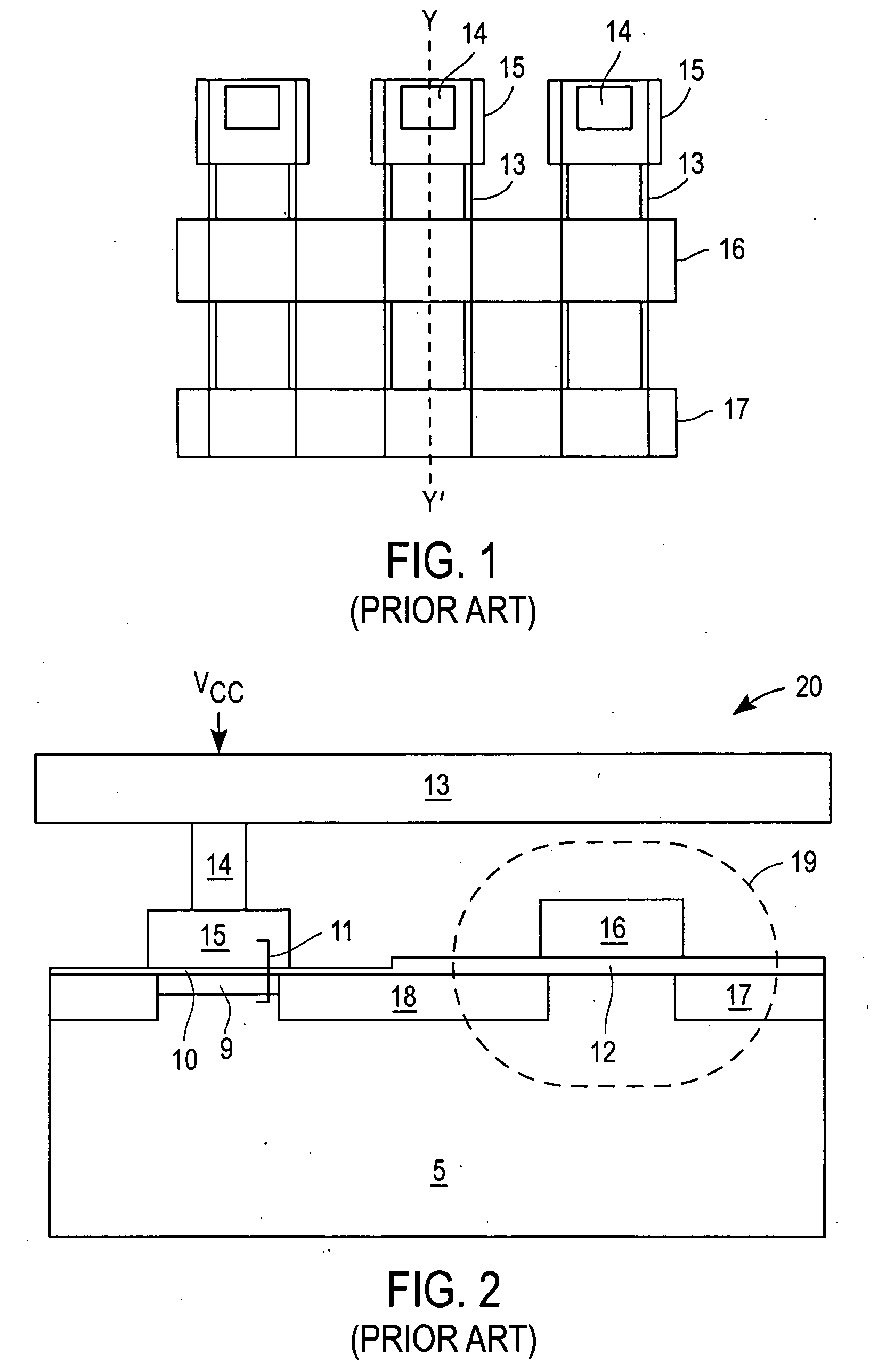

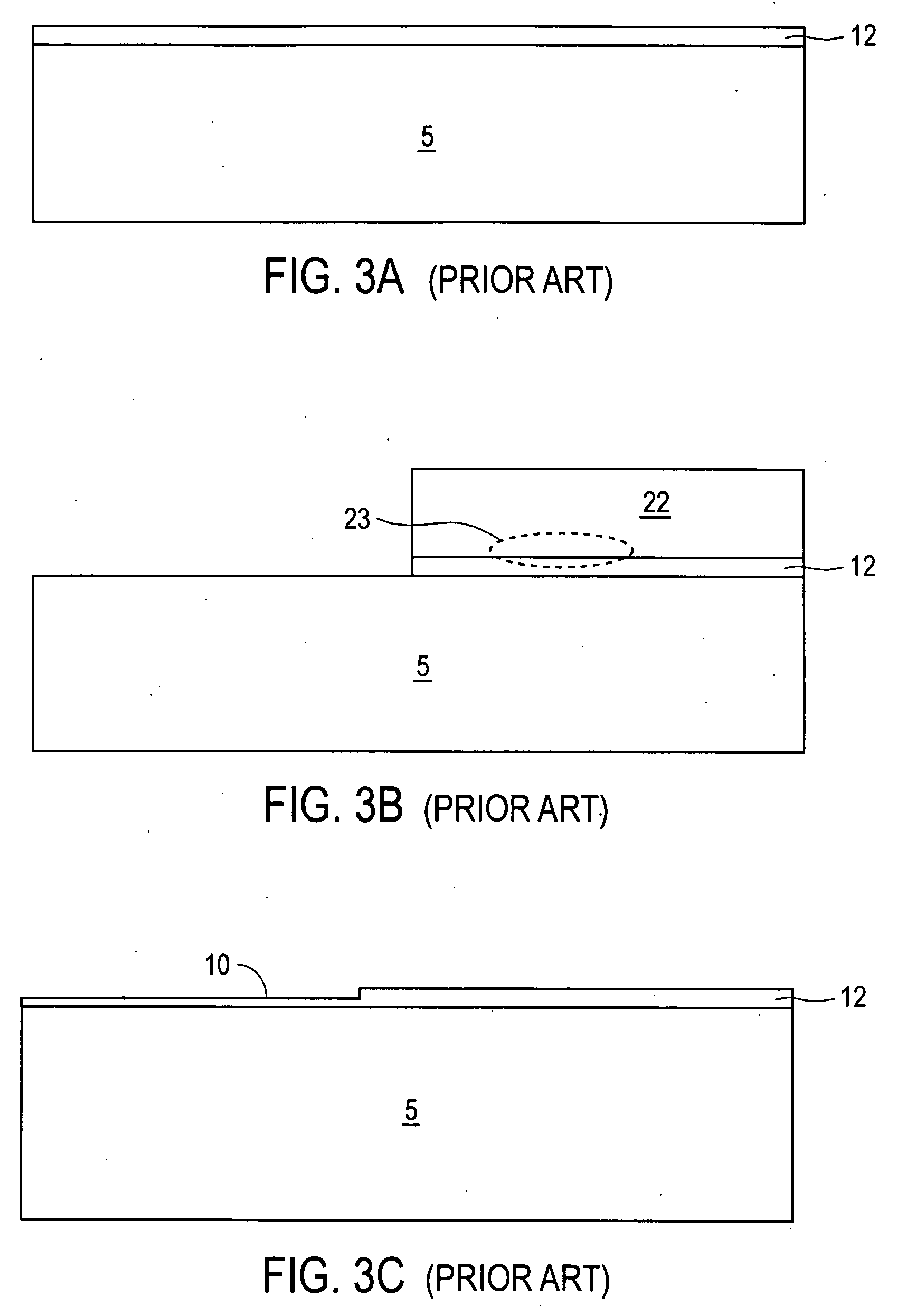

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F<2 >is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

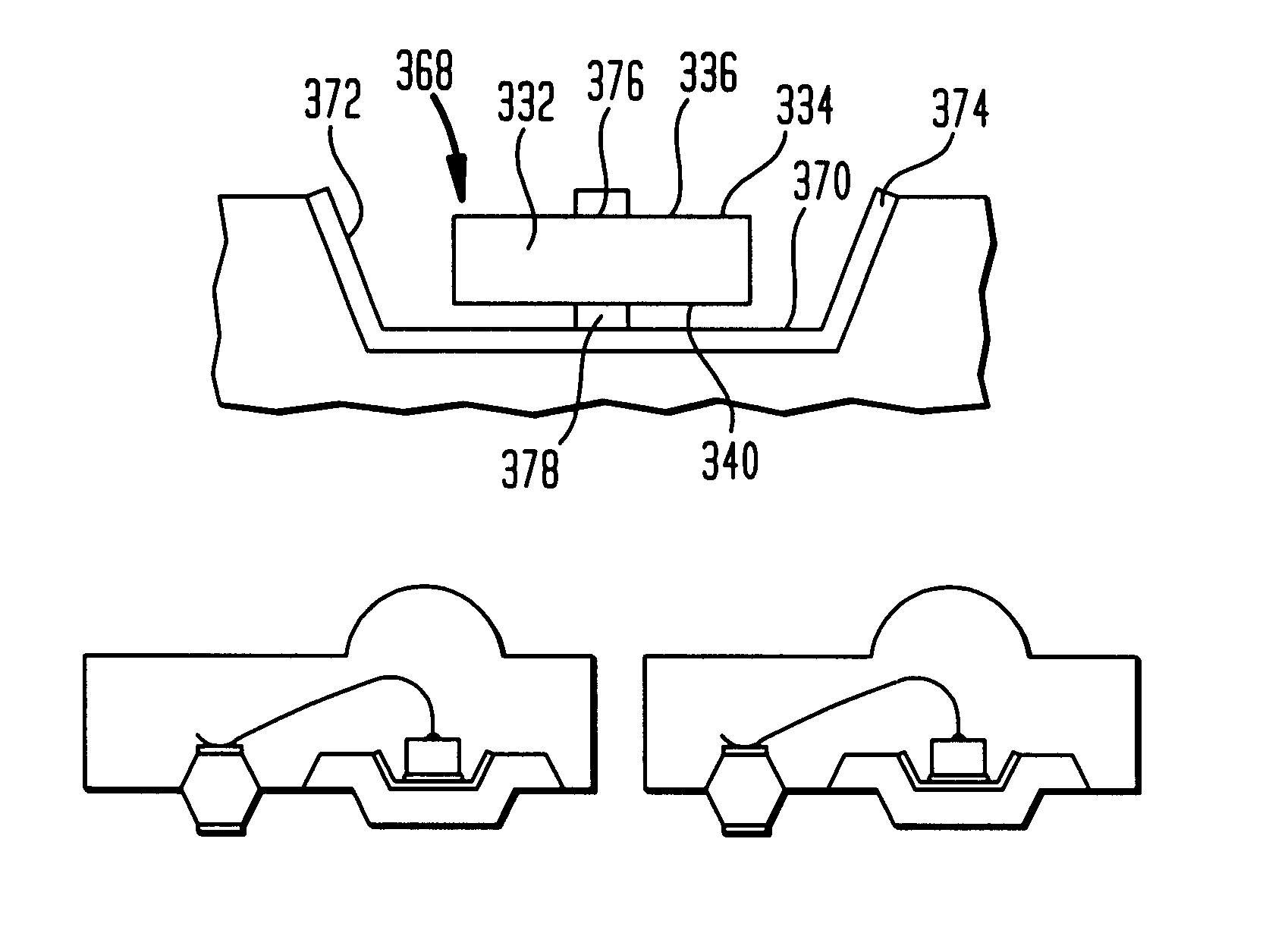

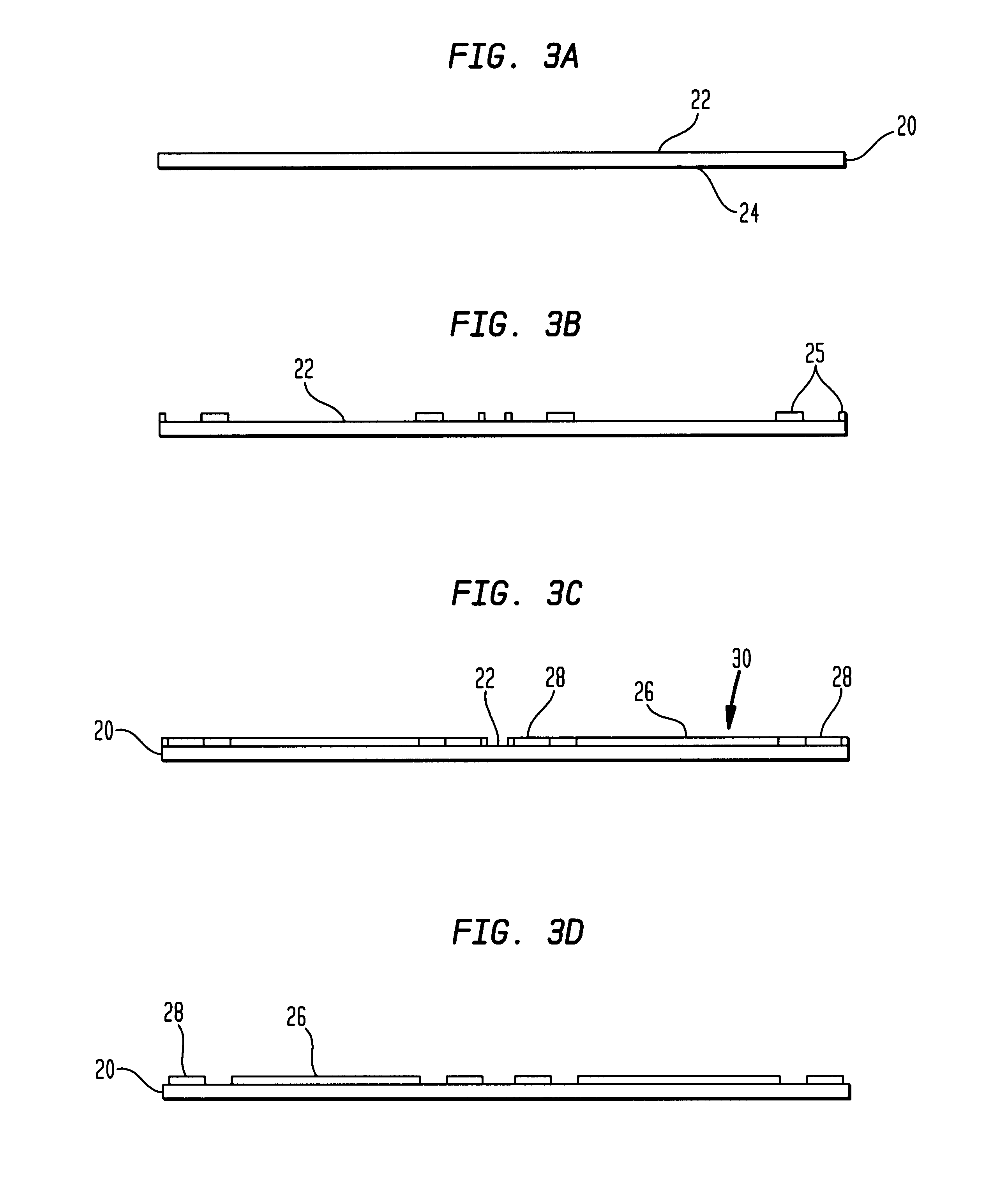

Semiconductor packages having light-sensitive chips

InactiveUS6583444B2Readily flexEasy to moveSemiconductor/solid-state device detailsSolid-state devicesProgrammable read-only memorySemiconductor package

A method of making a microelectronic package includes providing a sacrificial layer having a first surface and providing an optoelectronic element having a front face including one or more contacts and a rear surface and securing the rear surface of the optoelectronic element over the first surface of the sacrificial layer. The one or more contacts are then electrically interconnected with one or more conductive pads on the sacrificial layer and a curable and at least partially transparent encapsulant is provided over the first surface of the sacrificial layer so as to encapsulate the optoelectronic element and the conductive pads. The encapsulant is then cured the sacrificial layer is at least partially removed so as to leave said one or more conductive pads on a bottom surface of the encapsulant, the bottom surface of the encapsulant defining the bottom of the package. The optoelectronic element may include a light sensitive chip such as an ultraviolet-erasable programmable read-only memory (UV EPROM) or a light emitting chip, such as a light emitting diode (LED).

Owner:TESSERA INC

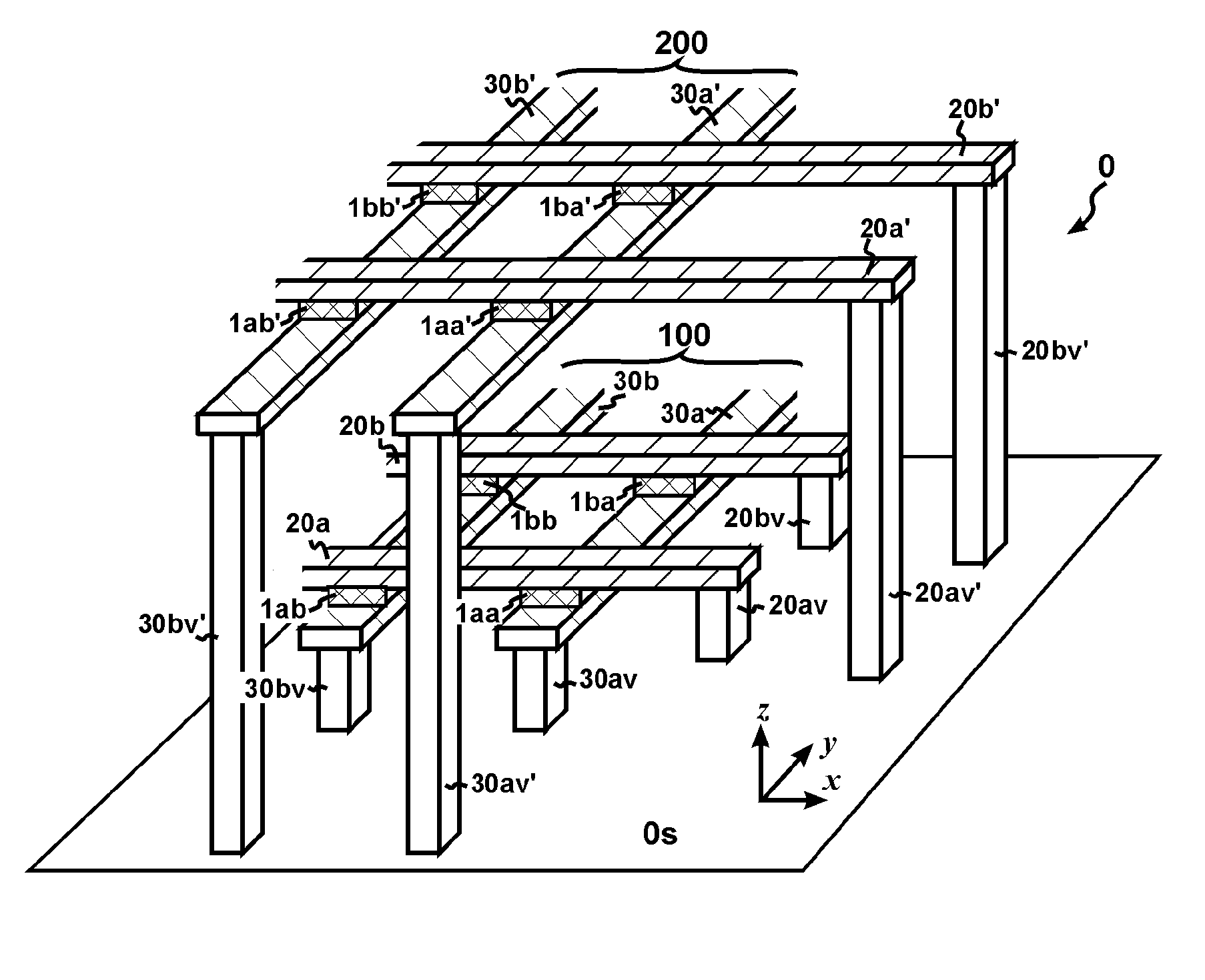

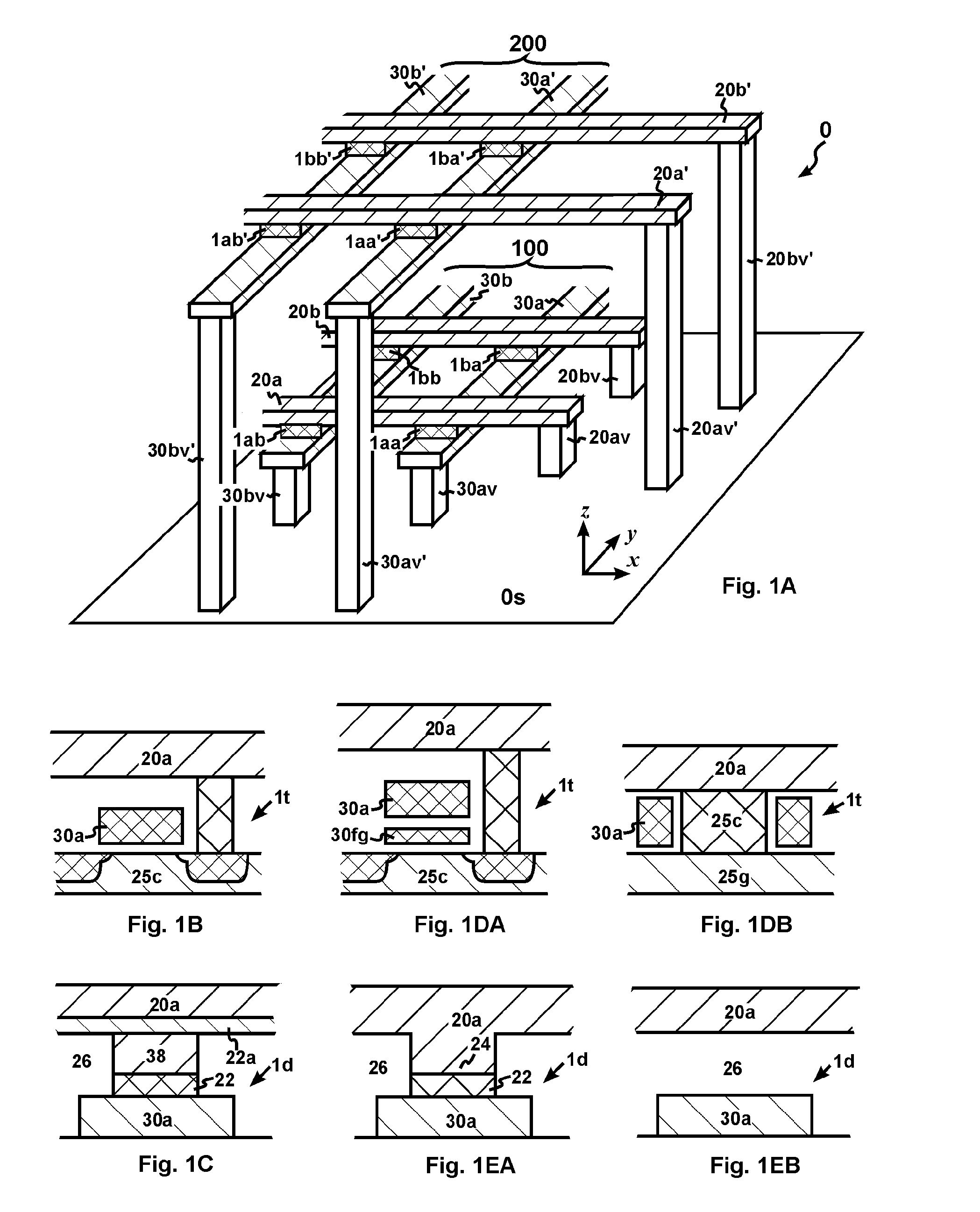

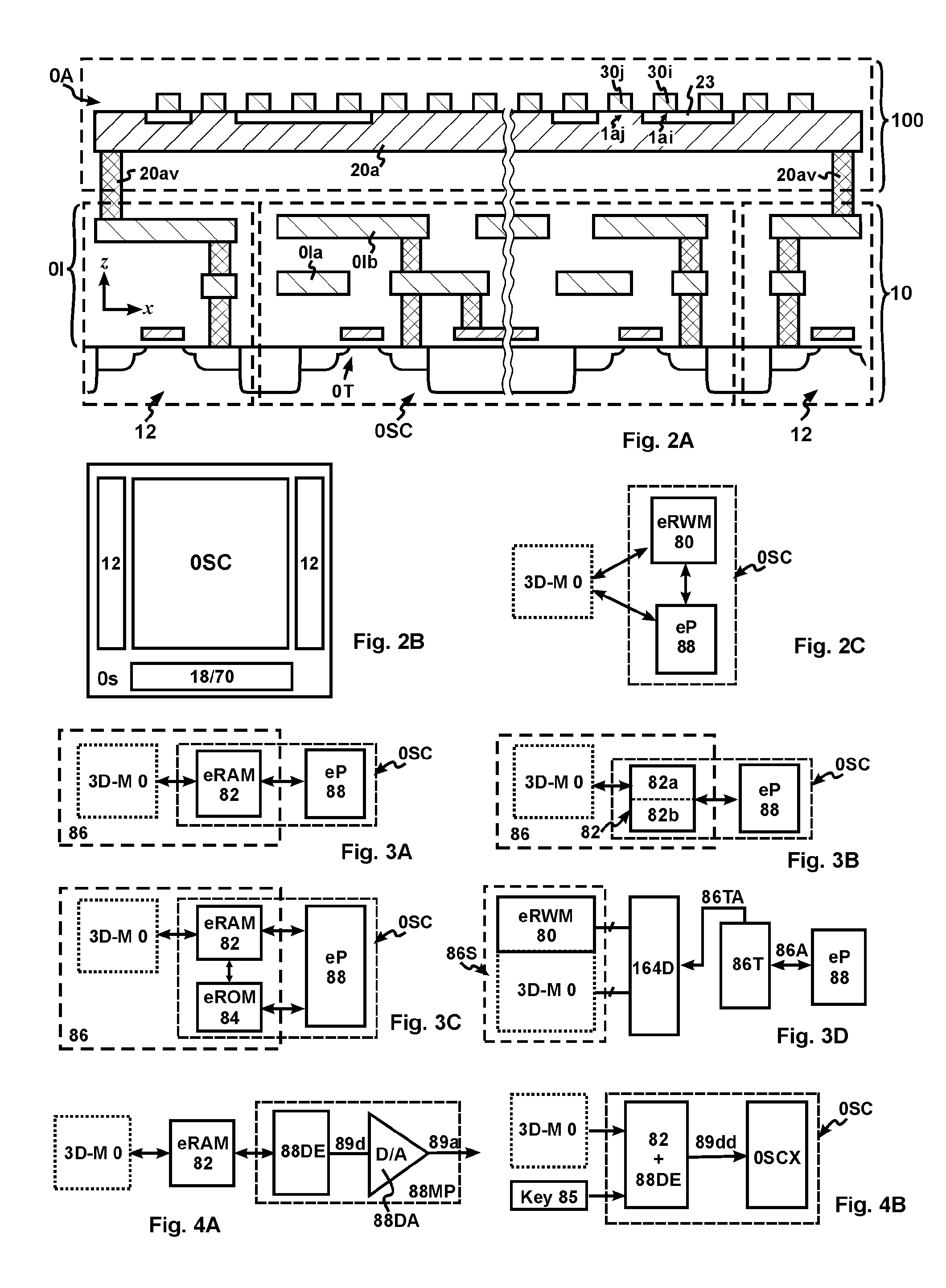

Three-Dimensional Mask-Programmable Read-Only Memory

The present invention discloses several improved three-dimensional mask-programmable read-only memories (3D-MPROM), including interleaved self-aligned pillar-shaped 3D-MPROM (ISP 3D-MPROM), separate self-aligned pillar-shaped 3D-MPROM (SSP 3D-MPROM), interleaved self-aligned natural-junction 3D-MPROM (ISN 3D-MPROM) and separate self-aligned natural-junction 3D-MPROM (SSN 3D-MPROM). They have larger memory capacity and lower manufacturing cost.

Owner:ZHANG GUOBIAO

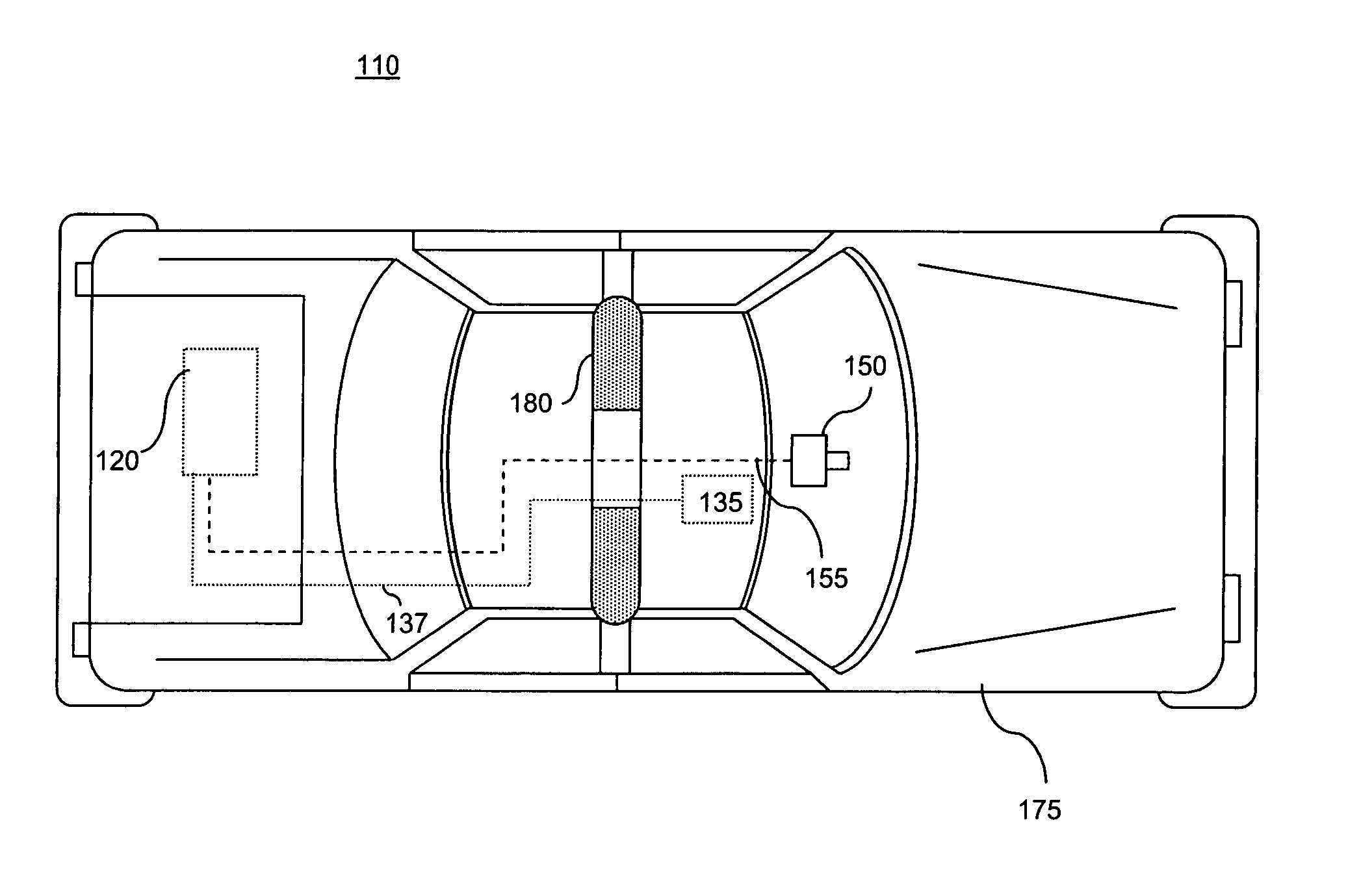

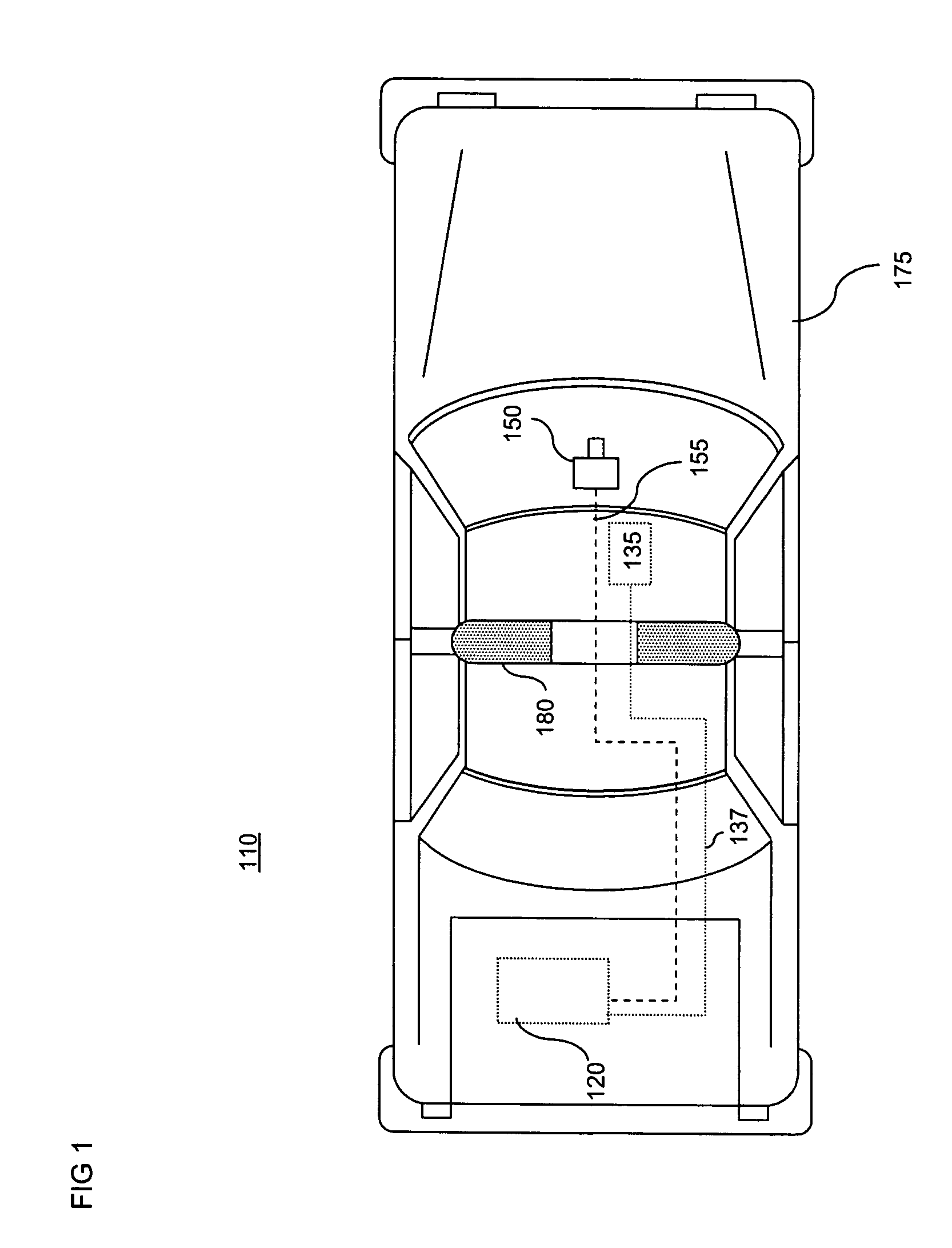

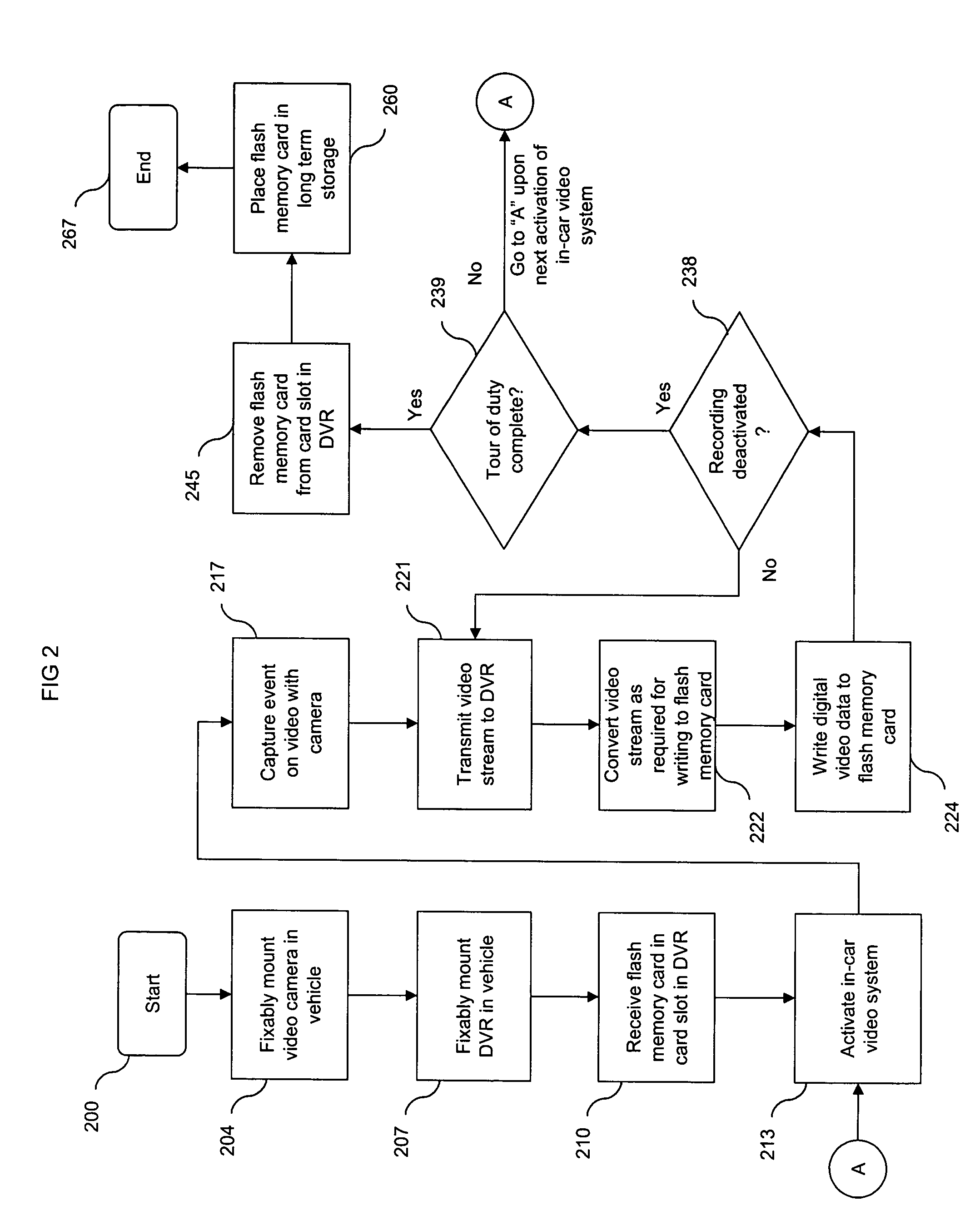

In-car video system using flash memory as a recording medium

InactiveUS20050088521A1Enhanced system packagingInherently reliableAnti-theft devicesColor television detailsDigital videoProgrammable read-only memory

An inventive system and method is provided by an in-car video system that uses a type of electrically erasable programmable read-only memory known as flash memory to store video of an incident or event. In an illustrative embodiment of the invention, a digital video recorder and video camera are fixably mounted in a vehicle such as a police cruiser. An event of interest is captured by a camera and the resulting video stream is converted into a form that writable to a flash memory. The video recorder writes the video to flash memory to thereby store a record of the event on the flash memory as a storage medium.

Owner:L 3 COMM MOBILE VISION

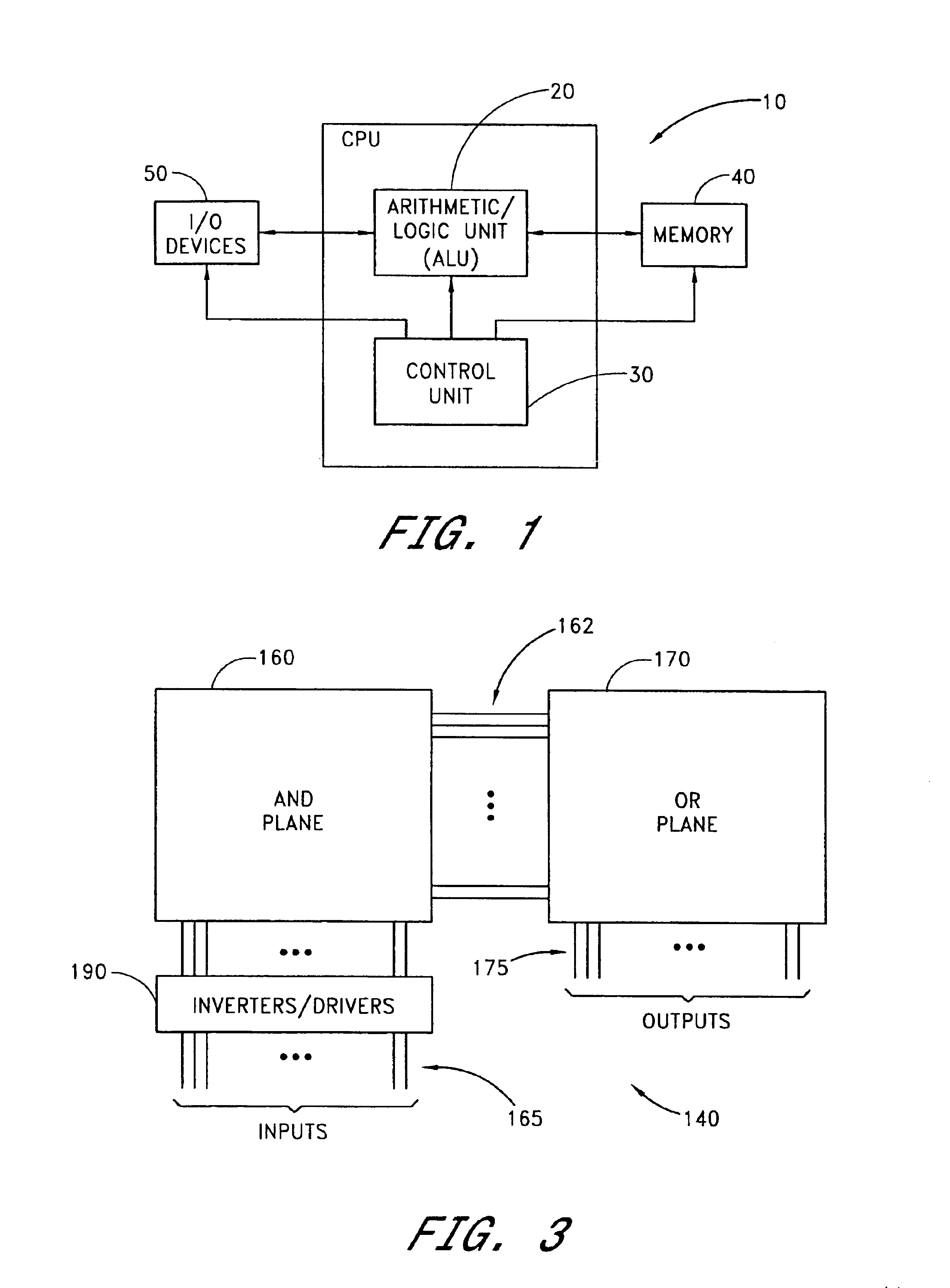

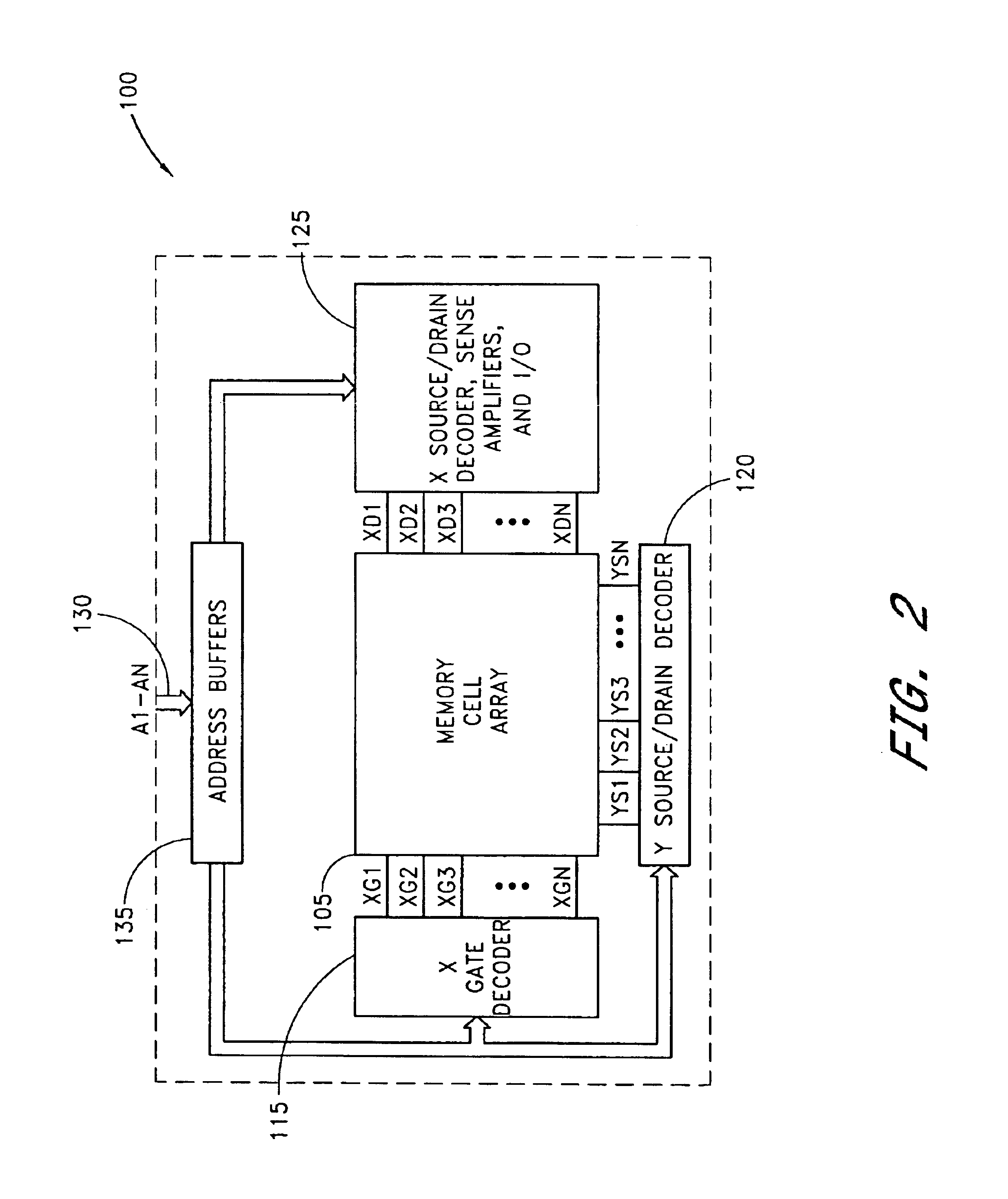

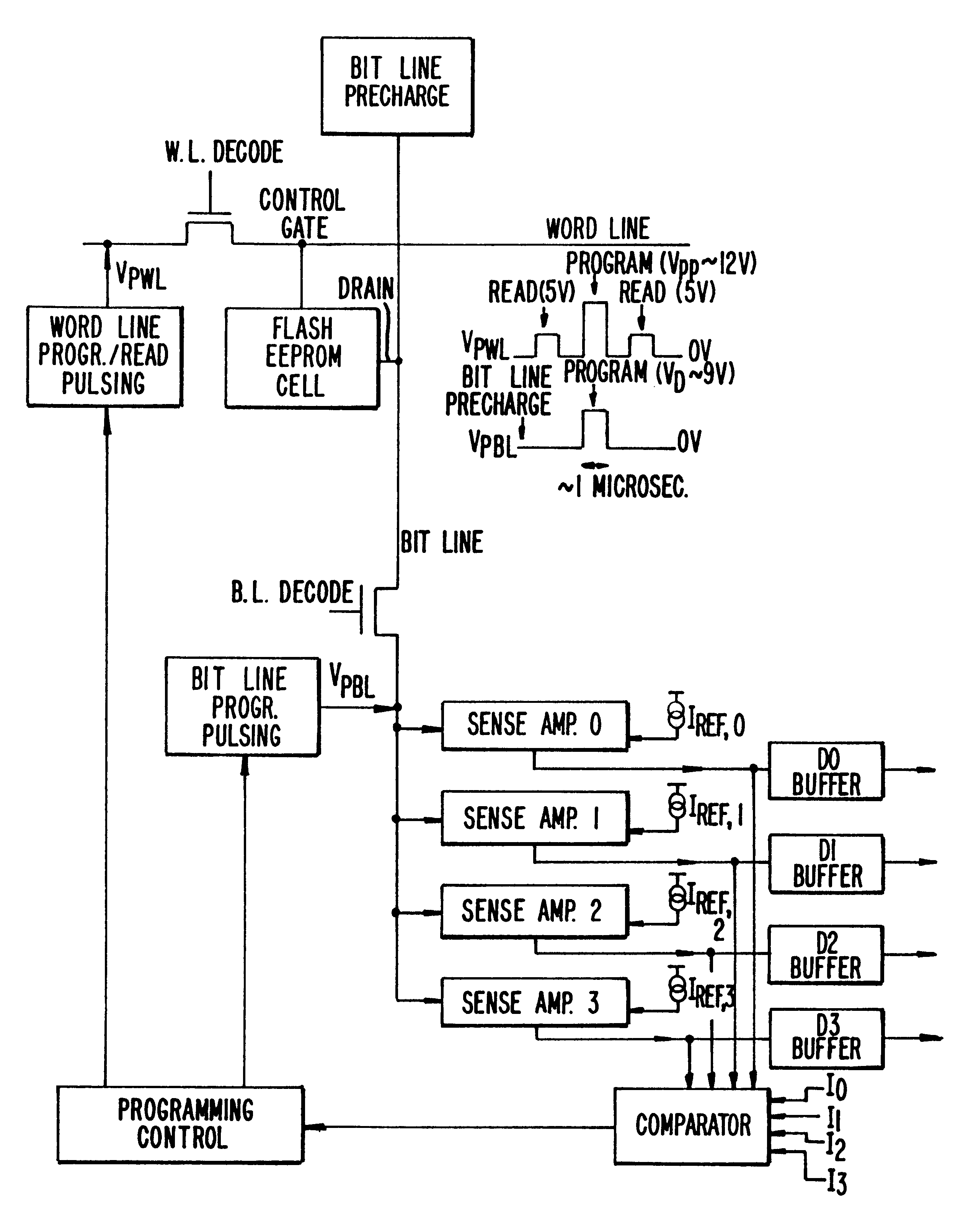

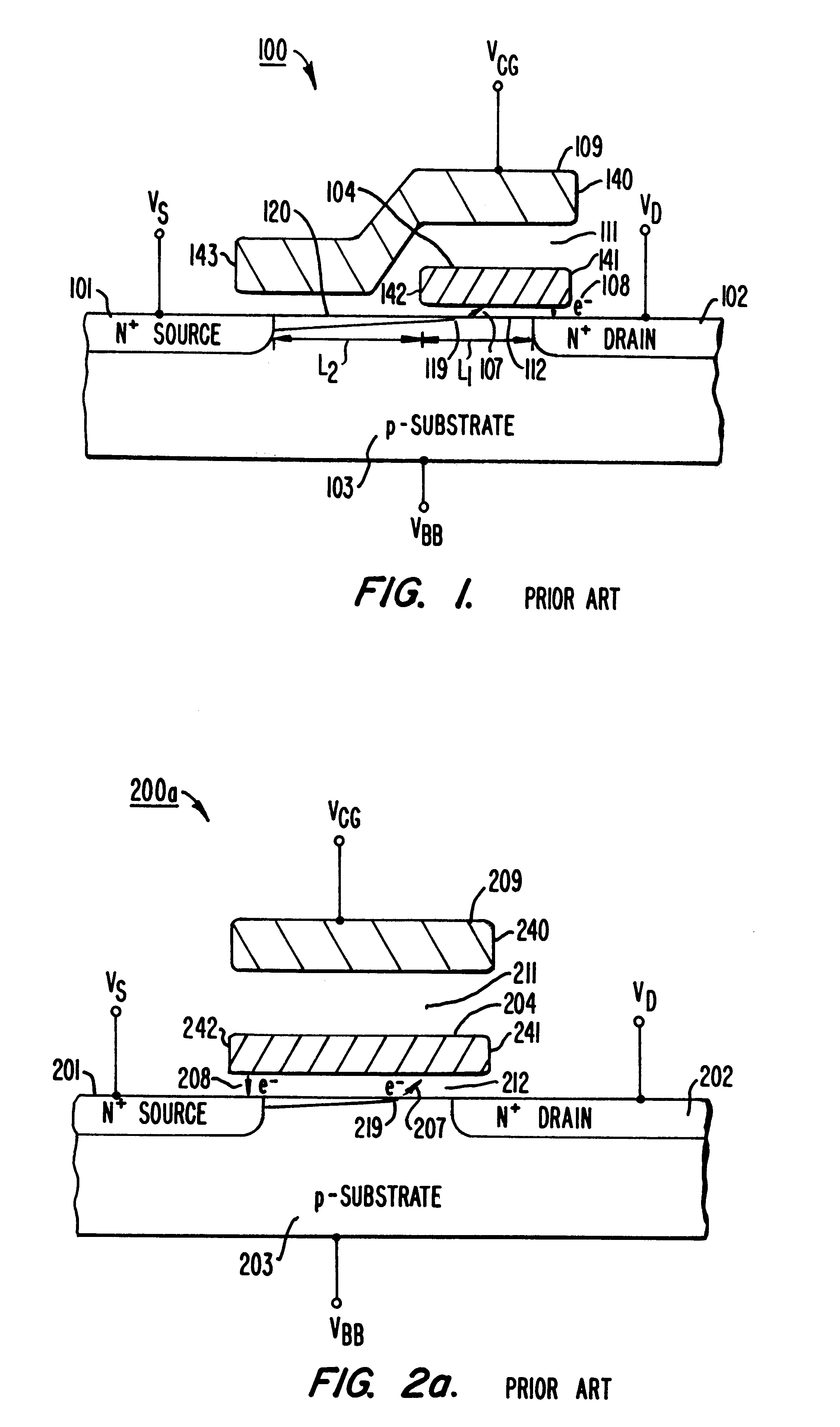

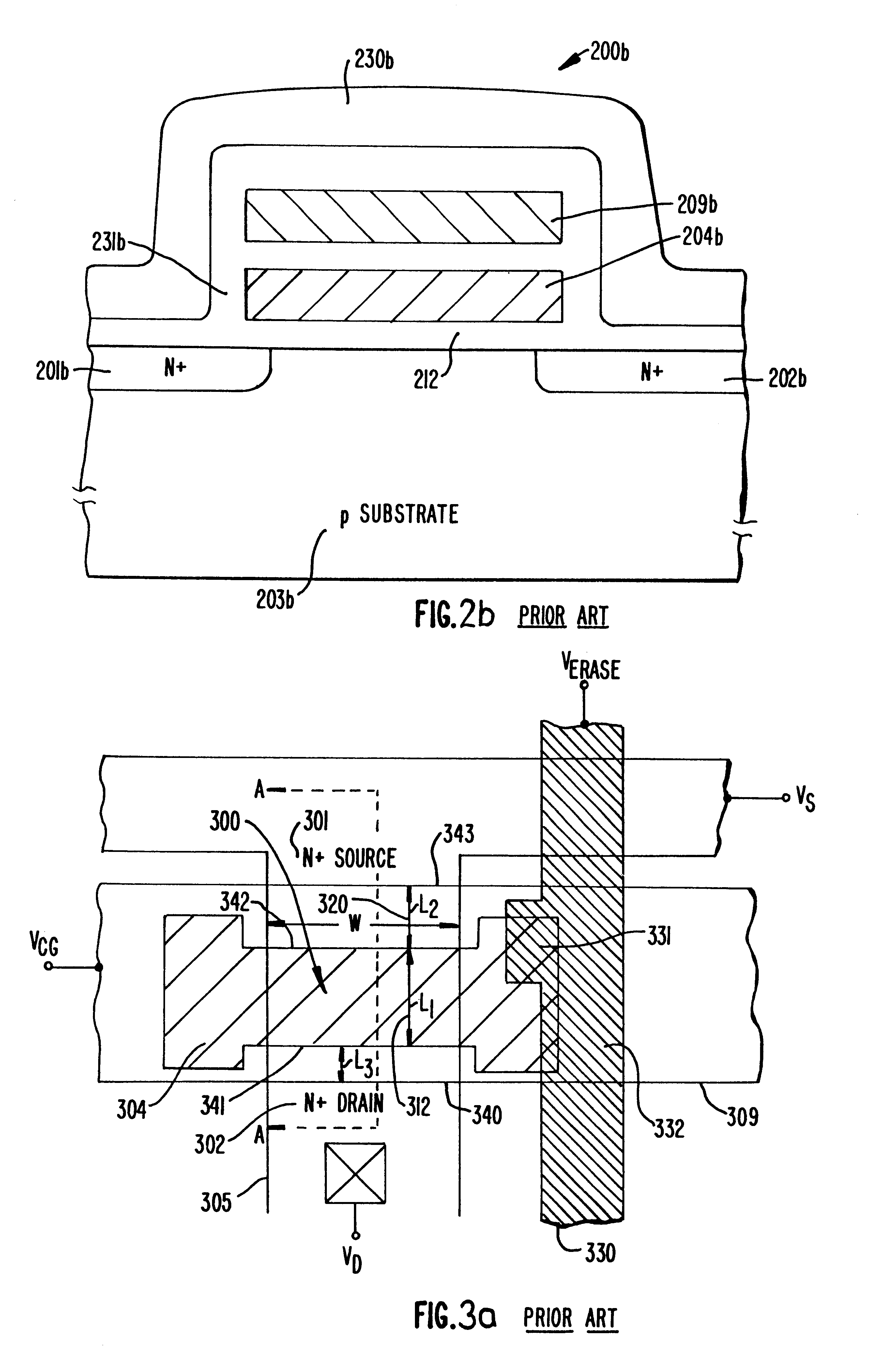

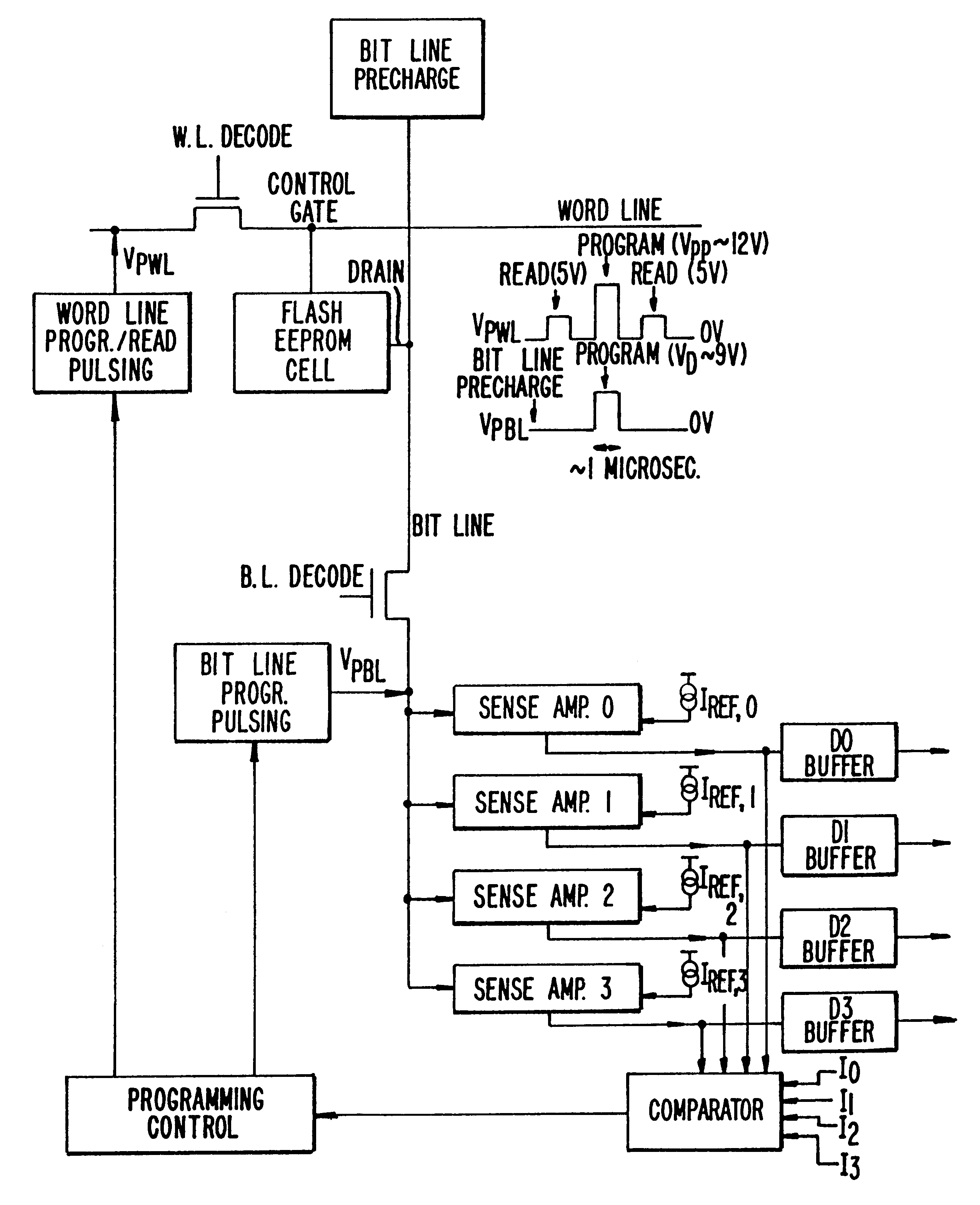

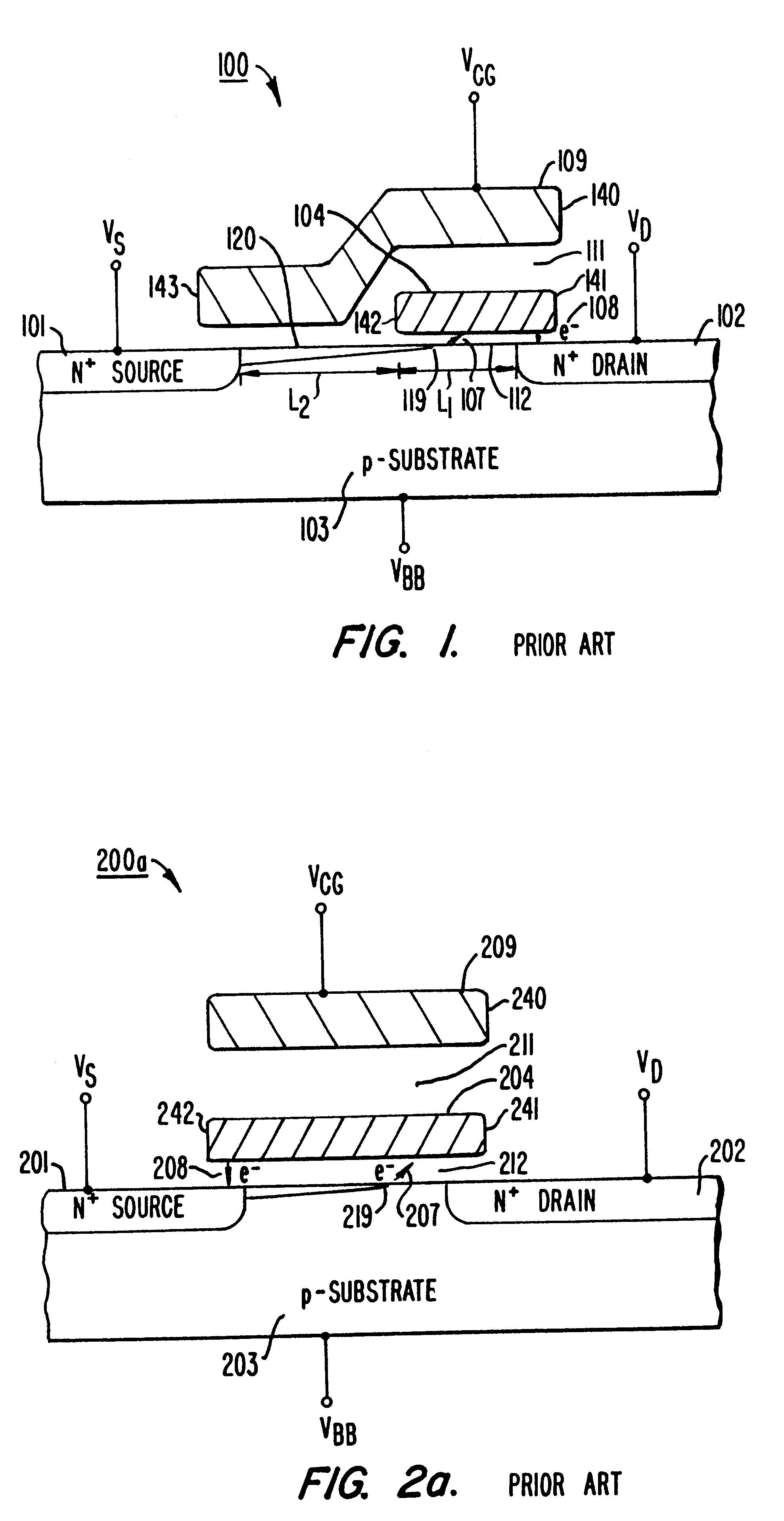

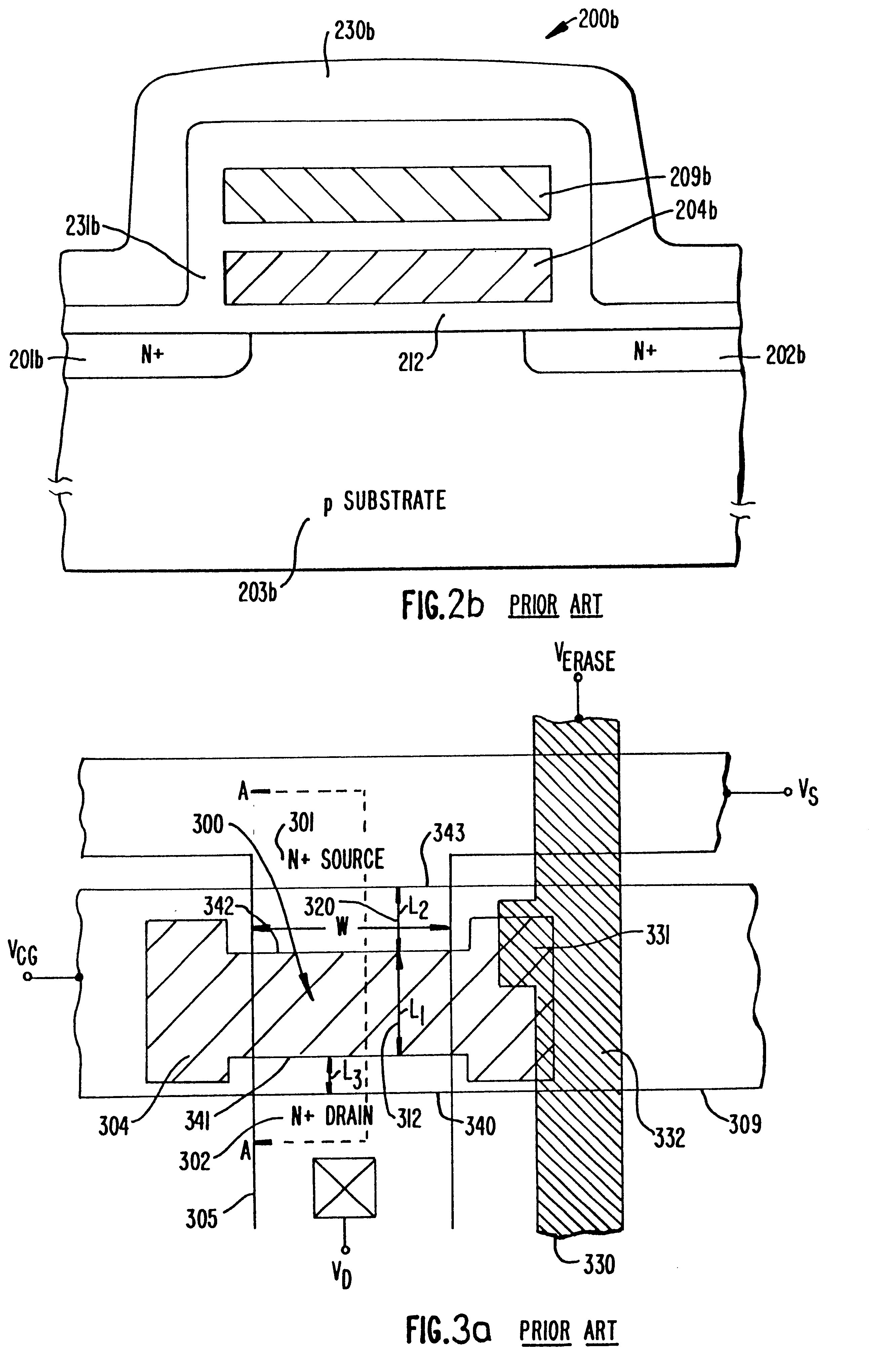

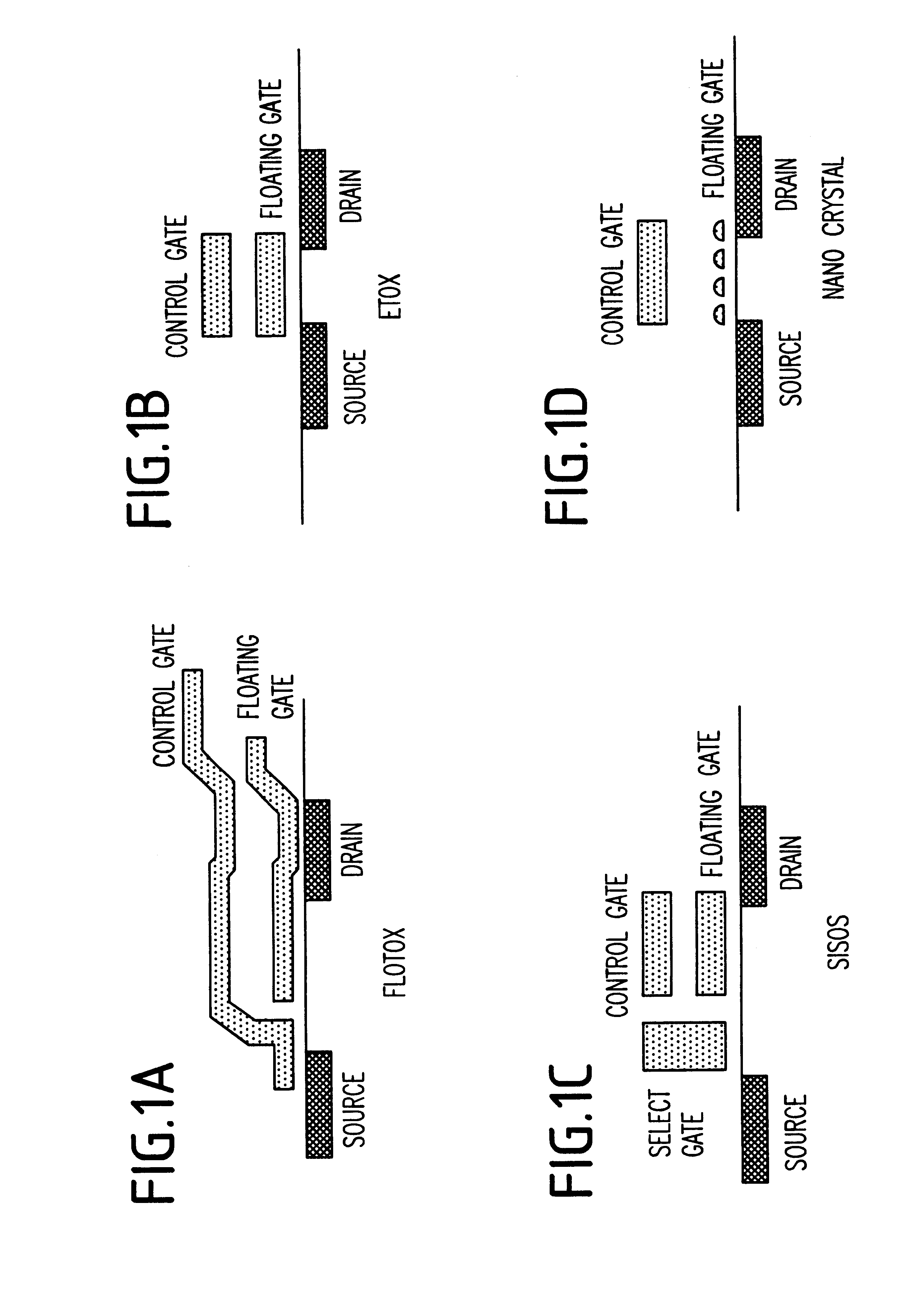

Highly compact EPROM and flash EEPROM devices

Structures, methods of manufacturing and methods of use of electrically programmable read only memories (EPROM) and flash electrically erasable and programmable read only memories (EEPROM) include split channel and other cell configurations. An arrangement of elements and cooperative processes of manufacture provide self-alignment of the elements. An intelligent programming technique allows each memory cell to store more than the usual one bit of information. An intelligent erase algorithm prolongs the useful life of the memory cells. Use of these various features provides a memory having a very high storage density and a long life, making it particularly useful as a solid state memory in place of magnetic disk storage devices in computer systems.

Owner:SANDISK TECH LLC

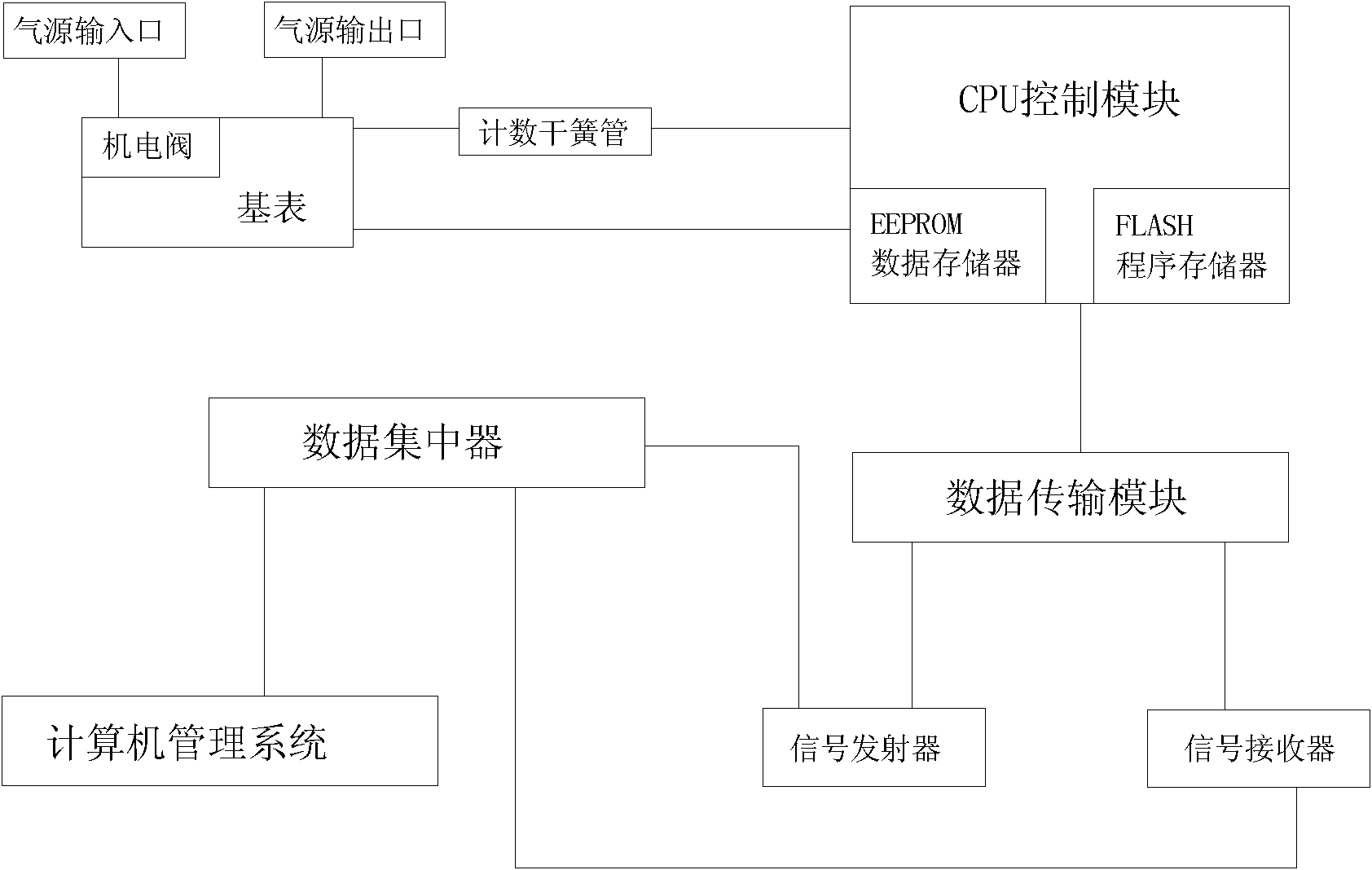

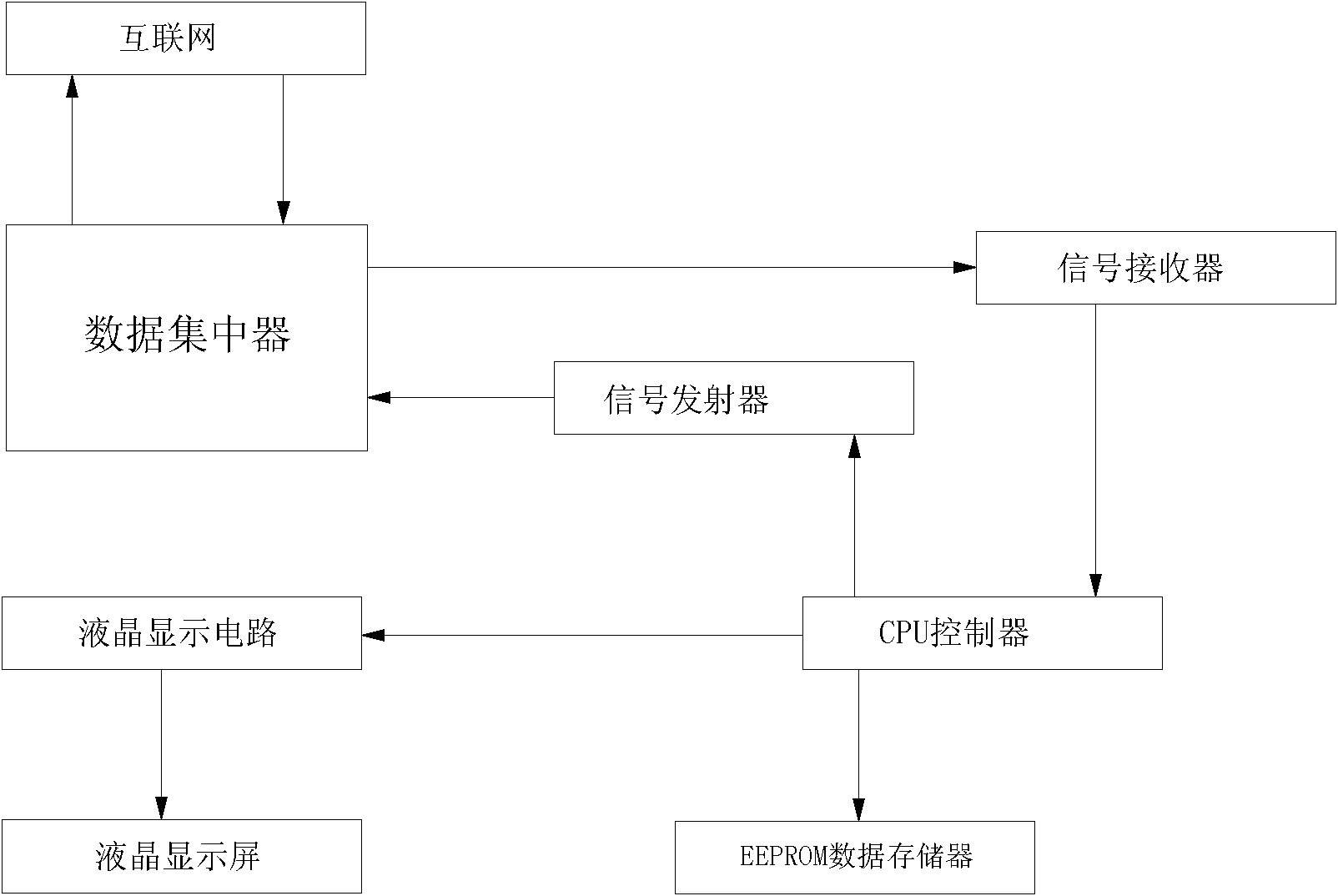

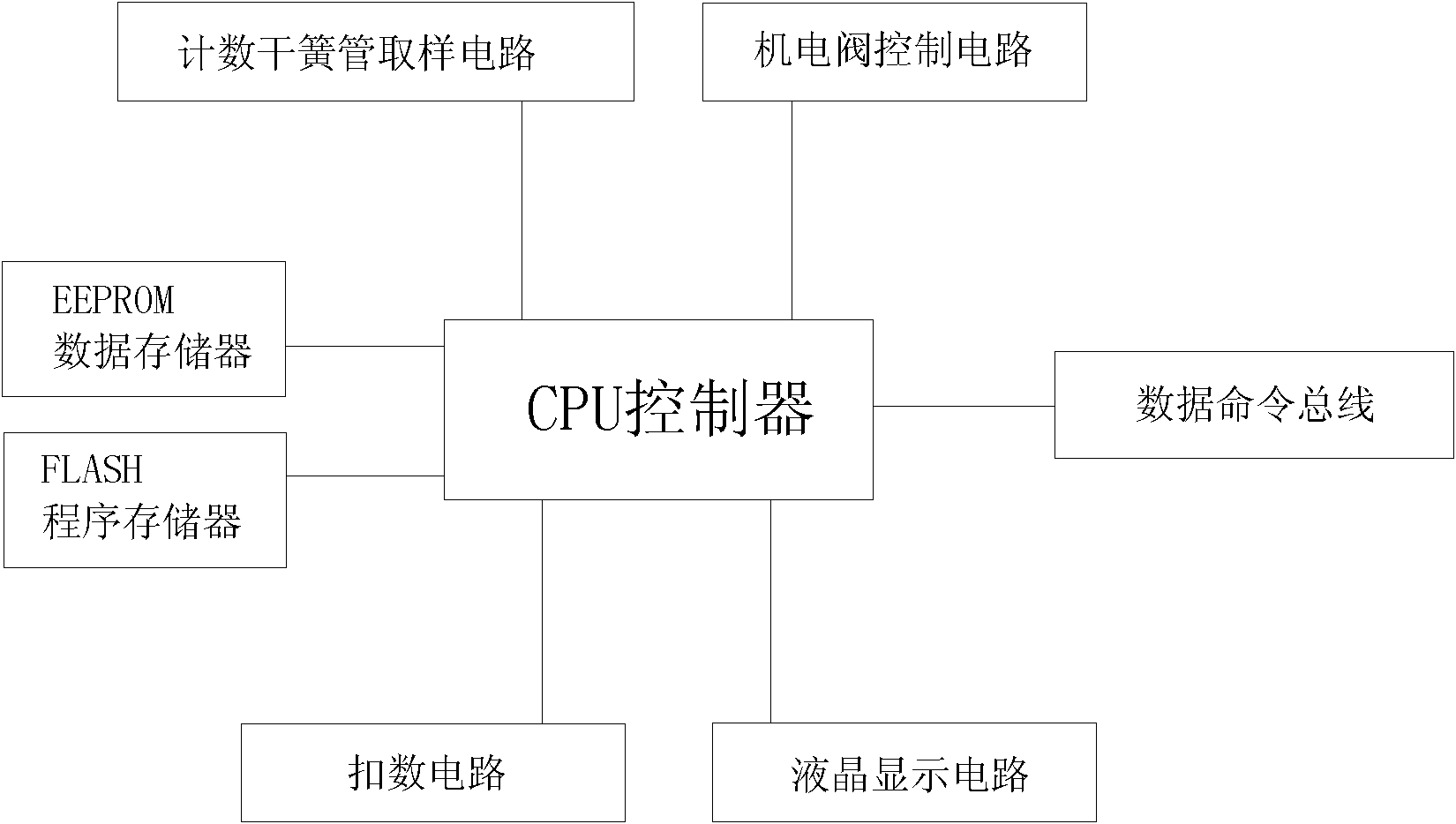

Intelligent gas meter of Internet of things and control system thereof

ActiveCN102063764AAvoid hoardingRealize remote control managementTariff metering apparatusVolume meteringProgrammable read-only memoryControl signal

The invention discloses an intelligent gas meter of the Internet of things and a control system thereof, belonging to an intelligent gas meter. The intelligent gas meter comprises a base meter, a CPU (Central Processing Unit) control module and a data transmission module. The base meter is provided with a source gas outlet and a source gas inlet. An electromechanical valve is installed close to the source gas inlet. The CPU control module is connected with the base meter and transmits a control signal to the base meter. The gas consumption standard of the base meter can be adjusted by the CPU control module. The CPU control module comprises an EEPROM (Electrically Erasable Programmable Read-Only Memory) data memory. The data transmission module is indirectly connected with the Internet of things and is also connected with a remote computer management system via the Internet of things. The data transmission module receives the control signal from the remote computer management system and feeds back the gas consumption information transmitted by the CPU control module to the computer management system. The intelligent gas meter of the Internet of things and the control system thereof are suitable for the gas use networks in areas and has the advantages of wide application range and easiness of generalization.

Owner:CHENGDU QINCHUAN IOT TECH CO LTD

Highly compact EPROM and flash EEPROM devices

Structures, methods of manufacturing and methods of use of electrically programmable read only memories (EPROM) and flash electrically erasable and programmable read only memories (EEPROM) include split channel and other cell configurations. An arrangement of elements and cooperative processes of manufacture provide self-alignment of the elements. An intelligent programming technique allows each memory cell to store more than the usual one bit of information. An intelligent erase algorithm prolongs the useful life of the memory cells. Use of these various features provides a memory having a very high storage density and a long life, making it particularly useful as a solid state memory in place of magnetic disk storage devices in computer systems.

Owner:SANDISK TECH LLC

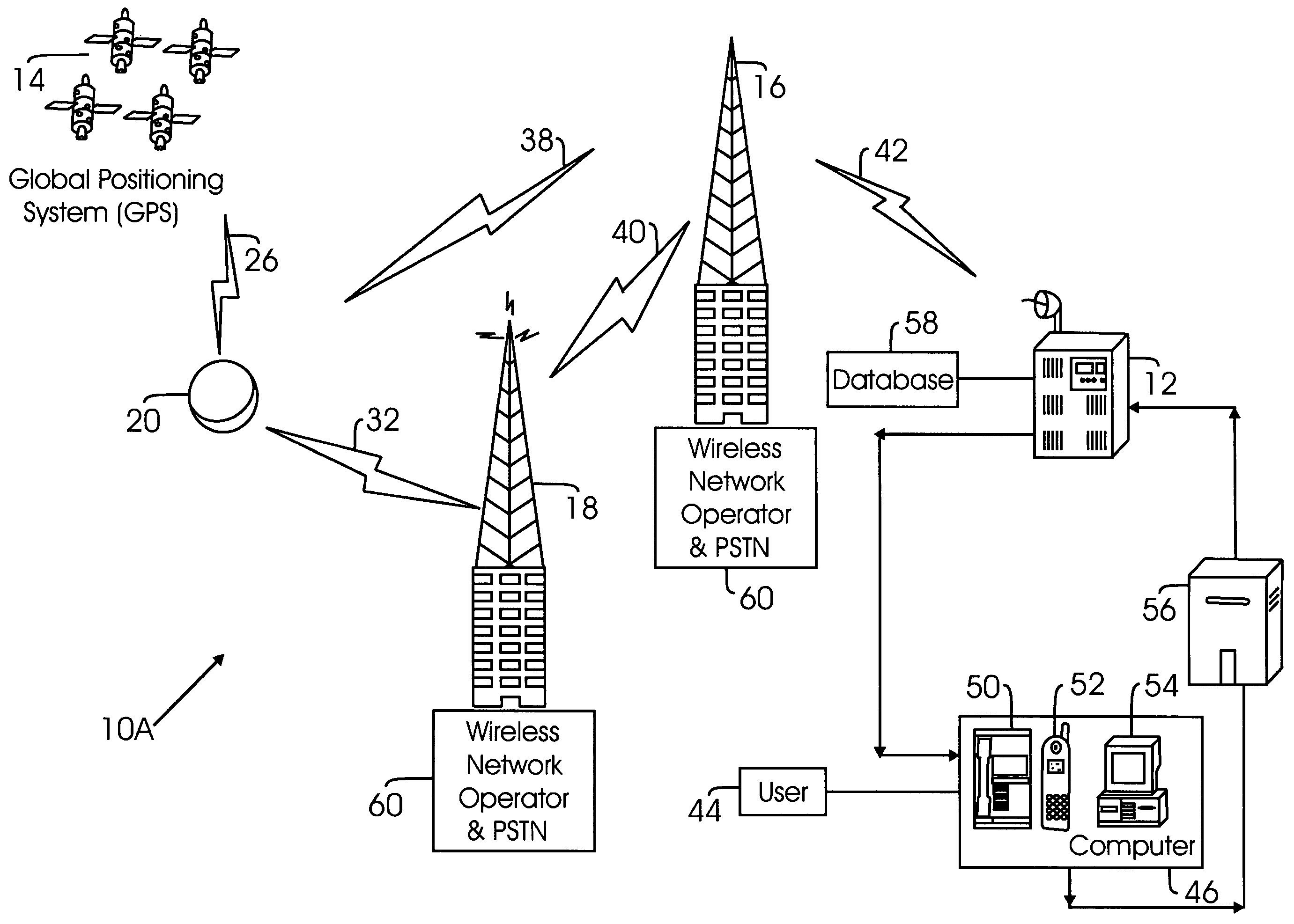

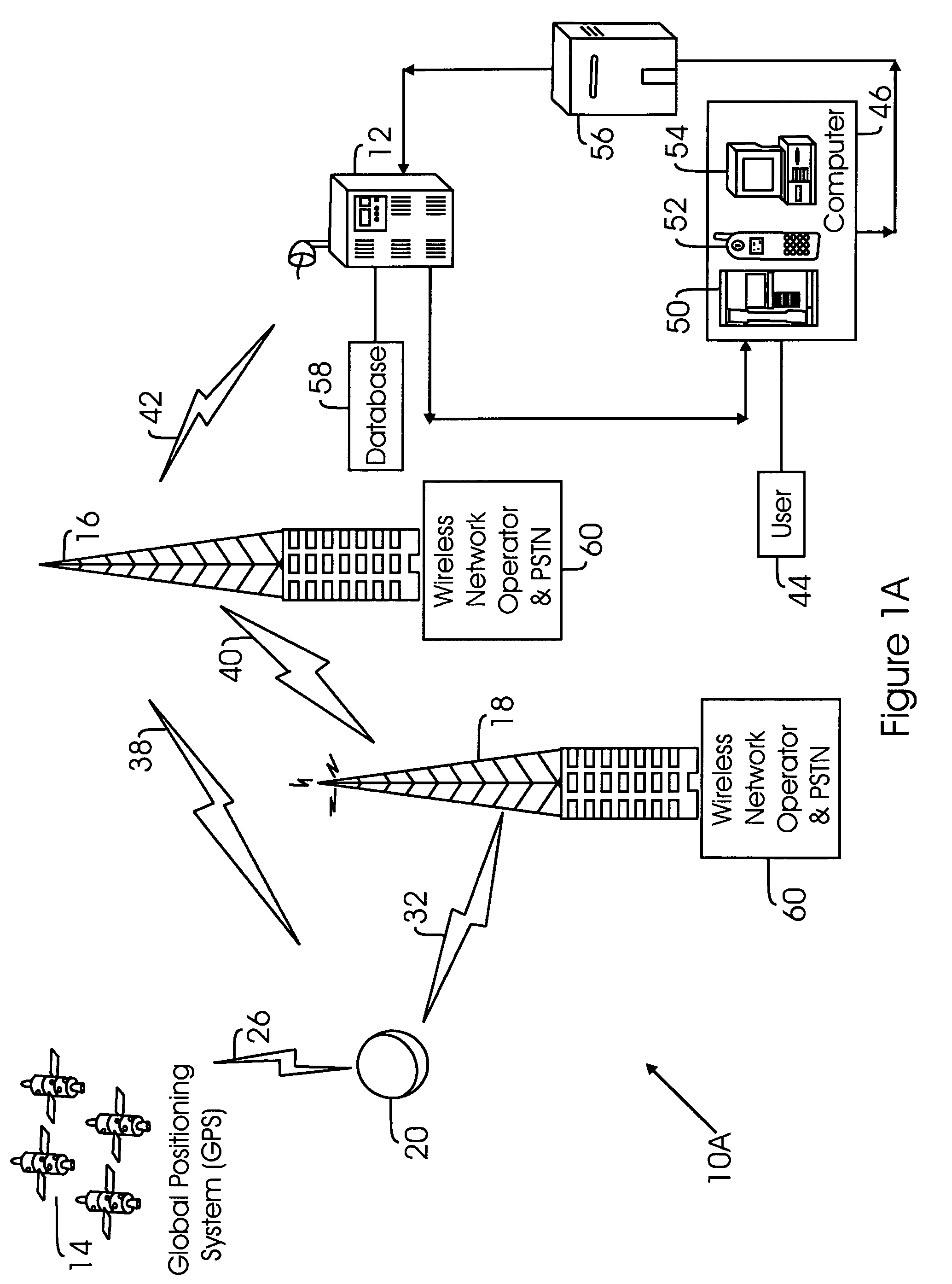

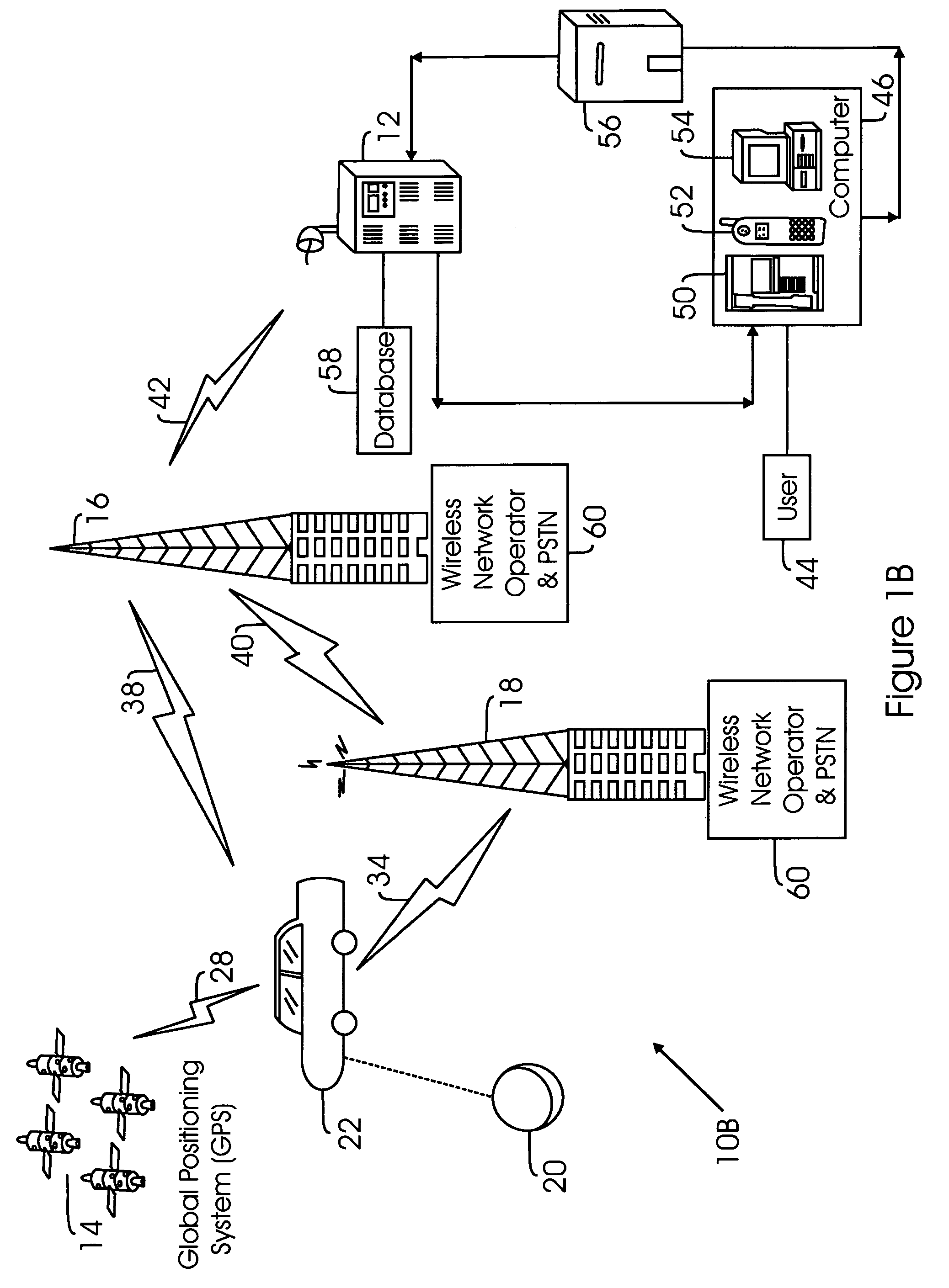

System for locating individuals and objects

ActiveUS7728724B1Position fixationElectric/electromagnetic visible signallingProgrammable read-only memoryGlobal Positioning System

A positioning and tracking system may comprise a monitoring station for receiving a location request and a user's identification code and transmitting a signal; a tracking device, which includes a signal receiver for receiving a signal from the monitoring station, including the user's identification code, a microprocessor / logic circuit for storing a first identification code, and generating a position signal; an erasable programmable read-only memory; a global positioning system logic circuit; a signal transmitter; and a plurality of transmitter / receiver stations for communicating between the tracking device and the monitoring station; wherein the tracking device compares the user's identification code to the stored identification code and upon determining that the user's identification code matches the stored identification code, the signal transmitter transmits the position signal to the monitoring station.

Owner:LBT IP II LLC

IC card with display screen

An IC card includes a card reader interface for receiving data from a card reader, a microprocessor for decoding, decrypting and categorizing the data or converting the data into displaying format, an electrically erasable programmable read only memory for storing the data, a display screen, a display driver for driving the display screen, and a solar battery for providing power, whereby it is unnecessary for a user to look for a card read in order to read the data stored in the IC card.

Owner:SMARTDISPLAYER TECH CO LTD

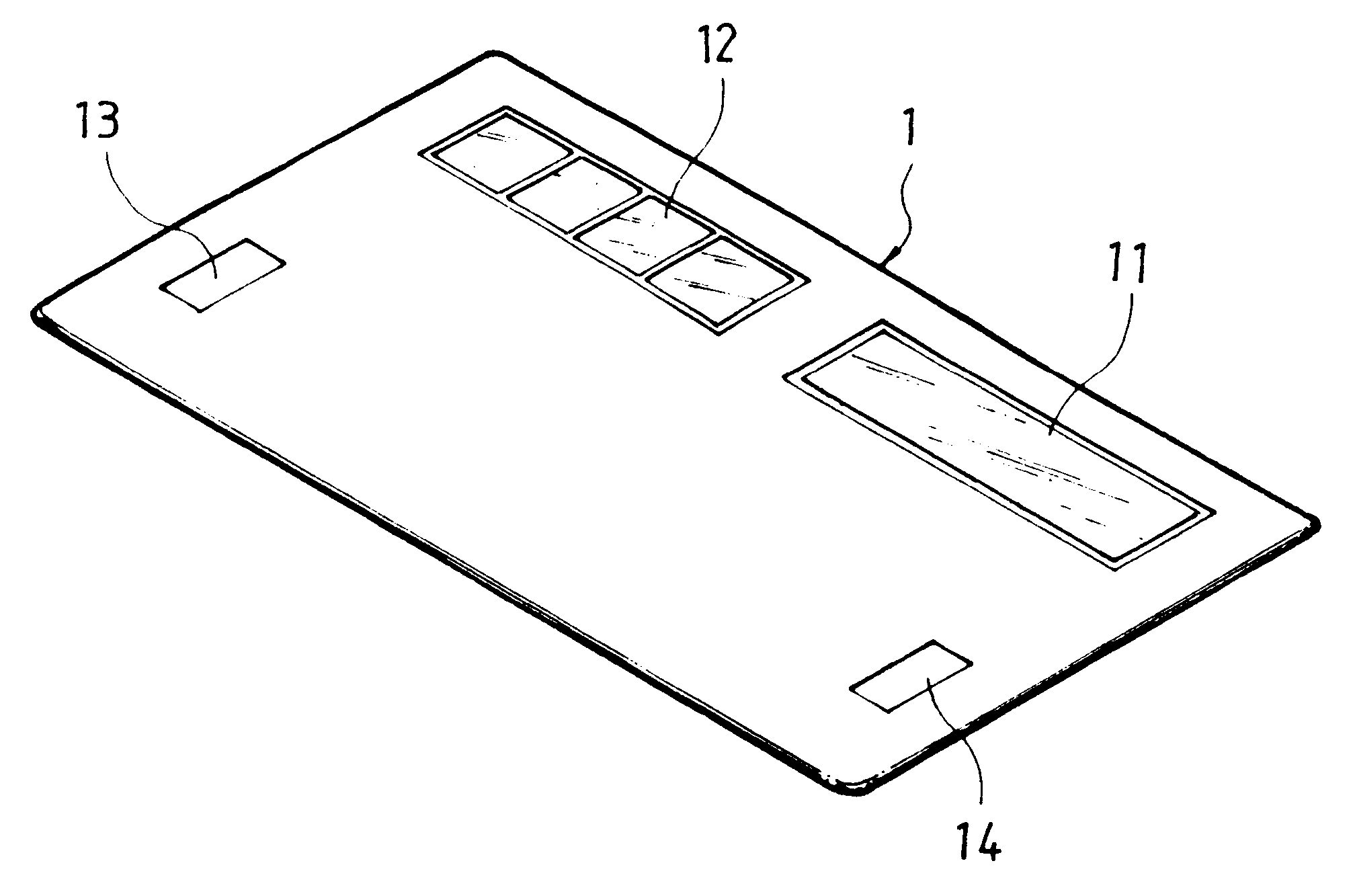

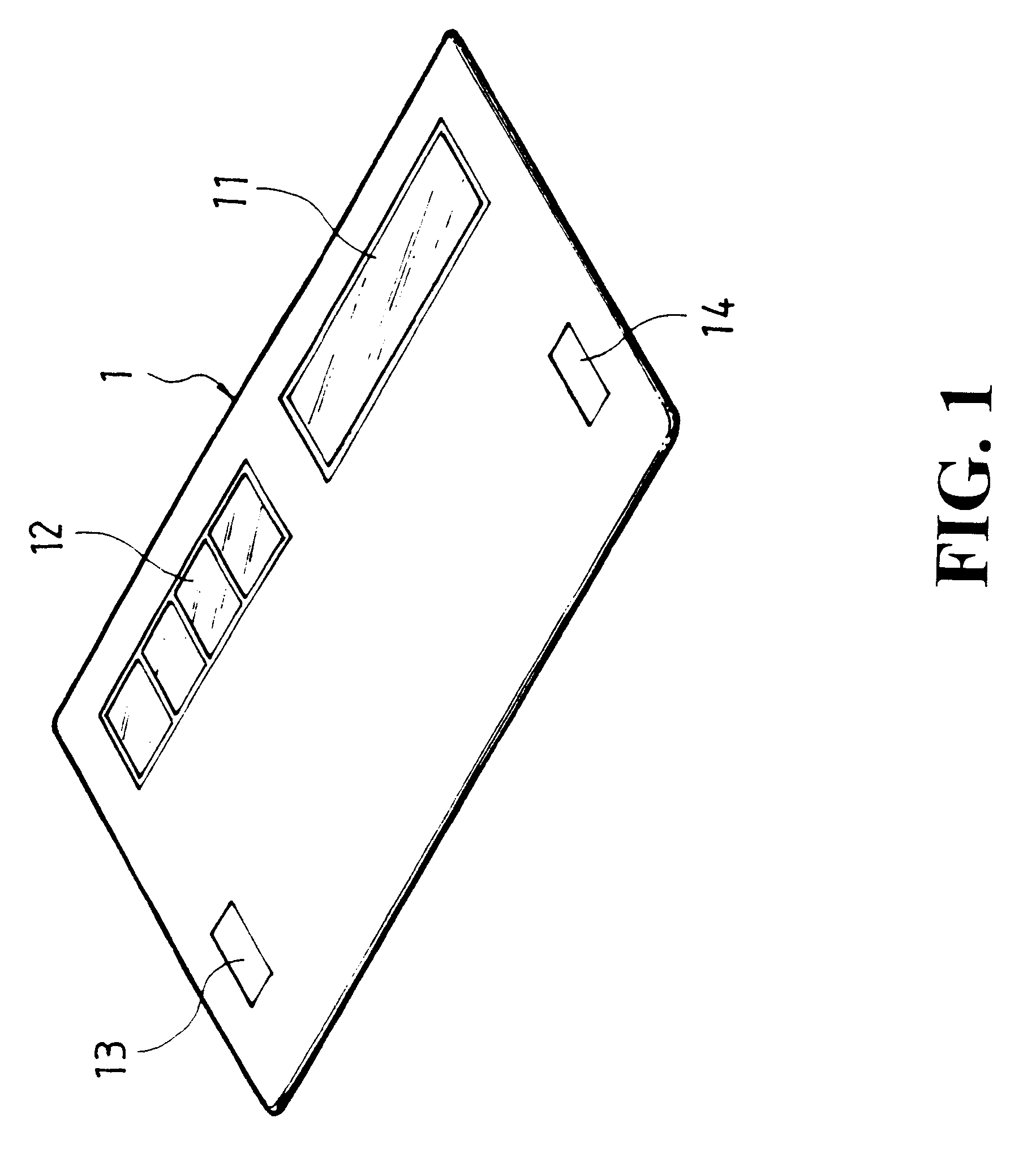

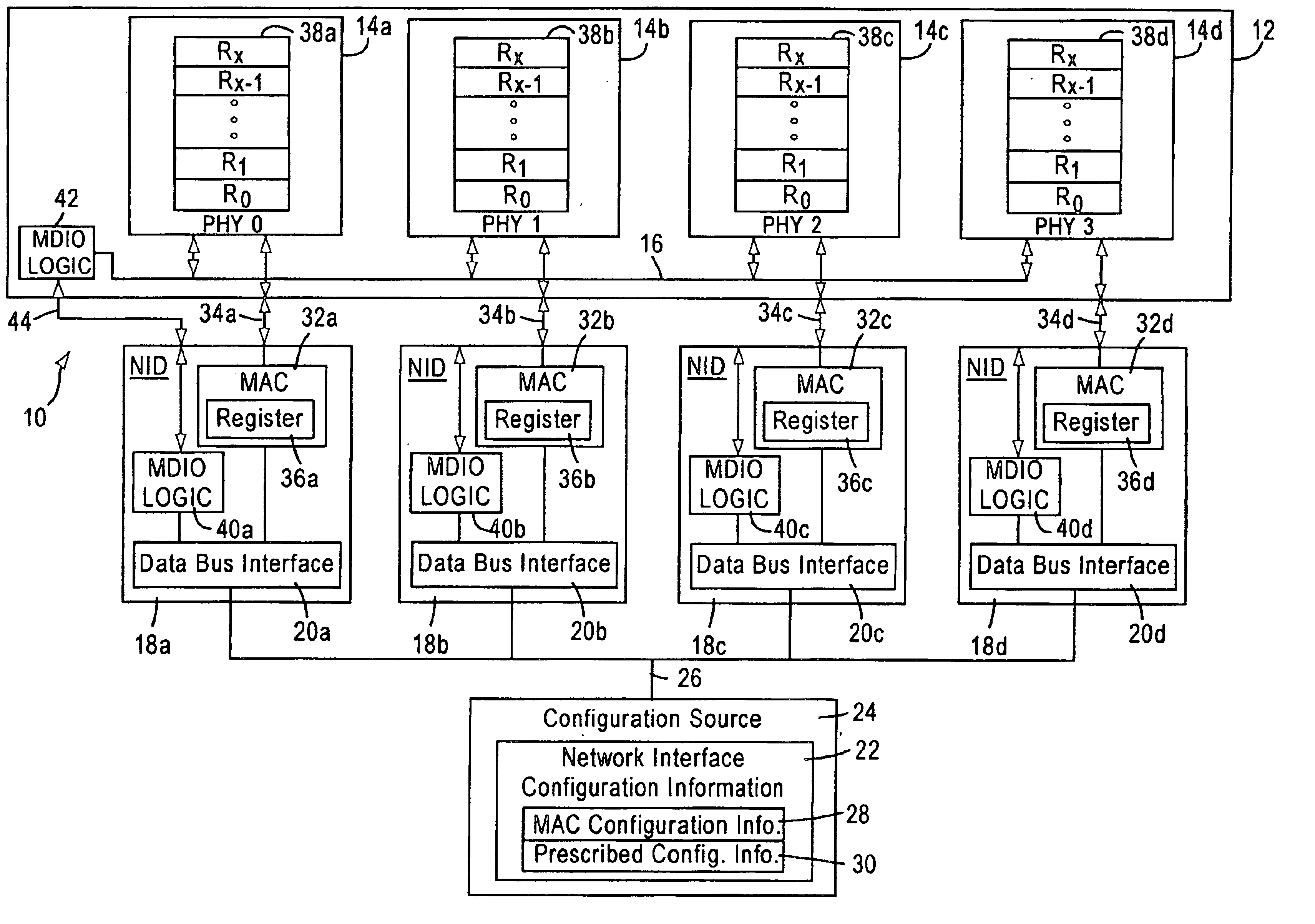

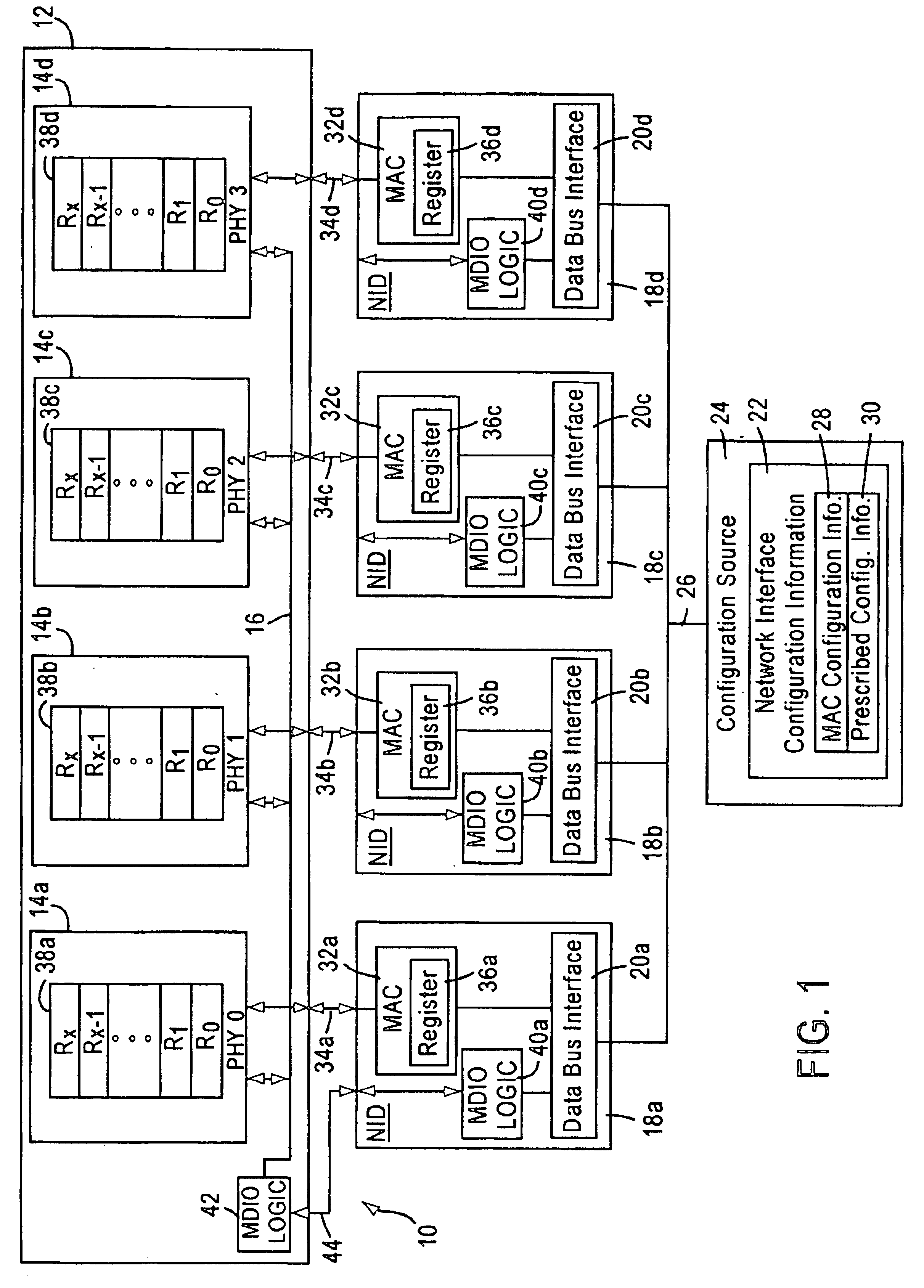

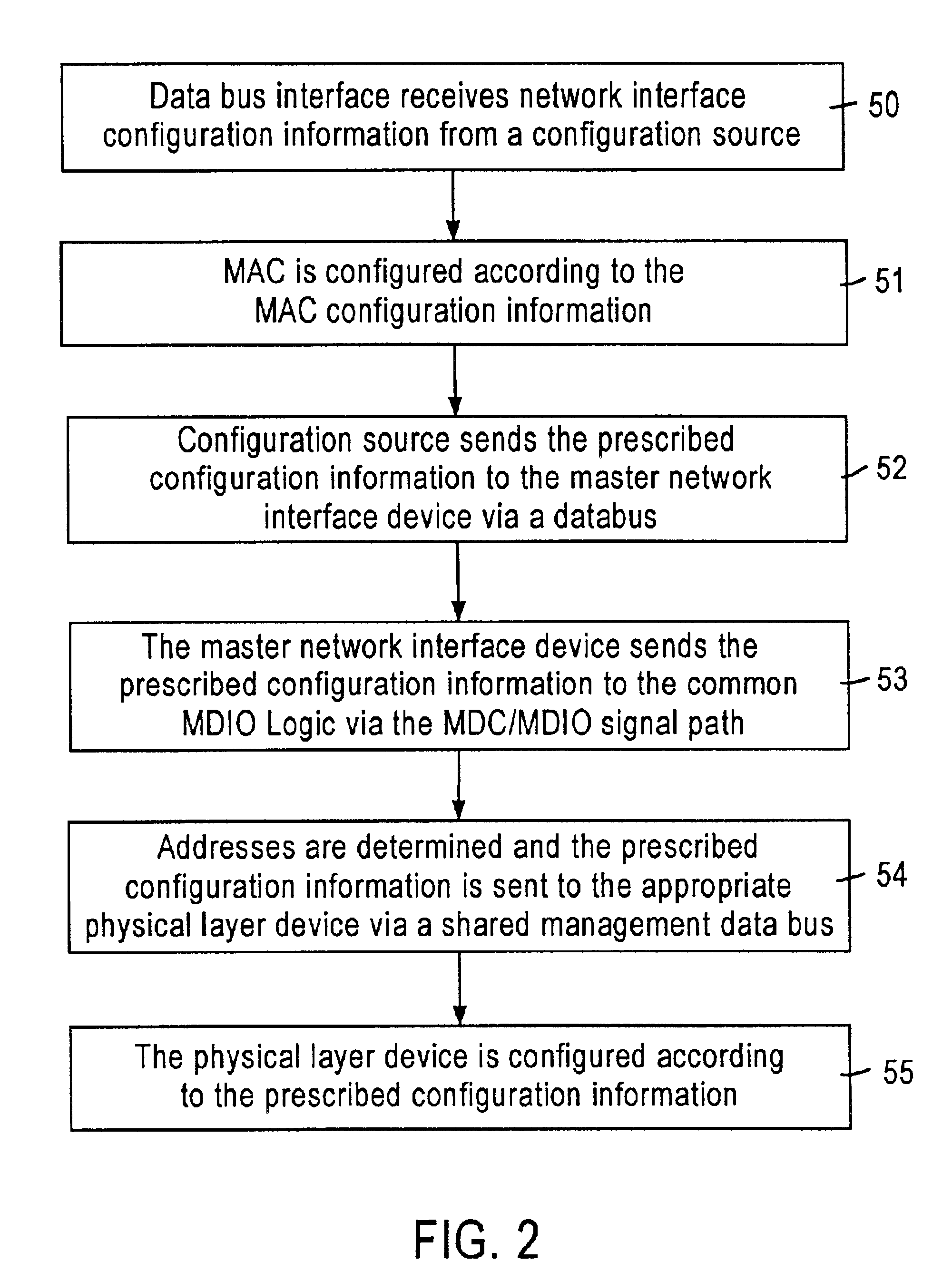

System and method enabling configuration of physical layer devices and corresponding link partners for communicating network data via a configuration source or auto-negotiation

InactiveUS6859825B1Multiple digital computer combinationsData switching networksProgrammable read-only memoryNetwork interface device

A network interface configures a plurality of physical layer devices and a corresponding plurality of network interface devices to allow for the communication of network data between the physical layer devices and corresponding link partners. At least one of the network interface devices is configured as a master device that communicates management information and autonegotiation results with the physical layer devices, while the other network interface devices do not. A configuration source, such as a central processing unit (CPU) or electronic erasable programmable read only memory (EEPROM), receives the autonegotiation results from the physical layer devices, through the master device, and configures the media access controllers (MACs) of each of the network interface devices in accordance with the autonegotiation results. This forces the MACs into their respective proper configurations even though the network interface devices that are not master devices do not receive the autonegotiation results directly from their corresponding physical layer devices.

Owner:ADVANCED MICRO DEVICES INC

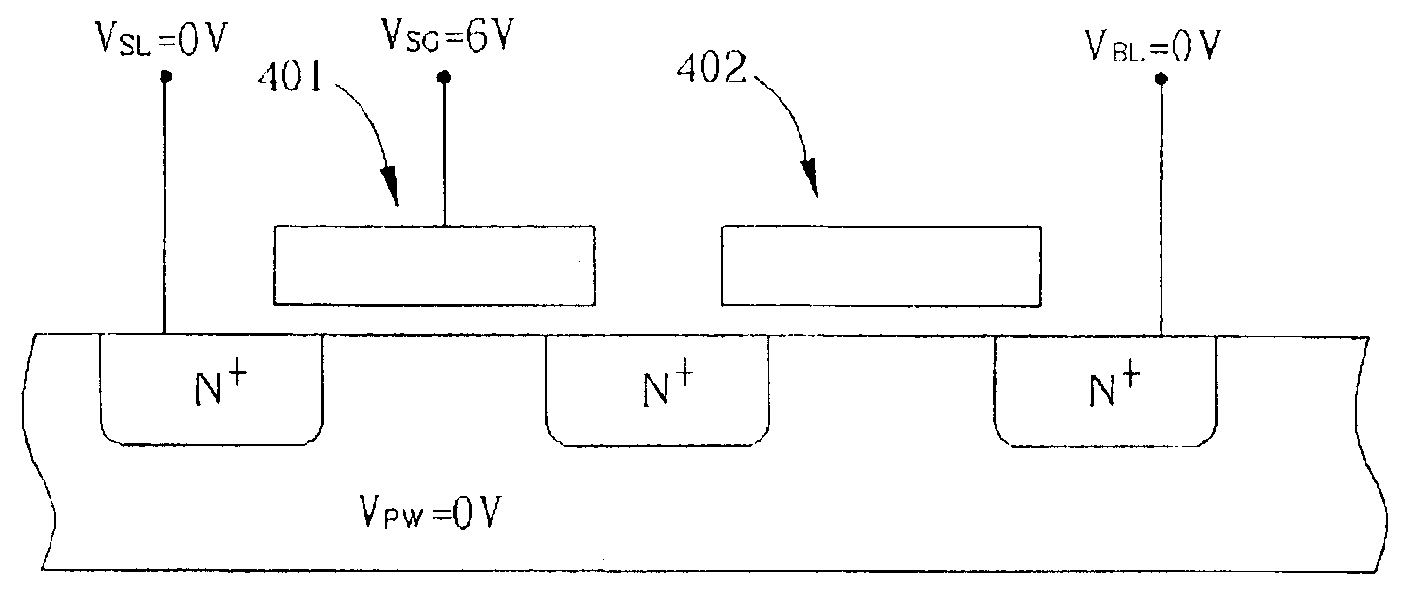

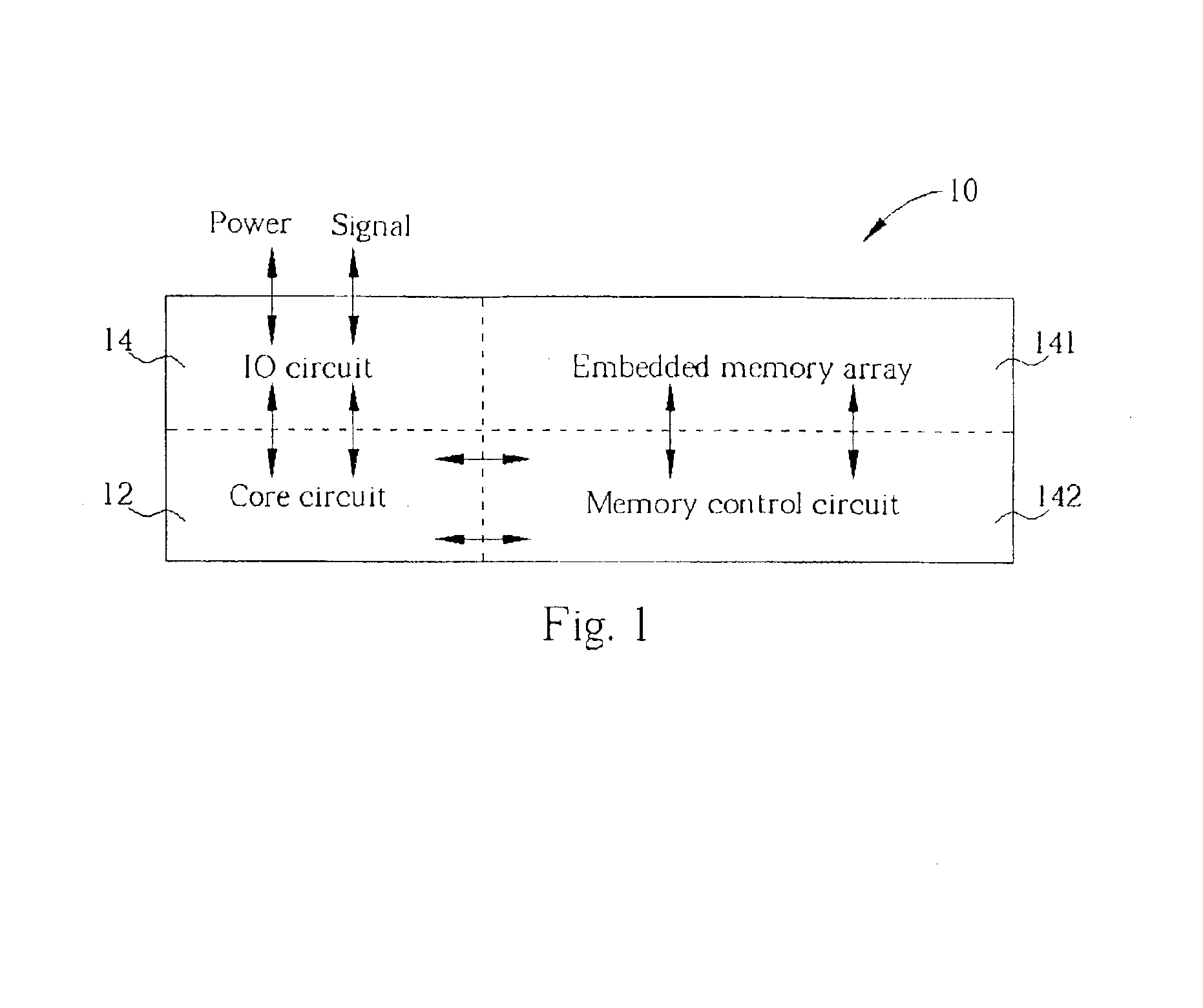

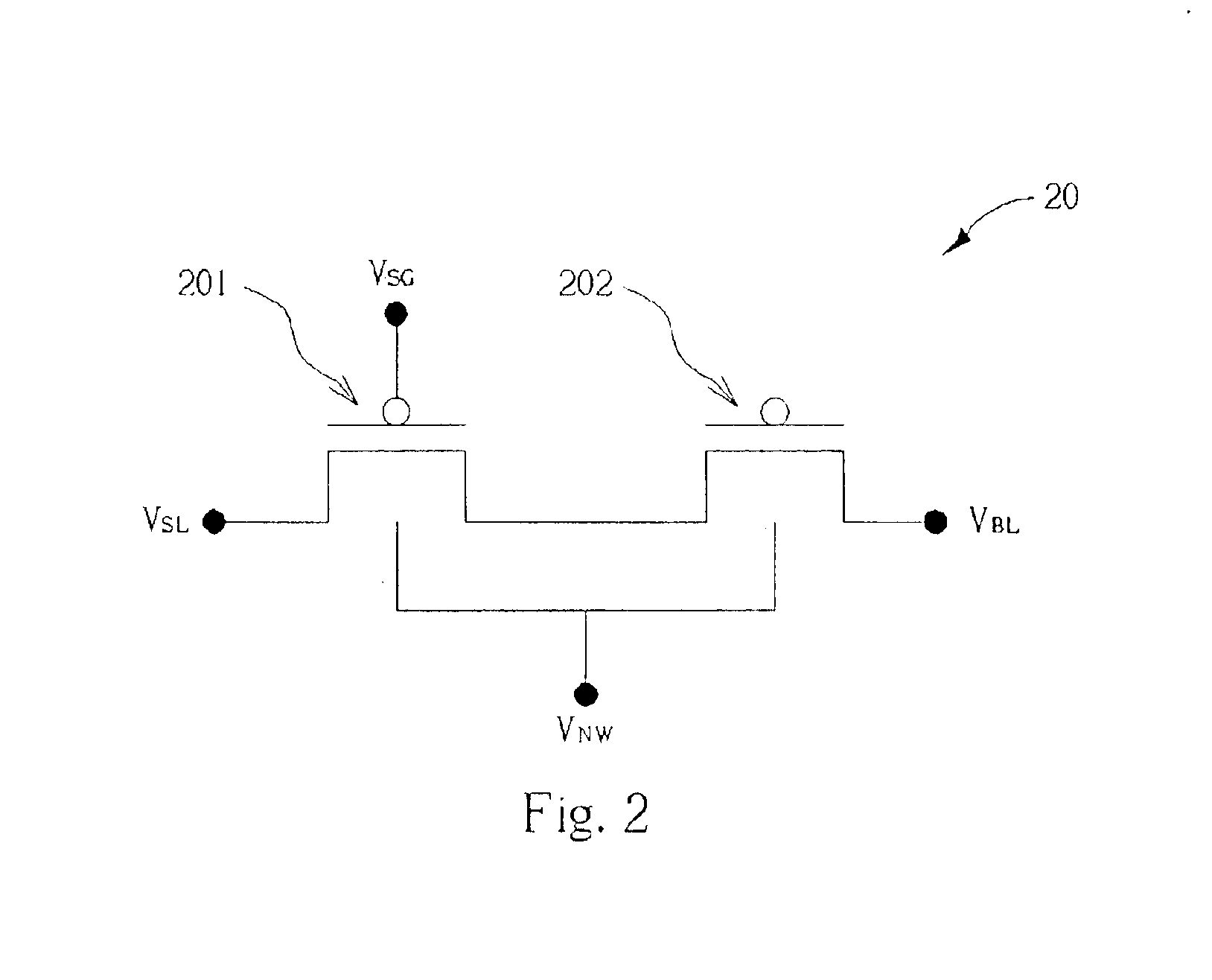

Integrated circuit embedded with single-poly non-volatile memory

InactiveUS6920067B2Reduce voltageReduce power consumptionTransistorSolid-state devicesProgrammable read-only memoryEngineering

A system on chip (SOC) contains a core circuit and an input / output (I / O) circuit embedded with an array of single-poly erasable programmable read only memory cells, each of which comprises a first PMOS transistor serially connected to a second PMOS transistor. The first and second PMOS transistors are both formed on an N-well of a P-type substrate. The first PMOS transistor includes a single-poly floating gate, a first P+ doped drain region and a first P+ doped source region, the second PMOS transistor includes a single-poly select gate and a second P+ doped source region, and the first P+ doped source region of the first PMOS transistor serves as a drain of the second PMOS transistor.

Owner:EMEMORY TECH INC

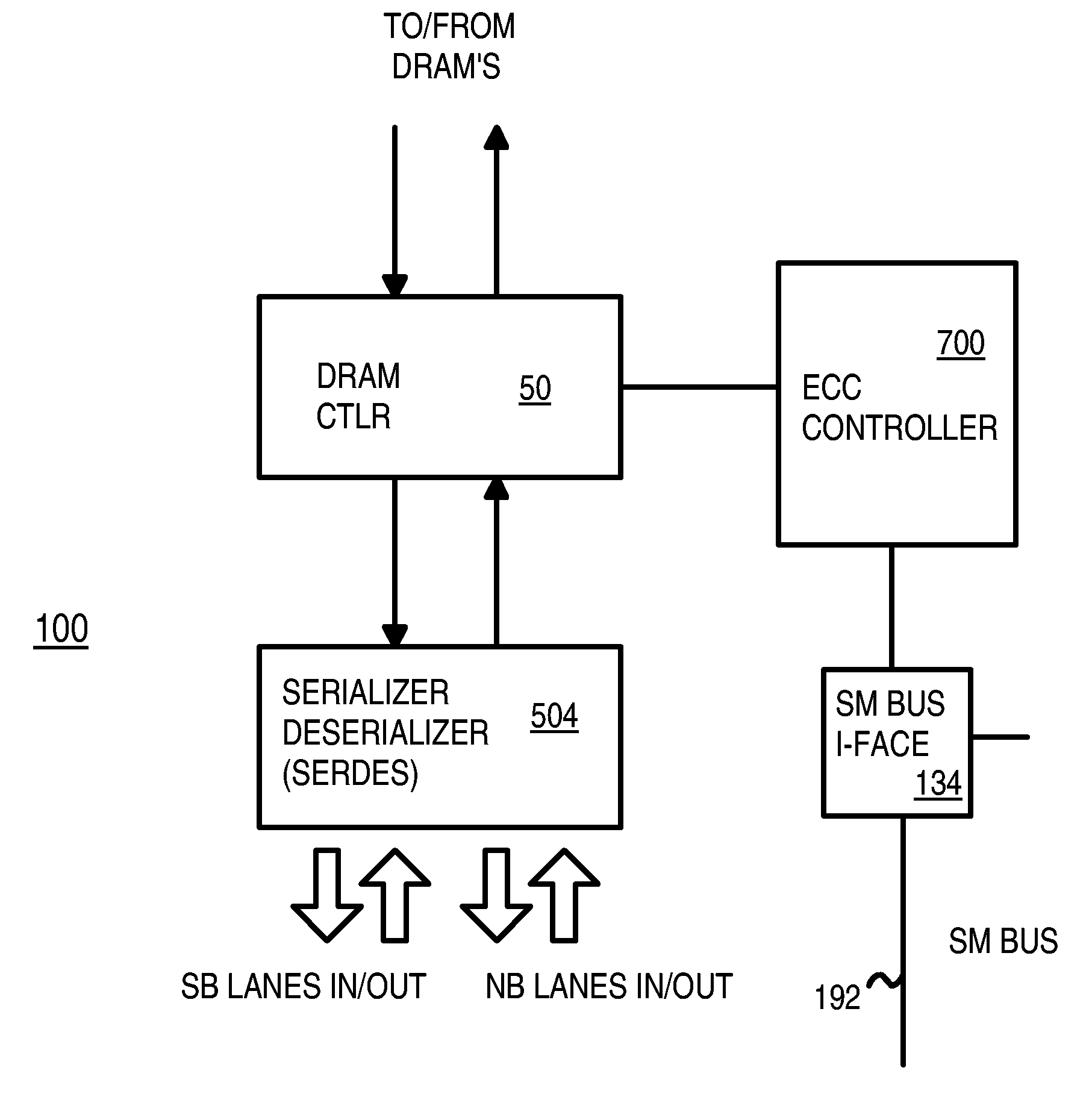

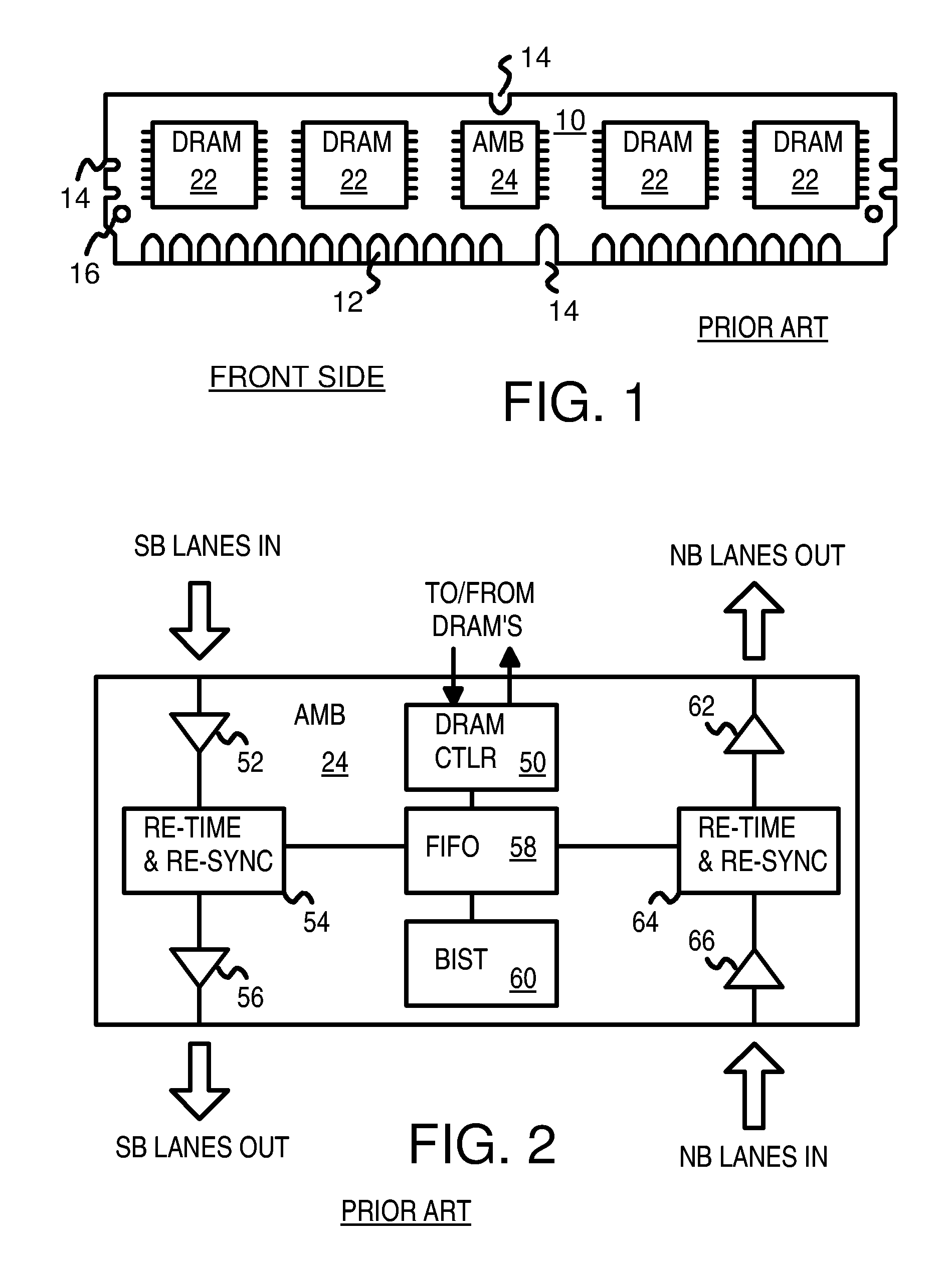

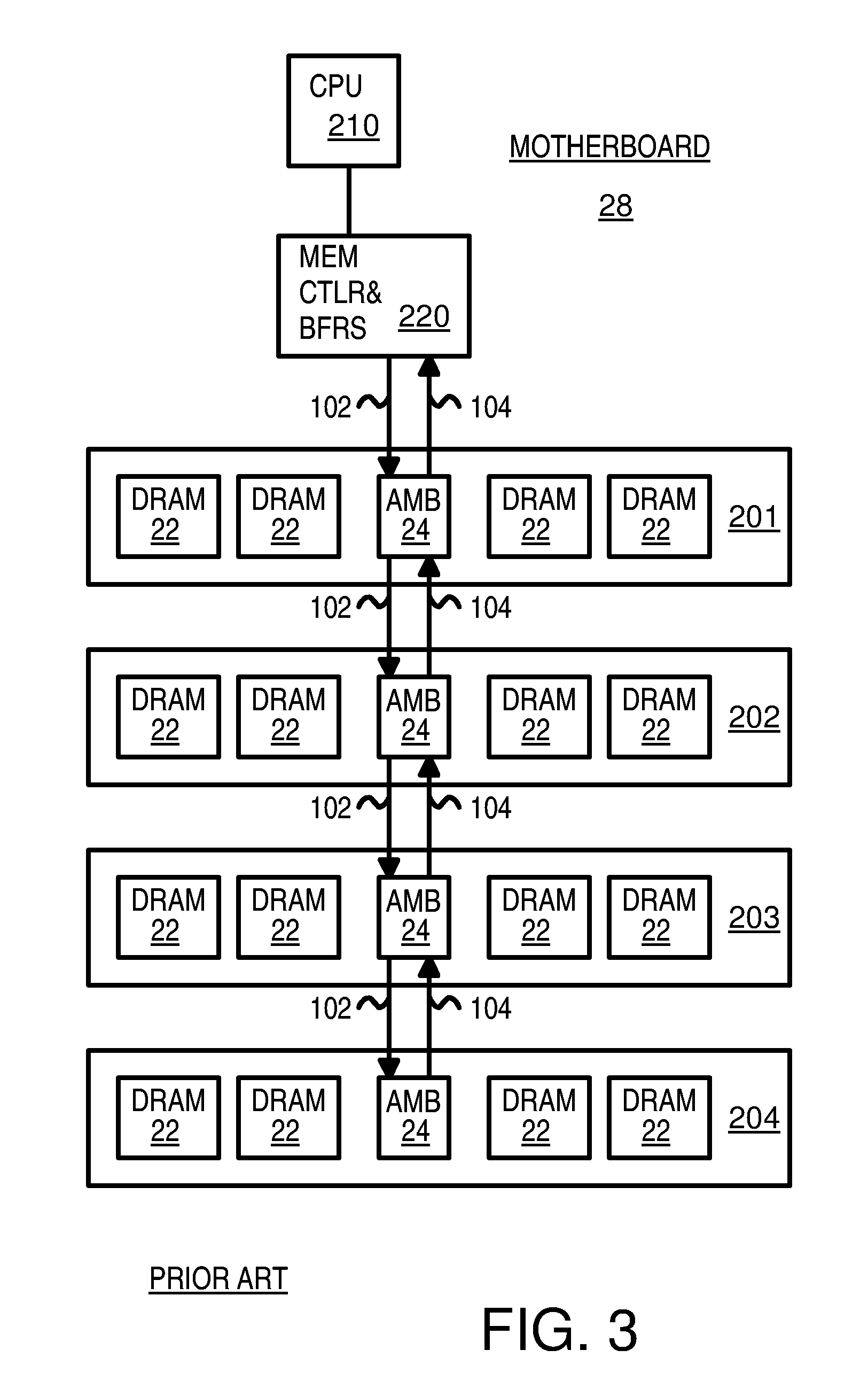

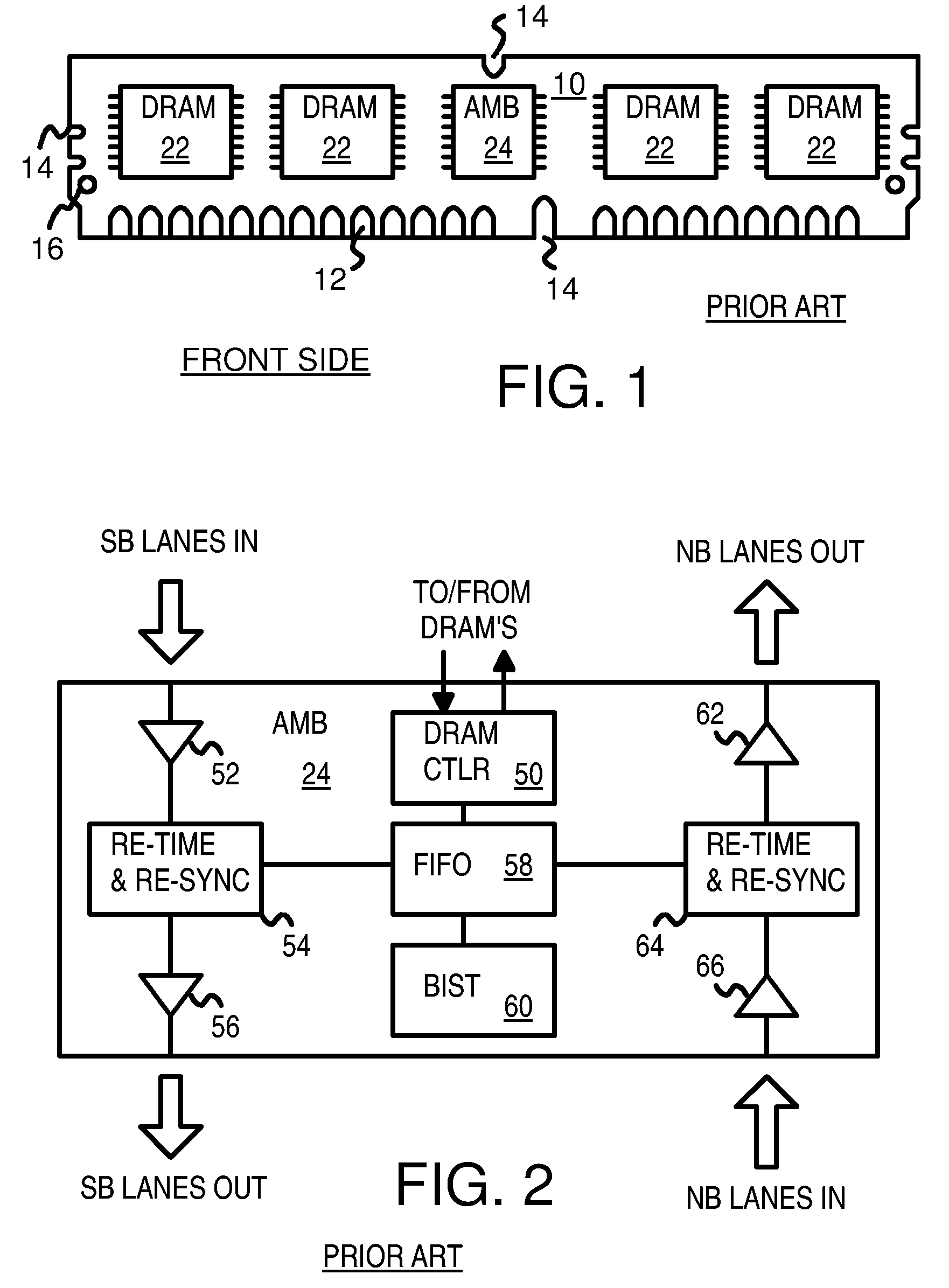

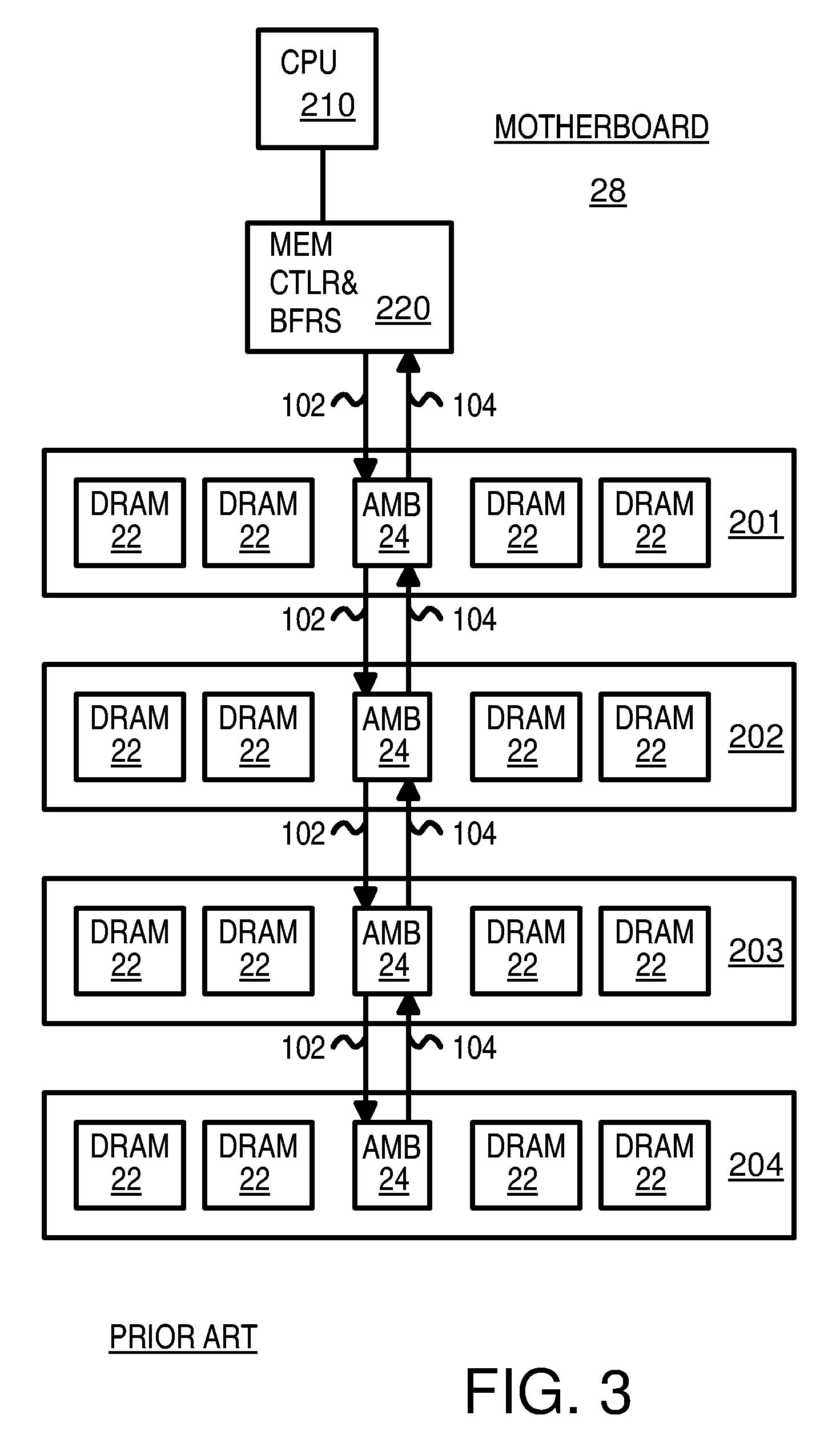

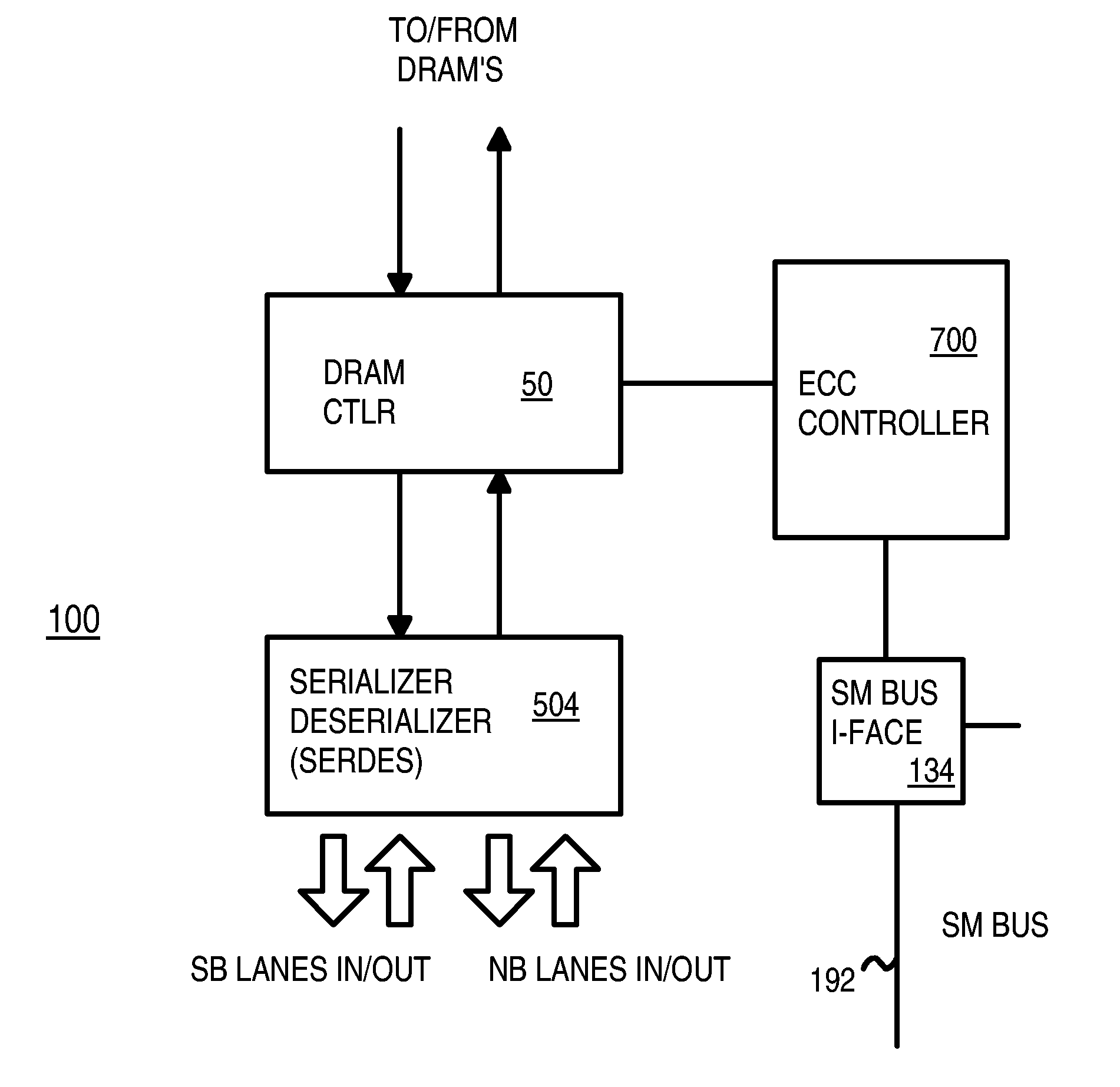

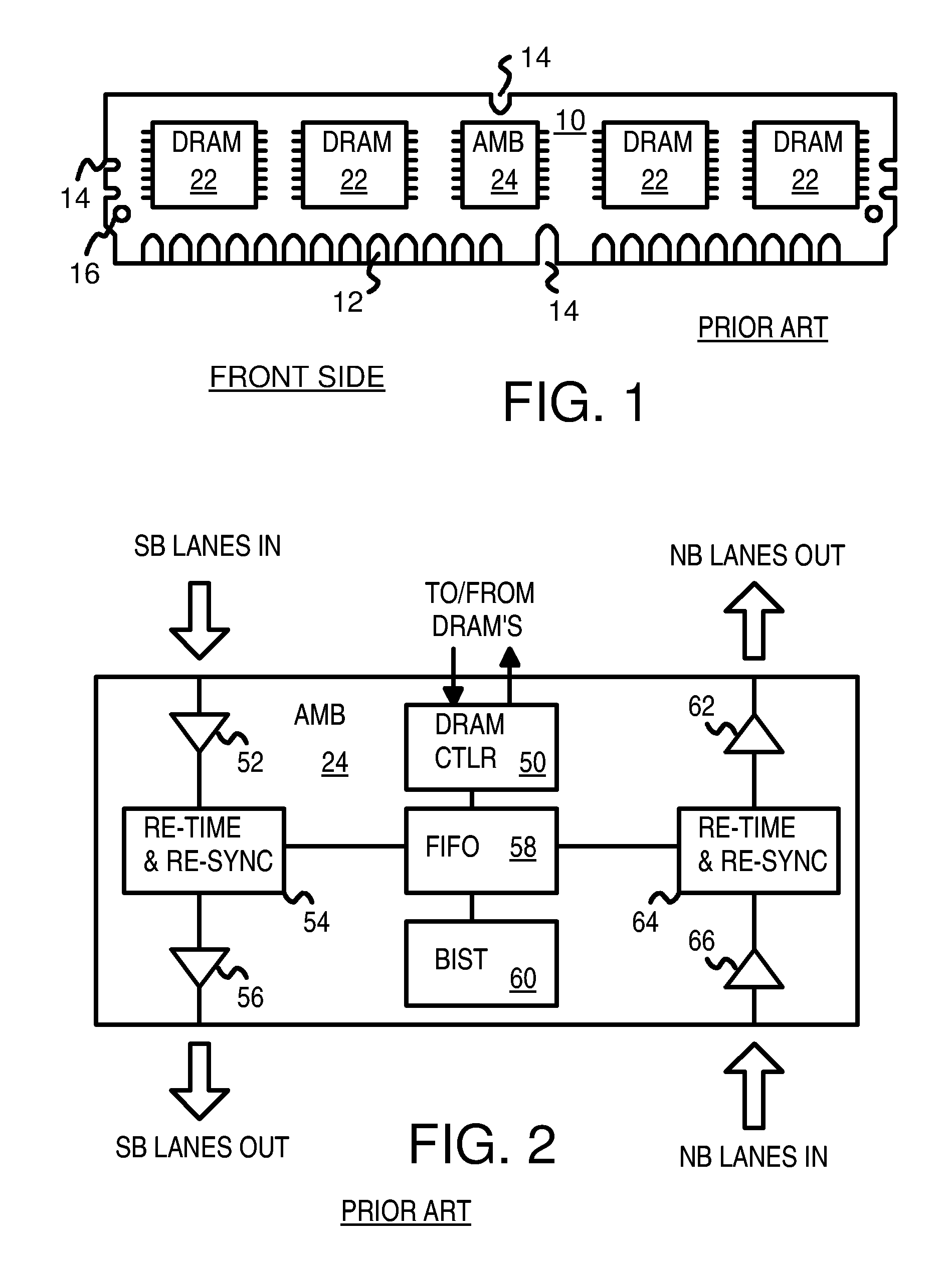

Fully-Buffered Memory-Module with Error-Correction Code (ECC) Controller in Serializing Advanced-Memory Buffer (AMB) that is transparent to Motherboard Memory Controller

ActiveUS20080022186A1Error detection/correctionStatic storageProgrammable read-only memoryError correcting

An error-correcting fully-buffered memory module can detect and correct some errors in data read from memory chips. An error correction code ECC controller is added to the Advanced Memory Buffer (AMB) on the memory module that fully buffers memory requests sent as serial packets. The error correction controller generates ECC bits for write data, and both the ECC bits and the write data are written to the memory chips by a DRAM controller in the AMB. During reads, an ECC checker generates a syndrome and can activate an error corrector to correct data or signal a non-correctable error. The corrected data is formed into serial packets sent back to the motherboard by the AMB. Configuration data for the ECC controller could be first programmed into a serial-presence-detect electrically-erasable programmable read-only memory (SPD-EEPROM) on the memory module, and then copied to error-correction configuration registers on the AMB during power-up.

Owner:KINGSTON DIGITAL CO LTD

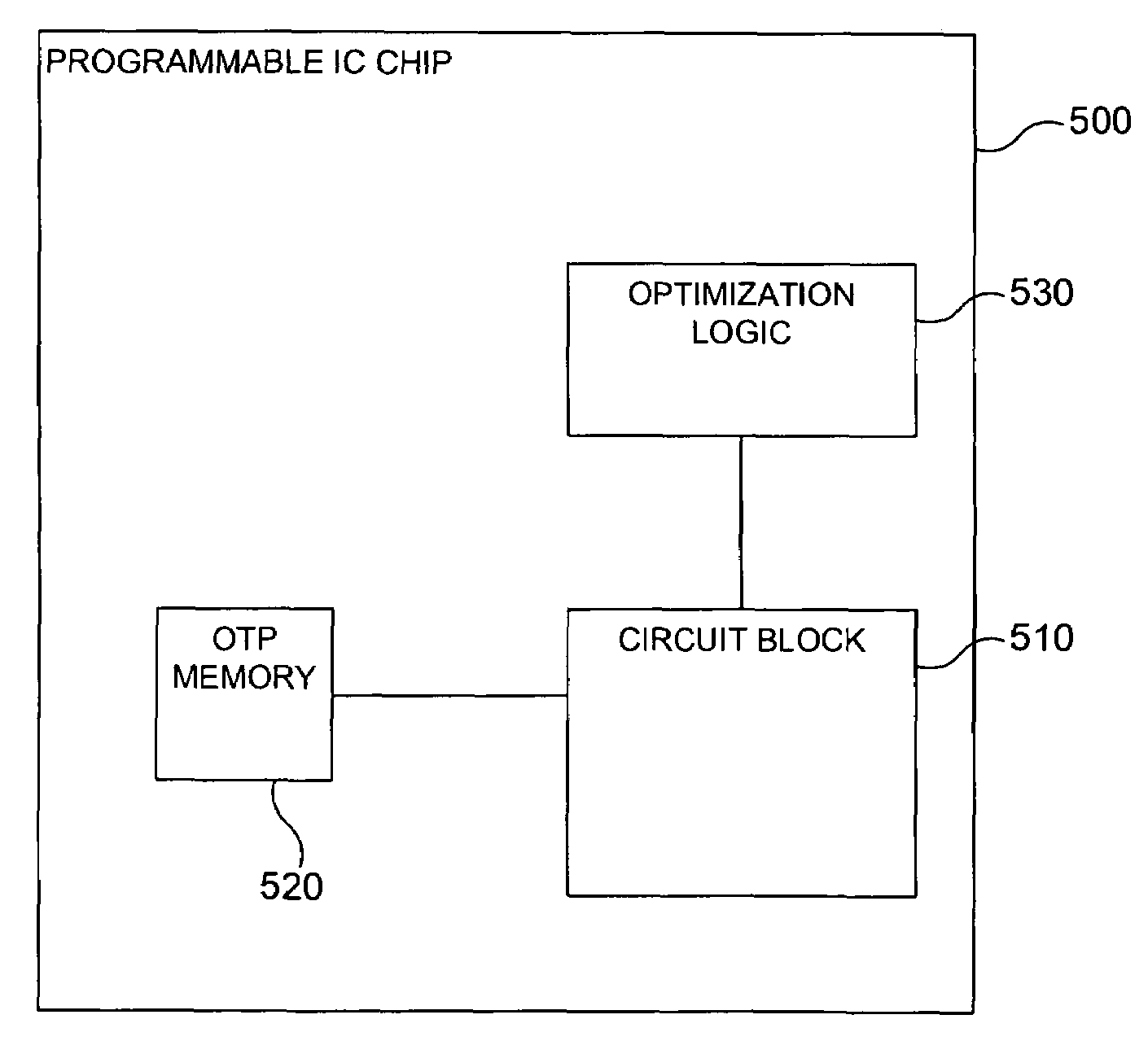

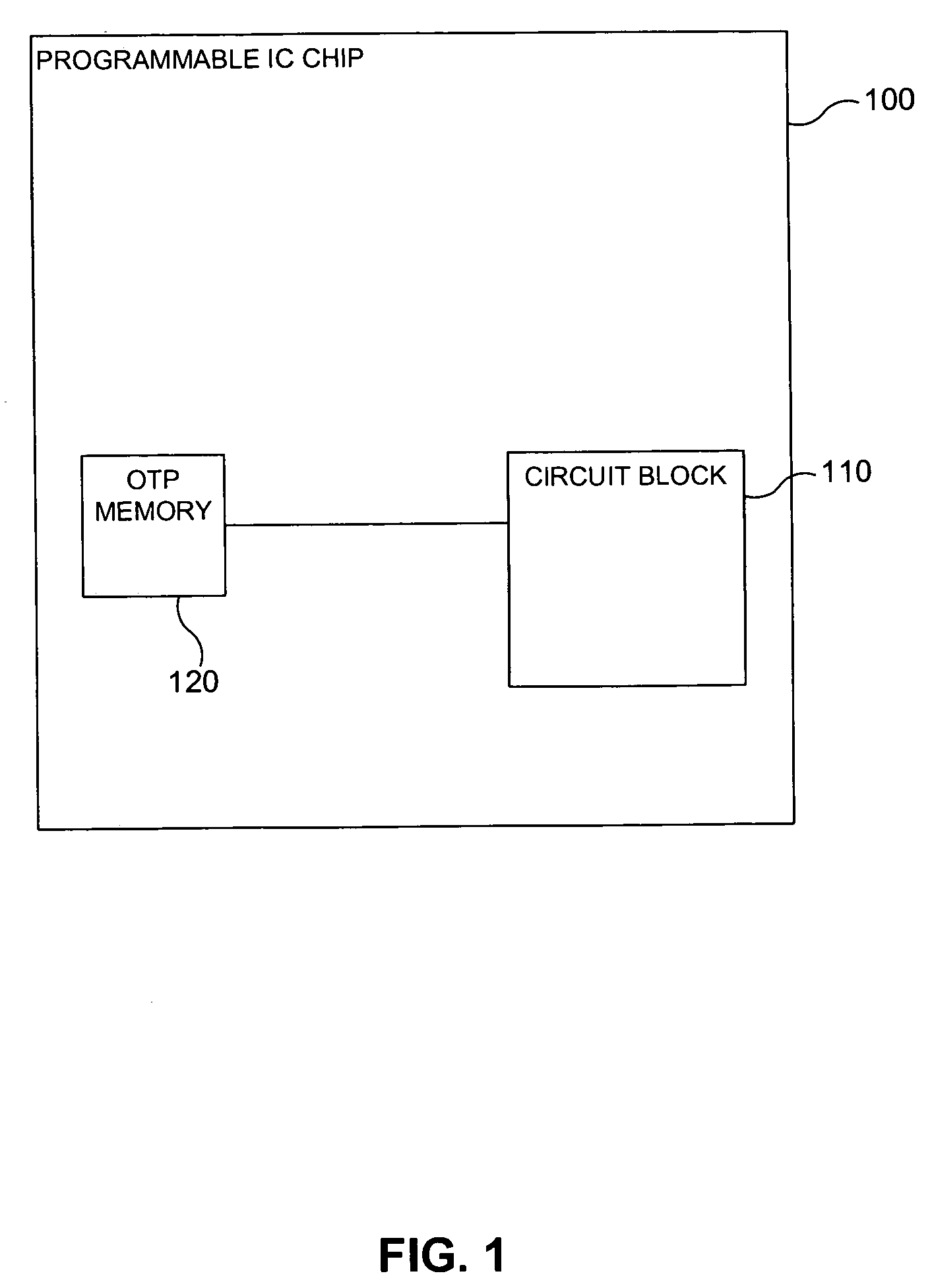

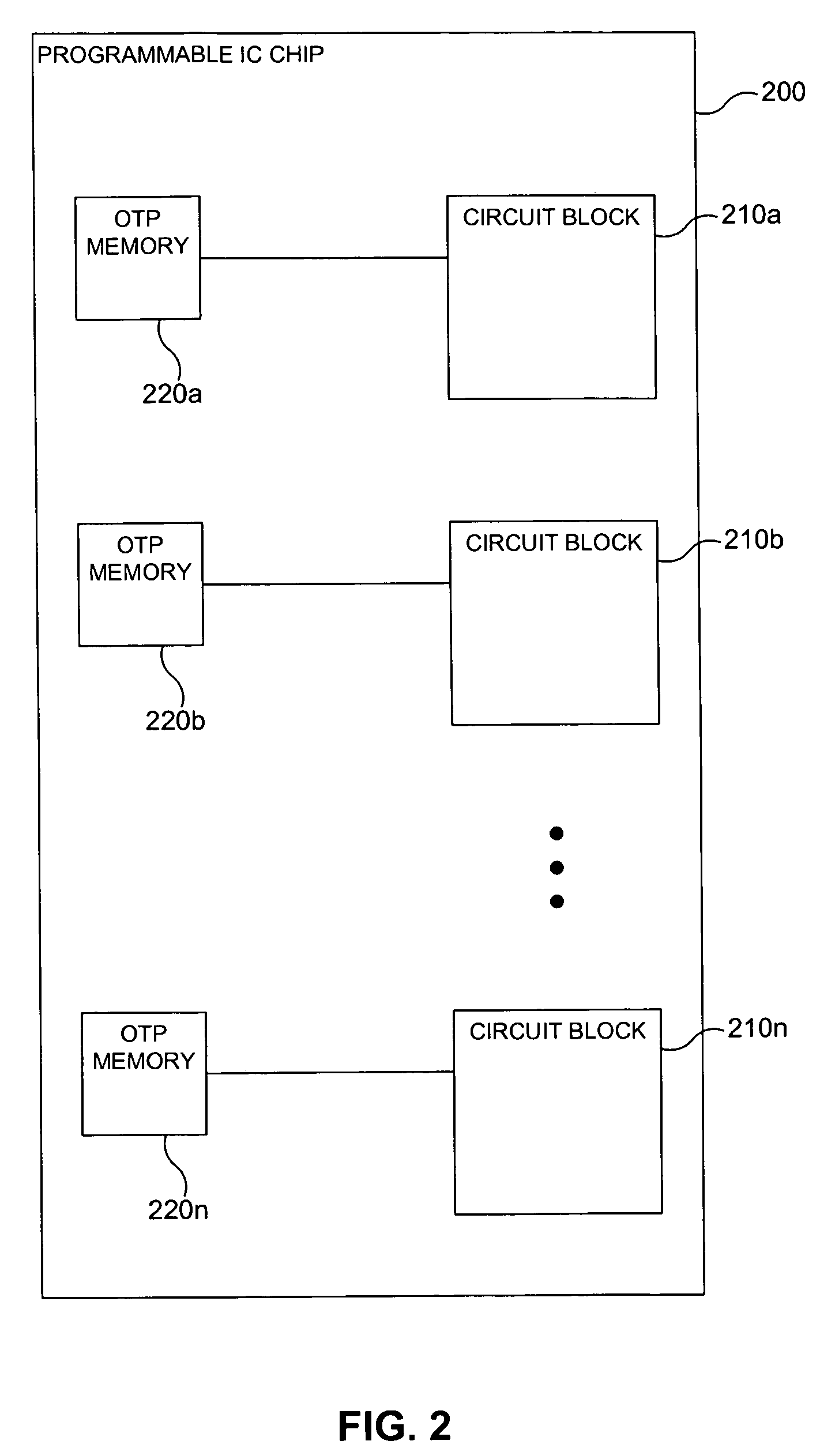

Integrated circuit chip having non-volatile on-chip memories for providing programmable functions and features

ActiveUS7263027B2Reduce areaLess-expensive and complexRead-only memoriesDigital storageElectricityCMOS

An integrated circuit chip having programmable functions and features in which one-time programmable (OTP) memories are used to implement a non-volatile memory function, and a method for providing the same. The OTP memories may be based on poly-fuses as well as gate-oxide fuses. Because OTP memories are small, less die area is utilized as compared to metal fuses. Addtionally, because OTP memories can be implemented as part of standard complementary metal oxide semiconductor (CMOS) processes, the method is less costly and complex than the use of electrically-erasable programmable read-only memories (E2PROMs).

Owner:AVAGO TECH INT SALES PTE LTD

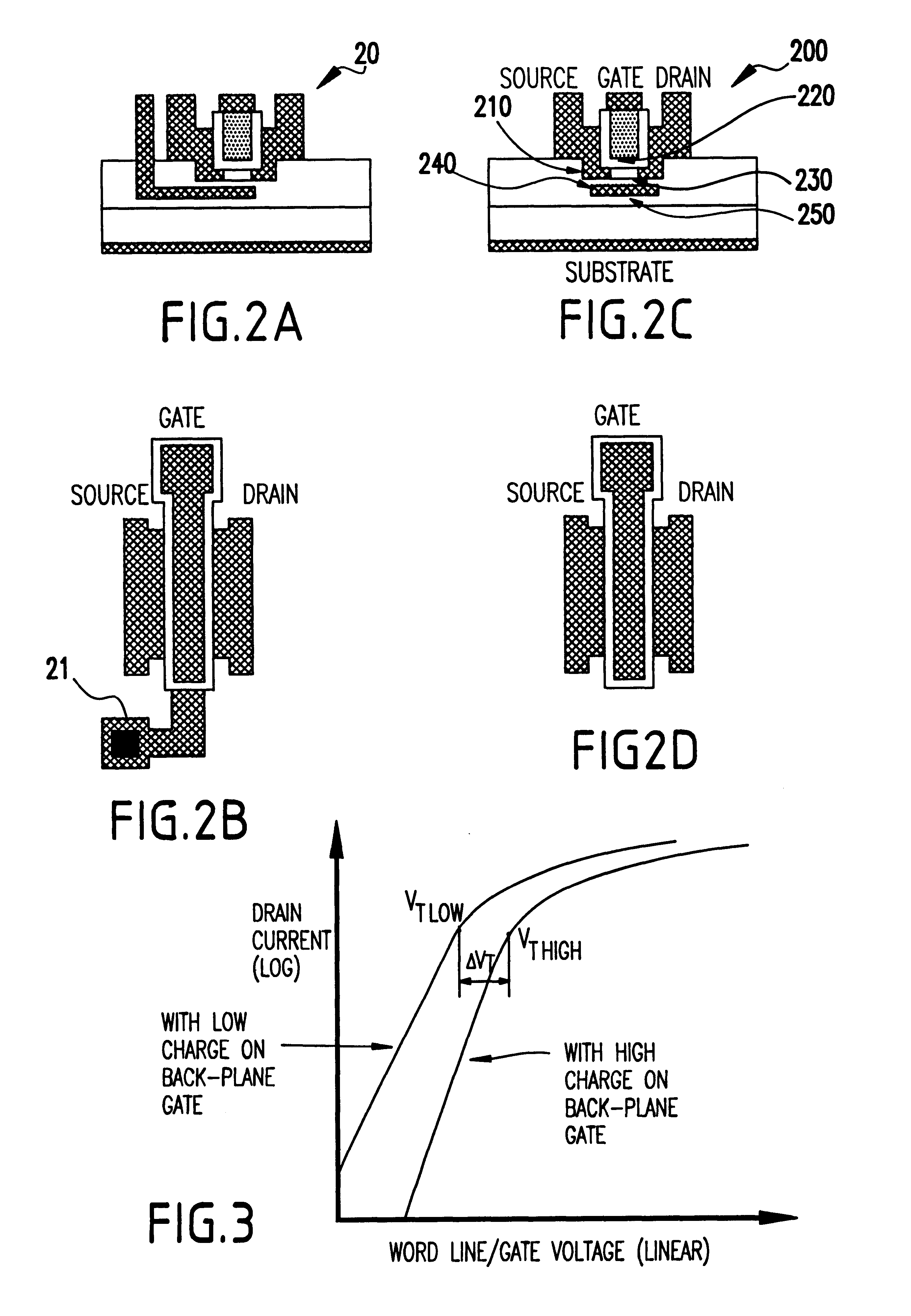

Floating back gate electrically erasable programmable read-only memory (EEPROM)

InactiveUS6248626B1TransistorIndividual molecule manipulationProgrammable read-only memoryEngineering

A semiconductor memory and a method of producing the memory, includes a transistor including a first gate having an oxide, and a channel, and a back-plane including a second gate and an oxide thereover, the second gate formed opposite to the channel of the transistor, the second gate including a floating gate, wherein a thickness of the oxide of the back-plane is separately scalable from an oxide of the first gate of the transistor.

Owner:GLOBALFOUNDRIES INC

Wear leveling techniques for flash EEPROM systems

InactiveUS20050114589A1Avoid uneven wearExtended service lifeMemory architecture accessing/allocationRead-only memoriesElectricityProgrammable read-only memory

A mass storage system made of flash electrically erasable and programmable read only memory (“EEPROM”) cells organized into blocks, the blocks in turn being grouped into memory banks, is managed to even out the numbers of erase and rewrite cycles experienced by the memory banks in order to extend the service lifetime of the memory system. Since this type of memory cell becomes unusable after a finite number of erase and rewrite cycles, although in the tens of thousands of cycles, uneven use of the memory banks is avoided so that the entire memory does not become inoperative because one of its banks has reached its end of life while others of the banks are little used. Relative use of the memory banks is monitored and, in response to detection of uneven use, have their physical addresses periodically swapped for each other in order to even out their use over the lifetime of the memory.

Owner:SANDISK TECH LLC

NAND-type non-volatile memory cell and method for operating same

ActiveUS6996011B2High densitySmall spacingSolid-state devicesRead-only memoriesProgrammable read-only memoryDevice form

Owner:MACRONIX INT CO LTD

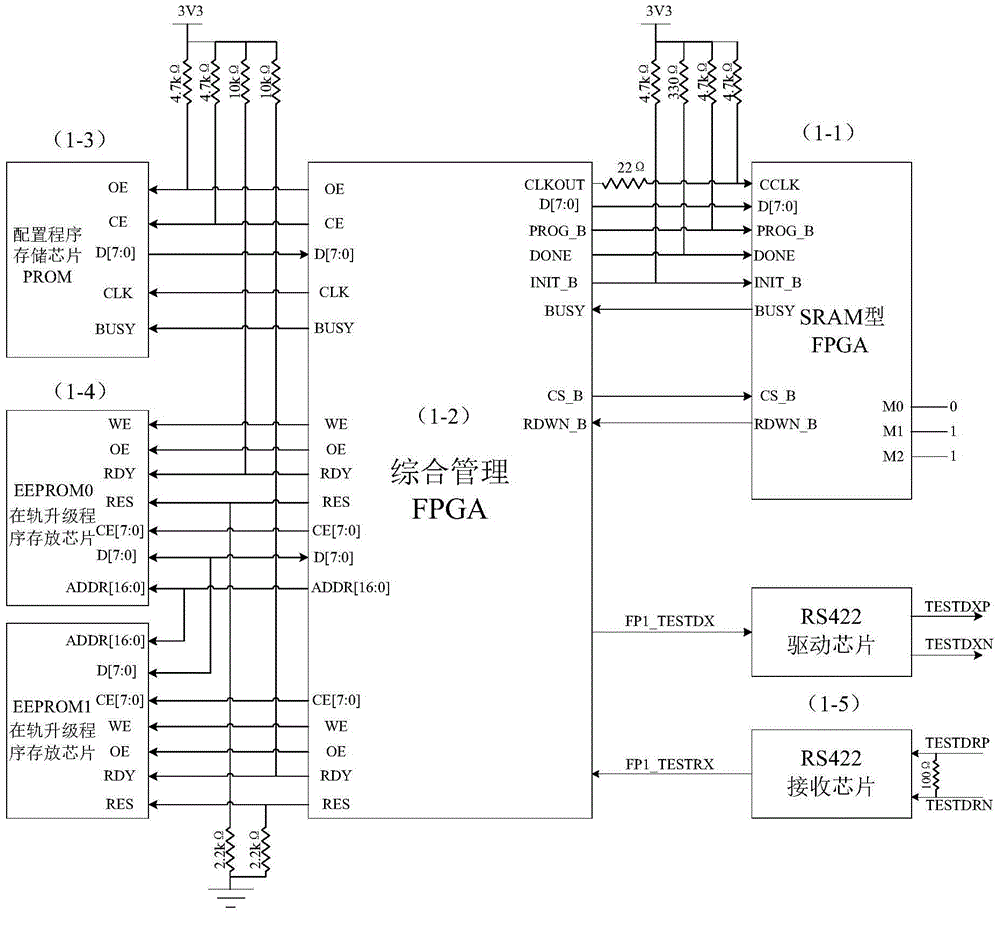

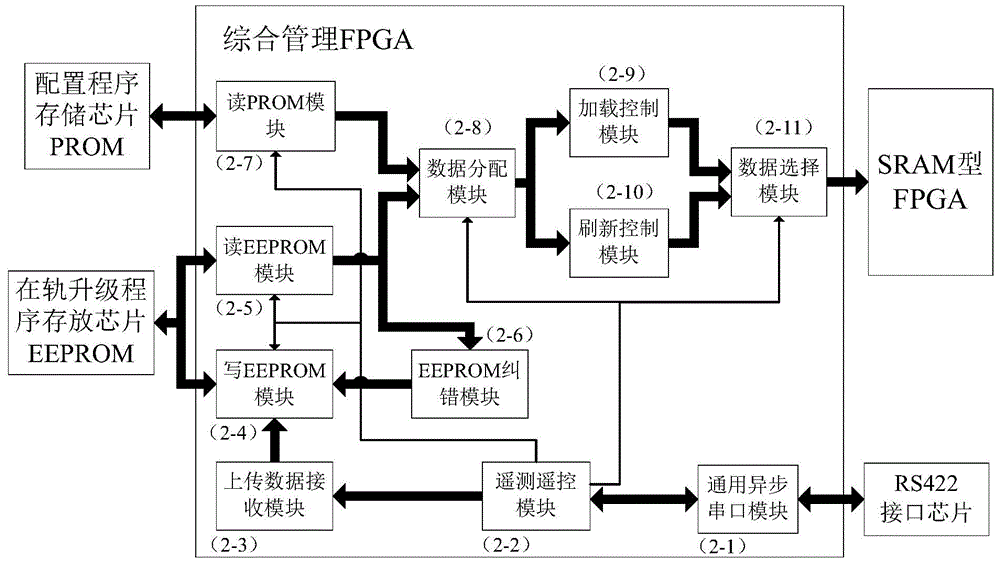

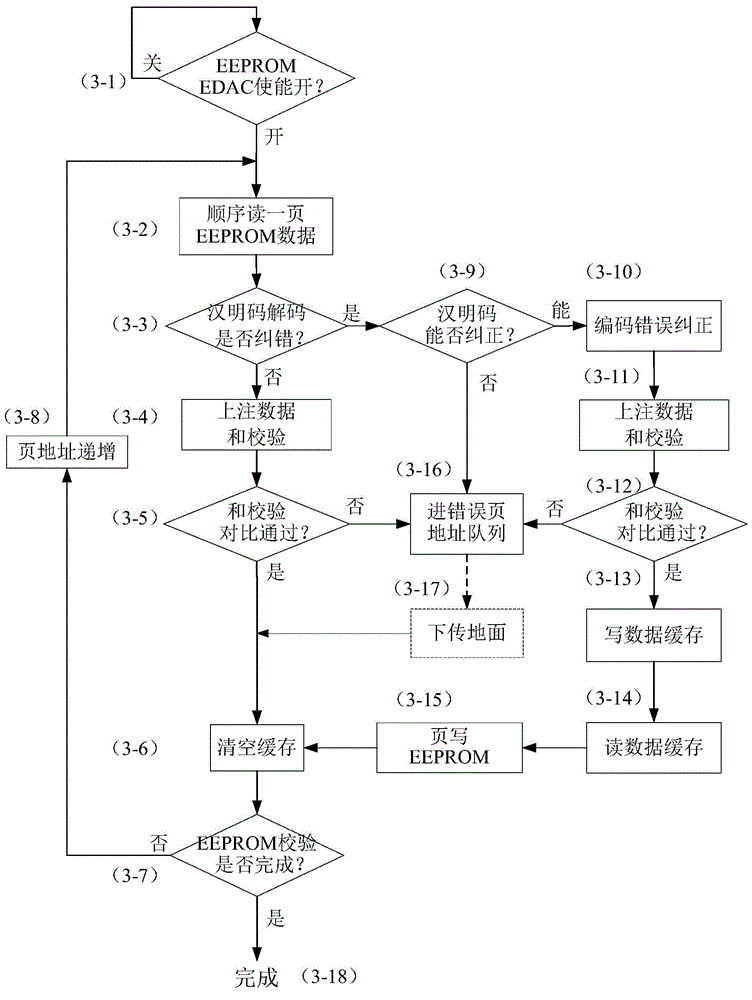

Configuration, refreshing and program upgrading integrated system for SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array)

ActiveCN104484214AIncrease flexibilityImprove versatilityProgram loading/initiatingProgrammable read-only memoryLogic gate

The invention discloses a configuration, refreshing and program upgrading integrated system for an SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array), belongs to the technical field of aerospace and aims to solve the problem of SEU (Single Event Upset) of the SRAM type FPGA in a spatial irradiation environment. The configuration, refreshing and program upgrading integrated system has a capability of performing program upgrading on the SRAM type FPGA which is in on-orbit work for a long time. The configuration, refreshing and program upgrading integrated system comprises an on-site programmable logic gate array SRAM type FPGA, a comprehensive management anti-fuse FPGA, a configuration program storage chip PROM (Programmable Read-Only Memory), an on-orbit upgrading program storage chip EEPORM (Electrically-Erasable Programmable Read-Only Memory) and an RS422 interface chip. The configuration, refreshing and program upgrading integrated system disclosed by the invention can be used for effectively solving the problem of the SEU of the SRAM type FPGA which is in on-orbit work for a long time and correcting the SEU and single event accumulation inside the SRAM type FPGA without being shut down, also has the function of on-orbit program upgrading of the SRAM type FPGA, and has the characteristics of instantaneity, reliability, flexibility, universality and low cost.

Owner:HUAZHONG UNIV OF SCI & TECH

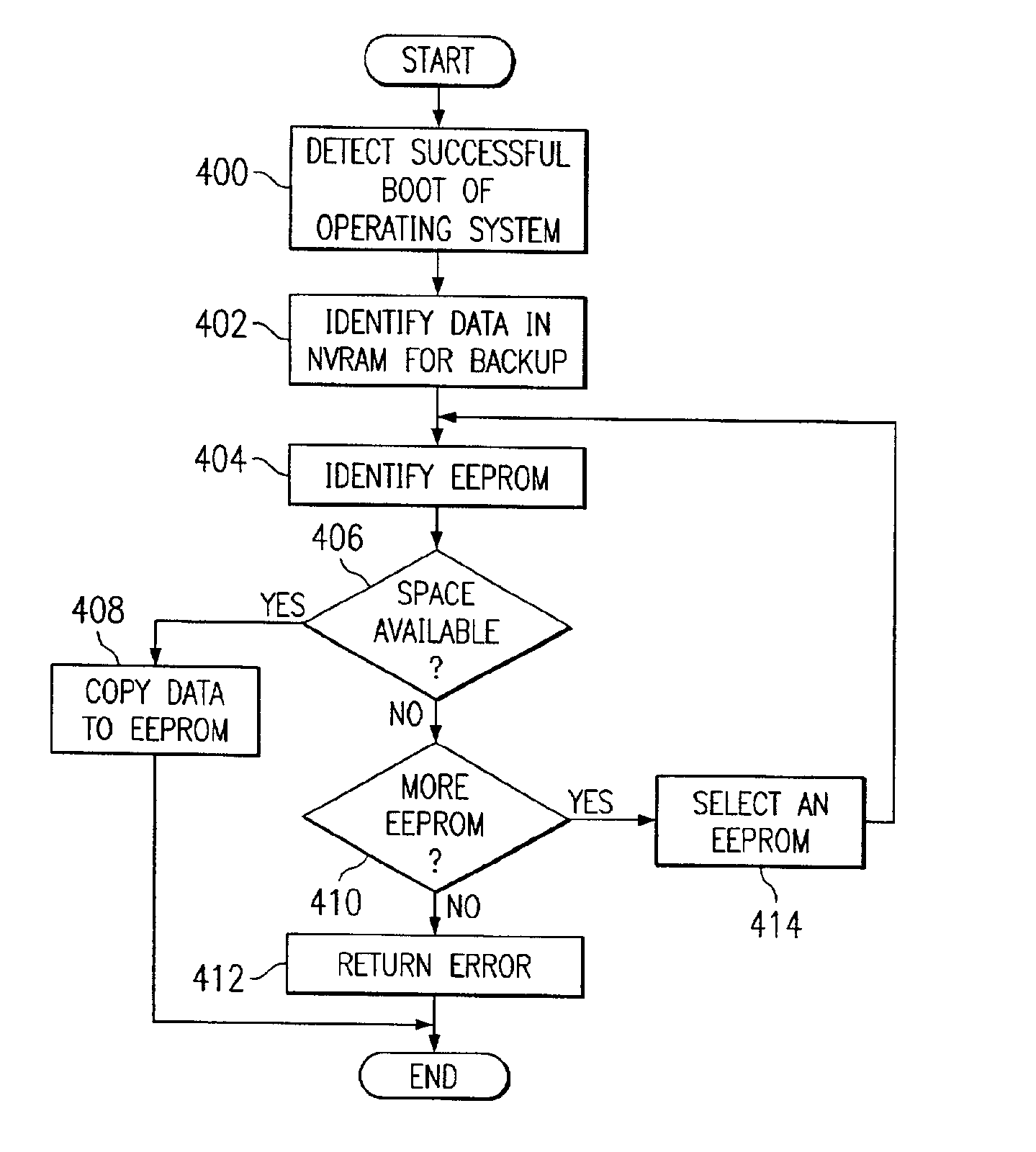

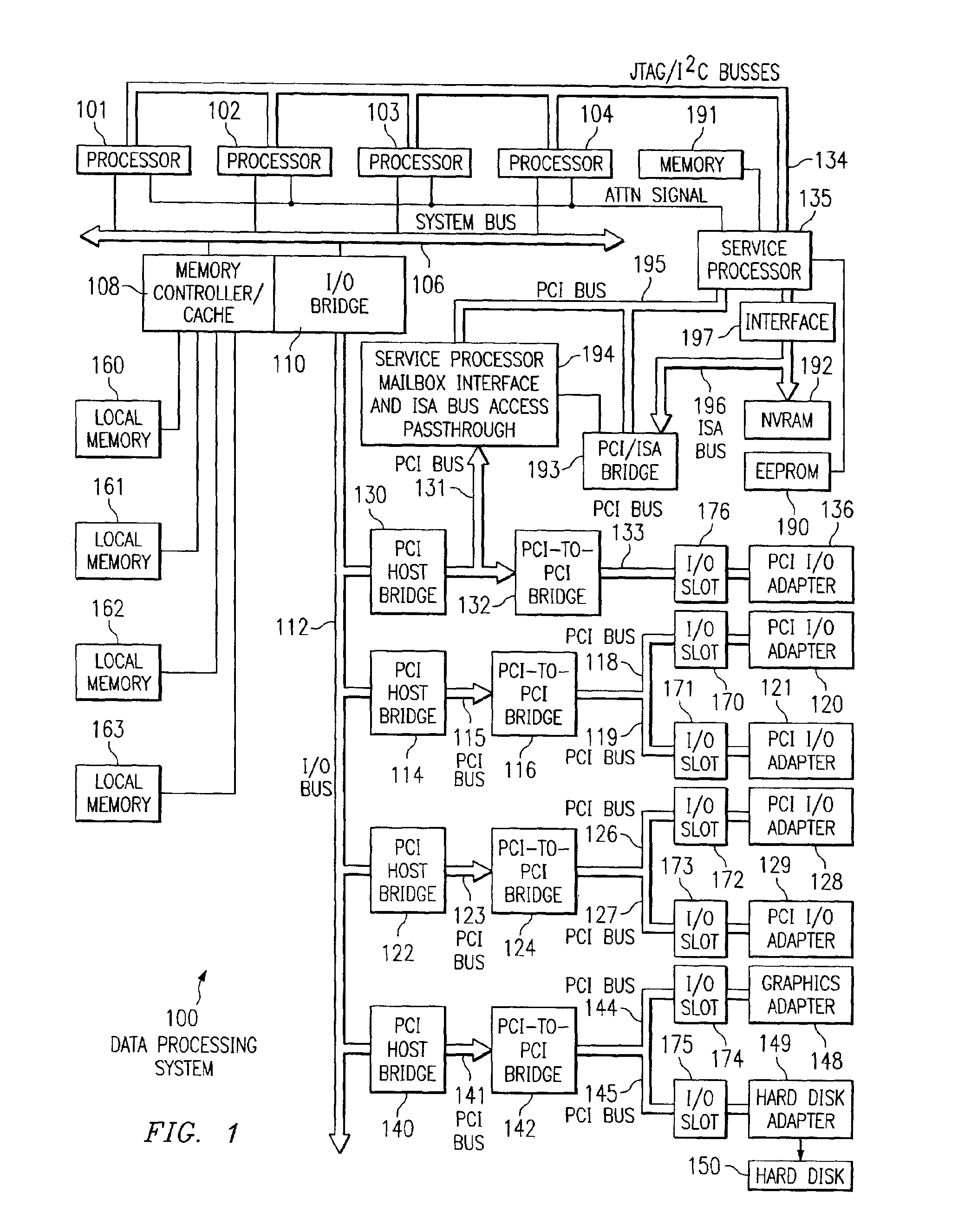

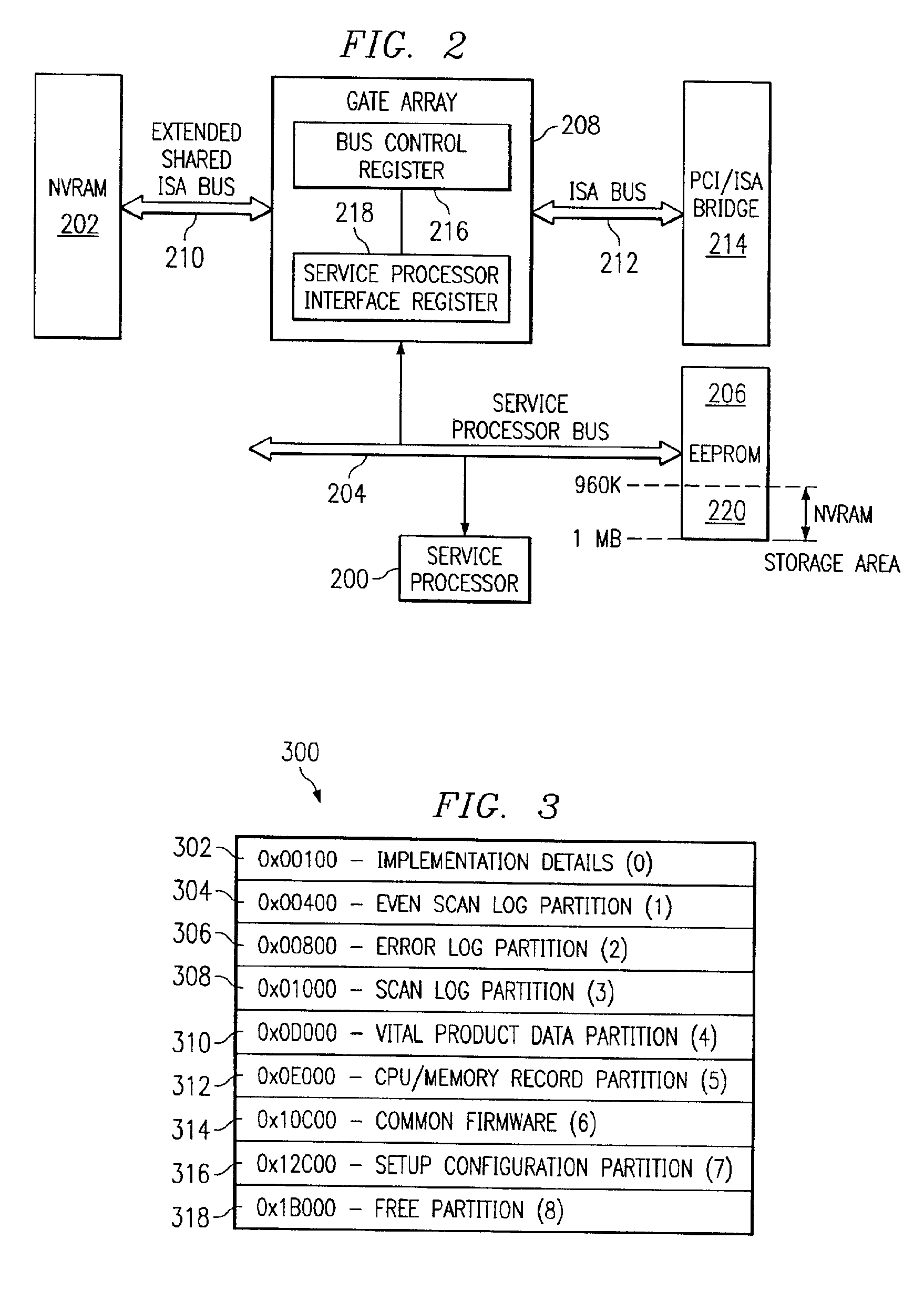

Method and apparatus for backing up and restoring data from nonvolatile memory

A method, apparatus, and computer instructions for backing up data in a nonvolatile random access memory. Selected data is stored in the nonvolatile random access memory in available space in at least one electrically erasable programmable read only memory in the data processing system to form stored data. The stored data is used to restore the nonvolatile random access memory if nonvolatile random access memory becomes corrupted.

Owner:IBM CORP

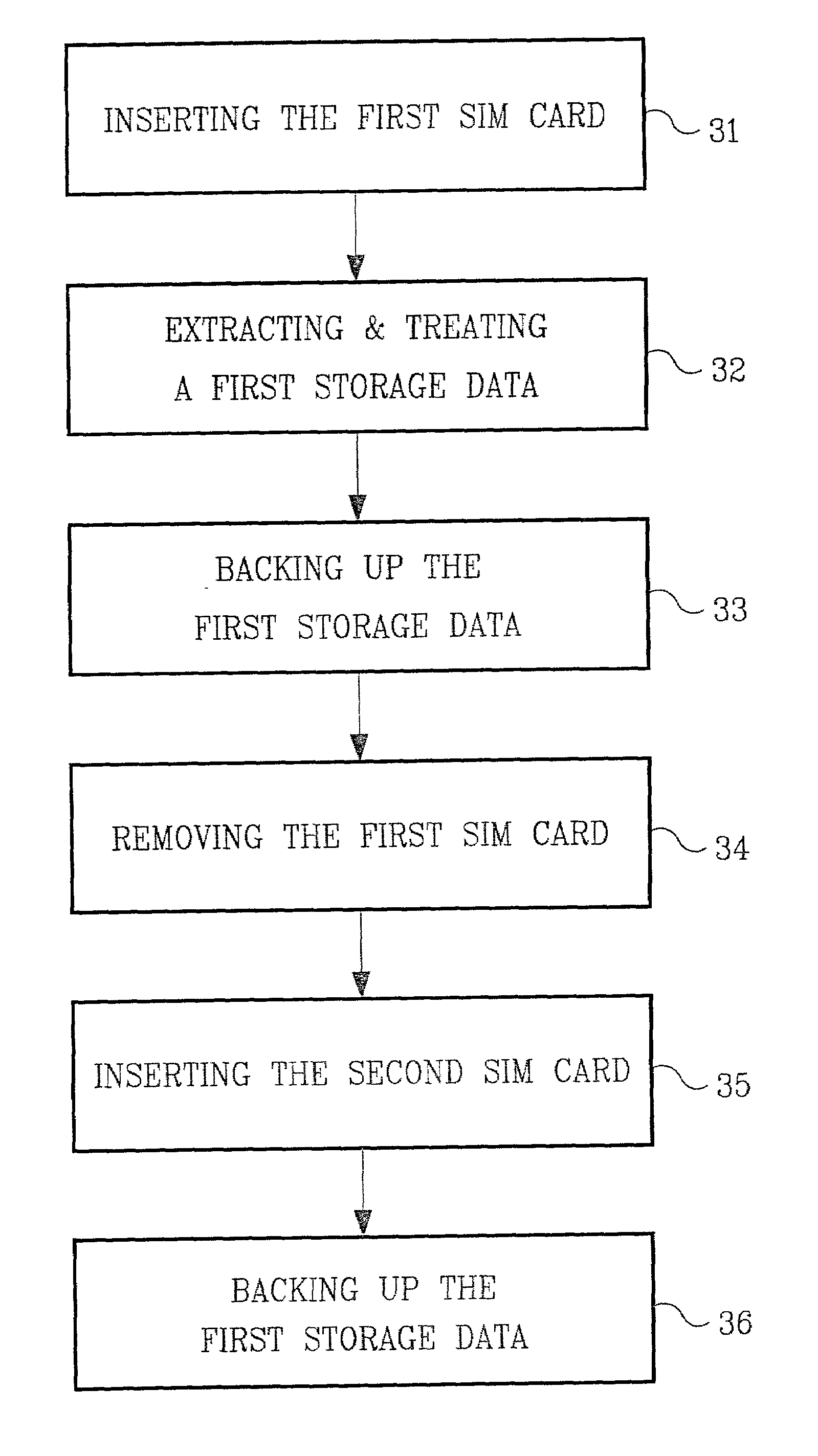

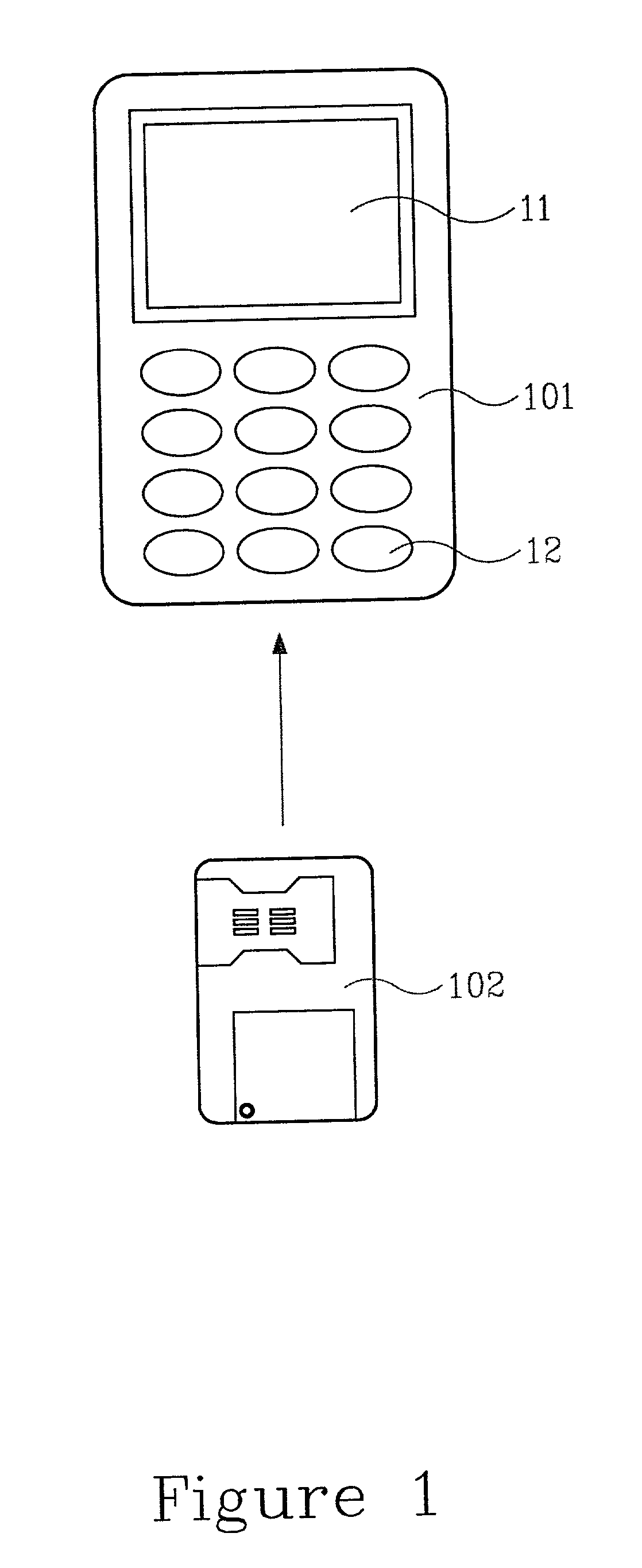

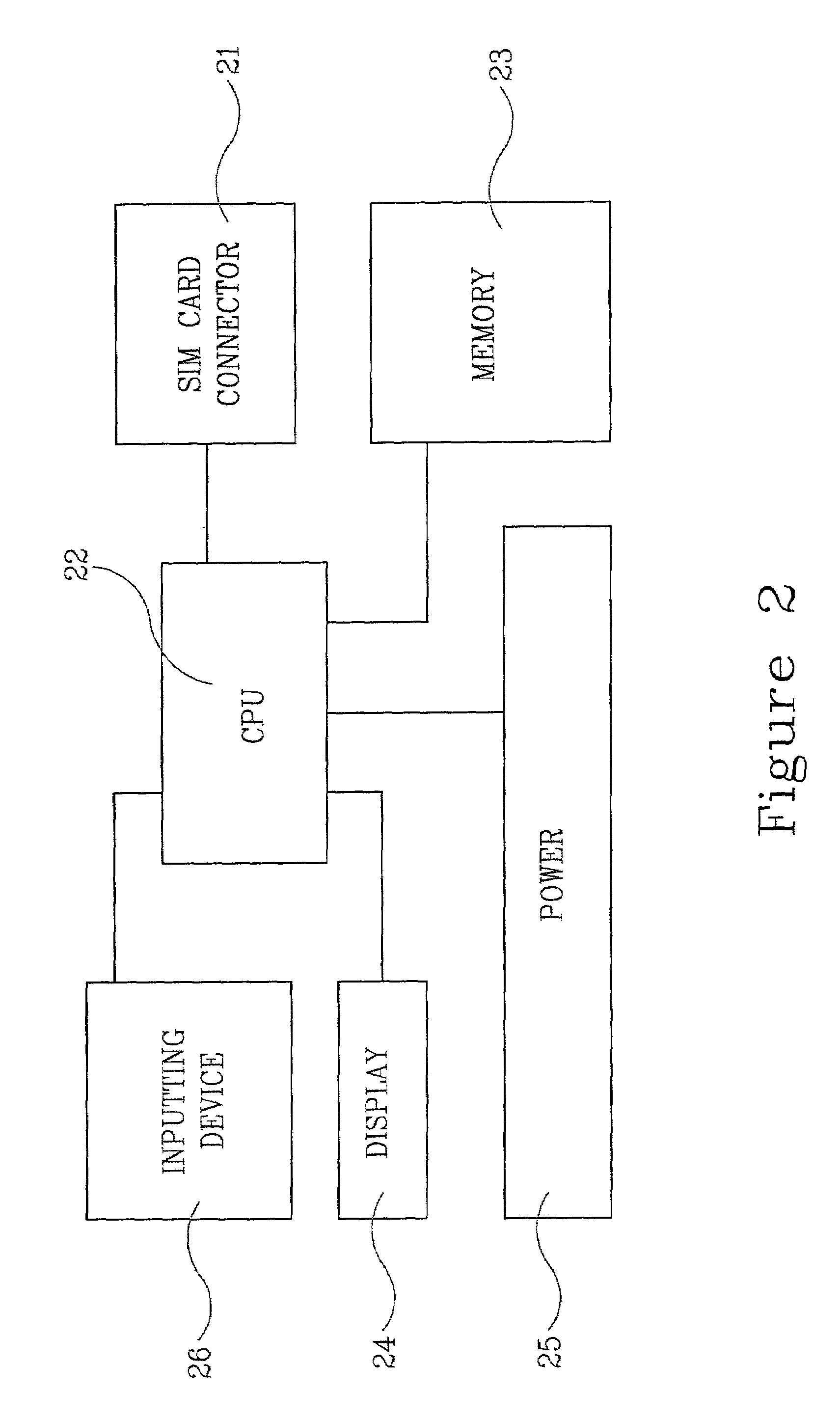

Subscriber identity module card backup system

InactiveUS7146161B2Improve securityEasy to updateCathode-ray tube indicatorsSubstation equipmentProgrammable read-only memorySubscriber identity module

An apparatus for backing up the storage data from a subscriber identity module card will comprise said followings: the subscriber identity module card connector, a central processing unit, a serial electrically erasable programmable read only memory, the displays, the power supply and the inputting device. Firstly, inserting a first subscriber identity module card into a subscriber identity module card connector of the subscriber identity module card backup system is carried out. Then, a first storage data from the subscriber identity module card is extracted and treated to a memory whereby a central processing unit. Next, backing up the first storage data into the memory whereby said central processing unit is achieved. Sequentially, the first subscriber identity module card can be removed from the subscriber identity module card connector. Next, a second subscriber identity module card is inserted into the subscriber identity module card connector. Finally, the first storage data is duplicated from the serial electrically erasable programmable read only memory into the second subscriber identity module card in order to back up the first storage data from the first subscriber identity module card to the second subscriber identity module card.

Owner:ENSKY TECH CO LTD

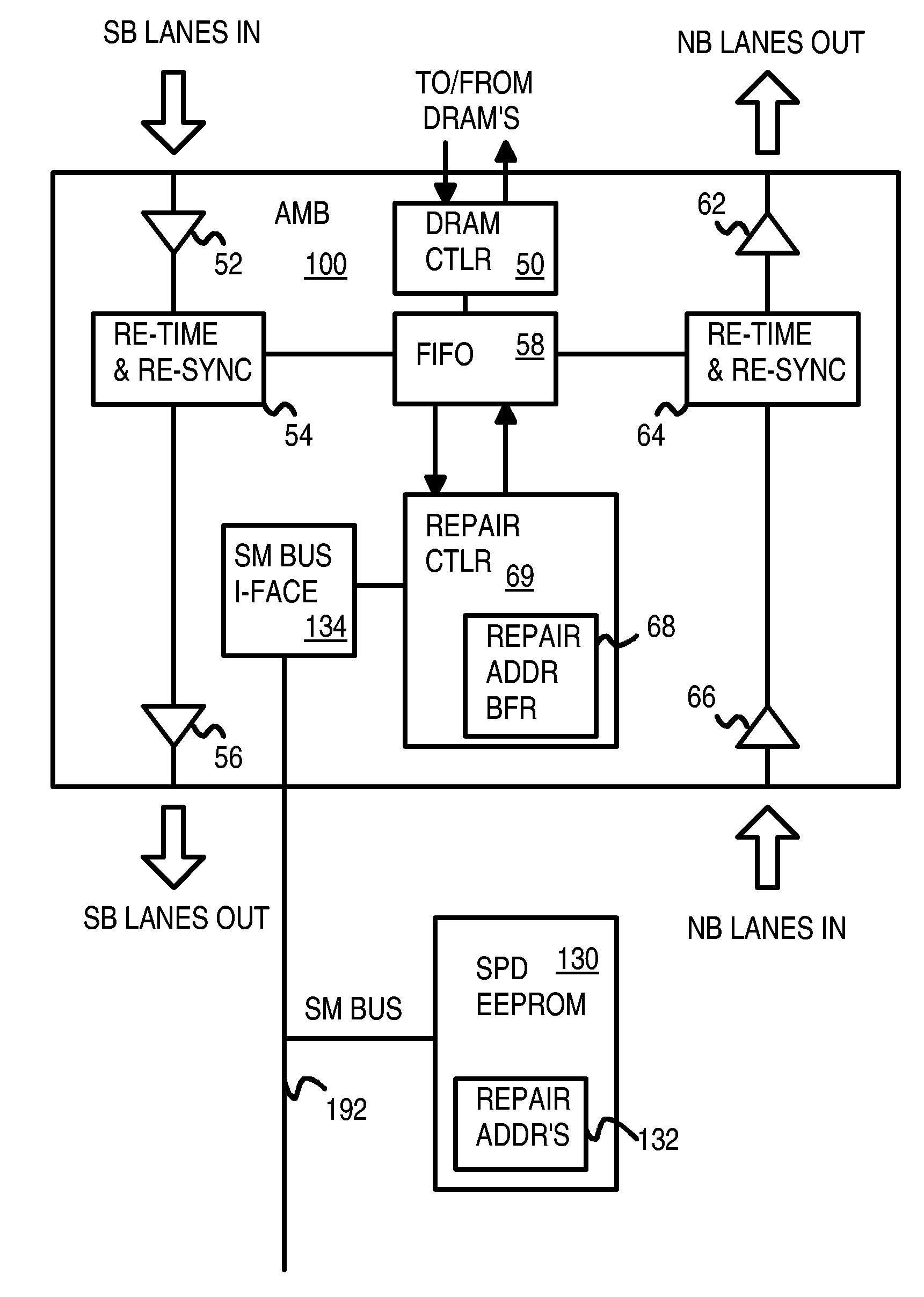

Fully-buffered memory-module with redundant memory buffer in serializing advanced-memory buffer (AMB) for repairing DRAM

A repairing fully-buffered memory module can have memory chips with some defects such as single-bit errors. A repair controller is added to the Advanced Memory Buffer (AMB) on the memory module. The AMB fully buffers memory requests that are sent as serial packets over southbound lanes from a host. Memory-access addresses are extracted from the serial packets by the AMB. The repair controller compares the memory-access addresses to repair addresses and diverts access from defective memory chips to a spare memory for the repair addresses. The repair addresses can be located during testing of the memory module and programmed into a repair address buffer on the AMB. The repair addresses could be first programmed into a serial-presence-detect electrically-erasable programmable read-only memory (SPD-EEPROM) on the memory module, and then copied to the repair address buffer on the AMB during power-up.

Owner:KINGSTON DIGITAL CO LTD

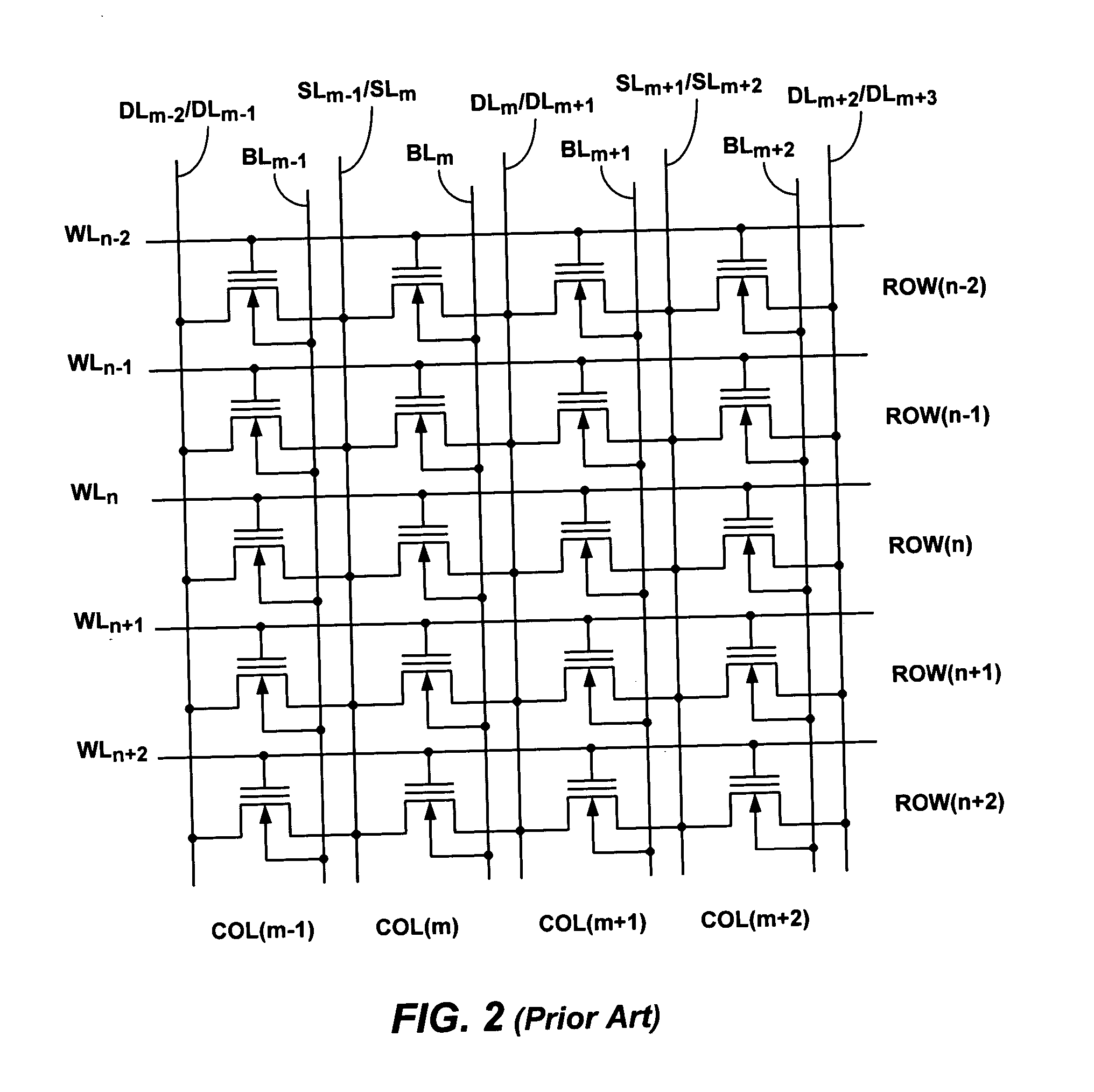

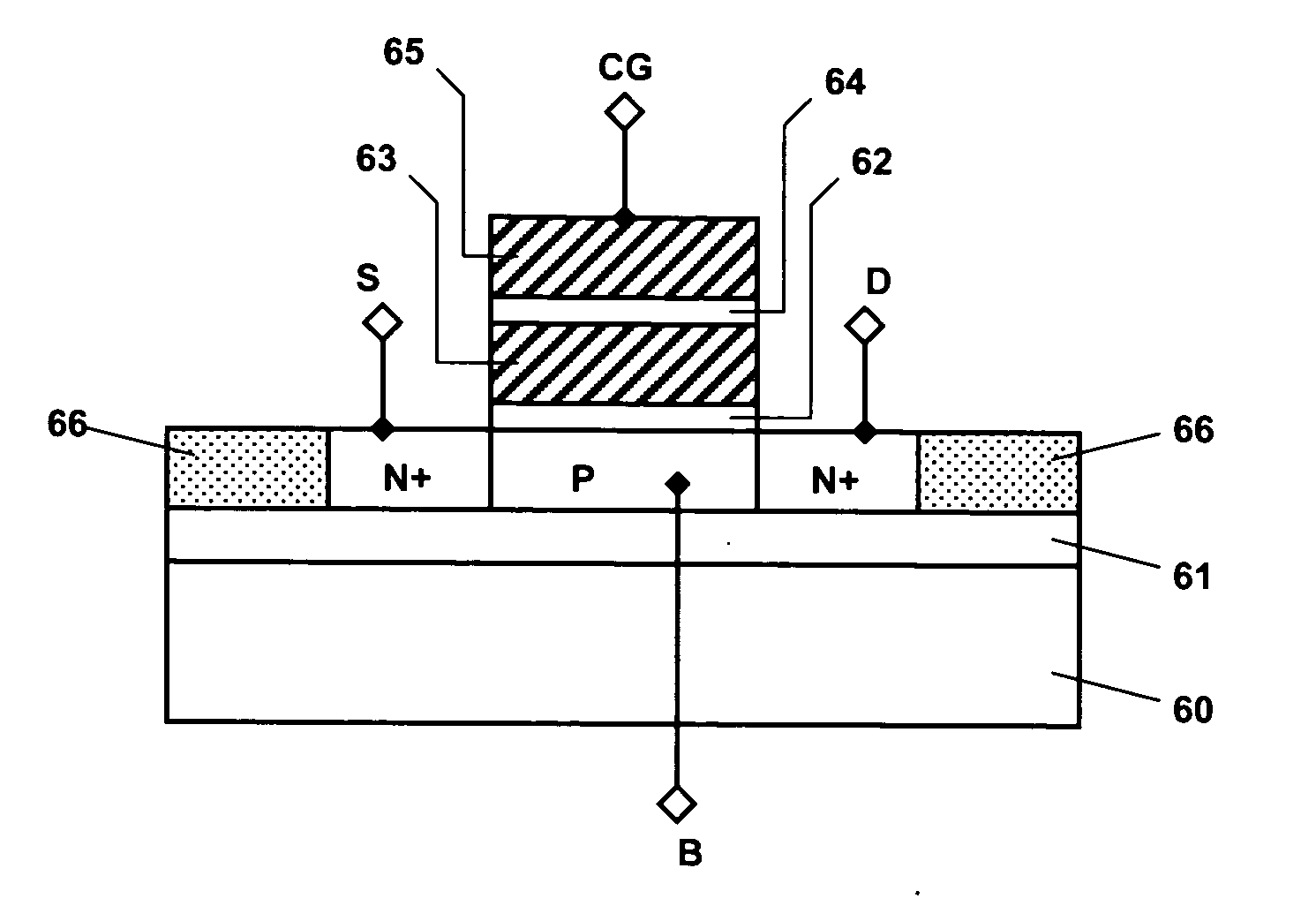

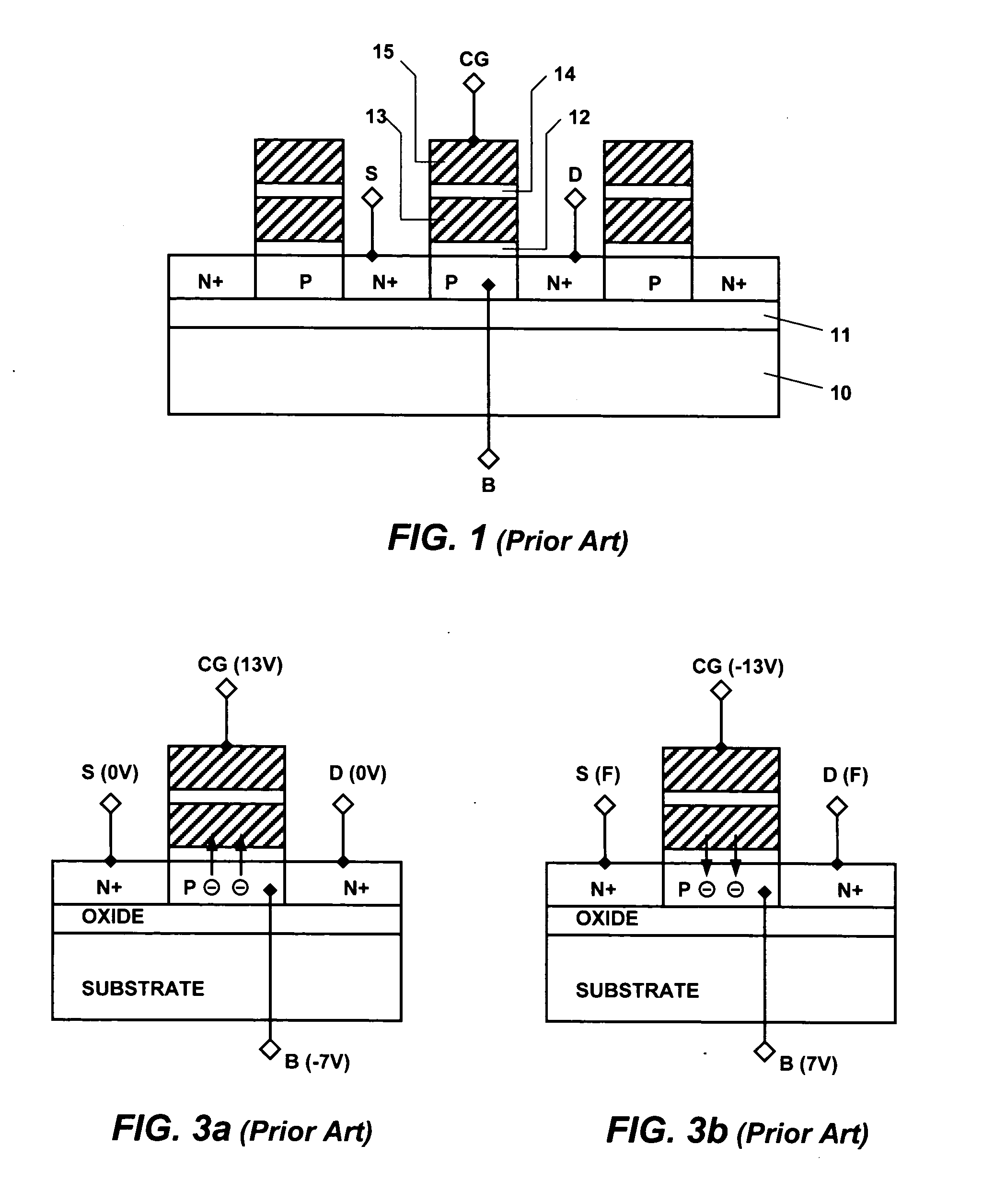

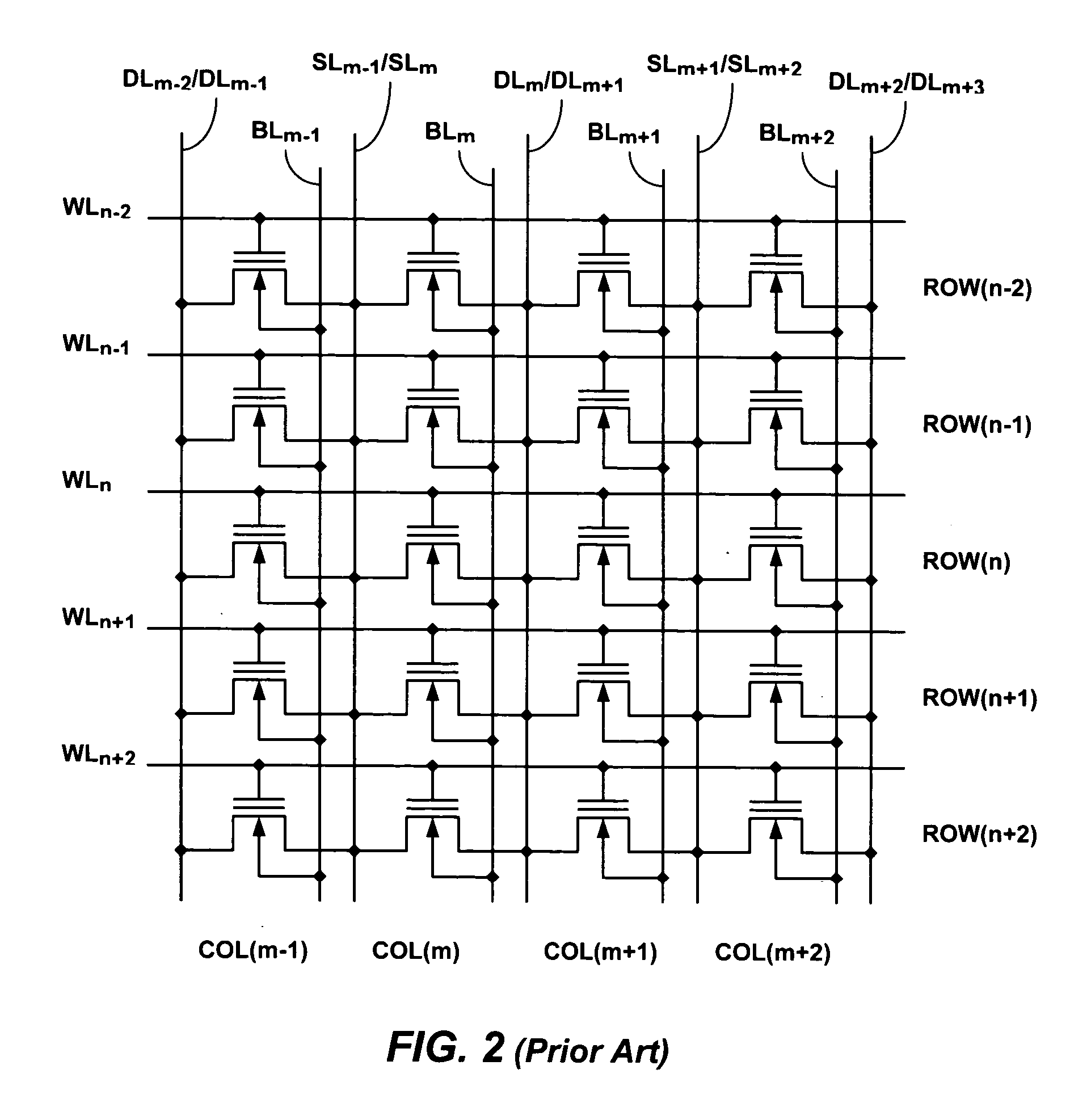

Nor-type channel-program channel-erase contactless flash memory on SOI

InactiveUS20060018164A1Improve good performanceImprove circuit performanceTransistorSolid-state devicesProgrammable read-only memoryDevice material

A semiconductor device having an electrically erasable programmable read only memory (EEPROM) comprises a contactless array of EEPROM memory cells disposed in rows and columns and constructed over a silicon-on-insulator wafer. Each EEPROM memory cell comprises a drain region, a source region, a gate region, and a body region. The semiconductor device further comprises a plurality of gate lines each connecting the gate regions of a row of EEPROM memory cells, a plurality of body lines each connecting the body regions of a column of EEPROM memory cells, a plurality of source lines each connecting the source regions of a column of EEPROM memory cells, and a plurality of drain lines each connecting the drain regions of a column of EEPROM memory cells. The source lines and the drain lines are buried lines, and the source regions and the drain regions of a column of EEPROM memory cells are insulated from the source regions and the drain regions of the adjacent columns of EEPROM memory cells.

Owner:WU KOUCHENG

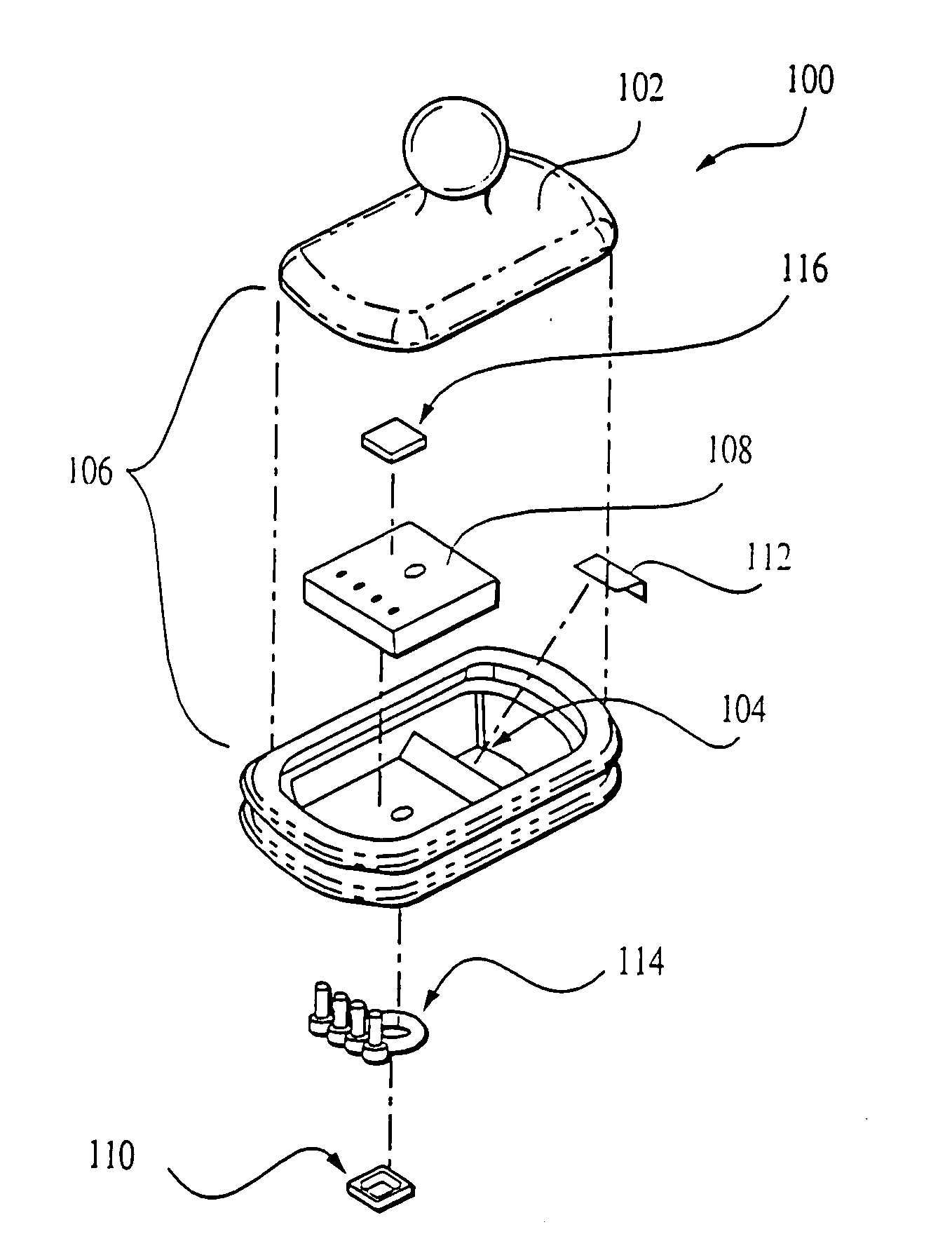

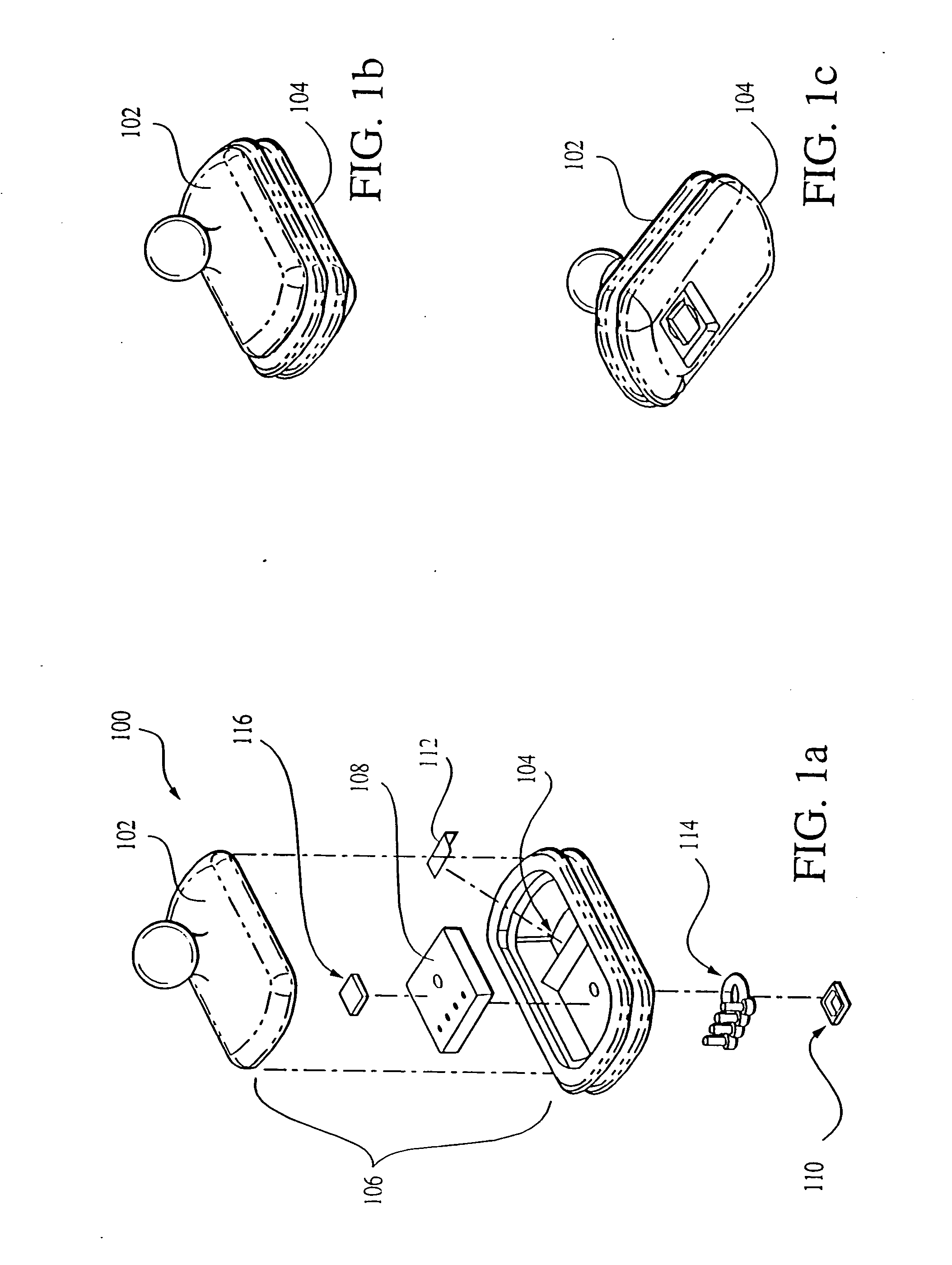

Smart physiologic parameter sensor and method

InactiveUS20050049501A1Low costEasy disposalBlood flow measurement devicesHeart/pulse rate measurement devicesUltrasonic sensorProgrammable read-only memory

A sensor assembly used for the measurement of one or more physiologic parameters of a living subject which is capable of storing both data obtained dynamically during use as well as that programmed into the device. In one embodiment, the sensor assembly comprises a disposable combined pressure and ultrasonic transducer incorporating an electrically erasable programmable read-only memory (EEPROM), the assembly being used for the non-invasive measurement of arterial blood pressure. The sensor EEPROM has a variety of information relating to the manufacture, run time, calibration, and operation of the sensor, as well as application specific data such as patient or health care facility identification. Portions of the data are encrypted to prevent tampering. In a second embodiment, one or more additional storage devices (EEPROMs) are included within the host system to permit the storage of data relating to the system and a variety of different sensors used therewith. In a third embodiment, one or more of the individual transducer elements within the assembly are made separable and disposable, thereby allowing for the replacement of certain selected components which may degrade or become contaminated. Methods for calibrating and operating the disposable sensor assembly in conjunction with its host system are also disclosed.

Owner:CONERO RONALD S +1

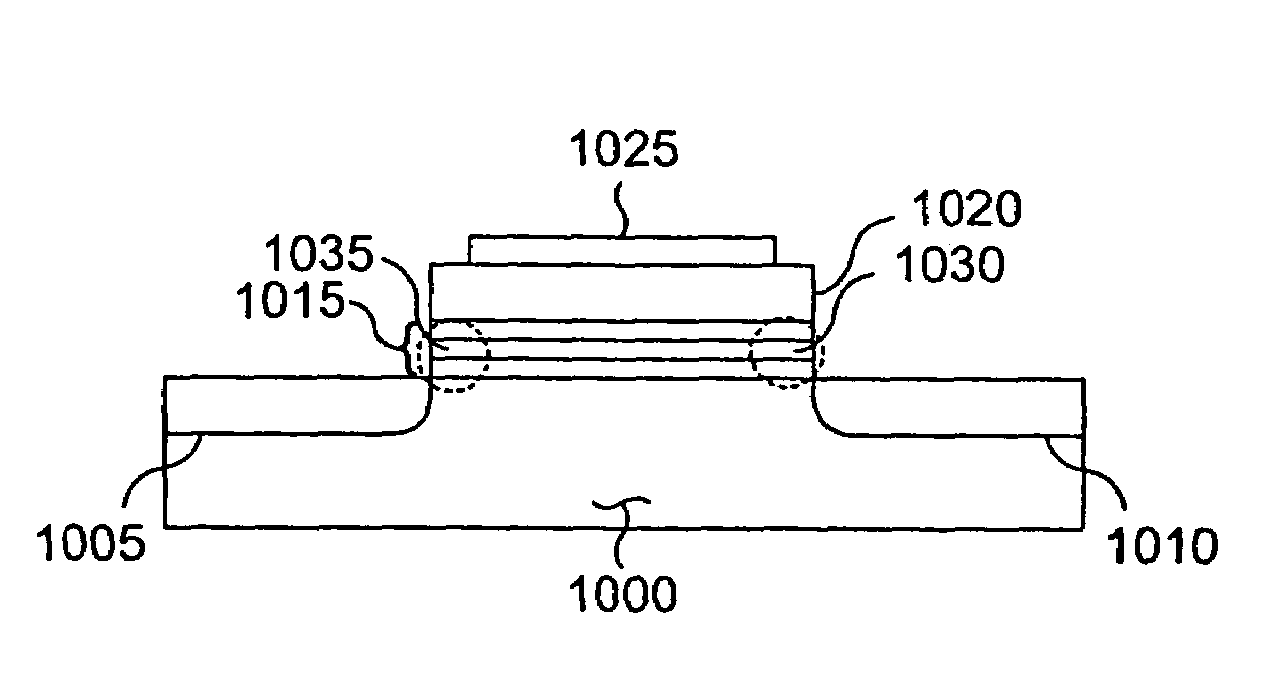

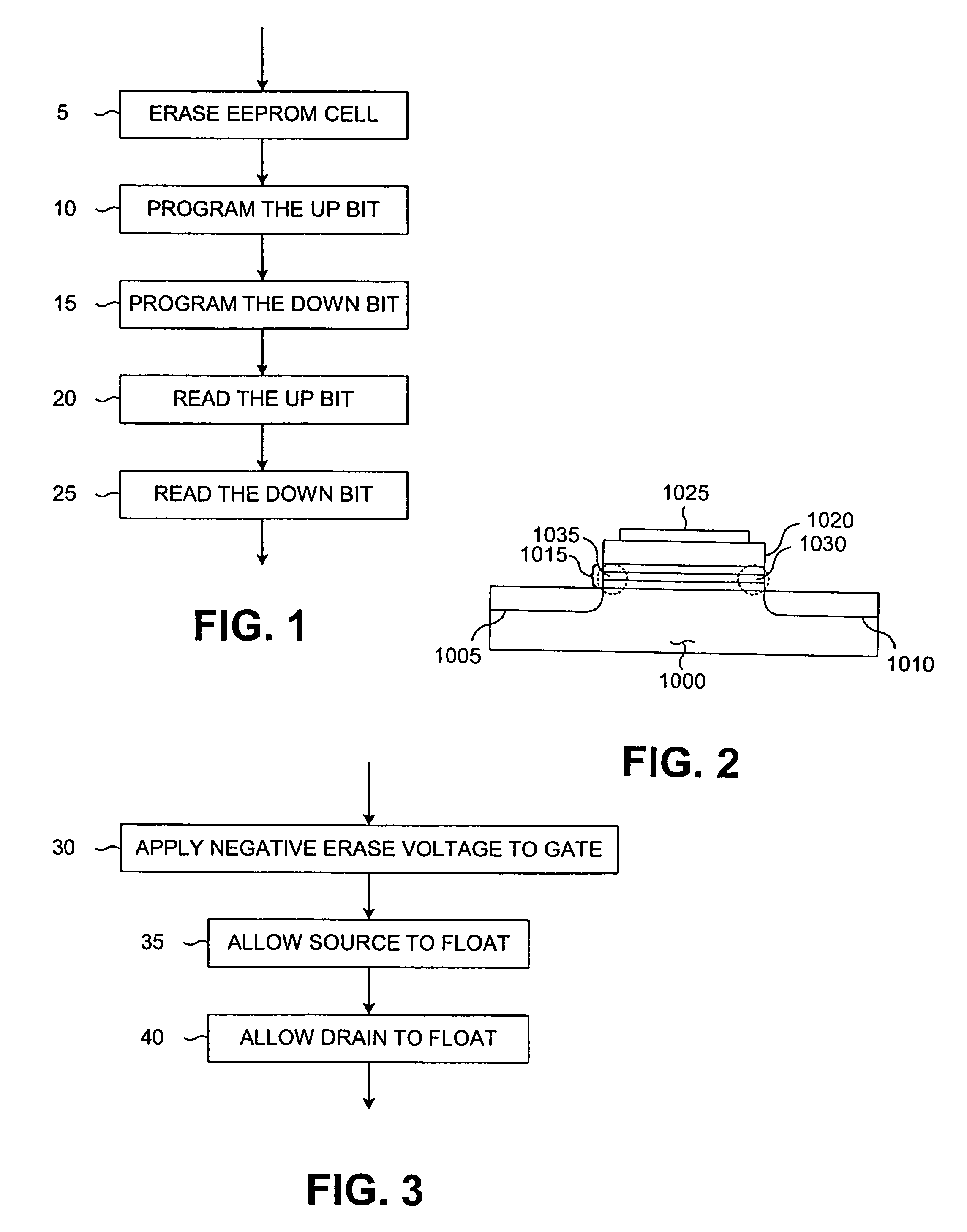

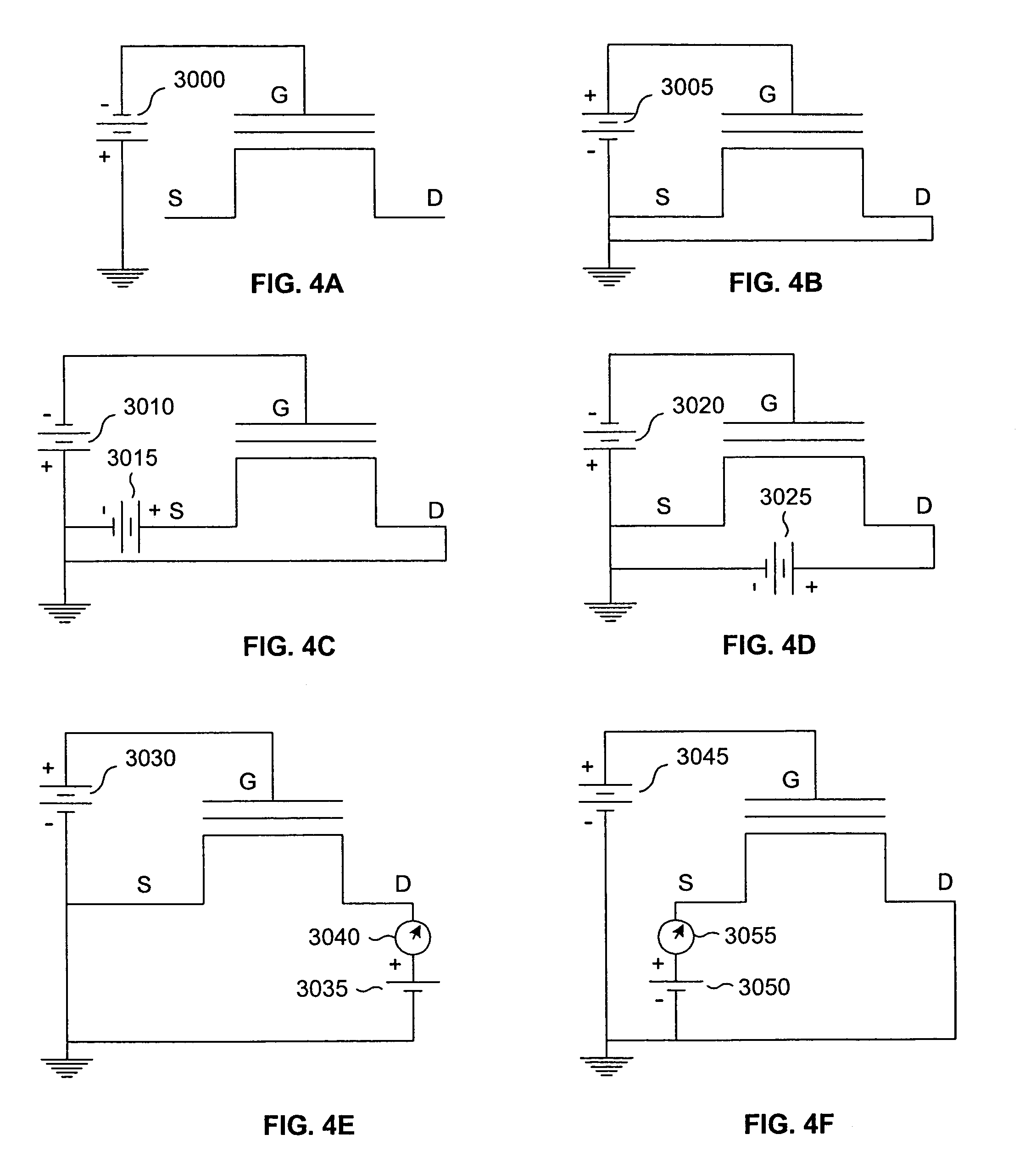

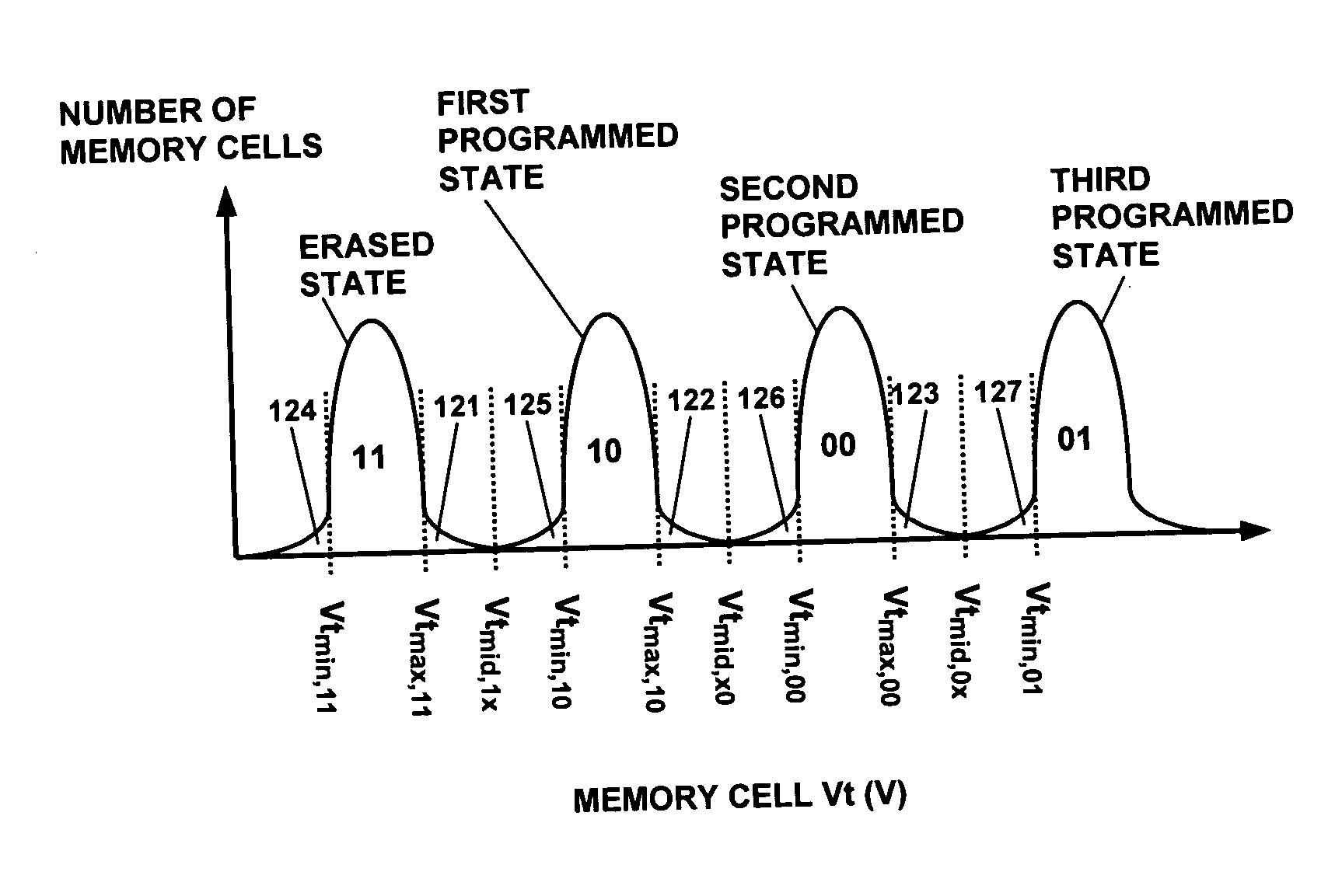

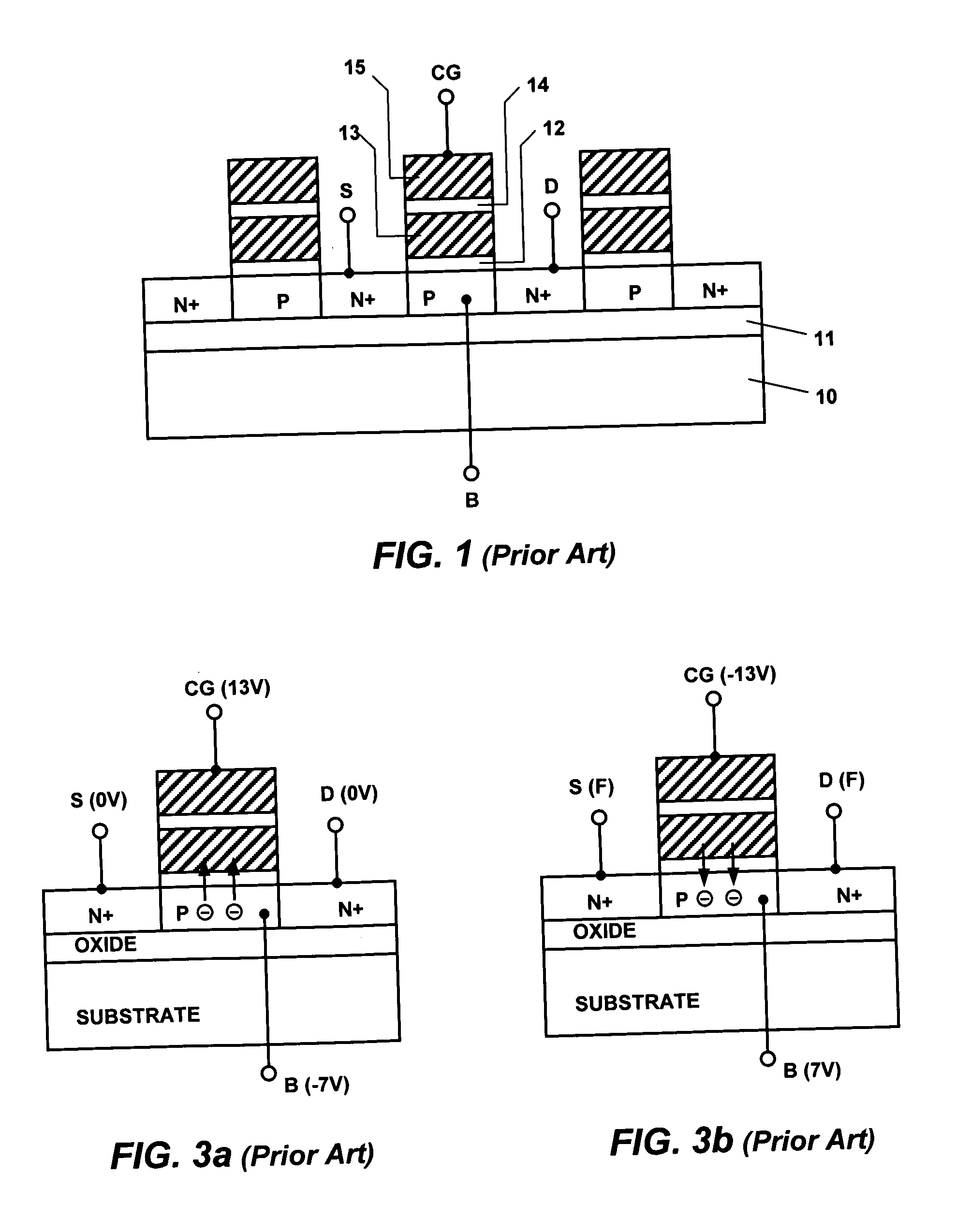

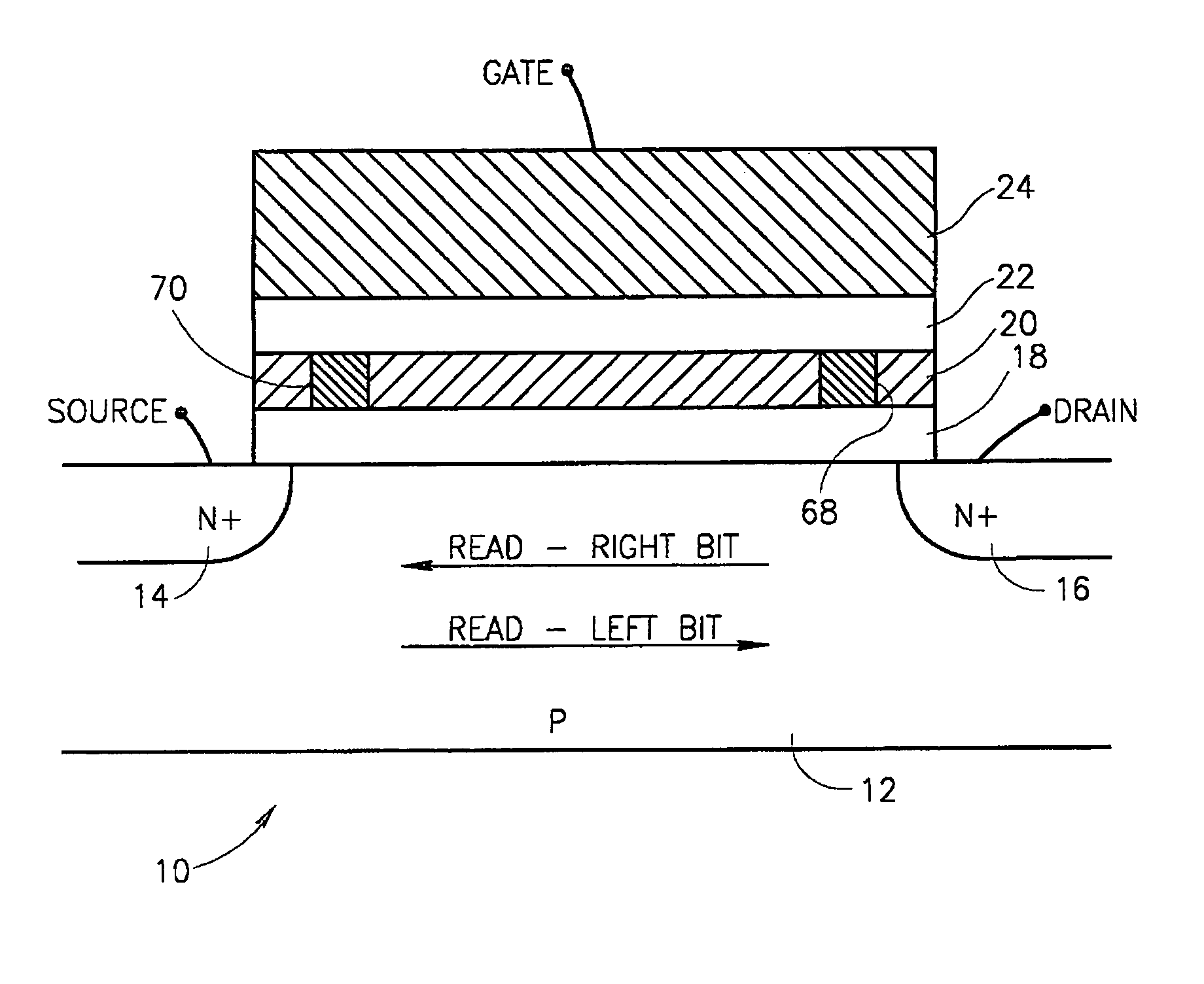

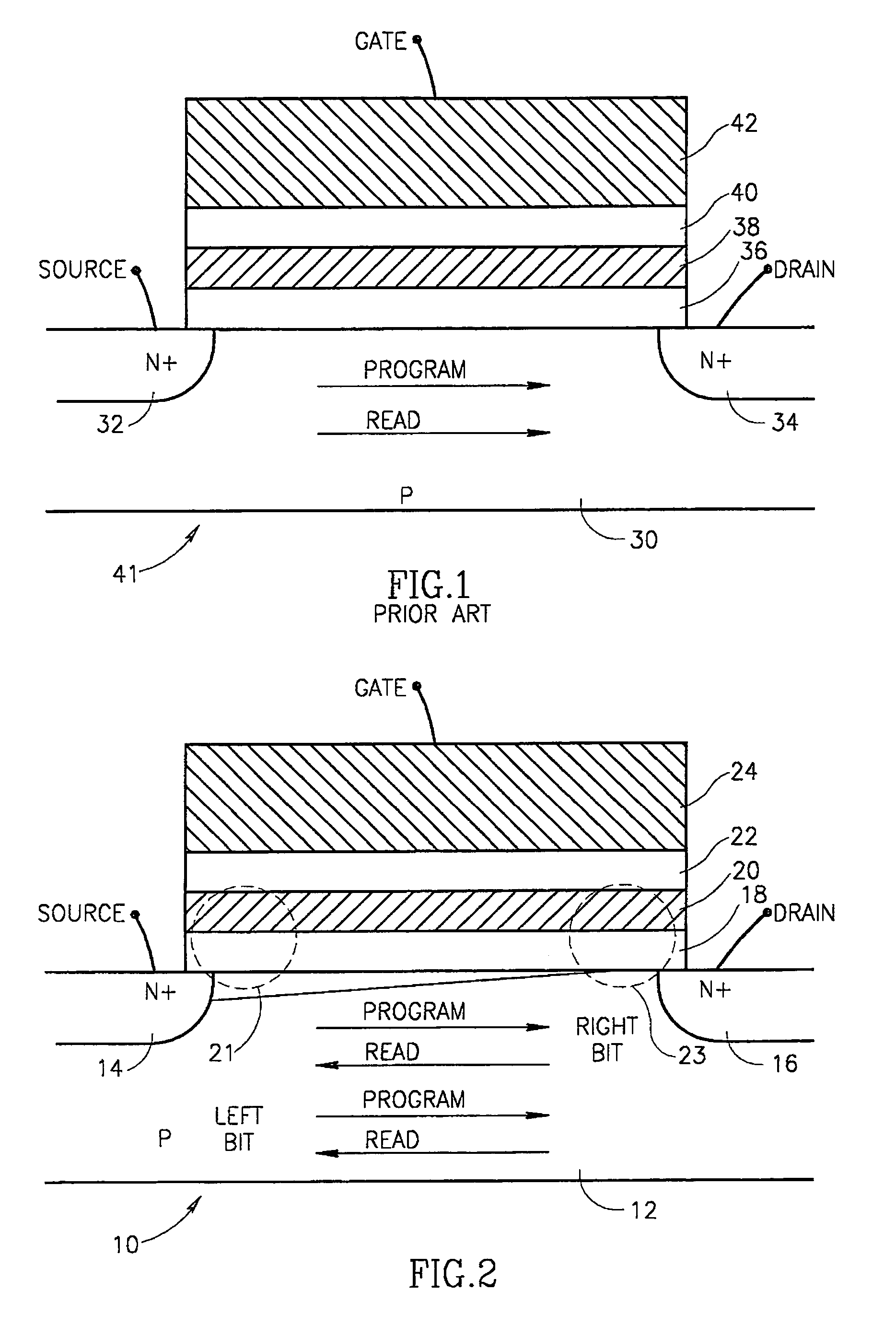

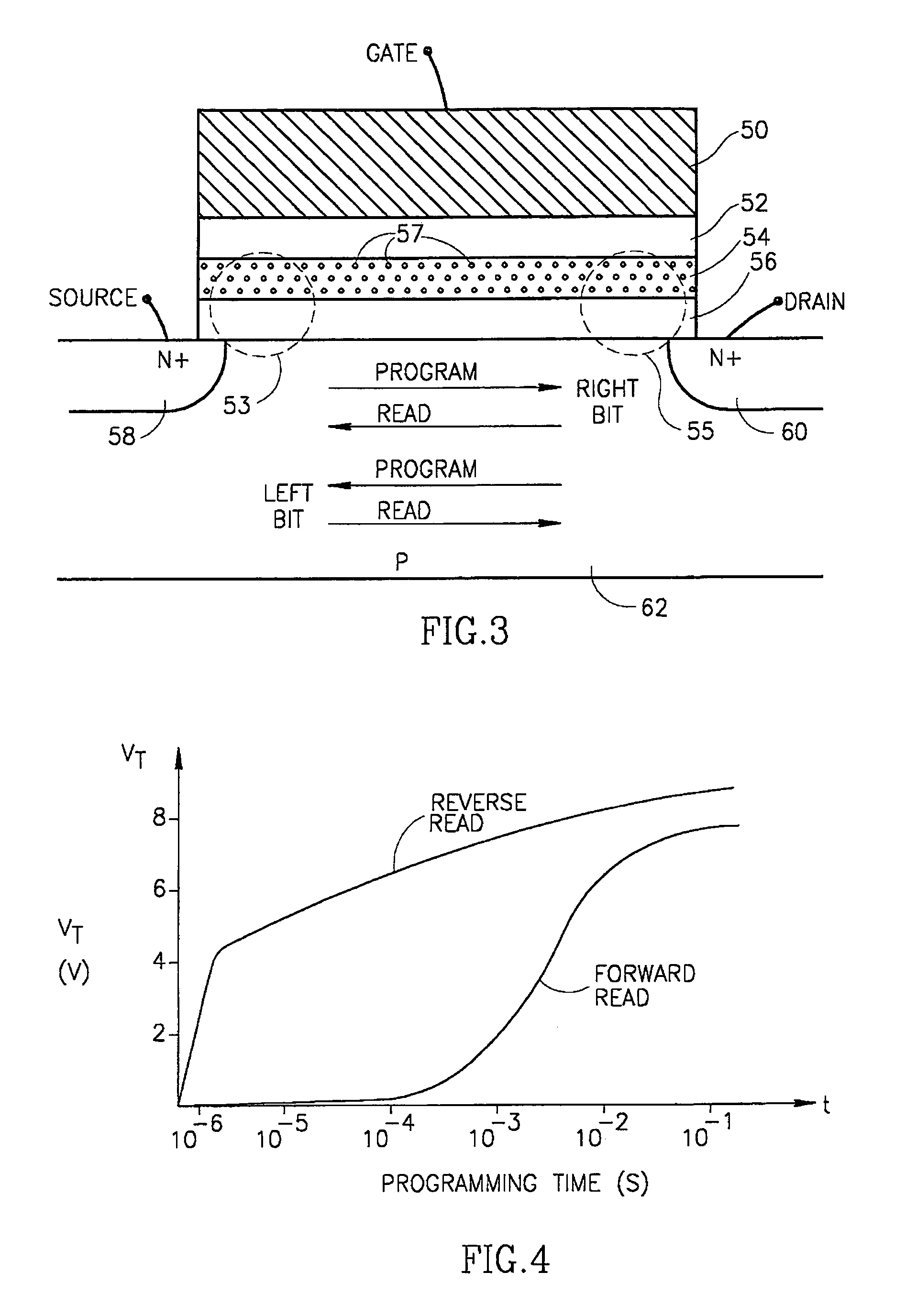

Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping

InactiveUS7116577B2Little effectShorten speedTransistorSolid-state devicesDielectricProgrammable read-only memory

A non-volatile electrically erasable programmable read only memory (EEPROM) capable of storing two bit of information having a nonconducting charge trapping dielectric, such as silicon nitride, sandwiched between two silicon dioxide layers acting as electrical insulators is disclosed. A left and a right bit are stored in physically different areas of the charge trapping layer, near left and right regions of the memory cell, respectively. Two bits are able to be programmed and read due to a combination of relatively low gate voltages with reading in the reverse direction. This greatly reduces the potential across the trapped charge region. This permits much shorter programming times by amplifying the effect of the charge trapped in the localized trapping region associated with each of the bits. In addition, both bits of the memory cell can be individually erased by applying suitable erase voltages to the gate and either left or right regions so as to cause electrons to be removed from the corresponding charge trapping region of the nitride layer.

Owner:SAIFUN SEMICON

Nor-type channel-program channel-erase contactless flash memory on SOI

InactiveUS20050179079A1Improve good performanceImprove circuit performanceTransistorSolid-state devicesProgrammable read-only memoryDevice material

A semiconductor device having an electrically erasable programmable read only memory (EEPROM) comprises a contactless array of EEPROM memory cells disposed in rows and columns and constructed over a silicon-on-insulator wafer. Each EEPROM memory cell comprises a drain region, a source region, a gate region, and a body region. The semiconductor device further comprises a plurality of gate lines each connecting the gate regions of a row of EEPROM memory cells, a plurality of body lines each connecting the body regions of a column of EEPROM memory cells, a plurality of source lines each connecting the source regions of a column of EEPROM memory cells, and a plurality of drain lines each connecting the drain regions of a column of EEPROM memory cells. The source lines and the drain lines are buried lines, and the source regions and the drain regions of a column of EEPROM memory cells are insulated from the source regions and the drain regions of the adjacent columns of EEPROM memory cells.

Owner:WU KOUCHENG

Fully-buffered memory-module with error-correction code (ECC) controller in serializing advanced-memory buffer (AMB) that is transparent to motherboard memory controller

ActiveUS7487428B2Error detection/correctionStatic storageProgrammable read-only memoryError correcting

An error-correcting fully-buffered memory module can detect and correct some errors in data read from memory chips. An error correction code ECC controller is added to the Advanced Memory Buffer (AMB) on the memory module that fully buffers memory requests sent as serial packets. The error correction controller generates ECC bits for write data, and both the ECC bits and the write data are written to the memory chips by a DRAM controller in the AMB. During reads, an ECC checker generates a syndrome and can activate an error corrector to correct data or signal a non-correctable error. The corrected data is formed into serial packets sent back to the motherboard by the AMB. Configuration data for the ECC controller could be first programmed into a serial-presence-detect electrically-erasable programmable read-only memory (SPD-EEPROM) on the memory module, and then copied to error-correction configuration registers on the AMB during power-up.

Owner:KINGSTON DIGITAL CO LTD

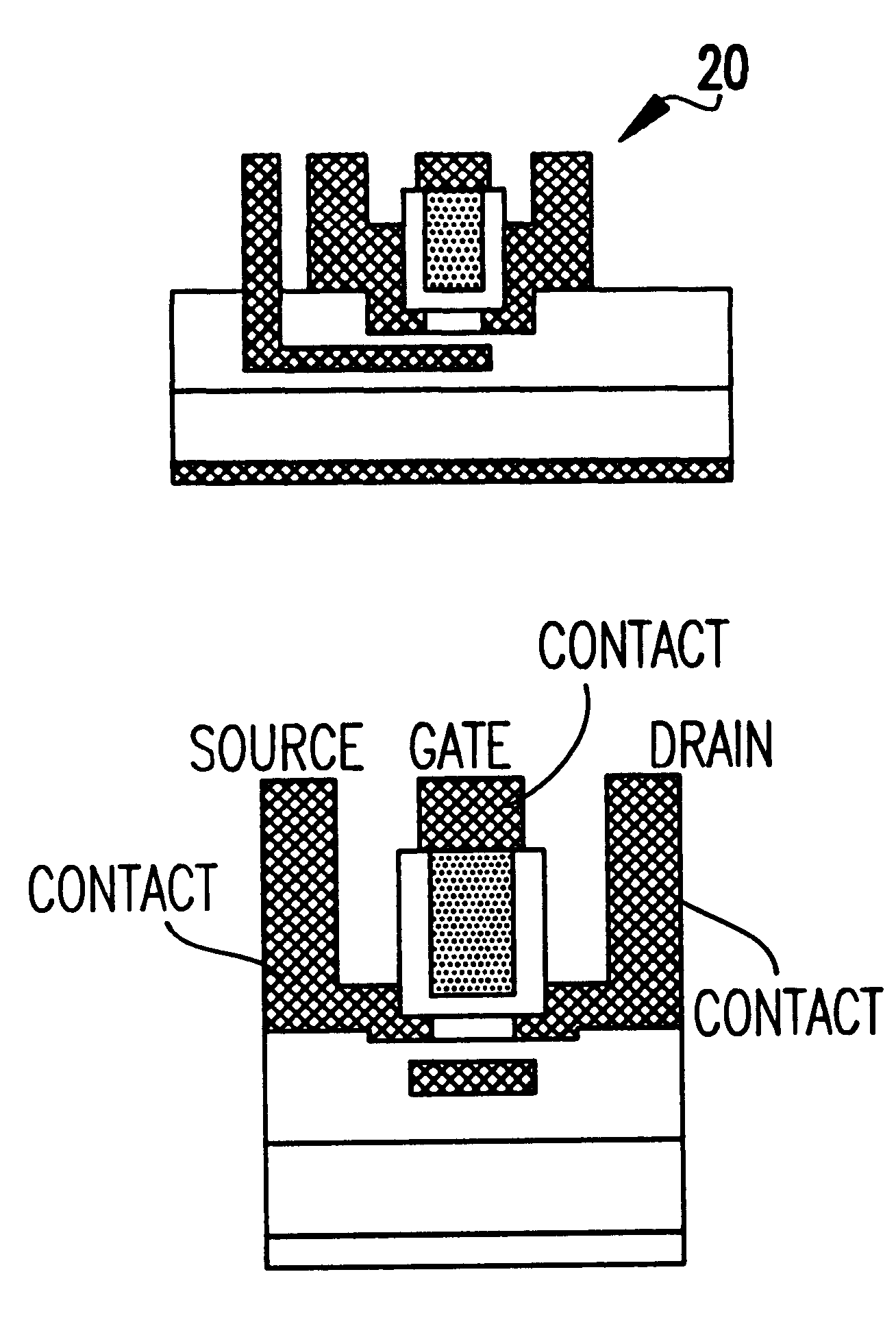

Vertical transistor with horizontal gate layers

InactiveUS20030038318A1TransistorSolid-state devicesProgrammable read-only memoryArray data structure

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F2 is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

One time programmable read-only memory comprised of fuse and two selection transistors

InactiveUS20060203591A1Reduce the differenceSimple processTransistorSolid-state devicesProgrammable read-only memoryInsulation layer

A one time programmable read-only memory (OTPROM) device includes a plurality of memory cells, where a memory cell of the OTPROM device comprises a fuse indicating a first memory state of the memory cell if the fuse is destroyed and a second memory state of the memory cell if the fuse is not destroyed, a first transistor coupled to the fuse, and a second transistor serially coupled to the first transistor. Both the first transistor and the second transistor are turned on to select the memory cell, and at least one of the first transistor and the second transistor are turned off to unselect the memory cell. The fuse insulation layer of the fuse and the gate insulation layers of the first and second transistors share a common insulation layer formed in the same fabrication process.

Owner:LEADIS TECH