Patents

Literature

294 results about "Field programmable logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

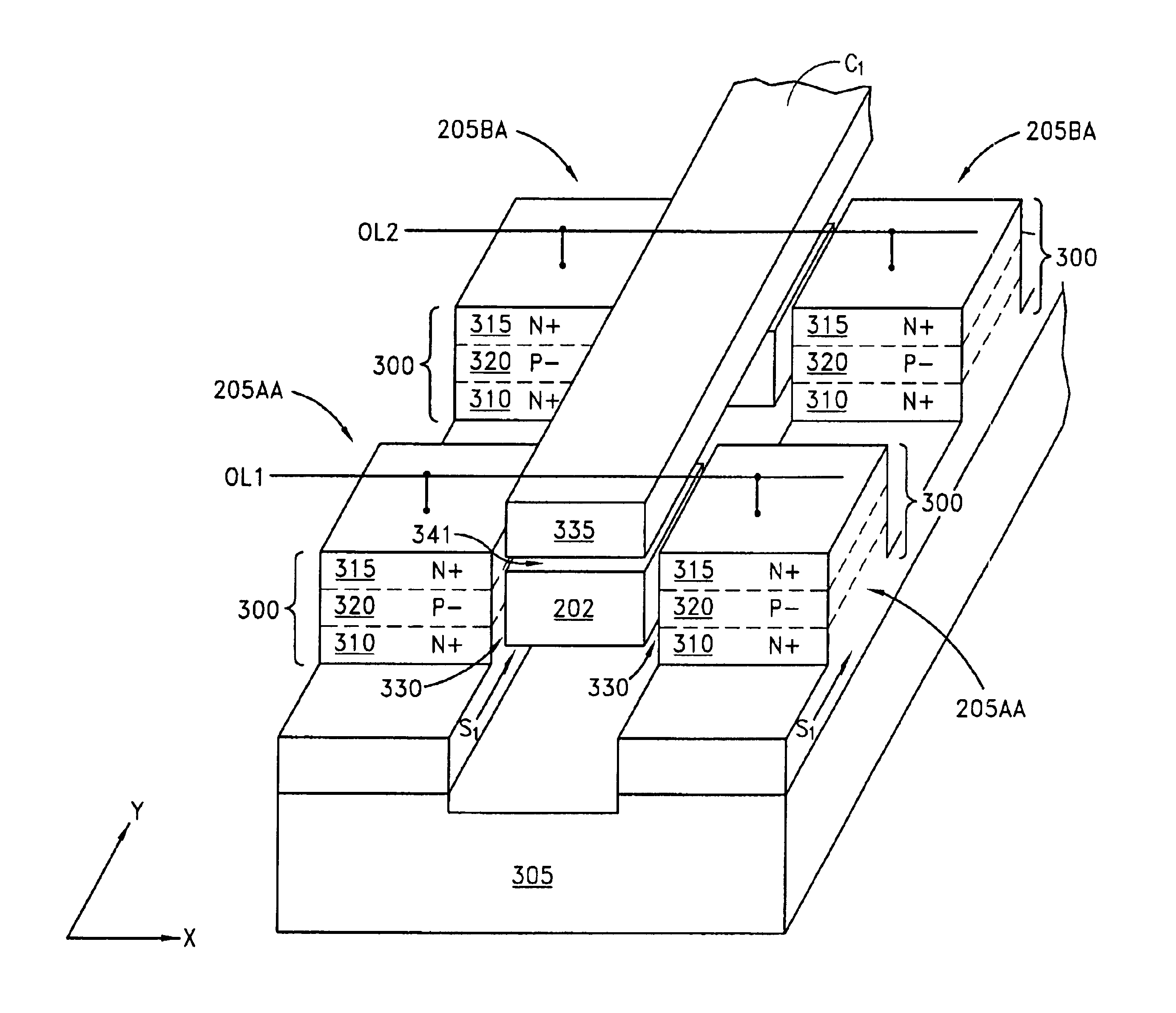

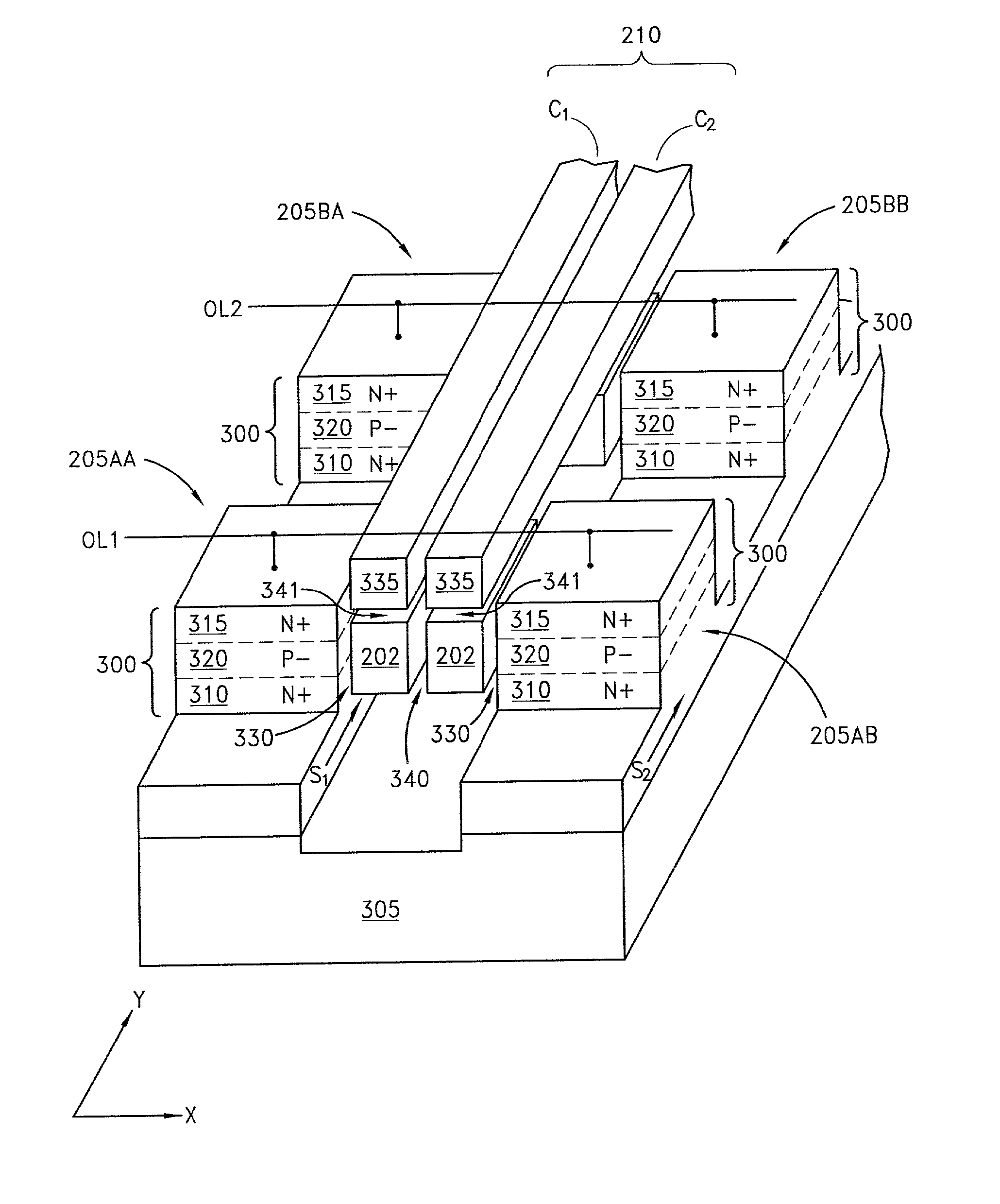

Floating gate transistor with horizontal gate layers stacked next to vertical body

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F<2 >is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

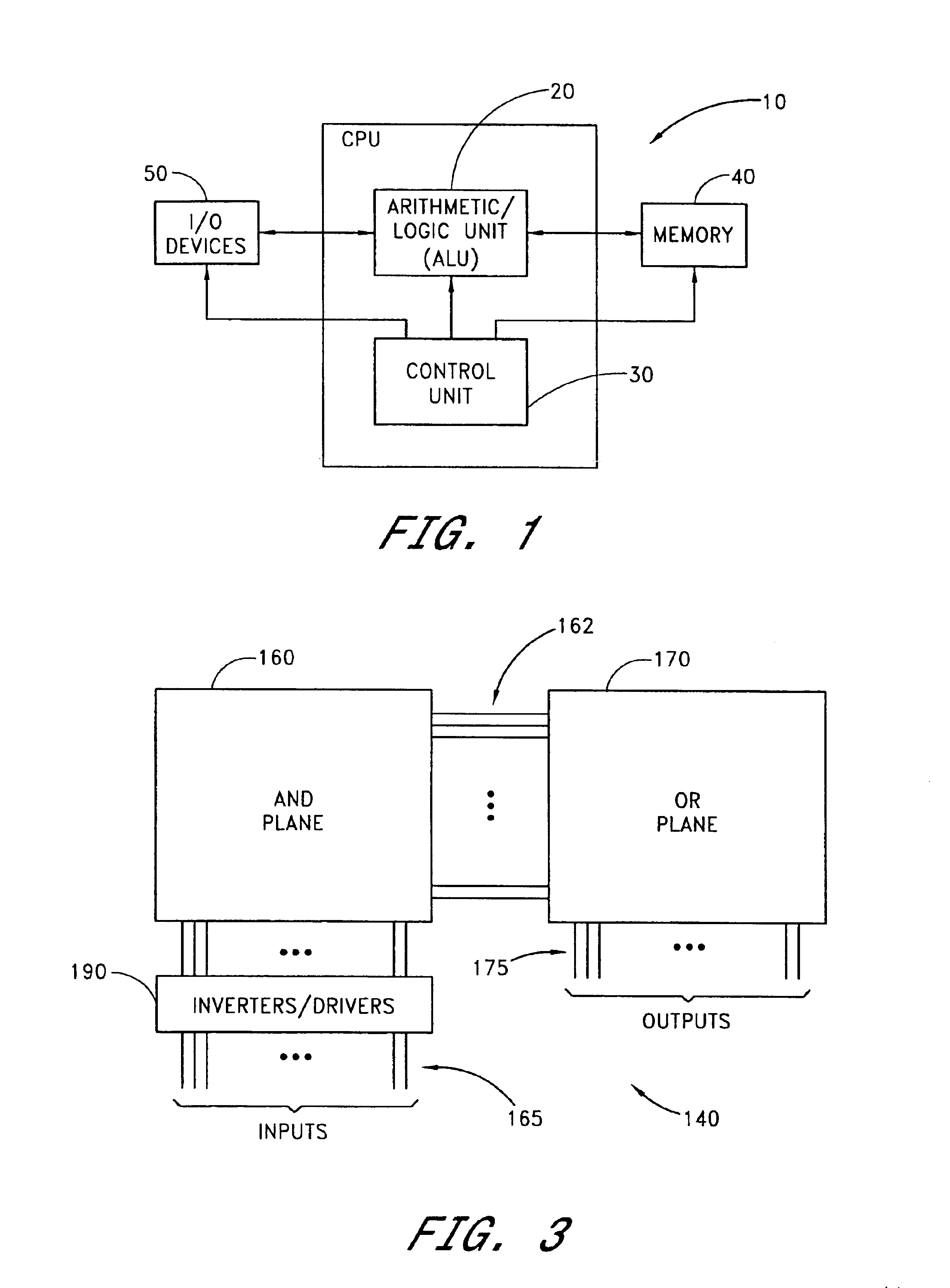

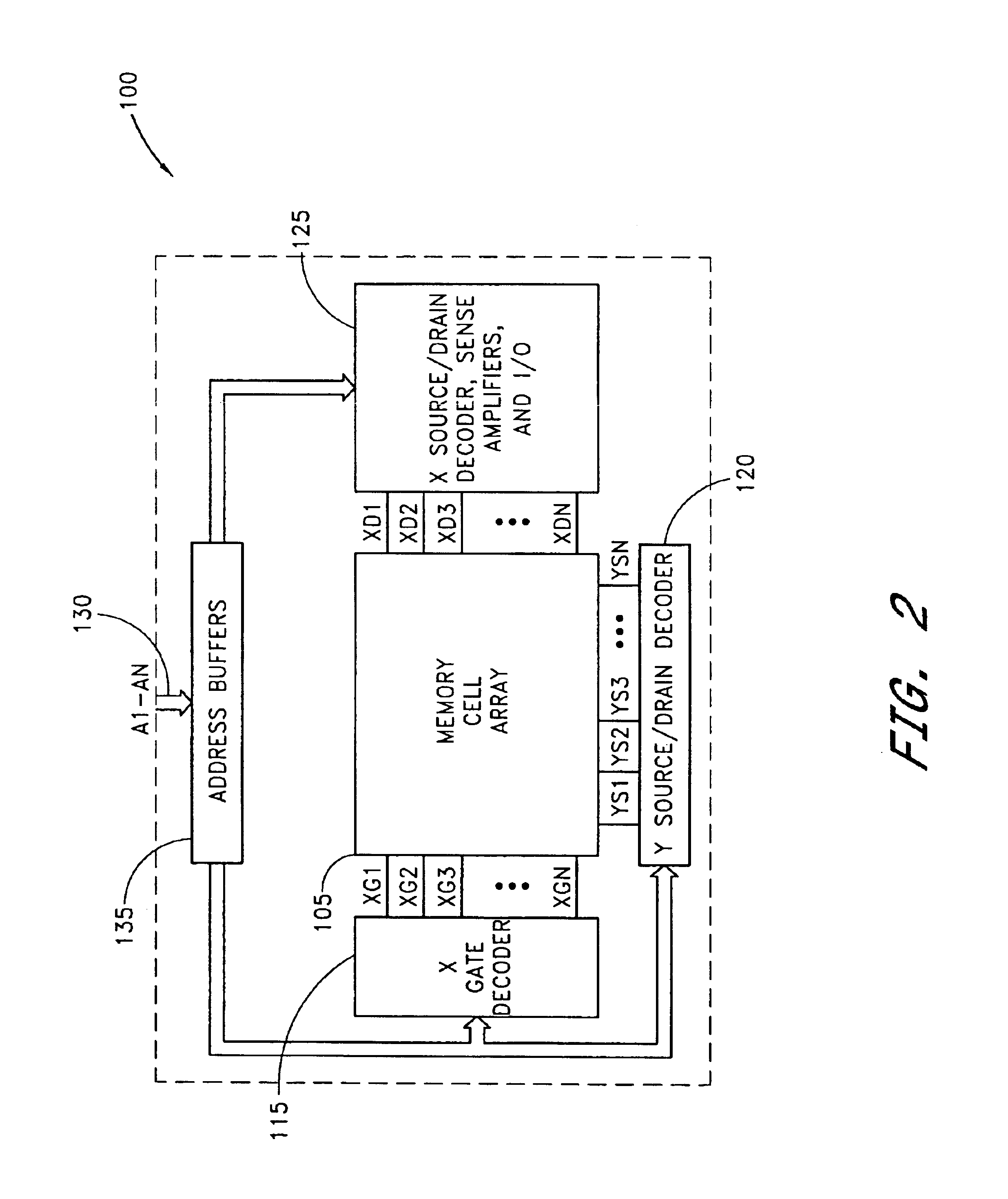

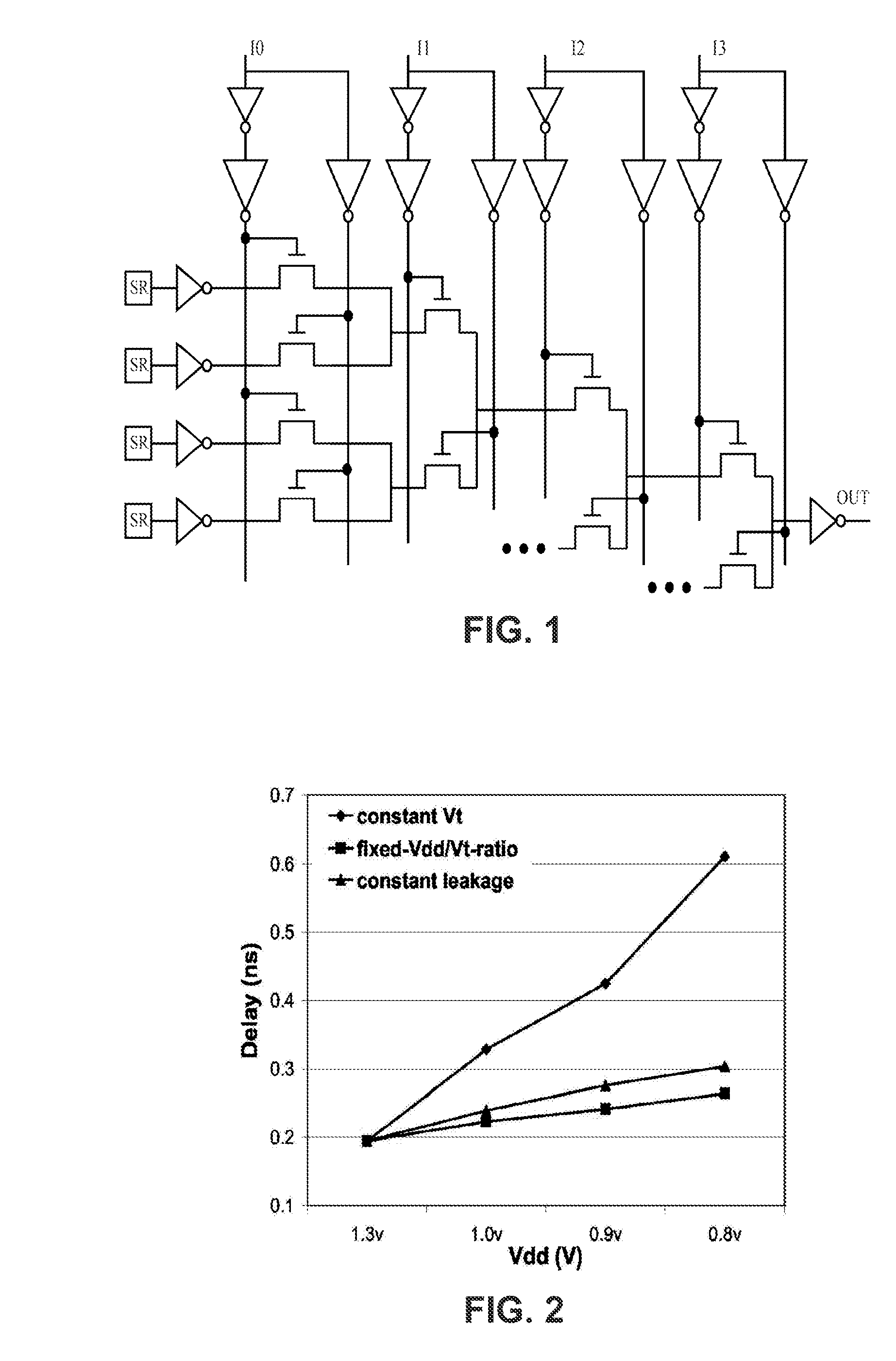

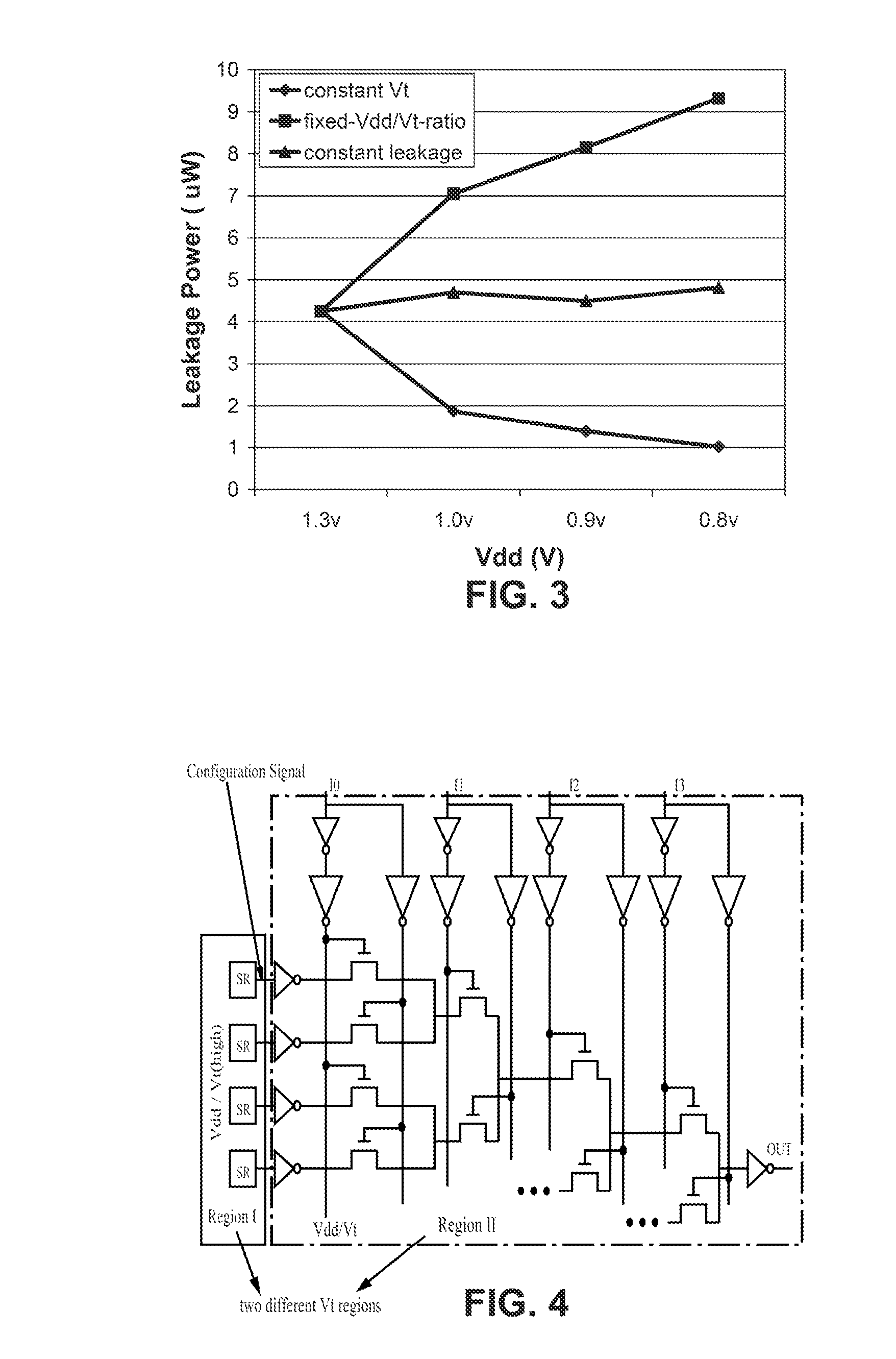

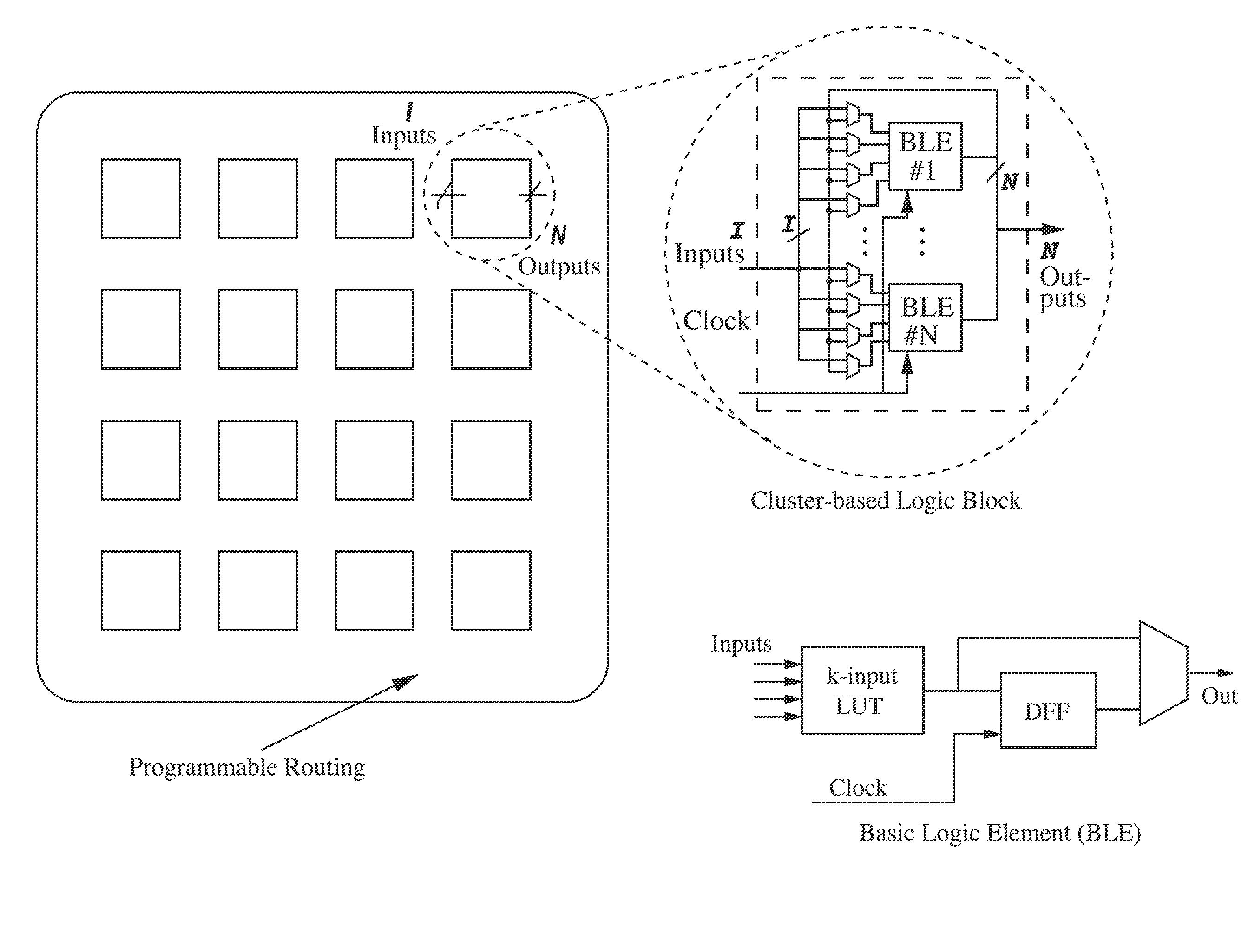

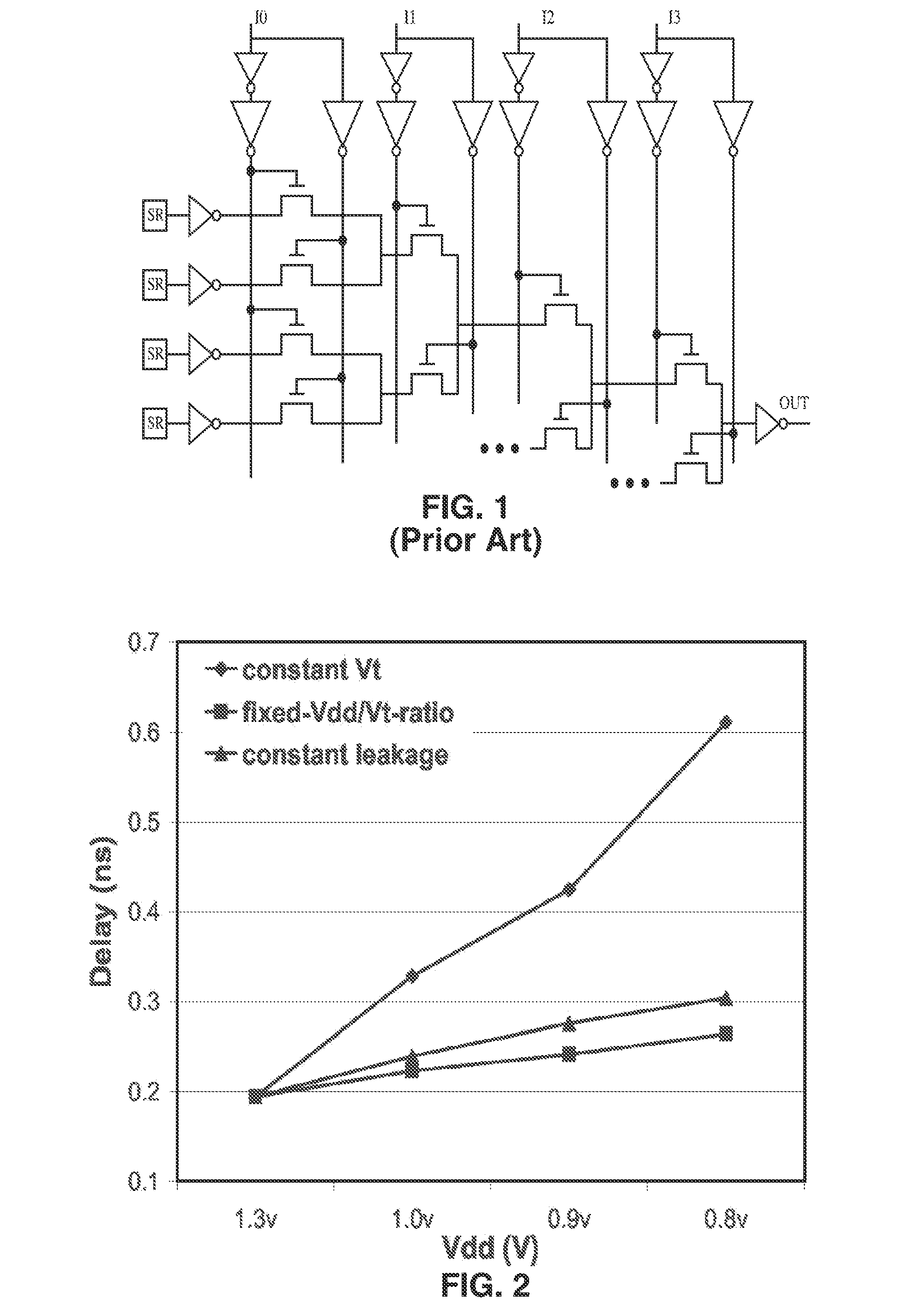

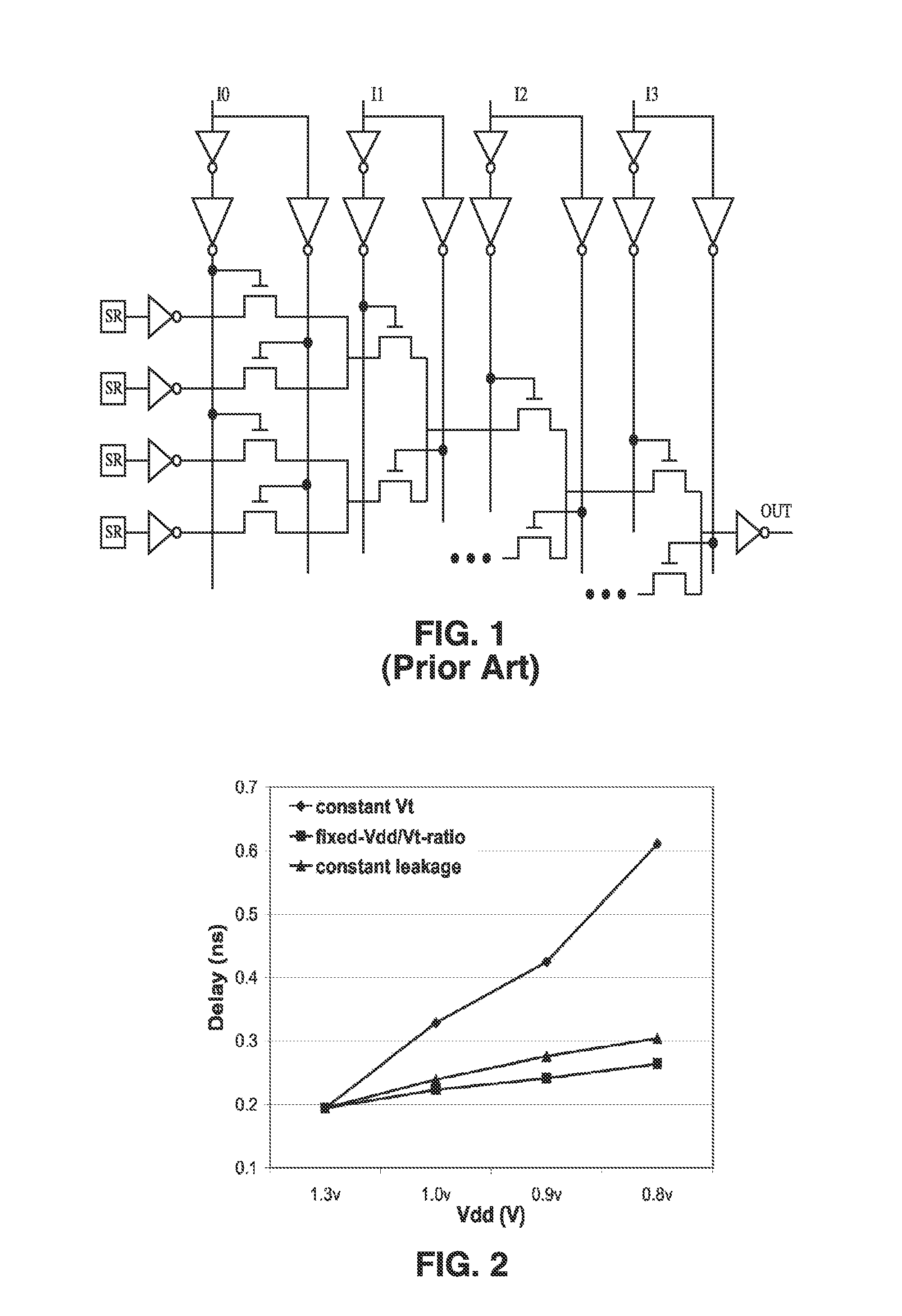

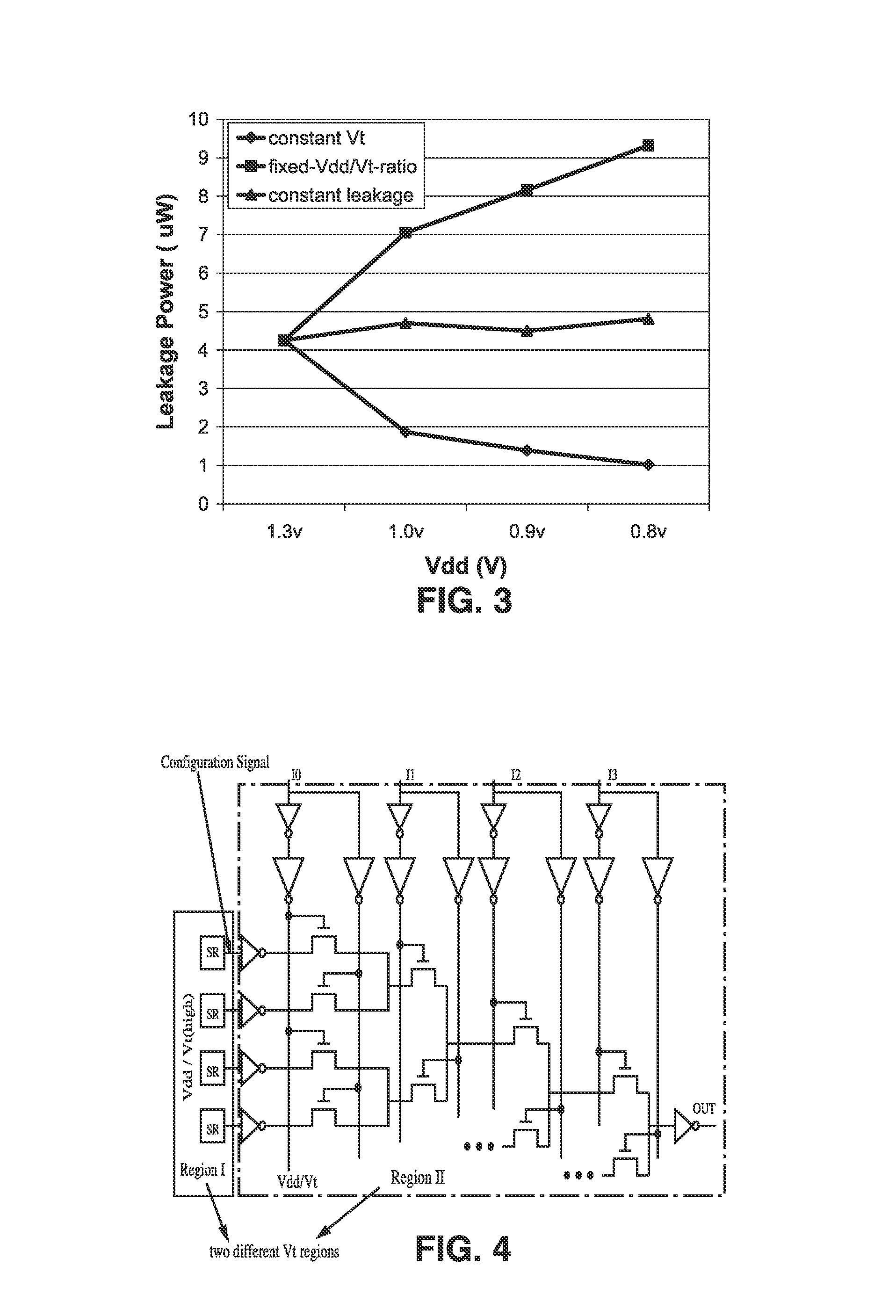

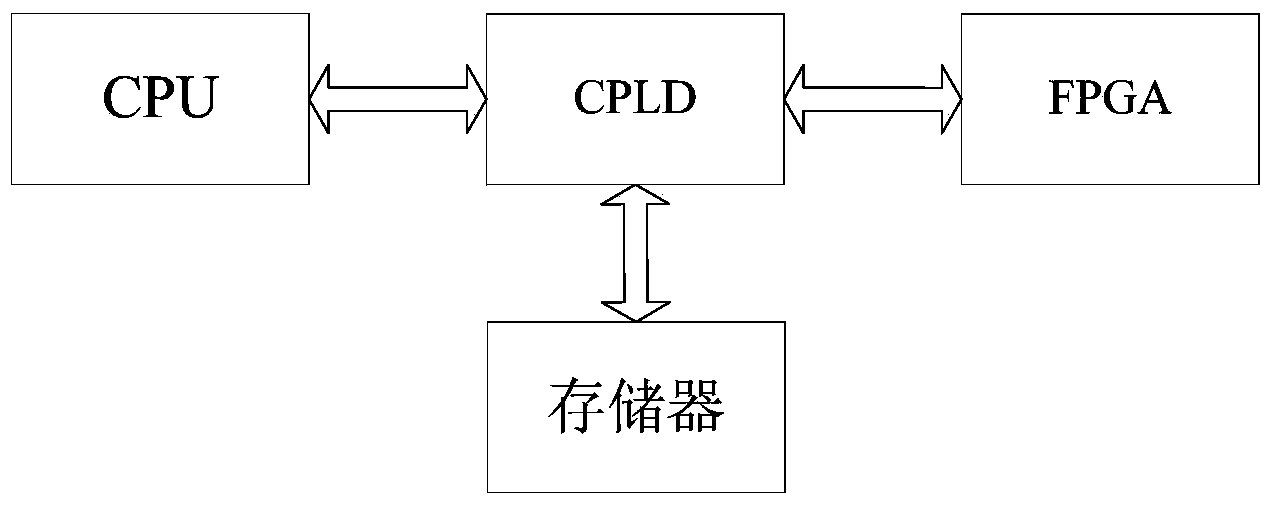

Low-power FPGA circuits and methods

InactiveUS20070164785A1Increase profitReduce needSolid-state devicesCAD circuit designEngineeringLeakage power

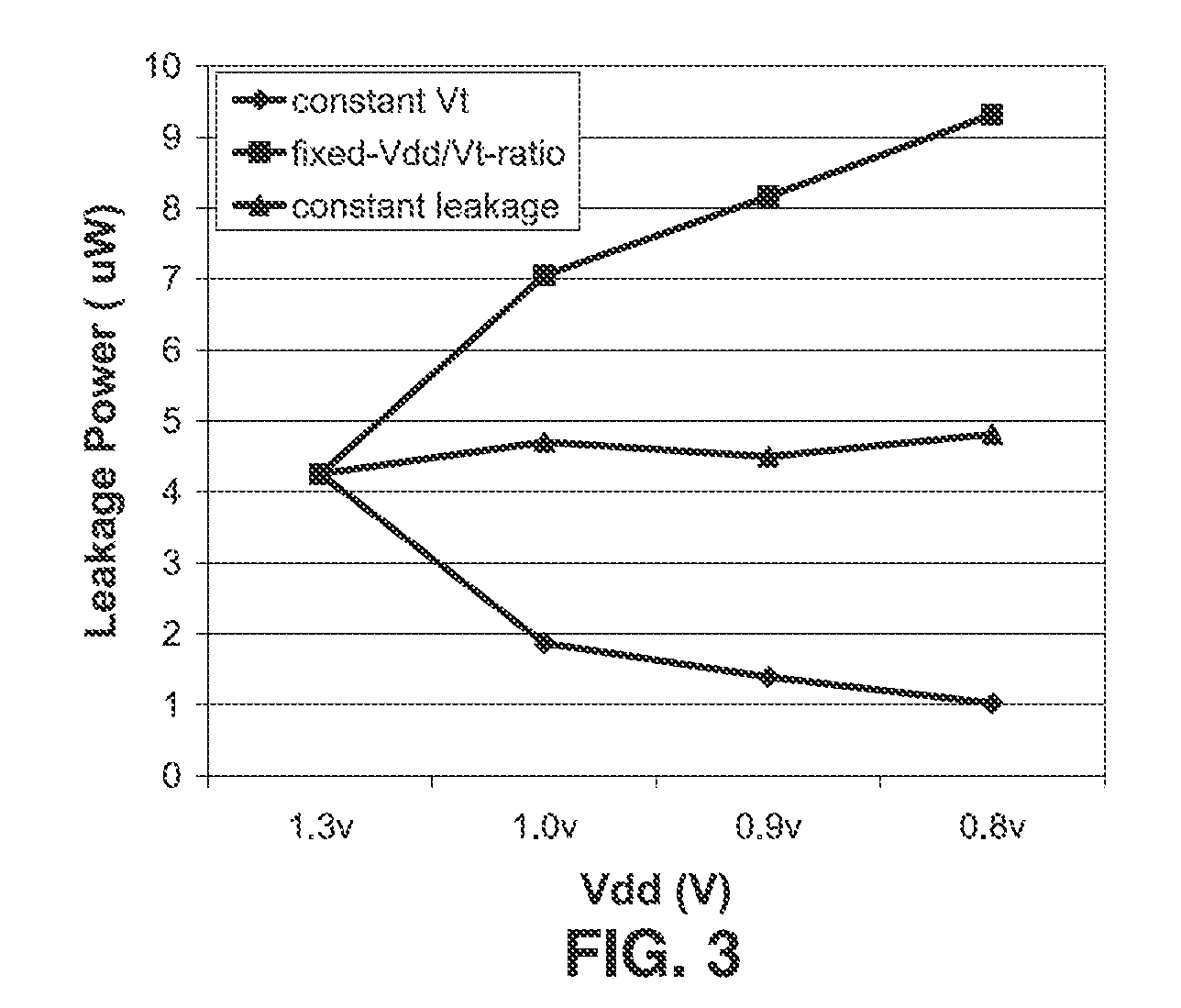

Field Programmable Logic Arrays (FPGAs) are described which utilize multiple power supply voltages to reduce both dynamic power and leakage power without sacrificing speed or substantially increasing device area. Power reduction mechanisms are described for numerous portions of the FPGA, including logic blocks, routing circuits, connection blocks, switch blocks, configuration memory cells, and so forth. Embodiments describe circuits and methods for implementing multiple supplies as sources of Vdd, multiple voltage thresholding Vt, signal level translators, and power gating of circuitry to deactivate portions of the circuit which are inactive. The supply voltage levels can be fixed, or programmable. Methods are described for performing circuit CAD in the routing and assignment process on FPGAs, in particular for optimizing FPGA use having the power reduction circuits taught. Routing methods describe utilizing slack timing, power sensitivity, trace-based simulations, and other techniques to optimize circuit utilization on a multi Vdd FPGA.

Owner:RGT UNIV OF CALIFORNIA

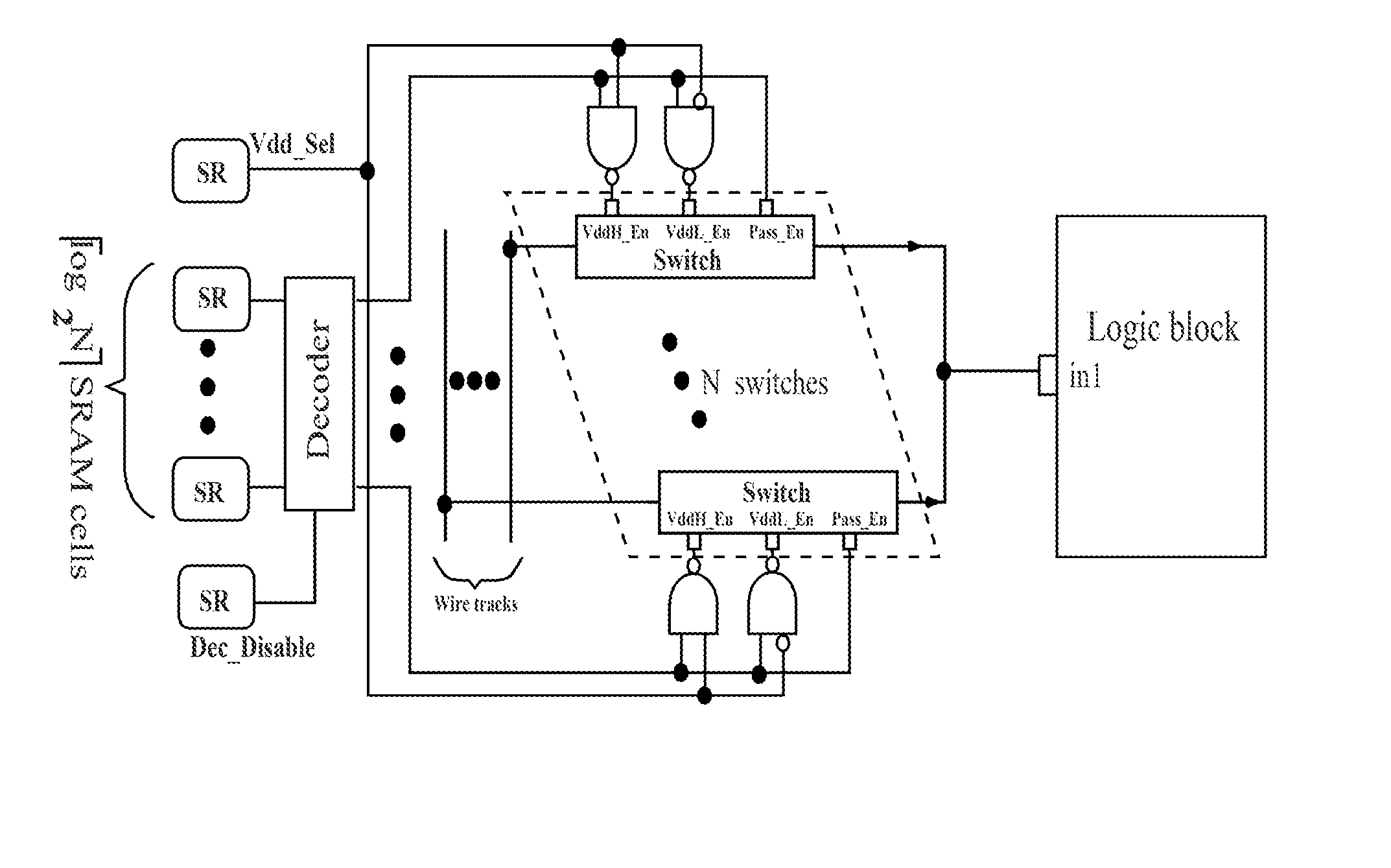

Low-power FPGA circuits and methods

InactiveUS20100281448A1Improve utilizationEasy to controlCAD circuit designMulti-objective optimisationComputer architectureMemory cell

Field Programmable Logic Arrays (FPGAs) are described which utilize multiple power supply voltages to reduce both dynamic power and leakage power without sacrificing speed or substantially increasing device area. Power reduction mechanisms are described for numerous portions of the FPGA, including logic blocks, routing circuits, connection blocks, switch blocks, configuration memory cells, and so forth. Embodiments describe circuits and methods for implementing multiple supplies as sources of Vdd, multiple voltage thresholding Vt, signal level translators, and power gating of circuitry to deactivate portions of the circuit which are inactive. The supply voltage levels can be fixed, or programmable. Methods are described for performing circuit CAD in the routing and assignment process on FPGAs, in particular for optimizing FPGA use having the power reduction circuits taught. Routing methods describe utilizing slack timing, power sensitivity, trace-based simulations, and other techniques to optimize circuit utilization on a multi Vdd FPGA.

Owner:RGT UNIV OF CALIFORNIA

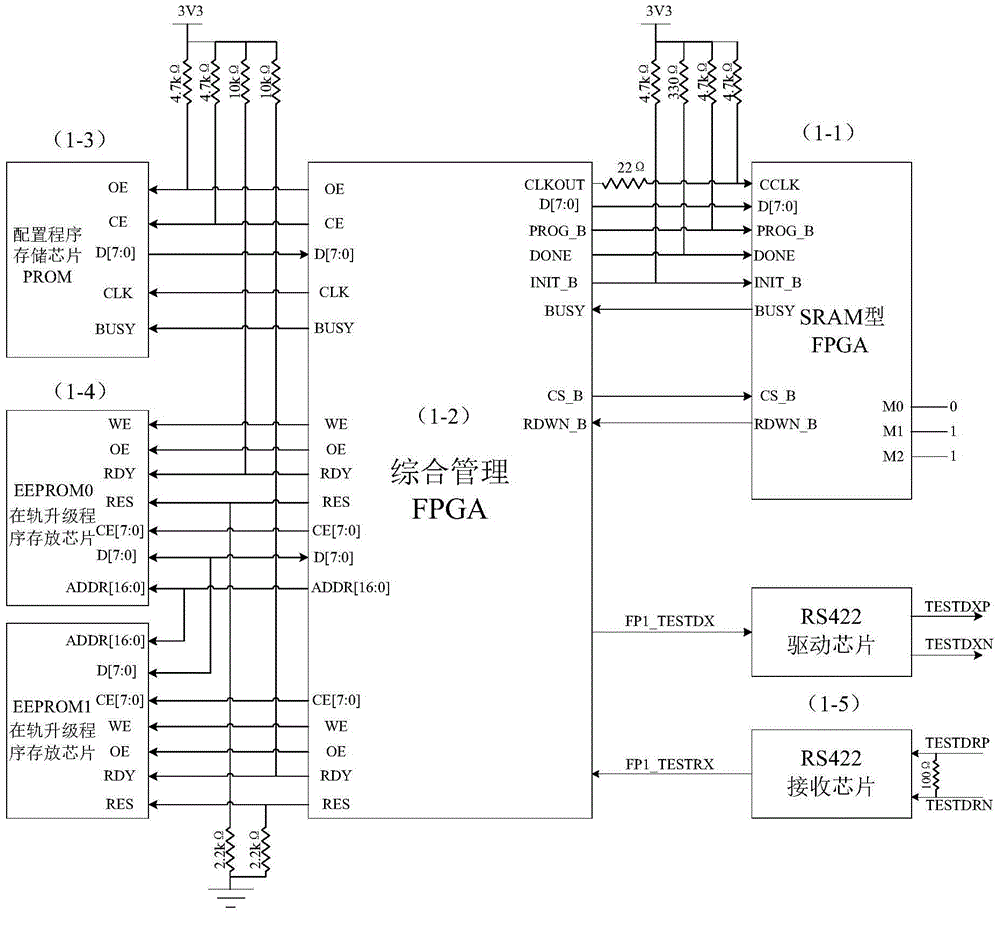

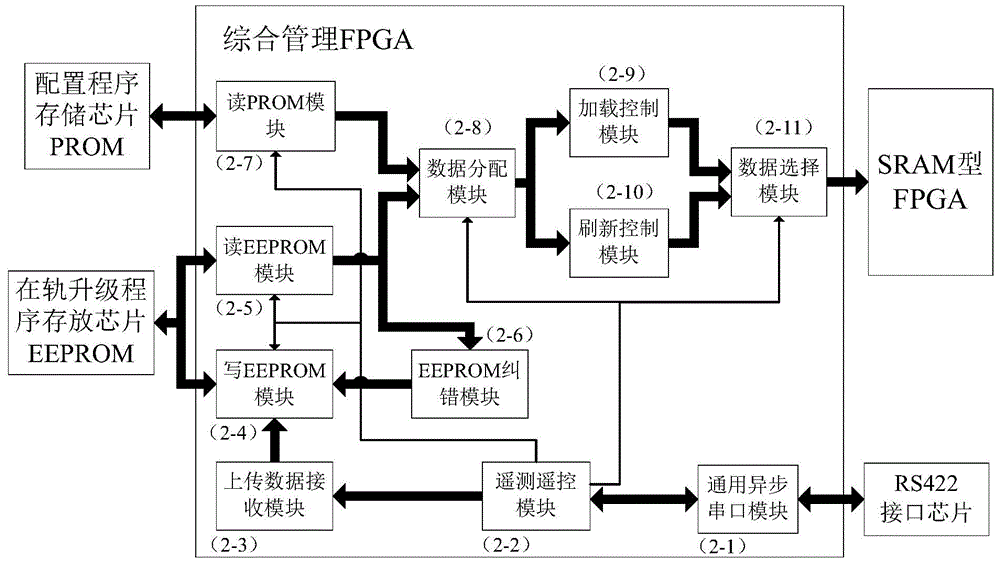

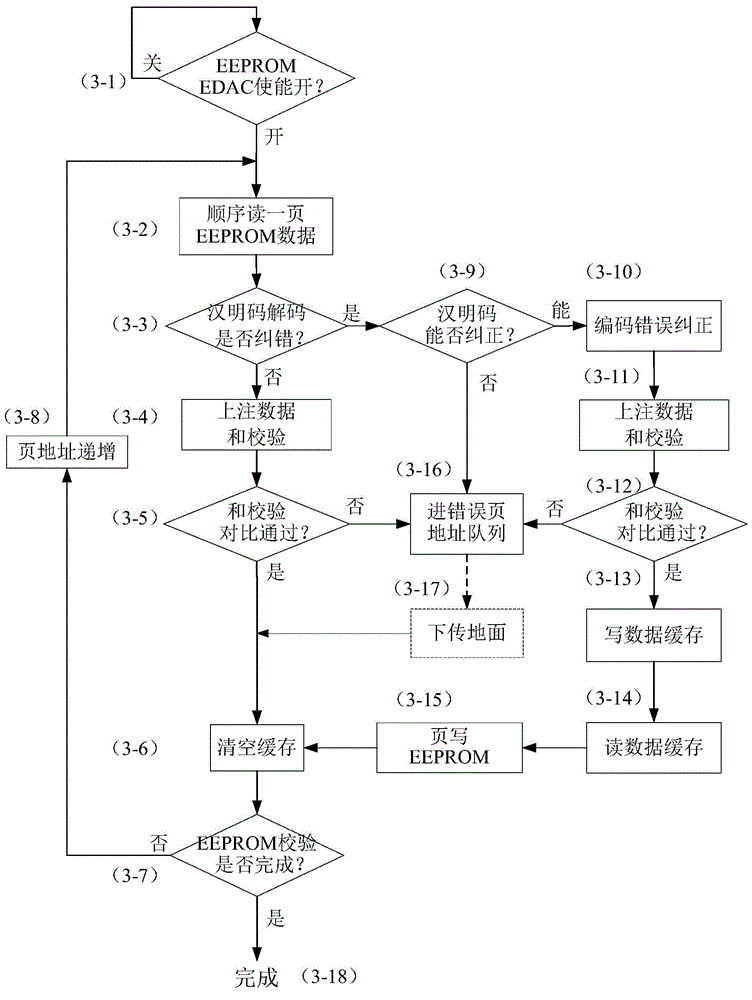

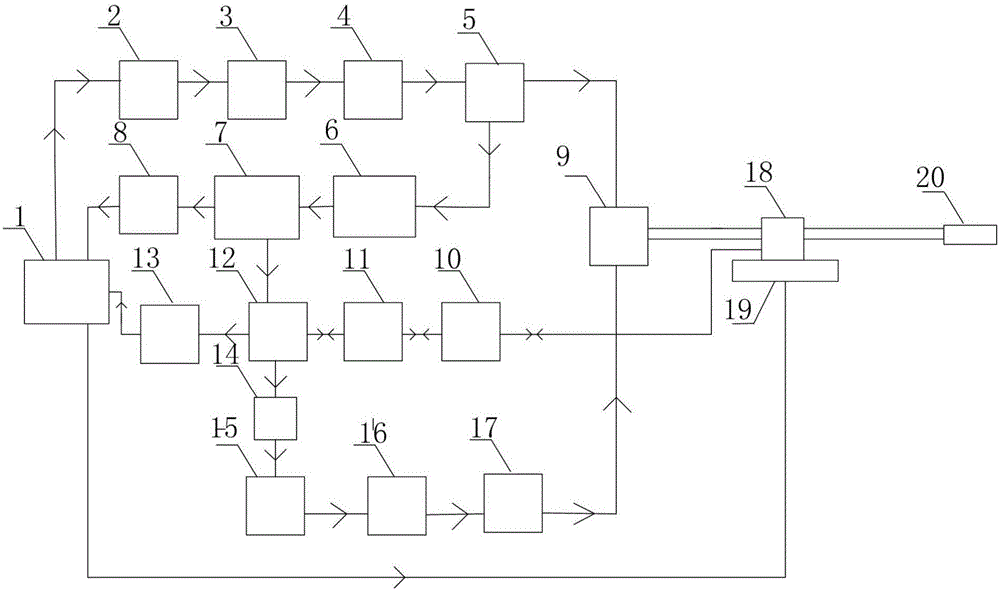

Configuration, refreshing and program upgrading integrated system for SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array)

ActiveCN104484214AIncrease flexibilityImprove versatilityProgram loading/initiatingProgrammable read-only memoryLogic gate

The invention discloses a configuration, refreshing and program upgrading integrated system for an SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array), belongs to the technical field of aerospace and aims to solve the problem of SEU (Single Event Upset) of the SRAM type FPGA in a spatial irradiation environment. The configuration, refreshing and program upgrading integrated system has a capability of performing program upgrading on the SRAM type FPGA which is in on-orbit work for a long time. The configuration, refreshing and program upgrading integrated system comprises an on-site programmable logic gate array SRAM type FPGA, a comprehensive management anti-fuse FPGA, a configuration program storage chip PROM (Programmable Read-Only Memory), an on-orbit upgrading program storage chip EEPORM (Electrically-Erasable Programmable Read-Only Memory) and an RS422 interface chip. The configuration, refreshing and program upgrading integrated system disclosed by the invention can be used for effectively solving the problem of the SEU of the SRAM type FPGA which is in on-orbit work for a long time and correcting the SEU and single event accumulation inside the SRAM type FPGA without being shut down, also has the function of on-orbit program upgrading of the SRAM type FPGA, and has the characteristics of instantaneity, reliability, flexibility, universality and low cost.

Owner:HUAZHONG UNIV OF SCI & TECH

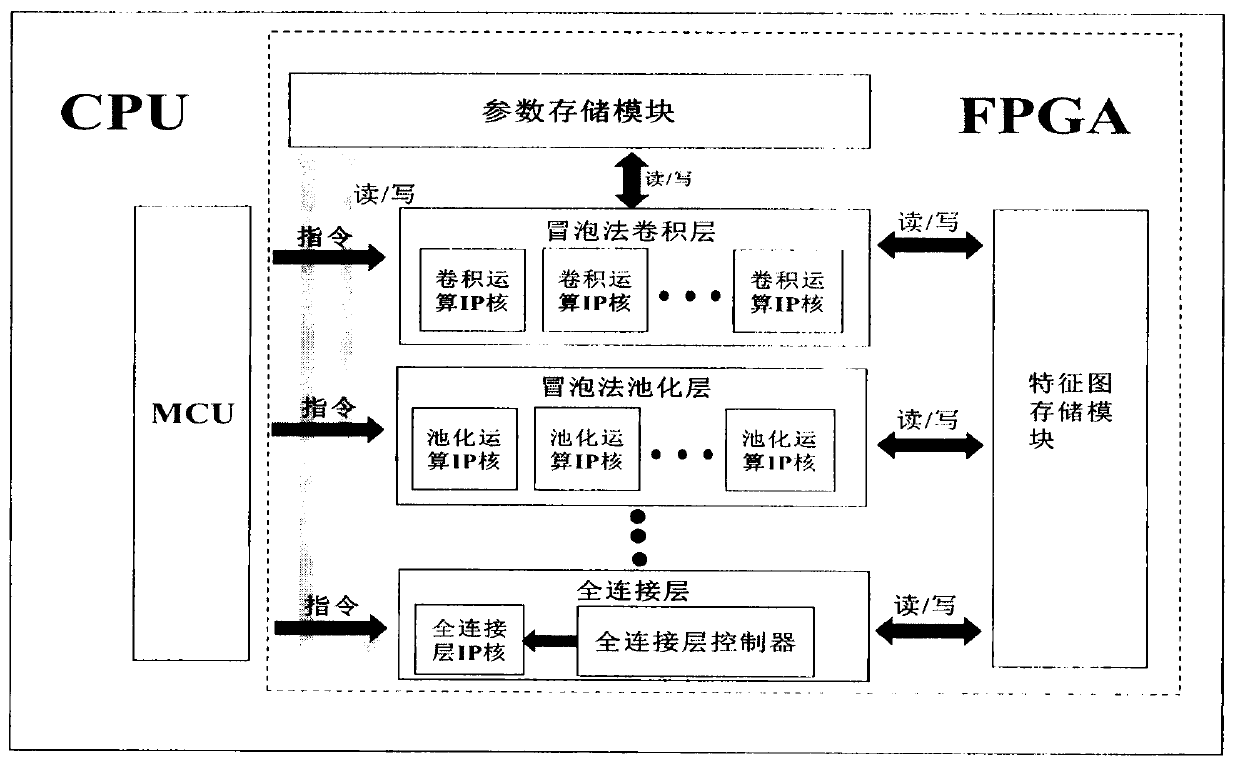

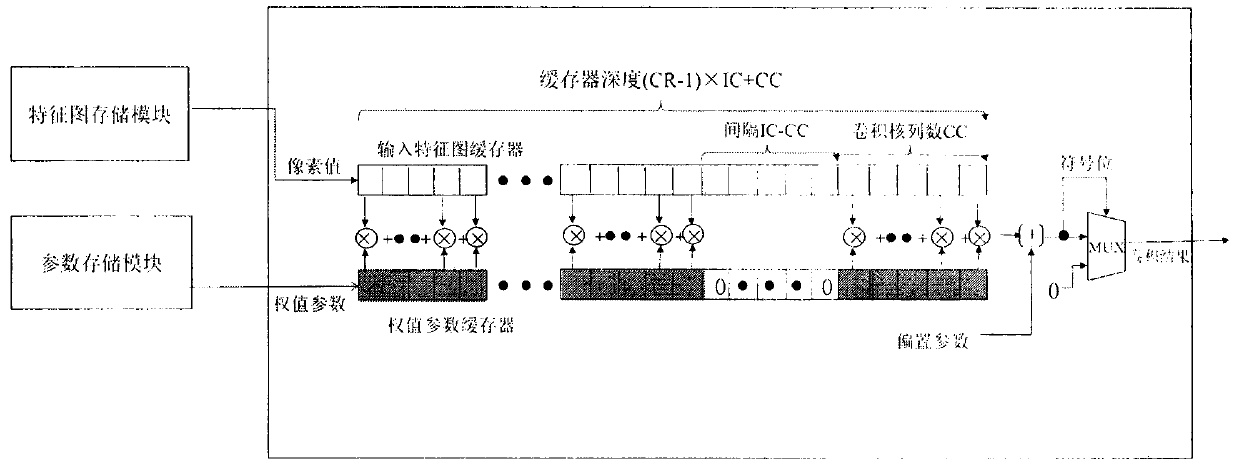

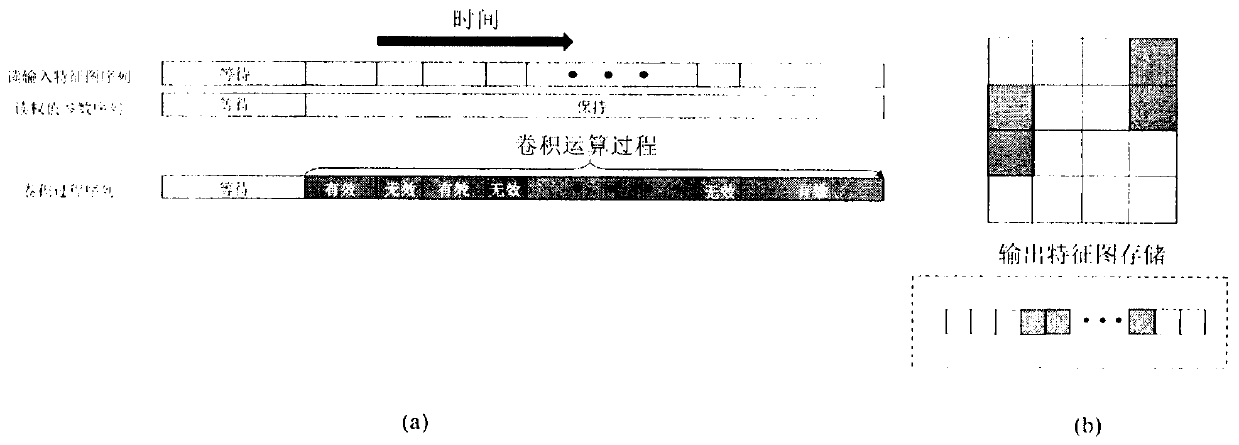

Convolutional neural network IP core based on FPGA

The invention discloses a convolutional neural network IP core based on FPGA, and aims to realize operation acceleration of a convolutional neural network on an FPGA. According to the basic model of the convolutional neural network, the specific architecture of the convolutional neural network comprises a convolution operation IP core, a pooling operation IP core, a full connection operation IP core, a bubbling method convolution layer, a bubbling method pooling layer, a full connection layer, a feature map storage module and a parameter storage module. The IP cores support construction of convolutional neural networks of different scales, and the IP cores of different types and numbers are instantiated according to the required network model. Different neural network layers are constructed by instantiating the IP core, and the parallelism of the FPGA is fully utilized to realize the operation acceleration of the convolutional neural network; and designing an IP core through a VerilogHDL language to realize transplantation of different FPGAs. The operation speed and efficiency of the convolutional neural network are greatly improved, and the processing power consumption of the convolutional neural network is reduced.

Owner:SCHOOL OF SOFTWARE & MICROELECTRONICS PEKING UNIV +4

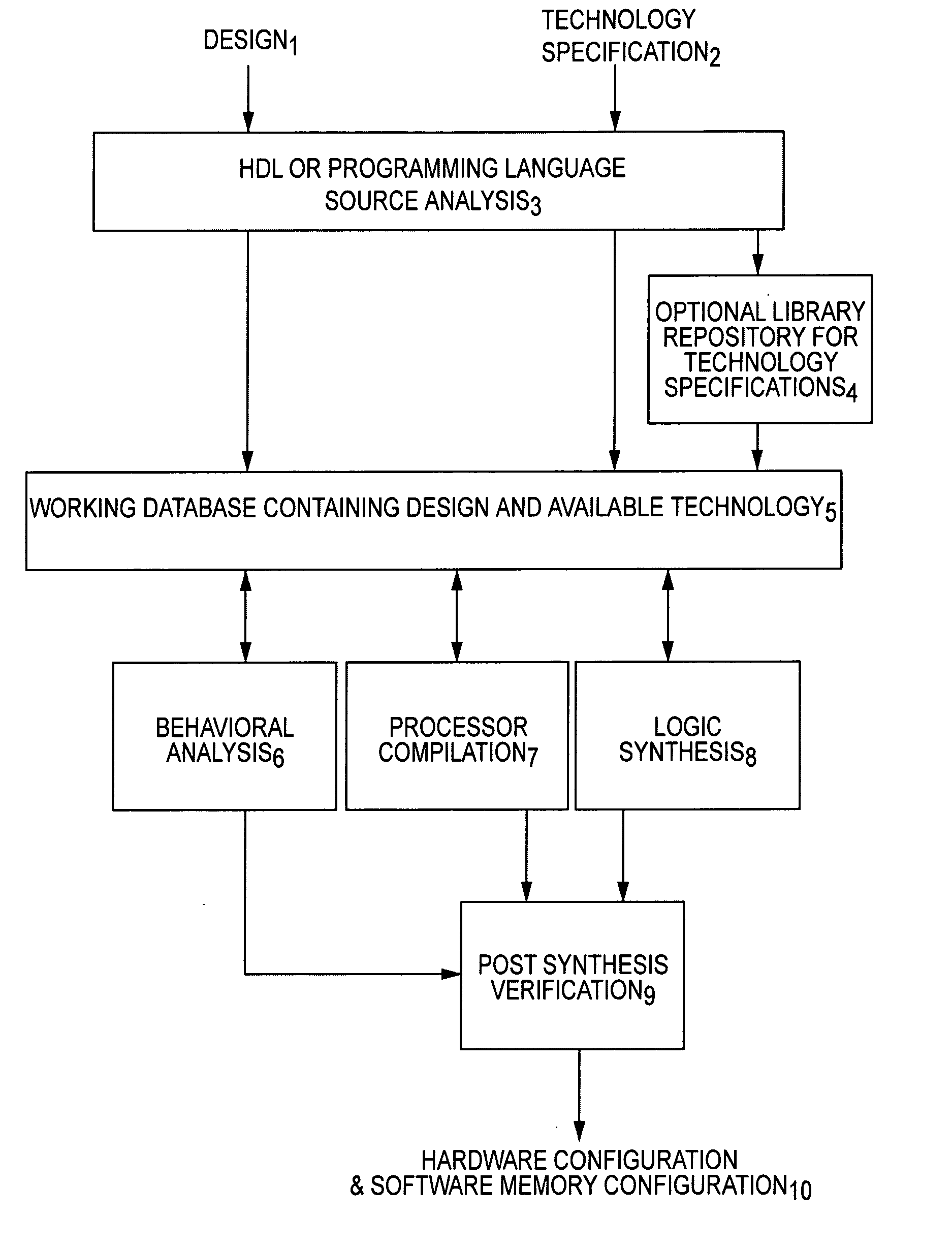

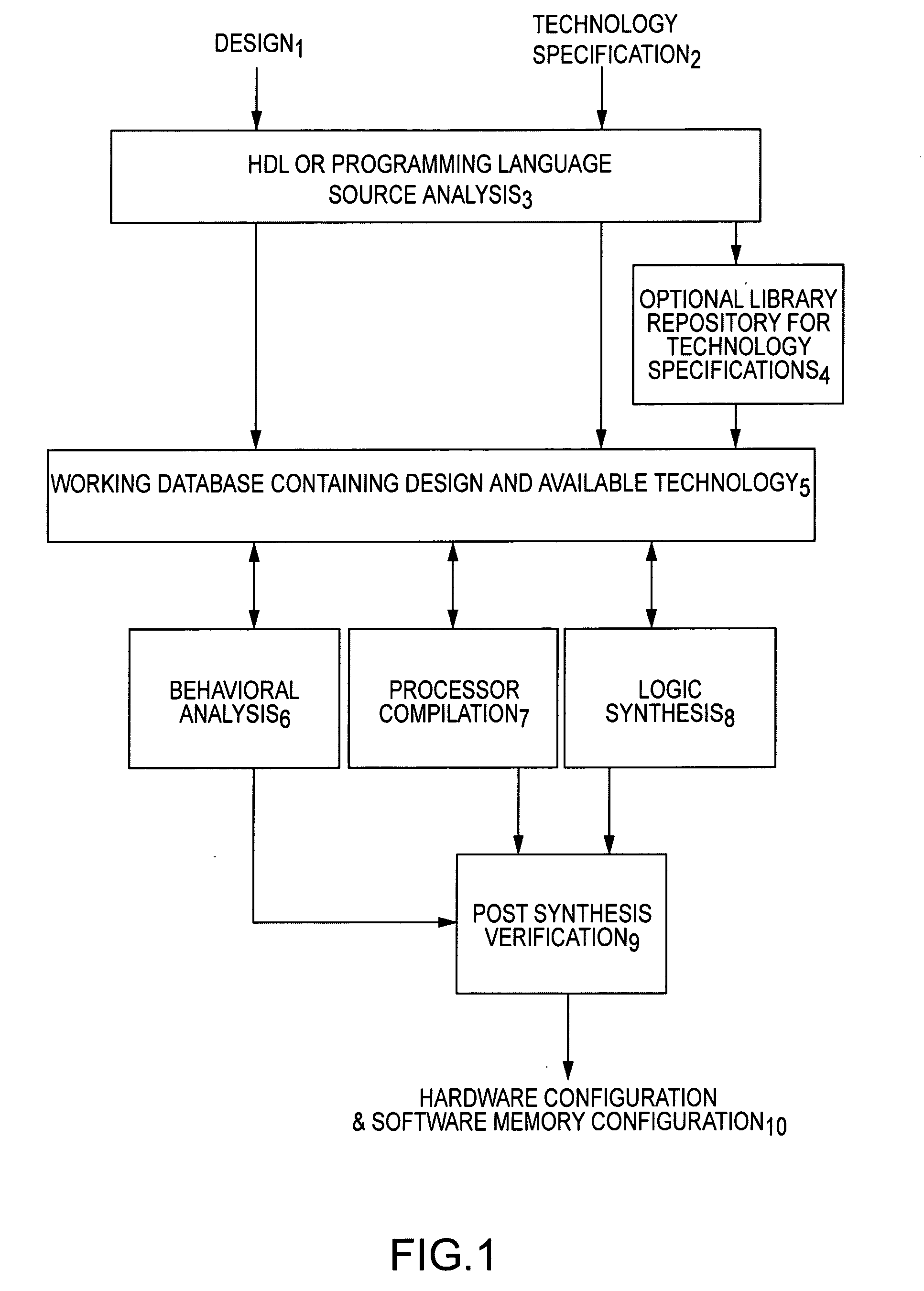

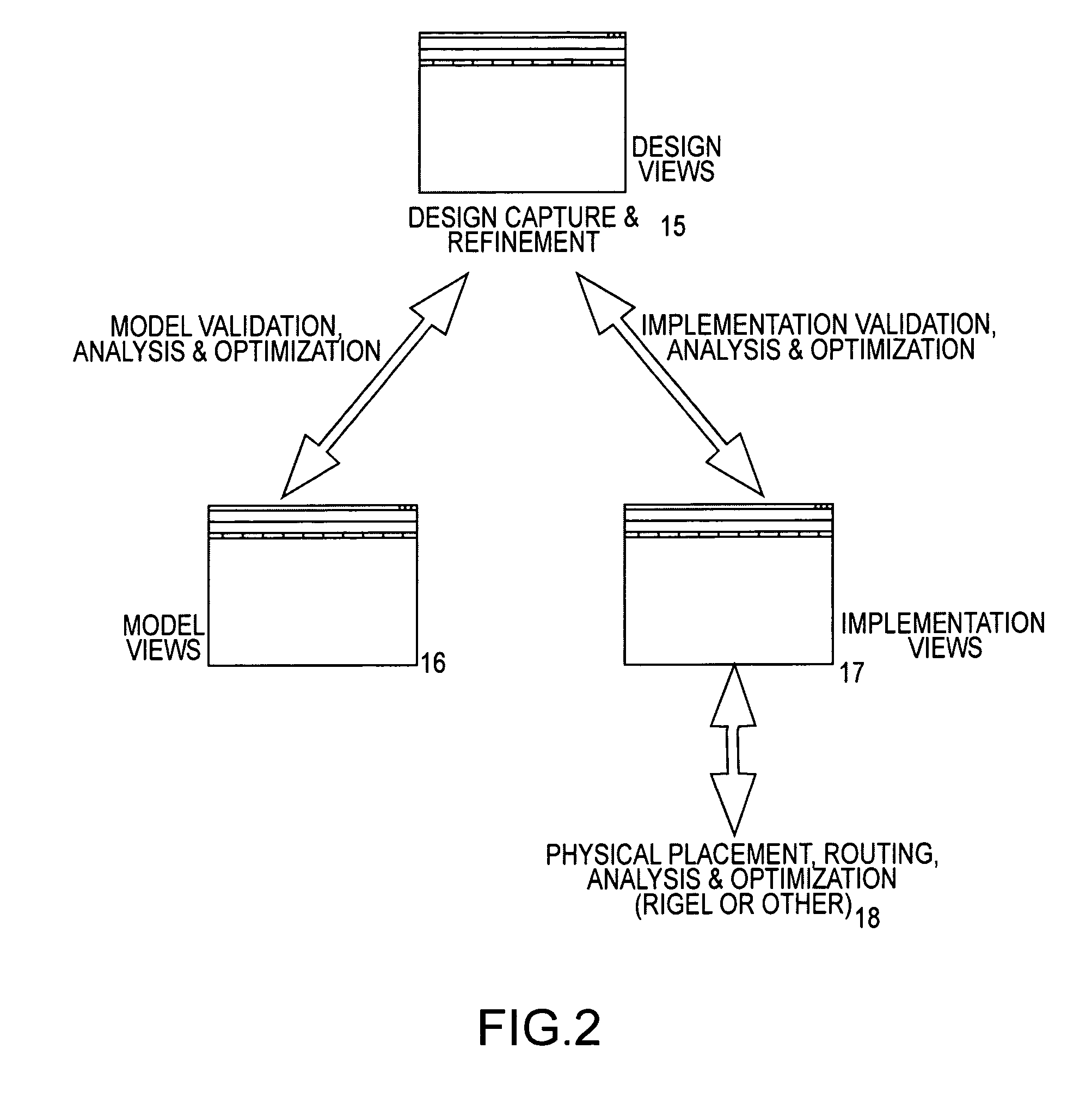

Hardware/software design tool and language specification mechanism enabling efficient technology retargeting and optimization

InactiveUS20050289485A1More compactEfficient designElectrical testingDigital computer detailsComputer architectureSoftware system

An innovative hardware / software design tool provides four modes of operation for converting an electronic design specification and zero or more technology specifications into realization of the electronic design in computer hardware, software and firmware. The first mode of operation compiles design and logic technology specifications into a model which can be utilized for behavioral analysis (such as simulation or formal verification) of logical characteristics (the model). The second mode of operation translates (compiles) partitions of the design and one or more logic technologies into one or more processor intermediates or binaries (embedded binary) suitable for execution on multi-purpose processing units (embedded or general purpose processors). The third mode of operation translates (synthesizes) partitions of the design and logic technology into a collection of cells and interconnects (net-list implementation) suitable for input to physical design processes such as is required to target a field-programmable logic array (FPGA), application specific integrated circuit (ASIC), system-on-a-chip (SOC) or custom logic). The fourth mode of operation analyzes (verifies) behavior of the embedded binaries running on processing units and implementations augmented by additional physical technology and parameters, yielding a more detailed (accurate) prediction of the resulting hardware / software system behavior when realized through manufacturing. Critically, the design specification, logic specifications, physical specifications and definition of each multi-purpose processing unit may be defined external to the hardware / software design tool using an innovative augmentation of standard hardware description or programming languages taught in this patent application. In the prior art, specification of the logic technology, physical technology and embedded or general purpose processor architecture are either incorporated directly into the design tool by the tool developer or are maintained entirely external to the design tool (such as an encapsulated component model or intermediate code interpreter). The present invention is an innovative and valuable improvement over prior art in that design specifications are combined by the tool from distinct specification(s) of generalized logic, physical and processor technology, leading to more efficient behavioral design, opportunities for third parties to add functionality by incorporating generalized logic and physical technology modules into the analysis and synthesis process and opportunities for semi-automatic, goal-directed optimization through application of various logic, physical and processor technologies by the design tool.

Owner:FTL SYST

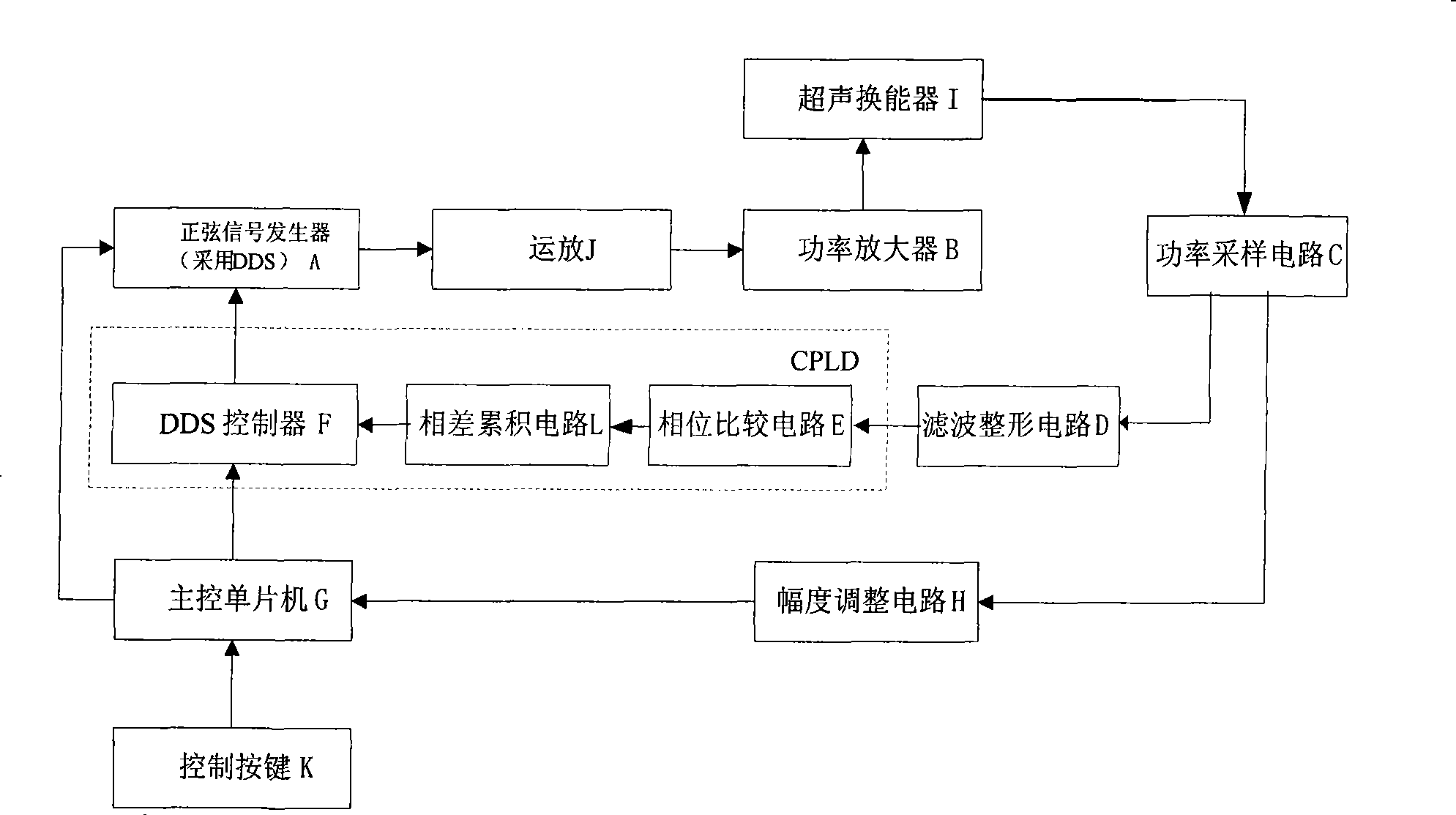

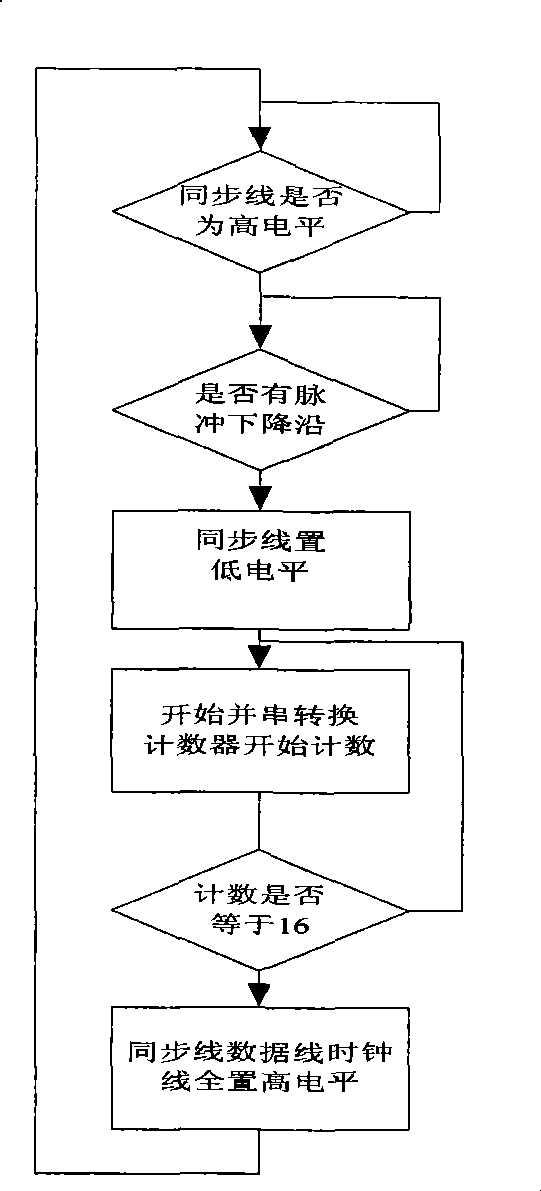

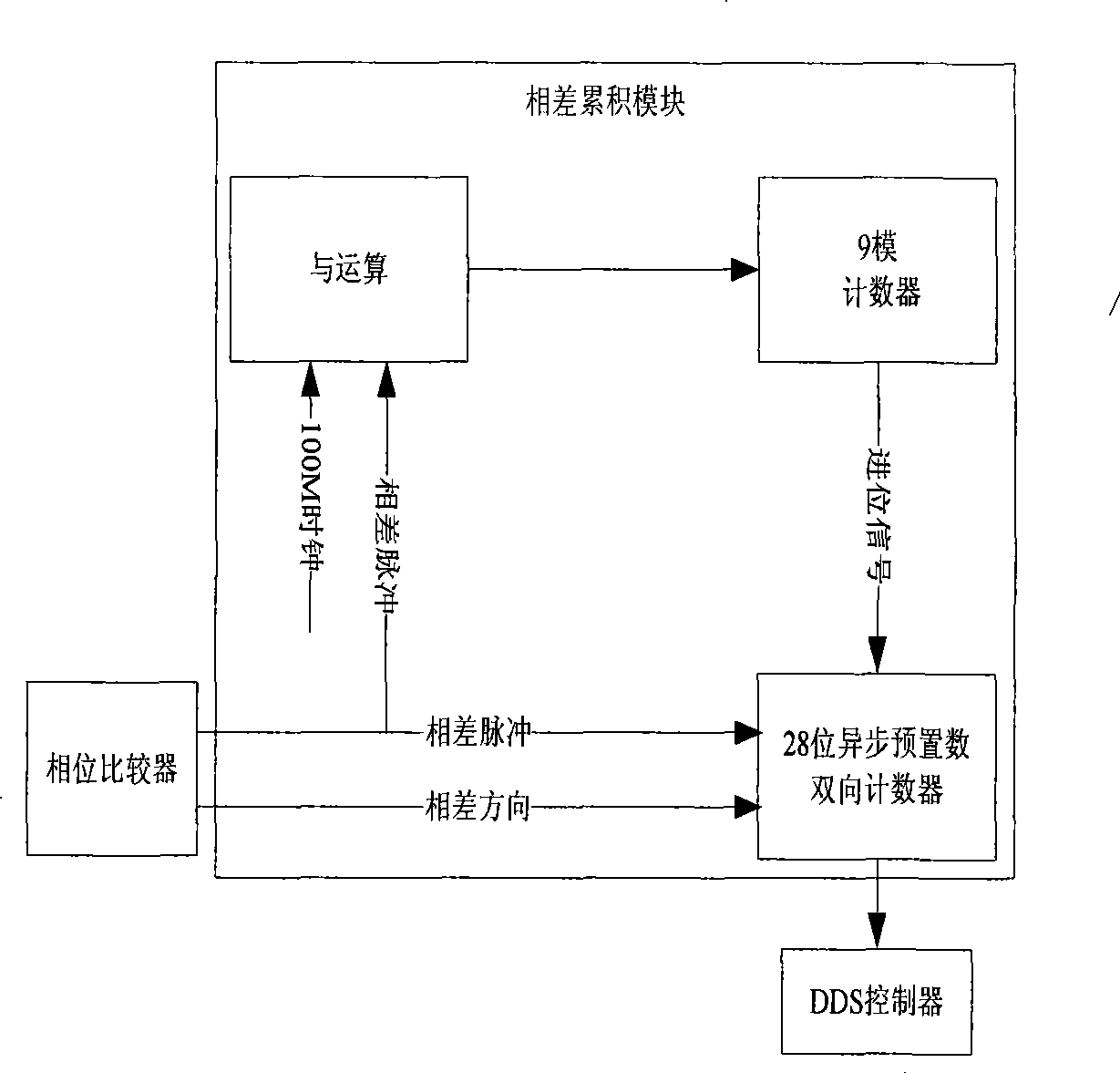

Automatic frequency tracking method of supersonic transducer and system thereof

ActiveCN101468347ARealize digital controlWork reliablyMechanical vibrations separationLogical elementUltrasonic sensor

The invention relates to an automatic frequency tracking method and a system for an ultrasonic transducer. A direct digital frequency synthesizer is used as a signal source, wherein the direct digital frequency synthesizer can be an independent integrated chip and also be achieved by the method that a digital part of a DDS is integrated in a site programmable logical element FPGA and then a digital-analog converter is additionally added. The design of the invention adopts a frequency sweeping and tracking policy, and an automatic frequency controller achieved by the programmable element controls the output frequency of the DDS according to a feedback signal sampled from the self transducer end so as to achieve the full digitization automatic frequency tracking and ensure that the ultrasonic transducer work near a resonance point all the time to obtain the optimal efficiency. A phase comparator utilizes a trigger to give out the arriving time difference of two riser edge signals of two input signals I ph and V ph aiming to the sensitive characteristics of the riser edge signals, and the sequence of the riser edge signals of the two input signals I ph and V ph is given out by a Dirrect pin.

Owner:BEIJING ANHEJIALIER TECH CO LTD

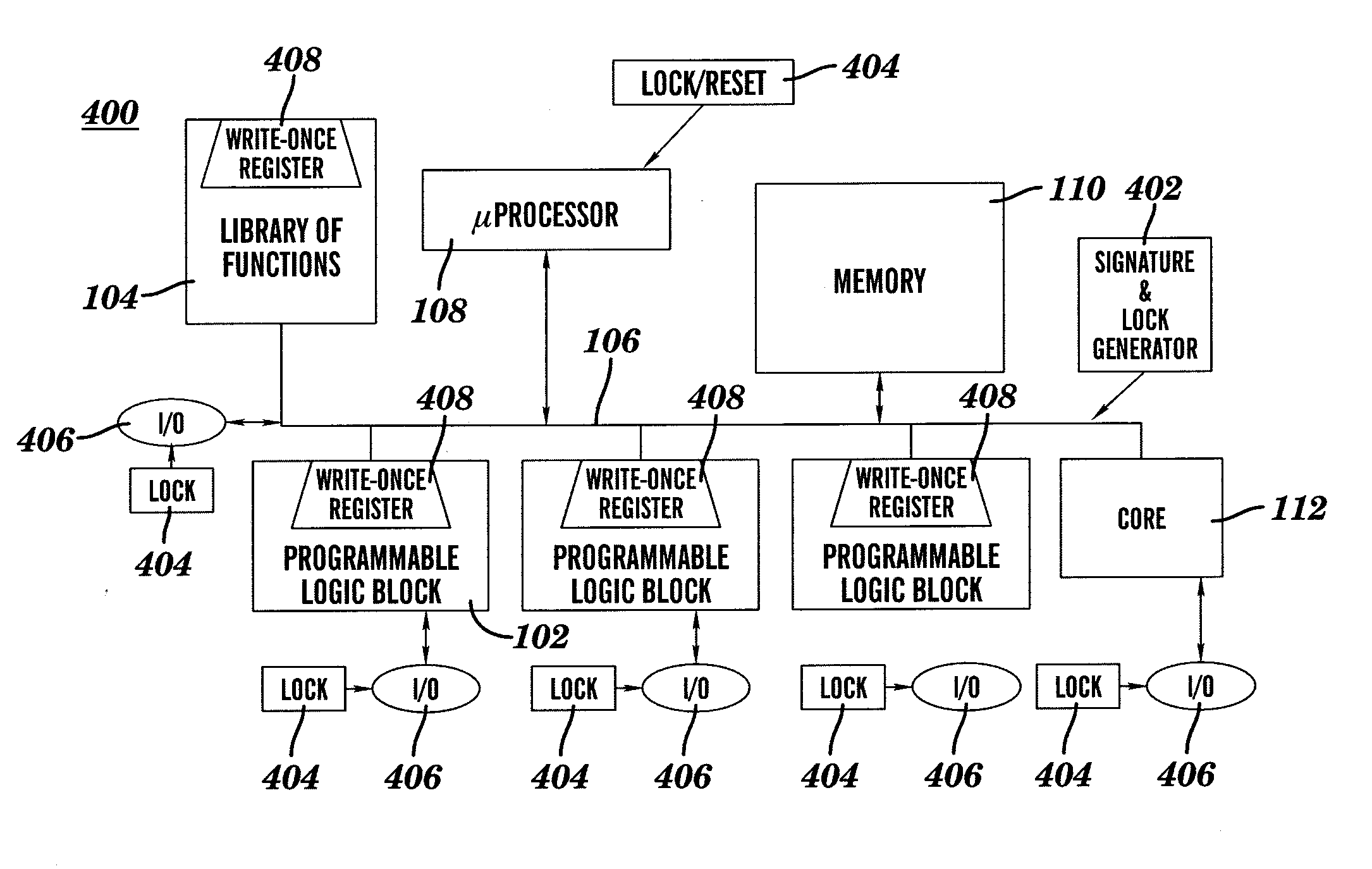

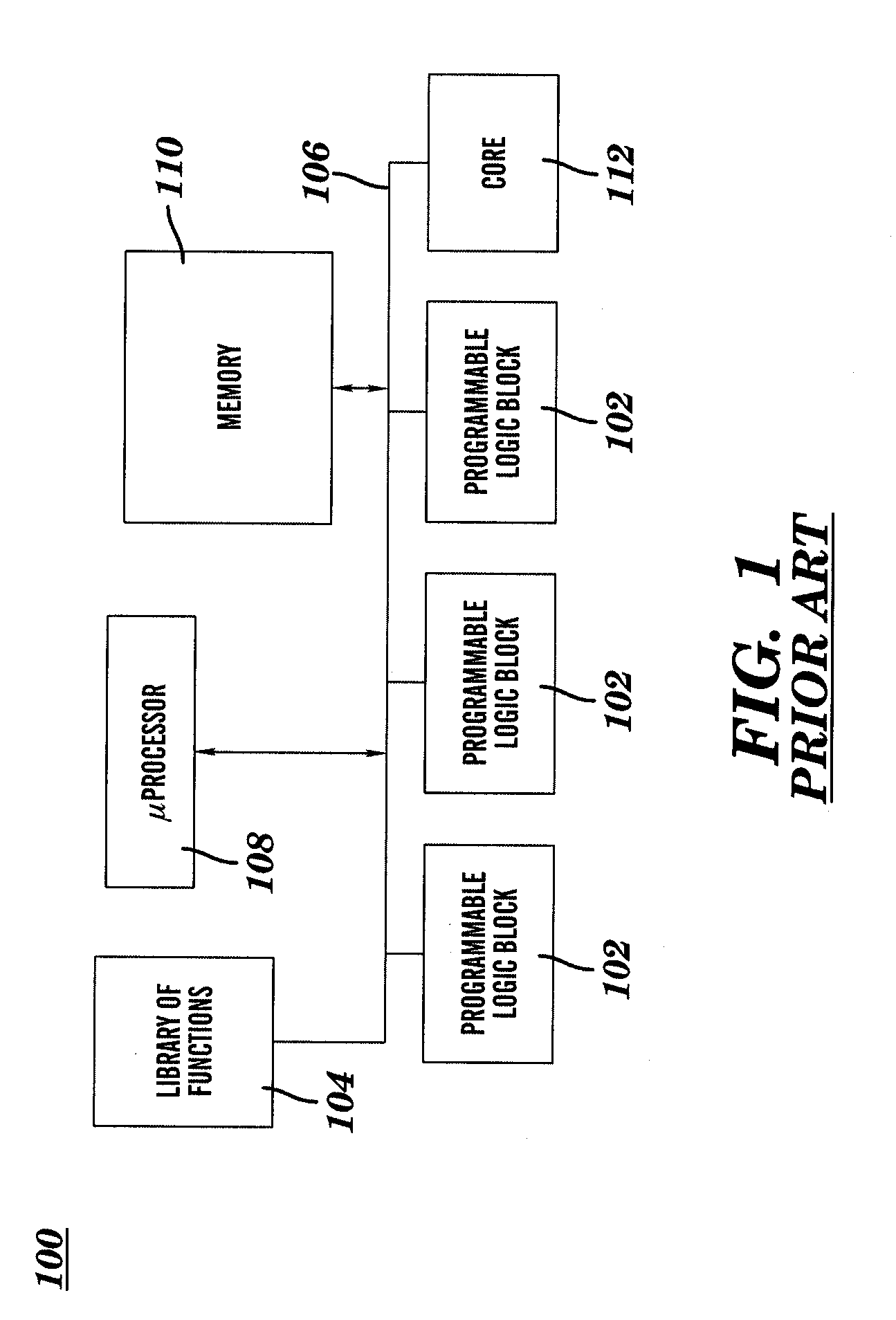

Method for system level protection of field programmable logic devices

InactiveUS20050278551A1Avoid accessDigital data processing detailsUser identity/authority verificationField programmable logic devicesProgrammable logic device

A method for protecting a dynamically reconfigurable computing system includes generating an encoding signature and passing the encoding signature, through a system level bus, to at least one field programmable logic device and to a function library included within the system. The function library contains a plurality of functions for selective programming into the at least one field programmable logic device. A lock is generated so as to prevent external resources with respect to the system from accessing the encoding signature during the passing thereof.

Owner:IBM CORP

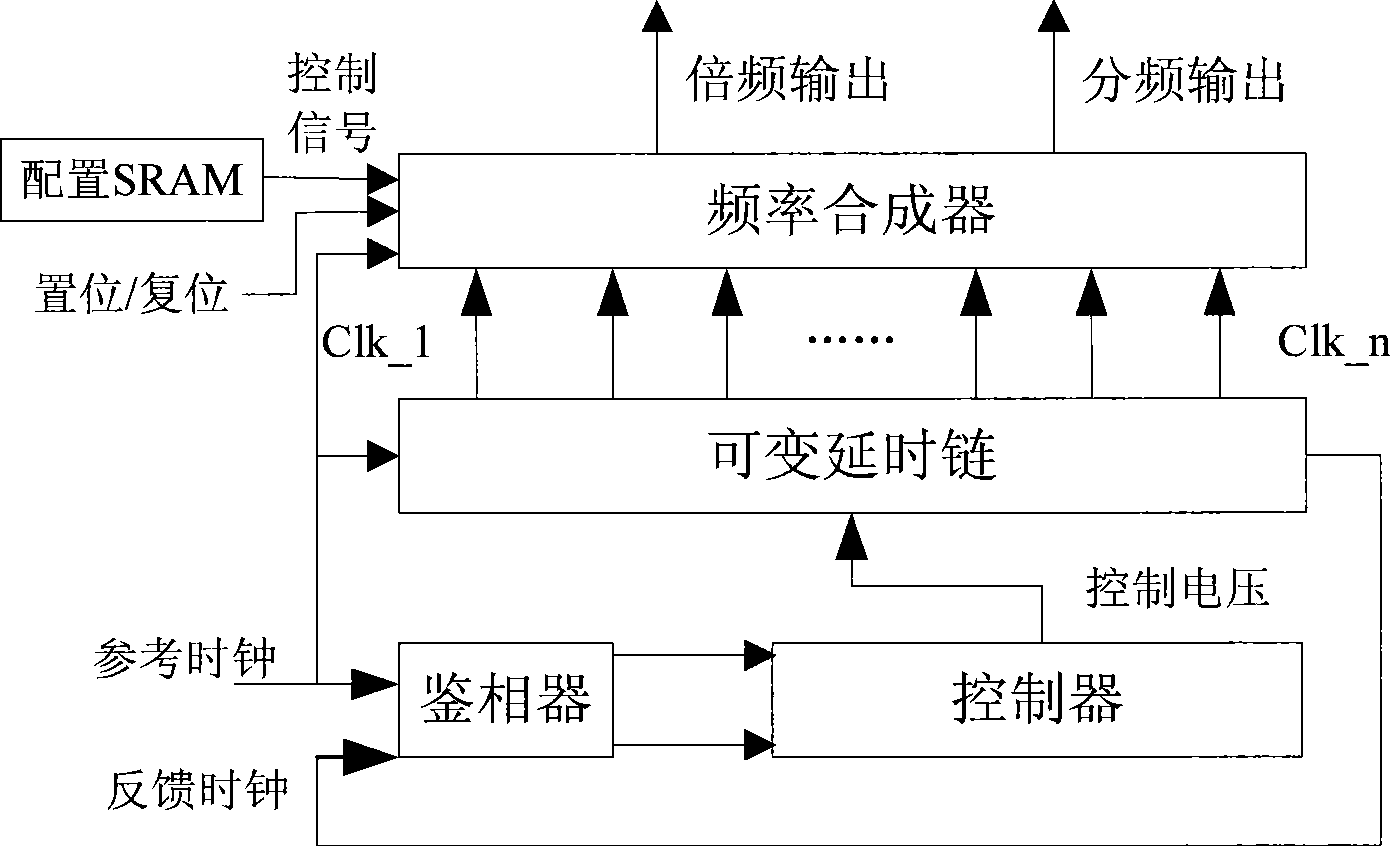

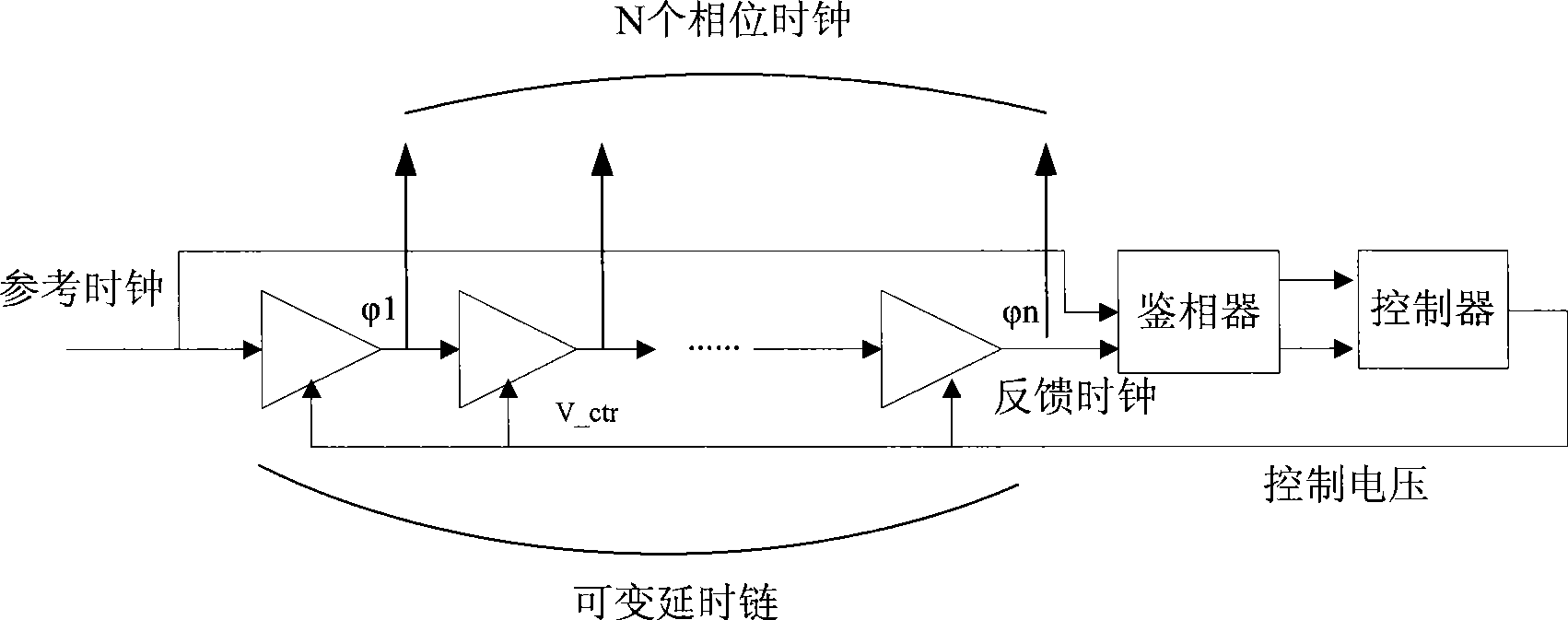

Configurable frequency synthesizer circuit based on time-delay lock loop

ActiveCN101478308AImprove reusabilityAbsolute stabilityPulse automatic controlDiscriminatorTime delays

The invention relates to a configurable frequency synthesis circuit based on a delay locked loop. The circuit comprises the delay locked loop, a frequency synthesizer and a configuring SRAM, wherein, the delay locked loop consists of a phase discriminator, a controller and a variable delay chain; and the frequency synthesizer consists of a frequency doubling synthesizer and a frequency division synthesizer. The phase discriminator receives a reference clock and a feedback clock and outputs comparison signals and locking signals after phase demodulation comparison; the comparison signals and the locking signals are processed by the controller, and the controller outputs control voltage then in order to enable the variable delay chain to generate N phase clocks that are output to the frequency synthesizer; and the frequency doubling synthesizer and the frequency division synthesizer enable the set / reset time of a R / S trigger in the frequency doubling synthesizer to generate frequency doubling clock signals under the control of the configuring SRAM, and lead the set / reset time of the R / S trigger in the frequency division synthesizer to generate frequency division clock signals. The configurable frequency synthesis circuit has simple circuit organization, flexibly changes a frequency synthesis coefficient by changing the code flow value in the embedded configuring SRAM so as to obtain a frequency division coefficient and a frequency doubling coefficient as required, and can be applied to a field programmable logic array.

Owner:BEIJING MXTRONICS CORP +1

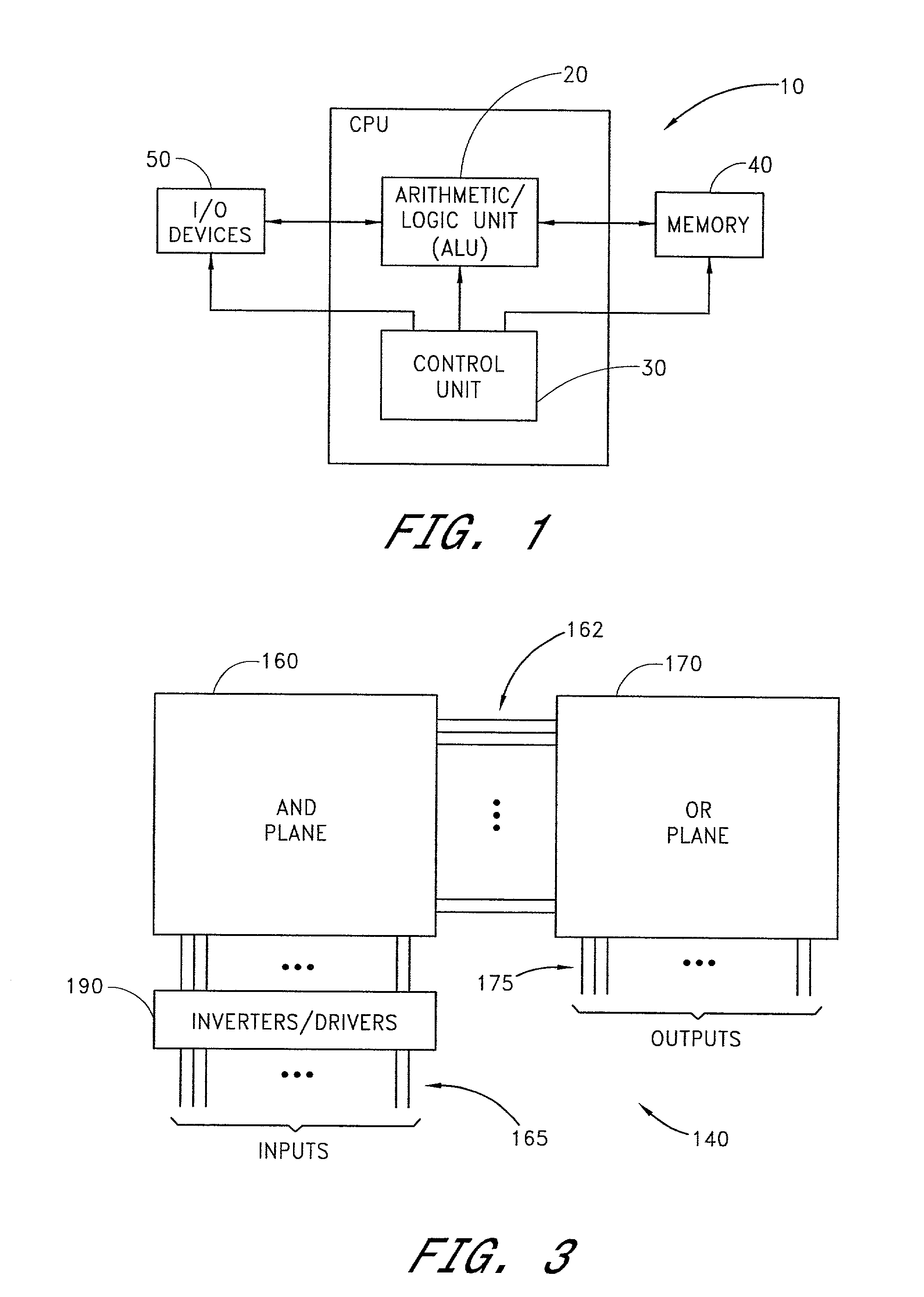

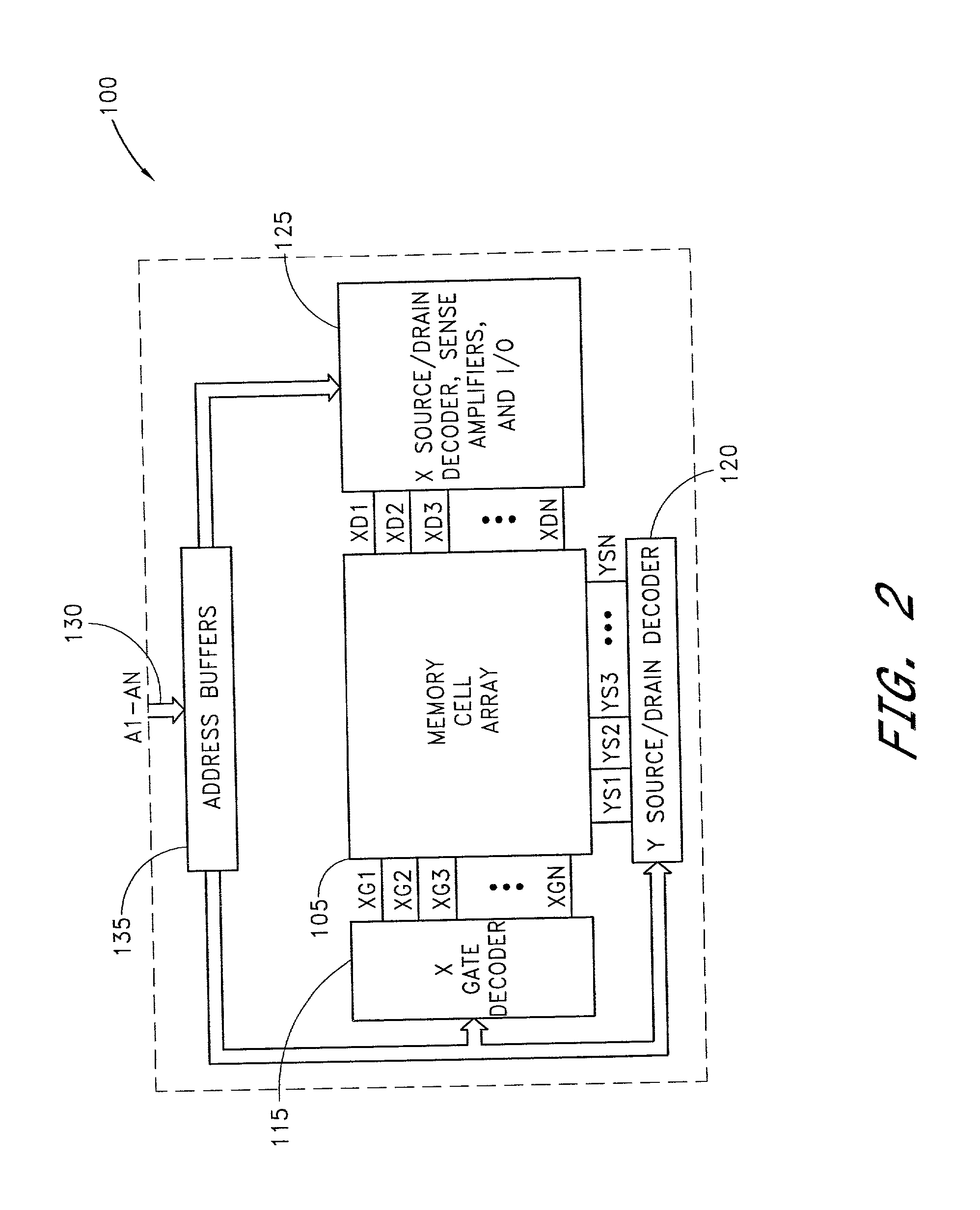

Vertical transistor with horizontal gate layers

InactiveUS20030038318A1TransistorSolid-state devicesProgrammable read-only memoryArray data structure

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F2 is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

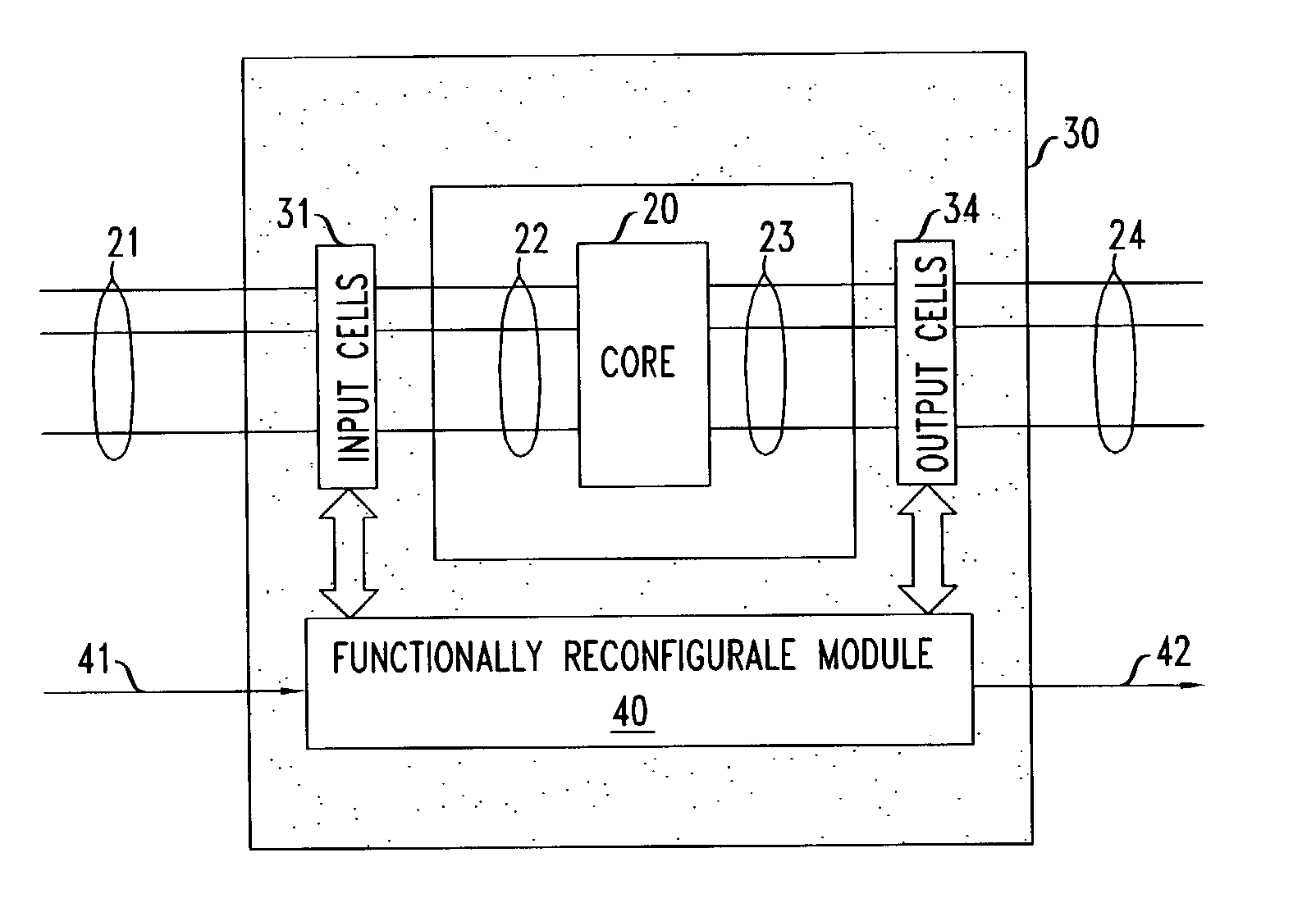

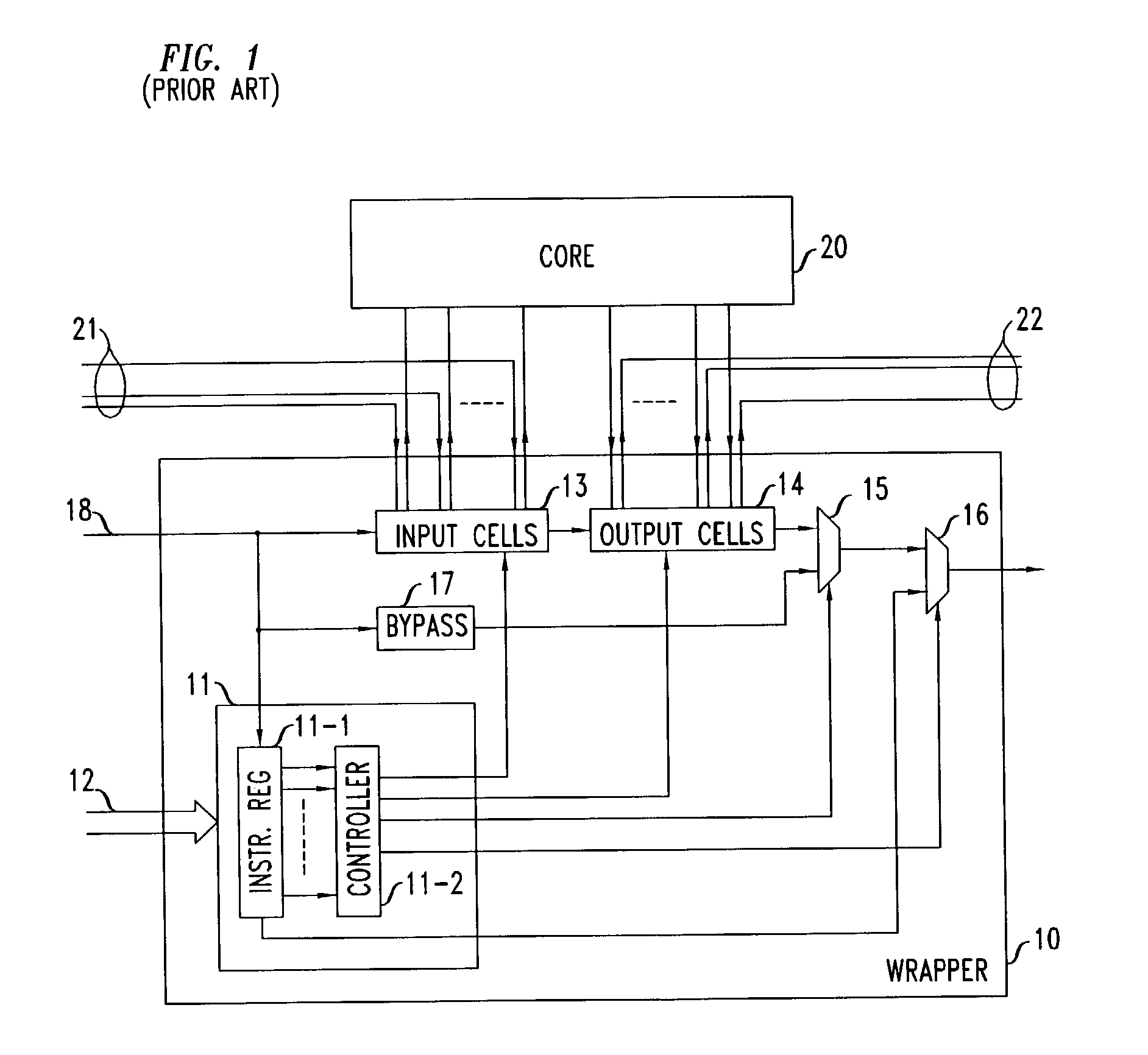

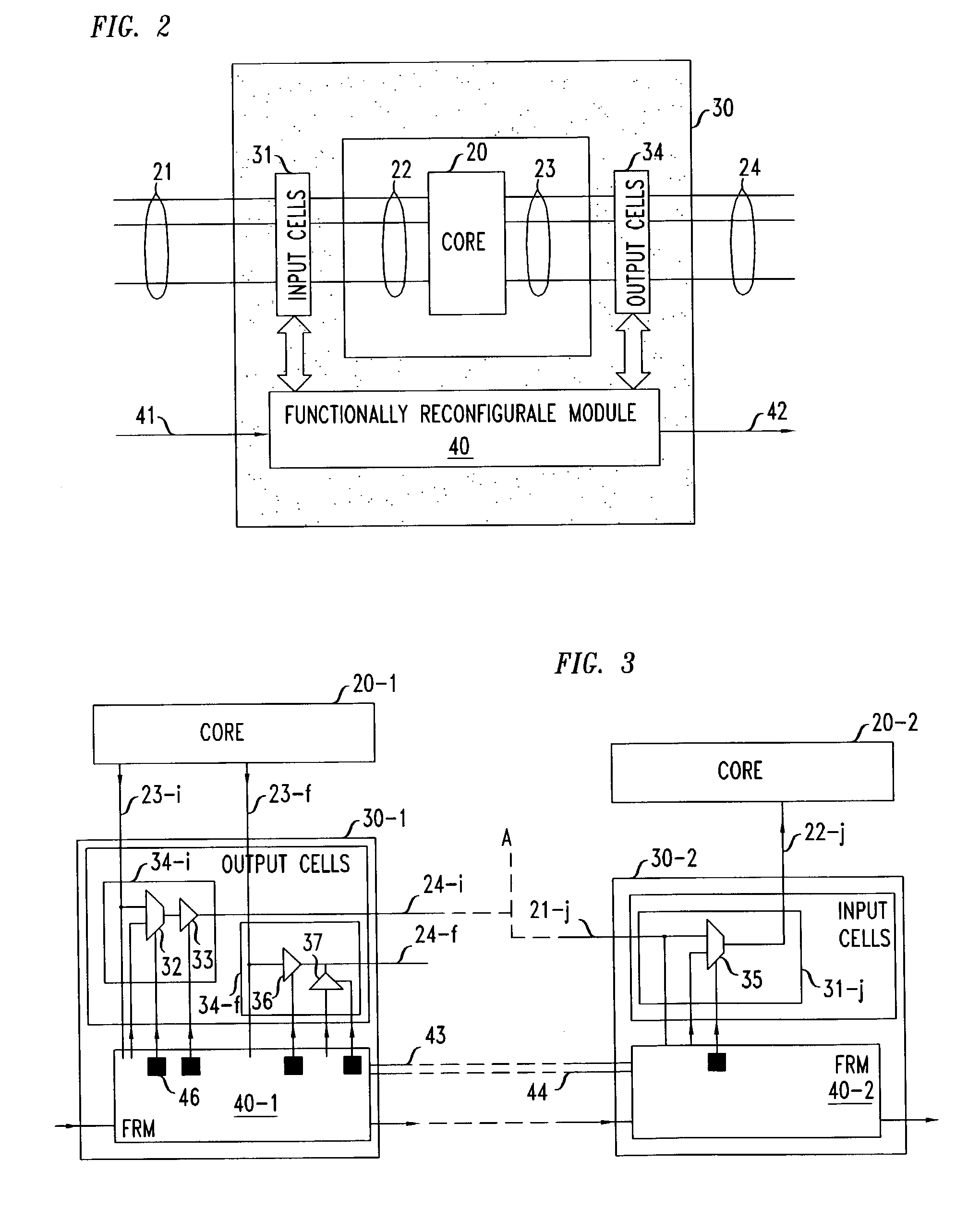

Reconfigurable fabric for SoCs using functional I/O leads

ActiveUS7058918B2Increase flexibilityIncrease the number ofElectrical testingSpecial data processing applicationsPath networkComputer module

An exceptionally effective SoC design is achieved by the user of wrappers that comprise a functionally reconfigurable module (FRM) that is capable of affecting the operational functionality of the wrapper and that, consequently, is capable of affecting the operational functionality of a designed SoC. One embodiment of a core+wrapper combination comprises distinct input and output cells within the wrapper, and a separate FRM. Another embodiment may embed the input and output cells within the FRM. The FRM may be implemented with, for example, a field programmable logic array (FPLA). An additional advance is realized by providing a number of spare leads in the signal paths network that interconnects the various SoC elements.

Owner:DAFCA

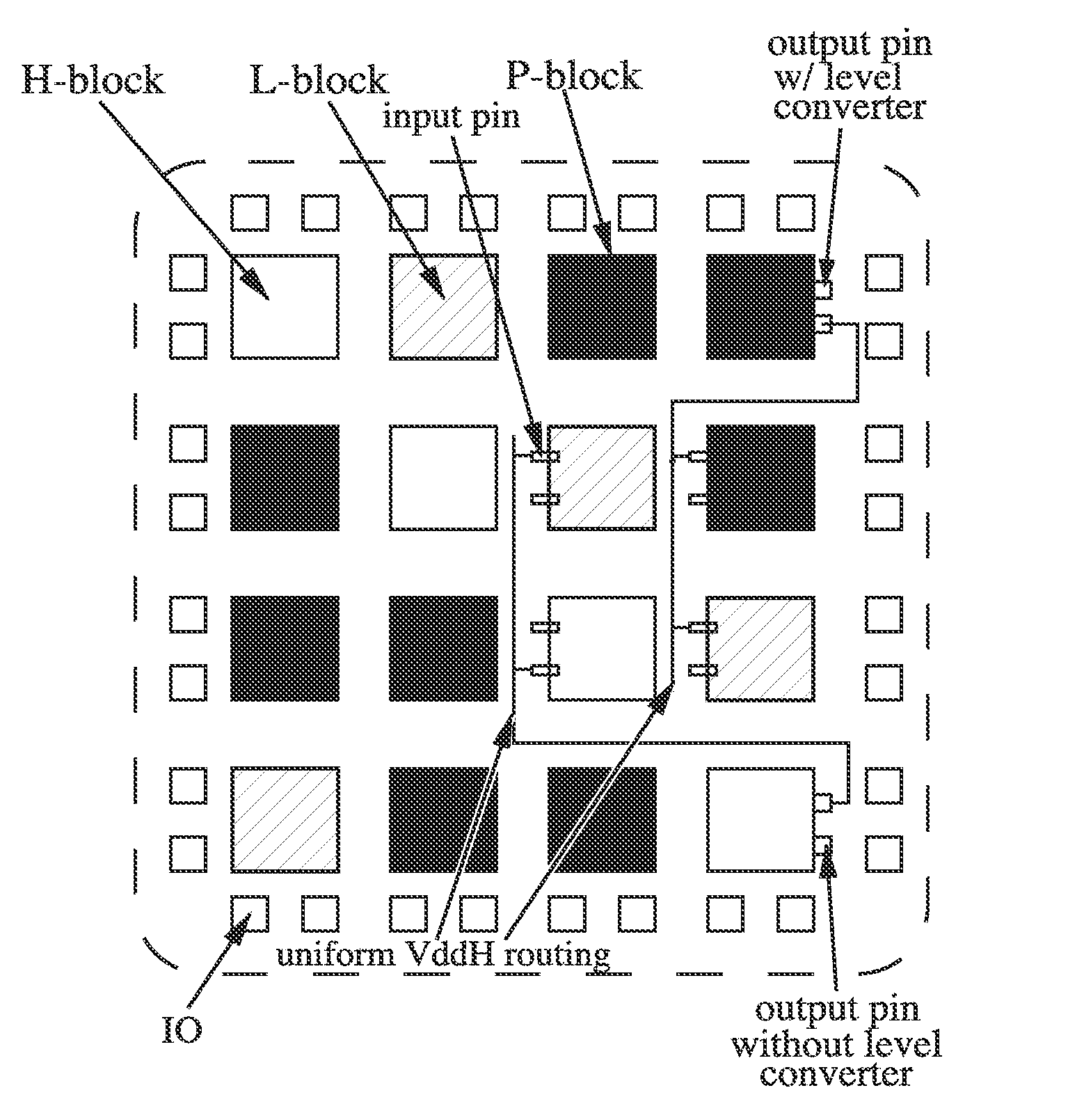

Low-power FPGA circuits and methods

InactiveUS7714610B2Increase profitEasy to controlSolid-state devicesCAD circuit designEngineeringLevel converter

Field Programmable Logic Arrays (FPGAs) are described which utilize multiple power supply voltages to reduce both dynamic power and leakage power without sacrificing speed or substantially increasing device area. Power reduction mechanisms are described for numerous portions of the FPGA, including logic blocks, routing circuits, connection blocks, switch blocks, configuration memory cells, and so forth. Embodiments describe circuits and methods for implementing multiple supplies as sources of Vdd, multiple voltage thresholding Vt, signal level translators, and power gating of circuitry to deactivate portions of the circuit which are inactive. The supply voltage levels can be fixed, or programmable. Methods are described for performing circuit CAD in the routing and assignment process on FPGAs, in particular for optimizing FPGA use having the power reduction circuits taught. Routing methods describe utilizing slack timing, power sensitivity, trace-based simulations, and other techniques to optimize circuit utilization on a multi Vdd FPGA.

Owner:RGT UNIV OF CALIFORNIA

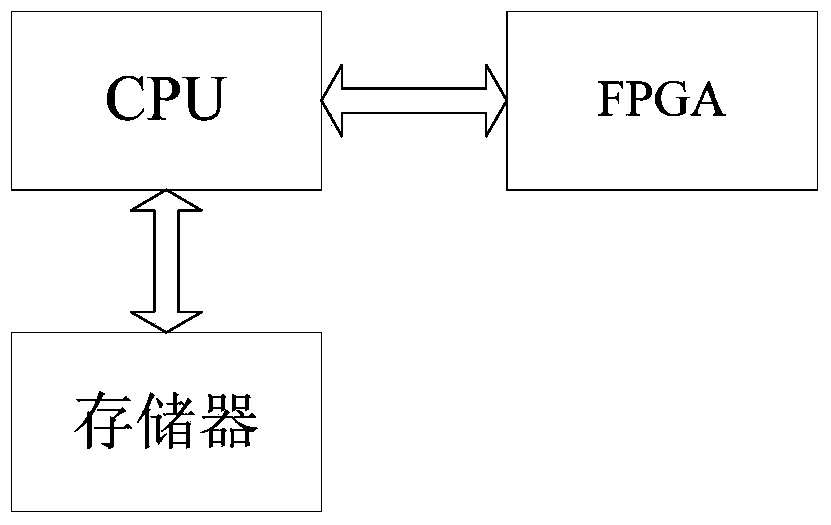

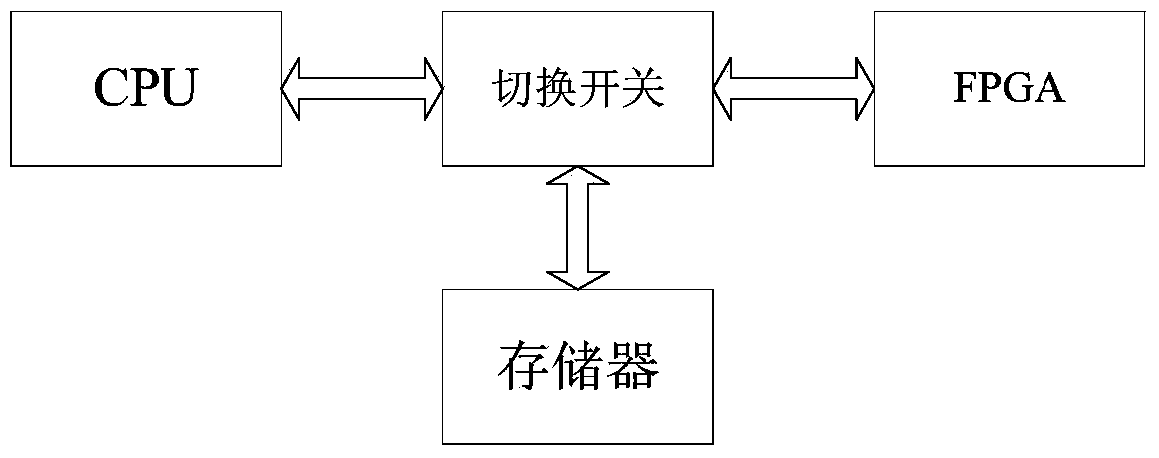

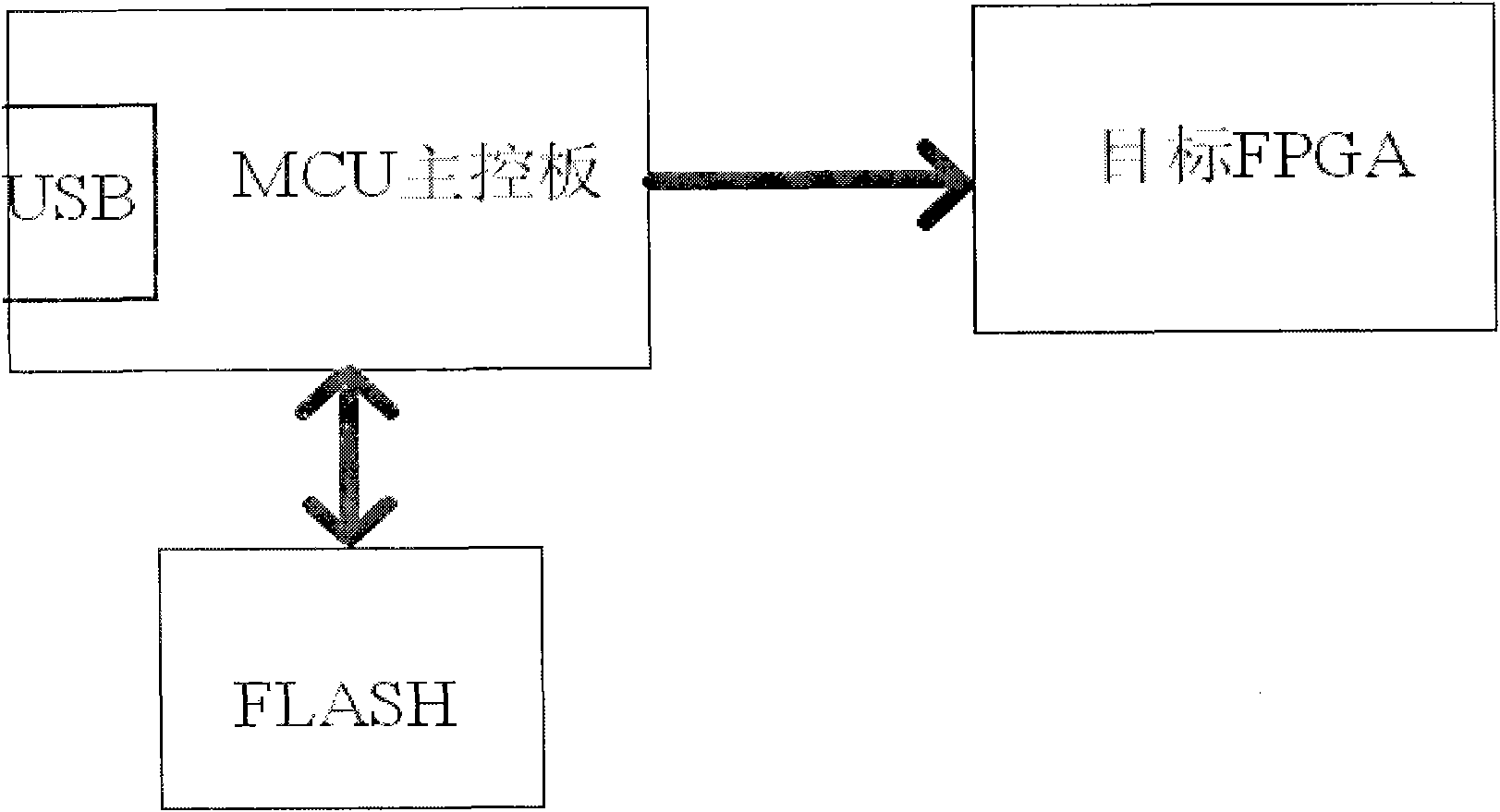

Board system and FPGA (Field Programmable Logic Array) online update method of communication interface cards

ActiveCN103559053AReduce design costImprove scalabilityProgram loading/initiatingCommunication interfaceComplex programmable logic device

The invention relates to the technical field of communication and discloses a board system, aiming at solving the problems that an FPGA (Field Programmable Logic Array) online update mode is inapplicable for the FPGA online update of a separated type system of a motherboard plus multiple communication interface cards in the prior art, and the update mode is high in cost and low in reliability. The system comprises a motherboard and n interface cards, wherein the motherboard comprises a CPU (Center Processing Unit), a CPLD (Complex Programmable Logic Device) unit and n slot positions; each slot position is connected with the CPLD unit; the CPLD unit is connected with the CPU; the n interface cards are connected onto the n slot positions in a plugging and one-to-one correspondence way through n connectors so as to realize signal interconnection with the motherboard; as an integer, n is greater than or equal to 2; the CPLD unit comprises a gating module and a counting module; the interface cards comprise an FPGA unit, a selector switch, a main flash module and a slave flash module; the main flash module and the slave flash module are connected with the FPGA unit through the selector switch. In addition, the invention also discloses an FPGA online update method of the communication interface cards, which is applicable for the separated type system of the motherboard plus the multiple interface cards.

Owner:MAIPU COMM TECH CO LTD

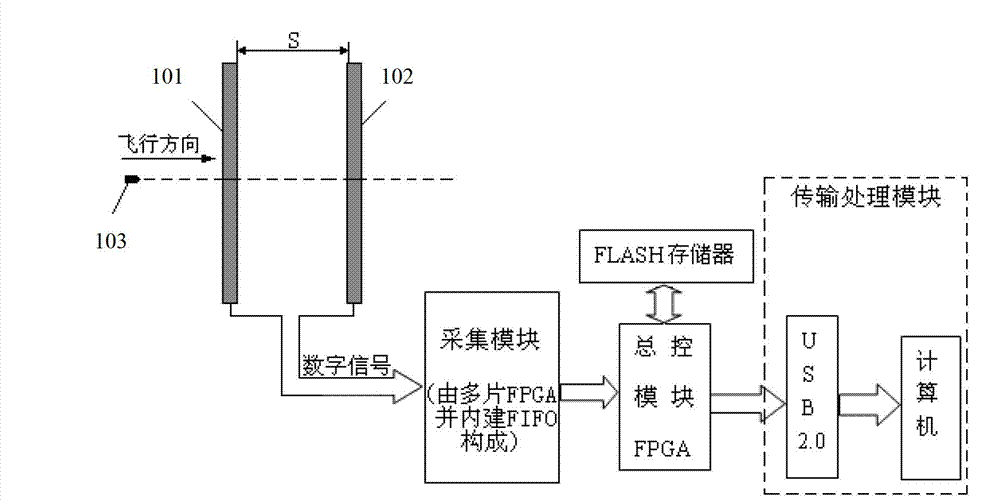

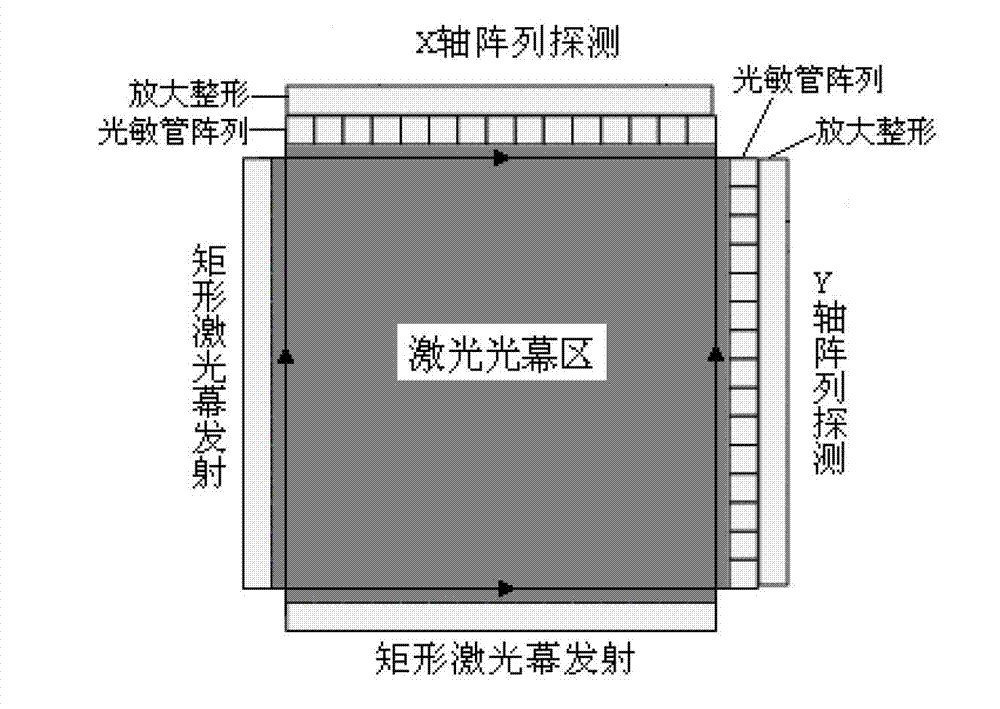

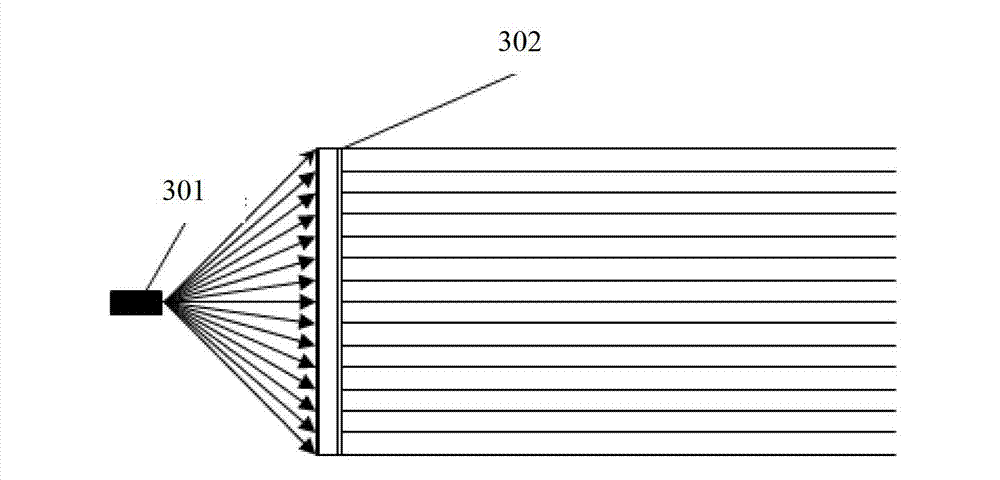

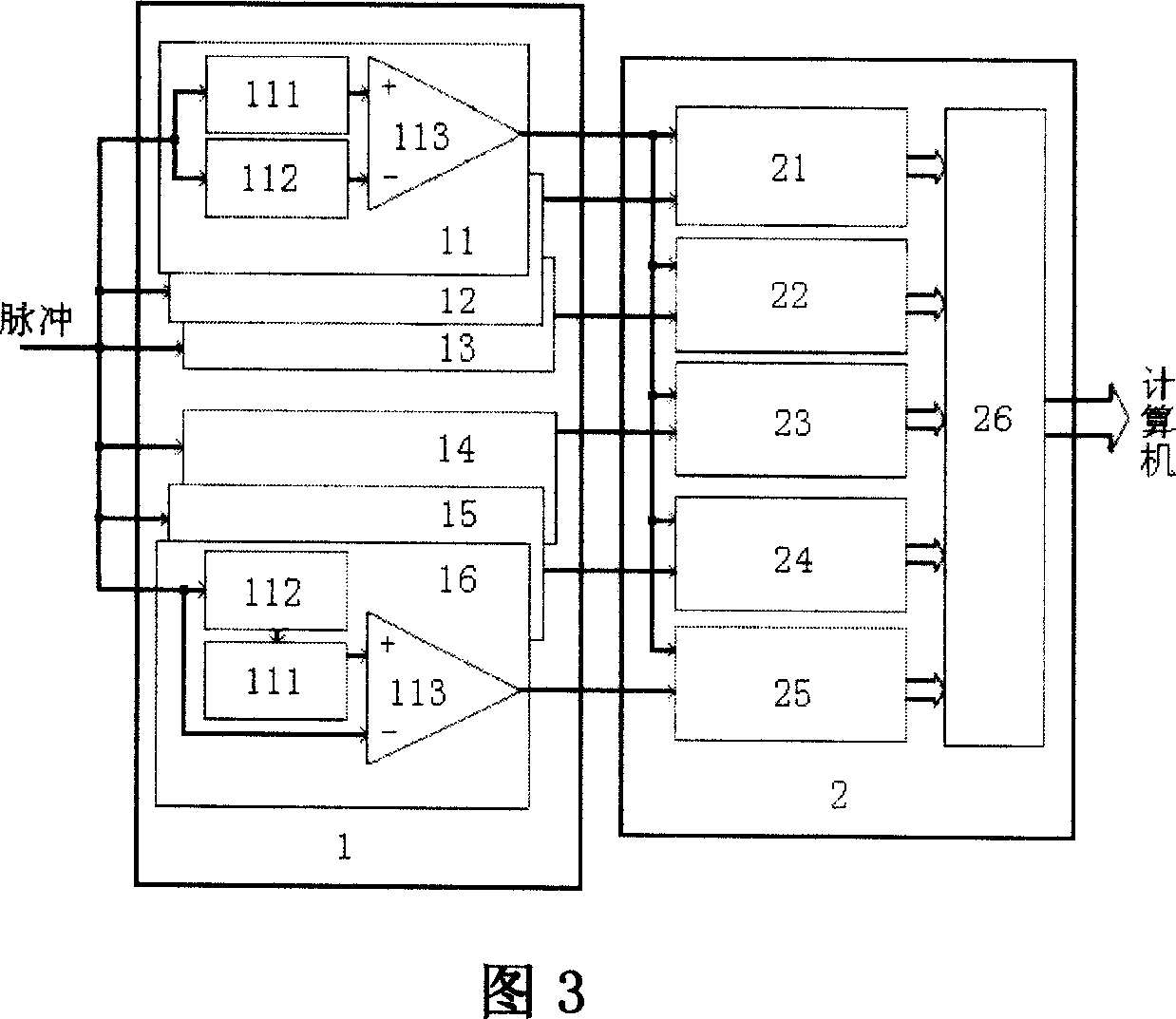

Parameter testing system and method for high-speed moving object

ActiveCN103206986ASimple compositionUsing optical meansDevices using time traversedTarget surfaceData acquisition

The invention discloses a parameter testing system and a parameter testing method for a high-speed moving object. The system mainly comprises a starting target, a stopping target, a data acquisition module, a master control module and a data transmission processing module, wherein each of the starting target and the stopping target consists of an X-axis and Y-axis rectangular laser light curtain emission unit, an X-axis and Y-axis photosensitive tube array and an amplification shaping unit; the starting target and the stopping target form two parallel virtual thin light curtain target surface which are at a determined interval; the data acquisition module consists of a plurality of field programmable logic arrays (FPGA) with built-in first in first out (FIFO) buffer memories; the master control module consists of an FPGA and a memory FLASH; and the data transmission processing module comprises a universal serial bus (USB) data interface and an upper computer. According to the system, the output level state of the X-axis and Y-axis photosensitive tube array at each moment when the object flies through thin light curtain areas is acquired and stored at high speed under the control of the FPGA of the master control module, and the speed of a fragment, landing coordinates and an overall dimension are calculated by data processing.

Owner:ZHONGBEI UNIV

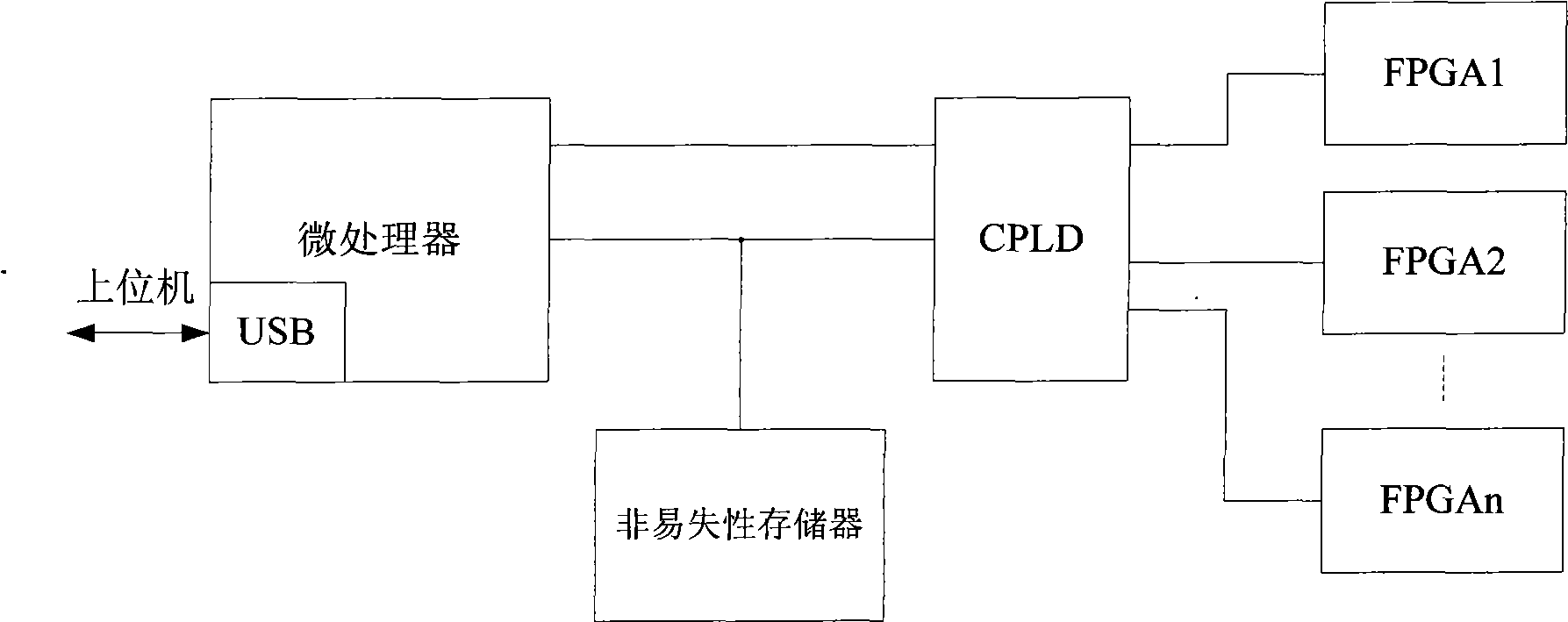

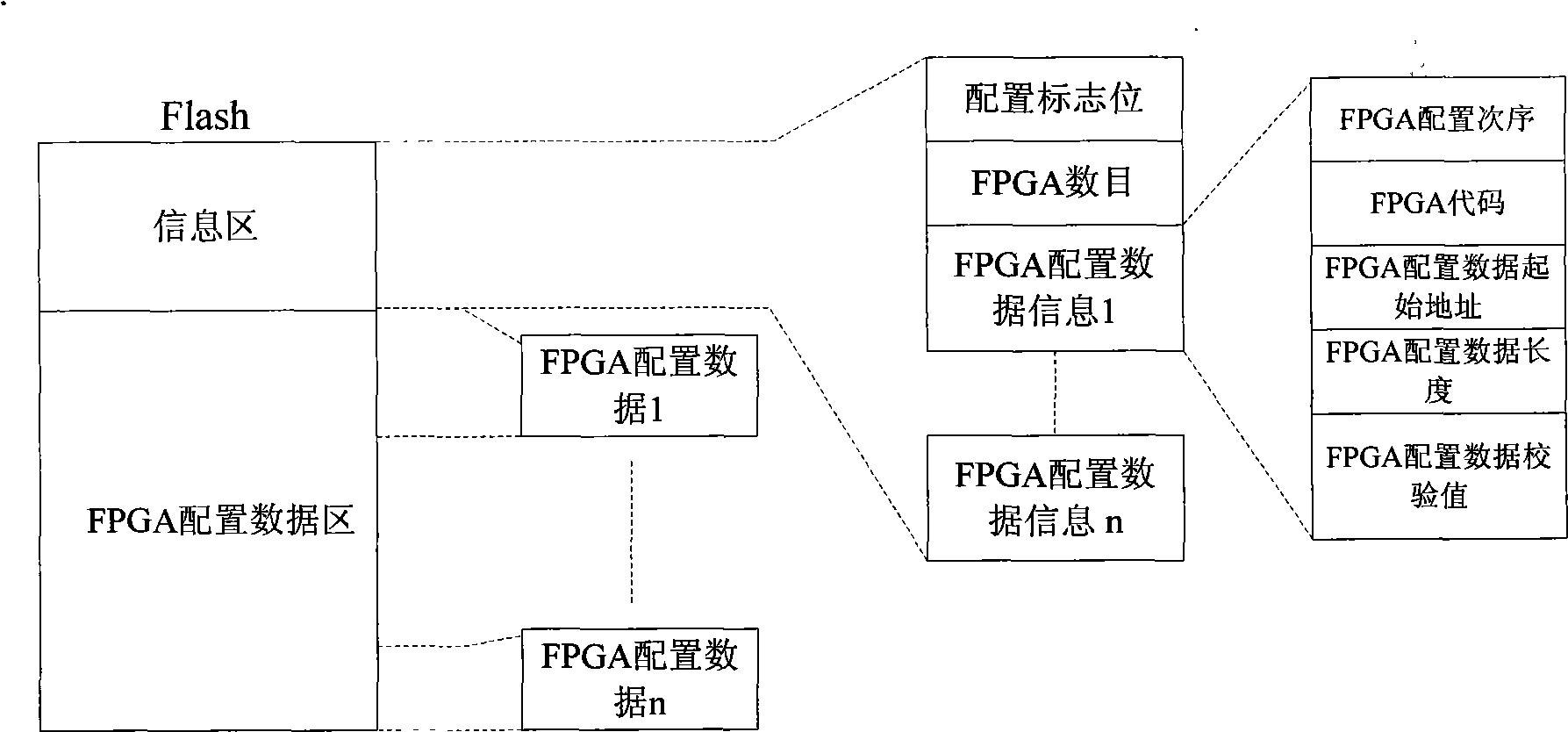

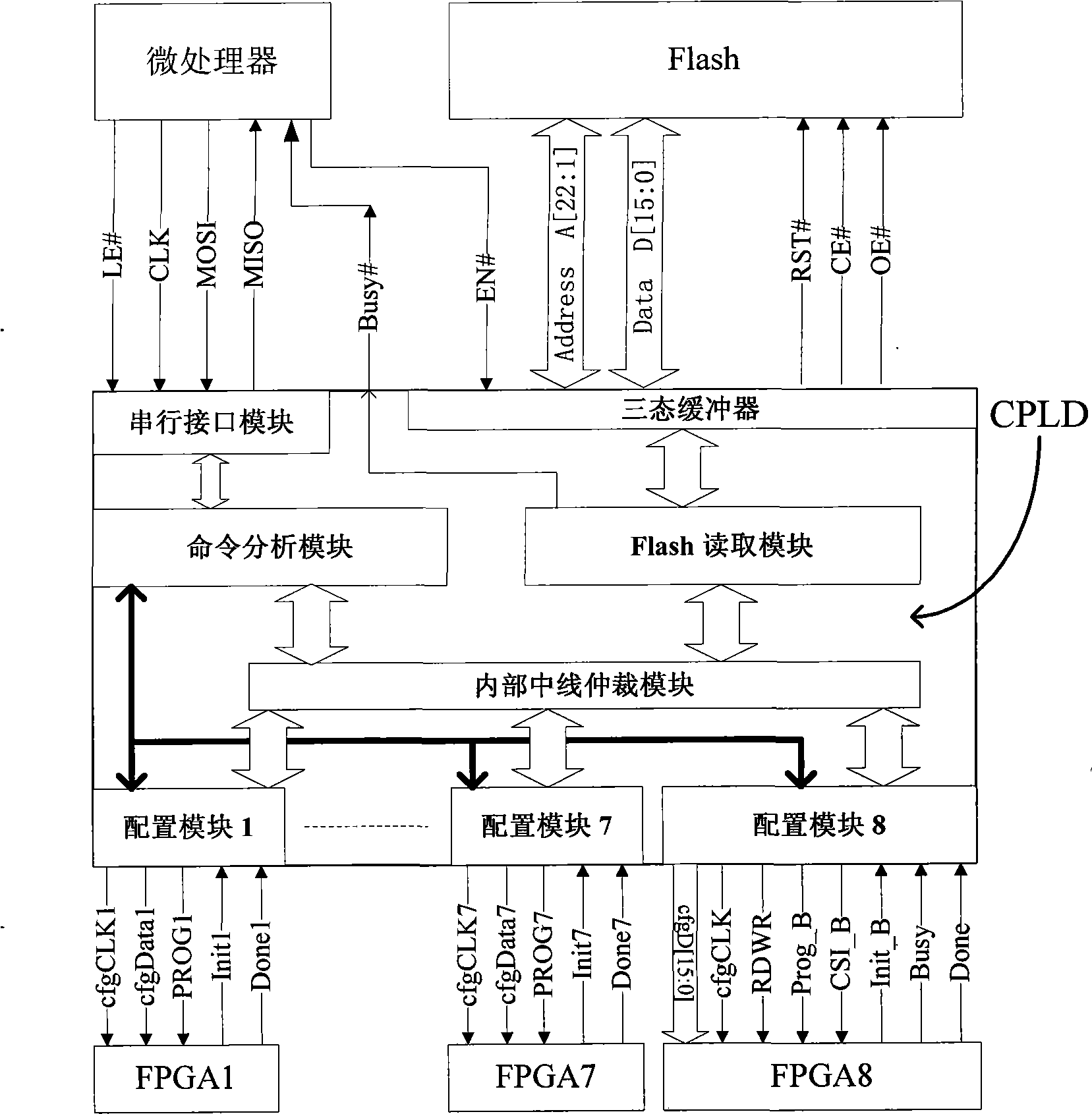

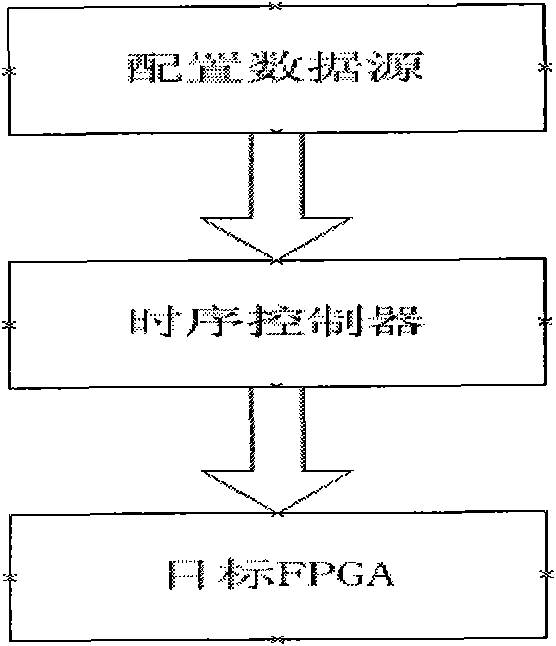

System for unified configuration and management of FPGA chip in equipment

InactiveCN101485576ARealize unified configurationRealize managementUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsComplex programmable logic deviceFpga chip

The invention discloses a system for unified configuration and management of FPGA chips inside equipment. The system comprises a configuration and management logic component and at least one field programmable gate array (FPGA) chip, wherein the configuration and management logic component is connected with the FPGA, and comprises a microprocessor, a nonvolatile memory and a complex programmable logic device (CPLD) which are connected with each another; the CPLD is connected with the FPGA; and the configuration and management logic component is used to realize the configuration of one or more pieces of the FPGA in a serial mode or a parallel mode. The system realizes unified configuration and management of the FPGA chips inside the equipment and greatly increases the configuration efficiency of the FPGA chips inside the equipment, thereby increasing equipment efficiency during use and maintenance.

Owner:SHENZHEN LANDWIND IND

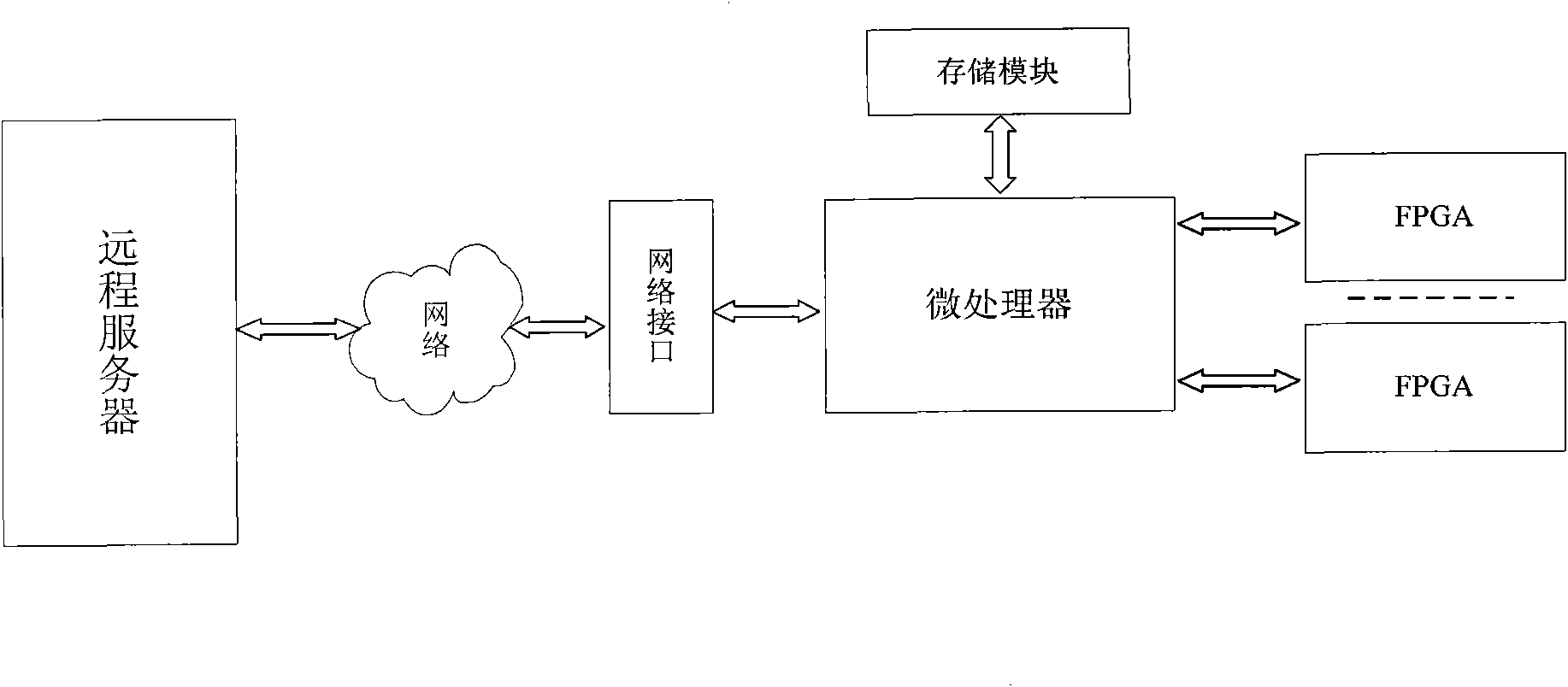

FPGA configuration system and configuration method based on network

InactiveCN101783812AImprove configuration efficiencyIncrease configuration flexibilityDigital computer detailsTransmissionNetwork connectionComputer module

The invention discloses an FPGA configuration system and a configuration method based on network. The configuration system comprises a remote server, a microprocessor, a network interface and a storage module, wherein the microprocessor is respectively connected with the network interface, the storage module and at least one field programmable gate array FPGA are connected; the remote server is connected with the network interface by the network; the remote server is used for storing the configuration data of the field programmable gate array FPGA and transmits the configuration data to the microprocessor by the network interface; and the microprocessor is used for writing the configuration data into the storage module or reads the configuration data from the storage module so as to configure the field programmable gate array FPGA.

Owner:SHENZHEN LANDWIND IND

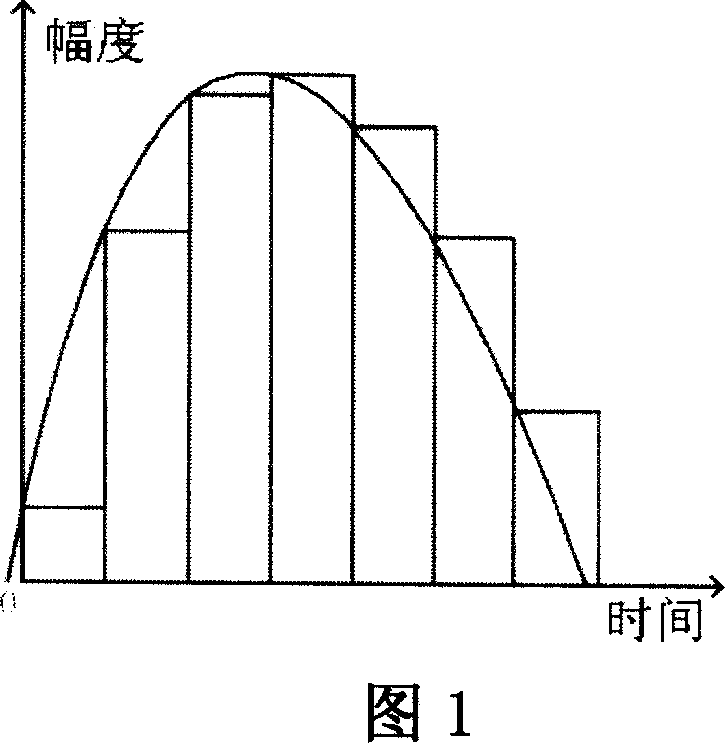

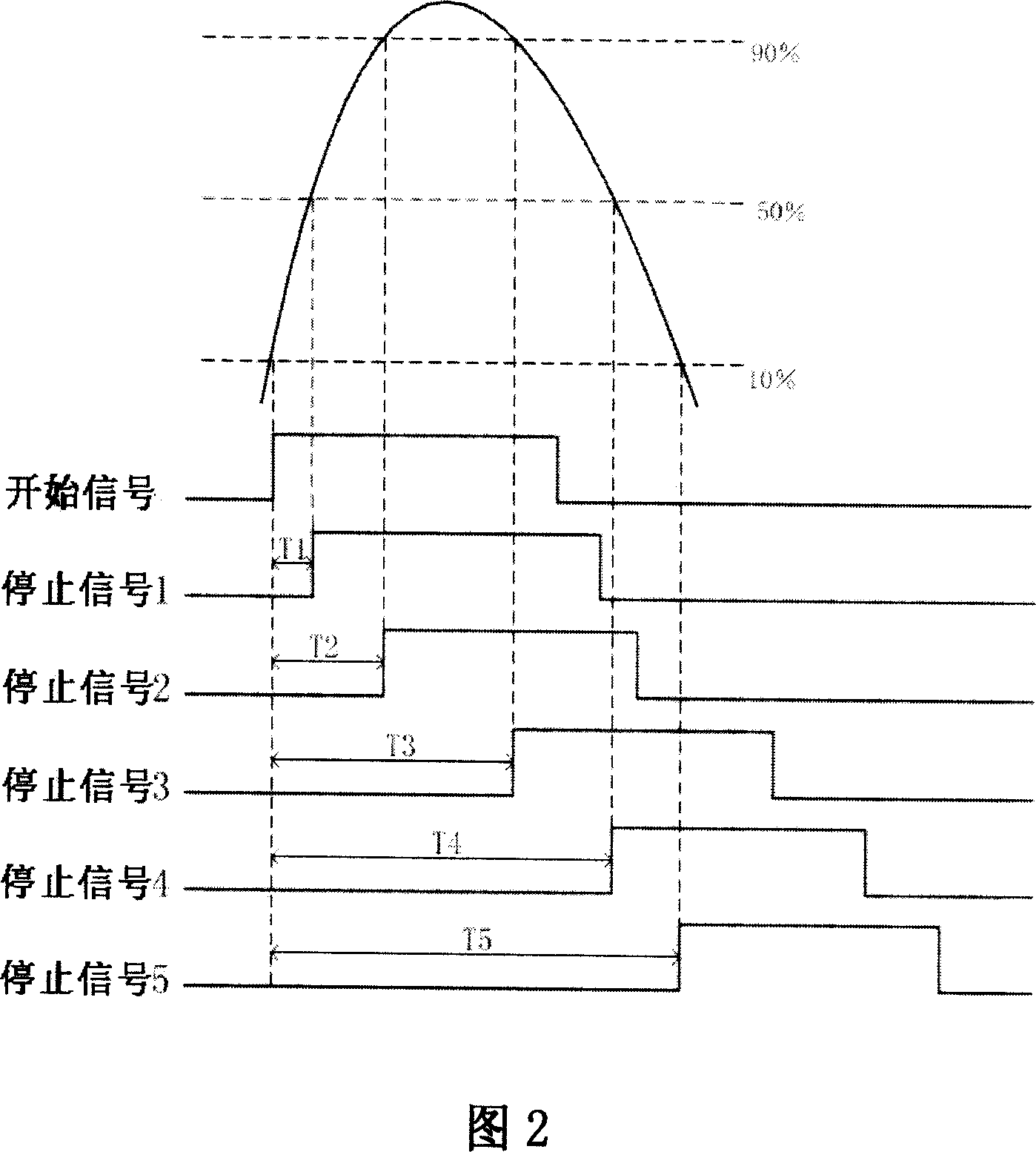

Pulse shape measuring device and measuring method thereof

InactiveCN101034120AHighly integratedGood value for moneyOptical rangefindersPulse characteristics measurementsDiscriminatorMeasurement device

This invention relates to a measuring method and device of impulse form. The invention includes one constant proportion timing discriminate module and one time-to-digital conversion module. Data of time-to-digital conversion modular enter calculator for handling. Constant proportion timing discriminate module has a group of leading edge discriminator and a group of back edge discriminator, which separately discriminate a series of points where the ratio of pulse front edge and back edge voltage and spike voltage are certain worth corresponding time. multipass time-to-digital conversion module convert time interval between first time and subsequently time to digital quantity, adopt digital counting method and combine digital delay line bracketing method, realize at a piece of field programmable logic array FPGA. sending obtained data into computer for calculation to gain time interval, base on voltage peak ratio of every time to indirectly reduce impulse form, and obtain pulsewidth. The invention has low cost, small bulk, and light weight, can apply to laser range finder.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

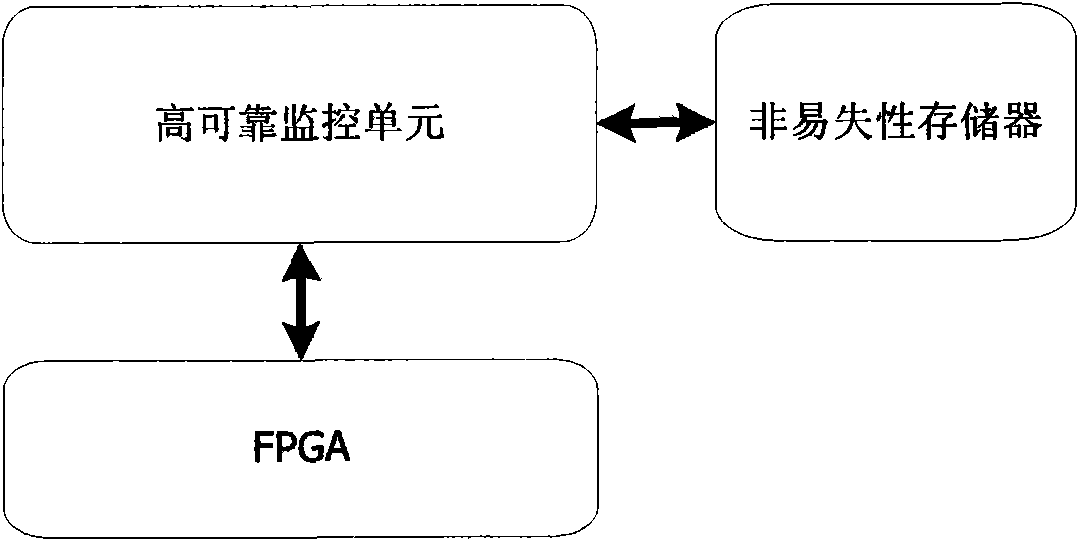

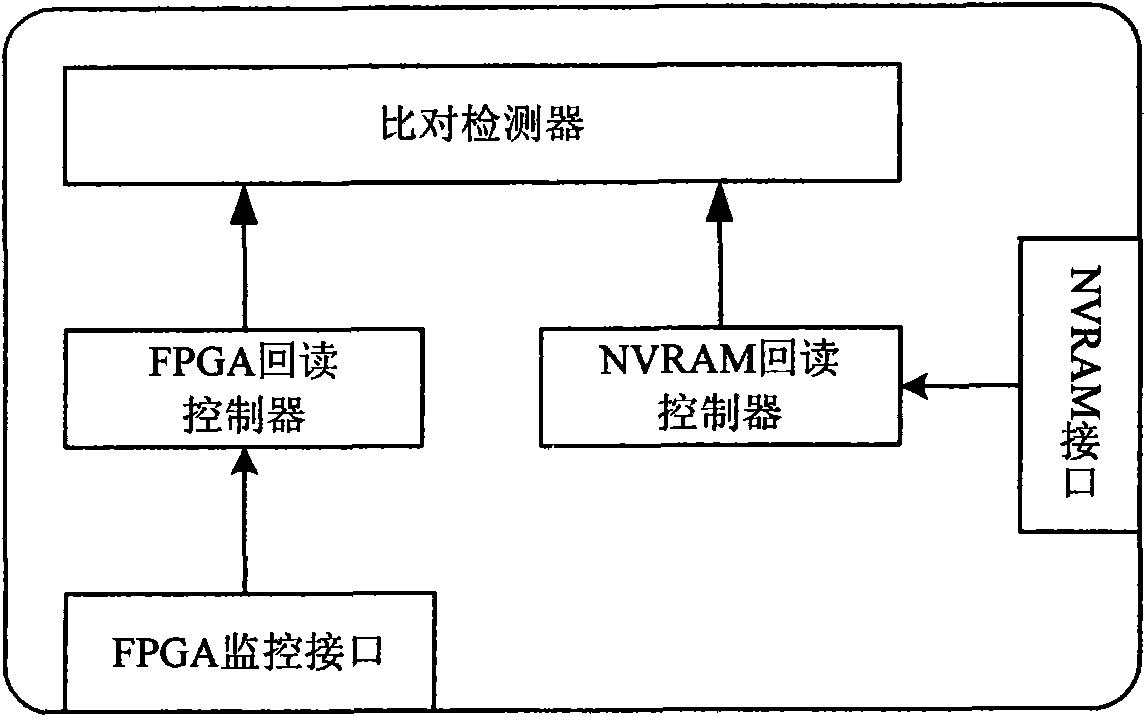

Method and device for testing single event upset in in-field programmable logic gate array

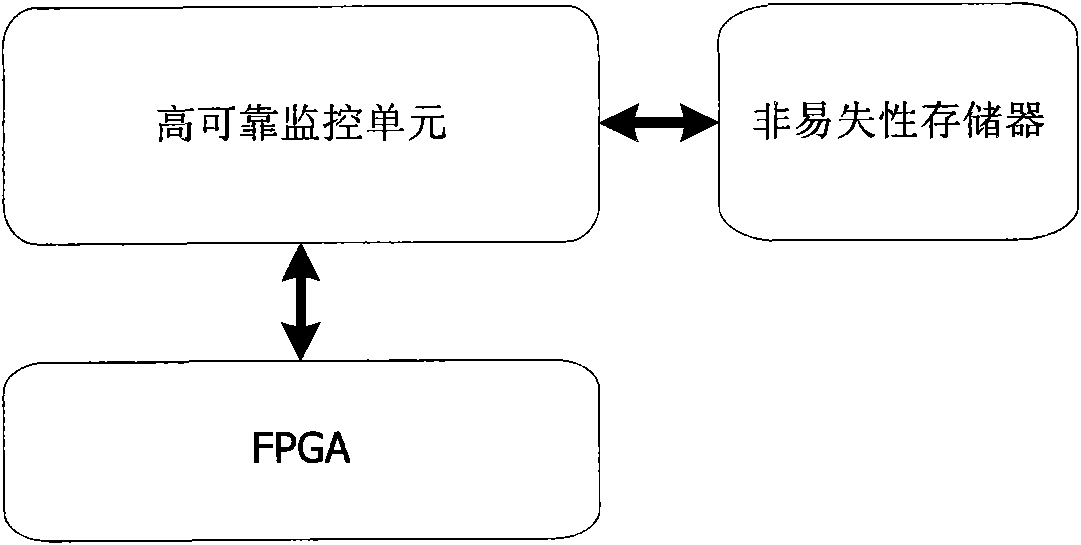

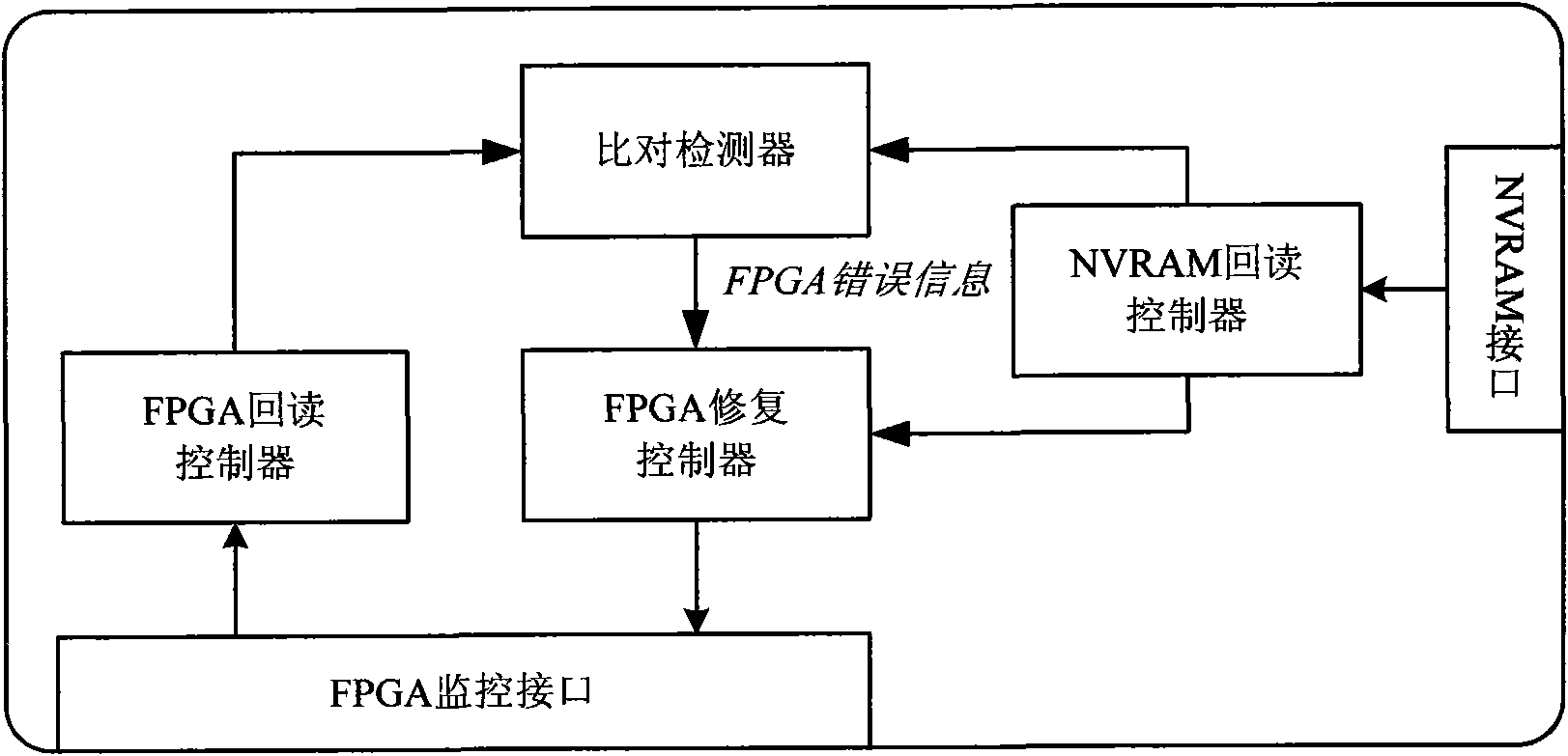

The invention discloses a method and a device for testing single event upset in in in-field programmable logic gate array, comprising the following steps: a highly reliable monitor unit which is connected with the field programmable logic gate array and used for realizing the testing flow of the single event upset is arranged; the highly reliable monitor unit executes the read back flow of the configuration memory of the field programmable logic gate array, reads the configuration frame of the field programmable logic gate array, and executes an original configuration frame which is read from a nonvolatile memory by a standard NVRAM interface; and the highly reliable monitor unit compares the read back configuration frame of the field programmable logic gate array with the original configuration frame by means of byte, when the configuration frame is wrong in comparing, namely, the configuration memory of the field programmable gate array is judged to have the single event upset. The device comprises the highly reliable monitor unit which is connected with the nonvolatile memory by a bus. The invention has the advantages of simple structural principle, high reliability, good stability, etc.

Owner:NAT UNIV OF DEFENSE TECH

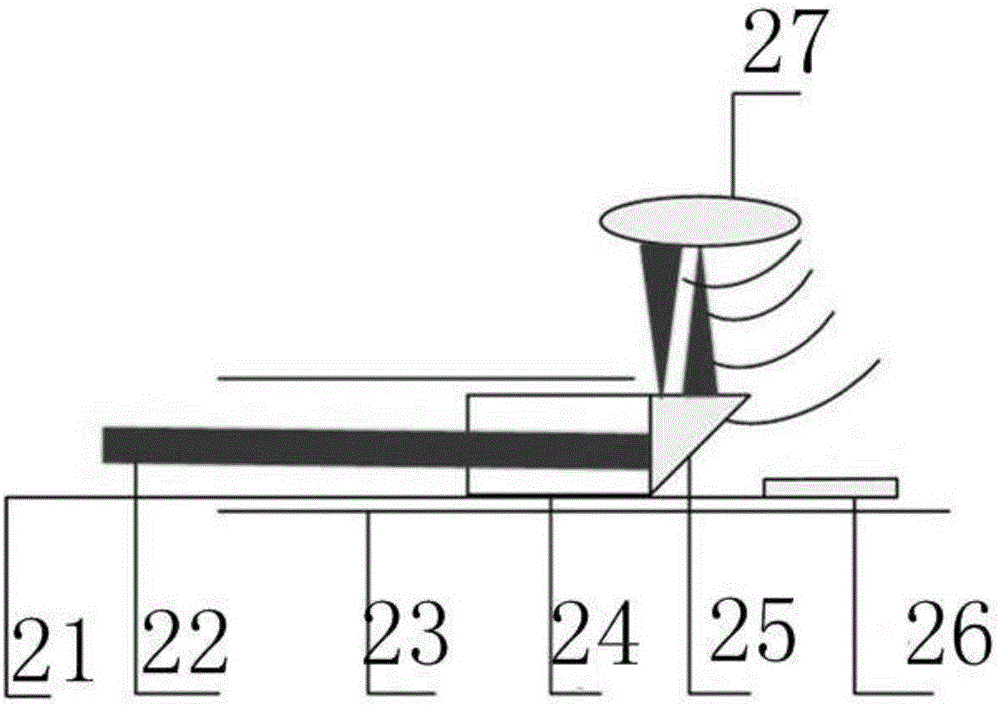

Device and method for endovascular optical coherence tomography - opto-acoustic - ultrasonic multimode imaging

ActiveCN106361294ASimplify testing proceduresReduce the difficulty of detectionSurgeryCatheterDiagnostic Radiology ModalitySonification

The invention belongs to the field of blood vessel endoscopic imaging and discloses a device and method for endovascular optical coherence tomography - opto-acoustic - ultrasonic multimode imaging. The device comprises a computer, an optical coherence tomography (OCT) excitation and collection system, an opto-acoustic signal excitation and collection system, an ultrasonic signal excitation and collection system and an integrated probe. The OCT excitation and collection system comprises a field programmable logic array (PFGA) panel, a superluminescent diode, an isolator, a first optical fiber coupler, a reference arm, a linear array charge coupled device (CCD) and a first collecting card. The opto-acoustic signal excitation and collection system comprises a pulsed laser, a diaphragm, a second optical fiber coupler and a doubly clad optical fiber. The ultrasonic signal excitation and collection system comprises a pulse ultrasonic emitter / receiver, a signal amplifier, a signal filter and a second collecting card. The OCT, opto-acoustic and ultrasonic tri-modal blood vessel endoscopic imaging system integrates three imaging modes and respective advantages thereof, and multi-parameter physiological function information and multiscale structural information of a blood vessel can be obtained.

Owner:SOUTH CHINA NORMAL UNIVERSITY

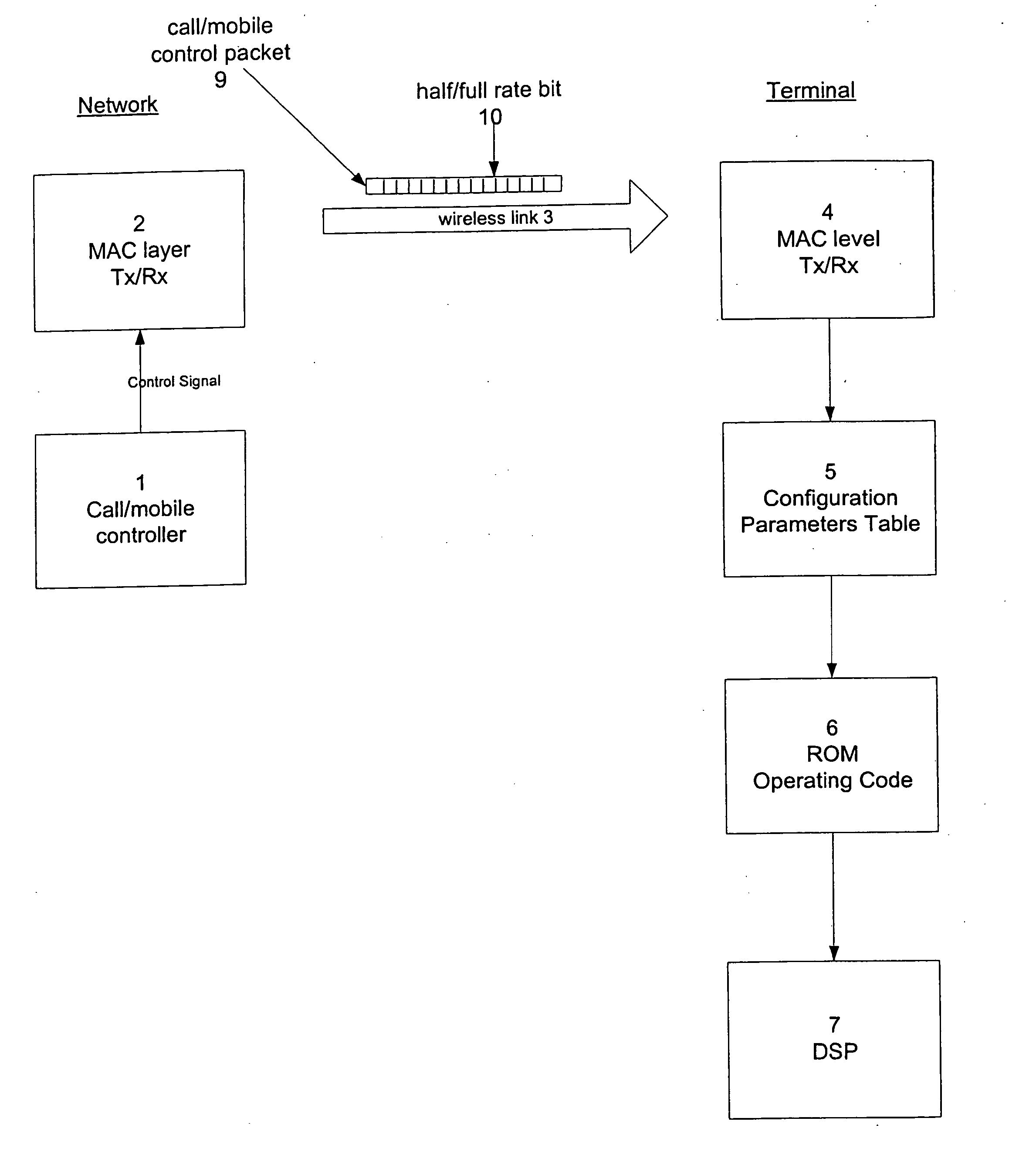

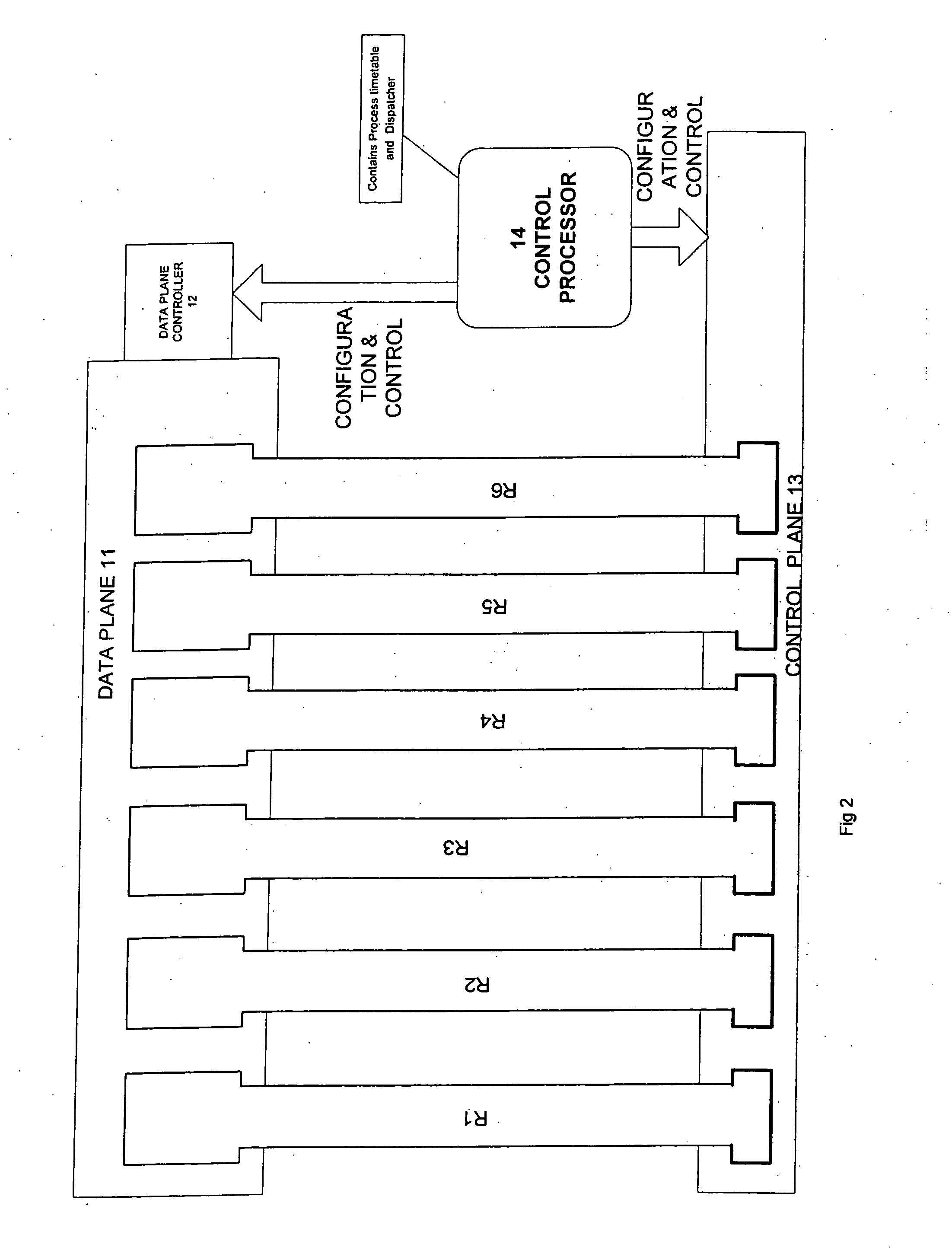

Reconfigurable signal processing module

InactiveUS20050152322A1Good flexibilityRadio/inductive link selection arrangementsAutomatic exchangesCommunications systemConfigurable hardware

The present invention relates to re-configurable signal processing modules in particular, although not exclusively, for wireless communications terminals. In general terms in one aspect the present invention provides a system for reconfiguring a signal processing module having a number of re-configurable resources such as re-configurable hardware blocks including ASIC's and field programmable logic gate arrays (FPGA's), as well as software modules for implementing different functions and which can be run on a DSP or other processing platform within the signal processing module. The module may be a mobile terminal or a base station in a wireless communications system for example. The system comprises means for generating a commands data structure comprising configuration commands for the resources, and may further comprise means for communicating this data structure to the signal processing module. The module has means for reconfiguring itself using this data structure. Typically the data structure will be a process timetable having time stamped configuration and run-time commands suitable for being dispatched to the appropriate resource.

Owner:KK TOSHIBA

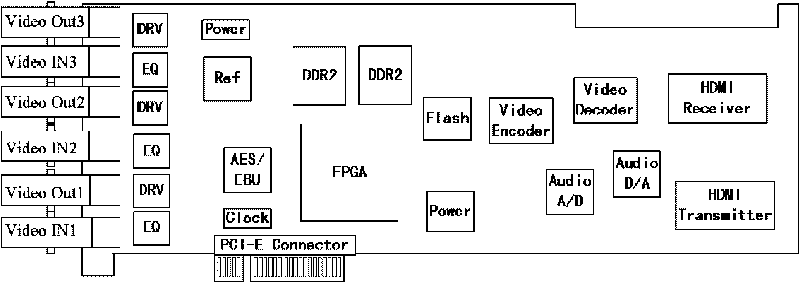

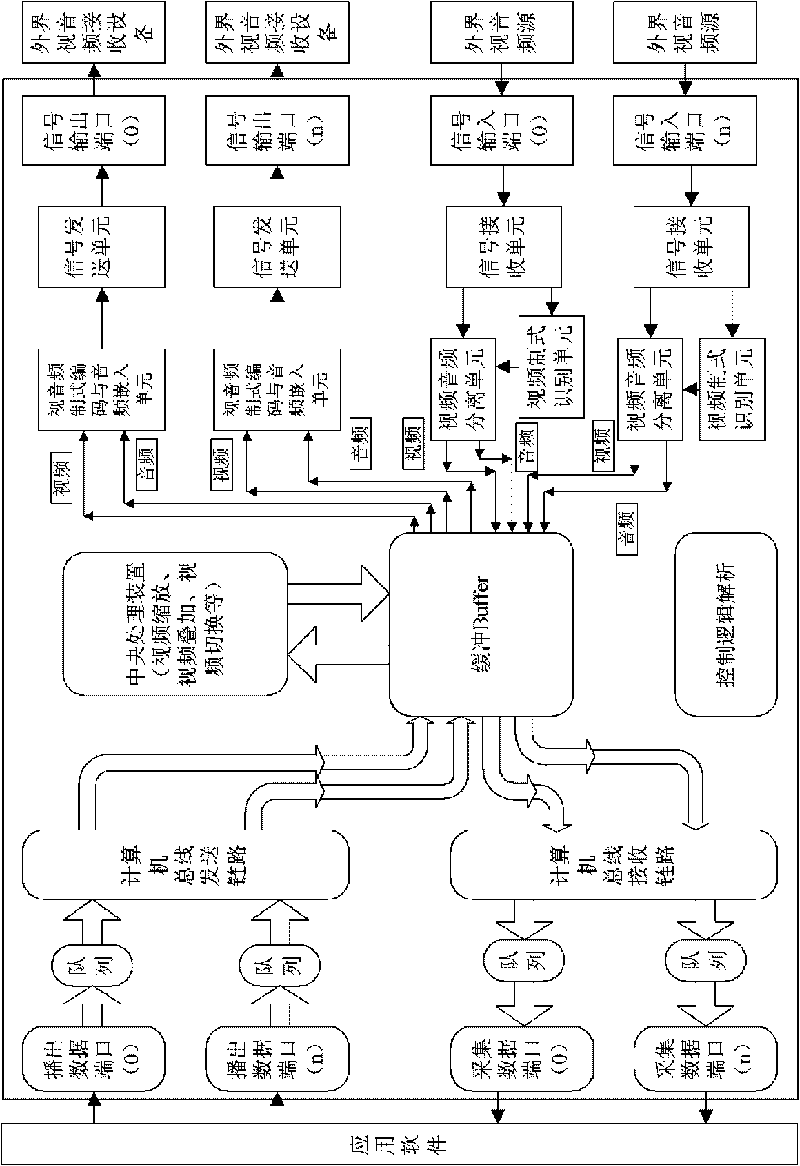

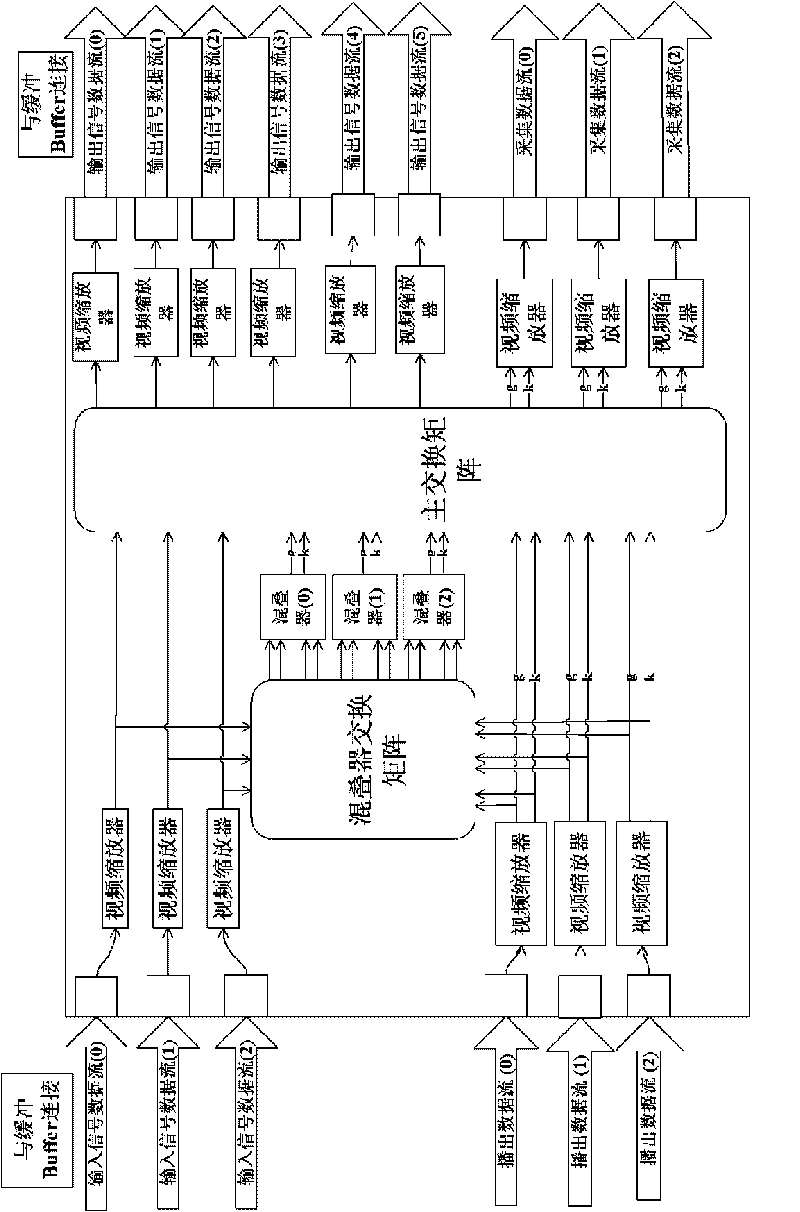

High standard-definition video-audio IO card with internal switching function

ActiveCN101706675AImprove economyExpand the scope of workTelevision system detailsColor television detailsComputer hardwareImage resolution

The invention relates to a high standard-definition video-audio IO card with an internal switching function. The high standard-definition video-audio IO card comprises a plurality of video-audio input ports and a plurality of video-audio output ports, wherein each input port is connected with a respective interface conversion chip of SDI input signals, the video-audio output ports are connected with respective SDI output driving chips, and the interface conversion chip of each SDI input signal and the SDI output driving chips are connected with a field programmable logic chip. Through the configuration of an internal switching mode, the high standard-definition video-audio IO card can achieve simultaneous acquisition of various videos with different resolution ratios on the videos input from the outside in one or more forms, achieve simultaneous broadcasting of various videos with different resolution ratios on the videos output by software in one or more forms, achieve aliasing of a plurality of paths of the videos input from the outside and a plurality of paths of the videos broadcast by the software, and achieve the functions of switching the videos and the audios input from the outside and the videos and the audios output by the software and the like. The high standard-definition video-audio IO card can be widely used in various types of devices of broadcasting television high standard-definition production and broadcasting processes.

Owner:BEIJING DAYANG TECH DEV

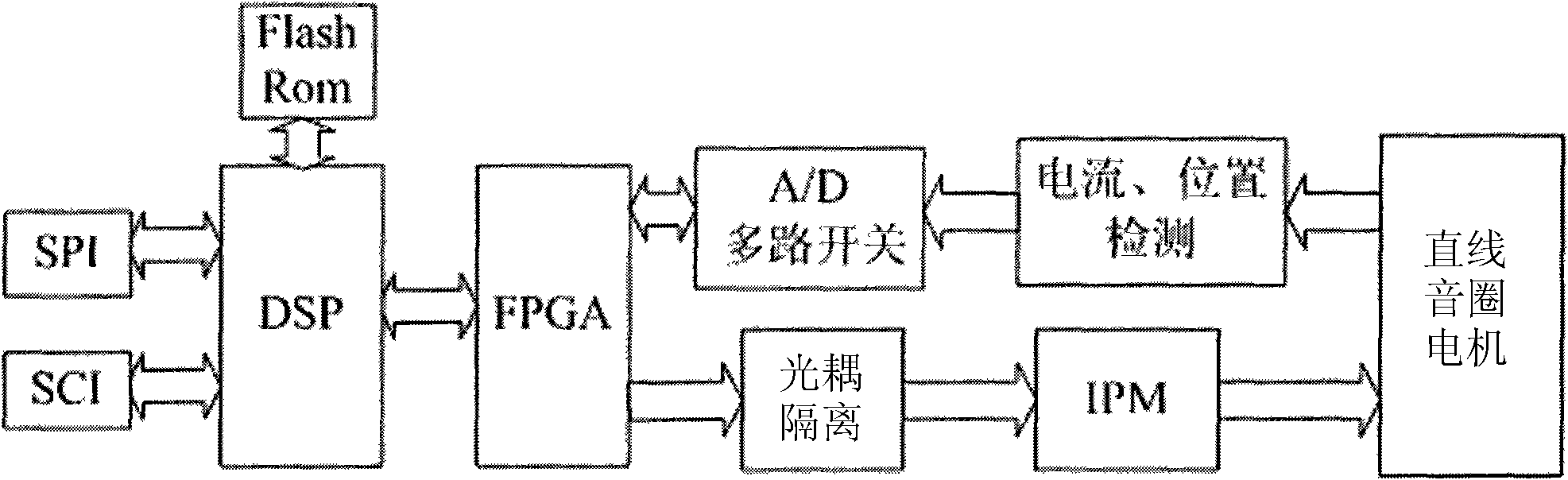

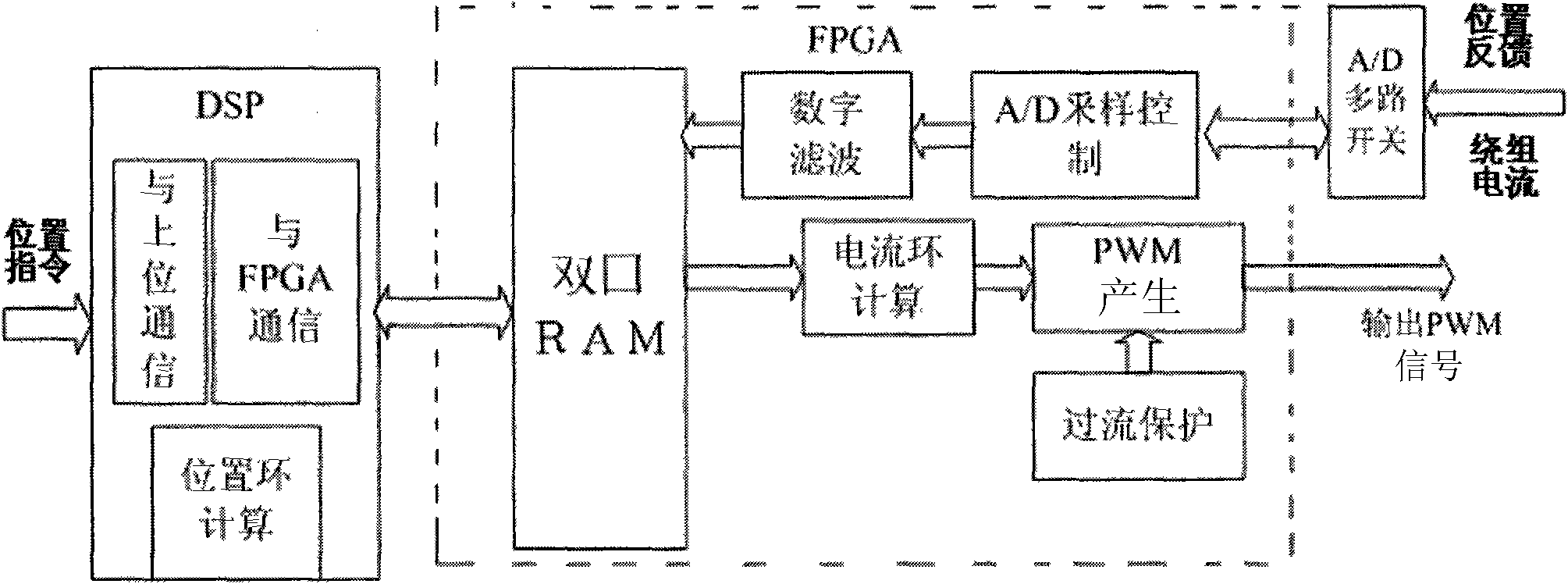

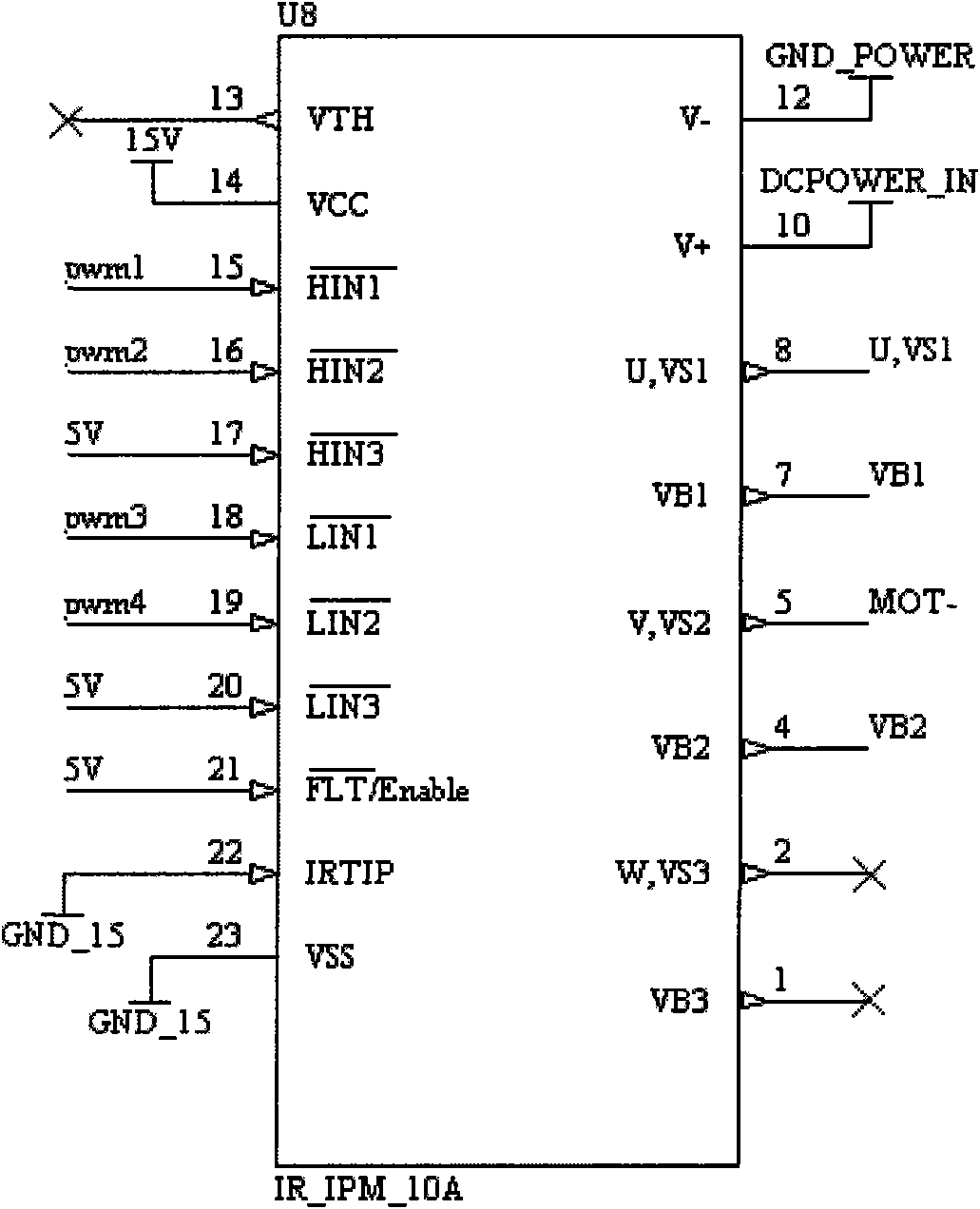

Full digital driving controller of permanent magnetic linear voice coil motor used for direct driving valve

InactiveCN101576745AIncrease sampling rateHighly integratedAC motor controlElectric motor controlExtensibilityField programmable logic devices

The invention relates to a full digital driving controller of a permanent magnetic linear voice coil motor used for a direct driving valve, consisting of three parts: a digital controller, a power circuit and a signal detection circuit; the digital controller circuit comprises a 32-bit floating point DSP, a field programmable logic device FPGA and an external Flash ROM; the power circuit comprises a high-speed optical coupling isolation circuit, and an H-bridge power main circuit consisting of intelligent power modules IPM; the signal detection circuit comprises an A / D converter, a multi-path analogue switch, a Hall current sensor used for detecting the moving coil winding current, a non-contact eddy current displacement sensor used for detecting the position of the moving coil and an amplification and active power filter circuit for analogue signals. The full digital driving controller of the permanent magnetic linear voice coil motor used for the direct driving valve has the advantages of high integration, good extensibility, high reliability, high frequency response and high precision.

Owner:BEIHANG UNIV

Method and device for repairing single event upset in field programmable logic gate array

InactiveCN101551763AImplement rollover detectionLow costError detection/correctionRead-only memoriesGate arrayByte

A method and a device for repairing single event upset in a field programmable logic gate array are disclosed, a high-reliability monitoring unit, which is connected with the field programmable logic gate array and used for realizing the detection and the repair of the single event upset, is set; a read-back process of a configuration memory of the field programmable logic gate array is implemented by the high-reliability monitoring unit in order to read configuration frames of the field programmable logic gate array, and original configuration frames, which are read from a non-volatile memory via a standard NVRAM interface, are then implemented by the high-reliability monitoring unit; the high-reliability monitoring unit compares the read-back configuration frames with the original configuration frames by bytes, when comparison error occurs on the configuration frames, it is judged that the single event upset in the configuration memory of the field programmable logic gate array occurs, and the high-reliability monitoring unit executes a repair process to repair the incorrect configuration frames of the field programmable logic gate array. The invention has the advantages of simple structural principal, convenient operation, high reliability and good stability.

Owner:NAT UNIV OF DEFENSE TECH

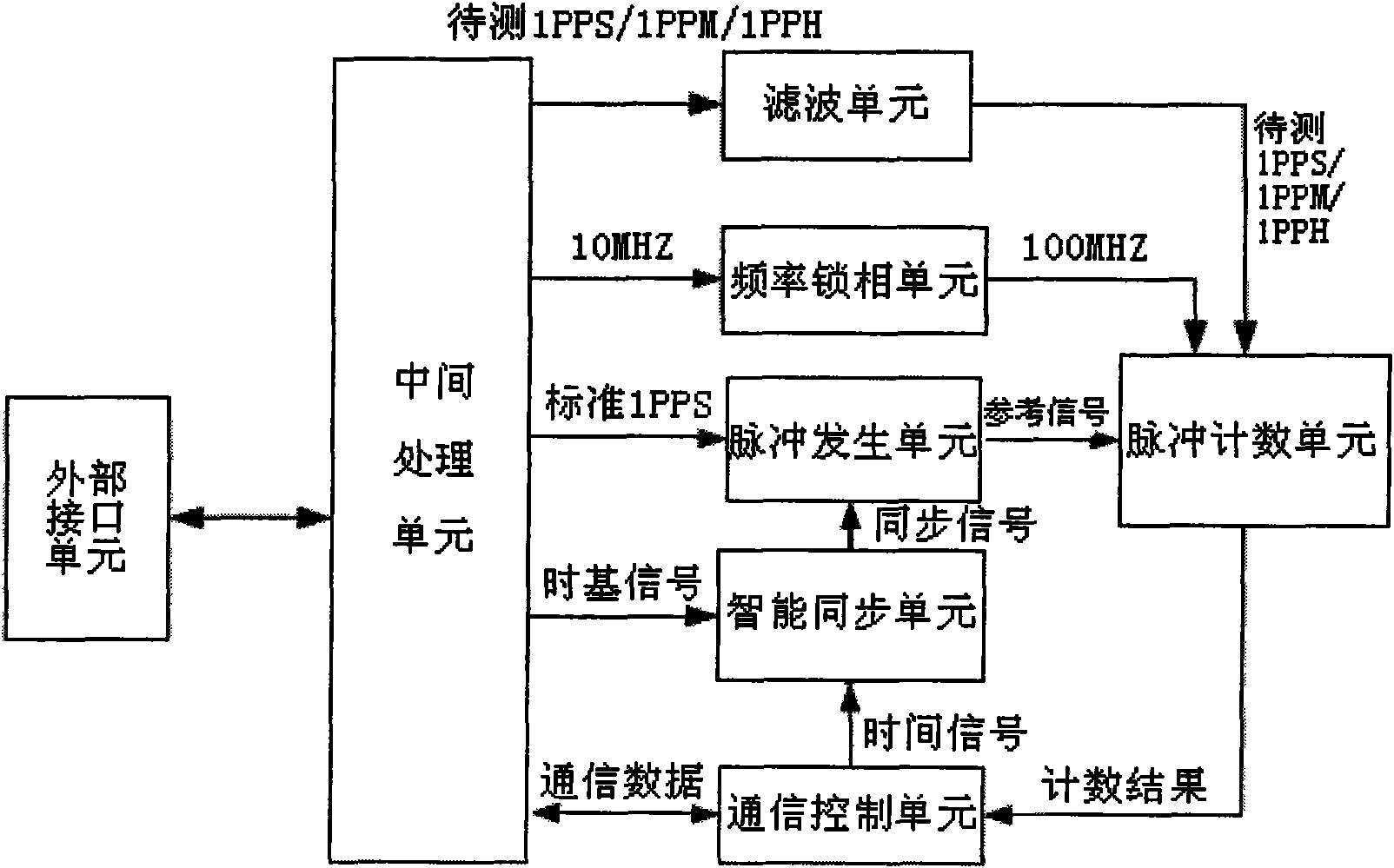

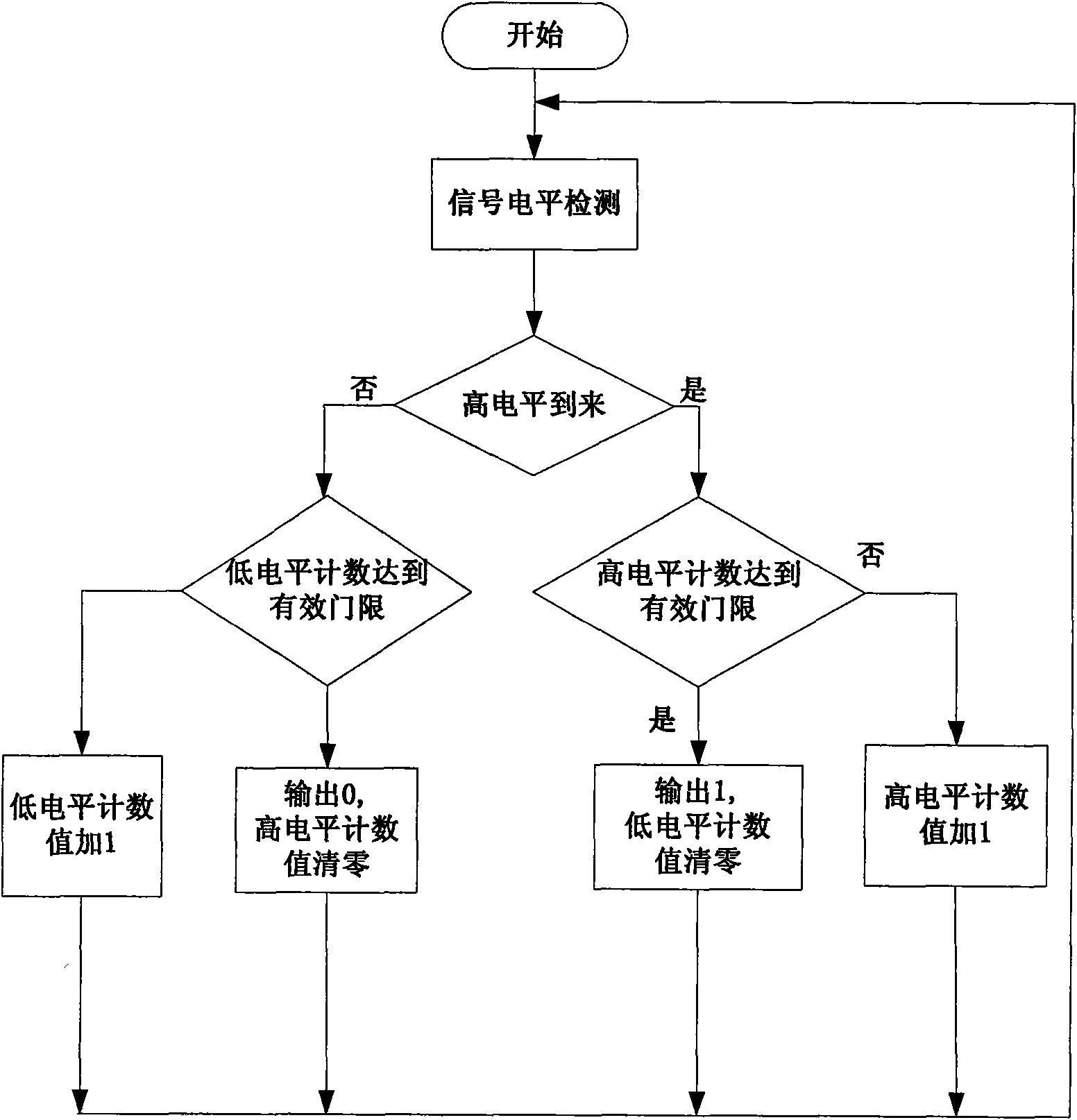

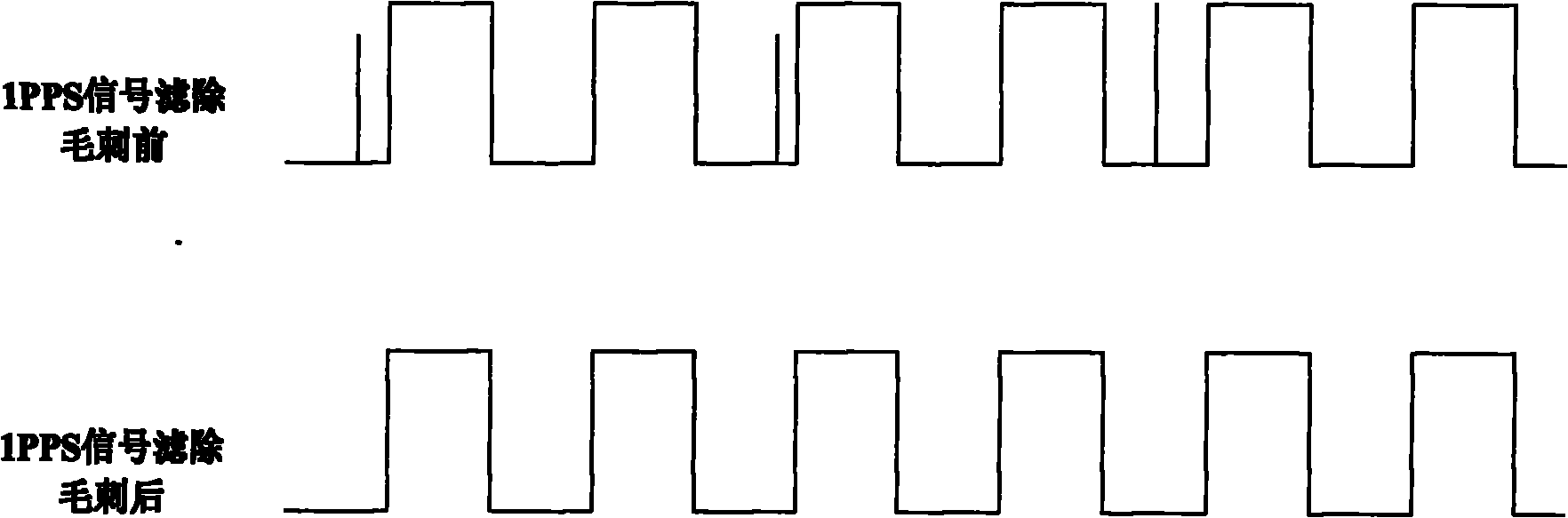

Reliable time scale pulse measurement method and measurement device thereof

ActiveCN101871968ASolve glitchesImprove performanceComputer controlPulse shapingTime markMeasurement device

The invention discloses a reliable time scale pulse measurement method, which comprises the following steps: 1) converting a 10MHz frequency signal of a precise clock source, a standard 1PPS signal and 1PPS, 1PPM and 1PPH signals to be measured to pulse signals; 2) carrying out frequency doubling on the 10MHz frequency signal of the precise clock source for obtaining a 100MHz frequency signal, and taking the 100MHz frequency signal as the working frequency of an FPGA; simultaneously carrying out frequency division on the standard 1PPS signal and respectively obtaining a 1PPM reference signal and a 1PPH reference signal; and 3) measuring the precision of the 1PPS, the 1PPM and the 1PPH signals to be measured according to the reference signals of 1PPS, 1PPM and 1PPH under the working frequency of 100MHz. The method can realize the high-speed and high-efficient counting operation by adopting a field programmable logic sequence, realize the multi-path and multi-group pulse fast detection, and send the detection result to a user and is characterized by stable performances and convenient maintenance.

Owner:郑州威科姆科技股份有限公司

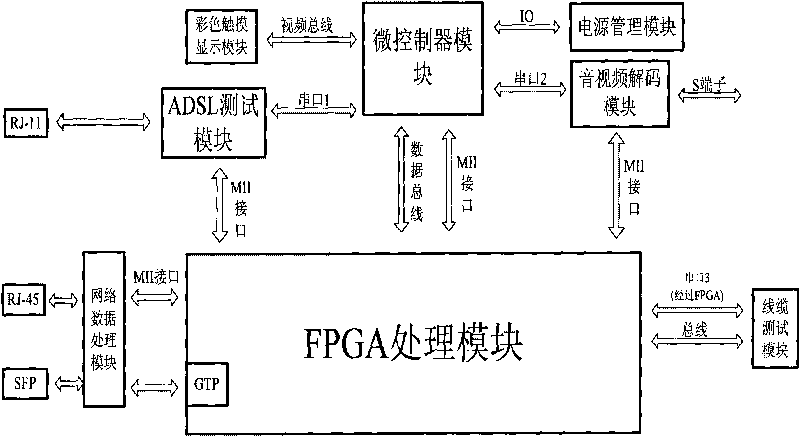

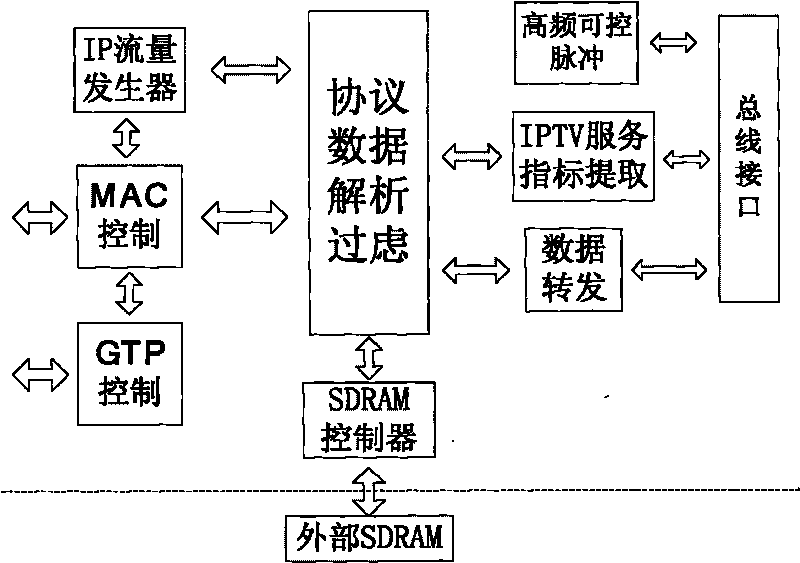

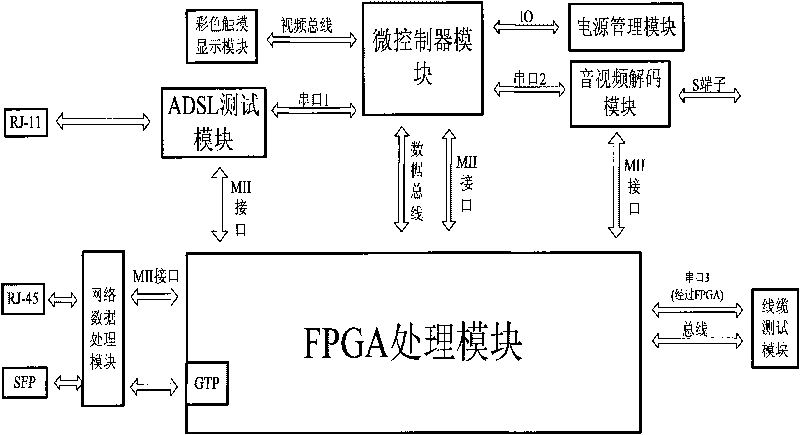

Method and device for testing quality of network television

The invention discloses a method and a device for testing the quality of a network television in order to solve the problems of single function, low testing efficiency, carrying inconvenience and the like of the method and device for testing the quality of the IPTV in the prior art. The method for testing the quality of the network television performs a test by actively sending test data to a target network and receiving test data fed back and can realize network connection in three different modes. The device for testing the quality of the network television of the invention is formed on thebasis of field programmable logic array FPGA on a large scale and a plurality of kinds of integrated circuits of specific purposes; and the device is integrated so highly as to meet the IPTV testing standards publicly known in the industry and easily realize expansion, so the device is a handheld IPTV tester which has the advantages of convenience, practicability, multifunction and strong operability.

Owner:重庆重邮汇测通信技术有限公司

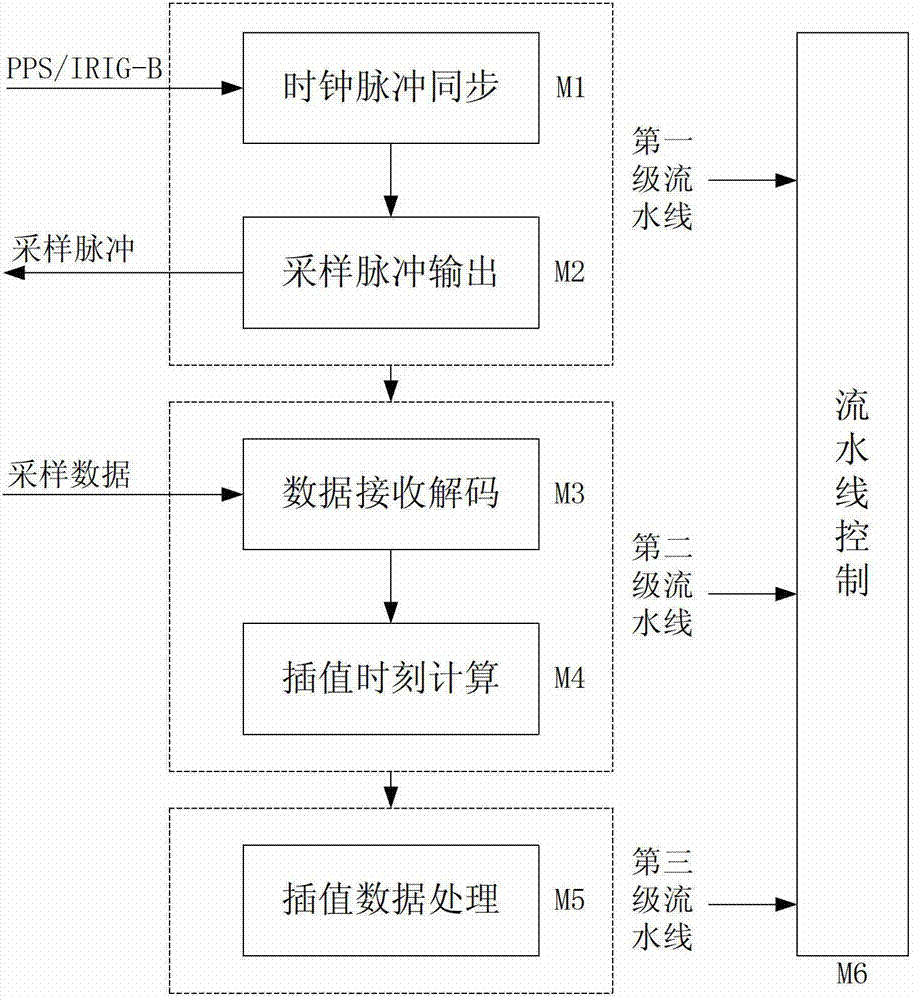

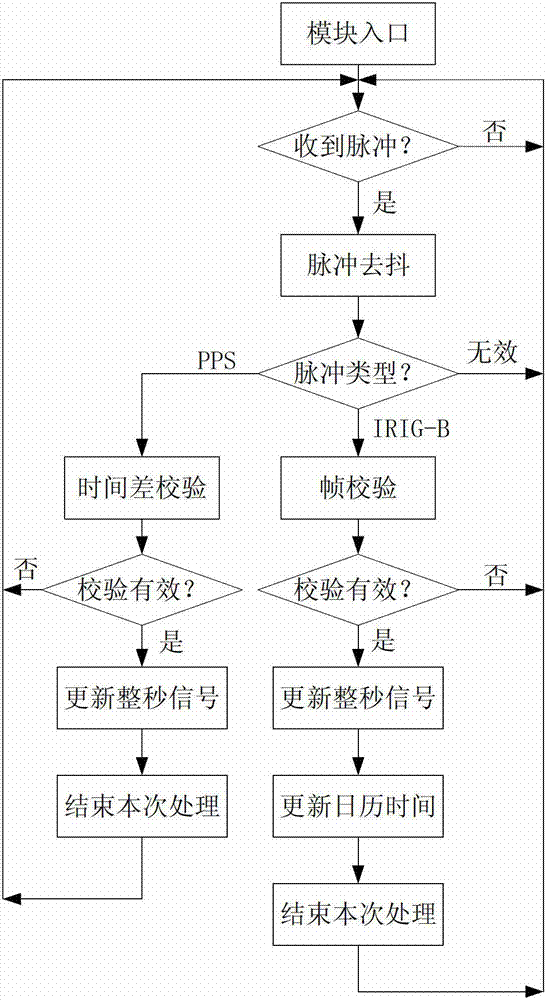

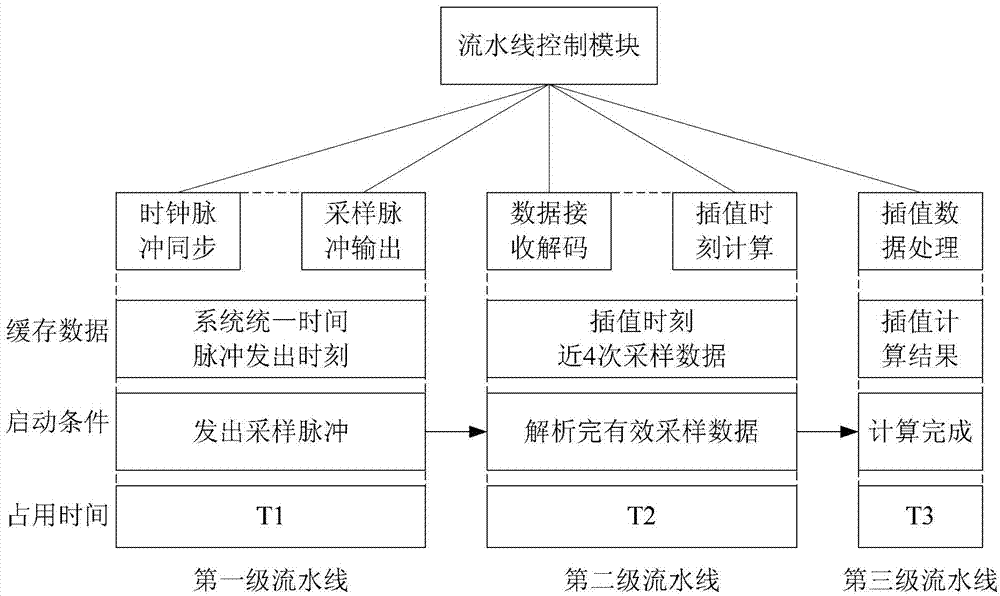

Integration unit for electric energy quality monitoring and synchronous sampling method of integration unit

ActiveCN103116096AAvoid the problem of low synchronization accuracySolve the problem of unstable sampling accuracyElectrical testingPower qualityAssembly line

An integration unit for electric energy quality monitoring comprises a clock pulse synchronizing module M1, a sampling pulse output module M2, a data receiving and decoding module M3, an interpolation moment calculating module M4, an interpolation data processing module M5 and an assembly line control module M6 which are implemented through field programmable gate array (FPGA). The invention further provides a synchronous sampling method of the integration unit. By combining the synchronous pulse method with the interpolation method, the problem about low synchronizing accuracy caused by the use of single synchronizing method is effectively solved. Secondly, the problem about instable sampling accuracy during long-term operating is solved by adopting the self-adaption adjustment interpolation moment algorithm, and the problem about low accuracy of ultraharmonics is solved by adopting the third-order newton interpolation algorithm. In addition, the integral system adopts assembly line control mode and is guaranteed to stably operate at high sampling speed. The integration unit creates conditions for an electric energy quality monitoring device to access a digital substation.

Owner:ELECTRIC POWER RES INST OF GUANGDONG POWER GRID +1

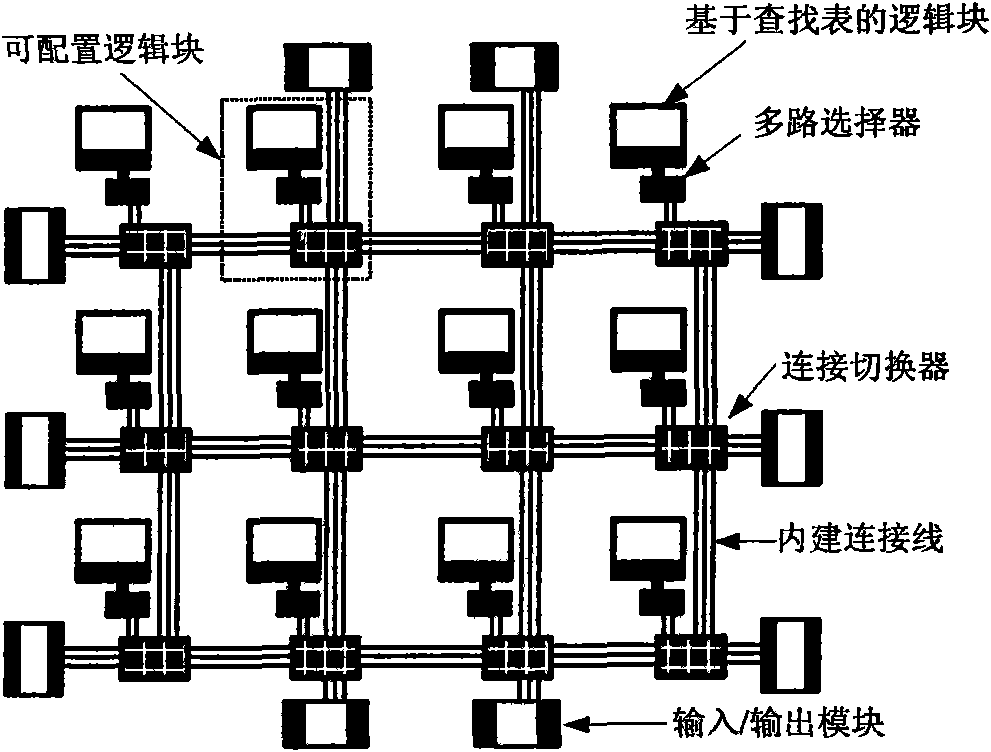

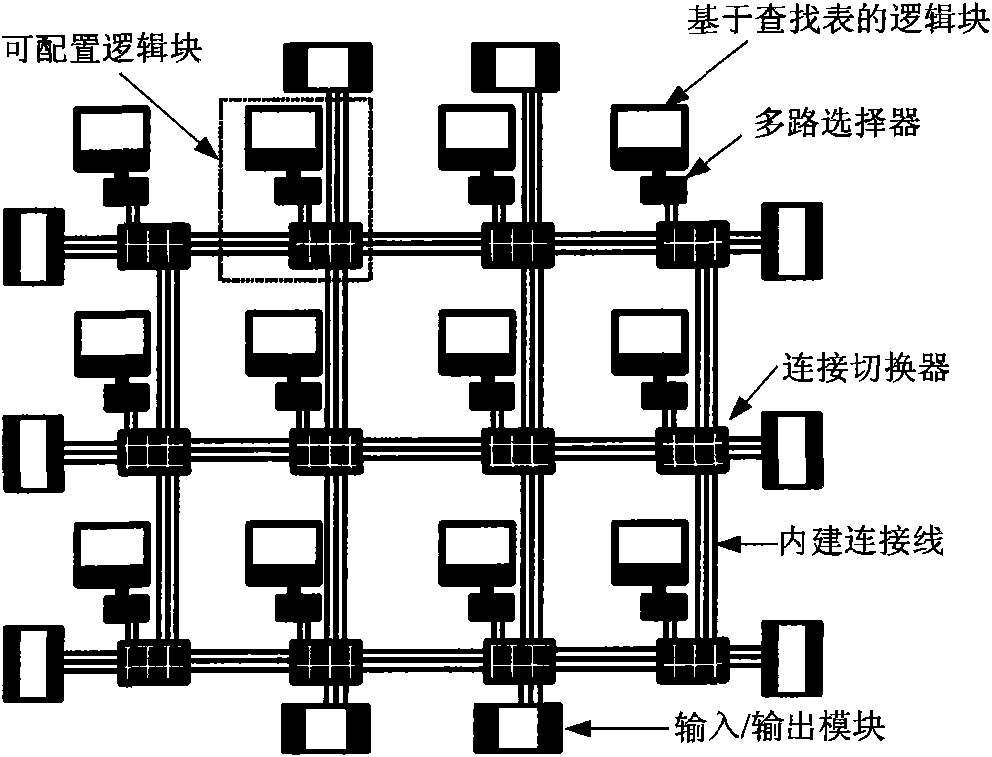

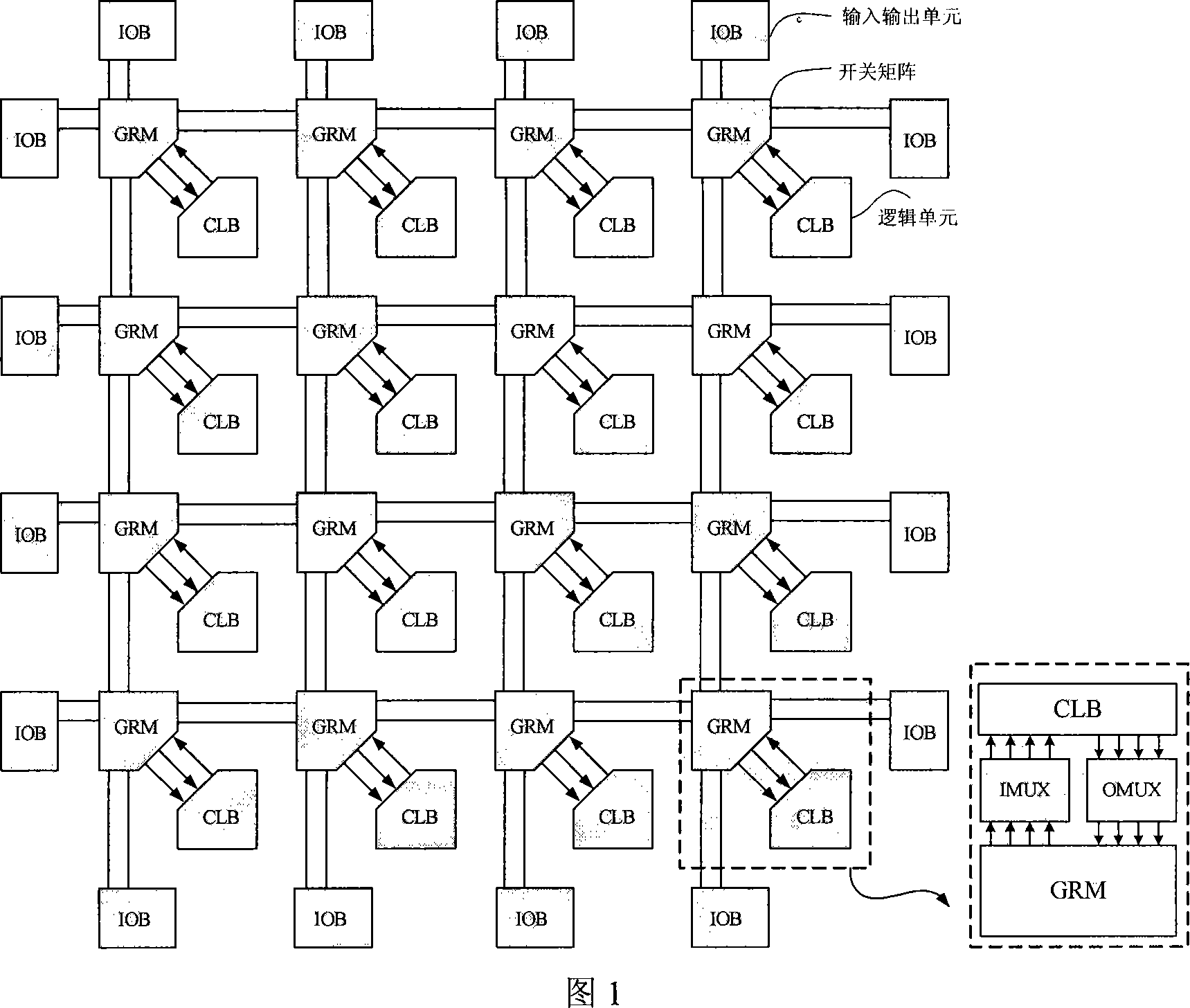

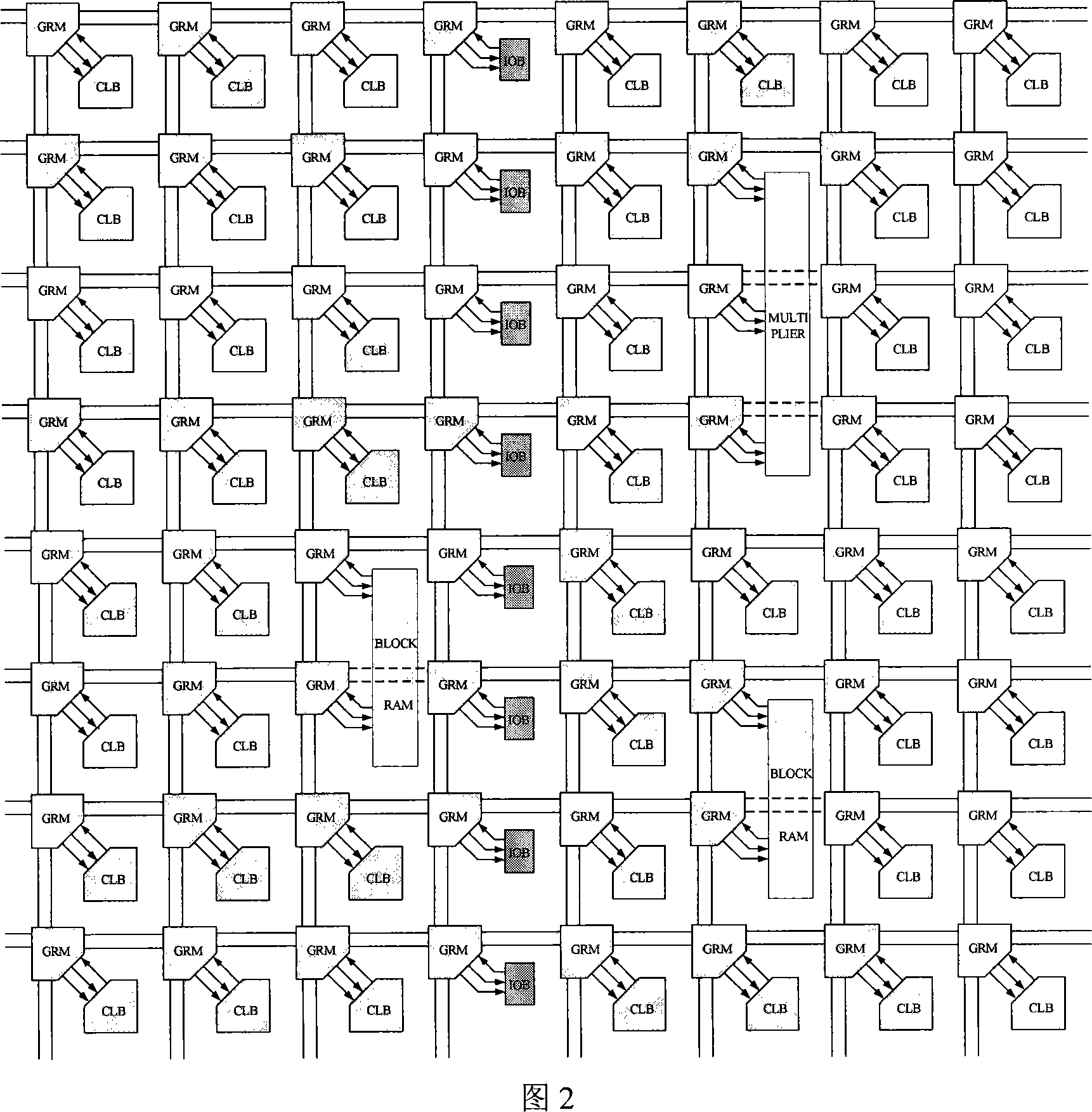

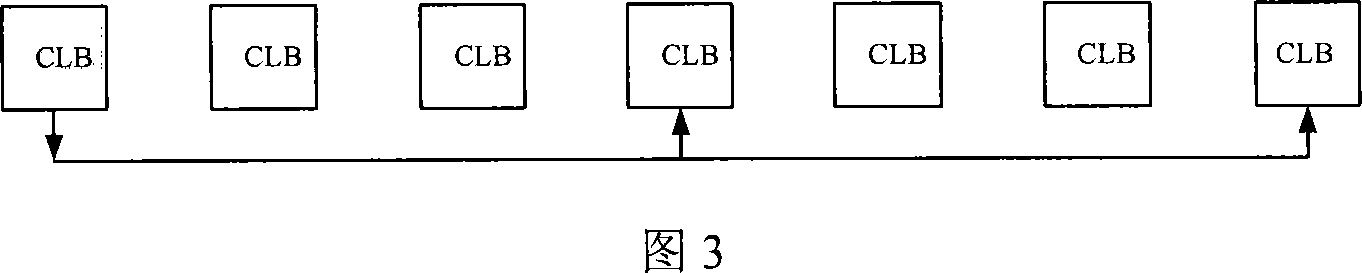

Field programmable logical array wiring resource structure and its modeling approach thereof

ActiveCN101043213AReduce duplicationFlexible descriptionLogic circuits using elementary logic circuit componentsAnd logic unitMulti path

The invention belongs to programmable component structure technology field, specially a local programmable logic array wiring resource structure and modeling method which supports the crutch line. The wiring resource structure of the invention includes: programmable interconnected line, uniform switch matrix, input and output multi path selector array and logic unit. It breaks the limit of level and uprightness interlinkage resource, introduces the concept of crutch line, makes the wiring path not pass the programmable switch, it gives attention to speed and agility. The description of wiring line resource, the interconnected line is distributed to the repeated unit then integral interconnected resource is described by describing an interconnected line resource in a repeated unit. This describing method is very flexible, the kind, amount, proportion of interconnected resource can be changed conveniently, and any switch array can be generated.

Owner:FUDAN UNIV

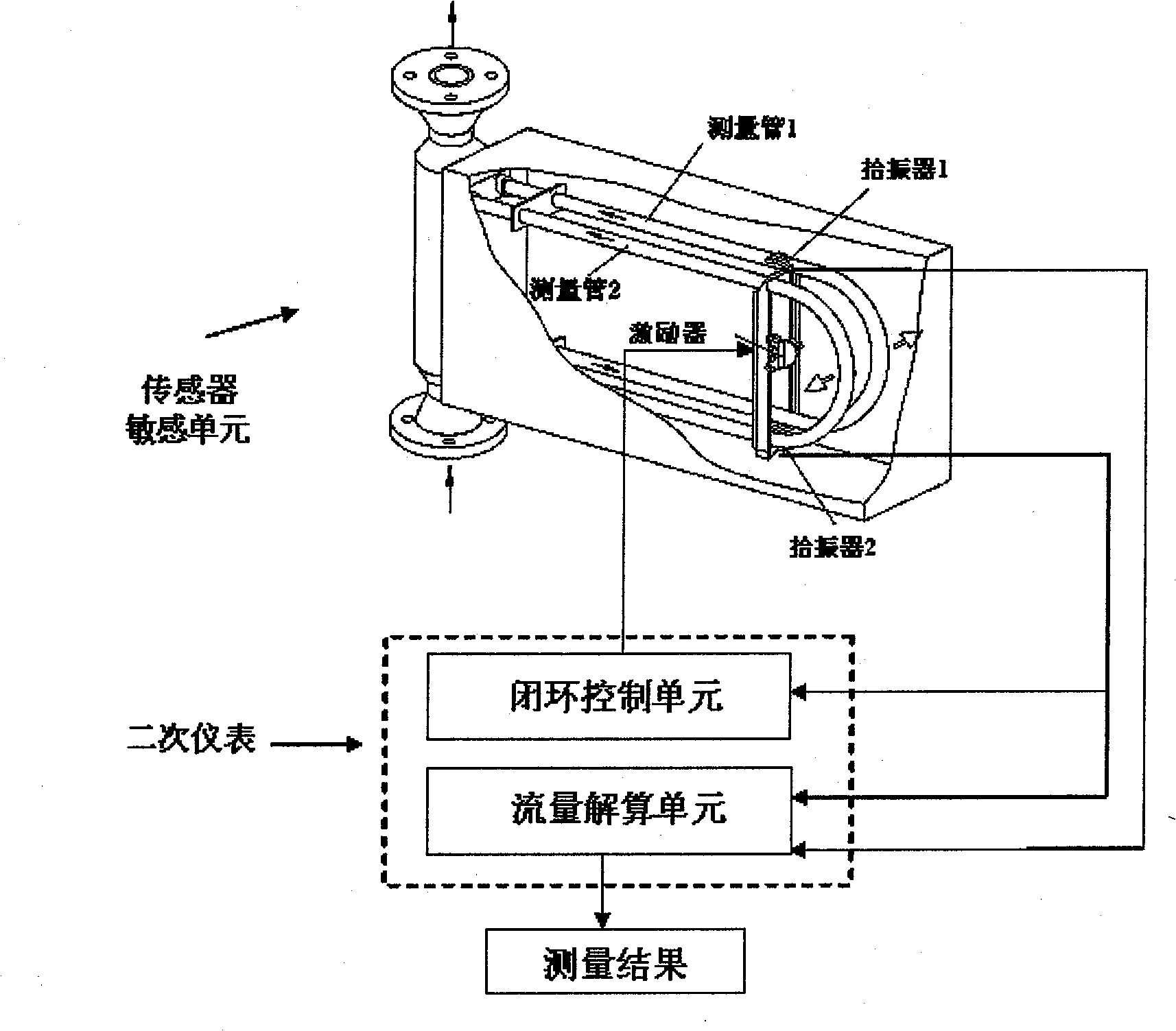

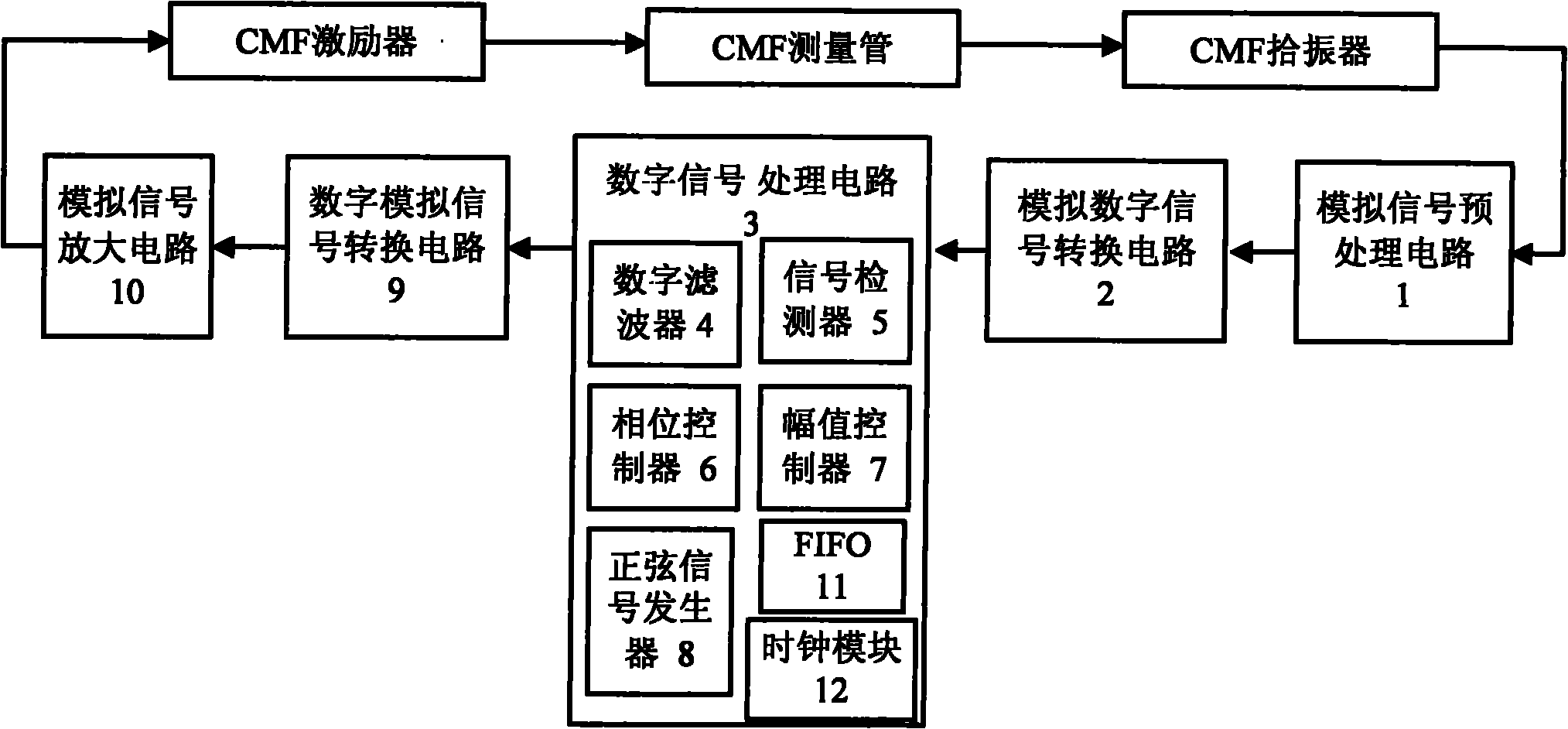

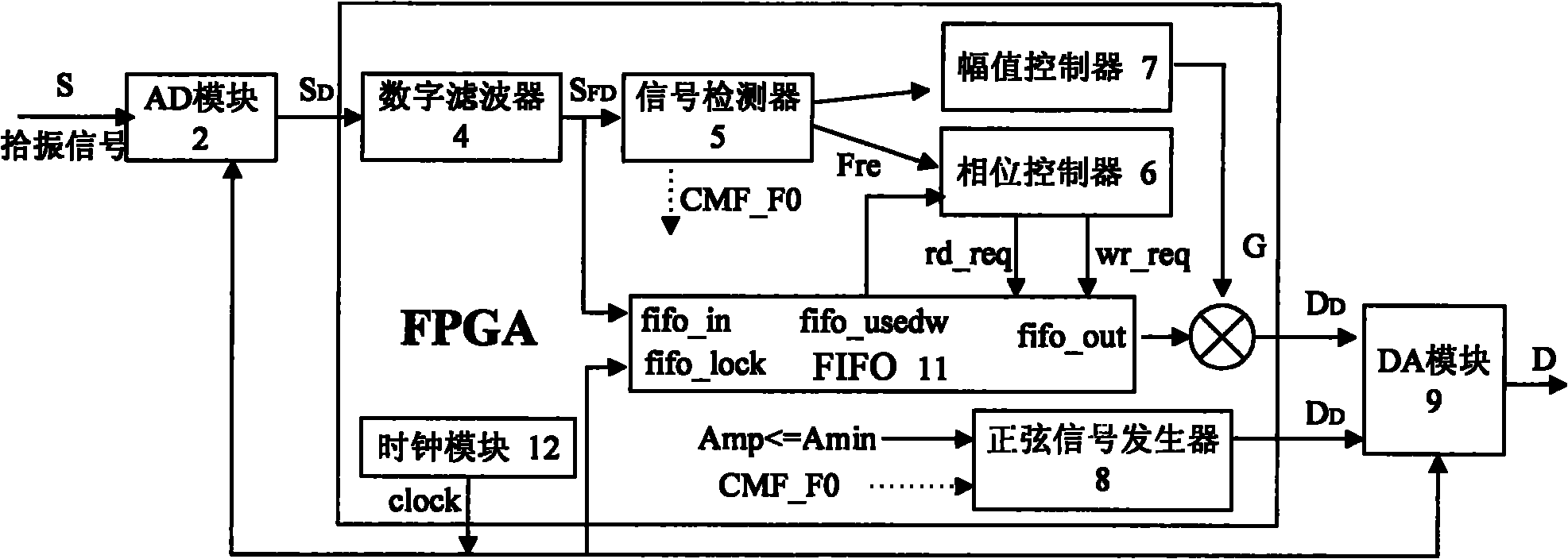

All-digital closed-loop system of Coriolis mass flowmeter

ActiveCN101881947AAvoid vibration stopGuaranteed measurementMass flow measurement devicesProgramme control in sequence/logic controllersDigital signal processingSignal processing circuits

The invention provides an all-digital closed-loop system of a Coriolis mass flowmeter (CMF). A hardware circuit is based on digital components to achieve the stable closed-loop control of the CMF, particularly, the digital signal processing circuit is mainly based on a field programmable gate array (FPGA), and a digital signal processing method is used in the FPGA to achieve the digital closed-loop control algorithm for the CMF and track the frequency on a real-time basis; by using the non-linear amplitude control method and introducing FIFO (first in, first out) components to the phase control, stable and accurate control can be achieved on the amplitude and phase; by better tracking the changes in the vibration of the measuring tube of the CMF to obtain vibration pickup signals reflecting the information of fluid more accurately and further output the vibration pickup signals at a stable amplitude, the invention is favorable for resolving a secondary meter, further improving the accuracy and stability in the measurement of the CMF and ensuring that the resource consumption and operation load are lower; and the invention further solves the problem of two-phase flow, particularly, when the CMF undergoes the problem of two-phase flow, the sinusoidal signal at the controllable amplitude and at the same frequency as the natural frequency of the measuring tubes of the CMF can be actively outputted to force the measuring tubes of the CMF to continue vibrating, thus ensuring the non-stop vibration and non-interrupted measurement when the CMF undergoes the problem of two-phase flow and enabling the CMF to carry out the flow measurement when undergoing the problem of the two-phase flow.

Owner:BEIHANG UNIV

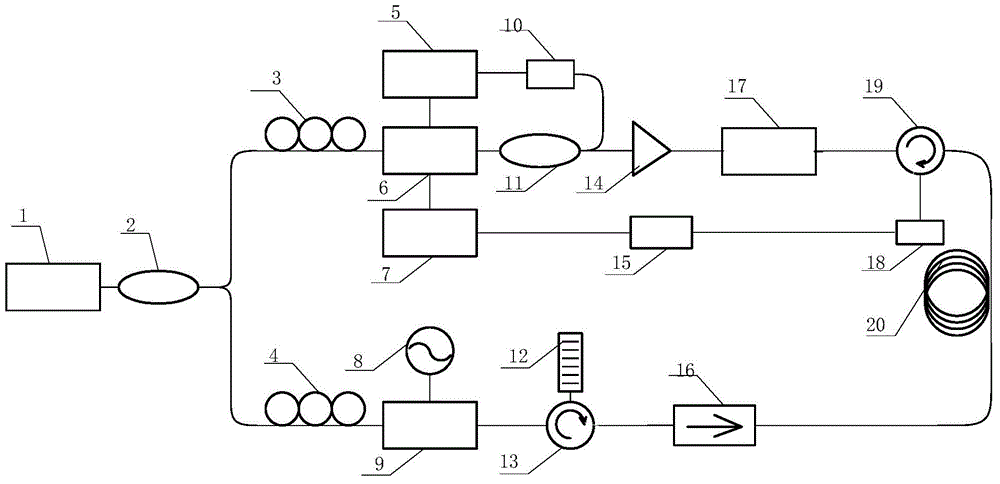

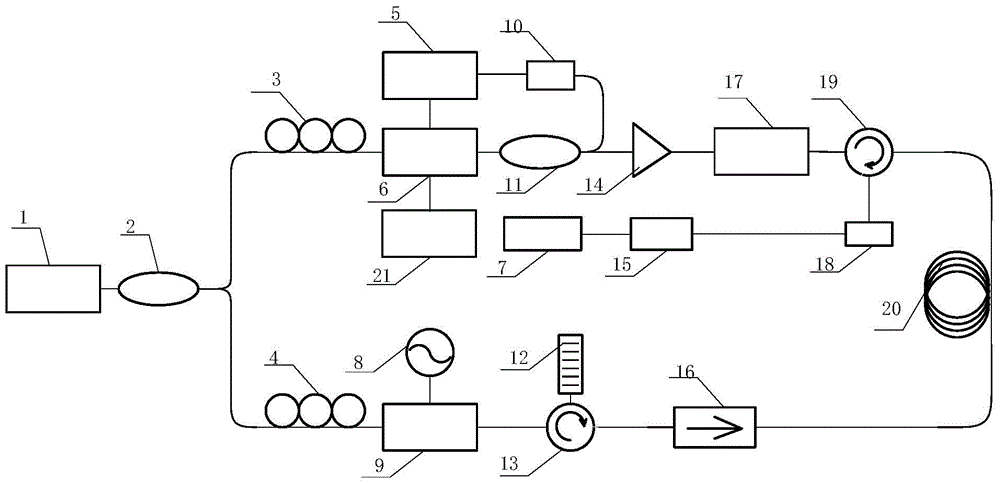

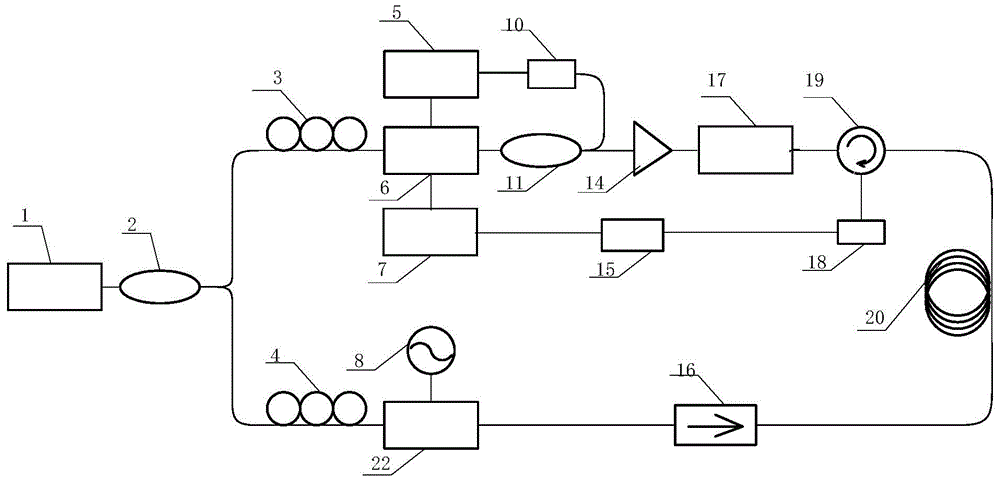

Brillouin optical-time-domain analyzer based on coherence dual-pulse pair sequence technology and method for restraining common-mode noise by utilizing same

ActiveCN104019836AReduced conversion timeAchieve inhibitionConverting sensor output opticallySpecial purpose recording/indication apparatusOptical fiber couplerSignal-to-quantization-noise ratio

The invention relates to a Brillouin optical-time-domain analyzer based on a coherence dual-pulse pair sequence technology and a method for restraining common-mode noise by utilizing the same, belongs to the field of optics, and solves the problems that a traditional Brillouin optical-time-domain analyzer is low in spatial resolution, long in measuring signal time and low in signal-to-noise ratio. A laser is adopted, an upper branch of light divided by an optical-fiber coupler I is used as pump light, pulse pairs with different pulse widths can be periodically generated by a field-programmable logic array in a programming manner, and the pulse pairs are continuously and optically modulated to form a coherence pulse pair sequence through a photoelectric modulator; a lower branch provides detection light, the detection light enters a photoelectric modulator after a polarization state is adjusted, upper marginal frequency light and lower marginal frequency light which having the frequency difference of Brillouin frequency shifting gamma B are generated on the basis of carrier light, the pump light consisting of the coherence pulse pair sequence and the modulated detection light has a Brillouin scattering phenomenon in a sensing optical fiber, and two Brillouin signals are detected by a photoelectric detector. The Brillouin optical-time-domain analyzer and the method are suitable for restraining the common-mode noise.

Owner:HARBIN INST OF TECH

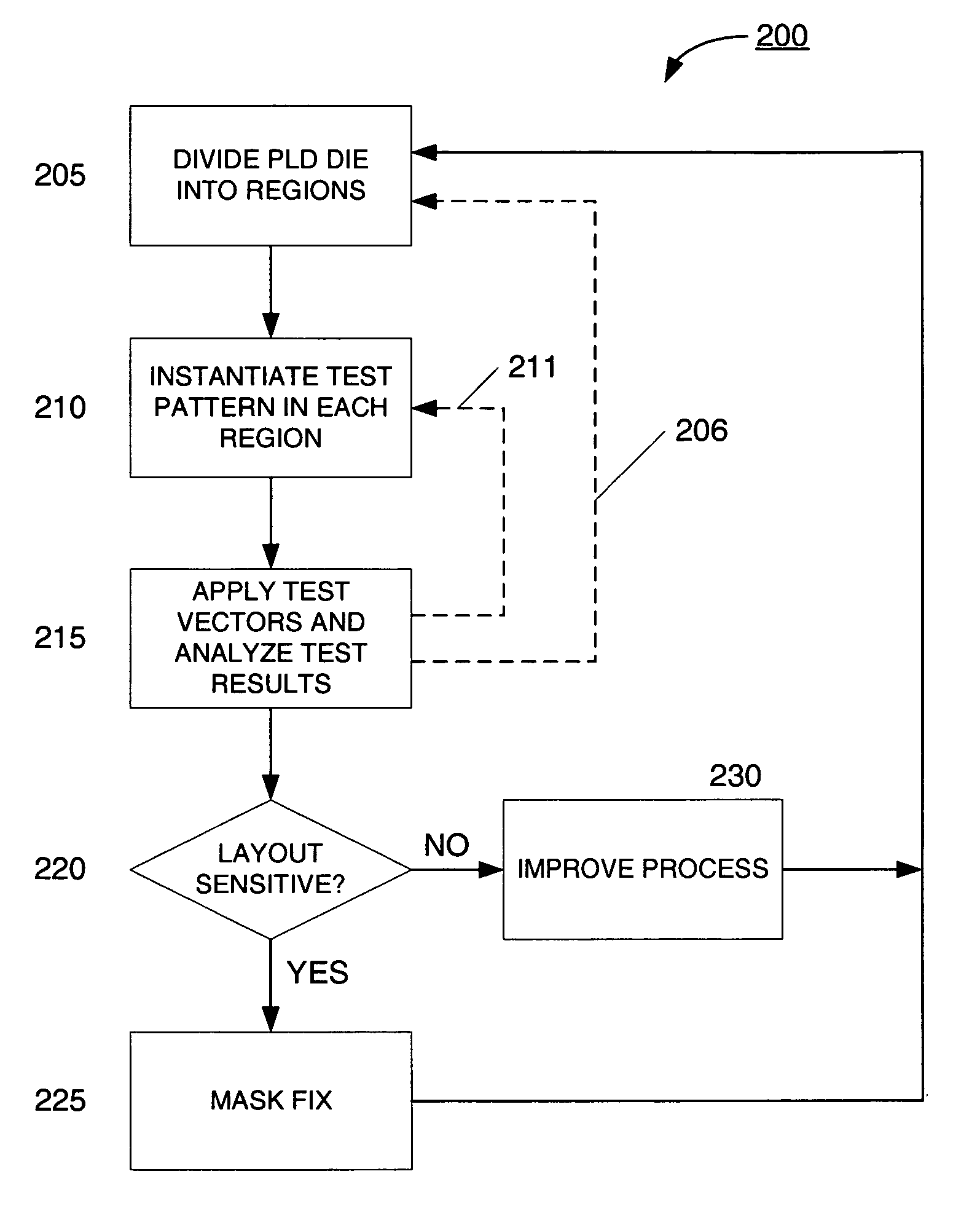

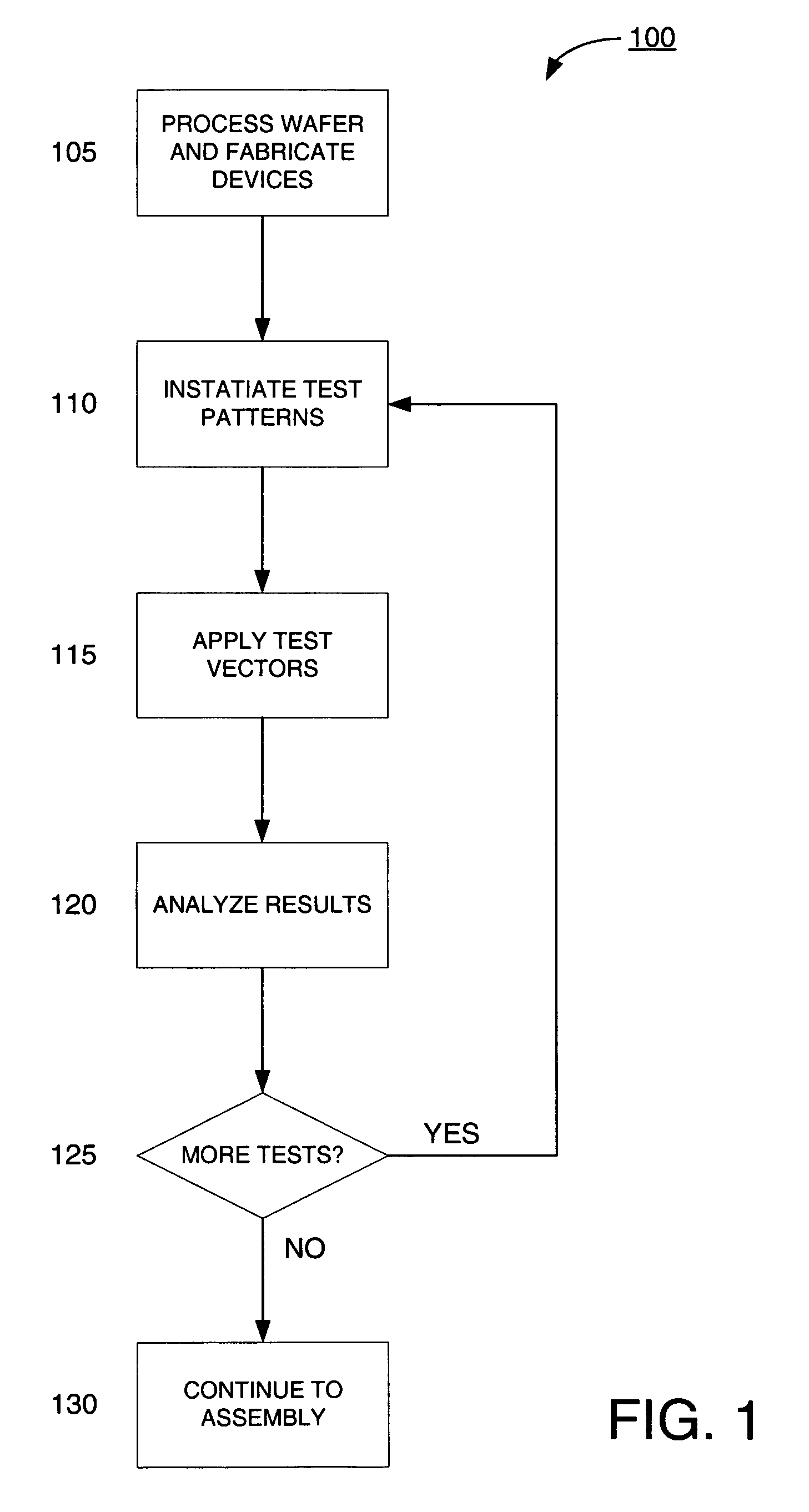

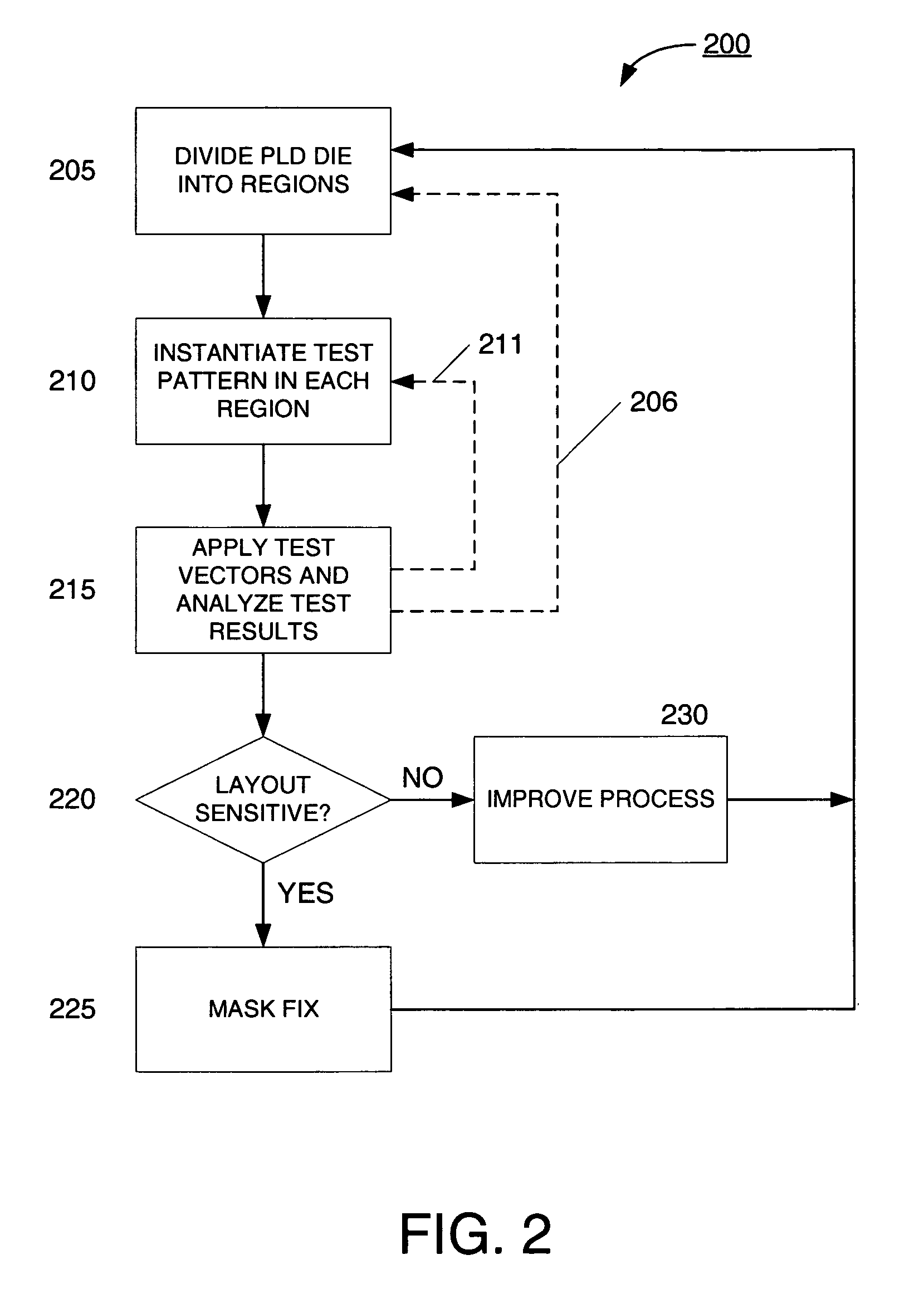

Method for monitoring and improving integrated circuit fabrication using FPGAs

ActiveUS7020860B1Monitoring and improving fabrication processDetecting faulty computer hardwareElectrical testingProgrammable logic deviceEngineering

Methods for monitoring and improving the fabrication process of integrated circuits using configurable devices are described. In one aspect, the method includes instantiating a test pattern on one or more configurable devices fabricated using the fabrication process, identifying an underperforming region of the configurable devices, and determining if the underperforming region is layout sensitive. At least one of the fabrication process and the layout of the configurable device can then be adjusted based on the determination. In some embodiments, the configurable device may be a programmable logic device, such as a field programmable logic array.

Owner:XILINX INC