Patents

Literature

84 results about "Physical design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

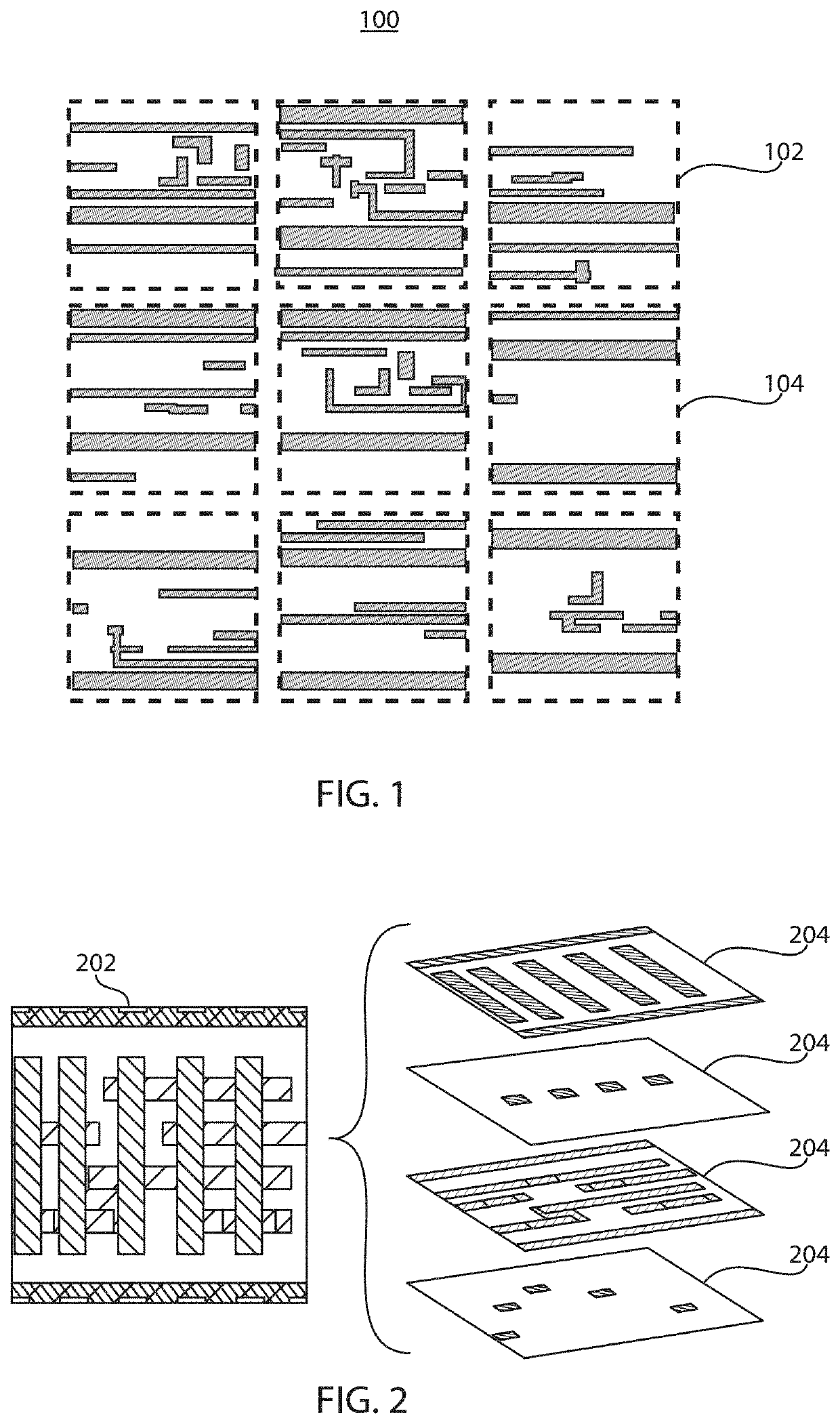

In integrated circuit design, physical design is a step in the standard design cycle which follows after the circuit design. At this step, circuit representations of the components (devices and interconnects) of the design are converted into geometric representations of shapes which, when manufactured in the corresponding layers of materials, will ensure the required functioning of the components. This geometric representation is called integrated circuit layout. This step is usually split into several sub-steps, which include both design and verification and validation of the layout.

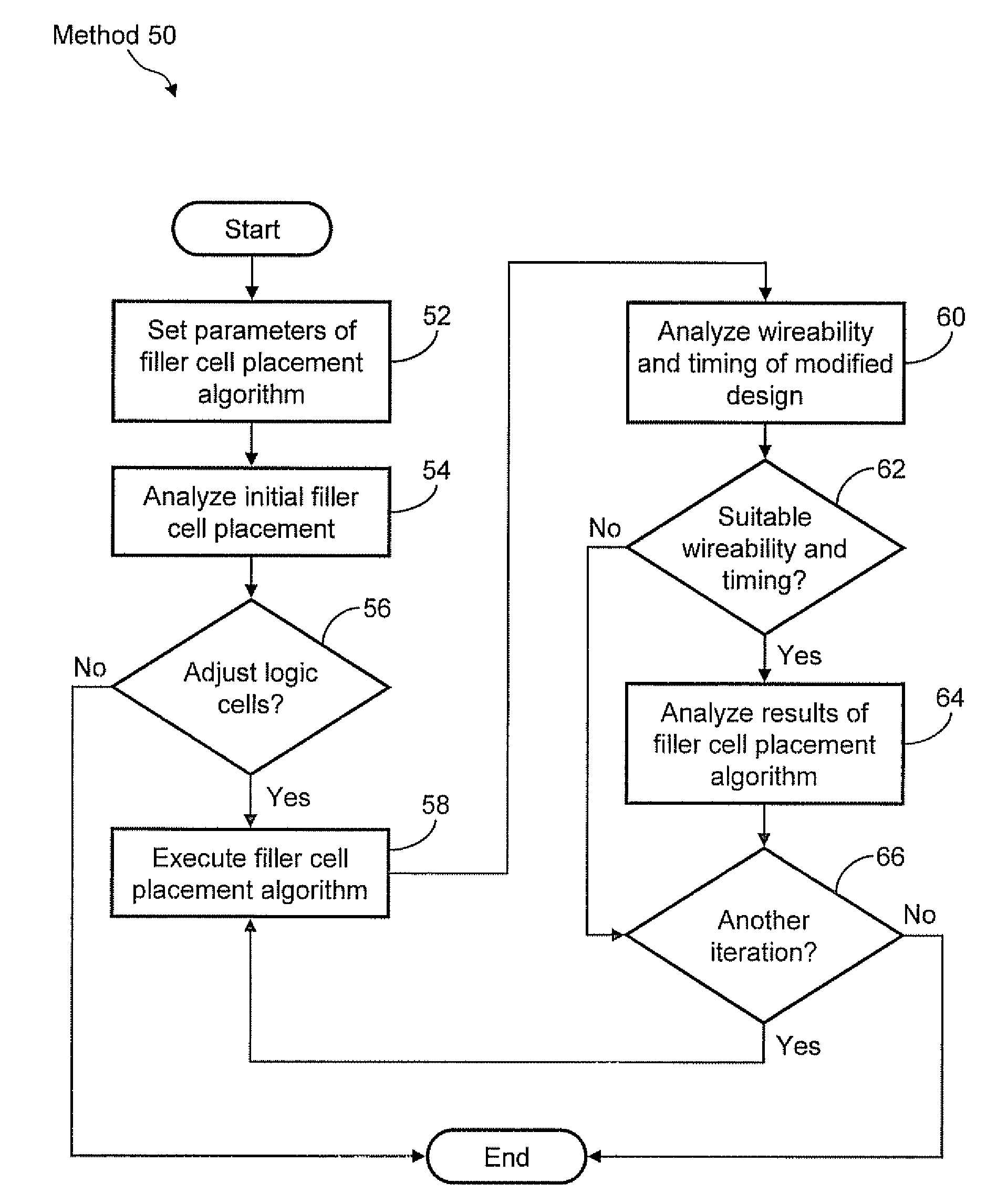

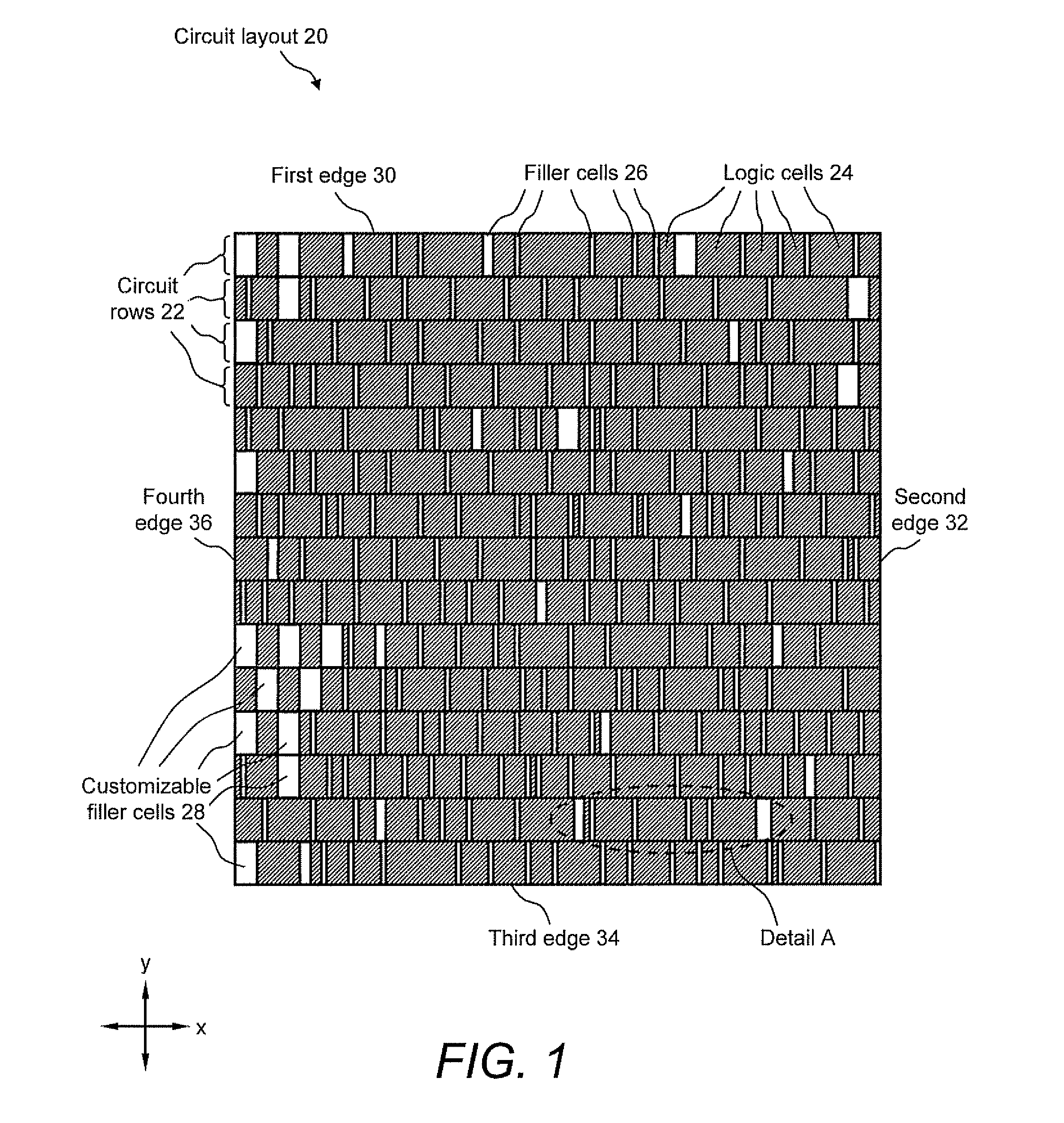

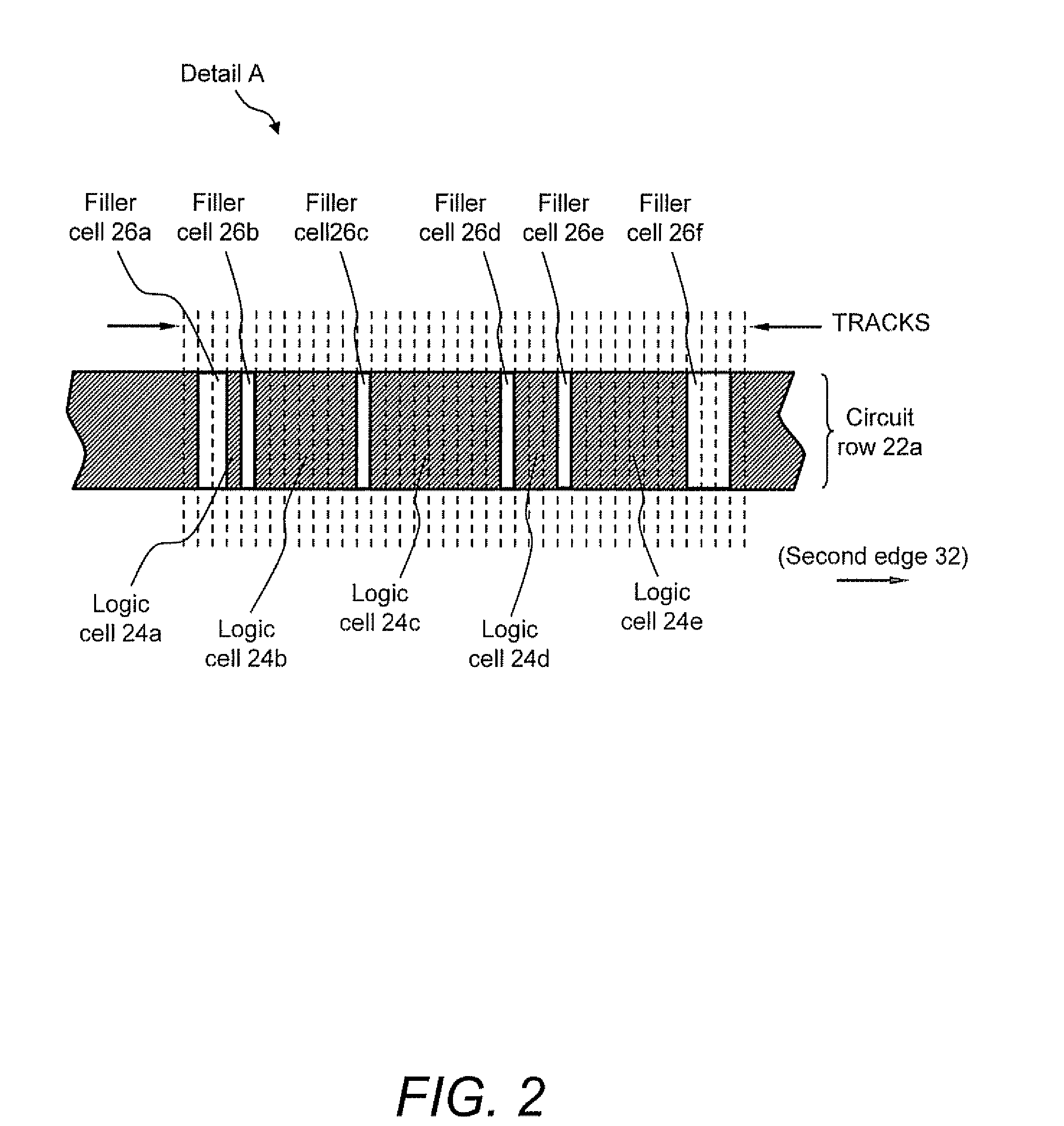

Method of optimizing customizable filler cells in an integrated circuit physical design process

ActiveUS20080005712A1Reduce traceabilityComputer aided designSoftware simulation/interpretation/emulationIntegrated circuitEngineering

A system and method for optimizing customizable filler cells in an integrated circuit physical design process. In particular, a filler cell placement algorithm of the present disclosure is utilized in the method to optimize the customizable filler cells in a circuit layout. The filler cell placement algorithm performs the operation of selecting a starting point within a given circuit layout, selecting a direction in which the position of logic cells is adjusted, adjusting the position of logic cells and, thereby, combining filler cells in order to increase the accumulated area thereof; suspending the adjustment operation when a customizable filler cell is formed; and resuming the adjustment operation from the point of the newly formed customizable filler cell. Additionally, a method of optimizing the locations, number, and distribution of the customizable filler cells in an integrated circuit design by use of the filler cell placement algorithm is provided.

Owner:GLOBALFOUNDRIES US INC

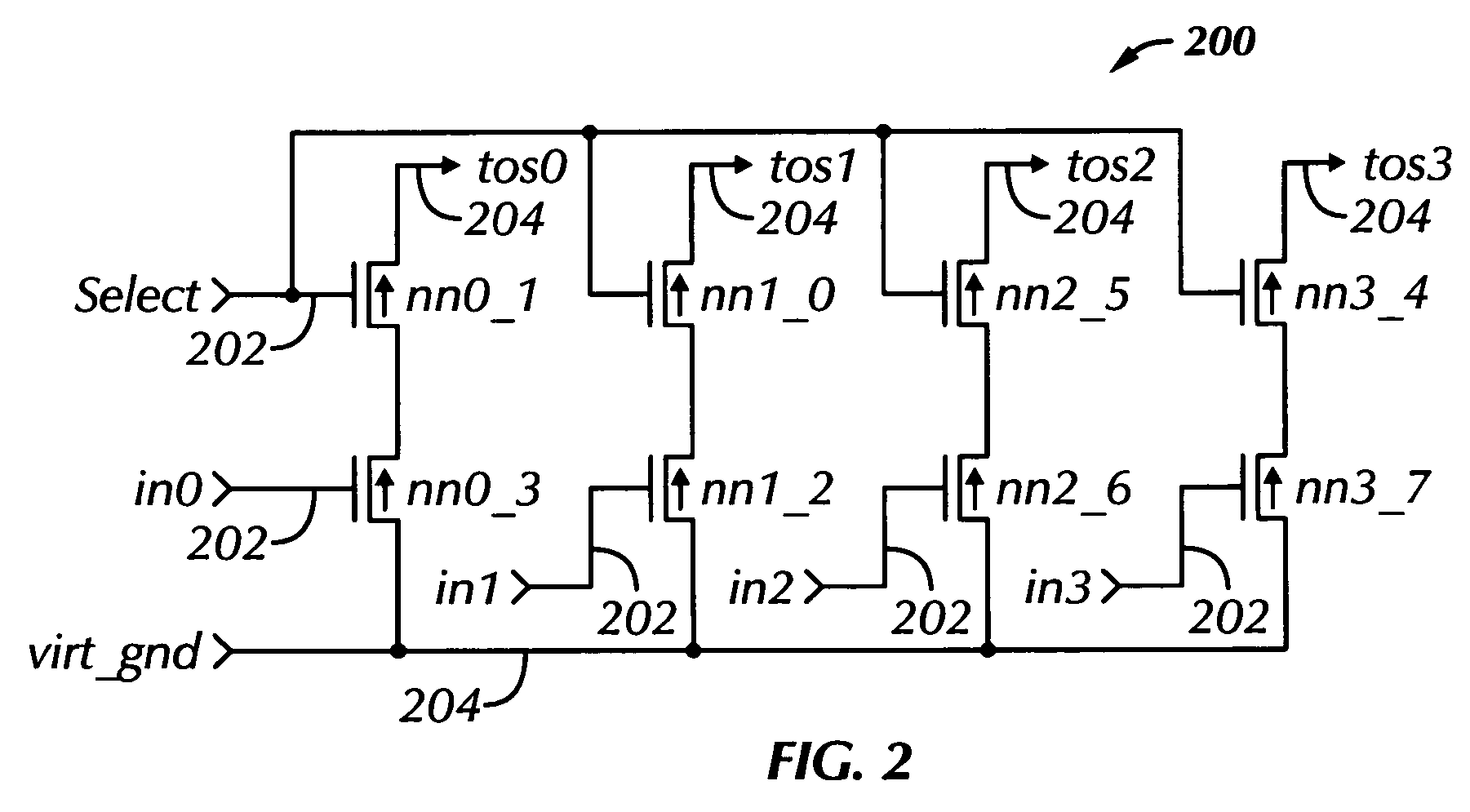

Physical realization of dynamic logic using parameterized tile partitioning

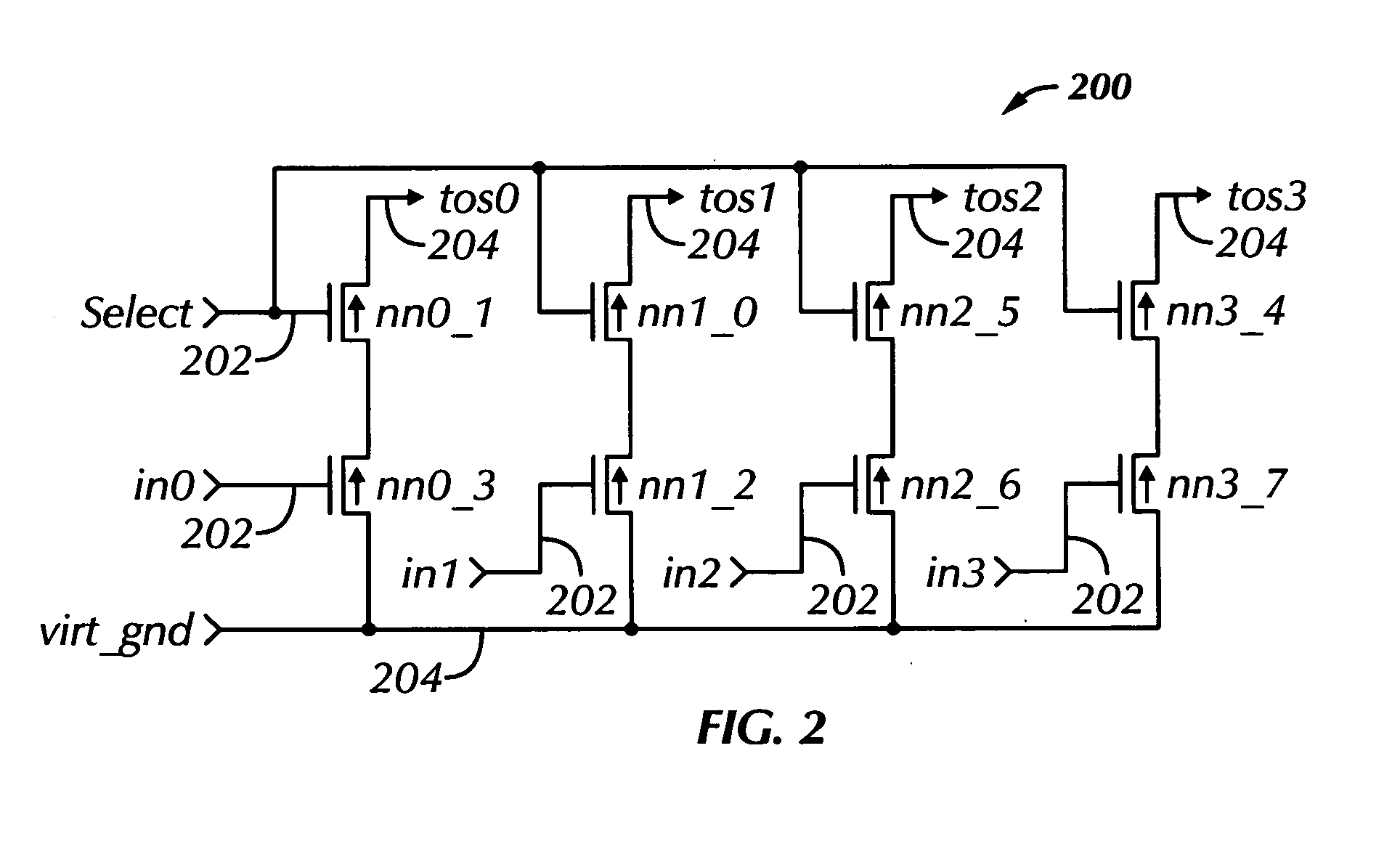

The matching algorithm of the layout synthesis method and apparatus disclosed locates transistor pattern matches in a design, links a parameterized tile to each identified match, and adjusts certain variable parameters of the linked parameterized tile to meet the physical design requirements of each located match. Each transistor pattern corresponds to a parameterized tile, which is an actual physical representation of the corresponding pattern and includes variable parameters, which may include transistor size. The matching algorithm locates matches in the design for an ordered list of patterns, names each located match, links the proper parameterized tile to each named match, and adjusts the tile's variable parameters as required. Transistors in the design are included in one and only one named located match.

Owner:APPLE INC

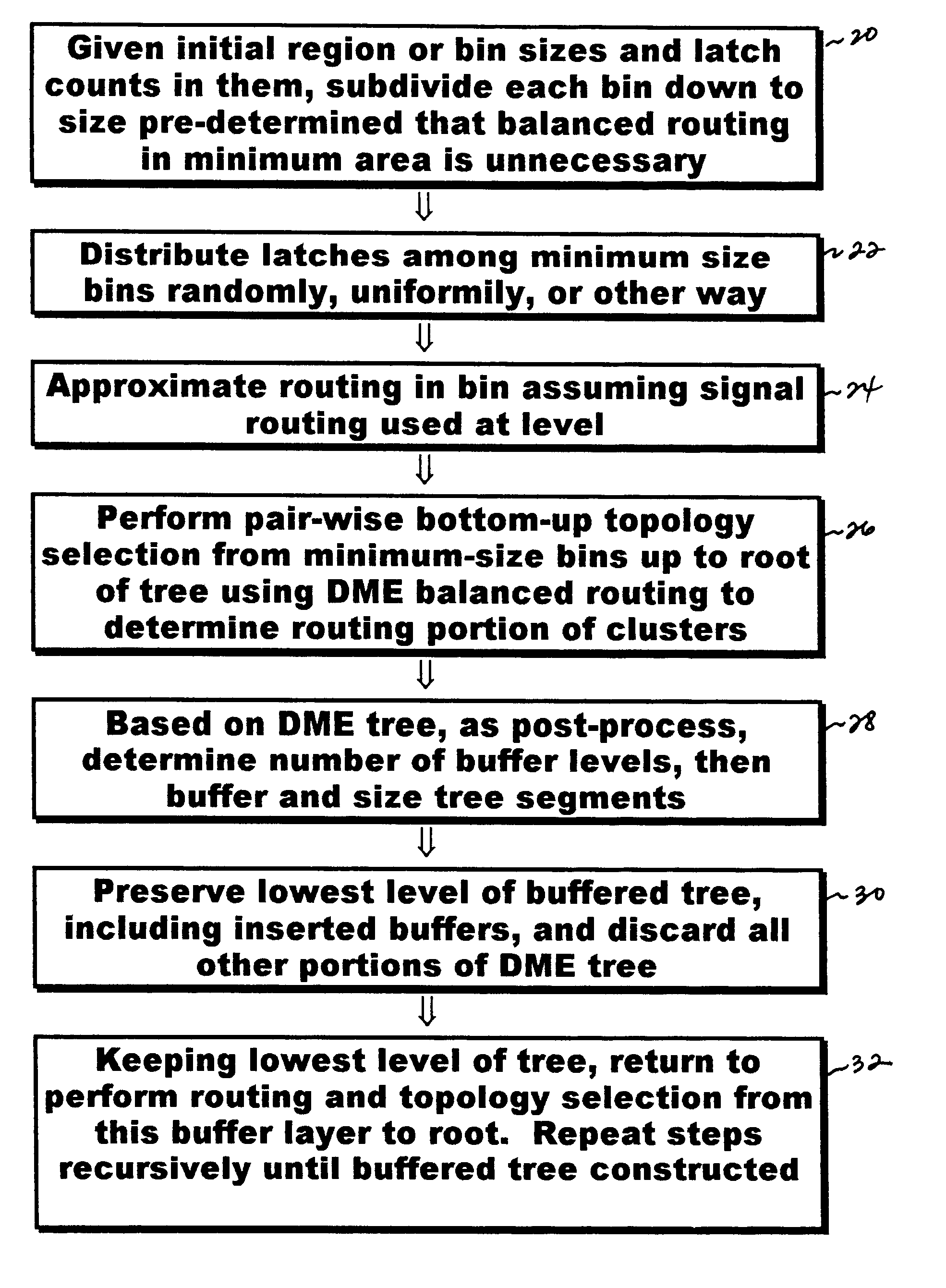

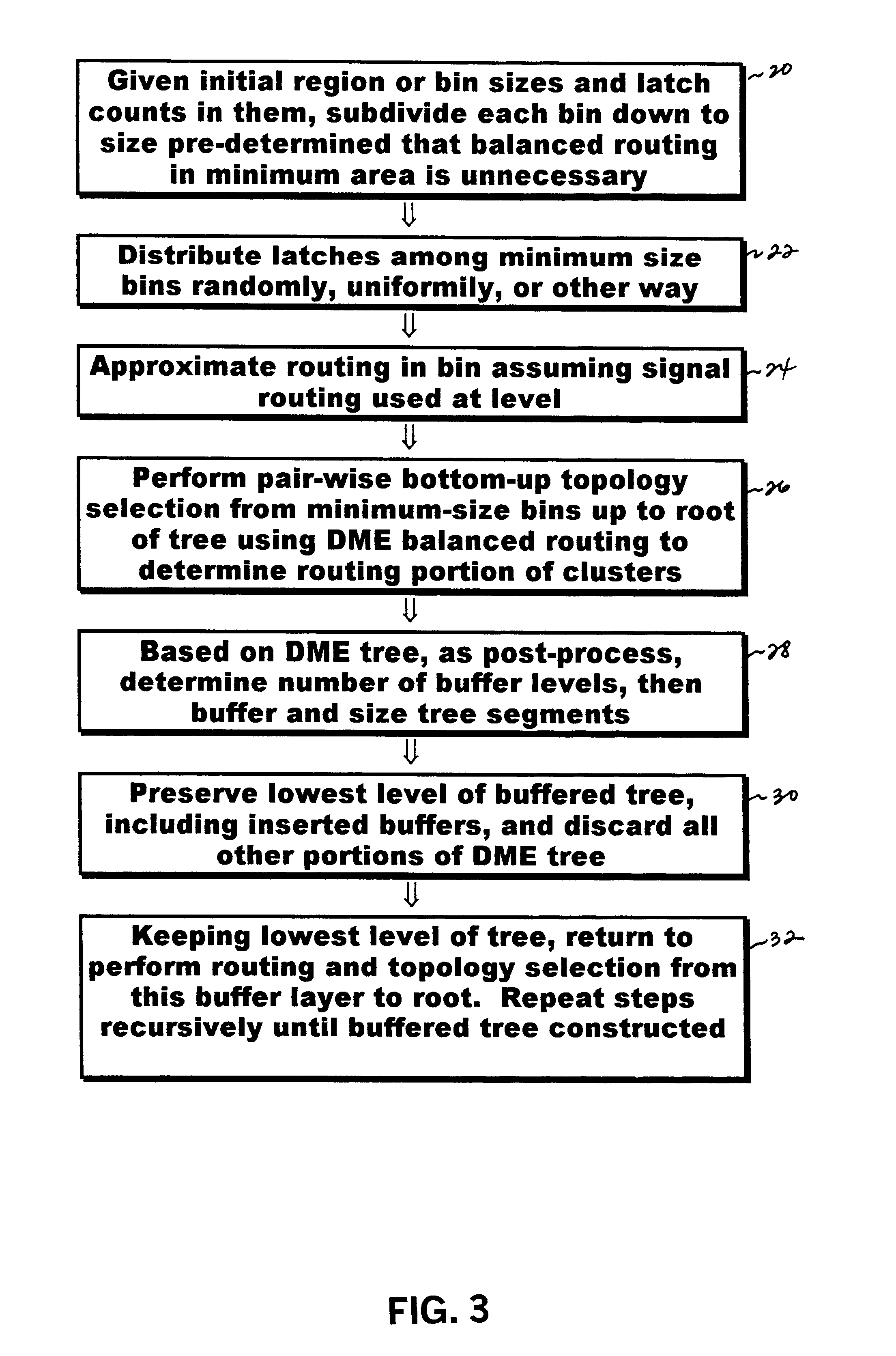

Method and system for progressive clock tree or mesh construction concurrently with physical design

InactiveUS6651232B1Generating/distributing signalsComputer aided designTopology constructionTheoretical computer science

Progressively optimized clock tree / mesh construction is performed concurrently with placement of all remaining objects. Clock tree / mesh is specified loosely for initial placement, then followed by progressive detailed placement. In particular, preferred approach provides automated and reliable solution to clock tree / mesh construction, occuring concurrently with placement process so that clock tree wiring and buffering considers and influences placement and wiring of all other objects, such as logic gates, memory elements, macrocells, etc. Hence, in this concurrent manner, clock tree / mesh pre-wiring and pre-buffering may be based on construction of approximate clock tree using partitioning information only, i.e., prior to object placement. Further, present approach provides modified DME-based clock tree topology construction without meandering, and recursive algorithm for buffered clock tree construction.

Owner:SYNOPSYS INC

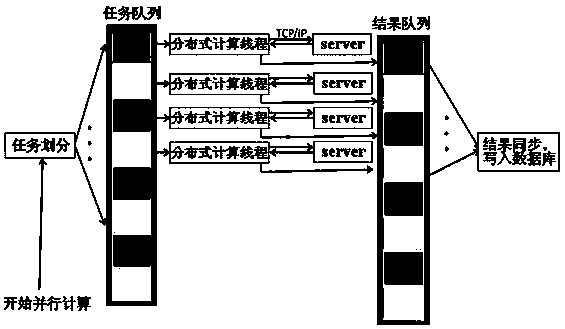

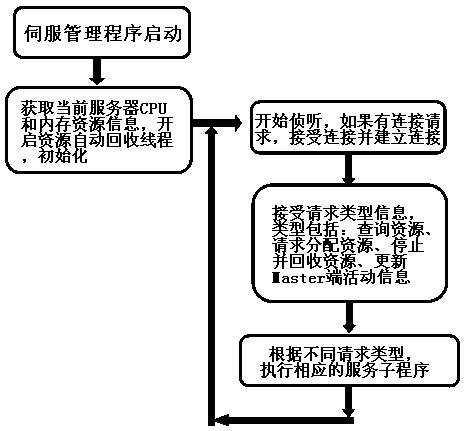

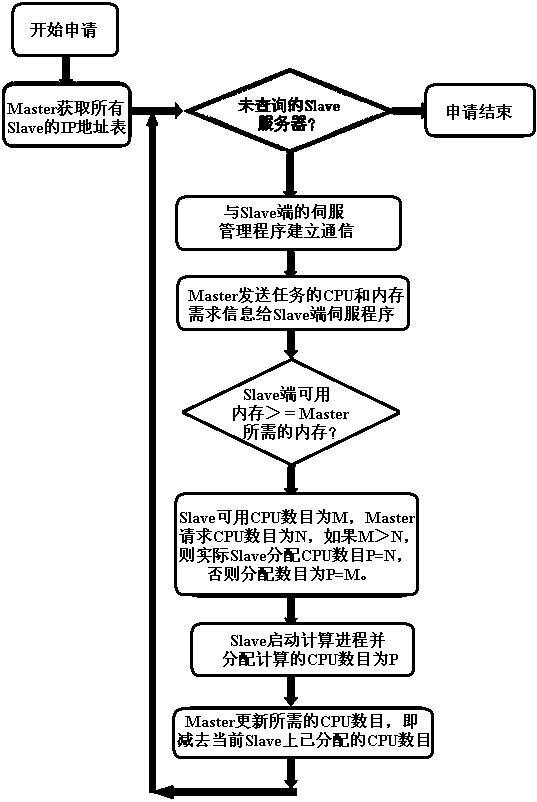

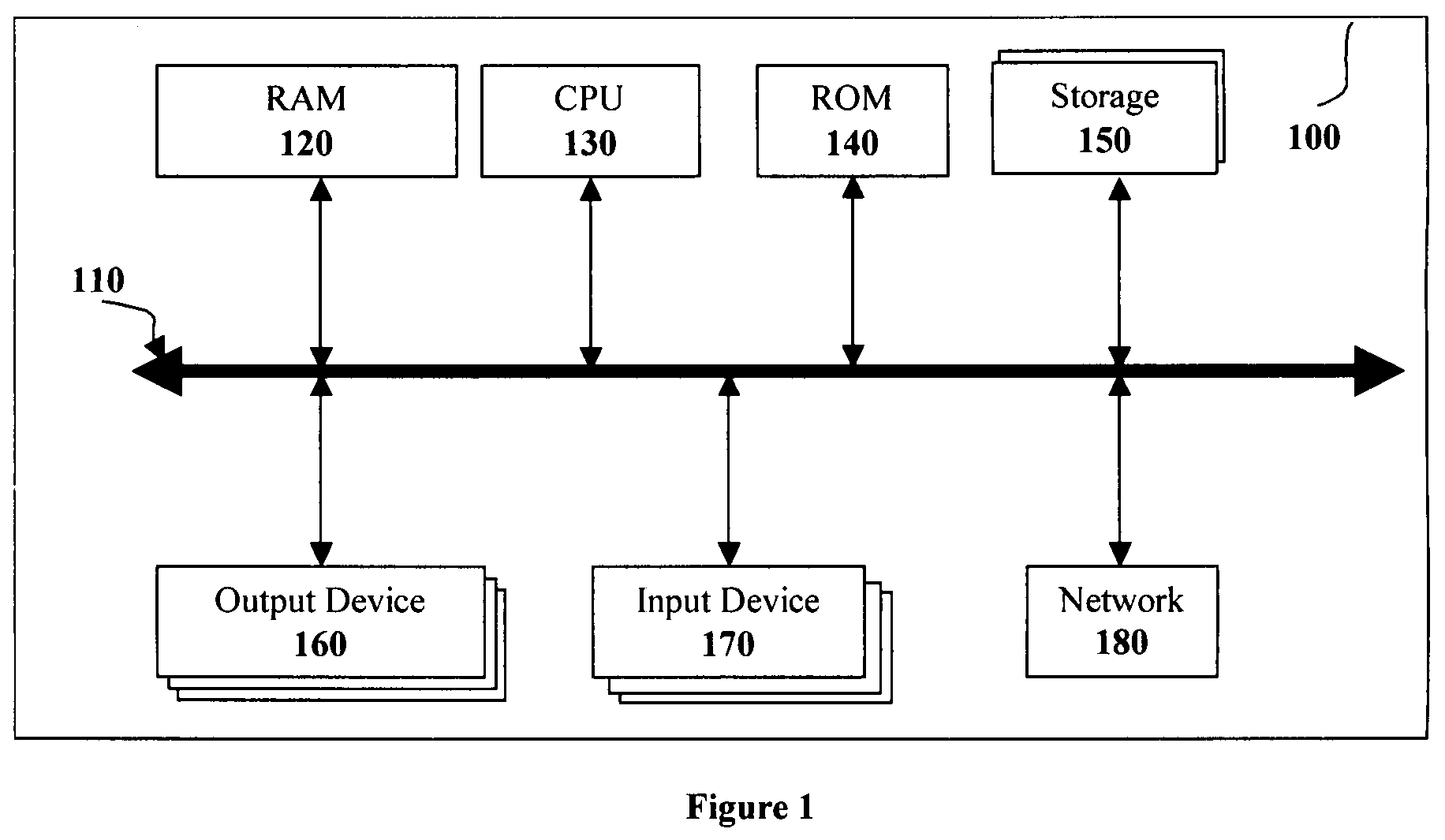

Distributed parallel computing method and system for physical implementation of large scale integrated circuit

InactiveCN104035817AFast Design AccelerationEasy to manageMultiprogramming arrangementsSpecial data processing applicationsResource recoveryNetwork communication

The invention discloses a distributed parallel computing method and system for physical implementation of a large scale integrated circuit. According to the method, physical design problems of different stages are divided into sub-problems on a host, different division methods are applied to the different stages, then the sub-problems are sent to distributed servers by the host in a network communication mode to be computed, and computing results are sent back to the host. The host and a computing cluster are respectively provided with a servo management program, the program is an impotent component of a distributed computing frame and is in charge of management of distributed computing resources, and management of the distributed computing resources comprises resource allocation, resource recovery and the like. According to the distributed parallel computing method and system for physical implementation of the large scale integrated circuit, the physical design problems of a super-large scale integrated circuit can be solved rapidly and effectively, physical design efficiency of the integrated circuit can be improved greatly, and rapider and more-effective physical design of the large scale integrated circuit can be achieved compared with multithreading computing on a single computer.

Owner:领佰思自动化科技(上海)有限公司

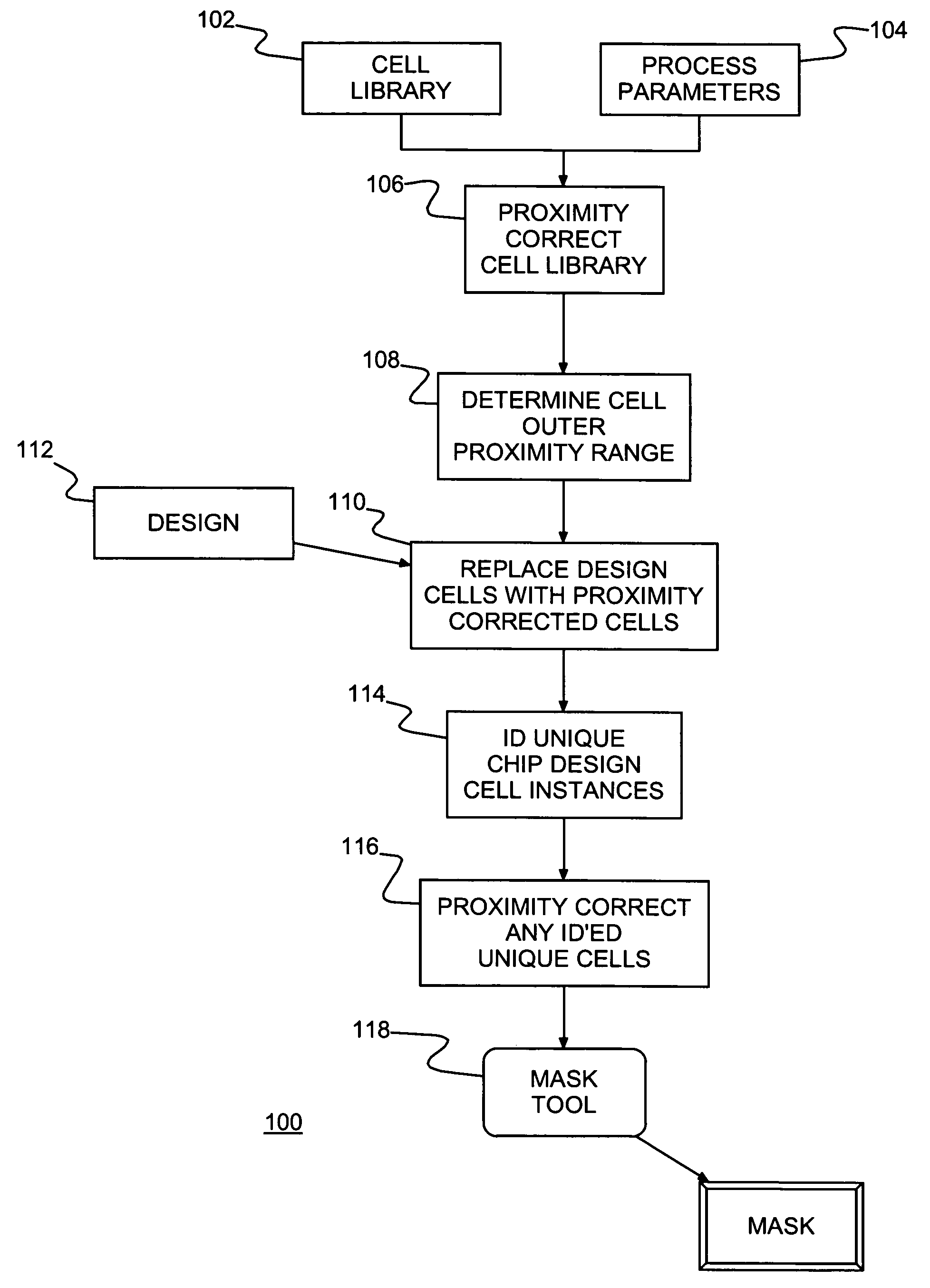

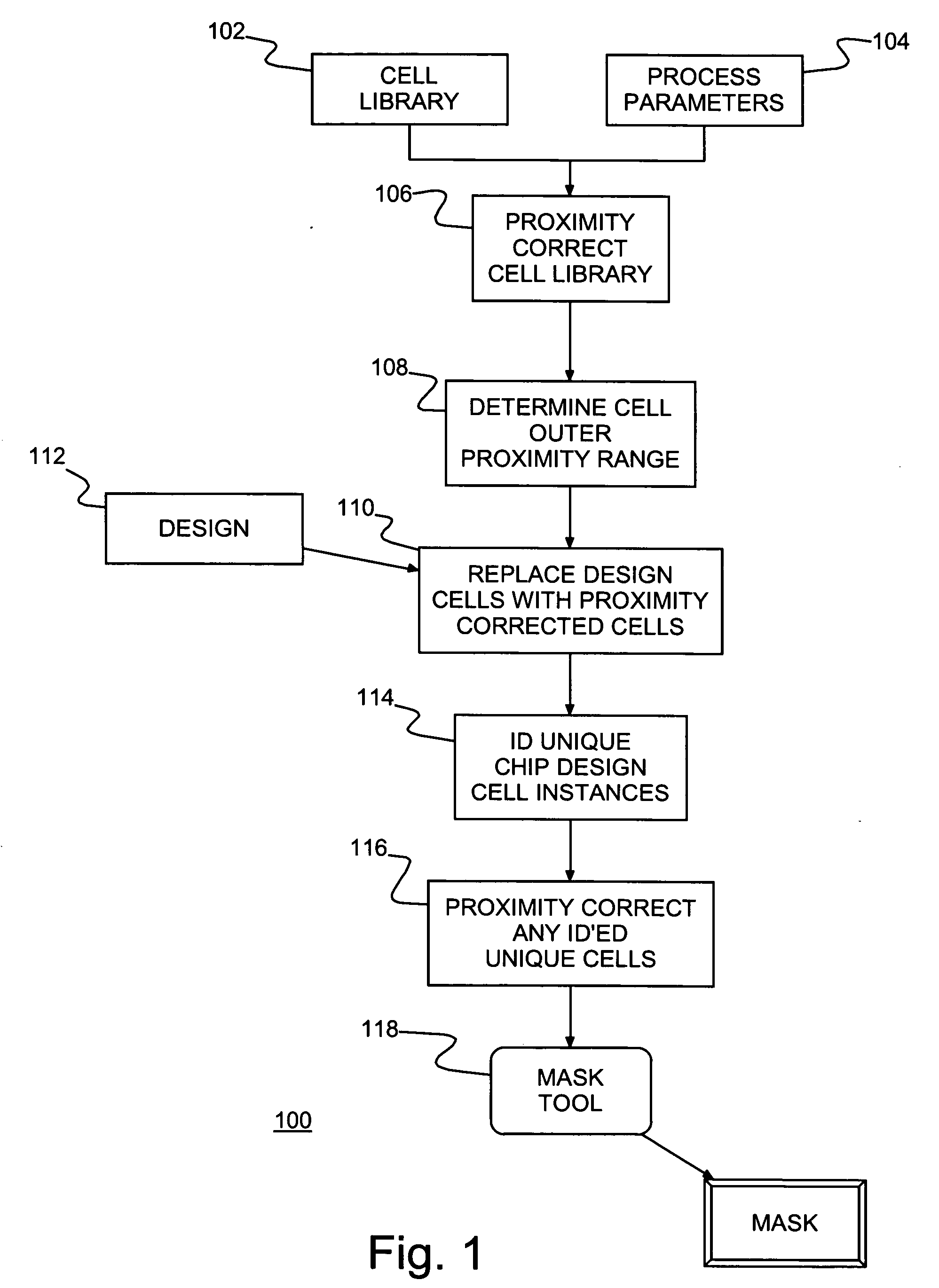

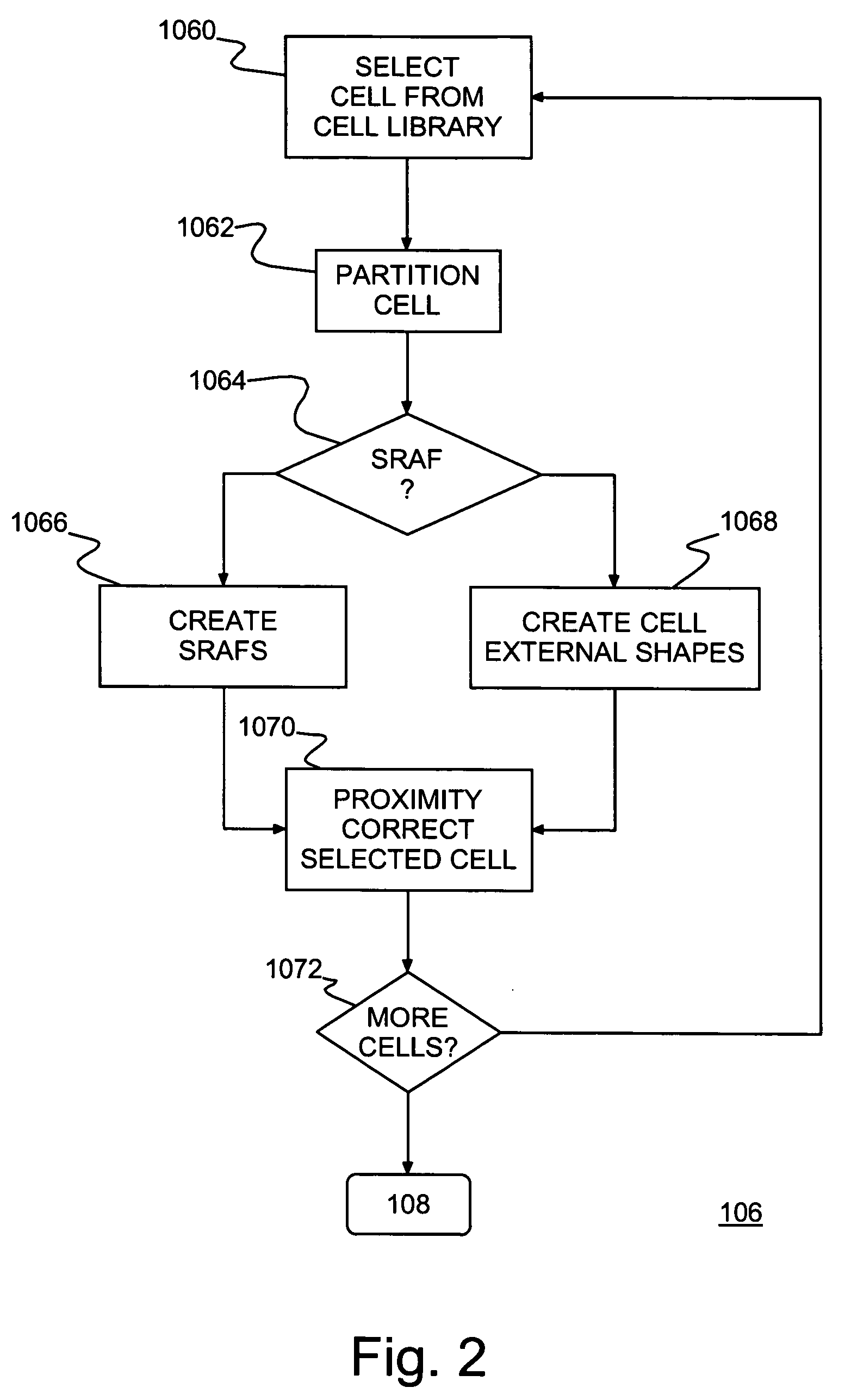

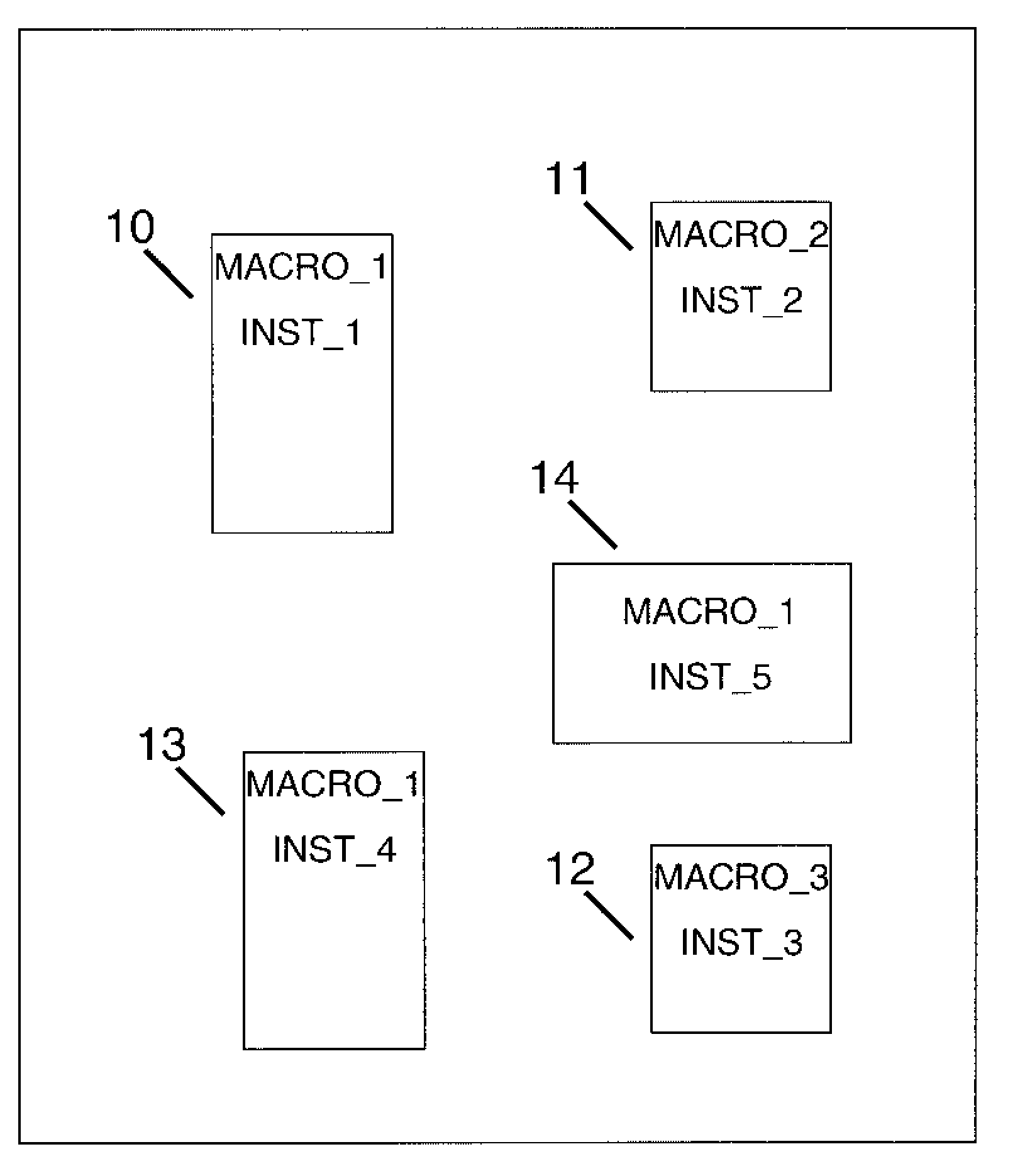

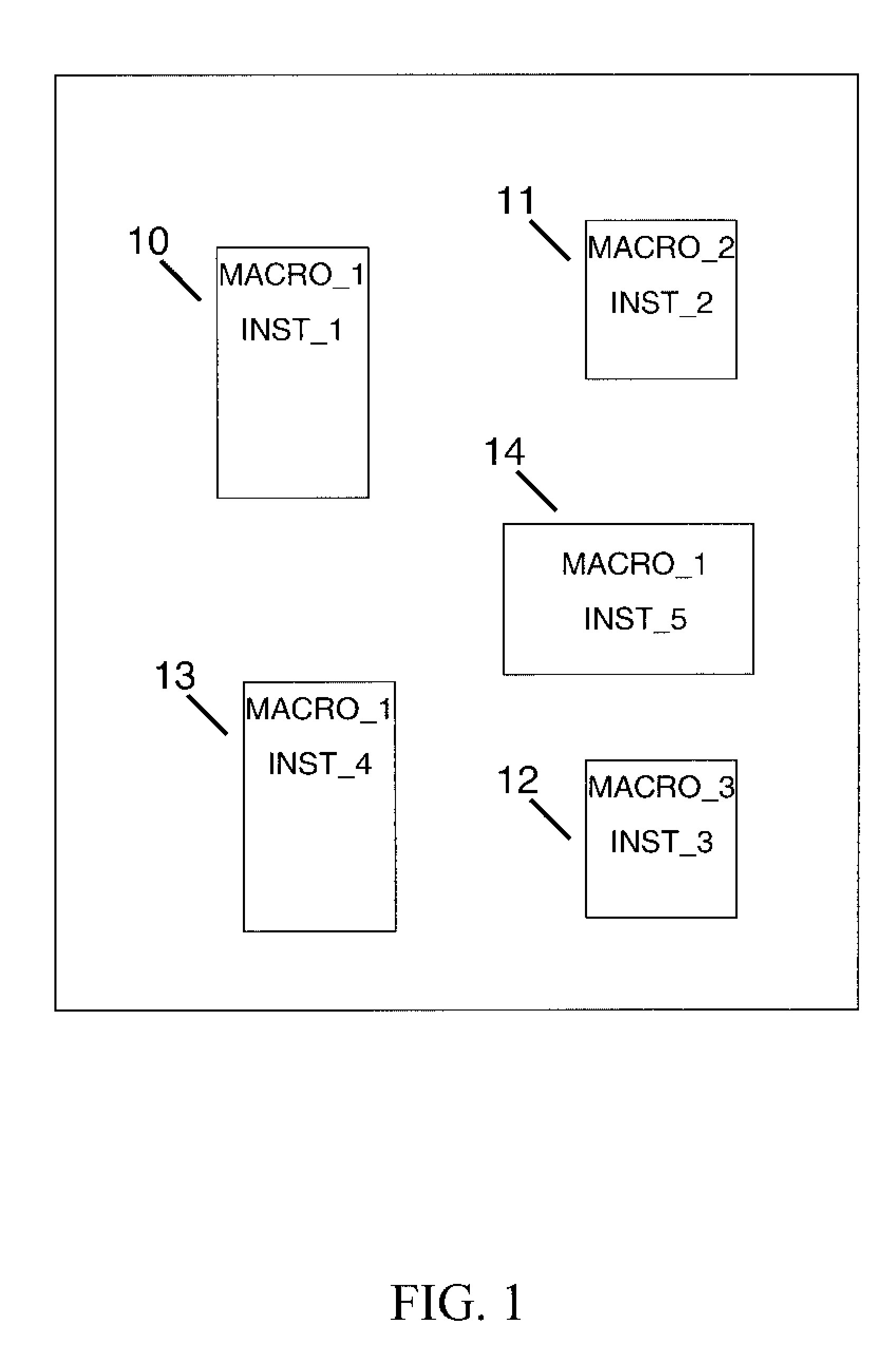

Method of IC fabrication, IC mask fabrication and program product therefor

InactiveUS20050193363A1Reduce designReduce resource consumptionPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringBoundary cell

A method of forming integrated circuit (IC) chip shapes and a method and computer program product for converting an IC design to a mask, e.g., for standard cell design. Individual book / macro physical designs (layouts) are proximity corrected before unnesting and an outer proximity range is determined for each proximity corrected physical design. Shapes with a unique design (e.g., in boundary cells and unique instances of books) are tagged and the design is unnested. Only the unique shapes are proximity corrected in the unnested design, which may be used to make a mask for fabricating IC chips / wafers.

Owner:GOOGLE LLC

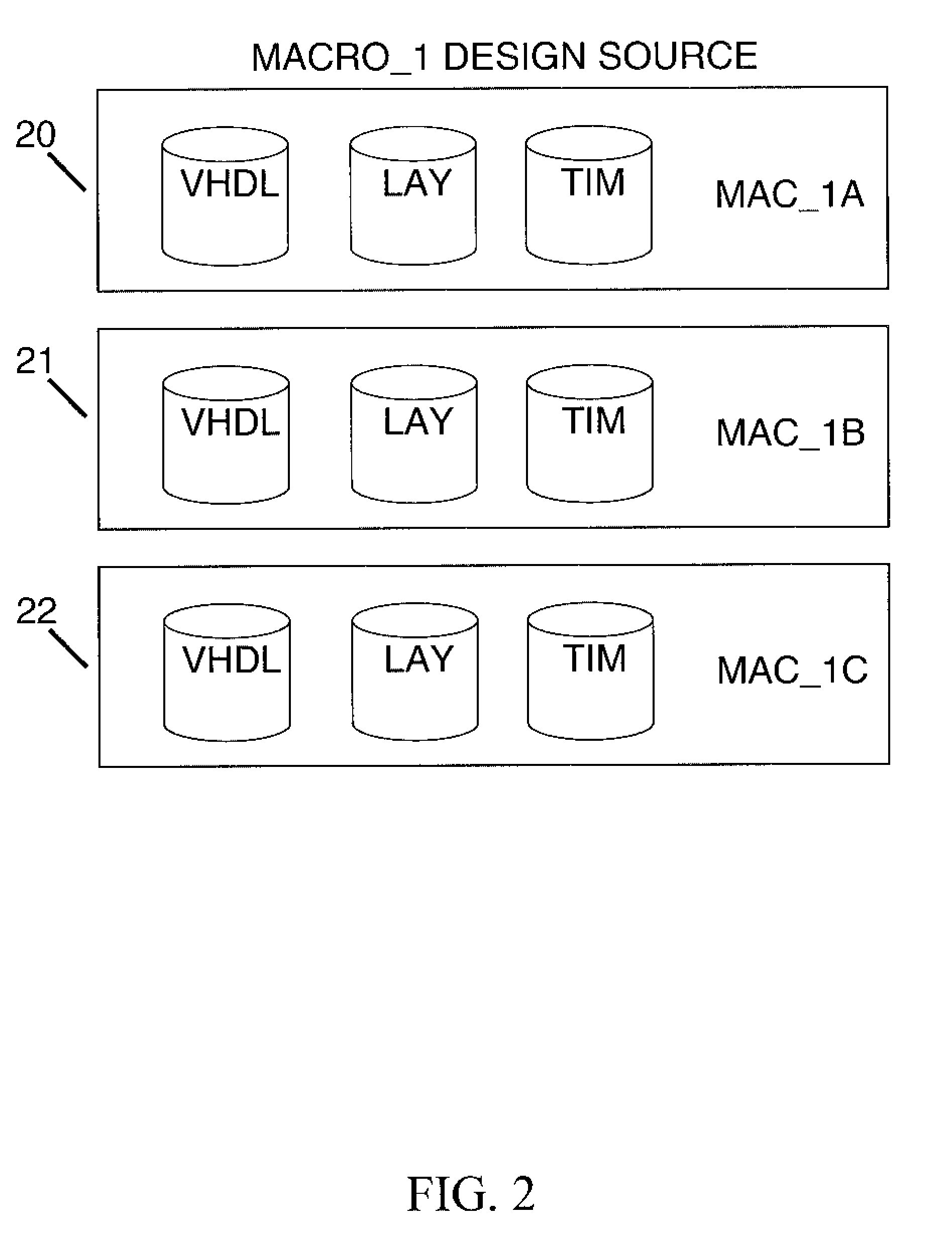

Method for Replicating and Synchronizing a Plurality of Physical Instances with a Logical Master

InactiveUS20080059952A1Minimal interventionError detection/correctionDatabase distribution/replicationData setData design

Design Data Management uses one copy of common data sets along with a plurality of instances, while continuing to utilize the existing design databases and existing CAD tools. Allowing a minimum amount of user intervention to create and maintain the common data set, Design Data Management employs replicating common data sets into one or more clone data sets. The method preferred provides for replicating and synchronizing one or more data sets with a master data set, comprises providing data design management of a master data set and at least one clone data set, and copying a master physical design data set into one or more physical instances to enable customization of said one or more physical instances. The master data set describes at least one of: a design component, a circuit macro, and a circuit entity, and comprises logical data sets, and it comprise physical design data sets. This permits all existing verification processes that are normally executed against the common data set to also be equally applied to the clones of said data set by way of automatic synchronization between of the common dataset and the clones.

Owner:IBM CORP

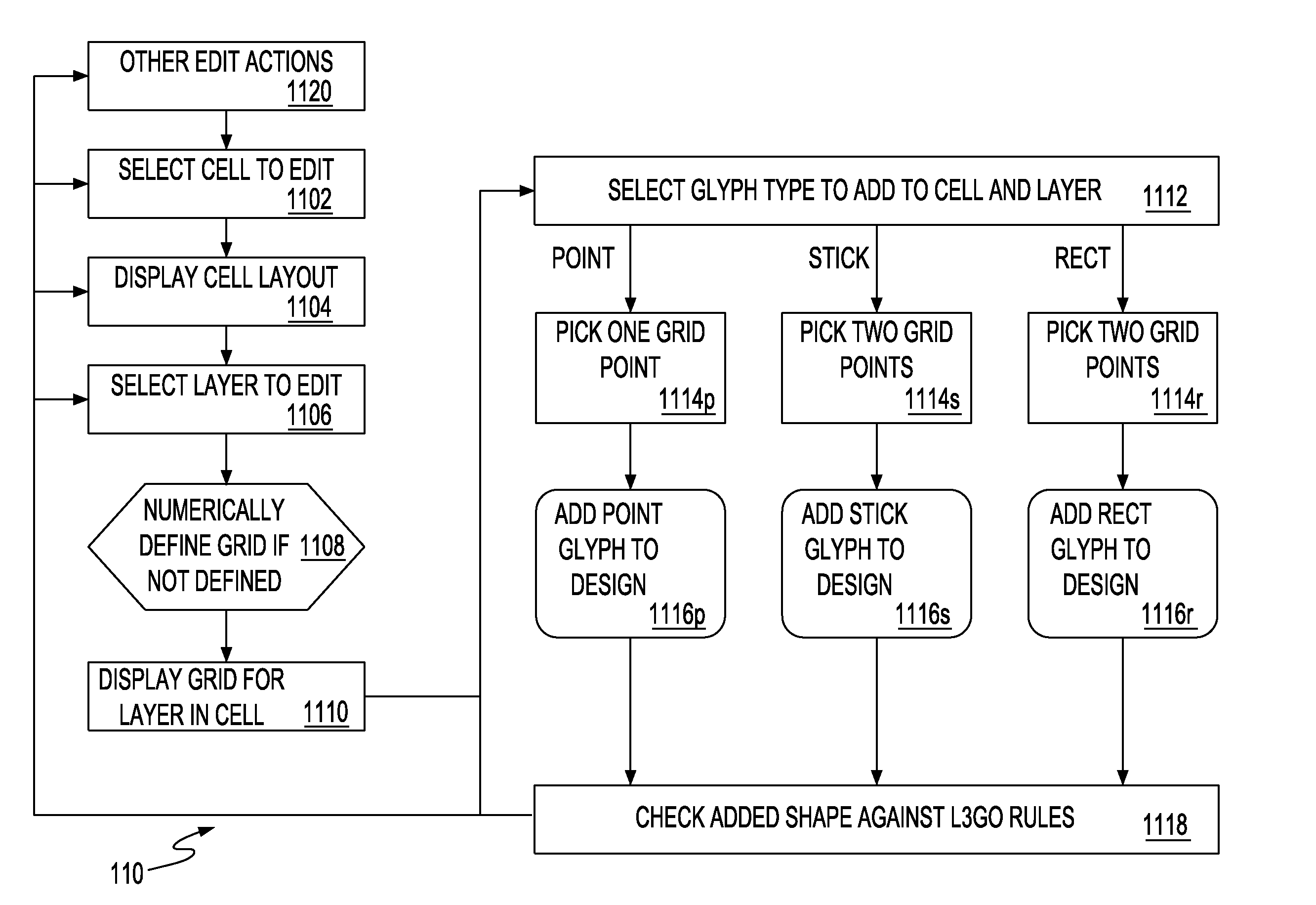

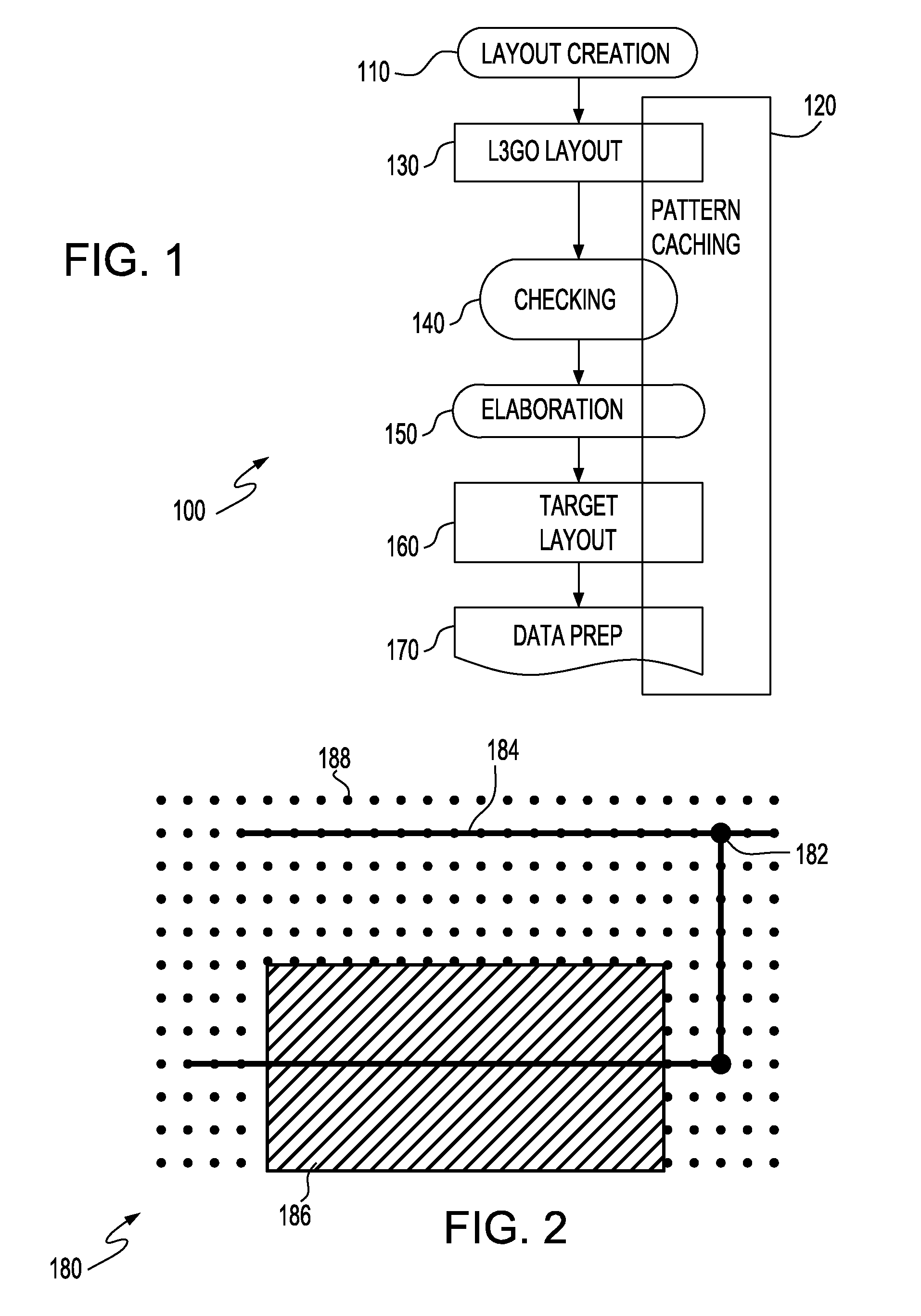

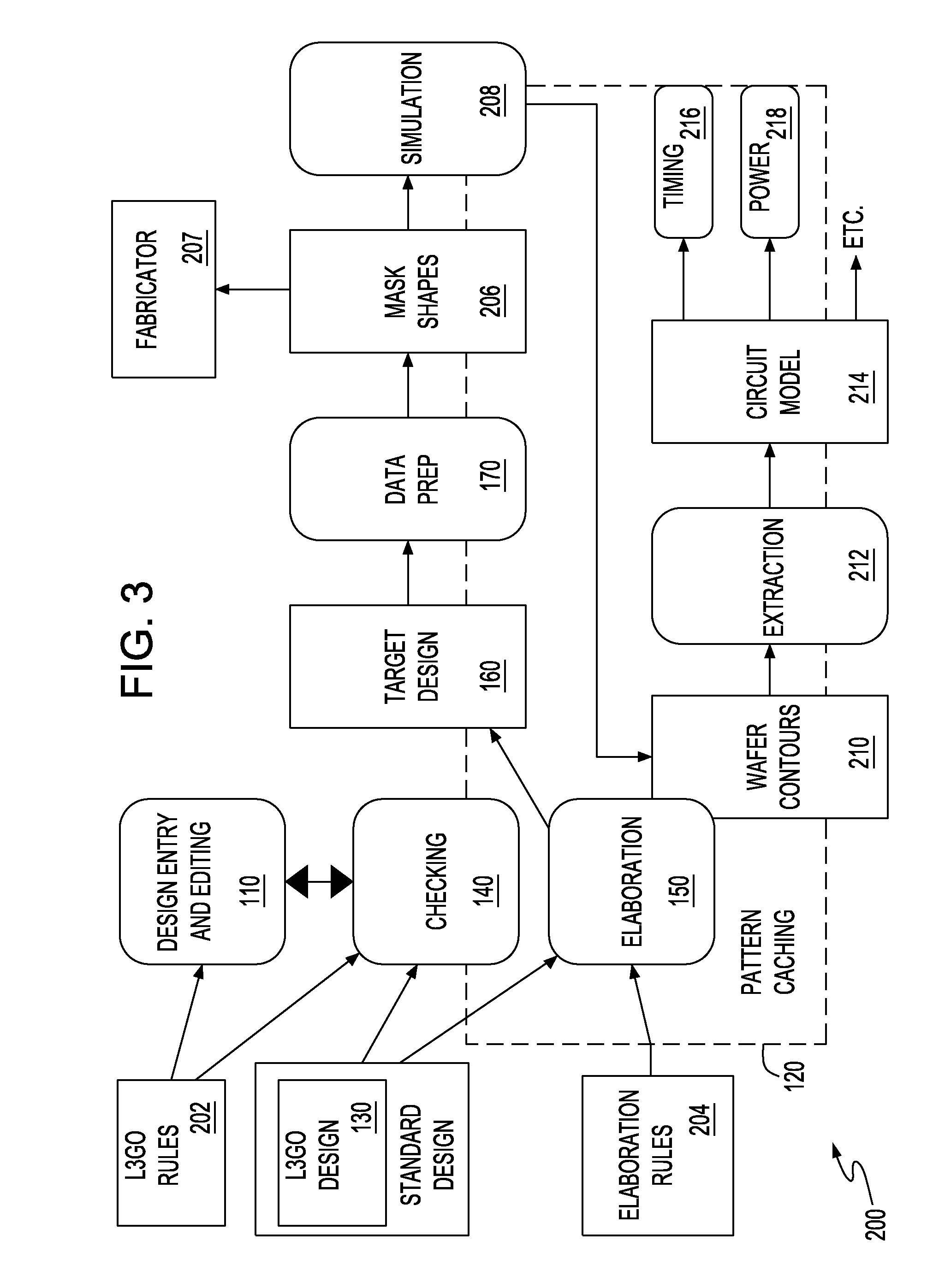

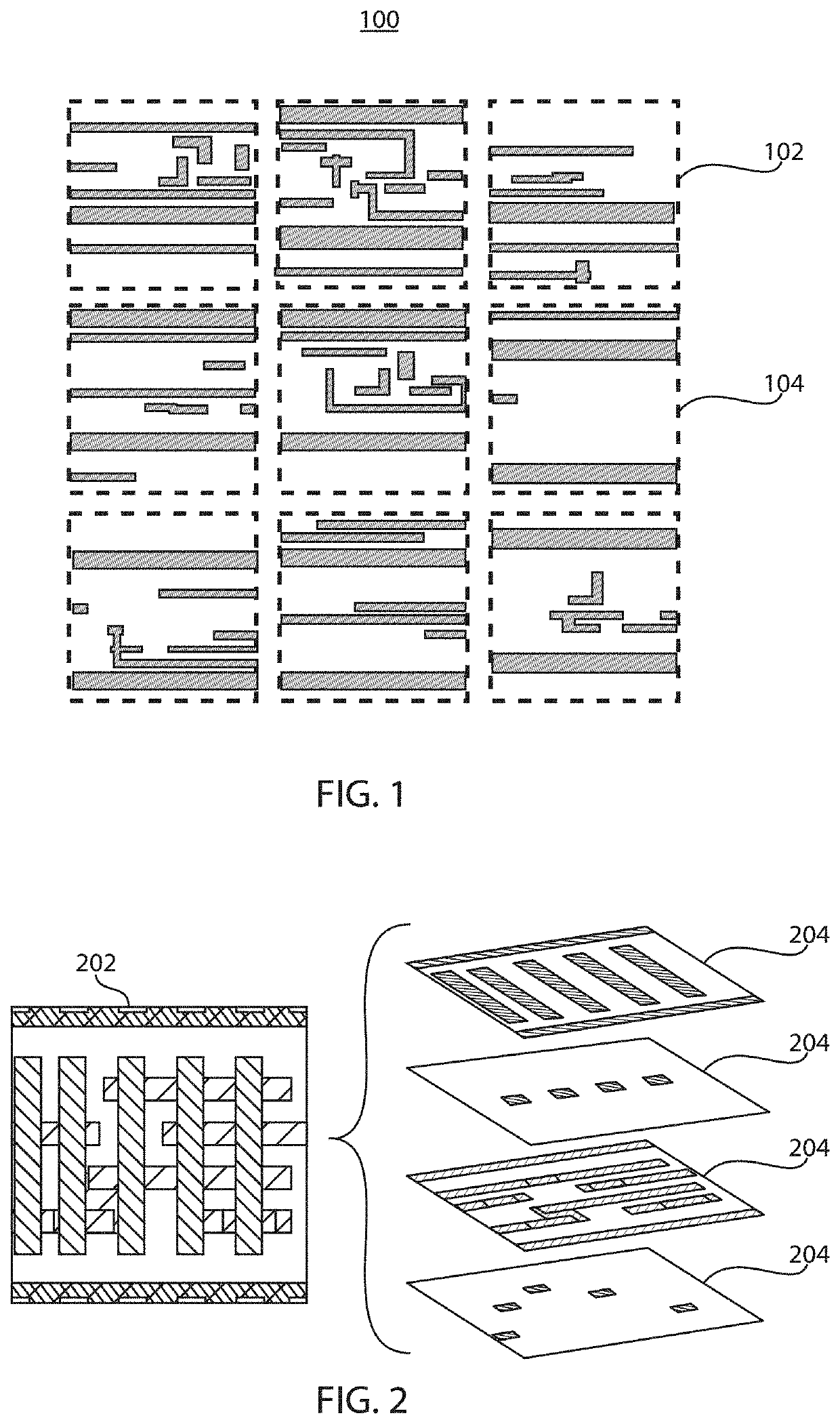

Iphysical design system and method

ActiveUS20090204930A1Low costReduce riskDesign optimisation/simulationSpecial data processing applicationsProgramming languageLayout

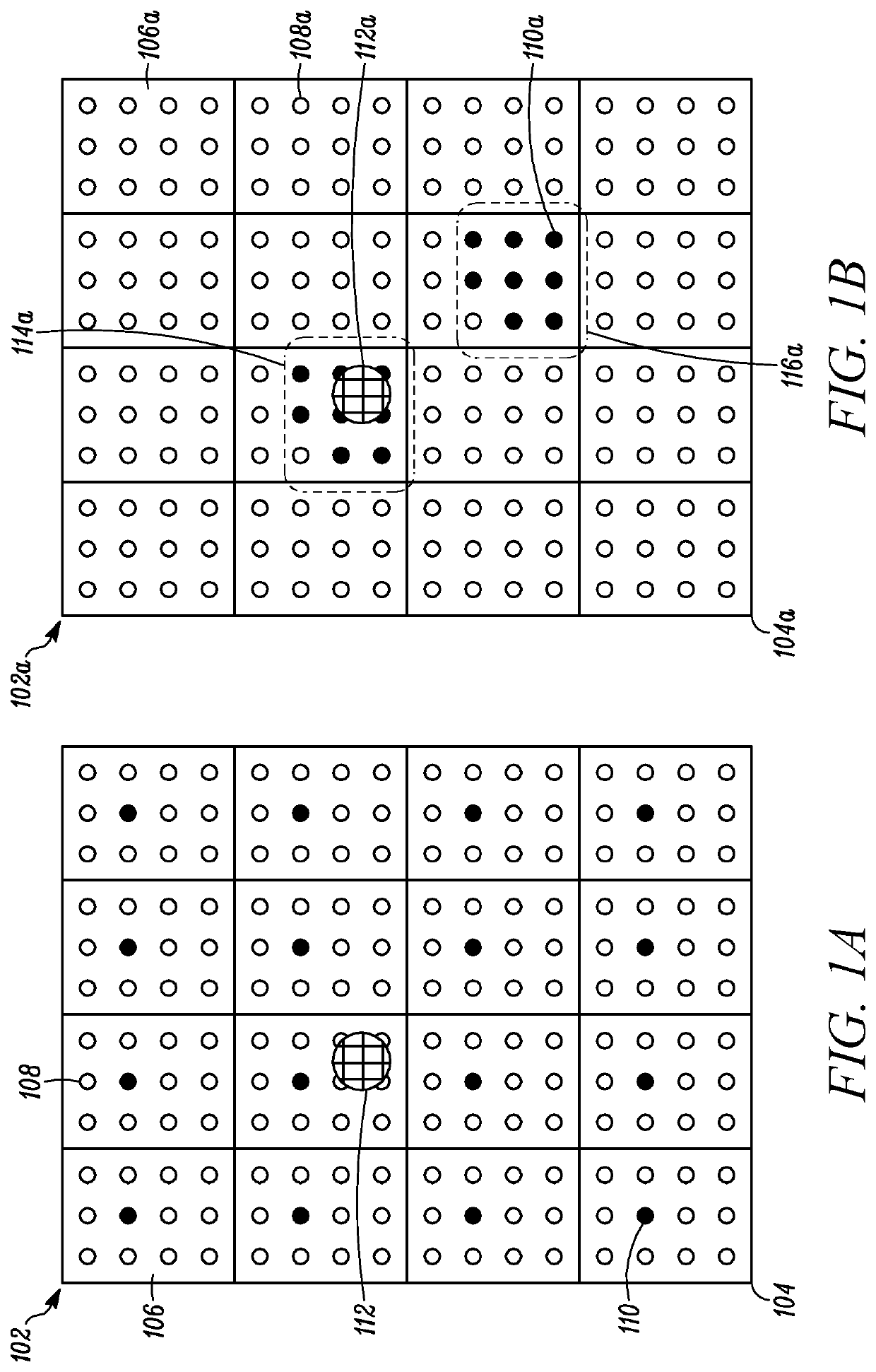

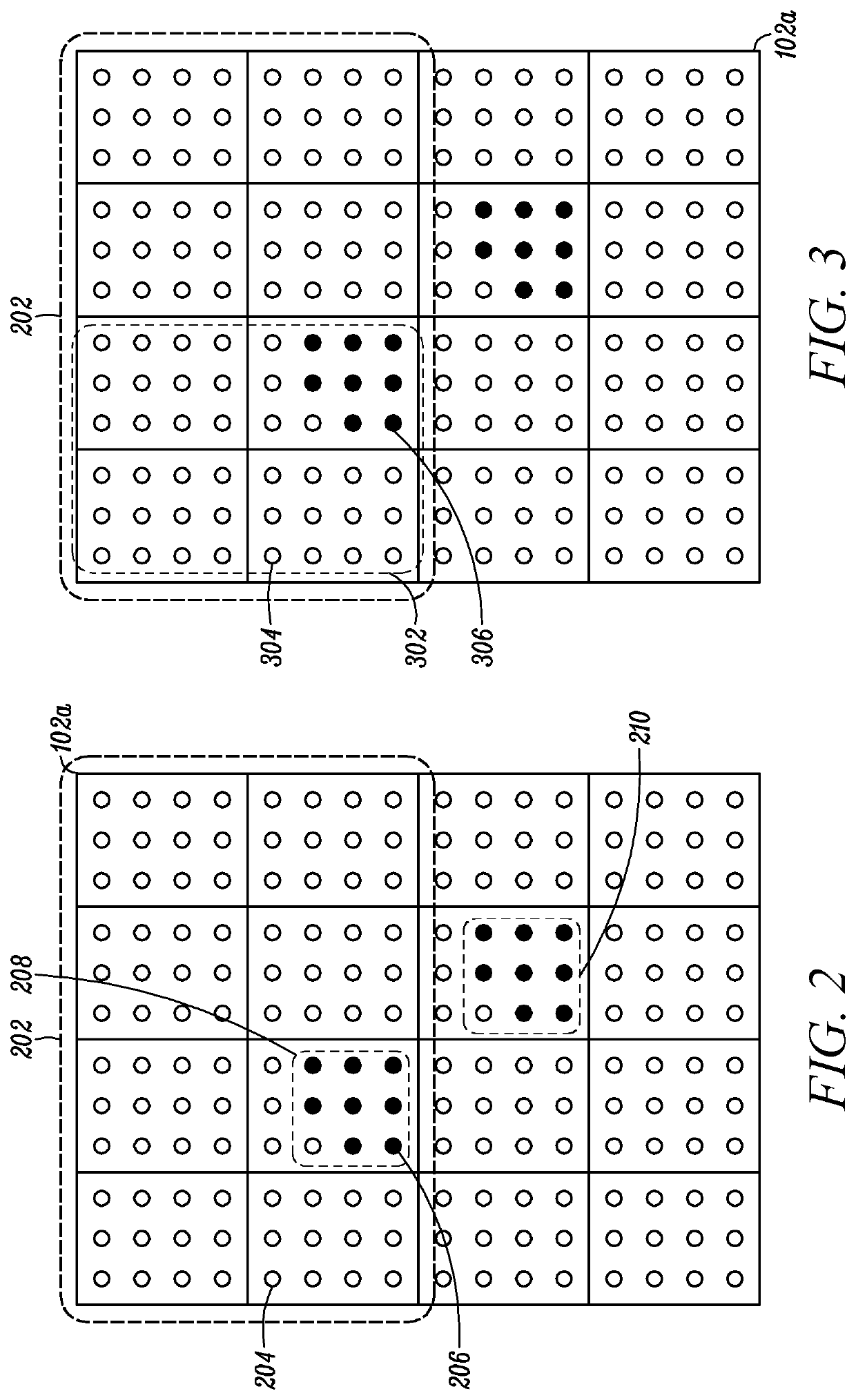

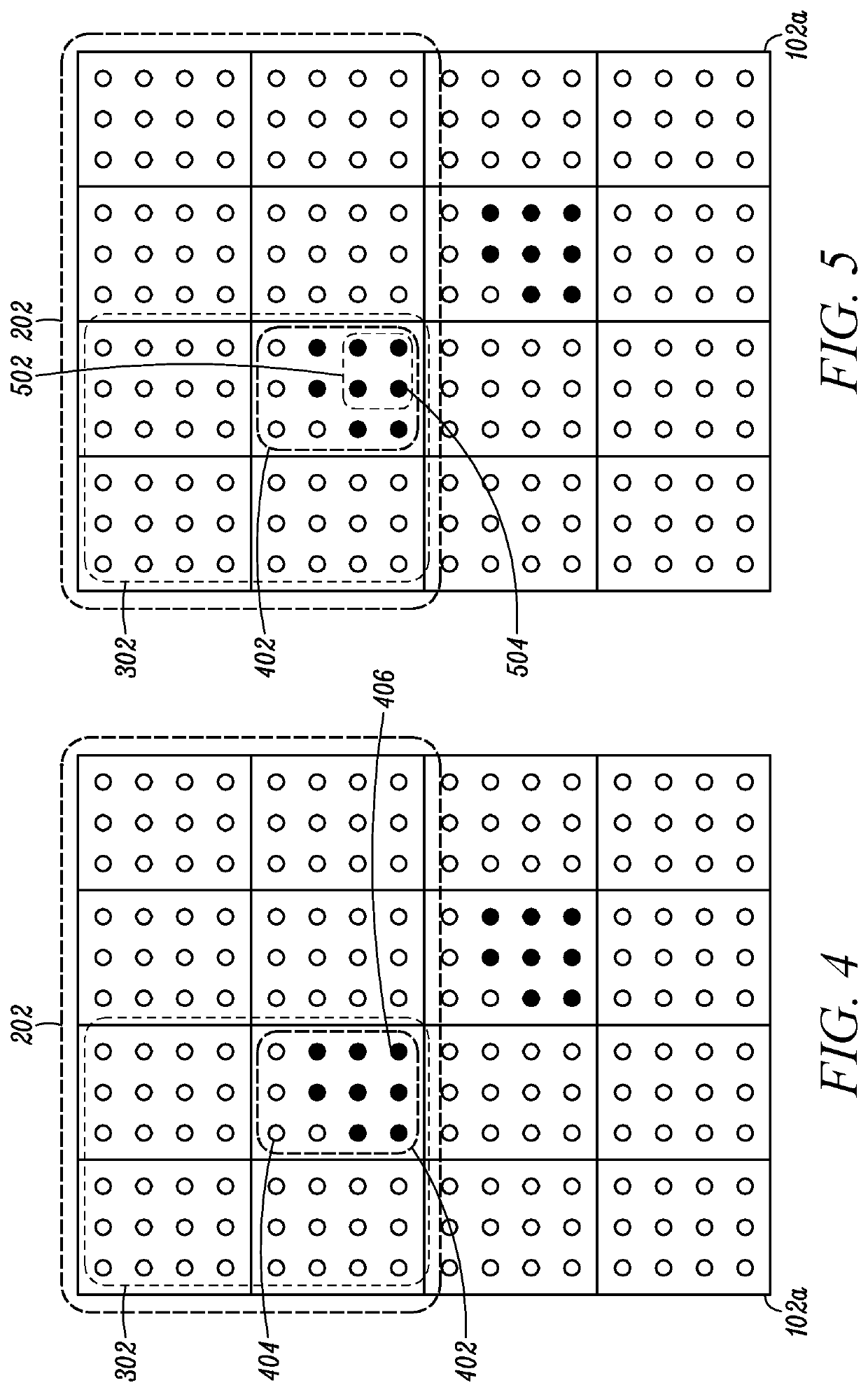

A design system for designing complex integrated circuits (ICs), a method of IC design and program product therefor. A layout unit receives a circuit description representing portions in a grid and glyph format. A checking unit checks grid and glyph portions of the design. An elaboration unit generates a target layout from the checked design. A data prep unit prepares the target layout for mask making. A pattern caching unit selectively replaces portions of the design with previously cached results for improved design efficiency.

Owner:GLOBALFOUNDRIES U S INC

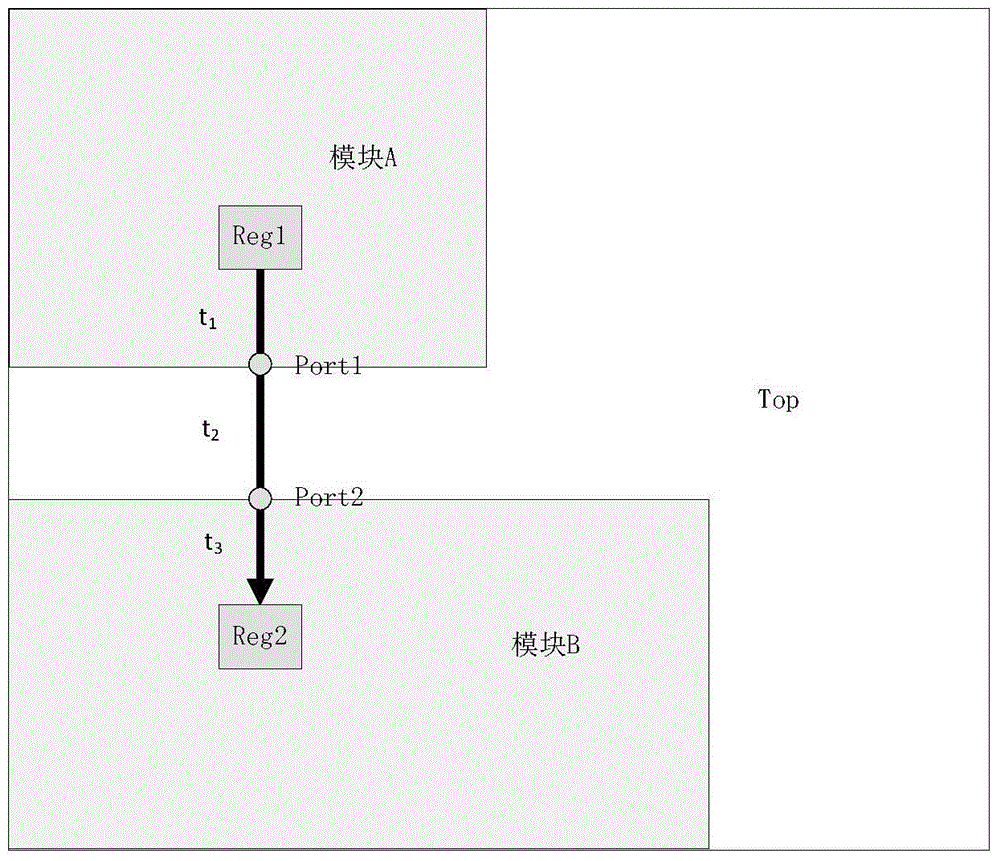

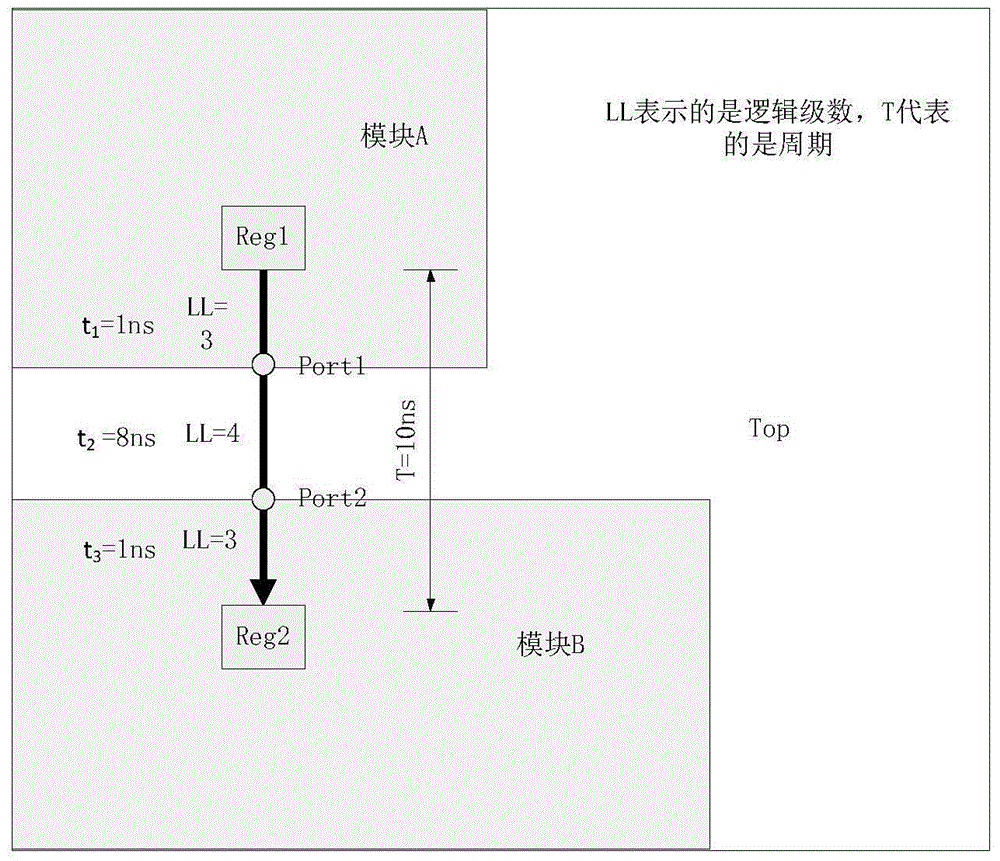

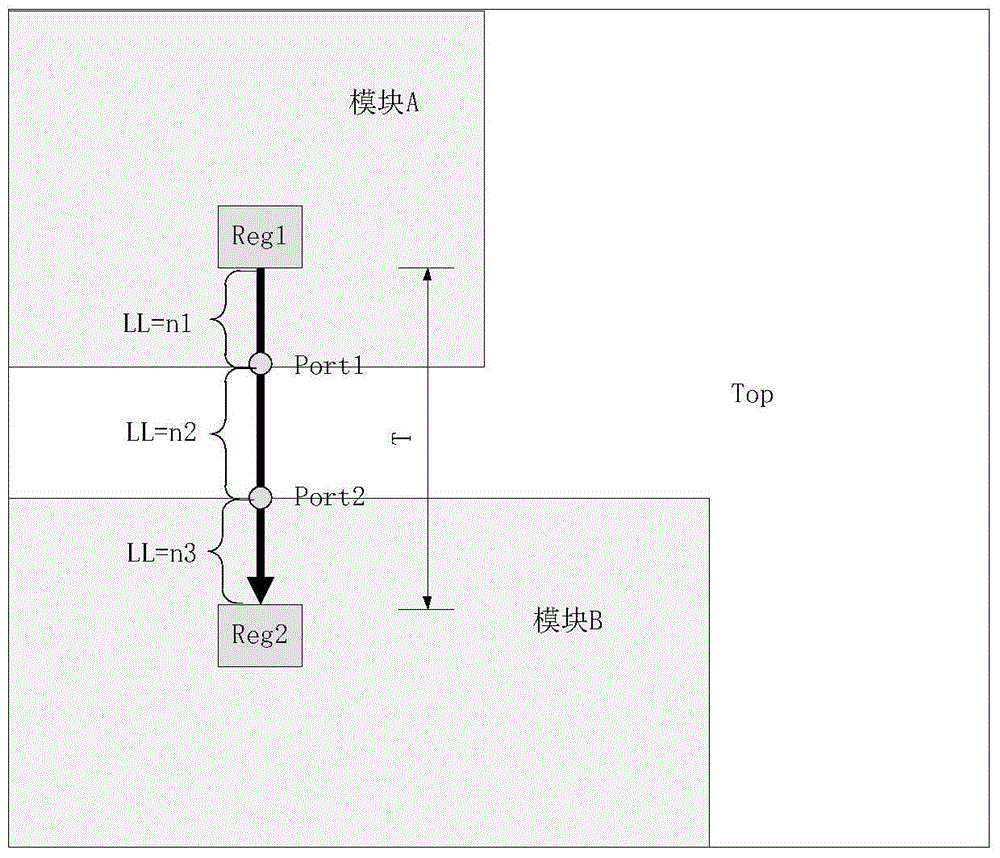

Time sequence budgeting method capable of considering distance and clock

ActiveCN105095604AGuaranteed reasonablenessAccurate Timing Budget ValuesSpecial data processing applicationsLogical depthProcessor register

The invention provides a time sequence budgeting method capable of considering a distance and a clock by aiming at the roughness and the boundness of the time sequence budgeting method with a shortest boundary in a hierarchical physical design and the time sequence budgeting method based on logical depth. The method fully considers influence caused on the time sequence of a cross-module path by the physical distance and a clock deviation between two modules and obtains a more accurate and reasonable time sequence budgeting numerical value of each module port through the following steps of carefully analyzing the physical positions of the module port and a relevant boundary register and the logic depth of the cross-module path and carrying out the time delay calculation of an interconnection line, the ratio calculation of logic depth and clock deviation estimation, so that the iterations of the time sequence optimization of the cross-module path are reduced, and time sequence convergence in a chip design is quickened.

Owner:NAT UNIV OF DEFENSE TECH

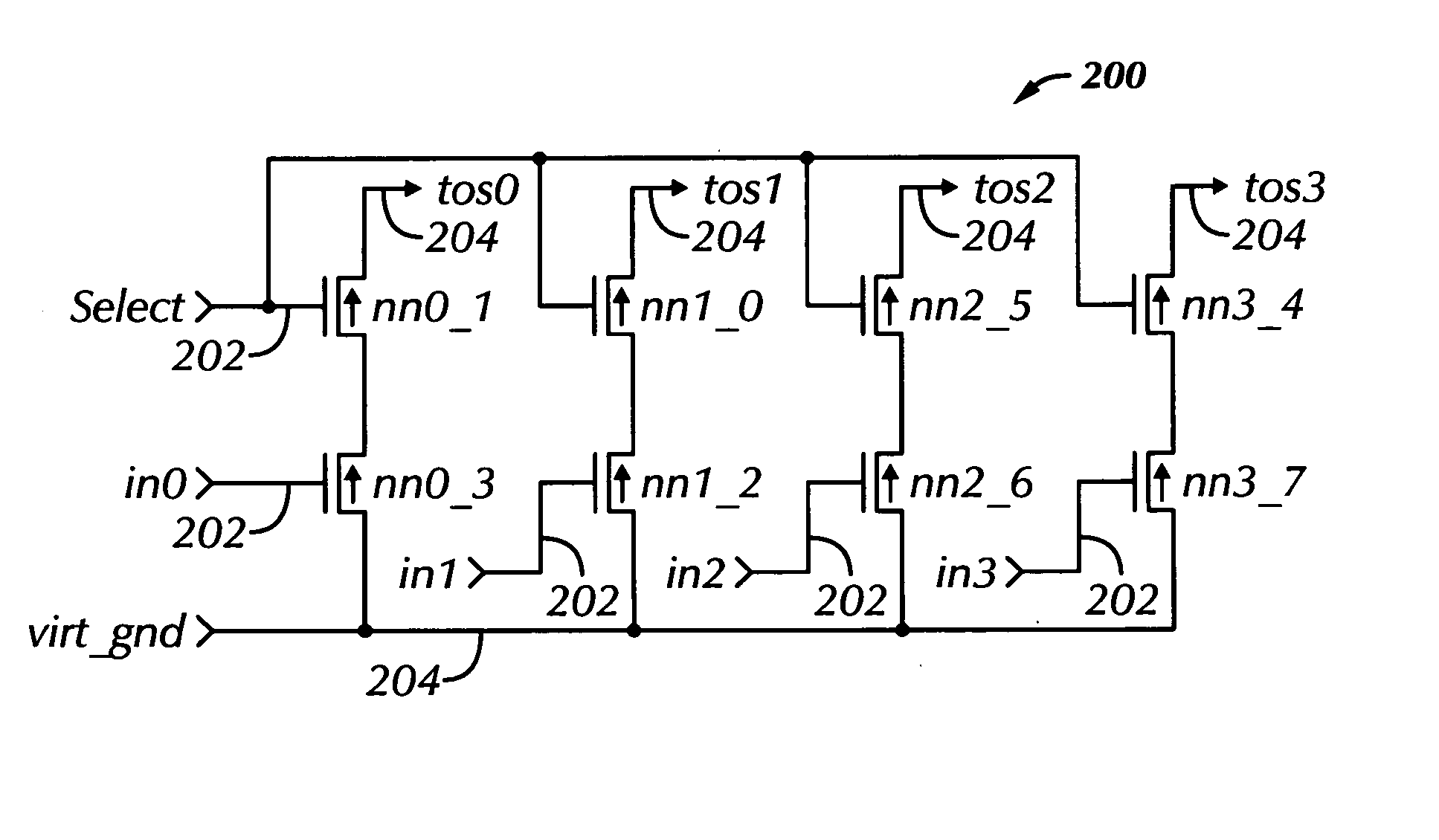

Physical realization of dynamic logic using parameterized tile partitioning

InactiveUS20050060128A1CAD circuit designSpecial data processing applicationsTransistor sizingEngineering

The matching algorithm of the layout synthesis method and apparatus disclosed locates transistor pattern matches in a design, links a parameterized tile to each identified match, and adjusts certain variable parameters of the linked parameterized tile to meet the physical design requirements of each located match. Each transistor pattern corresponds to a parameterized tile, which is an actual physical representation of the corresponding pattern and includes variable parameters, which may include transistor size. The matching algorithm locates matches in the design for an ordered list of patterns, names each located match, links the proper parameterized tile to each named match, and adjusts the tile's variable parameters as required. Transistors in the design are included in one and only one named located match.

Owner:APPLE INC

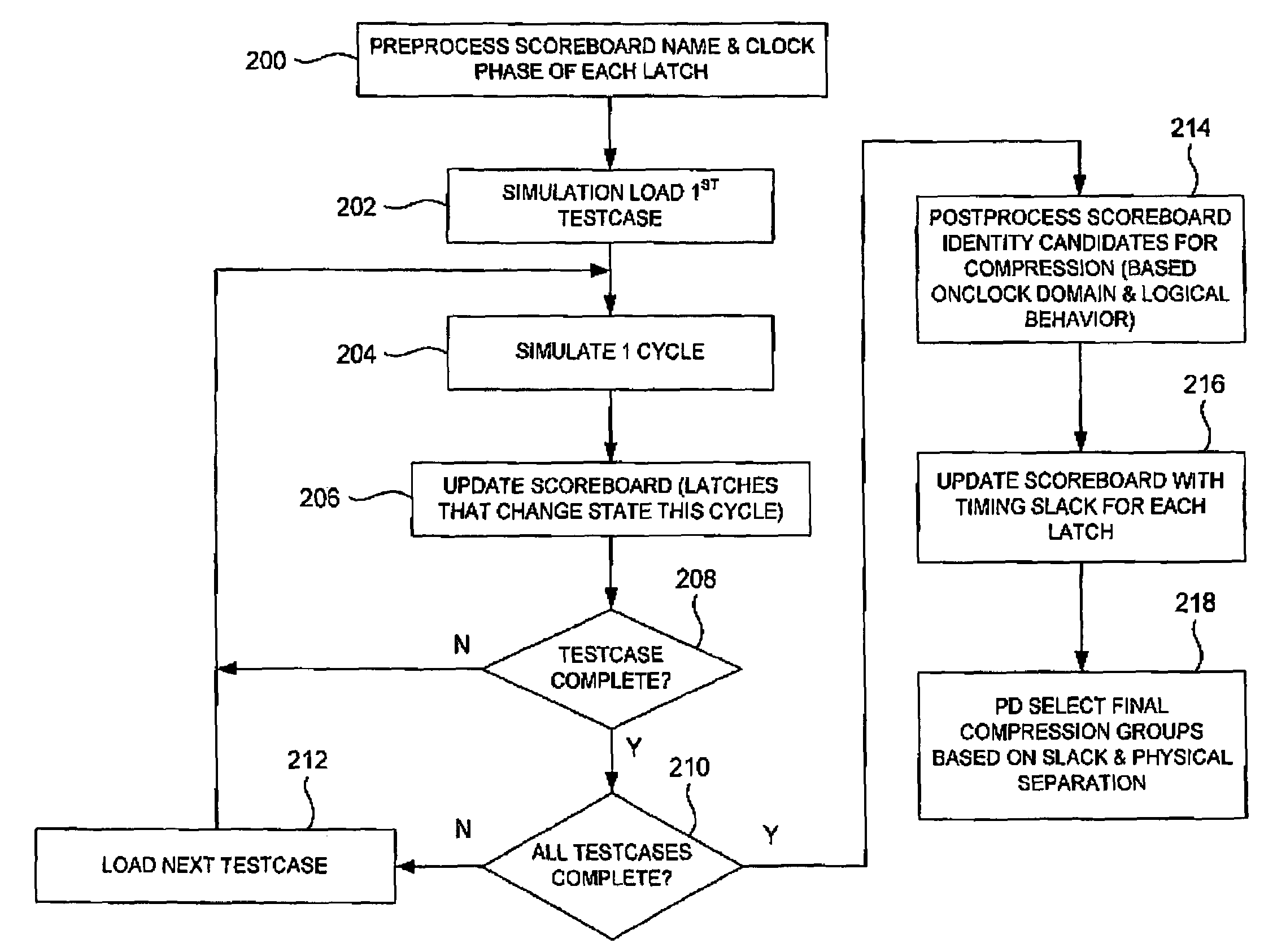

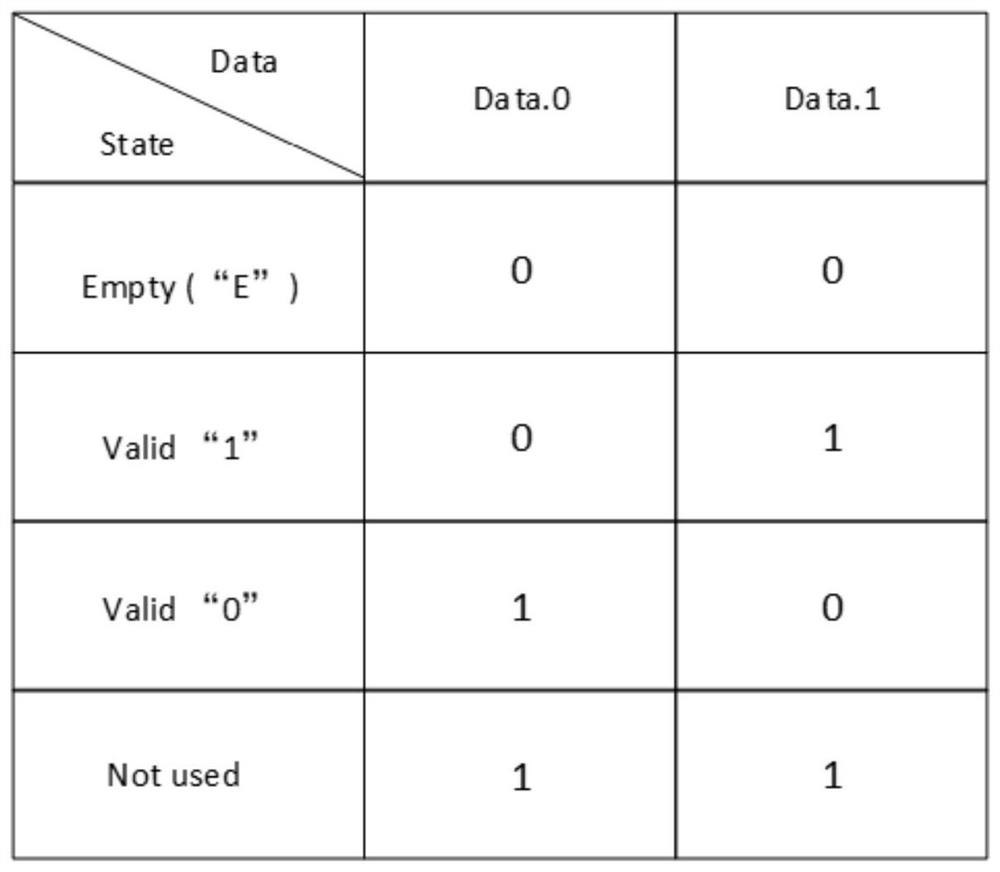

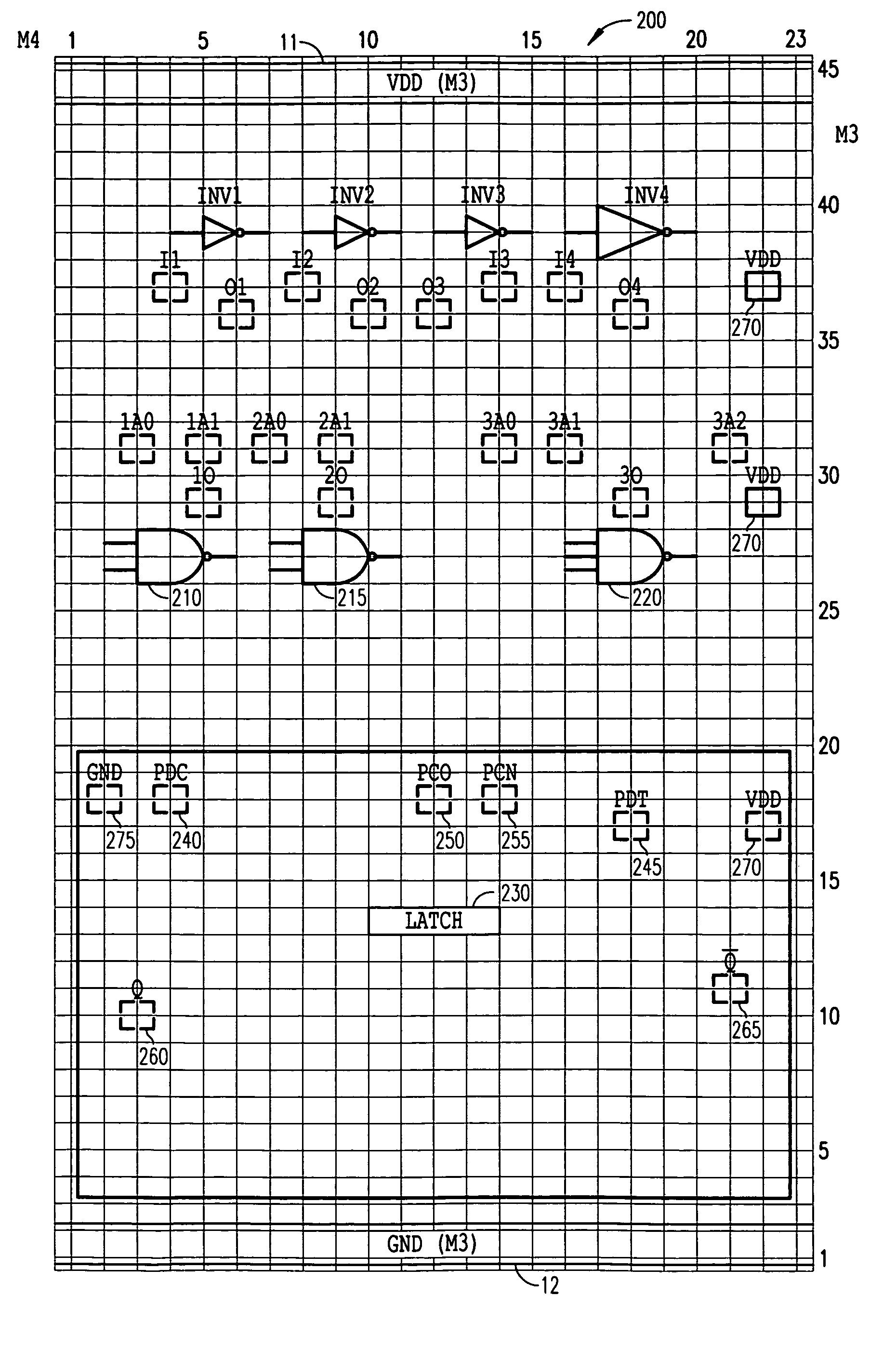

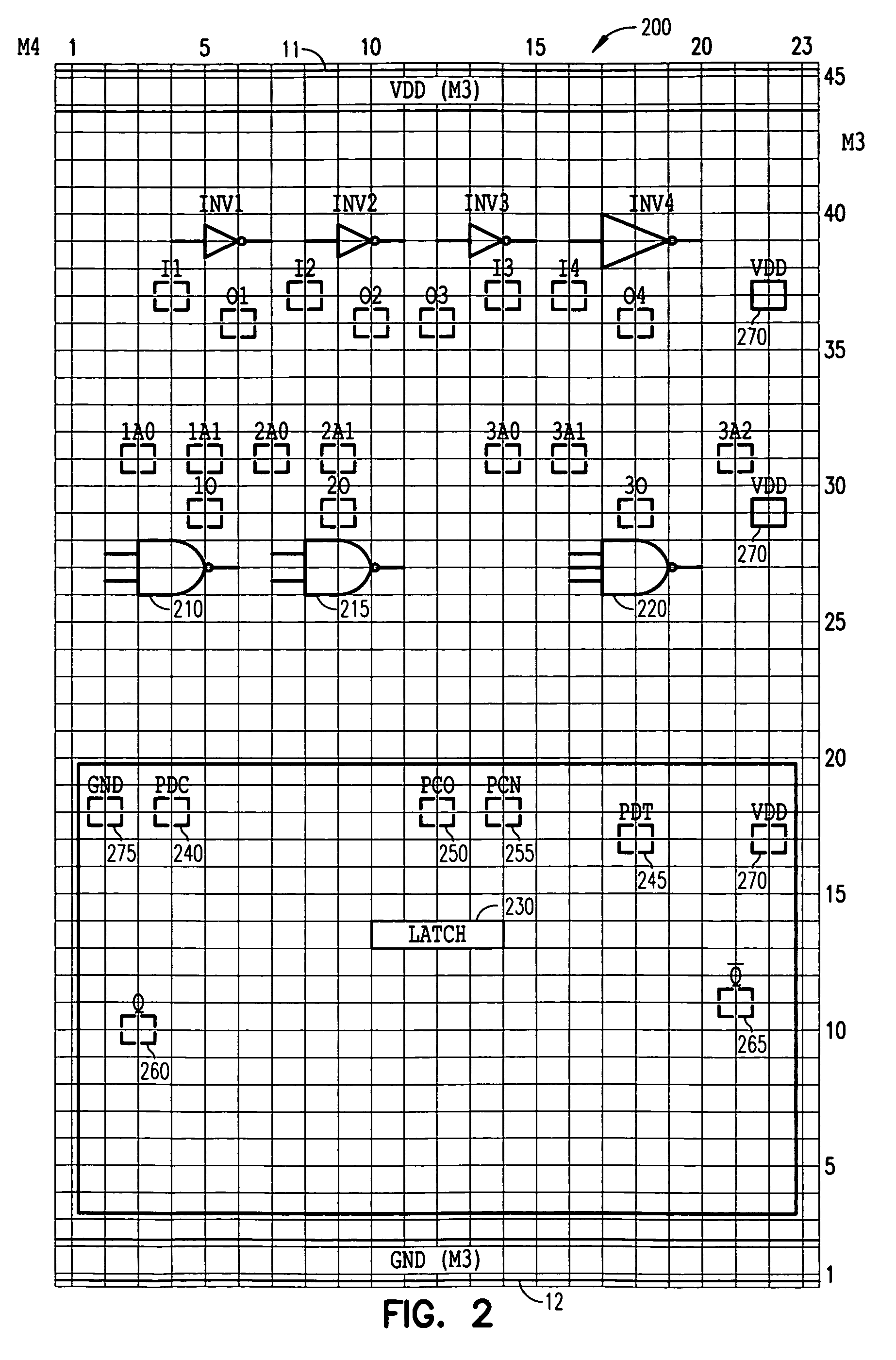

Automatic latch compression/reduction

ActiveUS7058914B2Eliminates redundant latchesCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareLogical Function

Owner:TWITTER INC

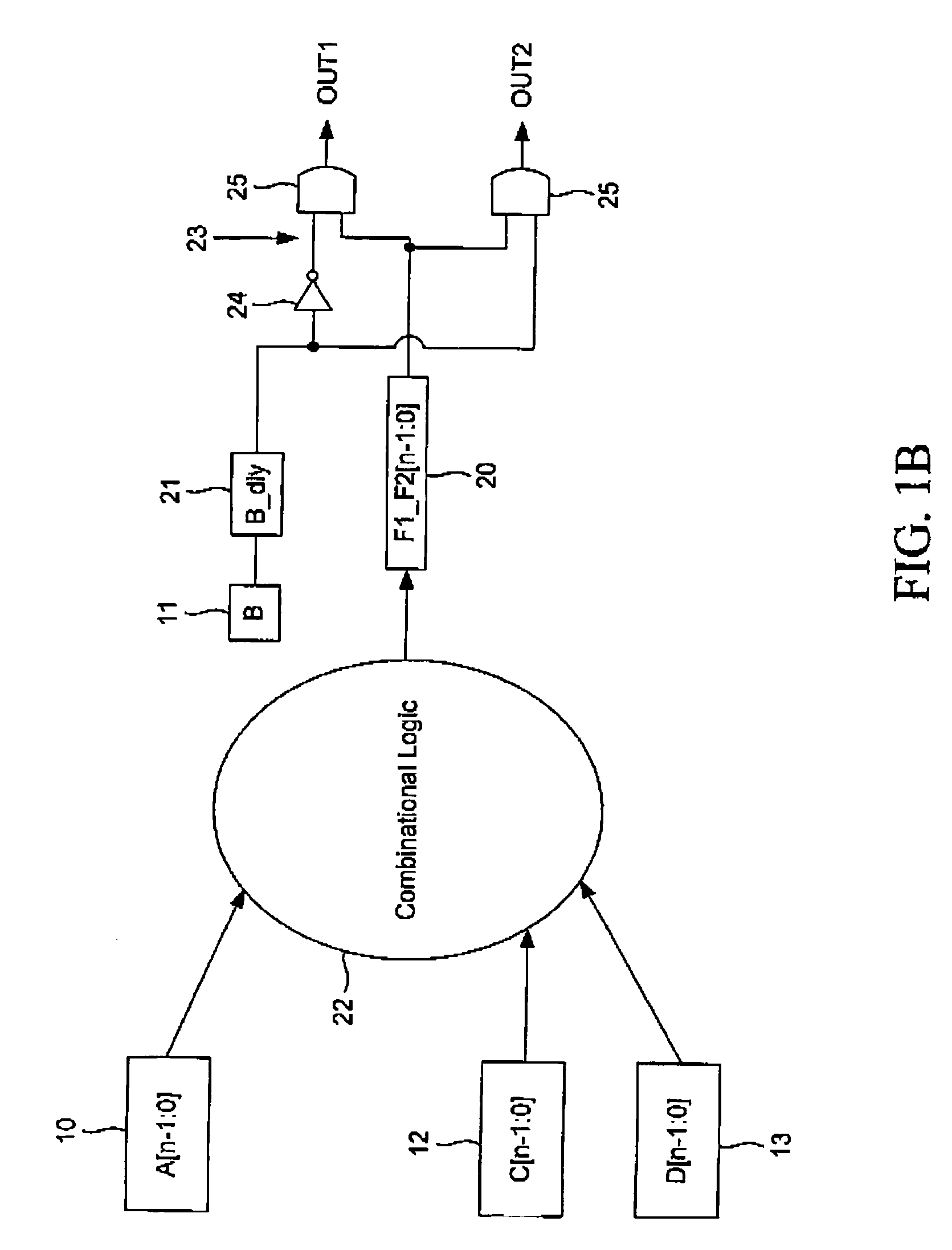

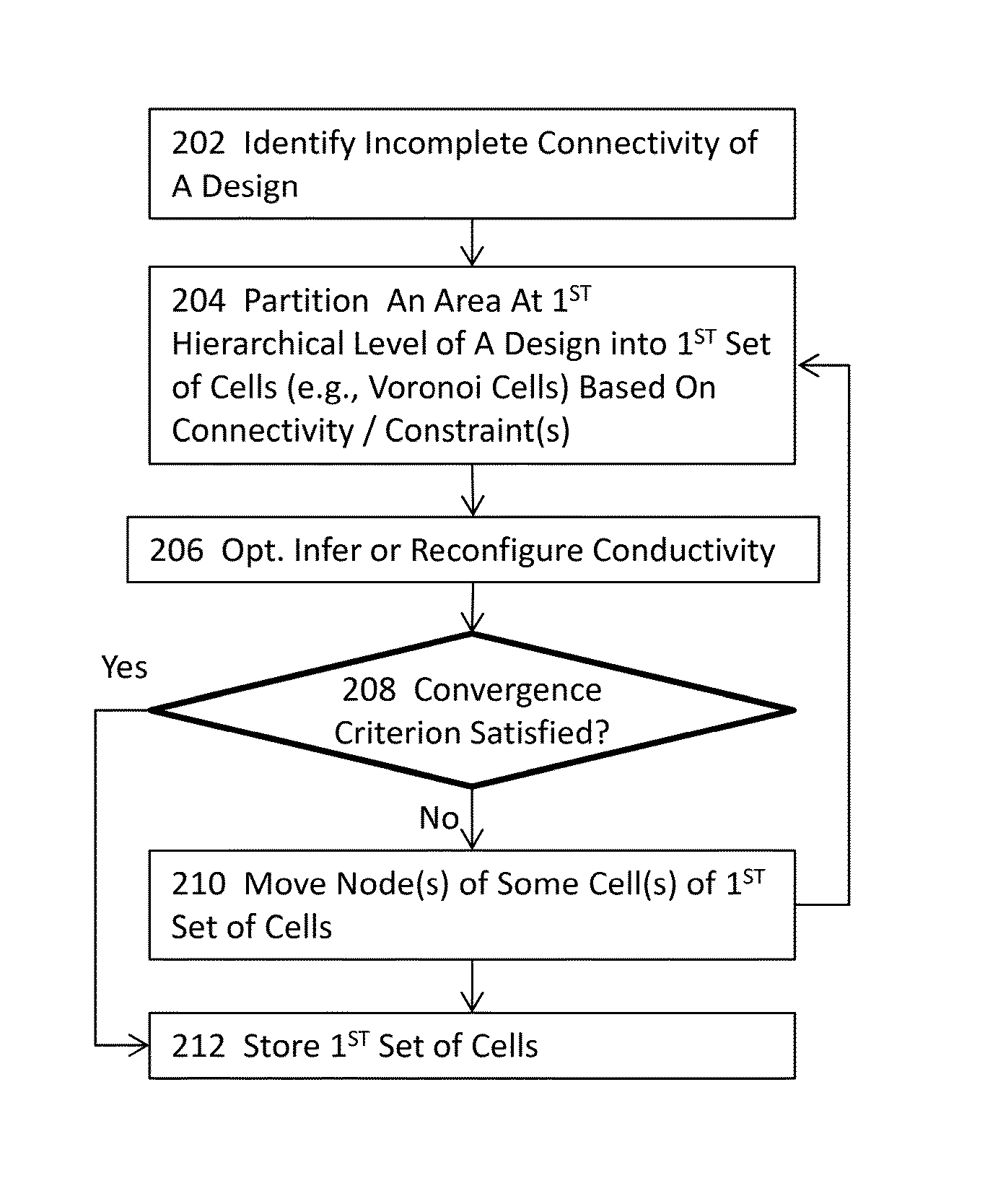

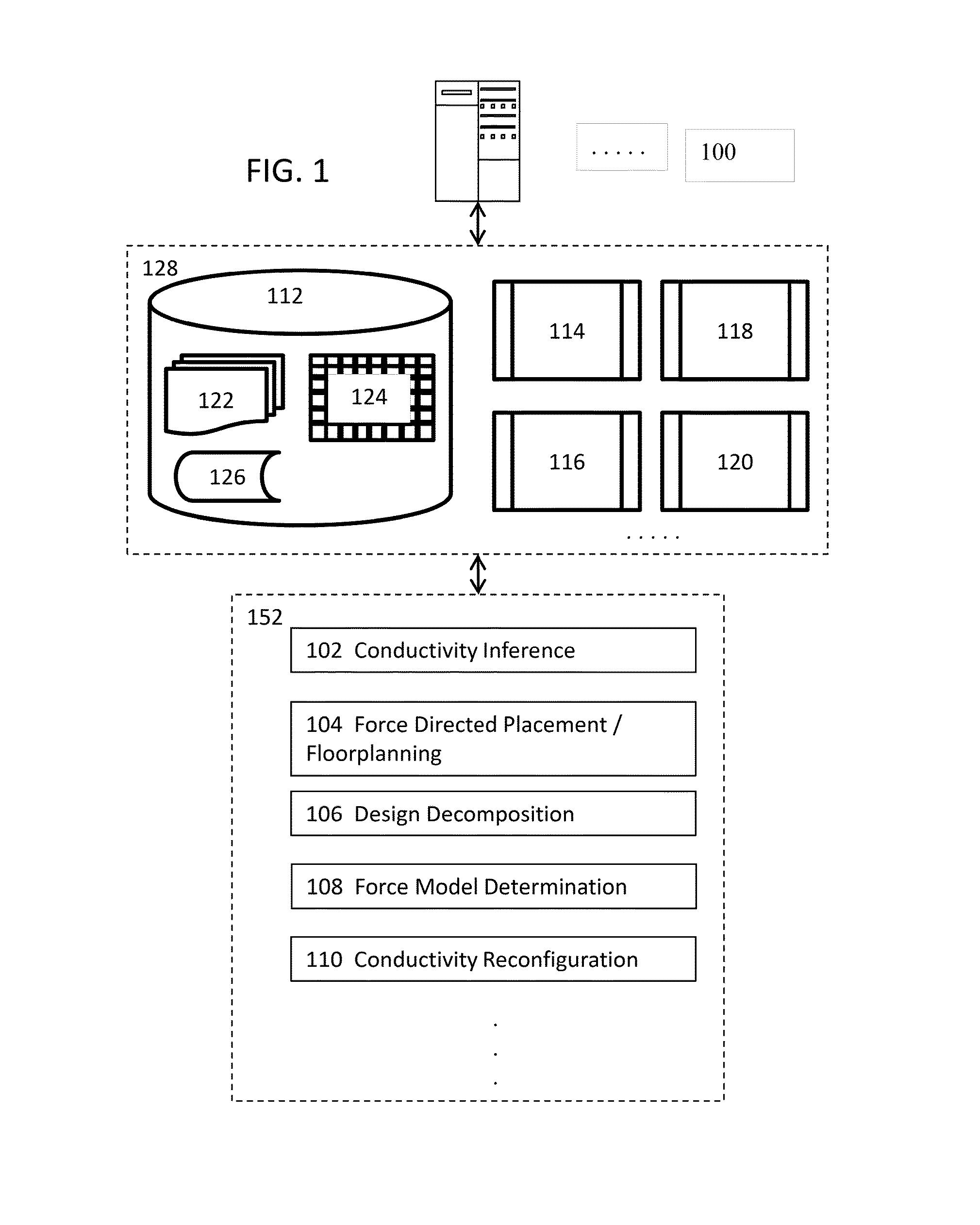

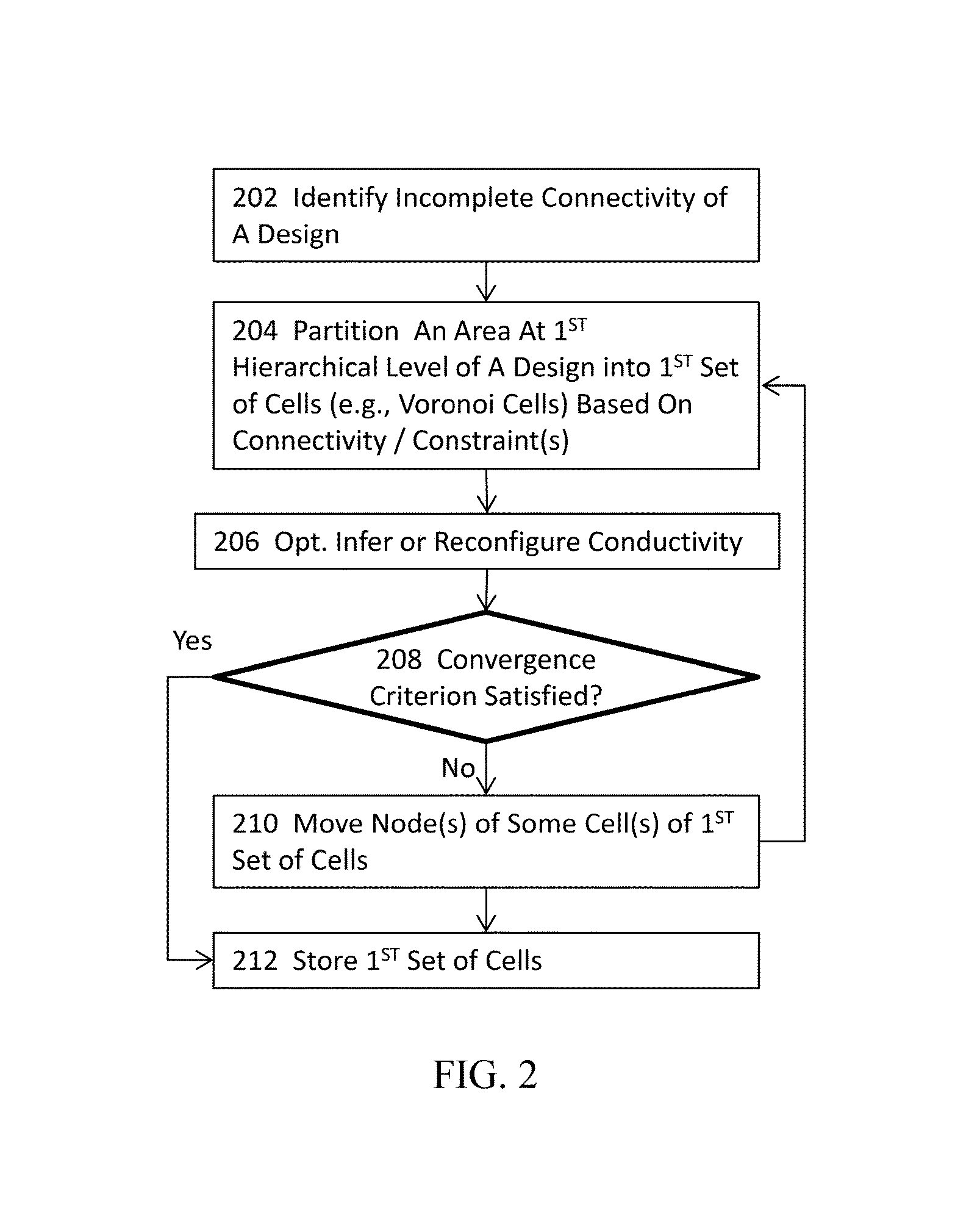

Methods, systems, and articles of manufacture for implementing physical design decomposition with custom connectivity

InactiveUS8918751B1Computer aided designSpecial data processing applicationsNODALComputer architecture

Disclosed are methods, systems, and articles of manufactures for implementing physical design decomposition with custom conductivity by identifying custom, incomplete conductivity for an electronic design, partitioning a physical design space multiple non-overlapping cells, and iteratively moving at least some of the nodes of these multiple cells to generate a floorplan or a placement layout until one or more convergence criteria are satisfied while maintaining the custom, incomplete conductivity. The floorplan or a placement layout generated resembles the final floorplan obtained through a floorplanner or the final placement layout through a placement tool without requiring that complete conductivity information be provided to the floorplanner or placement tool.

Owner:CADENCE DESIGN SYST INC

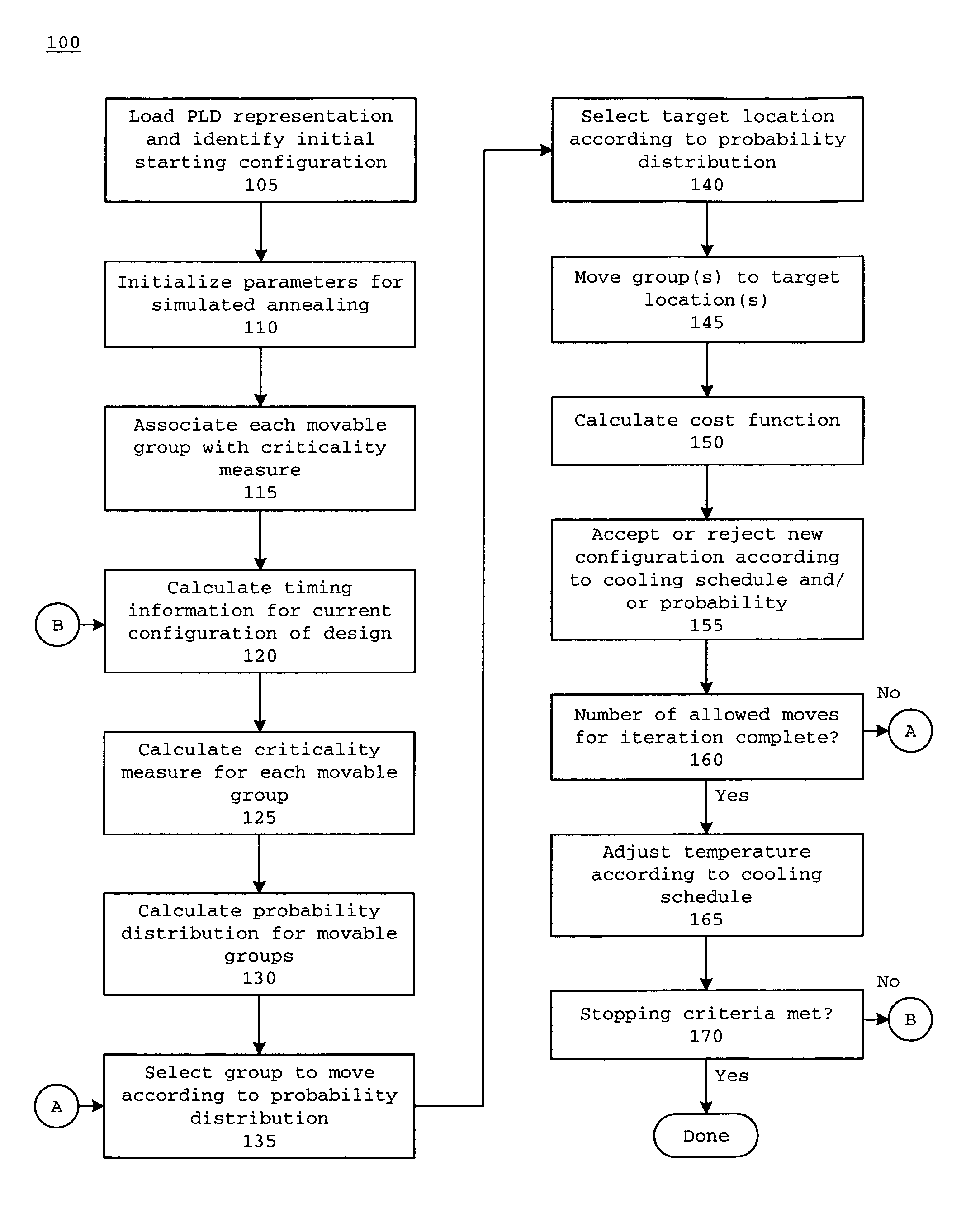

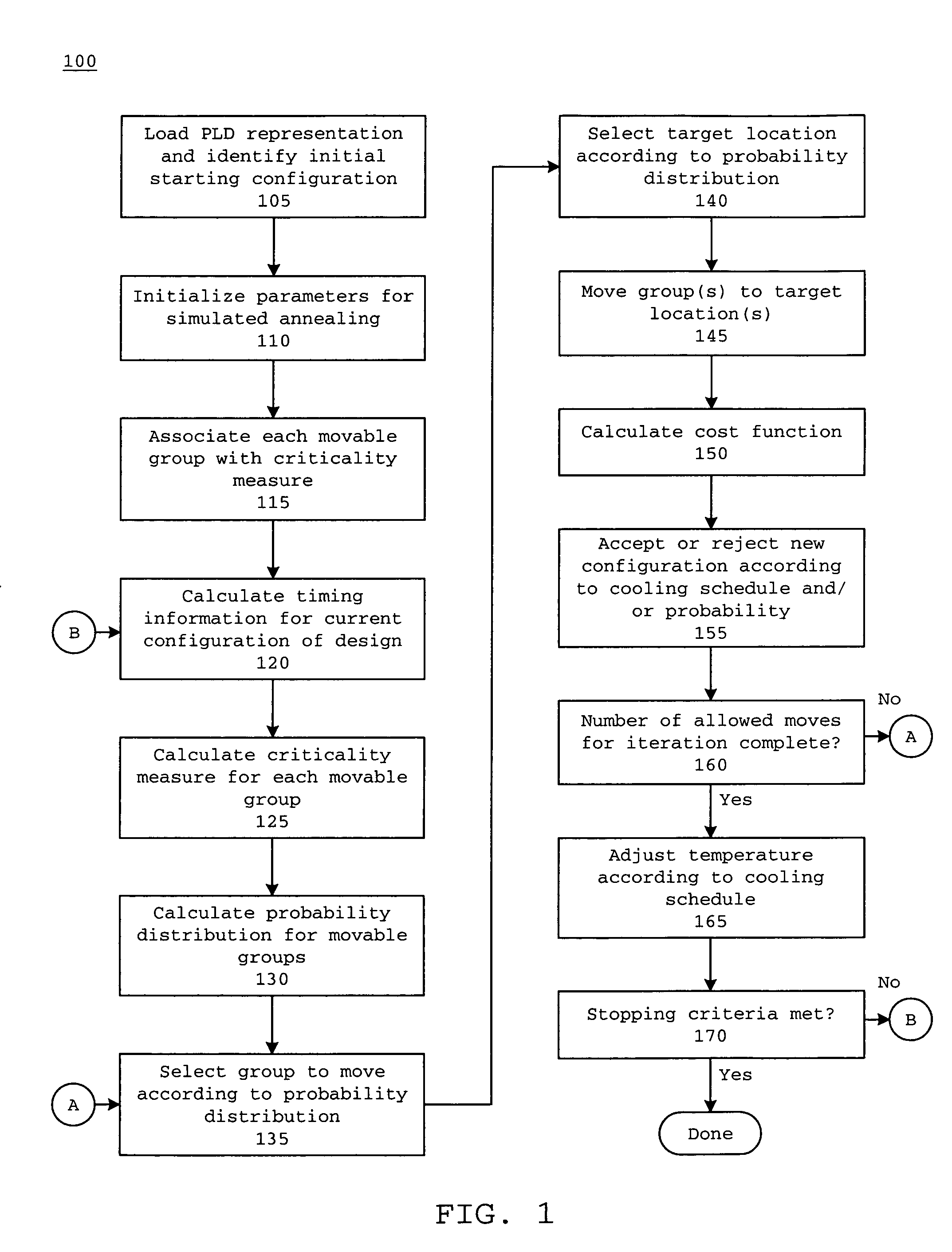

Cost-independent criticality-based move selection for simulated annealing

ActiveUS7194721B1Computer aided designSoftware simulation/interpretation/emulationProgrammable logic deviceSimulated annealing

A method of physical design for a programmable logic device (PLD) can include associating movable objects of the PLD with a criticality measure that is dependent upon timing information for a configuration of the PLD (115). The method further can include calculating the criticality measure for each movable object (125) and calculating a probability for each movable object (130). The probability can depend upon the criticality measure for the movable object. The method also can include selecting one or more of the movable objects for controlled move generation within a simulated annealing process (135). Movable objects are selected for controlled move generation according to the probabilities assigned to the movable objects.

Owner:XILINX INC

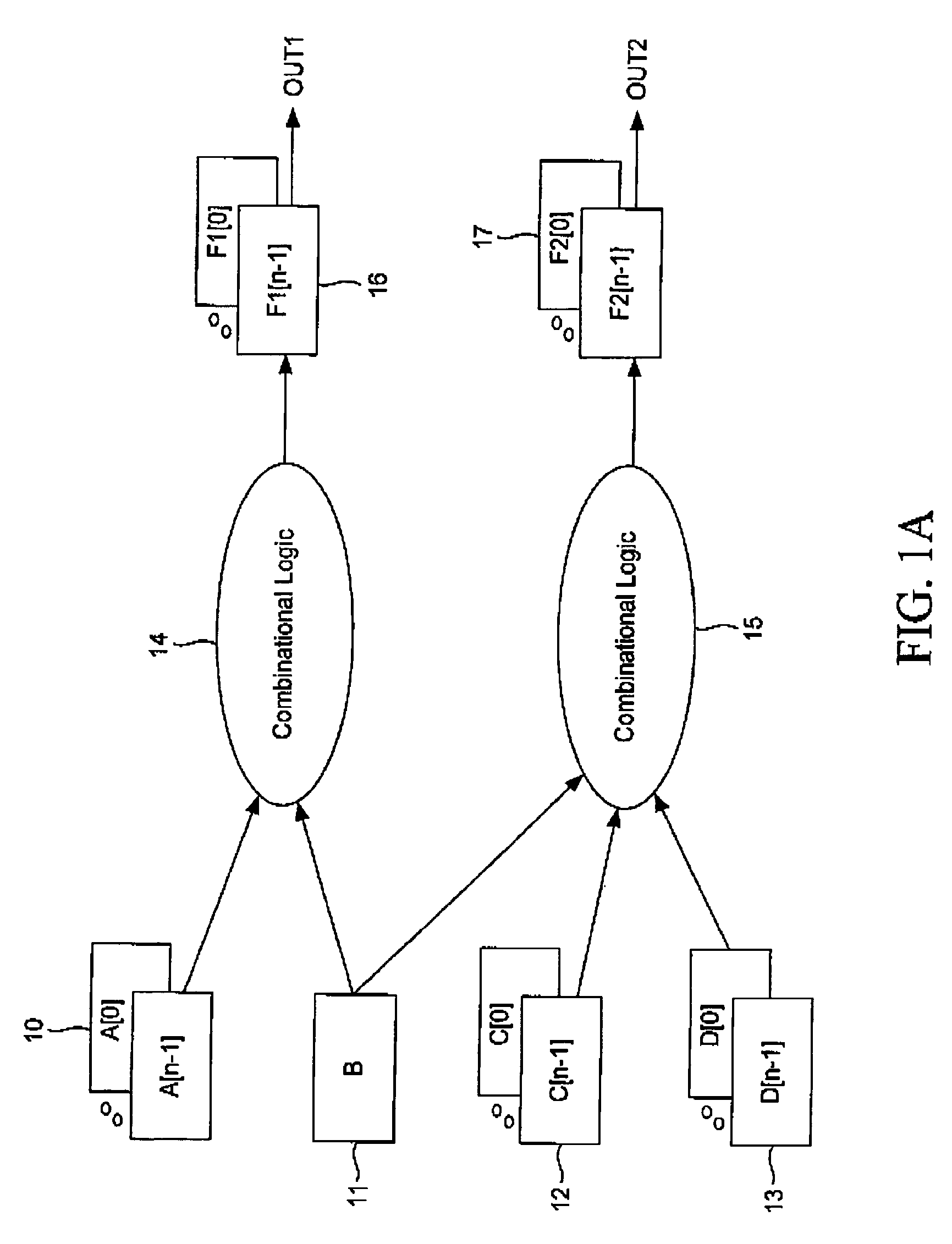

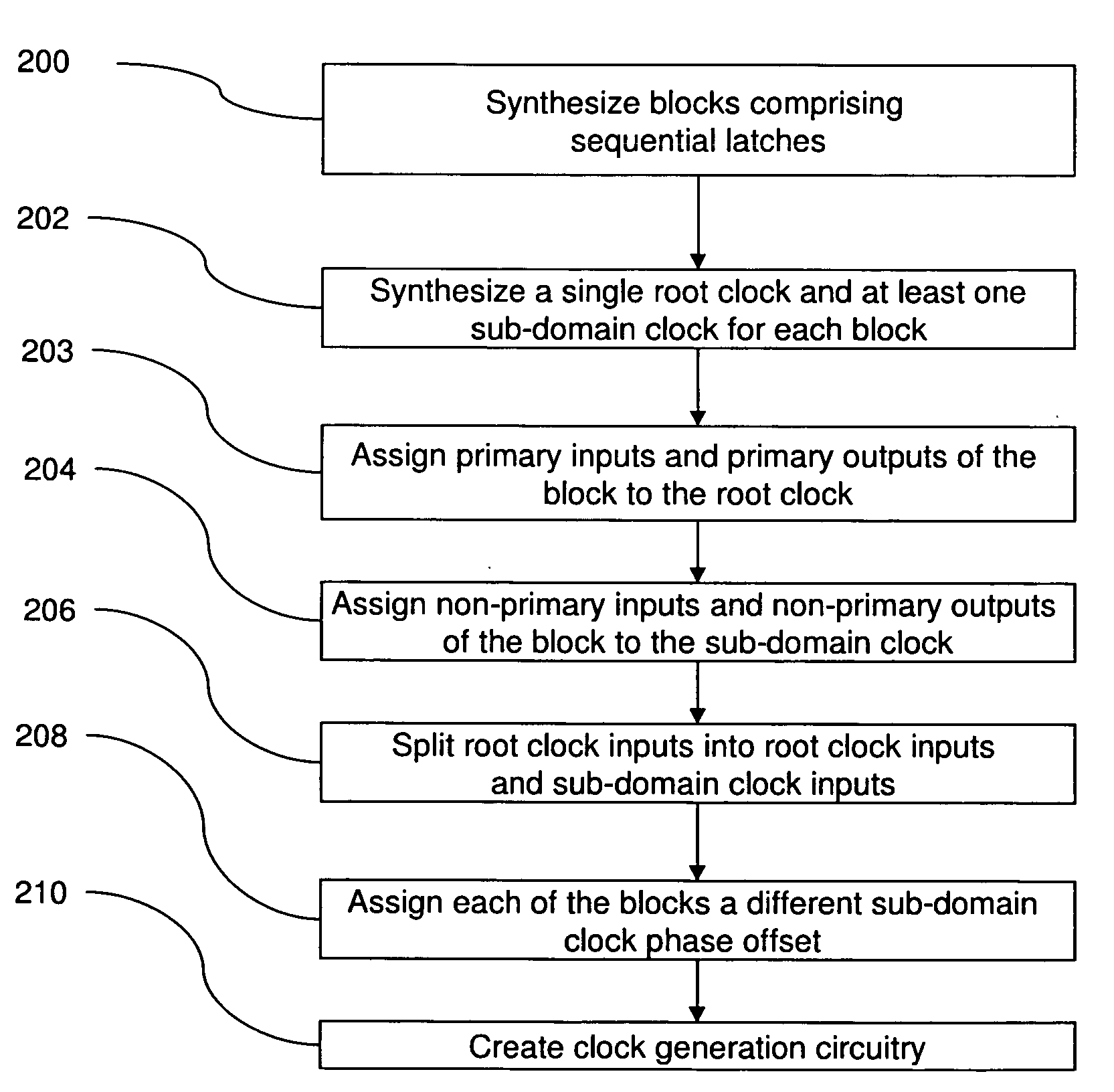

Transition Balancing For Noise Reduction/Di/Dt Reduction During Design, Synthesis, and Physical Design

InactiveUS20090106724A1Reduce noiseReduce noise valueCAD circuit designSpecial data processing applicationsPhase shiftedNoise reduction

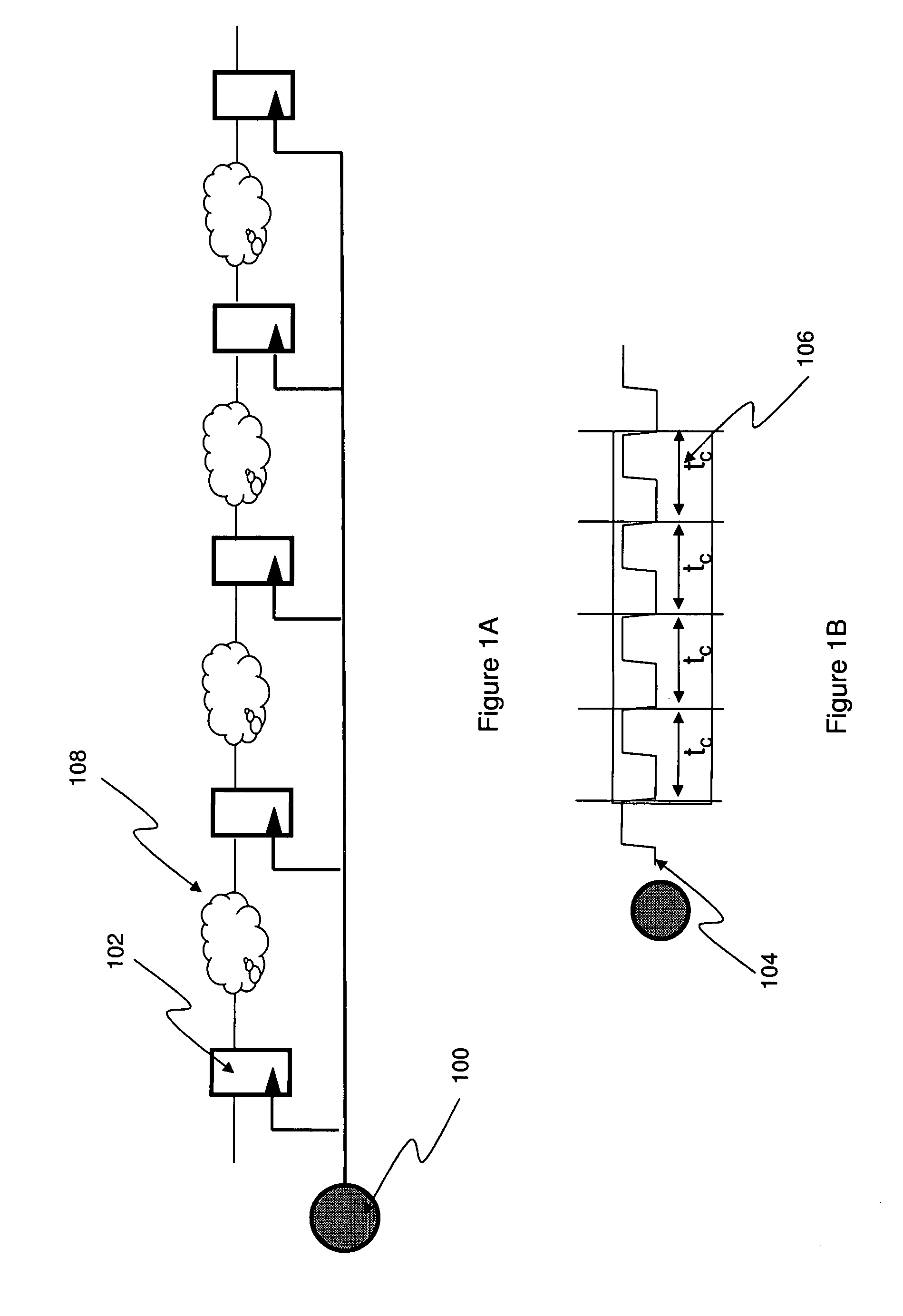

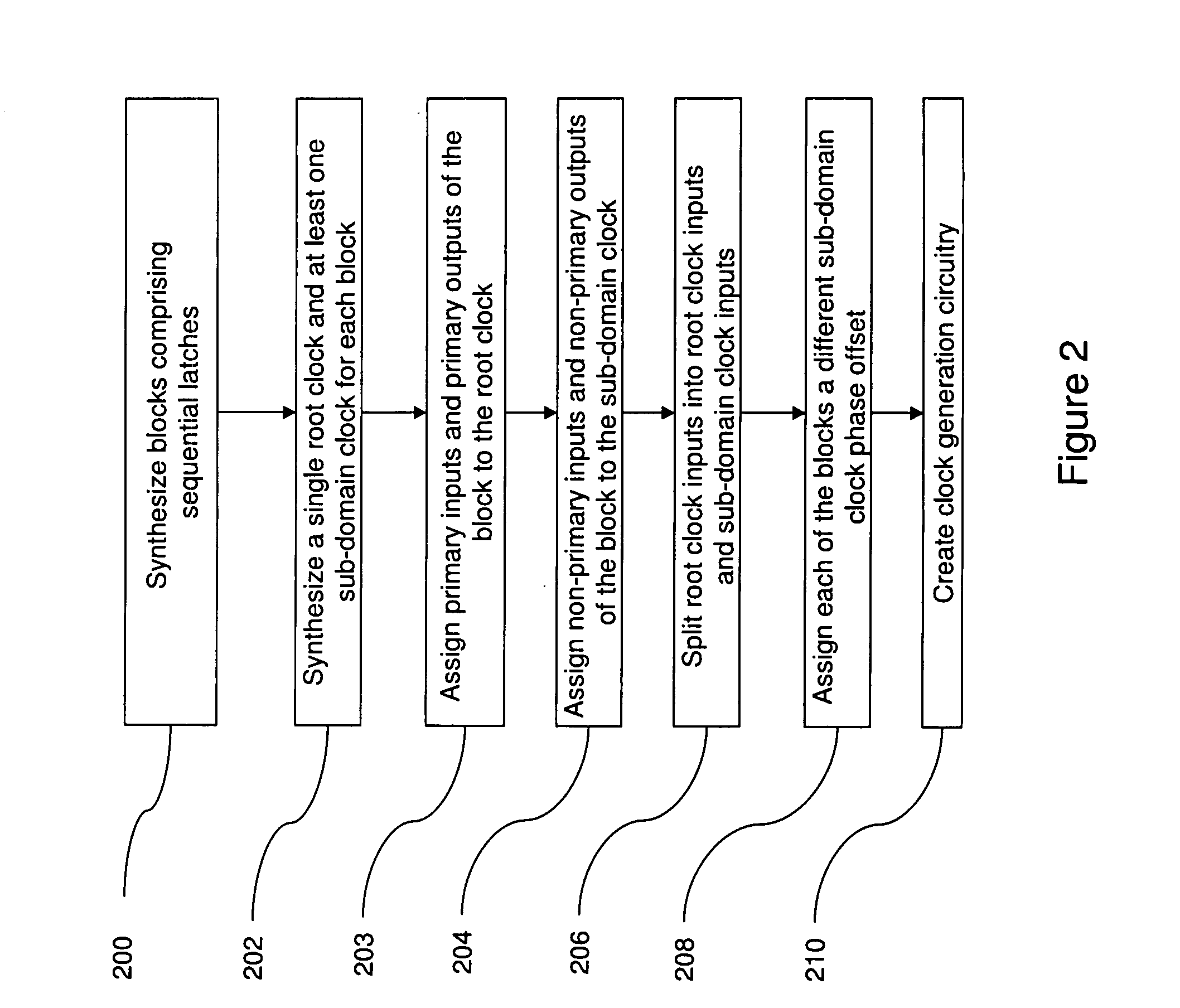

An embodiment of a design structure is shown for noise reduction comprising synthesizing blocks of sequential latches, e.g., a pipeline circuit architecture or clocking domain, which comprises combinational logic, synthesizing a root or a master clock and at least one phase-shifted sub-domain clock for each block, assigning primary inputs and primary outputs of the block to the root clock, assigning non-primary inputs and non-primary outputs of the block to the sub-domain clock, splitting root clock inputs into root clock inputs and phase-shifted sub-domain clock inputs, assigning each of the blocks a different phase-shifted sub-domain clock phase offset, creating a clock generation circuitry for the root clocks and the phase-shifted sub-domain clocks.

Owner:GLOBALFOUNDRIES INC

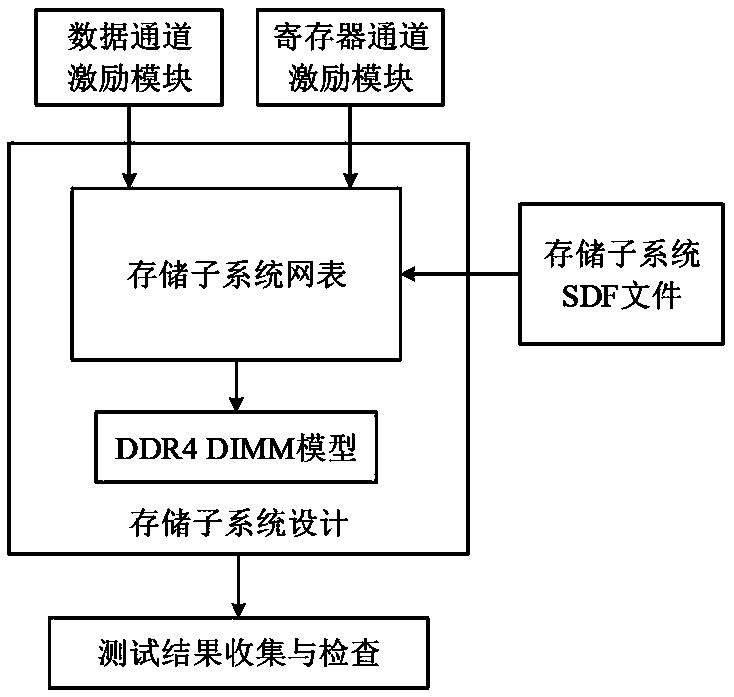

Method and system for accelerating storage component netlist simulation and medium

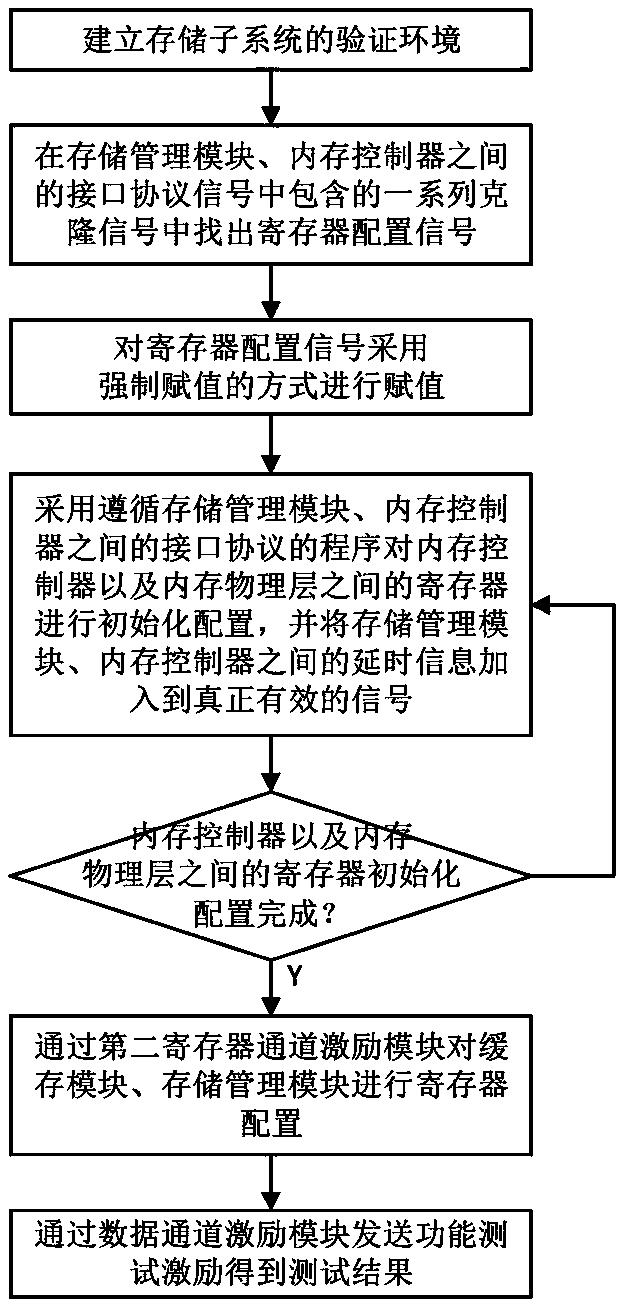

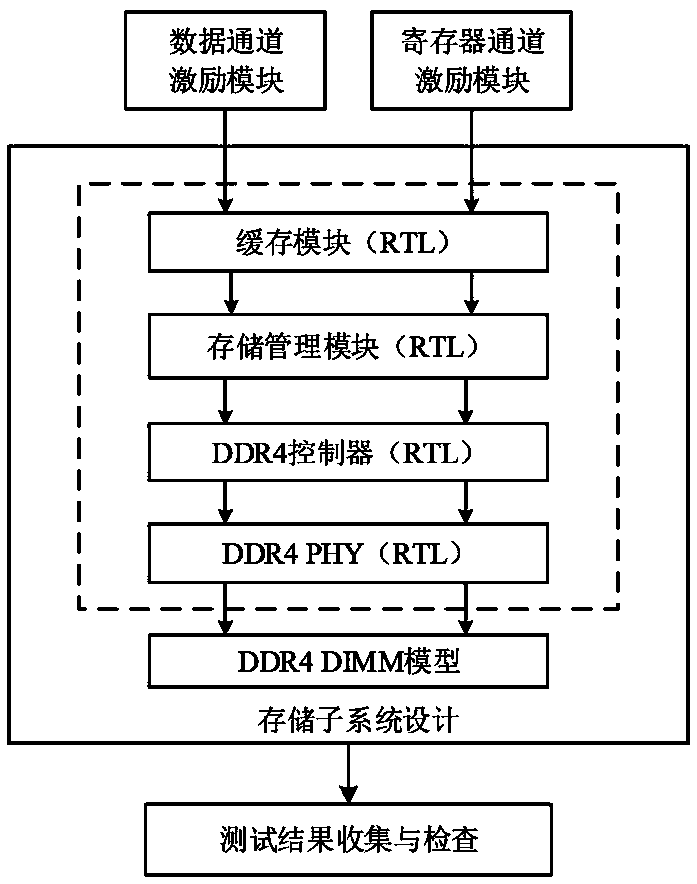

ActiveCN111427794AReduce development costsImprove efficiencySoftware testing/debuggingEnergy efficient computingRegister allocationComputer architecture

The invention discloses a method and system for accelerating storage component netlist simulation and a medium, and the method comprises the steps of enabling an original RTL design of a storage subsystem to be integrally replaced with a storage subsystem netlist in a verification environment of the subsystem; register configuration irrelevant to operation of the simulation test program in the memory controller and the memory physical interface is reduced; the clock frequency configured by registers in a memory controller and a memory physical interface is increased to the highest clock frequency tolerable by physical design, and the registers in the memory controller and the memory physical interface are independently configured in a forced assignment mode. The RTL verification environment of the original storage subsystem can be used, the original test case can be inherited, the original correctness checking mechanism is continuously used, and the development cost of the post-simulation verification environment is reduced. According to the method, the register configuration time can be shortened, a large amount of manpower and time cost is saved, the netlist simulation efficiencyis greatly improved, and the project period is shortened.

Owner:PHYTIUM TECH CO LTD

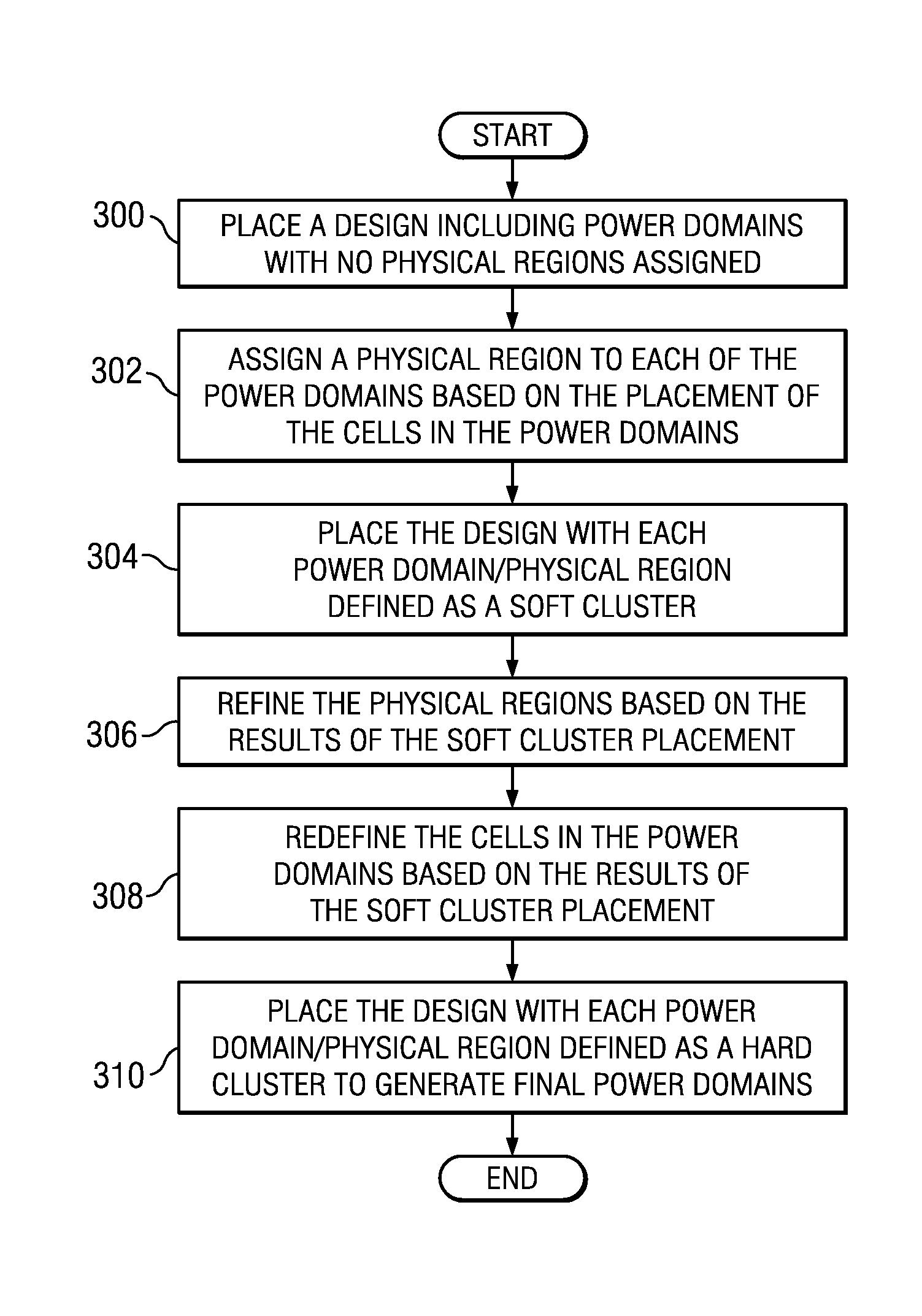

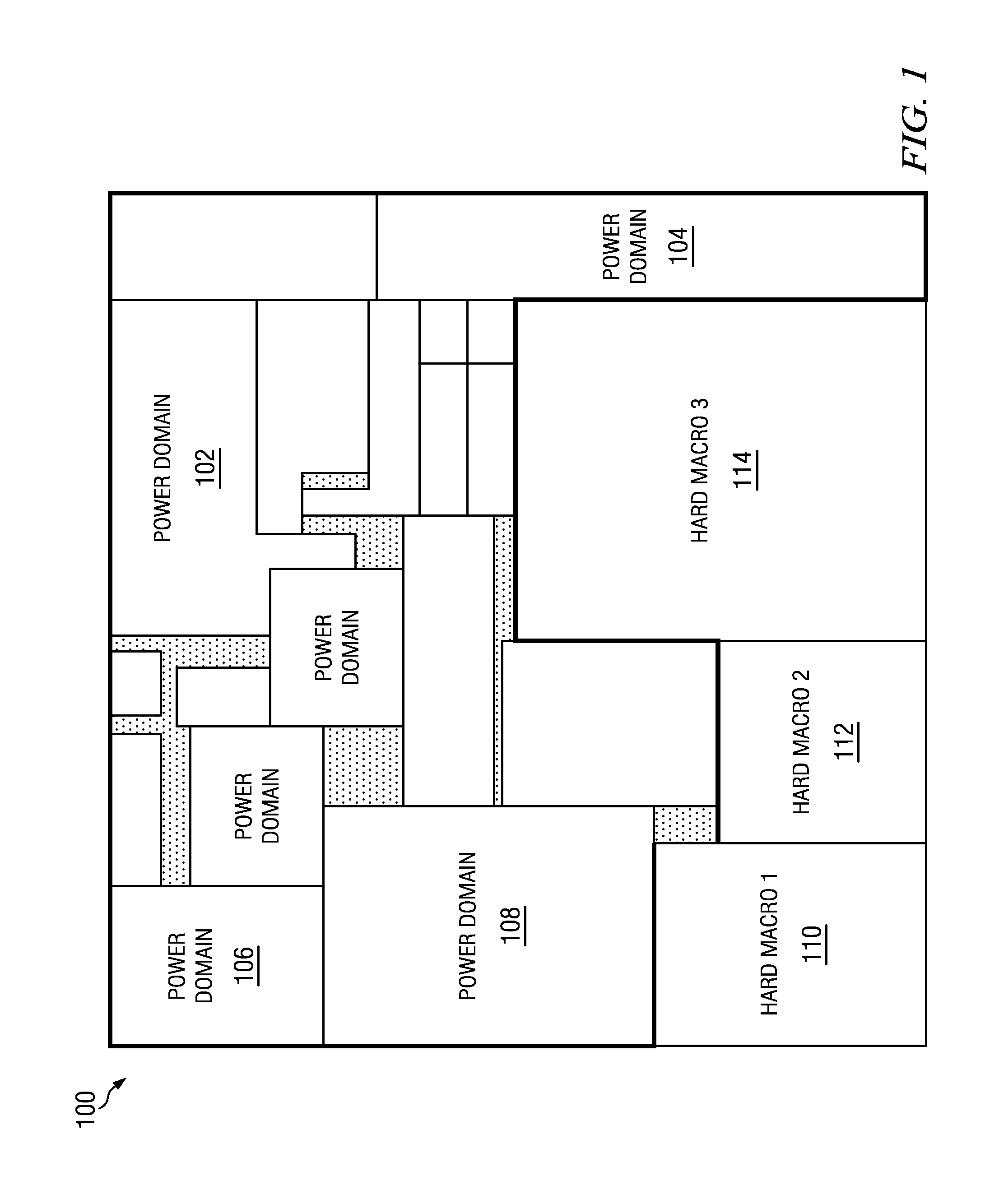

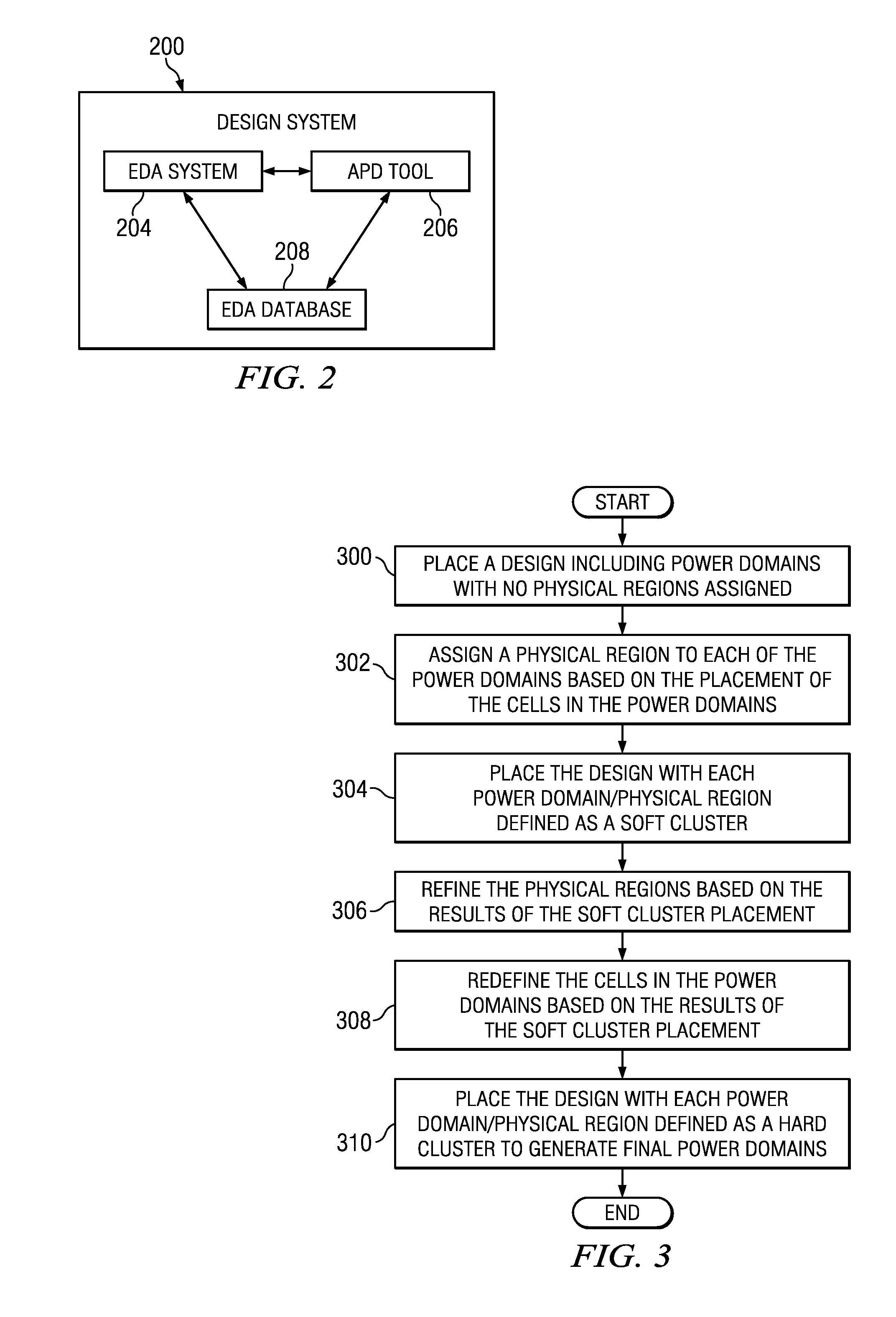

Method and system for adaptive physical design

A method is provided that includes performing a free placement of a system design comprising a plurality of power domains, wherein the power domains are not constrained to physical regions, assigning a physical region to each of the power domains based on the free placement of cells in the power domains, performing a soft cluster placement of the system design with each power domain and corresponding physical region defined as a soft cluster, refining at least one physical region based on the soft cluster placement, redefining cells in at least one power domain based on the soft cluster placement of the cells and the corresponding physical region, and performing a hard cluster placement of the system design with each power domain and corresponding physical region defined as a hard cluster to generate final power domains.

Owner:TEXAS INSTR INC

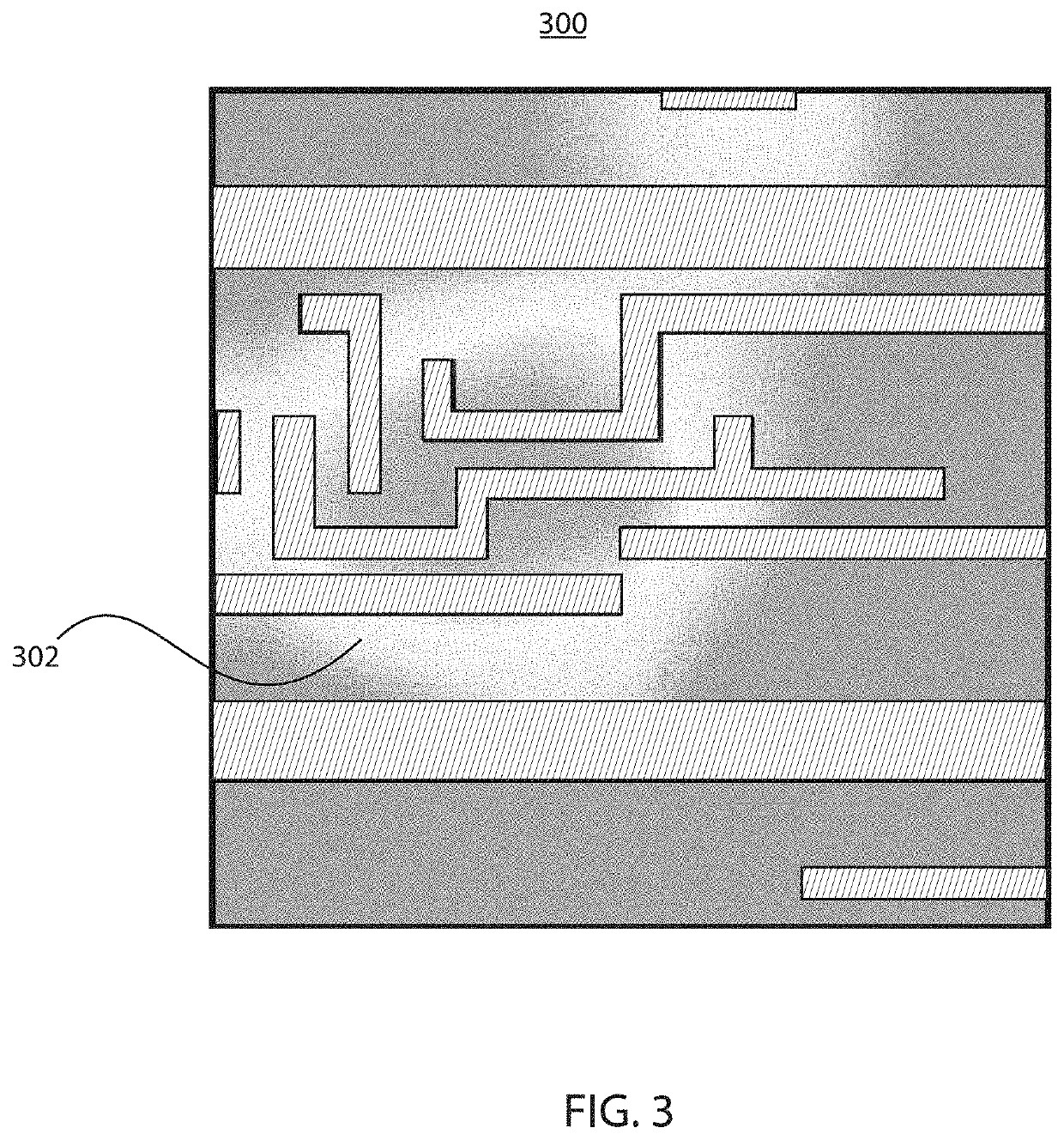

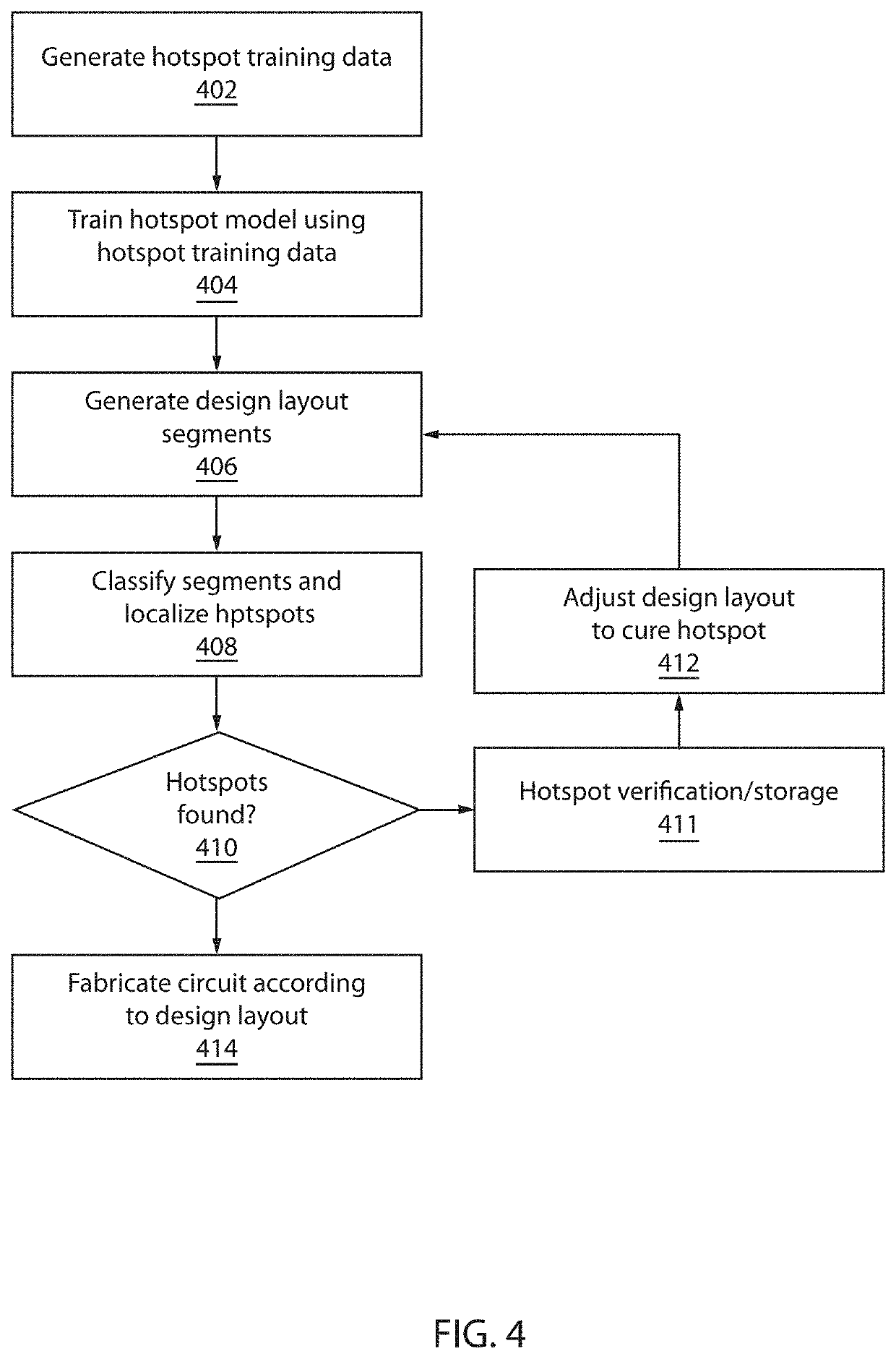

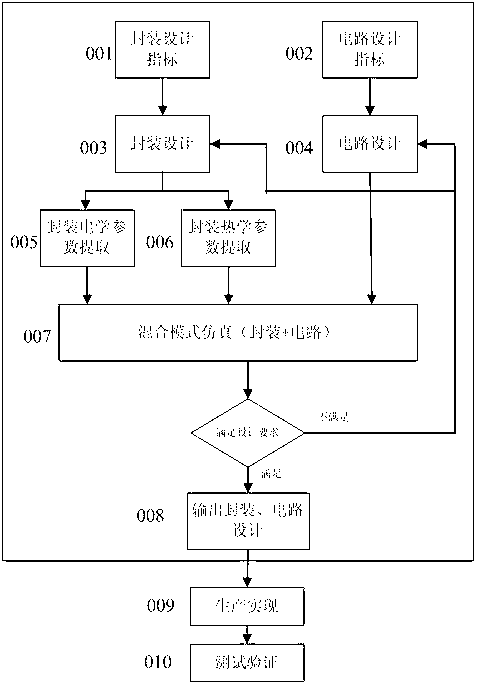

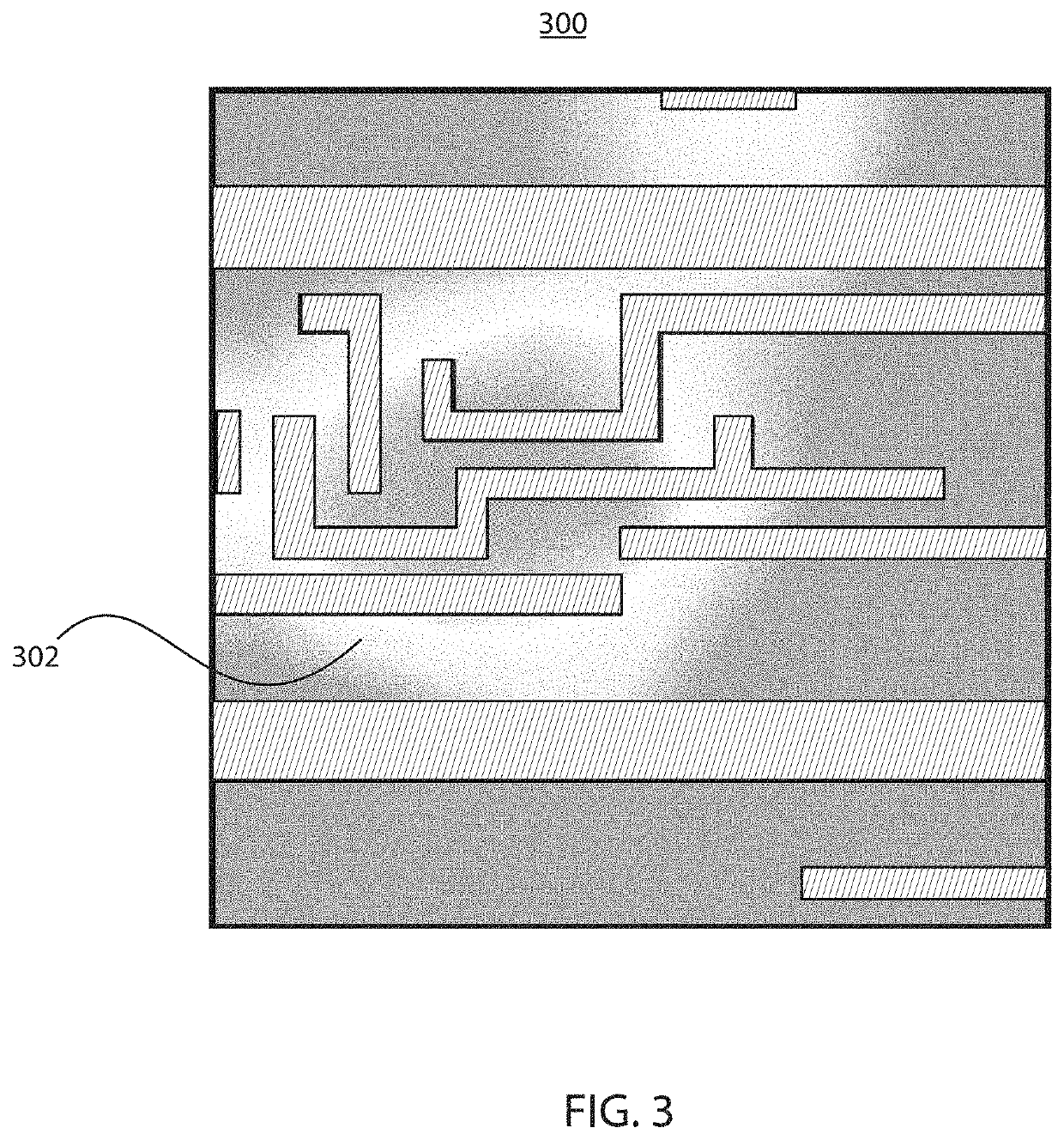

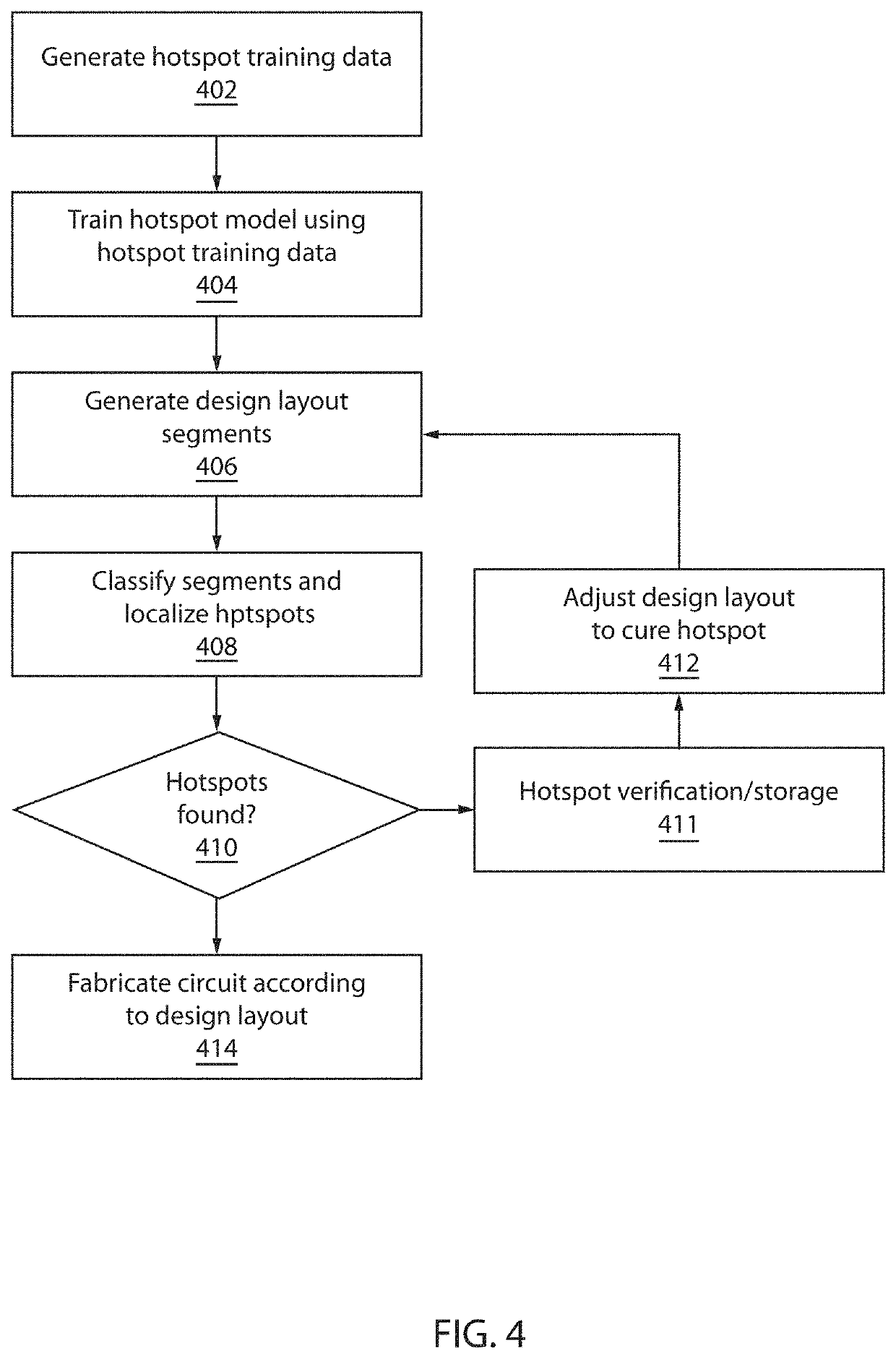

Classification and localization of hotspots in integrated physical design layouts

ActiveUS20200004918A1Raise the possibilityDesign optimisation/simulationPhotomechanical exposure apparatusLayoutHemt circuits

Methods and systems for fabricating an integrated circuit include training a machine learning model using a training set that includes known physical design layout patterns that are classified according to whether the patterns include a hotspot. It is determined whether an input physical design layout pattern includes a hotspot using the machine learning model. A hotspot localization is generated for the input physical design layout patterns. The input physical design pattern is adjusted to cure the hotspot. A circuit is fabricated in accordance with the adjusted input physical design layout pattern.

Owner:IBM CORP

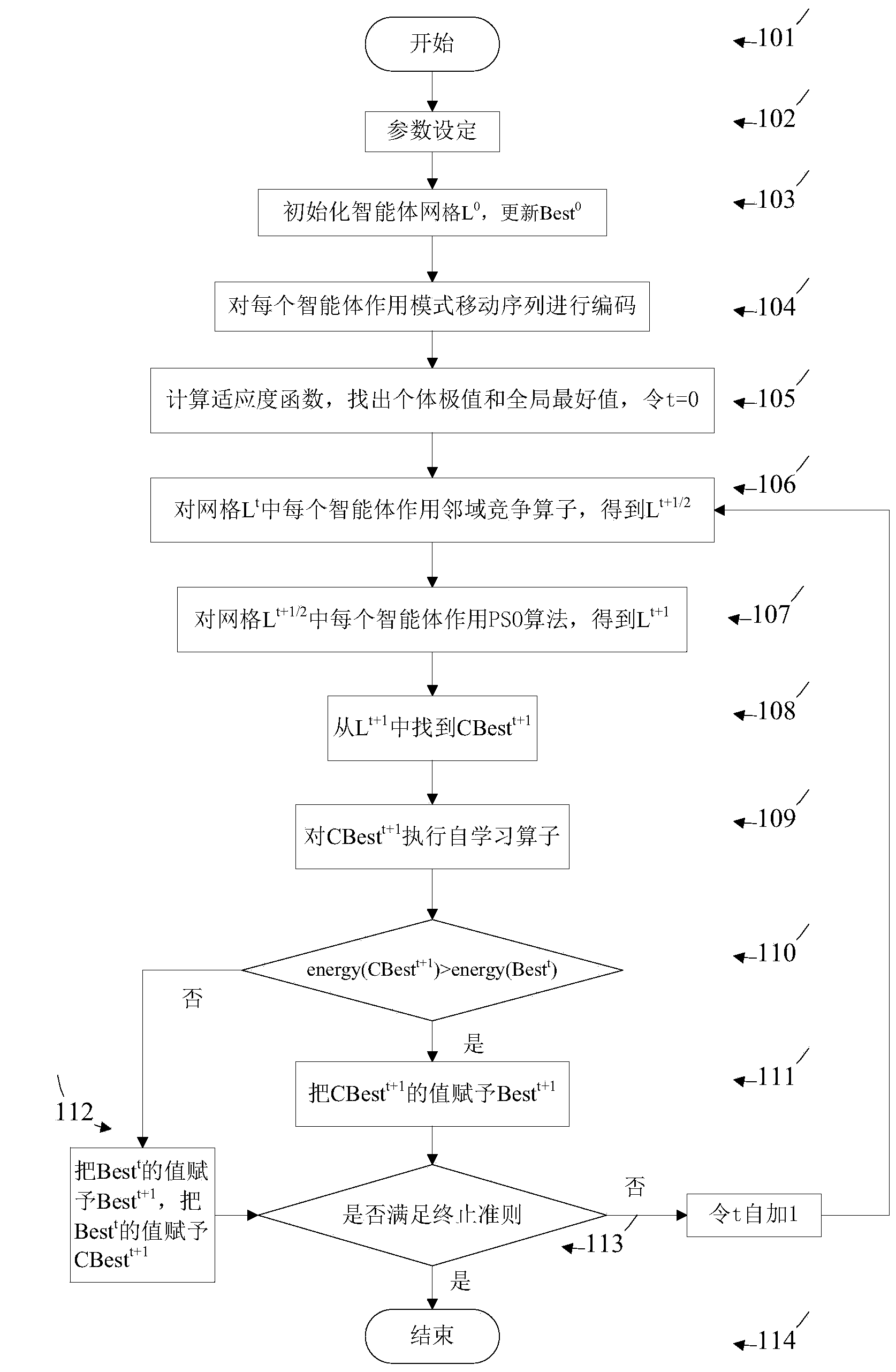

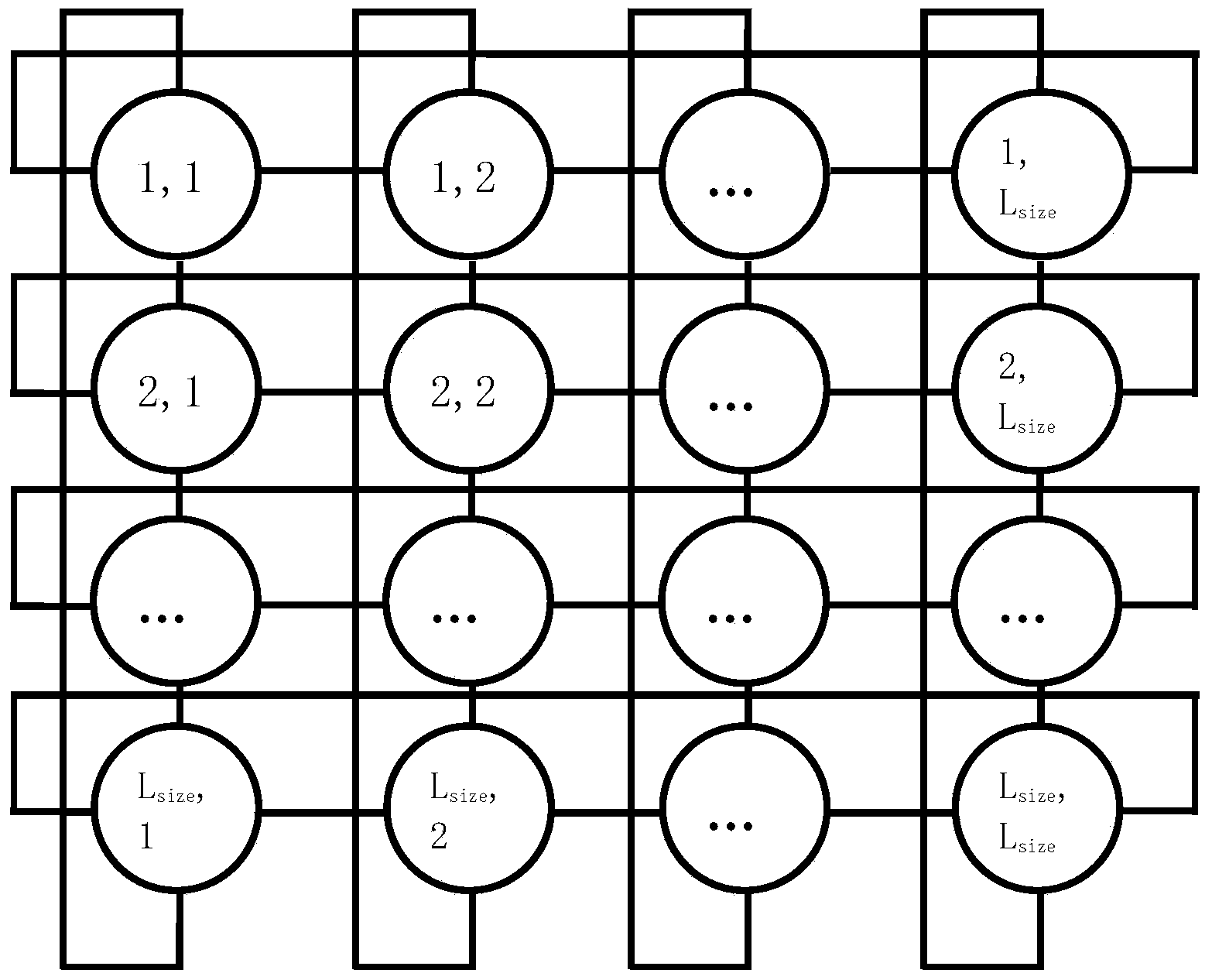

Integrated circuit floorplanning method based on moving block sequence and multi-agent particle swarm

ActiveCN103714211AImprove stabilitySmall scaleSpecial data processing applicationsPattern sequenceMulti-agent system

The invention discloses an integrated circuit floorplanning method based on a moving block sequence and a multi-agent particle swarm, and belongs to the technical field of physical design floorplanning. The moving block sequence is used as an encoding method, a multi-agent system and a particle swarm algorithm are combined, and the integrated circuit floorplanning method is used for solving the integrated circuit floorplanning problem. The integrated circuit floorplanning method is characterized in that firstly, each agent in an agent grid is initialized according to an adopted random generation method, then the moving block sequence is designed to encode each agent, and a neighbourhood competition operator, the particle swarm algorithm and a self-learning operator are designed at last to optimize the agents. Verification results show that the integrated circuit floorplanning method has advantages on one important aspect of methods and effectiveness for evaluating and solving the integrated circuit floorplanning problem, namely, the minimum rectangular coverage area, and the method effectively solves the integrated circuit floorplanning problem and can be expanded to solve multi-objective integrated circuit floorplanning problems.

Owner:XIDIAN UNIV

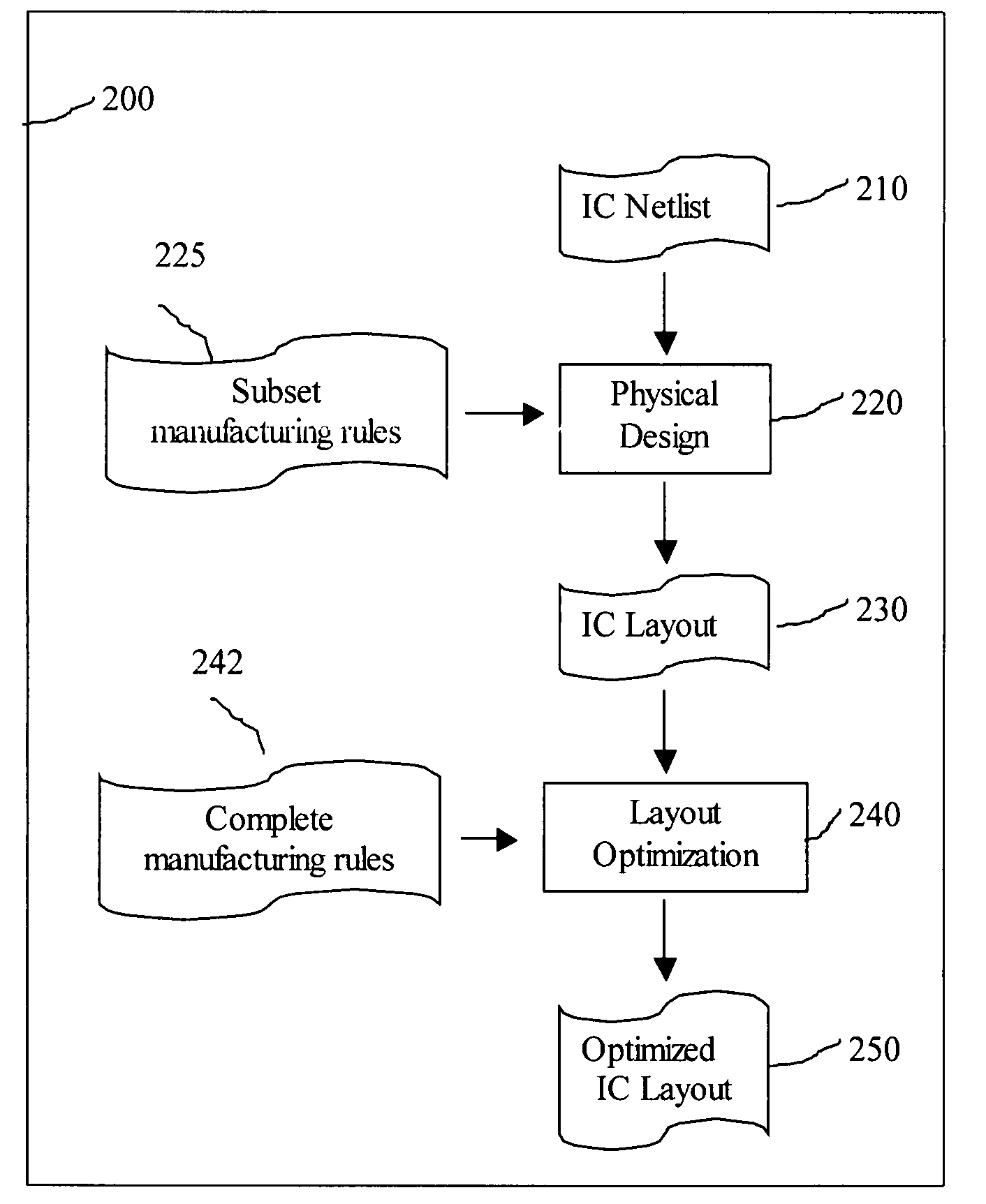

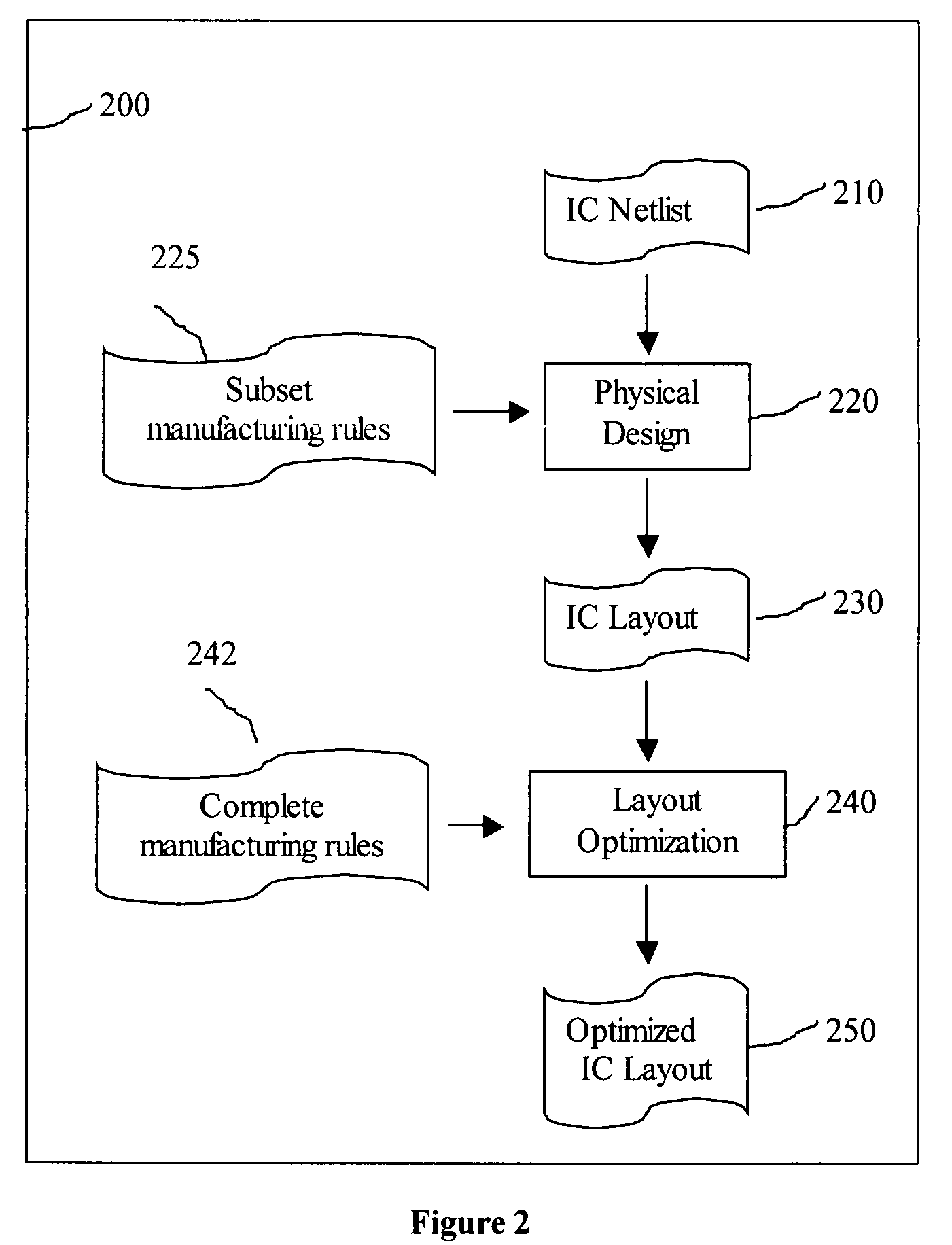

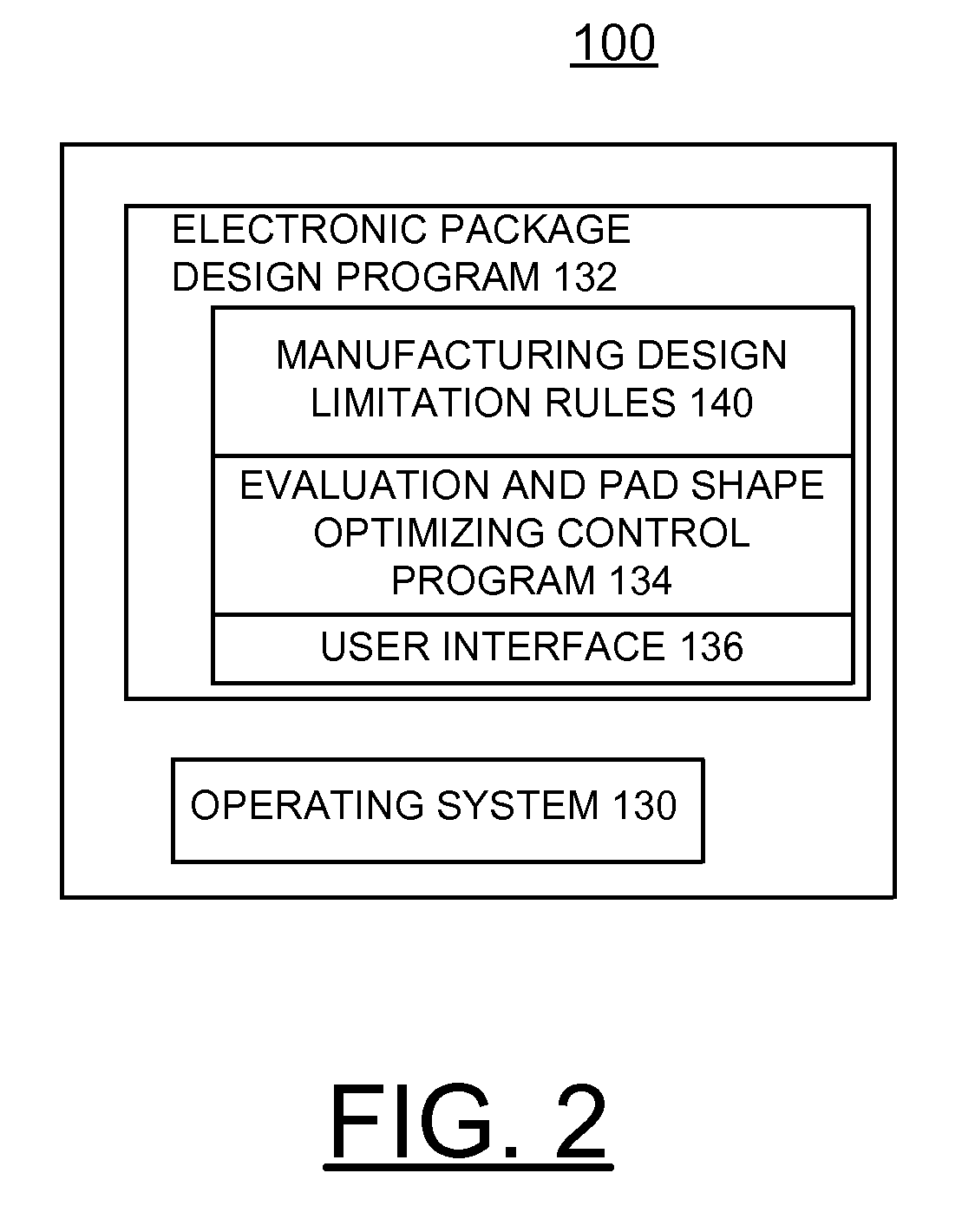

System and method to generate an IC layout using simplified manufacturing rule

InactiveUS7761824B2Increase probabilityReduce areaComputer aided designSoftware simulation/interpretation/emulationCompleteManufacturing line

Some embodiments of the invention provide a system and method where a physical design (“PD”) process can use simplified manufacturing rules to generate an integrated circuit (“IC”) layout. A layout optimization process transforms the PD generated layout to become more manufacturing rule compliant layout using a full set of manufacturing rules. The invention increases the probability of the PD process successfully generates an IC layout since the PD is not burdened with having to consider the full complexity of the manufacturing rules.

Owner:CHEW MARKO P +1

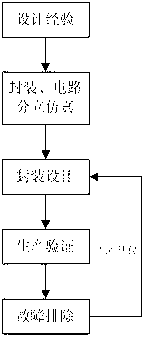

Method and flow for collaborative design of electric and thermal properties of integrated circuit package

The invention discloses a method and a flow for the collaborative design of the electric and thermal properties of an integrated circuit package. The method and the flow are characterized in that the influences of thermal and electric properties to the performance of an integrated circuit are taken into full consideration in a design stage, meanwhile, the collaborative optimization is performed together with a core integrated circuit design, and the system performance can be optimized from two aspects including package design and circuit design according to factors such as cost and implementation complexity, thereby improving the flexibility in package design. The method and the flow mainly comprise the steps of: physical design of the package, extraction of the electric parameters, extraction of the thermal parameters, design of the integrated circuit, consideration of mixed-mode simulation of a package and the integrated circuit, and output of integrated circuit design and package physical design in accordance with design requirements.

Owner:SHANGHAI RES INST OF MICROELECTRONICS SHRIME PEKING UNIV

Classification and localization of hotspots in integrated physical design layouts

ActiveUS10621302B2Design optimisation/simulationPhotomechanical exposure apparatusLayoutHemt circuits

Methods and systems for fabricating an integrated circuit include training a machine learning model using a training set that includes known physical design layout patterns that are classified according to whether the patterns include a hotspot. It is determined whether an input physical design layout pattern includes a hotspot using the machine learning model. A hotspot localization is generated for the input physical design layout patterns. The input physical design pattern is adjusted to cure the hotspot. A circuit is fabricated in accordance with the adjusted input physical design layout pattern.

Owner:INT BUSINESS MASCH CORP

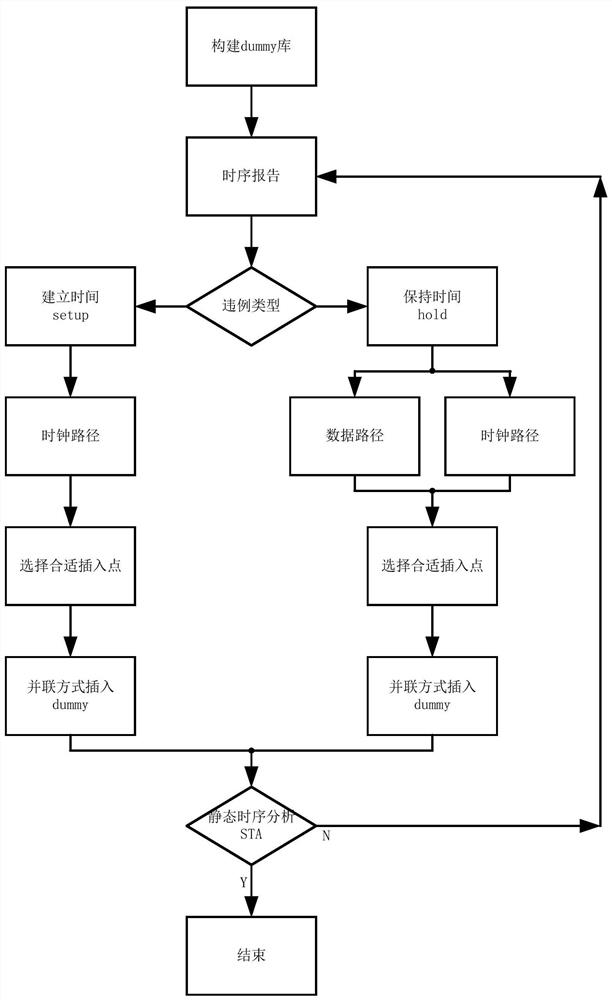

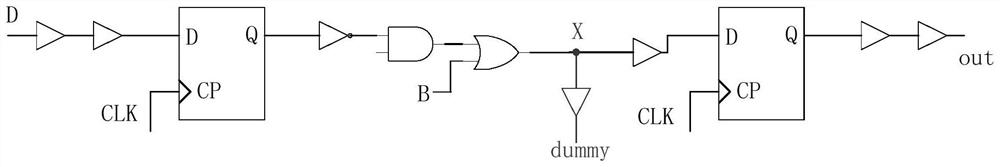

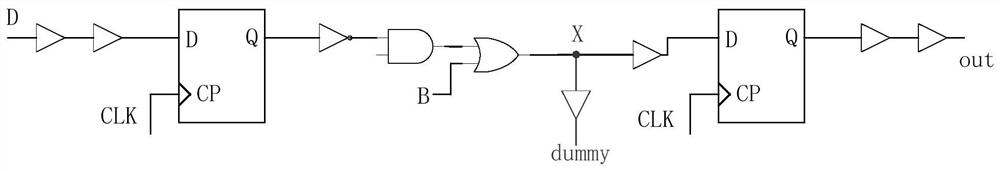

Time sequence optimization method based on dummy

ActiveCN113177380AThe principle is simpleLow costInternal combustion piston enginesComputer aided designStatic timing analysisRepair time

The invention discloses a time sequence optimization method based on dummy. The time sequence optimization method comprises the following steps: S1, constructing a dummy library; S2, analyzing a physical design time sequence, and preparing data for formulating a proper repair strategy; S3, processing the data in the step S2, classifying time sequence violations, and dividing the time sequence violations into data paths and clock paths according to different repair paths; wherein the data path can be used for repairing hold time violation, and the clock path can be used for repairing setup time and hold time violation; S4, repairing the data path by inserting the dummy; S5, repairing the clock path by inserting the dummy; and S6, performing static time sequence STA analysis again, and completing time sequence violation repairing. The method has the advantages of being simple in principle, low in implementation cost, capable of rapidly and accurately repairing time sequence violation and the like.

Owner:PHYTIUM TECH CO LTD

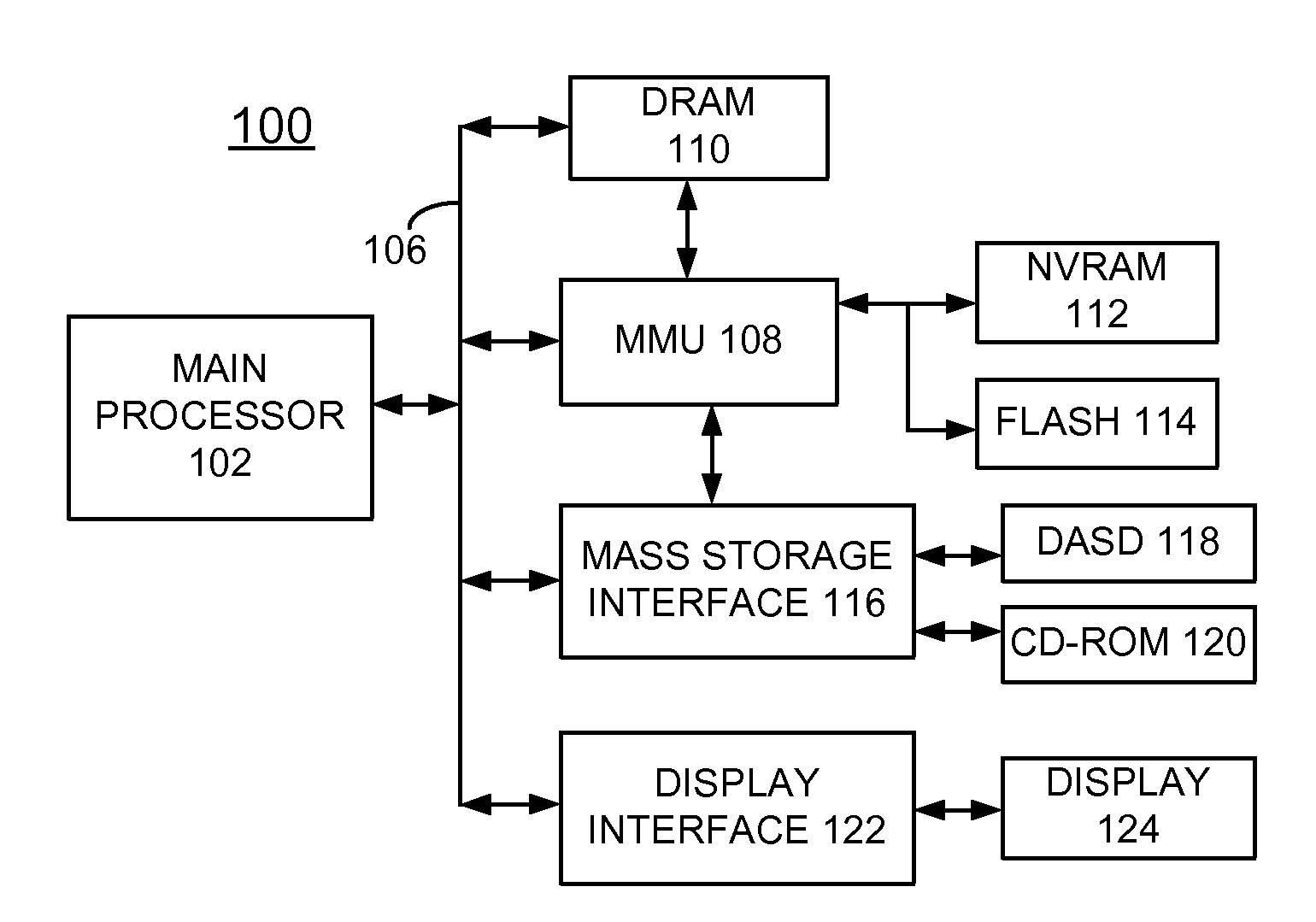

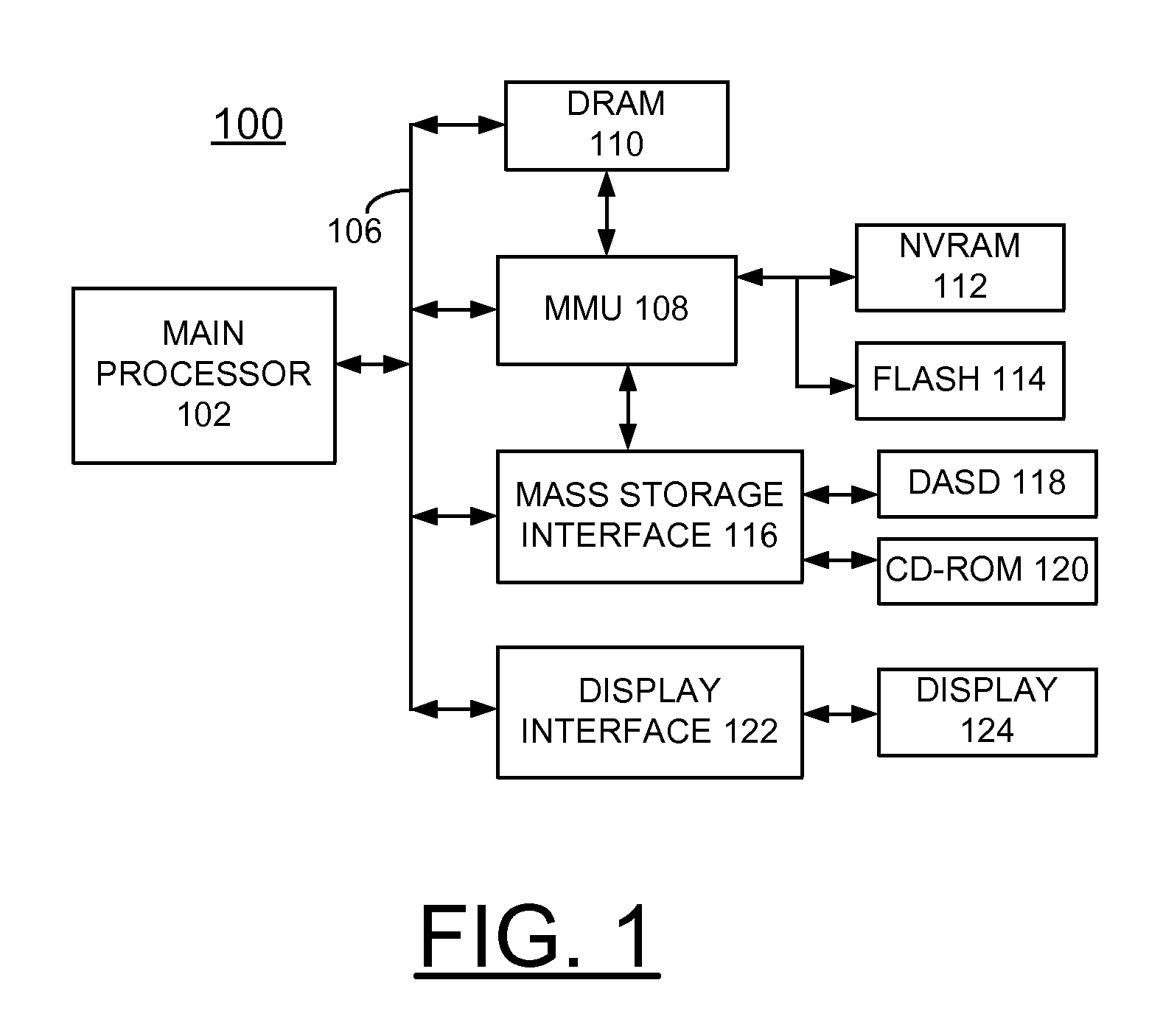

Implementing enhanced wiring capability for electronic laminate packages

InactiveUS20090138832A1Improve rendering capabilitiesNegative effectSemiconductor/solid-state device detailsSolid-state devicesPhysical designElectronic packages

Structures and a computer program product are provided for implementing enhanced wiring capability for electronic laminate packages. Electronic package physical design data are received. Instances of line width and space limit violations in the electronic package physical design data are identified. The identified instances of line width and space limit violations are evaluated using predefined qualified options and tolerance limitations and the electronic package physical design data are modified to optimize shapes to replace the instances of line width and space limit violations.

Owner:GLOBALFOUNDRIES INC

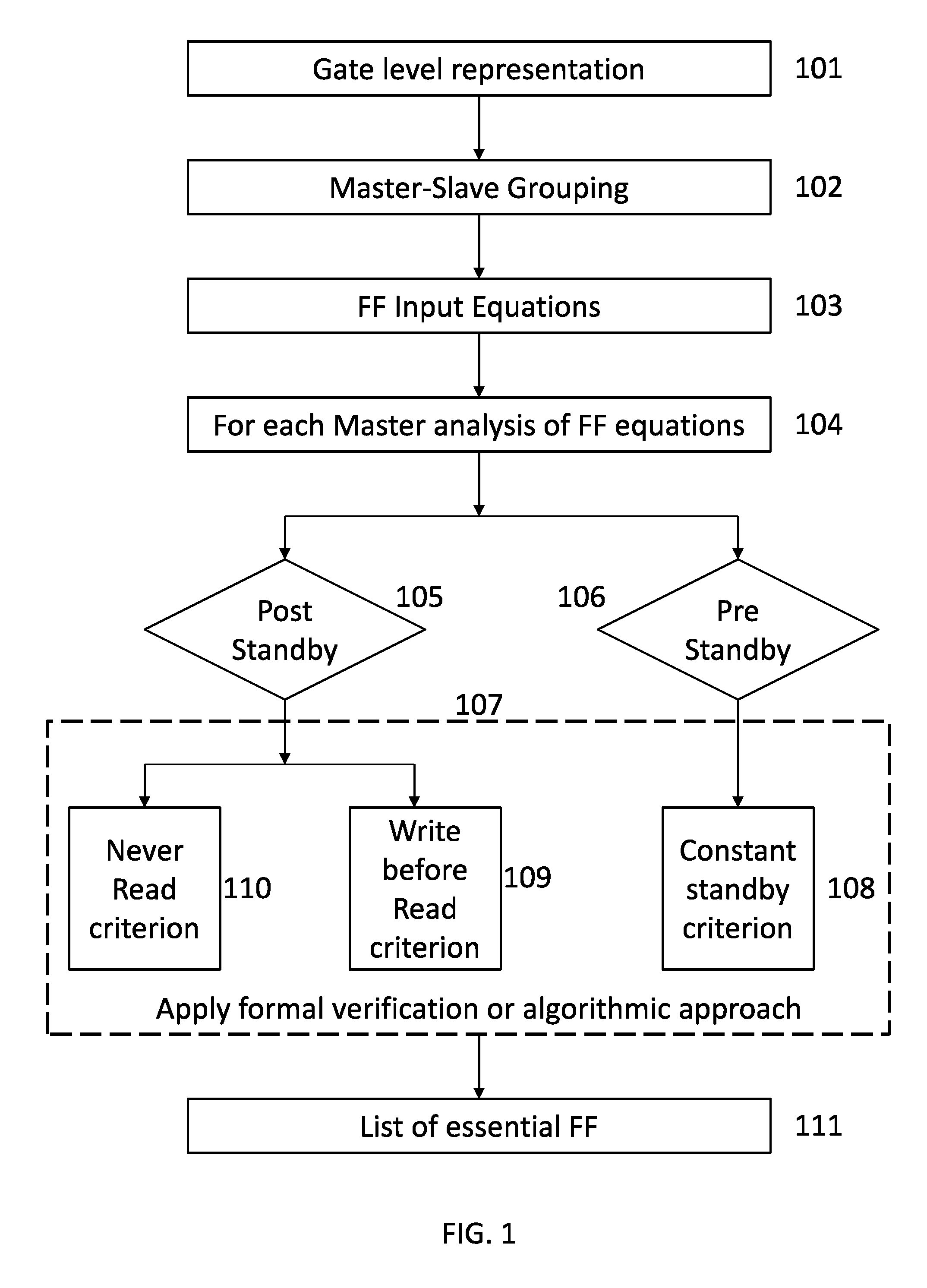

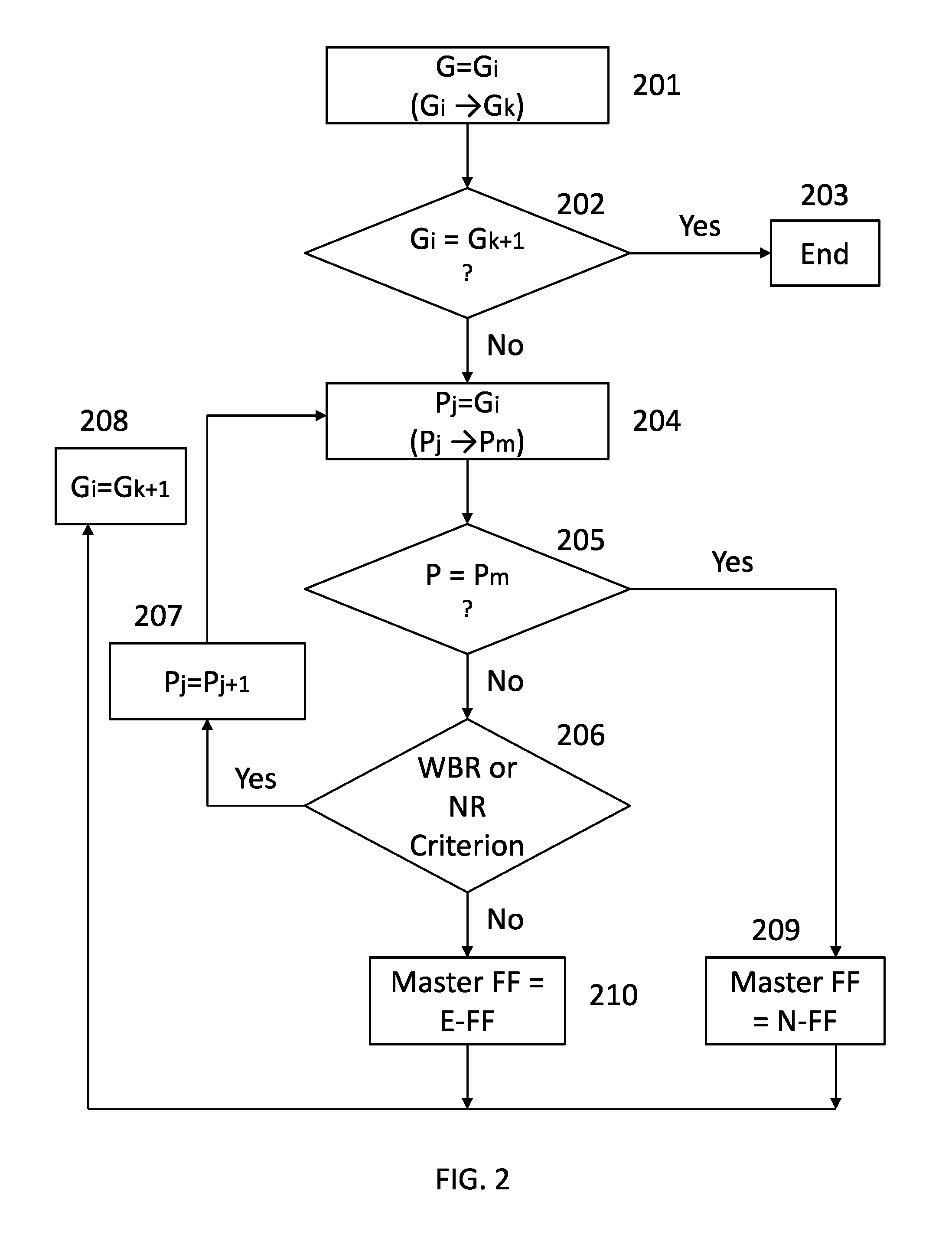

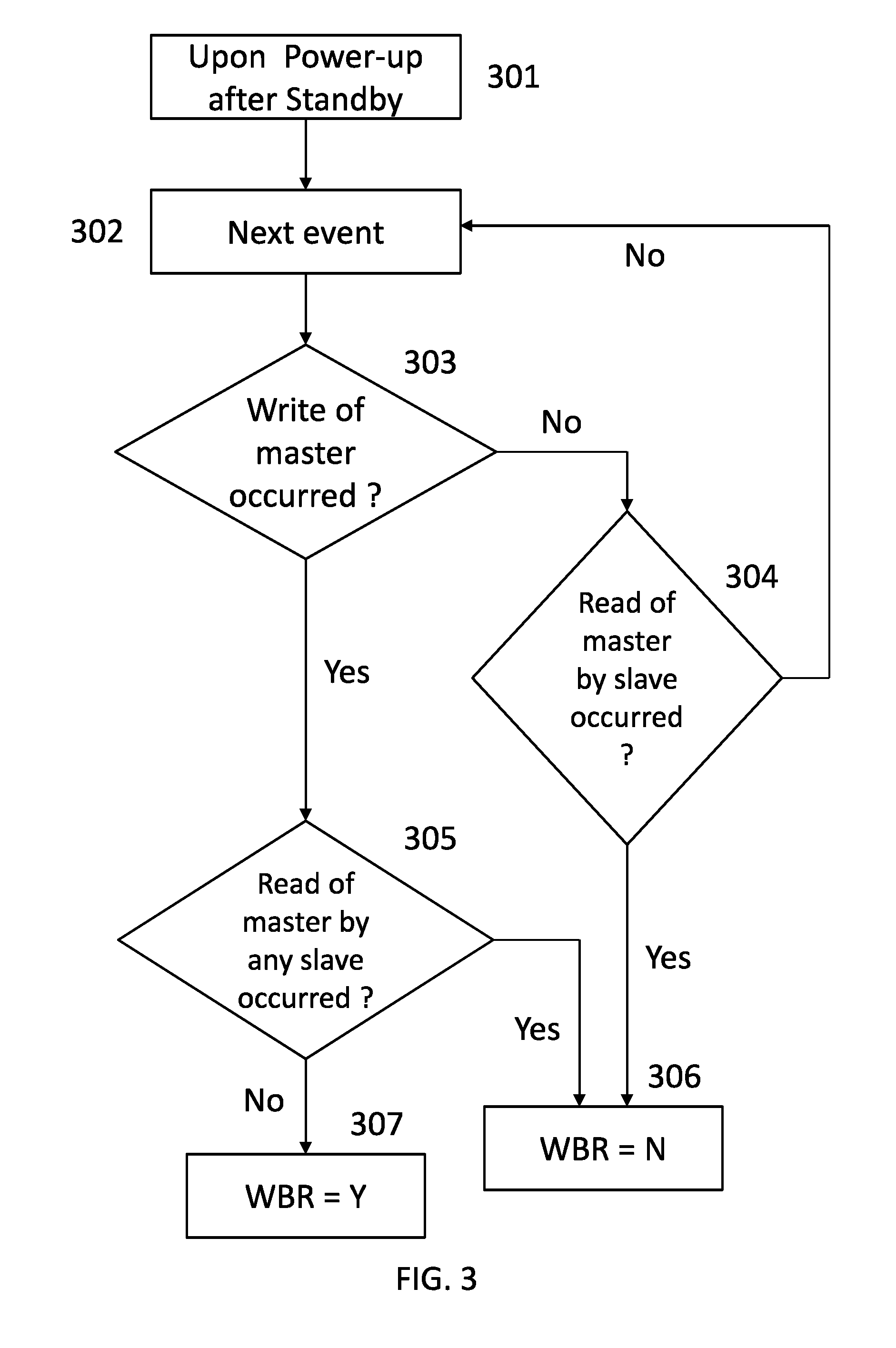

Method for finding non-essential flip flops in a VLSI design that do not require retention in standby mode

ActiveUS20150339435A1Reduce complexityMeet cutting requirementsCAD circuit designSoftware simulation/interpretation/emulationComputer architectureElectrical battery

The invention relates to a method for reducing the number of flip-flops in a VLSI design that require data retention, thereby eliminating the respective backup cells for those flip flops, the method comprises the steps of: (a) defining one or more criteria for non-essentiality of backup cells! (b) during the physical design stage, analyzing the VLSI design based on said one or more criteria for non-essentiality, and finding those flip-flops that meet these criteria, wherein said analysis is performed at the gate level, independent from any higher level representation of the design; and (c) eliminating from the VLSI design those backup cells for all non-essential flip-flops that meet one or more of said criteria for non-essentiality, thereby leaving in the design only those backup cells for those flip-flops that do not meet any of said criteria.

Owner:B G NEGEV TECH & APPL LTD

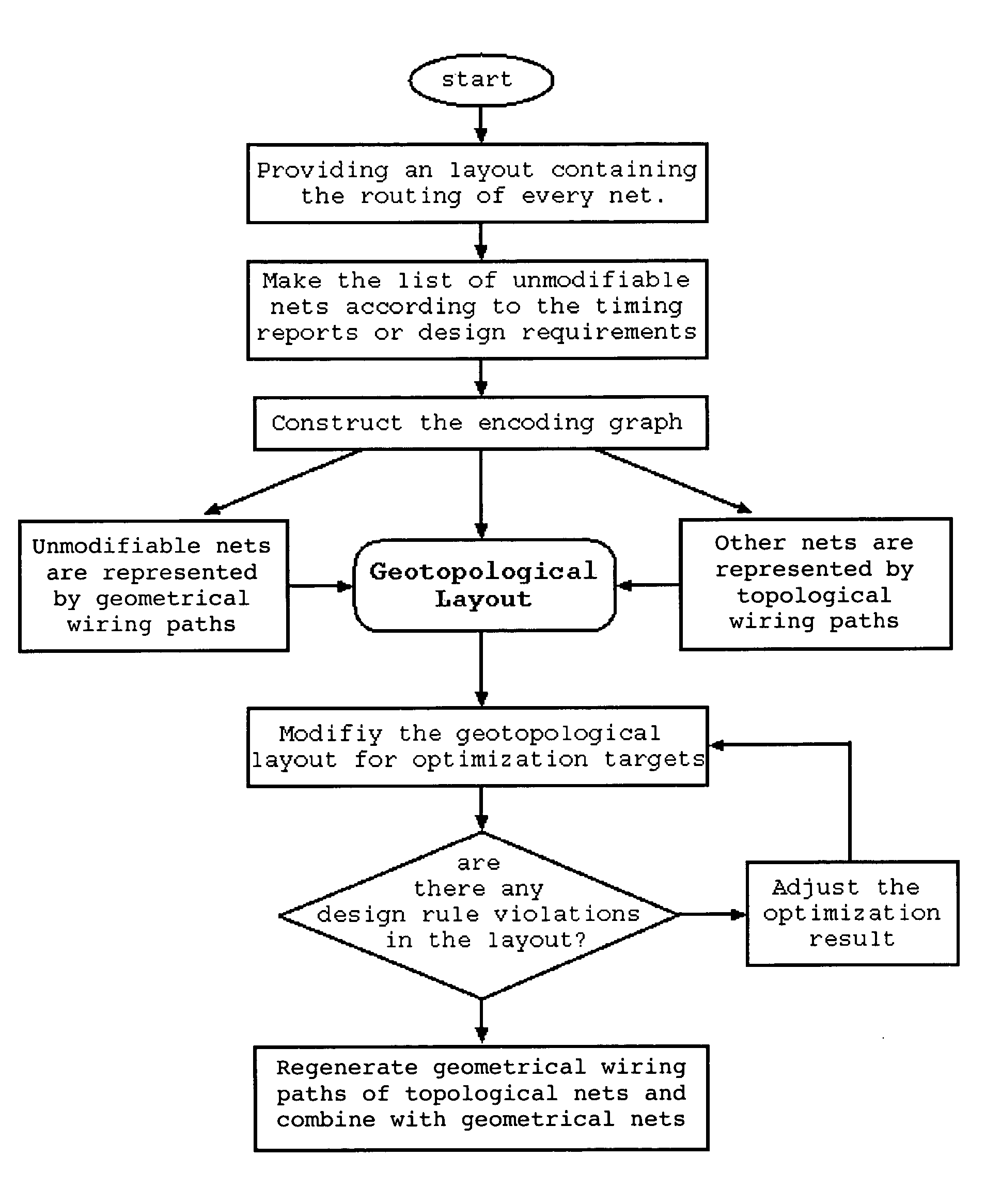

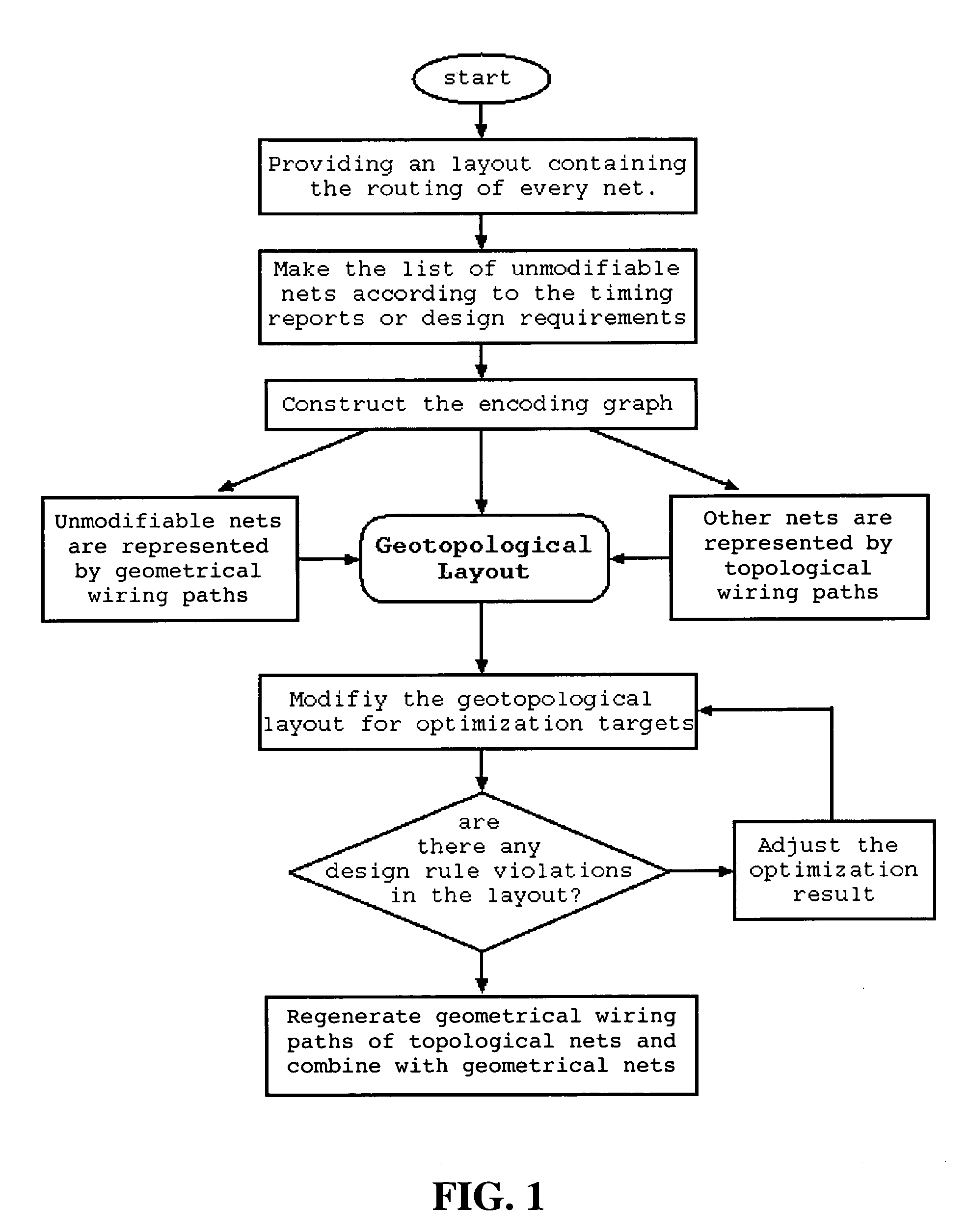

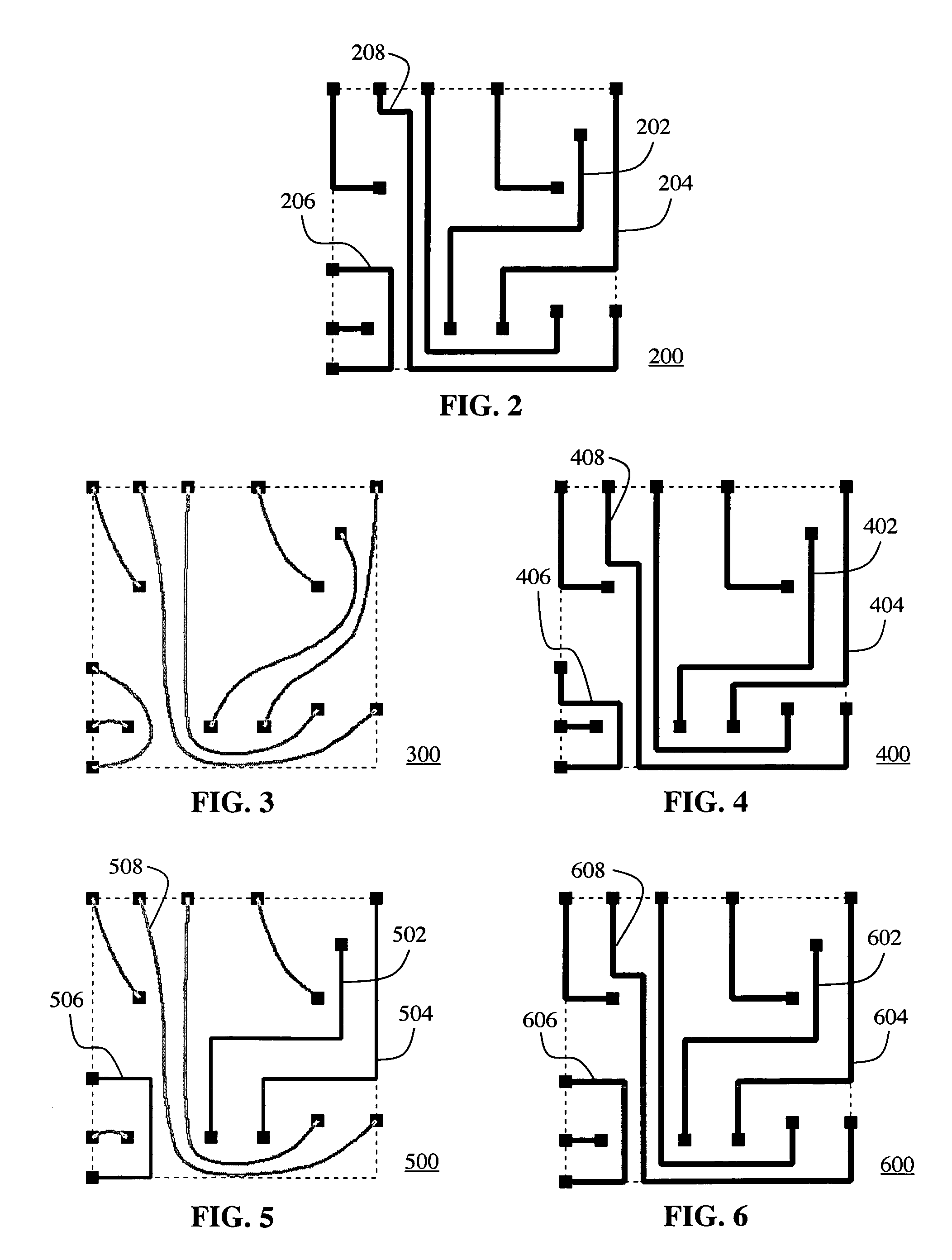

Routed layout optimization with geotopological layout encoding for integrated circuit designs

InactiveUS7131095B2Easy to modifyComputer aided designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit design

Owner:NANNOR TECH

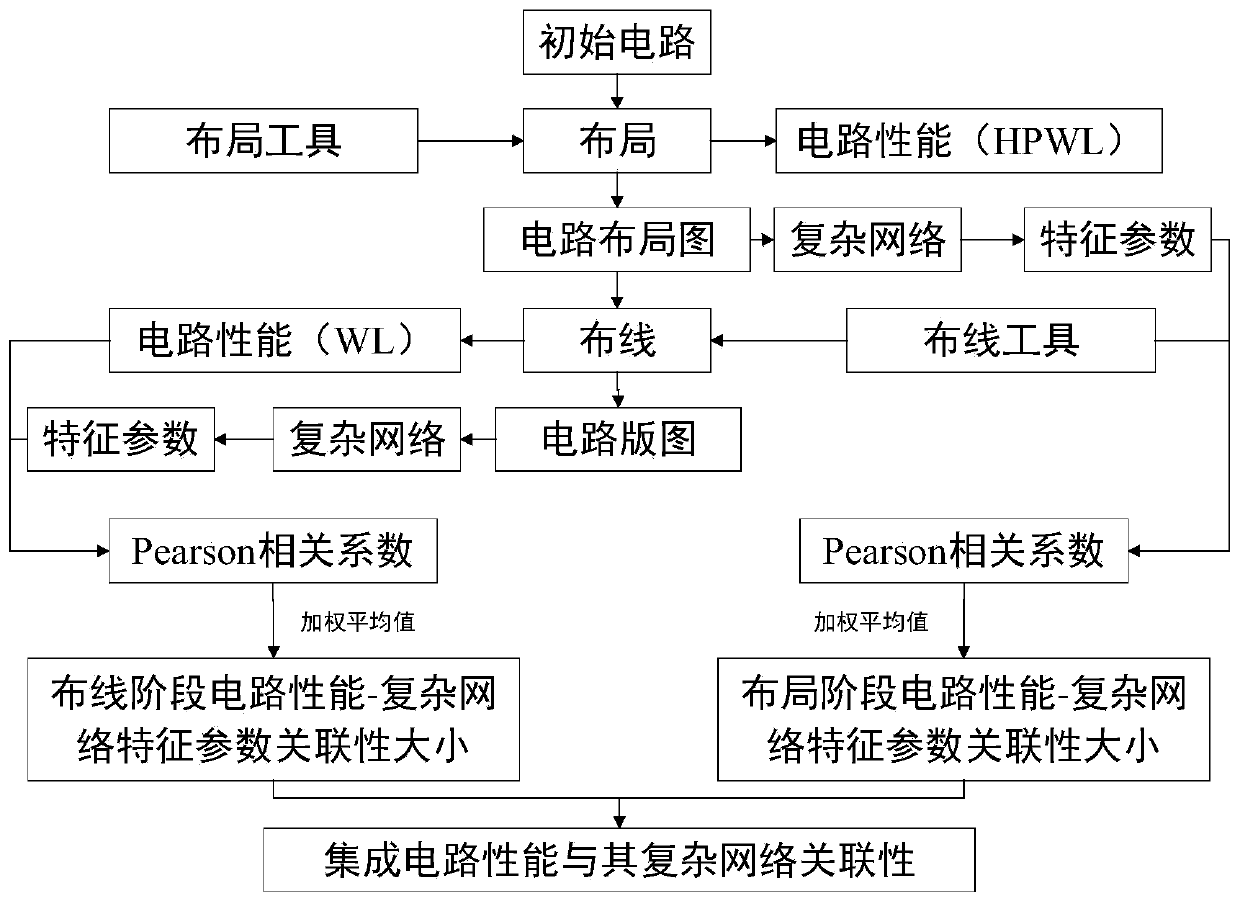

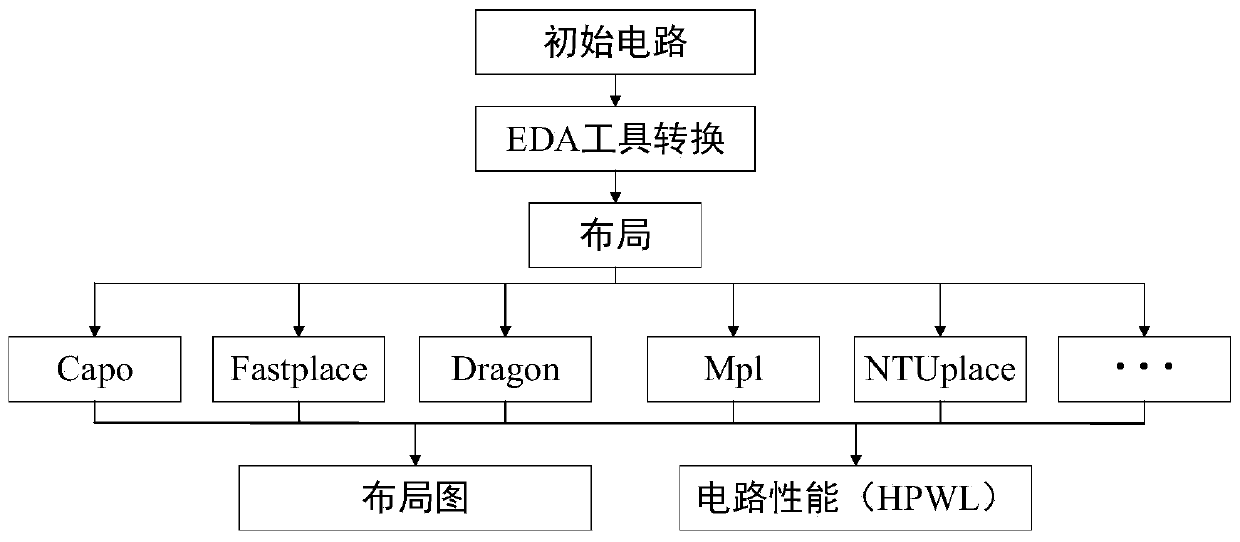

Method and system for judging relevance between integrated circuit performance and complex network characteristics

InactiveCN110941931AUniversalPlay a supporting roleCAD circuit designSpecial data processing applicationsComplex network analysisHemt circuits

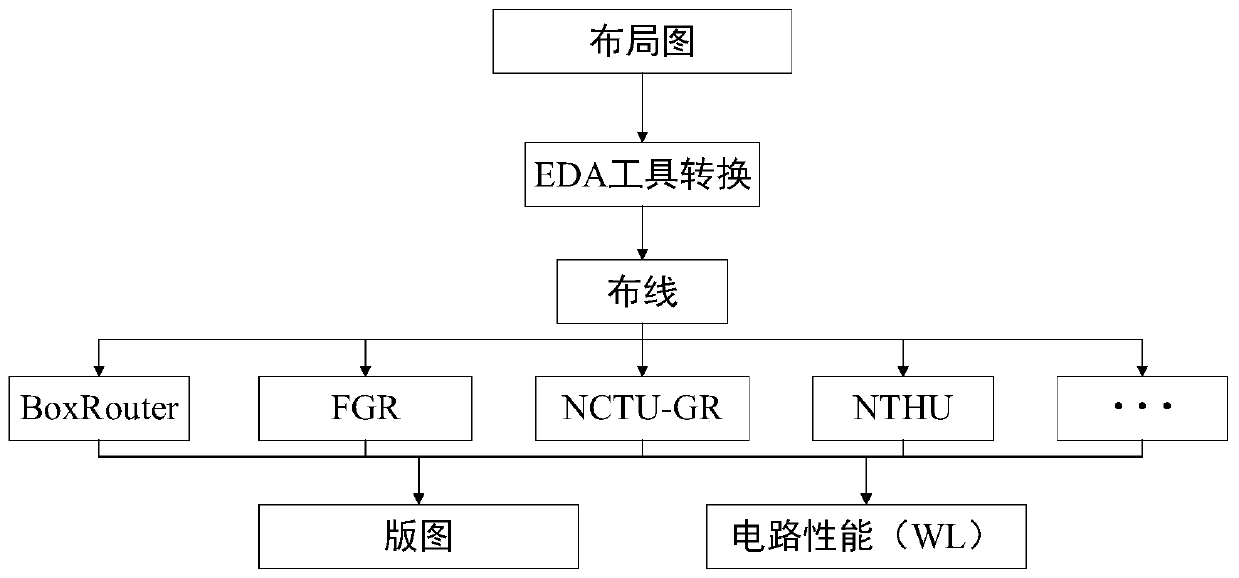

The invention discloses a method and a system for judging relevance between integrated circuit performance and complex network characteristics thereof. The method comprises the following steps: carrying out multi-tool physical design on a super-large-scale integrated circuit in a layout and wiring stage in the physical design, i.e., carrying out layout and wiring on an initial circuit by using different tools to obtain completely different layout diagrams and layouts so as to obtain different circuit performances; afterwards, complex network conversion is conducted on the layout diagram and the layout of the circuit, feature parameters of a complex network diagram of the circuit are calculated through a complex network analysis tool, network feature parameter-circuit performance correlation coefficients are calculated according to circuit performance changes and feature parameter changes, and the correlation between the performance of the integrated circuit and the feature parameters of the complex network is judged. According to the invention, the circuit performance and characteristics are not changed in the process of carrying out complex network conversion on the layout diagramand the layout, and the method has transparency.

Owner:QINGDAO TECHNOLOGICAL UNIVERSITY

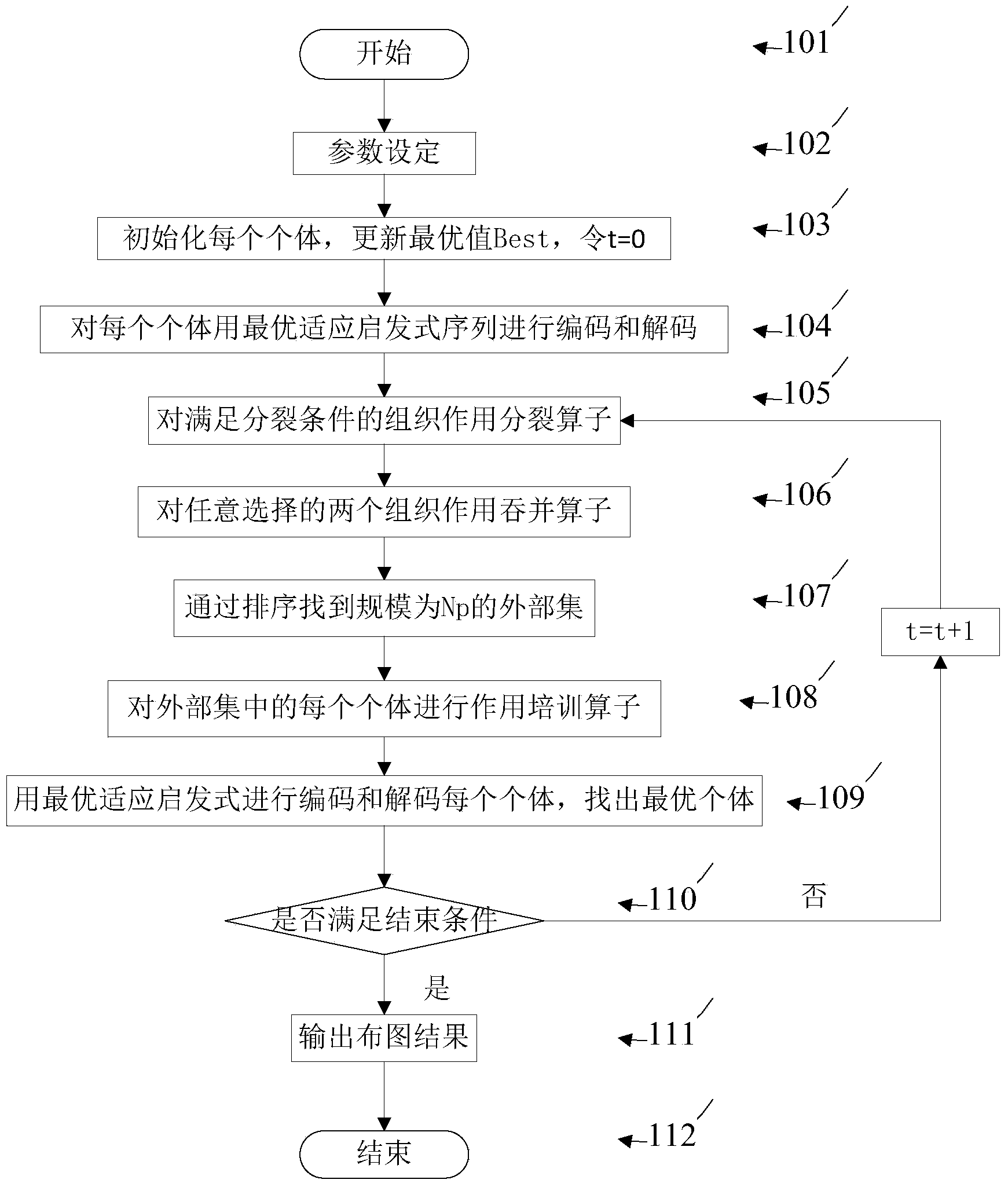

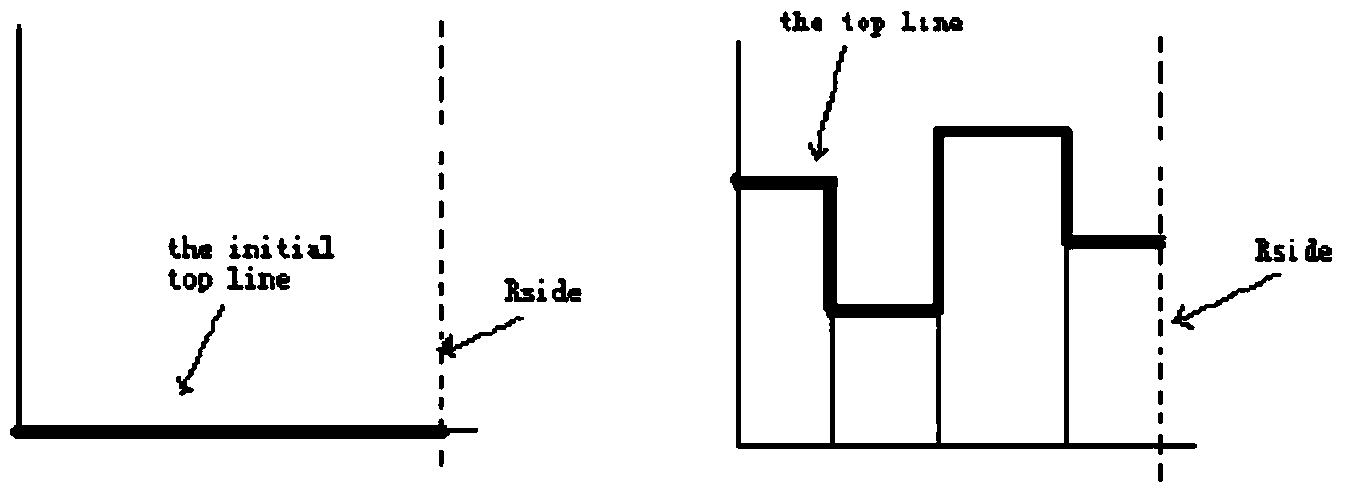

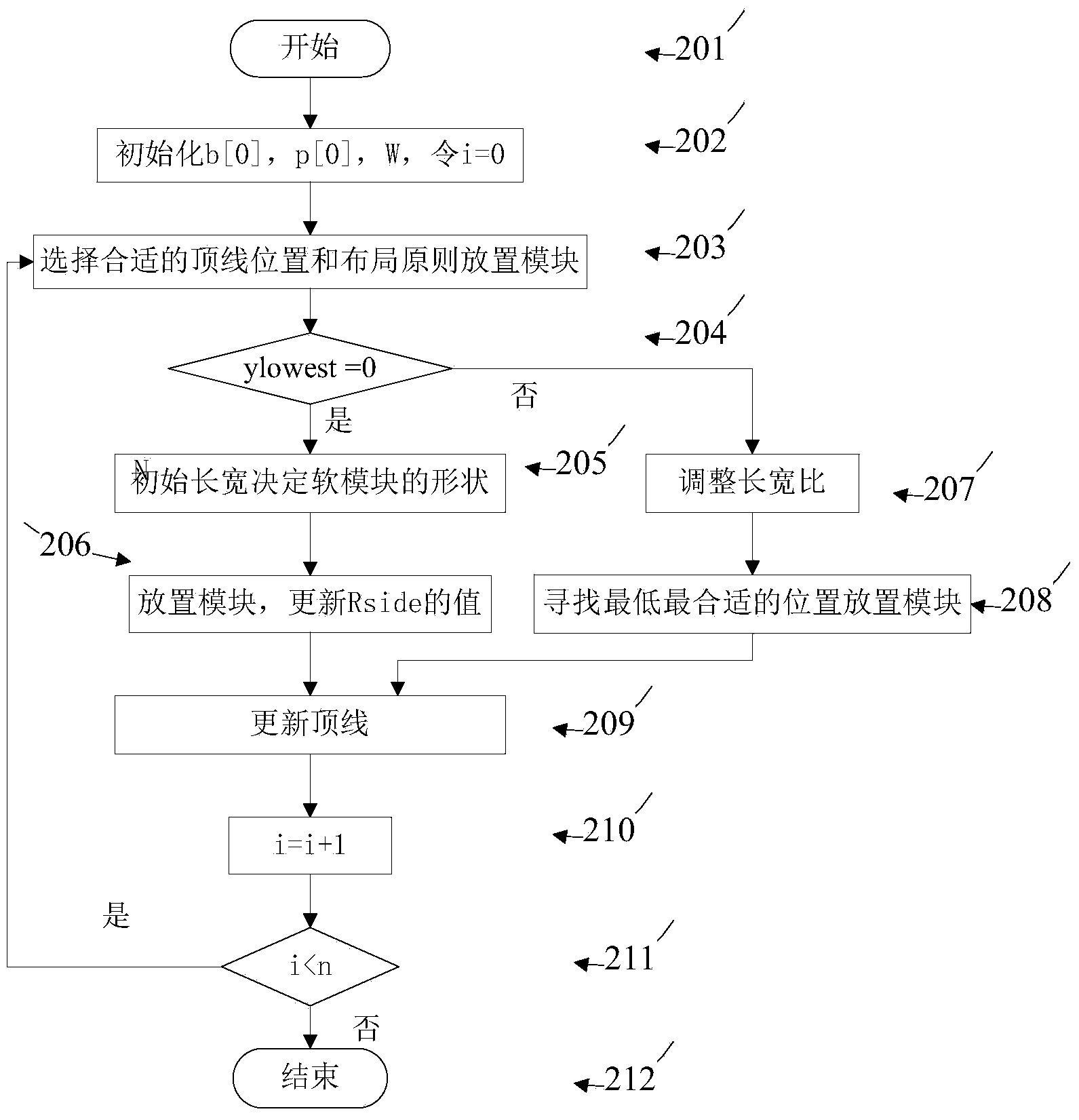

Integrated circuit floorplanning method based on best fit heuristic sequence and multi-objective organizational evolution

ActiveCN103714210AExcellent area utilizationGuaranteed arbitrarinessSpecial data processing applicationsVery large scale integrated circuitsOptimization problem

The invention discloses an integrated circuit floorplanning method based on a best fit heuristic sequence and multi-objective organizational evolution, and belongs to the technical field of physical design floorplanning. The method uses the best fit heuristic sequence for encoding and decoding, is combined with a multi-objective organizational evolutionary algorithm, and is used for solving the very large scale integration floorplanning problem. The method is characterized in that firstly each individual is initialized, then each individual is coded and decoded through the best fit heuristic sequence, and finally, a designed split operator, a designed annexation operator and a designed training operator are used for optimizing the multi-objective organization. Verification results show that the integrated circuit floorplanning method has advantages on two important aspects of methods and effectiveness for evaluating and solving the very large scale integration floorplanning problem, namely, the area utilization ratio and optimal line length of an optimal chip, and the method effectively solves the very large scale integration floorplanning problem and can be expanded to solve other multi-objective organizational optimization problems.

Owner:XIDIAN UNIV

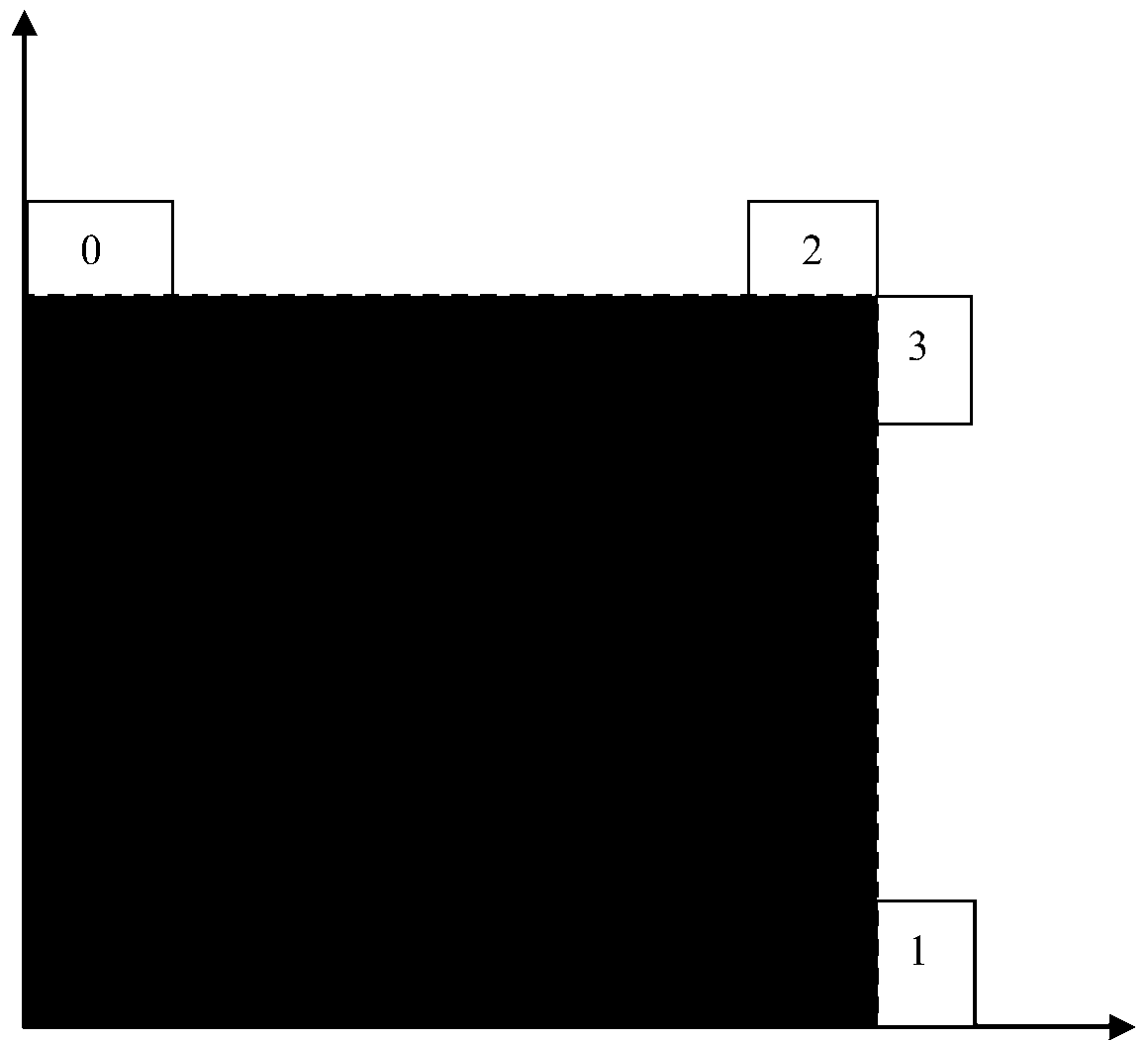

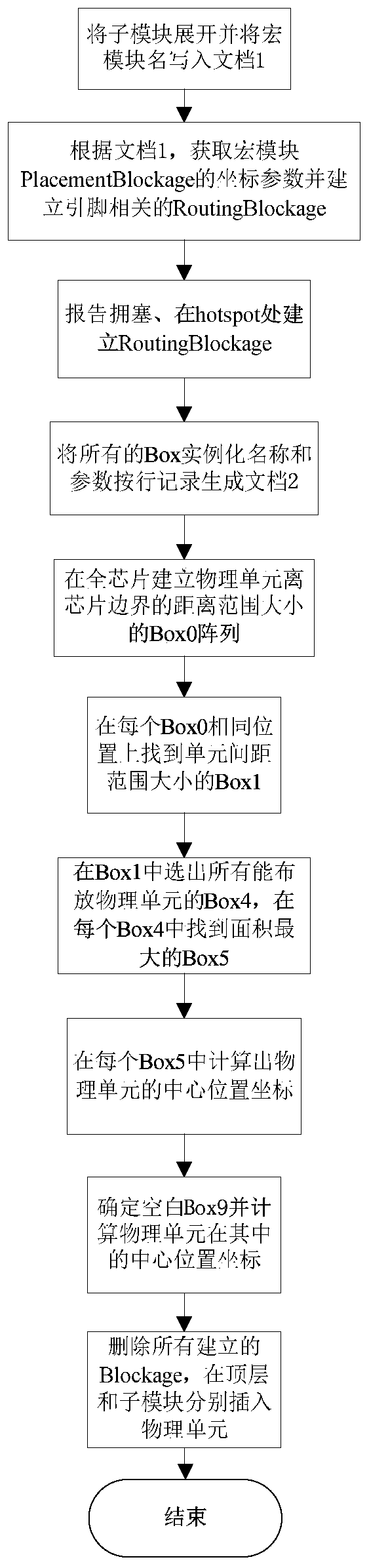

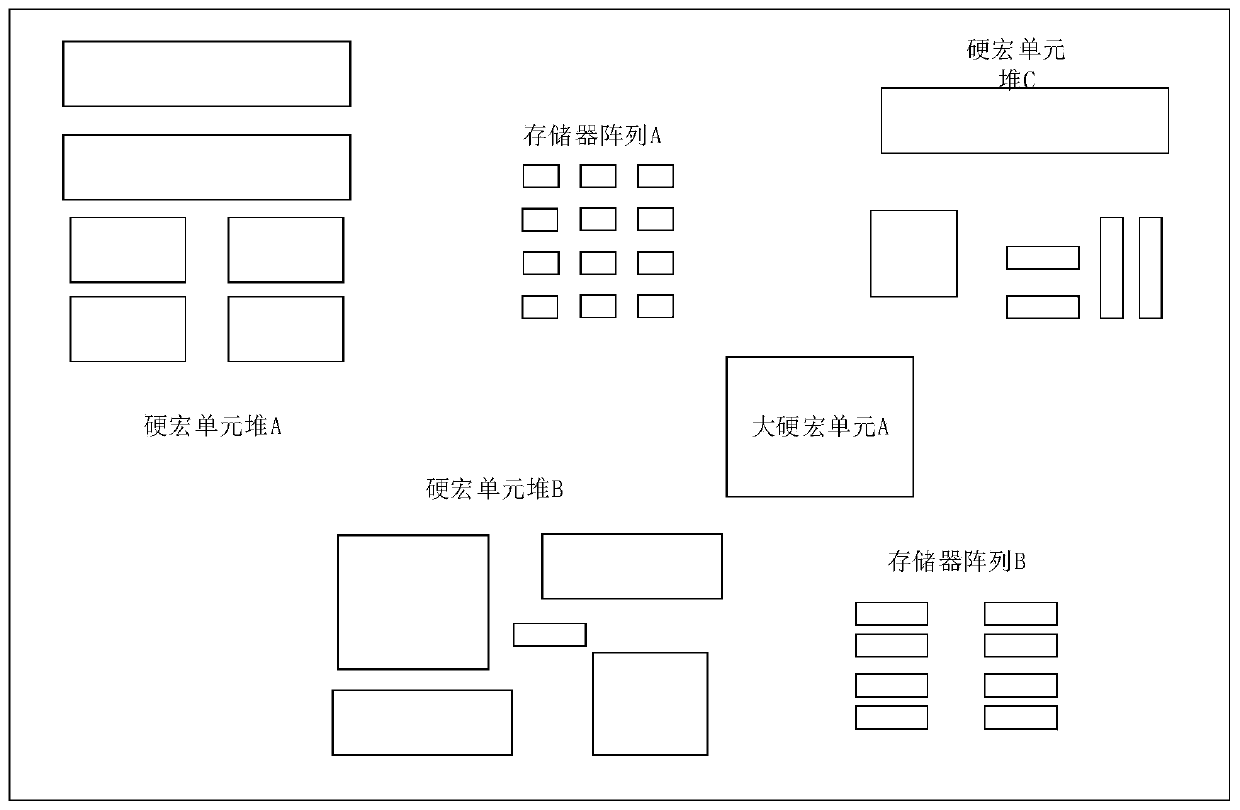

Automatic physical unit insertion method based on original layout planning

ActiveCN111259615AReduce the number of iterationsReduce runtime timeComputer aided designSpecial data processing applicationsLayout planningSoftware engineering

The invention discloses an automatic physical unit insertion method based on original layout planning. The method comprises the steps: S1, expanding the top layer of a chip, and recording the name ofa macro module in a document 1; s2, reading the document 1, and obtaining information of a hard macro unit Box; s3, reporting chip congestion information, and establishing a blocking rectangle Box ata hot spot; s4, recording all Box names and parameters into a document 2; s5, establishing a Box0 array with the distance range from the physical unit to the boundary of the chip; s6, Box1 of the unitspacing range is established at the same position of each Box0; s7, selecting Box4 capable of laying units from each Box1, and finding Box5 with the maximum area from the Box4; s8, calculating a central coordinate of each unit in each Box 5; s9, determining a central coordinate of the blank Box 9 calculation unit in the blank Box 9 calculation unit; s10, deleting the Block and inserting the Blockinto the physical unit; s11, ending is carried out. The method has the advantages of being simple in principle, easy to operate, capable of improving overall physical design efficiency and the like.

Owner:NAT UNIV OF DEFENSE TECH

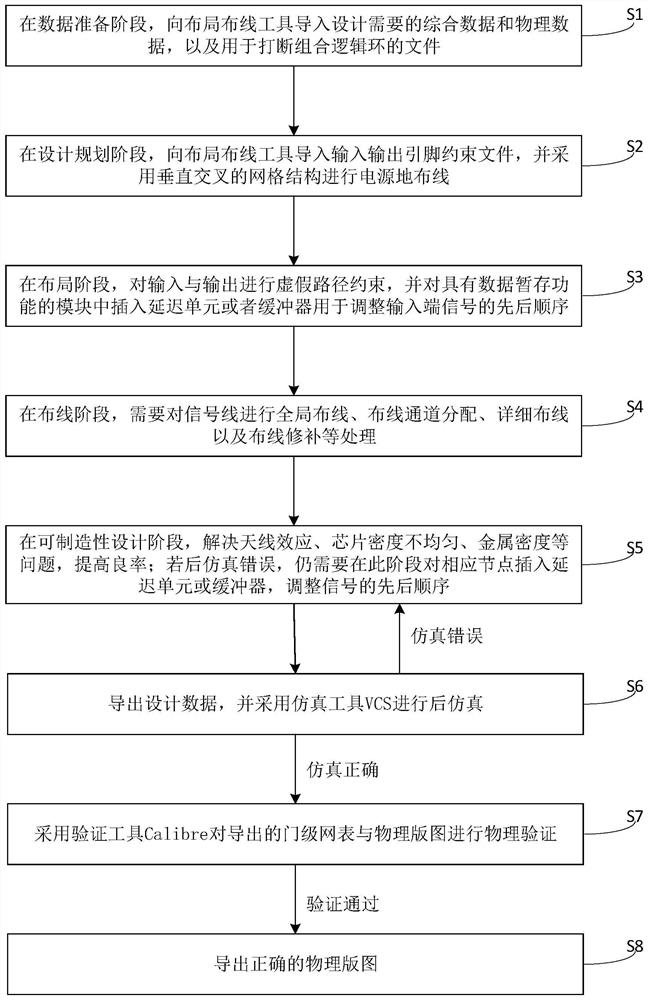

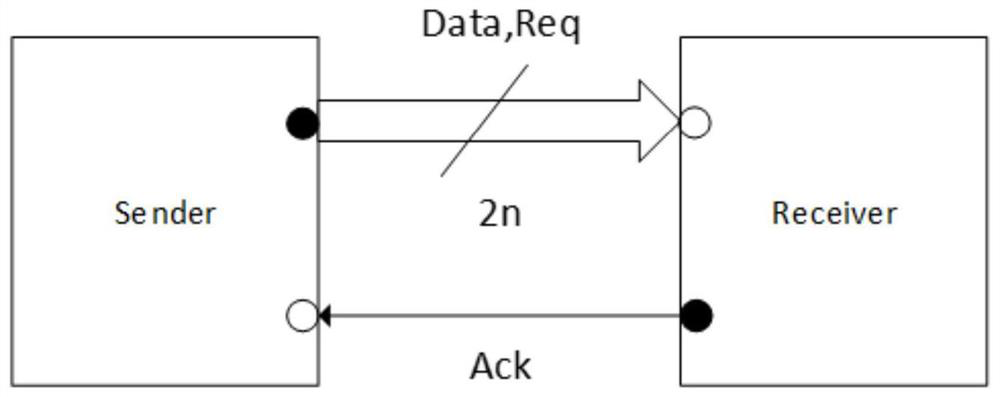

Asynchronous circuit physical implementation method and system

ActiveCN112651207ACompatible Design FlowRealize the physical designComputer aided designEnergy efficient computingAntenna effectPathPing

The invention discloses an asynchronous circuit physical implementation method and system, and the method comprises the steps: performing a data preparation stage: importing comprehensive data, physical data and a file for interrupting a combinational logic ring; in the design planning stage, inputting an IO pin constraint file; in the layout stage, carrying out false path constraint on IO; in the wiring stage, carrying out global wiring, wiring channel distribution, detailed wiring and wiring repair on the signal lines; in the manufacturability design stage, the antenna effect problem, the chip density non-uniformity problem and the metal density problem are solved; exporting design data, performing post-simulation, and returning to the manufacturability design stage for processing if errors occur in simulation; and performing physical verification on the exported gate-level netlist and the physical layout. The invention provides a novel asynchronous circuit physical implementation scheme, which can realize the physical design of a large-scale asynchronous integrated circuit based on a synchronous design tool, is compatible with the current synchronous circuit design process, and can be widely applied to the technical field of integrated circuits.

Owner:SUN YAT SEN UNIV

Method for designing structured ASICs in silicon processes with three unique masking steps

InactiveUS7895559B2Semiconductor/solid-state device detailsSolid-state devicesCore functionComputer architecture

A multi-function core base cell includes a set of functional microcircuits. These microcircuits are used to design a Library of Logic Function Macros. The functional macros consisting of one or more microcircuits have a fixed and complete physical layout similar to a conventional standard cell library macro set. In addition to a core functional macro set, primary input / output buffers and commonly used single and dual port memory blocks are also defined in the library. The library includes all the ASIC synthesis, simulation, and physical design rules.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Identifying test coverage gaps for integrated circuit designs based on node testability and physical design data

Test coverage for a circuit design may be determined by obtaining node testability data and physical location data for each node of a plurality of nodes in the circuit design. A determination is made that one or more low test coverage areas within the circuit design include untested nodes based on the node testability data and the physical location data of each node of the plurality of nodes. Test coverage data is generated for the circuit design including at least an identification of the one or more low test coverage areas.

Owner:NXP USA INC