Patents

Literature

497 results about "Power domains" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In denotational semantics and domain theory, power domains are domains of nondeterministic and concurrent computations. The idea of power domains for functions is that a nondeterministic function may be described as a deterministic set-valued function, where the set contains all values the nondeterministic function can take for a given argument. For concurrent systems, the idea is to express the set of all possible computations.

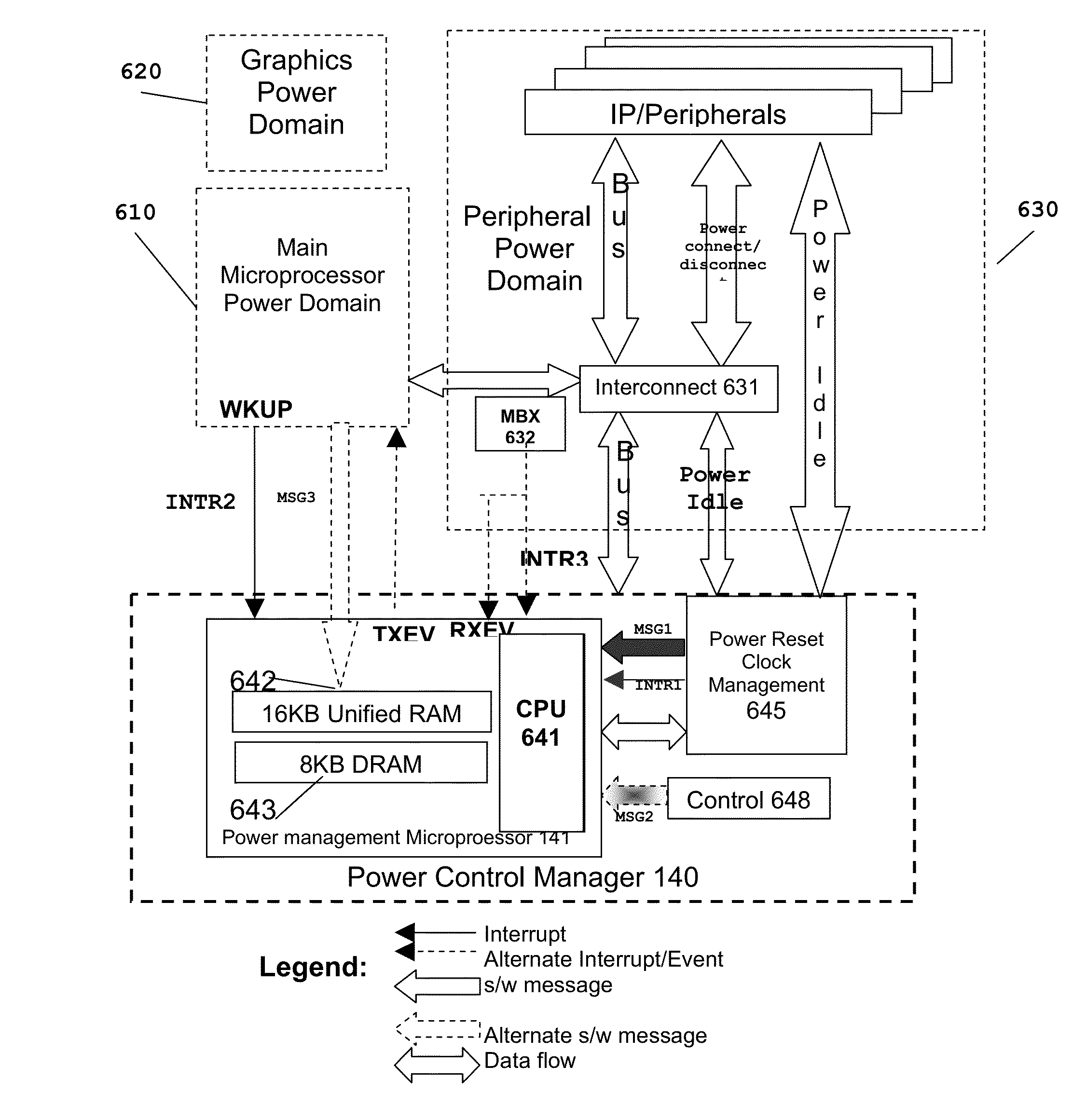

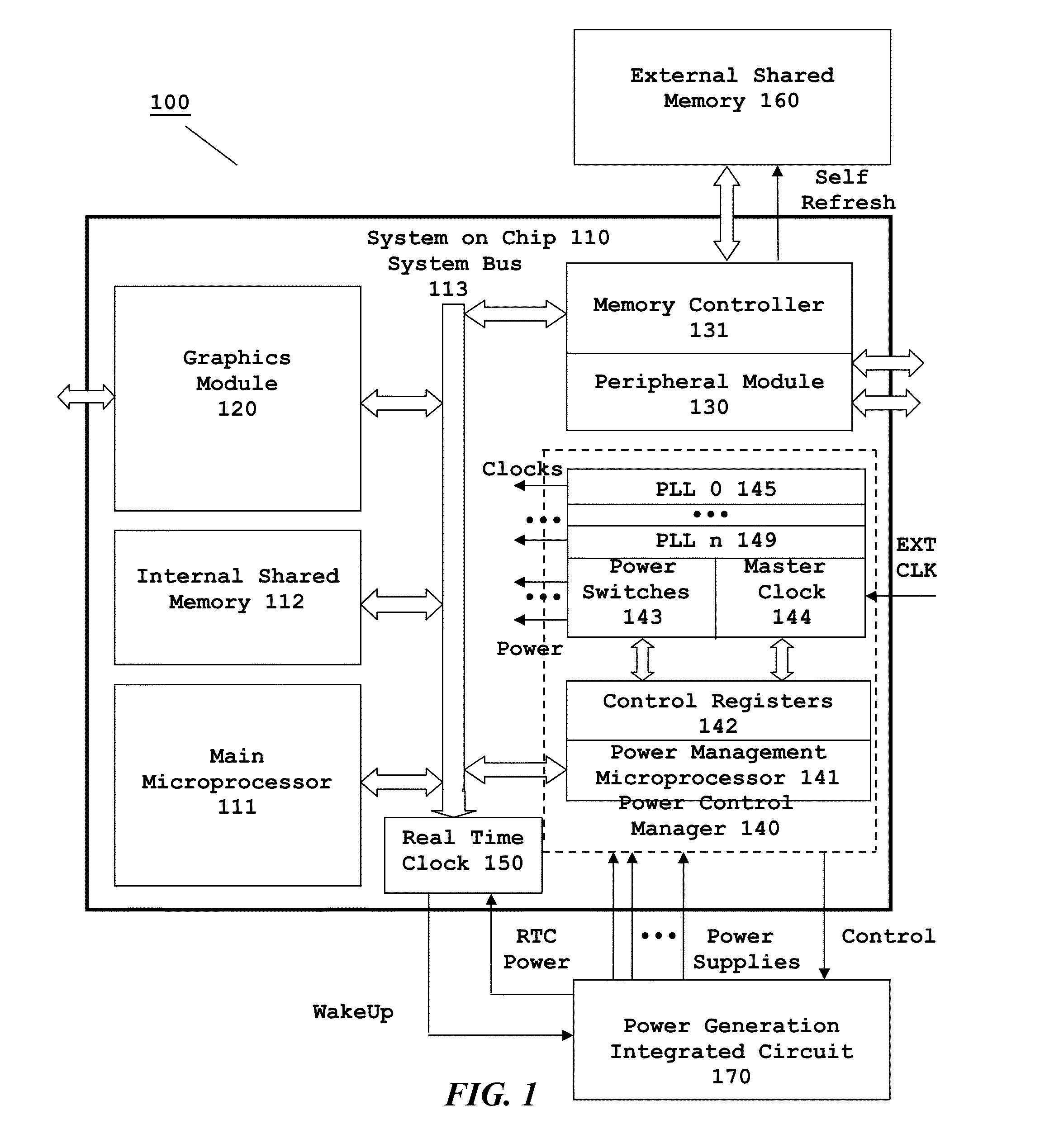

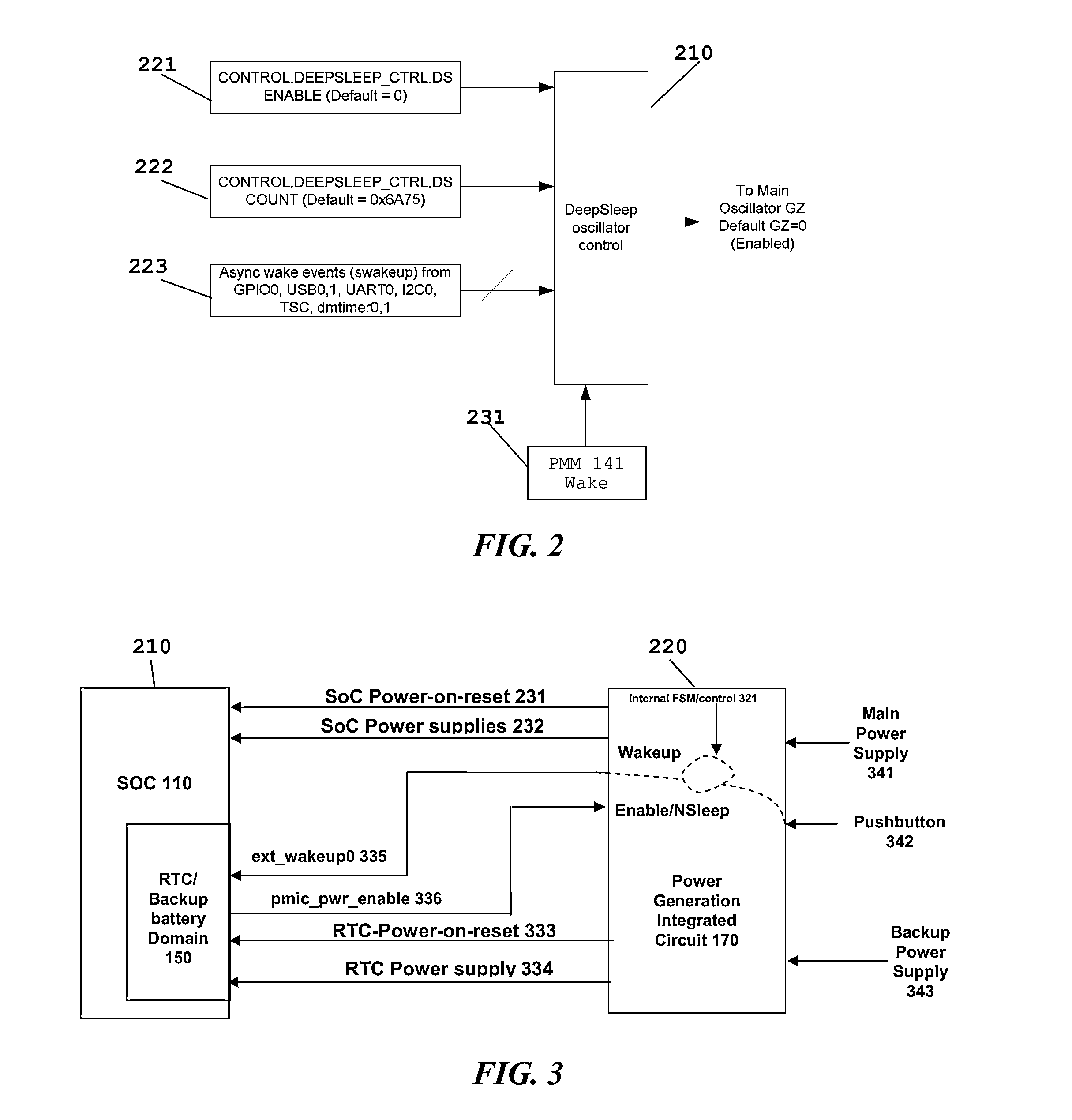

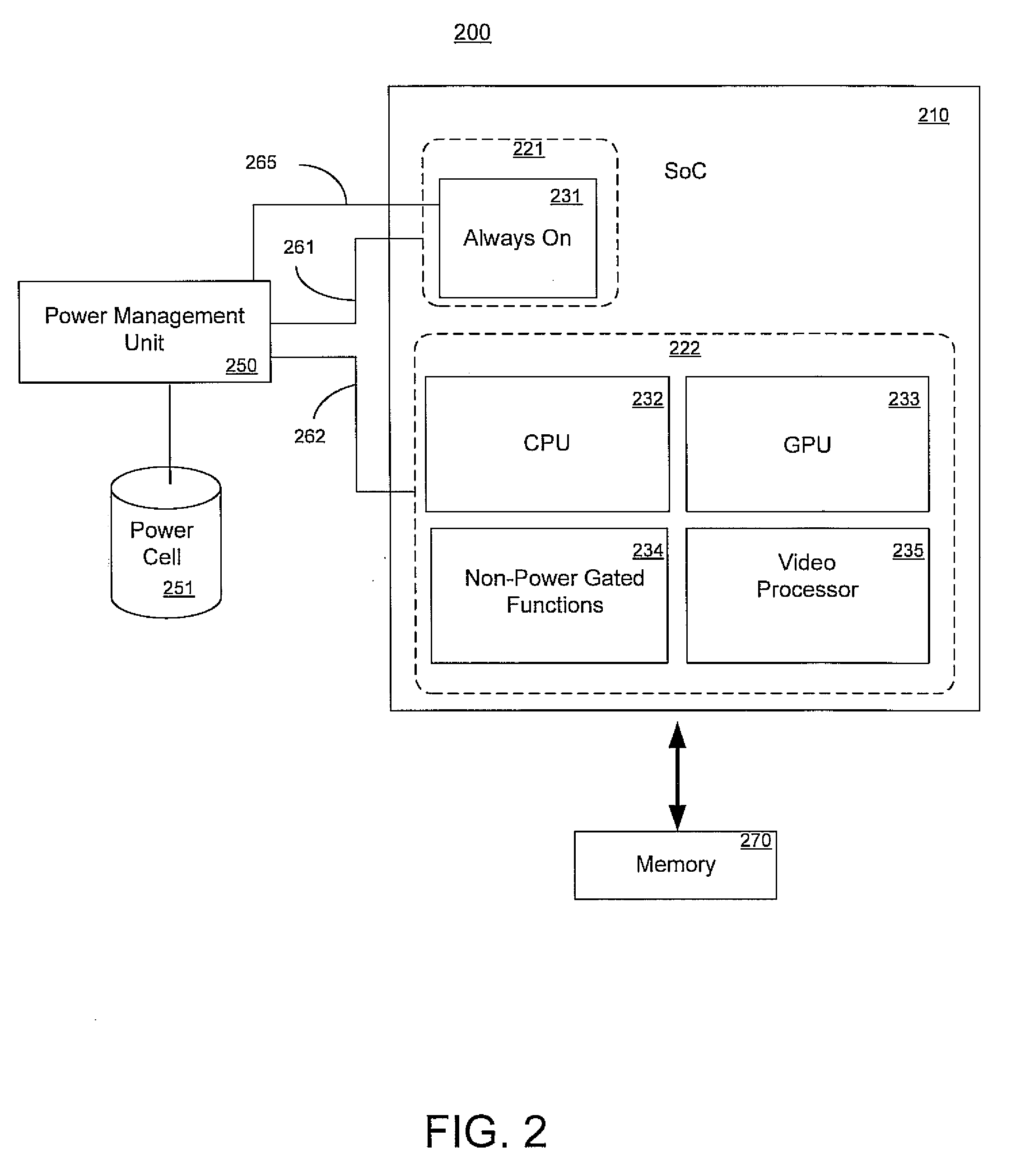

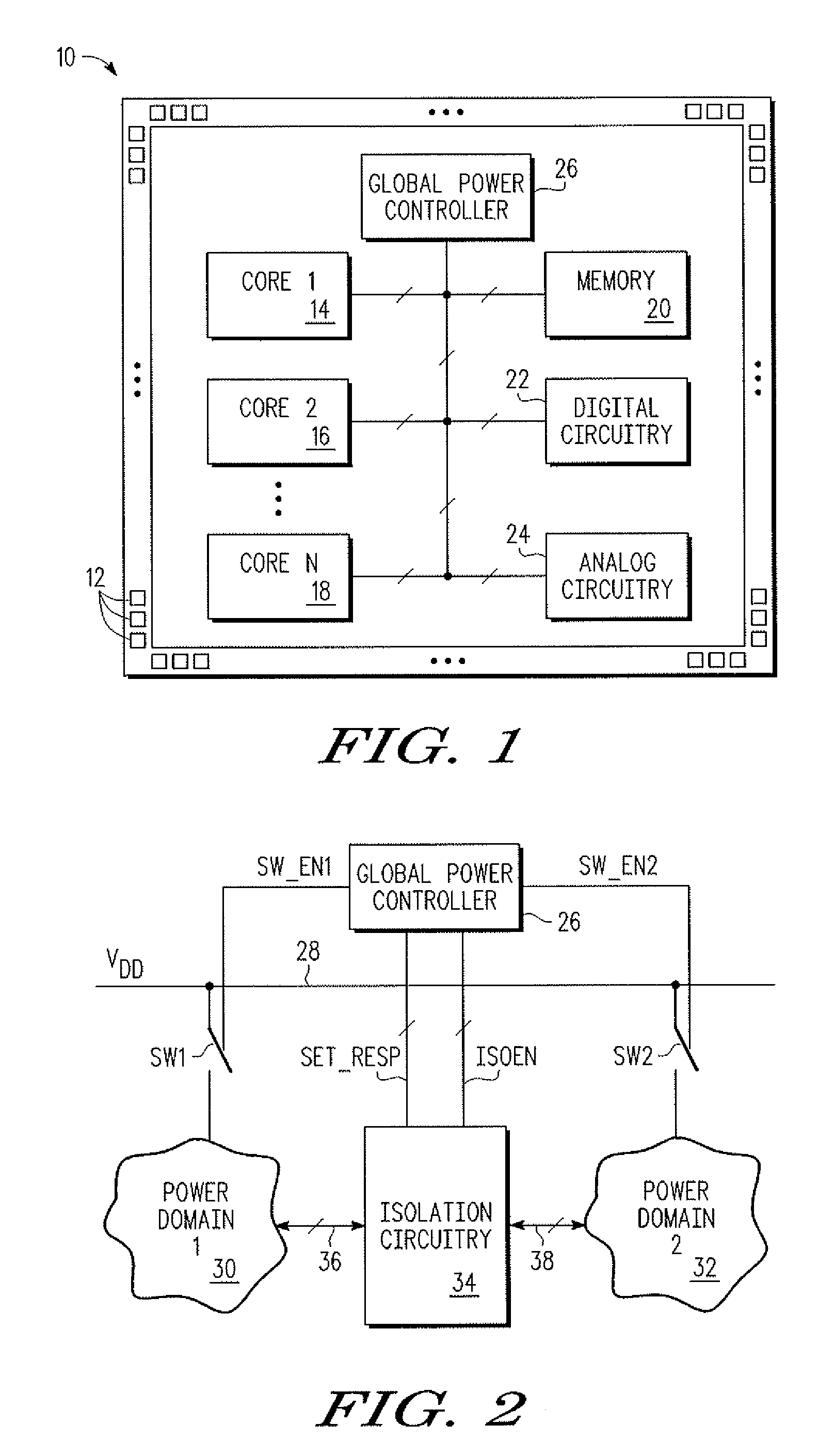

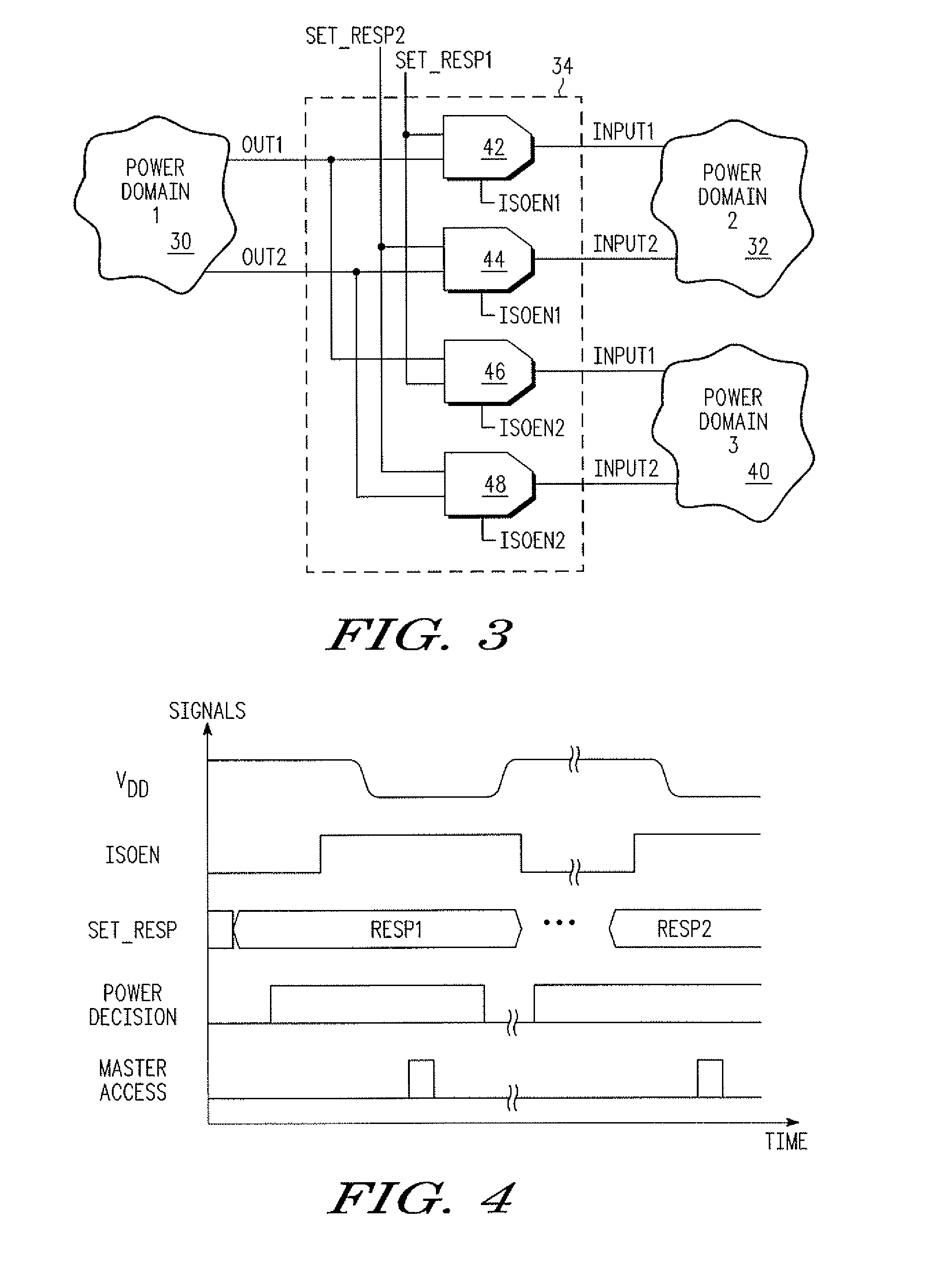

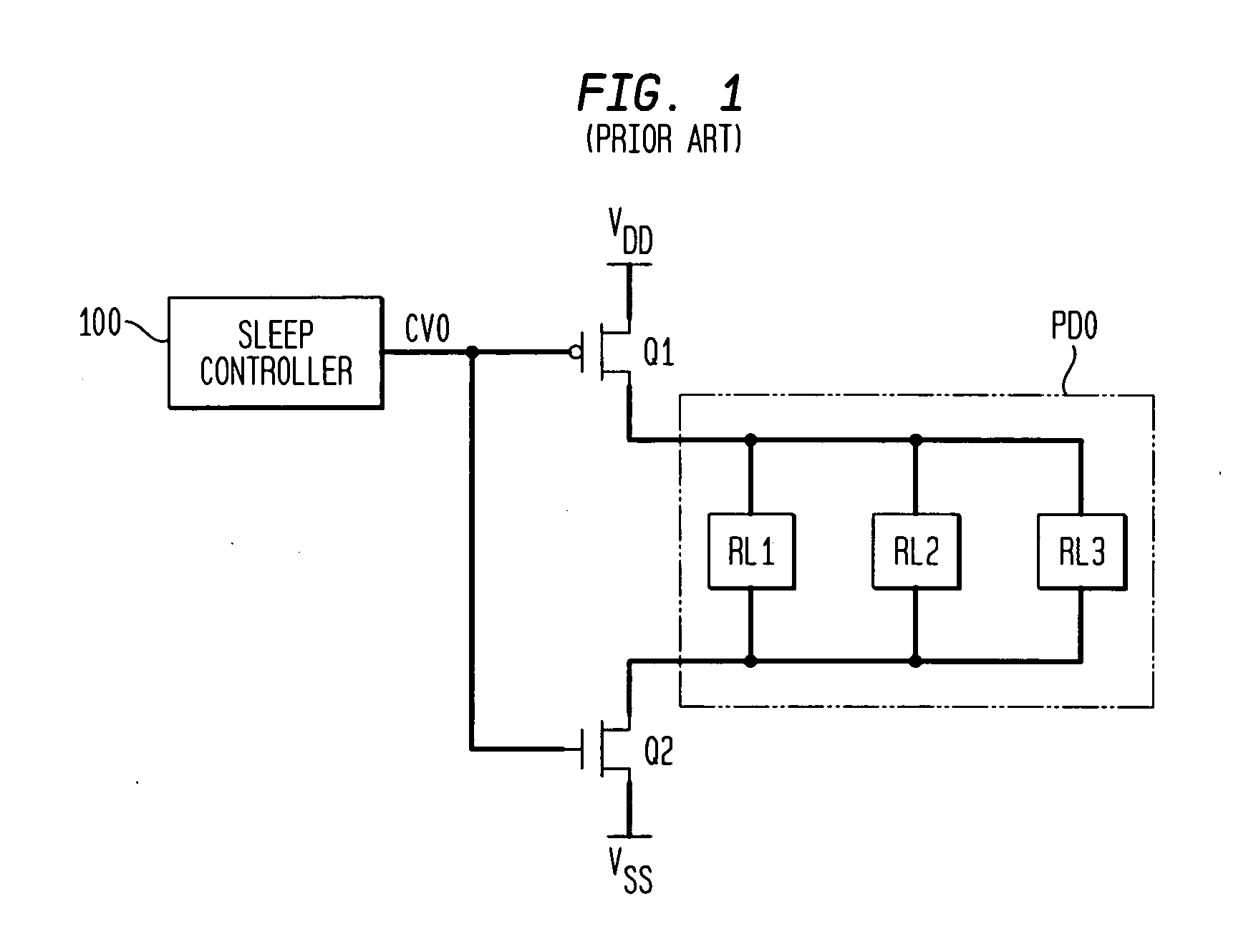

Microprocessor based power management system architecture

ActiveUS20130124895A1Low costLow powerEnergy efficient ICTVolume/mass flow measurementElectronic systemsPower switching

An electronic system is disposed on a single integrated circuit including a plurality of power domains and a power control manager. Each power domain may be independently powered. The power control manager includes a set of control registers storing individual control bits, a power switch for each power domain and a programmable microprocessor. The programmable microprocessor controls the digital state of individual bits within the control registers thereby controlling the ON and OFF state of the corresponding power domain.

Owner:TEXAS INSTR INC

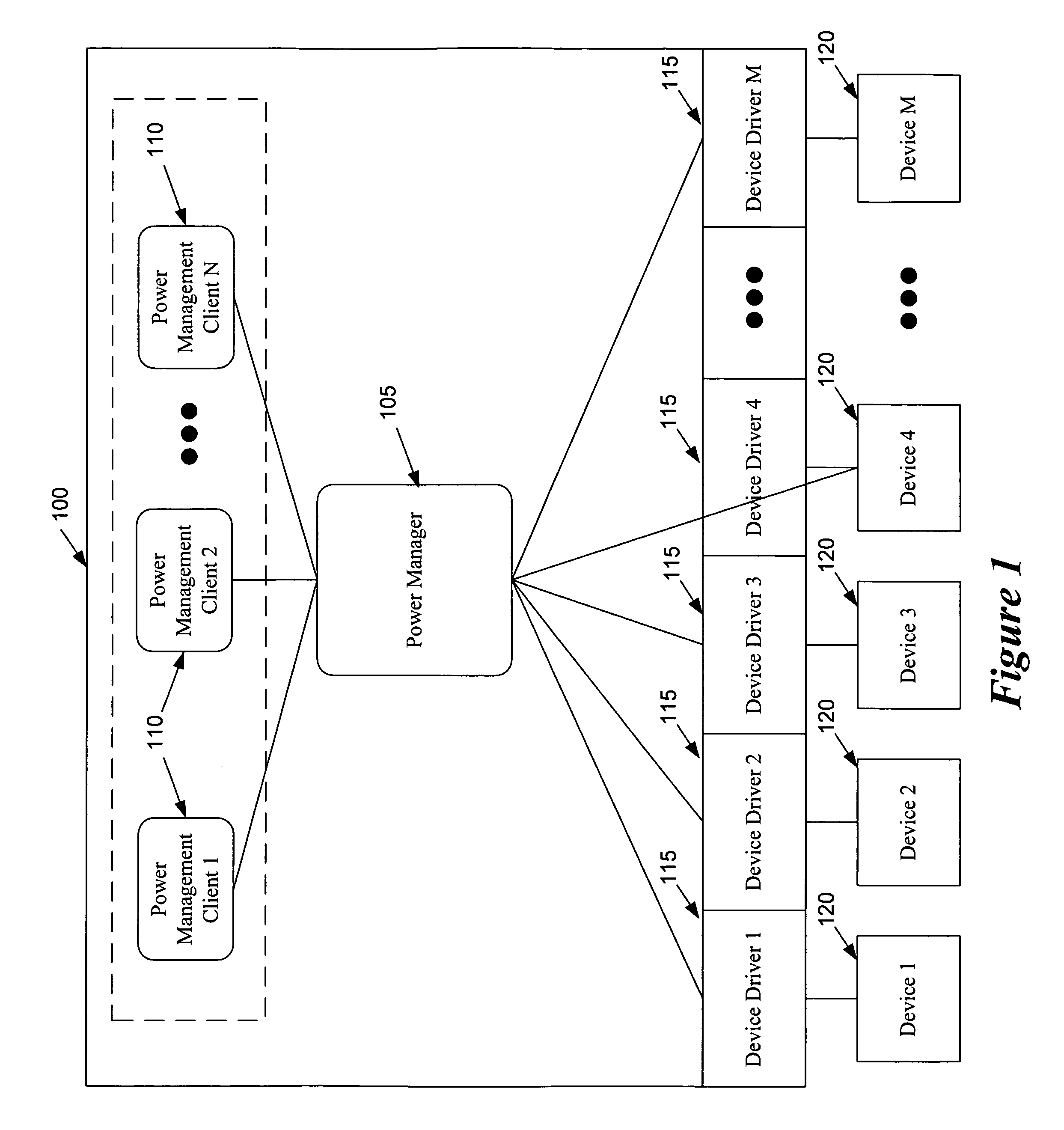

Method and apparatus for managing power in computer systems

InactiveUS7519838B1Energy efficient ICTVolume/mass flow measurementSoftware engineeringPower domains

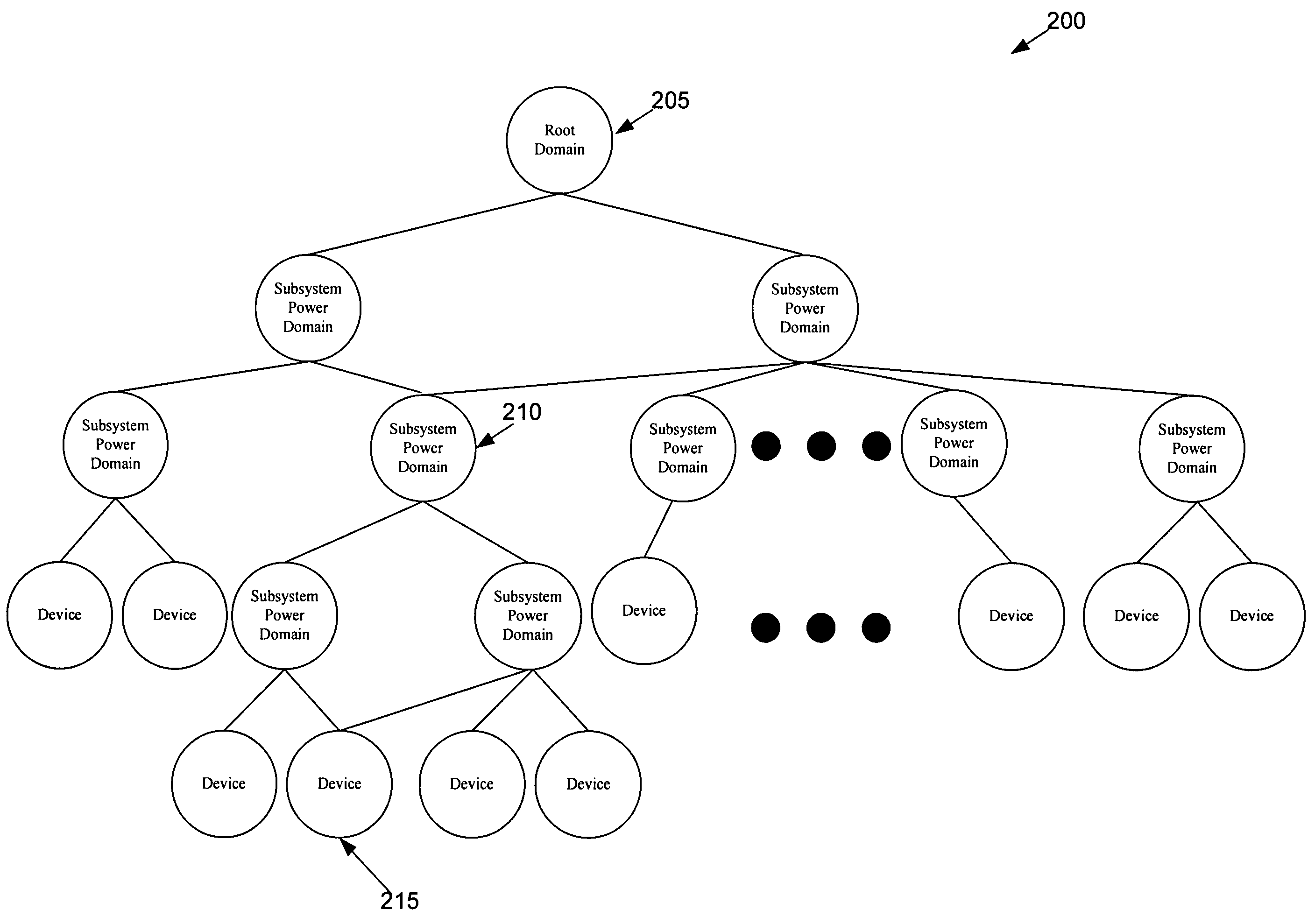

The invention is directed towards minimizing power consumption in computer systems. One embodiment of the invention is a power management system that is used for a computer system that has at least one device and one power domain. This embodiment uses two different power managers to manage the power consumption of the device and the power domain. Specifically, this embodiment has (1) a first power manager that determines when to change power state of the device, and (2) a second power manager that determines when to change power state of the power domain. Each of these power managers decides to change the power state of its corresponding device or domain based on information from several different sources. These sources can include power-management clients and power managers of related domains or devices.

Owner:APPLE INC

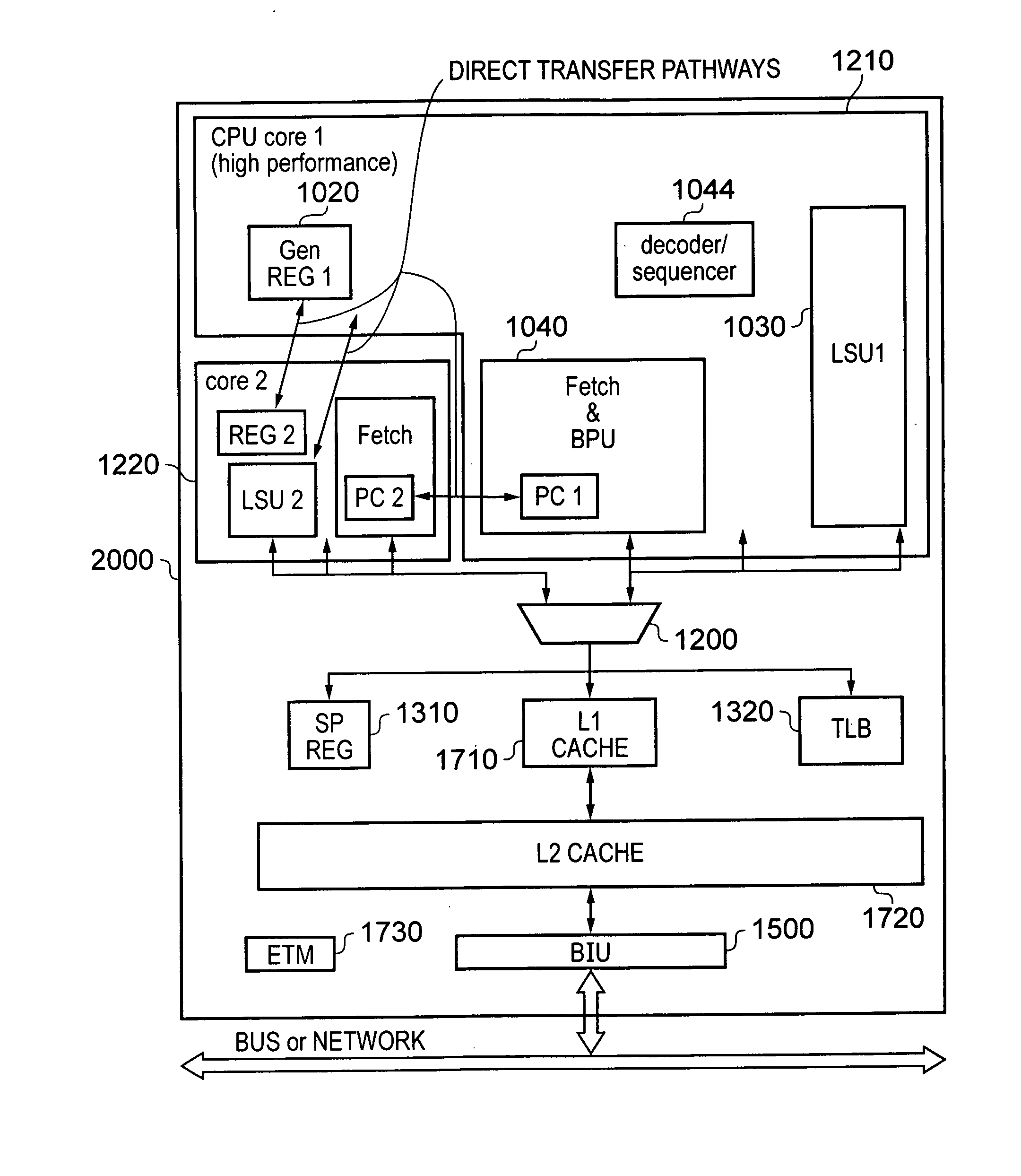

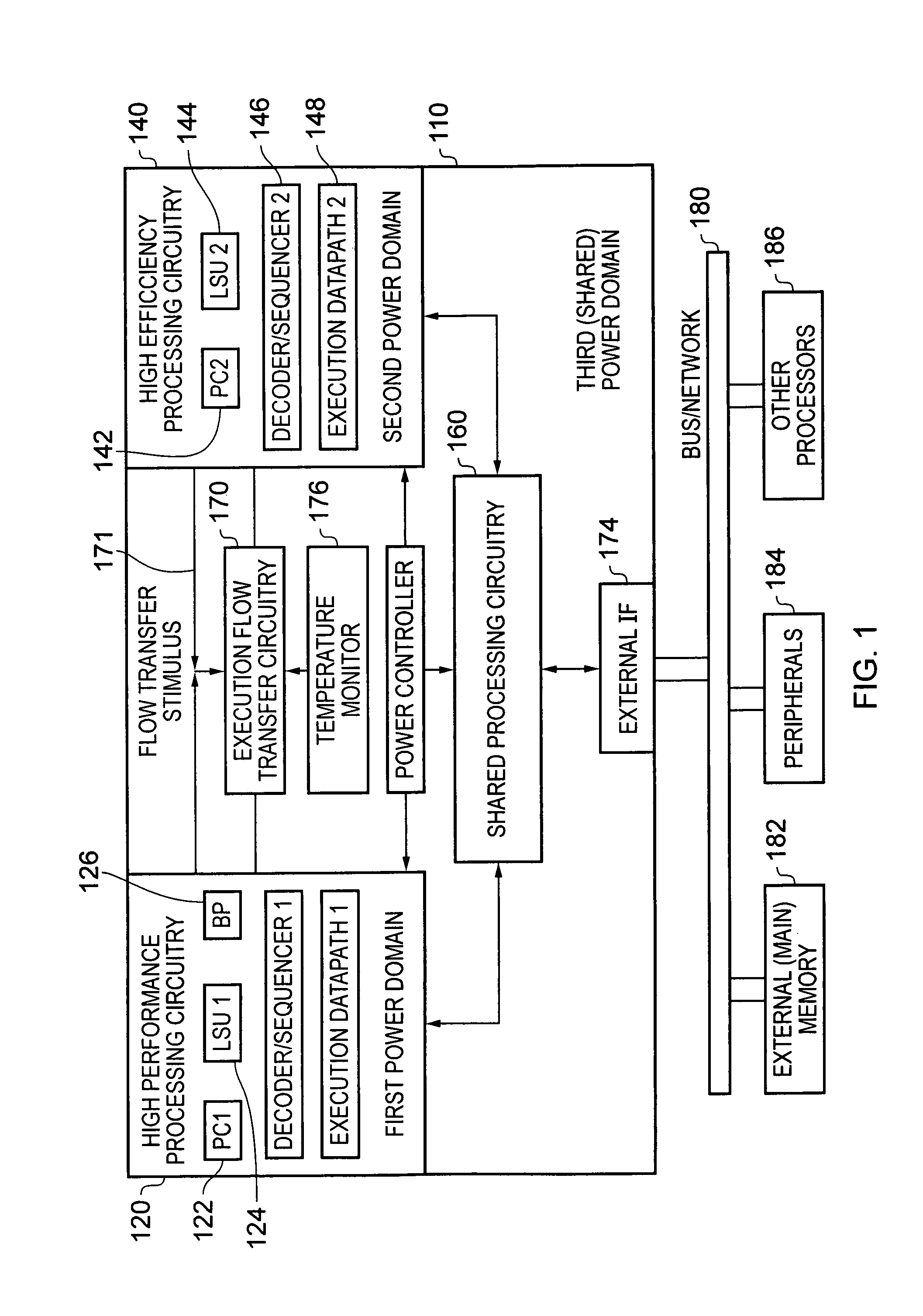

Data processing system

ActiveUS20110271126A1Easy to adaptData processing processEnergy efficient ICTVolume/mass flow measurementData processing systemPower domains

A data processing apparatus is provided comprising first processing circuitry, second processing circuitry and shared processing circuitry. The first processing circuitry and second processing circuitry are configured to operate in different first and second power domains respectively and the shared processing circuitry is configured to operate in a shared power domain. The data processing apparatus forms a uni-processing environment for executing a single instruction stream in which either the first processing circuitry and the shared processing circuitry operate together to execute the instruction stream or the second processing circuitry and the shared processing circuitry operate together to execute the single instruction stream. Execution flow transfer circuitry is provided for transferring at least one bit of processing-state restoration information between the two hybrid processing units.

Owner:ARM LTD

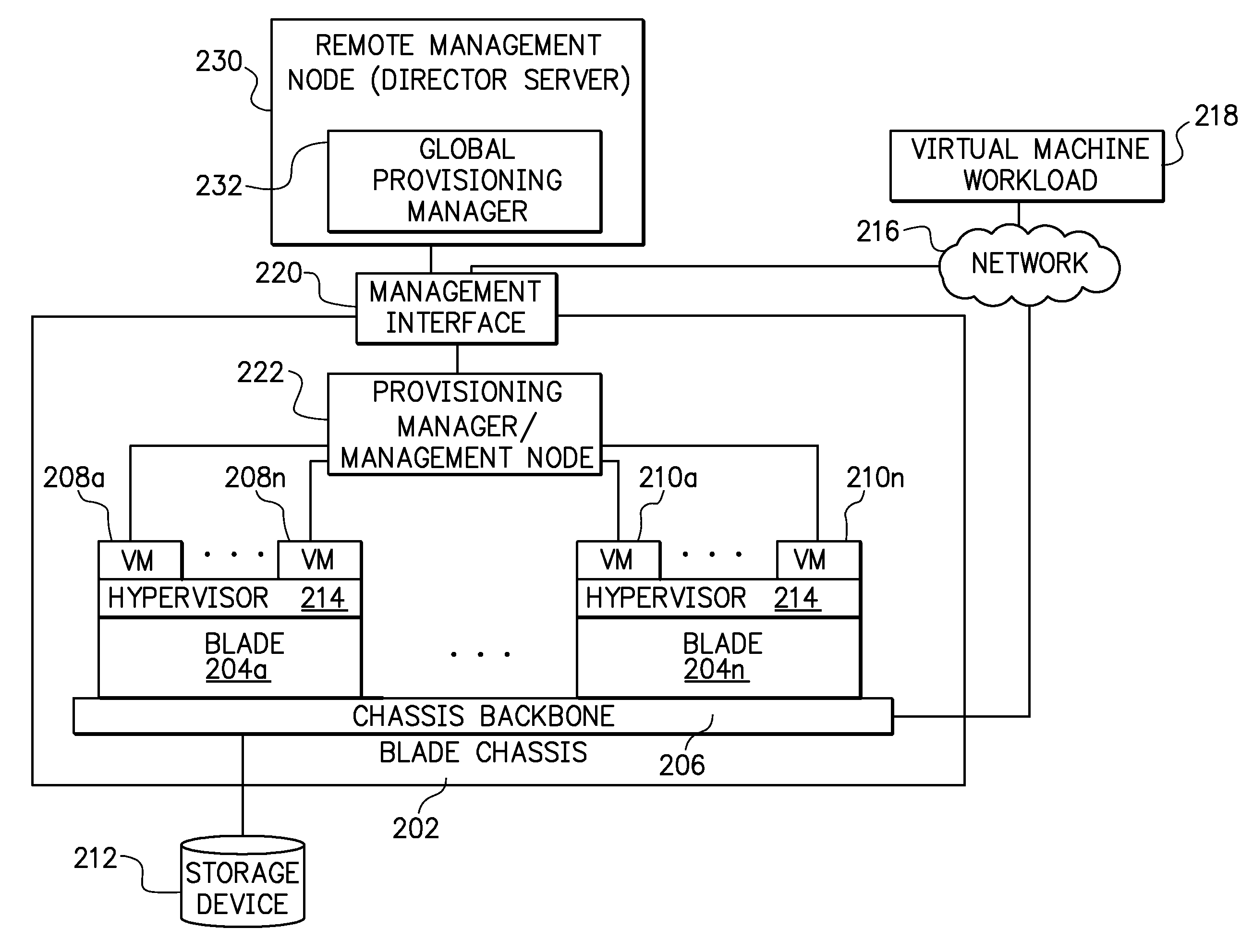

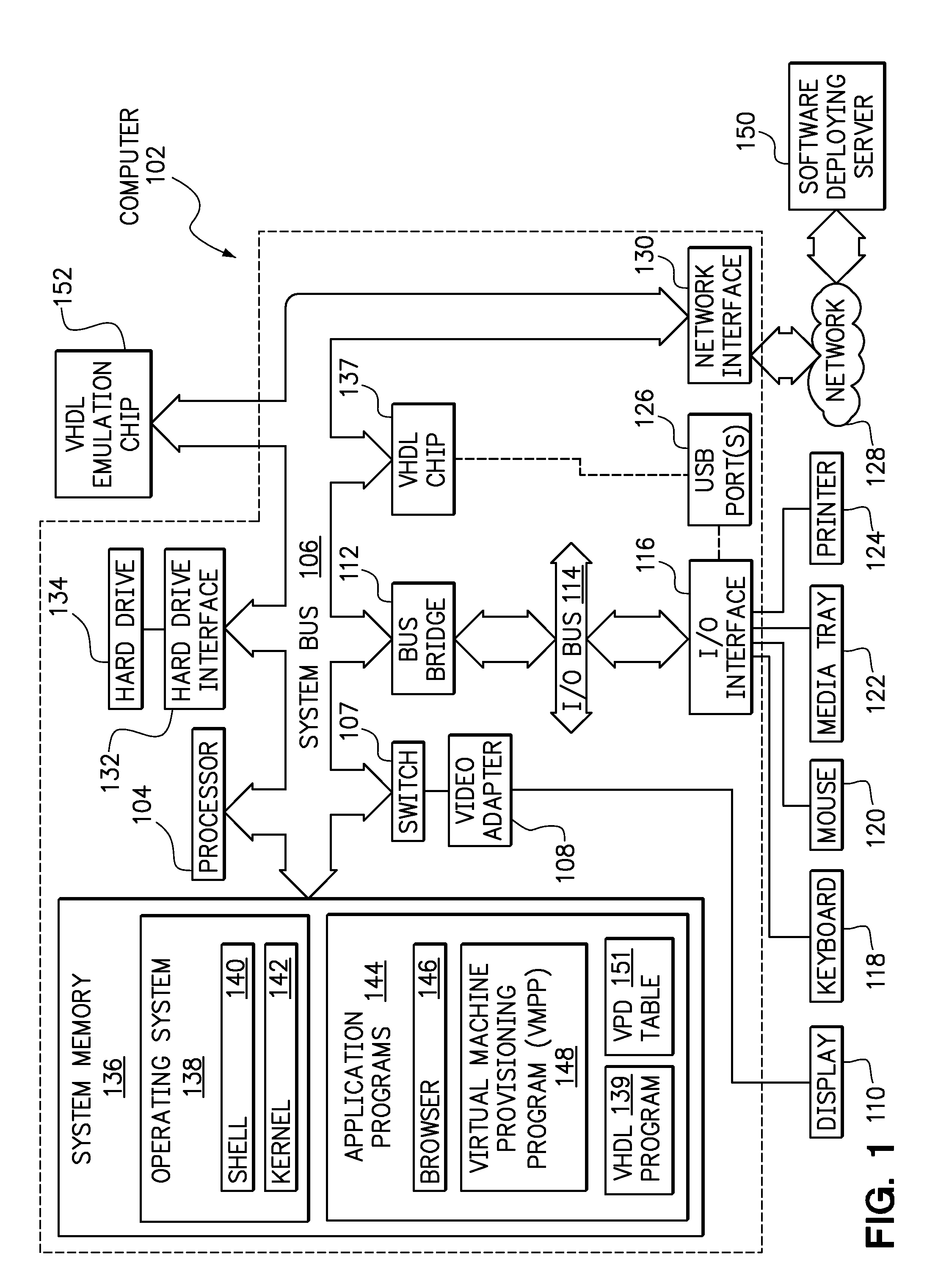

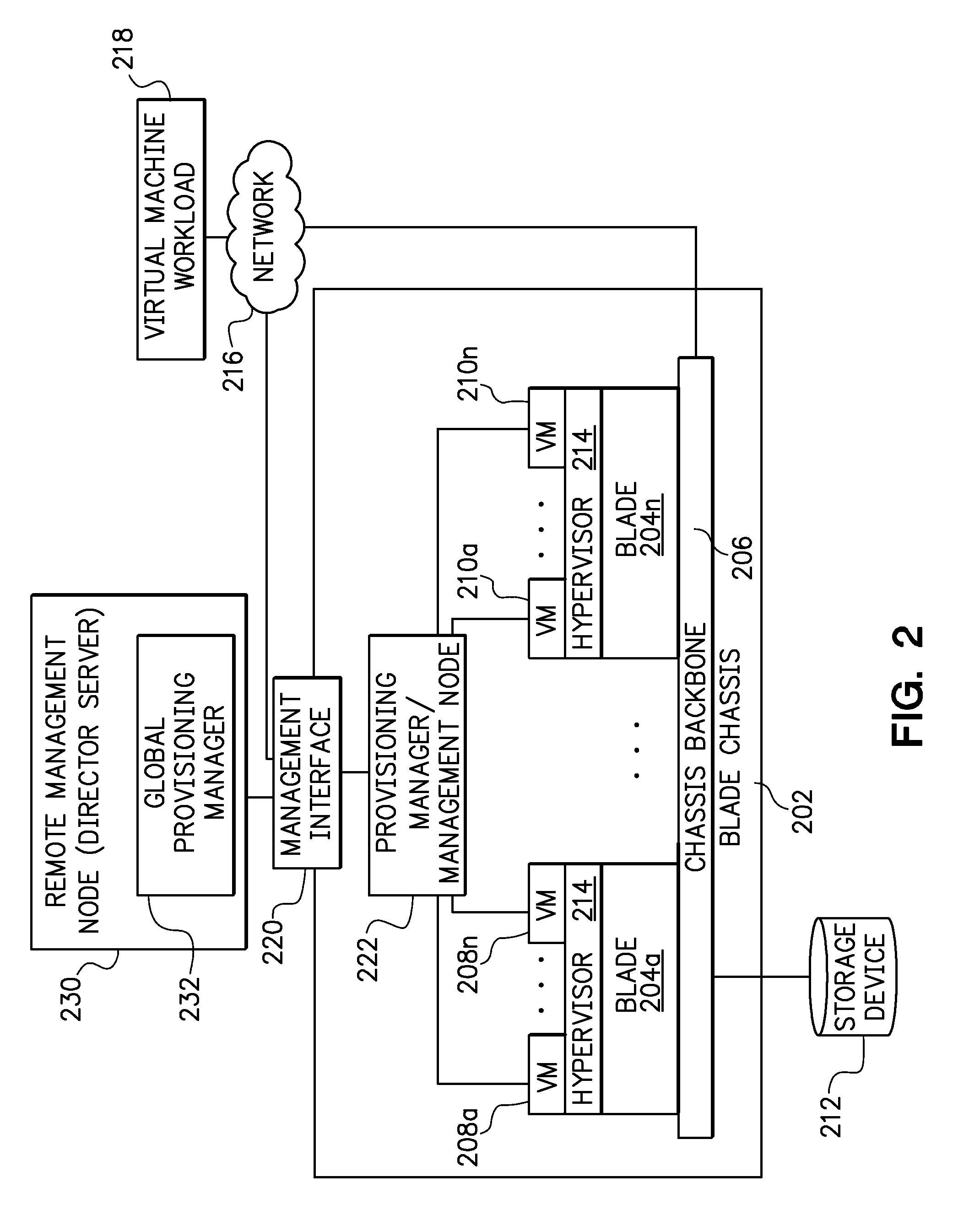

Protecting high priority workloads in a virtualized datacenter

A computer program product is provided, including computer usable program code for running a plurality of virtual machine workloads across a plurality of servers within a common power domain, and computer usable program code for setting an operating level for each of a plurality of hardware resources within the common power domain in response to receiving an early power off warning from a power source that supplies power to the common power domain, wherein the operating level for each of the hardware resources is determined as a function of the priority of the virtual machine workloads that are utilizing each of the hardware resources.

Owner:IBM CORP

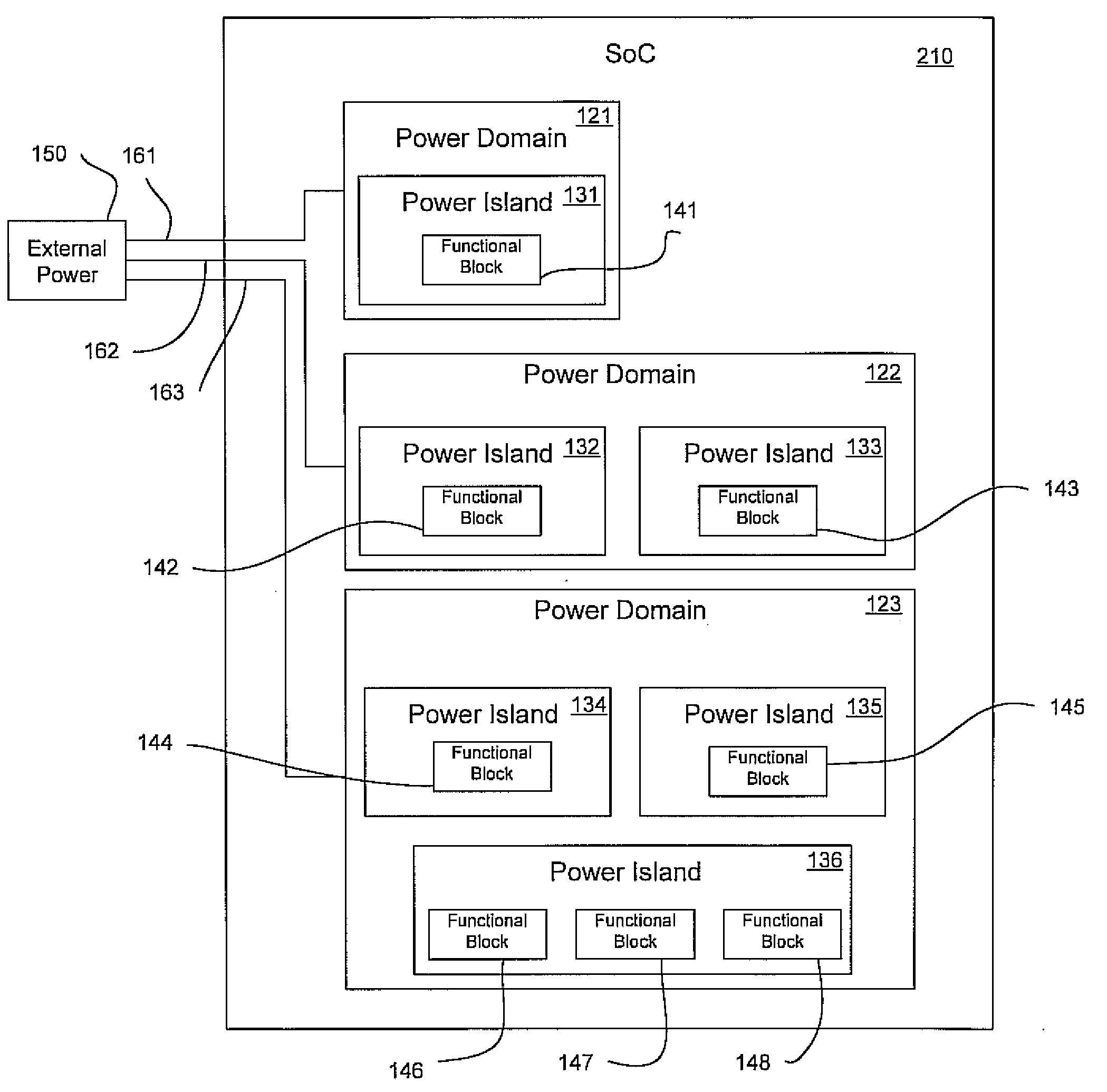

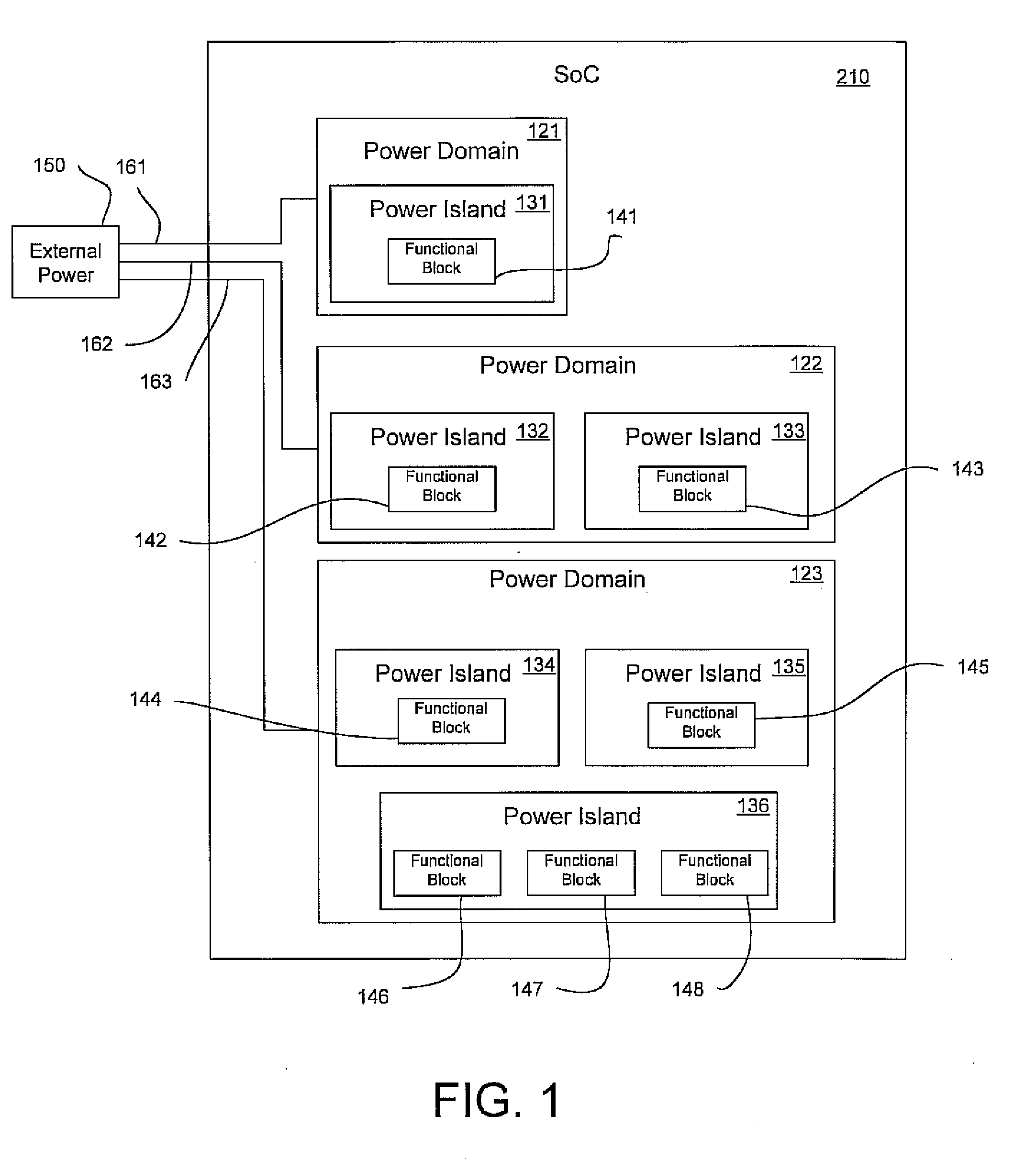

Integrated circuit device having power domains and partitions based on use case power optimization

ActiveUS20090201082A1Minimize leakage currentSolve the large leakage currentEnergy efficient ICTDigital data processing detailsEngineeringPower domains

A programmable SoC (system on a chip) having optimized power domains and power islands. The SoC is an integrated circuit device including a plurality of power domains, each of the power domains having a respective voltage rail to supply power to the power domain. A plurality of power islands are included within the integrated circuit device, wherein each power domain includes at least one power island. A plurality of functional blocks are included within the integrated circuit device, wherein each power island includes at least one functional block. Each functional block is configured to provide a specific device functionality. The integrated circuit device adjusts power consumption in relation to a requested device functionality by individually turning on or turning off power to a selected one or more power domains, and for each turned on power domain, individually power gating one or more power islands.

Owner:NVIDIA CORP

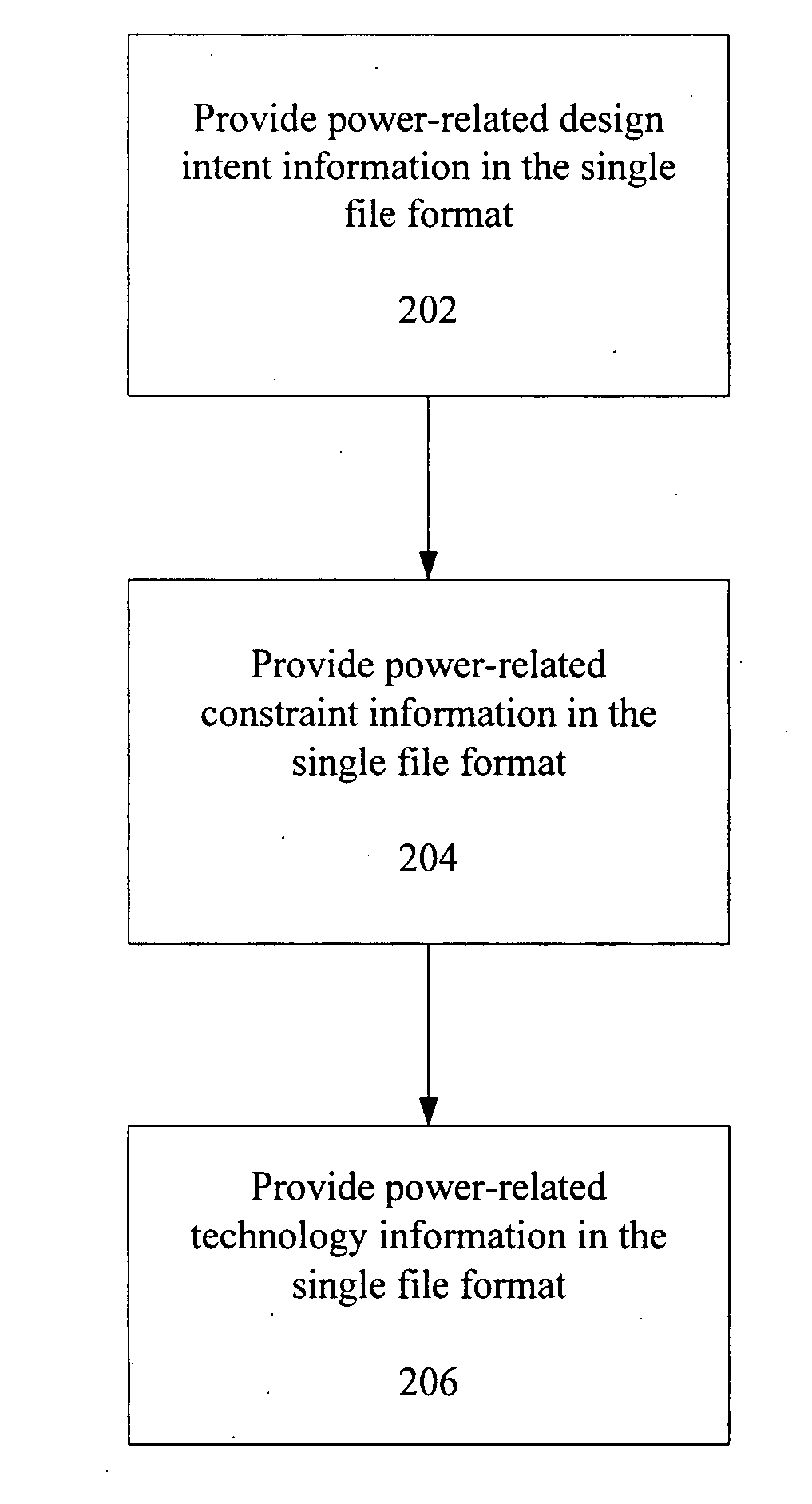

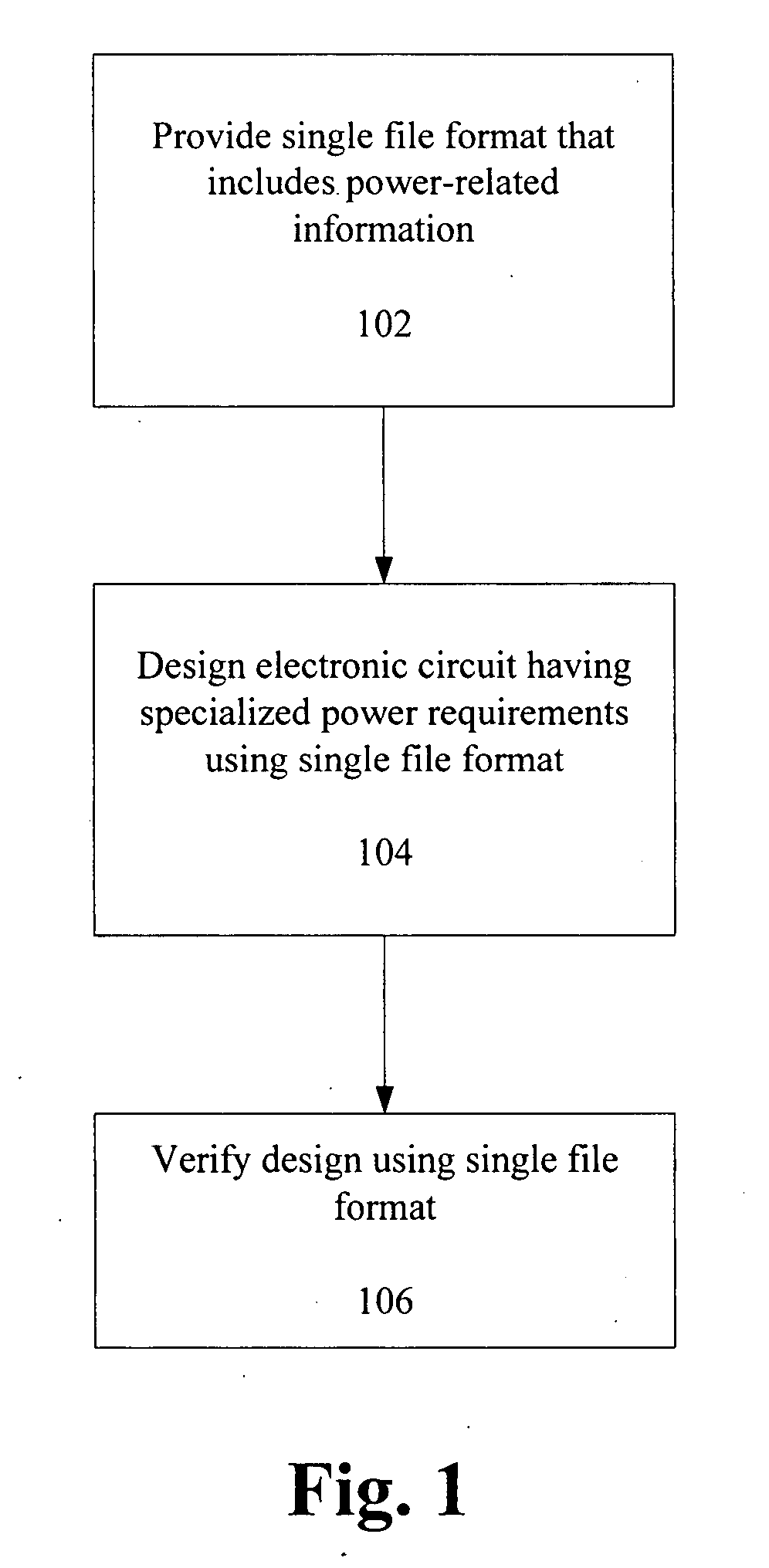

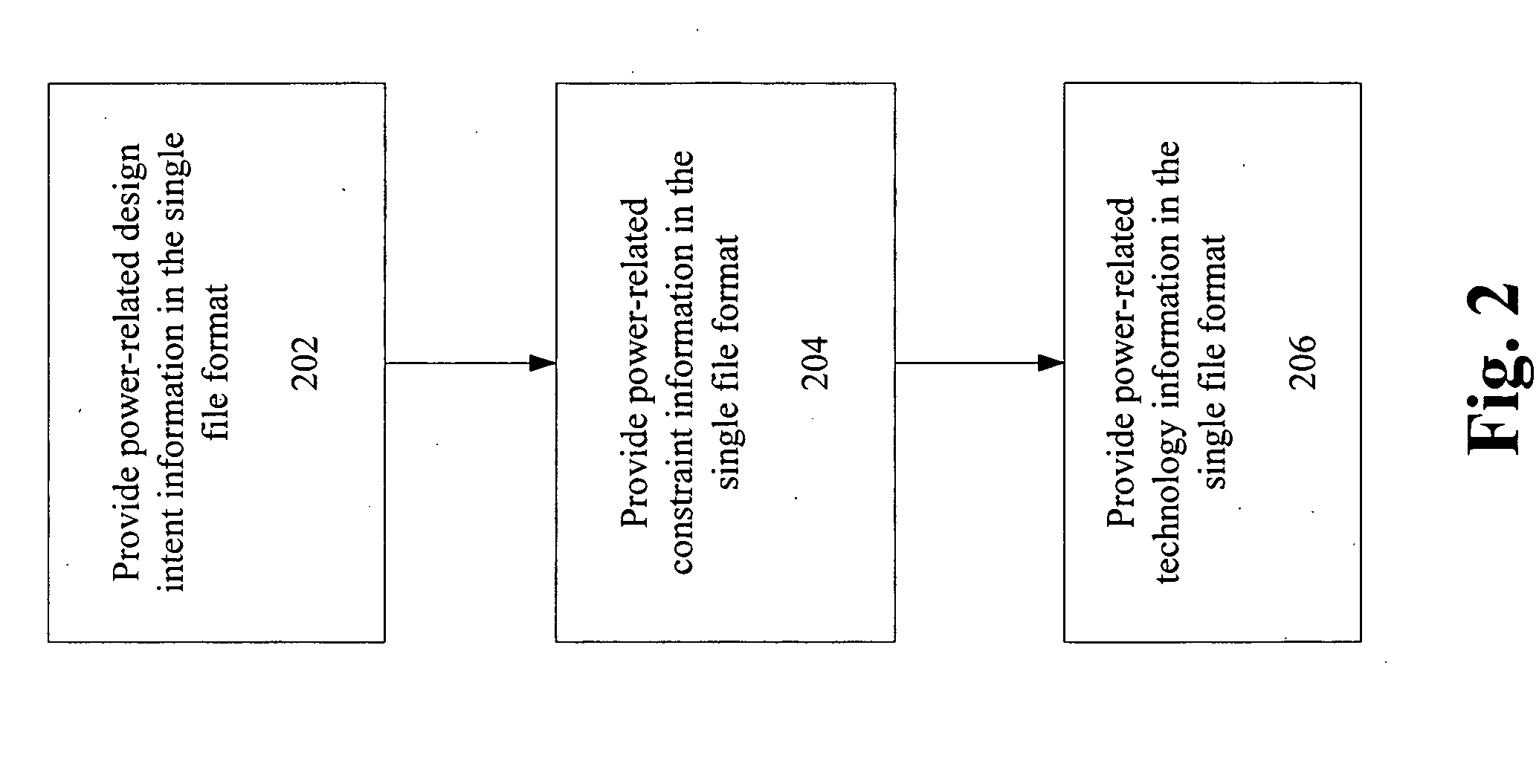

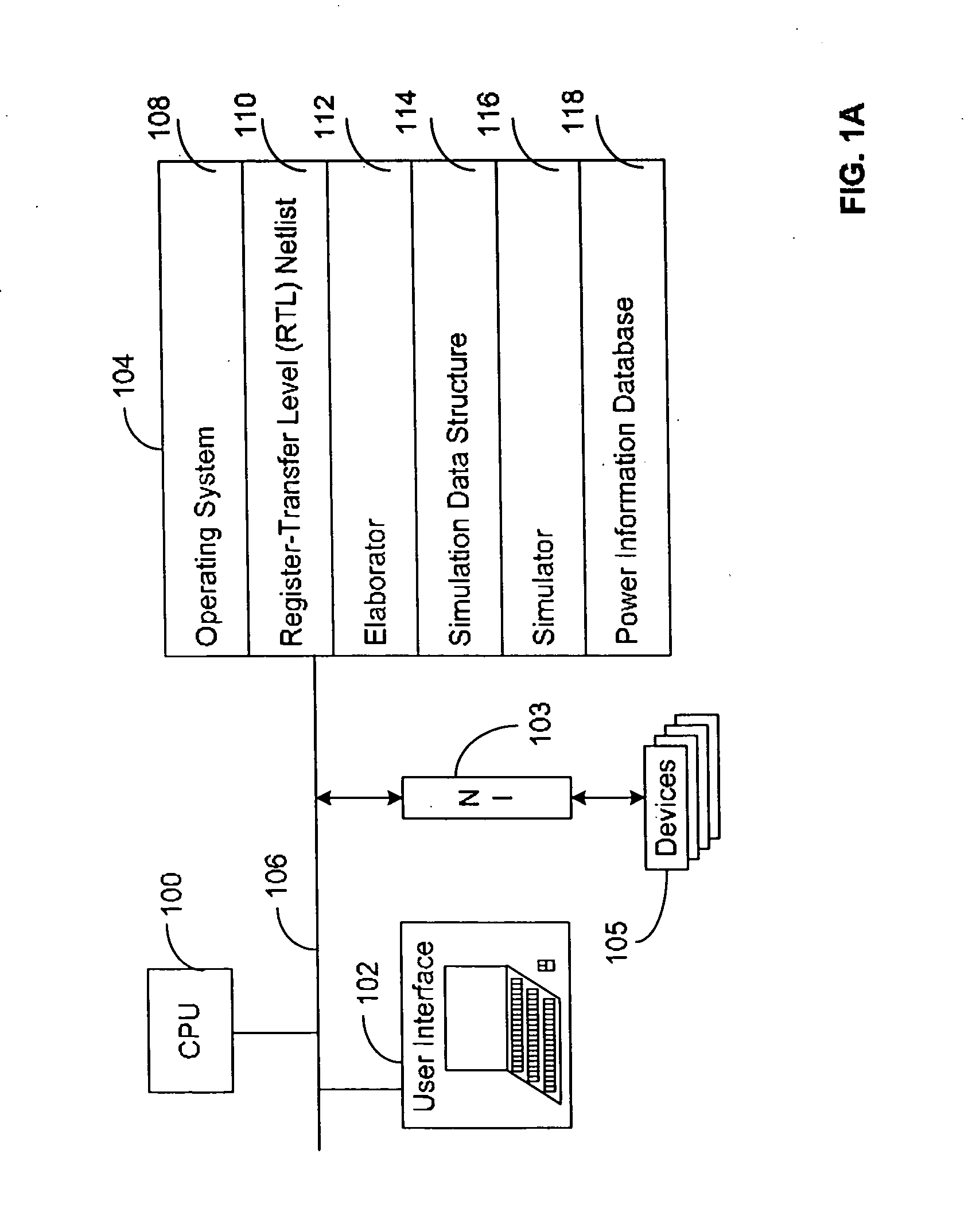

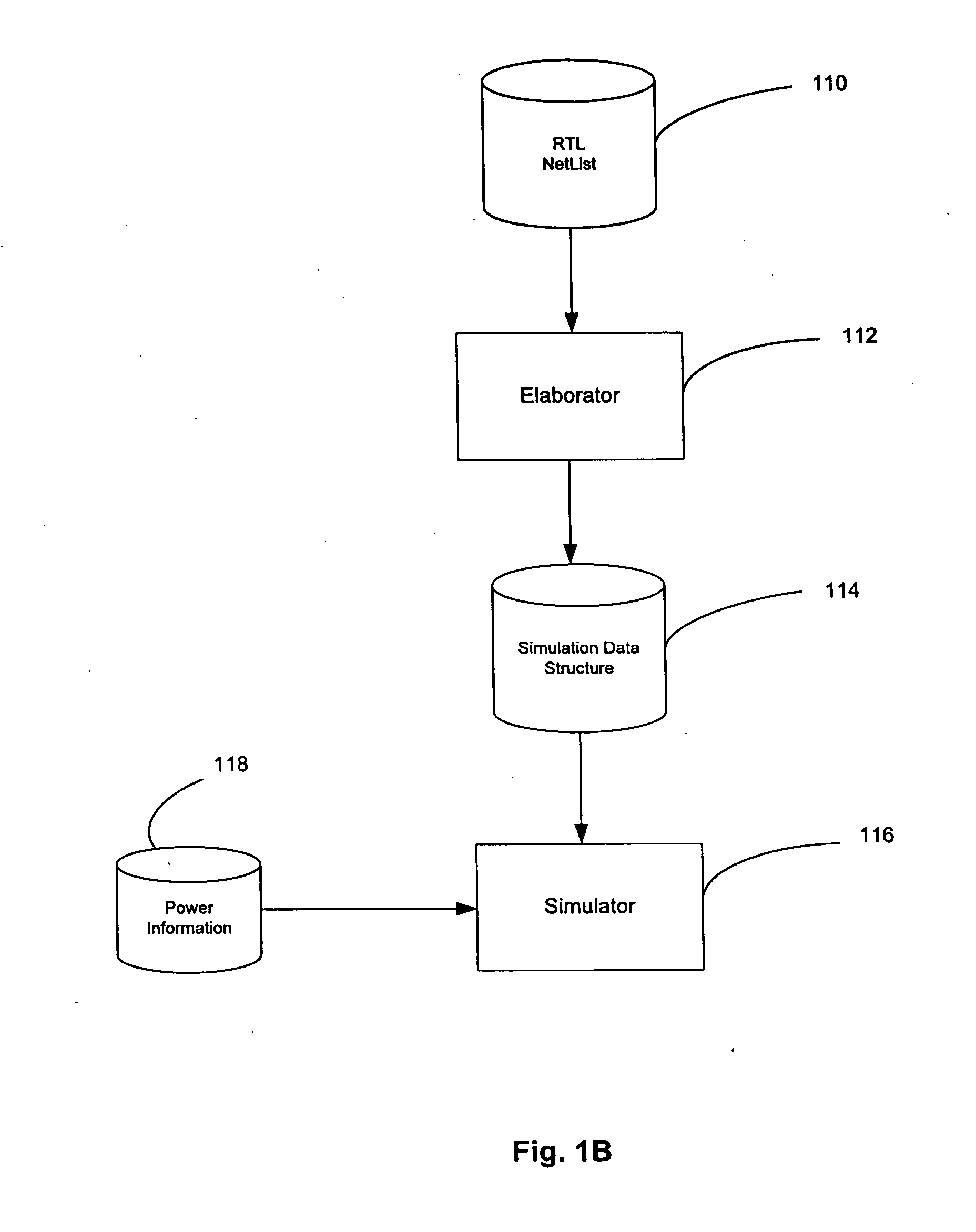

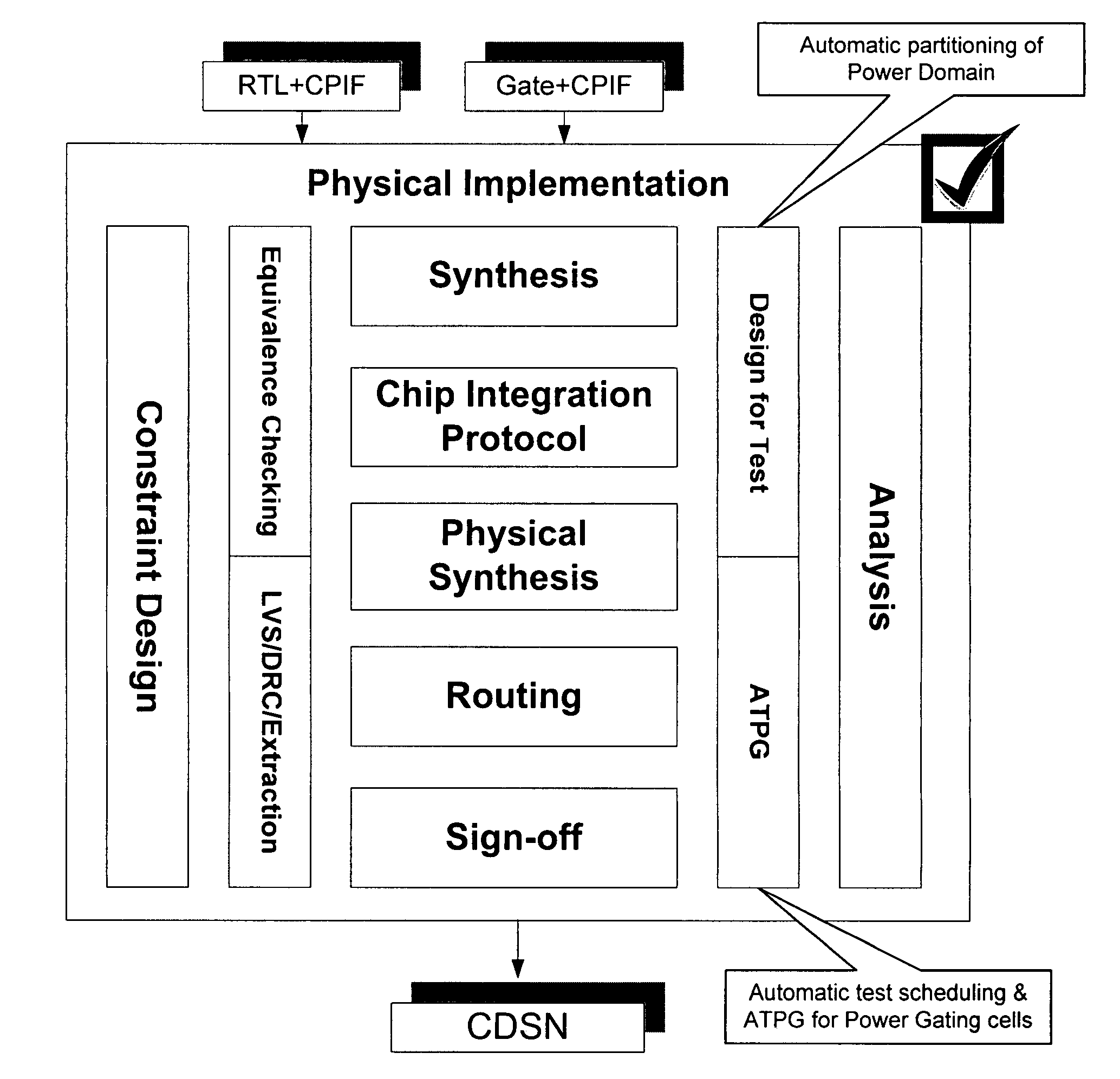

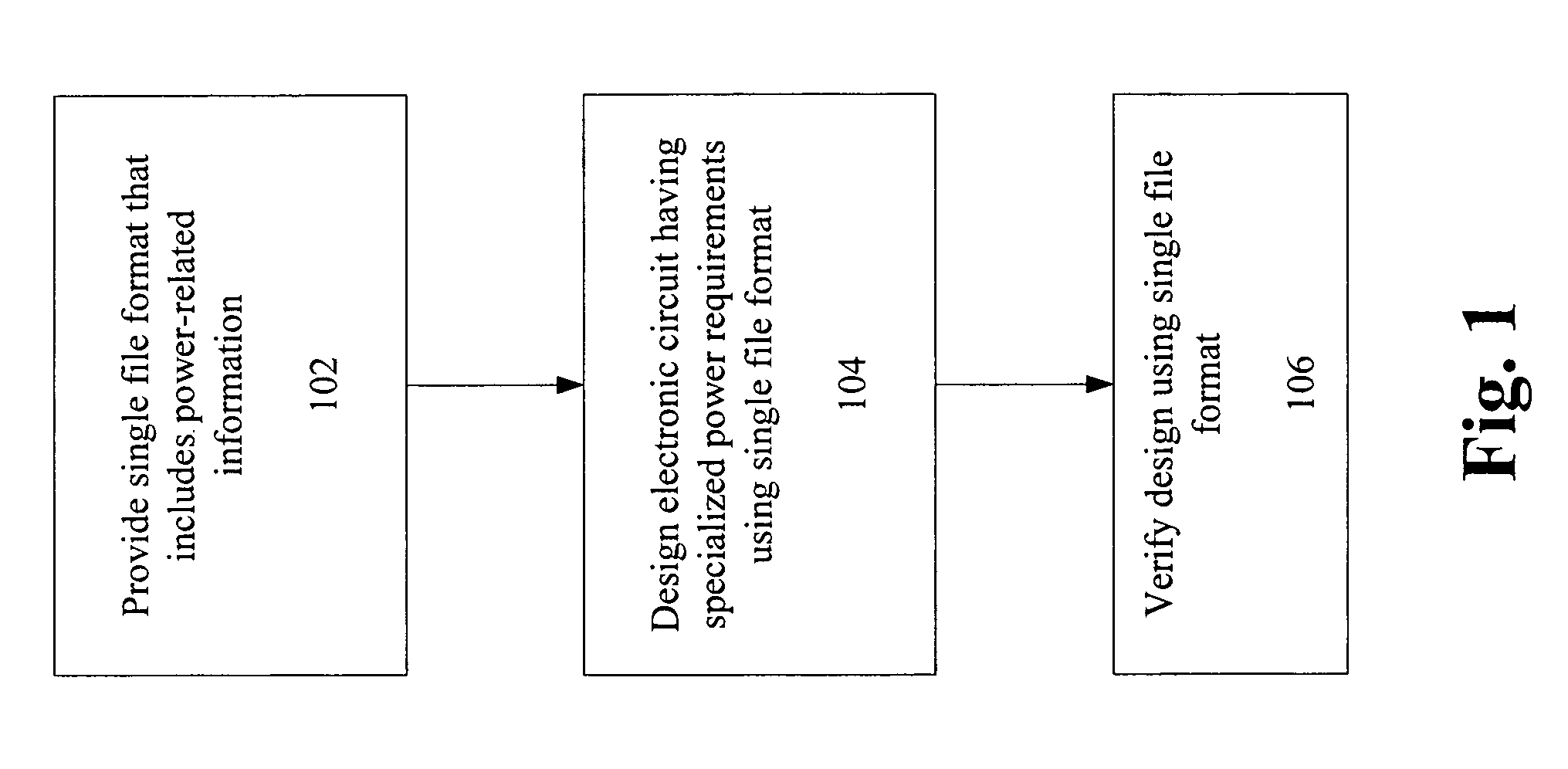

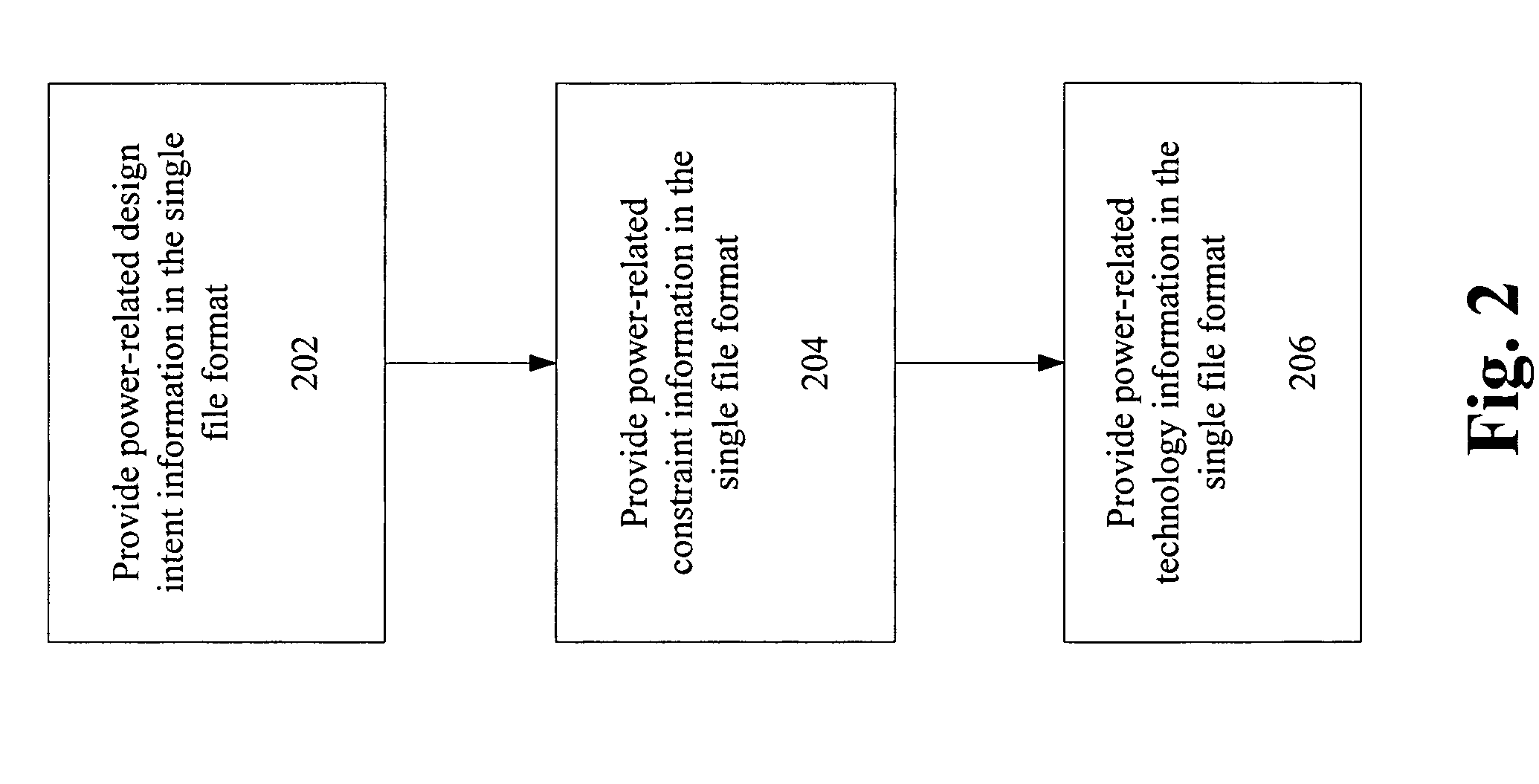

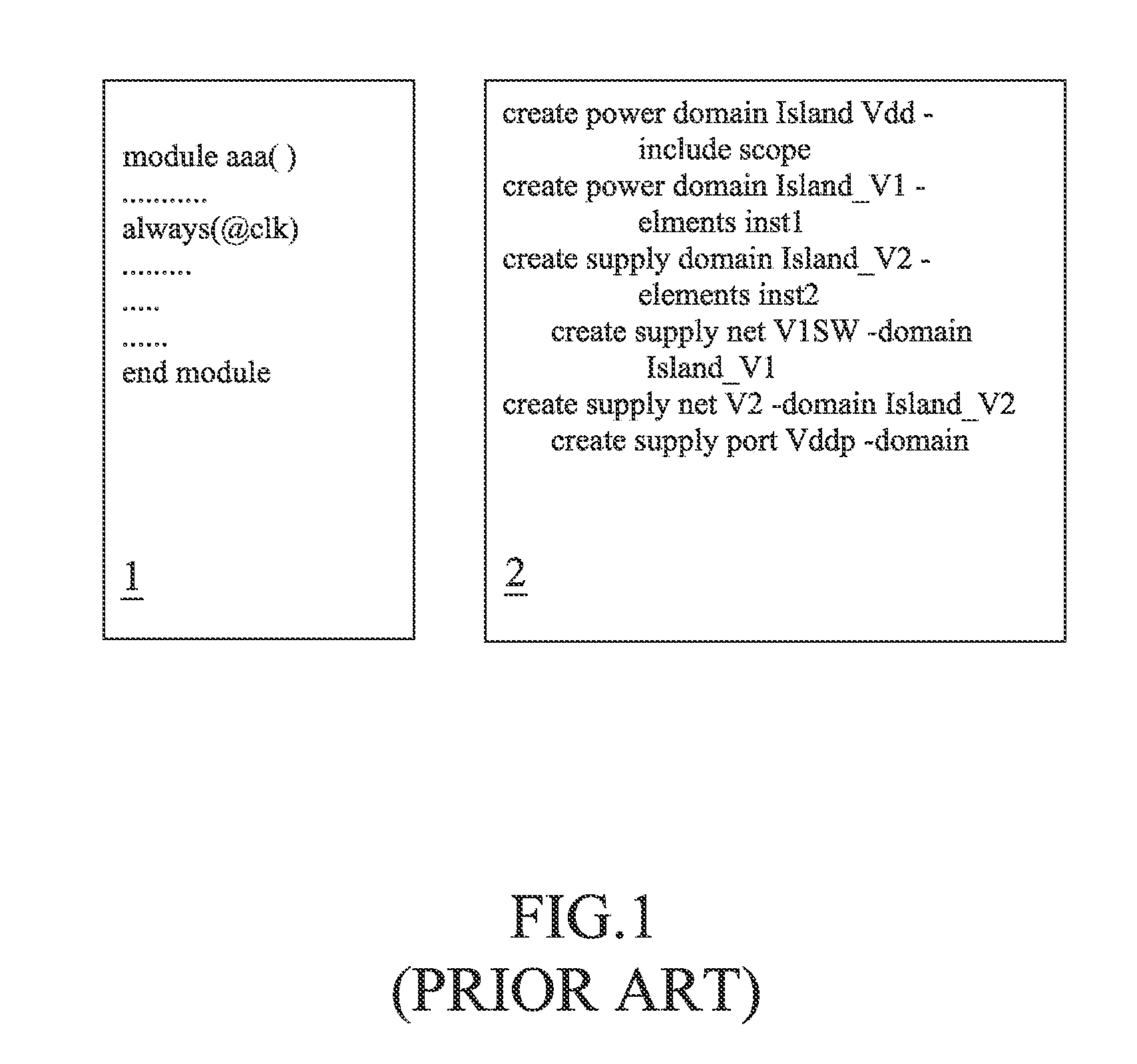

Method and mechanism for implementing electronic designs having power information specifications background

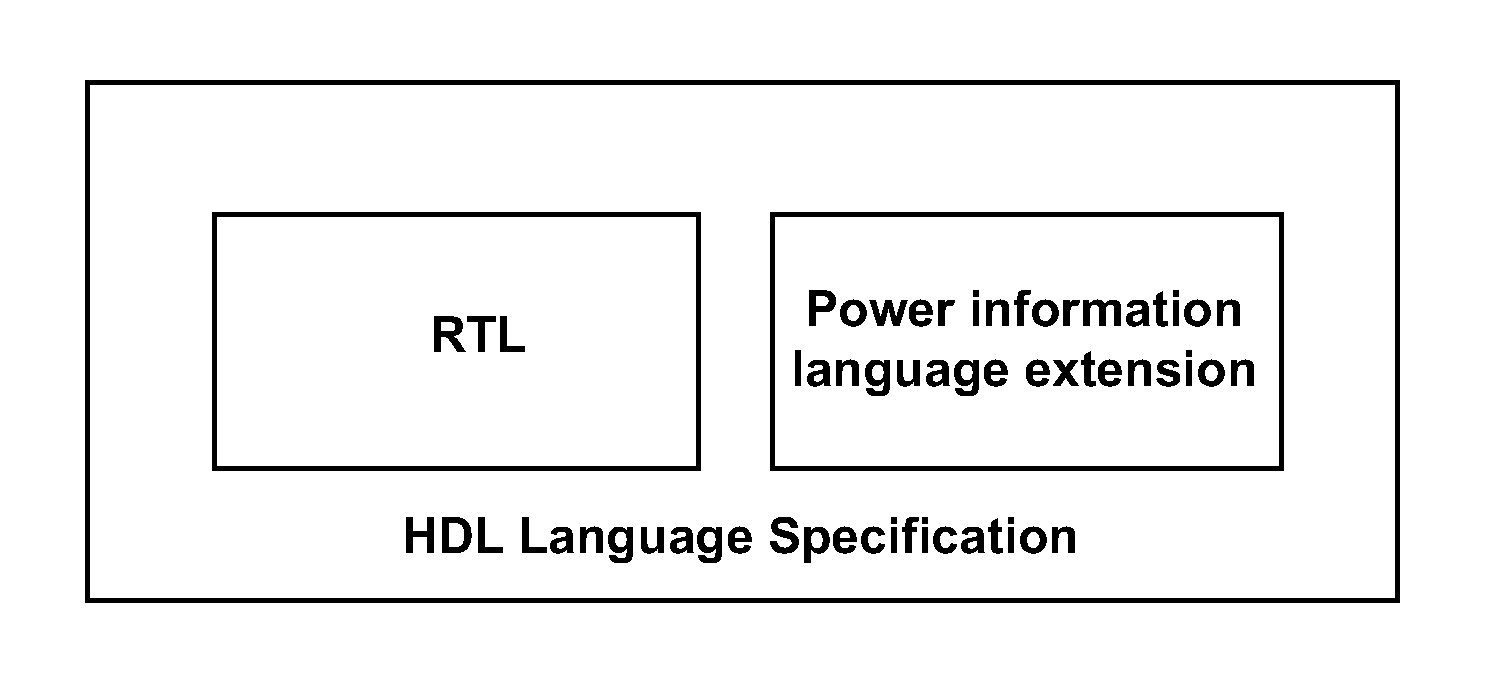

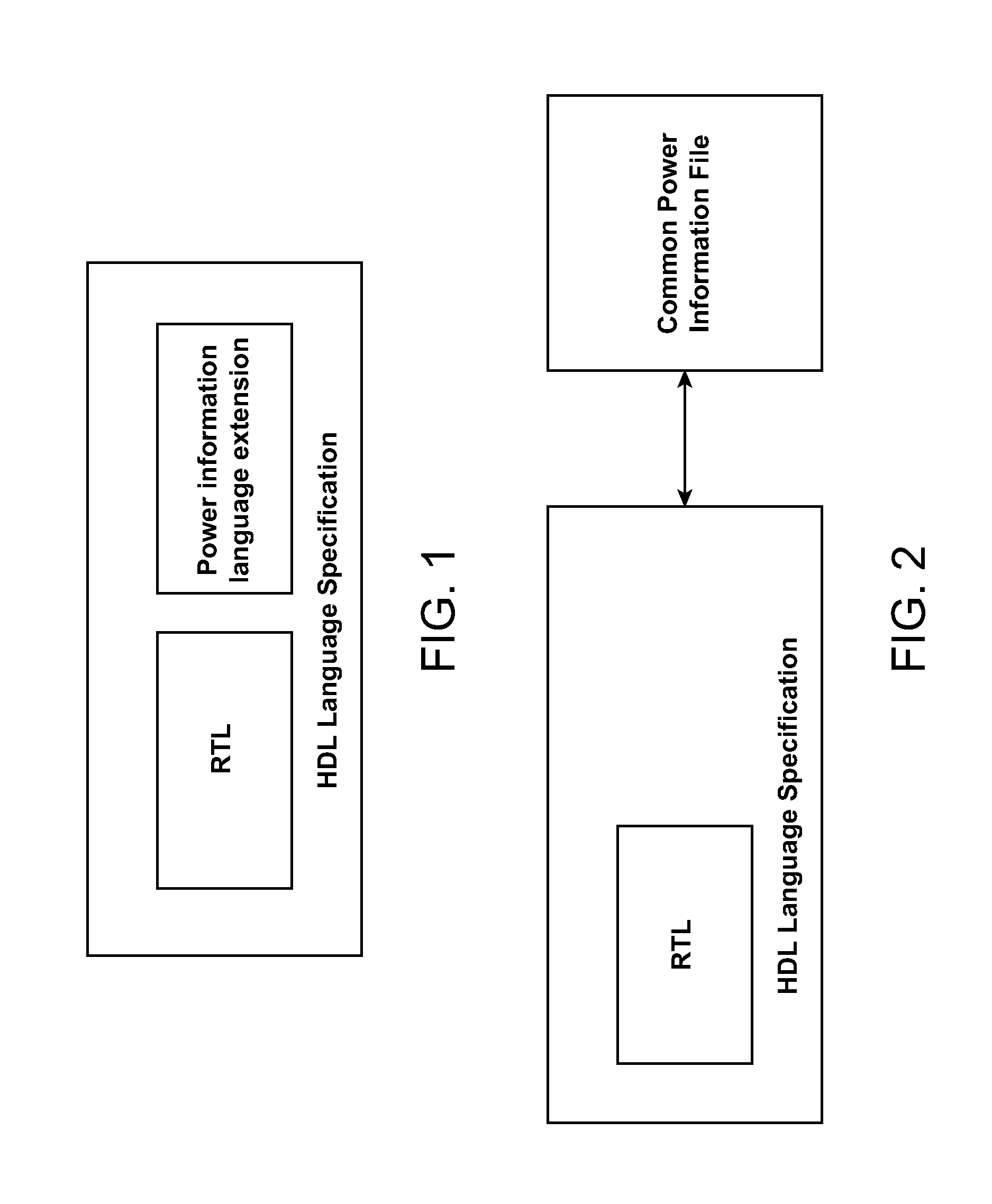

ActiveUS20070245285A1Low power designCAD circuit designSoftware simulation/interpretation/emulationPower modeElectronic design

A method of adding power control circuitry to a circuit design at each of an RTL and a netlist level comprising: demarcating multiple power domains within the circuit design; specifying multiple power modes each power mode corresponding to a different combination of on / off states of the multiple demarcated power domains; and defining isolation behavior relative to respective power domains.

Owner:CADENCE DESIGN SYST INC

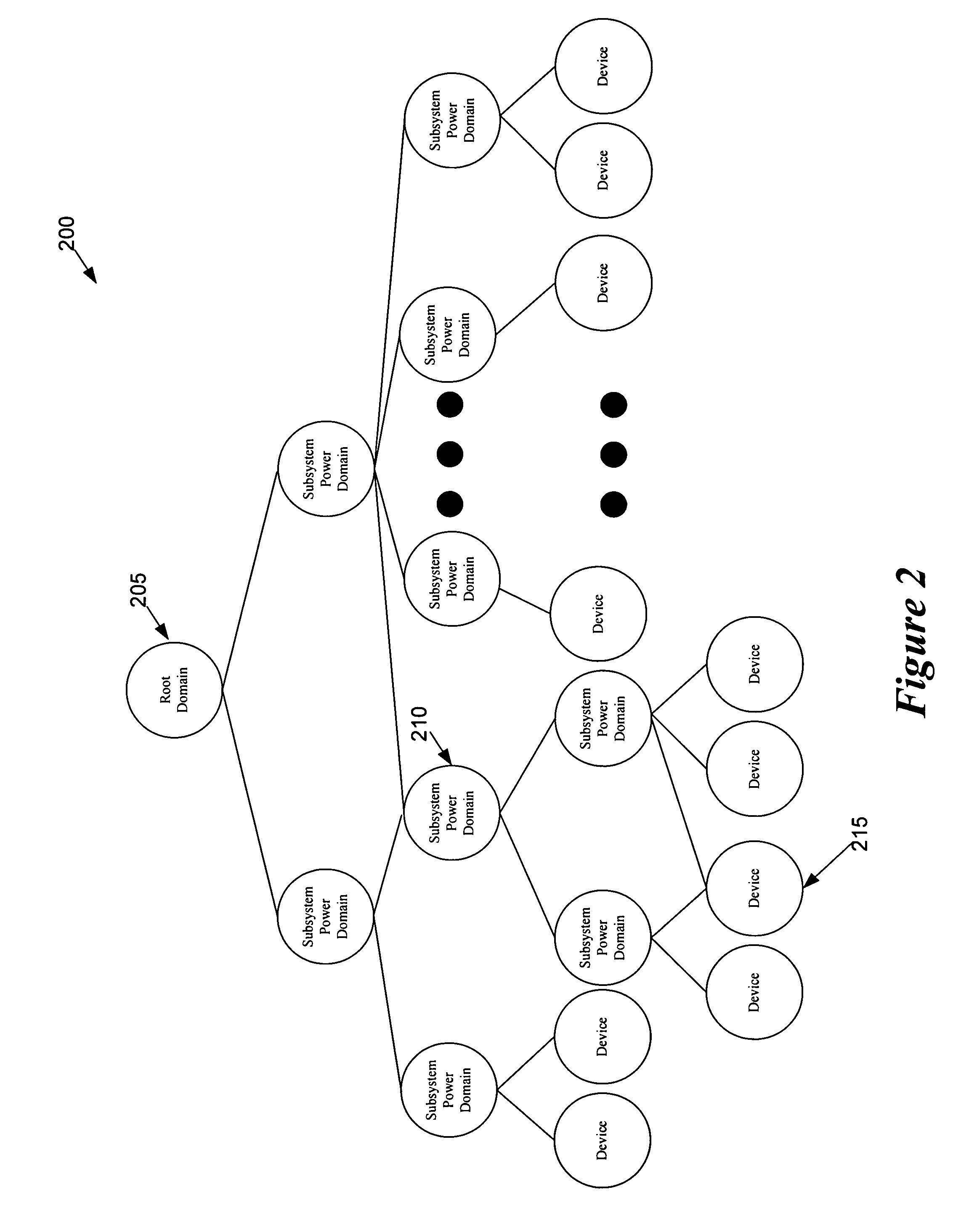

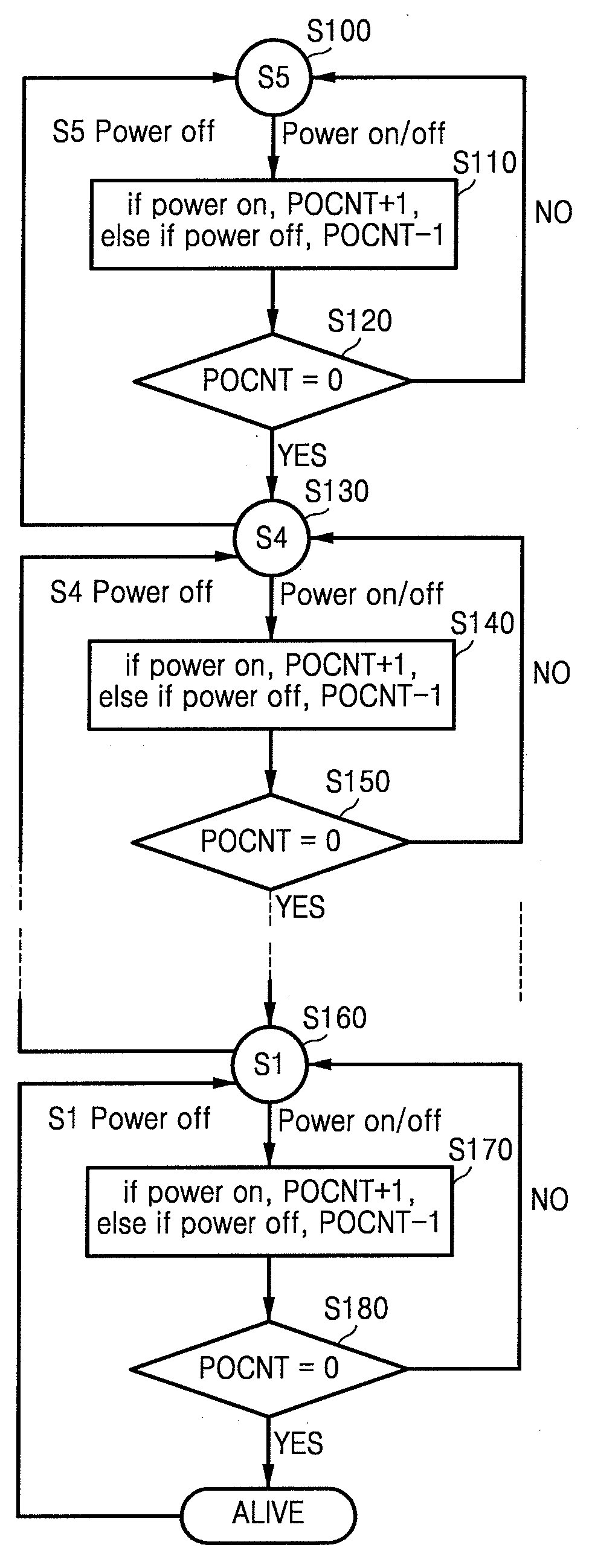

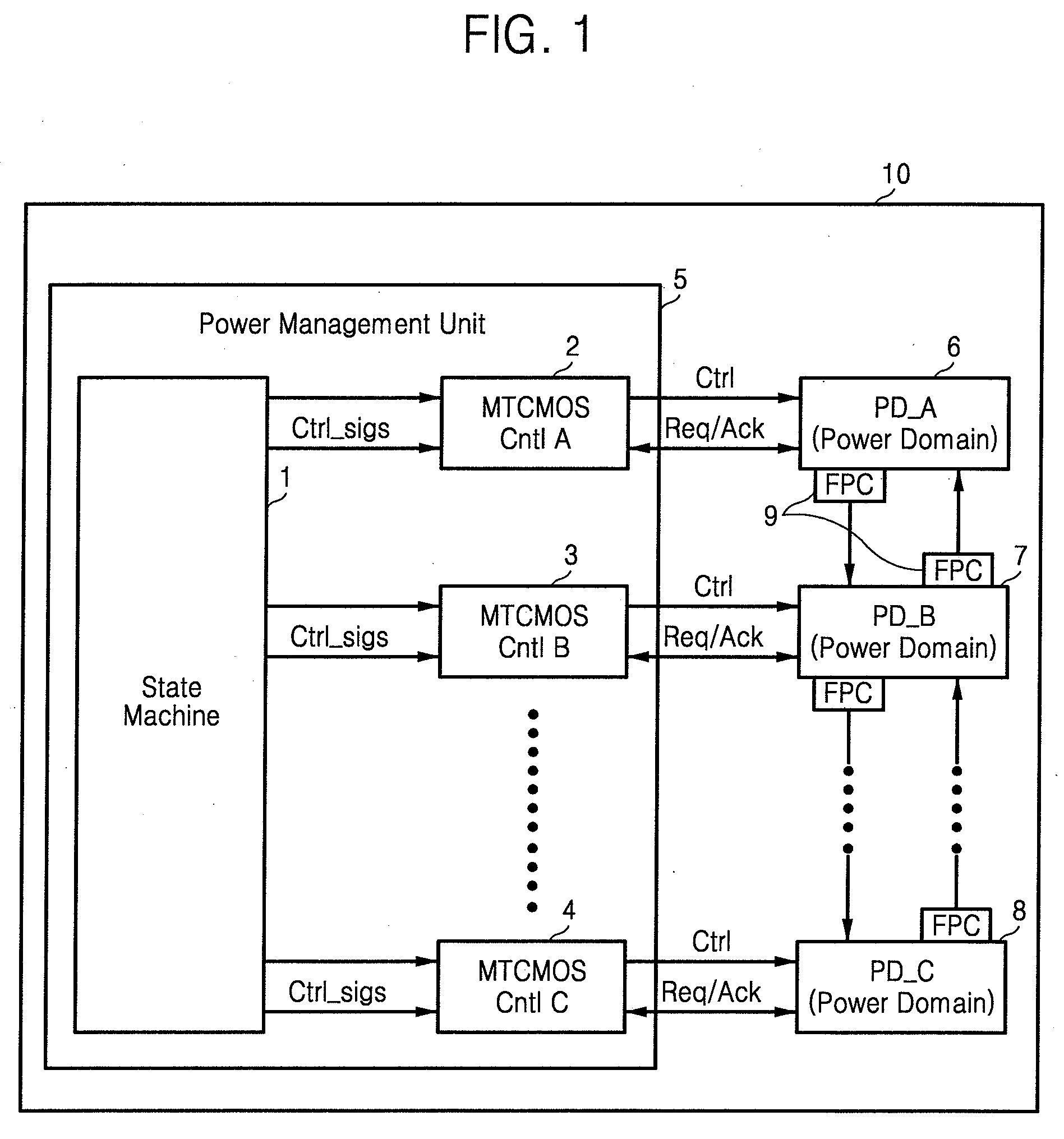

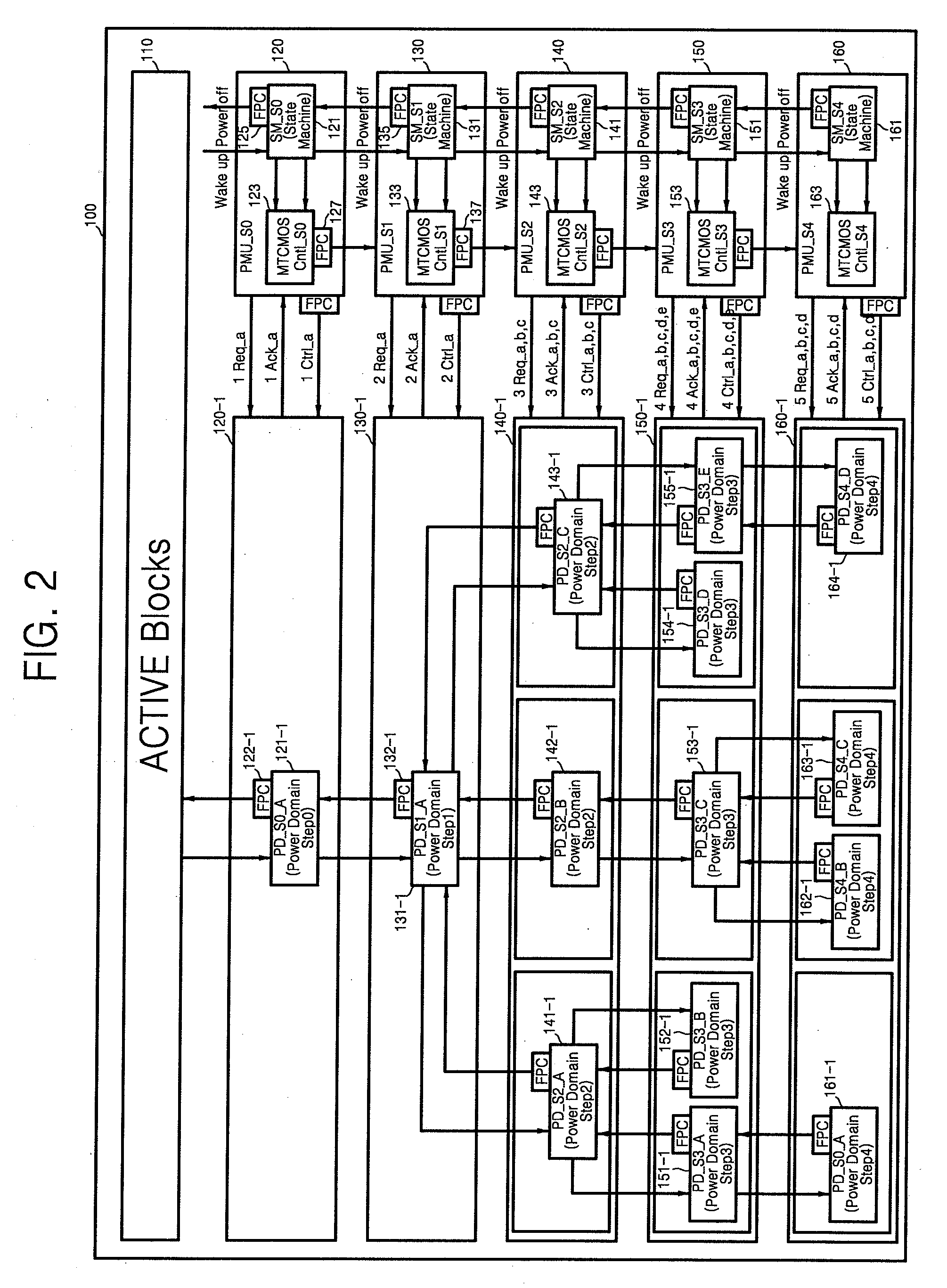

Power control apparatus and method thereof

InactiveUS20080178031A1Power controlEnergy efficient ICTVolume/mass flow measurementPower Management UnitEngineering

A power control apparatus including an active block in which power is always maintained in an on state and an N number of power management units having a hierarchical structure where N is a natural number greater than or equal to 1. Each of the power management units controls power of at least one power domain block Power of a first power management unit of the N number of the power management units is controlled by the active block, and power of an Nth power management unit of the N number of the power management units is controlled by an (N-1)th power management unit.

Owner:SAMSUNG ELECTRONICS CO LTD

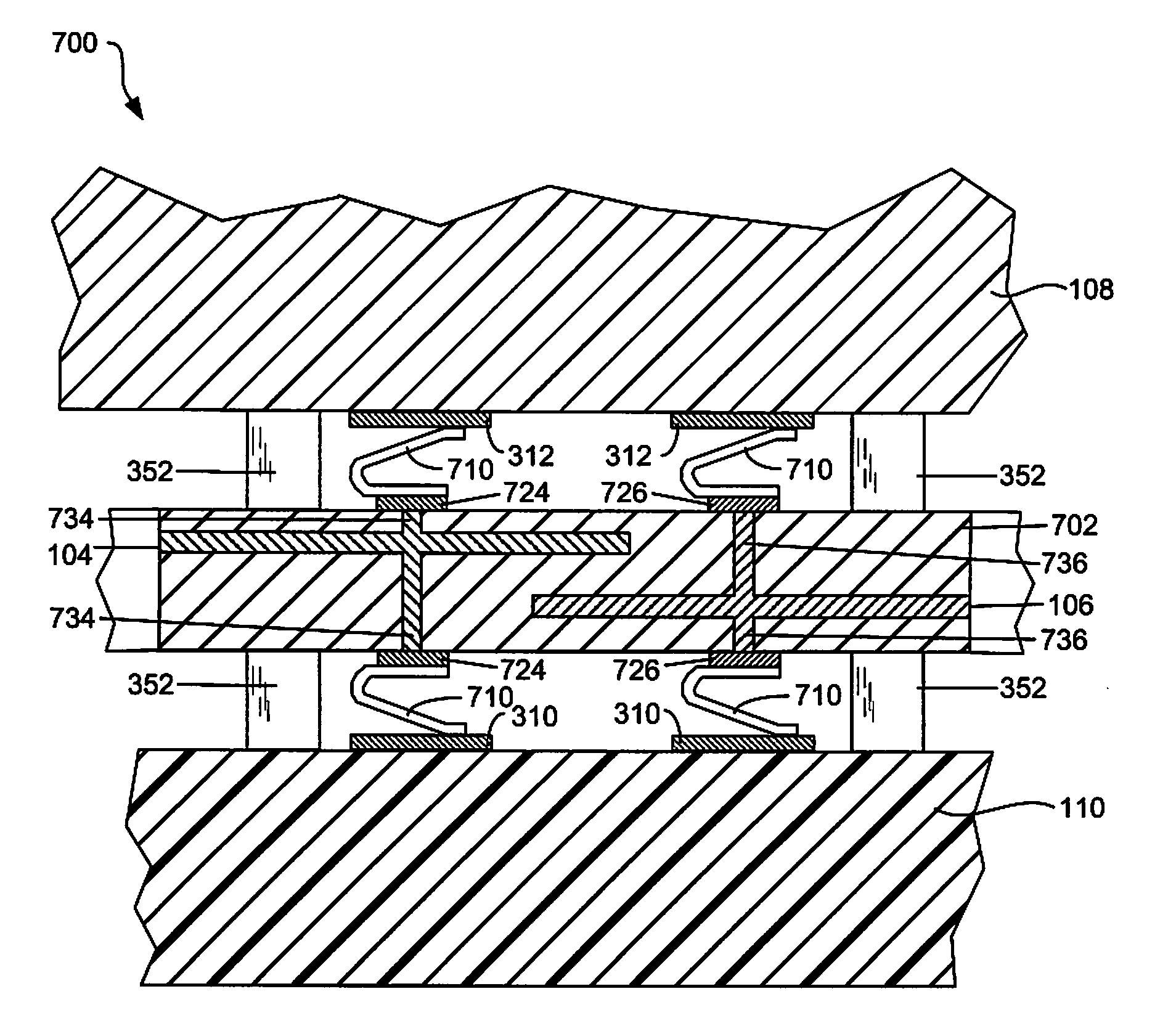

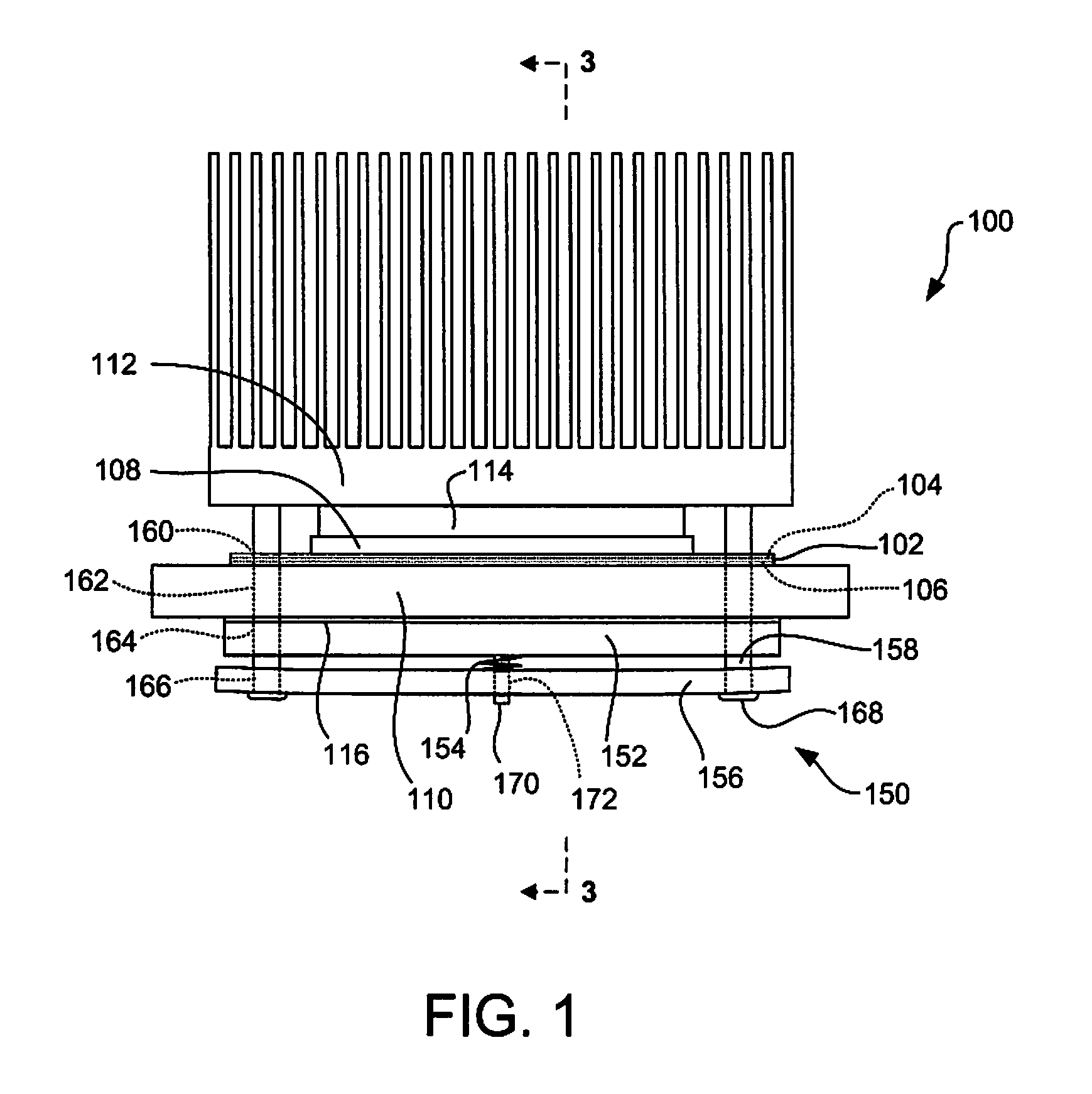

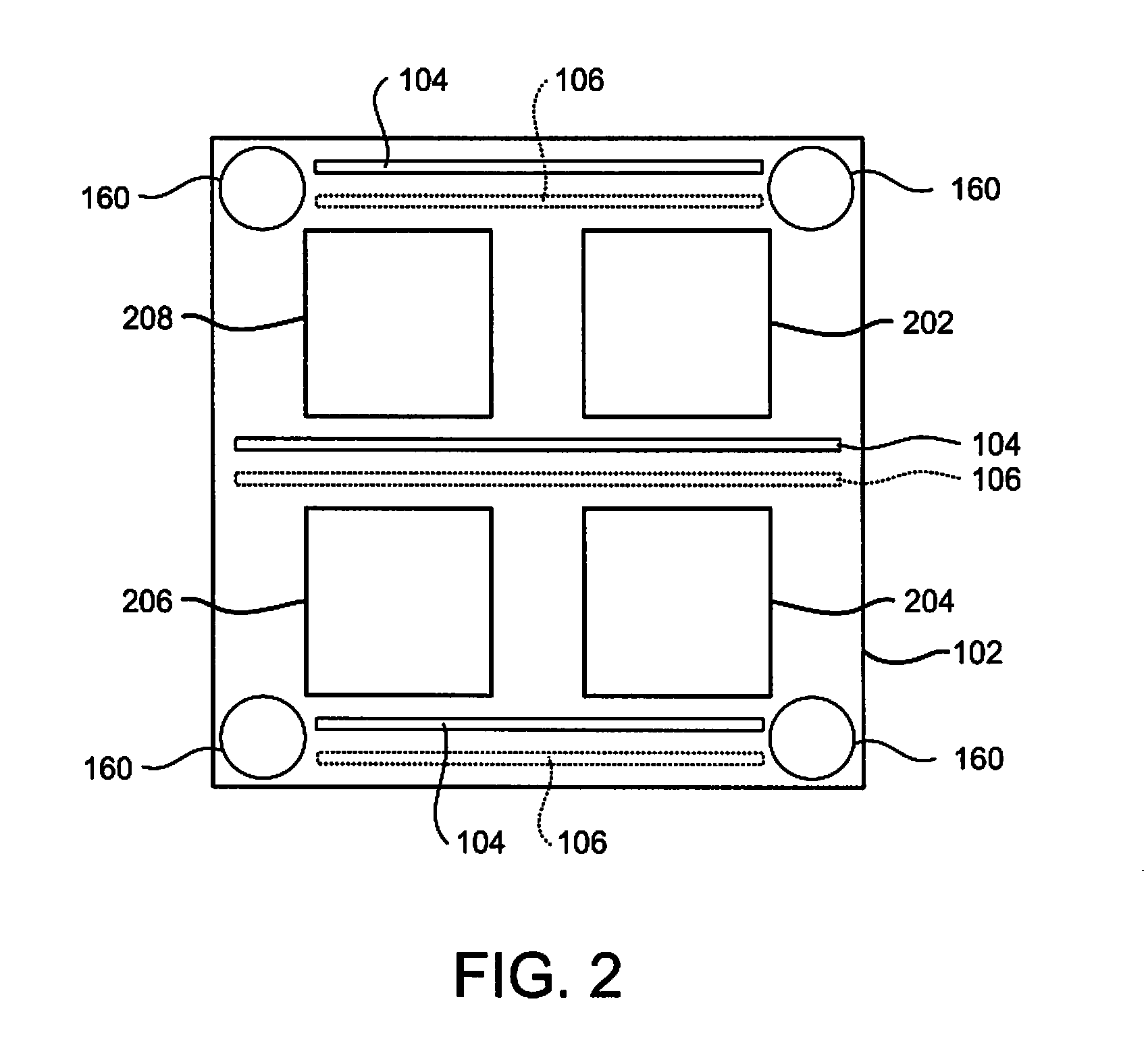

Method and Apparatus for Electrically Connecting Two Substrates Using a Land Grid Array Connector Provided with a Frame Structure Having Power Distribution Elements

InactiveUS20080239683A1Line/current collector detailsElectrically conductive connectionsPower cableInterposer

A method and apparatus for electrically connecting two substrates using a land grid array (LGA) connector provided with a frame structure having power distribution elements. In an embodiment, the frame structure includes a frame having one or more conductive layers sandwiched between non-conductive layers. The frame may, for example, be a printed wire board (PWB) having power planes that distribute power from a first substrate (e.g., a system PWB) and / or a power cable to a second substrate (e.g., an electronic module). The frame includes one or more apertures configured to receive an LGA interposer for electrically connecting the two substrates. Preferably, the frame includes four apertures arranged in quadrants that each receive an interposer, and at least one power plane extends between two quadrants and / or adjacent to a peripheral edge of one or more quadrants in the form of stacked and / or parallel bus bars each defining a power domain.

Owner:IBM CORP

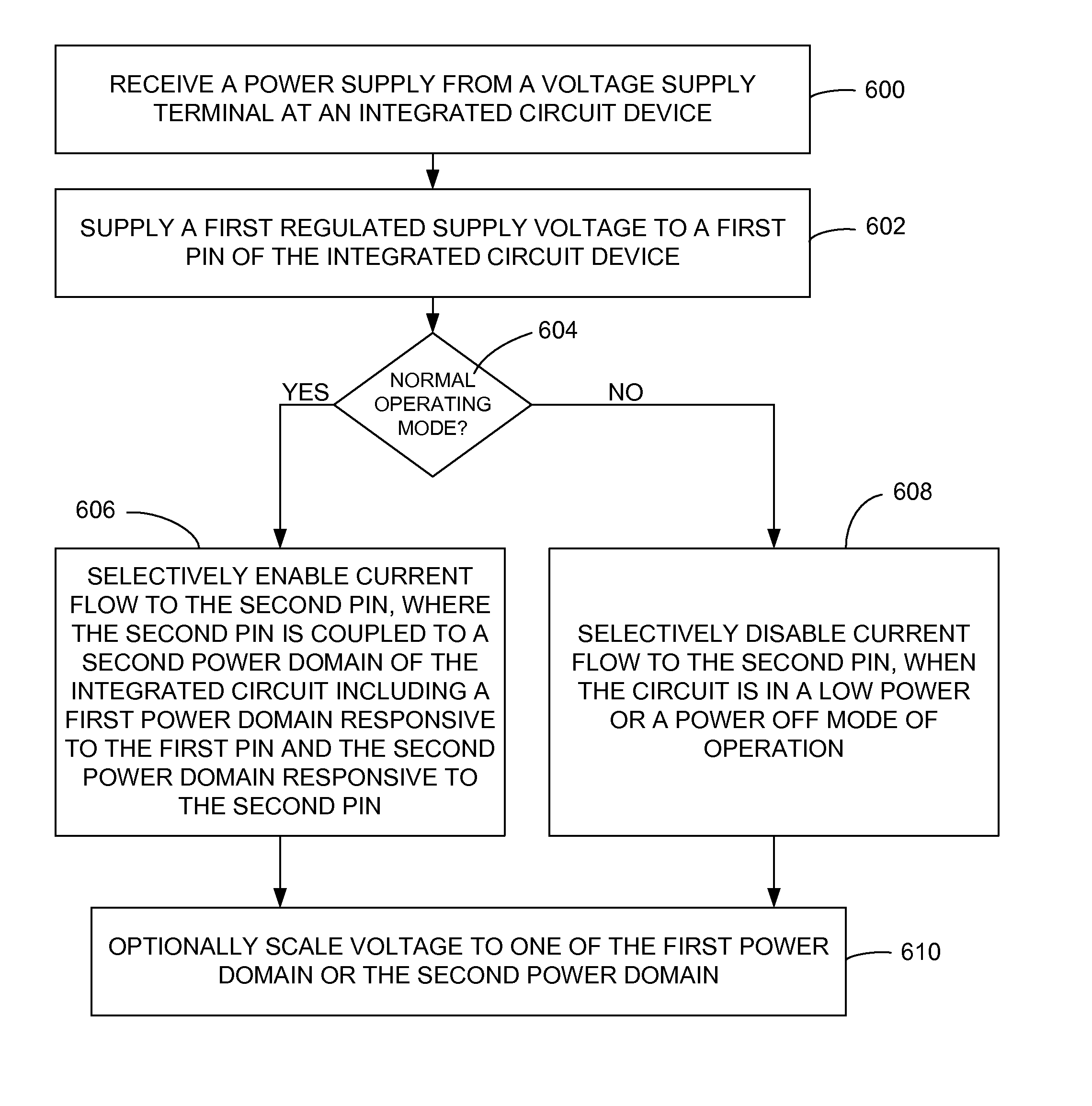

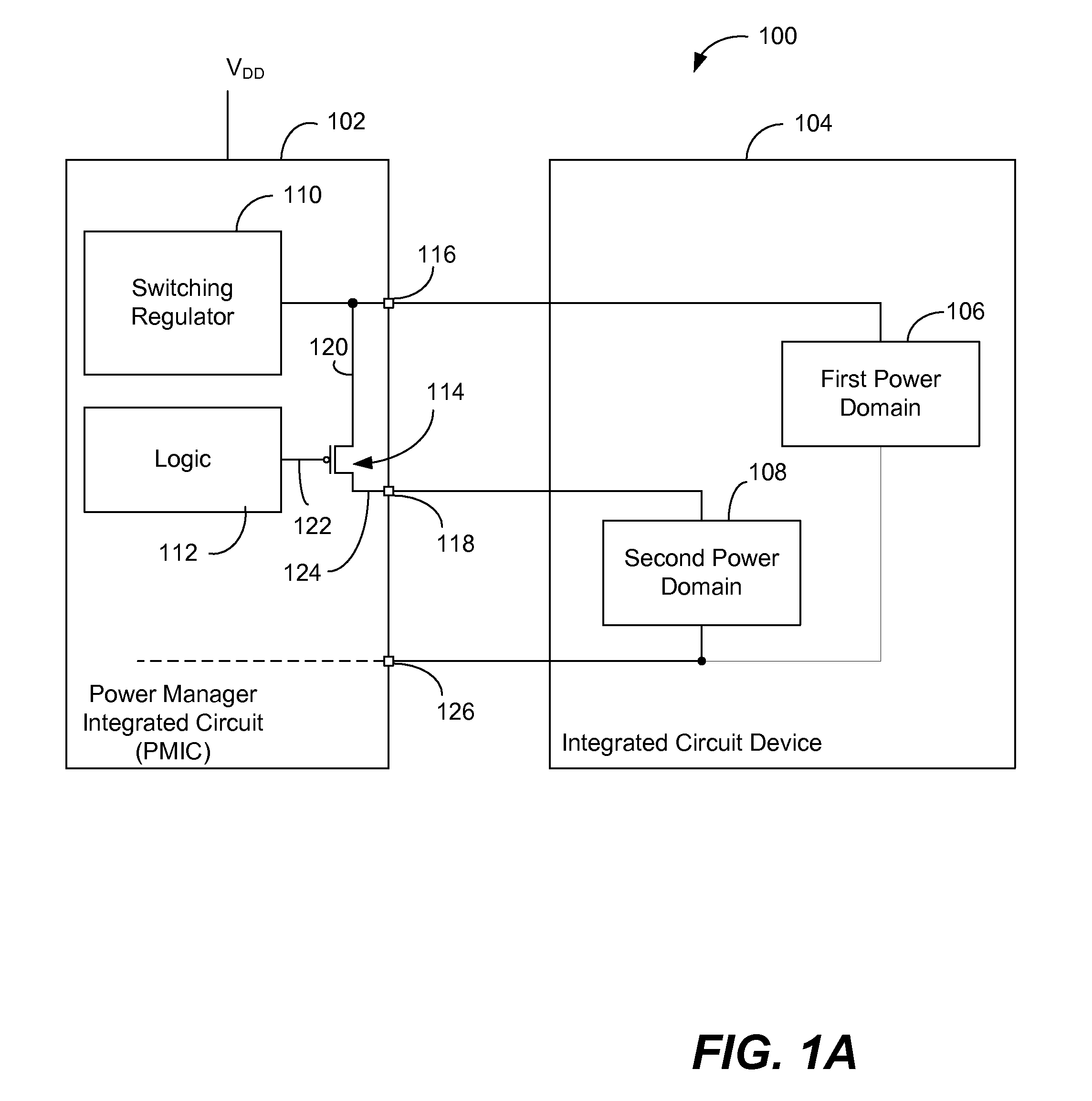

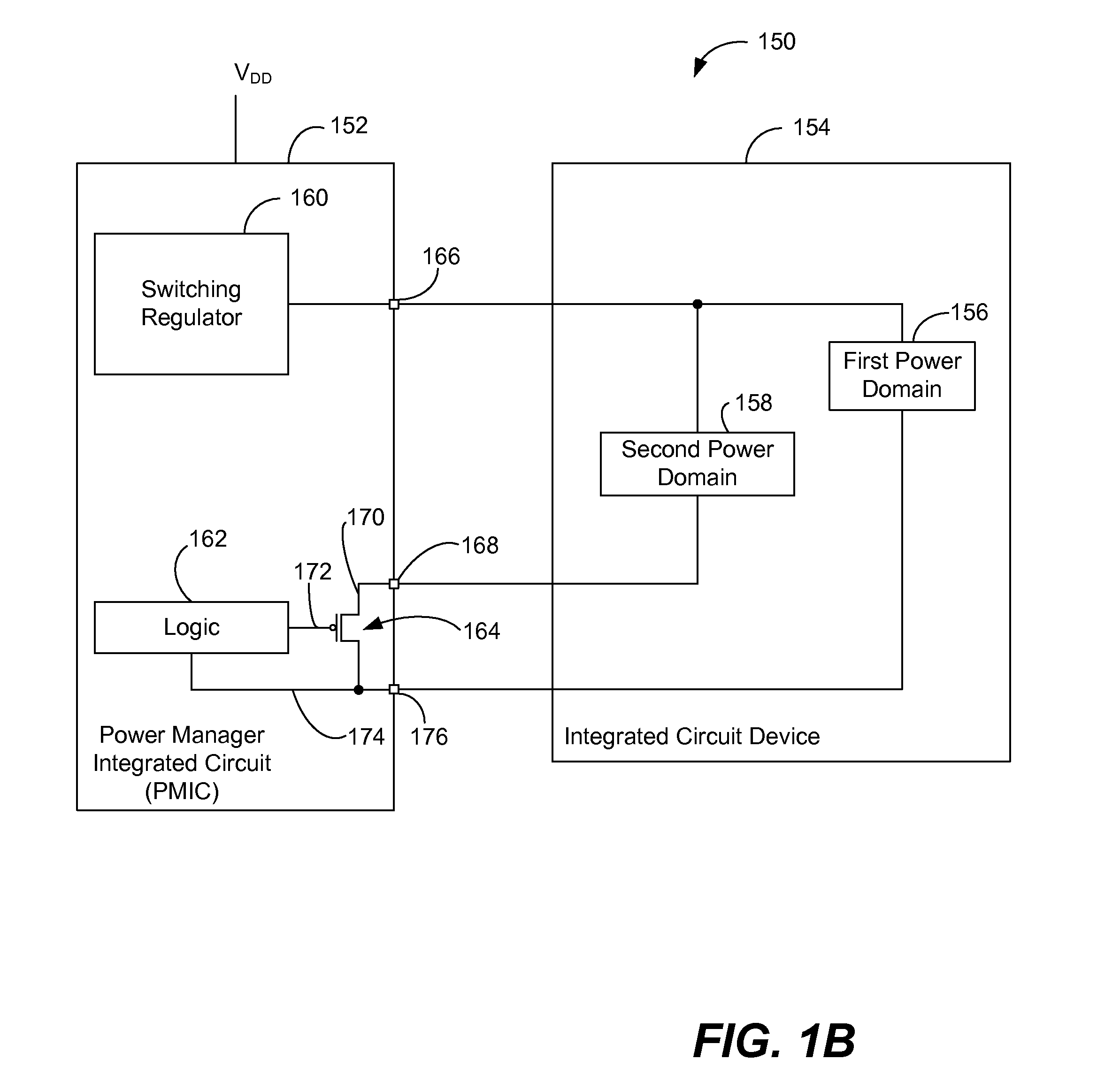

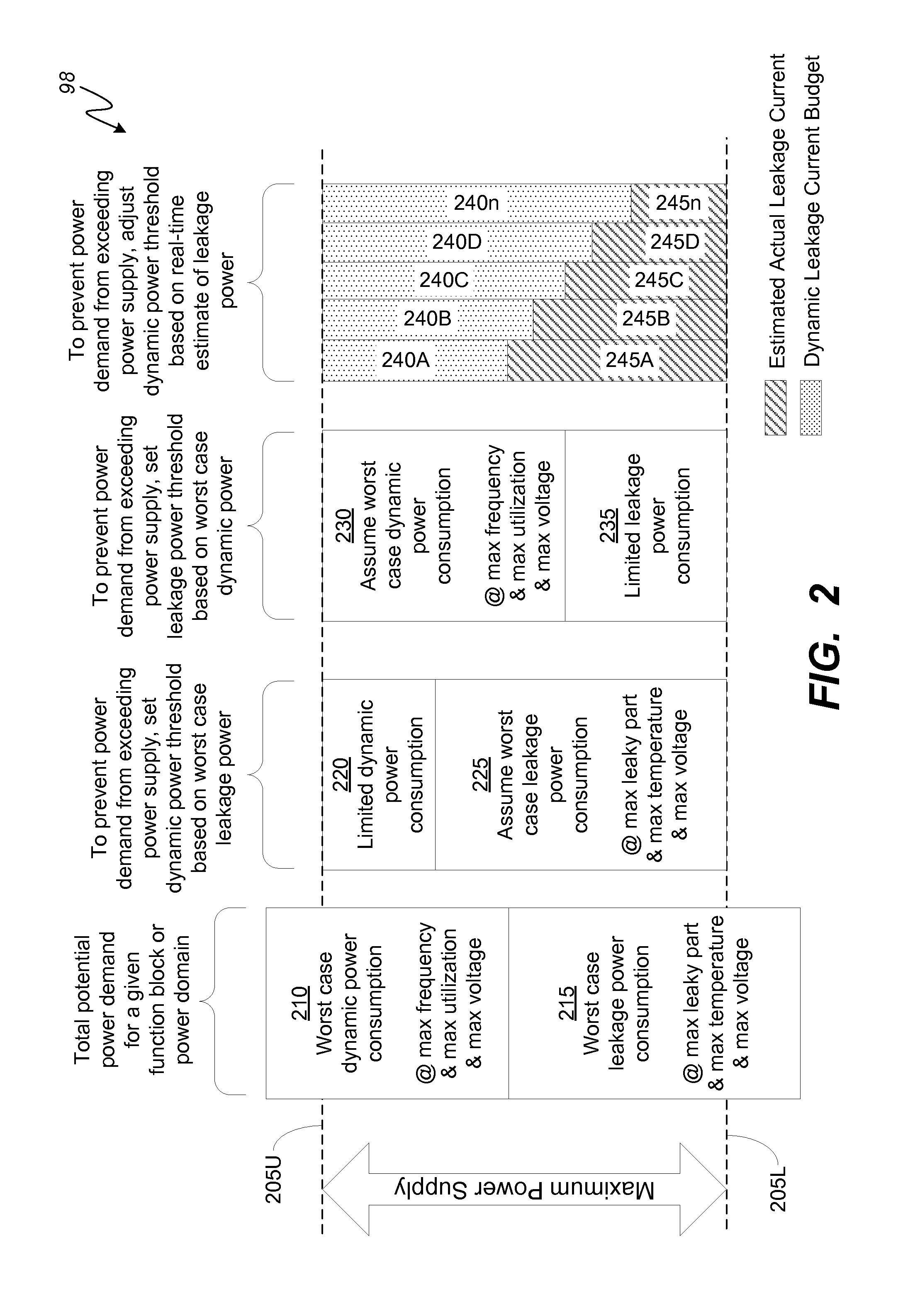

System and method of power distribution control of an integrated circuit

ActiveUS20080067995A1Limit current leakageLow costEfficient power electronics conversionDc-dc conversionDistribution controlControl system

Owner:QUALCOMM INC

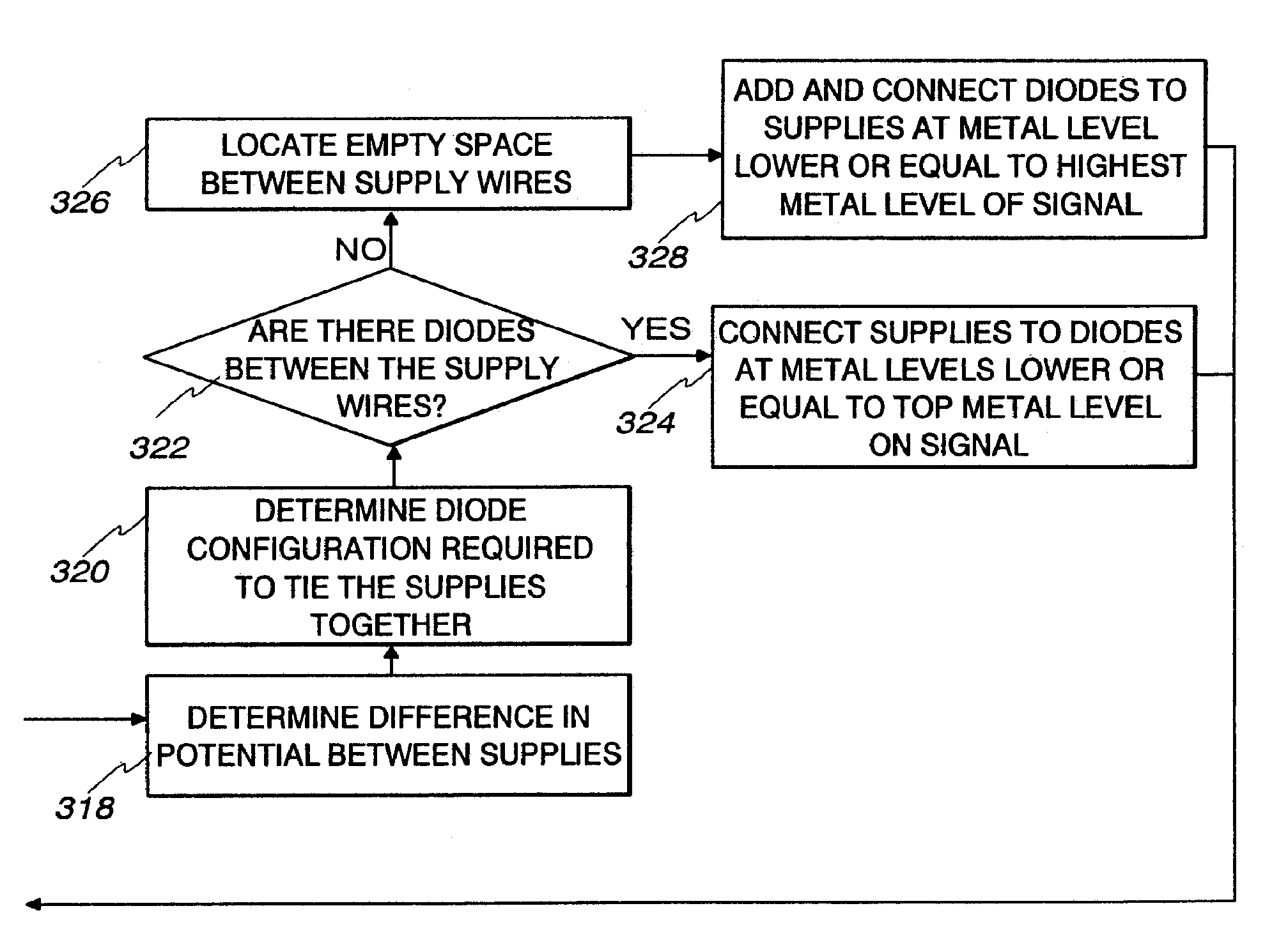

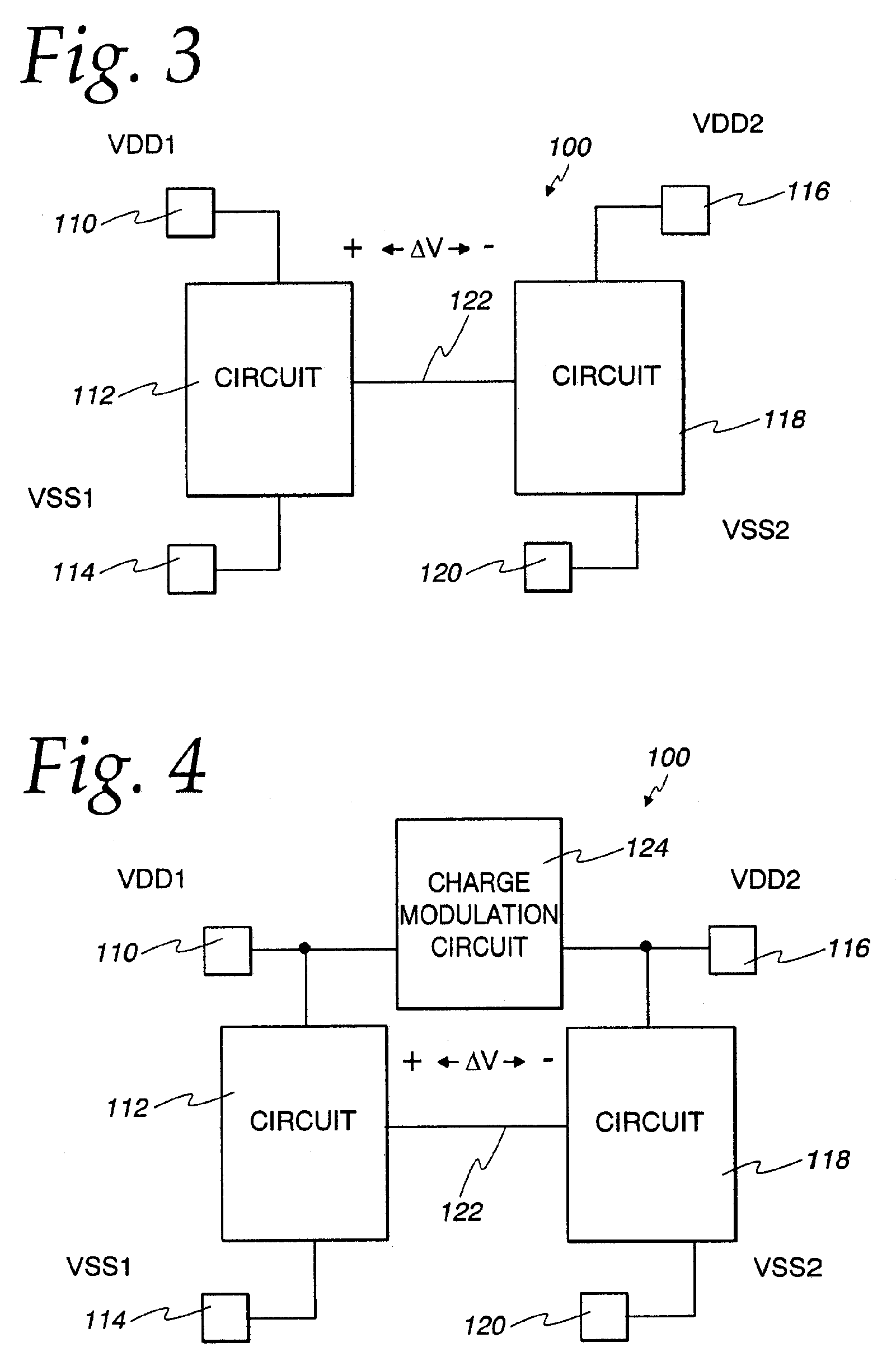

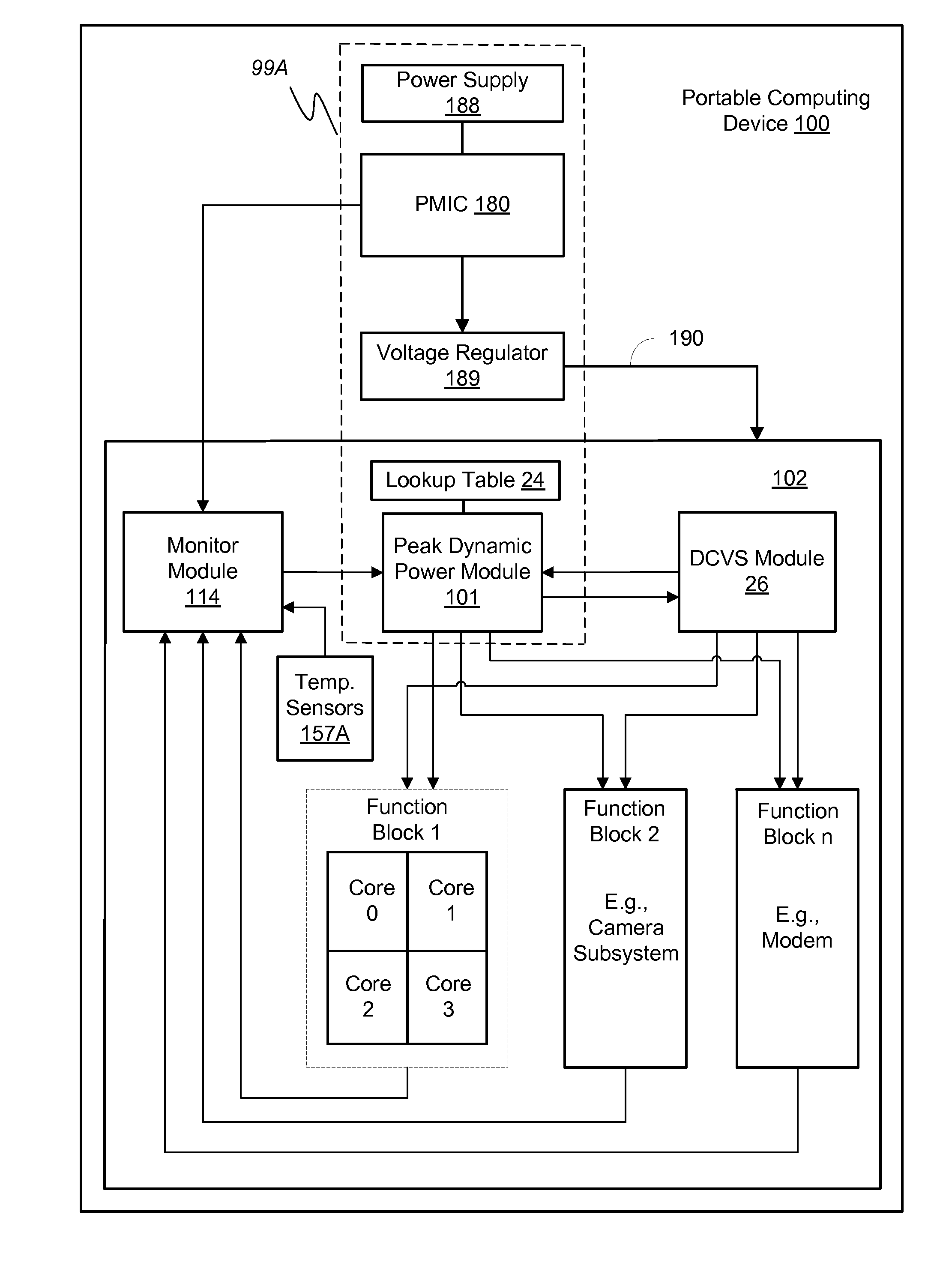

Charge modulation network for multiple power domains for silicon-on-insulator technology

InactiveUS7129545B2Reduce accumulationSemiconductor/solid-state device detailsSolid-state devicesElectricityEngineering

An SOI integrated circuit includes ESD protection on an SOI chip. A first power domain and a second power domain are provided in the SOI chip. In one embodiment, a charge modulation network in the SOI chip between the first power domain and the second power domain mitigates accumulation of electrical charge in an electrically isolated region of the SOI chip. In another embodiment, an ESD protection device in the SOI chip electrically connects the first power domain and the second power domain via a low metal layer to provide a discharge path for accumulated charge.

Owner:GLOBALFOUNDRIES INC

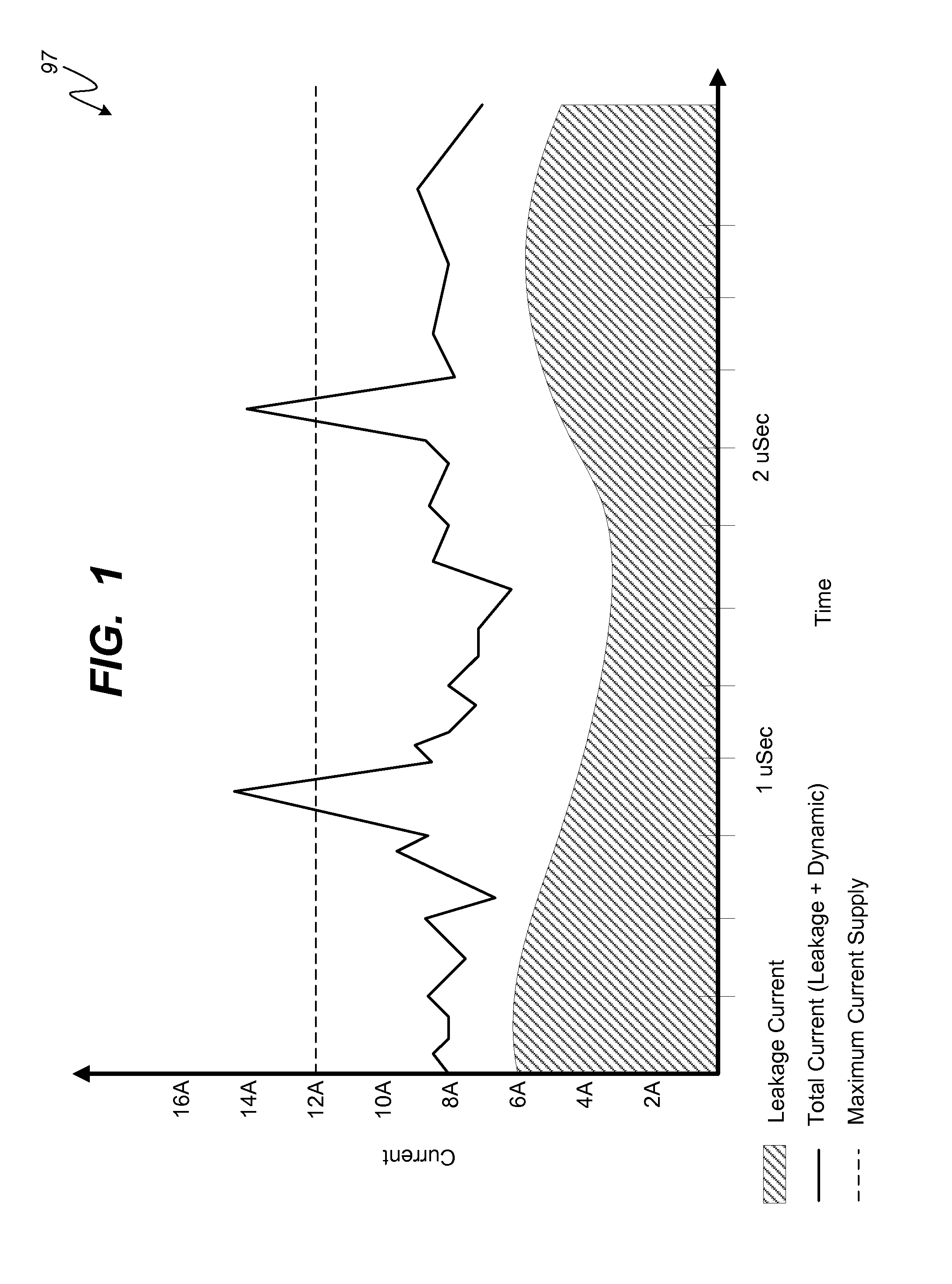

System and method for peak dynamic power management in a portable computing device

ActiveUS20160179164A1A large amountHardware monitoringPower supply for data processingQuality of serviceElectricity

Various embodiments of methods and systems for dynamically adjusting a peak dynamic power threshold are disclosed. Advantageously, embodiments of the solution for peak dynamic power management optimize a peak dynamic power threshold based on estimations of real-time leakage current levels and / or actual power supply levels to a power domain of a system on a chip (“SoC”). In this way, embodiments of the solution ensure that a maximum amount of available power supply is allocated to dynamic power consumption for processing workloads at an optimum performance or quality of service (“QoS”) level without risking that the total power consumption (leakage power consumption+dynamic power consumption) for the power domain exceeds the power supply capacity.

Owner:QUALCOMM INC

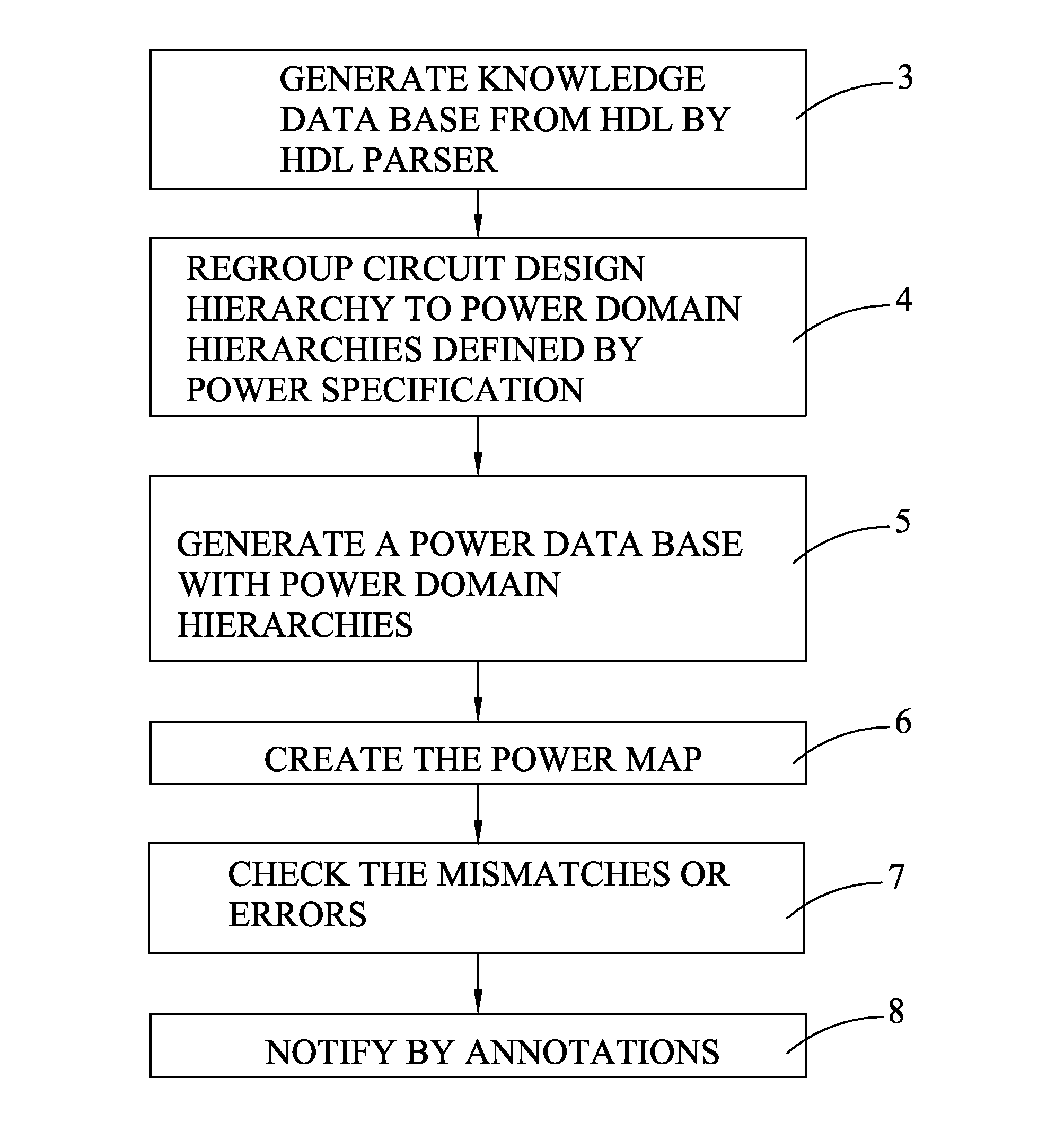

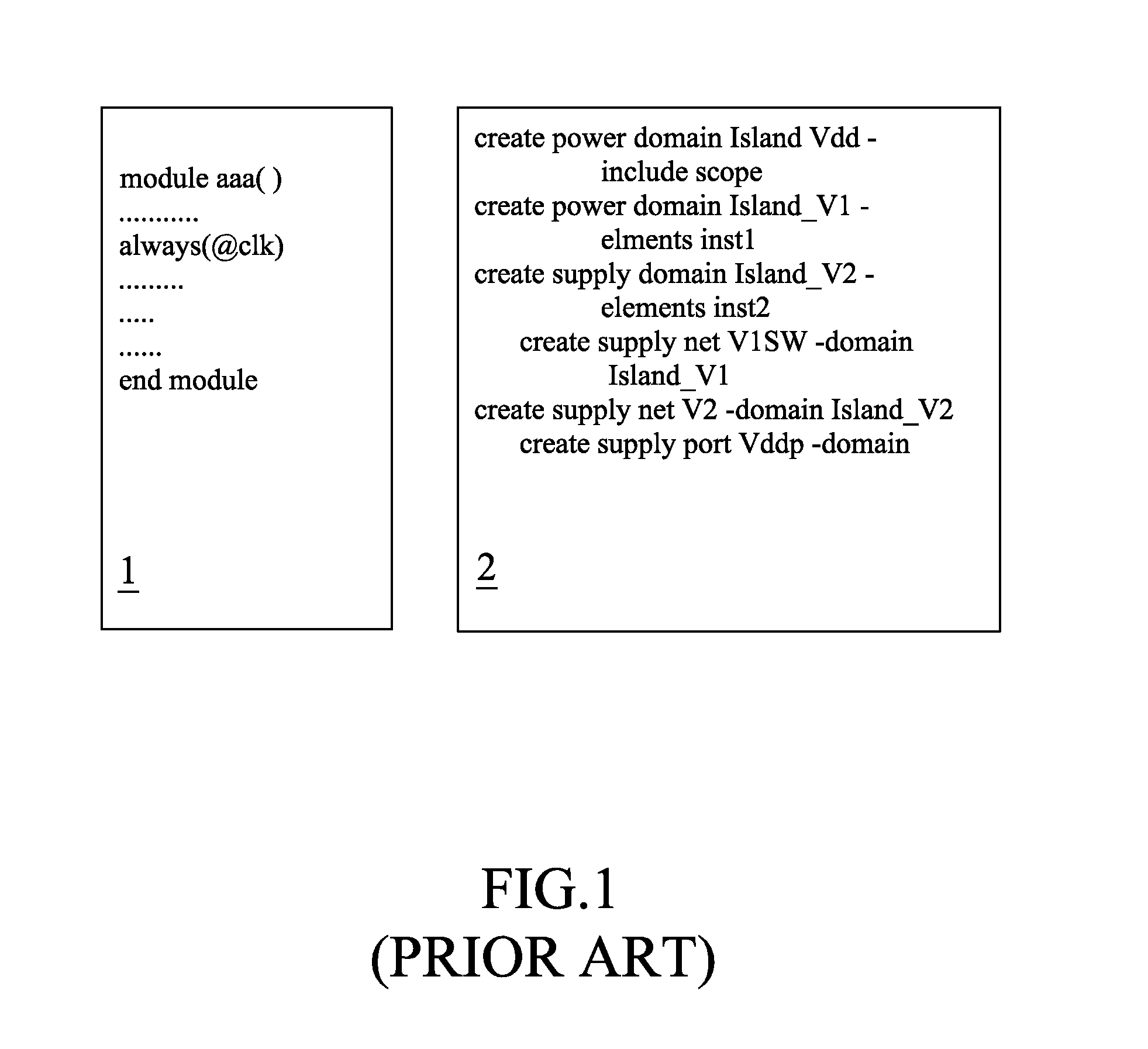

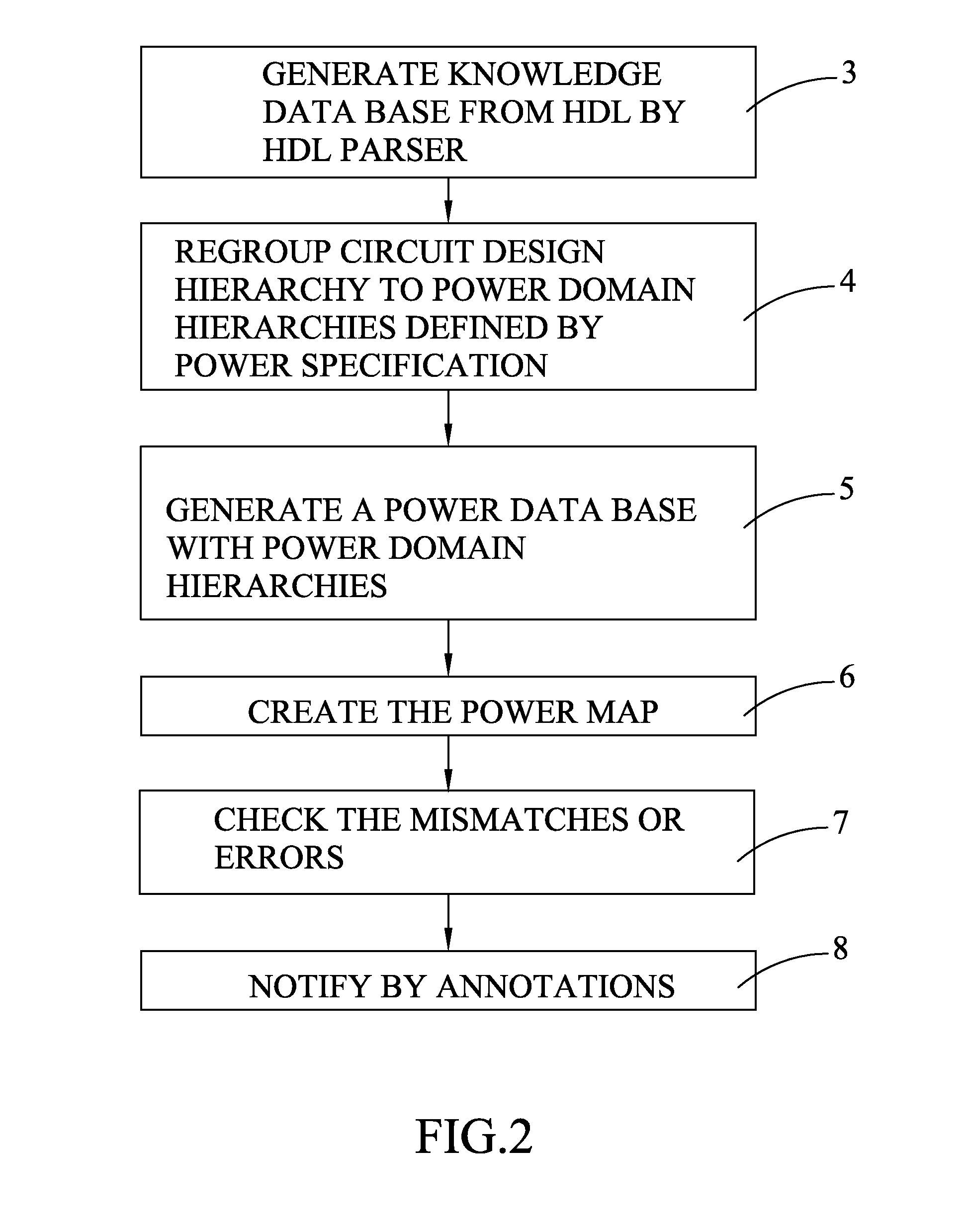

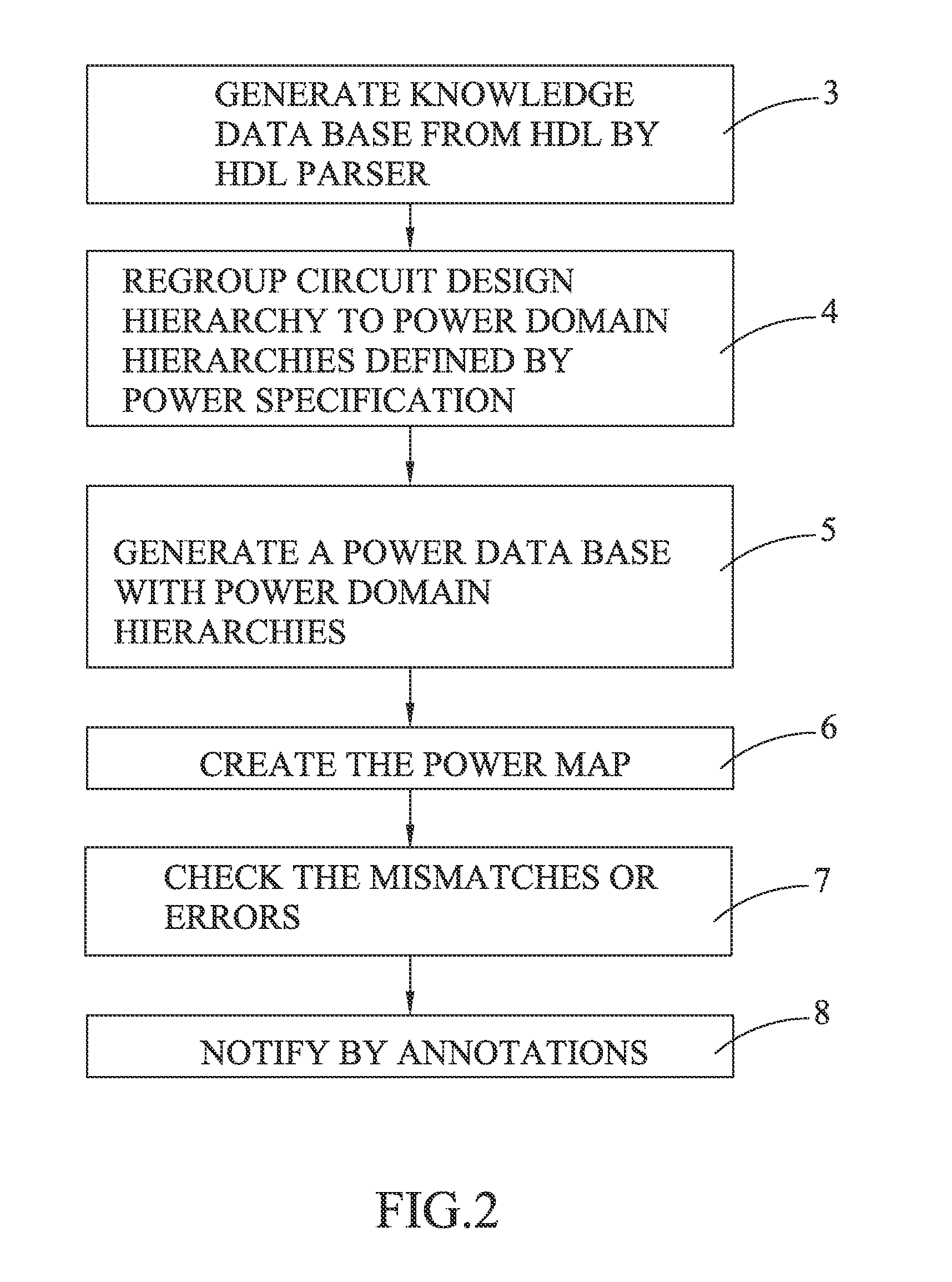

Hierarchial power map for low power design

ActiveUS20110320991A1Easy to debugQuick understandingCAD circuit designSoftware simulation/interpretation/emulationLow-power electronicsEngineering

A computer-implemented method for debugging the power aspect of an IC design by integrating the power specification expressed in certain power specification format and its corresponding circuit design within a power schematic diagram called power map. Power map is created by using a power data base generated by regrouping the original circuit design hierarchy to new hierarchies defined by the power specification. Power map contains power cell symbols (such as isolation cells, level shifters, power switches) and signal nets, and can show the relationship between power domains. Power map can also display mismatches or errors between the power specification and the circuit design for those signals connecting the power domains. Furthermore, power map can be used in conjunction with simulation result.

Owner:SYNOPSYS INC

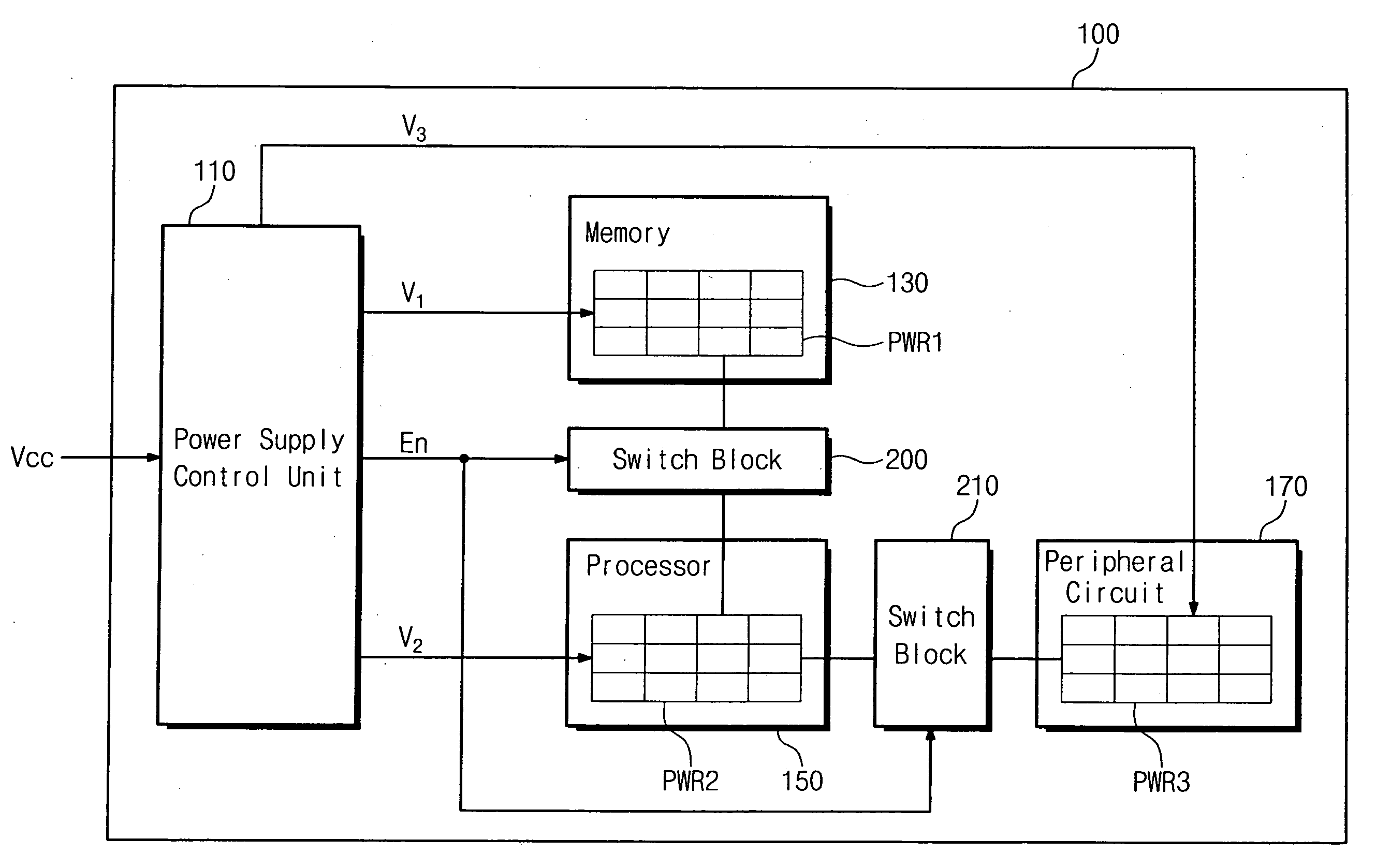

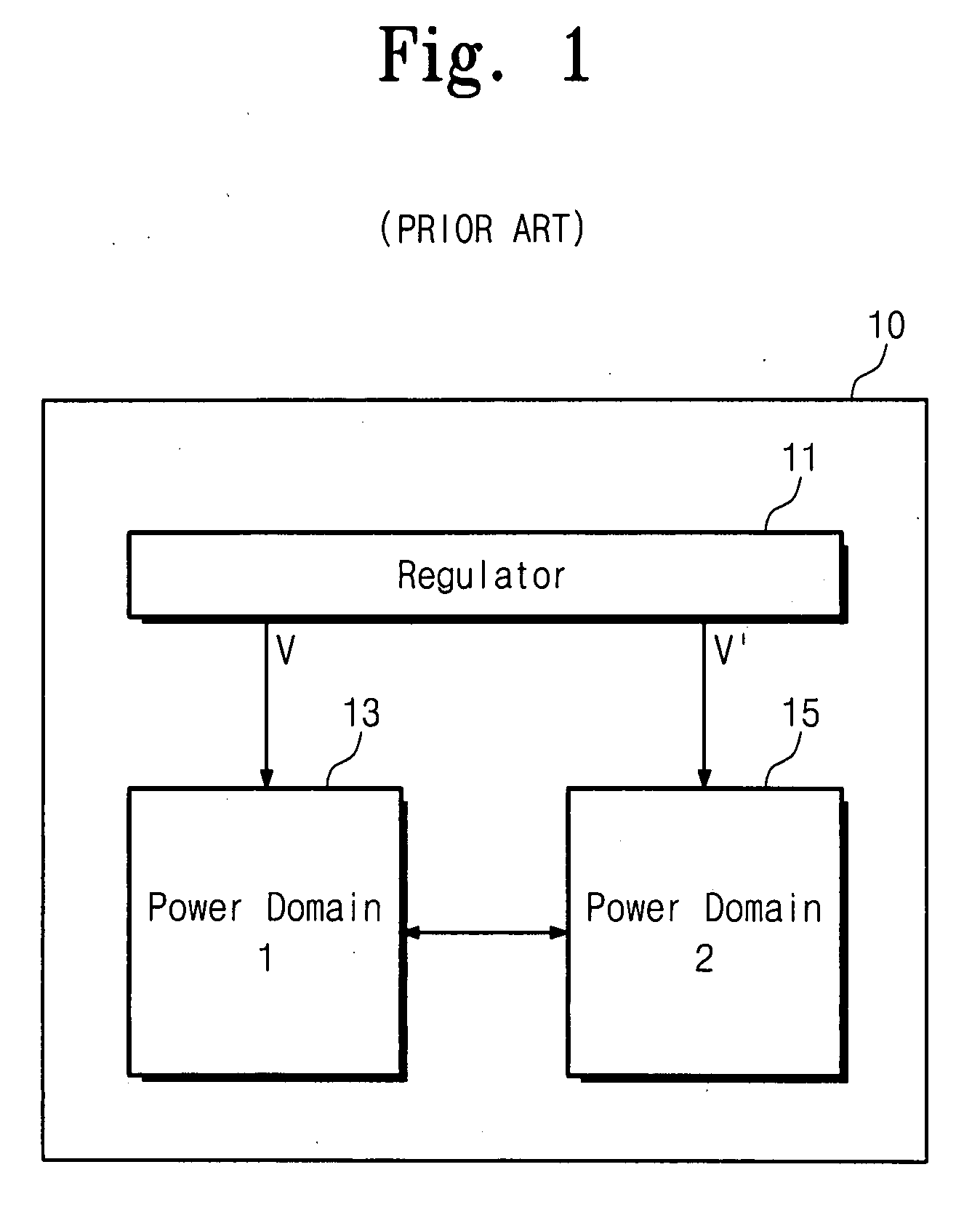

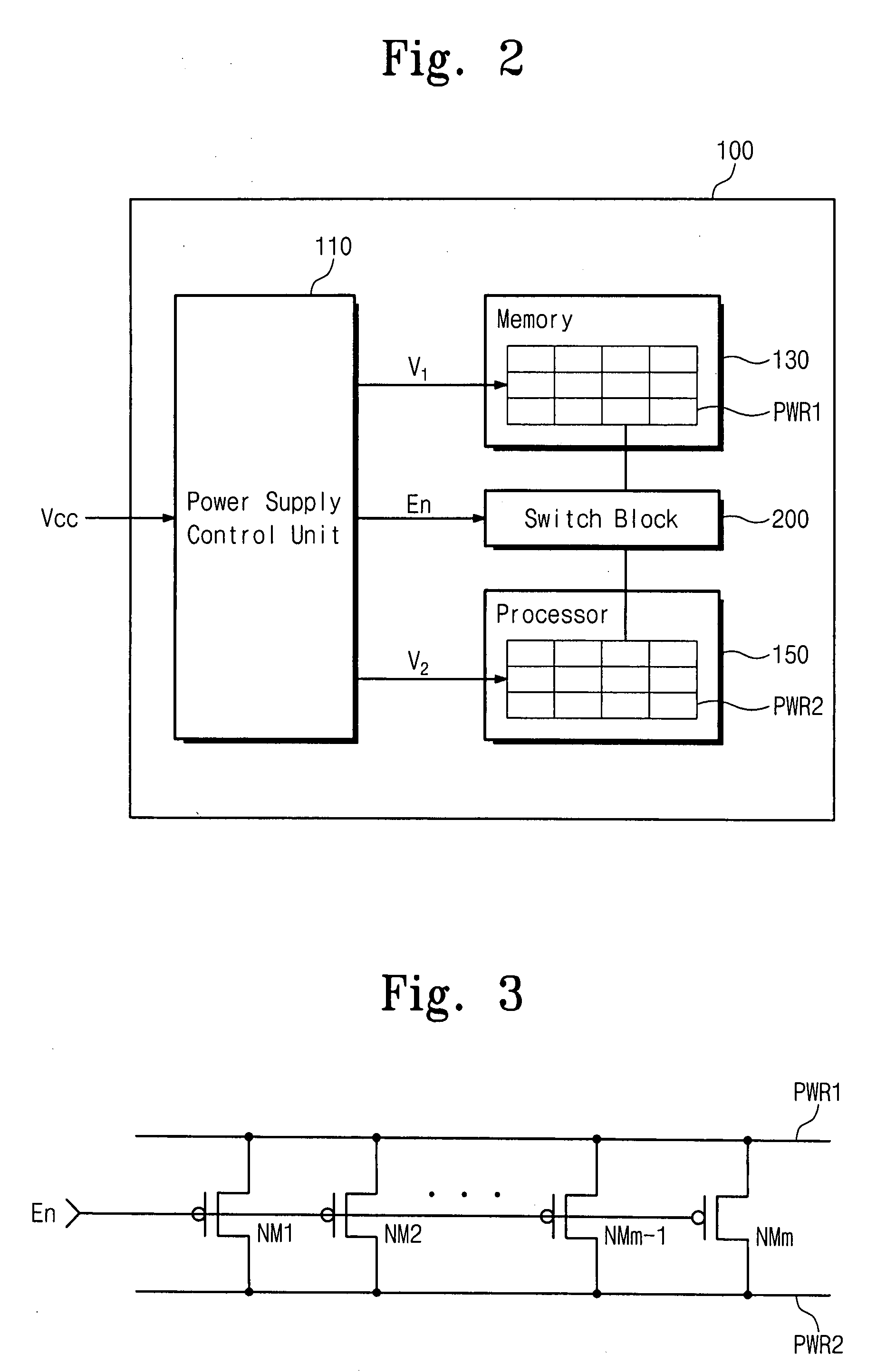

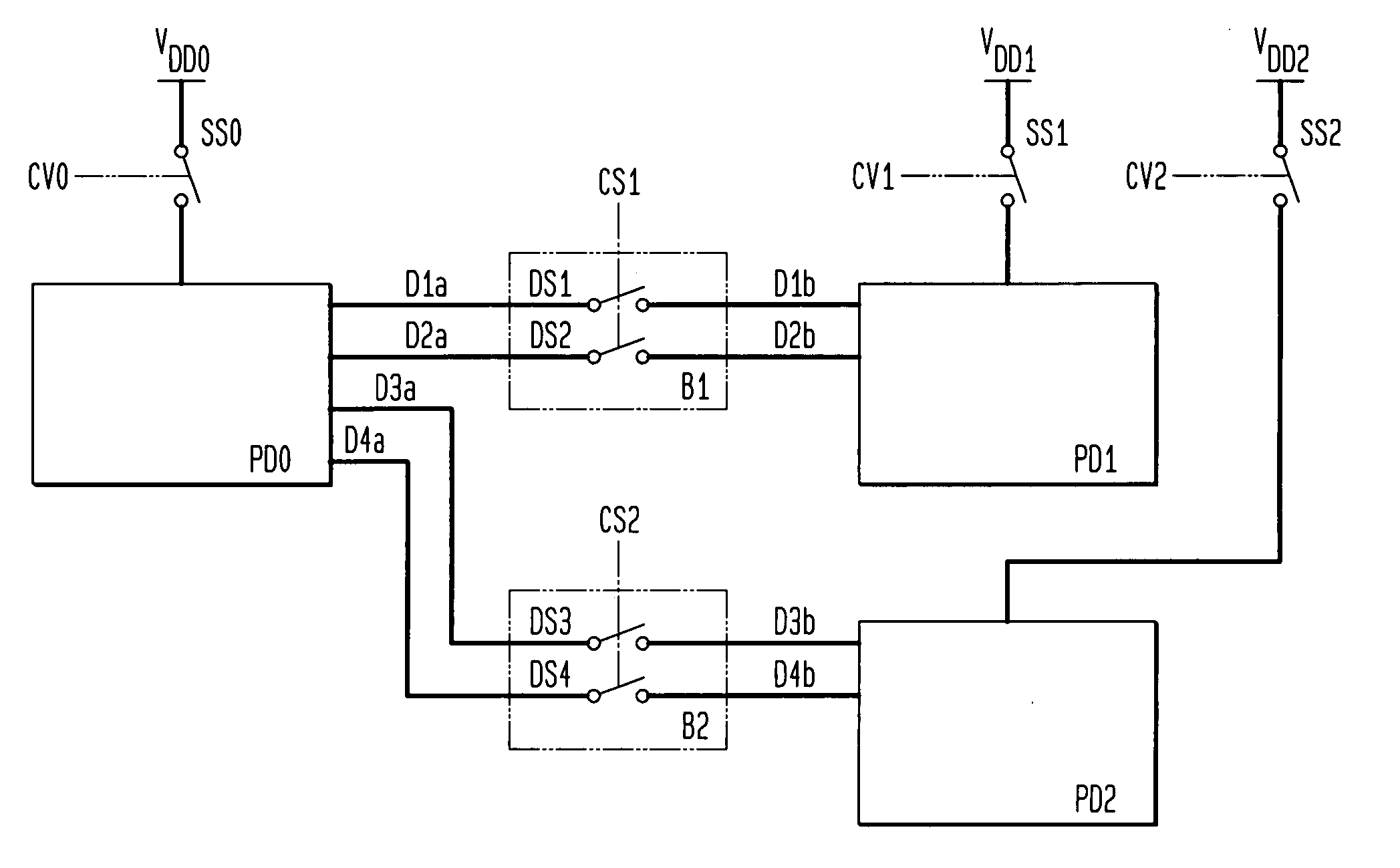

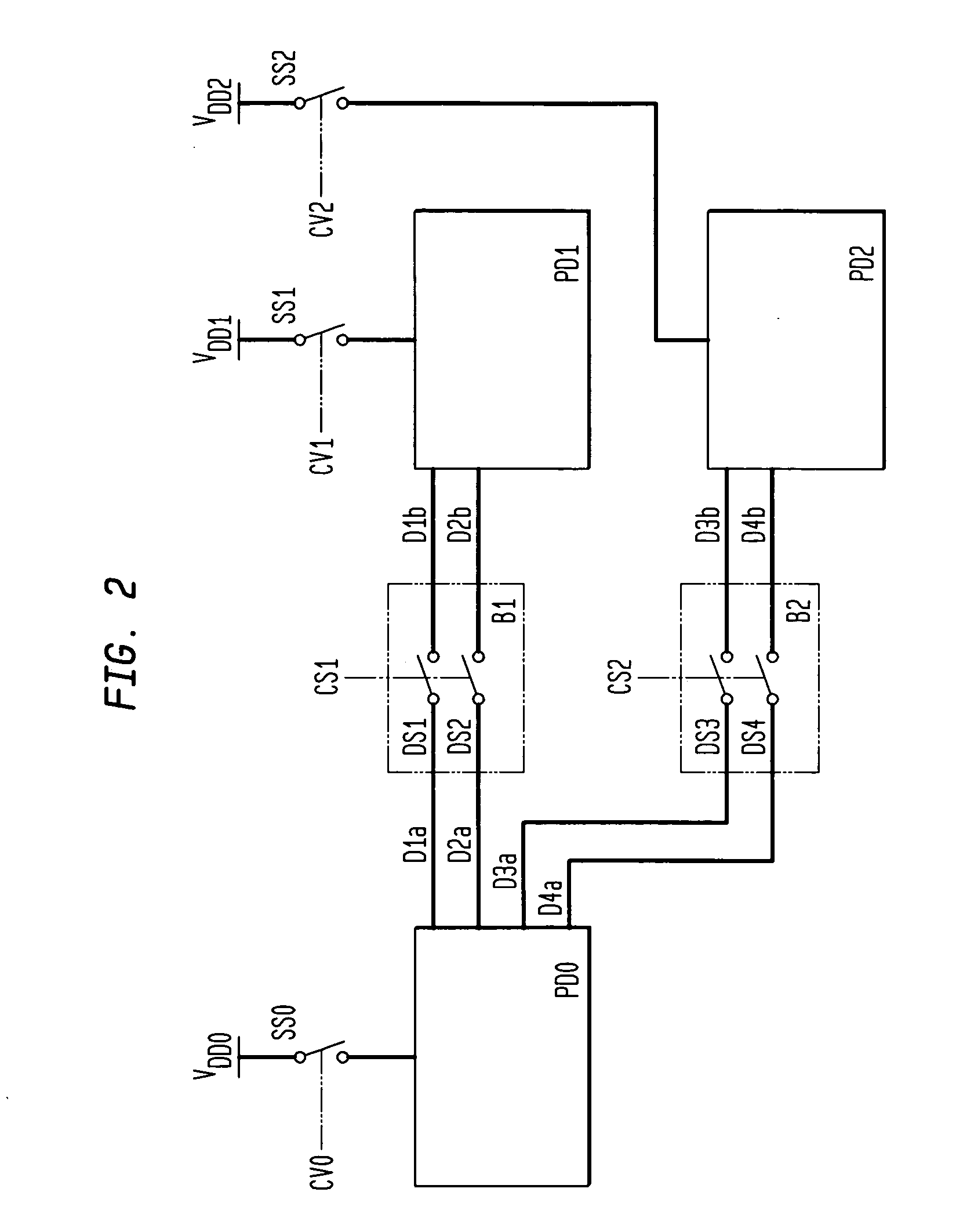

Integrated circuit having multiple power domains

ActiveUS20070234083A1Minimize power consumptionEnergy efficient ICTLighting and heating apparatusEngineeringOperation mode

An integrated circuit includes first and second power domains, a power supply control unit, and a switch block. The power supply control unit supplies a first voltage to the first power domain and a second voltage to the second power domain. The switch block provides at least one current path between the first and second power domains during a predetermined operating mode such as by connecting a first power line of the first power domain to a second power line of the second power domain.

Owner:SAMSUNG ELECTRONICS CO LTD

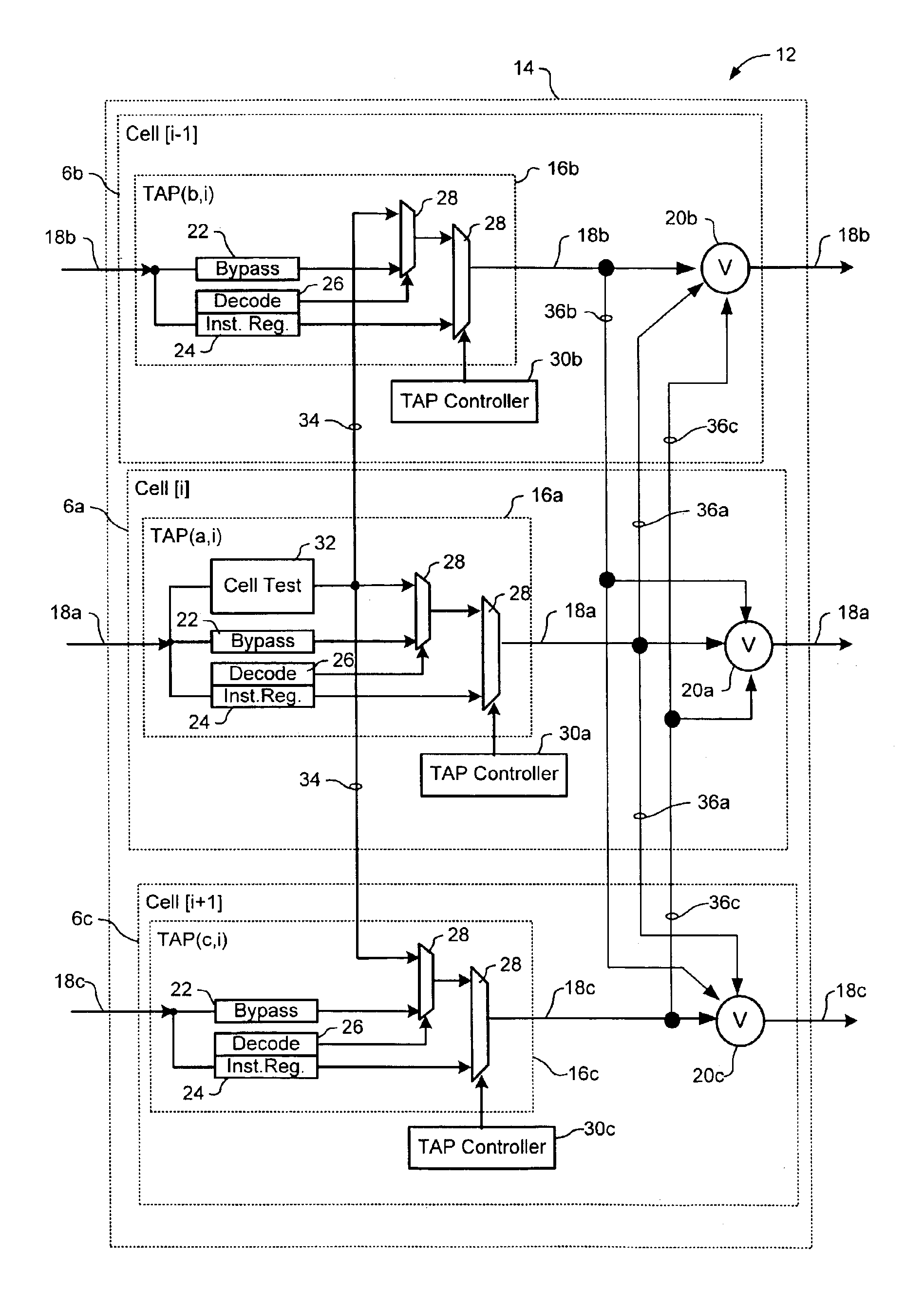

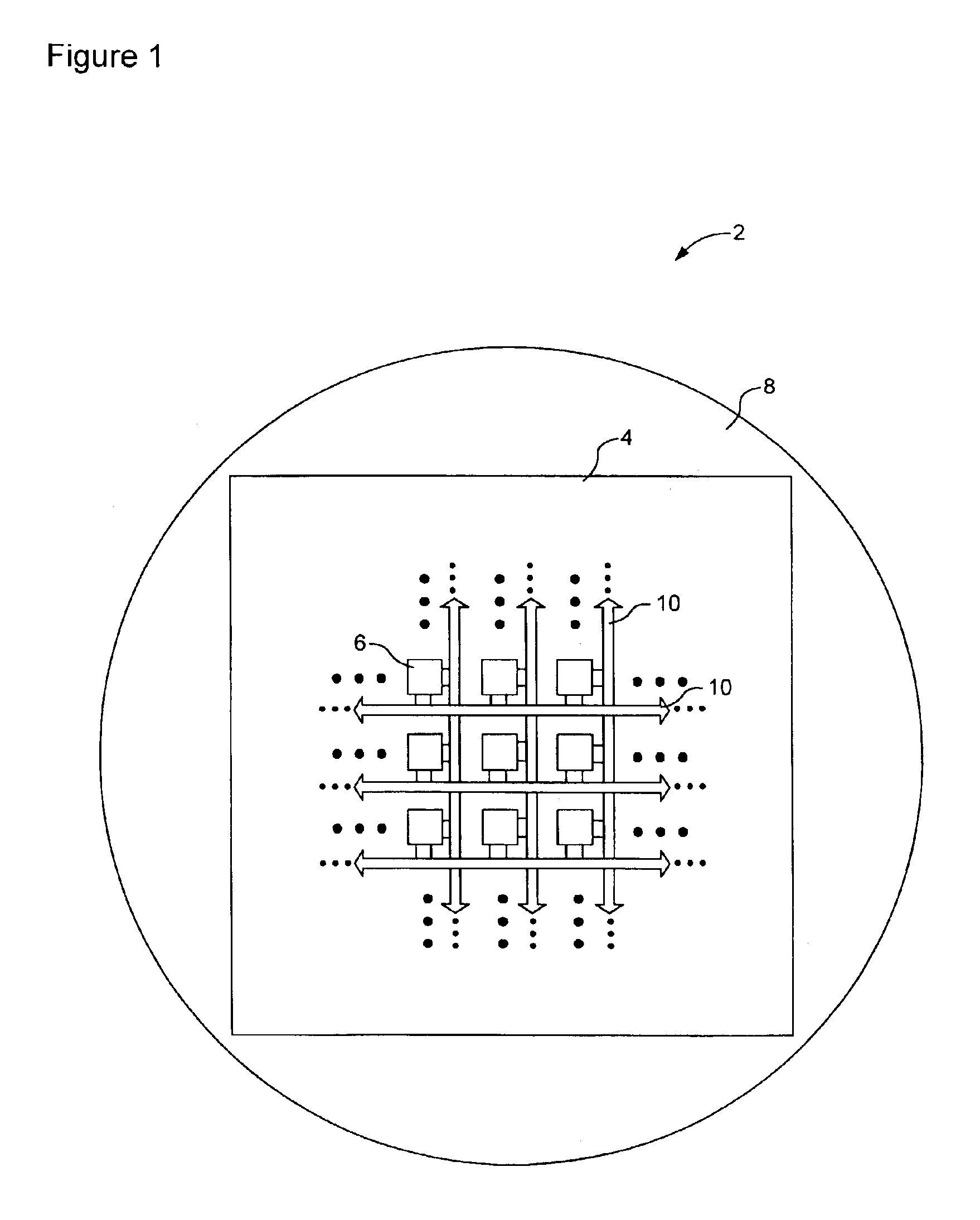

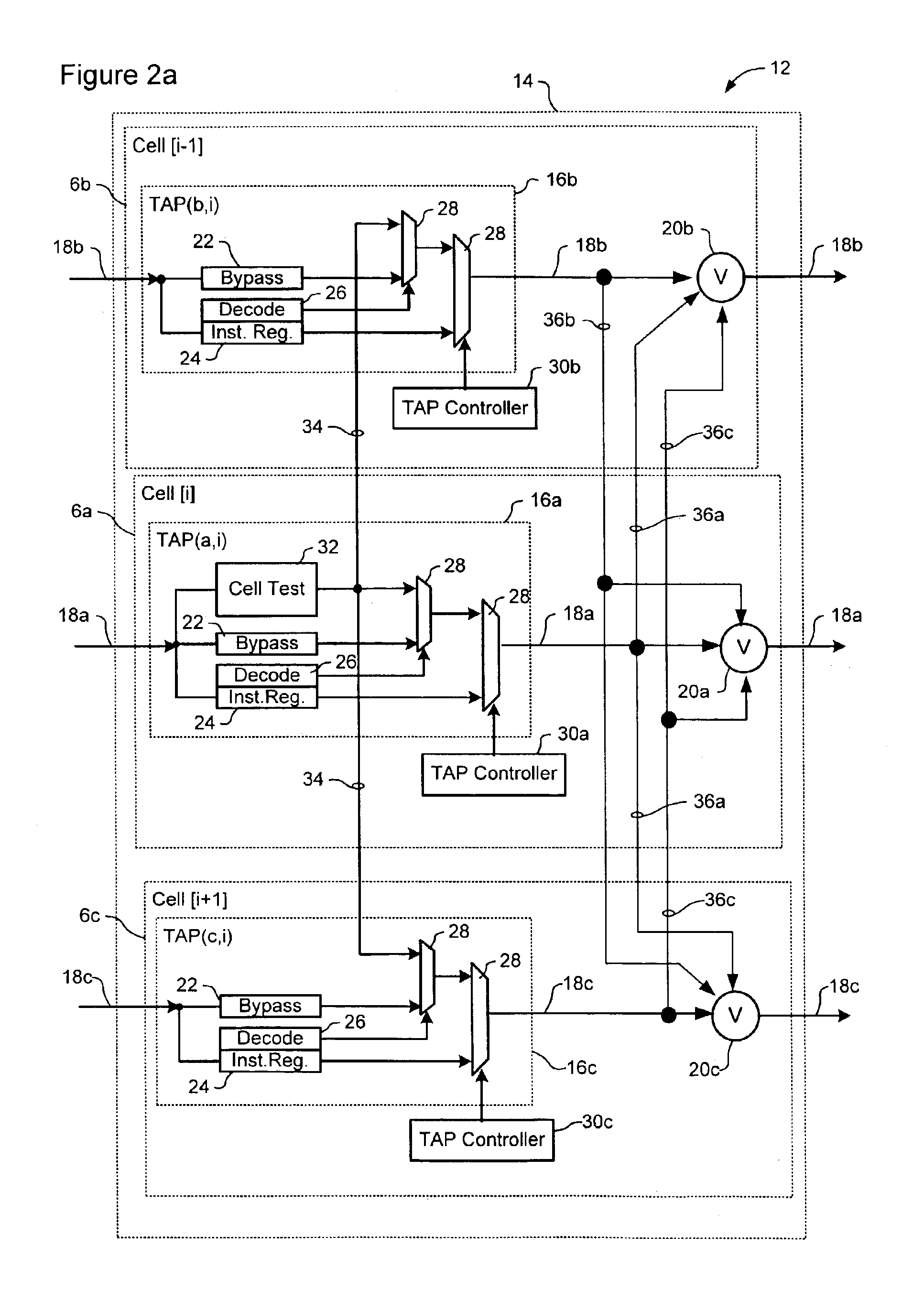

Fault tolerant scan chain for a parallel processing system

InactiveUS6928606B2Speed up preparationHighly robust fault tolerantElectronic circuit testingRedundant data error correctionVirtual cellControl signal

A highly robust fault tolerant scan chain is designed for scanning (and / or controlling a configuration of) a parallel processing system. The scan chain implements parallel redundant scan chains that follow physically diverse paths through the parallel processing system. For each IC under test, a set of redundant TAPs perform a boundary scan, and the test results are combined by voting. The TAPs of each set are physically diverse, in that they are physically located in separate power domains of the parallel processing system. As a result, the scan chain is robust to faults affecting power and / or control signal supply to any one power domain. Respective input and output dummy cells at opposite extreme ends of the scan chain provide a graceful separation and recombination of the redundant parallel scan chains, and so renders the architecture of the scan chain transparent to external boundary scan circuit elements.

Owner:NORMAN RICHARD S

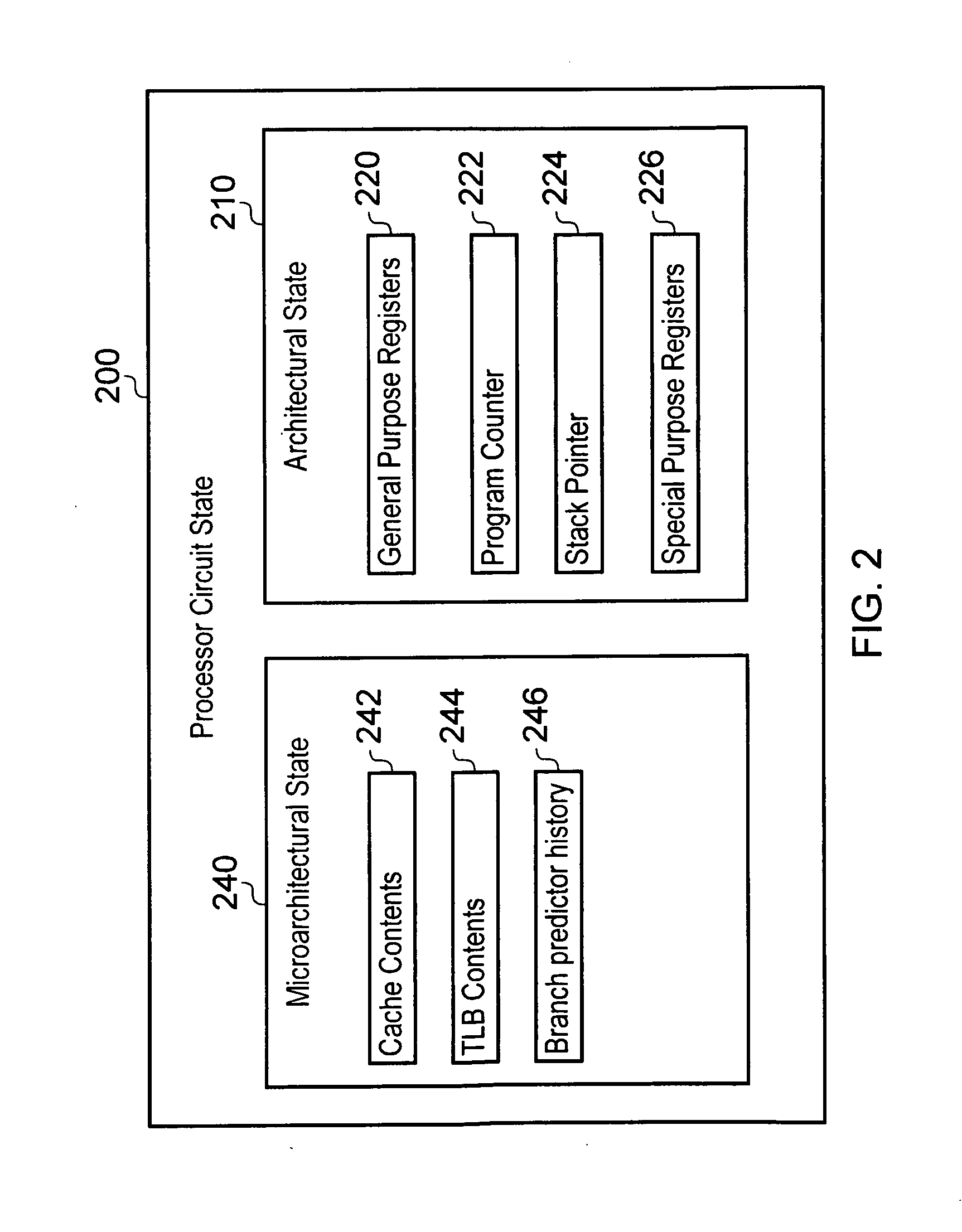

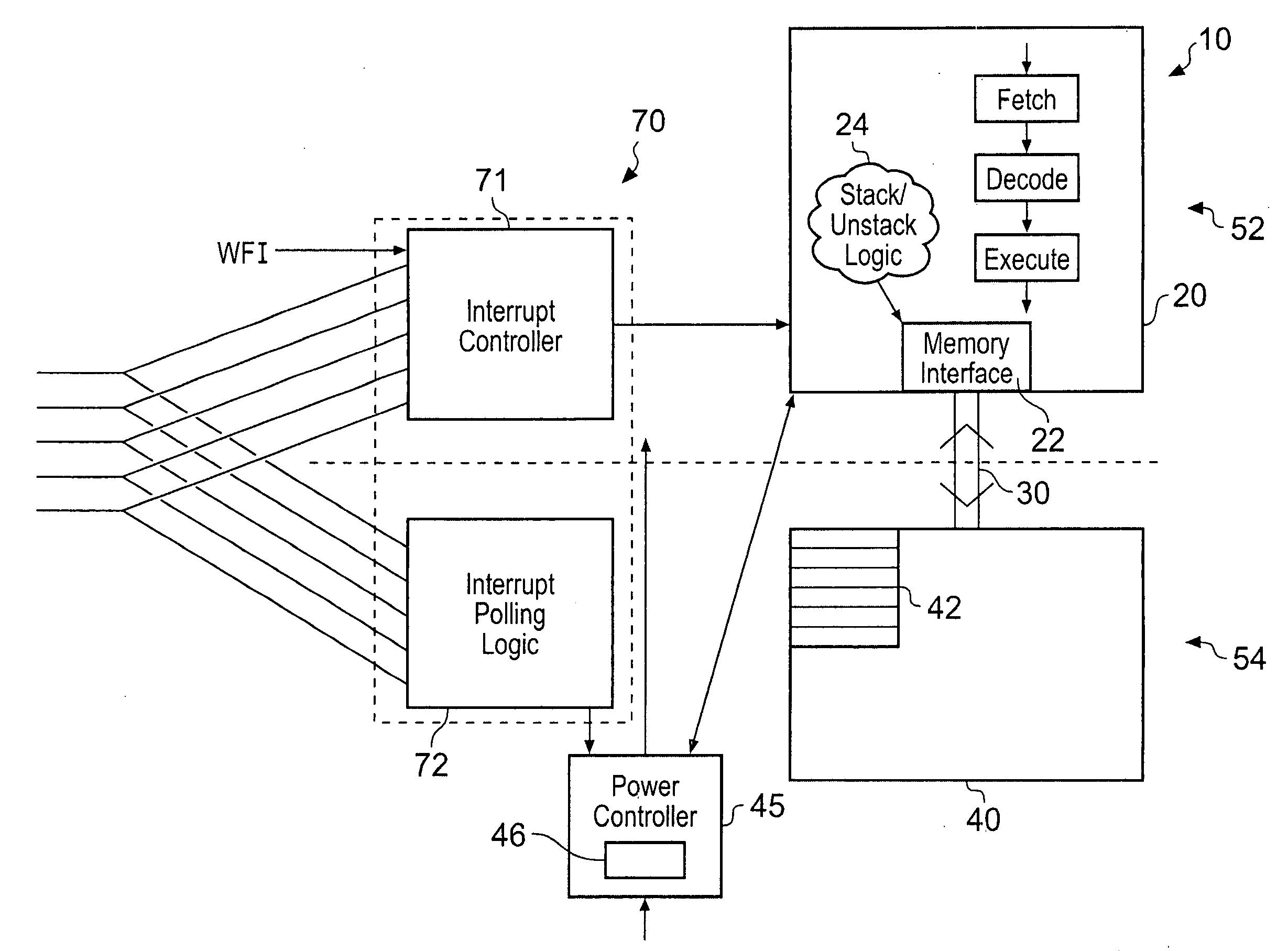

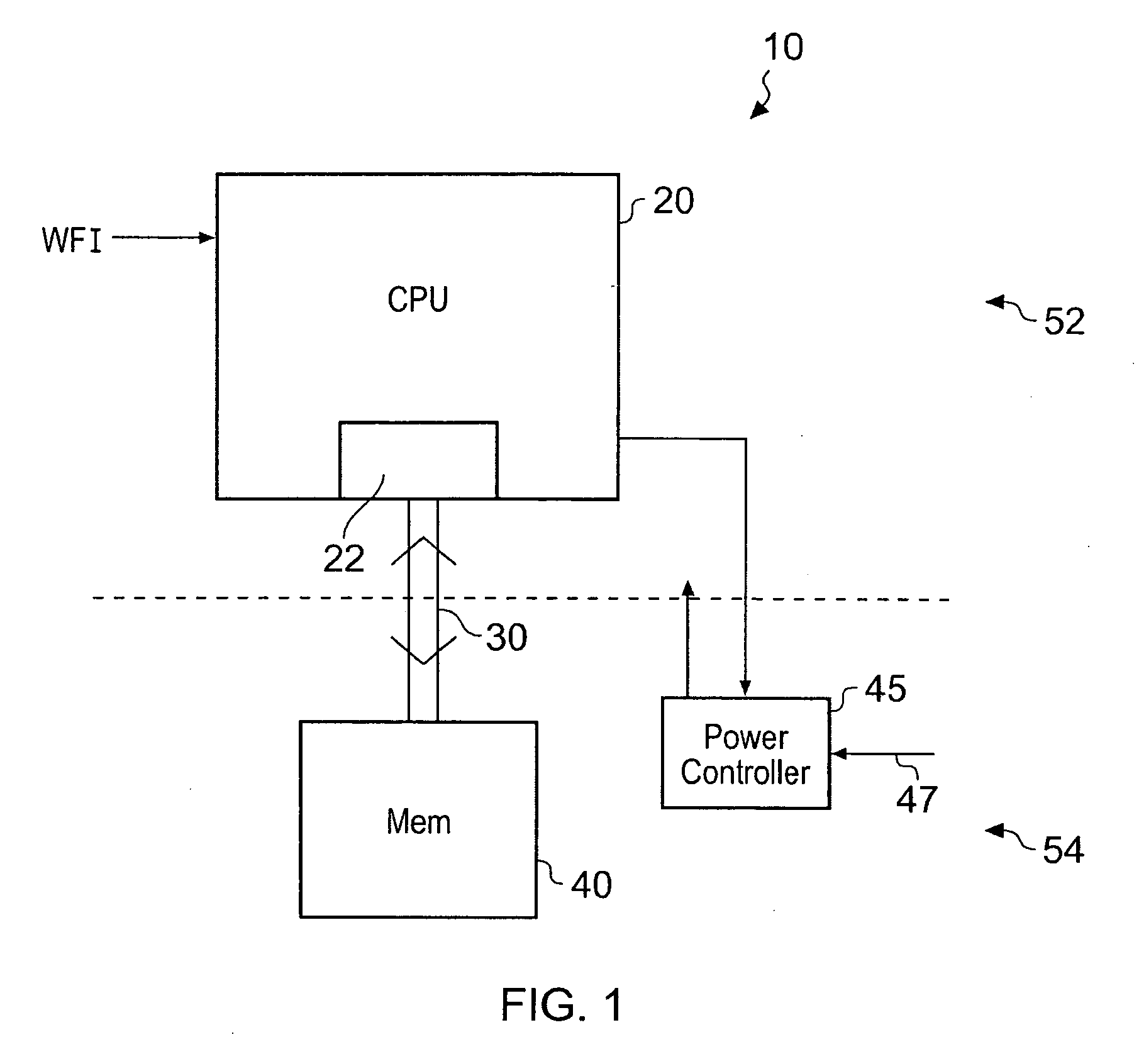

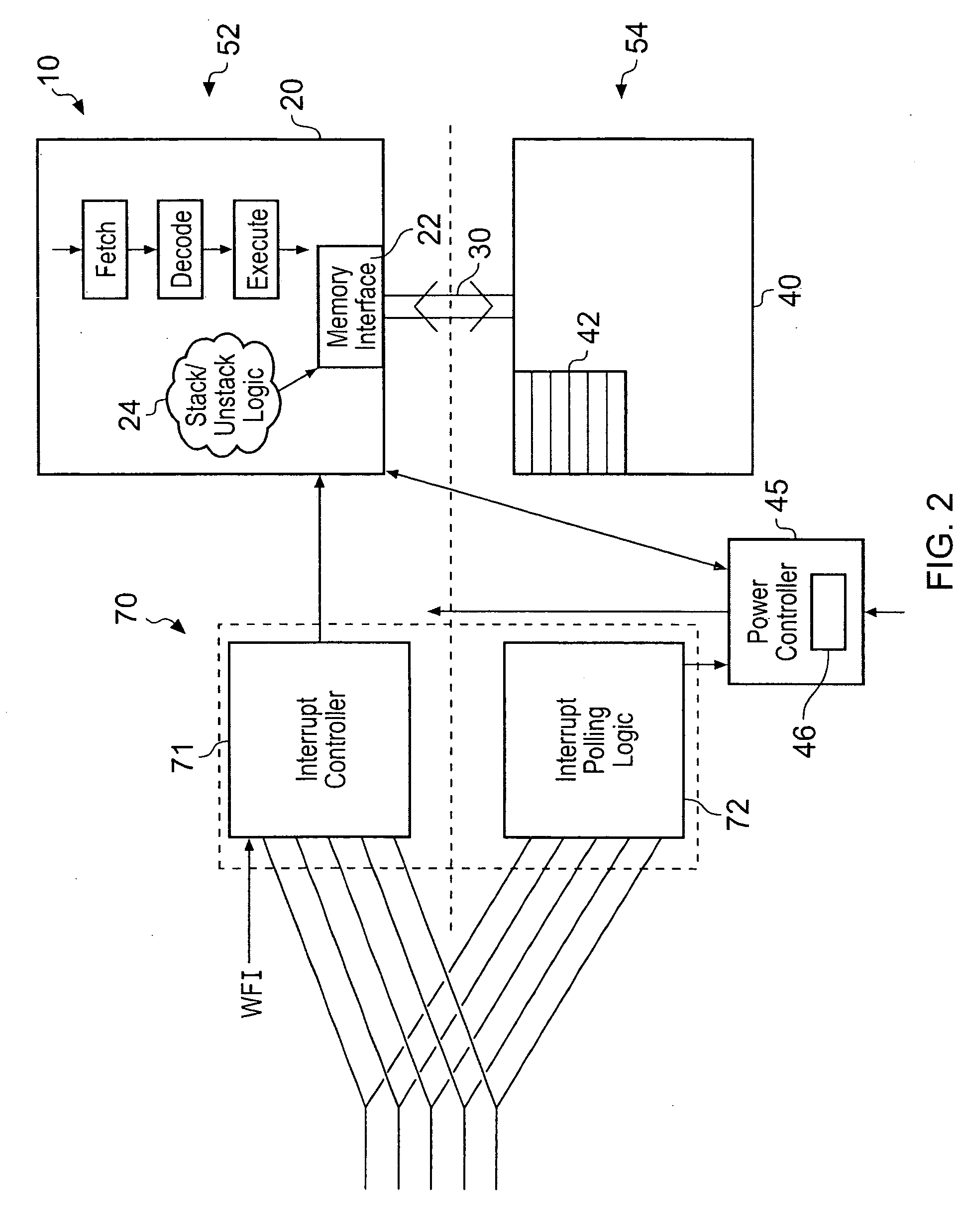

Hardware driven processor state storage prior to entering a low power mode

ActiveUS20090164814A1Reduced stateImprove processing speedEnergy efficient ICTVolume/mass flow measurementPower modeMemory interface

A data processing apparatus comprising: a processor for processing data, said processor comprising memory interface logic for controlling transfer of data to a memory, said processor being powered in a first power domain; a memory for storing data processed by said processor said memory being powered in a second power domain; a system bus coupled to said processor and said memory and operable to transfer data between said processor and said memory in response to memory transfer requests issued upon said system bus by said memory interface logic during normal processing operation of said processor and said memory; wherein said processor is responsive to a low power request indicating said data processing apparatus should enter a low power mode to: control transfer of state data indicating a current state of said processor to said memory via said system bus using said memory interface logic, said state data being sufficient data to restore said processor to an equivalent program state following exit from said low power mode; store said state data in said memory; and power down said first power domain.

Owner:ARM LTD

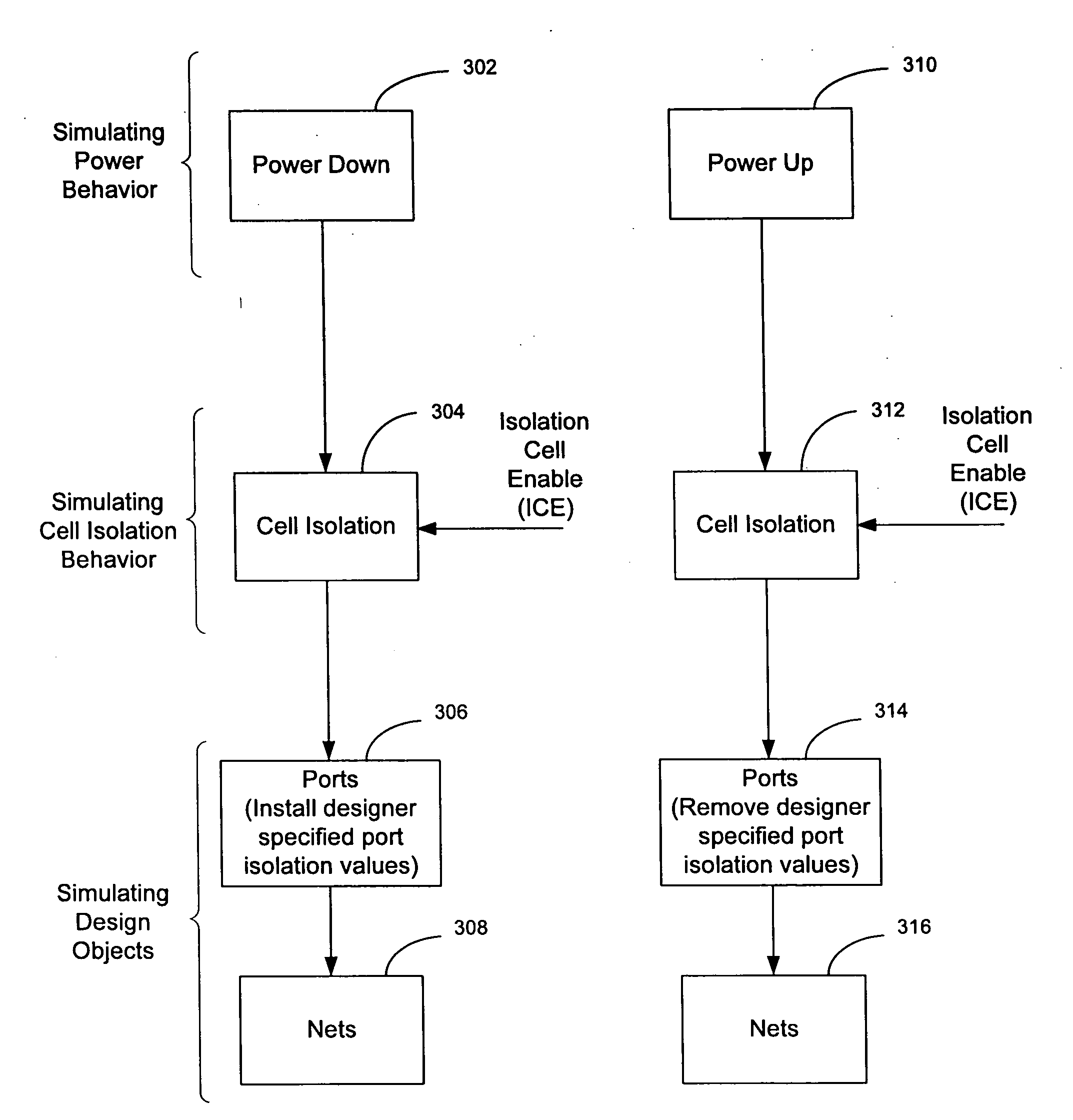

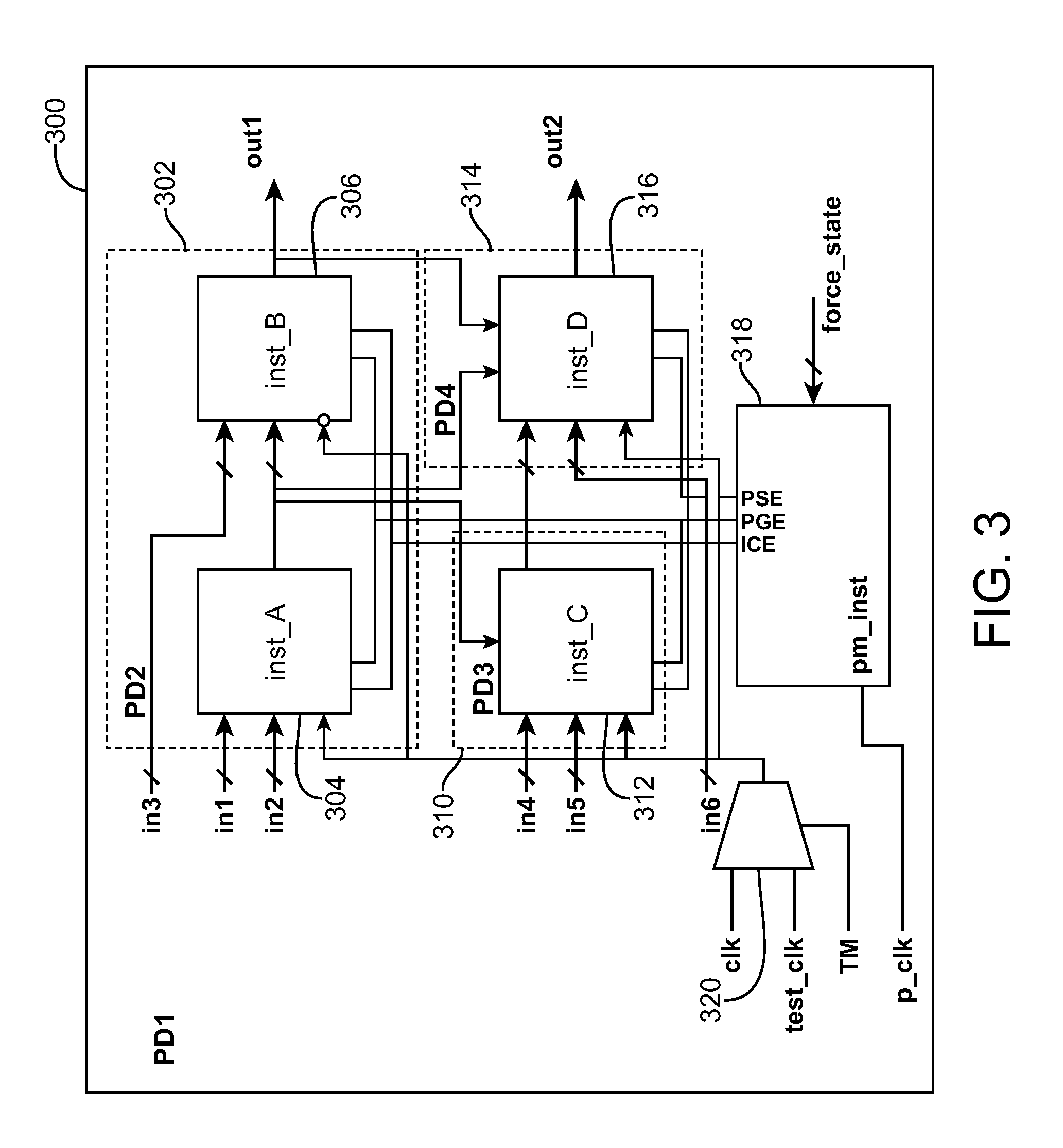

Simulation of power domain isolation

ActiveUS20070245278A1CAD circuit designSoftware simulation/interpretation/emulationControl signalProcessor register

Method and system for simulating isolation of a power domain are disclosed. The method includes receiving a netlist description of the circuit that is represented in a register-transfer-level (RTL) design environment, receiving power information specifications of the circuit, associating the plurality of power domains and the power information specifications in the RTL design environment, where the plurality of power domains are controlled by a set of power control signals through a power manager logic, isolating a power domain among the plurality of power domains for simulation, and simulating isolation behavior of the power domain in response to variations in power applied to the power domain.

Owner:CADENCE DESIGN SYST INC

Method and mechanism for implementing electronic designs having power information specifications background

A method of adding power control circuitry to a circuit design at each of an RTL and a netlist level comprising: demarcating multiple power domains within the circuit design; specifying multiple power modes each power mode corresponding to a different combination of on / off states of the multiple demarcated power domains; and defining isolation behavior relative to respective power domains.

Owner:CADENCE DESIGN SYST INC

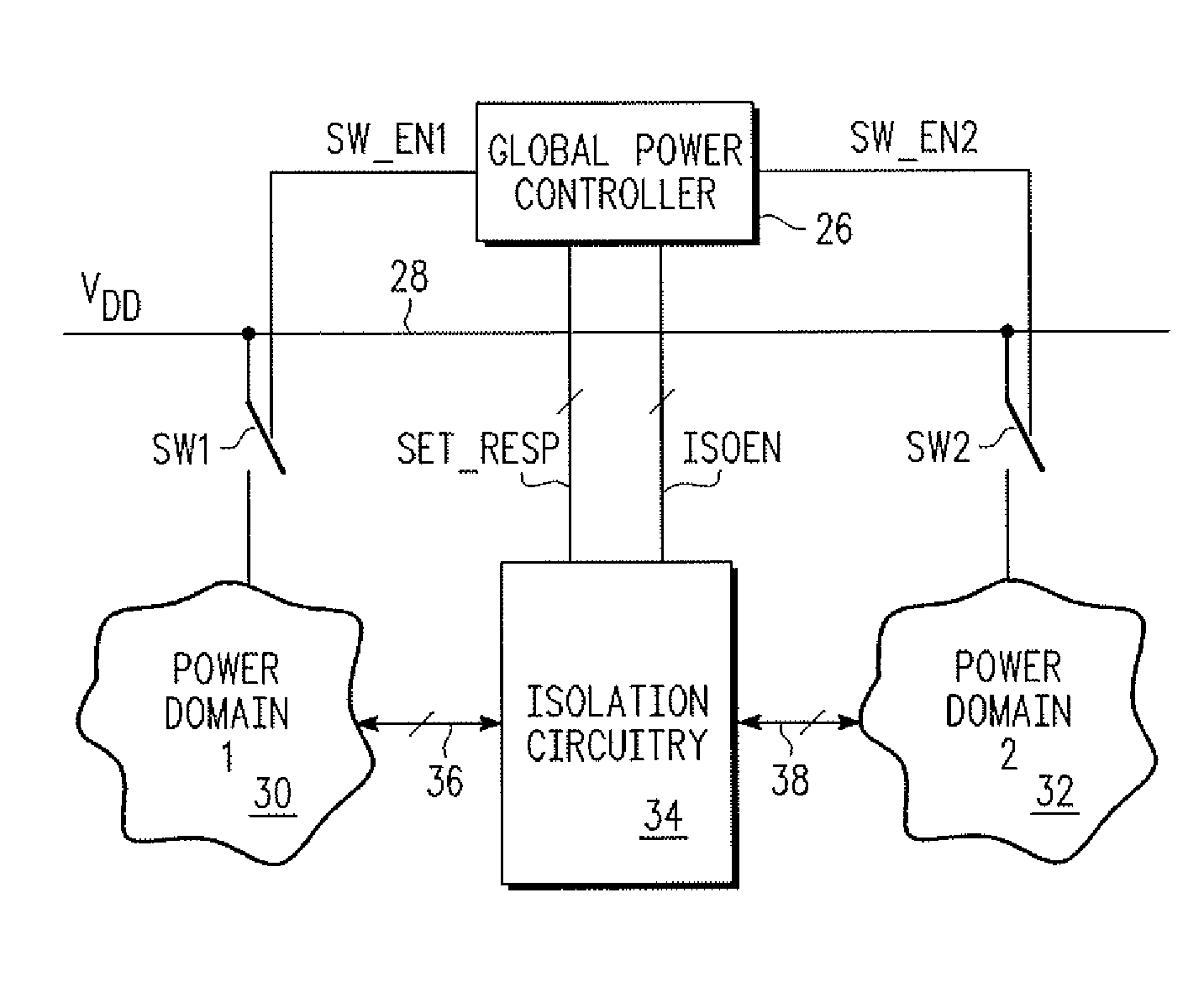

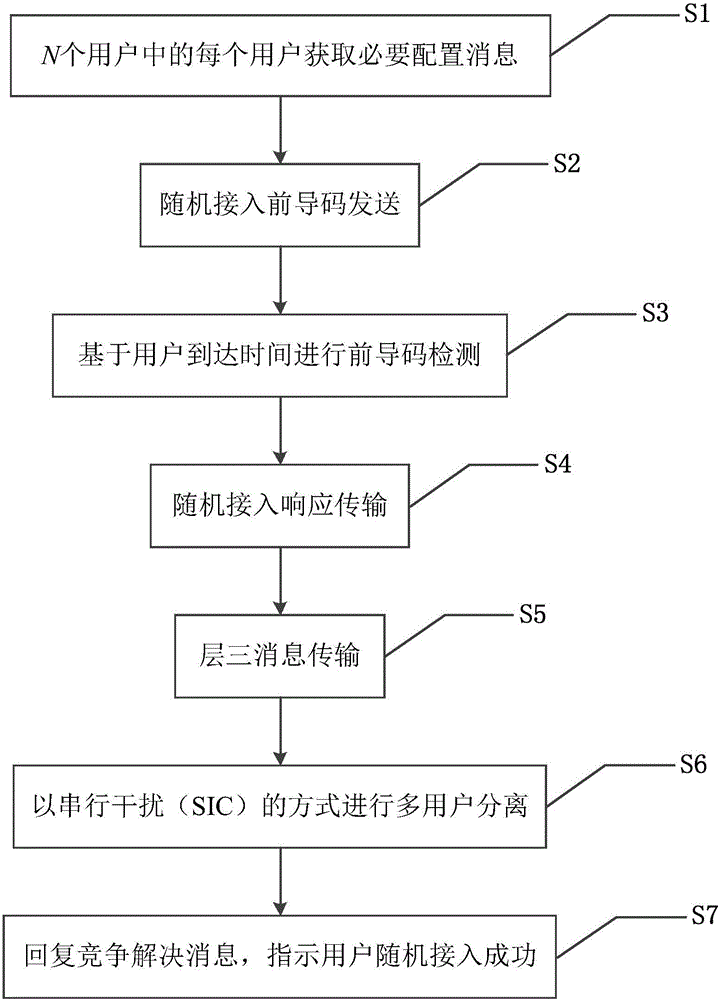

Management of power domains in an integrated circuit

A method of operating a circuit, including operating in a first mode, wherein in the first mode, a first power domain operates in an active power mode and a second power domain operates in an active power mode, wherein in the first mode, a first set of at least one terminal of a first circuit of the first power domain are coupled to a second set of at least one terminal of a second circuit of the second power mode via an isolation circuit for providing signals from the first circuit to the second circuit, is provided. The method further includes operating the circuit in a second mode, wherein in the second mode, the first power domain operates in a power gated mode and a second power domain operates in an active power mode.

Owner:NXP USA INC

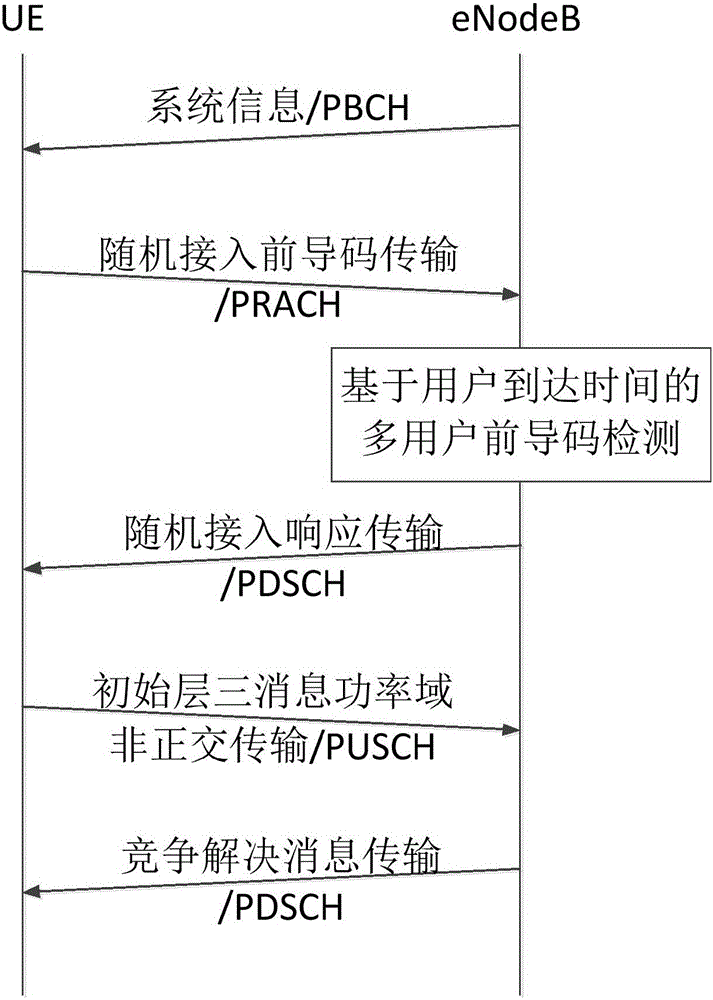

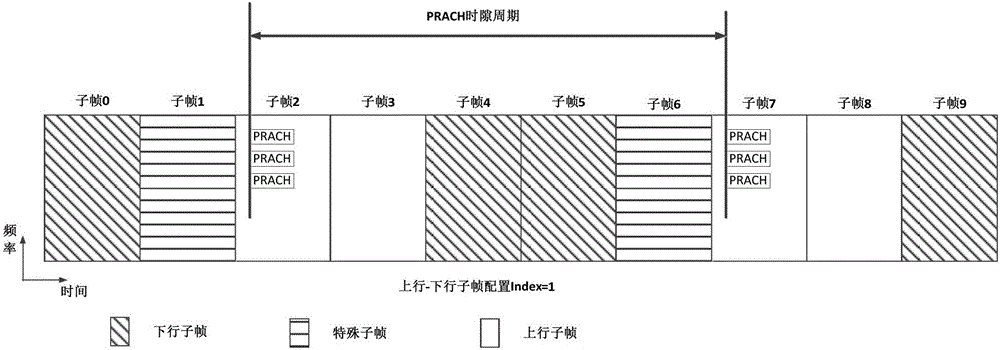

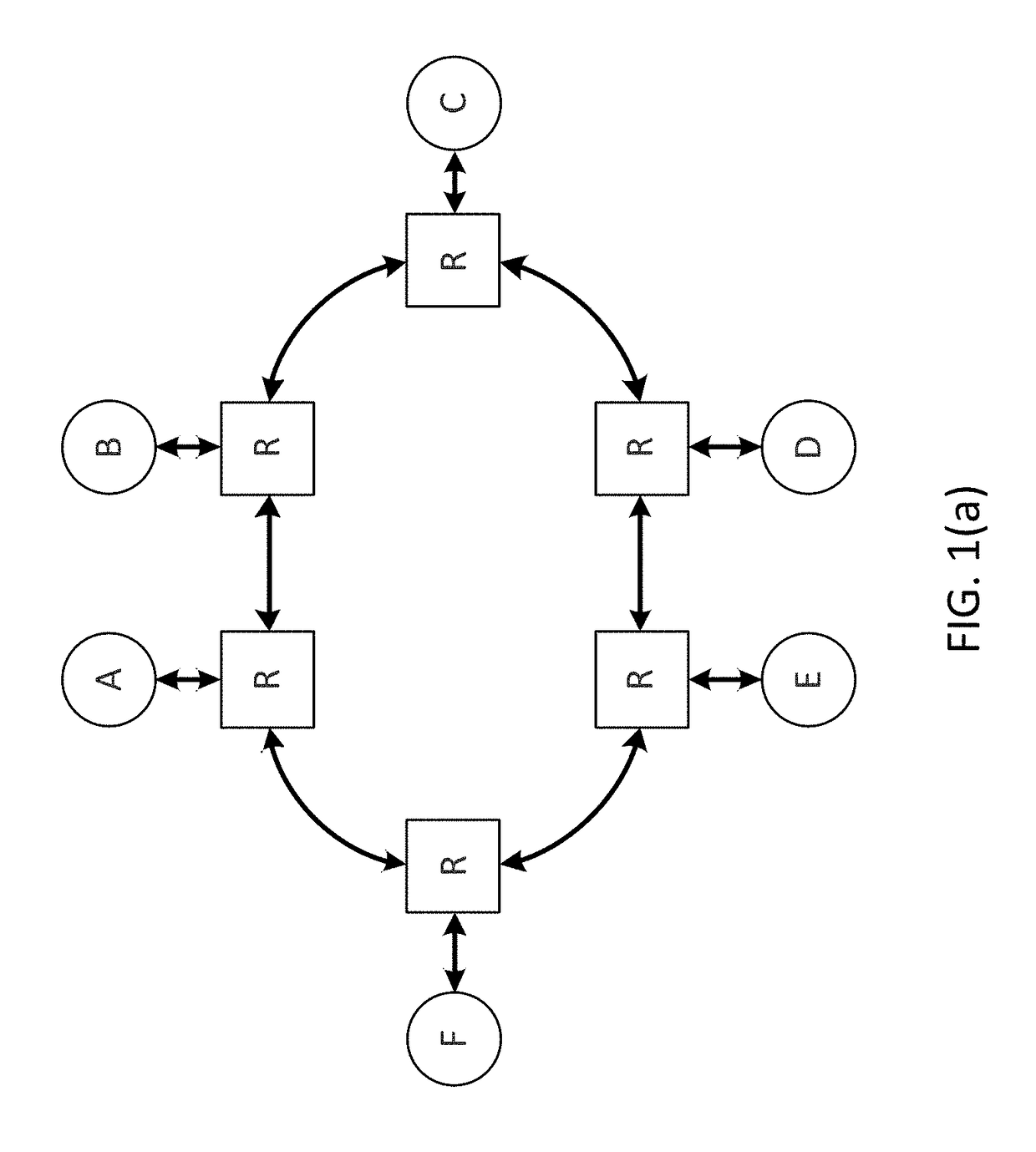

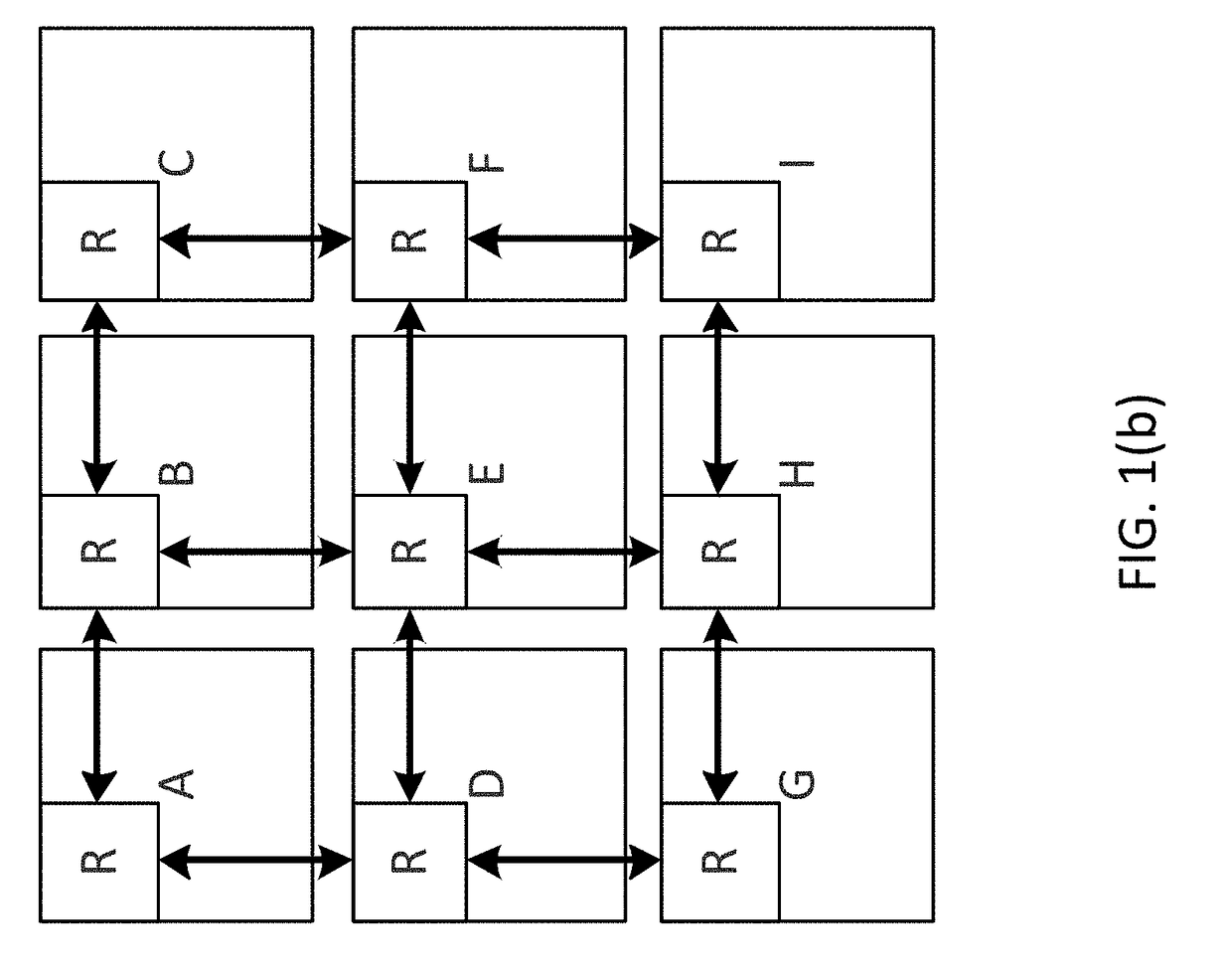

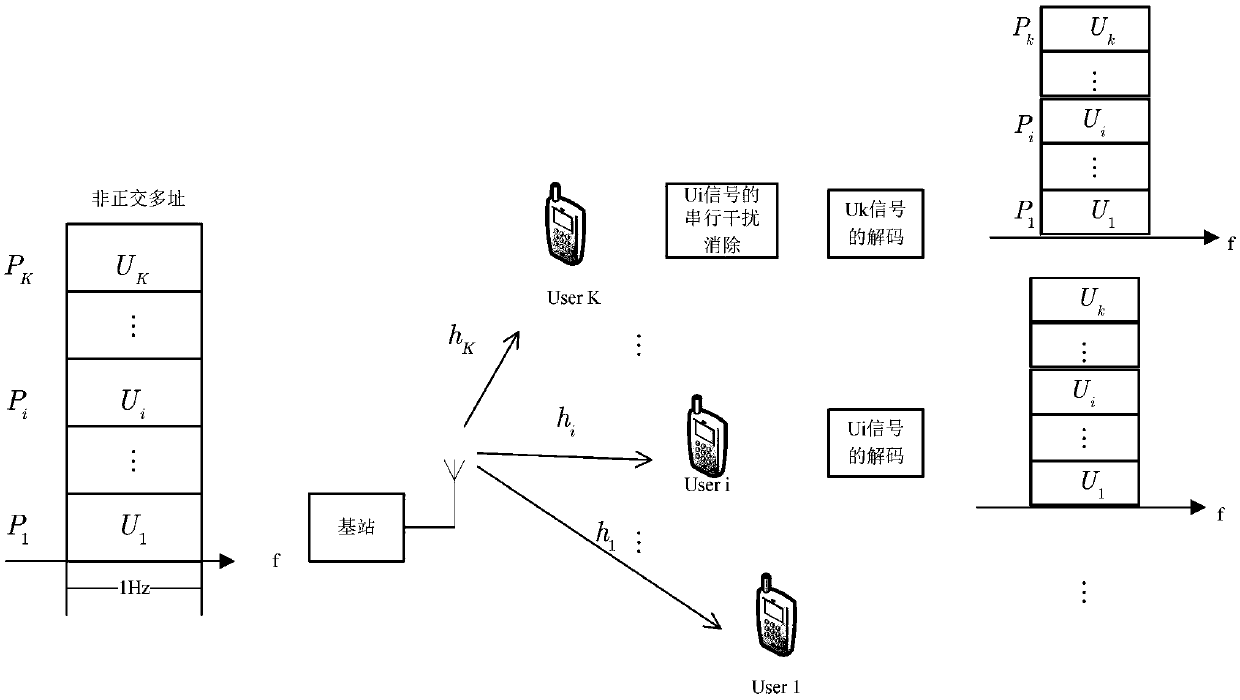

Non-orthogonal random access method

ActiveCN106102182AImproved chance of collisionImproved access success probabilityHigh level techniquesWireless communicationMultiplexingAccess time

The present invention discloses a non-orthogonal random access method. The method includes a first step of acquiring, by each of N users, necessary configuration information; a second step of sending a random access preamble; a third step of detecting, based on arrival time of the user, the preamble; a fourth step of transmitting a random access response; a fifth step of transmitting a layer III message; a sixth step of determining, according to a relationship between regular time and ahead of time of the user, a user demodulation sequence by eNodeB, so as to separate multiple users in a serial interference cancellation (SIC) manner; and a seventh step of replying, by the eNodeB, each identified cell radio network temporary identifier (C-RNTI) competition resolving information, so as to indicate that the user randomly accesses successfully. According to the non-orthogonal random access method, multiple users access randomly simultaneously due to adoption of a power domain multiplexing manner, user access success probability is effectively improved, access time delay is lowered, network users are greatly increased, and demands of a fifth-generation mobile communication system are met.

Owner:BEIJING JIAOTONG UNIV

Integrated circuit with multiple power domains

ActiveUS20050253462A1Save powerMinimize leakage currentReliability increasing modificationsLogic circuits characterised by logic functionLoad circuitElectricity

An integrated circuit having two or more power domains that include load circuits in different portions of the integrated circuit is disclosed. In order to conserve power, the circuits in one of the power domains are shut down by disconnecting the power source serving that domain. The load circuits in each power domain are buffered from the load circuits in other power domains by buffer cells. The buffer cells reduce leakage currents in the power domain that is shut down, by restricting data signals from the “live” power domain from reaching the shut-down power domain, and further by providing predetermined voltage signals to the load circuits in the shut-down power domain that are selected to minimize leakage currents in the inactive load circuits. The invention further provides a corresponding method for reducing power consumption in an integrated circuit having at least two power domains separated by a buffer cell.

Owner:AVAGO TECH INT SALES PTE LTD

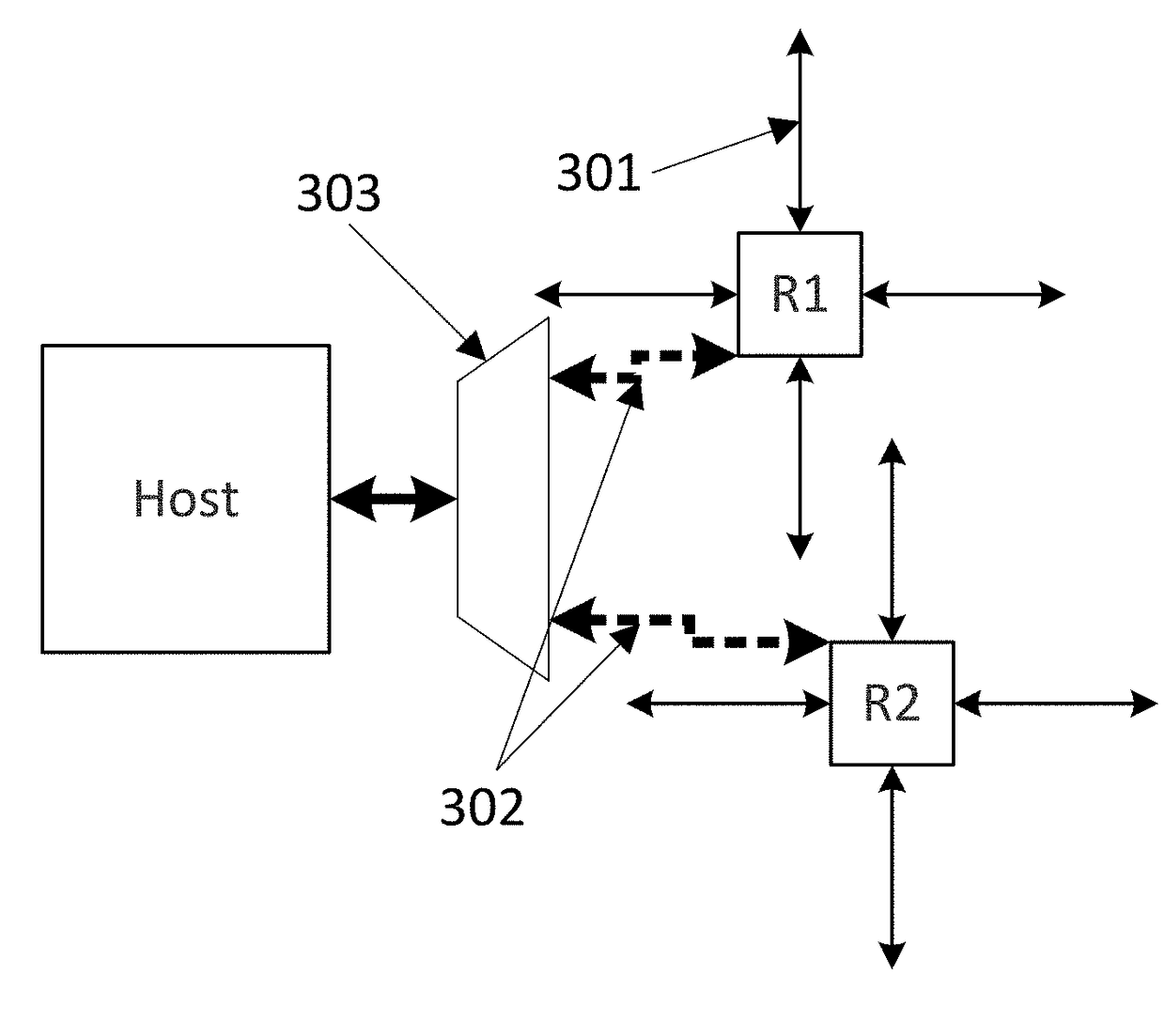

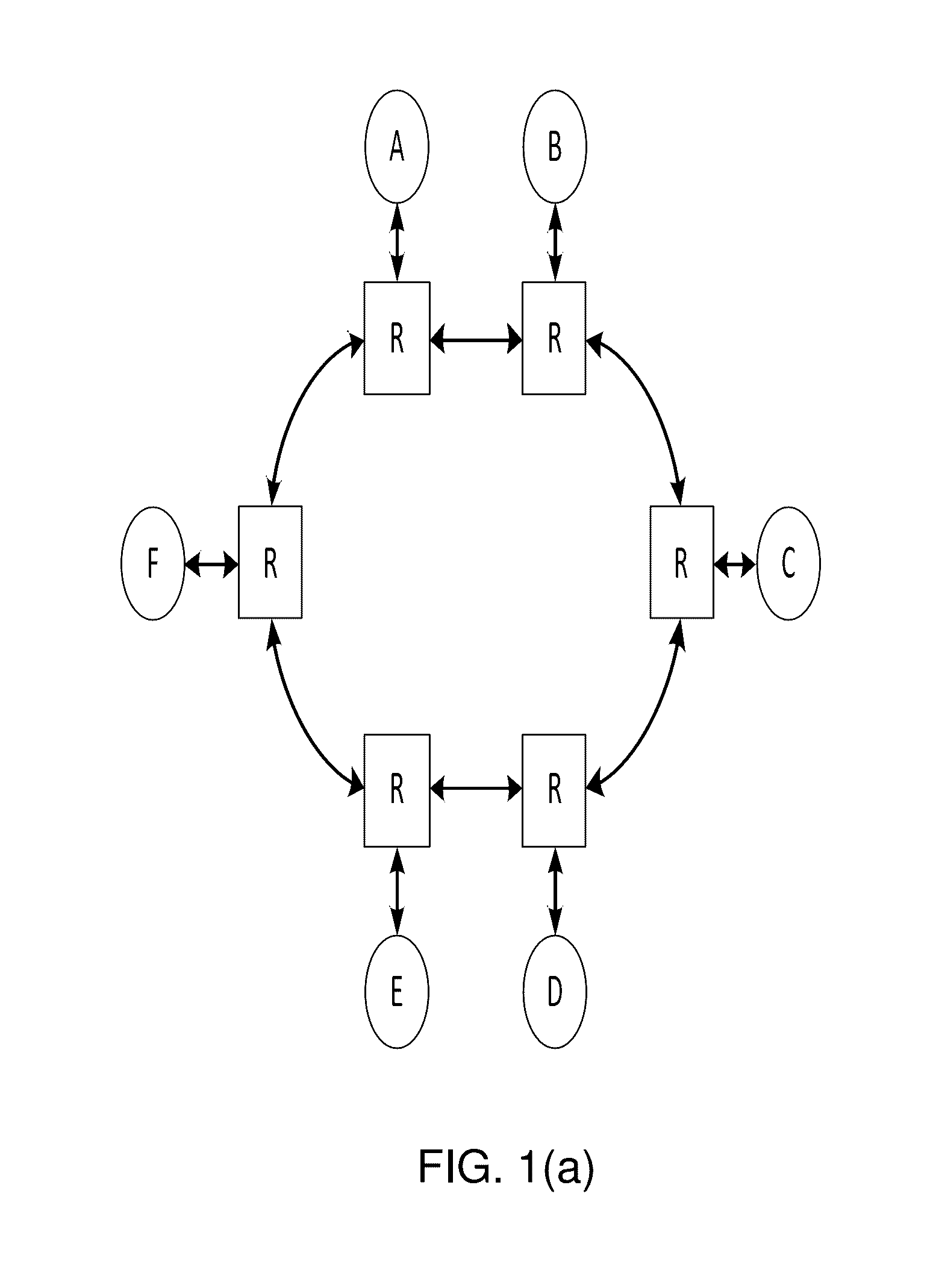

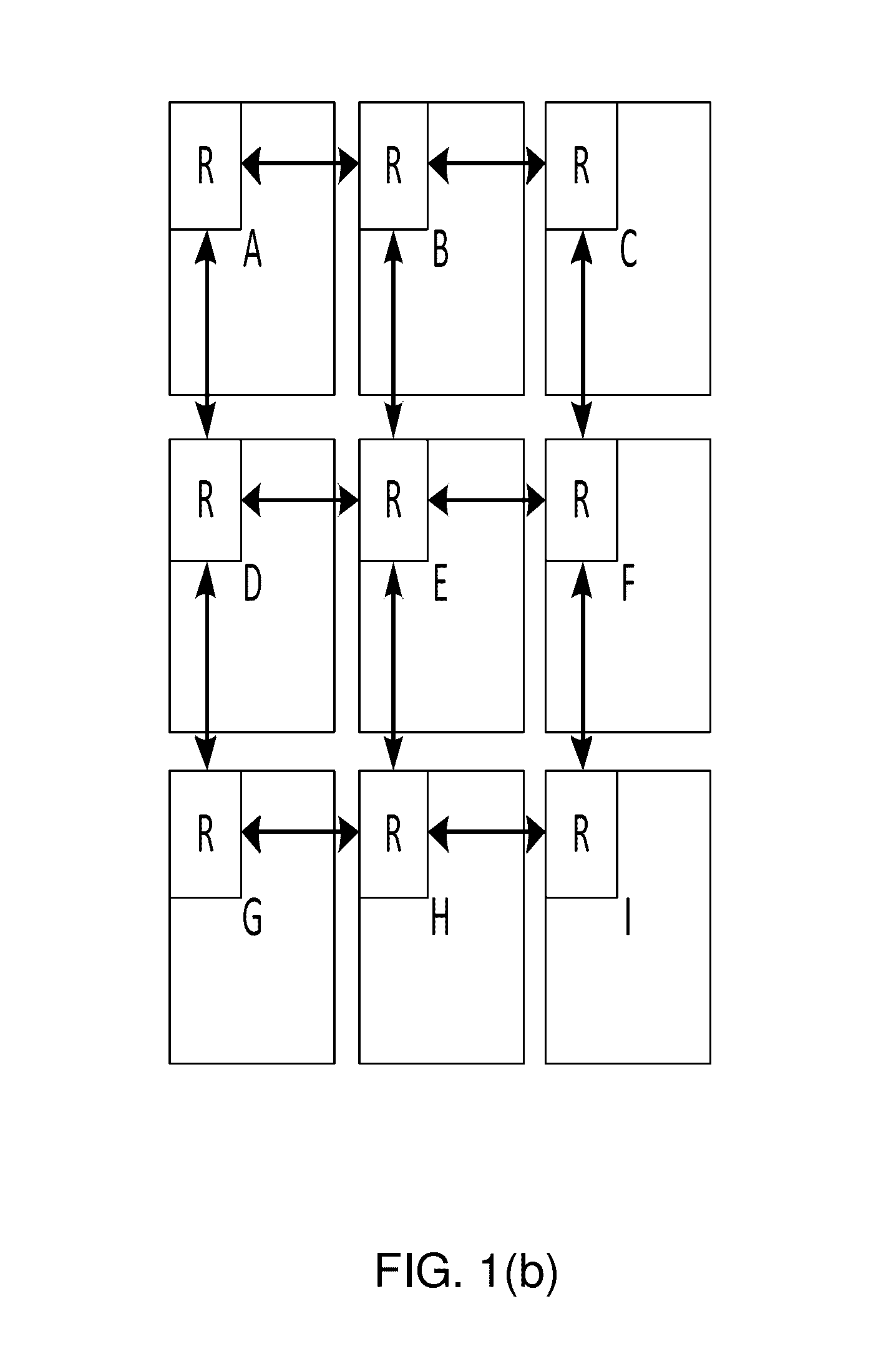

Systems and methods for facilitating low power on a network-on-chip

ActiveUS20180074572A1Power supply for data processingEnergy efficient computingFinite-state machineEngineering

Aspects of the present disclosure are directed to a power specification and Network on Chip (NoC) having a power supervisor (PS) unit. The specification is utilized to generate a NoC with power domains and clock domains. The PS is configured with one or more power domain finite state machines (PDFSMs) that drive signaling for the power domains of the NoC, and is configured to power the NoC elements of the power domain on or off. NoC elements are configured to conduct fencing or draining operations to facilitate the power state transitions.

Owner:TAHOE RES LTD

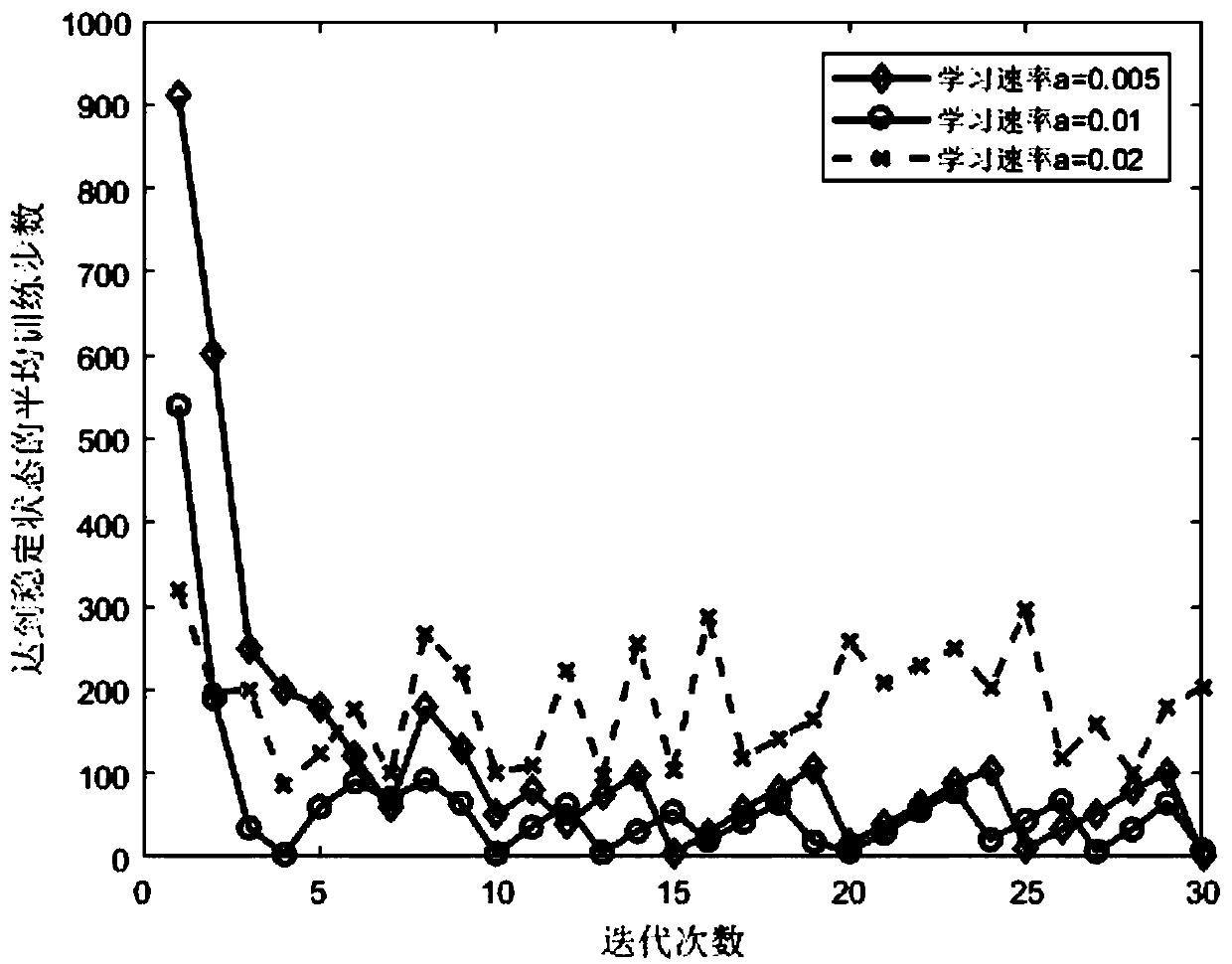

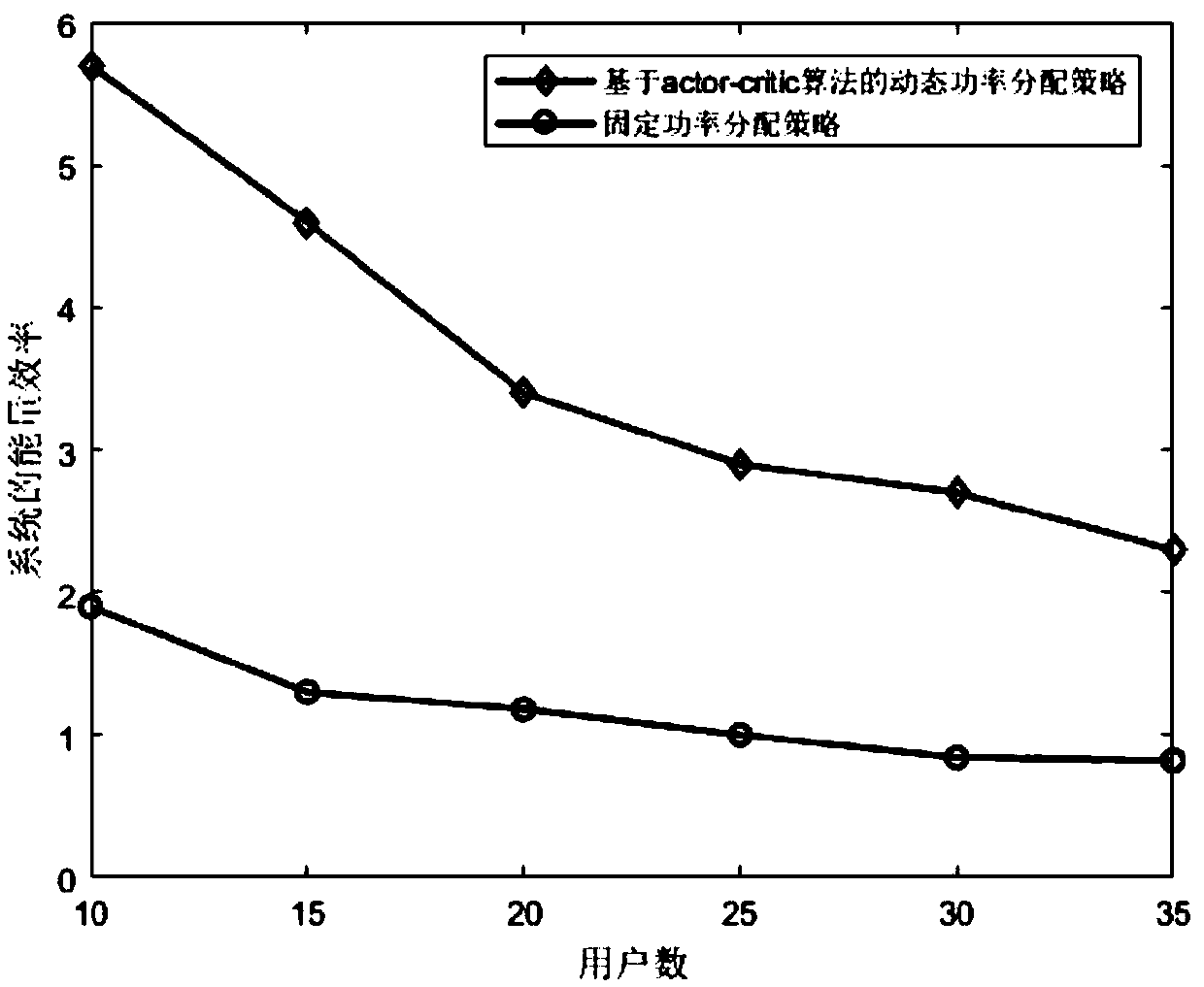

Power allocation method in power domain NOMA based on reinforcement learning algorithm

InactiveCN108924935AImprove energy efficiencyComputing modelsHigh level techniquesAlgorithmTheoretical computer science

The invention discloses a power allocation method in a power domain NOMA based on a reinforcement learning algorithm. Value function update is performed on a Critic part in an Actor-Critic algorithm,and then, an instant reward and a time difference error are fed back into an Actor part in the Actor-Critic algorithm to perform strategy update; and through continuous iteration, a state action valuefunction and a strategy finally tend to the optimal value function and the optimal strategy at last, the energy efficiency of the system is optimal at the moment, and the problems that the complexityof the existing power allocation method is high and that a good effect cannot be achieved on the optimization of the performance of the system are solved.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

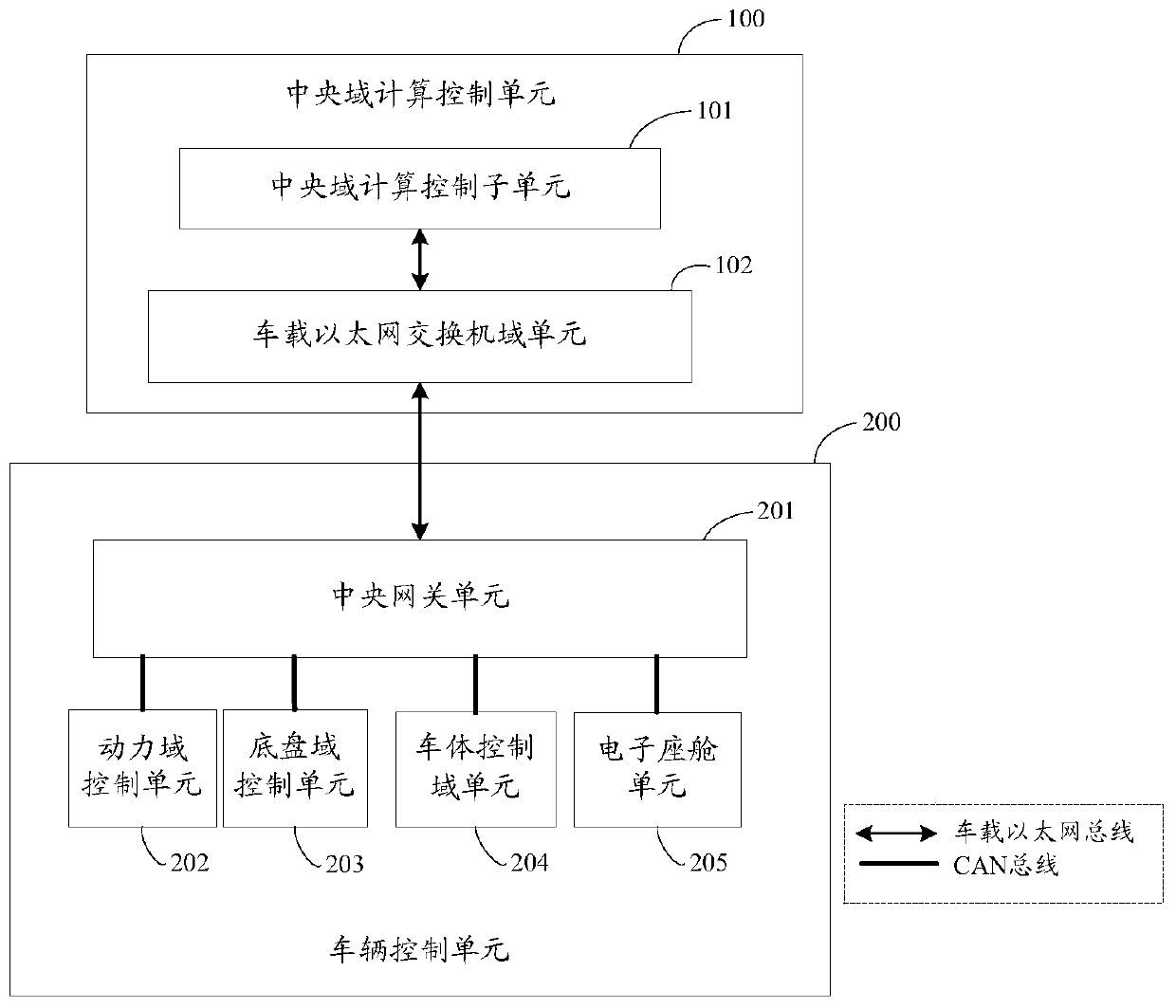

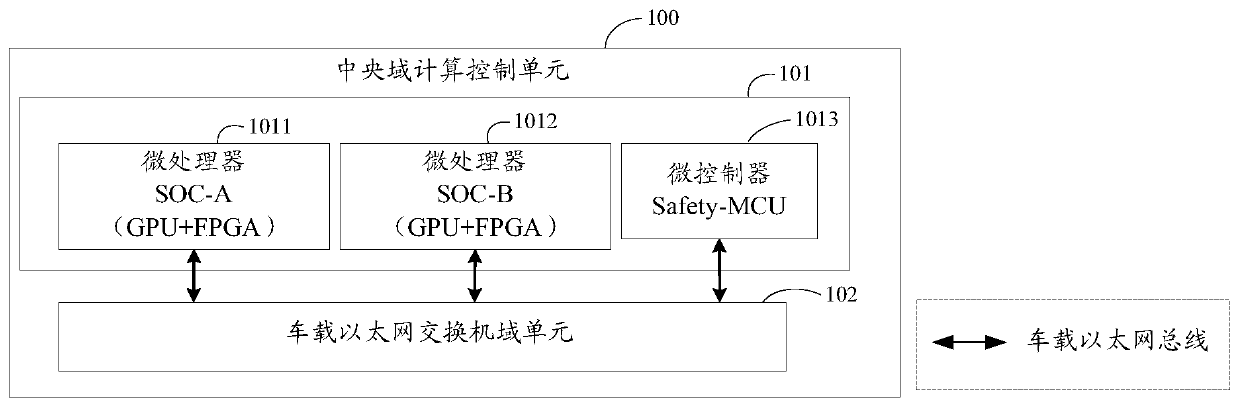

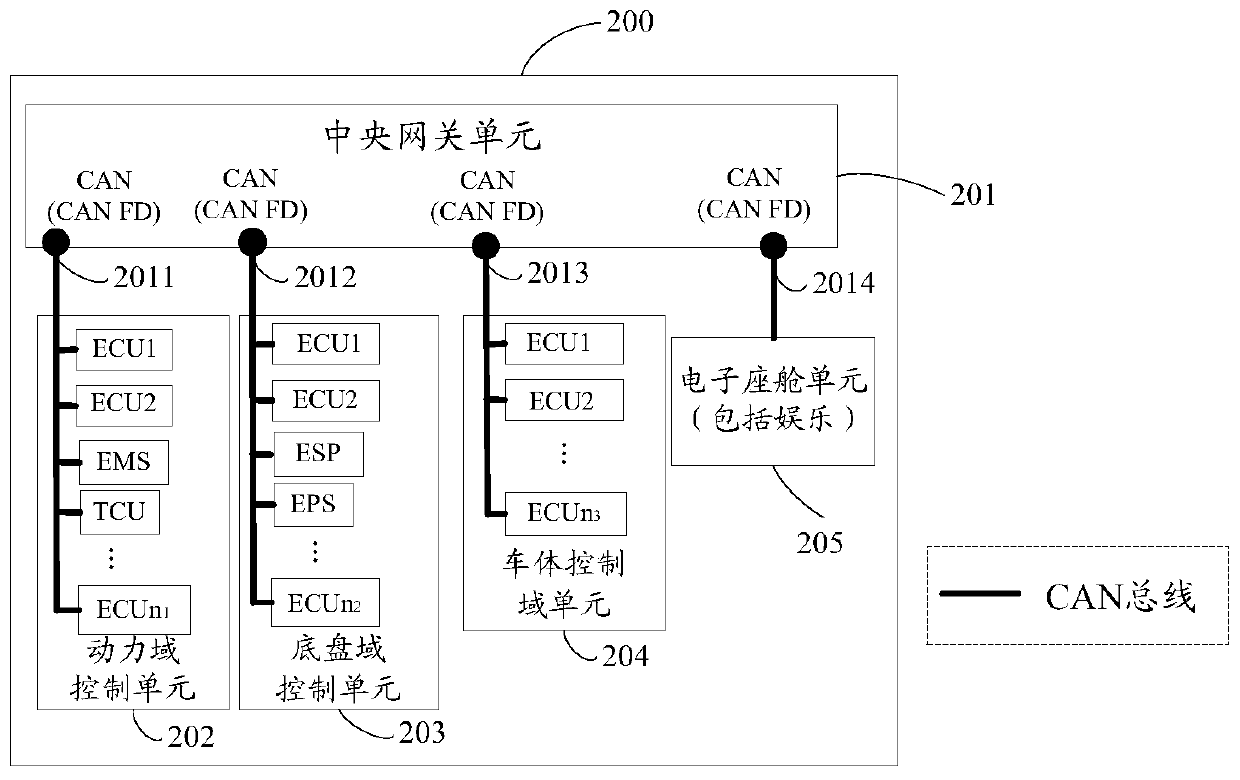

Distributed domain controller system based on network architecture of automatic driving system

ActiveCN109917765AImprove computing powerImprove controllabilityTotal factory controlProgramme total factory controlNetwork architectureEngineering

The invention discloses a distributed domain controller system based on the network architecture of an automatic driving system. The system is provided with a central domain calculation control unit including a central domain calculation control sub unit and a vehicle Ethernet switch domain unit, wherein the central domain calculation control sub unit is connected with the vehicle Ethernet switchdomain unit in a vehicle Ethernet mode, the system is provided with a vehicle control unit including a central gateway unit, a power domain control unit, a chassis domain control unit, a vehicle bodycontrol domain unit and an electronic cabin unit, the different-function units are connected with the central gateway unit through controlling a local area network CAN bus, and the central gateway unit is connected with the vehicle Ethernet switch domain unit in a vehicle Ethernet mode. The system is advantaged in that flexibility of overall configuration, efficiency of data calculation and command execution under different dedicated functional units, and convenience of fault and abnormality handling and component replacement can be improved.

Owner:NEUSOFT REACH AUTOMOBILE TECH (SHENYANG) CO LTD

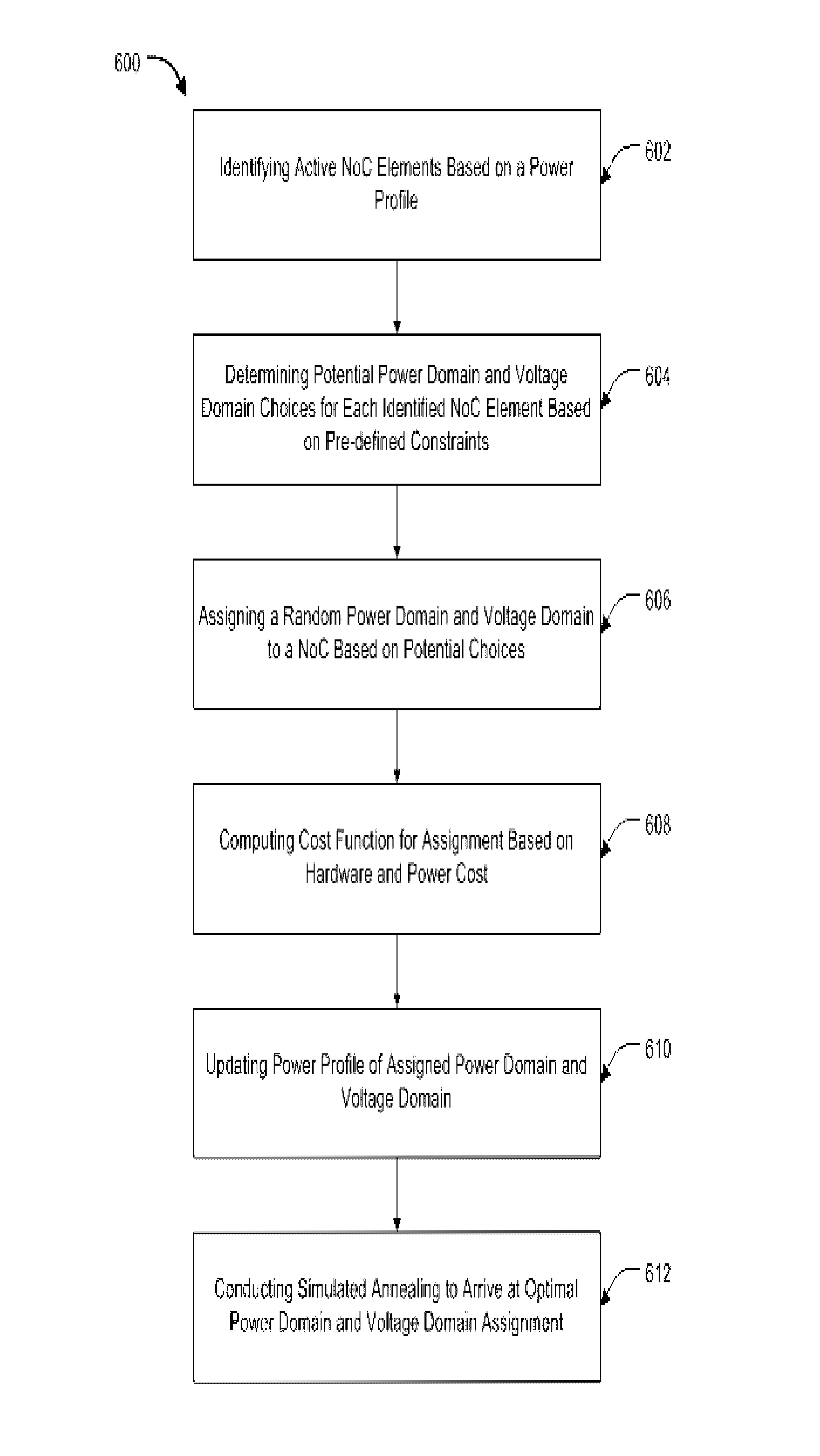

Automatic power domain and voltage domain assignment to system-on-chip agents and network-on-chip elements

ActiveUS9529400B1Reducing/minimizing static power consumptionVolume/mass flow measurementPower supply for data processingEngineeringPower domains

The present disclosure relates system and method for automatic assignment of power domain and voltage domain to one or more SoC and / or NoC elements based on one or a combination of NoC and / or SoC specification / design, traffic specification, connectivity between SoC hosts that the NoC element in context is a part of, power specification (power domain and voltage domain of each host) of the hosts / SoC, and power profile(s) applicable for the NoC element in context. In another example implementation, power domain and voltage domain can be assigned to each SoC and / or NoC element based on pre-defined constraints and with an objective of reducing / minimizing static power consumption, reducing / minimizing hardware area, or identifying a tradeoff between the two parameters.

Owner:INTEL CORP

High level IC design with power specification and power source hierarchy

ActiveUS7954078B1Computer aided designSoftware simulation/interpretation/emulationComputer architecturePower domains

A method to produce an information structure in computer readable memory that specifies power source hierarchy information for an RTL circuit design that includes multiple function instances encoded in computer readable memory, comprising: providing associations within the memory between respective function instances of the RTL design and respective power domains so as to define respective primary power domains relative to the RTL design; specifying in the memory respective secondary power domains; and providing associations within the memory that are indicative of respective power source relationships between respective primary power domains and corresponding respective secondary power domains.

Owner:CADENCE DESIGN SYST INC

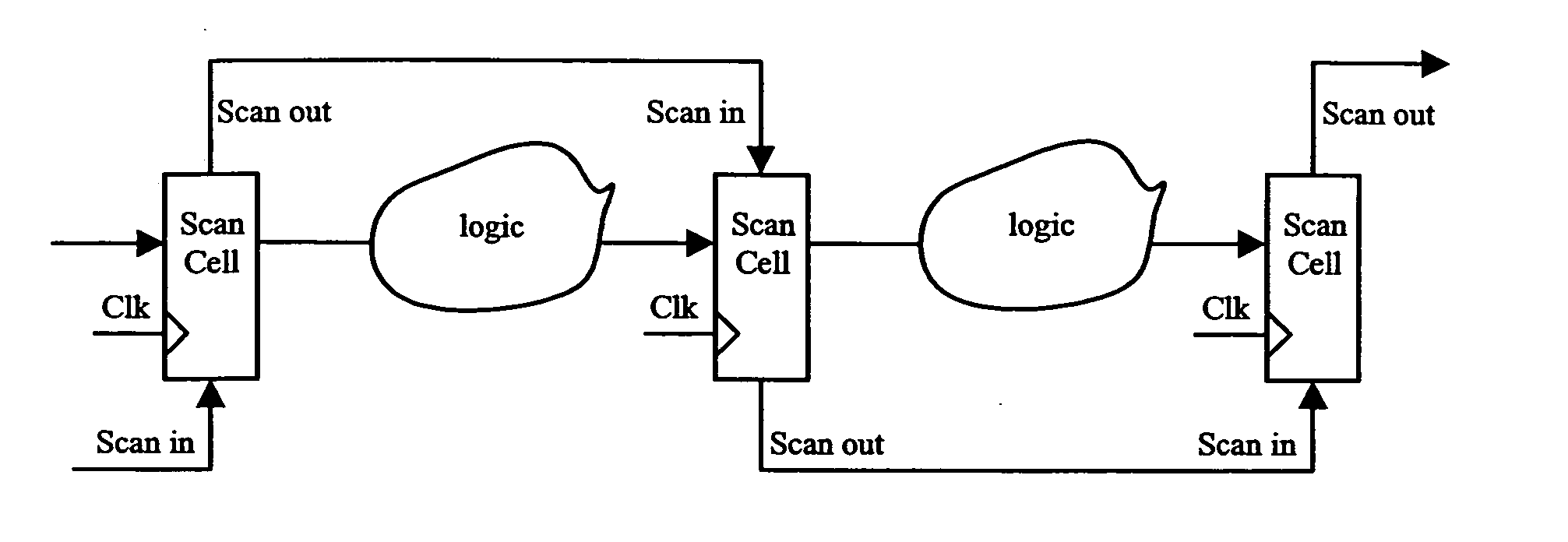

Integrated circuit with leakage control and method for leakage control

InactiveUS20050149799A1Improved leakage power controlReduce leakage powerPower reduction by control/clock signalDigital circuit testingPower modeState variable

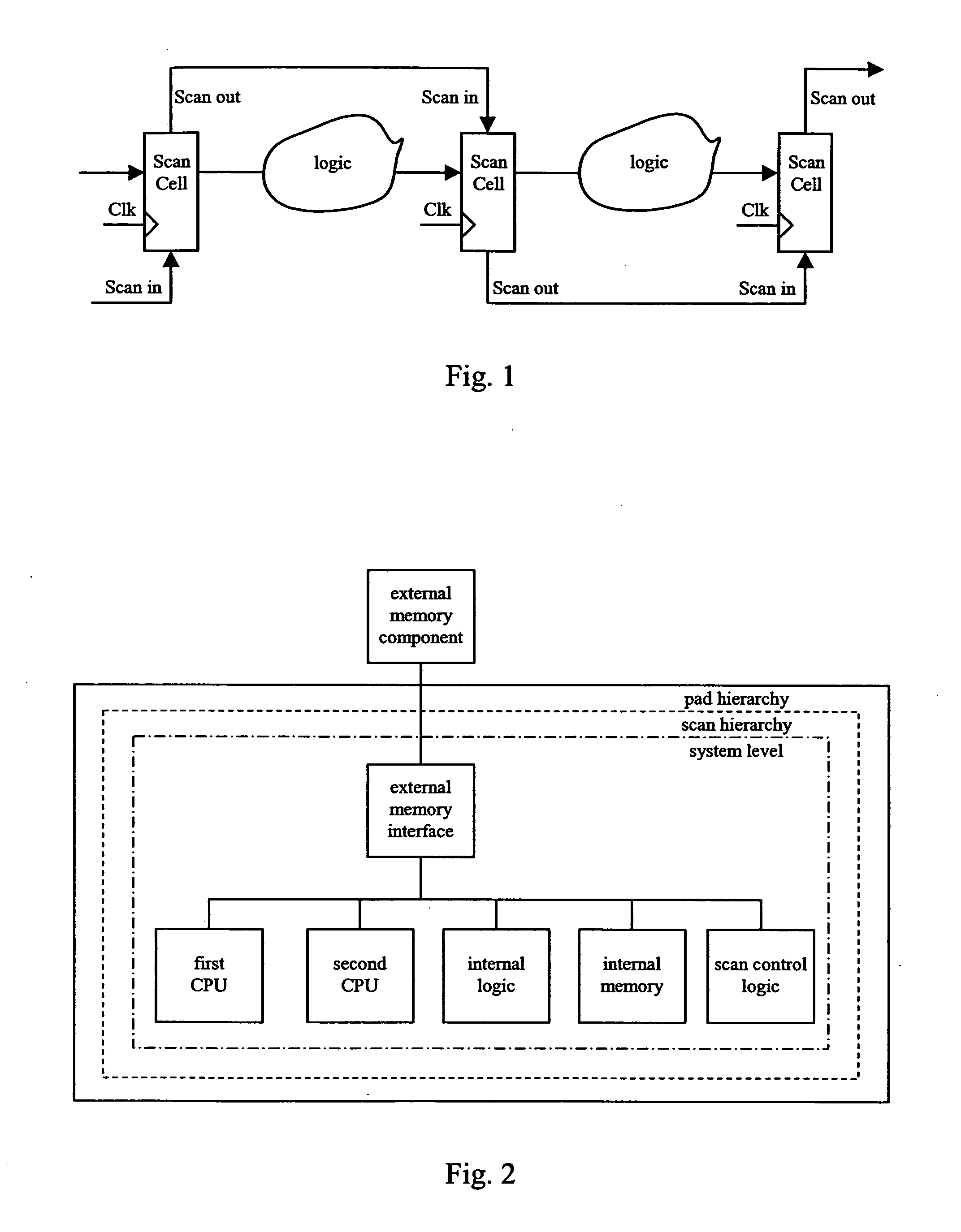

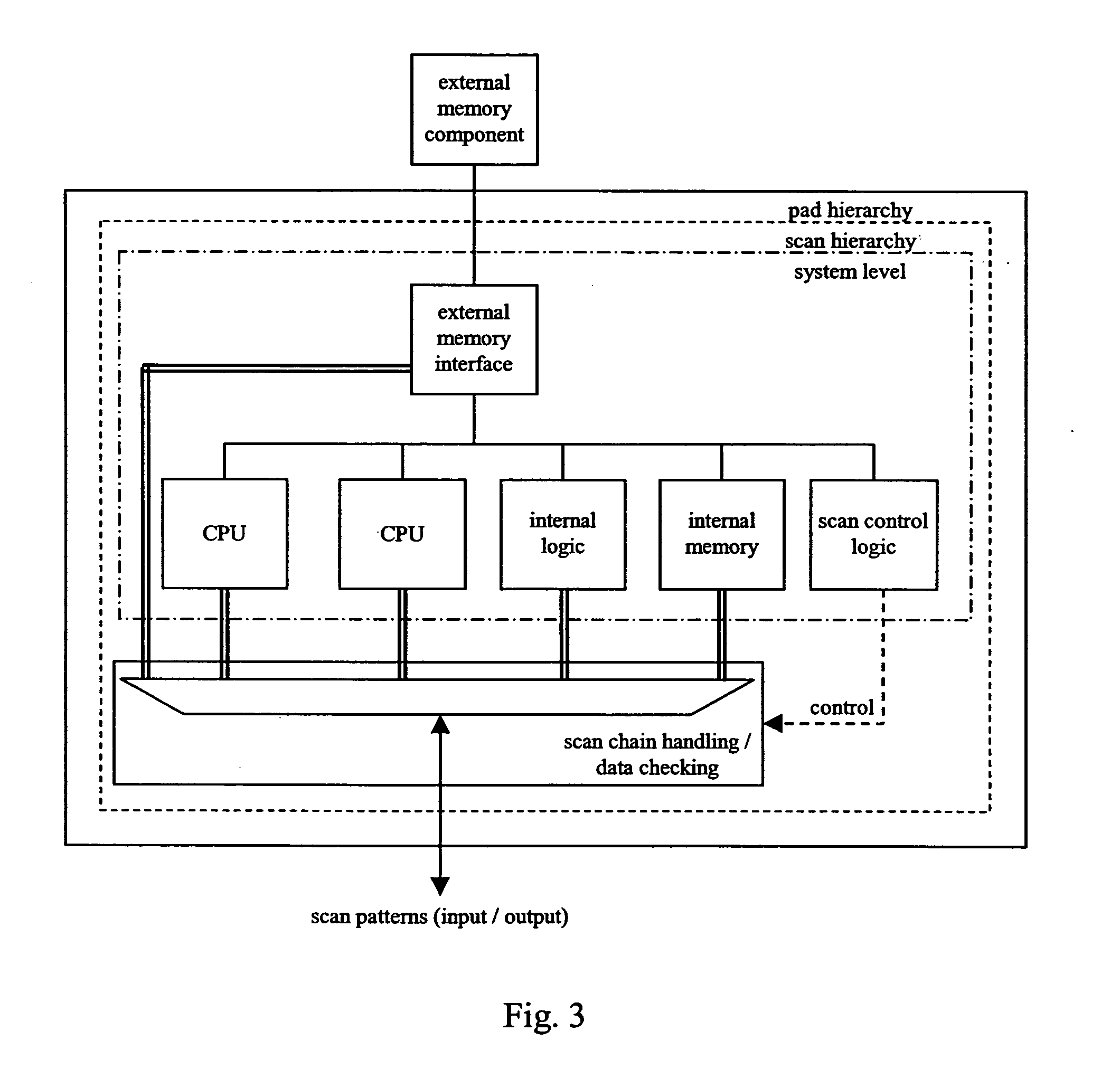

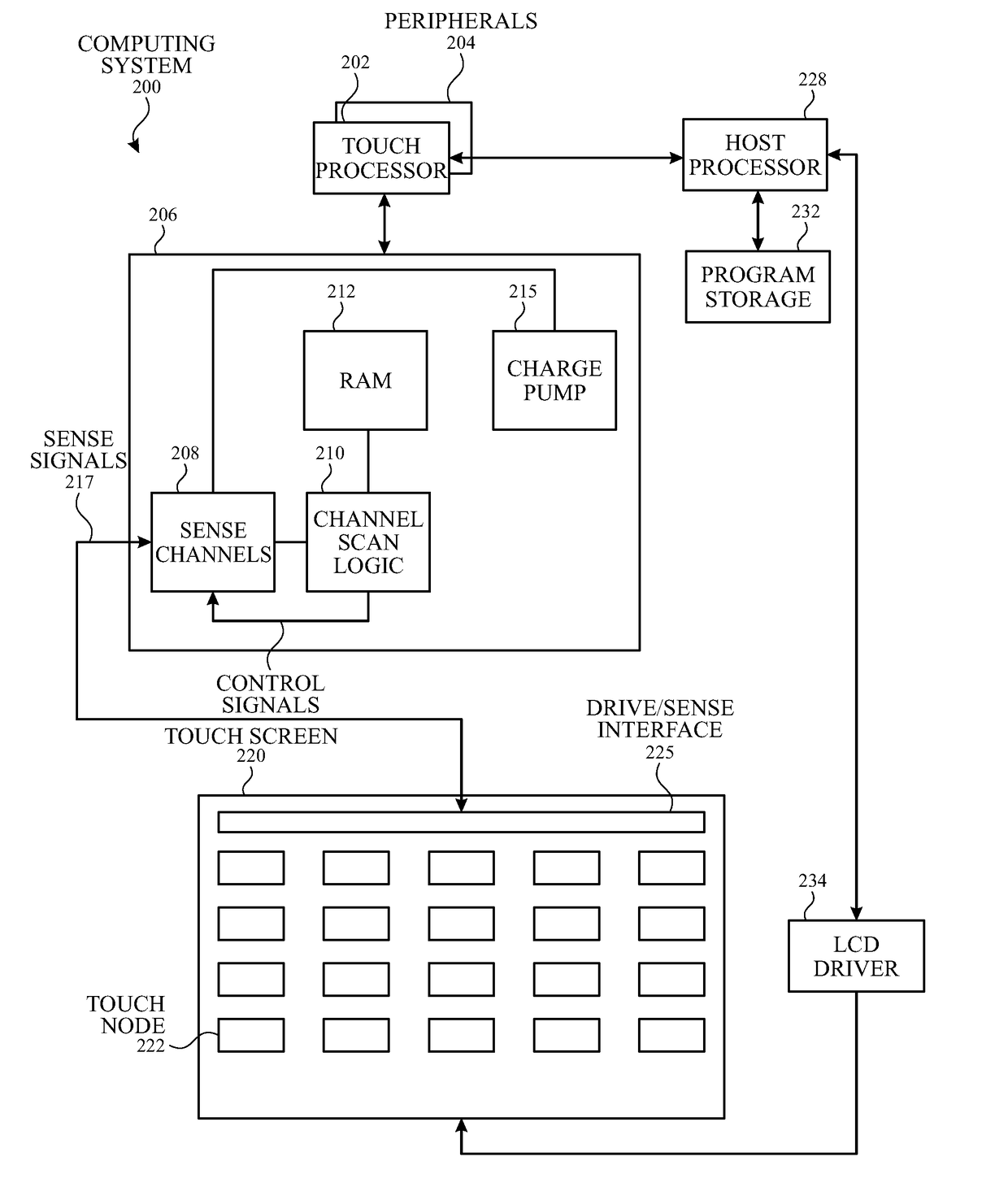

The present invention relates to integrated circuit with reduced leakage power and in particular to a methodology for retaining an operational state of at least a part of the integrated circuit while the part is in standby / low power mode. In detail, the inventive methodology is based on the use of scan chains being implemented in the integrated circuit for production testing purposes. Via the scan chains circuit-internal state-variable memory element content is read out and / or written in such that the operational state of for instance a specific part (power domain) of the integrated circuit may be captured on the basis of the circuit internal contents, retained in an adequately provided data storage and afterwards scanned into the specific part of the integrated circuit to restore the operational state thereof.

Owner:NOKIA CORP

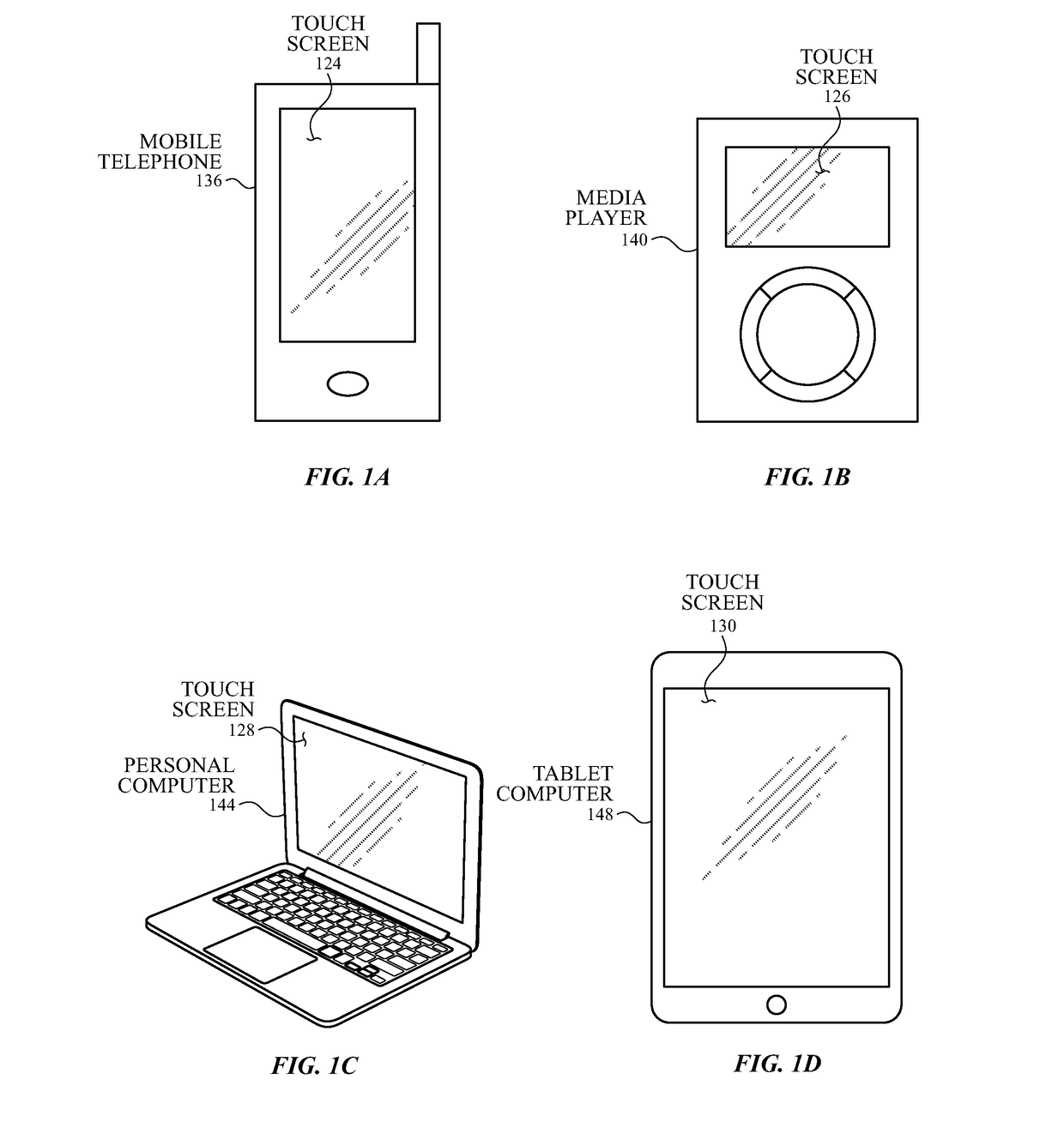

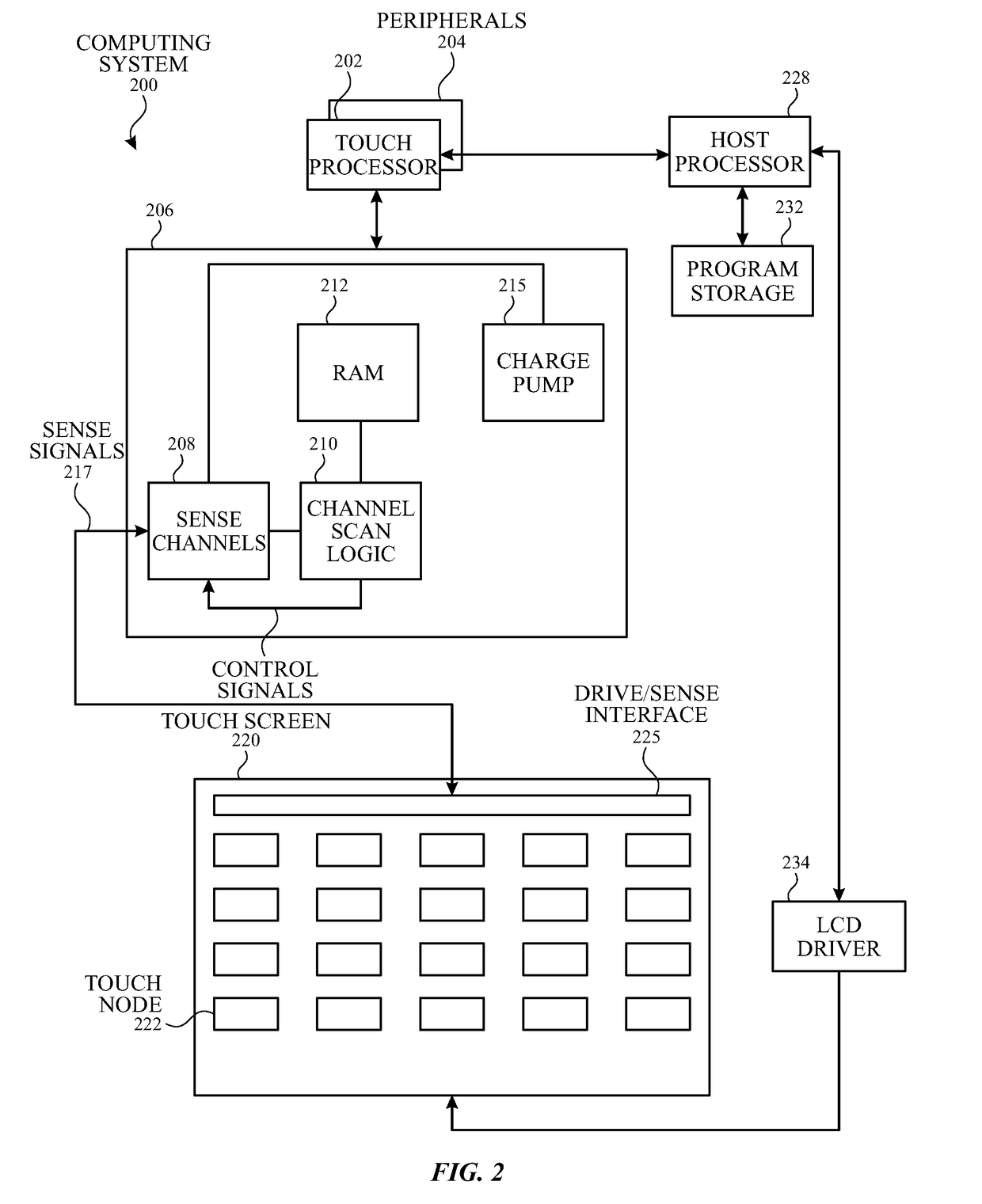

Touch sensor panel with multi-power domain chip configuration

ActiveUS20180032176A1Reduce and eliminate and parasitic capacitanceReduce and eliminate stray and capacitanceNon-linear opticsInput/output processes for data processingTouch SensesVoltage regulation

A touch sensing system is disclosed. The touch sensing system includes a guard signal generation chip operating in a first power domain referenced to a first voltage, the guard signal generation chip configured to generate a guard signal. A touch sensing chip operates in a second power domain, different from the first power domain, referenced to the guard signal, the touch sensing chip configured to sense touch at one or more touch electrodes included in a touch sensor panel operating in the second power domain referenced to the guard signal, and the touch sensing chip a different chip than the guard signal generation chip. A voltage regulator is configured to selectively regulate a voltage of the guard signal at the touch sensing chip.

Owner:APPLE INC

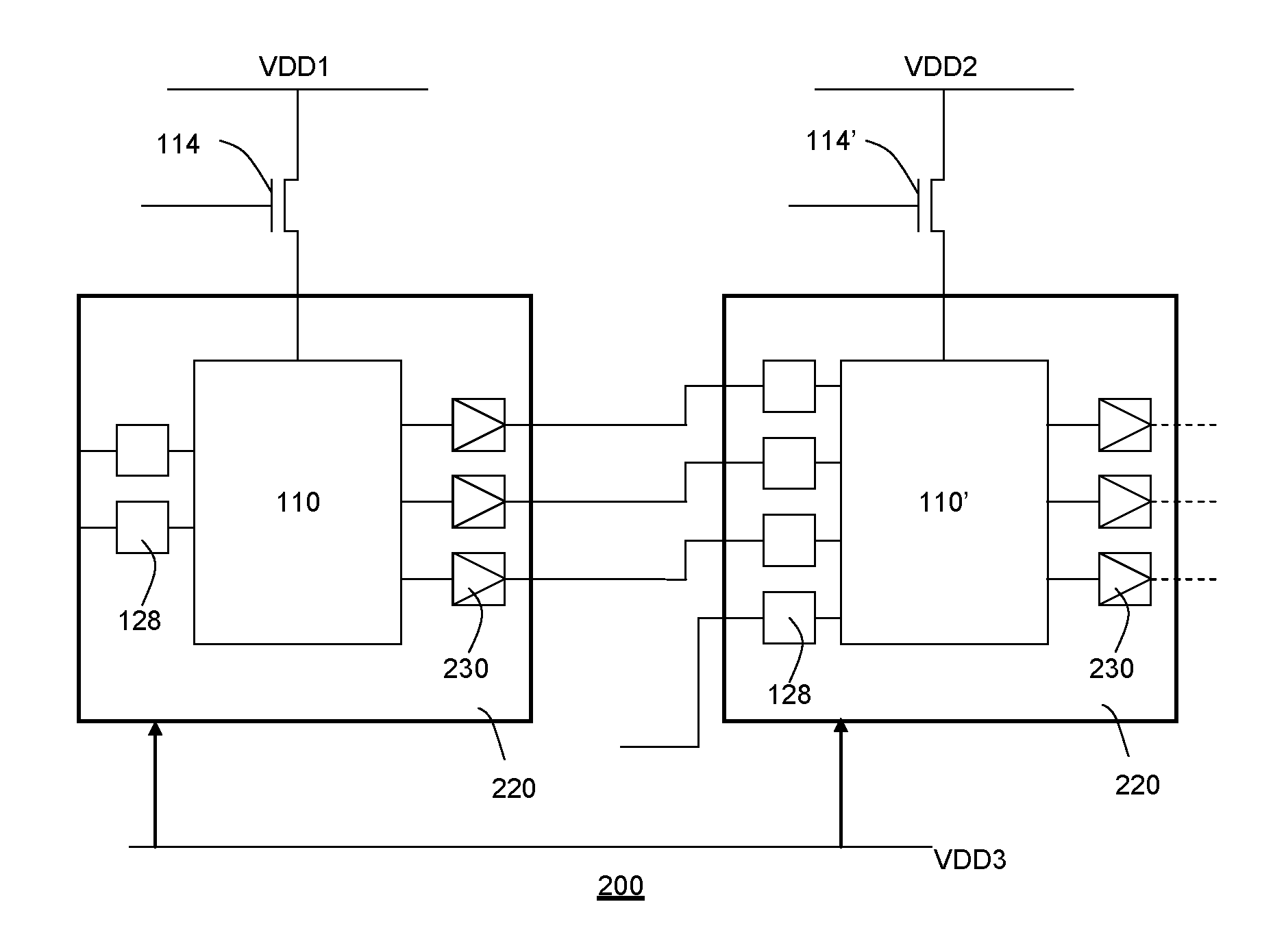

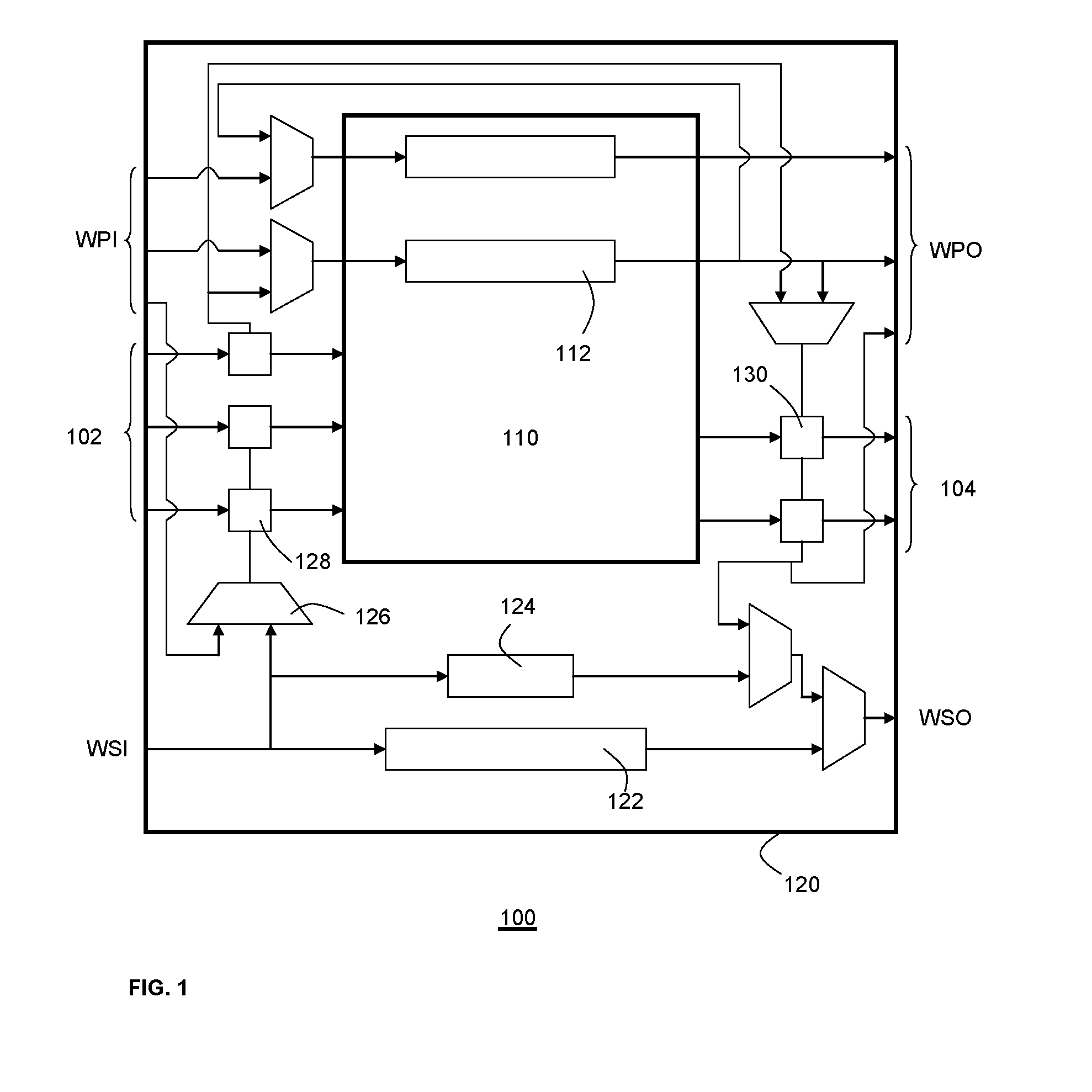

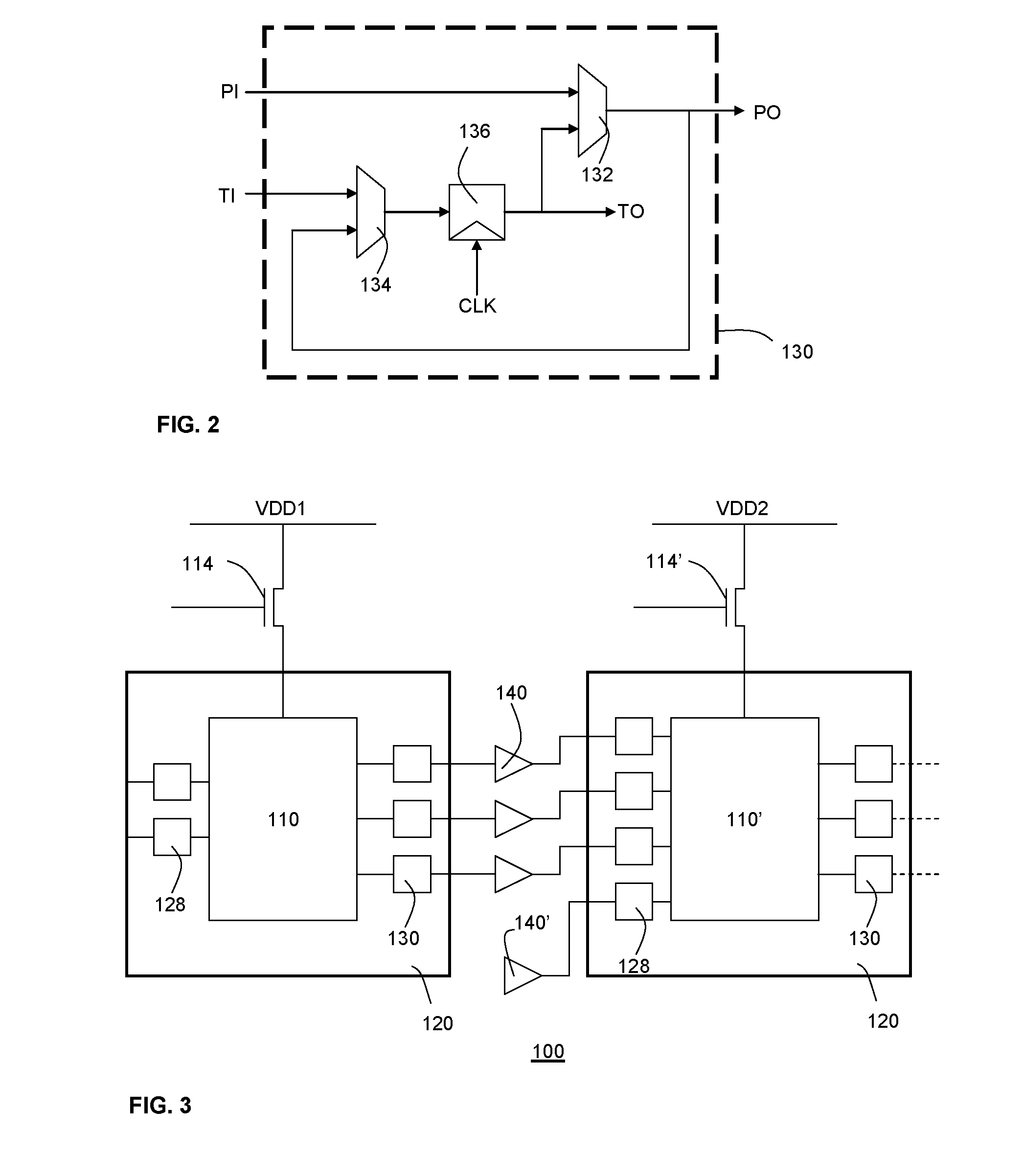

Testable integrated circuit and test method therefor

ActiveUS20110221502A1Reduce effortPulse automatic controlElectrical testingPower domainsIntegrated circuit

Disclosed is an integrated circuit (200) comprising a plurality of cores (110, 110), at least some of the cores being located in different power domains (VDD1, VDD2), each core being surrounded by a test wrapper (220) comprising a plurality of wrapper cells (128, 230), wherein each of said test wrappers are located in a single power domain (VDD3) and each plurality of wrapper cells comprises wrapper output cells (230) each arranged to output a signal from its associated core, each of said wrapper output cells comprising an output level shifter (232, 240) for shifting the voltage of said signal to the voltage of the single power domain (VDD3). A method for testing such an IC and standard library cells for designing such an IC are also disclosed.

Owner:III HLDG 6

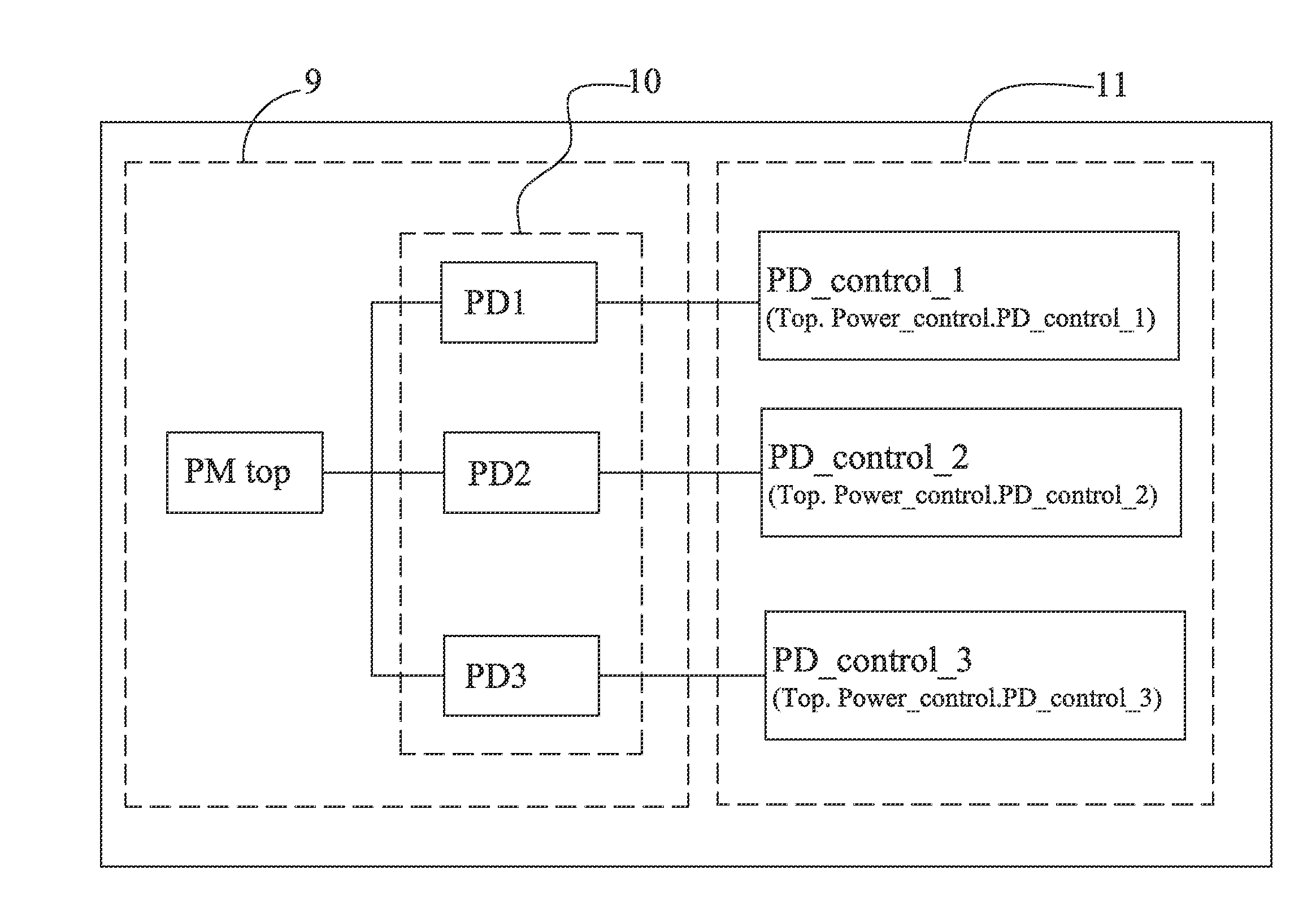

Hierarchical power map for low power design

InactiveUS20140013293A1Quick understandingEasy to debugCAD circuit designSoftware simulation/interpretation/emulationGraphicsLow-power electronics

Power information associated with an IC design is displayed graphically and hierarchically using a power map, thereby providing an intuitive way for describing the power distribution among various power domains of the IC and parent-child relationships within the power domains. Each power domain is associated with a power control for controlling the power domain. The status of the power control for each power domain is displayed on the power map. The power map may include a token to set and display current operating mode of the IC design to enable the IC design to be debugged under different operating modes.

Owner:SYNOPSYS INC

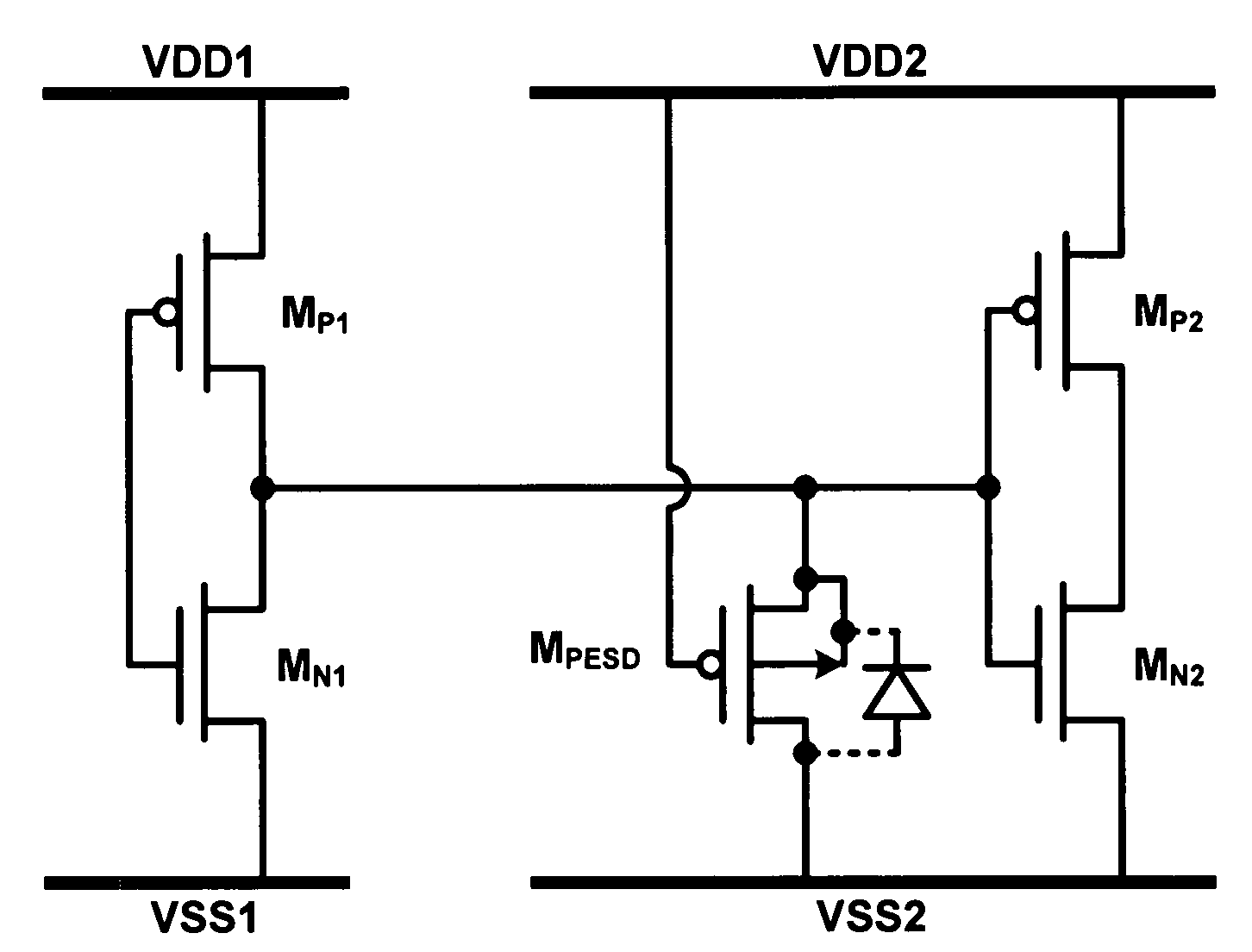

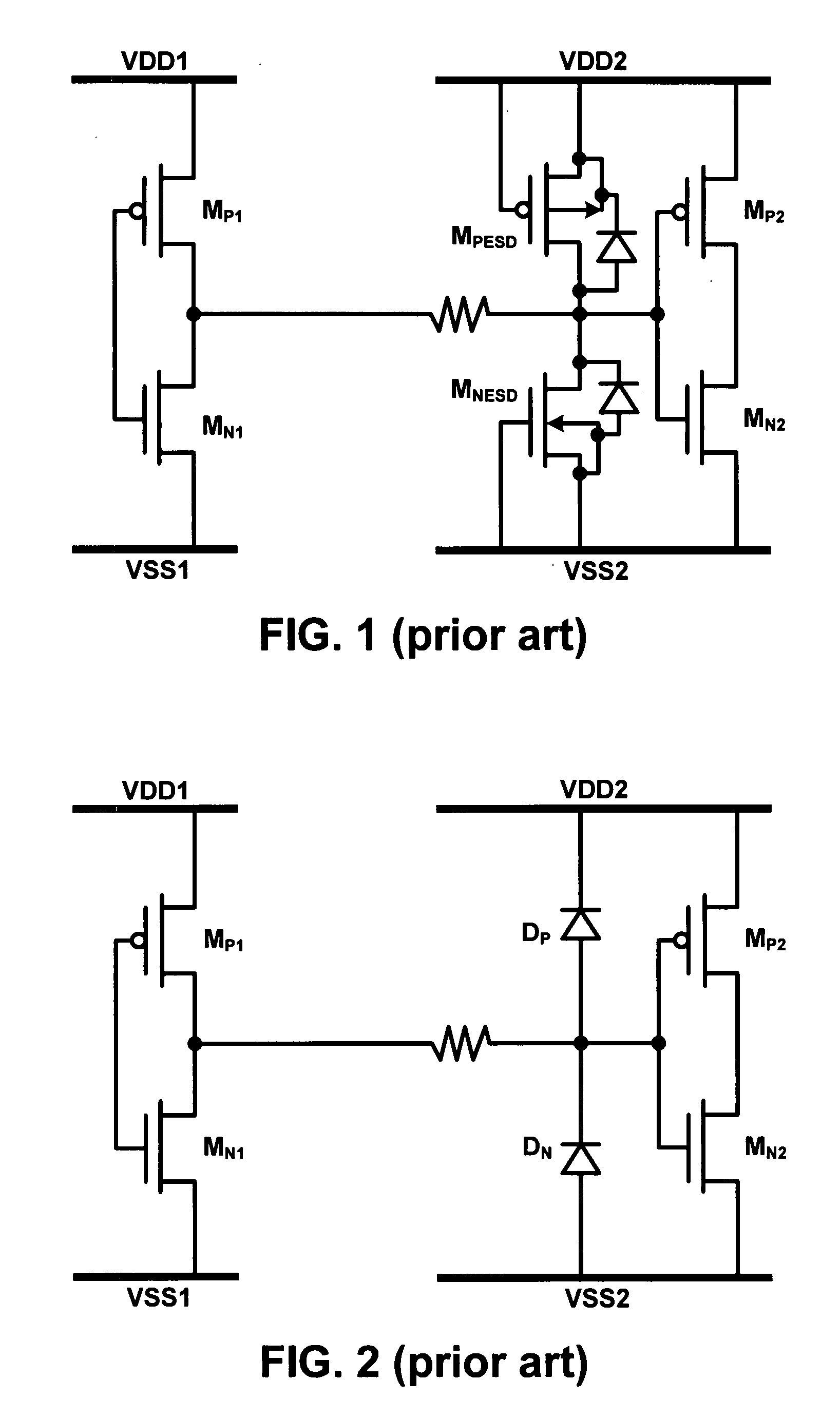

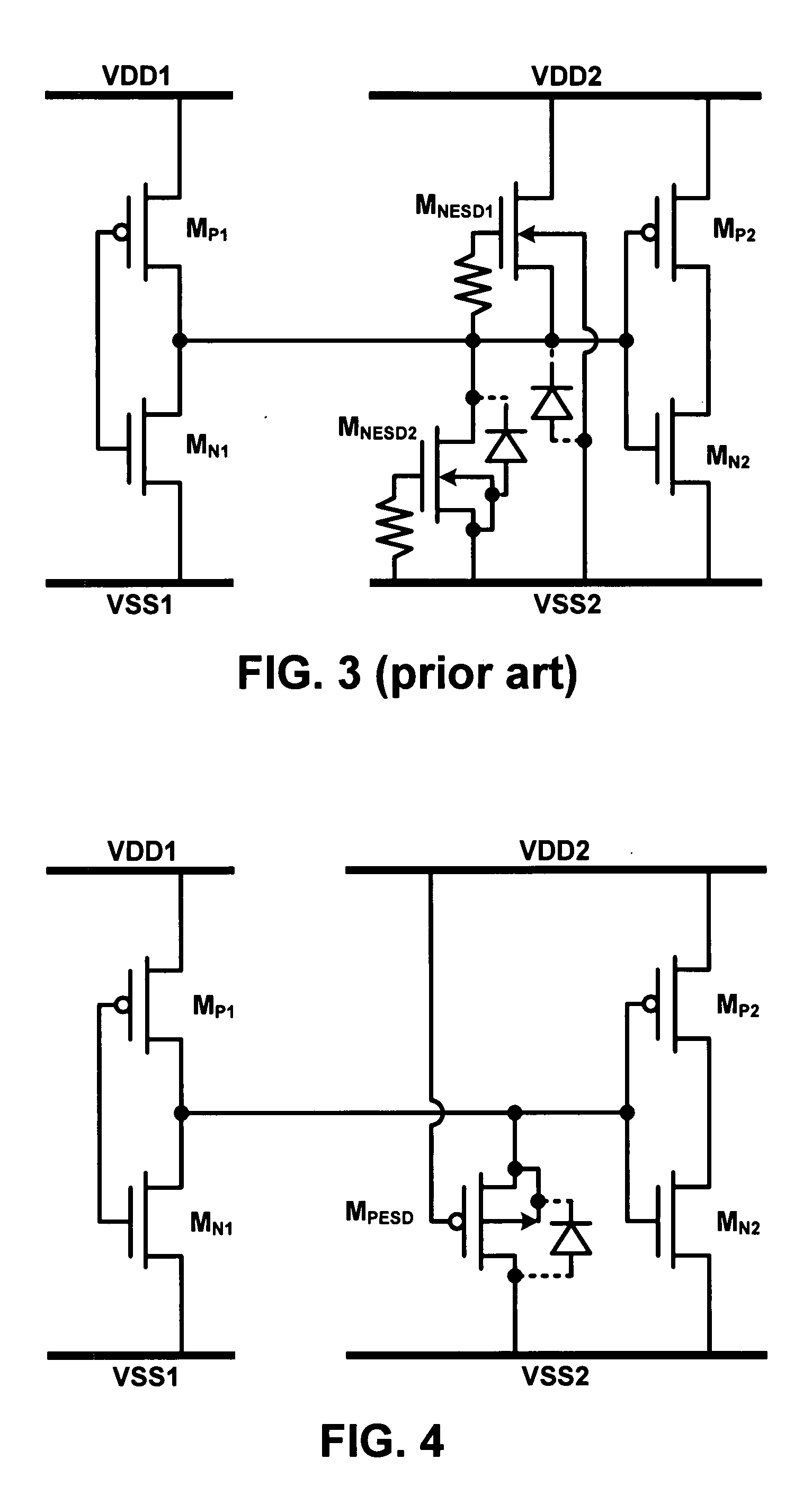

ESD protection circuit for IC with separated power domains

An ESD protection circuit suitable for applying in an integrated circuit with separated power domains is provided. The circuit includes a P-type MOSFET coupled between a first circuit in a first power domain and a second circuit in a second power domain. A source terminal of the P-type MOSFET is coupled to a connection node for connecting the first circuit and the second circuit. A gate terminal of the P-type MOSFET is coupled to a positive power line of the second power domain. A drain terminal of the P-type MOSFET is coupled to a negative power line of the second power domain. A body terminal of the P-type MOSFET is also coupled to the connection node.

Owner:AMAZING MICROELECTRONICS