Patents

Literature

584 results about "Shut down" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

To shut down or power off a computer is to remove power from a computer's main components in a controlled way. After a computer is shut down, main components such as CPUs, RAM modules and hard disk drives are powered down, although some internal components, such as an internal clock, may retain power.

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

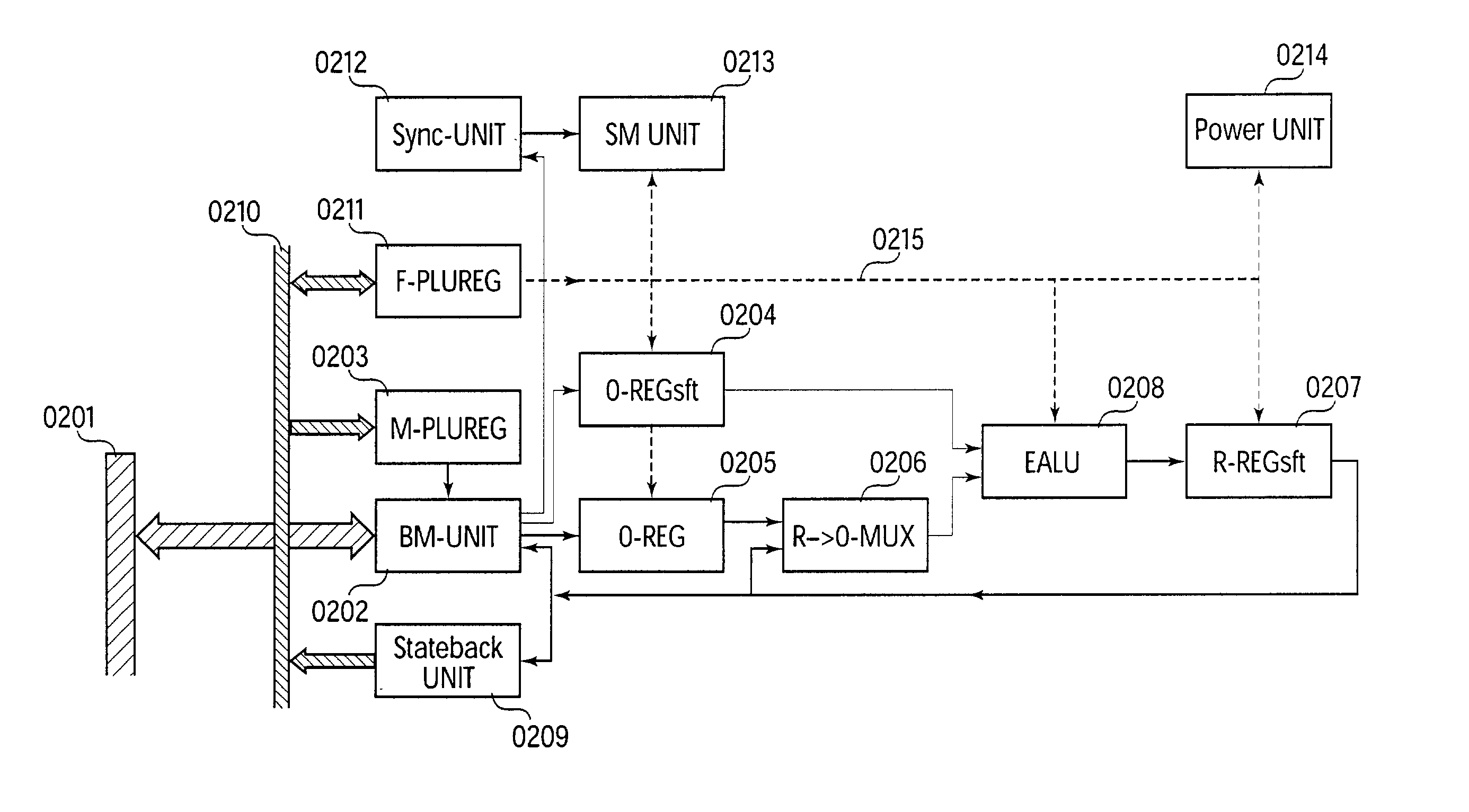

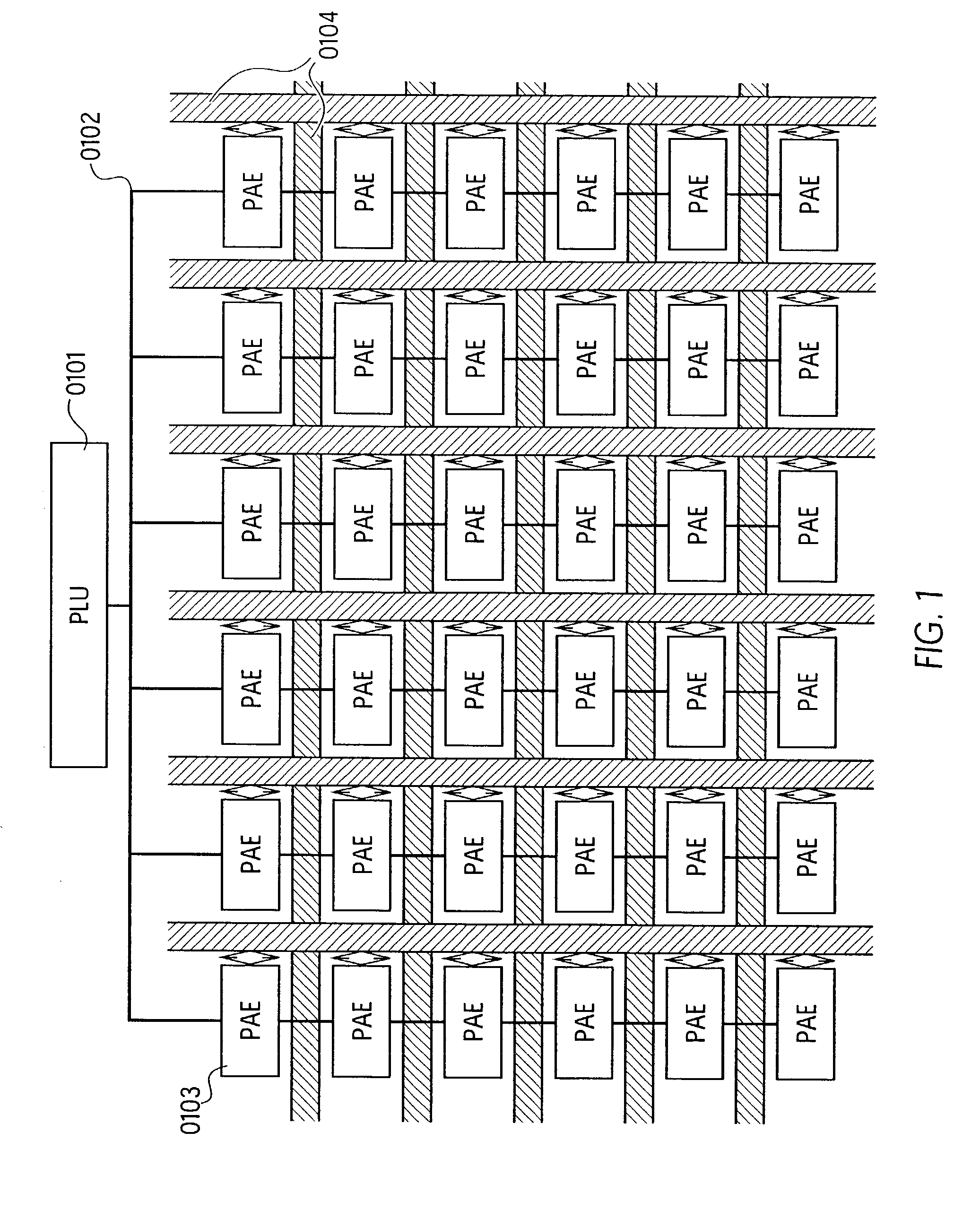

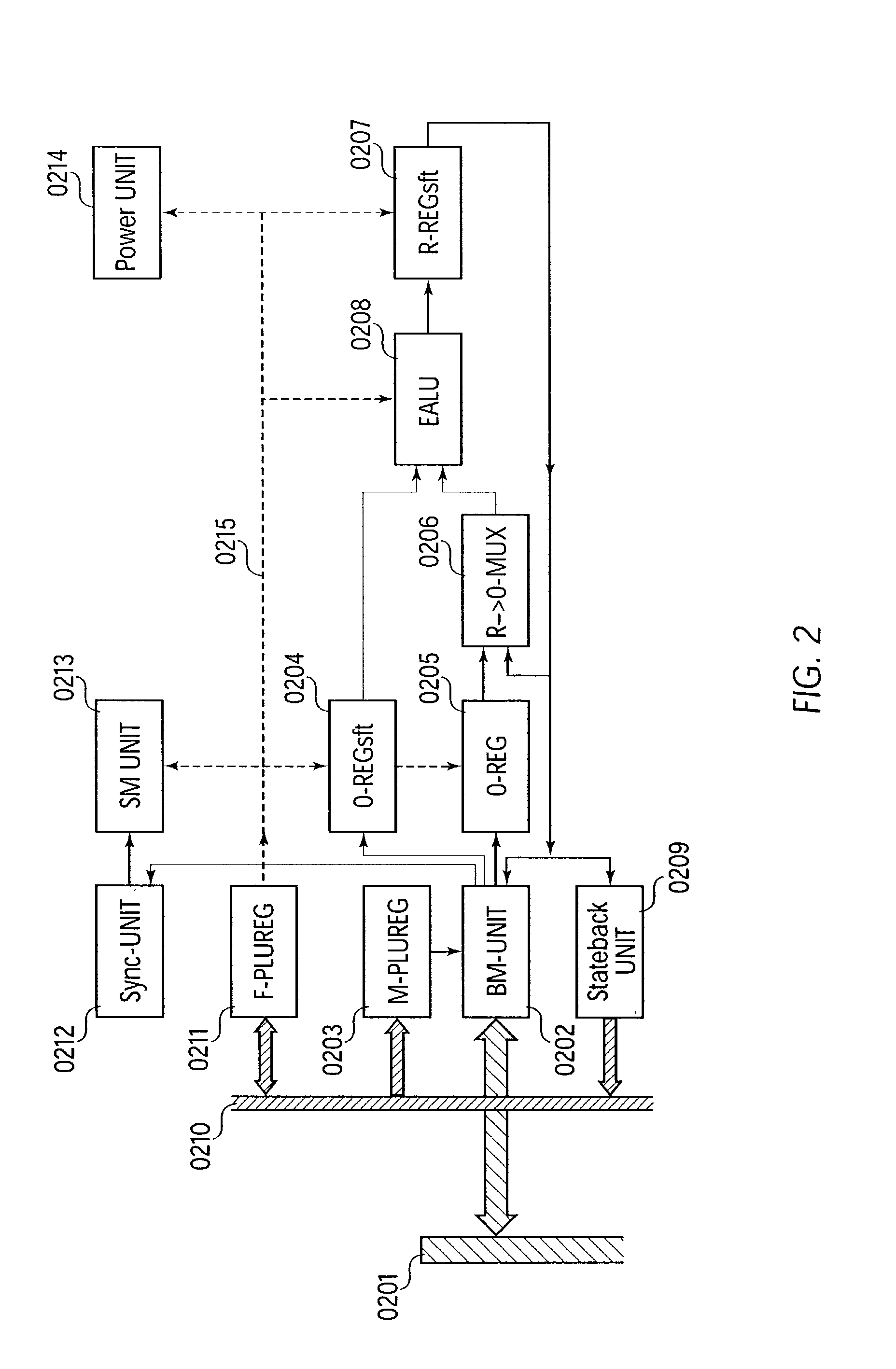

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

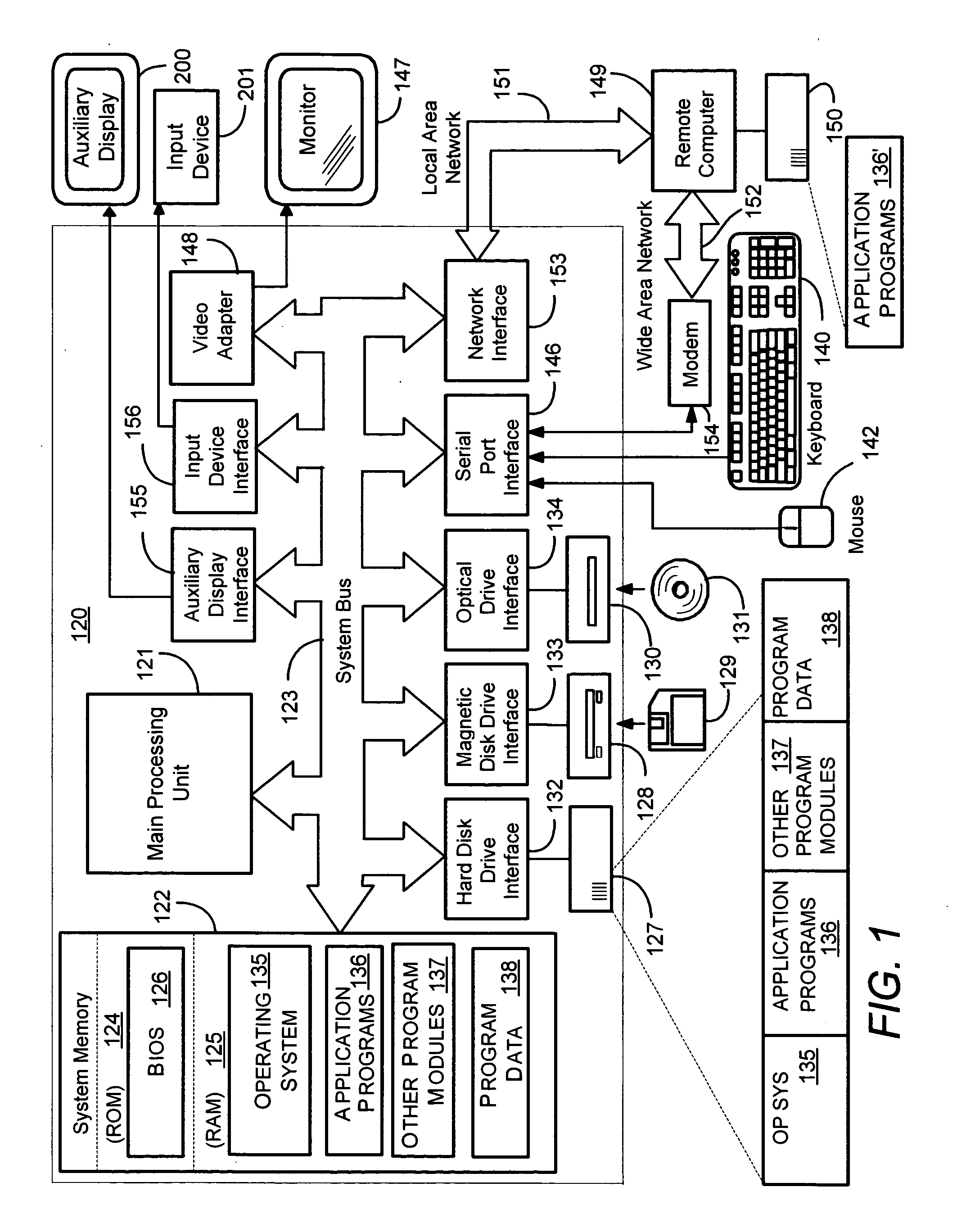

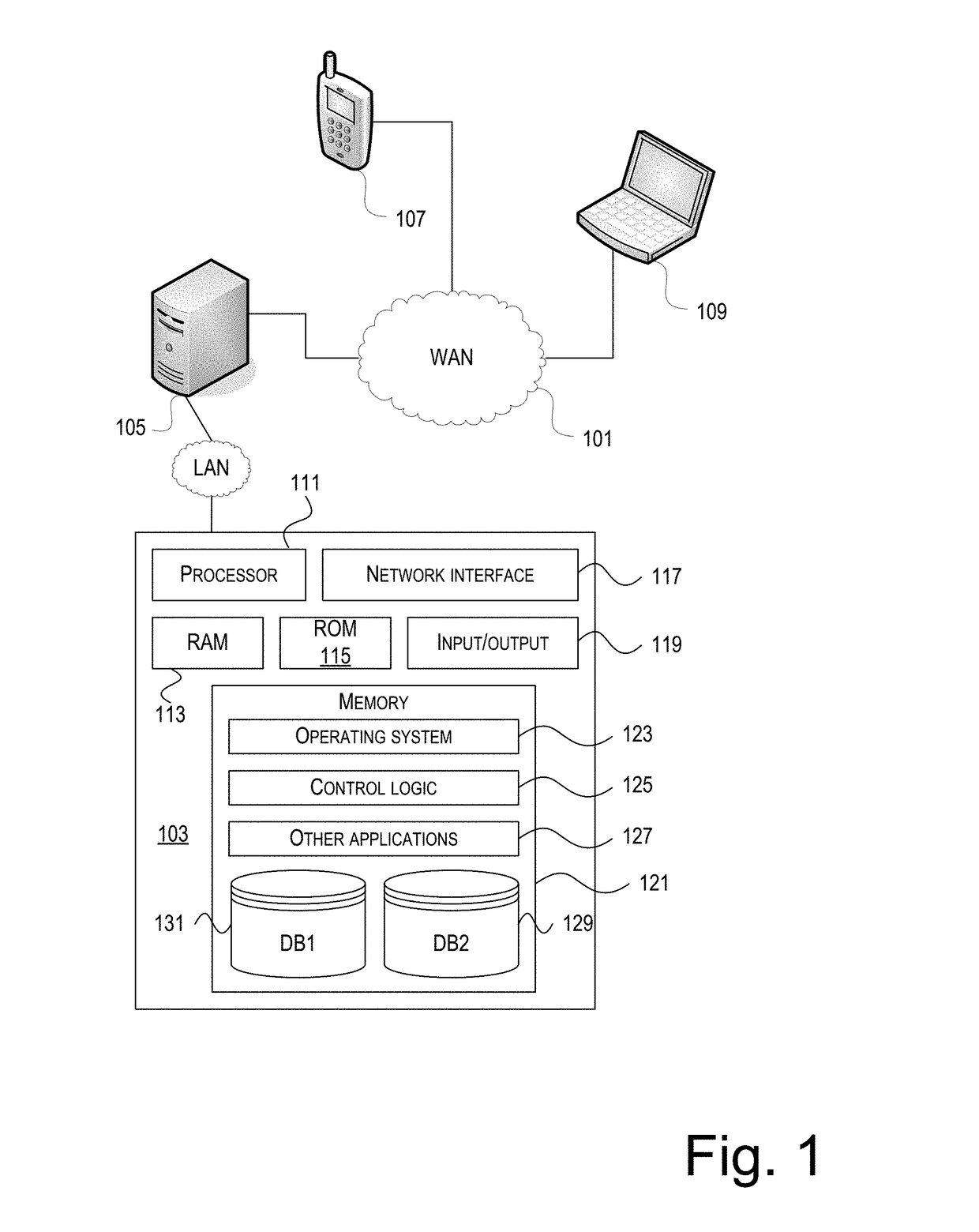

Processing information received at an auxiliary computing device

InactiveUS20050262302A1Digital data information retrievalProgram control using stored programsComputerized systemApplication software

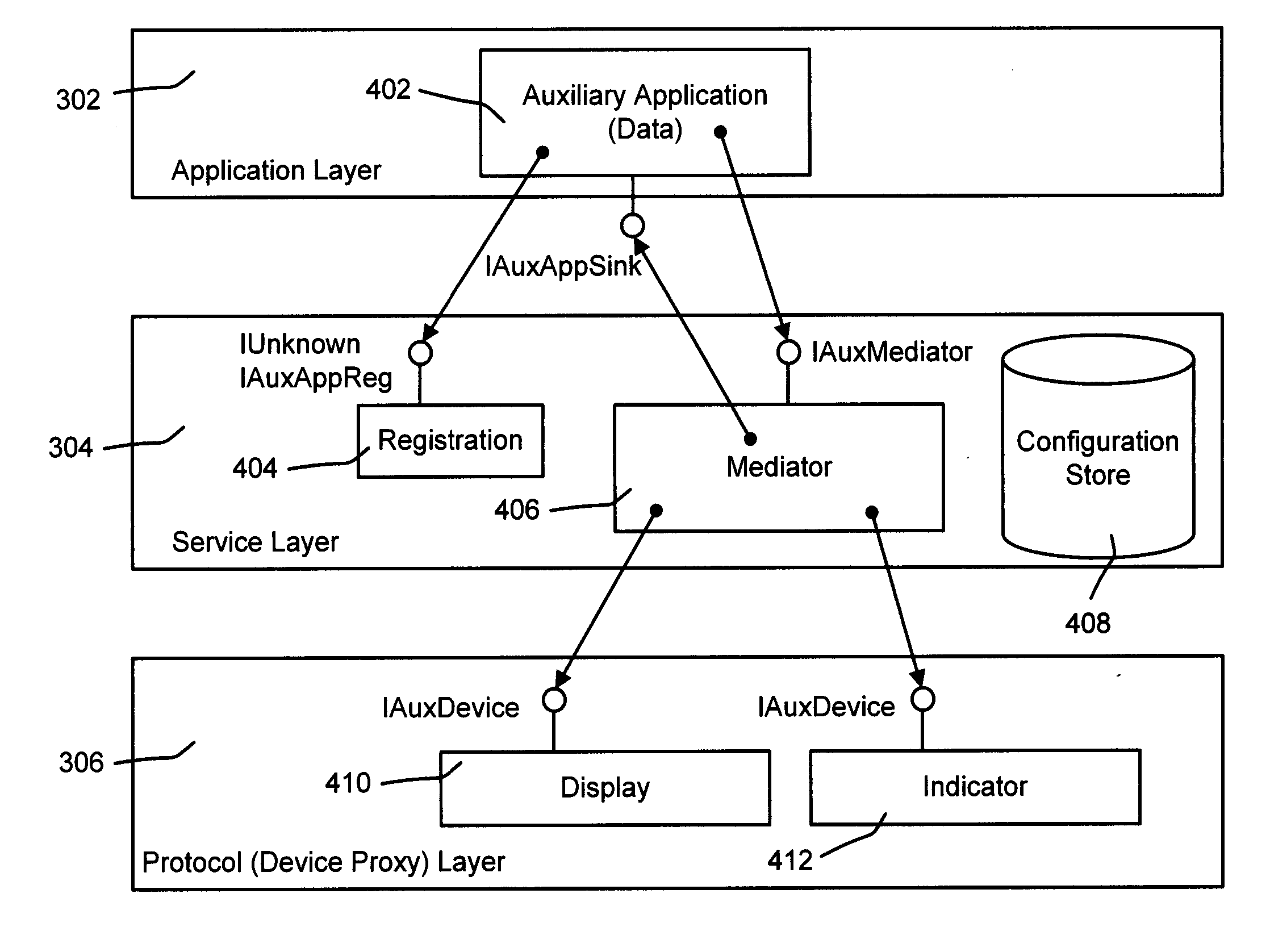

Described is a mechanism for receiving new data at an auxiliary device associated with a main computer system, and processing that new data within the auxiliary device firmware to take some action. The receipt and processing of the data is independent of whether the main computer system is in a powered-up state (online) or powered-down state (offline). A cache that maintains the user application data for offline navigation may be updated with new data, either to change existing data in the cache or add a new navigation path. The received data can be processed to perform other actions, depending on the context of that data as determined by auxiliary processing.

Owner:MICROSOFT TECH LICENSING LLC

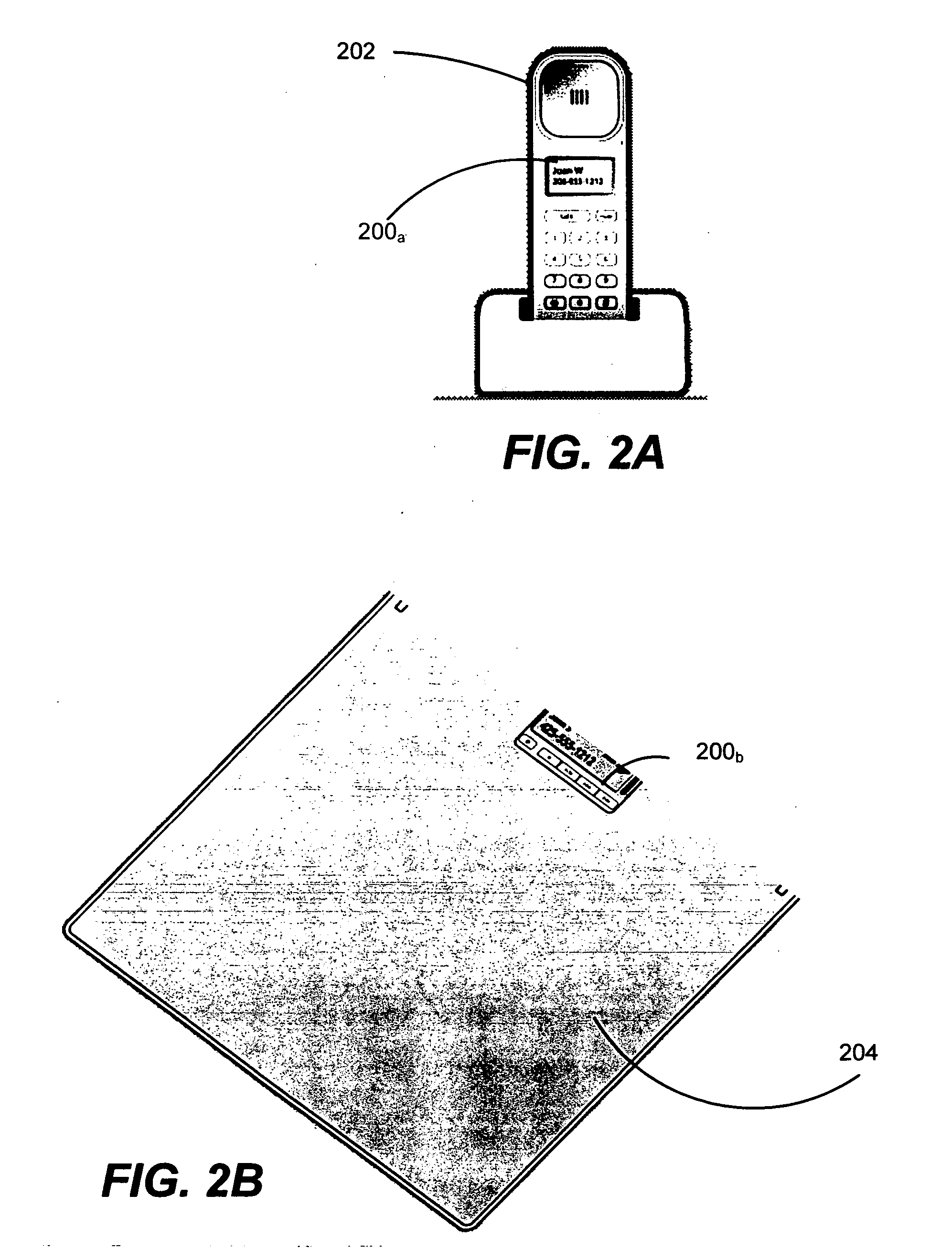

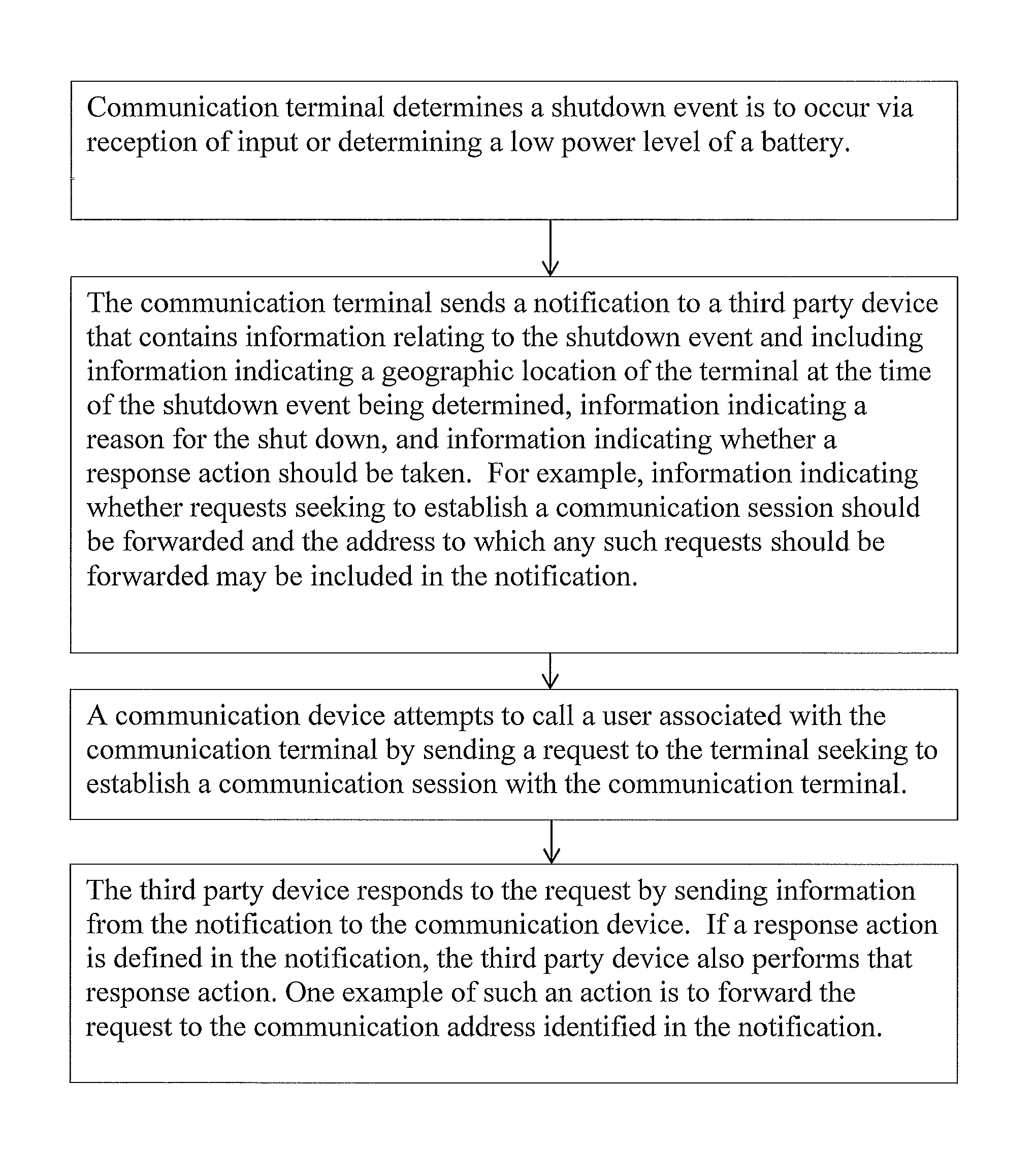

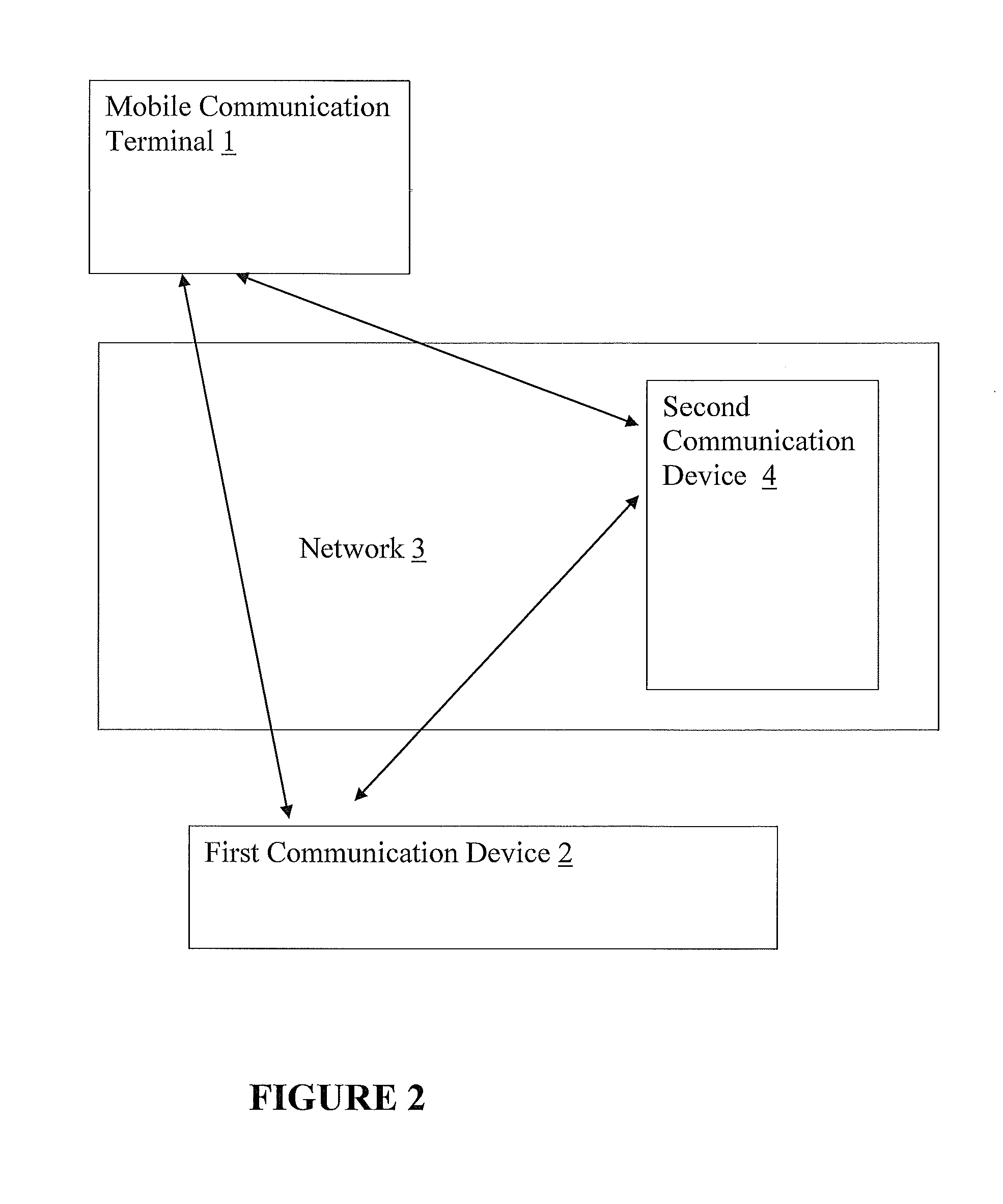

Method, device, and system for providing a notification of a shutdown

A method and apparatus for transmitting a notification of a shutdown event includes a communication terminal turning off or otherwise shutting down and prior to turning off sending a notification to a third party device such as an access point, base station, server, or proxy, that identifies information relating to the shutting down of the terminal such as a location, purpose for the shutdown and other relevant information. Subsequent devices that attempt to establish a communication connection with the terminal may then receive the notification or information from the notification via the third party device. The sending of information relating to the notification or the notification by the third party can also trigger another action. One example of such an action is the forwarding of the communication connection request to another device to receive that request based upon a predefined rule or a predefined forwarding address.

Owner:UNIFY GMBH & CO KG

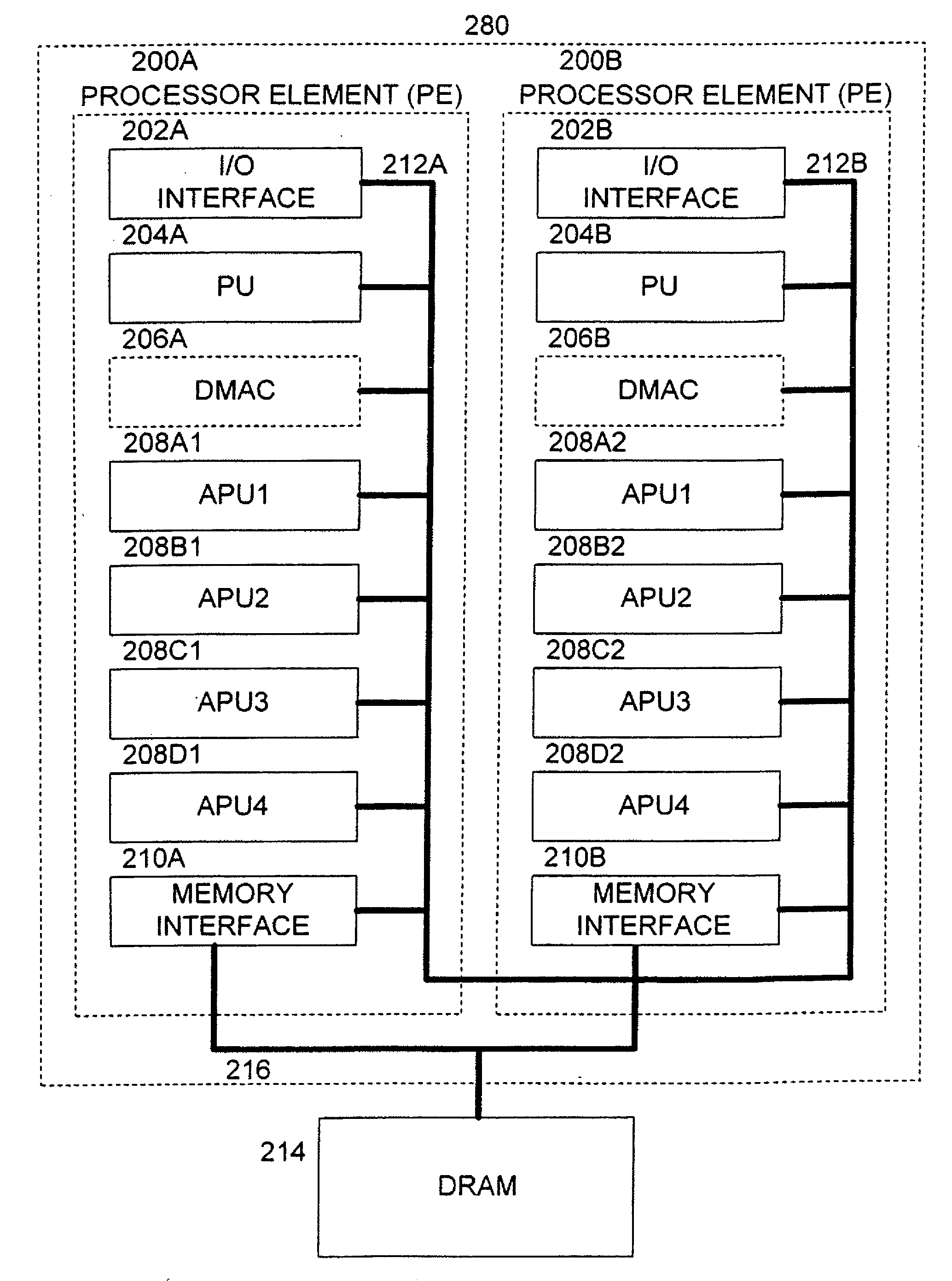

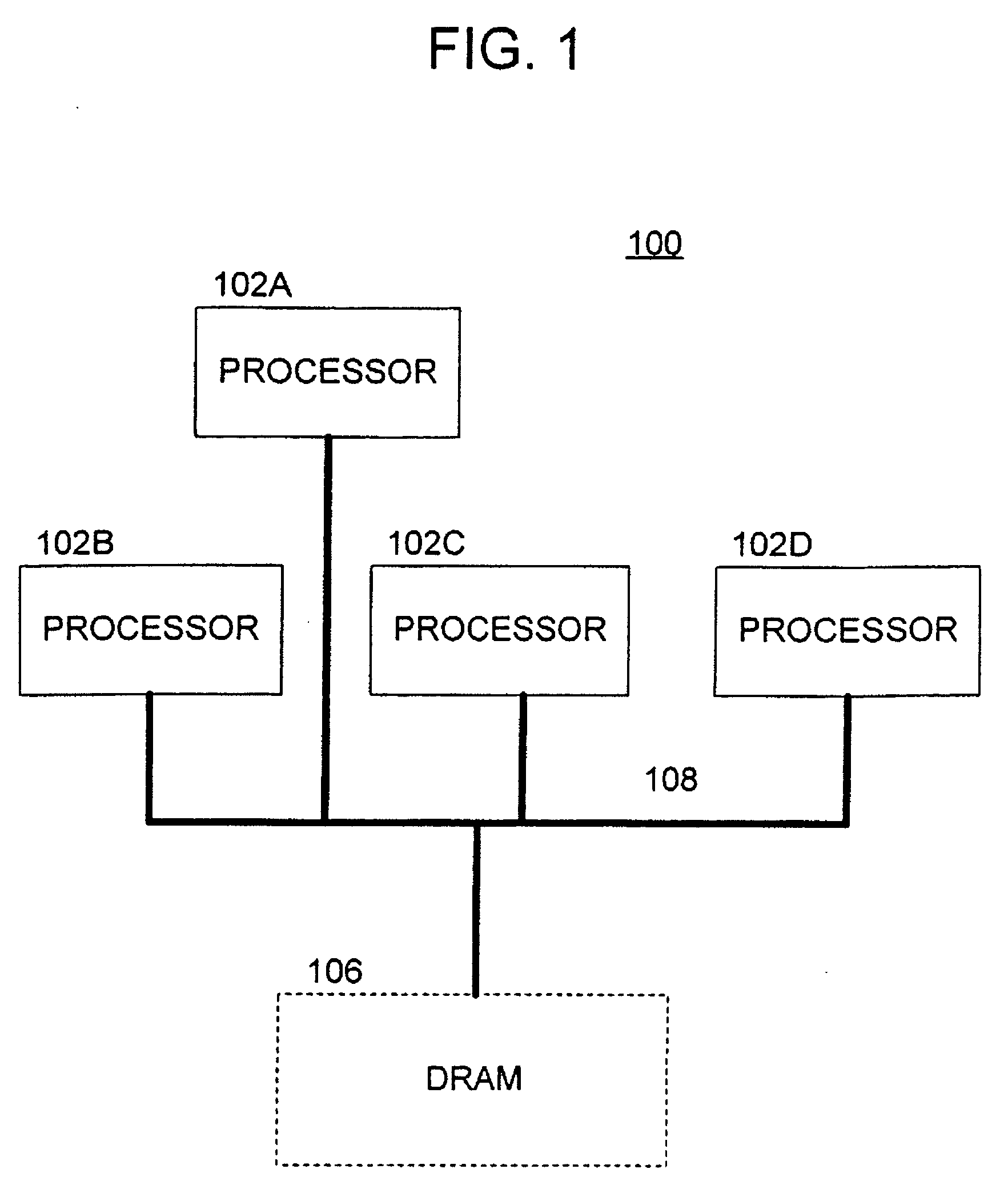

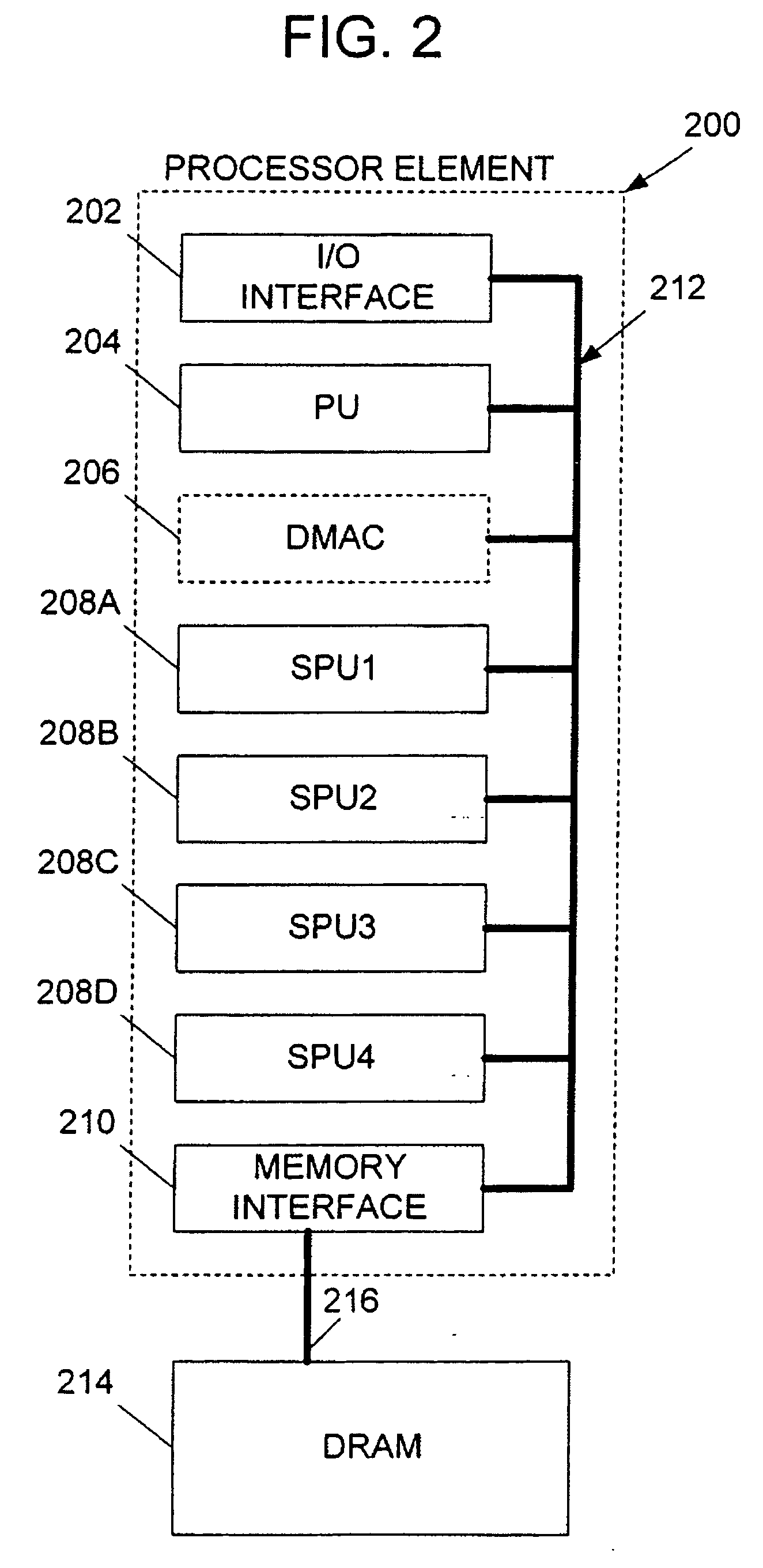

Methods and apparatus for handling processing errors in a multi-processing system

ActiveUS20080098260A1Resource allocationSpecific program execution arrangementsMain processing unitProcess error

Methods and apparatus are provided for: monitoring processor tasks and associated processor loads therefor that are allocated to be performed by respective sub-processing units associated with a main processing unit; detecting whether a processing error has occurred in a given one of the sub-processing units; re-allocating all of the processor tasks of the given sub-processing unit to one or more participating sub-processing units, including other sub-processing units associated with the main processing unit, based on the processor loads of the processor tasks of the given sub-processing unit and the processor loads of the participating sub-processing units; and at least one of: (i) shutting down, and (ii) re-booting the given sub-processing unit.

Owner:SONY COMPUTER ENTERTAINMENT INC

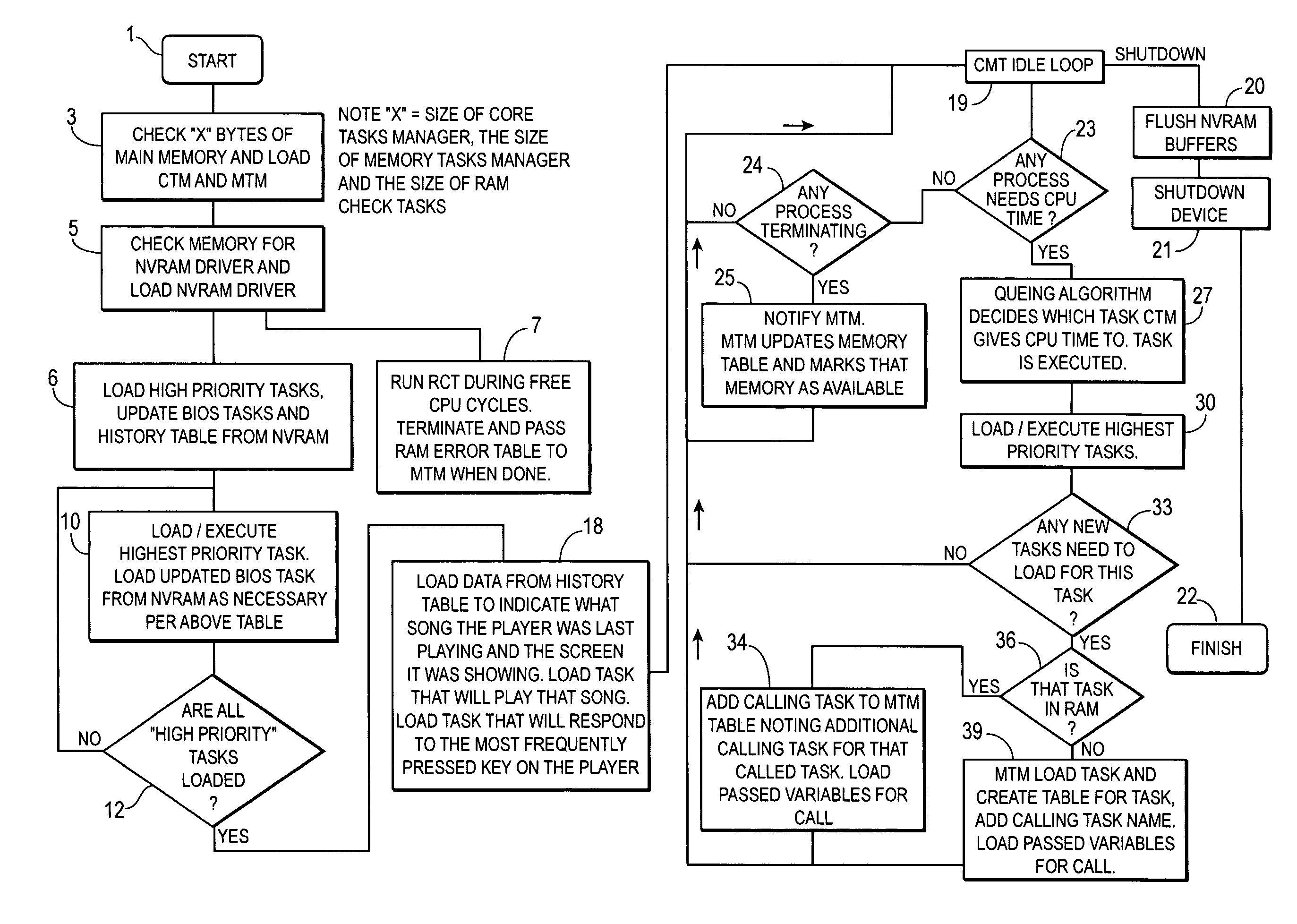

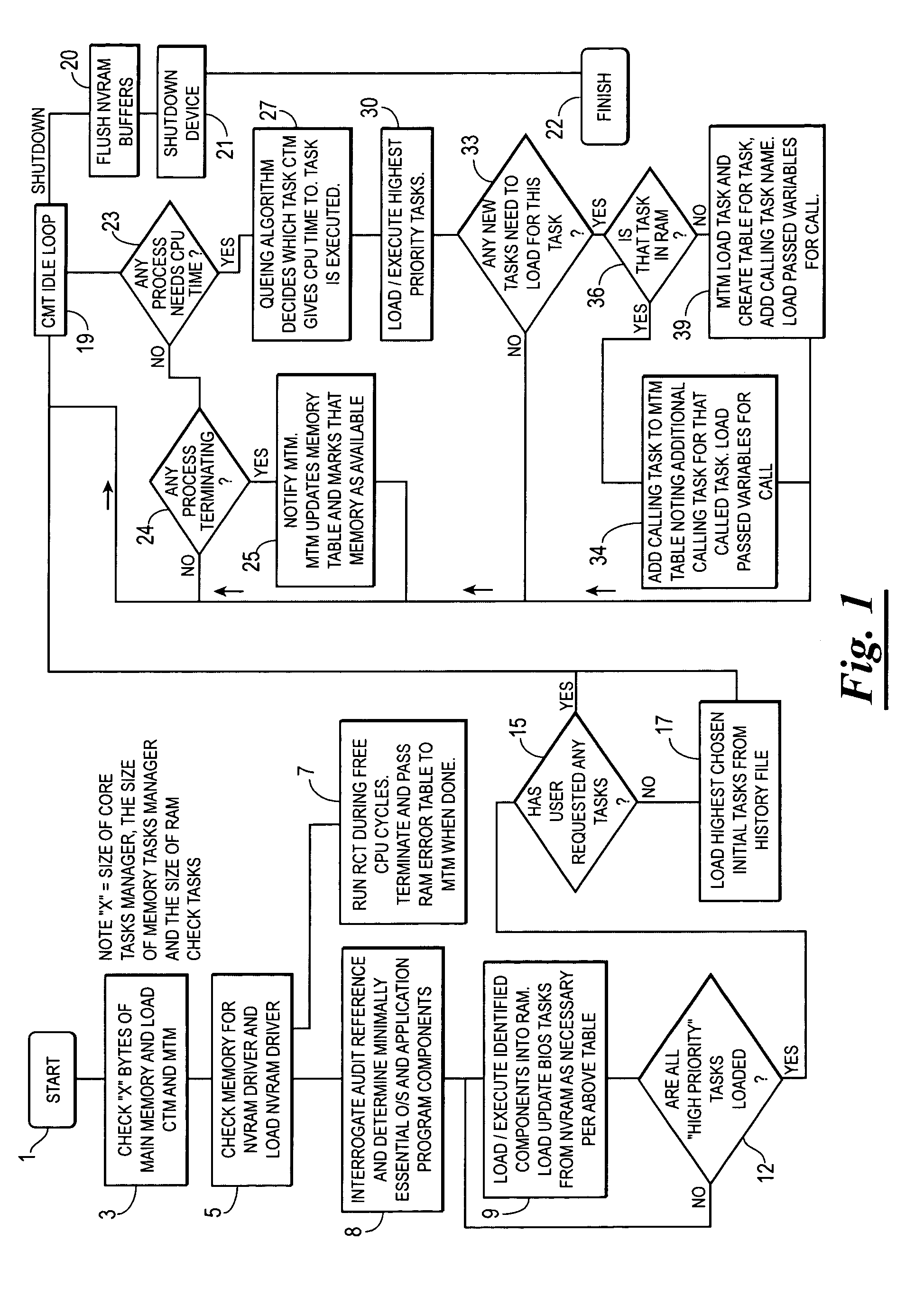

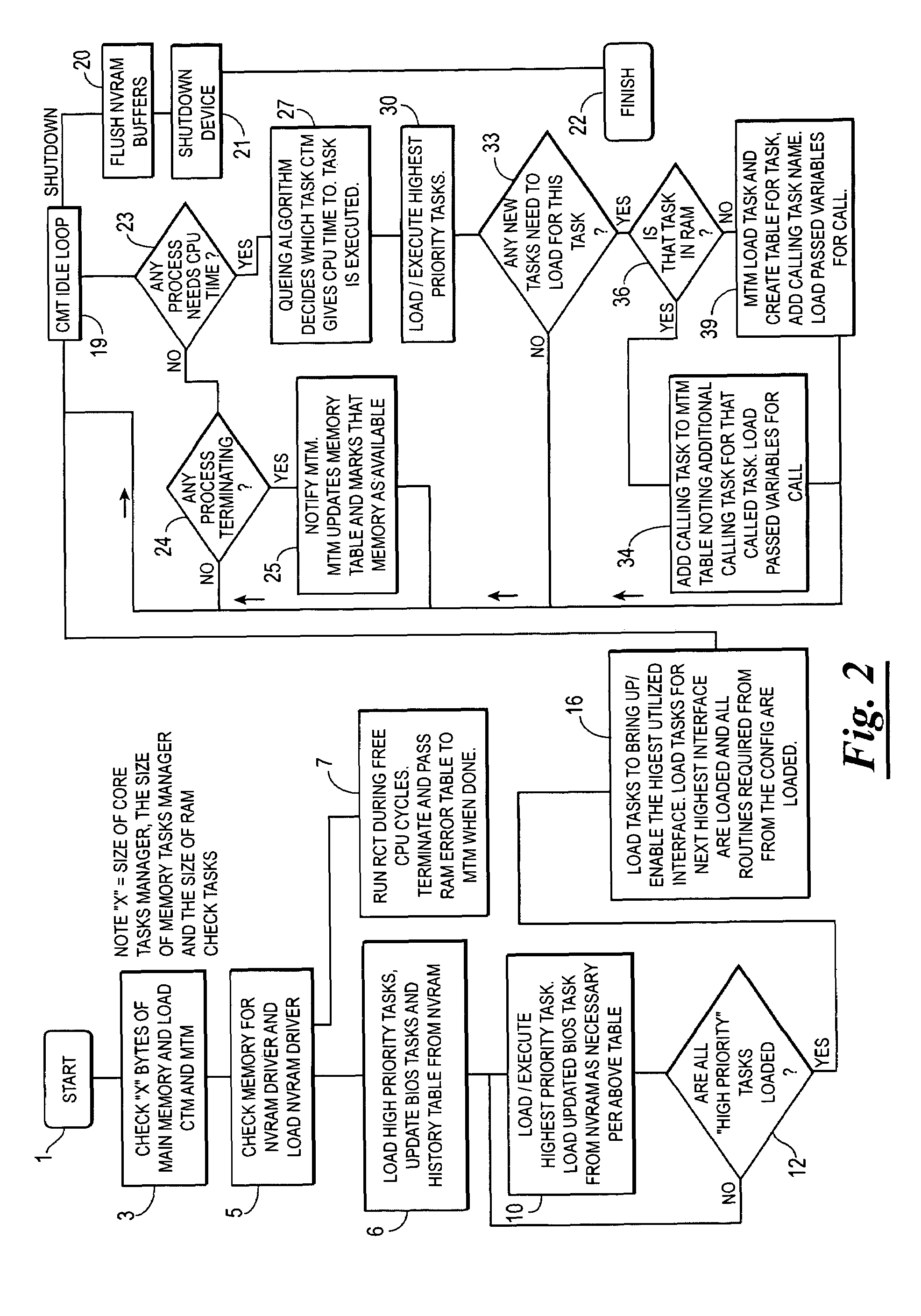

Method and apparatus to minimize computer apparatus initial program load and exit/shut down processing

A method to reduce and thereby improve the initial program load time of a computing apparatus operating system and thus provides for near instantaneous user interaction. When practicing the instant invention, a computing apparatus operating system or application processing component is loaded neither sequentially nor completely, but rather on an as required basis. The invention's “required only” loading of processing components persist through subsequent operation and shut down of the computing apparatus with each loaded task creating a checkpoint record of processing modifications to non-volatile memory. Such checkpointing allows shut down processing of the apparatus to consist of merely flushing memory buffers in the apparatus checkpointed non-volatile memory of the apparatus to permanent storage and powering off of the apparatus, with subsequent initial program load (IPL) sequencing referencing the checkpointed records to minimize future system initialization elapsed time.

Owner:III HLDG 1

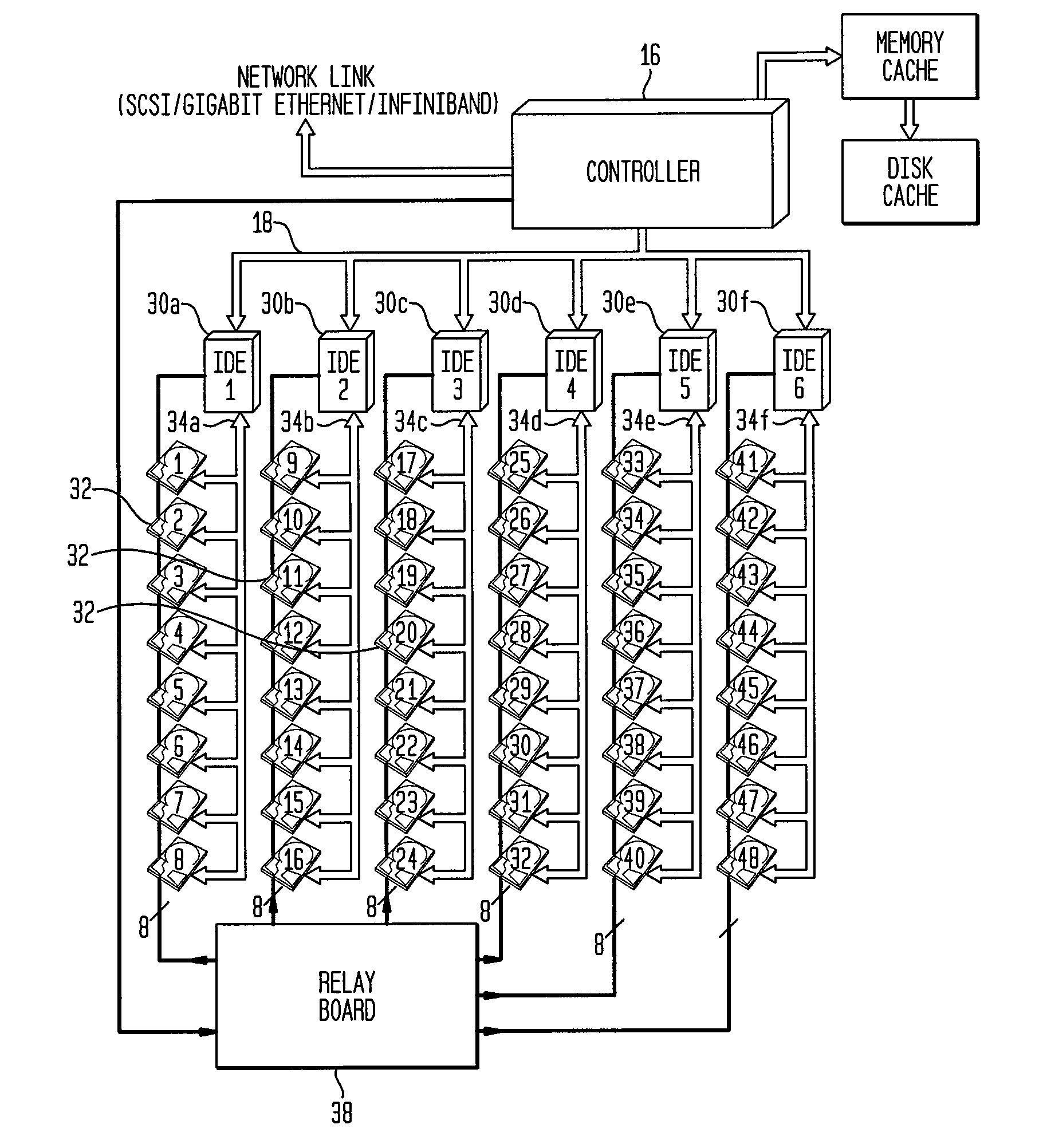

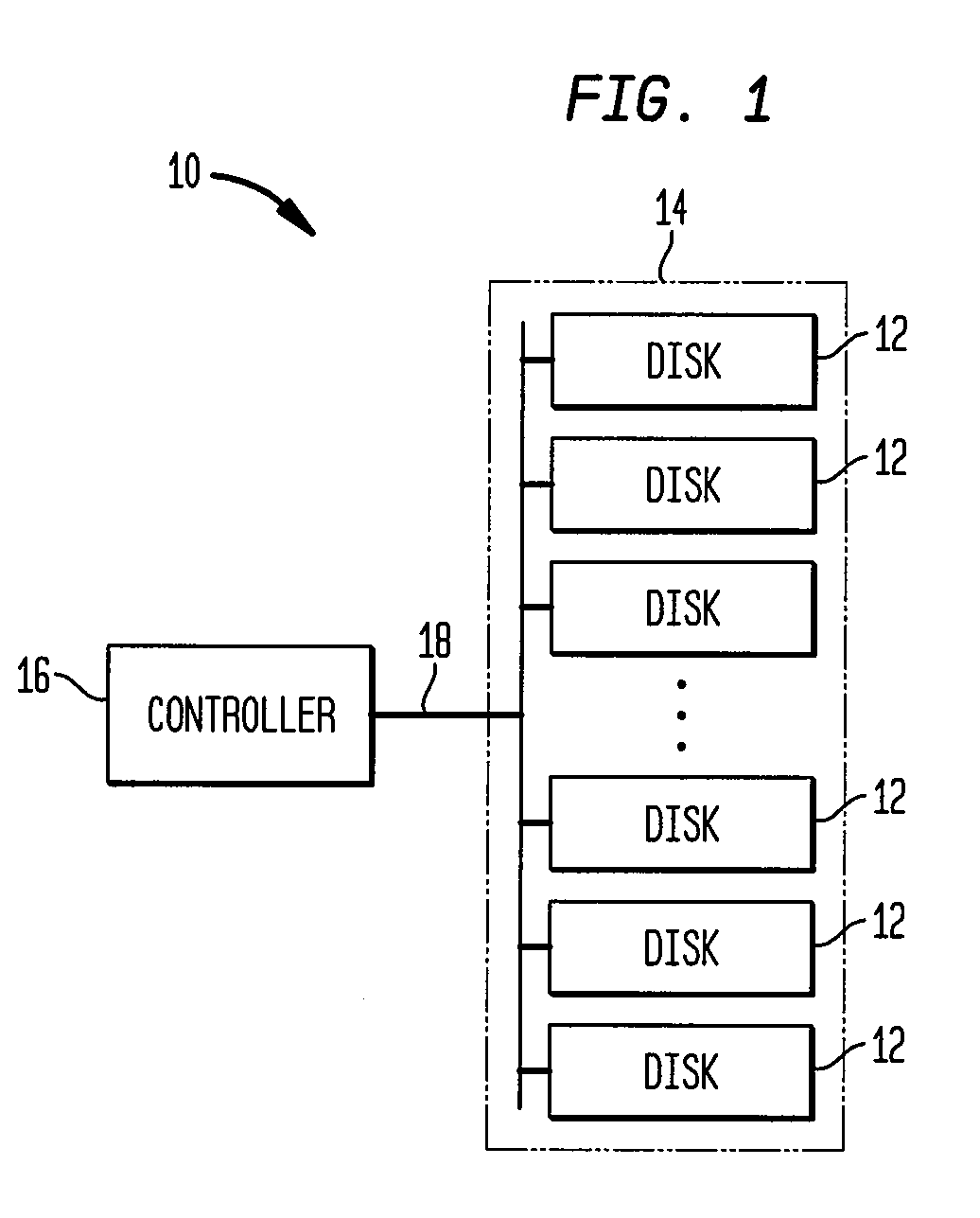

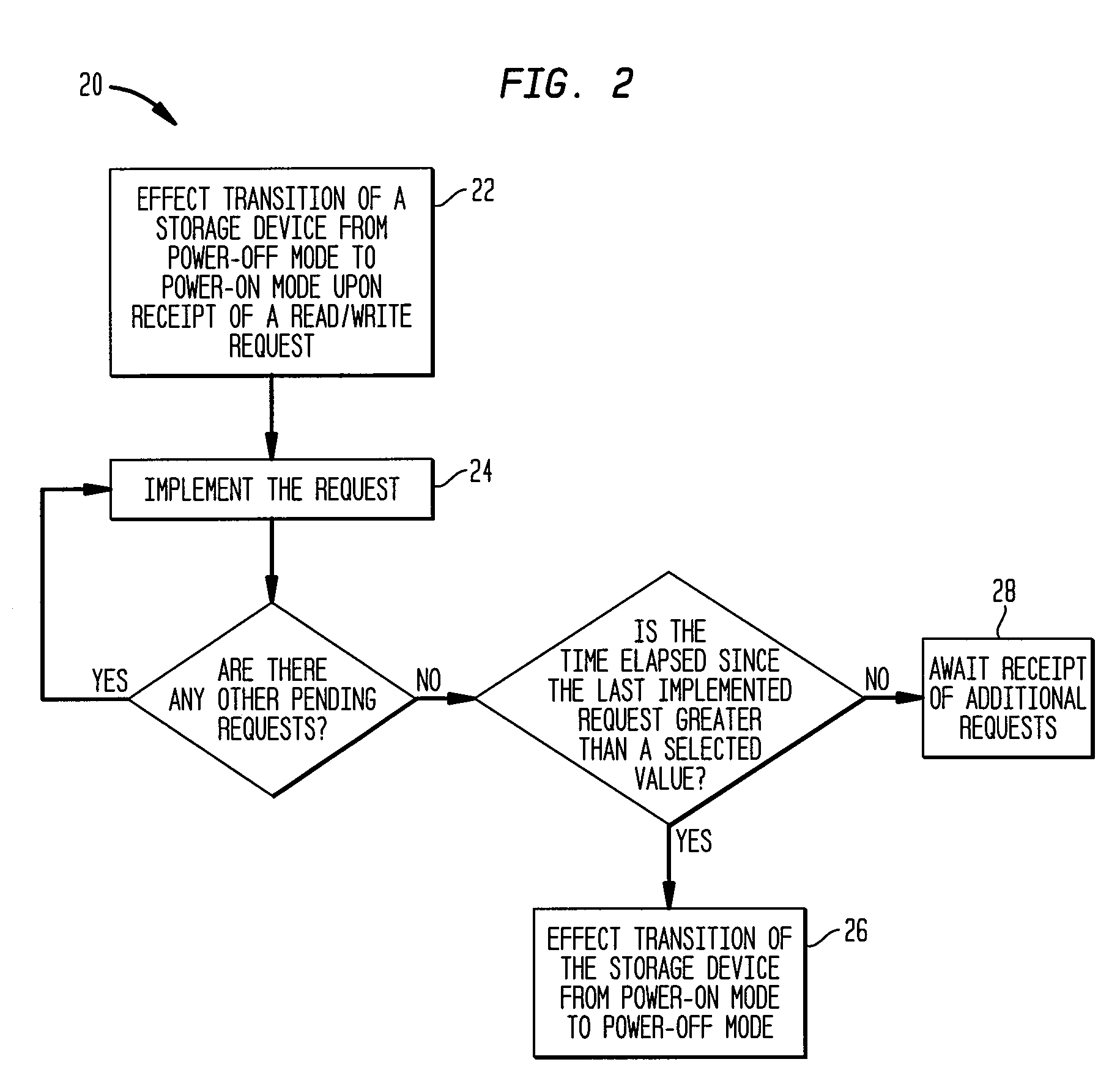

Lower power disk array as a replacement for robotic tape storage

The present invention provides methods and systems for storage of data. In one aspect, the invention provides a data storage system that includes a plurality of storage devices, such as, disks, for storing data, and a controller that implements a policy for managing distribution of power to the storage devices, which are normally in a power-off mode. In particular, the controller can effect transition of a storage device from a power-off mode to a power-on mode upon receipt of a request for reading data from or writing data to that storage device. The controller further effects transition of a storage device from a power-on mode to a power-off mode if no read / write request is pending for that storage device and a selected time period, e.g., a few minutes, has elapsed since the last read / write request for that storage device.

Owner:TEMPEST MICROSYST INC

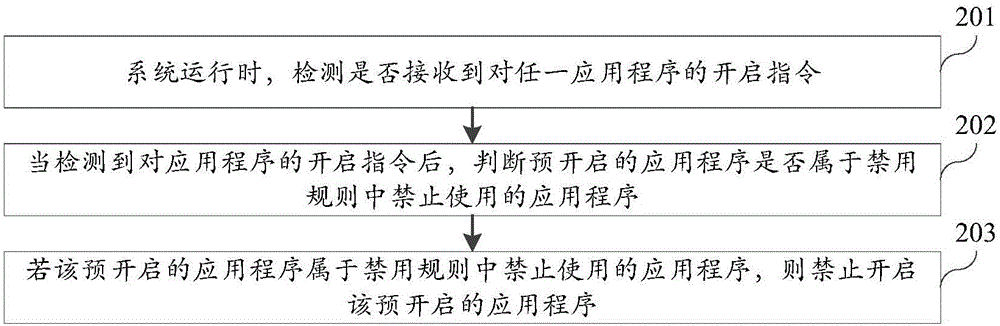

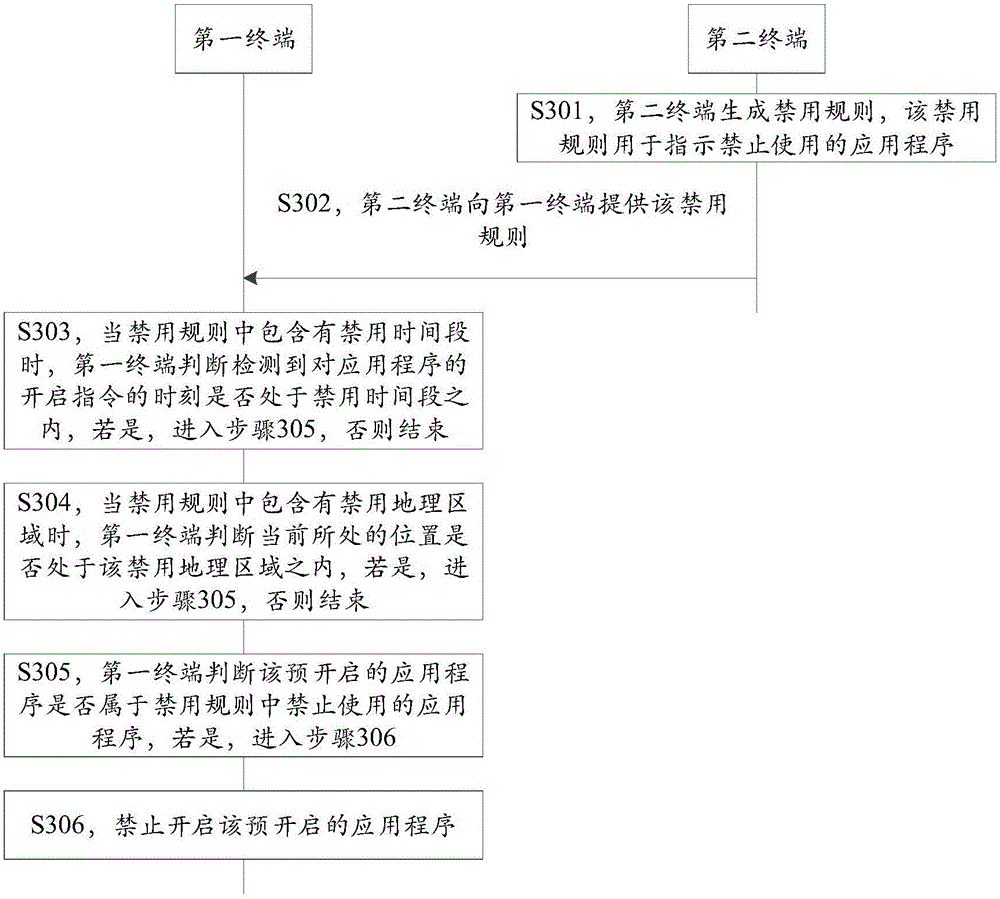

Application disabled method and apparatus

ActiveCN105094962AImprove experienceDoes not affect normal useMultiprogramming arrangementsComputer engineeringShut down

The present invention discloses an application disabled method and apparatus and belongs to the technical field of a mobile terminal. The method comprises: when a system operates, detecting whether an instruction of starting any application is received. after detecting the instruction of starting the application, detecting whether the prestarted application belongs to an application which is disabled to be used in a forbidding rule; and if yes, forbidding to start the prestarted application. According to the present invention, the prestarted application is judged whether to belong to the application forbidded to be used in the forbidding rule after the instruction of starting the application is detected, the prestarted application is forbidden to be started if the prestarted application belongs to the application forbidded to be used in the forbidding rule, the forbidding rule is used for indicating applications which need to be forbidden, startup of the applications is only forbidden as required without shutting down a terminal power supply and use of a user for other applications is not influenced, so that an effect of improving user experience is achieved.

Owner:XIAOMI INC

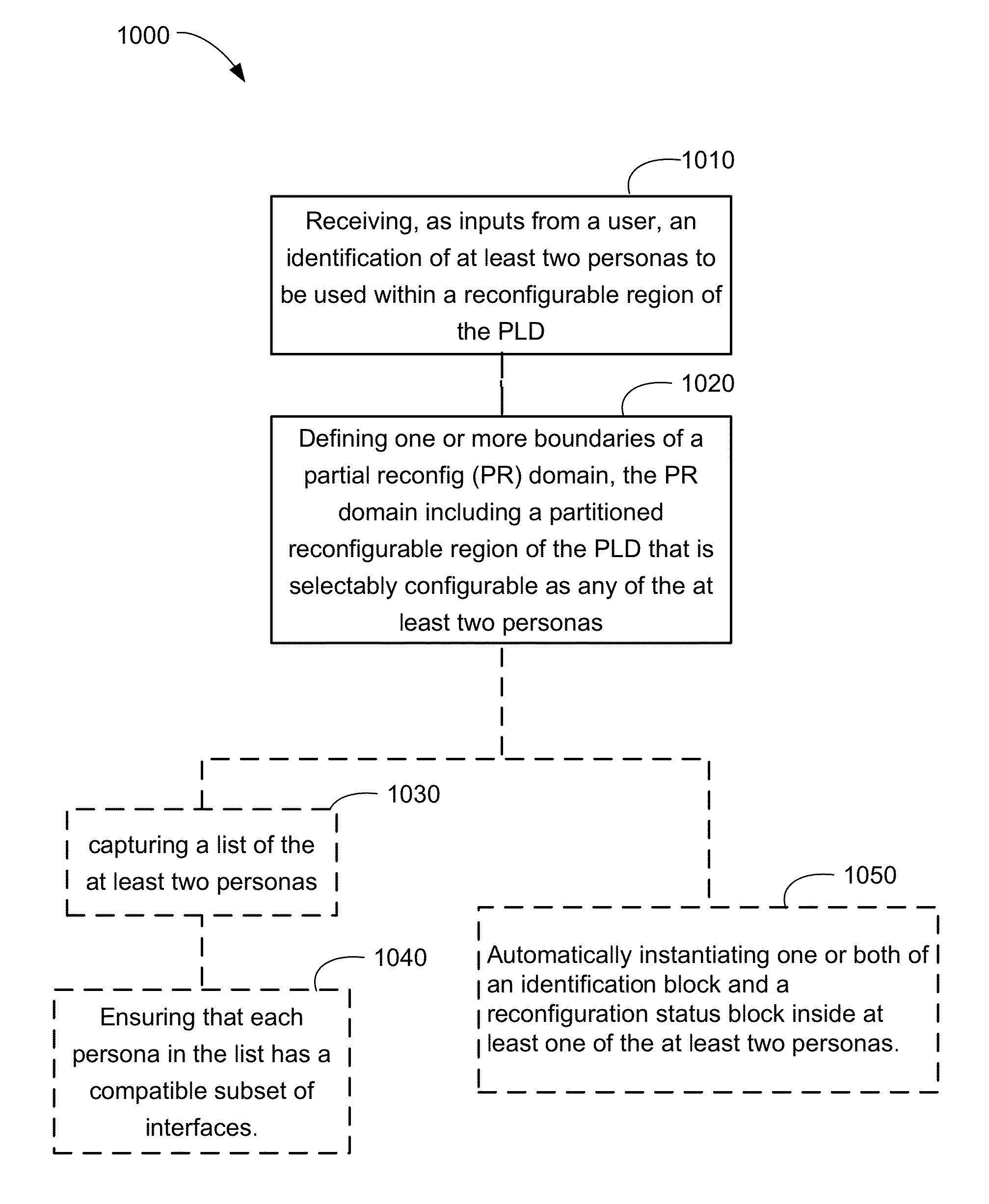

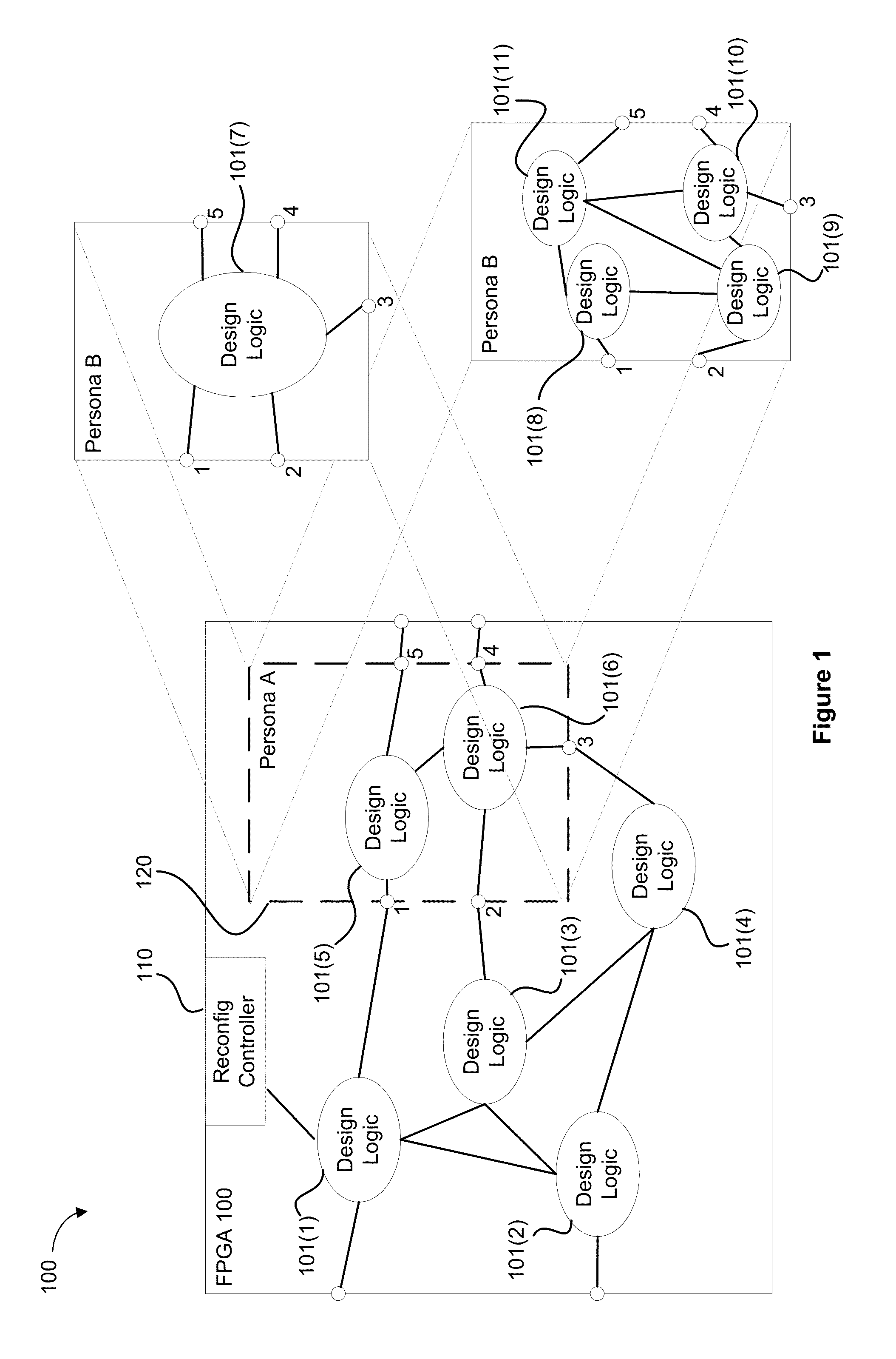

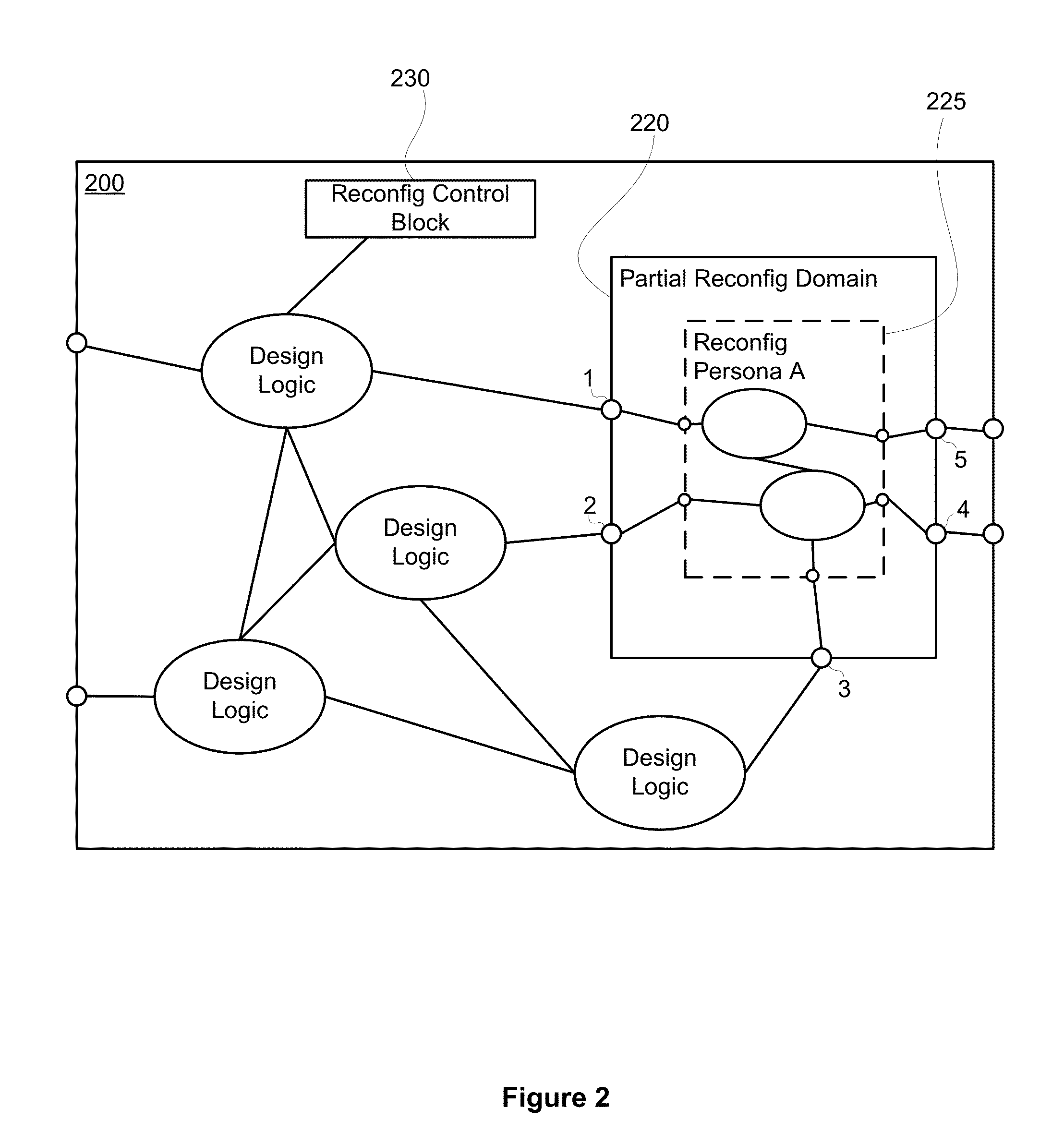

System level tools to support FPGA partial reconfiguration

ActiveUS9141747B1Efficient designReliability increasing modificationsComputer programmed simultaneously with data introductionProgrammable logic deviceComputer science

Various embodiments of the present disclosure provide techniques for enabling a user to efficiently design a programmable logic device (PLD) capable of partial reconfiguration. In some implementations, a processor is configured to run a system level design tool and accepts, as inputs from a user, an identification of at least two personas to be used within a reconfigurable region of the PLD. The design tool defines one or more boundaries of a partial reconfig (PR) domain, the PR domain including a partitioned reconfigurable region of the PLD that is selectably configurable as any of the at least two personas. In some implementations, the PR domain includes at least one IP component configured to safely shut down at least one signal, the at least one signal originating from or directed toward an element of the PLD outside of the PR domain.

Owner:ALTERA CORP

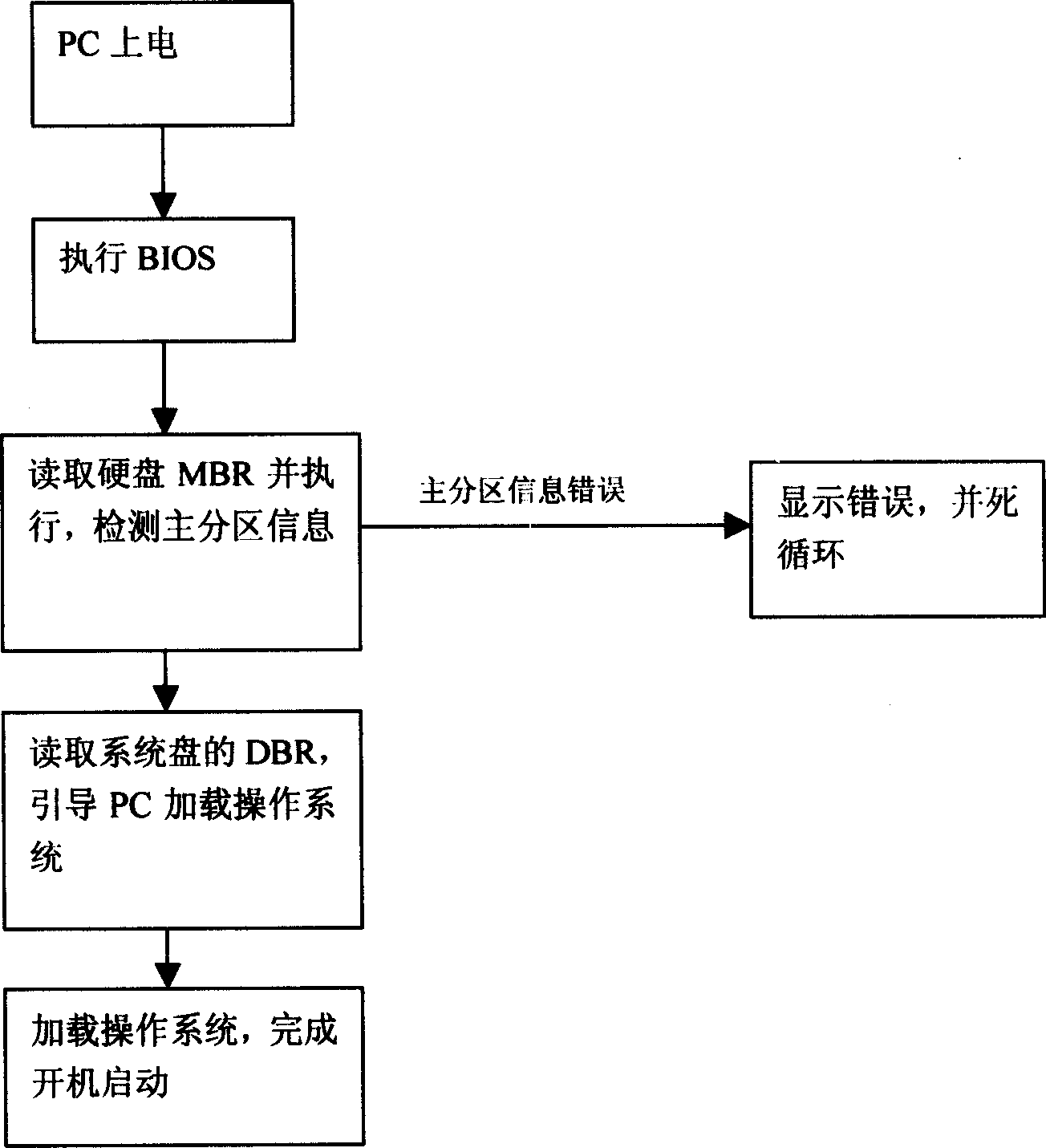

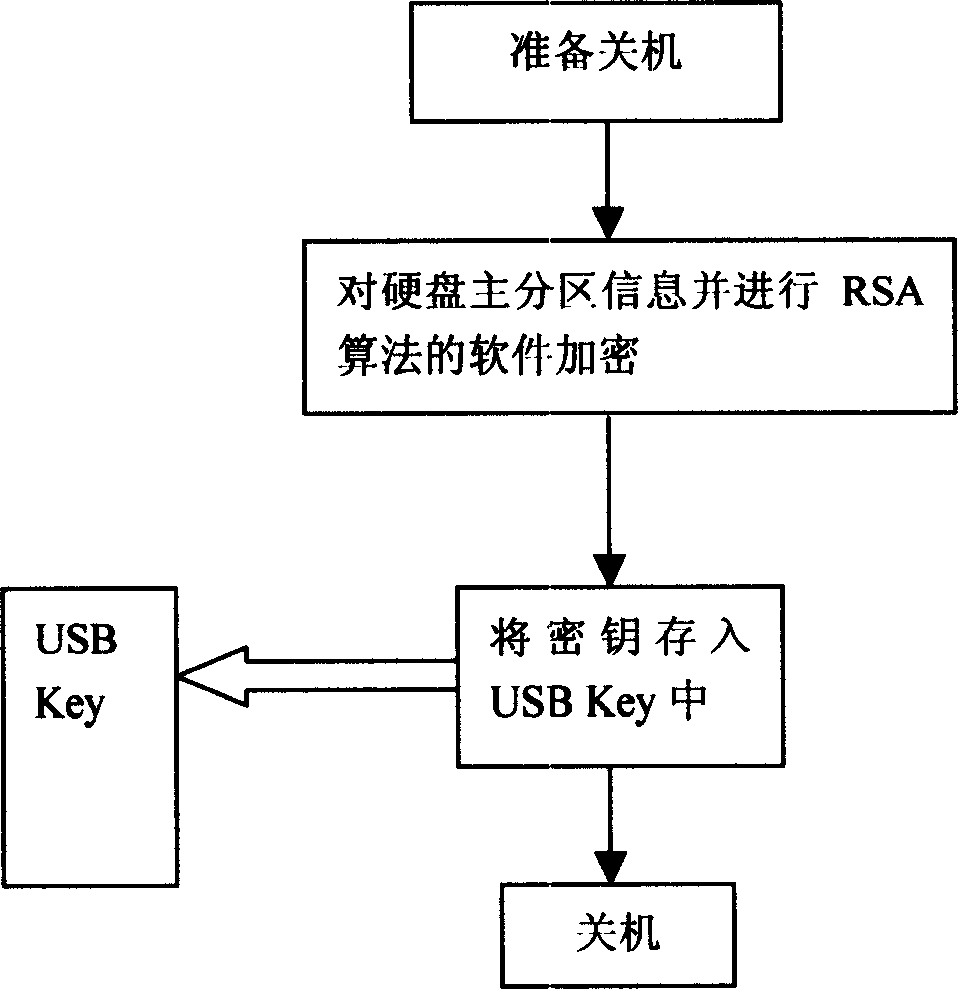

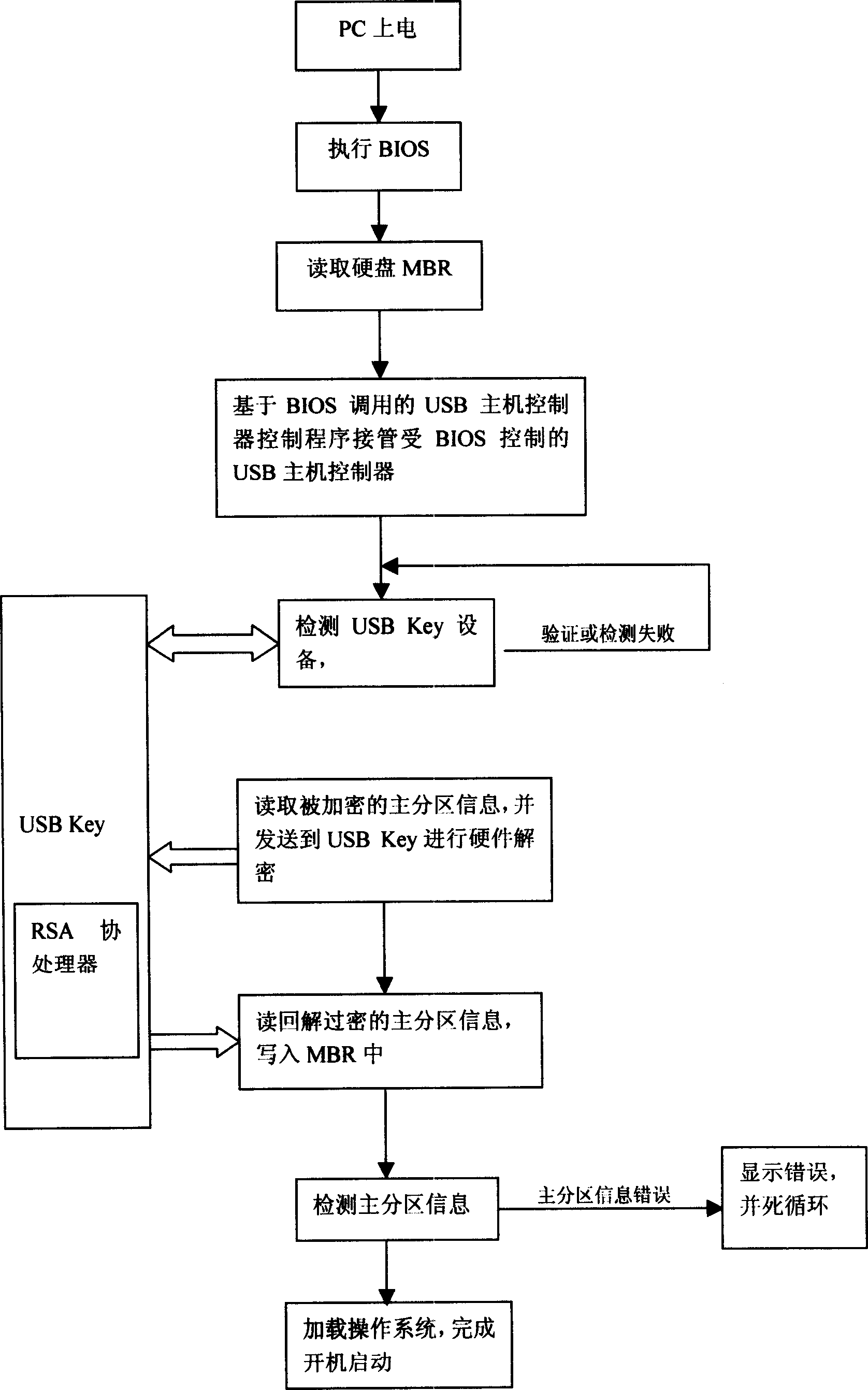

Method of carrying out hard disk protection by utilizing encryption of main zoning

InactiveCN1601430ADigital data processing detailsUnauthorized memory use protectionSoftwareMotherboard

The invention provides a method for more effectively implementing hard disk protection. In PC shutdown process said method adopts RS algorithm to make software encryption for hardware main partitioninformation. after the PC machine is started, in the stage of that the system is fed nito MBR the USB host controller control program is loaded so as to take over the USB host controller on them ain board, and can be used for making detection for USB key inserted onto the USB interface, and can utilize the RSA coprocessor on USB key to make hardware decryptment for main partion information stored in hard disk so as to implement the function of protecting hard disk.

Owner:苏州超锐微电子有限公司

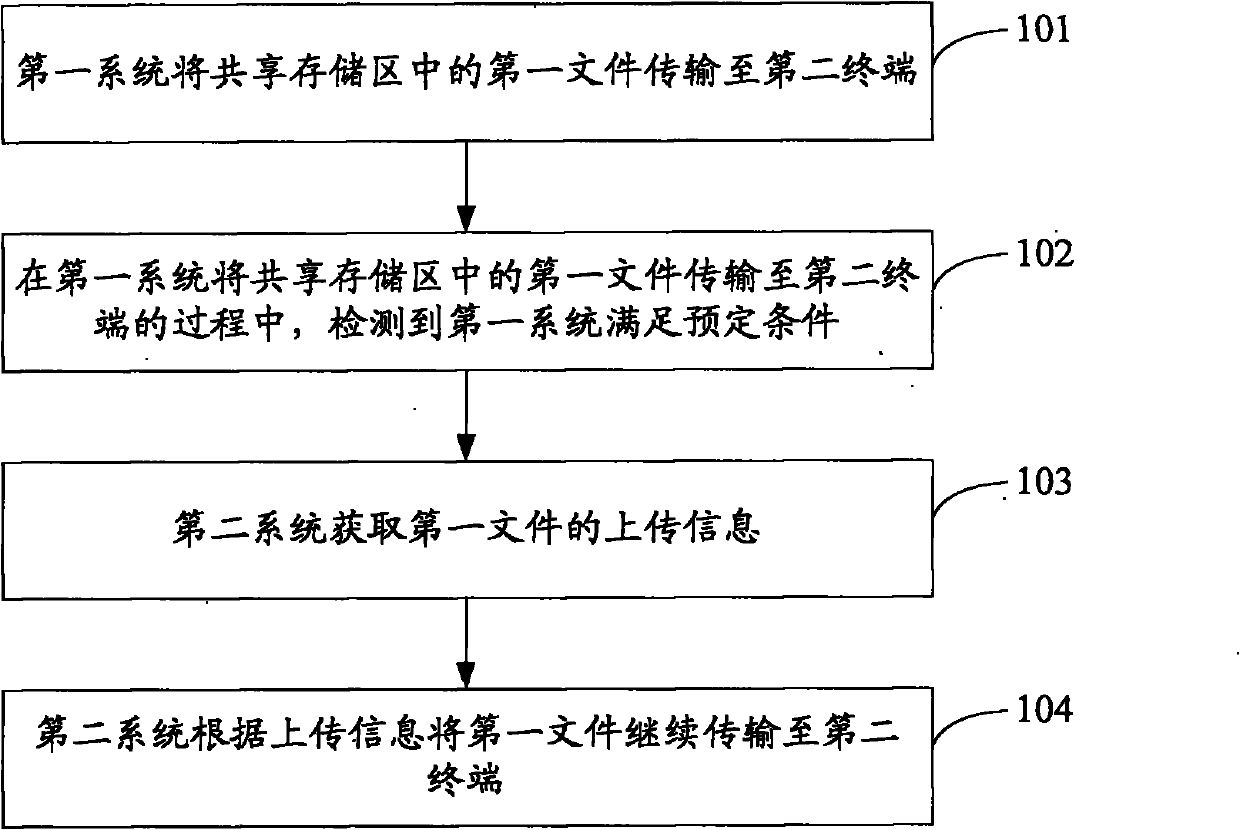

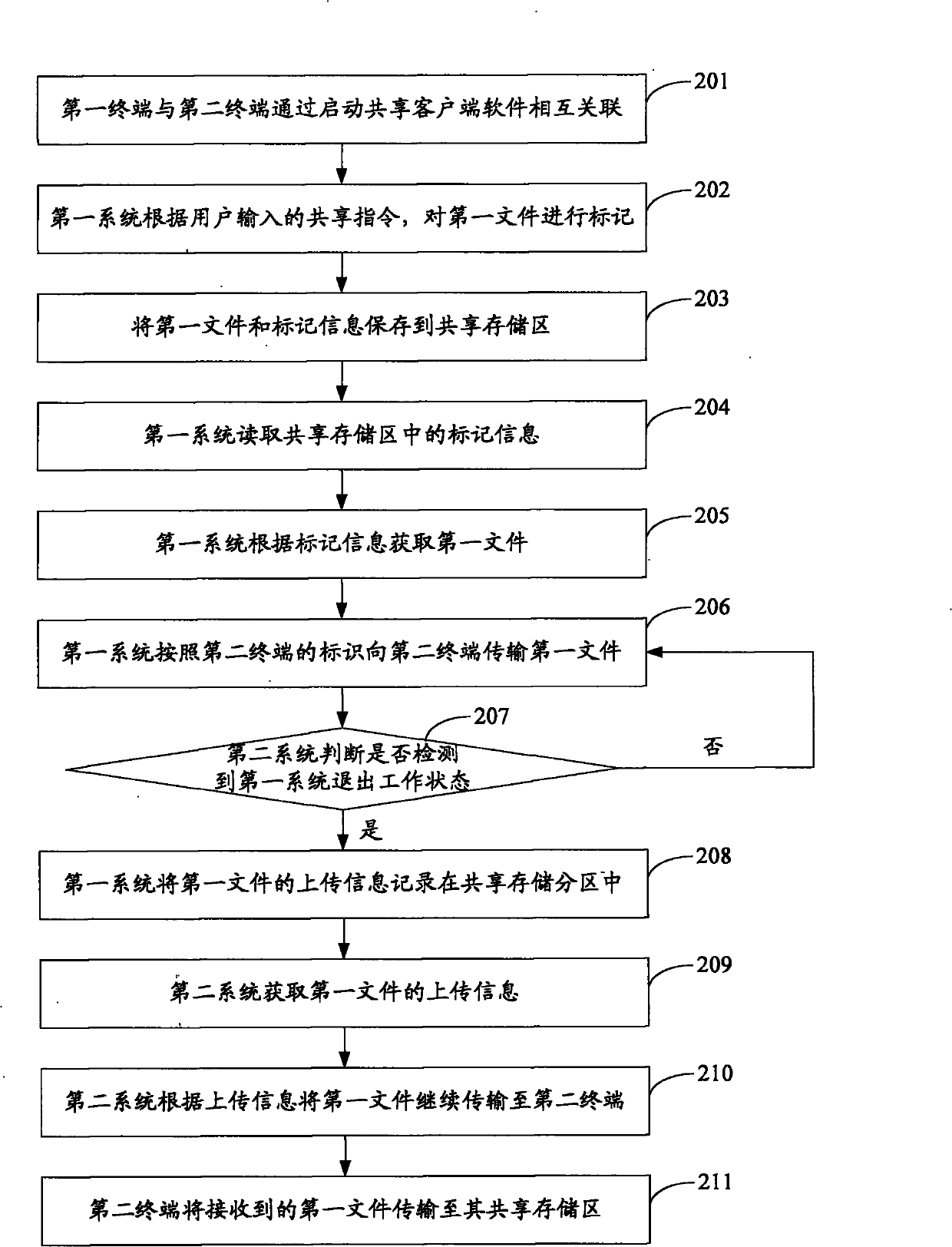

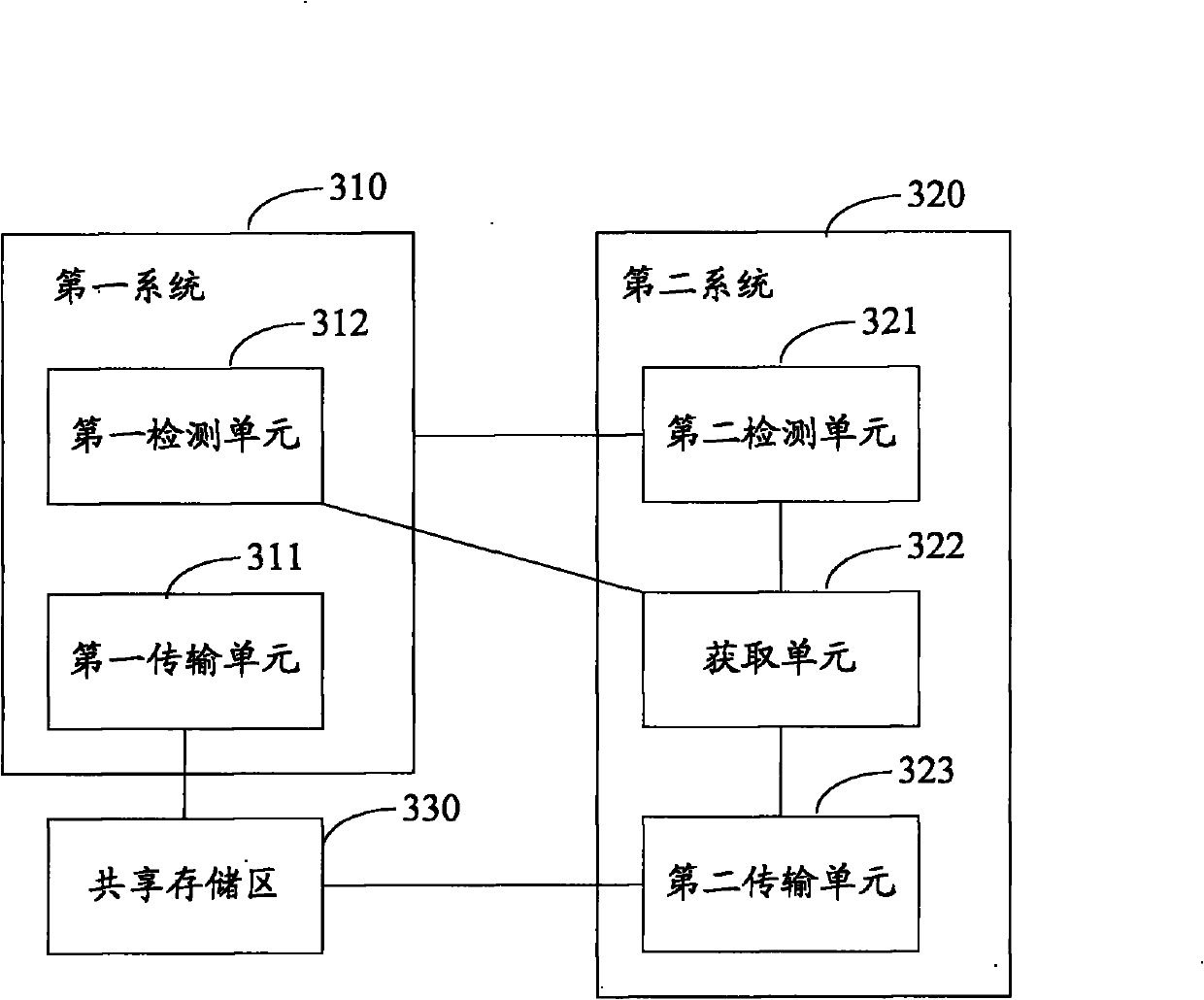

Data sharing method and portable terminal

The embodiment of the invention discloses a data sharing method and a portable terminal. The portable terminal is a first terminal with a first system and a second system, wherein the first system and the second system have capability of operating a sharing storage area. The method comprises the following steps: when the first system transmits a first file in the sharing storage area to a second terminal, if the first system is detected to meet the predetermined conditions, the second system obtains the uploaded information of the first file; and the second system continues transmitting the first file to the second terminal according to the uploaded information. By adopting the method and terminal disclosed by the invention to perform data sharing transmission, as the terminal has a mixed structure of double systems, if one system is shutdown or causes transmission interrupt due to an error, the other system can continue the data sharing transmission, thereby improving the experience of data sharing among users.

Owner:LENOVO (BEIJING) LTD

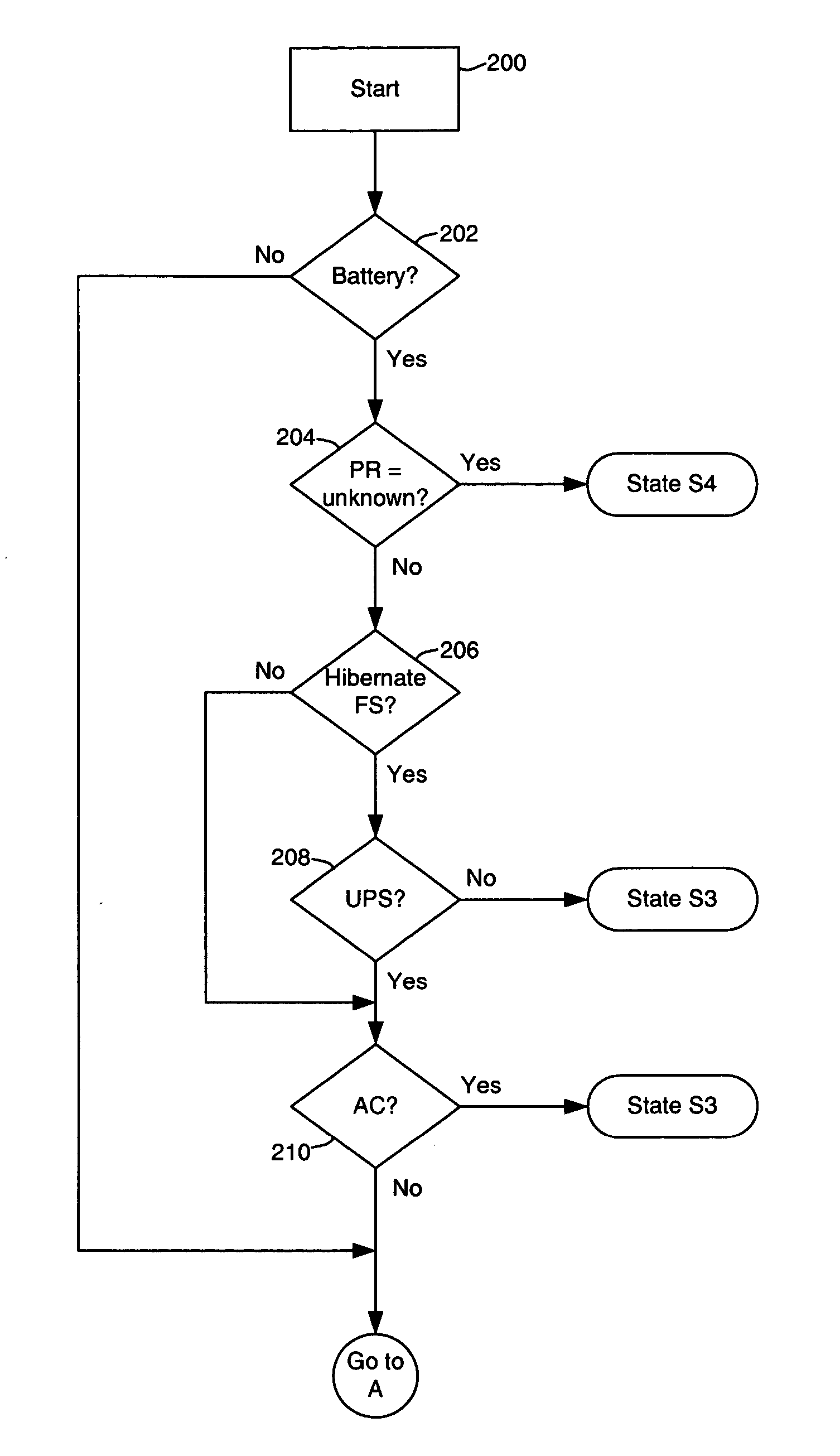

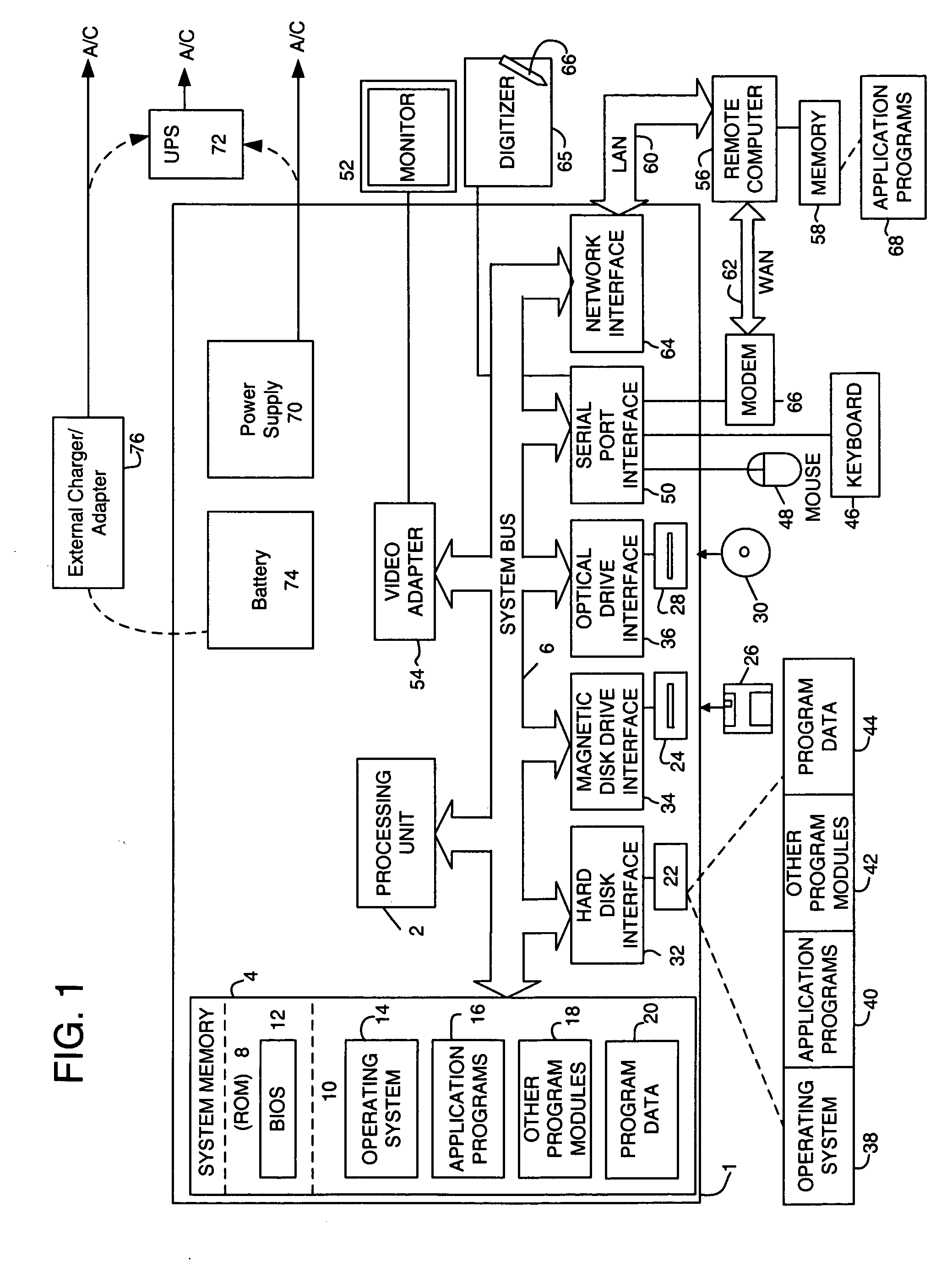

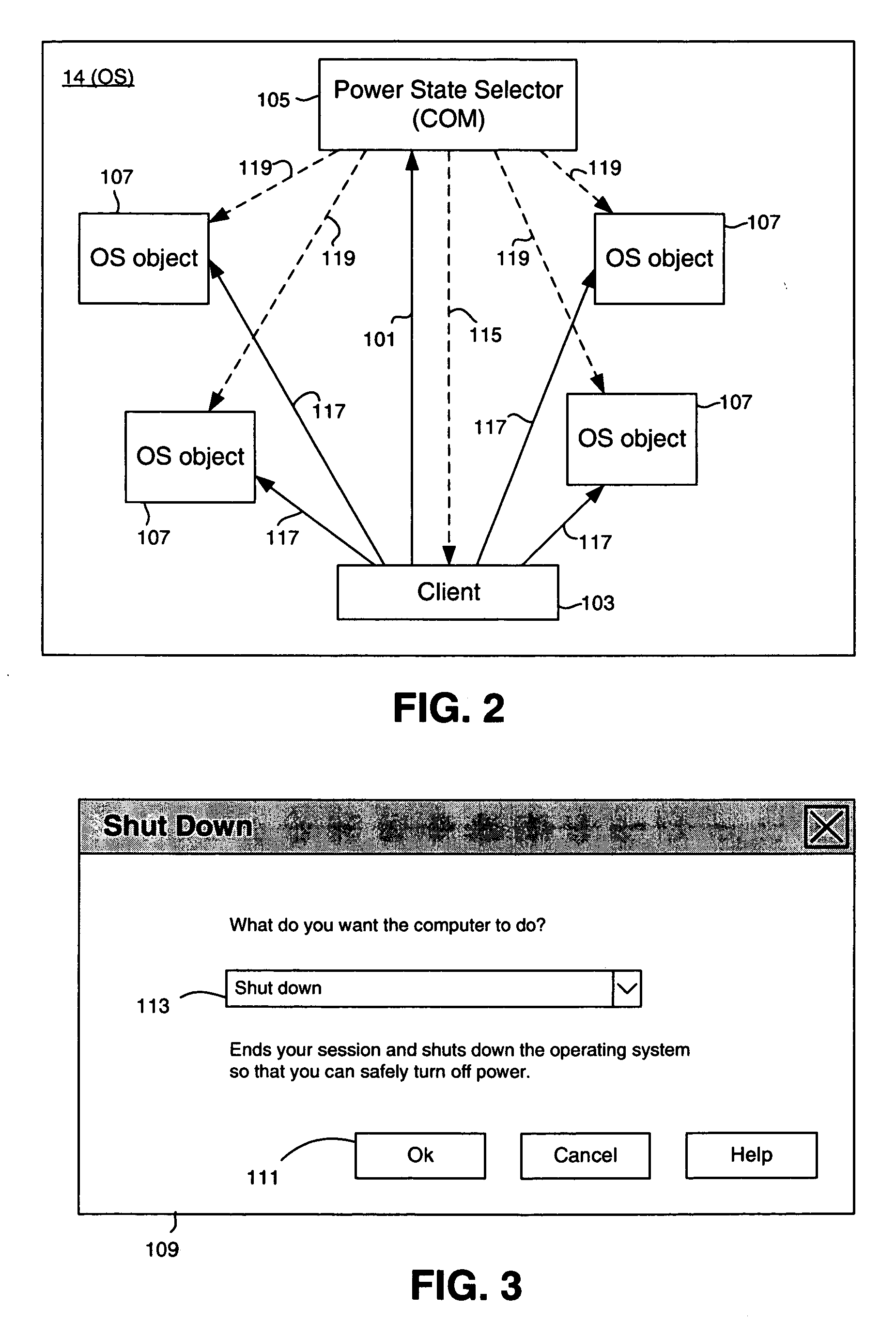

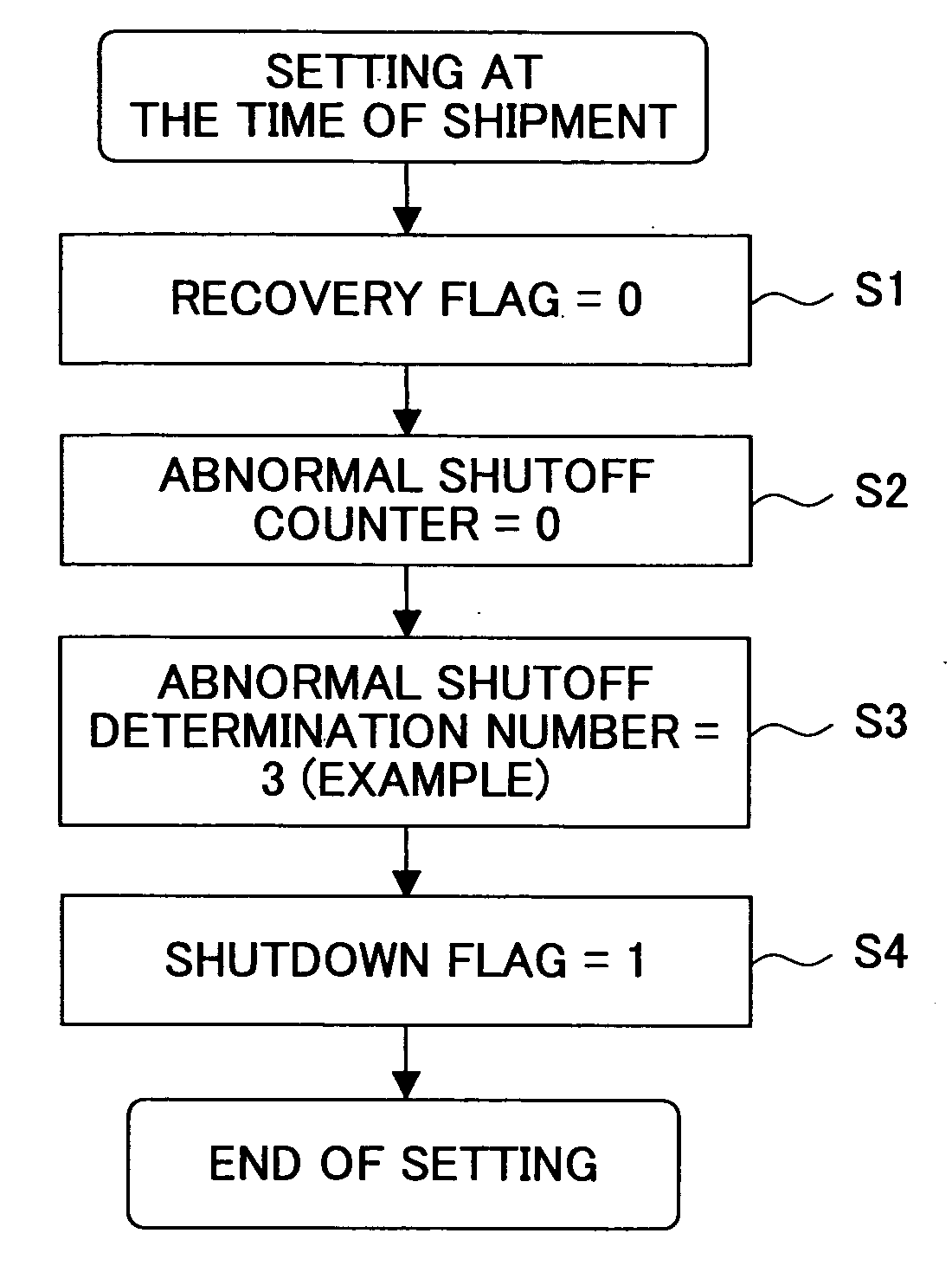

Power state selection heuristic

An algorithm automatically selects a power state based on device configuration parameters. The selected power state may then be returned and / or automatically implemented in a shutdown of the device. The parameters can include whether the device supports a system battery, whether the device is connected to an uninterruptible power supply, whether a value is available for remaining battery life, whether the device is receiving AC power and / or whether a hibernate fail safe feature is available. A shutdown failure algorithm may also be included. The shutdown failure algorithm detects a failed attempt to shut down the device using a selected power state. The power state selection is changed and shutdown is then re-attempted. If shutdown again fails, a force shutdown flag is set. If shutdown again fails, a shutdown failure is reported.

Owner:MICROSOFT TECH LICENSING LLC

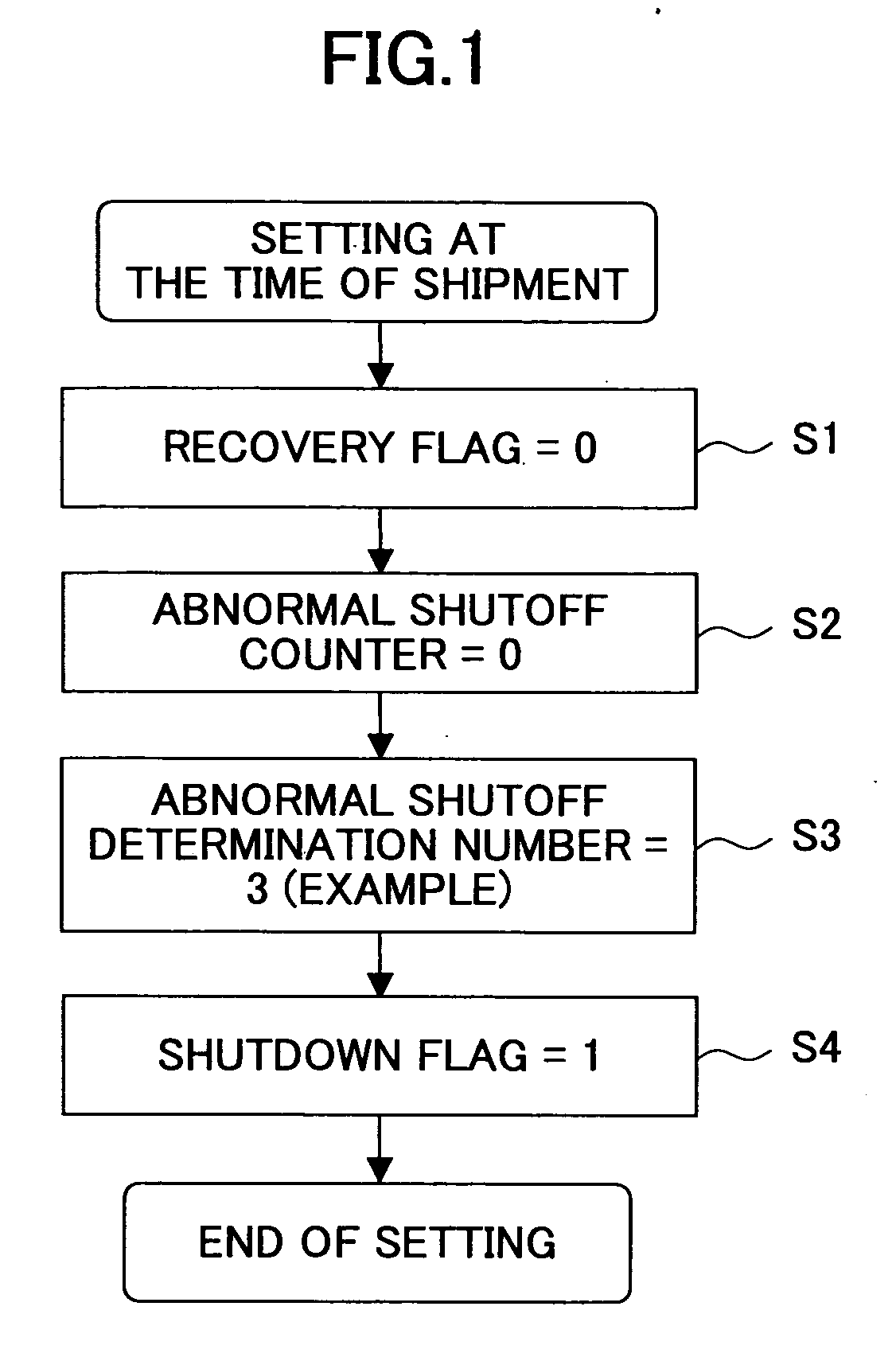

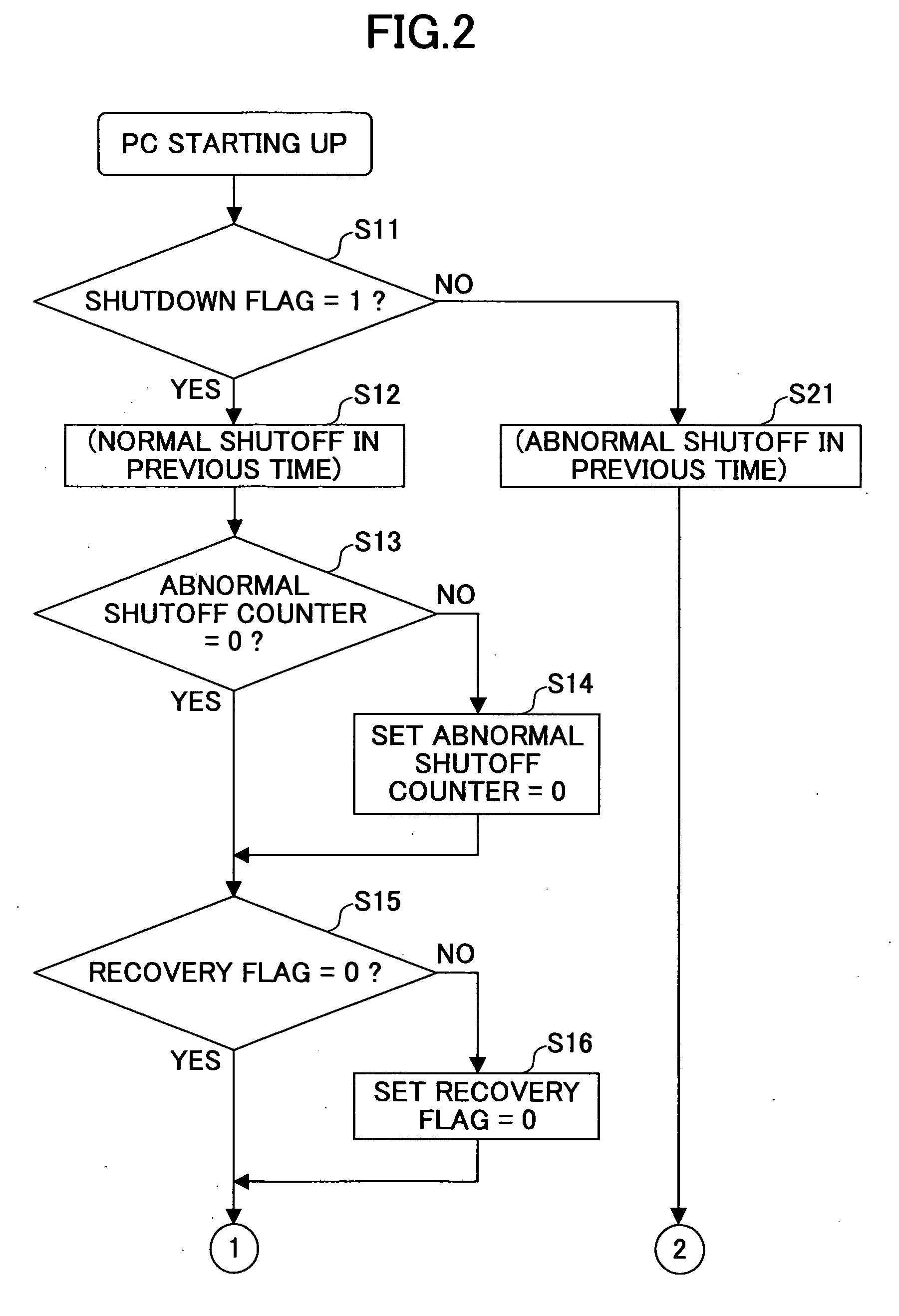

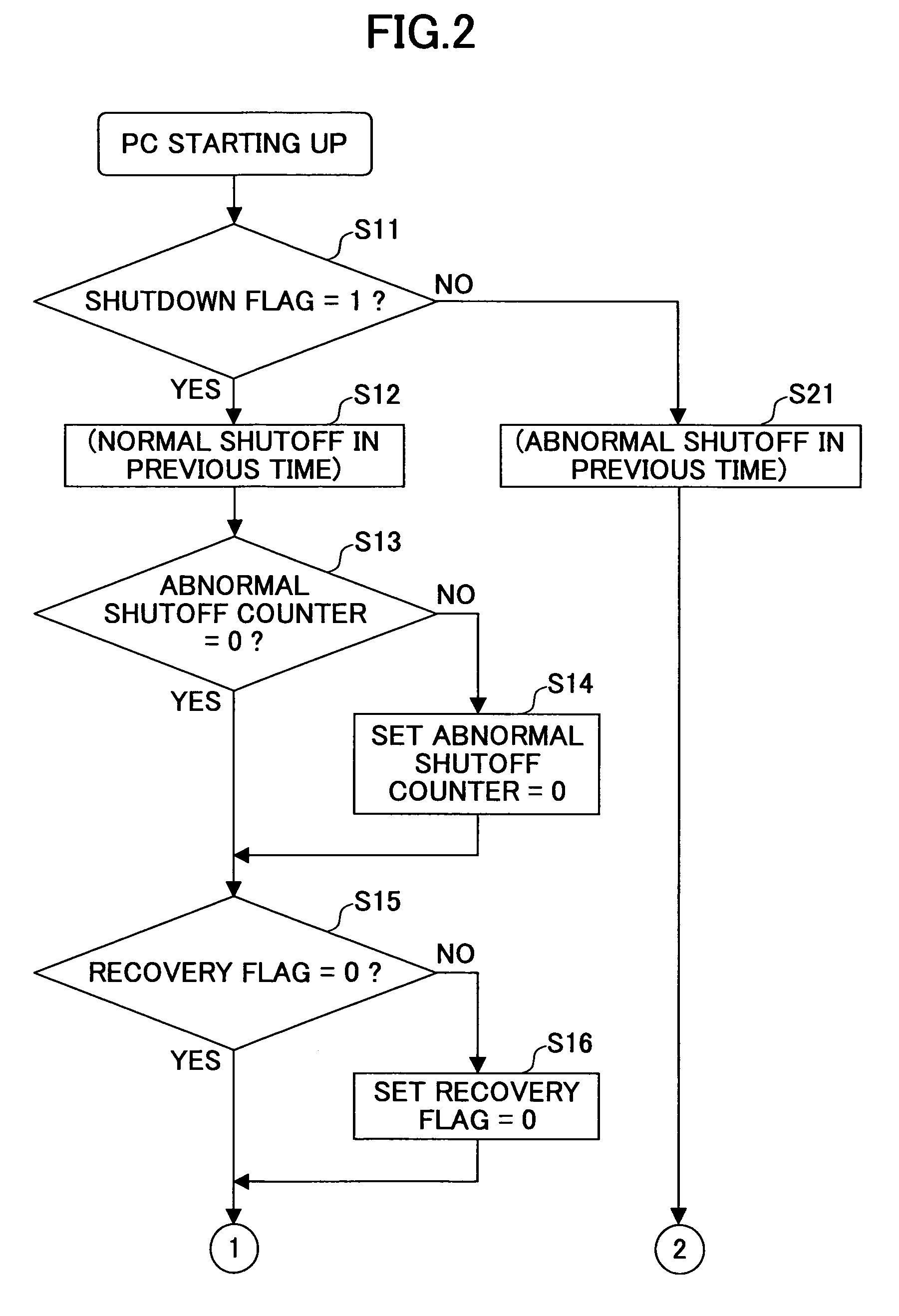

Computer shutoff condition monitoring method, information processing apparatus, program and computer readable information recording medium

InactiveUS20060179353A1Simple configurationError detection/correctionInformation processingSoftware engineering

A shutoff condition monitoring method for a computer, includes the steps of: a) determining that an abnormal shutoff has occurred when the computer shuts off without passing through predetermined shutoff processing; b) counting the number of times of repetitive occurrences of the abnormal shutoff; and c) determining that predetermined recovery processing should be carried out on the computer when the number of times of repetitive occurrences of abnormal shutoff exceeds a predetermined value.

Owner:FUJITSU CLIENT COMPUTING LTD

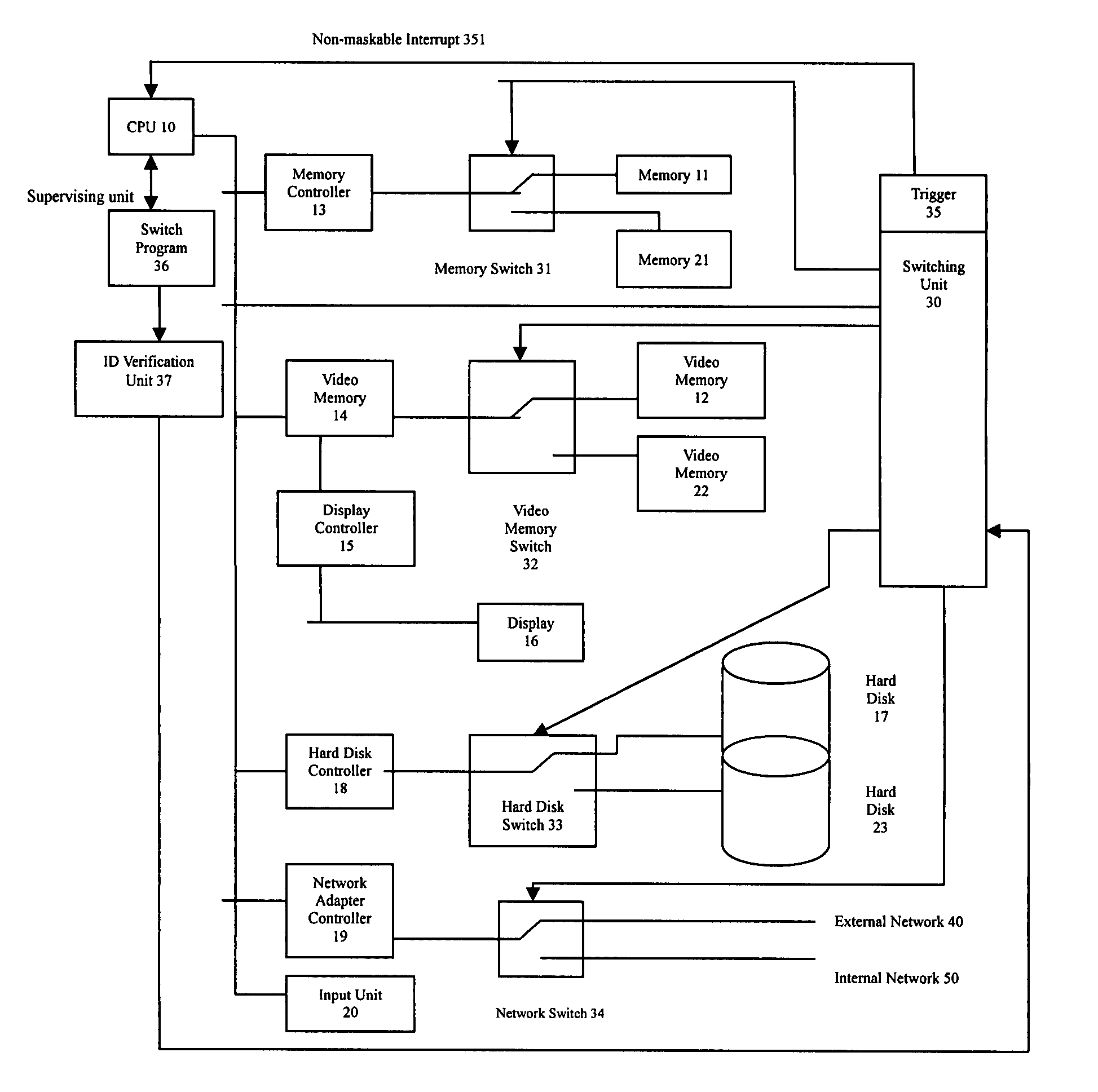

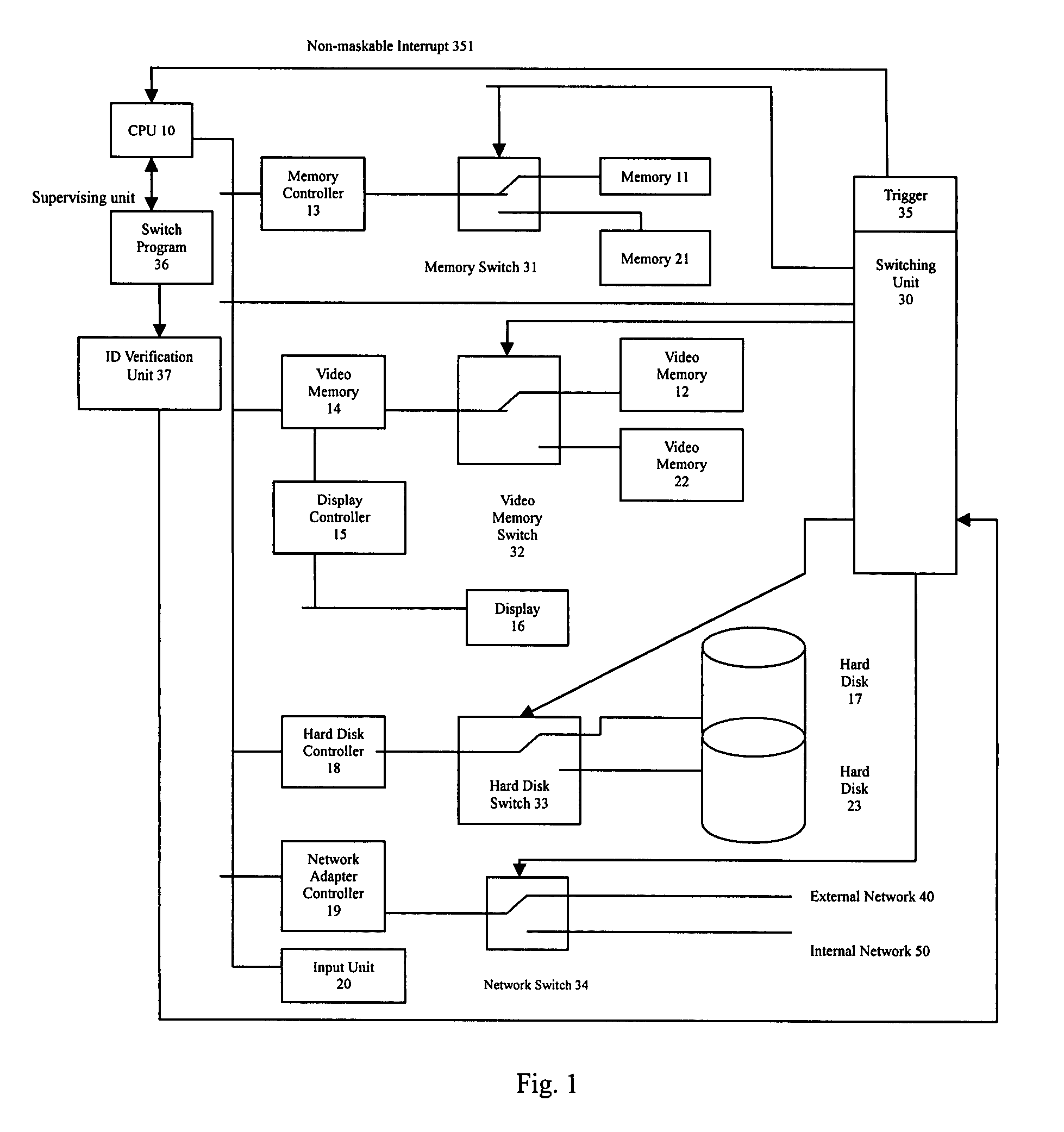

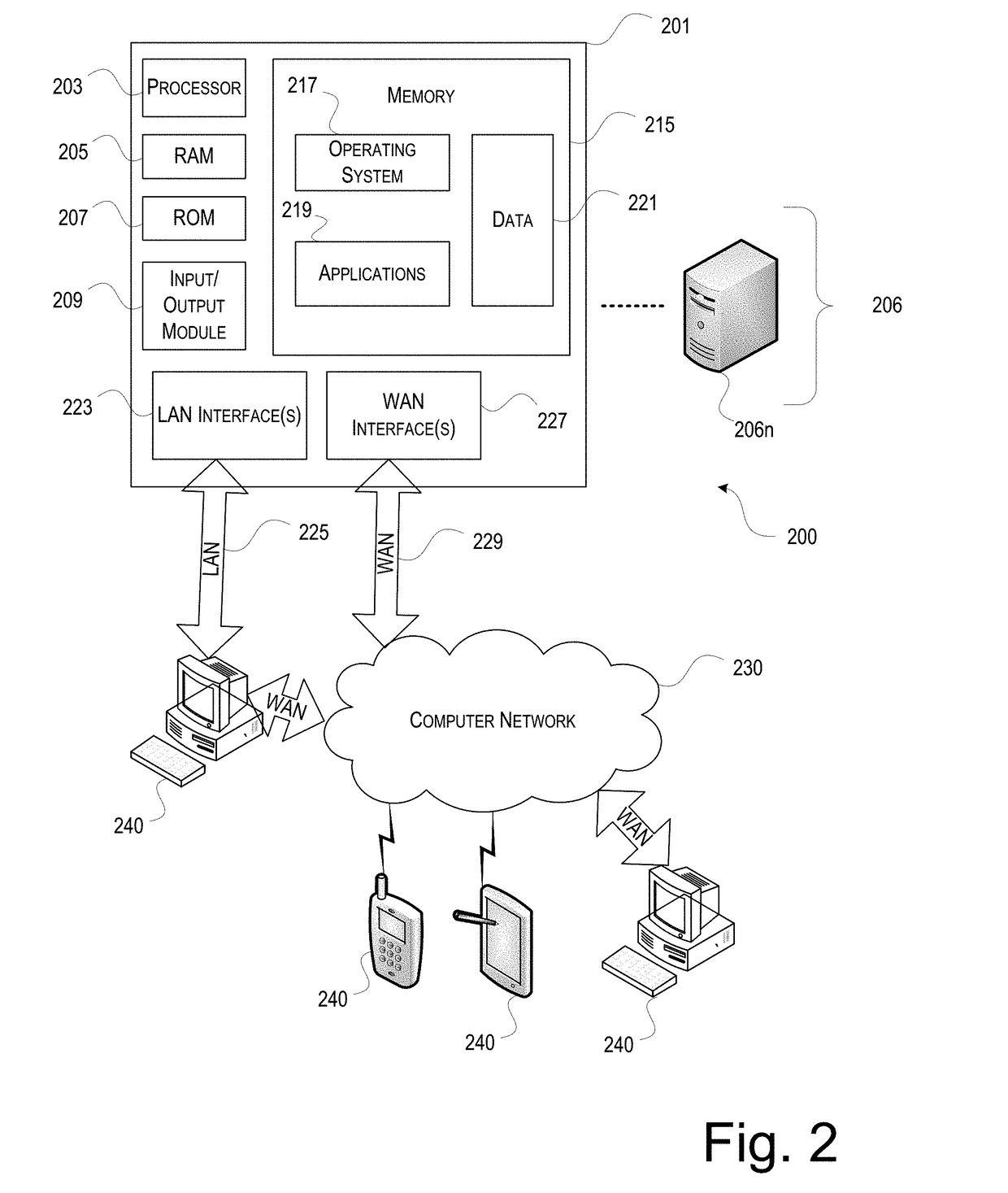

Computing system being able to quickly switch between an internal and an external networks and a method thereof

InactiveUS7370193B2Ensure physical separationQuick switchAnalogue secracy/subscription systemsData resettingNon-maskable interruptUser input

The invention discloses a computing system such as a computer, a Personal Digital Assistant, or a mobile phone, being connected both to an internal network and an external network and being able to quickly and safely switch therebetween without being shut down while ensuring a physical separation between the two networks. When a user inputs a request of switching, a switching unit will set a trigger thereof and generate a consequent non-maskable interrupt to CPU. After receives the NMI, the CPU controls the switching unit to run a switch program kept therein to back up a current status of the system. Then the switch program backs up a current status, controls the switching unit to interrupt all serving programs and loads the other status other than the current status to the computing system, and finally control the switching unit to reset the trigger.

Owner:SHAO TONG

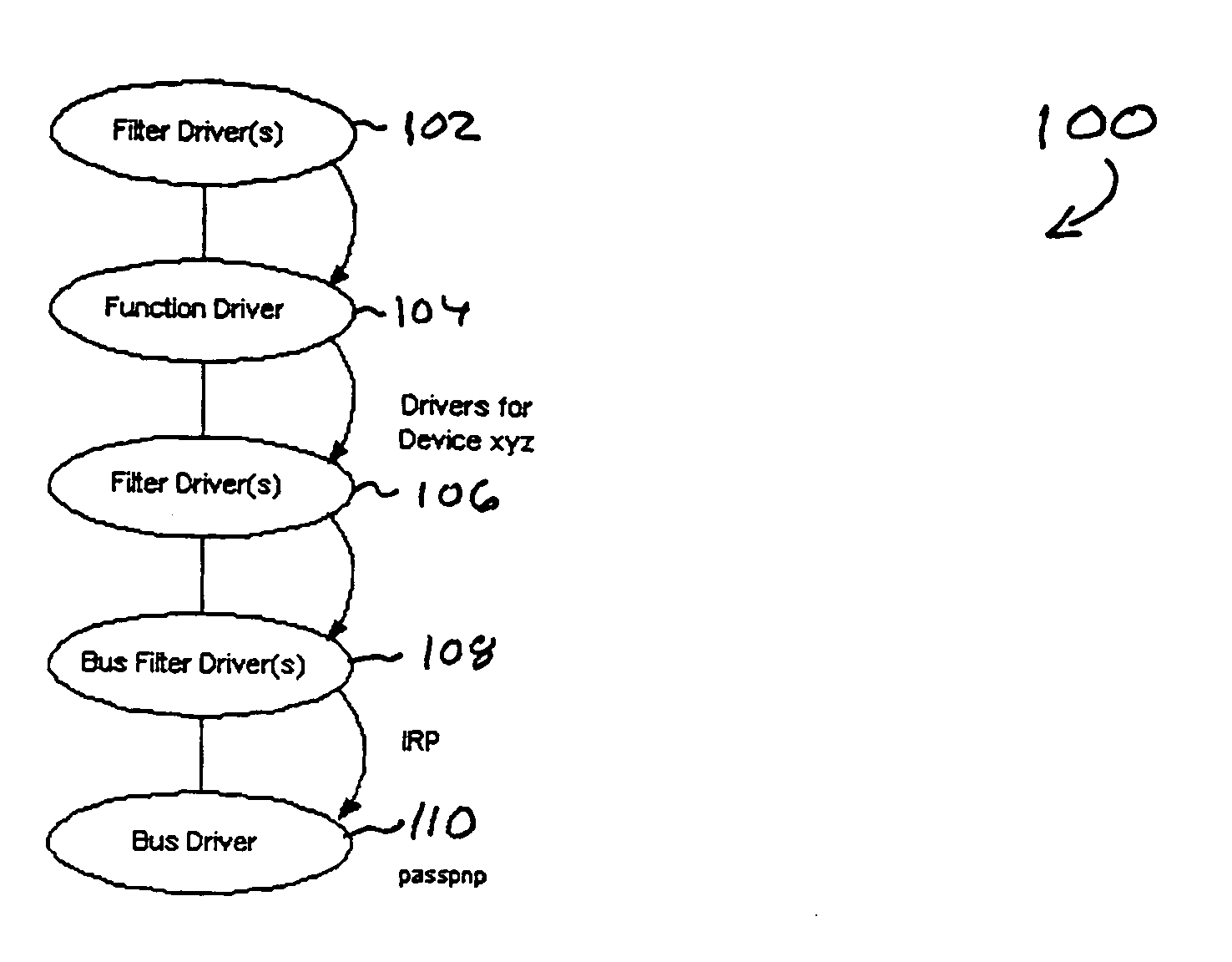

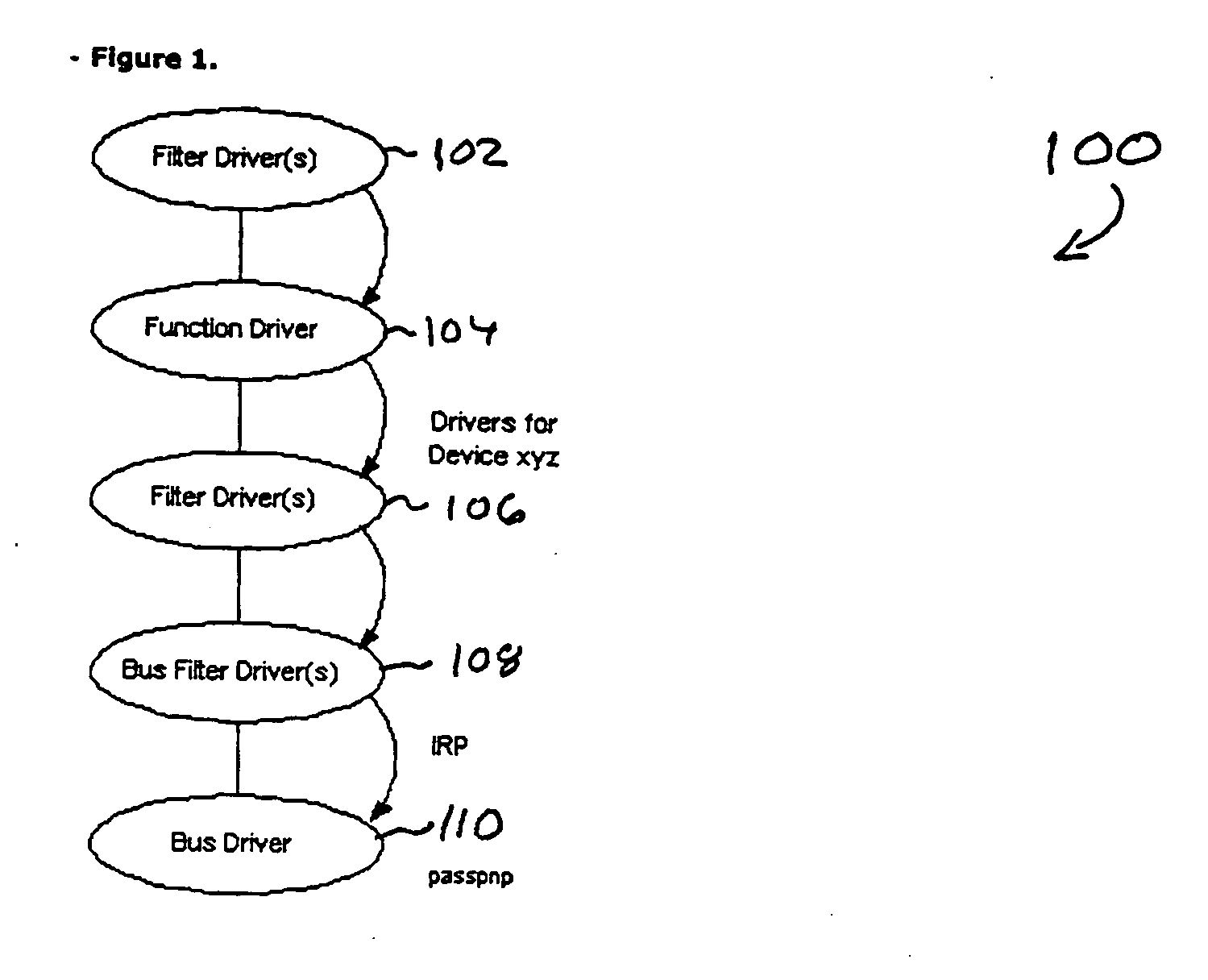

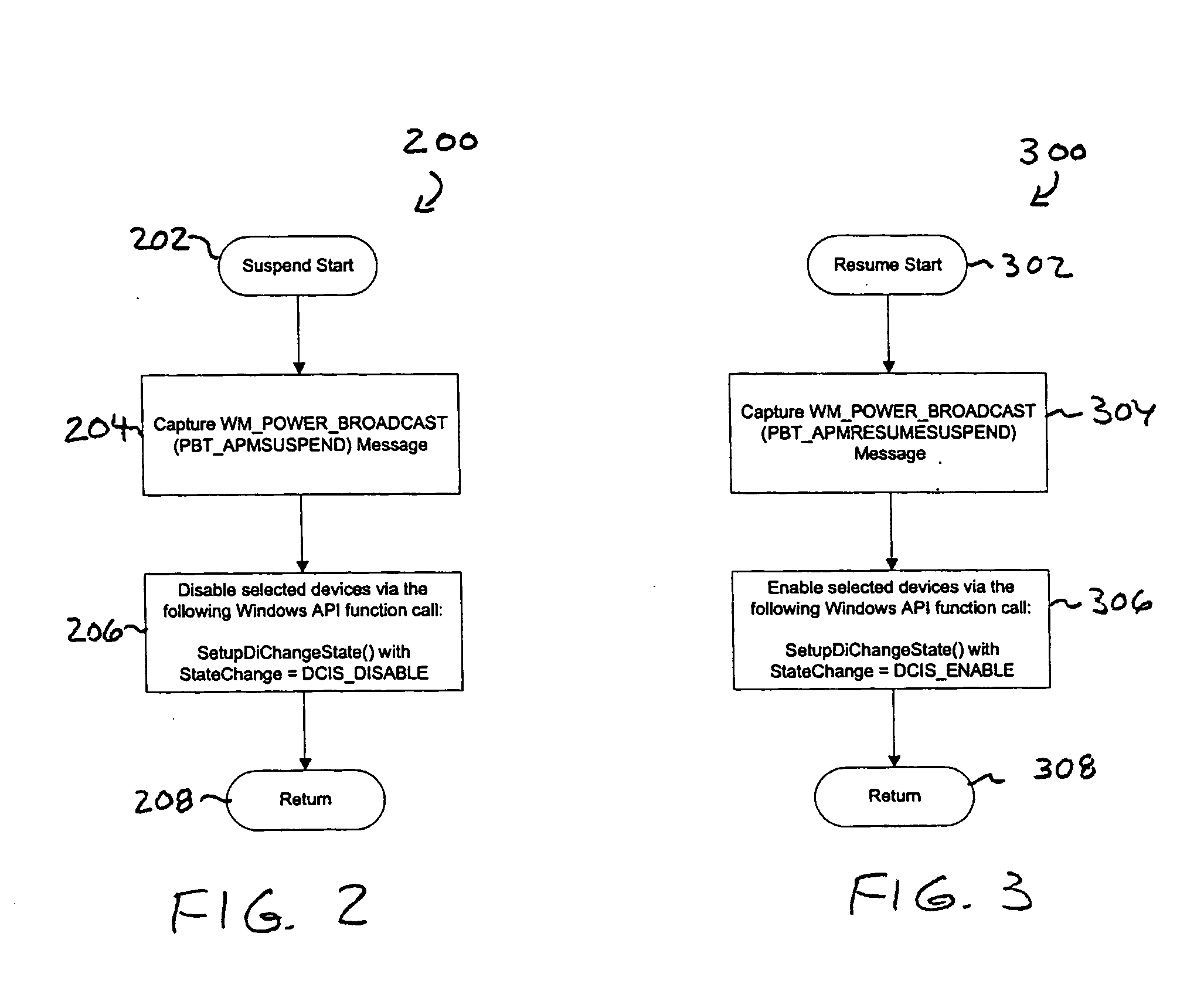

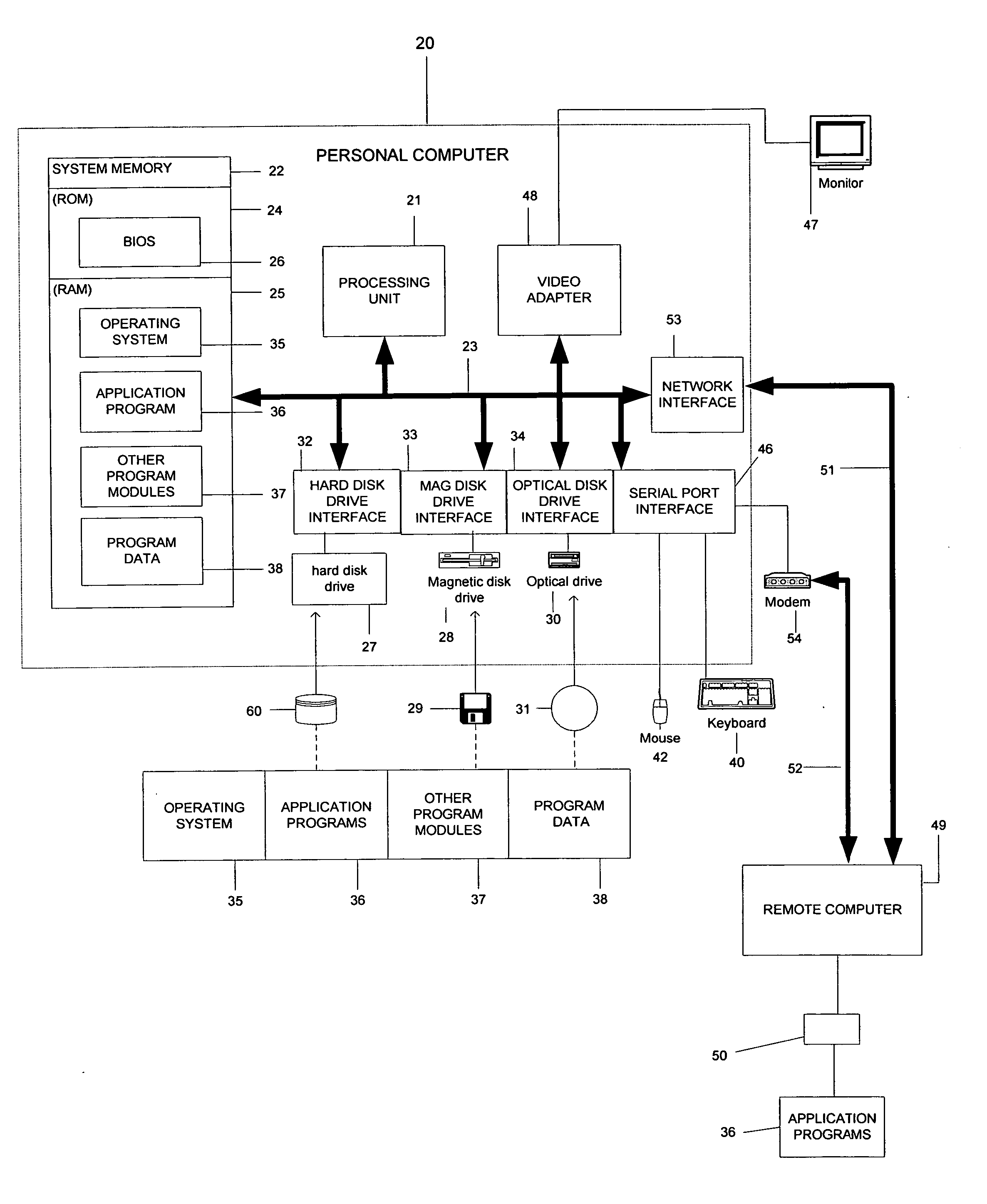

Fast resume to normal operation of a computer in a power saving mode

ActiveUS20050066158A1Faster resumeFaster resume to normal operation of a computerEnergy efficient ICTVolume/mass flow measurementPower modeOperational system

A fast resume of a computer from a low power mode to a normal operating mode captures a power down message from the operating system of the computer to devices connected thereto. In response to the captured message, the device manager is instructed to remove the device from the operating system. The computer is powered down with the device removed. The system is later powered up with the device removed, allowing for faster resume to normal operation. After the computer has returned to normal operation, the device manager reinstates the removed device. The program to capture the power down message can be above the device driver in the driver stock or be an application running in the user mode of the operating system.

Owner:TEXAS INSTR INC

Windows processing system of hand-hold equipment

ActiveCN101097521AFast startupCalculation speedMultiprogramming arrangementsPower supply for data processingOperational systemSoftware engineering

The invention discloses a Windows process system of hand-hold equipment, it includes: a data processor which can use several operation systems, thereinto: the first operation system guides all drive program of hardware and all application program of hand-hold equipment; a detecting module which detects hand-hold equipment in closing state and decides whether the guiding signal is sent; a program loading module is used to start when it receives guiding signal, it selects some operation system and guides the operation system to memory based on manual operation of user or hand-hold equipment automatically. User just needs to start the second operation system to realize some function, the function action can be accomplished in the second operation system, it possesses advantages that memory resource can be used fully, speed of starting is fast, speed of calculation is fast, energy is saved.

Owner:SICHUAN JIUZHOU ELECTRIC GROUP +1

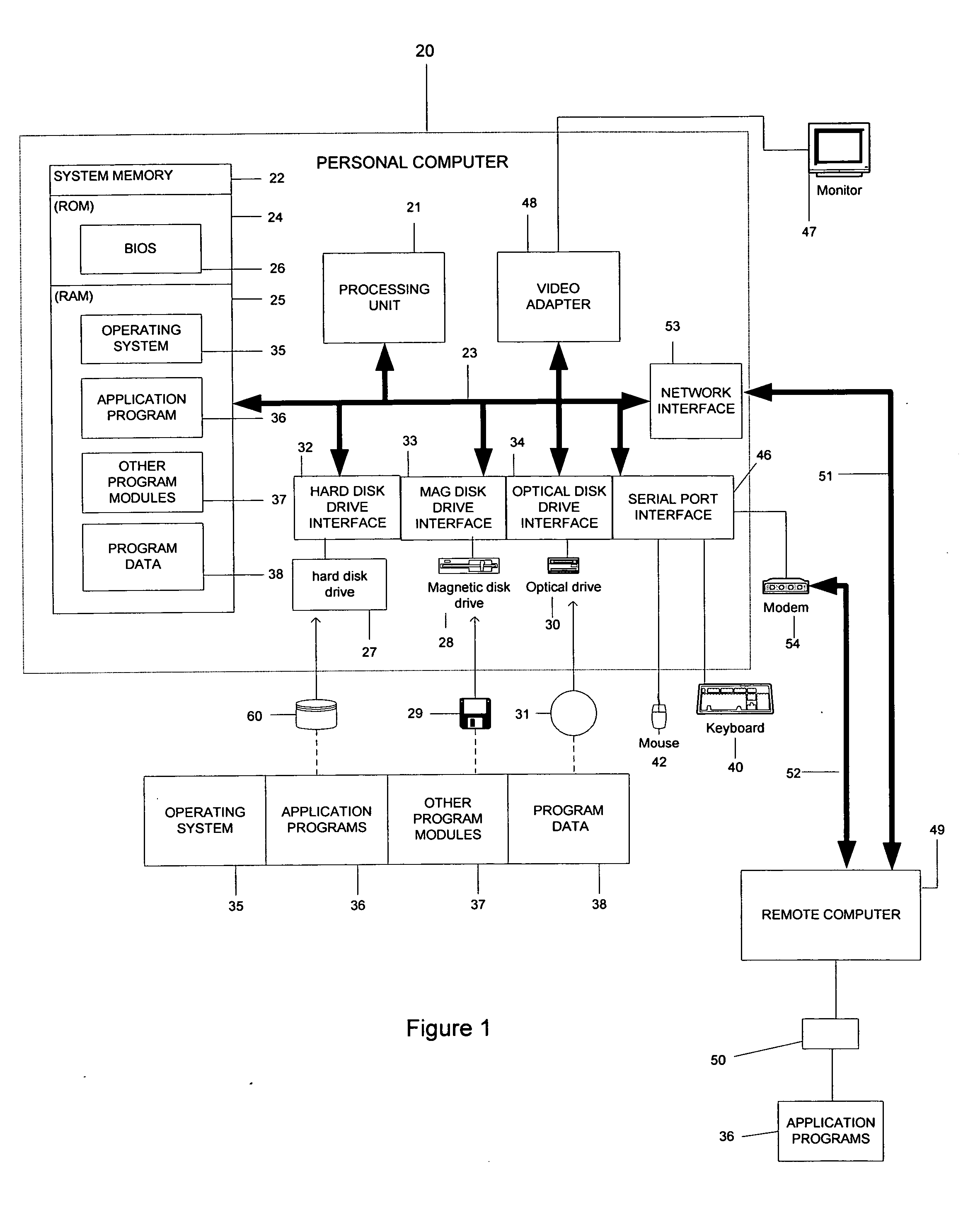

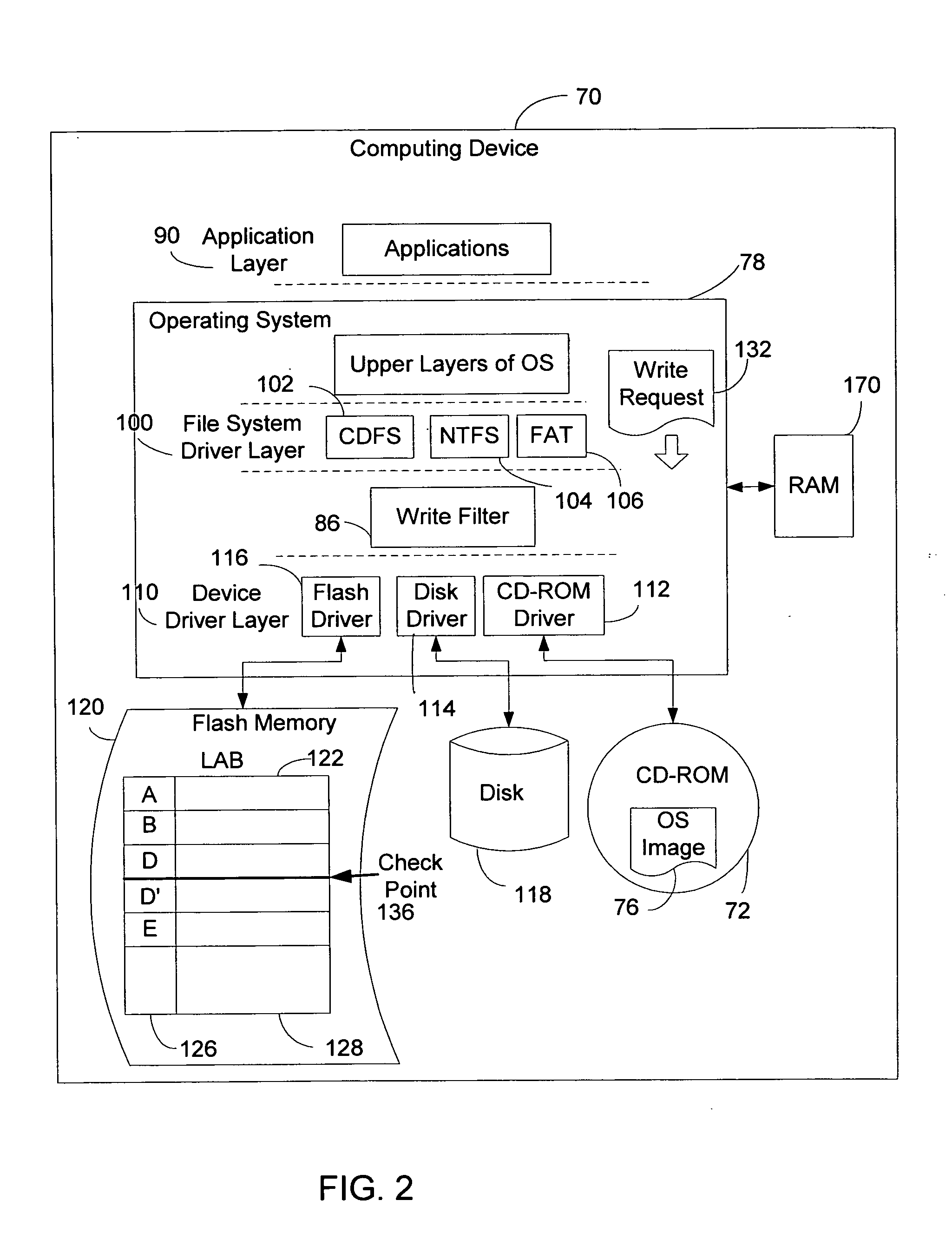

System and method for filtering write operations to a storage medium containing an operating system image

InactiveUS20050144519A1Avoid lossData processing applicationsError detection/correctionOperational systemOperating system

A write filter is used to handle write operations by an operating system of a computing device that has a main storage medium in which the operating system image is stored. The write filter is placed in the operating system to intercept write commands for writing state data into the main storage medium and to write the state data onto a non-volatile auxiliary storage medium to prevent the state data from being lost when the device is shut down. The write filter creates checkpoints (or watermarks) for the state data in the non-volatile memory to protect them from being written over and to allow the system to roll back to a previous state. The write filter also enables the operating system image in a writable main storage medium of the computing device to be replaced with a new operating system image while the operating system is still running through by gradually copying the new image into the main storage while moving the old image into a look-aside buffer in the RAM.

Owner:MICROSOFT TECH LICENSING LLC

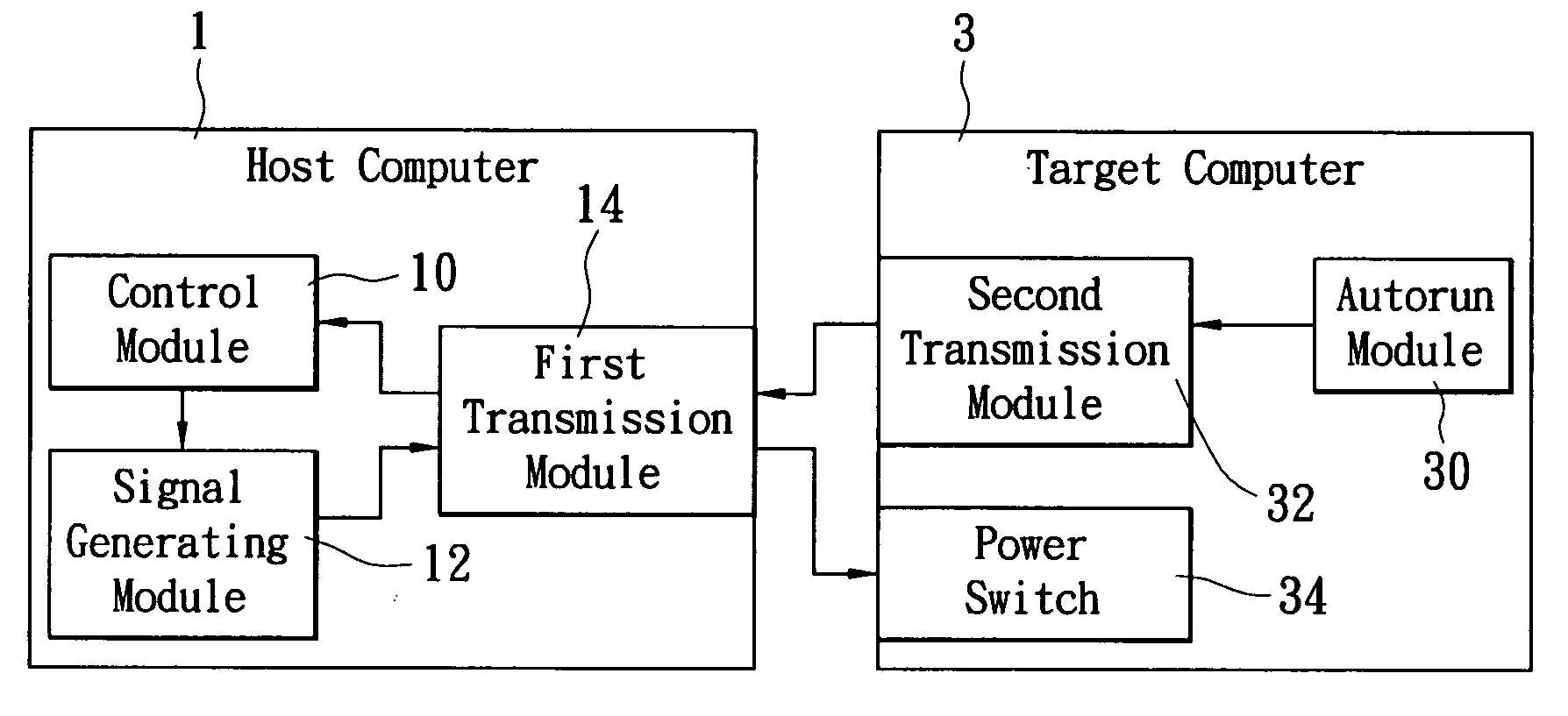

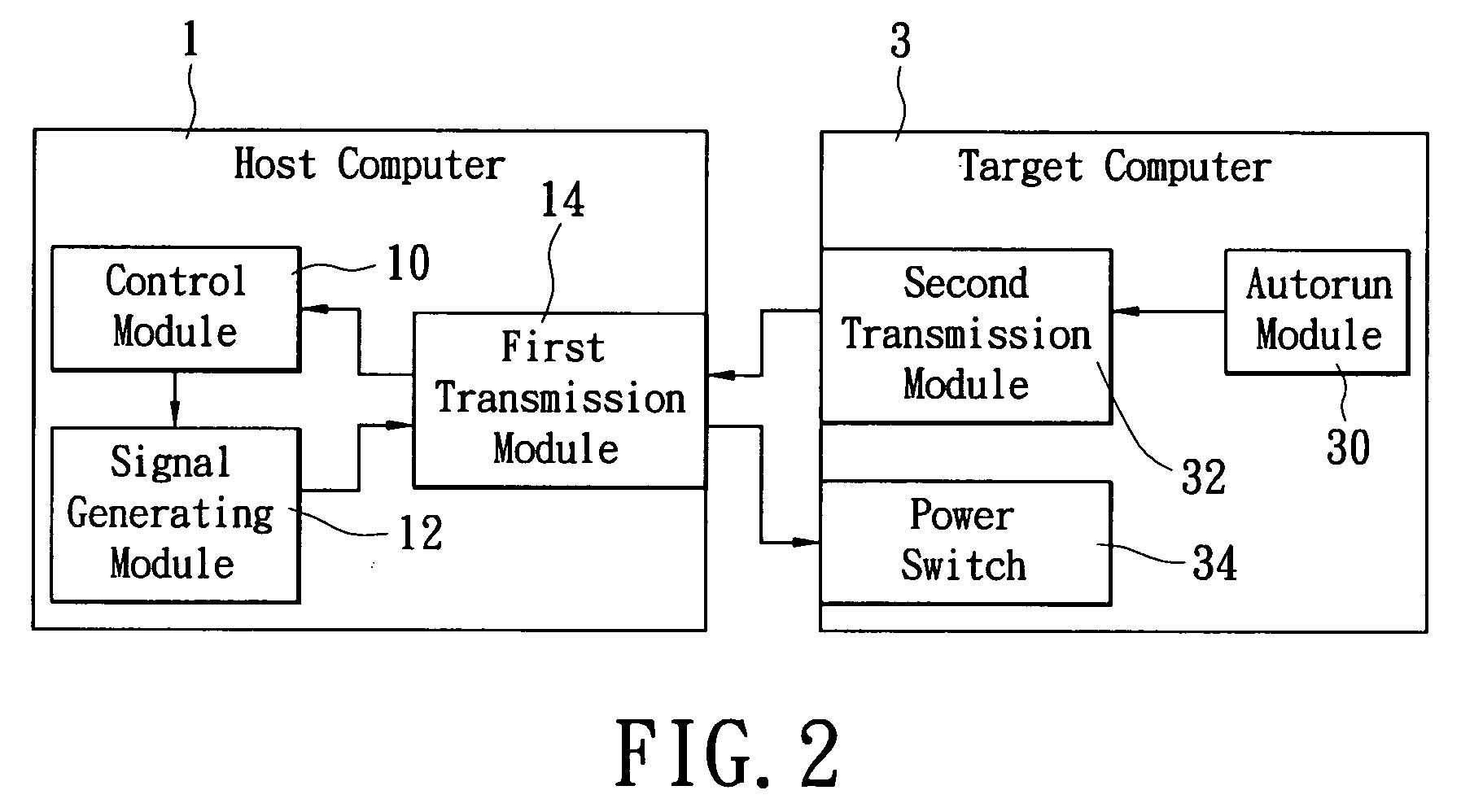

Boot test system and method thereof

ActiveUS20090292911A1Increased cost of testingLow costDetecting faulty hardware by power-on testDigital computer detailsEngineeringBootstrap test

A boot test system applied to test a cold boot in a target computer is provided. The boot test system includes a host computer and an autorun module. The host computer is used to test the target computer to turn power on / off and output a power-on signal and a power-off signal to the target computer based on a feedback signal. The autorun module installed in the target computer is used to output the feedback signal to the host computer during the boot of the target computer. Whereby, the present invention retains a fail result of the boot of the target computer for debugging by a worker.

Owner:UNIVERSAL SCIENTIFIC INDUSTRIAL (SHANGHAI) CO LTD +1

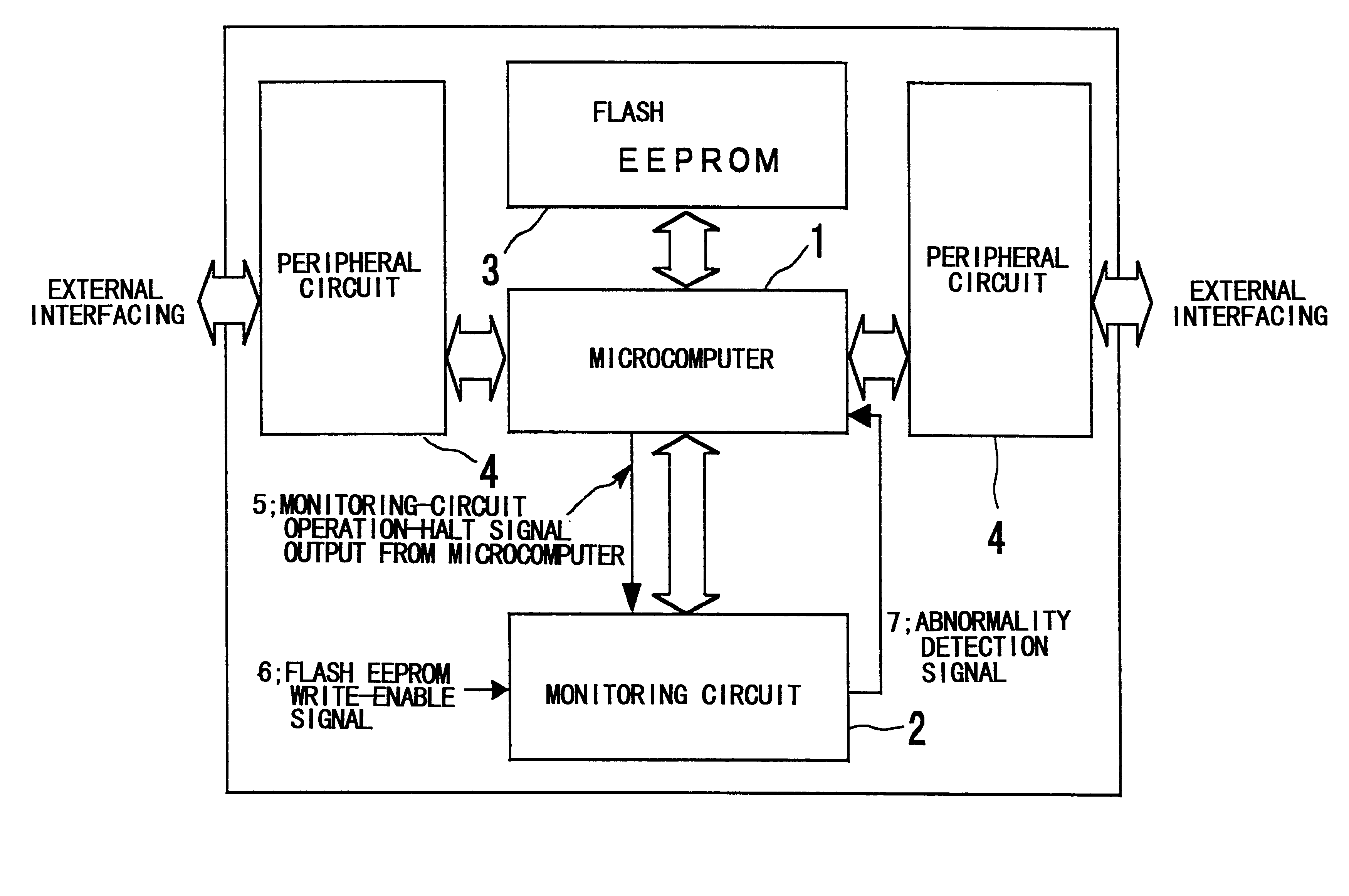

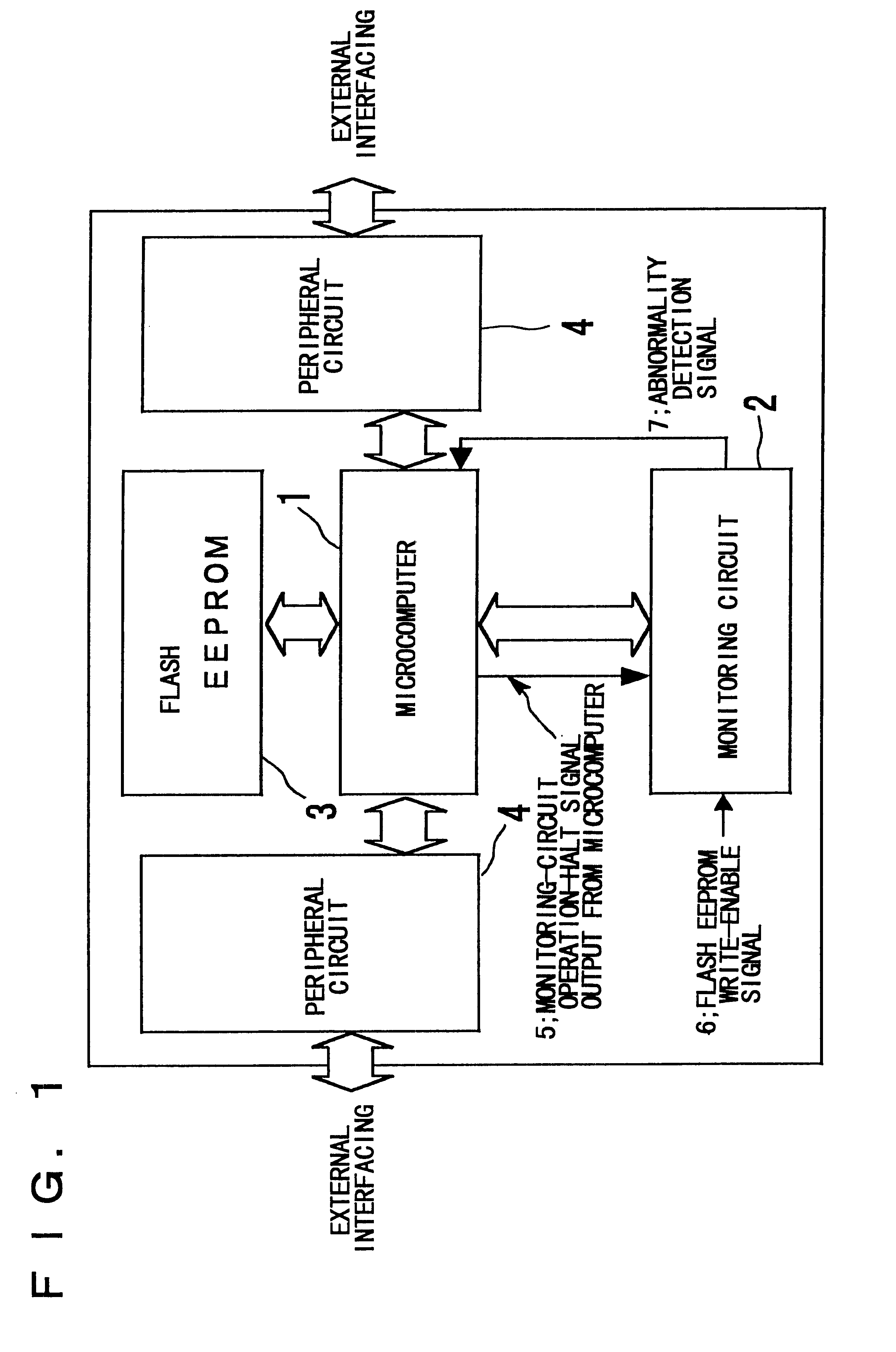

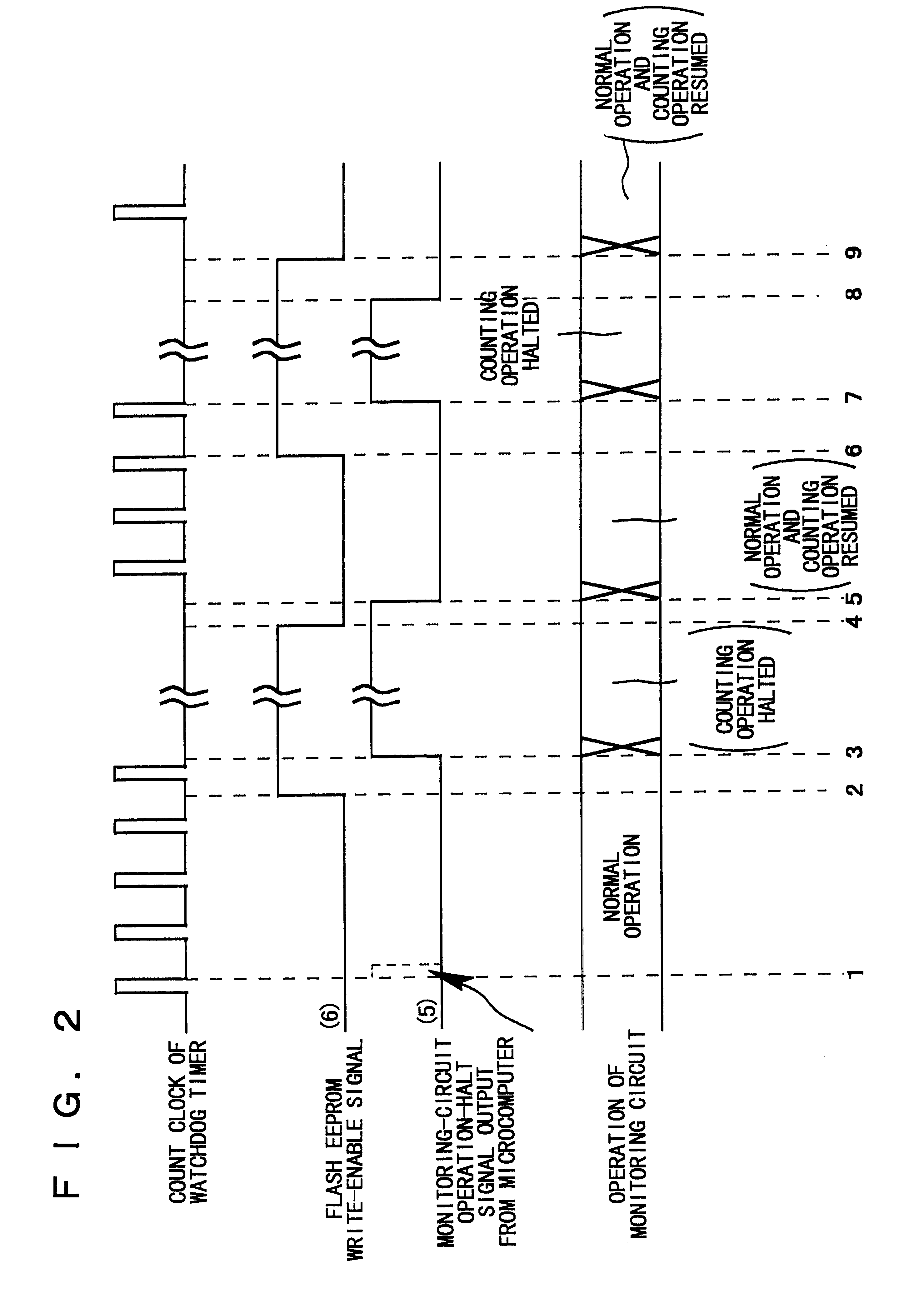

Method and apparatus for controlling writing of flash EEPROM by microcomputer

InactiveUS6567930B1Possible to executeHardware monitoringArchitecture with single central processing unitMicrocomputerSignal on

An apparatus that make it possible for a microcomputer to execute self-programming without the occurrence of shutdown or initialization (restart) includes a flash EEPROM for storing programs and data, a monitoring circuit for monitoring program runaway and malfunction, and the microcomputer. When rewriting of the content of said flash EEPROM (i.e., self-programming) is executed via control by the microcomputer, the monitoring circuit controls output / suppression of an abnormality detection signal on the basis of an externally entered flash EEPROM write-enable signal and a monitoring-circuit operation-control signal output from the microcomputer.

Owner:RENESAS ELECTRONICS CORP

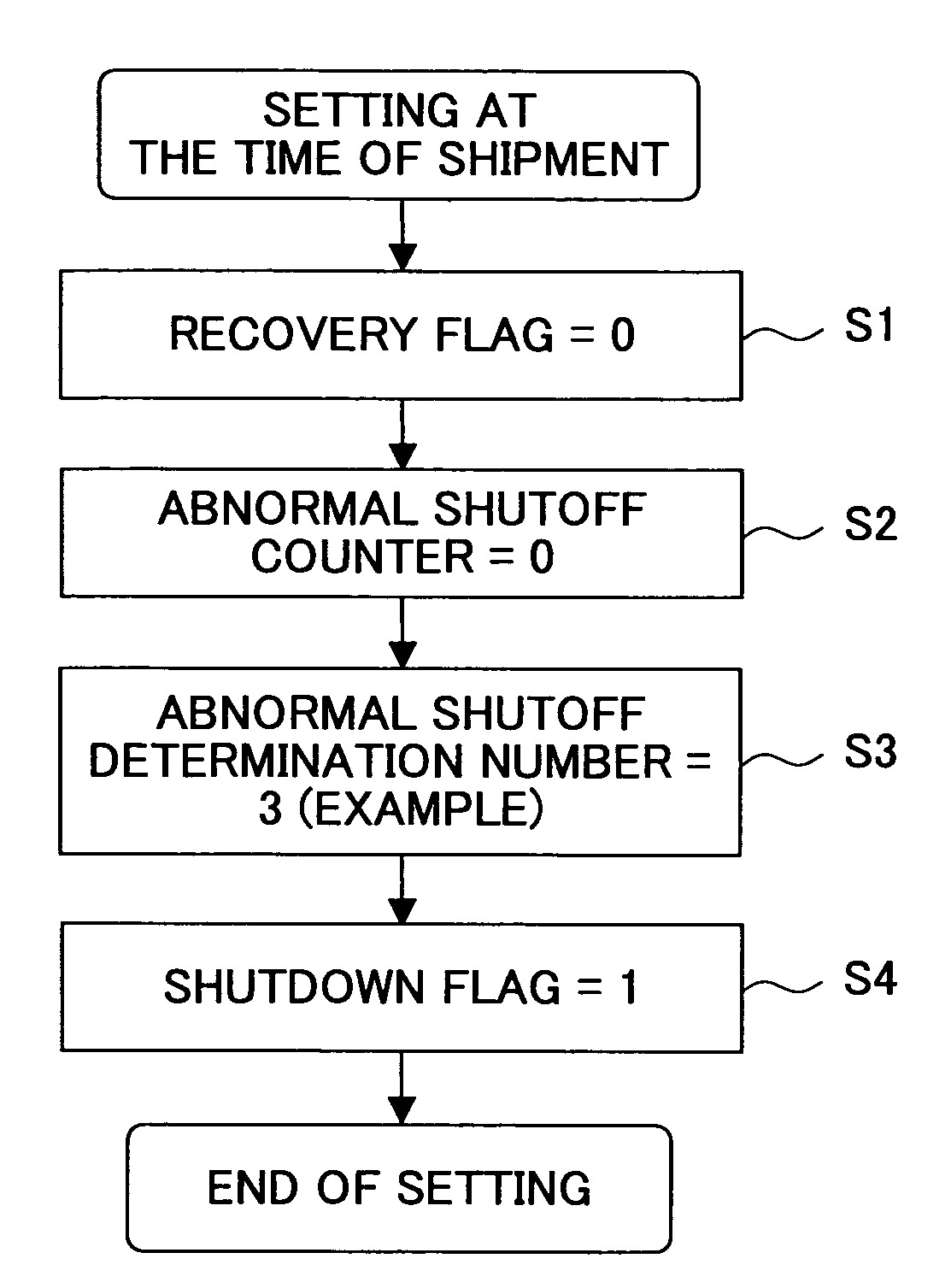

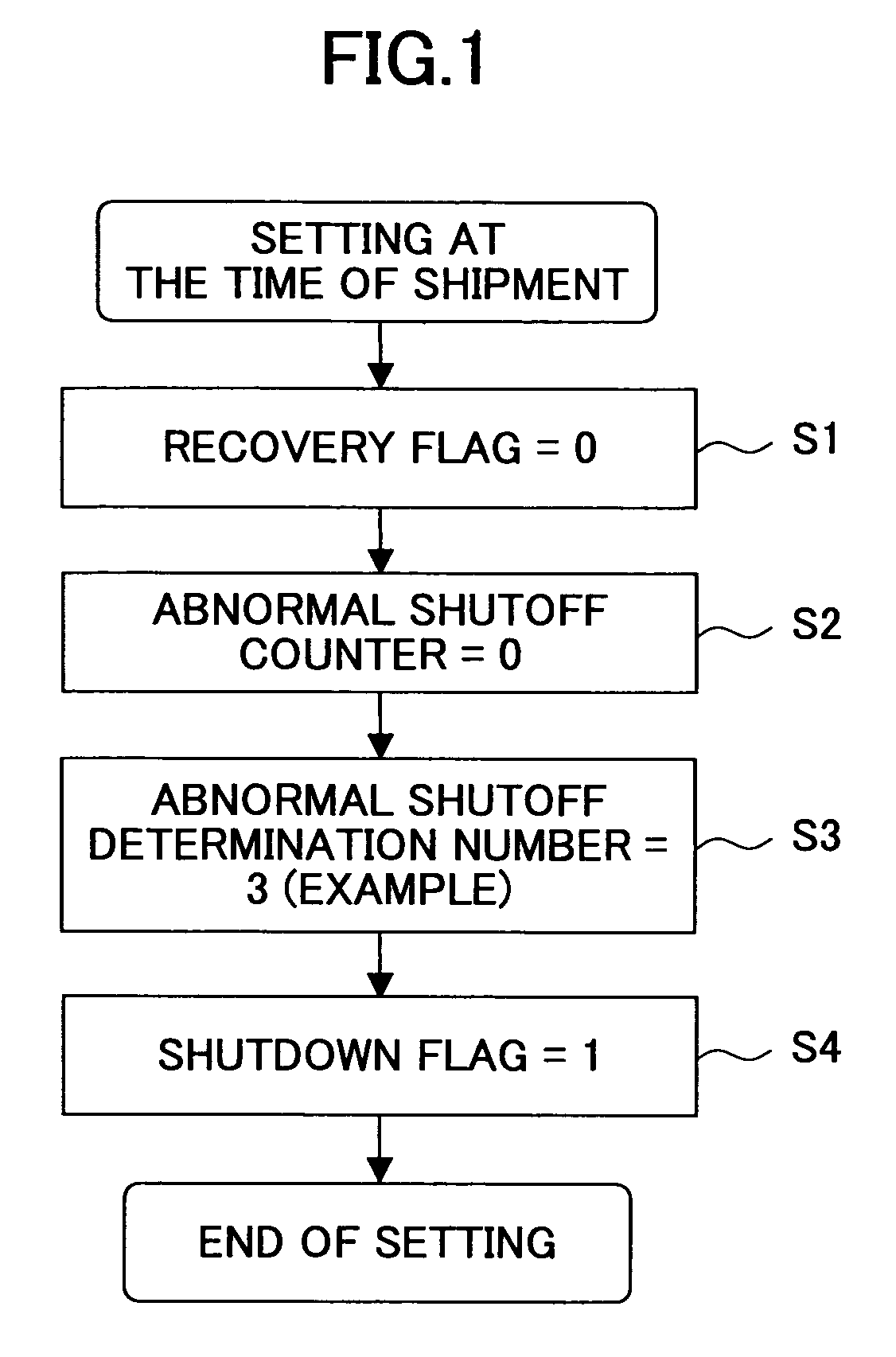

Computer shutoff condition monitoring method, information processing apparatus, program and computer readable information recording medium

InactiveUS7506209B2Simple configurationError detection/correctionInformation processingCondition monitoring

A shutoff condition monitoring method for a computer, includes the steps of: a) determining that an abnormal shutoff has occurred when the computer shuts off without passing through predetermined shutoff processing; b) counting the number of times of repetitive occurrences of the abnormal shutoff; and c) determining that predetermined recovery processing should be carried out on the computer when the number of times of repetitive occurrences of abnormal shutoff exceeds a predetermined value.

Owner:FUJITSU CLIENT COMPUTING LTD

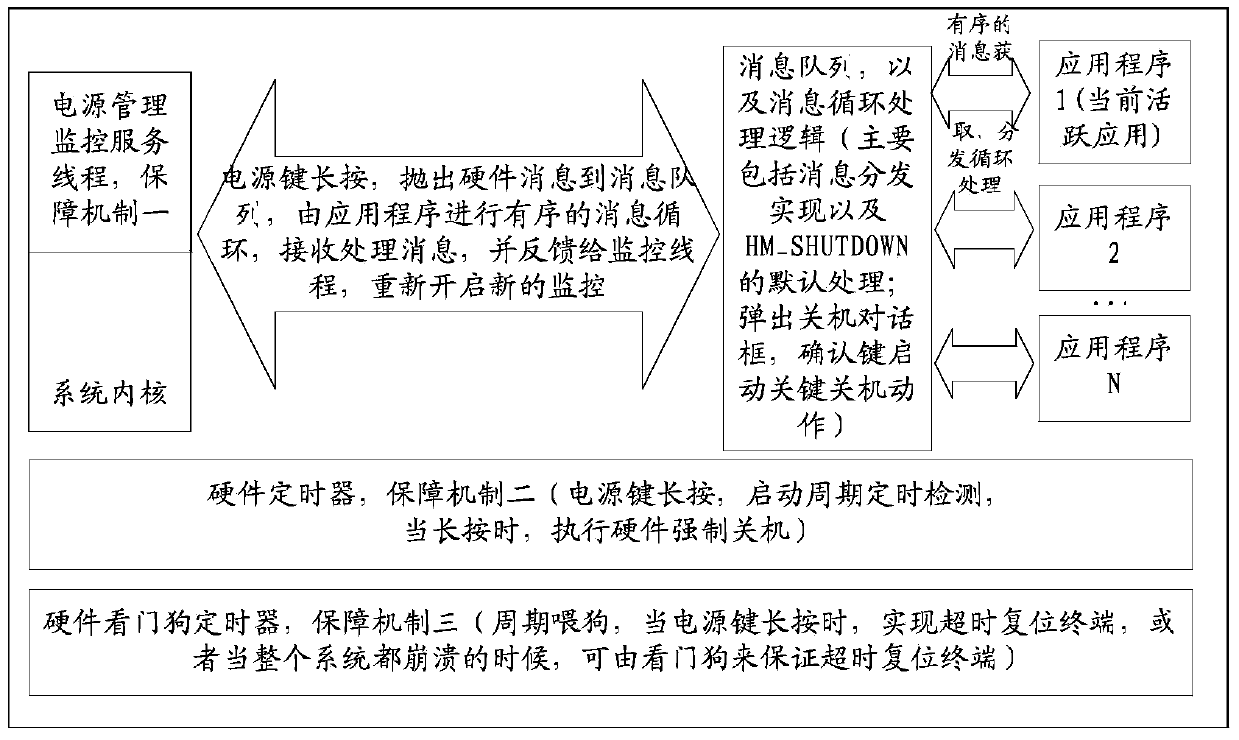

Startup control method for software-operated startup and shutdown in multitask systems

InactiveCN103473087AGuaranteed stabilityImprove experienceFault responseProgram loading/initiatingShut downSoftware switch

The invention provides a startup control method for software-operated startup and shutdown in multitask systems. The method is implemented by any one of three safeguard mechanisms. The first safeguard mechanism includes: a power management and monitoring service thread is established in a kernel of the multitask system, and shutdown is controlled through the power management and monitoring service thread which detects a long-press event of a power button. The second safeguard mechanism includes: a hardware timer interrupt service is established in the multitask system, and a hardware timer is started to regularly detect the long-press event of the power button so as to control shutdown. The third safeguard mechanism includes: a hardware watchdog timer is established in the multitask system, and the watchdog times out and restores so as to control shutdown. The design of three safeguard mechanisms allows a handheld terminal system to be able to shut down or reset and restart with no need for dismantling the system to remove a battery when the whole software-operated startup and shutdown mechanism collapses abnormally; accordingly, user experience is improved greatly, and products can be more competitive.

Owner:FUJIAN CENTM INFORMATION

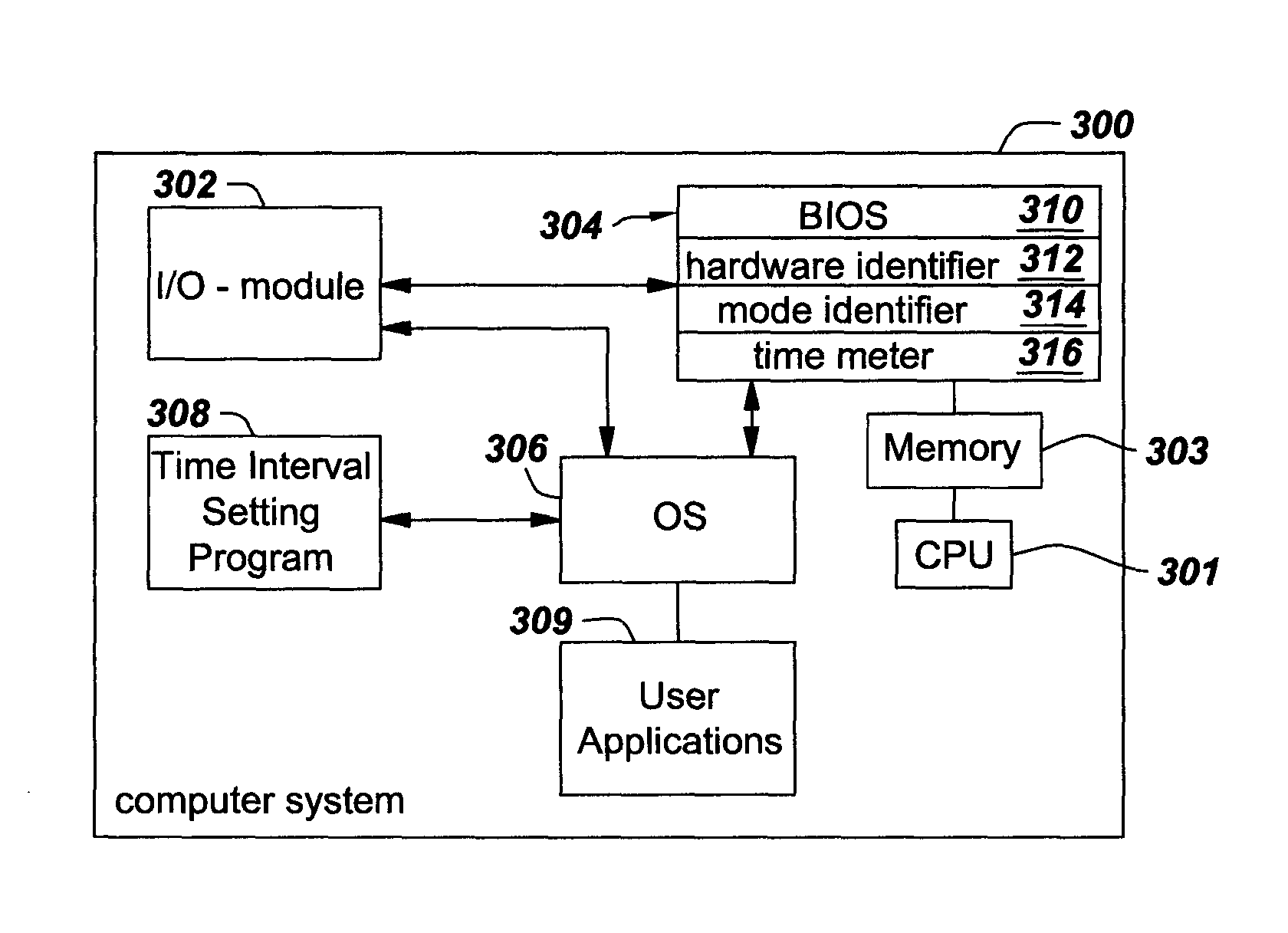

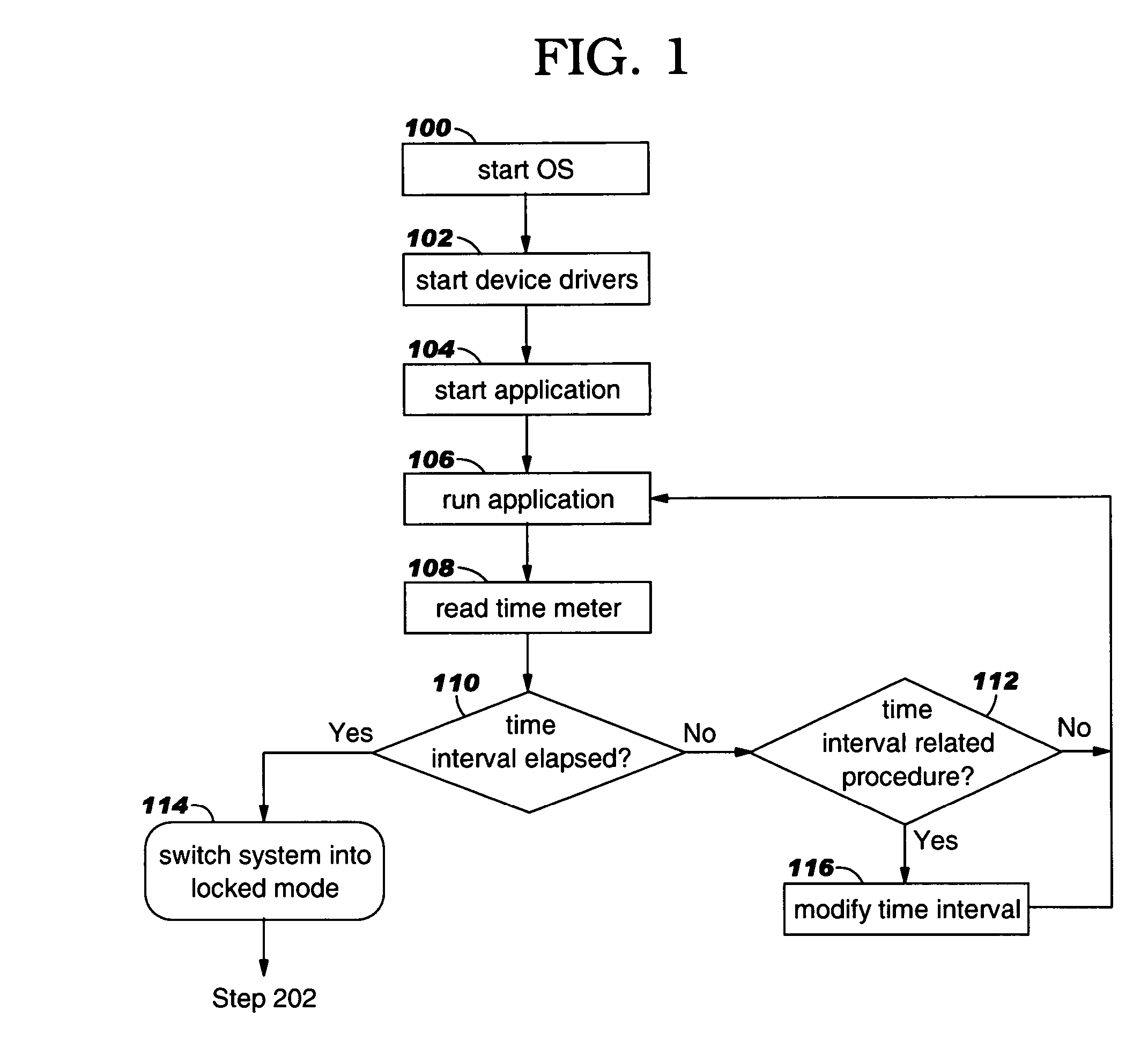

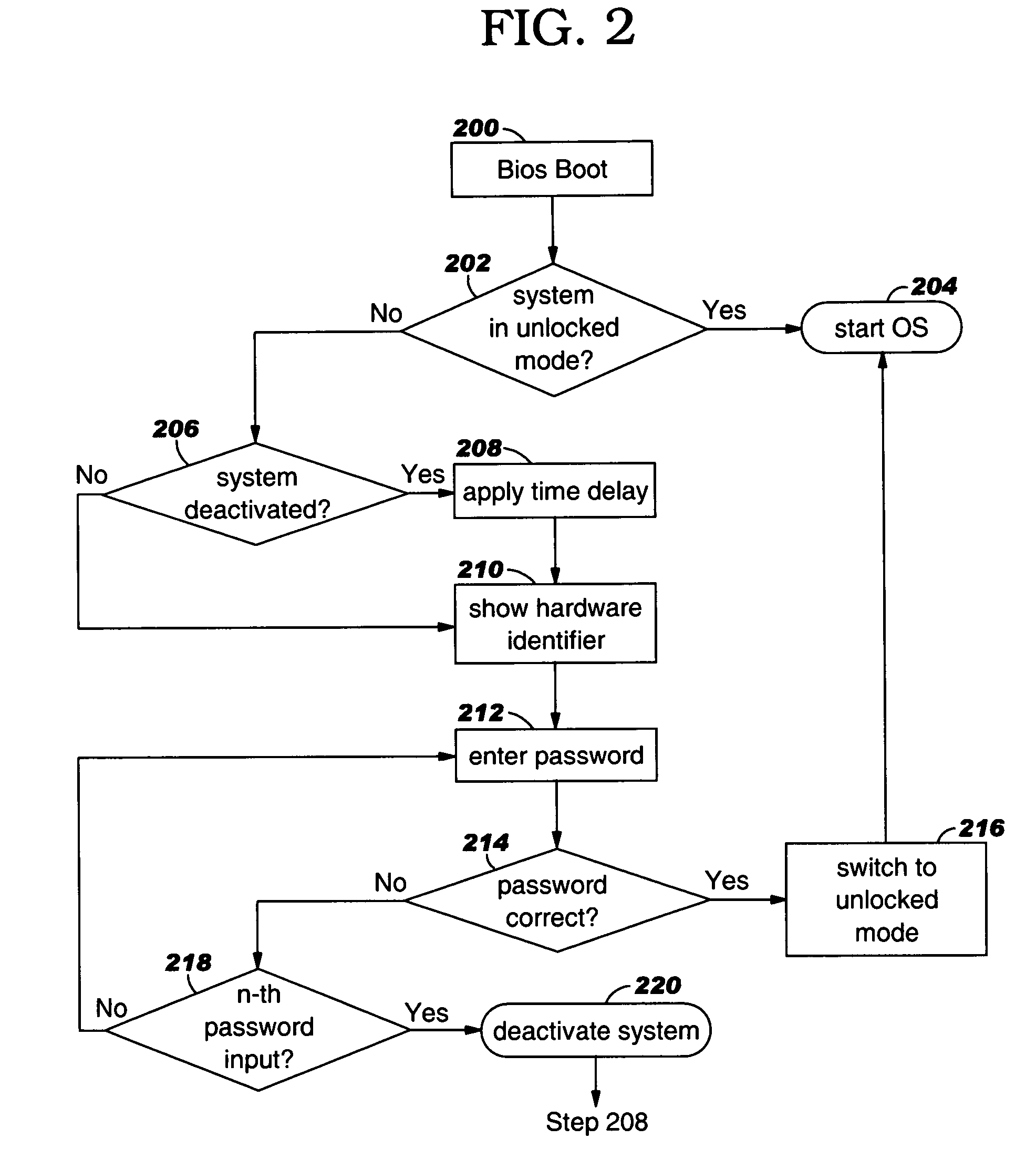

System, method and program product for controlling access to computer system

ActiveUS7870376B2Avoid accessDigital data processing detailsDigital computer detailsOperational systemPassword

The computer system initially operates in a fully operational mode in which an operating system in the computer system is operating and the computer system executes one or more user applications installed in the computer system. In response to a predefined time interval lapsing, the computer system automatically switches from the fully operational mode to a limited operational mode in which the one or more user applications are terminated, the operating system is shut down, and a BIOS within the computer system solicits entry of a password by a user. If the user fails to enter a valid password, operation of the operating system and execution of the one or more user applications are prevented. If a user attempts to activate the computer system for which the time interval has already lapsed, a BIOS within the computer system boots up, determines that the computer system is currently set for a limited operational mode, prevents boot up of an operating system of the computer system, and solicits a password from a user. If the user fails to enter a valid password, the BIOS continues to prevent boot up of the operating system. If the user enters a valid password, the operating system boots up and executes one or more user applications within the computer system.

Owner:GOOGLE LLC

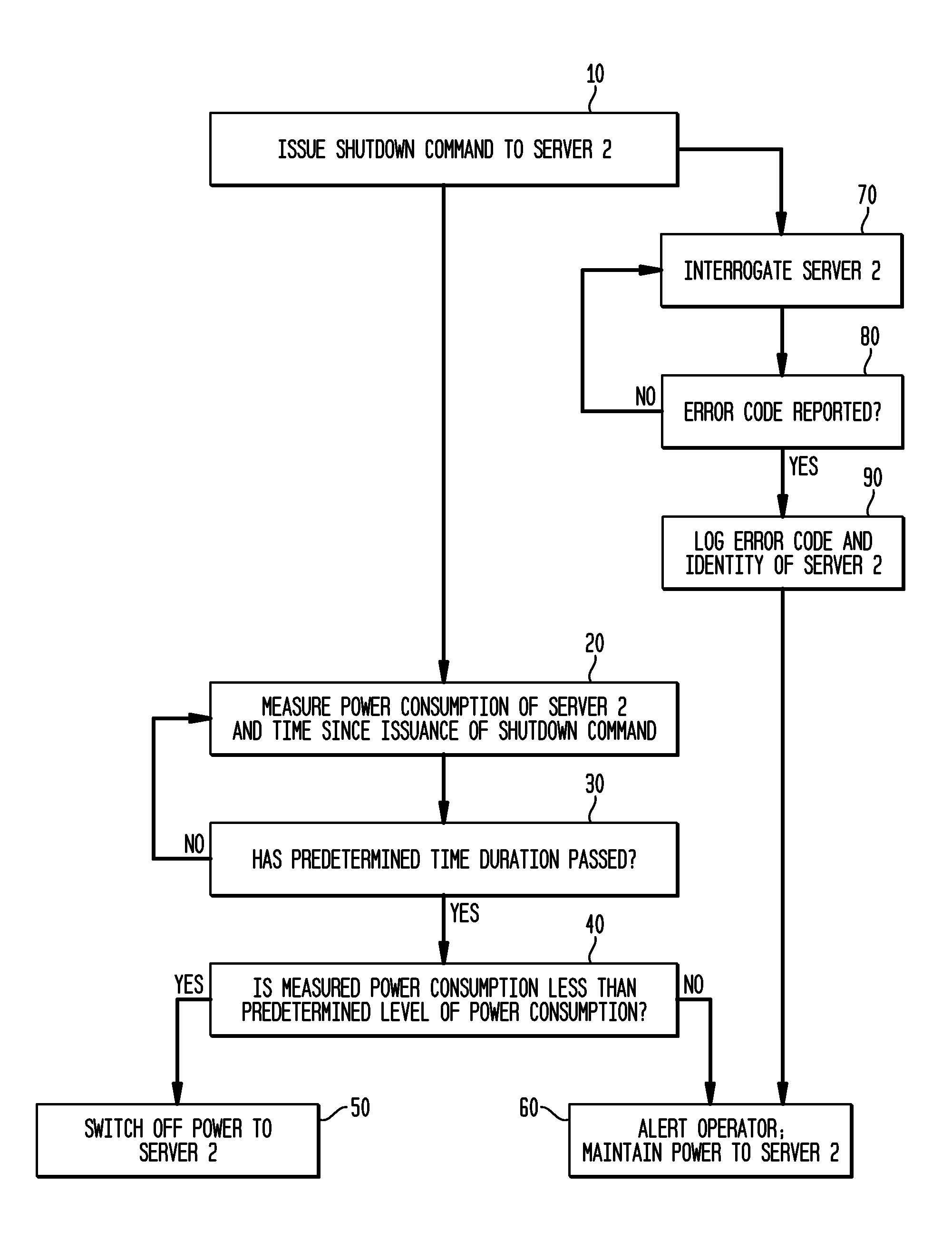

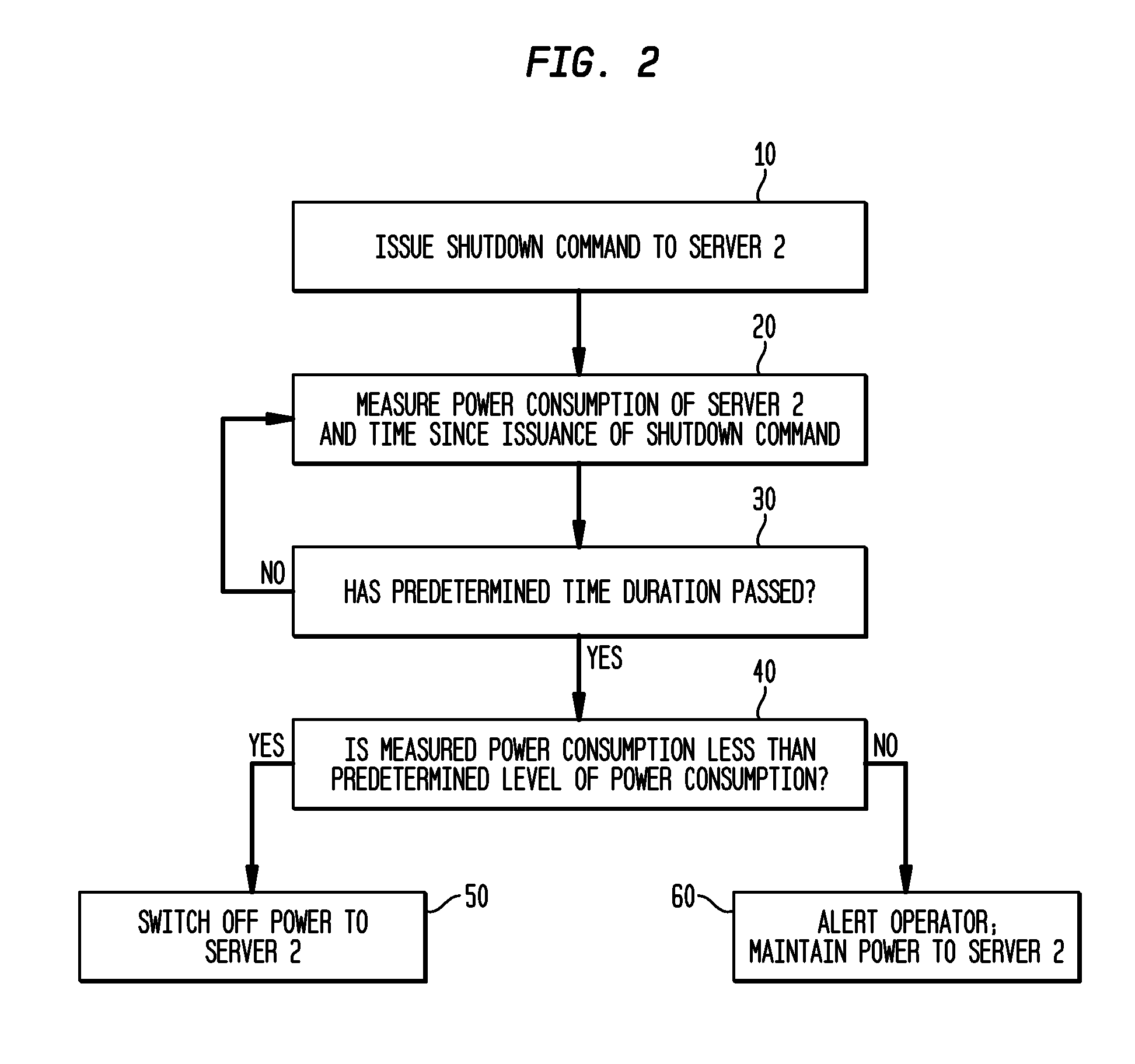

Method and system for detecting whether a computer server has shut down gracefully

A server in a data center is supplied with power by a power distribution unit (“PDU”) having outlet-level power monitoring and switching capability. A predetermined server-specific time after a shutdown command has been issued to the server, the level of power consumption of the server is compared with a predetermined server-specific level of power consumption. If the level of power consumption of the server at that time is less than the server-specific level of power consumption, the server is considered to have been gracefully shut down and power to the server is switched off by delivering an appropriate command to the PDU. If the level of power consumption of the server at that time is not less than the server-specific level of consumption, this indicates a malfunction and power to the server is maintained so the cause can be determined and remedied without unnecessarily corrupting data or damaging the server.

Owner:SUNBIRD SOFTWARE INC

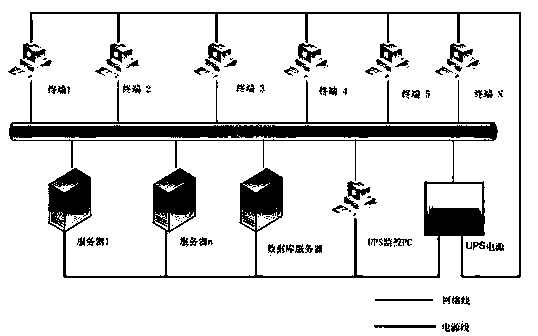

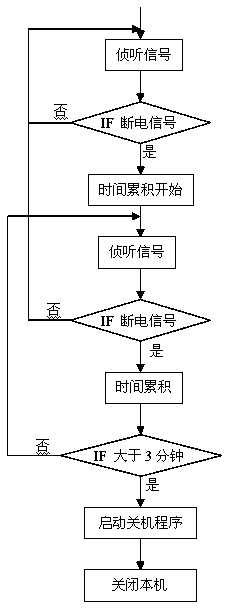

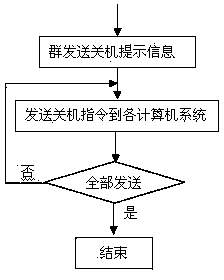

Method for protecting computer systems after outage of uninterrupted power supply (UPS)

InactiveCN104238714AEffective closeProtect resourcesPower supply for data processingComputer usersThe Internet

The invention relates to a method for protecting computer systems after an outage of an uninterrupted power supply (UPS). The method is characterized in that the method includes the following steps of (1) performing hardware configuration on a computer system protection mechanism: accessing UPS data signals to the internet through a network card configured by the UPS, and transmitting UPS operation process information to a personal computer (PC) for management; (2) designing monitoring programs: compiling UPS signal intercepting and monitoring programs in the PC, real-timely monitoring signals of an input power supply of the UPS, sending signals to the computer systems after exceeding accumulative three minutes from receipt of a UPS outage signal, prompting computer system information to be closed, and alerting a computer user to protect data; starting a shutdown process, and sequentially turning off the computer systems; (3) compiling independent computer shutdown strategies for different computer systems. The method is capable of effectively turning off the computer systems, guaranteeing security of the data and the systems, effectively protecting resources of the computer systems, and reducing loss of service objects as much as possible.

Owner:SHANGHAI MEISHAN IRON & STEEL CO LTD

Robust Suspension and Resumption of Desktop Virtualization

ActiveUS20170279927A1Easy retrievalFast rebuildTransmissionExecution for user interfacesClient-sideApplication software

A method for suspending and resuming a connection for desktop virtualization between two computing devices. In response to a client computing device shutting down, suspending, hibernating, or losing network connectivity during virtualization, the server computing device may itself shut down, suspend, or hibernate, or may pause or suspend the operation of one or more applications currently hosted by the server computing device. The server may detect that connectivity has been restored and resume operation of hosted applications. Alternatively, the client may transmit a command to the server indicating that the client is ready to resume virtualization. The client may also be configured to transmit a command that may cause the server to resume a powered-on state after the server was shut down or in a state of hibernation.

Owner:CITRIX SYST INC

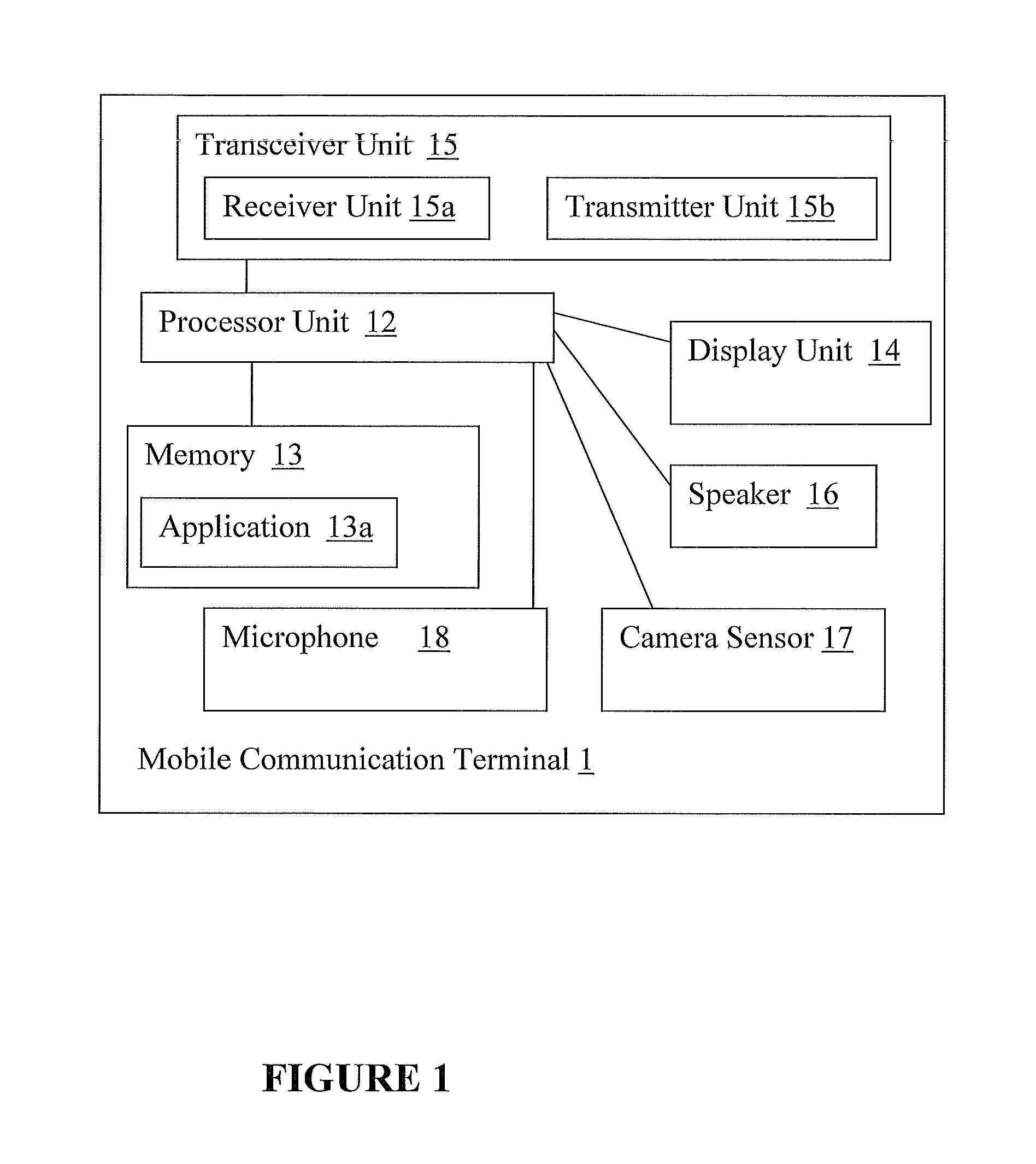

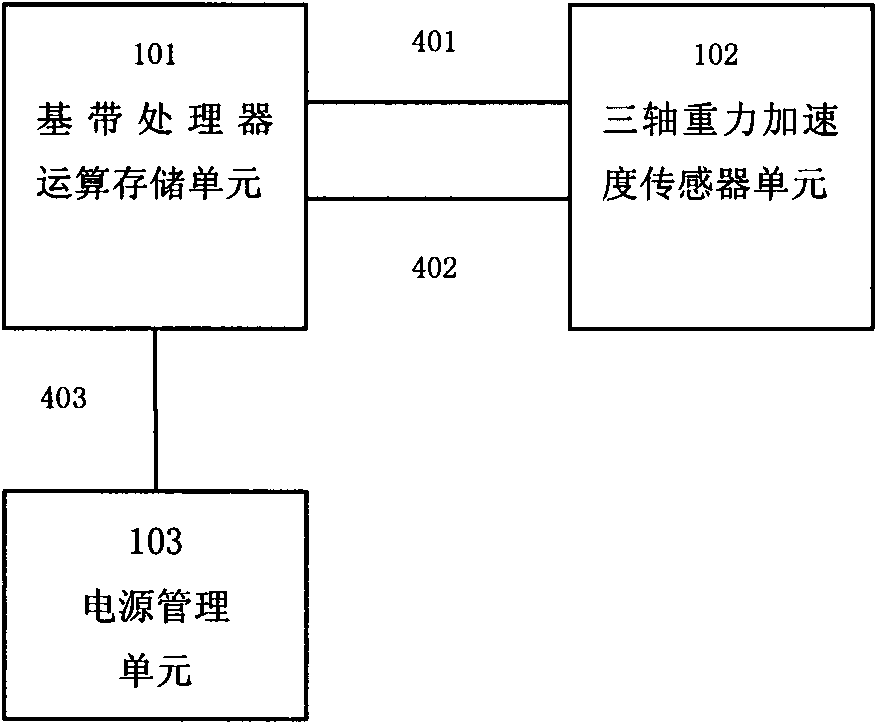

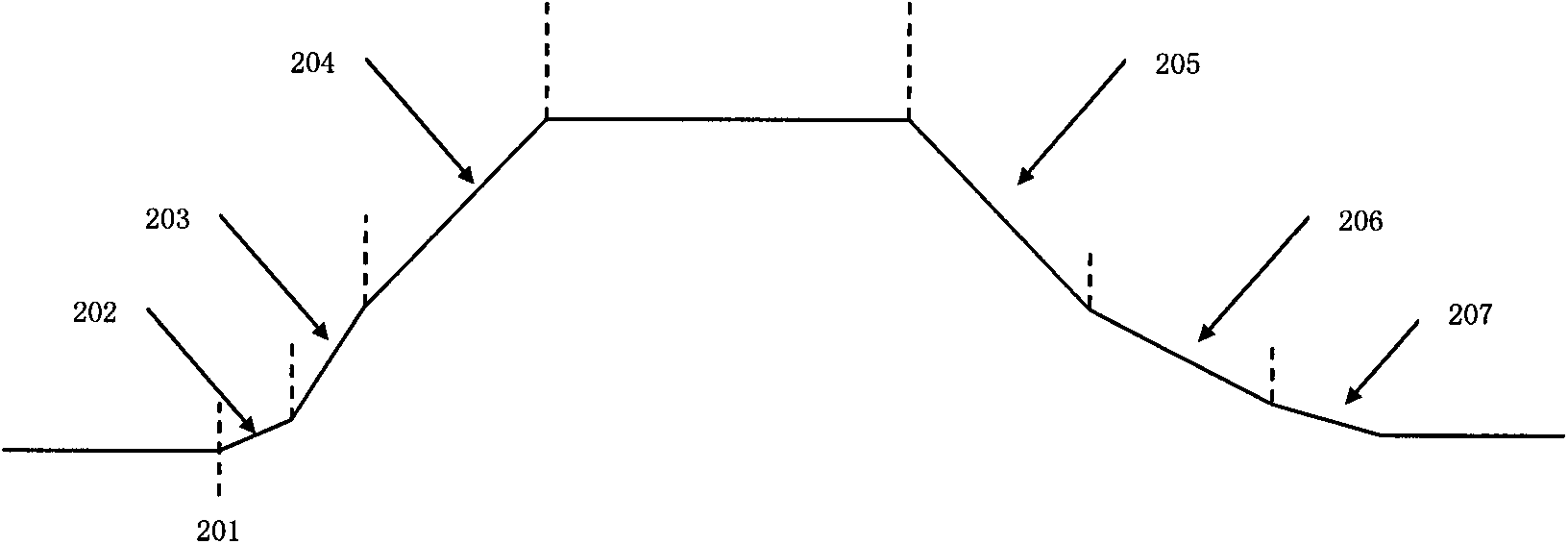

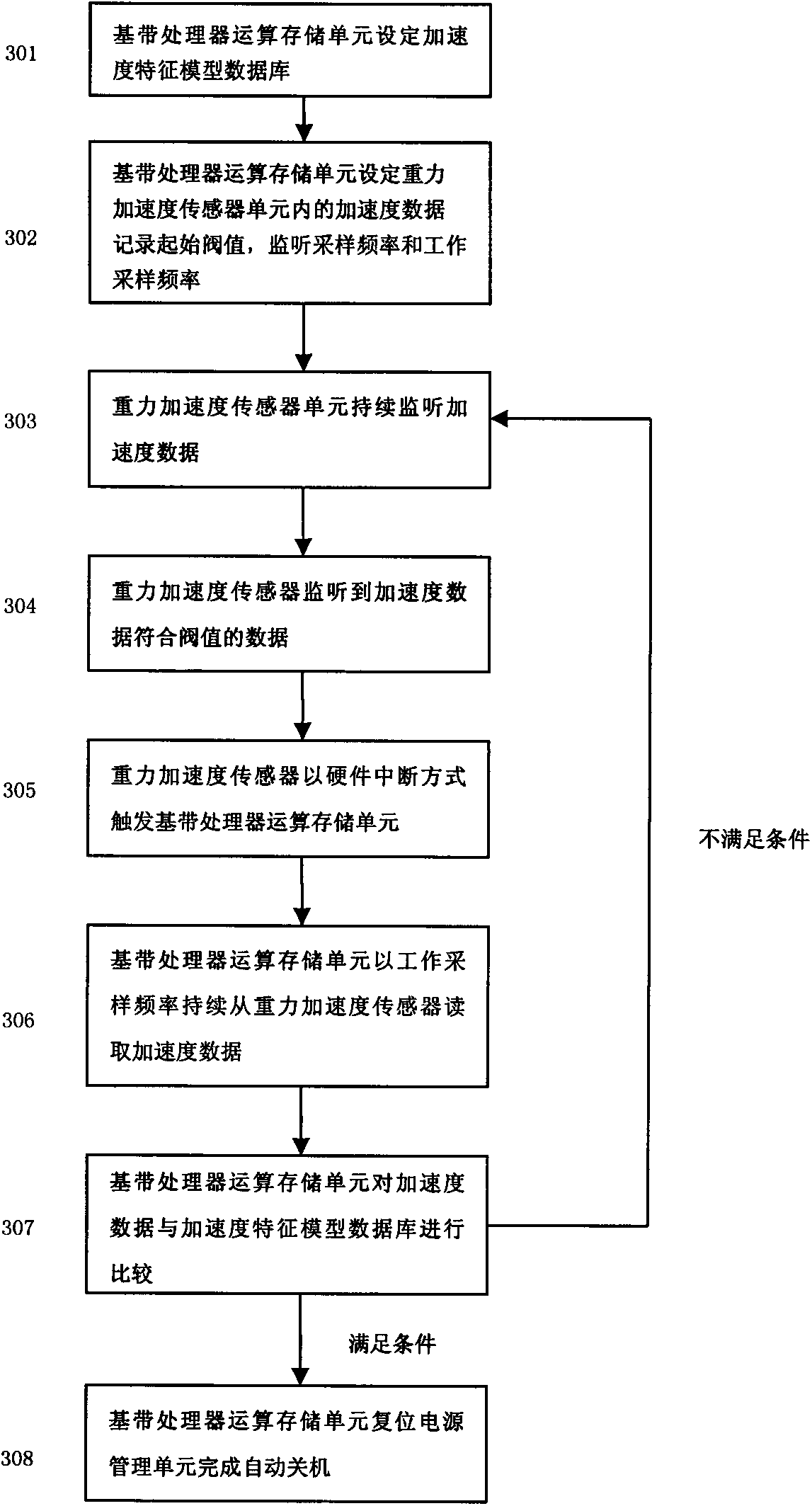

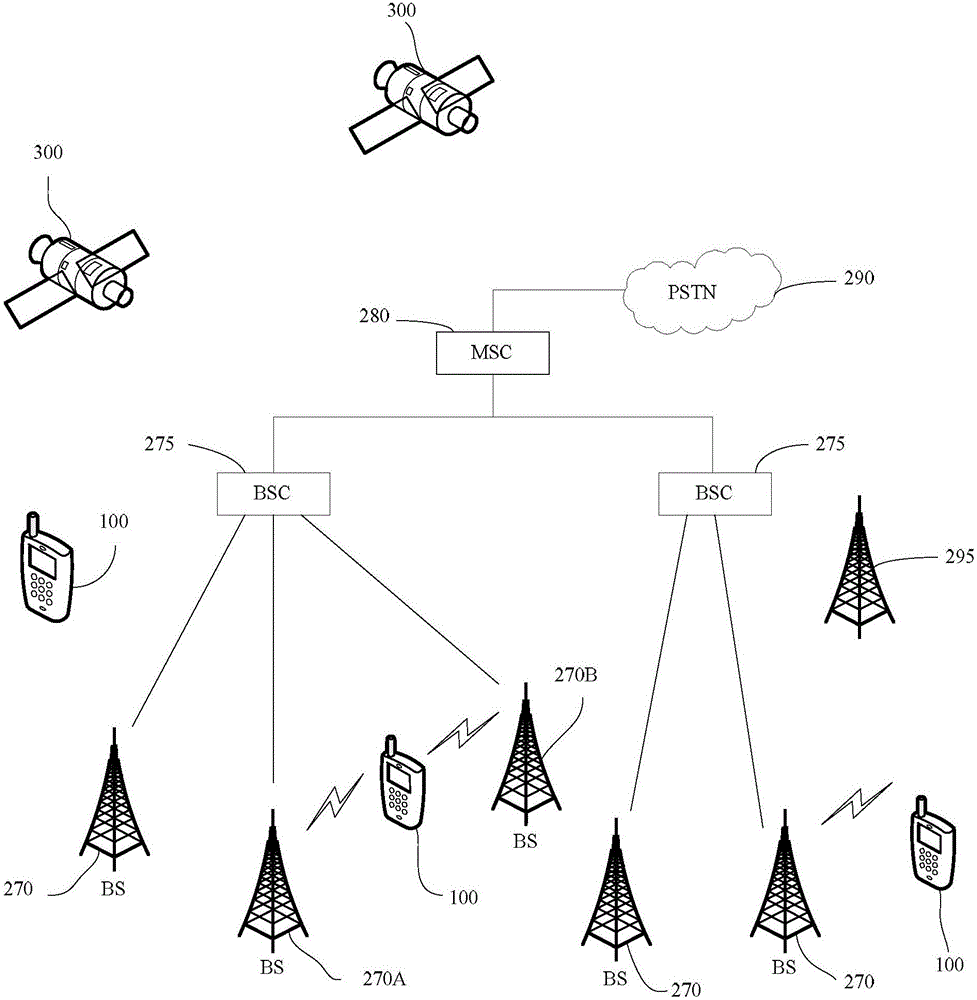

Automatic shutdown method for mobile communication terminal in civil aircraft

The invention discloses an automatic shutdown method for a mobile communication terminal in a civil aircraft. The automatic shutdown method is applied to the mobile communication terminal. The automatic shutdown method is characterized by comprising the following steps: the mobile communication terminal is used for acquiring real-time space acceleration data of the mobile communication terminal; comparison operation is conducted between the real-time space acceleration data of the mobile communication terminal and the space acceleration characteristic model data bases, preset at the mobile communication terminal, in all stages when the civil aircraft takes off and lands; when the real-time space acceleration data of the mobile communication terminal is judged to meet characteristic model requirements, the mobile communication terminal is recognized to be in the flight state of the civil aircraft, and automatic shutdown is executed. Therefore, flight security risks produced when the owner of the mobile communication terminal does not shut down the mobile communication terminal or the mobile communication terminal improperly starts up during a flight are avoided.

Owner:肖宁

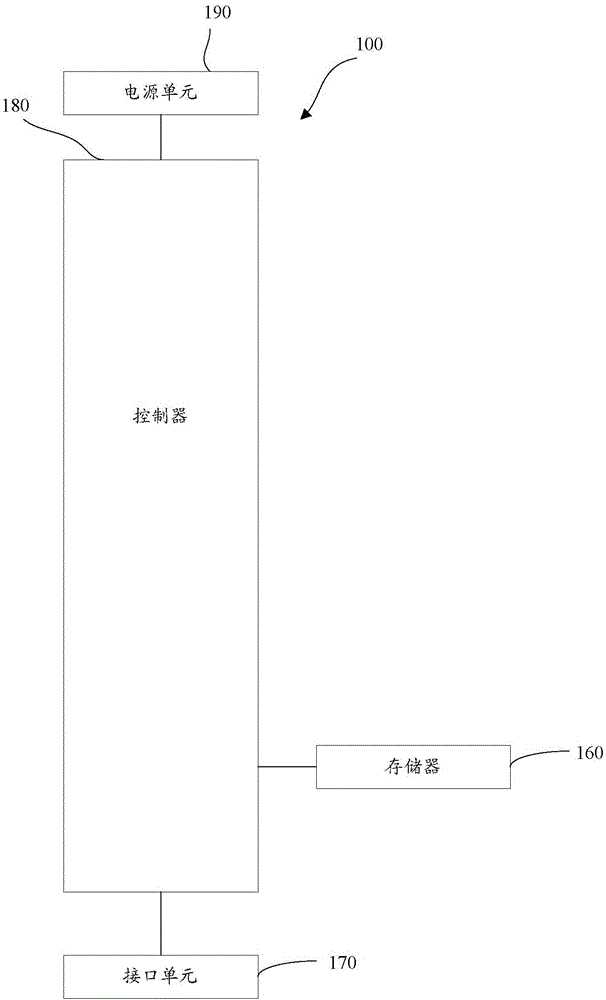

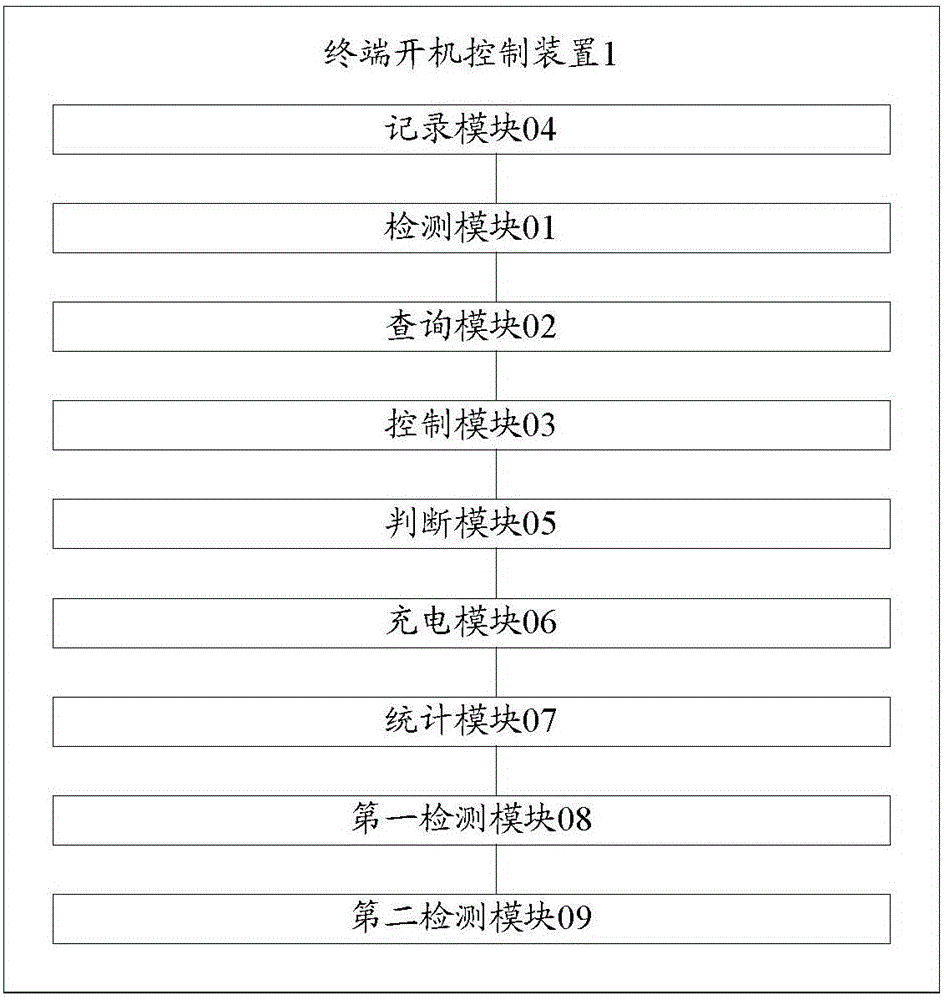

Terminal starting control device and method

InactiveCN106357903AReduce stepsImprove experienceSubstation equipmentState variationSoftware engineering

Owner:NUBIA TECHNOLOGY CO LTD

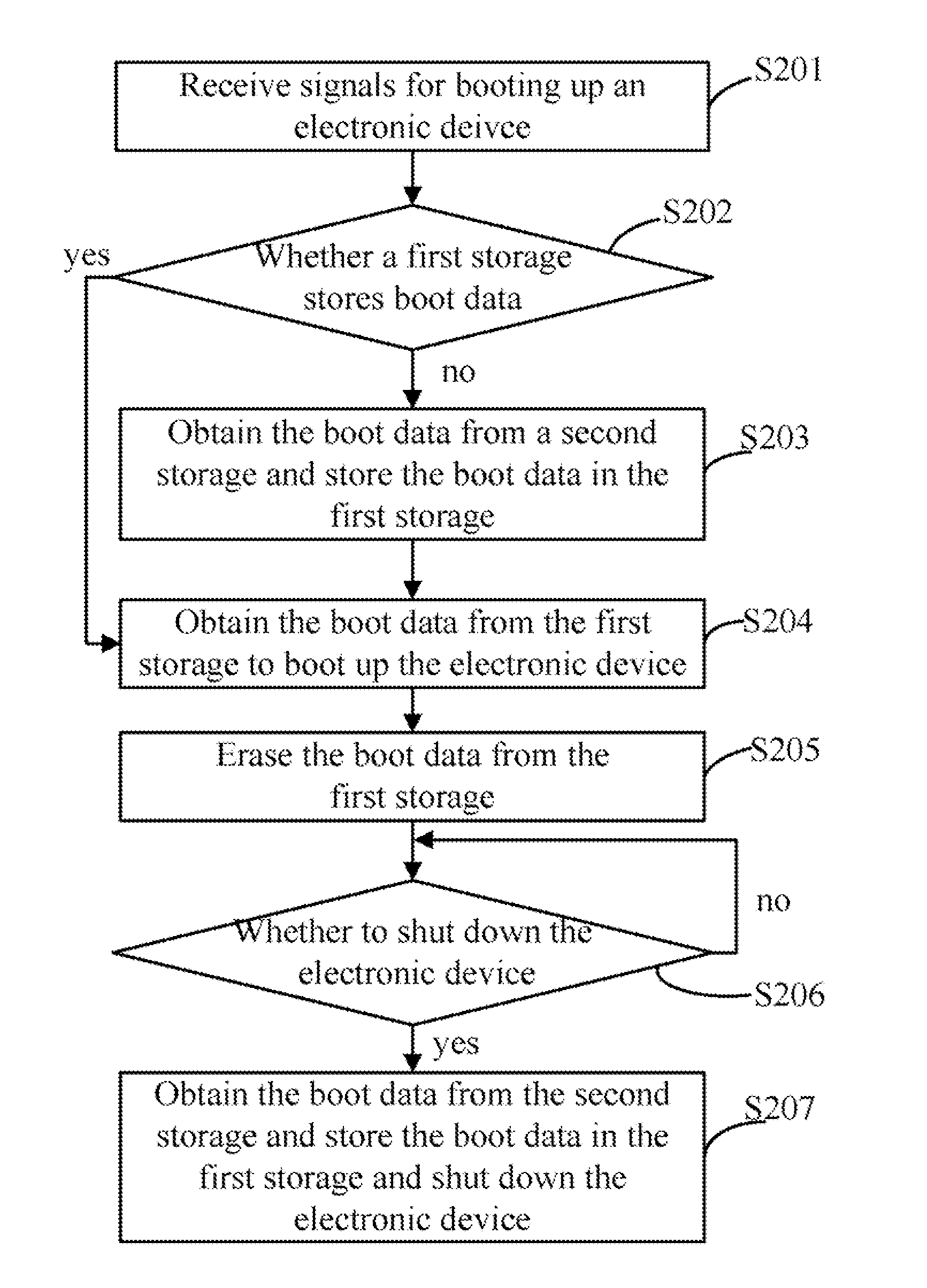

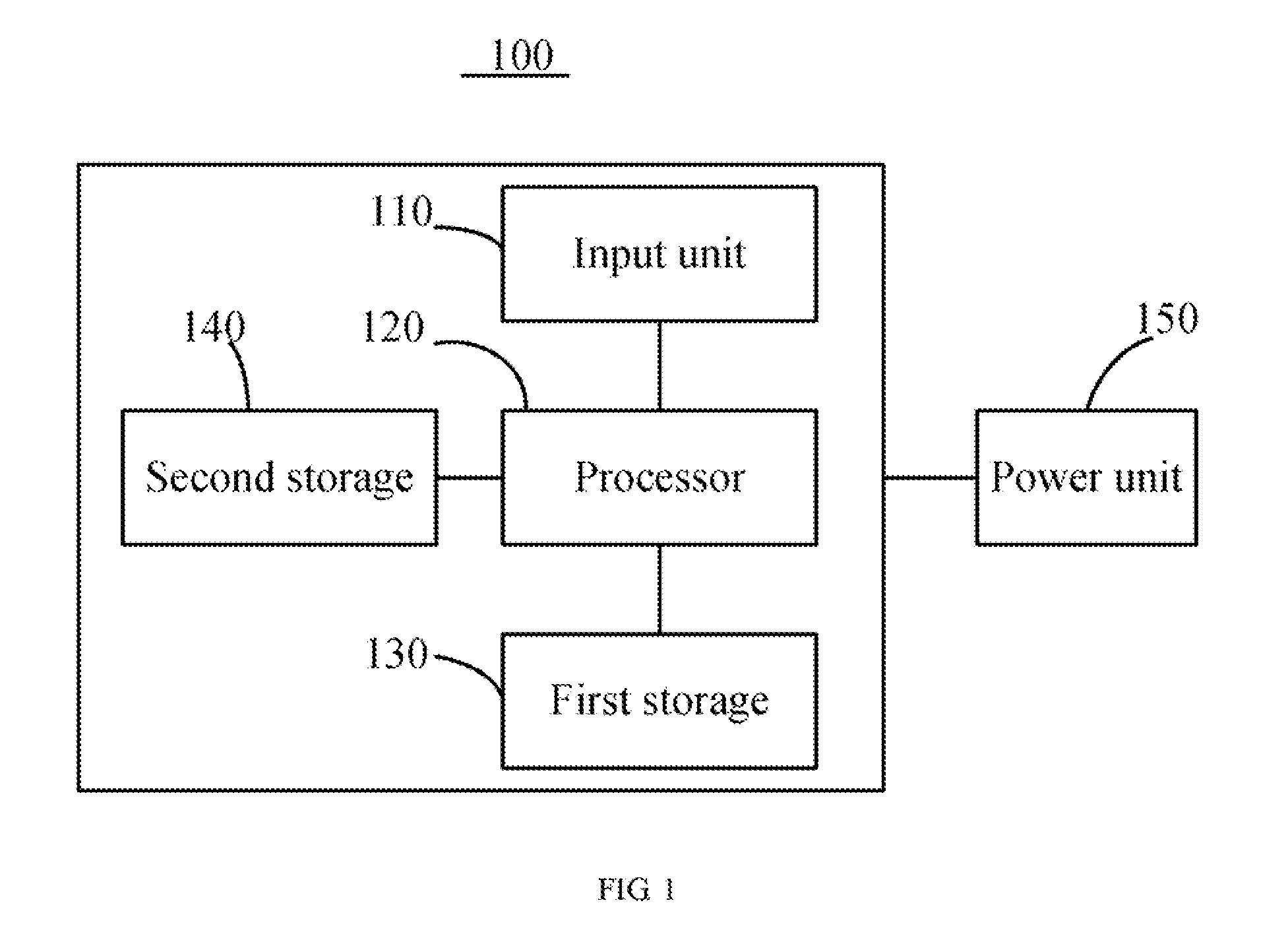

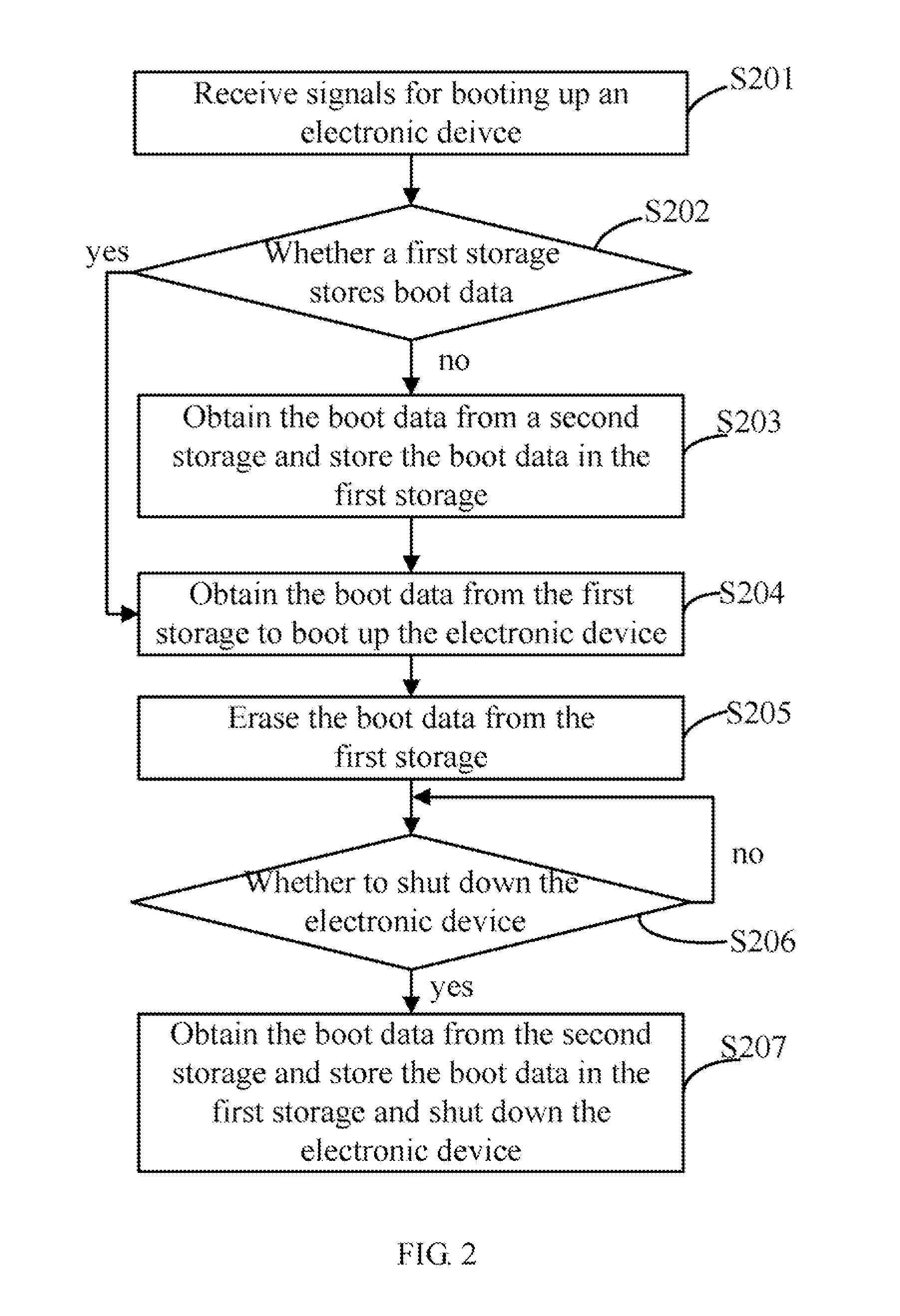

Electronic device and method for booting up and shutting down the electronic device

InactiveUS20110154008A1Increase speedTime consumingDigital data processing detailsDigital computer detailsComputer hardwareElectronic equipment

A method for booting up and shutting down an electronic device is applied in the electronic device. The electronic device includes a processor, a first storage, and a second storage. The speed of the processor accessing data from the first storage is faster than the speed of the processor accessing data from the second storage. The second storage stores the boot data for booting up the electronic device. The method includes: receiving signals for booting up the electronic device; detecting whether the first storage stores the boot data; and obtaining the boot data from the first storage to boot up the electronic device if the first storage stores the boot data. A related electronic device is also provided.

Owner:HON HAI PRECISION IND CO LTD

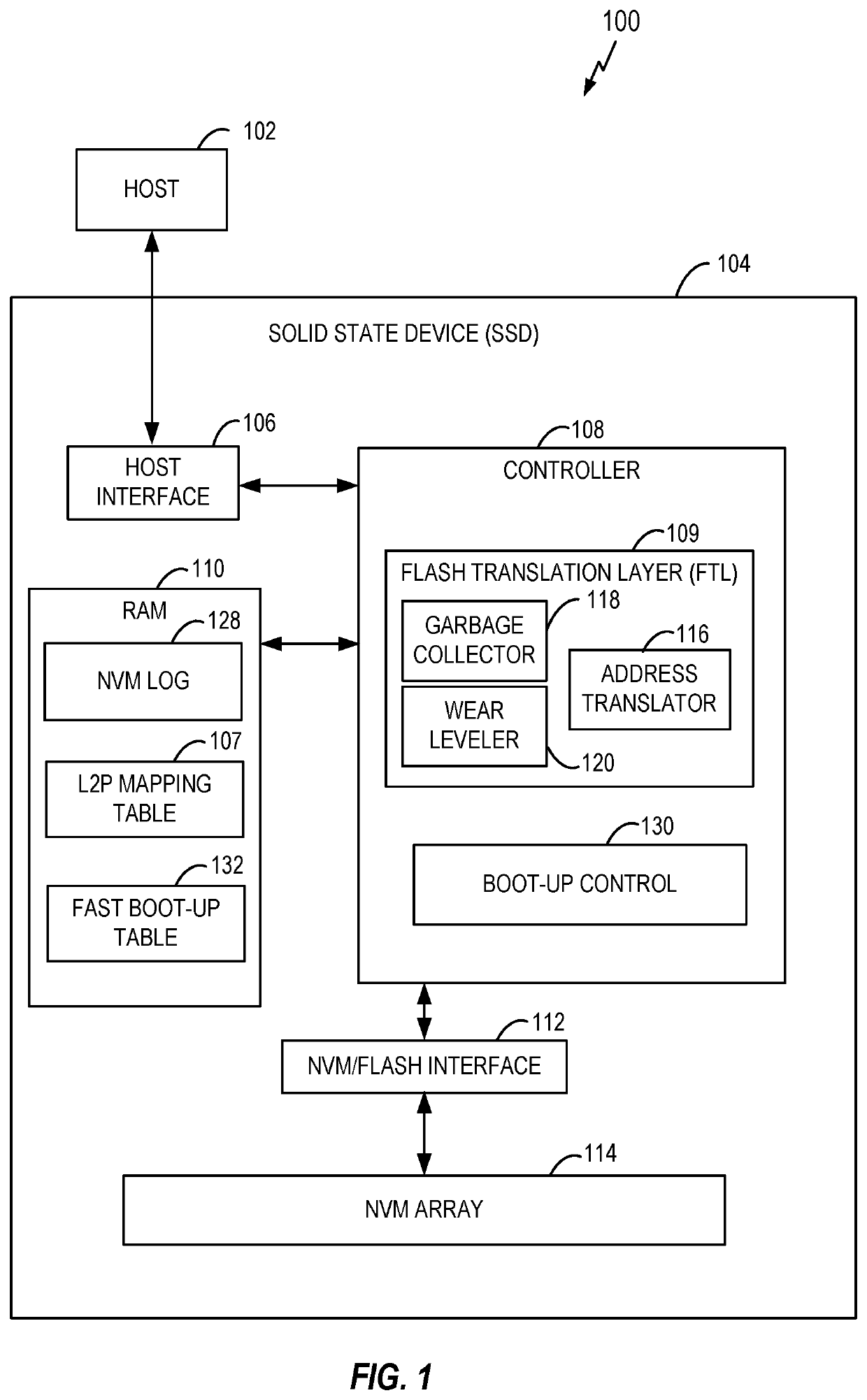

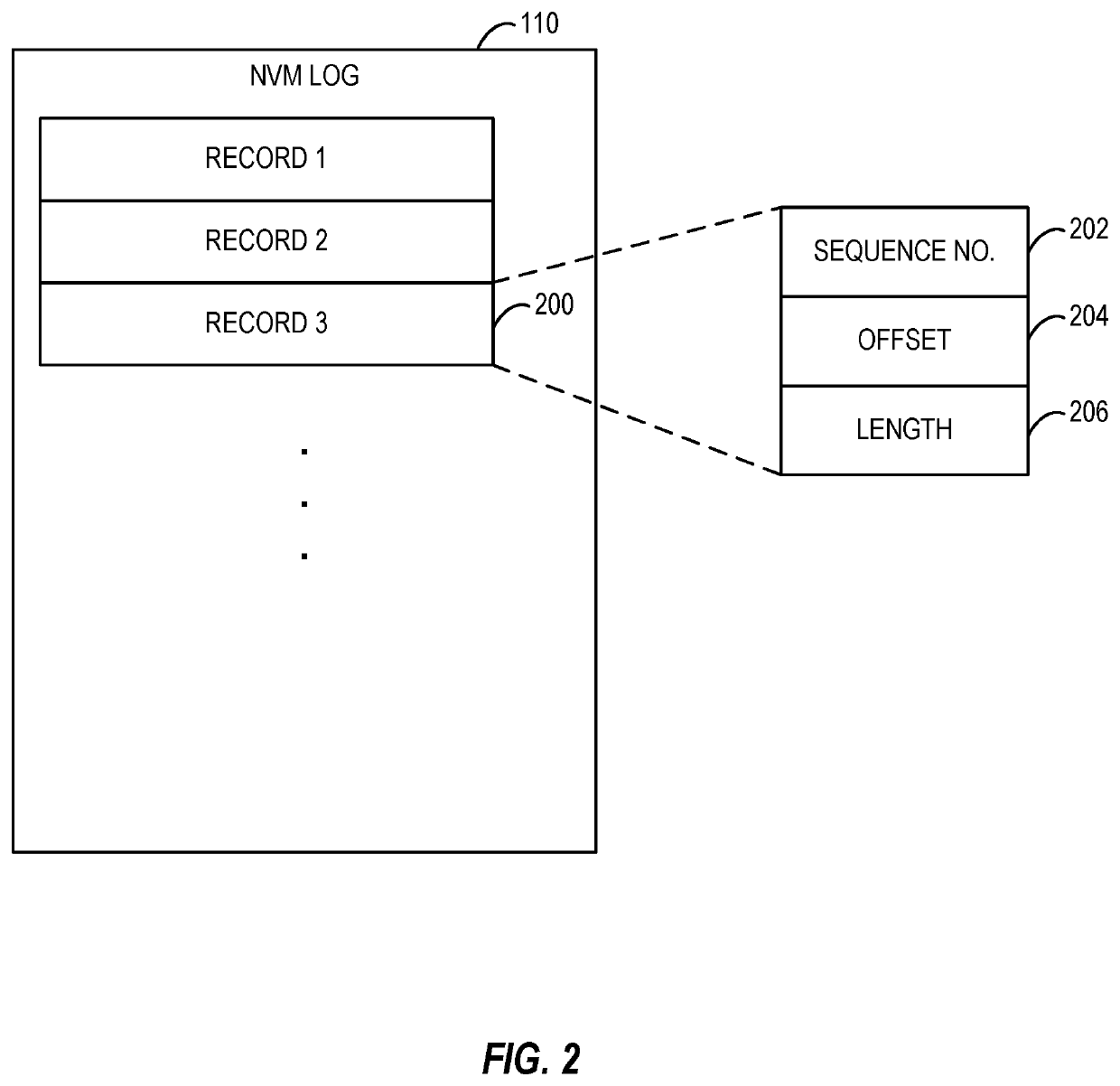

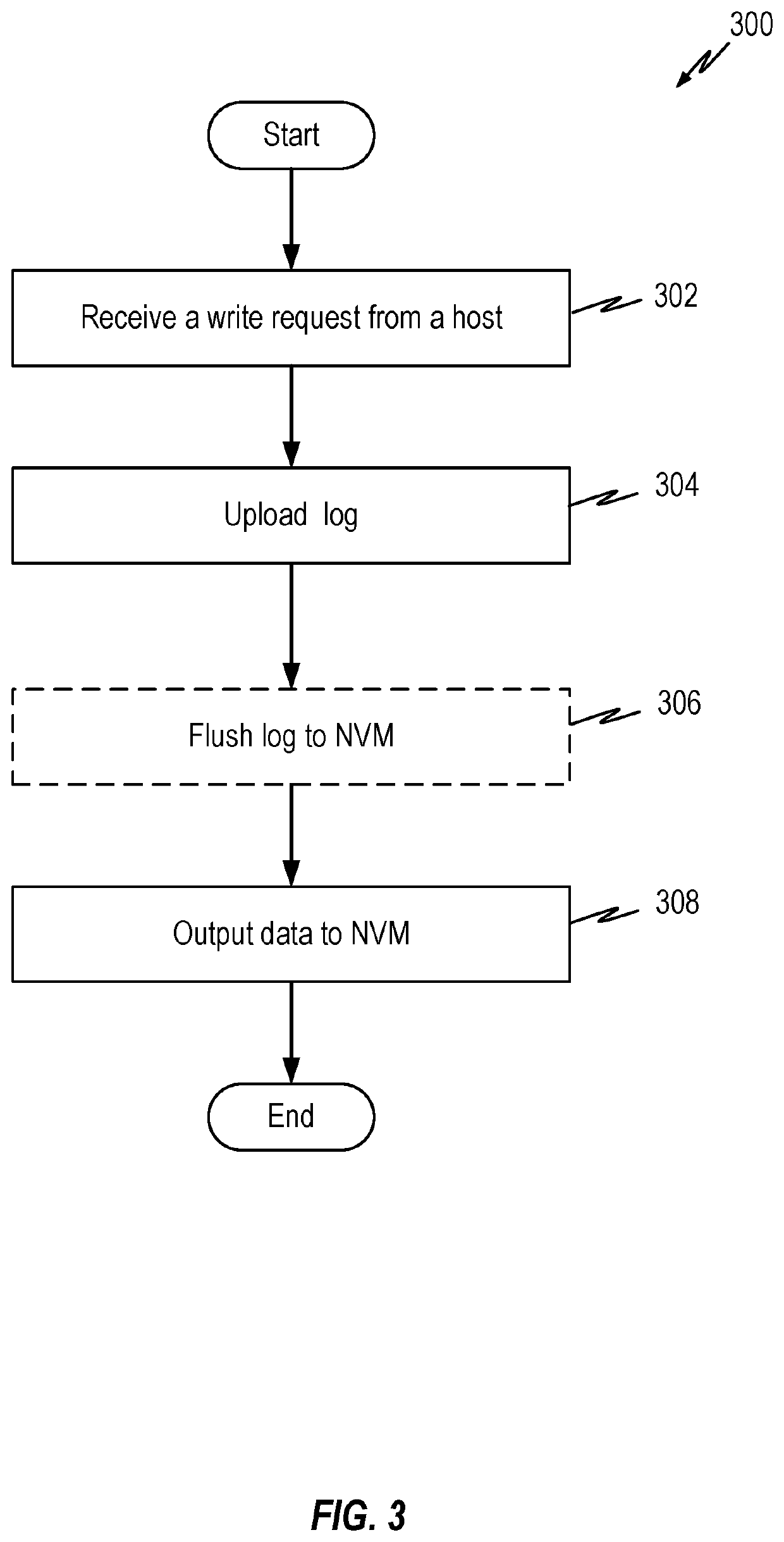

Solid state device with fast boot after ungraceful shutdown

ActiveUS20200097188A1Memory architecture accessing/allocationInput/output to record carriersLogical block addressingSoftware engineering

After an ungraceful shutdown (UGSD) event, a data storage apparatus restores a fast boot-up table from a copy stored in a non-volatile memory (NVM), and receives a first read command from a host. The first read command includes a request to read data from a logical block address (LBA). The apparatus maintains a fast boot-up table that includes a plurality of entries, and each entry includes an LBA and an associated physical block address of the NVM. If the LBA is contained in the fast boot-up table, the apparatus determines a first physical block address associated with the LBA using the fast boot-up table. The apparatus reads data from the NVM at the first physical block address, prior to completing an initialization process of the data storage apparatus, and transmits the data read from the NVM to the host.

Owner:WESTERN DIGITAL TECH INC

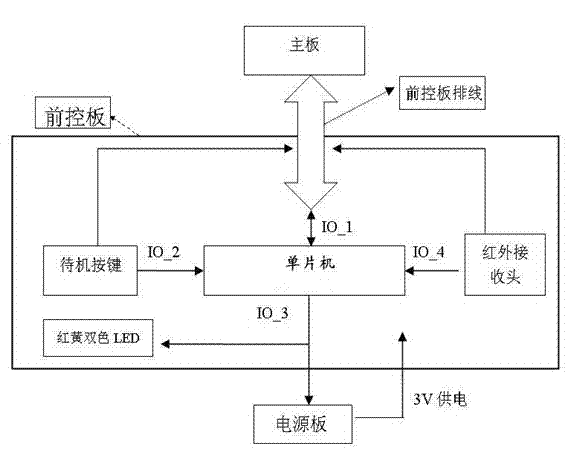

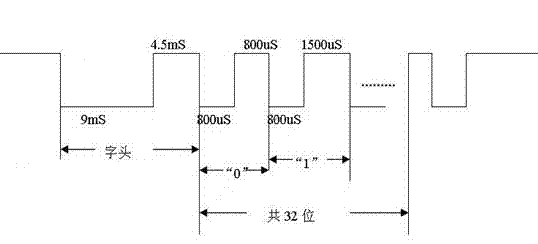

Skytop box standby and timing shutdown control device

InactiveCN102281467ALow power standbyStatus information out of timeSelective content distributionShut downSingle chip

The invention discloses a standby, timing shutdown and timing boot controlling device of a set top box. The device comprises a mainboard, a front control plate and a power strip. The power strip connects with the mainboard through a flat cable. The front control plate connects with the power strip and the mainboard respectively through two flat cables. The front control plate is provided with a one-chip microcomputer processor used for controlling standby and boot. A host on the mainboard monitors a standby button signal and sends a command to the one-chip microcomputer, the one-chip microcomputer sends a standby signal to the power strip, the power strip reduces power supplied to the mainboard, operation of the mainboard is stopped, only power supply of the one-chip microcomputer and an infrared receiving terminal are reserved, thus low-power standby is realized. A standby control command is sent by the mainboard, an abnormal condition appeared at next boot time caused by that a plurality of state information is not saved timely when power is off is avoided. When detecting a timing shutdown time period, the host sends a command to the one-chip microcomputer, the one-chip microcomputer outputs low level to the power strip, the power strip starts power supply of the mainboard, the set top box restarts, thus timing boot and shutdown functions are realized.

Owner:SICHUAN JIUZHOU ELECTRONICS TECH

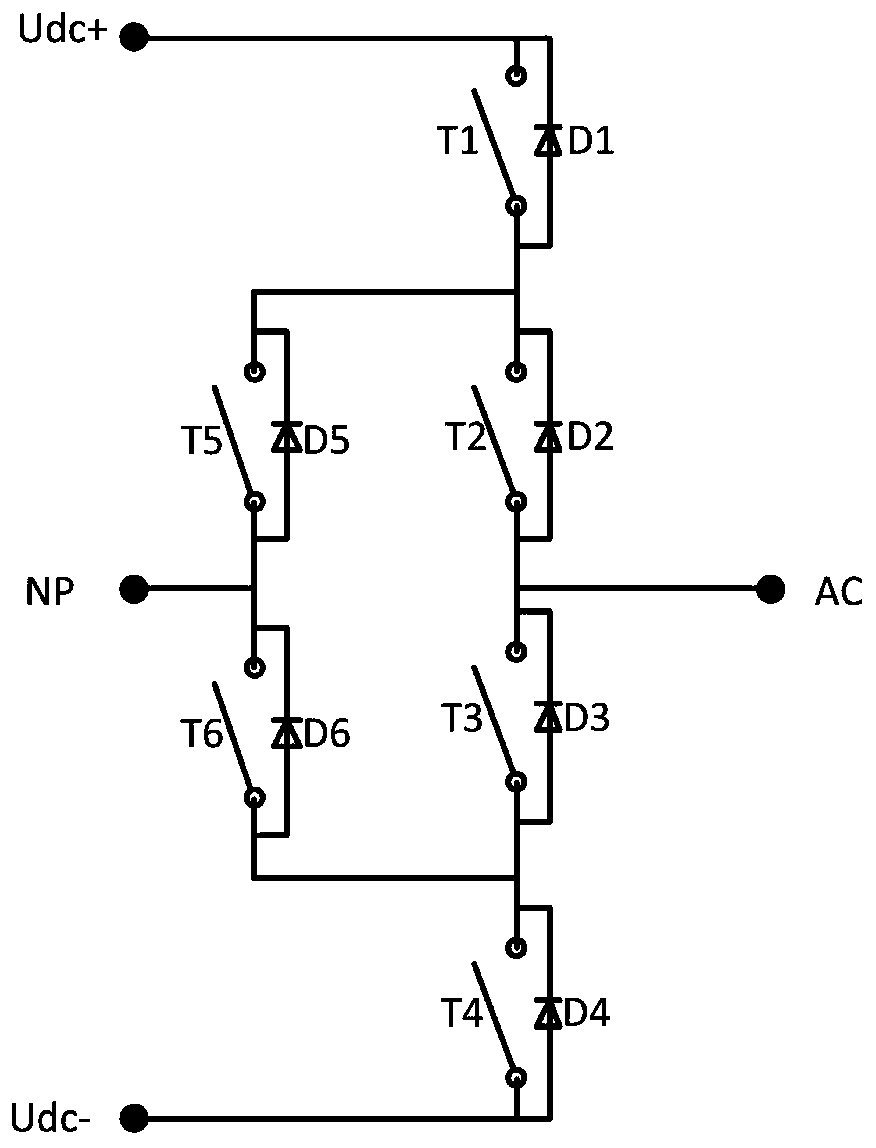

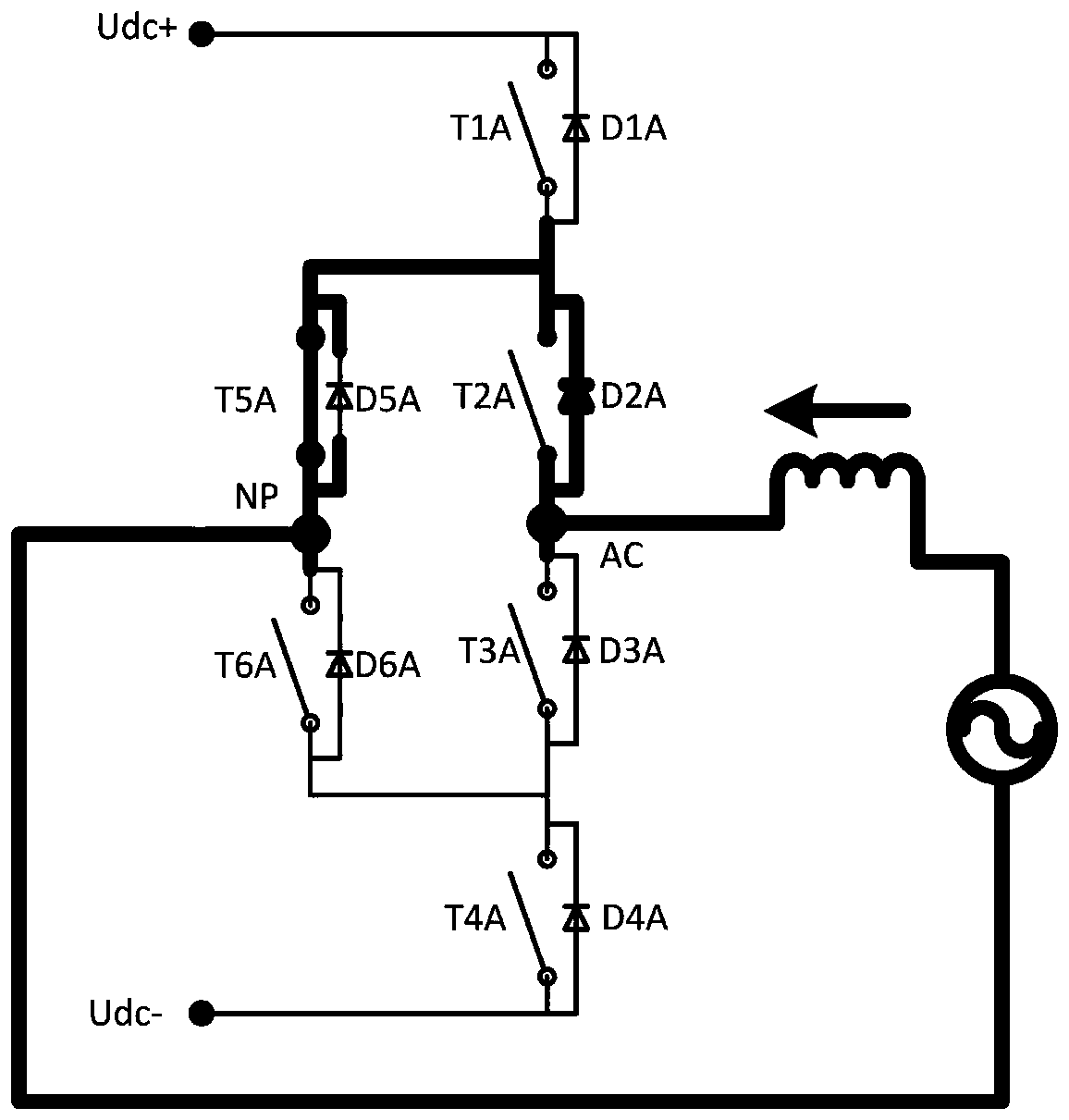

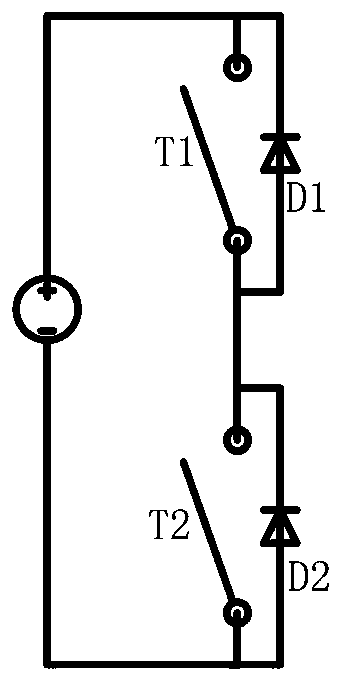

Shutdown wave sealing control method of multi-level inverter circuit and application device thereof

ActiveCN110649831AReduced risk of overvoltageEmergency protective circuit arrangementsSingle network parallel feeding arrangementsOvervoltageHandoff control

The invention provides a shutdown wave sealing control method of a multi-level inverter circuit and an application device thereof. After shutdown instruction issuing, a multi-level inverter circuit iscontrolled to be in a free state that each switching tube is switched off, and specific switching tubes are combined and closed, so that the switching tubes which are not subjected to clamping protection in the multi-level inverter circuit are switched between specific closed states in which the voltage stress borne by the switching tubes is zero so as to destroy difference accumulation of natural voltage division caused by inconsistent switching tube parameters when the switching tubes which are not subjected to clamping protection are in a free state. The method is advantaged in that by carrying out multiple times of back-and-forth switching control between a free state and a specific closed state, the voltage stress borne by the switching tubes which are not subjected to clamping protection is controlled within a controlled range, and the overvoltage risk possibly caused by the inconsistent switching tube parameters is reduced.

Owner:SUNGROW POWER SUPPLY CO LTD