Patents

Literature

1091 results about "Bus mastering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

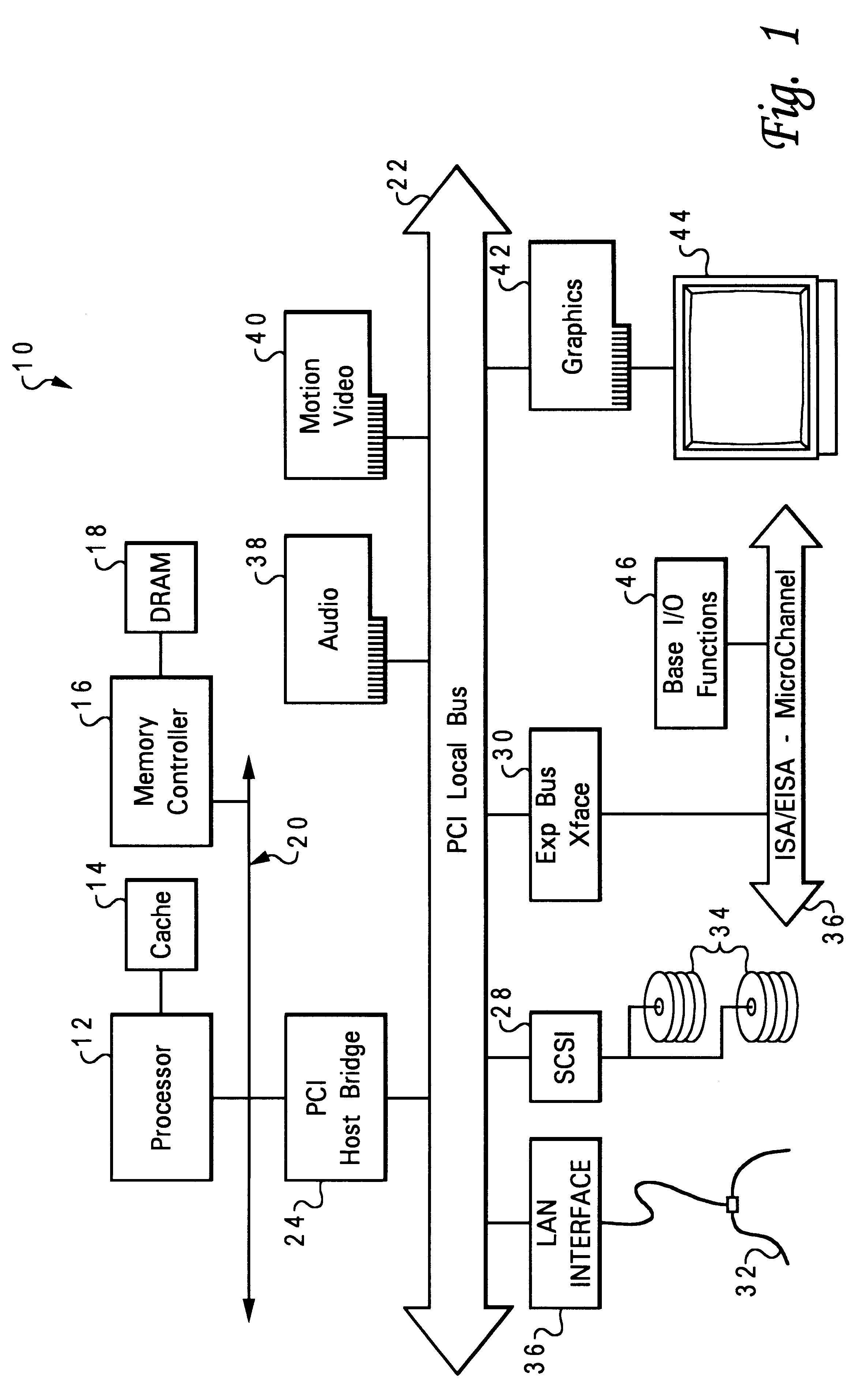

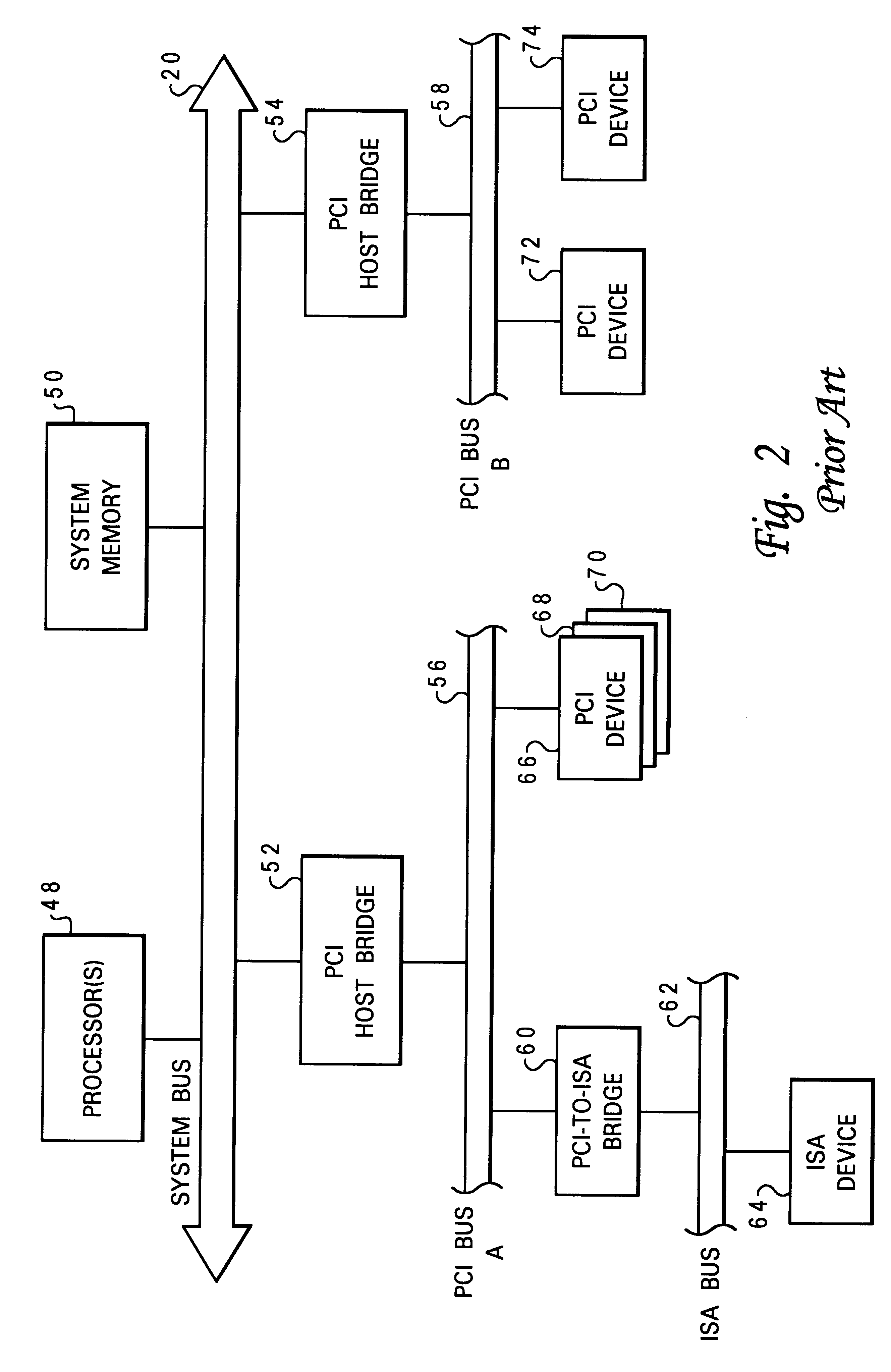

In computing, bus mastering is a feature supported by many bus architectures that enables a device connected to the bus to initiate direct memory access (DMA) transactions. It is also referred to as first-party DMA, in contrast with third-party DMA where a system DMA controller actually does the transfer.

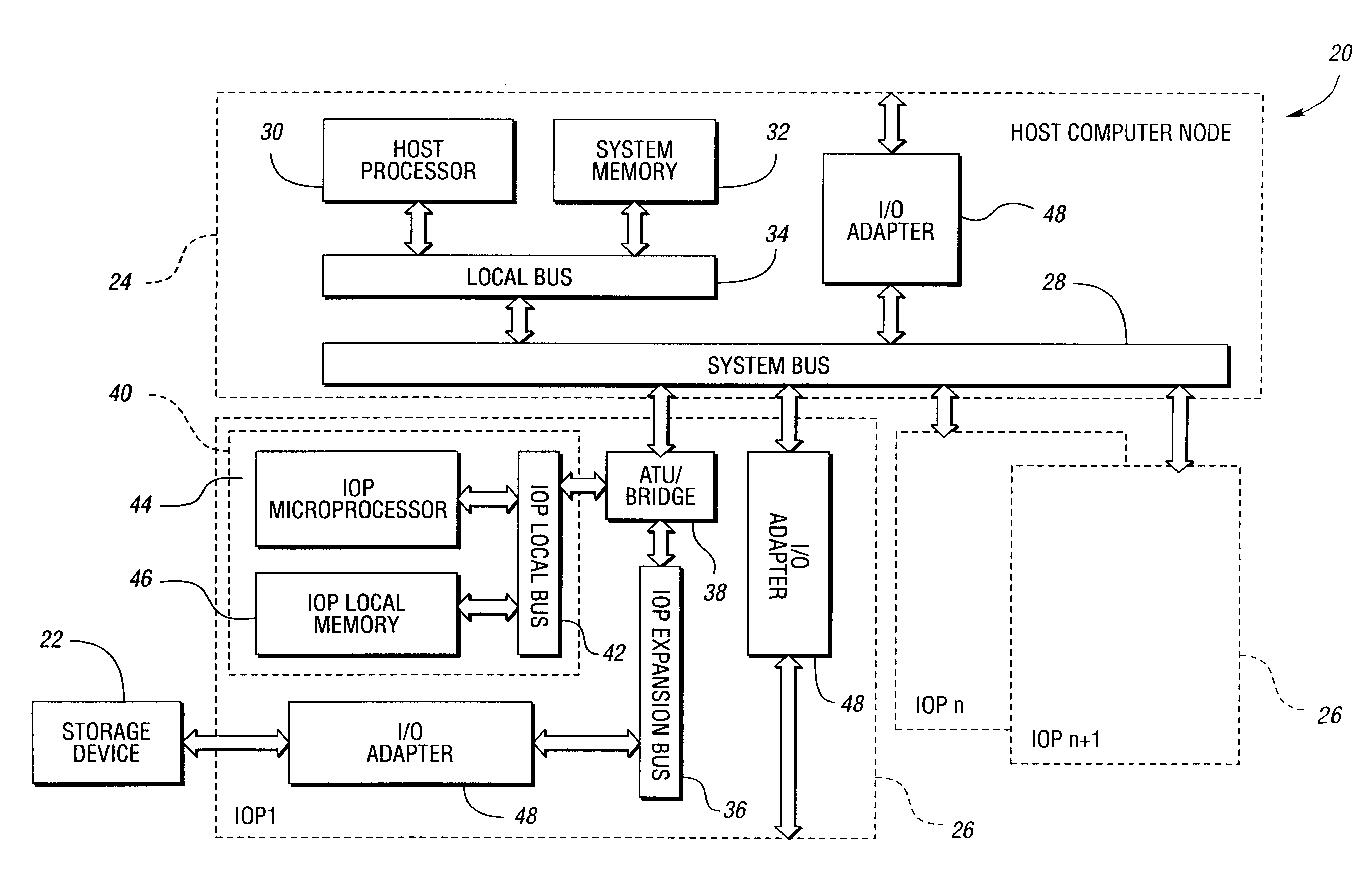

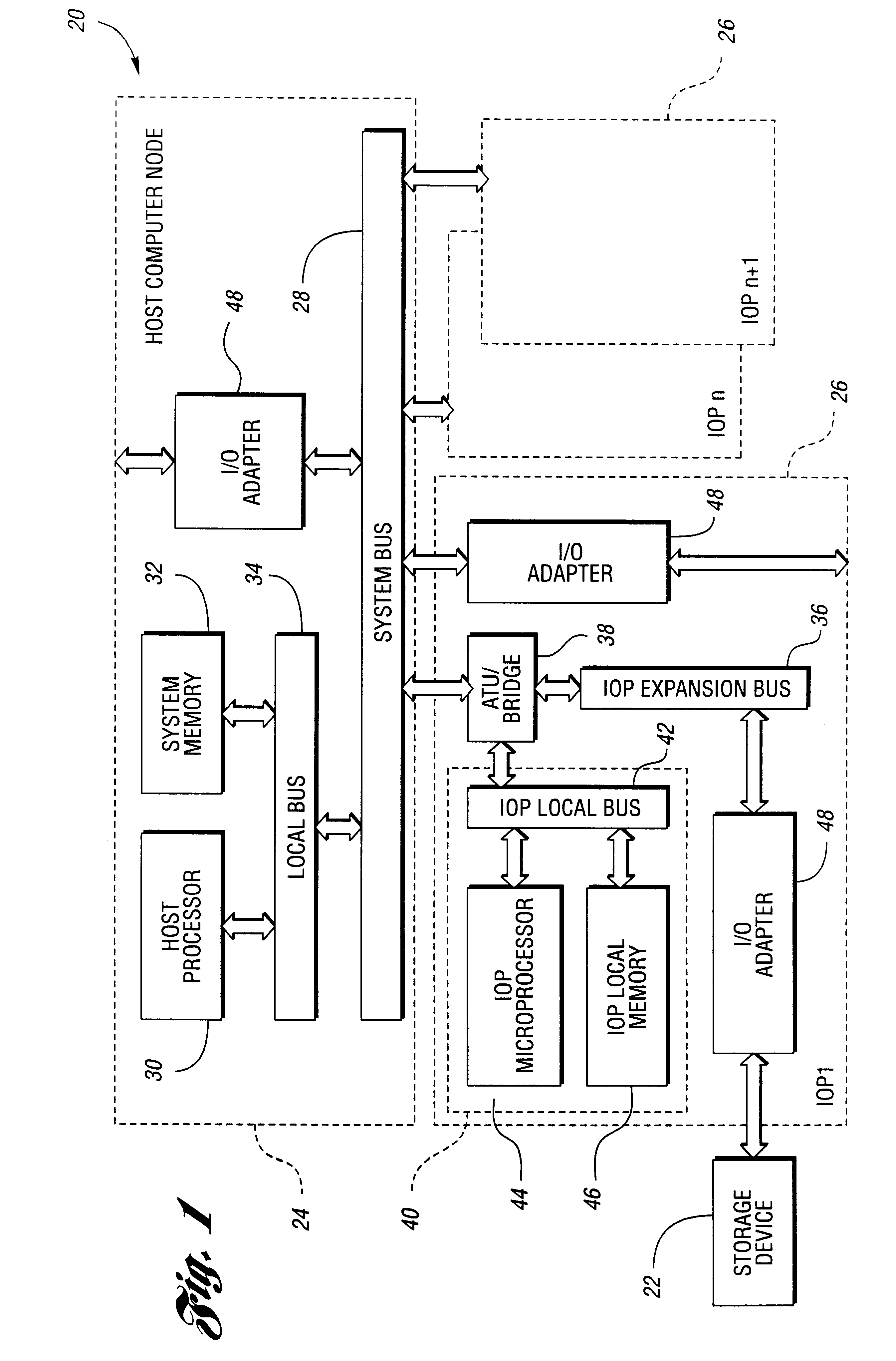

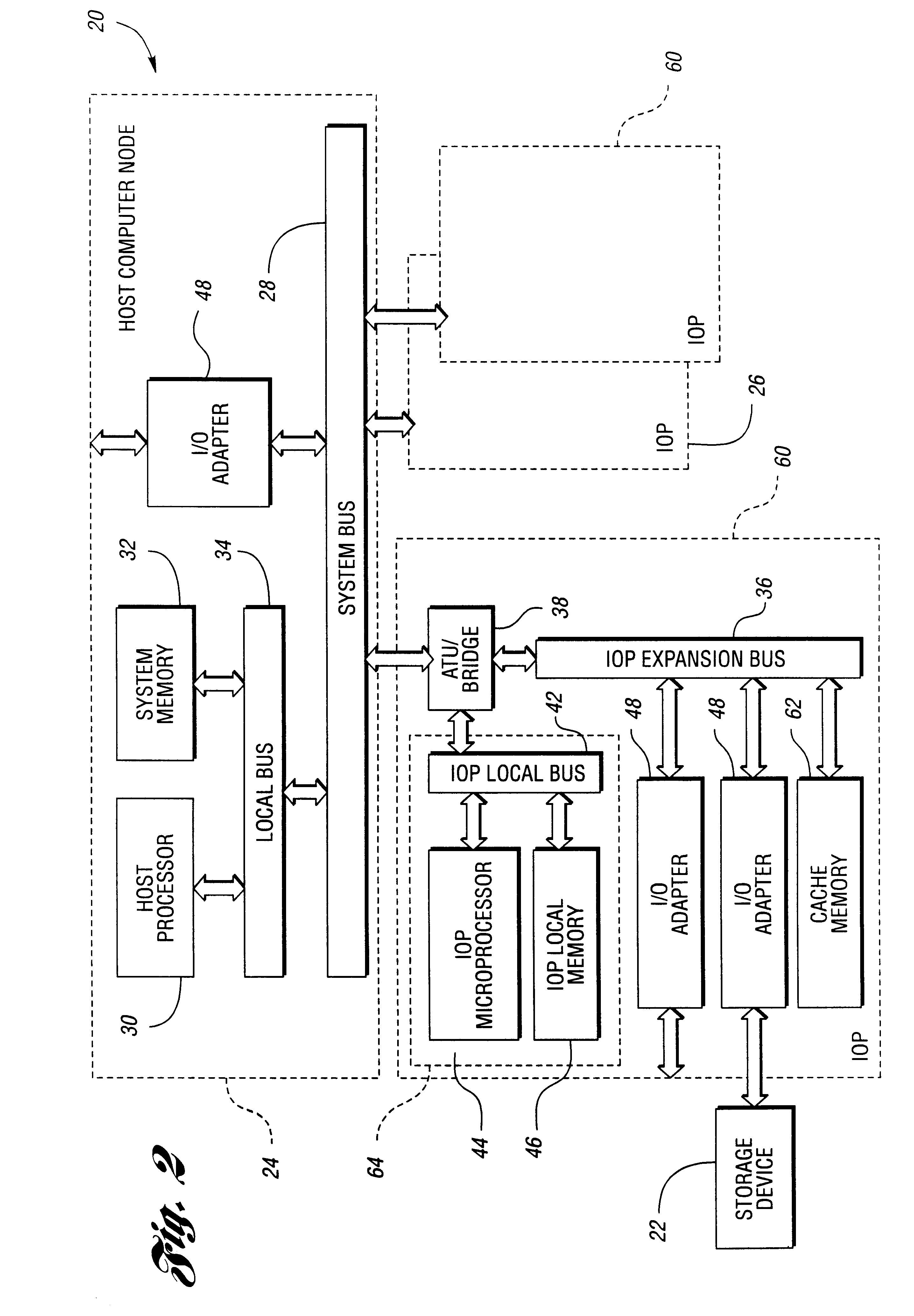

Computer system with storage device mapping input/output processor

InactiveUS6195730B1Memory adressing/allocation/relocationUnauthorized memory use protectionVirtualizationData transmission

An input / output processor provides device virtualization "on-board" through the use of a dedicated IO cache memory. A computer system includes at least one host processor and associated main memory each with access to a system bus. Each input / output processor is also connected to the system bus through an expansion bus. IO adapters within the input / output processor each connect at least one storage device to the expansion bus. Also connected to the expansion bus is the cache memory and a control logic. The control logic receives a data transfer request from a requesting host processor. The data transfer request is mapped to a cache device object. The cache device object has associated data maintained in the cache memory. If any storage device is required for the data transfer, the data transfer request is mapped to the storage device capable of servicing the request. A location in cache memory is determined based on the mapped cache device object. The data transfer is performed based on the location and, if needed, the determined storage devices. This provides the host computer with a virtual view of the storage devices.

Owner:ORACLE INT CORP

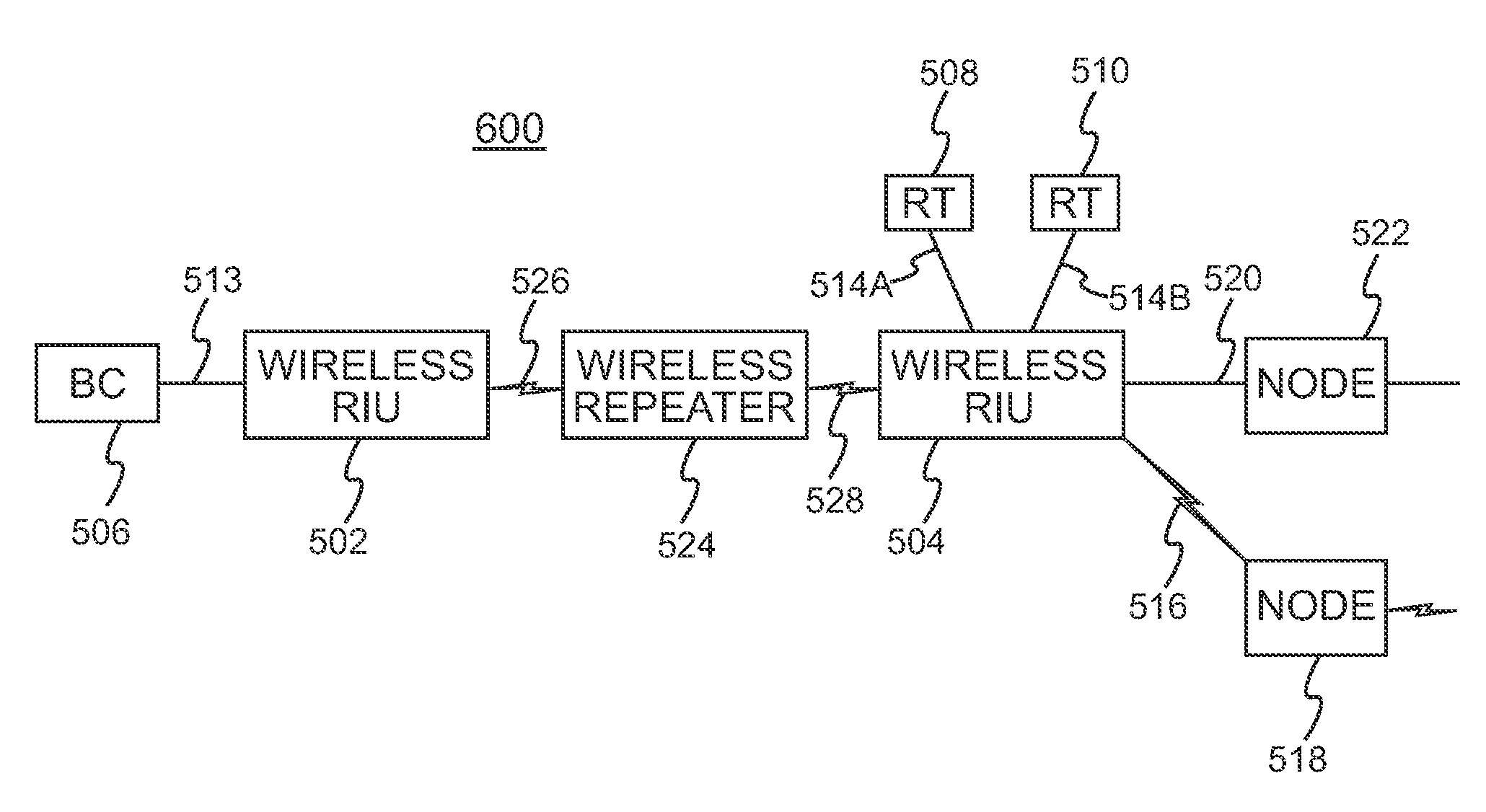

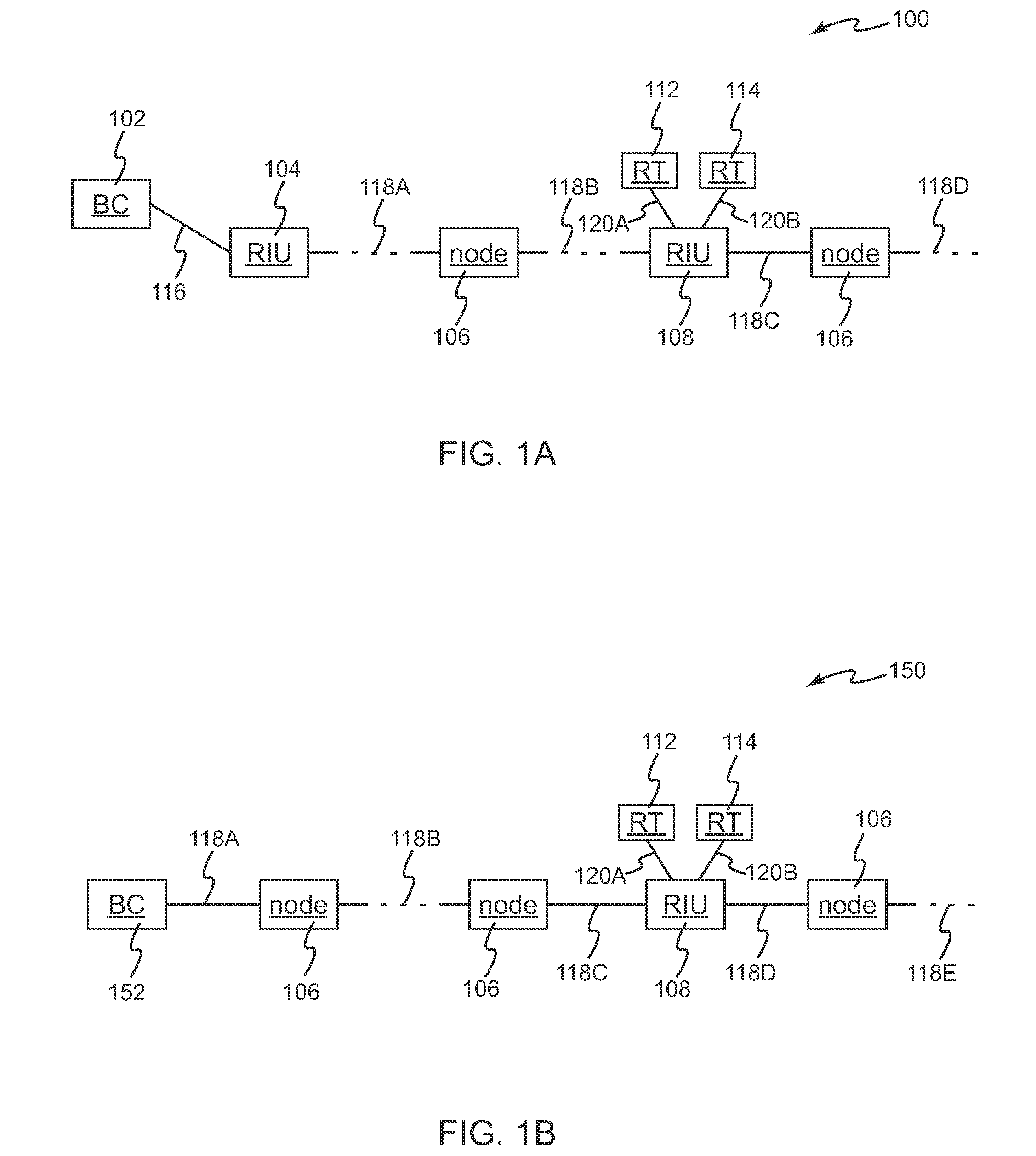

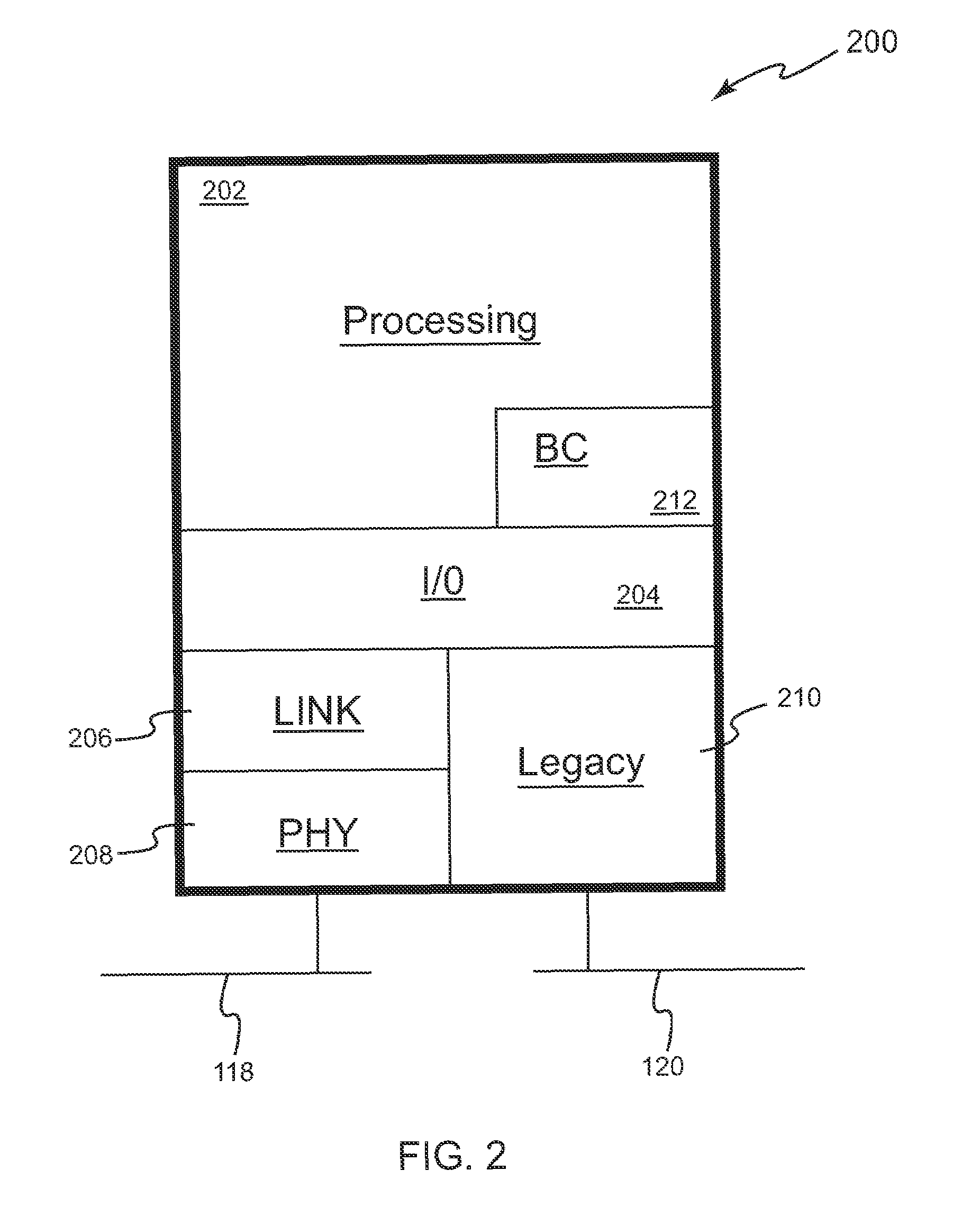

Interfacing a legacy data bus with a wideband wireless data resource utilizing an embedded bus controller

InactiveUS7558903B2Digital computer detailsElectric digital data processingMIL-STD-1553Wireless Application Protocol

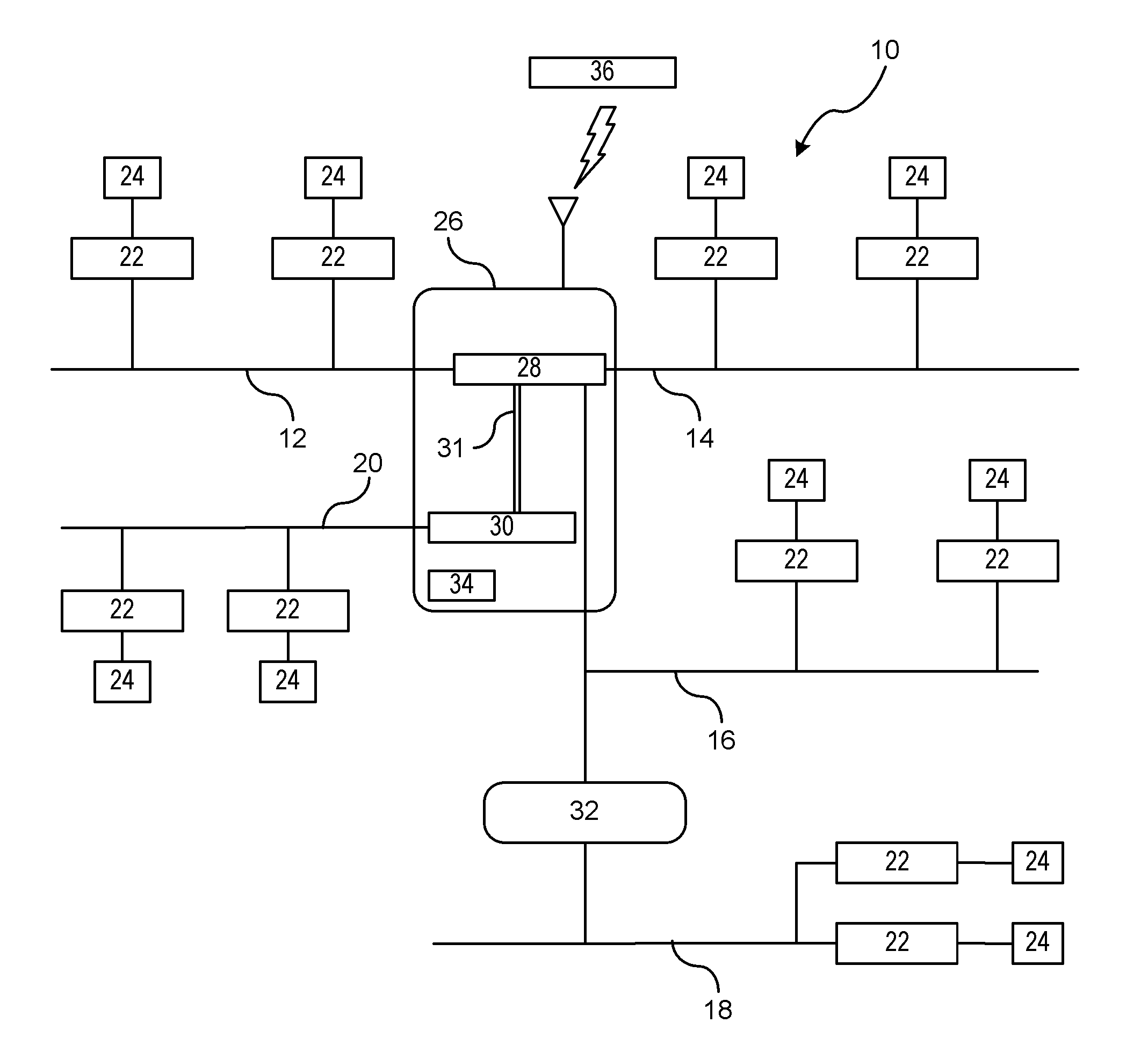

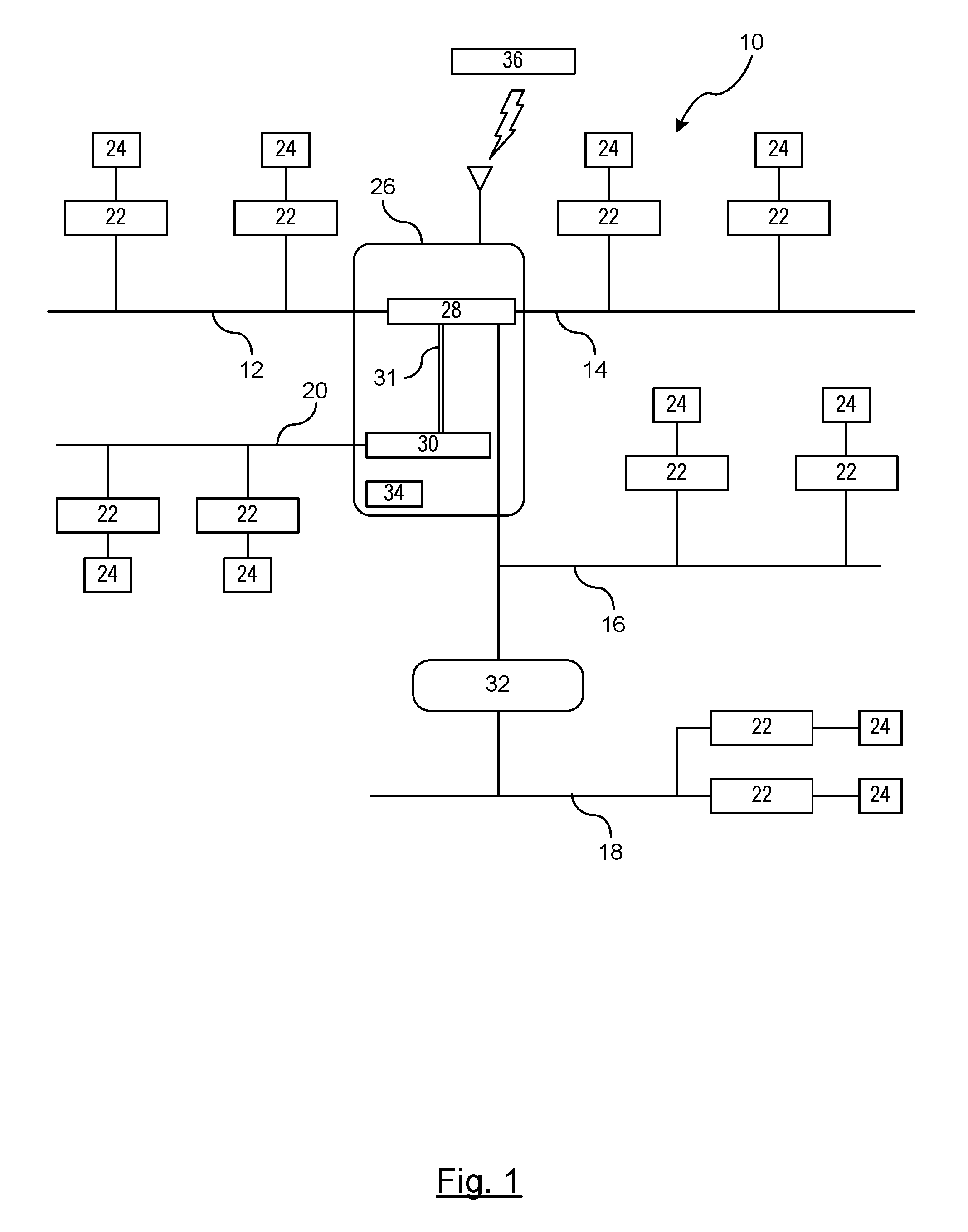

Various methods and systems provide interfaces between legacy data buses such as MIL-STD 1553 buses and wideband wireless data links such as links compatible with IEEE 802.11 or IEEE 802.16e. One technique for interfacing a legacy bus to a wideband wireless data communication link involves providing a hybrid bus controller / remote interface unit as an interface between the two data communication architectures. In operation, the legacy interface suitably receives data intended for a legacy node from a wireless radio module that is compatible with a designated broadband wireless data communication protocol. The legacy data is converted in the legacy interface / remote interface unit to at least one legacy word having a legacy format for transmission on the legacy data bus. The legacy interface may be further configured to receive a reply message from the legacy component on the legacy data bus, and to forward a reply to the wireless radio module in a format that is compatible with the designated wireless data communication protocol.

Owner:THE BOEING CO

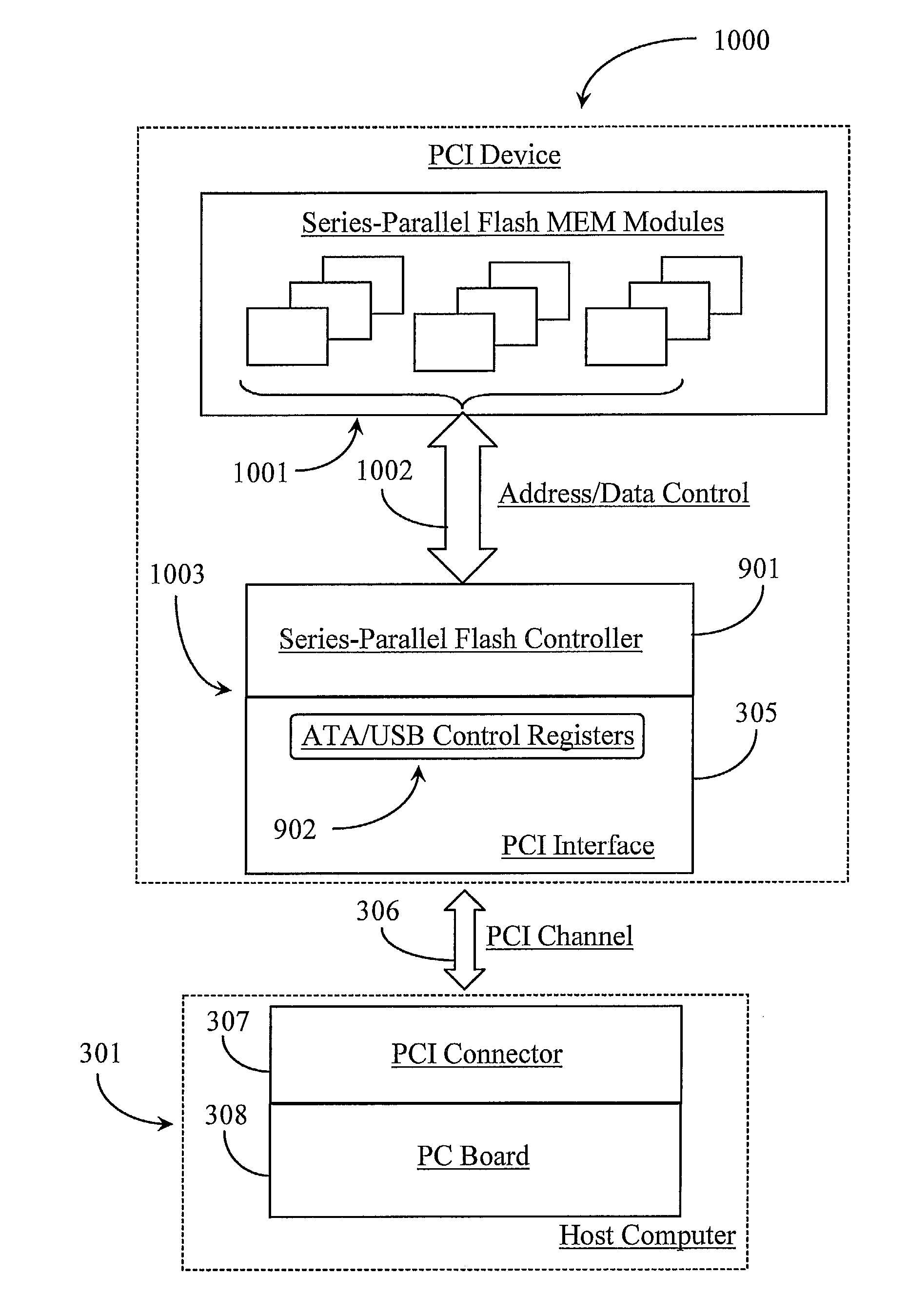

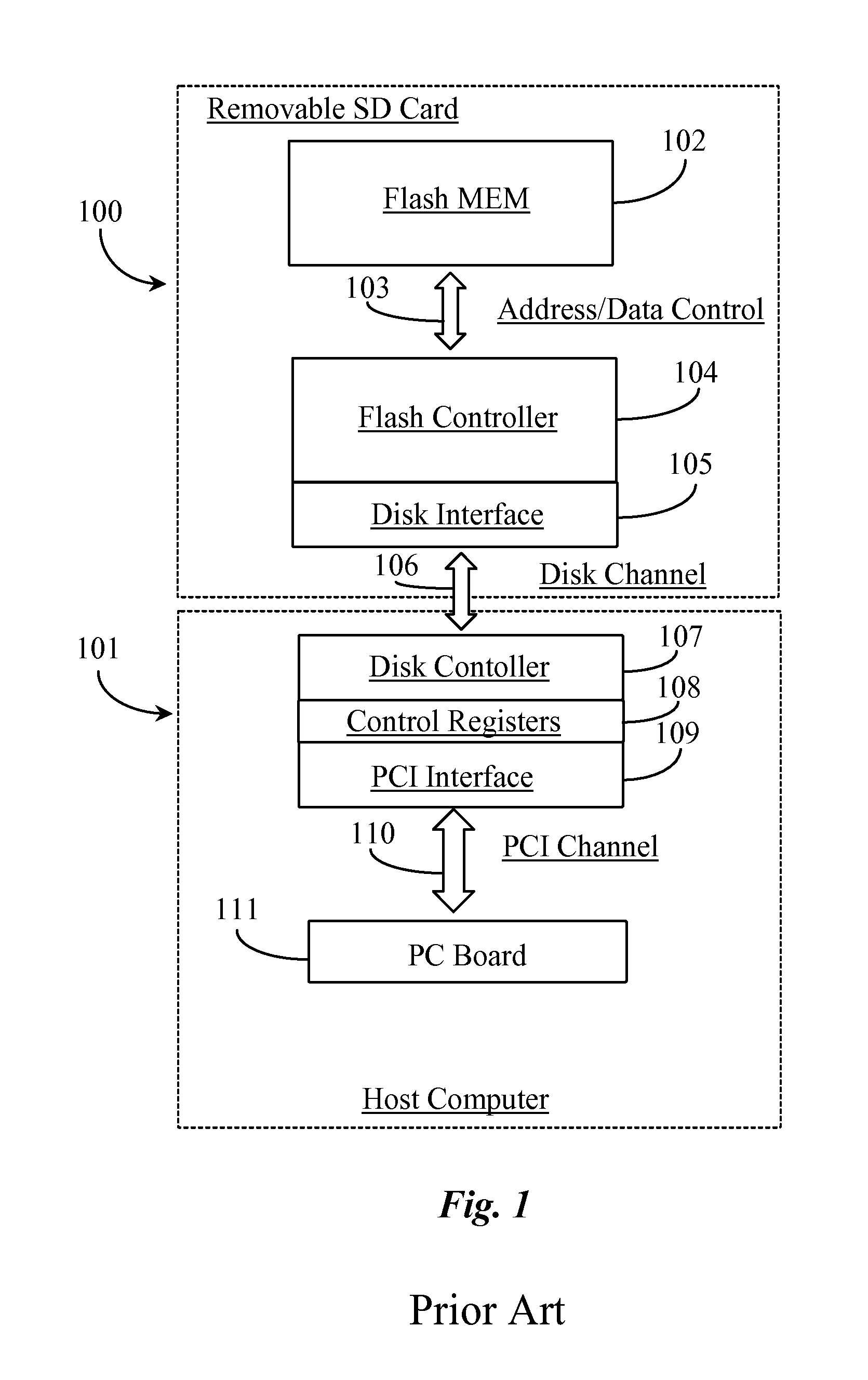

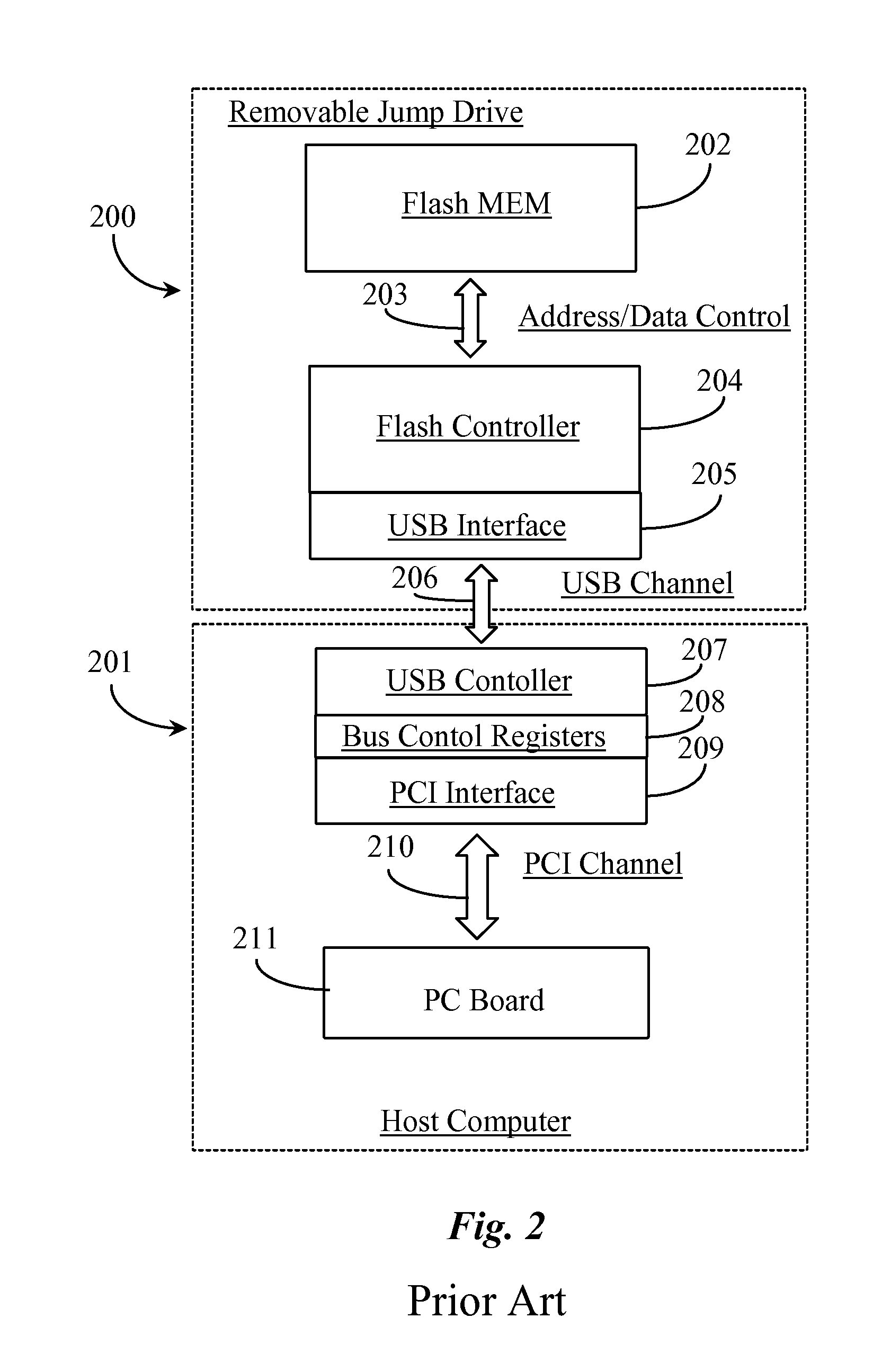

Solid state memory device with PCI controller

ActiveUS8086791B2Memory systemsInput/output processes for data processingSolid-state storageProcessor register

Owner:SK HYNIX INC

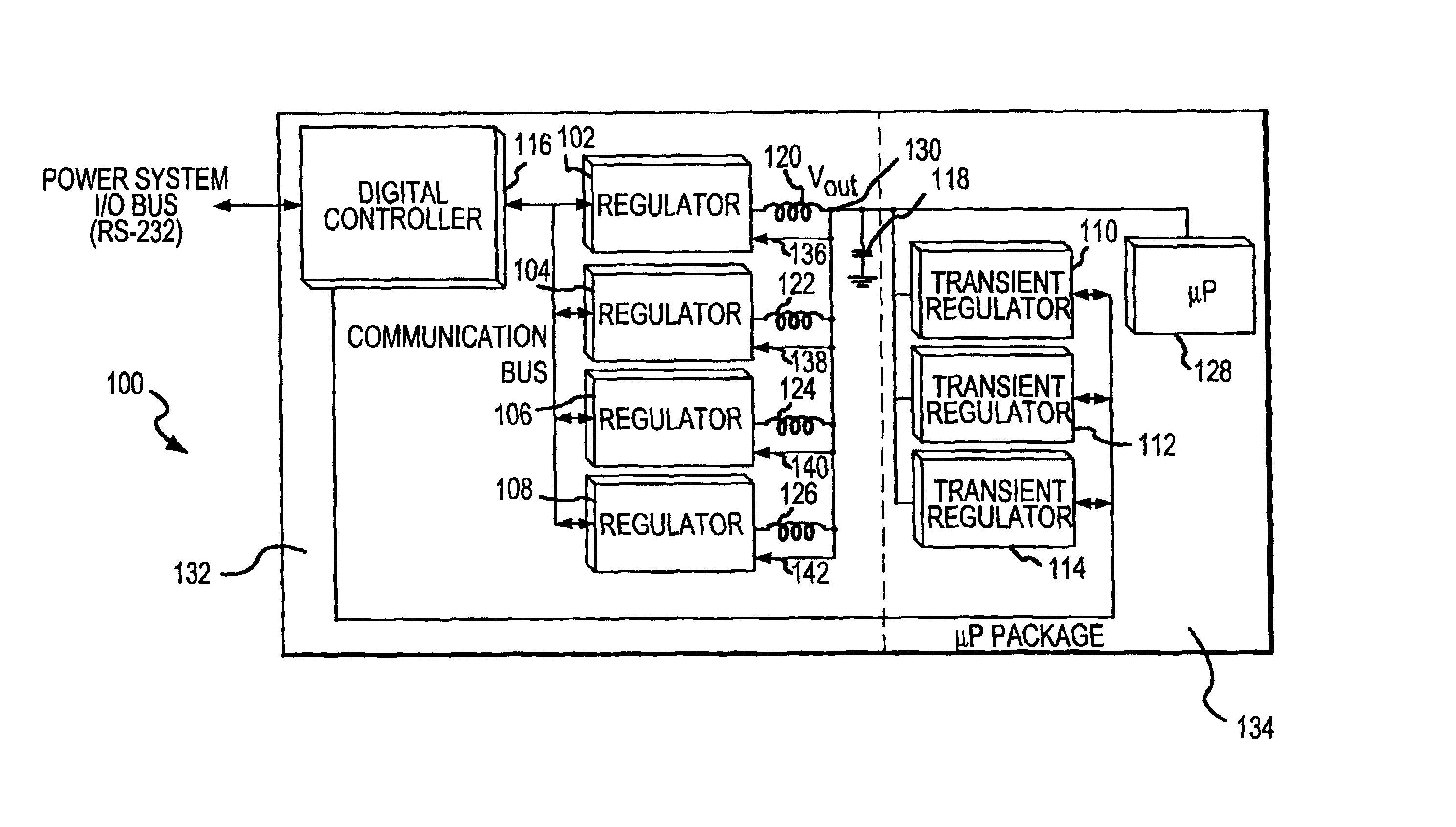

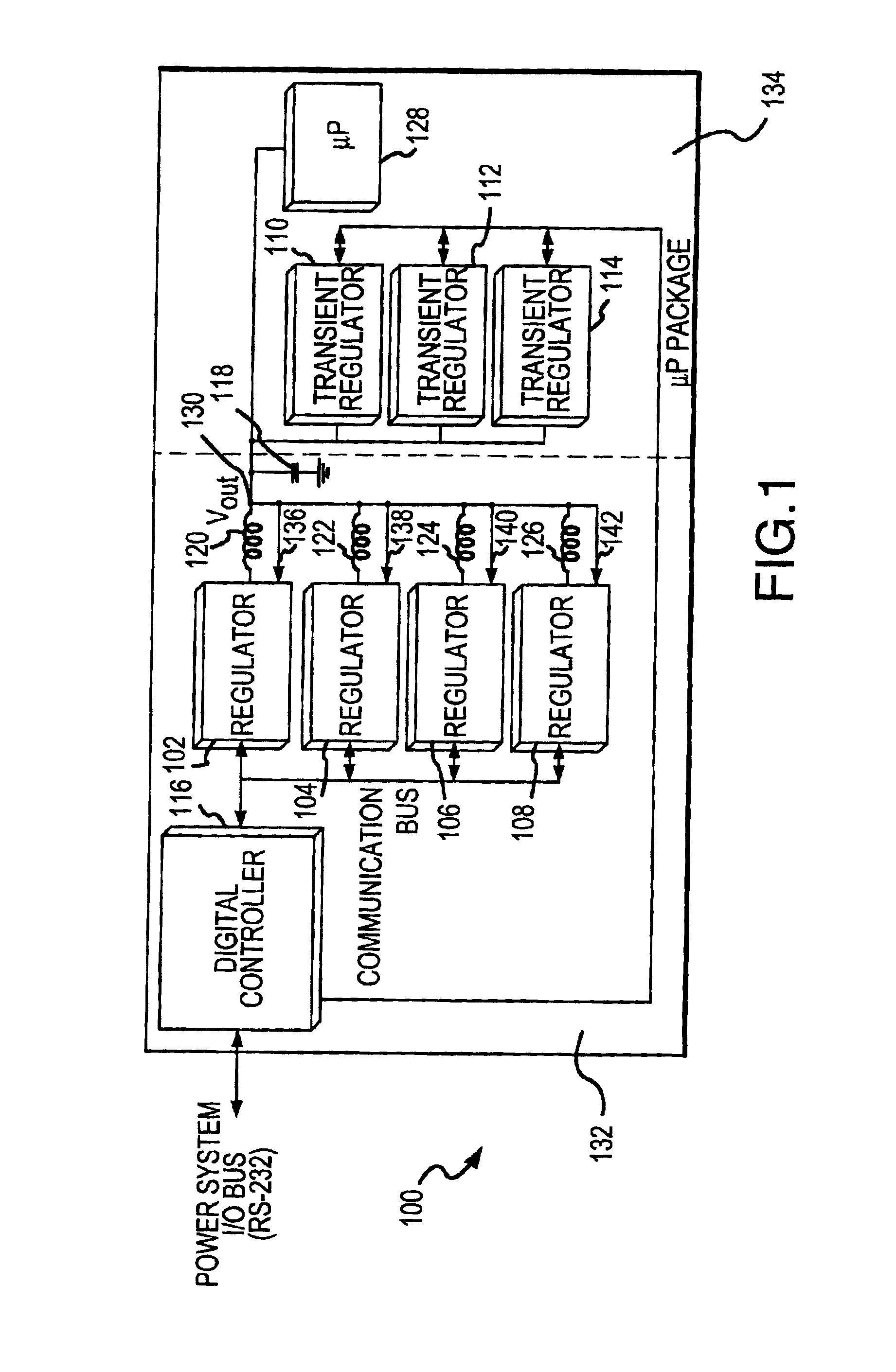

Serial bus control method and apparatus for a microelectronic power regulation system

InactiveUS6788035B2Dc source parallel operationPrinted circuit non-printed electric components associationEngineeringBus mastering

A serial bus control method, apparatus, and system for transmitting signals between a master controller and a slave controller associated with a power regulator are disclosed. The serial bus control scheme allows for information to be written to or read from individual regulators or be written to read from all regulators that are coupled to the master controller.

Owner:INFINEON TECH AUSTRIA AG

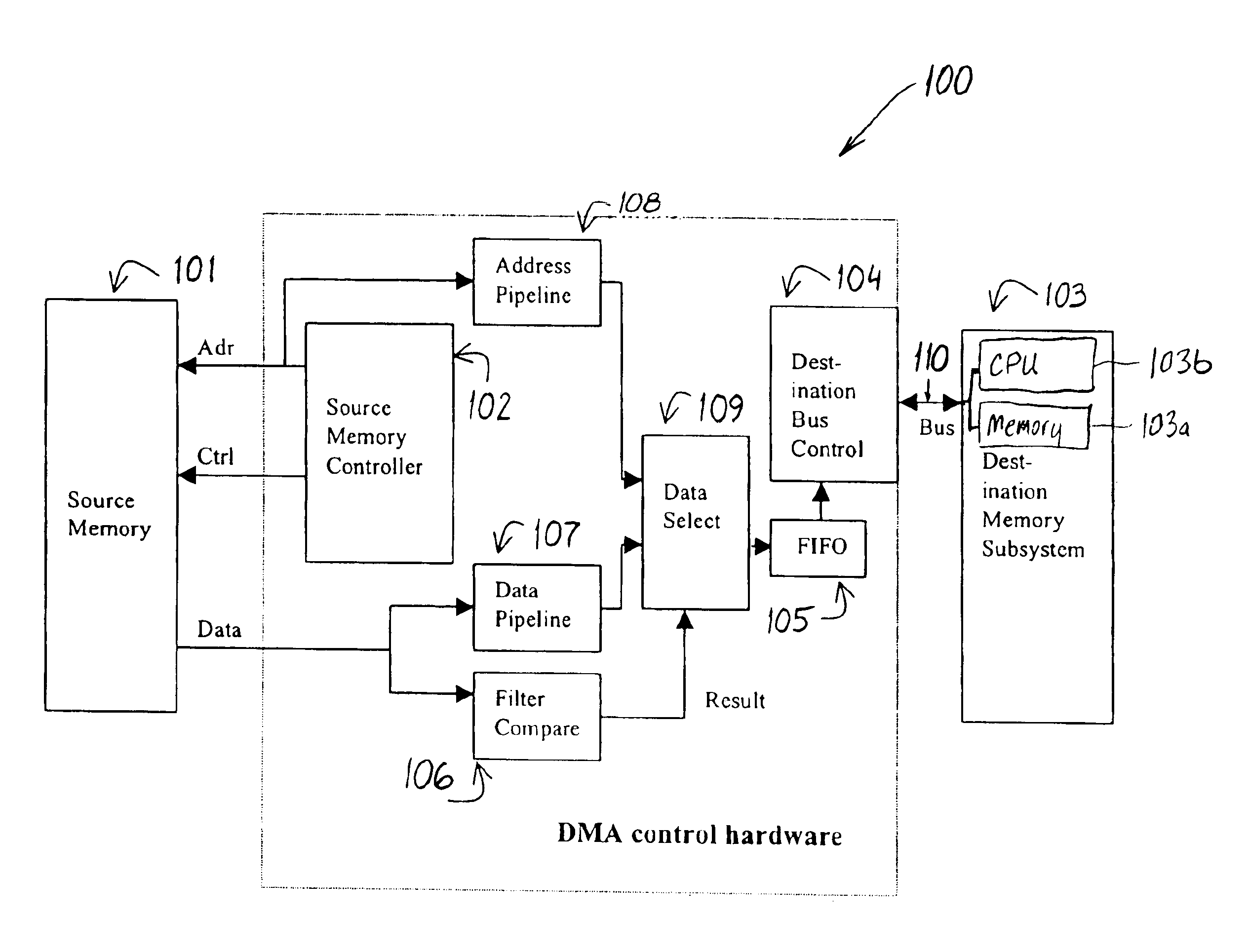

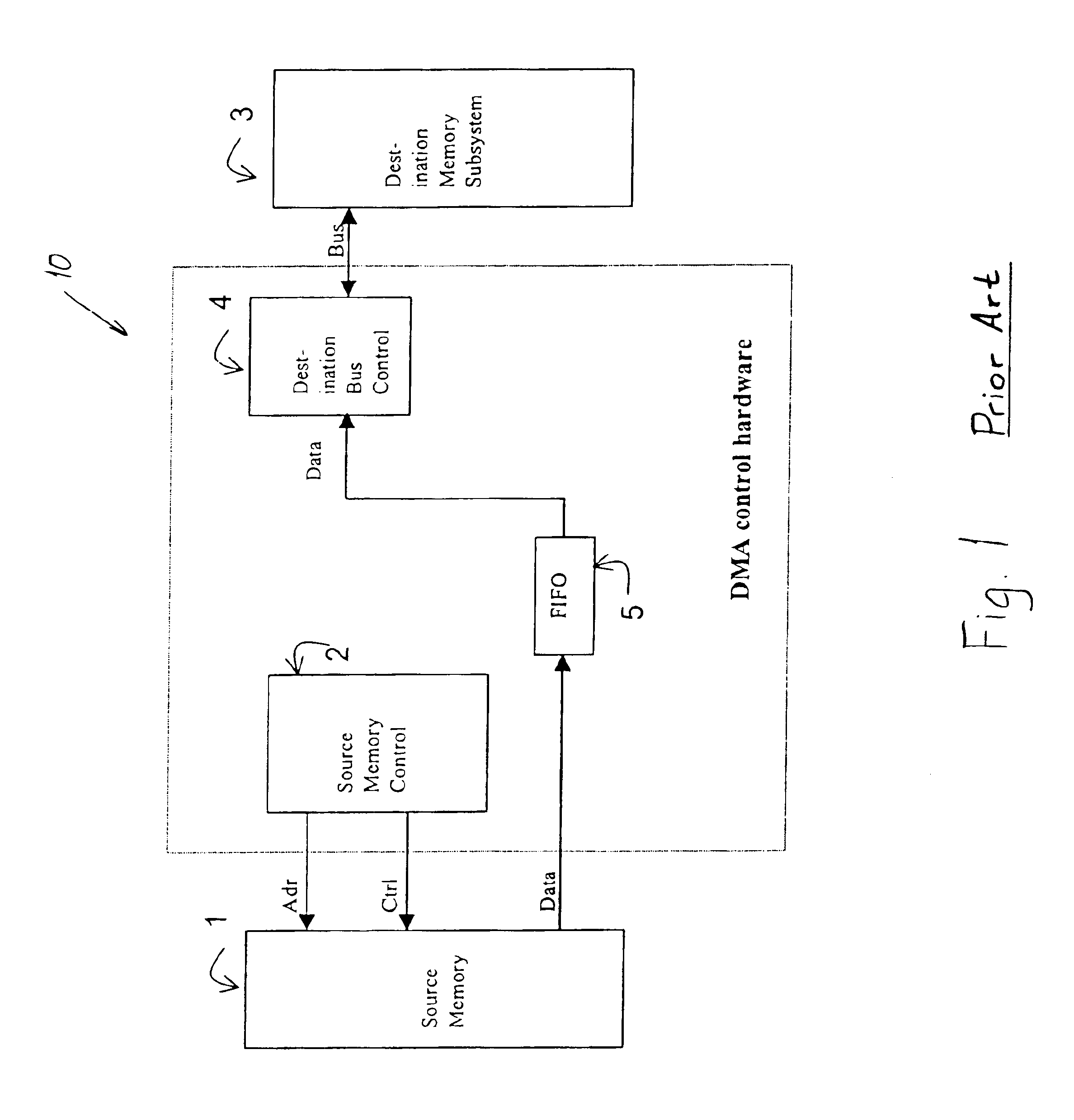

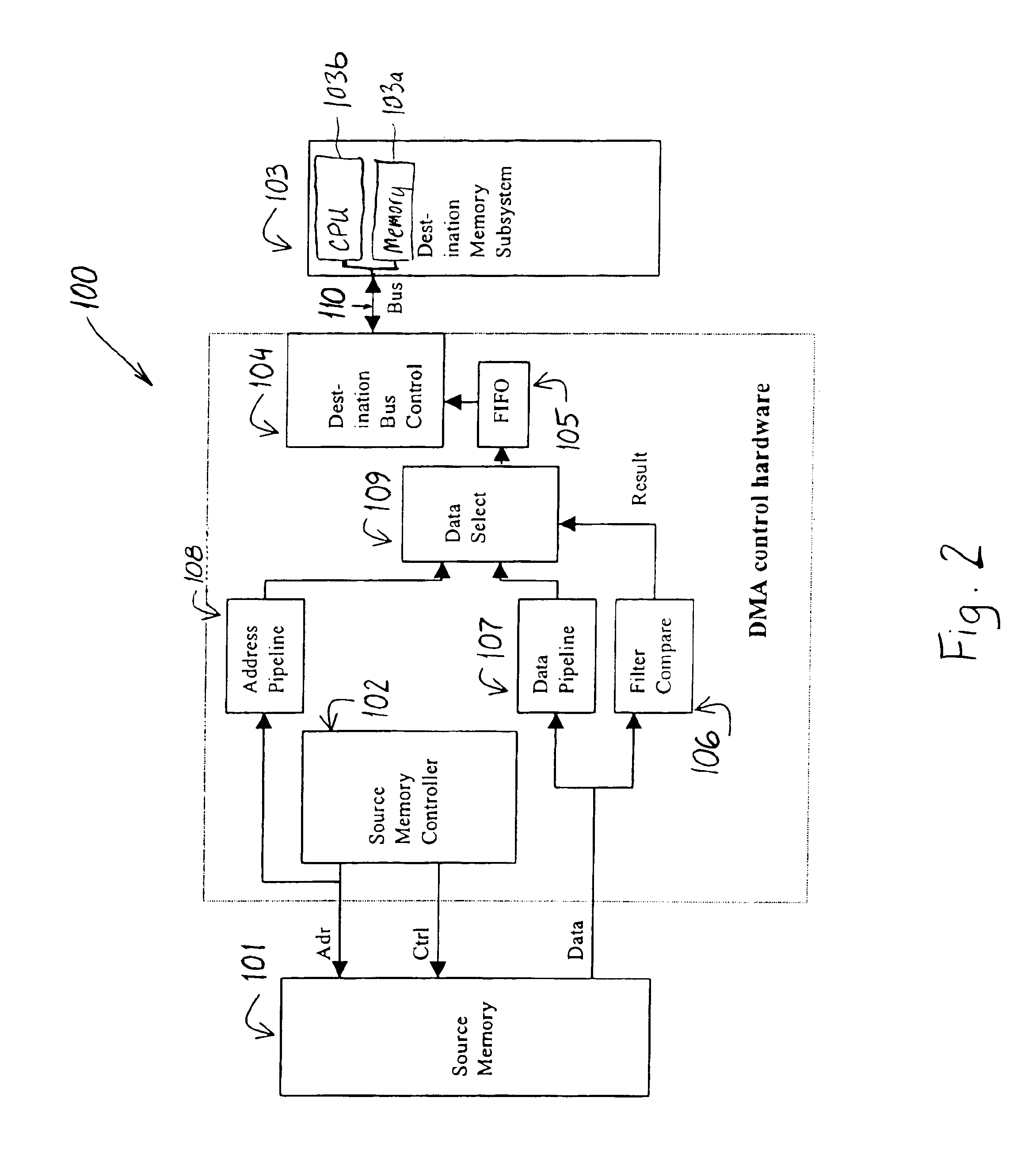

Direct memory access controller and method of filtering data during data transfer from a source memory to a destination memory

InactiveUS6904473B1Convenient and efficient transferEfficient transferData processing applicationsElectric digital data processingDirect memory accessMemory controller

A direct memory access controller includes a source memory controller for controlling a source memory, a destination bus controller for controlling the transfer of data to a destination memory, a first-in-first-out memory buffer for receiving data from the source memory, and a filter connected upstream of the first-in-first-out memory buffer for comparing the source memory data to a filter criterion and passing to the first-in-first-out memory buffer only that data which matches the filter criterion.

Owner:XYRATEX TECH LTD

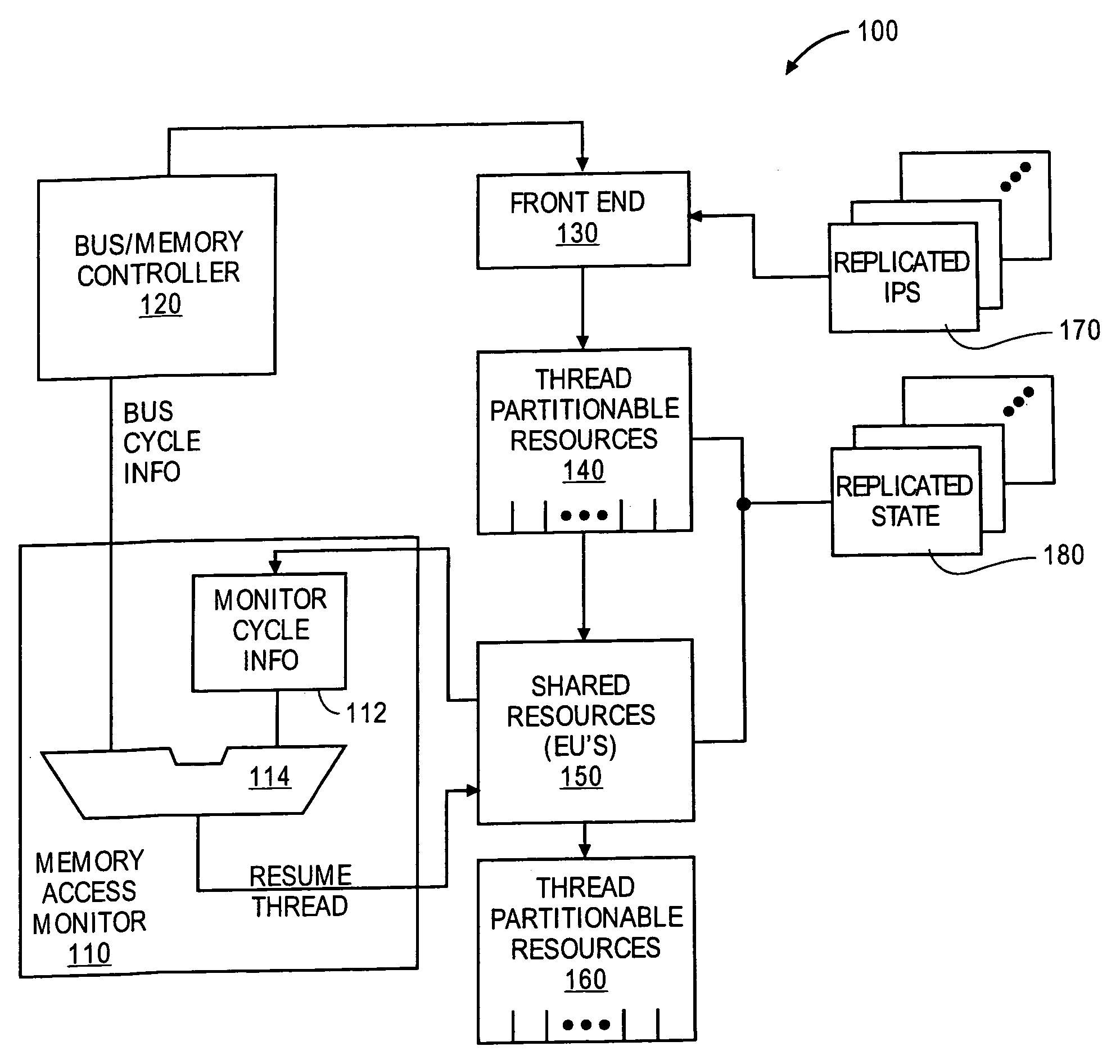

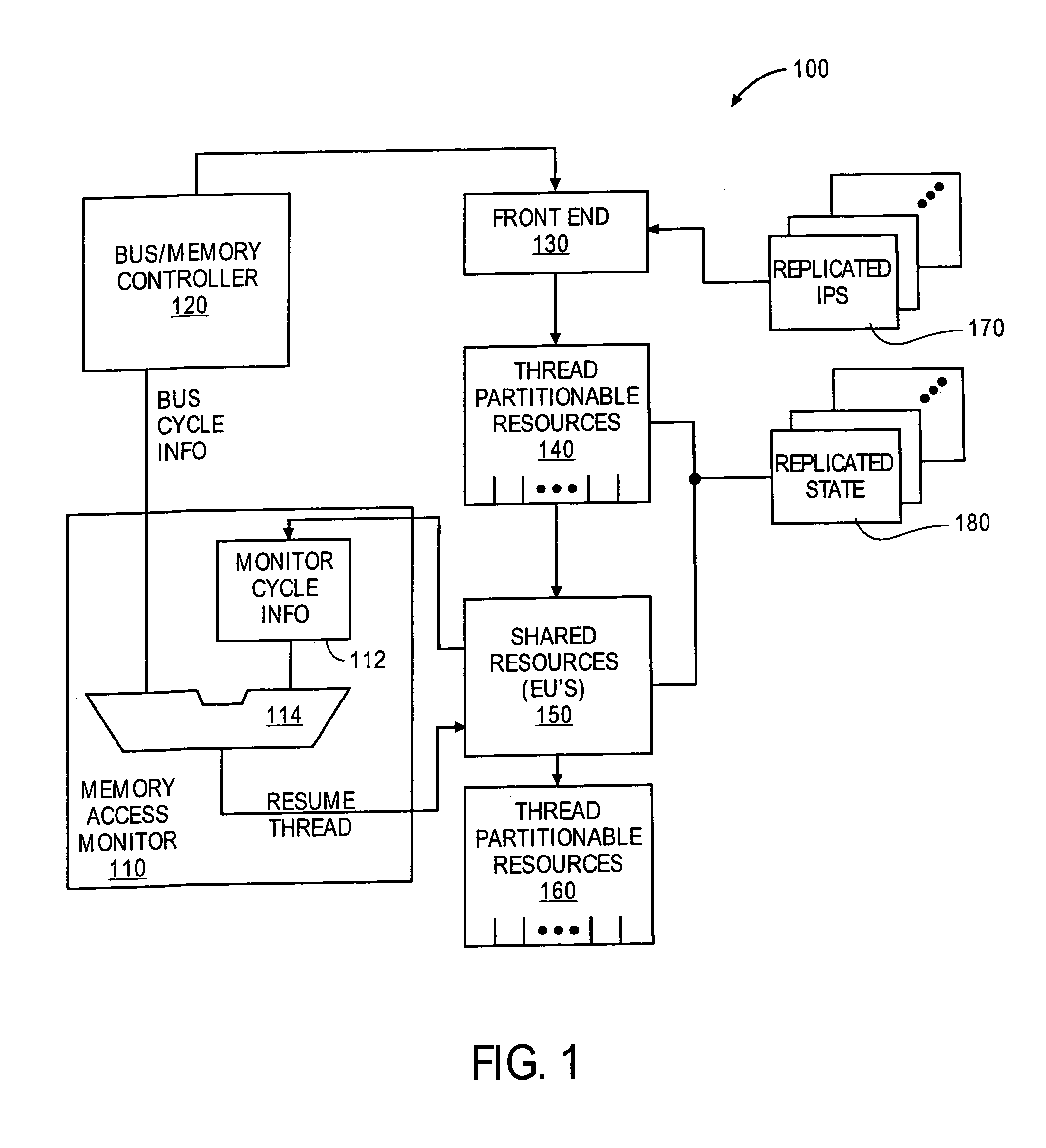

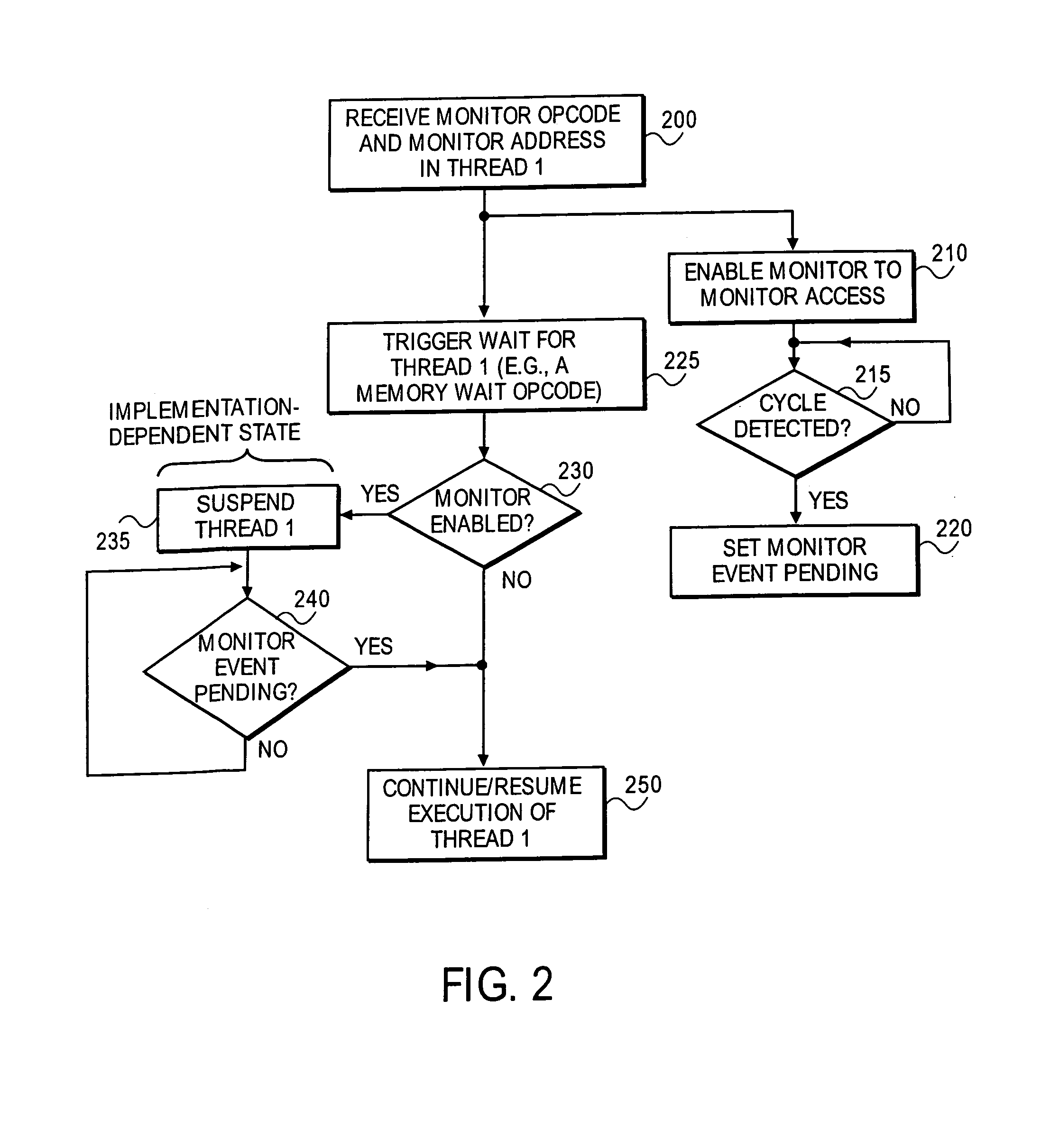

Coherency techniques for suspending execution of a thread until a specified memory access occurs

InactiveUS7127561B2Memory adressing/allocation/relocationMultiprogramming arrangementsBus masteringOperand

Coherency techniques for suspending execution of a thread until a specified memory access occurs. In one embodiment, a processor includes a cache, execution logic to execute an instruction having an operand indicating a monitor address and a bus controller. In one embodiment, the bus controller is to assert a preventative signal in response to receiving a memory access attempting to gain sufficient ownership of a cache line associated with said monitor address to allow modification of said cache line without generation of another transaction indicative of the modification. In another embodiment, the bus controller is to generate a bus cycle in response to the instruction to eliminate any ownership of the cache line by another processor that would allow a modification of the cache line without generation of another memory access indicative of the modification.

Owner:INTEL CORP

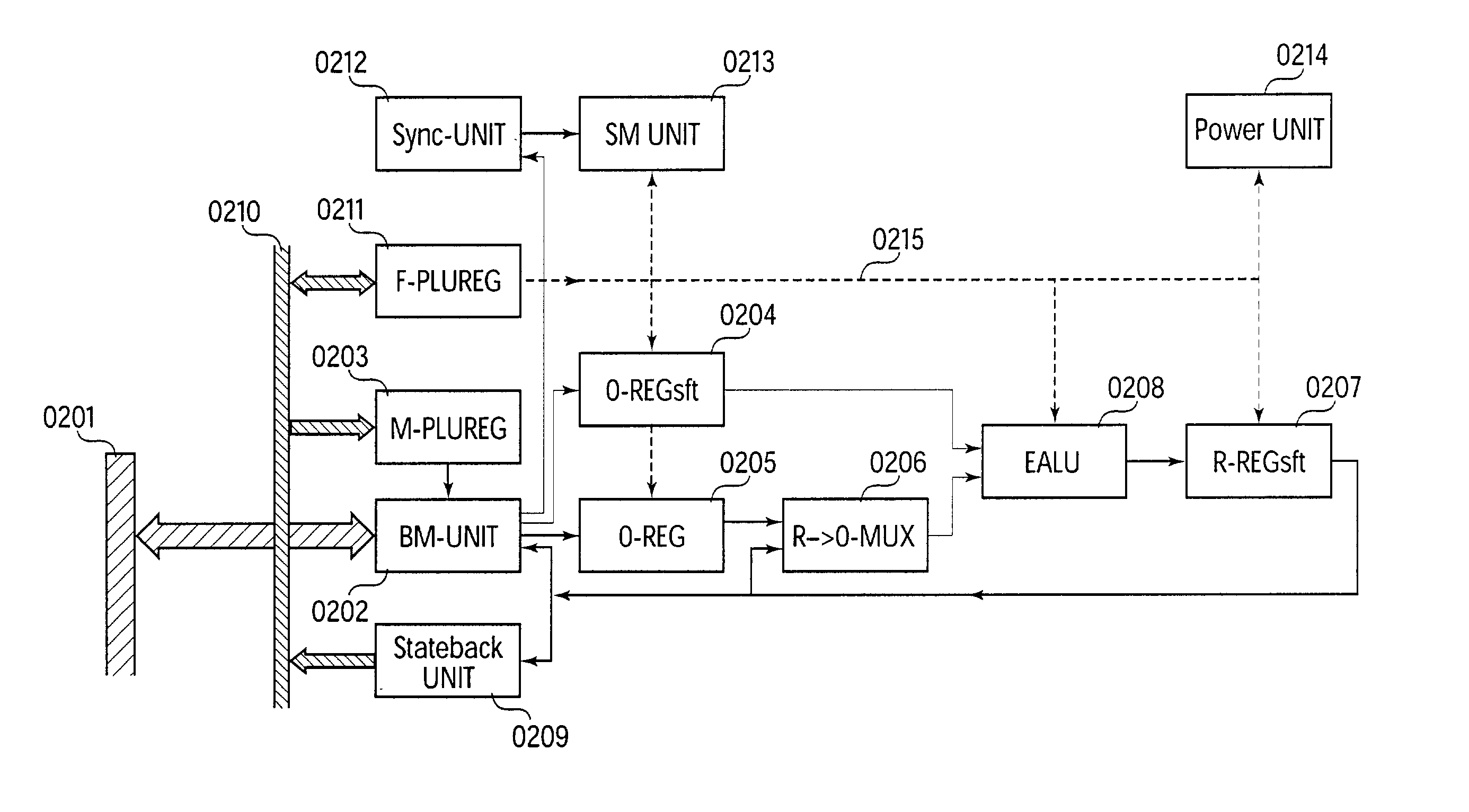

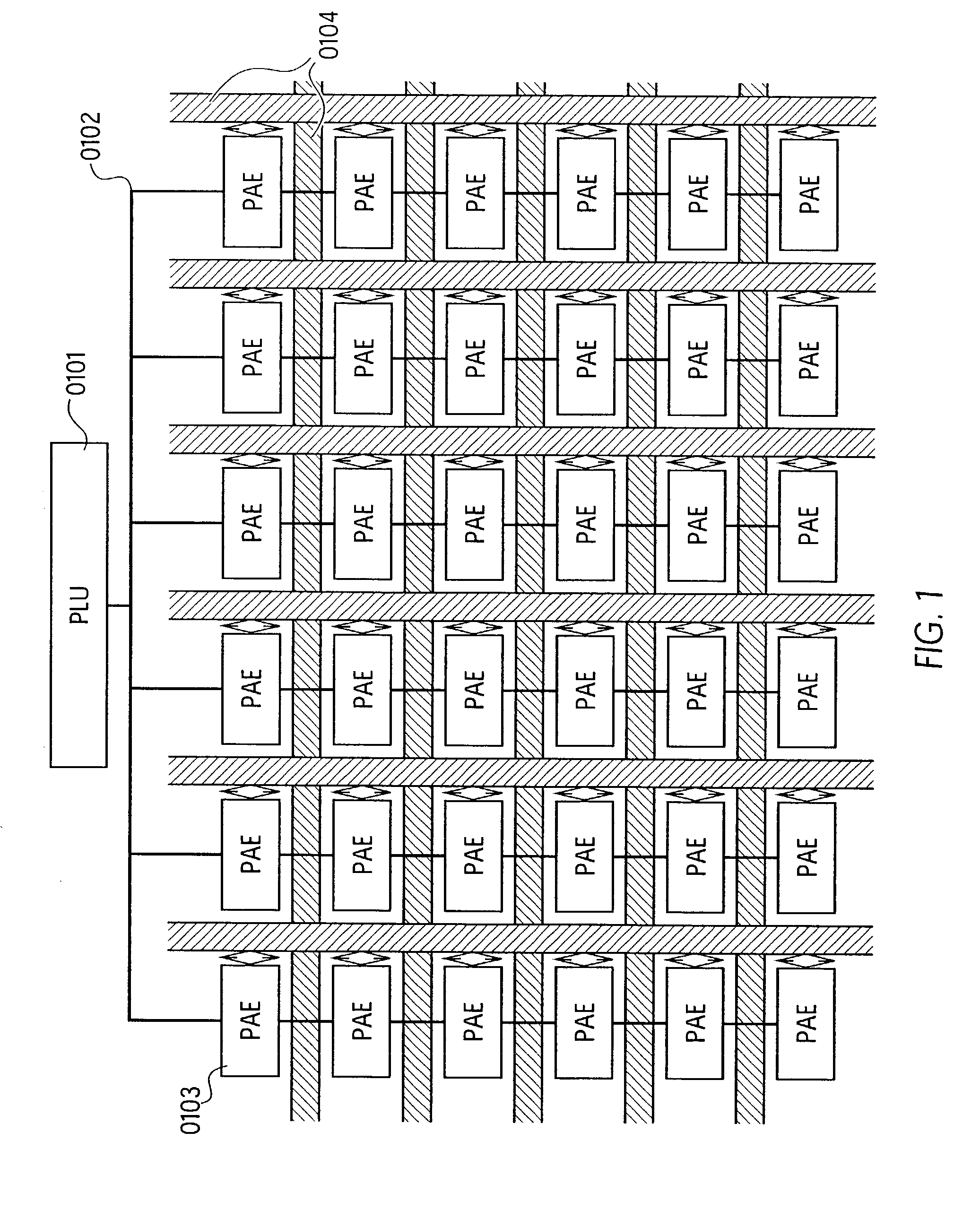

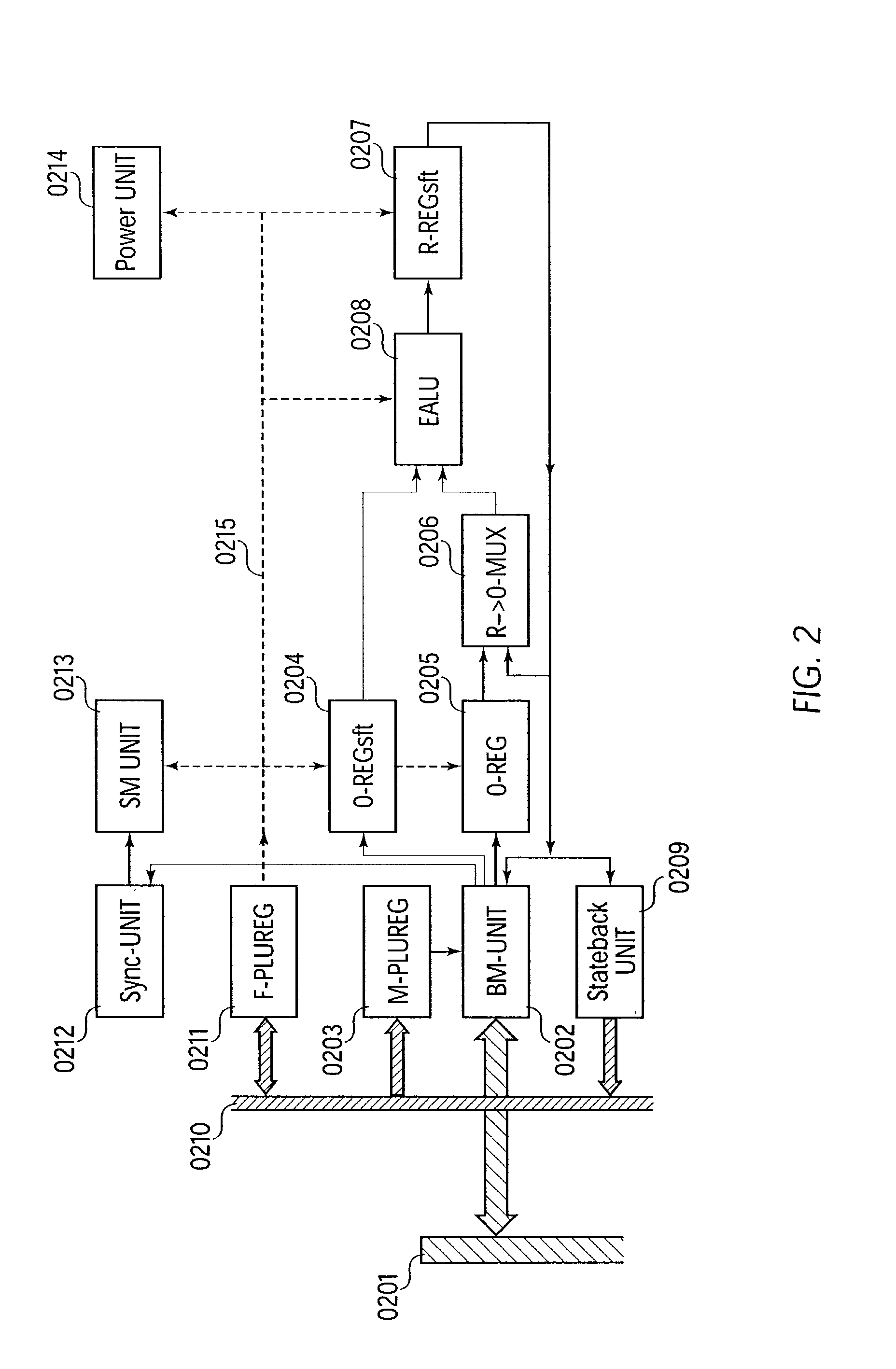

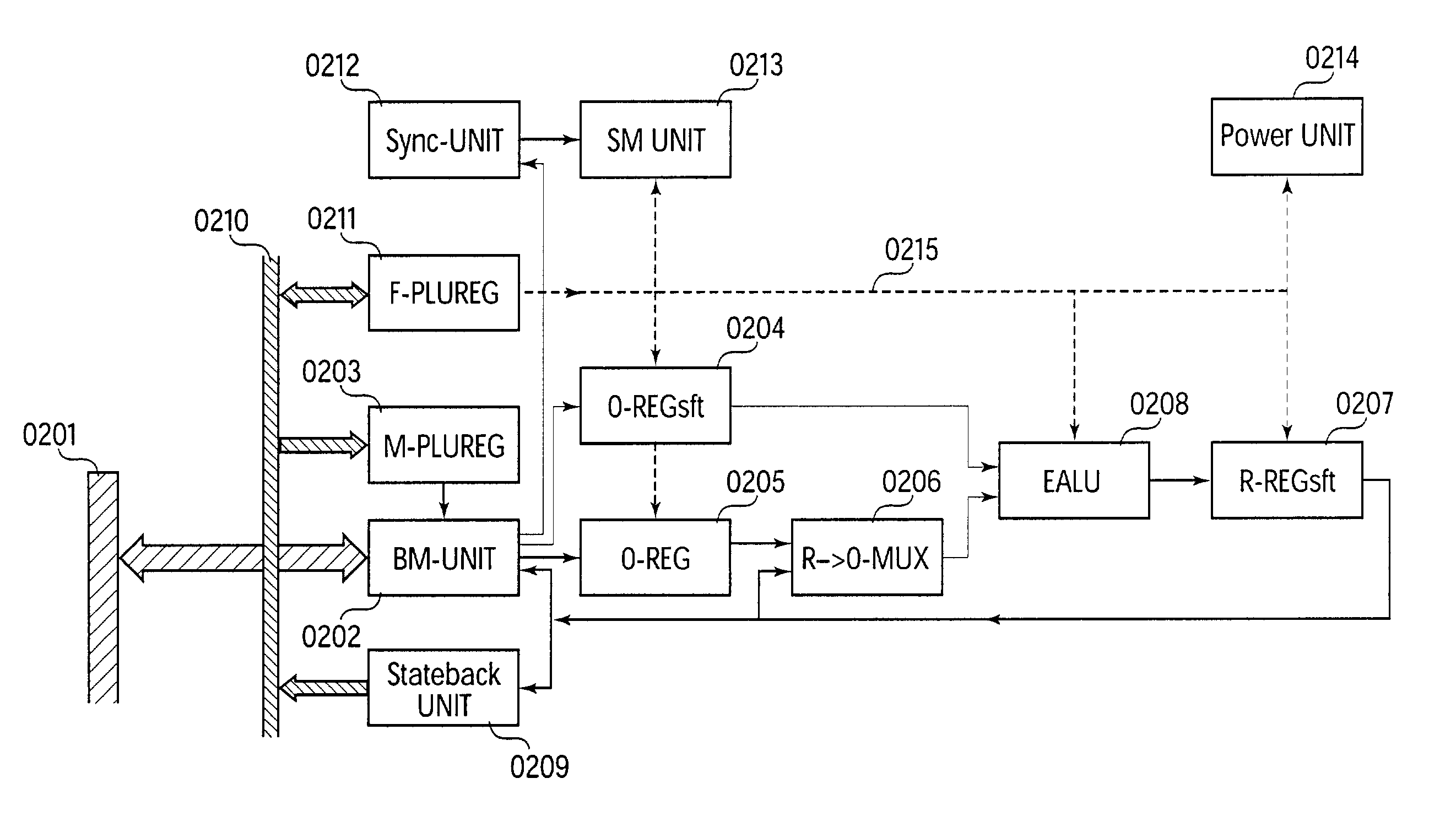

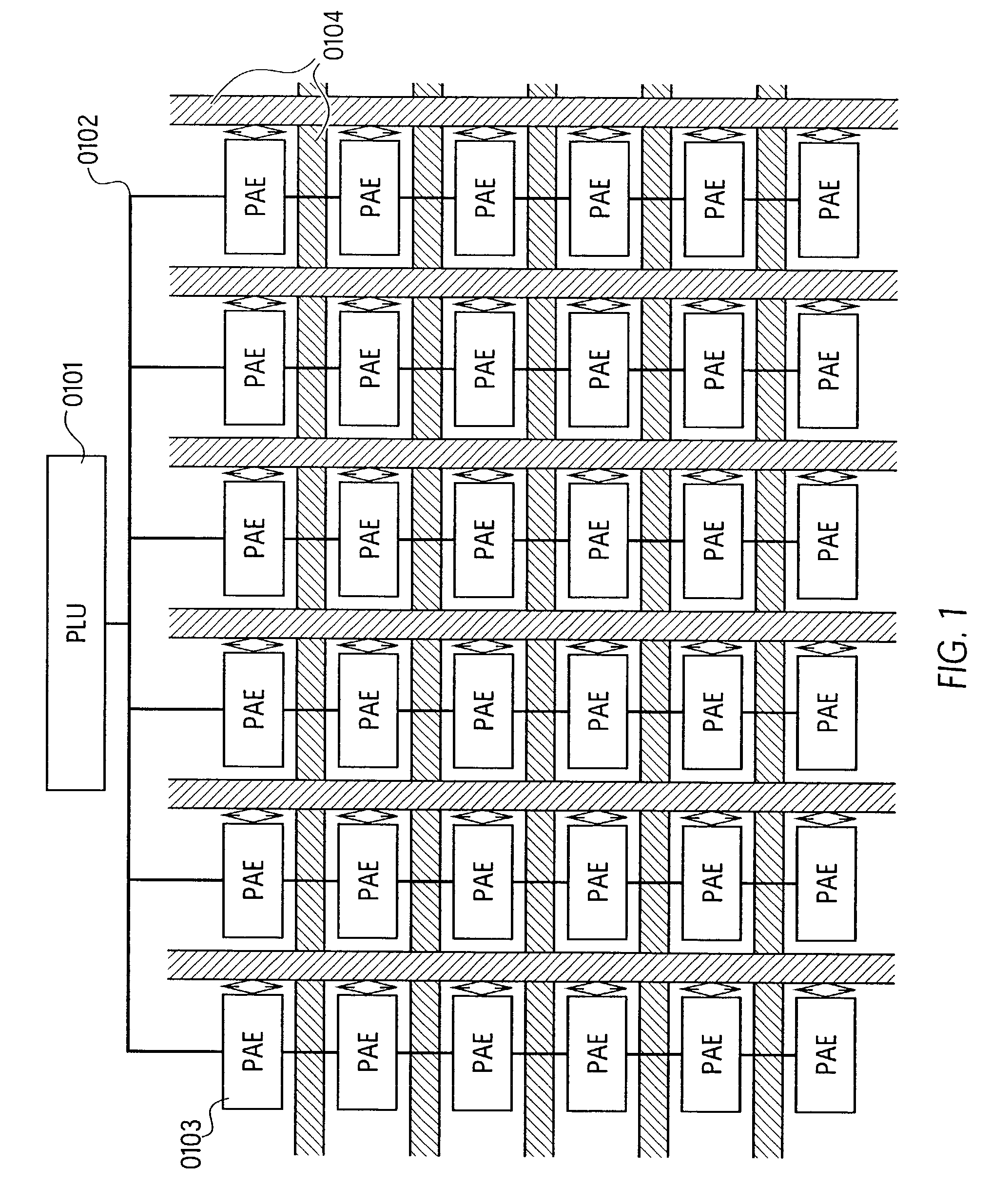

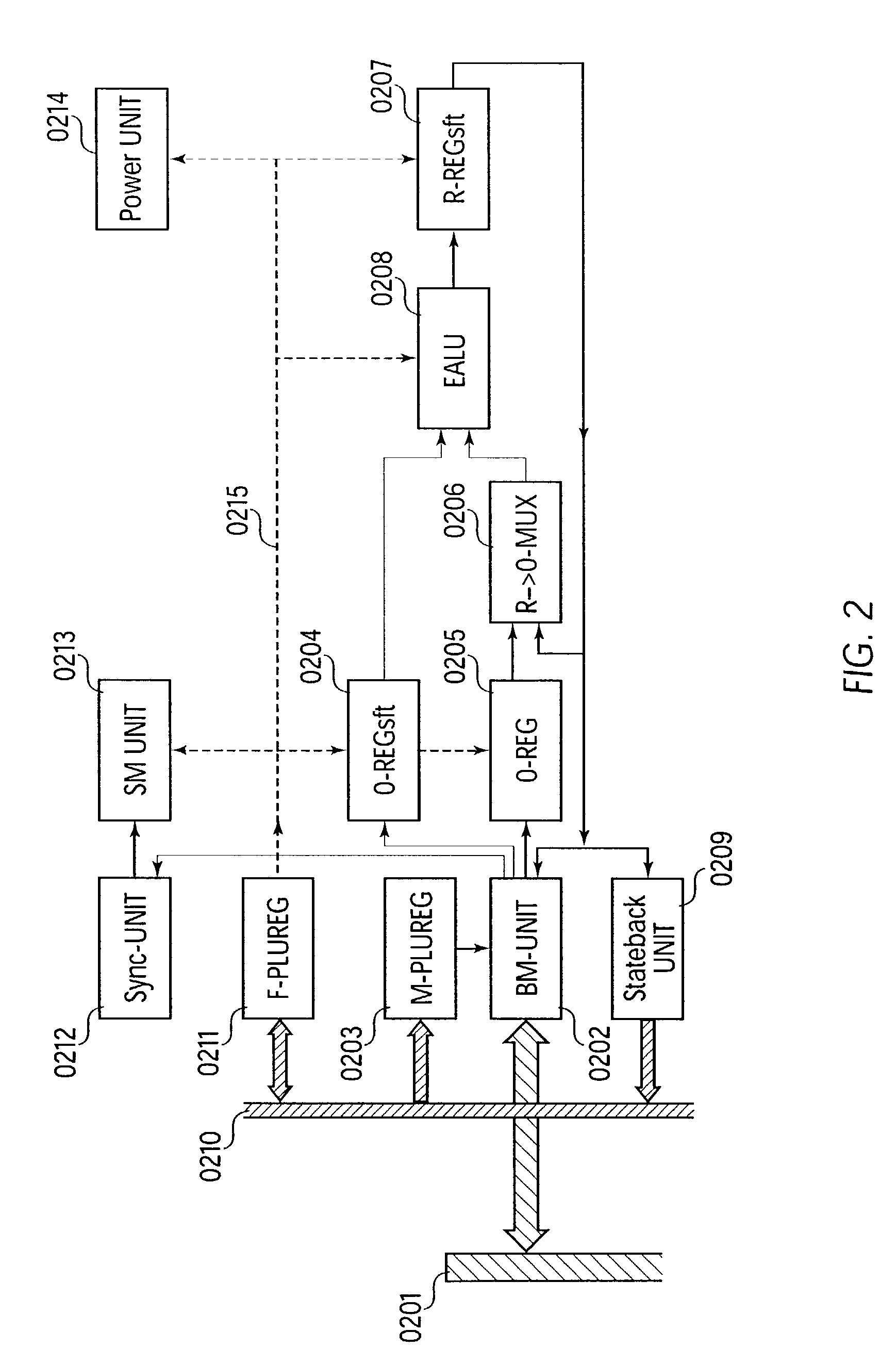

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

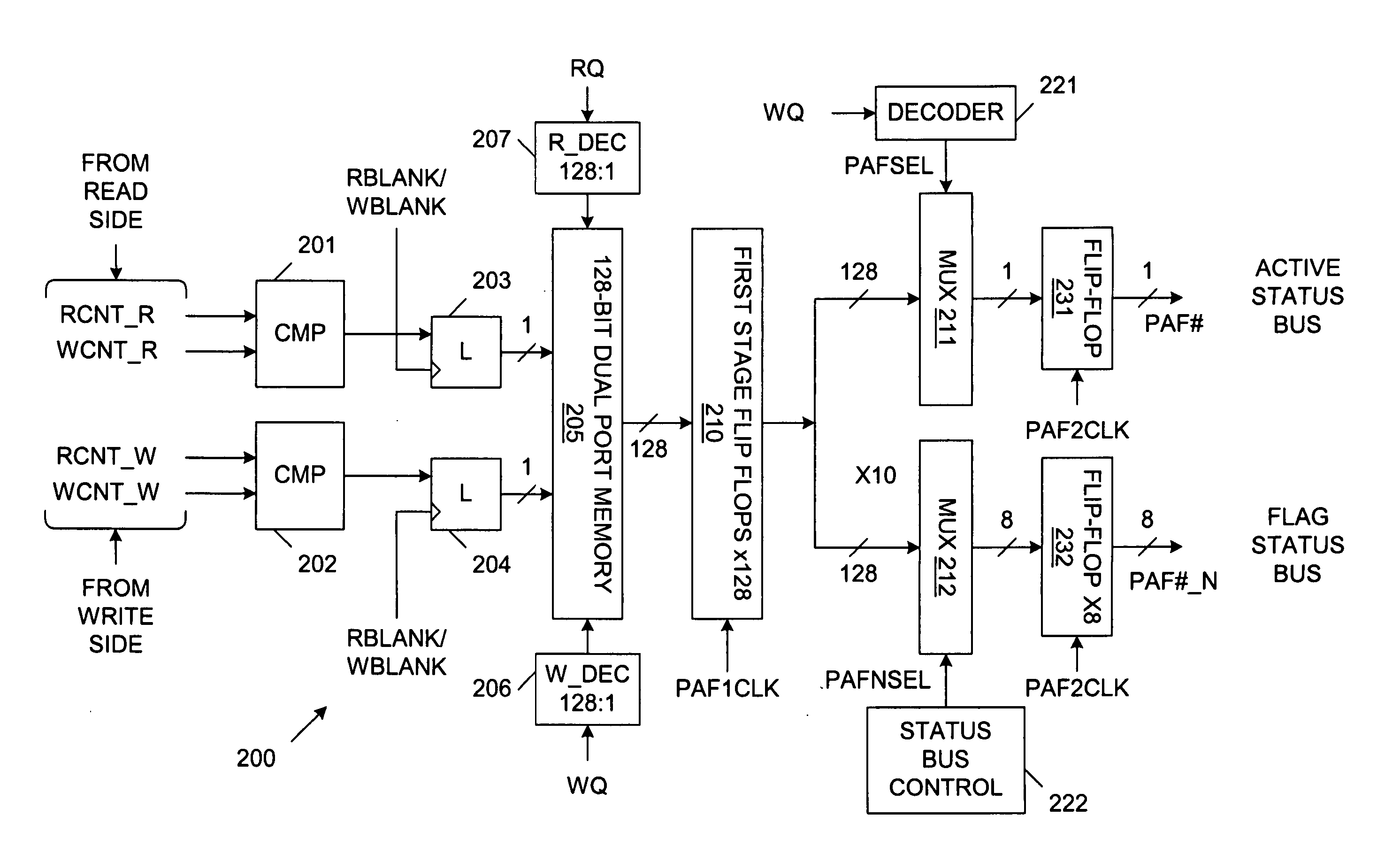

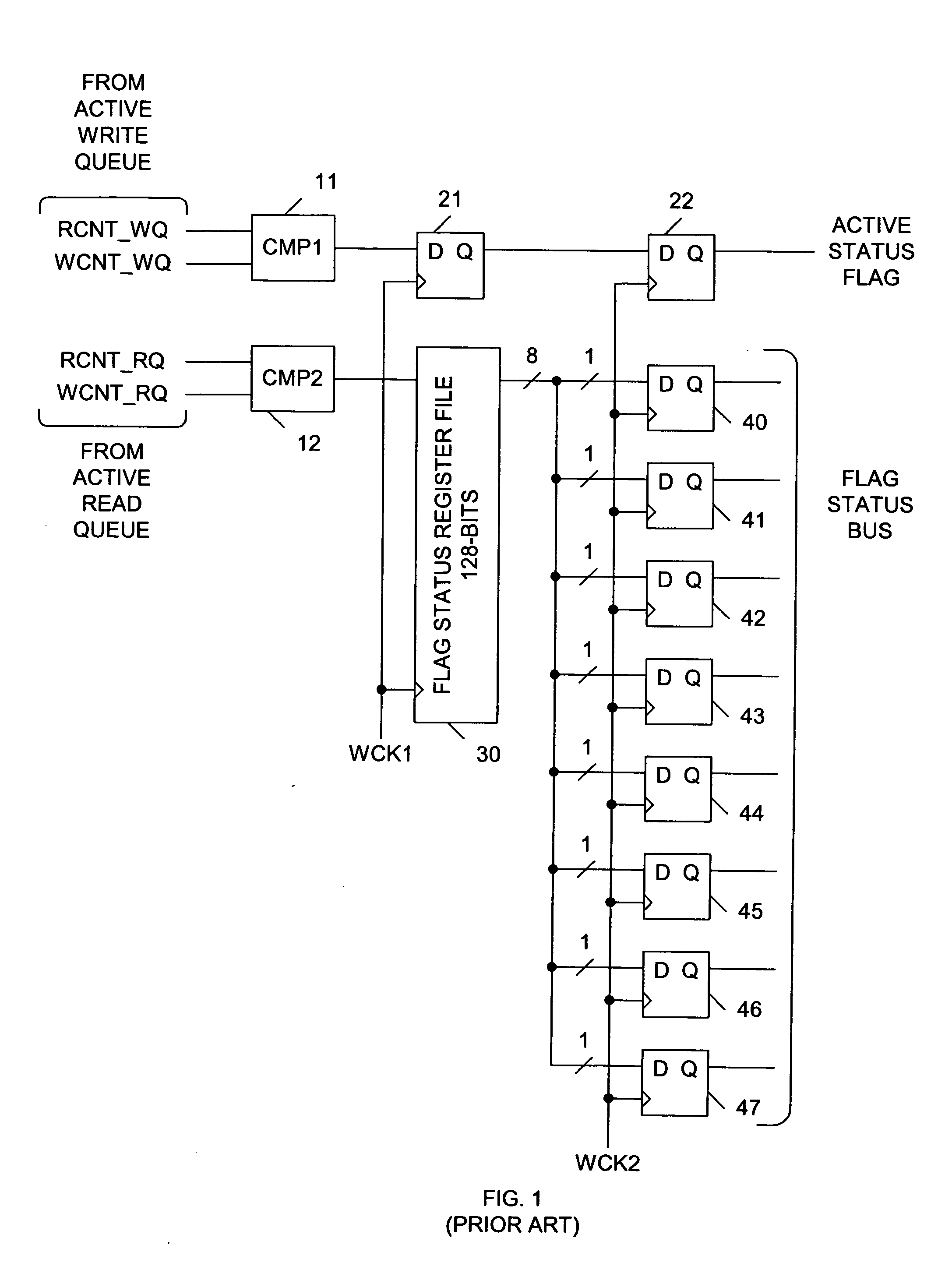

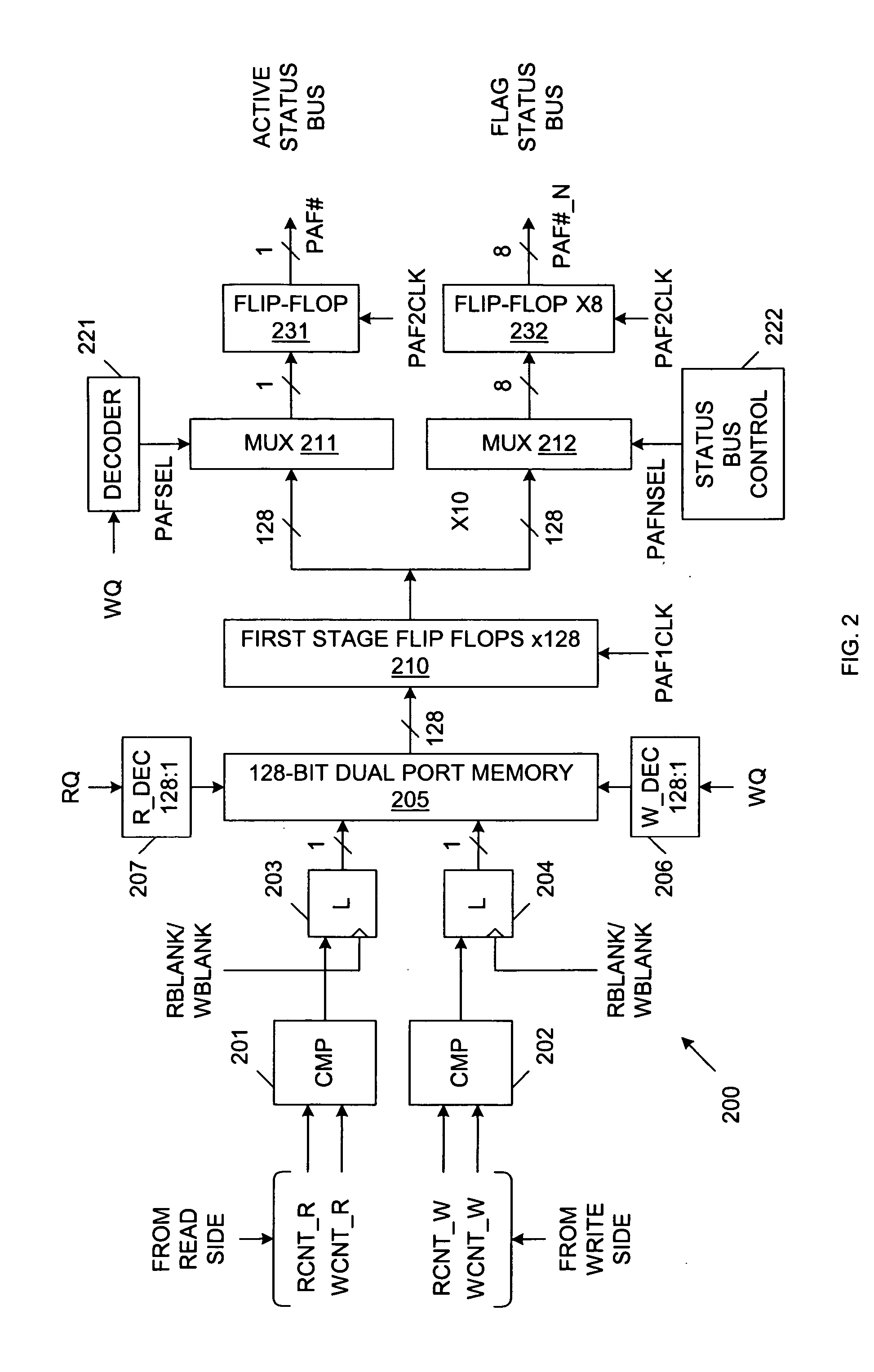

Status bus accessing only available quadrants during loop mode operation in a multi-queue first-in first-out memory system

ActiveUS20060020742A1Efficient routingMemory systemsInput/output processes for data processingBus masteringControl circuit

A flag logic circuit is provided for use in a multi-queue memory device having a plurality of queues. A first stage memory stores a flag value for each of the queues in the multi-queue memory device. Flag values are routed from the first stage memory to a flag status bus having a width N in the manner described below. A status bus control circuit receives a signal that identifies the number of queues M actually used by the multi-queue memory device, and in response, generates a repeating pattern of X control values, wherein X is equal to (M−(M mod N)) / N+1. A selector circuit sequentially routes X sets of N flag values from the first stage memory to the flag status bus in response to the repeating pattern of X control values. The X sets of N flag values include the flag values associated with the queues actually used.

Owner:INTEGRATED DEVICE TECH INC

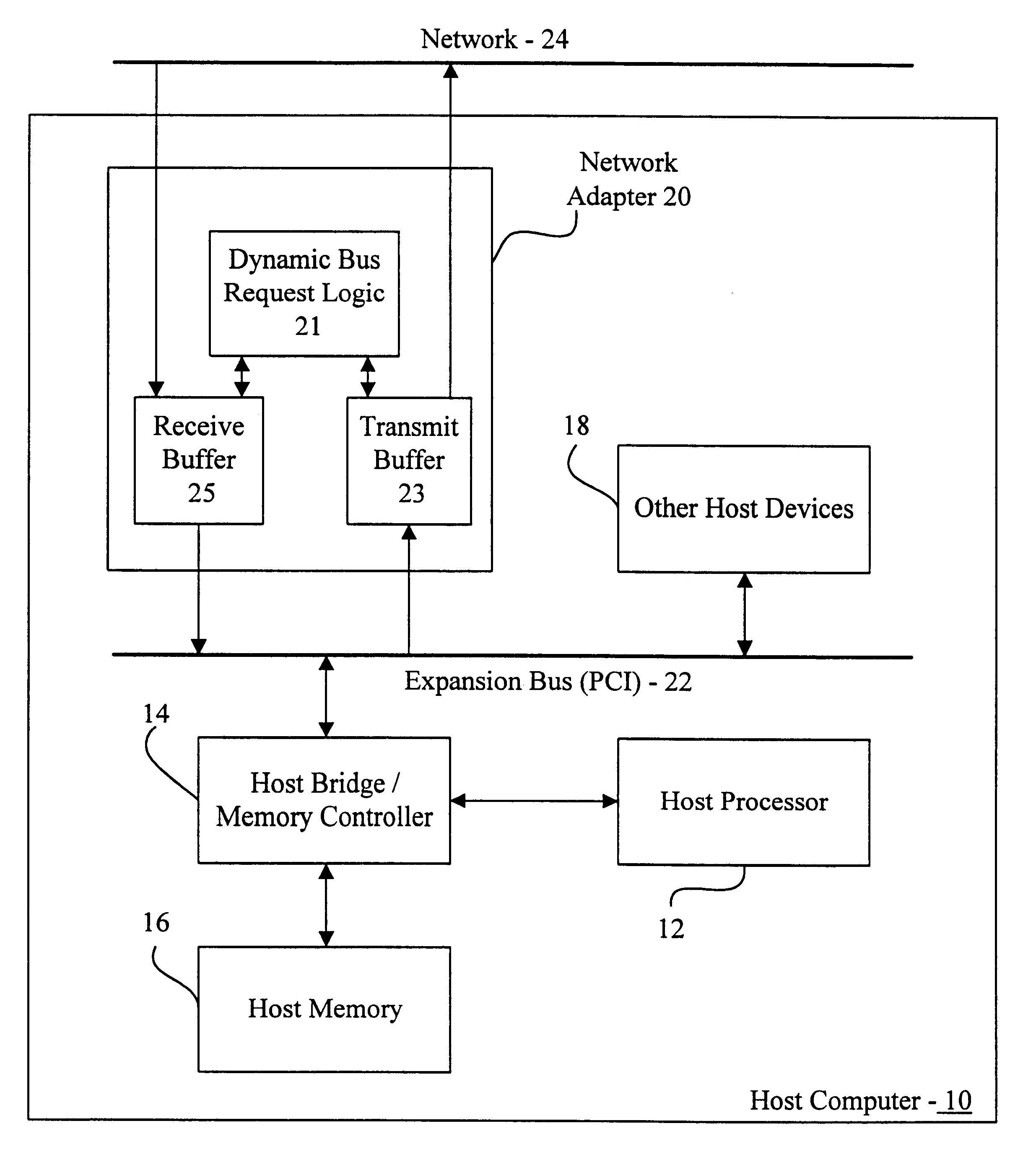

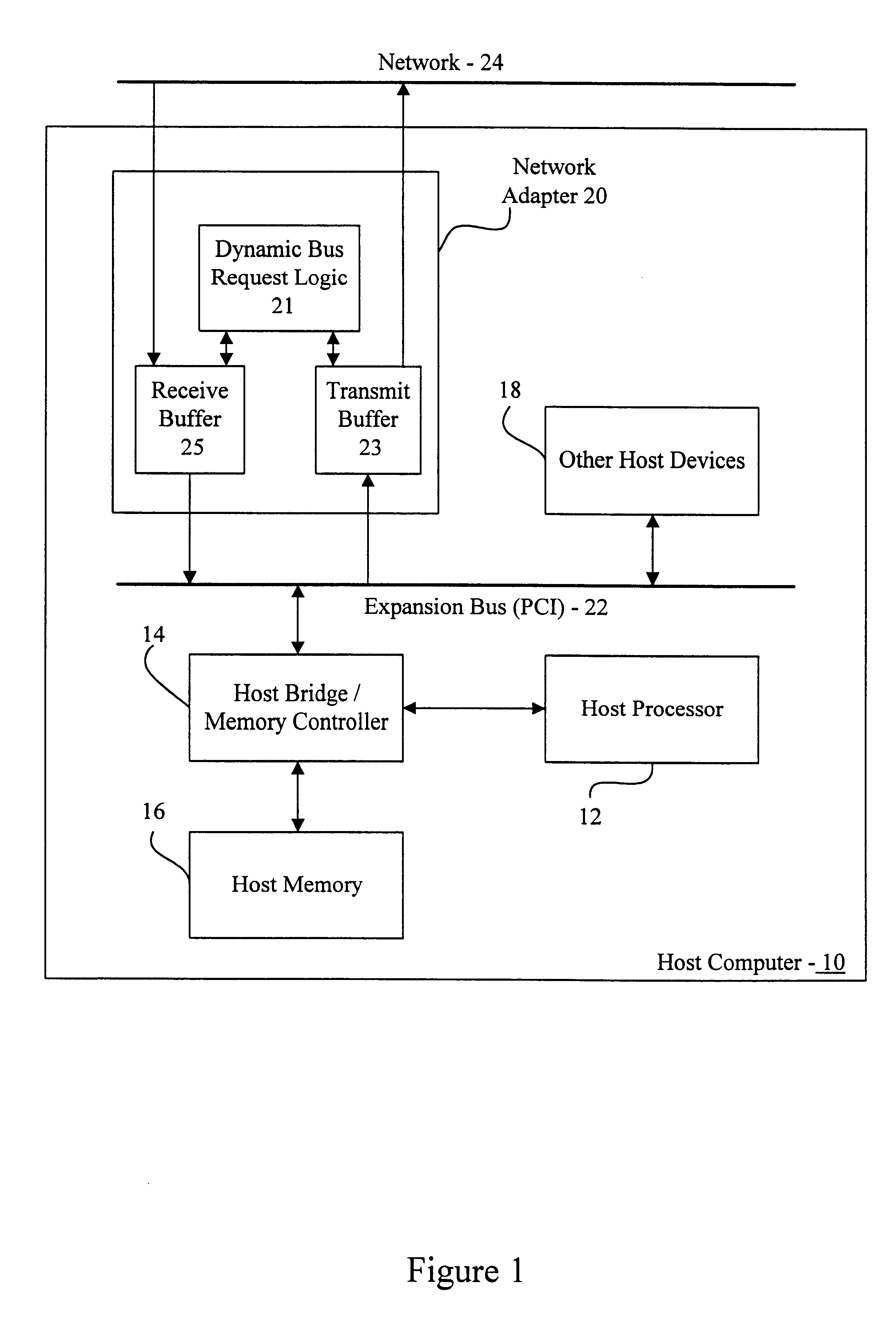

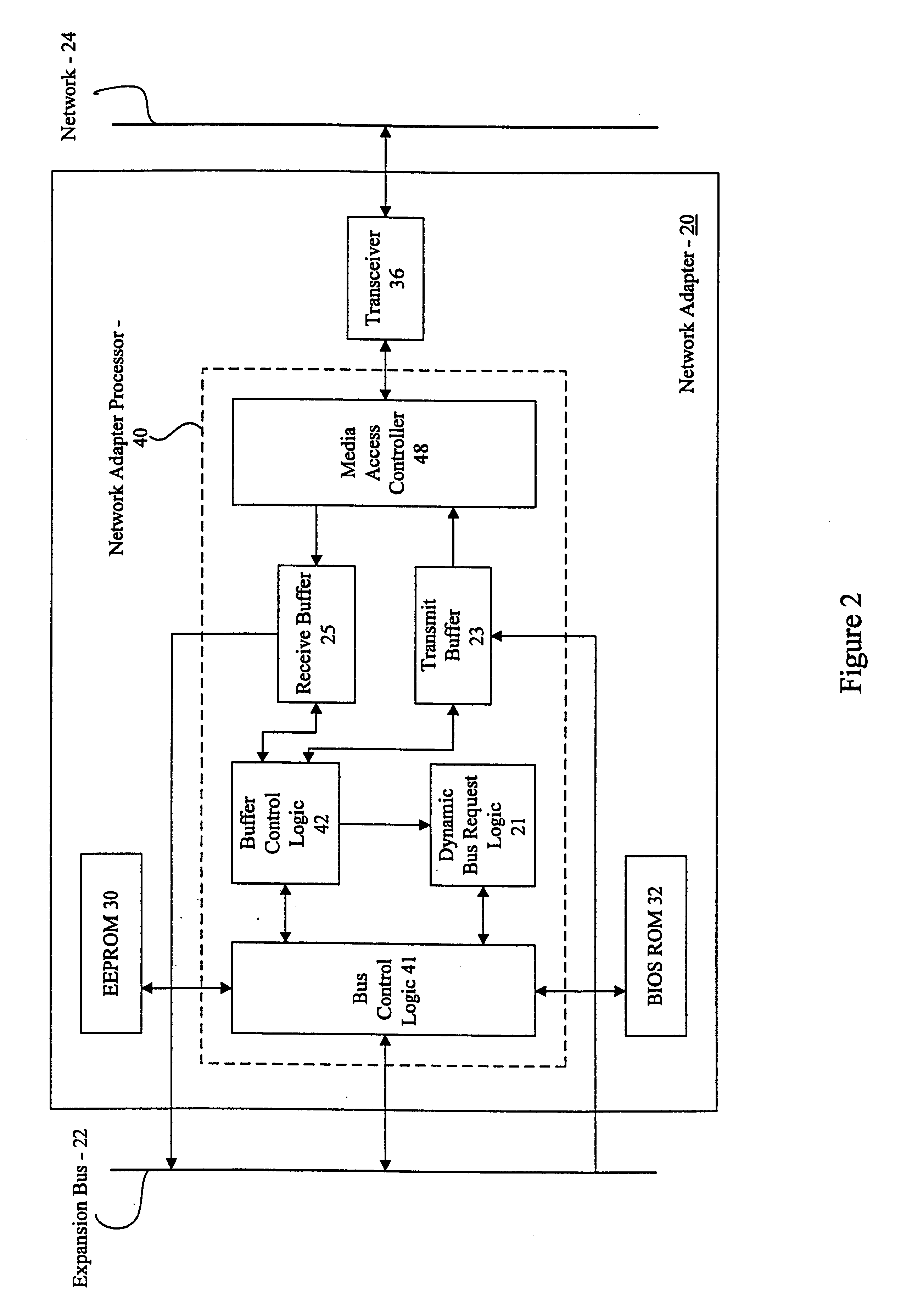

Method and apparatus for dynamic bus request and burst-length control

InactiveUS6397287B1Minimizing of overrunEasy transferMultiple digital computer combinationsInput/output processes for data processingData signalBus mastering

A network adapter is provided that controls the transfer of data between a host computer and a network medium in a manner which optimizes the amount of data transferred between the host computer and the buffer of the network adapter during a contemporaneous transfer of data between the network medium and the buffer. The network adapter optimizes the data transfer by dynamically determining when to make a bus request such that the buffer is capable of transferring a data packet of a particular target burst size at the end of an estimated latency period. The network adapter includes a buffer memory that transfers data between the host computer and the network medium and a buffer control logic that generates a first buffer data signal in response to the amount of data in the buffer memory. The adapter further includes a bus control logic that generates a second buffer data signal in response to previous transfers of data between the host computer and the network medium, and a dynamic bus request logic that asserts a bus request signal at a time responsive to the first and second buffer data signals to initiate an optimized data transfer between the host computer and the buffer memory during a contemporaneous transfer of data between the buffer memory and the network medium. In one instance, the target burst size is equal to the maximum amount of data transferred between the host computer and the buffer in a single transaction since the host computer has been powered on. Further, in one instance the estimated latency is set as the latency of the previous data transfer between the buffer and the host computer.

Owner:HEWLETT PACKARD DEV CO LP

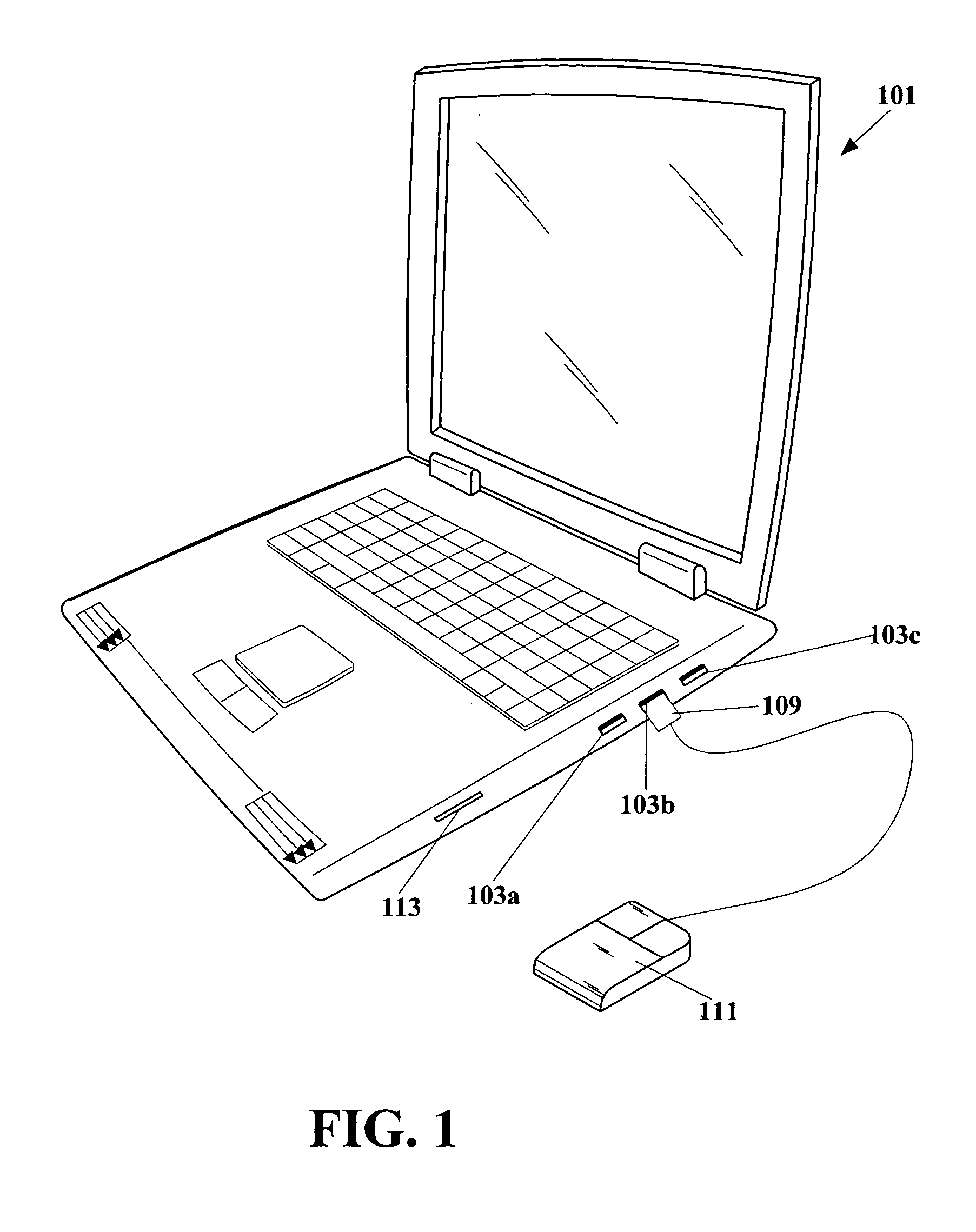

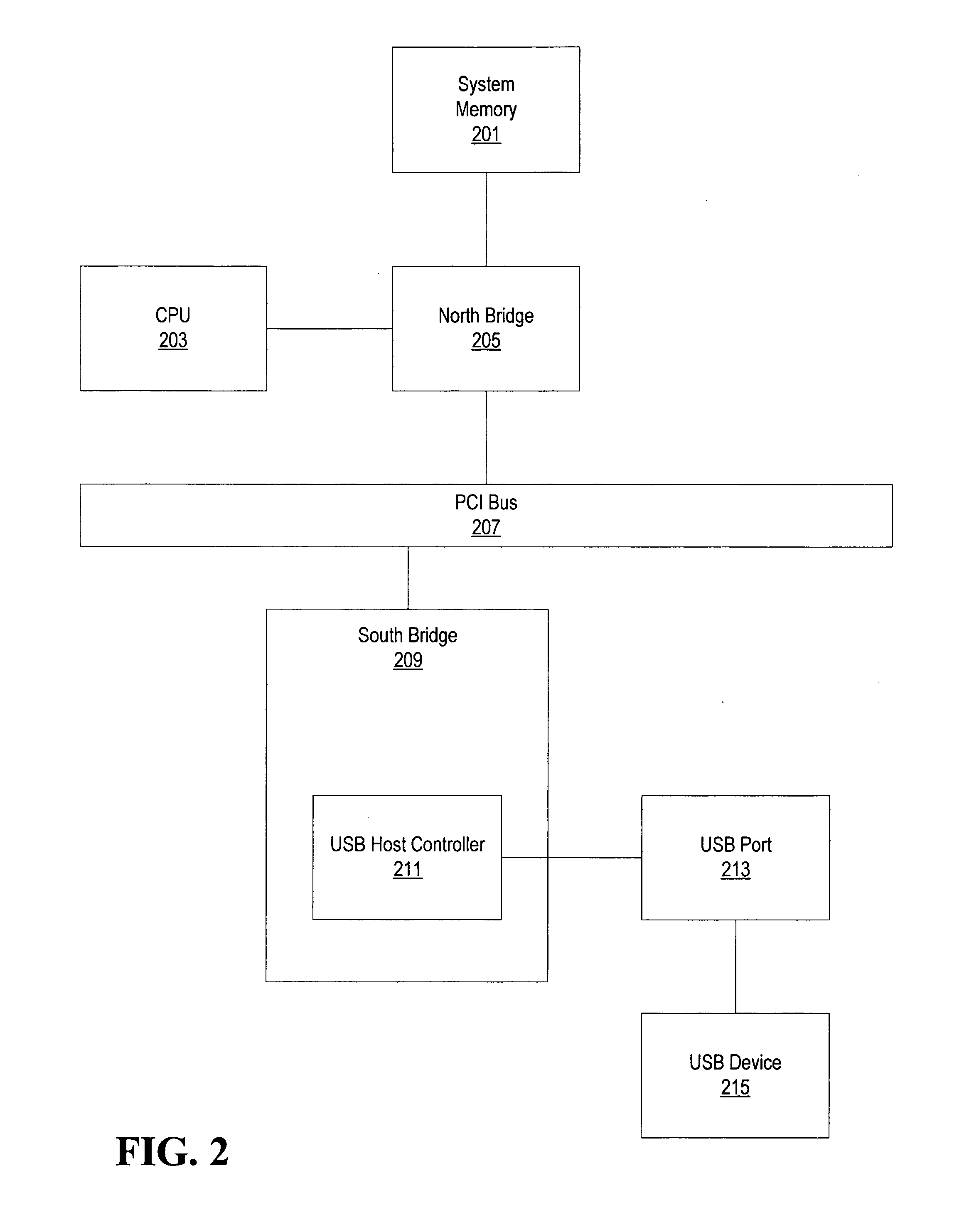

Peripheral device feature allowing processors to enter a low power state

ActiveUS20050156038A1Volume/mass flow measurementCo-operative working arrangementsElectricityWaiting period

If a USB device is turned off or is not active, the device may be electrically disconnected from a USB host controller. The device may be electrically disconnected through a physical interface on the device. In some embodiments, if the device becomes active during a wait period (e.g., 2-3 seconds) prior to electrically disconnecting the device, the device may not be electrically disconnected. In some embodiments, when the device is electrically disconnected from the USB host controller and no system activity of a bus mastering peripheral is occurring, the CPU may enter a low power state if other conditions are met. In some embodiments, if the USB device becomes active after electrically disconnecting, the electrical disconnection may be discontinued.

Owner:SONRAI MEMORY LTD

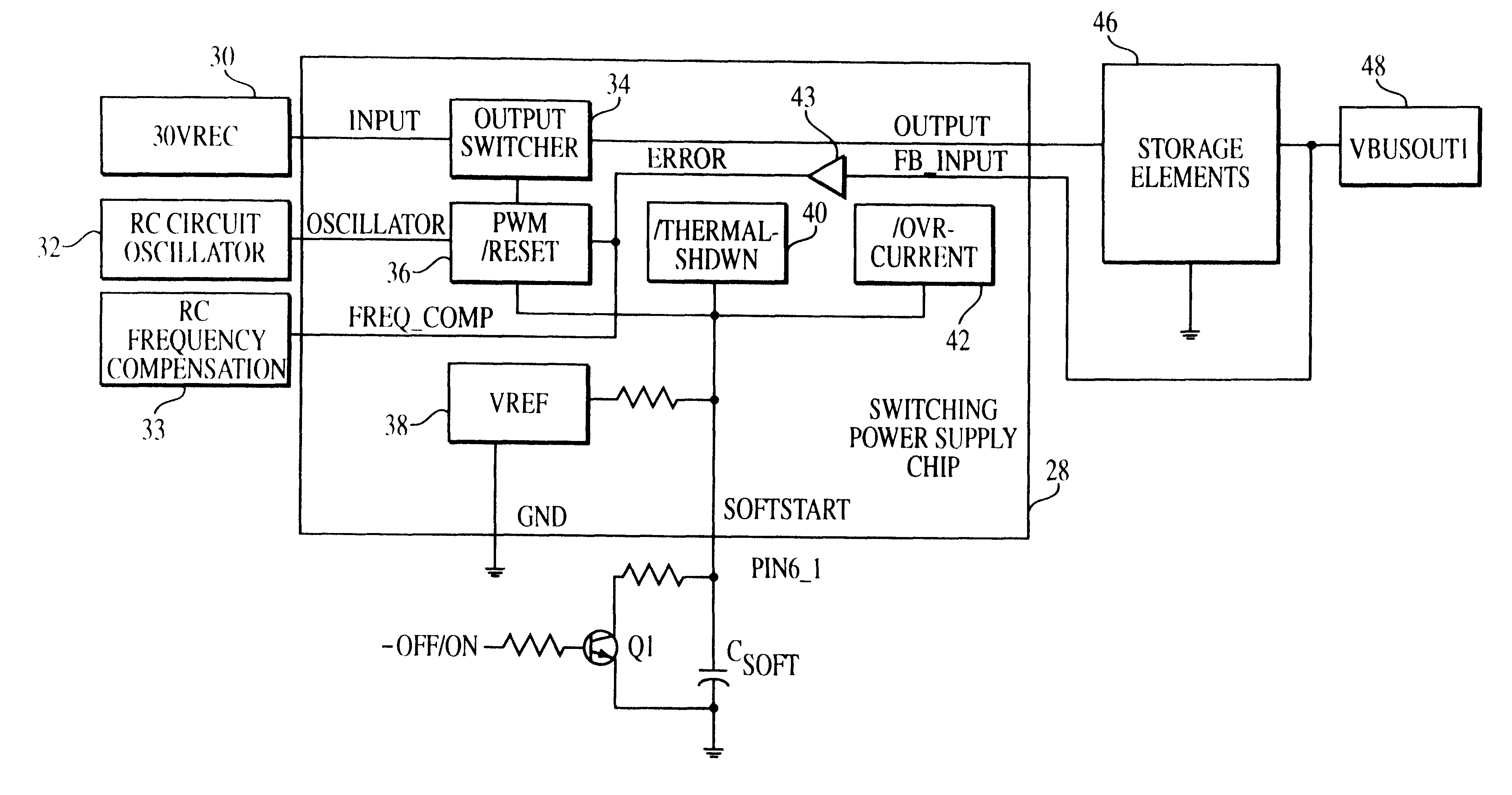

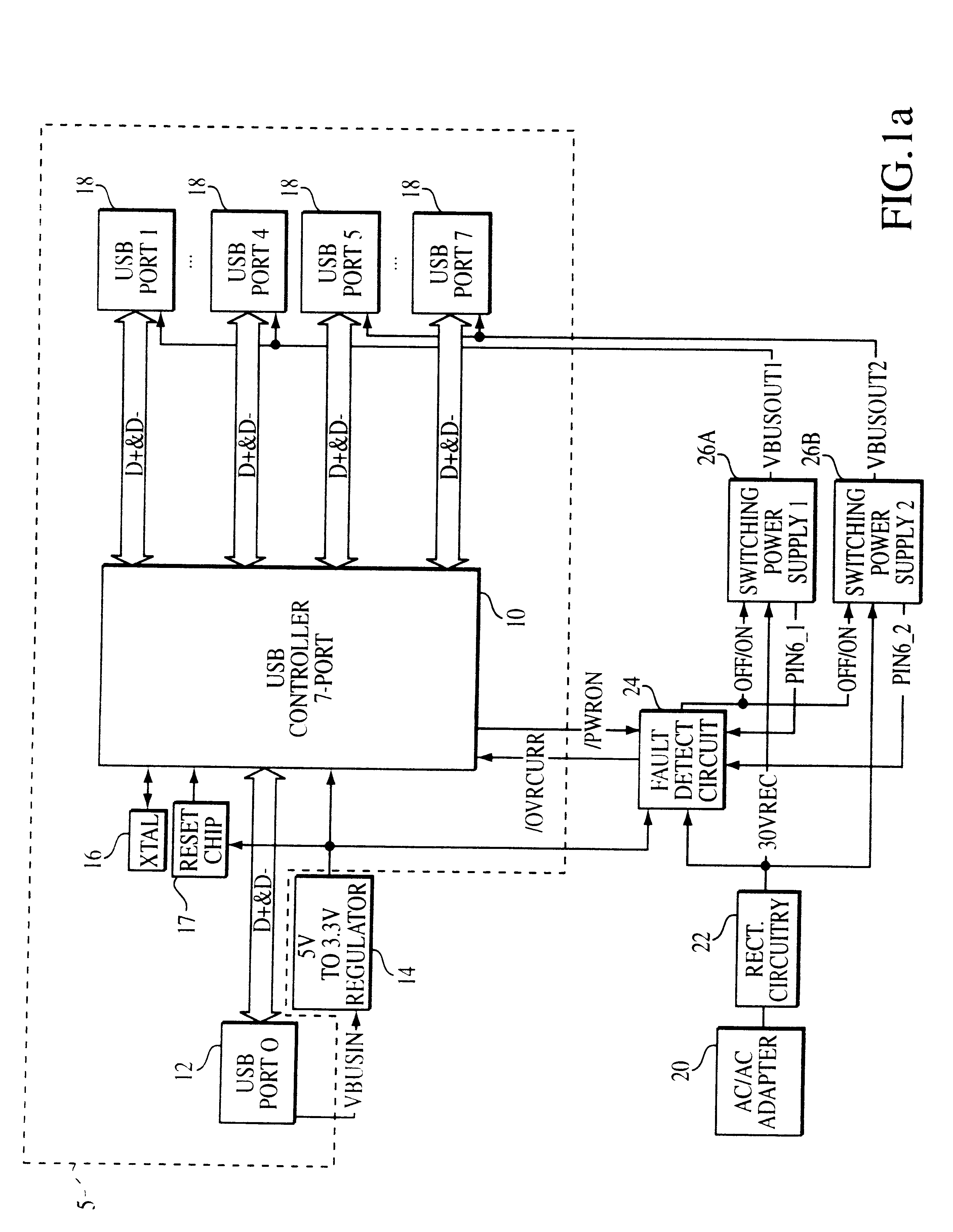

Fault detection on dual supply system for a universal serial bus system

InactiveUS6170062B1Easy to manufactureVolume/mass flow measurementMarginal checkingElectric power systemBus mastering

A method and apparatus for a dual power supply on a universal serial bus system using an overcurrent detect circuit. Dual power supplies in the universal serial bus system allows for greater flexibility of operation and is based on two separate power systems. The first power system is achieved using the power line on the bus connecting to the universal serial bus controller. The second power system is a separate power supply to power the downstream ports. Moreover, the universal serial bus system has an overcurrent and thermal error detect circuit based on the power system in order to achieve an efficient and cost effective method and apparatus in which to notify the universal serial bus controller of any error in the power system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Reconfigurable multidimensional array processor allowing runtime reconfiguration of selected individual array cells

InactiveUS7237087B2Small volumeEffects spaceEnergy efficient ICTMultiple digital computer combinationsClock rateAnd logic unit

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

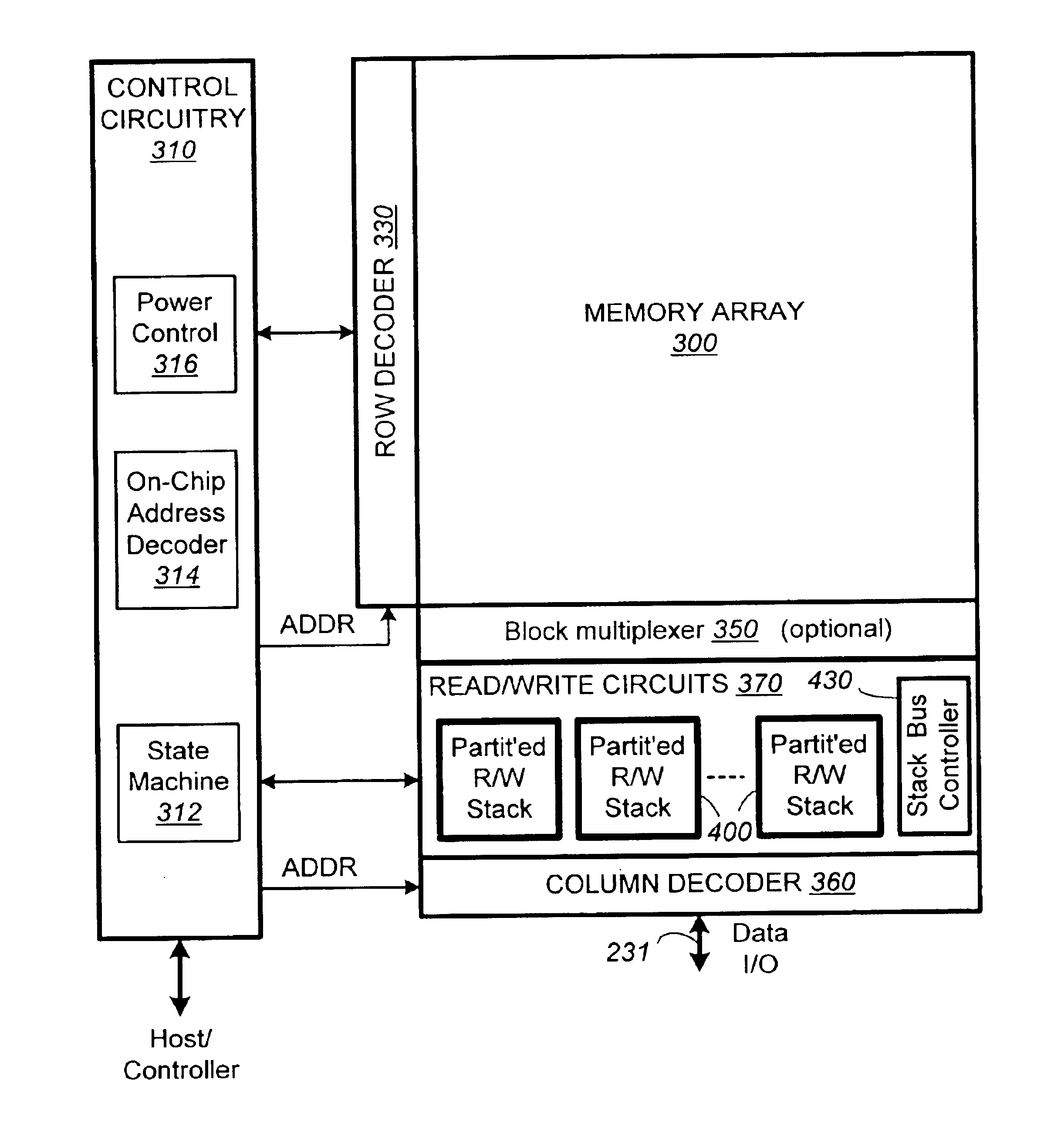

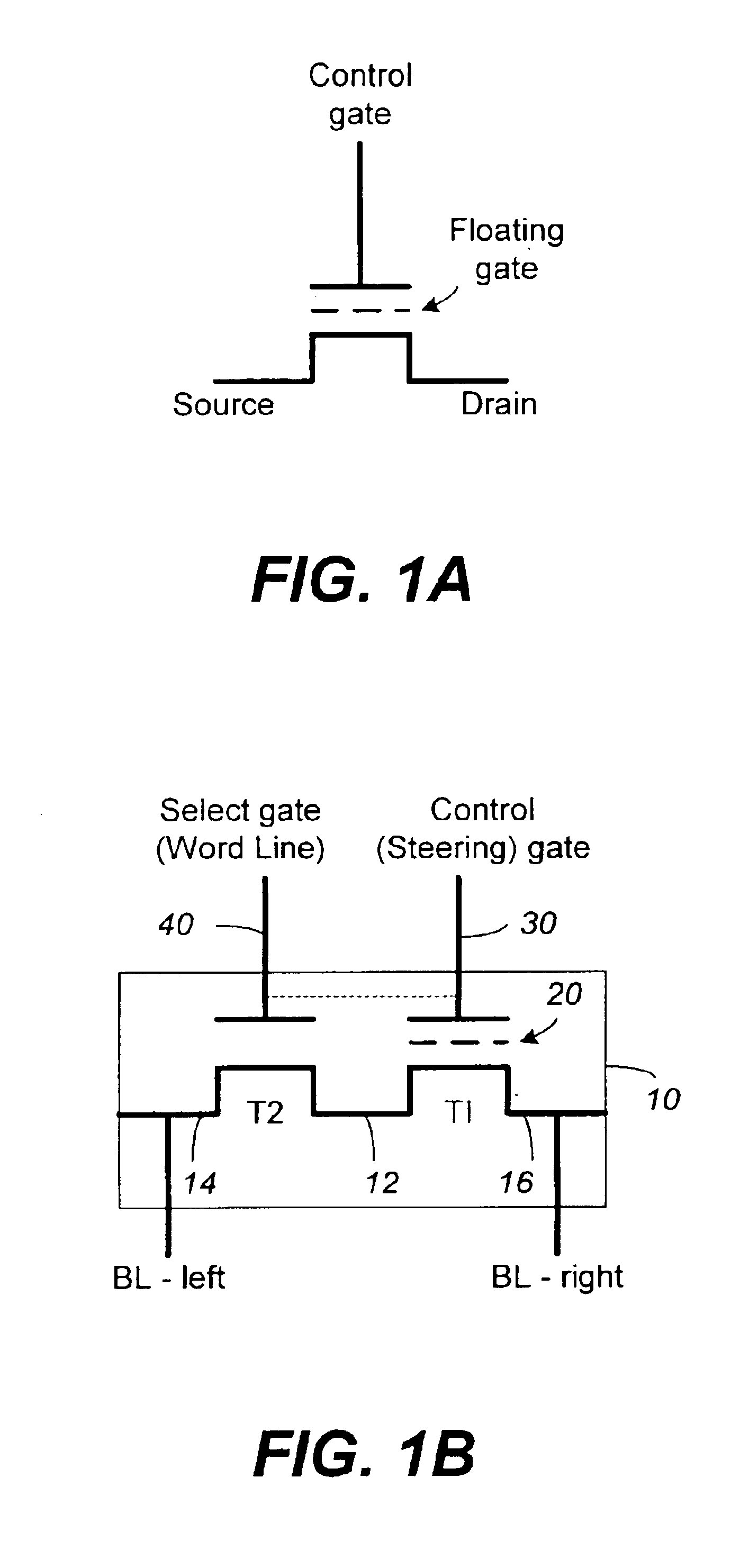

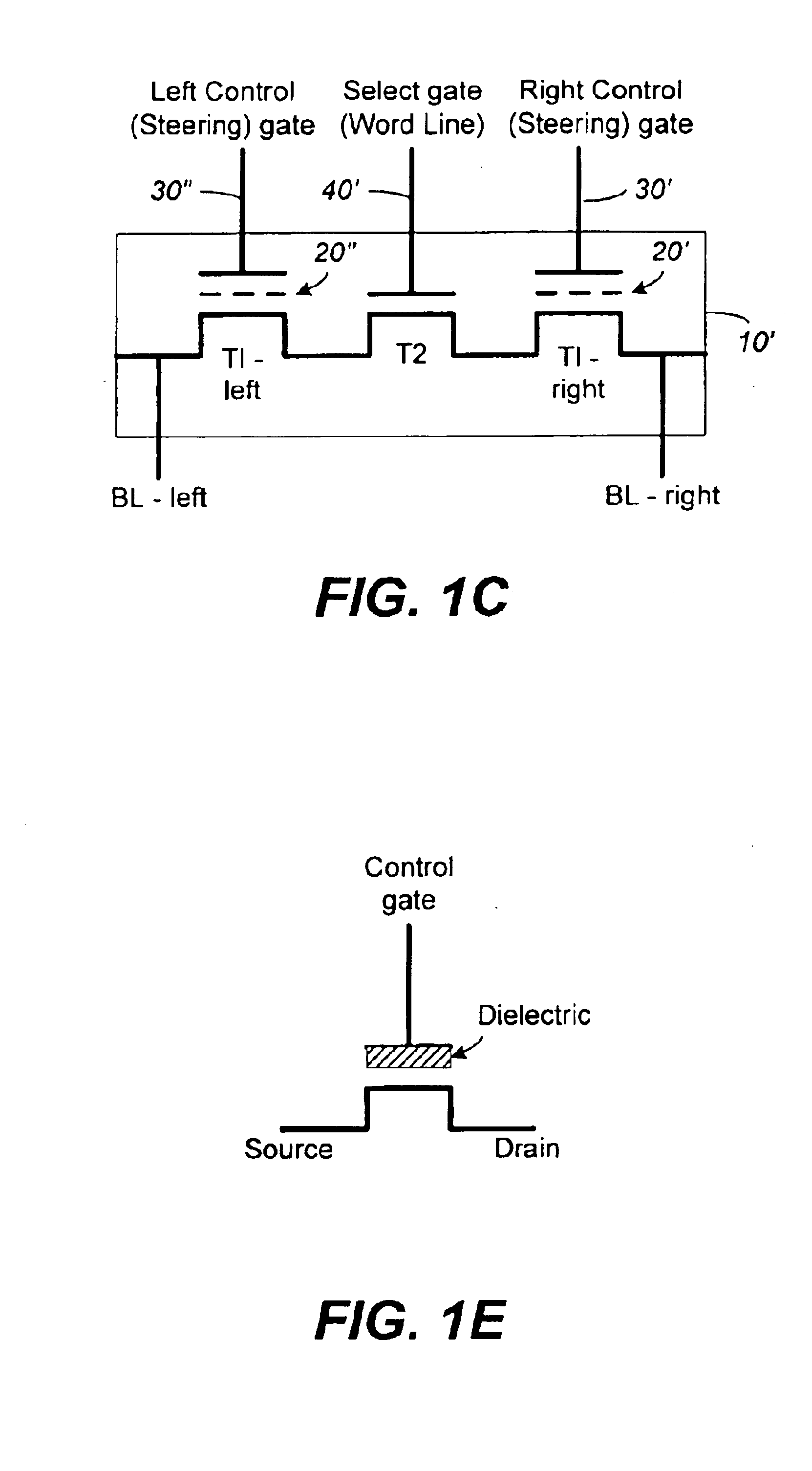

Highly compact non-volatile memory and method therefor with internal serial buses

InactiveUS6891753B2Improve performanceReduce redundancyRead-only memoriesDigital storageBus masteringComputer science

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. The multiple read / write circuits are organized into a bank of similar stacks of components. Redundant circuits among each stack are factored out. In one aspect, a serial bus allows communication between components in each stack, thereby reducing the number of connections in a stack to a minimum. A bus controller sends control and timing signals to control the operation of the components and their interactions through the serial bus. In a preferred embodiment, the bus transactions of corresponding components in all the similar stacks are controlled simultaneously.

Owner:INNOVATIVE MEMORY SYST INC

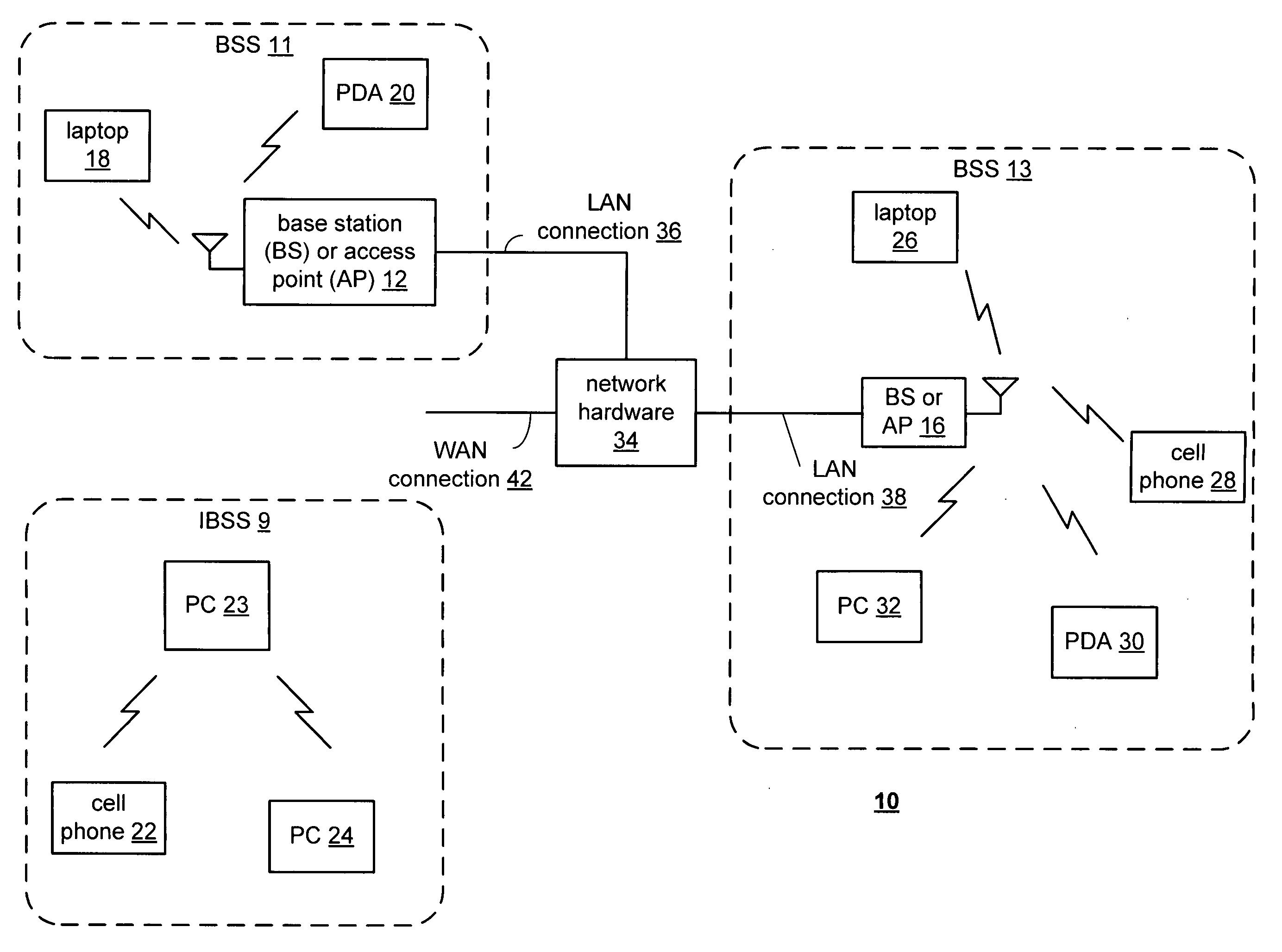

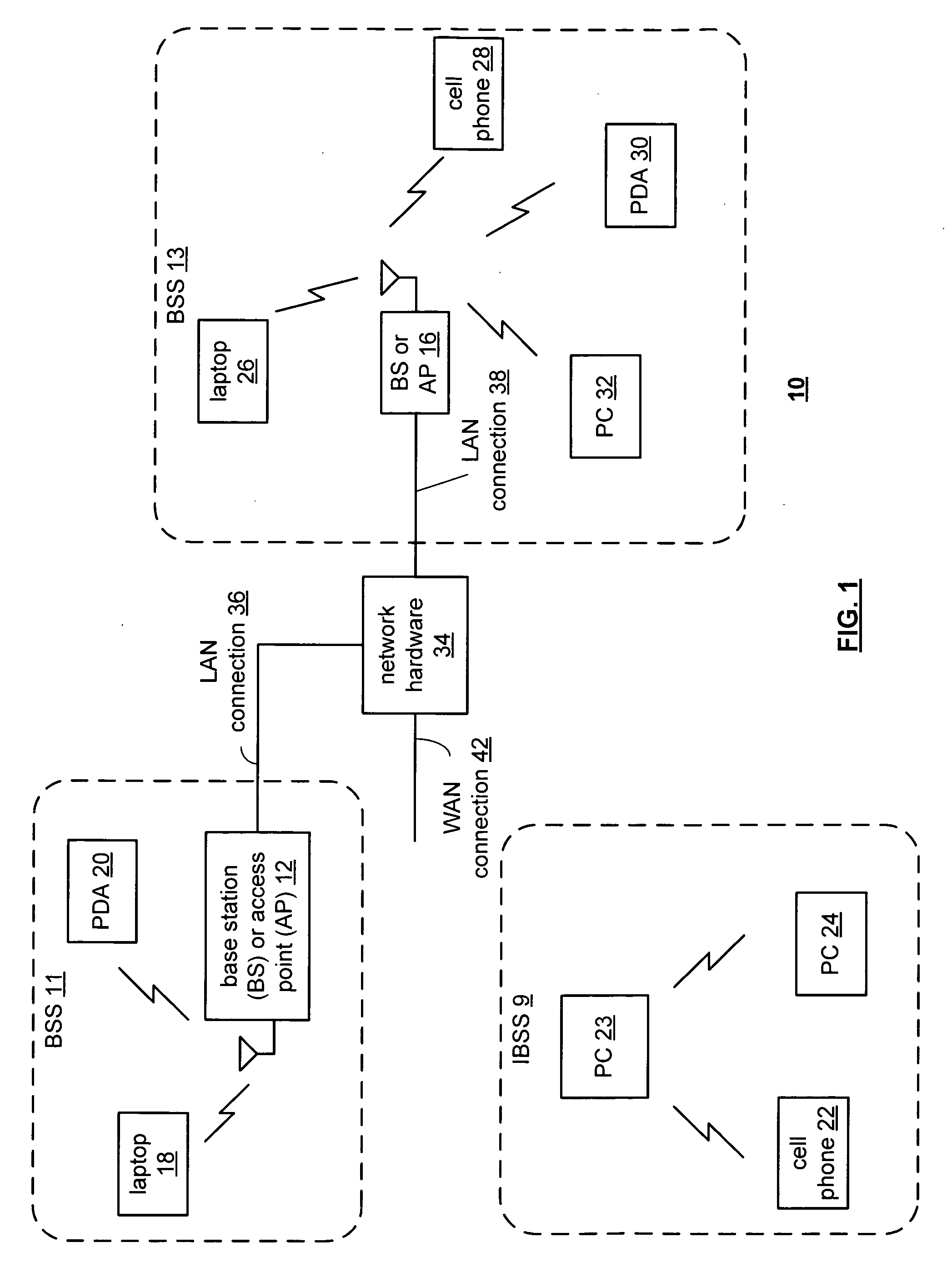

RF bus controller

ActiveUS20080181252A1Semiconductor/solid-state device detailsSolid-state devicesBus masteringRadio frequency

A radio frequency (RF) bus controller includes an interface and a processing module. The interface is coupled for communicating intra-device RF bus access requests and allocations. The processing module is coupled to receive an access request to an RF bus via the interface; determine RF bus resource availability; and when sufficient RF bus resources are available to fulfill the access request, allocate, via the interface, at least one RF bus resource in response to the access request.

Owner:AVAGO TECH INT SALES PTE LTD

Scalable DMA remapping on a computer bus

InactiveUS20060277348A1Eliminate needMemory architecture accessing/allocationMemory systemsMemory addressMemory map

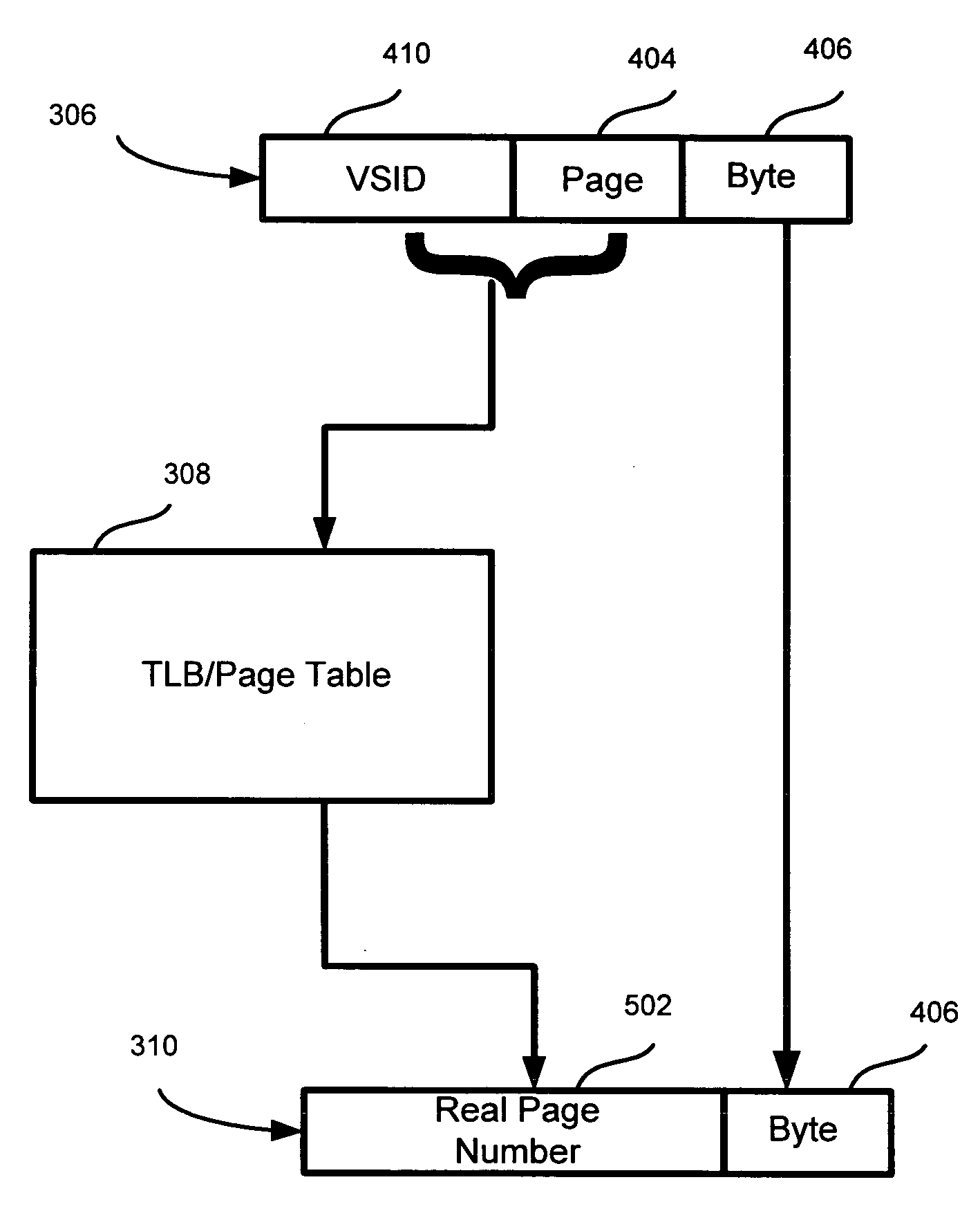

A system for addressing bus components comprises a bus controller component that controls access between a CPU and a memory address space. A plurality of bus components connected to said bus controller over a bus are addressable via a memory mapped address within the address space. An address translation table is stored on at least one of the plurality of bus components. The bus translation table stores a translation between a virtual address and a real address.

Owner:MICROSOFT TECH LICENSING LLC

Non-blocking bus controller for a pipelined, variable latency, hierarchical bus with point-to-point first-in first-out ordering

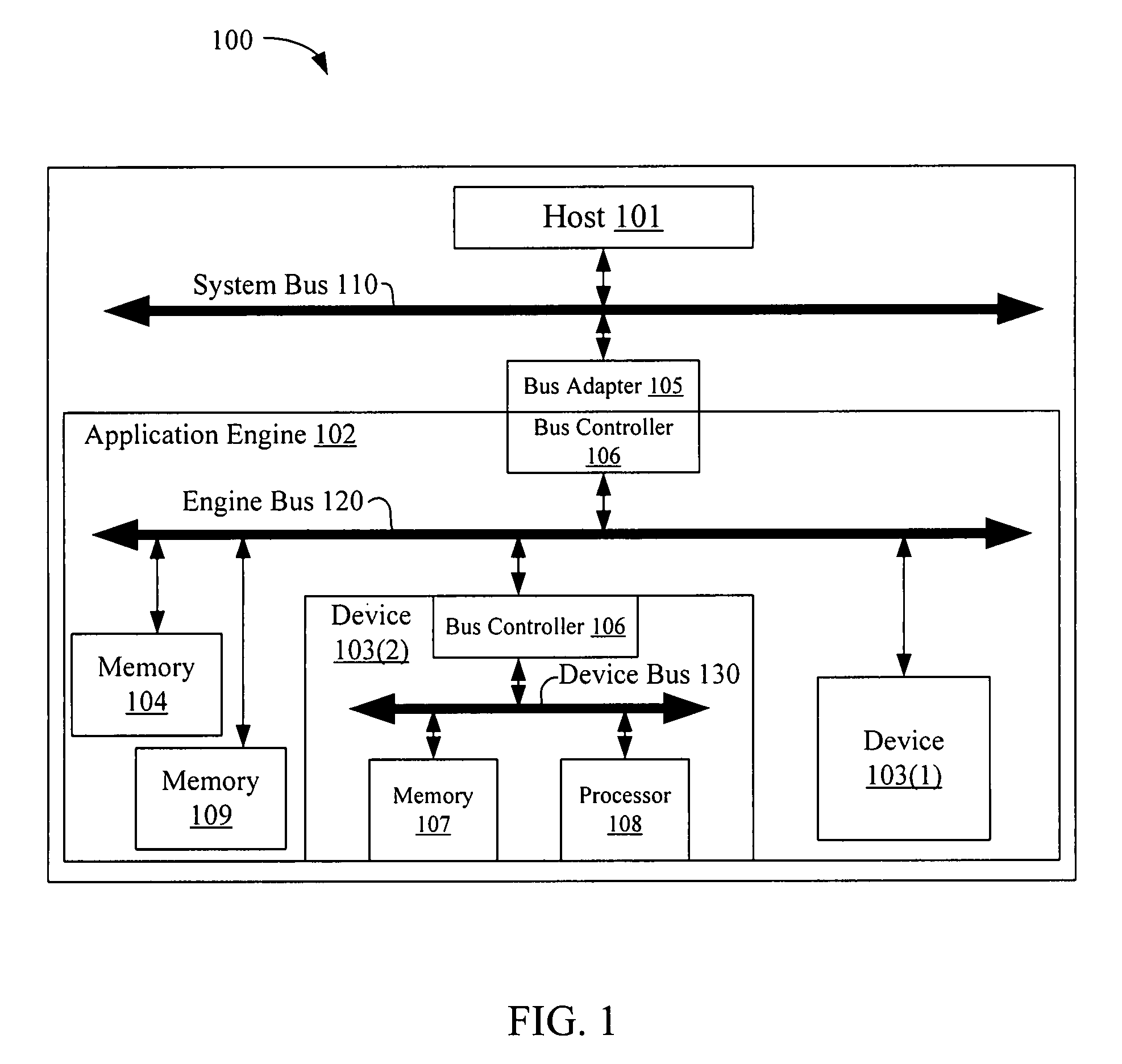

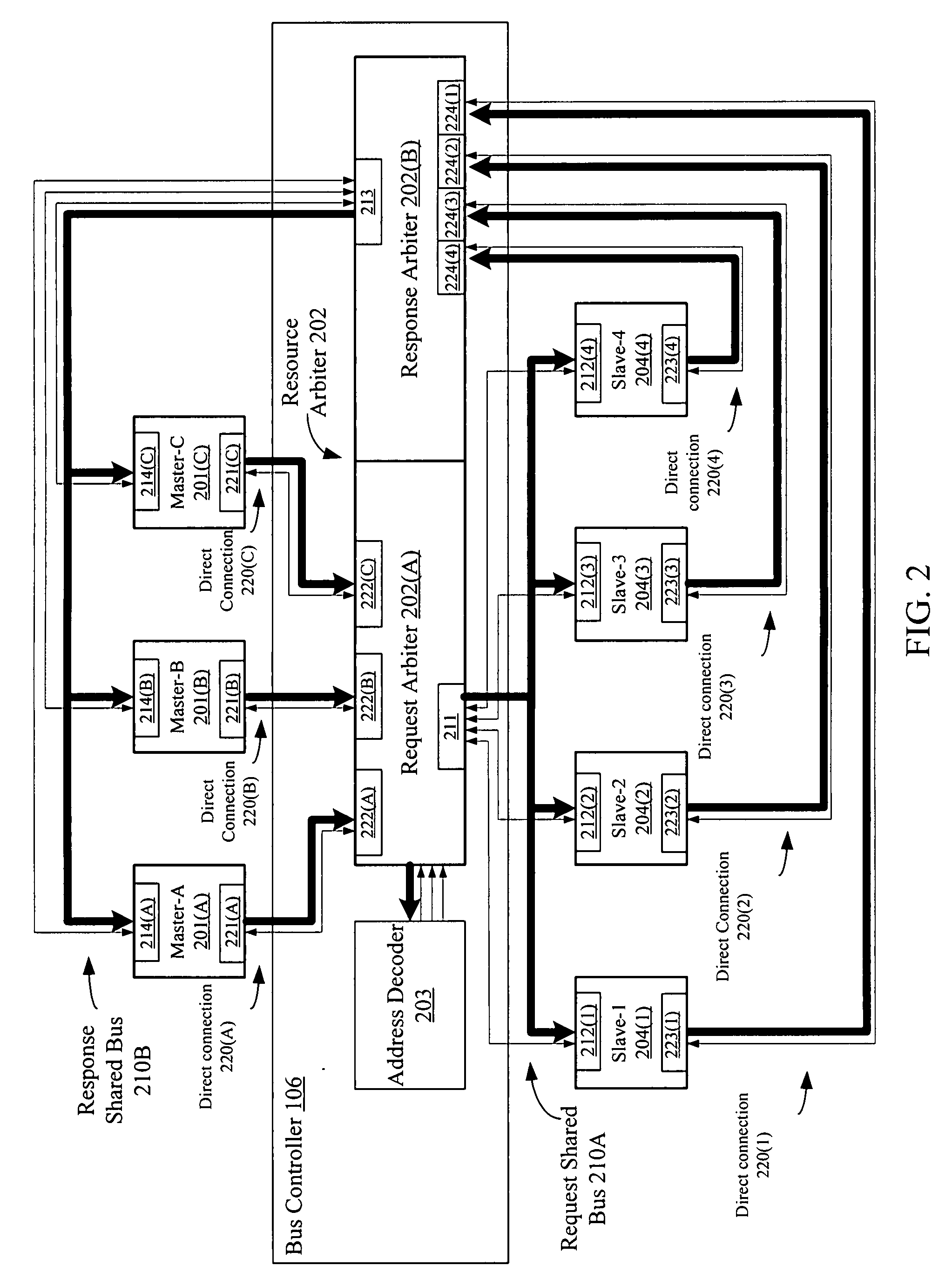

A method and apparatus is disclosed herein for a bus controller that supports a flexible bus protocol that handles pipelined, variable latency bus transactions while maintaining point-to-point (P2P) FIFO ordering of transactions in a non-blocking manner. In one embodiment, the apparatus includes a bus controller to receive a plurality of bus transactions at a first incoming port from a bus. The bus controller is configured to process the plurality of bus transactions in a pipelined manner, maintaining P2P FIFO ordering of the plurality of bus transactions even when the plurality of bus transactions take a variable number of cycles to complete.

Owner:SYNFORA

Data Sensor Coordination Using Time Synchronization in a Multi-Bus Controller Area Network System

A method is provided for synchronizing time in an unsynchronized vehicle controller area network system. A master control unit receives a global time from a time synchronization source. The master control unit estimates a respective time delay in transmitting messages by electronic control units on each controller area network bus. The time delay is a difference between a time when a message is generated by a respective electronic control unit for transmission on a respective controller area network bus and a time when the message is transmitted on the respective controller area network bus. The global time is adjusted for each respective controller area network bus based on the estimated time delays associated with each respective controller area network bus. Global time messages from the master control unit are transmitted to each electronic control unit that include the adjusted global times for an associated controller area network bus.

Owner:GM GLOBAL TECH OPERATIONS LLC

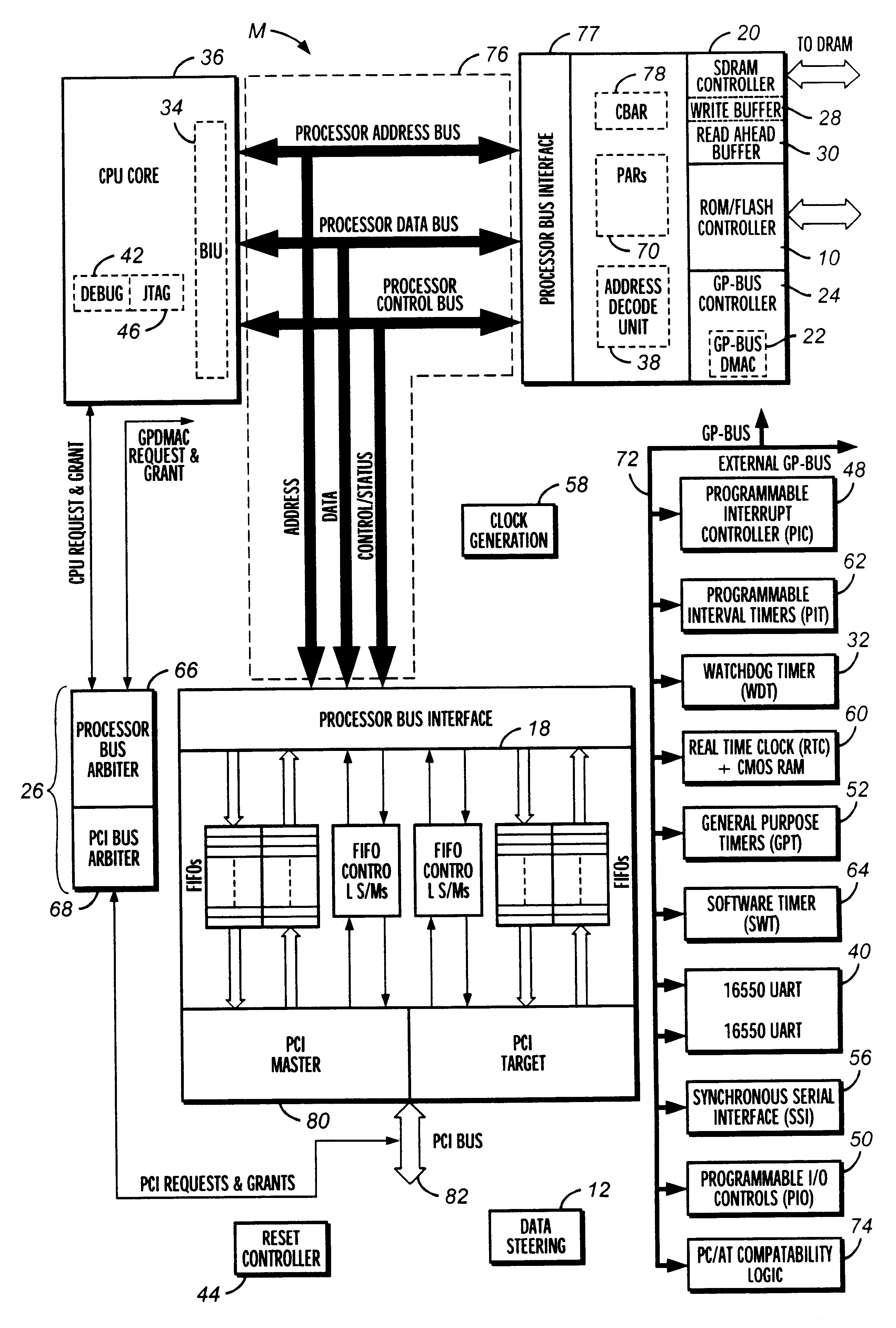

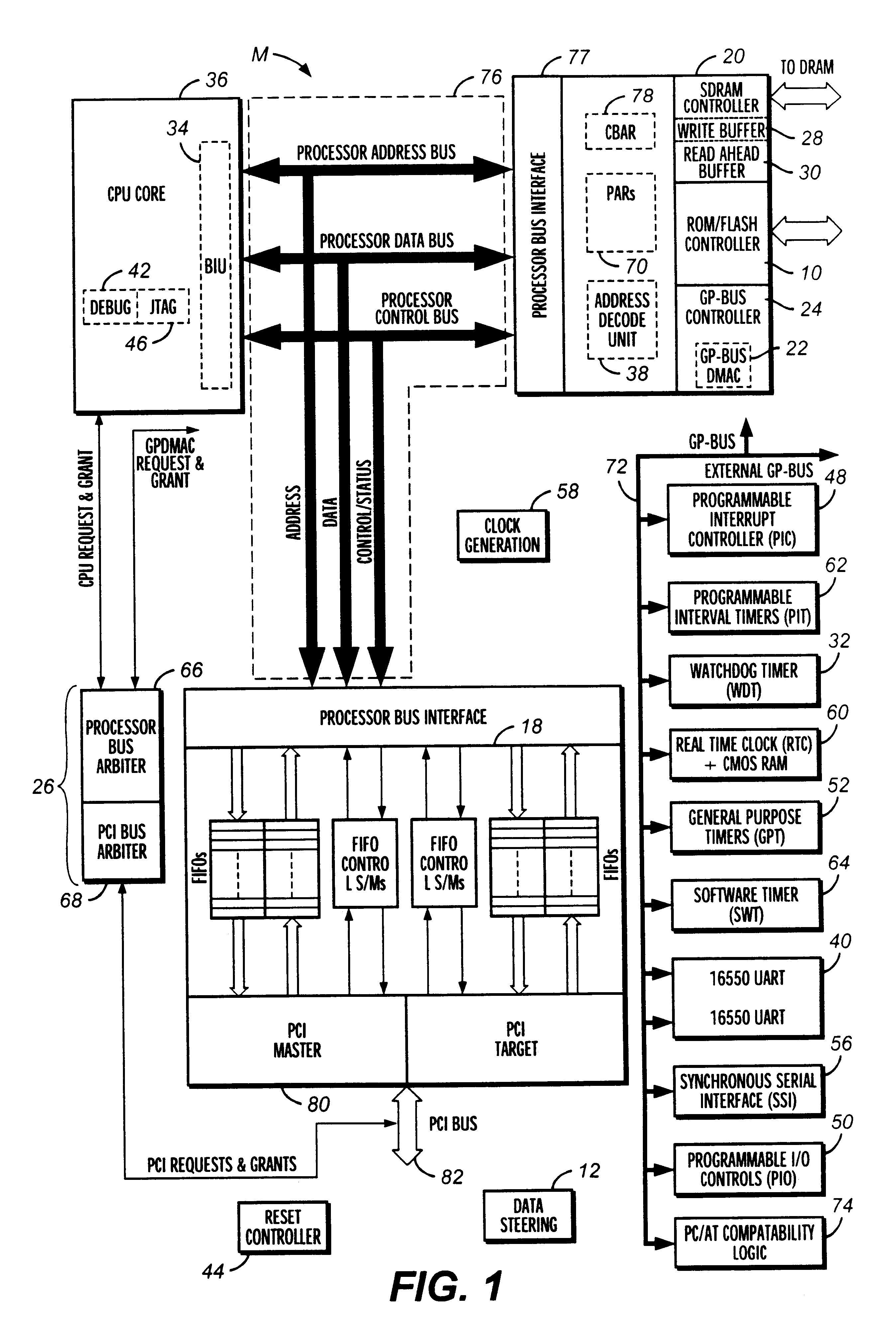

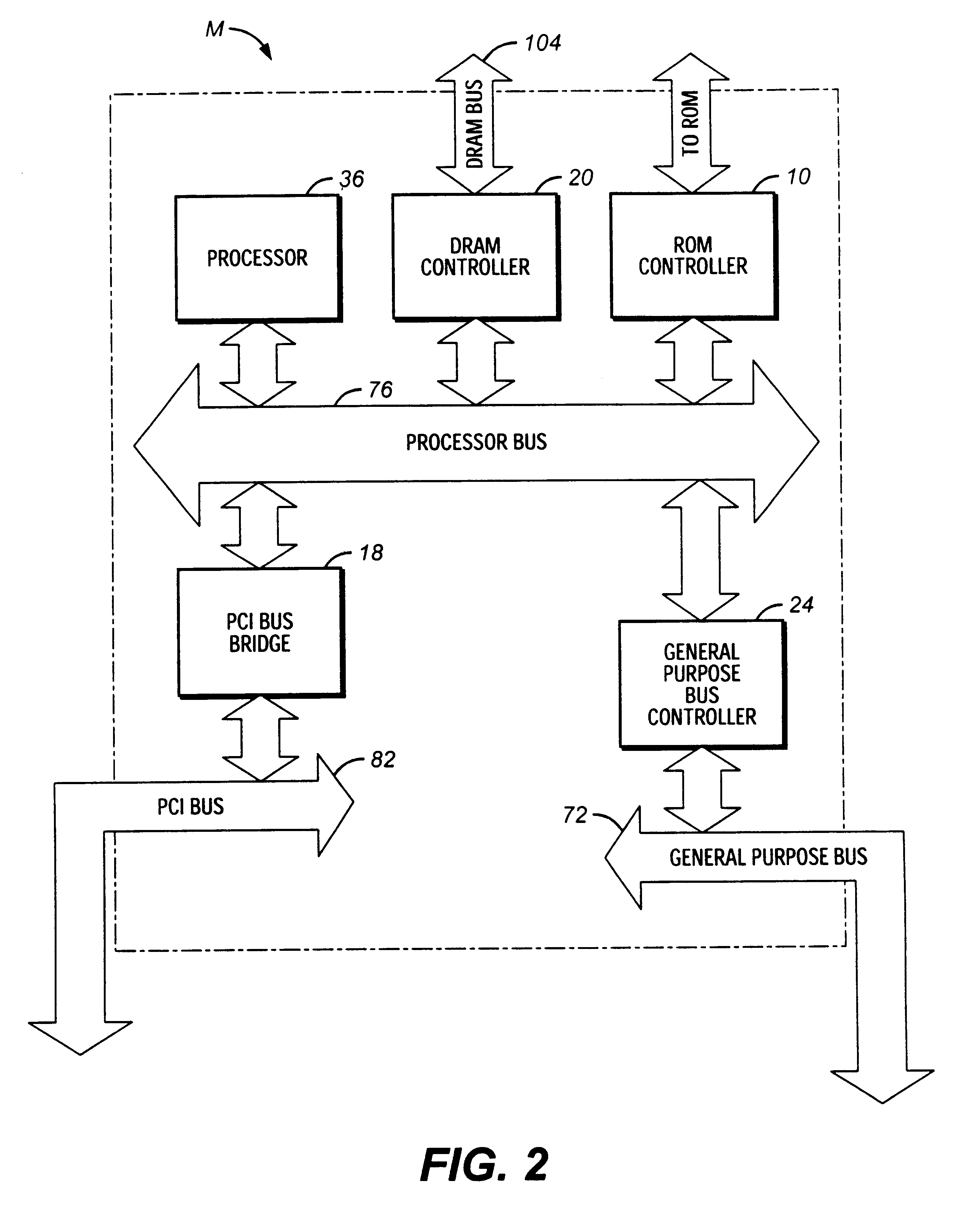

Flexible microcontroller architecture

A microcontroller provides a flexible architecture to readily support both general embedded applications and communications applications. The microcontroller includes an embedded processor, a relatively low-speed general purpose peripheral bus controller, a relatively high-speed peripheral bus host bridge, a primary memory controller, and a secondary memory controller, each coupled to a processor bus. The general purpose peripheral bus controller is coupled to a relatively low-speed general purpose peripheral bus which is coupled to a plurality of integrated general purpose peripherals. The relatively high-speed peripheral bus host bridge is coupled to a relatively high-speed peripheral bus capable of supporting a plurality of communication-oriented peripherals. The secondary memory controller shares an address bus with the general purpose peripheral bus controller and shares a data bus with either the primary memory controller or the general purpose peripheral bus controller. The control timing of the secondary memory controller is independent of the control timing of the general purpose peripheral bus controller. Also, a processor arbiter is coupled to the embedded processor, and a relatively high-speed peripheral bus arbiter is coupled to the peripheral bus host bridge. Aside from the microcontroller, an embedded system can include a relatively low-speed general purpose peripheral bus and a relatively high-speed peripheral bus, both external to the microcontroller. The external relatively lowspeed general purpose bus can be coupled to the relatively low-speed general purpose peripheral bus controller, and the external relatively high-speed peripheral bus can be coupled to the relatively high-speed peripheral bus host bridge.

Owner:ADVANCED MICRO DEVICES INC

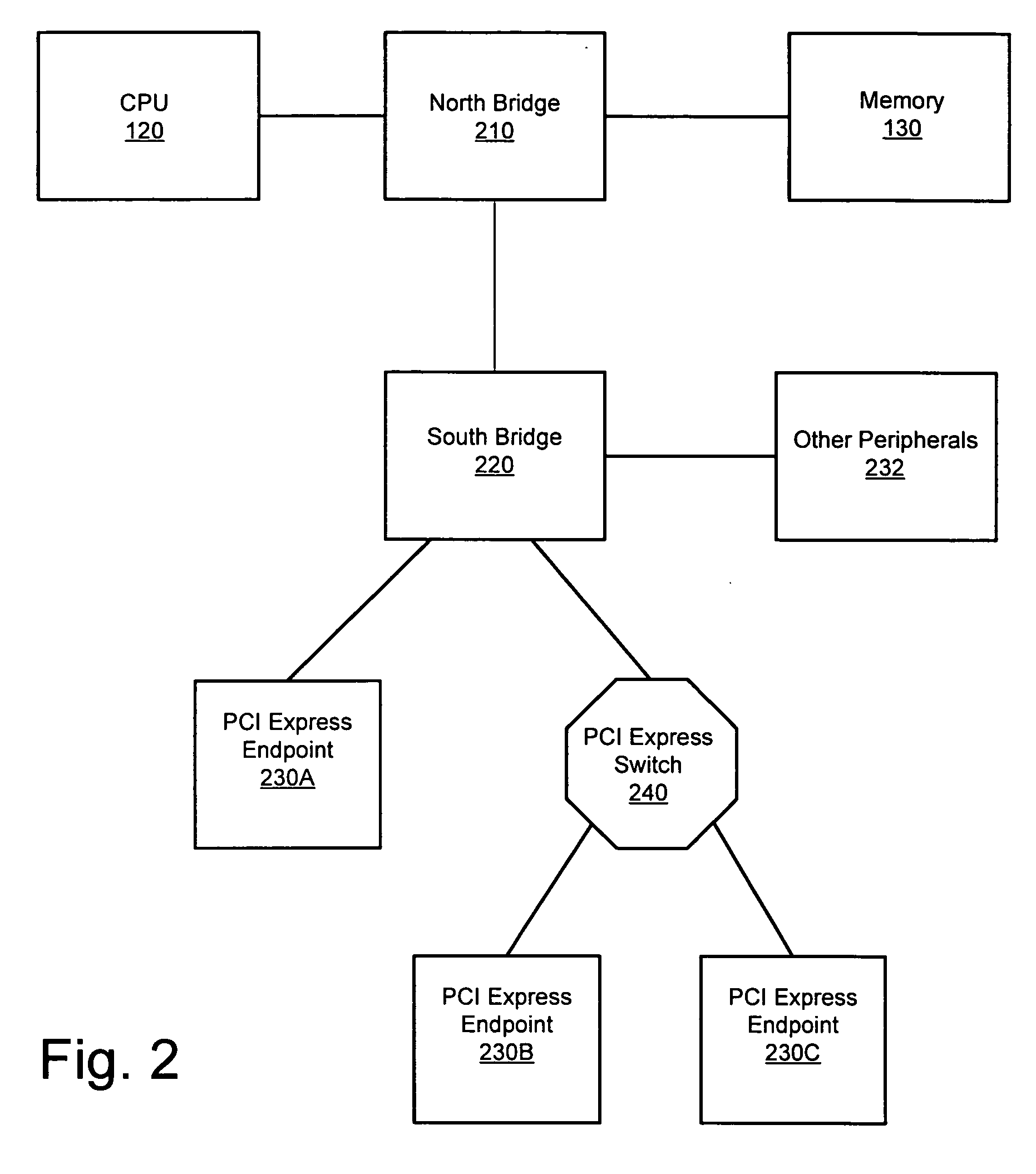

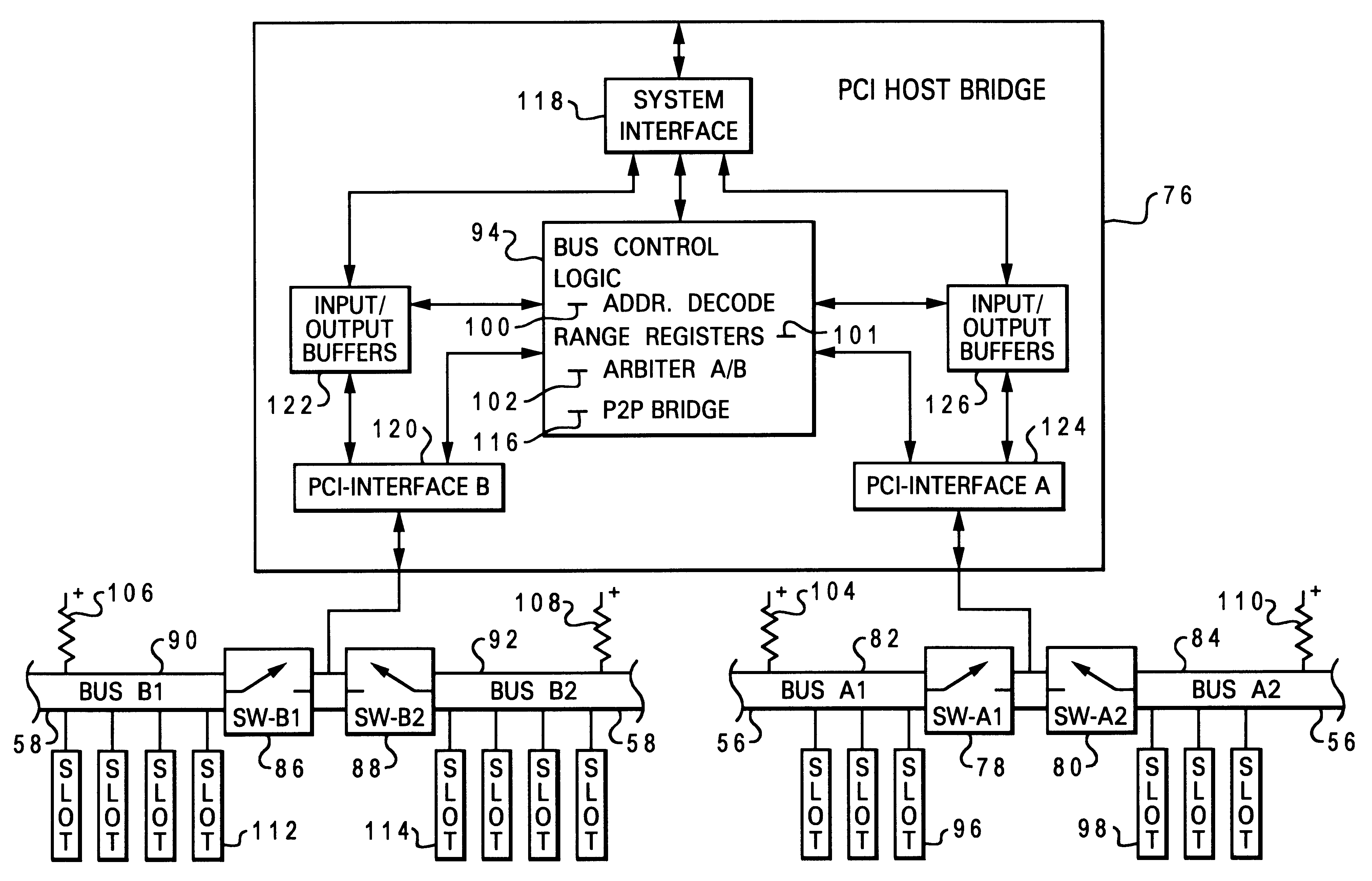

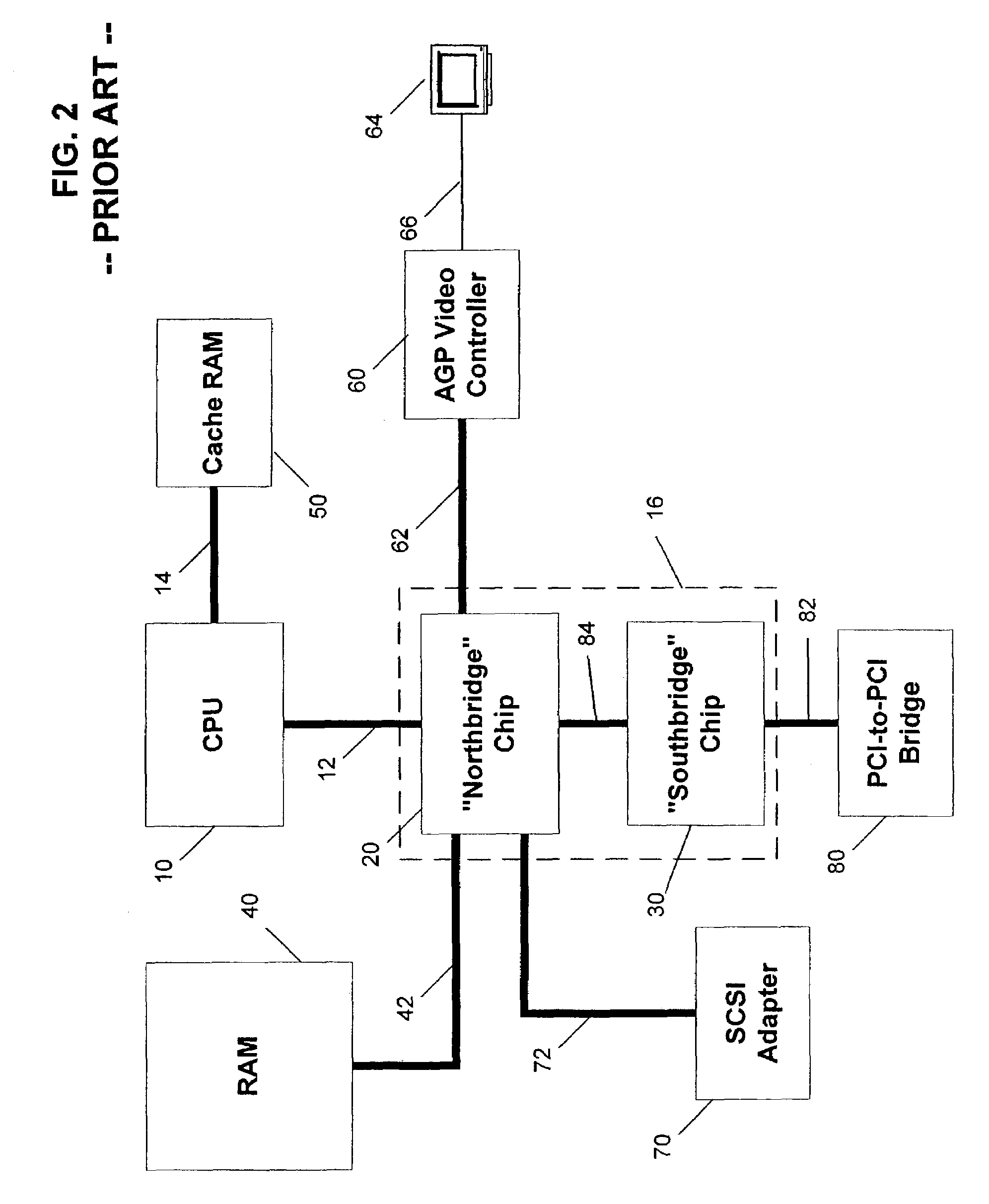

Method and system for supporting peripheral component interconnect (PCI) peer-to-peer access across a PCI host bridge supporting multiple PCI buses

A method and system for supporting multiple Peripheral Component Interconnect (PCI) local buses through a single PCI host bridge having multiple PCI interfaces within a data-processing system are disclosed. In accordance with the method and system of the present invention, a processor and a system memory are connected to a system bus. First and second PCI local buses are connected to the system bus through a PCI host bridge. The first and second PCI local buses have sets of in-line electronic switches, dividing the PCI local buses into PCI local bus segments supporting a plurality of PCI peripheral component slots for connecting PCI devices. The sets of in-line electronic switches are open and closed in accordance with bus control logic within the PCI host bridge allowing up to fourteen or more PCI peripheral component slots for connecting up to fourteen PCI devices to have access through a single PCI host bridge to the system bus. An internal PCI-to-PCI bridge is provided to allow a PCI device to share data with another PCI device as peer-to-peer devices across the first and second PCI local bus segments.

Owner:IBM CORP

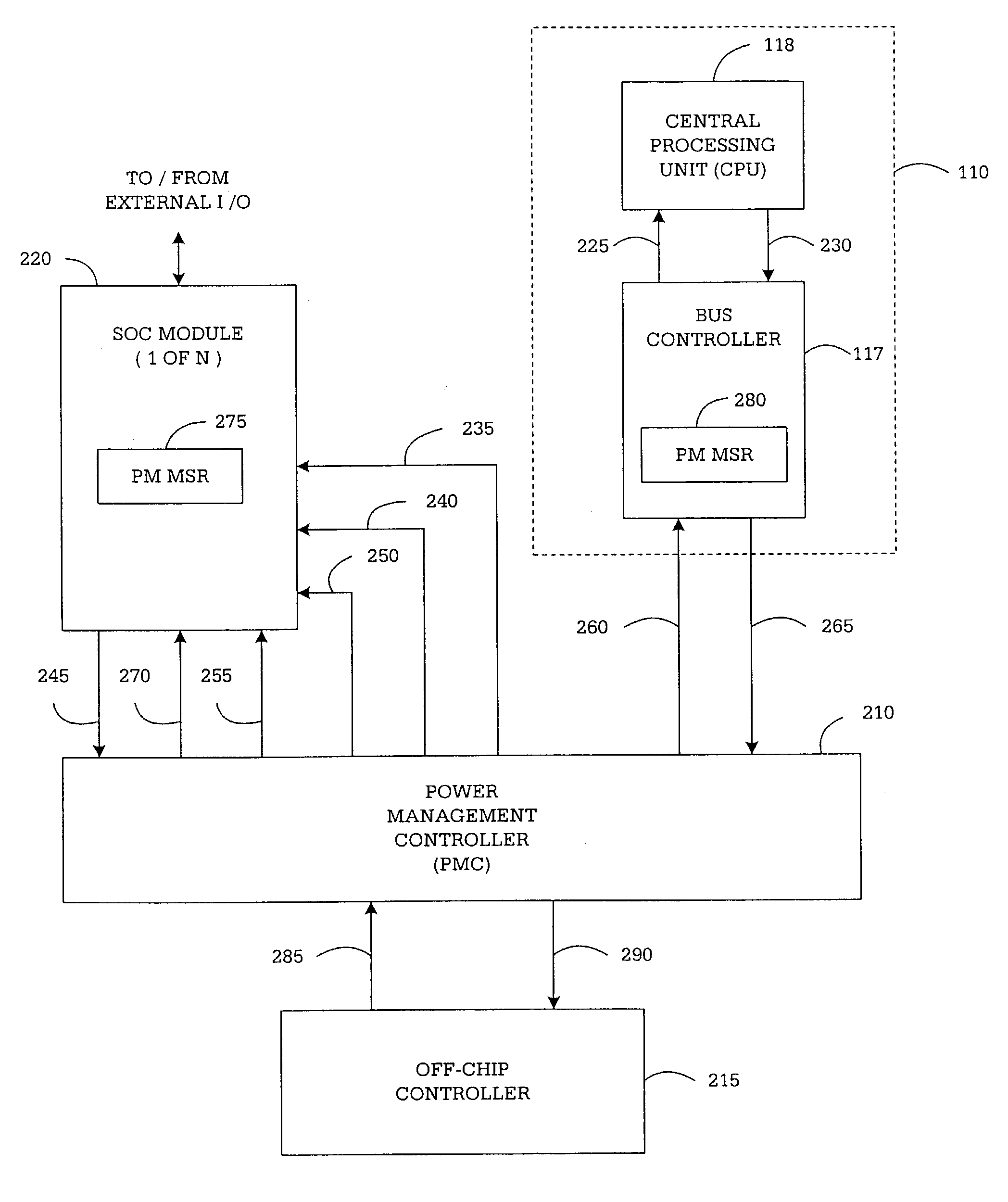

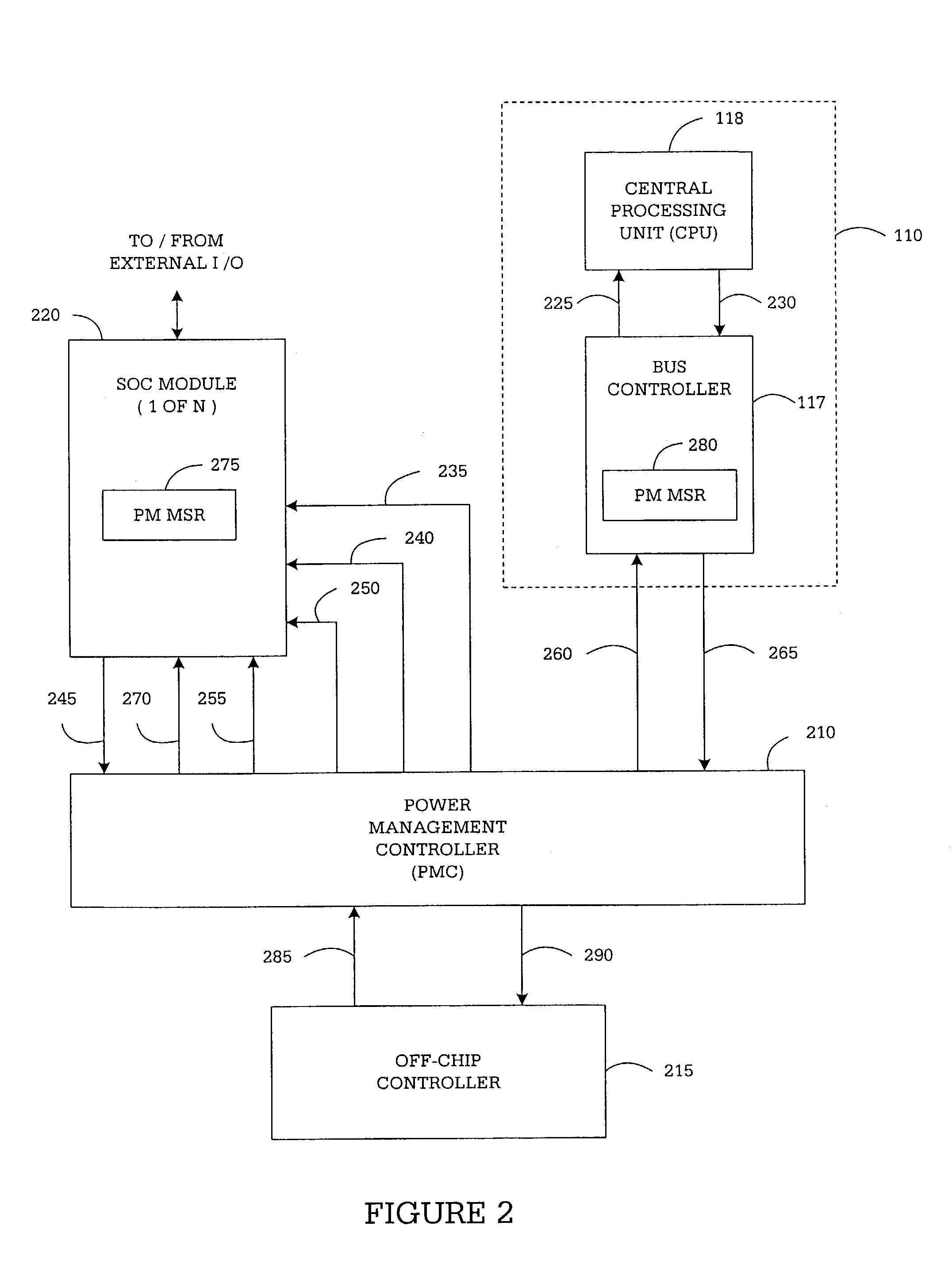

Apparatus and method for initiating a sleep state in a system on a chip device

ActiveUS7039819B1Efficiently initiating sleep stateEfficient coordinationEnergy efficient ICTVolume/mass flow measurementSleep stateControl signal

An apparatus and method is disclosed for initiating a sleep state in a system-on-a-chip (SOC) device. The apparatus comprises a bus controller coupled to a central processing unit (CPU) and a power management controller that is coupled to the bus controller and to a plurality of SOC modules. The power management controller sends control signals to the bus controller and to the SOC modules to coordinate the shutting down of power to the SOC modules during a process in which the power management controller places the SOC modules of the system-on-a-chip (SOC) device into a sleep state.

Owner:GLOBALFOUNDRIES US INC

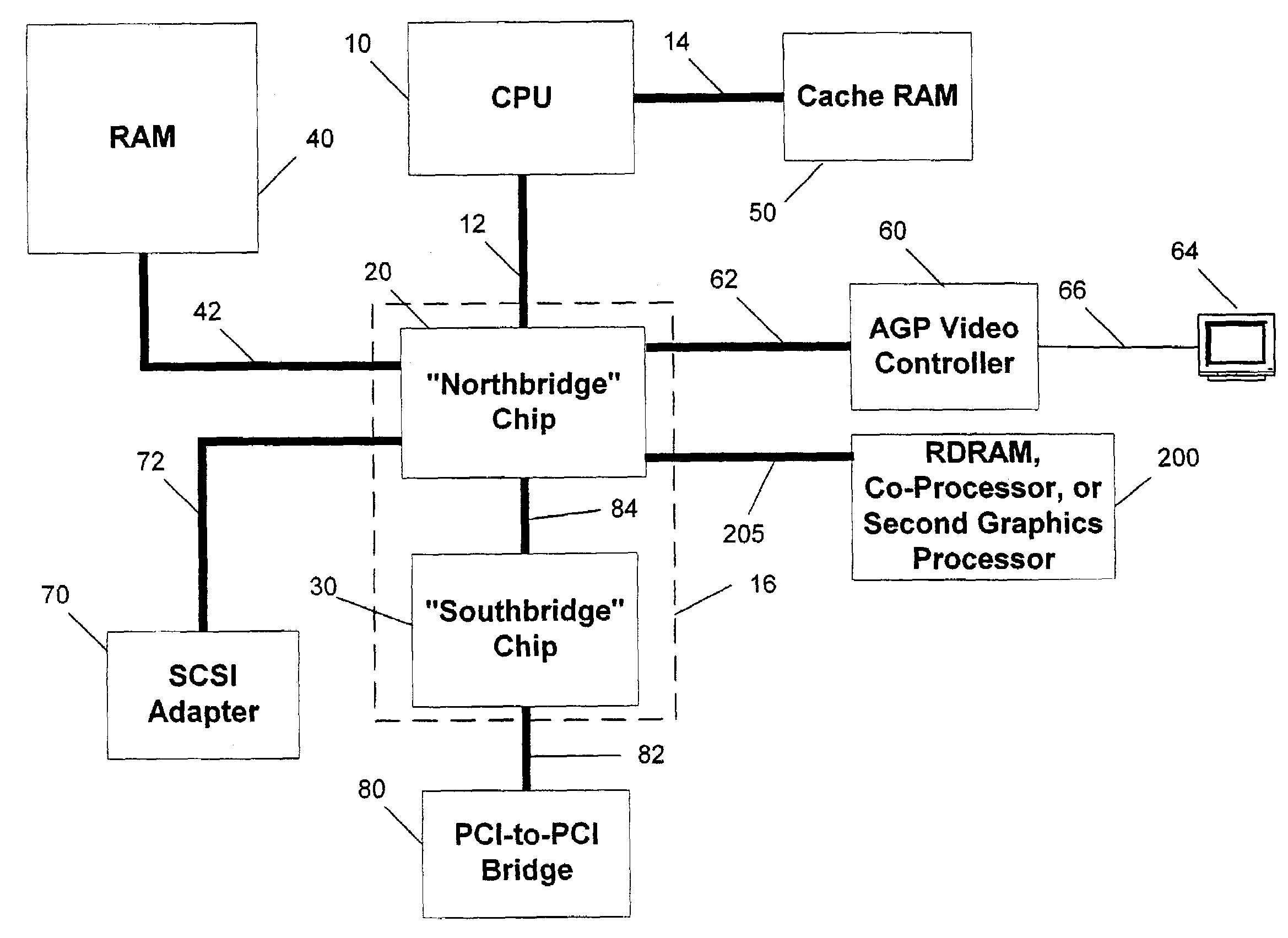

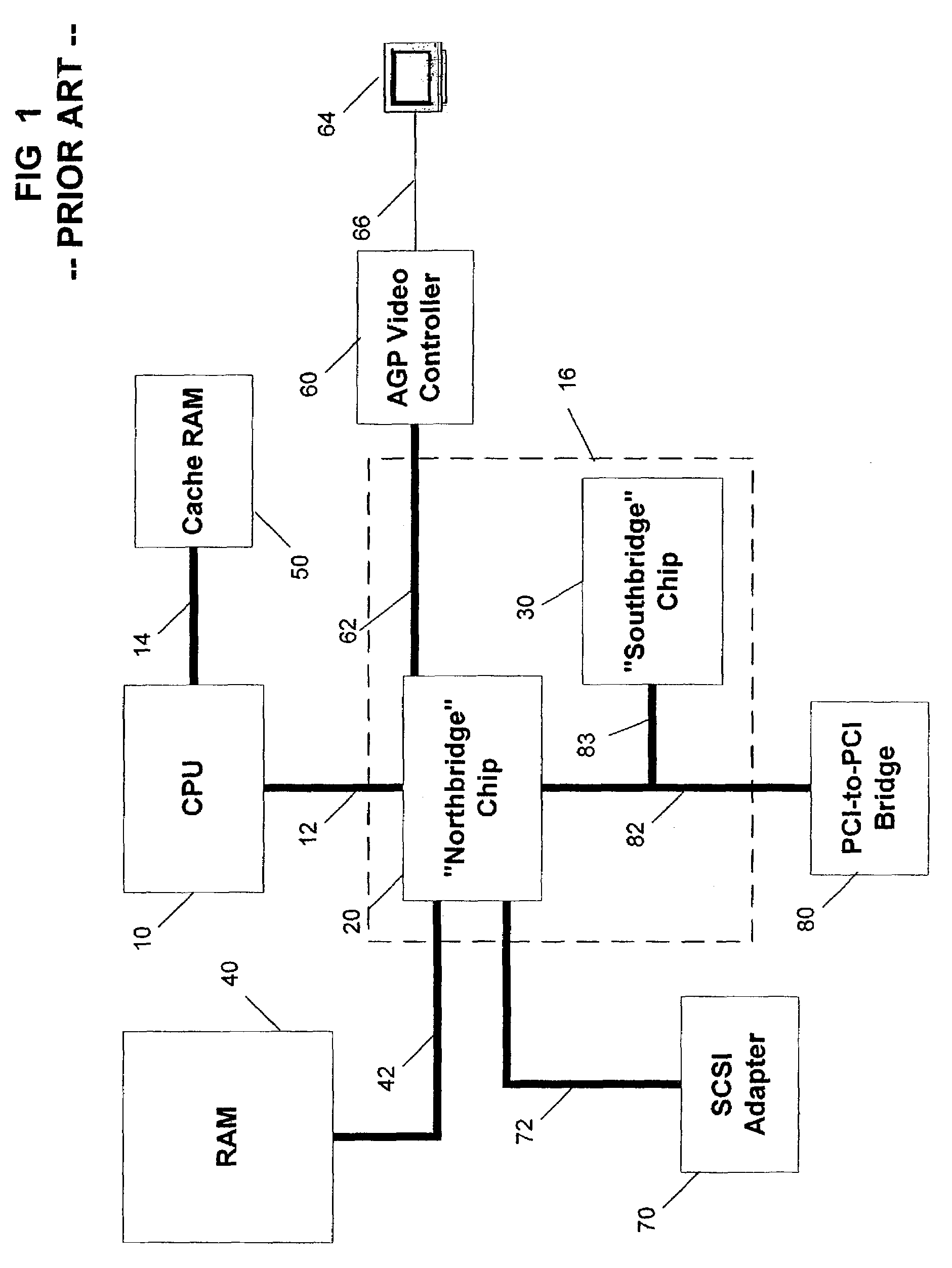

CPU expandability bus

Embodiments of the present invention provide a computer system with a high speed, high bandwidth expandability bus for integrated and non-integrated CPU products. The computer system includes a processor, a chipset coupled to the processor, a graphics processor coupled to the chipset for controlling a video display and a main memory coupled to the chipset. The computer system further includes an expandability bus, which is coupled at one end to the chipset and at the other end to a replaceable electronic component. The expandability bus can be changeably configured to enable or disable bus mastering at both ends, as required, to operate with whichever replaceable electronic component is installed.

Owner:INTEL CORP

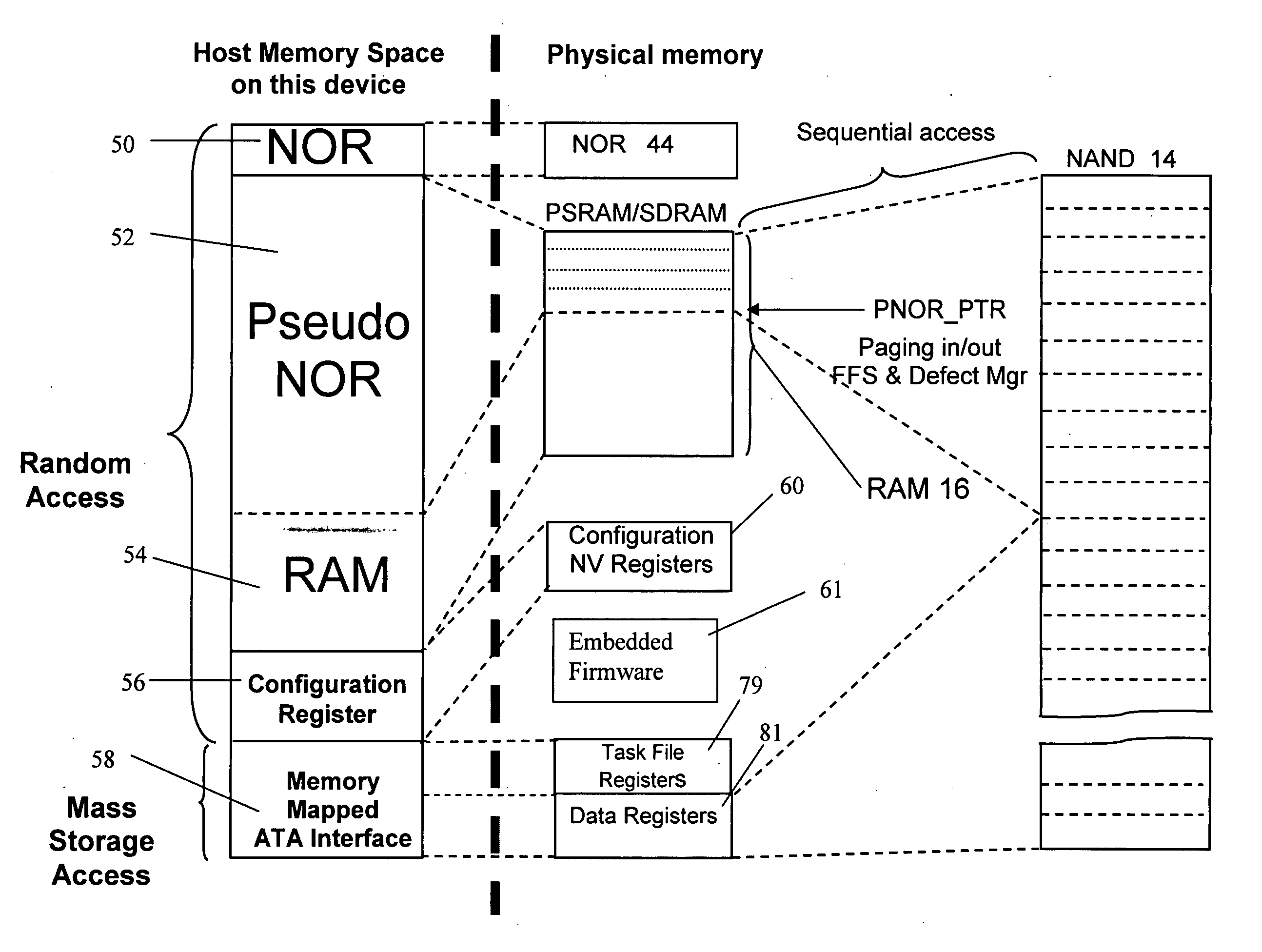

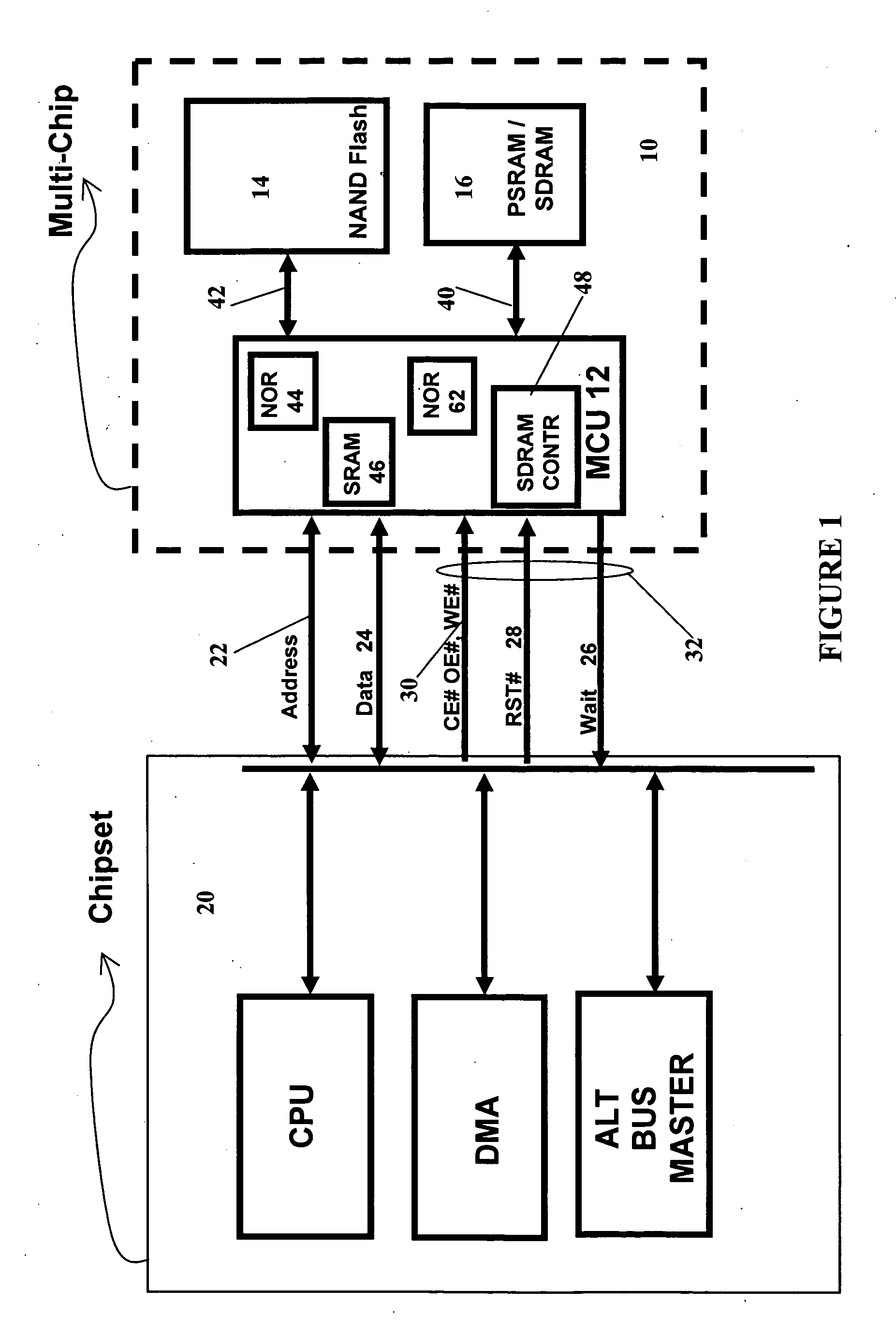

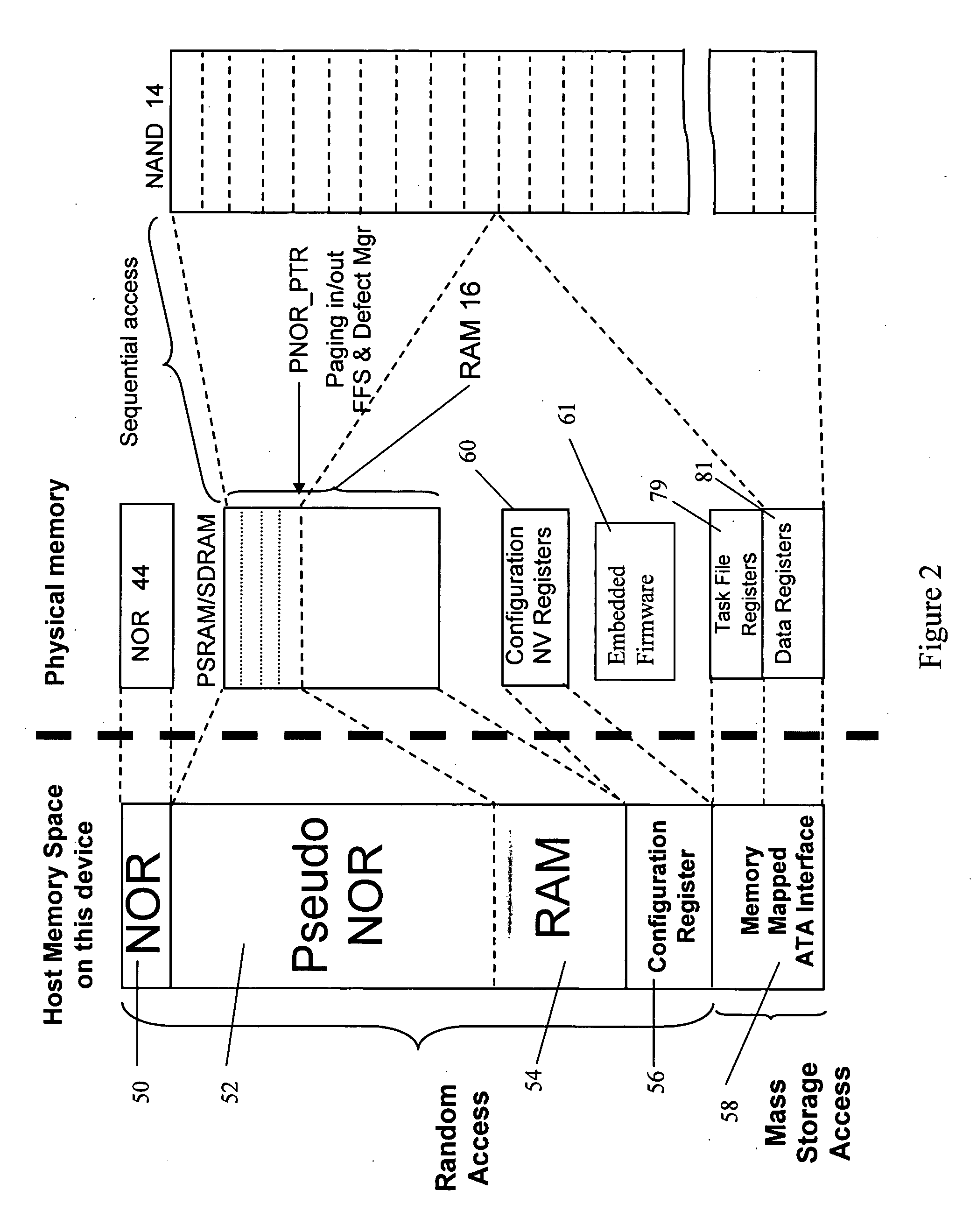

Unified memory and controller

InactiveUS20070147115A1Memory adressing/allocation/relocationDigital storageData coherenceControl signal

A memory device has a controller. The controller has a first address bus for receiving a RAM address signals, a first data bus for receiving RAM data signals, and a first control bus for receiving RAM control signals. The controller further has a second address bus for interfacing with a volatile RAM memory, a second data bus for interfacing with the volatile RAM memory, and a second control bus for interfacing with the volatile RAM memory. The controller further has a third address / data bus for interfacing with a non-volatile NAND memory, and a third control bus for interfacing with non-volatile NAND memory. The memory device further having a RAM memory connected to said second address bus, said second data bus, and said second control bus. The memory device further having a non-volatile NAND memory connected to the third address / data bus and to the third control bus. The controller also has a non-volatile bootable memory, and further has means to receive a first address on the first address bus and to map the first address to a second address in the non-volatile NAND memory, with the volatile RAM memory serving as cache for data to or from the second address in the non-volatile NAND memory, and means for maintaining data coherence between the data stored in the volatile RAM memory as cache and the data at the second address in the non-volatile NAND memory.

Owner:GREENLIANT

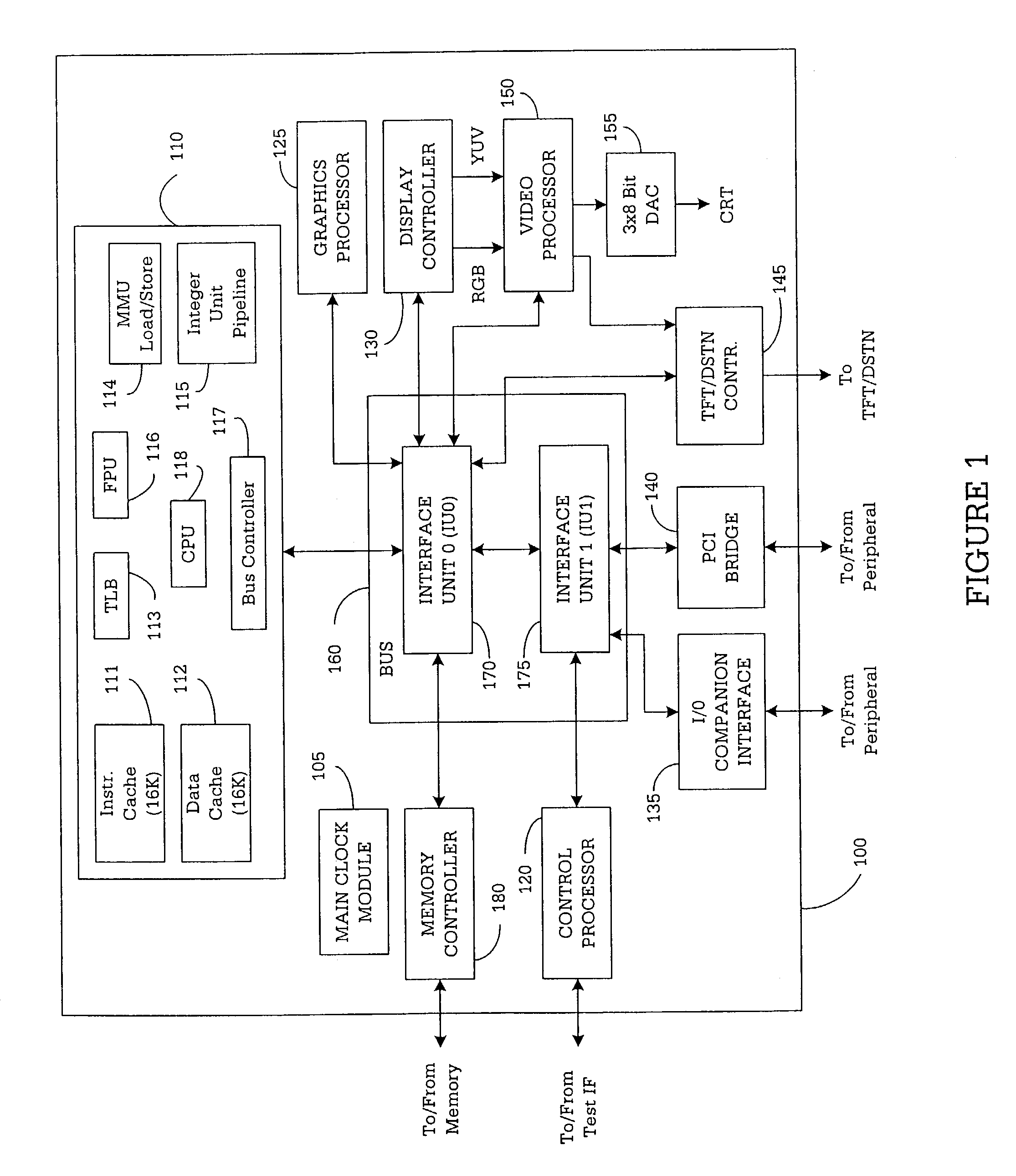

Integrated CPU and memory controller utilizing a communication link having isochronous and asynchronous priority modes

InactiveUS6148357AInput/output processes for data processingData conversionTelecommunications linkTransfer mode

An integrated circuit includes a central processing unit, a memory controller circuit for interfacing to system memory, and an interconnect bus controller for interfacing to an interconnect bus. The interconnect bus controller gives priority to transfer of asynchronous data during a first transfer mode and priority to transfer of isochronous data during a second transfer mode. A switch selectively couples the CPU, the memory controller circuit and the interconnect bus controller.

Owner:ADVANCED MICRO DEVICES INC

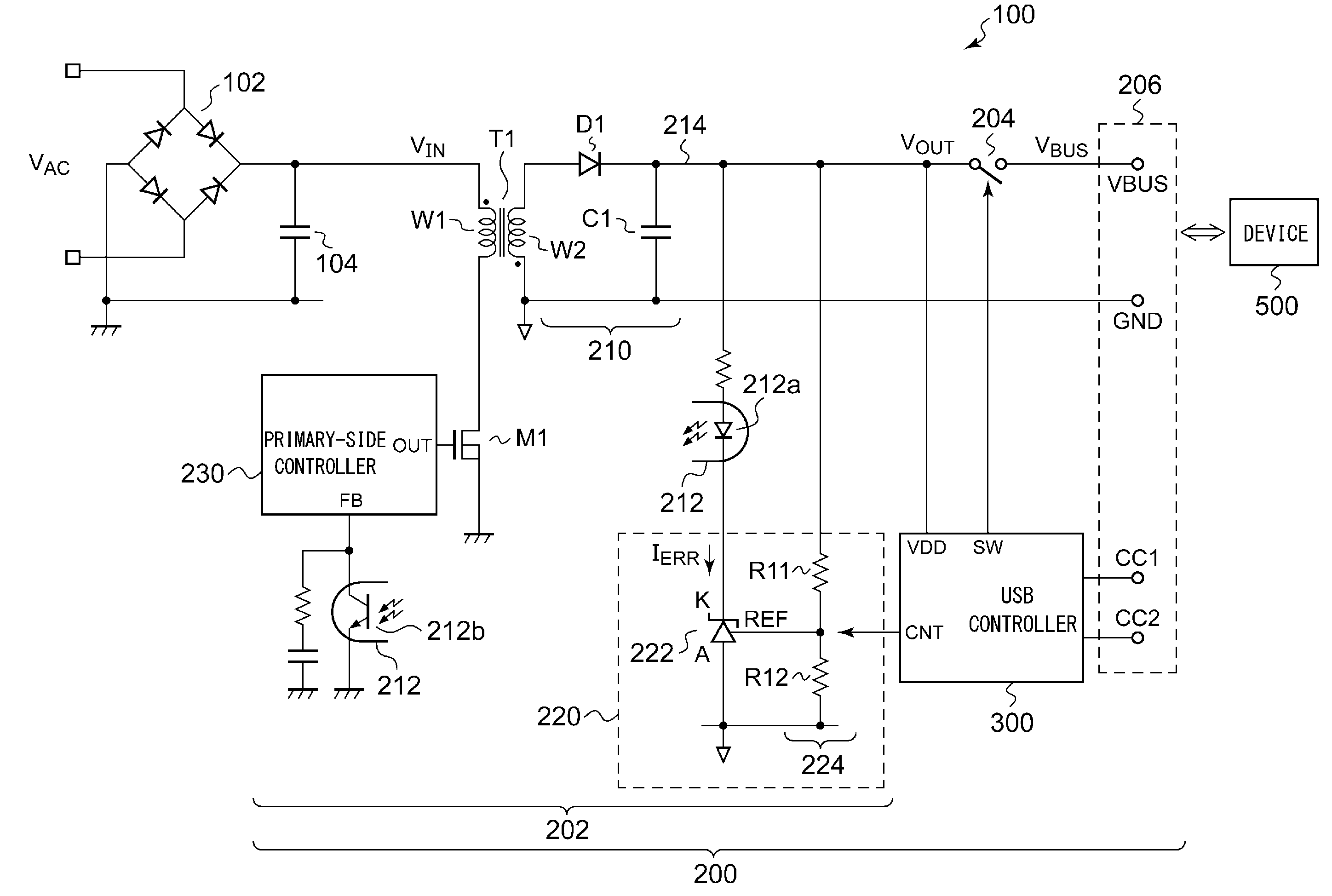

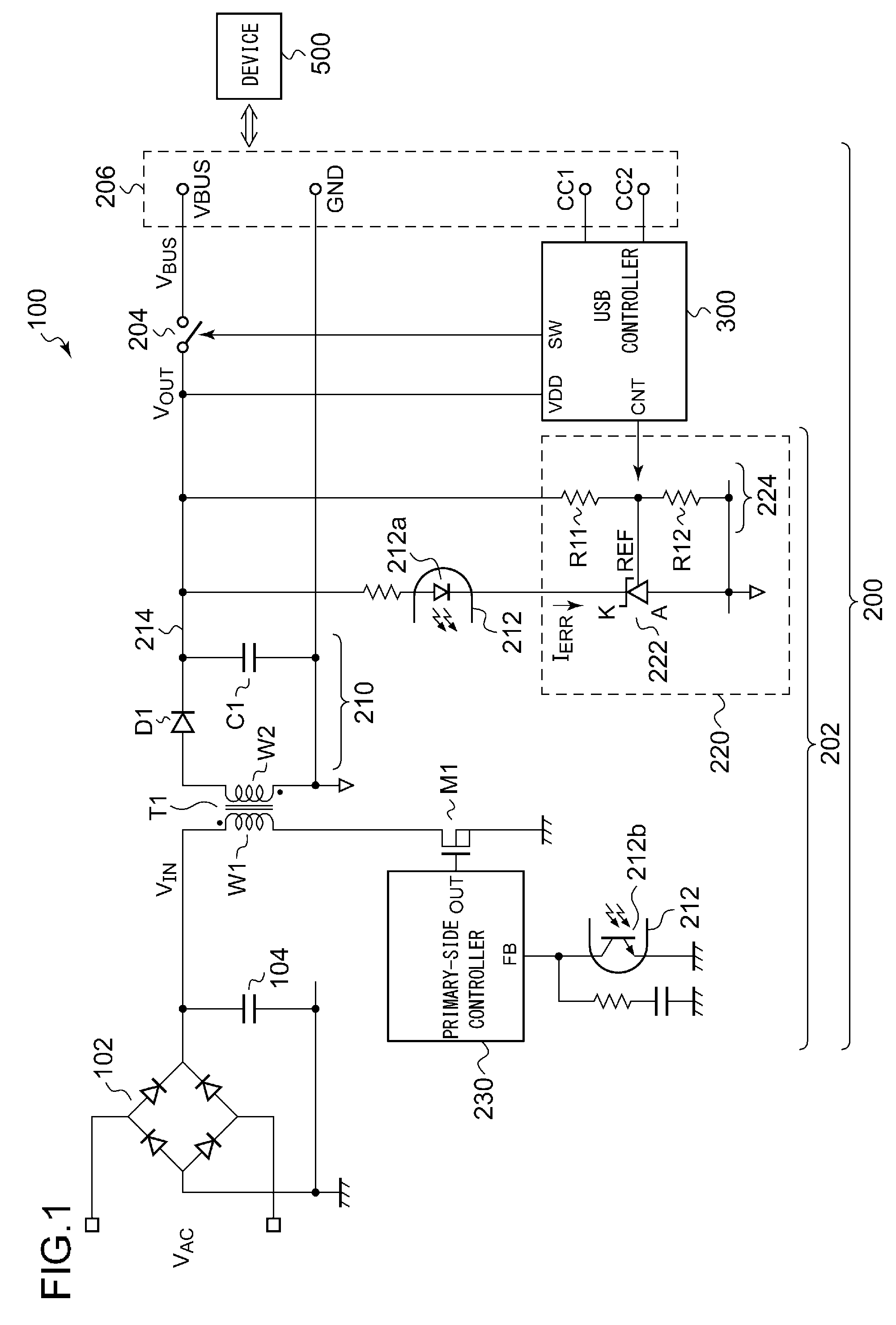

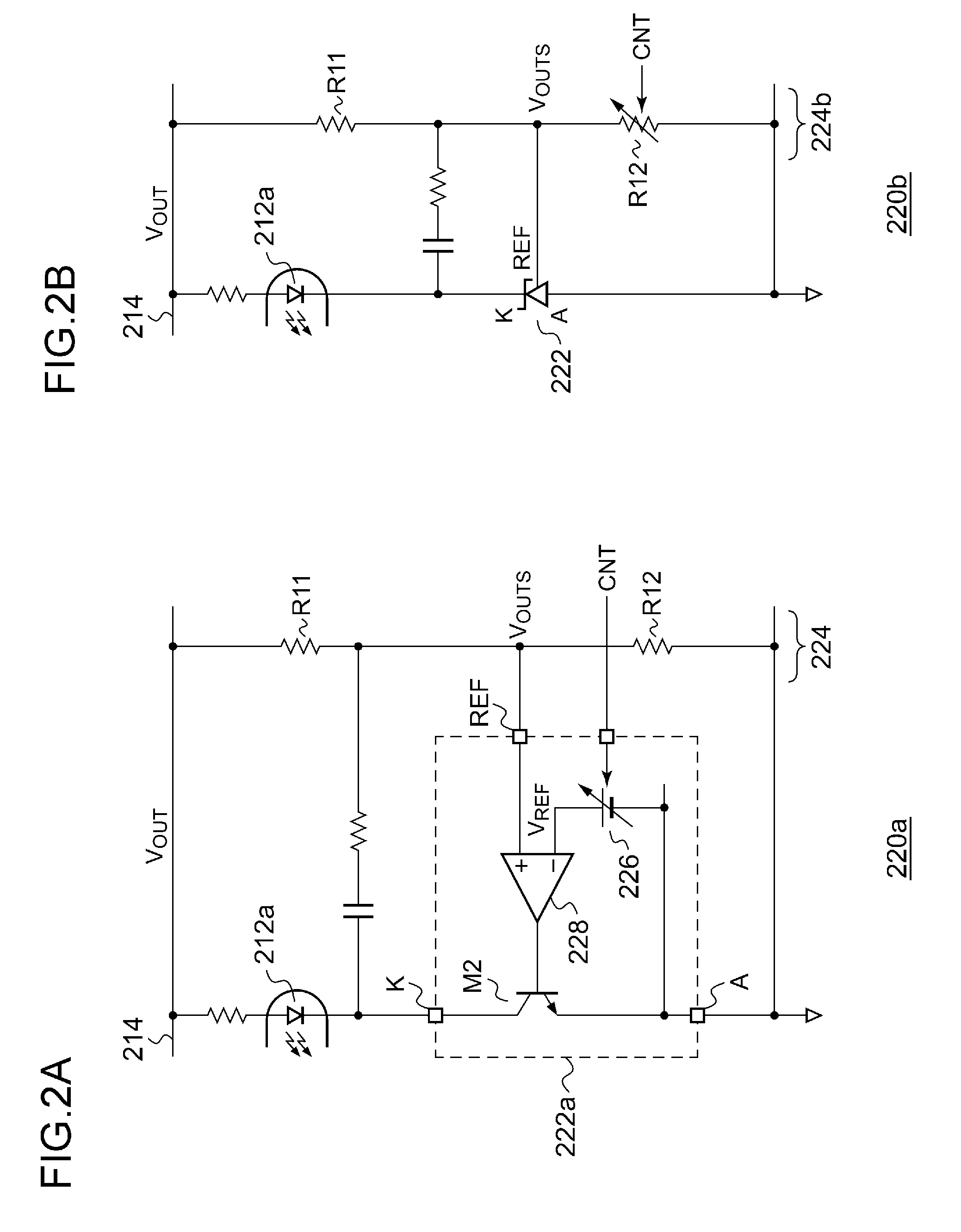

Bus controller

ActiveUS20160308452A1Reduce power consumptionUniform characteristicsBatteries circuit arrangementsAc-dc conversion without reversalDc converterUSB

A power supply apparatus is provided, that supplies a bus voltage VBUS to a detachable device. A DC / DC converter generates a DC voltage VOUT used as the bus voltage VBUS. A USB controller receives the DC voltage VOUT as a power supply voltage, and detects whether or not the device is connected. The DC / DC converter generates the DC voltage VOUT such that (i) when the device is detected, the DC voltage VOUT has a specified voltage level, and such that (ii) when the device is not detected, the DC voltage VOUT has a voltage level that is lower than the specified voltage level and that is higher than a minimum operating voltage level required to operate the USB controller.

Owner:ROHM CO LTD

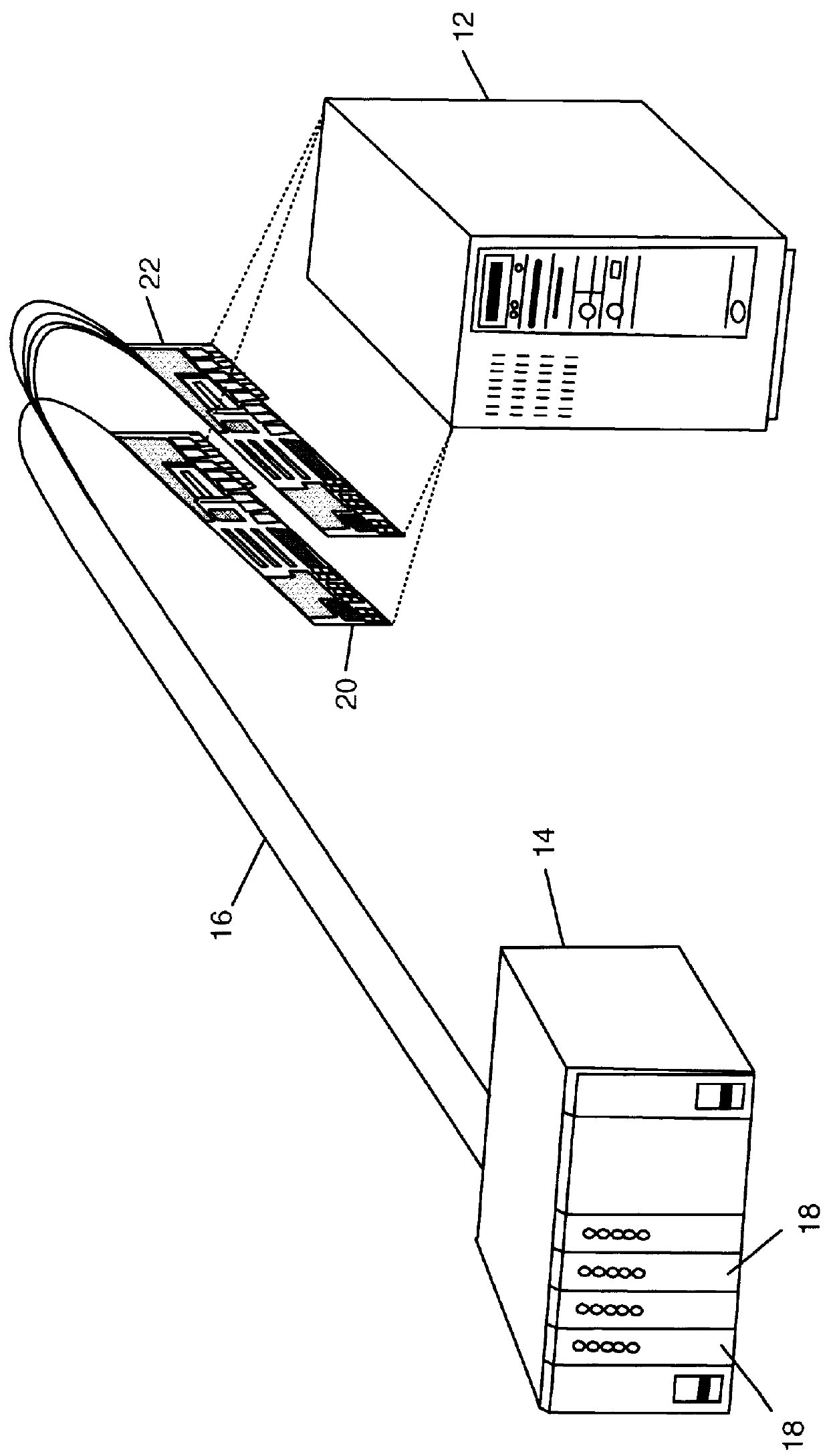

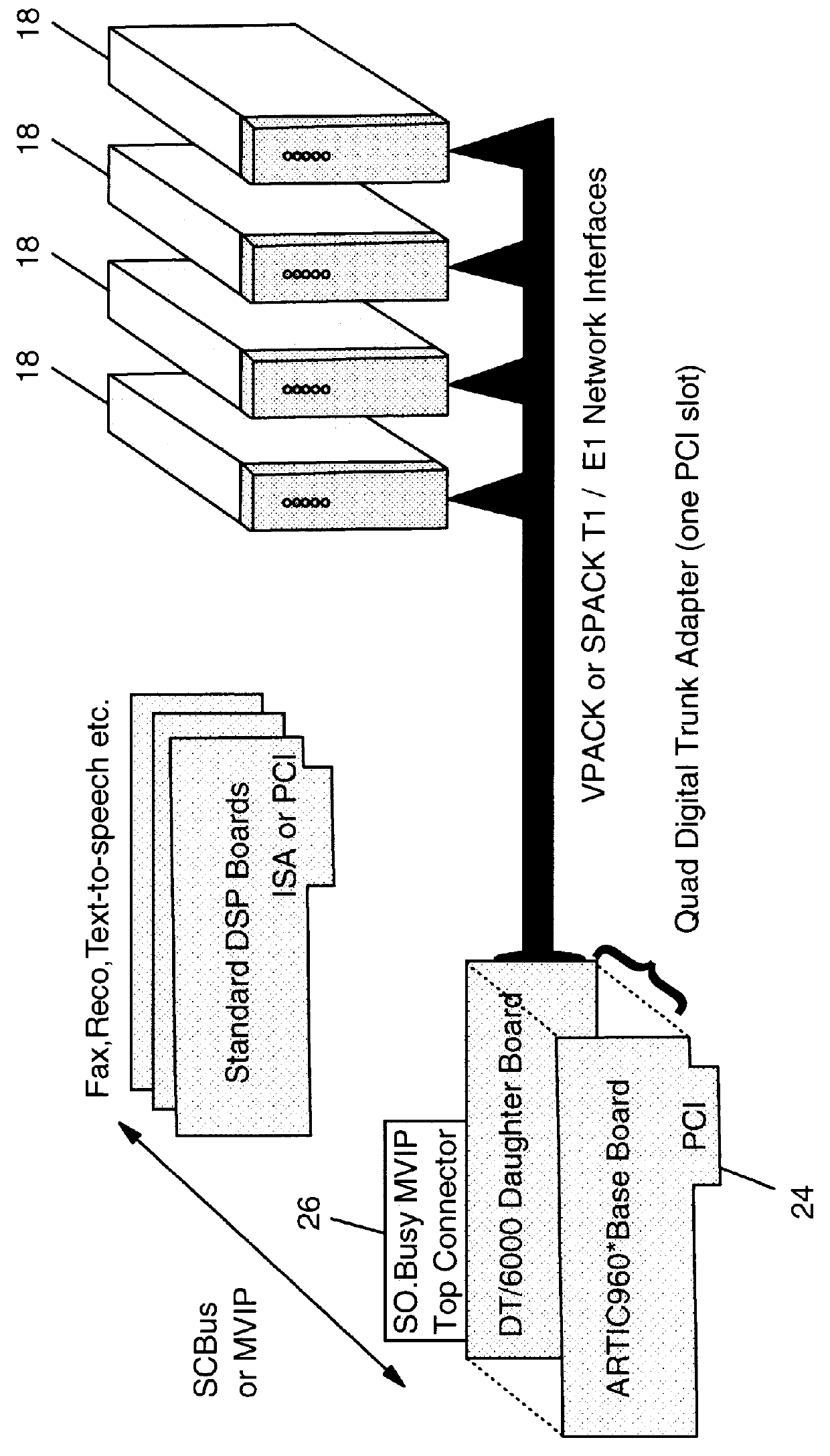

Timed division multiplex bus connection controller

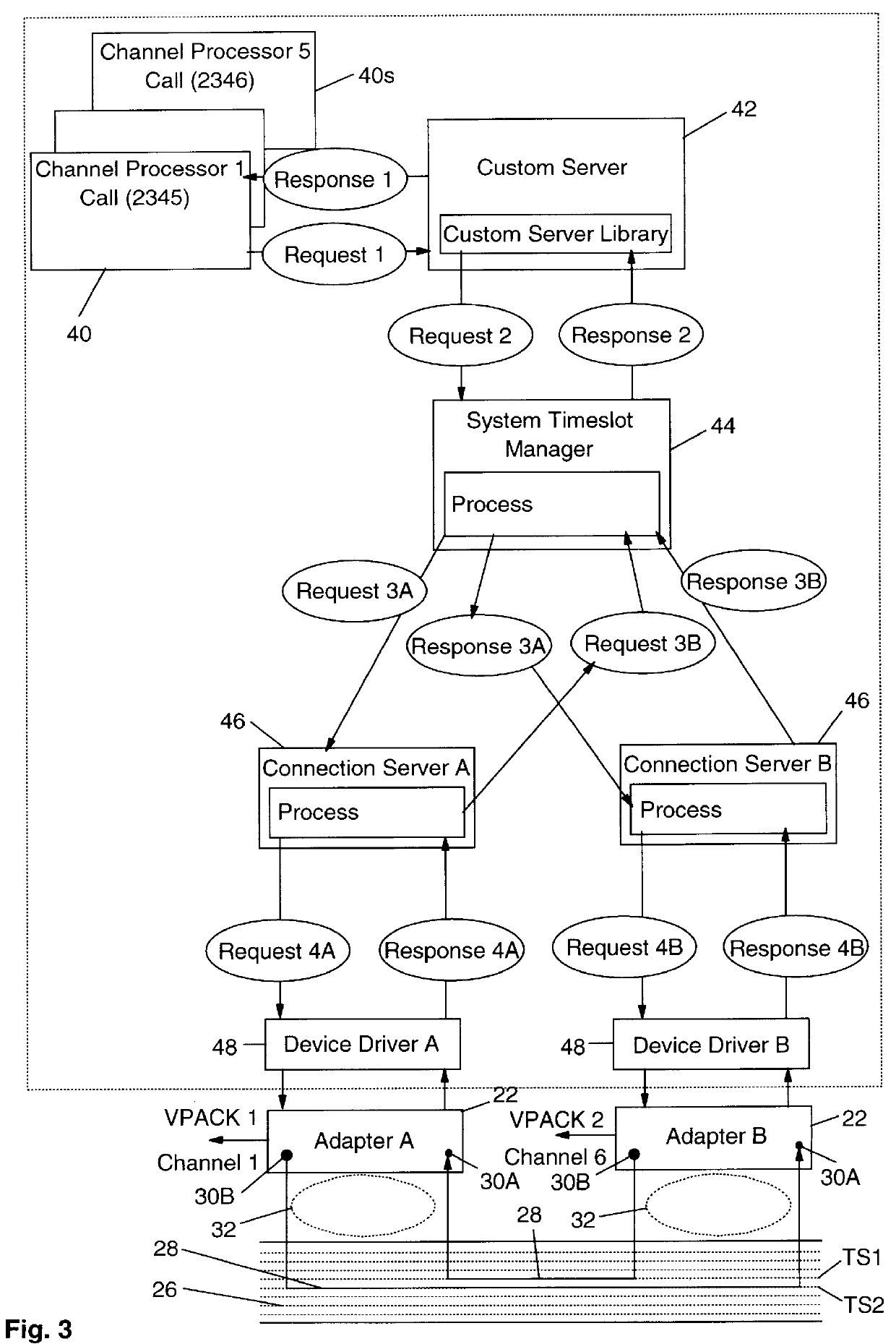

A bus connection controller in a voice processing is for managing the connection of a timeslot on a time-division multiplex (TDM) bus to a port on an adapter. The voice processing system includes basic time-division multiplex (TDM) connection management to enable the coordination of connections between resources such as channels on line cards (SPacks or VPacks), and channels on digital signal processor (DSPs) cards that provide, amongst others things, voice recognition, text-to-speech, fax capabilities and so on. One of the problems with known voice processing systems having a TDM bus is that there is no facility to allow the use of third party devices without modifications being made to the TDM connection controller. The bus controller comprises: a custom server 42 for sending a first request including a port identifier and using a first protocol for connection or disconnection of a port indicated by said port identifer on an adapter to the TDM bus 26; a timeslot manager for analyzing the first request to determine the port availability and state and for making a second request; device driver means (48), corresponding to the particular adapter, for sending the appropriate signals to the adapter to connect or disconnect the port on the adapter to a time slot 28 on the TDM; and a connection server 46, corresponding to a particular adapter, for analyzing the second request and for making a third request to the device driver means (48) using a second protocol for connection or disconnection of the port on that adapter to the TDM bus 26.

Owner:IBM CORP

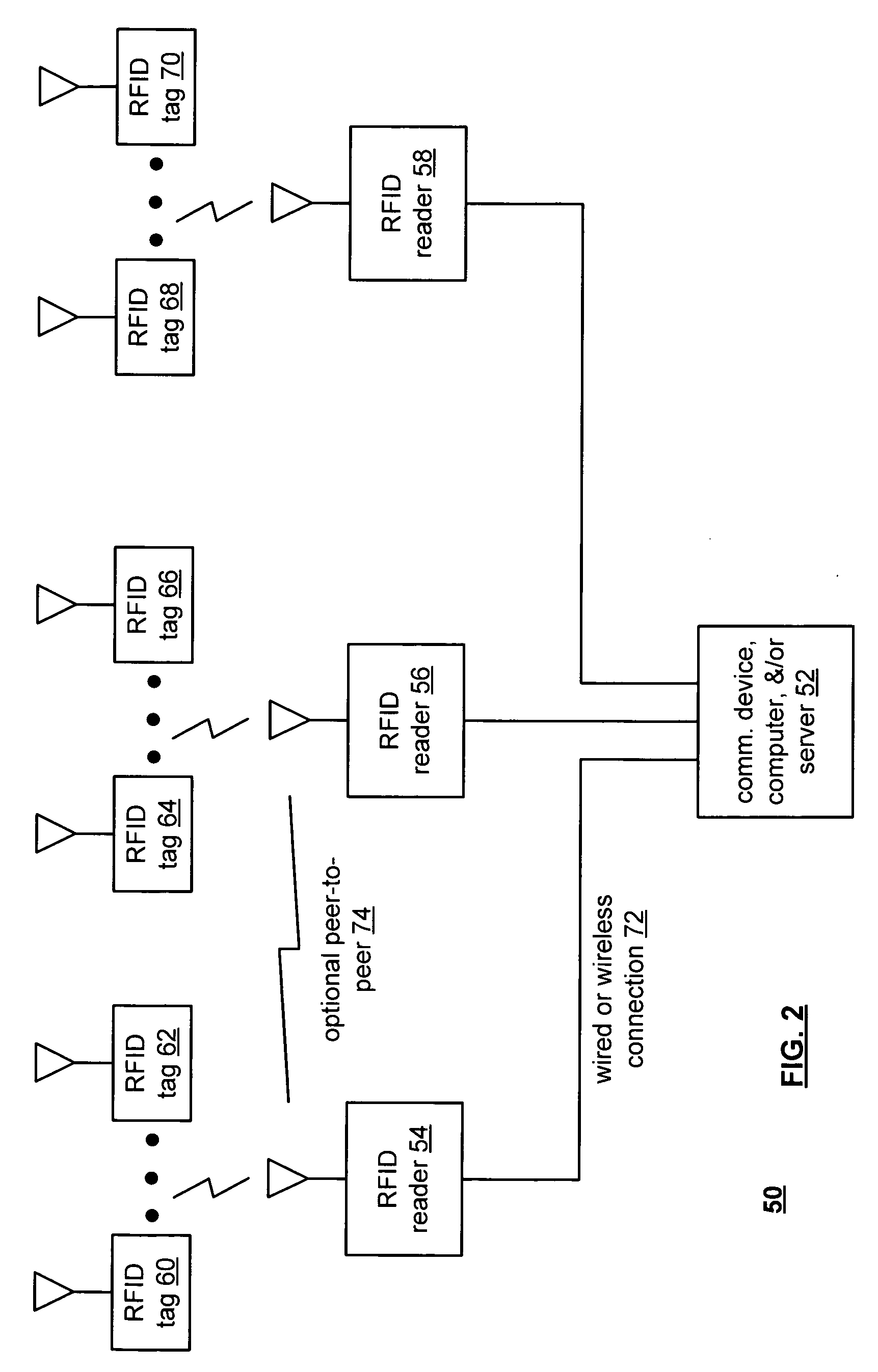

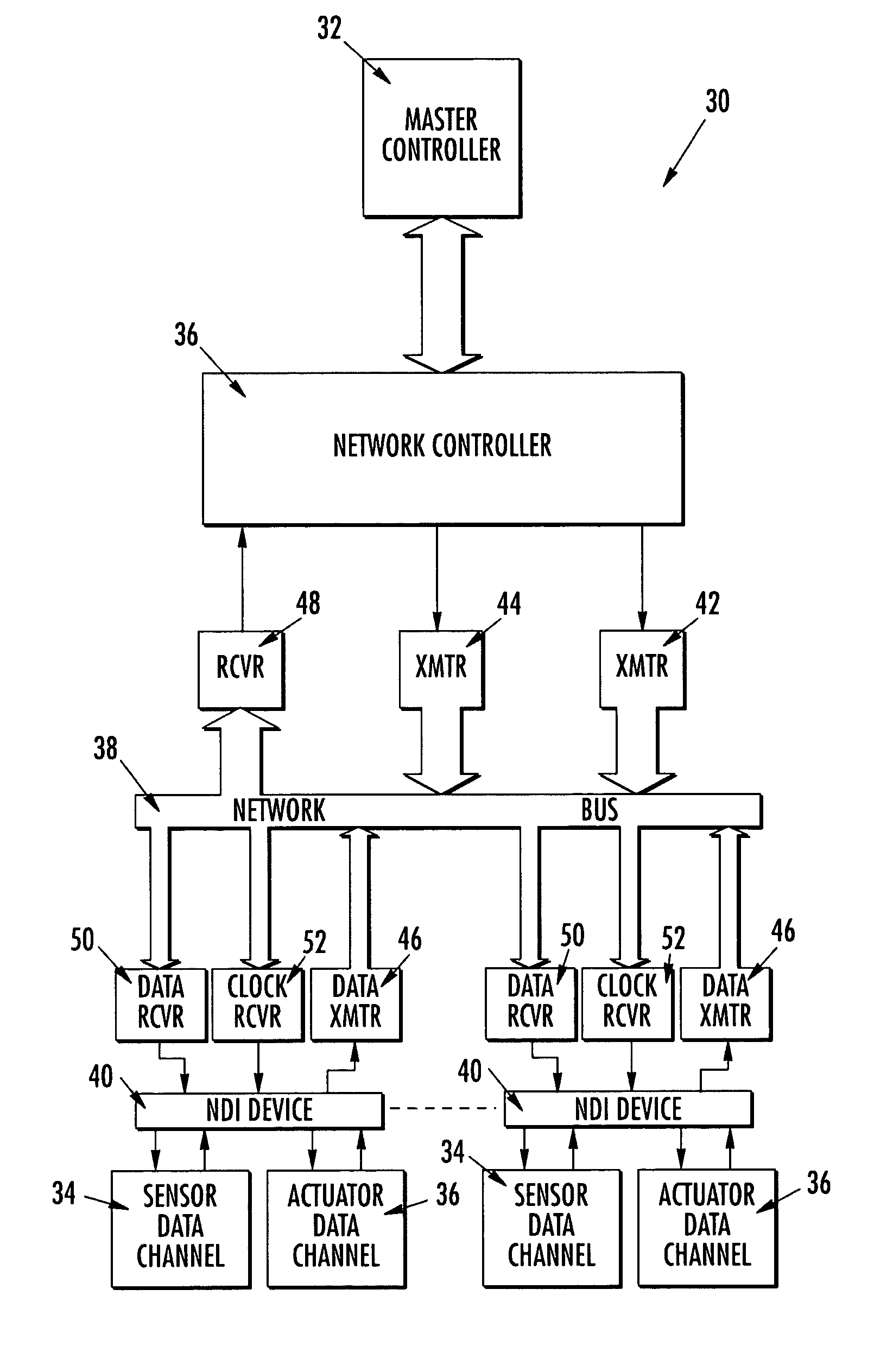

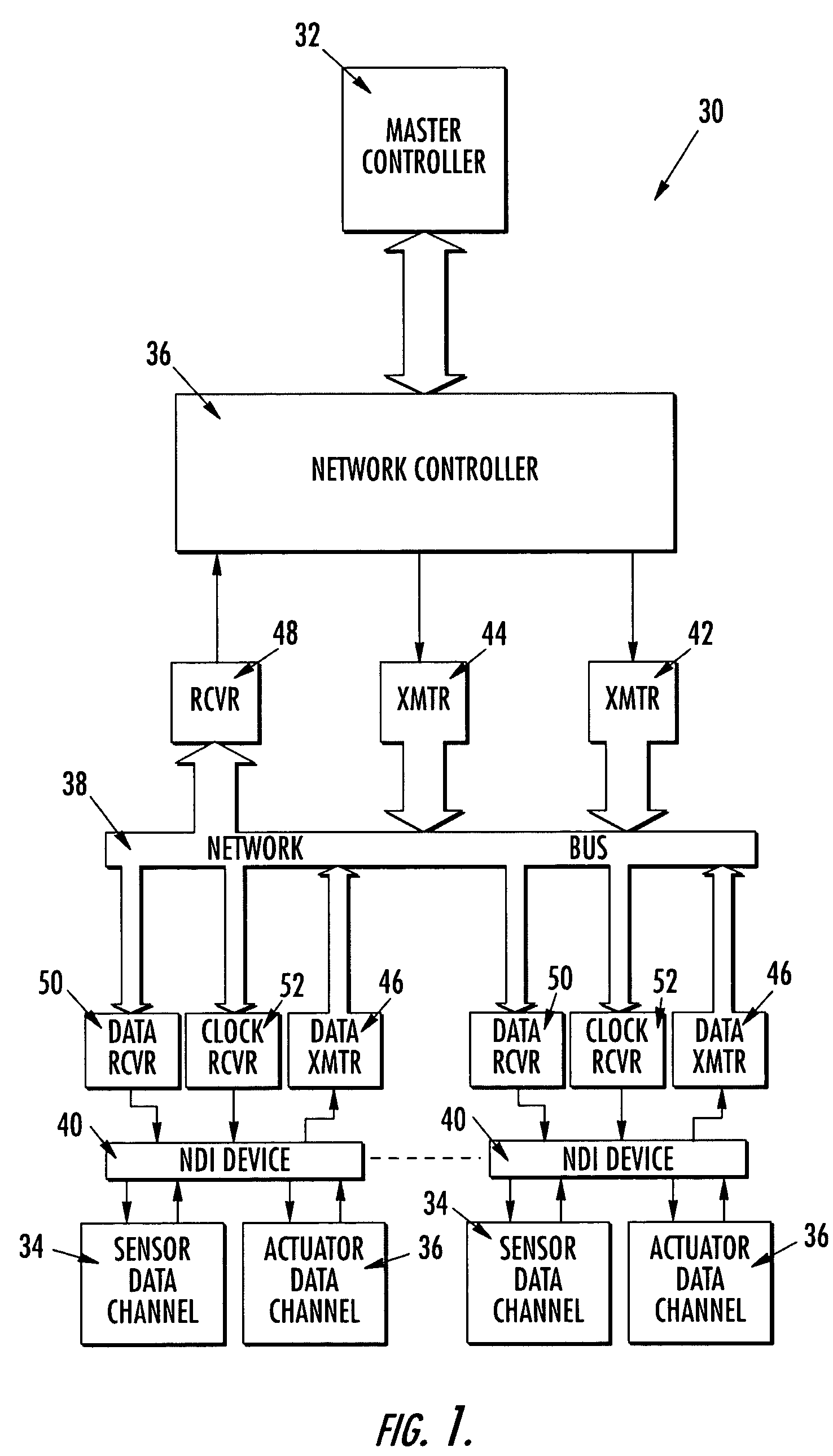

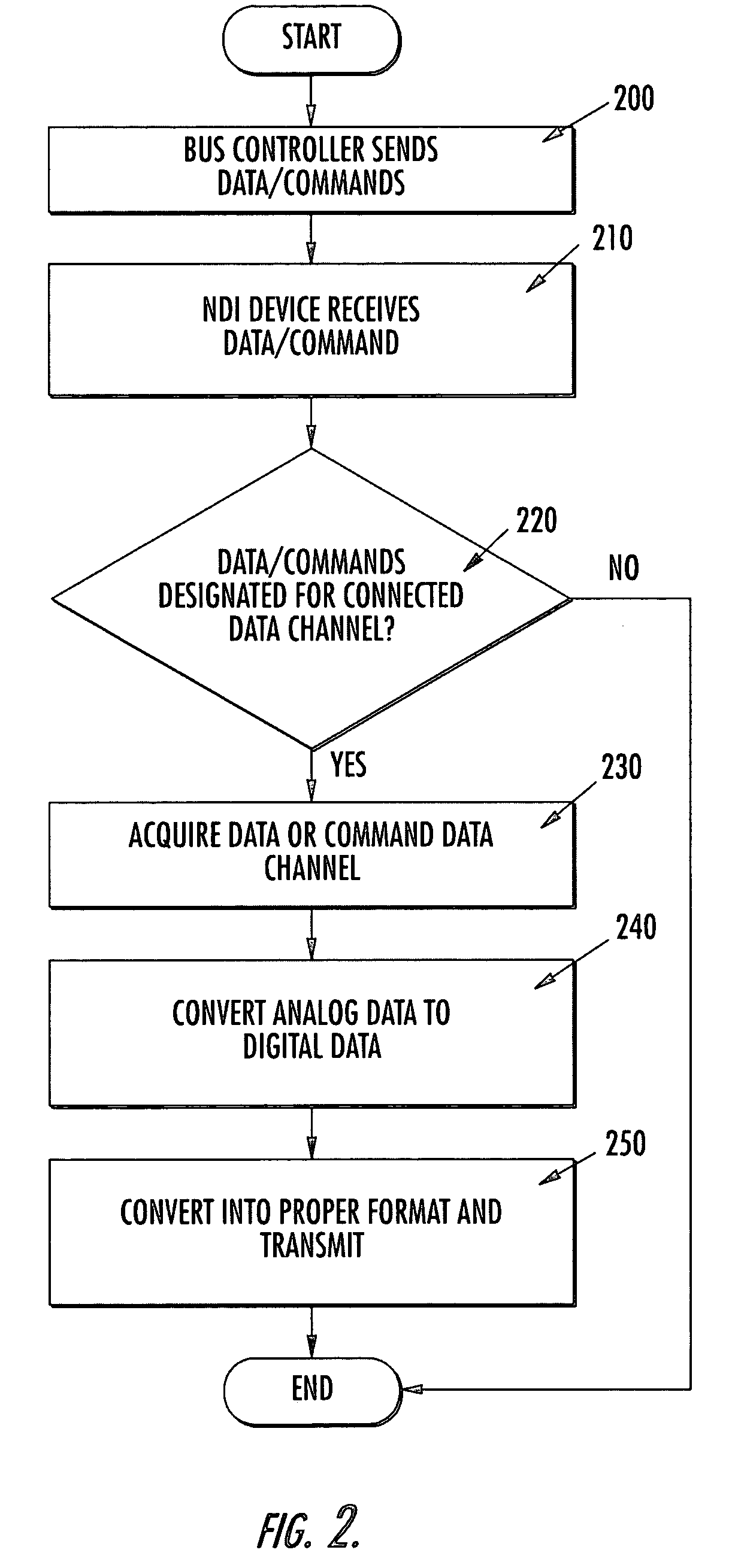

Network device interface for digitally interfacing data channels to a controller via a network

InactiveUS7058737B2Less susceptible to noise and degradationEasy extractionSynchronisation signal speed/phase controlData switching networksBus masteringActuator

The present invention provides a network device interface and method for digitally connecting a plurality of data channels, such as sensors, actuators, and subsystems, to a controller using a network bus. The network device interface interprets commands and data received from the controller and polls the data channels in accordance with these commands. Specifically, the network device interface receives digital commands and data from the controller, and based on these commands and data, communicates with the data channels to either retrieve data in the case of a sensor or send data to activate an actuator. Data retrieved from the sensor is then converted into digital signals and transmitted back to the controller. In one embodiment, the bus controller sends commands and data a defined bit rate, and the network device interface senses this bit rate and sends data back to the bus controller using the defined bit rate.

Owner:THE BOEING CO

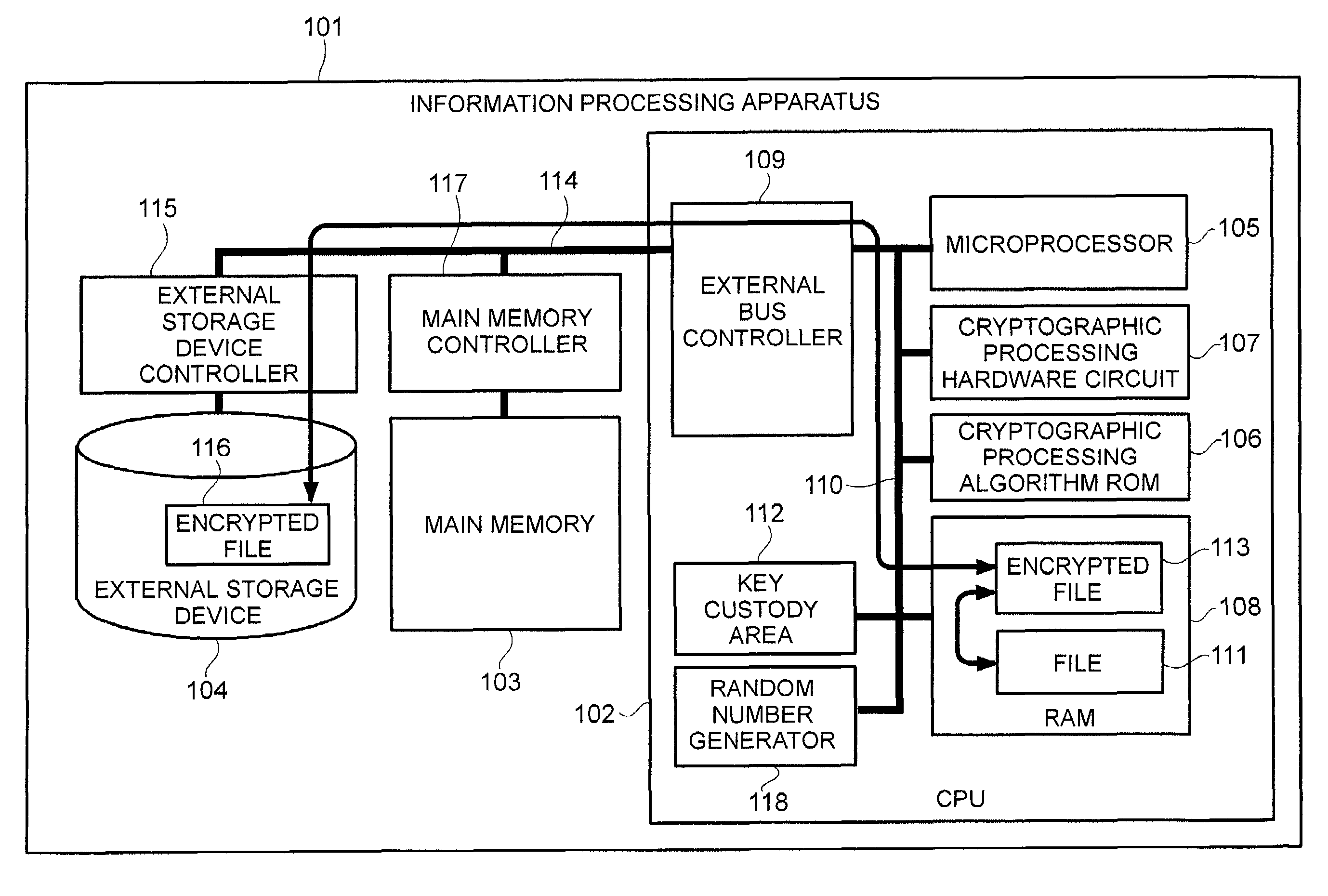

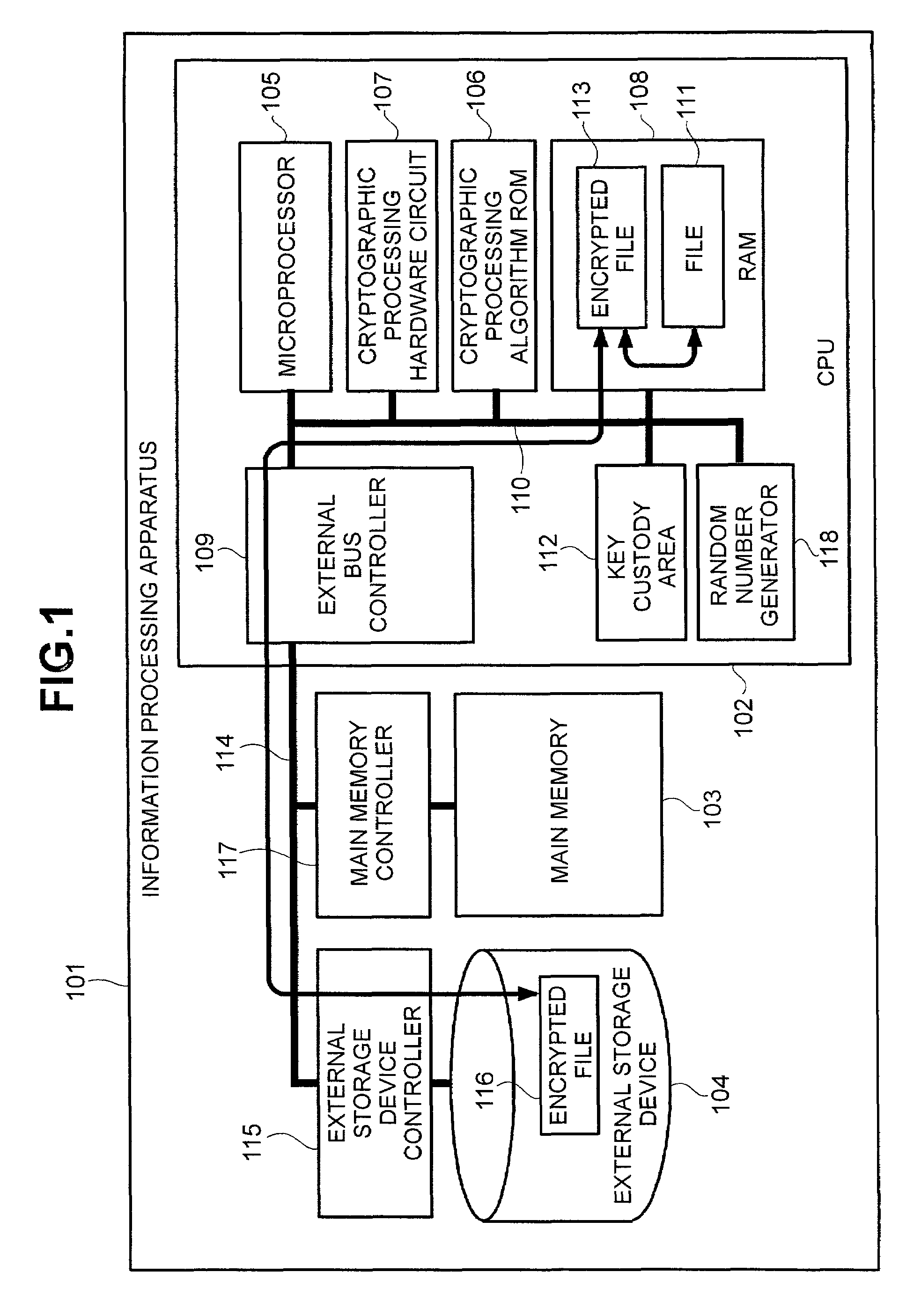

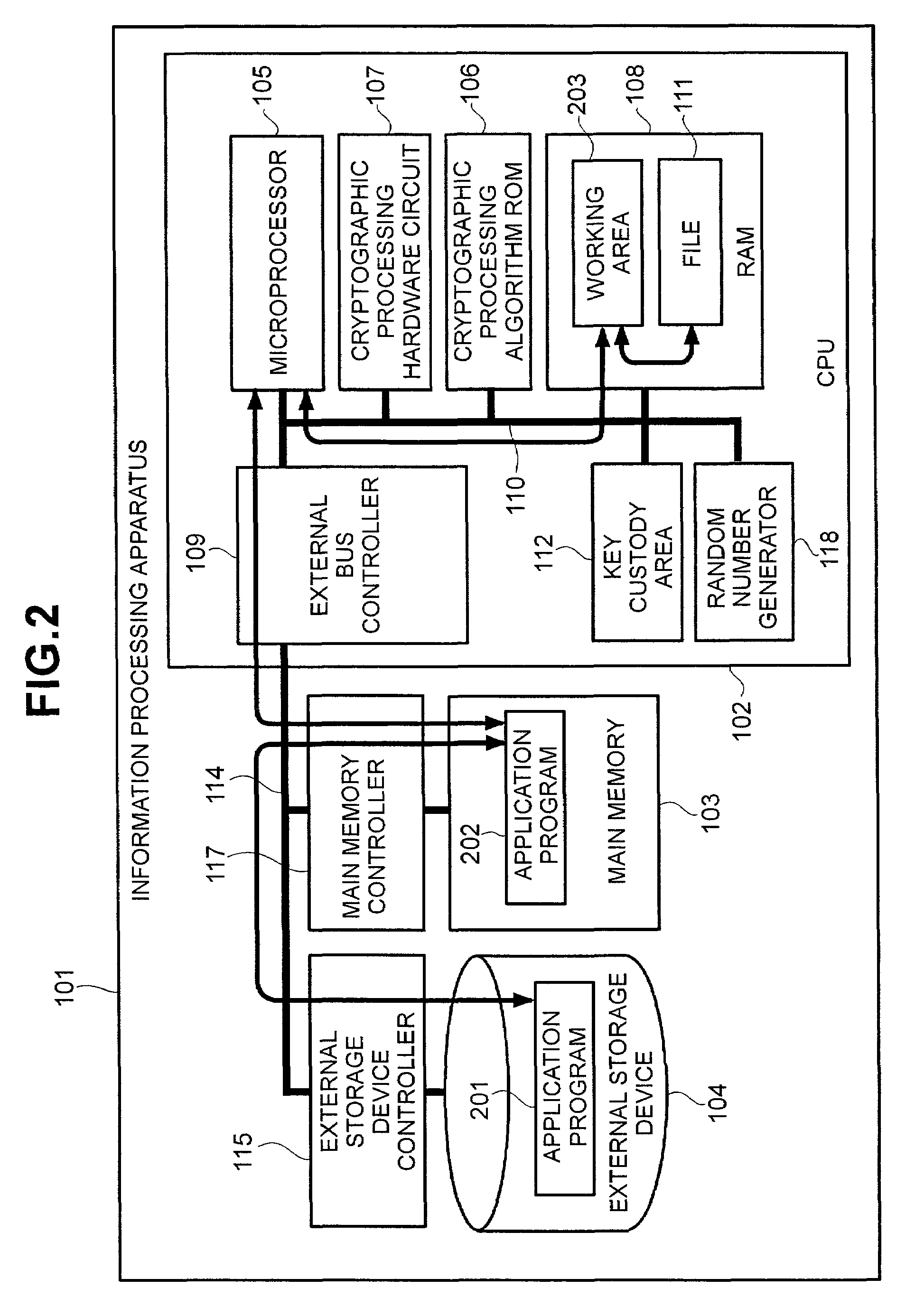

Information processing apparatus

InactiveUS7082539B1Memory loss protectionUnauthorized memory use protectionInformation processingSemiconductor chip

Since a conventional information processing apparatus includes a plurality of semiconductor devices, there is a problem that sensitive information may reside on a system bus in the apparatus or a semiconductor memory device serving as main memory therein. To obviate this problem, each information processing apparatus has a CPU which includes a microprocessor, a cryptographic processing algorithm ROM, a cryptographic processing hardware circuit, a RAM, a key custody area, and an external bus controller, which are all integrated on a single semiconductor chip. Thus, encryption / decryption processing is carried out only in the CPU, and internal operations of the CPU are made non-analyzable from an external signal of the CPU.

Owner:HITACHI LTD

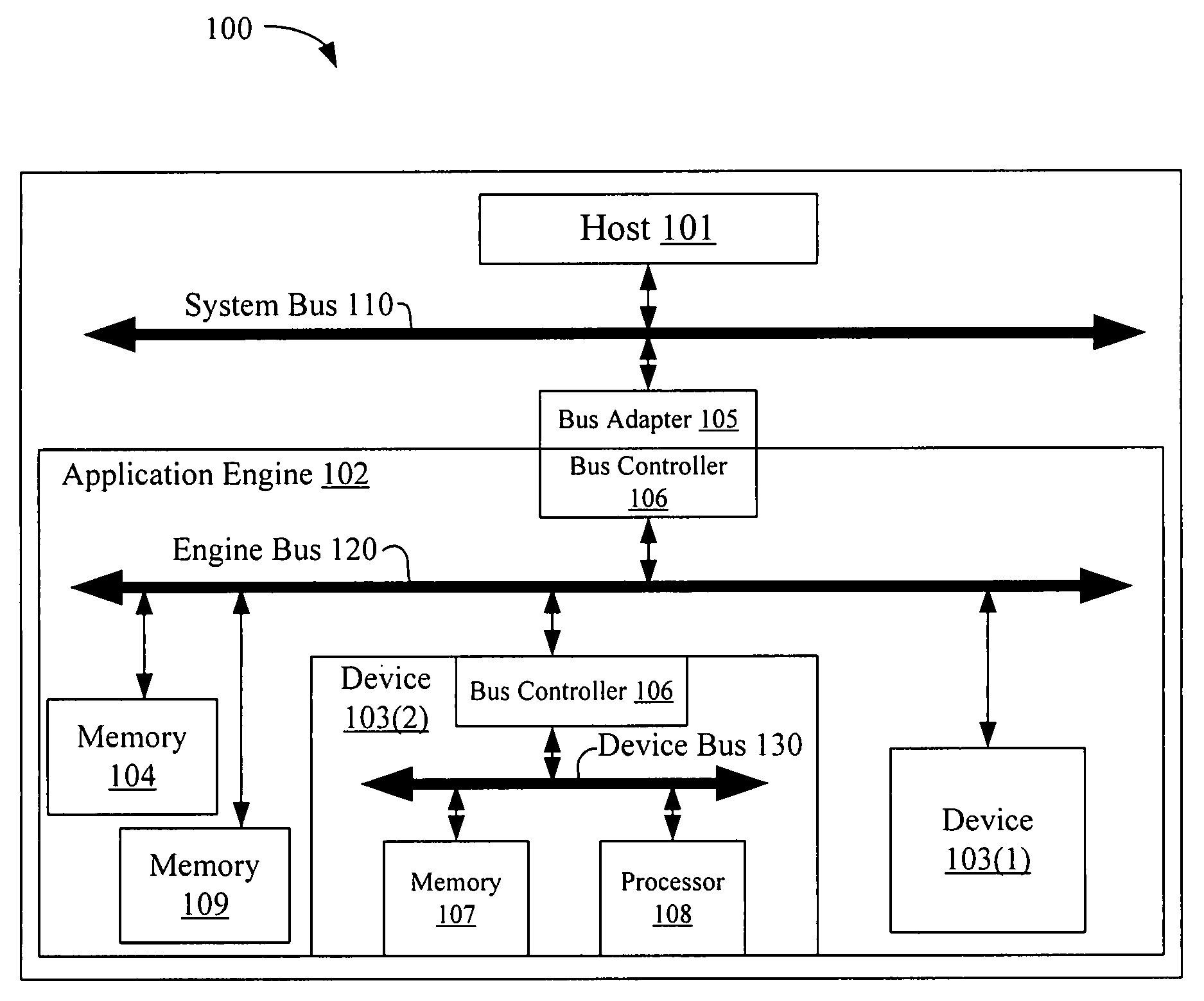

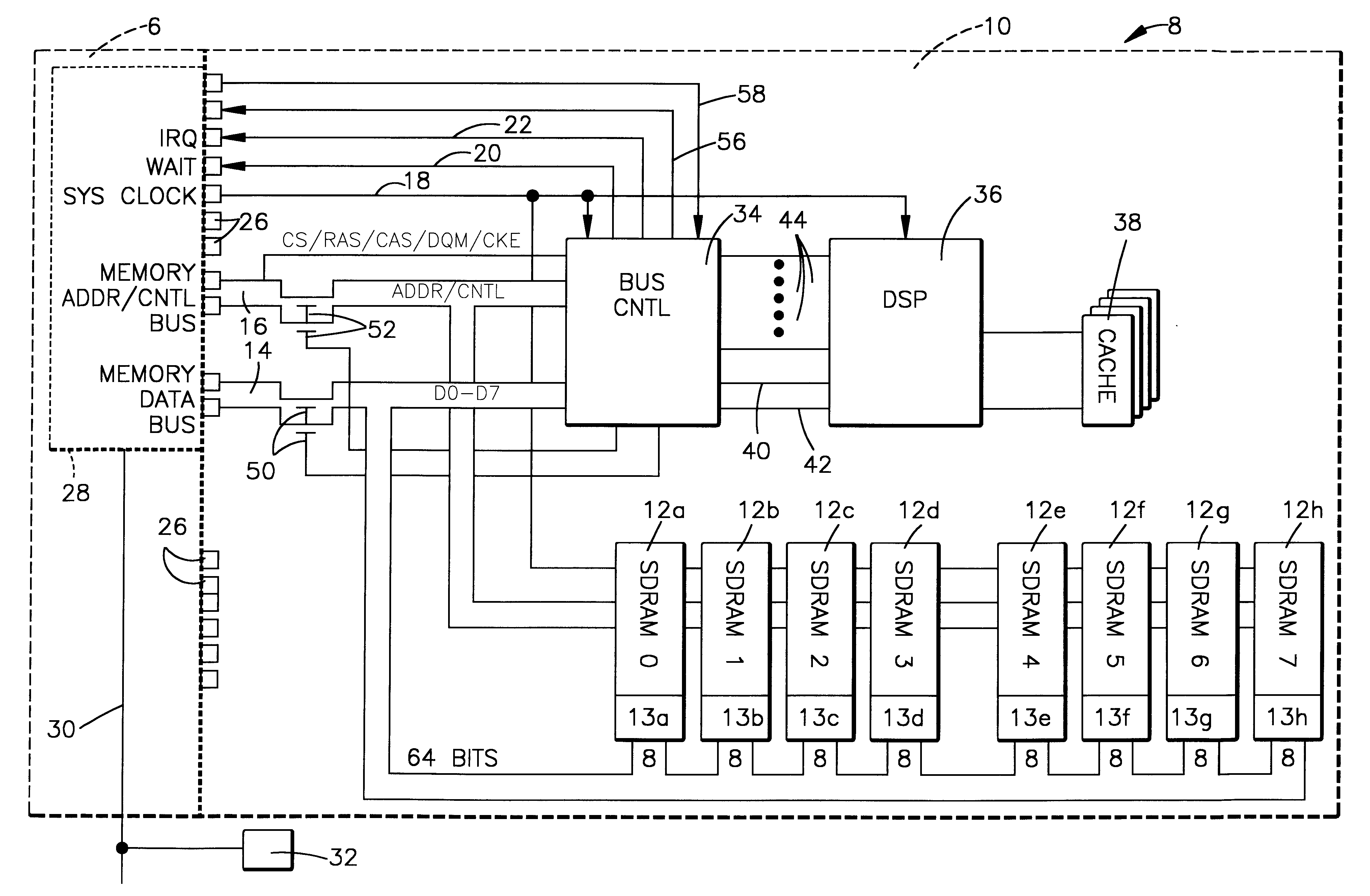

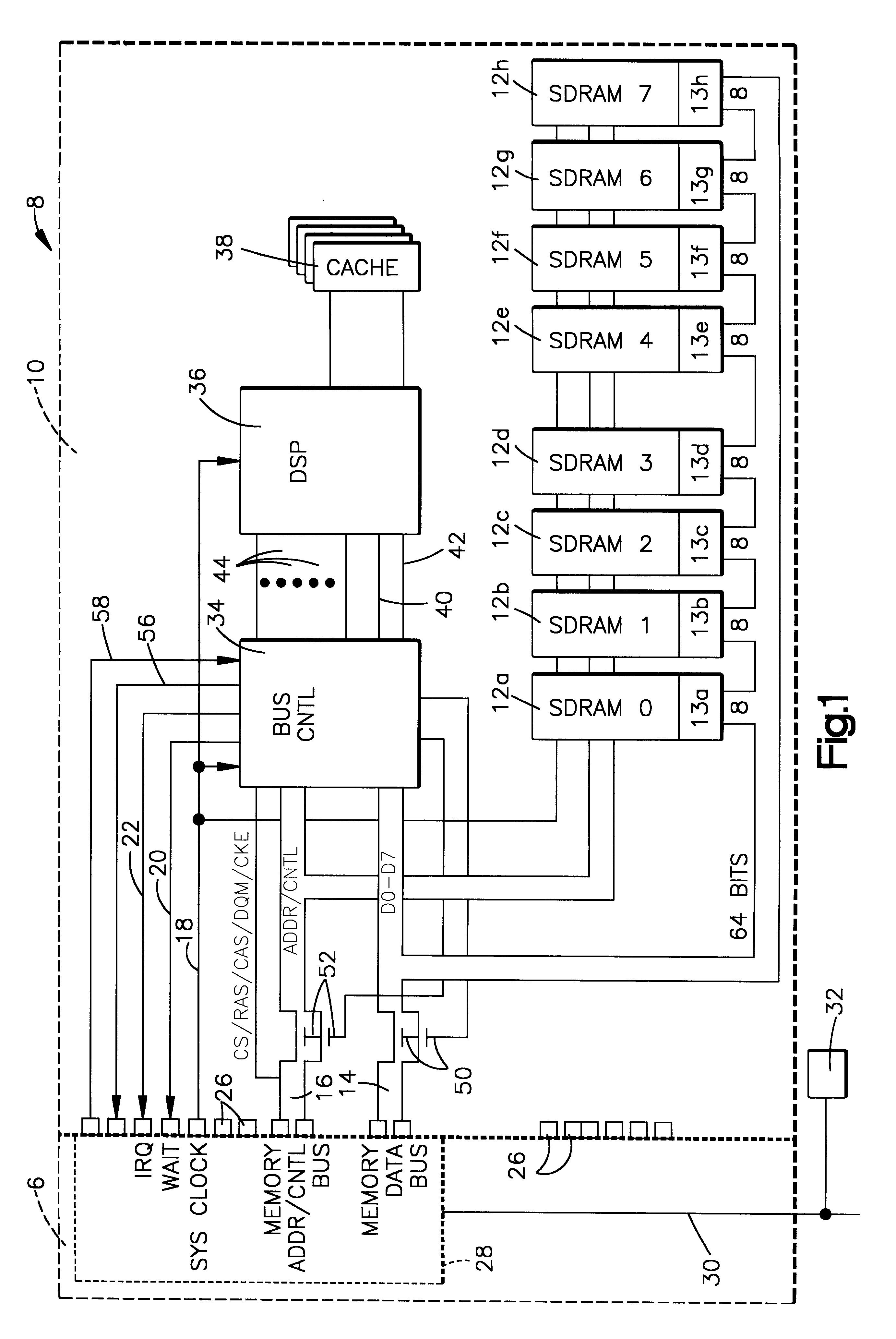

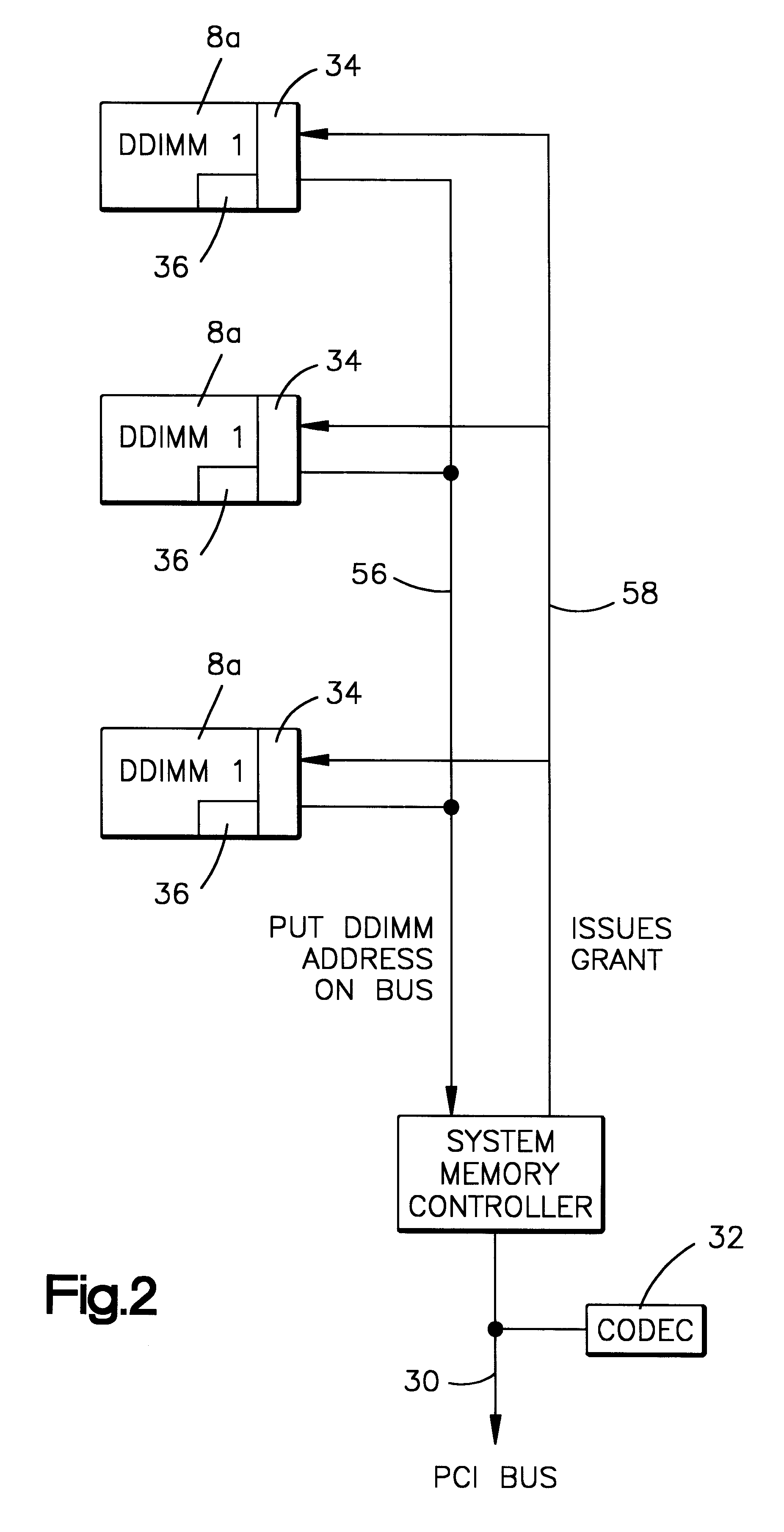

Memory card utilizing two wire bus

A serial bus and connection to a device on a computer system through a system memory controller is provided on a memory card having a DSP and a memory bus controller to allow the DSP on the memory card to gain access to the system device without using the system memory bus. The serial bus is a two wire serial bus connecting the device to the DSP through the system memory controller. If more than one memory card is present with DSPs or more than one device is contending for access, the system memory controller or arbitrate the access of each memory card or contending device. In such case the serial bus will signal the system memory controller when it wants access to the particular device, and the system memory controller will act as arbitrator to grant or not grant access to the particular memory card or device requesting access. If access is granted the bus memory controller outputs the required control or command word on the serial bus followed by the address and the required data. This serial information is received by the system memory controller which packets it, and, upon completion, outputs the information rapidly on a parallel bus, e.g. a PCI bus to the device which needs the information.

Owner:IBM CORP

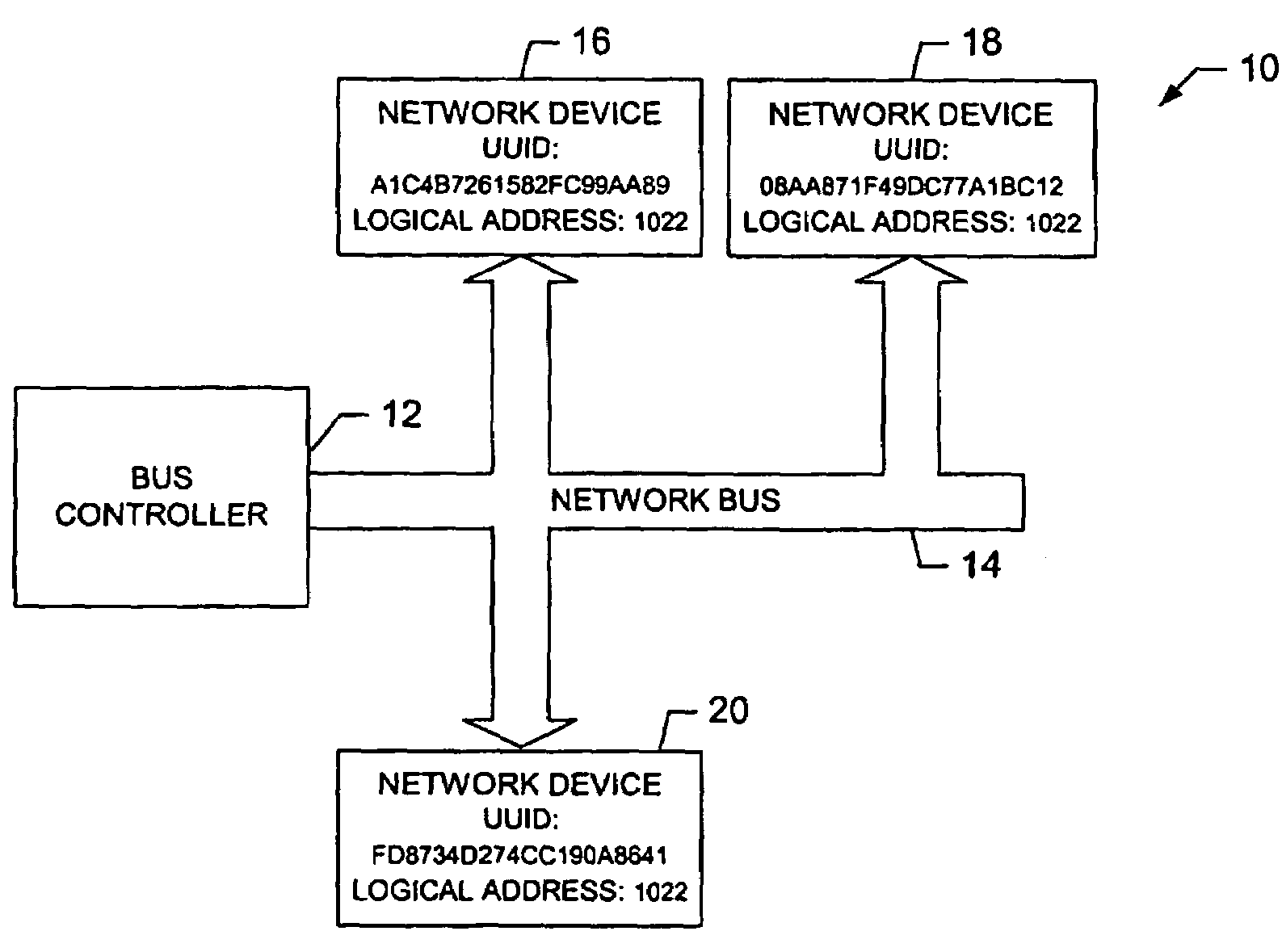

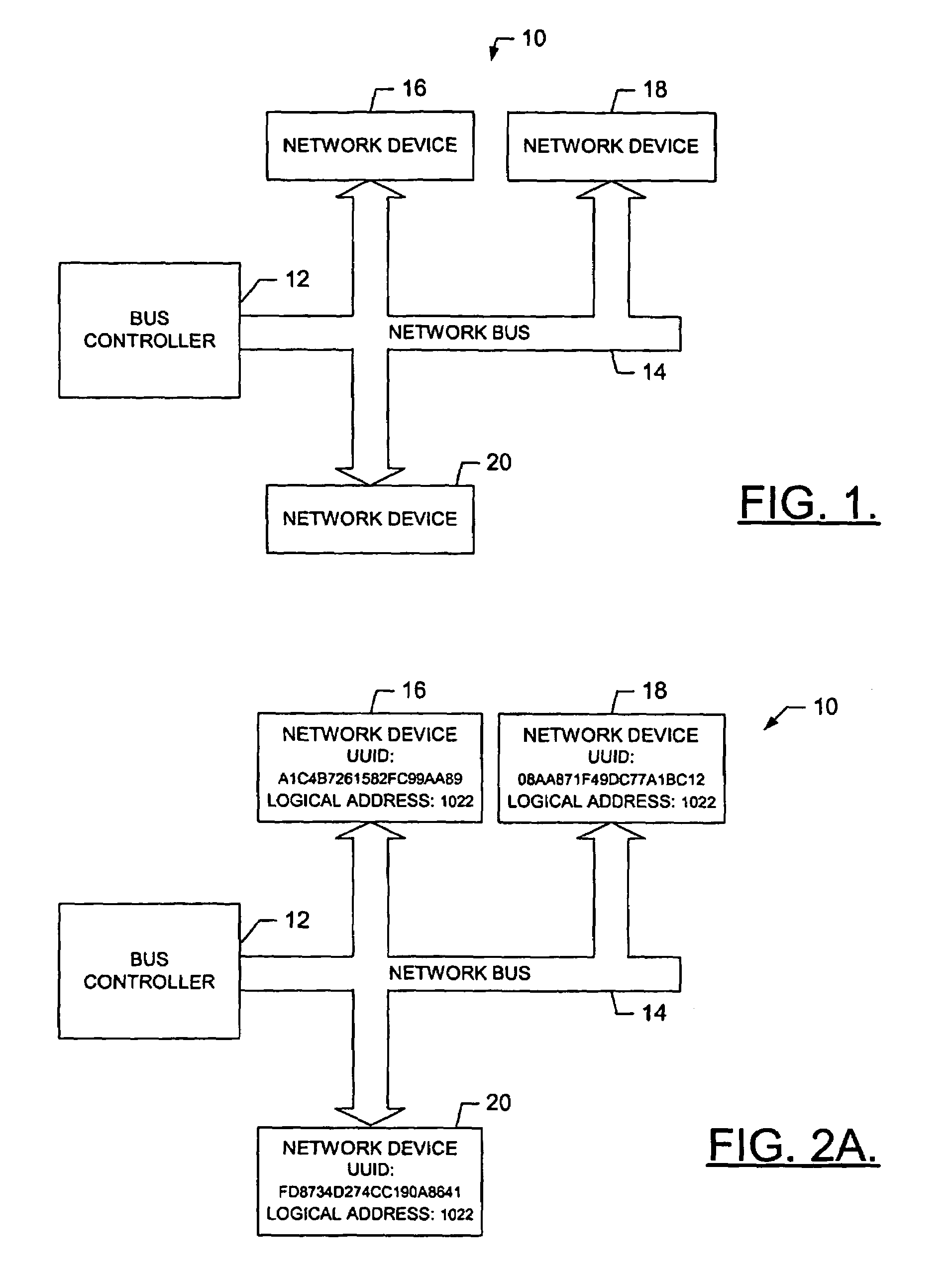

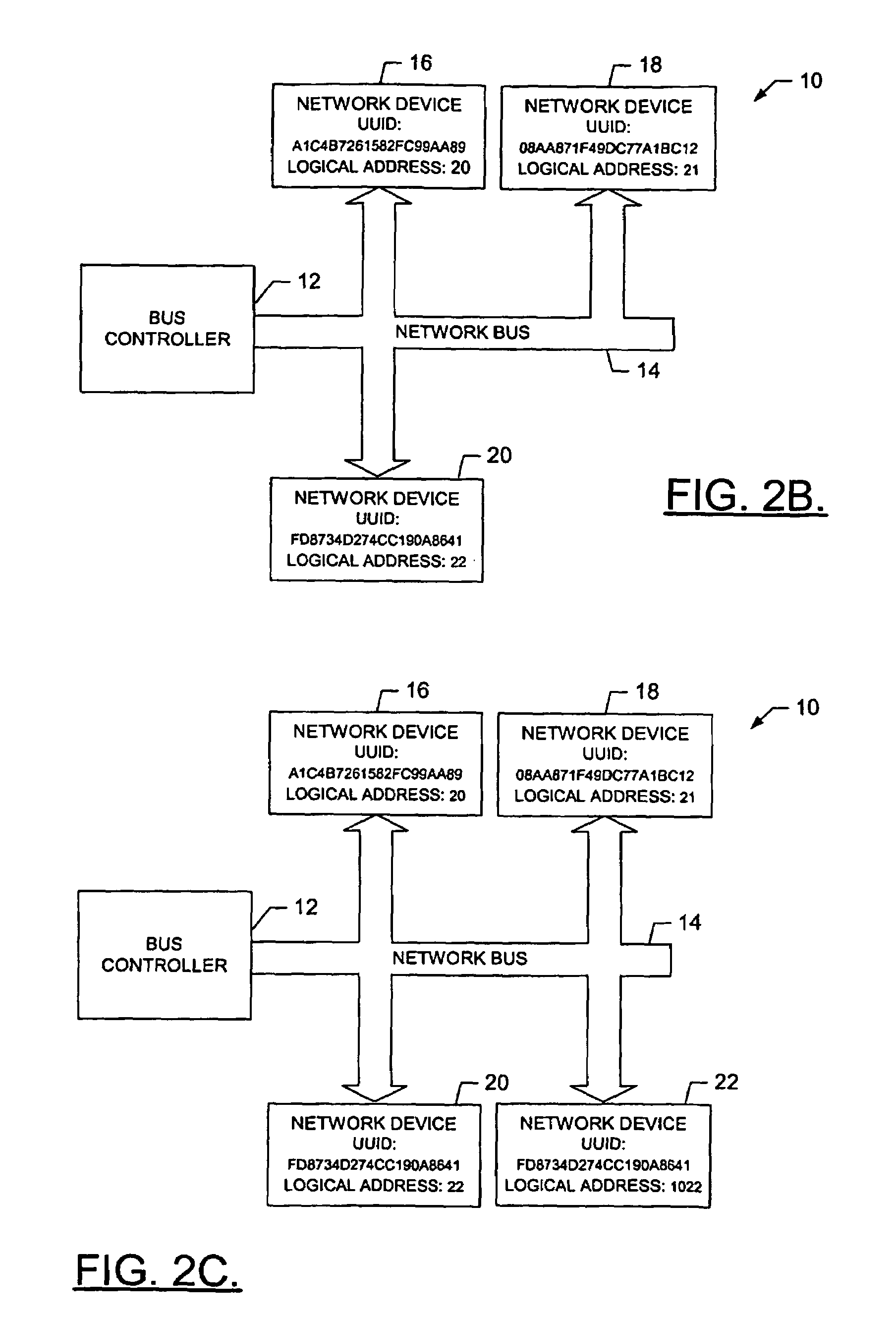

Systems and methods for assigning an address to a network device added to an existing network

InactiveUS7111100B2Component plug-in assemblagesData switching networksNetworked systemNetwork Access Device

The present invention provides systems, methods, and bus controllers (12) for establishing communication with various network systems located on a network system (10). Importantly, the systems, methods, and bus controllers (12) of the present invention are capable recognizing that a new network device (16, 18, 20) has been added to an existing network and assigning it an address such that the added network device is identifiable on the network. Further, the systems, methods, and bus controllers (12) of the present invention may update the operating schedule that outlines communication in the network system between the bus controller (12) and the network devices (16, 18, 20) to include commands for communicating with the added network device. The systems, methods, and bus controllers (12) of the present invention may also detect when a network device (16, 18, 20) has been disconnected from a network system (10) and remove the commands associated with the networked device from the command schedule.

Owner:THE BOEING CO

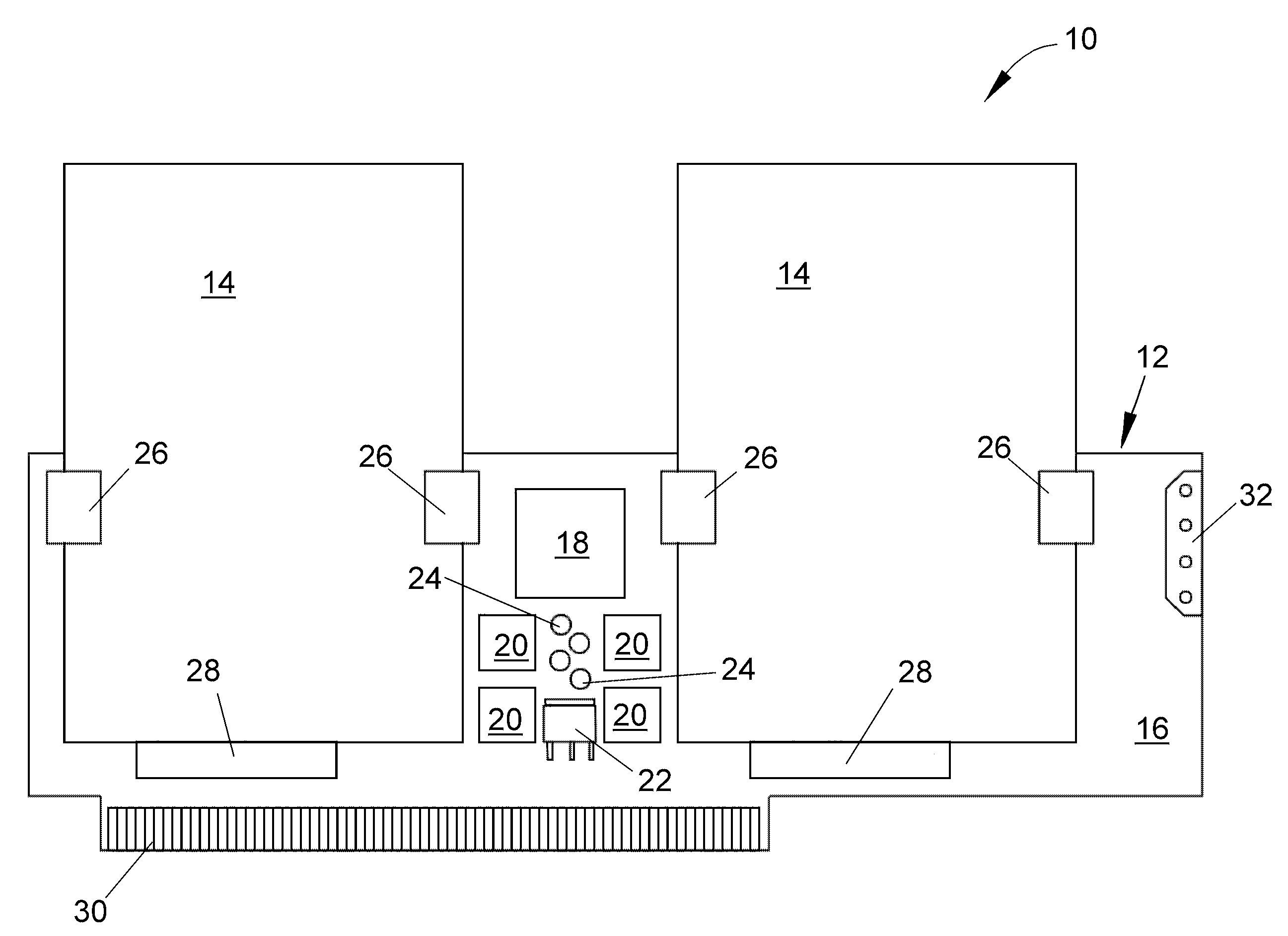

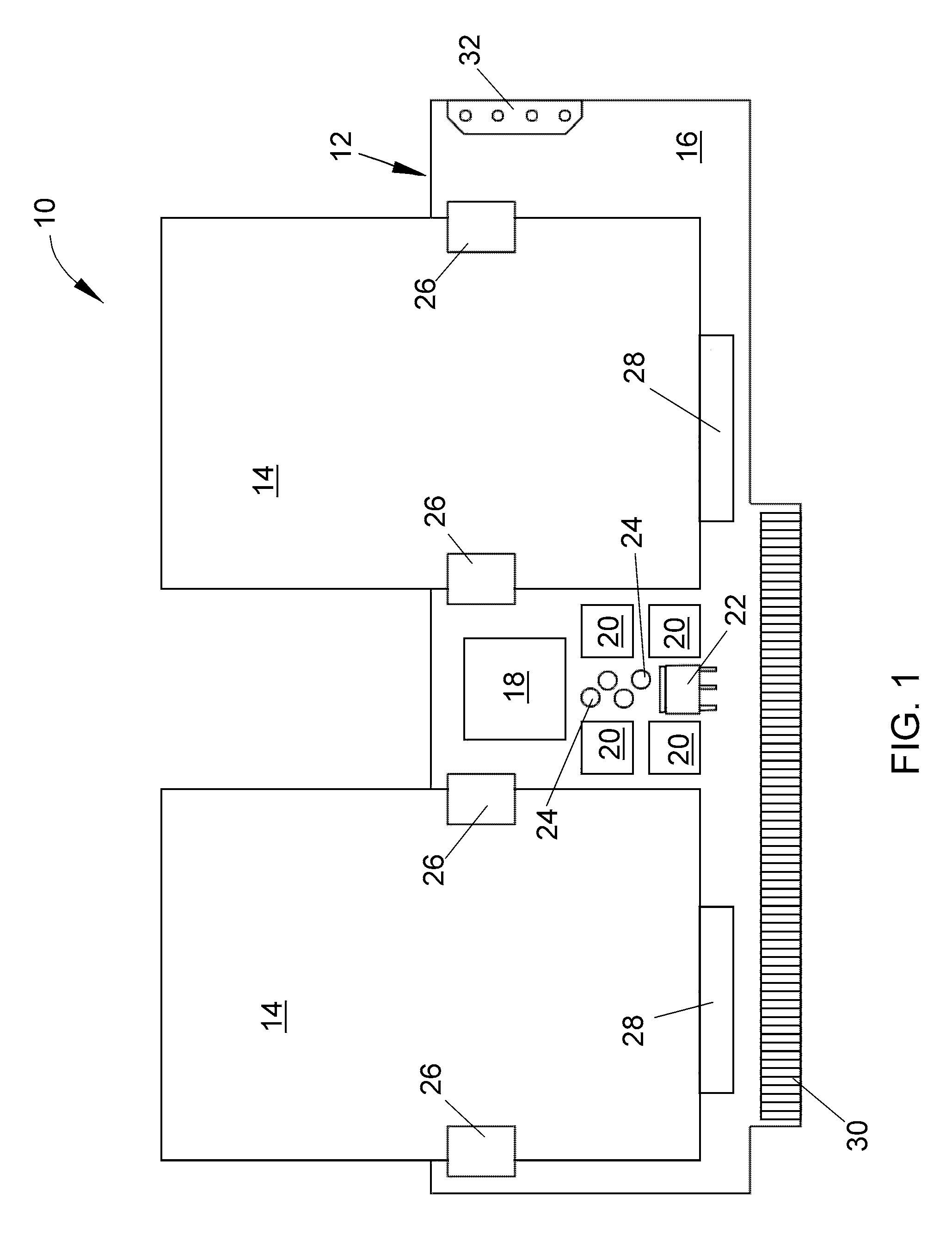

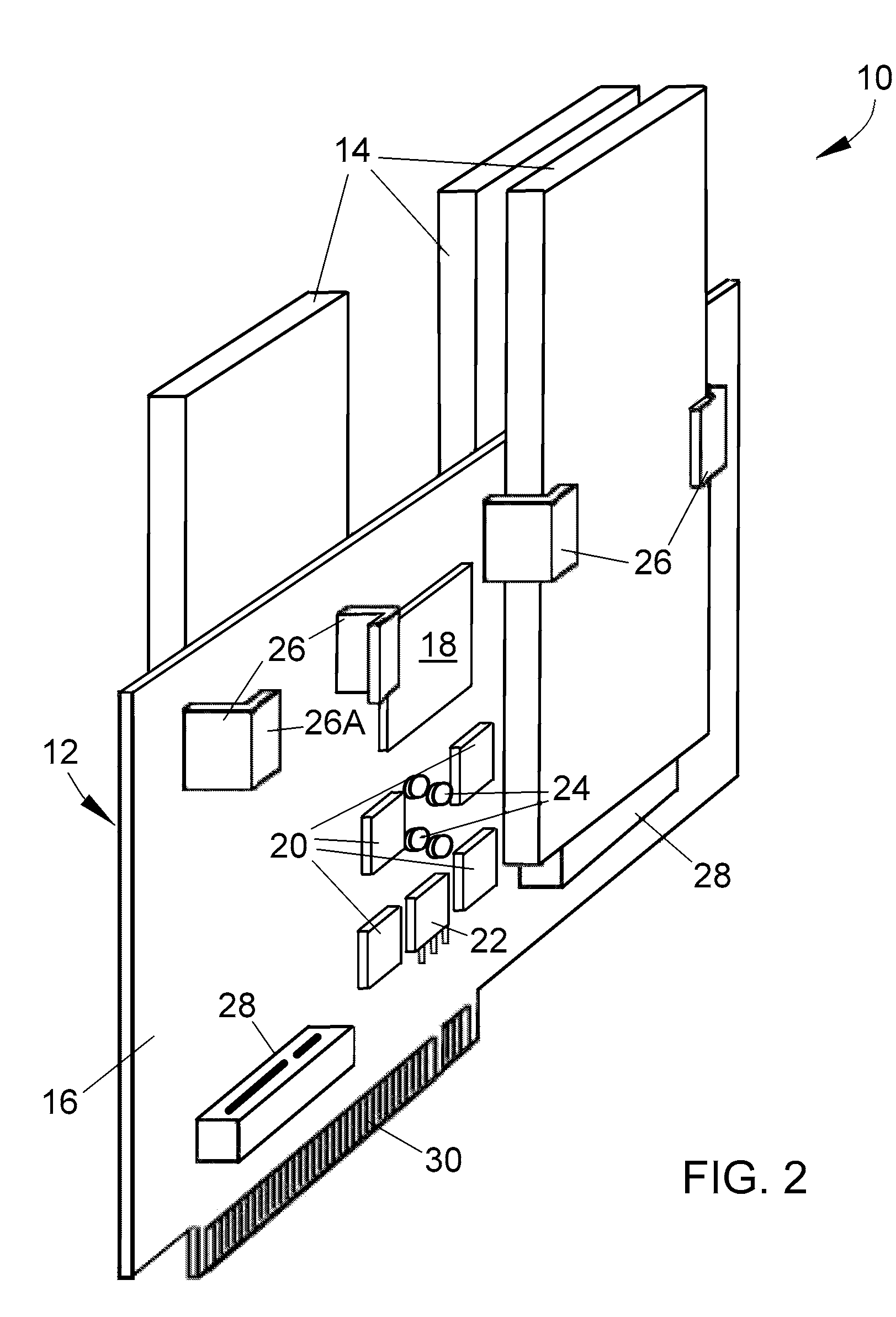

Modular mass storage sysgtem and method therefor

ActiveUS20100241799A1Eliminate the problemCheap replacementMemory loss protectionElectric discharge tubesDevices fixationEngineering

A modular mass storage system and method that enables cableless mounting of ATA and / or similar high speed interface-based mass storage devices in a computer system. The system includes a printed circuit board, a system expansion slot interface on the printed circuit board and comprising power and data pins, a host bus controller on the printed circuit board and electrically connected to the system expansion slot interface, docking connectors connected with the host bus controller to receive power and exchange data therewith and adapted to electrically couple with industry-standard non-volatile memory devices without cabling therebetween, and features on the printed circuit board for securing the memory devices thereto once coupled to the docking connectors.

Owner:KIOXIA CORP