Patents

Literature

25472 results about "Input/output" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, input/output or I/O (or, informally, io or IO) is the communication between an information processing system, such as a computer, and the outside world, possibly a human or another information processing system. Inputs are the signals or data received by the system and outputs are the signals or data sent from it. The term can also be used as part of an action; to "perform I/O" is to perform an input or output operation.

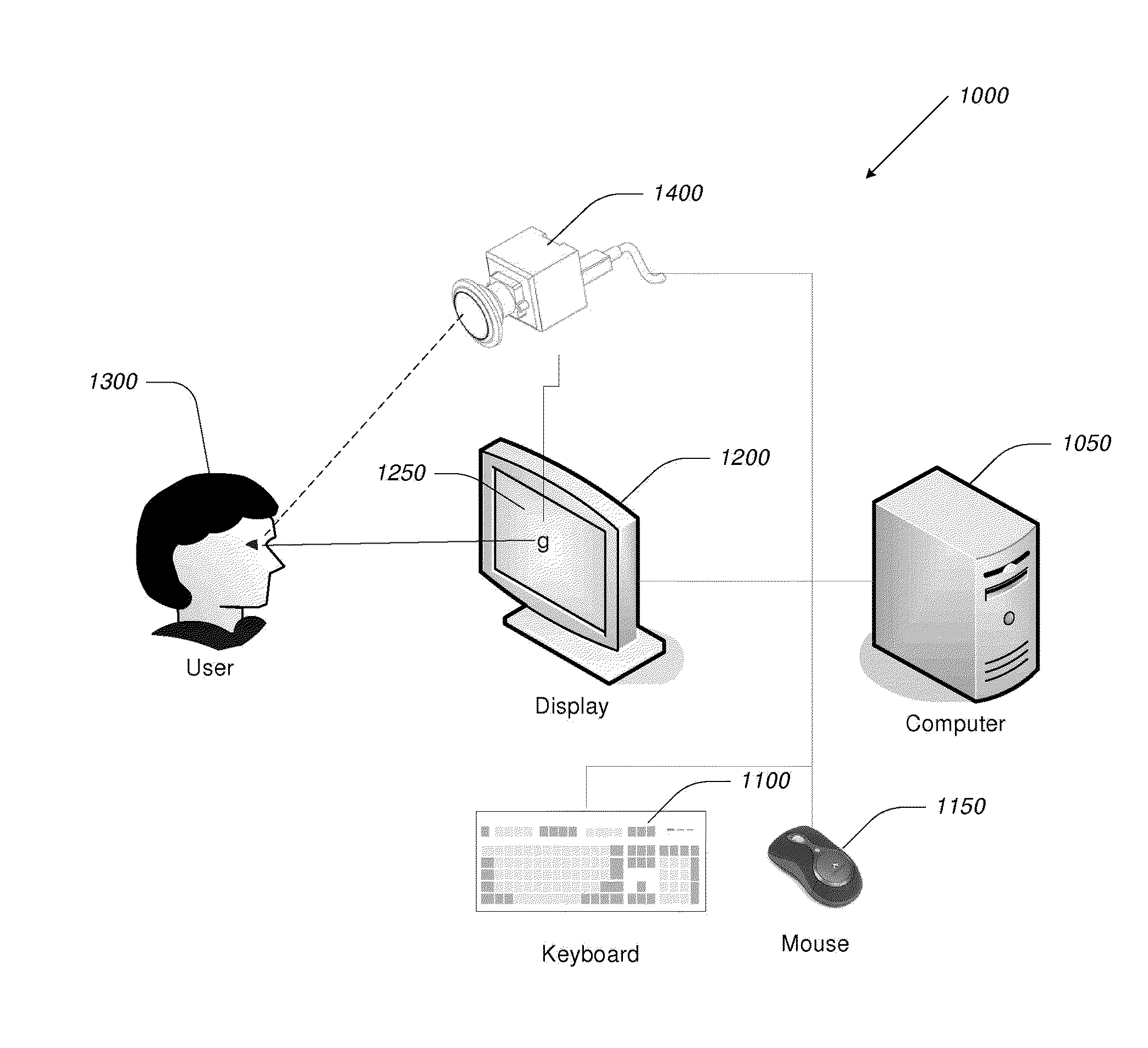

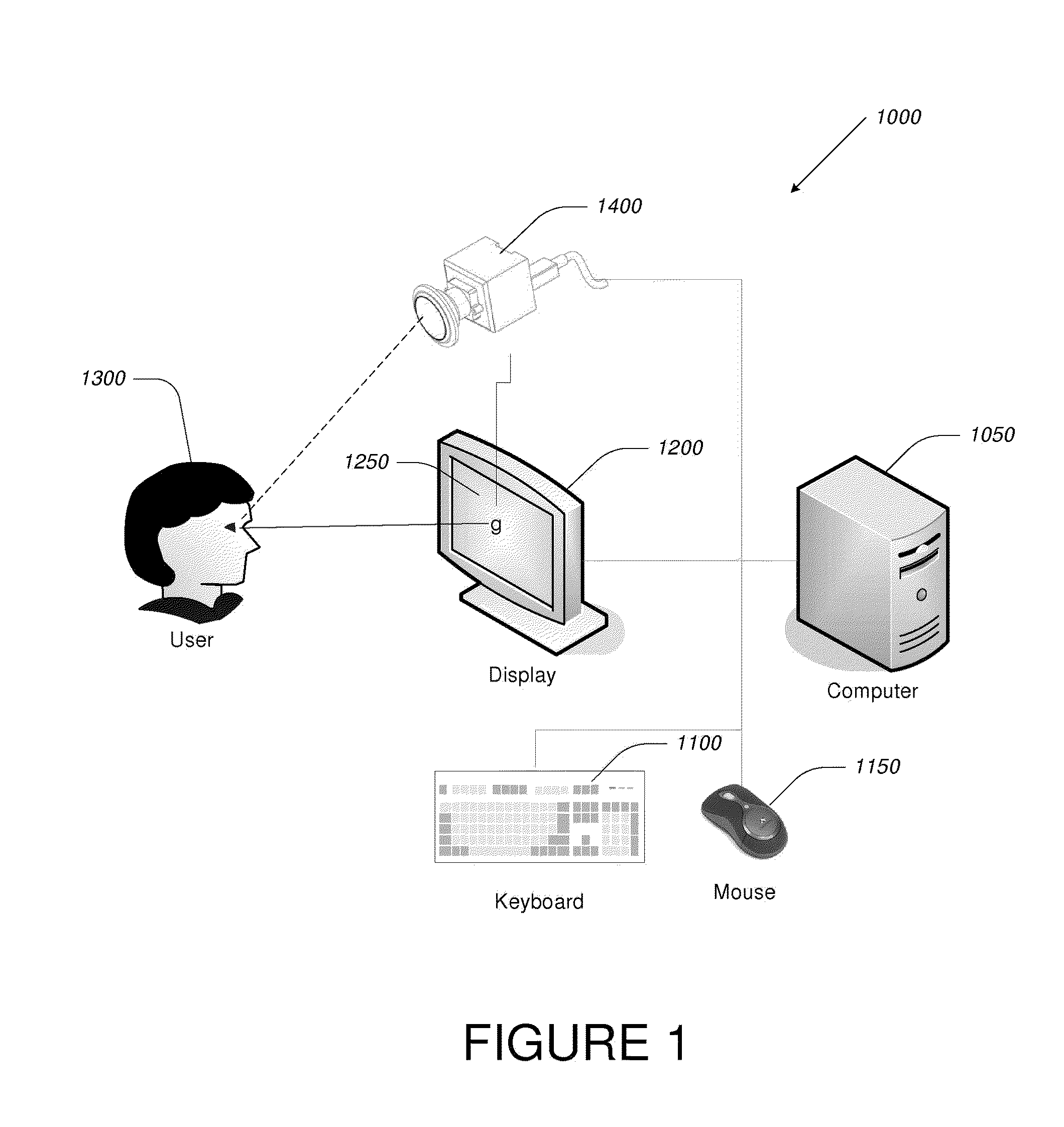

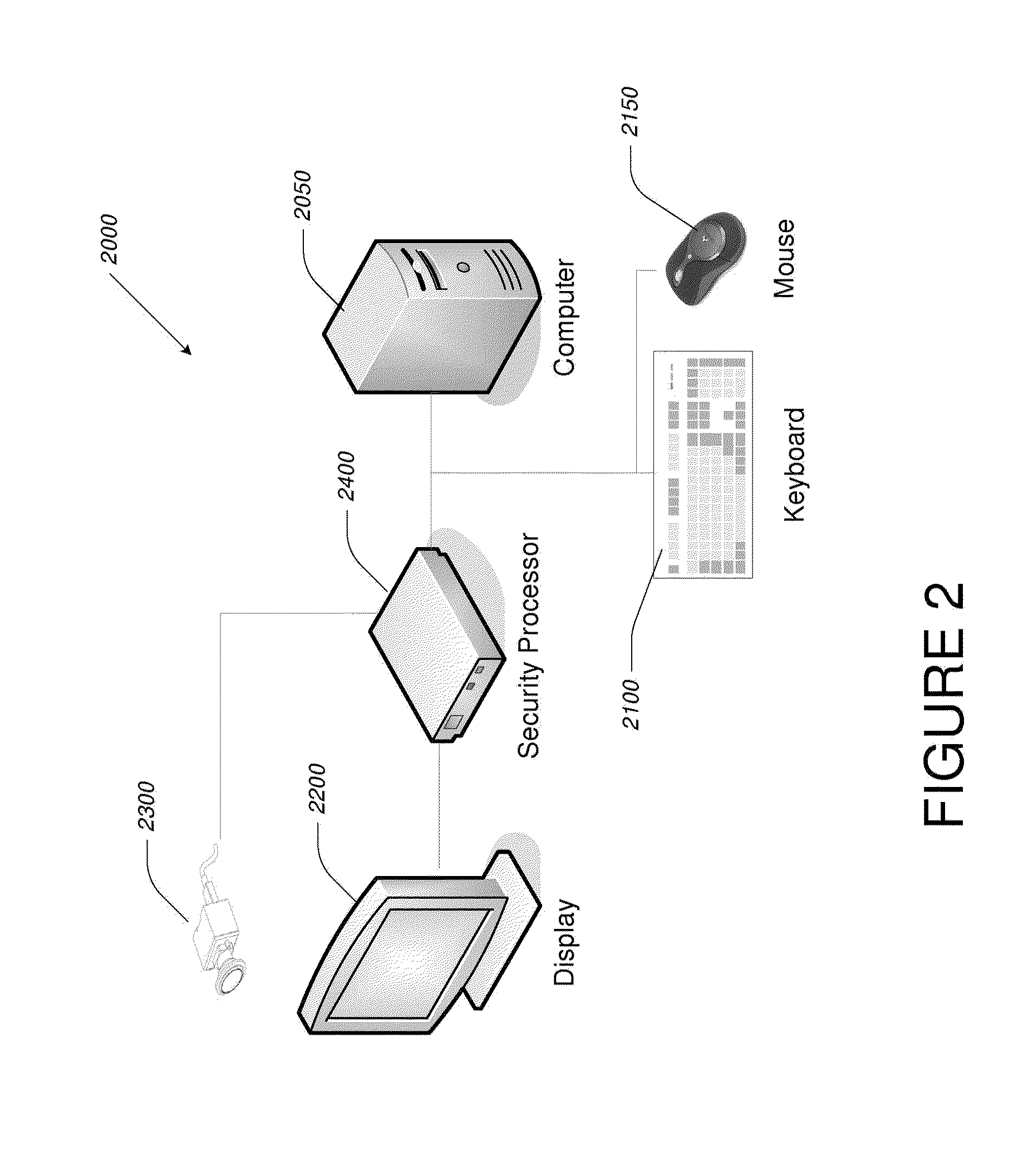

Video-Based Privacy Supporting System

ActiveUS20100205667A1Improve securityPrivacy protectionDigital data processing detailsUnauthorized memory use protectionDisplay deviceOutput device

Computer display privacy and security for computer systems. In one aspect, the invention provides a computer-controlled system for regulating the interaction between a computer and a user of the computer based on the environment of the computer and the user. For example, the computer-controlled system provided by the invention comprises an input-output device including an image sensor configured to collect facial recognition data proximate to the computer. The system also includes a user security parameter database encoding security parameters associated with the user; the database is also configured to communicate with the security processor. The security processor is configured to receive the facial recognition data and the security parameters associated with the user, and is further configured to at least partially control the operation of the data input device and the data output device in response to the facial recognition data and the security parameters associated with the user.

Owner:TOBII TECH AB

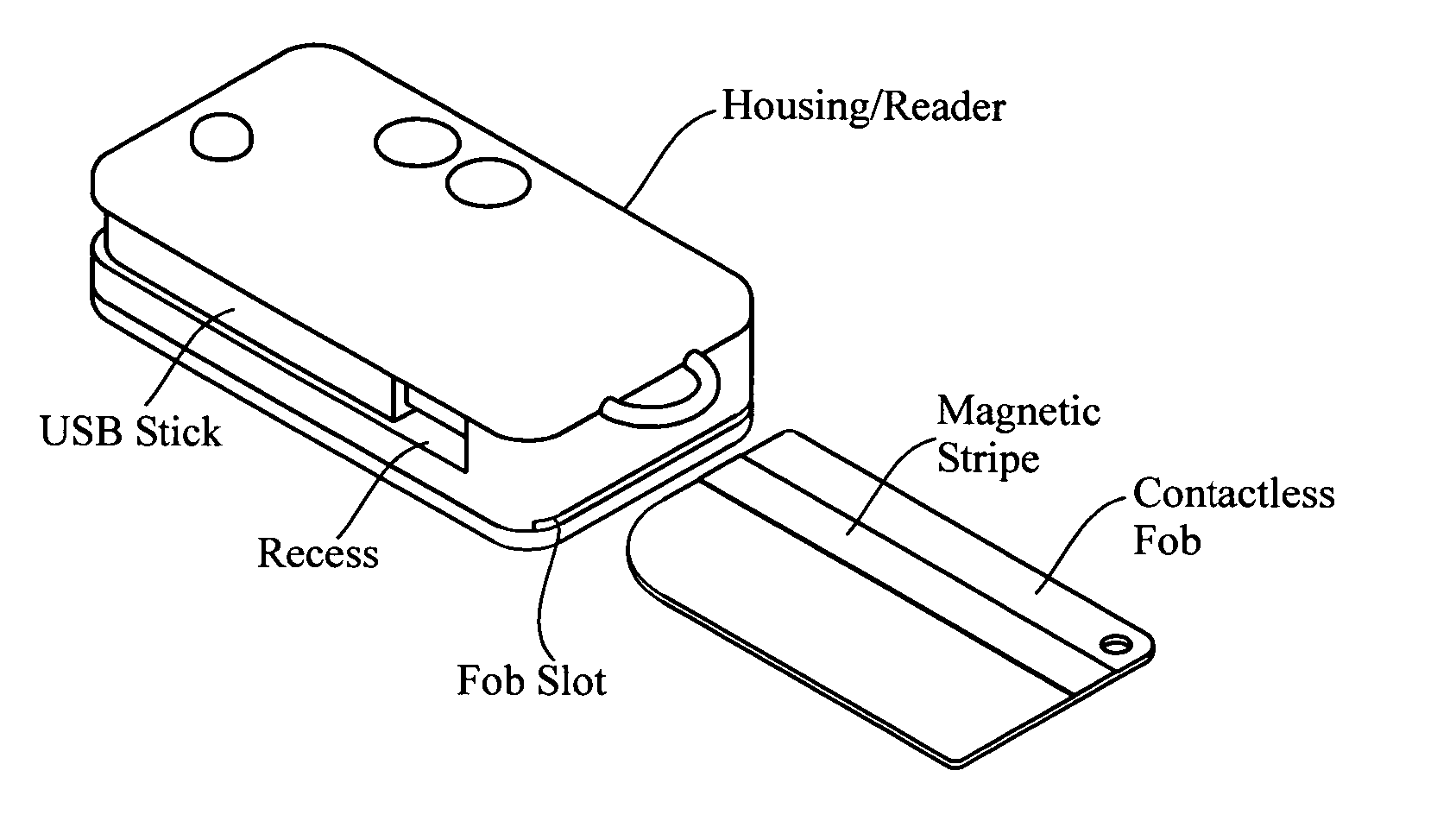

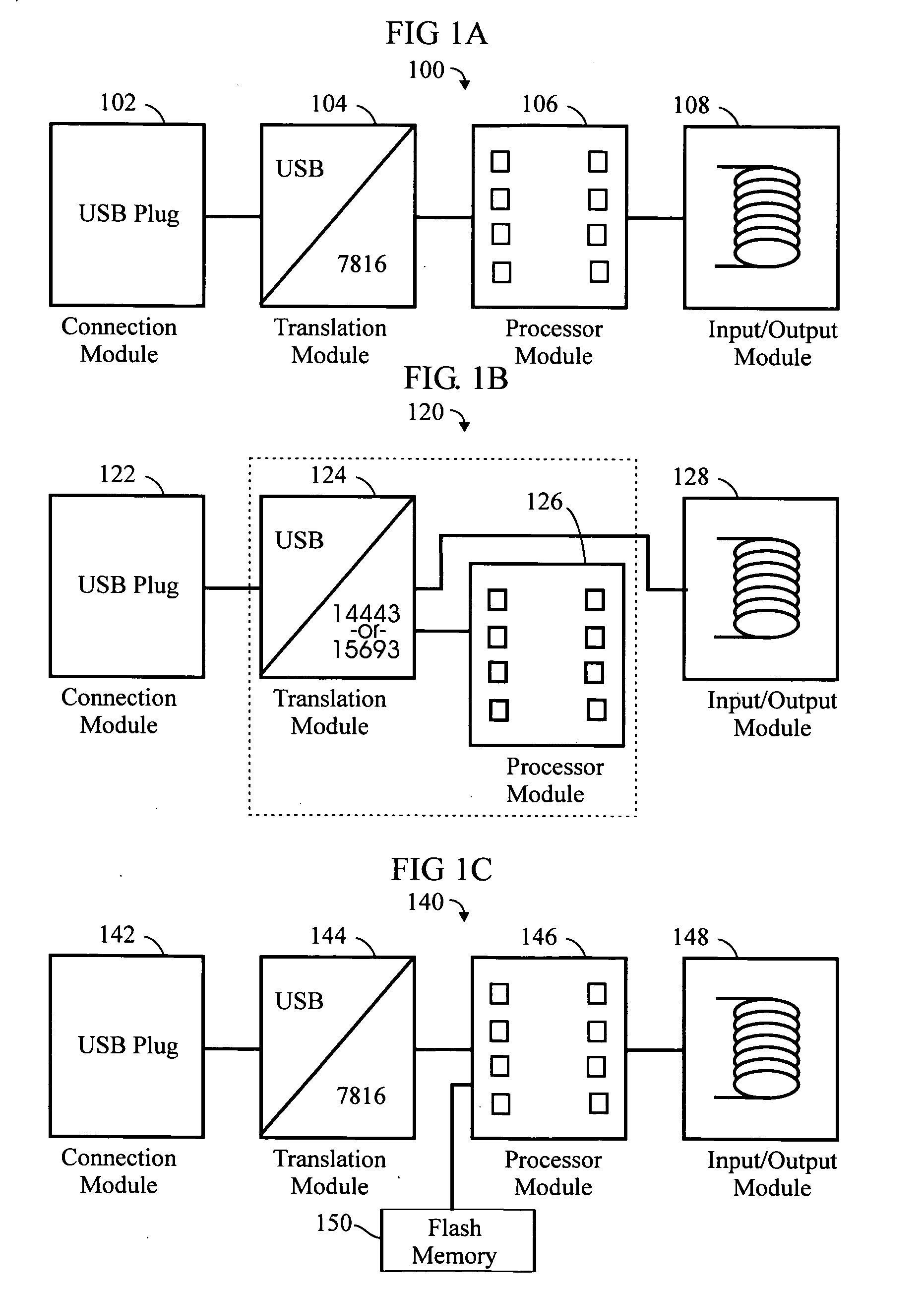

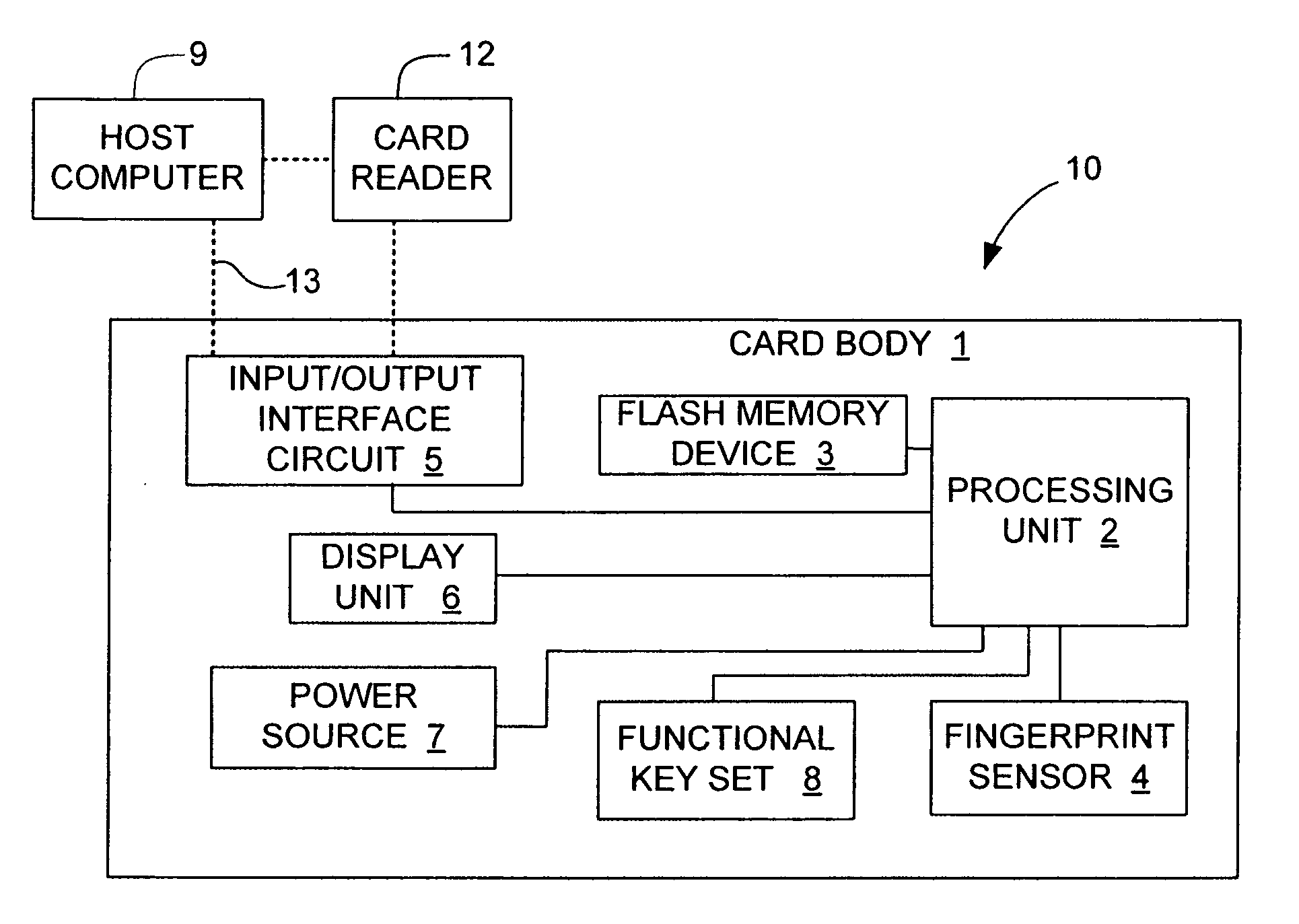

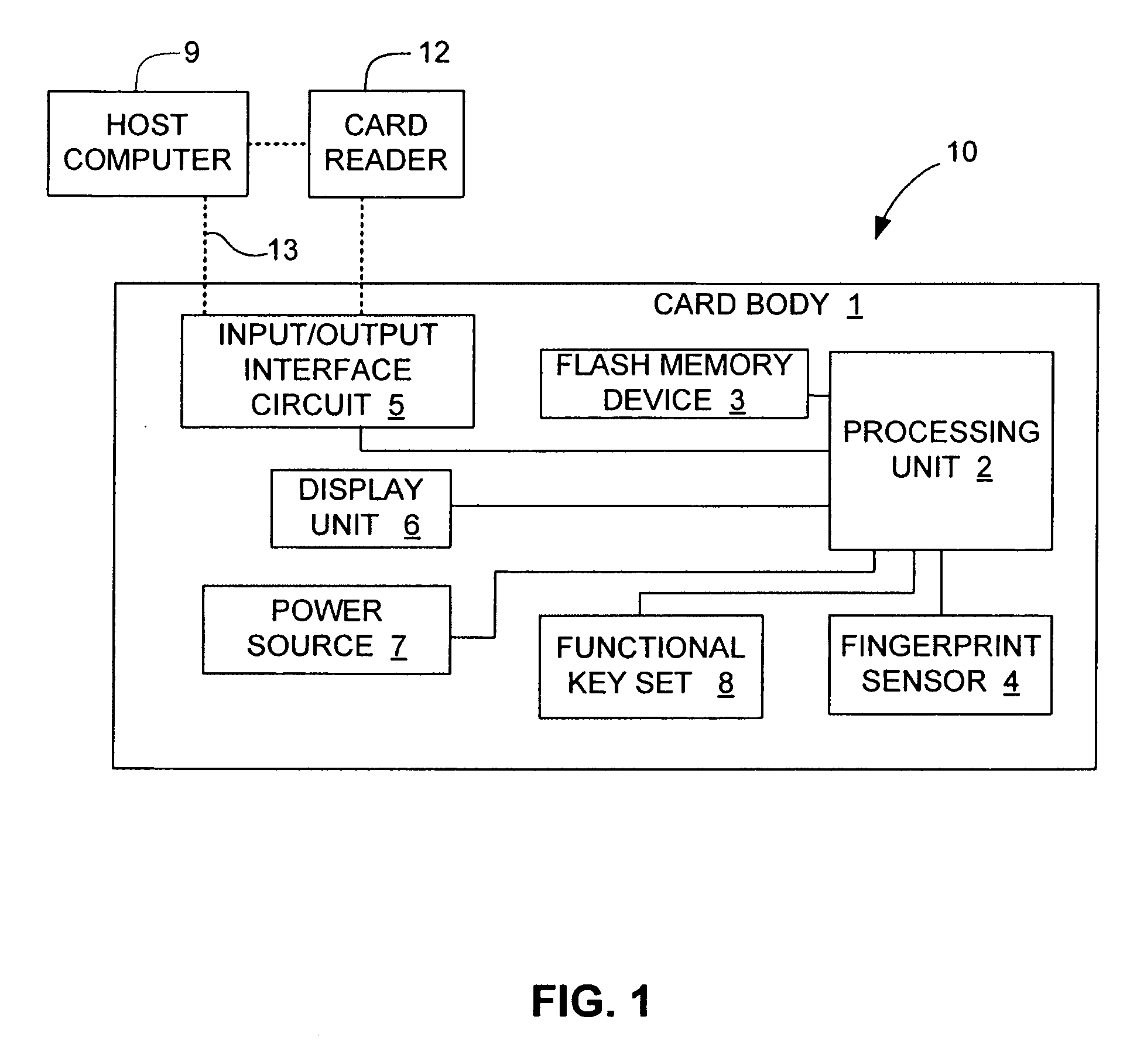

RFID token with multiple interface controller

InactiveUS20060208066A1Acutation objectsBroadcast information characterisationComputer moduleSmart card

An RFID token apparatus has a connection module for interfacing with an appliance capable of communicating and interacting with remote servers and networks, a translation module for moving signals between a USB interface and a smart card interface, a processor module which may be capable of operating as a dual-interface (DI) chip; and an input / output module having at least one RF antenna and a modulator. An RFID-contactless interface according to ISO 14443 & ISO 15693 and / or NFC. A wireless interface according to Zigbee, Bluetooth, WLAN 802.11, UWB, USB wireless and / or any similar interface. An RFID reader apparatus has a housing; a slot for a contact or contactless fob; and a USB stick alternately protruding from the housing and retracted within the housing.

Owner:DPD PATENT TRUST

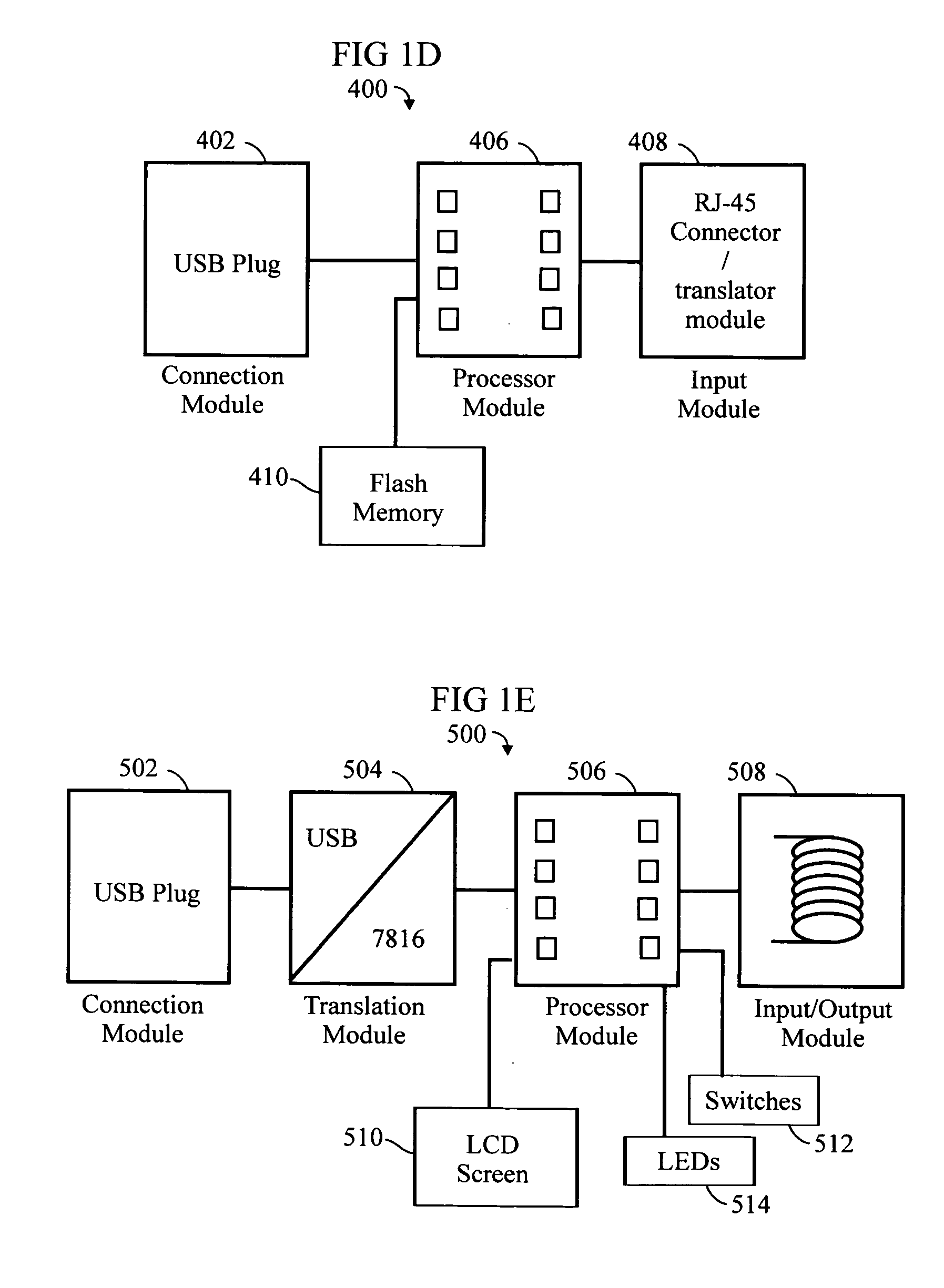

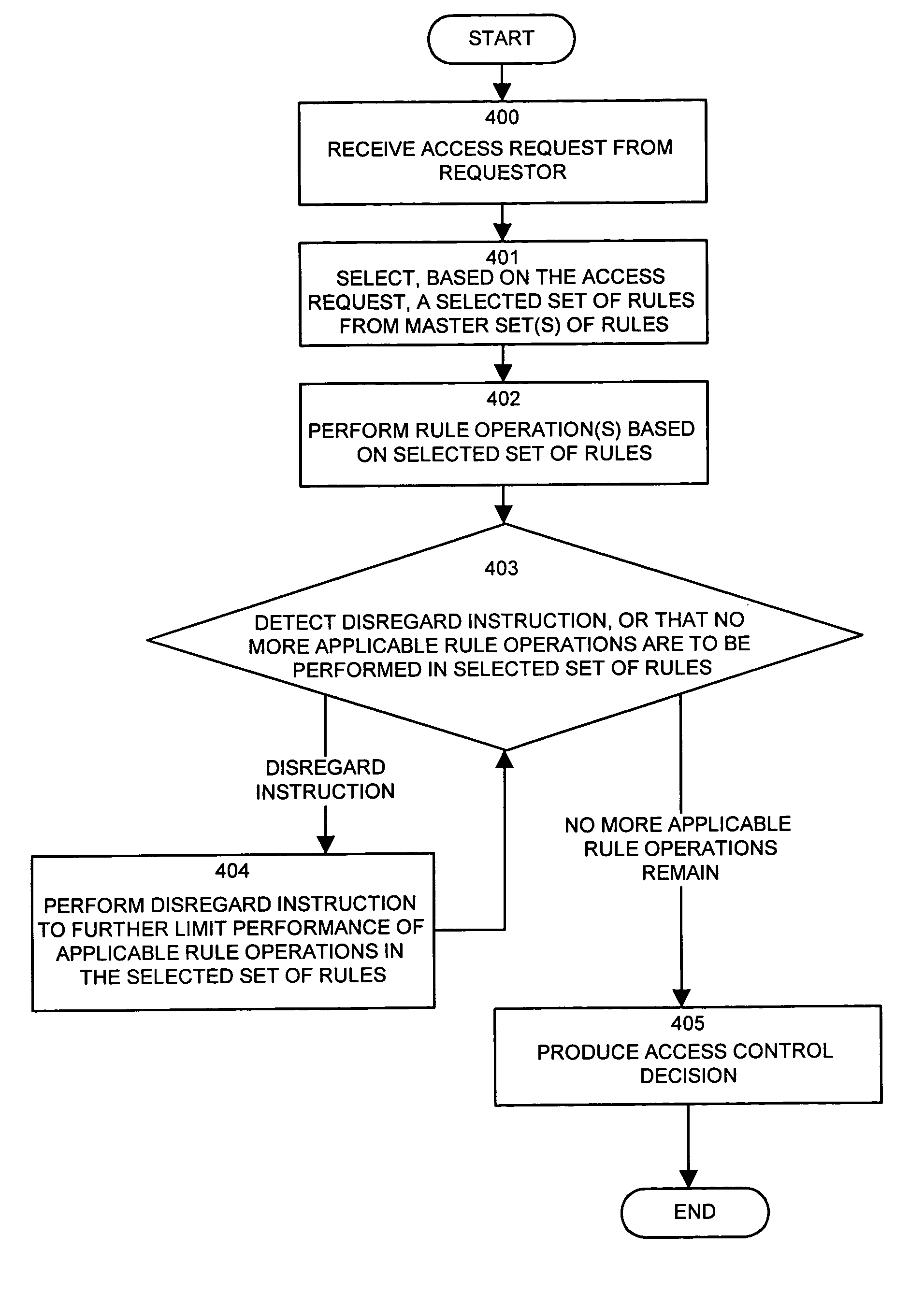

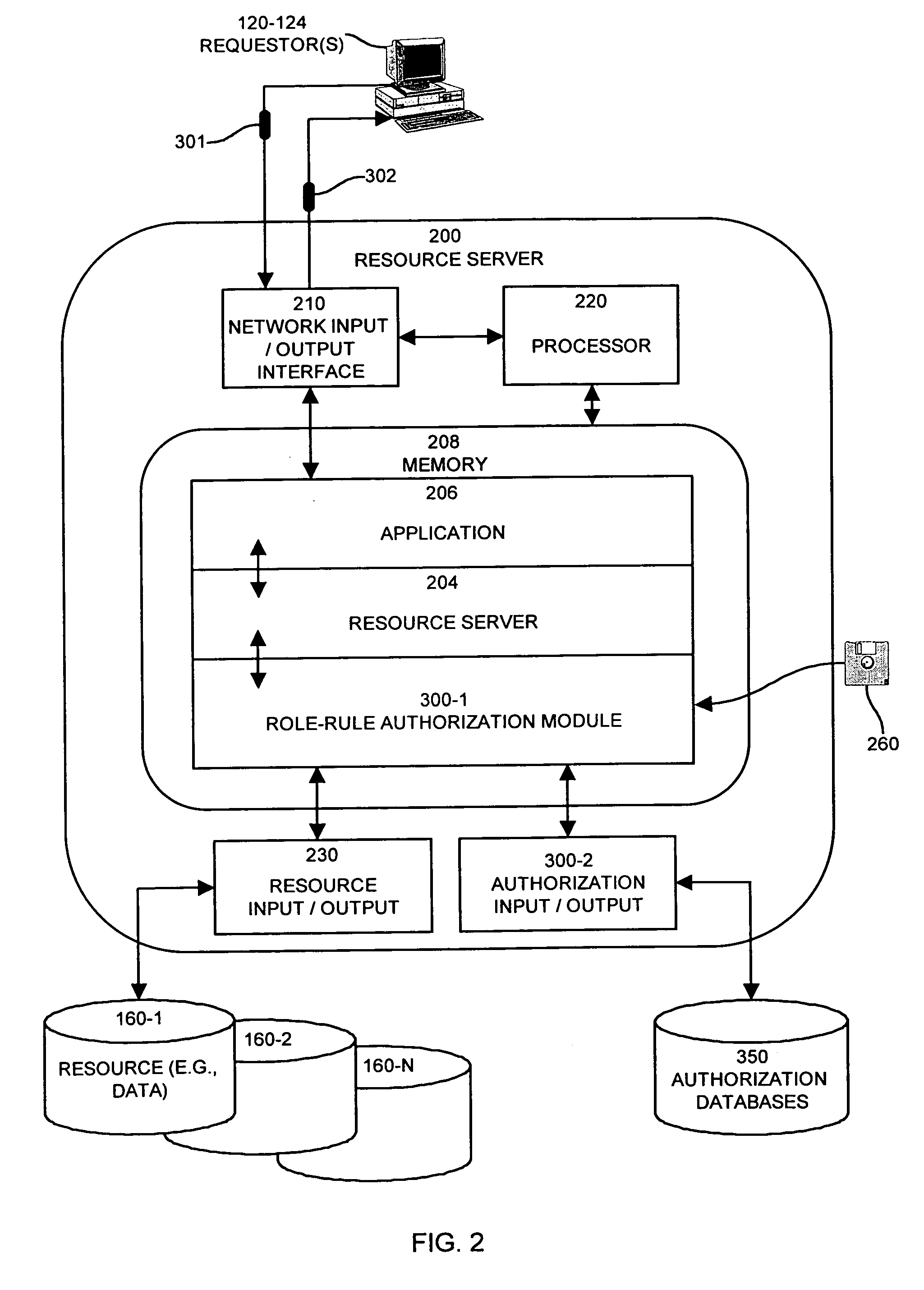

Methods and apparatus for controlling access to a resource

InactiveUS7185192B1Limit staff employee accessVerification of the security policy more straightforwardData processing applicationsDigital data processing detailsProgramming languageDecision taking

An input / output interface receives an access request from a requester. A processor associated with the input / output interface applies a filter operation to select a subset of rules from a master set of rules maintained within an authorization database. Rules can be selected in this manner using filter operations so that all rules in the rule set need not be processed. A rule may include a disregard instruction. The processor further performs at least one rule operation based on the subset of rules to produce an access control decision in the memory system until either a rule operation including a disregard instruction is performed to limit performance of rule operations in the selected set of rules or until all rule operations in the selected set of rules that are applicable to the access control decision are performed.

Owner:EMC IP HLDG CO LLC

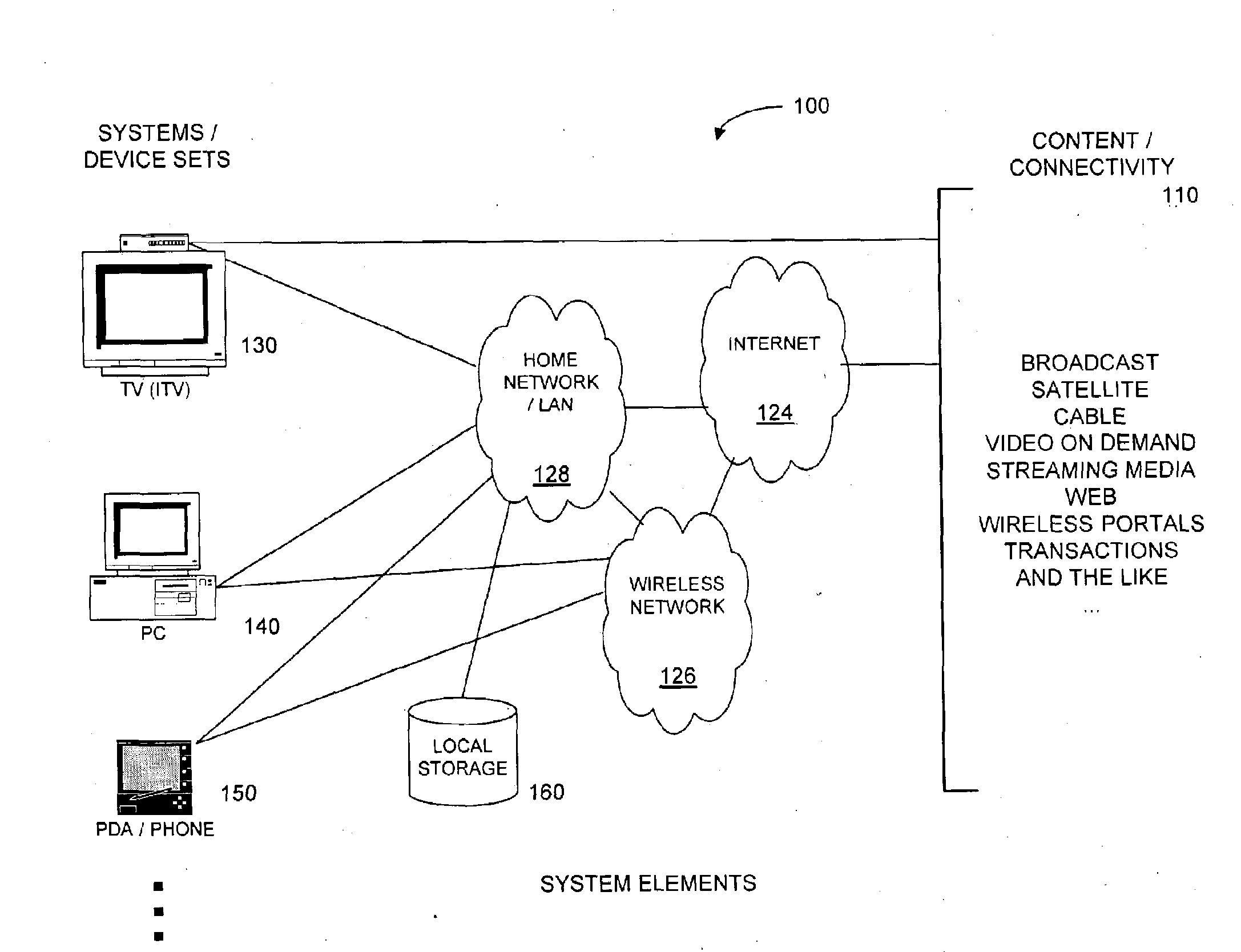

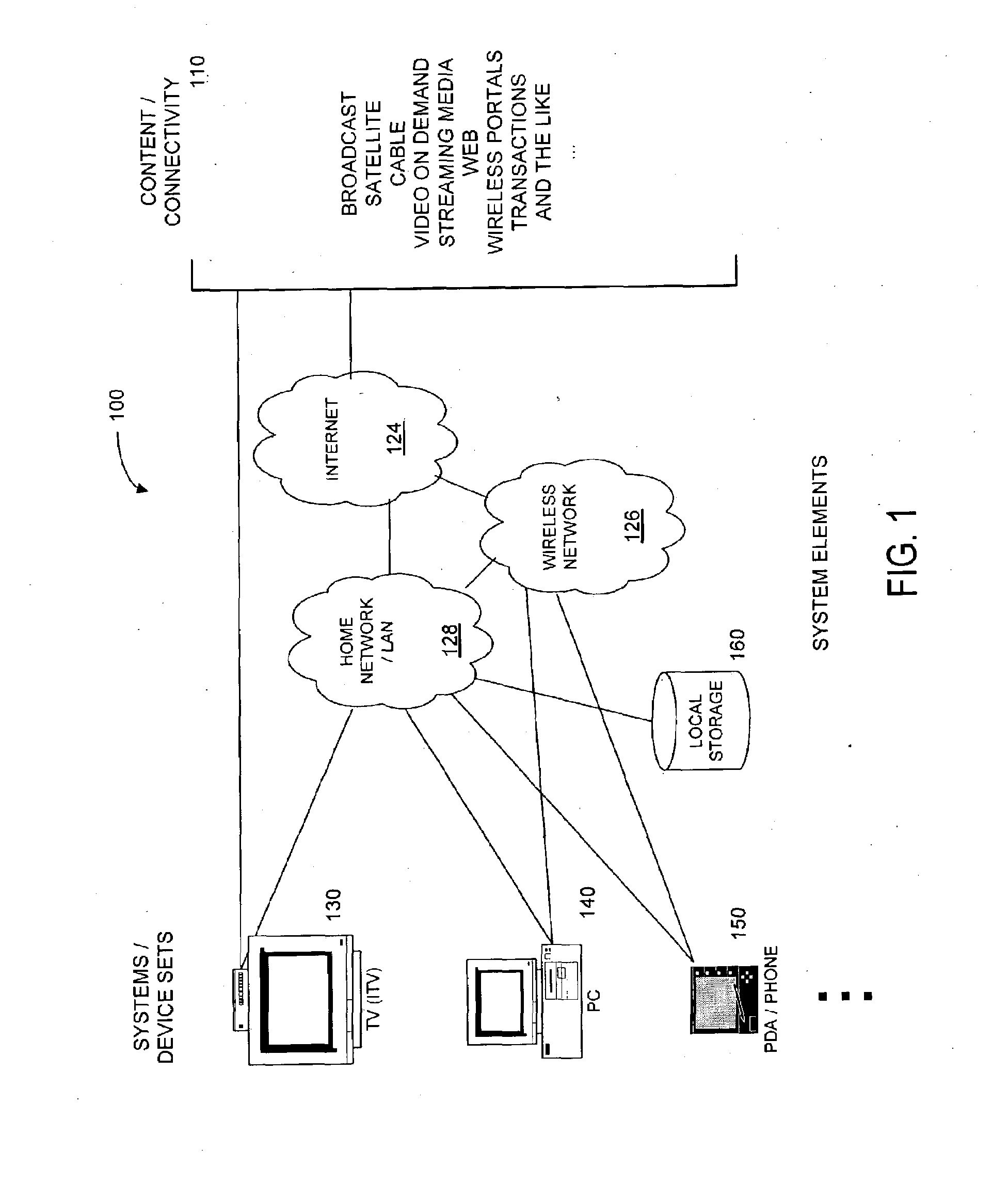

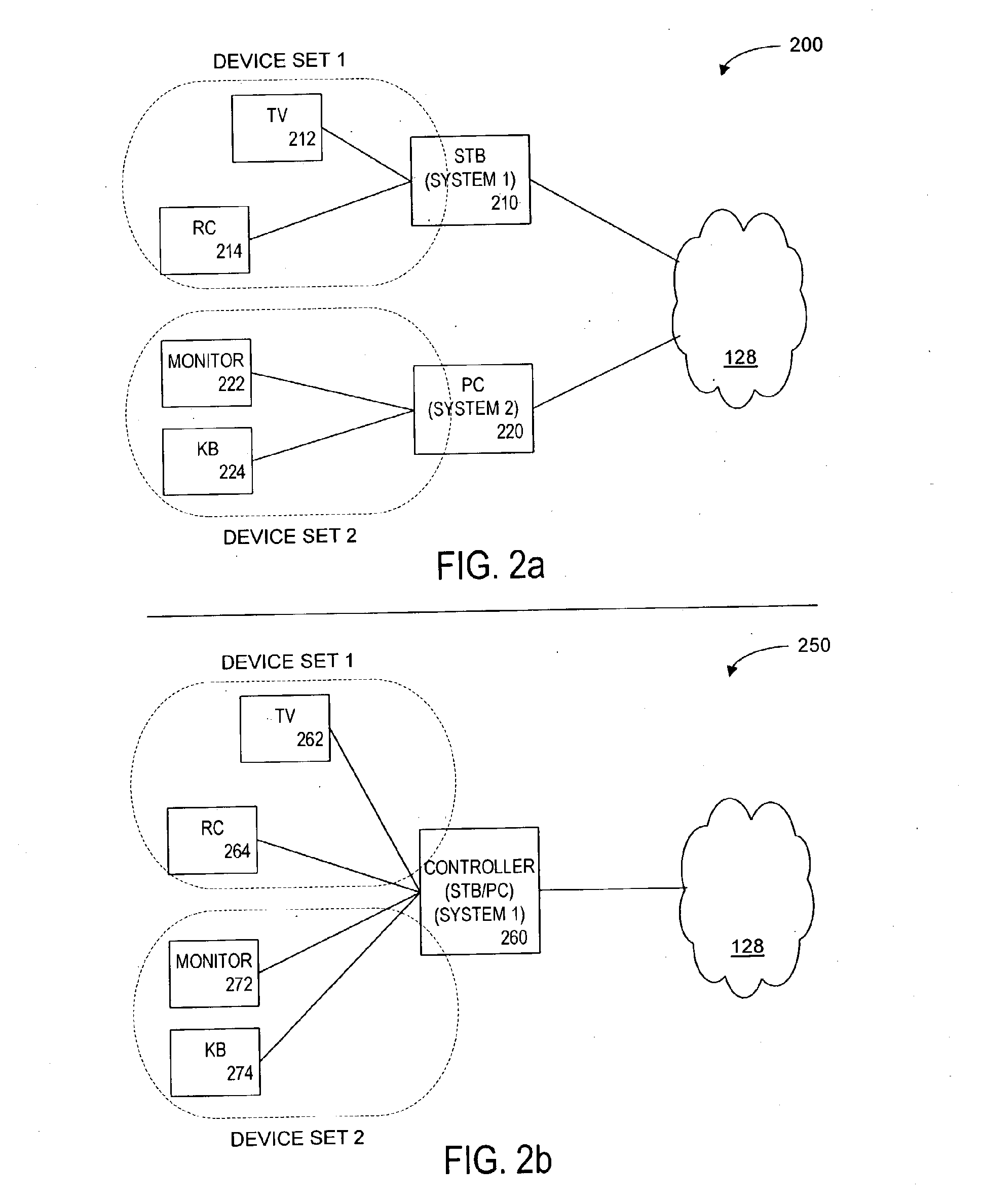

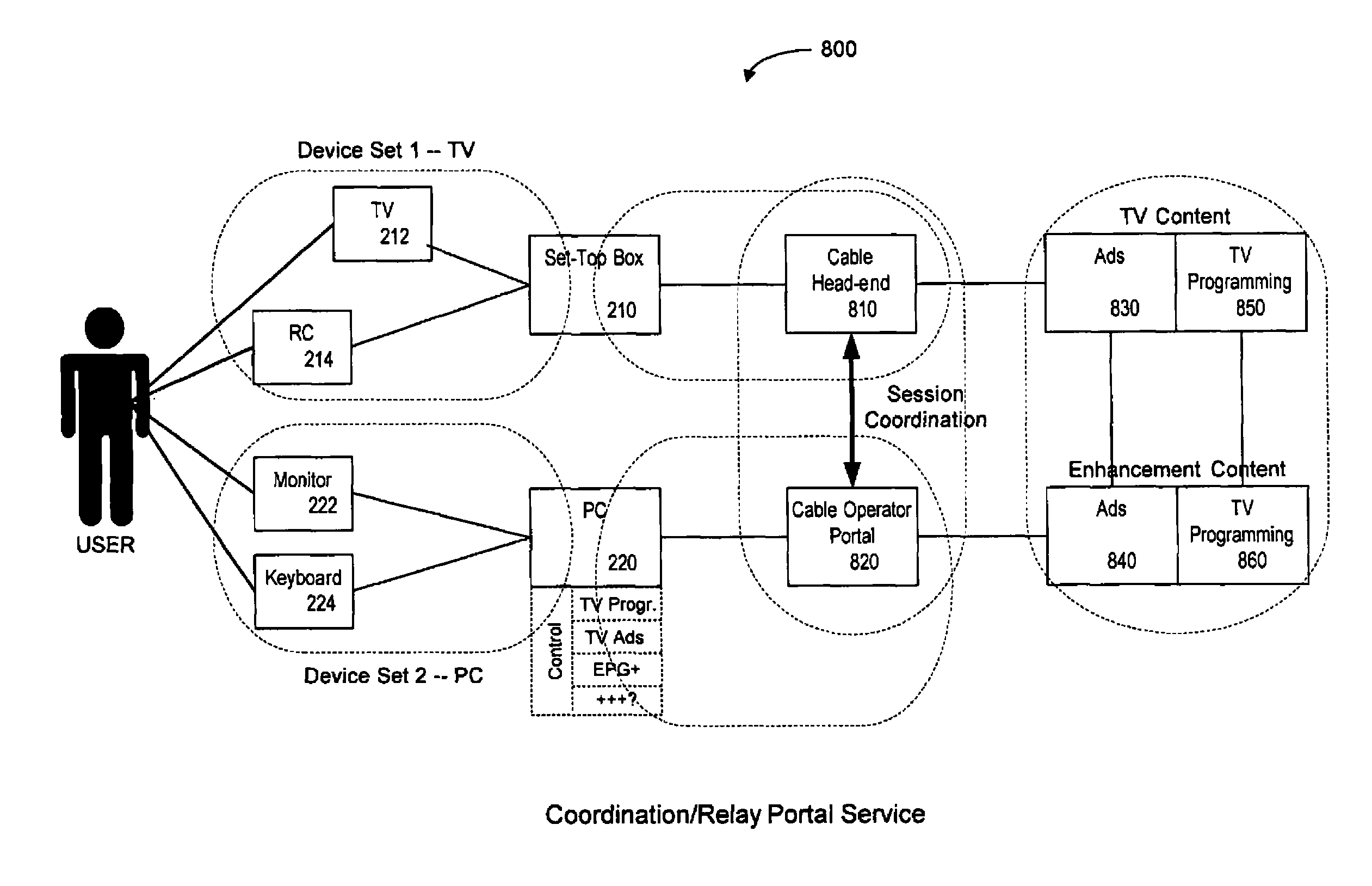

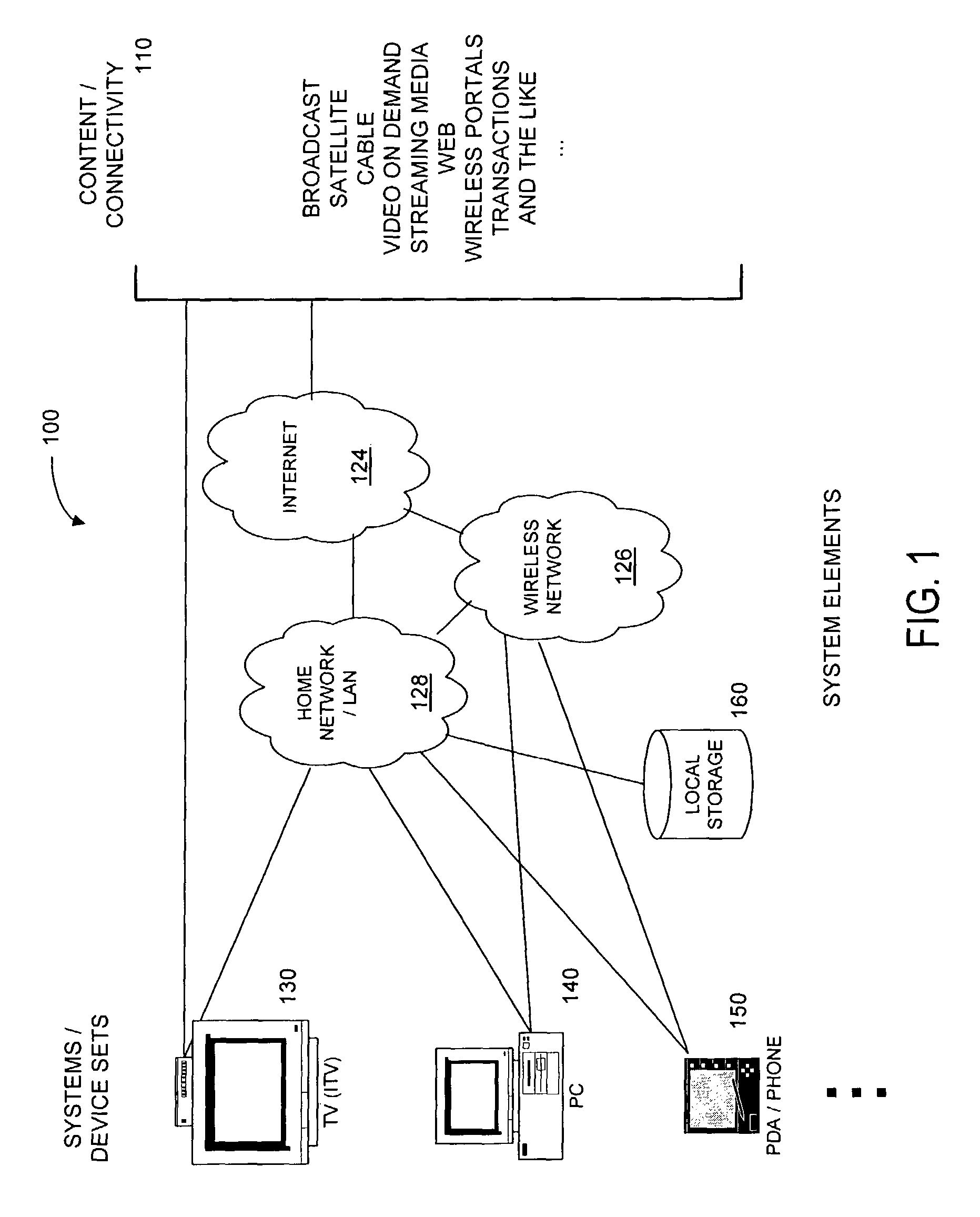

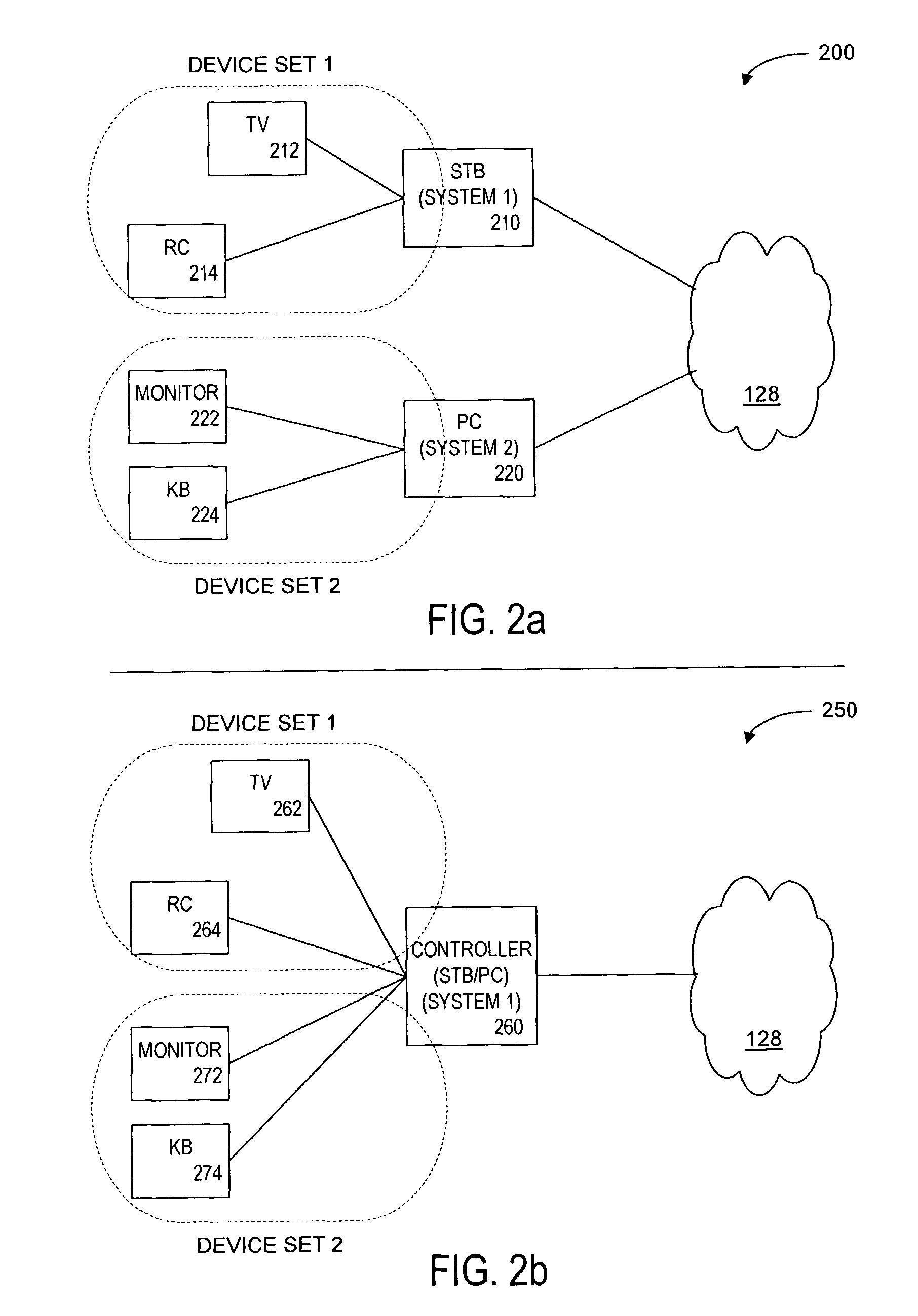

Method and Apparatus for Browsing Using Multiple Coordinated Device Sets

Systems and methods for navigating hypermedia using multiple coordinated input / output device sets. Disclosed systems and methods allow a user and / or an author to control what resources are presented on which device sets (whether they are integrated or not), and provide for coordinating browsing activities to enable such a user interface to be employed across multiple independent systems. Disclosed systems and methods also support new and enriched aspects and applications of hypermedia browsing and related business activities.

Owner:CONVERGENT MEDIA SOLUTIONS

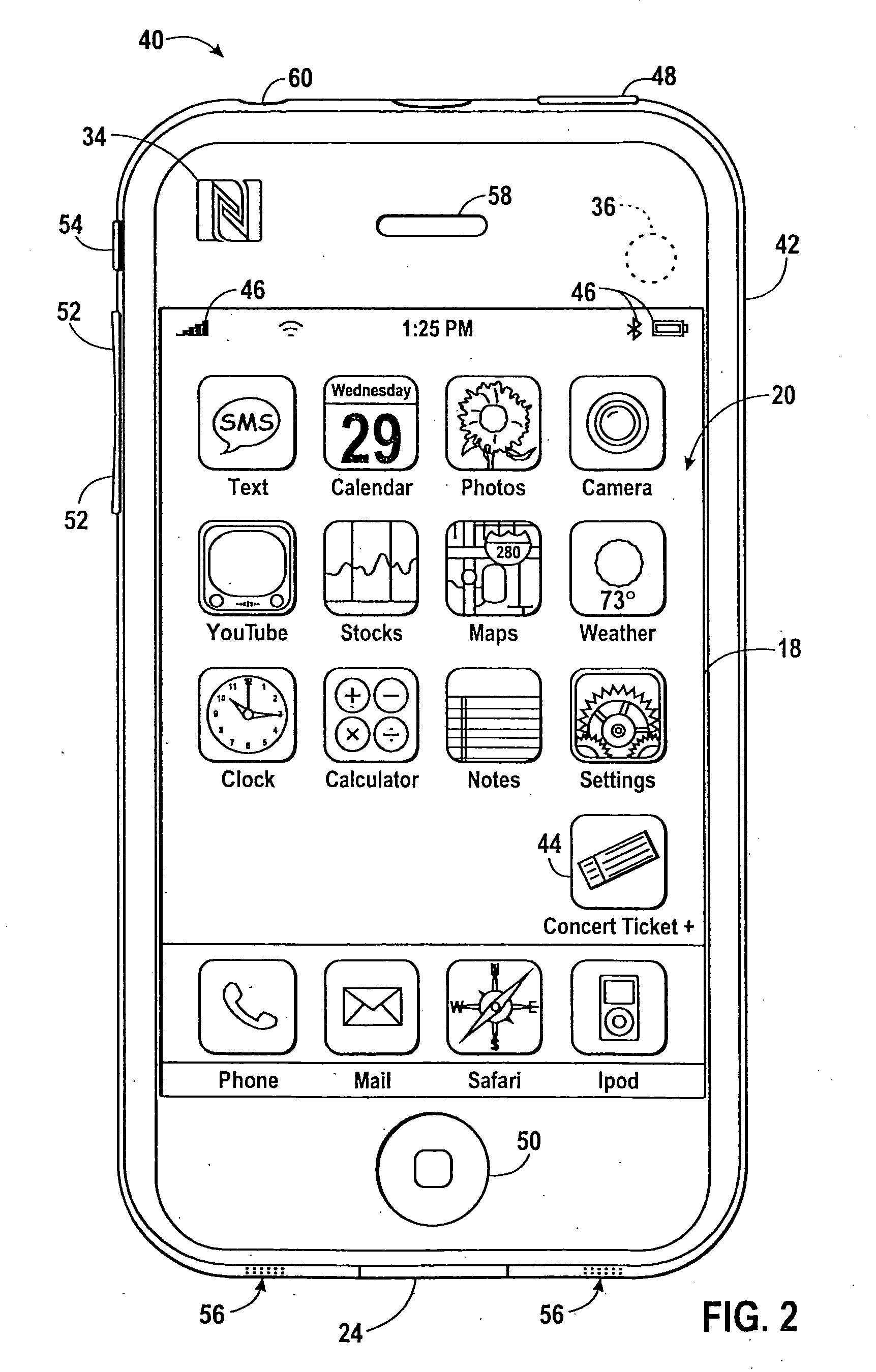

System and method for providing electronic event tickets

Systems, methods, and devices for providing and managing electronic event tickets are provided. For example, a device for managing an electronic event ticket may include a processor configured to run an electronic ticket management application, a memory device configured to store data associated with the electronic ticket management application, an electronic display configured to display at least a portion of the data associated with the electronic ticket management application, and an input / output interface configured to receive an electronic ticket and the data associated with the electronic ticket for management by the electronic ticket management application. The electronic ticket management application may be configured to enable the electronic device to gain entry to an event and to obtain at least one other event-related benefit after the electronic ticket is received by the input / output interface.

Owner:APPLE INC

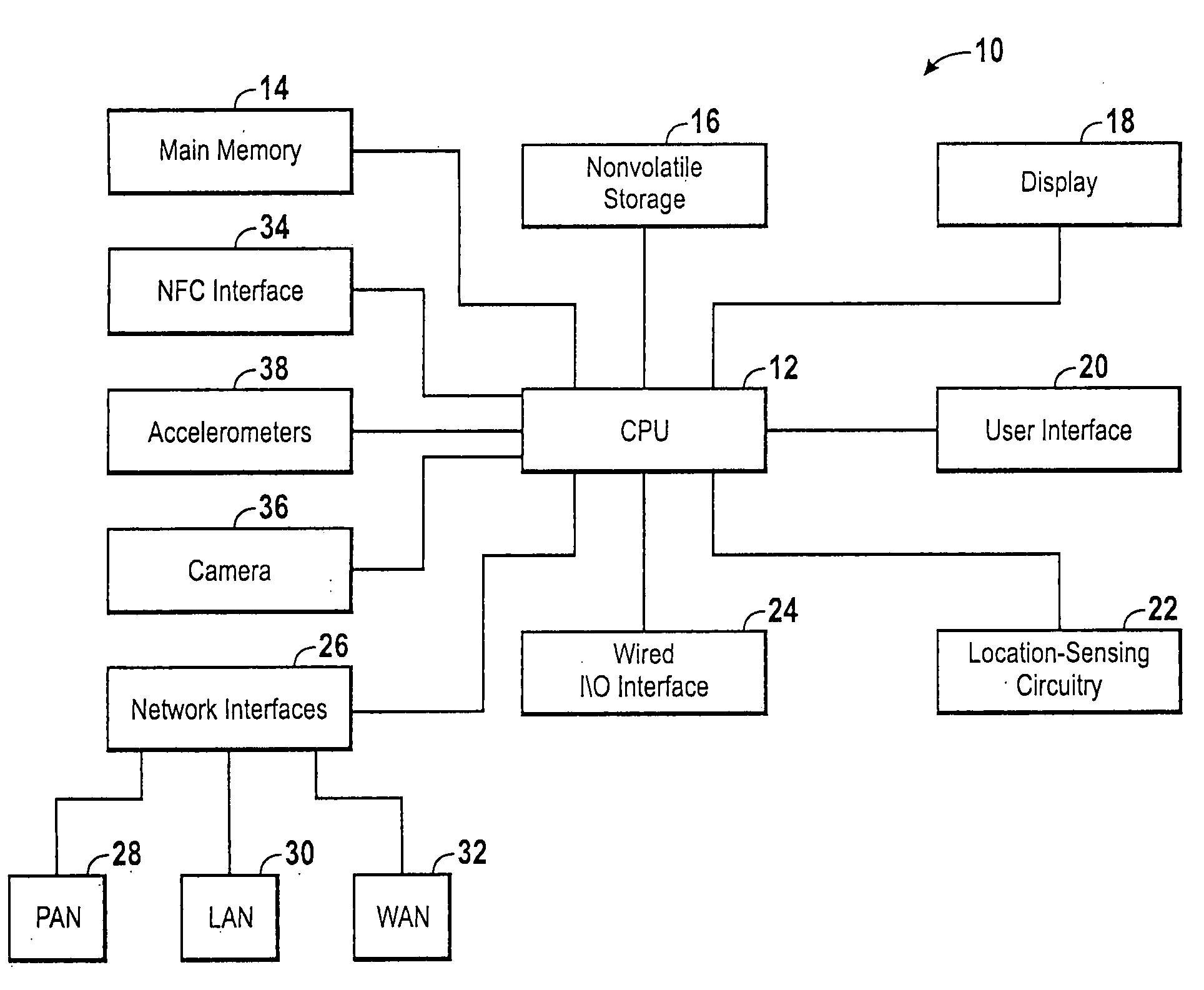

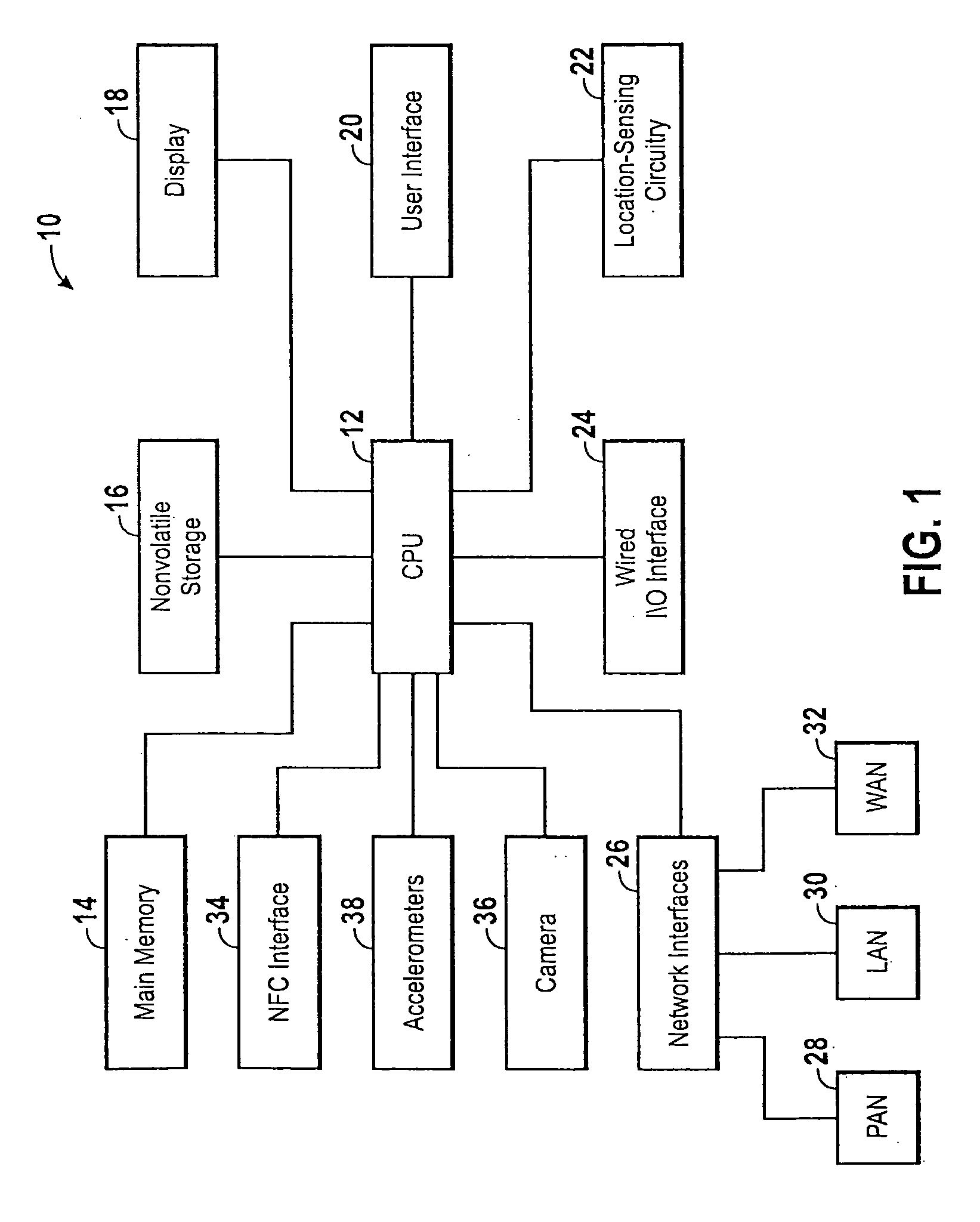

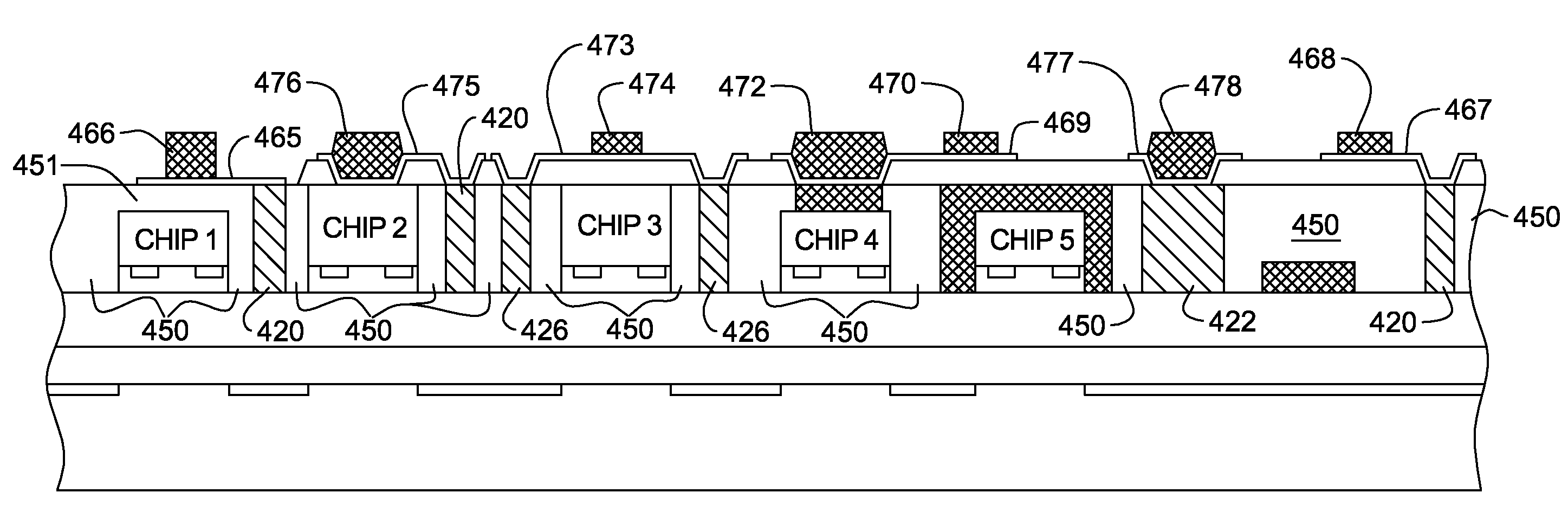

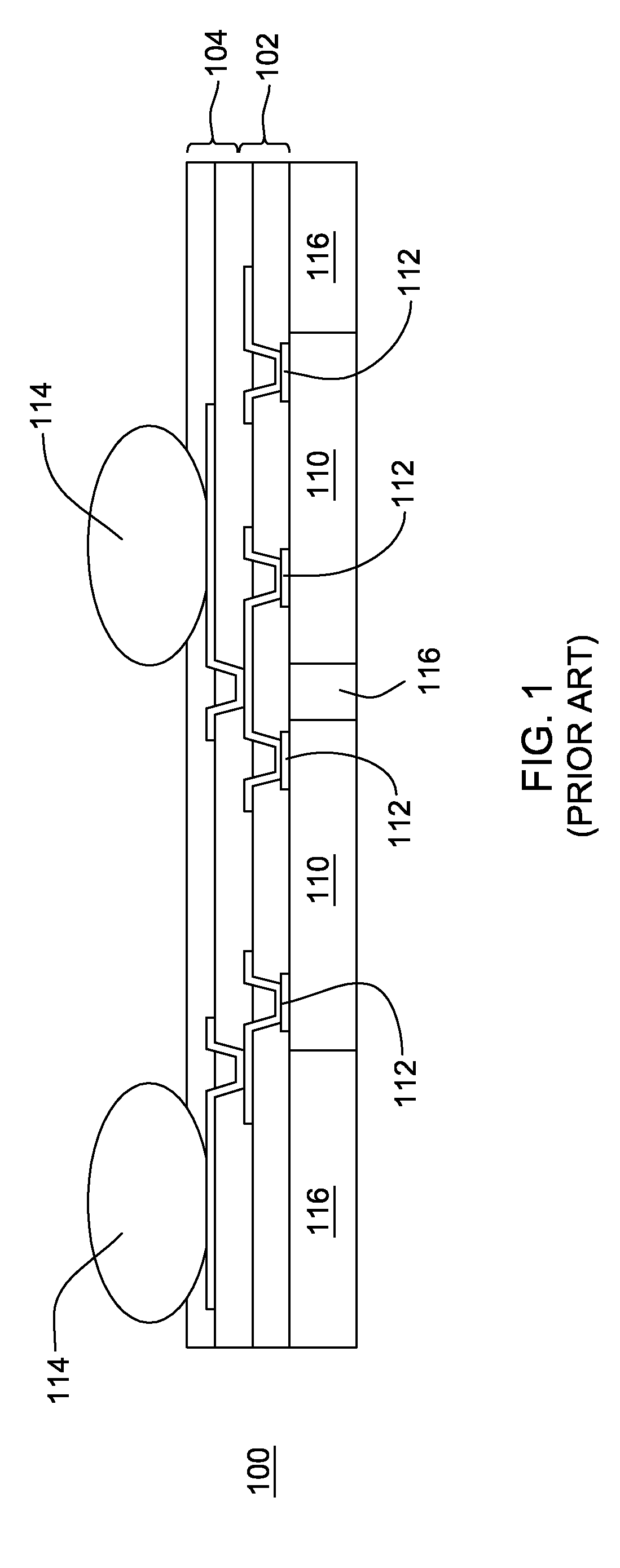

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS7619901B2Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

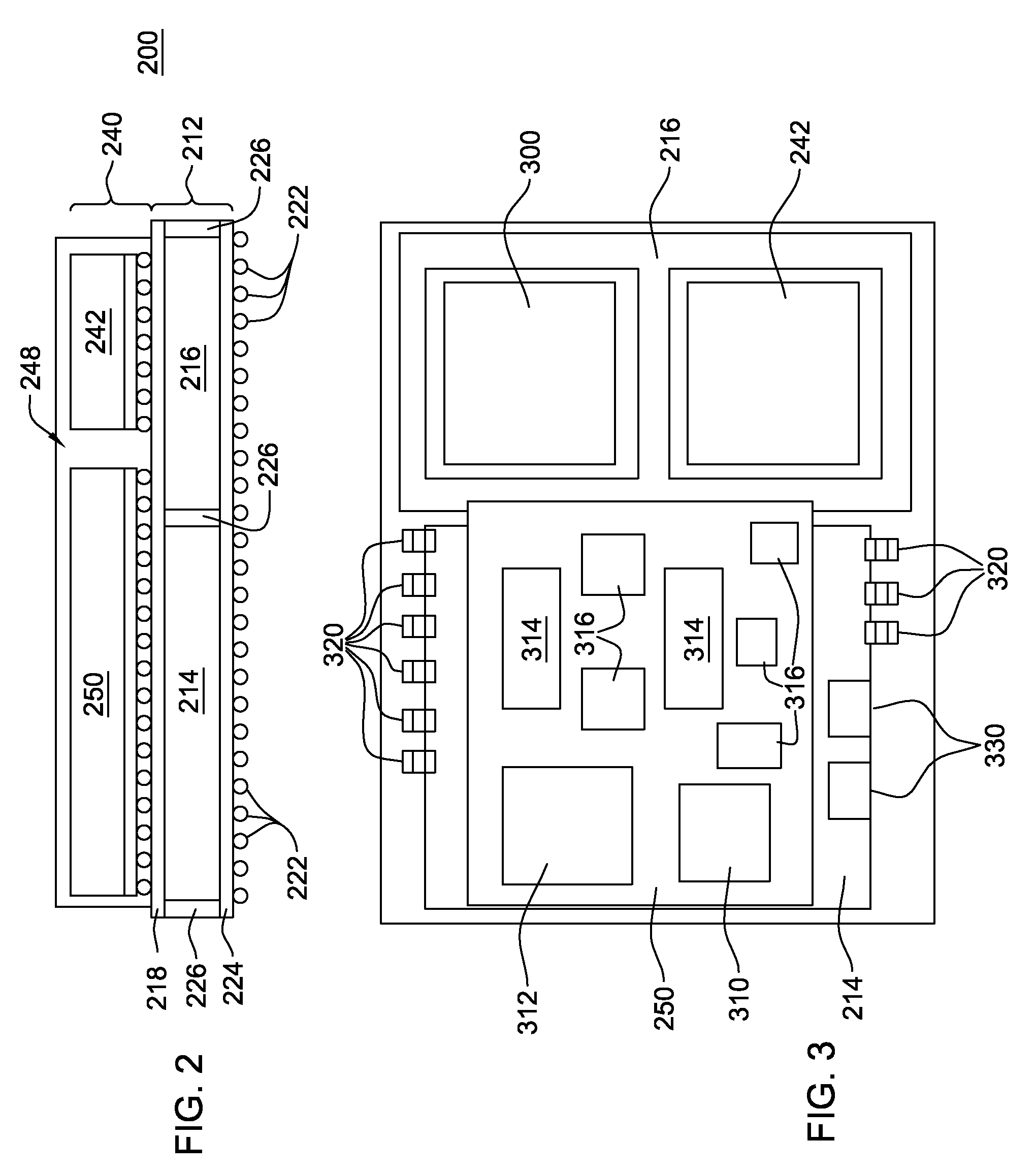

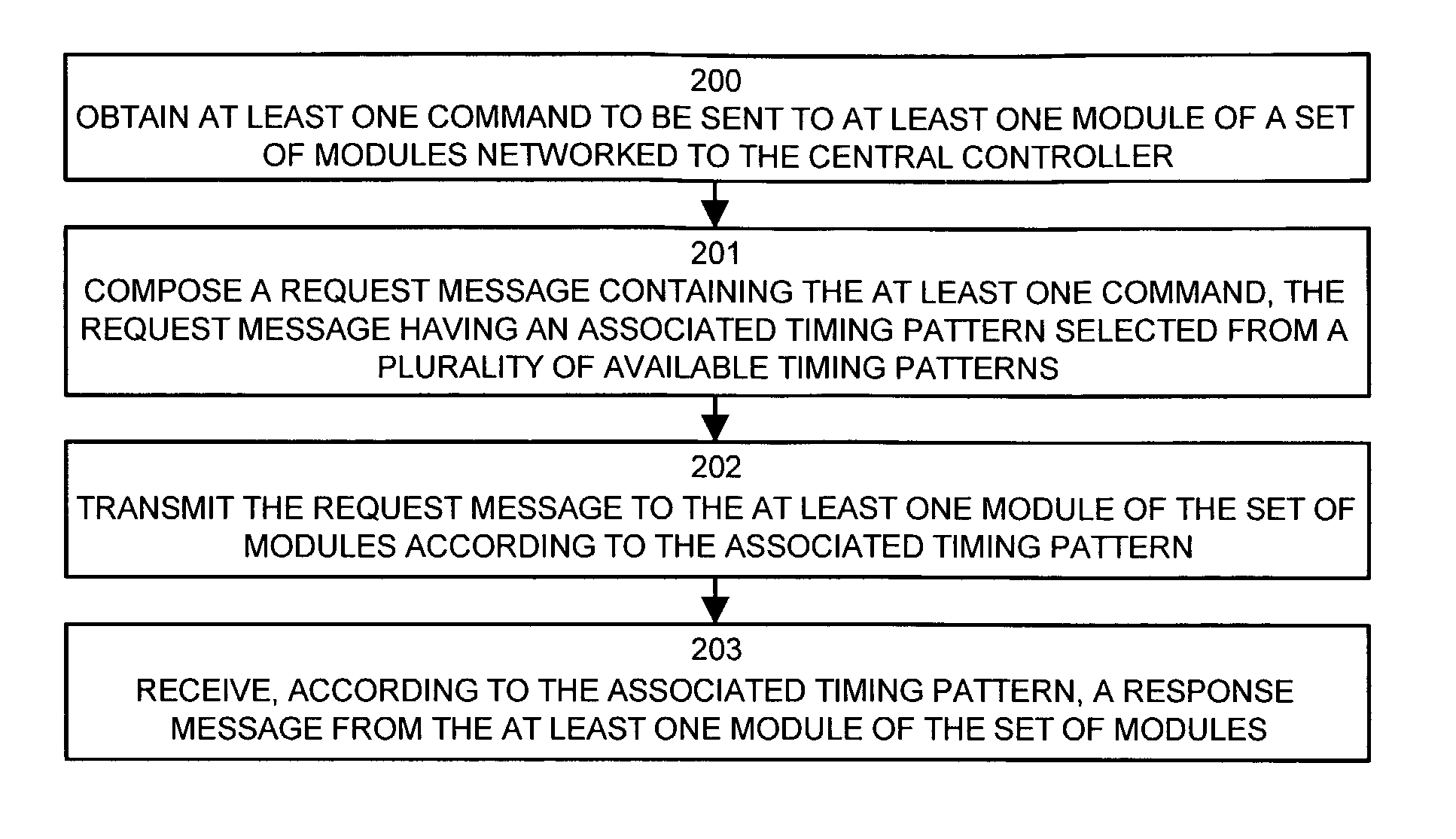

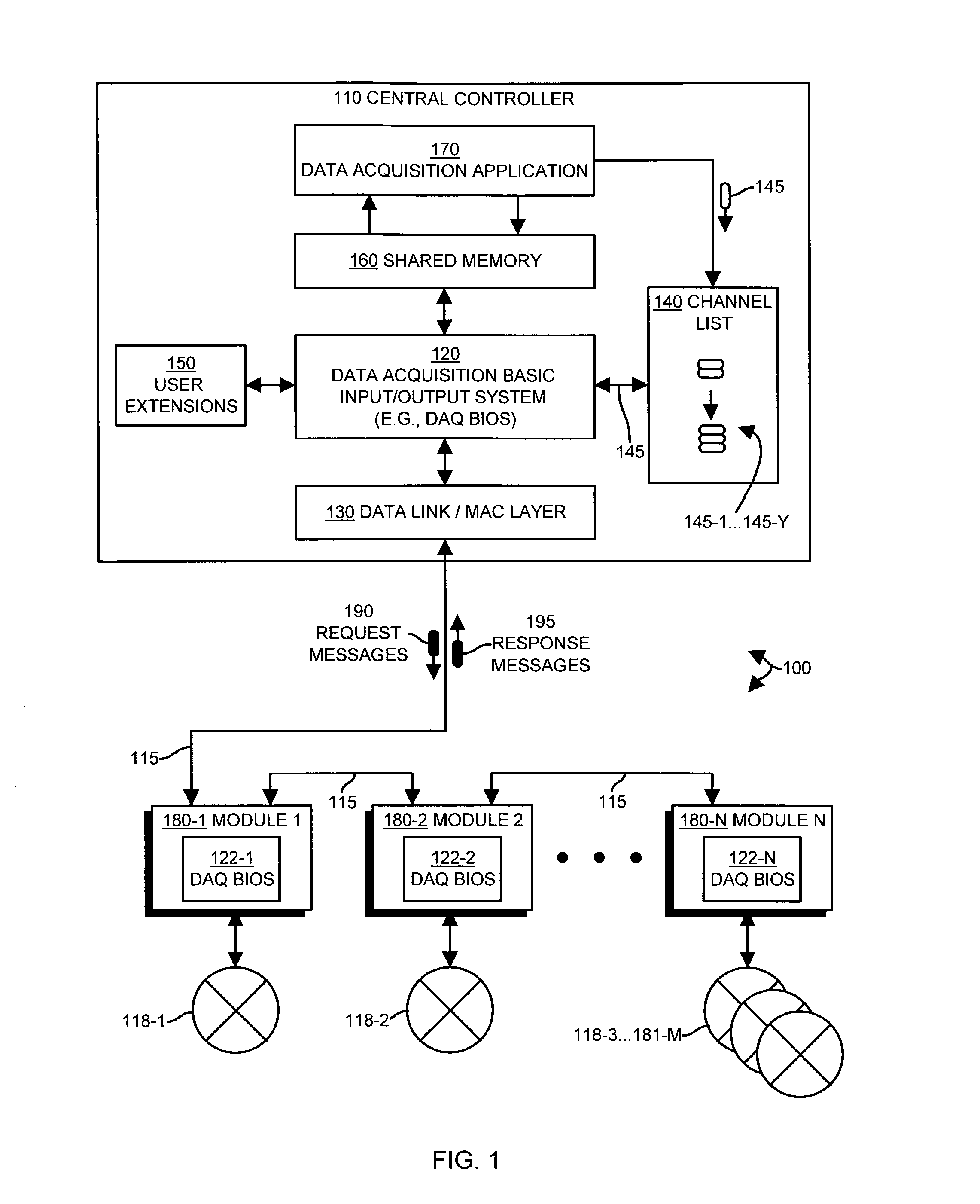

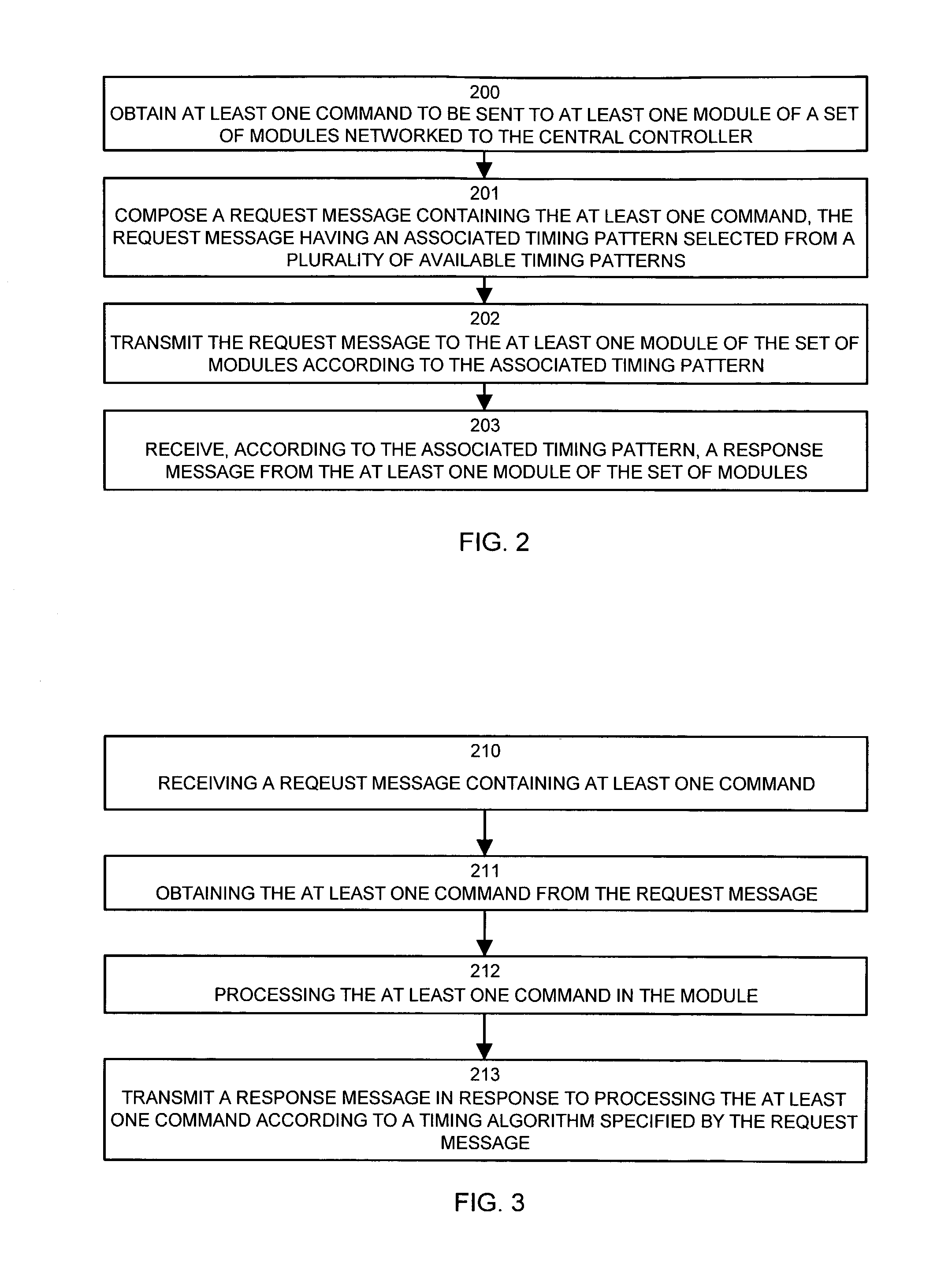

Methods and apparatus for performing data acquisition and control

ActiveUS7007107B1Avoid collisionOvercome deficienciesMultiple digital computer combinationsData switching networksInput/outputReal-time computing

Mechanisms and techniques provide a data acquisition basic input output system between a central controller and a set of modules networked to the central controller. The central controller obtains at least one command to be sent to at least one module of the set of modules networked to the central controller and composing a request message containing the command. The request message has an associated timing pattern selected from a plurality of available timing patterns, such as a fixed timing pattern or a variable timing pattern. The central controller transmits the request message to the module(s) according to the associated timing pattern and receives, according to the associated timing pattern, a response message from the module(s). The data acquisition basic input output system communications do not require reliance on transport layer protocols or collision avoidance techniques.

Owner:UNITED ELECTRONICS IND

Method and apparatus for browsing using multiple coordinated device sets

InactiveUS7899915B2Synchronised browsingBroadcast information characterisationOutput deviceBusiness activities

Owner:CONVERGENT MEDIA SOLUTIONS

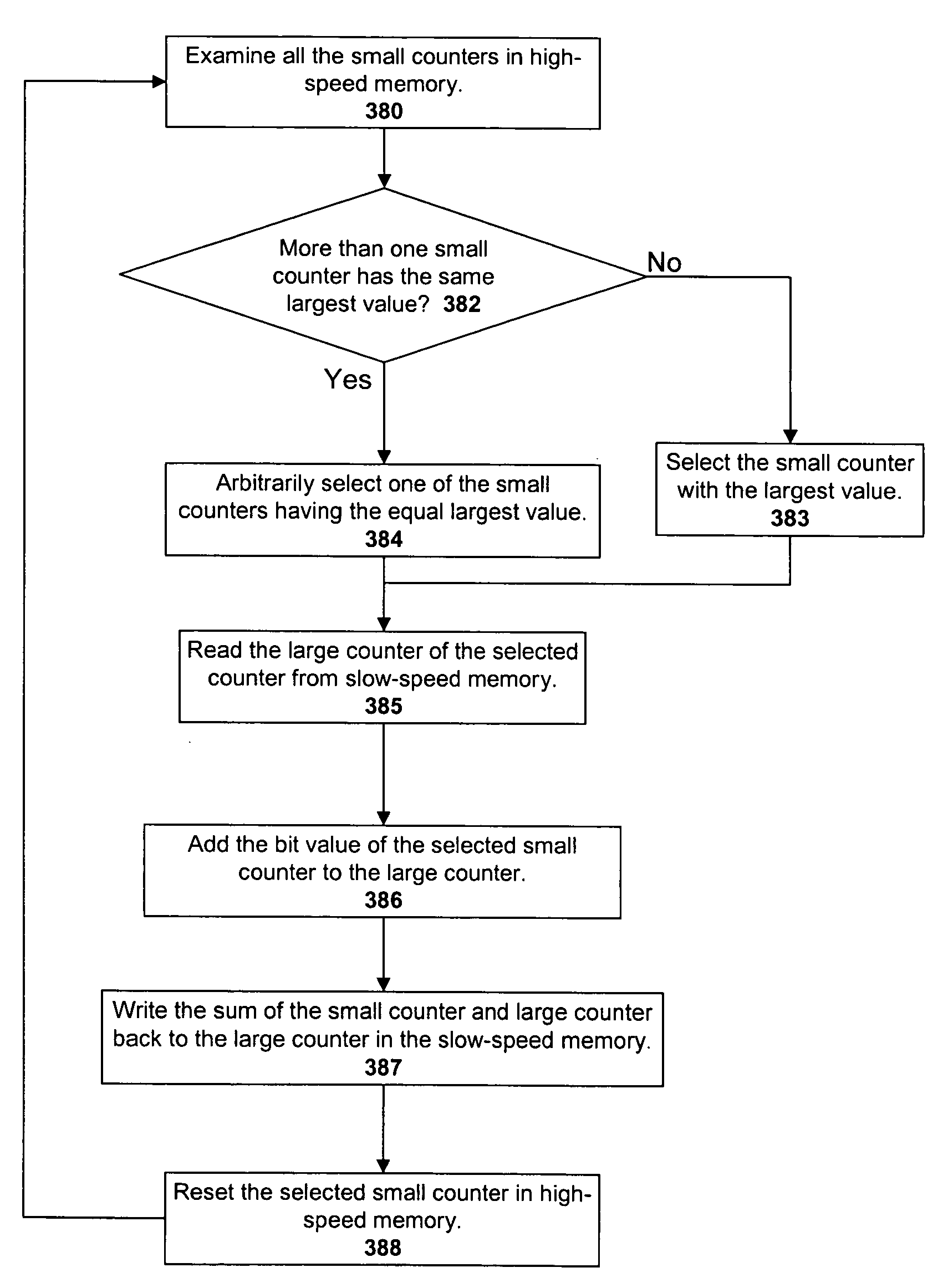

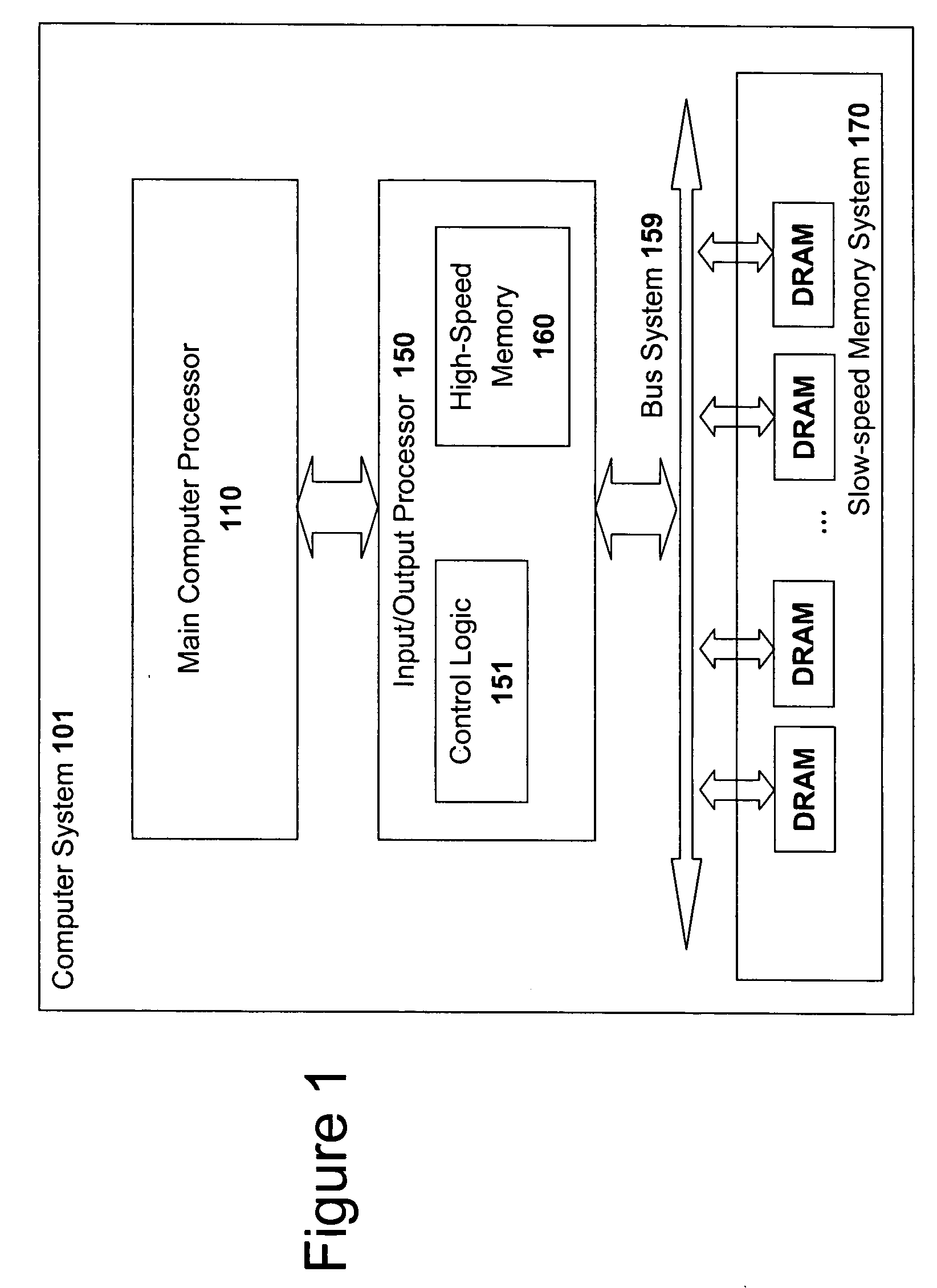

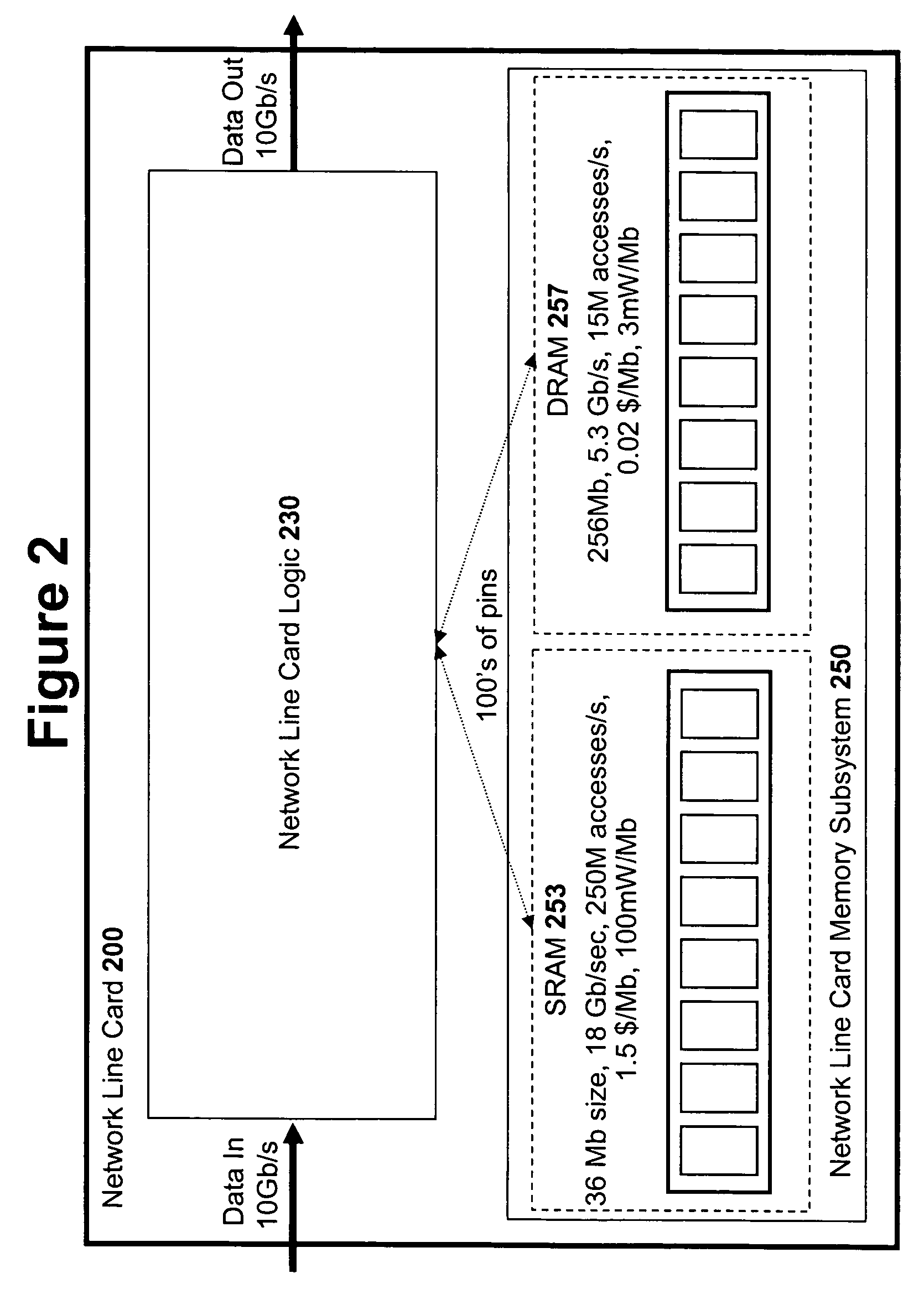

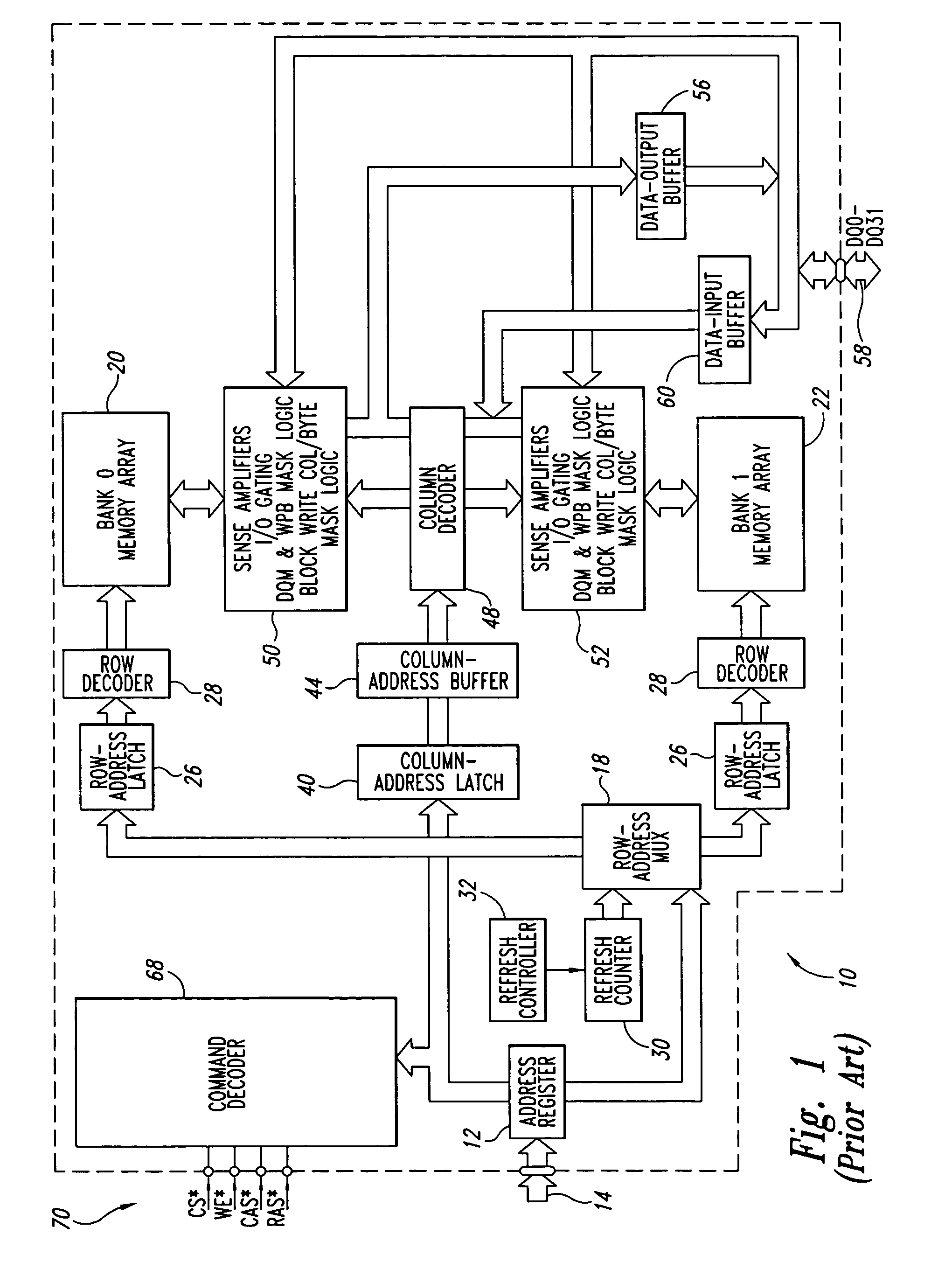

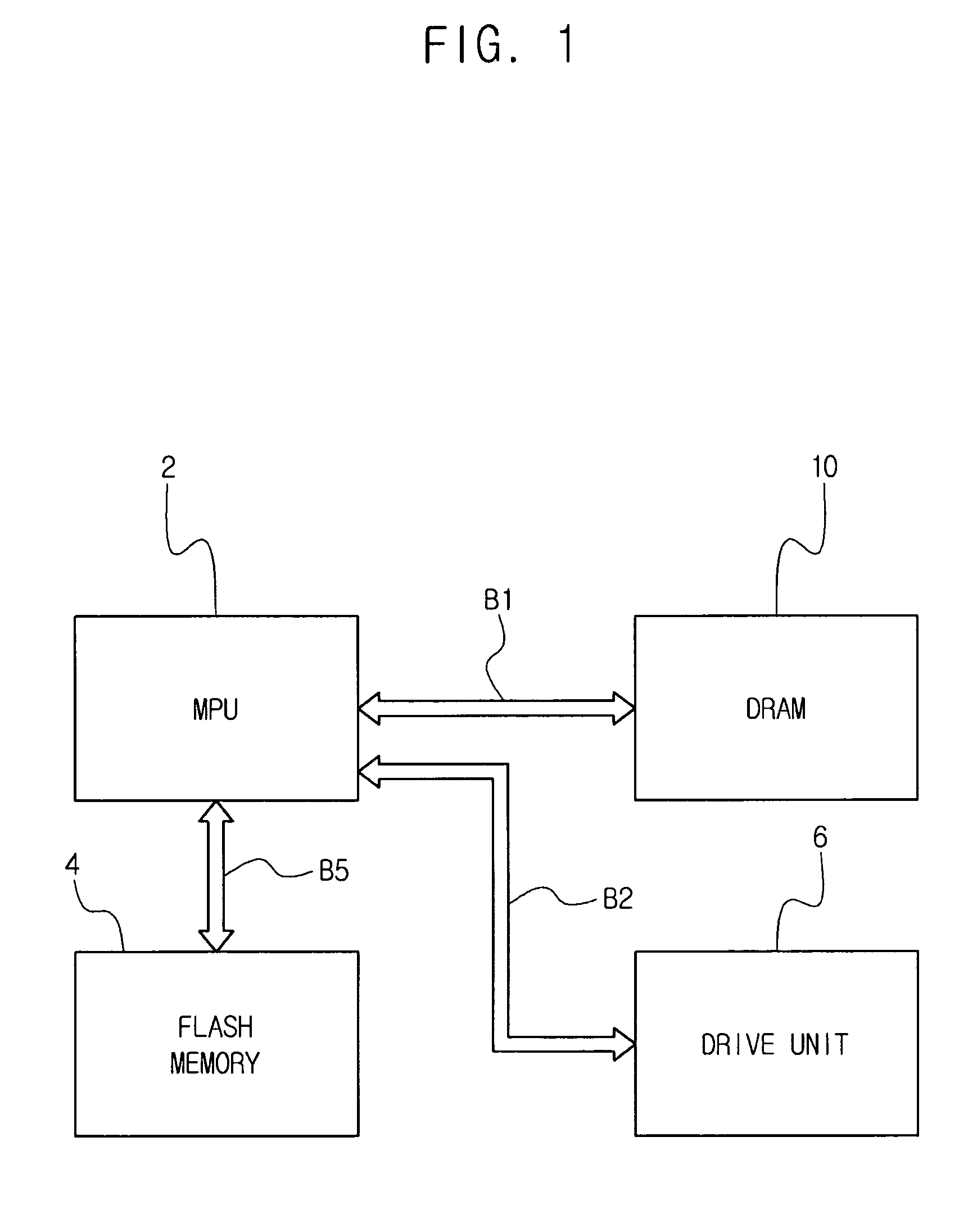

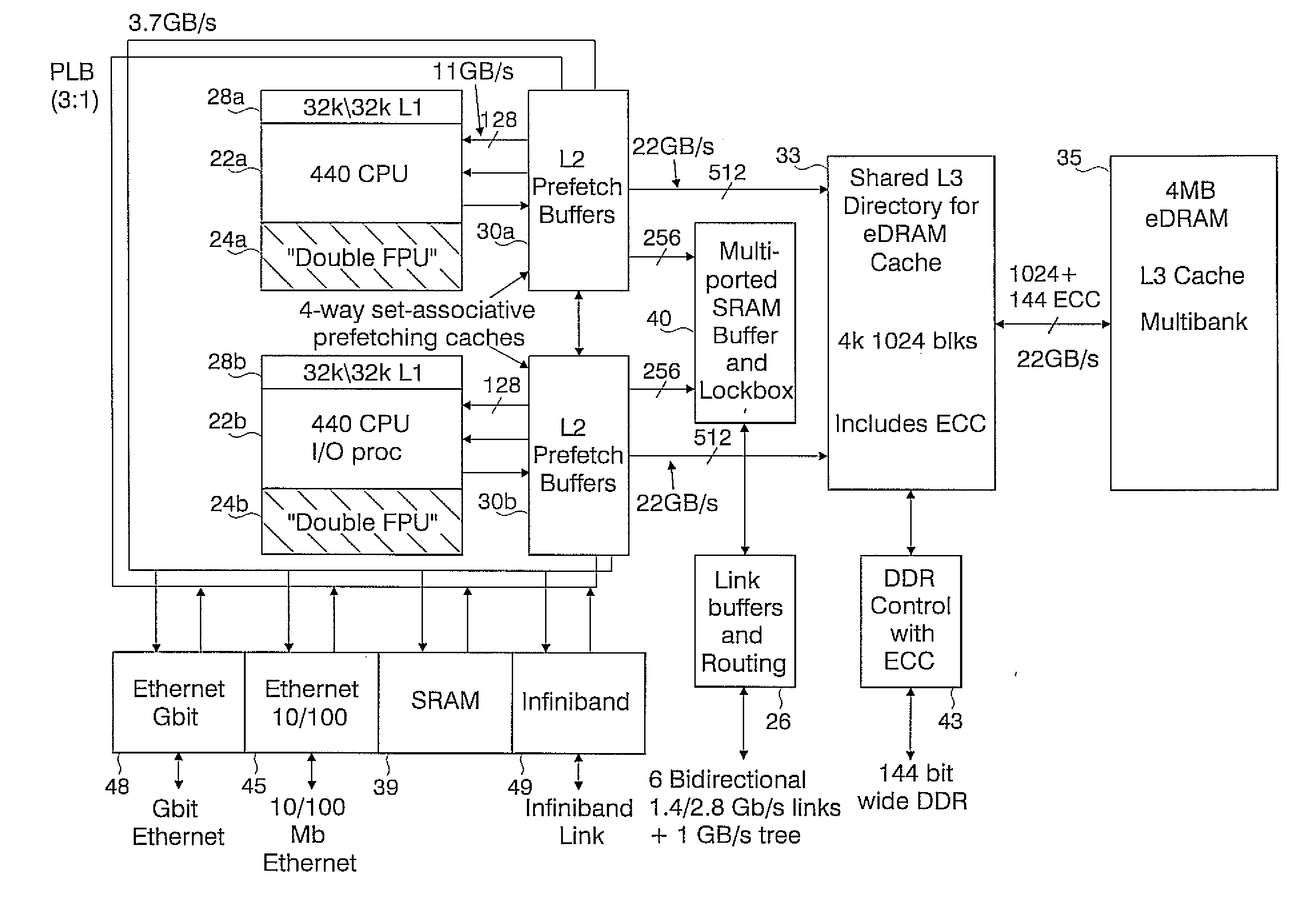

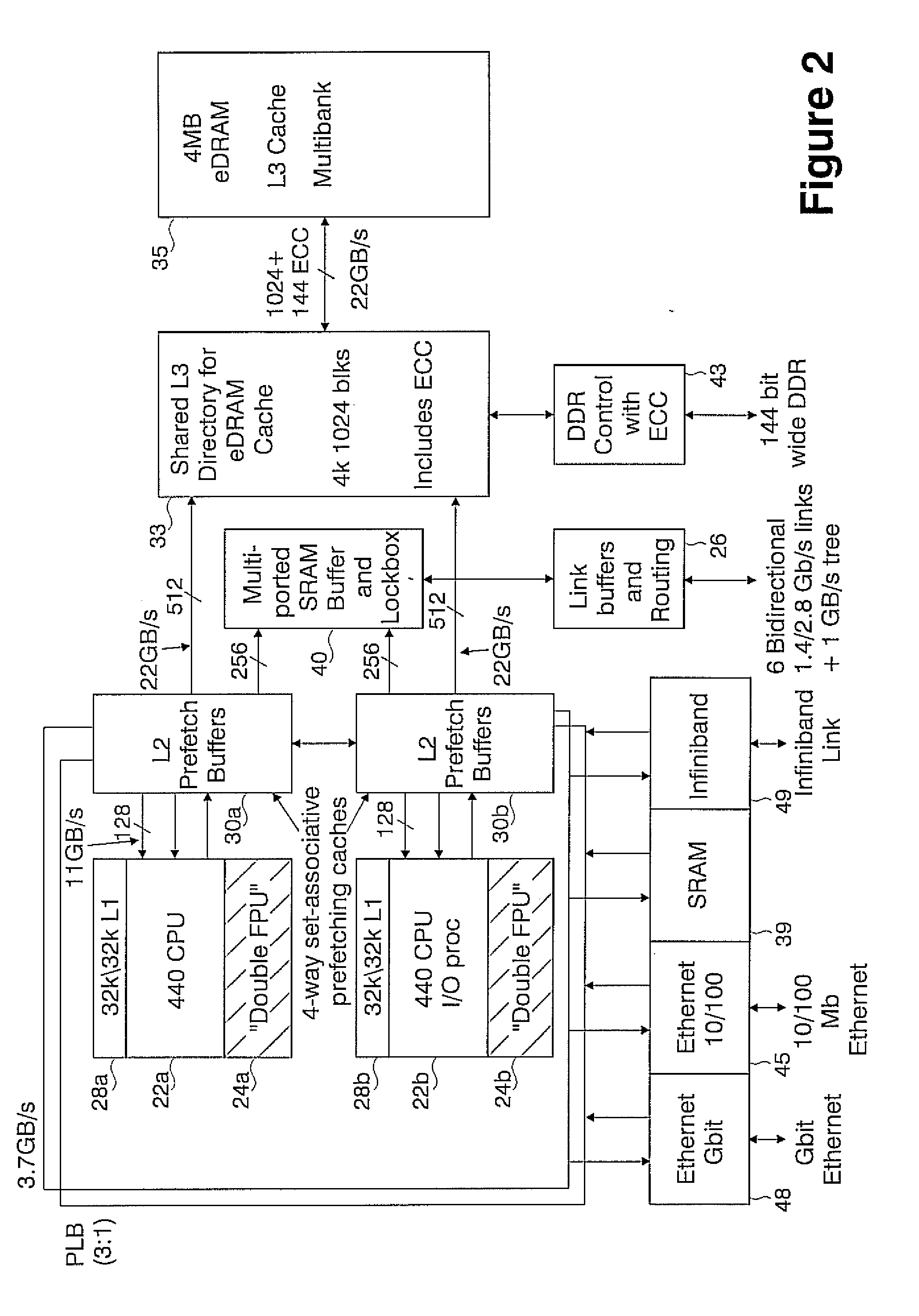

High speed memory control and I/O processor system

ActiveUS20050240745A1Easy to handleSimplify memory access taskMemory architecture accessing/allocationMemory adressing/allocation/relocationHigh speed memoryTailored approach

An input / output processor for speeding the input / output and memory access operations for a processor is presented. The key idea of an input / output processor is to functionally divide input / output and memory access operations tasks into a compute intensive part that is handled by the processor and an I / O or memory intensive part that is then handled by the input / output processor. An input / output processor is designed by analyzing common input / output and memory access patterns and implementing methods tailored to efficiently handle those commonly occurring patterns. One technique that an input / output processor may use is to divide memory tasks into high frequency or high-availability components and low frequency or low-availability components. After dividing a memory task in such a manner, the input / output processor then uses high-speed memory (such as SRAM) to store the high frequency and high-availability components and a slower-speed memory (such as commodity DRAM) to store the low frequency and low-availability components. Another technique used by the input / output processor is to allocate memory in such a manner that all memory bank conflicts are eliminated. By eliminating any possible memory bank conflicts, the maximum random access performance of DRAM memory technology can be achieved.

Owner:CISCO TECH INC

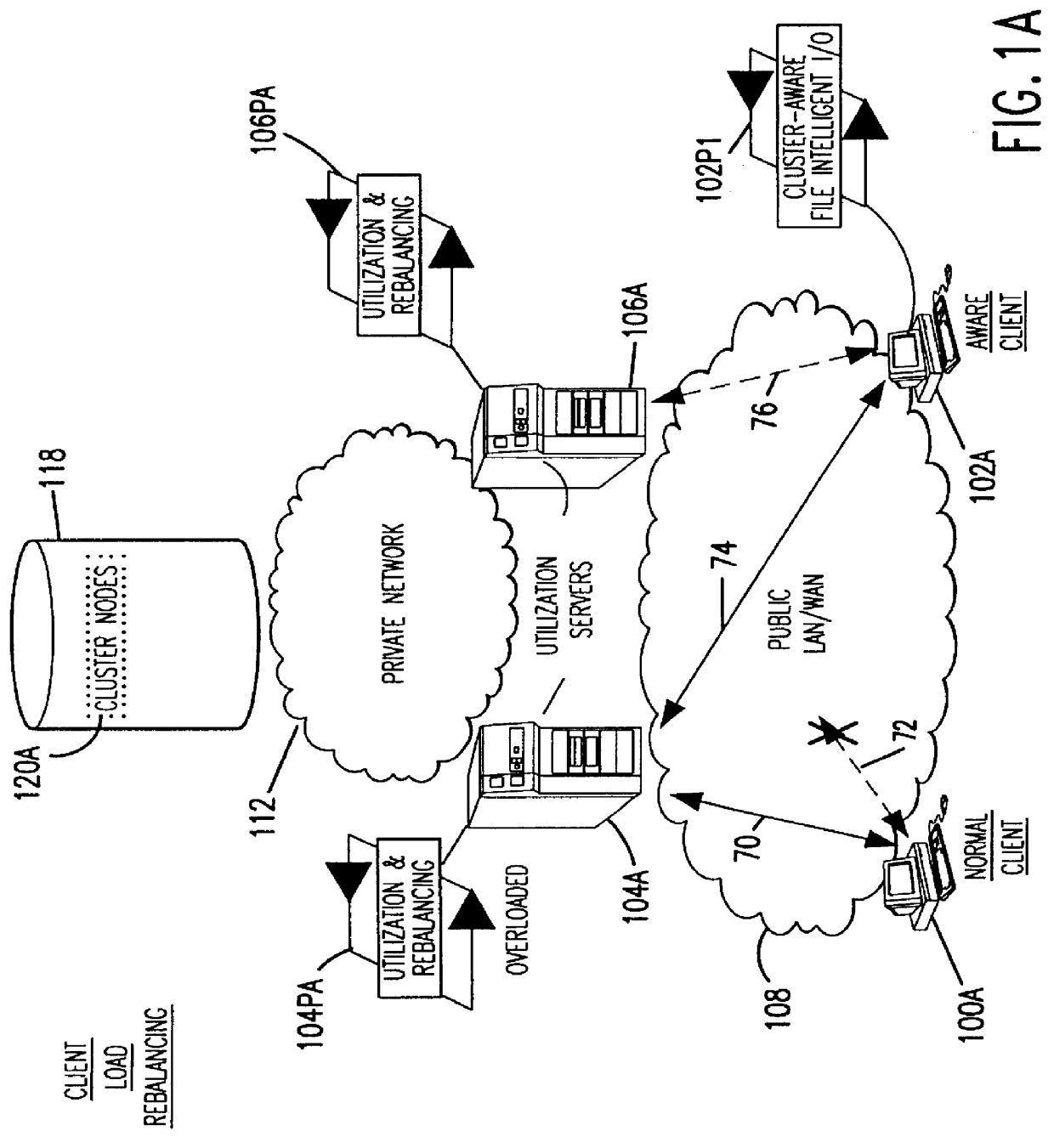

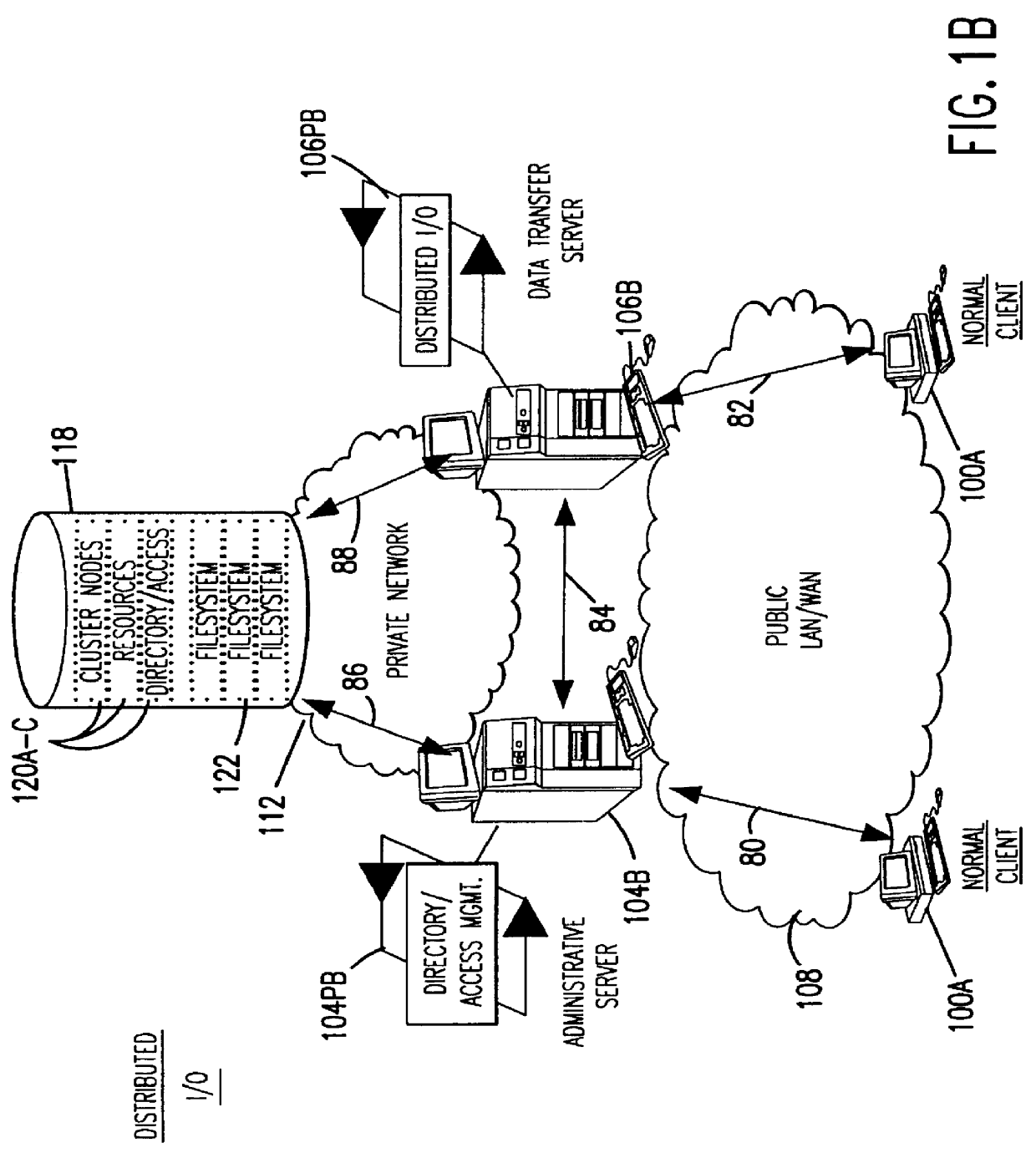

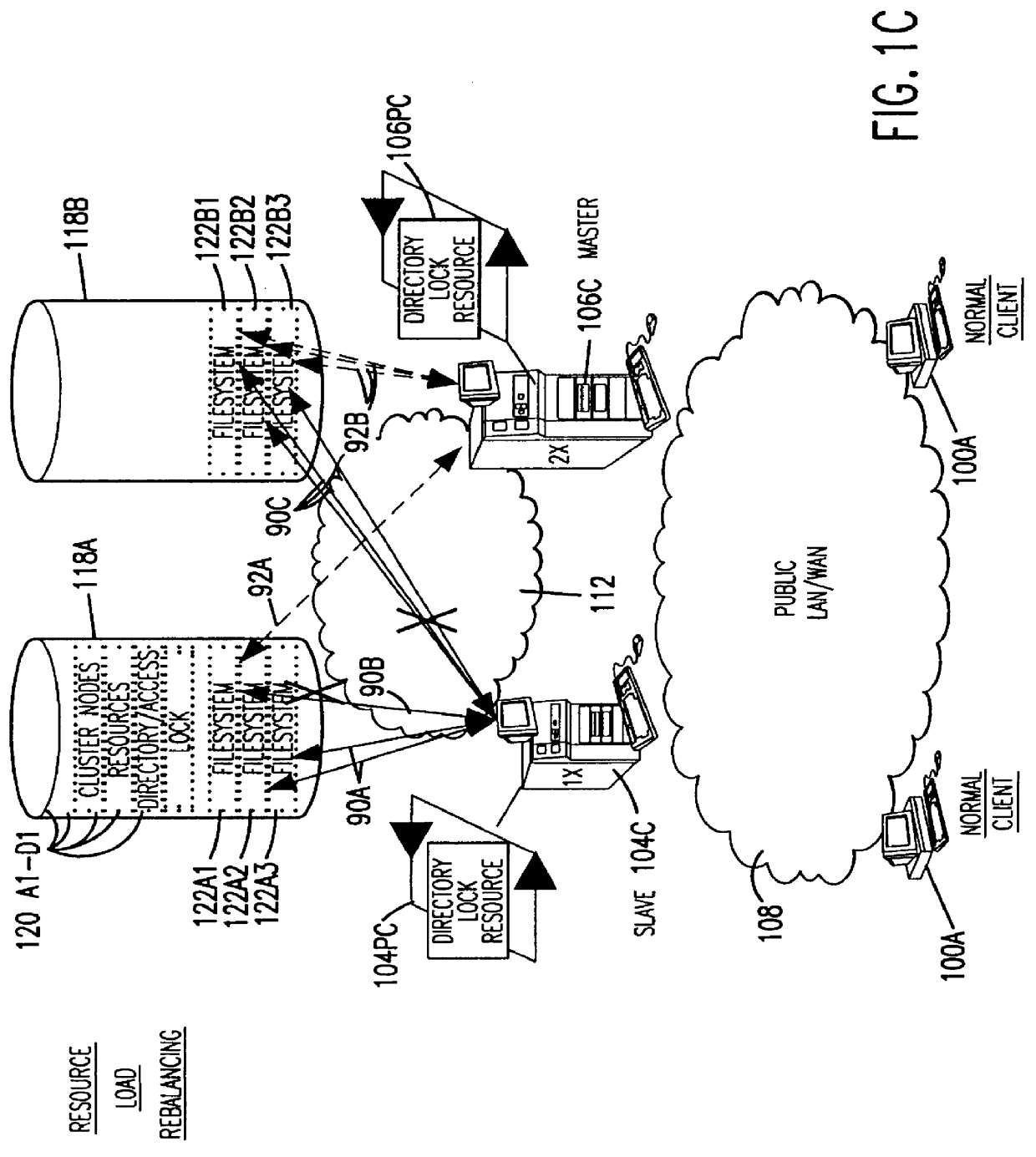

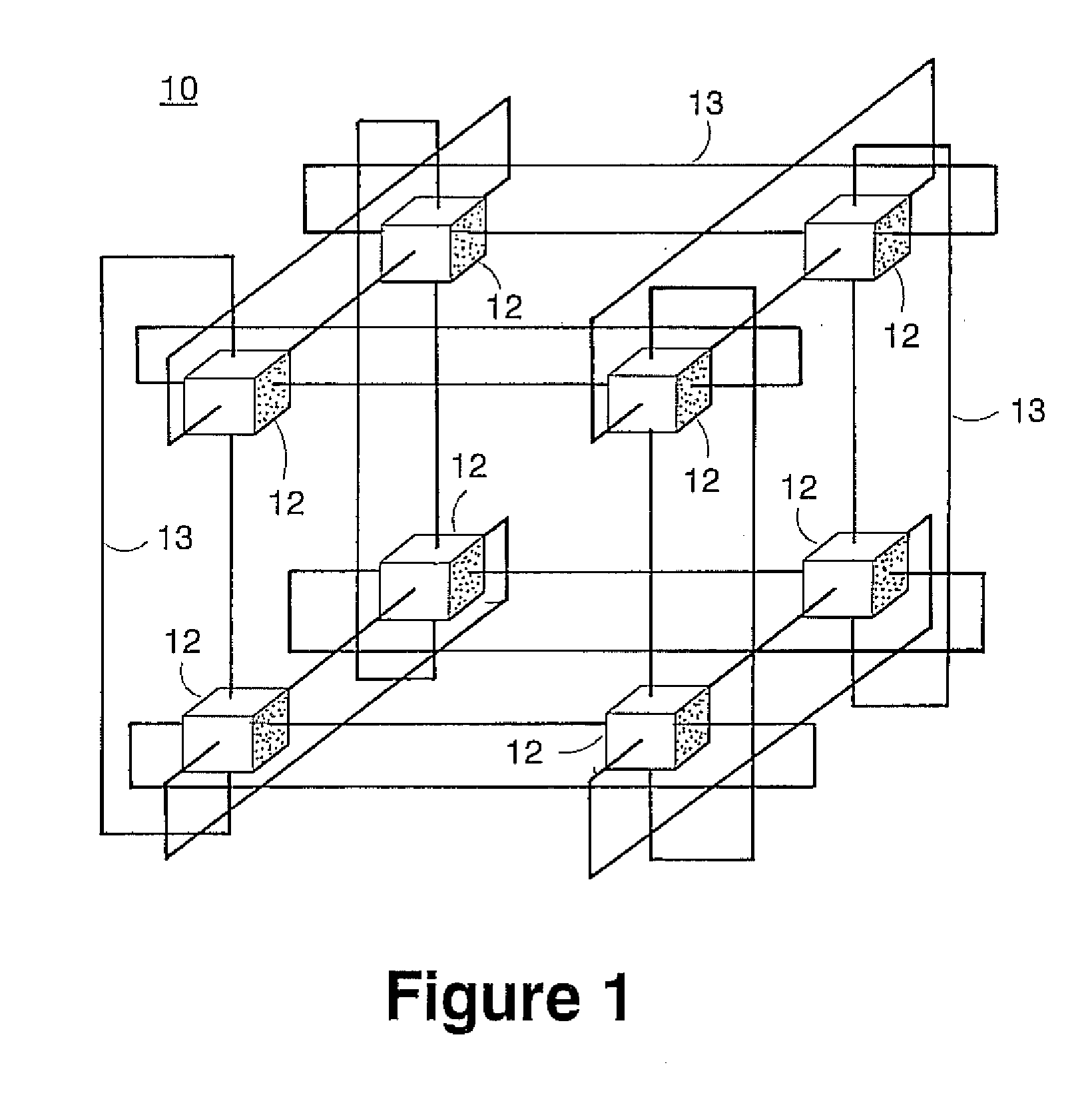

Clustered file management for network resources

InactiveUS6101508AData processing applicationsProgram synchronisationFile systemClustered file system

Methods for operating a network as a clustered file system is disclosed. The methods involve client load rebalancing, distributed Input and Output (I / O) and resource load rebalancing. Client load rebalancing refers to the ability of a client enabled with processes in accordance with the current invention to remap a path through a plurality of nodes to a resource. Distributed I / O refers to the methods on the network which provide concurrent input / output through a plurality of nodes to resources. Resource rebalancing includes remapping of pathways between nodes, e.g. servers, and resources, e.g. volumes / file systems. The network includes client nodes, server nodes and resources. Each of the resources couples to at least two of the server nodes. The method for operating comprising the acts of: redirecting an I / O request for a resource from a first server node coupled to the resource to a second server node coupled to the resource; and splitting the I / O request at the second server node into an access portion and a data transfer portion and passing the access portion to a corresponding administrative server node for the resource, and completing at the second server nodes subsequent to receipt of an access grant from the corresponding administrative server node a data transfer for the resource. In an alternate embodiment of the invention the methods may additionally include the acts of: detecting a change in an availability of the server nodes; and rebalancing the network by applying a load balancing function to the network to re-assign each of the available resources to a corresponding available administrative server node responsive to the detecting act.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

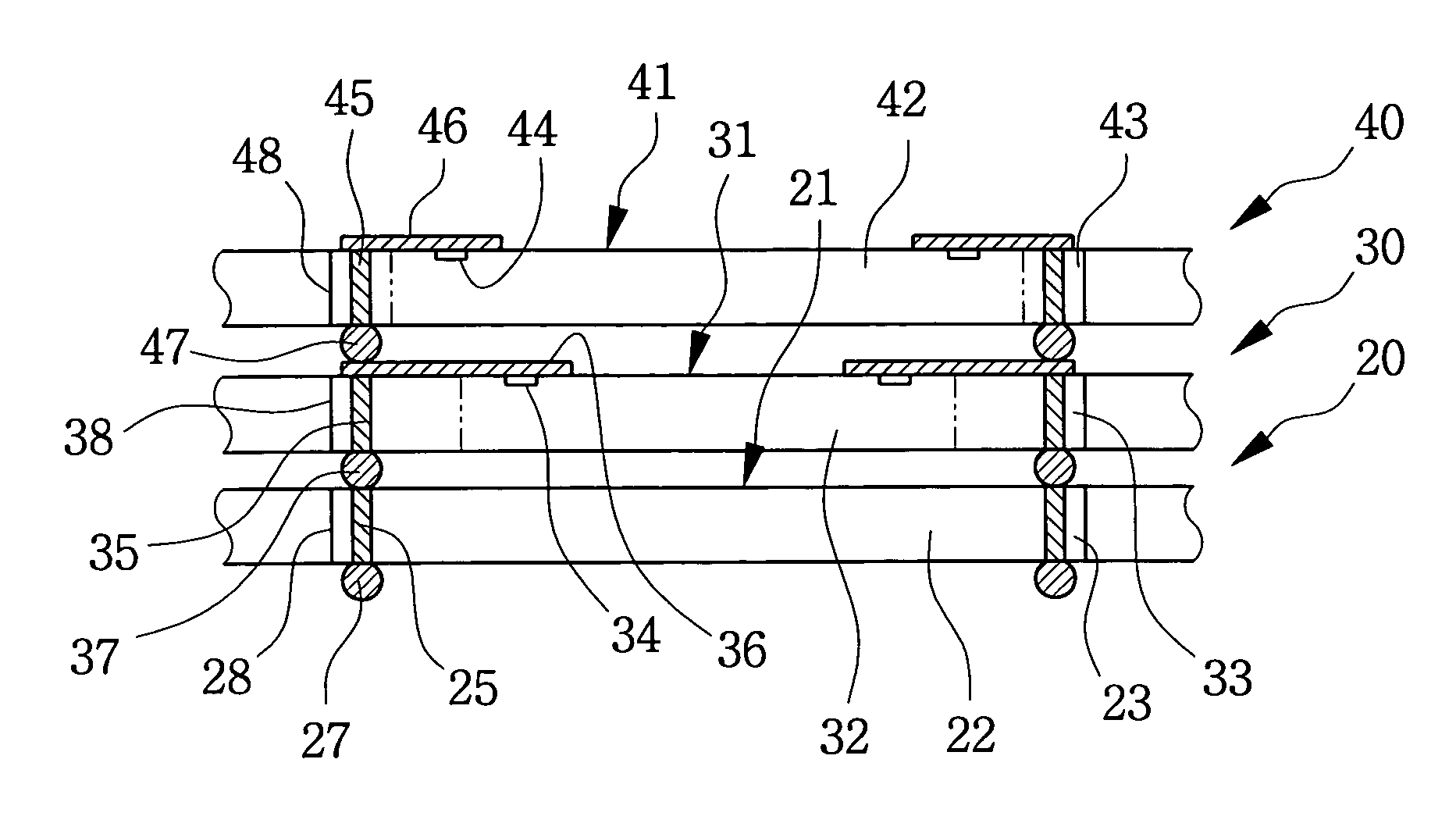

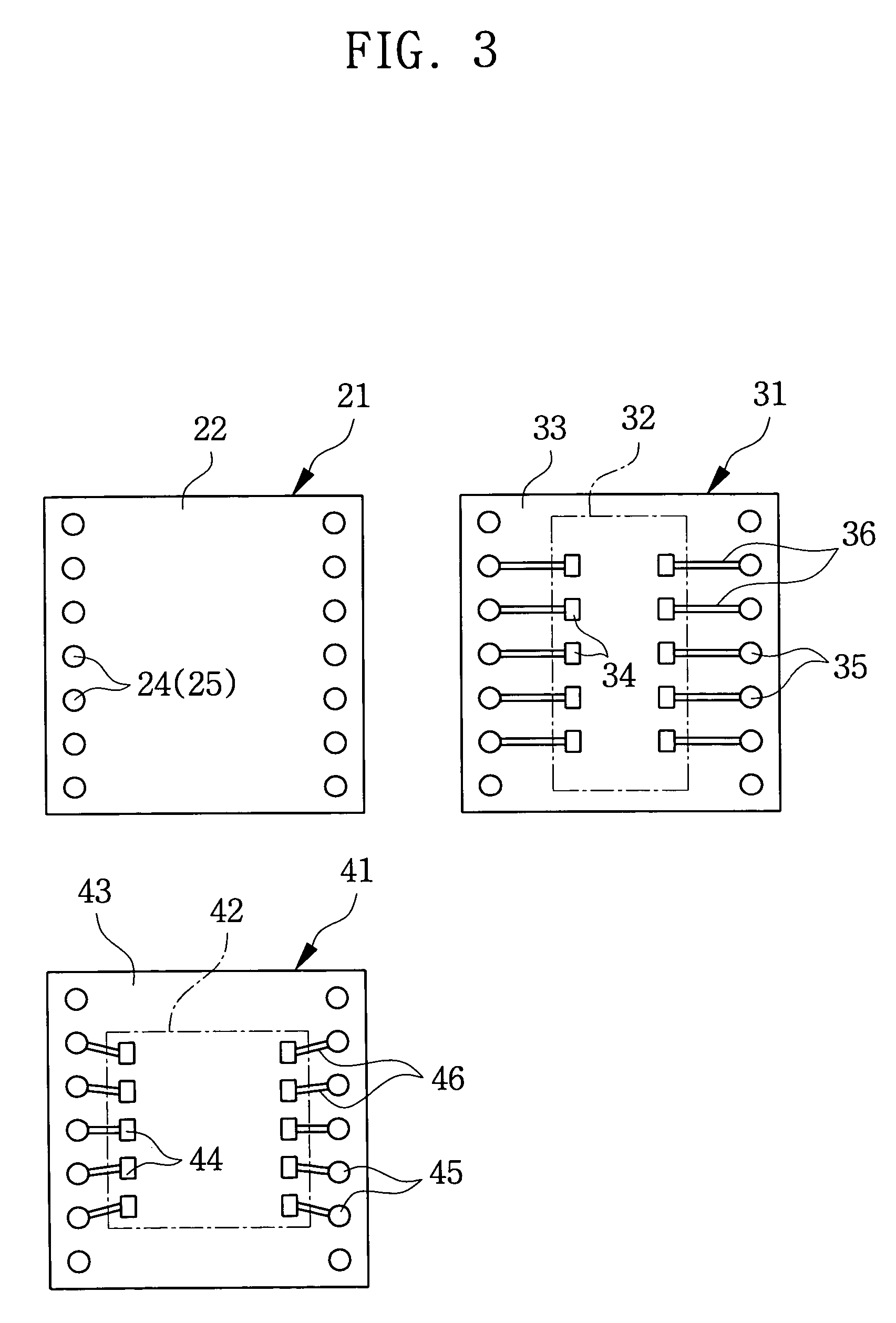

Wafer level stack structure for system-in-package and method thereof

ActiveUS7215033B2Semiconductor/solid-state device detailsSolid-state devicesChip sizeSystem in package

A wafer level stack structure, including a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, wherein the first wafer and the second wafer are stacked, and wherein the first wafer and the second wafer are coupled to each other. A method of forming a wafer level stack structure, including forming a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, forming a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, stacking the first wafer and the second wafer, and coupling the first wafer and the second wafer to each other. A system-in-package, including a wafer level stack structure including at least one first device chip with a first plurality of input / output (I / O) pads and at least one second device chip with a second plurality of I / O pads, and a common circuit board to which the wafer level stack structure is connected.

Owner:SAMSUNG ELECTRONICS CO LTD

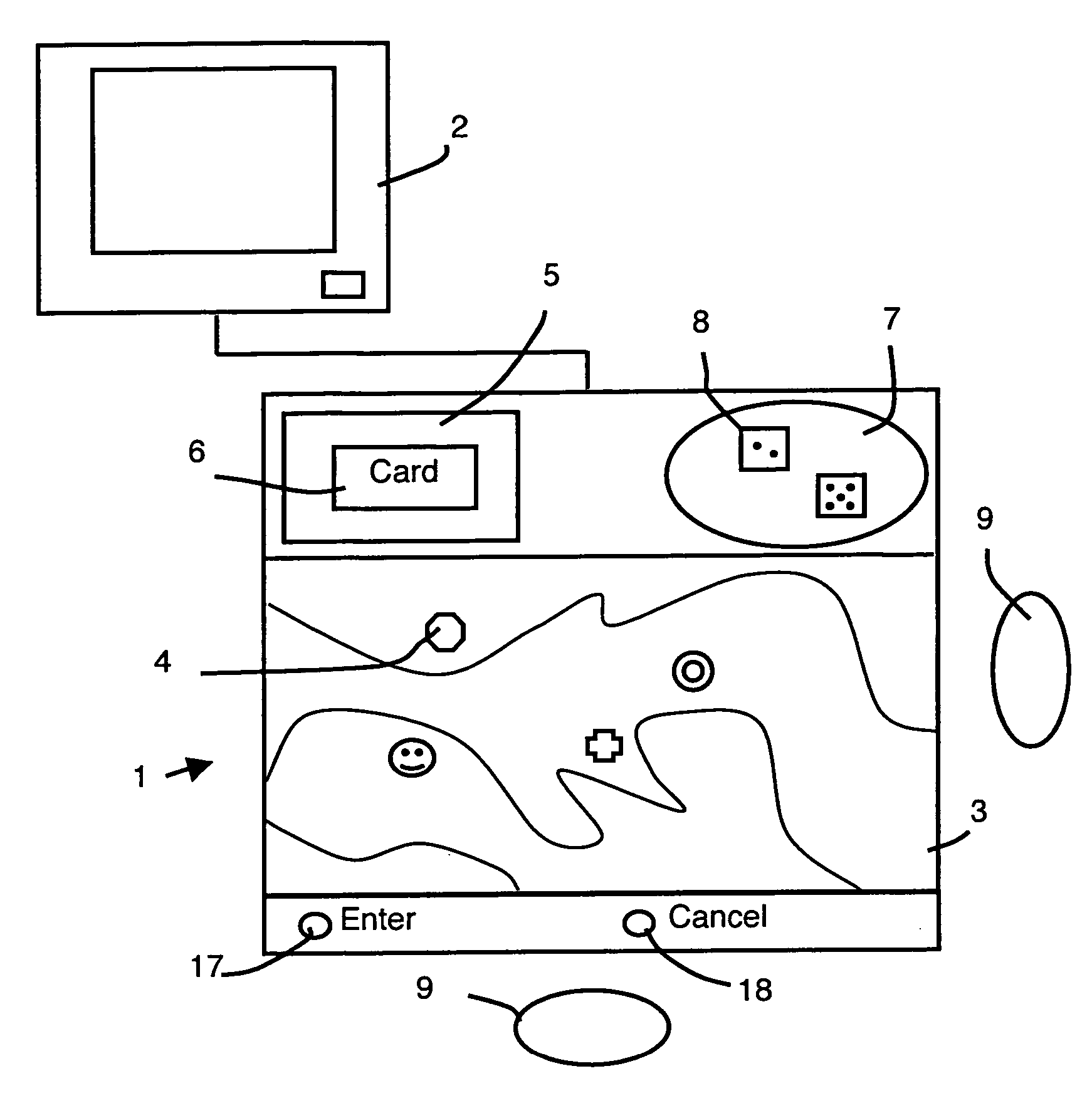

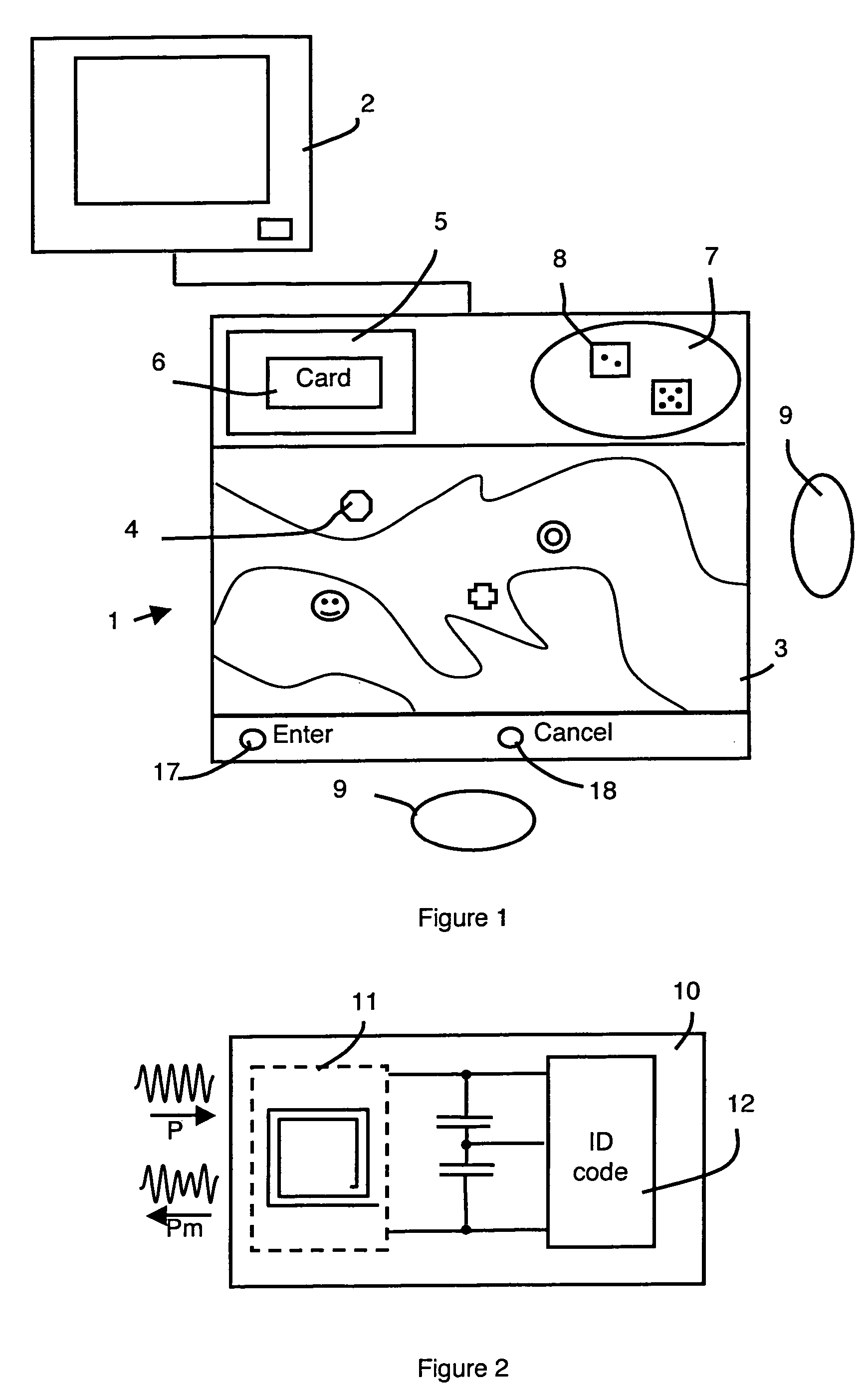

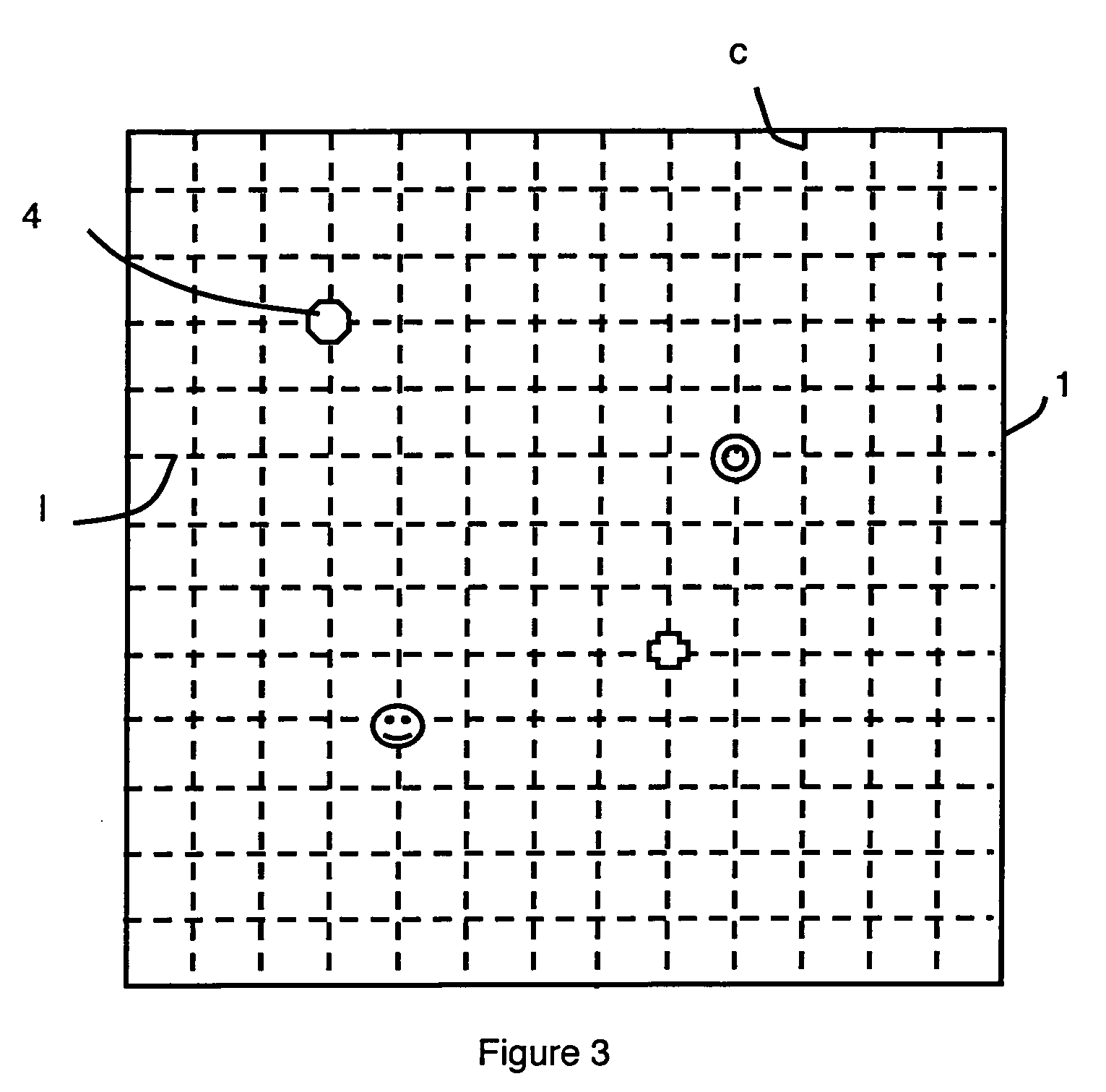

Electronic educational game set having communicating elements with a radio-frequency tag

InactiveUS20060246403A1Short response timeLower average response timeBoard gamesInput/output processes for data processingEducational gamePersonal identification number

The invention relates to a game set which comprises communicating elements, in the form of pieces, figurines, cards or dice, each having a radio-frequency tag provided with an individual identification code. A game board comprises a digital processing circuit which is connected to a plurality of antennas, arranged such as to form a sensor matrix, for detecting the presence, type and position of the communicating elements. Radio-frequency readers are respectively connected to m corresponding input / output terminals of the digital processing circuit. Each radio-frequency reader is connected to an associated group of antennas, preferably by means of a corresponding multiplexer. The game board may consist of a removable assembly of basic boards, each comprising a basic digital processing circuit which is connected to the antennas of the corresponding basic board.

Owner:FRANCE TELECOM SA

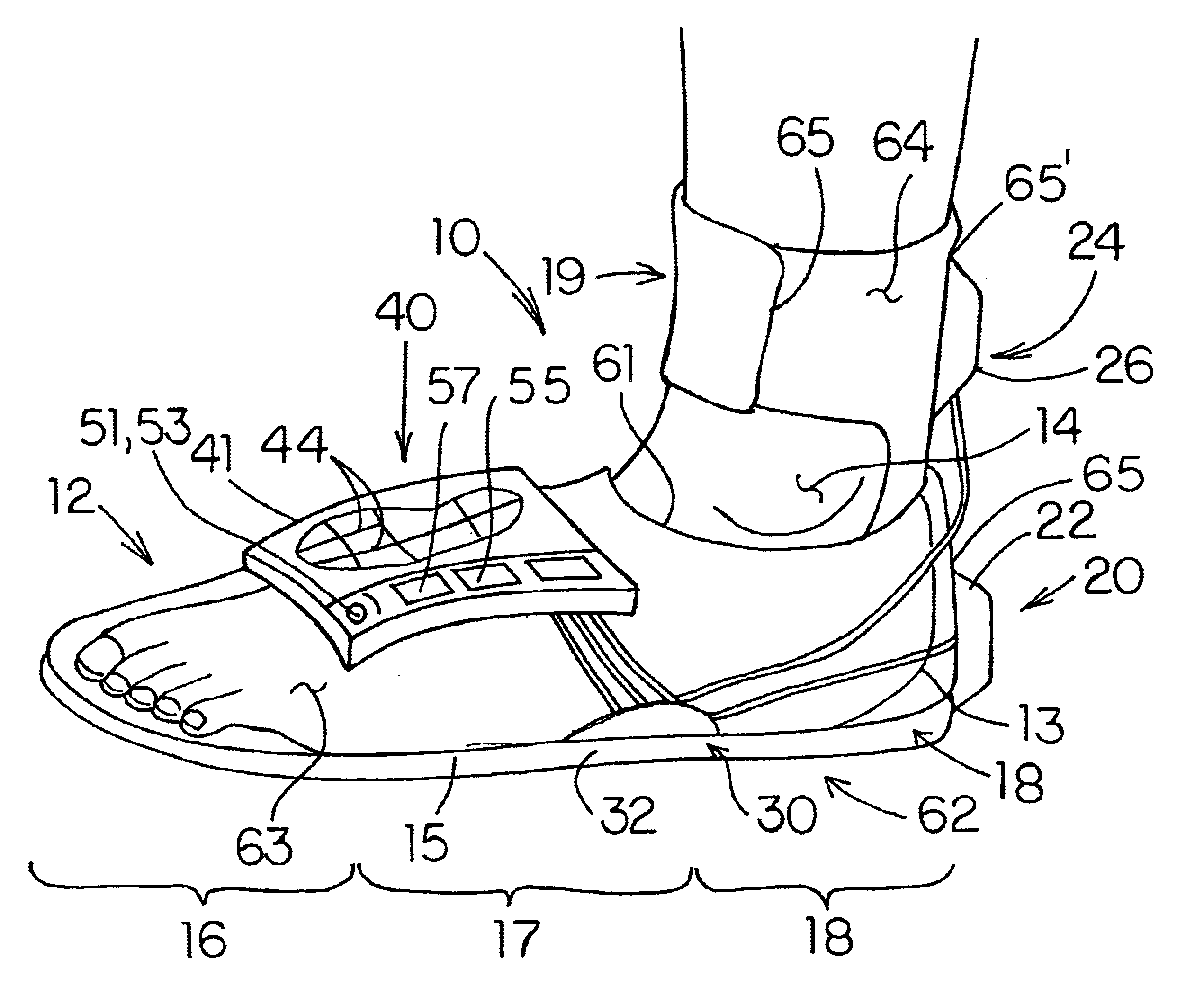

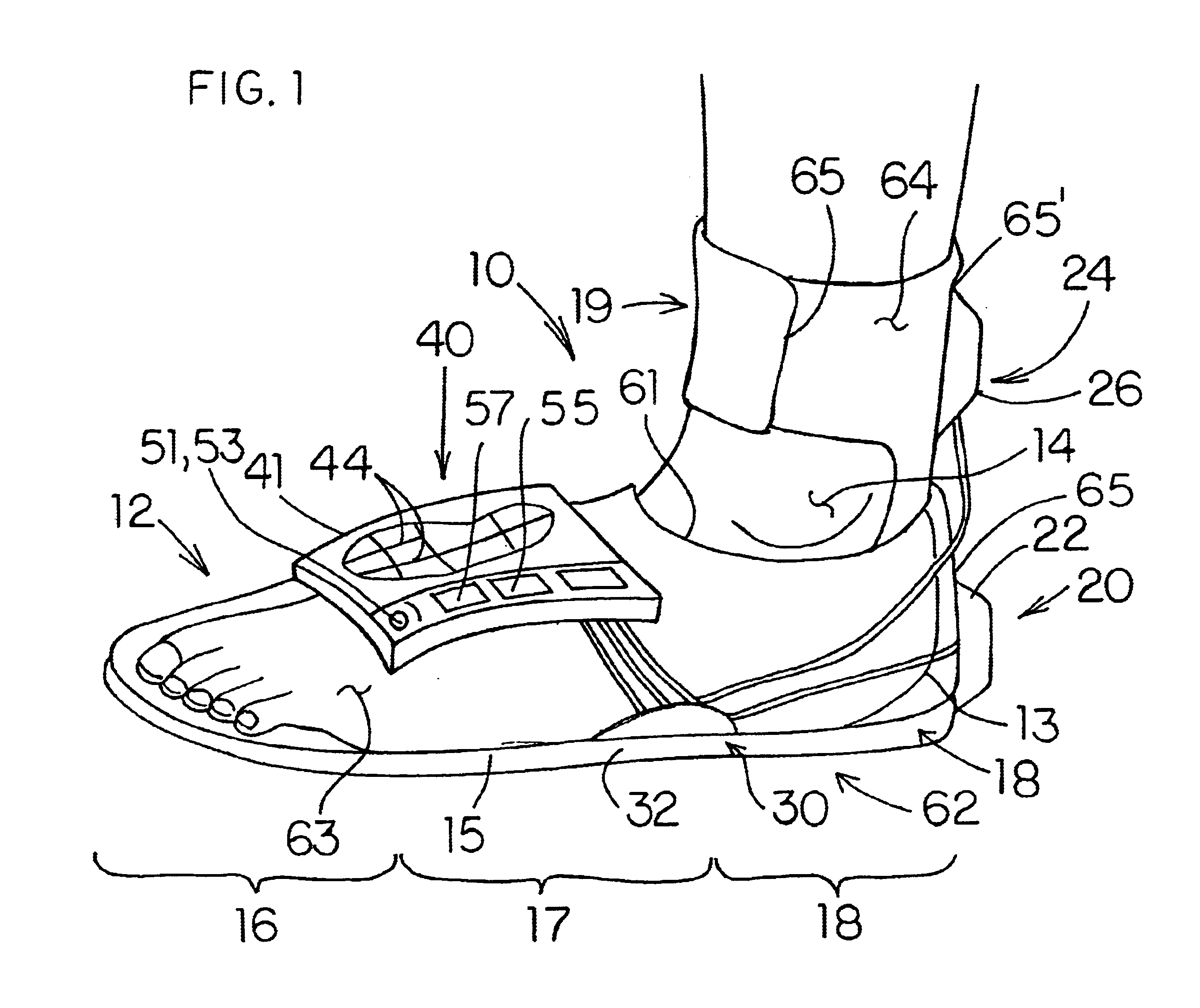

Portable system for analyzing human gait

InactiveUS6836744B1Input/output for user-computer interactionInertial sensorsAccelerometerAngular velocity

The invention is a portable gait analyzer comprising of at least one independent rear foot motion collection unit, at least one independent lower shank motion collection unit, plantar pressure collection unit, at least one processing and display unit, and a soft casing unit. A plurality of accelerometers, rate sensors, force sensor resistors, and pressure sensors provide for the acquisition of acceleration signals, angular velocity signals, foot force signals, and foot pressure signals to be processed. At least one central processing unit, a plurality of memory components, input / output components and ports, telemetry components, calibration components, liquid crystal displays components for the processing and outputting of three dimensional acceleration, angular velocity, tilt, and position. The rearfoot motion collection unit and lower shank motion collection unit interact with the processing and display unit to calculate rear foot kinematic data crucial to identify the motions of pronation and supination. The plantar pressure collection unit interacts with the processing and display unit to calculate plantar pressure data crucial to identify the center of pressure line and excessive and abnormal loads on the sole of the foot. These factors of rear-foot kinematics and plantar pressure lead to gait style identification.

Owner:ADVANCED MOTION TECH INC

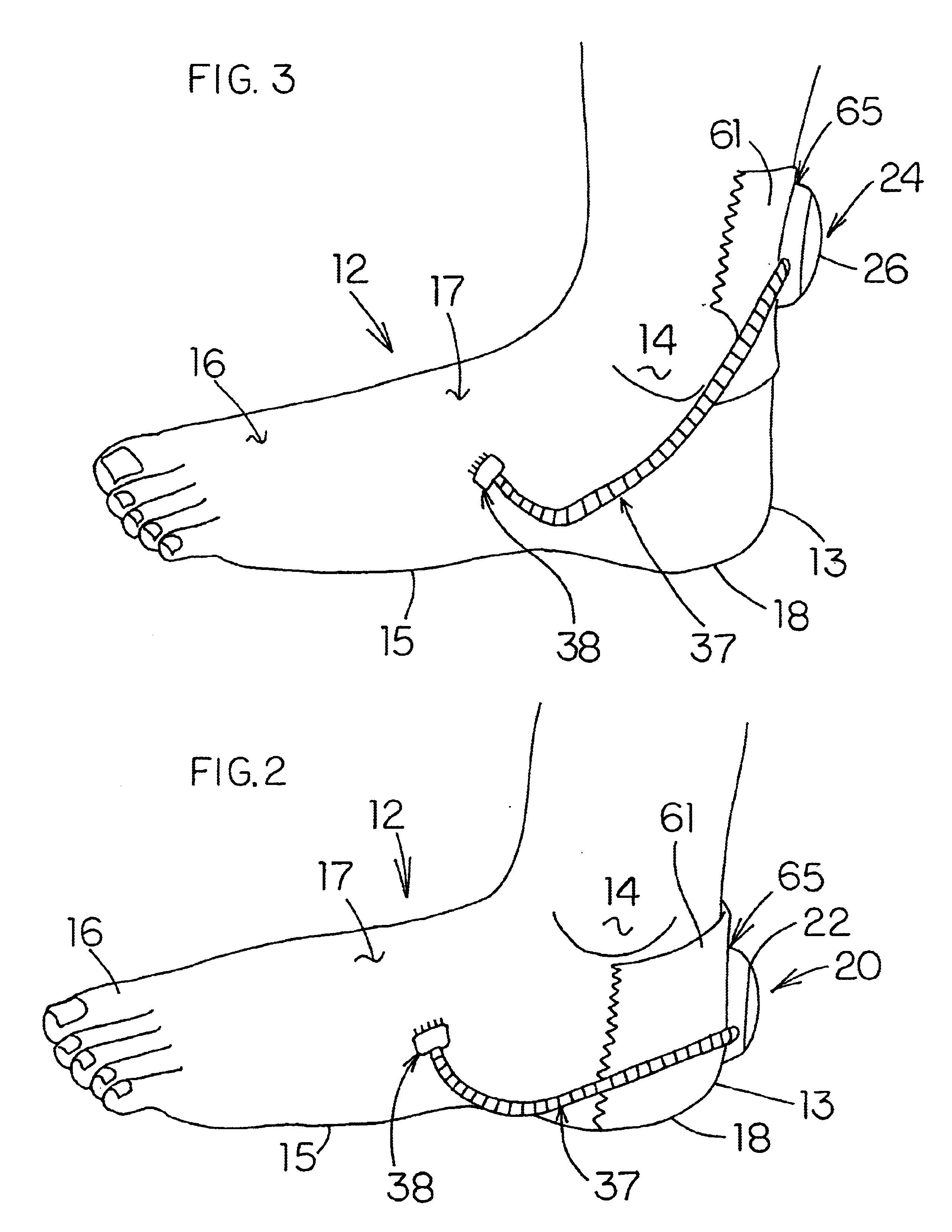

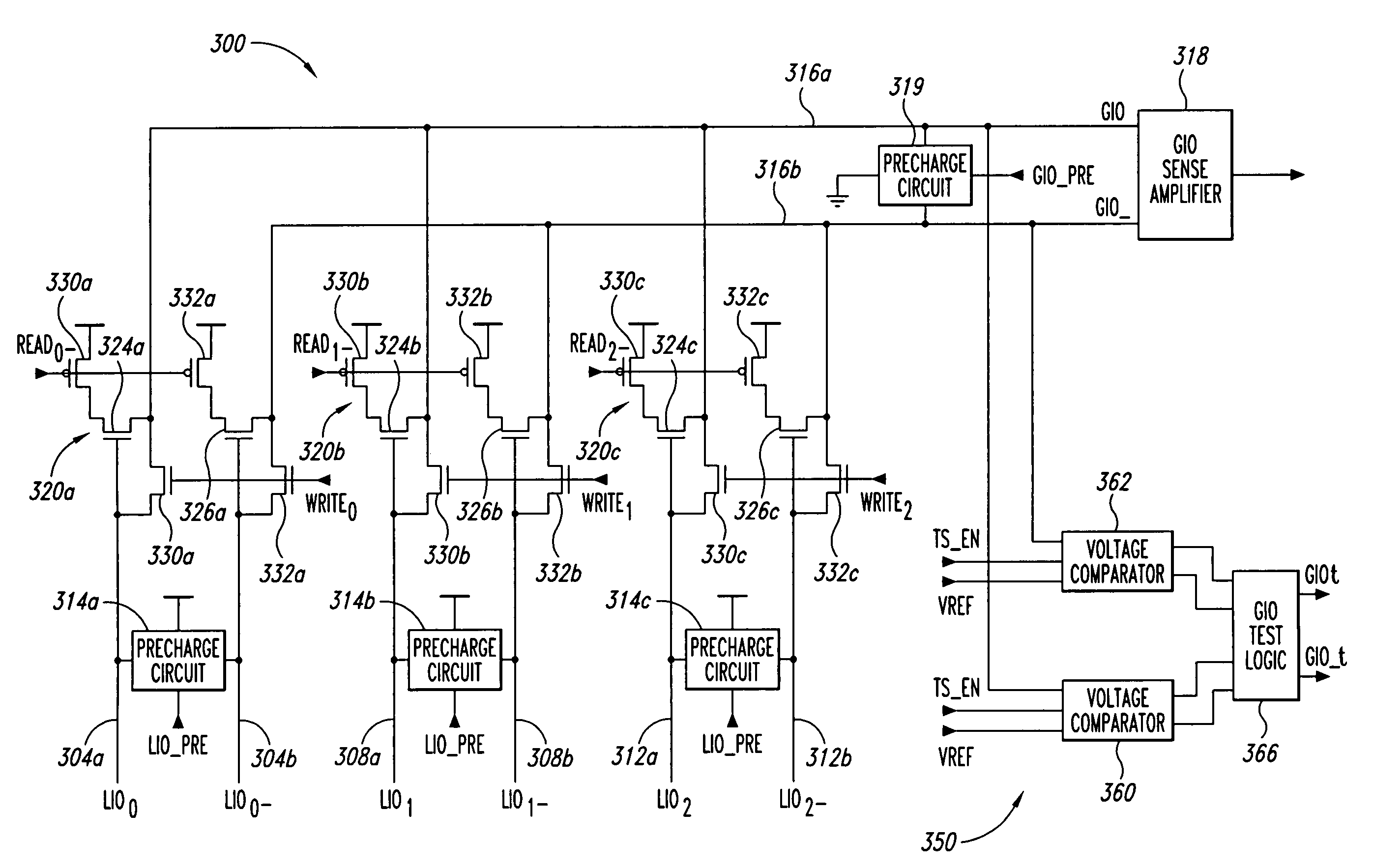

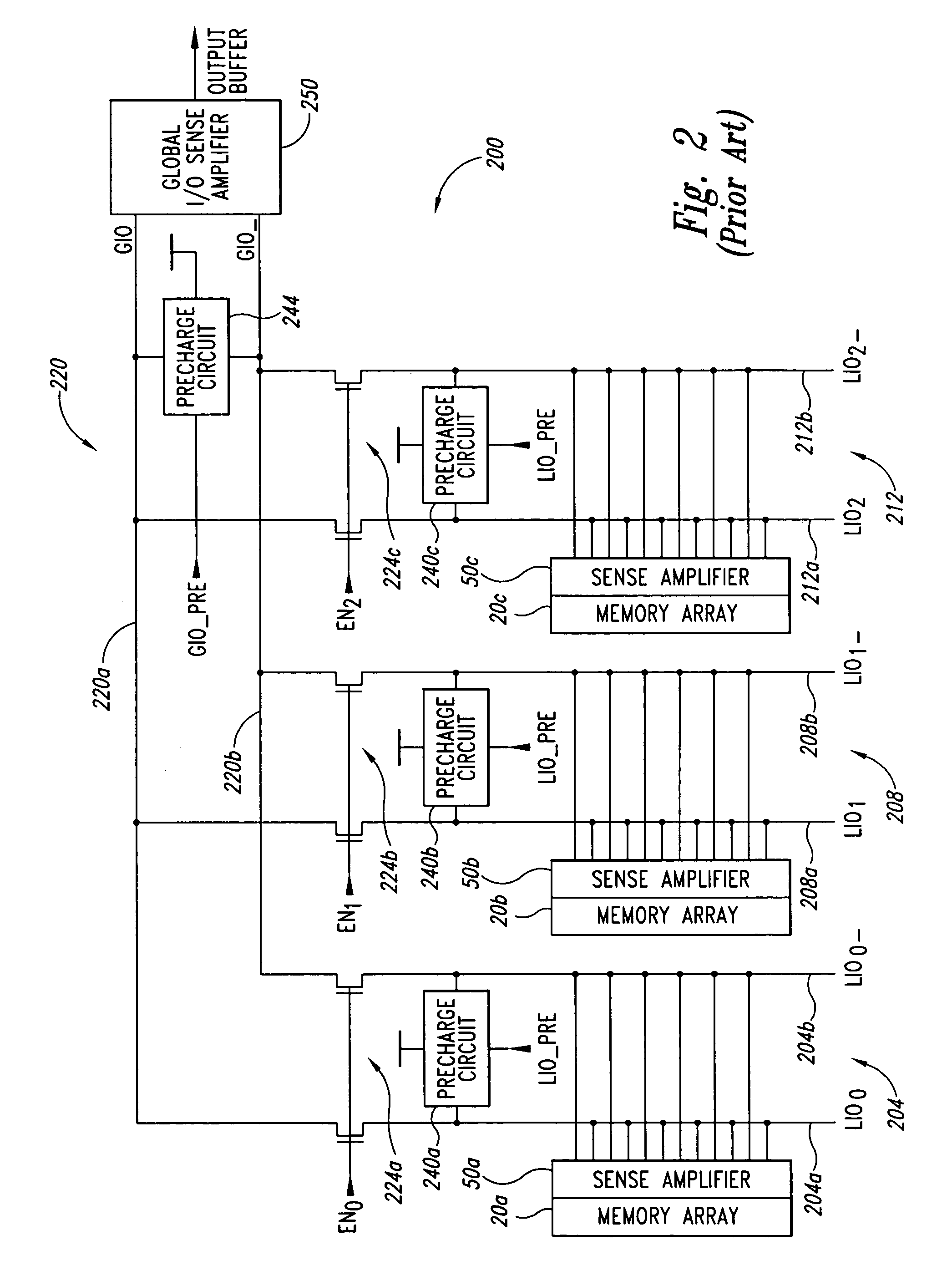

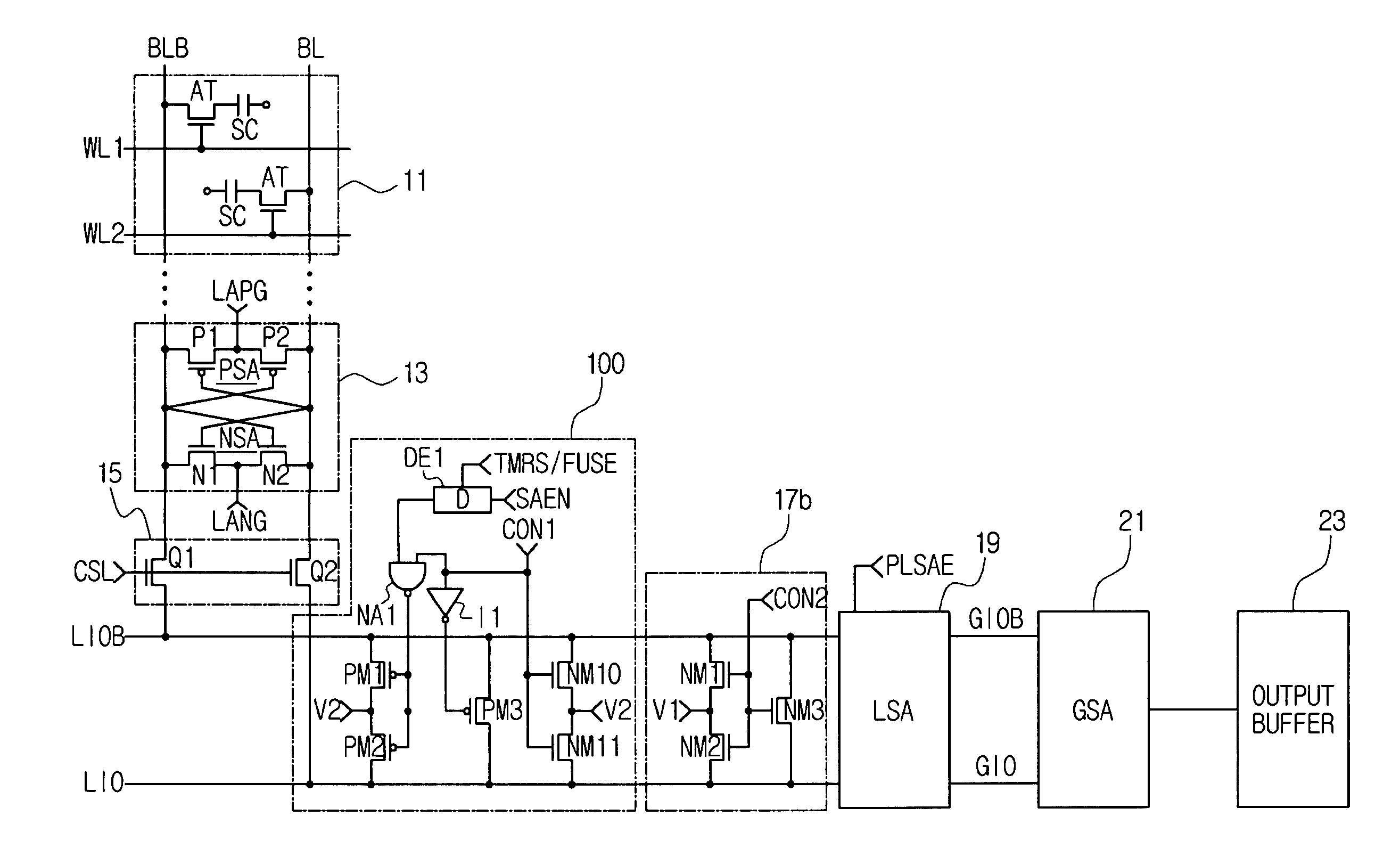

Data path having grounded precharge operation and test compression capability

A data path for coupling data between a memory cell and an input / output (IO) line sense amplifier. An IO line coupling circuit is coupled to a pair of global data lines and a pair of local data lines to couple and decouple each of the global data lines to and from a voltage supply based on the voltage levels of the local data lines for the memory read operation. For the memory write operation, the IO line coupling circuit couples and decouples each of the global data lines to and from a respective one of the local data lines. The data path also includes a first precharge circuit coupled to the global data lines to couple the global data lines to ground to precharge the signal lines prior to a memory read or write operation, and can further include a test compression circuit coupled to the global data lines.

Owner:MOSAID TECH

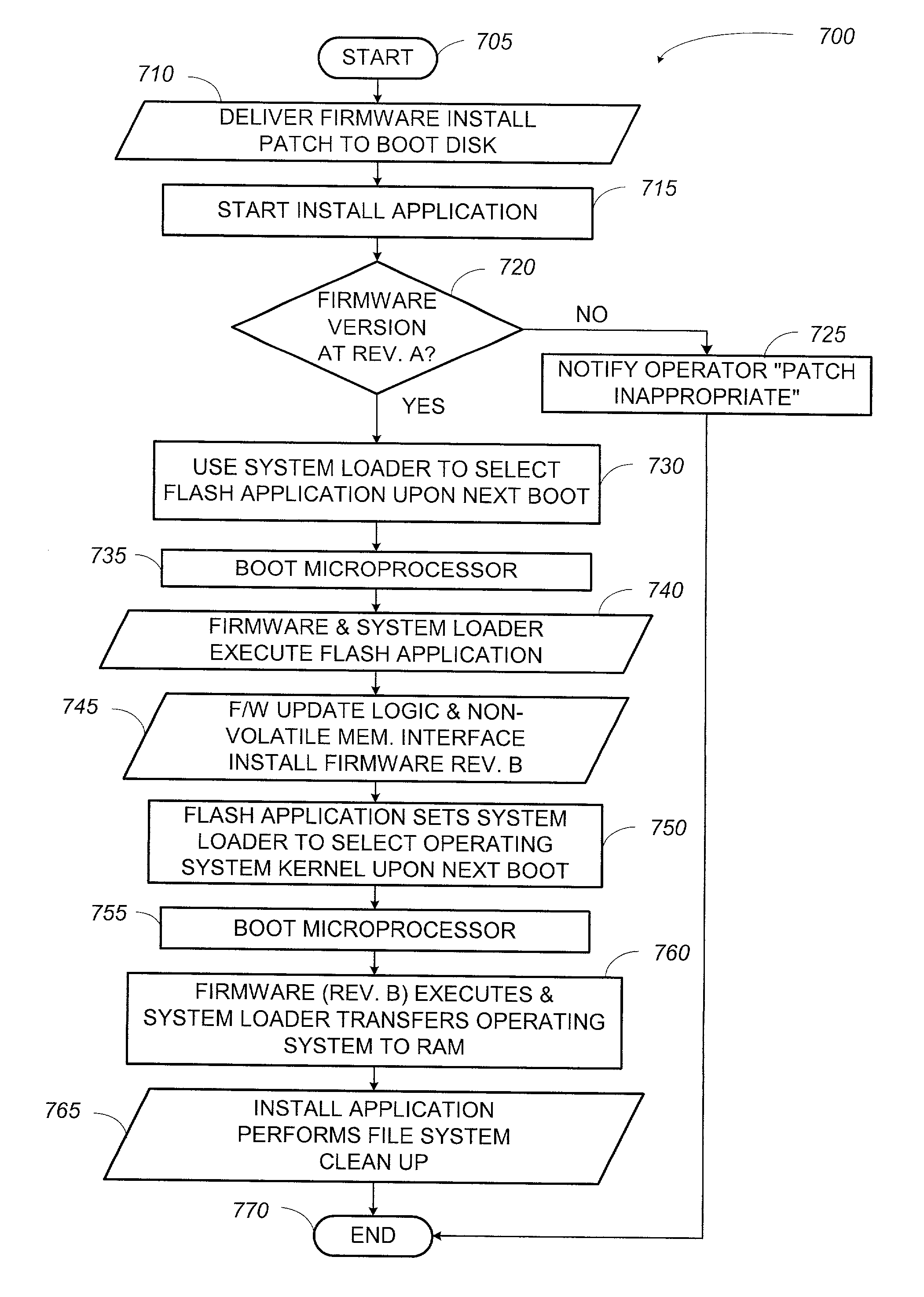

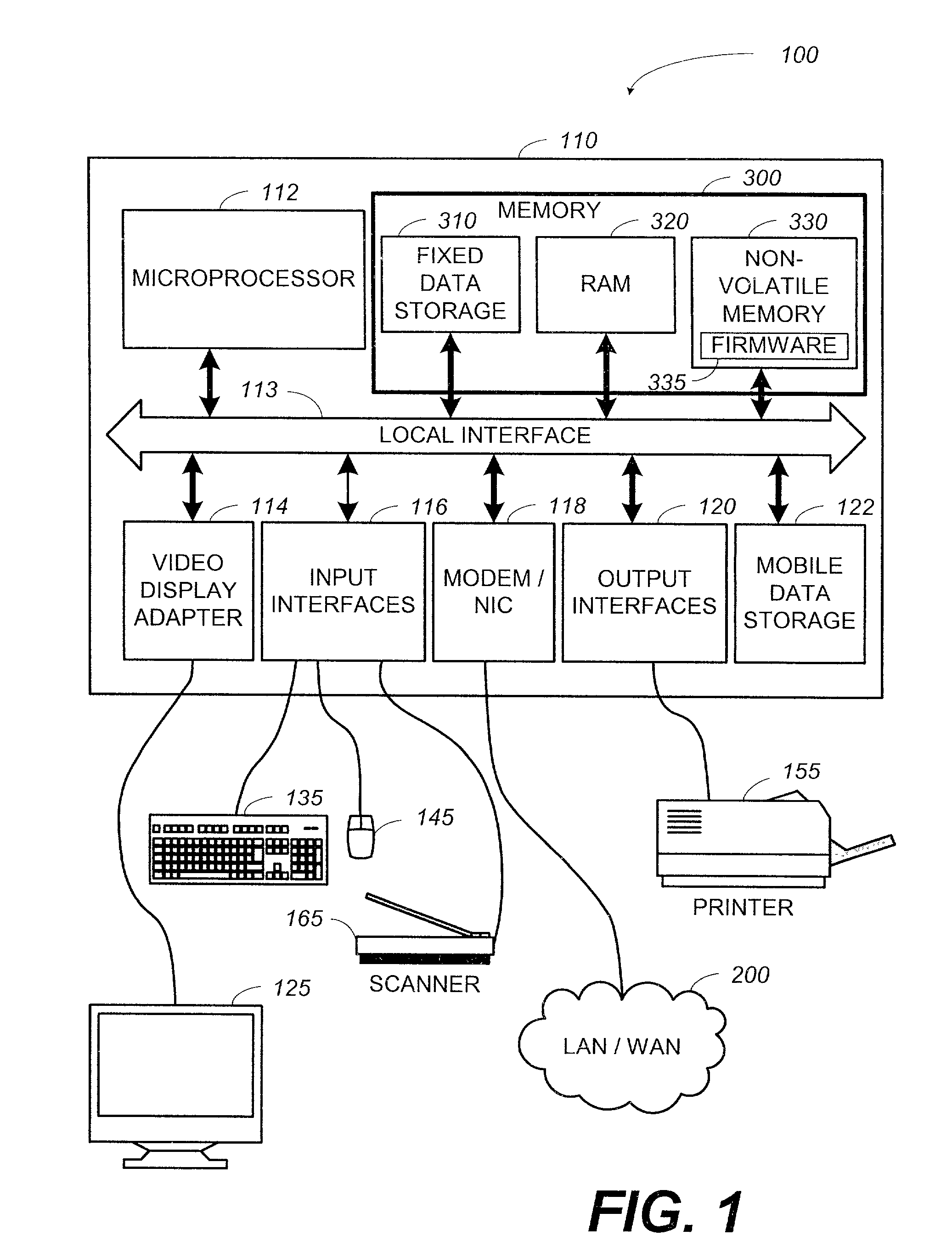

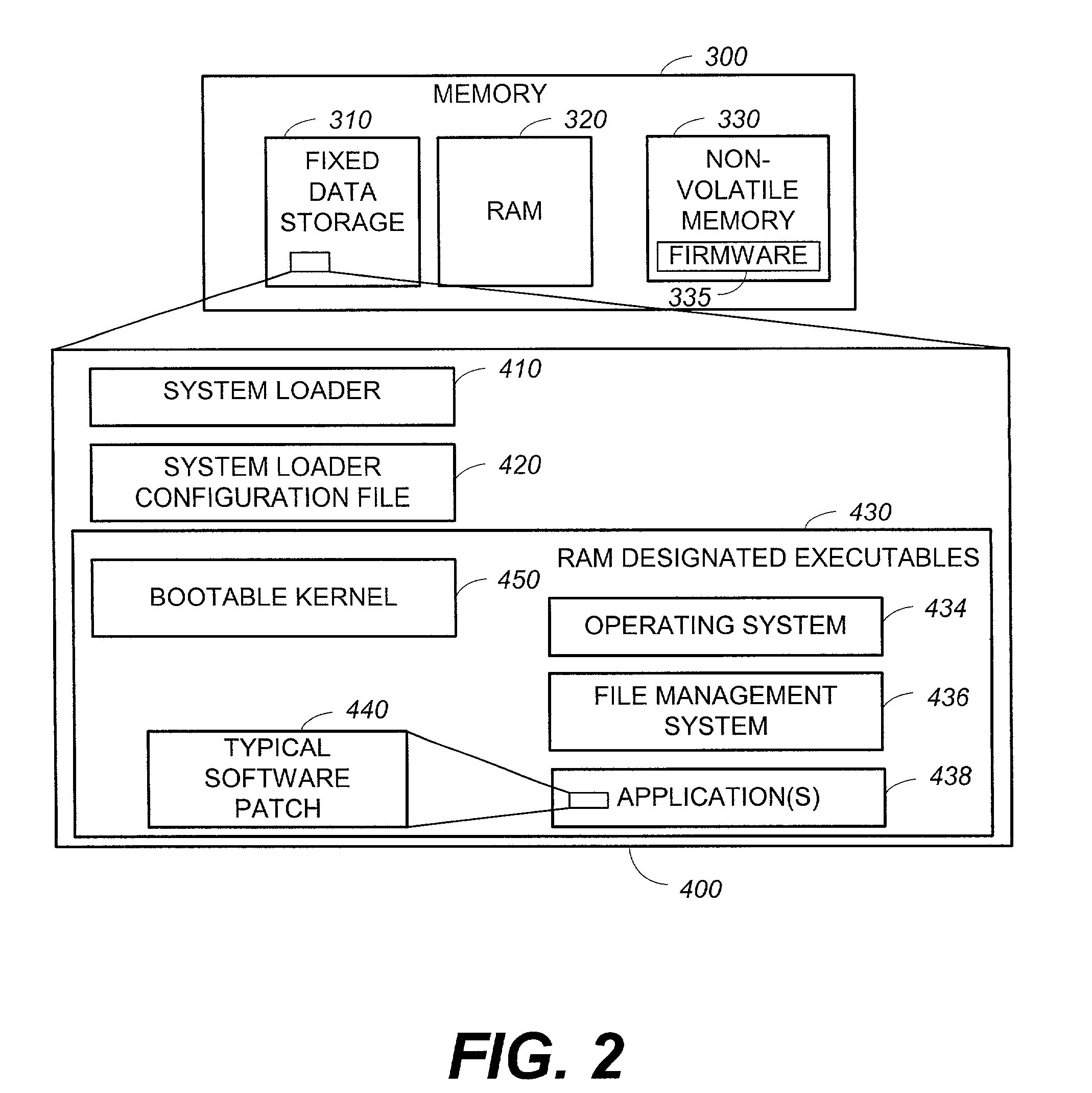

System and method for updating firmware

InactiveUS7055148B2Avoid manual interventionDigital computer detailsProgram loading/initiatingOperational systemFirmware version

A system and a method that uses a software application operable under a current firmware / operating system configuration to install a new firmware version without “compromising” the operating system are presented. The software application may configure a computer system to install a plurality of software fixes configured to enhance functionality under a new firmware / operating system environment after the firmware has been successfully upgraded. Such functionality enhancements may be associated with external peripherals, as well as, input / output circuit cards, processors, and the like. In addition, the software application may configure the computing device to “boot” under the new firmware / operating system environment upon subsequent system initializations. Furthermore, the software application permits the distribution of firmware upgrades via a network. The capability to install firmware remotely permits a system administrator to “push” the new firmware to a plurality of network coupled computing devices, thus avoiding manual intervention at each device.

Owner:HEWLETT PACKARD DEV CO LP

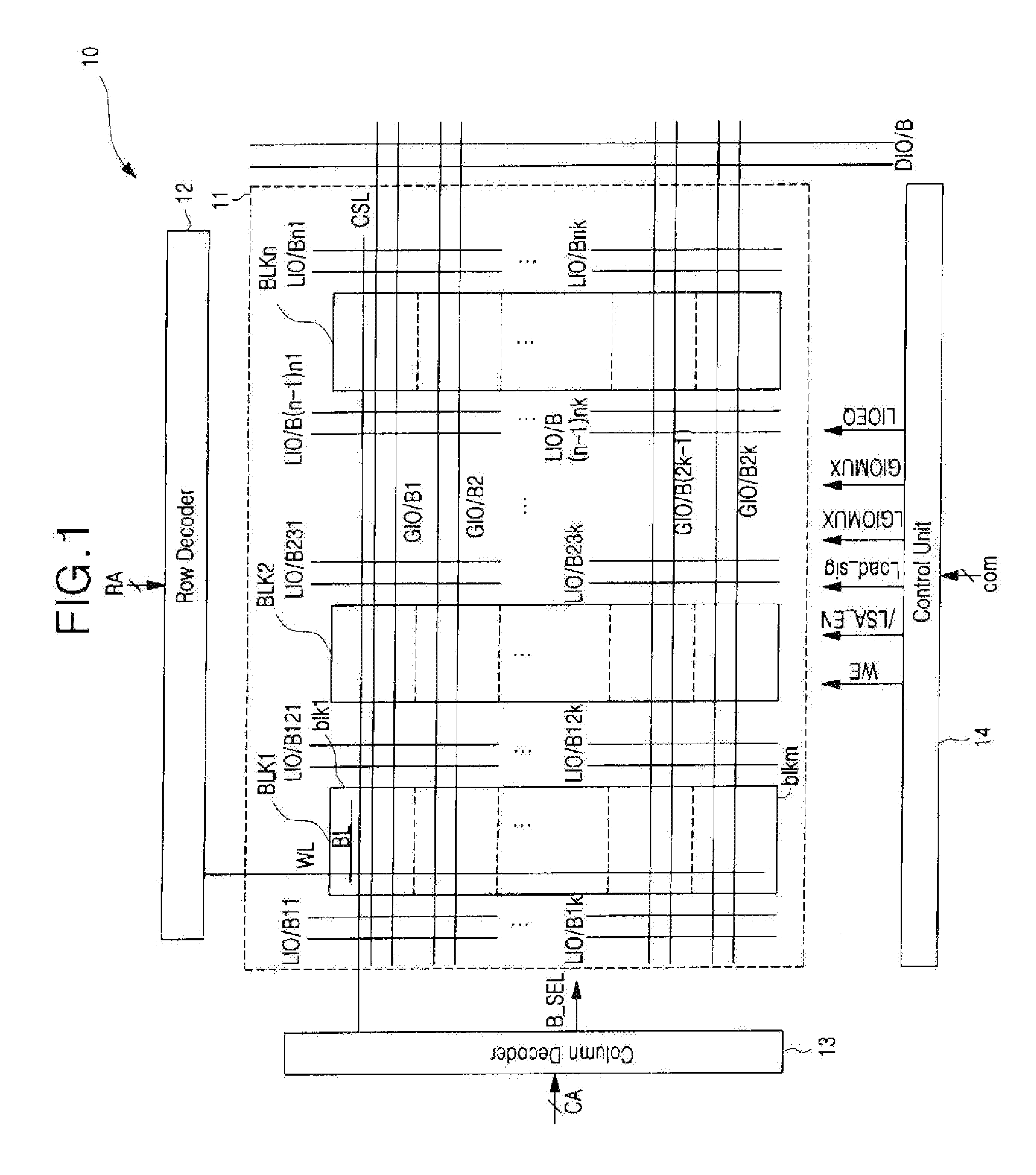

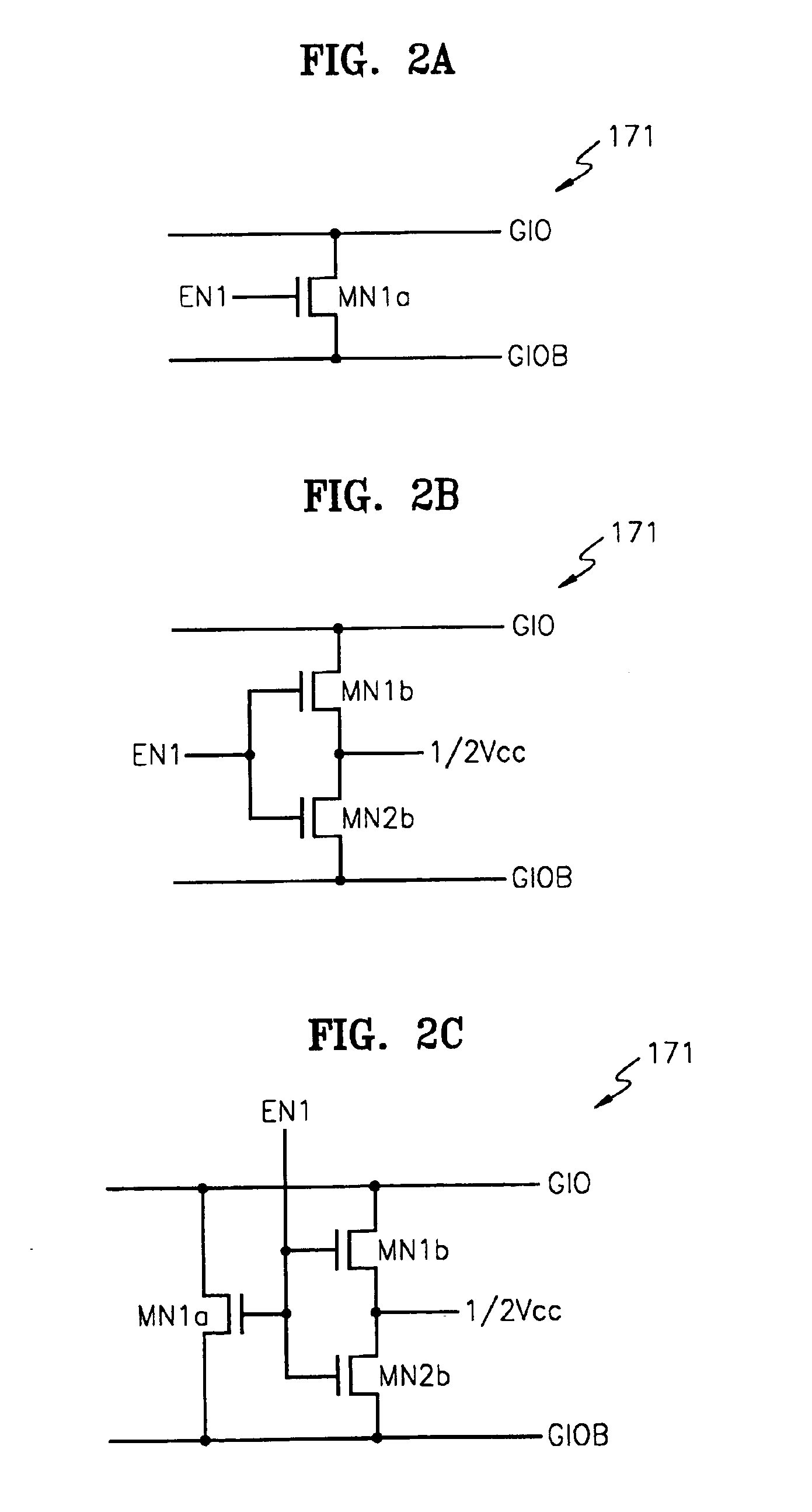

Memory device with separate read and write gate voltage controls

A circuit and method are provided for controlling the gate voltage of a transistor acting between local and global input / output lines of a memory device, the circuit including a local input / output line, a local from / to global input / output multiplexer in signal communication with the local input / output line, a global input / output line in signal communication with the local from / to global input / output multiplexer, and a local from / to global input / output controller having an input node and an output node, the input node disposed for receiving a signal indicative of an input or output operation, and the output node in signal communication with a gate of the local from / to global input / output multiplexer for providing a gate signal of a first or second level in the presence of the output operation, and a gate signal of a third level in the presence of the input operation.

Owner:SAMSUNG ELECTRONICS CO LTD

Integrated circuit devices including input/output line pairs and precharge circuits and related memory devices

An integrated circuit device may include a pair of first and second input / output lines on a substrate and a precharge circuit connected to the first and second input / output lines. More particularly, portions of the first and second input / output lines may extend in a parallel direction along first lengths thereof, portions of the first and second input / output lines may cross one another in a twist region so that portions of the first and second input / output lines in the twist region extend in directions different than the parallel direction, and portions of the first and second input / output lines may extend in the parallel direction along second lengths. Accordingly, relative positions of the first and second input / output lines may be reversed in the first and second lengths thereof. In addition, the precharge circuit may be connected to portions of the first and second input / output lines in the twist region extending in the directions different than the parallel direction, and the precharge circuit may be configured to provide that the first and second input / output lines have a same electrical potential responsive to an enable signal. Related memory devices are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

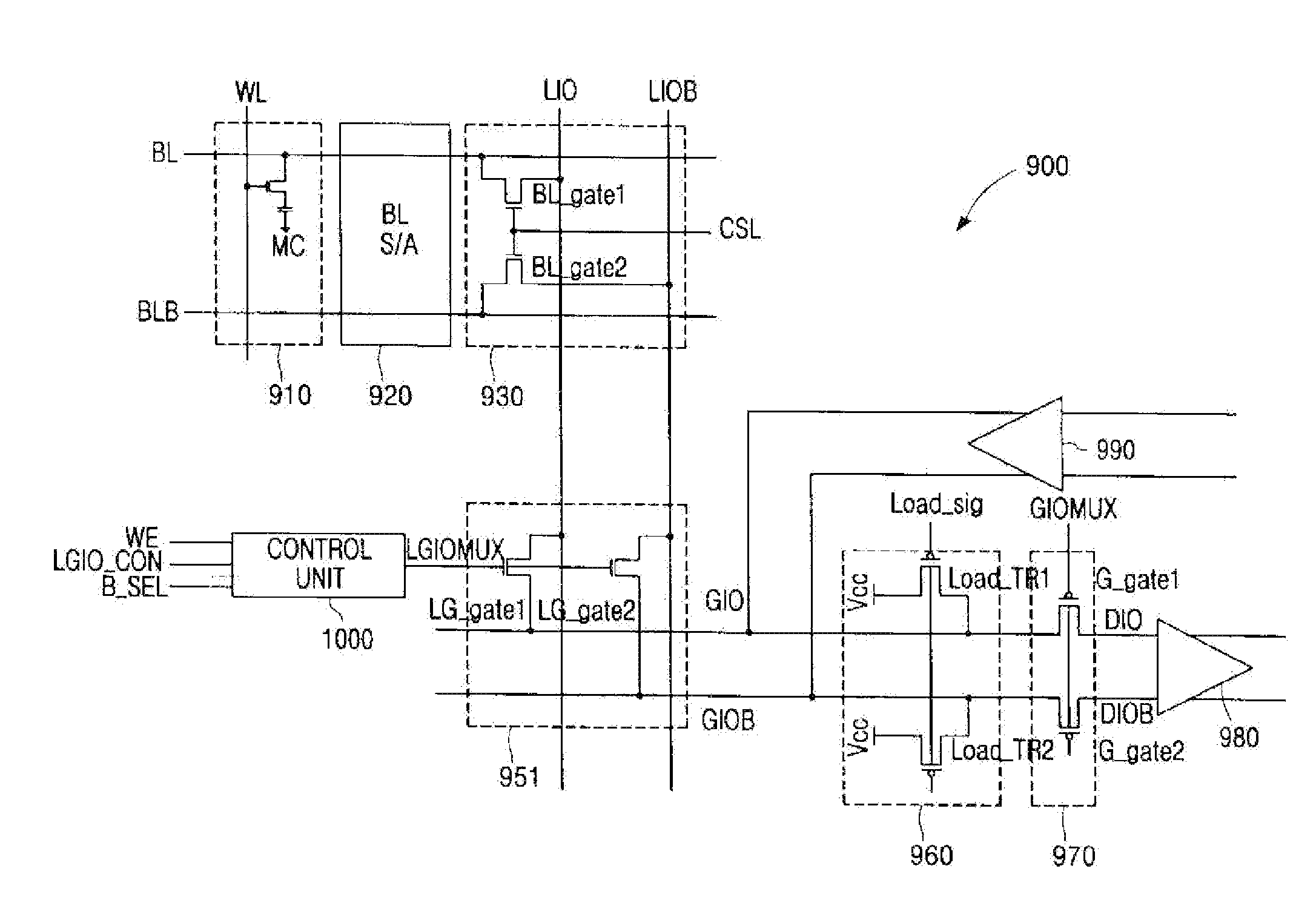

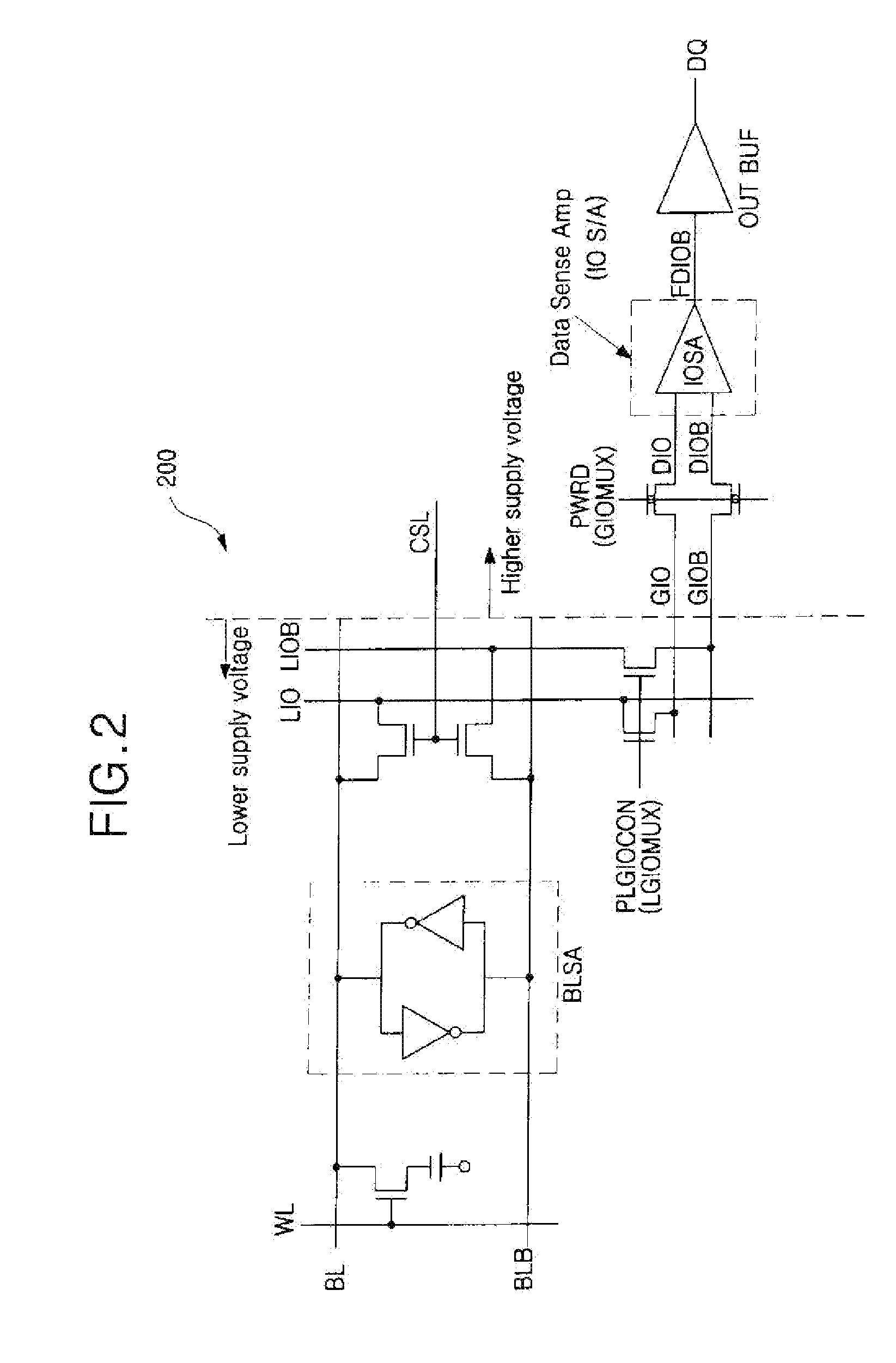

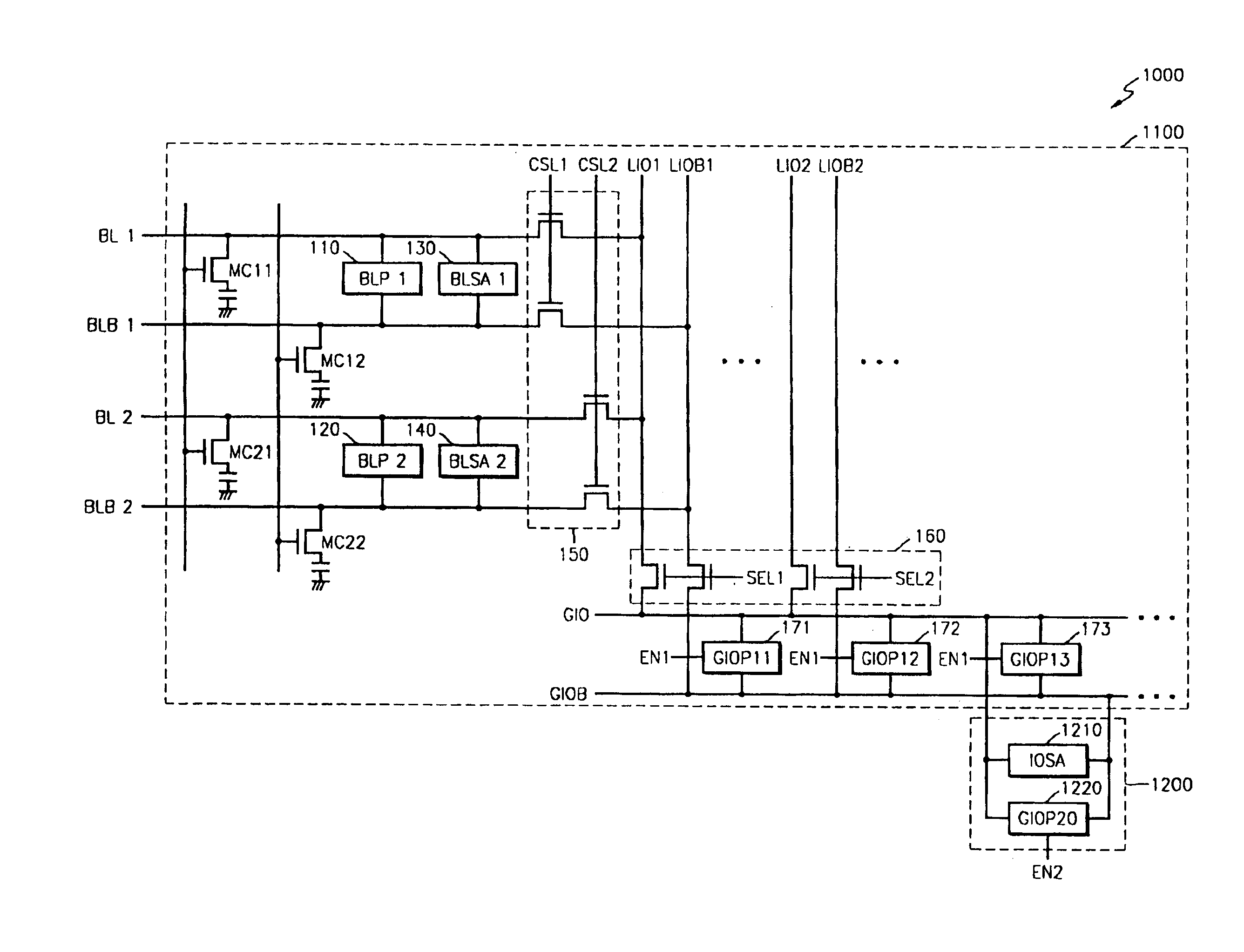

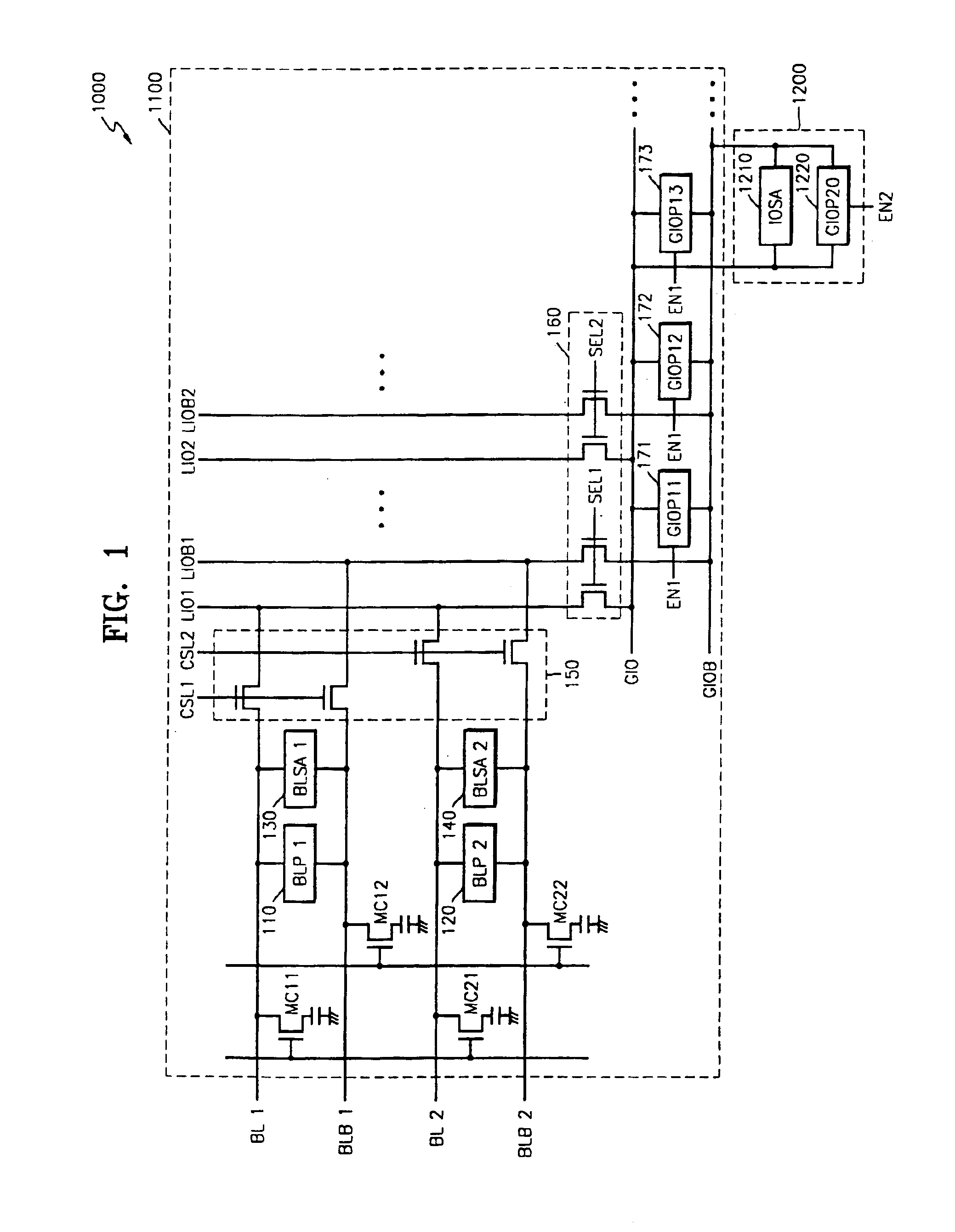

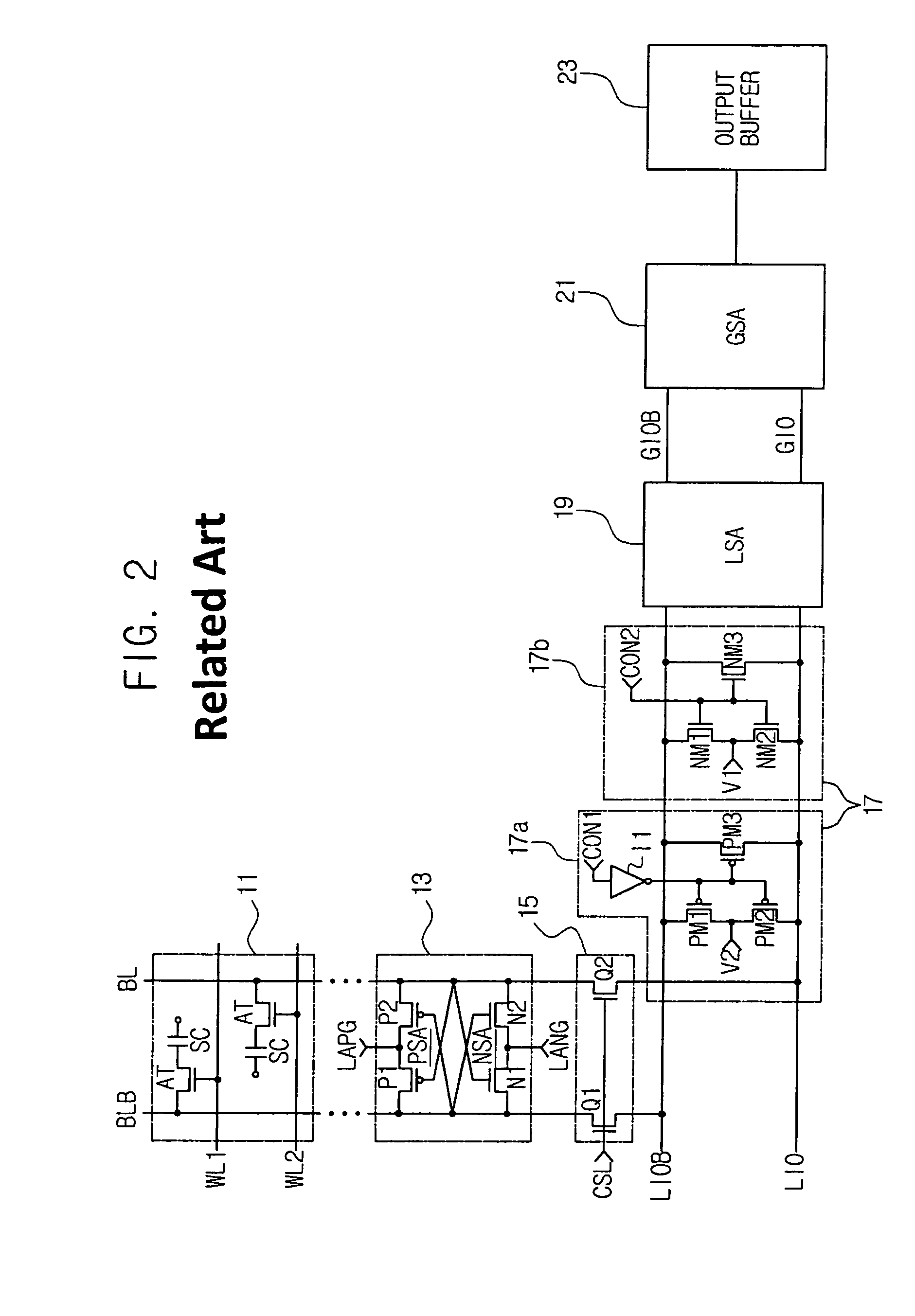

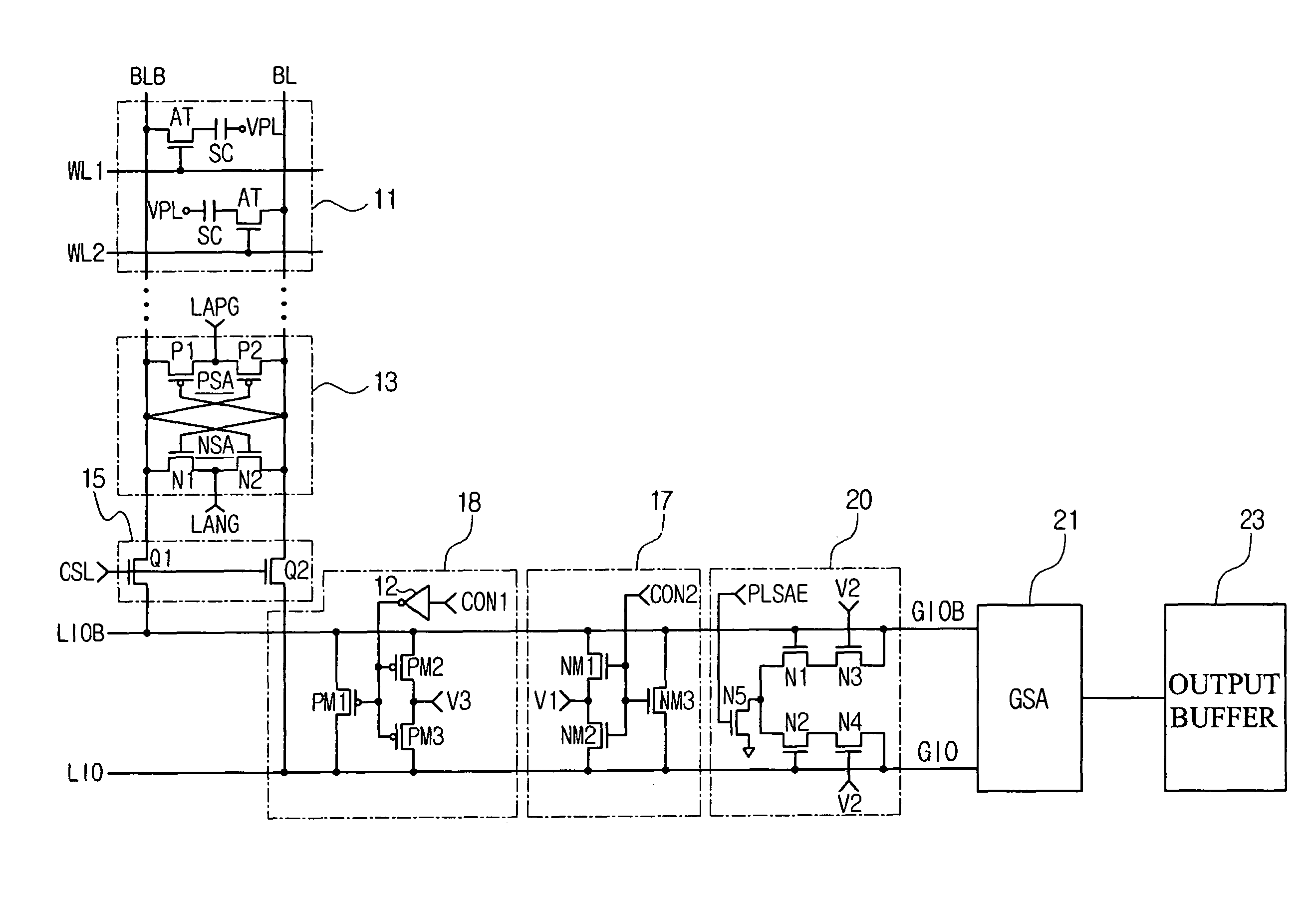

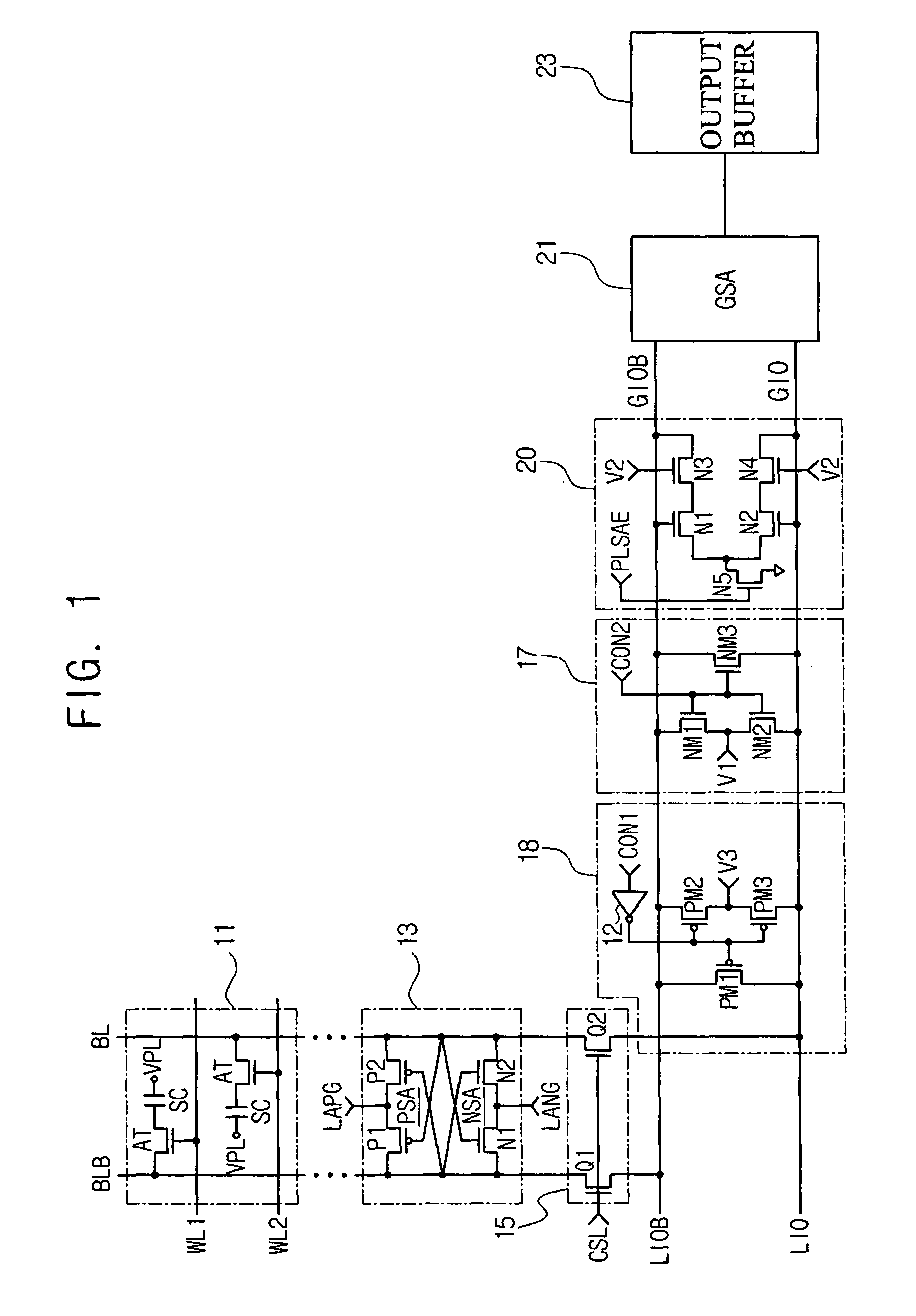

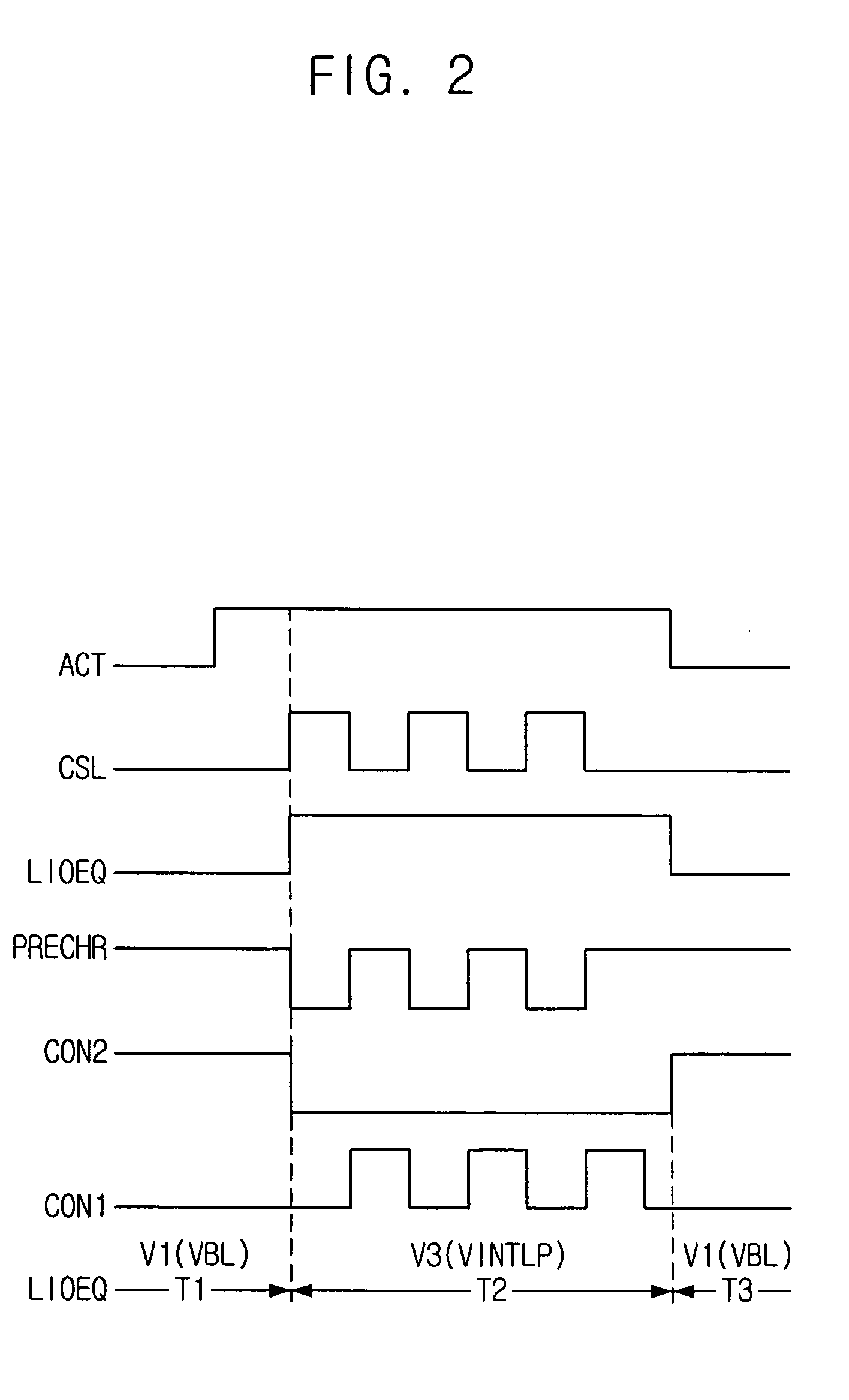

Semiconductor memory device adopting improved local input/output line precharging scheme

A semiconductor memory device capable of preventing or minimizing bit line disturbance and performing a low-voltage high-speed operation includes a read data path circuit including a bit line sense amplifier, a local input / output line sense amplifier, a column selecting unit to operationally connect bit lines connected to the bit line sense amplifier to local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal, and a local input / output line precharging unit to precharge the pair of local input / output lines by a first precharging unit, equalizing the pair of local input / output lines by an equalizing unit, and to precharge the local input / output lines by a second precharging unit following an elapsed time after the bit line sense amplifier is activated, while the column selection is deactivated.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device having improved local input/output line precharge scheme

ActiveUS8213248B2Preventing bit line disturbanceRun at high speedDigital storageBit lineDatapath circuits

A data path circuit of a semiconductor memory device includes: a bit line sense amplifier driven by a first power supply voltage; a local input / output line sense amplifier; a column selecting unit operatively connecting a pair of bit lines connected to the bit line sense amplifier and a pair of local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal; and a local input / output line precharge unit precharging the pair of local input / output lines with a second power supply voltage different from the first power supply voltage during a period for which the column selection signal is in an inactive state.

Owner:SAMSUNG ELECTRONICS CO LTD

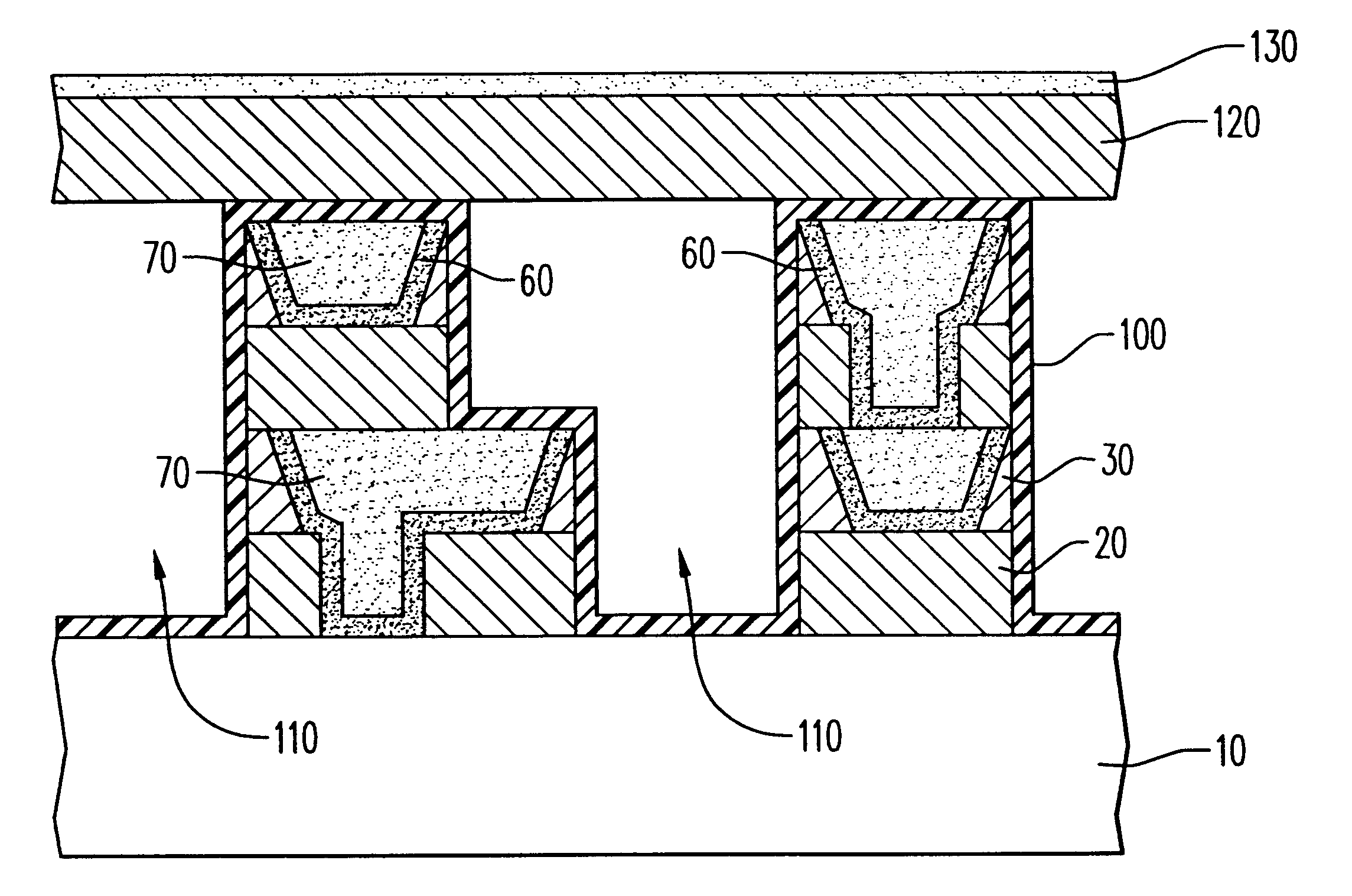

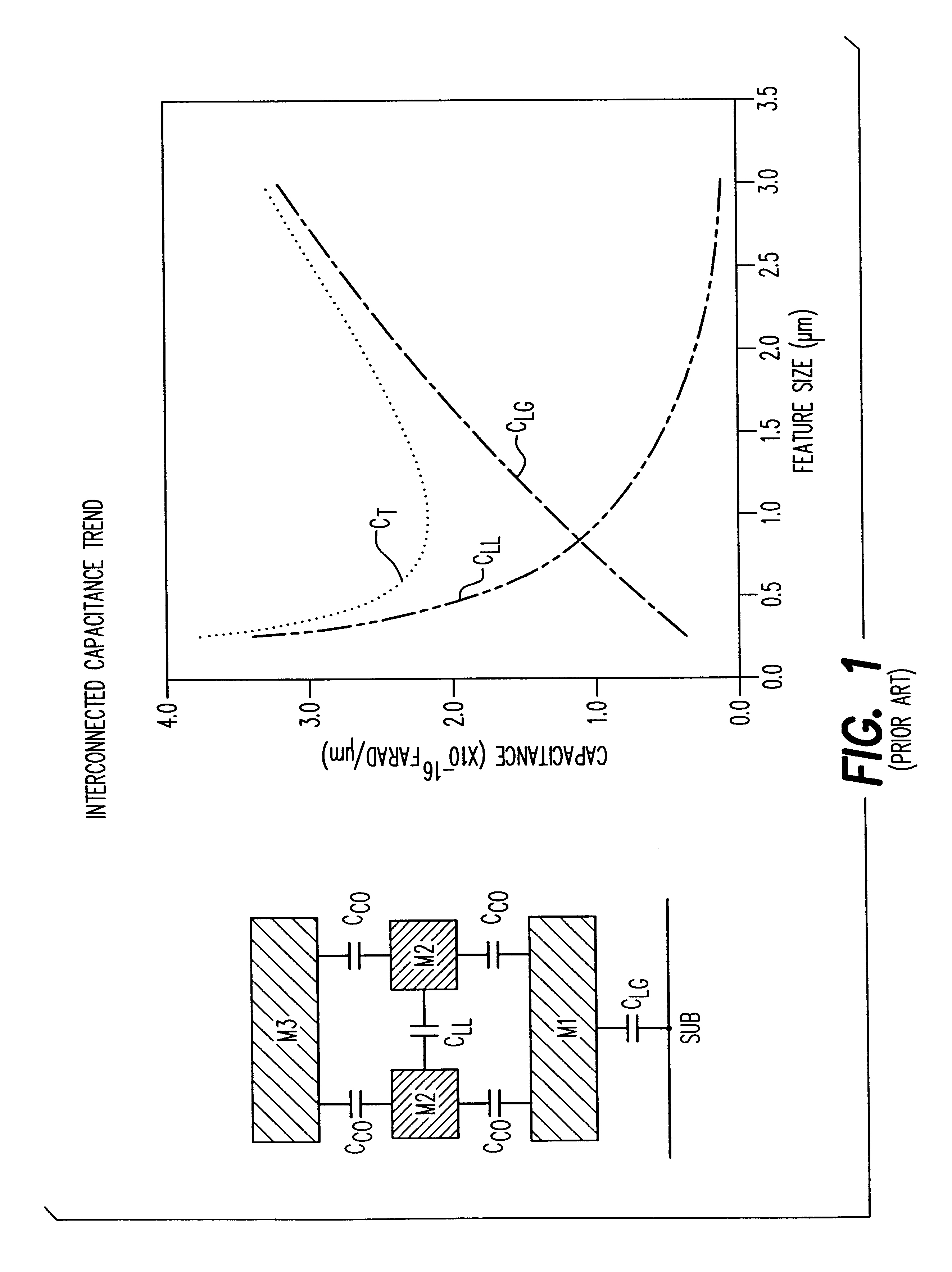

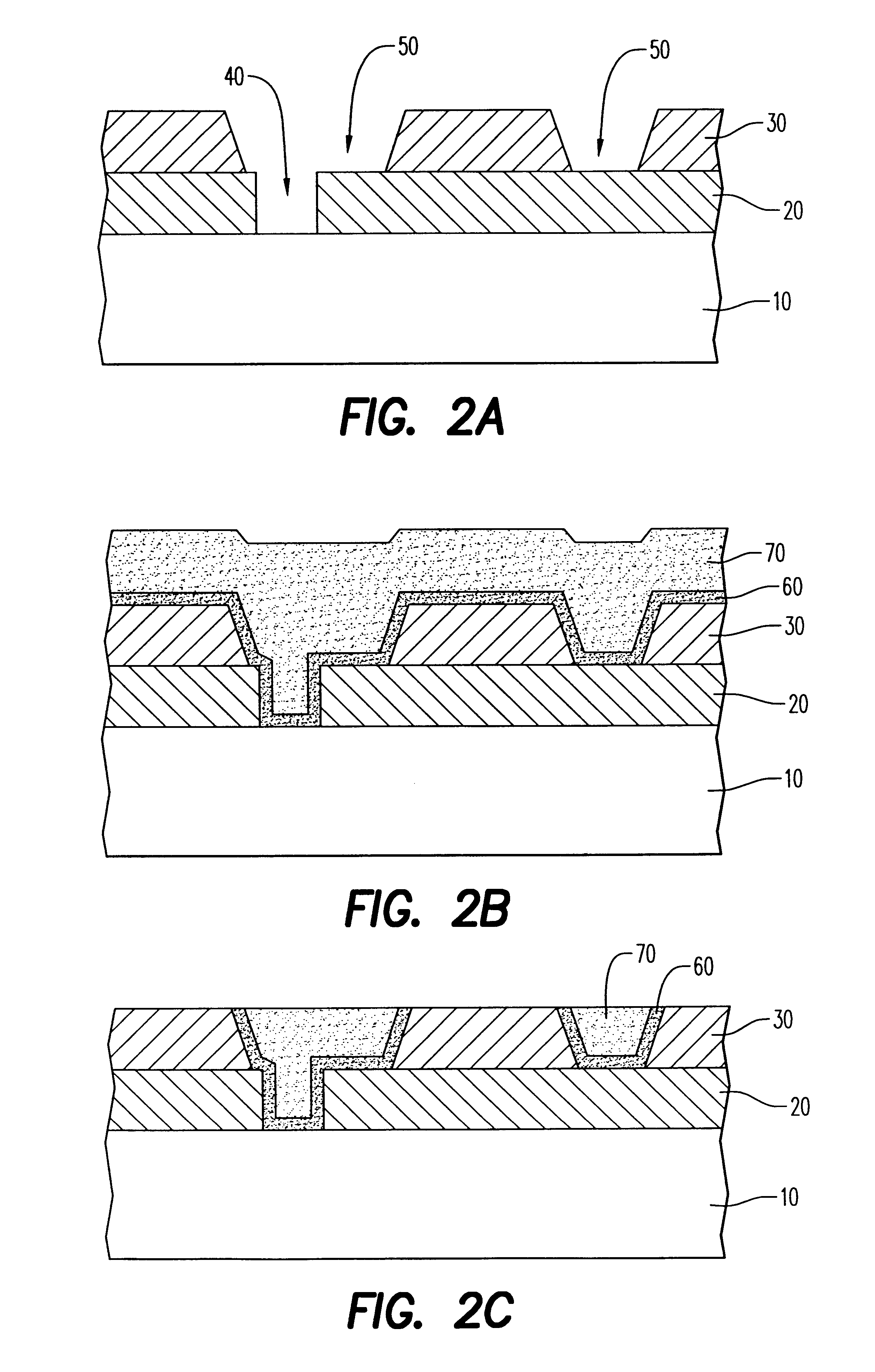

Chip interconnect wiring structure with low dielectric constant insulator and methods for fabricating the same

A method to achieve a very low effective dielectric constant in high performance back end of the line chip interconnect wiring and the resulting multilayer structure are disclosed. The process involves fabricating the multilayer interconnect wiring structure by methods and materials currently known in the state of the art of semiconductor processing; removing the intralevel dielectric between the adjacent metal features by a suitable etching process; applying a thin passivation coating over the exposed etched structure; annealing the etched structure to remove plasma damage; laminating an insulating cover layer to the top surface of the passivated metal features; optionally depositing an insulating environmental barrier layer on top of the cover layer; etching vias in the environmental barrier layer, cover layer and the thin passivation layer for terminal pad contacts; and completing the device by fabricating terminal input / output pads. The method obviates issues such as processability and thermal stability associated with low dielectric constant materials by avoiding their use. Since air, which has the lowest dielectric constant, is used as the intralevel dielectric the structure created by this method would possess a very low capacitance and hence fast propagation speeds. Such structure is ideally suitable for high density interconnects required in high performance microelectronic device chips.

Owner:GLOBALFOUNDRIES INC

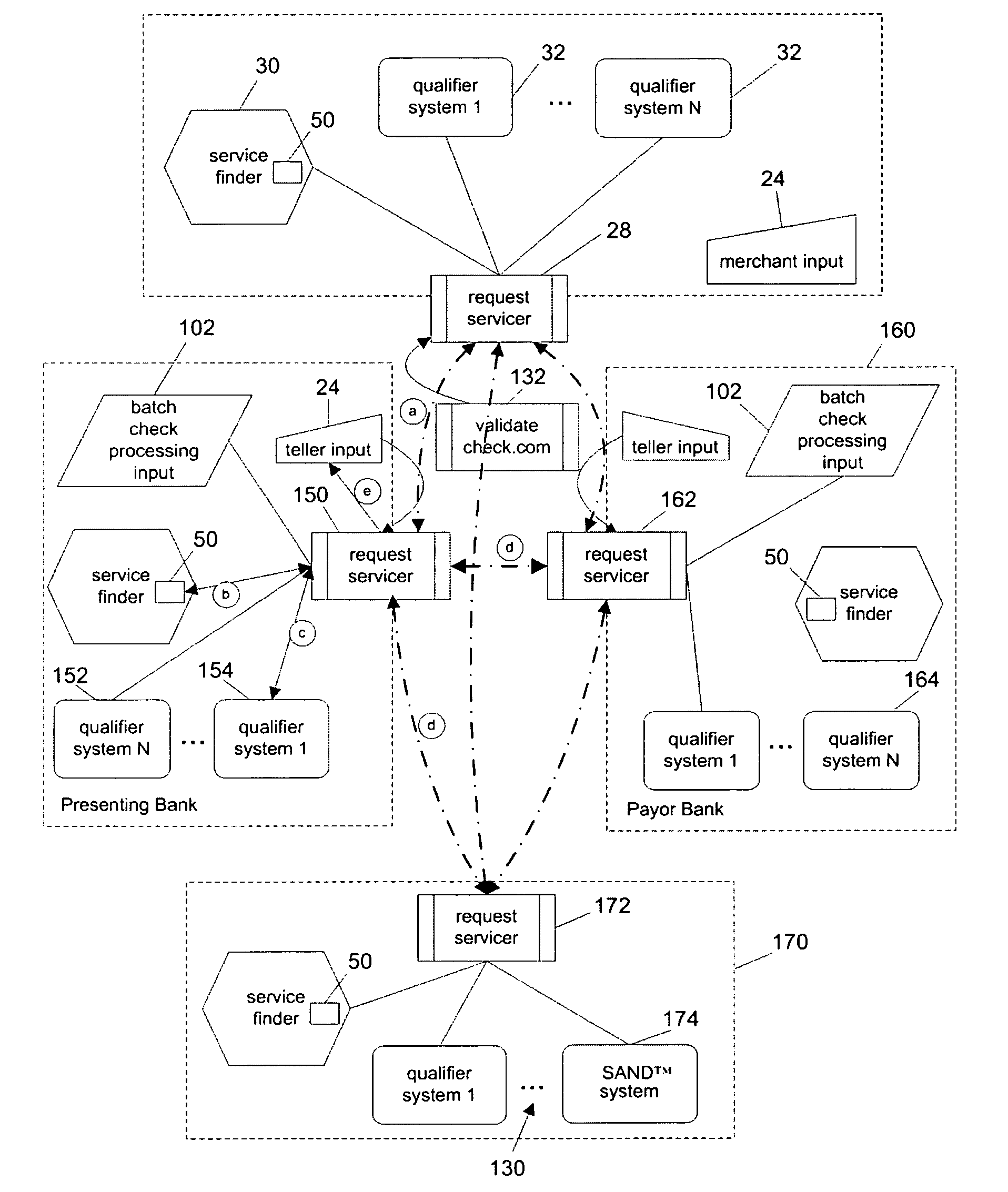

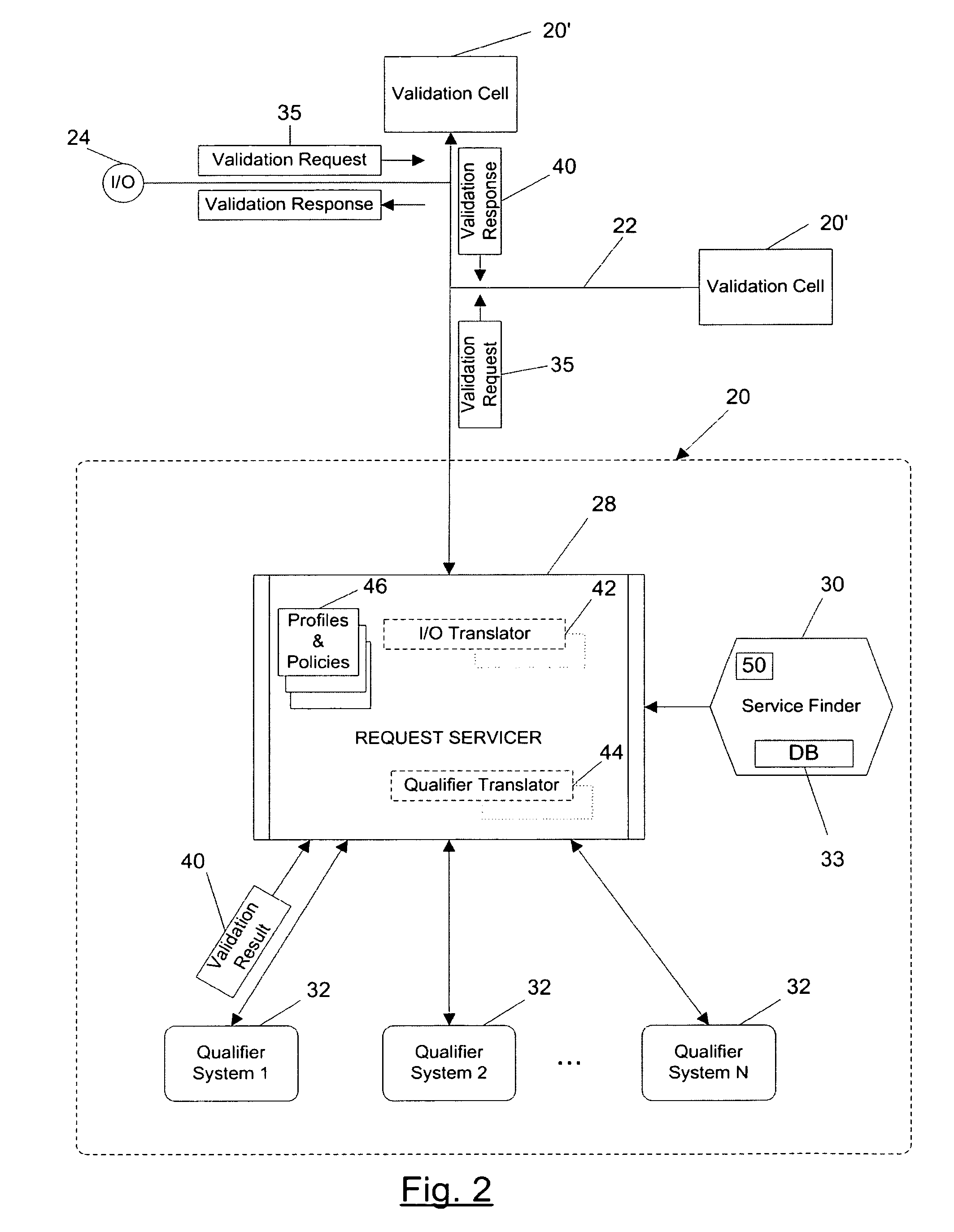

Payment validation network

ActiveUS7004382B2Easy to analyzeReduce riskComplete banking machinesSpecial service provision for substationPaymentTransaction data

A payment validation network having network of payment validation cells, each of which includes: one or more local qualifier systems for assessing the risk of loss in accepting a check; a service finder for identifying the scope of coverage provided by each of the local qualifier systems and for identifying the scope of coverage provided by other cells; and one or more input / output (I / O) sources for obtaining transaction data associated with a check at a point of presentment. The request servicer interfaces with the I / O sources, service finder and the qualifier systems in order to (i) receive transaction data from an I / O source in connection with the check, including the routing / transit number, (ii) maintain a user profile for the I / O source, (iii) consult the service finder to identify which local qualifier systems cover the routing / transit (R / T) number associated with the check, (iv) transmit a payment validation request to the identified local qualifier systems and at least one other remote request servicer in accordance with the user profile, (v) receive one or more validation results from local qualifier systems or remote request servicers, and (vi) process said results to provide a homogeneous validation assessment to the requesting I / O source.

Owner:ADVANCED SOFTWARE DESIGN

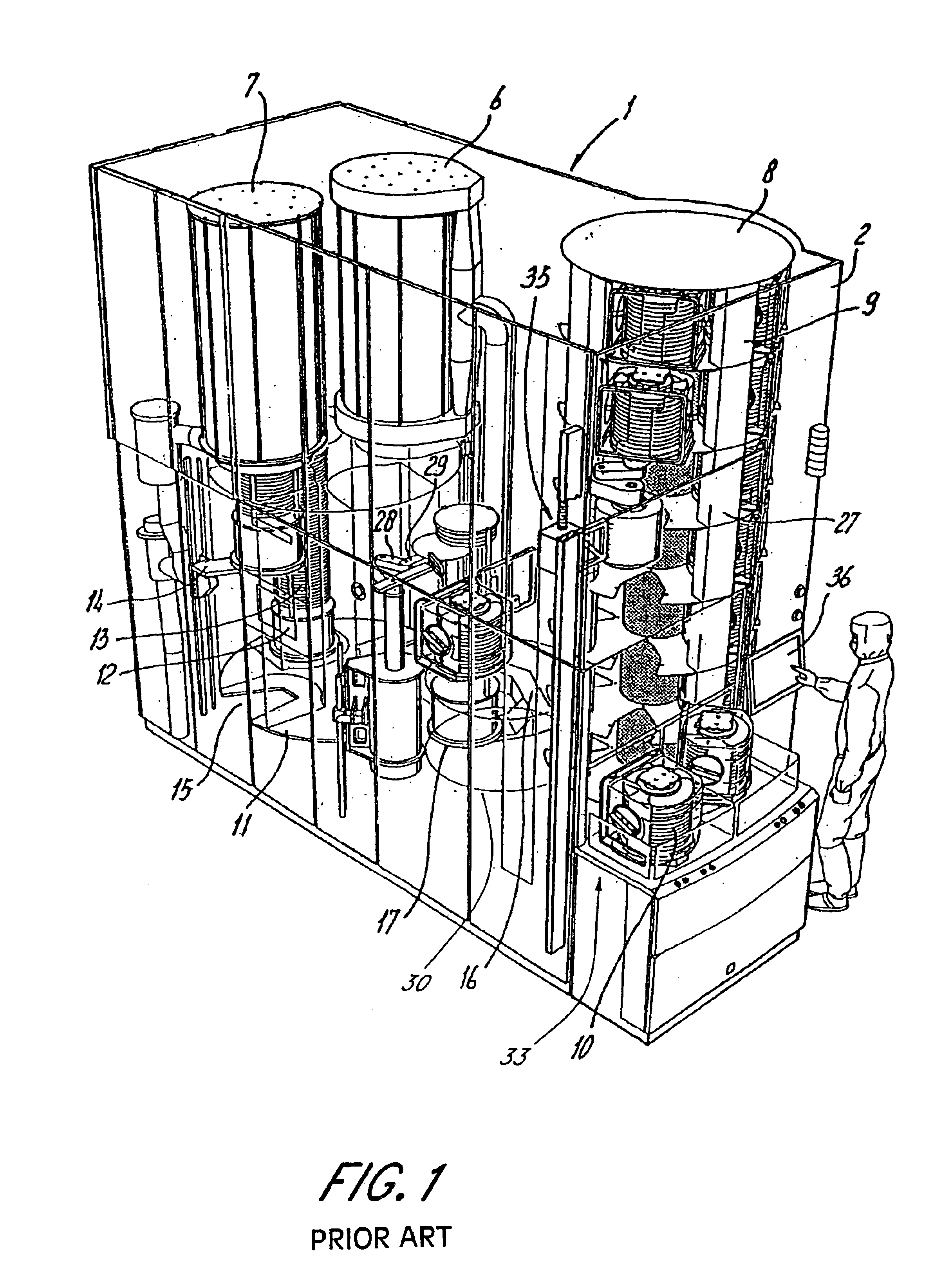

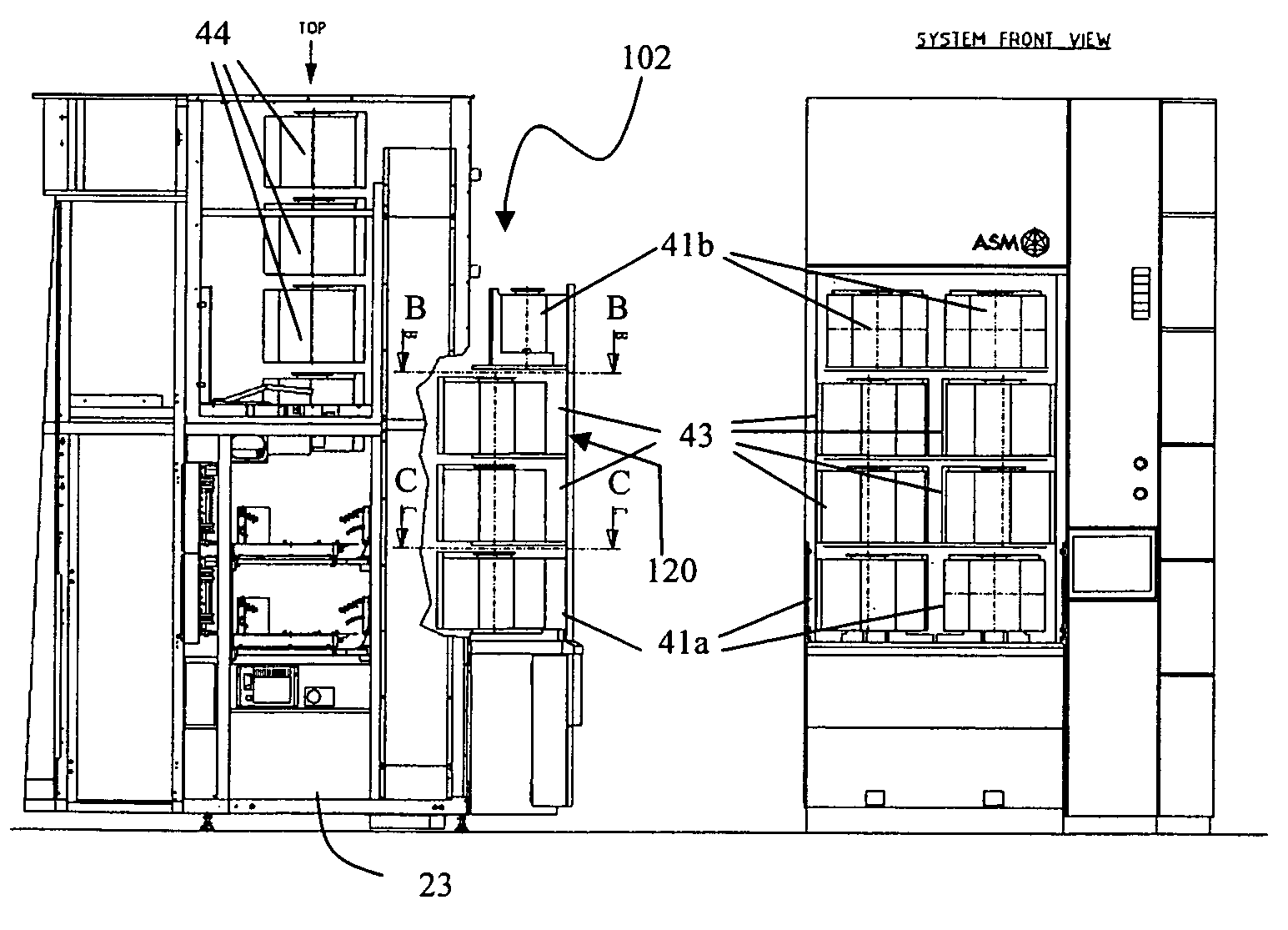

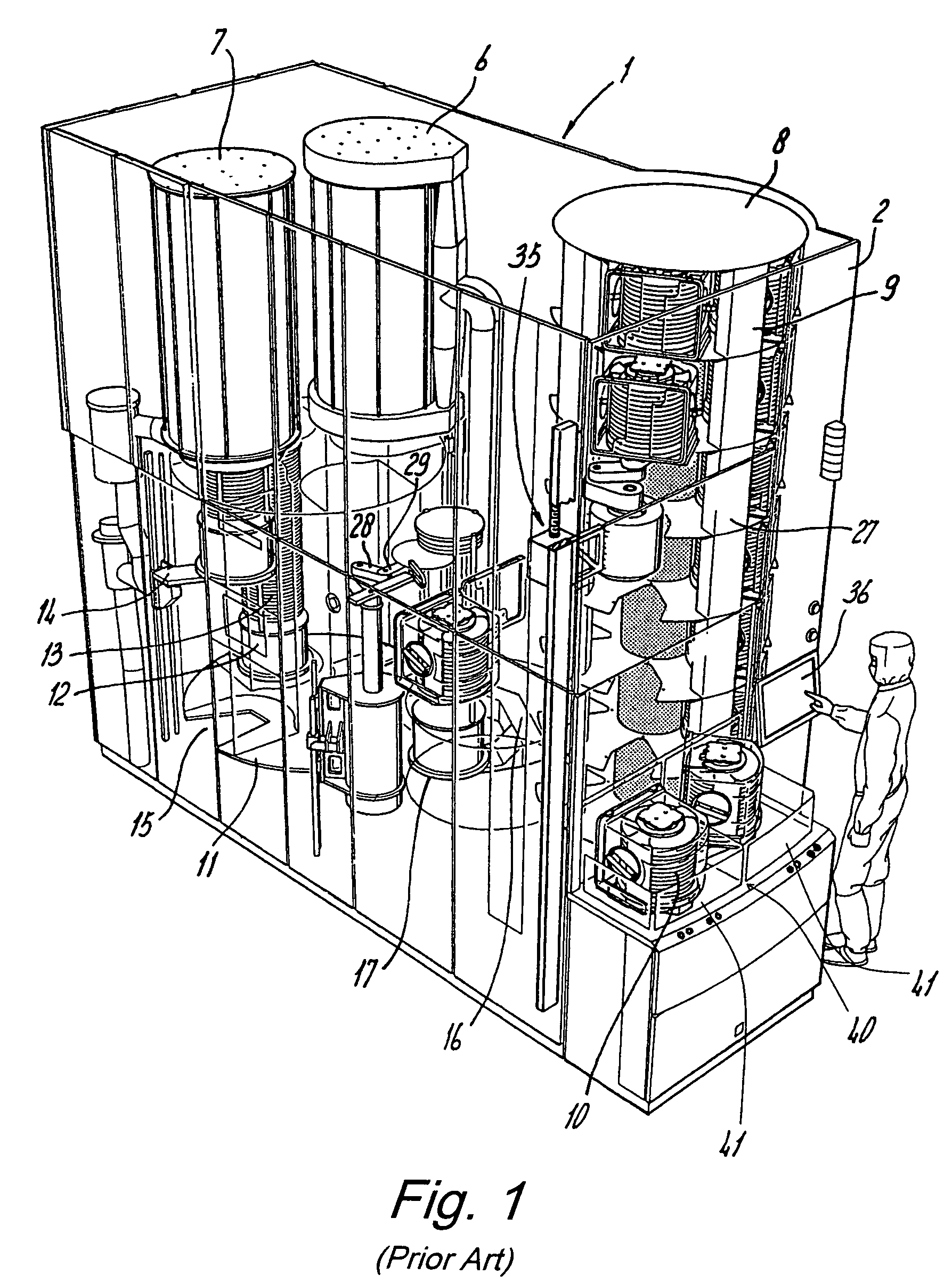

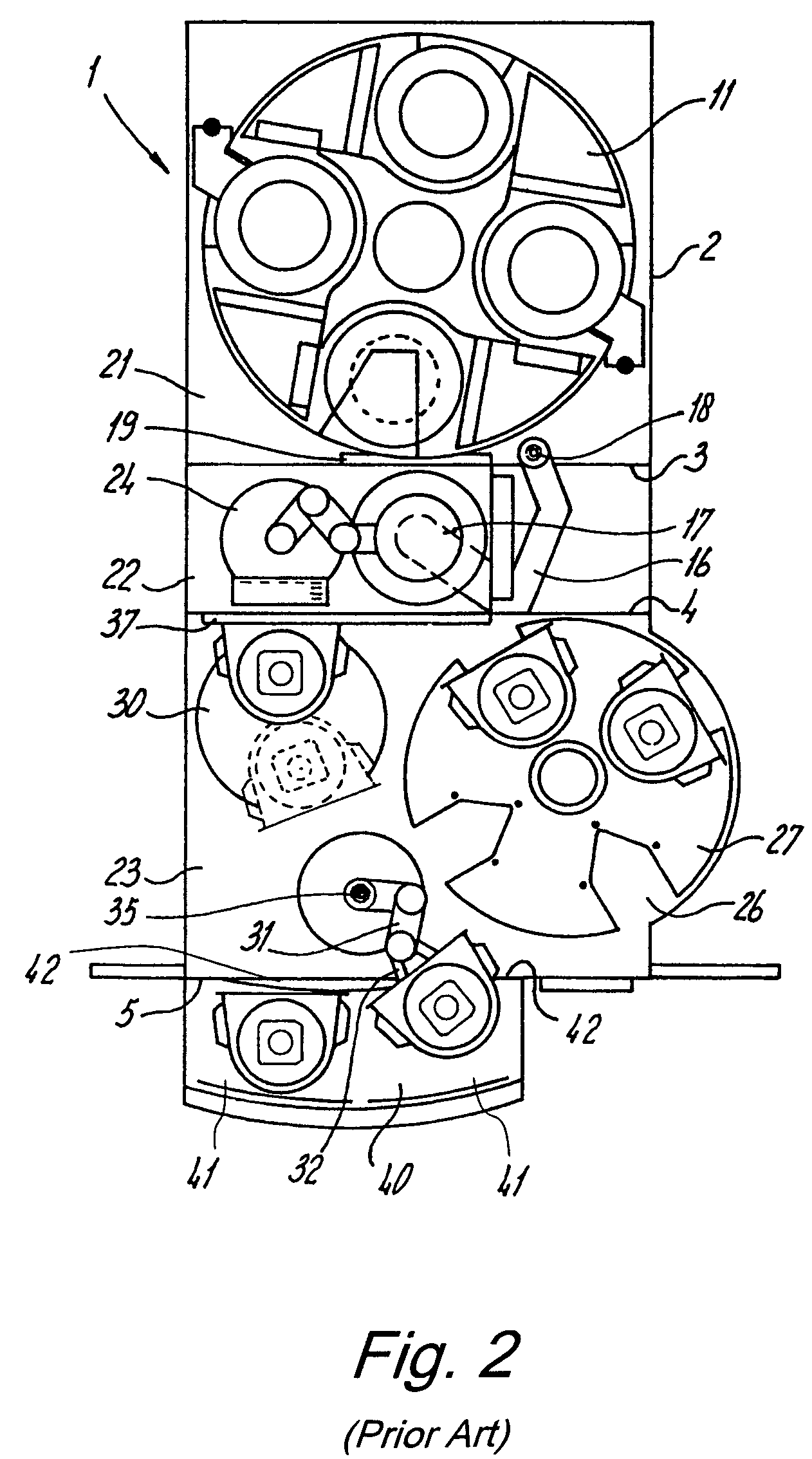

Wafer handling system

InactiveUS6981832B2Semiconductor/solid-state device manufacturingStorage devicesMagnetic tapeEngineering

A system for processing semiconductor wafers includes adaptations allowing the selective handling of cassettes for both 200-mm wafers and 300-mm wafers. The system is configured initially for handling standard 300-mm FOUP cassettes. Adaptions for handling 200-mm wafer open cassettes include a load port adapter frame for receiving such cassettes on a input / output platform; a cassette handler adapter configured for reversibly mounting on a cassette handler end effector and for receiving 200-mm open cassettes; a store adapter frame for converting 300-mm FOUP storage compartments into compartments for storing 200-mm open cassettes; and a Transhipment FOUP for holding 200-mm open cassettes upon a cassette transfer platform and bringing such cassettes into an interface with a wafer handler. The Transhipment FOUP has outer surfaces resembling a standard 300-mm FOUP cassette, but is configured to receive a 200-mm open cassette therein.

Owner:ASM INTERNATIONAL

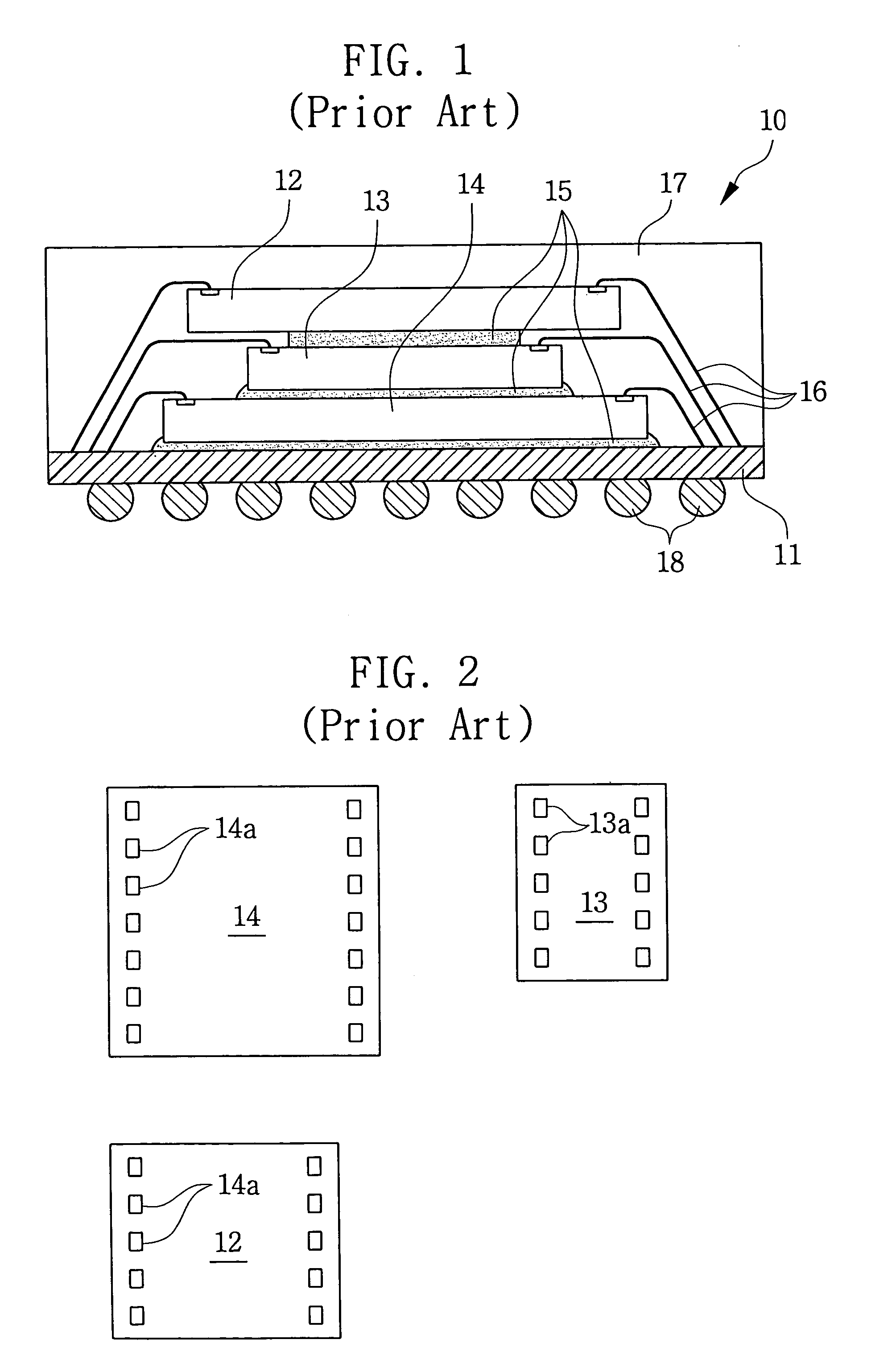

Semiconductor package and method for fabricating the same

InactiveUS6395578B1Improve cooling effectUniform encapsulationSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

Semiconductor packages having a thin structure capable of easily discharging heat from a semiconductor chip included therein, and methods for fabricating such semiconductor packages, are disclosed. An embodiment of a semiconductor package includes a semiconductor chip having a first major surface and a second major surface, the semiconductor chip being provided at the second major surface with a plurality of input / output pads; a circuit board including a resin substrate having a first major surface and a second major surface, a first circuit pattern formed at the first major surface and provided with a plurality of ball lands, a second circuit pattern formed at the second major surface and provided with a plurality of bond fingers connected with he ball lands by conductive via holes through the resin substrate, cover coats respectively coating the first and second circuit patterns while allowing the bond fingers and the ball lands to be exposed therethrough, and a central through hole adapted to receive the semiconductor chip therein; electrical conductors that electrically connect the input / output pads of the semiconductor chip with the bond fingers of the circuit board, respectively; a resin encapsulate that covers the semiconductor chip, the electrical conductors, and at least part of the circuit board; and, a plurality of conductive balls fused on the ball lands of the circuit board, respectively.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

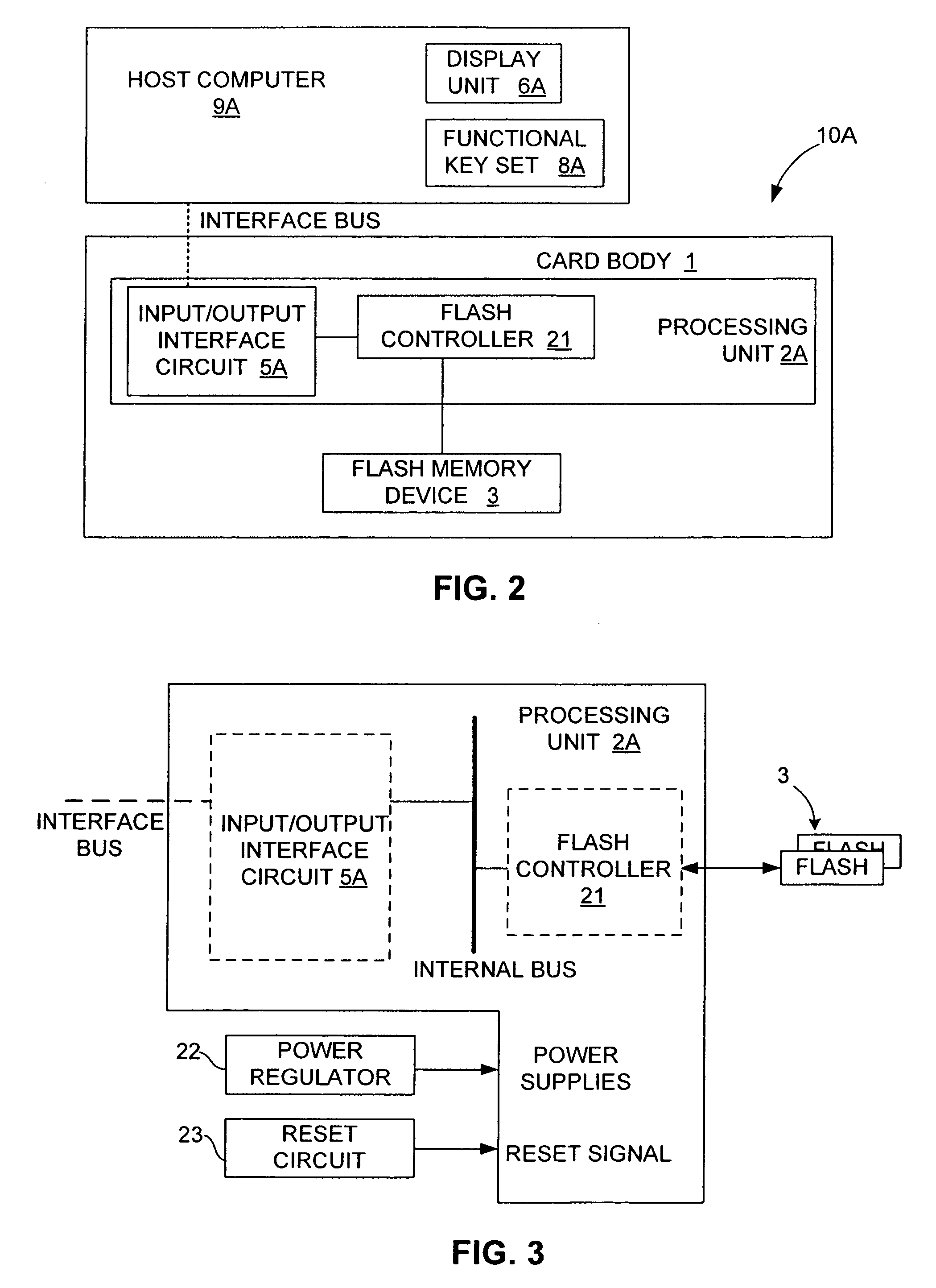

Managing bad blocks in various flash memory cells for electronic data flash card

InactiveUS20080082736A1Small sizeLow costMemory architecture accessing/allocationMemory systemsComputer accessFlash memory controller

An electronic data flash card accessible by a host computer, includes a flash memory controller connected to a flash memory device, and an input-output interface circuit activated to establish a communication with the host. In an embodiment, the flash card uses a USB interface circuit for communication with the host. A flash memory controller includes an arbitrator for mapping logical addresses with physical block addresses, and for performing block management operations including: storing reassigned data to available blocks, relocating valid data in obsolete blocks to said available blocks and reassigning logical block addresses to physical block addresses of said available blocks, finding bad blocks of the flash memory device and replacing with reserve blocks, erasing obsolete blocks for recycling after relocating valid data to available blocks, and erase count wear leveling of blocks, etc. Furthermore, each flash memory device includes an internal buffer for accelerating the block management operations.

Owner:SUPER TALENT ELECTRONICS

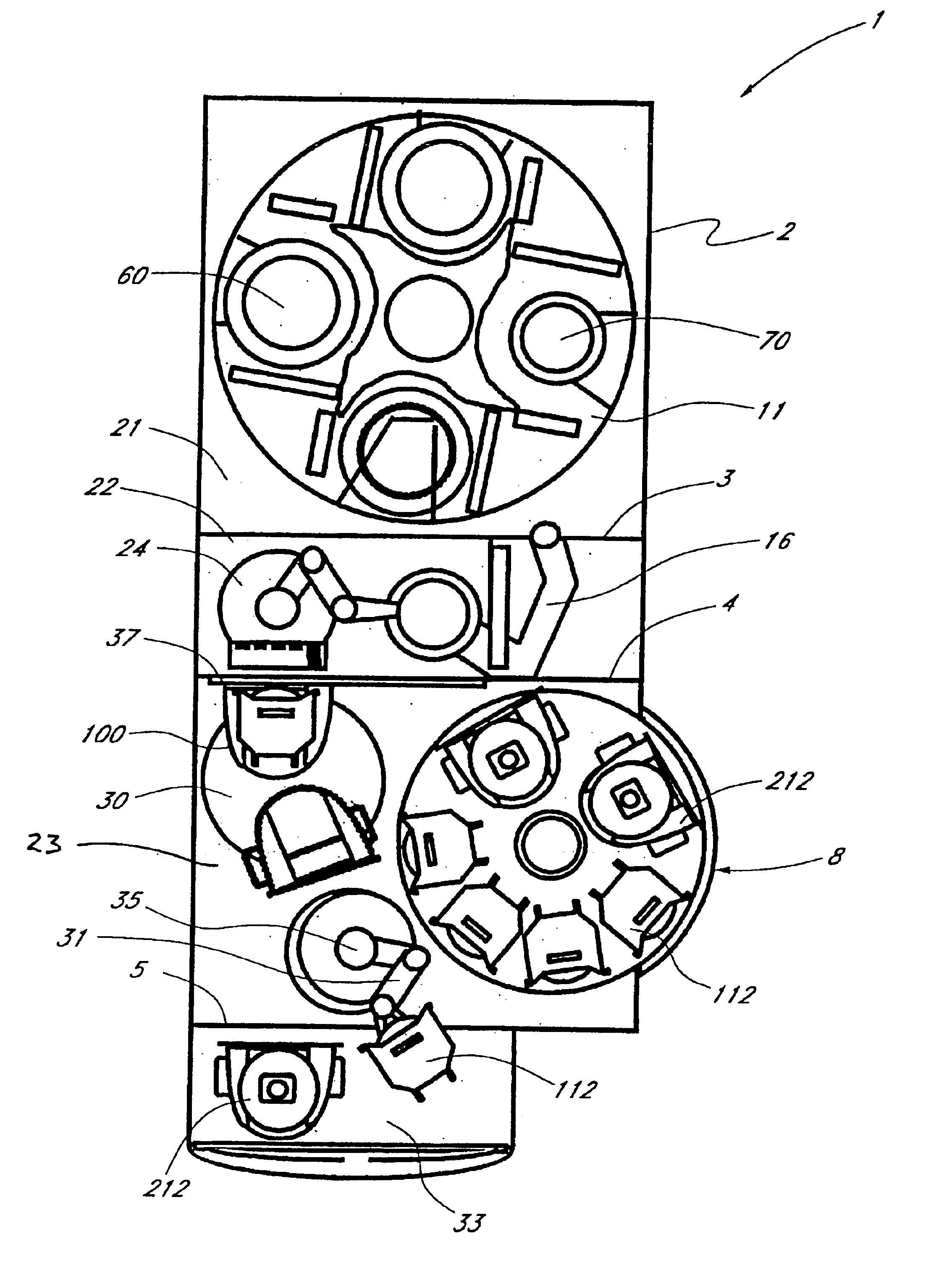

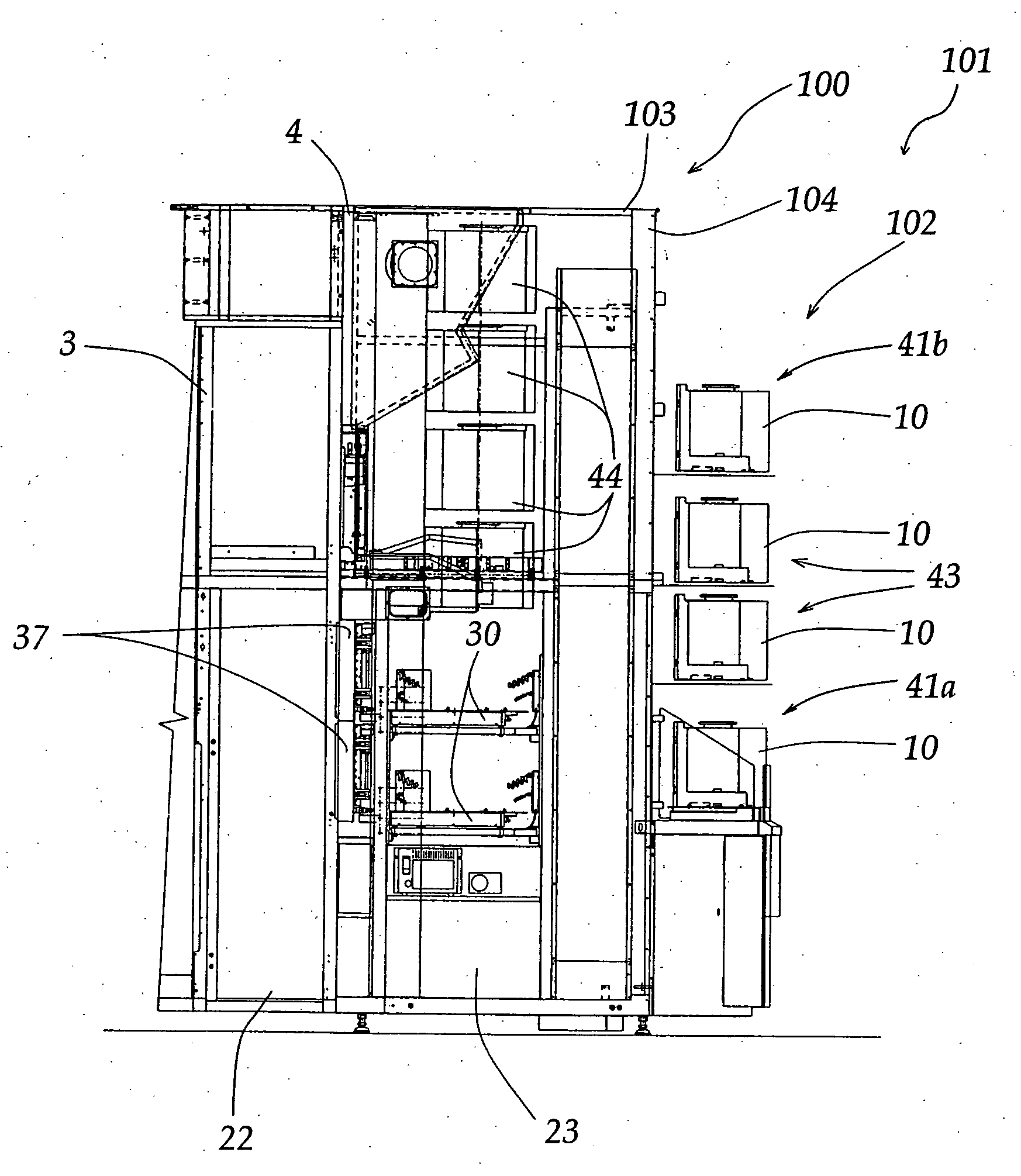

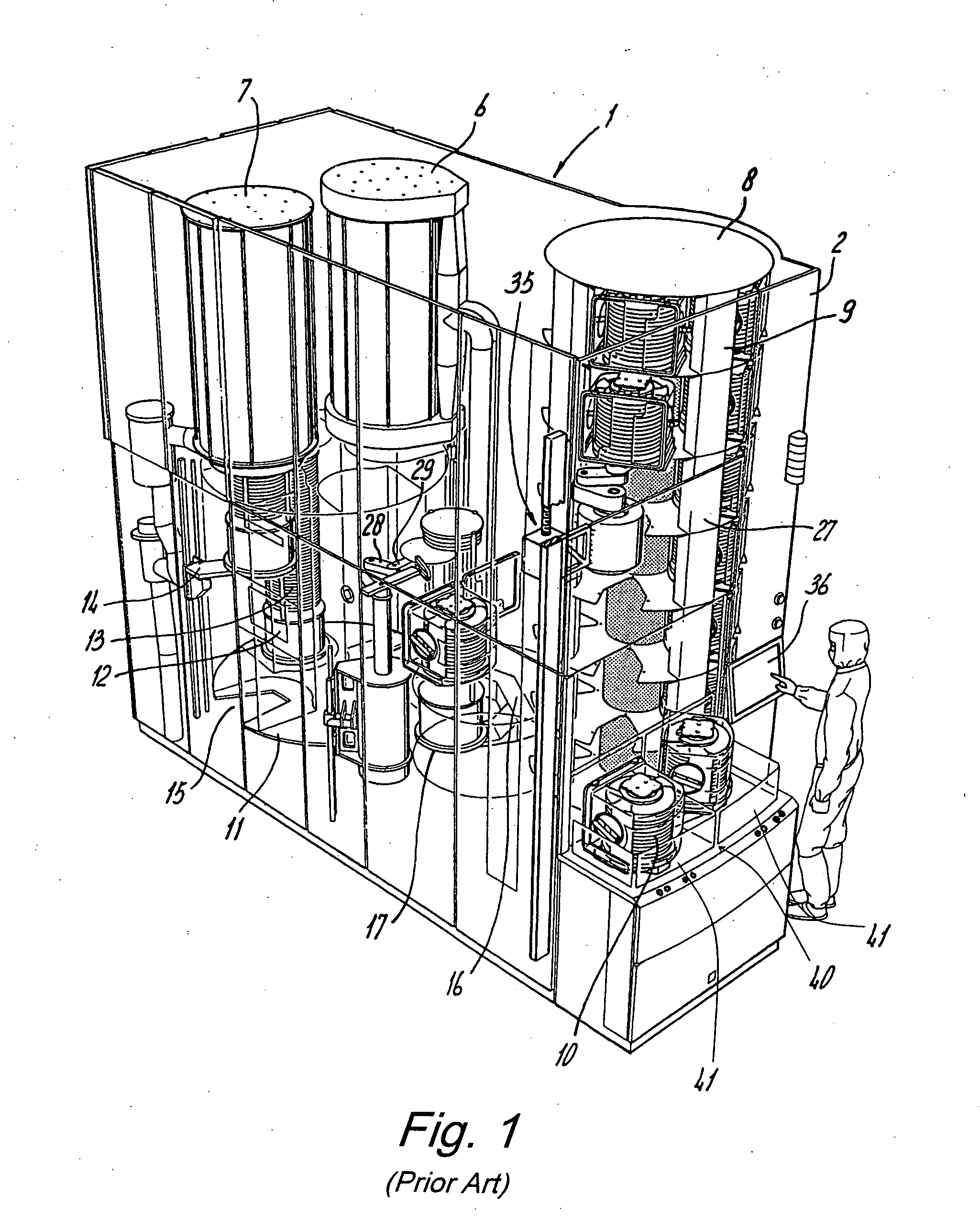

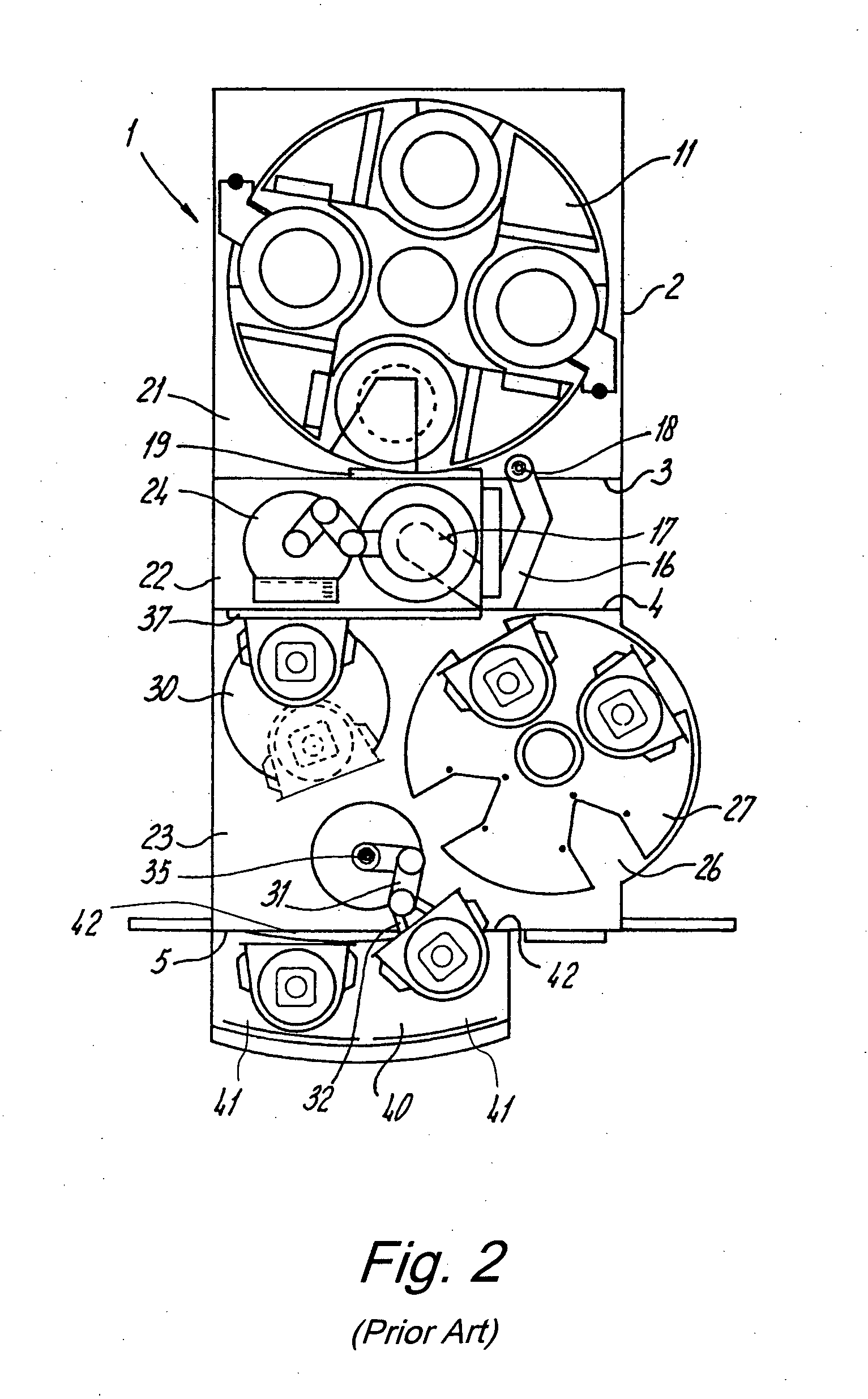

Processing system with increased cassette storage capacity

ActiveUS7740437B2Semiconductor/solid-state device manufacturingCharge manipulationMagnetic tapeEngineering

Owner:ASM IP HLDG BV

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

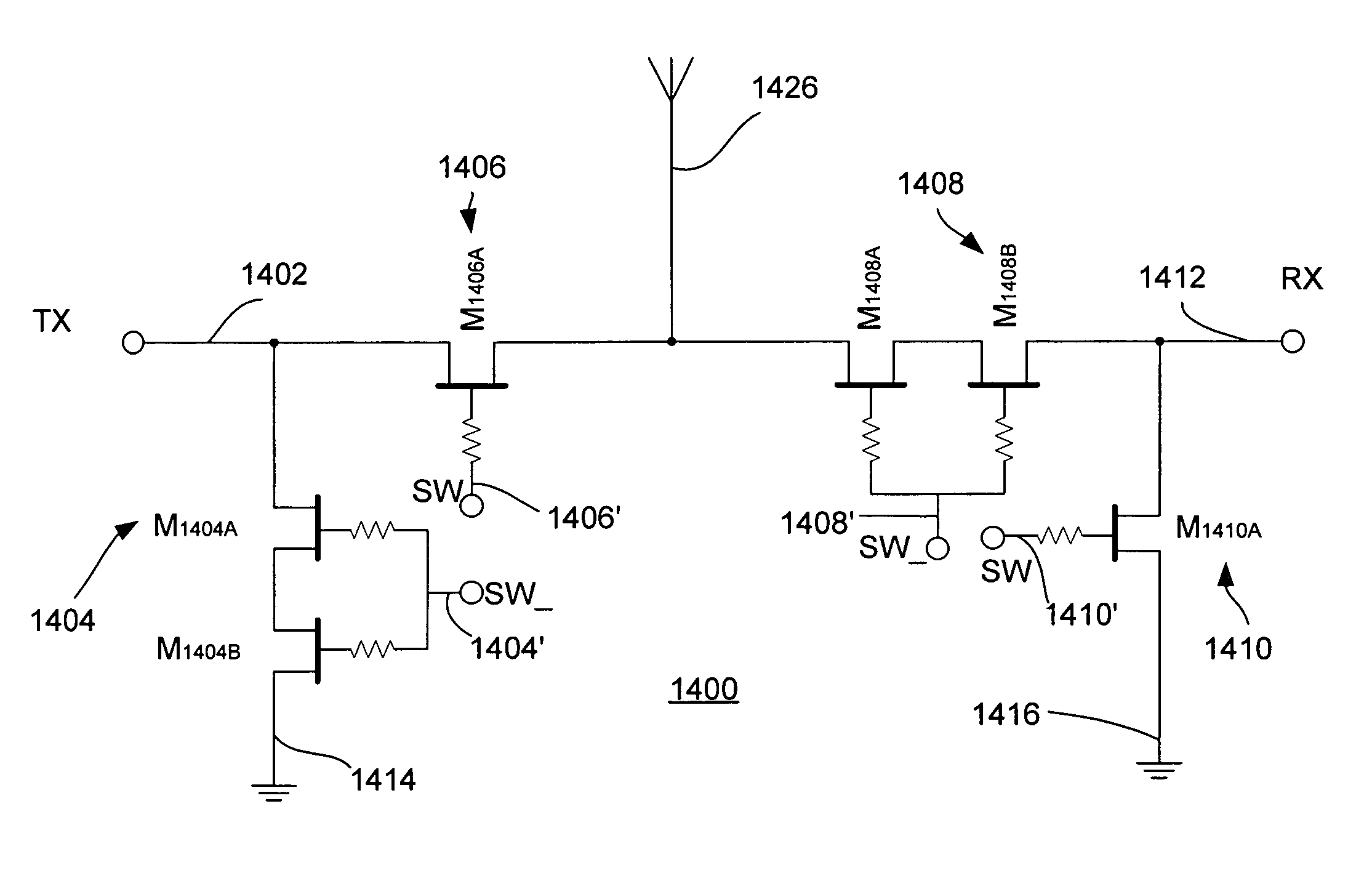

Symmetrically and asymmetrically stacked transistor group RF switch

A silicon-on-insulator (SOI) RF switch adapted for improved power handling capability using a reduced number of transistors is described. In one embodiment, an RF switch includes pairs of switching and shunting stacked transistor groupings to selectively couple RF signals between a plurality of input / output nodes and a common RF node. The switching and shunting stacked transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. In one embodiment, the transistor groupings are “symmetrically” stacked in the RF switch (i.e., the transistor groupings all comprise an identical number of transistors). In another embodiment, the transistor groupings are “asymmetrically” stacked in the RF switch (i.e., at least one transistor grouping comprises a number of transistors that is unequal to the number of transistors comprising at least one other transistor grouping). The stacked configuration of the transistor groupings enable the RF switch to withstand RF signals of varying and increased power levels. The asymmetrically stacked transistor grouping RF switch facilitates area-efficient implementation of the RF switch in an integrated circuit. Maximum input and output signal power levels can be withstood using a reduced number of stacked transistors.

Owner:PSEMI CORP

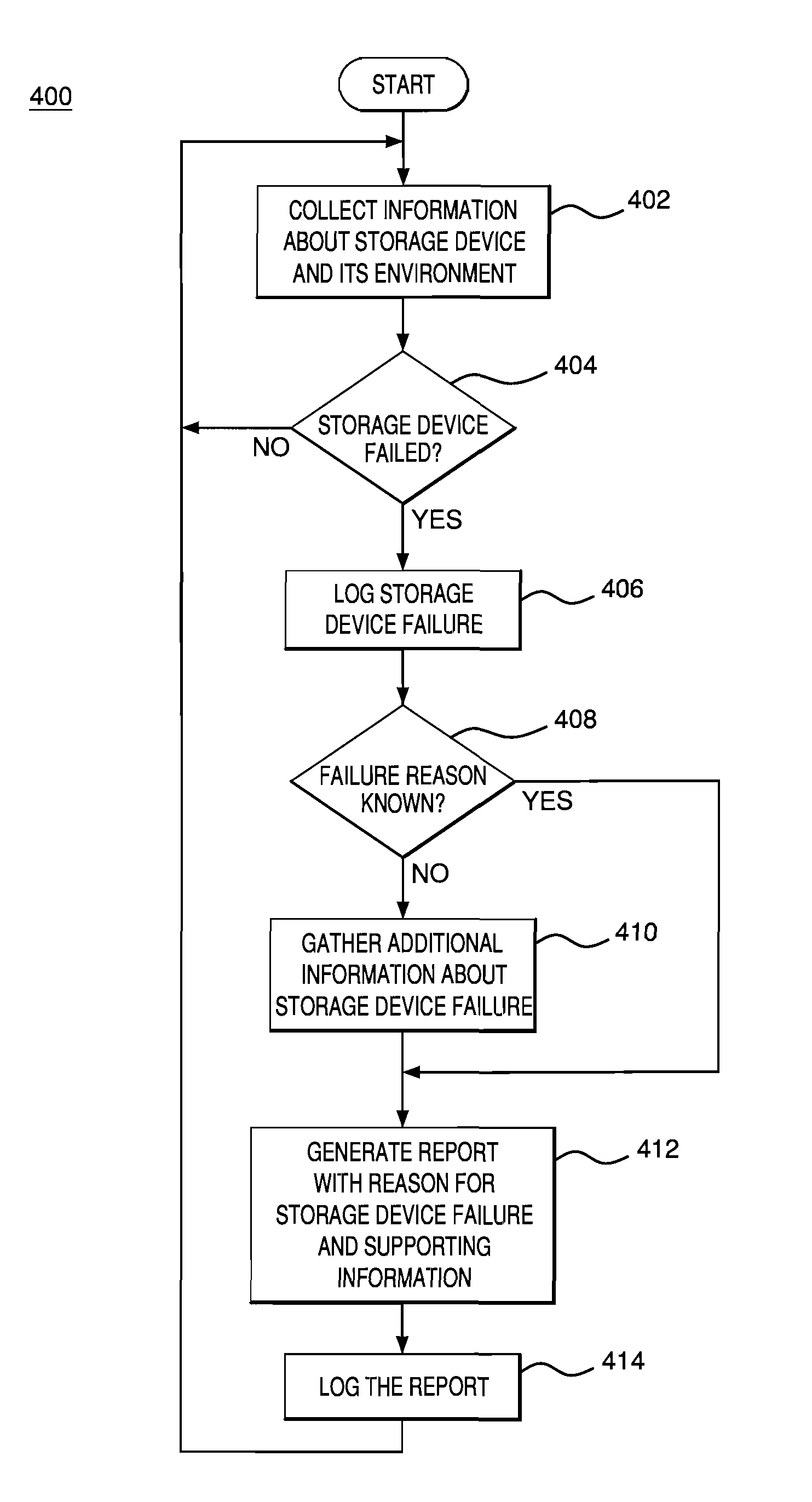

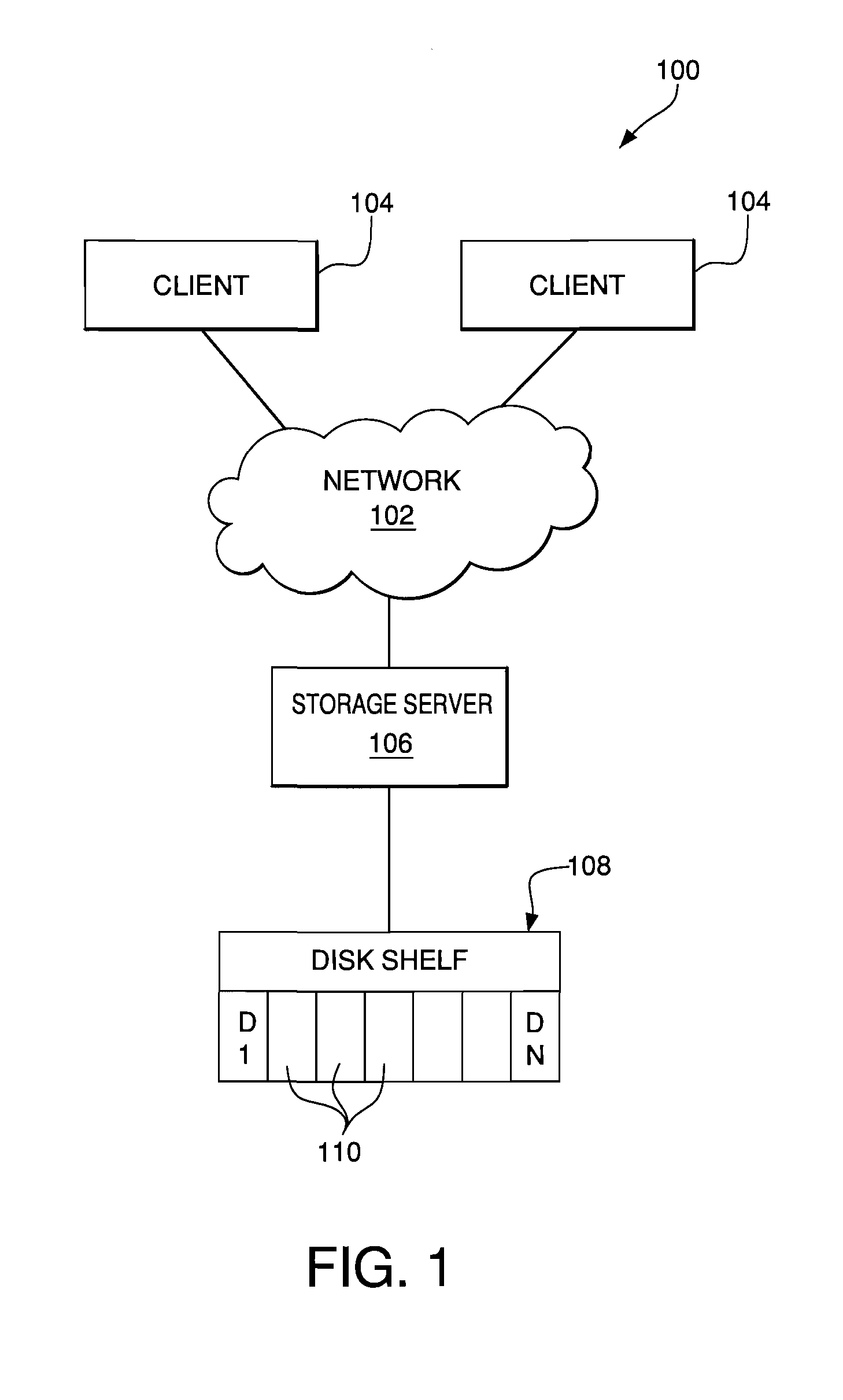

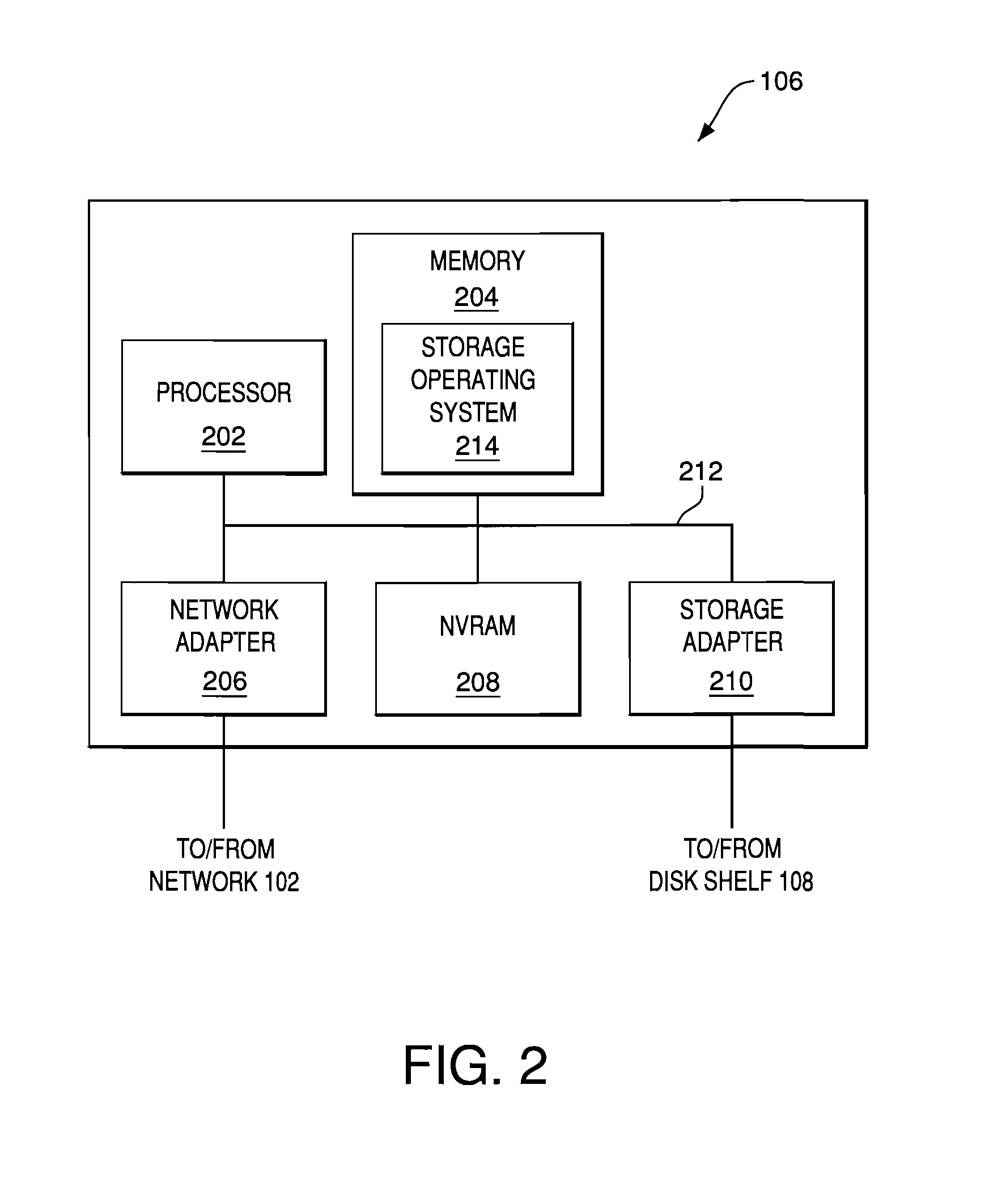

Creating environmental snapshots of storage device failure events

InactiveUS8949863B1Interprogram communicationNon-redundant fault processingRelevant informationDevice failure

A storage device failure in a computer storage system can be analyzed by the storage system by examining relevant information about the storage device and its environment. Information about the storage device is collected in real-time and stored; this is an on-going process such that some information is continuously available. The information can include information relating to the storage device, such as input / output related information, and information relating to a storage shelf where the storage device is located, such as a status of adjacent storage devices on the shelf. All of the relevant information is analyzed to determine a reason for the storage device failure. Optionally, additional information may be collected and analyzed by the storage system to help determine the reason for the storage device failure. The analysis and supporting information can be stored in a log and / or presented to a storage system administrator to view.

Owner:NETWORK APPLIANCE INC

Processing system with increased cassette storage capacity

ActiveUS20080075562A1Semiconductor/solid-state device manufacturingStorage devicesMagnetic tapeEngineering

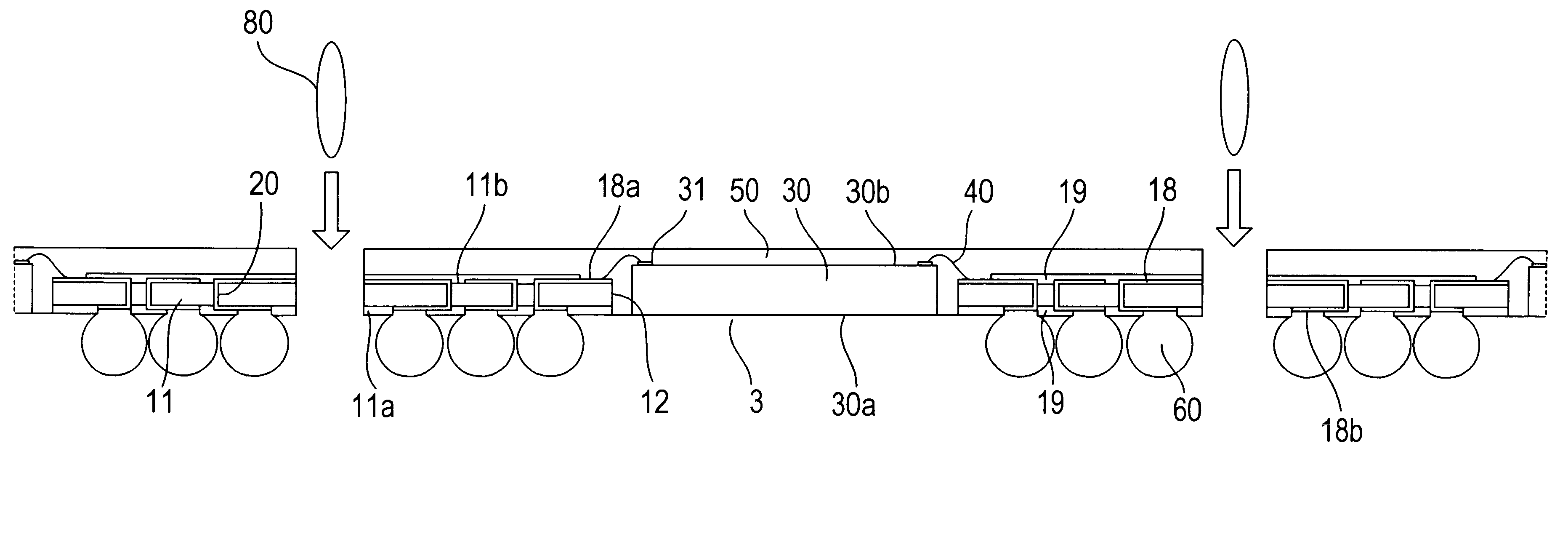

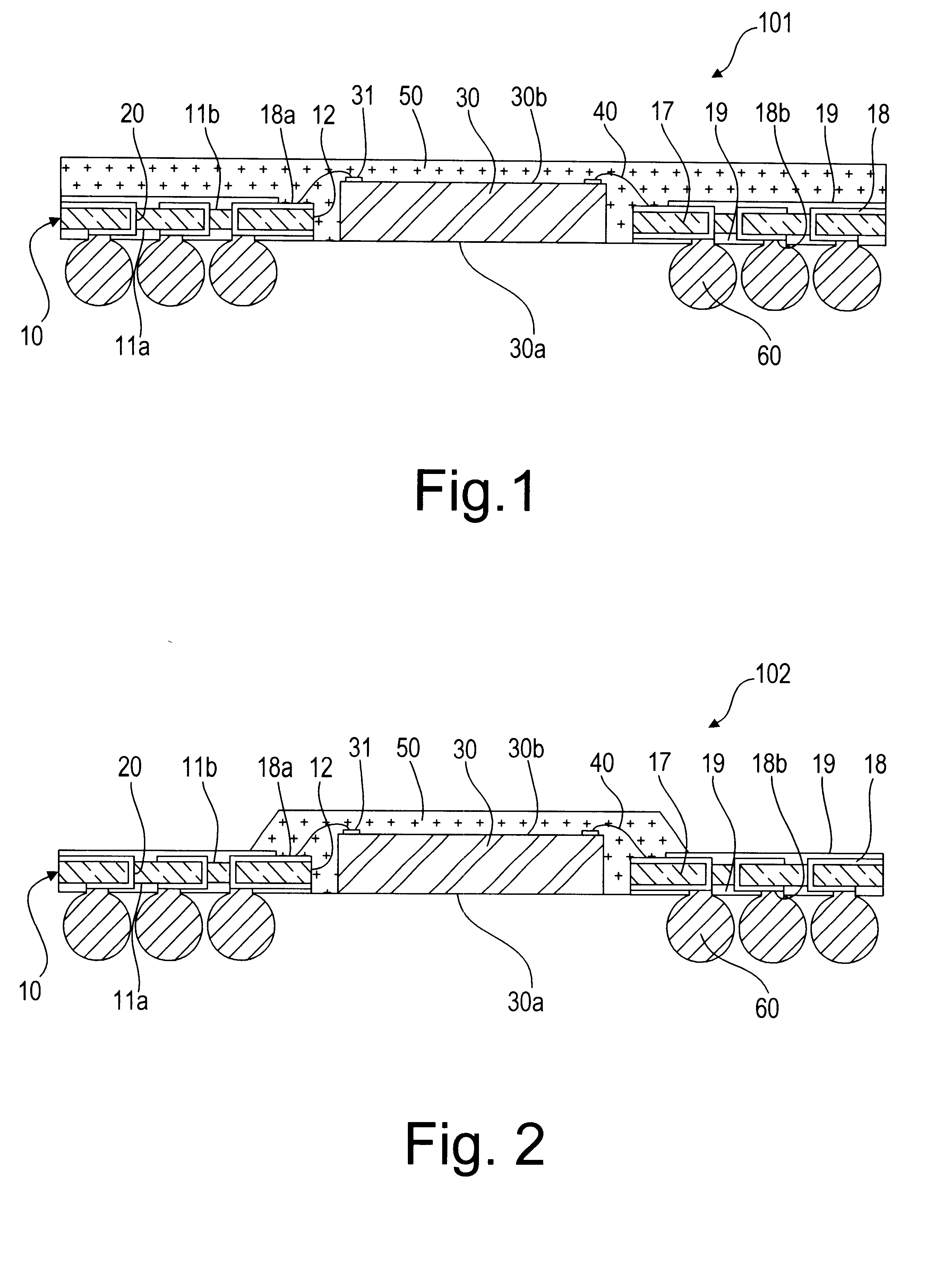

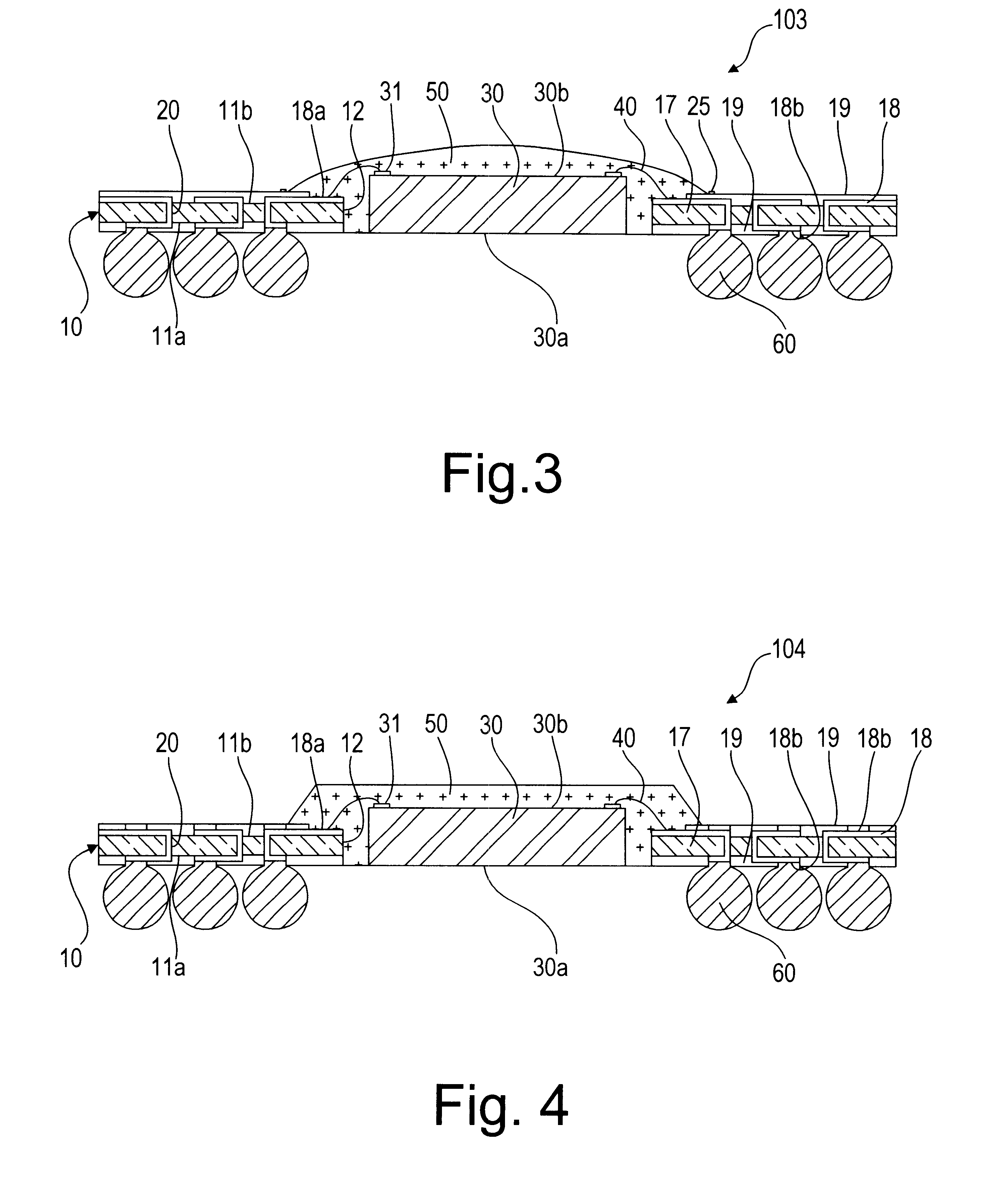

A system for processing semiconductor substrates includes a front-end with at least two vertical levels of input / output ports for transferring substrate cassettes into or out of the housing of the processing system. The front-end also includes at least one level of storage positions, e.g., two levels of storage positions, which can be disposed between the two vertical levels of the input / output ports. The two vertical levels of storage positions can each be provided with two storage positions and each of two levels of input / output ports can be provided with accommodations for two cassettes, allowing for a total of eight cassettes to be accommodated at the front-end of the processing system. Inside the housing of the processing system, interior storage positions can be provided adjacent a wafer handling chamber and spaced apart from a cassette store having rotary platforms for housing cassettes. A single cassette handler can be used to access cassettes at each of the input / output ports and the interior storage positions.

Owner:ASM IP HLDG BV

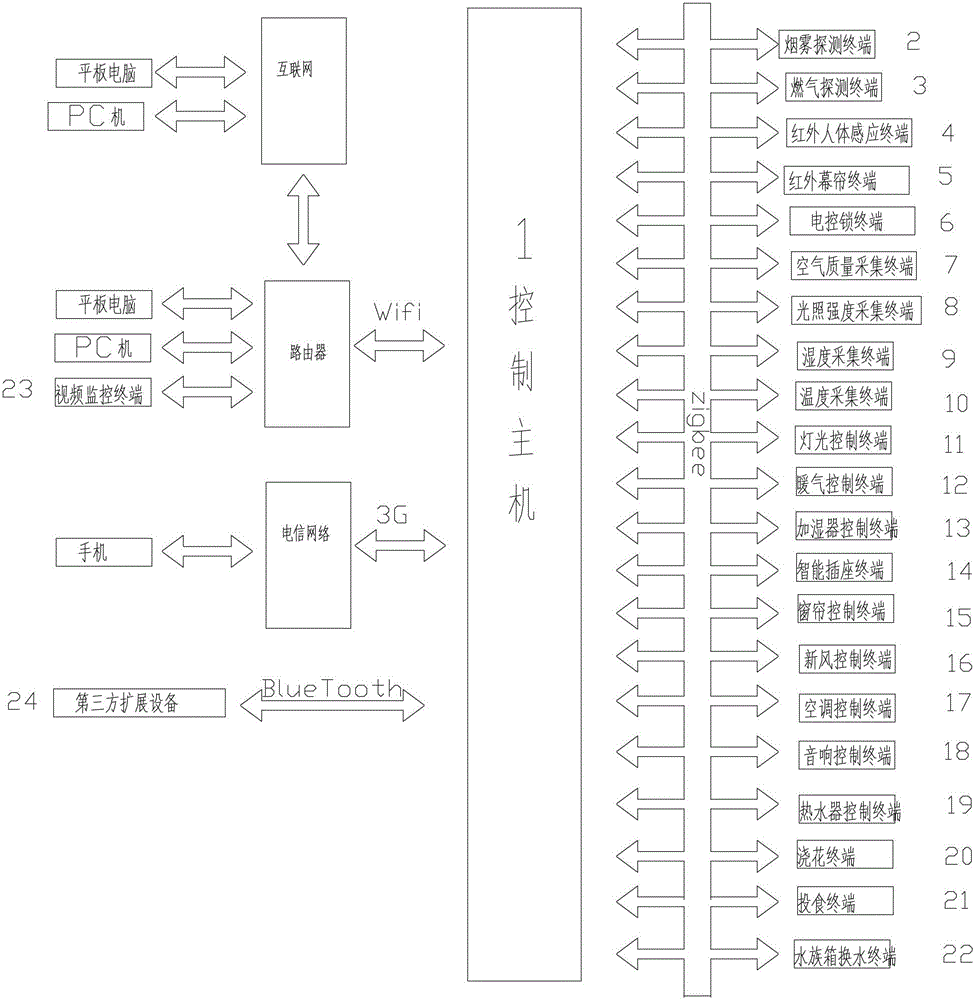

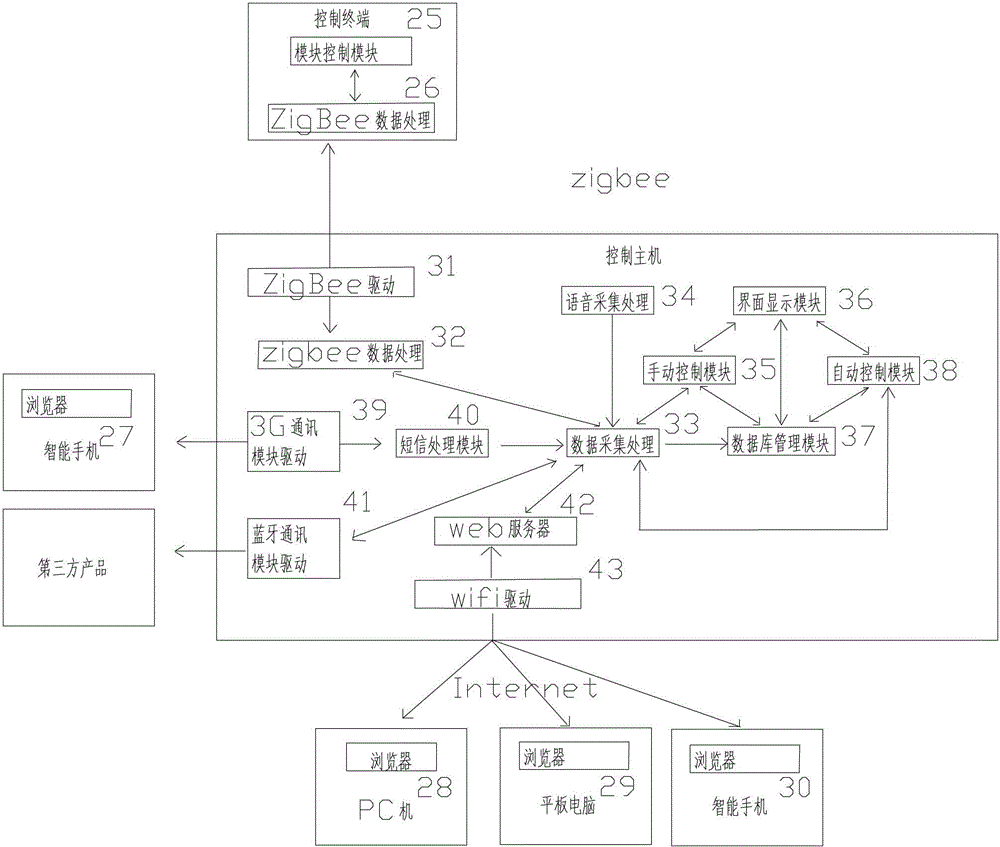

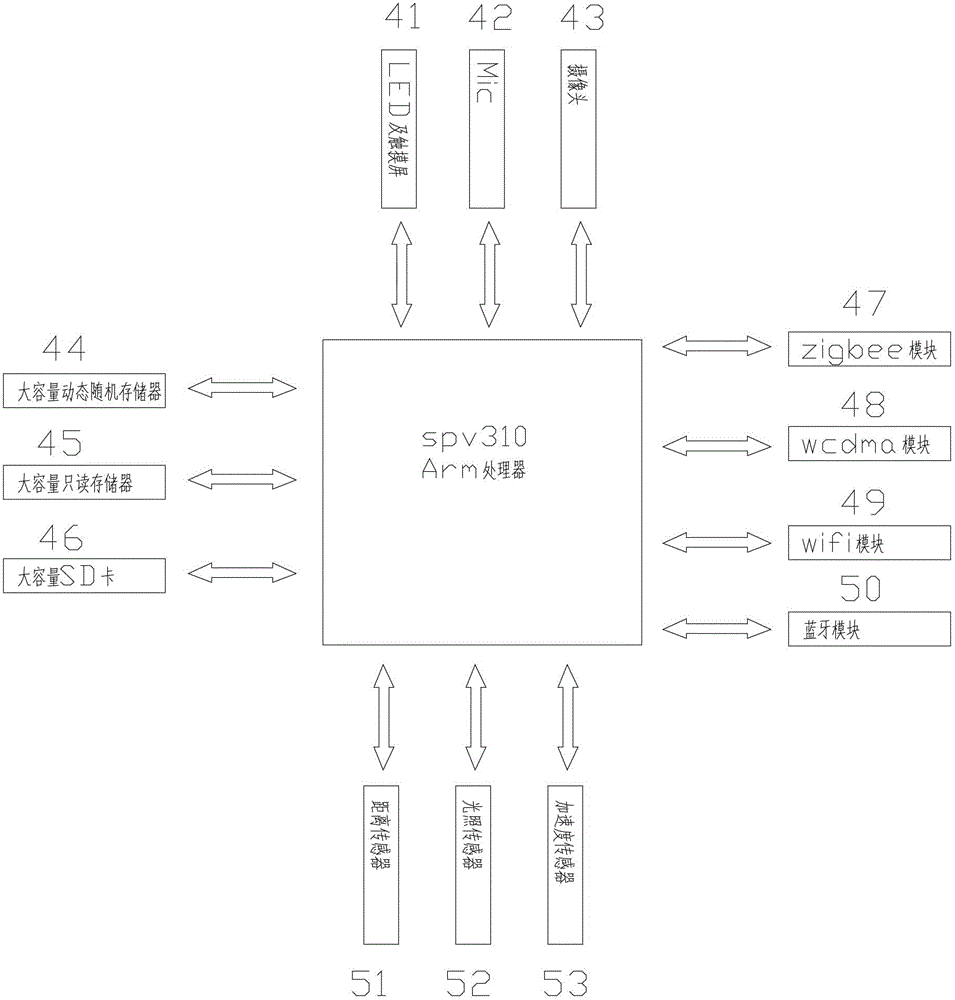

Internet-of-things and android system based intelligent home system and control method

InactiveCN102882752ARealize automatic arming and disarmingReduce complexityData switching by path configurationAutomatic controlWeb service

The invention discloses an internet-of-things and android system based intelligent home system which comprises a control host and a plurality of terminal devices. The control host is provided with a high-performance arm processor, a touch screen and an android operation system, supports zigbee, blueTooth, wifi (wireless fidelity), 3G (the third generation) communication, is provided with a built-in web server and a built-in database, has functions of display, operation, control data storage, server, energy management, and particularly has functions of automatic control, hand-operated control, voice control and remote control. The terminal devices include a sensor terminal, a security terminal and a control terminal, are provided with independent processors and network addresses, have functions of data acquisition, data transmission, instruction receiving, transmitting and processing and IO (input / output) control, and support one or multiple wireless communication manners of zigbee, blueTooth, wifi and 3G.

Owner:TIANJIN GUANGHONG TECH