Patents

Literature

2567 results about "Memory bank" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A memory bank is a logical unit of storage in electronics, which is hardware-dependent. In a computer, the memory bank may be determined by the memory controller along with physical organization of the hardware memory slots. In a typical synchronous dynamic random-access memory (SDRAM) or double data rate synchronous dynamic random-access memory (DDR SDRAM), a bank consists of multiple rows and columns of storage units, and is usually spread out across several chips. In a single read or write operation, only one bank is accessed, therefore the number of bits in a column or a row, per bank and per chip, equals the memory bus width in bits (single channel). The size of a bank is further determined by the number of bits in a column and a row, per chip, multiplied by the number of chips in a bank.

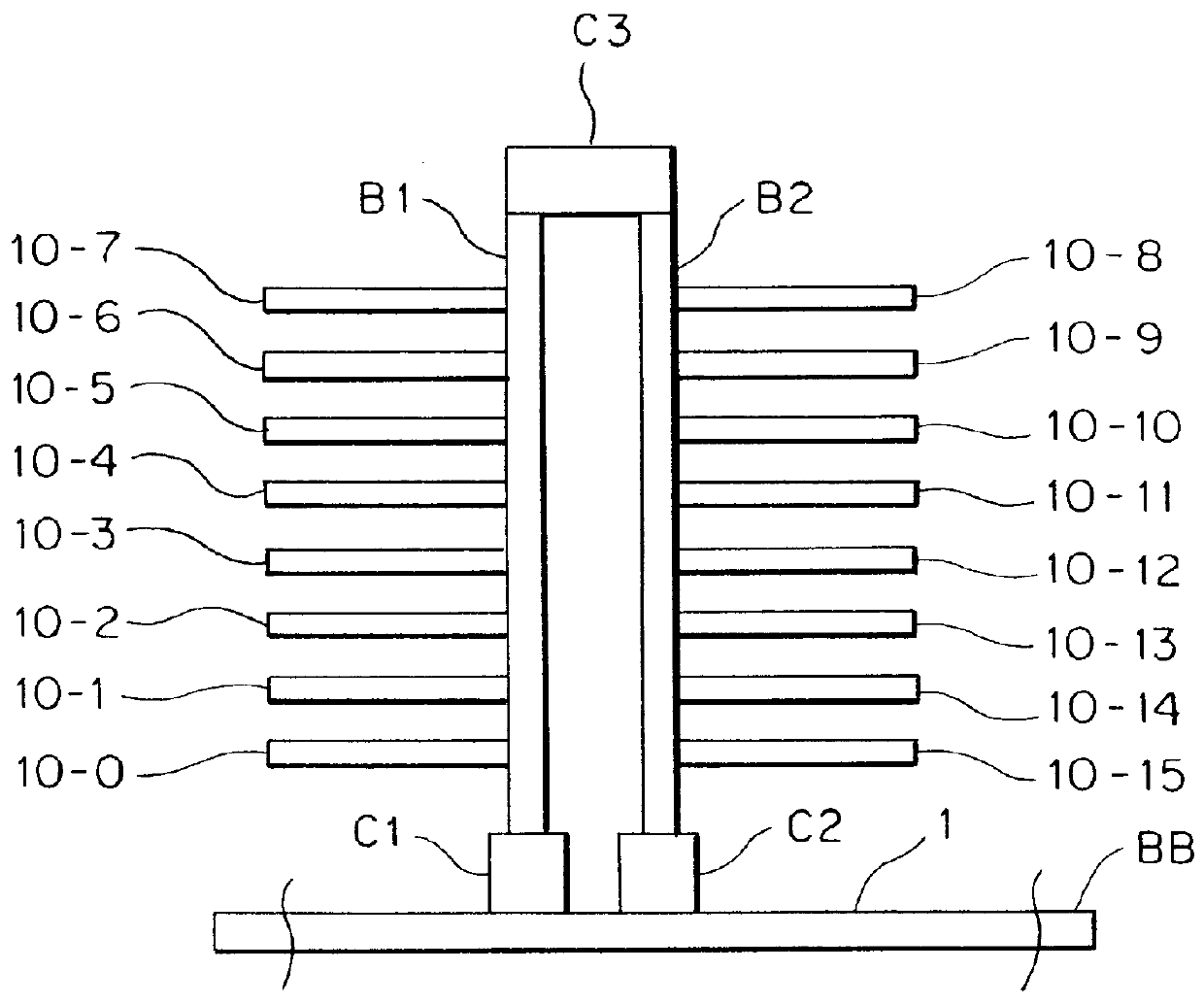

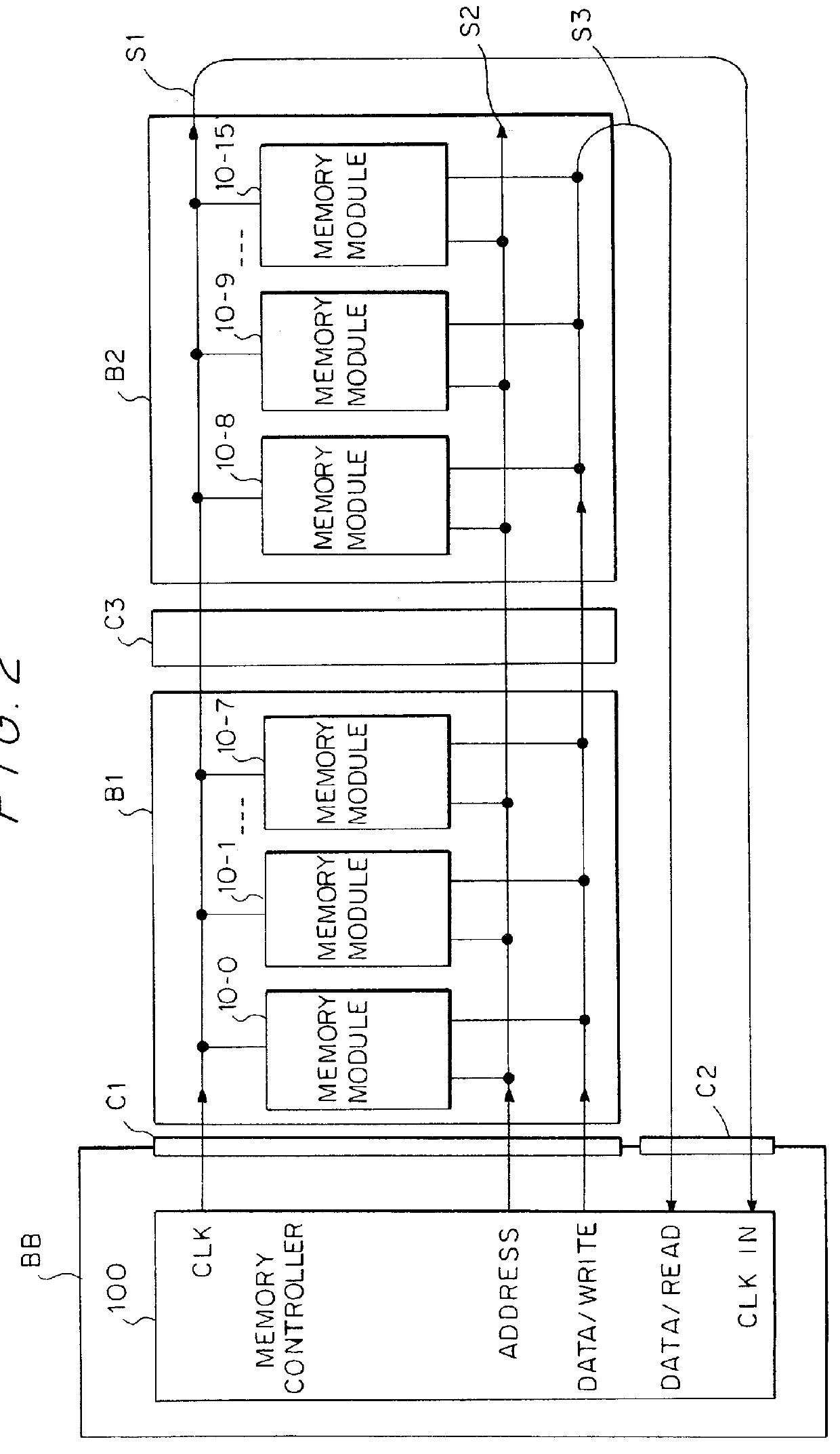

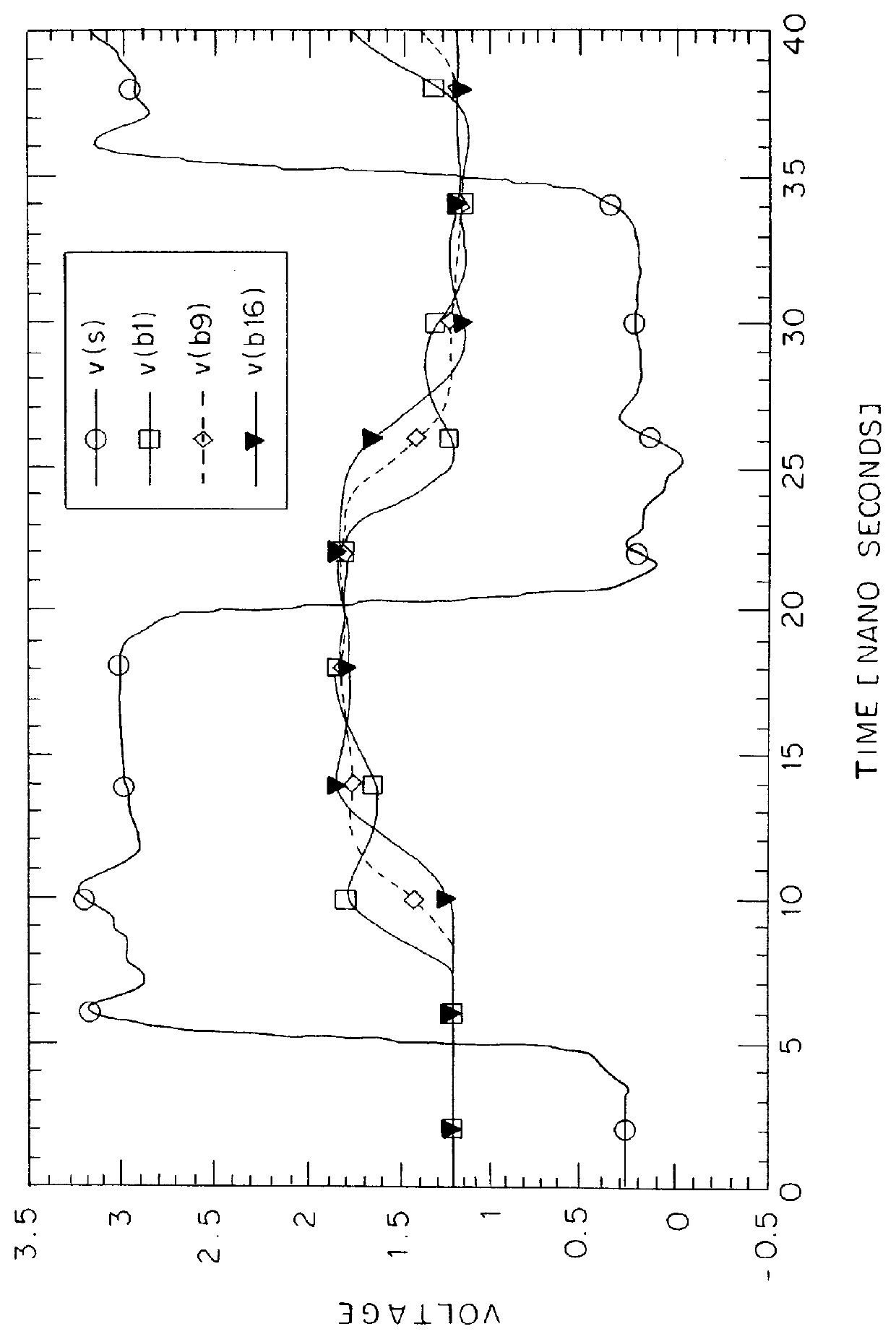

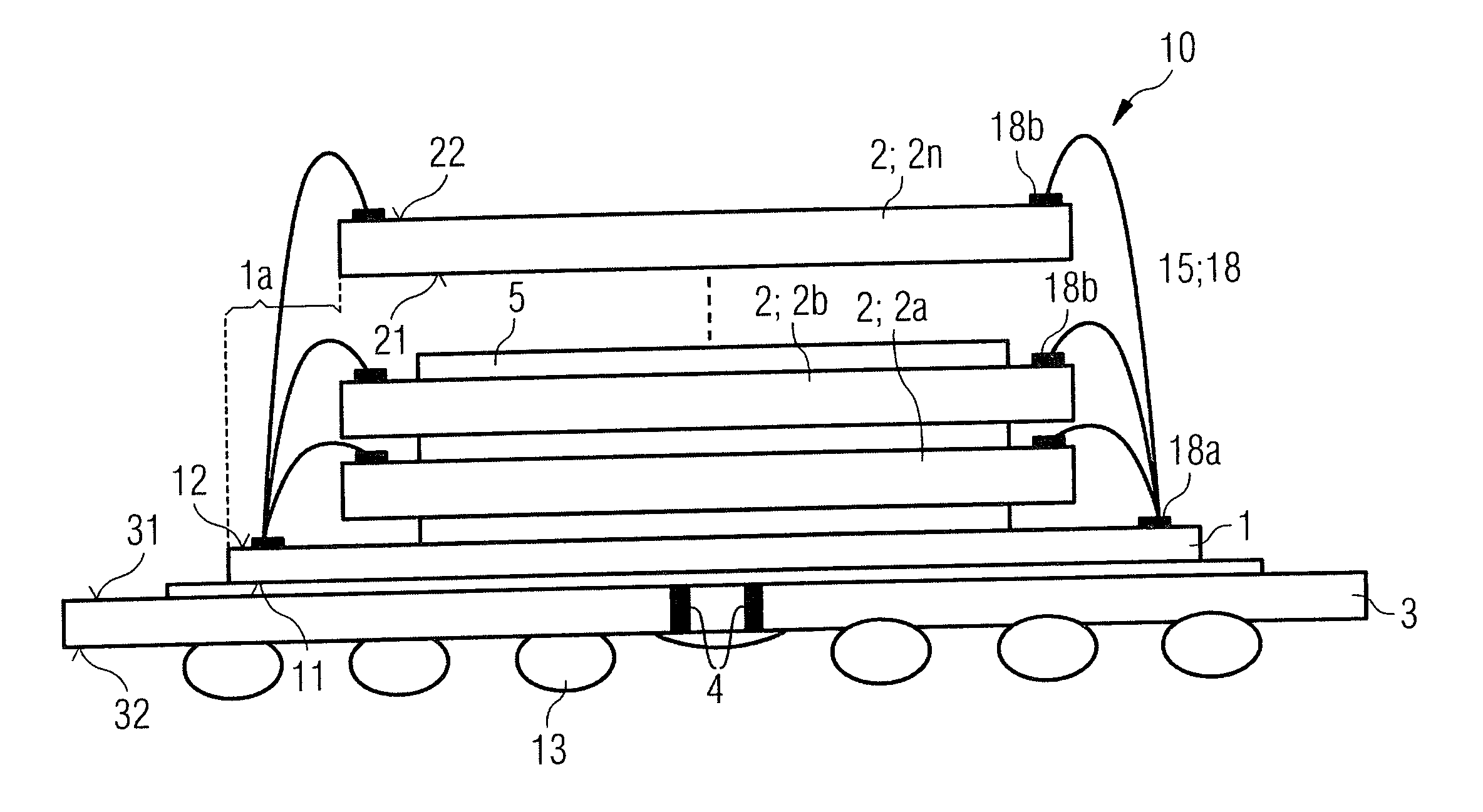

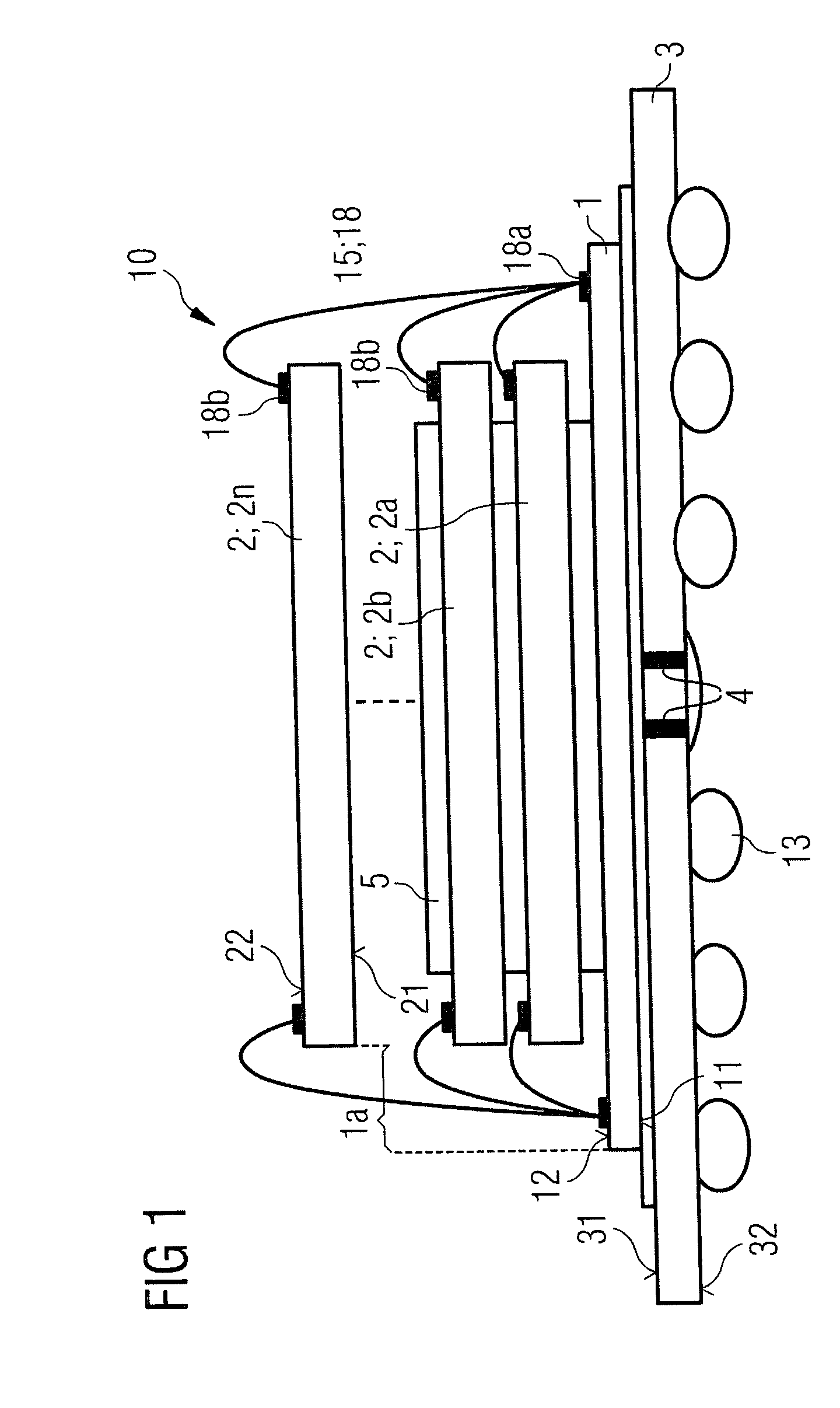

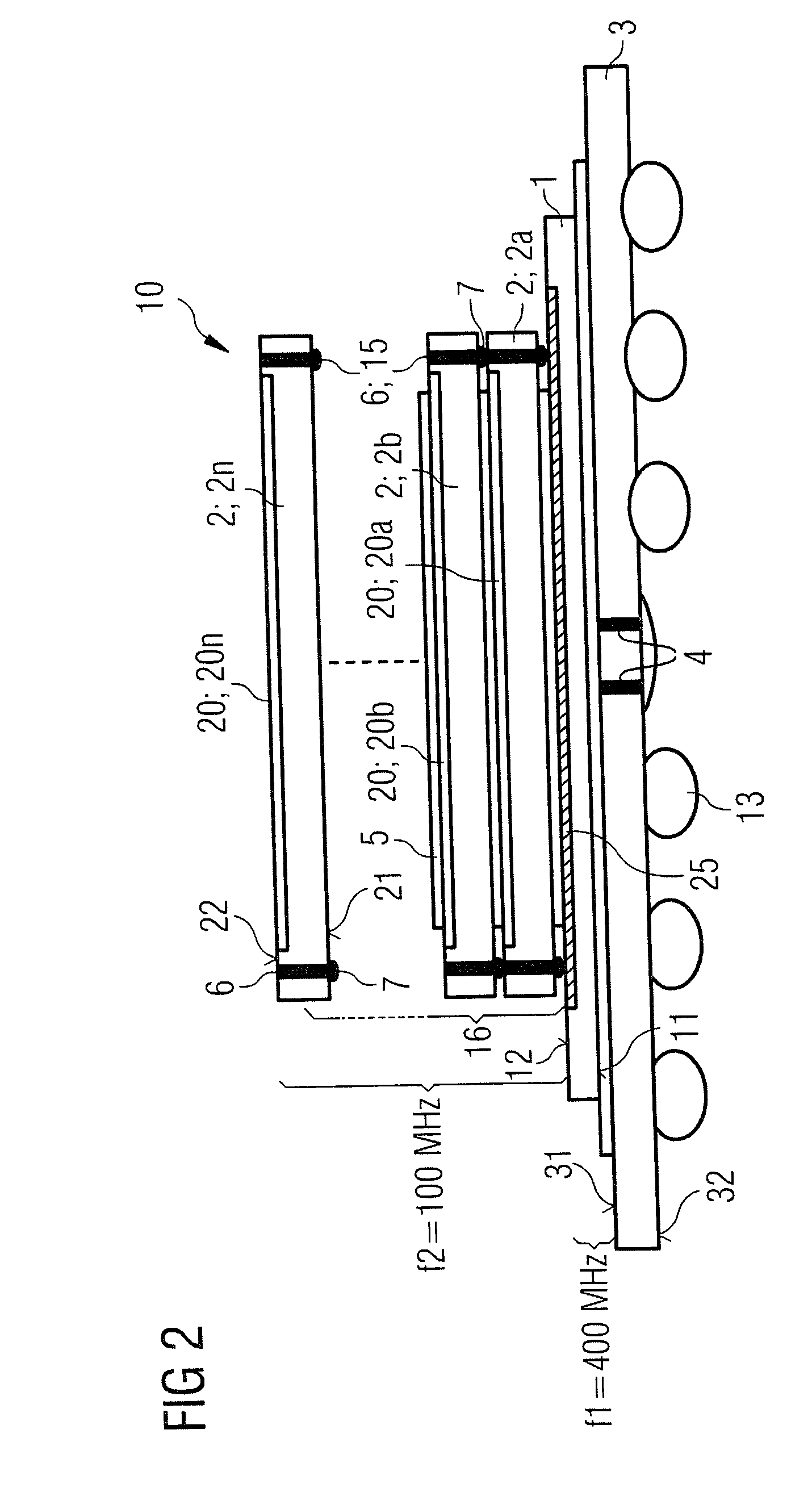

Source-clock-synchronized memory system and memory unit

InactiveUS6034878ALarge data storage capacity per memoryImprove installation densityMemory adressing/allocation/relocationDigital storageMemory bankComputer module

A source-clock-synchronized memory system having a large data storage capacity per memory bank and a high mounting density. The invention includes a memory unit having a first memory riser board B1 mounted on a base board through a first connector C1 and a second memory riser board B2 mounted on the base board BB through a second connector C2. The first memory riser board has a plurality of first memory modules mounted on the front surface thereof and the second memory riser board has a plurality of second memory modules mounted on the front surface thereof. The first and second memory riser boards are arranged in such a way that the back surface of the first memory riser board faces the back surface of the second memory riser board. The invention further includes a board linking connector for connecting signal lines on the first memory riser board to corresponding signal lines on the second memory riser board.

Owner:DELTA KOGYO CO LTD +1

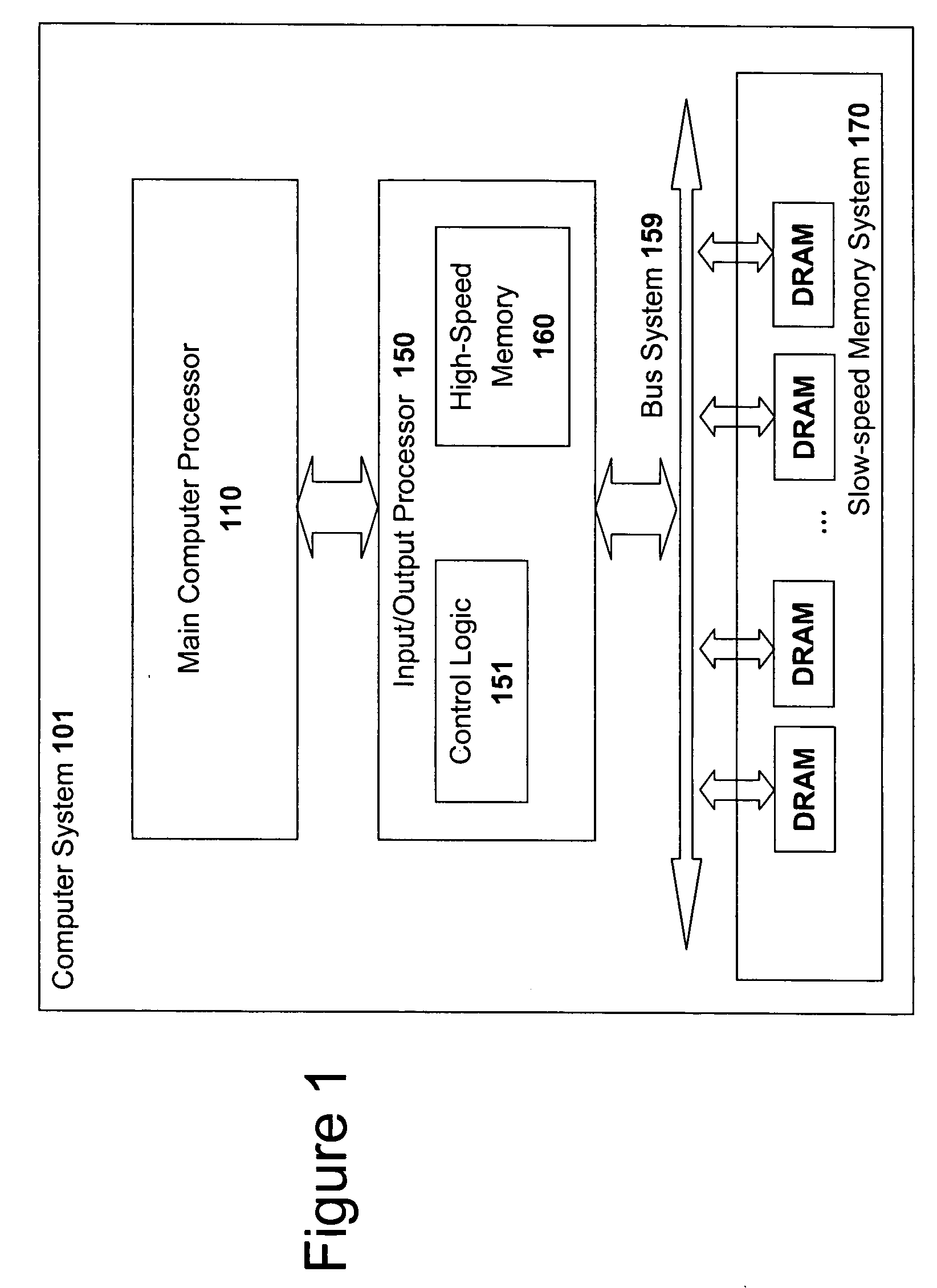

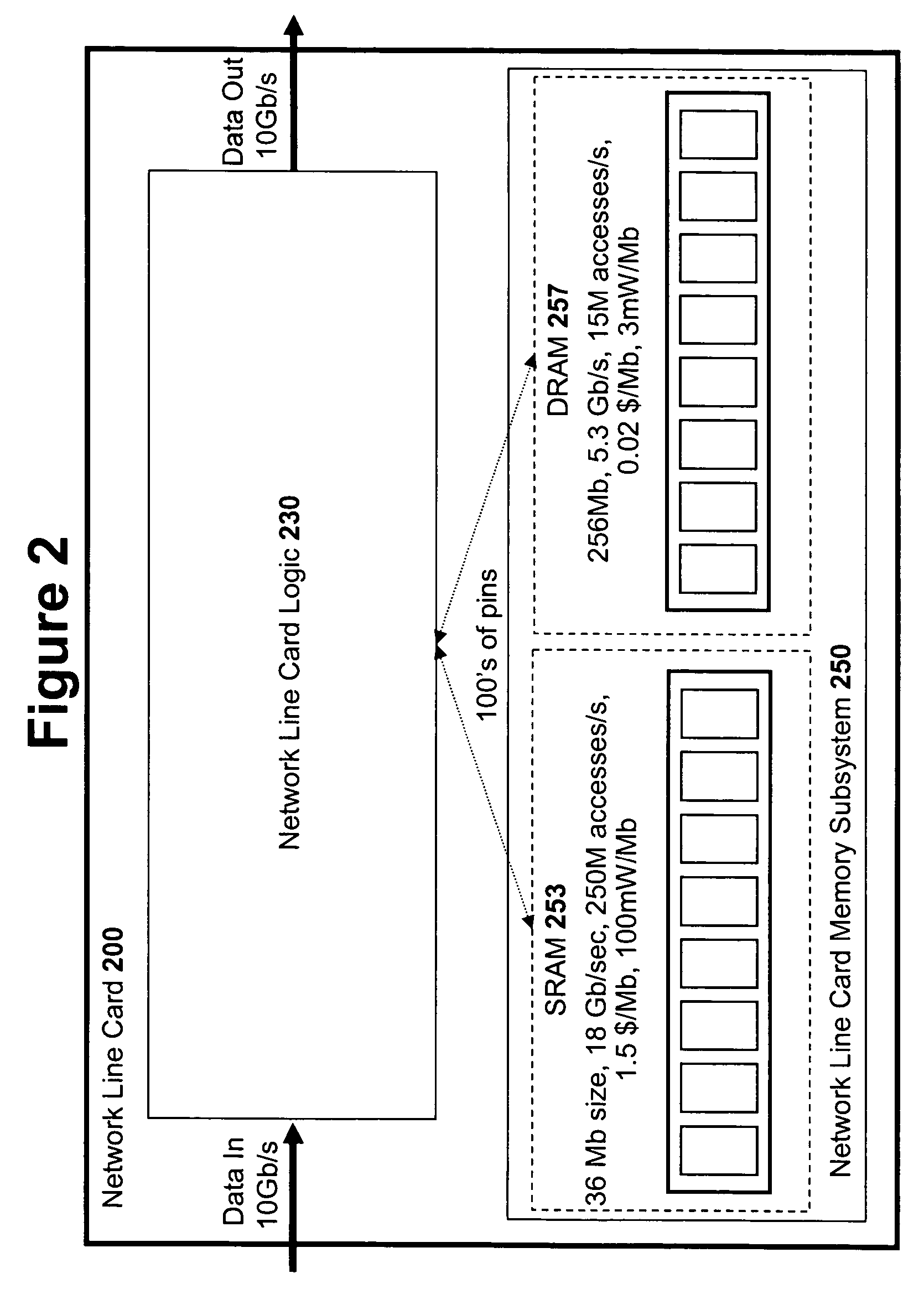

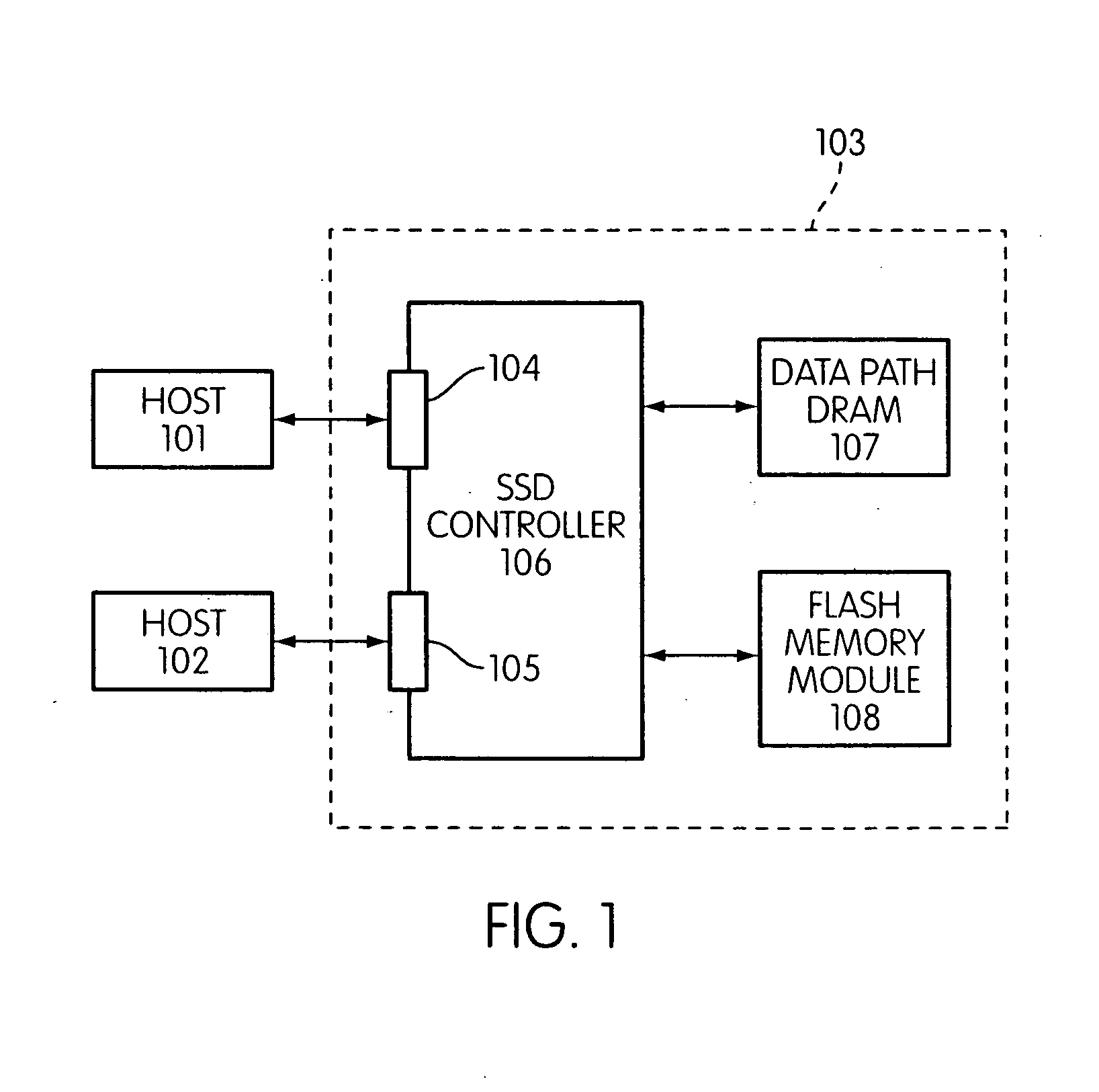

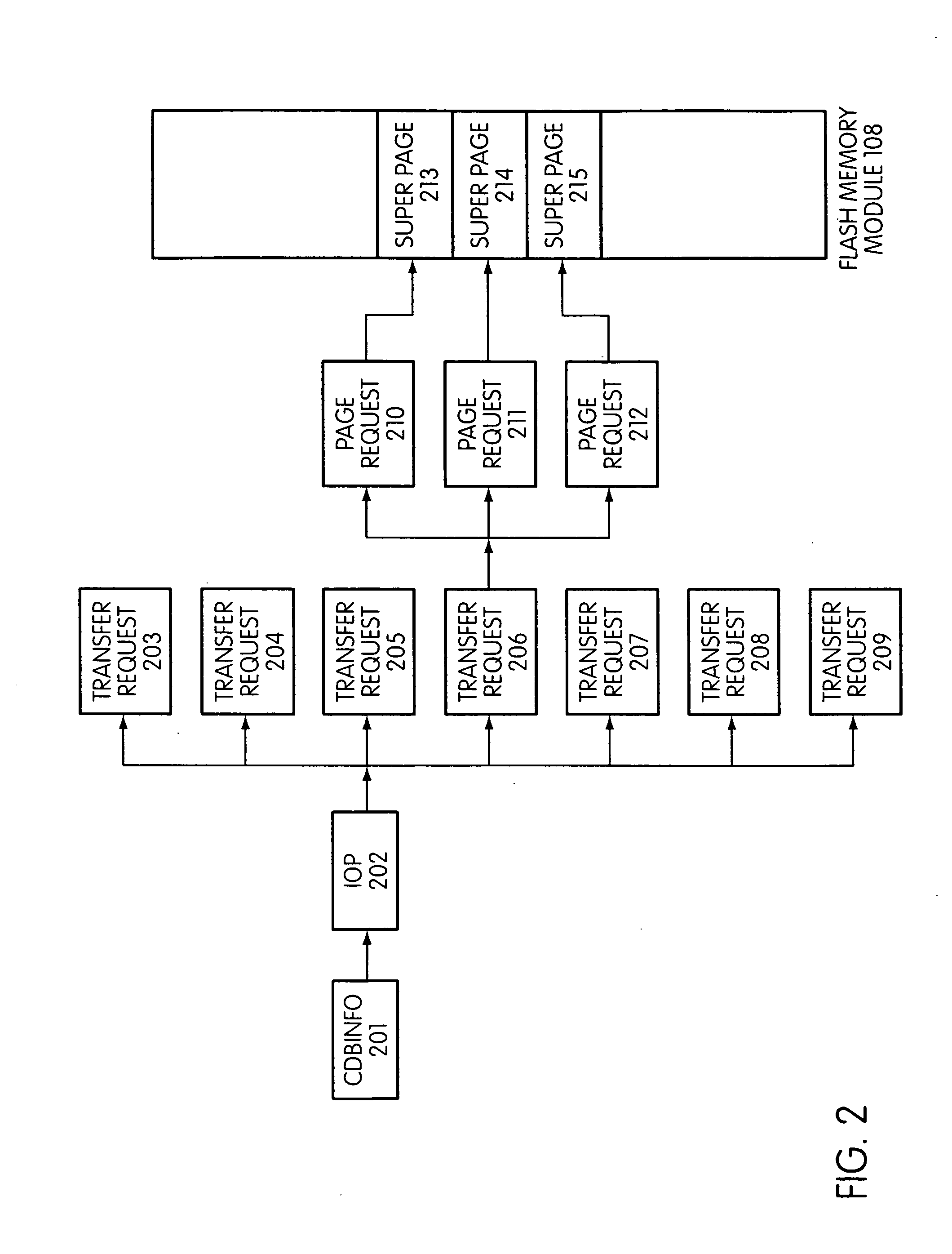

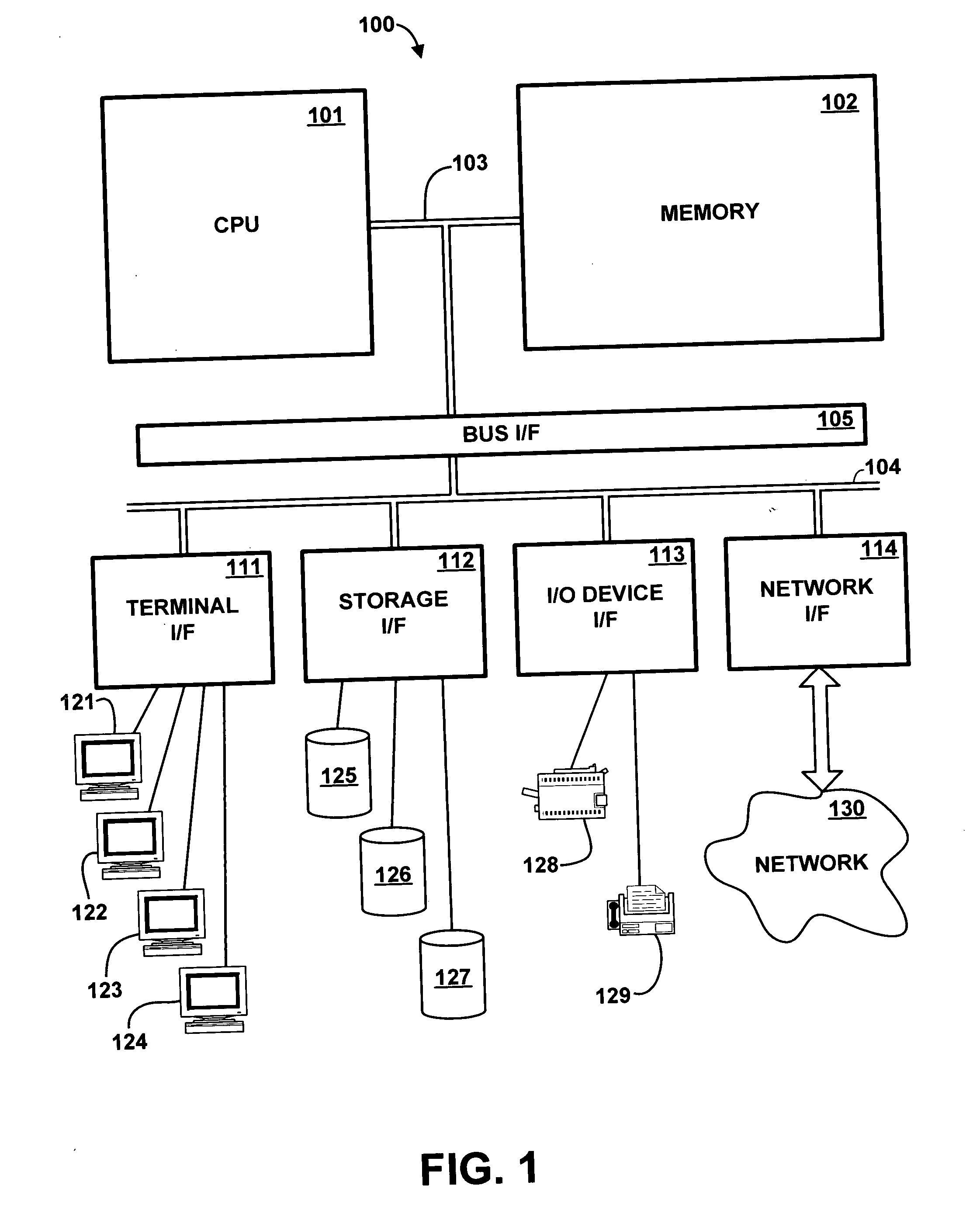

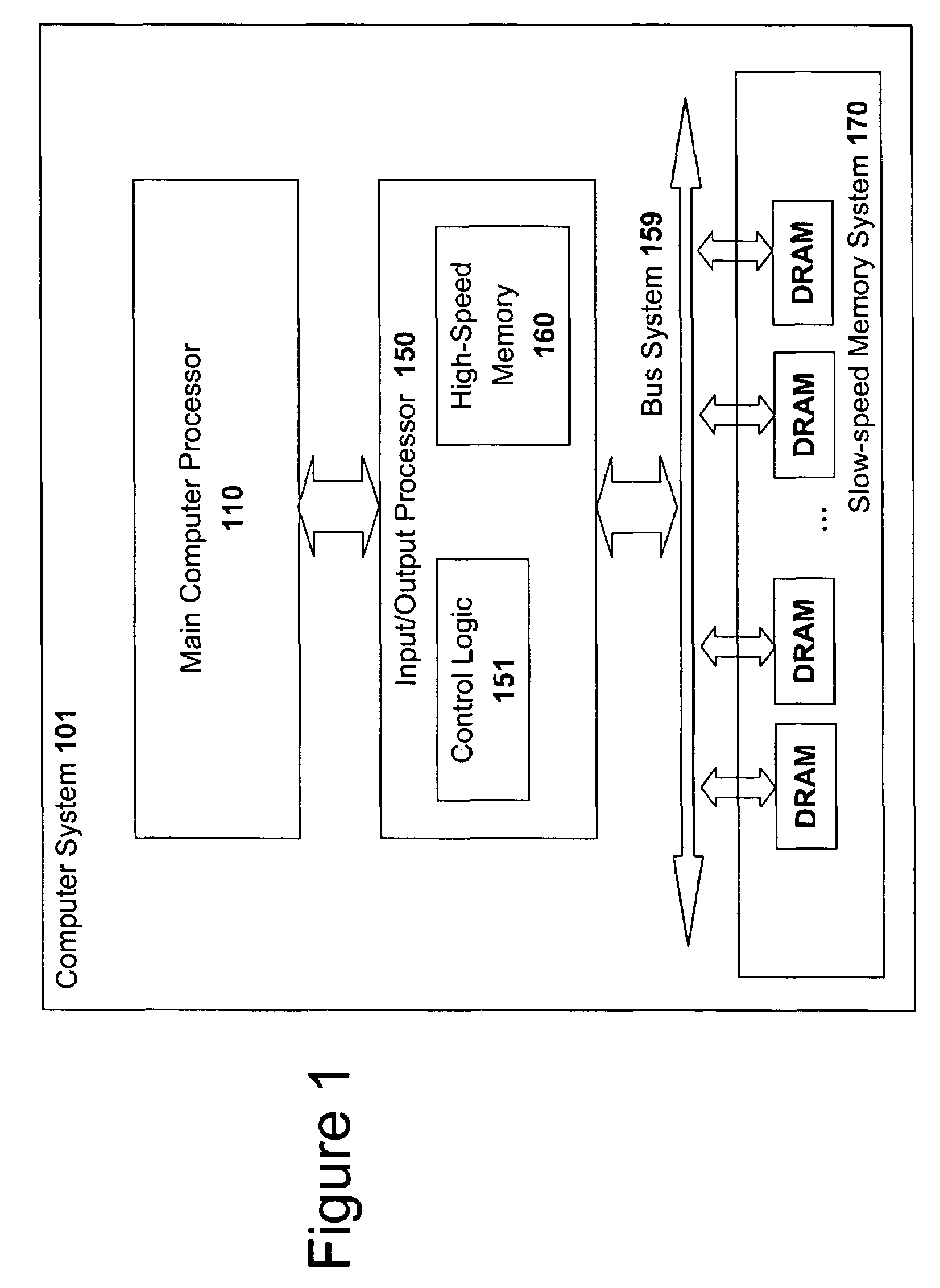

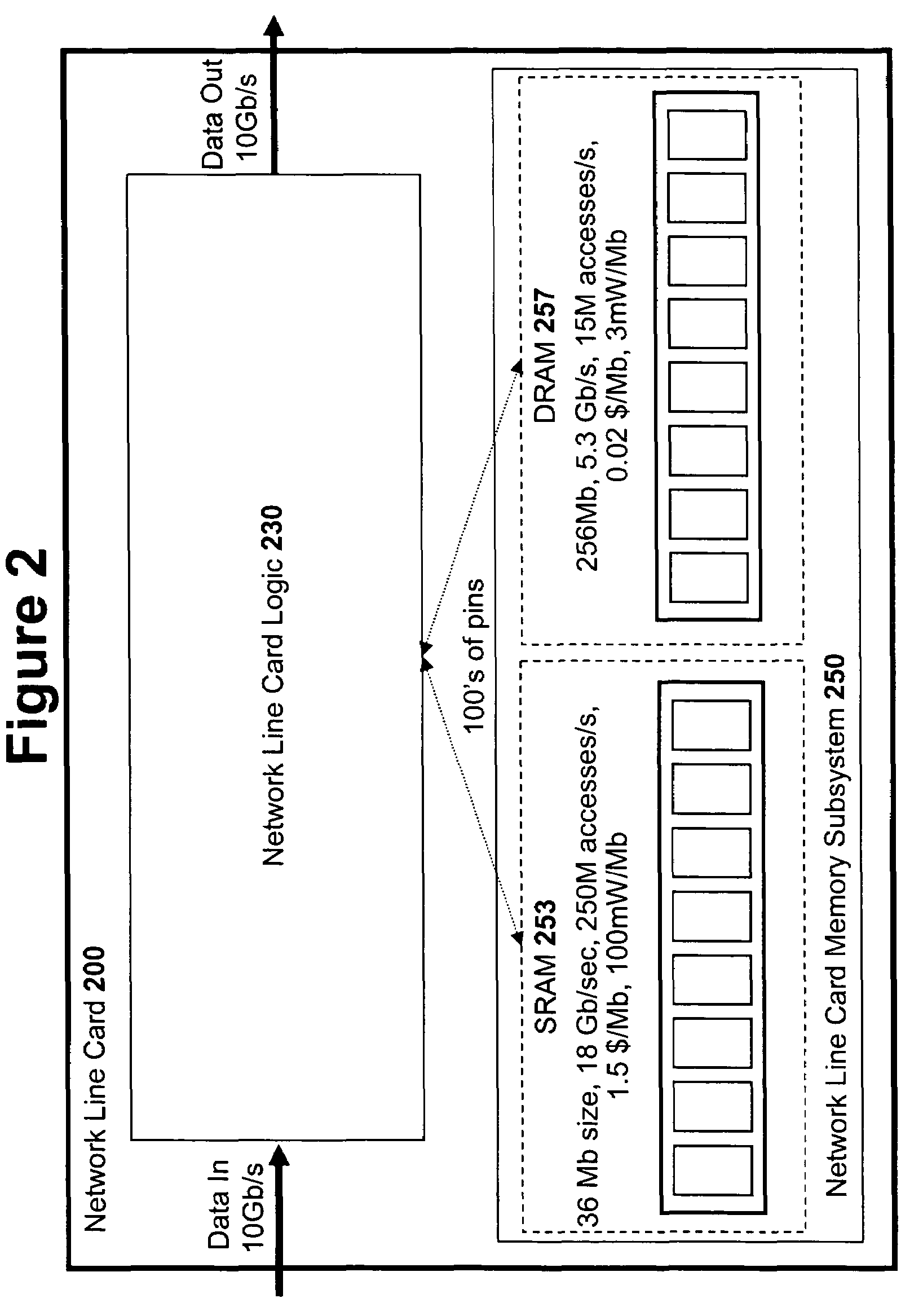

High speed memory control and I/O processor system

ActiveUS20050240745A1Easy to handleSimplify memory access taskMemory architecture accessing/allocationMemory adressing/allocation/relocationHigh speed memoryTailored approach

An input / output processor for speeding the input / output and memory access operations for a processor is presented. The key idea of an input / output processor is to functionally divide input / output and memory access operations tasks into a compute intensive part that is handled by the processor and an I / O or memory intensive part that is then handled by the input / output processor. An input / output processor is designed by analyzing common input / output and memory access patterns and implementing methods tailored to efficiently handle those commonly occurring patterns. One technique that an input / output processor may use is to divide memory tasks into high frequency or high-availability components and low frequency or low-availability components. After dividing a memory task in such a manner, the input / output processor then uses high-speed memory (such as SRAM) to store the high frequency and high-availability components and a slower-speed memory (such as commodity DRAM) to store the low frequency and low-availability components. Another technique used by the input / output processor is to allocate memory in such a manner that all memory bank conflicts are eliminated. By eliminating any possible memory bank conflicts, the maximum random access performance of DRAM memory technology can be achieved.

Owner:CISCO TECH INC

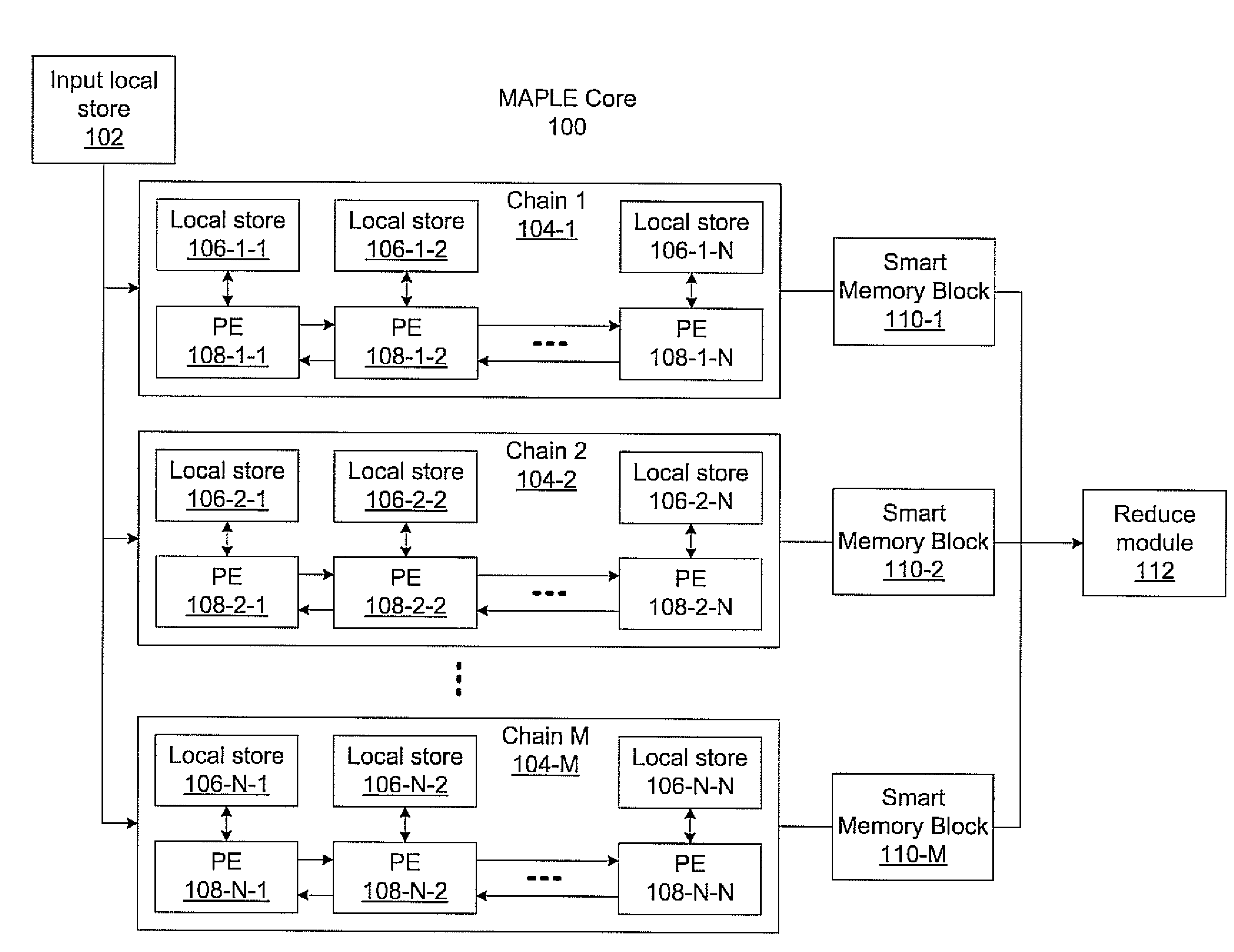

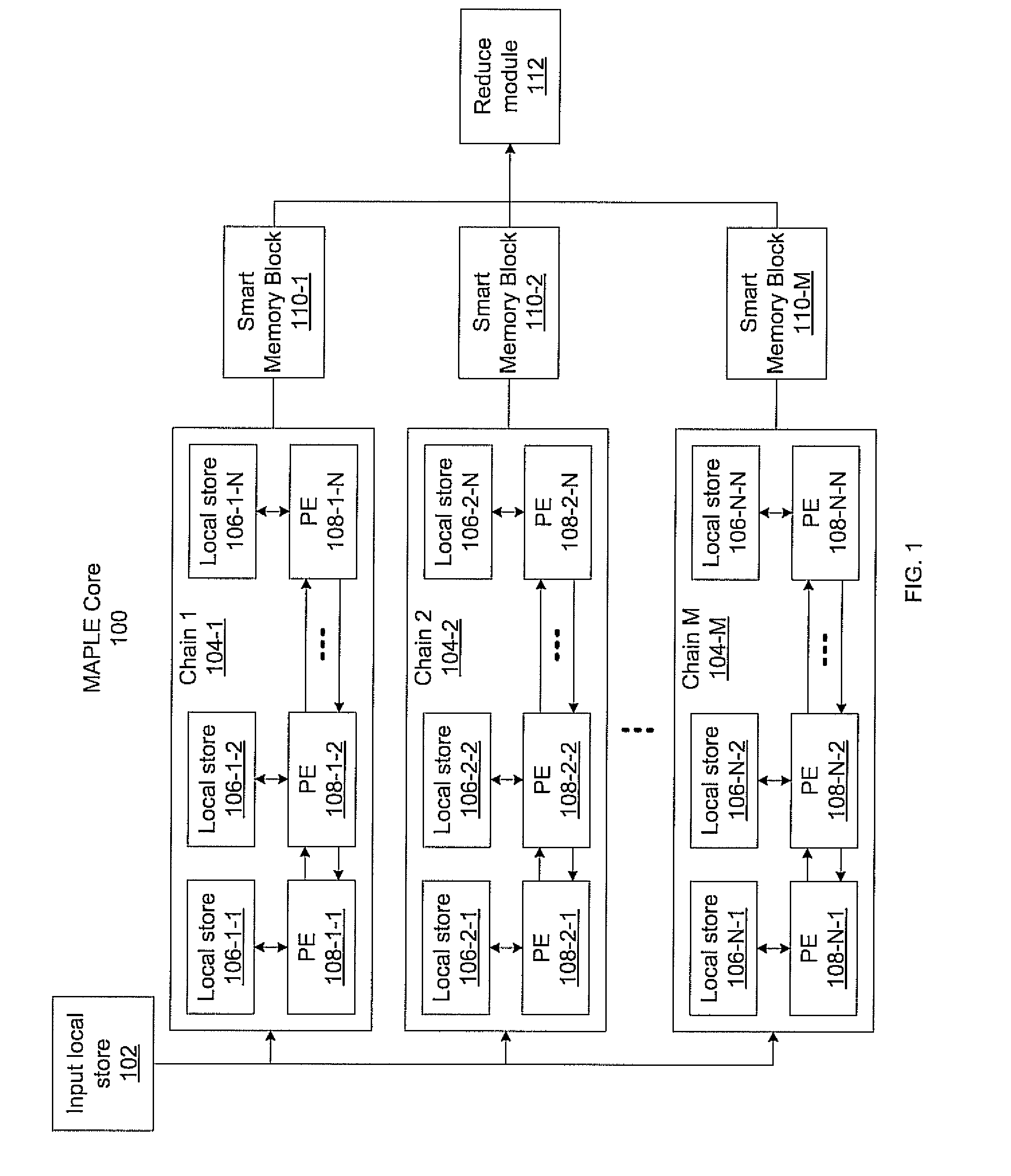

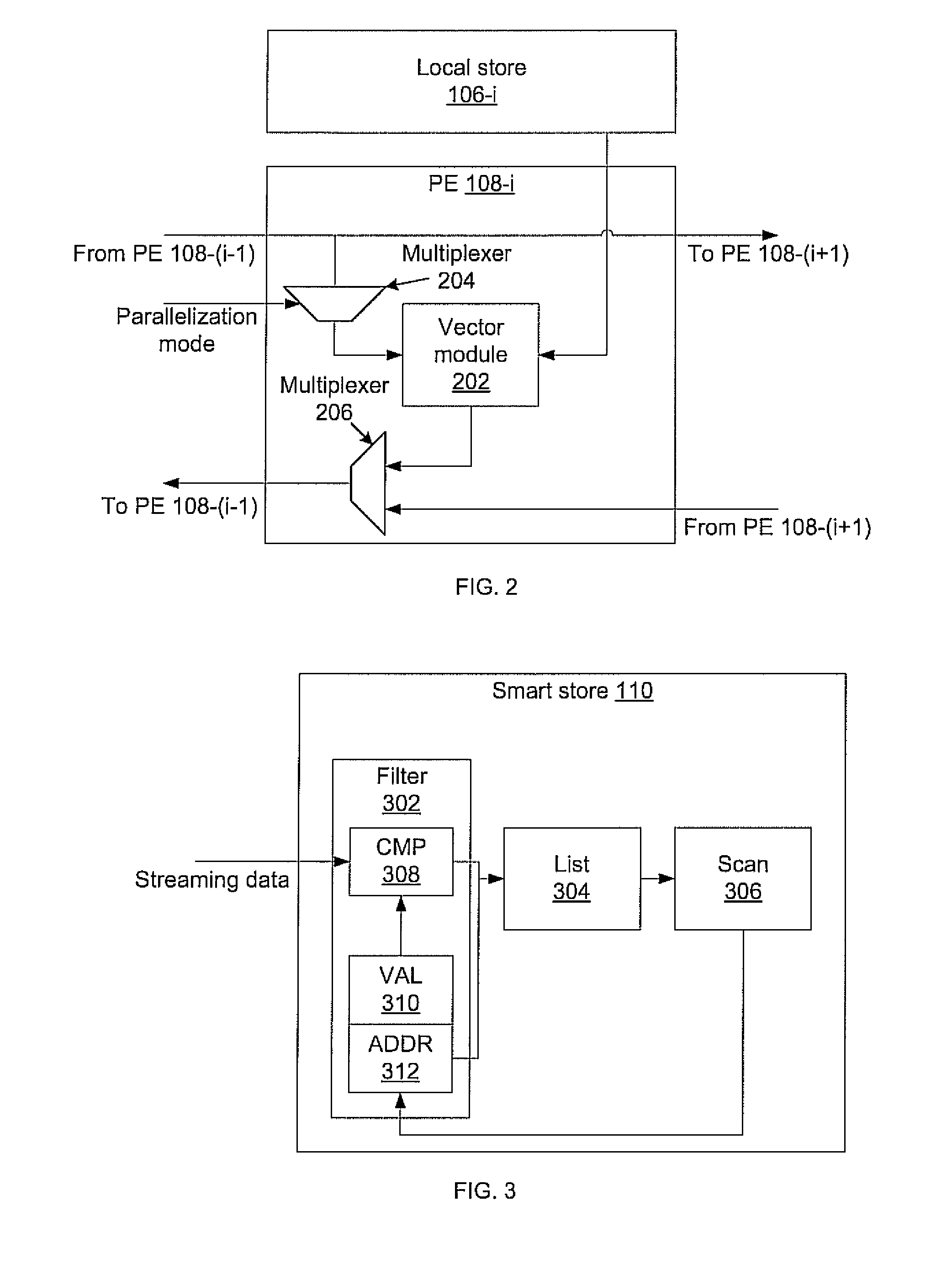

Massively parallel, smart memory based accelerator

Systems and methods for massively parallel processing on an accelerator that includes a plurality of processing cores. Each processing core includes multiple processing chains configured to perform parallel computations, each of which includes a plurality of interconnected processing elements. The cores further include multiple of smart memory blocks configured to store and process data, each memory block accepting the output of one of the plurality of processing chains. The cores communicate with at least one off-chip memory bank.

Owner:NEC CORP

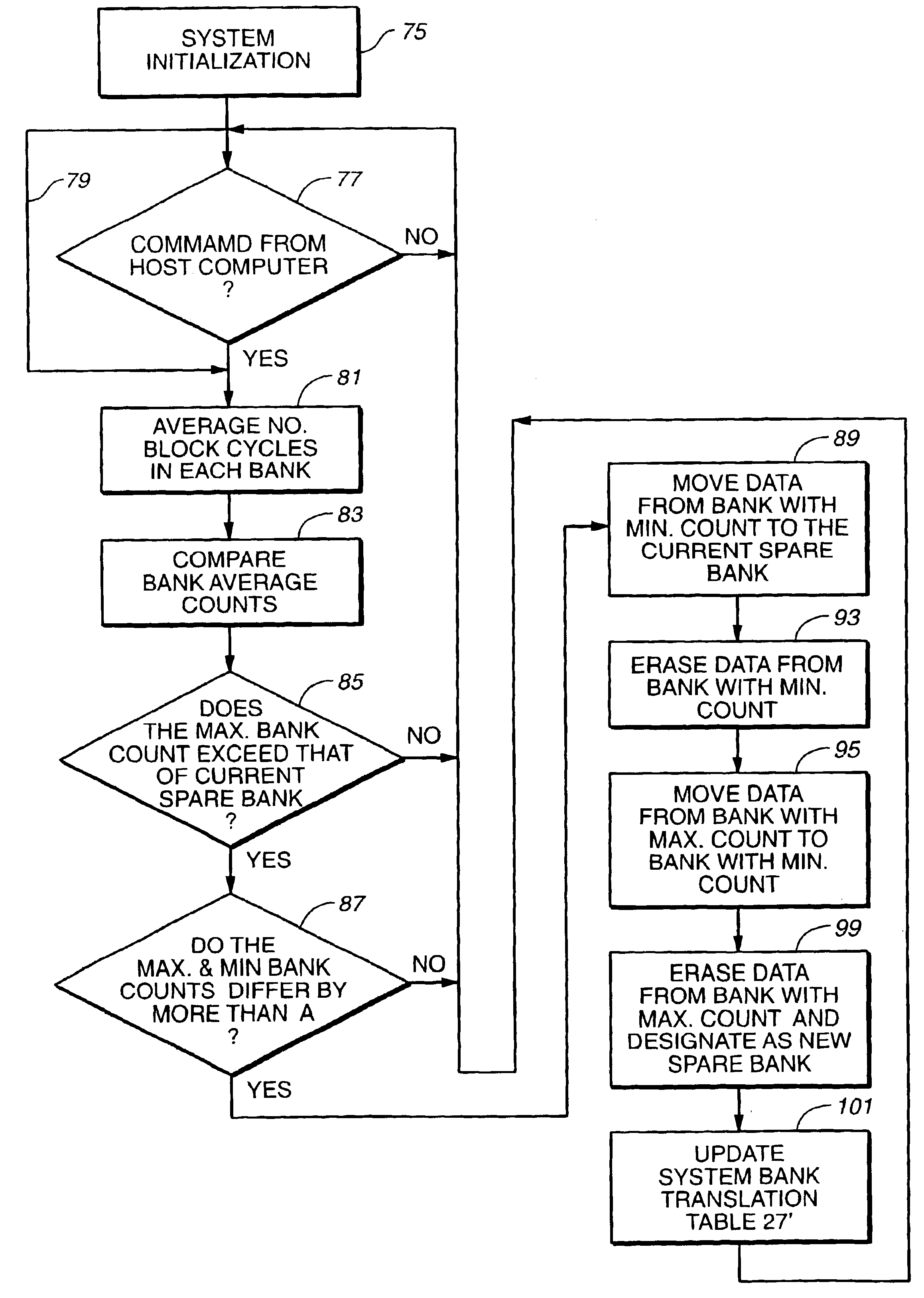

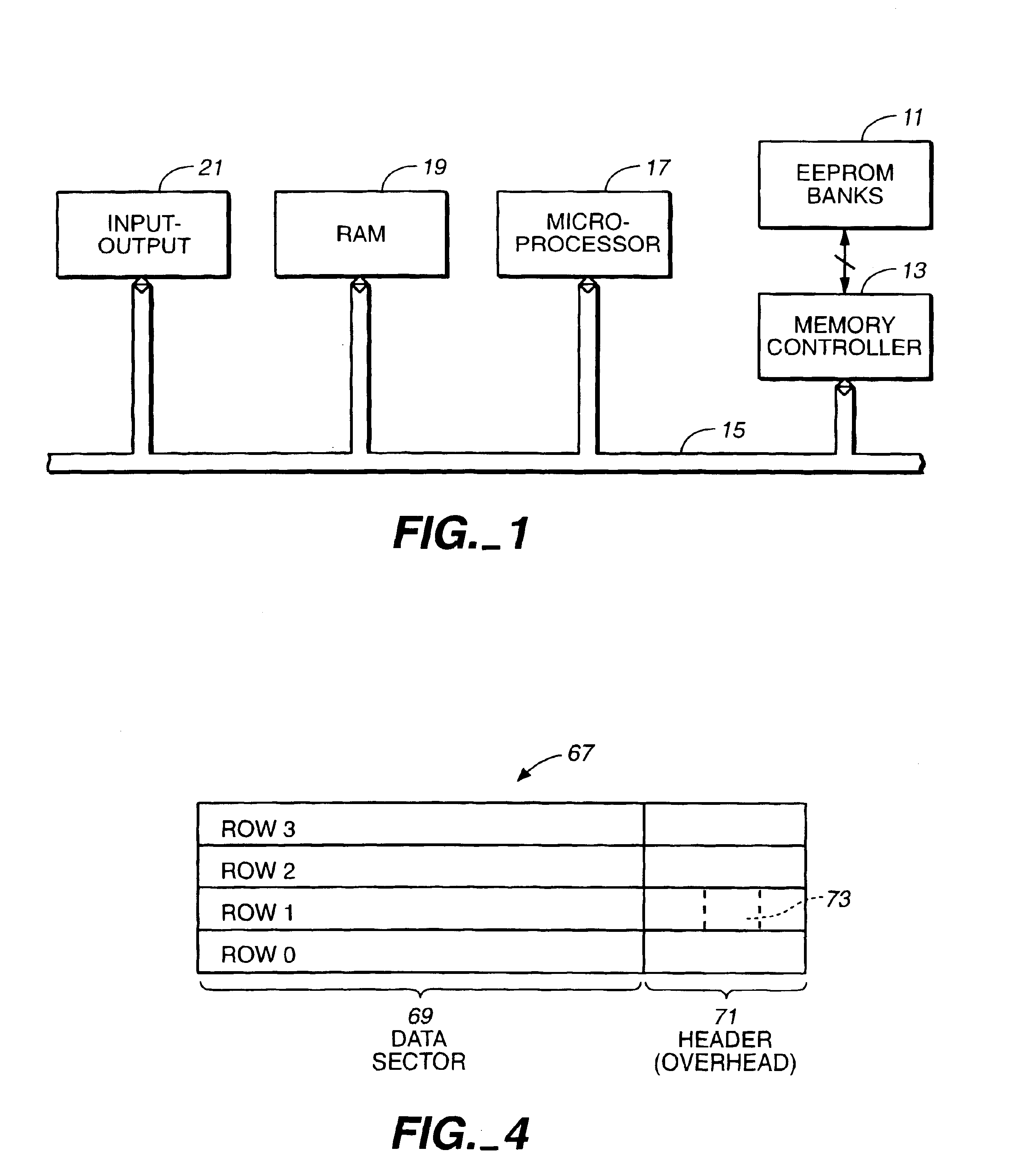

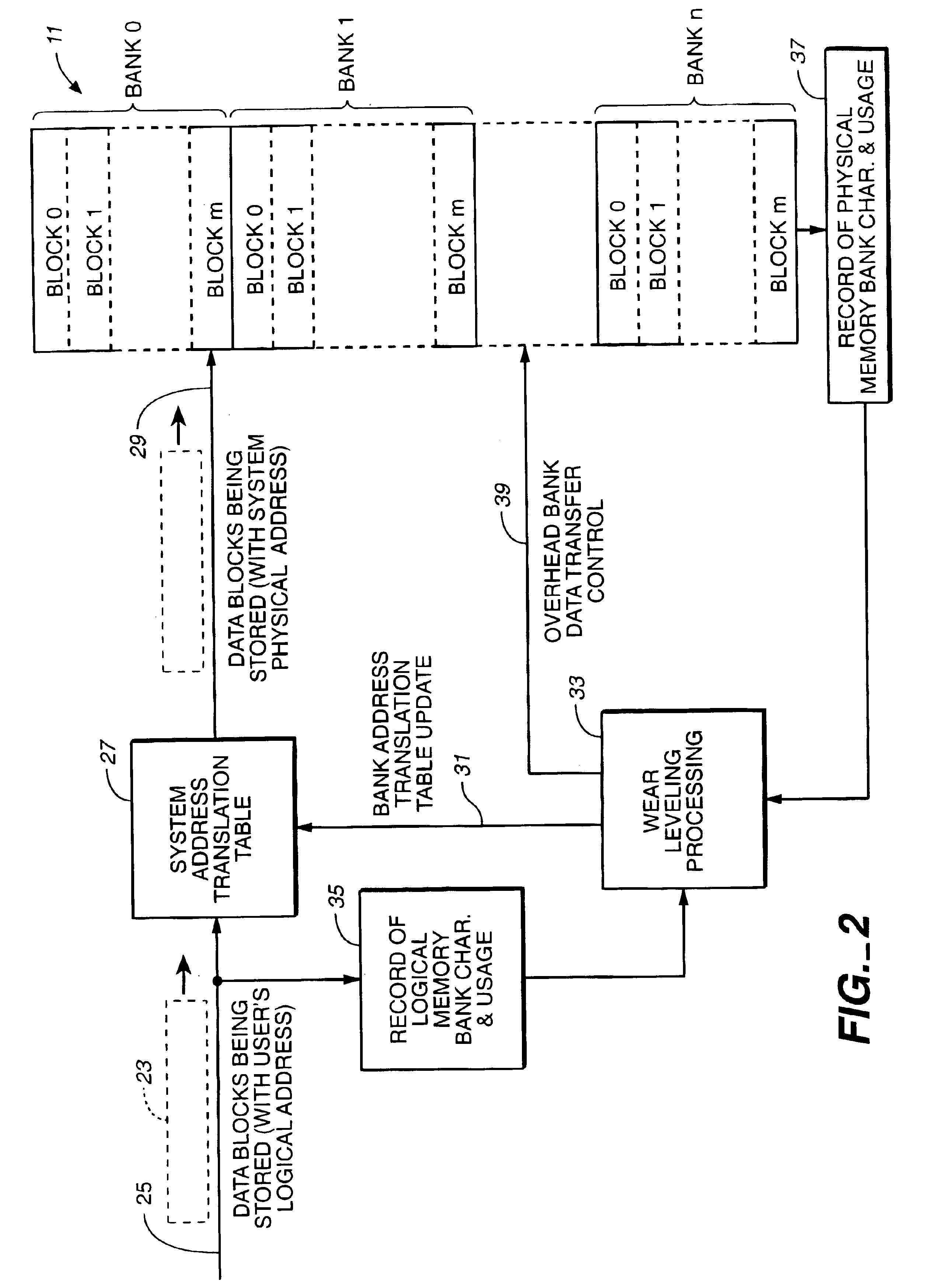

Wear leveling techniques for flash EEPROM systems

InactiveUS6850443B2Avoid uneven wearExtended service lifeMemory architecture accessing/allocationRead-only memoriesElectricityProgrammable read-only memory

A mass storage system made of flash electrically erasable and programmable read only memory (“EEPROM”) cells organized into blocks, the blocks in turn being grouped into memory banks, is managed to even out the numbers of erase and rewrite cycles experienced by the memory banks in order to extend the service lifetime of the memory system. Since this type of memory cell becomes unusable after a finite number of erase and rewrite cycles, although in the tens of thousands of cycles, uneven use of the memory banks is avoided so that the entire memory does not become inoperative because one of its banks has reached its end of life while others of the banks are little used. Relative use of the memory banks is monitored and, in response to detection of uneven use, have their physical addresses periodically swapped for each other in order to even out their use over the lifetime of the memory.

Owner:SANDISK TECH LLC

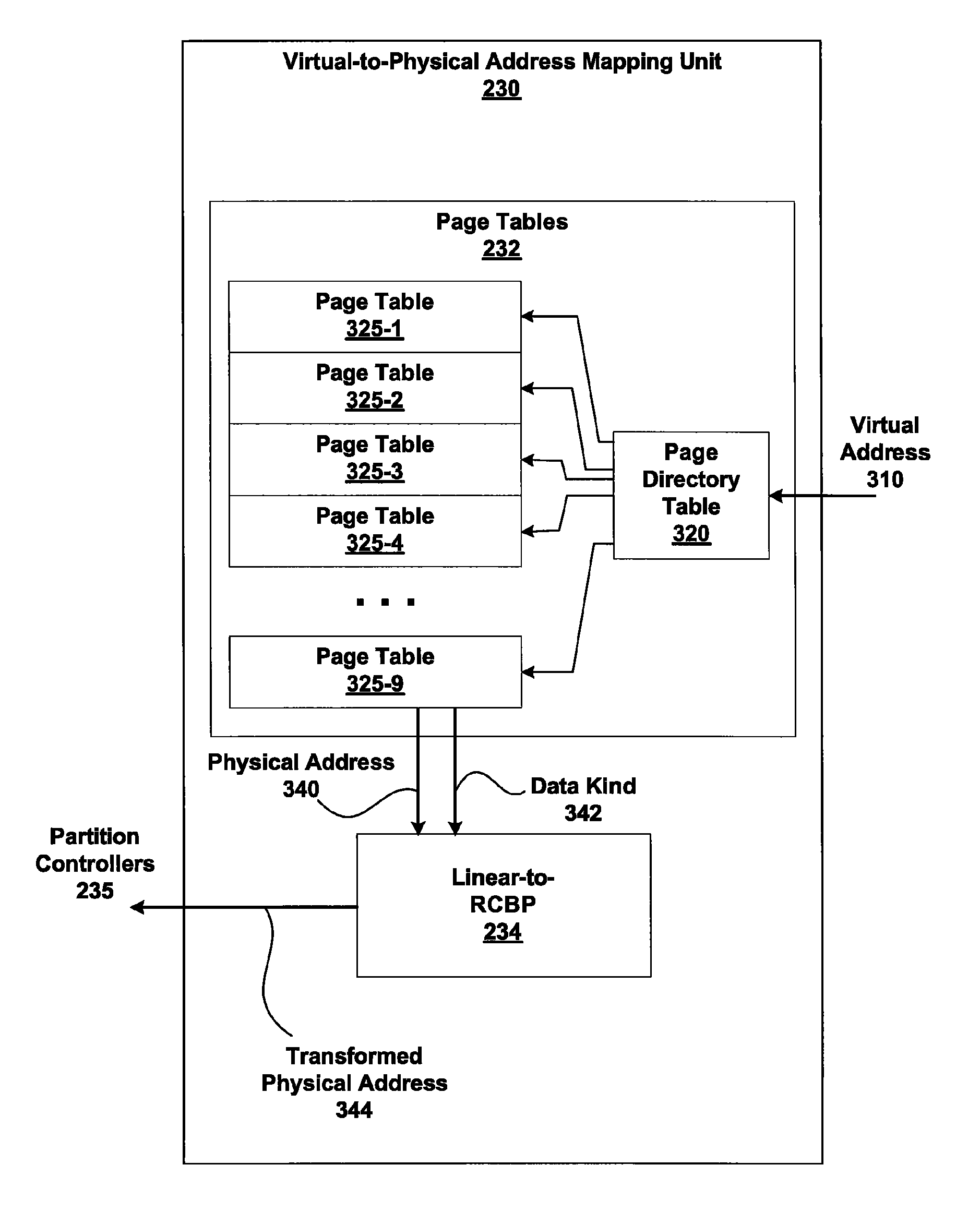

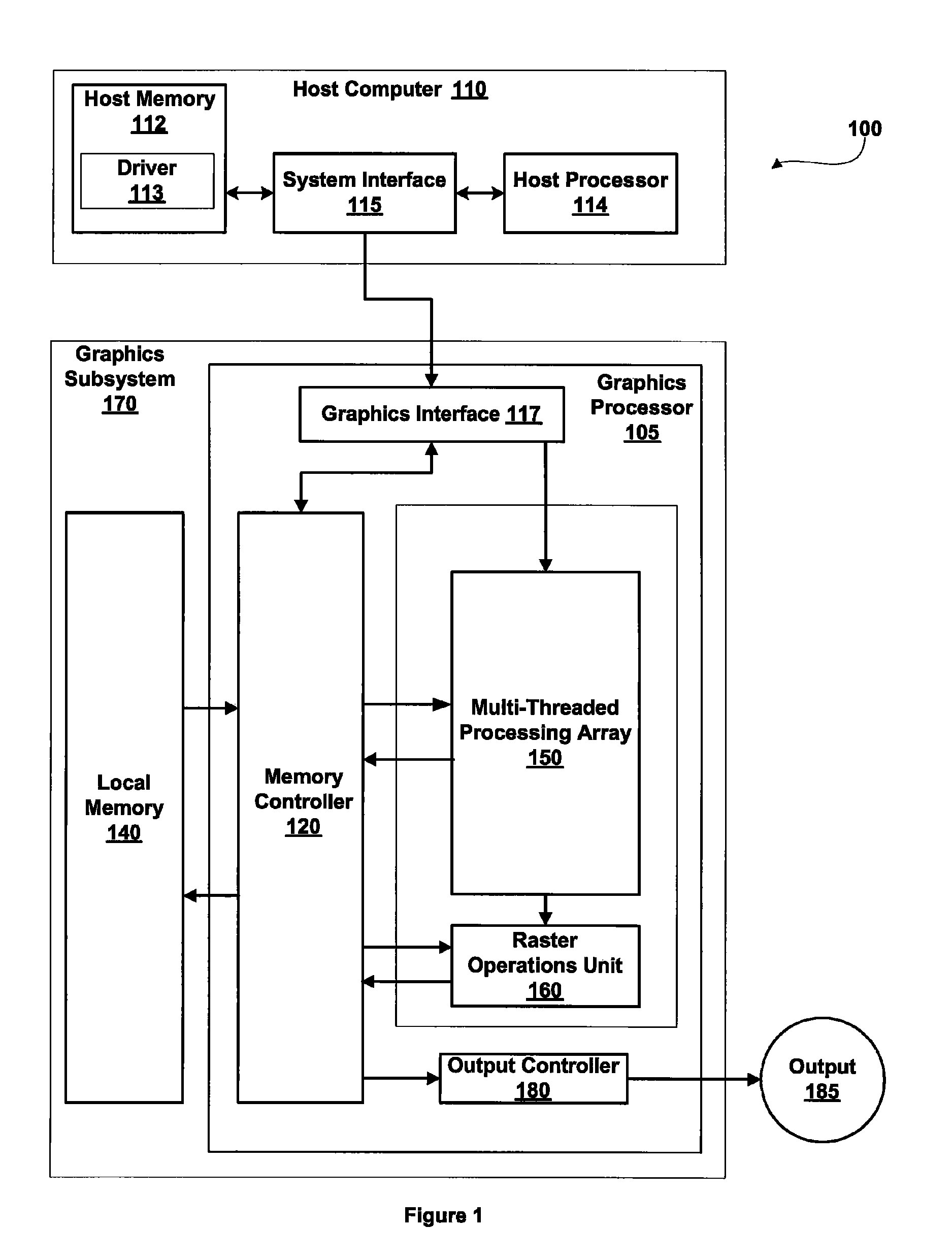

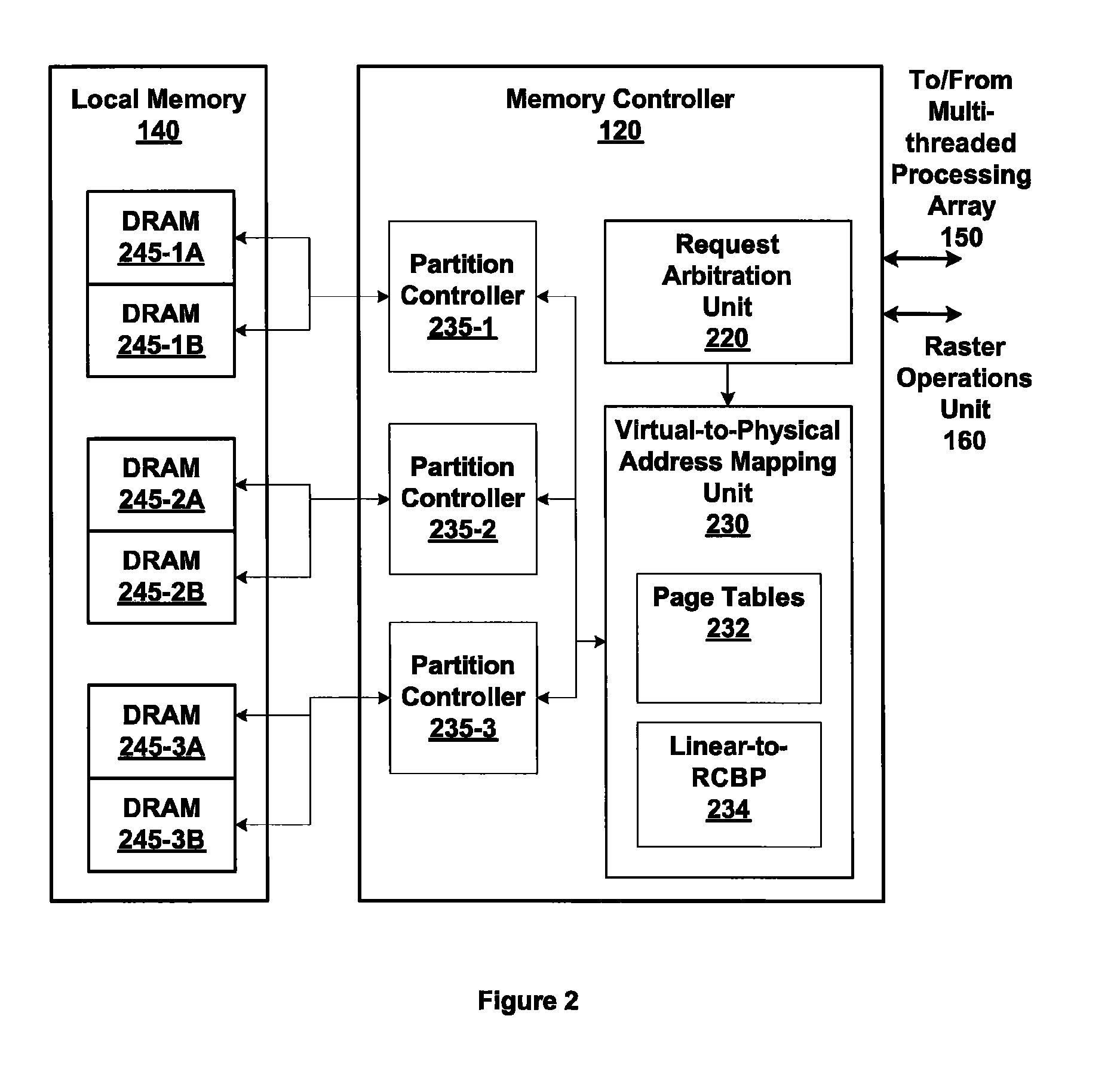

Memory addressing controlled by PTE fields

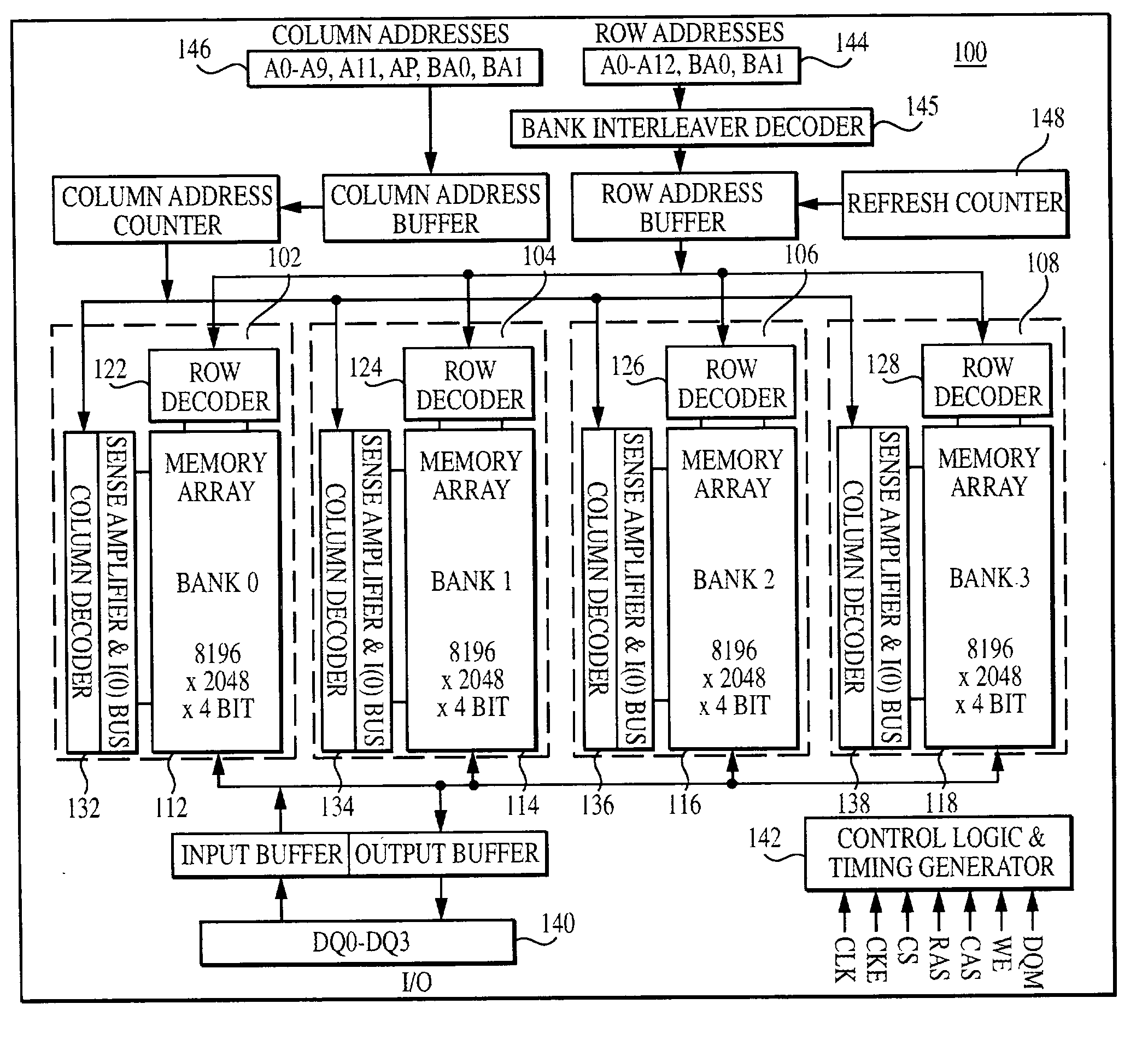

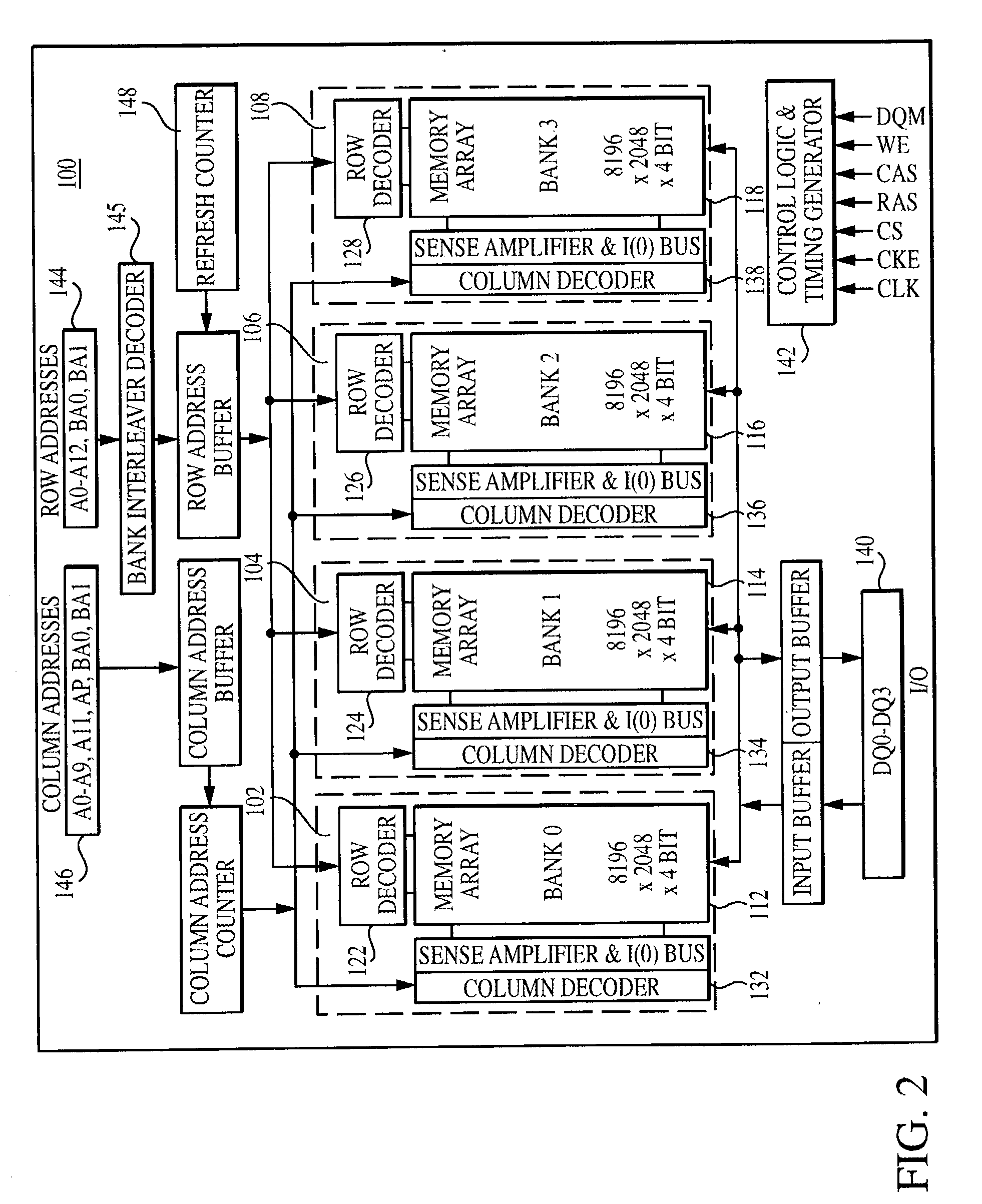

ActiveUS7805587B1Reduce accessMemory adressing/allocation/relocationComputer security arrangementsMemory addressDram memory

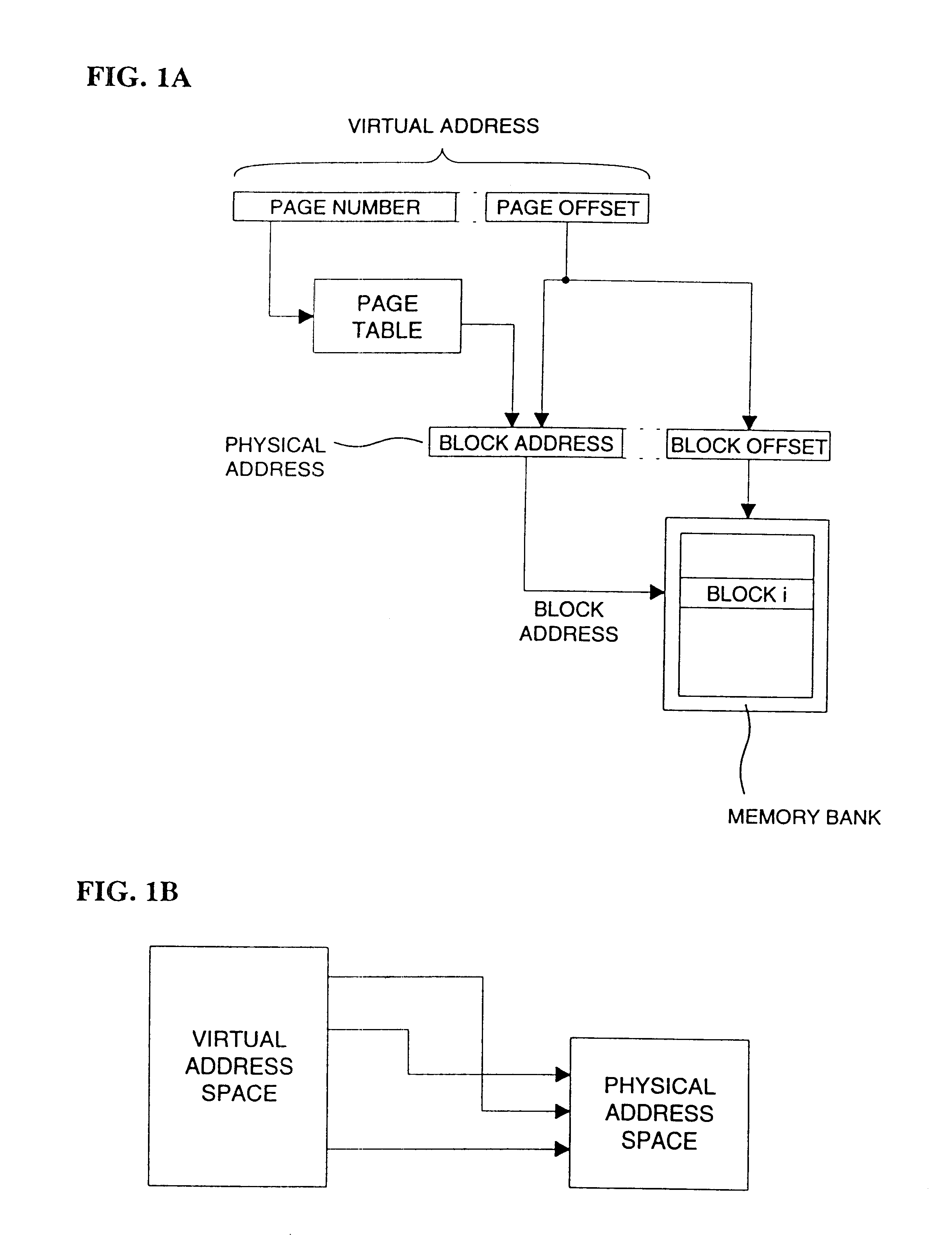

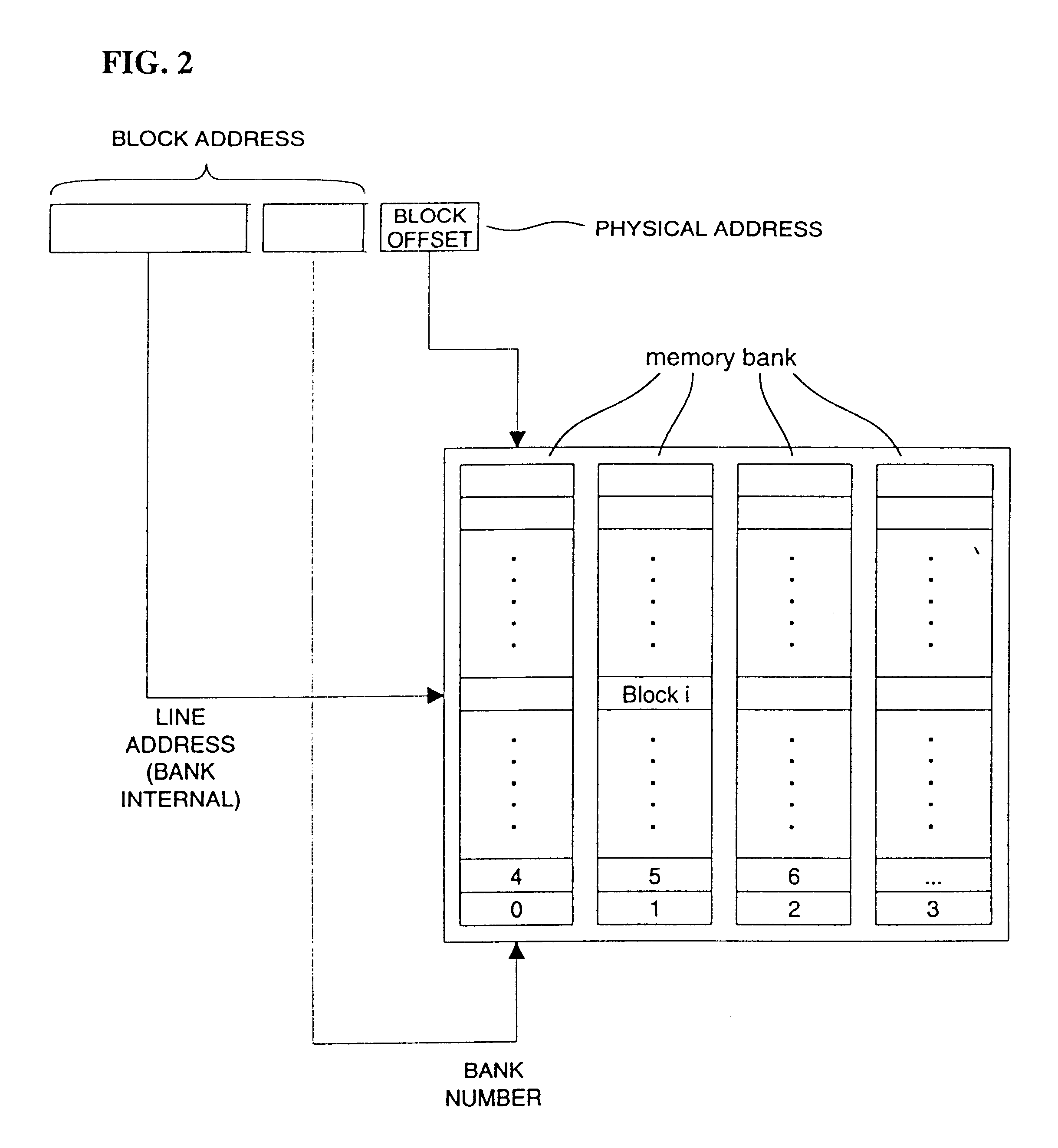

Embodiments of the present invention enable virtual-to-physical memory address translation using optimized bank and partition interleave patterns to improve memory bandwidth by distributing data accesses over multiple banks and multiple partitions. Each virtual page has a corresponding page table entry that specifies the physical address of the virtual page in linear physical address space. The page table entry also includes a data kind field that is used to guide and optimize the mapping process from the linear physical address space to the DRAM physical address space, which is used to directly access one or more DRAM. The DRAM physical address space includes a row, bank and column address. The data kind field is also used to optimize the starting partition number and partition interleave pattern that defines the organization of the selected physical page of memory within the DRAM memory system.

Owner:NVIDIA CORP

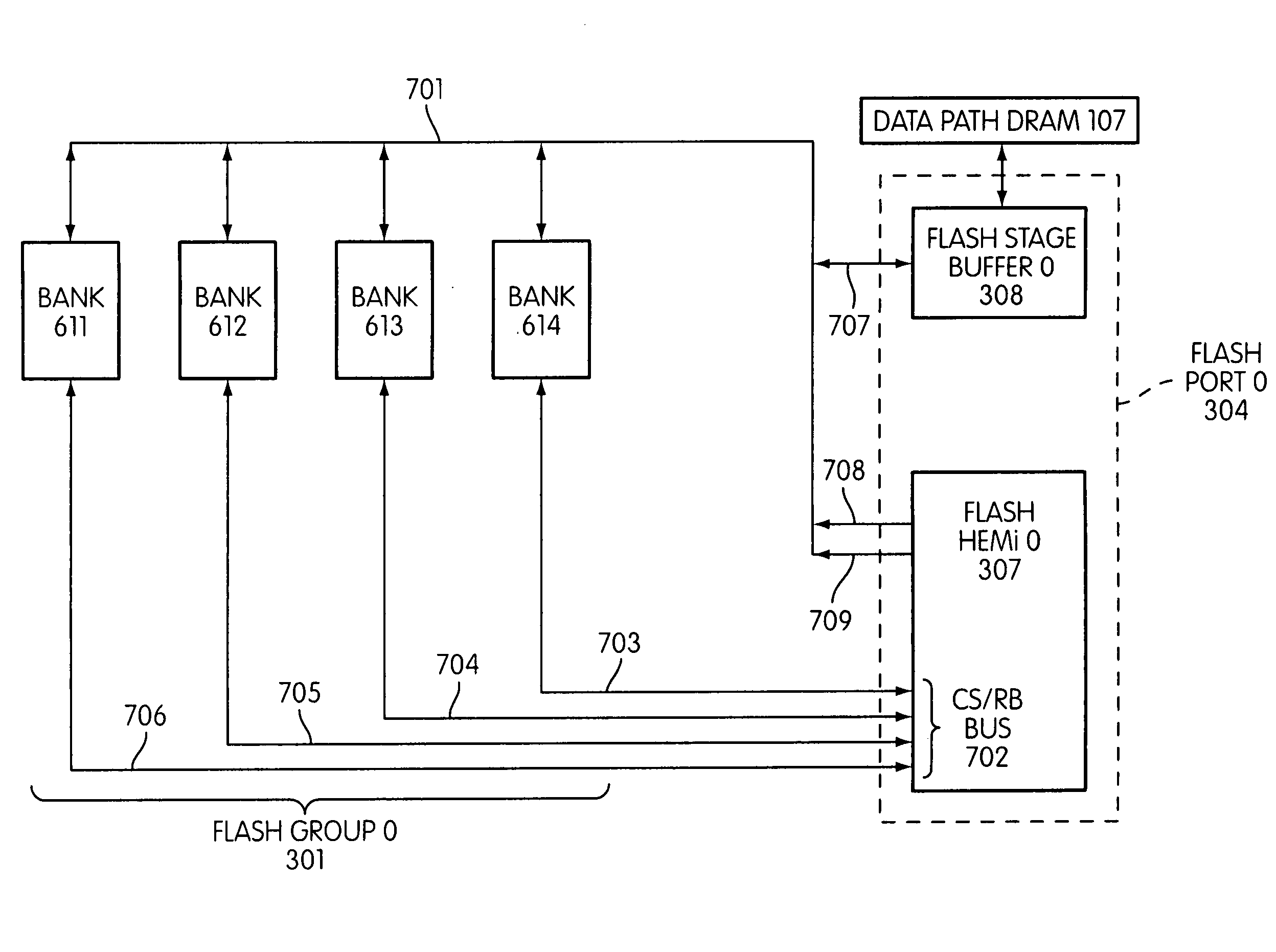

Flash memory controller having reduced pinout

InactiveUS20090168525A1Affect performanceMaximize useMemory architecture accessing/allocationMemory adressing/allocation/relocationChip selectFlash memory controller

Disclosed is a flash memory controller connected to a flash memory module. The pin-out of the flash memory controller combines ready-busy and chip-select signals. In one embodiment, the flash memory module is made up of a set of banks, each consisting of a plurality of devices, with each bank sharing a single chip-select / ready-busy connection to the controller.

Owner:SANDISK TECH LLC

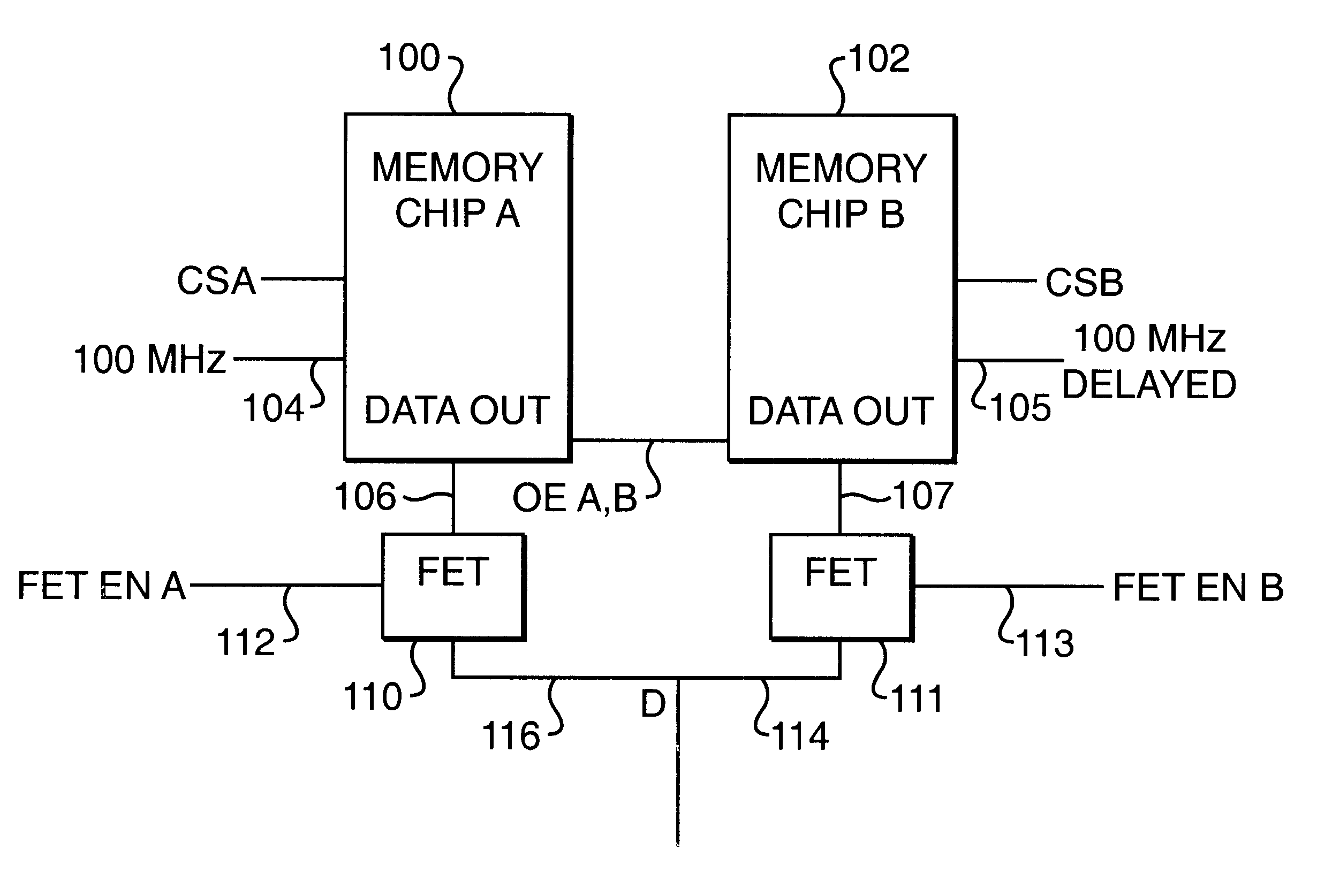

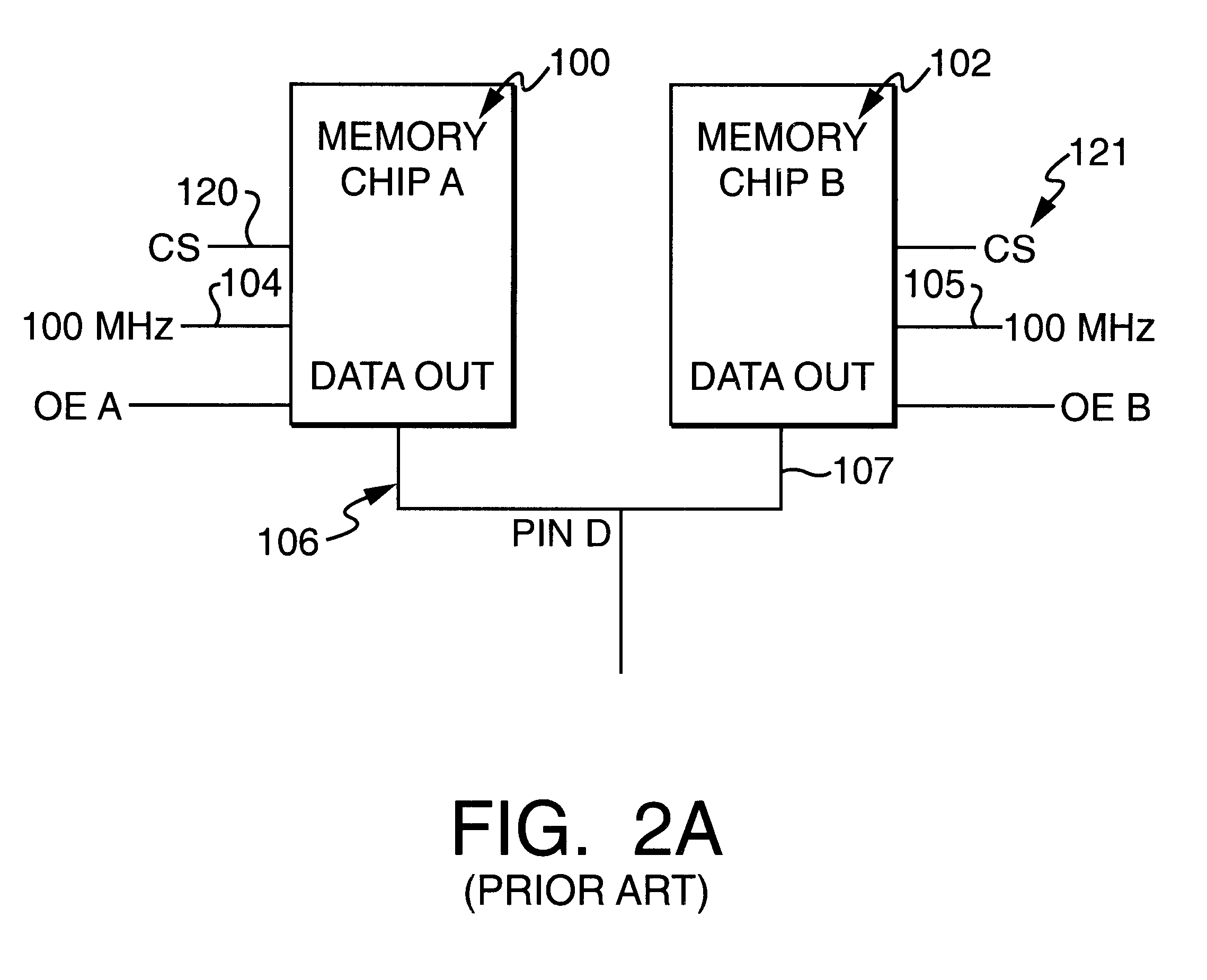

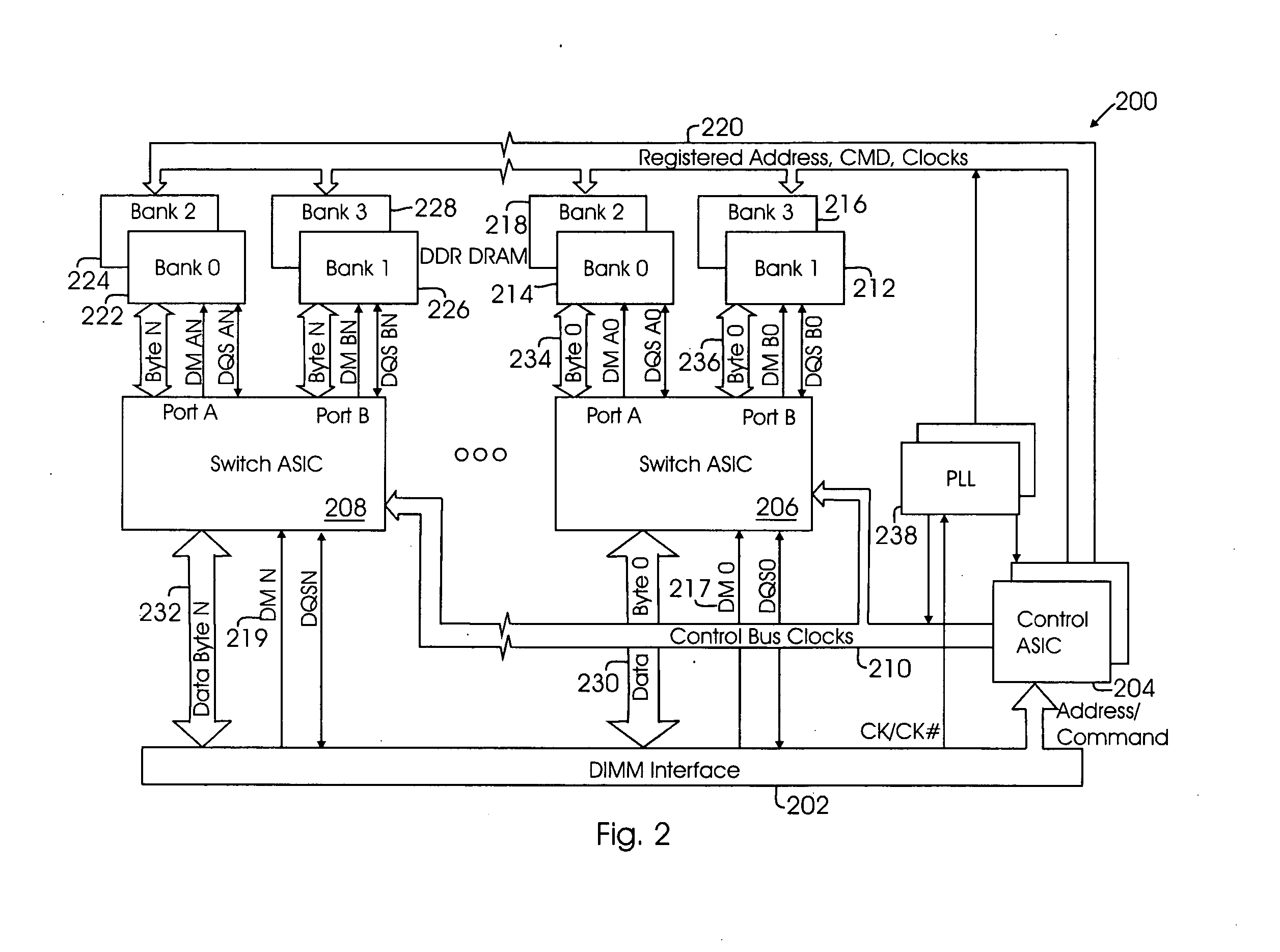

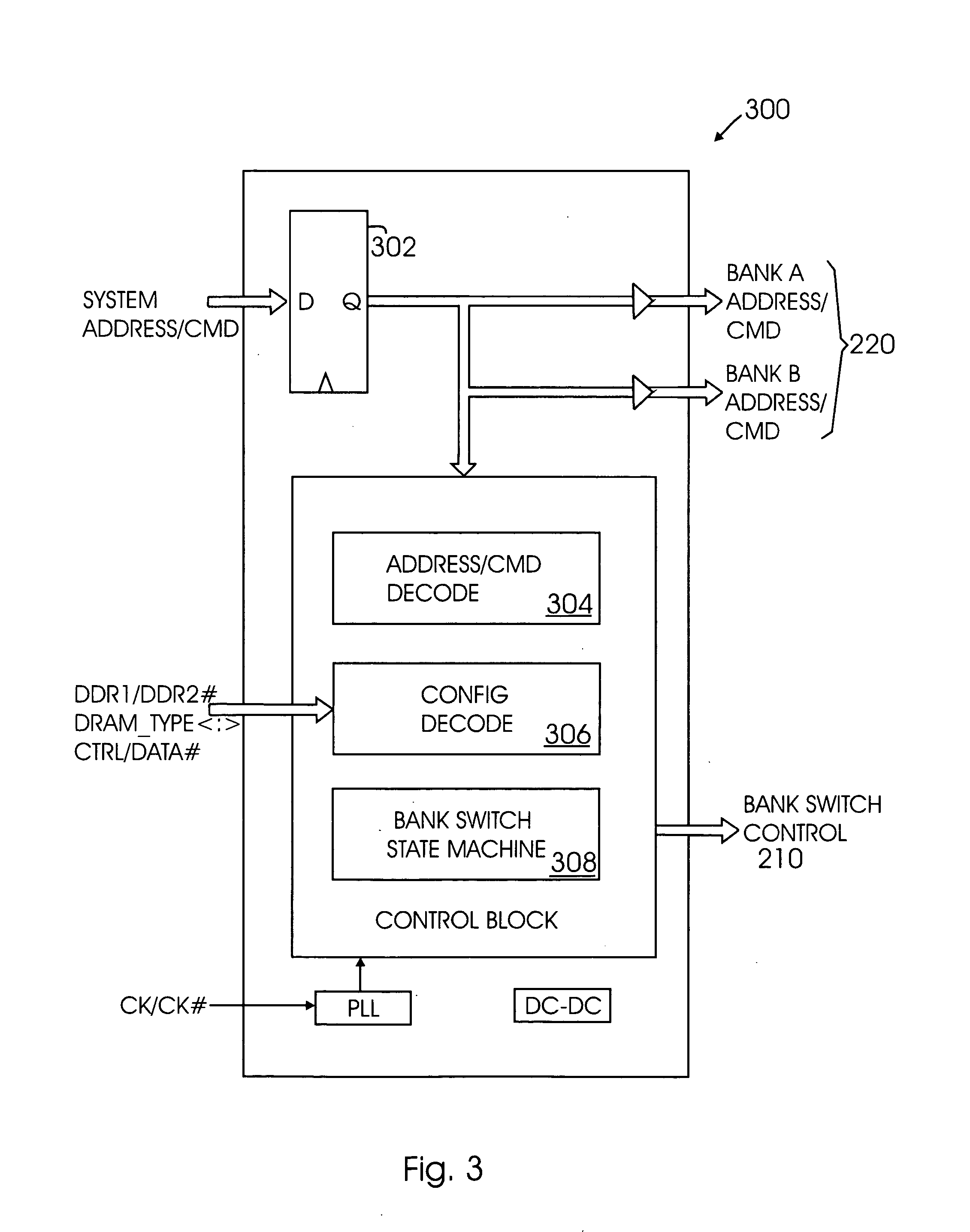

Memory system using FET switches to select memory banks

A computer memory system provides a double data rate (DDR) memory output while requiring memory chips with only half the frequency limit of the prior art DDR memory chips. The system contains a first memory bank having data lines and a second memory bank having data lines. The first and second memory banks are associated with first and second clock signals, respectively, where the second clock signal is delayed from the first clock signal such that the data lines of the first memory bank are connected to a data bus in synchronism with the first clock signal while the data lines of the second memory bank are connected with the data bus in synchronism with the second clock signal. In one embodiment, a first FET switch connects the data lines of the first memory bank with the data bus and a second FET switch connects the data lines of the second memory bank with the data bus. The second FET switch is connected to the data bus at a time delayed from the beginning after the start of each clock cycle of the second clock signal. As a result, the data bus is never connected to the data lines of both memory banks at the same time, but rather, the data bus is alternately connected with the first memory bank and then the second memory bank.

Owner:FOOTHILLS IP LLC

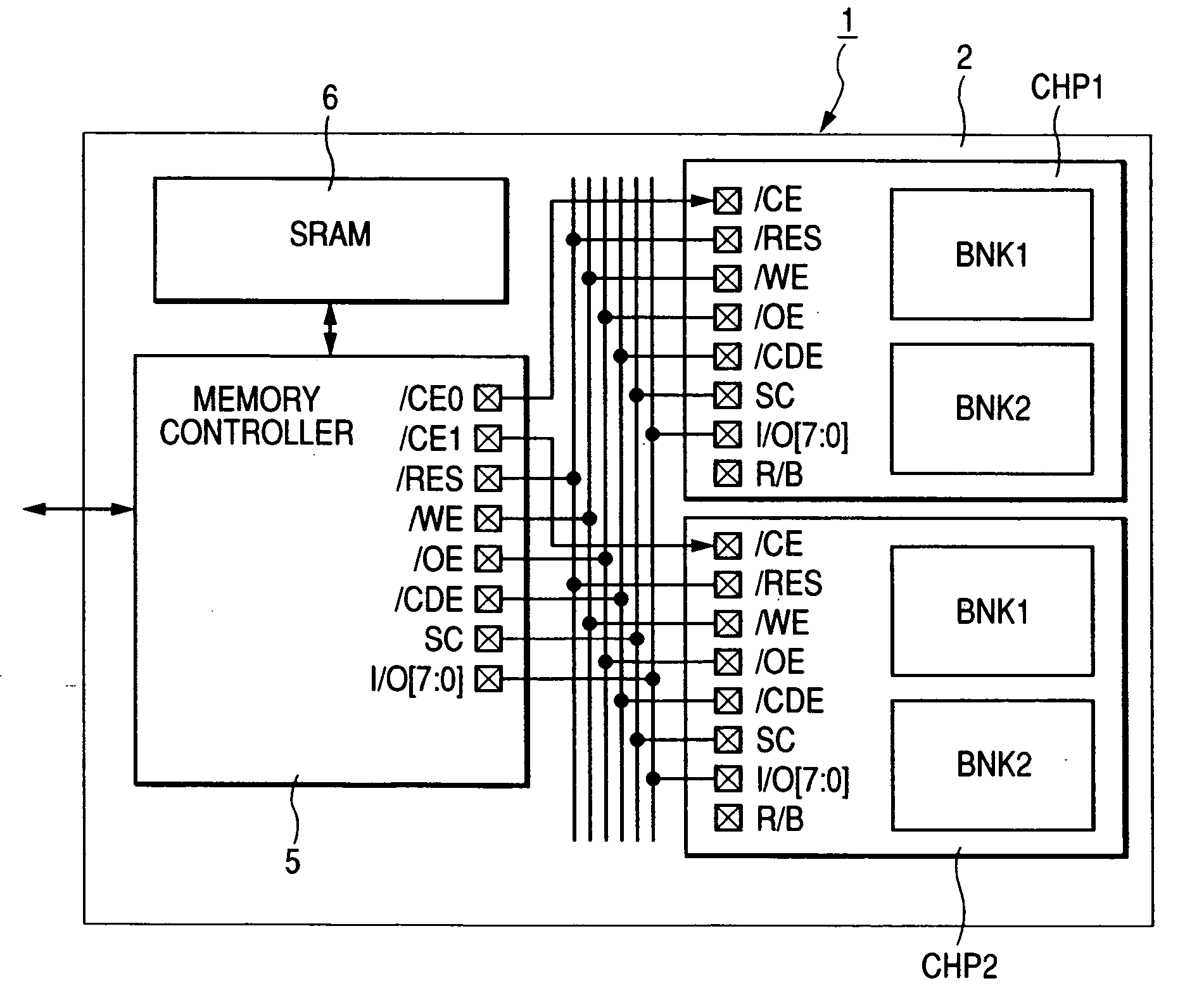

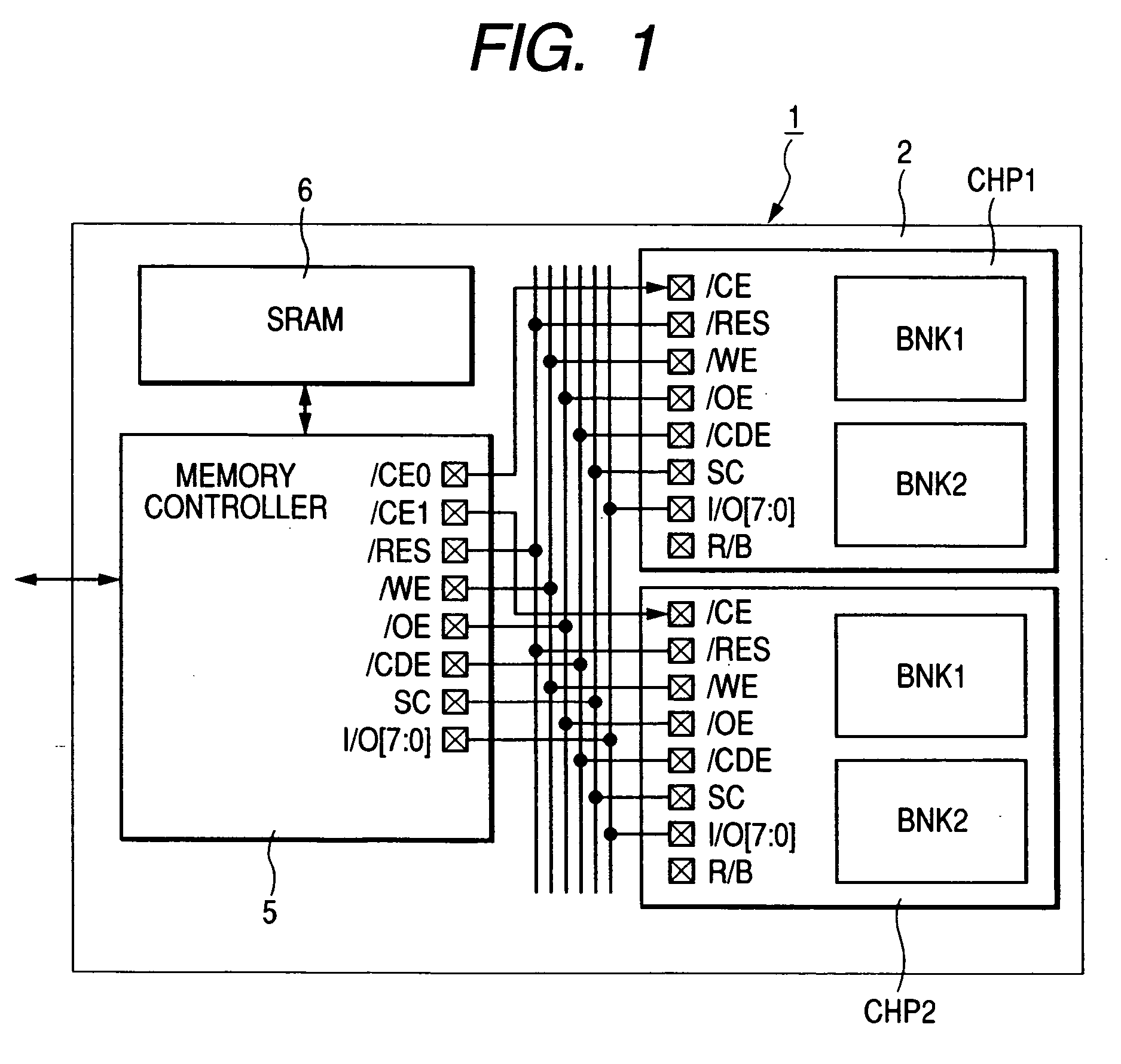

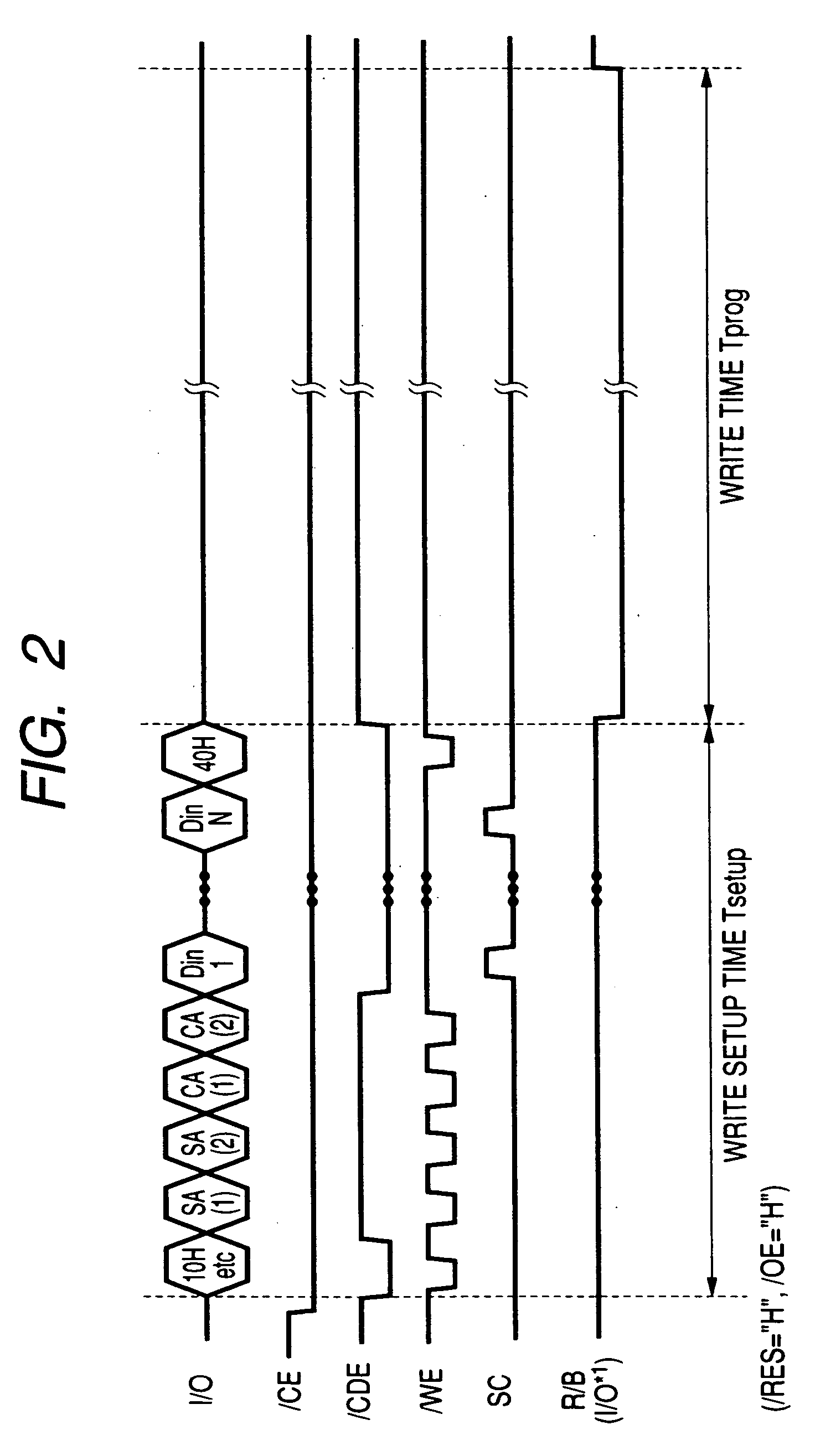

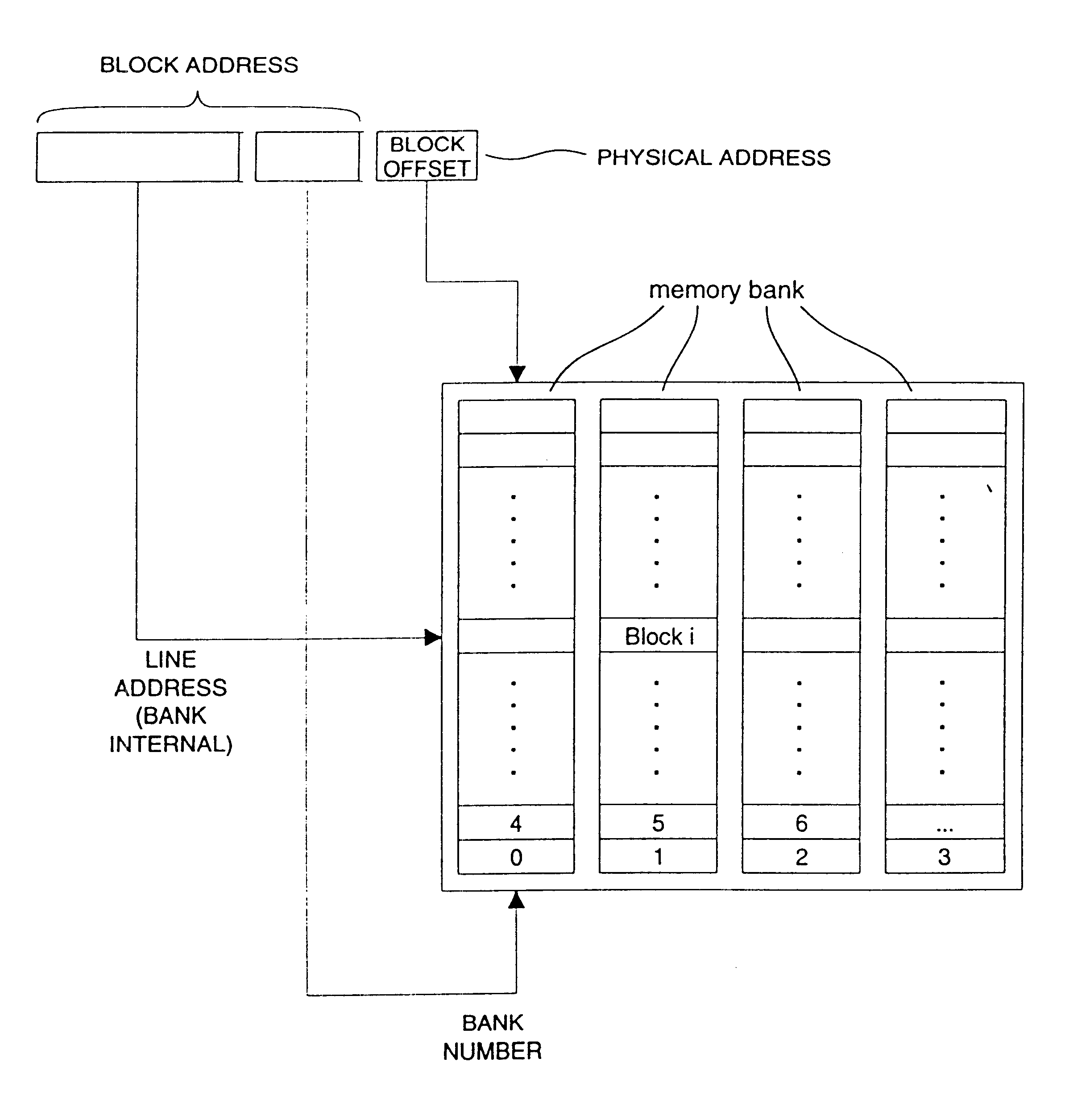

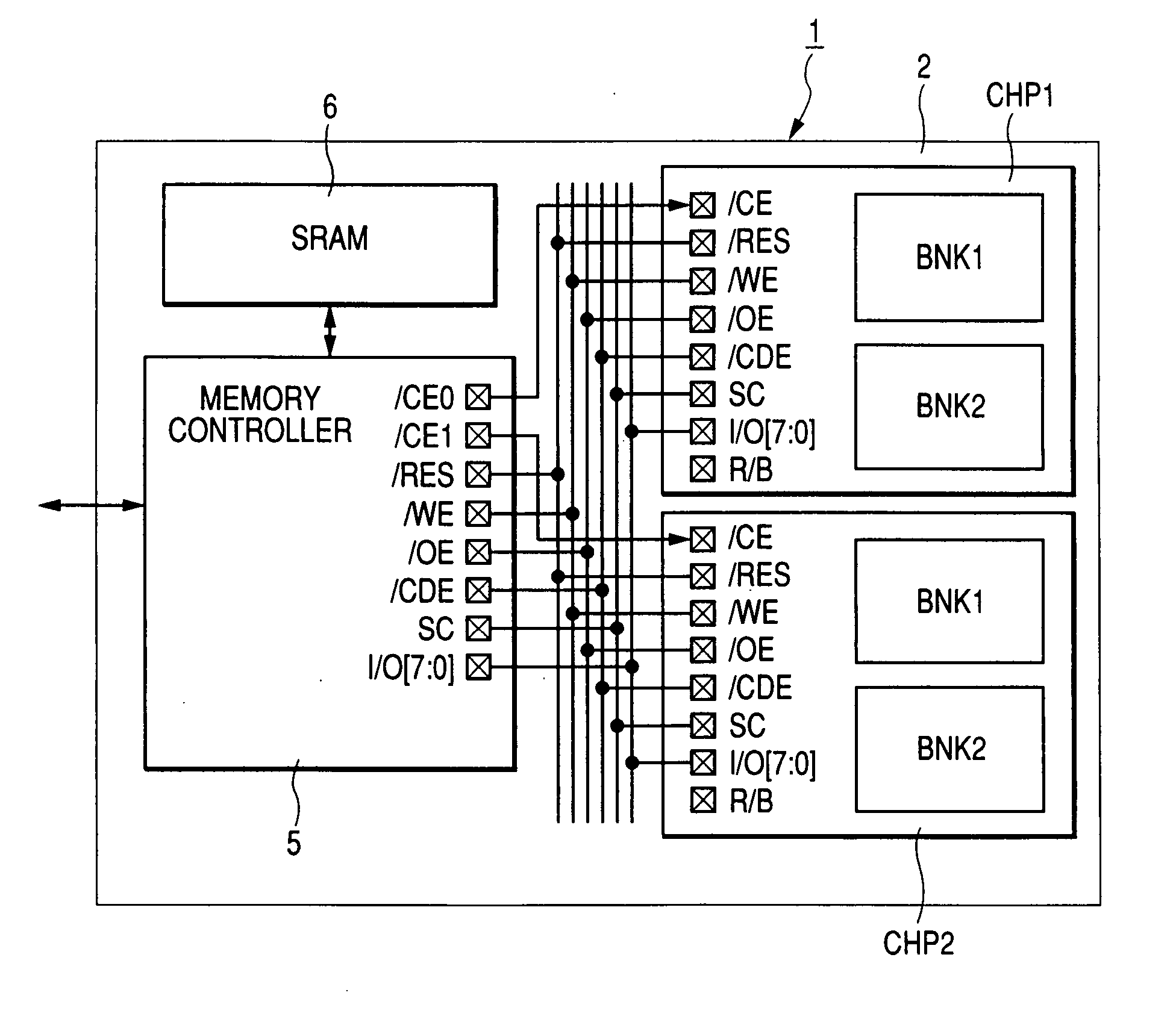

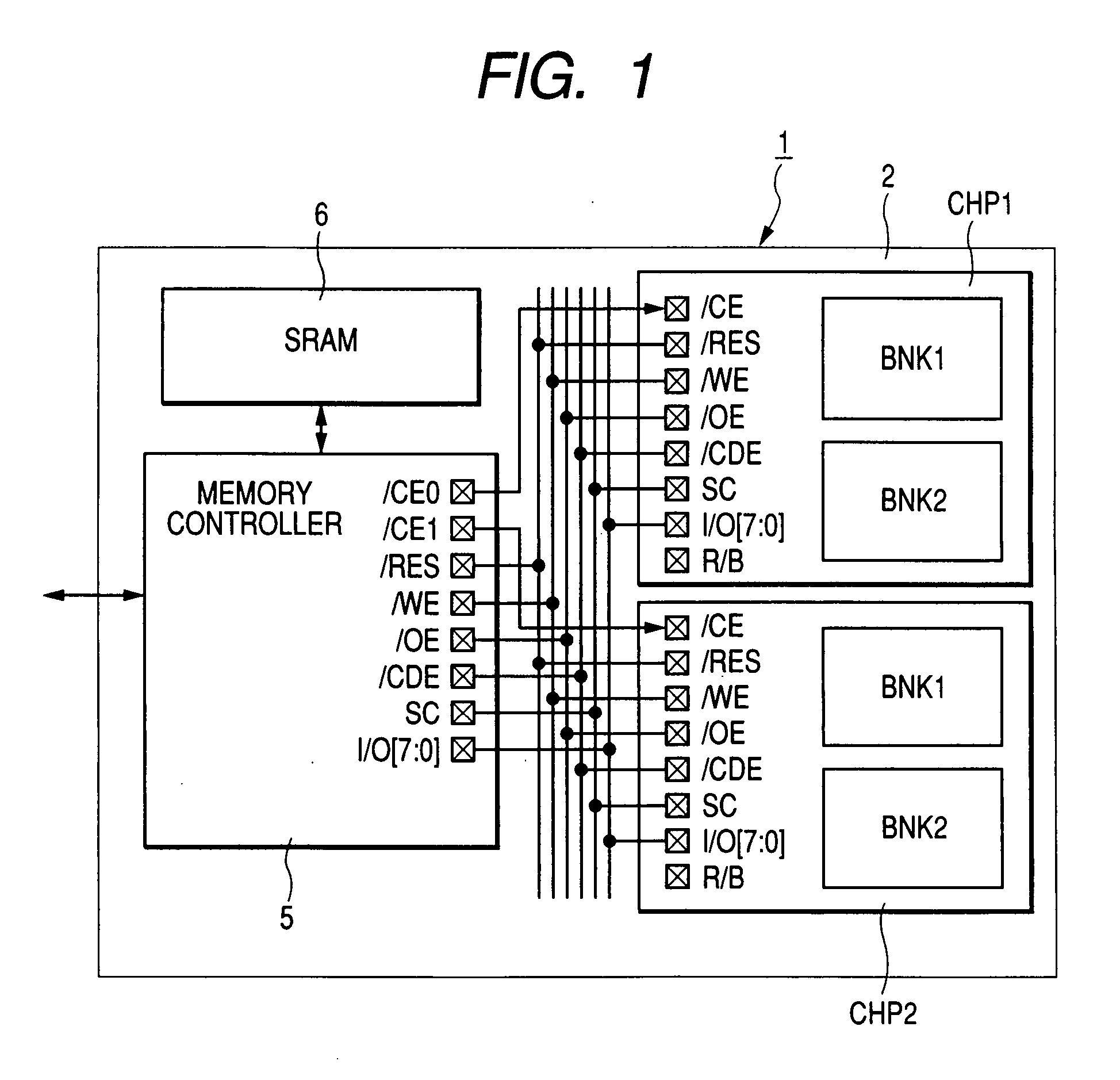

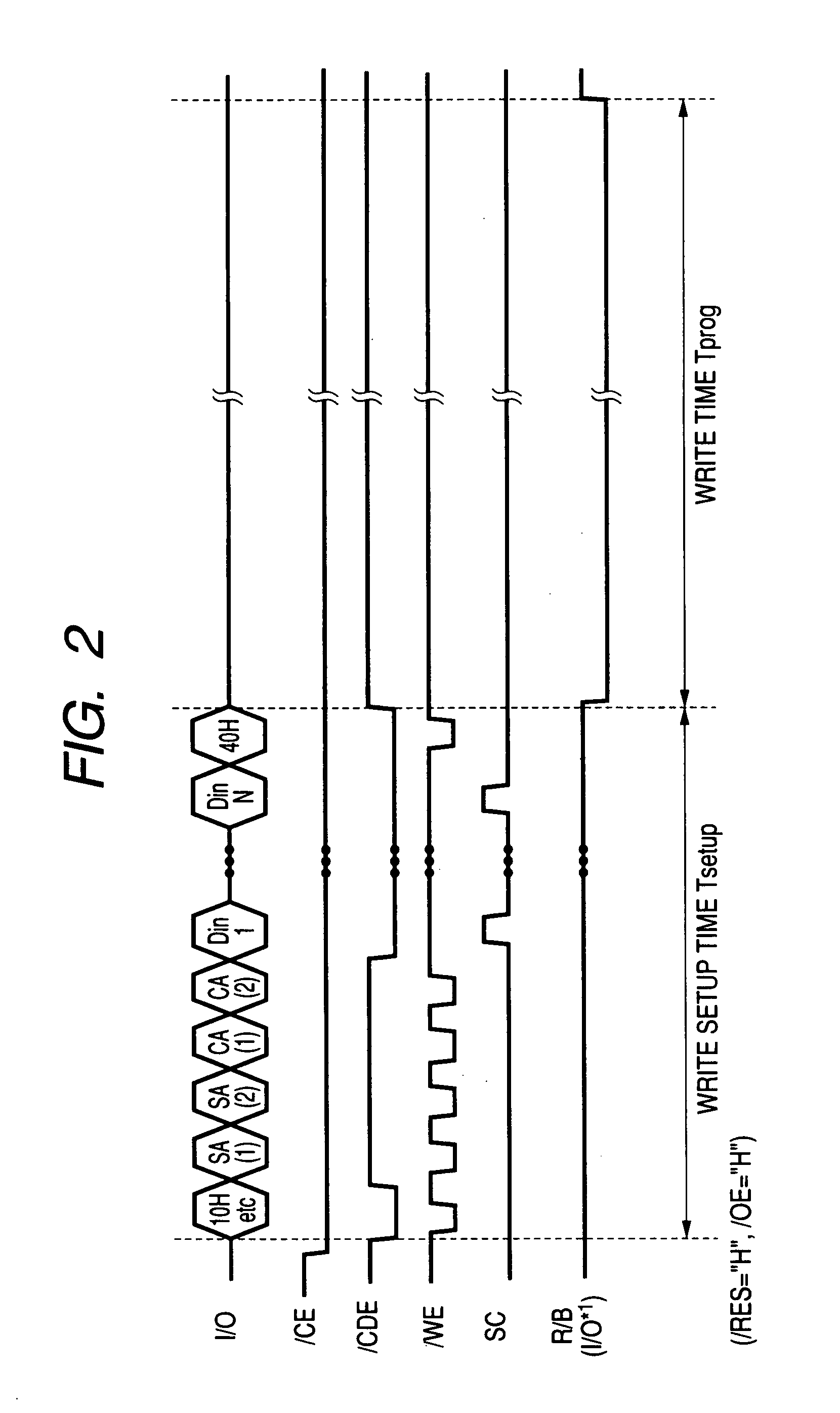

Memory system and memory card

InactiveUS20050015539A1Increase costIncrease speedMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:RENESAS ELECTRONICS CORP

Address mapping for system memory

InactiveUS6381668B1Flexible choiceEasy to changeMemory adressing/allocation/relocationMicro-instruction address formationMemory bankParallel computing

For optimizing access to system memory having a plurality of memory banks, interleaving can be used when storing data so that data sequences are distributed over memory banks. The invention introduces an address-mapping method applying a table lookup procedure so that arbitrary, non-power-of-two interleave factors and numbers of memory banks are possible for various strides.

Owner:TWITTER INC

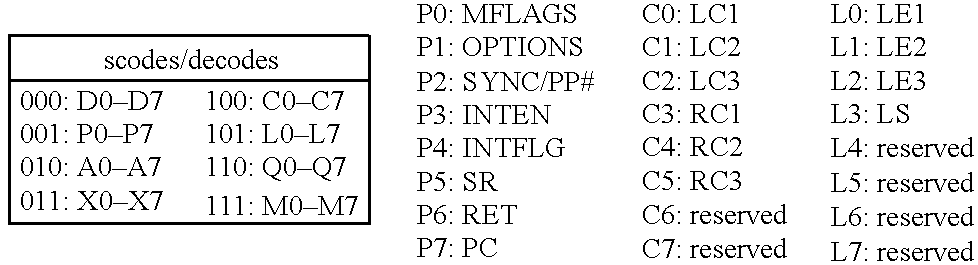

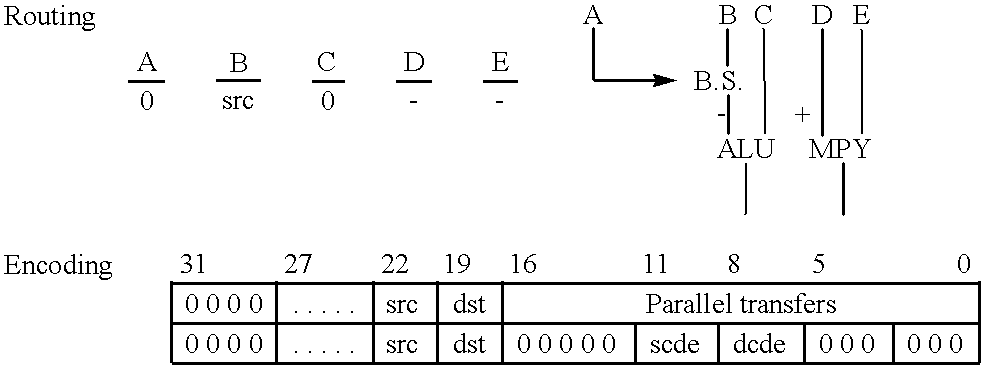

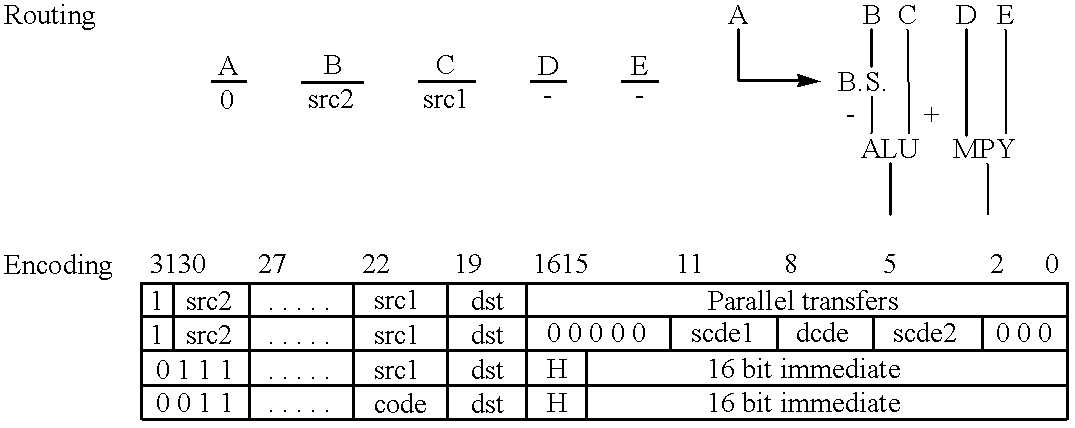

Single integrated circuit embodying a risc processor and a digital signal processor

InactiveUS6260088B1Save spaceImprove versatilityGeneral purpose stored program computerMultiple digital computer combinationsDigital signal processingComputer image

A single integrated circuit includes first and second data processors operating on different instruction sets independently operating on disjoint programs and data. The single integrated circuit preferably includes an external interface, a shared data transfer controller and shared memory divided into plural independently accessible memory banks. The two data processors are preferably a digital signal processor (DSP) and a reduced instruction set computer (RISC) processor. The DSP and RISC processors are suitably programmed to perform differing aspects of computer image processing.

Owner:TEXAS INSTR INC

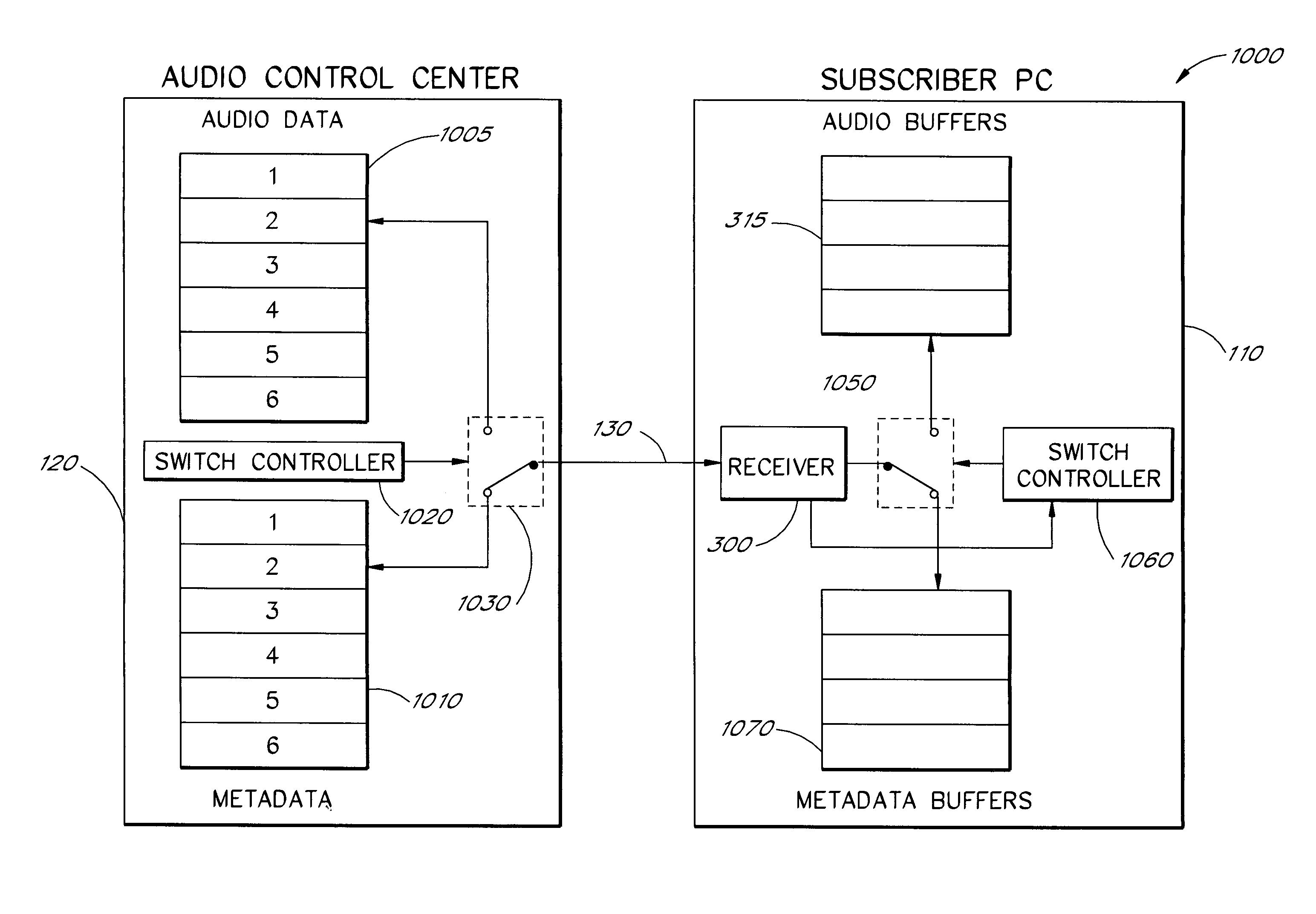

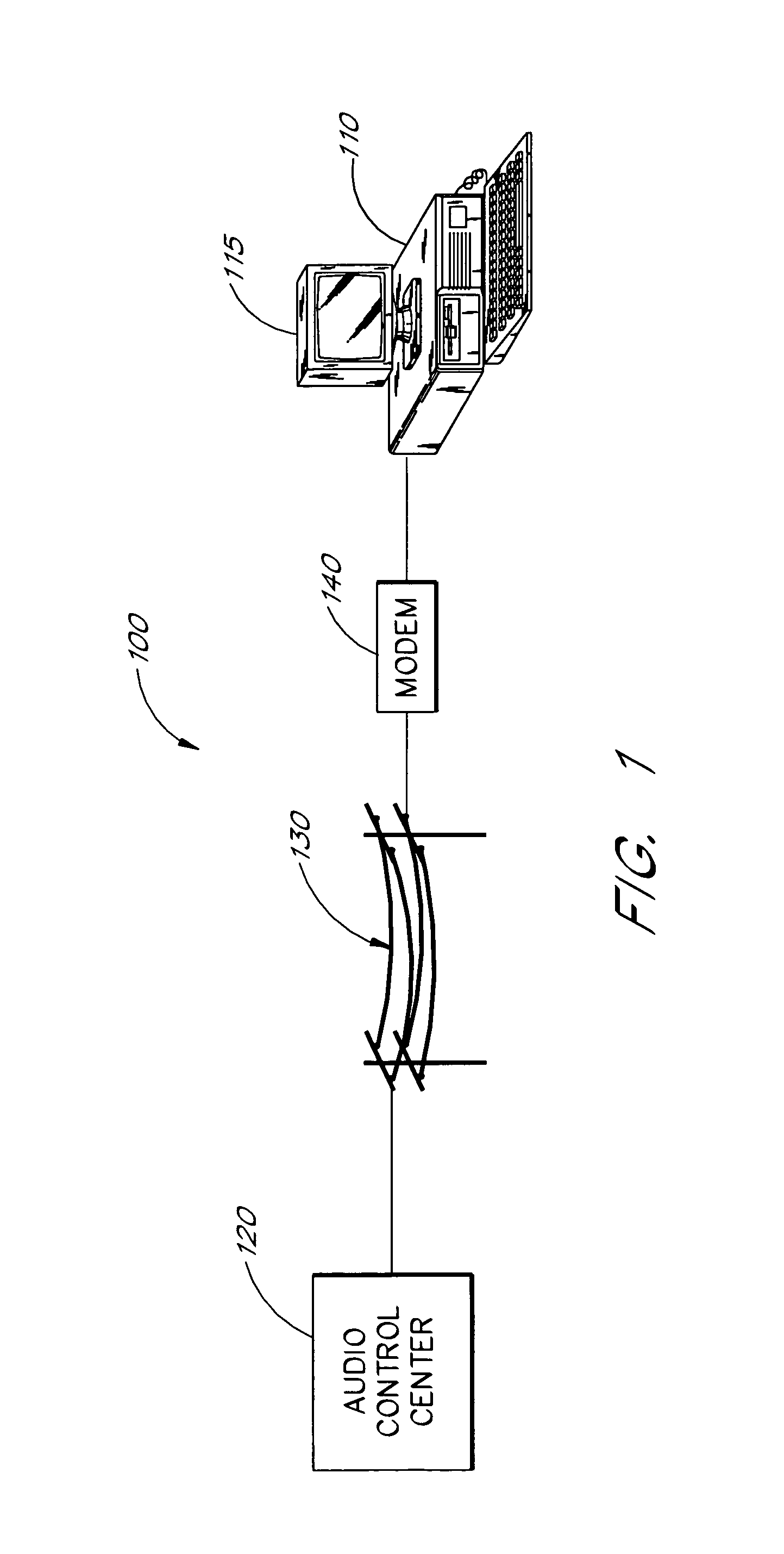

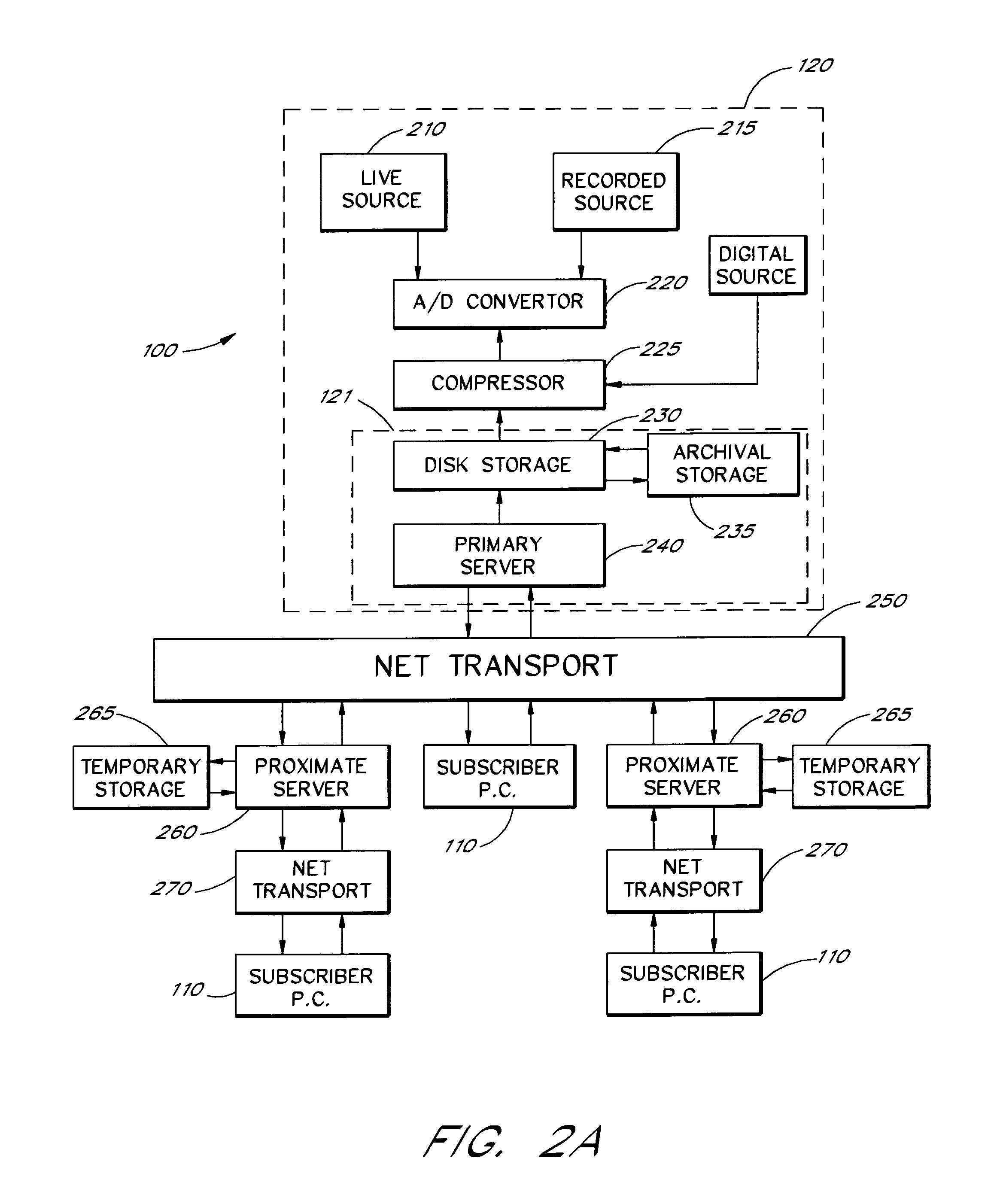

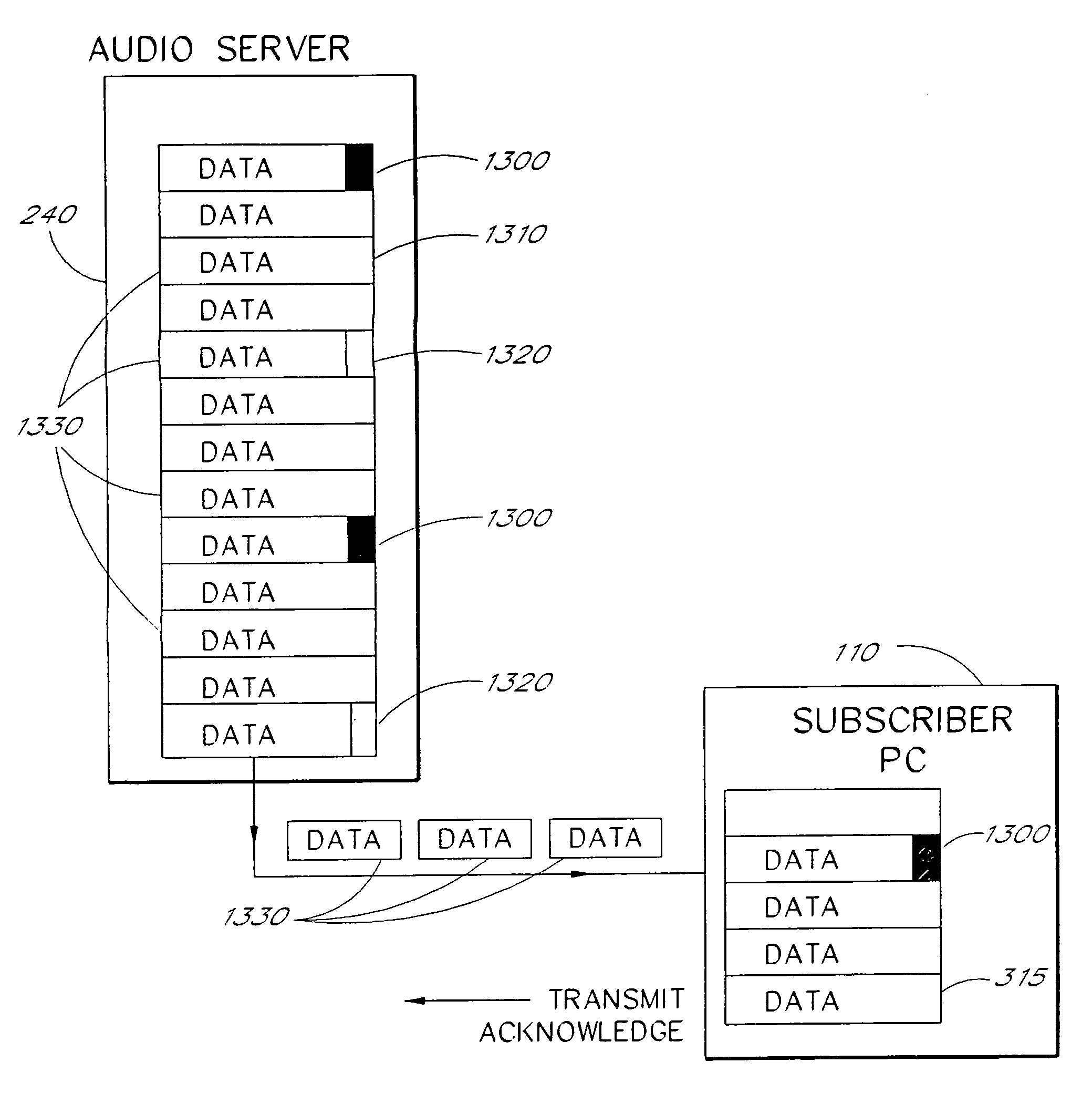

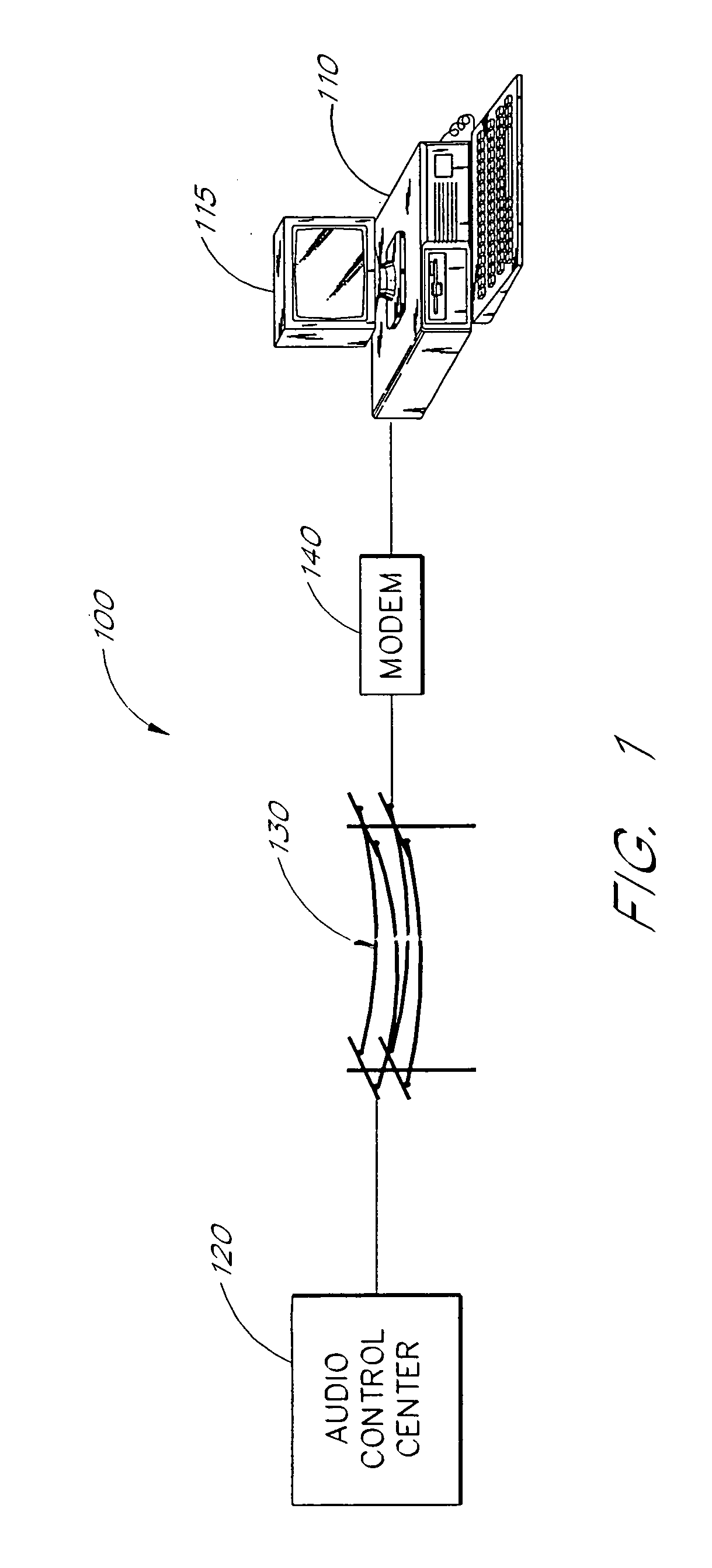

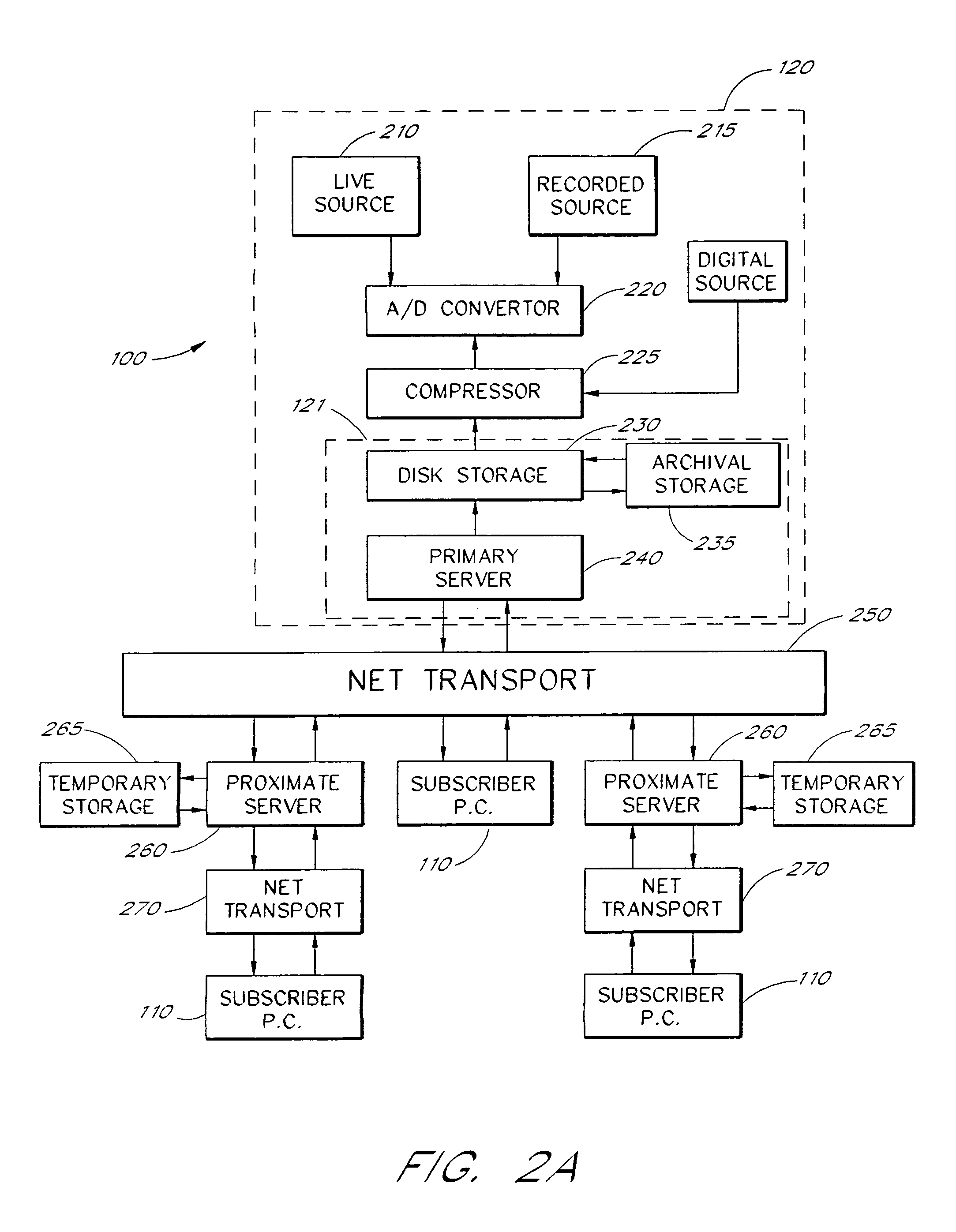

Multimedia communications system and method for providing audio on demand to subscribers

InactiveUS6985932B1Quality improvementHigh audio signalSpecific information broadcast systemsBroadcast transmission systemsCommunications systemTelecommunications link

An audio-on-demand communication system provides real-time playback of audio data transferred via telephone lines or other communication links. One or more audio servers include memory banks which store compressed audio data. At the request of a user at a subscriber PC, an audio server transmits the compressed audio data over the communication link to the subscriber PC. The subscriber PC receives and decompresses the transmitted audio data in less than real-time using only the processing power of the CPU within the subscriber PC. According to one aspect of the present invention, high quality audio data compressed according to lossless compression techniques is transmitted together with normal quality audio data. According to another aspect of the present invention, metadata, or extra data, such as text, captions, still images, etc., is transmitted with audio data and is simultaneously displayed with corresponding audio data. The audio-on-demand system also provides a table of contents indicating significant divisions in the audio clip to be played and allows the user immediate access to audio data at the listed divisions. According to a further aspect of the present invention, servers and subscriber PCs are dynamically allocated based upon geographic location to provide the highest possible quality in the communication link.

Owner:INTEL CORP

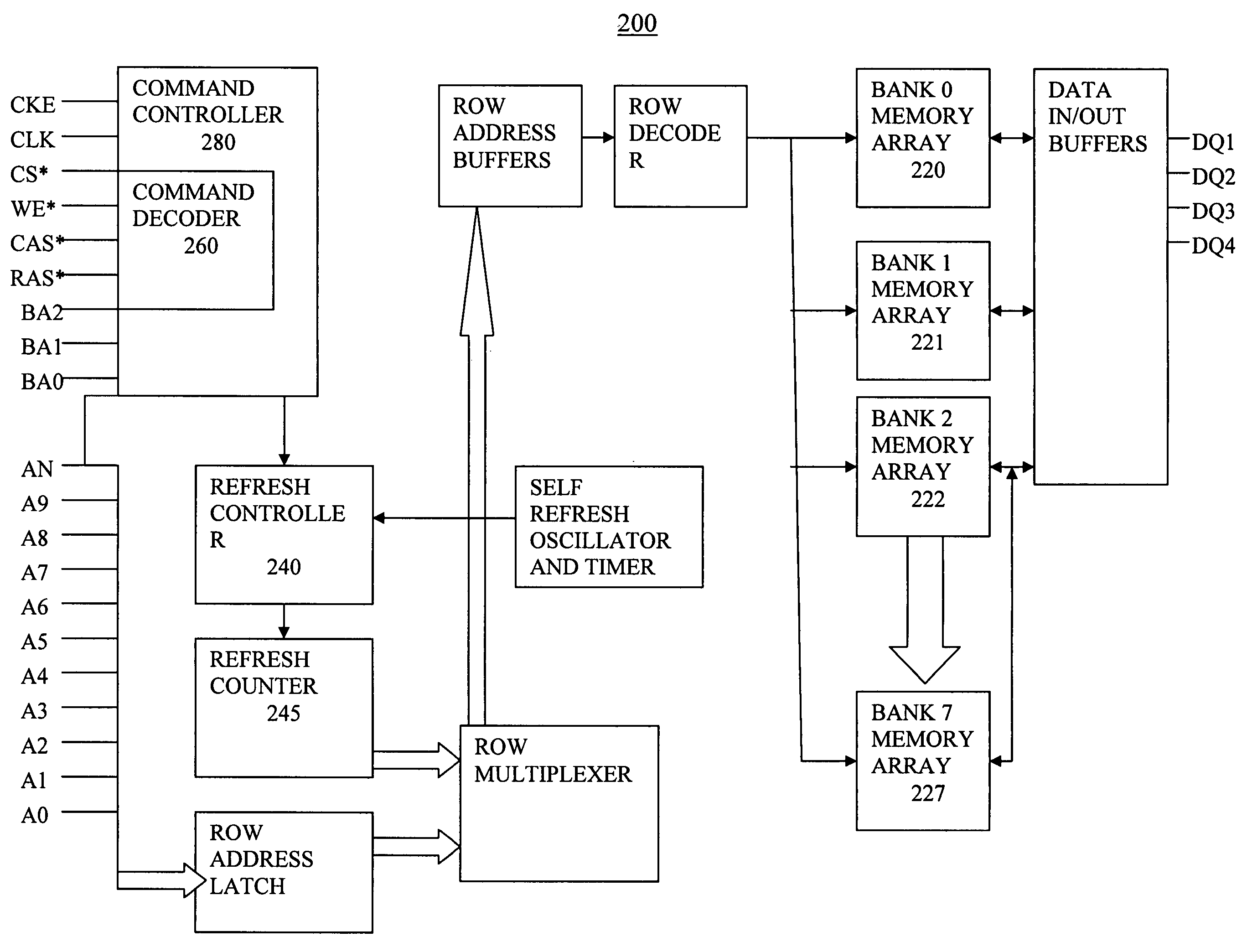

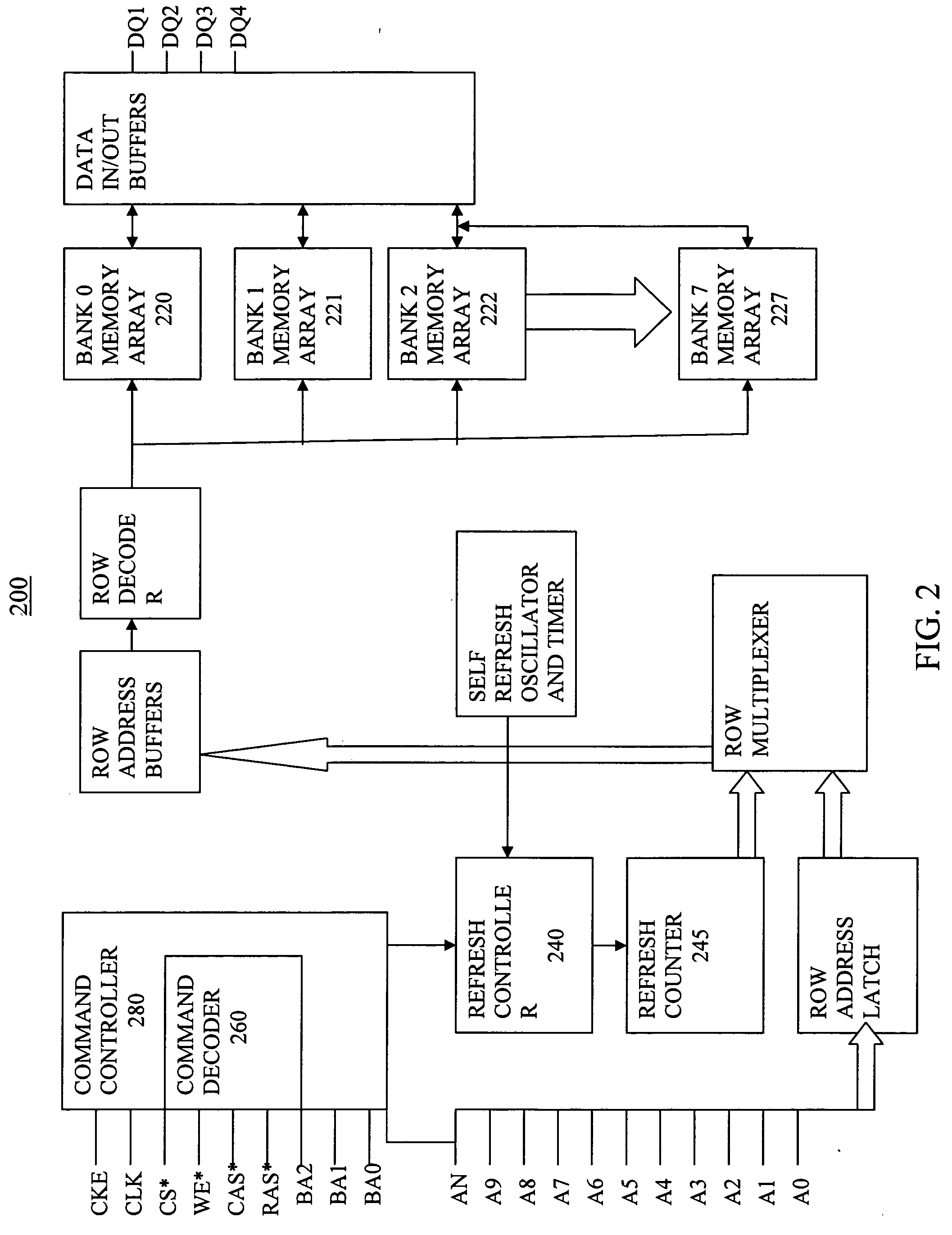

Partial bank DRAM refresh

InactiveUS20050108460A1Memory adressing/allocation/relocationDigital storageComputer hardwareMemory bank

A “partial refresh command” is used to refresh a fraction of the banks in a multi-bank DRAM. In a first implementation the command refreshes one half of the banks. In a second implementation the command refreshes one quarter of the banks. The power drawn by the upper or lower bank refresh on the eight bank DRAM is the same as the power drawn by an “all bank” refresh on a four bank DRAM, without requiring the refresh period to be extended.

Owner:INTEL CORP

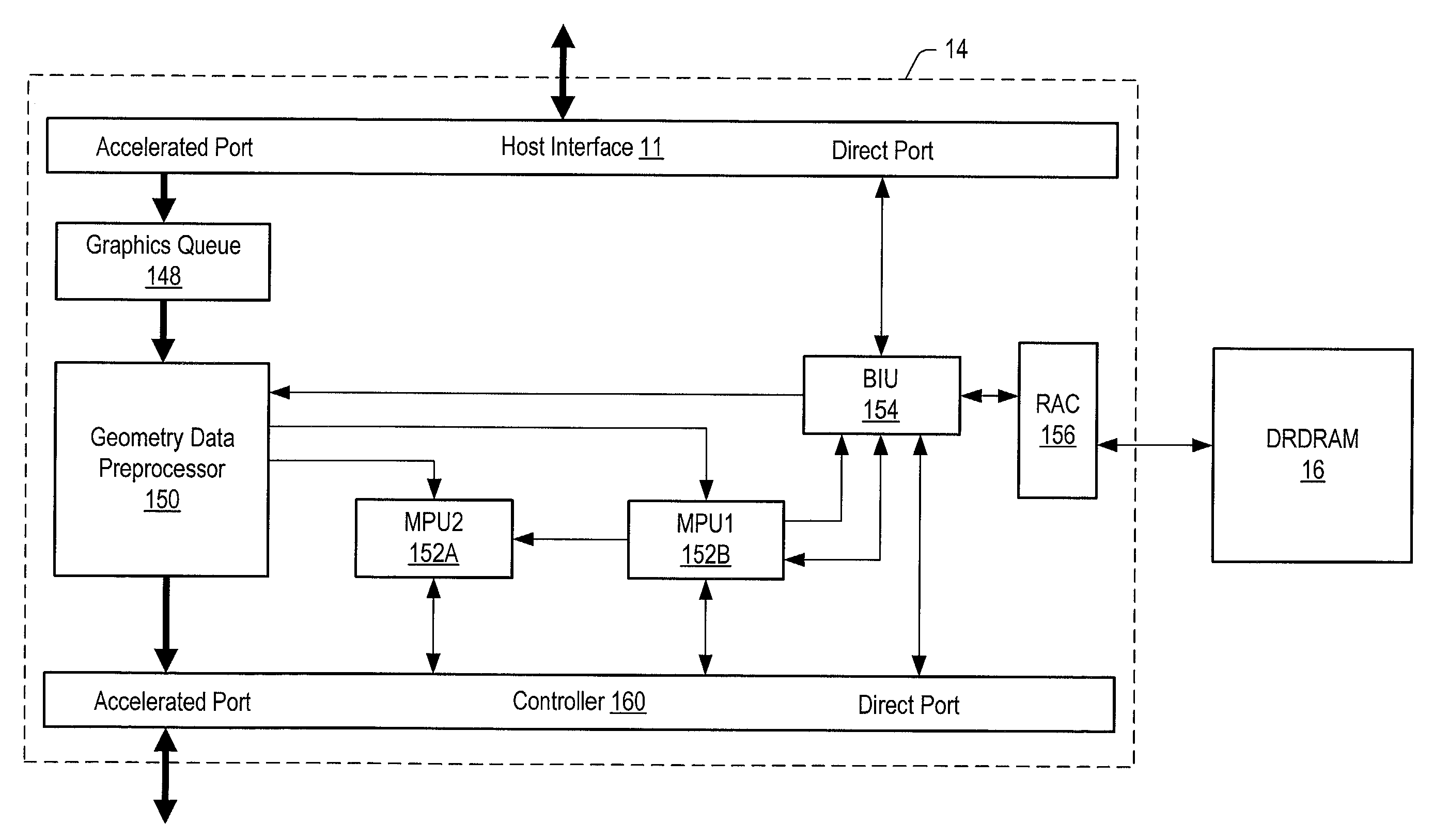

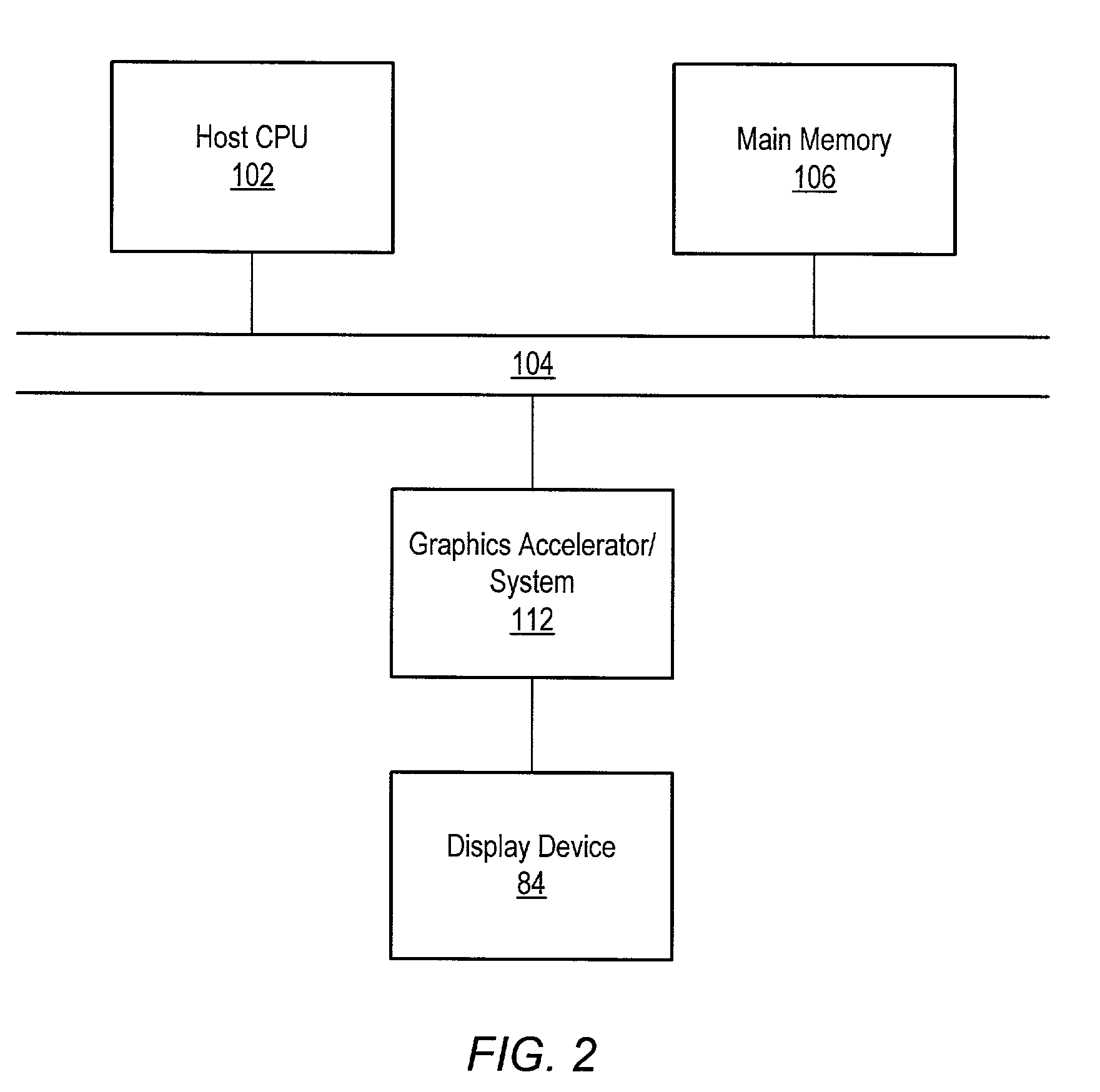

System and method for handling display device requests for display data from a frame buffer

InactiveUS20030169262A1Memory adressing/allocation/relocationCathode-ray tube indicatorsGraphic systemMemory bank

A graphics system may include a frame buffer, a processing device coupled to access data in the frame buffer, a frame buffer interface coupled to the frame buffer, and an output controller configured to assert a request for display data to provide to a display device. The frame buffer interface may receive the request for display data from the output controller and delay providing the request for display data to the frame buffer if the processing device is currently requesting access to a portion of the frame buffer targeted by the request for display data. For example, if the frame buffer includes several memory banks and the request for display data targets a first bank, the frame buffer interface may delay providing the request for display data to the frame buffer if the processing device is currently requesting access to the first bank.

Owner:ORACLE INT CORP

Memory system and memory card

InactiveUS20070198770A1Rise in cost is suppressedRequirement for numberMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:HORII TAKASHI +2

Combined command set

InactiveUS20030217223A1Memory adressing/allocation/relocationDigital storageStatic random-access memoryMemory bank

A circuit and method of operation for combining commands in a DRAM (dynamic random access memory) are revealed. The method applies to DRAMs having a plurality of memory banks or arrays. The method combines commands to rows on different memory banks, and the method also combines row and column commands on different memory banks. The method eliminates steps in a sequence of commands, and may significantly increase speed of input / output to a DRAM.

Owner:INFINEON TECH AG

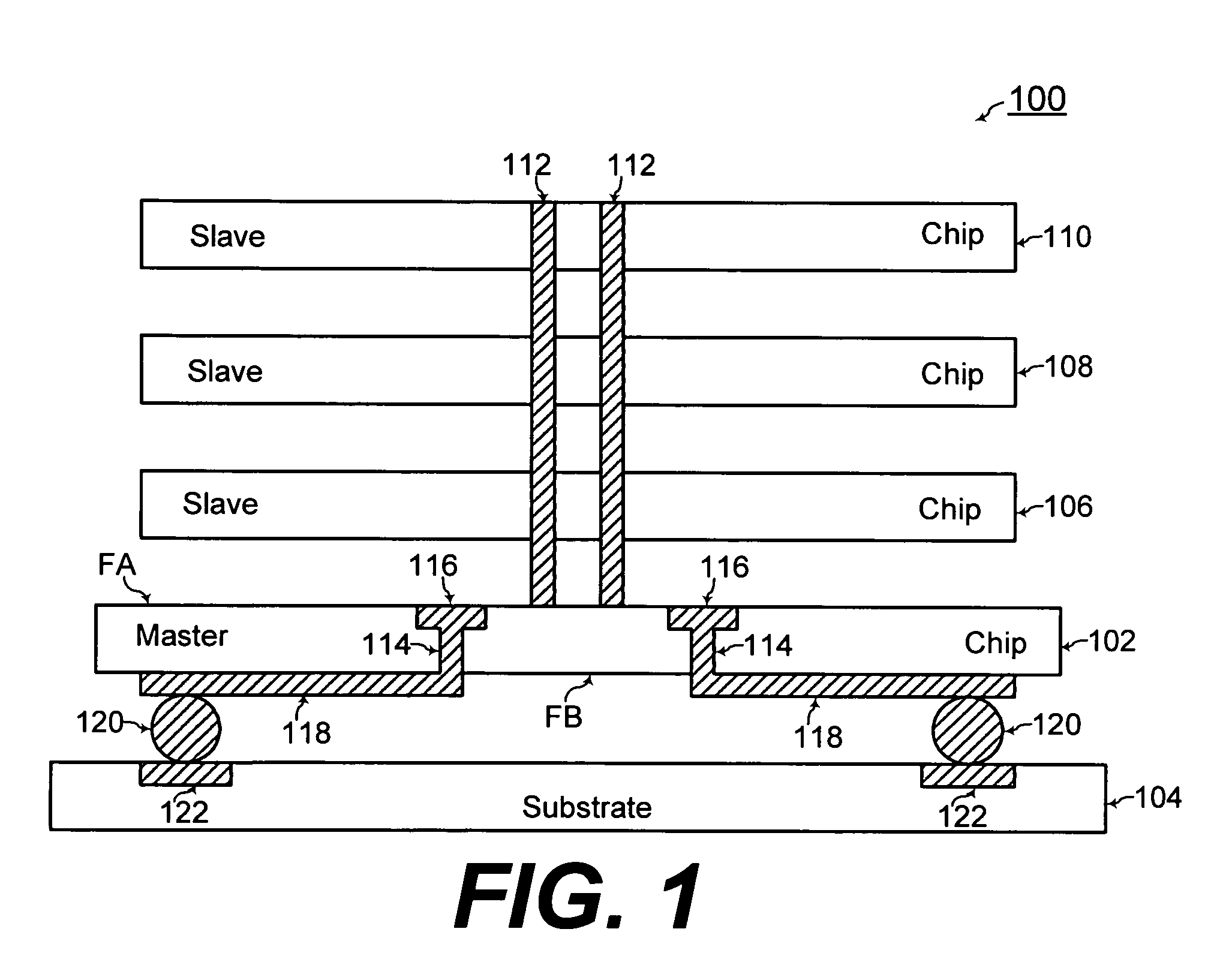

Semiconductor product and method for forming a semiconductor product

InactiveUS20070109831A1Increase storage capacityIncrease the number ofSolid-state devicesStatic storageMemory bankSemiconductor chip

A semiconductor product includes a first semiconductor chip that includes input / output circuitry enabling transfer of data from memory banks of the semiconductor product to an external electronic device and / or from an external electronic device to the memory banks of the semiconductor product. A number of second semiconductor chips are stacked on and electrically coupled to the first semiconductor chip. The second semiconductor chips are stacked on one another. Each second semiconductor chip of the plurality of second semiconductor chips comprises at least one of the memory banks of the semiconductor product. The memory banks of the second semiconductor chips are accessible by the input / output circuitry arranged on the first semiconductor chip.

Owner:INFINEON TECH AG

Audio-on-demand communication system

InactiveUS7349976B1Quality improvementHigh audio signalAnalogue secracy/subscription systemsMultiple digital computer combinationsTelecommunications linkCommunications system

An audio-on-demand communication system provides real-time playback of audio data transferred via telephone lines or other communication links. One or more audio servers include memory banks which store compressed audio data. At the request of a user at a subscriber PC, an audio server transmits the compressed audio data over the communication link to the subscriber PC. The subscriber PC receives and decompresses the transmitted audio data in less than real-time using only the processing power of the CPU within the subscriber PC. According to one aspect of the present invention, high quality audio data compressed according to lossless compression techniques is transmitted together with normal quality audio data. According to another aspect of the present invention, metadata, or extra data, such as text, captions, still images, etc., is transmitted with audio data and is simultaneously displayed with corresponding audio data. The audio-on-demand system also provides a table of contents indicating significant divisions in the audio clip to be played and allows the user immediate access to audio data at the listed divisions. According to a further aspect of the present invention, servers and subscriber PCs are dynamically allocated based upon geographic location to provide the highest possible quality in the communication link.

Owner:INTEL CORP

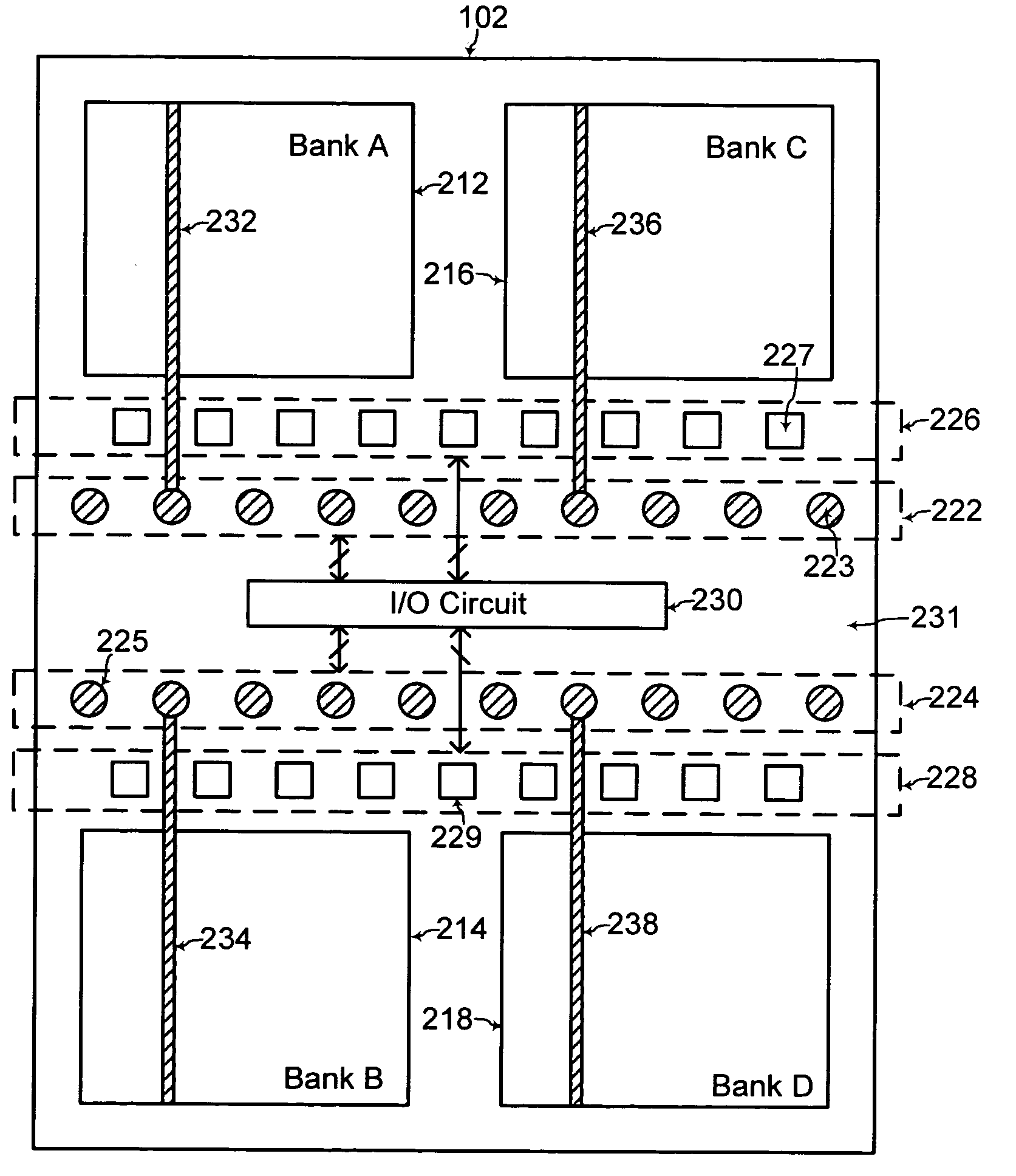

Stacked memory module and system

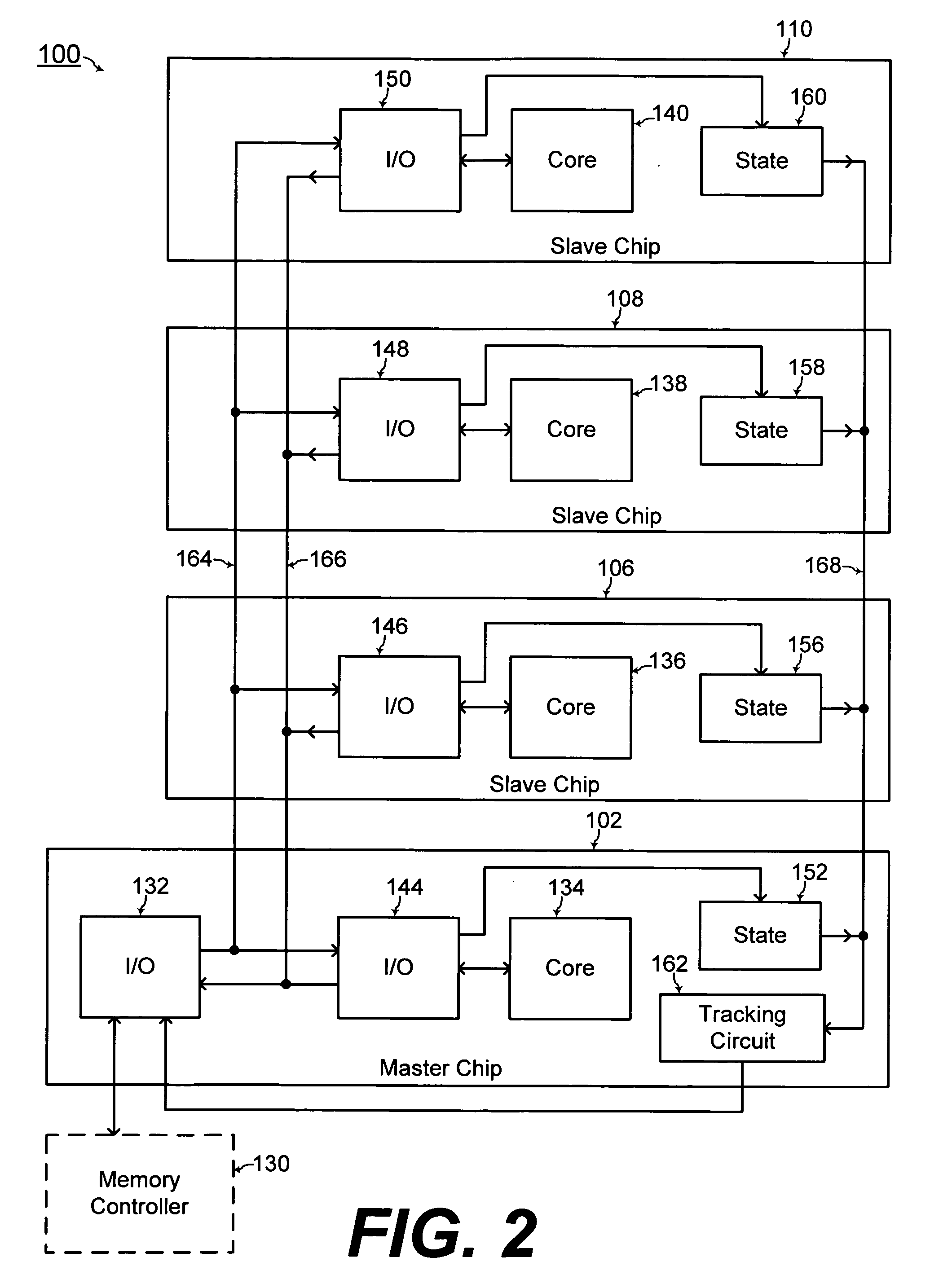

ActiveUS20100020583A1Increase memory capacityEfficient wiring and capacity organizationSemiconductor/solid-state device detailsSolid-state devicesMemory bankComputer module

A three dimensional memory module and system are formed with at least one slave chip stacked over a master chip. Through semiconductor vias (TSVs) are formed through at least one of the master and slave chips. The master chip includes a memory core for increased capacity of the memory module / system. In addition, capacity organizations of the three dimensional memory module / system resulting in efficient wiring is disclosed for forming multiple memory banks, multiple bank groups, and / or multiple ranks of the three dimensional memory module / system.

Owner:SAMSUNG ELECTRONICS CO LTD

Capacity-expanding memory device

InactiveUS20060277355A1Increase memory capacityReduce loadMemory adressing/allocation/relocationMemory bankMemory module

Owner:SANMINA-SCI CORPORATION

Method and apparatus for maintaining cache coherency in a computer system having multiple processor buses

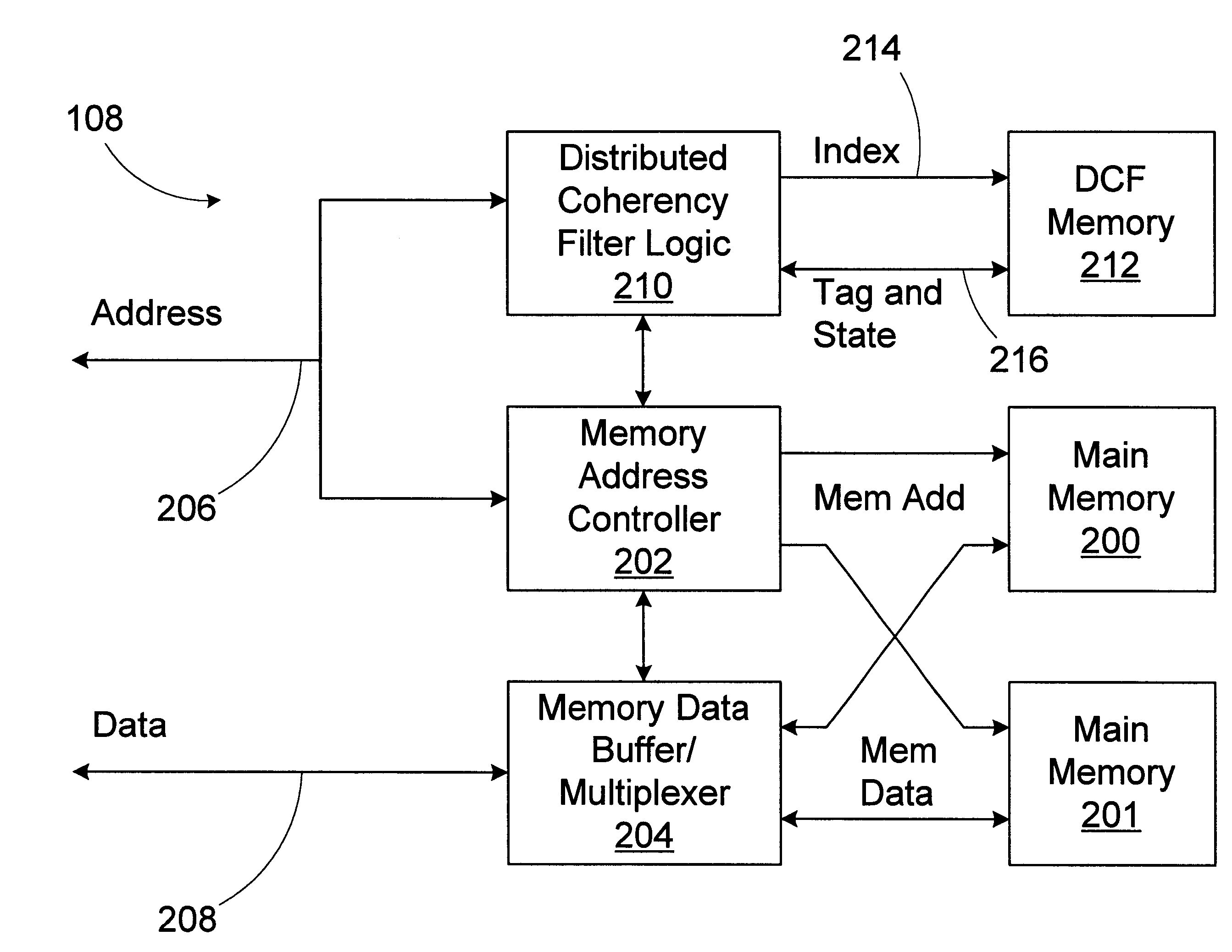

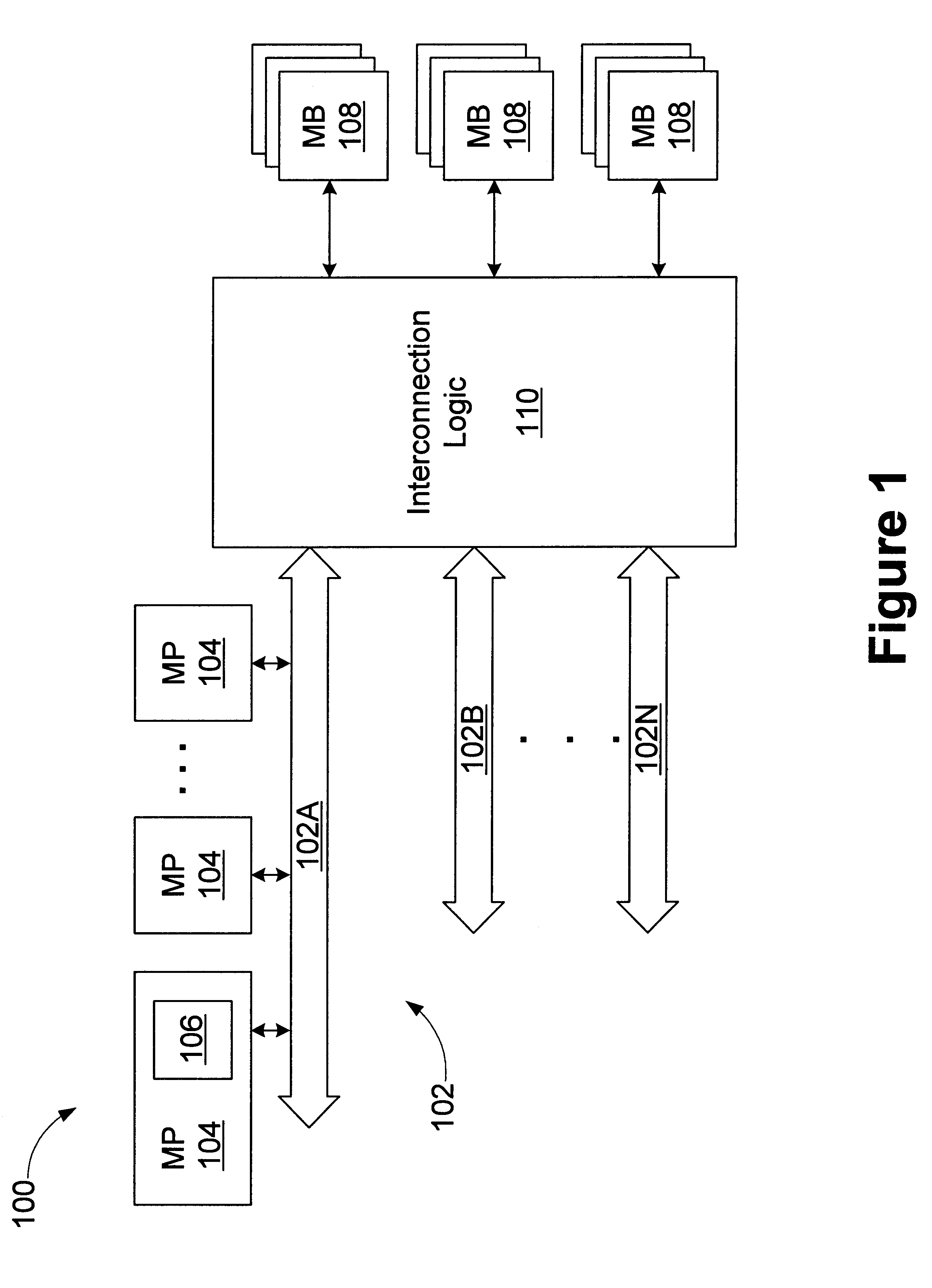

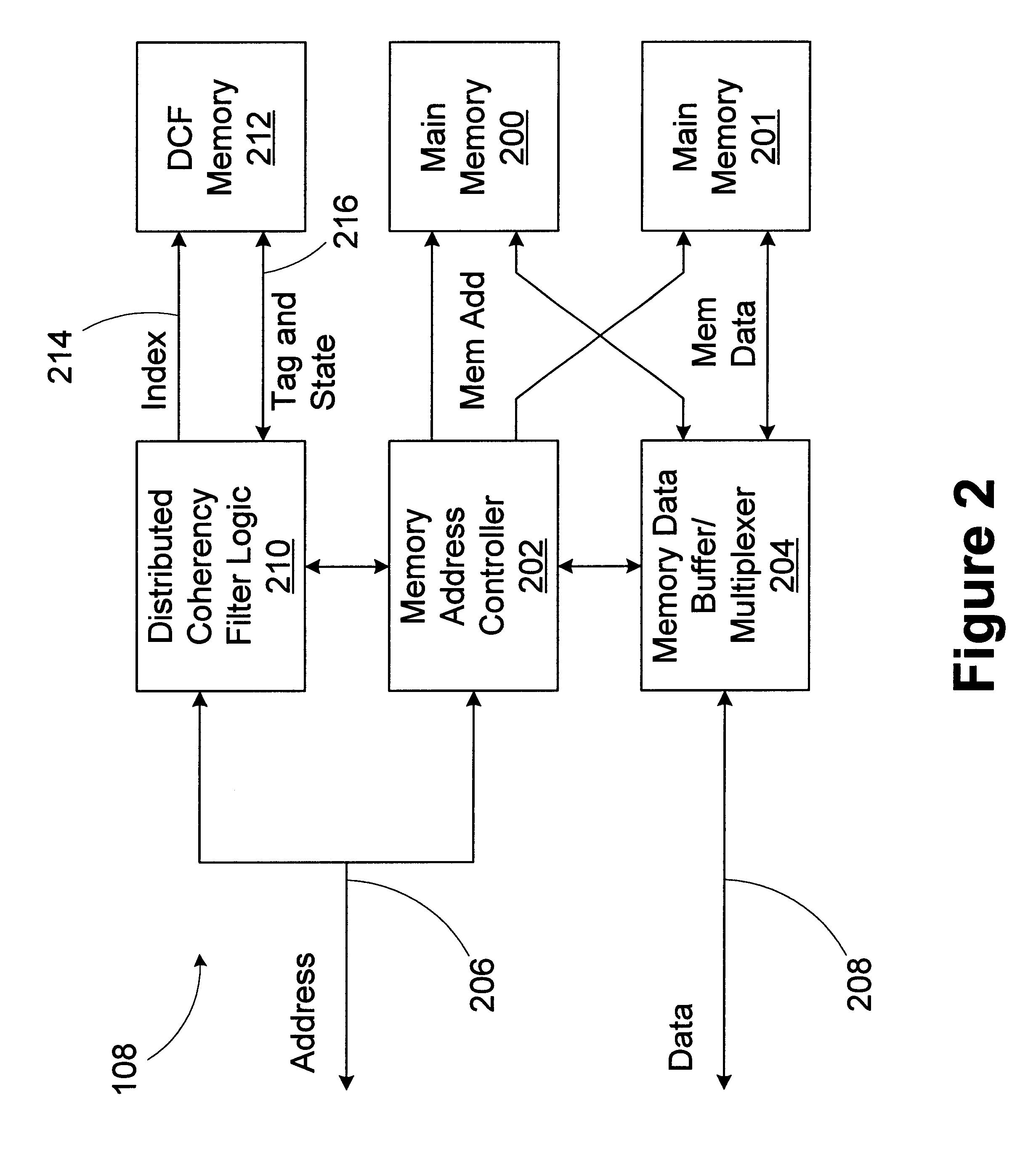

A computer system includes a plurality of processor buses, and a memory bank. The plurality of processors is coupled to the processor buses. At least a portion of the processors have associated cache memories arranged in cache lines. The memory bank is coupled to the processor buses. The memory bank includes a main memory and a distributed coherency filter. The main memory is adapted to store data corresponding to at least a portion of the cache lines. The distributed coherency filter is adapted to store coherency information related to the cache lines associated with each of the processor buses. A method for maintaining cache coherency among processors coupled to a plurality of processor buses is provided. Lines of data are stored in a main memory. A memory request is received for a particular line of data in the main memory from one of the processor buses. Coherency information is stored related to the lines of data associated with each of the processor buses. The coherency information is accessed based on the memory request.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

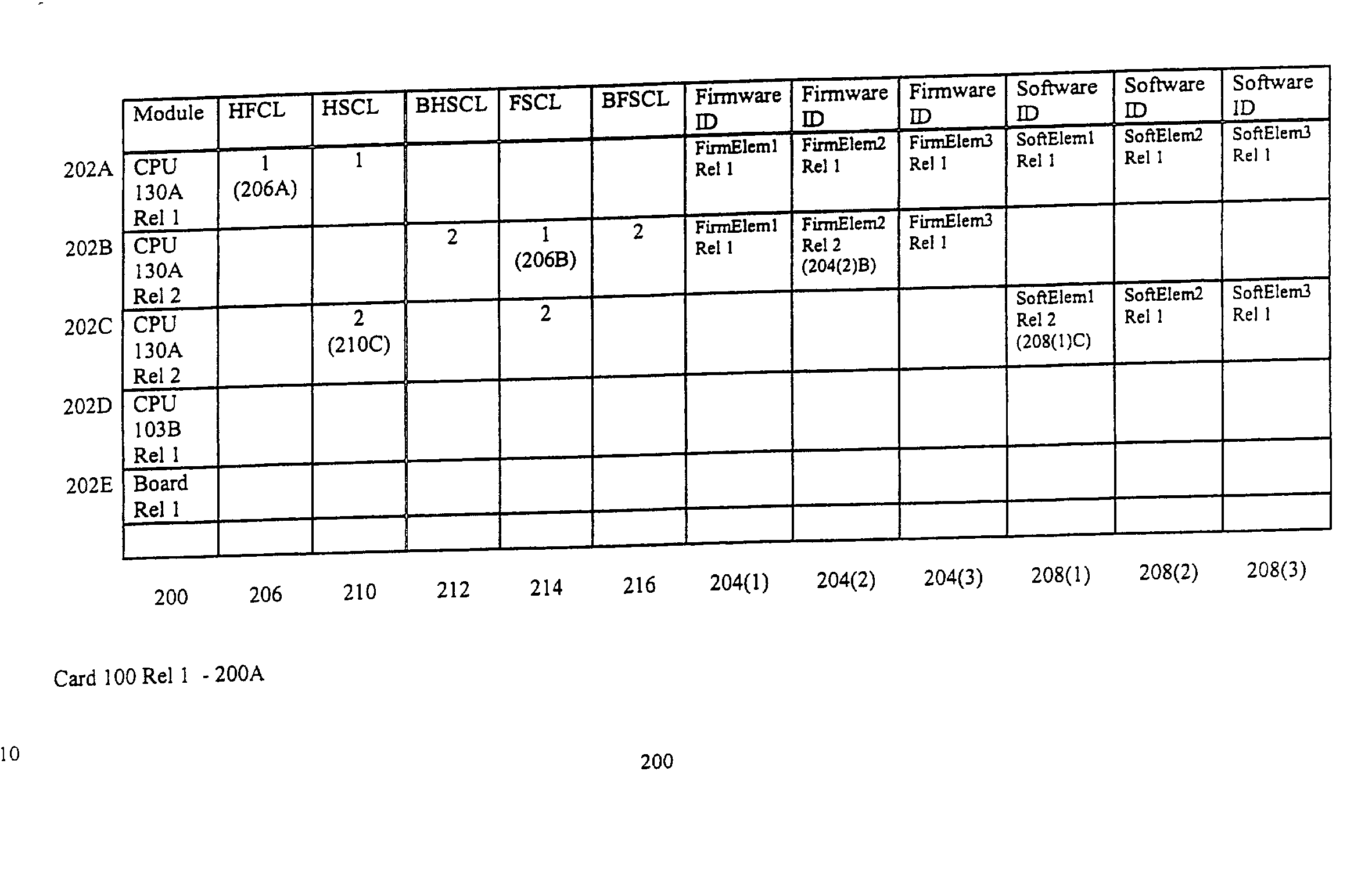

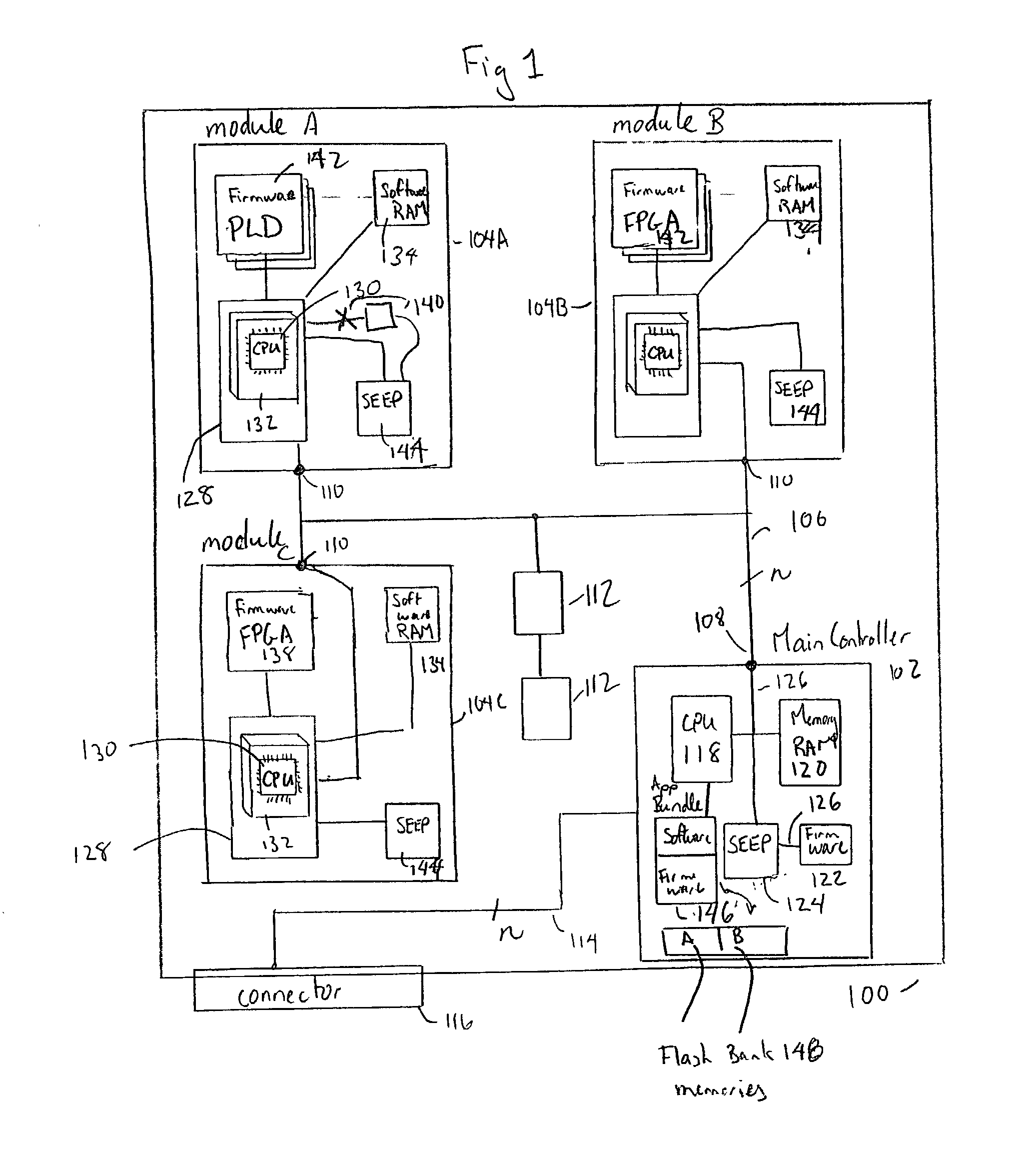

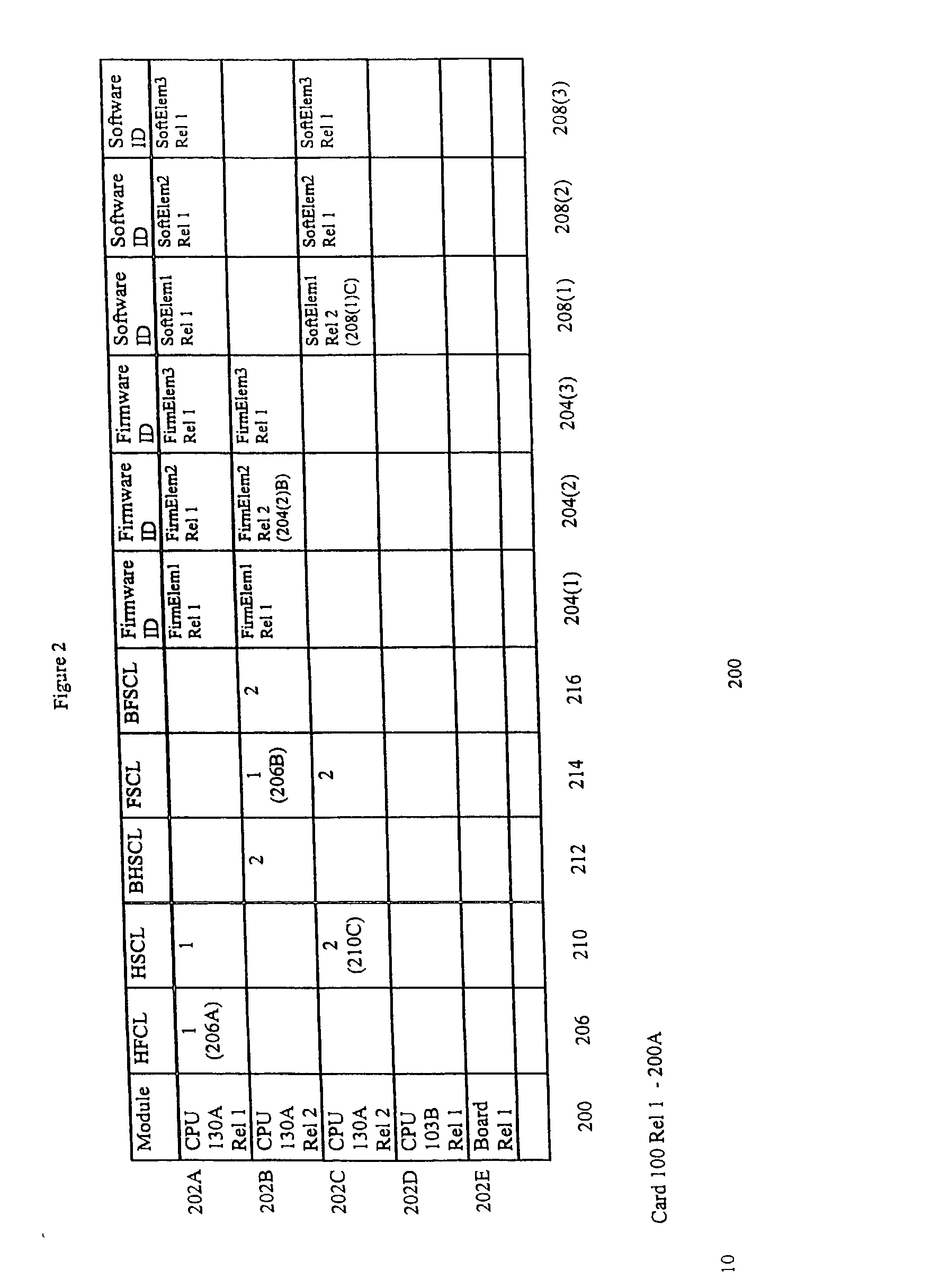

System and method for managing configurable elements of devices in a network element and a network

InactiveUS20030140134A1Digital computer detailsProgram loading/initiatingMemory bankComputer compatibility

The invention provides a system and a method of selecting a version of a program code from a series of program codes for a program element associated with a hardware element for a circuit board. The invention identifies a compatible program code for a particular hardware element and downloads the compatible program code. A record is associated with the hardware element to identify its compatible program codes. The program codes are stored in a bundle and are associated with a software code. A program loader, associated with each bundle, checks the compatibilities of the hardware element to both the software code and the selected program code. Another record stores compatibility information of the program codes with hardware element versions and is also associated with the bundle. Code downloads are made first to an inactive memory bank and after the codes are verified, the inactive memory bank is made active.

Owner:ALCATEL CANADA

GPS receiver with efficient signal acquisition

InactiveUS6118808AReduce power consumptionShorten the timePosition fixationSynchronisation signal speed/phase controlMemory bankGps receiver

A direct sequence spread spectrum receiver samples an incoming signal and translates the signal to an IF signal. The IF signal is sampled and stored in memory. In one embodiment, the memory consists of two memory banks which alternately receive sample segments. During a write period to one of the memory banks, the other memory bank supplies its output to a processor. This continues in a ping-pong manner. In another embodiment, a single memory bank is filled and read as necessary, the receiver ignoring incoming signal until the processor has completed processing the sample available at the output of the memory. Such a receiver is useful in global positioning satellite (GPS) signal processing where the incoming signal contains several satellite transmissions encoded with CDMA encoding.

Owner:GENERAL ELECTRIC CO

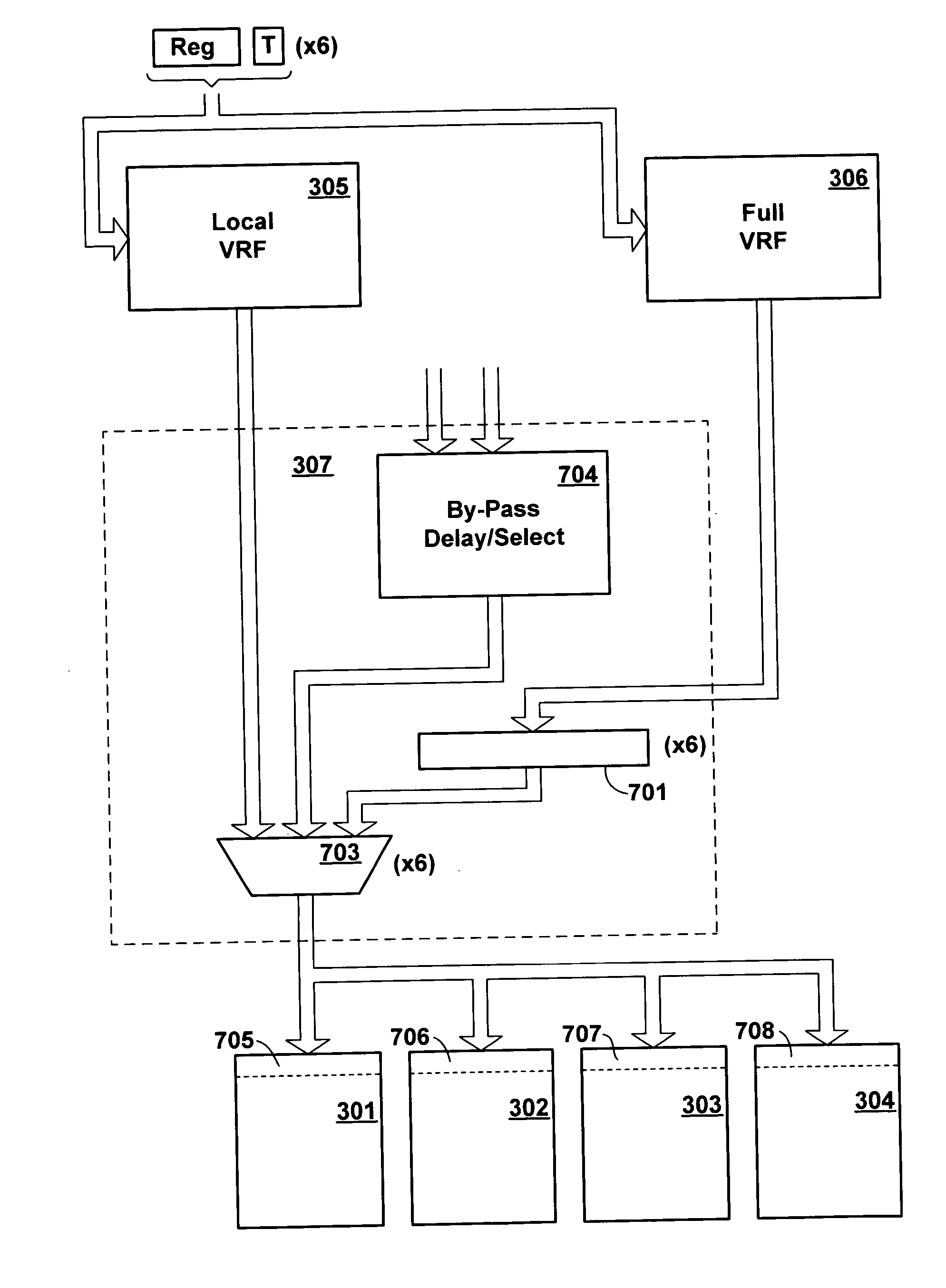

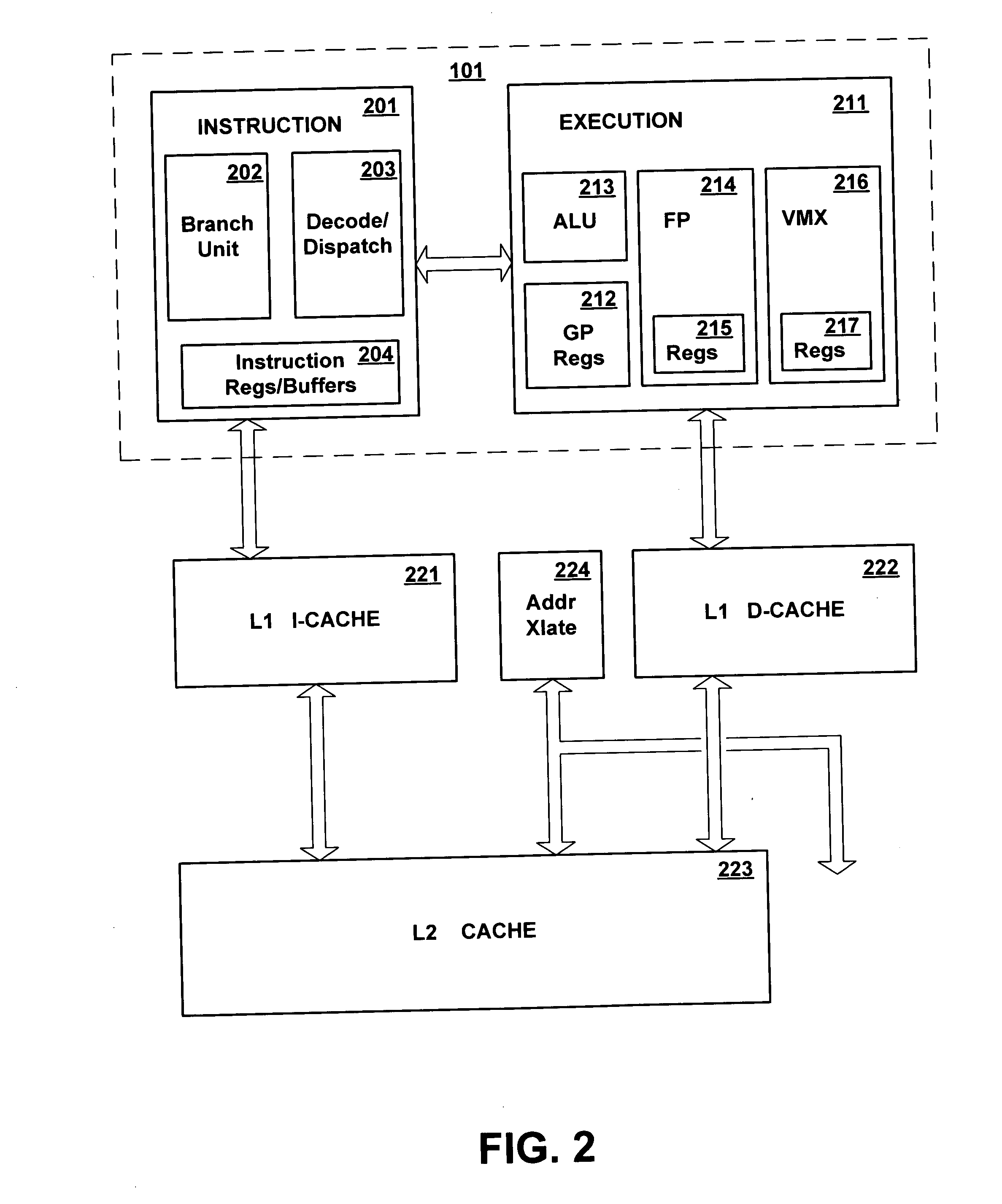

Digital data processing apparatus having multi-level register file

InactiveUS20050289299A1Faster access latency timeSlow access latency timeRegister arrangementsMemory adressing/allocation/relocationDigital dataMemory bank

A processor contains multiple levels of registers having different access latency. A relatively smaller set of registers is contained in a relatively faster higher level register bank, and a larger, more complete set of the registers is contained in a relatively slower lower level register bank. Physically, the higher level register bank is placed closer to functional logic which receives inputs from the registers. Preferably, the lower level bank includes a complete set of all processor registers, and the higher level bank includes a smaller subset of the registers, duplicating information in the lower level bank. The higher level bank is preferably accessible in a single clock cycle.

Owner:IBM CORP

Selective replication of data structures

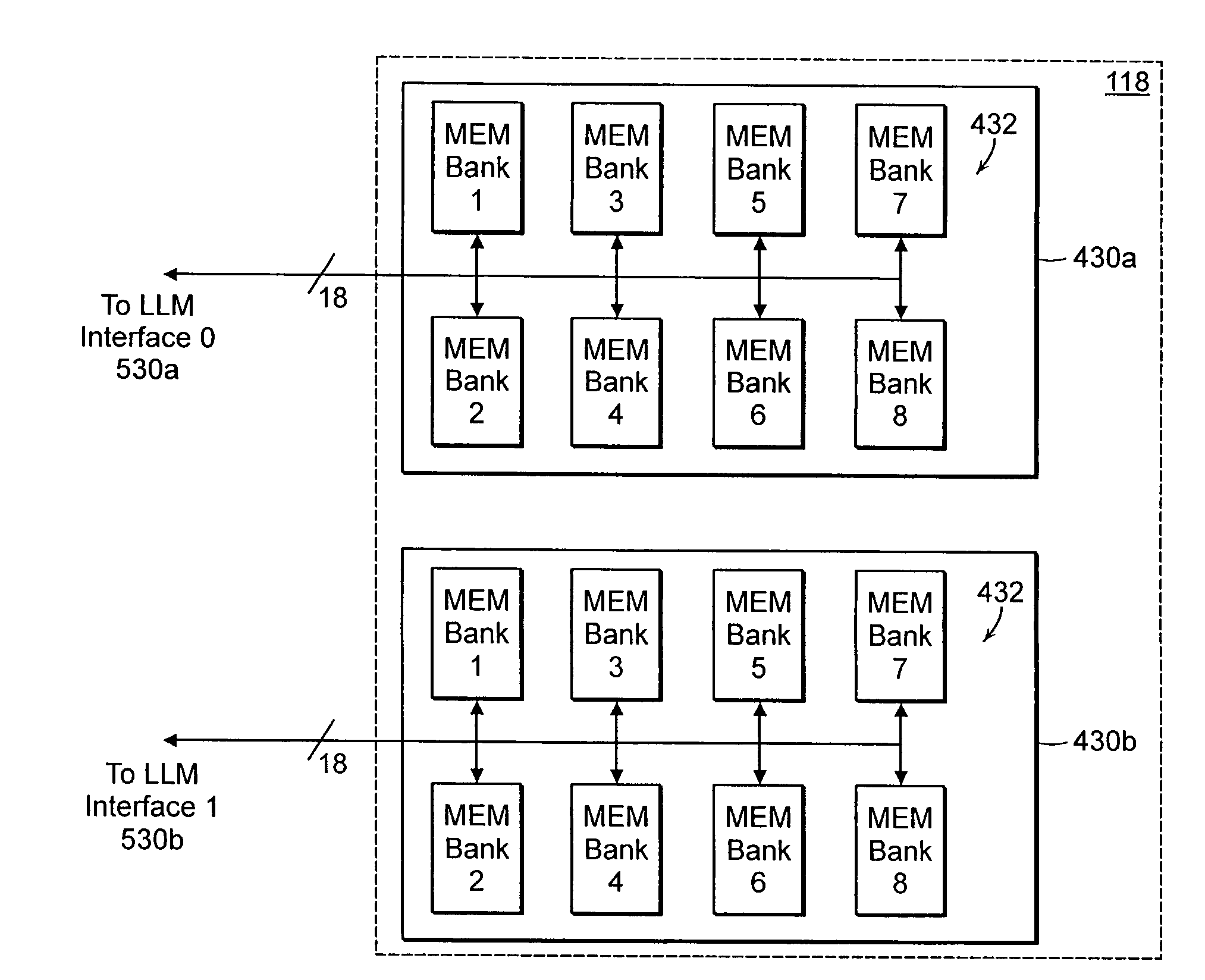

ActiveUS7558925B2Reduce delaysLow-latency memoryMemory architecture accessing/allocationMemory adressing/allocation/relocationArray data structureMemory bank

Methods and apparatus are provided for selectively replicating a data structure in a low-latency memory. The memory includes multiple individual memory banks configured to store replicated copies of the same data structure. Upon receiving a request to access the stored data structure, a low-latency memory access controller selects one of the memory banks, then accesses the stored data from the selected memory bank. Selection of a memory bank can be accomplished using a thermometer technique comparing the relative availability of the different memory banks. Exemplary data structures that benefit from the resulting efficiencies include deterministic finite automata (DFA) graphs and other data structures that are loaded (i.e., read) more often than they are stored (i.e., written).

Owner:MARVELL ASIA PTE LTD

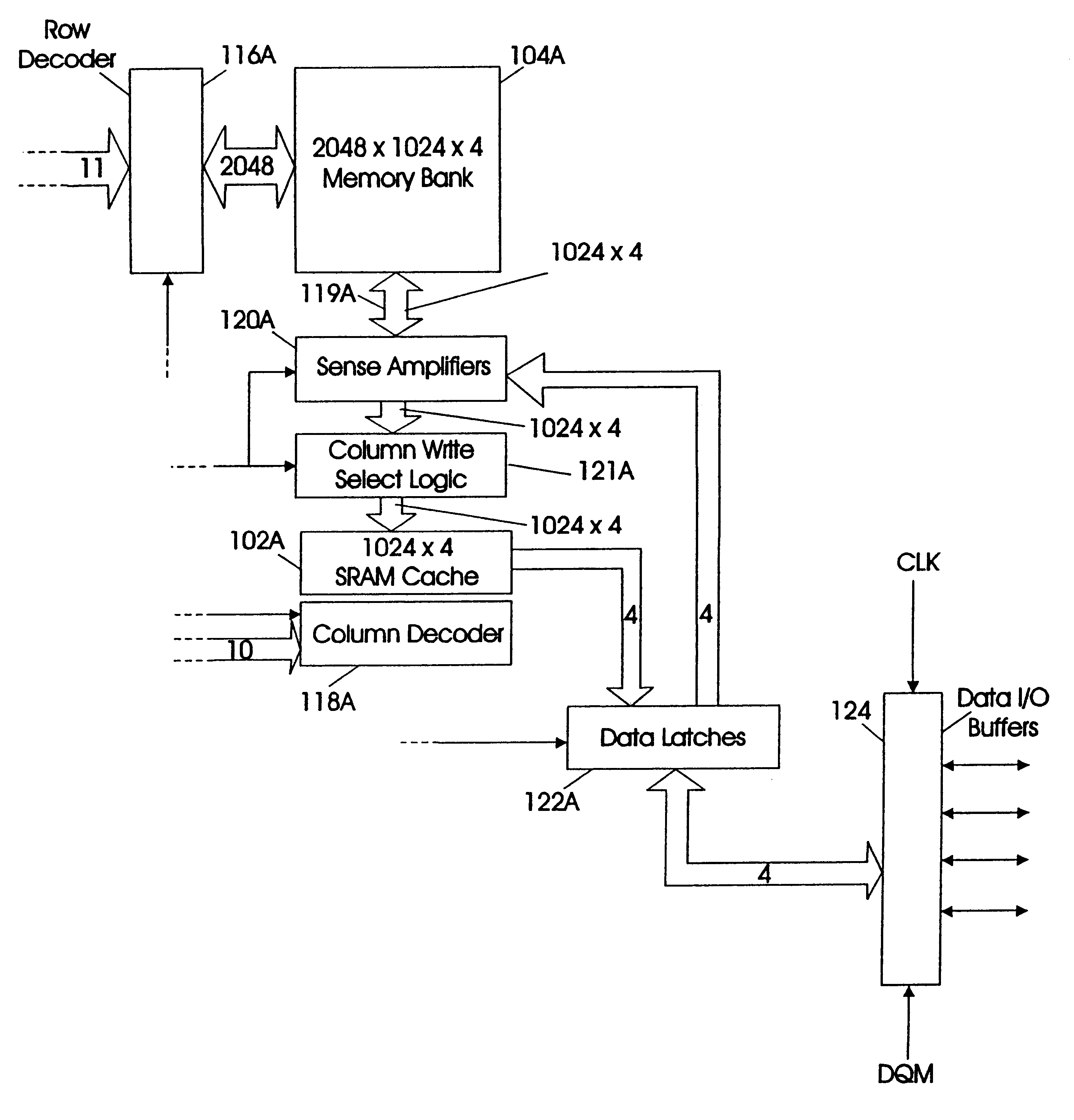

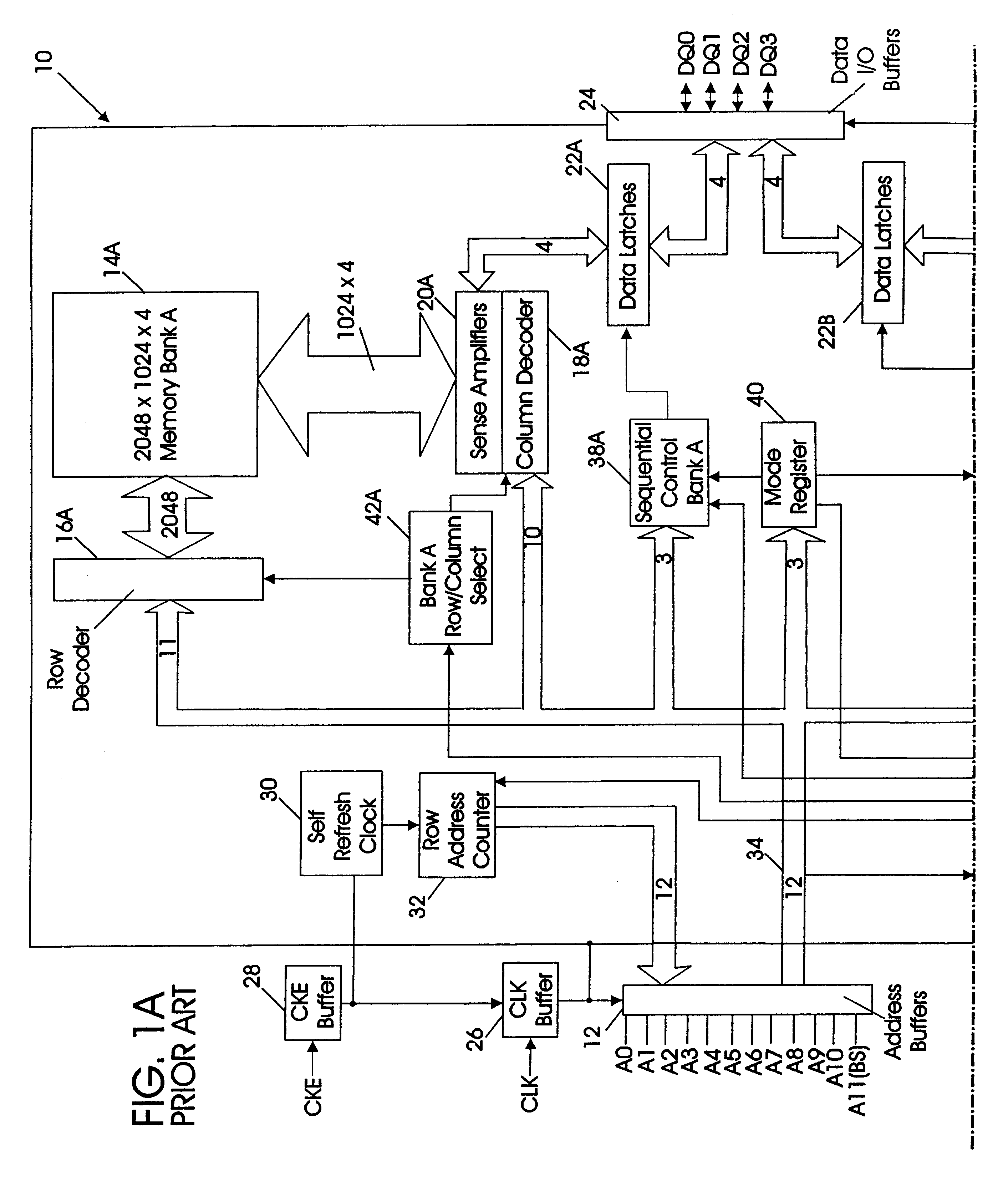

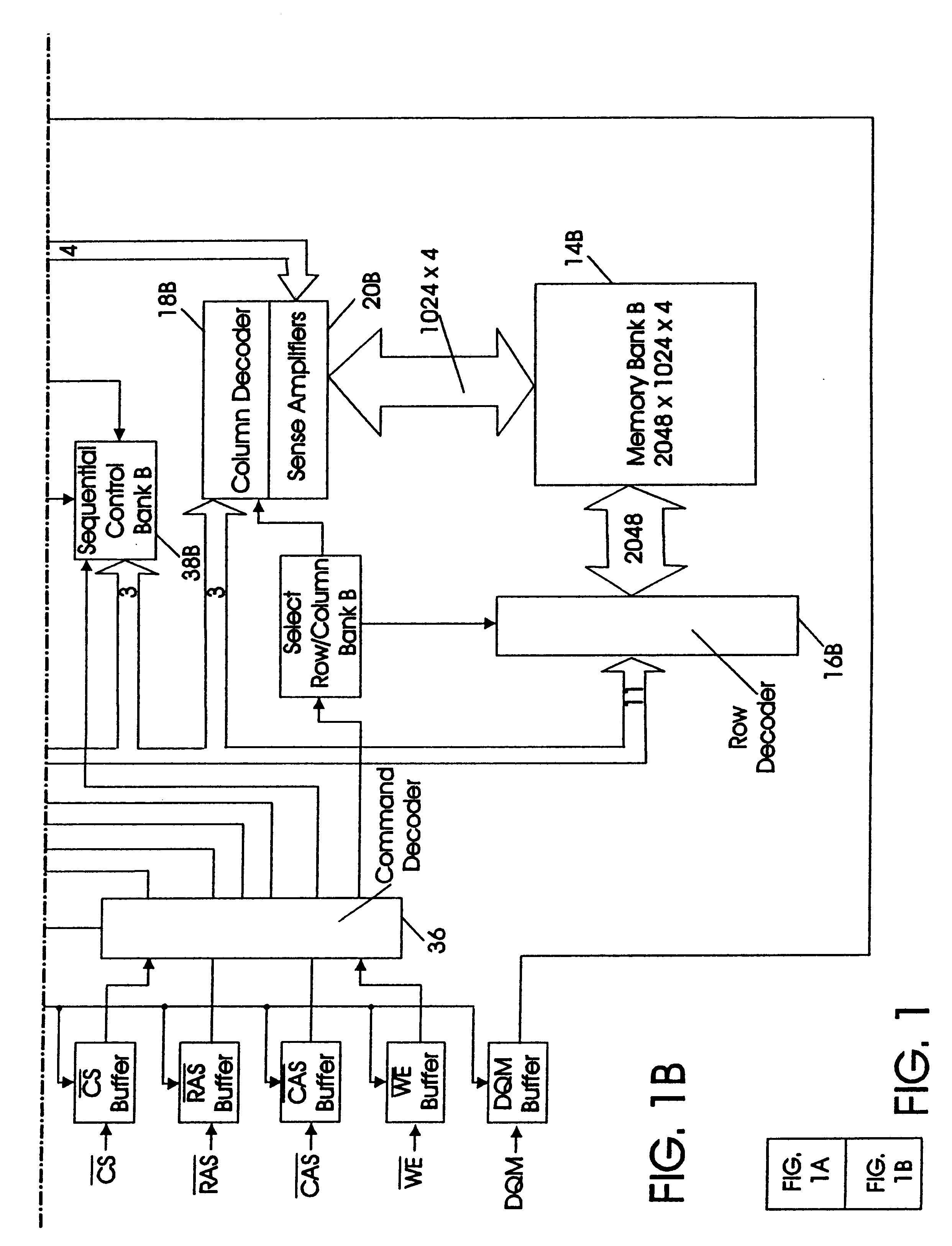

Cached synchronous DRAM architecture having a mode register programmable cache policy

InactiveUS6289413B1Memory adressing/allocation/relocationDigital storageBit lineAudio power amplifier

A cached synchronous dynamic random access memory (cached SDRAM) device having a multi-bank architecture and a programmable caching policy includes a synchronous dynamic random access memory (SDRAM) bank, a synchronous static randomly addressable row register, a select logic gating circuit, and mode register for programming of the cached SDRAM to operate in a Write Transfer mode corresponding to a Normal Operation mode of a standard SDRAM during a Write cycle, and to operate in a No Write Transfer mode according to an alternate operation mode during a Write cycle, thereby operating under a first and a second caching policy, respectively. The SDRAM includes a row decoder for selecting a row of data in a memory bank array, sense amplifiers for latching the row of data selected by the row decoder, and a synchronous column selector for selecting a desired column of the row of data. The row register stores a row of data latched by the sense amplifiers and the select logic gating circuit, disposed between the sense amplifiers and the row register, selectively gates the row of data present on the bit lines to the row register in accordance to particular synchronous memory operations being performed.

Owner:IBM CORP +2

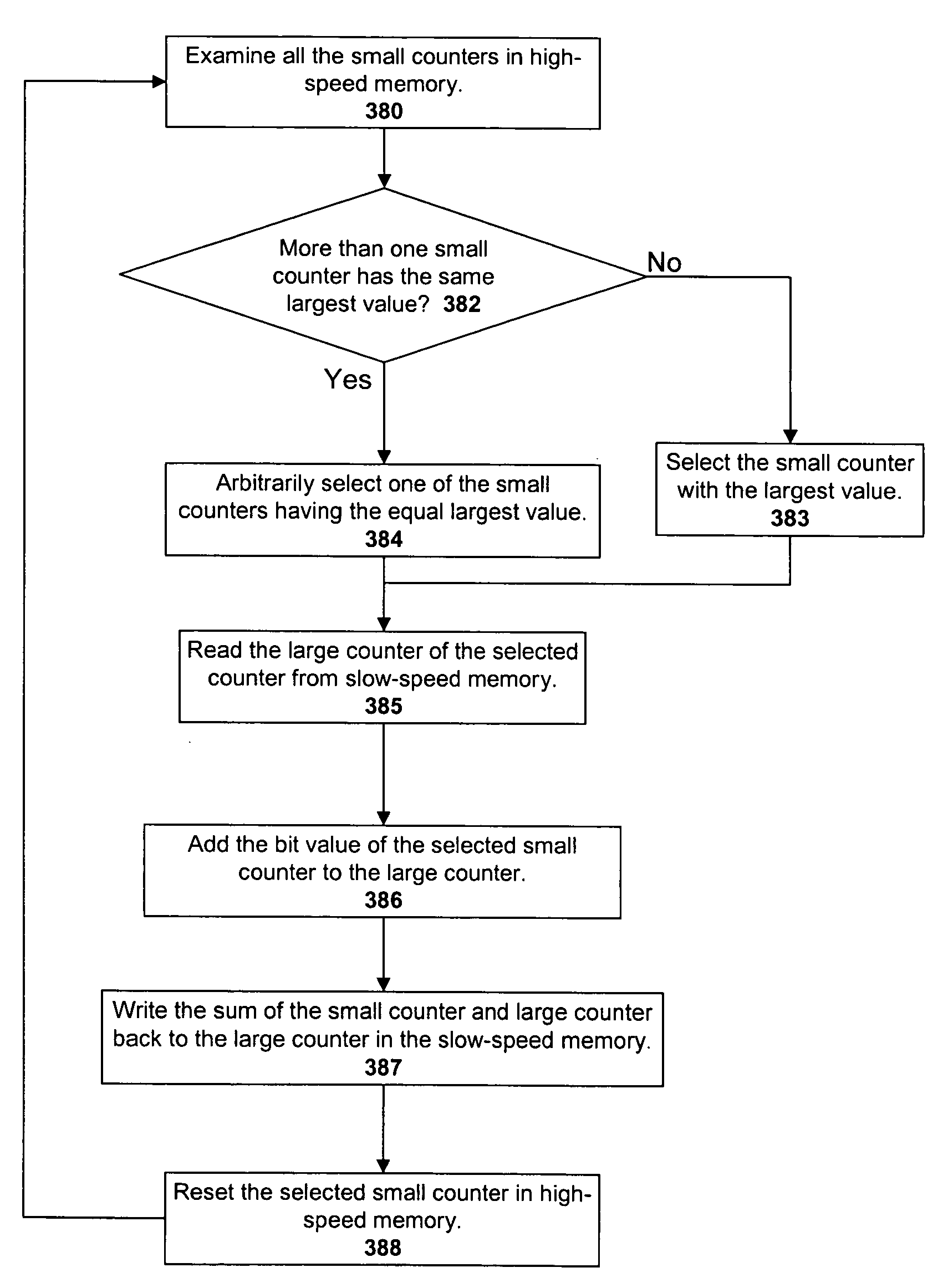

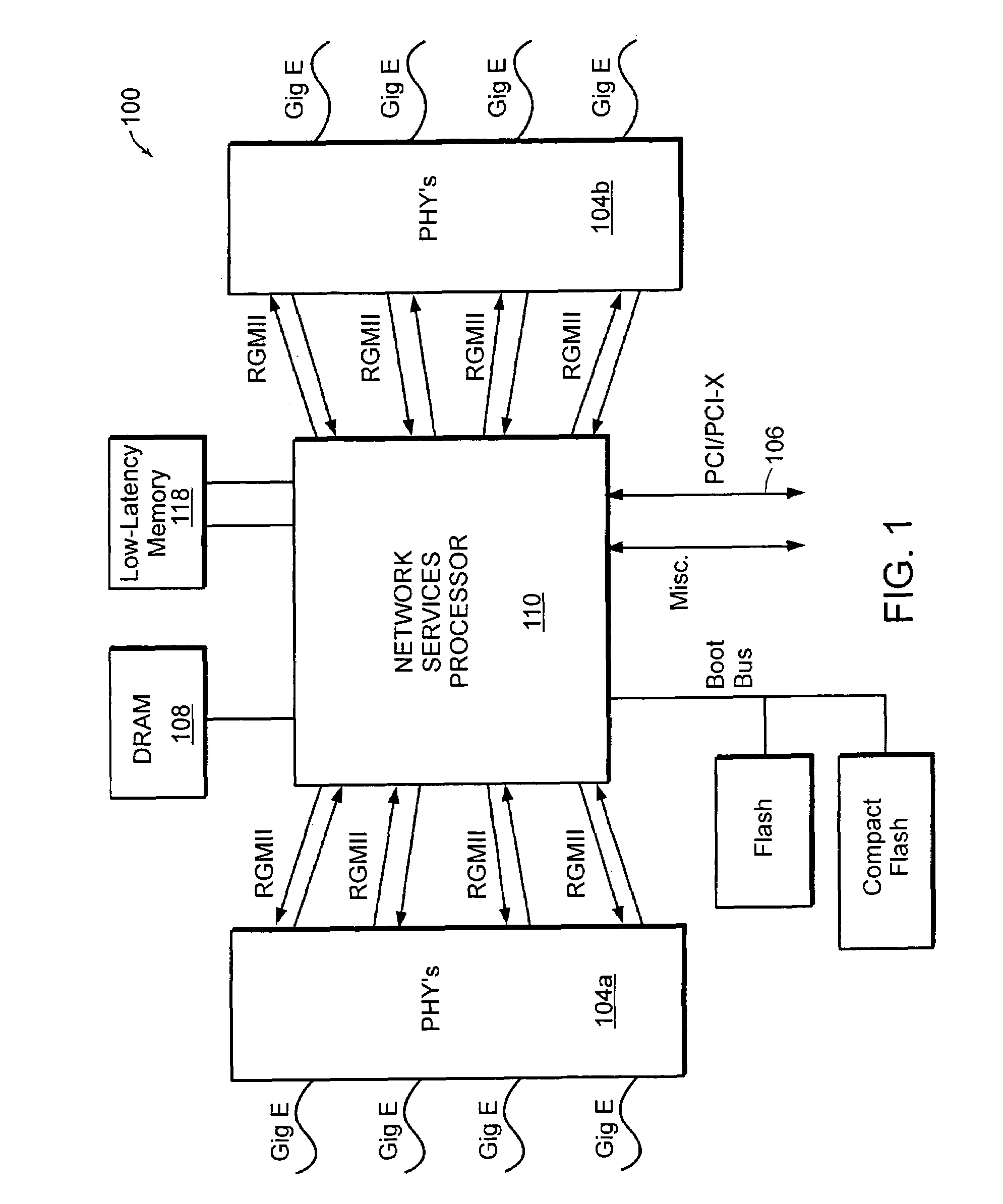

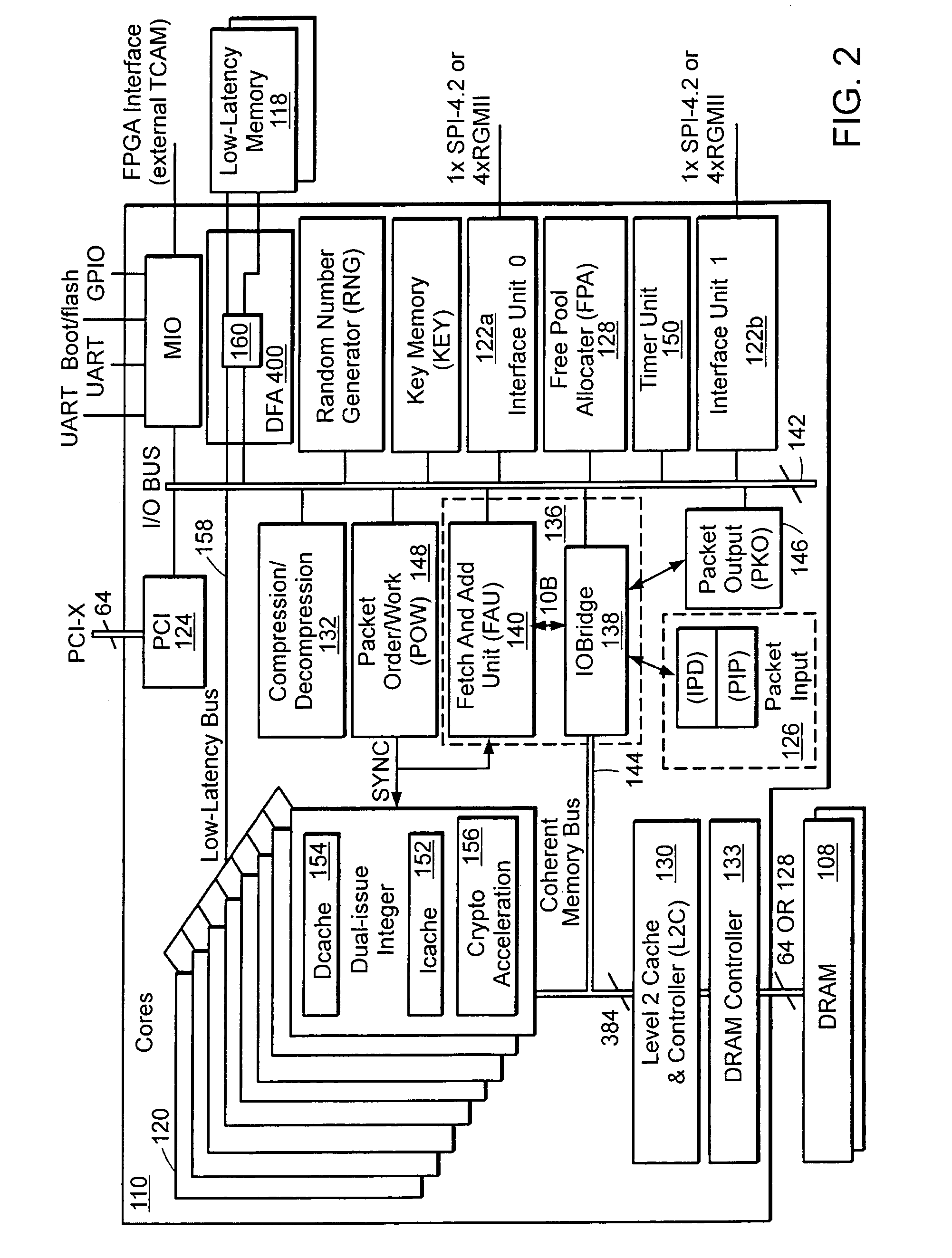

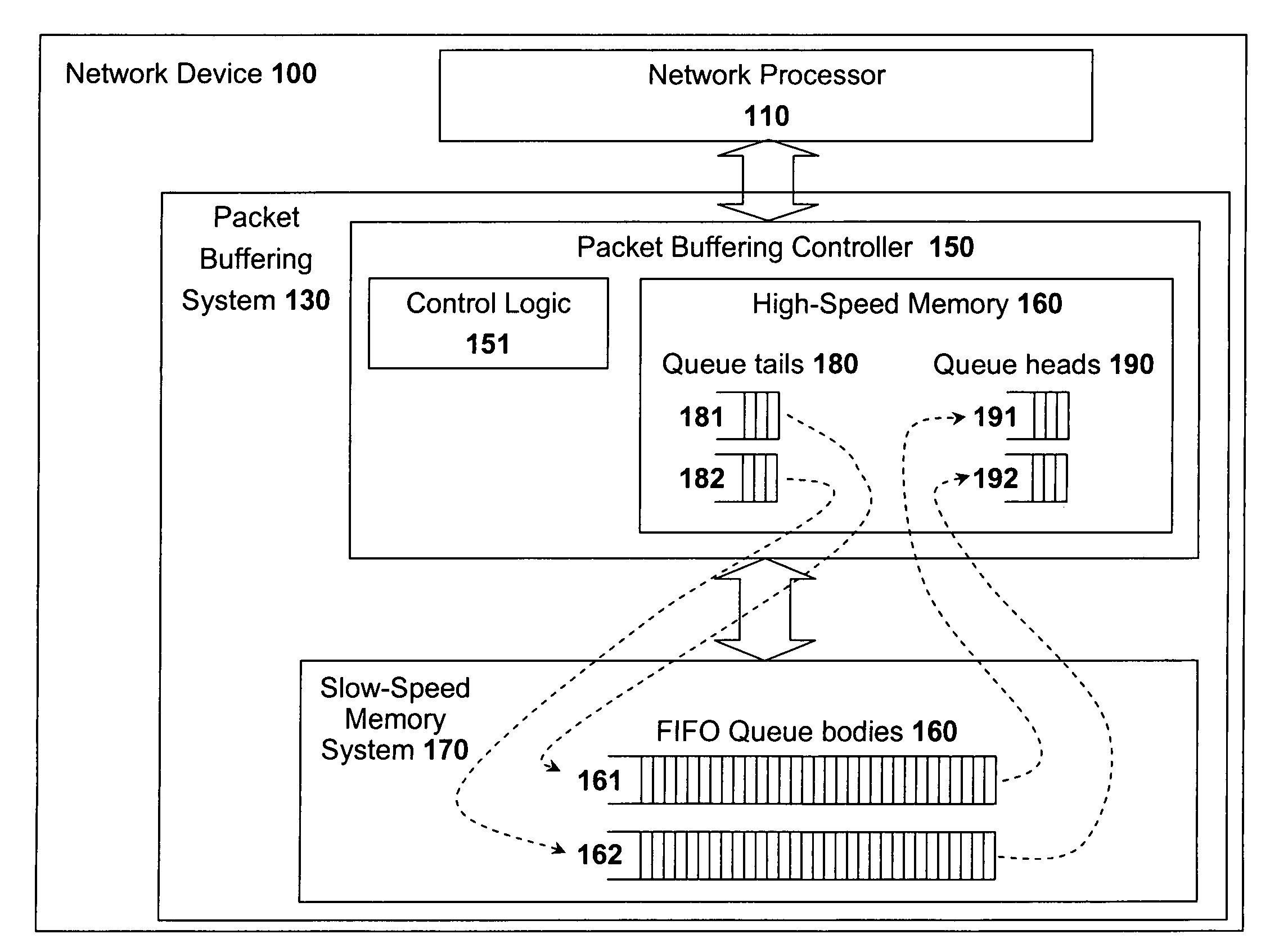

High speed memory and input/output processor subsystem for efficiently allocating and using high-speed memory and slower-speed memory

ActiveUS7657706B2Easy to handleSimple taskMemory architecture accessing/allocationMemory adressing/allocation/relocationHigh speed memoryMemory bank

An input / output processor for speeding the input / output and memory access operations for a processor is presented. The key idea of an input / output processor is to functionally divide input / output and memory access operations tasks into a compute intensive part that is handled by the processor and an I / O or memory intensive part that is then handled by the input / output processor. An input / output processor is designed by analyzing common input / output and memory access patterns and implementing methods tailored to efficiently handle those commonly occurring patterns. One technique that an input / output processor may use is to divide memory tasks into high frequency or high-availability components and low frequency or low-availability components. After dividing a memory task in such a manner, the input / output processor then uses high-speed memory (such as SRAM) to store the high frequency and high-availability components and a slower-speed memory (such as commodity DRAM) to store the low frequency and low-availability components. Another technique used by the input / output processor is to allocate memory in such a manner that all memory bank conflicts are eliminated. By eliminating any possible memory bank conflicts, the maximum random access performance of DRAM memory technology can be achieved.

Owner:CISCO TECH INC

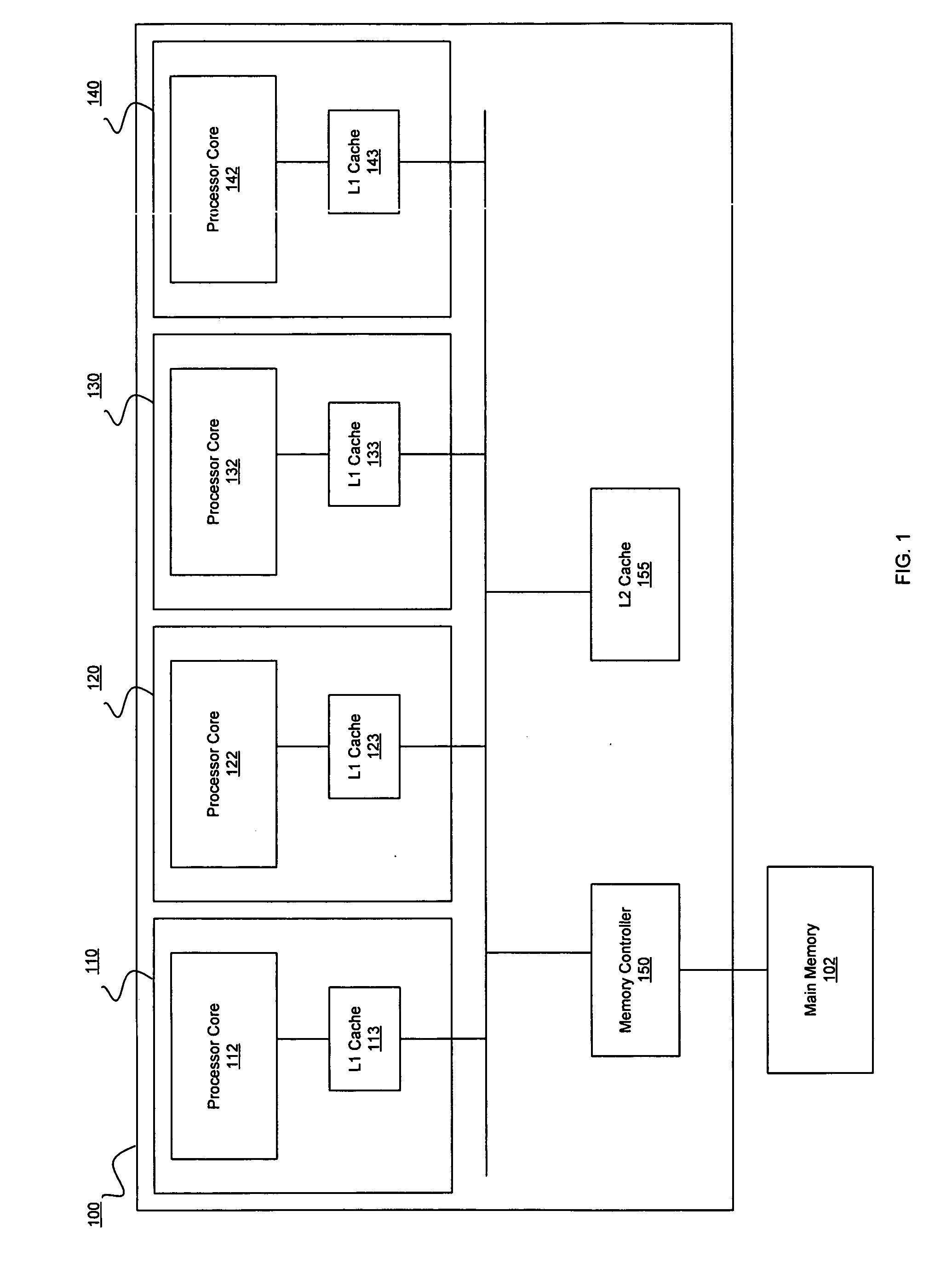

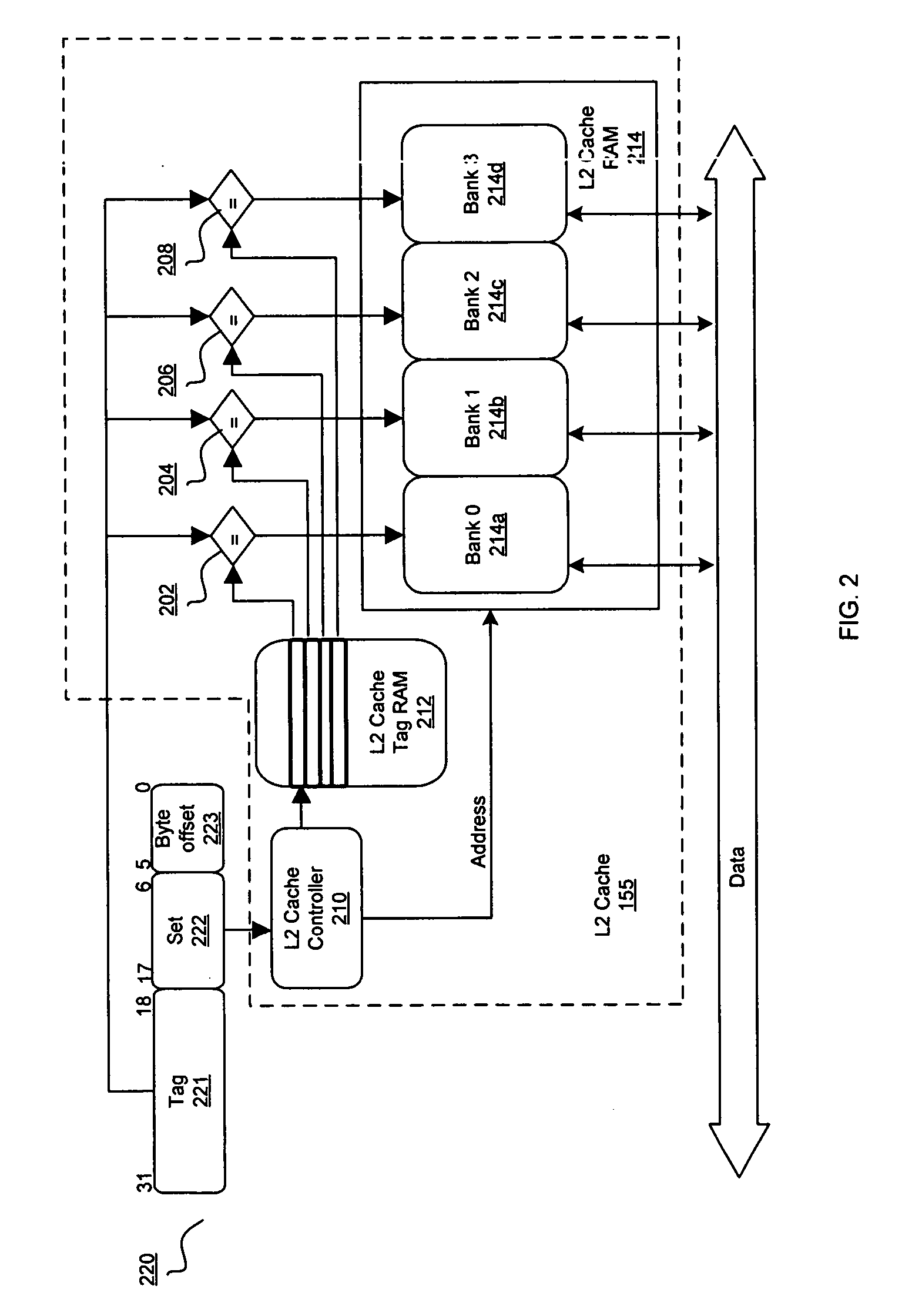

Method and system for on-chip configurable data ram for fast memory and pseudo associative caches

InactiveUS20060277365A1Memory architecture accessing/allocationEnergy efficient ICTMemory addressMemory bank

Aspects of a method and system for an on-chip configurable data RAM for fast memory and pseudo associative caches are provided. Memory banks of configurable data RAM integrated within a chip may be configured to operate as fast on-chip memory or on-chip level 2 cache memory. A set associativity of the on-chip level 2 cache memory may be same after configuring the memory banks as prior to the configuring. The configuring may occur during initialization of the memory banks, and may adjusted the amount of the on-chip level 2 cache. The memory banks configured to operate as on-chip level 2 cache memory or as fast on-chip memory may be dynamically enabled by a memory address.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Multisection memory bank system

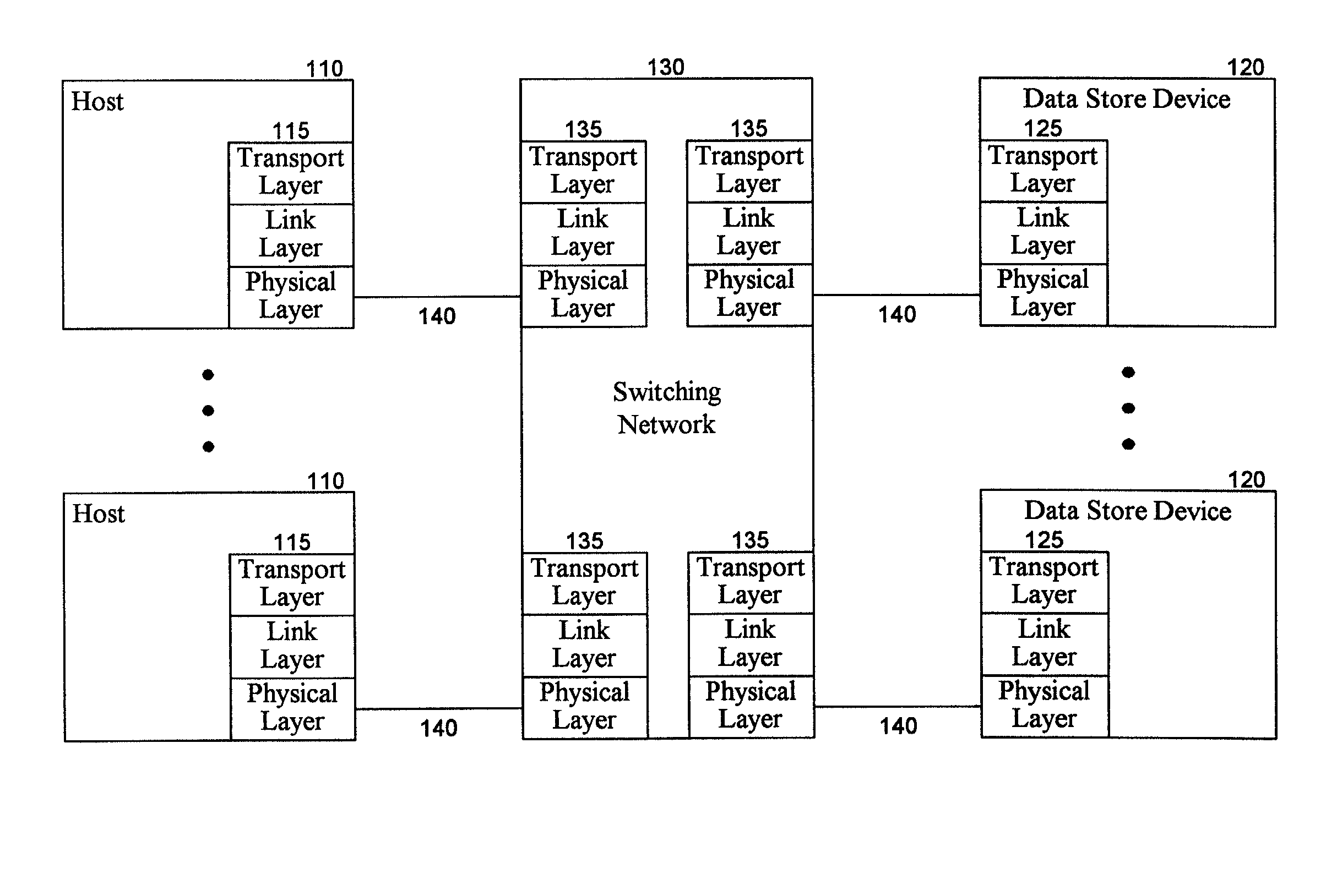

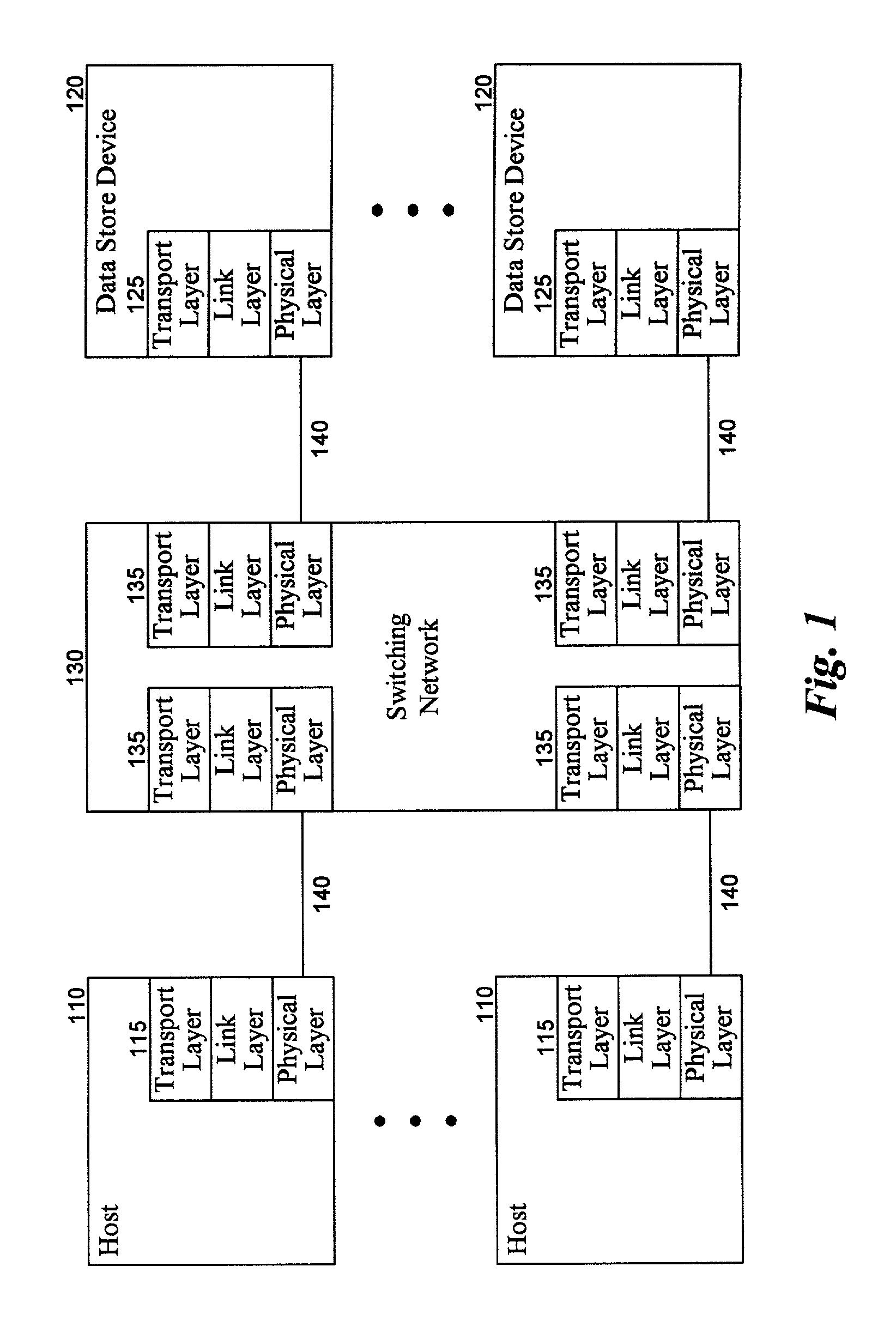

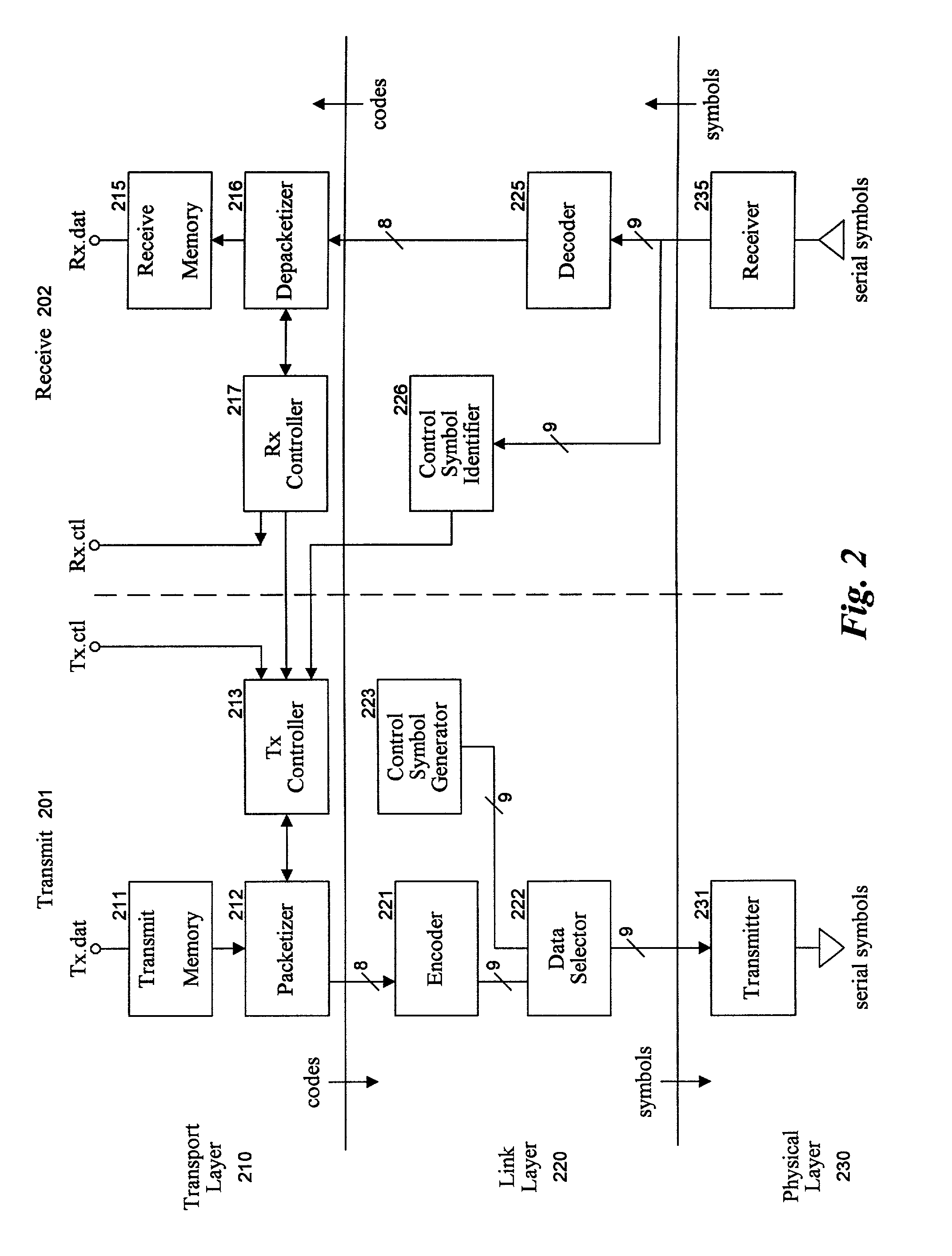

ActiveUS7340558B2Error preventionFrequency-division multiplex detailsExchange networkStorage area network

A serial communications architecture for communicating between hosts and data store devices. The Storage Link architecture is specially adapted to support communications between multiple hosts and storage devices via a switching network, such as a storage area network. The Storage Link architecture specifies various communications techniques that can be combined to reduce the overall cost and increase the overall performance of communications. The Storage Link architecture may provide packet ordering based on packet type, dynamic segmentation of packets, asymmetric packet ordering, packet nesting, variable-sized packet headers, and use of out-of-band symbols to transmit control information as described below in more detail. The Storage Link architecture may also specify encoding techniques to optimize transitions and to ensure DC-balance.

Owner:UNIVERSAL CONNECTIVITY TECH INC

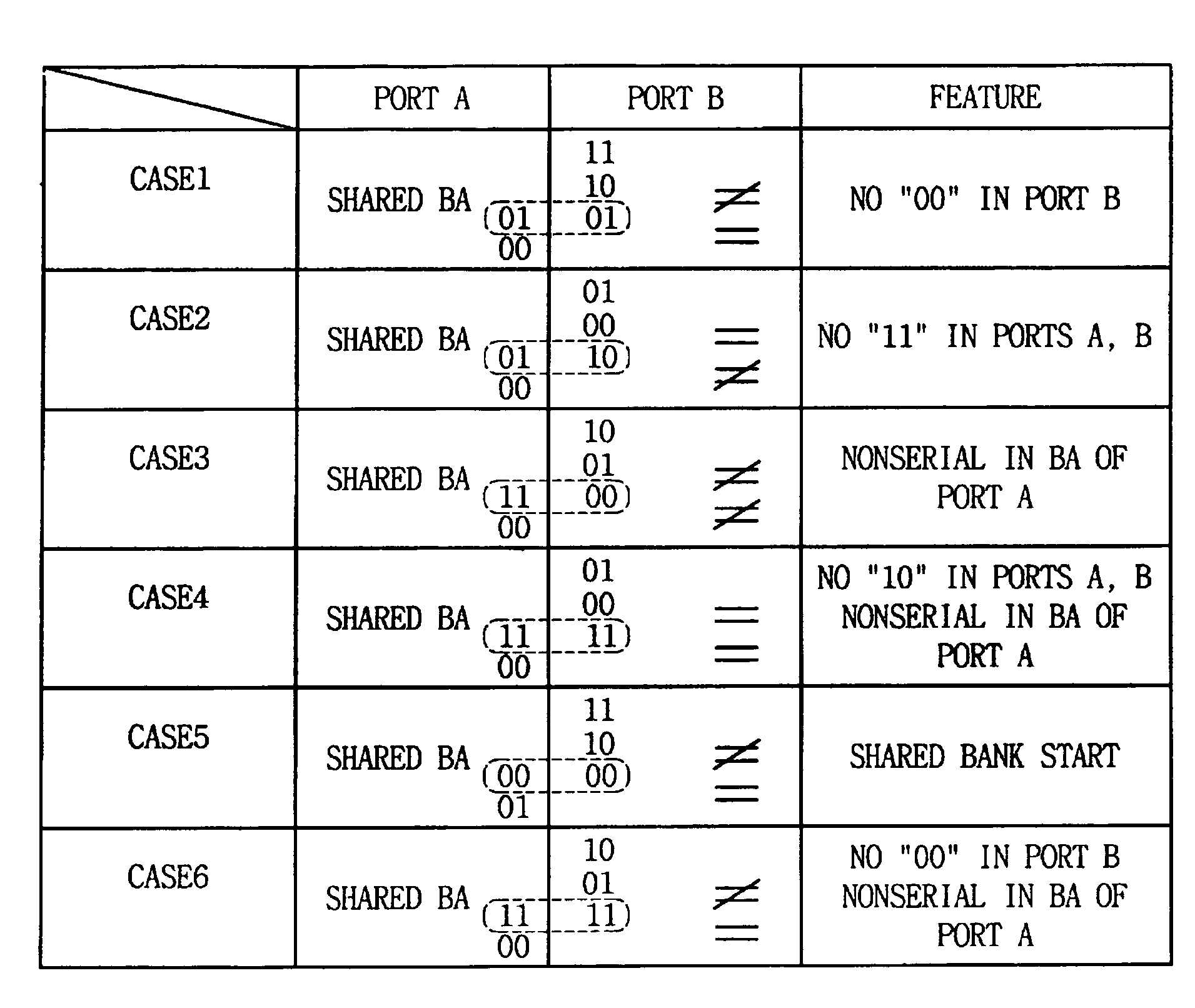

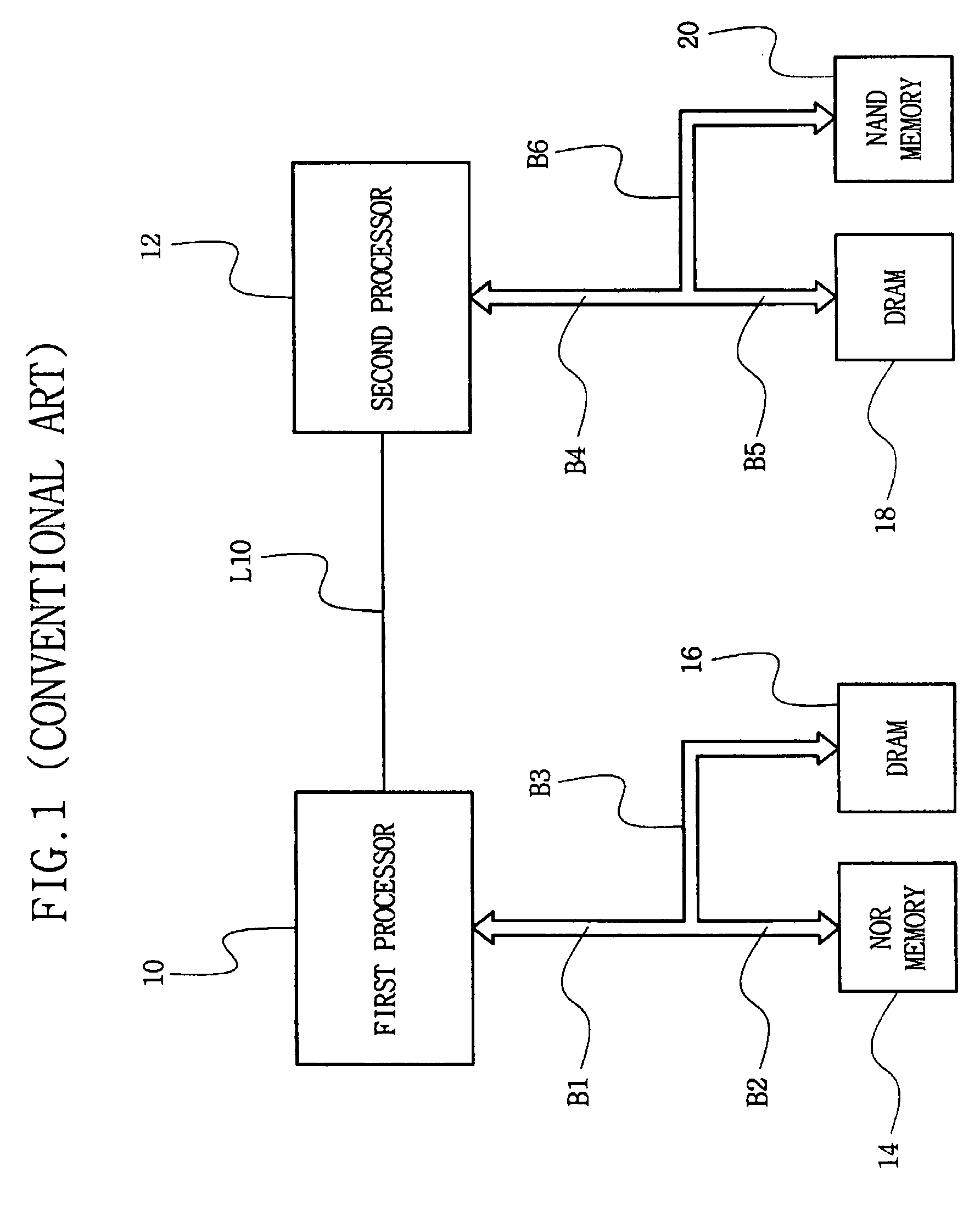

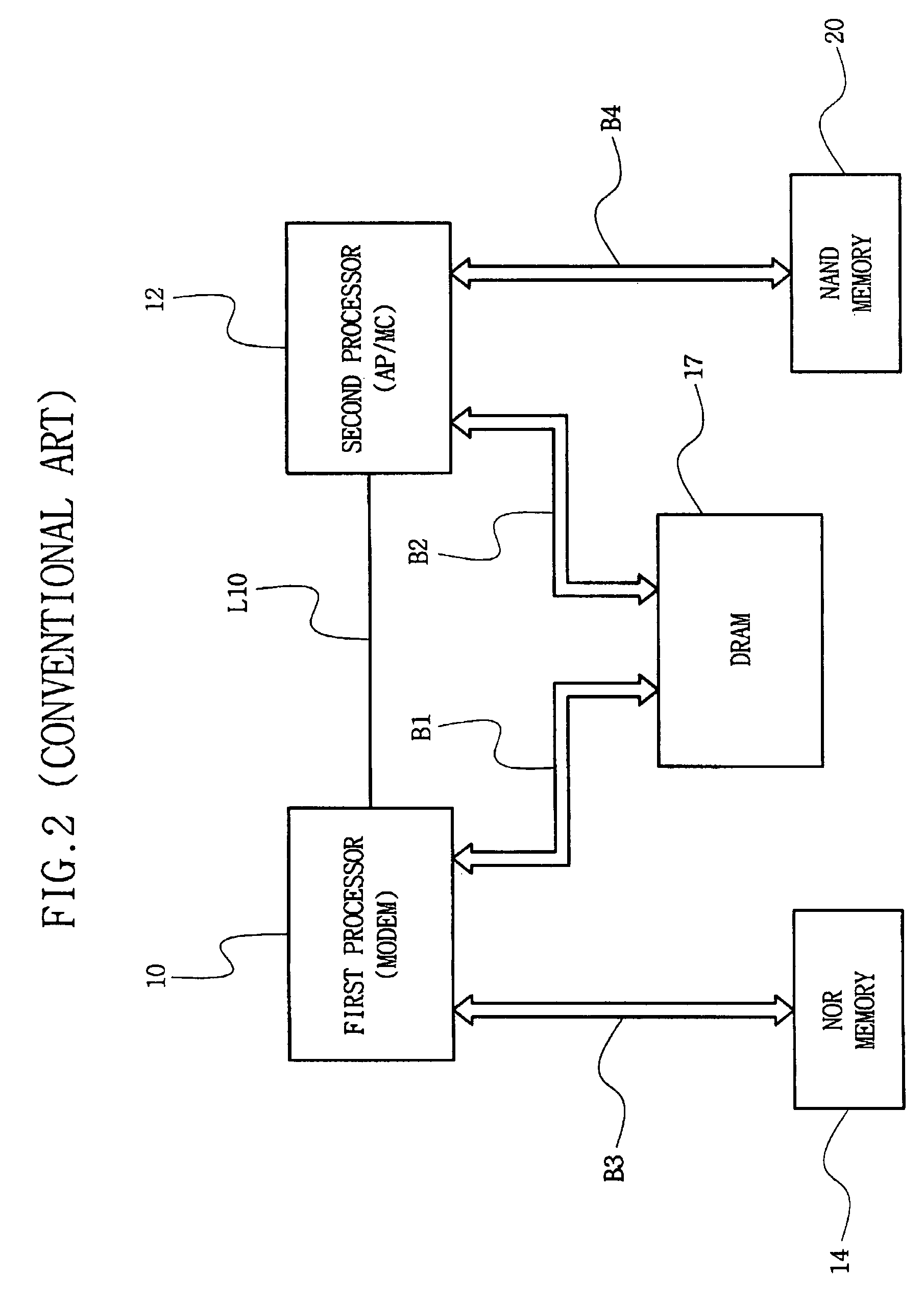

Multiprocessor system and method thereof

A multiprocessor system and method thereof are provided. The example multiprocessor system may include first and second processors, a dynamic random access memory having a memory cell array, the memory cell array including a first memory bank coupled to the first processor through a first port, second and fourth memory banks coupled to the second processor through a second port, and a third memory bank shared and connected with the first and second processors through the first and second ports, and a bank address assigning unit for assigning bank addresses to select individually the first and second memory banks, as the same bank address through the first and second ports, so that starting addresses for the first and second memory banks become equal in booting, and assigning bank addresses to select the third memory bank, as different bank addresses through the first and second ports, and assigning, through the second port, bank addresses to select the fourth memory bank, as the same bank address as a bank address to select the third memory bank through the first port.

Owner:SAMSUNG ELECTRONICS CO LTD

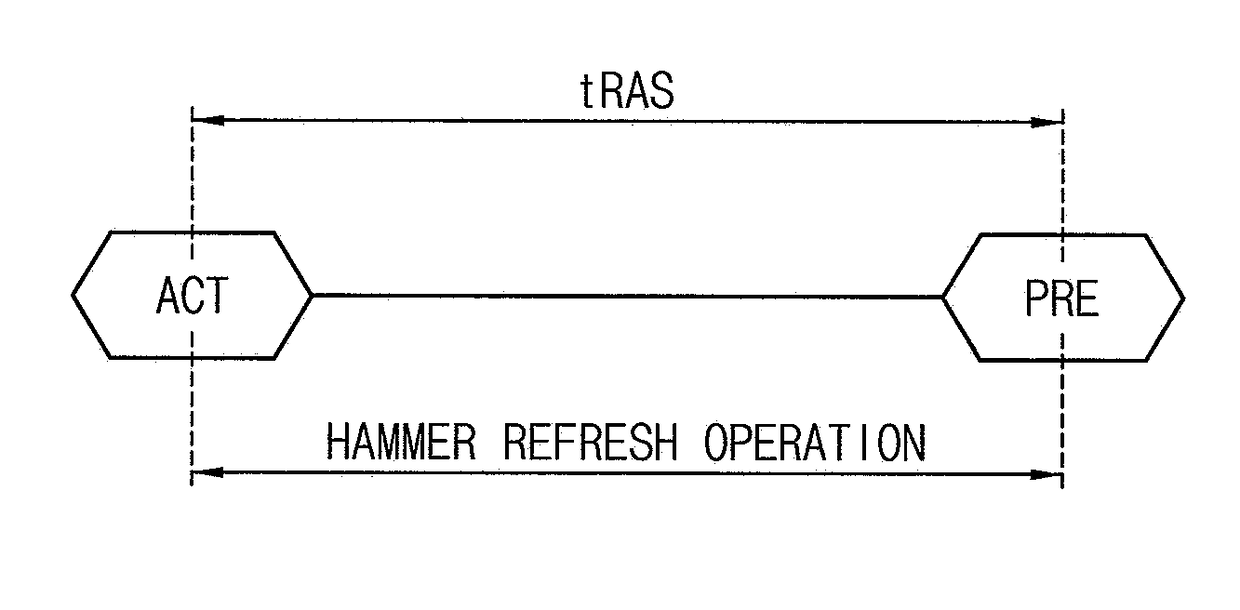

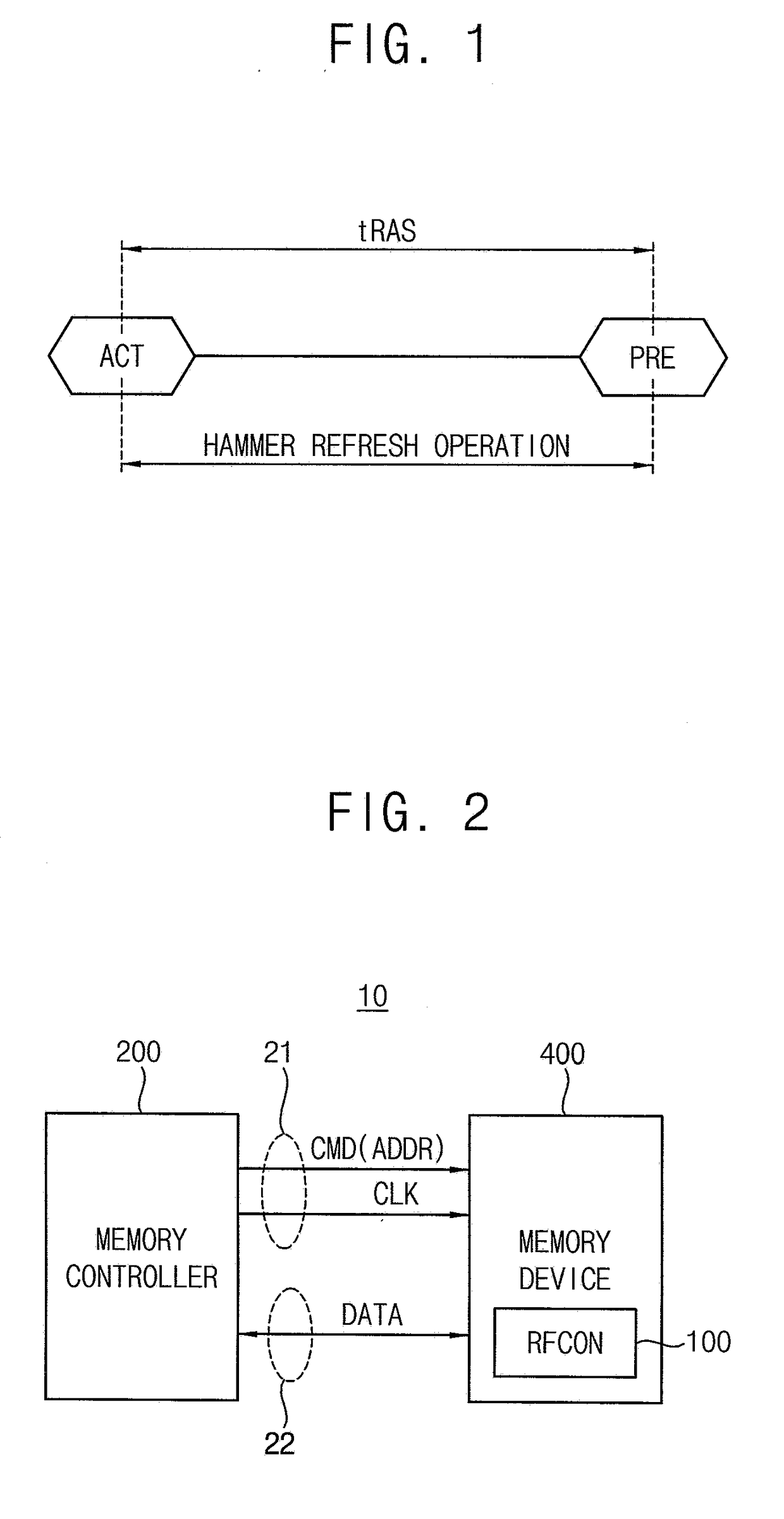

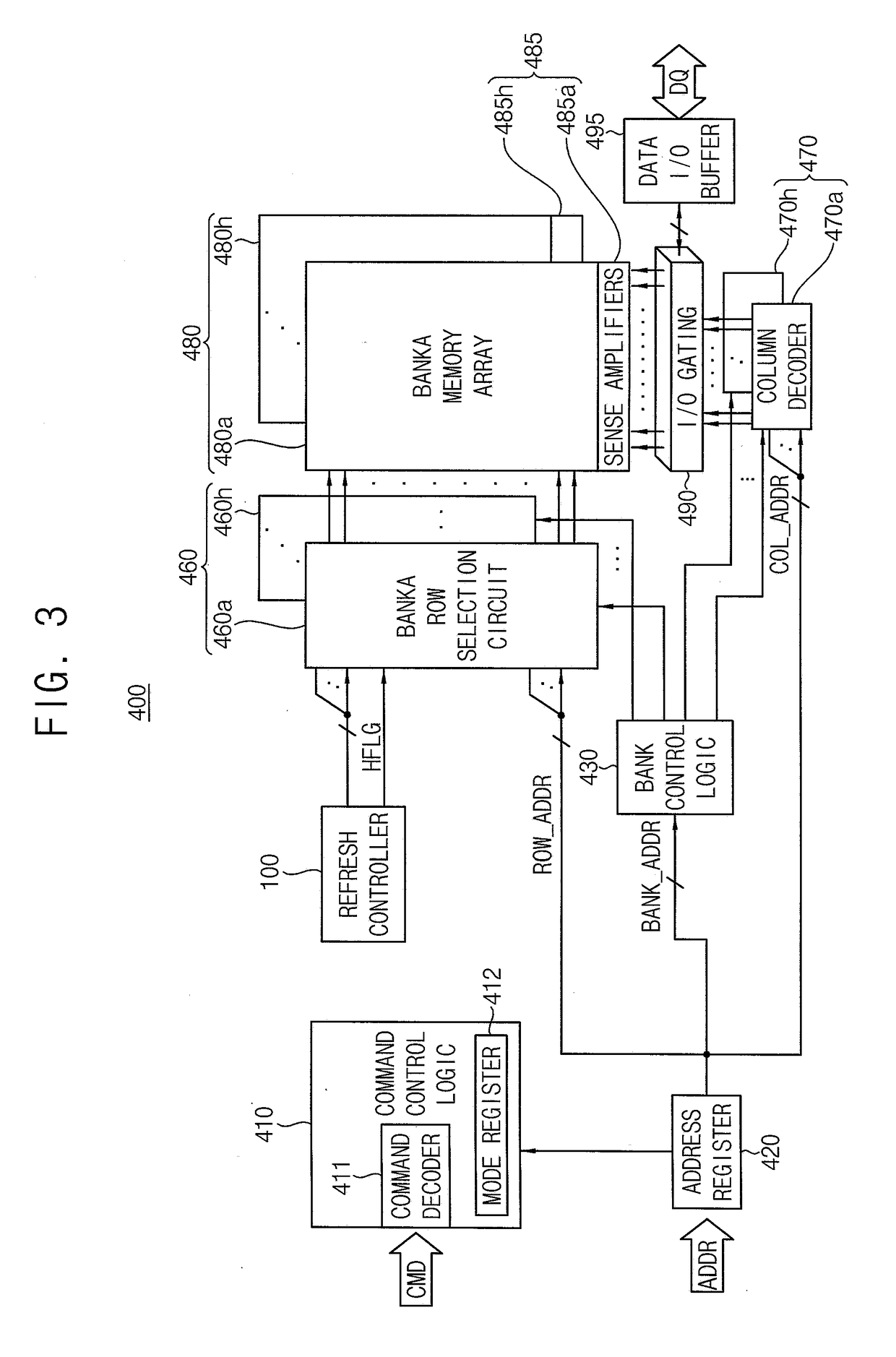

Memory device performing hammer refresh operation and memory system including the same

ActiveUS20170213586A1Efficiently performing hammer refresh operationInput/output to record carriersDigital storageActive timeMemory bank

A memory device includes a memory bank, a row selection circuit and a refresh controller. The memory bank includes a plurality of memory blocks, and each memory block includes a plurality of memory cells arranged in rows and columns. The row selection circuit performs an access operation with respect to the memory bank and a hammer refresh operation with respect to a row that is physically adjacent to a row that is accessed intensively. The refresh controller controls the row selection circuit such that the hammer refresh operation is performed during a row active time for the access operation. The hammer refresh operation may be performed efficiently and performance of the memory device may be enhanced by performing the hammer refresh operation during the row active time for the access operation.

Owner:SAMSUNG ELECTRONICS CO LTD