Patents

Literature

1114 results about "Memory operation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory operations per second or MOPS is a metric for an expression of the performance capacity of semiconductor memory. It can also be used to determine the efficiency of RAM in the Windows operating environment.

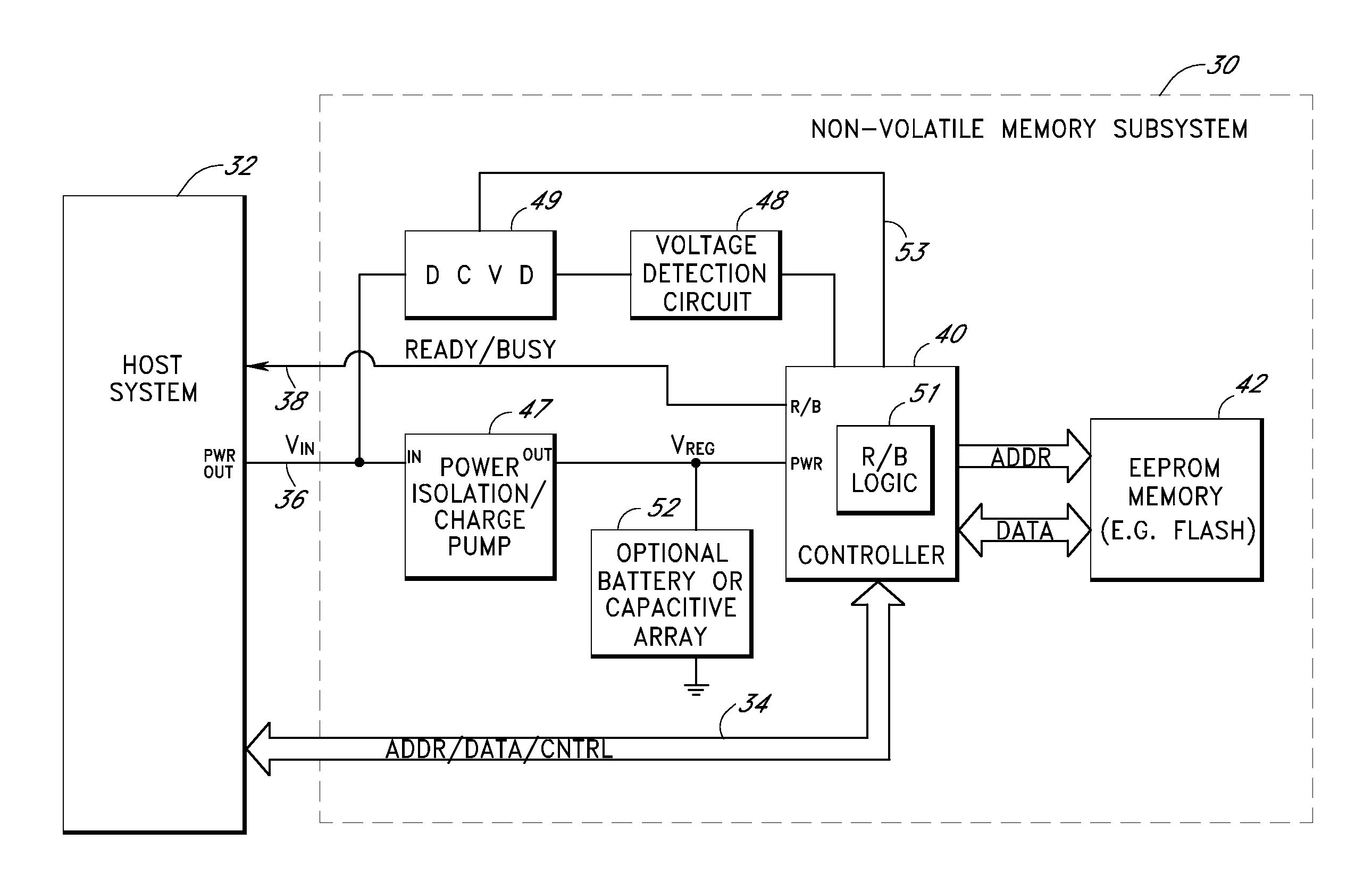

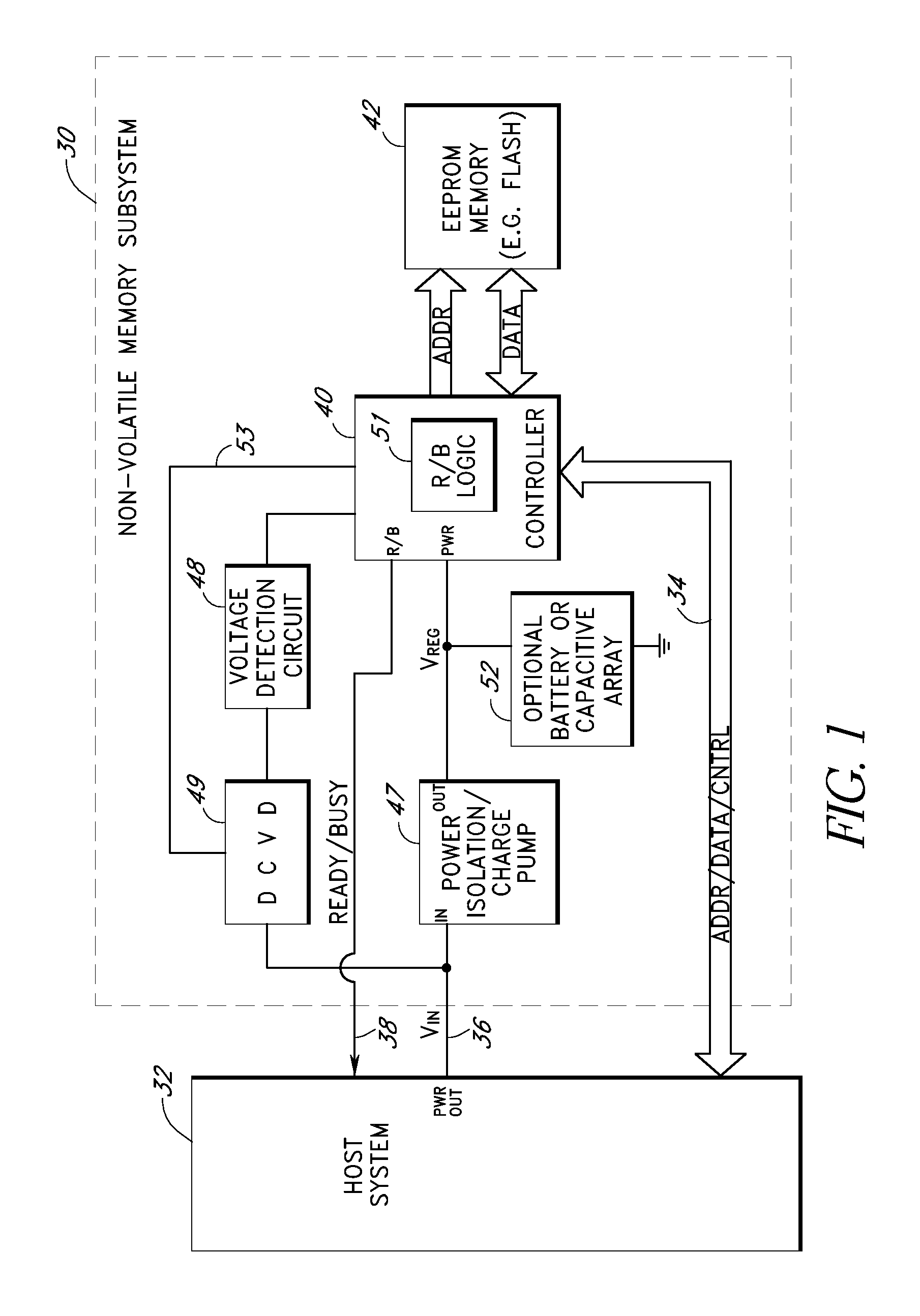

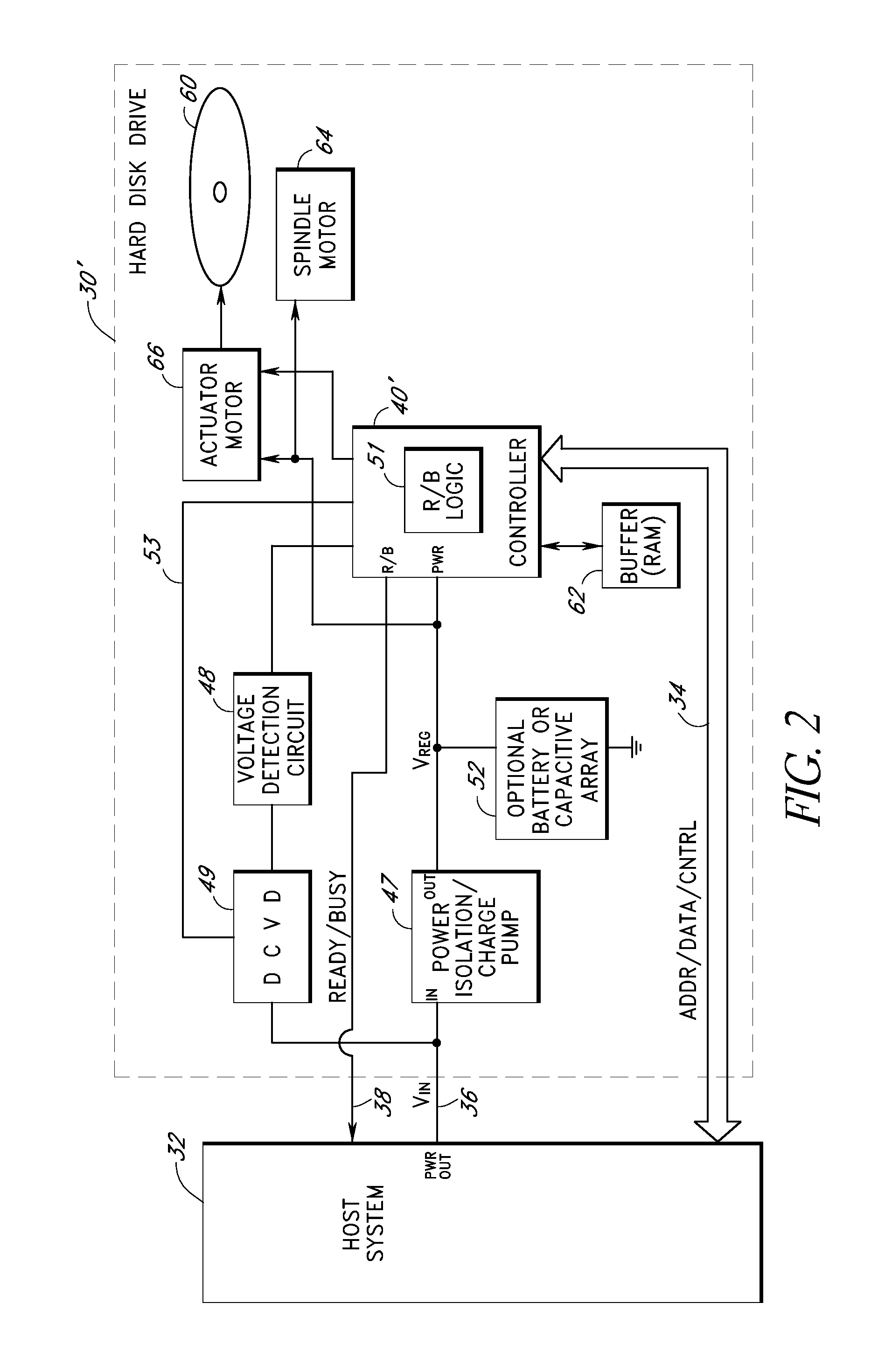

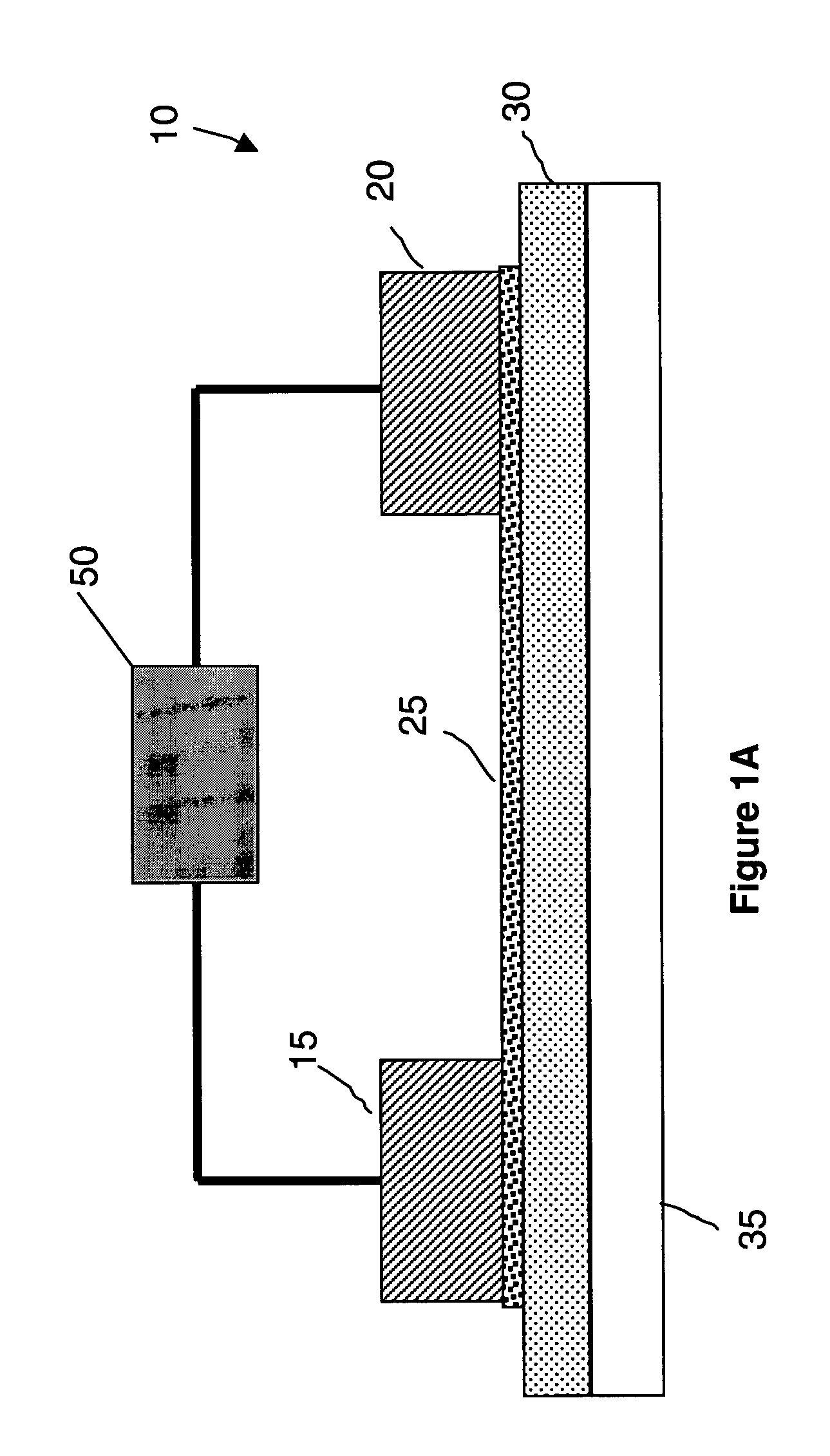

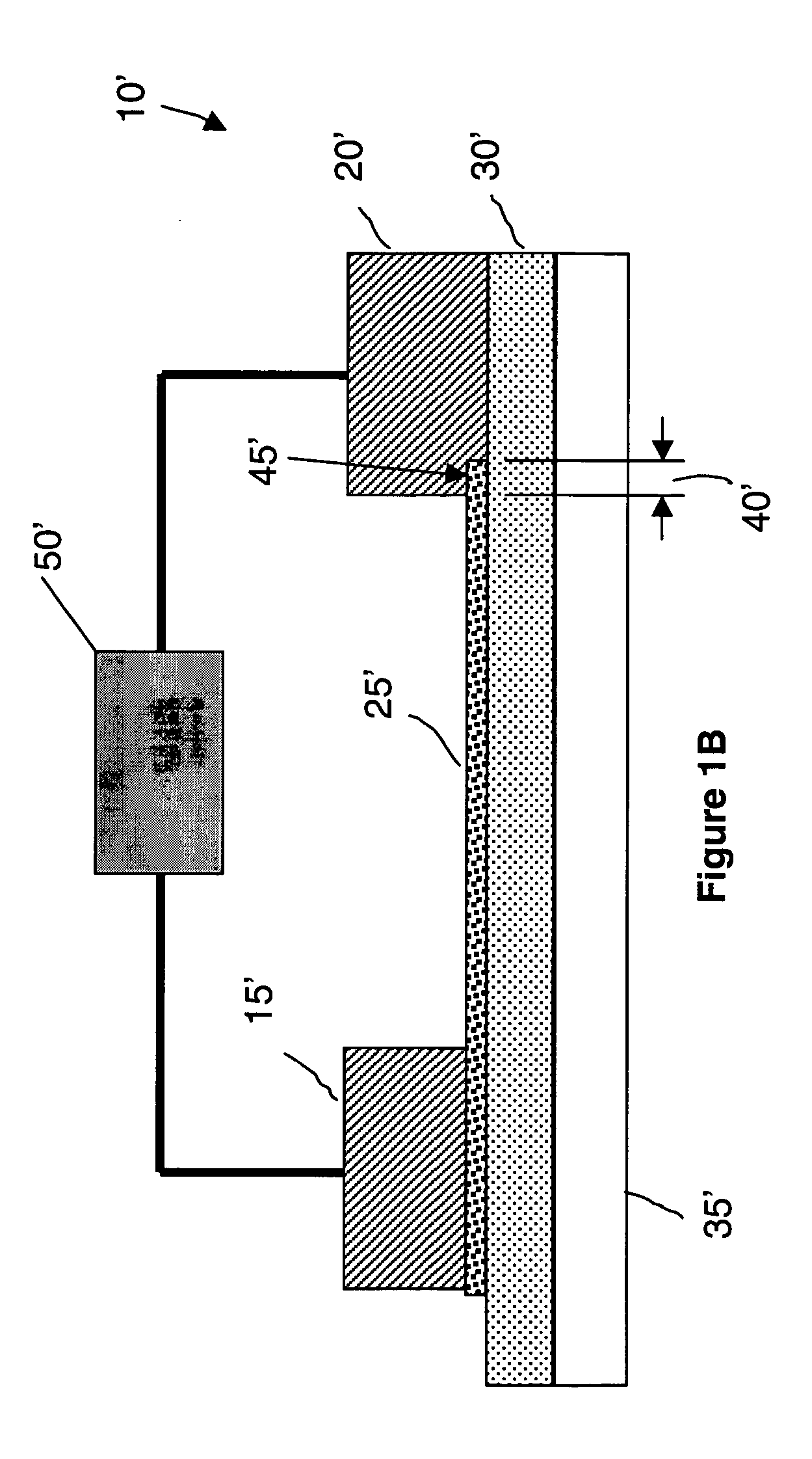

Storage subsystem with embedded circuit for protecting against anomalies in power signal from host

ActiveUS7733712B1Extended runtimeProvide powerRead-only memoriesDigital storageStandby powerEngineering

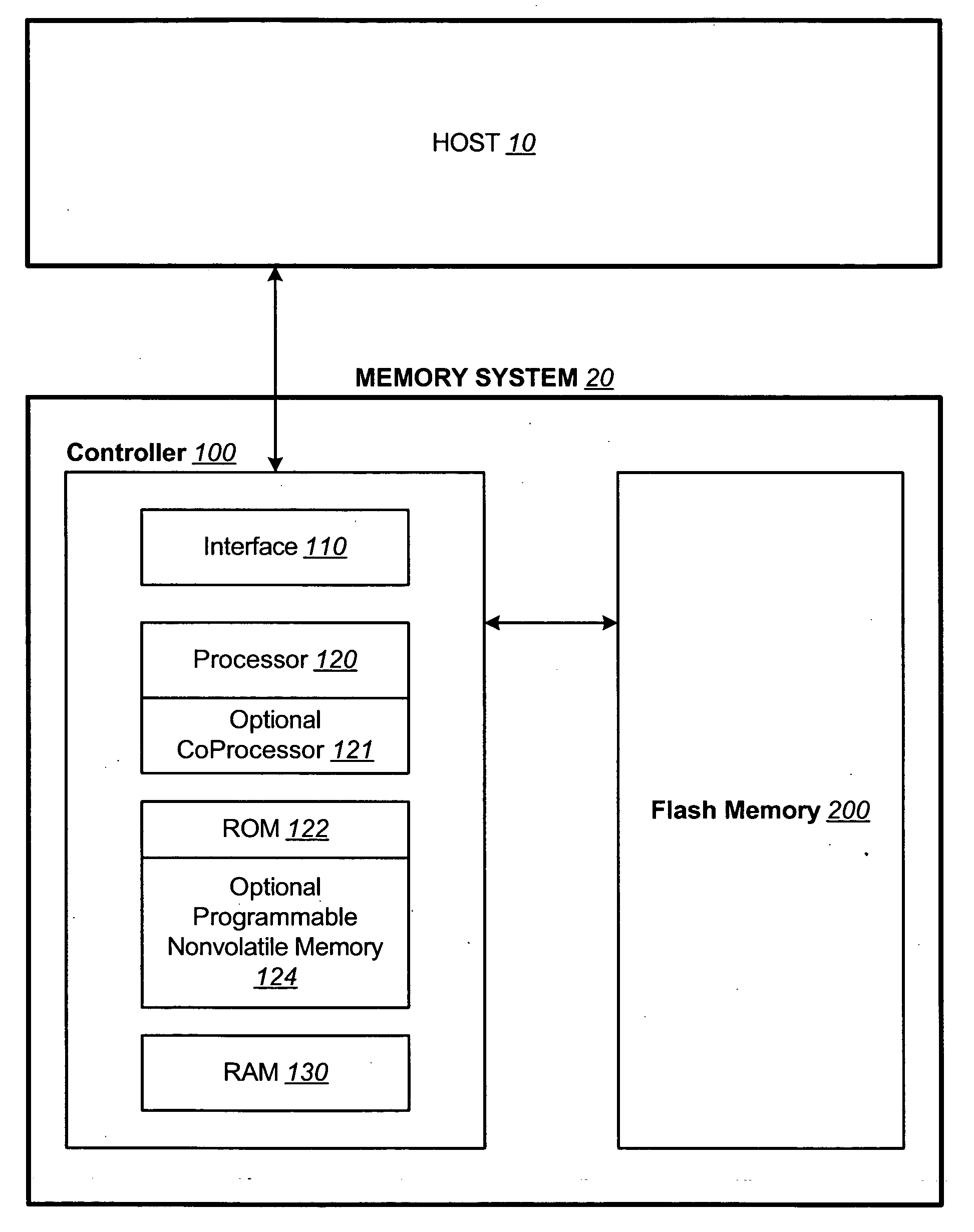

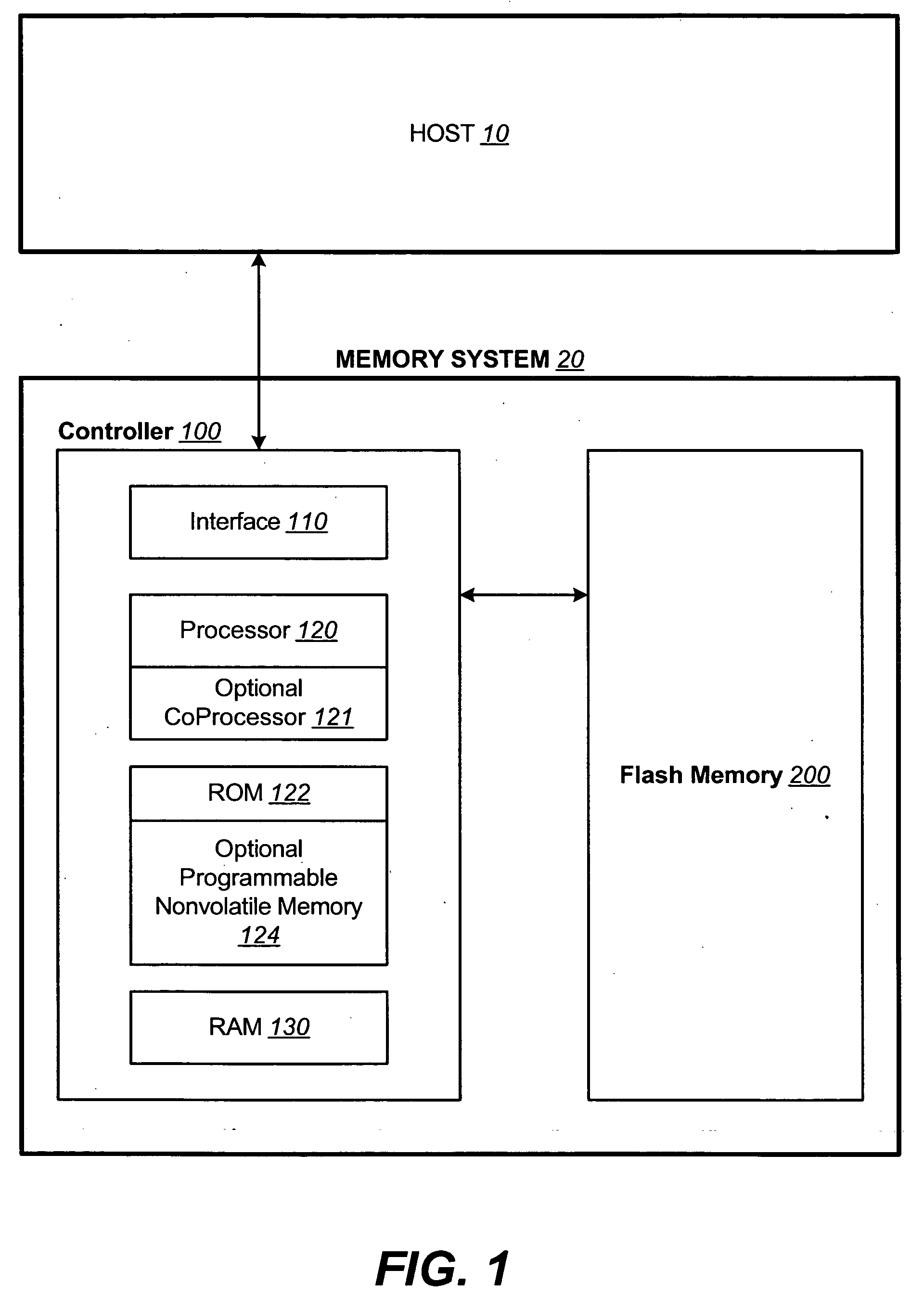

A storage subsystem includes a charge pump that receives a power signal from a host system, and generates a regulated power signal that is provided to the storage subsystem's controller. When the power signal from the host is interrupted, the charge pump additionally acts as a backup power supply to enable the storage subsystem to continue to operate temporarily, and power isolation circuitry in the storage subsystem prevents power from flowing back to the host system. The storage subsystem further includes a digitally programmable voltage detection circuit that accepts various supply voltages and asserts a busy signal to the controller when an anomaly in the power signal is detected. The controller includes logic circuitry that will block the host system from performing write operations to the storage subsystem either when the voltage detection circuit asserts a busy signal or when the controller is busy executing memory operation commands.

Owner:WESTERN DIGITAL TECH INC

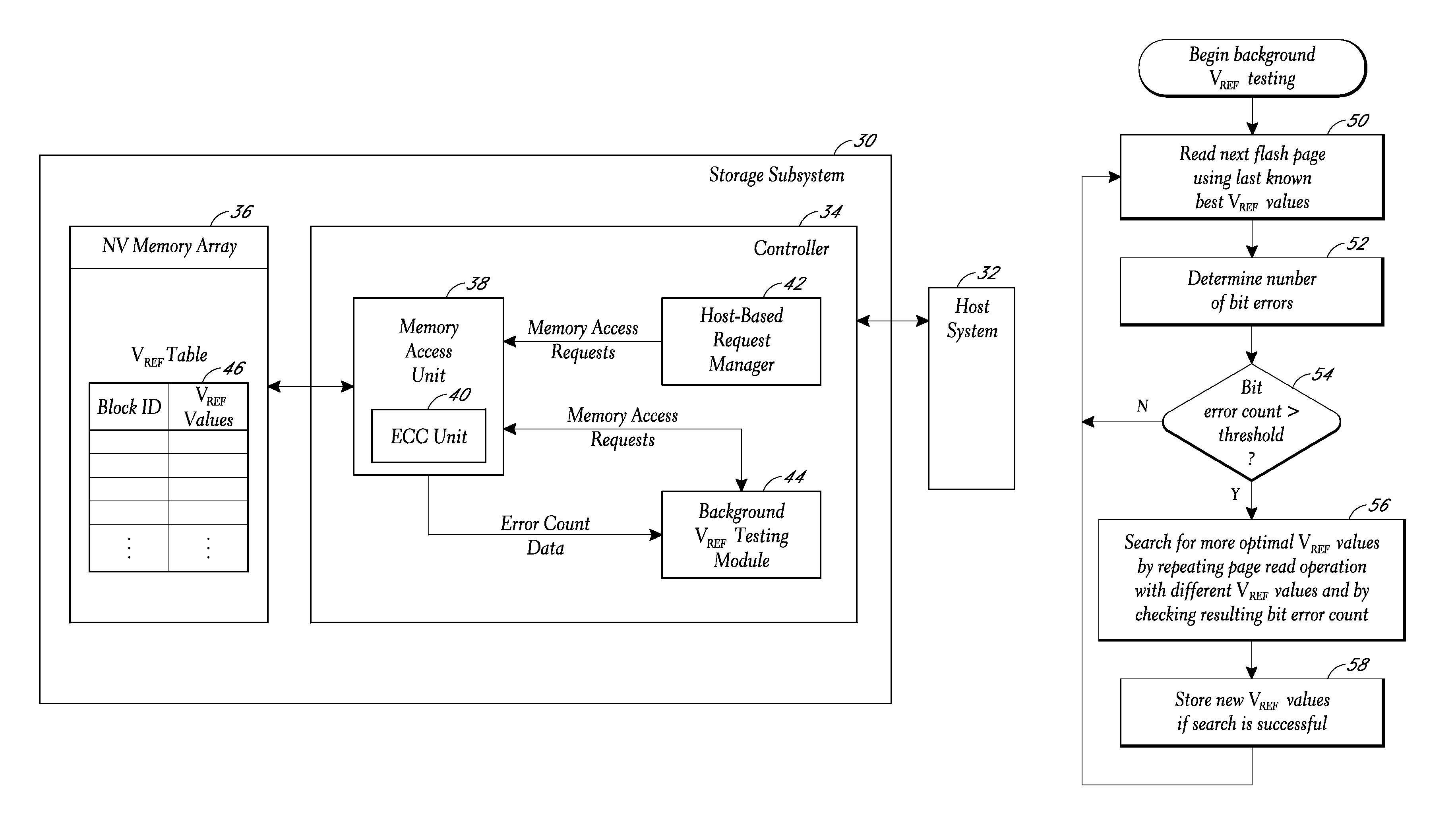

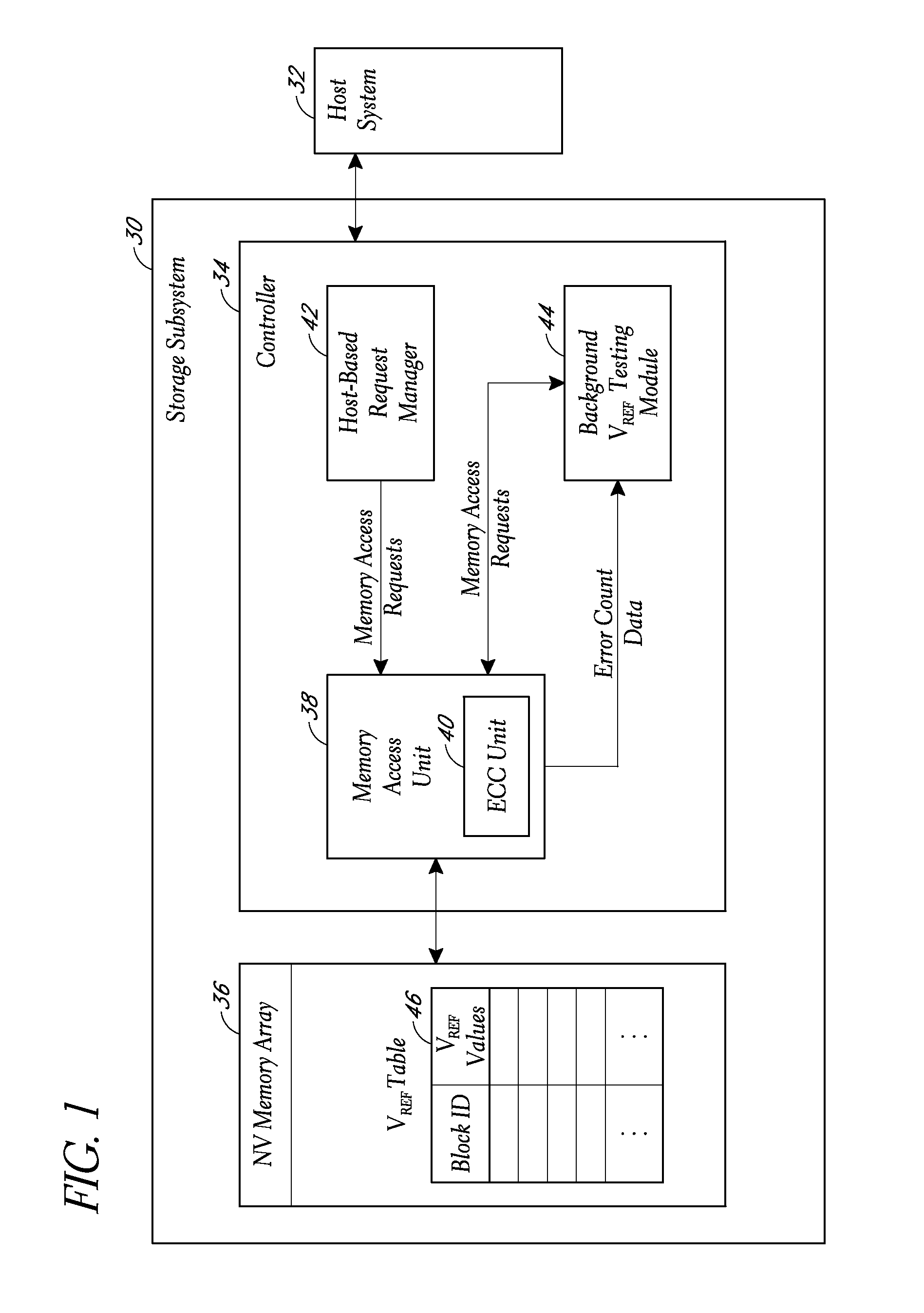

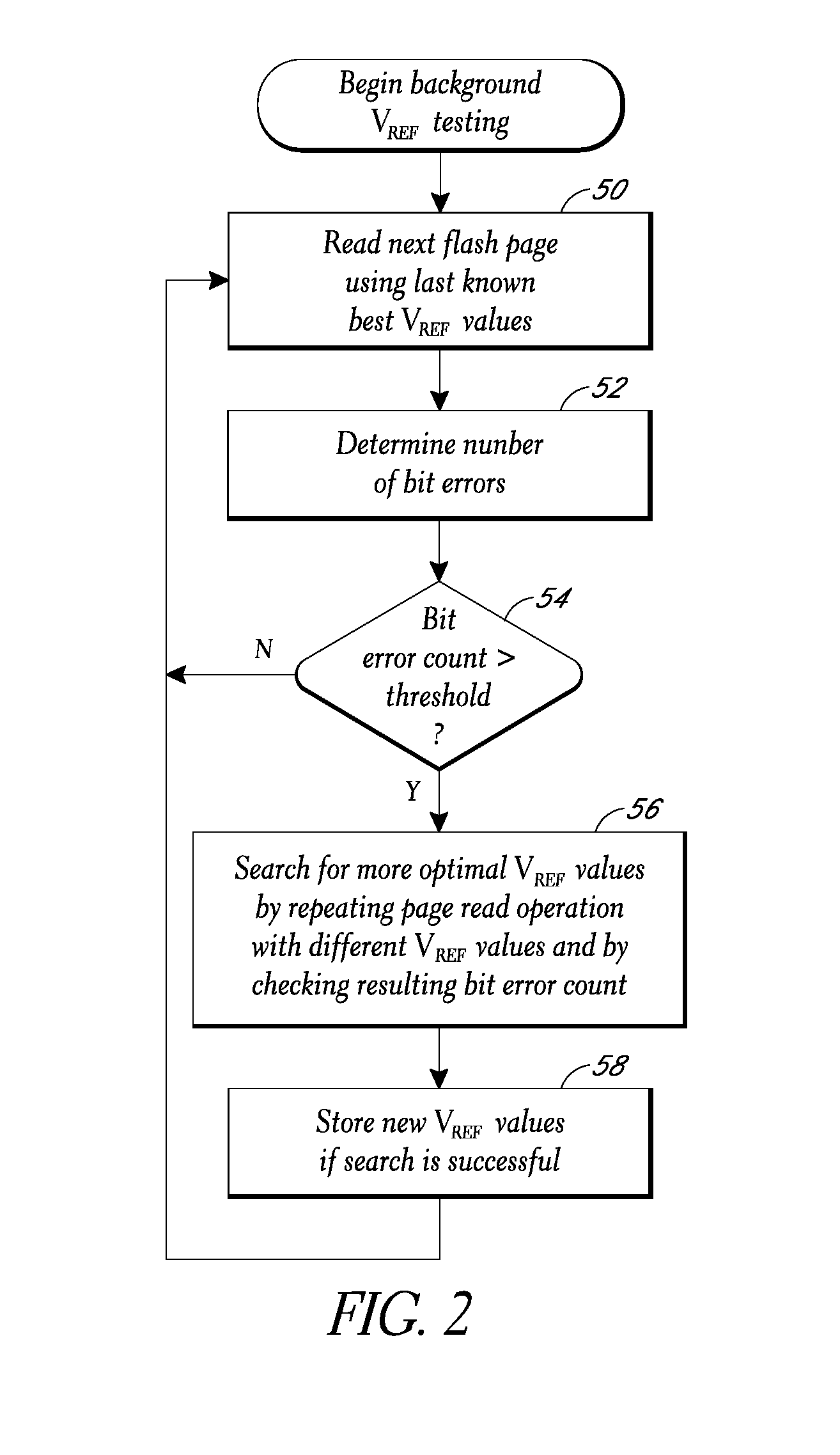

Background selection of voltage reference values for performing memory read operations

A storage subsystem implements a background process for selecting voltage reference values to use for reading data from a non-volatile memory array, such as an array of multi-level cell (MLC) flash memory. The process involves performing background read operations using specific sets of voltage reference values while monitoring the resulting bit error counts. The selected voltage reference values for specific pages or other blocks of the array are stored in a table. Read operations requested by a host system are executed using the corresponding voltage reference values specified by the table.

Owner:WESTERN DIGITAL TECH INC

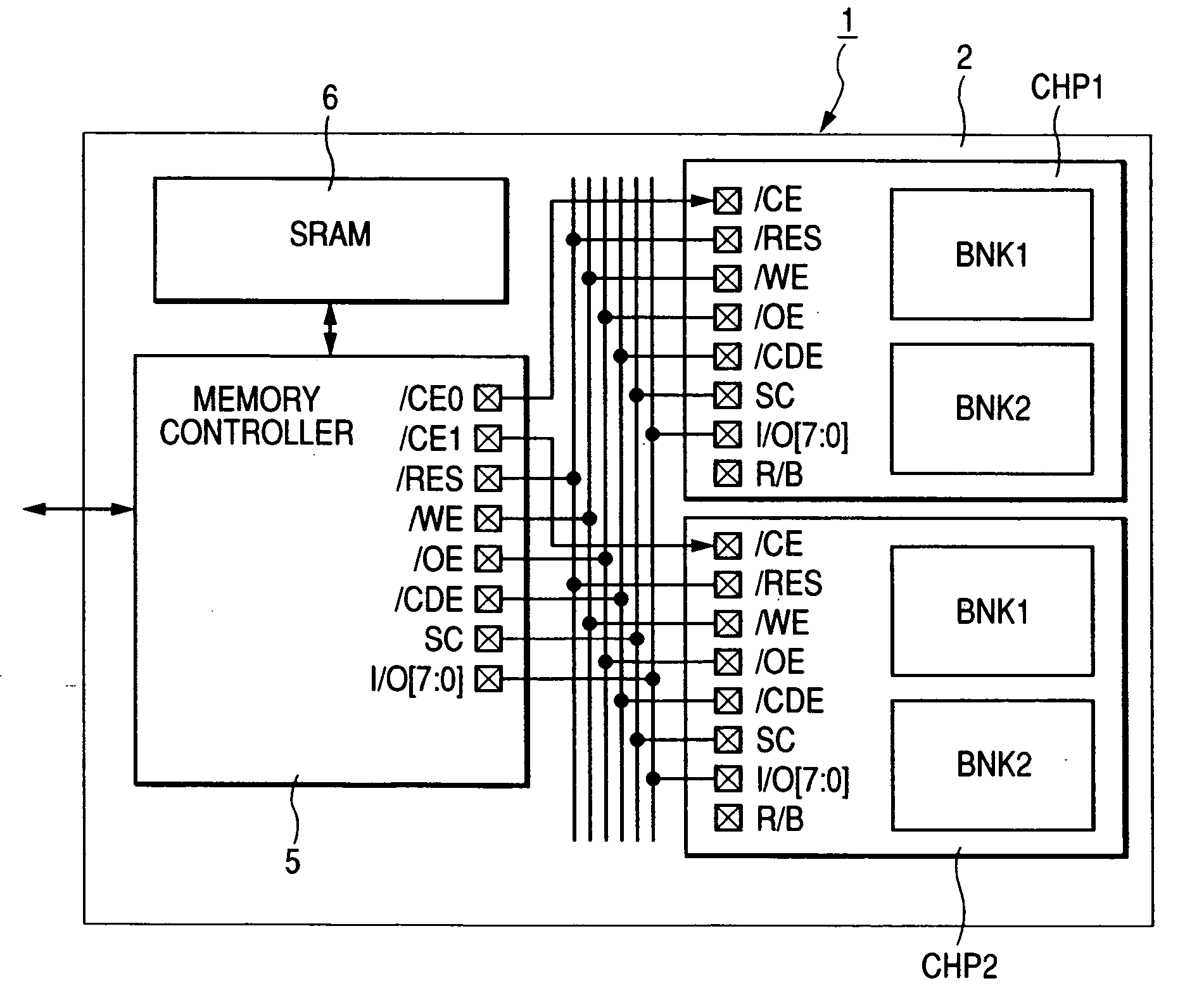

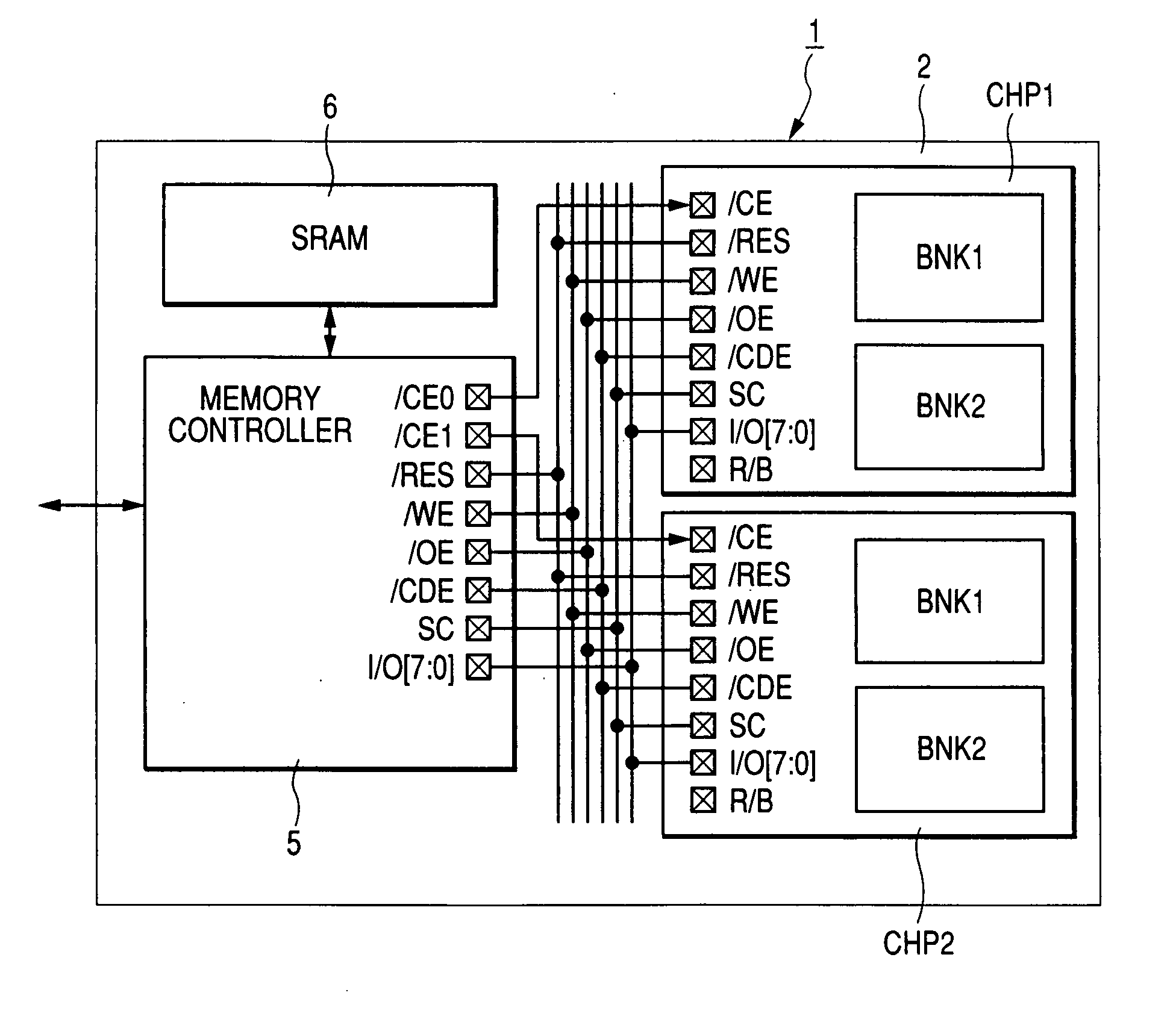

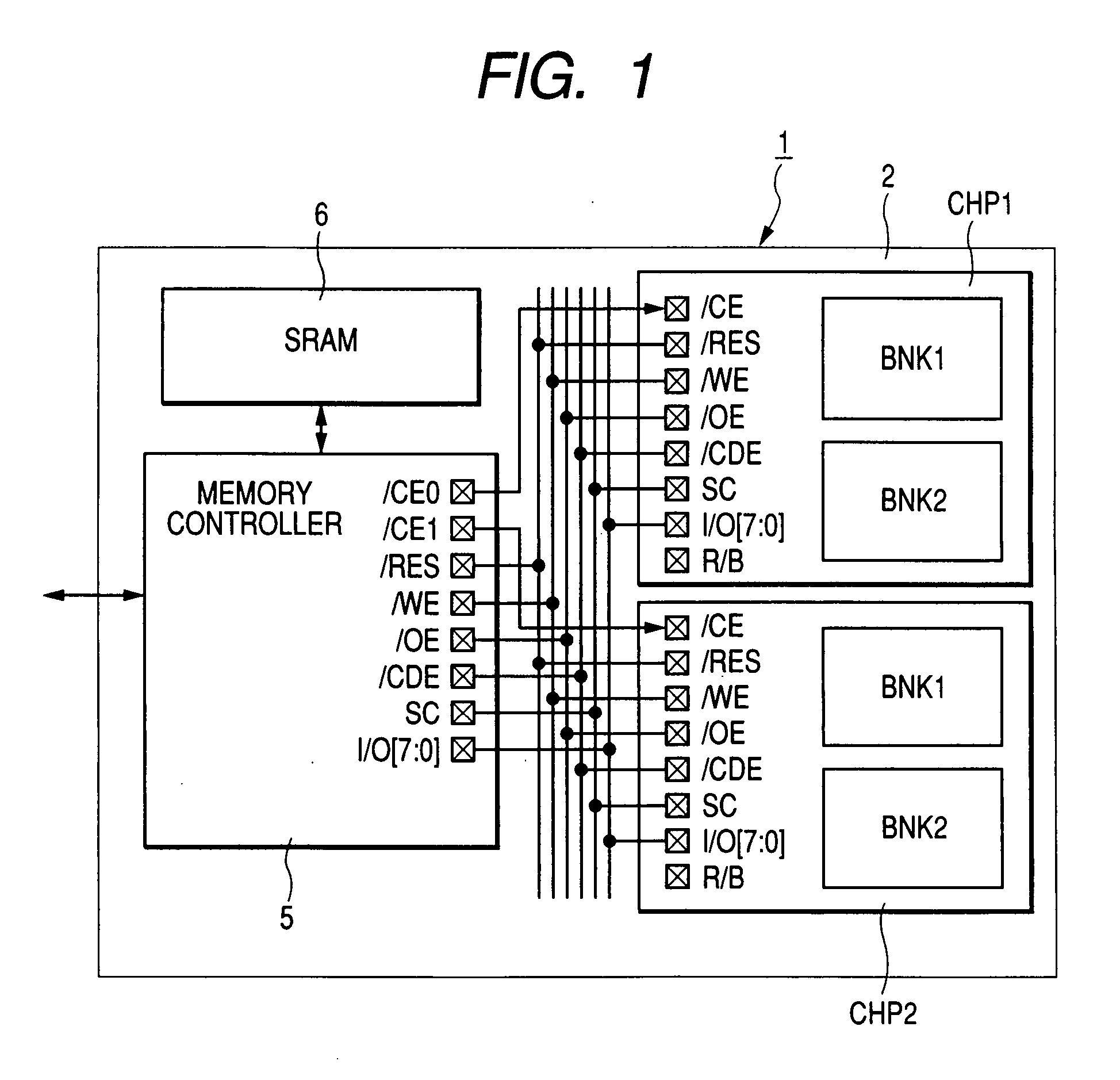

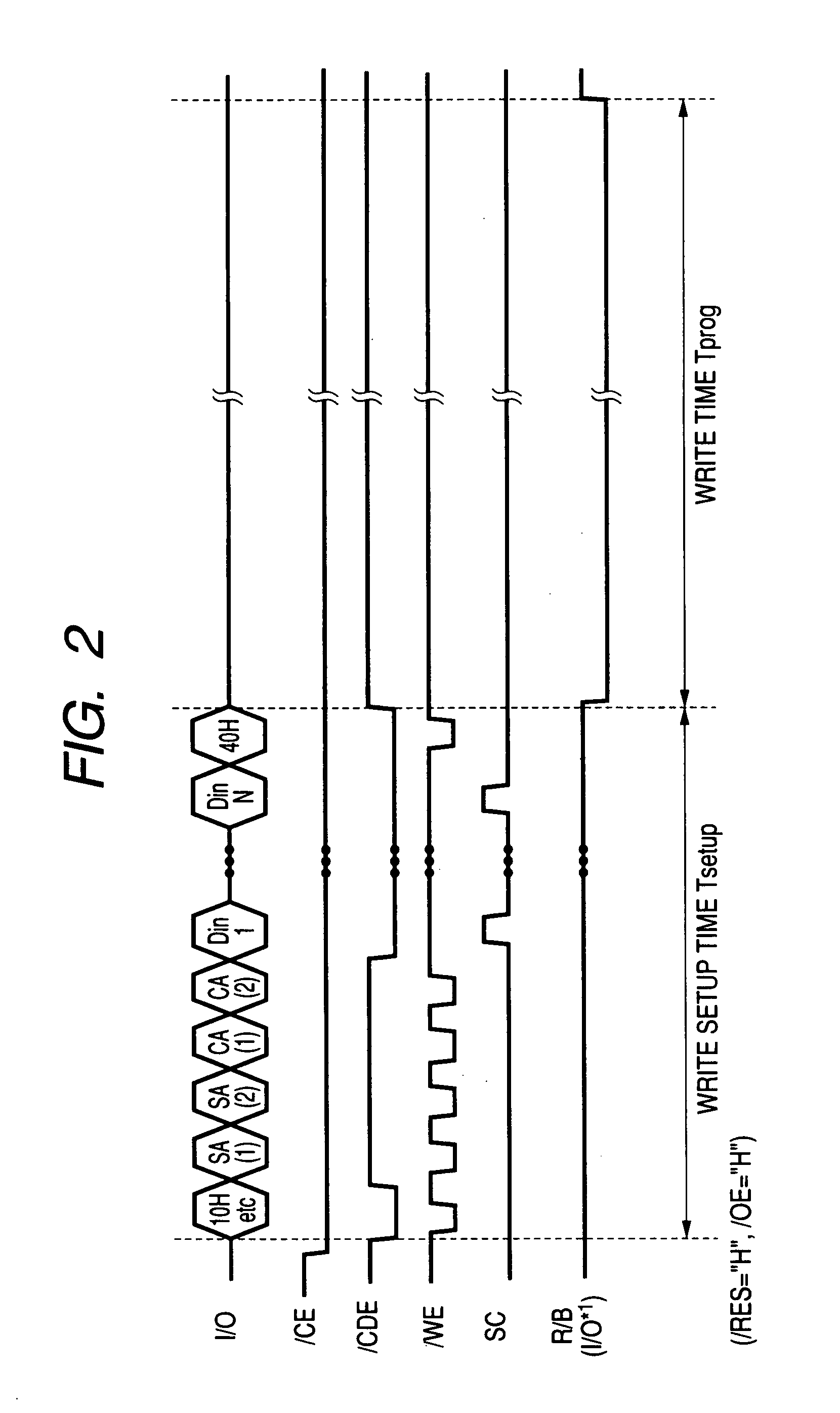

Memory system and memory card

InactiveUS20050015539A1Increase costIncrease speedMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

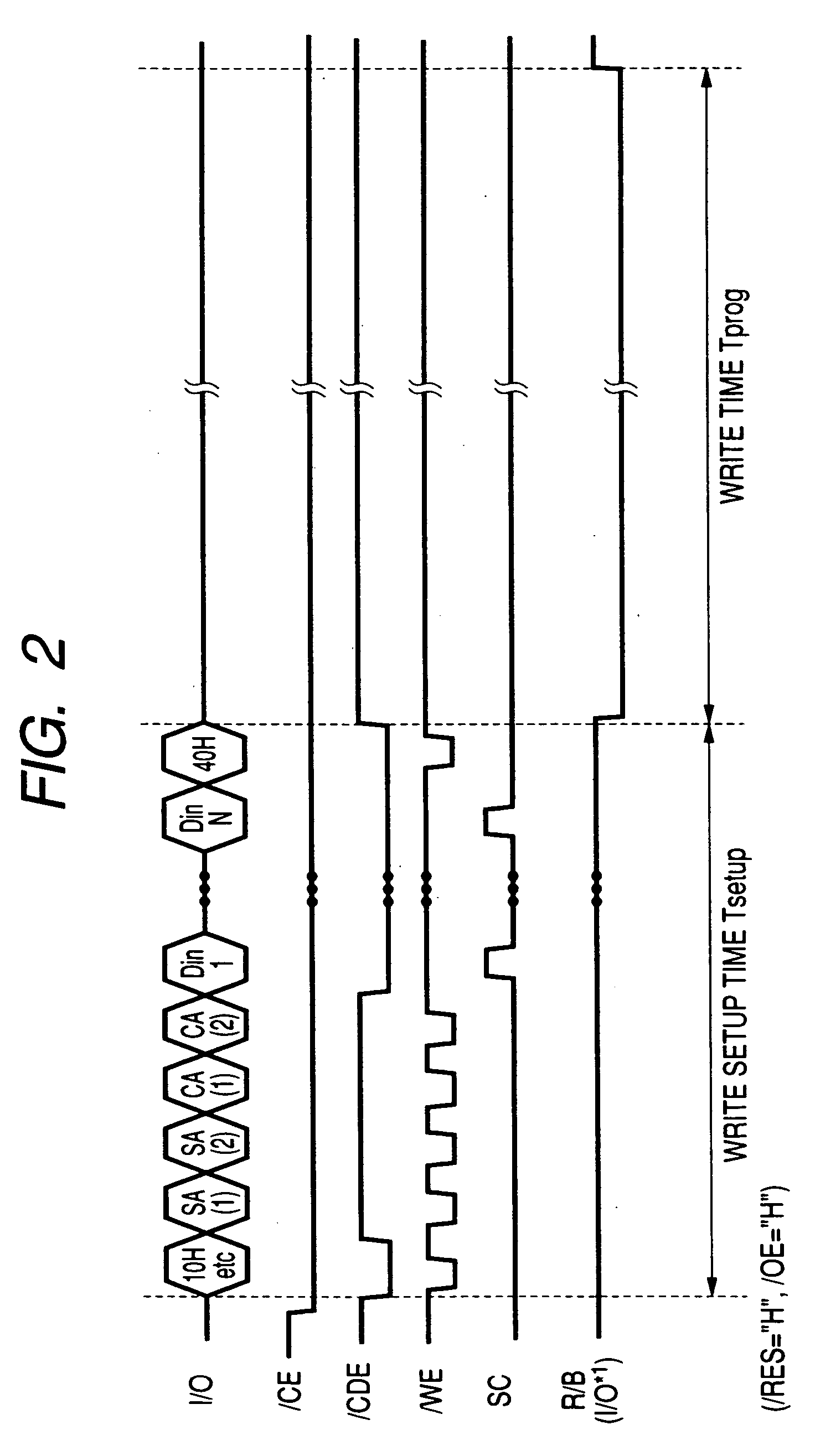

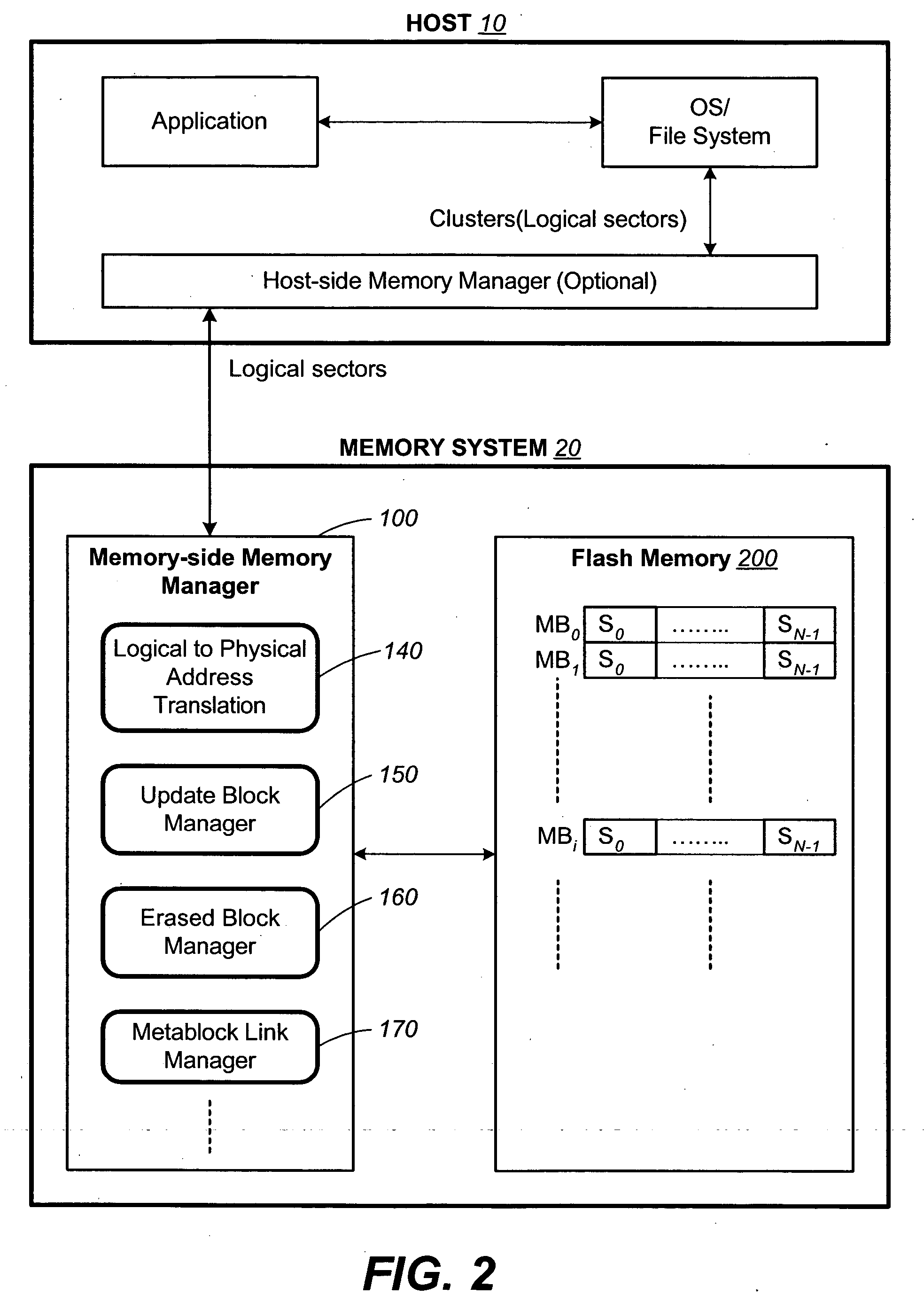

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:RENESAS ELECTRONICS CORP

Non-volatile memory and method with phased program failure handling

InactiveUS20050166087A1Improve efficiencyReduce overheadMemory architecture accessing/allocationMemory adressing/allocation/relocationError processingTime critical

In a memory with block management system, program failure in a block during a time-critical memory operation is handled by continuing the programming operation in a breakout block. Later, at a less critical time, the data recorded in the failed block prior to the interruption is transferred to another block, which could also be the breakout block. The failed block can then be discarded. In this way, when a defective block is encountered during programming, it can be handled without loss of data and without exceeding a specified time limit by having to transfer the stored data in the defective block on the spot. This error handling is especially critical for a garbage collection operation so that the entire operation need not be repeated on a fresh block during a critical time. Subsequently, at an opportune time, the data from the defective block can be salvaged by relocation to another block.

Owner:SANDISK TECH LLC

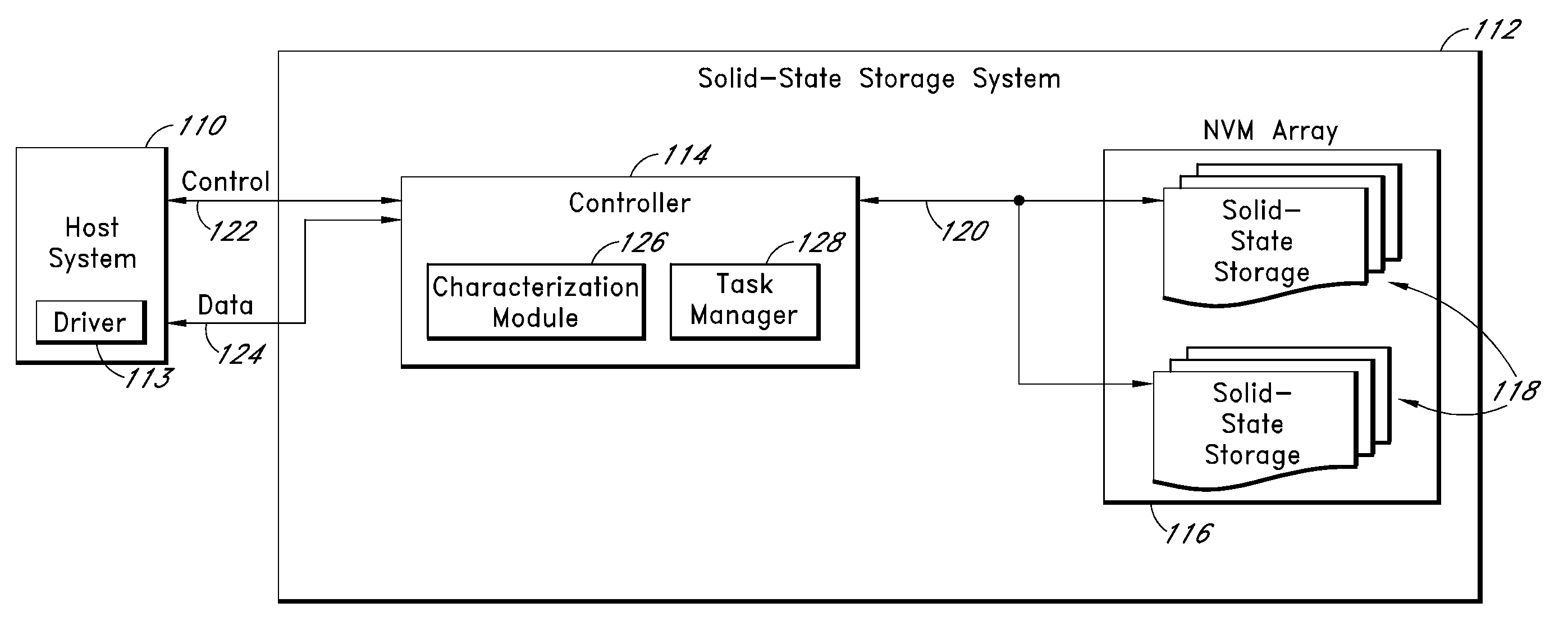

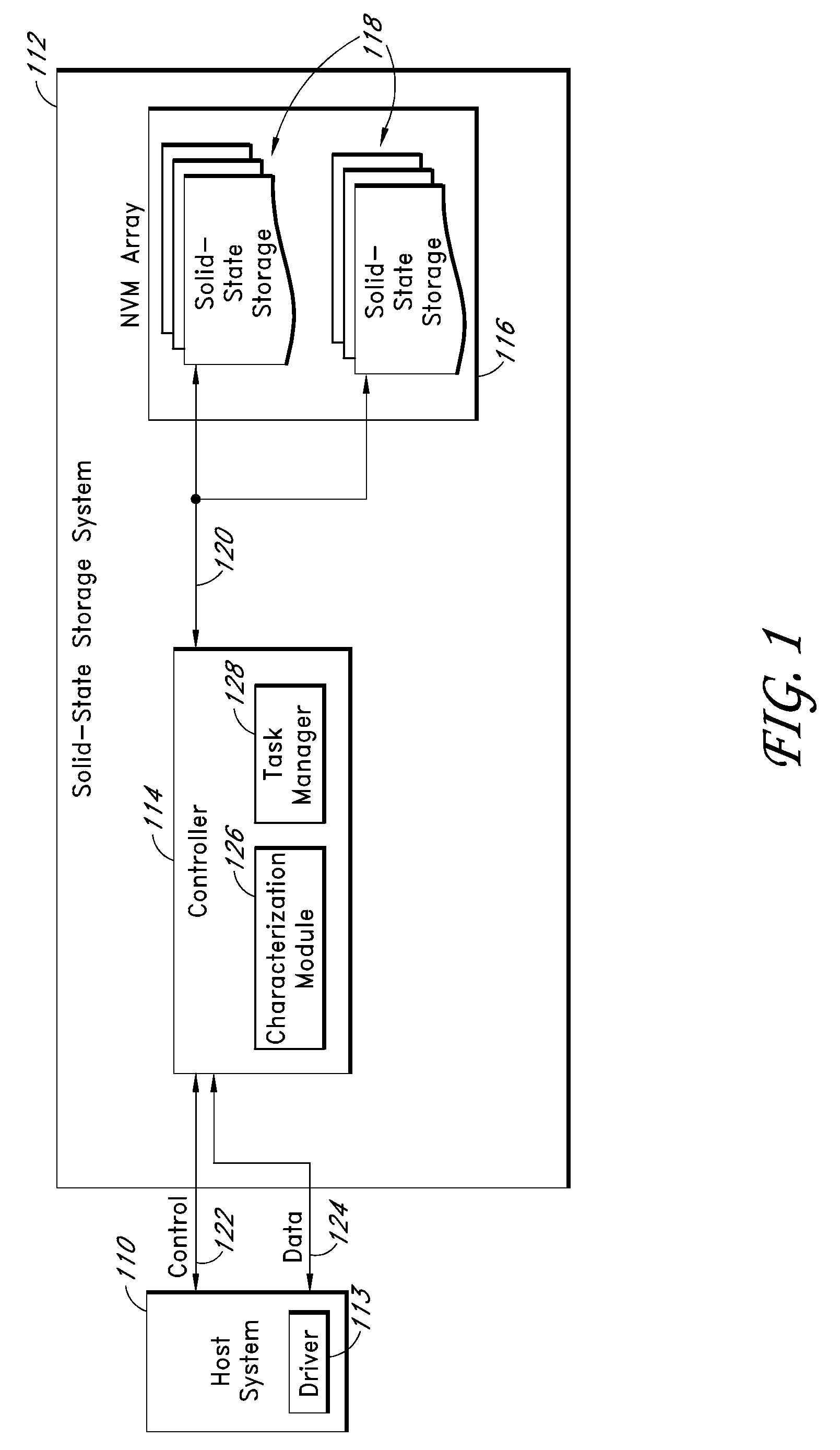

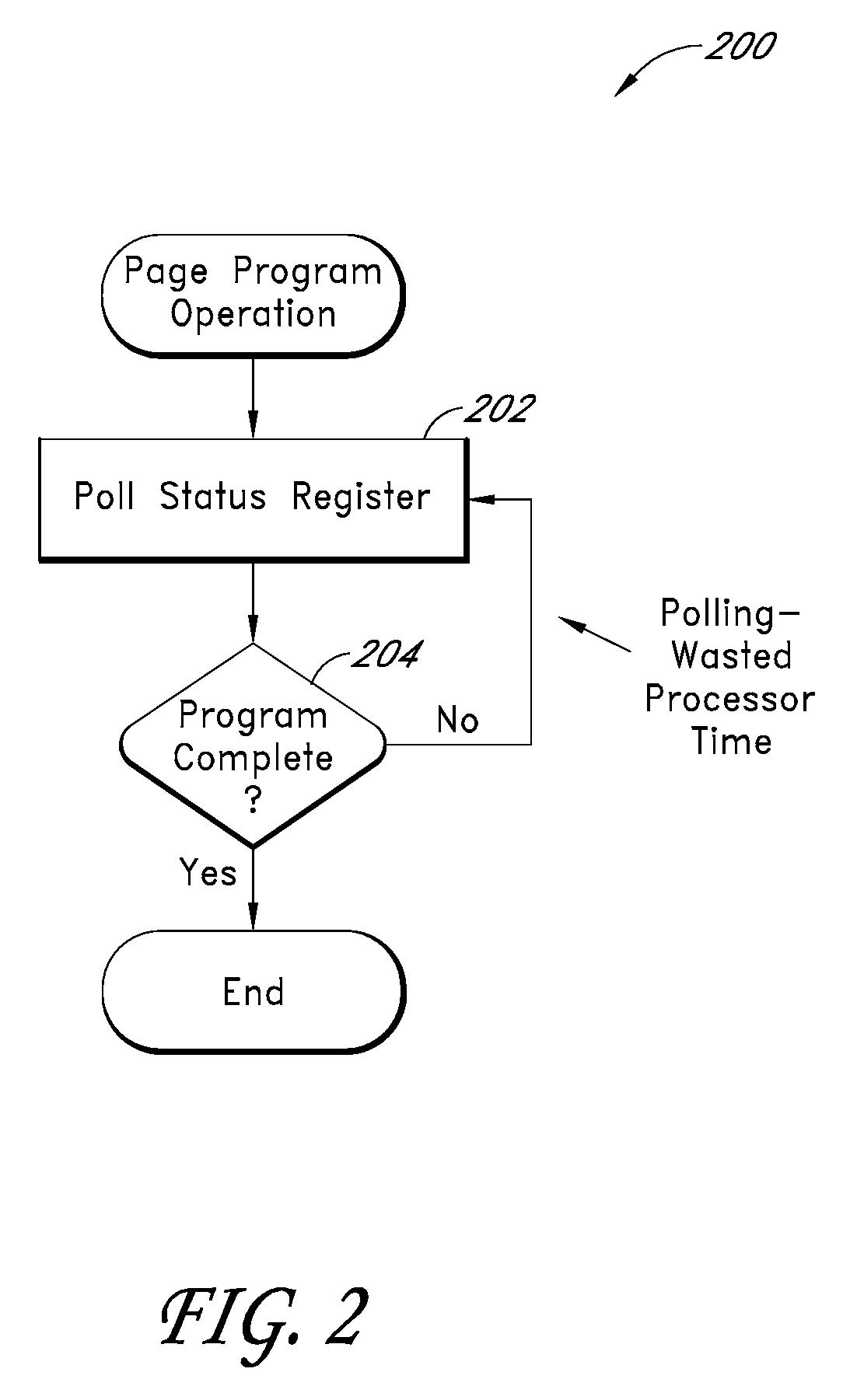

Systems and methods for improving the performance of non-volatile memory operations

ActiveUS20100174849A1Efficient use ofMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingStart up

Disclosed herein are systems and methods that recognize and recapture potentially unused processing time in typical page program and block erase operations in non-volatile memory (NVM) devices. In one embodiment, a characterization module within a controller executes a characterization procedure by performing page program and block erase operations on one or more NVM devices in an array and storing execution time data of the operations in a calibration table. The procedure may be executed at start-up and / or periodically so that the time values are reflective of the actual physical condition of the individual NVM devices. A task manager uses the stored time values to estimate the time needed for completing certain memory operations in its task table. Based on the estimated time for completion, the task manager assigns tasks to be executed during page program and / or block erase cycles, so that otherwise unused processing time can be utilized.

Owner:WESTERN DIGITAL TECH INC

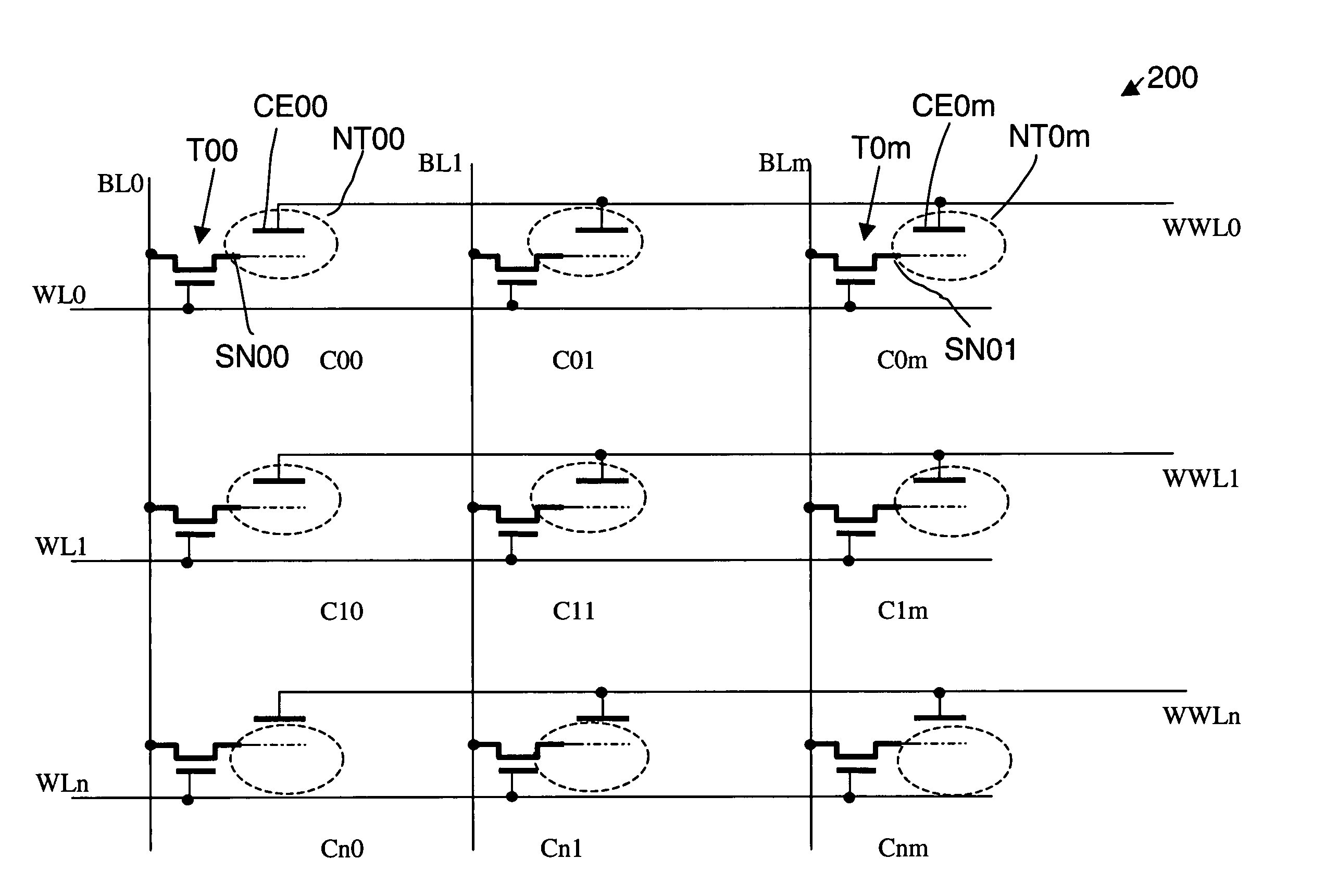

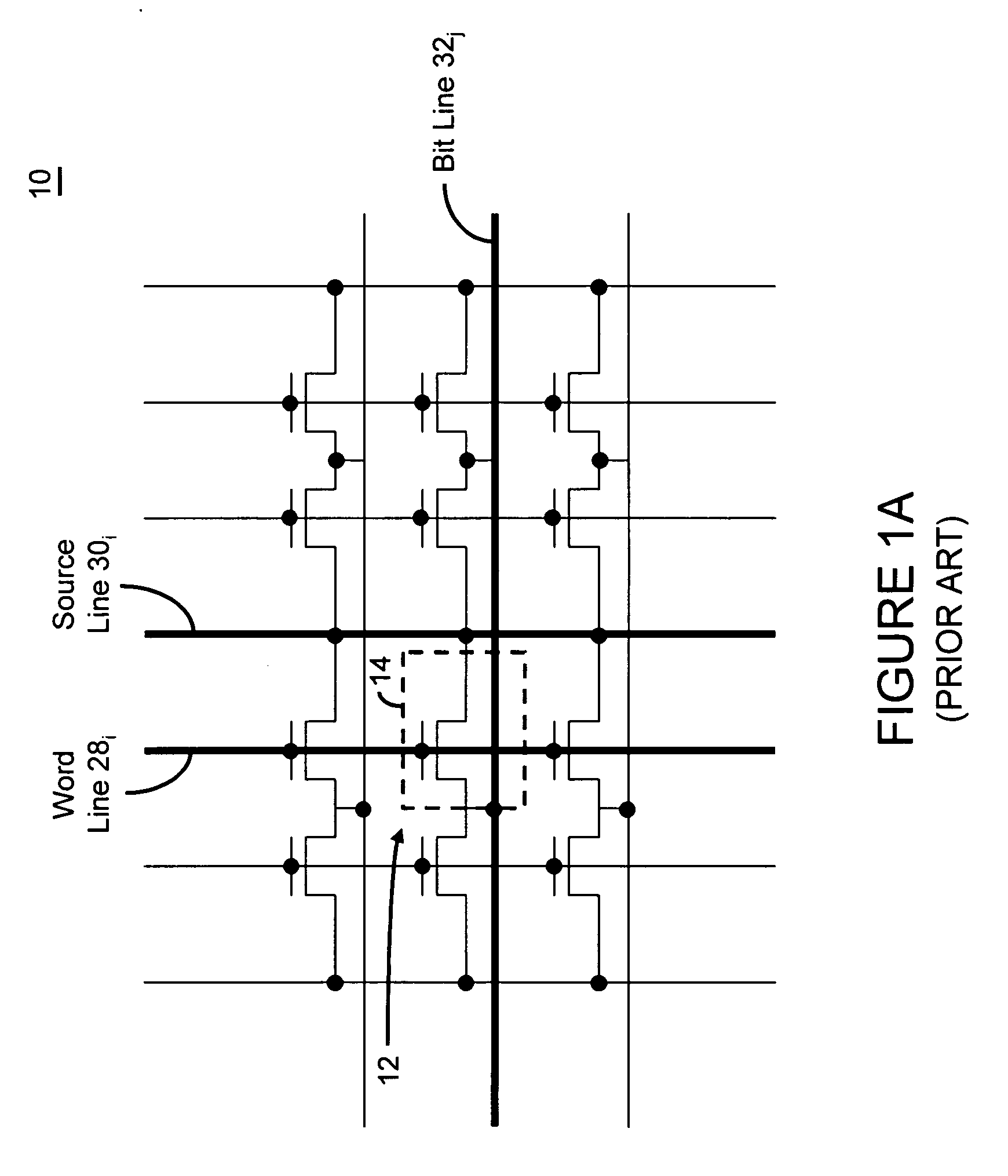

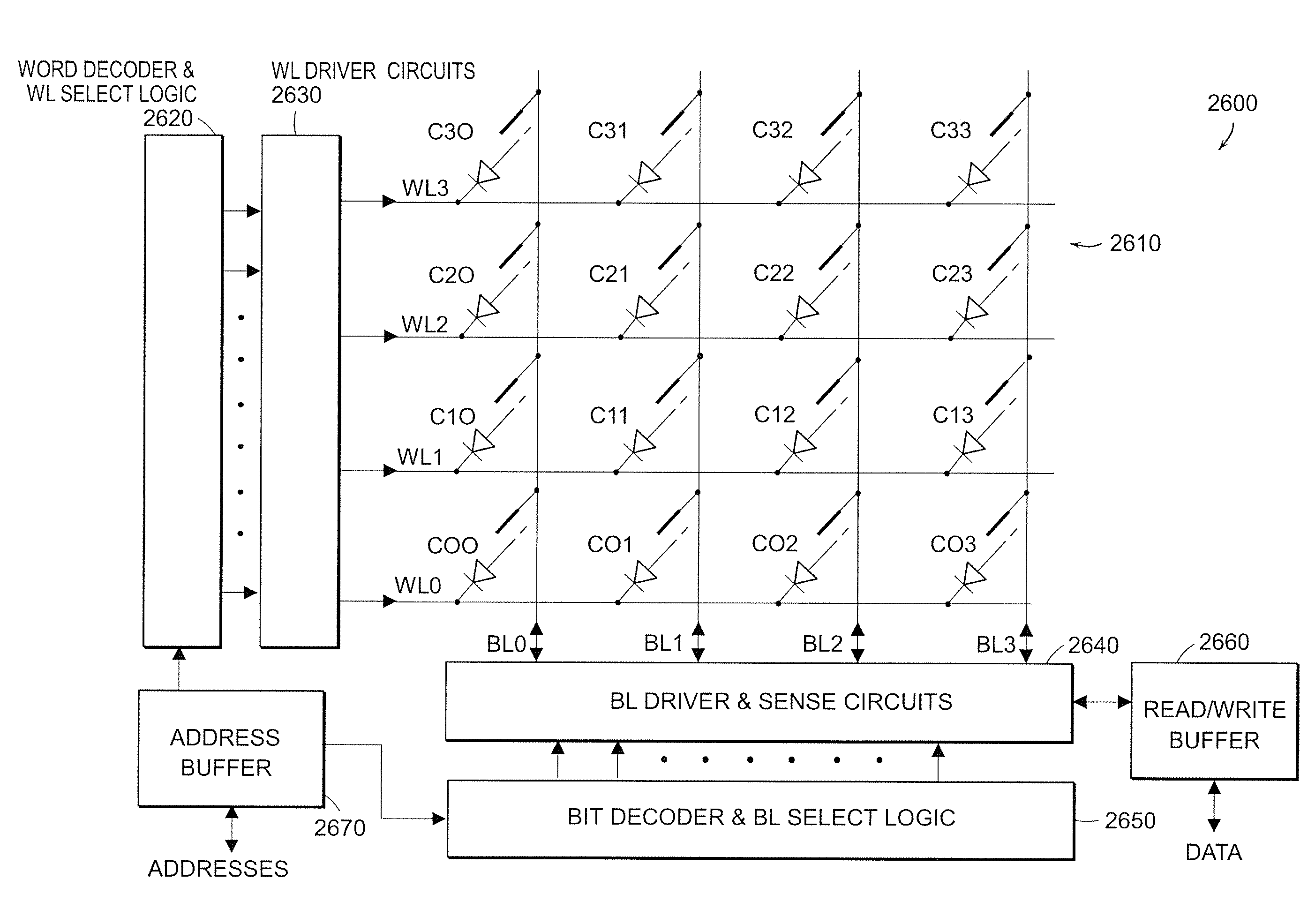

Memory arrays using nanotube articles with reprogrammable resistance

A memory array includes a plurality of memory cells, each of which receives a bit line, a first word line, and a second word line. Each memory cell includes a cell selection circuit, which allows the memory cell to be selected. Each memory cell also includes a two-terminal switching device, which includes first and second conductive terminals in electrical communication with a nanotube article. The memory array also includes a memory operation circuit, which is operably coupled to the bit line, the first word line, and the second word line of each cell. The circuit can select the cell by activating an appropriate line, and can apply appropriate electrical stimuli to an appropriate line to reprogrammably change the relative resistance of the nanotube article between the first and second terminals. The relative resistance corresponds to an informational state of the memory cell.

Owner:NANTERO

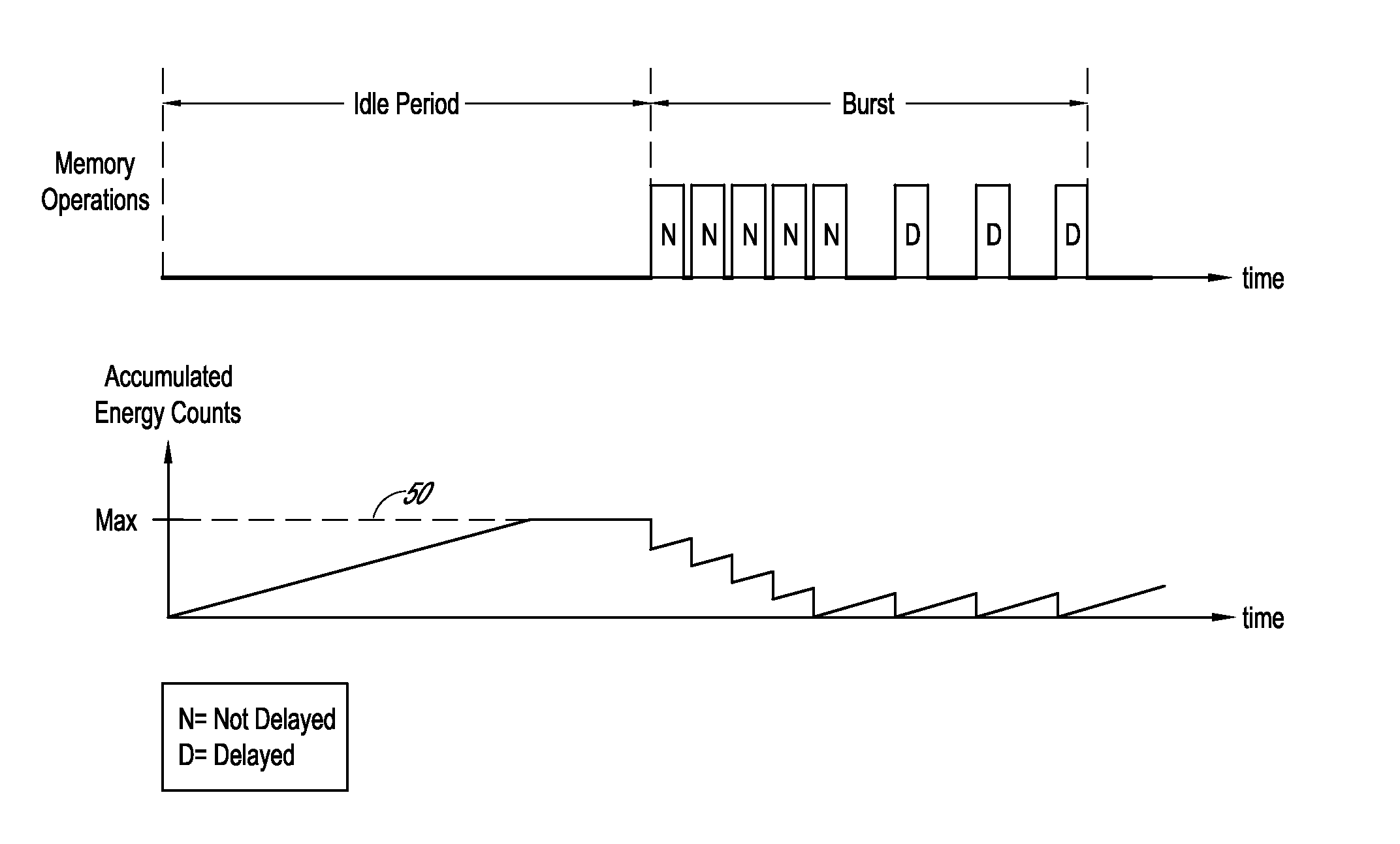

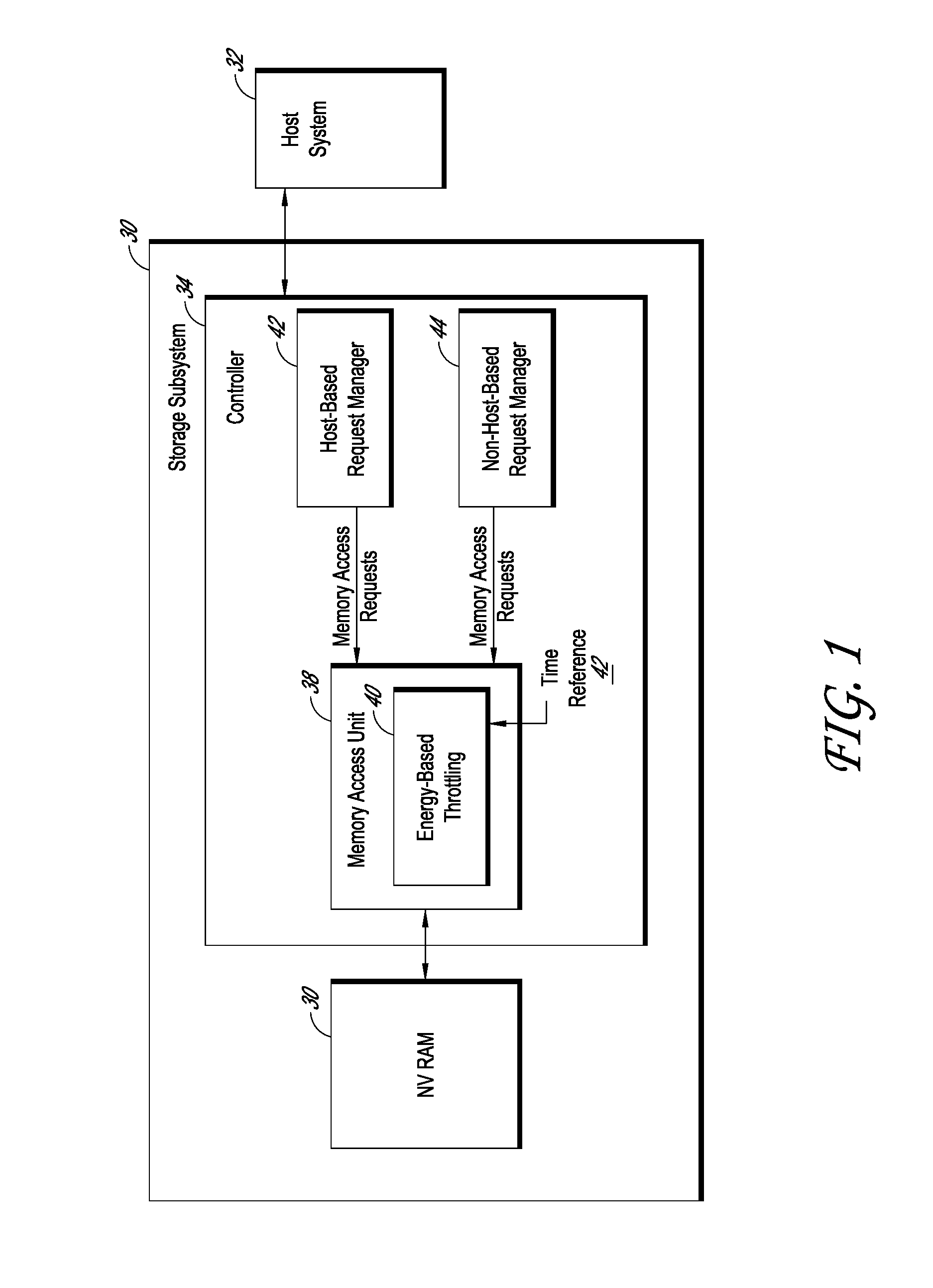

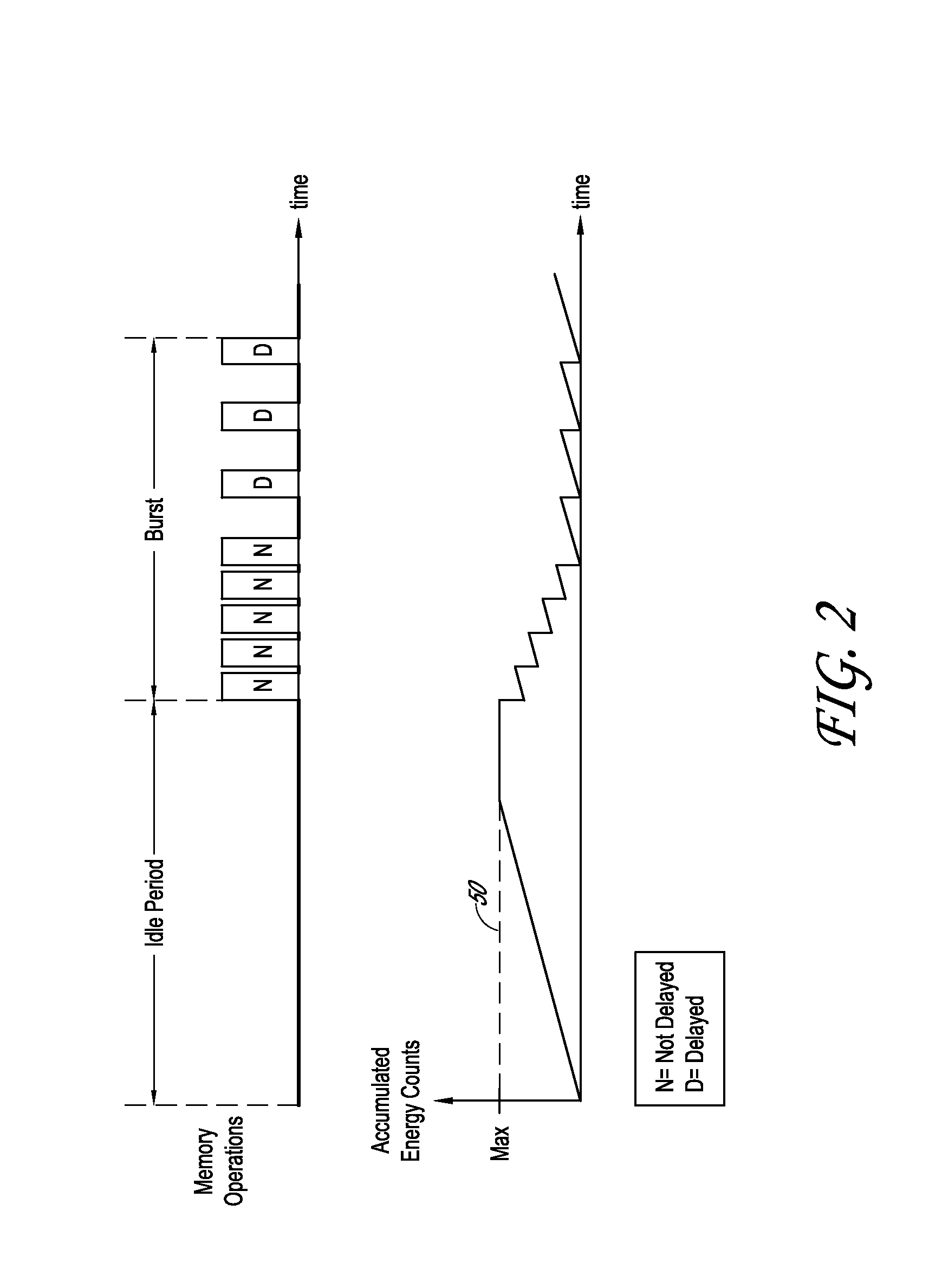

Non-volatile storage subsystem with energy-based performance throttling

A non-volatile storage subsystem regulates energy consumption by controlling or “throttling” the rate at which memory operations are performed. During relatively idle periods in which few or no memory operations are performed, energy allotments or “counts” are accumulated to reflect unused energy. These accumulated energy counts may then be effectively allocated for use during bursts or other periods of relatively heavy memory activity, such that the memory operations are performed at a relatively high rate without causing a maximum average power consumption to be exceeded.

Owner:WESTERN DIGITAL TECH INC

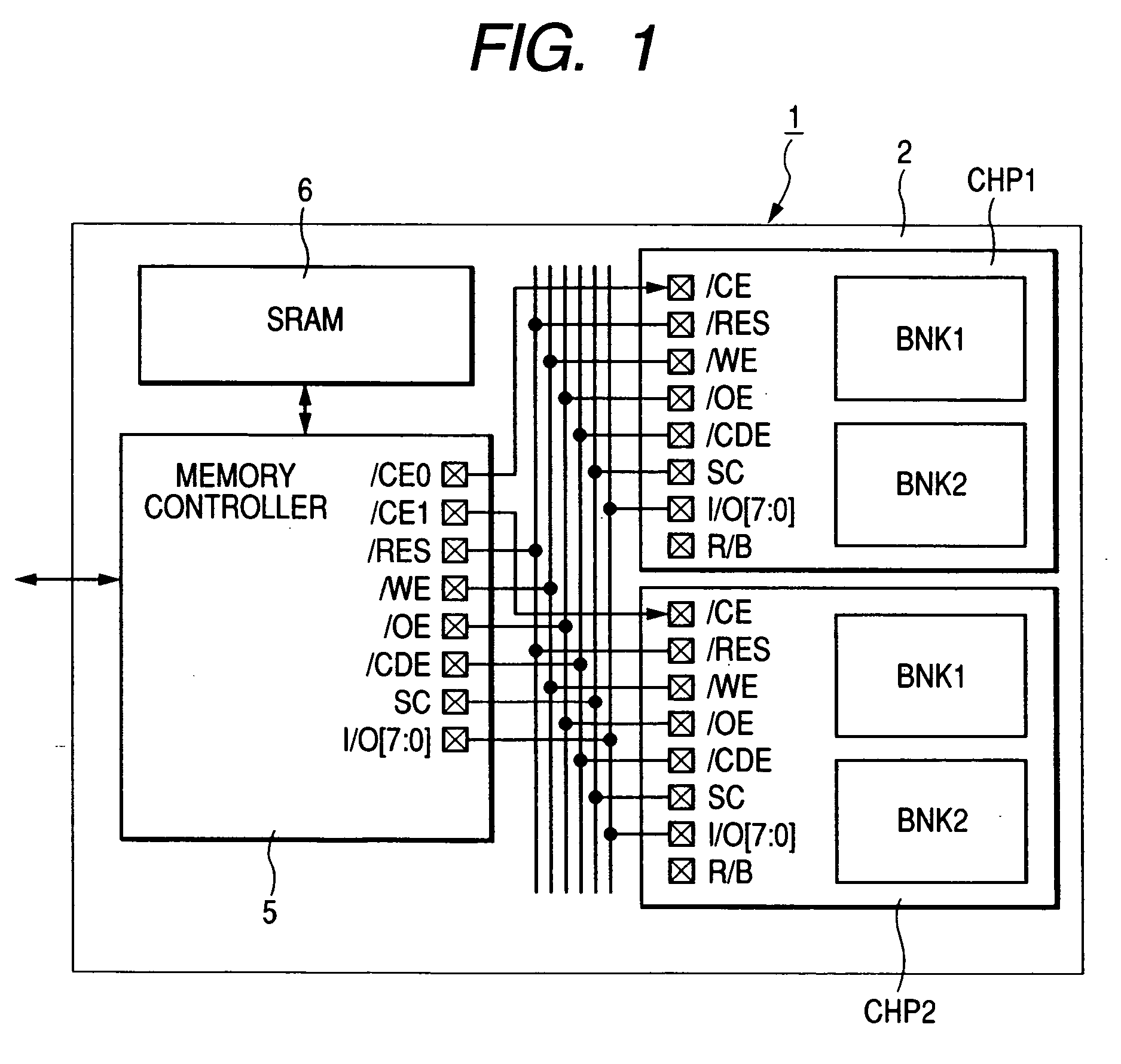

Memory system and memory card

InactiveUS20070198770A1Rise in cost is suppressedRequirement for numberMemory adressing/allocation/relocationRead-only memoriesMemory chipMemory bank

A memory system includes a plurality of nonvolatile memory chips (CHP1 and CHP2) each having a plurality of memory banks (BNK1 and BNK2) which can perform a memory operation independent of each other and a memory controller (5) which can control to access each of said nonvolatile memory chips. The memory controller can selectively instruct either a simultaneous writing operation or an interleave writing operation on a plurality of memory banks of the nonvolatile memory chips. Therefore, in the simultaneous writing operation, the writing operation which is much longer than the write setup time can be performed perfectly in parallel. In the interleave writing operation, the writing operation following the write setup can be performed so as to partially overlap the writing operation on another memory bank. As a result, the number of nonvolatile memory chips constructing the memory system of the high-speed writing operation can be made relatively small.

Owner:HORII TAKASHI +2

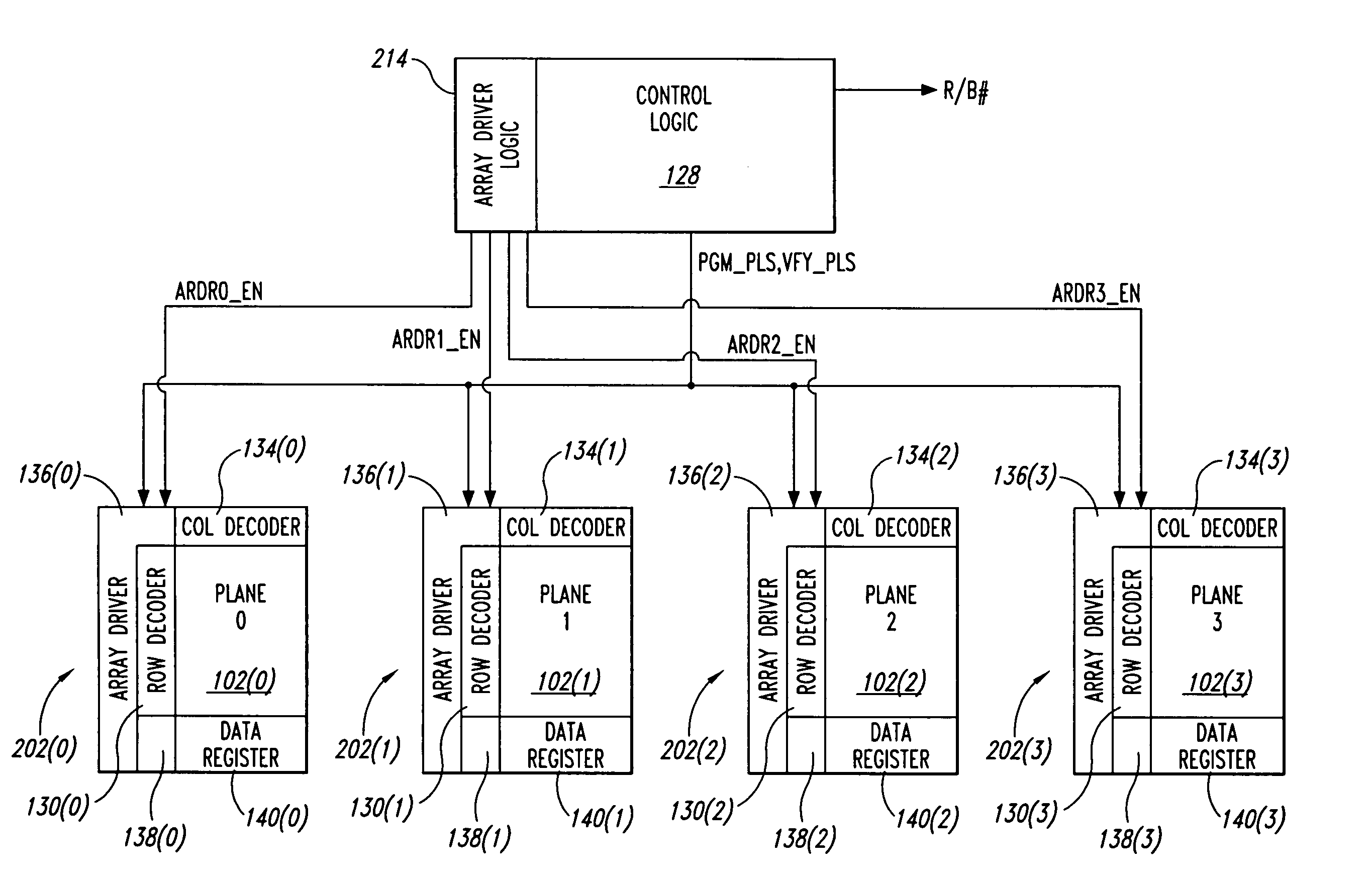

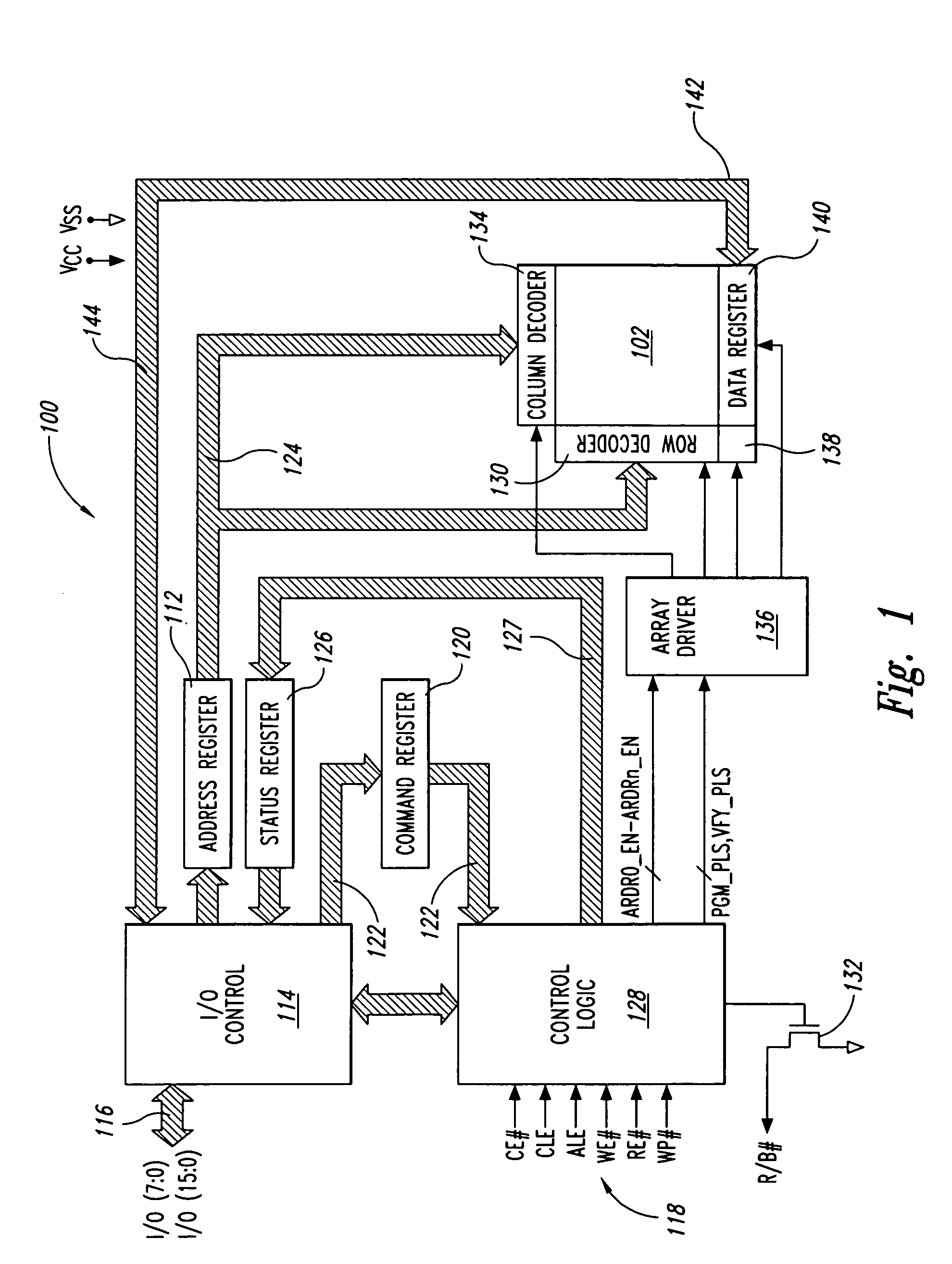

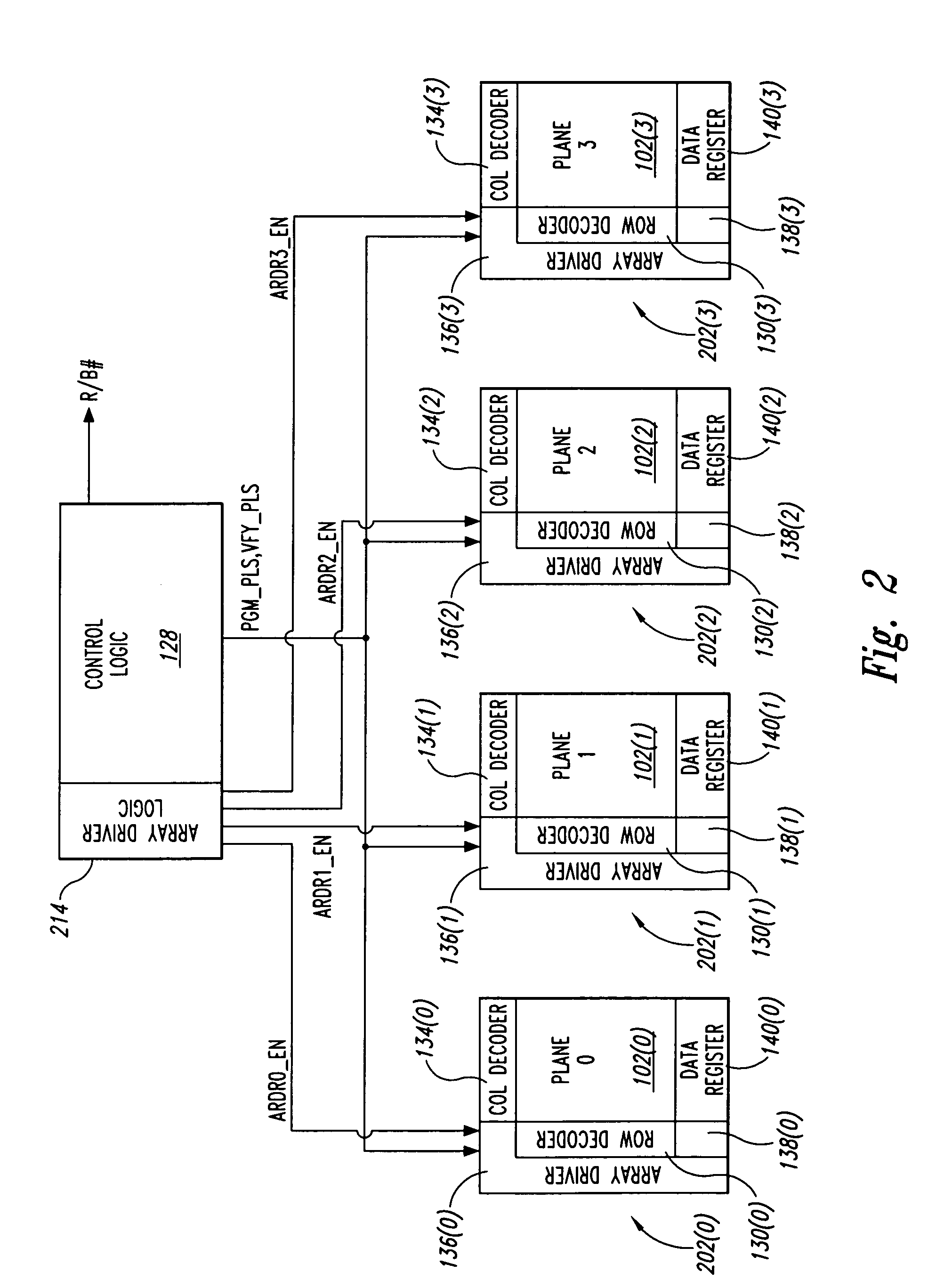

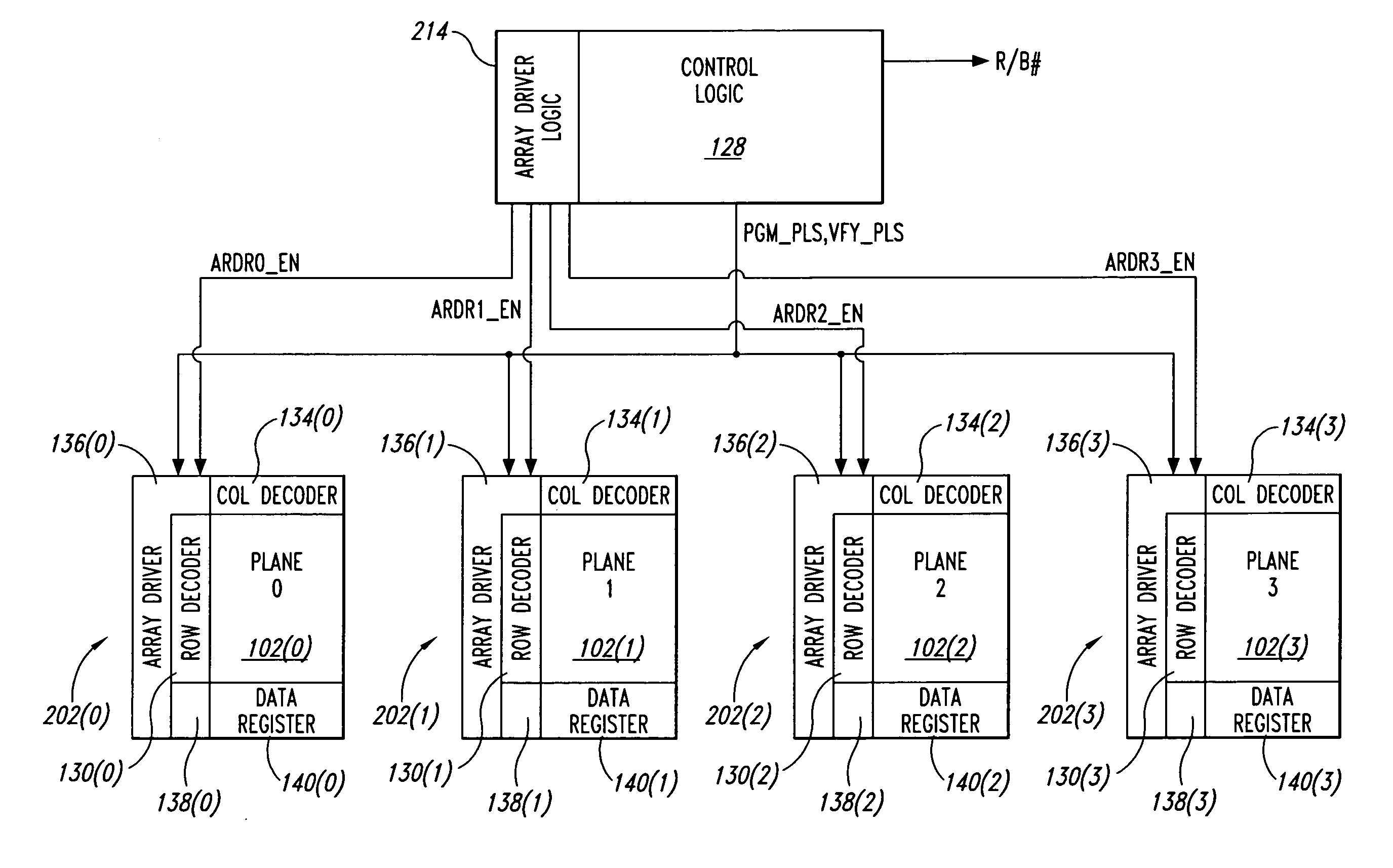

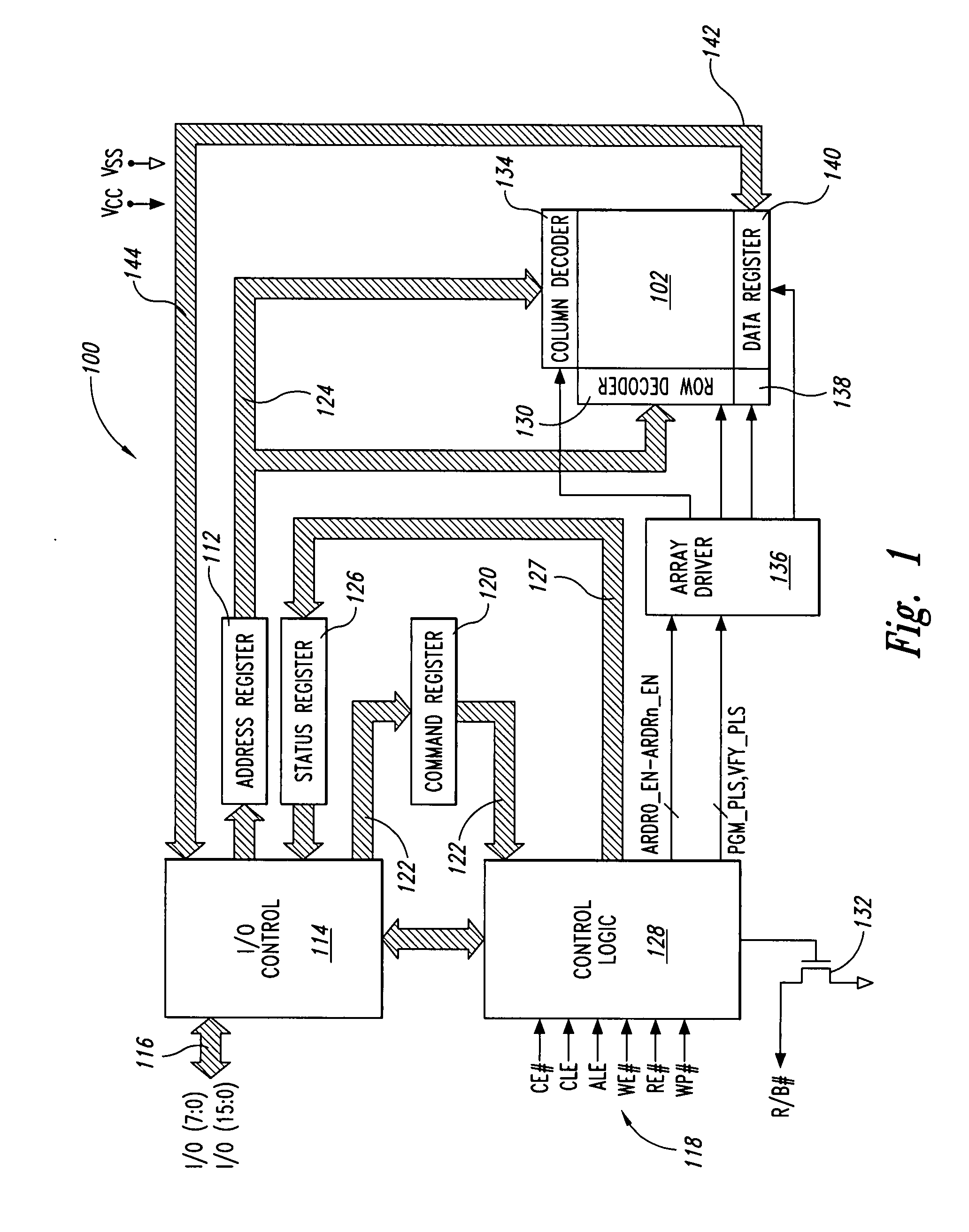

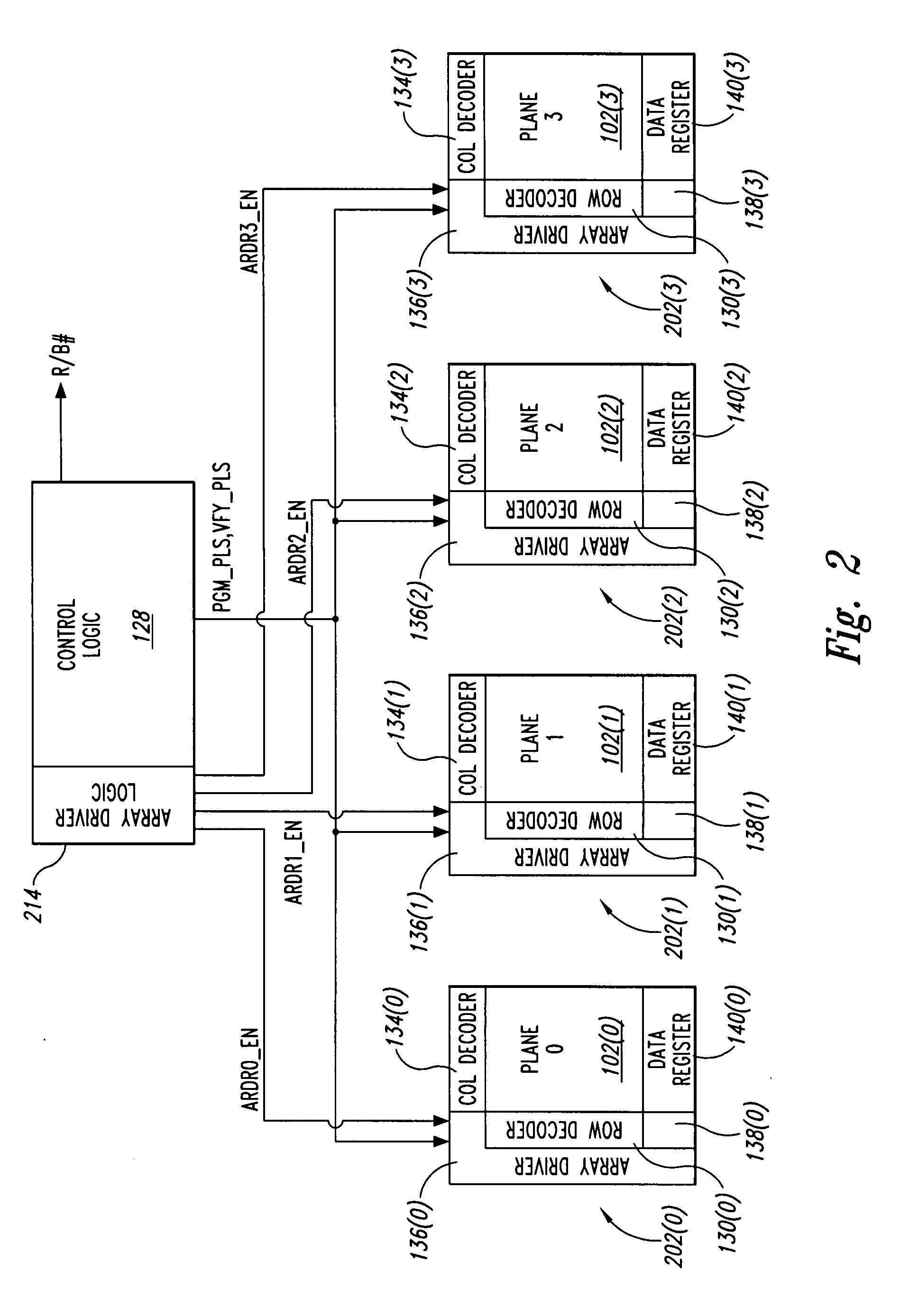

System and memory for sequential multi-plane page memory operations

A system and method for performing memory operations in a multi-plane flash memory. Commands and addresses are sequentially provided to the memory for memory operations in memory planes. The memory operations are sequentially initiated and the memory operation for at least one of the memory planes is initiated during the memory operation for another memory plane. In one embodiment, each of a plurality of programming circuits is associated with a respective memory plane and is operable to program data to the respective memory plane in response to programming signals and when it is enabled. Control logic coupled to the plurality of programming circuits generates programming signals in response to the memory receiving program commands and further generates programming enable signals to individually enable each of the programming circuits to respond to the programming signals and stagger programming of data to each of the memory planes.

Owner:ROUND ROCK RES LLC

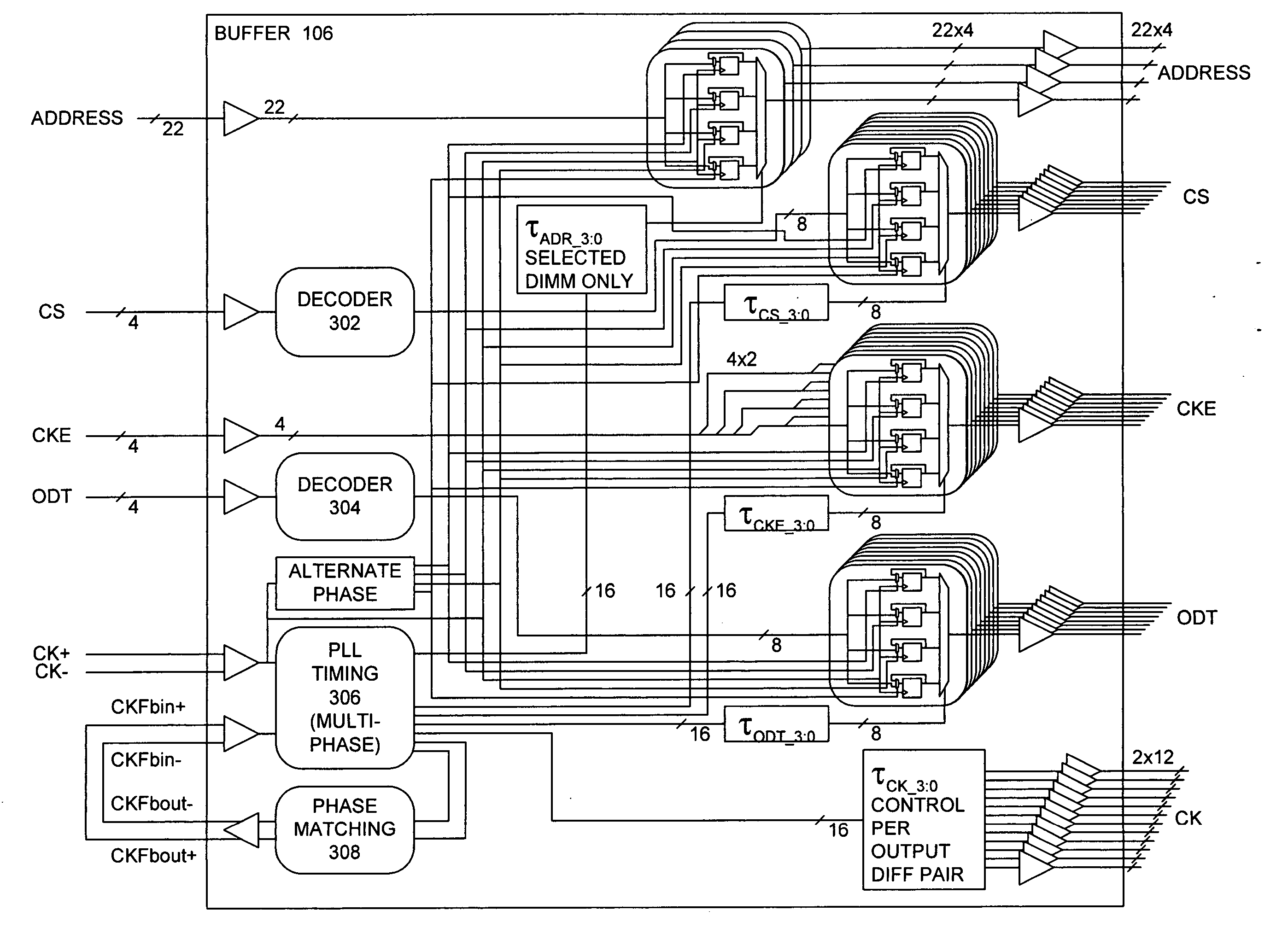

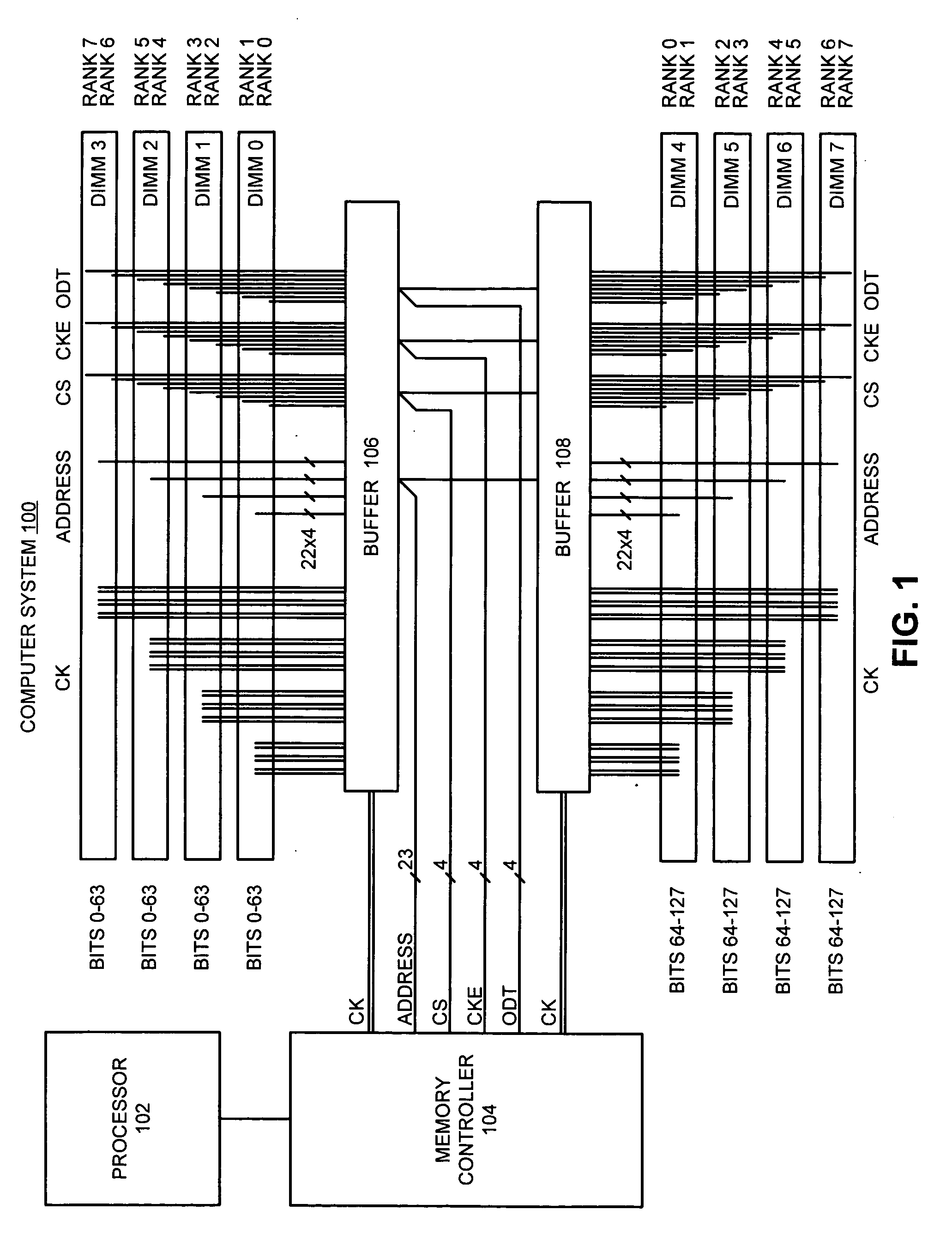

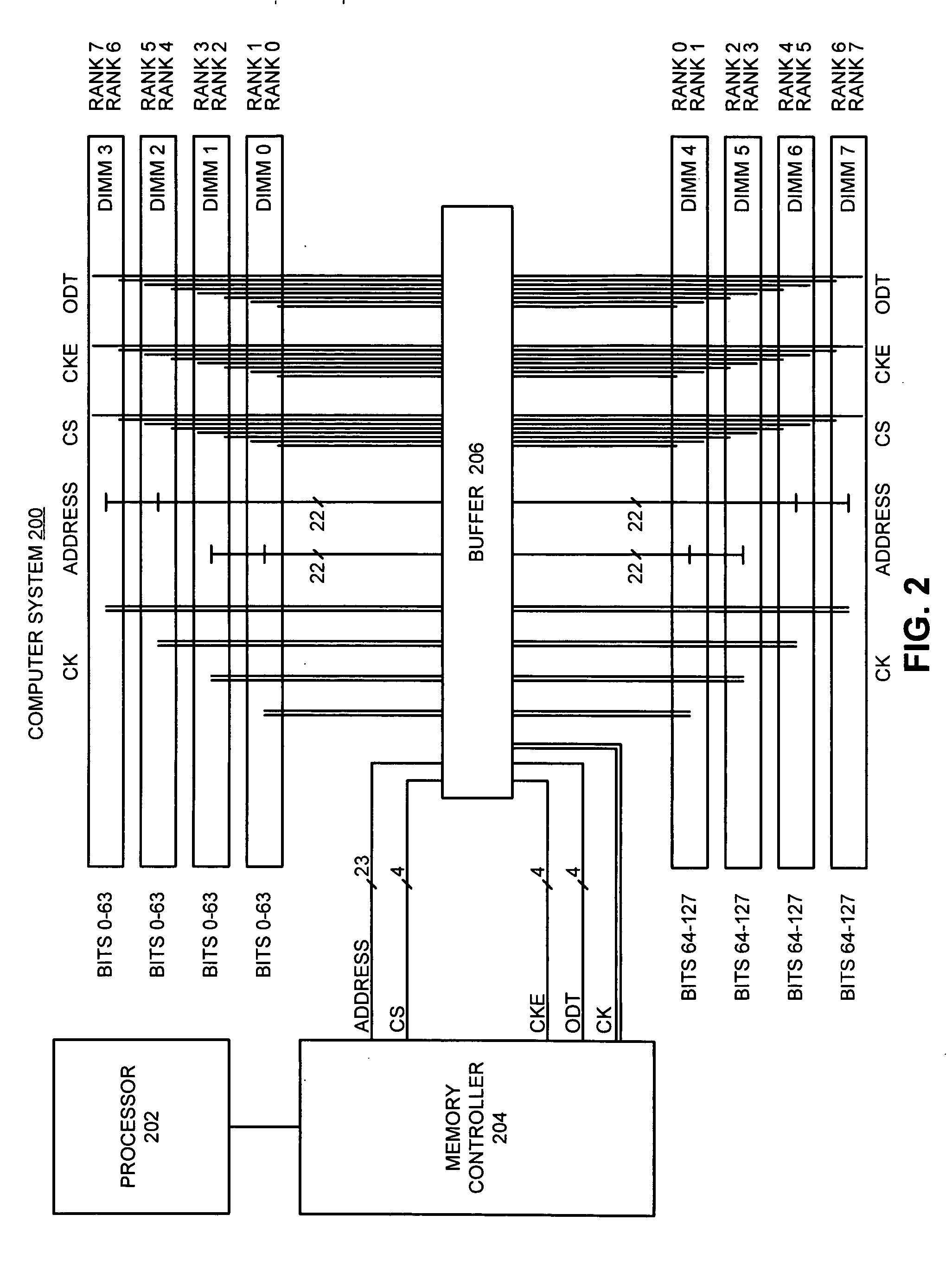

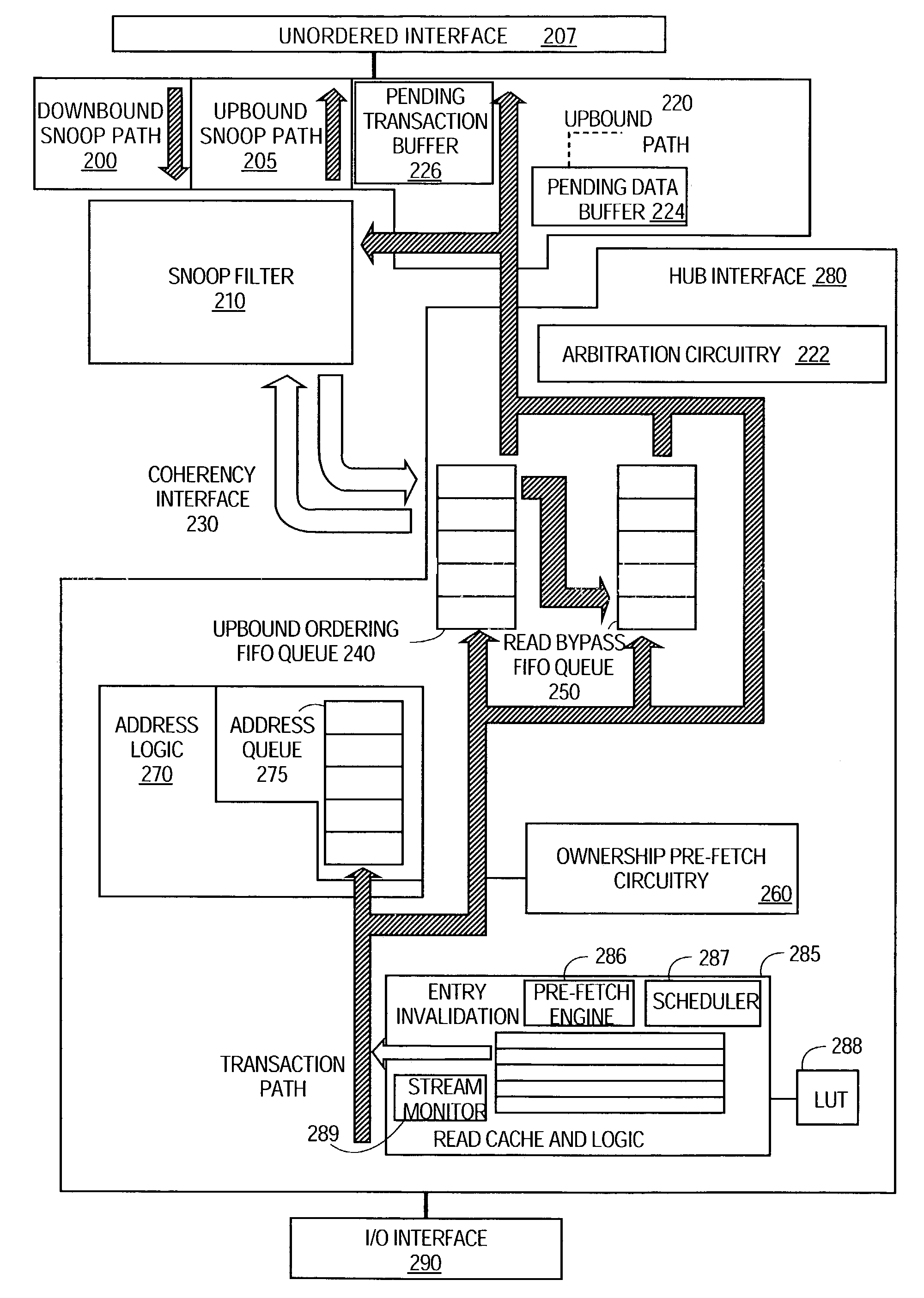

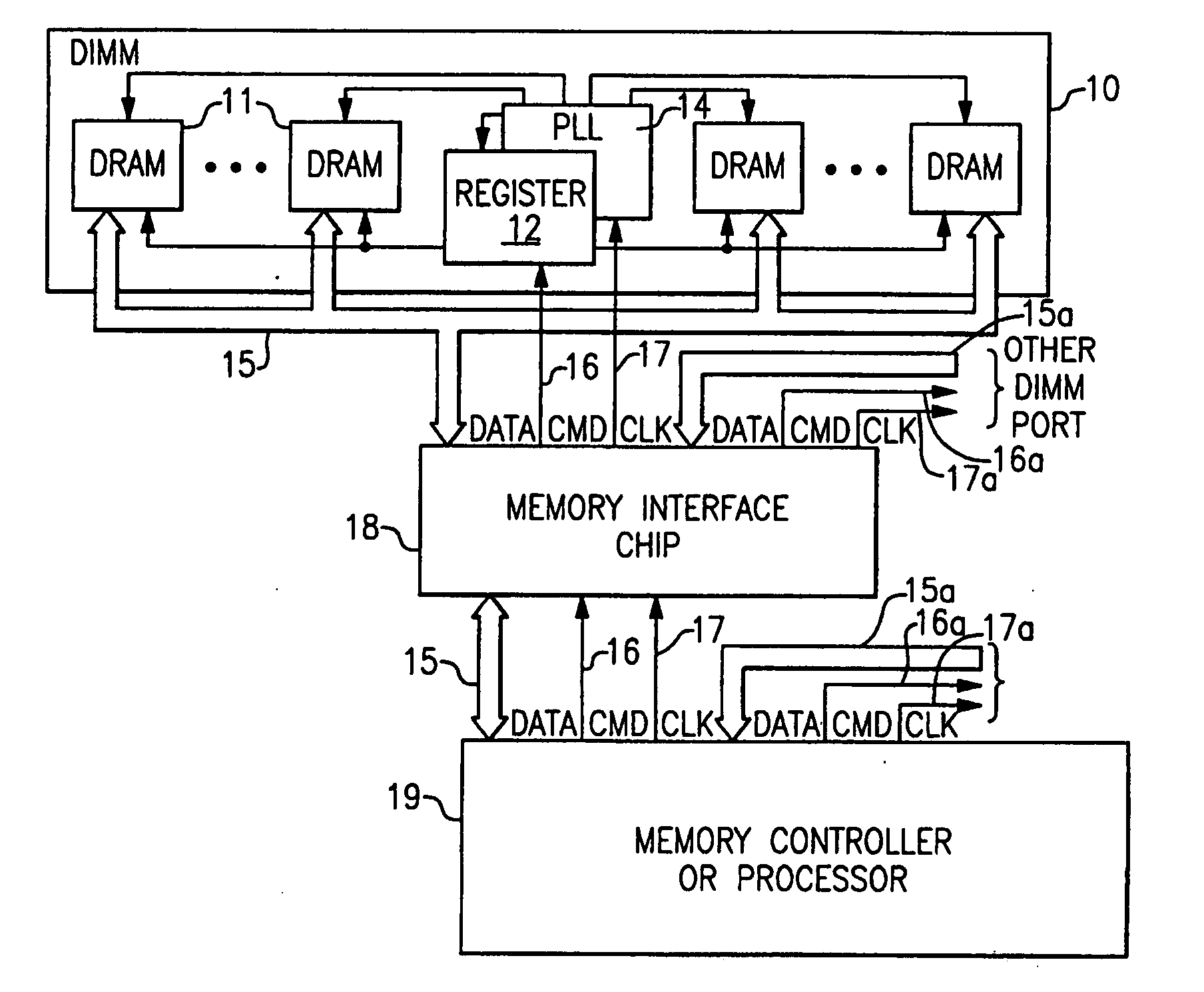

Reducing the number of power and ground pins required to drive address signals to memory modules

InactiveUS20060039205A1Reduced pin countReduce in quantityEnergy efficient ICTDigital storageChip selectEngineering

One embodiment of the present invention provides a system that reduces the number of power and ground pins required to drive address signals to system memory. During operation, the system receives address signals associated with a memory operation from a memory controller, wherein the address signals are received at a buffer chip, which is external the memory controller. The system also receives chip select signals associated with the memory operation at the buffer chip. Next, the system uses the chip select signals to identify an active subset of memory modules in the system memory, which are active during the memory operation. The system then uses address drivers on the buffer chip to drive the address signals only to the active subset of memory modules, and not to other memory modules in the system memory. In this way, the buffer chip requires fewer power and ground pins for the address drivers because the address signals are only driven to the active subset of memory modules, instead of being driven to all memory modules in the system memory.

Owner:APPLE INC

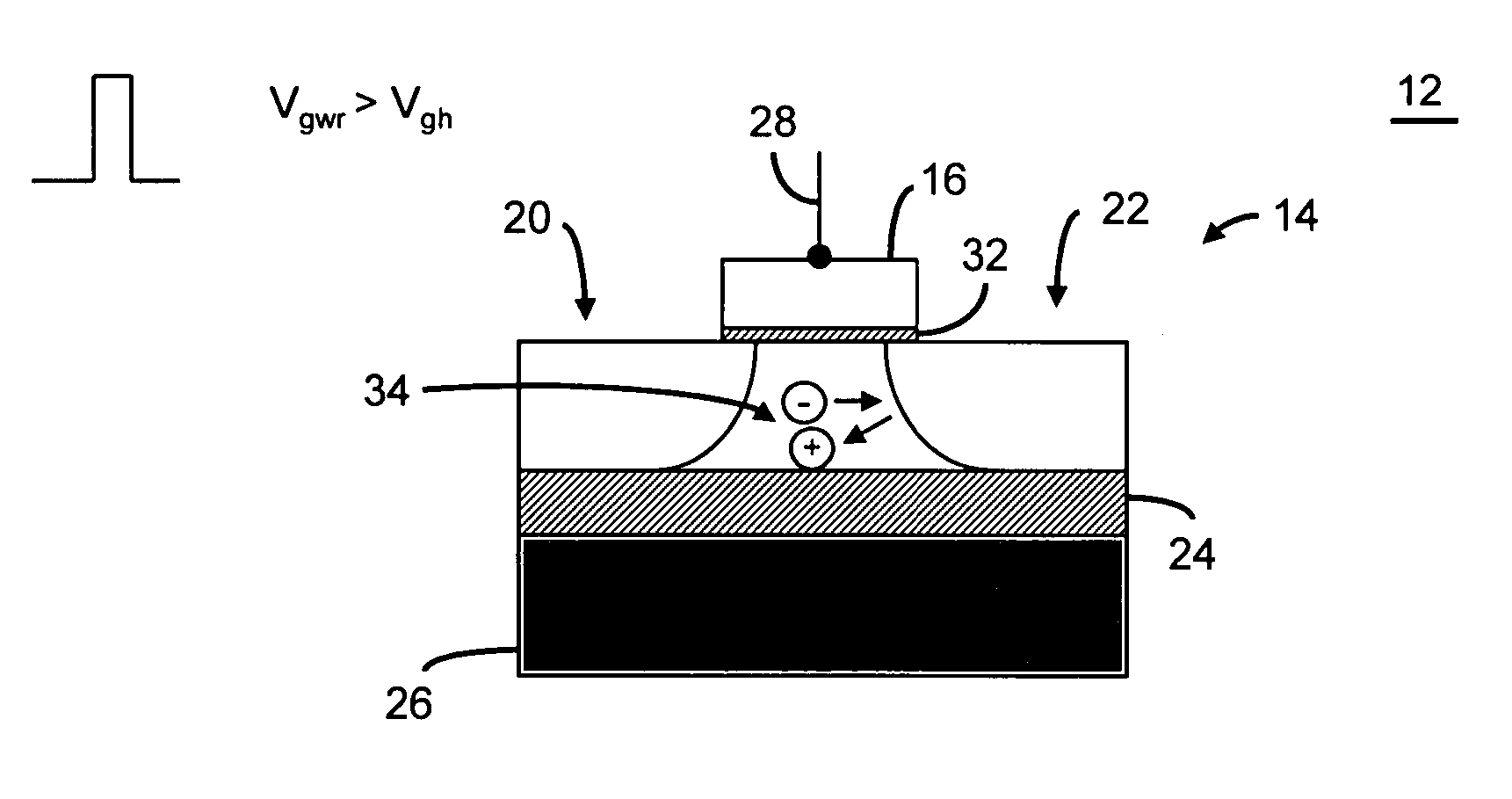

Method and apparatus for varying the programming duration and/or voltage of an electrically floating body transistor, and memory cell array implementing same

There are many inventions described herein as well as many aspects and embodiments of those inventions, for example, circuitry and techniques for reading, writing and / or operating a semiconductor memory cells of a memory cell array, including electrically floating body transistors in which an electrical charge is stored in the body of the transistor. In one aspect, the present inventions are directed to one or more independently controllable parameters of a memory operation (for example, restore, write, refresh), to program or write a data state into a memory cell. In one embodiment, the parameter is the amount of time of programming or writing a predetermined data state into a memory cell. In another embodiment, the controllable parameter is the amplitude of the voltage of the control signals applied to the gate, drain region and / or source region during programming or writing a predetermined data state into a memory cell. Indeed, the controllable parameters may be both temporal and voltage amplitude. Notably, the memory cell array may comprise a portion of an integrated circuit device, for example, logic device (for example, a microprocessor) or a portion of a memory device (for example, a discrete memory).

Owner:MICRON TECH INC

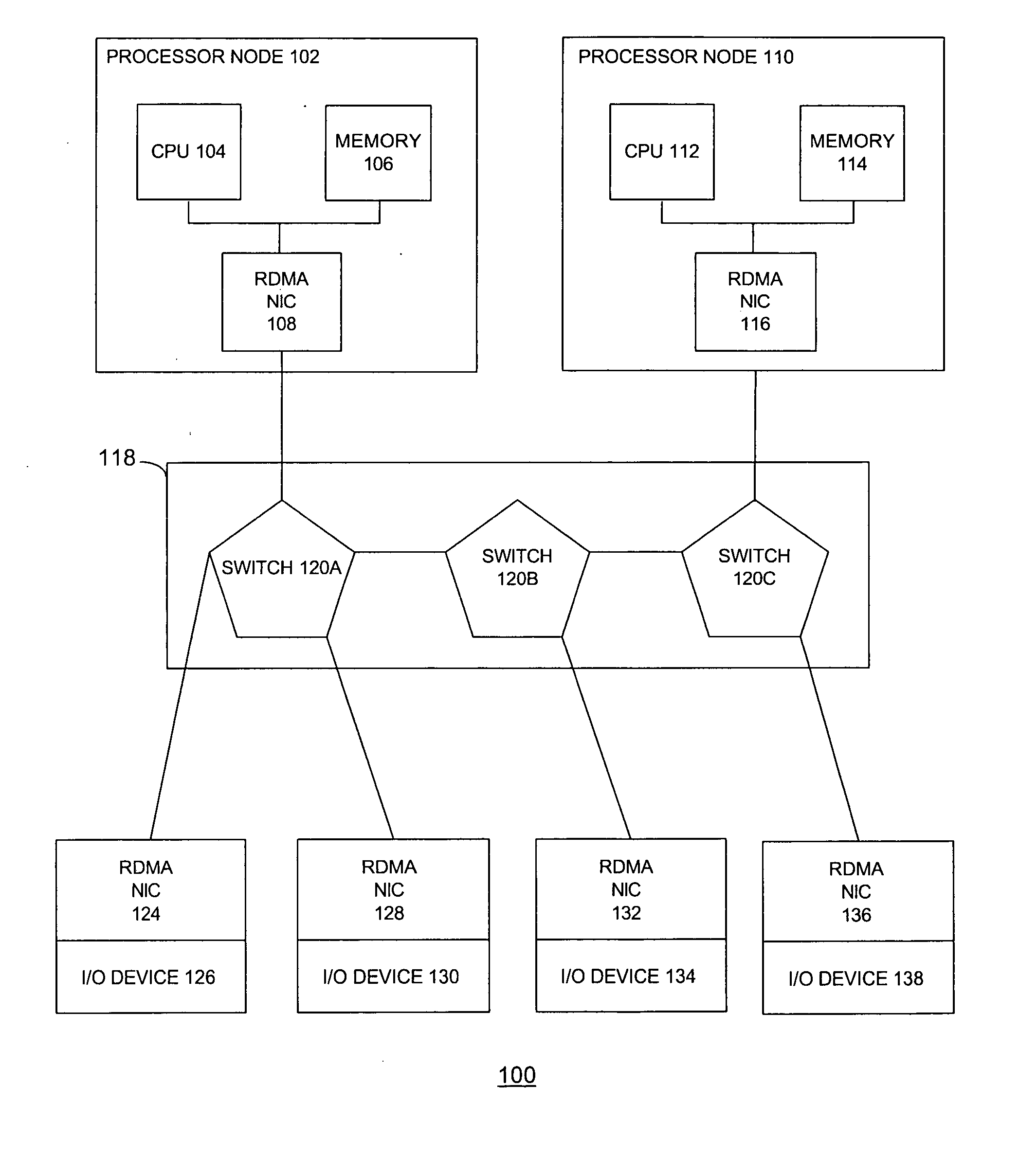

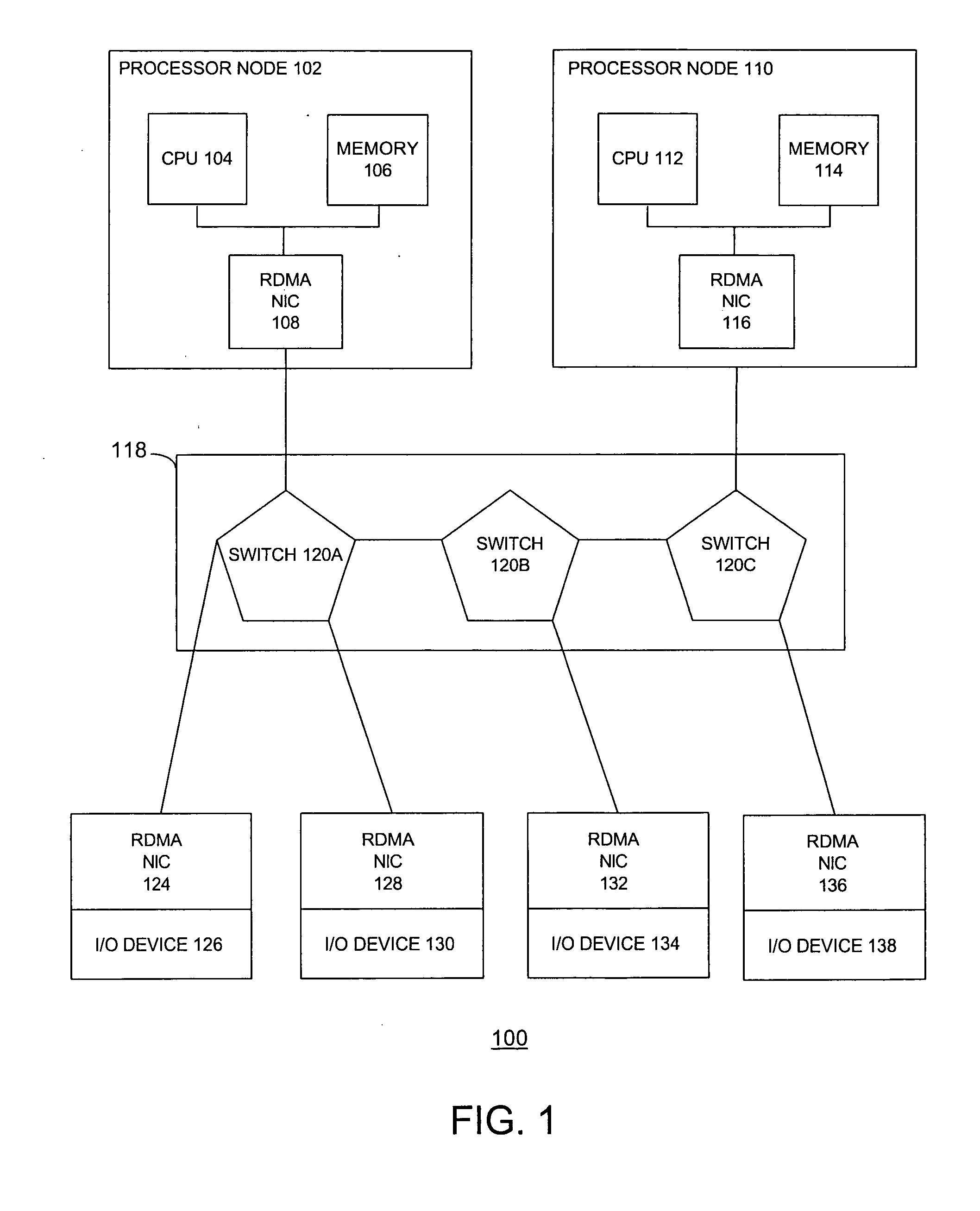

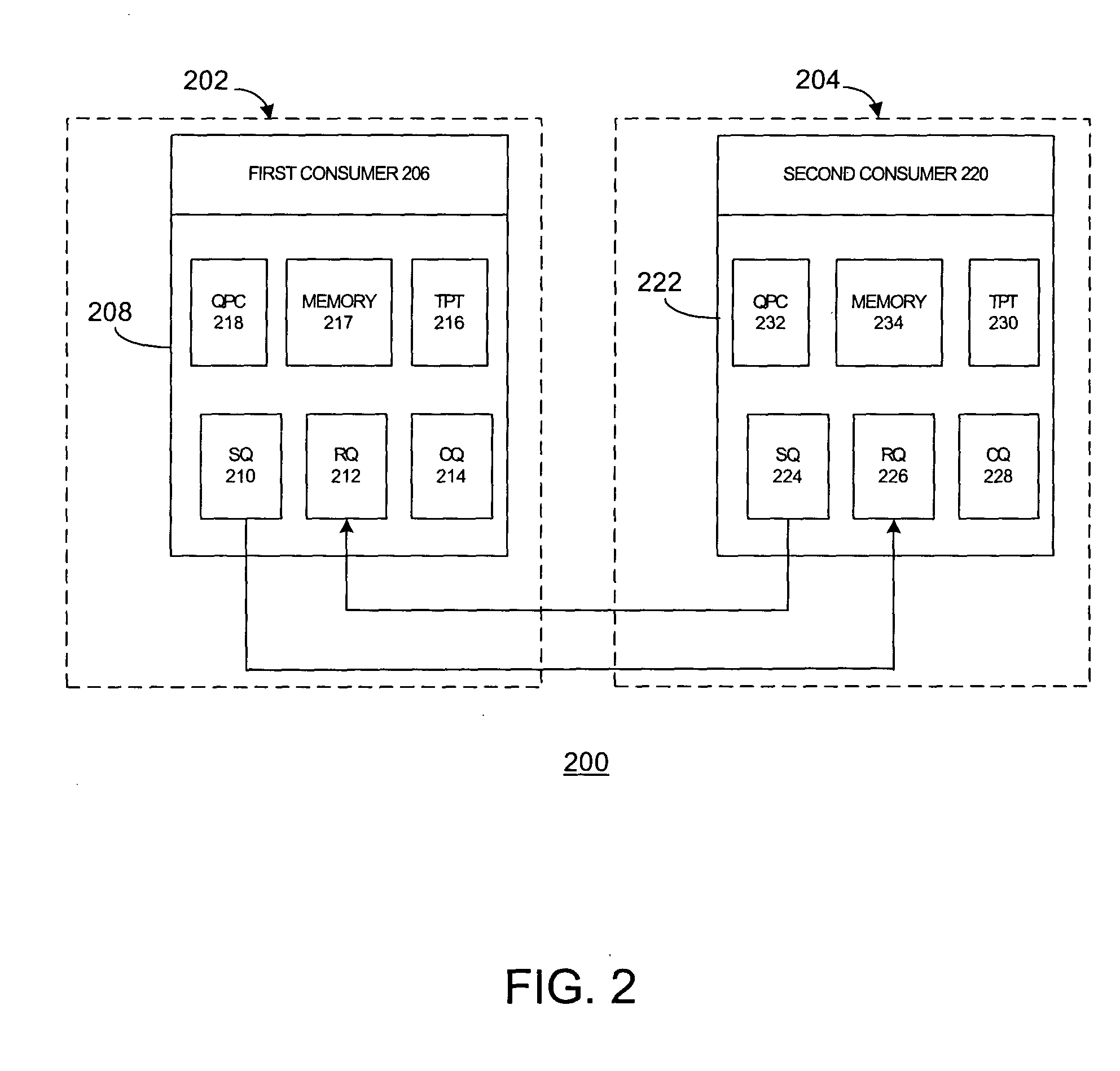

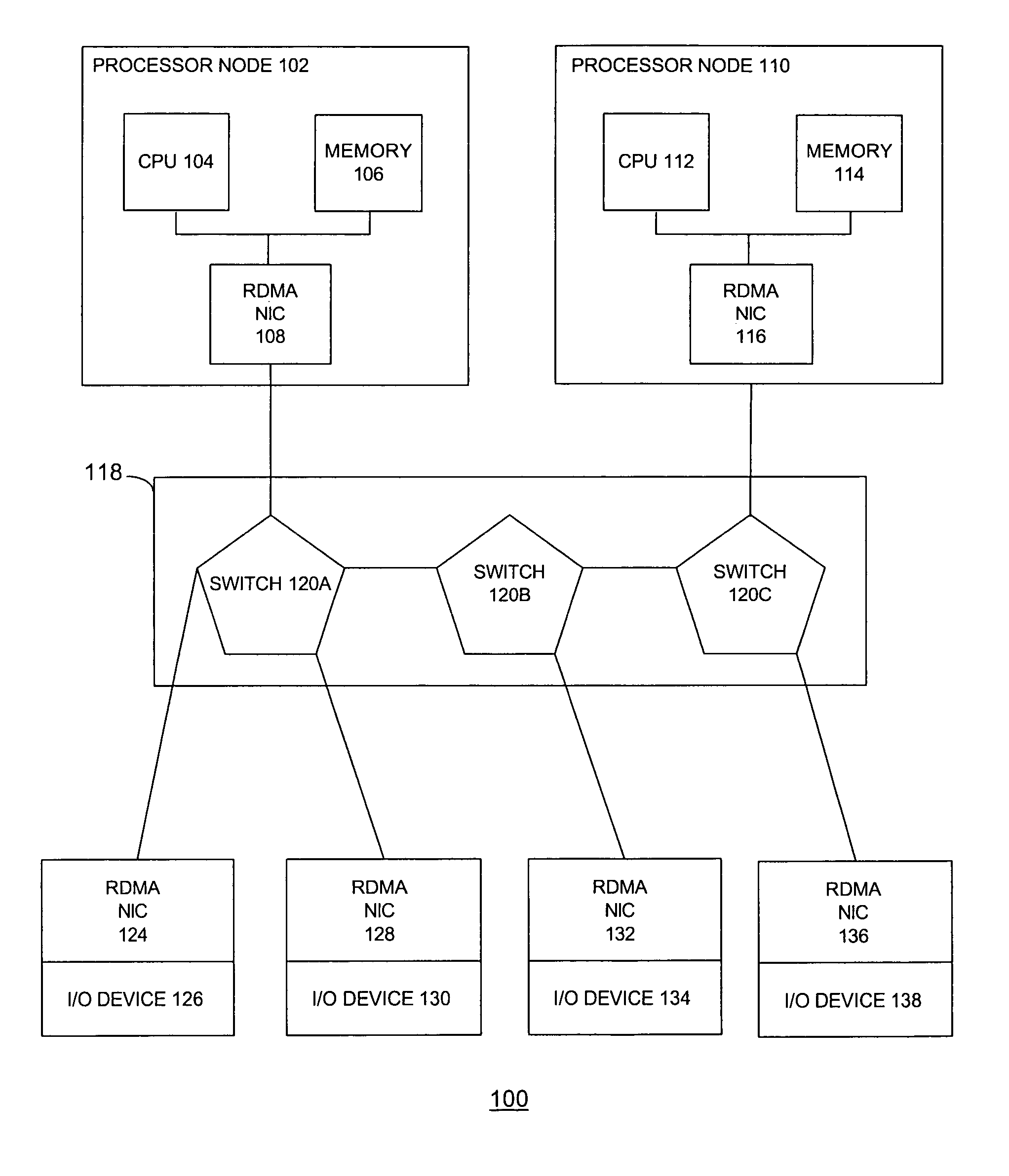

Method and apparatus for accessing a memory

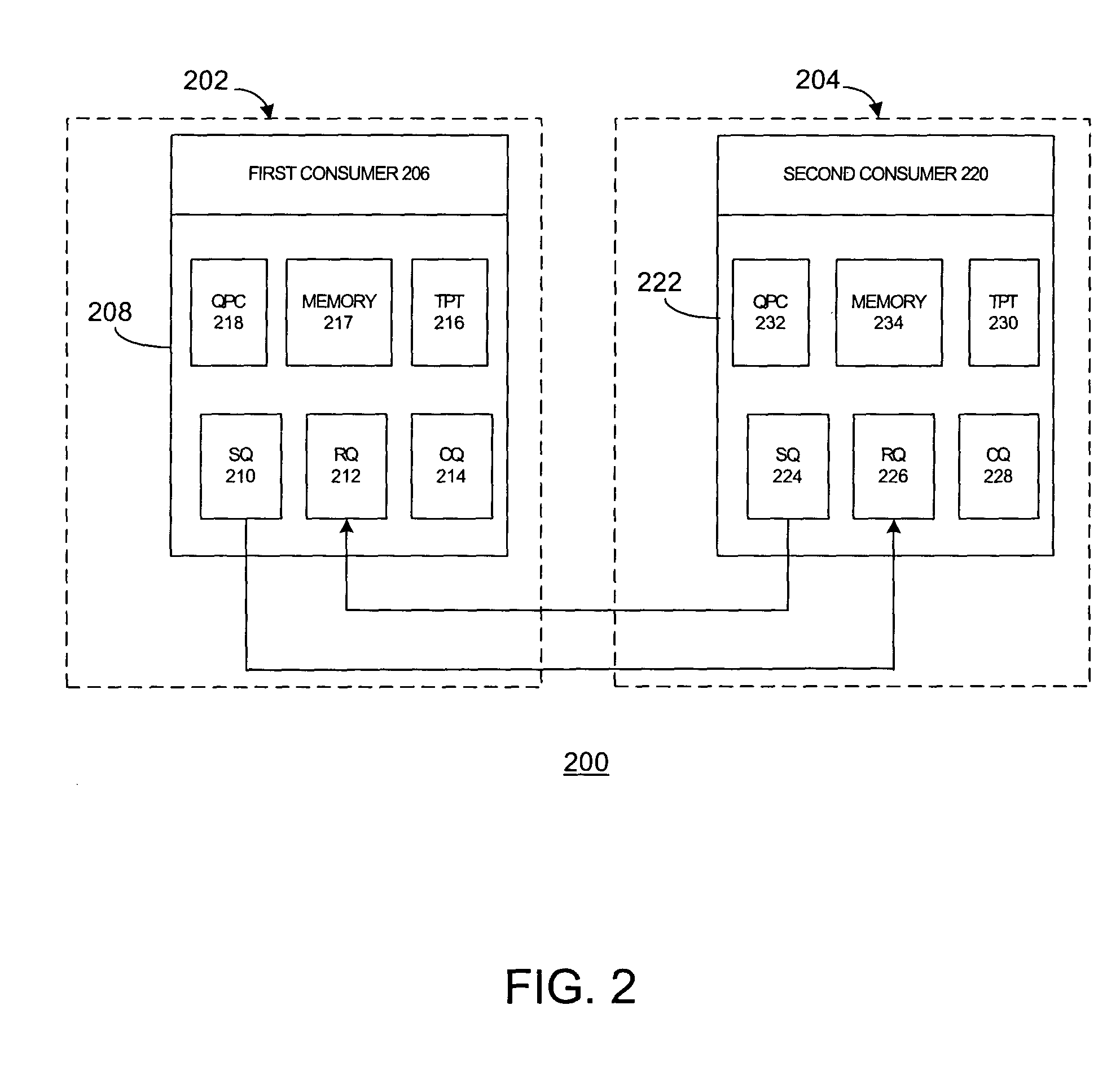

InactiveUS20050038941A1Minimized on demandMemory adressing/allocation/relocationTransmissionTerm memoryPage table

The disclosed embodiments relate to an optimized memory registration mechanism that may comprise an upper layer protocol that associates I / O buffers with memory regions and that manages steering tags. The memory regions may be associated with a translation page table. The upper layer protocol may allocate one of the steering tags associated with at least one of the memory regions for a memory operation.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

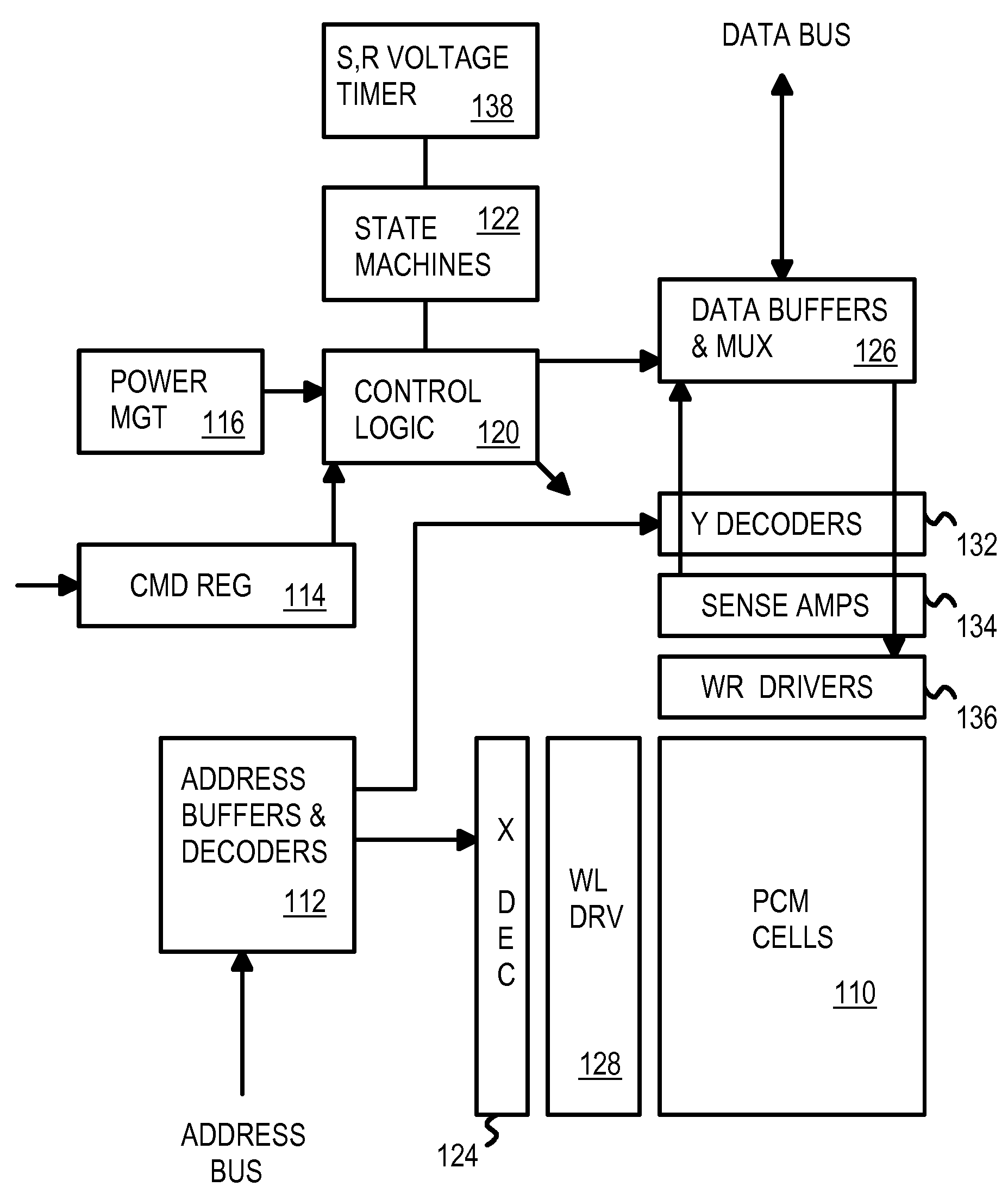

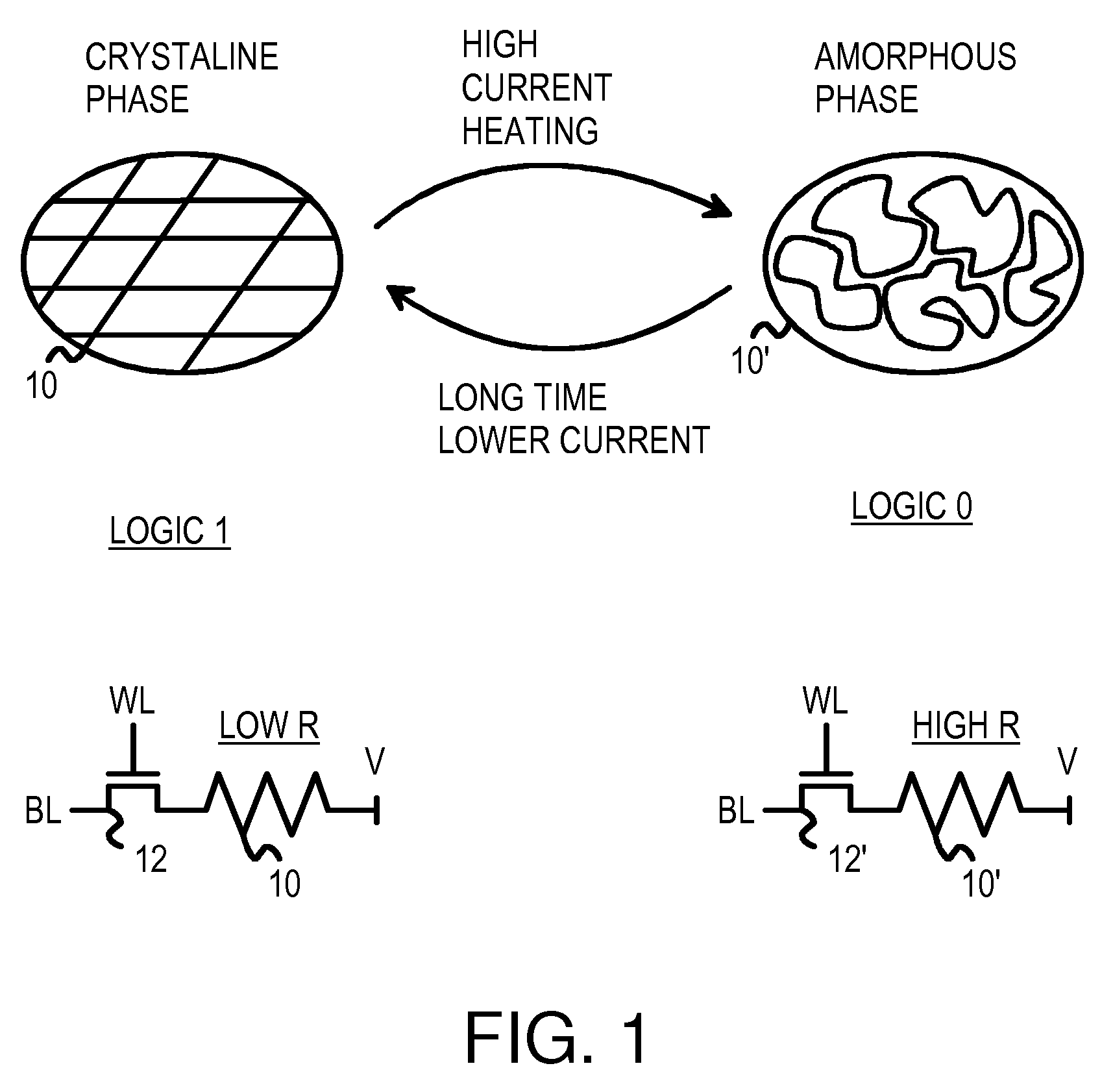

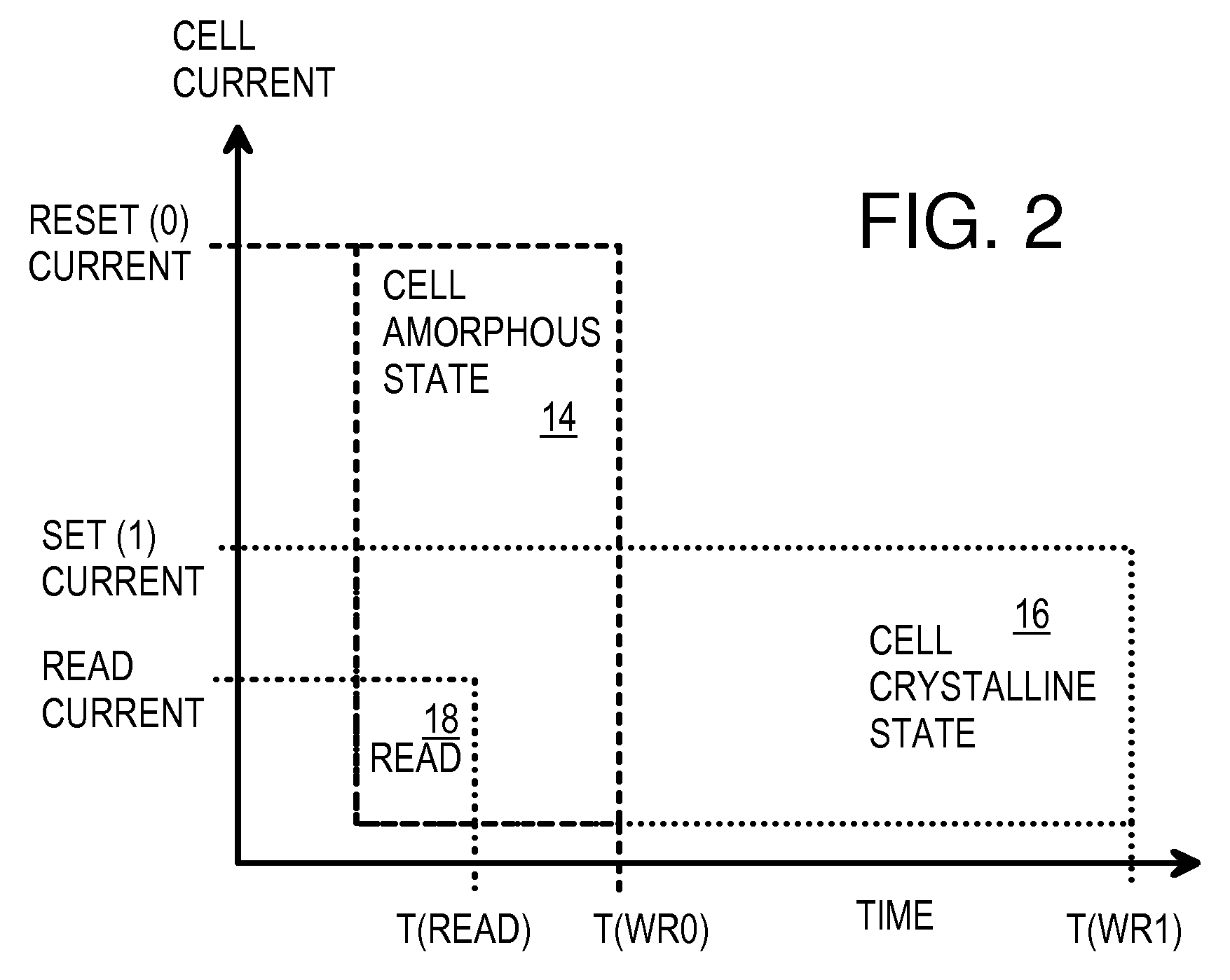

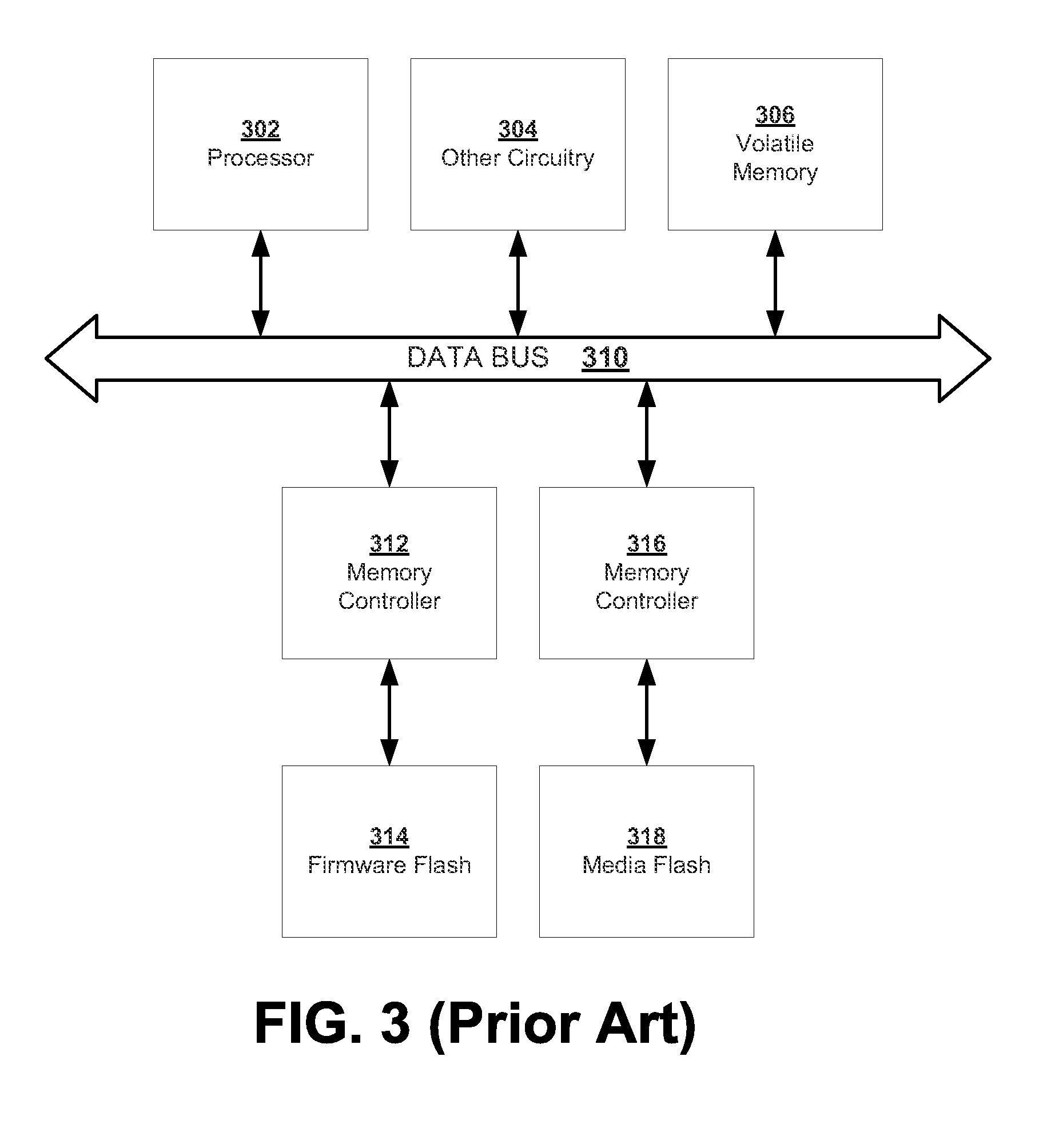

High-Speed Controller for Phase-Change Memory Peripheral Device

InactiveUS20070255891A1Memory architecture accessing/allocationDigital storageHigh resistancePhase-change memory

Peripheral devices store data in non-volatile phase-change memory (PCM). PCM cells have alloy resistors with high-resistance amorphous states and low-resistance crystalline states. The peripheral device can be a Multi-Media Card / Secure Digital (MMC / SD) card. A PCM controller accesses PCM memory devices. Various routines that execute on a CPU in the PCM controller are activated in response to commands in the host-bus transactions. The PCM system increases the throughput of one or more phase-change memory devices by performing one or more of a read-ahead memory operation, a write-ahead memory write operation, a larger page memory write operation, a wider data bus memory write operation, a multi-channel concurrent multi-bank interleaving memory read or write operation, a write-cache memory write operation, and any combination thereof.

Owner:SUPER TALENT TECH CORP

System and memory for sequential multi-plane page memory operations

A system and method for performing memory operations in a multi-plane flash memory. Commands and addresses are sequentially provided to the memory for memory operations in memory planes. The memory operations are sequentially initiated and the memory operation for at least one of the memory planes is initiated during the memory operation for another memory plane. In one embodiment, each of a plurality of programming circuits is associated with a respective memory plane and is operable to program data to the respective memory plane in response to programming signals and when it is enabled. Control logic coupled to the plurality of programming circuits generates programming signals in response to the memory receiving program commands and further generates programming enable signals to individually enable each of the programming circuits to respond to the programming signals and stagger programming of data to each of the memory planes.

Owner:ROUND ROCK RES LLC

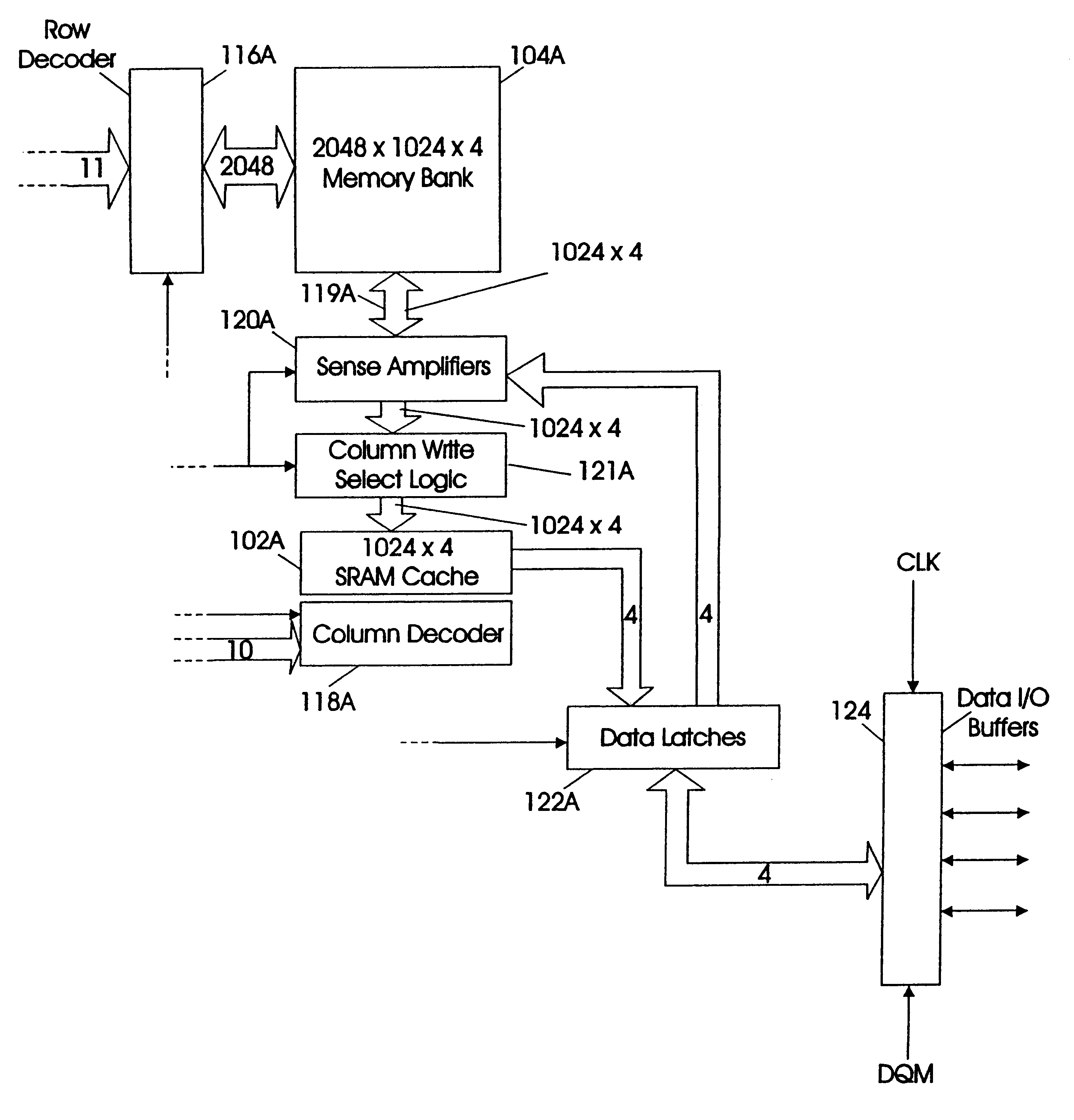

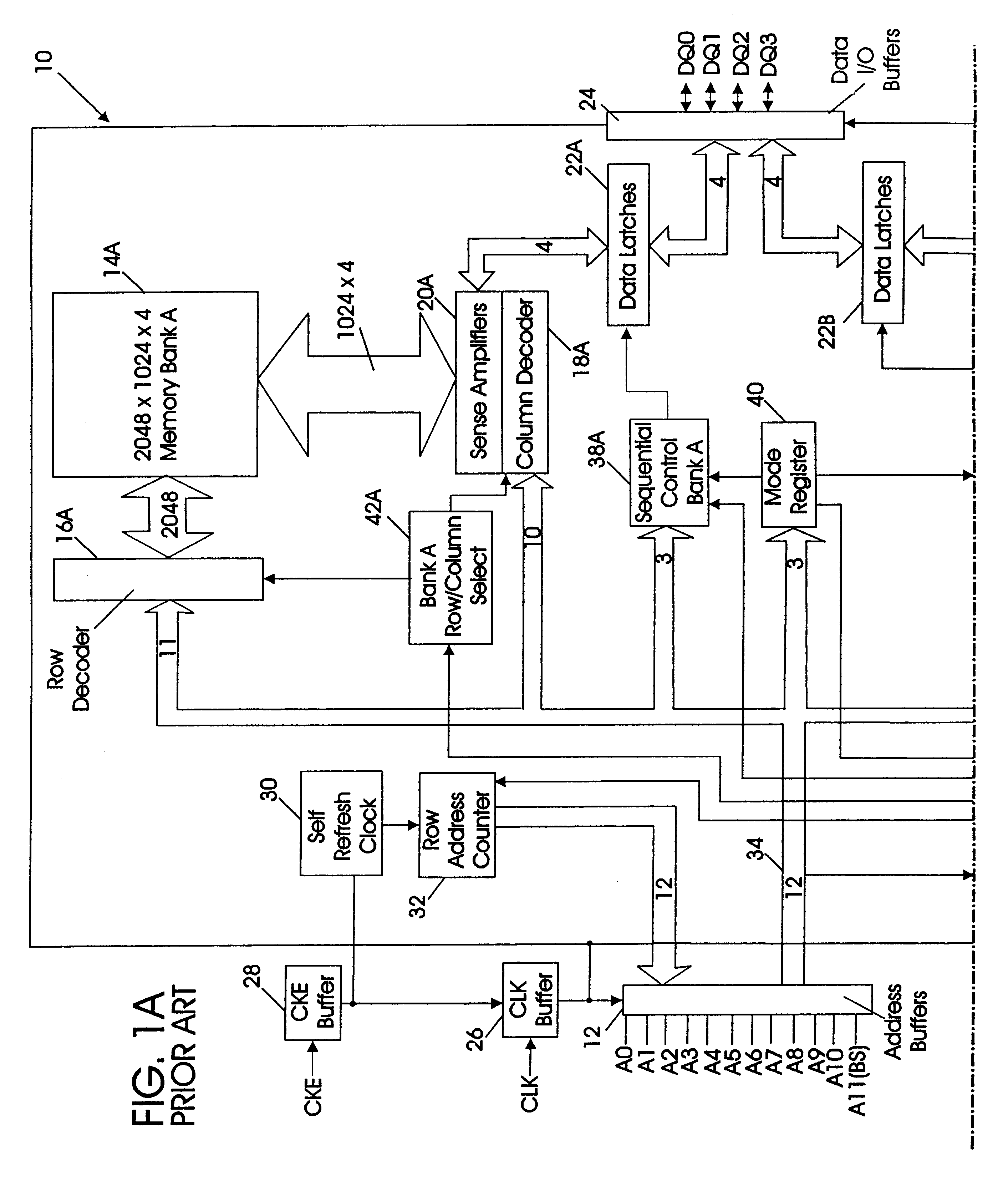

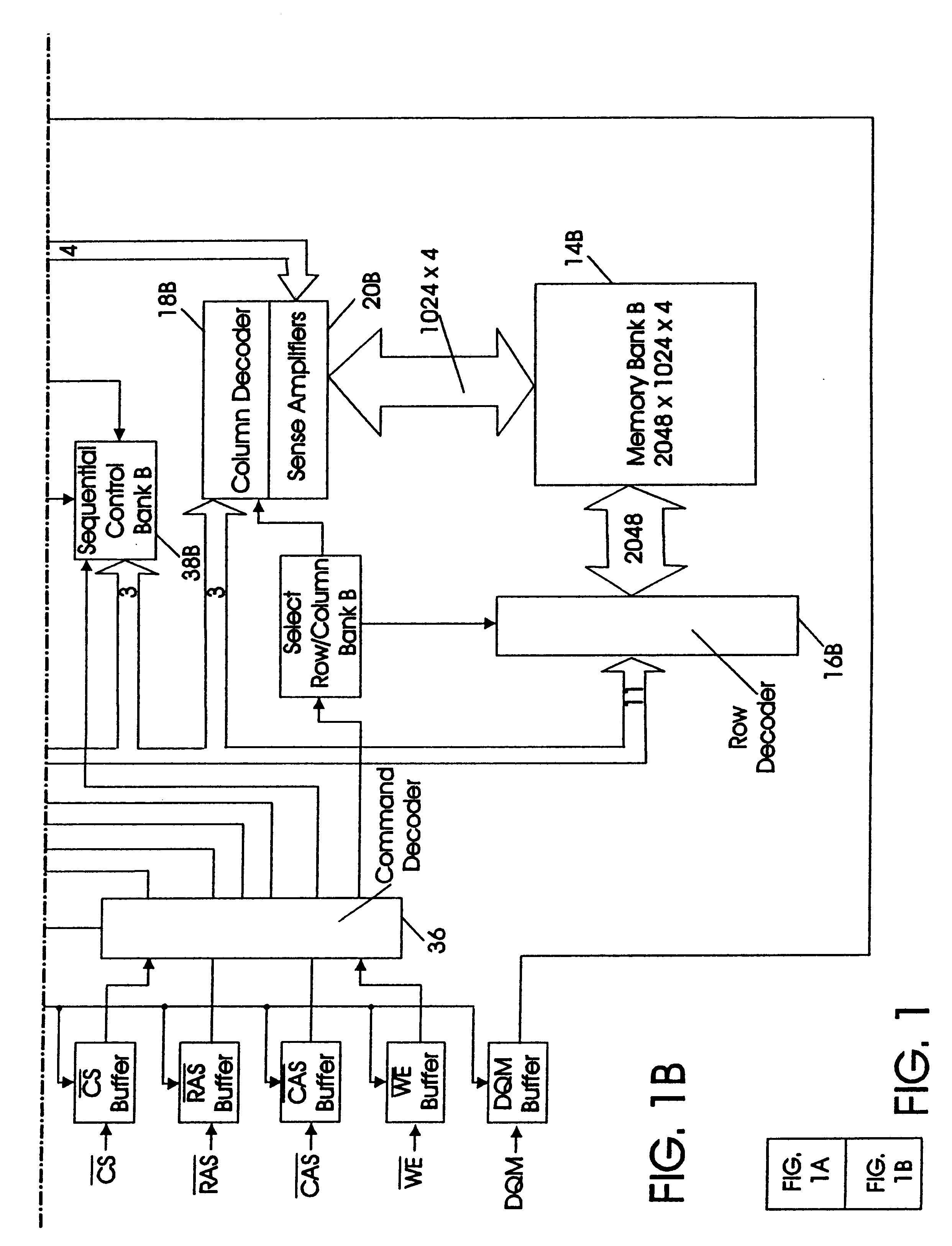

Cached synchronous DRAM architecture having a mode register programmable cache policy

InactiveUS6289413B1Memory adressing/allocation/relocationDigital storageBit lineAudio power amplifier

A cached synchronous dynamic random access memory (cached SDRAM) device having a multi-bank architecture and a programmable caching policy includes a synchronous dynamic random access memory (SDRAM) bank, a synchronous static randomly addressable row register, a select logic gating circuit, and mode register for programming of the cached SDRAM to operate in a Write Transfer mode corresponding to a Normal Operation mode of a standard SDRAM during a Write cycle, and to operate in a No Write Transfer mode according to an alternate operation mode during a Write cycle, thereby operating under a first and a second caching policy, respectively. The SDRAM includes a row decoder for selecting a row of data in a memory bank array, sense amplifiers for latching the row of data selected by the row decoder, and a synchronous column selector for selecting a desired column of the row of data. The row register stores a row of data latched by the sense amplifiers and the select logic gating circuit, disposed between the sense amplifiers and the row register, selectively gates the row of data present on the bit lines to the row register in accordance to particular synchronous memory operations being performed.

Owner:IBM CORP +2

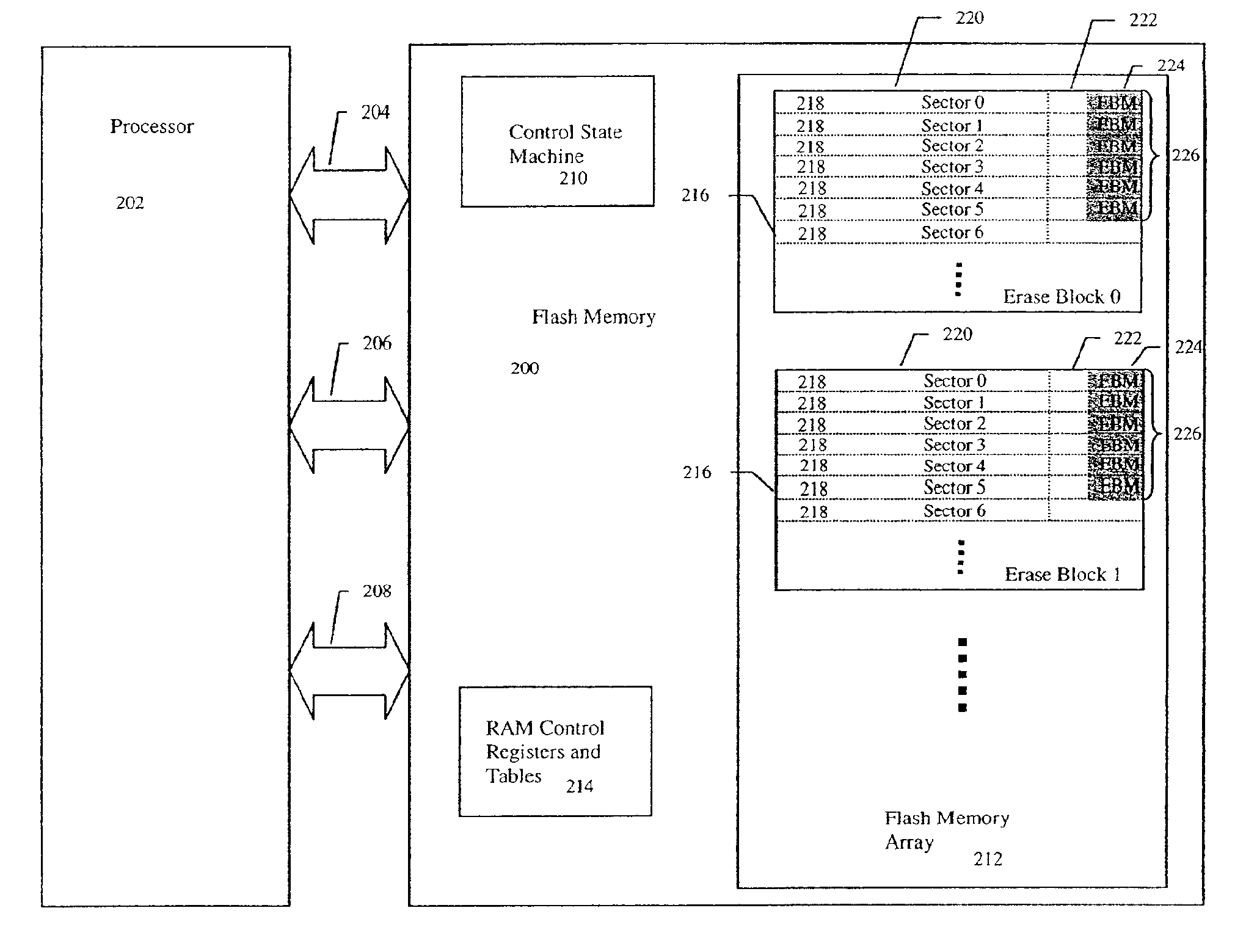

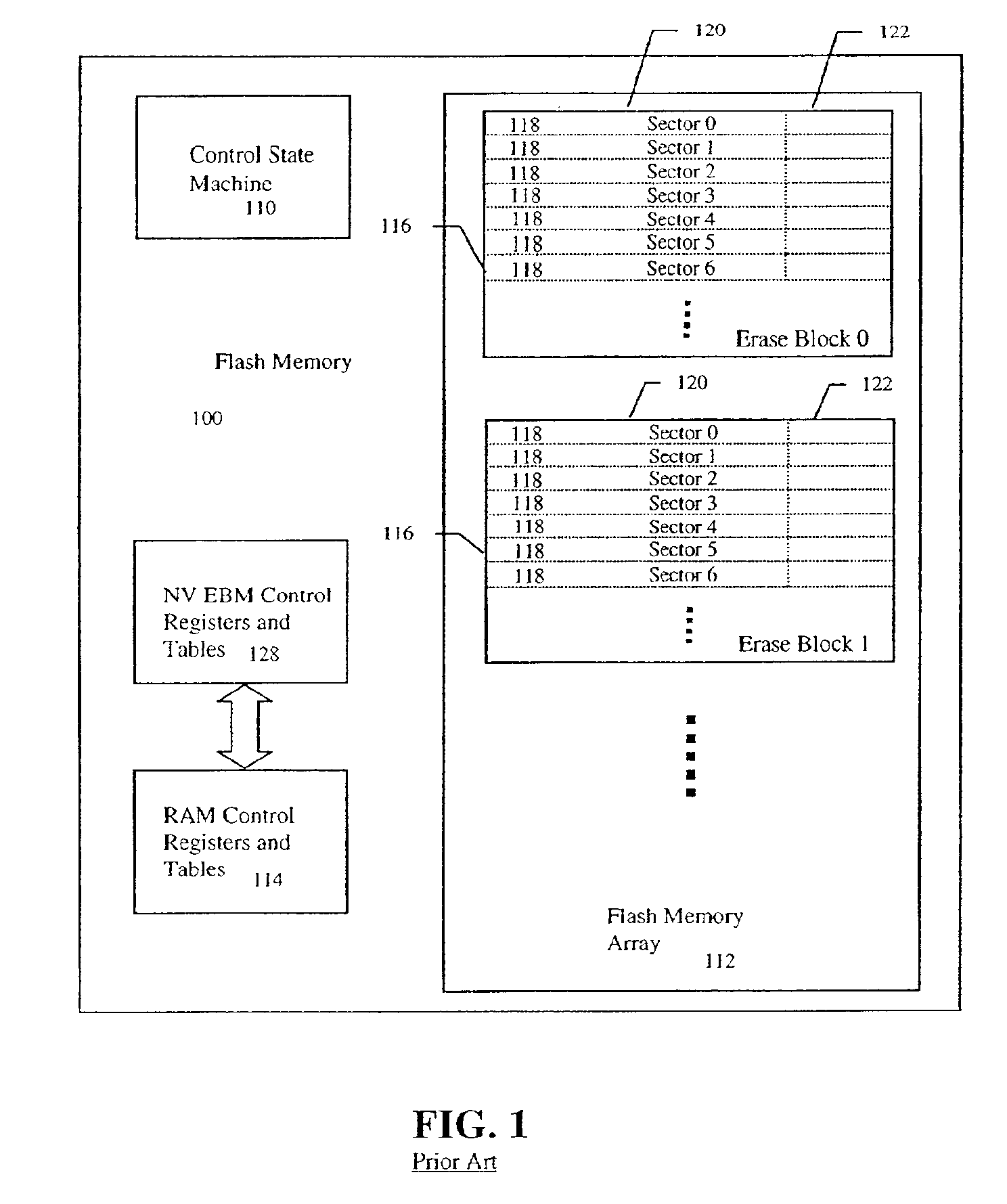

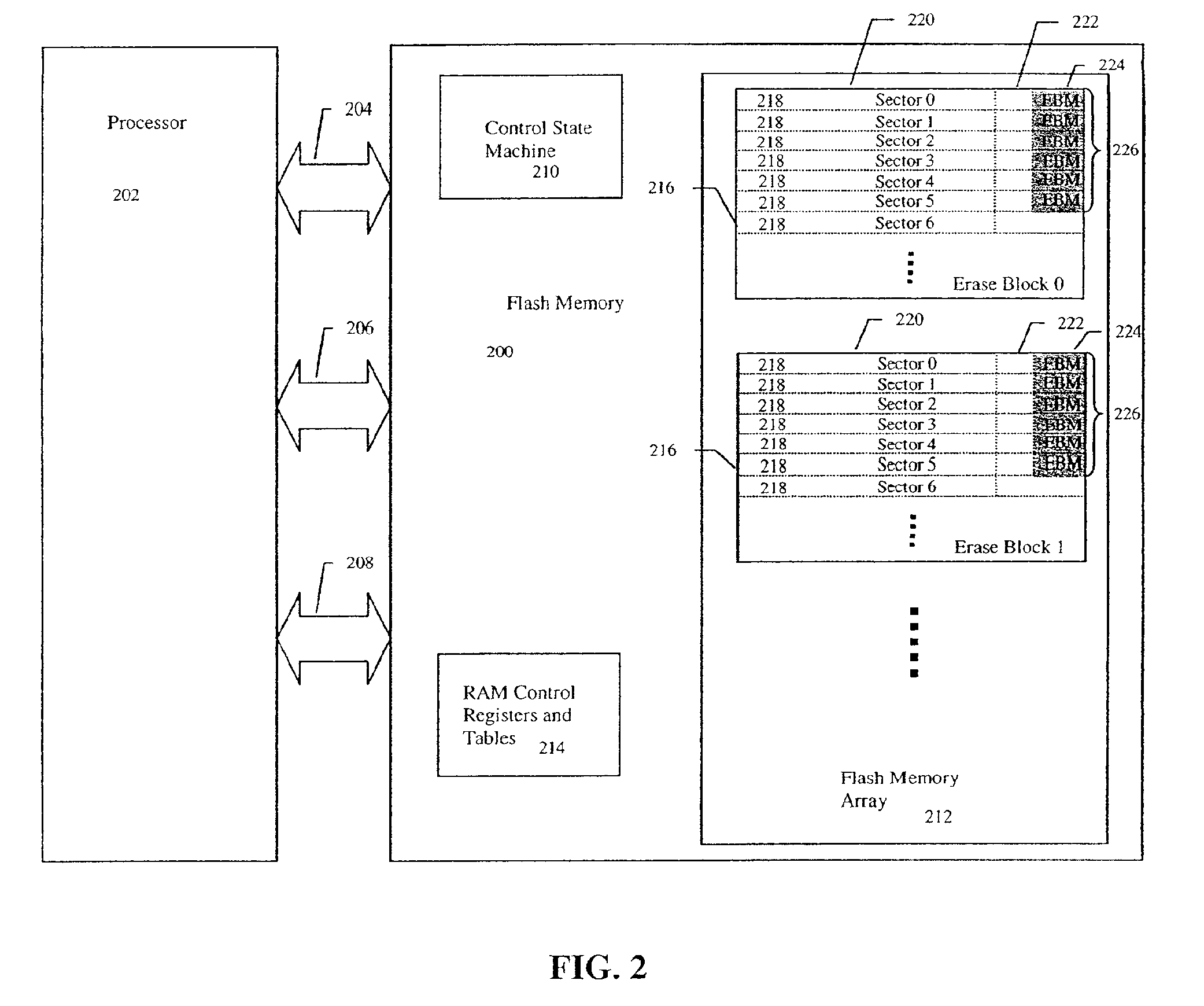

Erase block management

InactiveUS6948026B2Slowing overall Flash device operationMemory architecture accessing/allocationError detection/correctionData fieldControl data

An improved Flash memory device with a distributed erase block management (EBM) scheme is detailed that enhances operation and helps minimize write fatigue of the floating gate memory cells of the Flash memory device. In the prior art, erase block management of a Flash memory device, which provides logical sector to physical sector mapping and provides a virtual rewriteable interface for the host, requires that erase block management data be kept in specialized EBM data tables to keep the state of the Flash memory device in case of loss of power. This placement of EBM data in a separate erase block location from the user data slows the Flash memory operation by requiring up to two writes and / or block erasures for every update of the user data. Additionally, one of the goals of the EBM control is to minimize write fatigue of the non-volatile floating gate memory cells of the Flash memory device erase blocks by re-mapping and distributing heavily rewritten user data sectors in a process called load leveling so that no one erase block gets overused too quickly and reduce the expected lifespan of the Flash memory device. The EBM data structures, however, are some of the most heavily rewritten non-volatile floating gate memory cells in the device and thus, while helping to reduce write fatigue in the Flash memory device, are some of the data structures most susceptible to the process of fatigue. The Flash memory device of the invention combines the EBM data in a user data erase block by placing it in an EBM data field of the control data section of the erase block sectors. Therefore distributing the EBM data within the Flash memory erase block structure. This allows the Flash memory to update and / or erase the user data and the EBM data in a single operation, to reduce overhead and speed operation. The Flash memory also reduces the process of EBM data structure write fatigue by allowing the EBM data fields to be load leveled by rotating them with the erase blocks they describe.

Owner:MICRON TECH INC

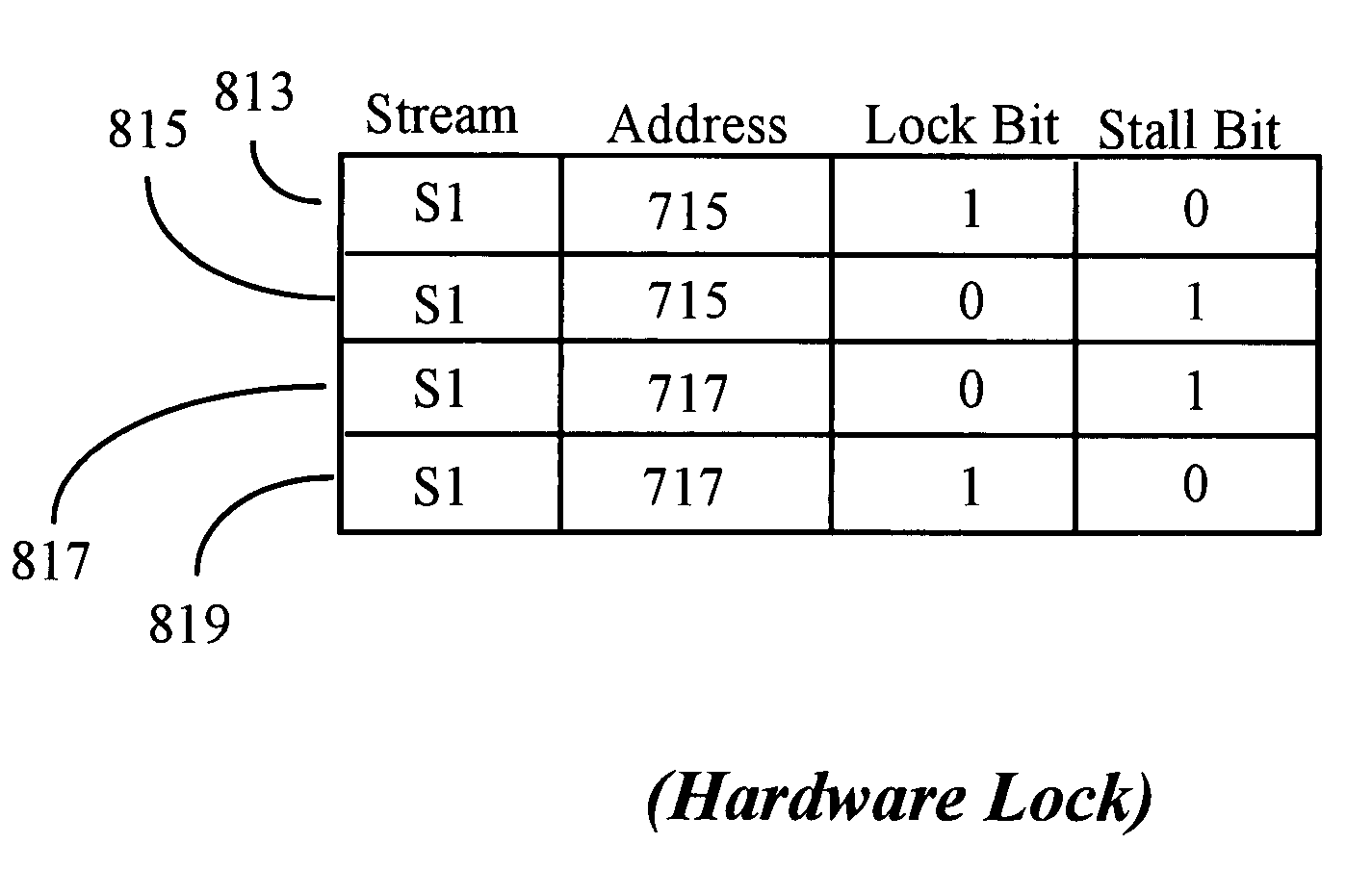

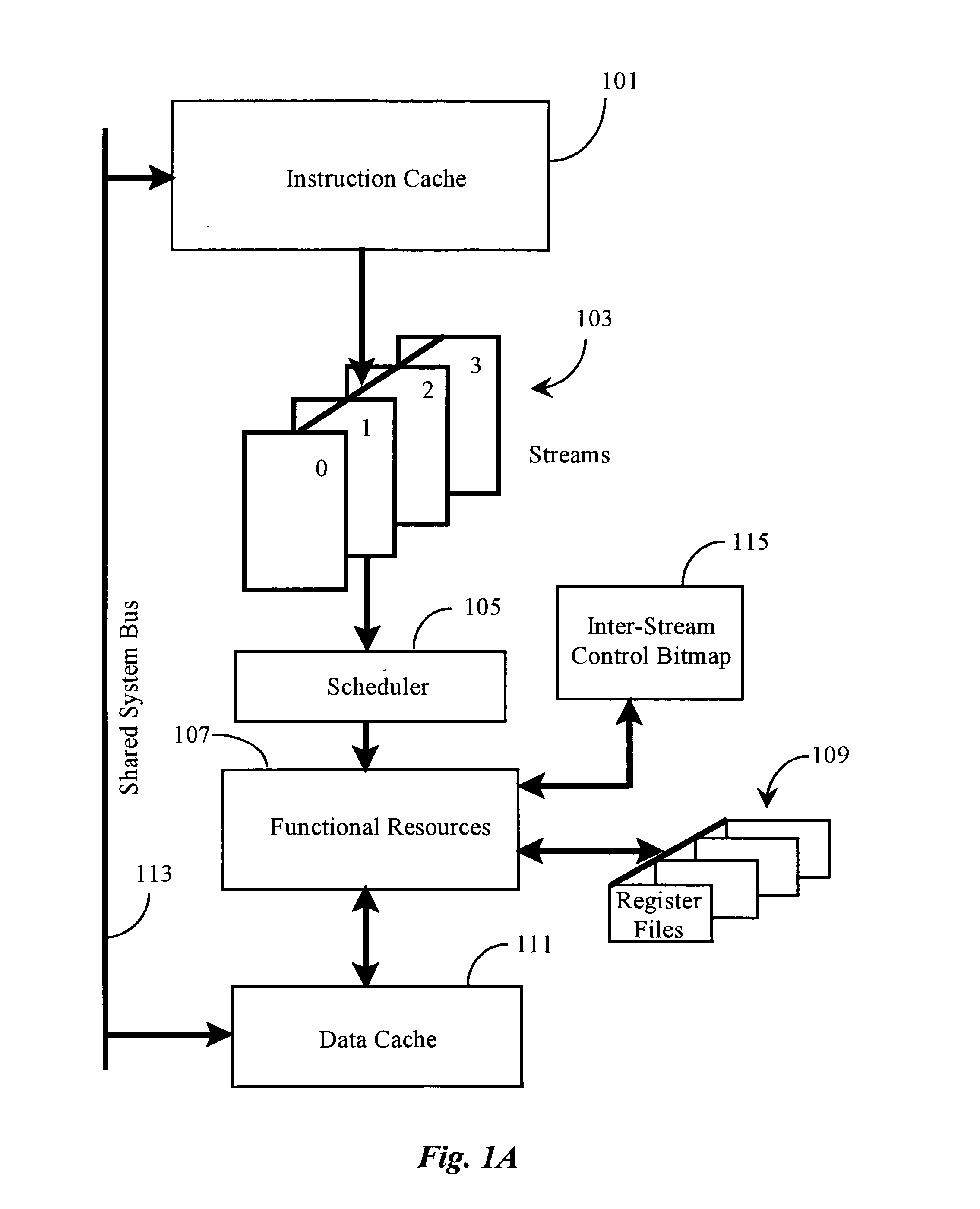

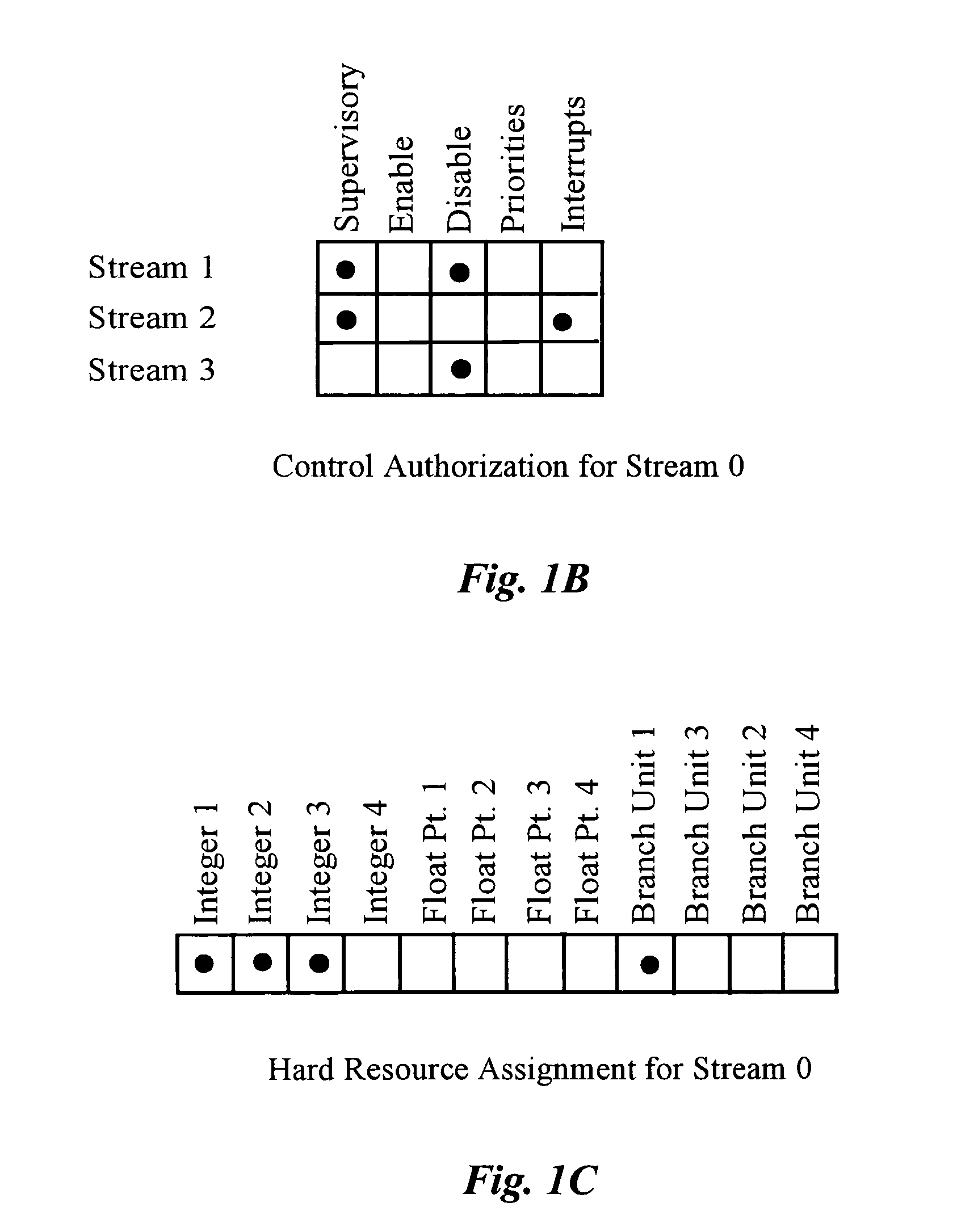

Method and apparatus for implementing atomicity of memory operations in dynamic multi-streaming processors

InactiveUS7257814B1Digital computer detailsUnauthorized memory use protectionMemory addressLocking mechanism

A multi-streaming processor has a plurality of streams for streaming one or more instruction threads, a set of functional resources for processing instructions from streams, and a lock mechanism for locking selected memory locations shared by streams of the processor, the hardware-lock mechanism operating to set a lock when an atomic memory sequence is started and to clear a lock when an atomic memory sequence is completed. In preferred embodiments the lock mechanism comprises one or more storage locations associated with each stream of the processor, each storage location enabled to store a memory address a lock bit, and a stall bit. Methods for practicing the invention using the apparatus are also taught.

Owner:ARM FINANCE OVERSEAS LTD

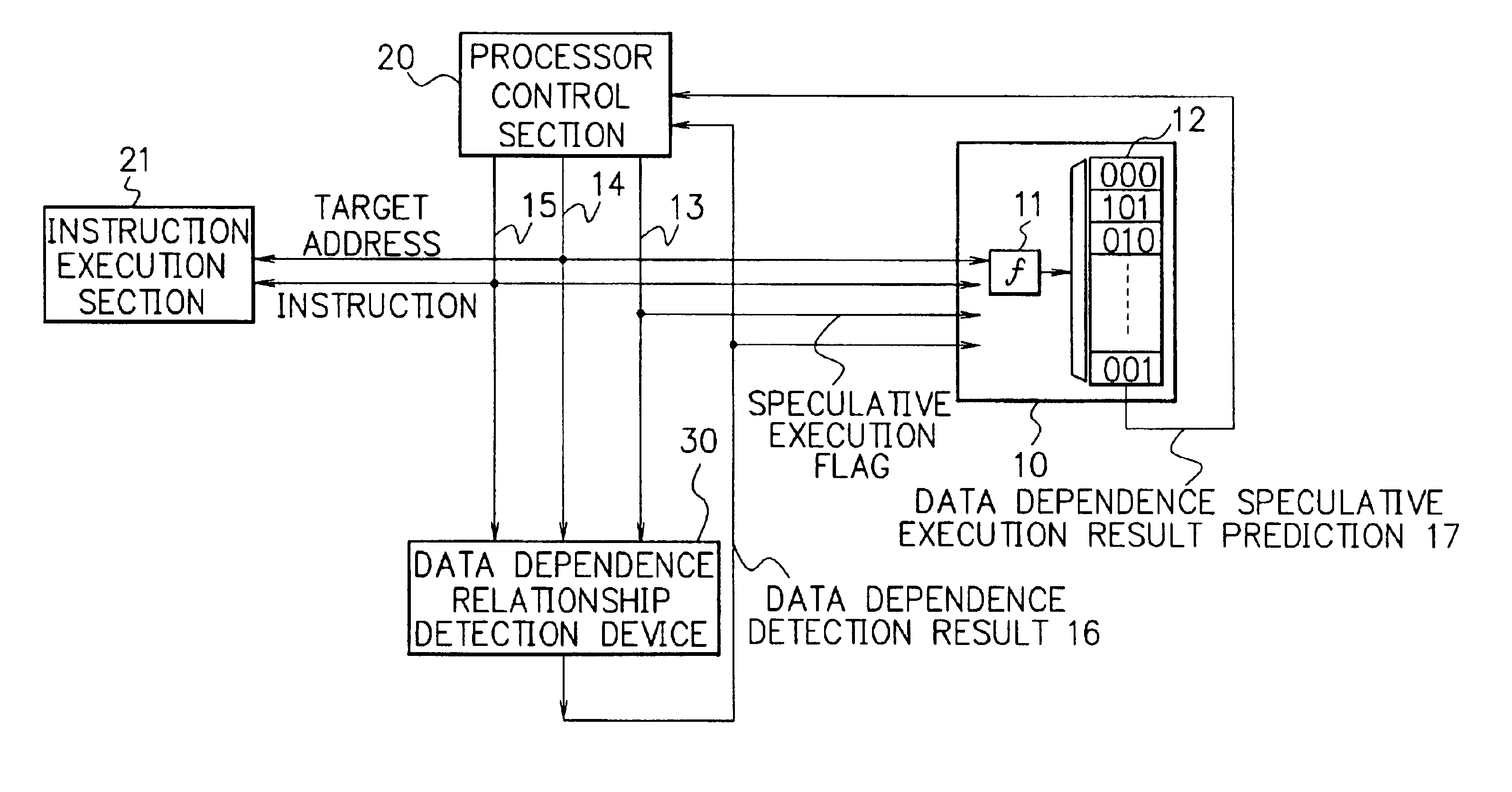

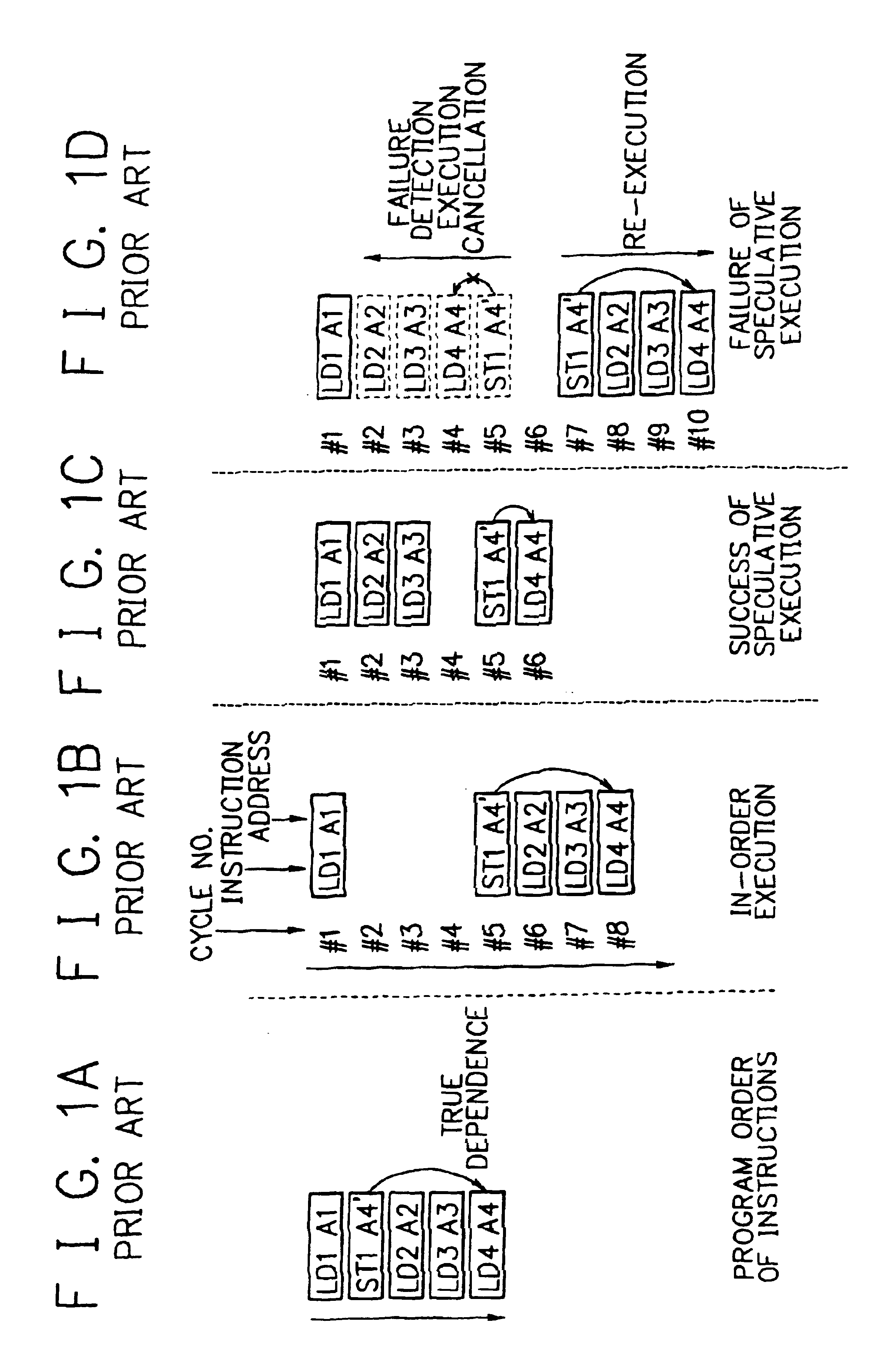

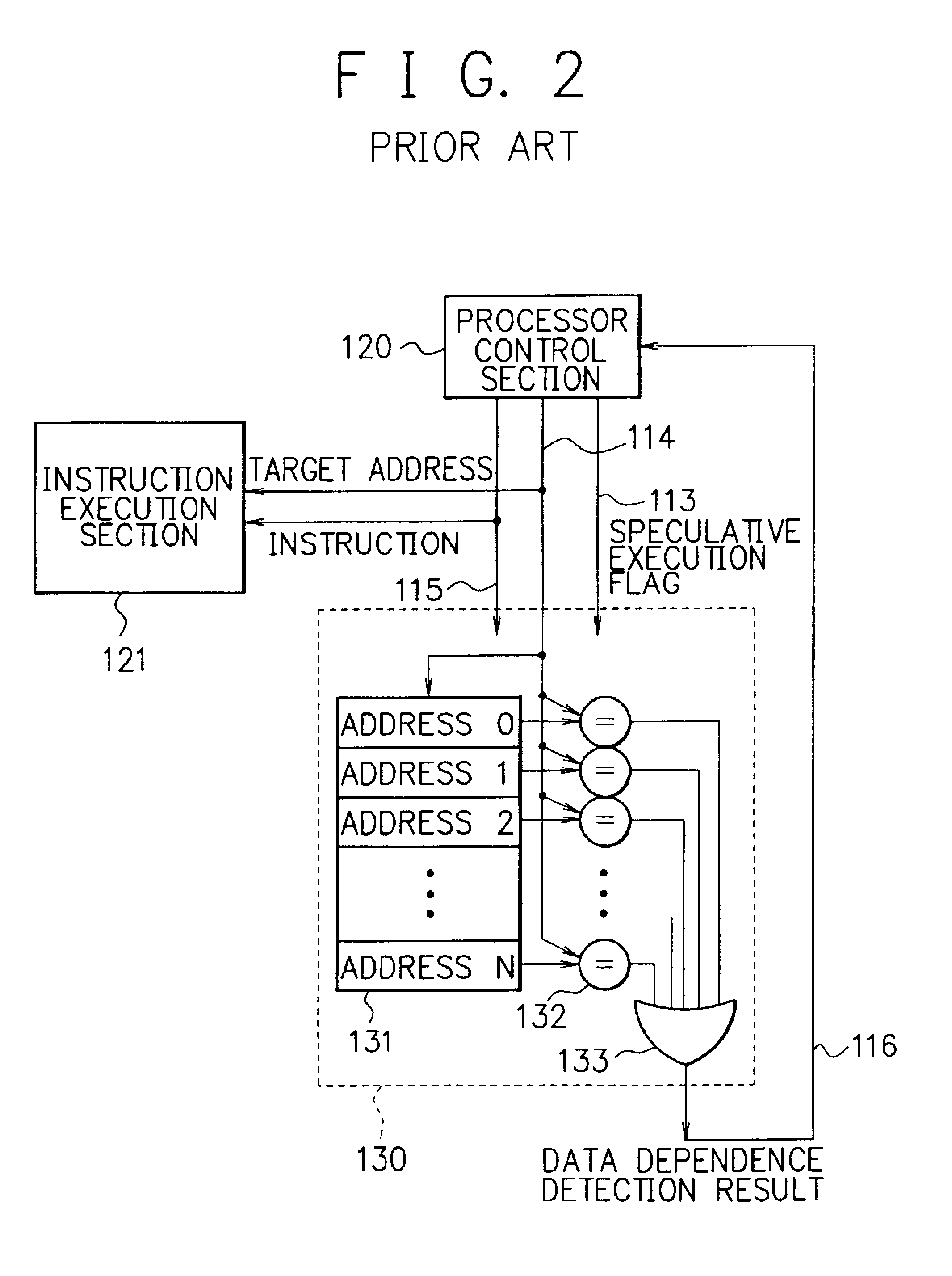

Processor, multiprocessor system and method for speculatively executing memory operations using memory target addresses of the memory operations to index into a speculative execution result history storage means to predict the outcome of the memory operation

InactiveUS6970997B2Low failure rateImprove execution performanceDigital computer detailsConcurrent instruction executionMemory addressSpeculative execution

When a processor executes a memory operation instruction by means of data dependence speculative execution, a speculative execution result history table which stores history information concerning success / failure results of the speculative execution of memory operation instructions of the past is referred to and thereby whether the speculative execution will succeed or fail is predicted. In the prediction, the target address of the memory operation instruction is converted by a hash function circuit into an entry number of the speculative execution result history table (allowing the existence of aliases), and an entry of the table designated by the entry number is referred to. If the prediction is “success”, the memory operation instruction is executed in out-of-order execution speculatively (with regard to data dependence relationship between the instructions). If the prediction is “failure”, the speculative execution is canceled and the memory operation instruction is executed later in the program order non-speculatively. Whether the speculative execution of the memory operation instructions has succeeded or failed is judged by detecting the data dependence relationship between the memory operation instructions, and the speculative execution result history table is updated taking the judgment into account.

Owner:NEC CORP

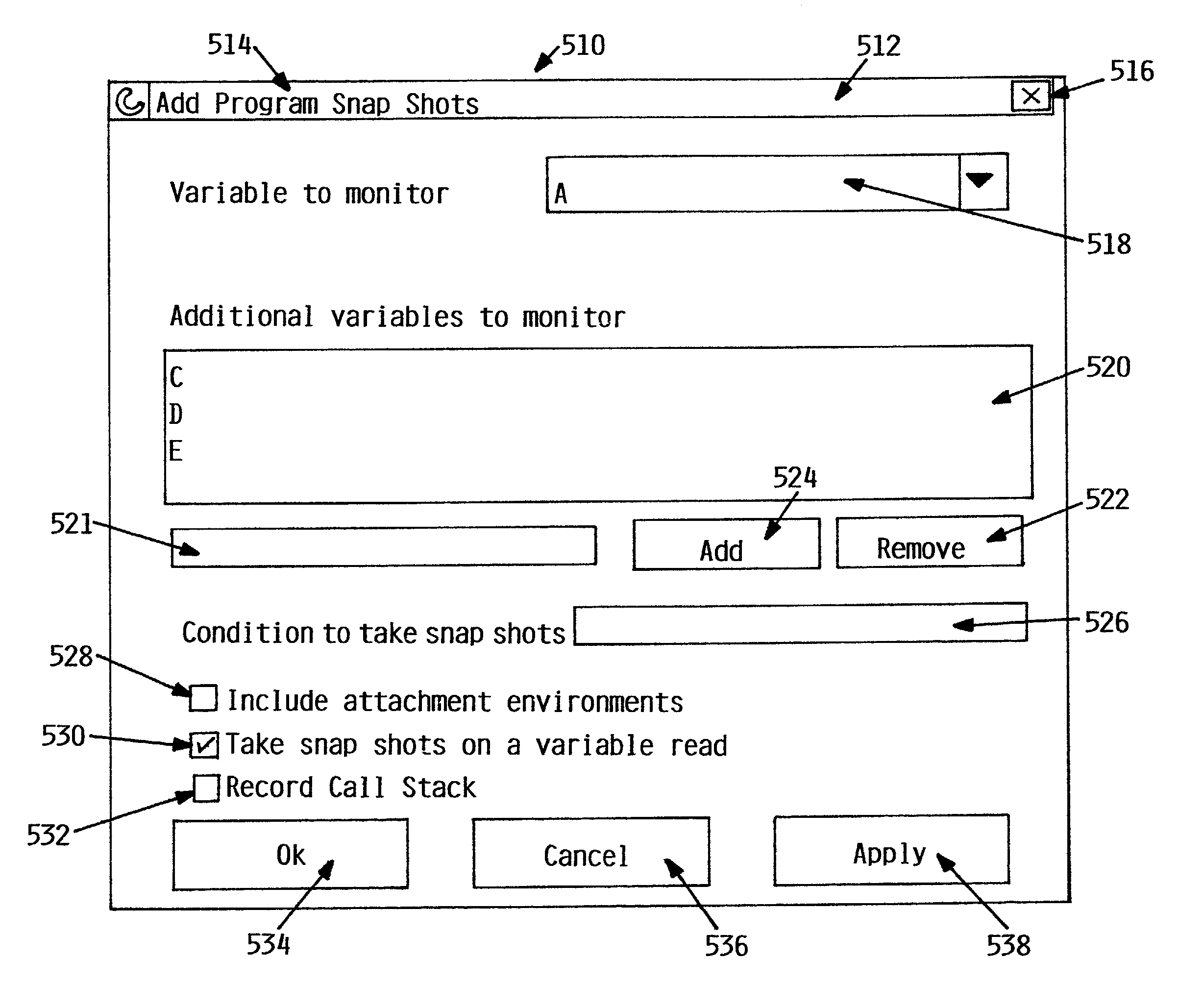

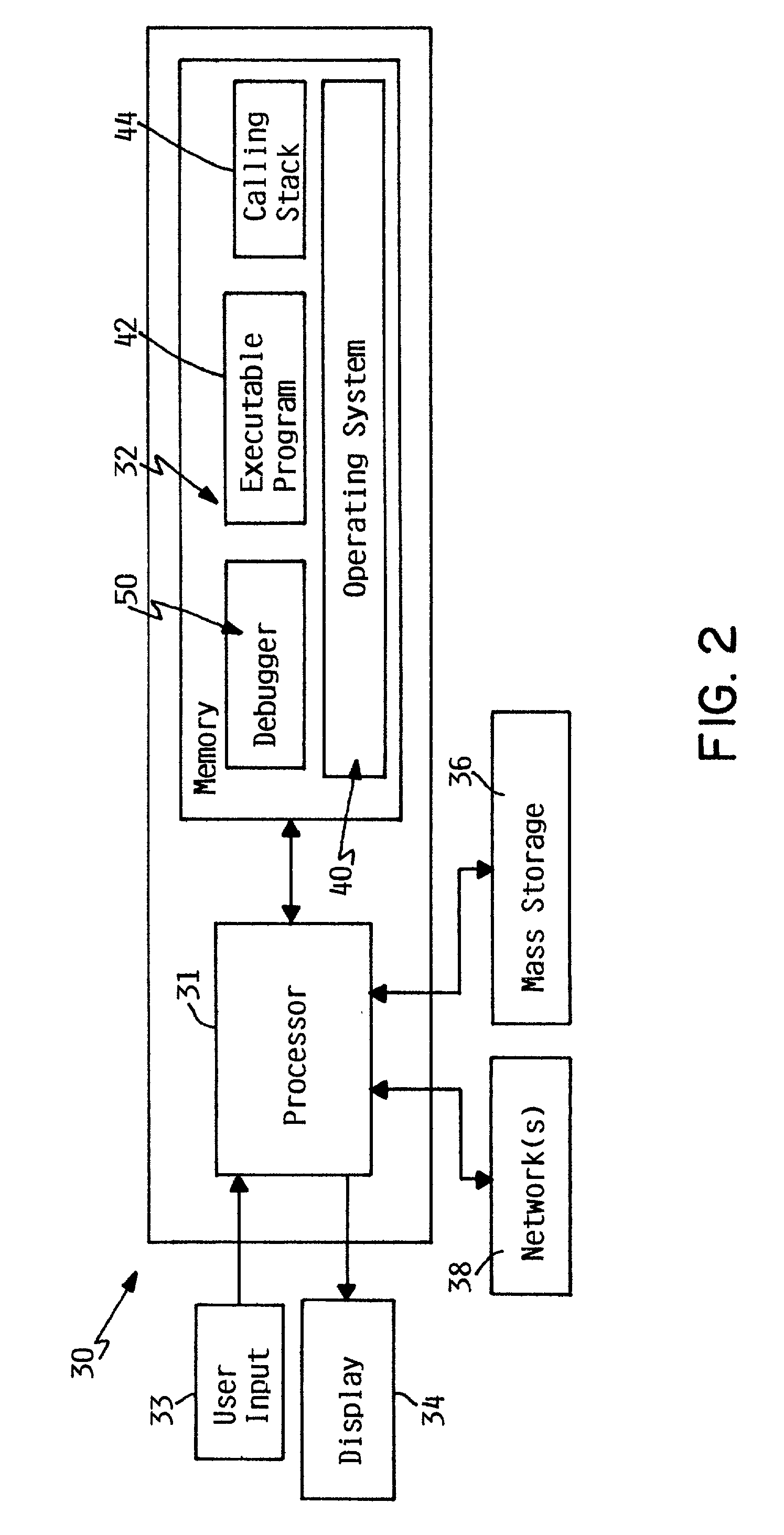

Storing and restoring snapshots of a computer process

InactiveUS7383538B2Maintain abilitySoftware testing/debuggingSpecific program execution arrangementsMemory operationComputer program

A method to trace a variable or other expression through a computer program is disclosed. A user determines the variable and the conditions upon which activity of the variable will be monitored. As a result of the invention, every time that variable is referenced in a memory operation or other activity by the program and the conditions set forth by the user are satisfied, the state of that variable is saved as a snapshot without interrupting or stopping execution of the program. The snapshots are accumulated in a history table. The history table can be retrieved and the state of the variable in any given snapshot can be restored. Other variables and expressions can be attached to the trigger variable and the states of these other variables at the time of the activity of the trigger variable may also be saved in the snapshot. The method may be incorporated into a program as a tracing device or a program product separate from the logical processing device executing the program.

Owner:IBM CORP

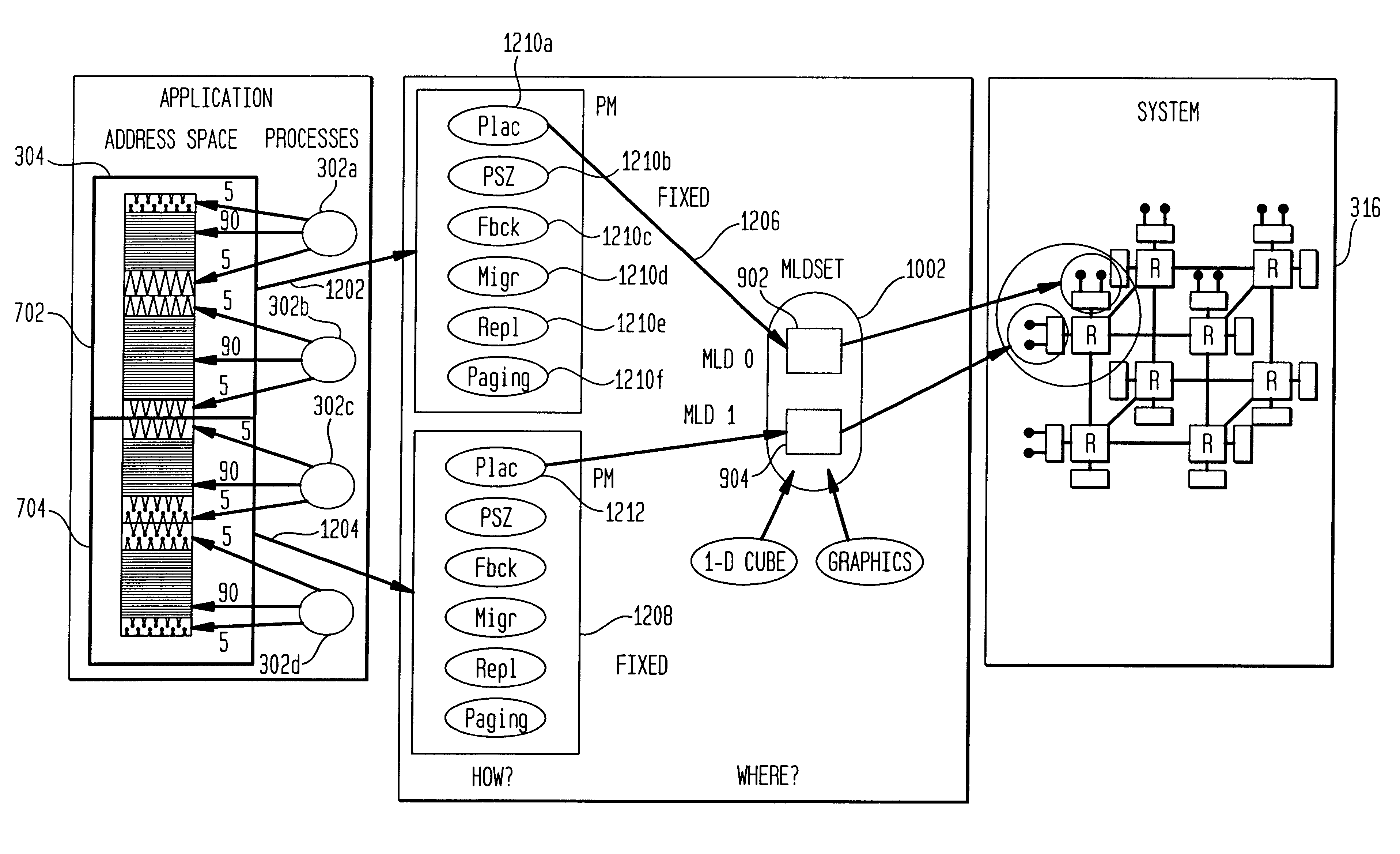

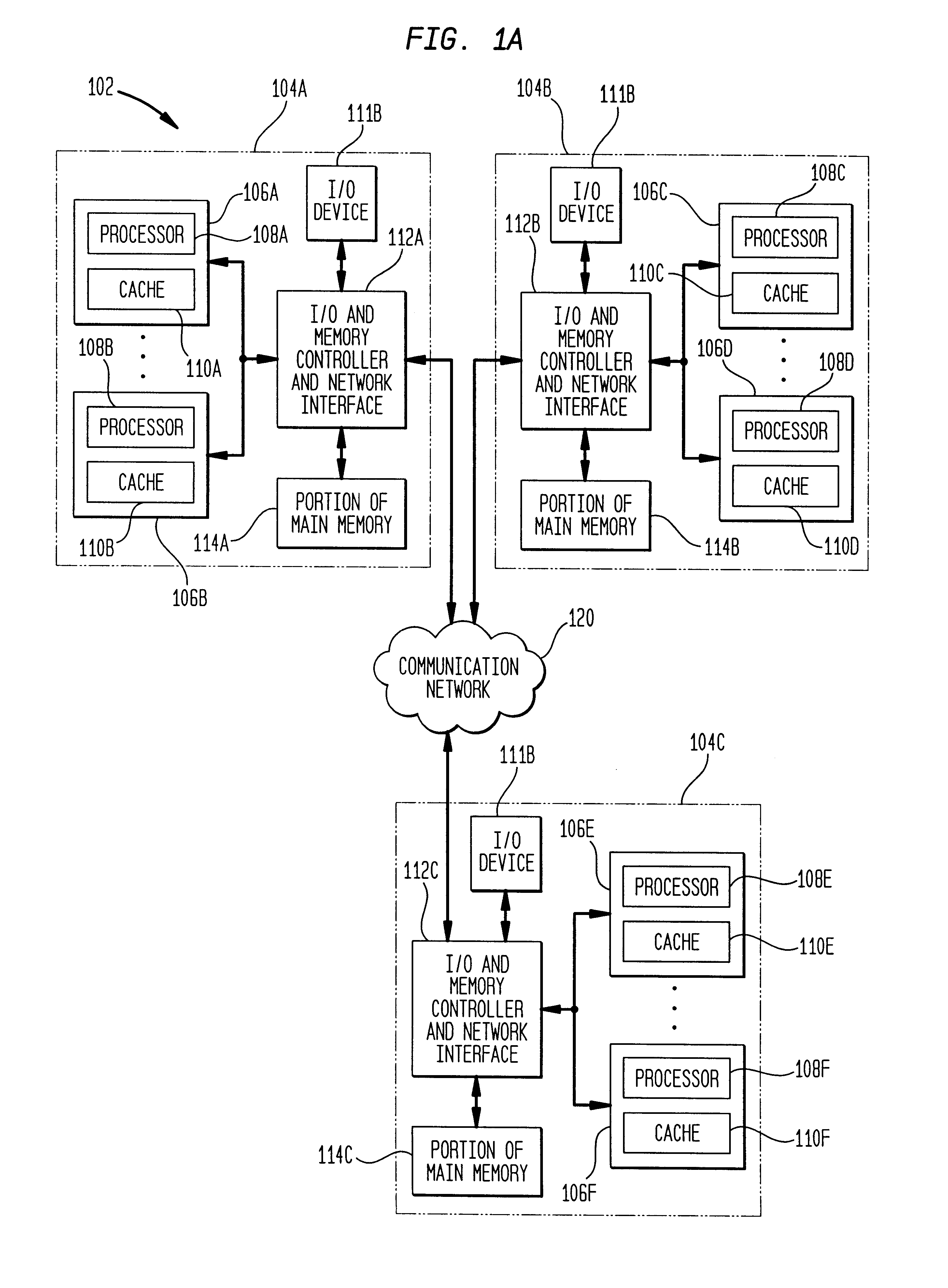

Method, system and computer program product for managing memory in a non-uniform memory access system

InactiveUS6289424B1Easy to carryMemory architecture accessing/allocationResource allocationControl systemComputerized system

A memory management and control system that is selectable at the application level by an application programmer is provided. The memory management and control system is based on the use of policy modules. Policy modules are used to specify and control different aspects of memory operations in NUMA computer systems, including how memory is managed for processes running in NUMA computer systems. Preferably, each policy module comprises a plurality of methods that are used to control a variety of memory operations. Such memory operations typically include initial memory placement, memory page size, a migration policy, a replication policy and a paging policy. One method typically contained in policy modules is an initial placement policy. Placement policies may be based on two abstractions of physical memory nodes. These two abstractions are referred to herein as "Memory Locality Domains" (MLDs) and "Memory Locality Domain Sets" (MLDSETs). By specifying MLDs and MLDSETs, rather than physical memory nodes, application programs can be executed on different computer systems regardless of the particular node configuration and physical node topology employed by the system. Further, such application programs can be run on different machines without the need for code modification and / or re-compiling.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

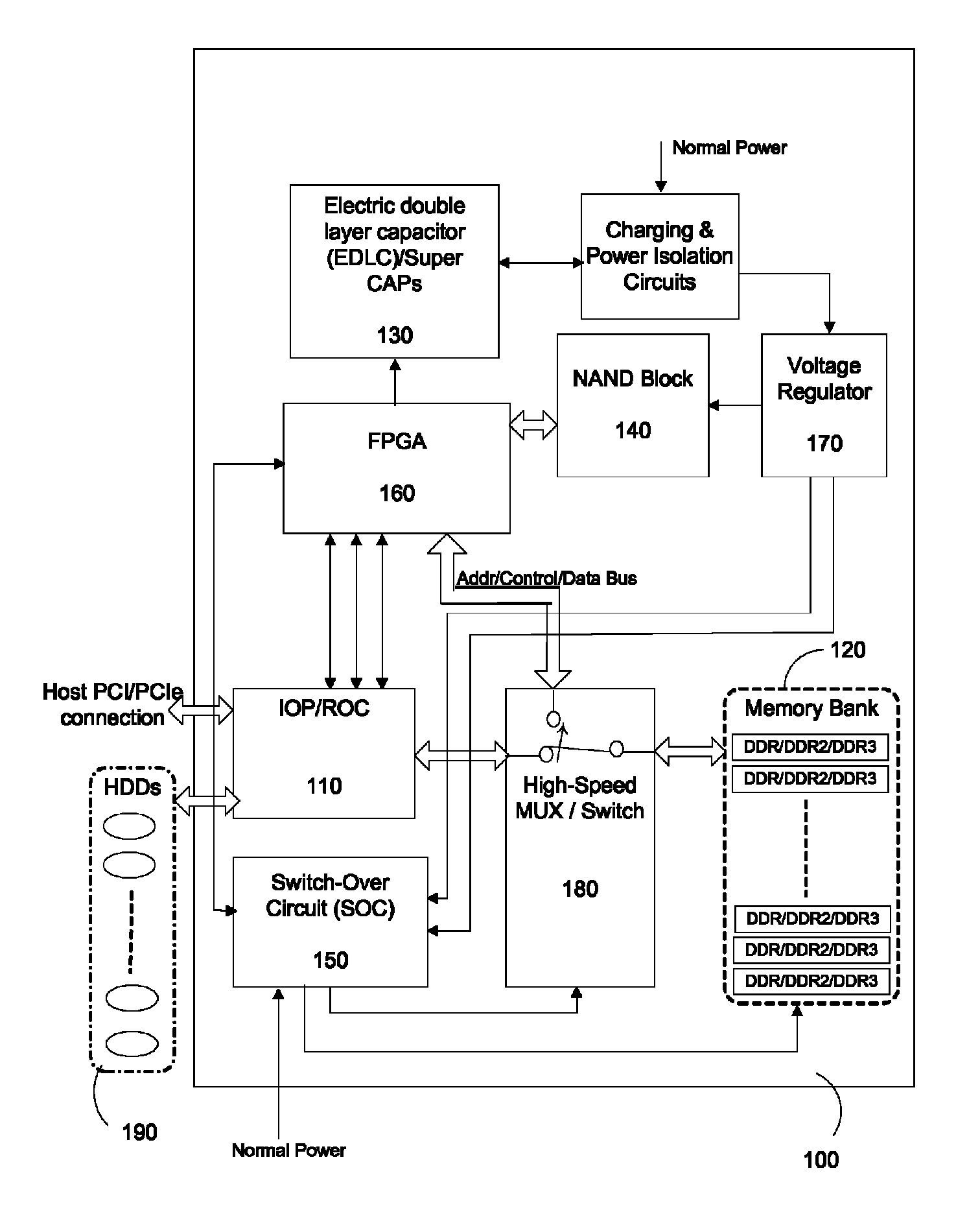

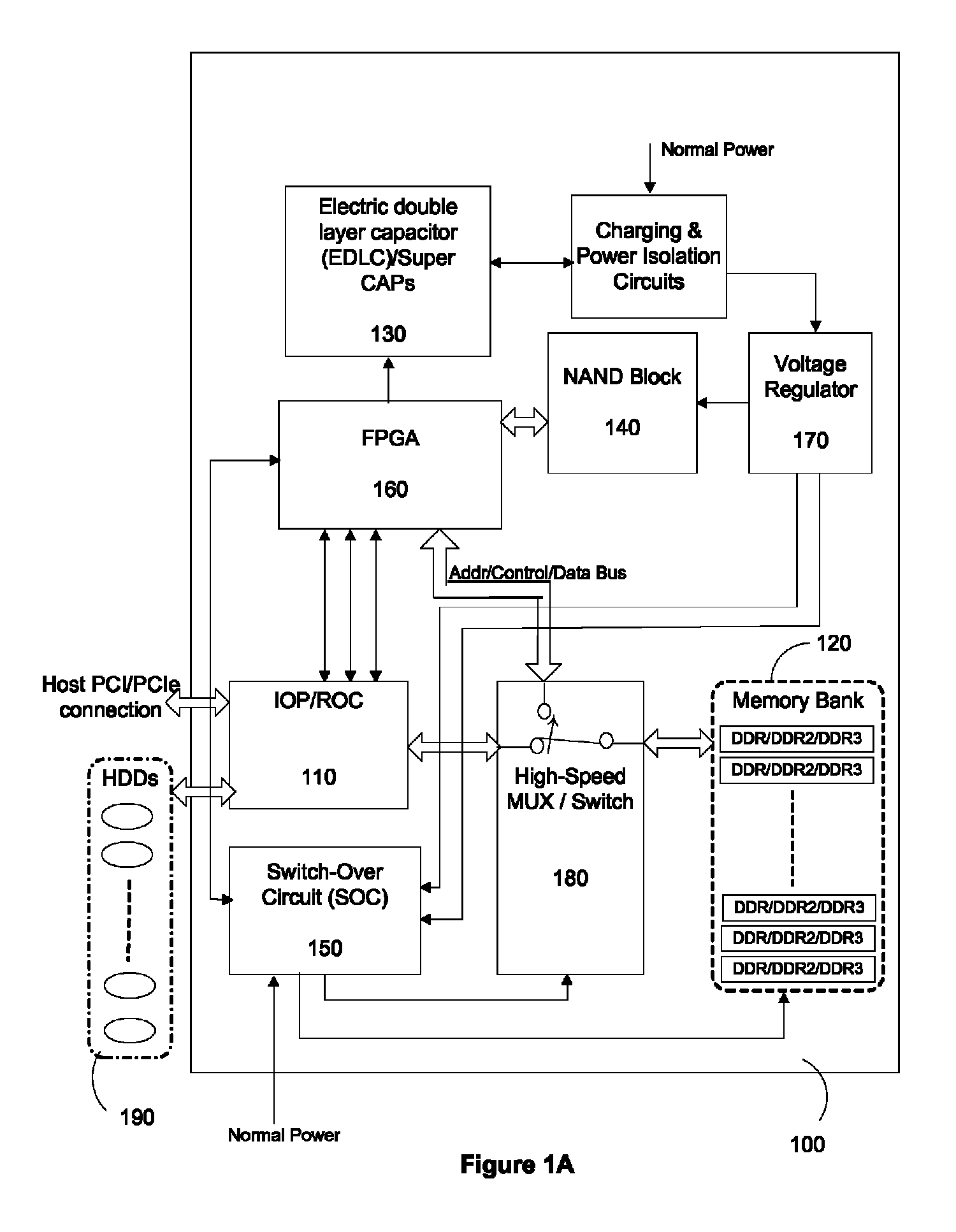

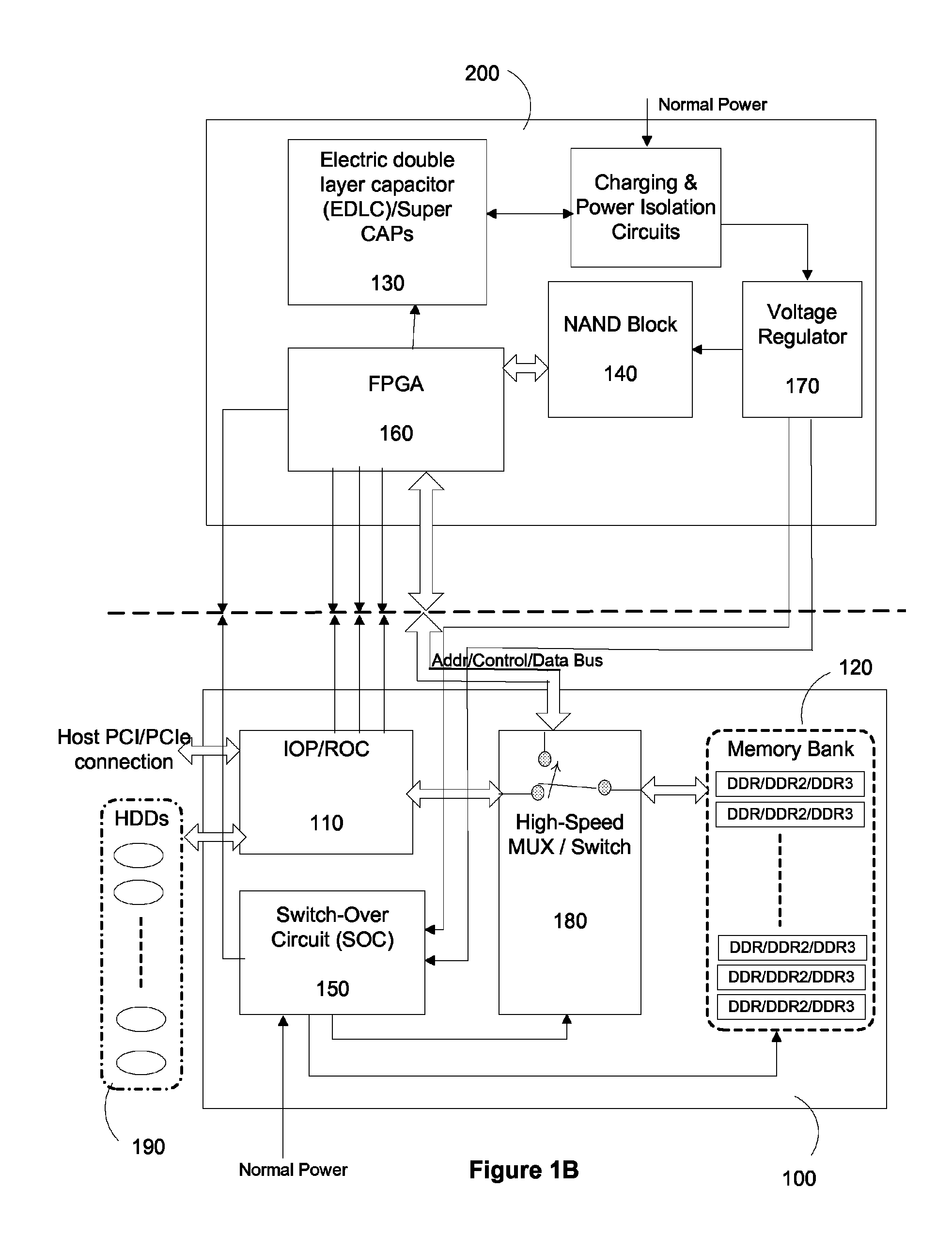

Method and apparatus for archiving data during unexpected power loss

ActiveUS7954006B1Sufficient powerAvoid data lossHardware monitoringPower supply for data processingParallel computingData loss

A method and system for preventing loss of data in a computer interface board during power failure includes providing a secondary data path to a non-volatile storage element from a cache memory of the computer interface board. Components in the secondary data path, such as the cache memory and non-volatile storage element, are powered by a secondary power supply. The cache memory of the computer interface board is a volatile memory. The secondary data path with the non-volatile storage element enables reliable memory operation during both normal and power fail modes. A power failure at the computer interface board is detected. The power failure may result in incomplete transactional data within the cache memory. Upon detection of power failure, the incomplete transactional data at the cache memory is transmitted to the non-volatile storage element through the secondary data path using the power from the secondary power supply. The non-volatile storage element preserves the transactional data of the cache memory during power failure.

Owner:PMC-SIERRA

Method and apparatus for accessing a memory

InactiveUS7617376B2Minimized on demandMemory adressing/allocation/relocationTransmissionPage tableMemory operation

The disclosed embodiments relate to an optimized memory registration mechanism that may comprise an upper layer protocol that associates I / O buffers with memory regions and that manages steering tags. The memory regions may be associated with a translation page table. The upper layer protocol may allocate one of the steering tags associated with at least one of the memory regions for a memory operation.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

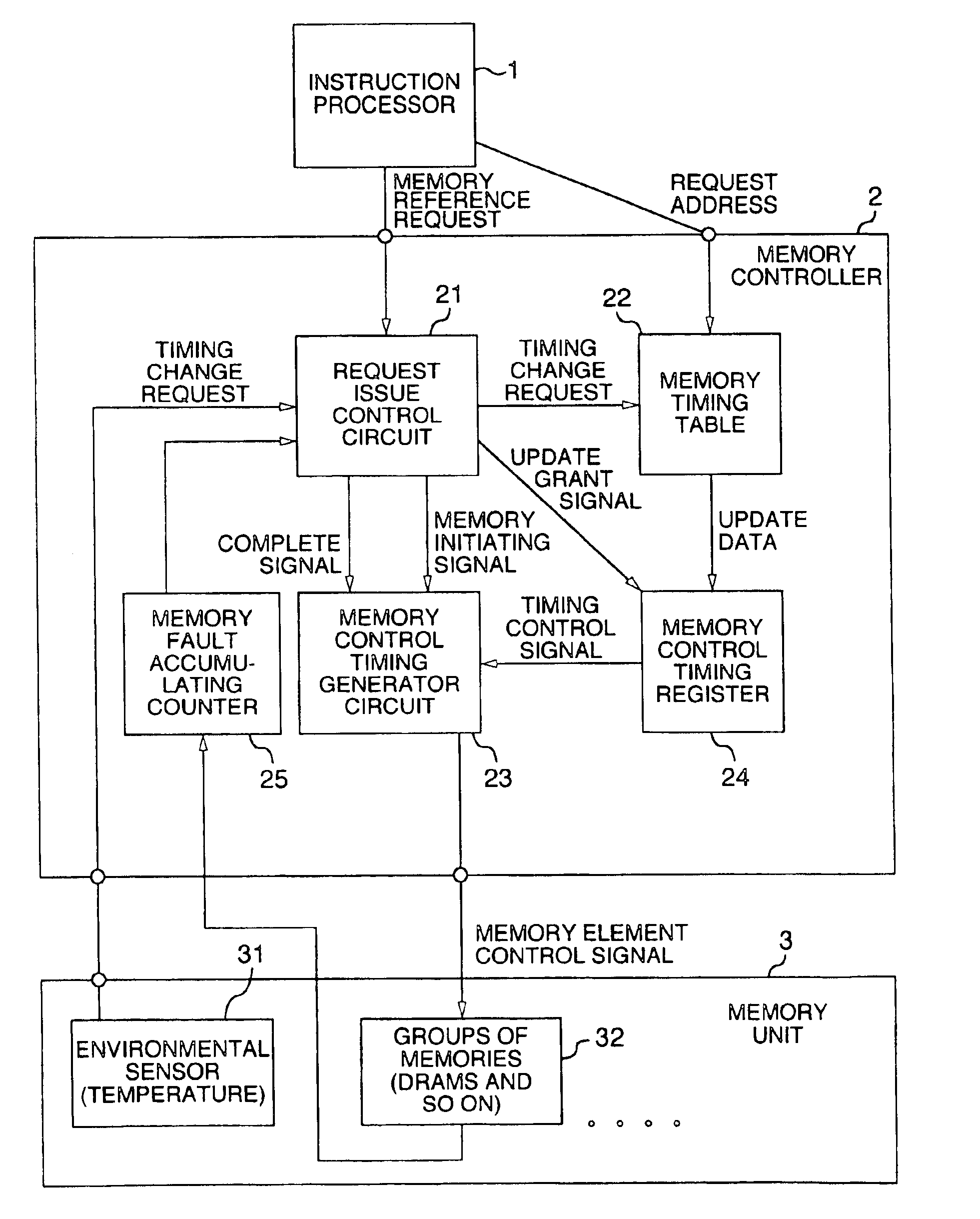

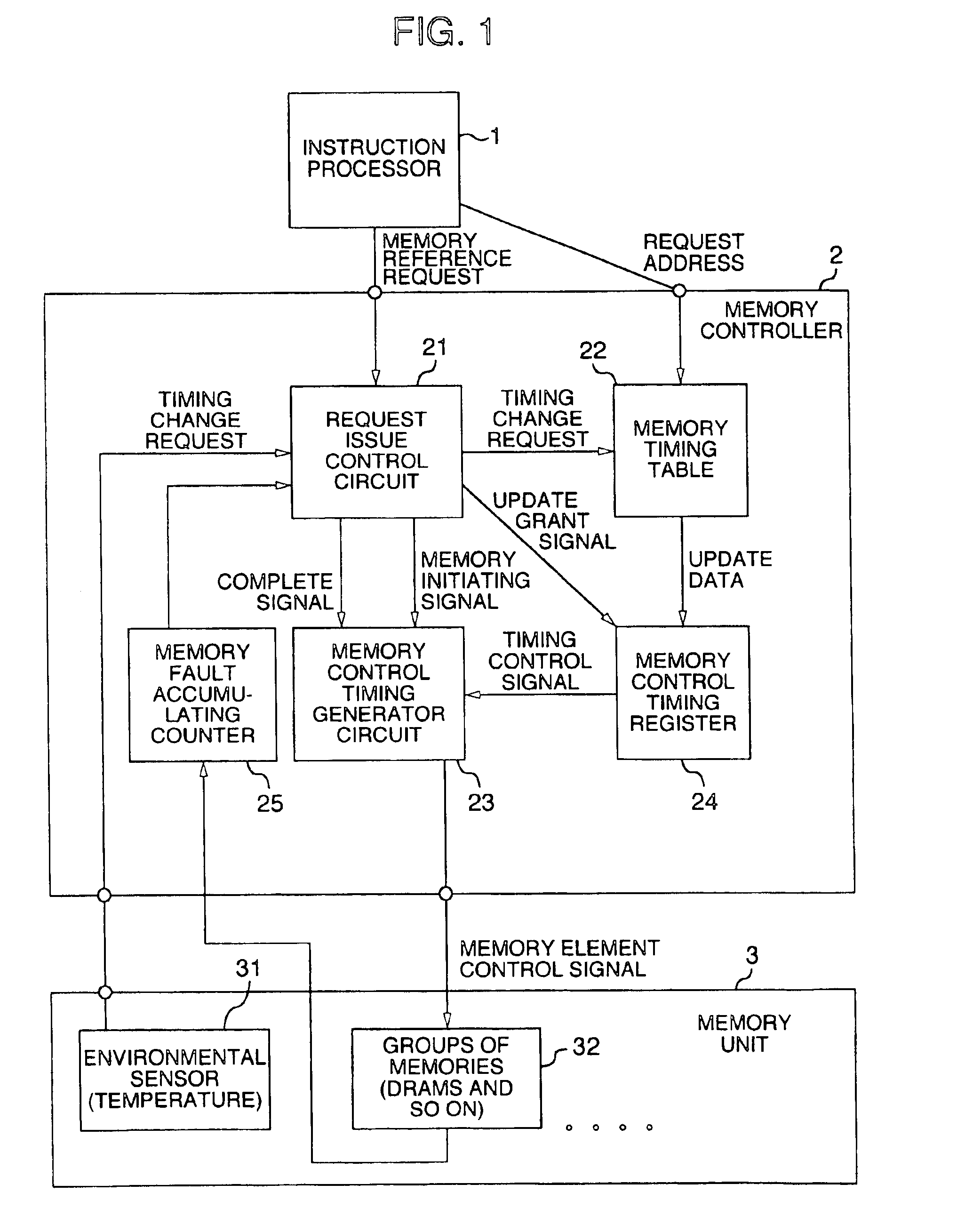

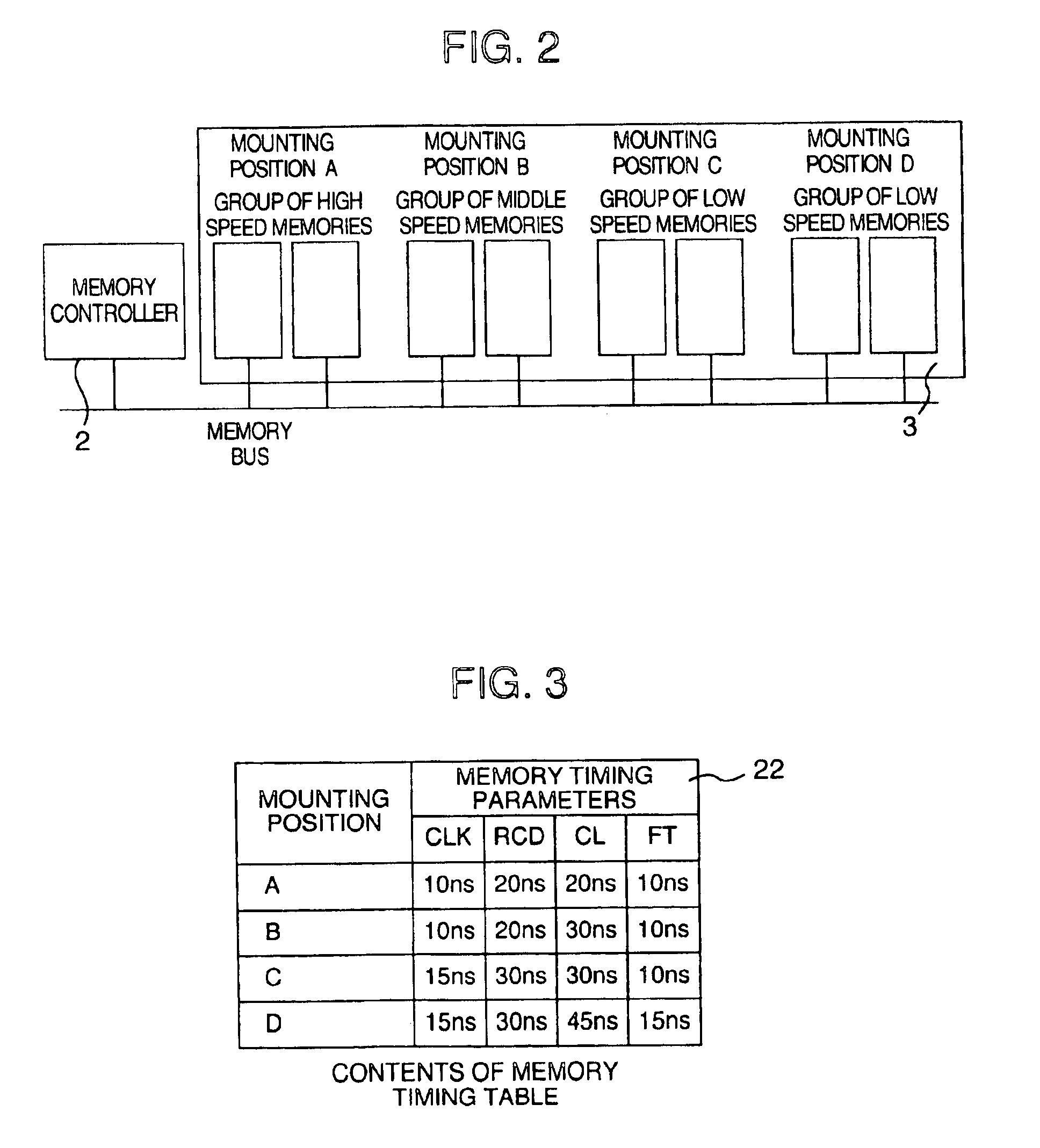

Information processing system with memory element performance-dependent memory control

InactiveUS6877078B2Improve performanceGuaranteed uptimeMemory adressing/allocation/relocationHardware monitoringInformation processingMemory controller

An information processing system which self-detects a change in the actual performance of memory elements due to mounting positions, change in environment, and aging changes to enable the memory elements to stably operate at the highest possible performance without shutting down the system. For implementing an optimal memory access for each of memory elements mounted in a memory unit, a memory controller is provided with a memory timing table which stores operation timings corresponding to the respective memory elements. The timing table is updated in response to an instruction from an apparatus for monitoring the memory operation, and the updated table is applied to a processing request after the update instruction. The apparatus for monitoring the memory operation includes an environmental sensor disposed around the memory elements, a counter for accumulating error information which is generated each time the memory unit is accessed, and so on.

Owner:HITACHI LTD

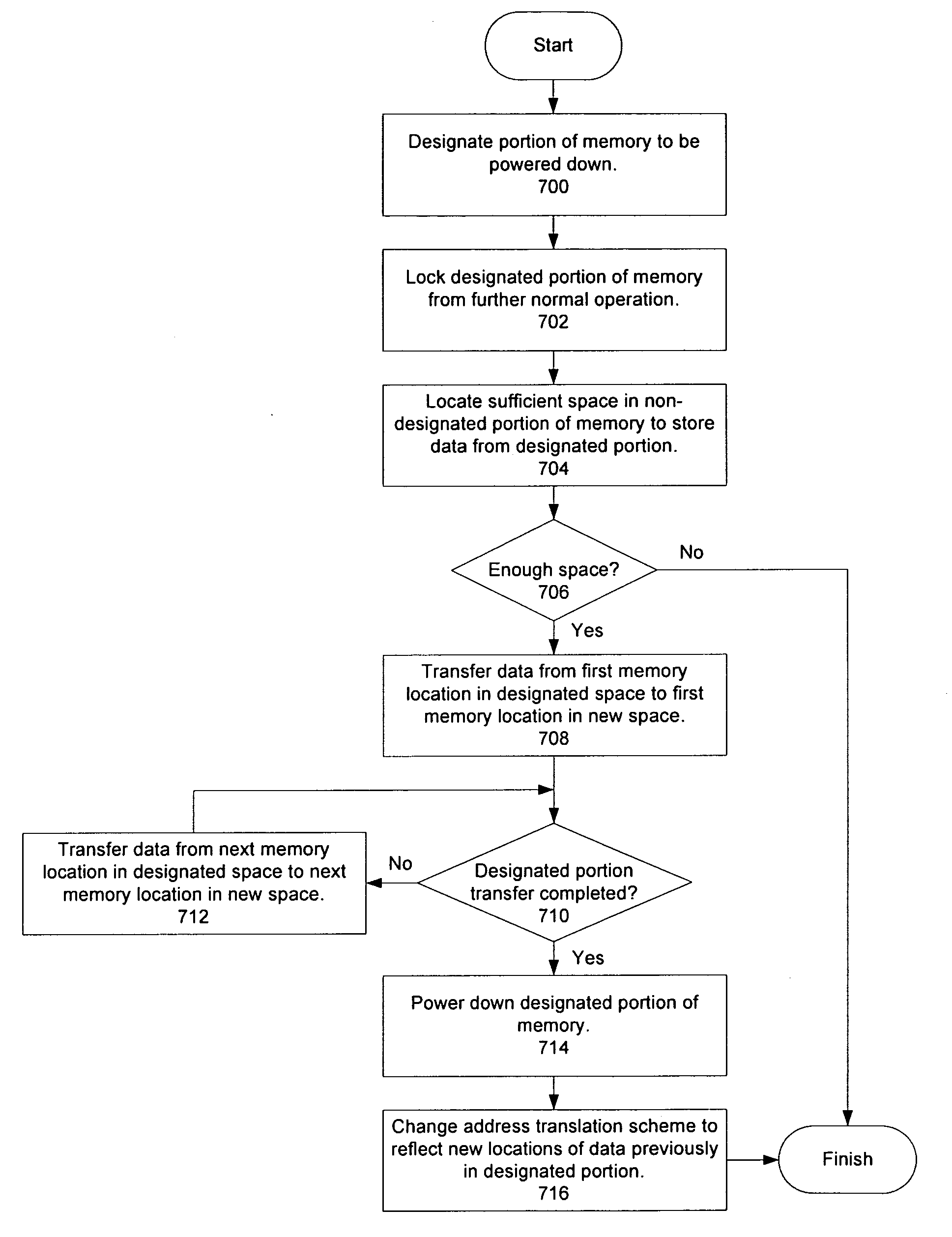

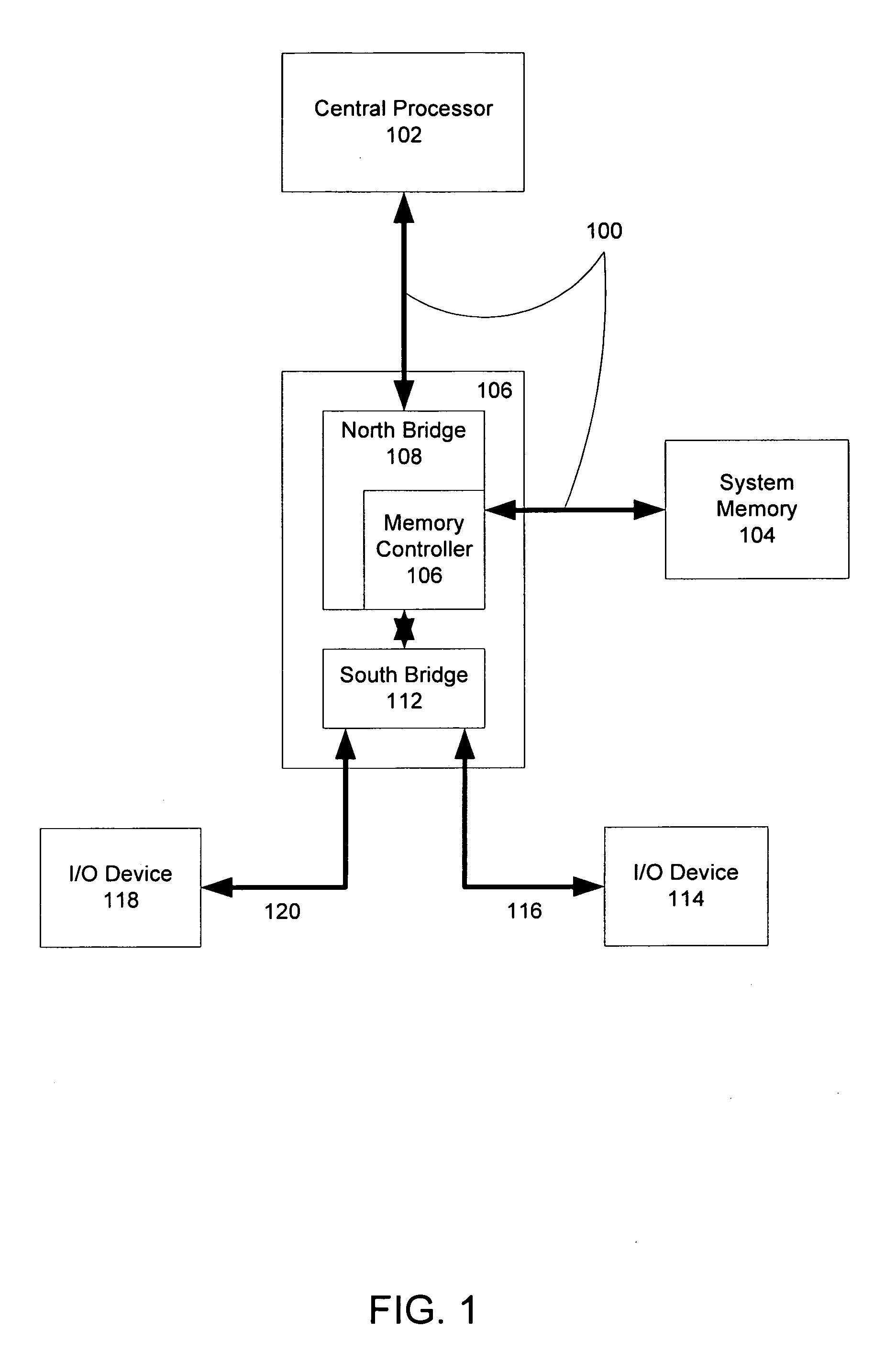

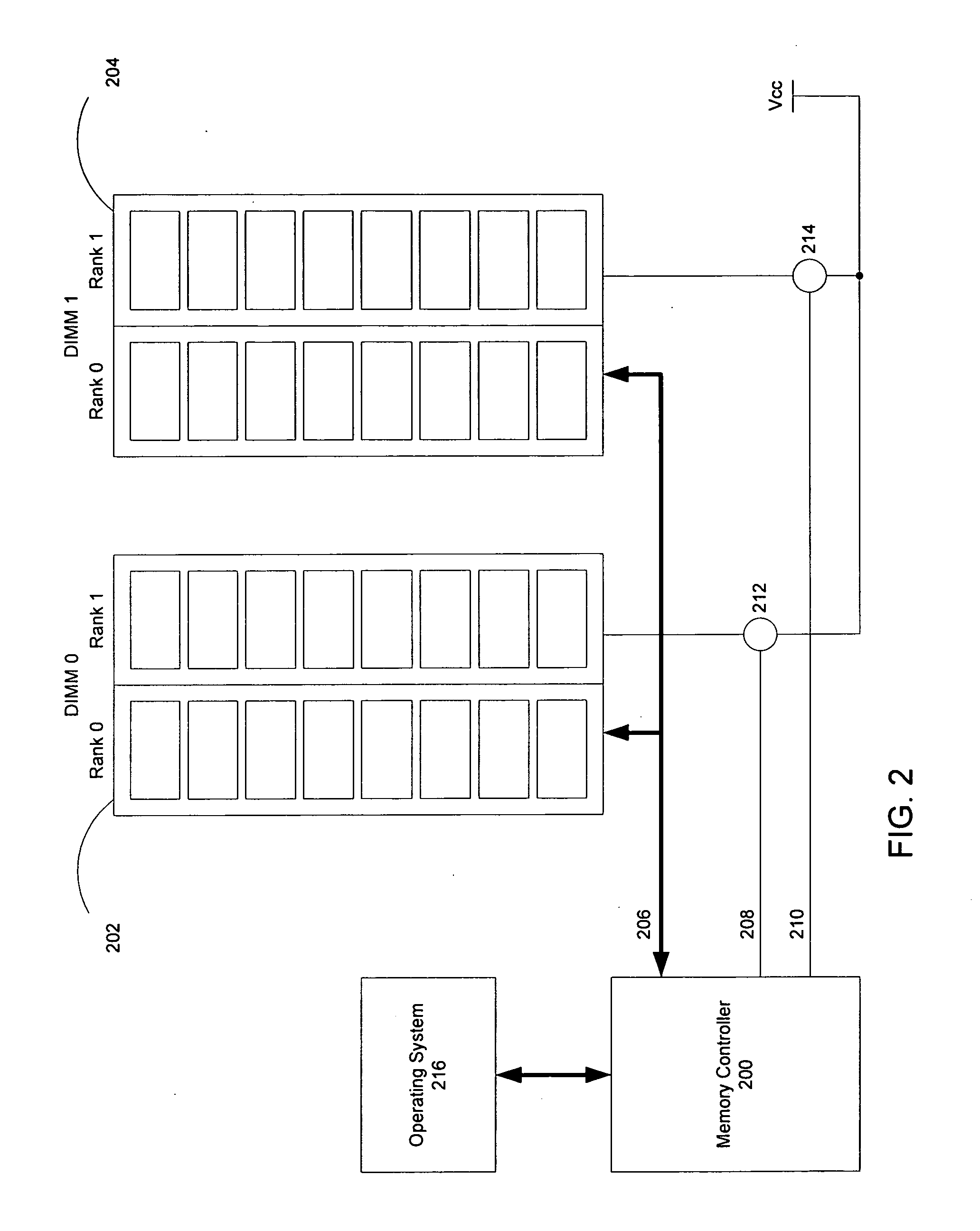

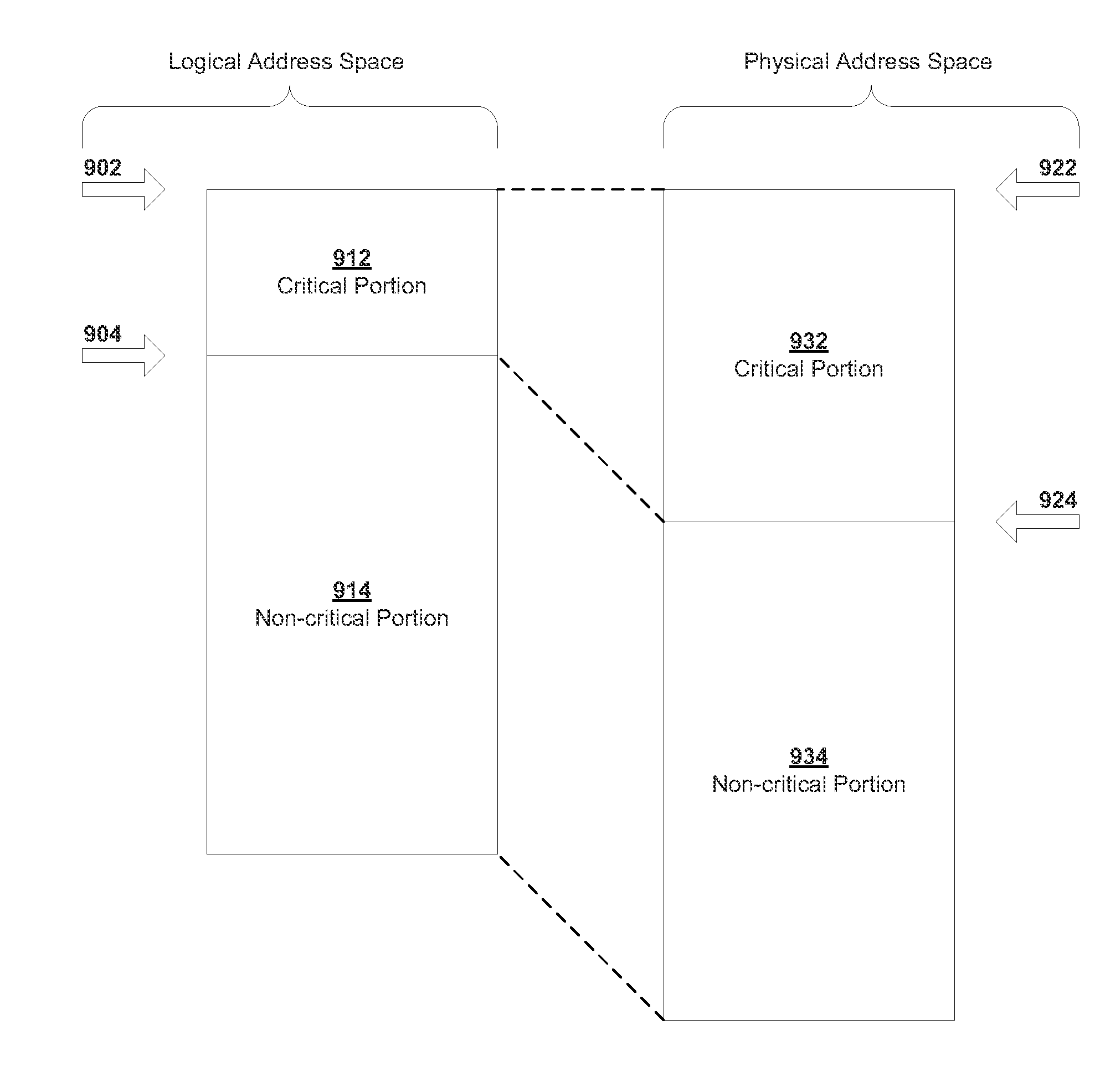

Memory power management through high-speed intra-memory data transfer and dynamic memory address remapping

InactiveUS20080005516A1Memory architecture accessing/allocationEnergy efficient ICTMemory addressData transmission

A method, circuit, and system are disclosed. In one embodiment, the method comprises designating a contiguous portion of the physical memory in one or more dual in-line memory modules (DIMMs) to be powered down, locking the designated portion of memory to halt memory operations between the memory and any device that requests access to the designated portion of memory, relocating any data currently residing in the designated portion of the one or more DIMMs to one or more locations in the non-designated portion of the one or more DIMMs, and powering down the designated portion of the one or more DIMMs.

Owner:INTEL CORP

Nonvolatile nanotube diodes and nonvolatile nanotube blocks and systems using same and methods of making same

ActiveUS20080212361A1High resistance stateLow resistance stateNanotechSolid-state devicesBit lineElectricity

Under one aspect, a memory array includes word lines; bit lines; memory cells; and a memory operation circuit. Each memory cell responds to electrical stimulus on a word line and on a bit line and includes: a two-terminal non-volatile nanotube switching device having first and second terminals, a semiconductor diode element, and a nanotube fabric article capable of multiple resistance states. The semiconductor diode and nanotube article are between and in electrical communication with the first and second terminals, which are coupled to the word line bit line respectively. The operation circuit selects cells by activating bit and / or word lines, detects a resistance state of the nanotube fabric article of a selected memory cell, and adjusts electrical stimulus applied to the cell to controllably induce a selected resistance state in the nanotube fabric article. The selected resistance state corresponds to an informational state of the memory cell.

Owner:NANTERO

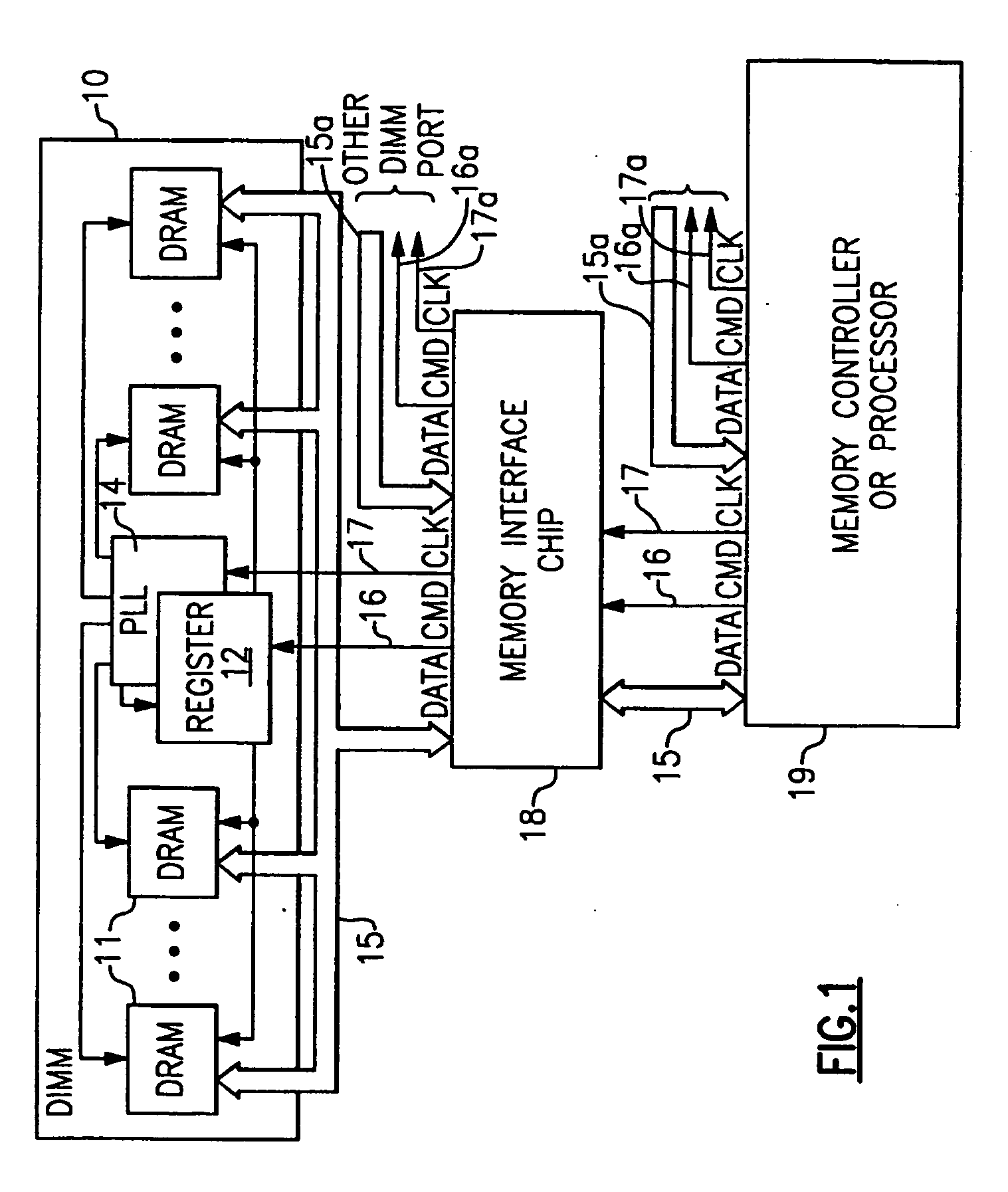

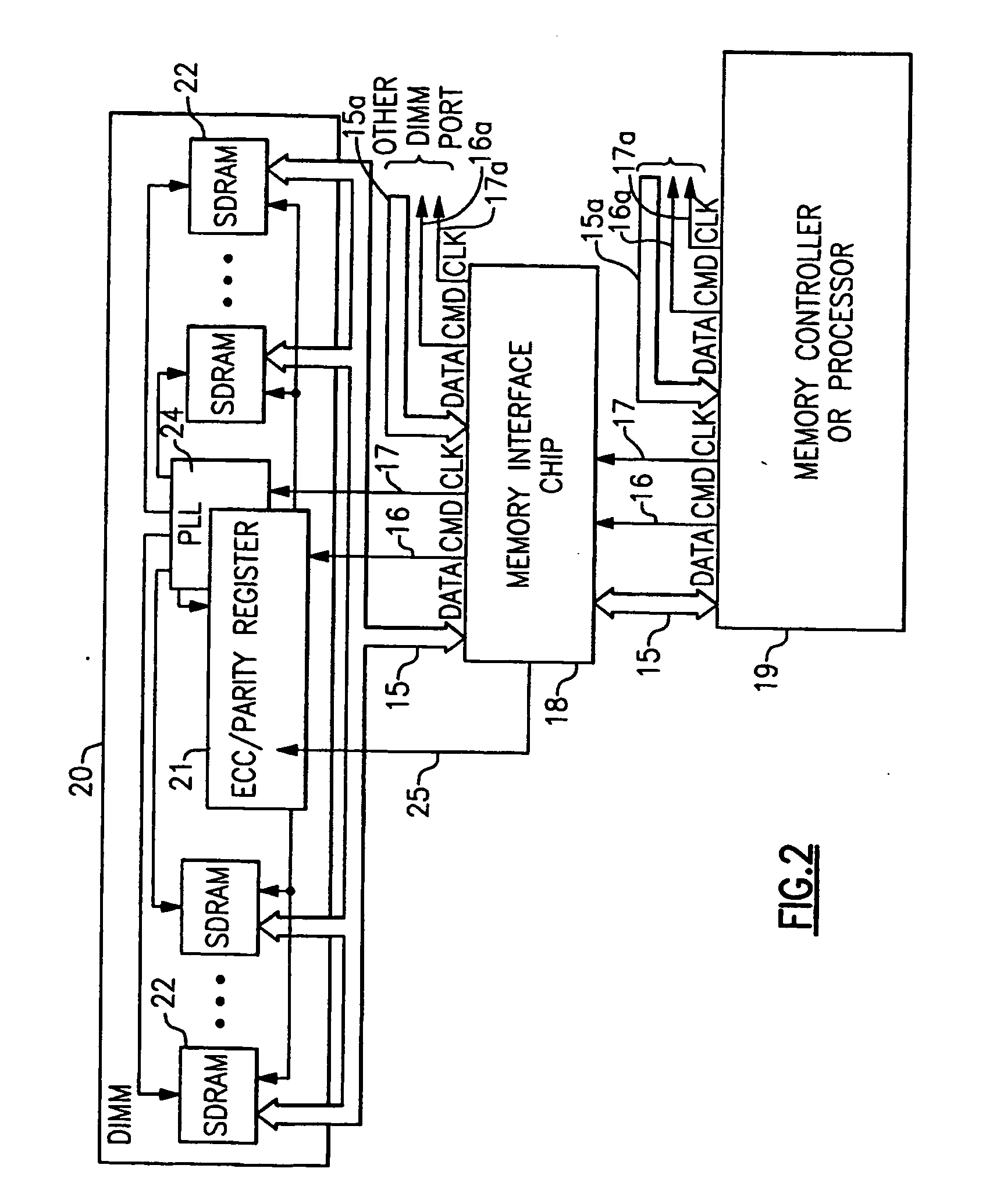

Memory read/write reordering

InactiveUS7047374B2Memory adressing/allocation/relocationInput/output processes for data processingDIMMMemory bandwidth

Owner:INTEL CORP

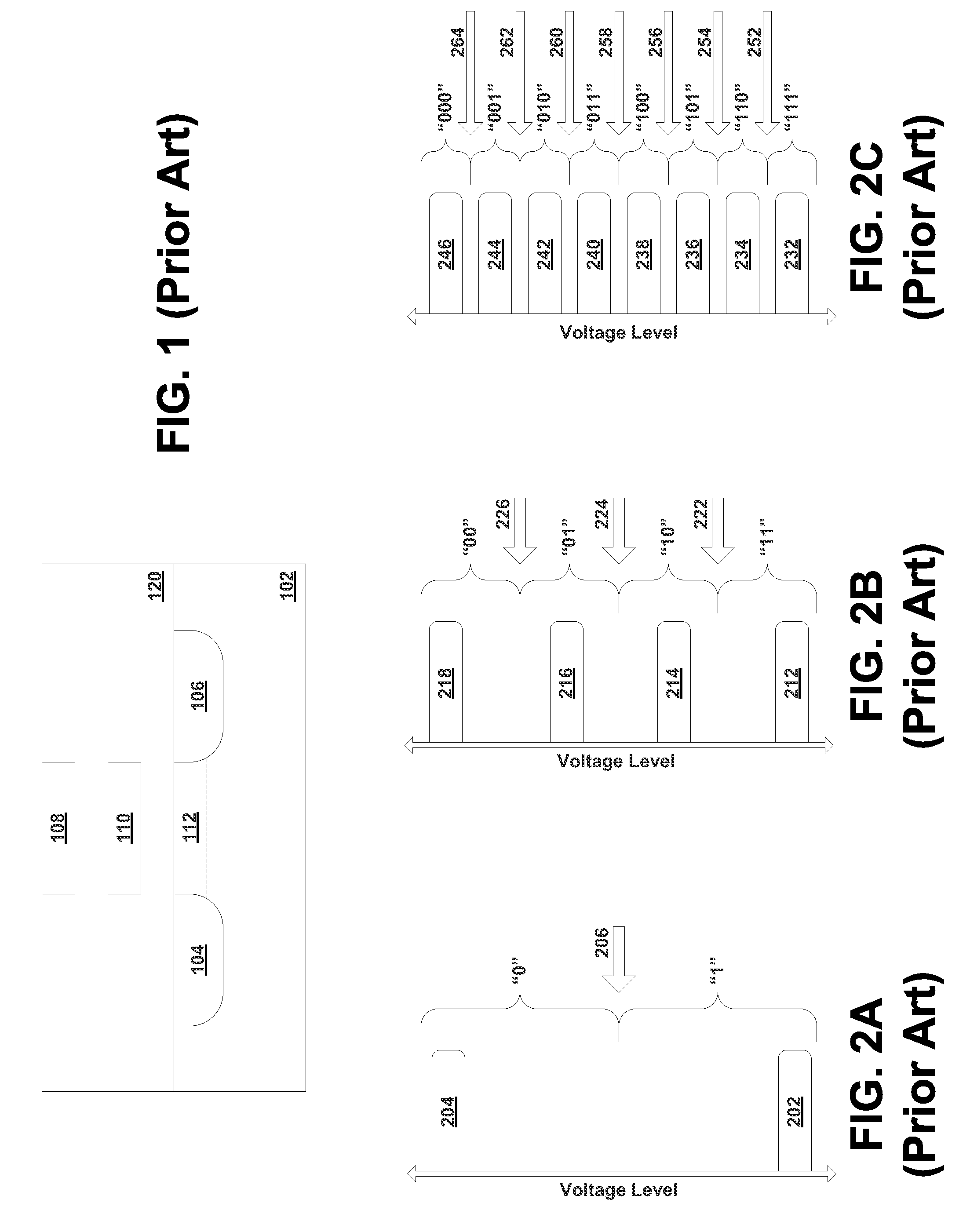

Systems and methods for reliable multi-level cell flash storage

ActiveUS20110302354A1Memory adressing/allocation/relocationRead-only memoriesSingle levelMulti-level cell

Multi-level cell (MLC) flash memory has become widely used due to their capacity to store more information in the same area as a single-level cell (SLC) flash memory. This makes MLC flash memory very attractive for storing media. Flash has also traditionally been used in electronic devices for firmware, but MLC flash is less reliable than SLC flash. For critical memory operations, MLC flash memory can be made as reliable as SLC flash by mapping one binary value to an MLC state corresponding to the highest threshold voltage and the other binary value to the MLC state corresponding the lowest threshold voltage when writing to the MLC flash, and by mapping all MLC states with corresponding threshold voltages above a central cutoff threshold voltage to one binary value and by mapping all MLC states with corresponding threshold voltages below a central cutoff threshold voltage to the other binary value.

Owner:SYNAPTICS INC

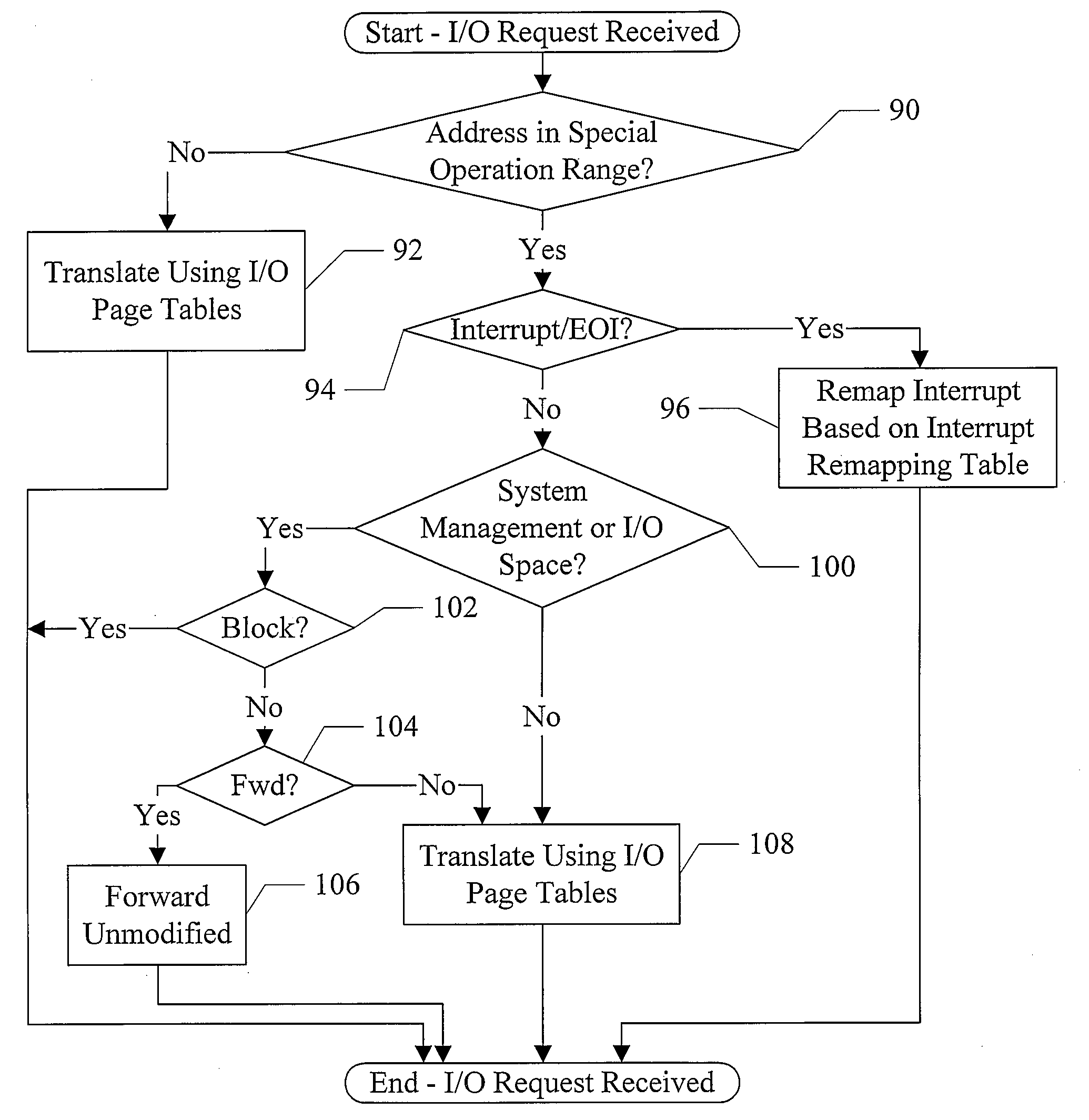

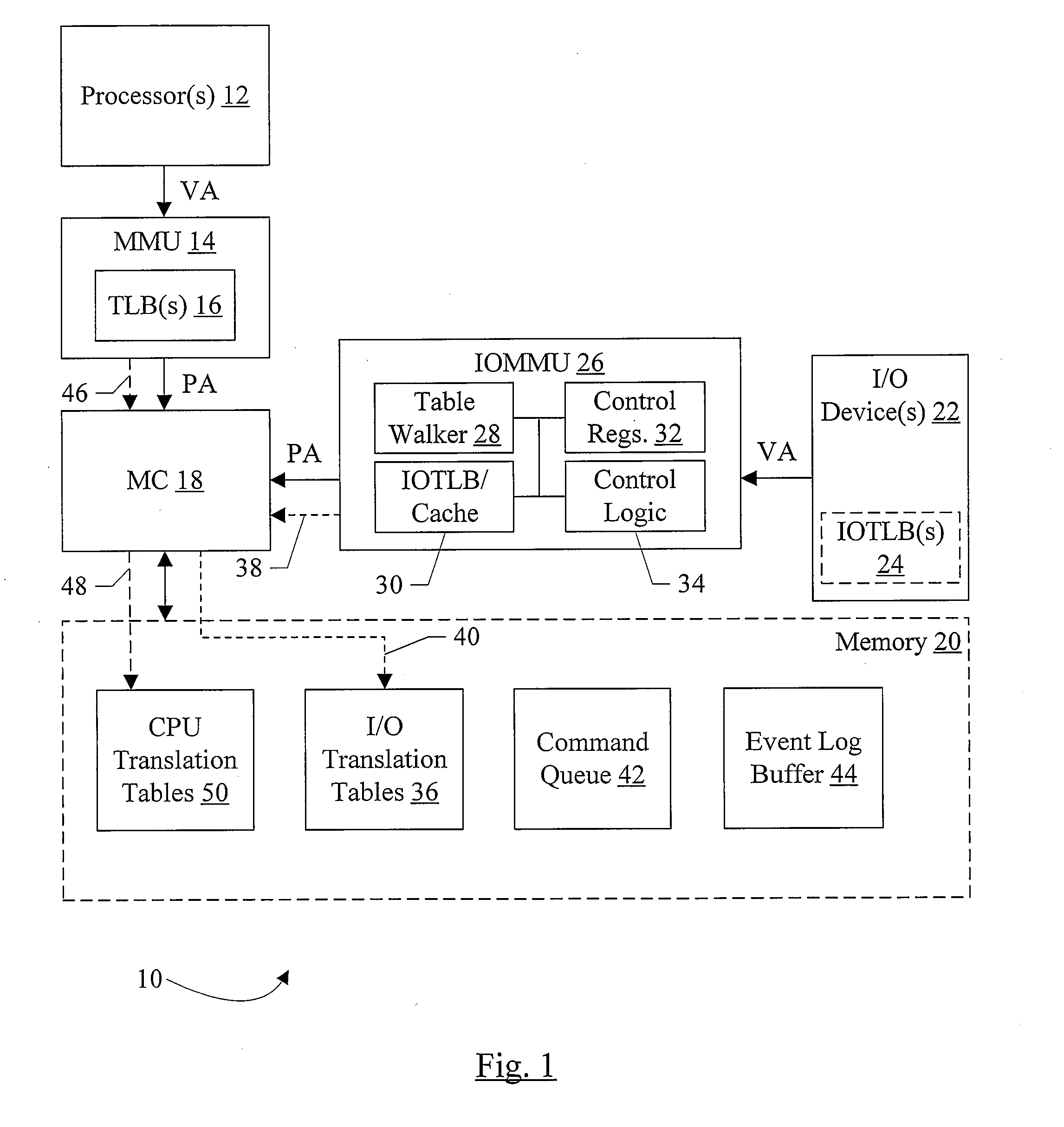

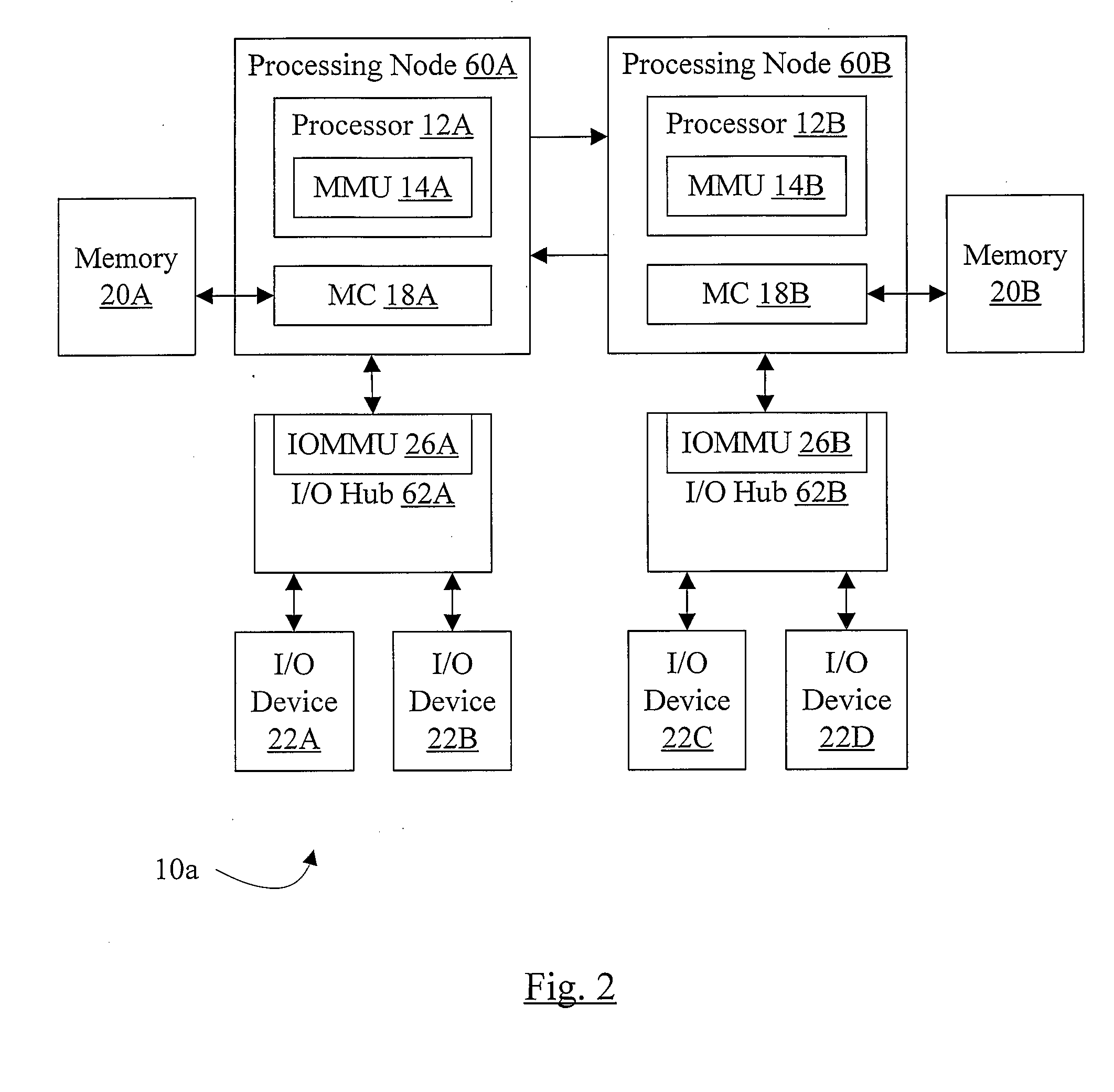

Efficiently Controlling Special Memory Mapped System Accesses

ActiveUS20080114906A1Memory architecture accessing/allocationMemory systemsManagement unitControl register

In one embodiment, an input / output memory management unit (IOMMU) comprises a control register configured to store a base address of a set of translation tables and control logic coupled to the control register. The control logic is configured to respond to an input / output (I / O) device-initiated request having an address within an address range of an address space corresponding to a peripheral interconnect. One or more operations other than a memory operation are associated with the address range, and the control logic is configured to translate the address to a second address outside of the address range if the translation tables specify a translation from the address to the second address, whereby a memory operation is performed in response to the request instead of the one or more operations associated with the address range.

Owner:ADVANCED MICRO DEVICES INC

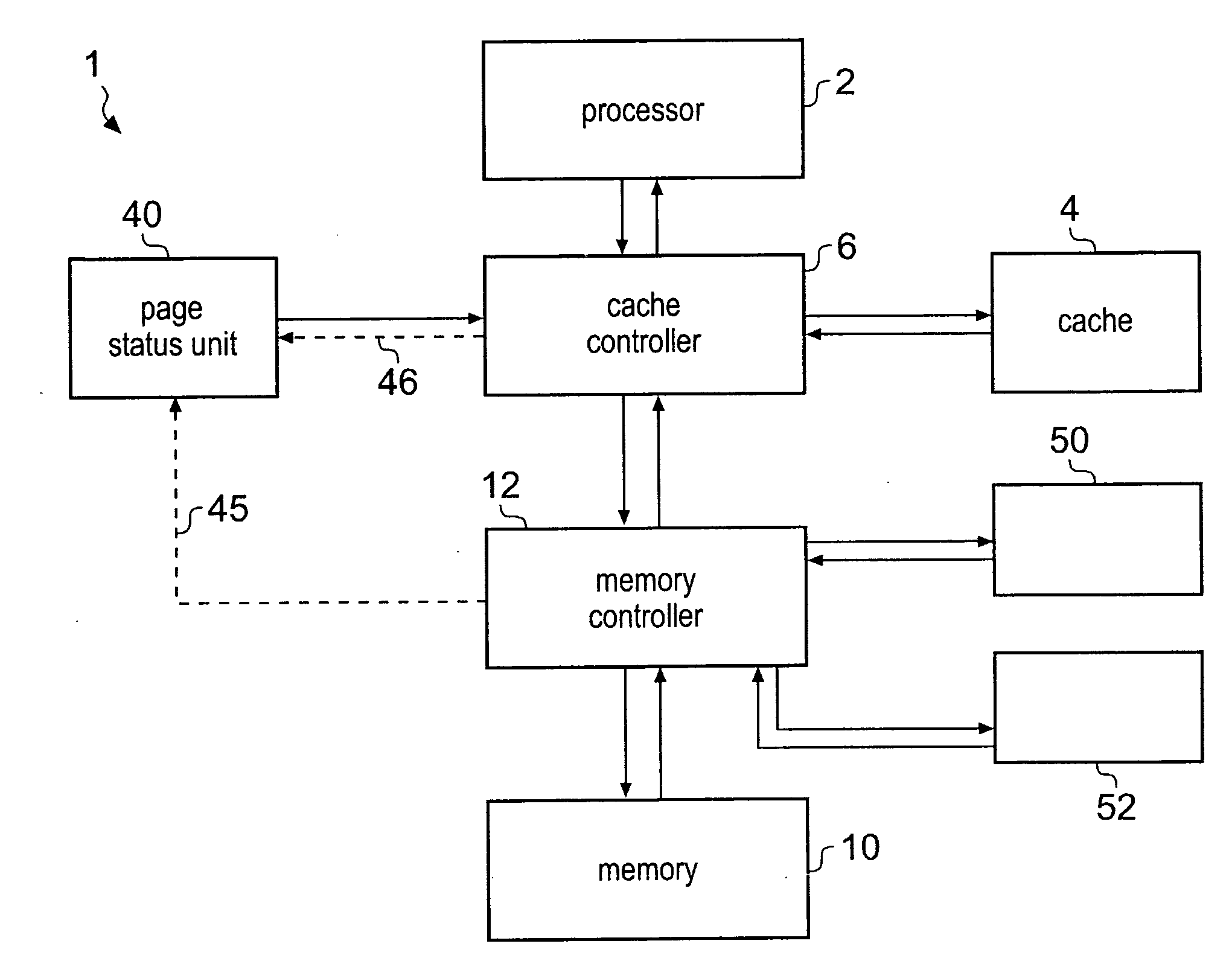

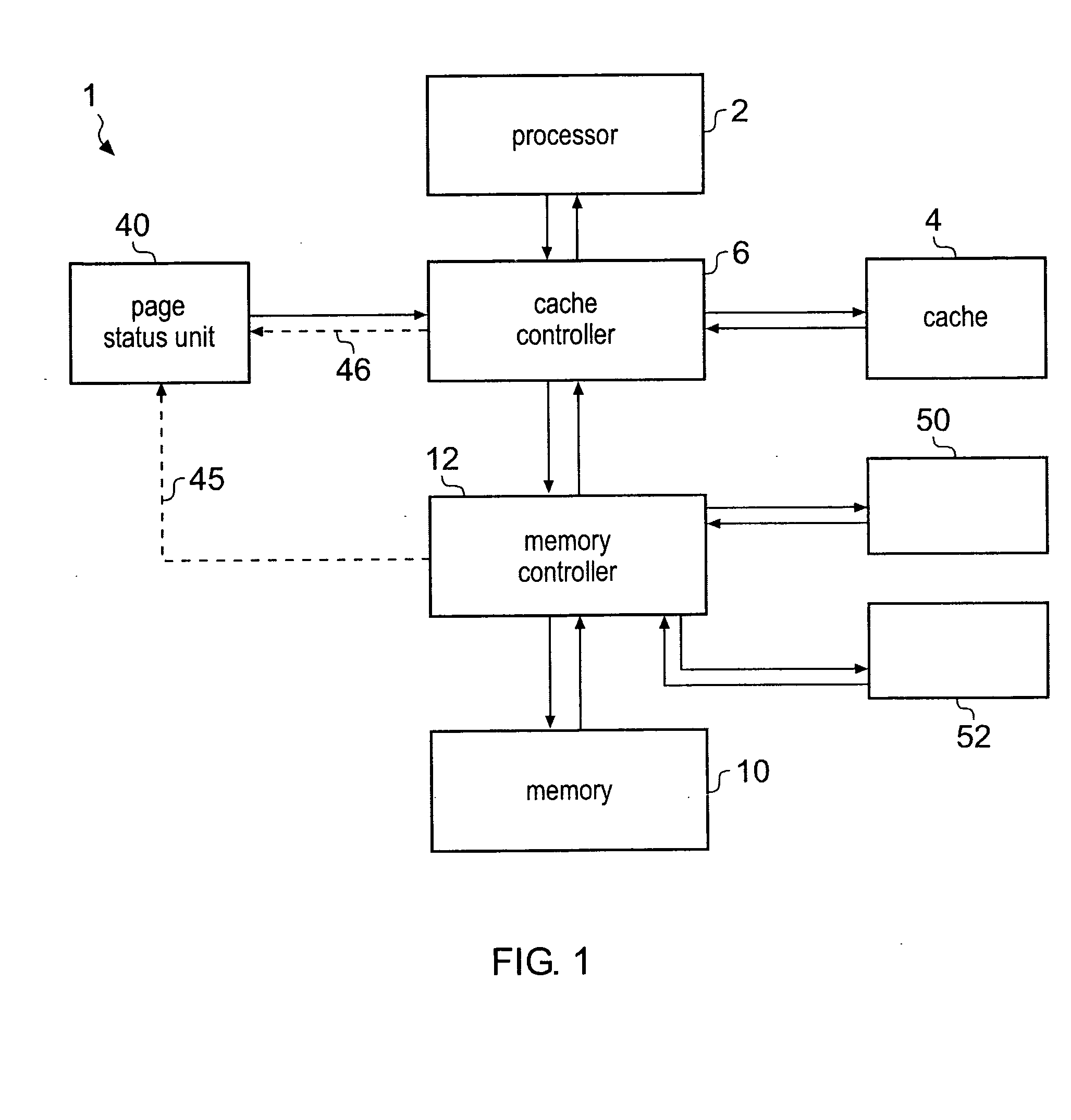

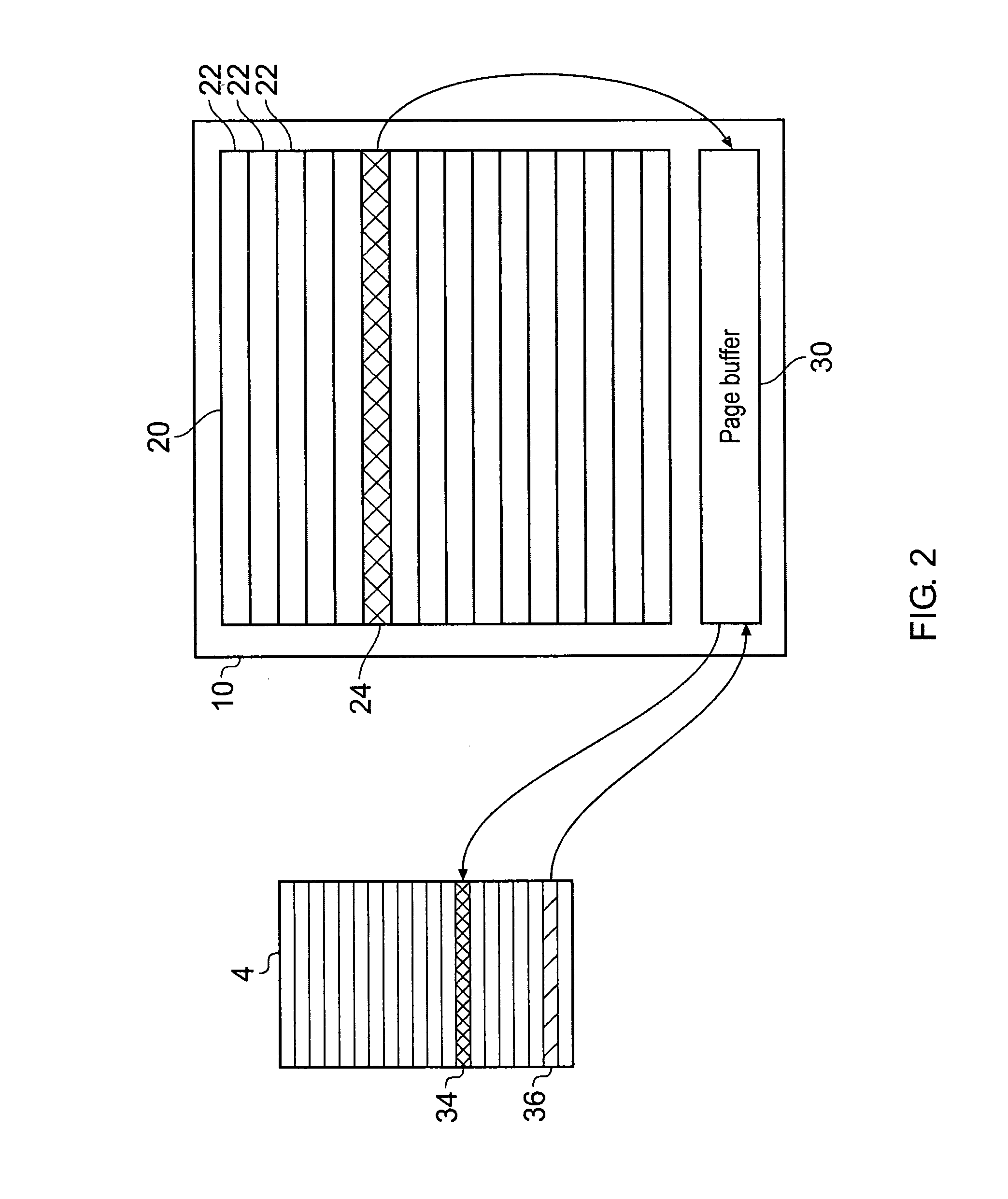

Efficiency of cache memory operations

InactiveUS20090265514A1Improve caching efficiencyEasy accessMemory systemsParallel computingCache management

A processing system 1 including a memory 10 and a cache memory 4 is provided with a page status unit 40 for providing a cache controller with a page open indication indicating one or more open pages of data values in memory. At least one of one or more cache management operations performed by the cache controller is responsive to the page open indication so that the efficiency and / or speed of the processing system can be improved.

Owner:ARM LTD