Patents

Literature

2800 results about "Phase-change memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

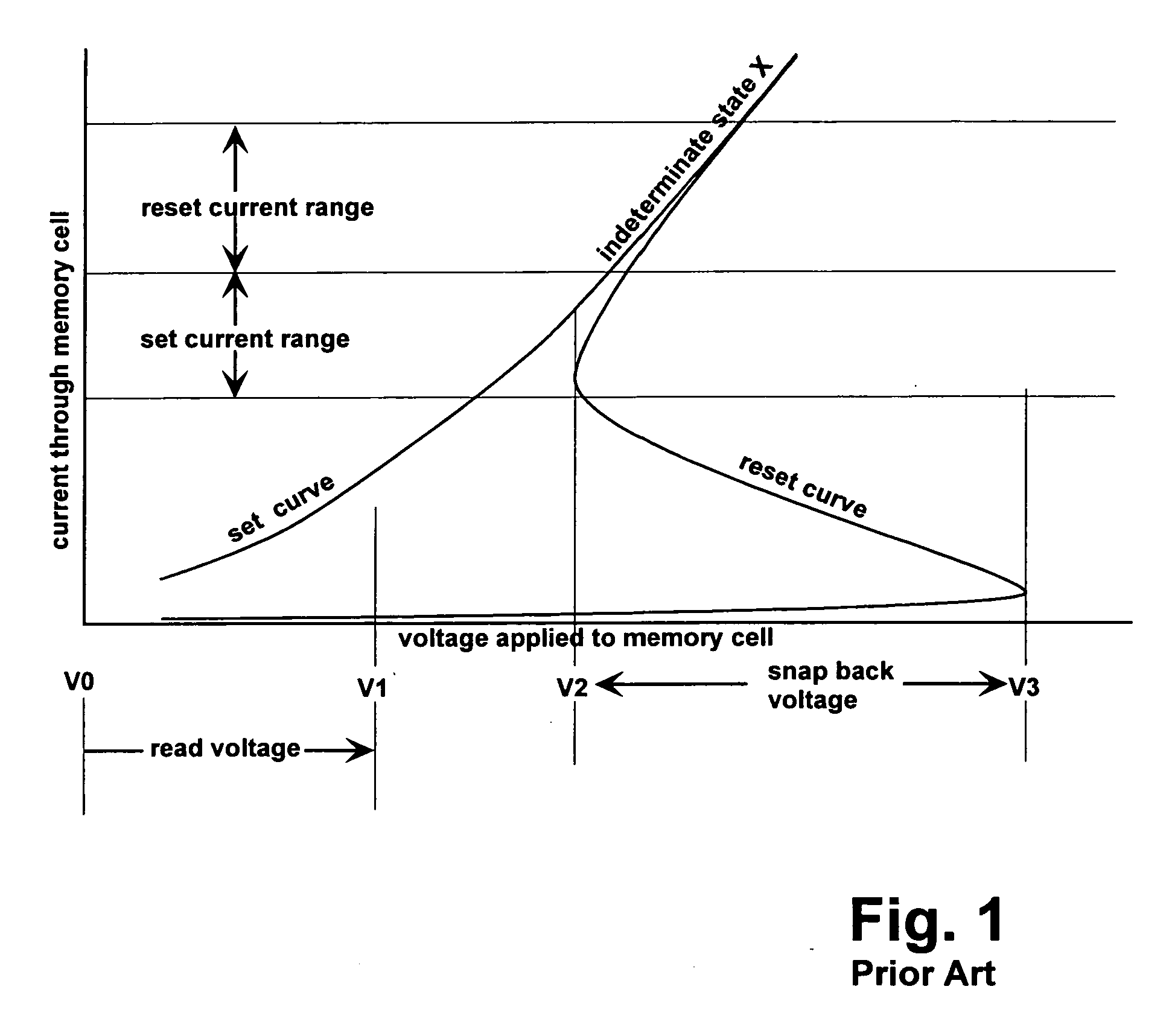

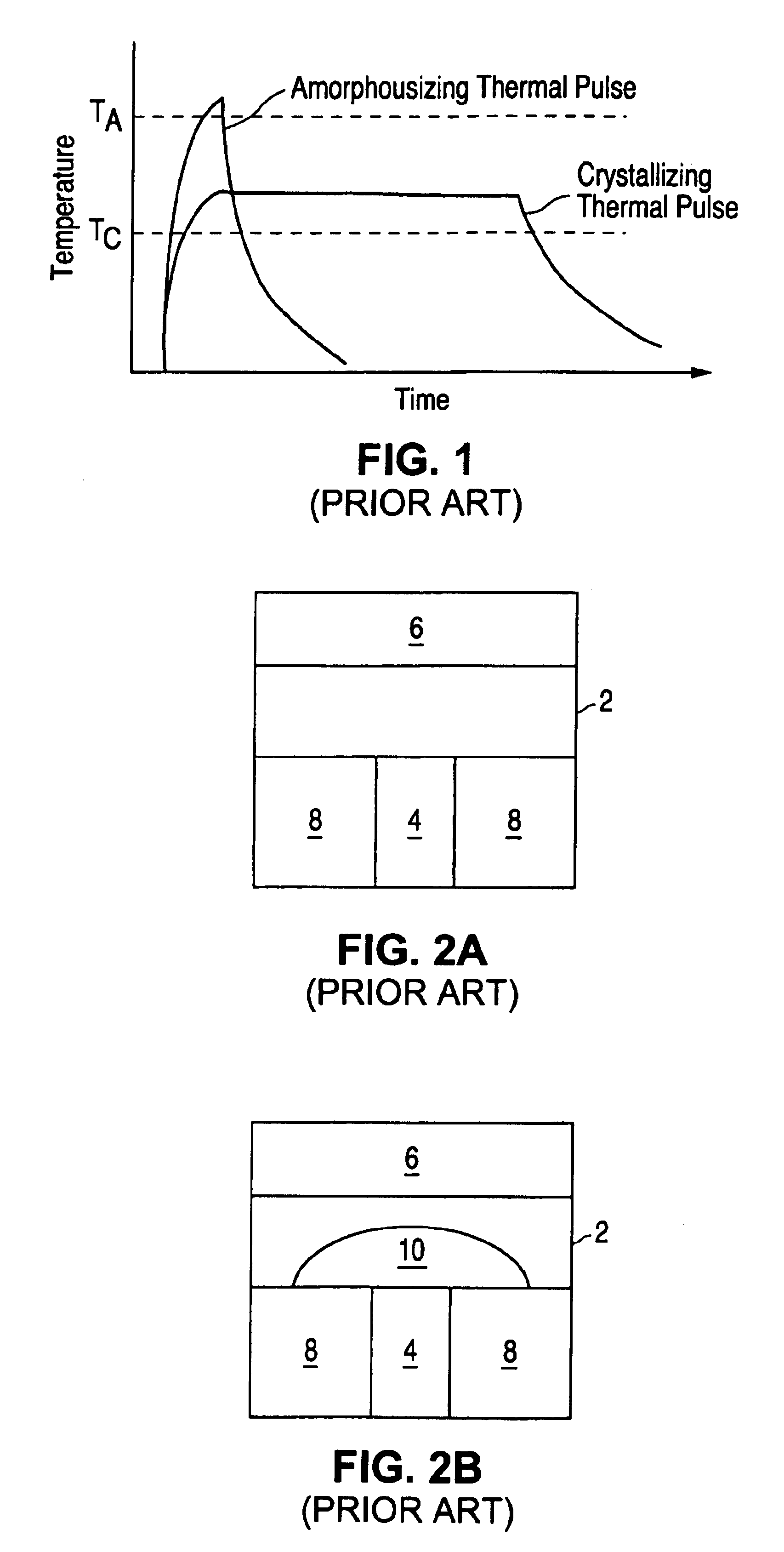

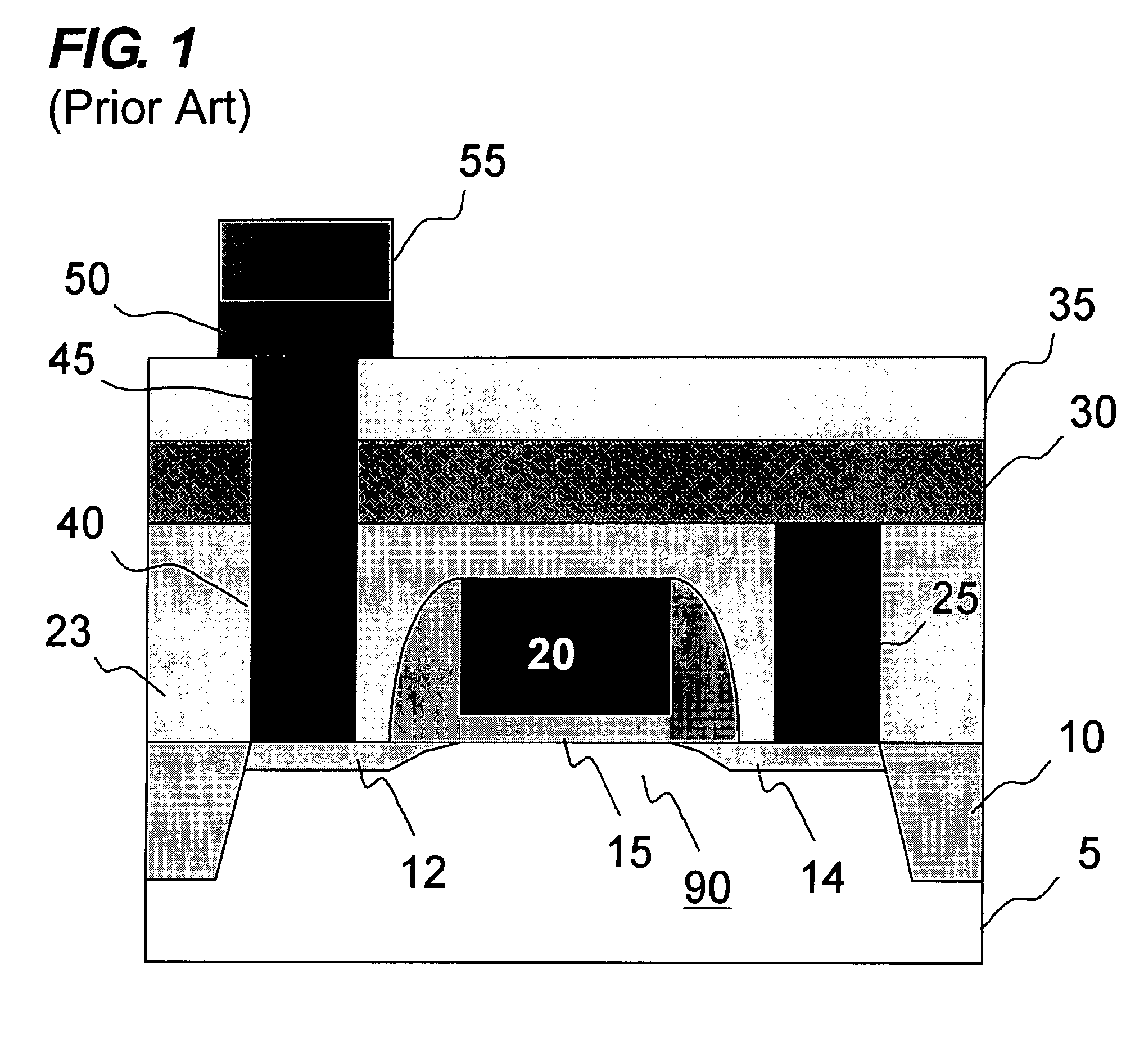

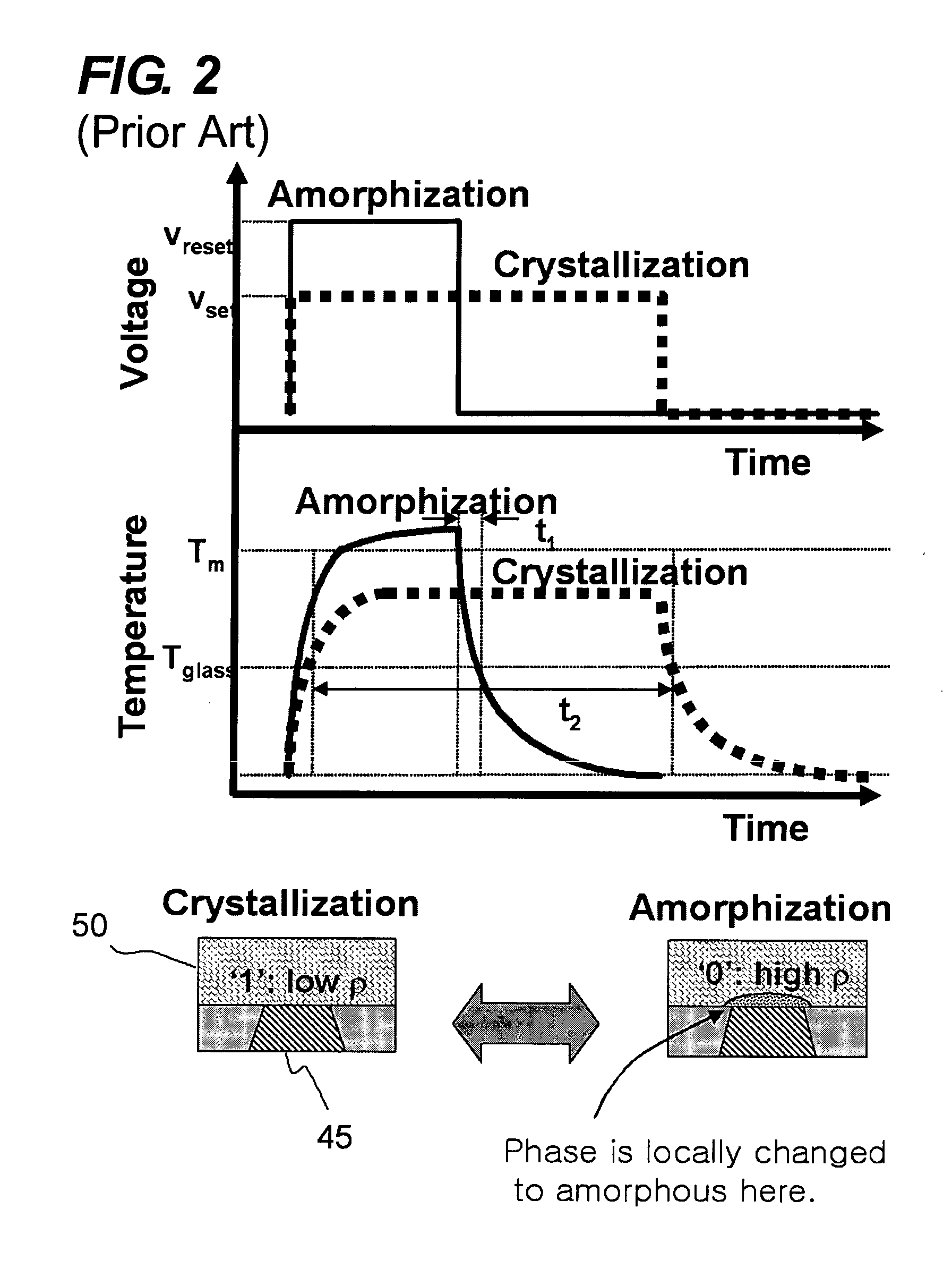

Phase-change memory (also known as PCM, PCME, PRAM, PCRAM, OUM (ovonic unified memory) and C-RAM or CRAM (chalcogenide RAM) is a type of non-volatile random-access memory. PRAMs exploit the unique behaviour of chalcogenide glass. In the older generation of PCM, heat produced by the passage of an electric current through a heating element generally made of TiN was used to either quickly heat and quench the glass, making it amorphous, or to hold it in its crystallization temperature range for some time, thereby switching it to a crystalline state. PCM also has the ability to achieve a number of distinct intermediary states, thereby having the ability to hold multiple bits in a single cell, but the difficulties in programming cells in this way has prevented these capabilities from being implemented in other technologies (most notably flash memory) with the same capability.

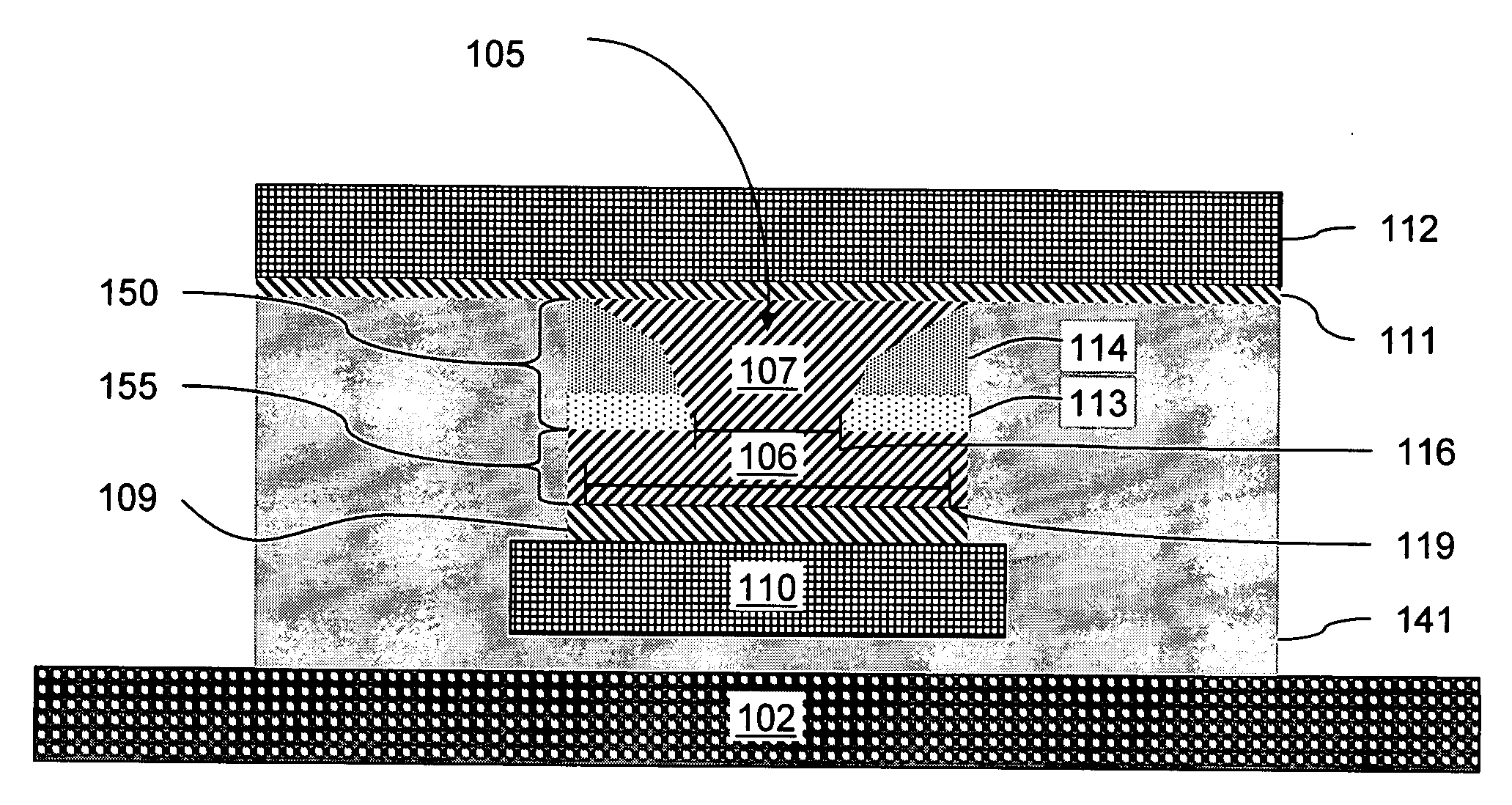

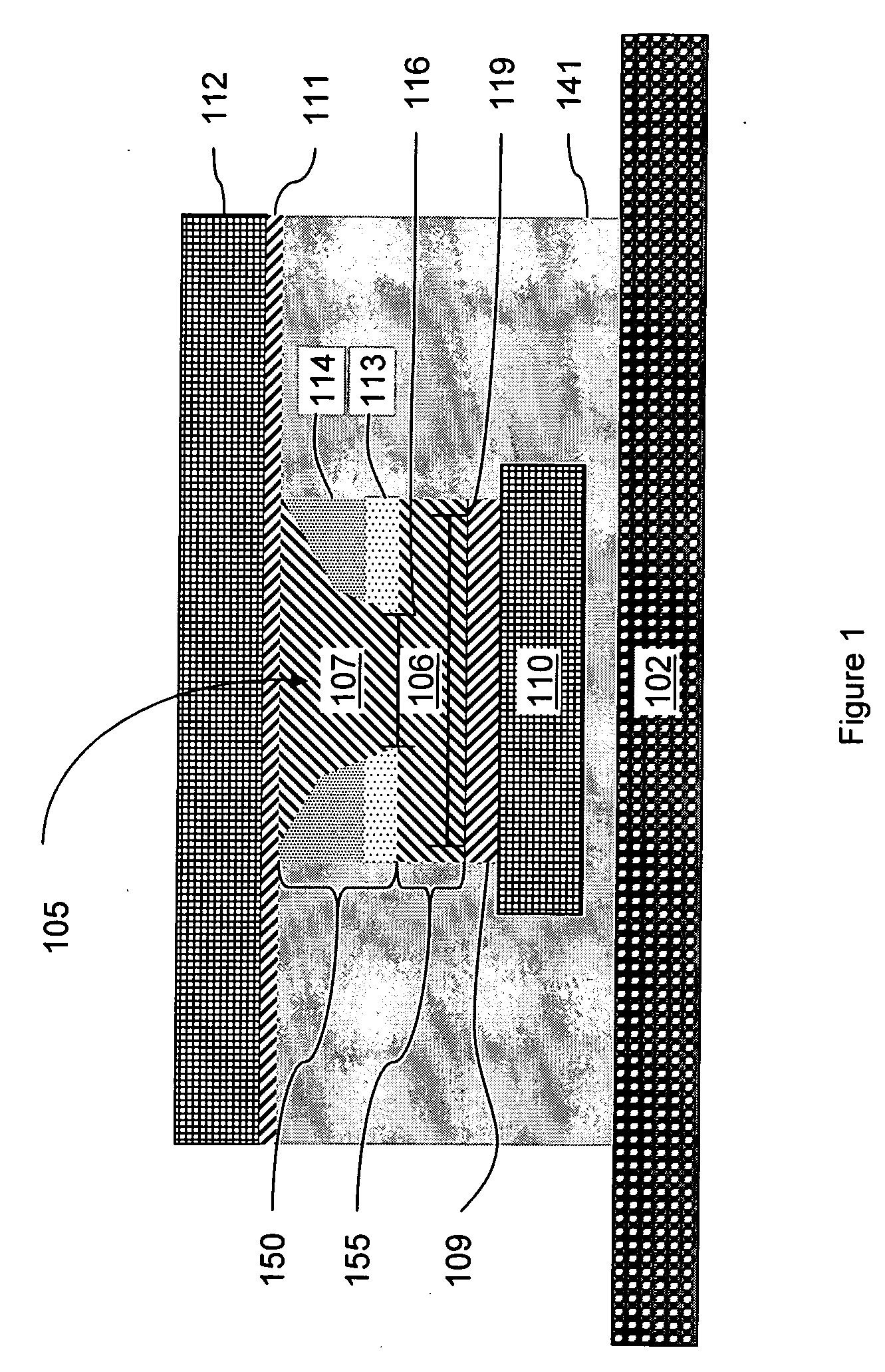

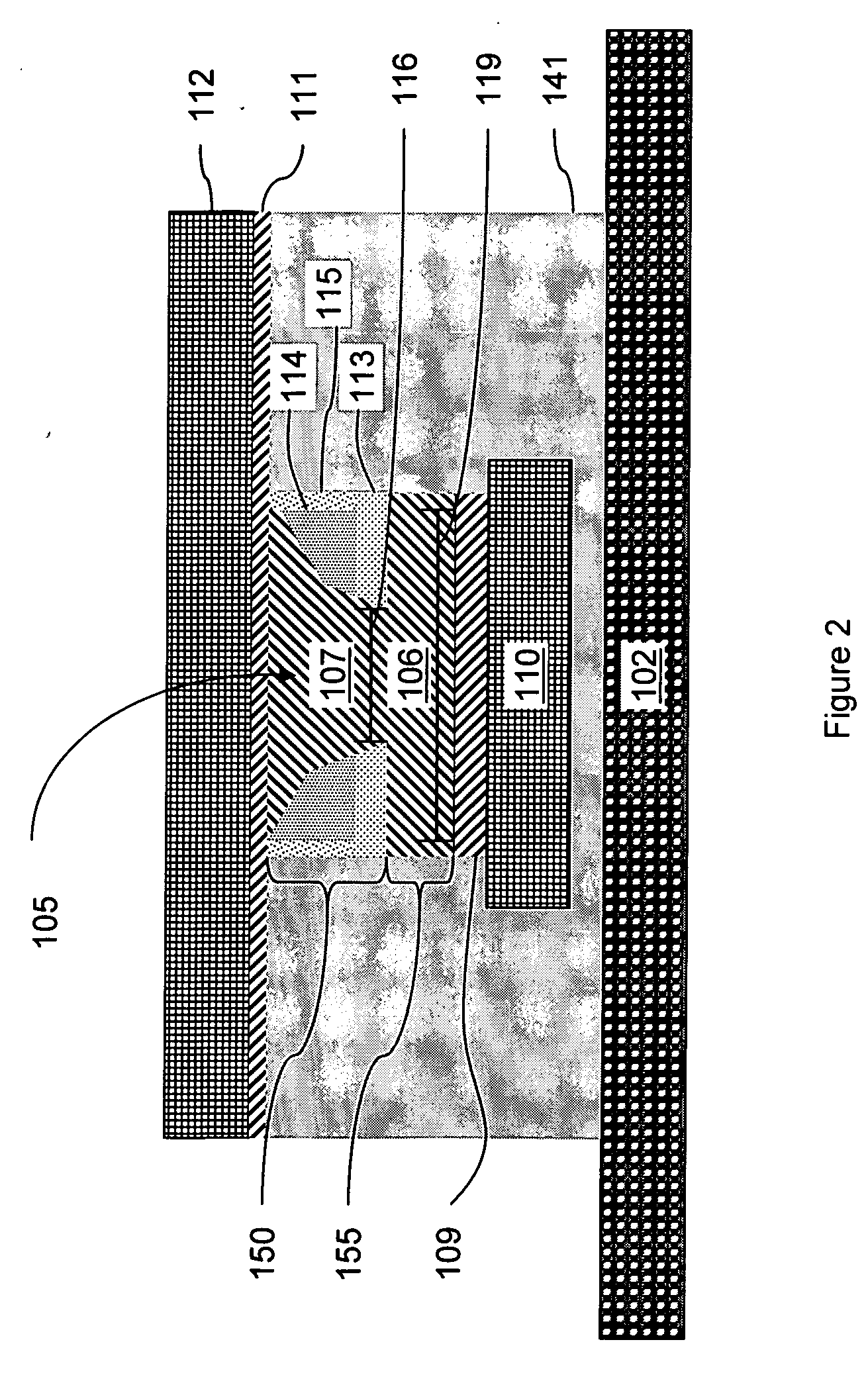

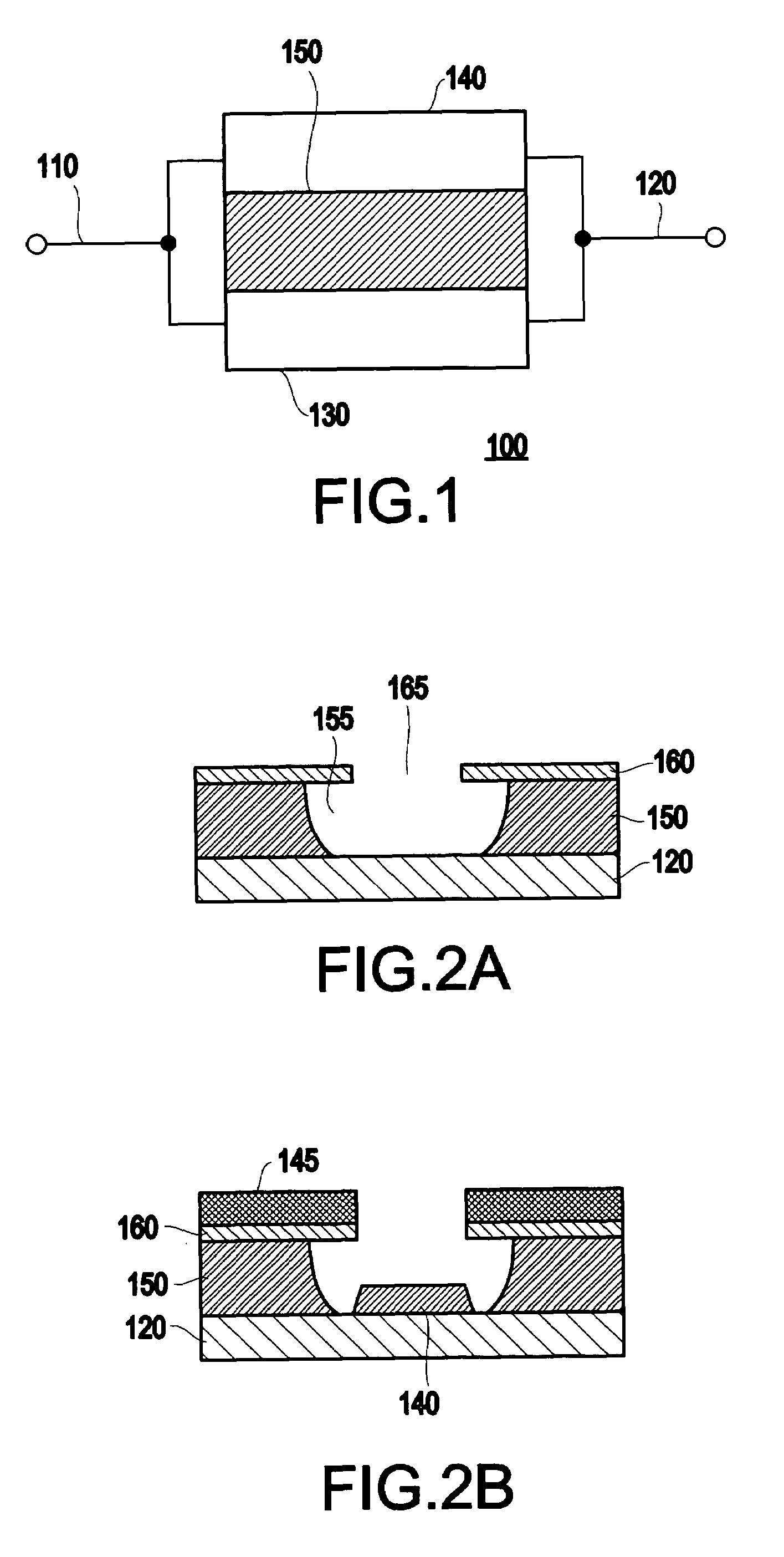

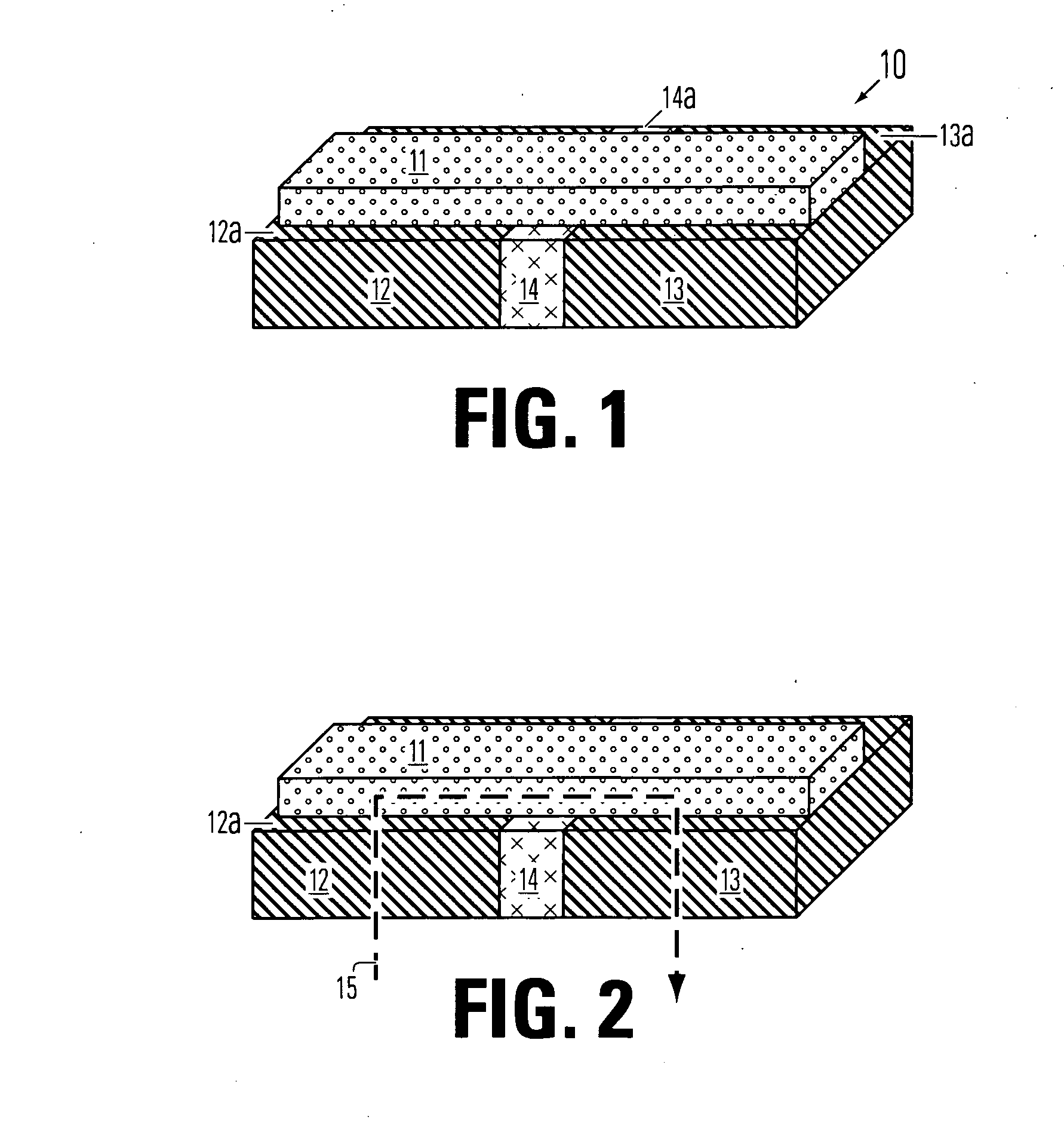

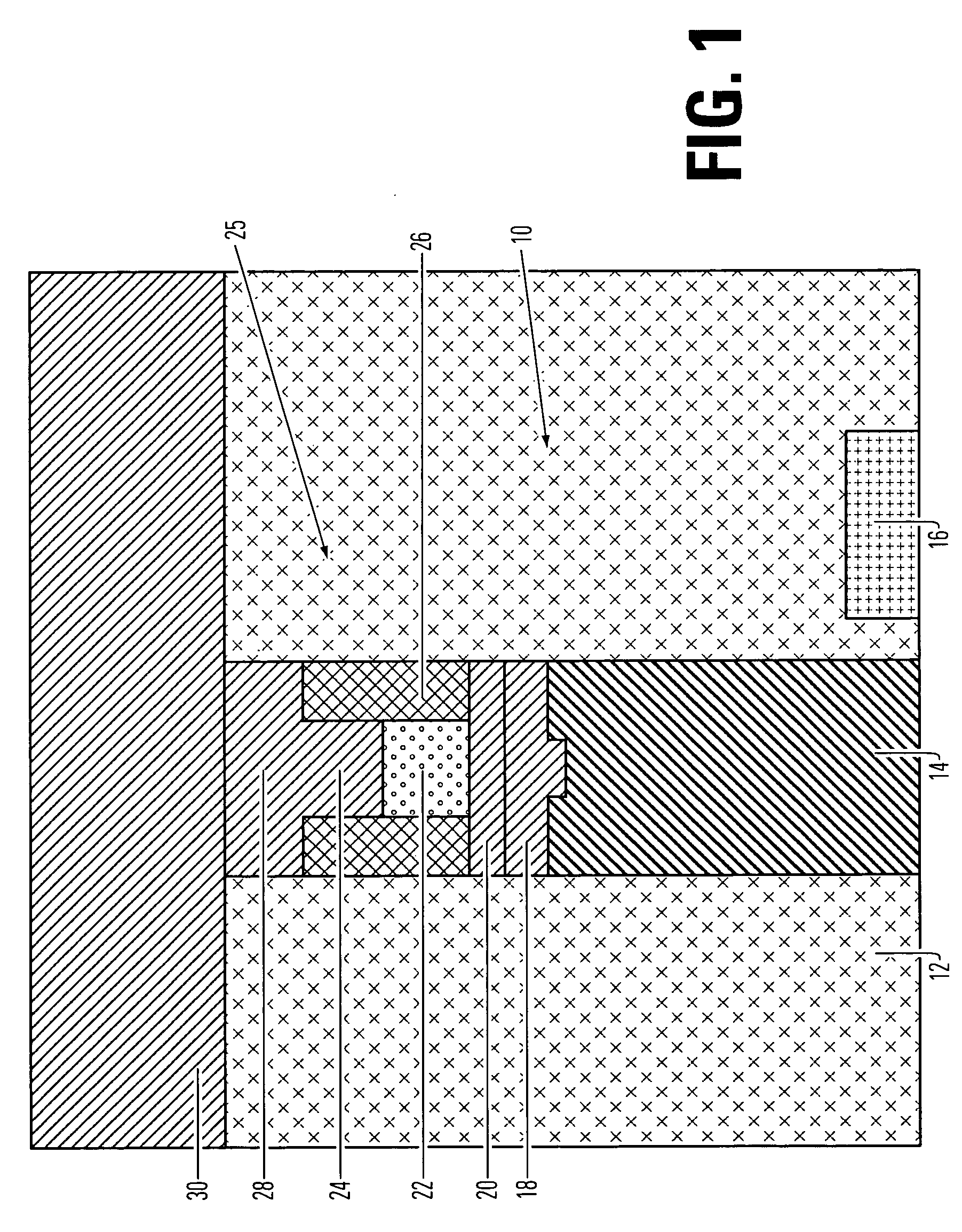

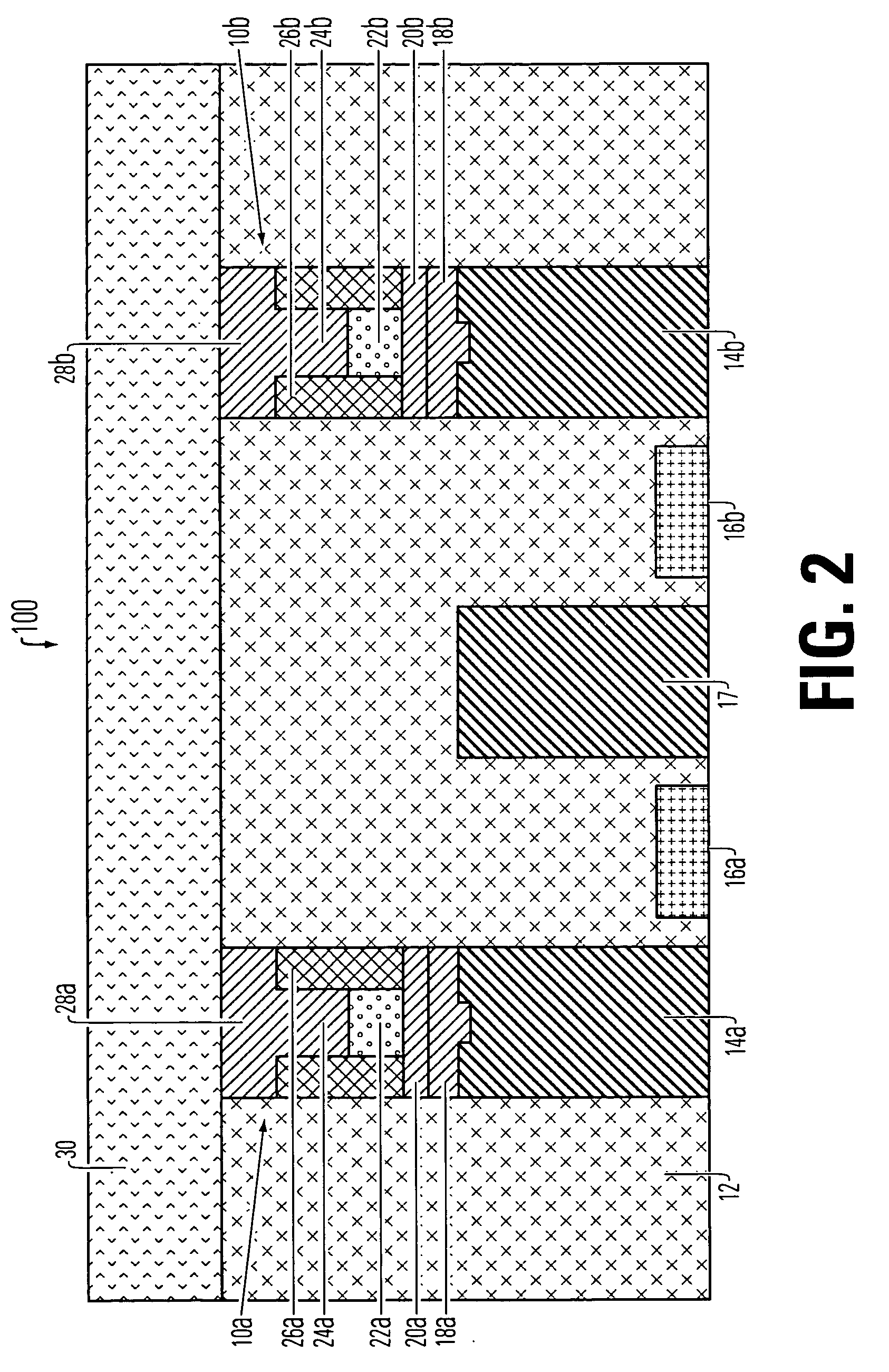

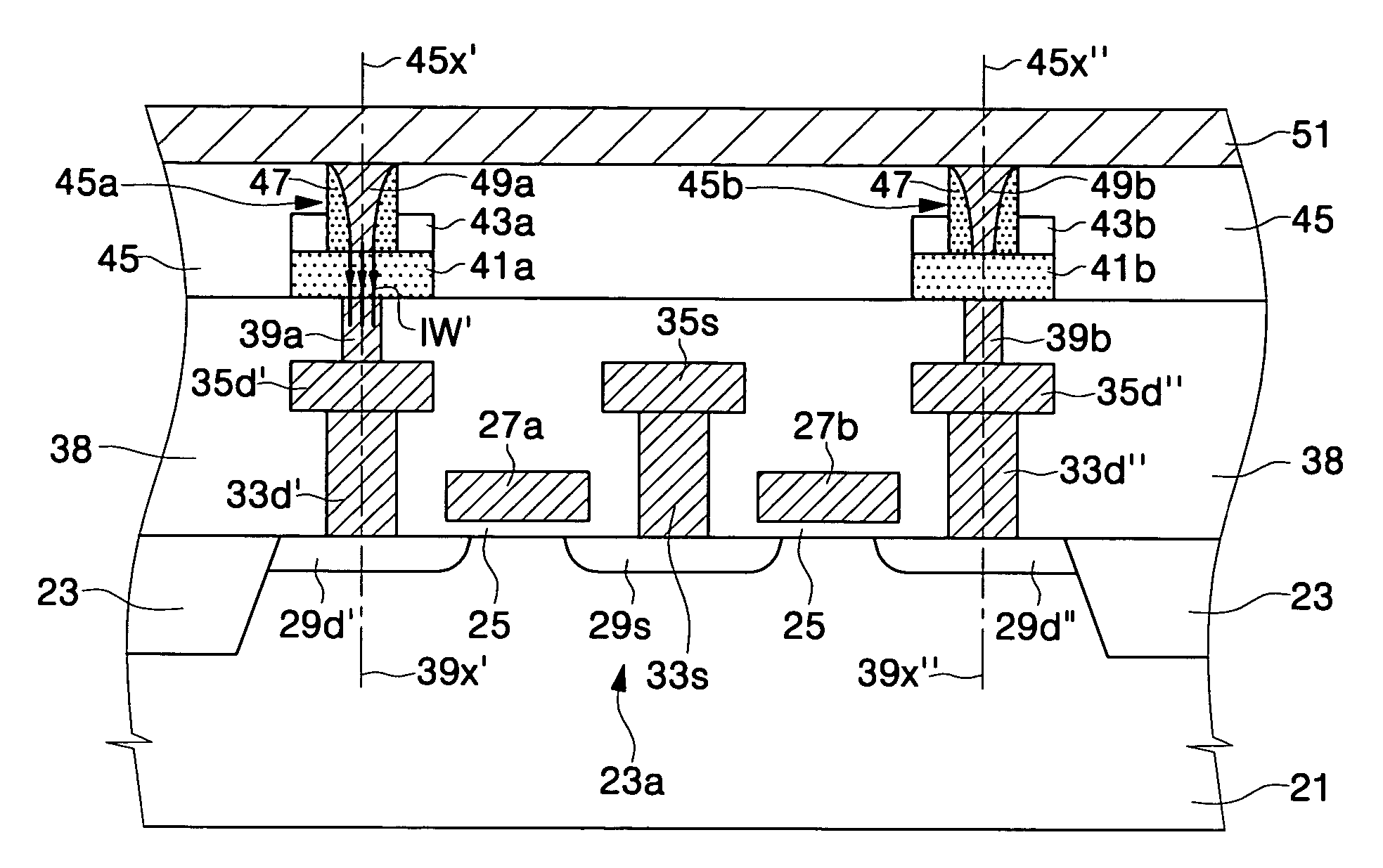

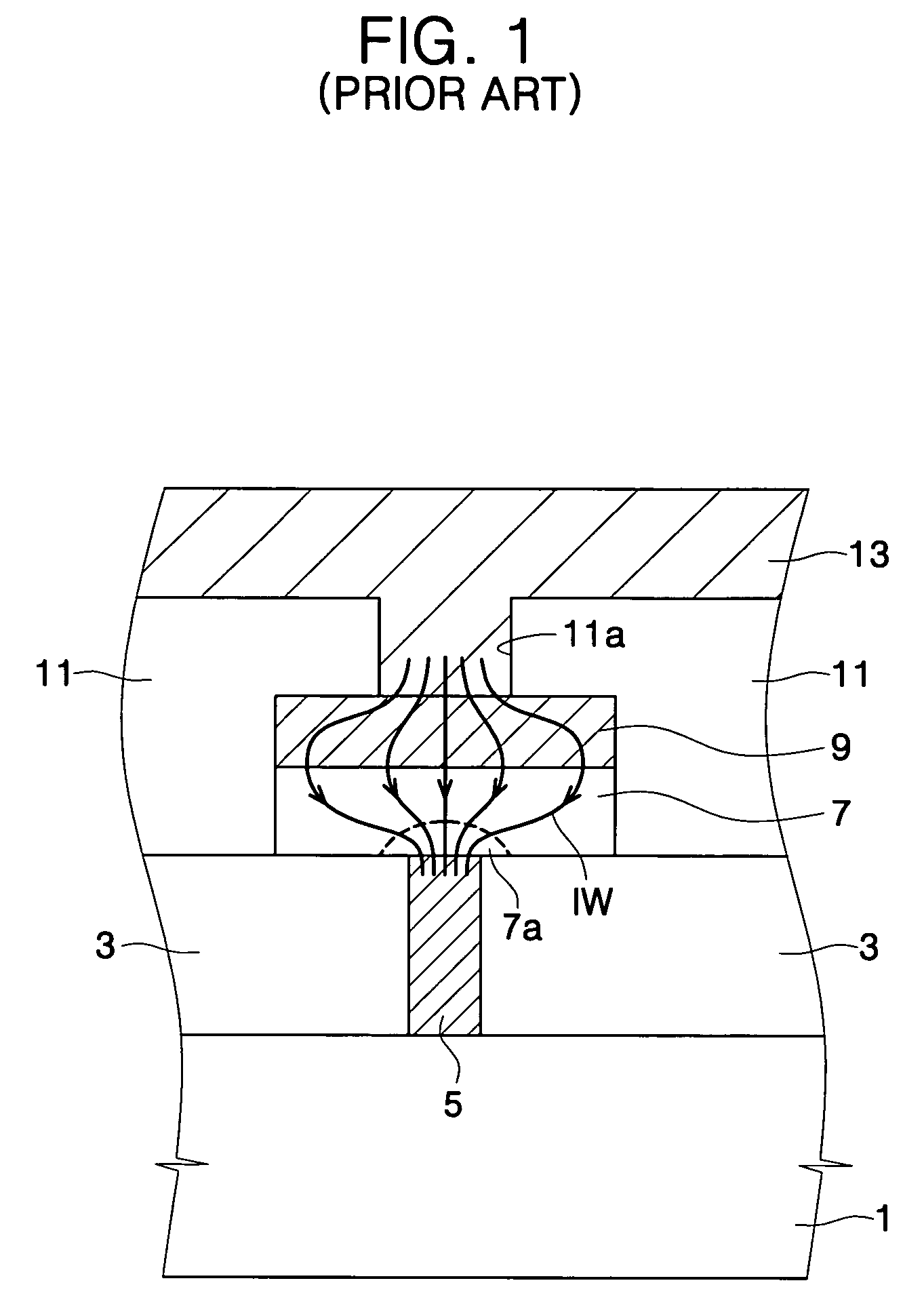

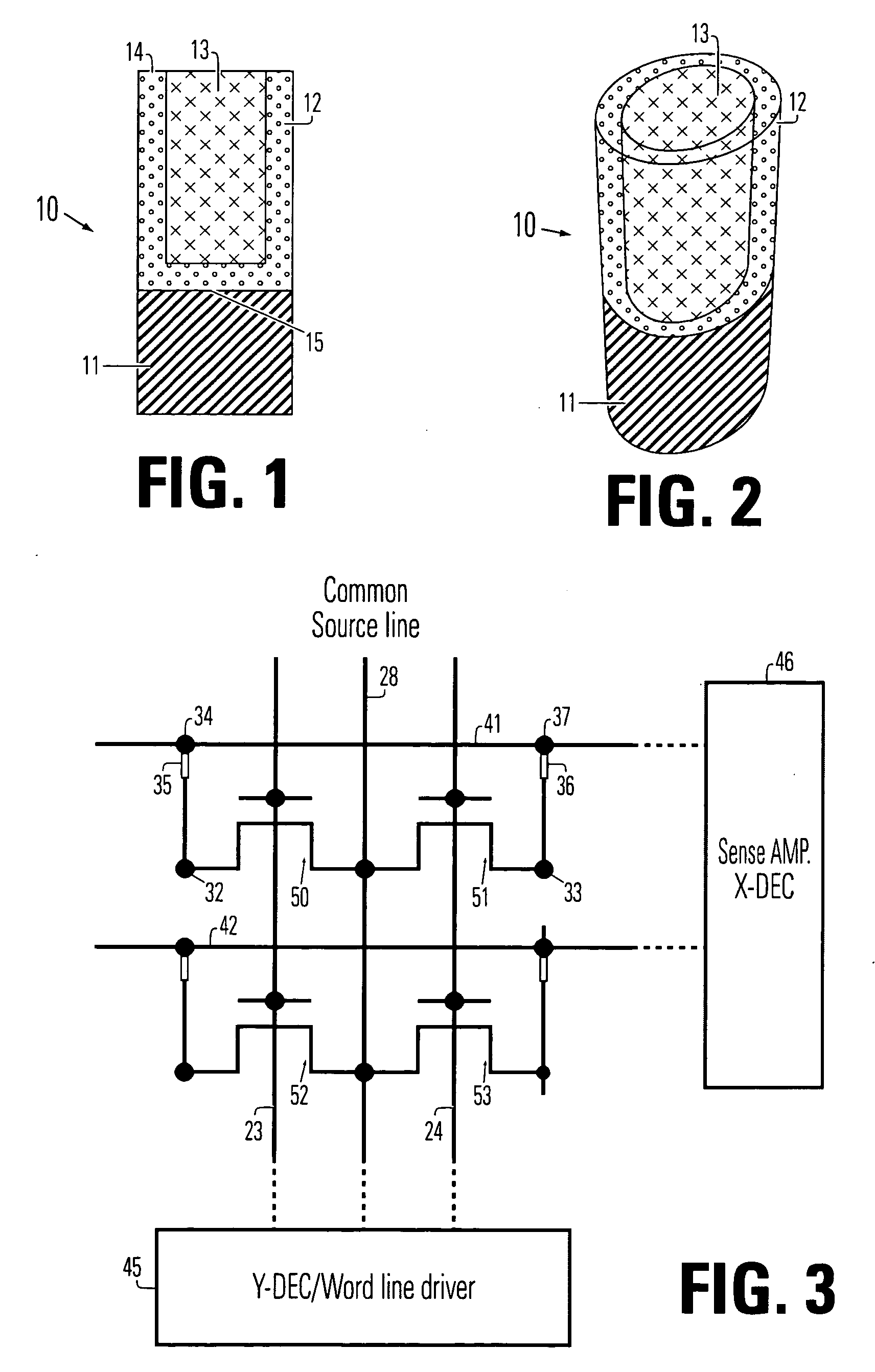

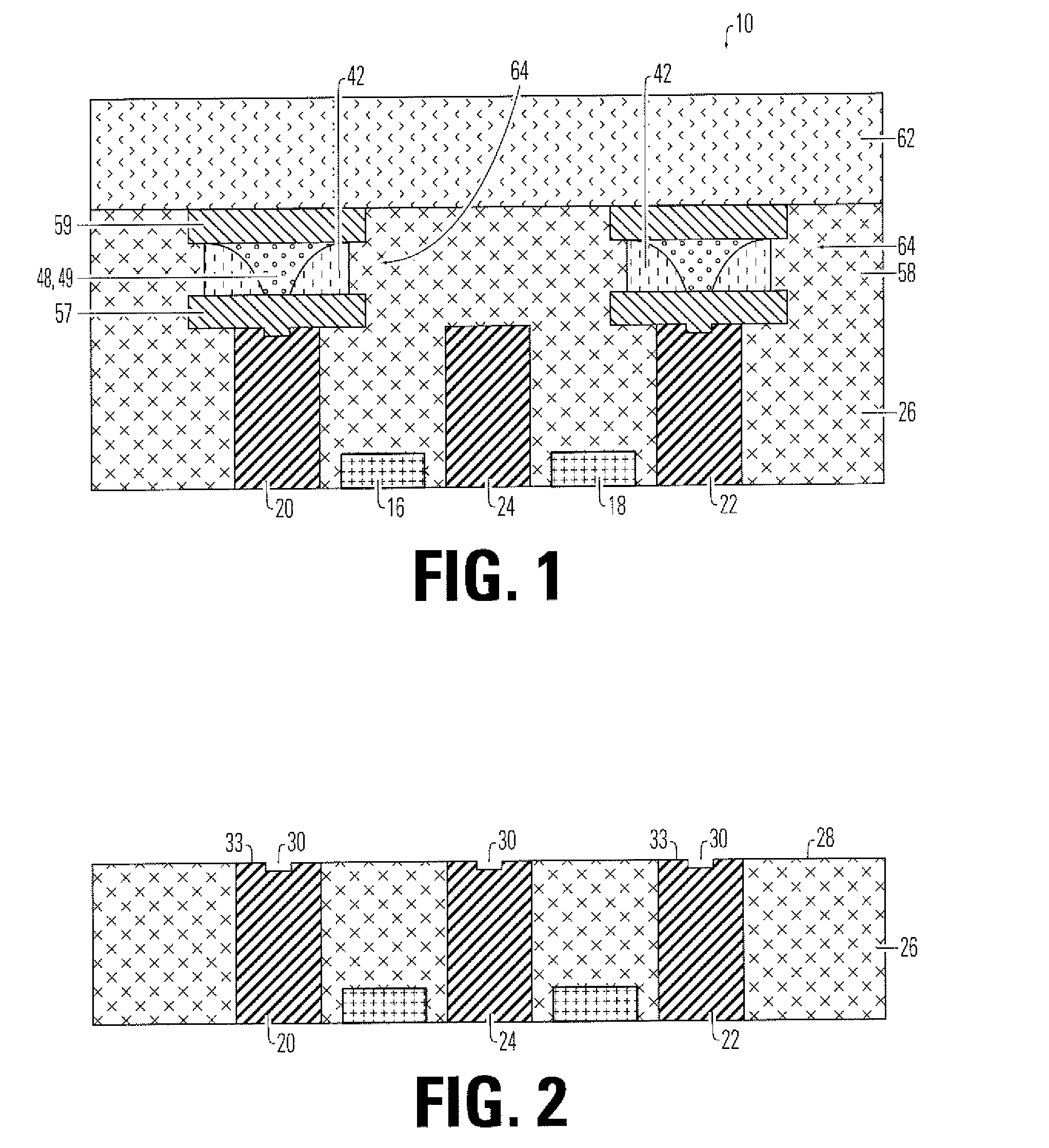

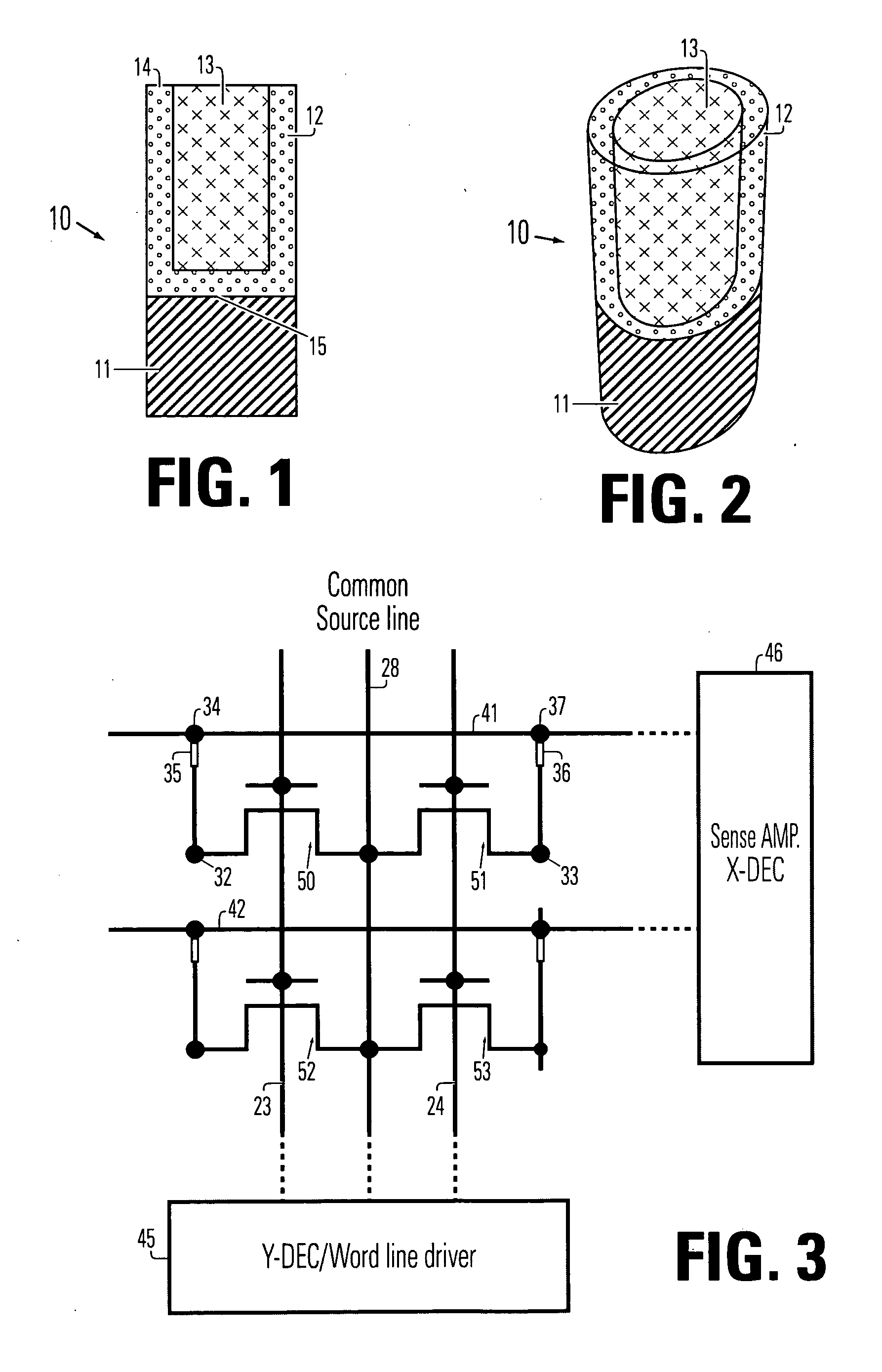

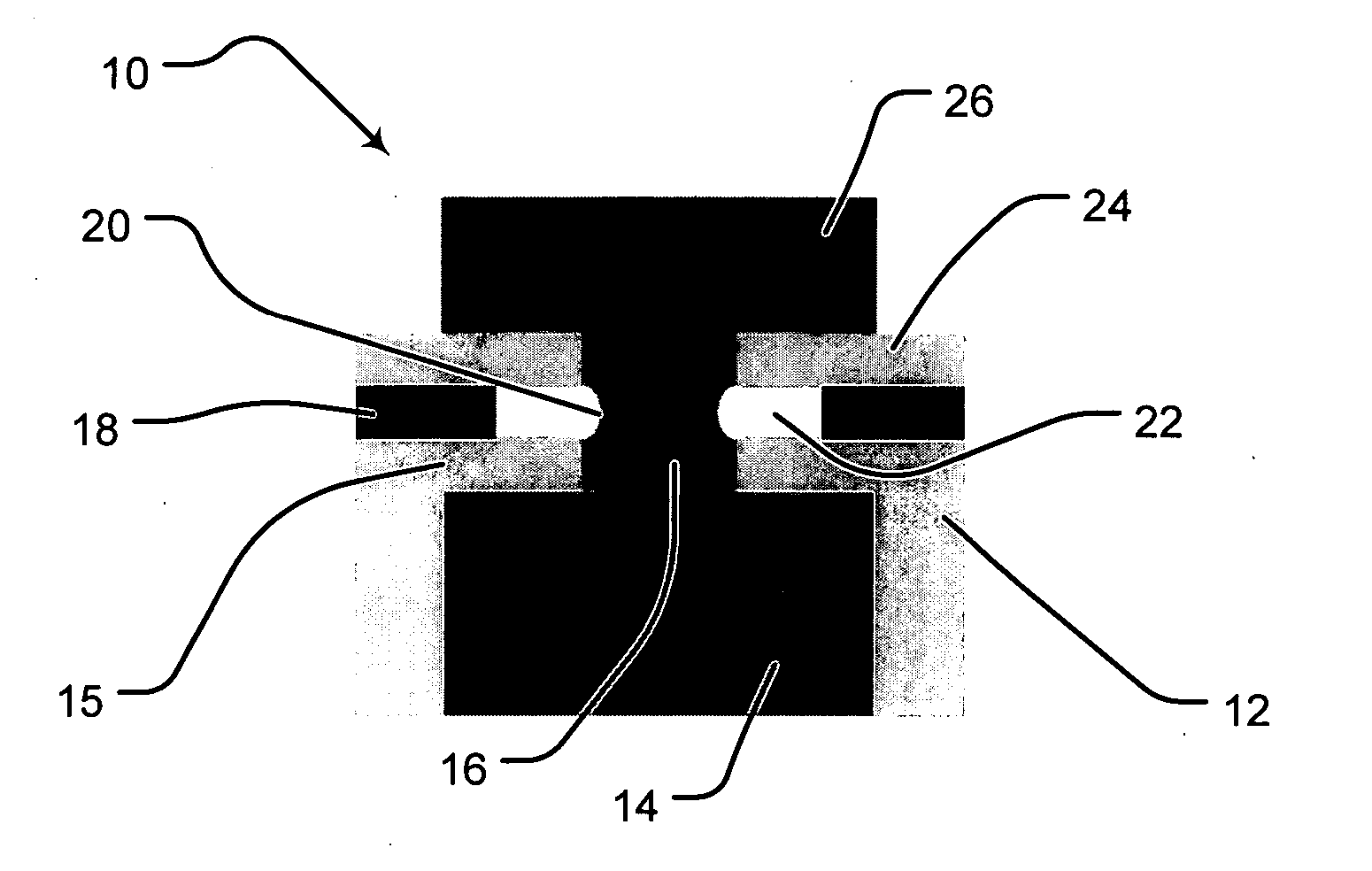

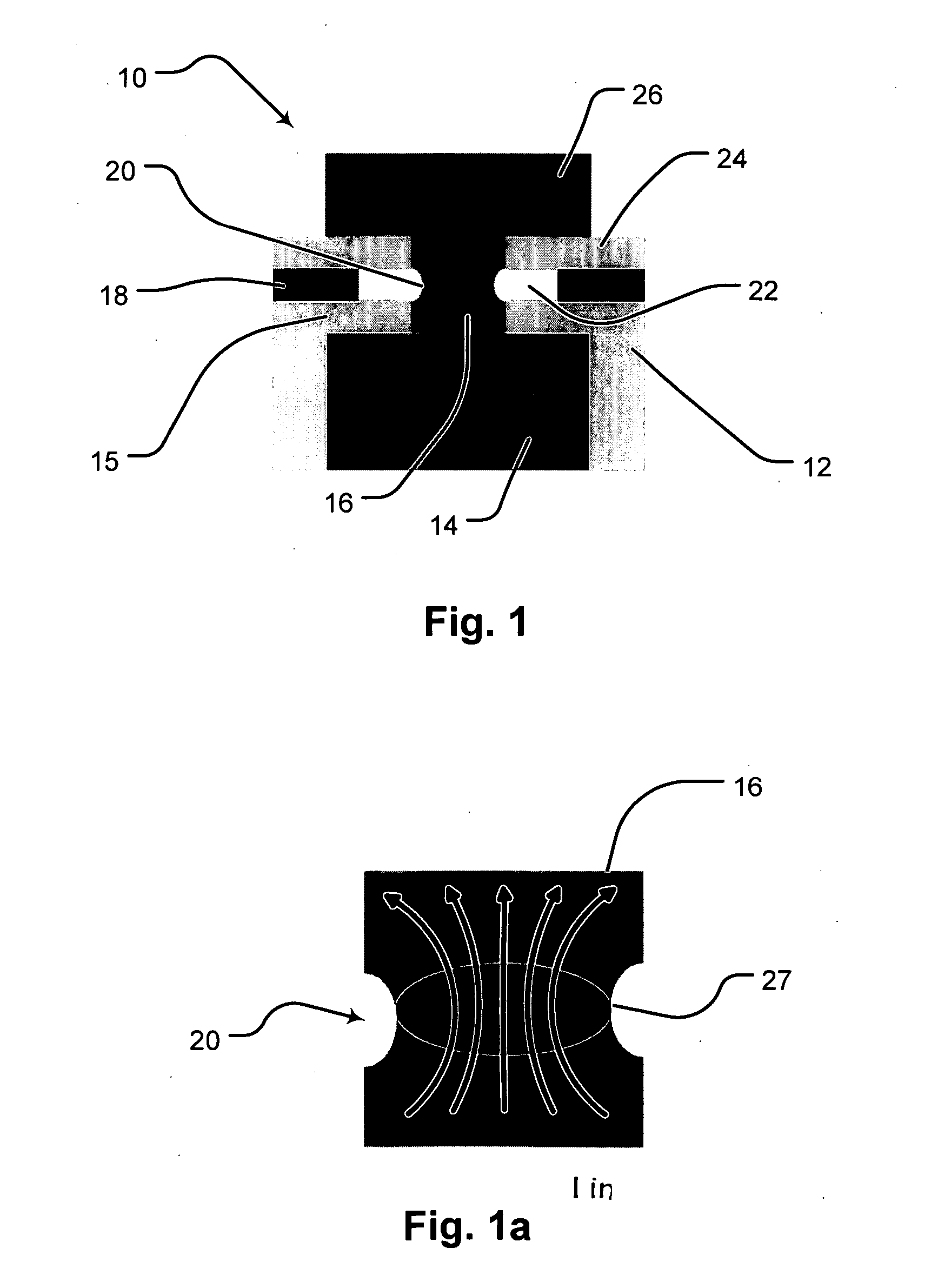

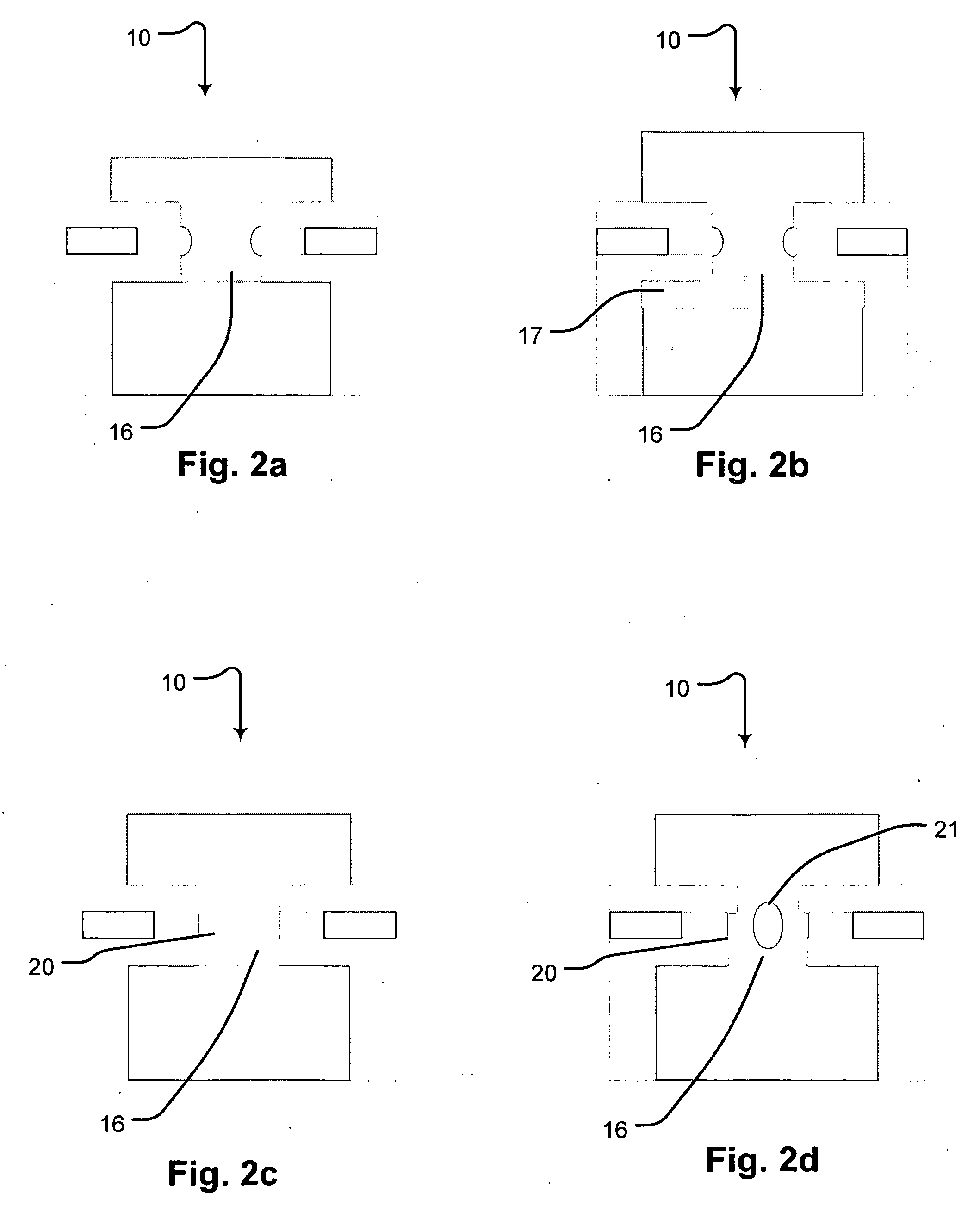

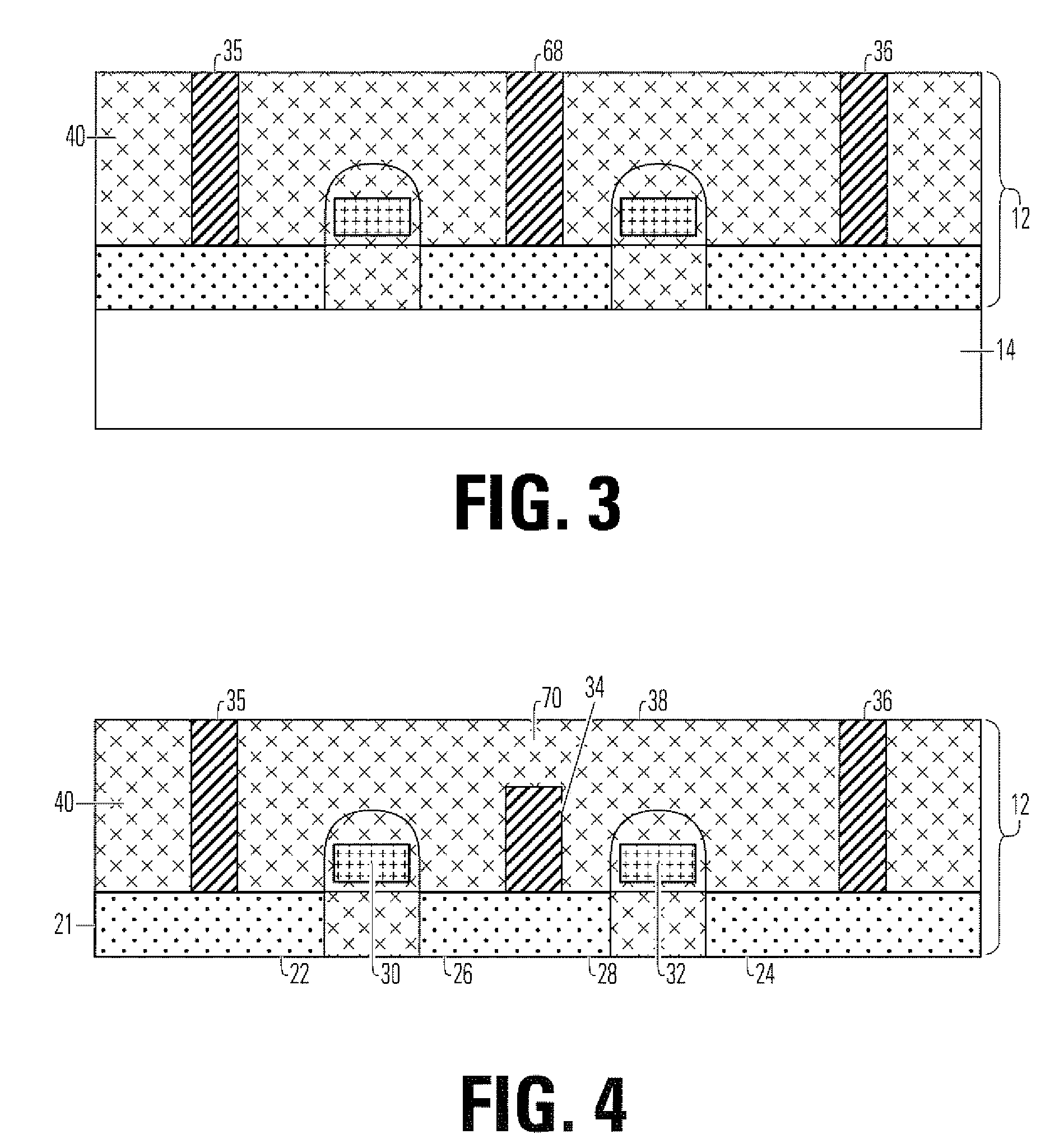

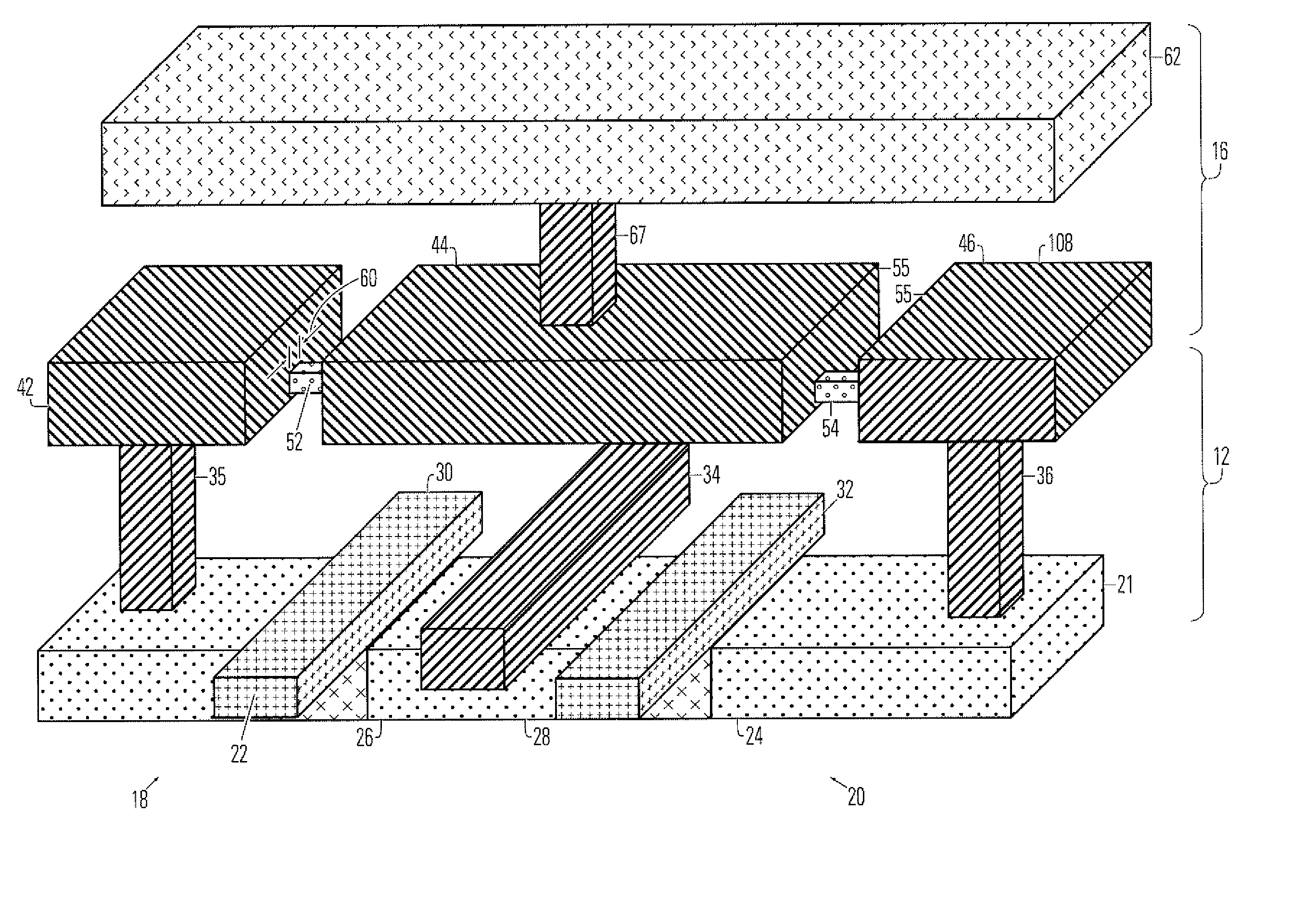

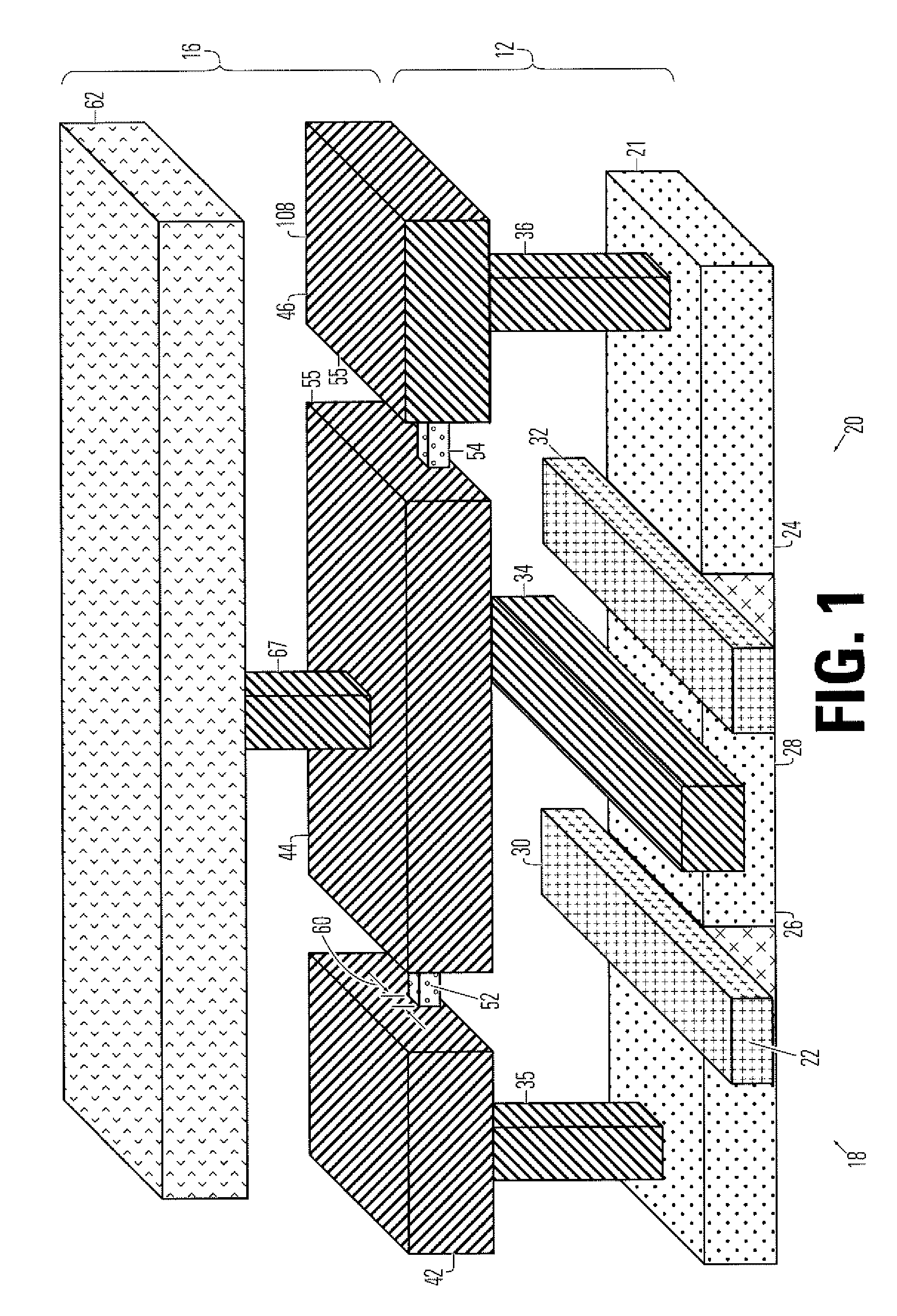

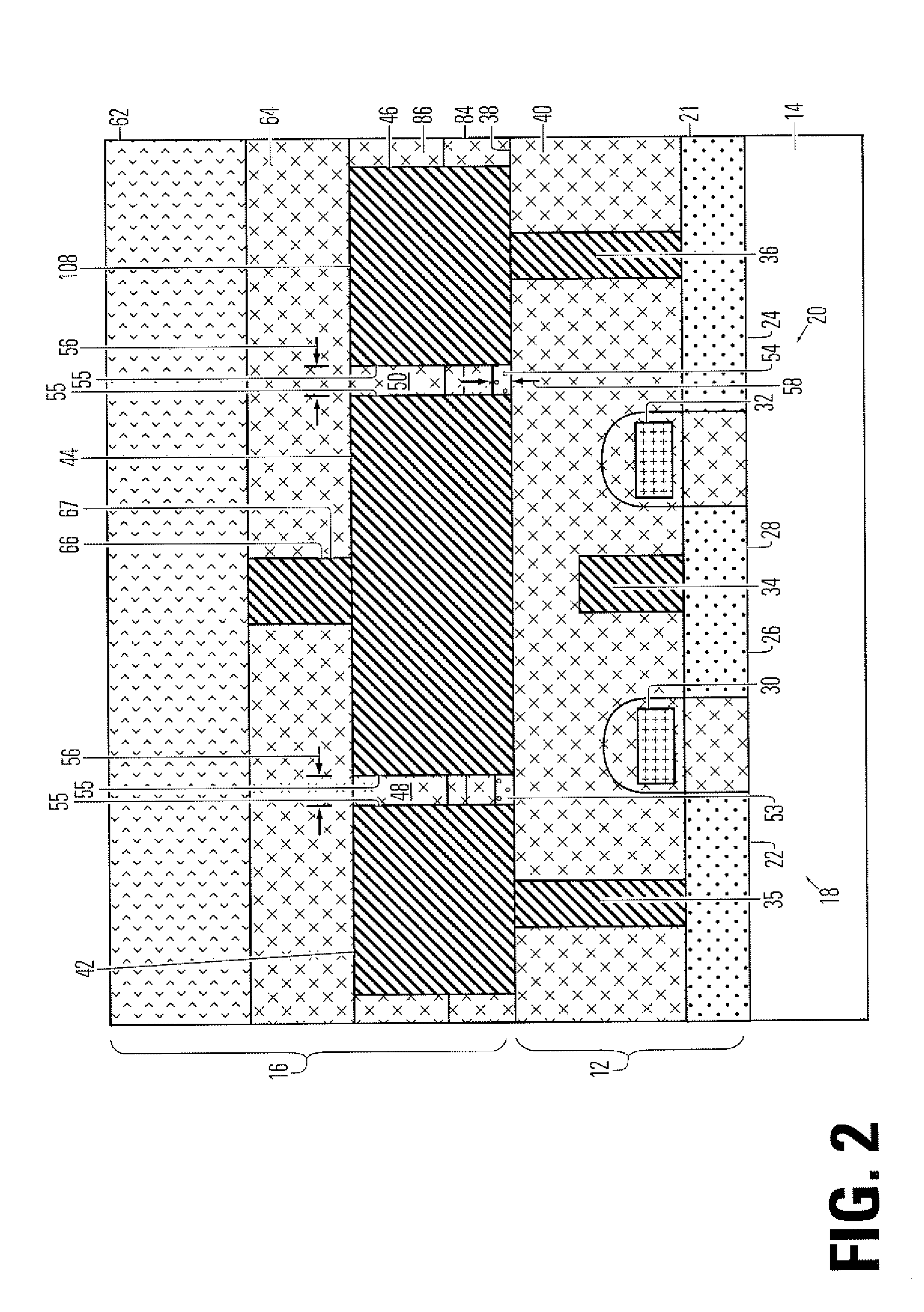

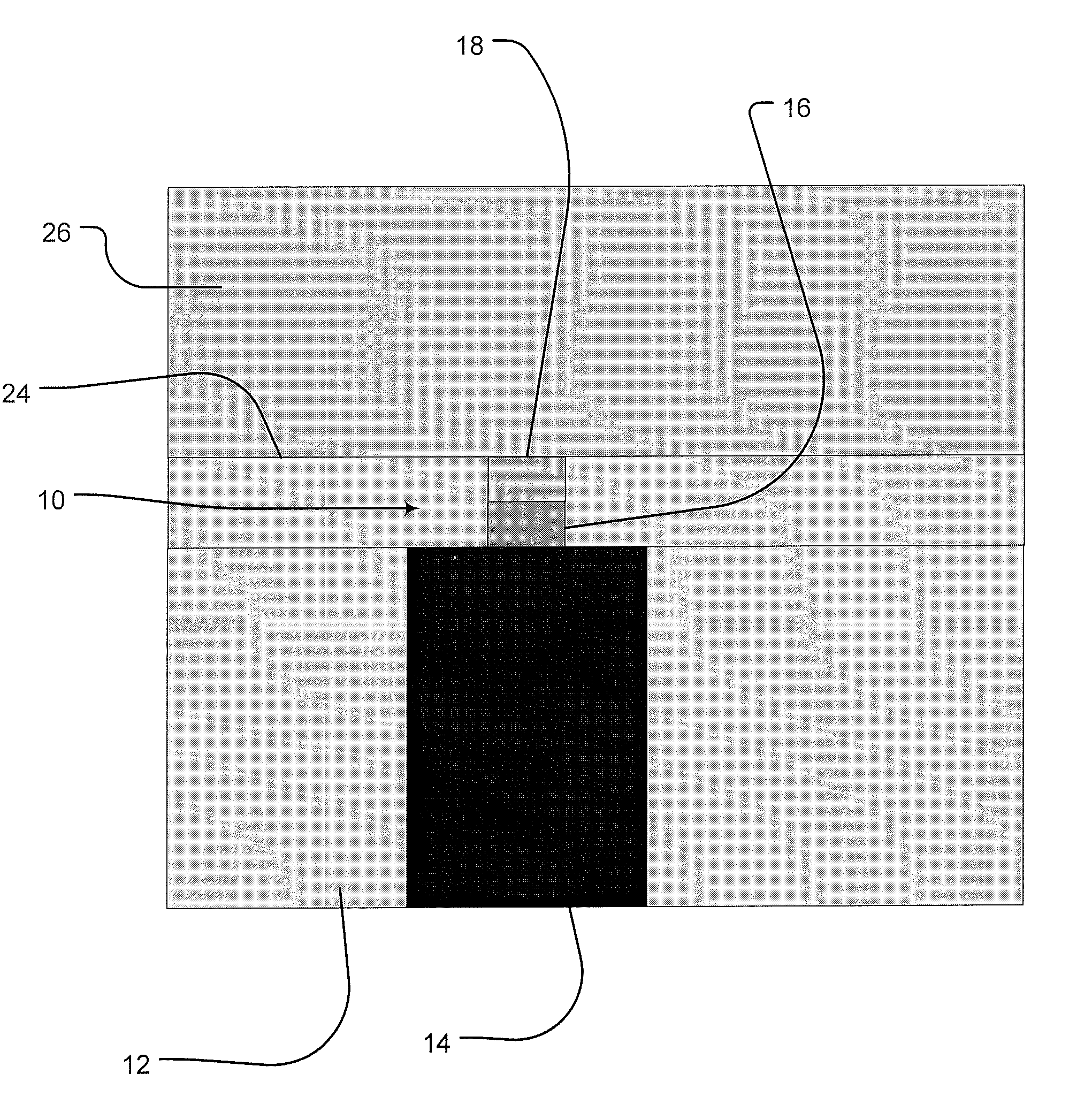

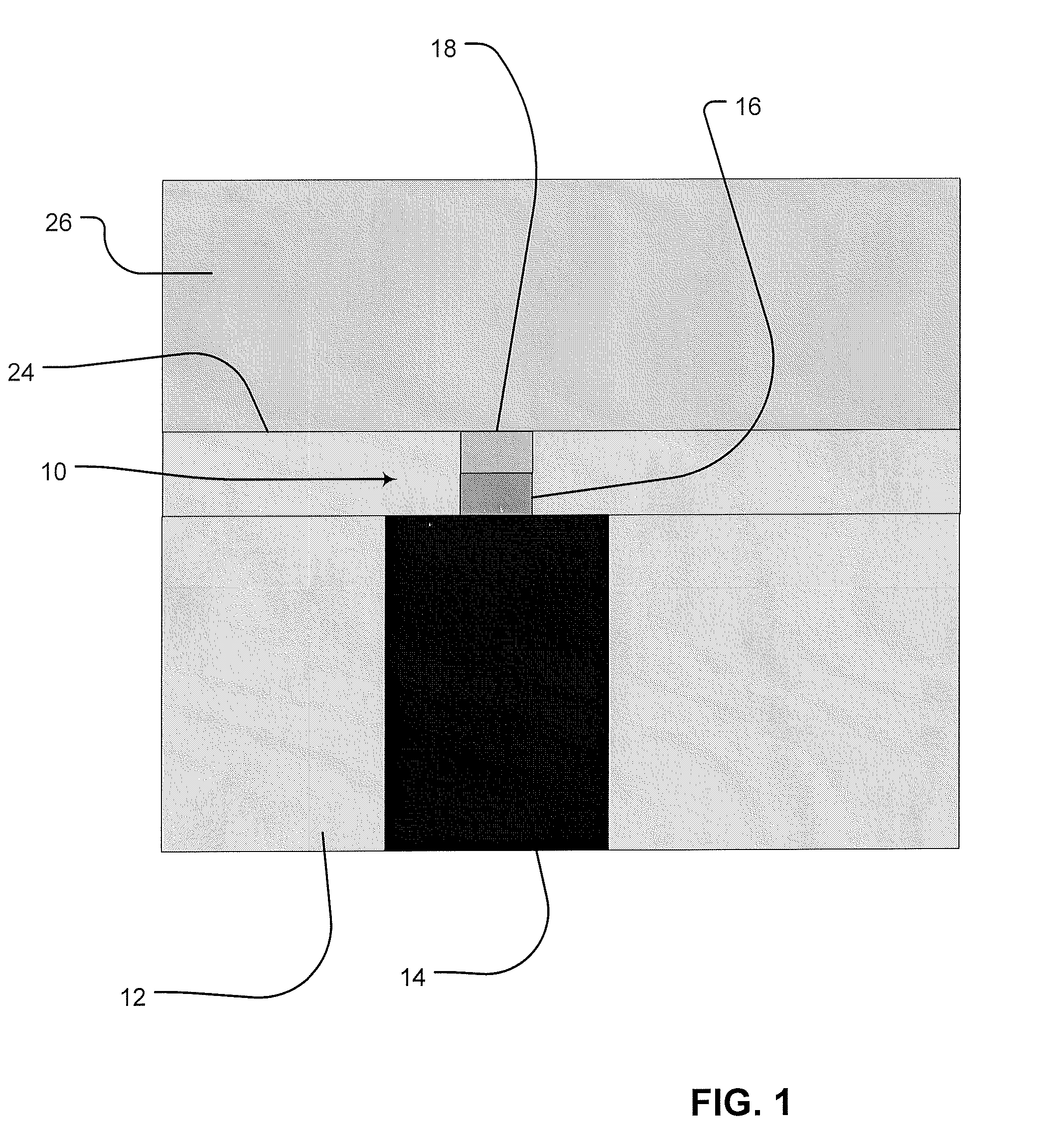

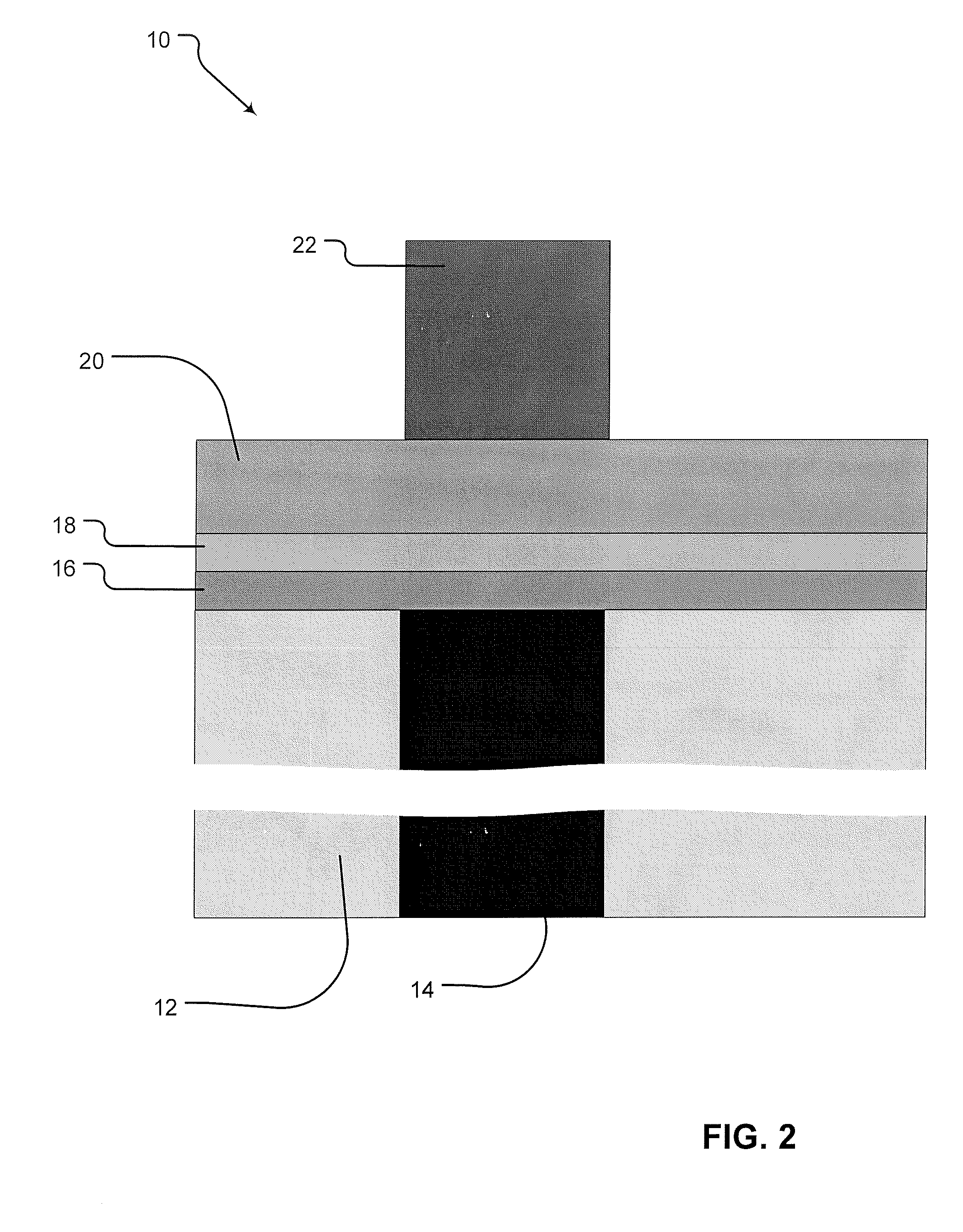

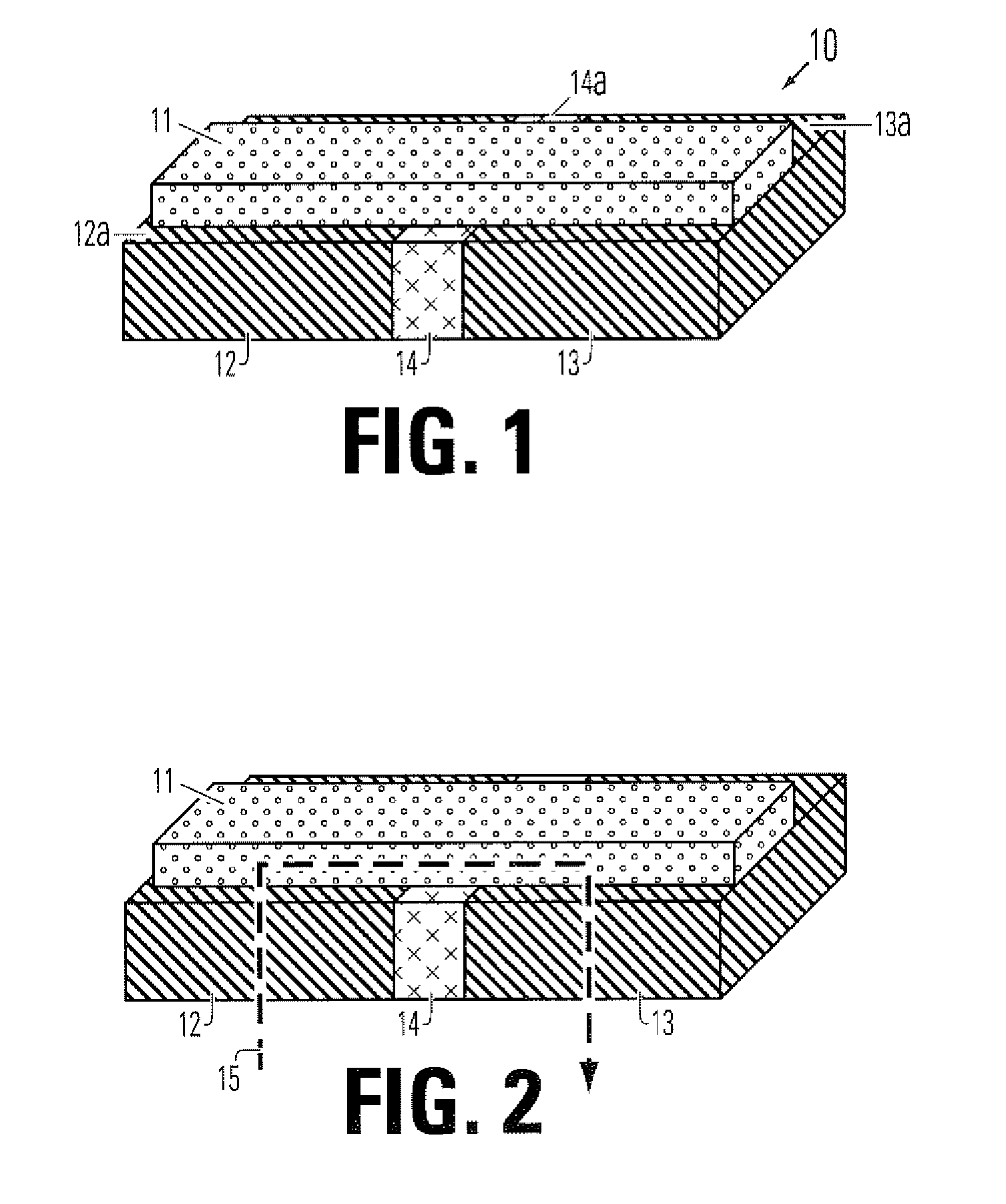

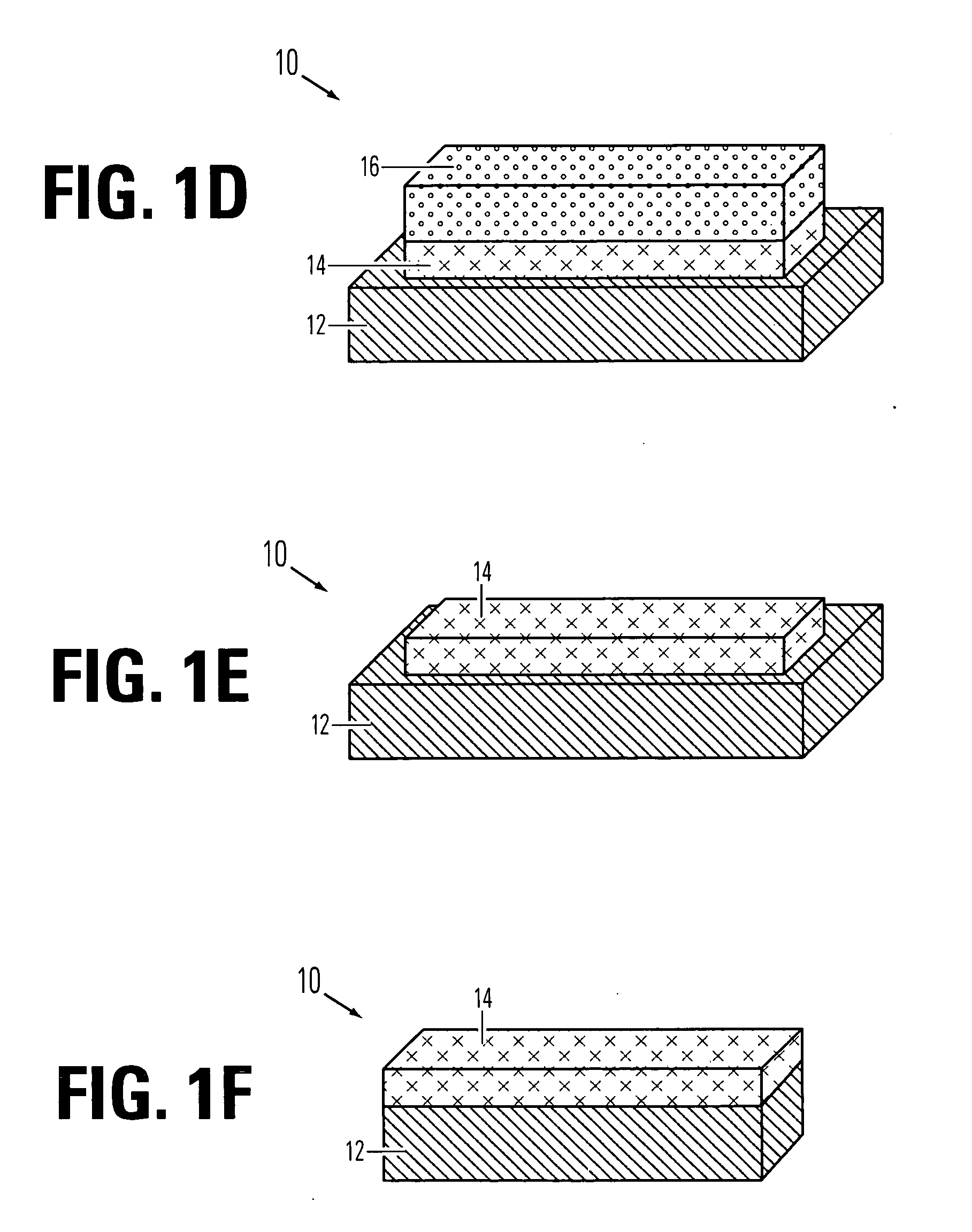

Phase-change memory devices with a self-heater structure

ActiveUS6894305B2Semiconductor/solid-state device detailsSolid-state devicesPhase-change memorySemiconductor

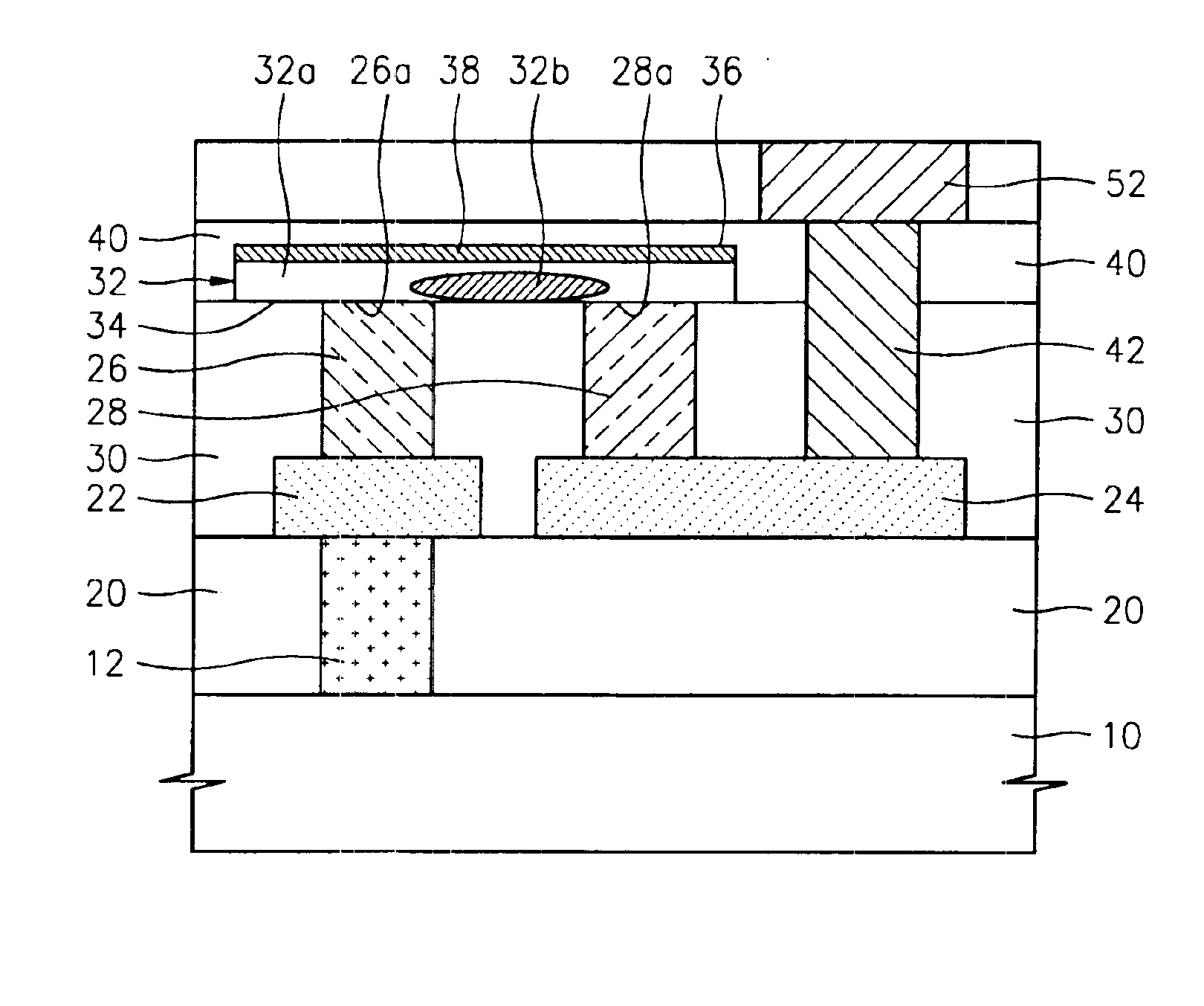

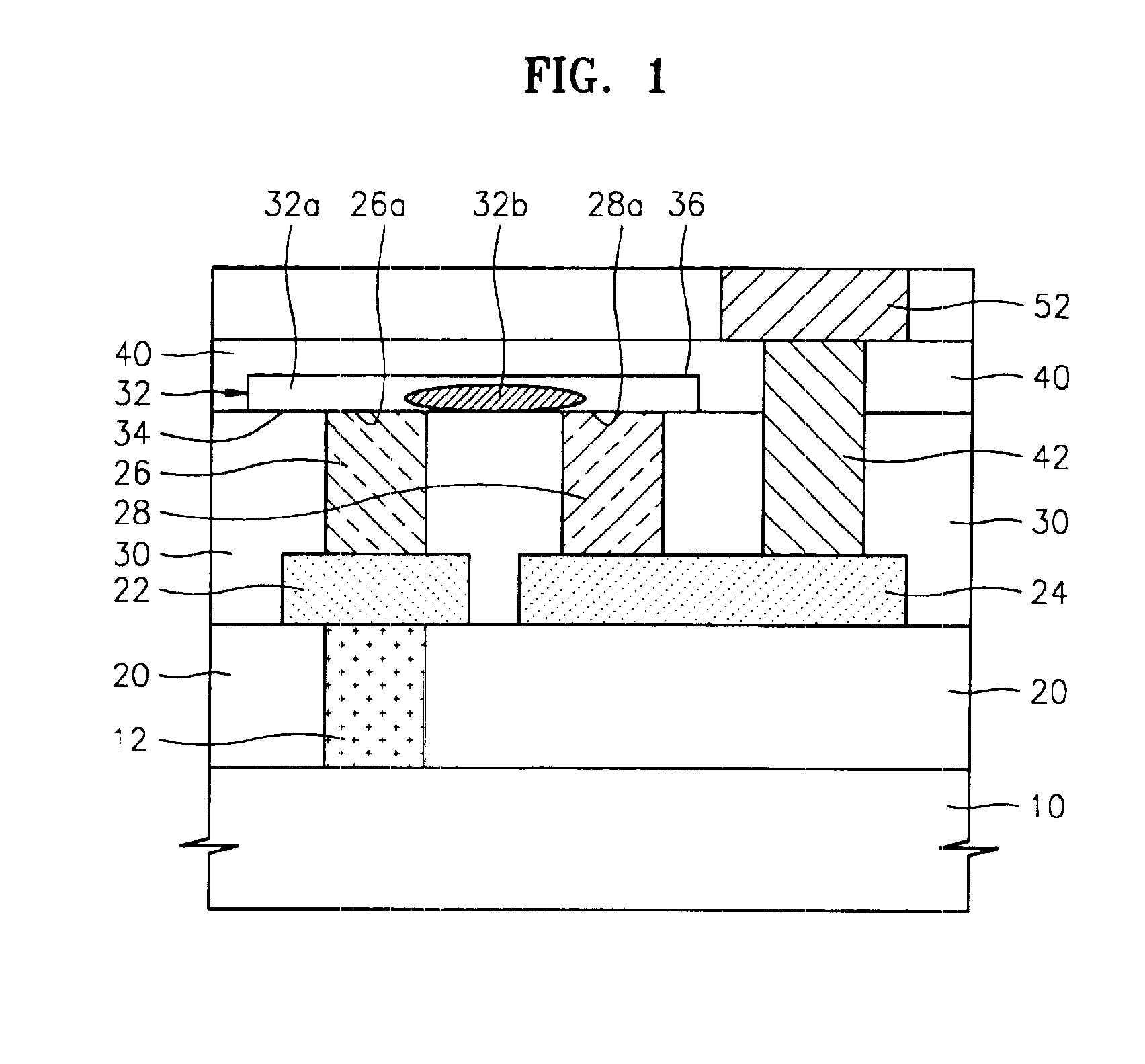

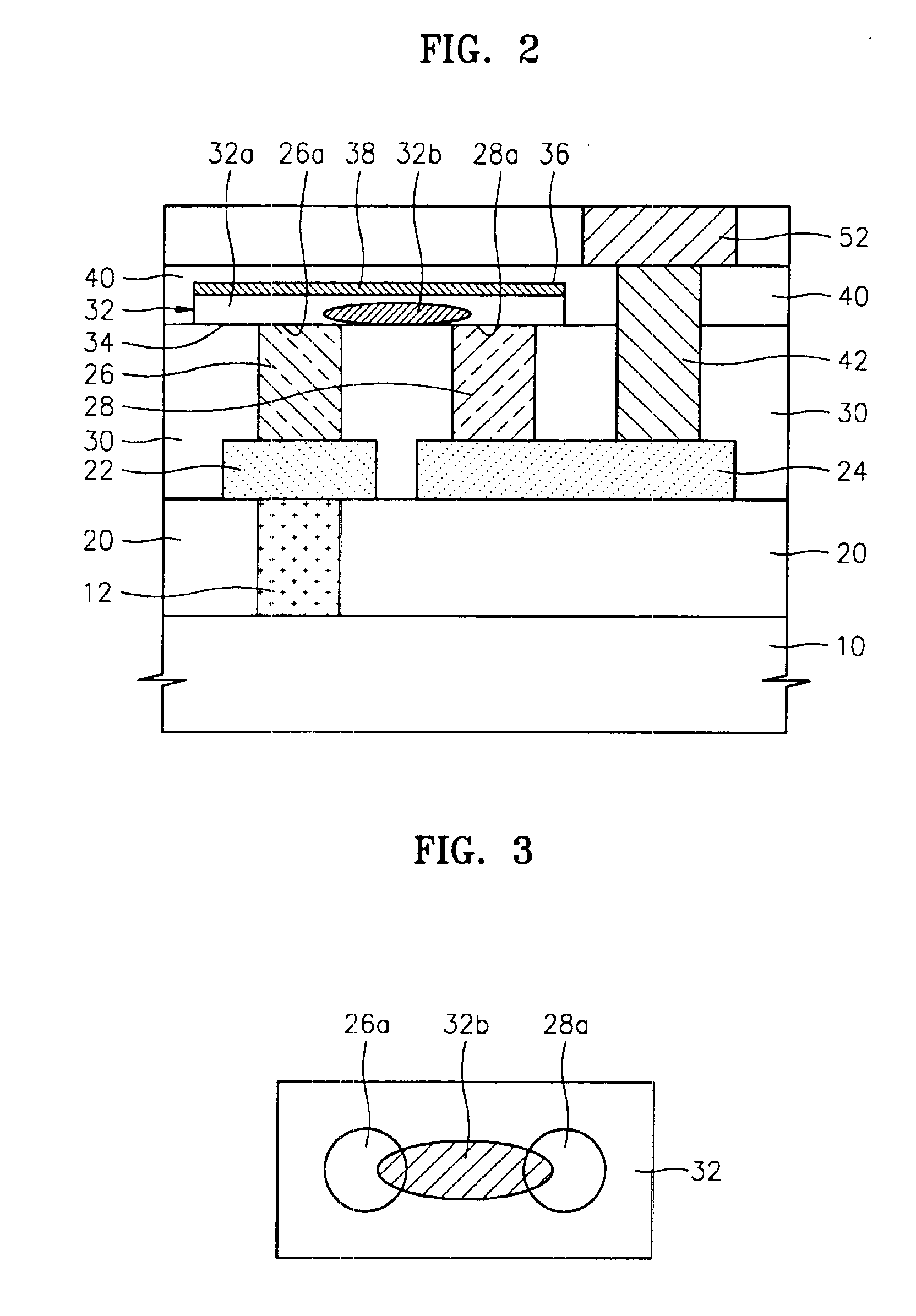

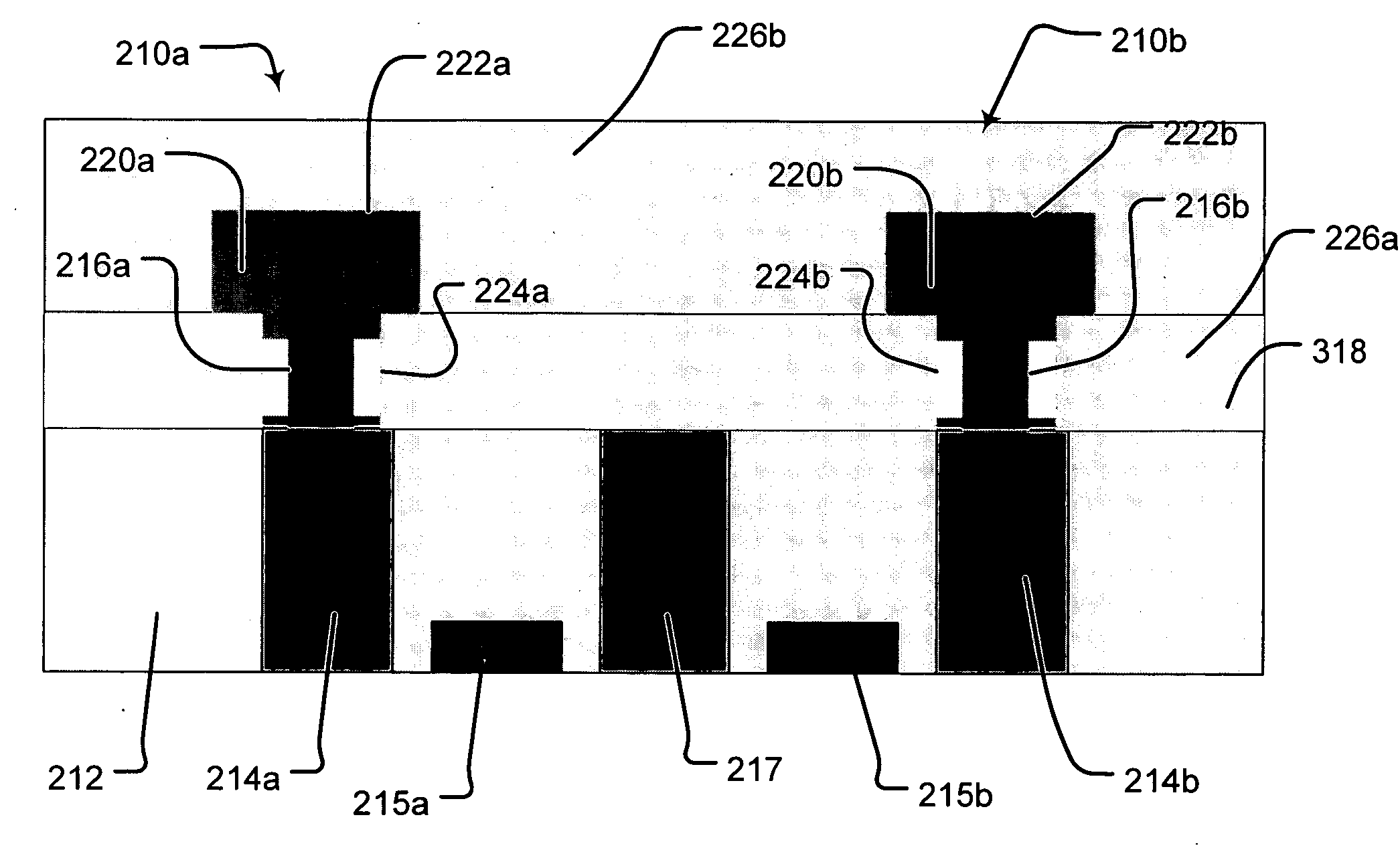

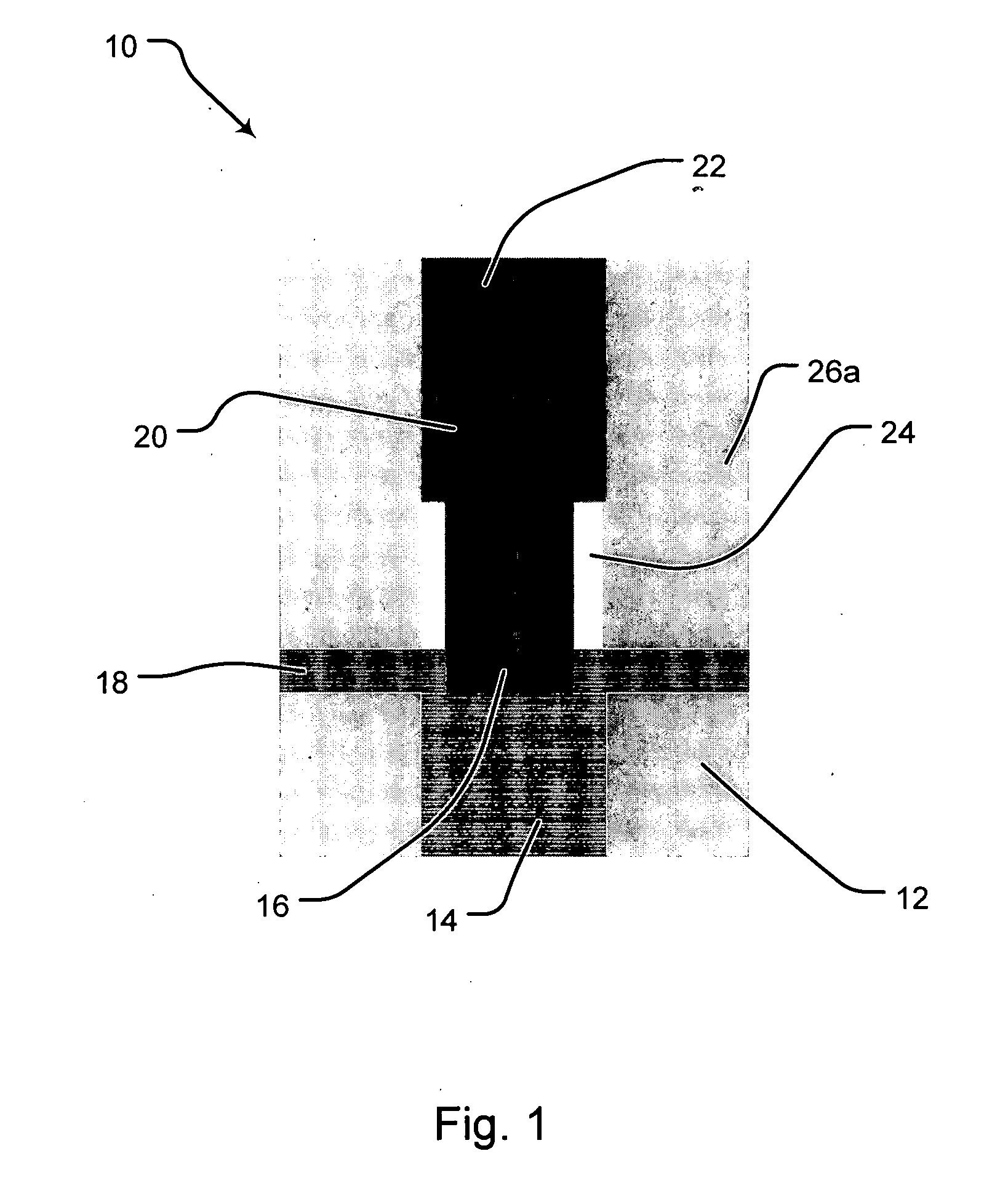

Phase change memory devices include a phase-change memory layer on a semiconductor substrate. The phase-change memory layer has a major axis that is substantially parallel to a major axis of the semiconductor substrate and has a first surface and a second surface opposite the first surface that are substantially parallel to the major axis of the phase-change memory layer. A first electrode is provided on the semiconductor substrate that is electrically connected to the first surface of the phase-change memory layer in a first contact region of the phase-change memory layer. A second electrode is provided on the semiconductor substrate that is electrically connected to the phase-change memory layer in a second contact region of the phase-change memory layer. The second contact region is space apart from the first contact region.

Owner:SAMSUNG ELECTRONICS CO LTD

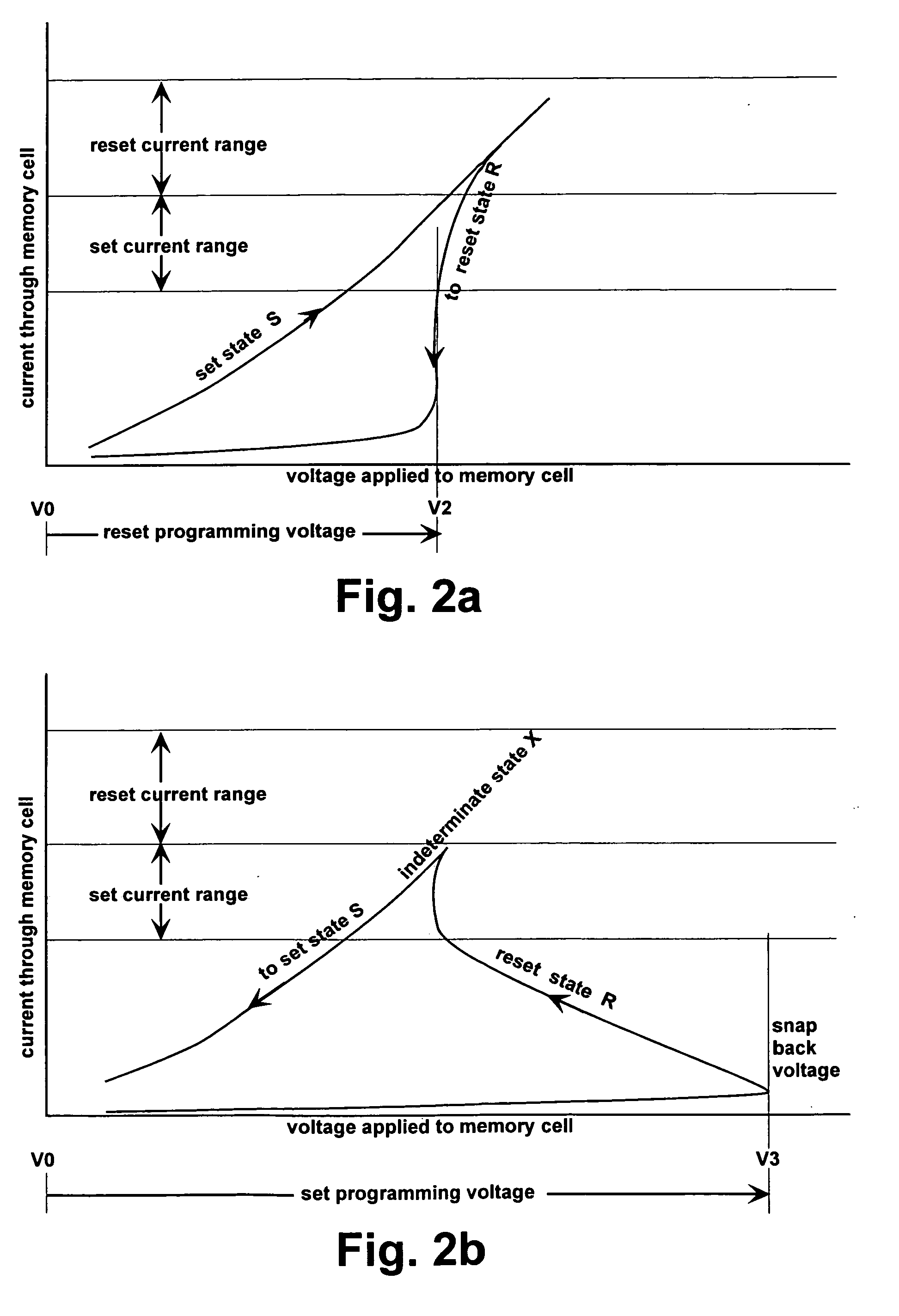

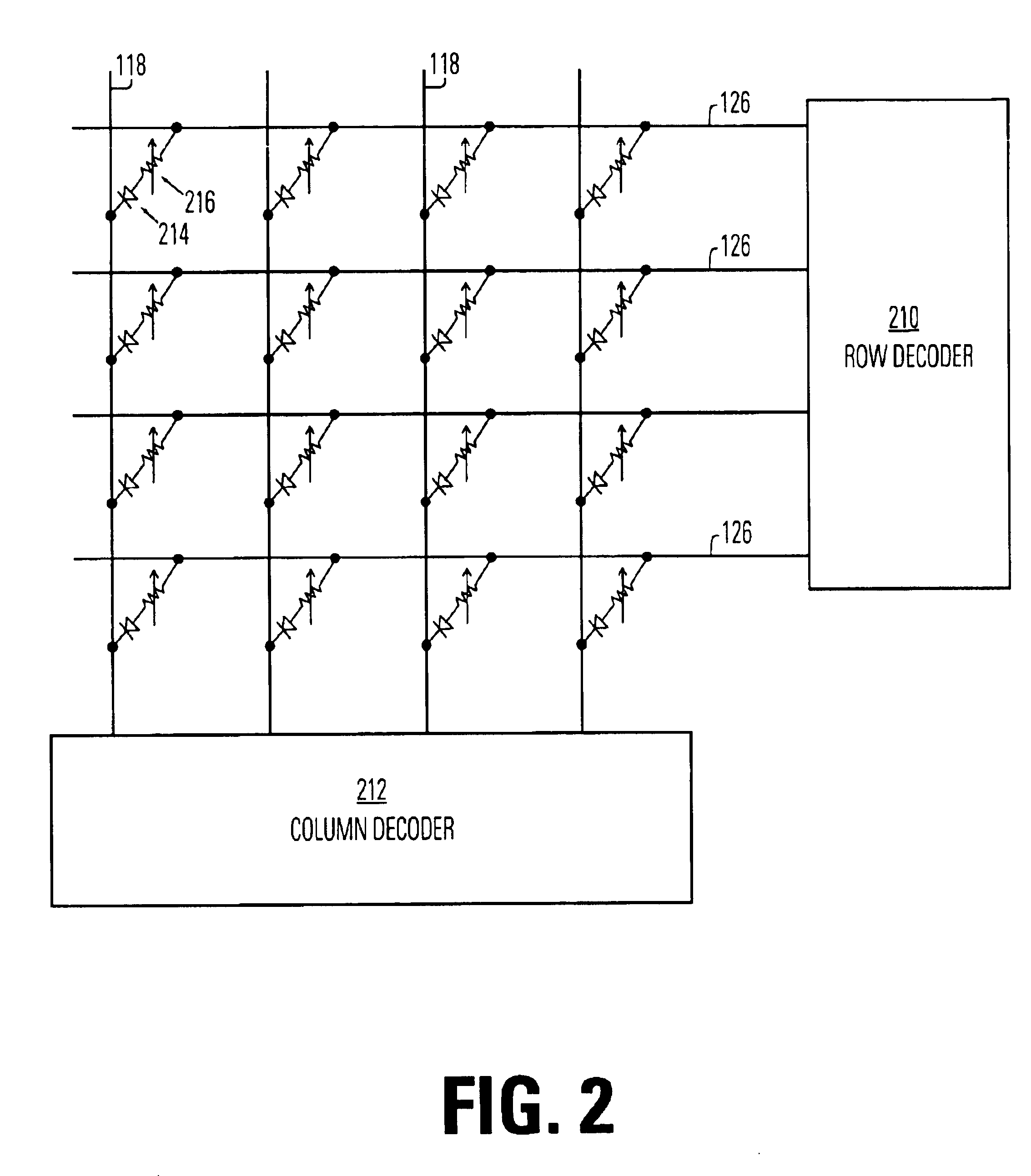

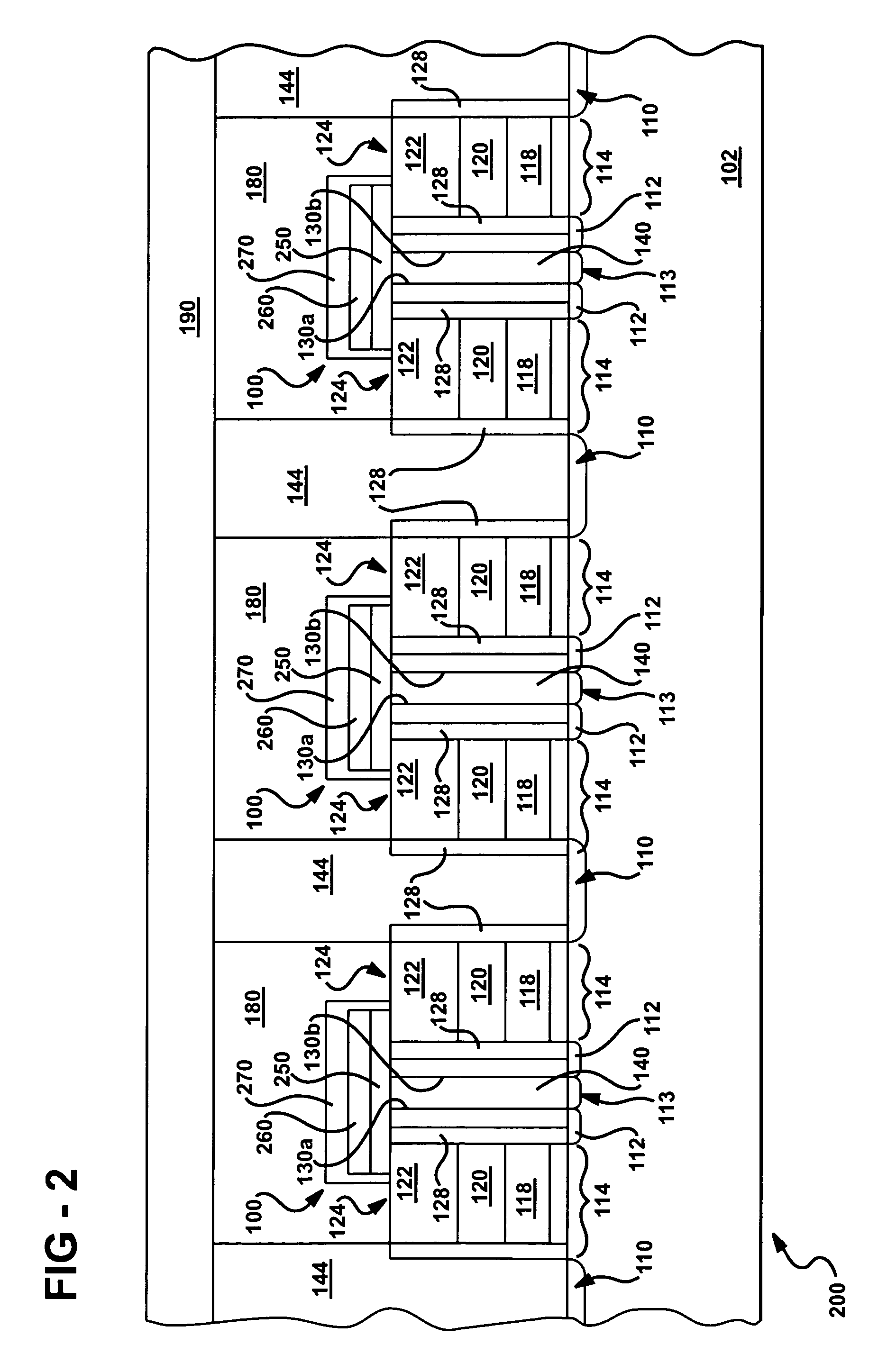

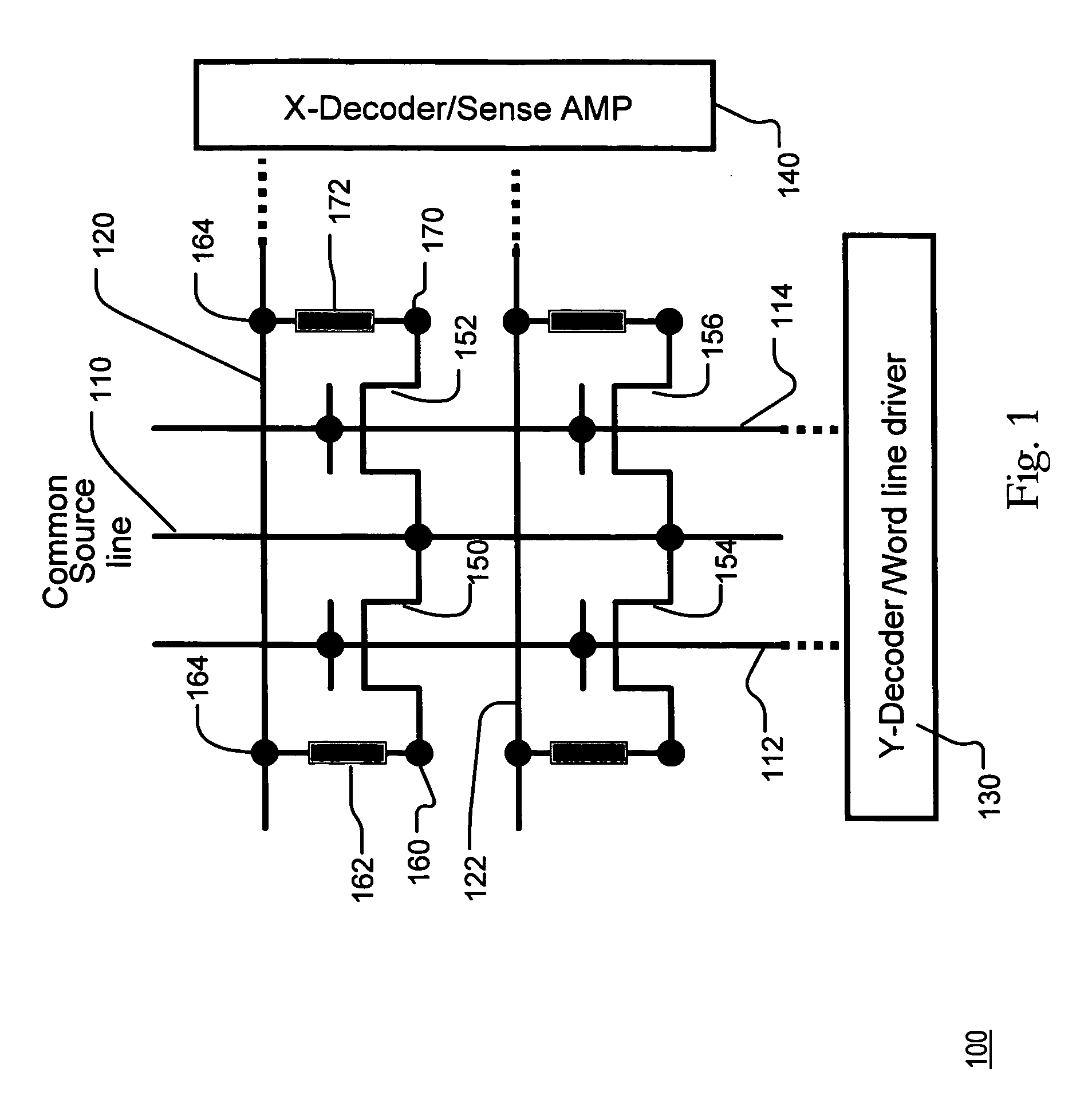

Memory device and method of operating same

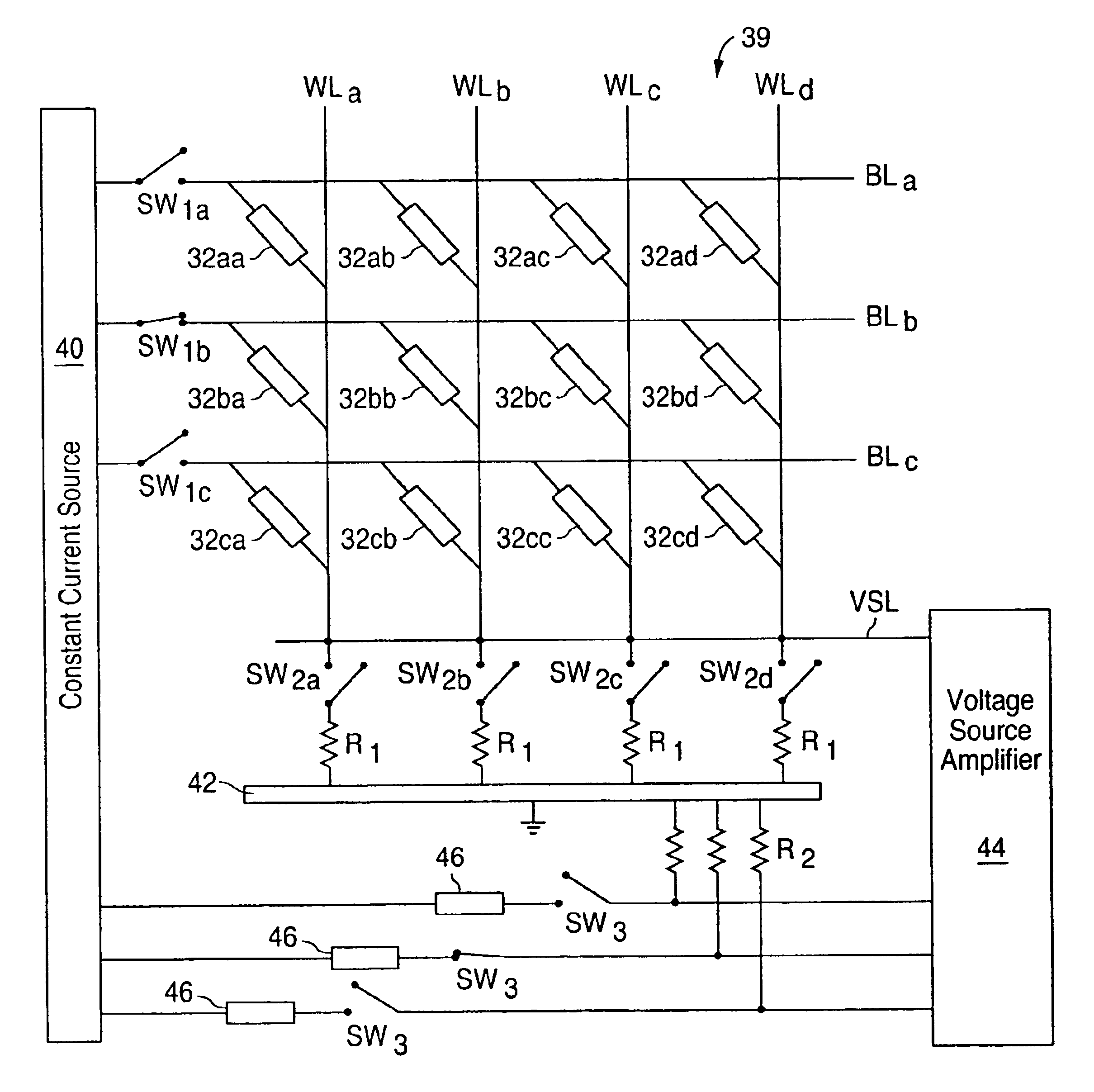

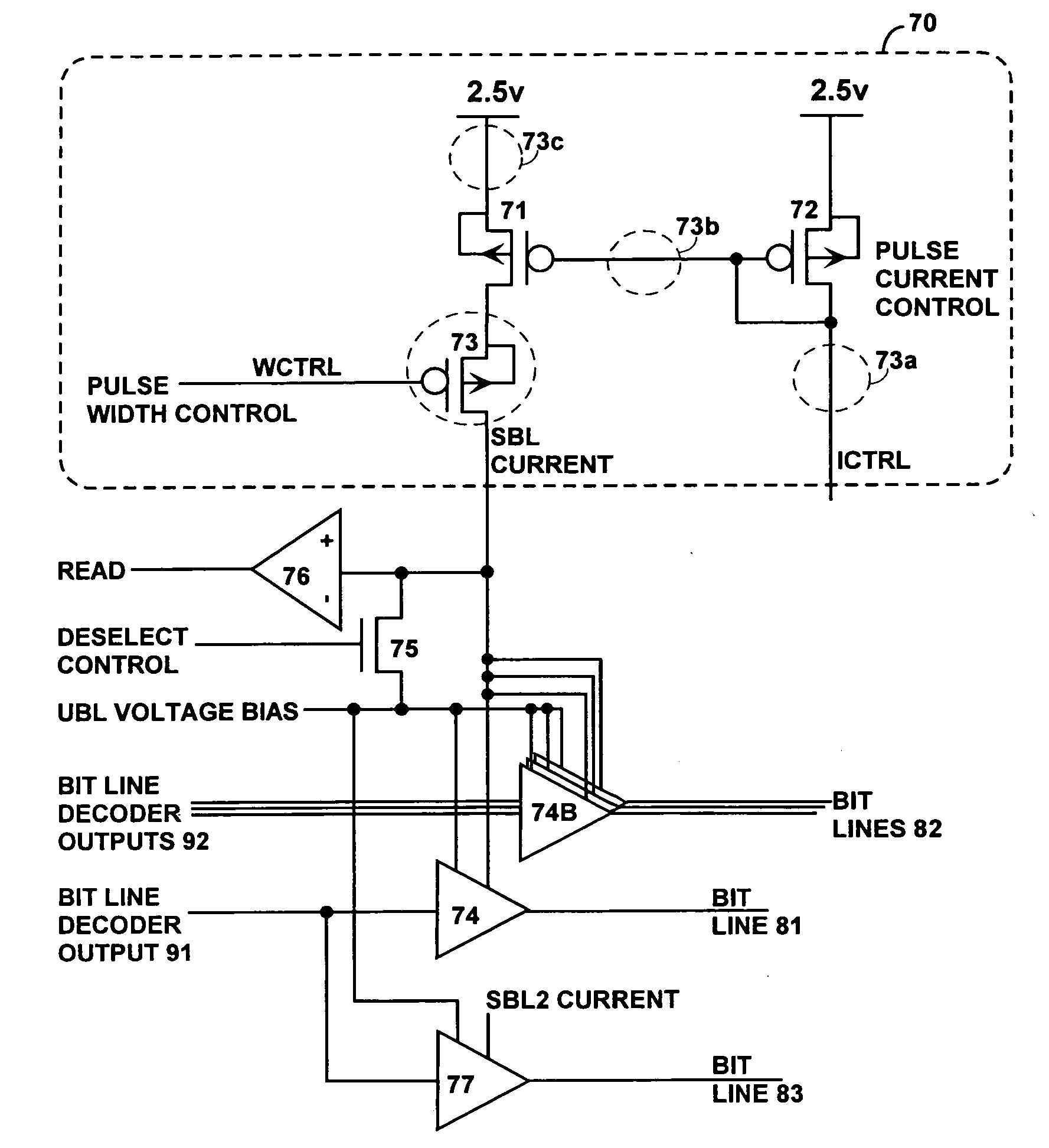

An array of phase changing memory cells that includes a current source, a voltage sensor, a plurality of conductive bit lines electrically connected to the current source, a plurality of conductive word lines each electrically connected to a ground plane via a first resistor and to the voltage sensor, and a plurality of memory cells. Each memory cell is connected between one of the bit lines and one of the word lines and includes phase change memory material. One of the memory cells is selected by turning on switches just on the bit line and word line connected thereto, or by turning a switch connected in series between the corresponding bit and word lines, where the read current flows through the selected memory cell and the voltage sensor measures a voltage drop across the selected memory cell.

Owner:SILICON STORAGE TECHNOLOGY

Structure and method for biasing phase change memory array for reliable writing

ActiveUS20060157679A1Minimize leakage currentReduce the possibilitySolid-state devicesDigital storageBit linePhase-change memory

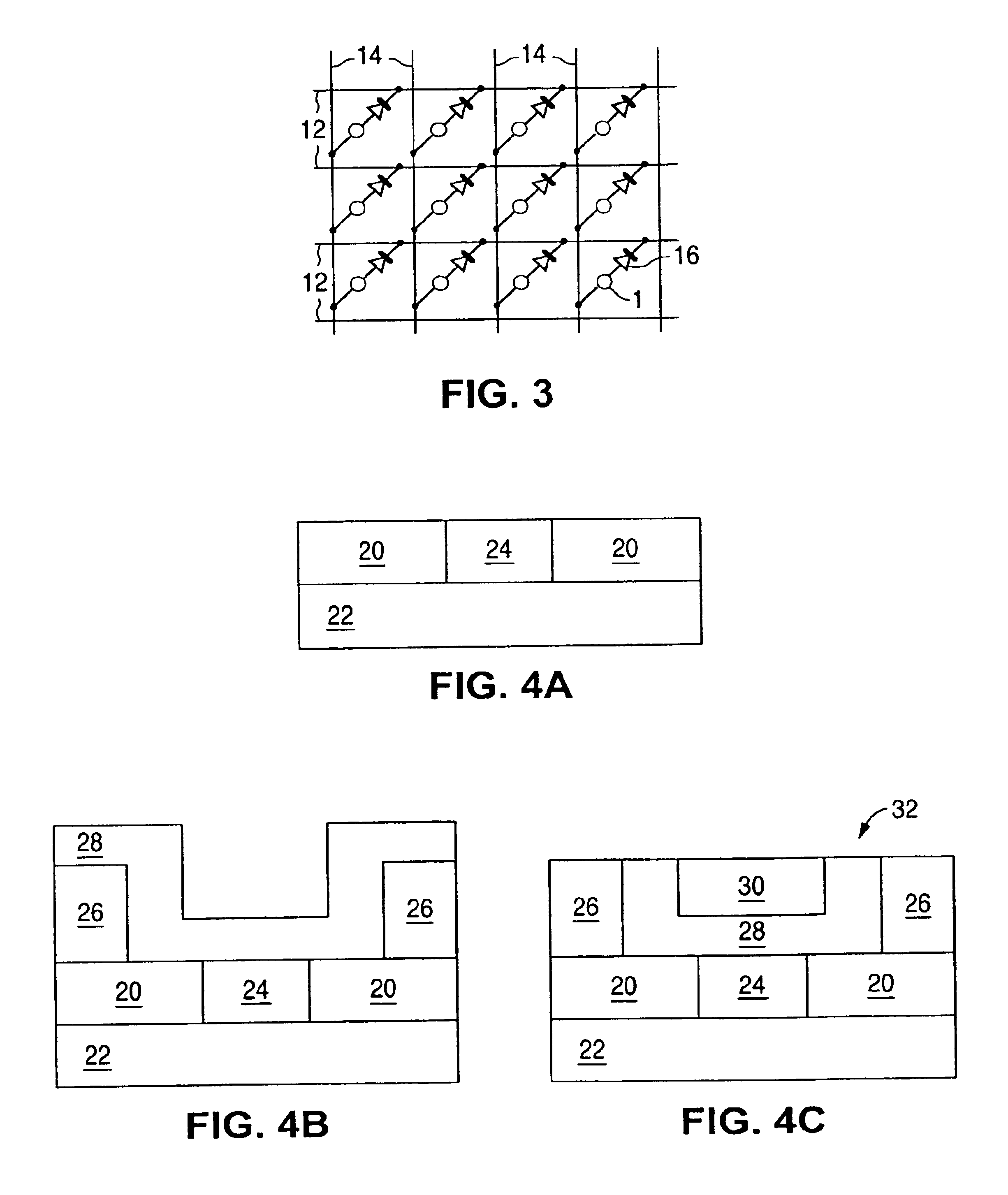

A memory array having memory cells comprising a diode and a phase change material is reliably programmed by maintaining all unselected memory cells in a reverse biased state. Thus leakage is low and assurance is high that no unselected memory cells are disturbed. In order to avoid disturbing unselected memory cells during sequential writing, previously selected word and bit lines are brought to their unselected voltages before new bit lines and word lines are selected. A modified current mirror structure controls state switching of the phase change material.

Owner:SANDISK TECH LLC

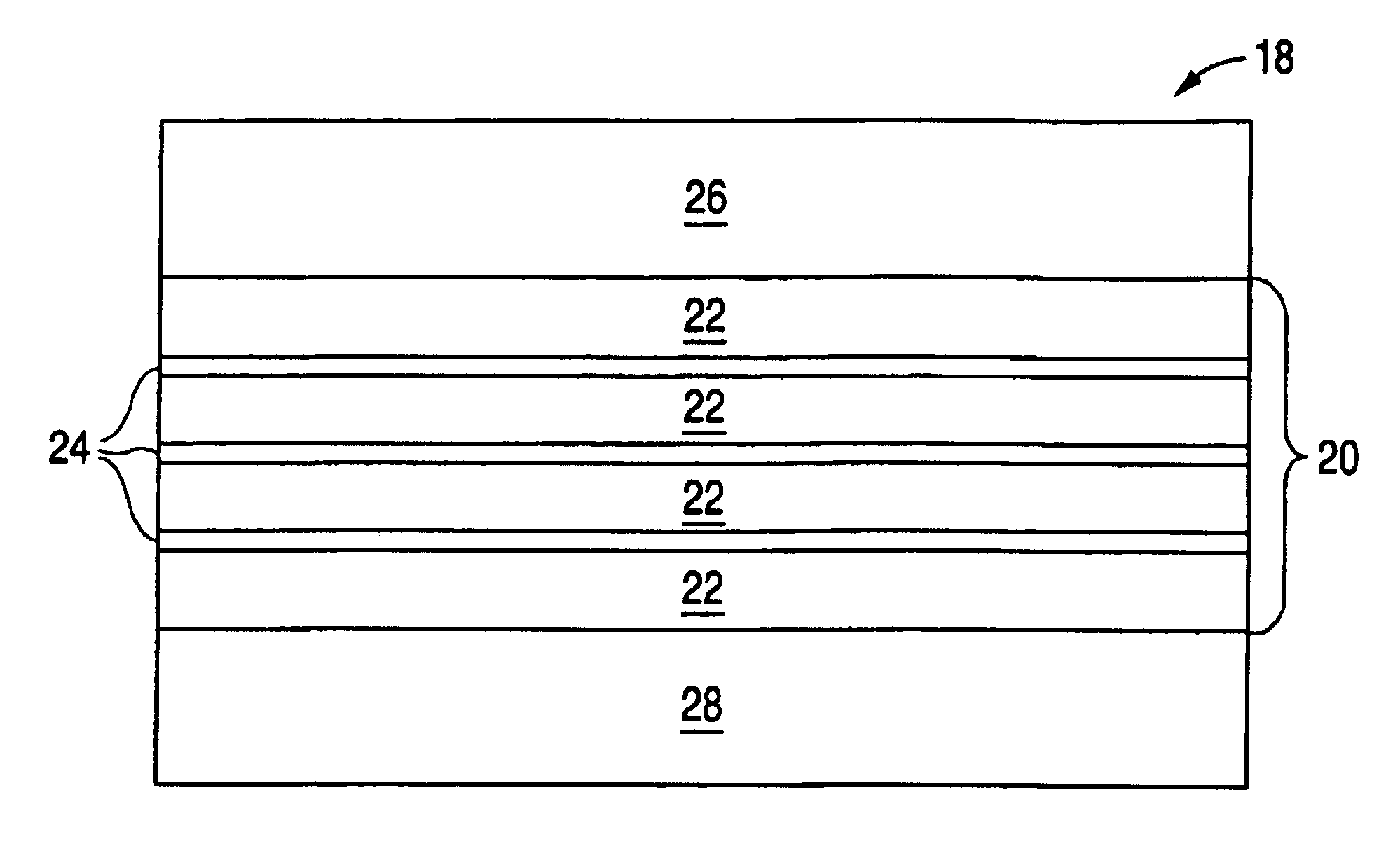

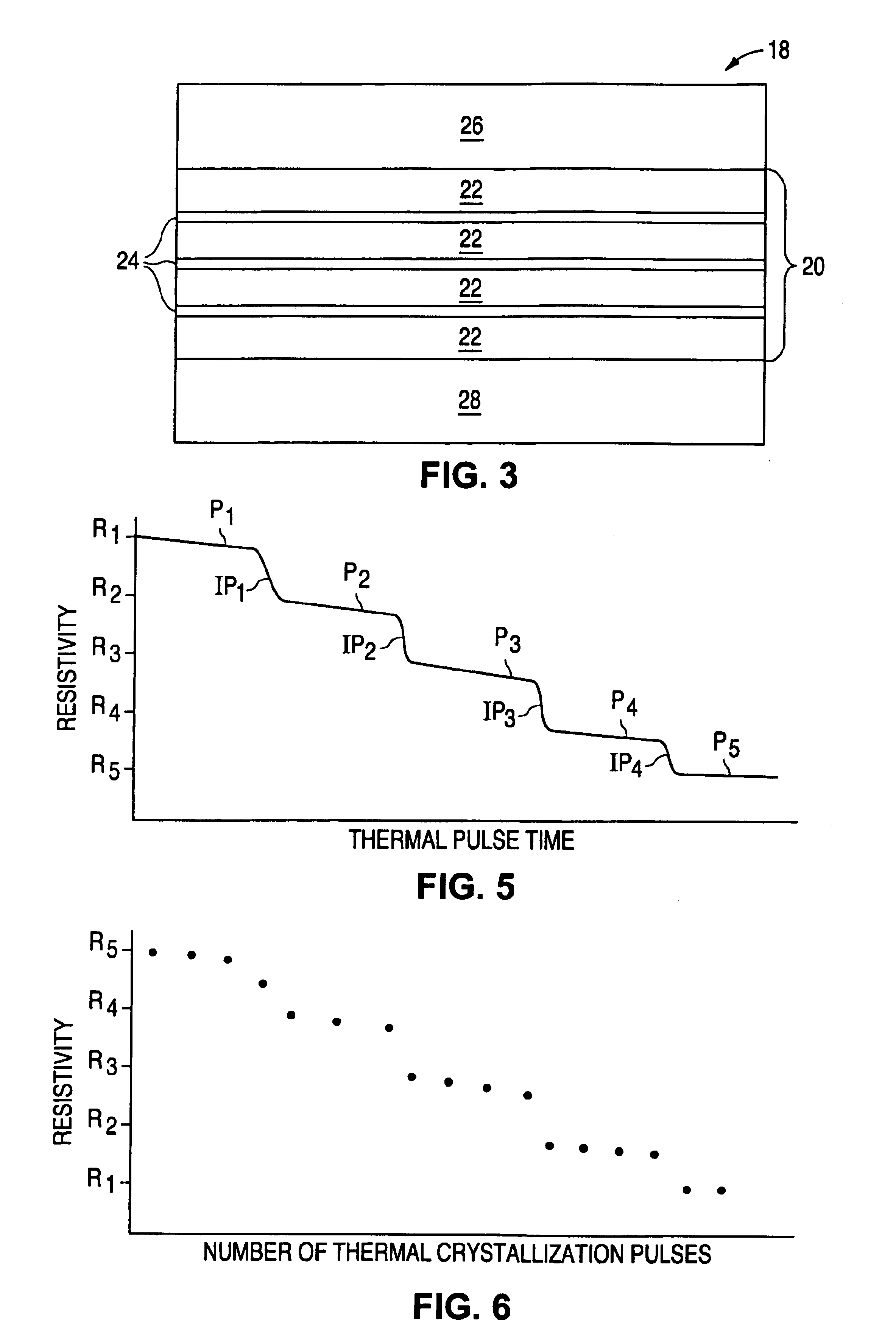

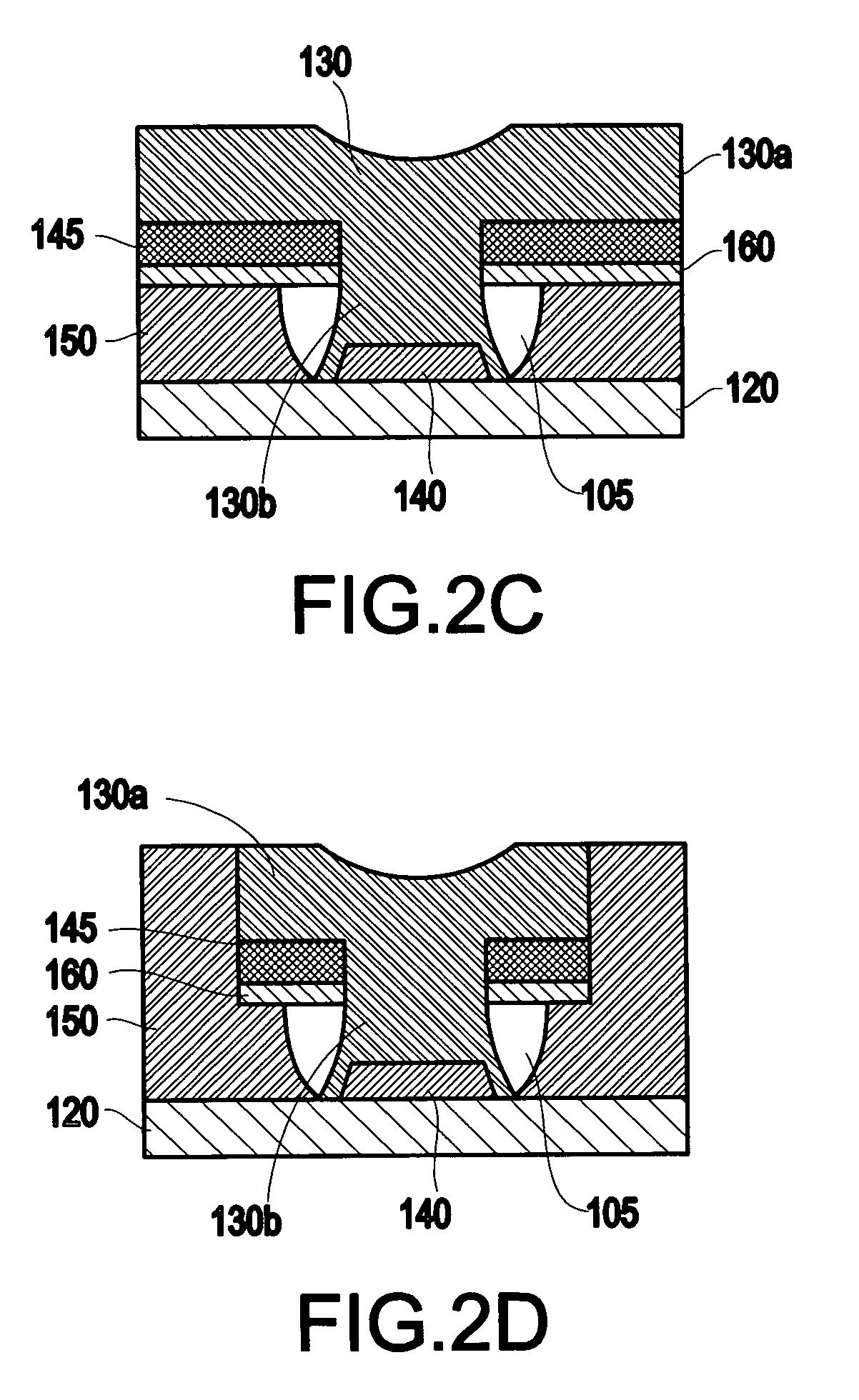

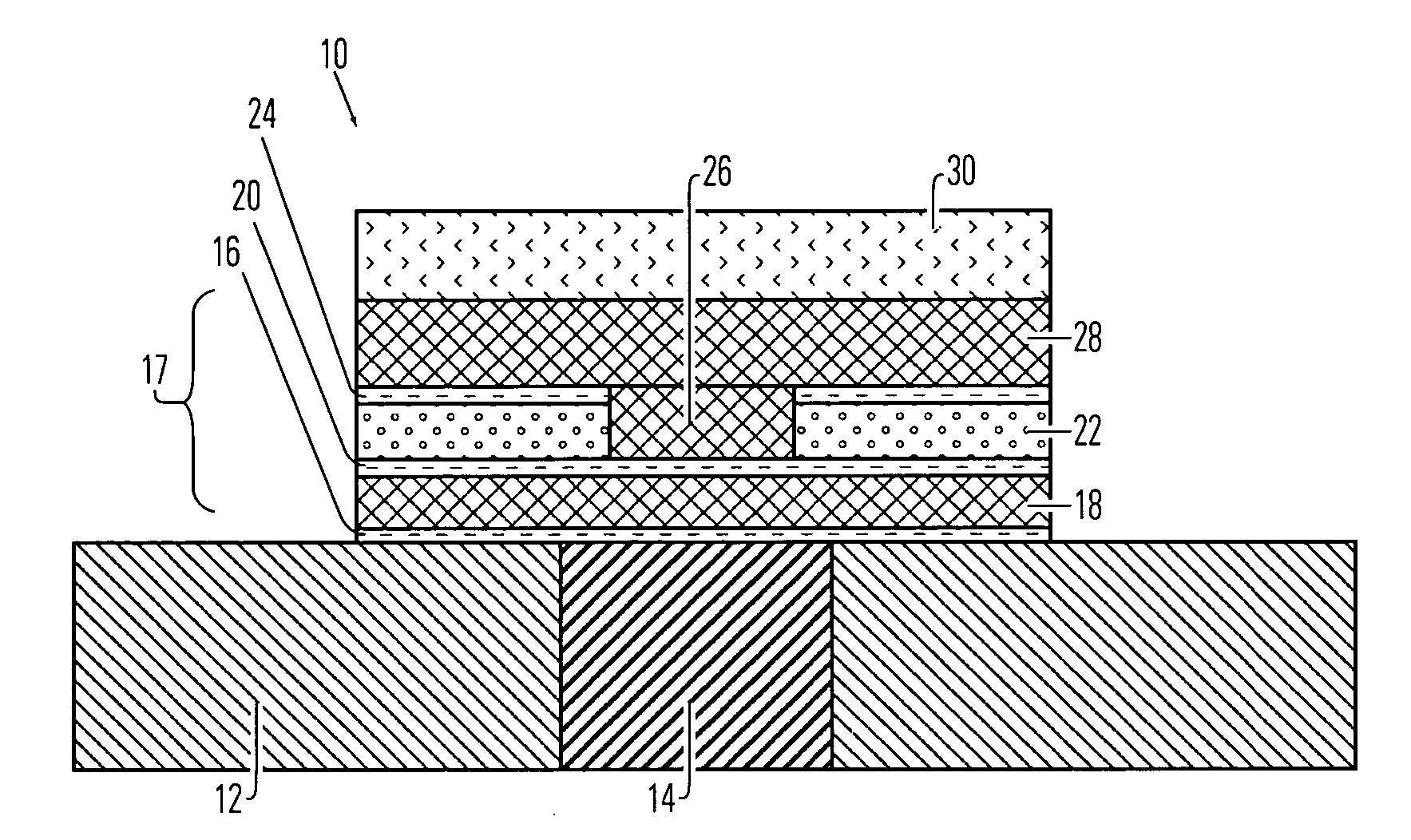

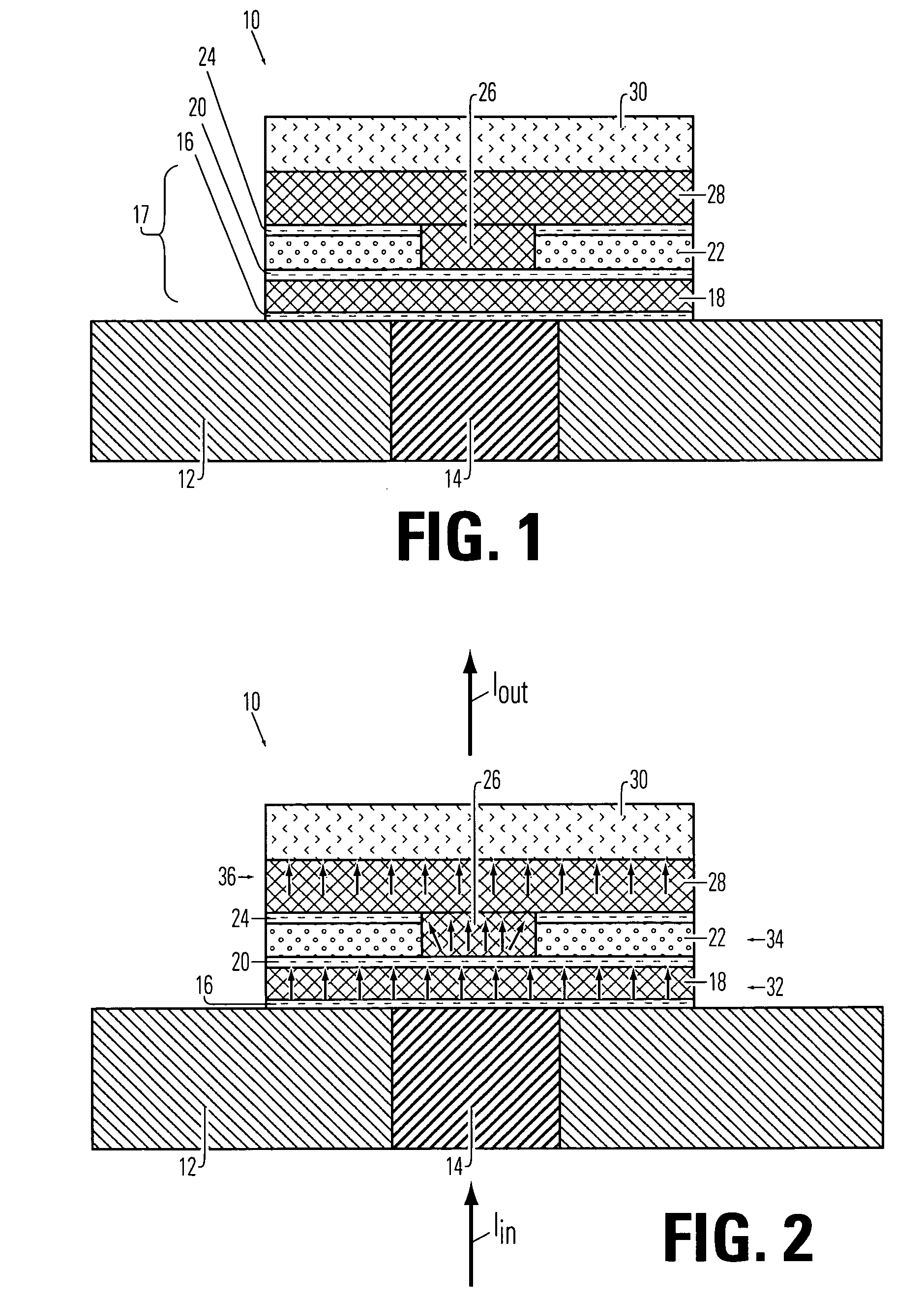

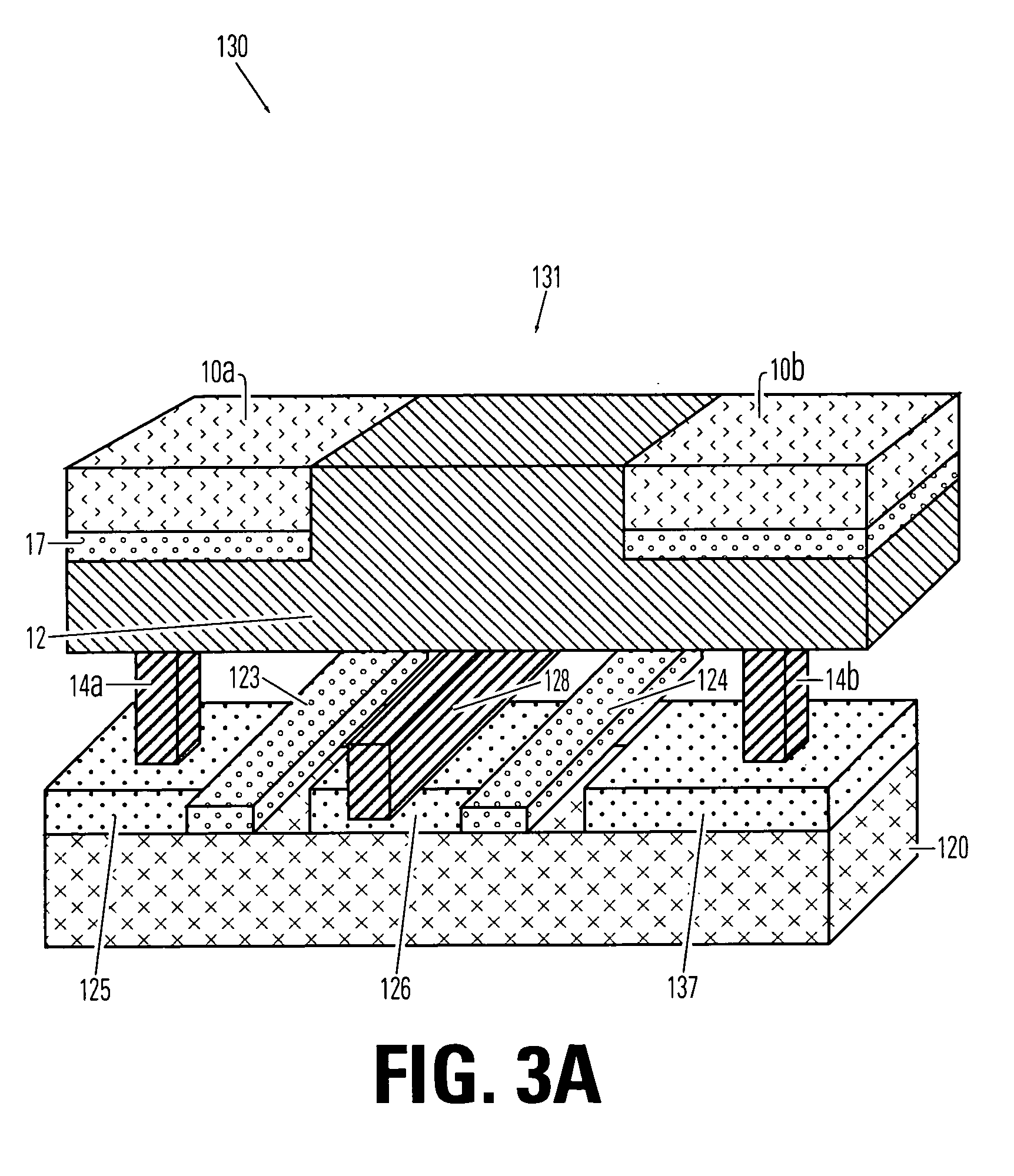

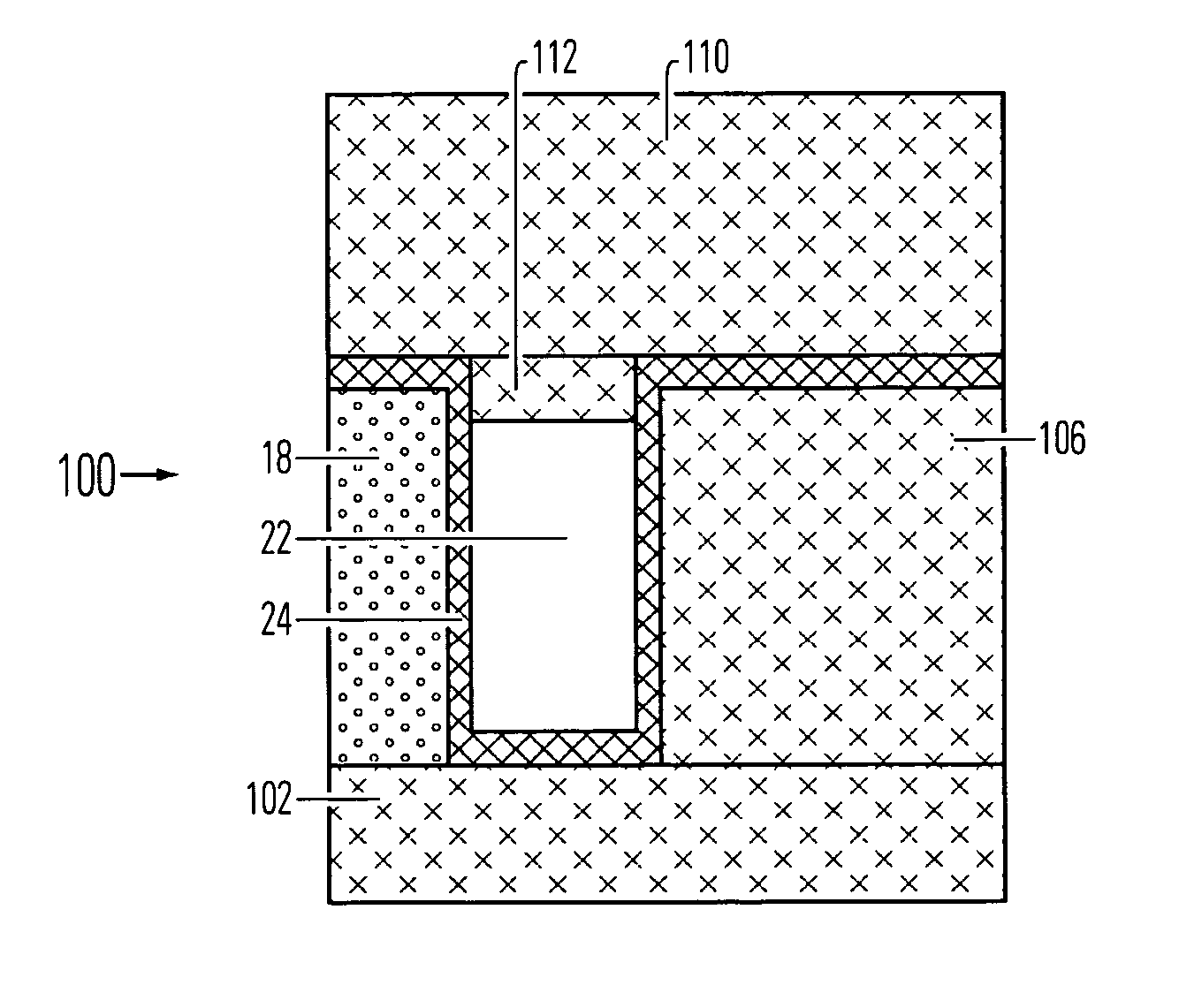

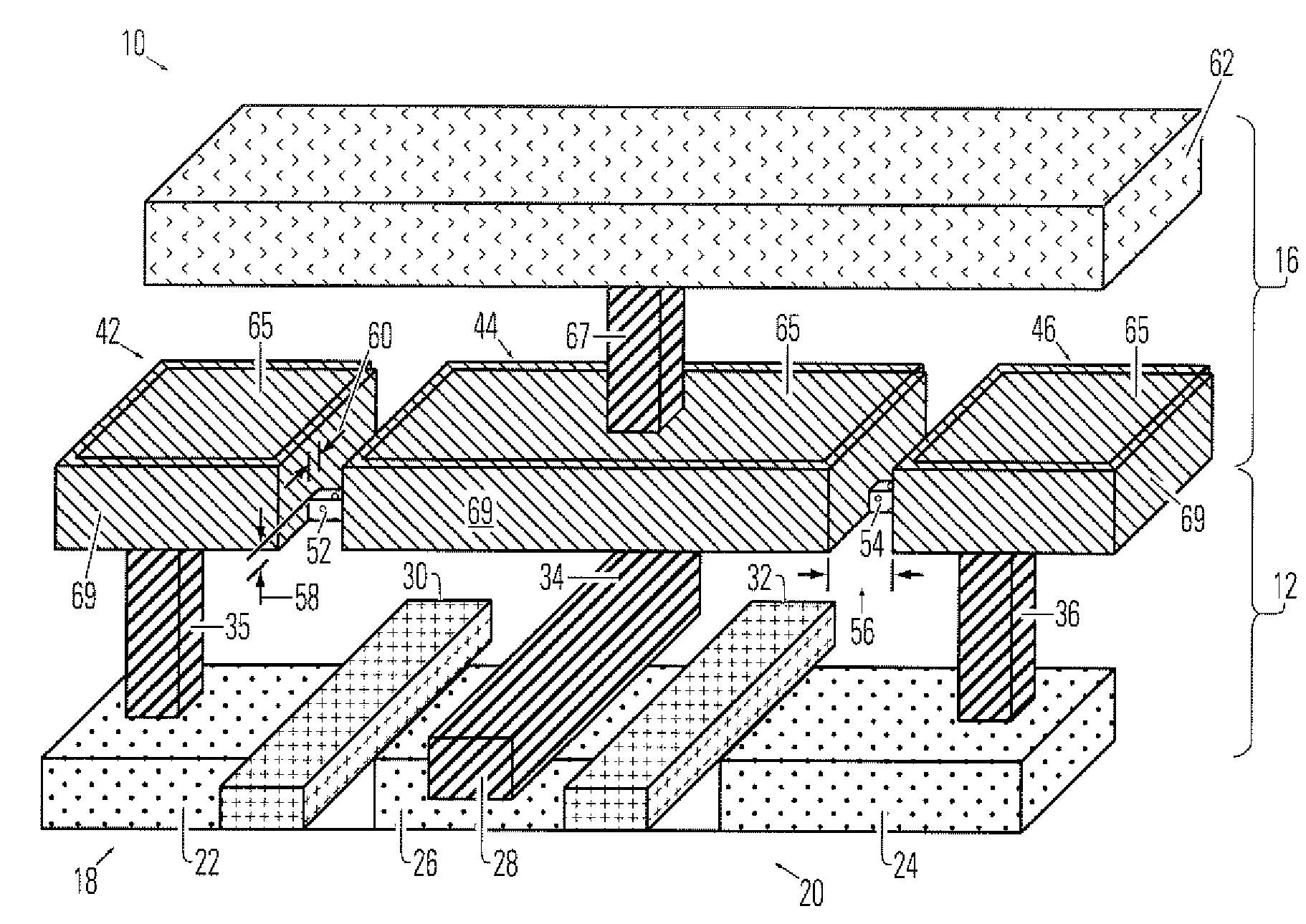

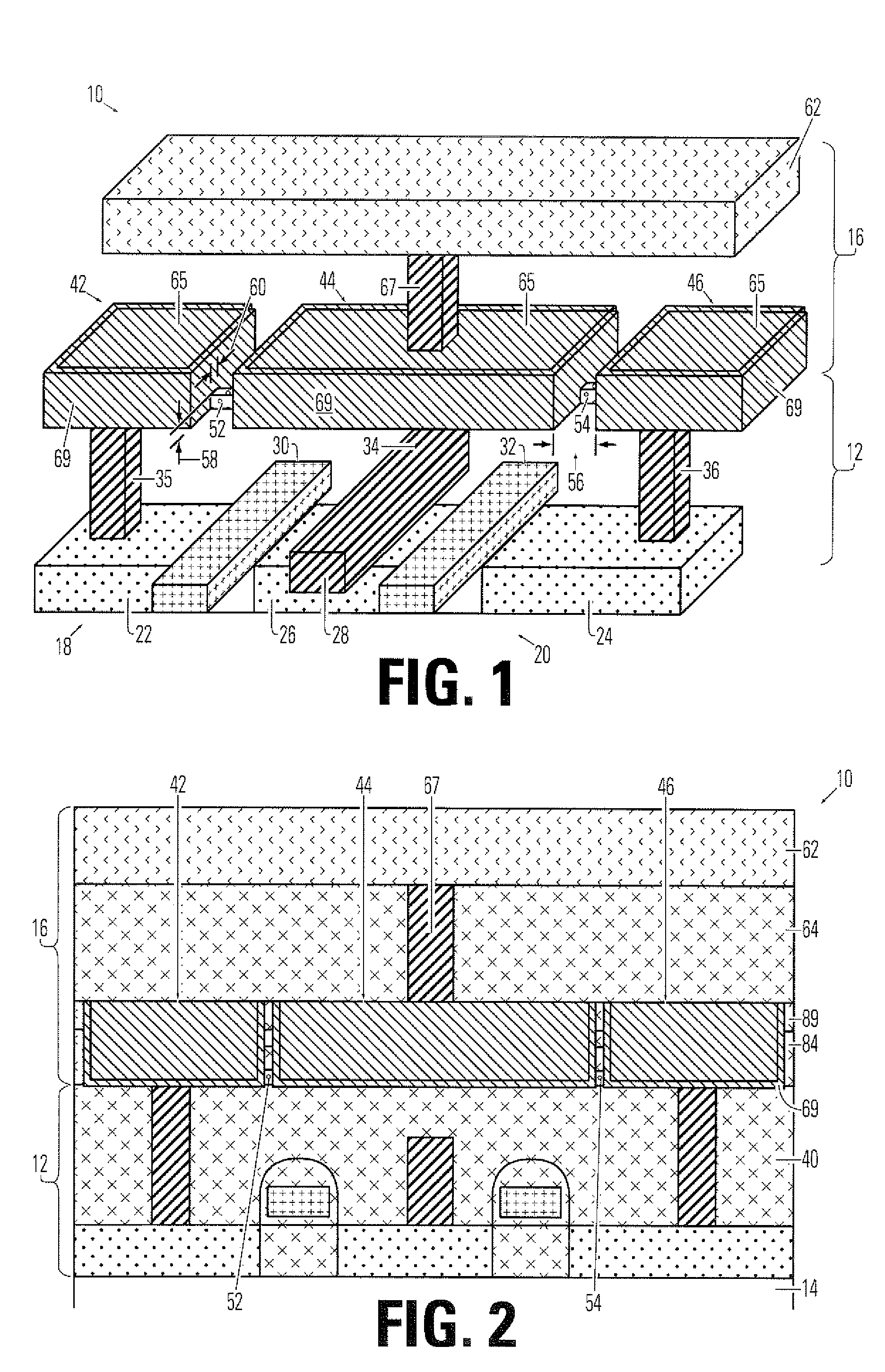

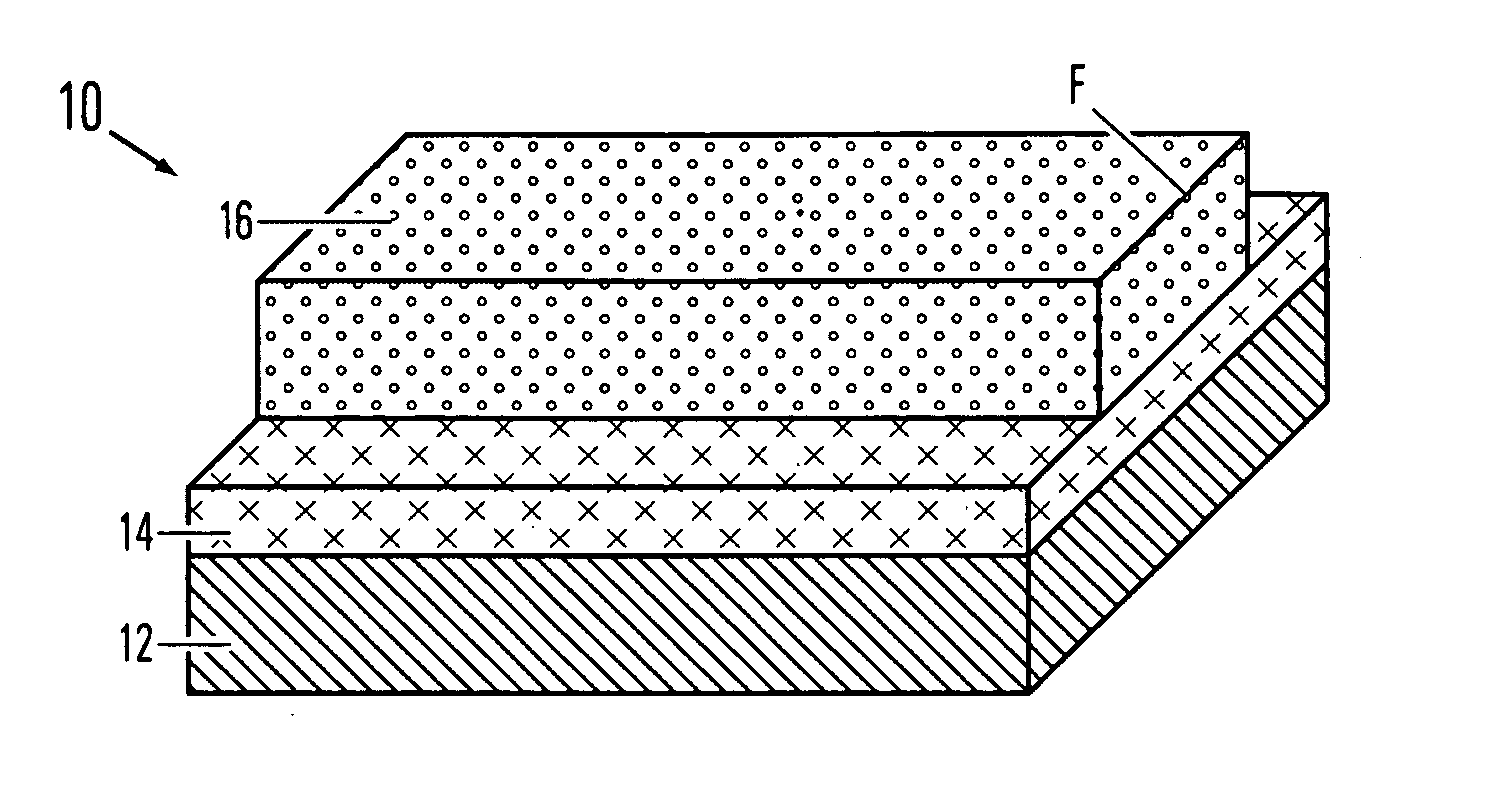

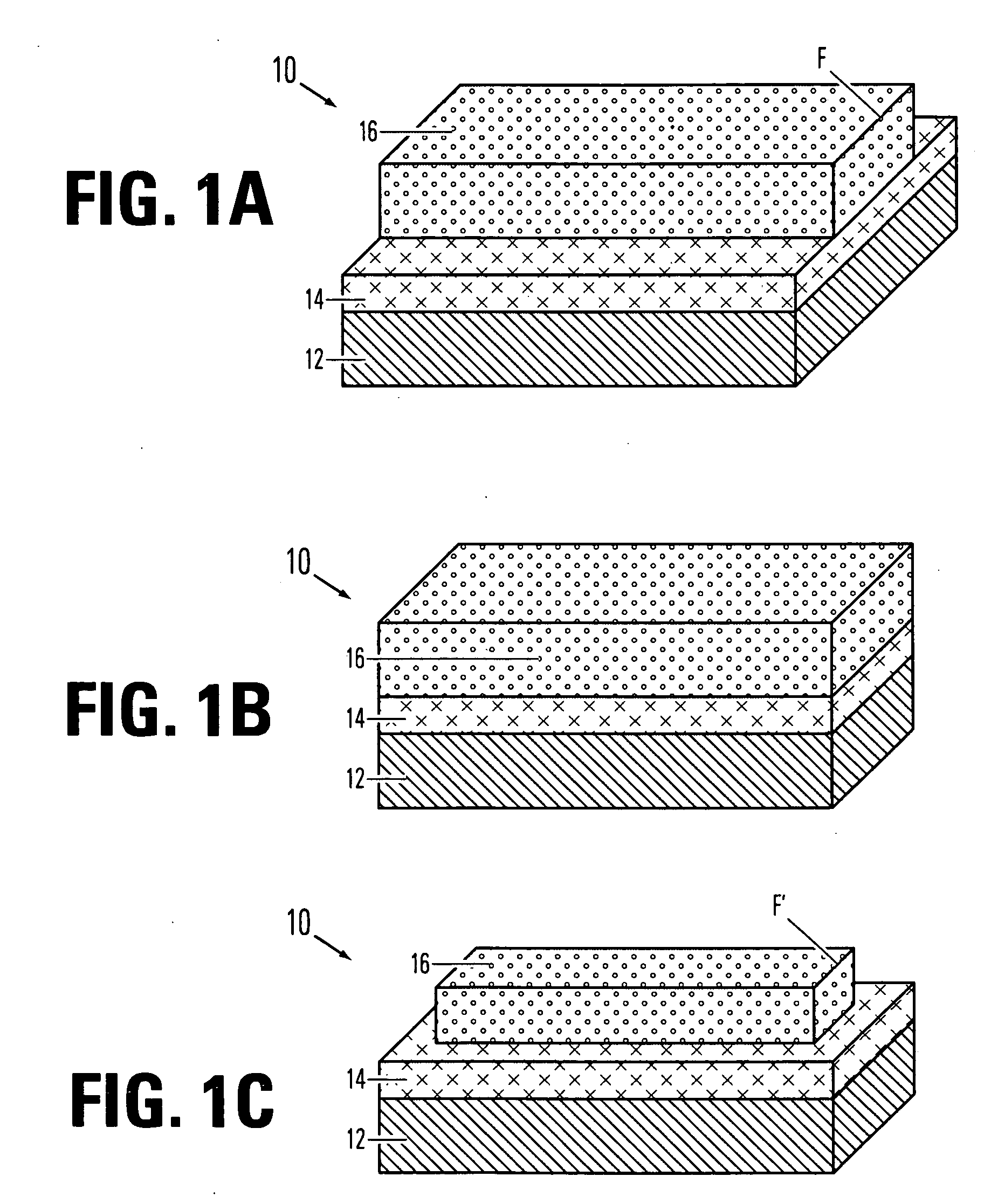

Memory device with discrete layers of phase change memory material

InactiveUS6927410B2Reliably and more repeatedly programmableSemiconductor/solid-state device detailsSolid-state devicesPhase-change memoryInterface layer

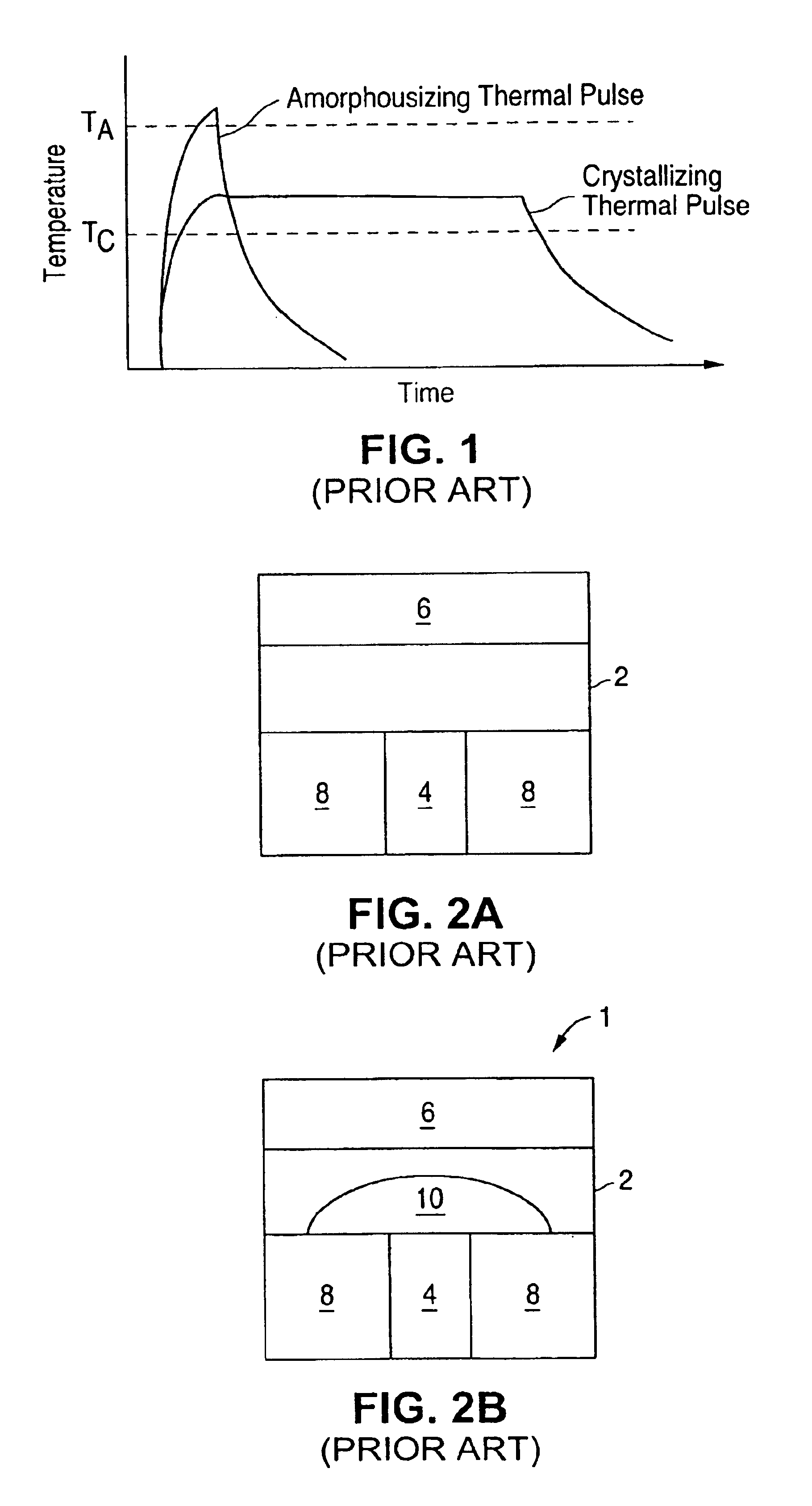

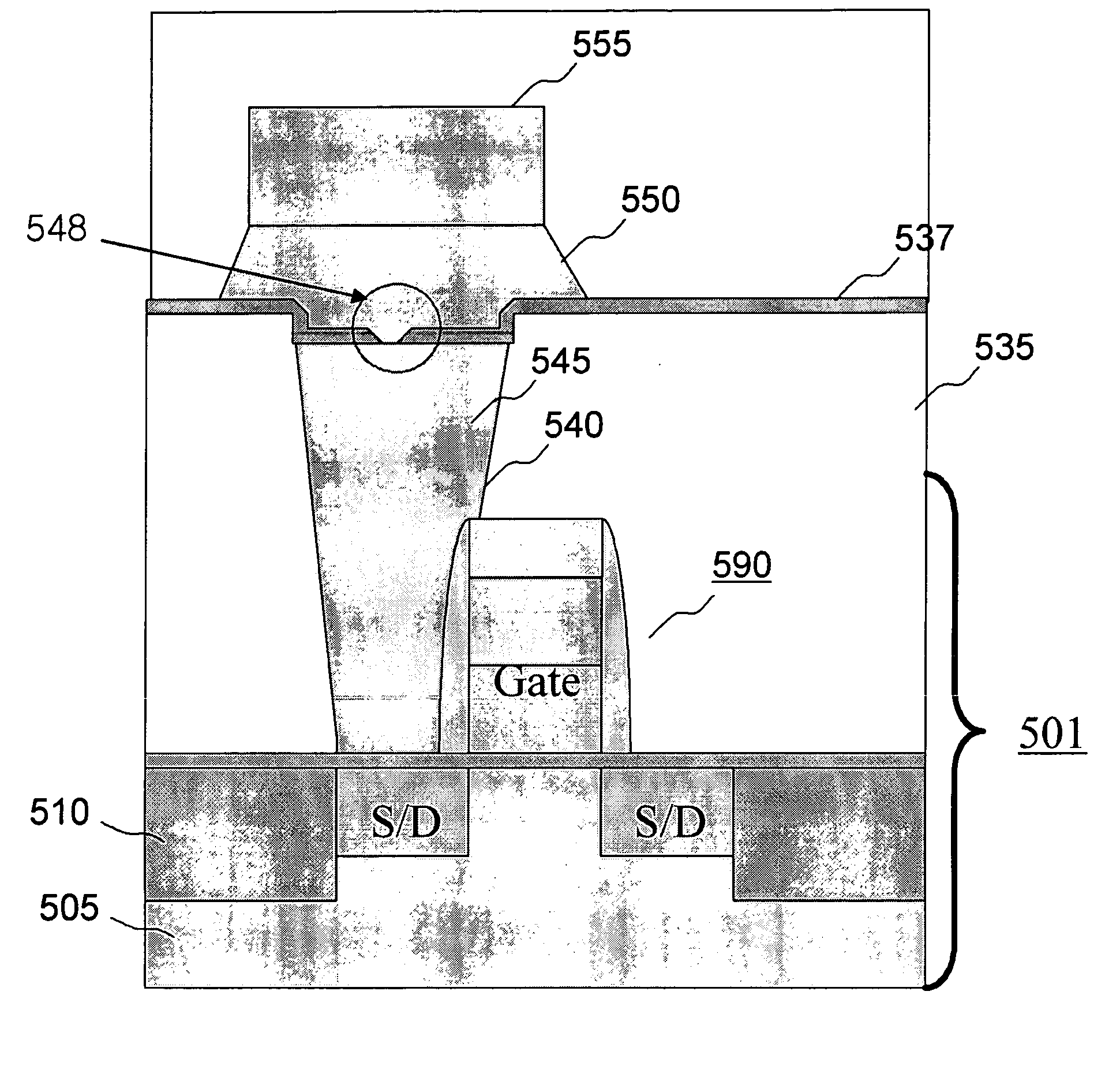

A phase changing memory device, and method of making the same, that includes programmable memory material disposed between a pair of electrodes. The programmable memory material includes discrete layers of phase change material, separated by conductive interface layers, that exhibits relatively stable resistivity values over discrete ranges of crystallizing and amorphousizing thermal pulses applied thereto, for multi-bit storage. The memory material and one of the electrodes can be disposed along spacer material surfaces to form an electrical current path that narrows in width as the current path approaches the other electrode, such that electrical current passing through the current path generates heat for heating the memory material disposed between the electrodes.

Owner:SILICON STORAGE TECHNOLOGY

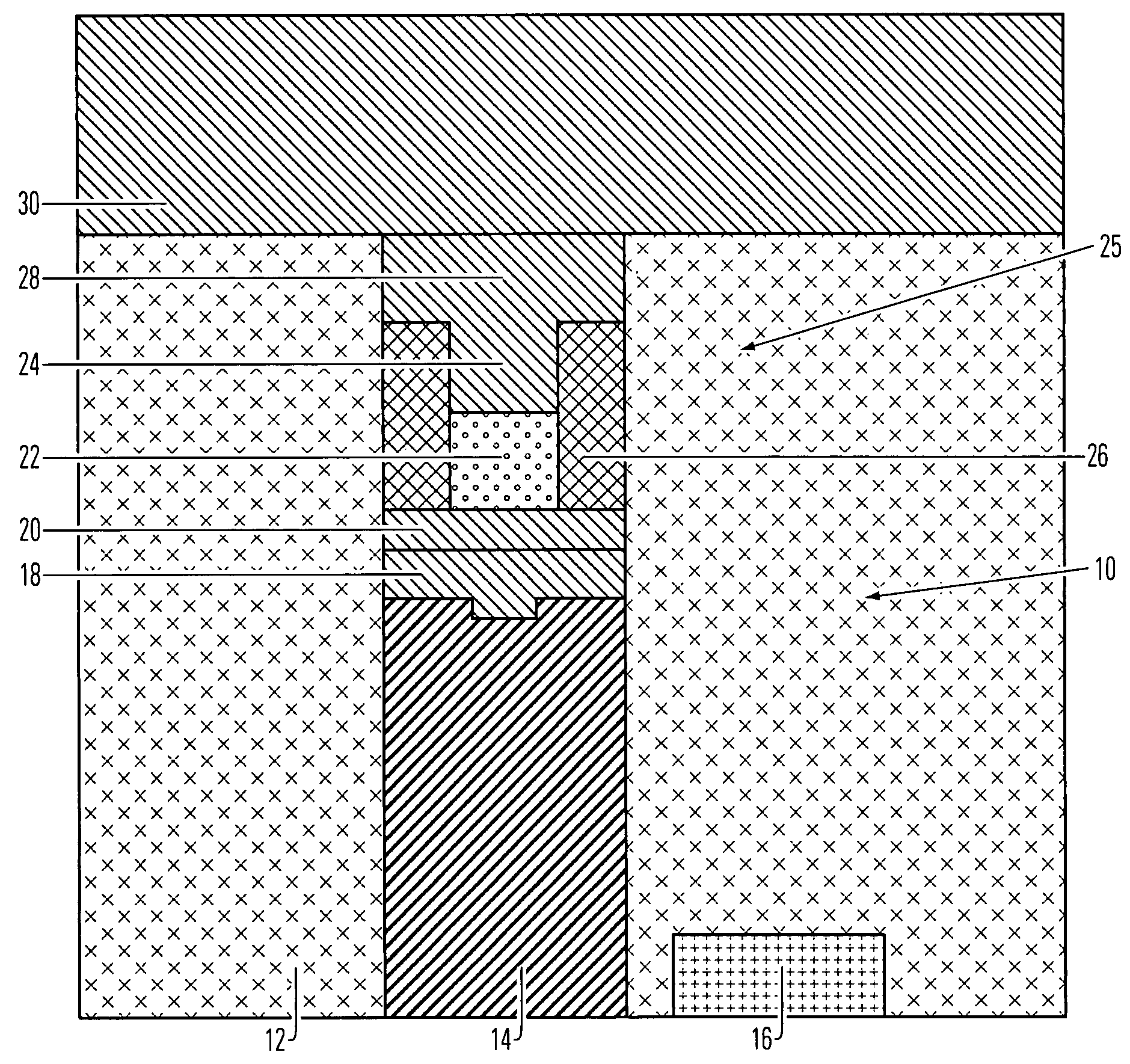

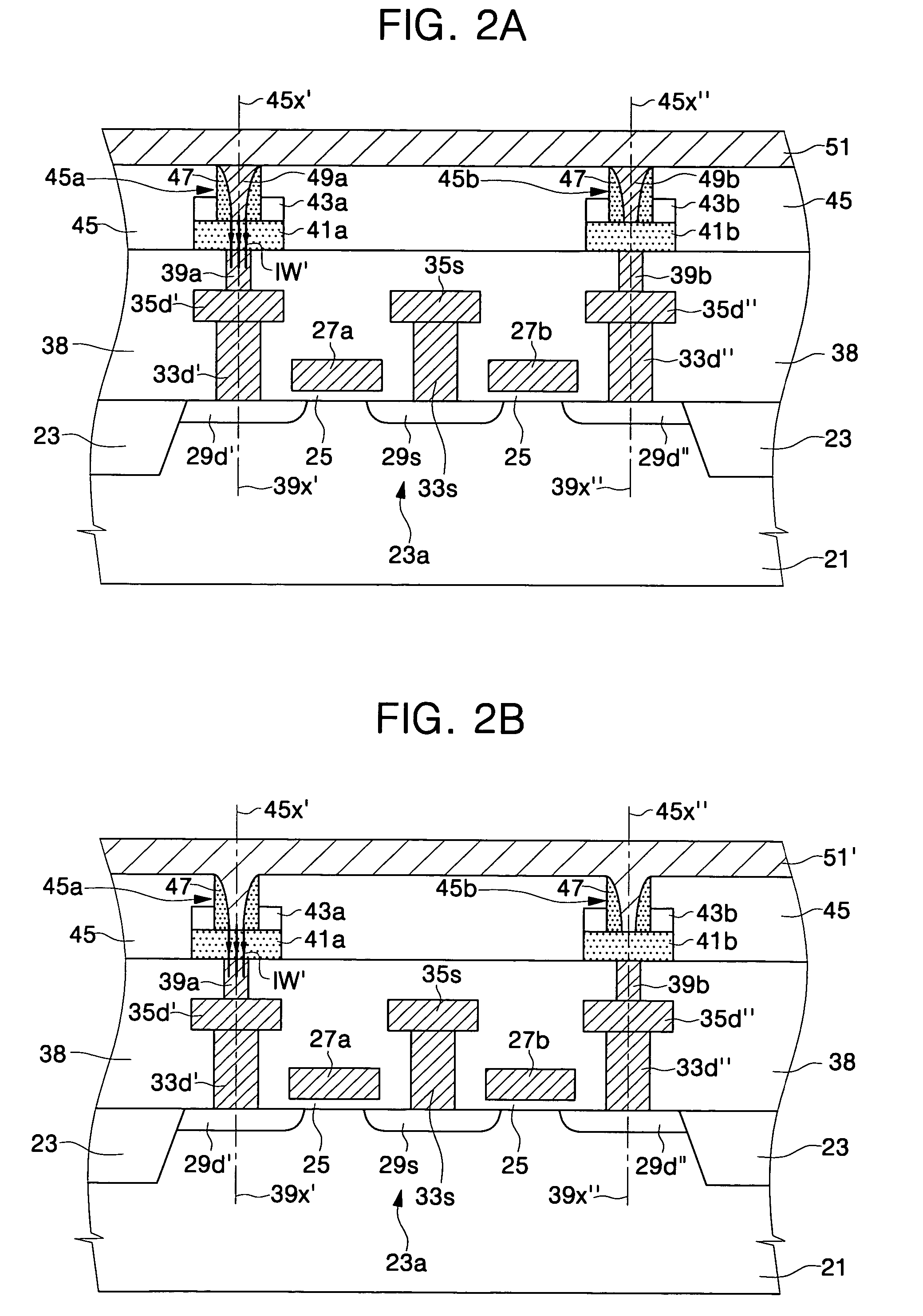

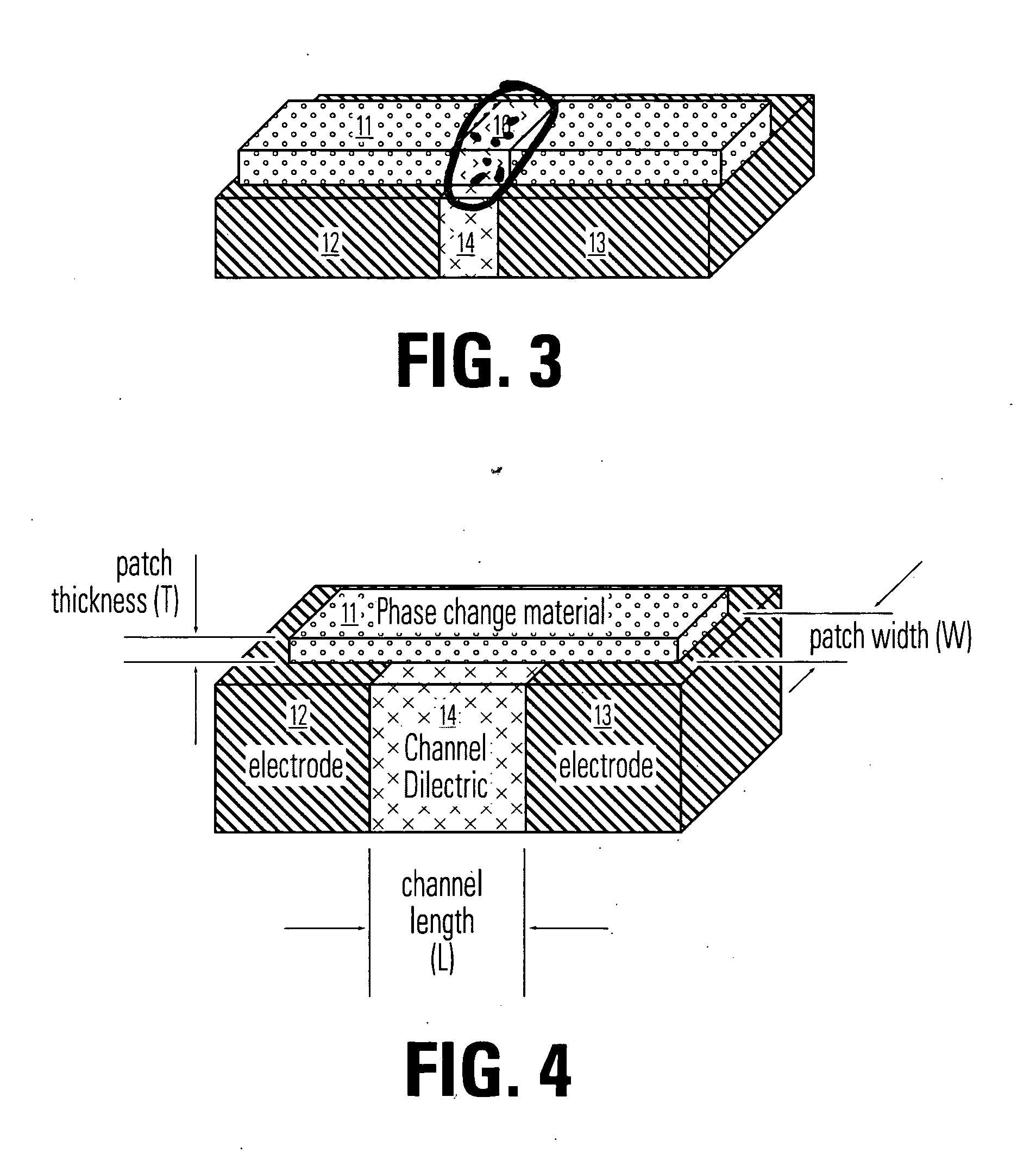

Structure for confining the switching current in phase memory (PCM) cells

InactiveUS20060226409A1Heat dissipation is limitedHigh densityBulk negative resistance effect devicesSemiconductor devicesPhase-change memorySwitched current

Disclosed are a phase change memory cell and a method of forming the memory cell. The memory cell comprises a main body of phase change material connected directly to a bottom contact and via a narrow channel of phase change material to a top contact. The channel is tapered from the top contact towards the main body. A minimum width of the channel has a less than minimum lithographic dimension and is narrower than a width of the main body. Therefore, the channel provides a confined region for the switching current path and restricts phase changing to within the channel. In addition an embodiment of the memory cell isolates the main body of phase change material by providing a space between the phase change material and the cell walls. The space allows the phase change material to expand and contract and also limits heat dissipation.

Owner:IBM CORP

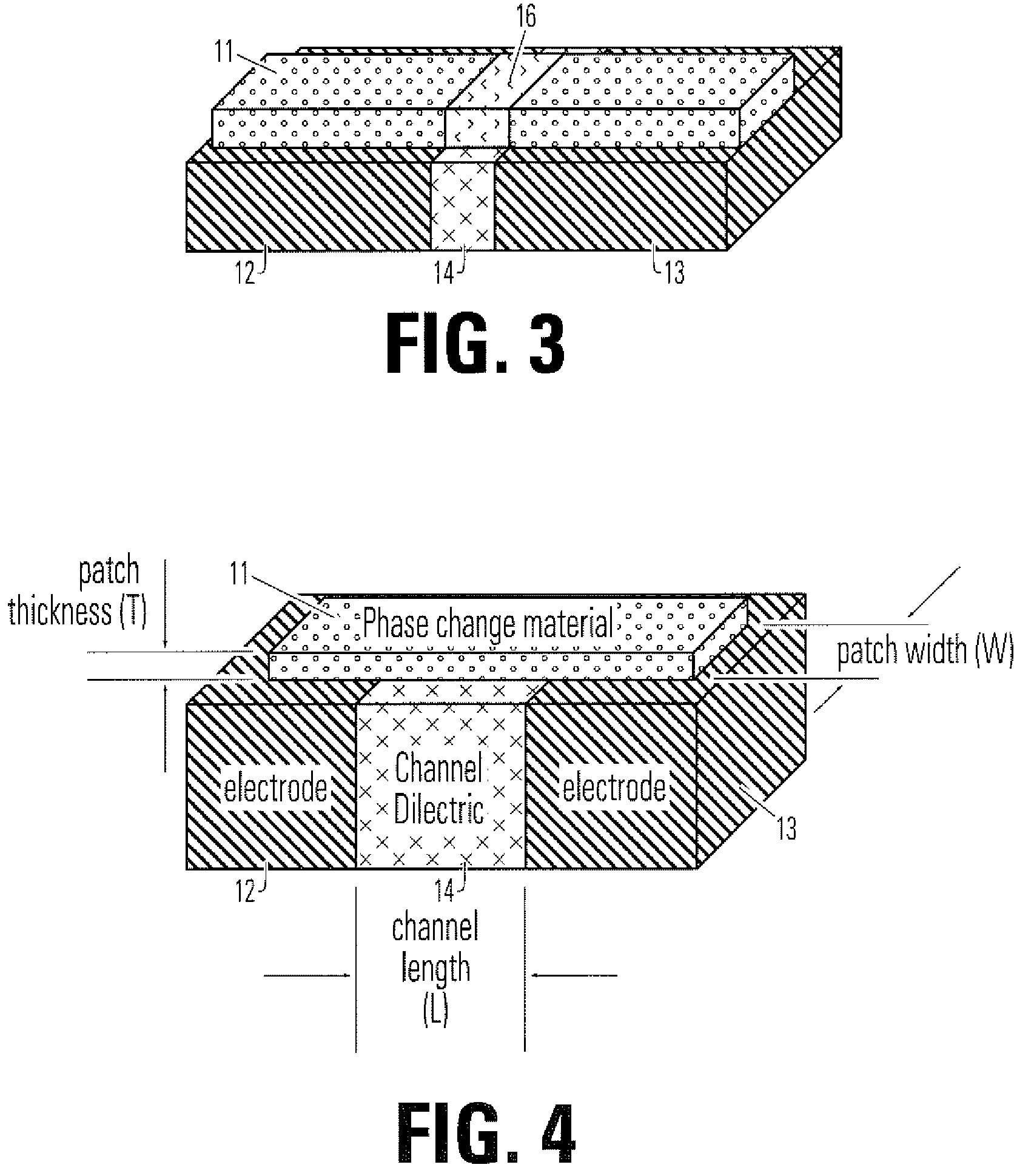

Phase-change memory cell and method of fabricating the phase-change memory cell

InactiveUS6936840B2Improve reliabilityHigh yieldTransistorSolid-state devicesPhase-change memoryEngineering

A memory cell and method of fabricating the memory cell includes an insulating layer formed on a first electrode layer, the insulating layer having a first opening, a stencil layer formed on the insulating layer, and having a second opening formed in an area of the first opening, a phase-change material layer formed on a surface of the first electrode layer in the first opening, and an electrically conductive layer including a first portion formed on the stencil layer and defining a second electrode layer and a second portion formed on the phase-change material layer.

Owner:GLOBALFOUNDRIES INC

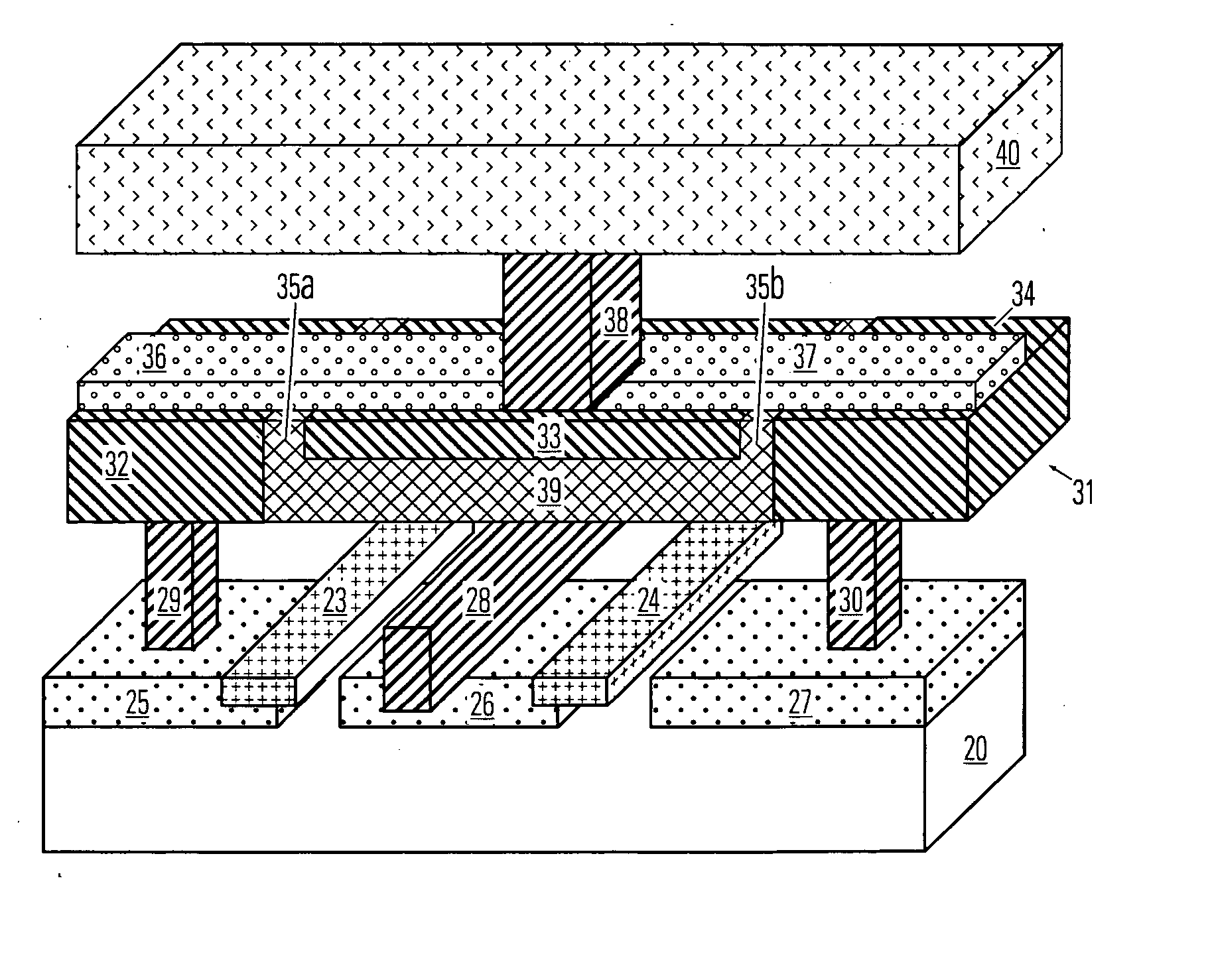

I-shaped phase change memory cell

A memory device includes two electrodes, vertically separated and having mutually opposed contact surfaces, between which lies a phase change cell. The phase change cell includes an upper phase change member, having a contact surface in electrical contact with the first electrode; a lower phase change member, having a contact surface in electrical contact with the second electrode; and a kernel member disposed between and in electrical contact with the upper and lower phase change members. The phase change cell is formed of material having at least two solid phases, and the lateral extent of the upper and lower phase change members is substantially greater than that of the kernel member. An intermediate insulating layer is disposed between the upper and lower phase change members adjacent to the kernel member.

Owner:MACRONIX INT CO LTD

Manufacturing methods for thin film fuse phase change ram

InactiveUS20060286709A1Simple structureReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryOptoelectronics

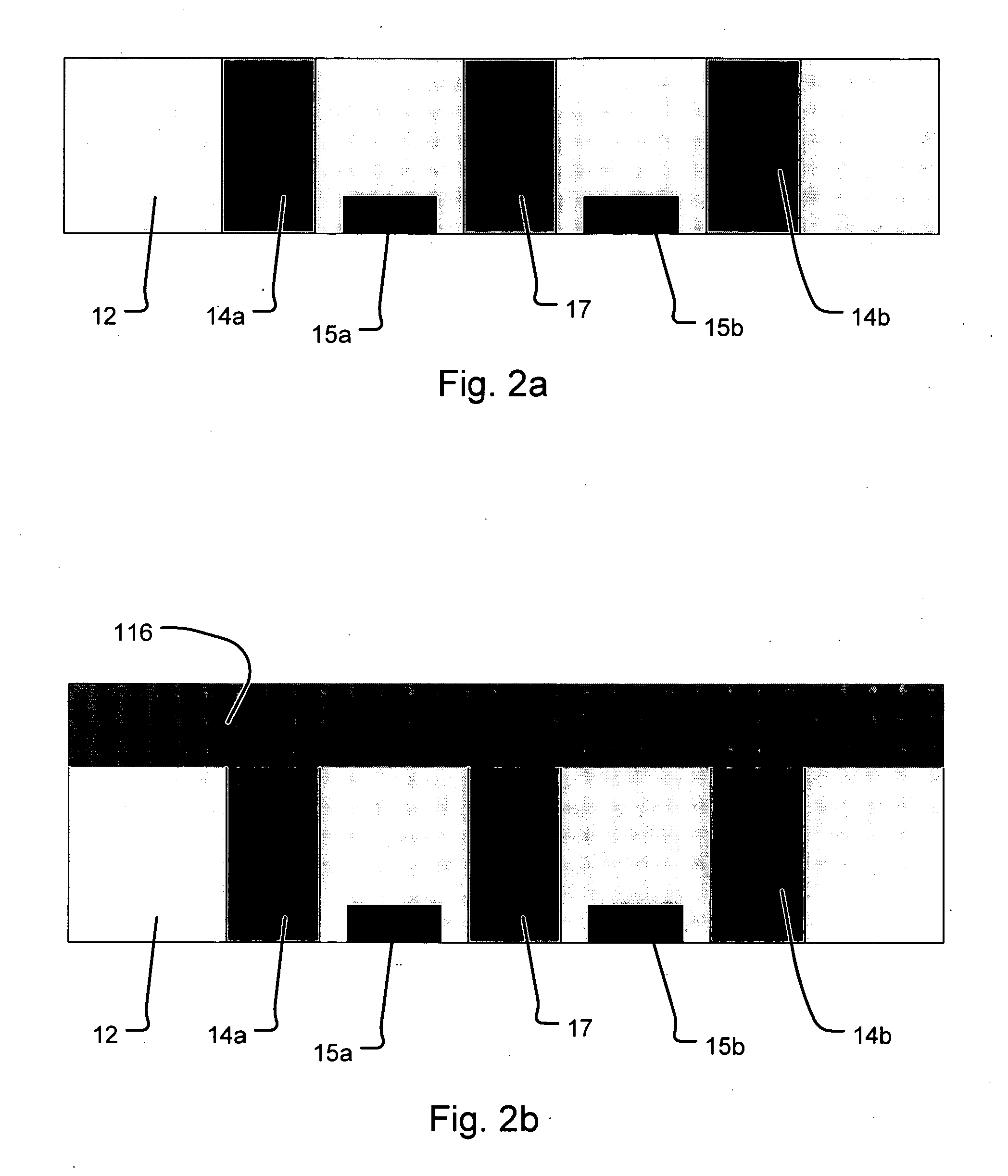

A method for manufacturing a memory device comprises forming an electrode layer on a substrate which comprises circuitry made using front-end-of-line procedures. The electrode layer includes a first electrode and a second electrode, and an insulating member between the first and second electrodes for each phase change memory cell to be formed. A bridge of memory material is formed on the top surface of the electrode layer across the insulating member for each memory cell to be formed. An access structure over the electrode layer is made by forming a patterned conductive layer over said bridge, and forming a contact between said first electrode and said patterned conductive layer.

Owner:MACRONIX INT CO LTD

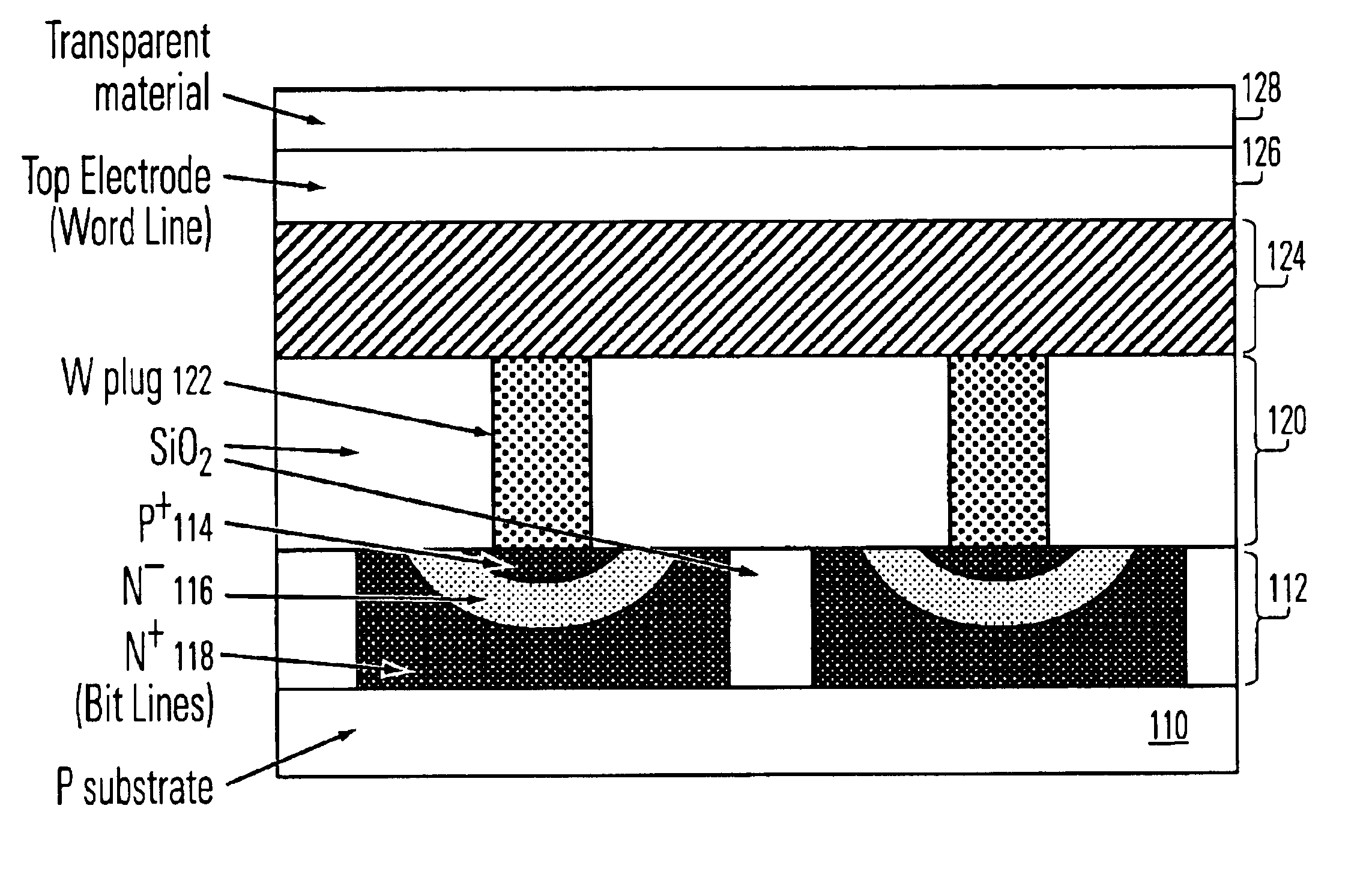

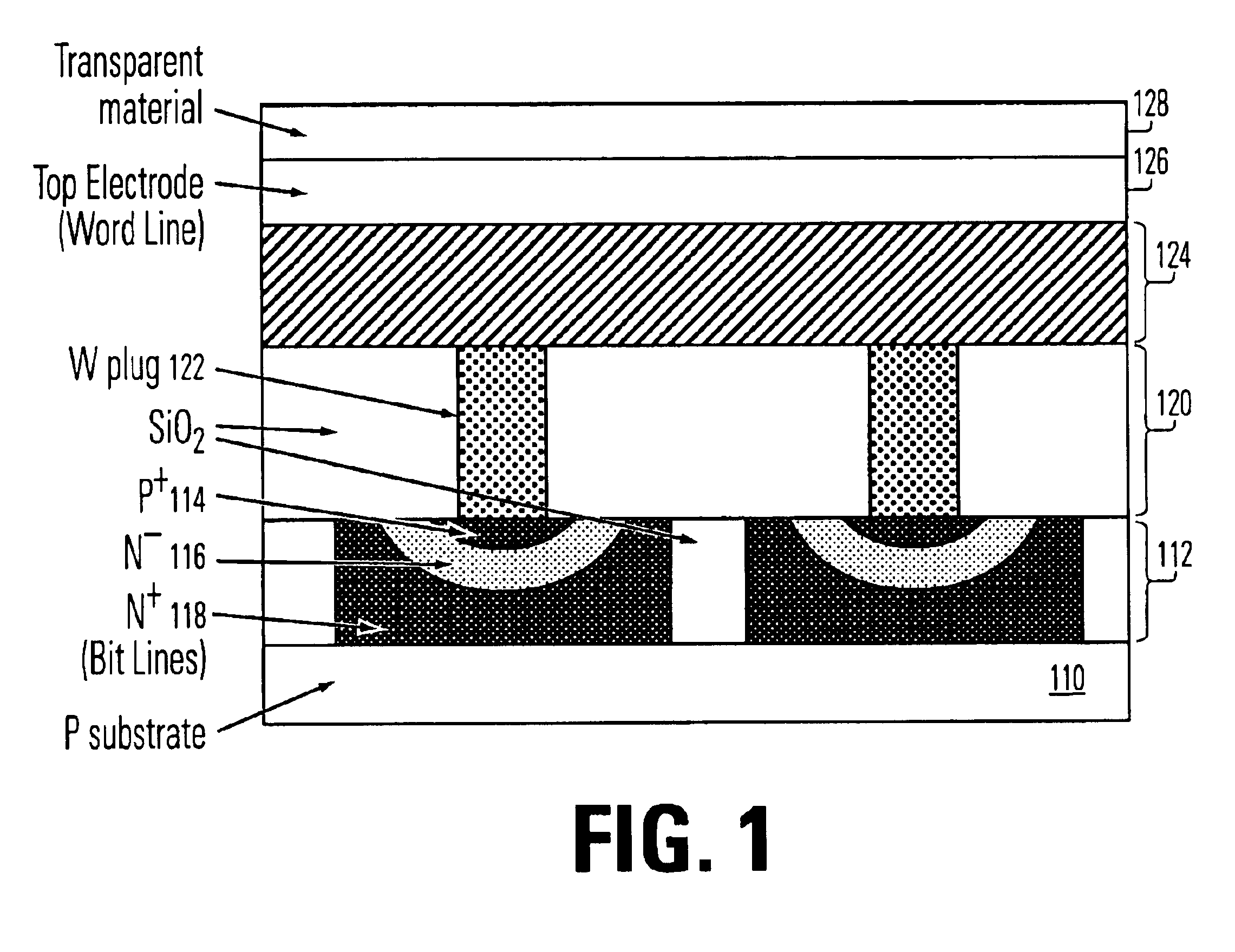

Laser programmable electrically readable phase-change memory method and device

InactiveUS6850432B2Simple and low power-consumingSimple and low and electrical circuitRead-only memoriesDigital storagePhase-change memoryEngineering

Roughly described, a phase-change memory such as a chalcogenide-based memory is programmed optically and read electrically. No complex electrical circuits are required for programming the cells. On the other hand, this memory can be read by electrical circuitry directly. The read out speed is much faster than for optical disks, and integrated circuit chips made this way are more compatible with other electrical circuits than are optical disks. Thus memories according to the invention can have simple, low power-consuming, electrical circuits, and do not require slow and power-hungry disk drives for reading. The invention therefore provides a unique low power, fast read / write memory with simple electrical circuits.

Owner:MACRONIX INT CO LTD

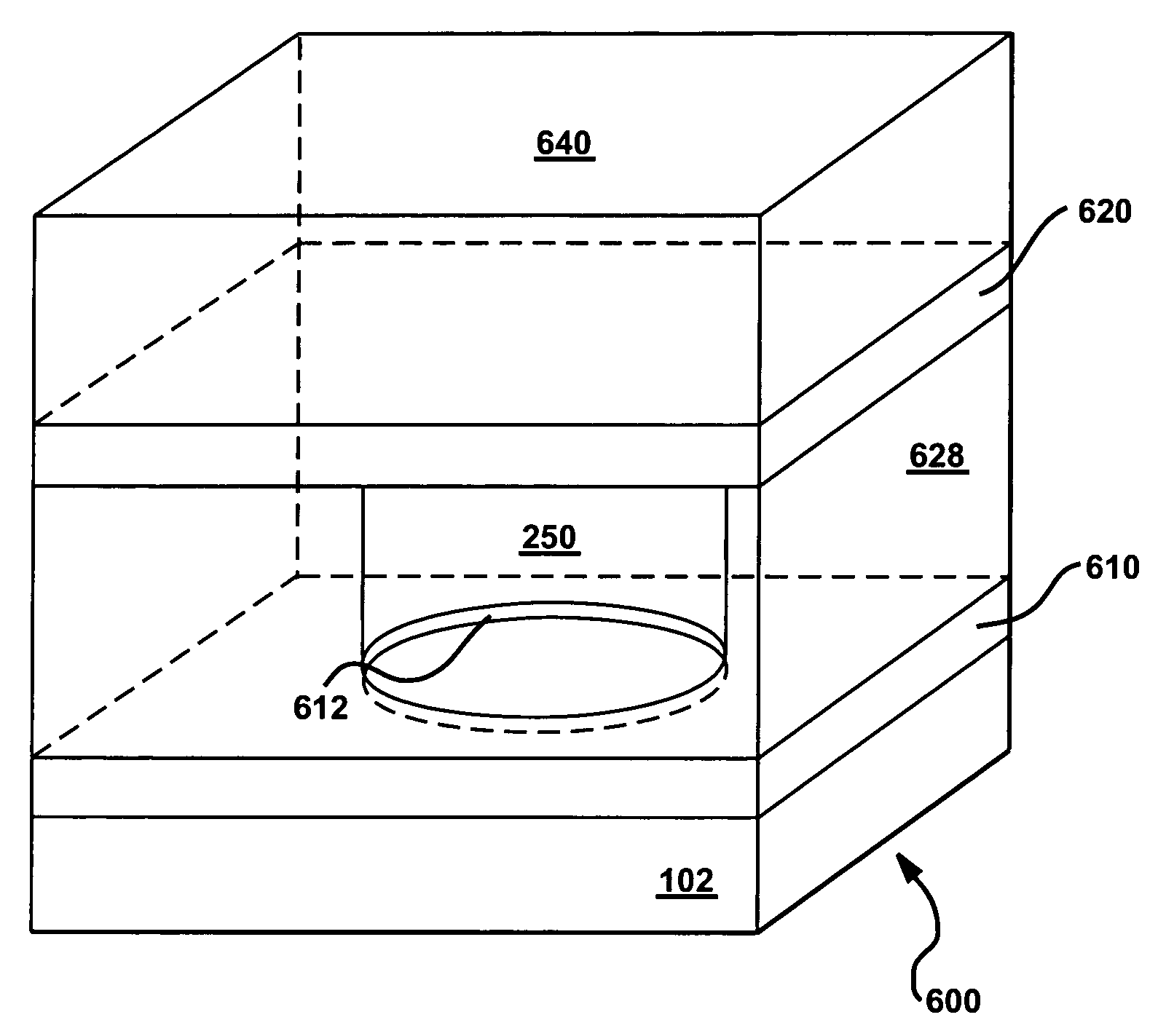

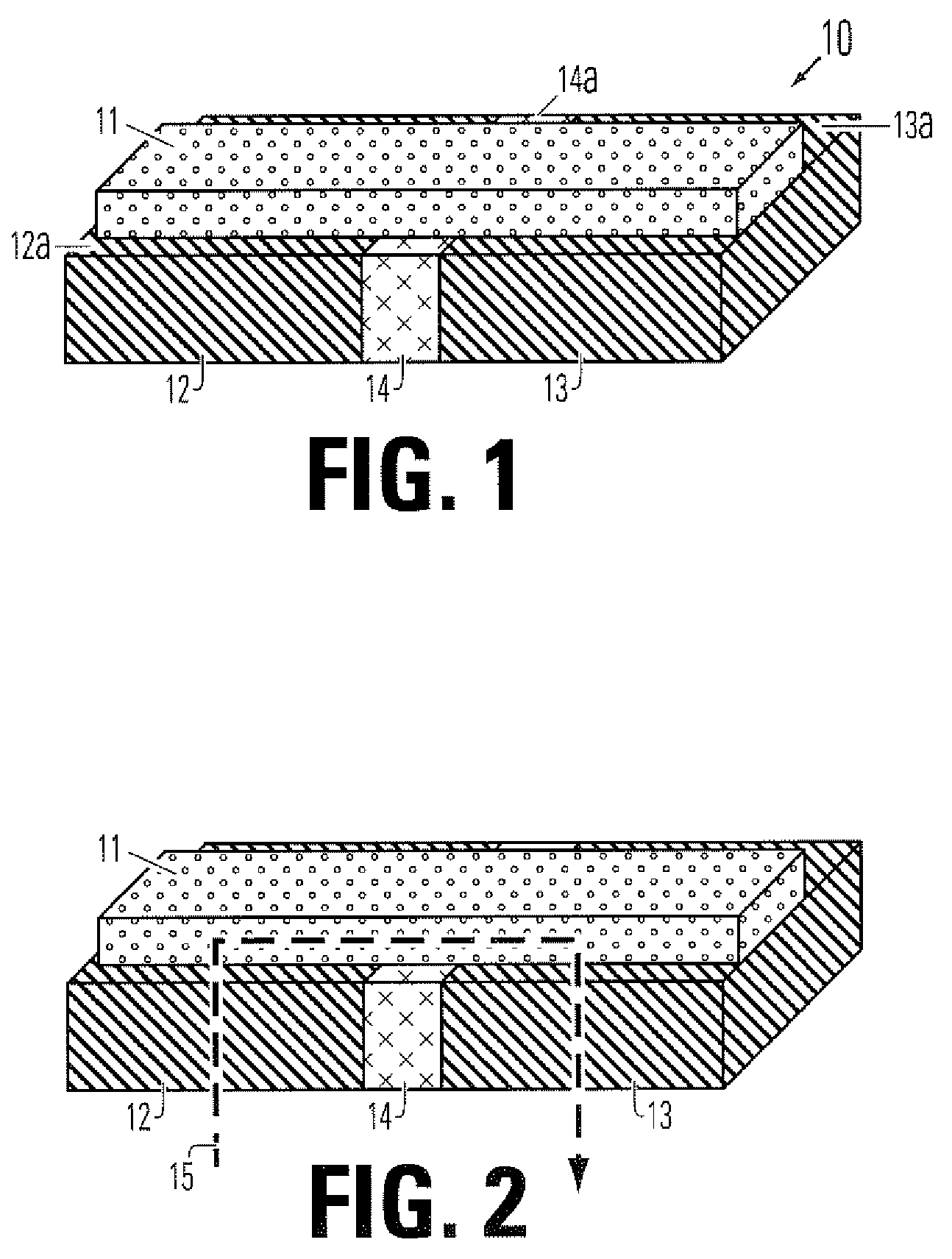

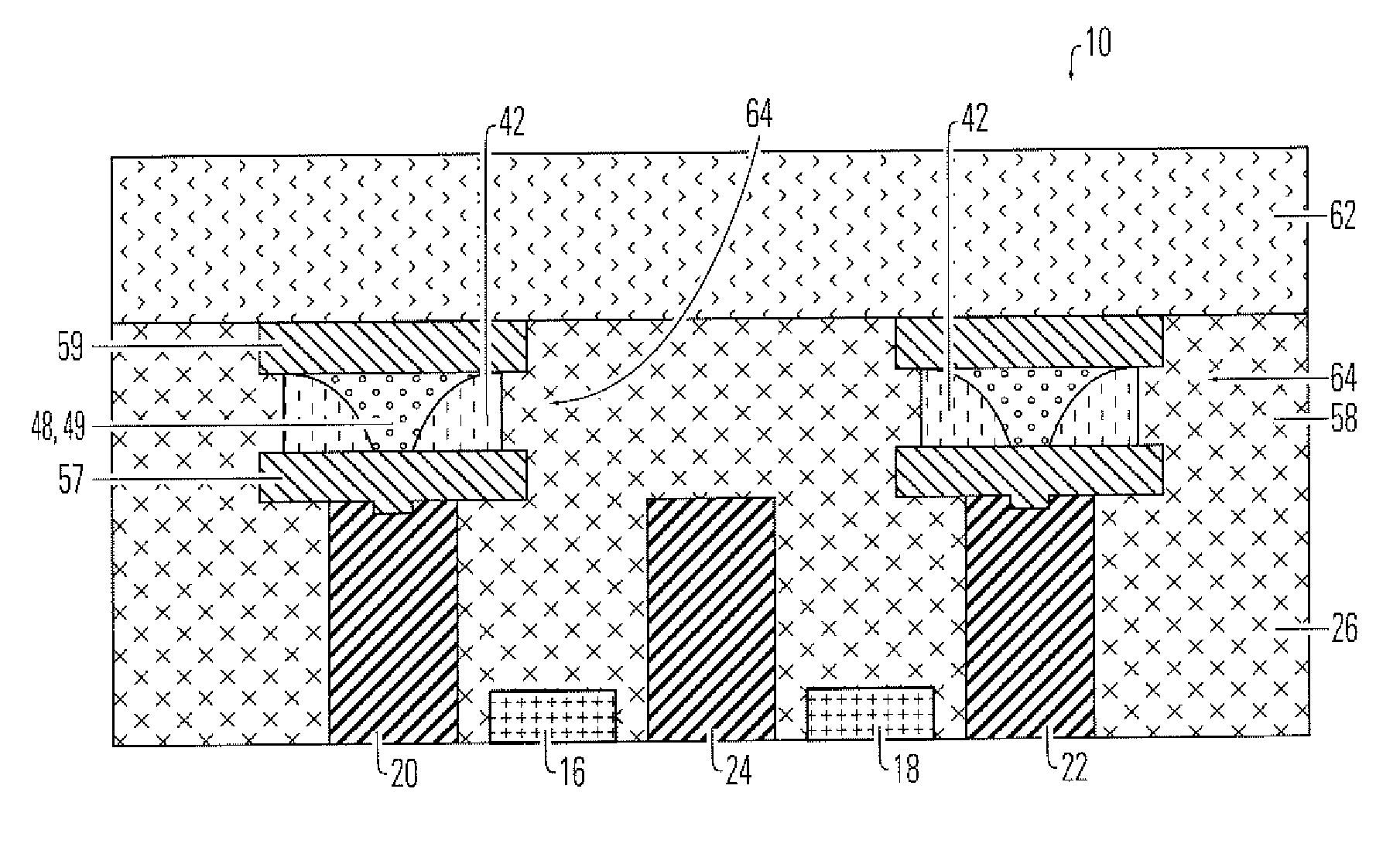

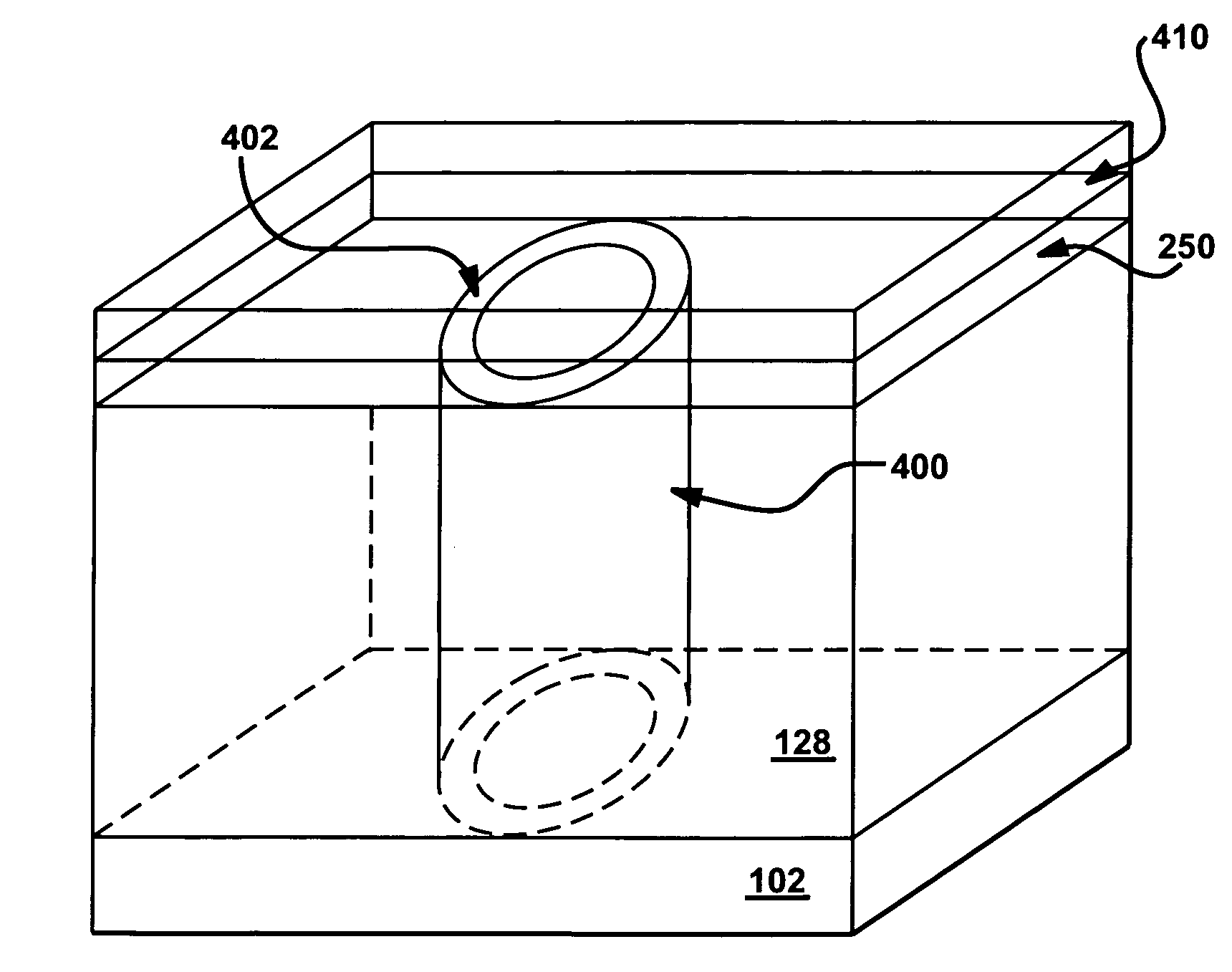

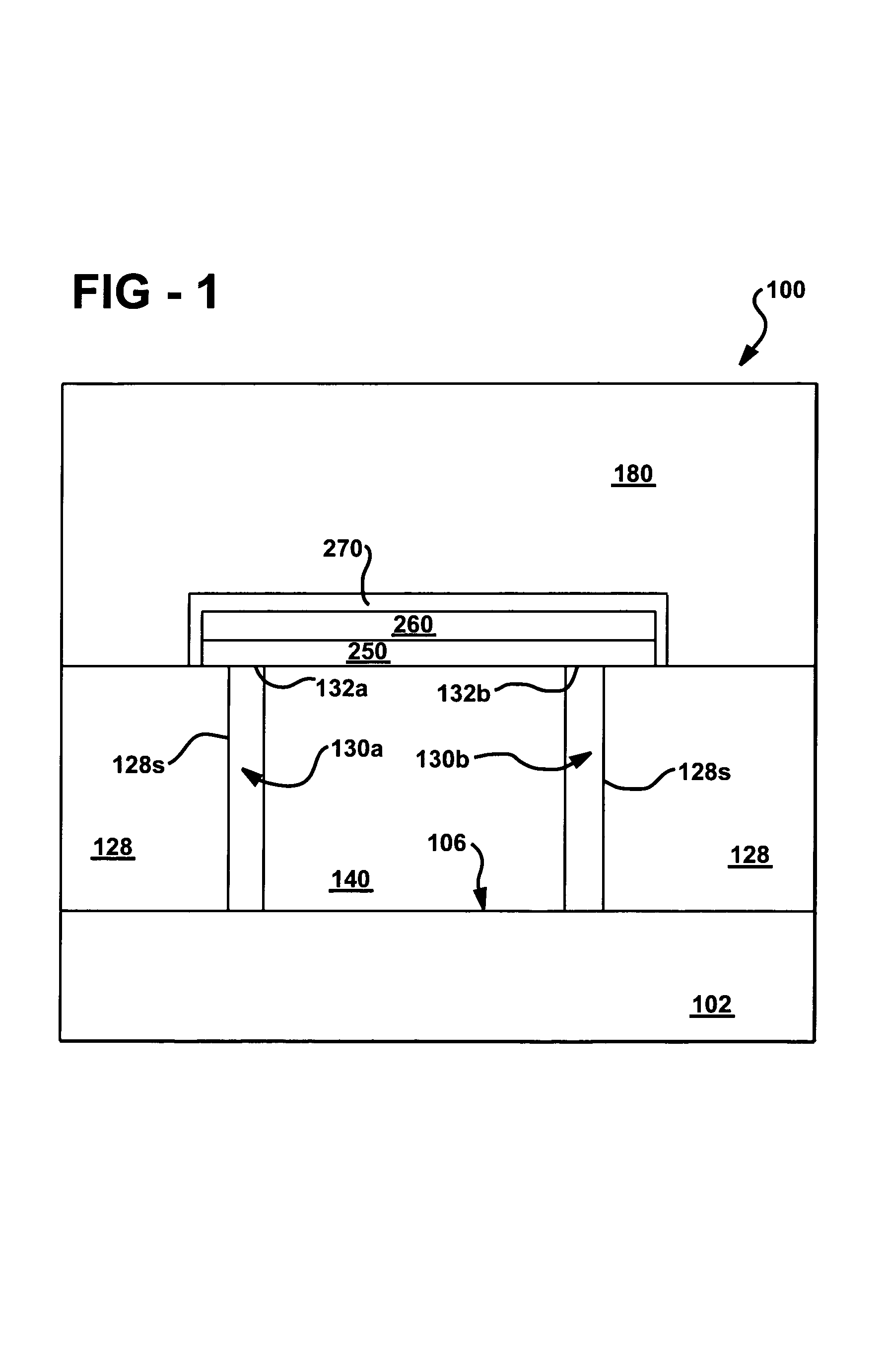

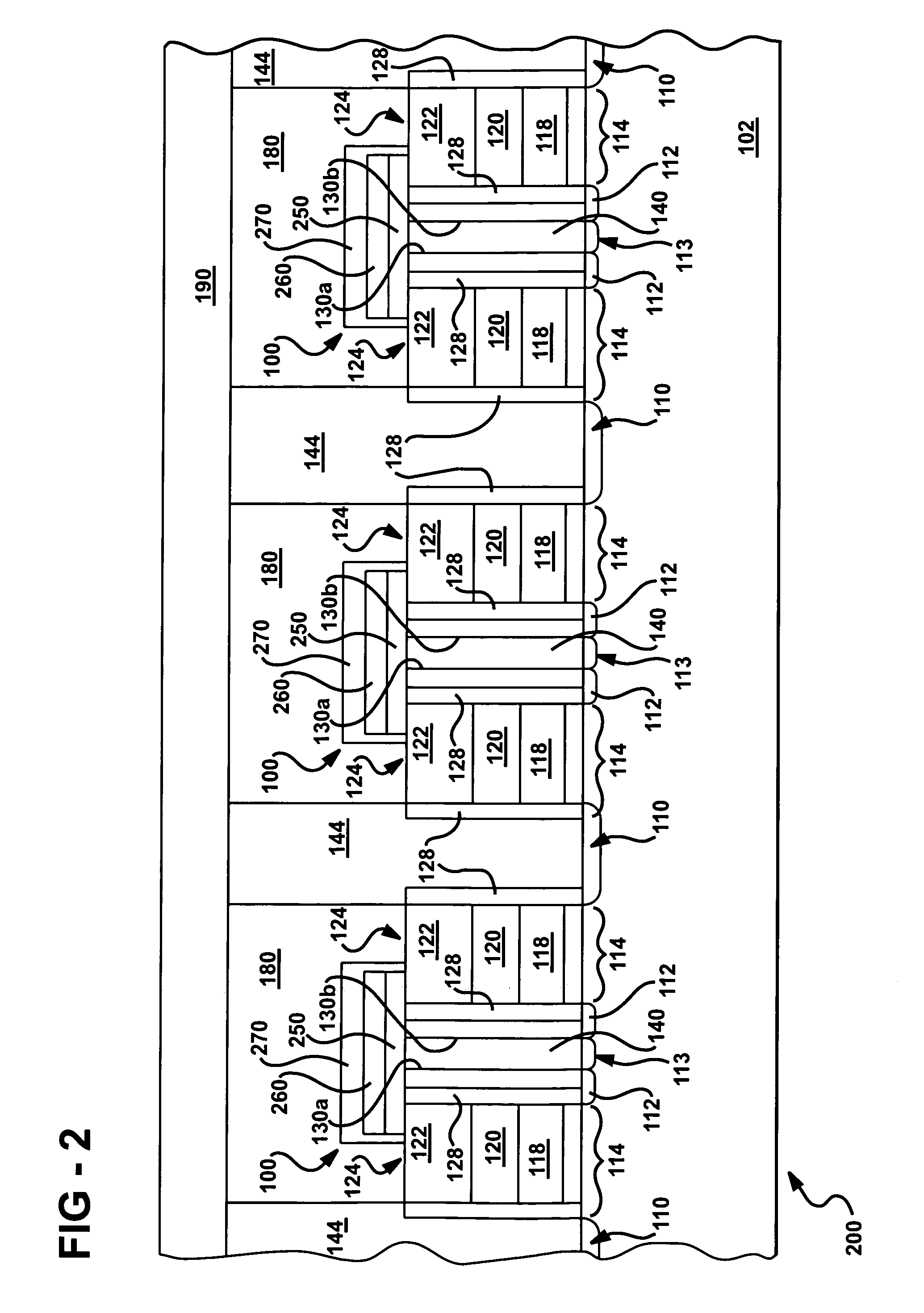

Thermally contained/insulated phase change memory device and method (combined)

ActiveUS20070108430A1Improve heat transfer characteristicsImprove insulation performanceSolid-state devicesBulk negative resistance effect devicesPhase-change memoryDielectric layer

A memory device with improved heat transfer characteristics. The device first includes a dielectric material layer; first and second electrodes, vertically separated and having mutually opposed contact surfaces. A phase change memory element is encased within the dielectric material layer, including a phase-change layer positioned between and in electrical contact with the electrodes, wherein the lateral extent of the phase change layer is less than the lateral extent of the electrodes. An isolation material is positioned between the phase change layer and the dielectric layer, wherein the thermal conductivity of the isolation material is lower than the thermal conductivity of the dielectric material.

Owner:MACRONIX INT CO LTD

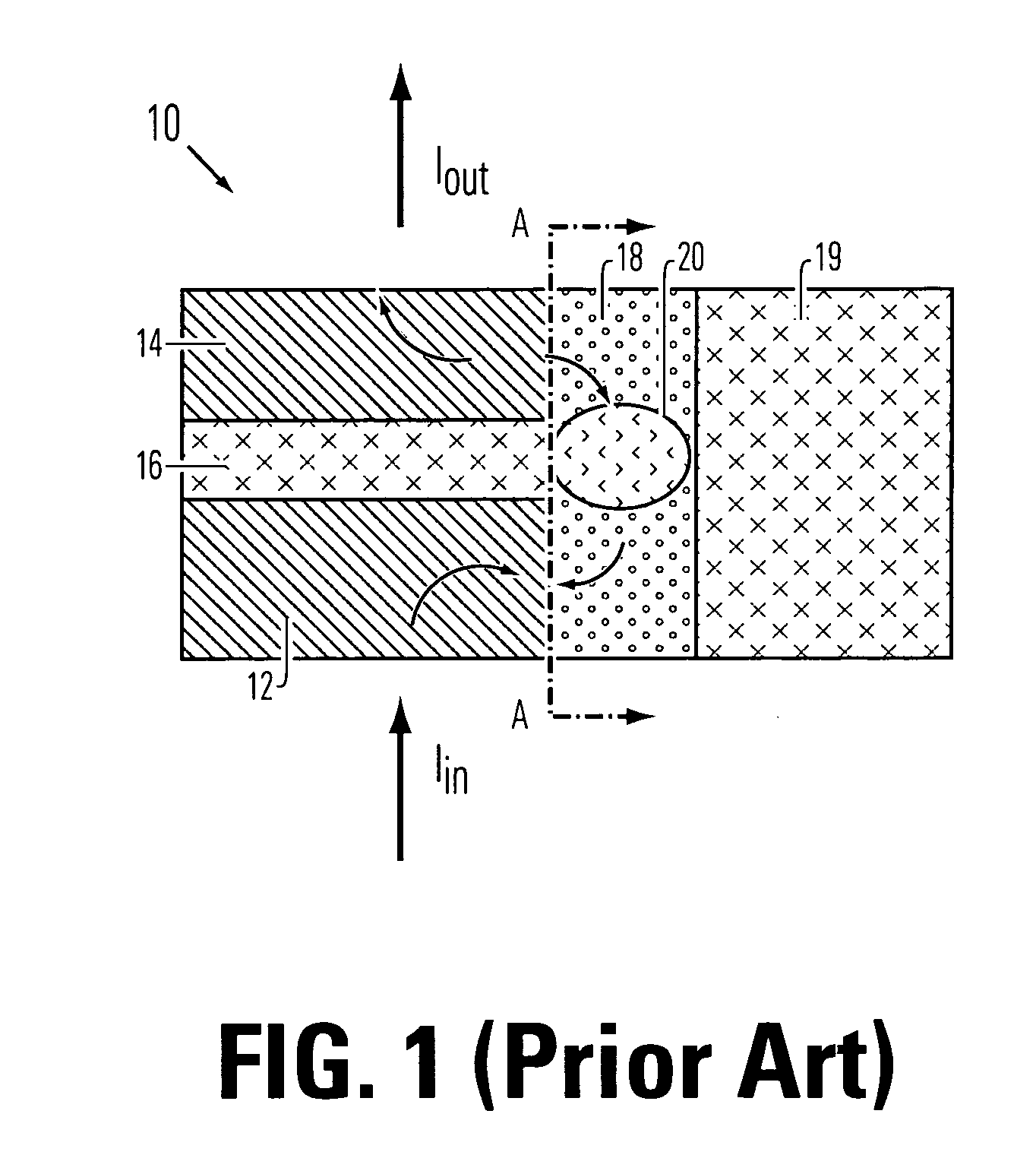

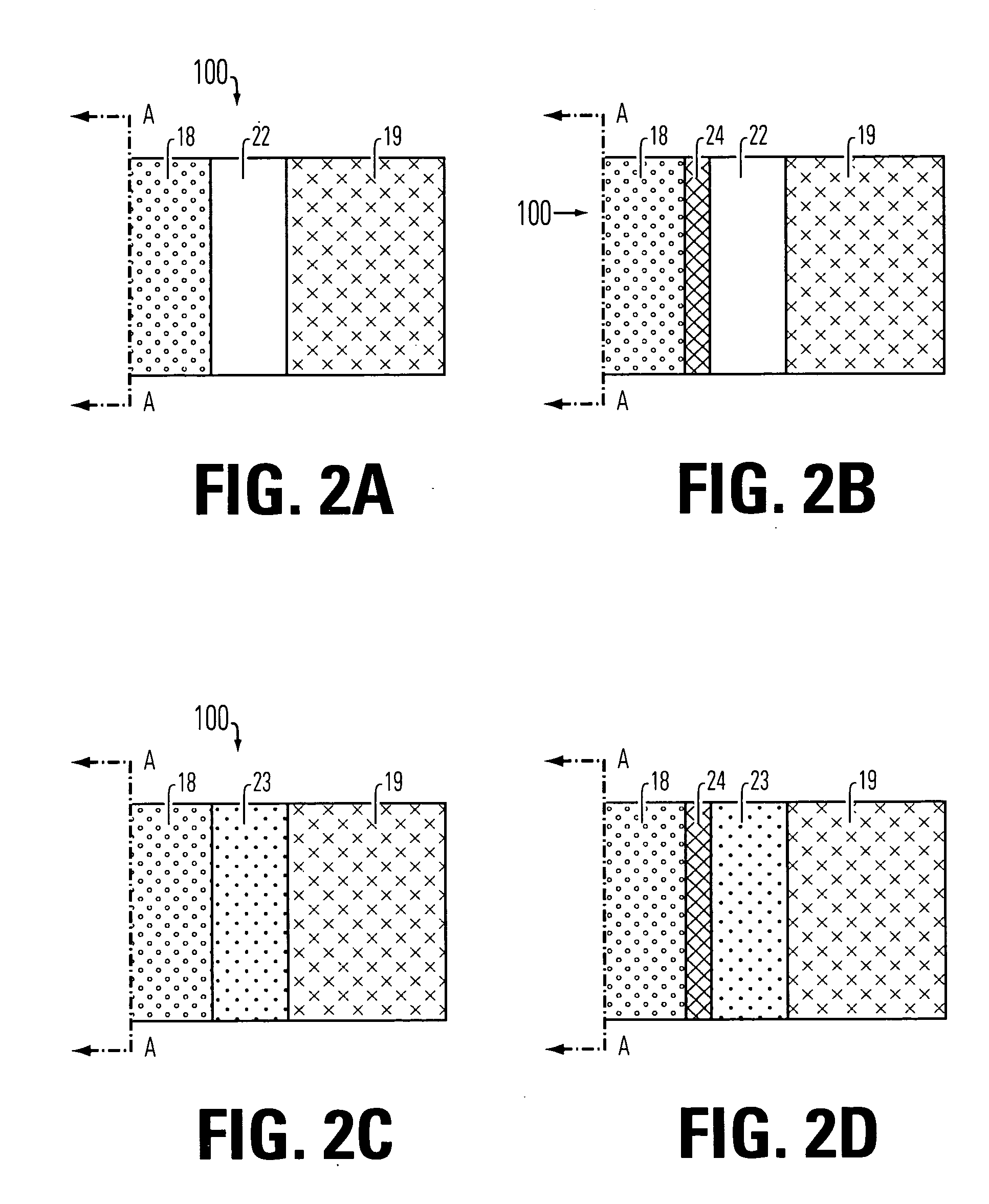

Electrically programmable memory element with improved contacts

Owner:OVONYX MEMORY TECH LLC

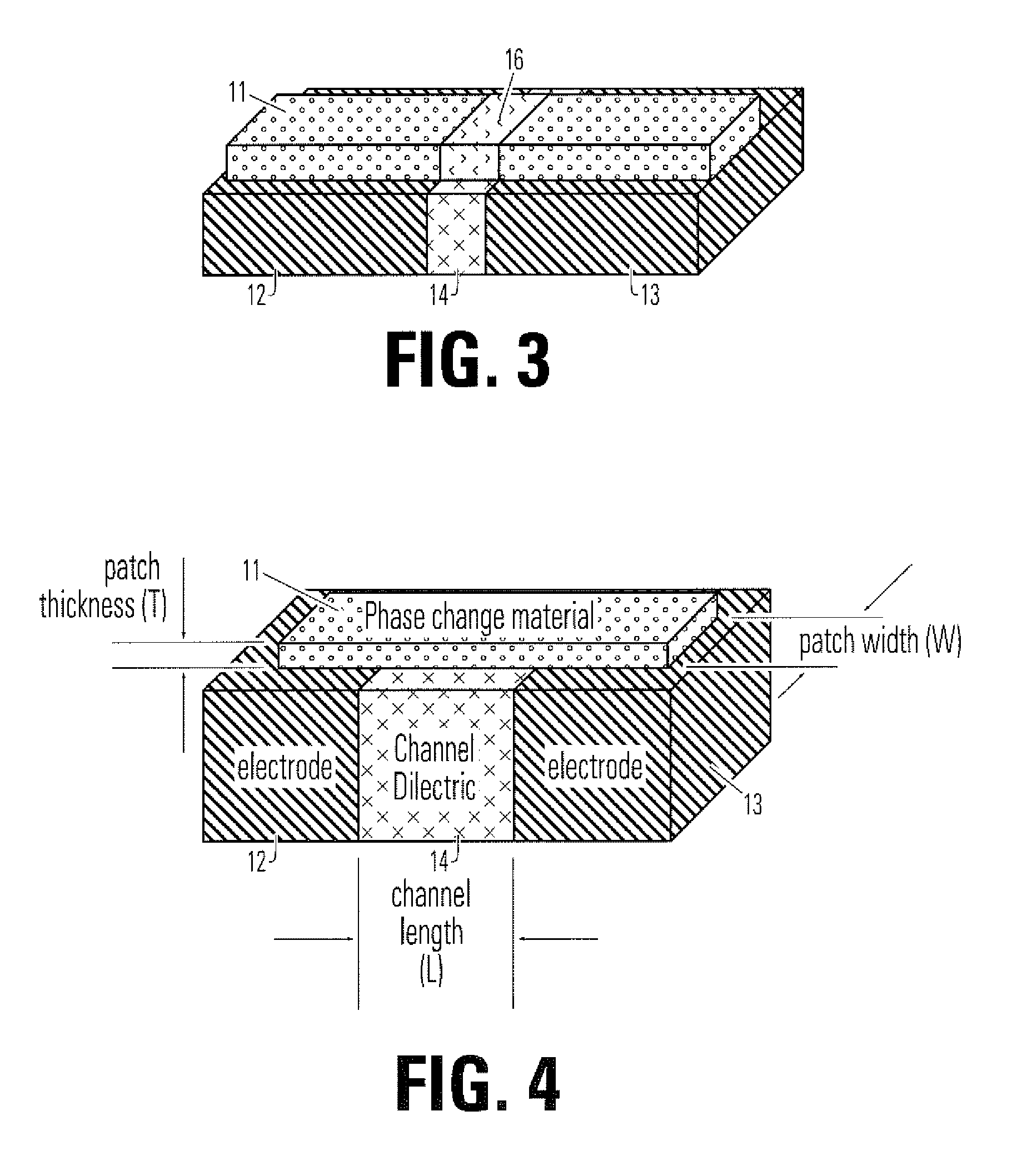

Phase Change Memory Cell and Manufacturing Method

ActiveUS20070121363A1Raise the transition temperatureLower transition temperatureSolid-state devicesDigital storageElectricityPhase-change memory

A phase change memory cell includes first and second electrodes having generally coplanar surfaces spaced apart by a gap and a phase change bridge electrically coupling the first and second electrodes. The phase change bridge may extend over the generally coplanar surfaces and across the gap. The phase change bridge has a higher transition temperature bridge portion and a lower transition temperature portion. The lower transition temperature portion comprises a phase change region which can be transitioned from generally crystalline to generally amorphous states at a lower temperature than the higher transition temperature portion. A method for making a phase change memory cell is also disclosed.

Owner:MACRONIX INT CO LTD

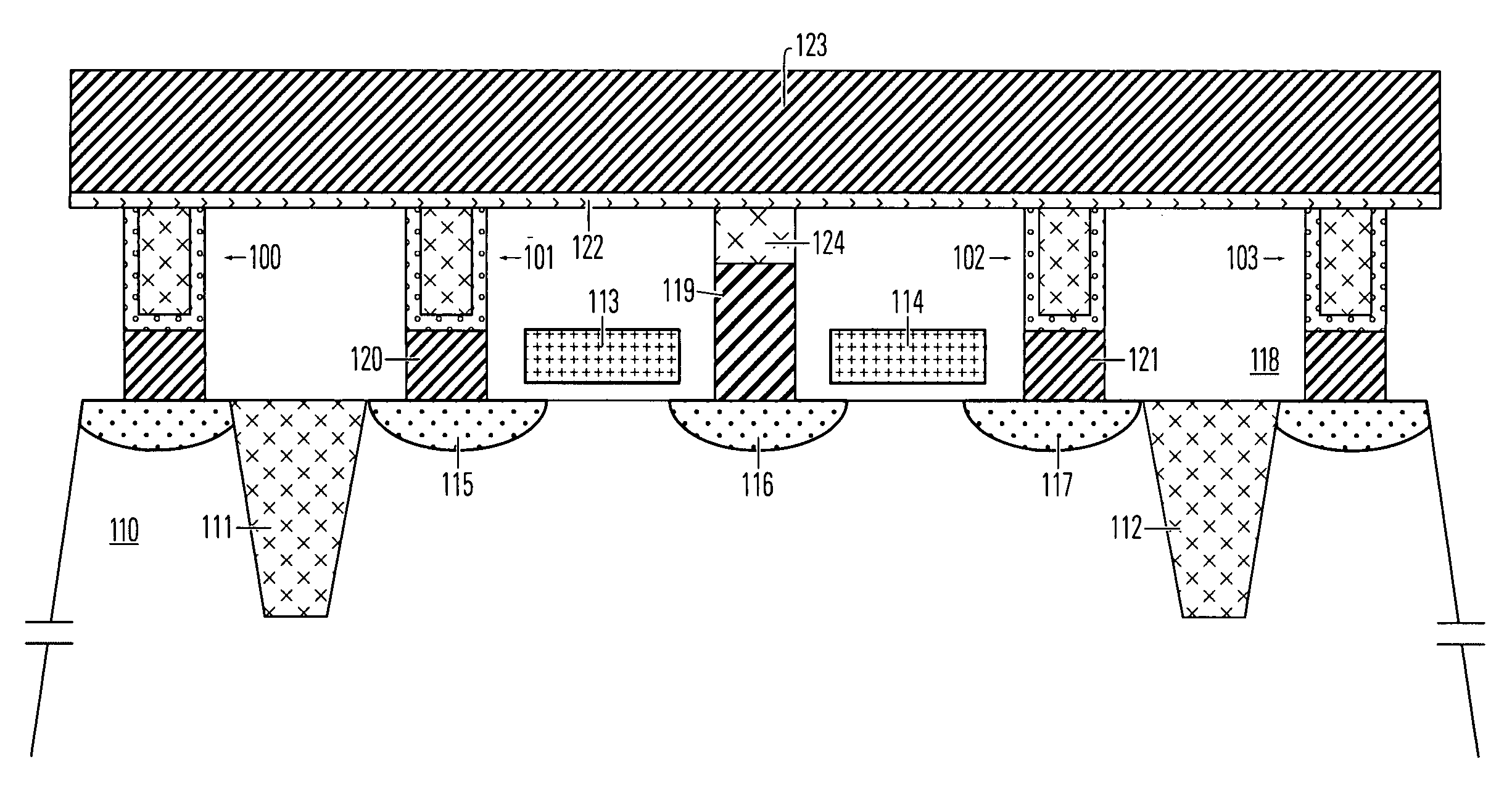

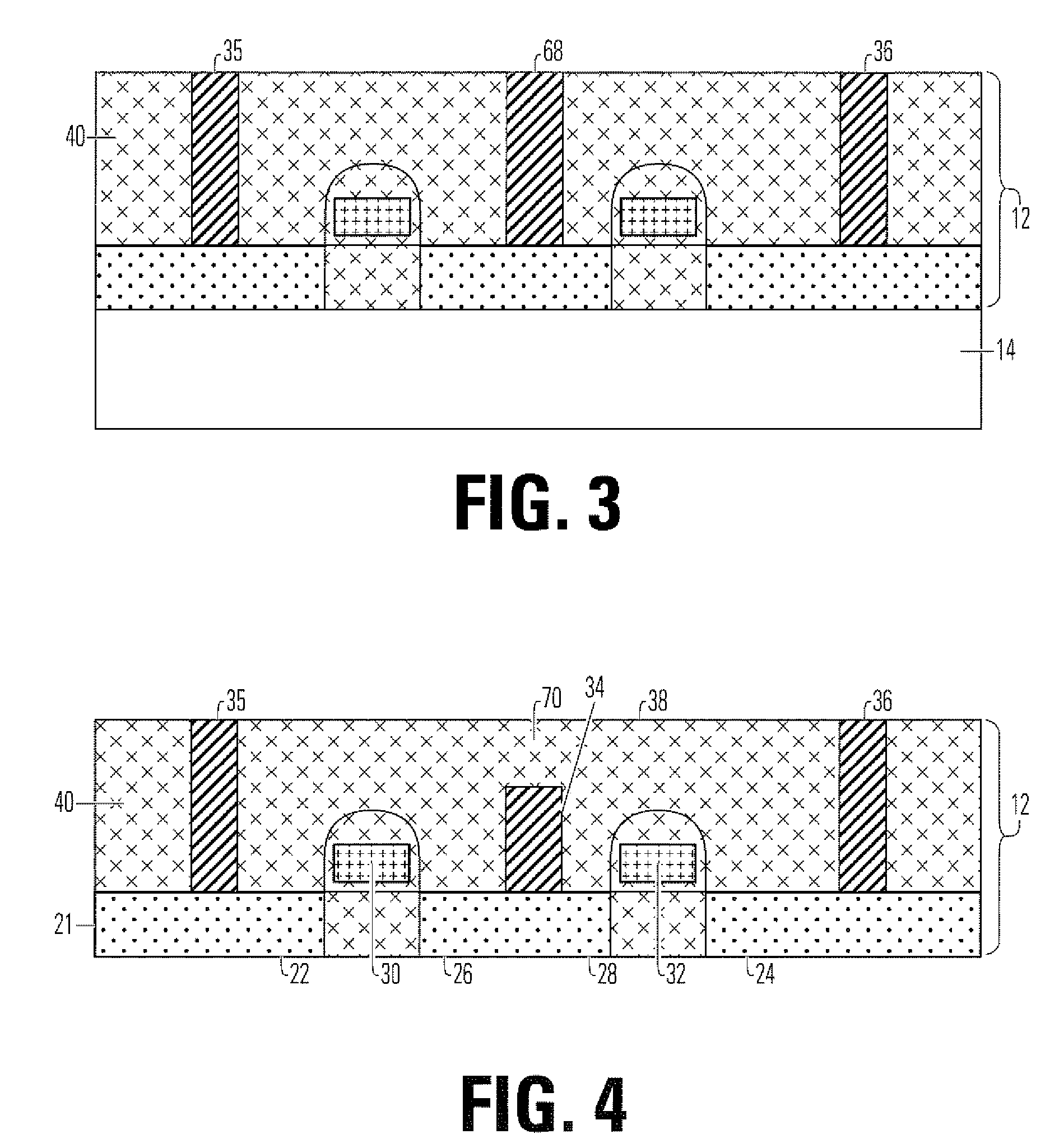

Phase changeable memory cells and methods of forming the same

InactiveUS20060118913A1Solid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryPhase-change material

A phase changeable memory cell is provided. The phase changeable memory cell includes a lower interlayer dielectric layer formed on a semiconductor substrate and a lower conductive plug passing through the lower interlayer dielectric layer. The lower conductive plug is in contact with a phase change material pattern disposed on the lower interlayer dielectric layer. The phase change material pattern and the lower interlayer dielectric layer are covered with an upper interlayer dielectric layer. The phase change material pattern is in direct contact with a conductive layer pattern, which is disposed in a plate line contact hole passing through the upper interlayer dielectric layer. Methods of fabricating the phase changeable memory cell is also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

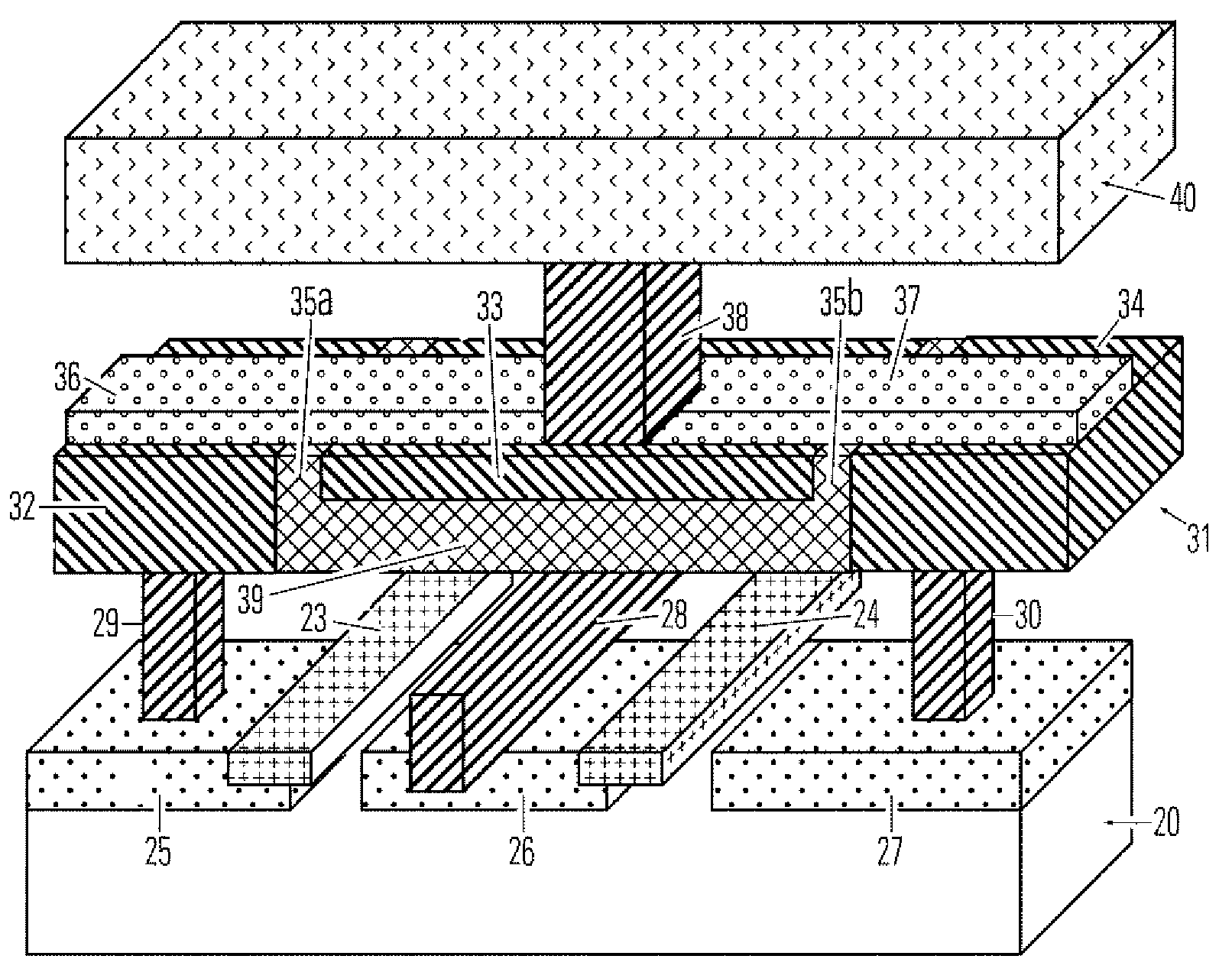

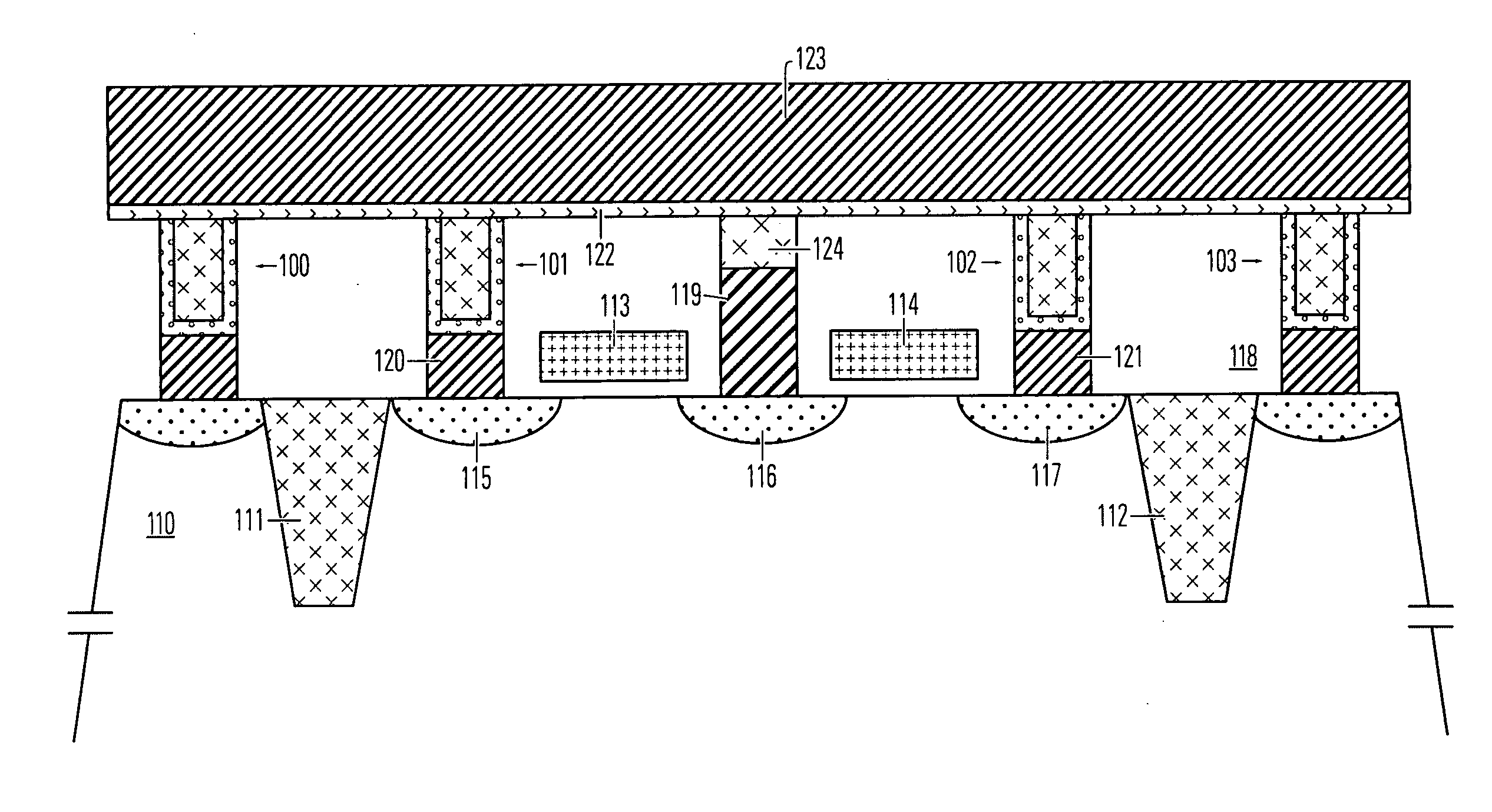

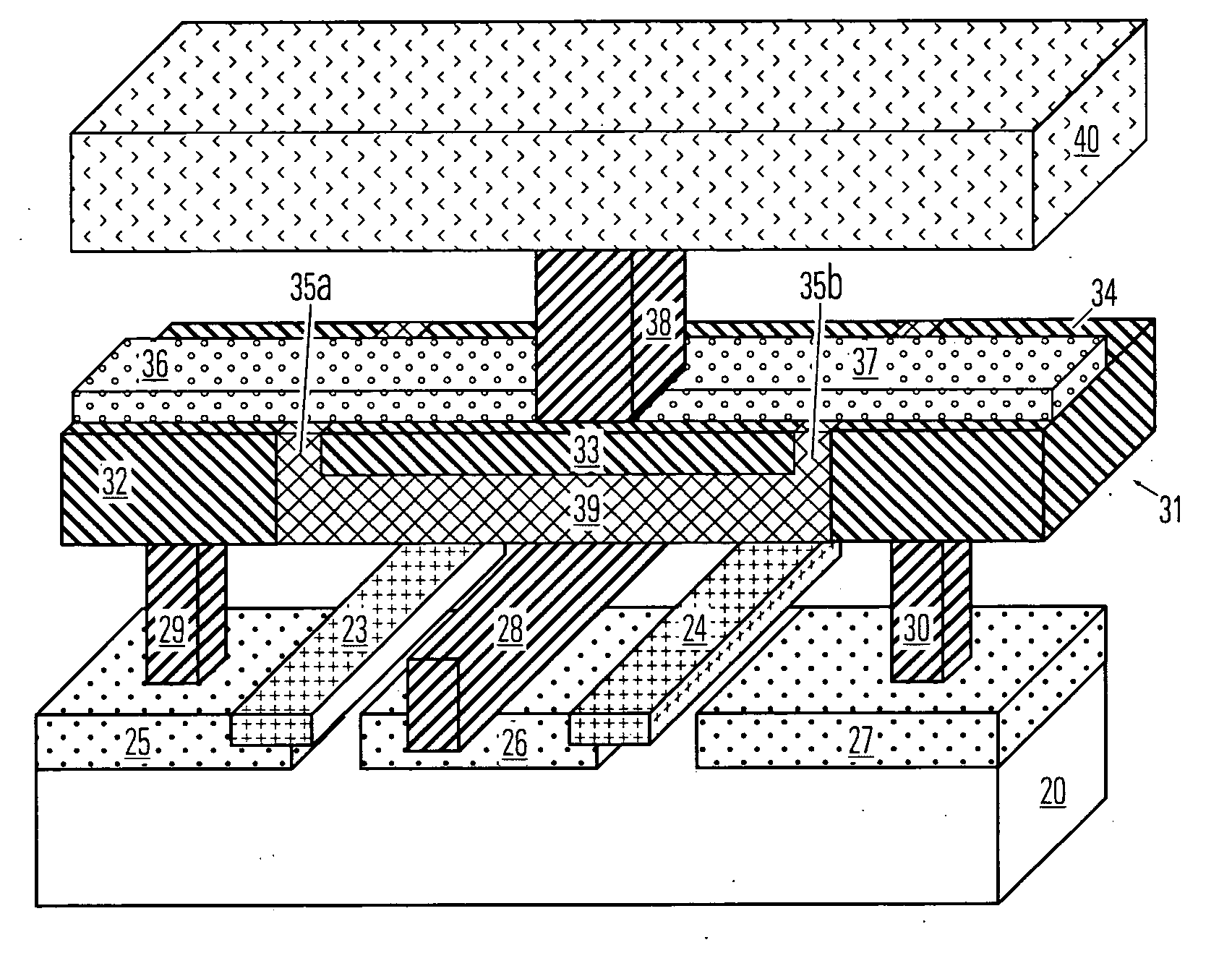

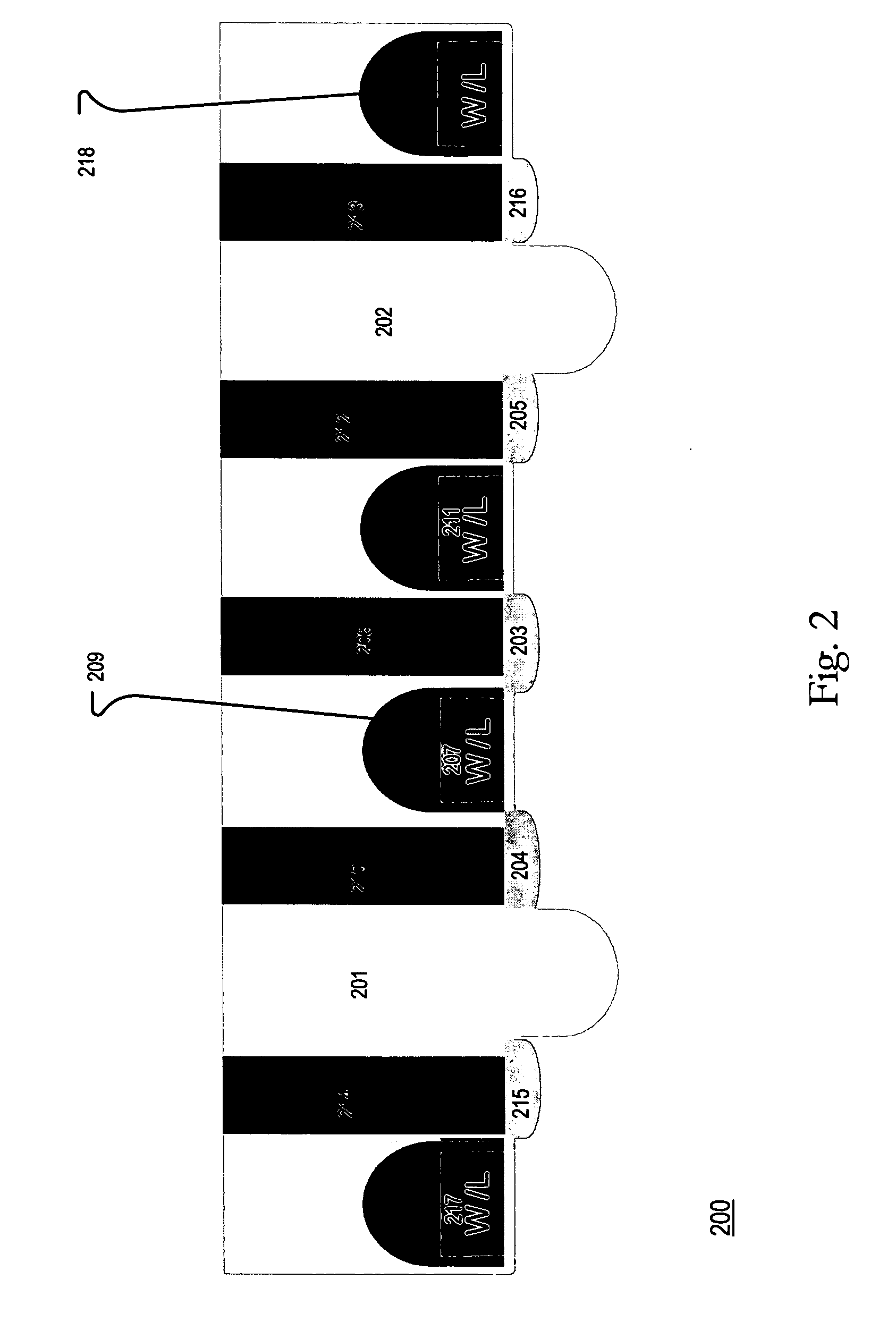

Method of manufacturing a pipe shaped phase change memory

InactiveUS20070111429A1Low thermal conductivityLower average currentSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryEngineering

A manufacturing method for a pipe-shaped memory cell device includes forming a bottom electrode having a top surface; forming a fill layer over the electrode, with a via having sides, extending from a top surface of the fill layer to the top surface of the bottom electrode; forming a conformal layer of programmable resistive material within the via, the conformal layer contacting the electrode and extending along the sides of the via to the top surface; and forming a top electrode in contact with the conformal layer over the fill layer.

Owner:MACRONIX INT CO LTD

Phase change memory cell and manufacturing method

A phase change memory cell includes first and second electrodes electrically coupled by a phase change element. At least a section of the phase change element comprises a higher reset transition temperature portion and a lower reset transition temperature portion. The lower reset transition temperature portion comprises a phase change region which can be transitioned, by the passage of electrical current therethrough, from generally crystalline to generally amorphous states at a lower temperature than the higher reset transition temperature portion. The phase change element may comprise an outer, generally tubular, higher reset transition temperature portion surrounding an inner, lower reset transition temperature portion.

Owner:MACRONIX INT CO LTD

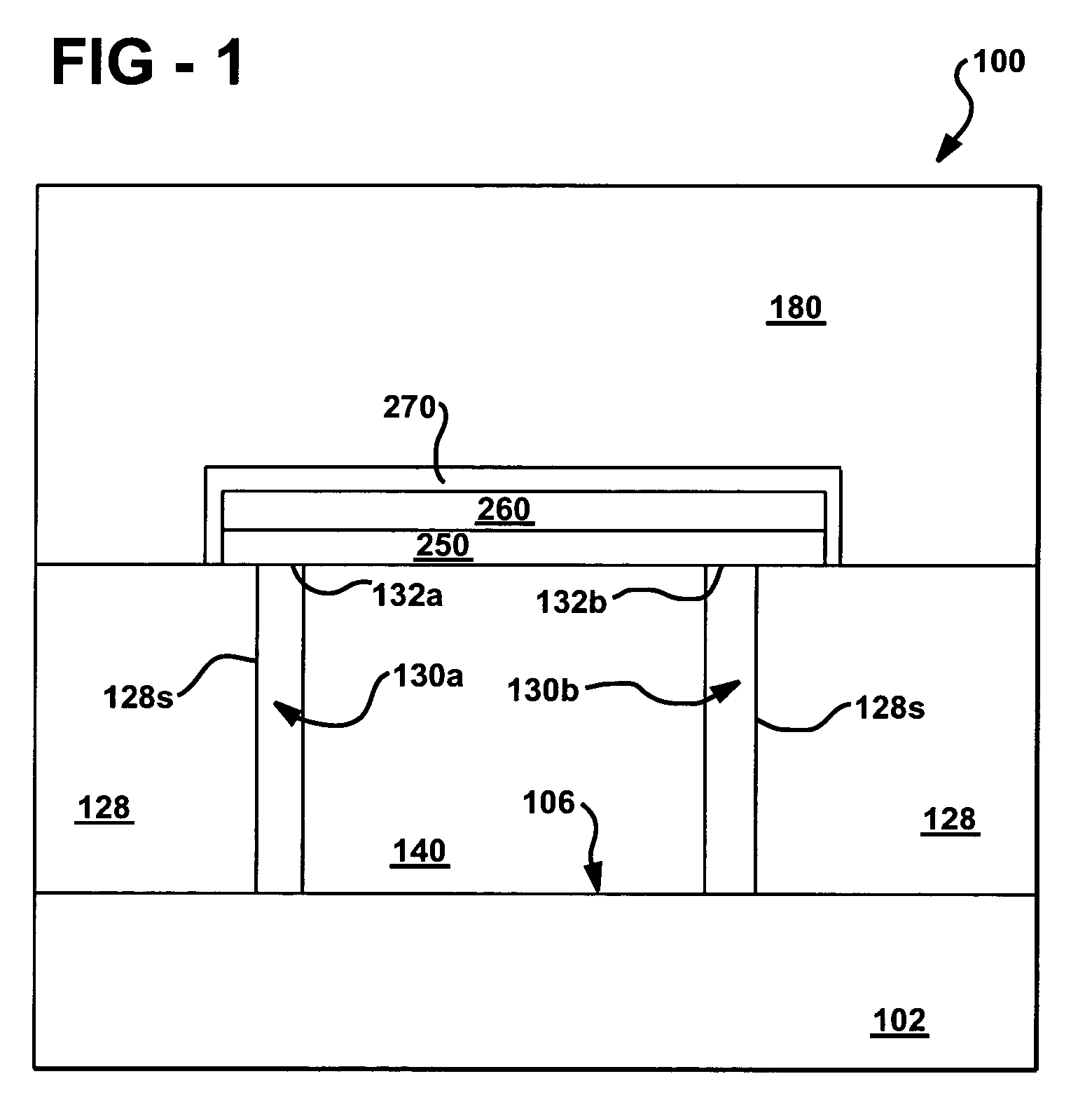

Thermally insulated phase change memory device and manufacturing method

ActiveUS20070109836A1Reduce the required powerImprove flatnessSolid-state devicesDigital storagePhase-change memoryEngineering

A thermally insulated memory device comprises a memory cell, the memory cell having electrodes with a via extending therebetween, a thermal insulator within the via and defining a void extending between the electrode surfaces. A memory material, such as a phase change material, is within the void and electrically couples the electrodes to create a memory material element. The thermal insulator helps to reduce the power required to operate the memory material element. An electrode may contact the outer surface of a plug to accommodate any imperfections, such as the void-type imperfections, at the plug surface. Methods for making the device and accommodating plug surface imperfections are also disclosed.

Owner:MACRONIX INT CO LTD

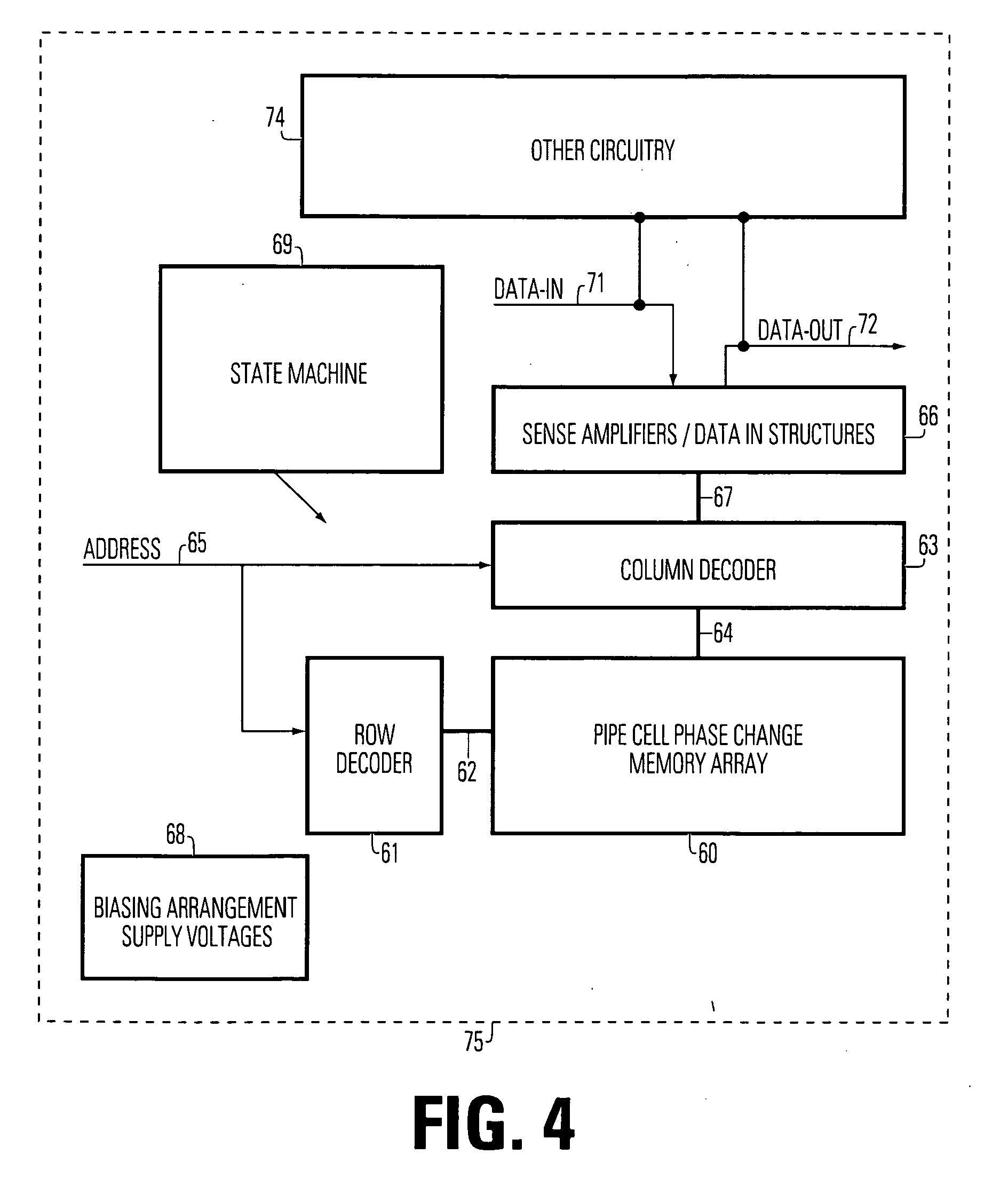

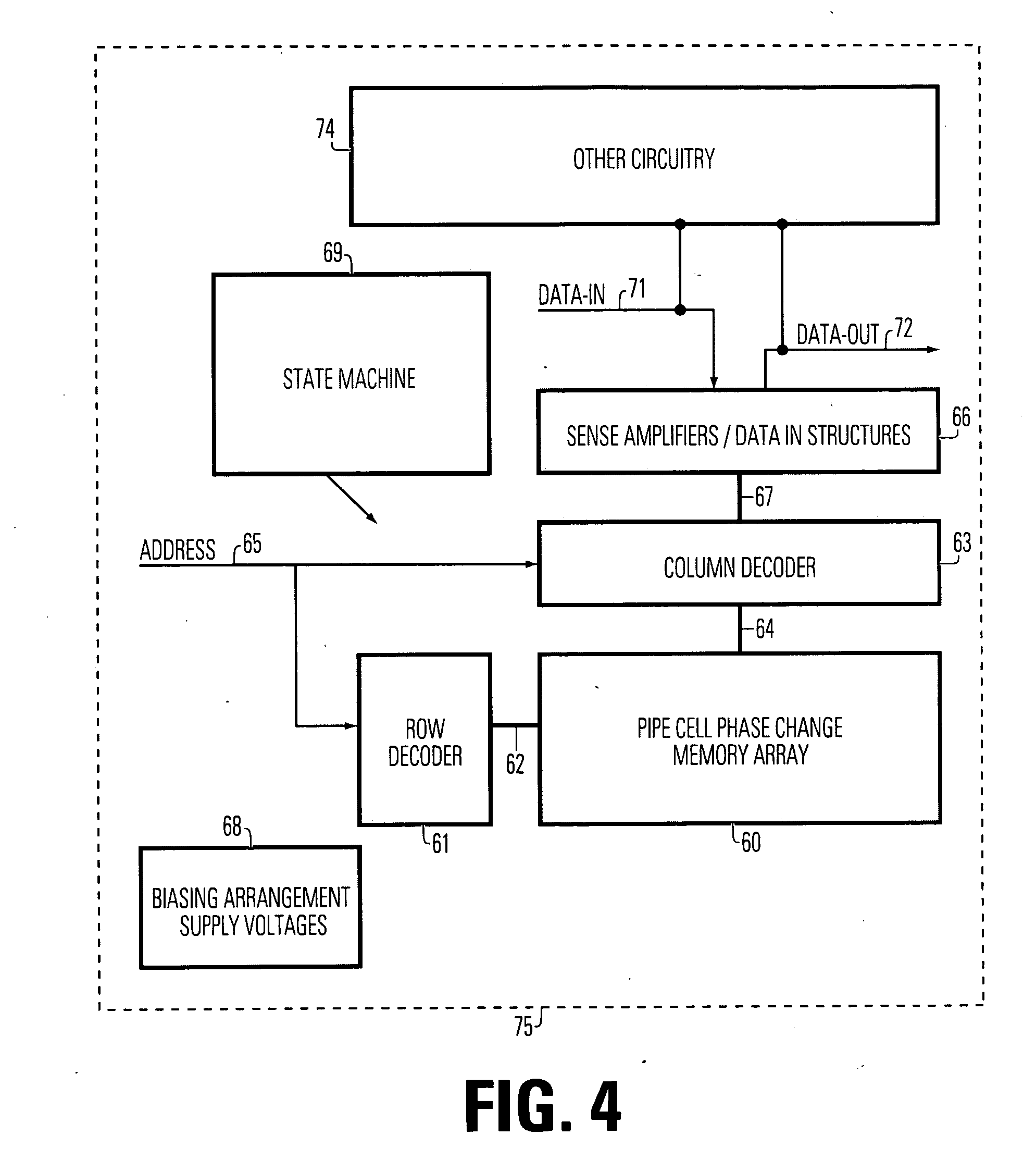

Pipe shaped phase change memory

ActiveUS20070108429A1High resistivityLow thermal conductivitySolid-state devicesBulk negative resistance effect devicesPhase-change memoryEngineering

A memory cell device includes a bottom electrode, pipe shaped member comprising phase change material and a top electrode in contact with the pipe-shaped member. An electrically and thermally insulating material is inside the pipe-shaped member. An integrated circuit including an array of pipe-shaped phase change memory cells is described.

Owner:MACRONIX INT CO LTD

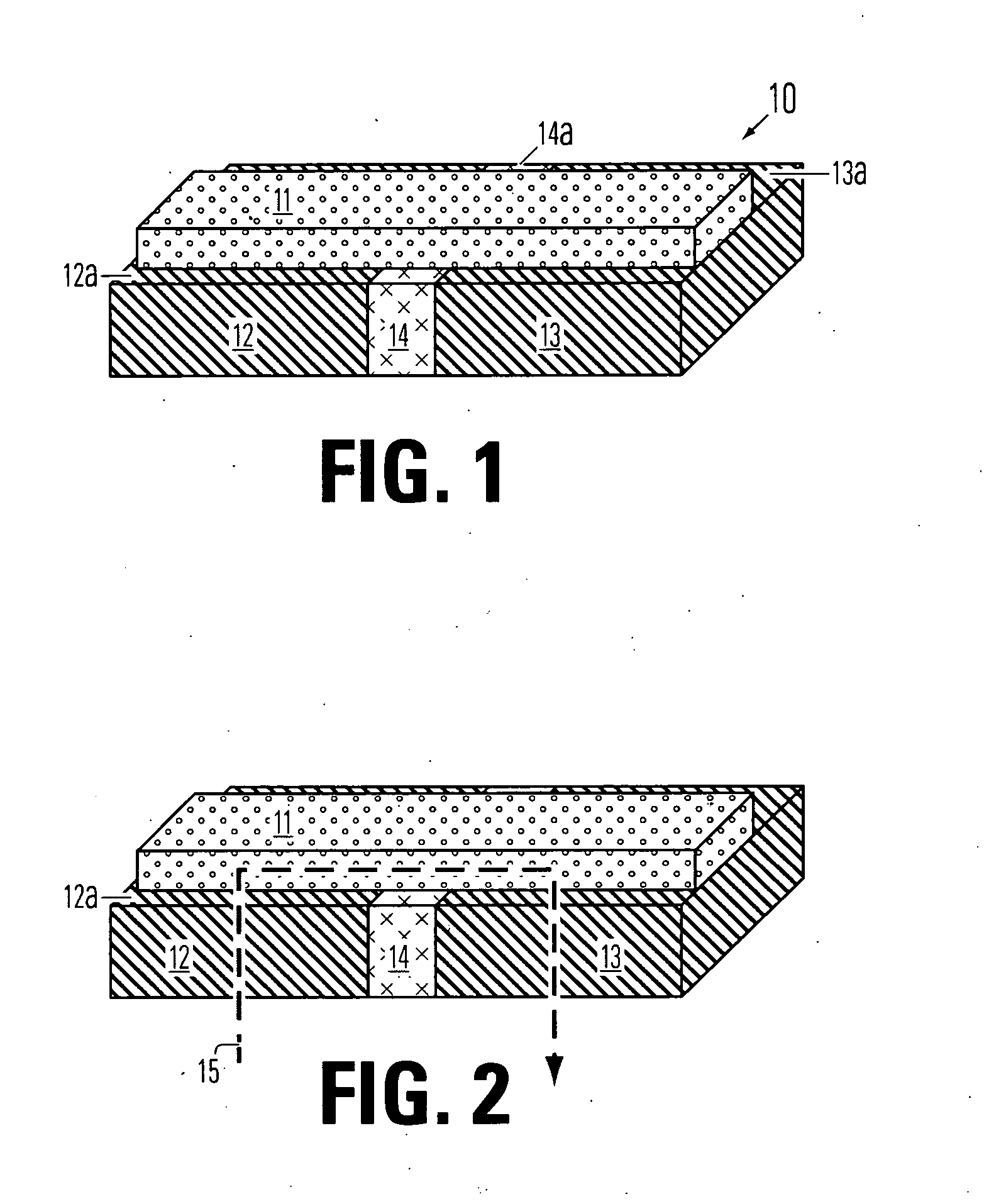

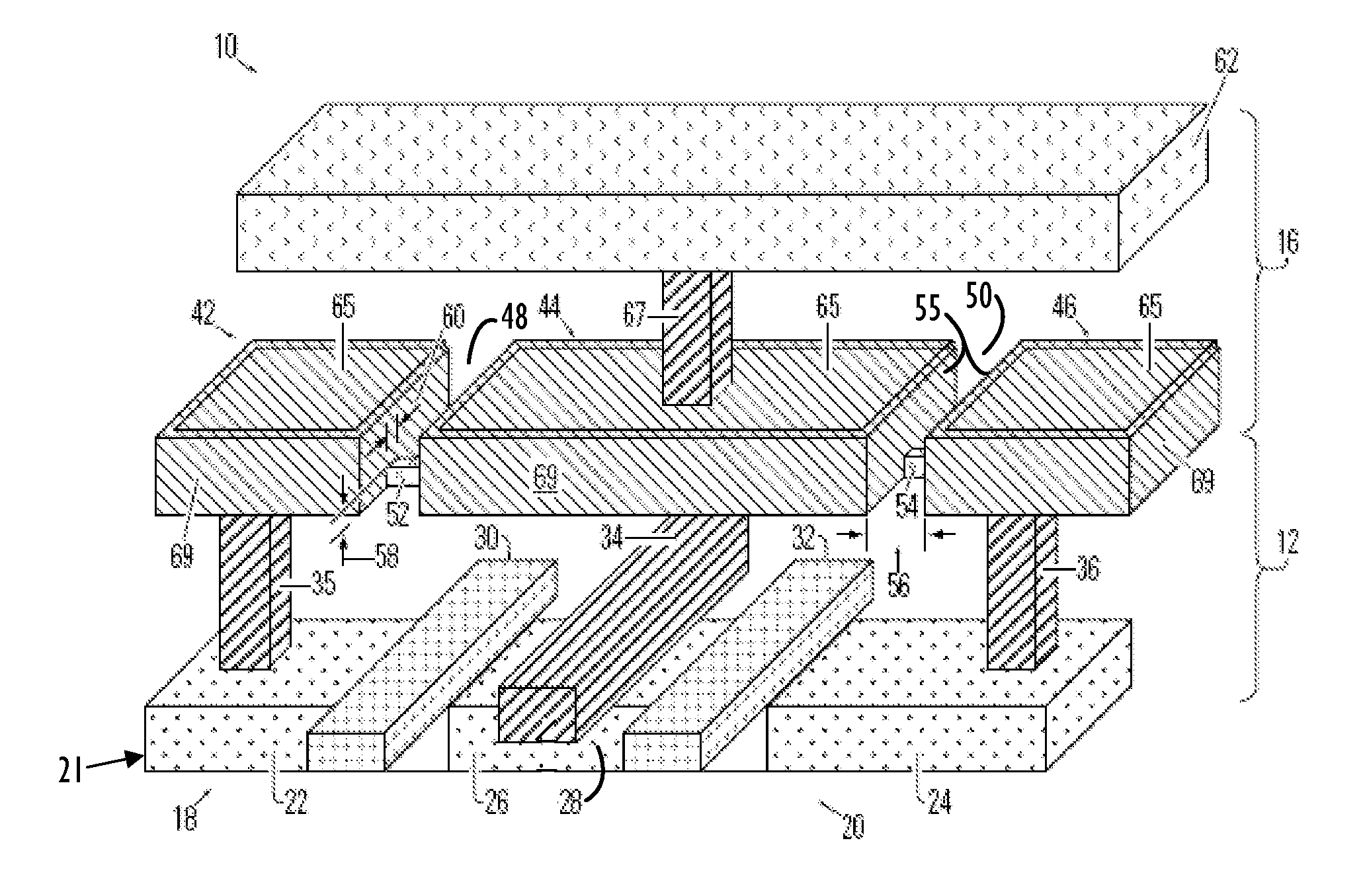

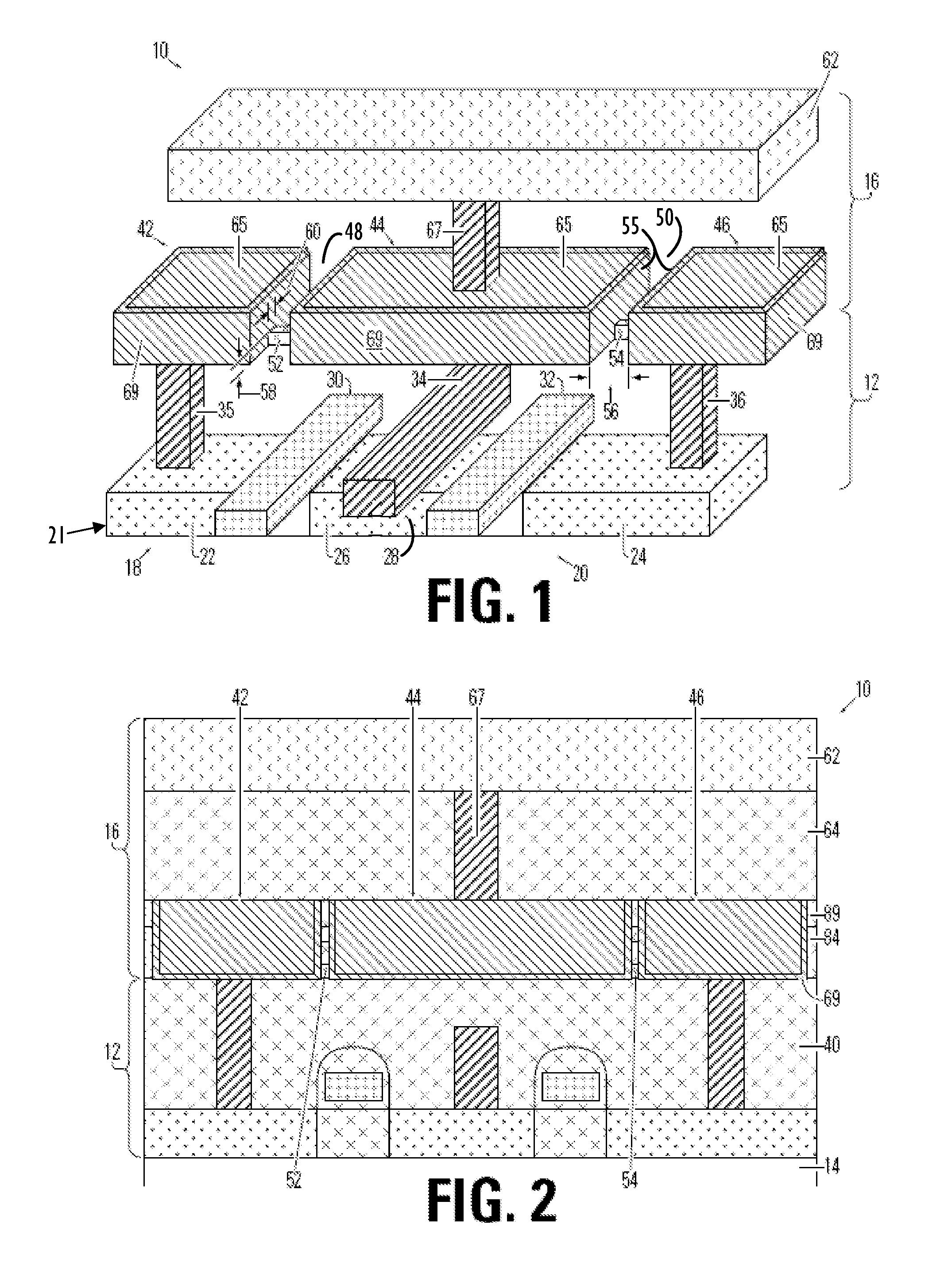

Thin film plate phase change RAM circuit and manufacturing method

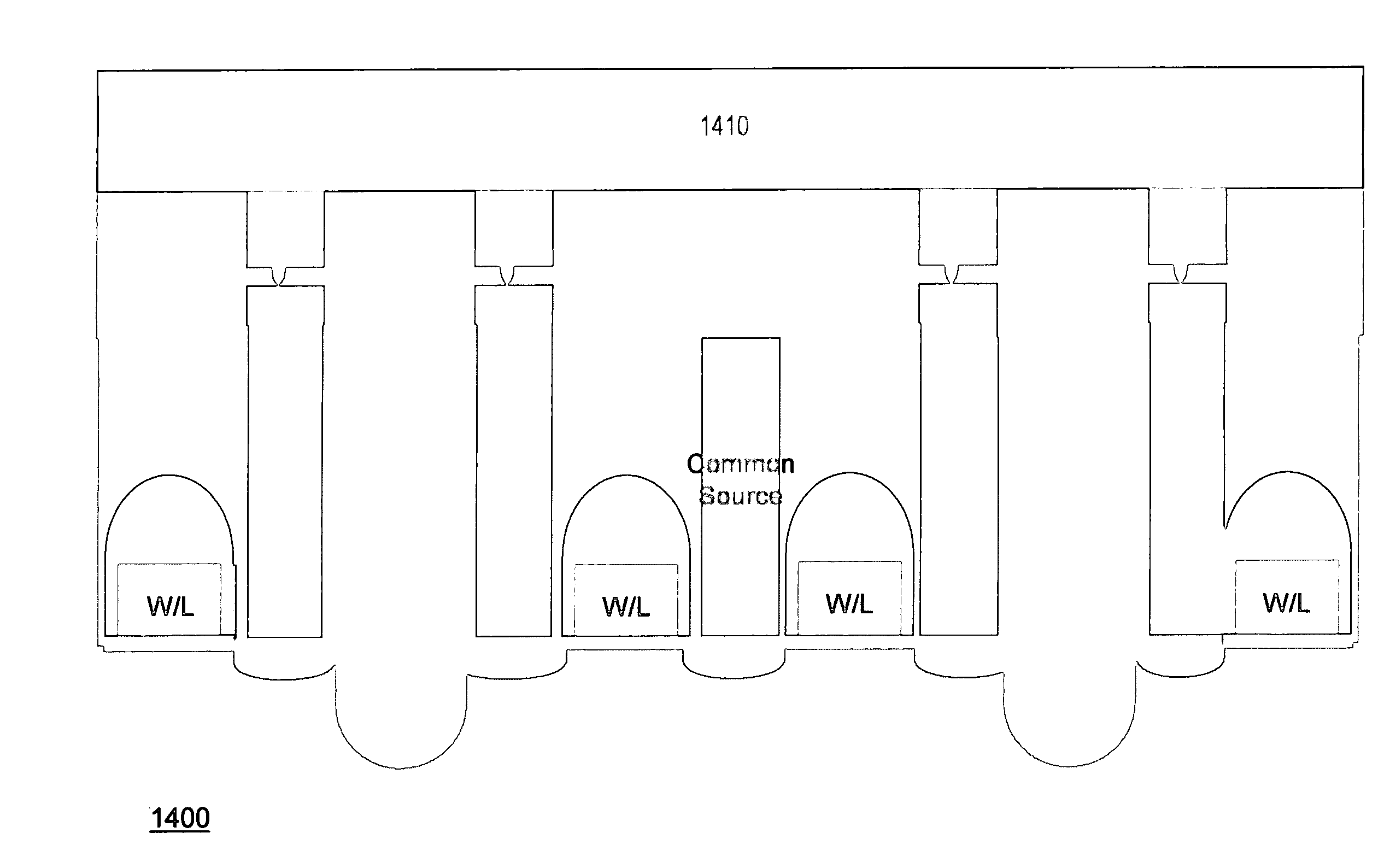

ActiveUS20060284157A1Simple structureReduce power consumptionSolid-state devicesBulk negative resistance effect devicesBit linePhase-change memory

A memory device comprising a access circuits, an electrode layer over the access circuits, an array of phase change memory bridges over the electrode layer, and a plurality of bit lines over the array of phase change memory bridges. The electrode layer includes electrode pairs. Electrode pairs include a first electrode having a top side, a second electrode having a top side and an insulating member between the first electrode and the second electrode. A bridge of memory material crosses the insulating member, and defines an inter-electrode path between the first and second electrodes across the insulating member.

Owner:MACRONIX INT CO LTD

Thermal isolation for an active-sidewall phase change memory cell

ActiveUS20070115794A1Improve insulation performanceMechanical recordingRecord information storageDielectricThermal isolation

A phase change memory device with improve thermal isolation. The device includes an electrode stack, including a first and second electrode elements, generally planar in form, separated by and in mutual contact with a dielectric spacer element, wherein the electrode stack includes a side surface; a phase change element having a bottom surface in contact with the electrode stack side surface, including electrical contact with the first and second electrode elements; and dielectric fill material surrounding and encasing the memory device, wherein the dielectric fill material is spaced from the phase change element, such that the phase change element and the dielectric fill material define a cavity adjacent the phase change element, and wherein the cavity contains a low pressure environment.

Owner:MACRONIX INT CO LTD

Vacuum cell thermal isolation for a phase change memory device

ActiveUS20070126040A1Improve insulation performanceSemiconductor/solid-state device manufacturingSemiconductor devicesThermal isolationPhase-change memory

A memory device with improved thermal isolation. The memory cell includes a first electrode element, having an upper surface; an insulator stack formed on the first electrode element, including first, second and third insulating members, all generally planar in form and having a central cavity formed therein and extending therethrough, wherein the second insulator member is recessed from the cavity; a phase change element, generally T-shaped in form, having a base portion extending into the cavity to make contact with the first electrode element and making contact with the first and third insulating members, and a crossbar portion extending over and in contact with the third insulating member, wherein the base portion of the phase change element, the recessed portions of the second insulating member and the surfaces of the first and third insulating members define a thermal isolation void; and a second electrode formed in contact with the phase change member.

Owner:MACRONIX INT CO LTD

Phase-change memory device and manufacturing method thereof

InactiveUS20050018526A1Easy to manufactureHigh yield rateSolid-state devicesDigital storagePhase-change memoryDielectric layer

The present invention is to provide a phase change memory device having a new structure which can be easily manufactured by mass-production with a high yield rate, therefore, reducing the cost of process and providing reliable device characteristics, and a manufacturing method thereof. The present invention provides a phase-change memory device comprising: a lower dielectric layer; a lower electrode, at least a part of the lateral surface of the lower electrode being surrounded by the lower dielectric layer; a thin dielectric layer including a pore having smaller area than the top surface of the lower electrode, aligned to the top surface of the lower electrode and extending to the top surface of the lower electrode; and a phase-change resistor filling the pore and formed on the thin dielectric layer. In the proposed structure of the present invention, the pores or local damaged spots can provide a micro path of current and localize the phase-changing volume in the phase-change resistor. Thus, the phase-change memory device can be operated with very low power.

Owner:LEE HEON

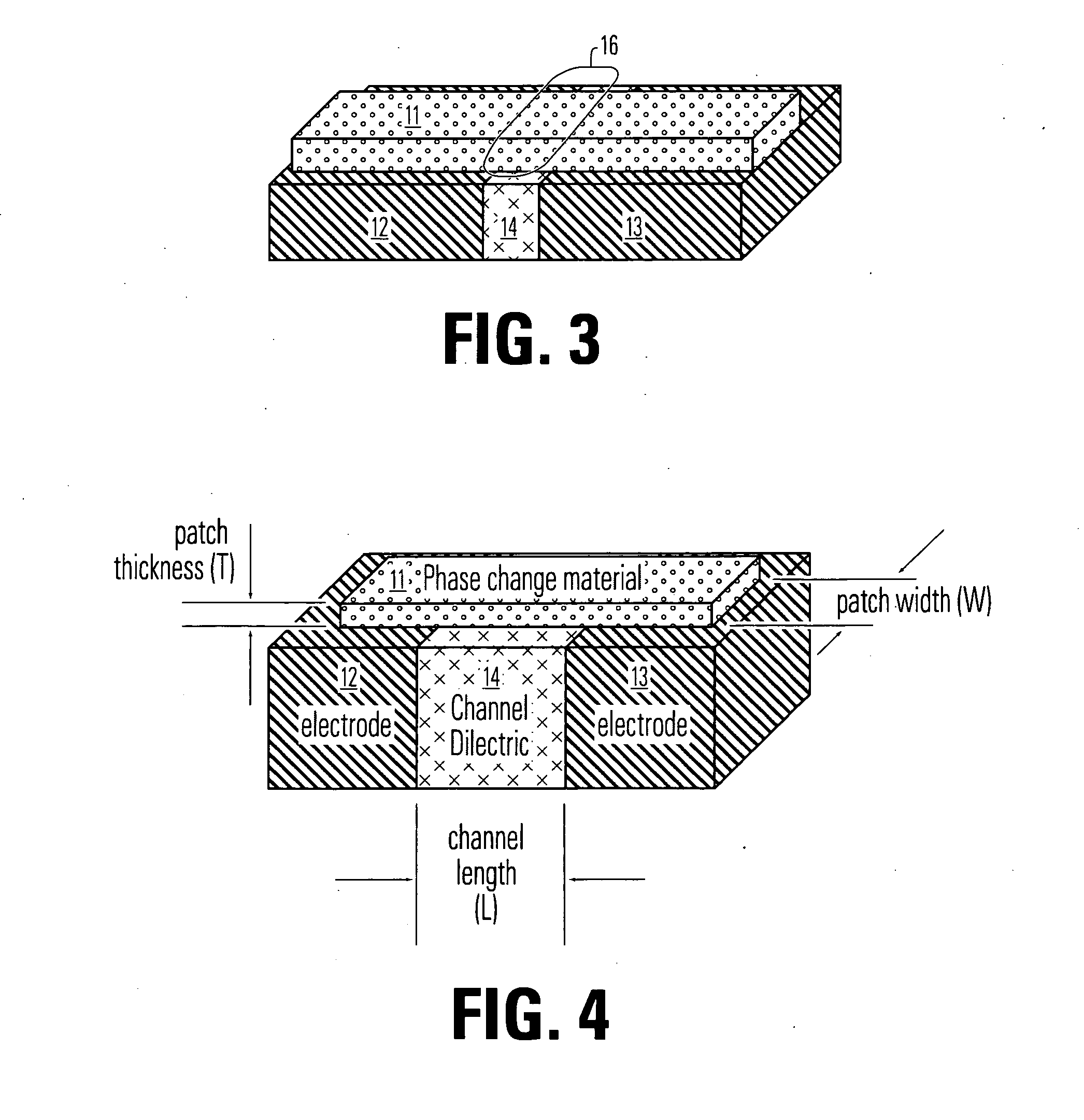

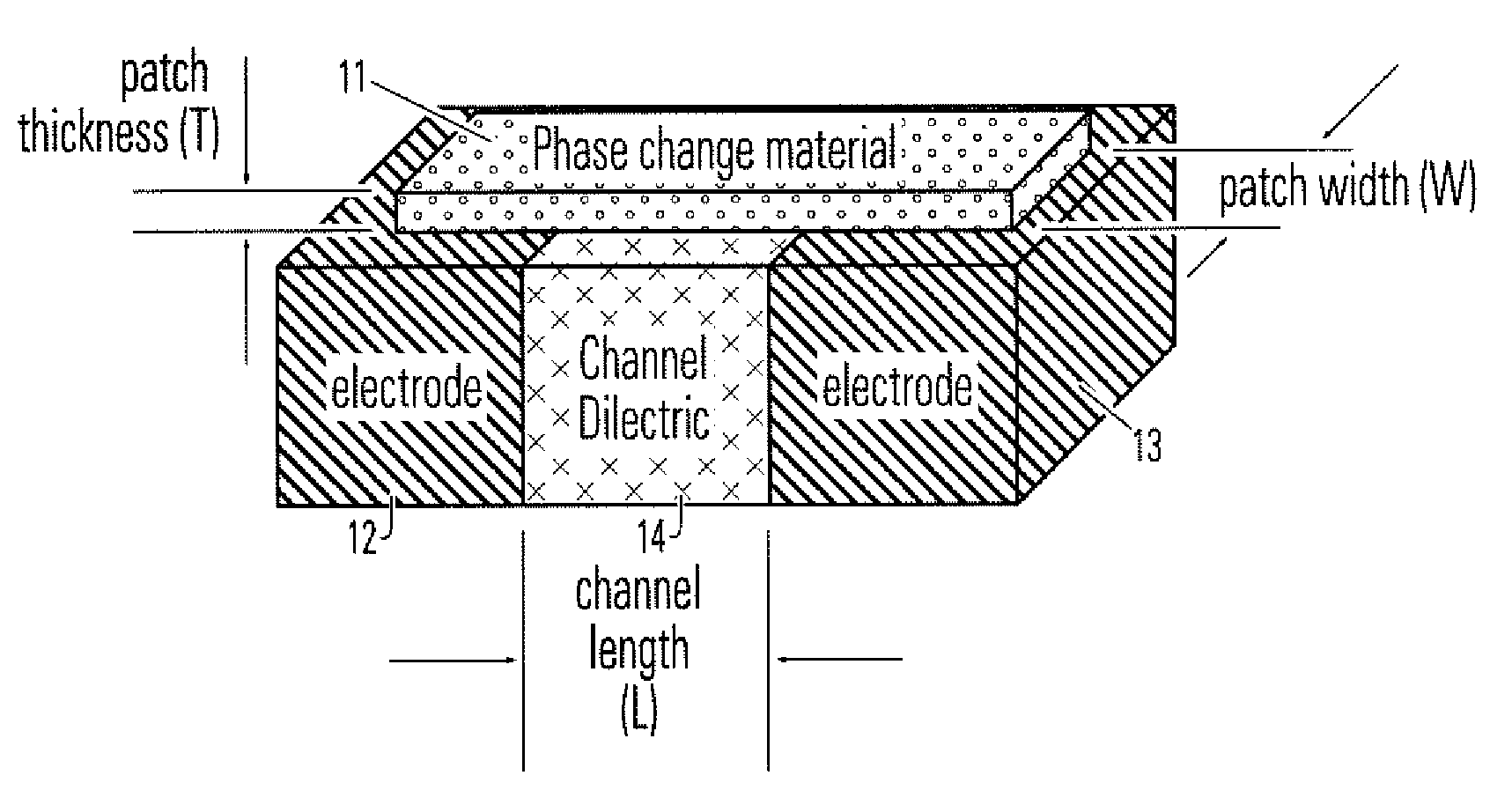

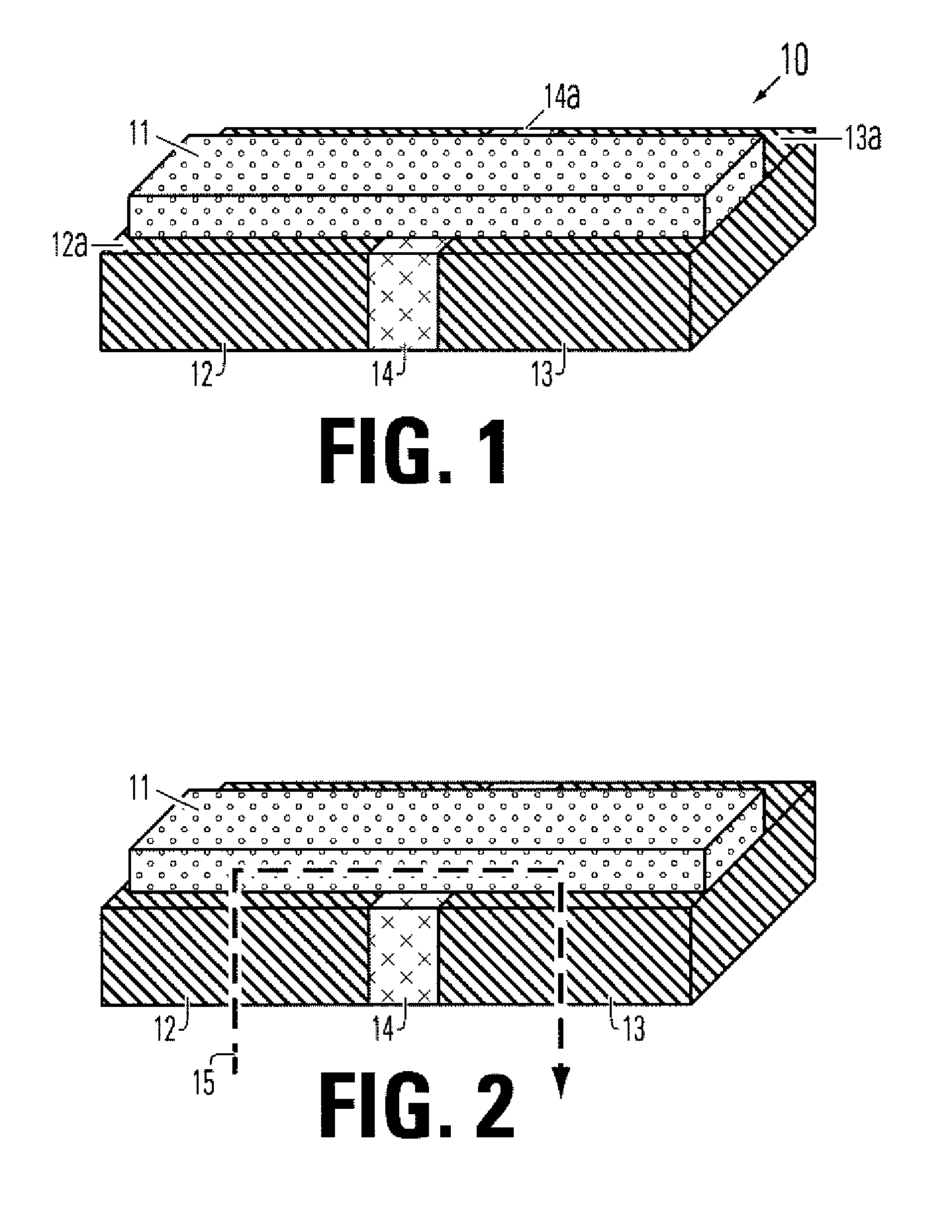

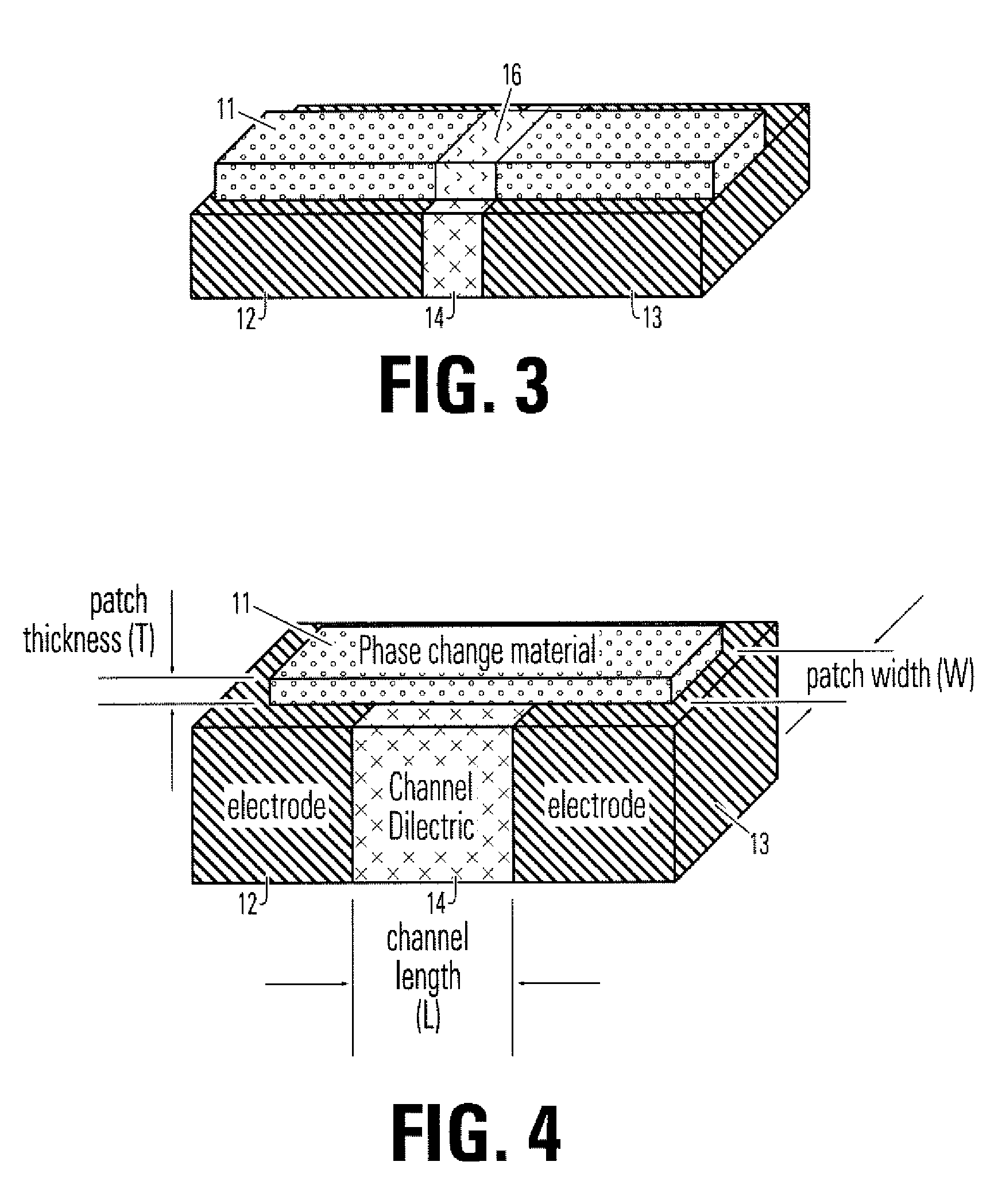

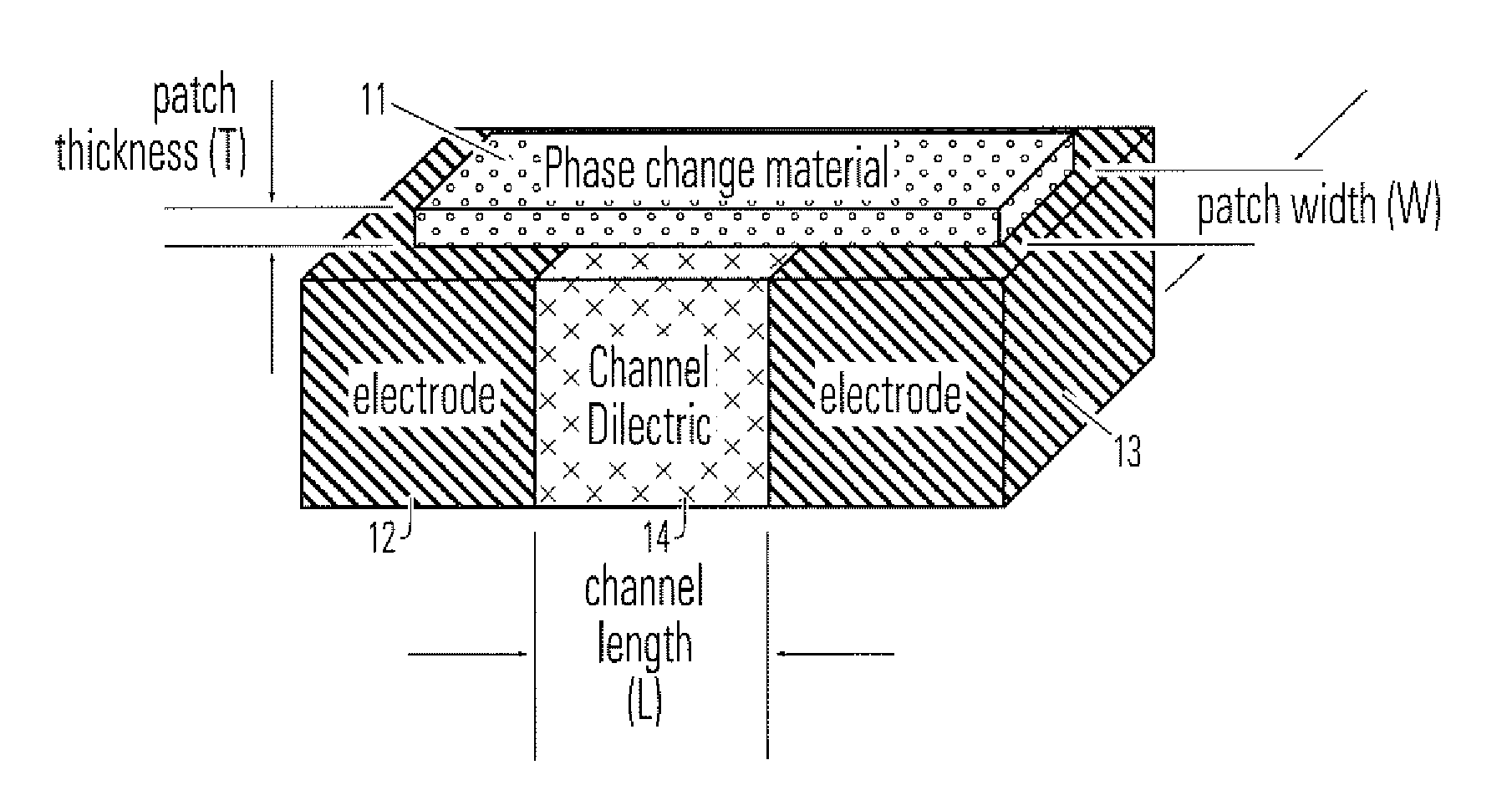

Phase Change Memory Device and Manufacturing Method

InactiveUS20070109843A1Solid-state devicesSemiconductor/solid-state device manufacturingElectricityPhase-change memory

A phase change memory device comprises a photolithographically formed phase change memory cell having first and second electrodes and a phase change element positioned between and electrically coupling the opposed contact elements of the electrodes to one another. The phase change element has a width, a length and a thickness. The length, the thickness and the width are less than a minimum photolithographic feature size of the process used to form the phase change memory cell. The size of the photoresist masks used in forming the memory cell may be reduced so that the length and the width of the phase change element are each less than the minimum photolithographic feature size.

Owner:MACRONIX INT CO LTD

Phase Change Memory Device and Manufacturing Method

A phase change memory device comprises a photolithographically formed phase change memory cell having first and second electrodes and a phase change bridge positioned between and electrically coupling the opposed sides of the electrodes to one another. The phase change bridge has a length, a width and a thickness. The width, the thickness and the length are less than a minimum photolithographic feature size of the process used to form the phase change memory cell. The size of the photoresist masks used in forming the memory cell may be reduced so that the width and the length of the phase change bridge are each less than the minimum photolithographic feature size.

Owner:MACRONIX INT CO LTD

Method for Fabricating a Pillar-Shaped Phase Change Memory Element

InactiveUS20070158632A1Photomechanical apparatusSemiconductor/solid-state device manufacturingPhase-change memoryPhase-change material

A method of fabricating a sub-feature size pillar structure on an integrated circuit. The process first provides a substrate having formed thereon a phase change layer, an electrode layer and a hard-mask layer. Then there is formed a feature-size hard-mask, by lithographically patterning, etching and stripping a photoresist layer, followed by trimming the hard-mask to a selected sub-feature size, wherein the trimming step is highly selective between the electrode and phase change material layers and the hard-mask. The final steps are trimming the electrode and phase change layers to the size of the hard-mask and removing the hard-mask.

Owner:MACRONIX INT CO LTD

Phase Change Memory Cell and Manufacturing Method

ActiveUS20070147105A1Improve thermal conductivityRaise the transition temperatureSolid-state devicesDigital storageElectricityPhase-change memory

A phase change memory cell includes first and second electrodes electrically coupled by a phase change element. At least a section of the phase change element comprises a higher reset transition temperature portion and a lower reset transition temperature portion. The lower reset transition temperature portion comprises a phase change region which can be transitioned, by the passage of electrical current therethrough, from generally crystalline to generally amorphous states at a lower temperature than the higher reset transition temperature portion. The phase change element may comprise an outer, generally tubular, higher reset transition temperature portion surrounding an inner, lower reset transition temperature portion.

Owner:MACRONIX INT CO LTD

Phase change memory device and manufacturing method

InactiveUS7786460B2Solid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryContact element

A phase change memory device comprises a photolithographically formed phase change memory cell having first and second electrodes and a phase change element positioned between and electrically coupling the opposed contact elements of the electrodes to one another. The phase change element has a width, a length and a thickness. The length, the thickness and the width are less than a minimum photolithographic feature size of the process used to form the phase change memory cell. The size of the photoresist masks used in forming the memory cell may be reduced so that the length and the width of the phase change element are each less than the minimum photolithographic feature size.

Owner:MACRONIX INT CO LTD

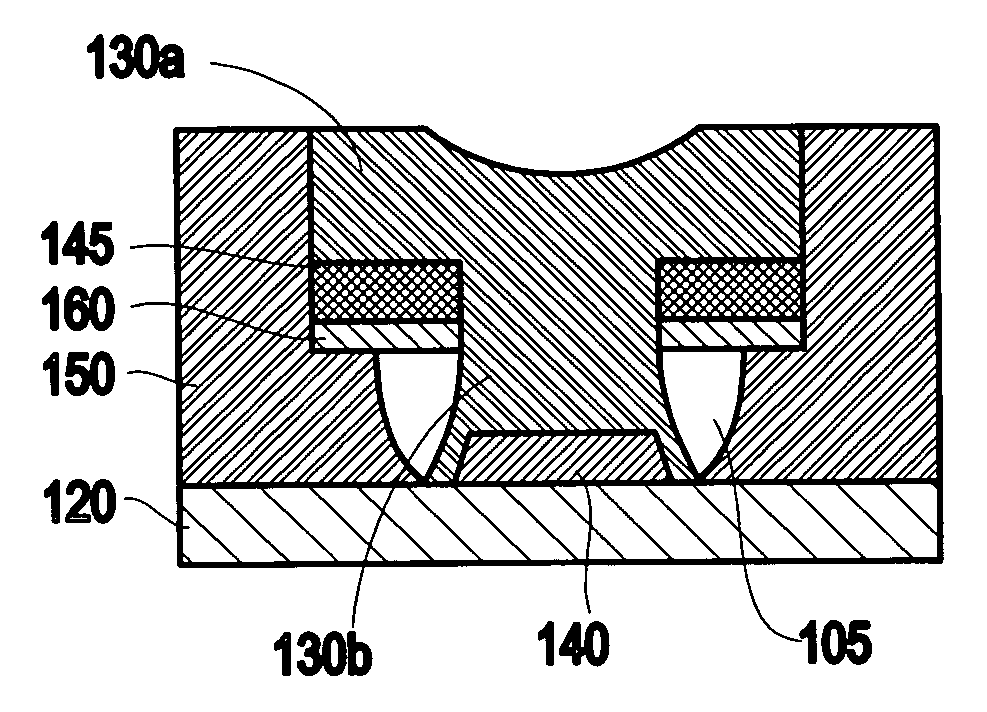

Electrically programmable memory element with improved contacts

InactiveUS6969866B1Reduced programming energyReduce cell areaSemiconductor/solid-state device detailsSolid-state devicesPhase-change memoryEngineering

A memory element comprising a volume of phase change memory material; and first and second contact for supplying an electrical signal to the memory material, wherein the first contact comprises a conductive sidewall spacer. Alternately, the first contact may comprise a contact layer having an edge adjacent to the memory material.

Owner:OVONYX MEMORY TECH LLC

Vacuum jacketed electrode for phase change memory element

ActiveUS20070158862A1Improve insulation performanceTransistorSolid-state devicesThermal isolationPhase-change memory

A memory device having a vacuum jacket around the first electrode element for improved thermal isolation. The memory unit includes a first electrode element; a phase change memory element in contact with the first electrode element; a dielectric fill layer surrounding the phase change memory element and the first electrode element, wherein the dielectric layer is spaced from the first electrode element to define a chamber between the first electrode element and the dielectric fill layer; and wherein the phase change memory layer is sealed to the dielectric fill layer to define a thermal isolation jacket around the first electrode element.

Owner:MACRONIX INT CO LTD

Self-align planerized bottom electrode phase change memory and manufacturing method

ActiveUS20070158645A1Solid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryRandom access memory

A method is described for self-aligning a bottom electrode in a phase change random access memory PCRAM device where a top electrode serves as a mask for self-aligning etching of the bottom electrode. The bottom electrode has a top surface that is planarized by chemical mechanical polishing. The top electrode also has a top surface that is planarized by chemical mechanical polishing. A bottom electrode layer like TiN is formed over a substrate and prior to the formation of a via during subsequent process steps. A first dielectric layer is formed over the bottom electrode layer, and a second dielectric layer is formed over the first dielectric layer. A via is formed at a selected section that extends through the first and second dielectric layers.

Owner:MACRONIX INT CO LTD

Self-aligned manufacturing method, and manufacturing method for thin film fuse phase change ram

ActiveUS20070173063A1Semiconductor/solid-state device manufacturingDigital storagePhase-change memoryEngineering

A method for manufacturing a self aligned narrow structure over a wider structure based on mask trimming. A method for manufacturing a memory device comprises forming an electrode layer on a substrate which comprises circuitry made using front-end-of-line procedures. The electrode layer includes a first electrode and a second electrode, and an insulating member between the first and second electrodes for each phase change memory cell to be formed. A patch of memory material is formed on the top surface of the electrode layer across the insulating member for each memory cell to be formed. The patch and the first and second electrodes are formed using a self-aligned process based on mask trimming.

Owner:MACRONIX INT CO LTD