Patents

Literature

454 results about "Narrow channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Narrow-Channel Rule Law and Legal Definition. Narrow channel rule is a navigational requirement that a vessel traveling down a slim fairway must keep as near to the fairway wall on the vessel's starboard side as is safe and practicable.

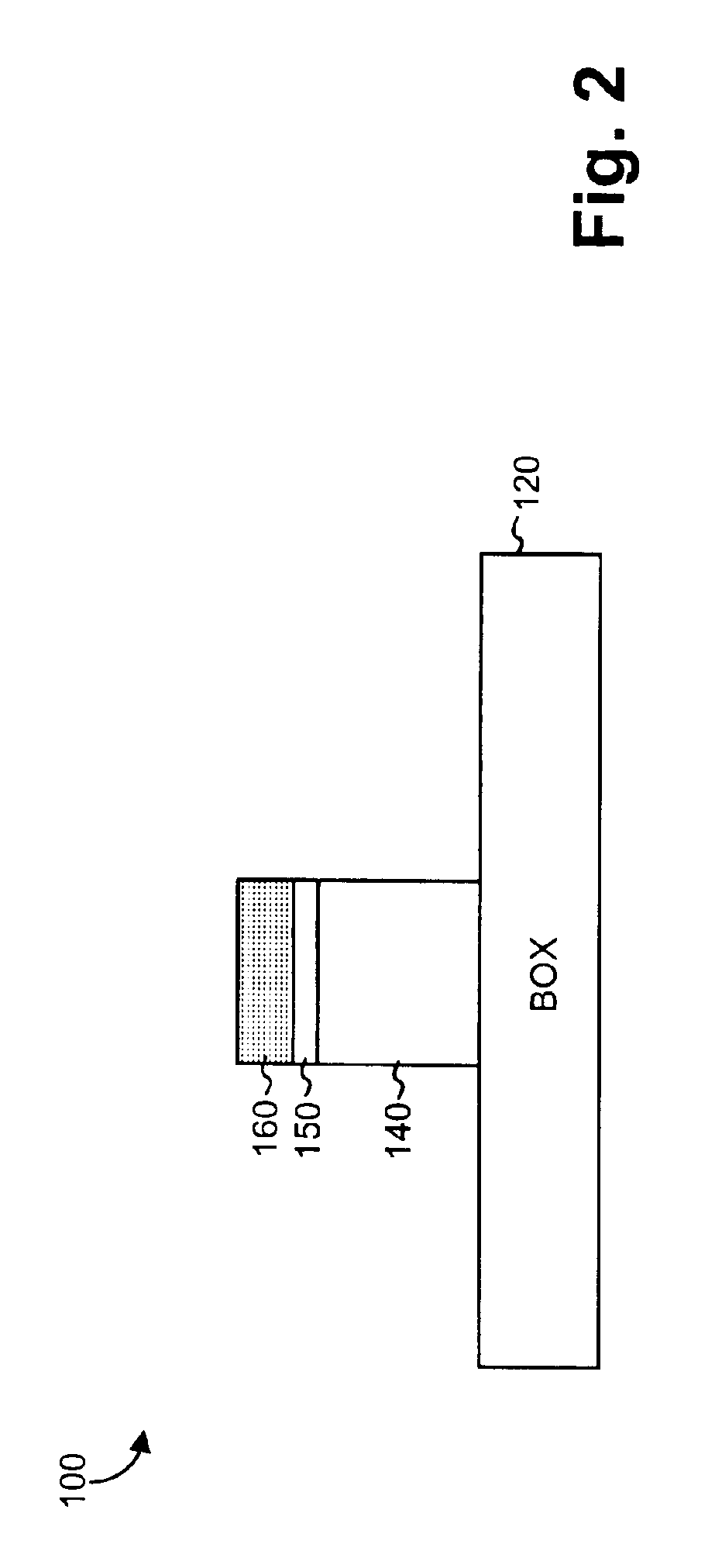

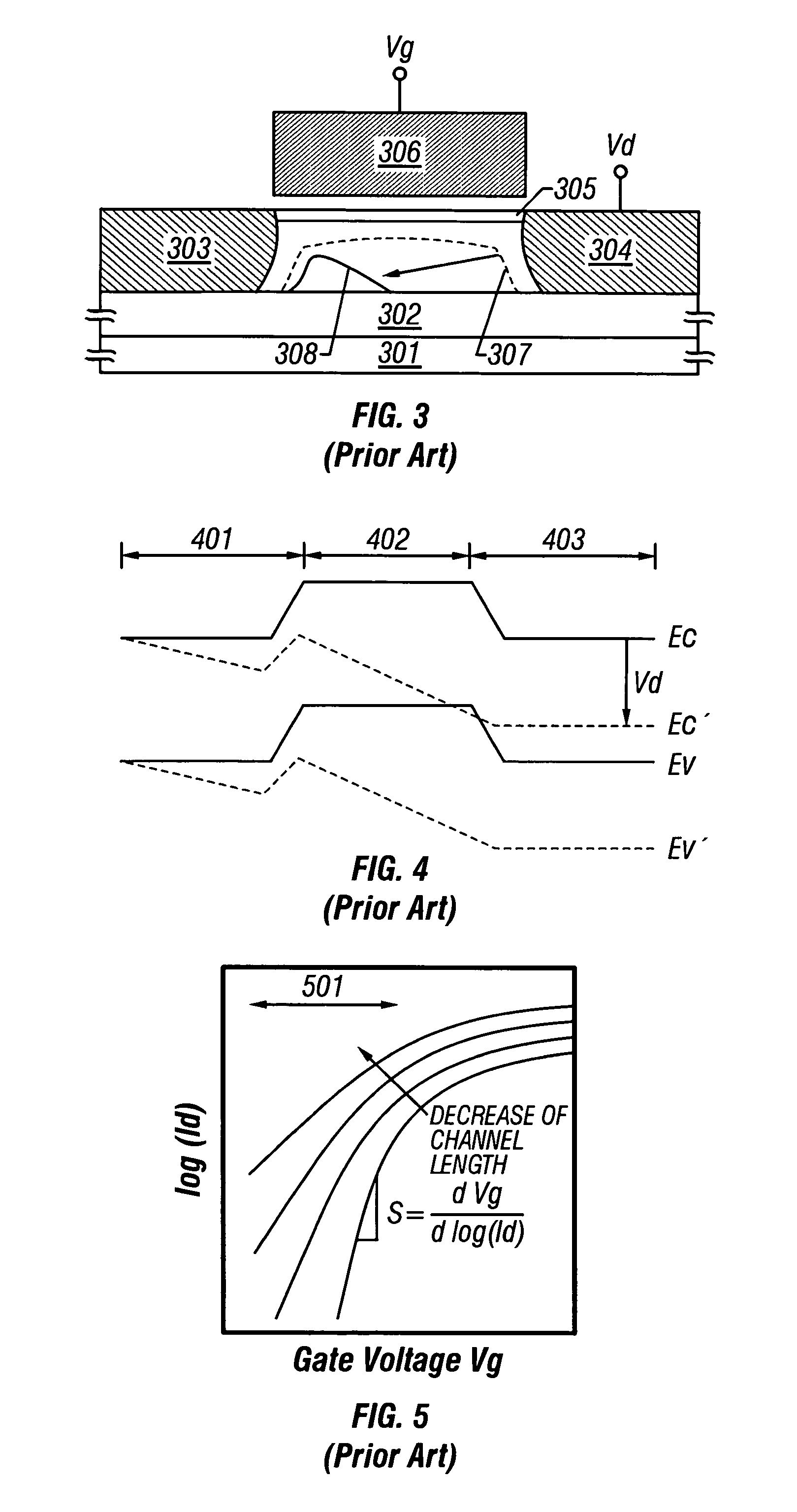

Structure for confining the switching current in phase memory (PCM) cells

InactiveUS20060226409A1Heat dissipation is limitedHigh densityBulk negative resistance effect devicesSemiconductor devicesPhase-change memorySwitched current

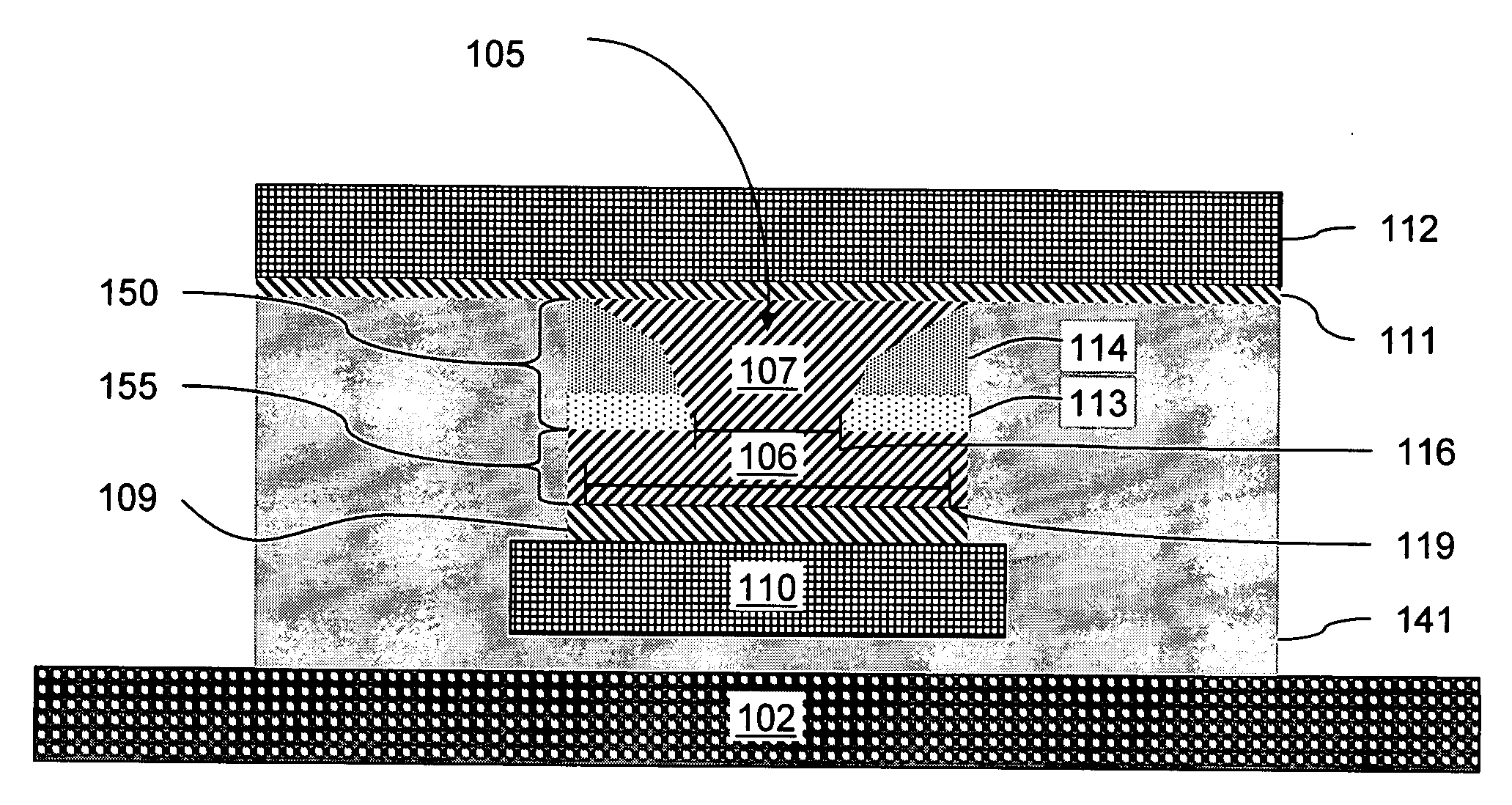

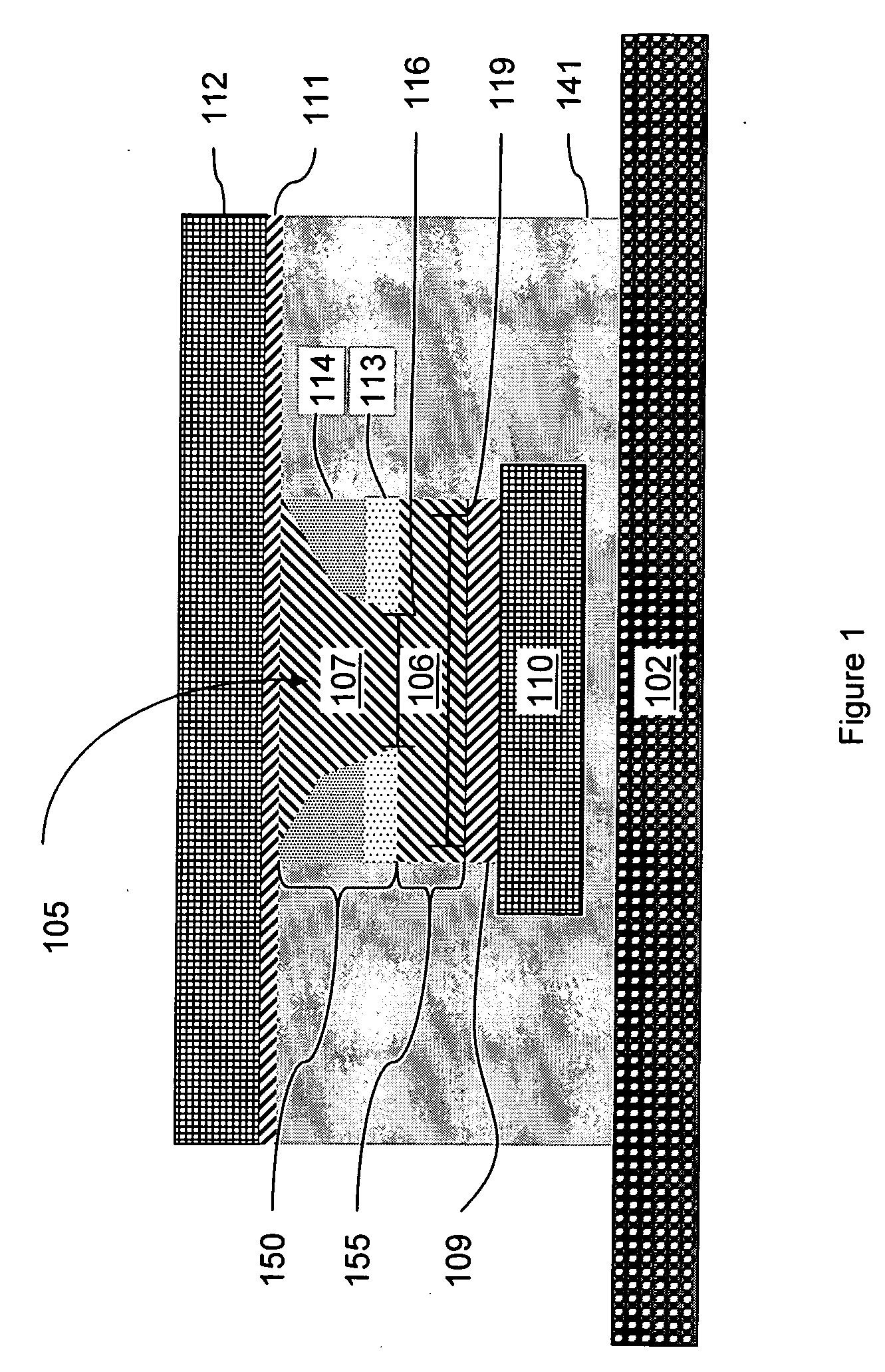

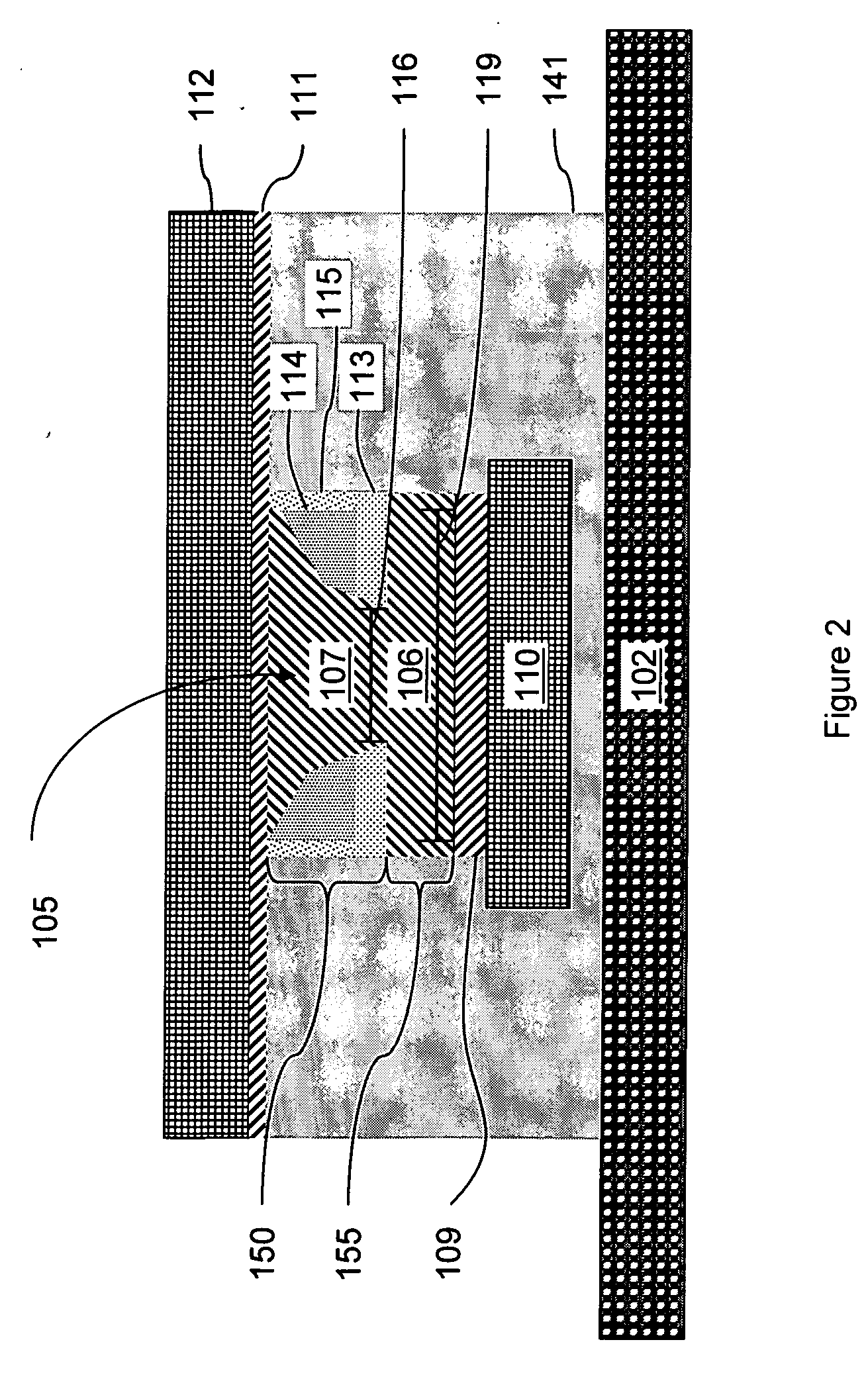

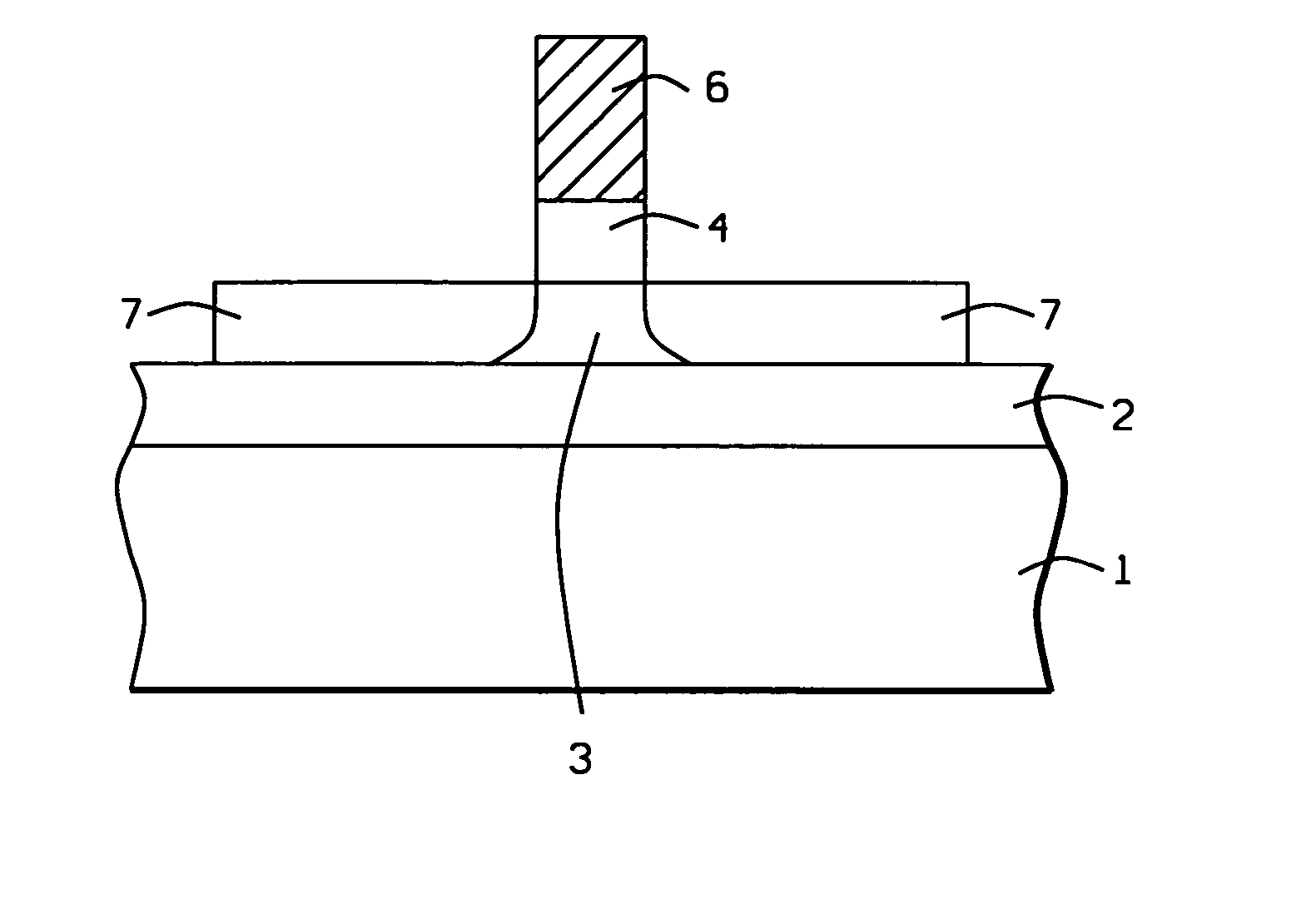

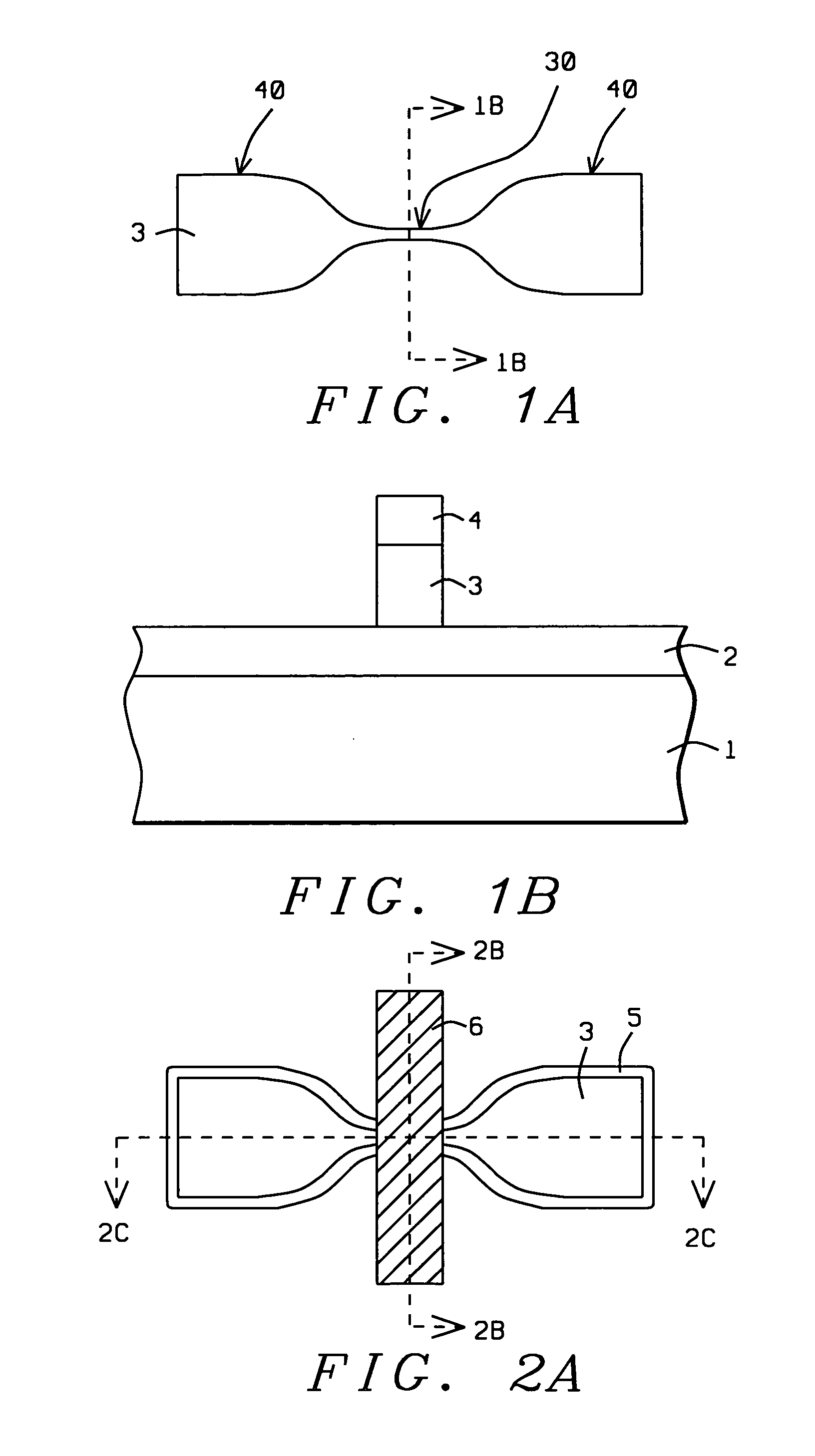

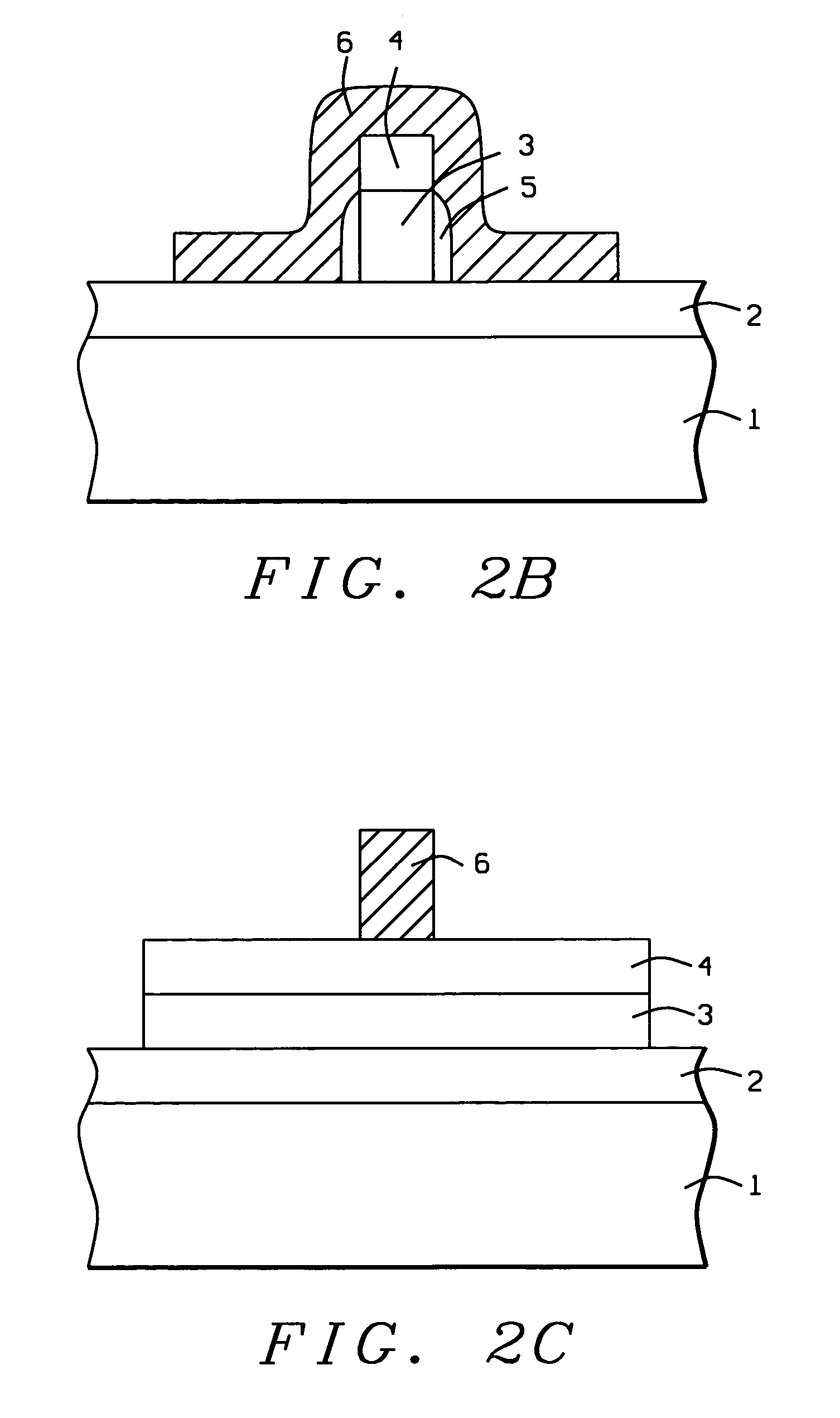

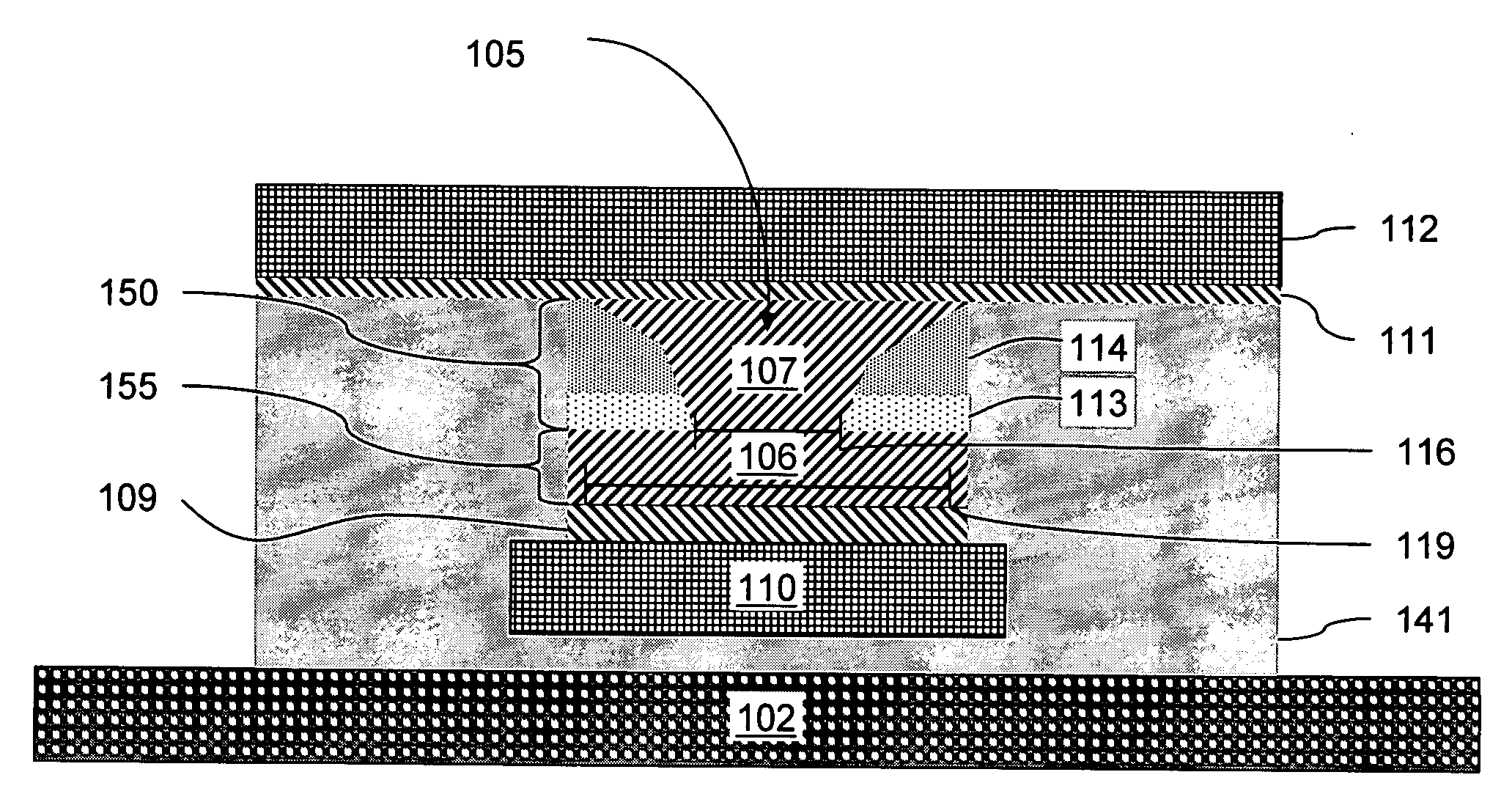

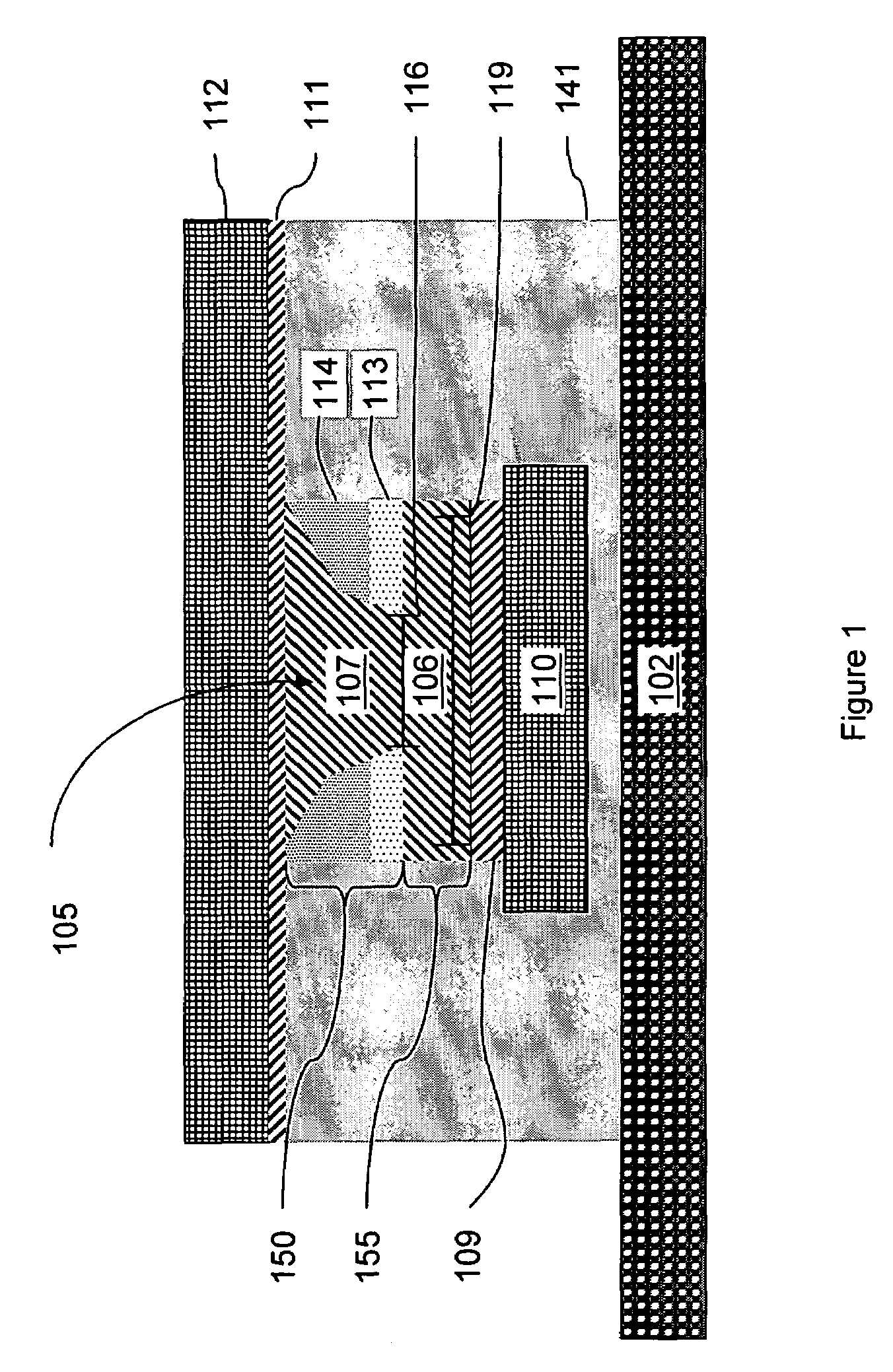

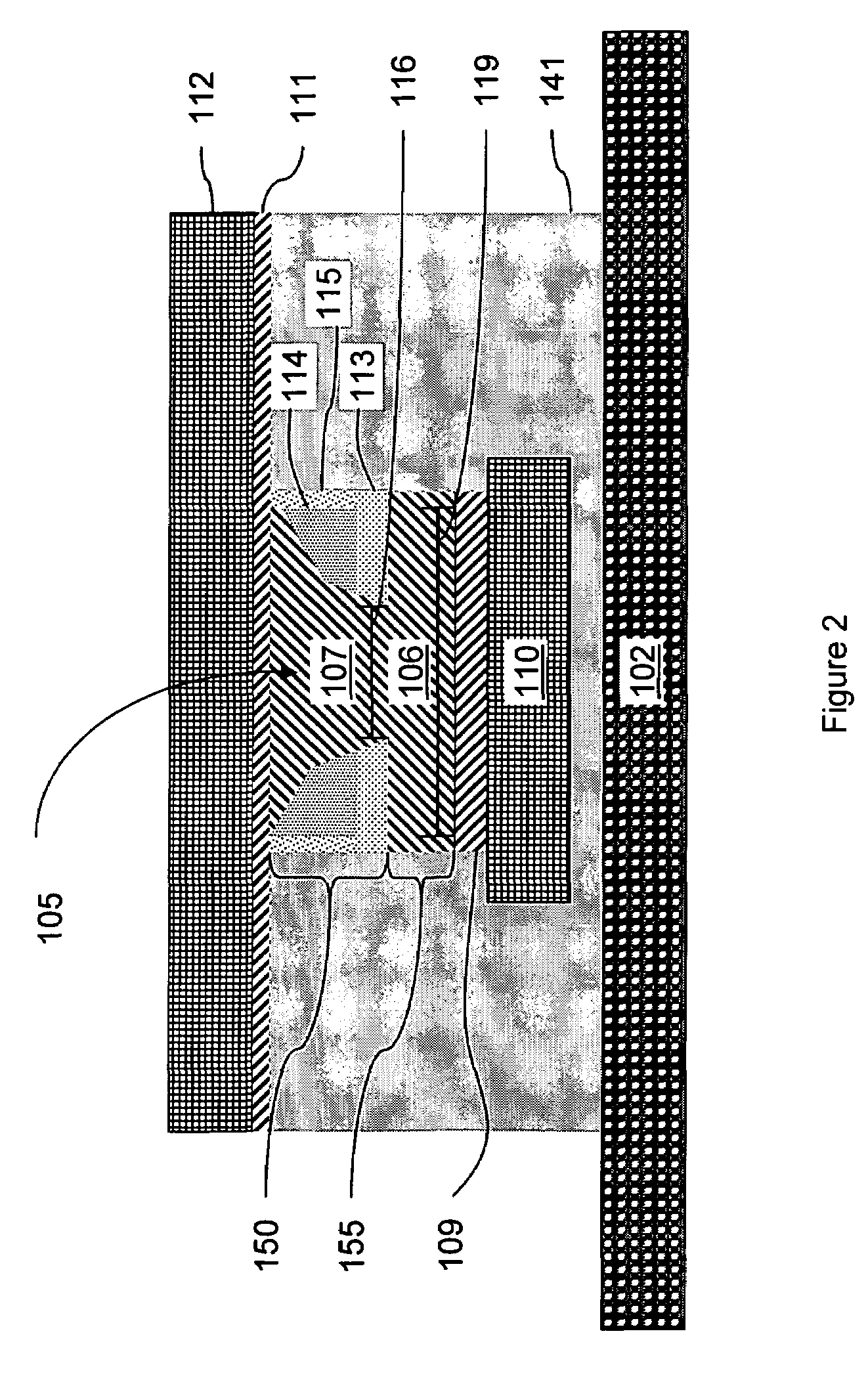

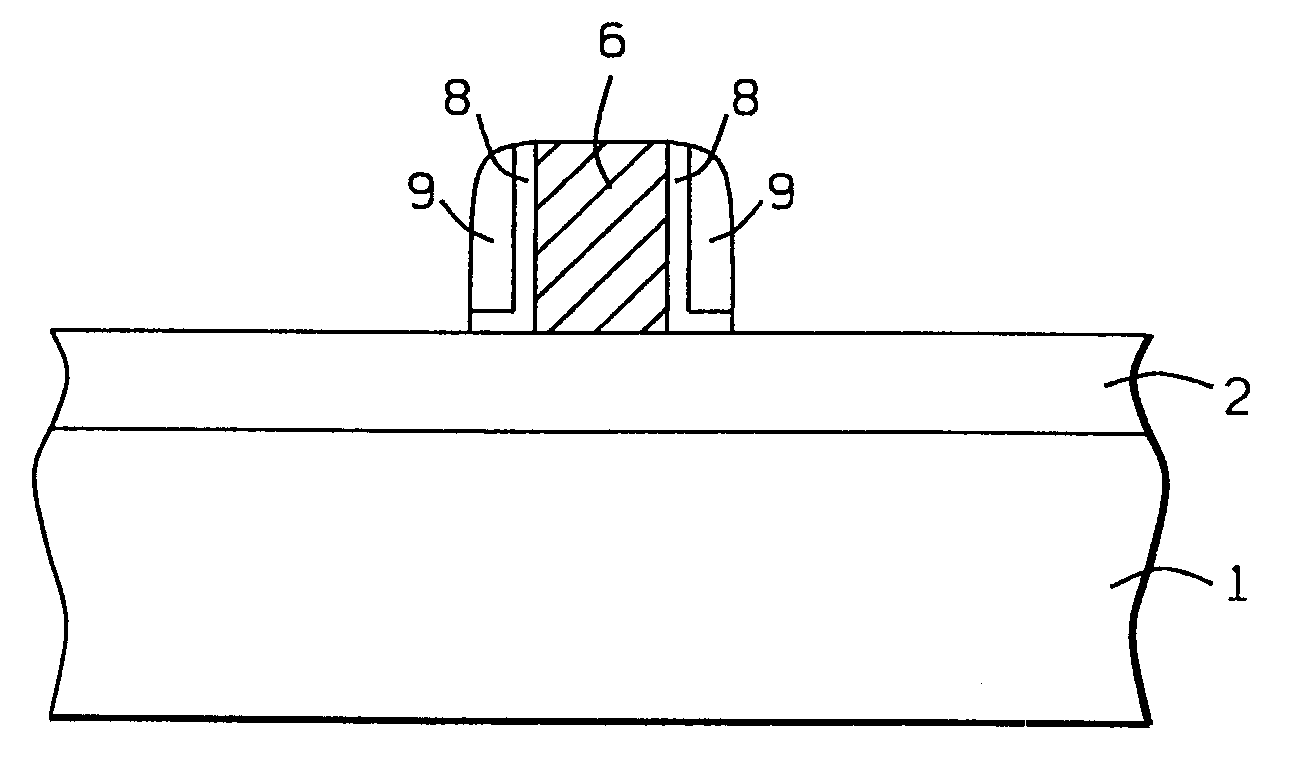

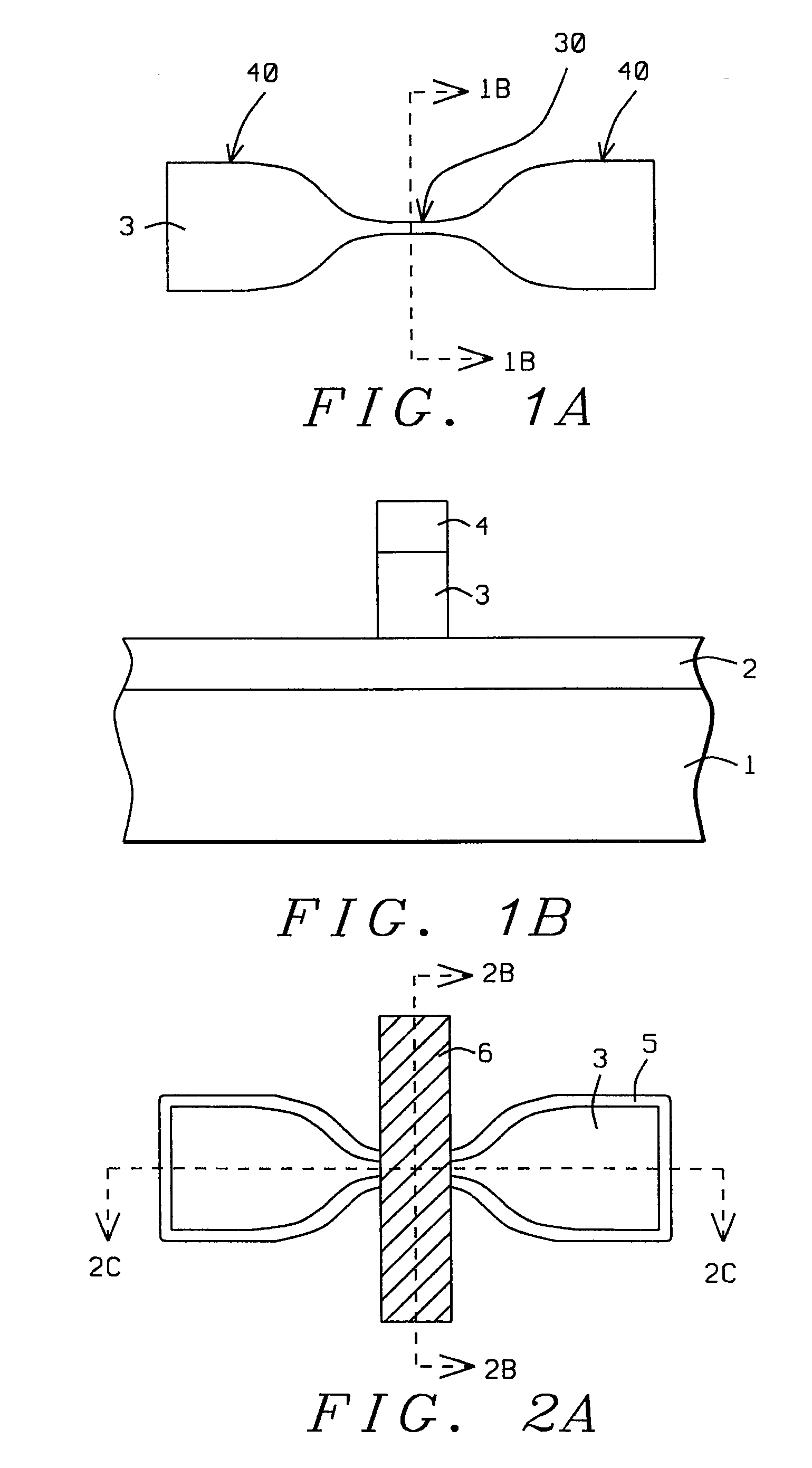

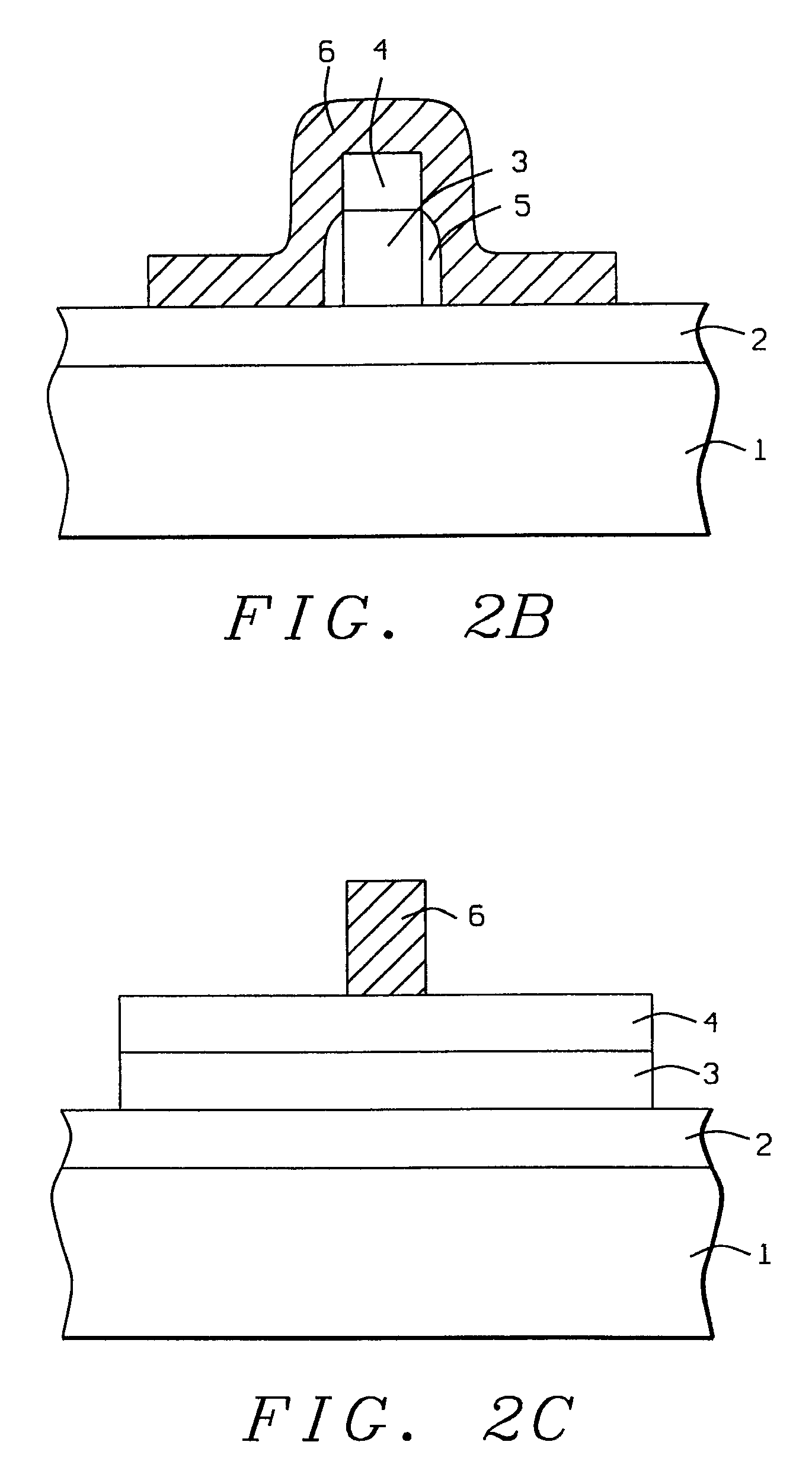

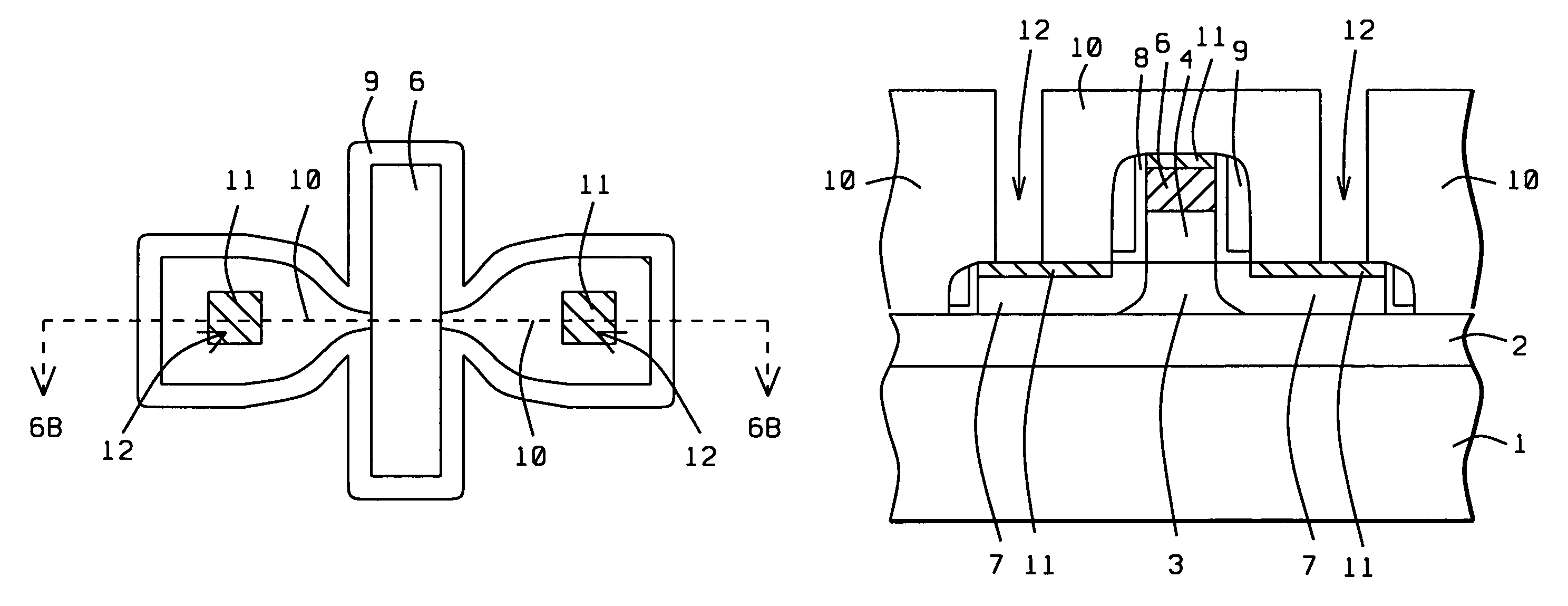

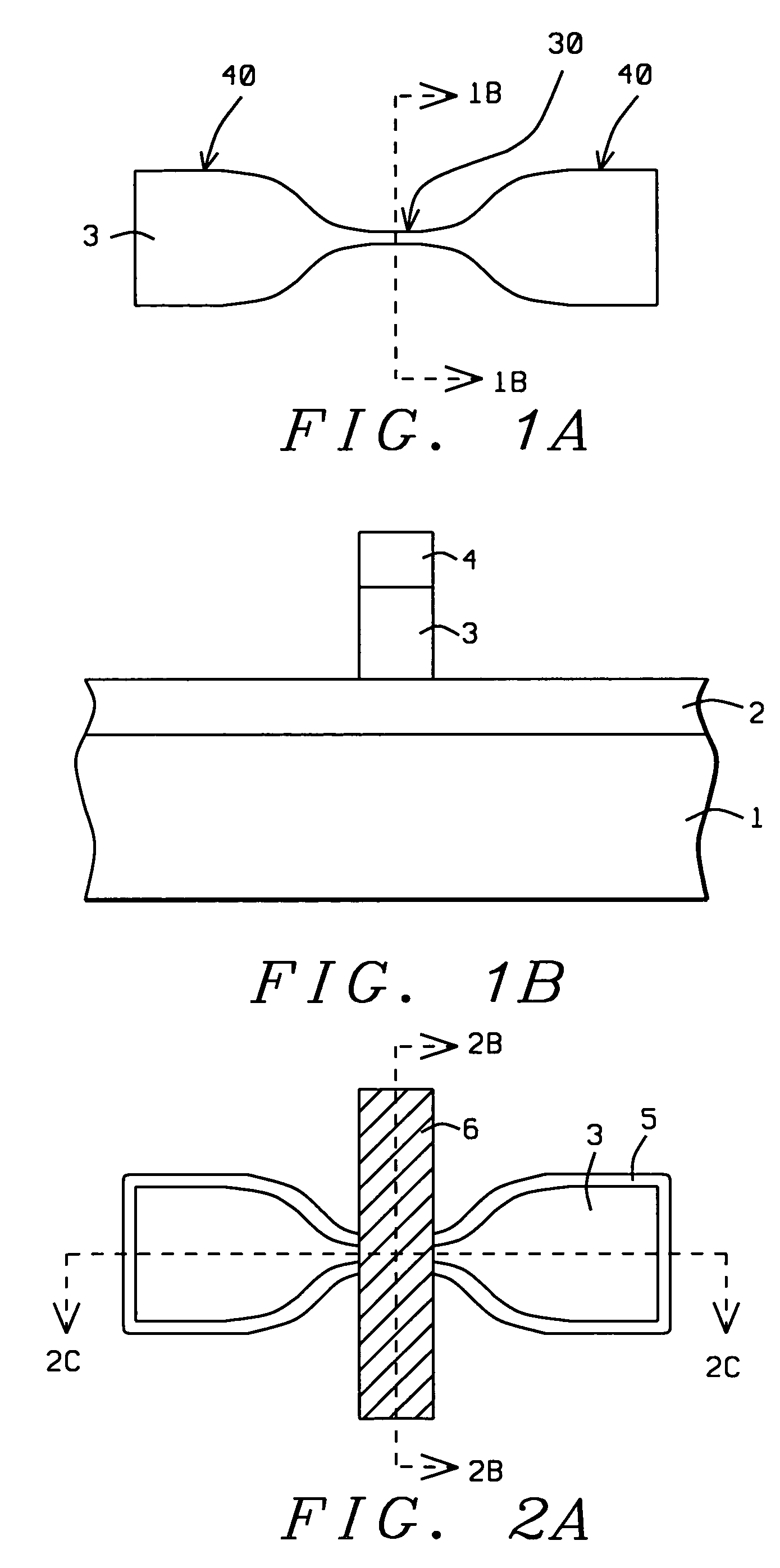

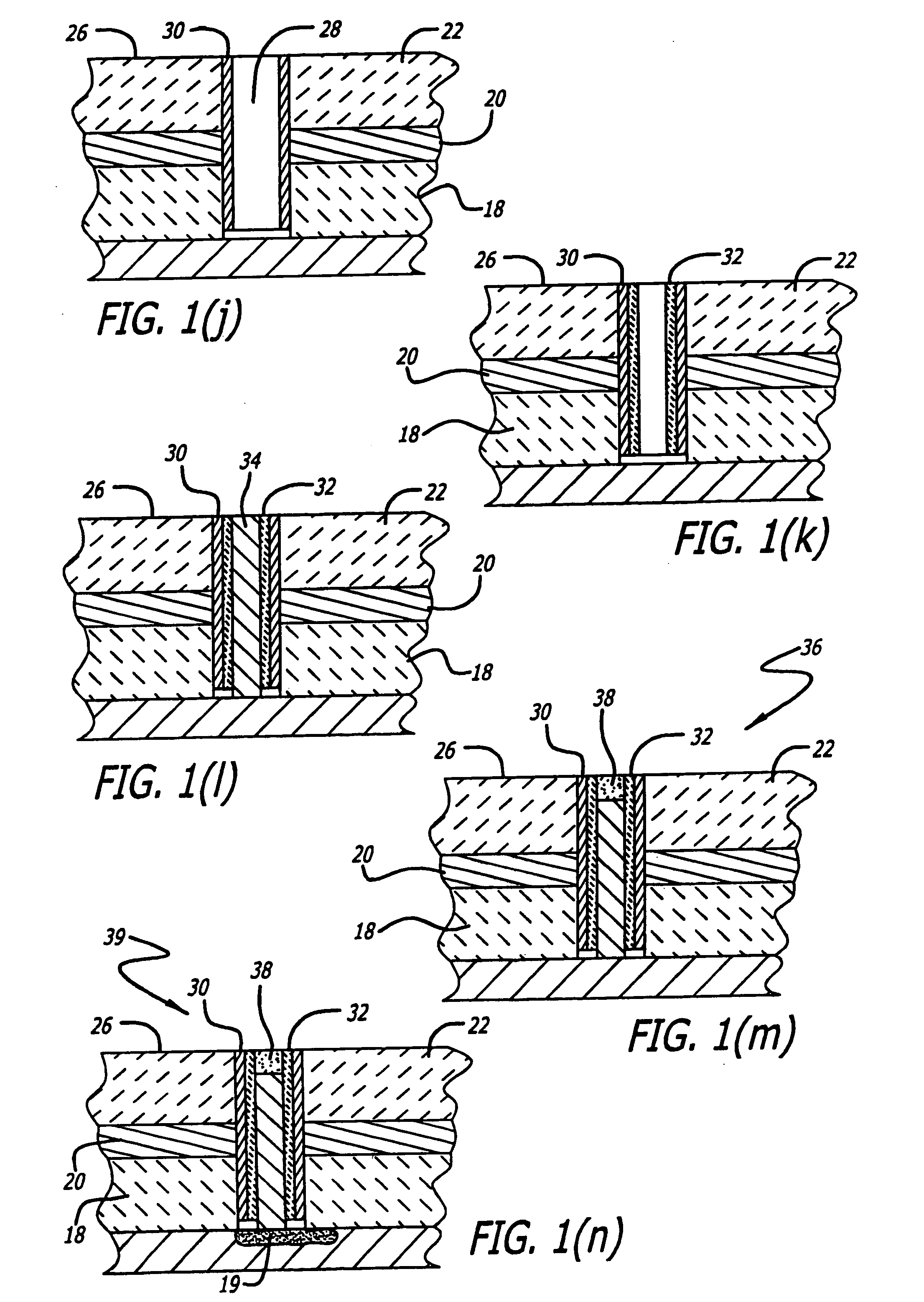

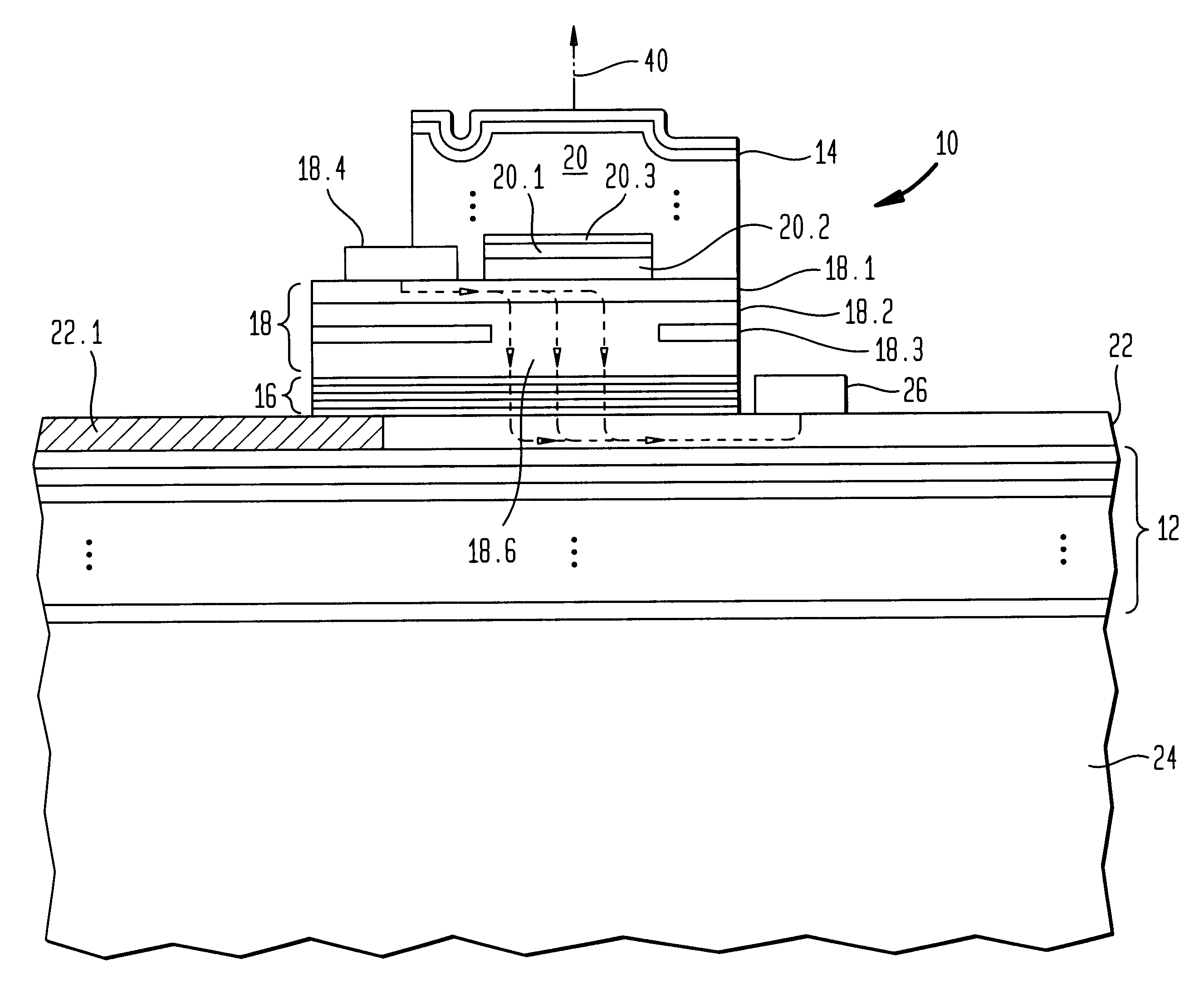

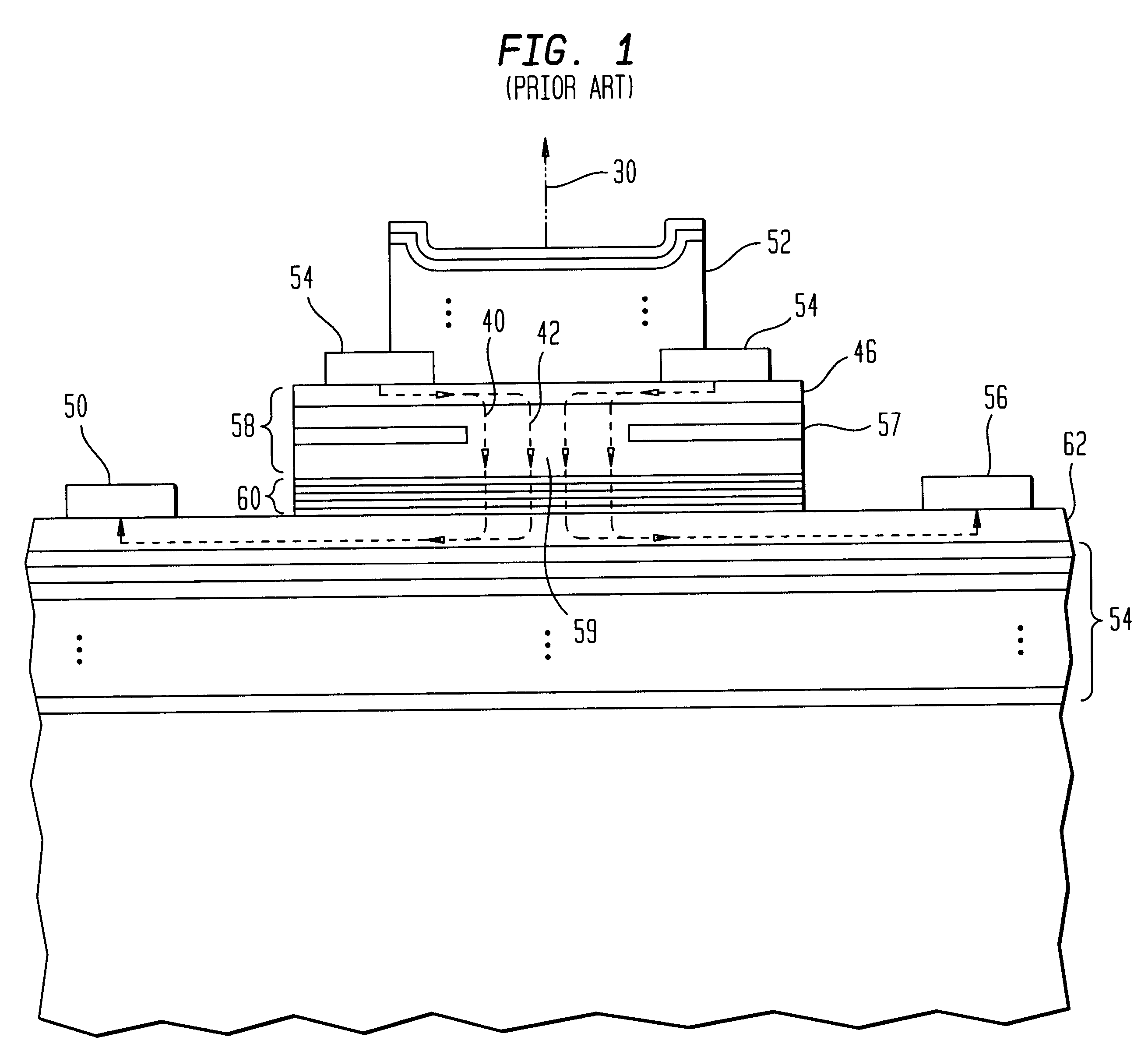

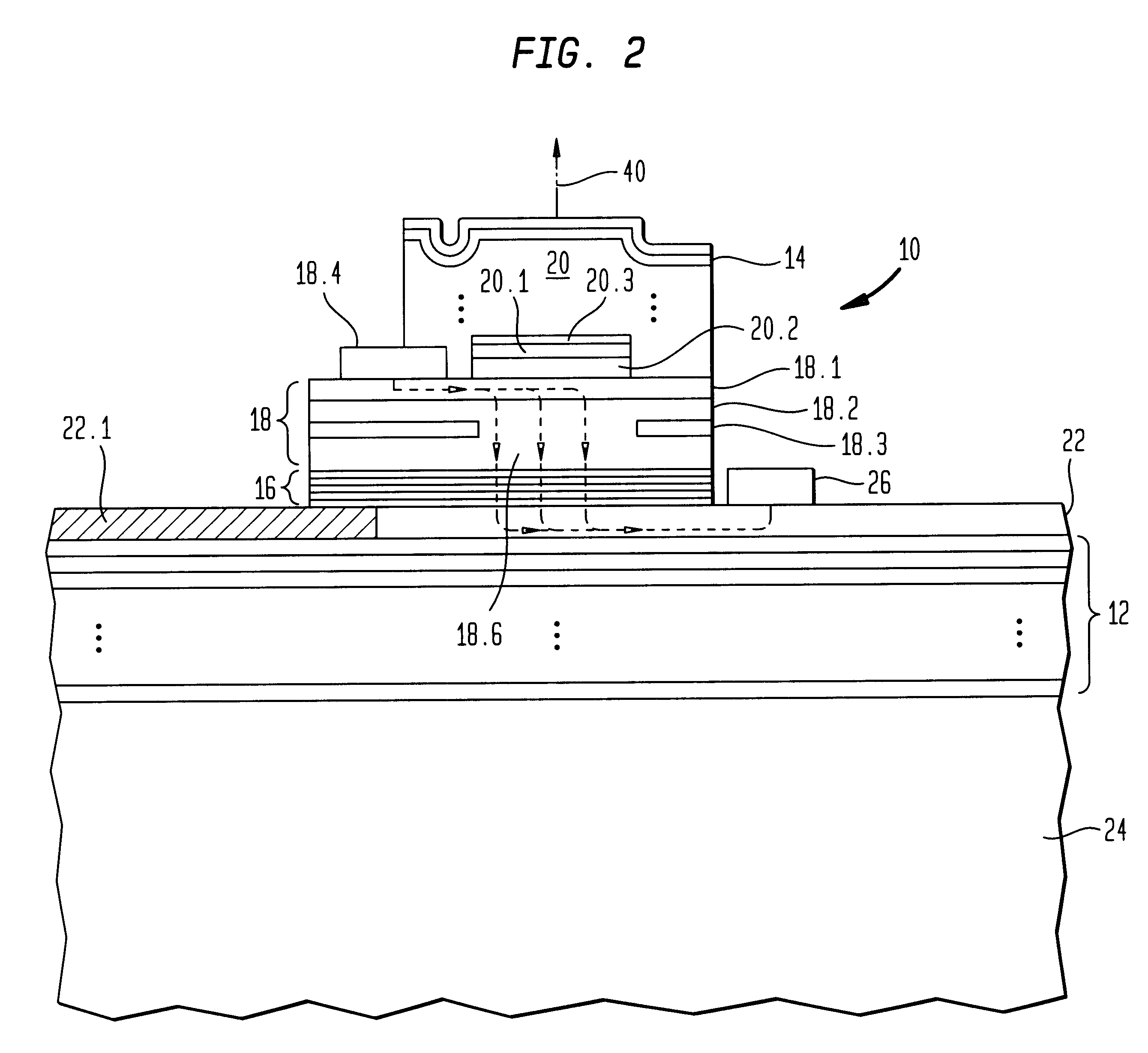

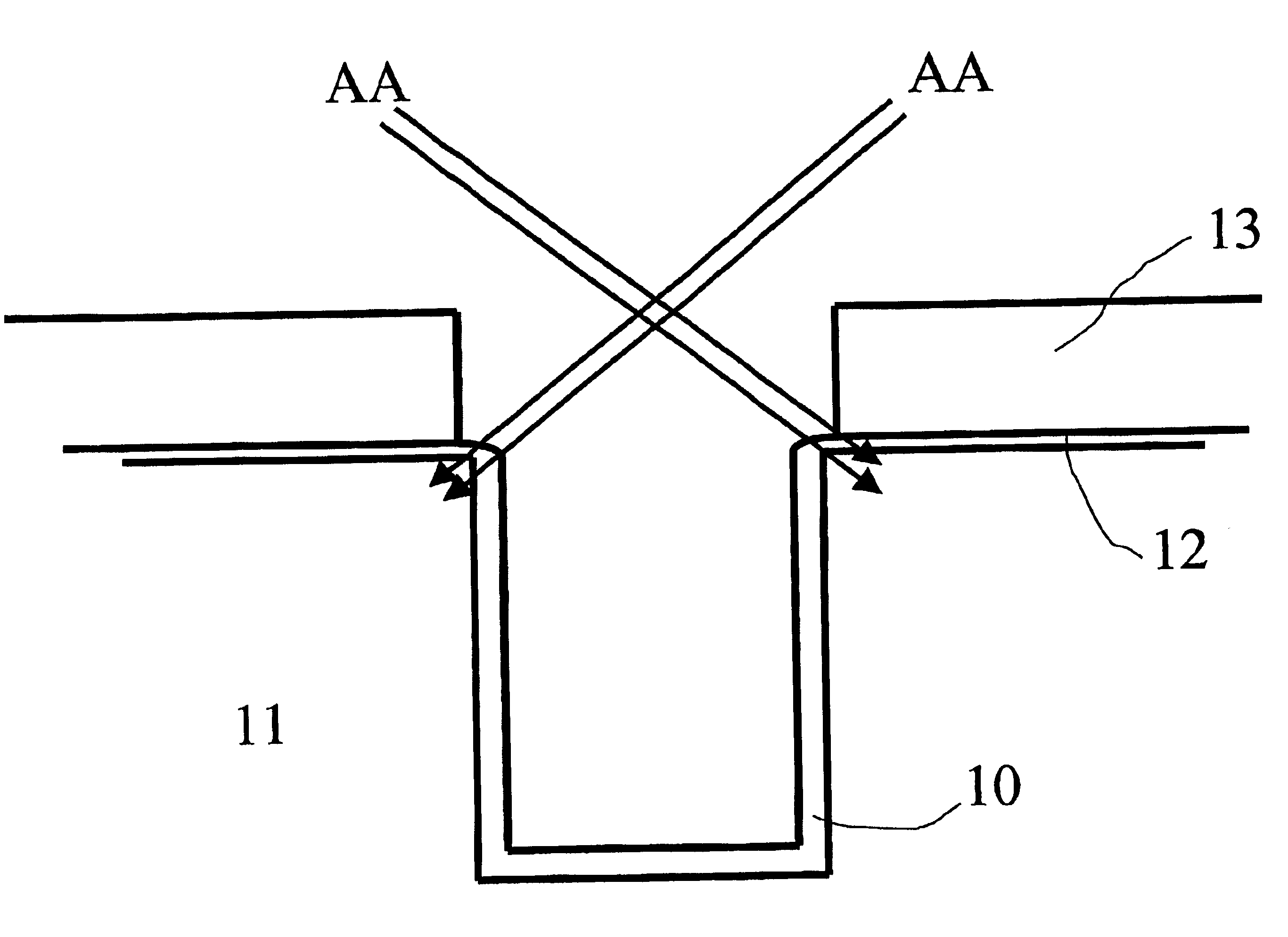

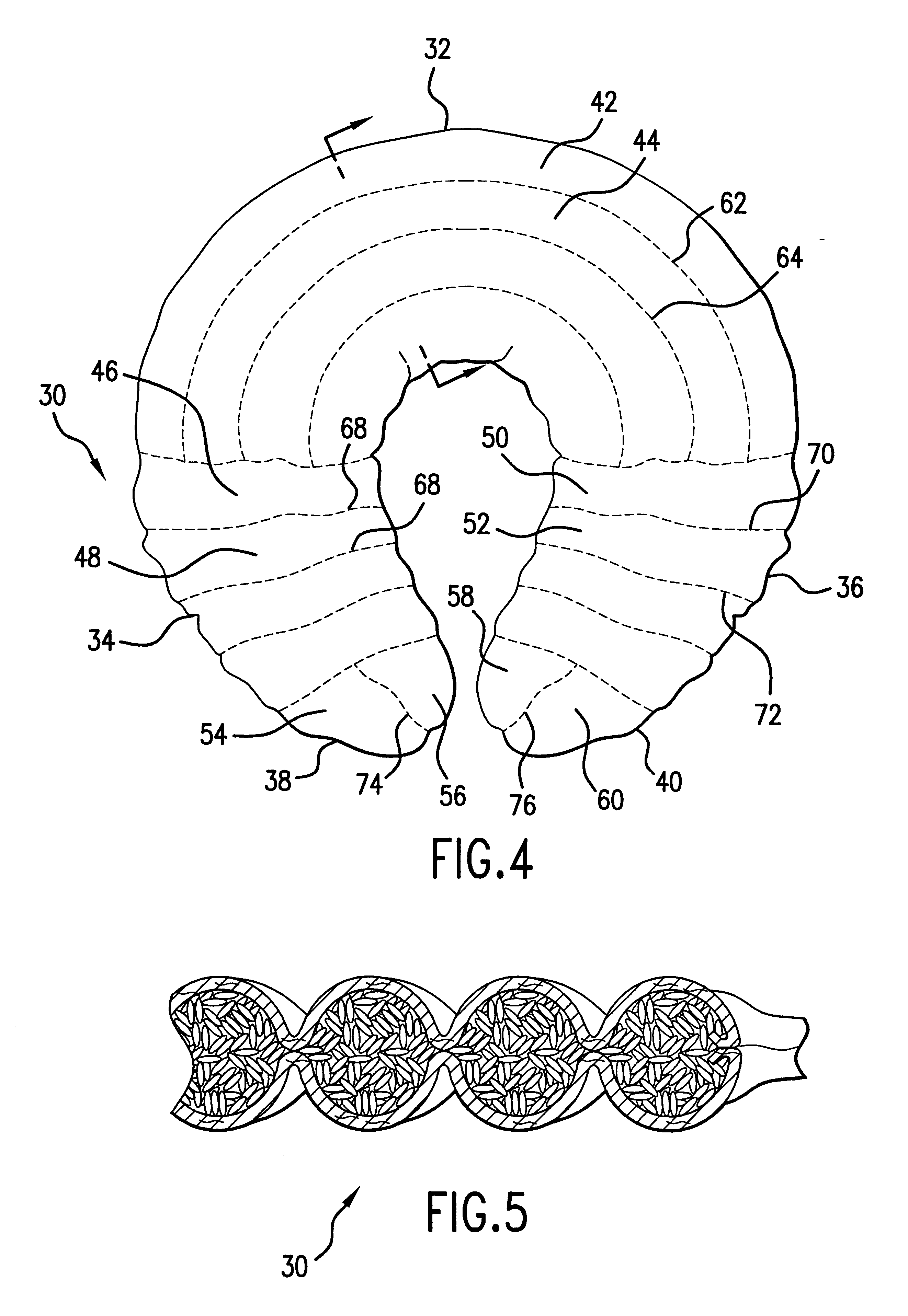

Disclosed are a phase change memory cell and a method of forming the memory cell. The memory cell comprises a main body of phase change material connected directly to a bottom contact and via a narrow channel of phase change material to a top contact. The channel is tapered from the top contact towards the main body. A minimum width of the channel has a less than minimum lithographic dimension and is narrower than a width of the main body. Therefore, the channel provides a confined region for the switching current path and restricts phase changing to within the channel. In addition an embodiment of the memory cell isolates the main body of phase change material by providing a space between the phase change material and the cell walls. The space allows the phase change material to expand and contract and also limits heat dissipation.

Owner:IBM CORP

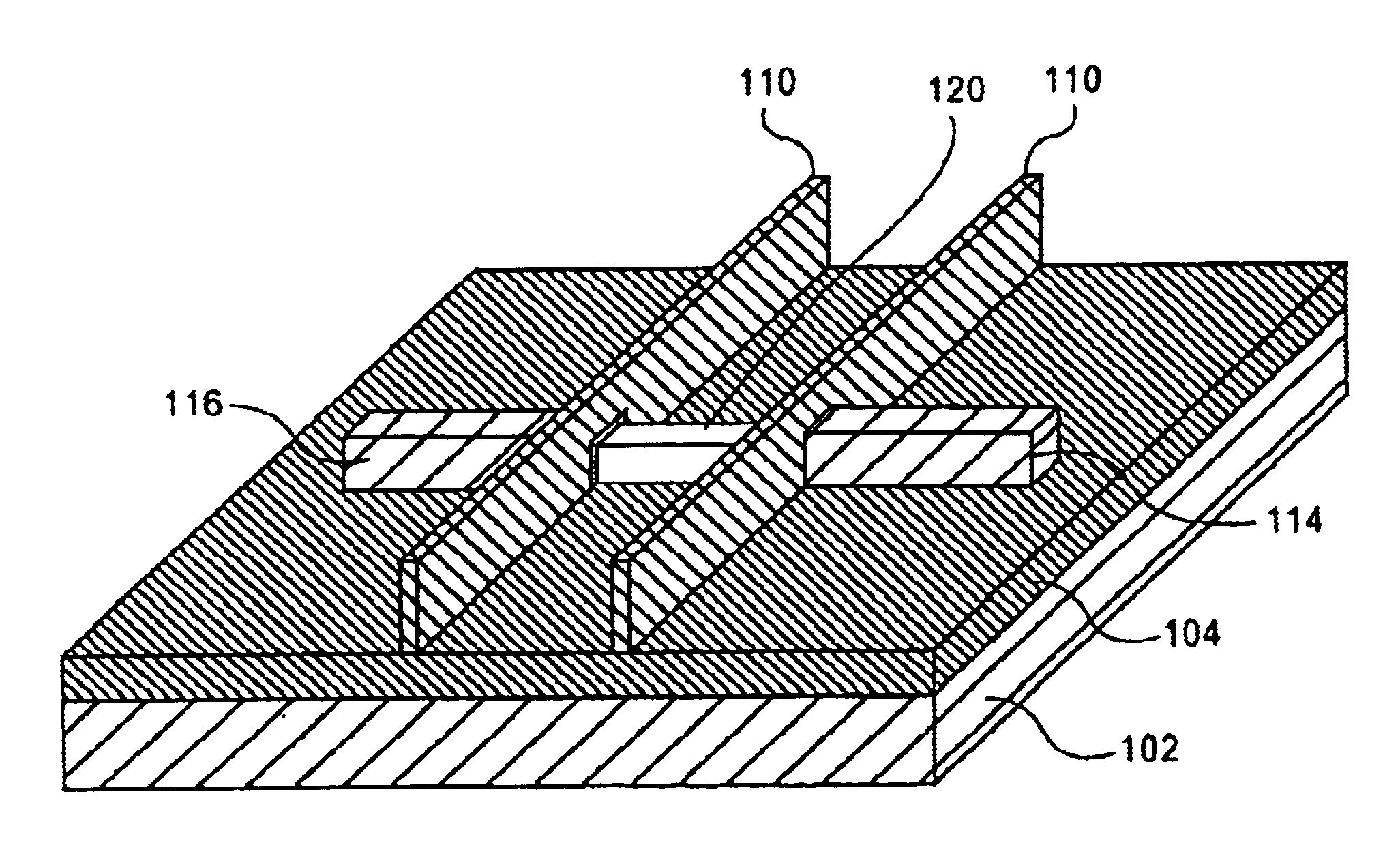

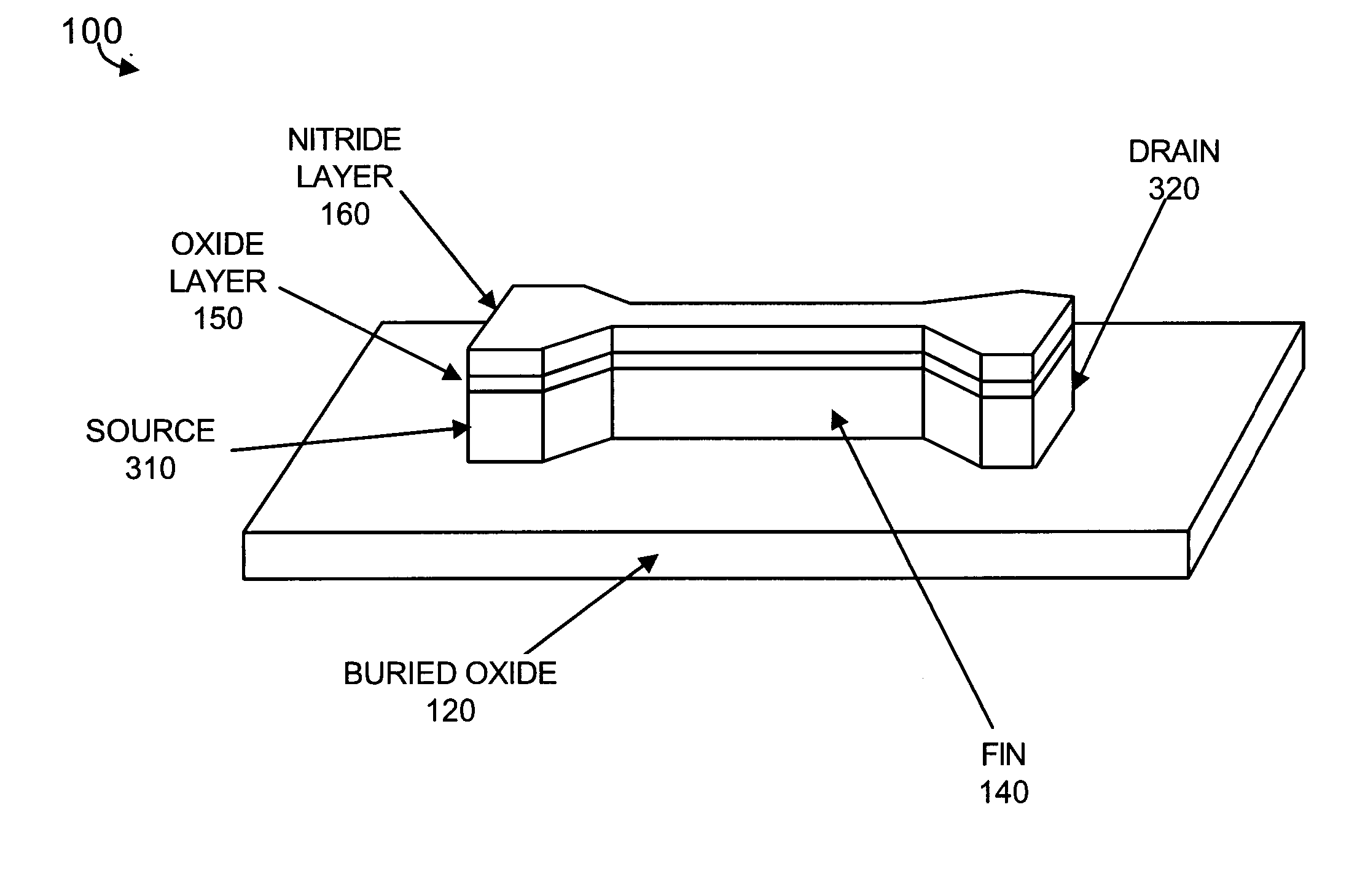

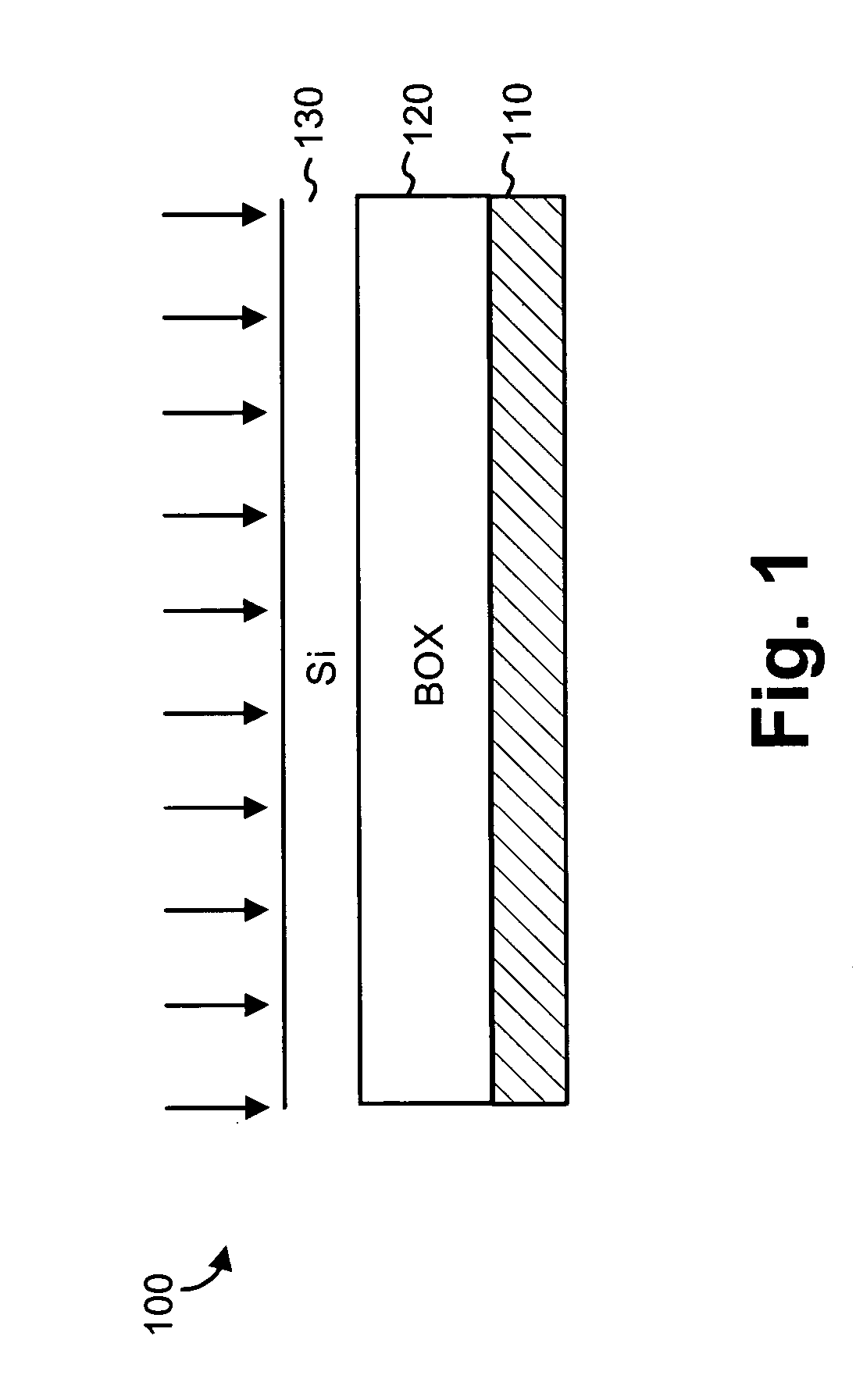

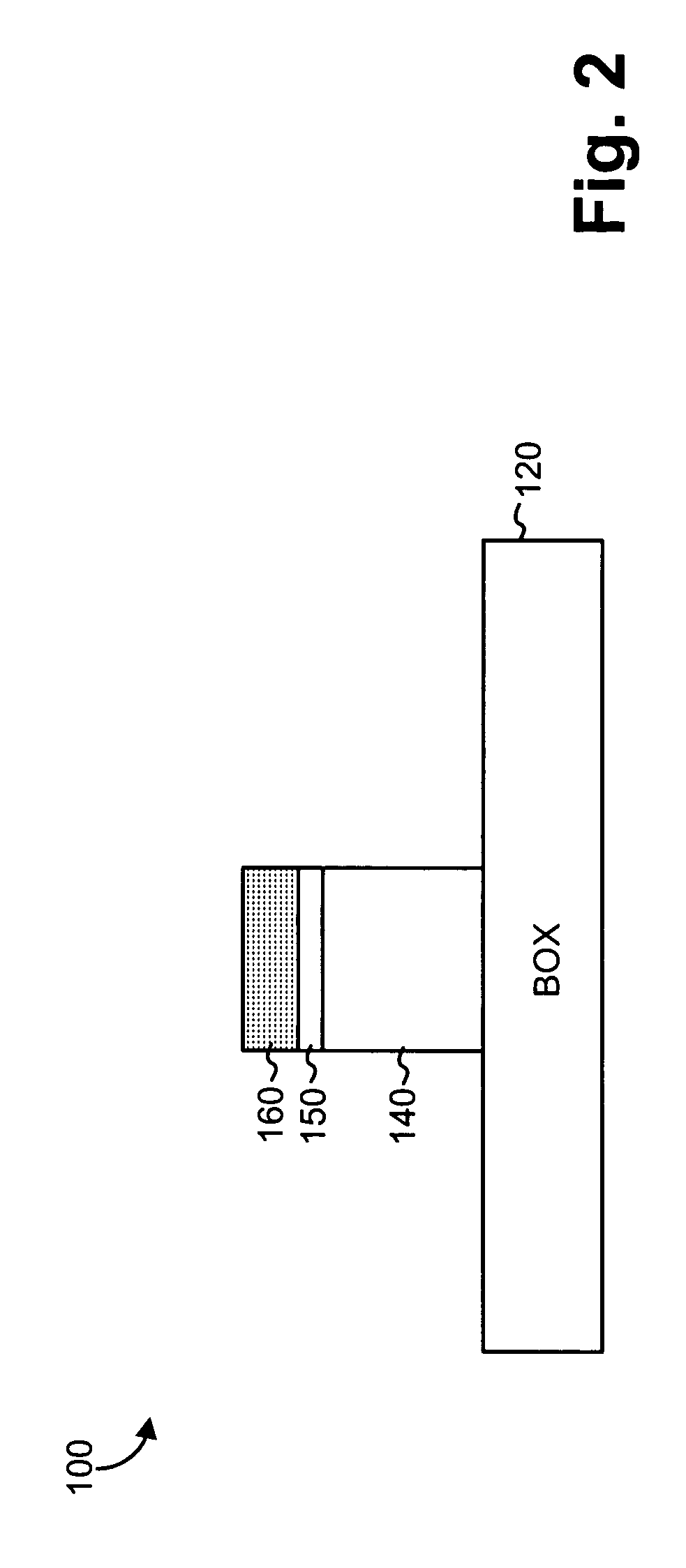

Narrow fin FinFET

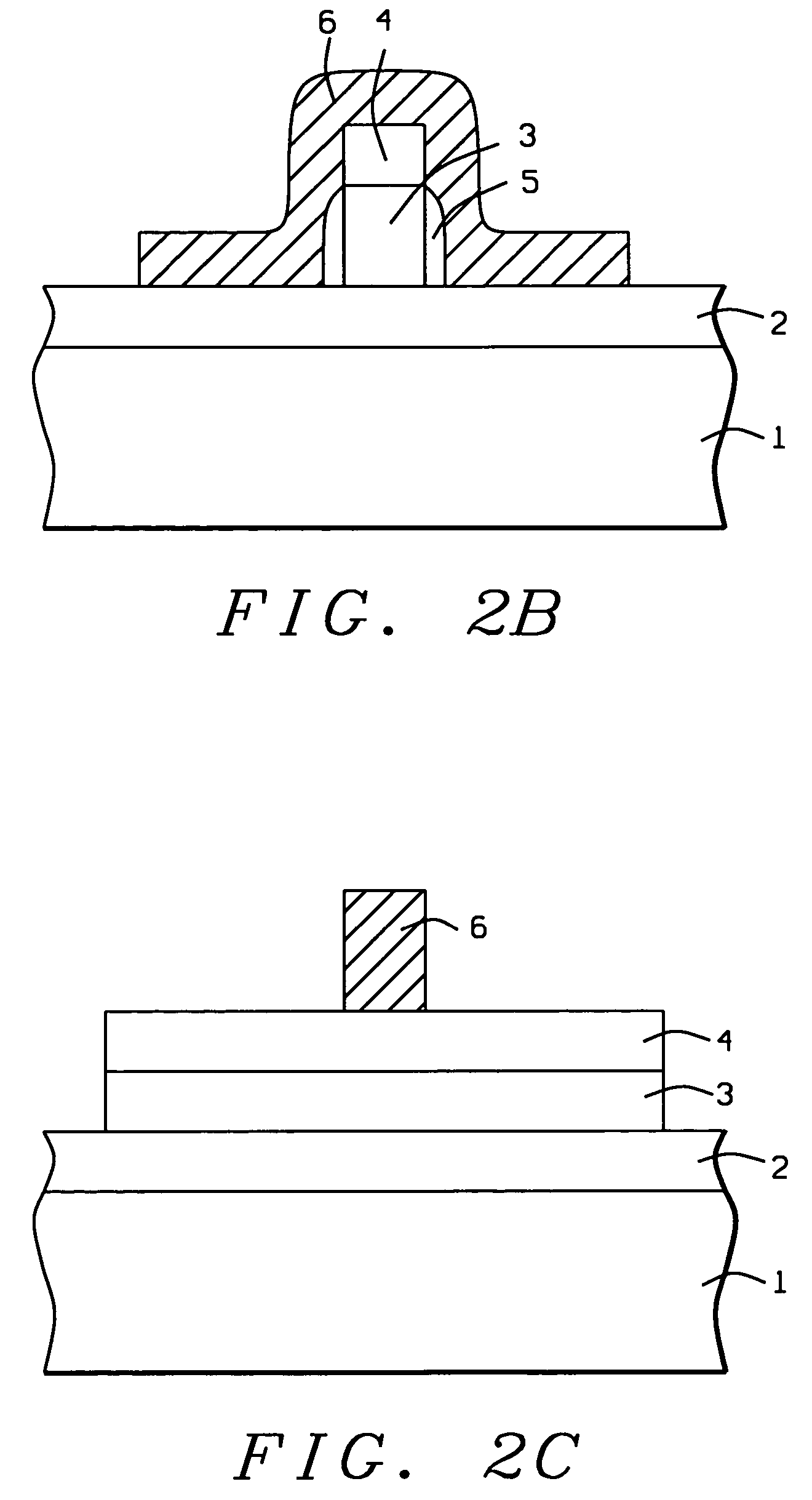

A narrow channel FinFET is described herein with a narrow channel width. A protective layer may be formed over the narrow channel, the protective layer being wider than the narrow channel.

Owner:GLOBALFOUNDRIES U S INC

Method of fabricating an ultra-narrow channel semiconductor device

A method of forming a nanowire is disclosed. A nanowire having a first dimension is deposited on a first dielectric layer that is formed on a substrate. A sacrificial gate stack having a sacrificial dielectric layer and a sacrificial gate electrode layer is deposited over a first region of the nanowire leaving exposed a second region and a third region of the nanowire. A first spacer is deposited on each side of the sacrificial gate stack. A second dielectric layer is deposited over the first dielectric layer to cover the second region and third region. The sacrificial gate stack is removed. The first region of the nanowire is thinned by at least one thermal oxidation process and oxide removal process to thin said first region from said first dimension to a second dimension.

Owner:TAHOE RES LTD

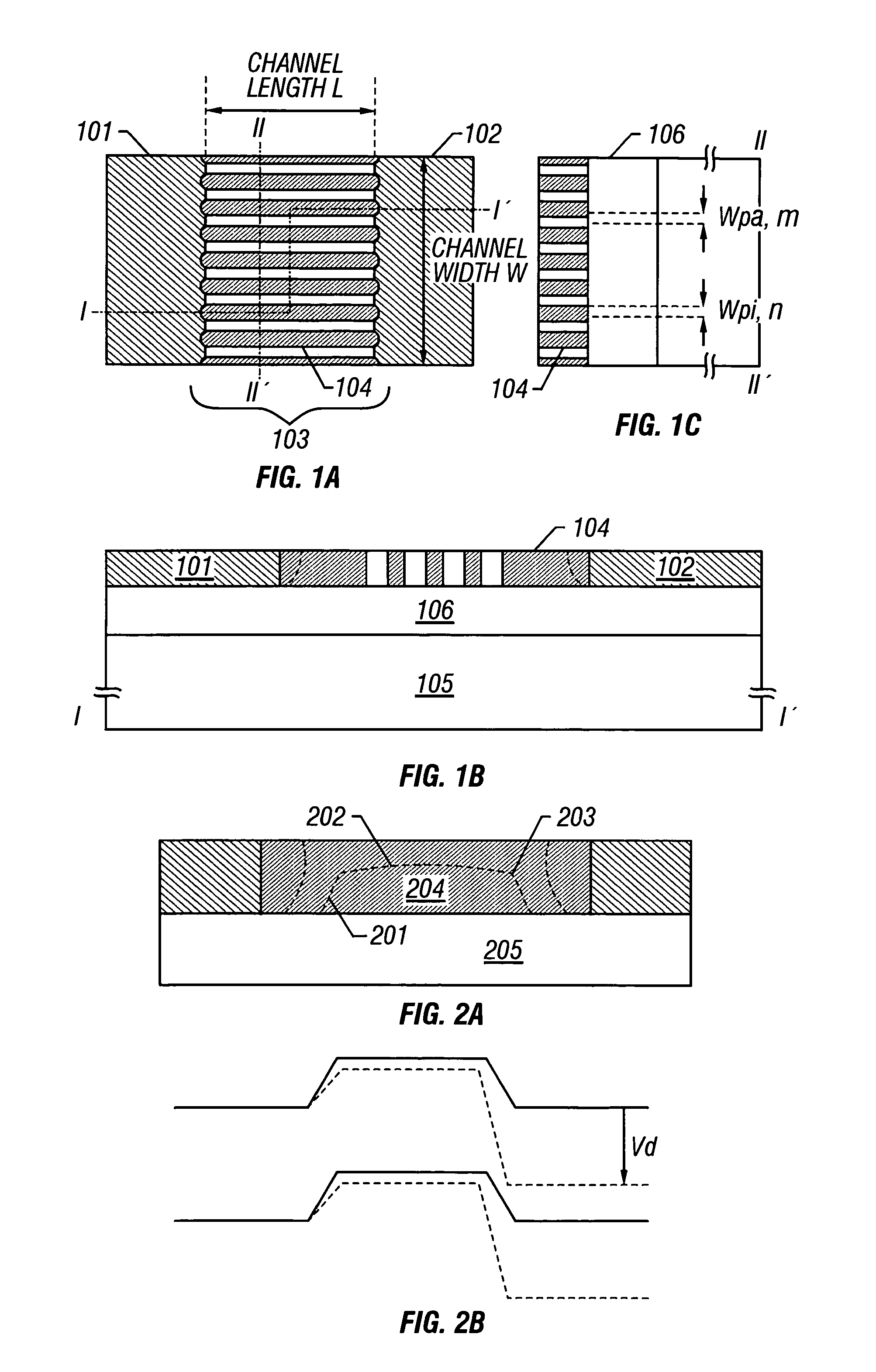

Insulated gate semiconductor device and method of manufacturing the same

Dot-pattern-like impurity regions are artificially and locally formed in a channel forming region. The impurity regions restrain the expansion of a drain side depletion layer toward the channel forming region to prevent the short channel effect. The impurity regions allow a channel width W to be substantially fined, and the resultant narrow channel effect releases the lowering of a threshold value voltage which is caused by the short channel effect.

Owner:SEMICON ENERGY LAB CO LTD

Method of fabricating semiconductor side wall fin

InactiveUS20050001216A1Tolerance channel thicknessGrowth is not complicatedTransistorSolid-state devicesGate insulatorEngineering

Owner:GLOBALFOUNDRIES INC

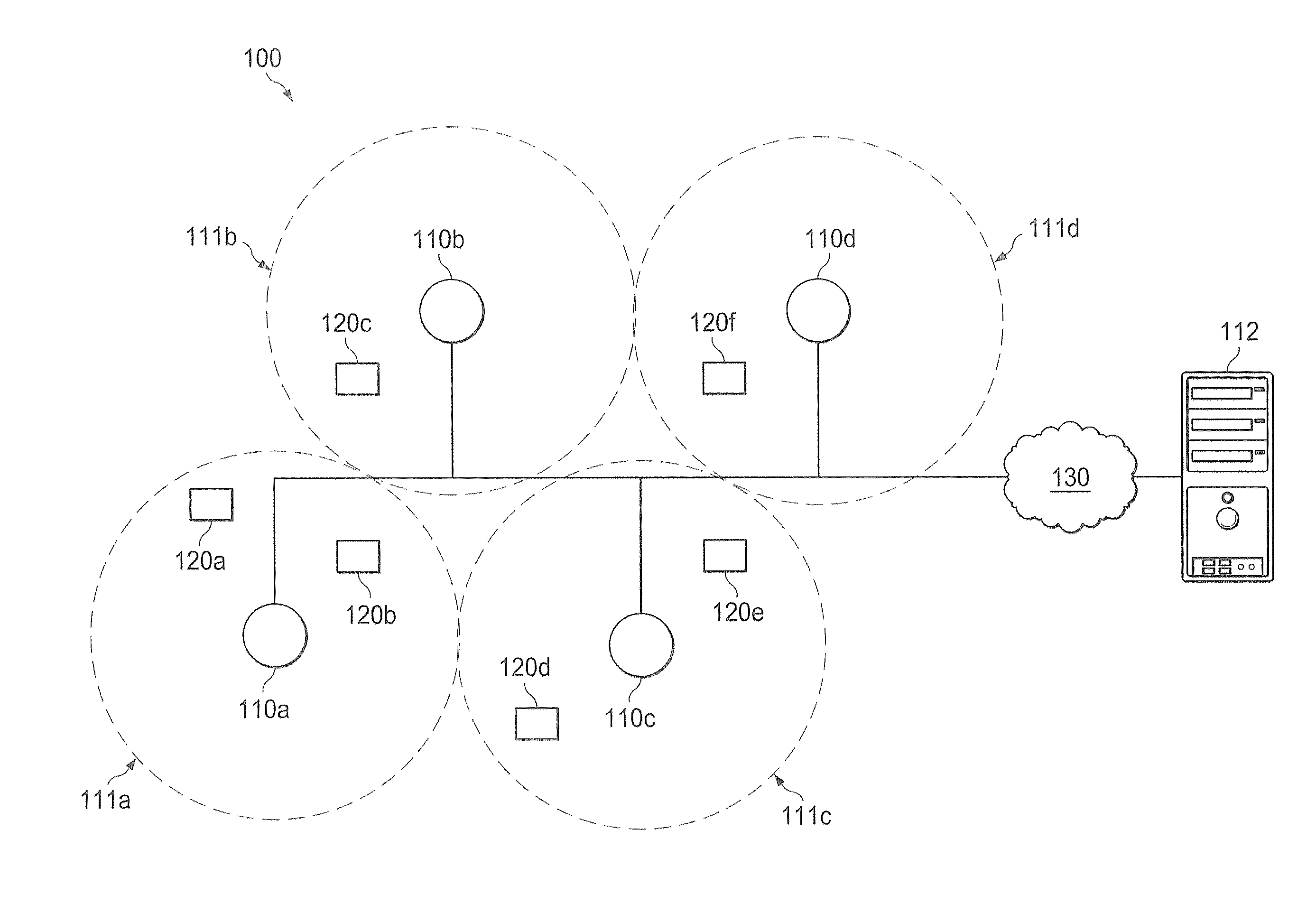

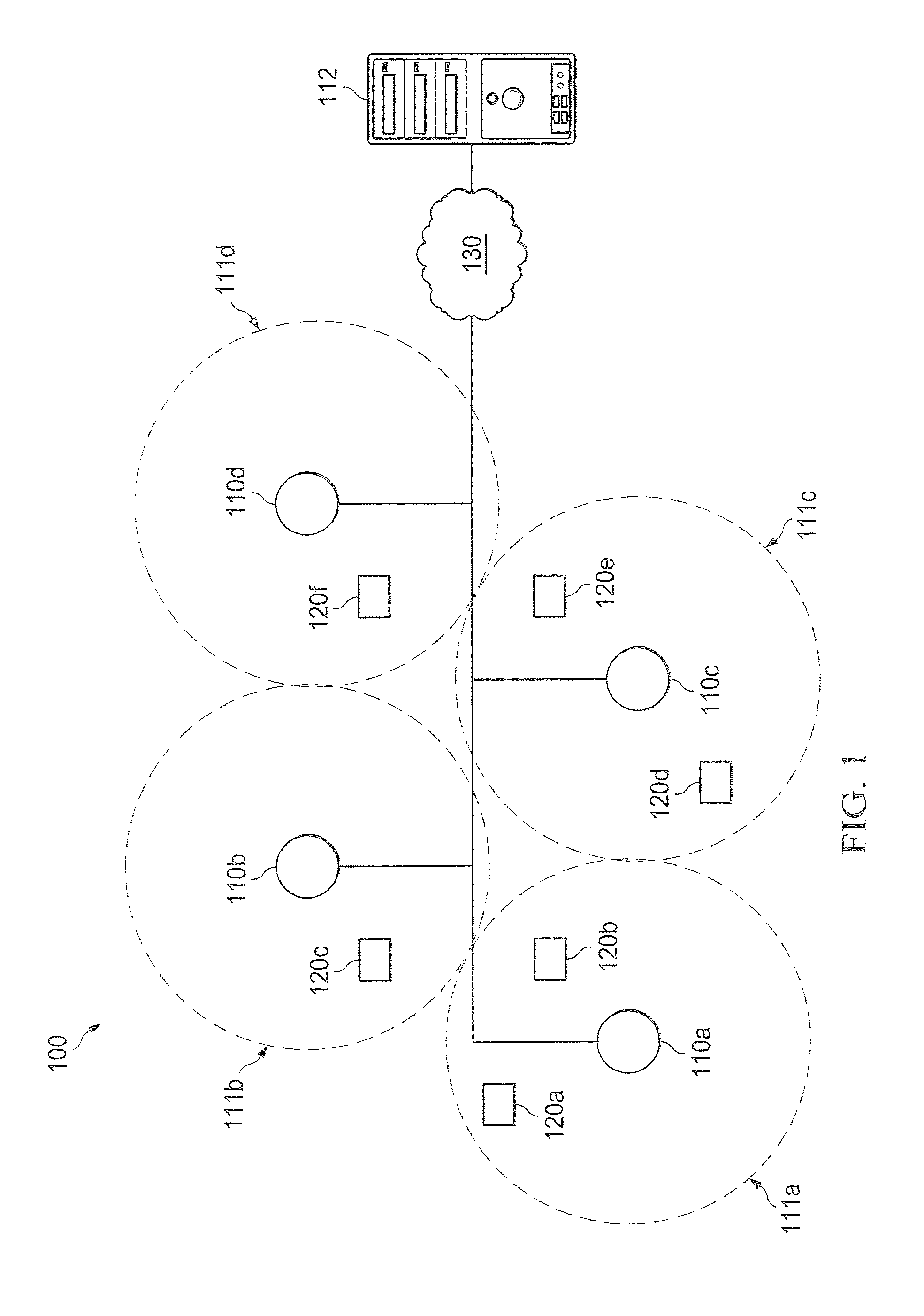

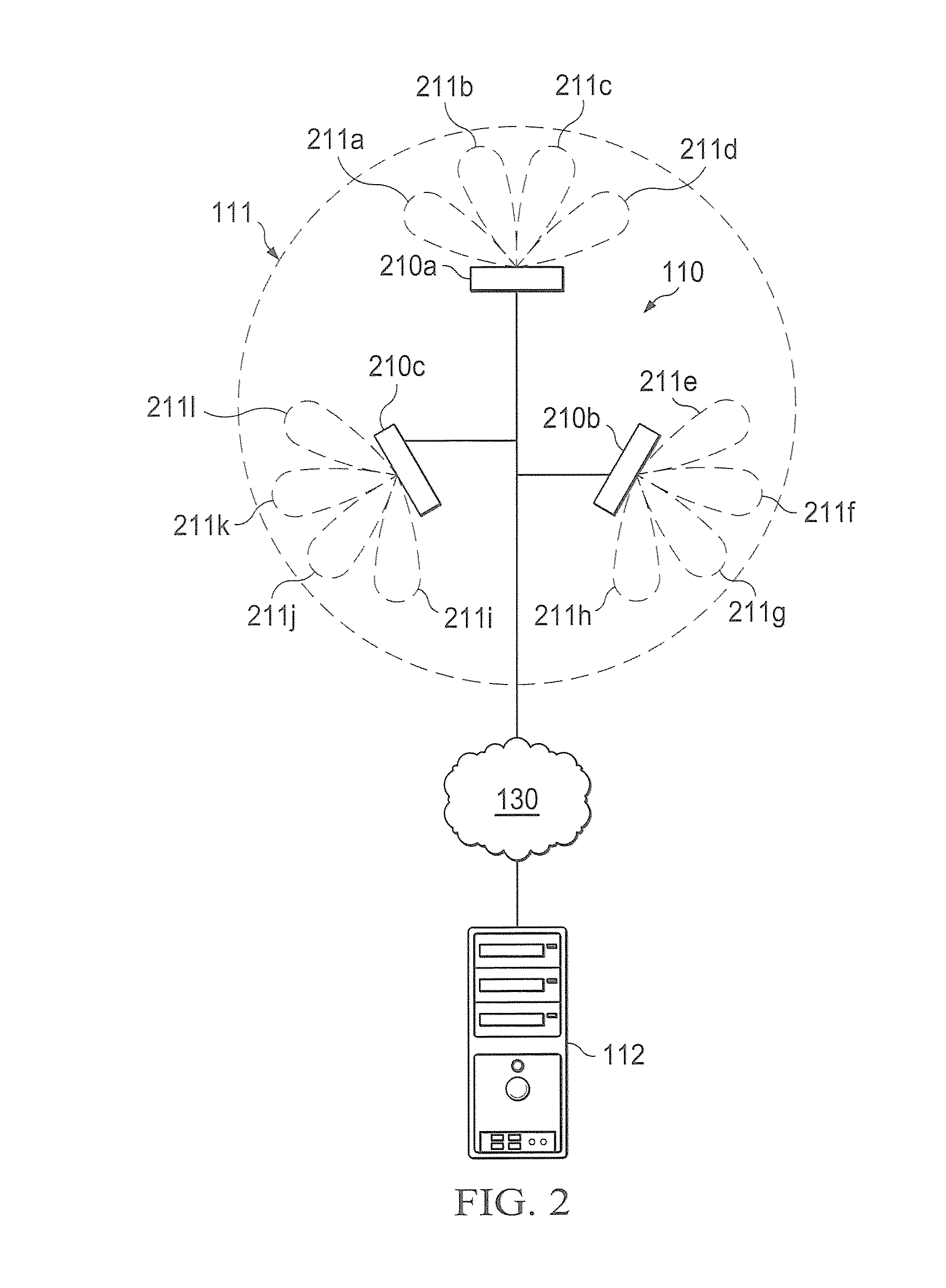

Systems and methods for mitigating interference between access points

InactiveUS20110032849A1Easy to useDense reuseTime-division multiplexRadio transmissionEngineeringPoint system

Systems and methods which implement cooperative techniques at wireless network access points to provide interference mitigation are shown. Embodiments utilize cooperative antenna beam adaptation techniques wherein antenna beam selection, selective antenna beam transmission power, and / or antenna beam null selection is implemented based upon the communication environment created by a plurality of access points. Additionally or alternatively, embodiments utilize cooperative antenna beam isolation techniques wherein narrow channel filters are implemented with respect to antenna beam signals and / or shielding is provided between various antenna beams based upon the communication environment created by a plurality of access points. Embodiments additionally or alternatively utilize cooperative antenna beam coordination techniques wherein transmission and / or reception of signals is coordinated, the use of antenna beams is coordinated, and / or interference cancellation is implemented based upon the communication environment created by a plurality of access points.

Owner:FIMAX TECH

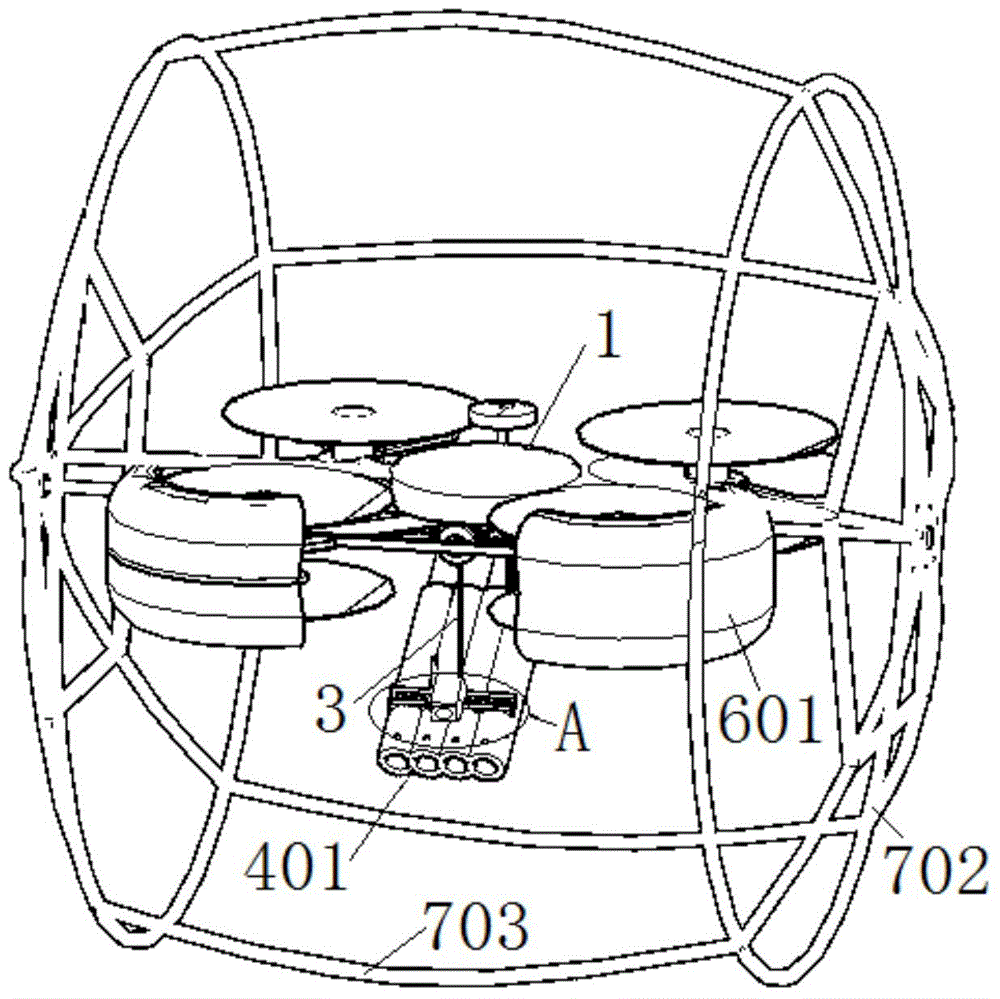

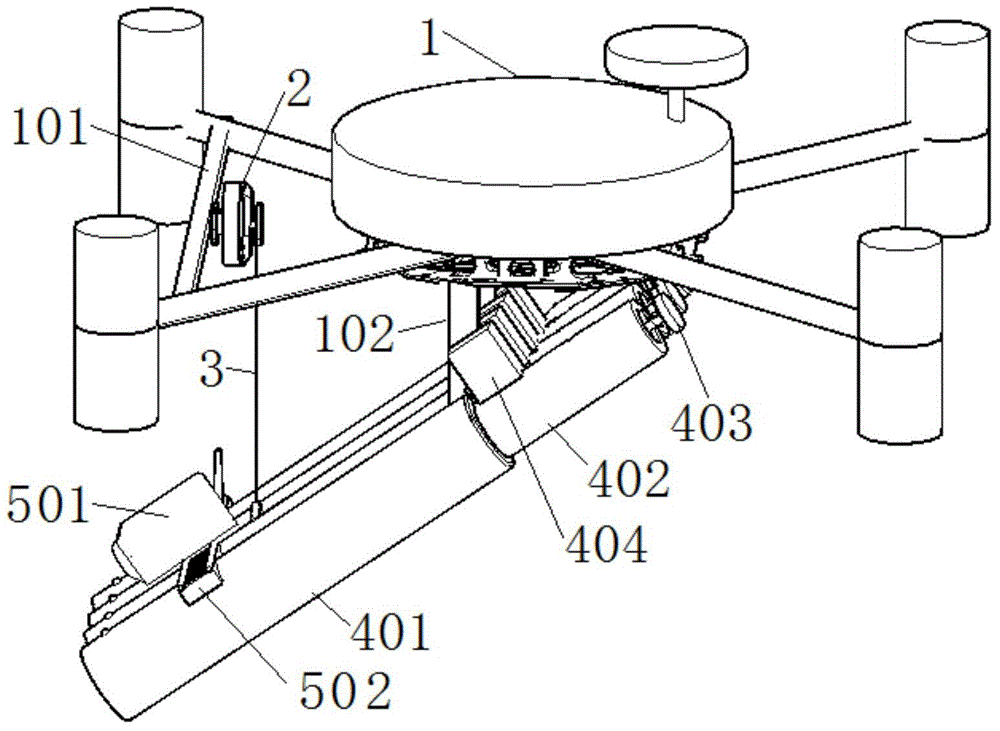

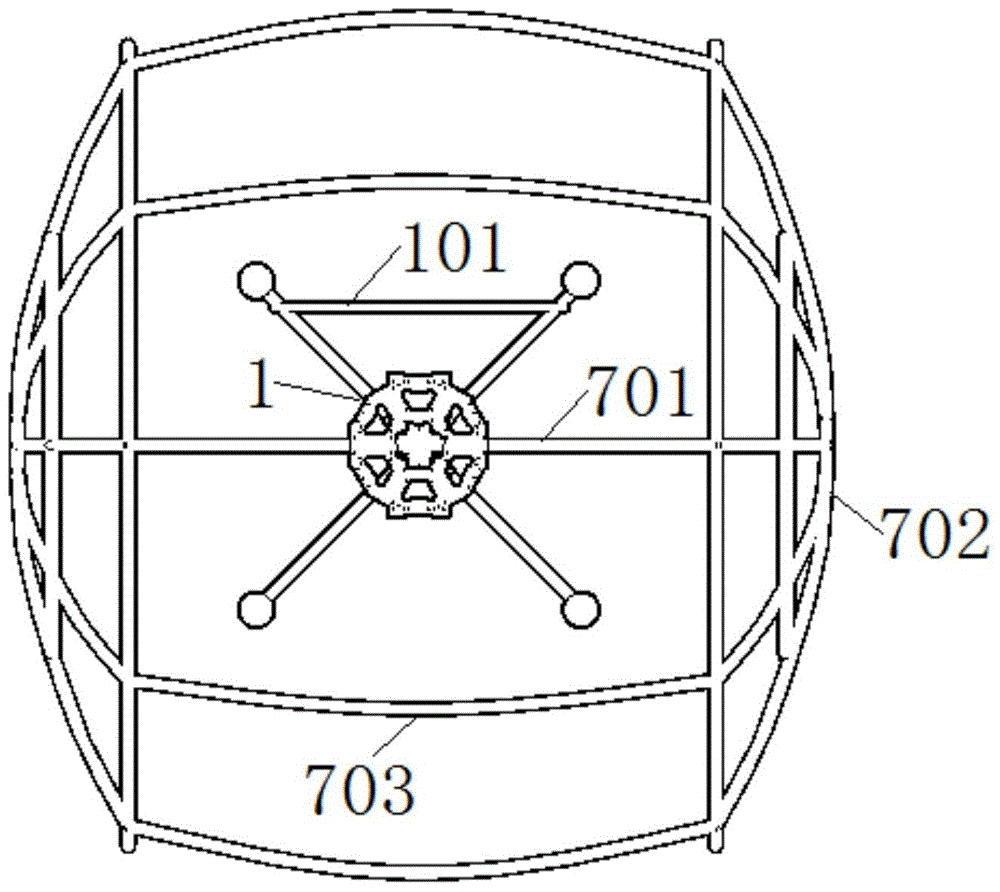

Anti-collision fixed-point unmanned aerial vehicle for fire control

The invention discloses an anti-collision fixed-point unmanned aerial vehicle for fire control, and belongs to the field of unmanned aerial vehicles. The anti-collision fixed-point unmanned aerial vehicle for fire control comprises an unmanned aerial vehicle body, a bomb-dropping gun and an anti-collision cover, wherein the bomb-dropping gun is arranged below the unmanned aerial vehicle body; a steering engine is mounted on the bomb-dropping gun and is used for controlling the bomb-dropping gun to launch a fire extinguishing bomb; a collimation mechanism is mounted on the parallelly arranged bomb-dropping gun, so that the bomb-dropping accuracy is improved; the anti-collision cover adopts a cage-shaped structure; the cage-shaped structure encircles the periphery of the unmanned aerial vehicle body to protect the unmanned aerial vehicle body from being collided; a waterproof cover is also arranged on a spiral paddle support to prevent the spraying of flames. According to the anti-collision fixed-point unmanned aerial vehicle, fixed-point fire extinguishment on high-rise buildings and narrow channels is carried out without geographical environment limitation, and the unmanned aerial vehicle is unlikely to collide and damage, high in flying speed, sensitive in actions and wide in application range.

Owner:如东道博智能设备有限公司

Narrow fin finfet

InactiveUS20040197975A1TransistorSolid-state devicesNarrow channelElectrical and Electronics engineering

A narrow channel FinFET is described herein with a narrow channel width. A protective layer may be formed over the narrow channel, the protective layer being wider than the narrow channel.

Owner:GLOBALFOUNDRIES US INC

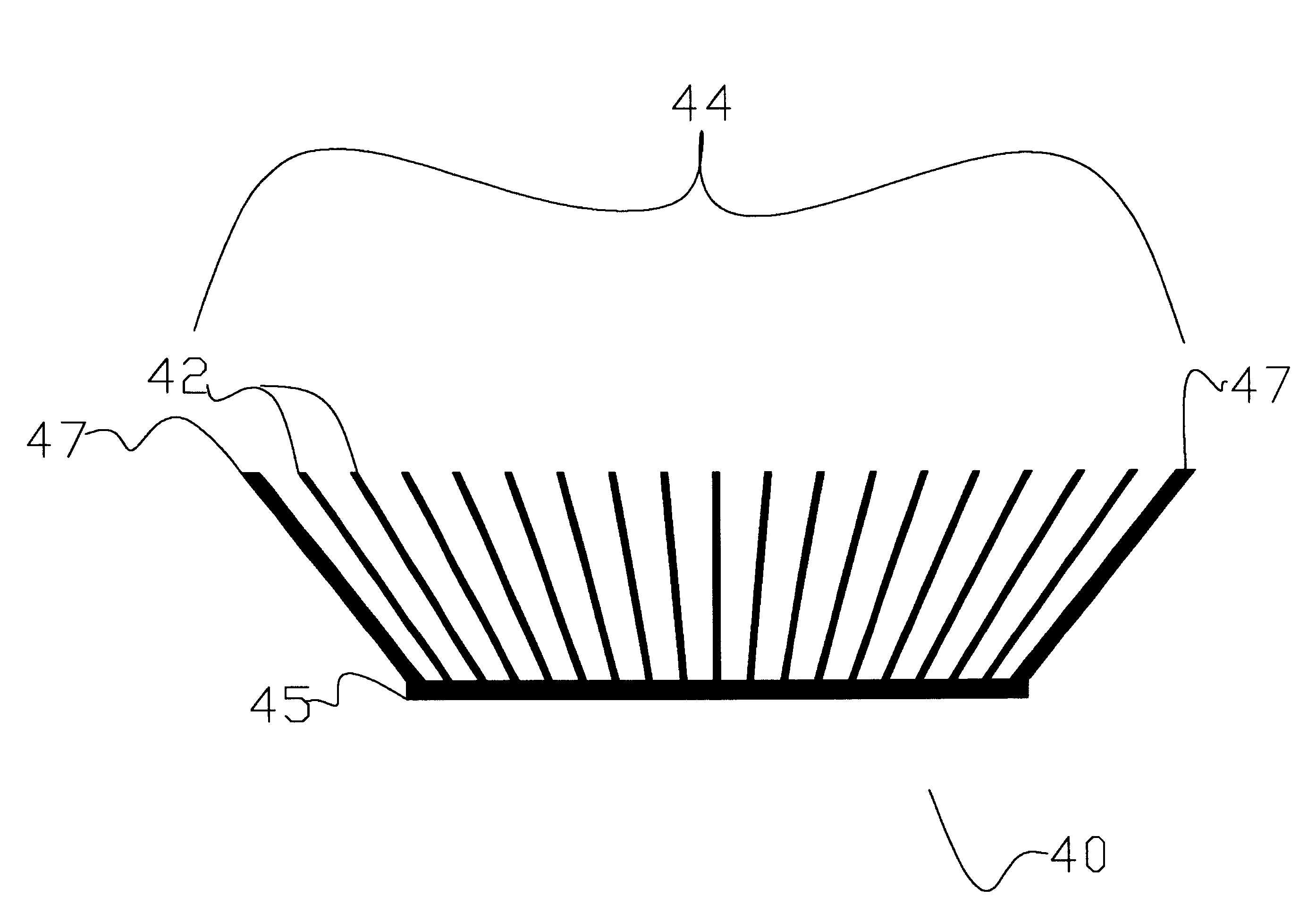

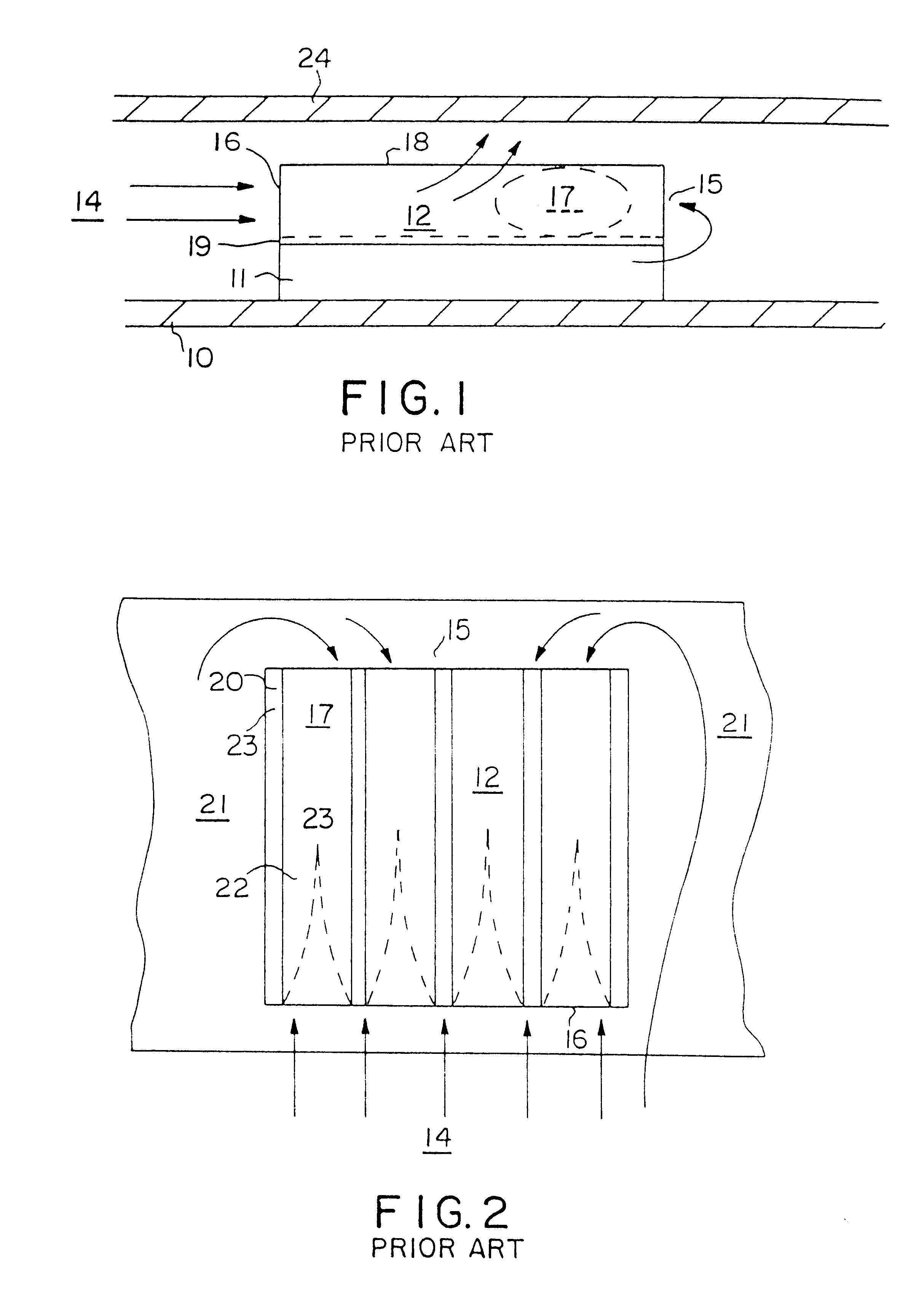

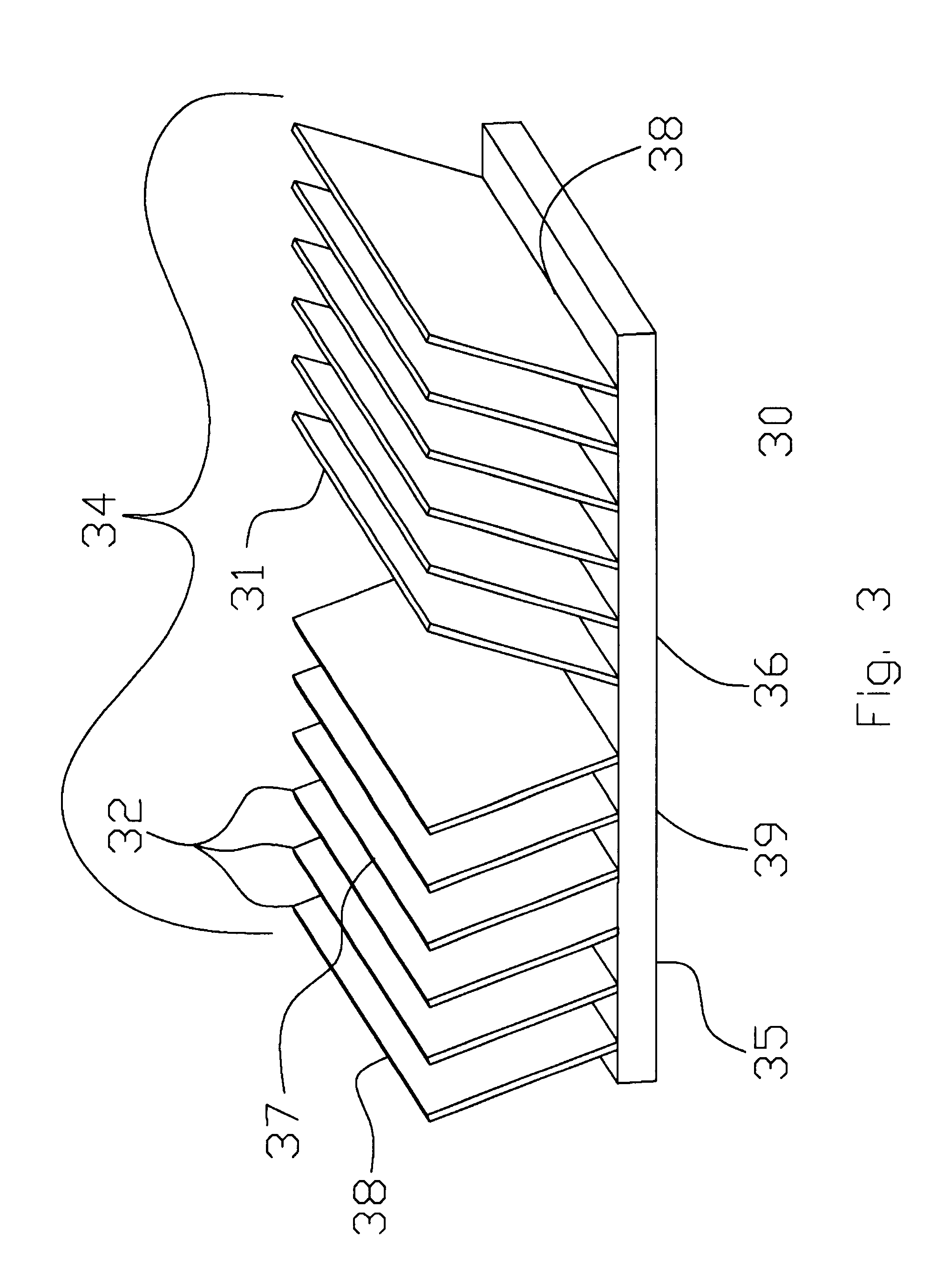

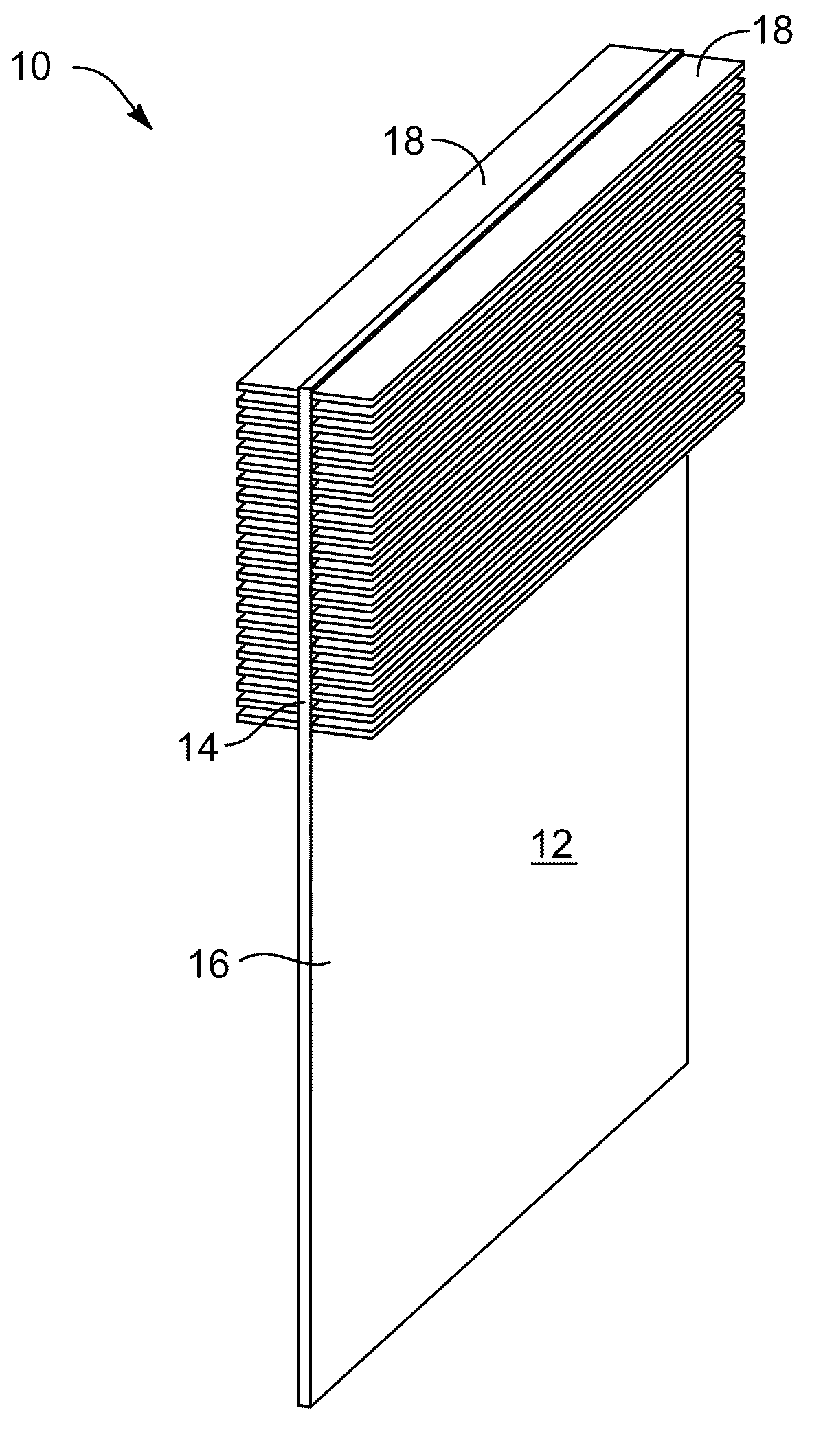

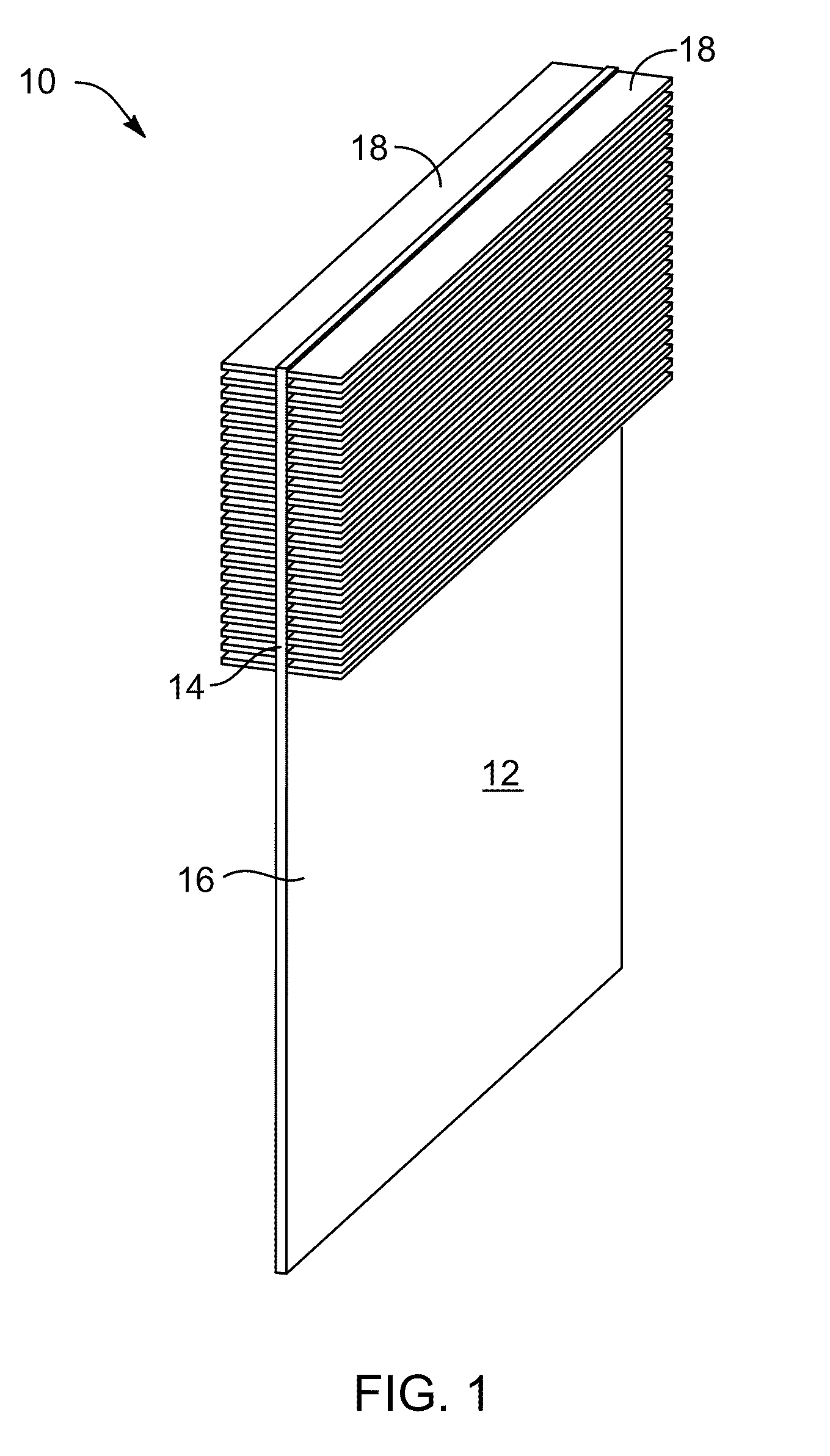

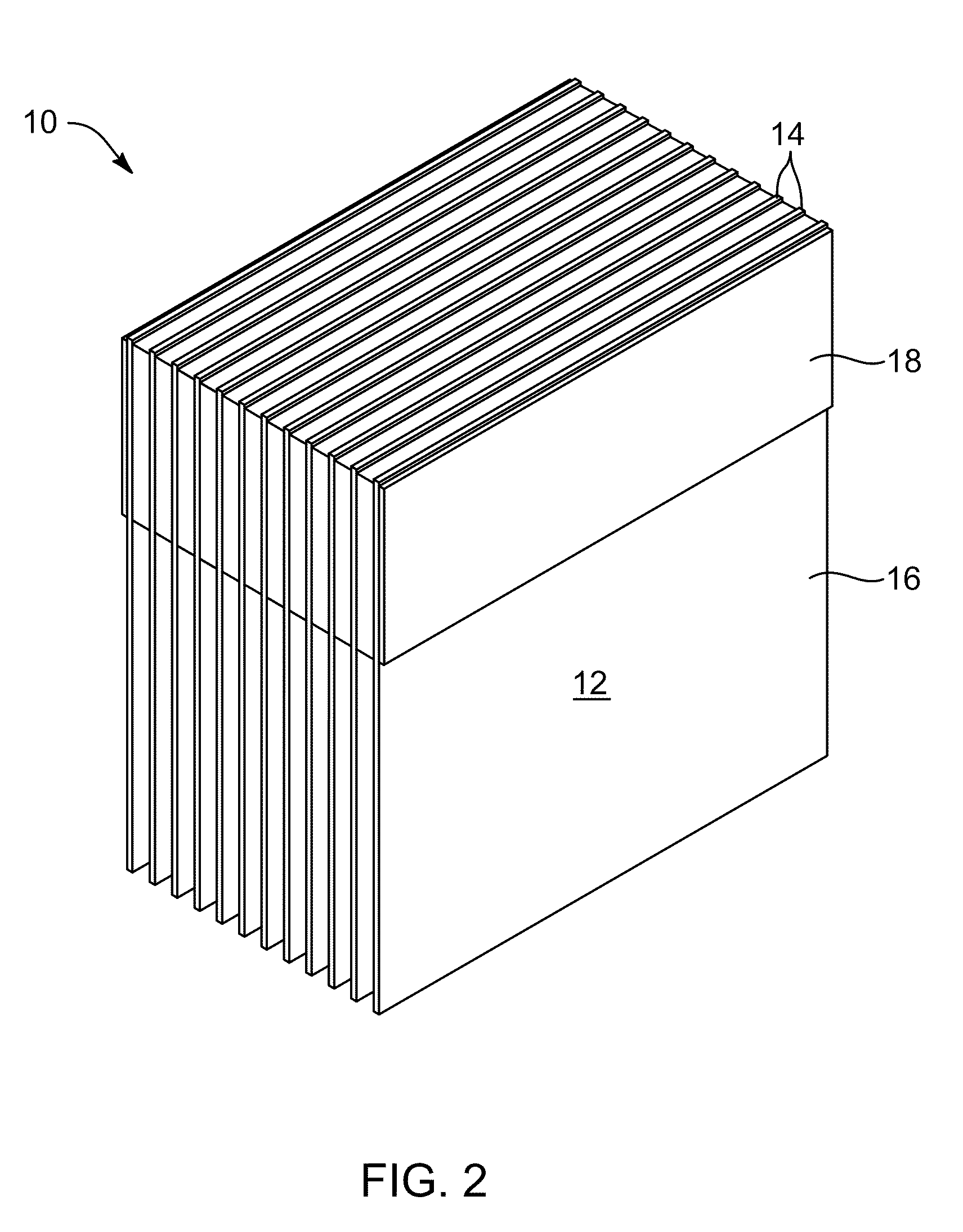

High performance fan tail heat exchanger

InactiveUS6308771B1Increased control volumeOptimize volumeSemiconductor/solid-state device detailsSolid-state devicesAcute angleEngineering

A novel plate fin heat exchanger adapted for high and low velocity fluid flows for dissipating heat from a heat generating component. The heat exchanger comprises an array of fins being affixed to and in thermal communication with a thermally conductive base, wherein the fins are arranged in a fan tail configuration for minimizing flow bypass, and further providing reduced thermal resistance for fluid passing through the fin field. The fins are affixed to and in thermal communication with the base at an acute angle, such that the effective width of the array of fins exceeds the width of the base. The enlarged effective width of the fin array in comparison to conventional heat exchanger provides an increased volume for fluid flow, thereby allowing a greater volume of fluid to enter the fin field and a greater surface area of plate fins for cooling the fluid passing through the heat exchanger. In addition, the heat exchanger comprises a fin density of at least ten fins per inch or greater of base length thereby providing a narrow channel heat exchanger with a fan tail. The aspect ratio of the individual channels between the fins, as compared to parallel fins affixed perpendicular to the base through an extrusion method, generates a reduced pressure drop across the heat exchanger. Accordingly, the heat exchanger of the present invention expands the envelope of cooling performance provided by fluid flow over an array of thermally conductive plates.

Owner:ADVANCED THERMAL SOLUTION

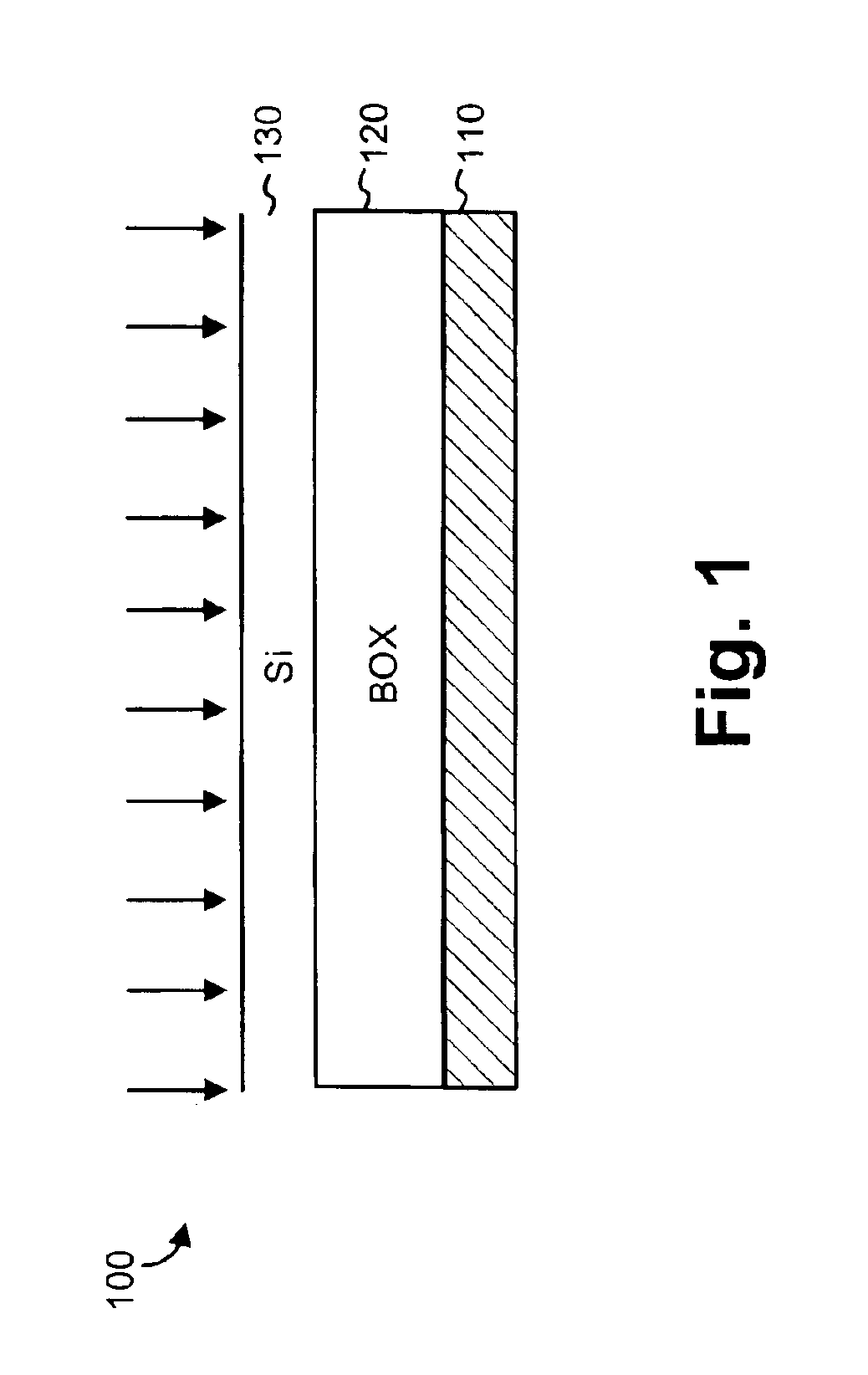

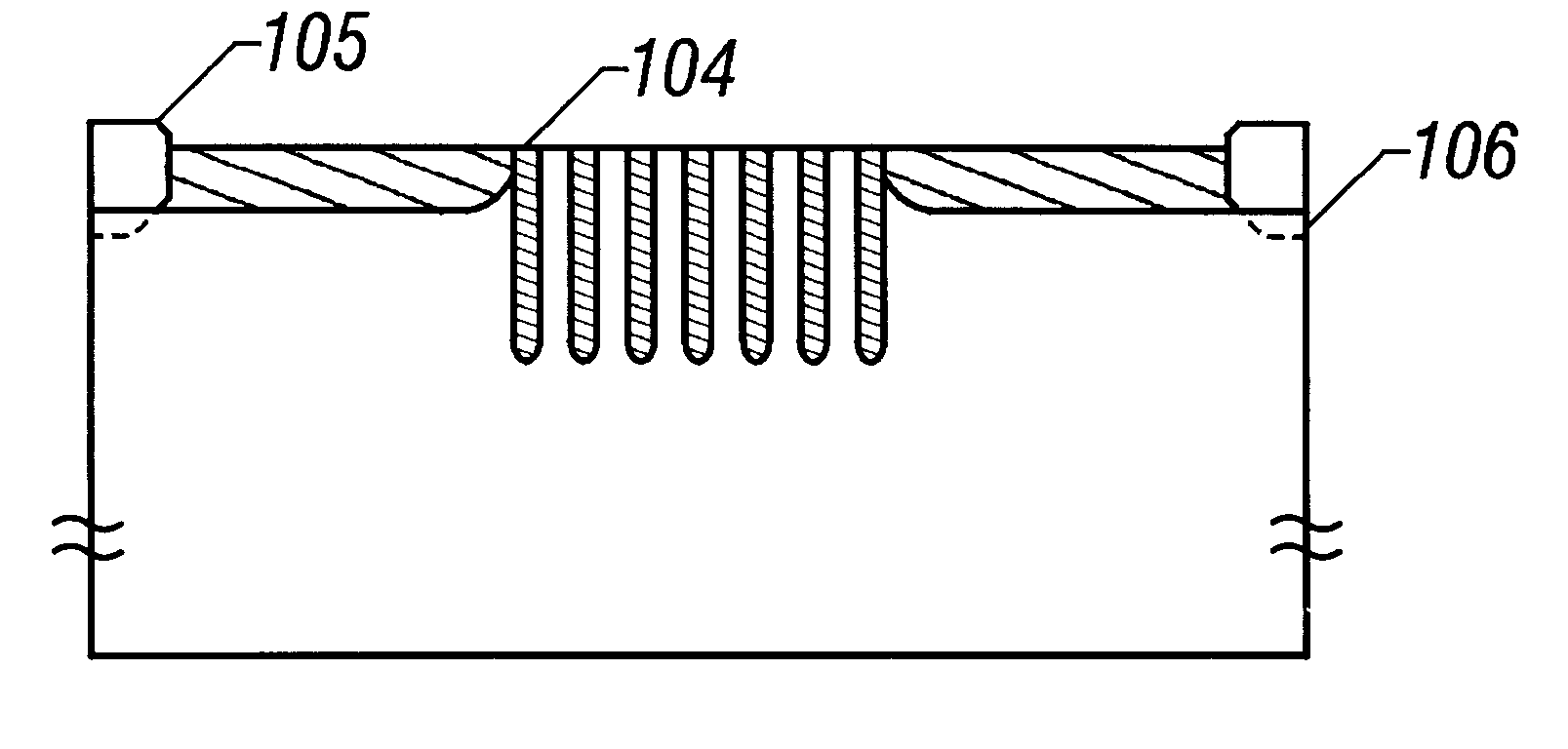

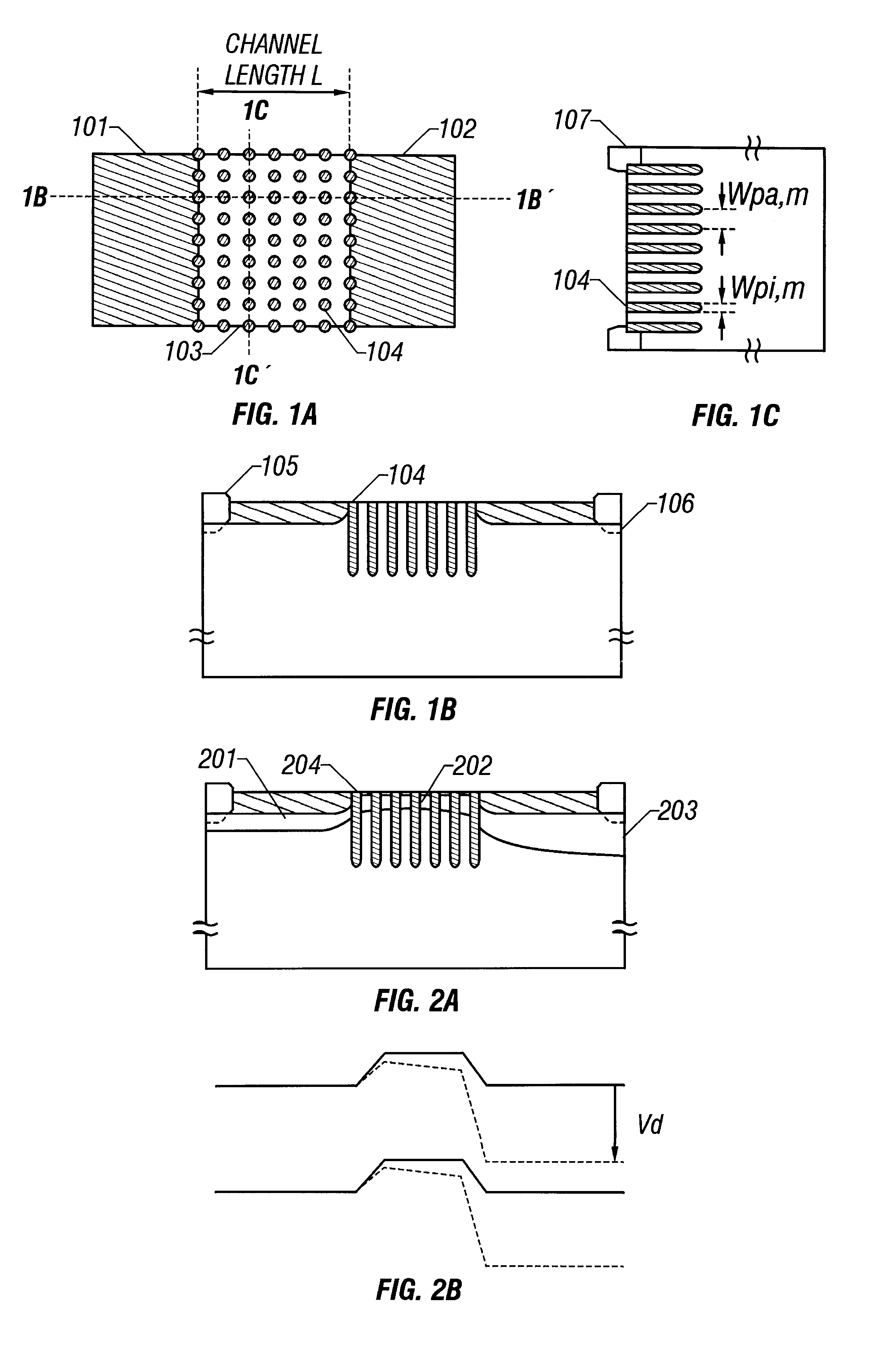

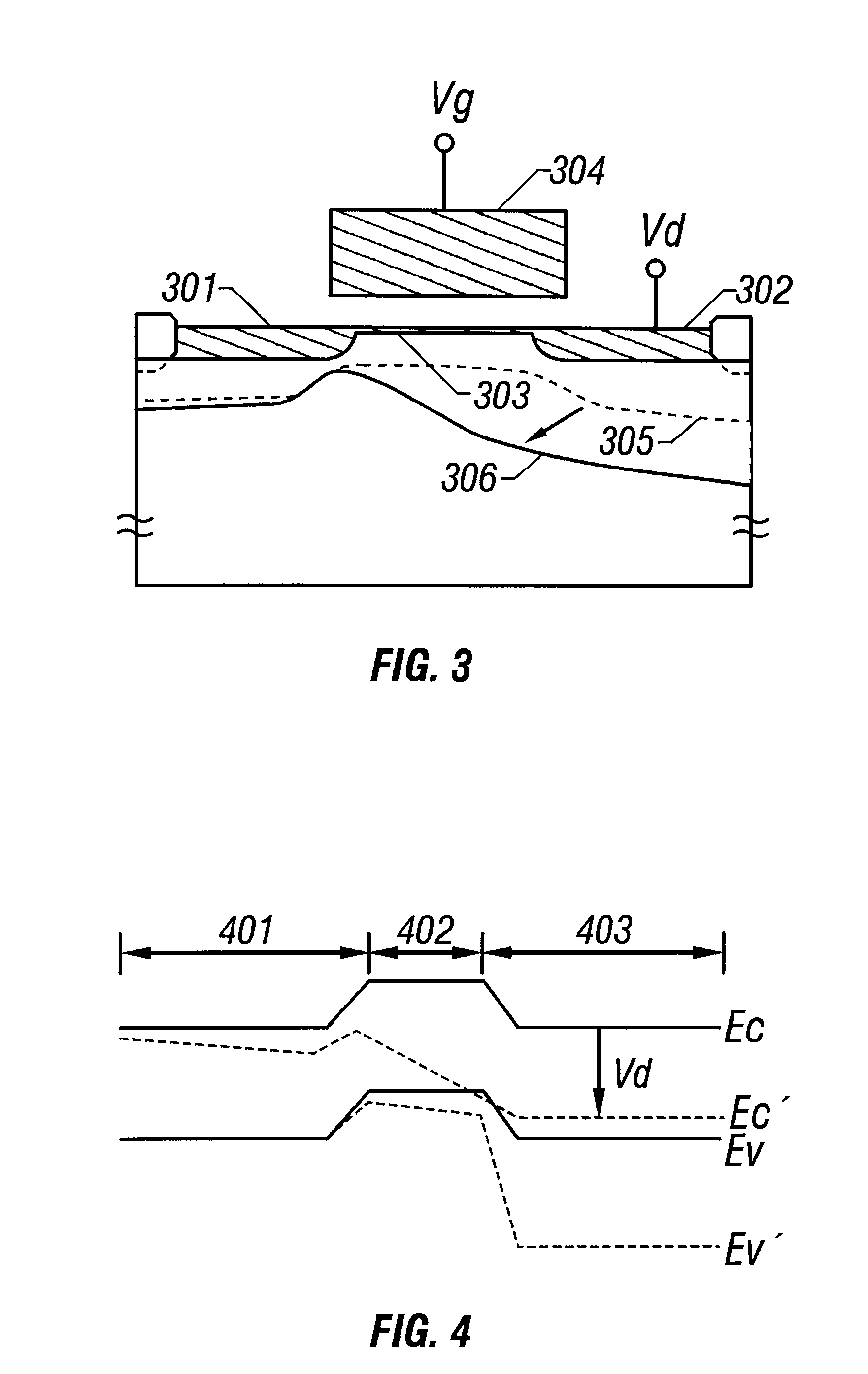

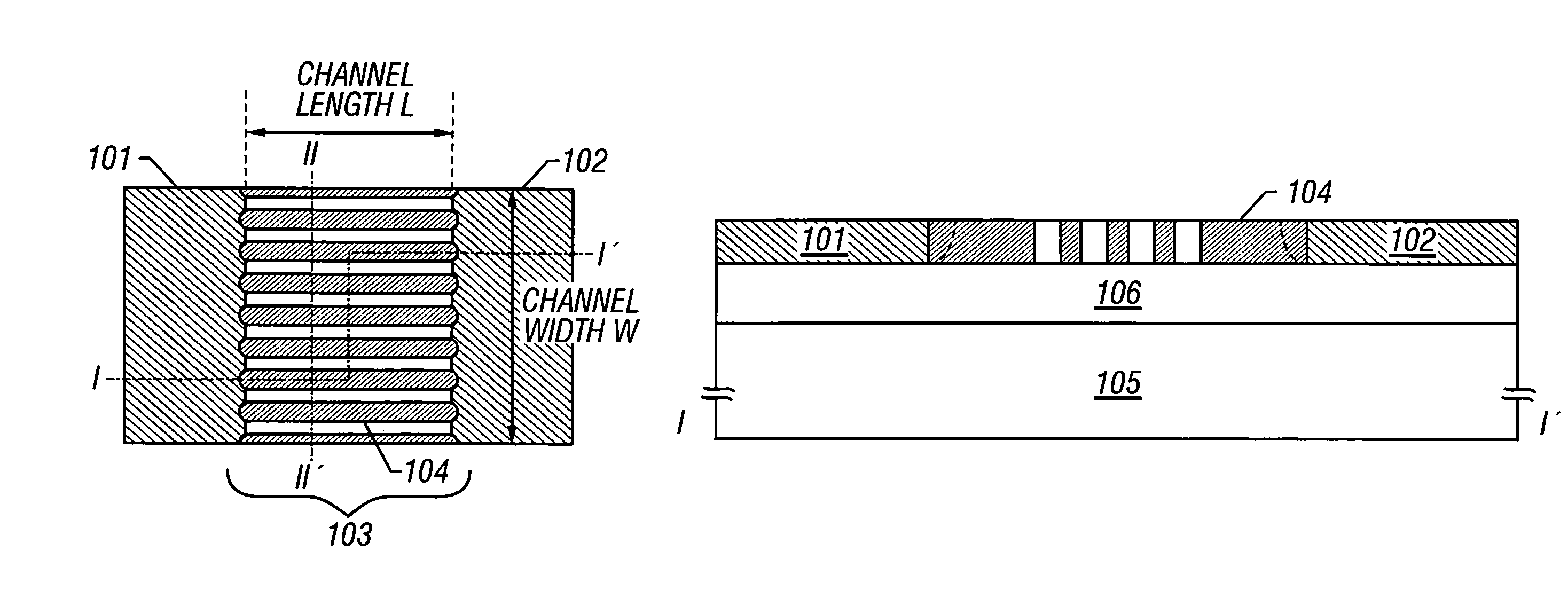

Semiconductor device having SOI structure and manufacturing method thereof

InactiveUS7339235B1Suppression of short channel effectsEffectively suppress a depletion layerTransistorIndividual molecule manipulationEngineeringSemiconductor

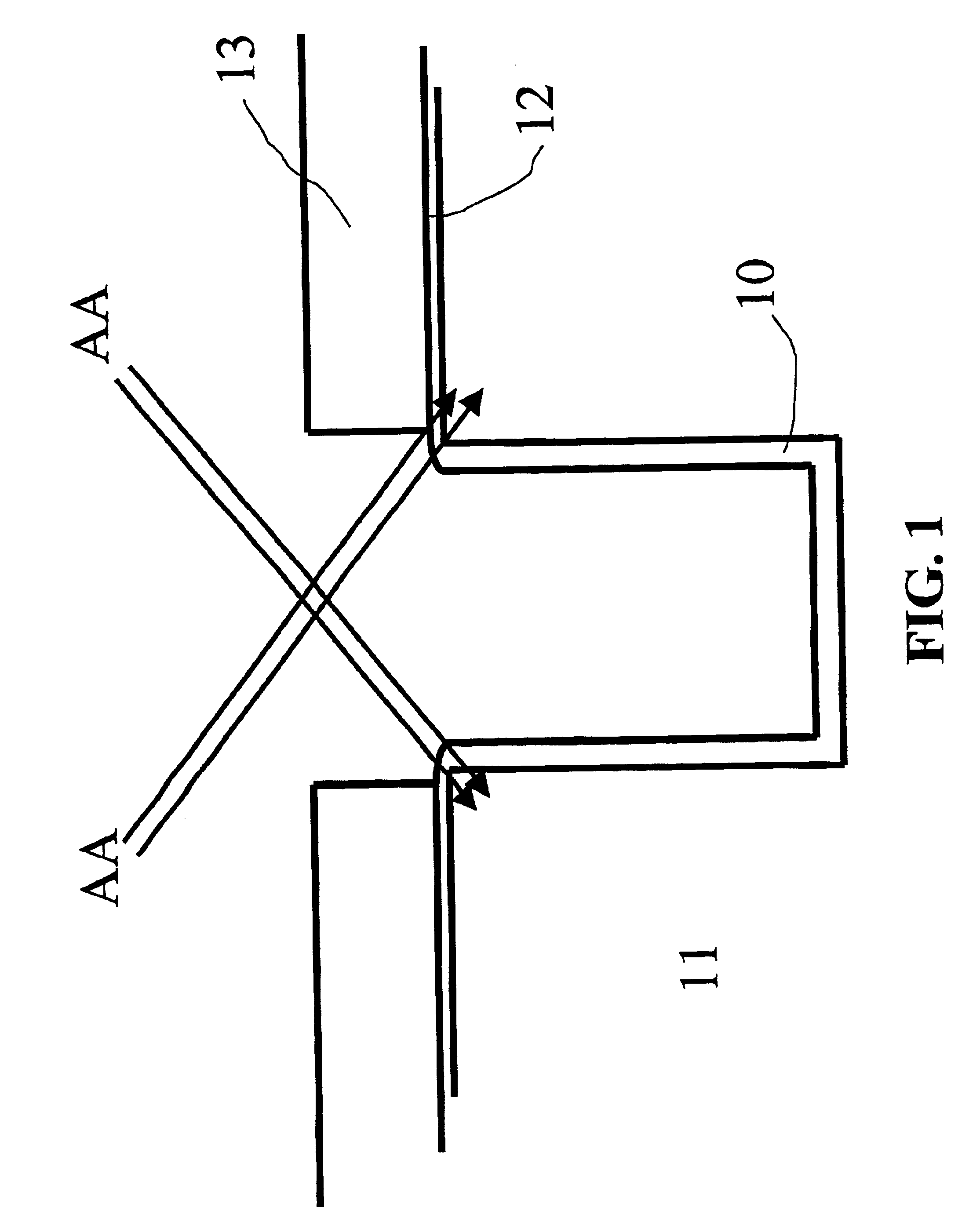

A fine semiconductor device having a short channel length while suppressing a short channel effect. Linearly patterned or dot-patterned impurity regions 104 are formed in a channel forming region 103 so as to be generally parallel with the channel direction. The impurity regions 104 are effective in suppressing the short channel effects. More specifically, the impurity regions 104 suppress expansion of a drain-side depletion layer, so that the punch-through phenomenon can be prevented. Further, the impurity regions cause a narrow channel effect, so that reduction in threshold voltage can be lessened.

Owner:SEMICON ENERGY LAB CO LTD

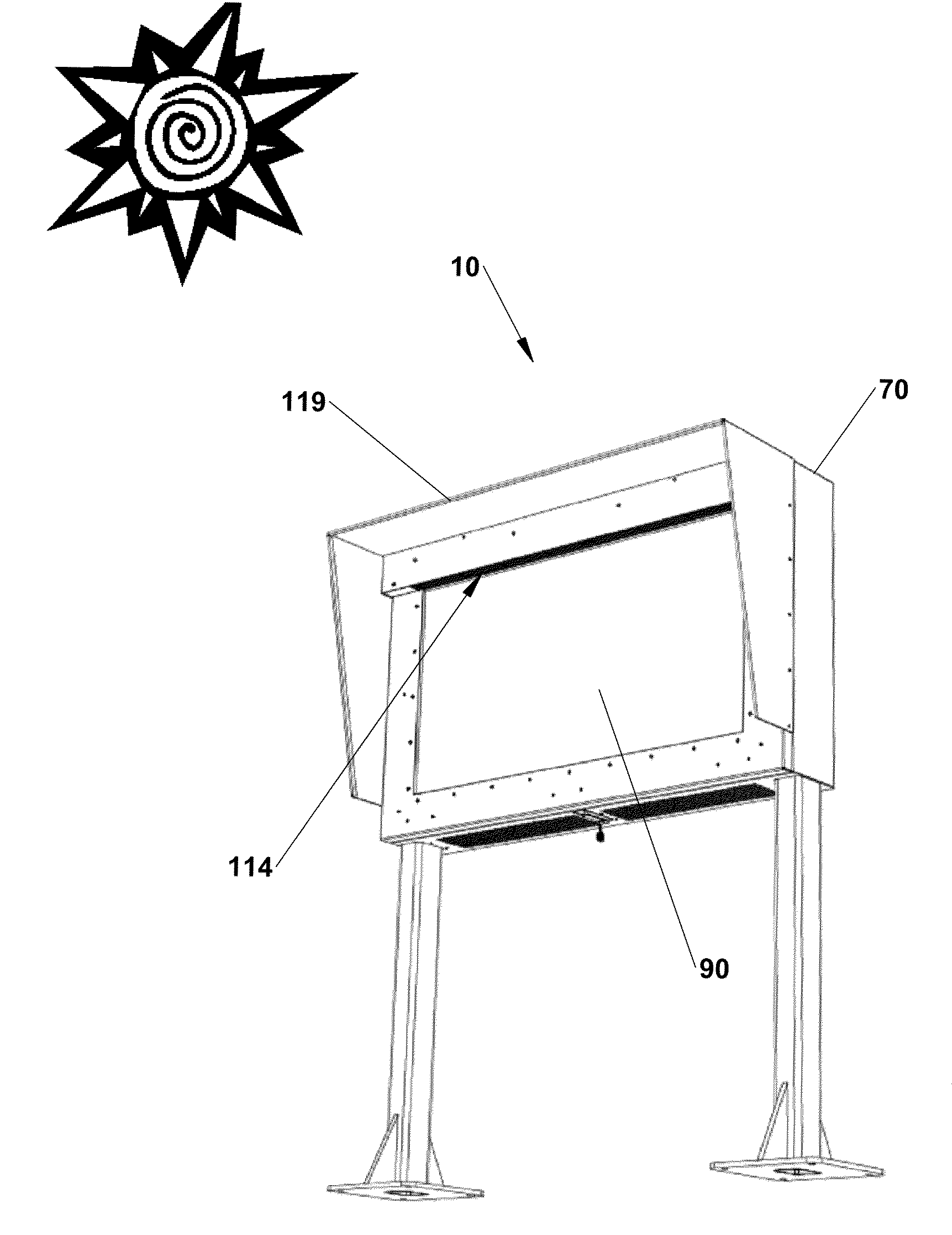

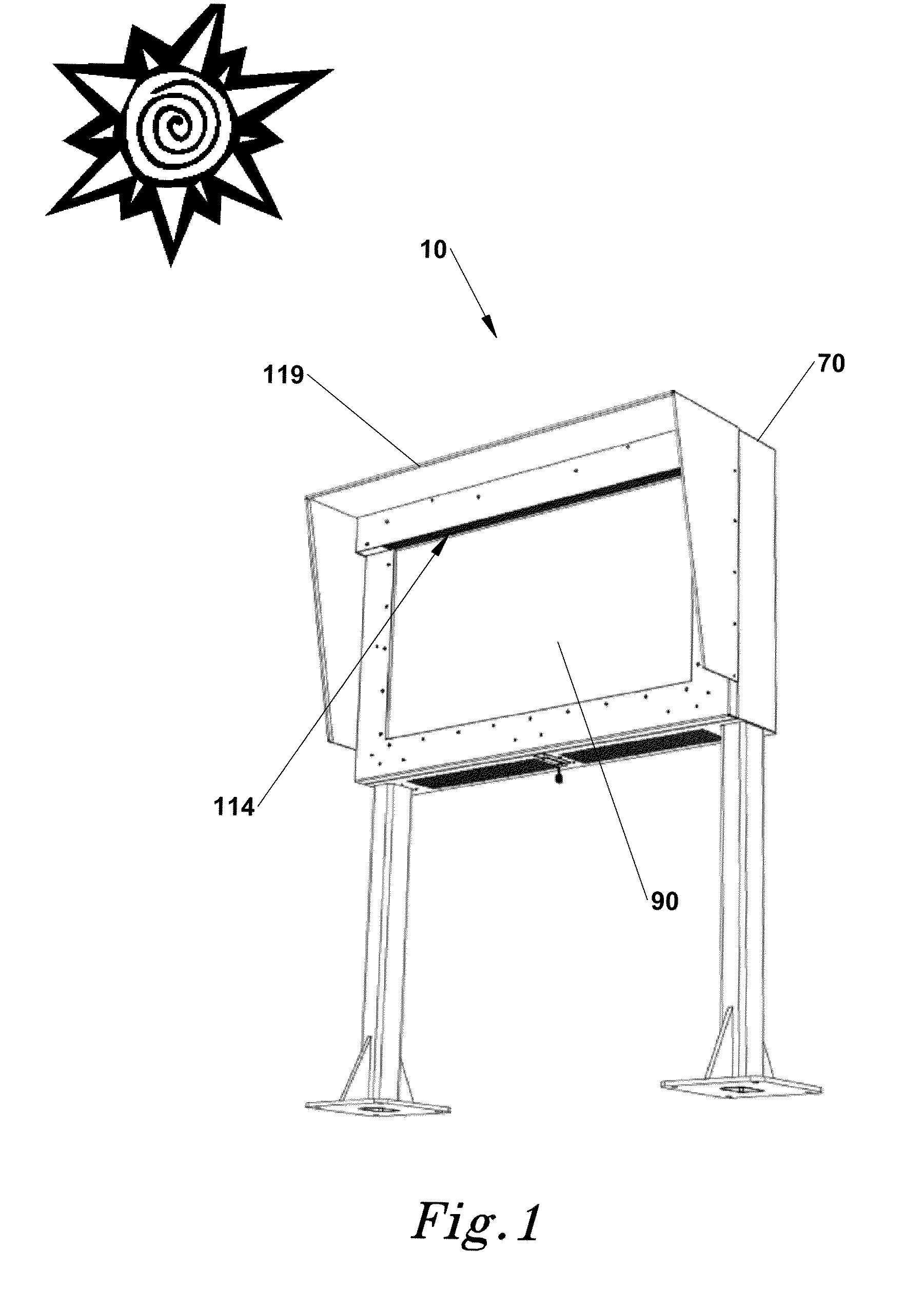

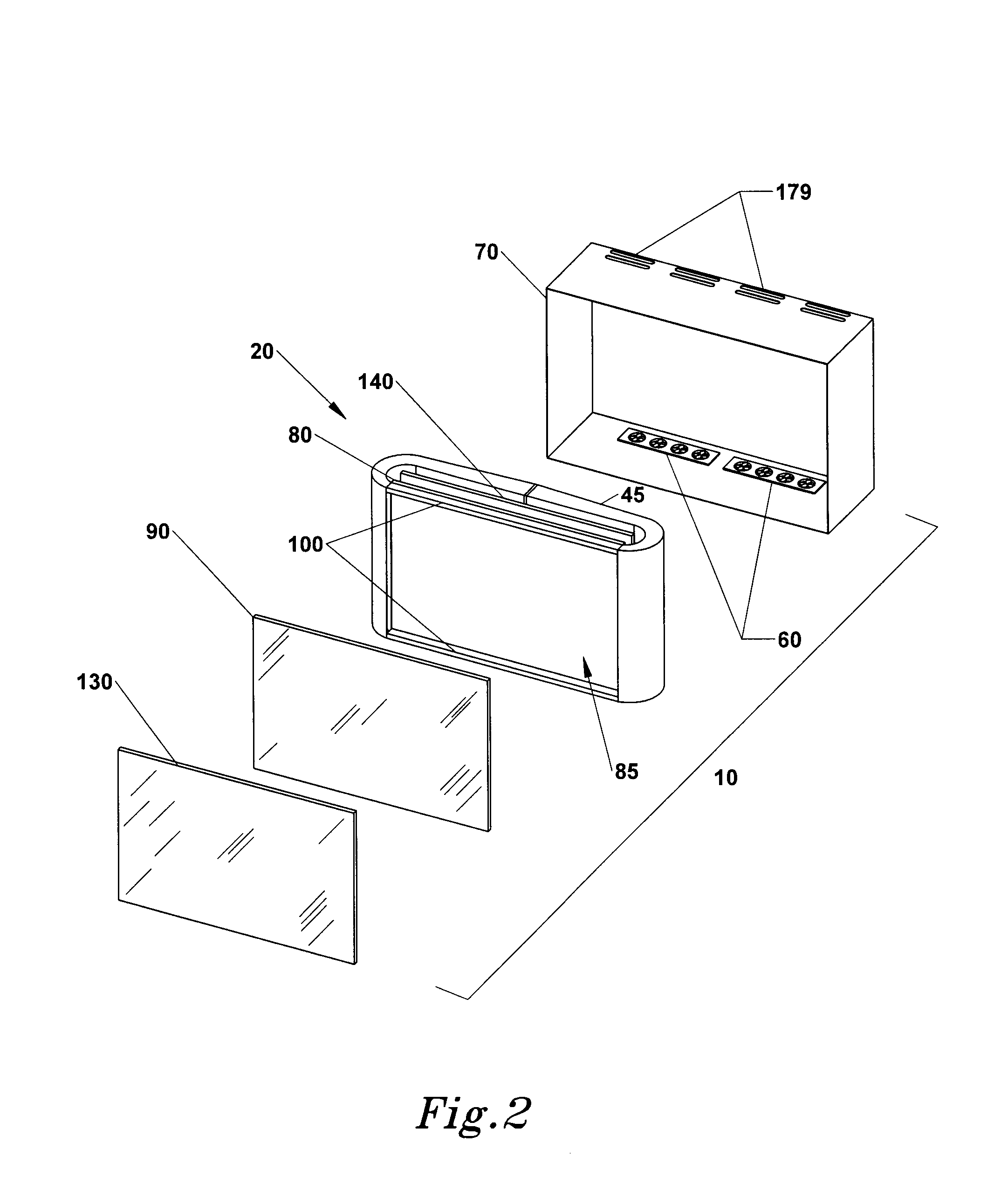

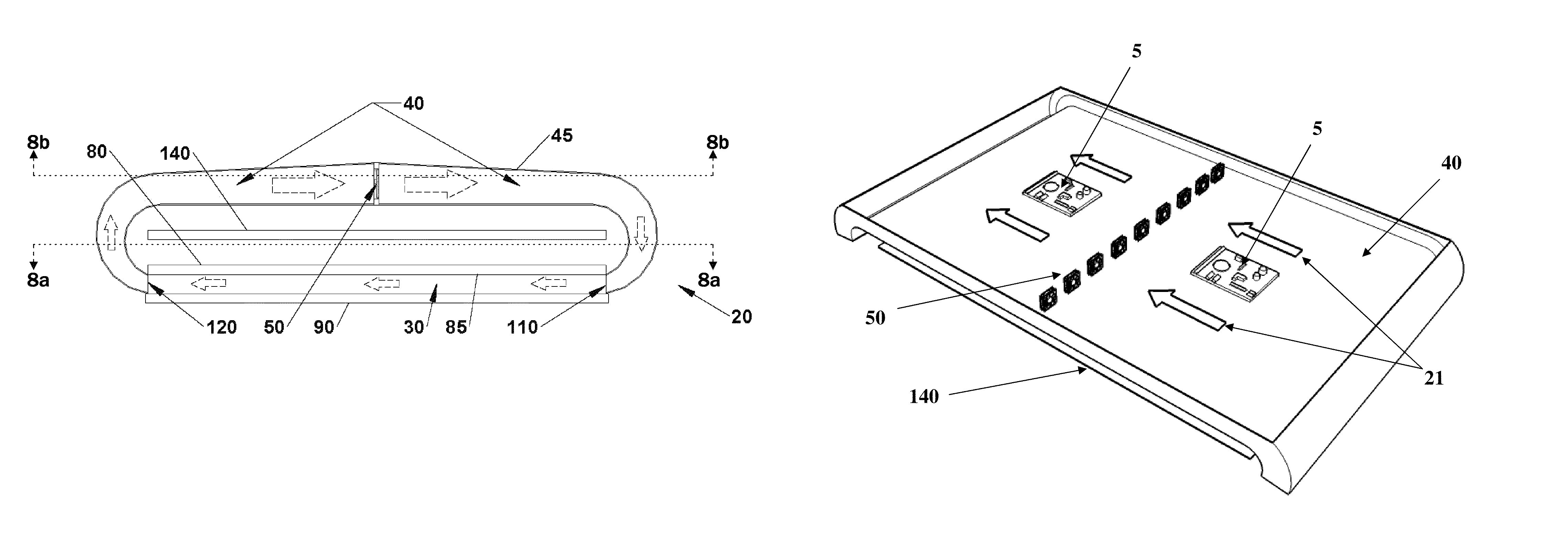

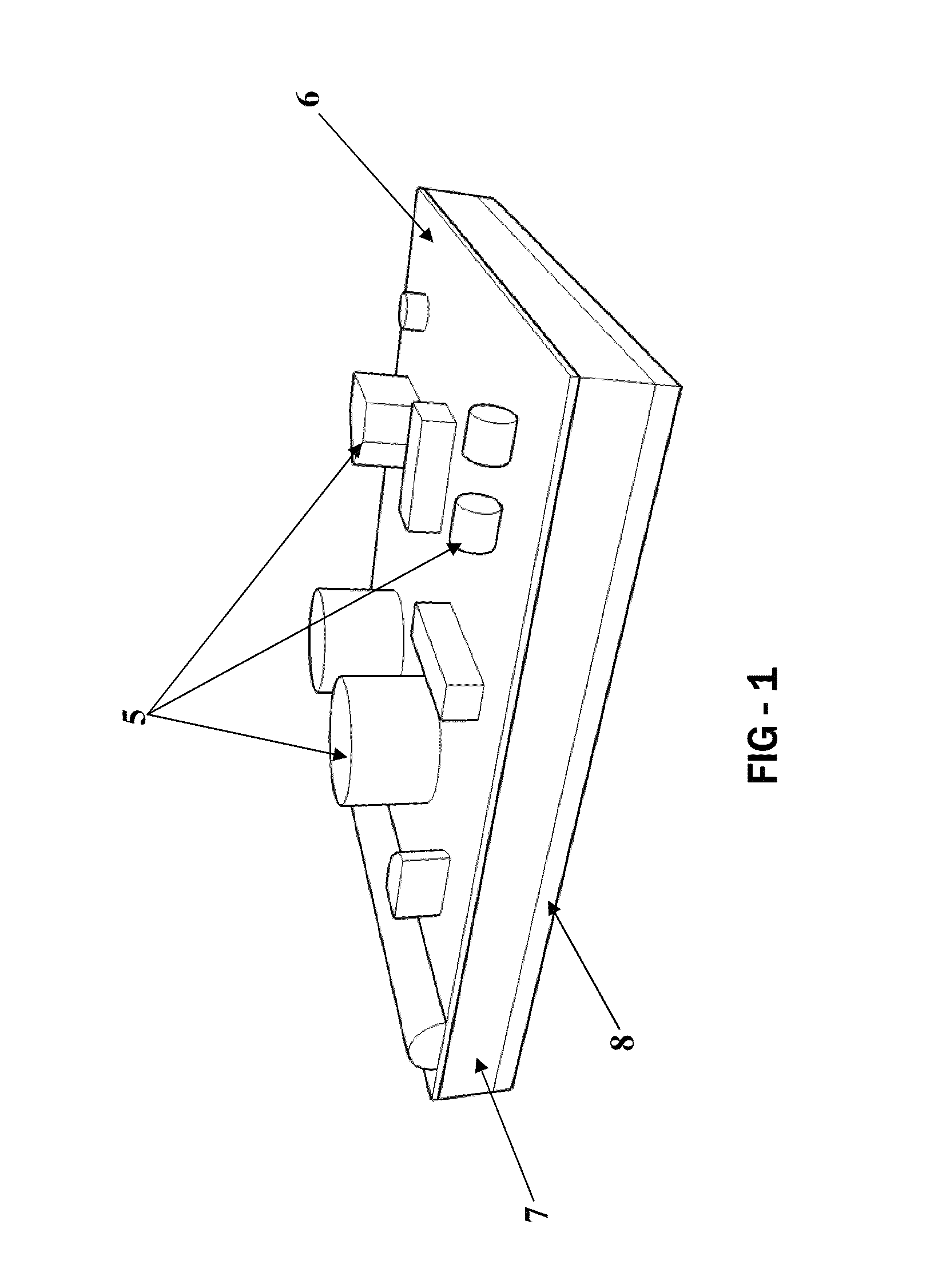

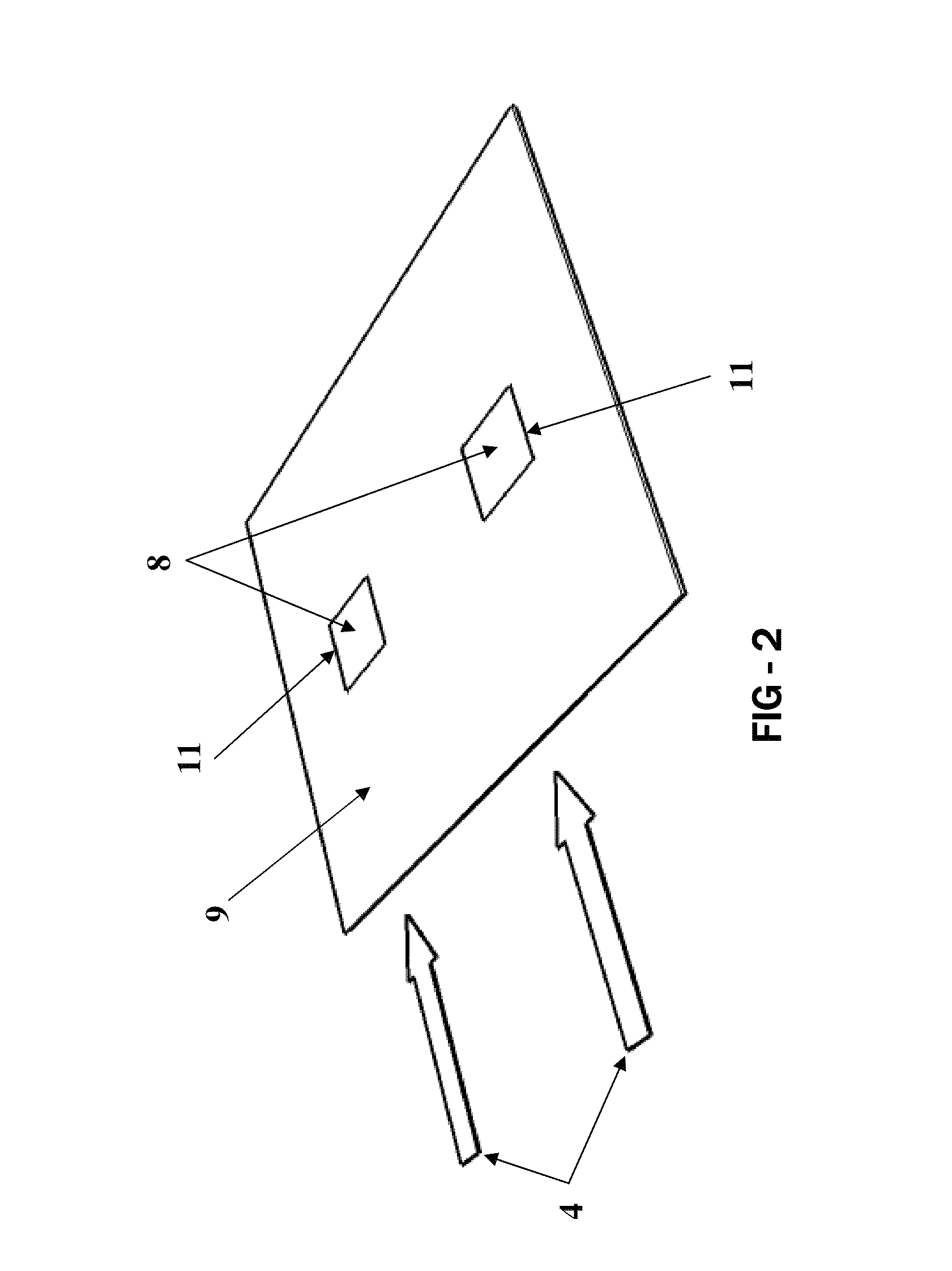

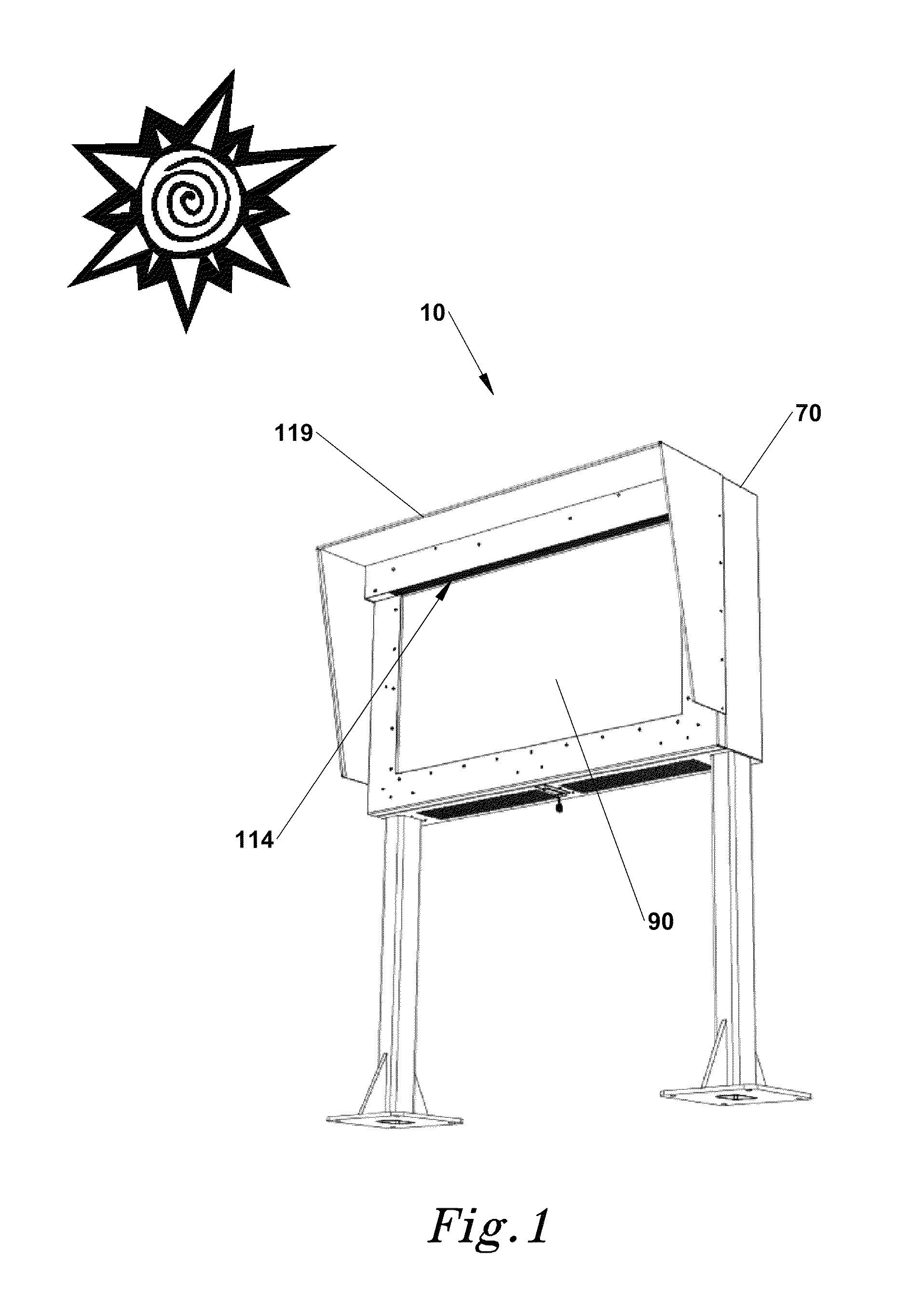

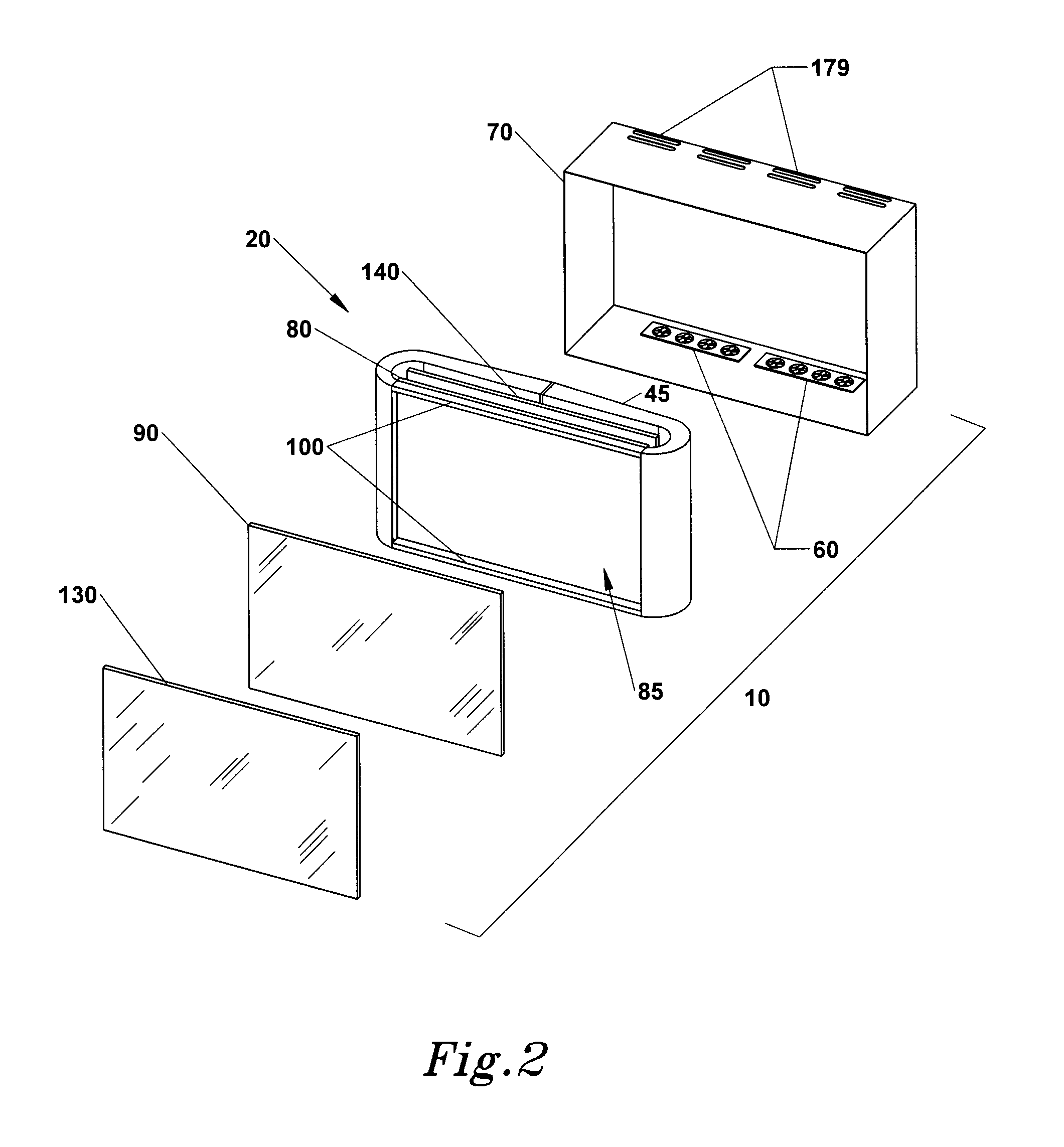

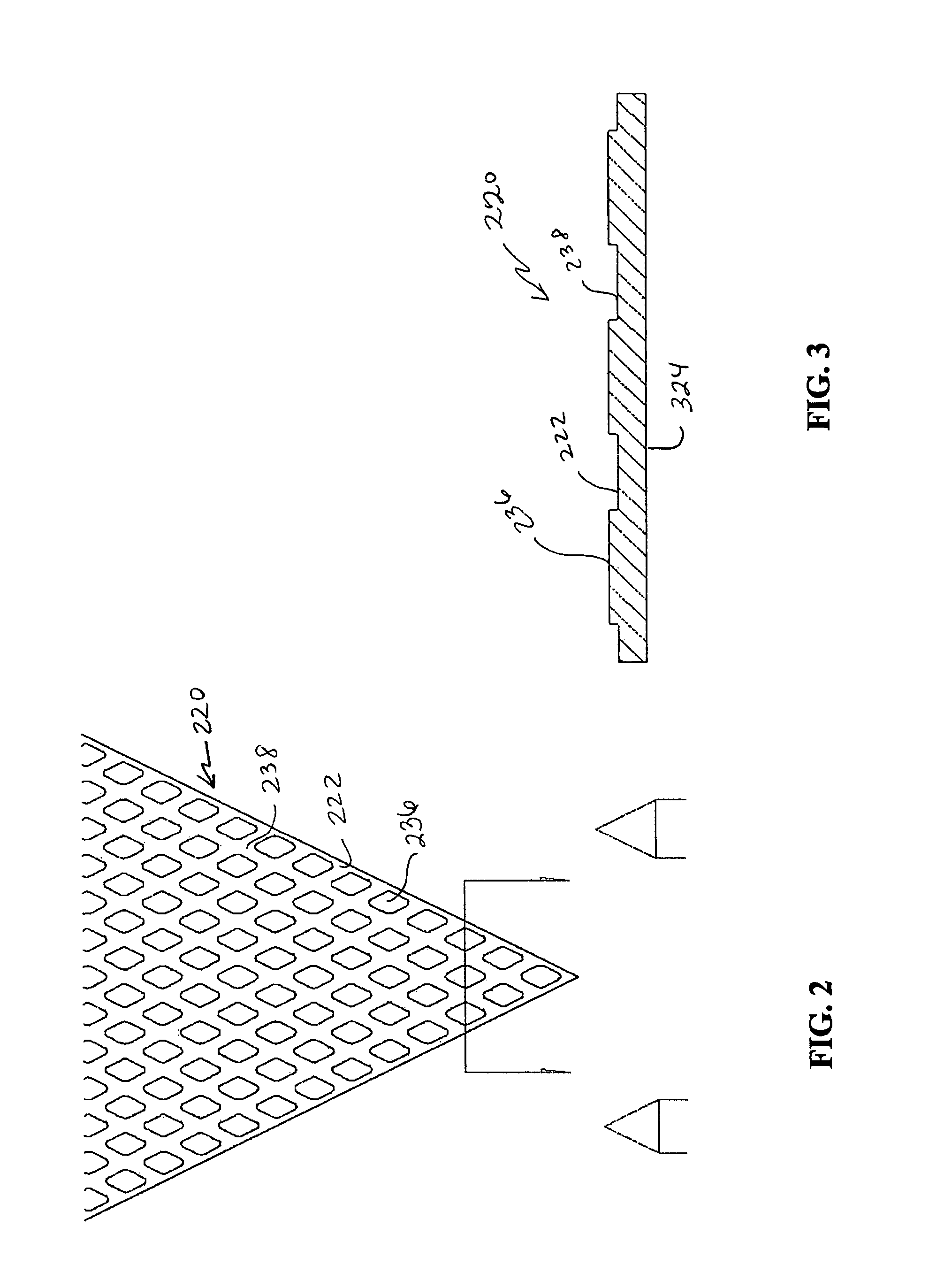

Isolated Cooling System Having an Insulator Gap and Front Polarizer

ActiveUS20090135365A1Guard against solar loadingReduce displayNon-linear opticsCooling/ventilation/heating modificationsImaging qualityNuclear engineering

An exemplary embodiment relates to a cooling system and a method for cooling an electronic display. A preferred embodiment includes a transparent gas cooling chamber. The transparent gas cooling chamber may have a linear polarizer. The components in the system are preferably housed within the electronic display housing. The cooling chamber defines a gas compartment that is anterior to and coextensive with the electronic display surface. Fans may be used to propel the isolated gas through the cooling chamber. The circulating gas removes heat directly from the electronic display surface by convection. The isolated gas is transparent or at least semi-transparent. The image quality of an exemplary embodiment remains essentially unchanged, even though the gas is flowing through a narrow channel over the visible face of the electronic display surface.

Owner:MFG RESOURCES INT INC

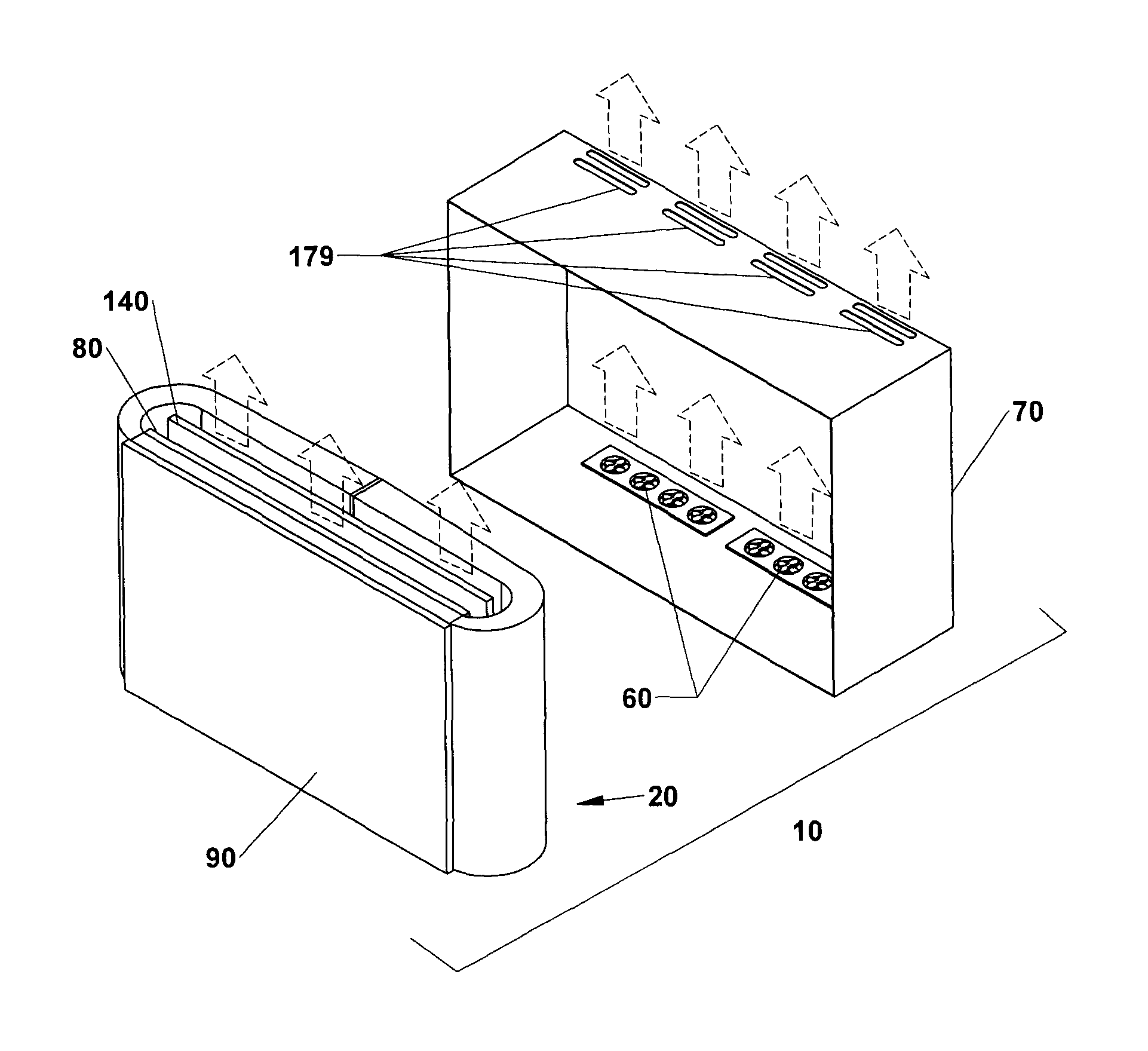

System for cooling an electronic display

ActiveUS8358397B2Low level of resistanceHeat dissipationSolid cathode detailsStructural circuit elementsComputer moduleClosed loop

A system for cooling an electronic display where an isolating structure may be used to allow ambient air to cool power modules. The isolating structure substantially prohibits containments which may be present within the ambient air from contacting sensitive electrical components on the power modules or otherwise. A gasket may be used to seal the interface between the power modules and the isolating structure. Heat sinks may be placed in thermal communication with the power supplies and fans may draw air through a narrow channel in which the heat sinks are located. In some embodiments the narrow channel may have the opposing surface of the channel defined by the rear portion of an LED assembly. Exemplary embodiments may use the ambient air to cool both the power modules and a closed loop of isolated gas within the electronic display.

Owner:MFG RESOURCES INT INC

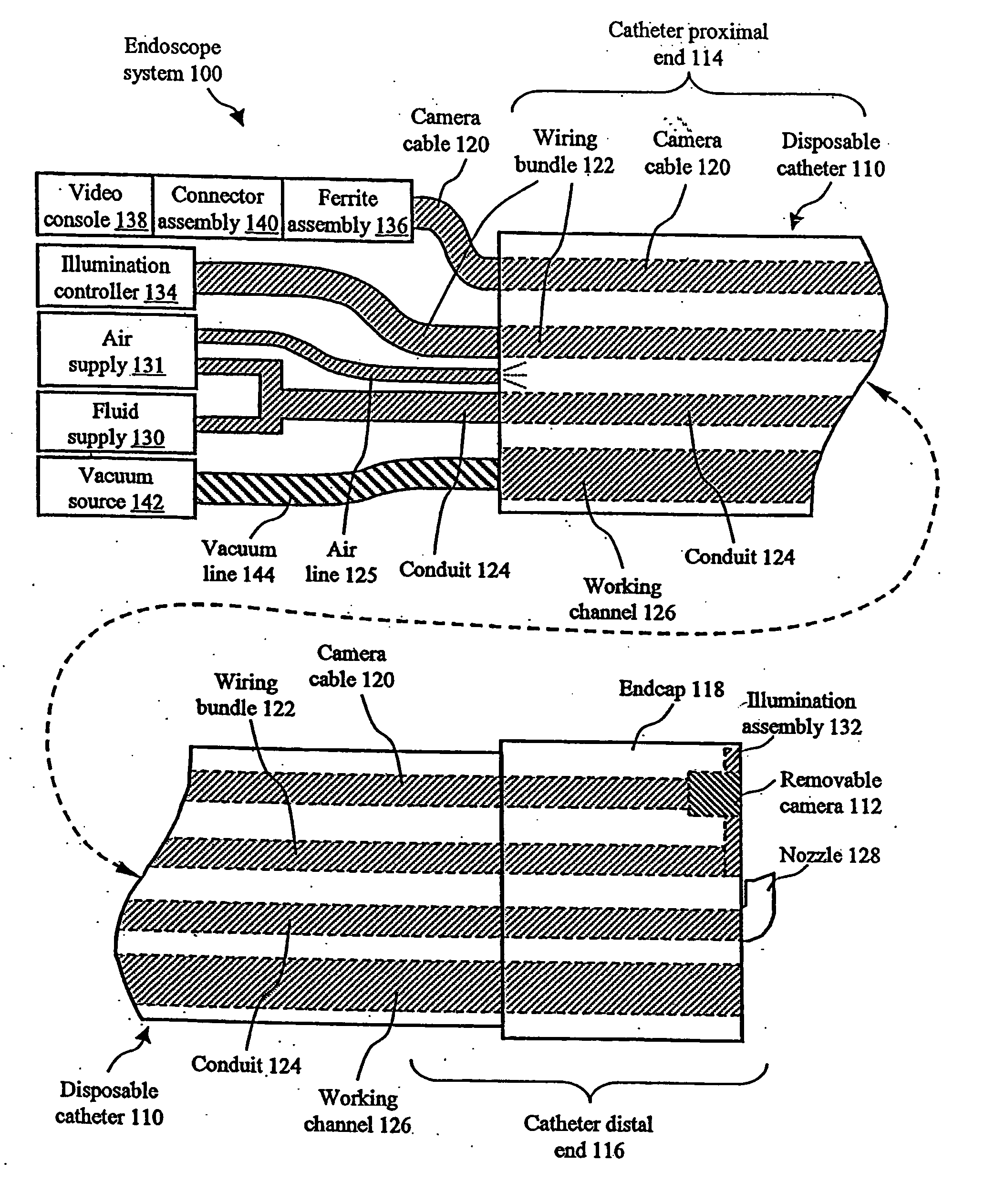

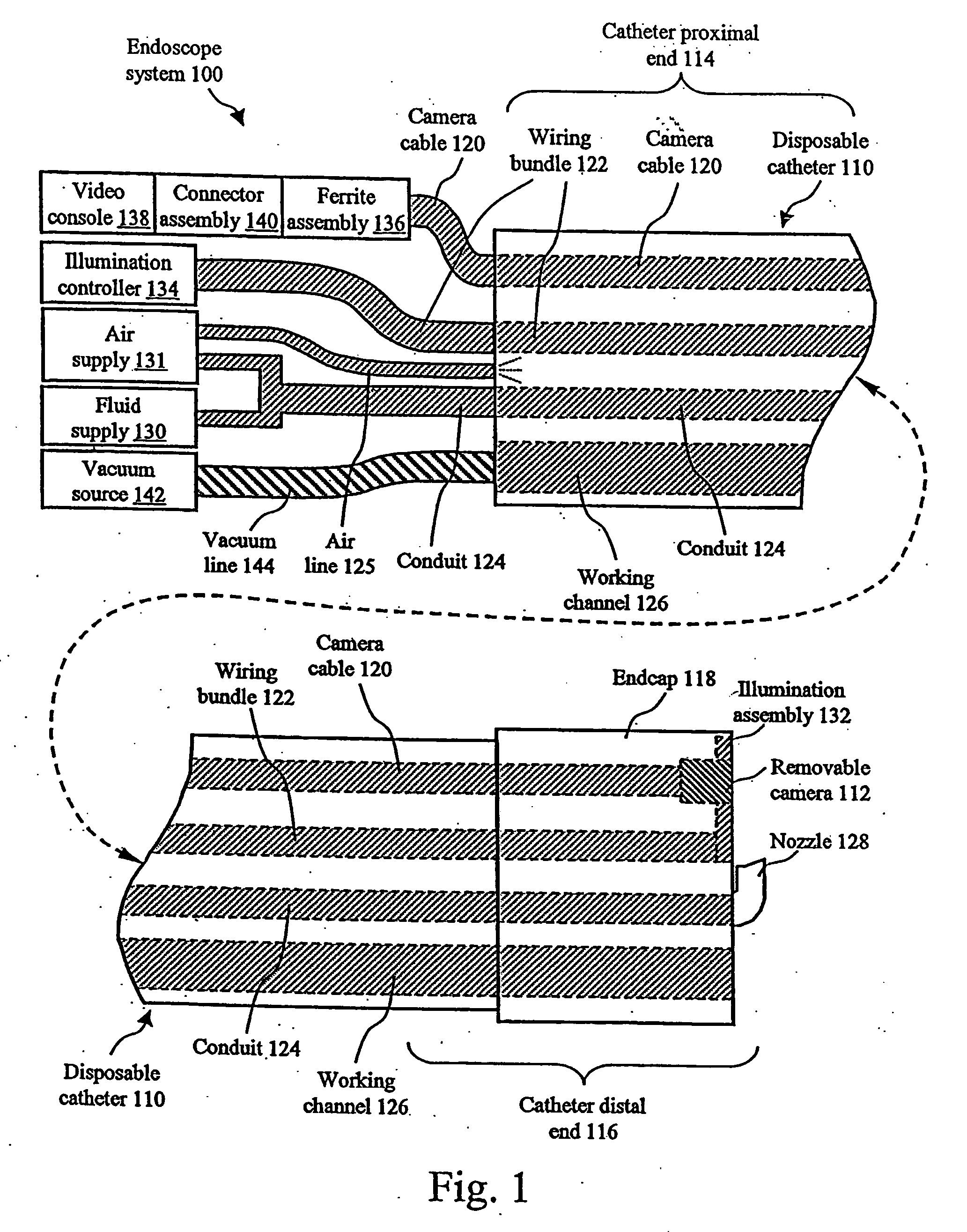

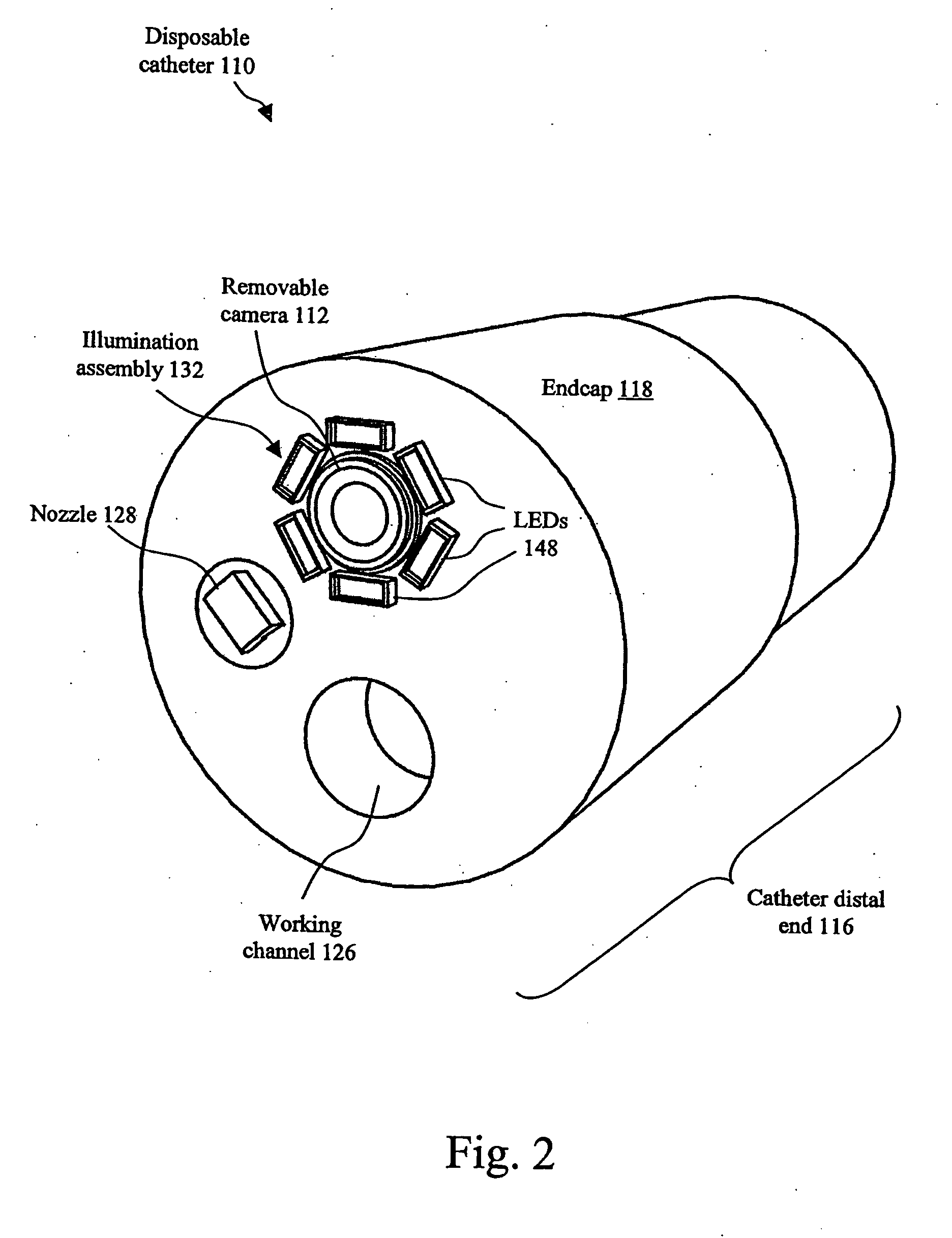

Device employing camera connector

An endoscopic system is disclosed, and can include a disposable catheter, a reusable camera assembly, and a camera connector system. A small cable and cable connector for feeding through a narrow channel of the disposable catheter is disclosed. A connector for connecting to a video console via an improved connector assembly system is also disclosed.

Owner:ETHICON ENDO SURGERY INC

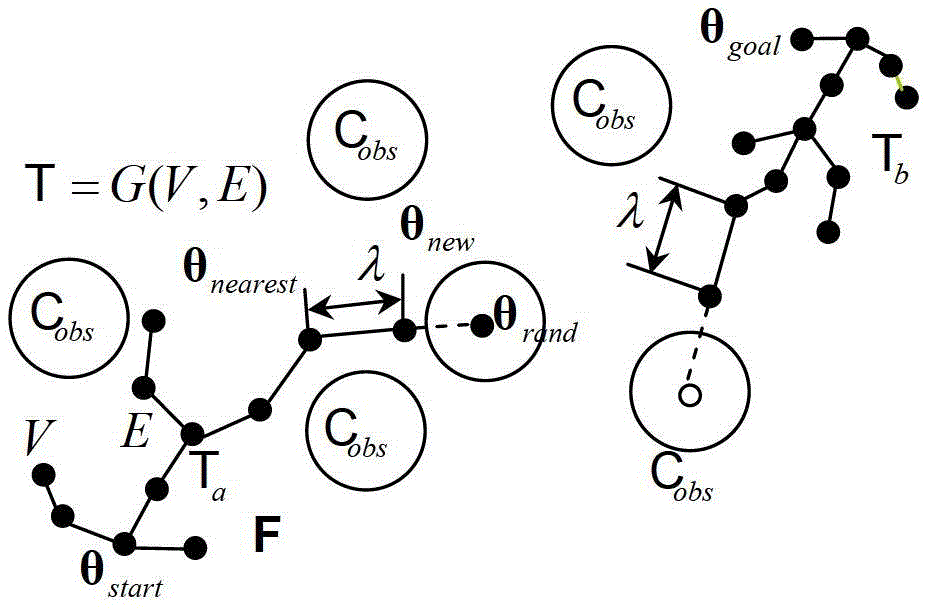

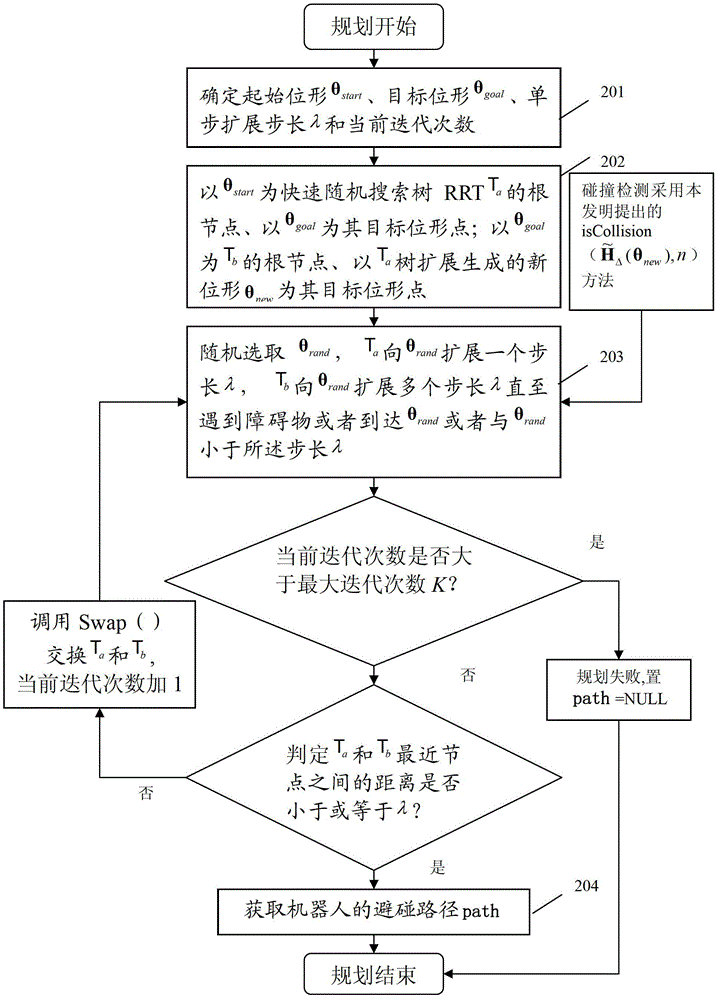

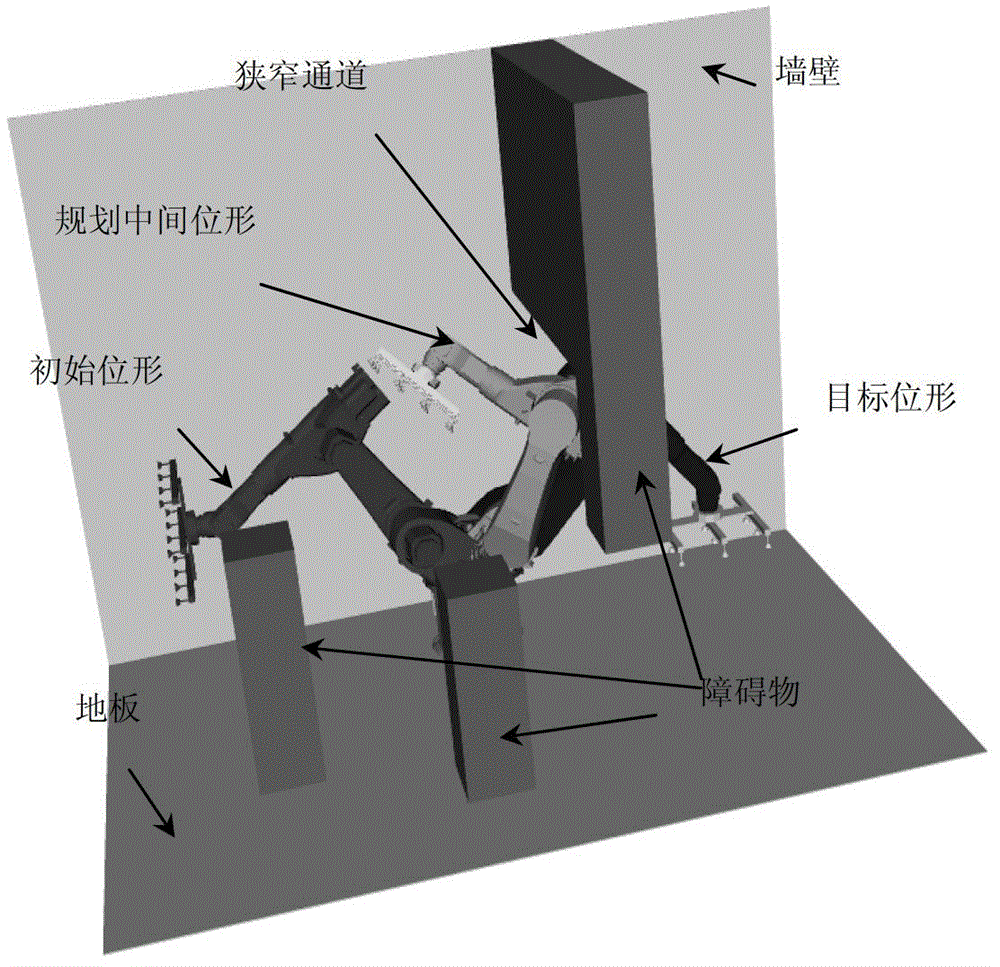

Path planning method and apparatus for robot fast collision avoidance

InactiveCN104155974AImprove execution efficiencyGuaranteed stabilityPosition/course control in two dimensionsCollision detectionSimulation

Owner:SHENZHEN INSTITUTE OF INFORMATION TECHNOLOGY

Isolated cooling system having an insulator gap and front polarizer

ActiveUS8879042B2Guard solar loadingReduce loadSubstation/switching arrangement cooling/ventilationNon-linear opticsImaging qualityNuclear engineering

An exemplary embodiment relates to a cooling system and a method for cooling an electronic display. A preferred embodiment includes a transparent gas cooling chamber. The transparent gas cooling chamber may have a linear polarizer. The components in the system are preferably housed within the electronic display housing. The cooling chamber defines a gas compartment that is anterior to and coextensive with the electronic display surface. Fans may be used to propel the isolated gas through the cooling chamber. The circulating gas removes heat directly from the electronic display surface by convection. The isolated gas is transparent or at least semi-transparent. The image quality of an exemplary embodiment remains essentially unchanged, even though the gas is flowing through a narrow channel over the visible face of the electronic display surface.

Owner:MFG RESOURCES INT INC

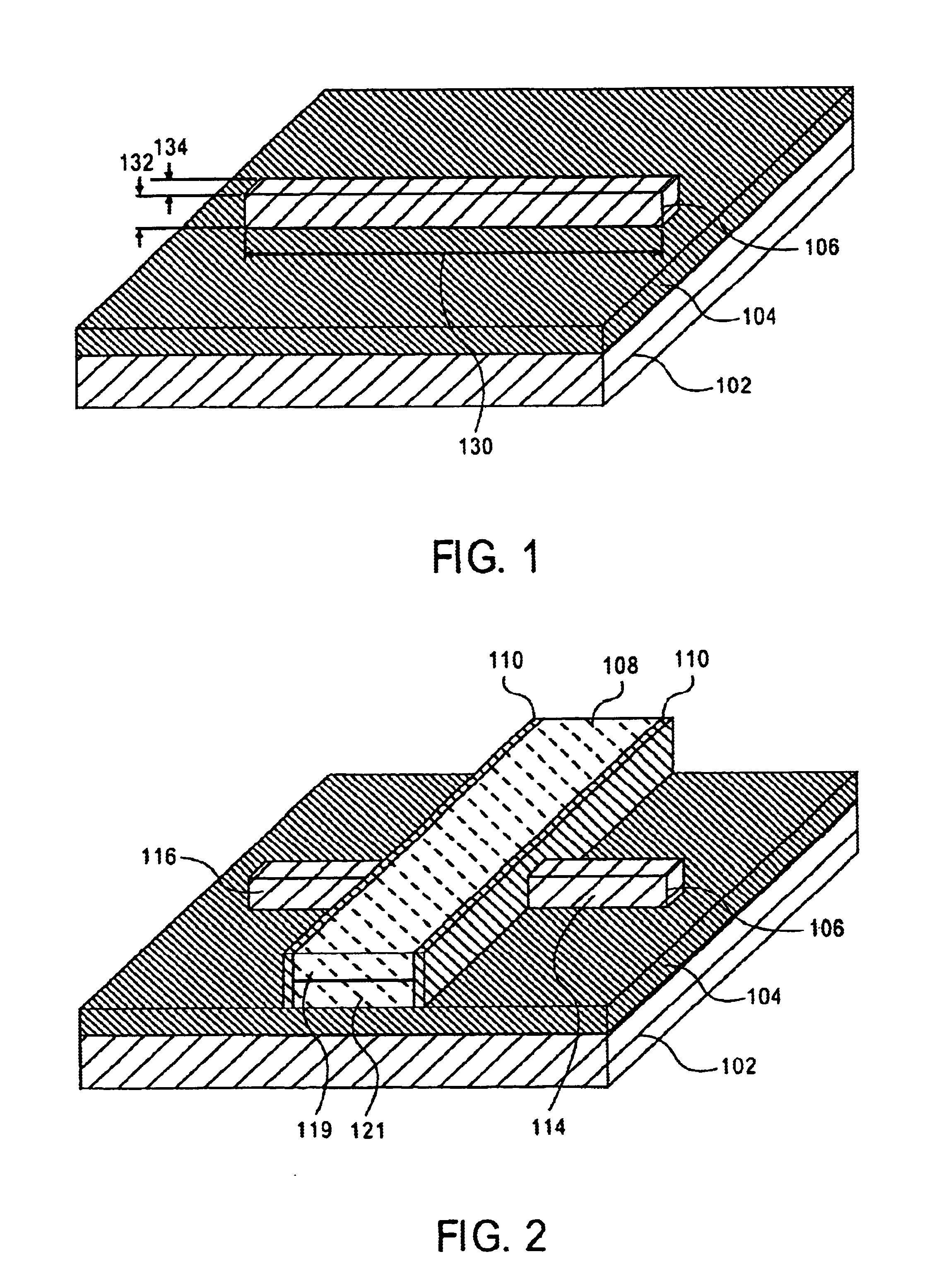

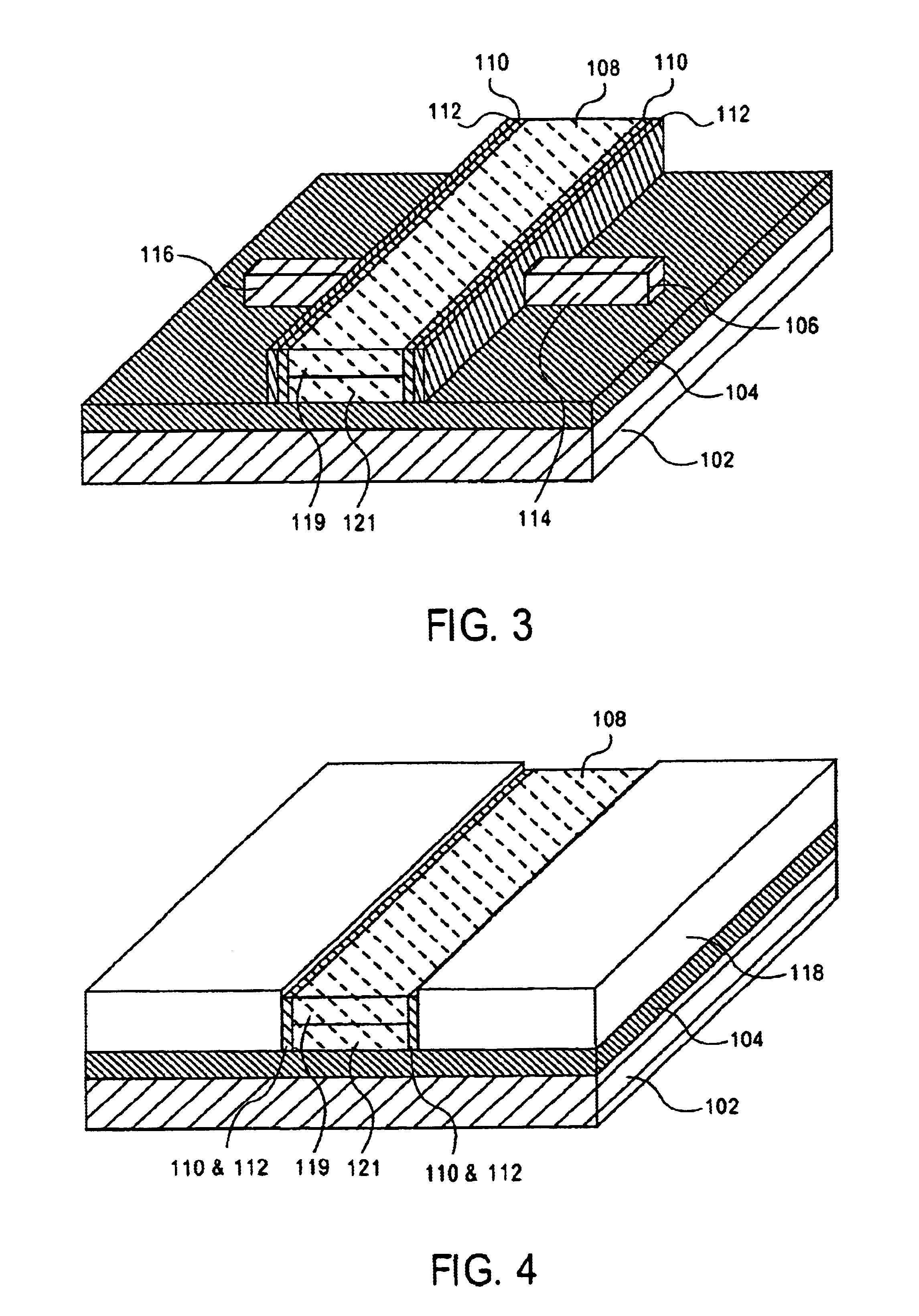

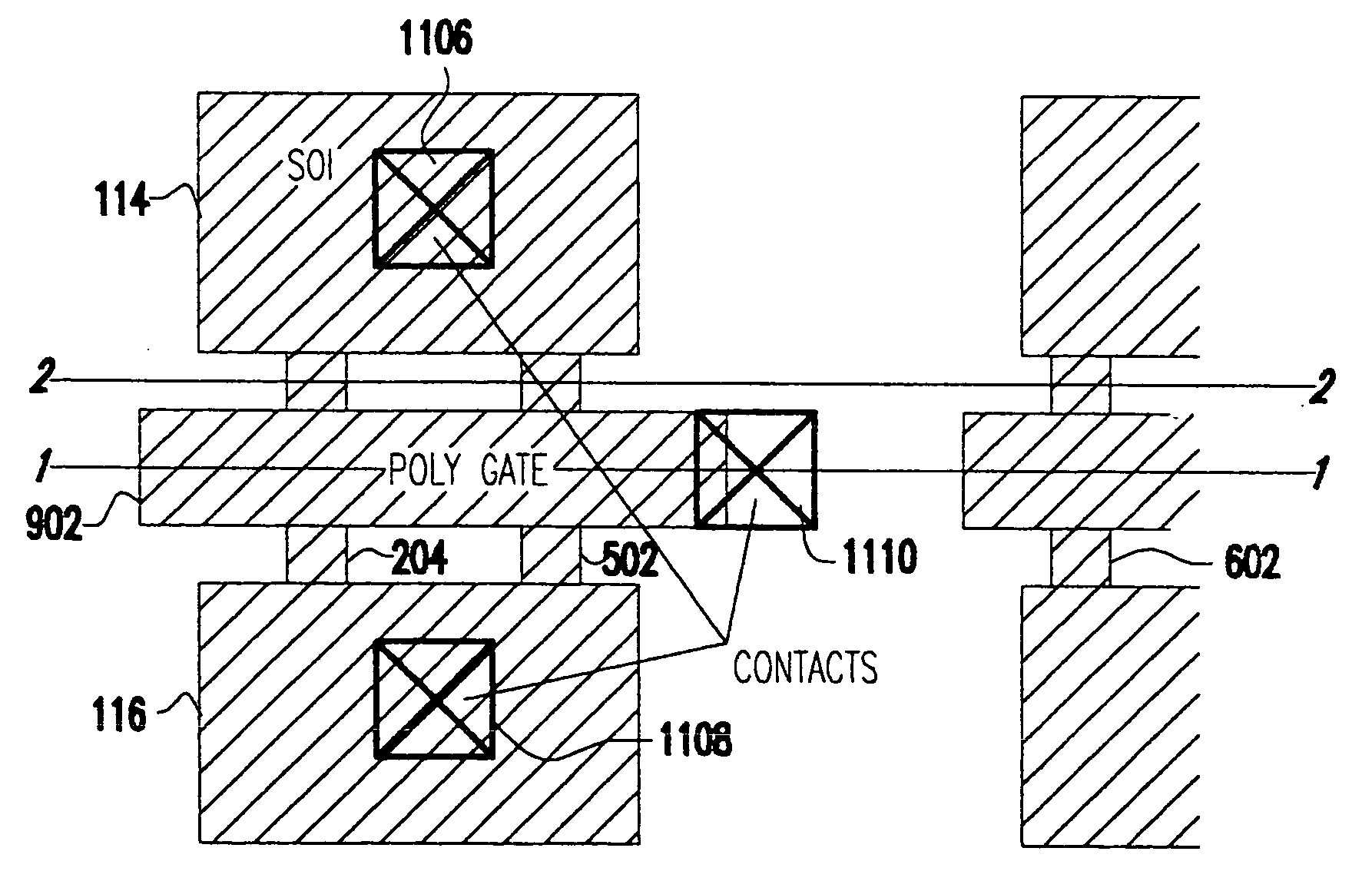

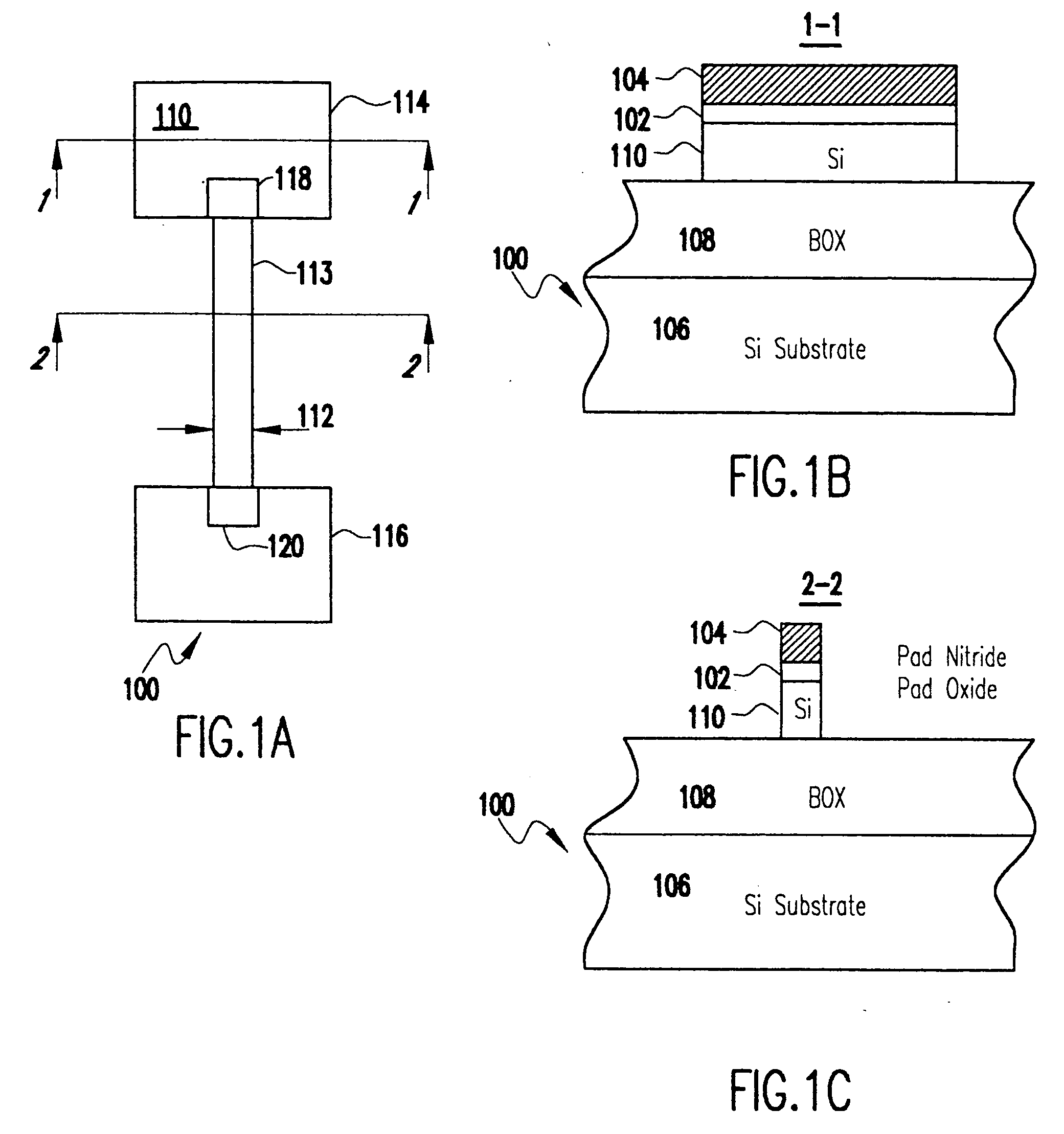

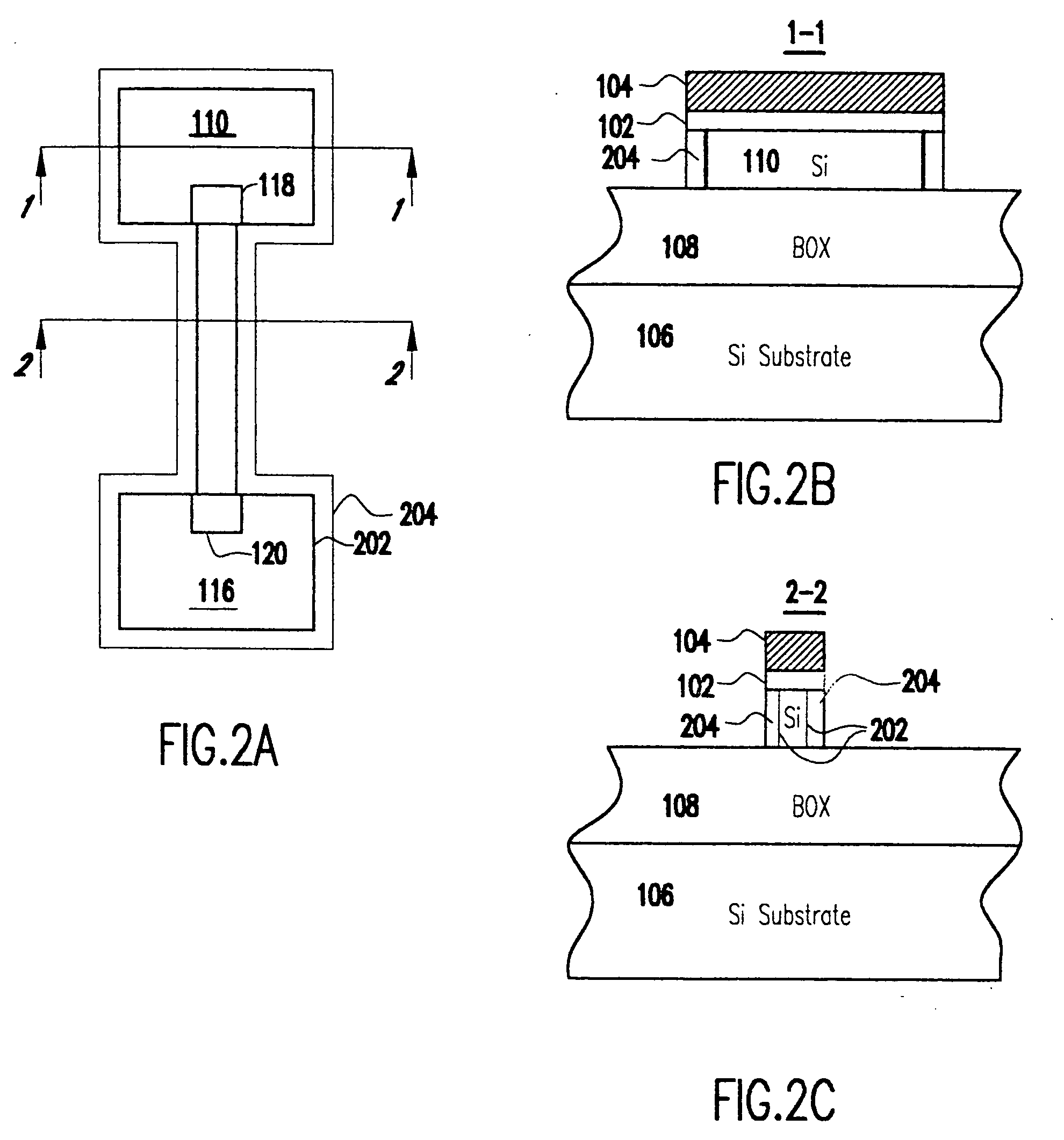

Method of fabricating a necked finfet device

ActiveUS20050253193A1Reduce FINFET channel resistancePrevent silicide formationTransistorSolid-state devicesComposite insulatorsMetal silicide

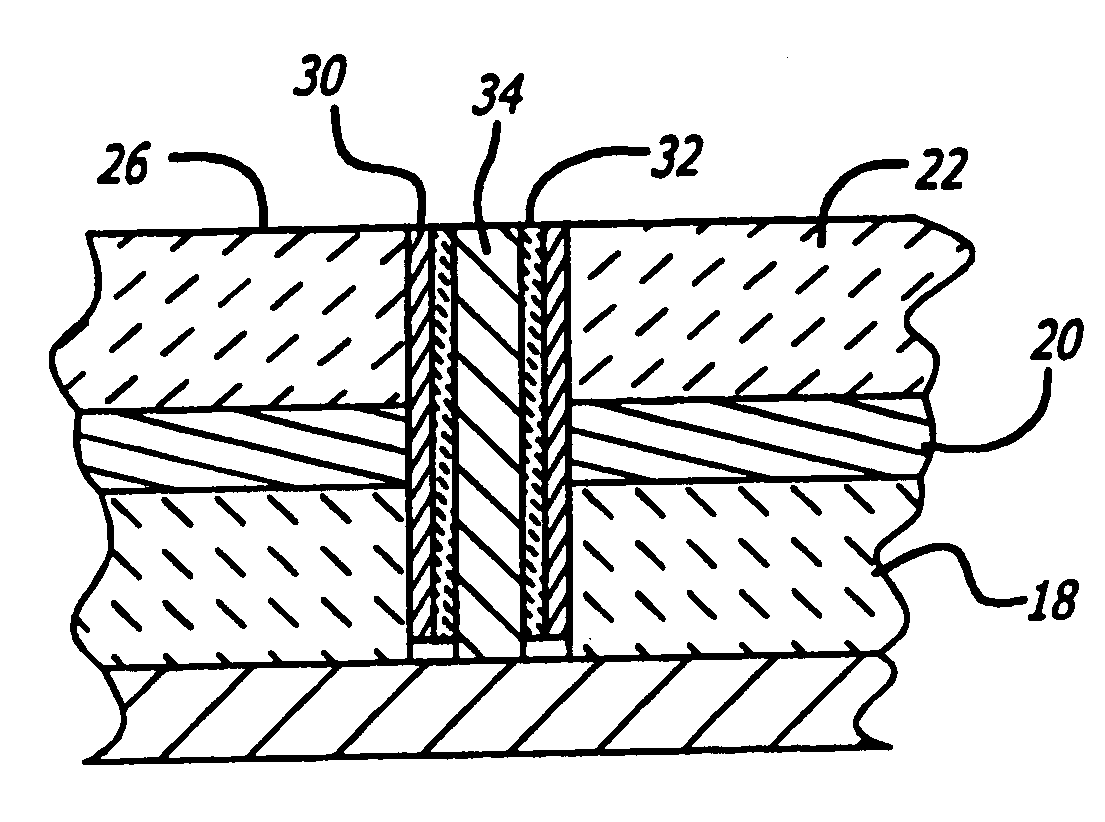

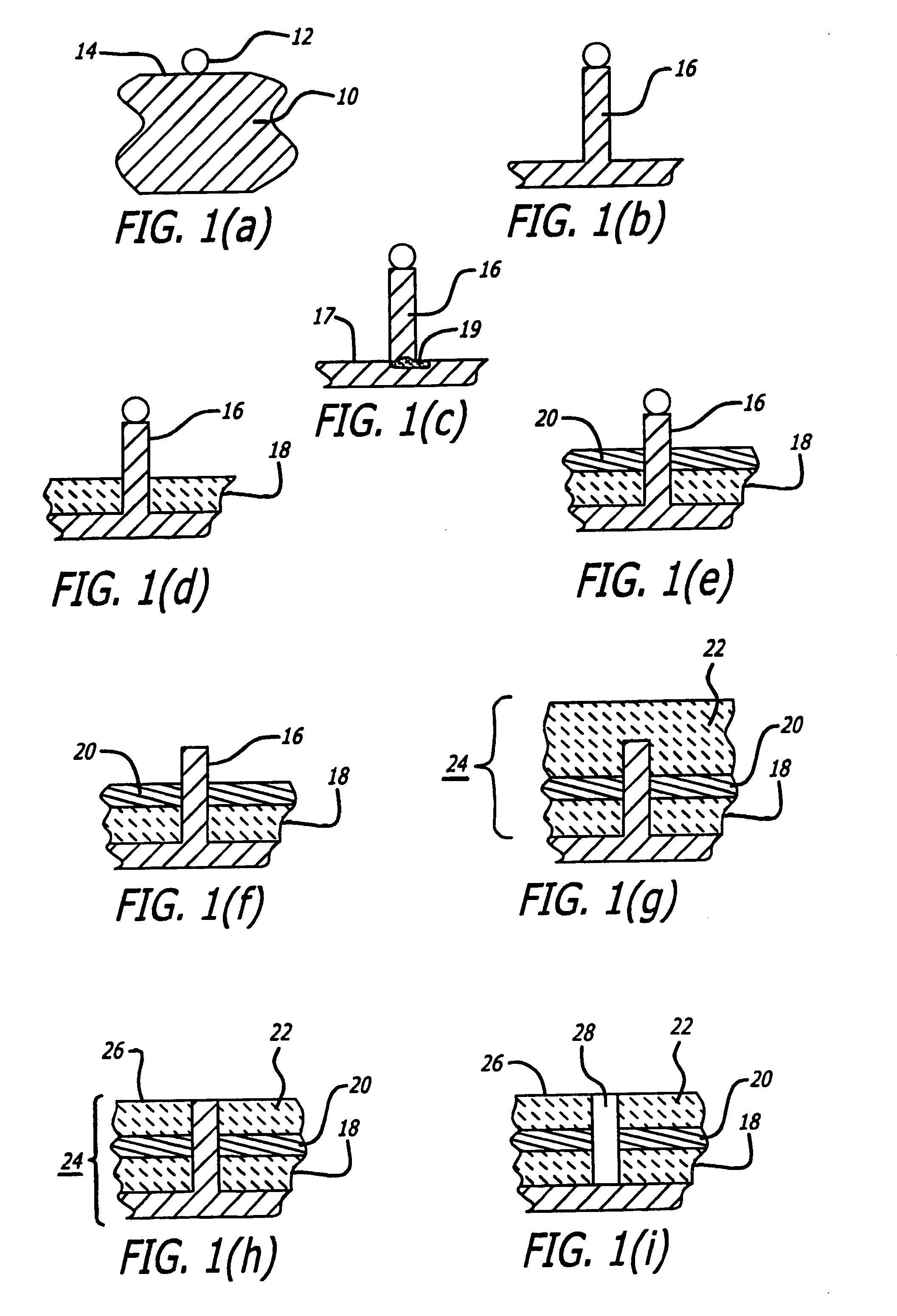

A method of fabricating a double gate, FINFET device structure in a silicon on insulator layer, in which the channel region formed in the SOI layer is defined with a narrowed, or necked shape, and wherein a composite insulator spacer is formed on the sides of the device structure, has been developed. A FINFET device structure shape is formed in an SOI layer via anisotropic RIE procedures, followed by a growth of a silicon dioxide gate insulator layer on the sides of the FINFET device structure shape. A gate structure is fabricated traversing the device structure and overlying the silicon dioxide gate insulator layer located on both sides of the narrowest portion of channel region. After formation of a source / drain region in wider, non-channel regions of the FINFET device structure shape, composite insulator spacers are formed on the sides of the FINFET shape and on the sides of the gate structure. Metal silicide is next formed on source / drain regions resulting in a FINFET device structure featuring a narrow channel region, and surrounded by composite insulator spacers located on the sides of the device structure.

Owner:TAIWAN SEMICON MFG CO LTD

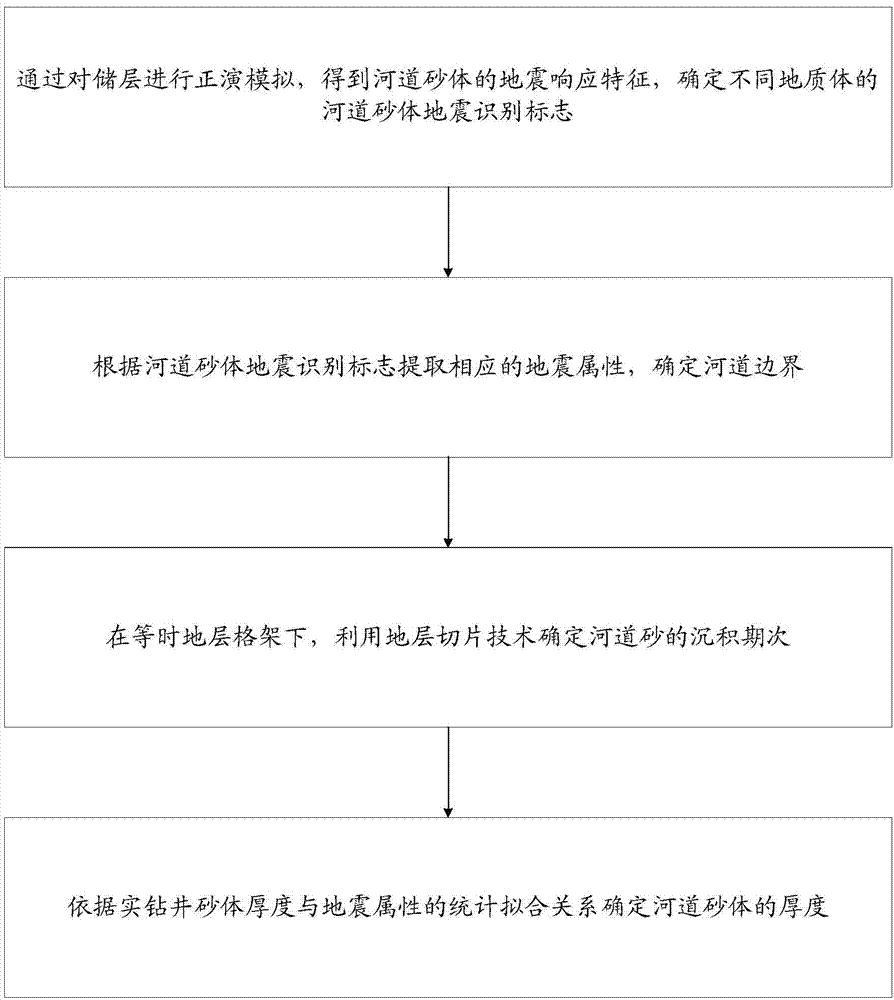

Channel sandstone reservoir identification method

ActiveCN104502969AAccurate identificationSmall impact on seismic resolutionSeismic signal processingWell drillingImage resolution

The invention discloses a channel sandstone reservoir identification method. The method includes: acquiring seismic response features of channel sand by performing forward modelling on reservoirs, and determining channel-sand seismic identification marks of different geologic bodies; extracting corresponding seismic attributes according to the channel sand seismic identification marks, and determining a channel boundary; under an isochronous stratigraphic frame, determining sedimentary periods of the channel sand by the aid of the stratal slice technique; determining the thickness of the channel sand according to the statistical fitting relation of the real well-drilling sand thickness and the seismic attributes. According to the method, the channel sand identification and description technology is created by going deep into seismic attribute extraction and analysis, utilizing the reservoir of the fixed well, reservoir calibration results and statistical analysis of well drilling and combining forward model analysis results. Channel sandstone reservoirs of ultra-deep layers, thin sand layers and narrow channels can be identified and described accurately, and influence of seismic resolution is less.

Owner:CHINA PETROLEUM & CHEM CORP

Structure for confining the switching current in phase memory (PCM) cells

InactiveUS7488967B2Heat dissipation is limitedHigh densityBulk negative resistance effect devicesSemiconductor devicesPhase-change memorySwitched current

Disclosed are a phase change memory cell and a method of forming the memory cell. The memory cell comprises a main body of phase change material connected directly to a bottom contact and via a narrow channel of phase change material to a top contact. The channel is tapered from the top contact towards the main body. A minimum width of the channel has a less than minimum lithographic dimension and is narrower than a width of the main body. Therefore, the channel provides a confined region for the switching current path and restricts phase changing to within the channel. In addition an embodiment of the memory cell isolates the main body of phase change material by providing a space between the phase change material and the cell walls. The space allows the phase change material to expand and contract and also limits heat dissipation.

Owner:INT BUSINESS MASCH CORP

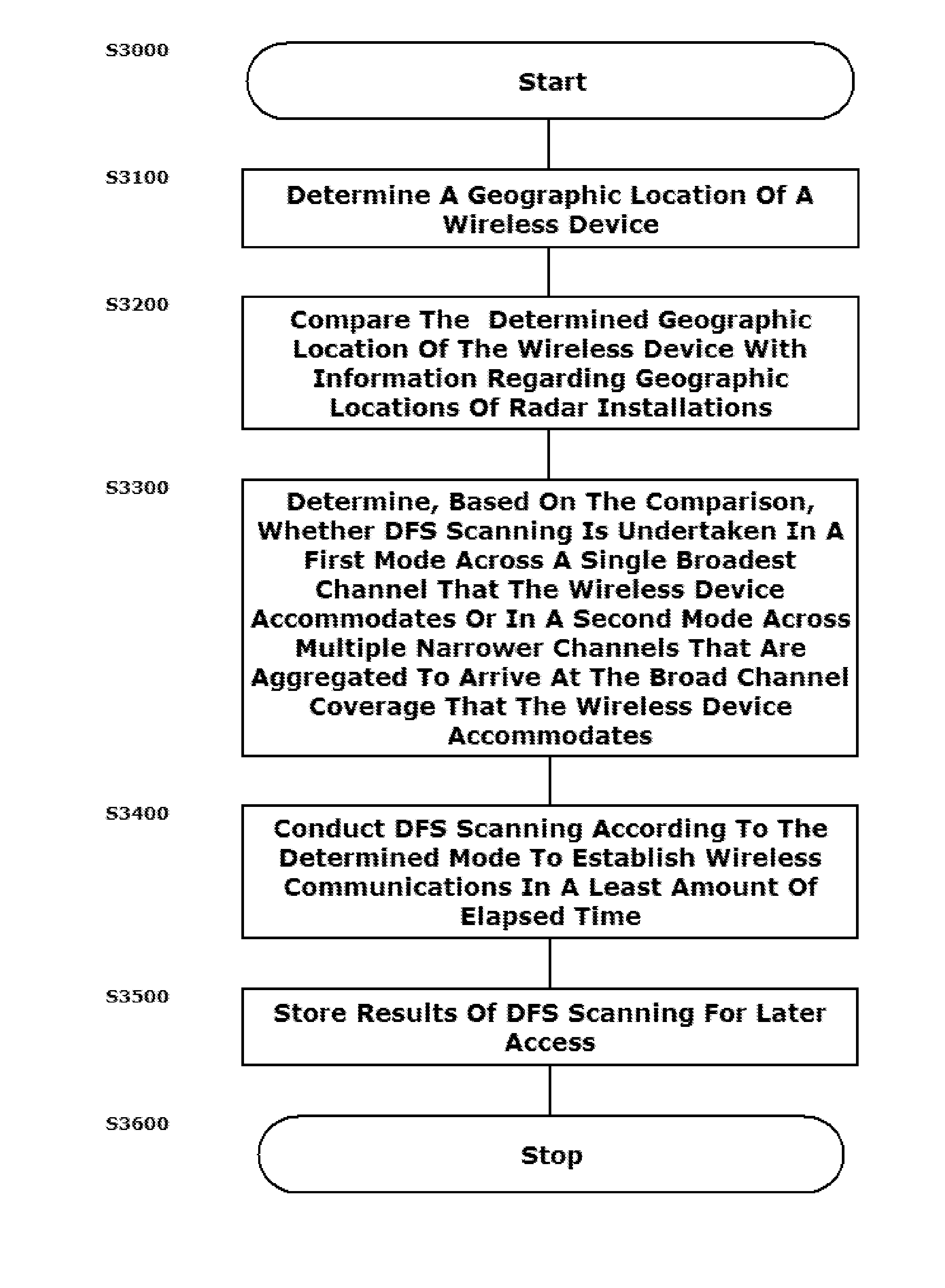

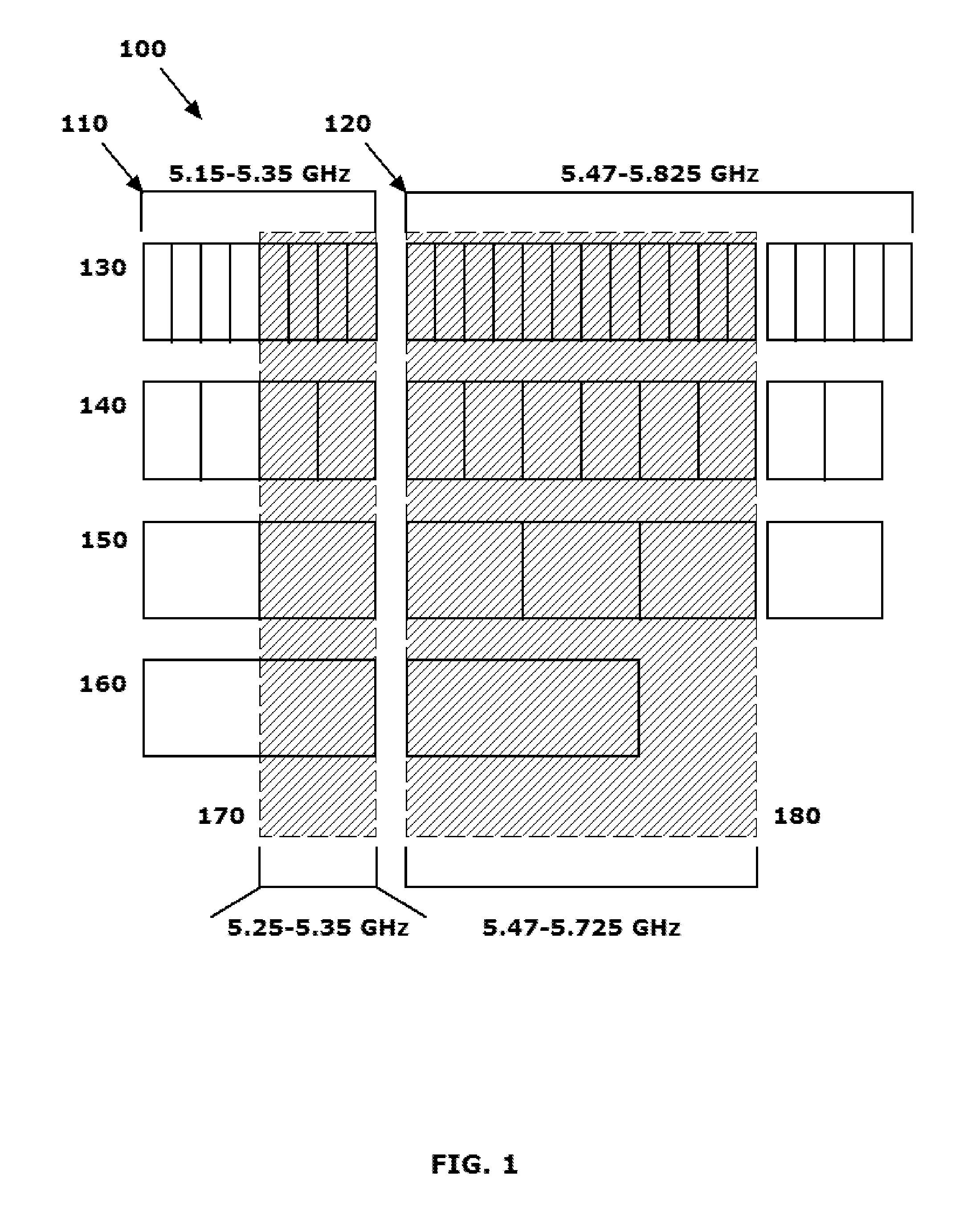

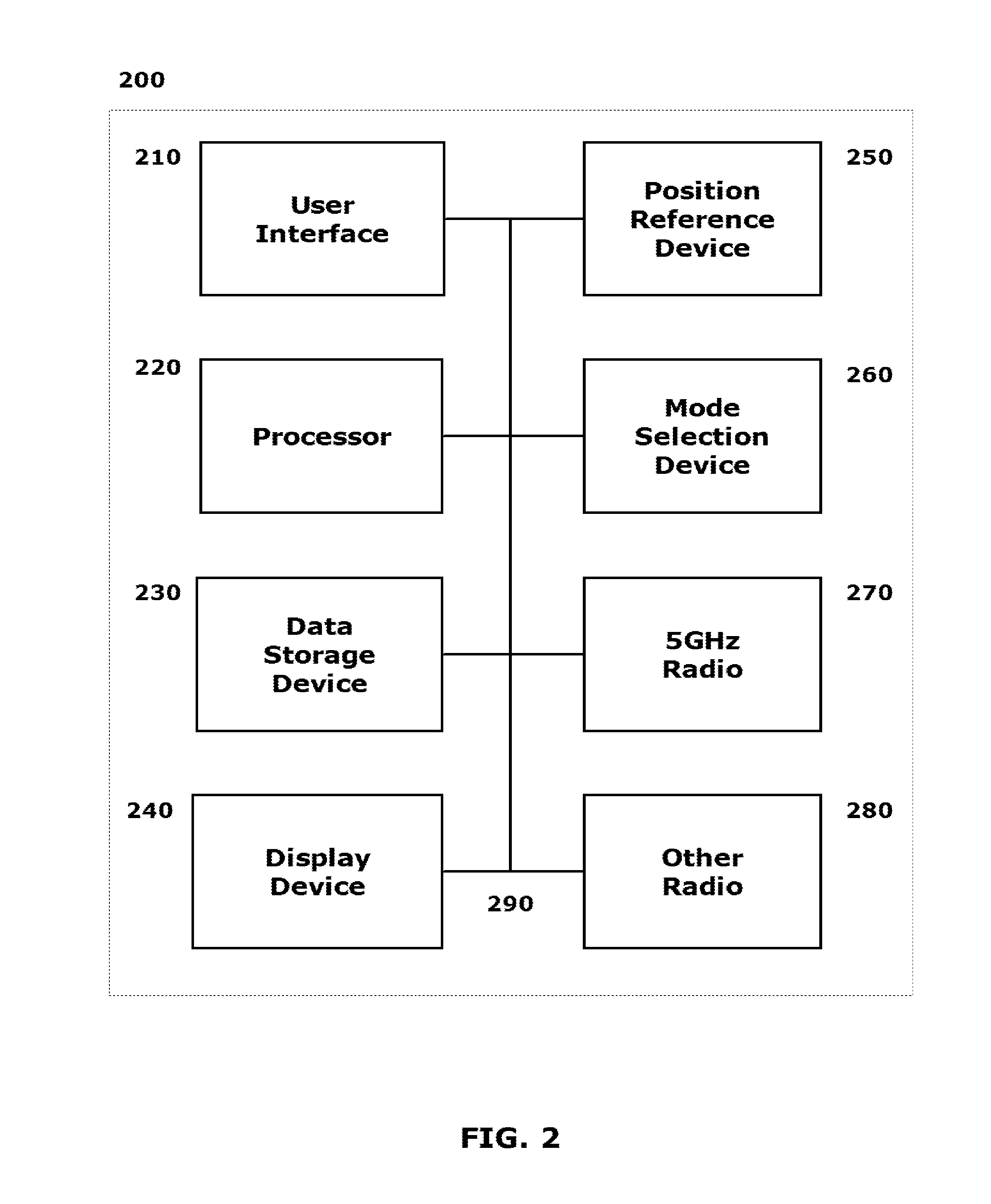

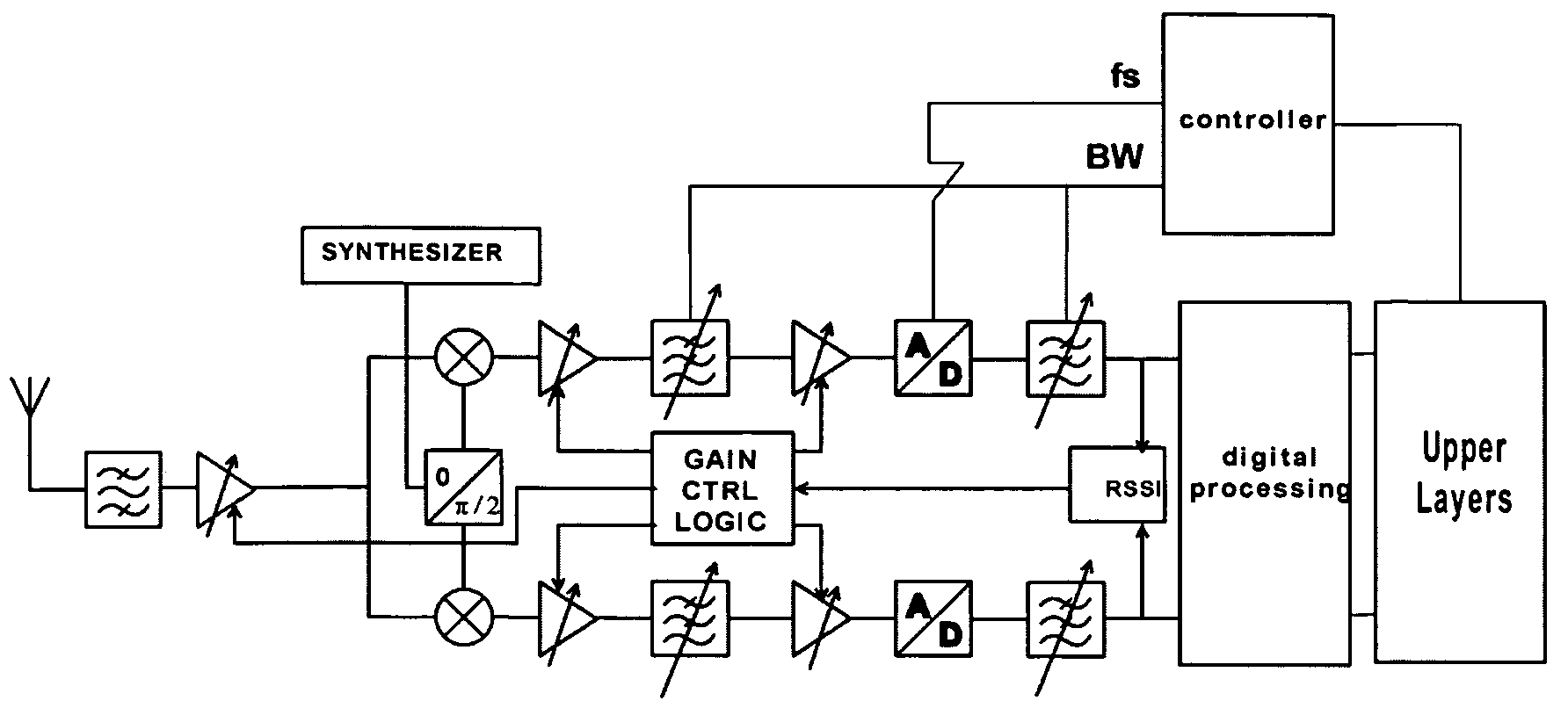

Systems and methods for implementing intelligent wideband digital frequency selection scanning

InactiveUS20130252640A1Detected satisfactorilyReduce riskAssess restrictionMilitary installationBroadband

A system and method are provided to intelligently undertake mandated scanning for radar signals prior to operating a particular wireless device in the 5 GHz band. The disclosed systems and methods provide a capability by which wireless devices are enabled to intelligently scan using a 160 MHz signal, or the largest bandwidth that the wireless device has the capacity to occupy. The disclosed scheme makes use of information about the location of the wireless device to determine characteristic of the environment in which the wireless device is operating. Locations of potentially conflicting radar installations, such as at airports and on military installations, are generally “known.” This information is used to compare to a determined geographic location of the wireless device to assess whether full broad bandwidth DFS scanning cane be reasonably undertaken or whether some narrower channel scanning is appropriate for the wireless device based on proximity to radar installations.

Owner:INTEL CORP

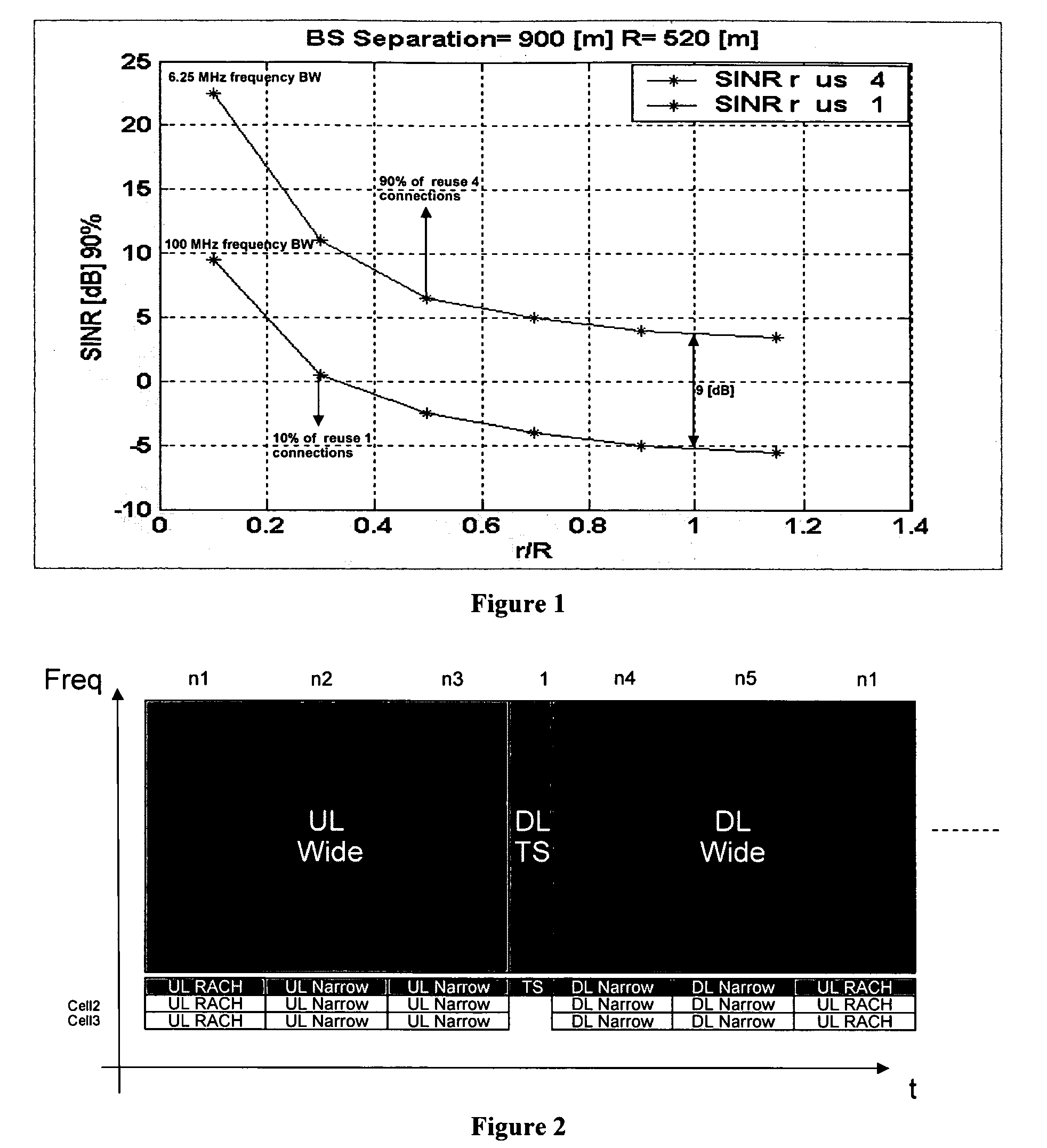

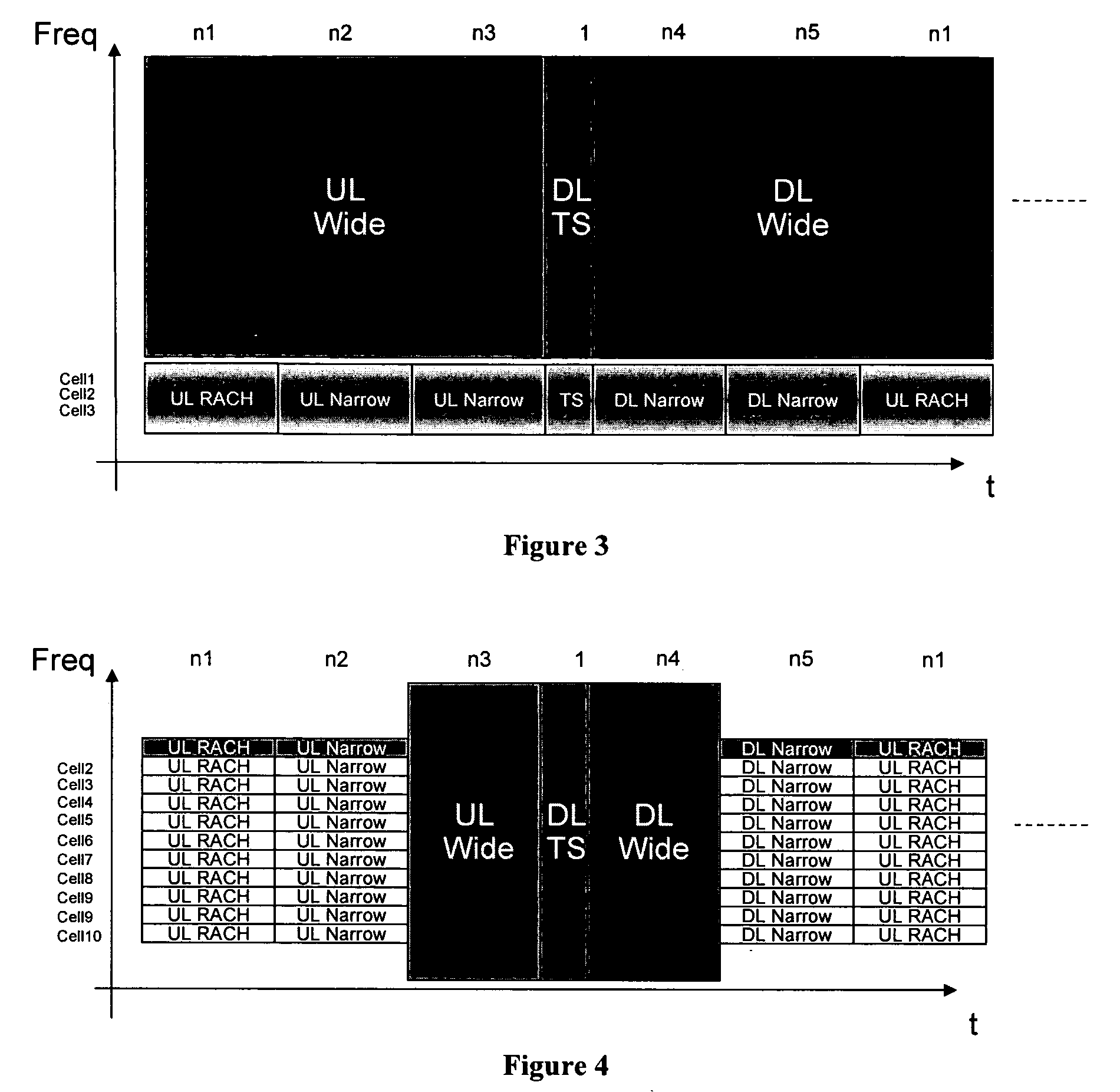

Variable bandwidth in a communication system

InactiveUS20050170839A1Improve reuseHigh frequency re-useSubstation equipmentRadio/inductive link selection arrangementsCommunications systemFrequency spectrum

A method, device, and system that use narrowband channels to provide higher re-use without multiplying the operator spectrum requirement. If a communication system supports variable carrier bandwidth channels, the narrow channel capacity can be divided among adjacent cells to provide higher re-use.

Owner:NOKIA TECHNOLOGLES OY

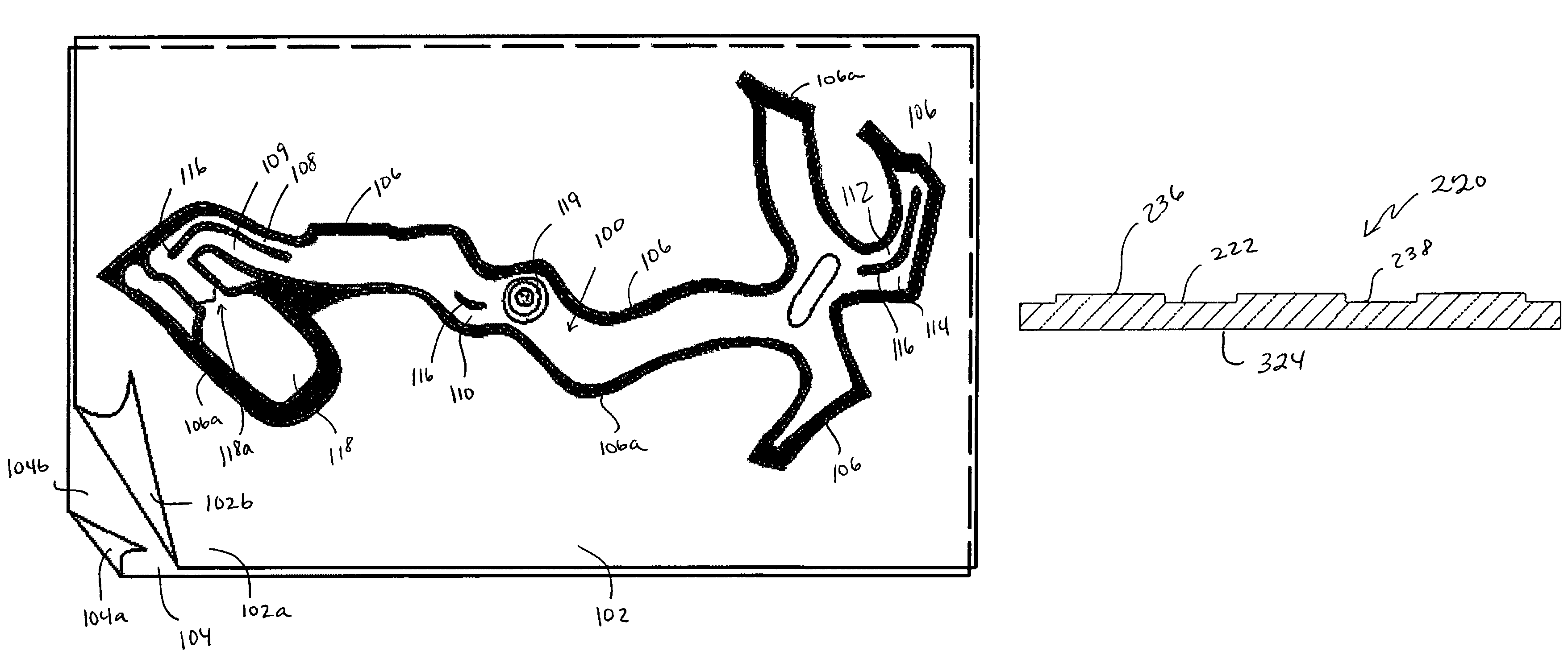

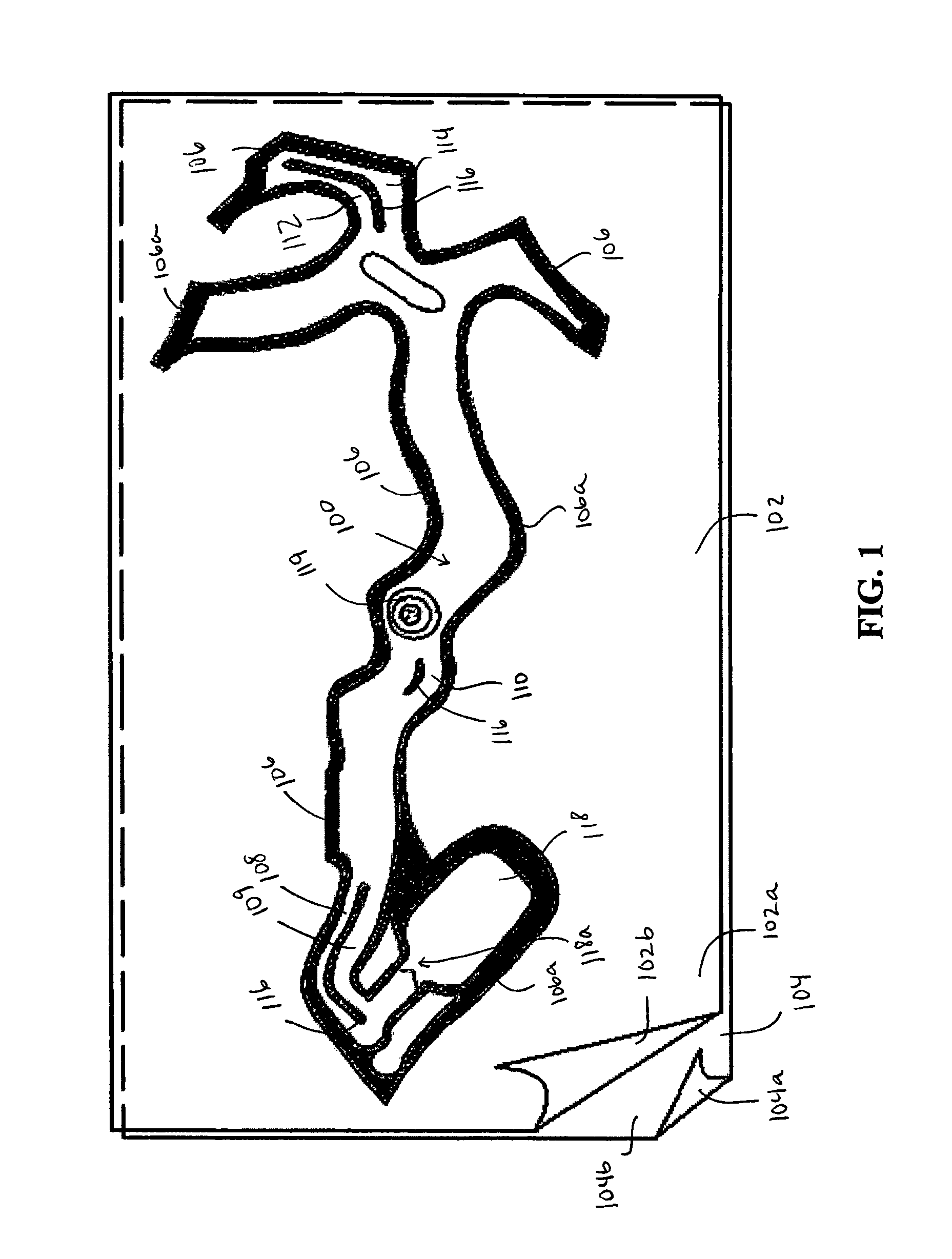

Air passage device for inflatable shoe bladders

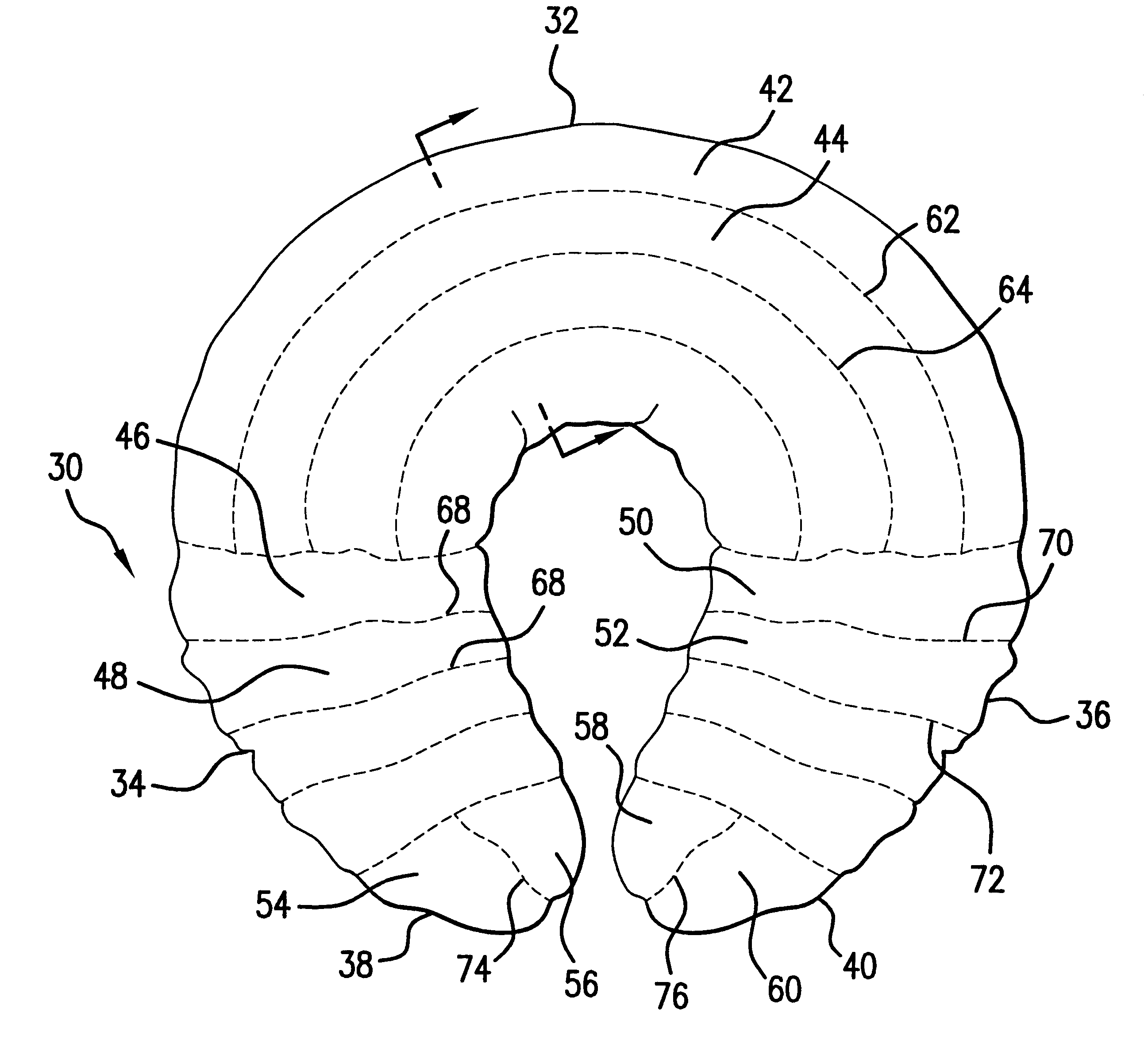

An inflatable bladder for use in an article of footwear including a first sheet of a flexible fluid-impervious material and a second sheet of flexible fluid-impervious material. The first sheet and the second sheet are sealed along air-tight weld lines forming at least one narrow channel. The inflatable bladder includes an air passage device for maintaining air flow within the narrow channel. In one embodiment, the first sheet has an embossed interior surface to limit the contact between the first sheet and second sheet. Another embodiment includes the use of a mechanical device to separate the first sheet and the second sheet within a narrow channel. A method of manufacturing an inflatable bladder, a method of increasing localized air flow though a narrow channel of an inflatable bladder for use in an article of footwear and an article of footwear incorporating the inflatable bladder are also described.

Owner:REEBOK

Necked Finfet device

InactiveUS20070063261A1Reduce channel resistanceInhibition formationTransistorSolid-state devicesComposite insulatorsMetal silicide

Owner:TAIWAN SEMICON MFG CO LTD

Method of fabricating a necked FINFET device

ActiveUS7122412B2Reduce channel resistanceInhibition formationTransistorSemiconductor/solid-state device manufacturingComposite insulatorsGate insulator

A method of fabricating a double gate, FINFET device structure in a silicon on insulator layer, in which the channel region formed in the SOI layer is defined with a narrowed, or necked shape, and wherein a composite insulator spacer is formed on the sides of the device structure, has been developed. A FINFET device structure shape is formed in an SOI layer via anisotropic RIE procedures, followed by a growth of a silicon dioxide gate insulator layer on the sides of the FINFET device structure shape. A gate structure is fabricated traversing the device structure and overlying the silicon dioxide gate insulator layer located on both sides of the narrowest portion of channel region. After formation of a source / drain region in wider, non-channel regions of the FINFET device structure shape, composite insulator spacers are formed on the sides of the FINFET shape and on the sides of the gate structure. Metal silicide is next formed on source / drain regions resulting in a FINFET device structure featuring a narrow channel region, and surrounded by composite insulator spacers located on the sides of the device structure.

Owner:TAIWAN SEMICON MFG CO LTD

Field effect transistor fabrication including formation of a channel in a pore

A field effect transistor having a narrow channel and a method for forming such a device. An upstanding nanopillar is formed from a substrate by directional etching of the substrate preferentially masked by a nanoparticle. A stack of planar layers of material is formed adjacent and around the nanopillar. The bottom layer, adjacent the substantially planar top substrate surface, comprises insulating material. A conductive gate layer overlies the bottom layer while a second insulating layer overlies the gate layer. The pillar material is etched to leave a nanopore into which semiconductor material is deposited, forming an upstanding channel, after insulating material has been deposited on the interior of the nanopore. The source or drain may be a conductive substrate or a doped region of the substrate formed immediately beneath the nanopillar with the other electrode formed by doping the region adjacent the top of the channel.

Owner:HEWLETT PACKARD DEV CO LP

Lateral injection vertical cavity surface-emitting laser

InactiveUS6493368B1Optical resonator shape and constructionSemiconductor lasersVertical-cavity surface-emitting laserParasitic capacitance

A lateral injection VCSEL comprises upper and lower mirrors forming a cavity resonator, an active region disposed in the resonator, high conductivity upper and lower contact layers located on opposite sides of the active region, upper and lower electrodes disposed on the upper and lower contact layers, respectively, and on laterally opposite sides of the upper mirror, and a current guide structure including an apertured high resistivity layer for constraining current to flow in a relatively narrow channel through the active region, characterized in that a portion of the lower contact layer that extends under the top electrode has relatively high resistivity. This feature of our invention serves two purposes. First, it suppresses current flow in parallel paths and, therefore, tends to make the current density distribution in the aperture more favorable for the fundamental mode. Second, it reduces parasitic capacitance.

Owner:LUCENT TECH INC

Two-phase-flow, panel-cooled, battery apparatus and method

InactiveUS20100252238A1Eliminate needEnhancing free convectionSemiconductor/solid-state device detailsSolid-state devicesHeat fluxWorking fluid

Two-phase, boiling heat transfer in confined channels close to a source of heat, such as an electrical component or device, carries the latent heat of vapors away to remote locations where “real estate” demands of air convection are tolerable operationally, economically, and technologically. Liquid-to-vapor, phase-change, heat transfer in a narrow channel (e.g., typically less than 0.200 inches total thickness, and often less than 0.150 in the channel itself) improves by several hundred percent the heat extraction from modest temperature (e.g., about 120 degree F.) devices, when compared to heat fluxes in pool boiling. Saturated working fluids provide nearly isothermal conditions in the working fluid. Minimal conduction paths provide minimal temperature gradients, and capillary action may maintain nearly constant temperature conditions about a surface of a heat source, while carrying heat of vaporization away to a condensation location.

Owner:BATTY J CLAIR +1

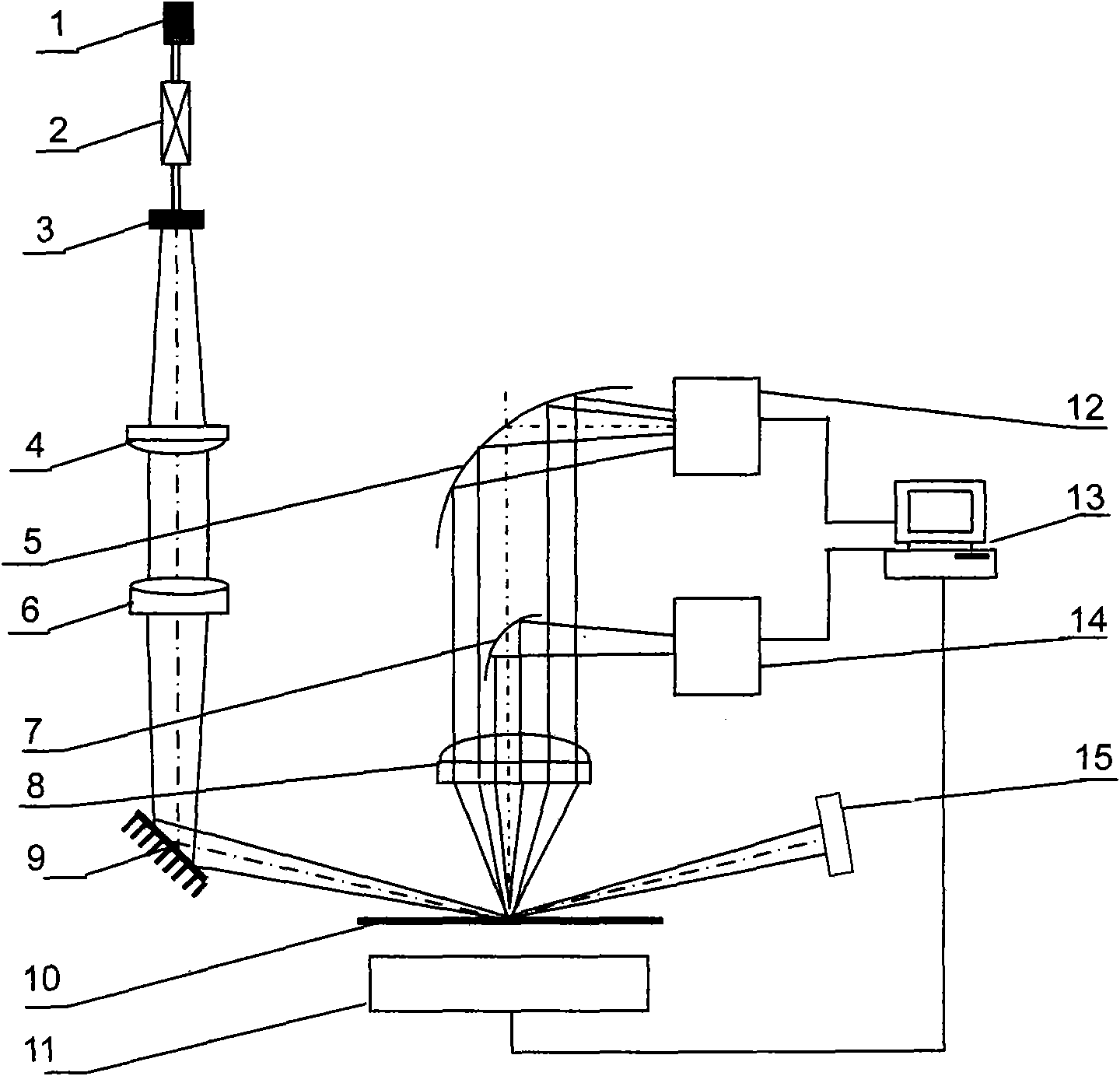

Silicon chip surface defect detector capable of classifying defects and defect classifying method

InactiveCN101672801AEasy to detectImplement classificationScattering properties measurementsOptically investigating flaws/contaminationPhotovoltaic detectorsSilicon chip

The invention relates to a silicon chip surface defect detector capable of classifying defects and a defect classifying method. The flat surface of the silicon chip to be detected on a highly reliablesilicon chip working platform is irradiated by a laser from an inclination direction. Circular narrow channel collection and annular narrow channel collection are carried out on scattered lights produced by the silicon chip surface defect by two paraboloidal mirrors with different calibers in a direction near the silicon chip face normal and parallel with silicon chip face. Two photoelectric detectors detect intensities of the collected electrooptical signals in two channels respectively and then take a ratio of two intensities, then compare the ratio with a given threshold value, and at lastthe silicon chip surface defects can be classified. The defect detector has the advantages of simple structure, high sensitivity, fast detecting speed, capability of classifying the defects on the silicon chip surface, etc.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

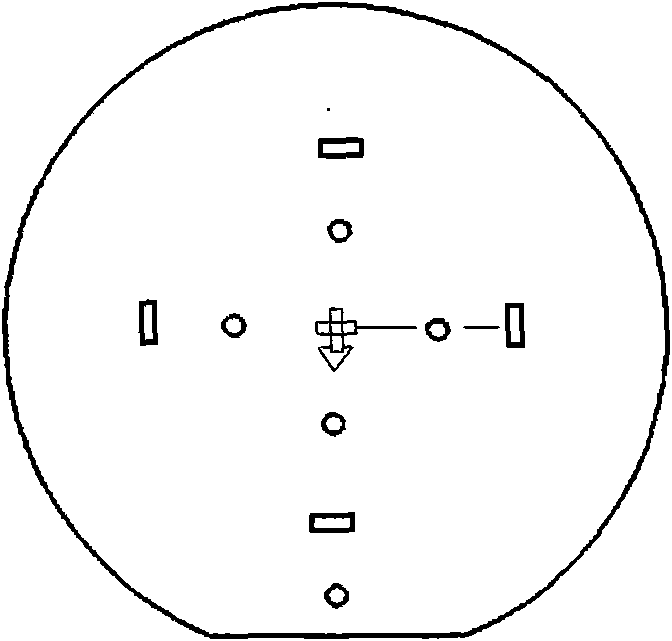

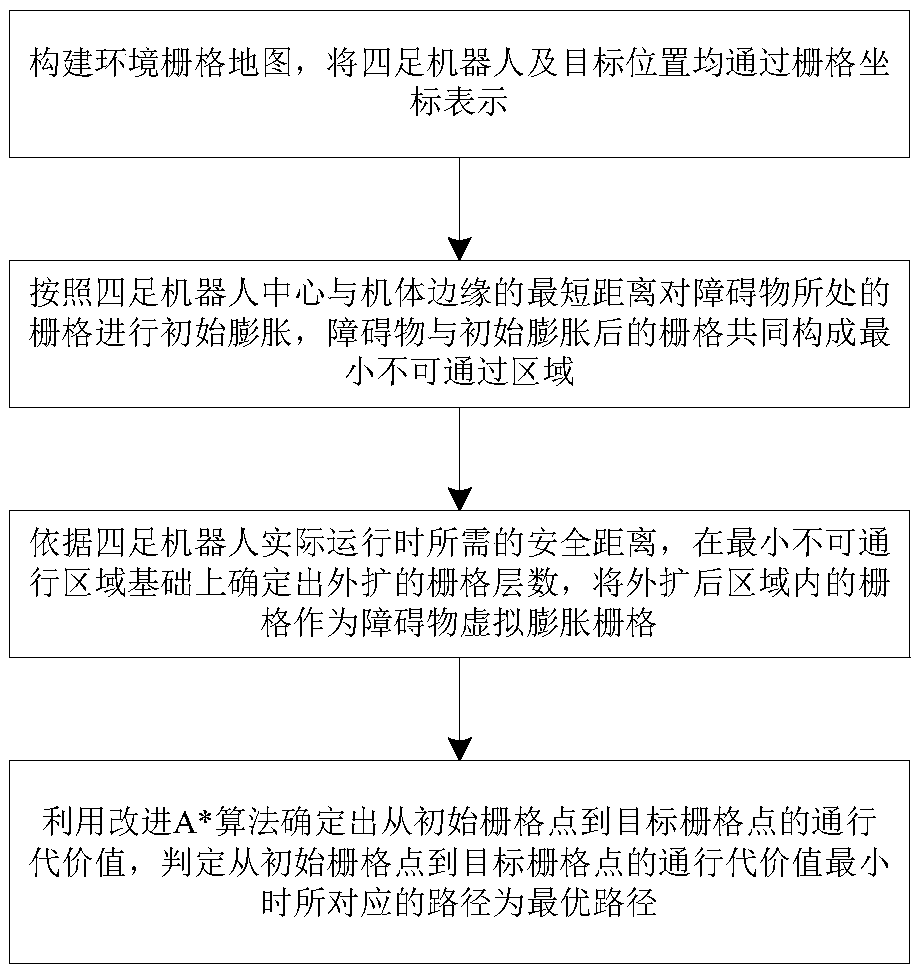

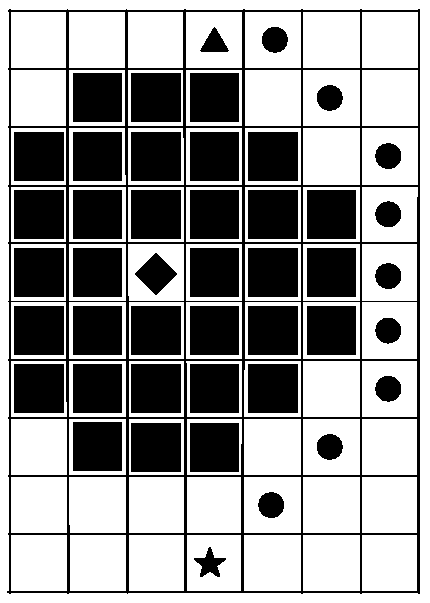

Quadruped robot path planning method and system based on improved A* algorithm

InactiveCN108646765ARealize virtual inflationSolve the blockagePosition/course control in two dimensionsSimulationRobot path planning

The invention discloses a quadruped robot path planning method and system based on an improved A* algorithm. The method comprises the steps of constructing an environment raster map,and representing aquadruped robot and a target position through raster coordinates; on the basis of the smallest distance between the edge of a robot body and the center of the quadruped robot,performing initial expansion on the raster where a barrier is located,and enabling the barrier and the raster obtained after initial expansion to jointly form the minimum impassable region; according to the the safe distanceneeded by actual operation of the quadruped robot,determining the outward expansion raster layer number on the basis of the minimum impassable region,and adopting the raster obtained after outward expansion inside the region as a barrier virtual expansion raster; utilizing the improved A* algorithm for determining a passing price value from the initial raster and the target raster,and determiningthe corresponding path obtained when the passing price value from the initial raster point to the target raster point is minimum is determined as the optimal path. The problem that a narrow channel is blocked can be avoided while the quadruped robot is driven to move away from the barrier.

Owner:QILU UNIV OF TECH

Reduction of negative bias temperature instability in narrow width PMOS using F2 implantation

InactiveUS6780730B2Suppress instabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh densityEngineering

In a process of fabricating a narrow channel width PMOSFET device, the improvement of affecting reduction of negative bias temperature instability by use of F2 side wall implantation, comprising:a) forming a shallow trench isolation (STI) region in a substrate;b) forming a gate on a gate oxide in the substrate;c) forming a liner layer in said shallow trench isolation region and subjecting the liner layer to oxidation to form a STI liner oxidation layer;d) implanting F2 into side walls of the STI liner oxidation layer at a large tilted angle in sufficient amounts to affect reduction of negative bias temperature instability after a high density plasma fill of the STI F2 implanted liner oxidation layer; ande) filling the STI F2 implanted structure from step d) with a high density plasma (HDP) fill to affect reduction of negative bias temperature instability.

Owner:INFINEON TECH AG

Therapeutic wraps

Owner:CLAYTON NEVA A