Patents

Literature

46527results about "Cooling/ventilation/heating modifications" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

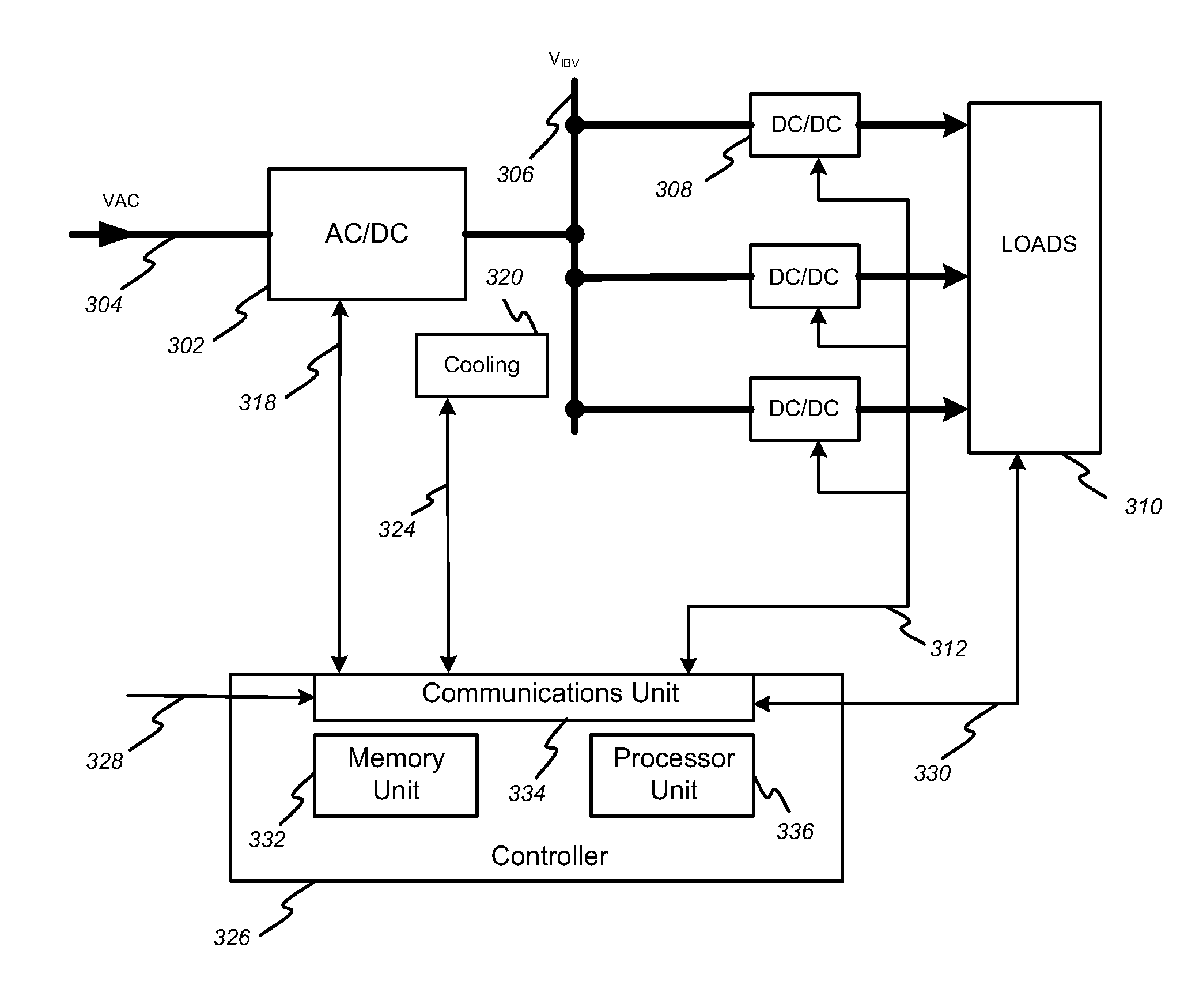

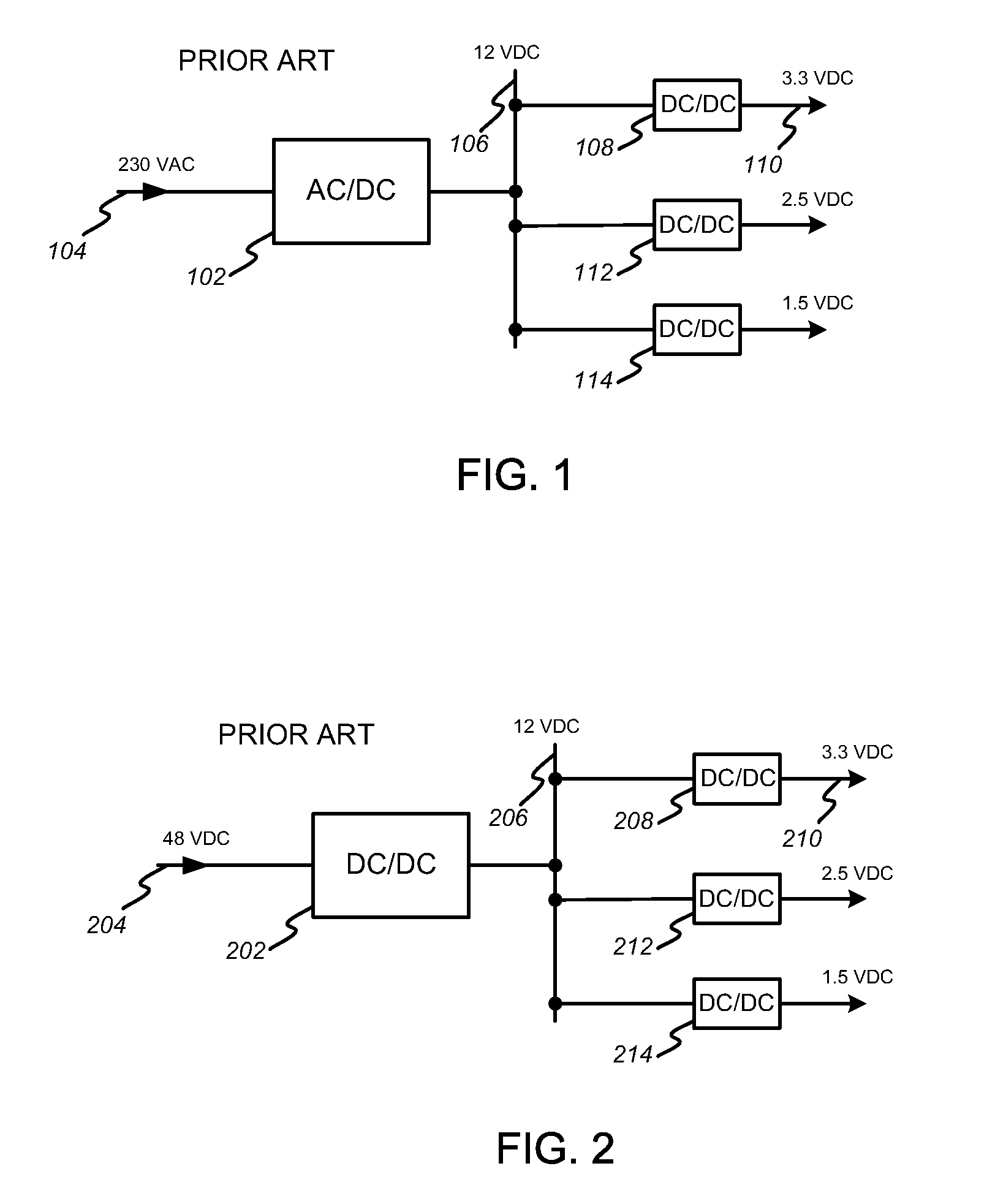

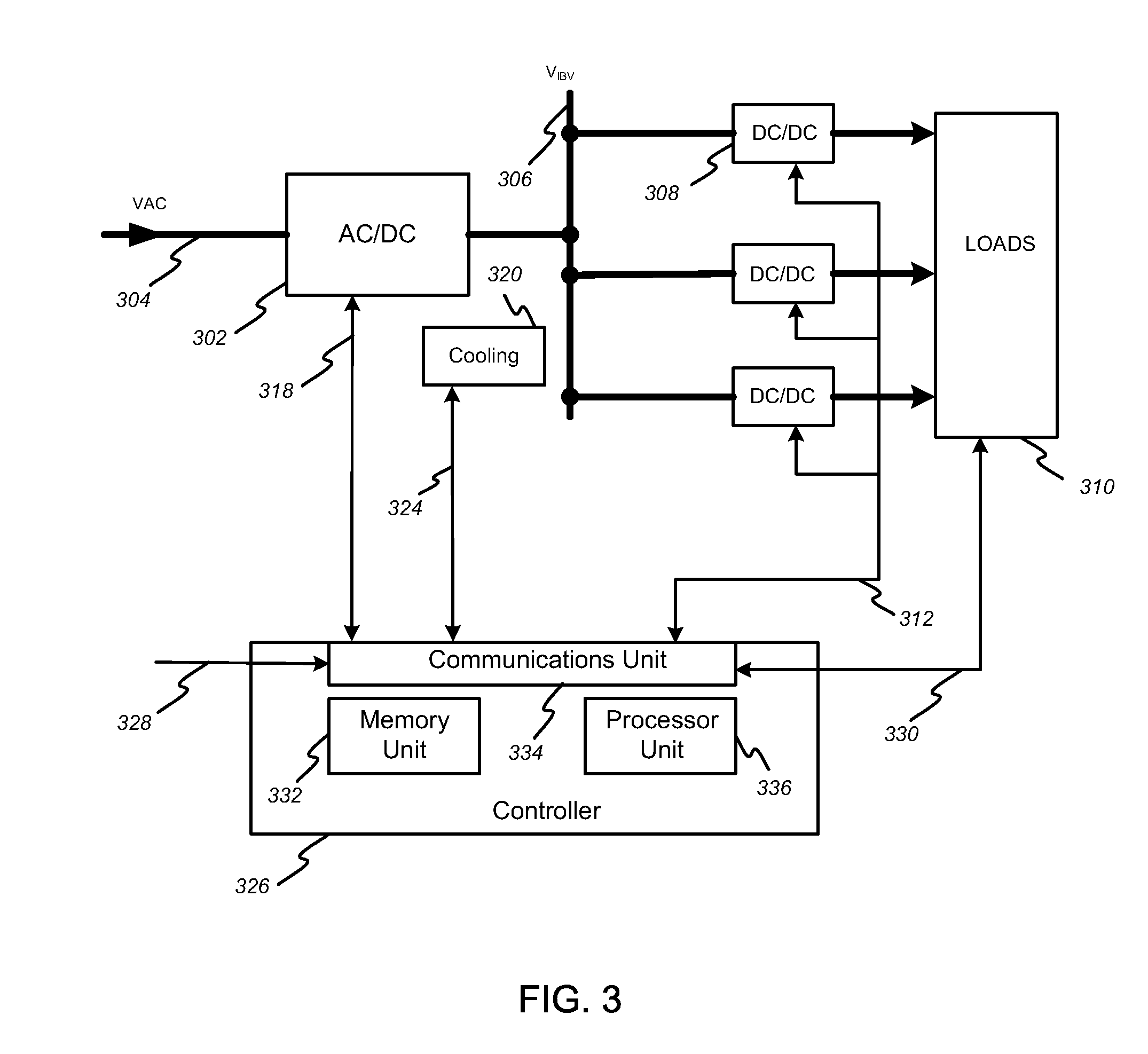

Apparatus and method of optimizing power system efficiency using a power loss model

ActiveUS8179705B2Maximize efficiencyImprove efficiencyMechanical power/torque controlLevel controlPower flowMeasurement device

A power subsystem is actively optimized to improve total subsystem efficiency in a way that is responsive to changes in load requirements, power supply variations, and subsystem temperature variations. Detailed, multidimensional power loss models are developed for constituent devices which are then combined into a power subsystem containing a controller and circuity for measuring device operating parameters such as input and output voltage, output current, and temperature. Operating parameters are continually monitored, and set points are correspondingly changed based on the detailed power loss models to achieve maximum overall efficiency for the instantaneous operating state of the system.

Owner:BEL POWER SOLUTIONS INC

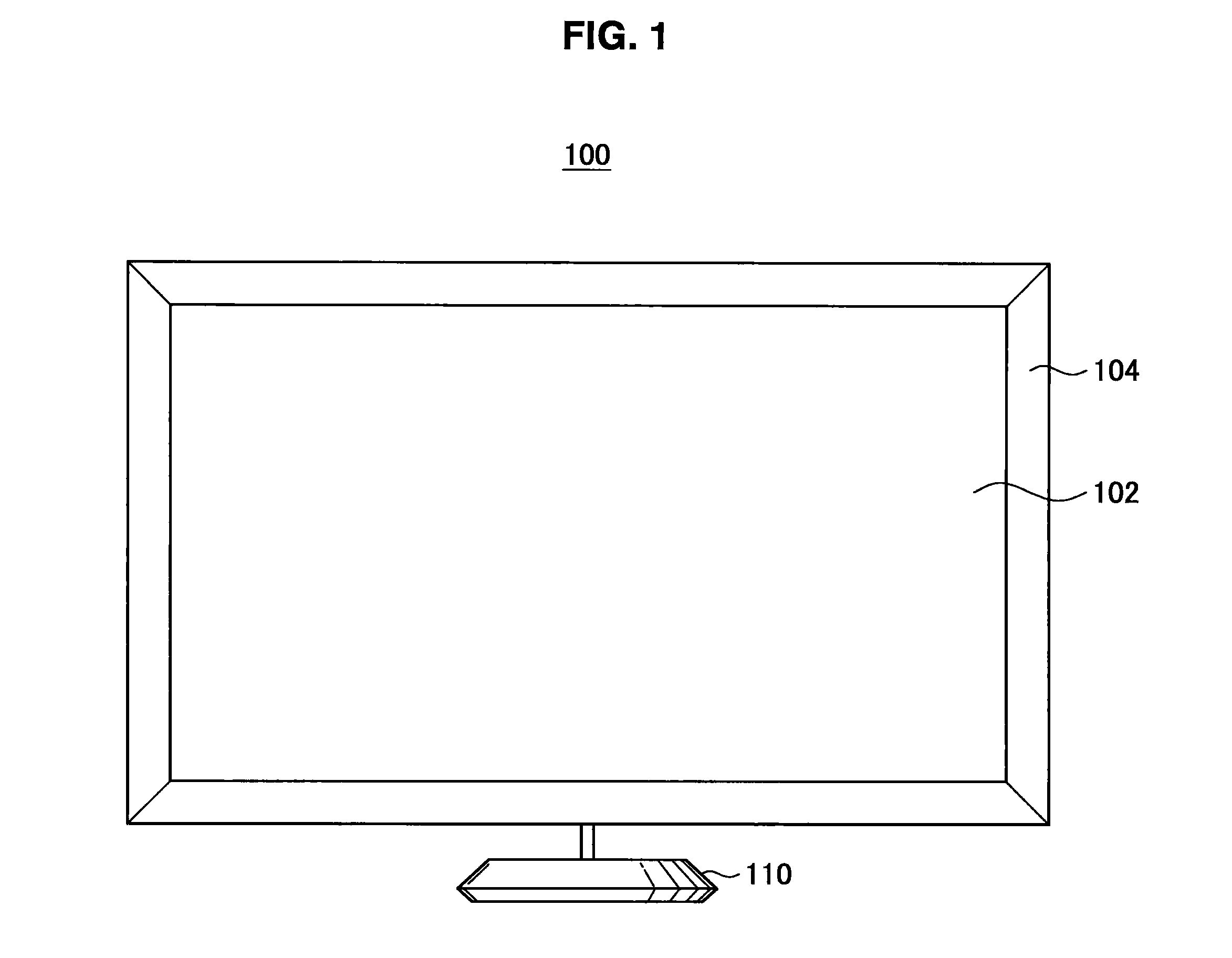

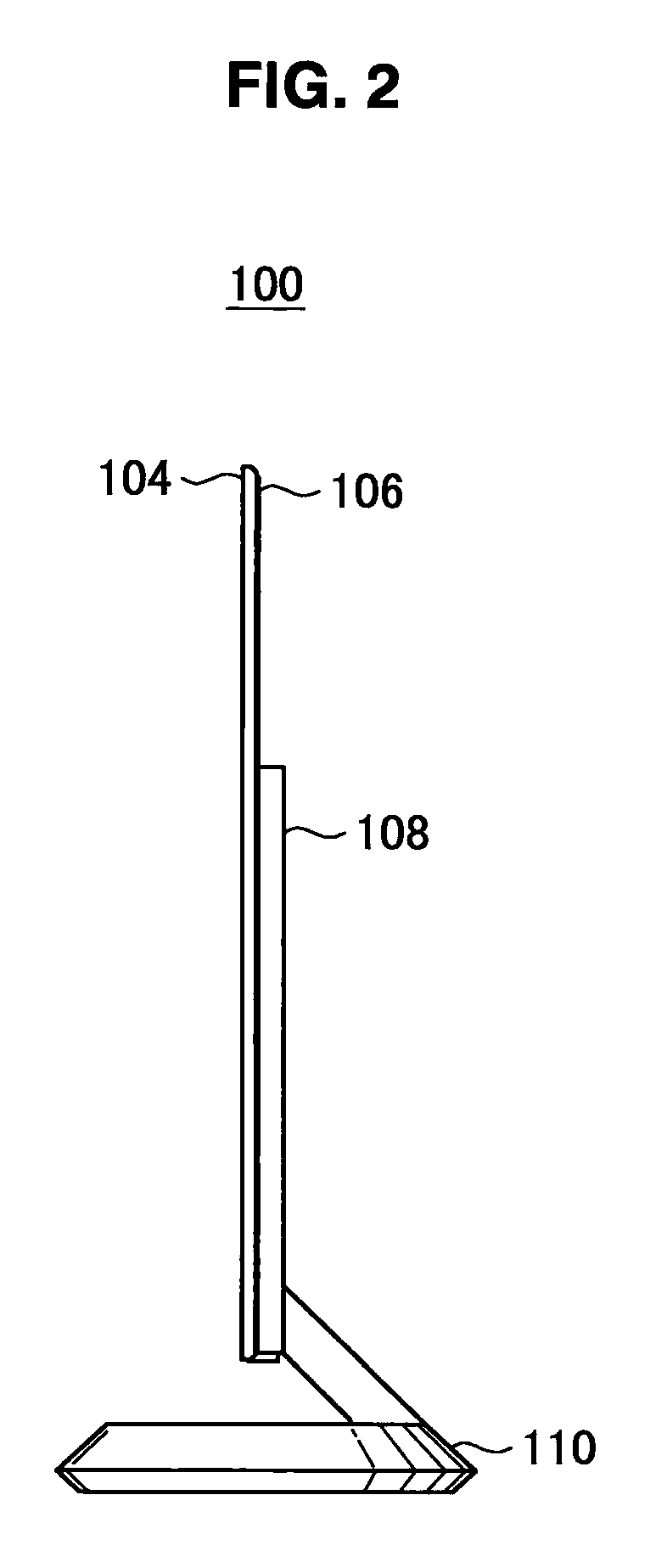

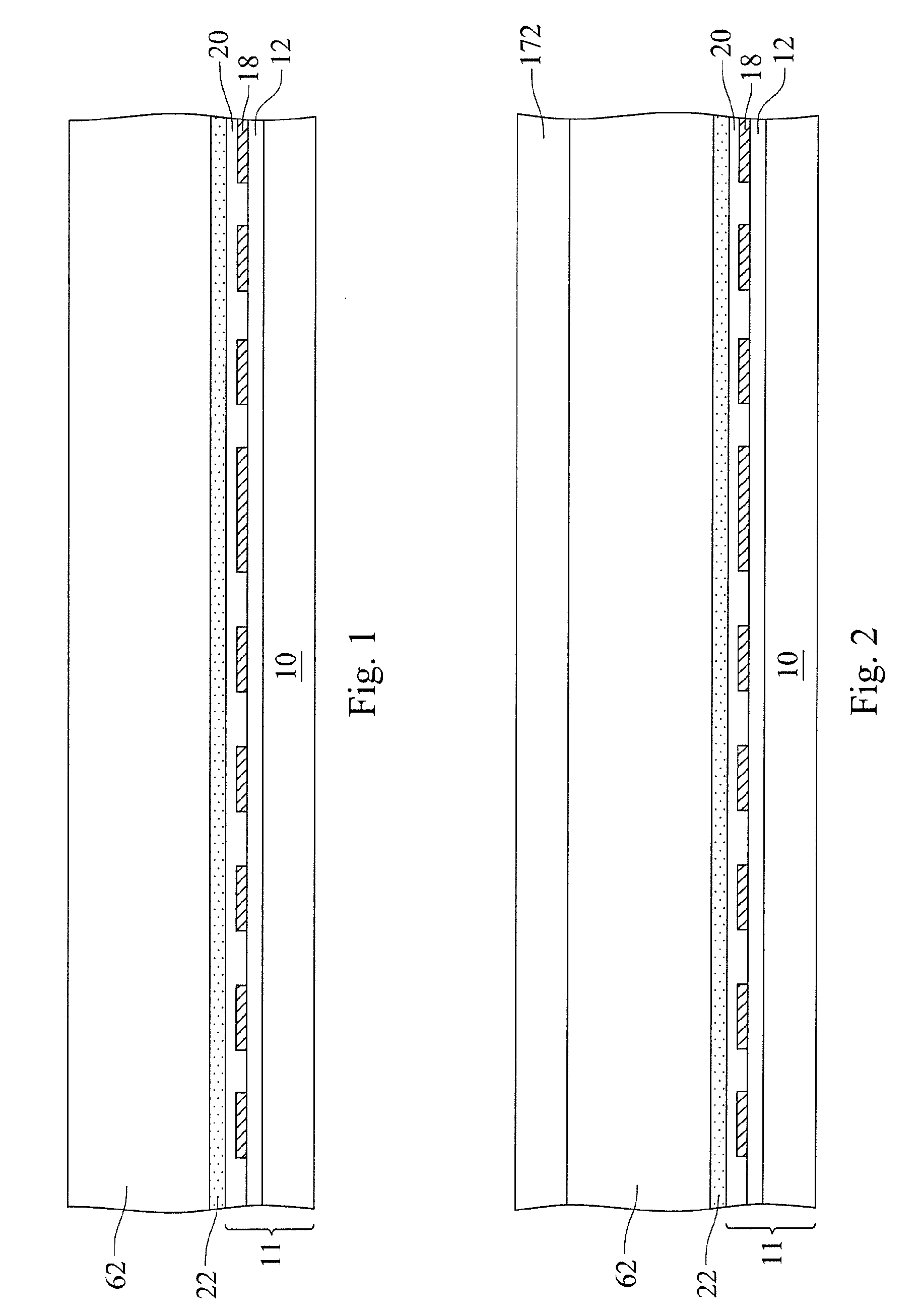

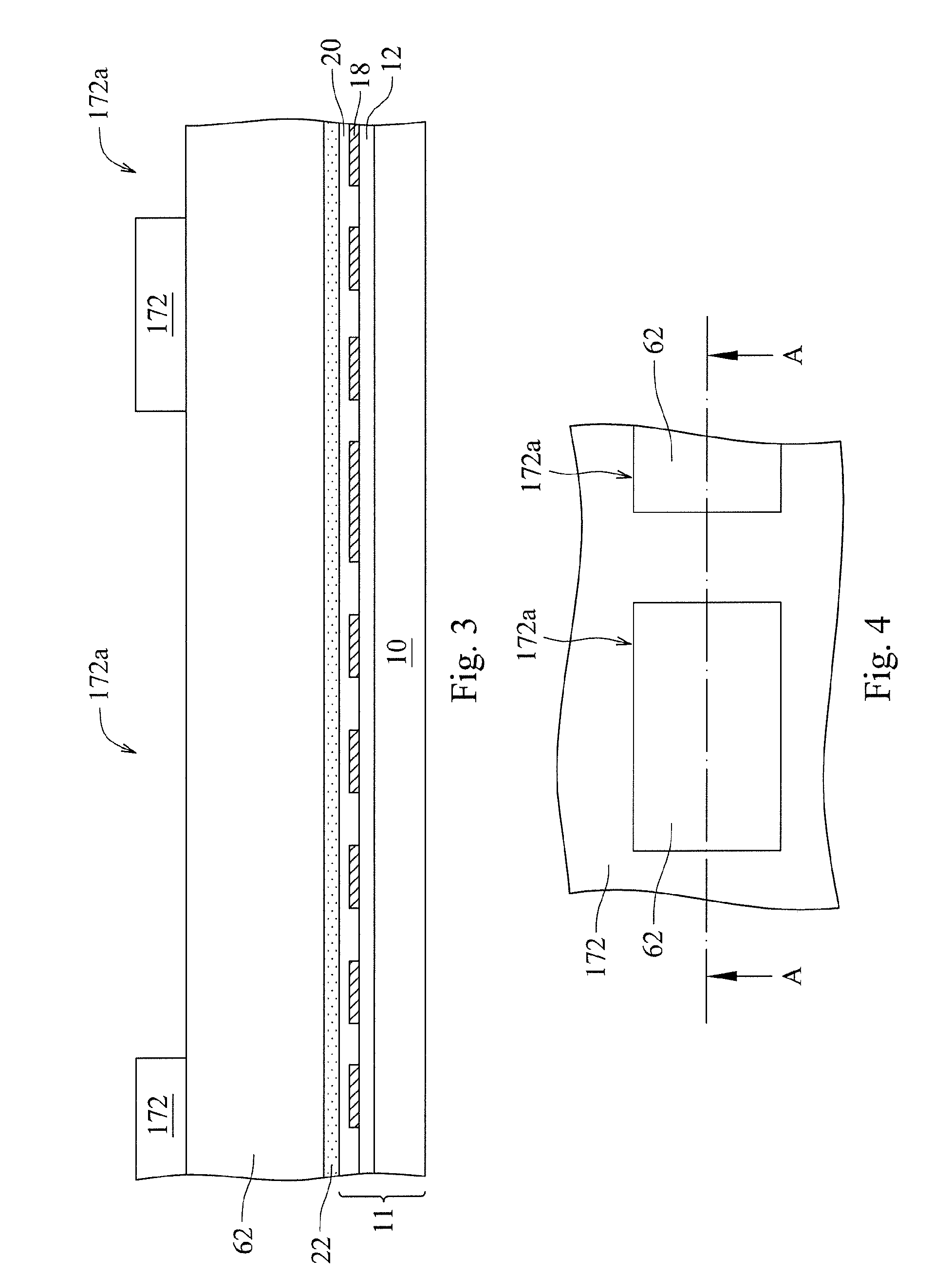

Display apparatus

ActiveUS8811017B2Effective diffusionTelevision system detailsElectric discharge tubesEngineeringClose contact

Provided is a display apparatus including a display panel for displaying an image, a heat source arranged at a side surface of at least one side of the display panel, a heat absorbing section for absorbing heat generated by the heat source, a back surface plate arranged at a back surface side of the display panel and made of a metal, a portion of the back surface plate being in close contact with the heat absorbing section, a front surface plate arranged at a front surface side of the display panel and made of a metal, and a middle chassis arranged between the front surface plate and the heat absorbing section.

Owner:SATURN LICENSING LLC

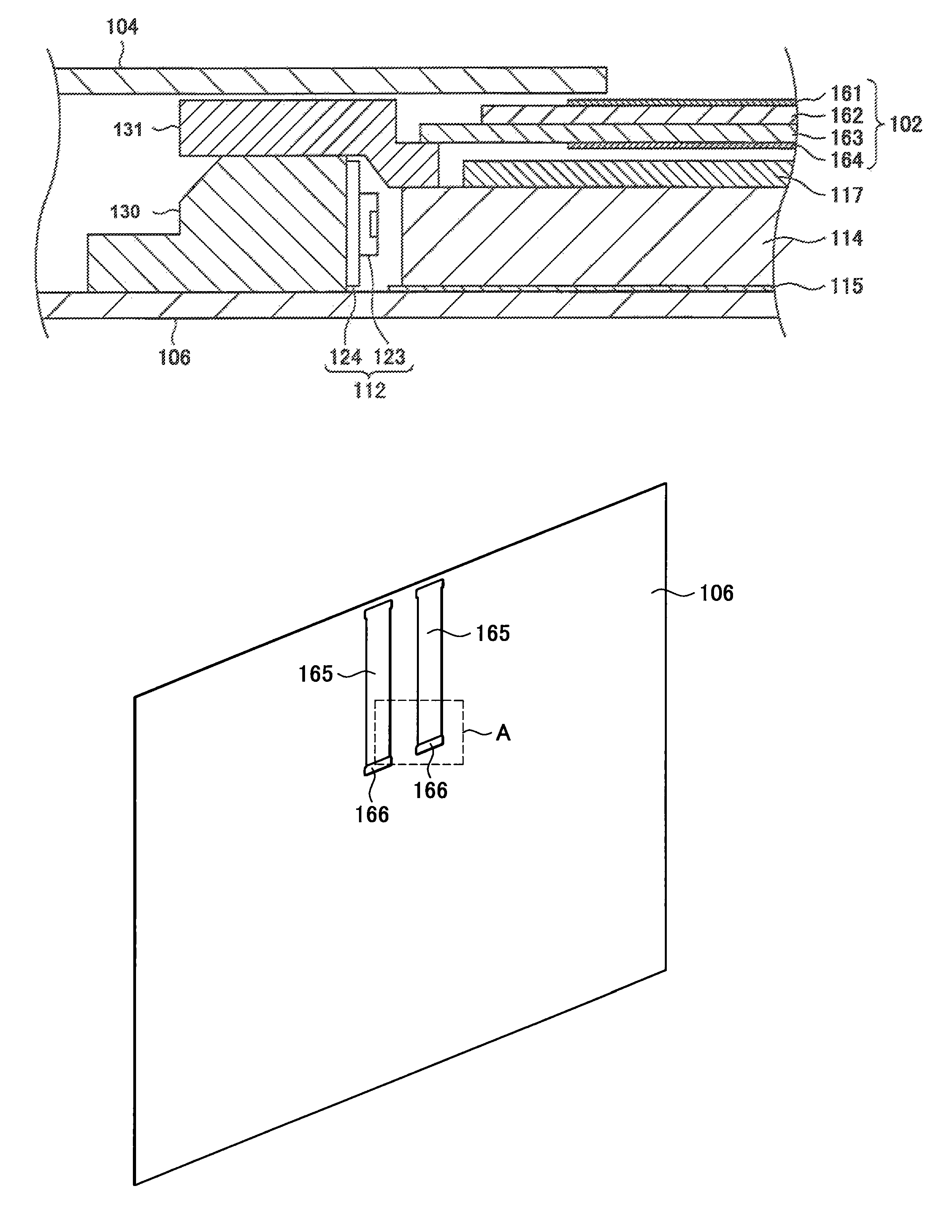

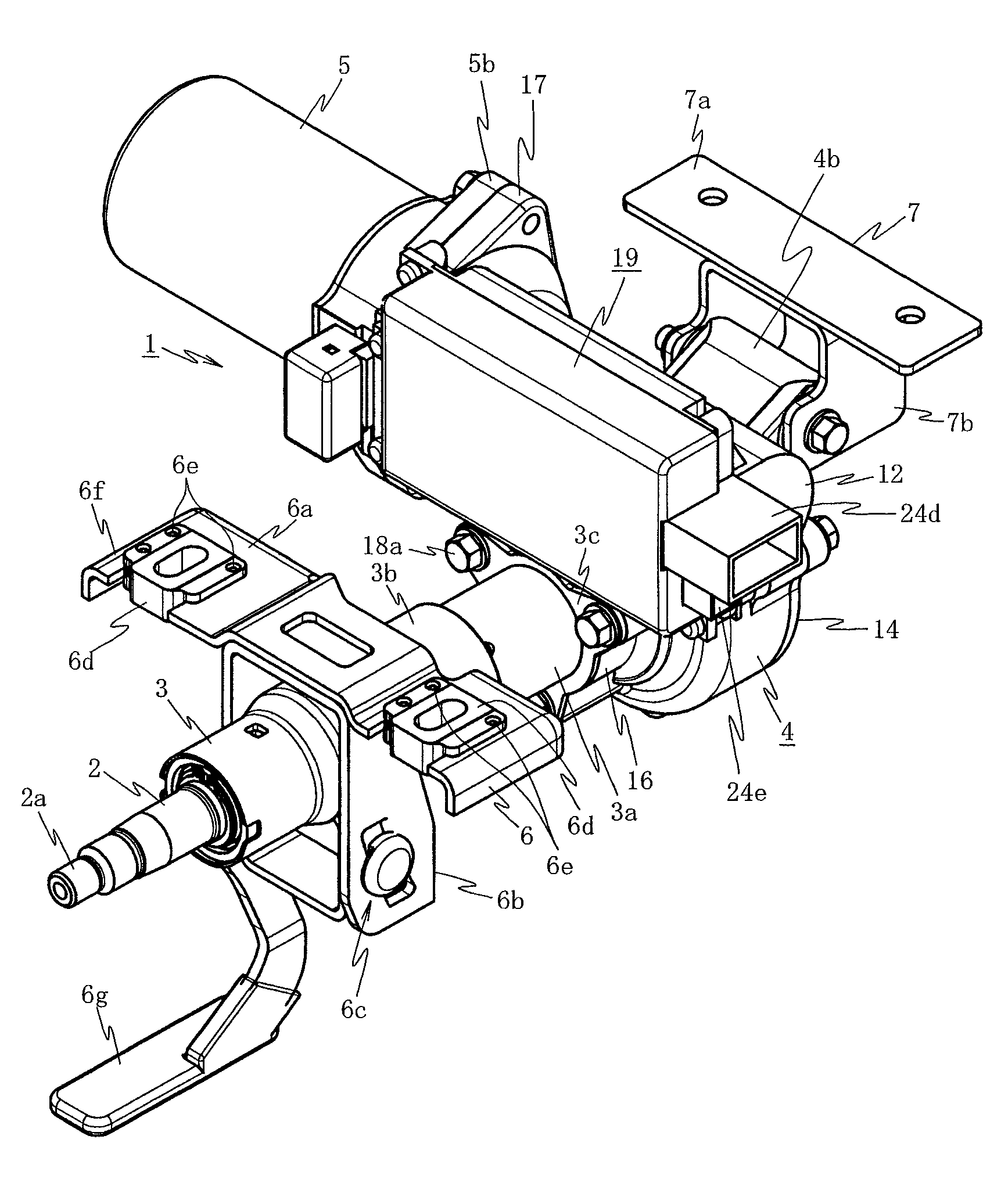

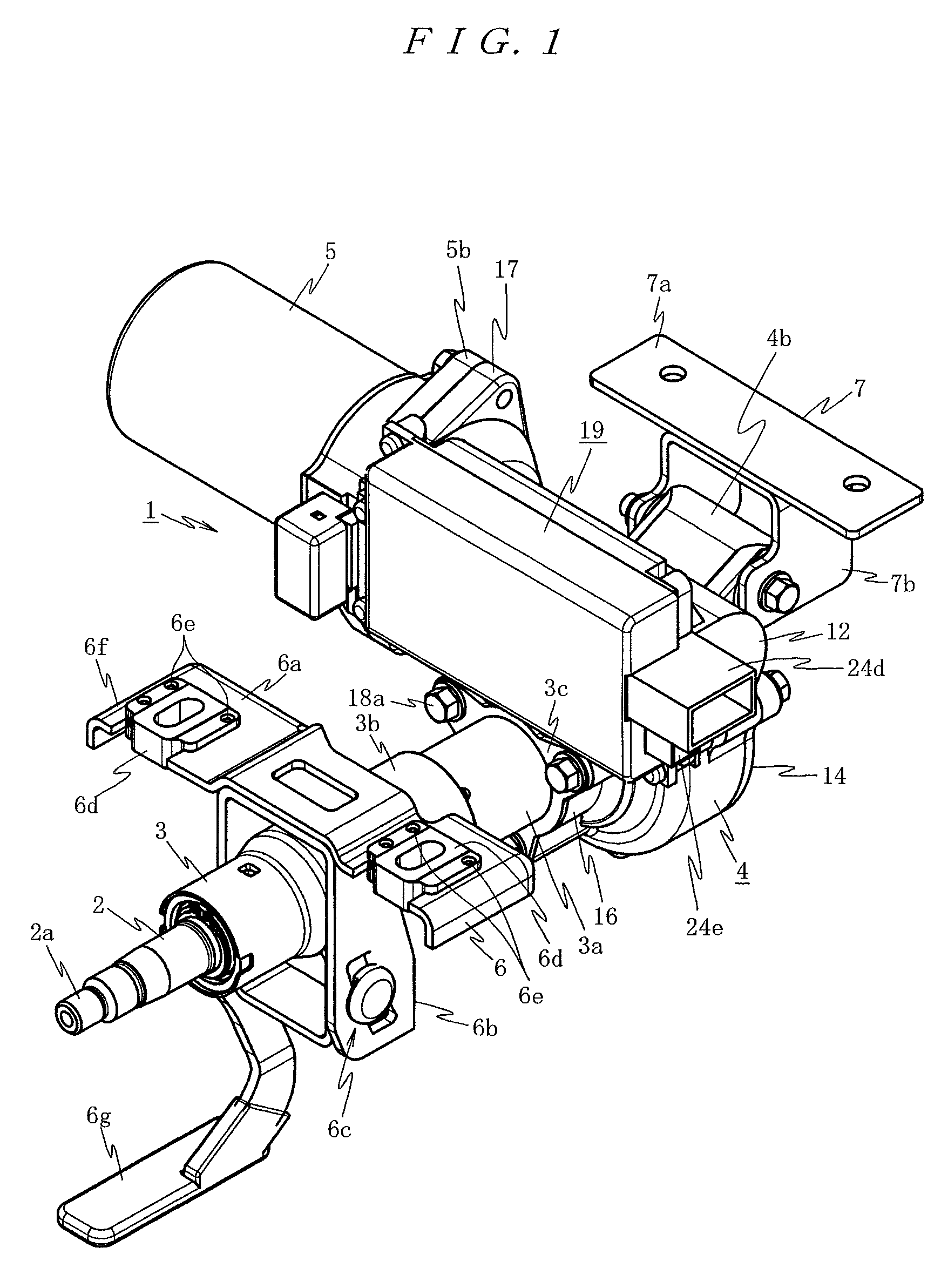

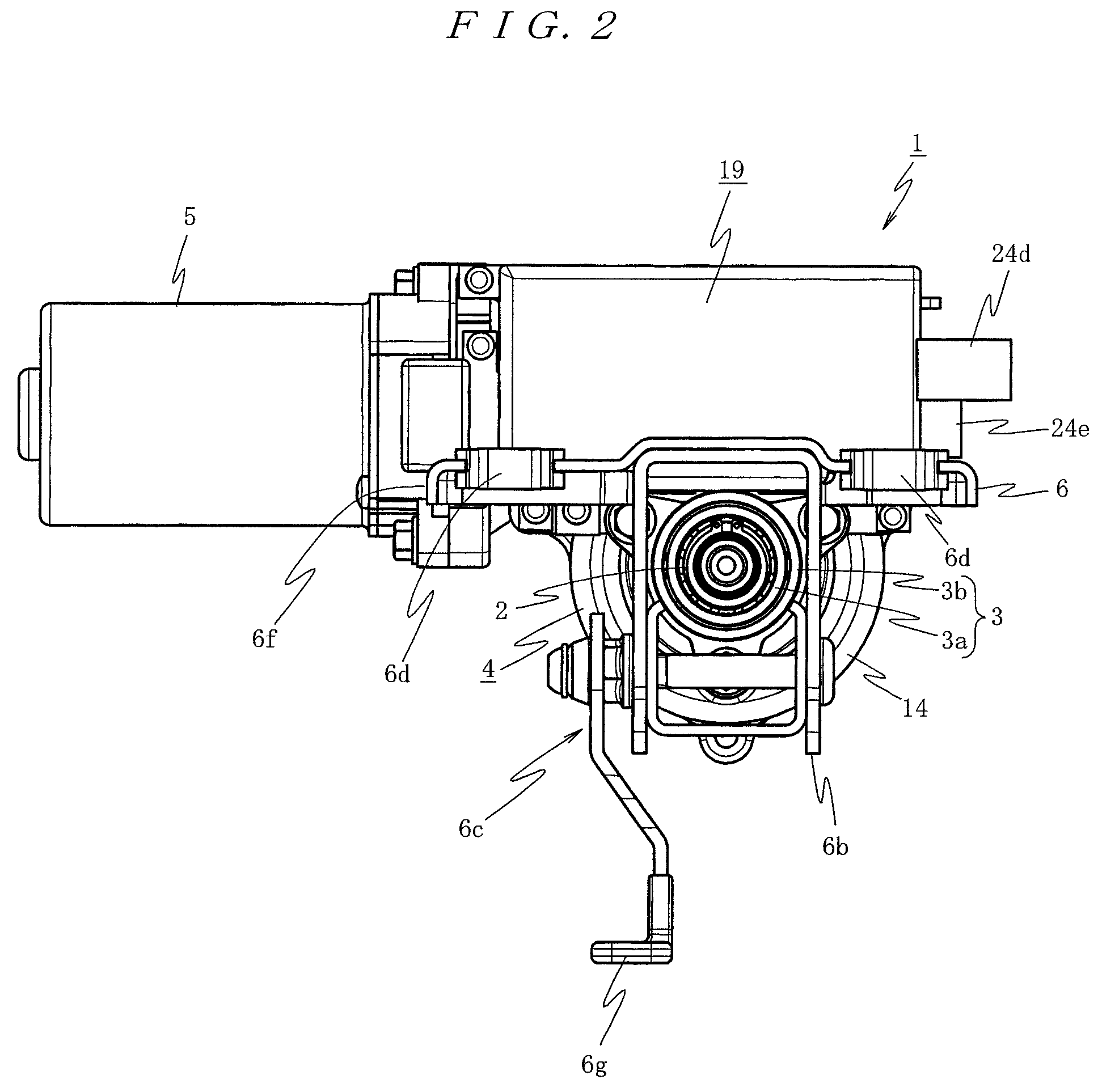

Electric power steering apparatus and method of assembling the same

ActiveUS8102138B2Large massDC motor speed/torque controlElement comparisonElectricityElectric power steering

A motor control apparatus includes a steering column having inserted therein a steering shaft to which steering torque is transmitted, a reduction gear box coupled to the steering shaft, and an electric motor that transmits a steering assisting force to the steering shaft via a reduction mechanism in the reduction gear box. The electric motor and its control unit including a control board mounted with a control circuit, are provided side by side in the reduction gear box. A connection terminal of the electric motor is electrically connected to the control unit directly. This minimizes a connection distance between the control unit and the electric motor.

Owner:NSK LTD

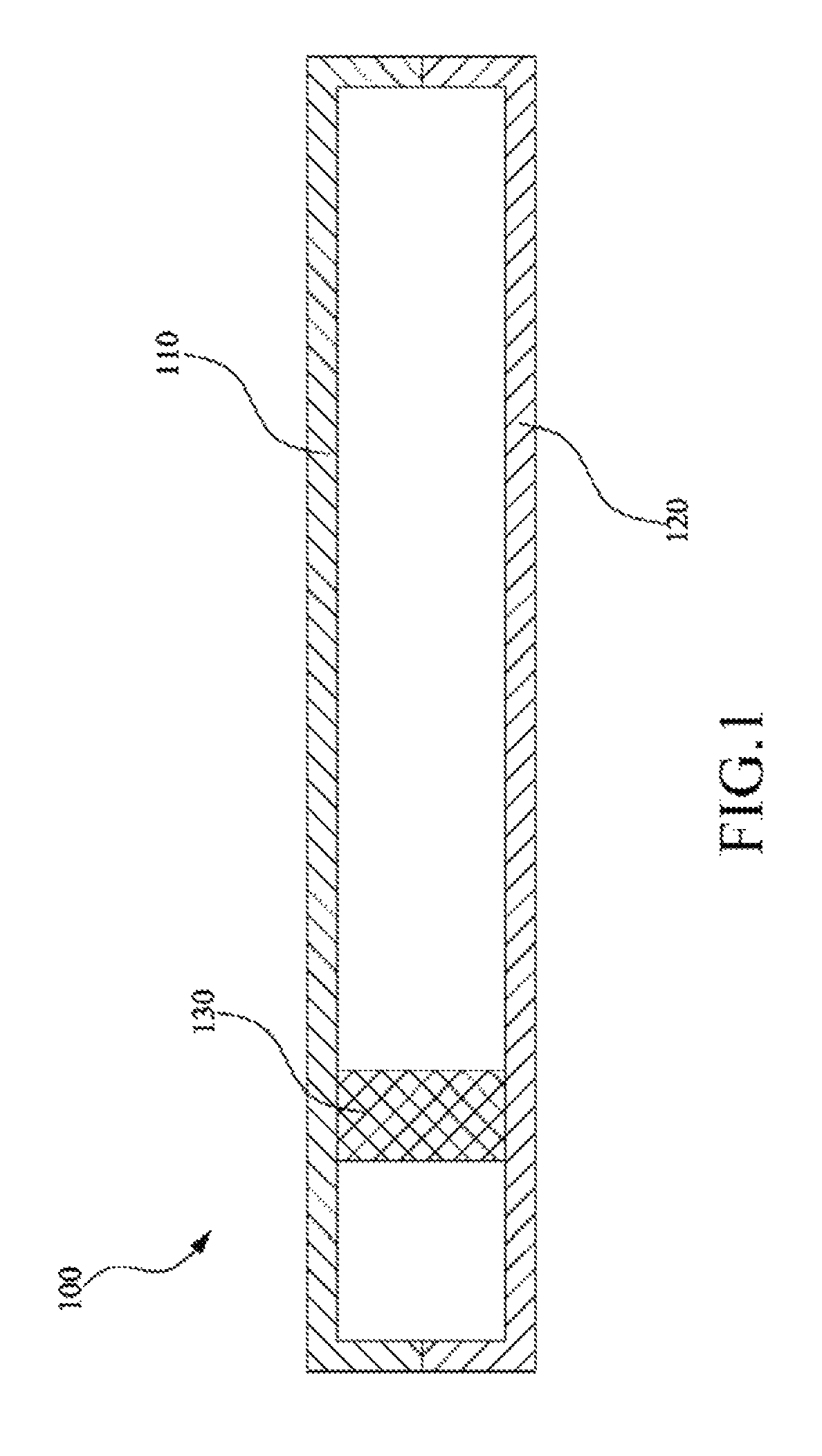

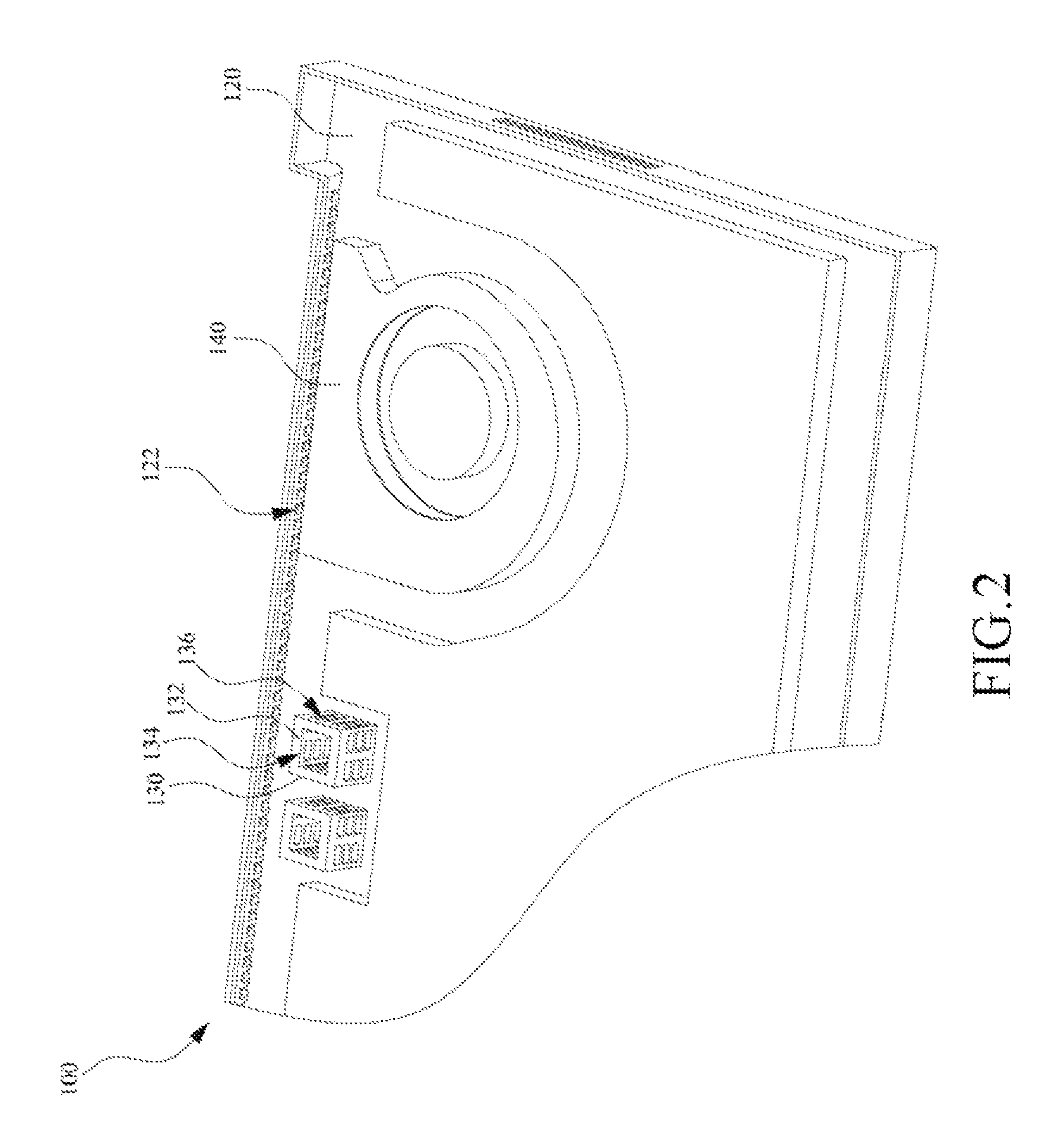

Electronic device

ActiveUS9313915B2Improve cooling efficiencyPump componentsDigital data processing detailsHeat conductingElectron device

An electronic device includes an upper cover, a lower cover combined with the upper cover, and a heat conducting pillar. An accommodating space is formed by the upper cover and the lower cover. The heat conducting pillar is disposed in the accommodating space and physically connected with the upper cover and the lower cover to balance the temperature of the upper cover and the lower cover.

Owner:ASUSTEK COMPUTER INC

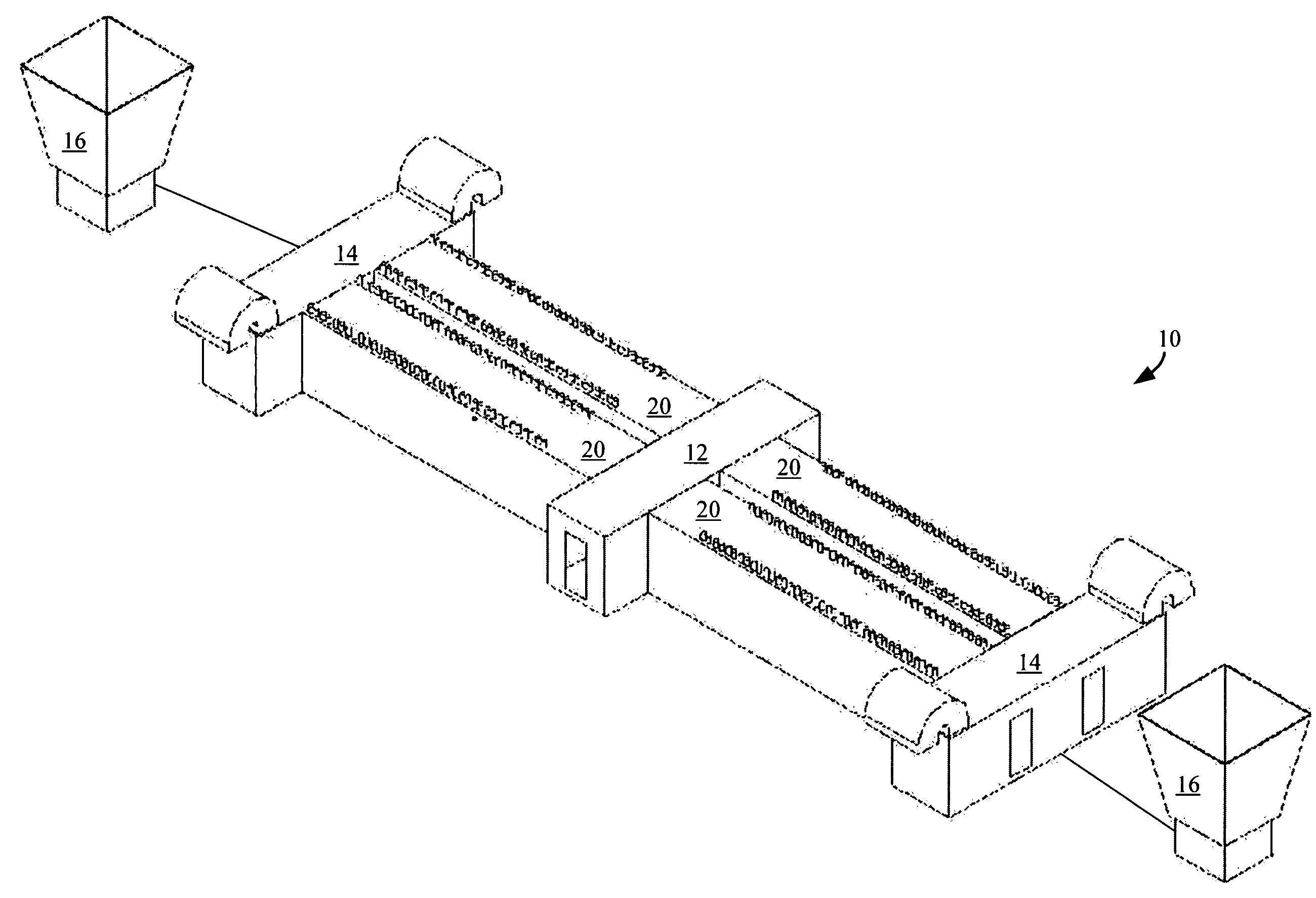

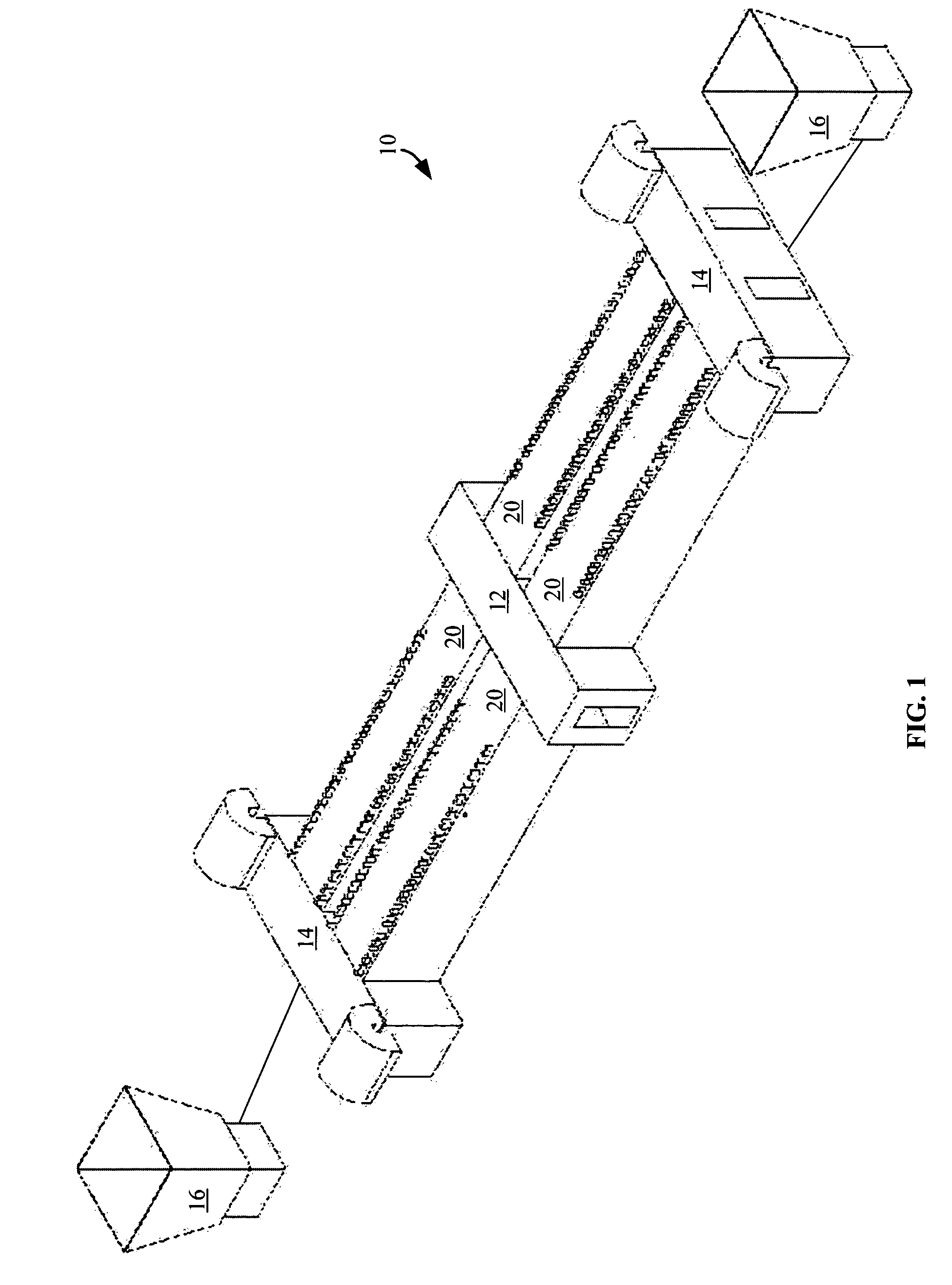

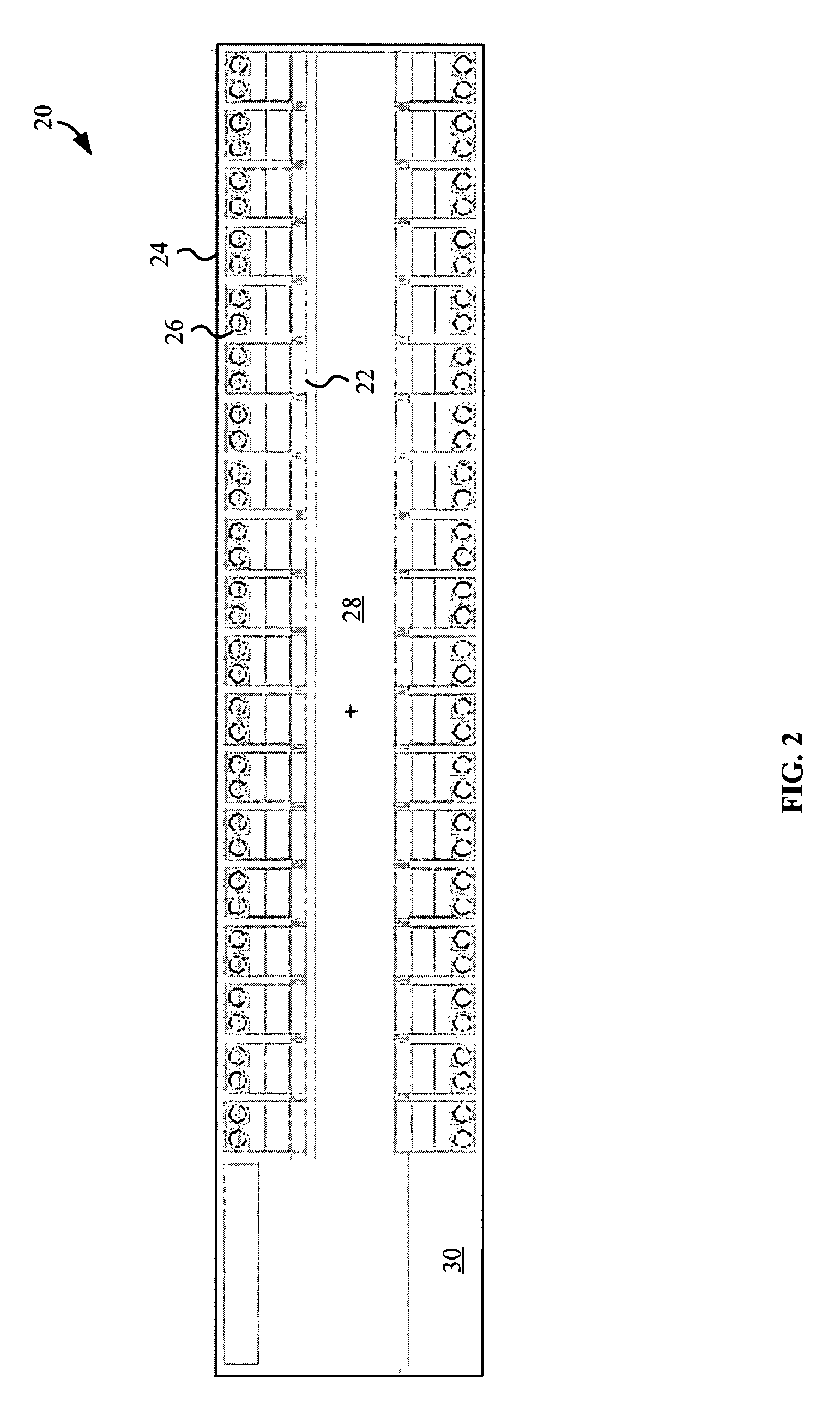

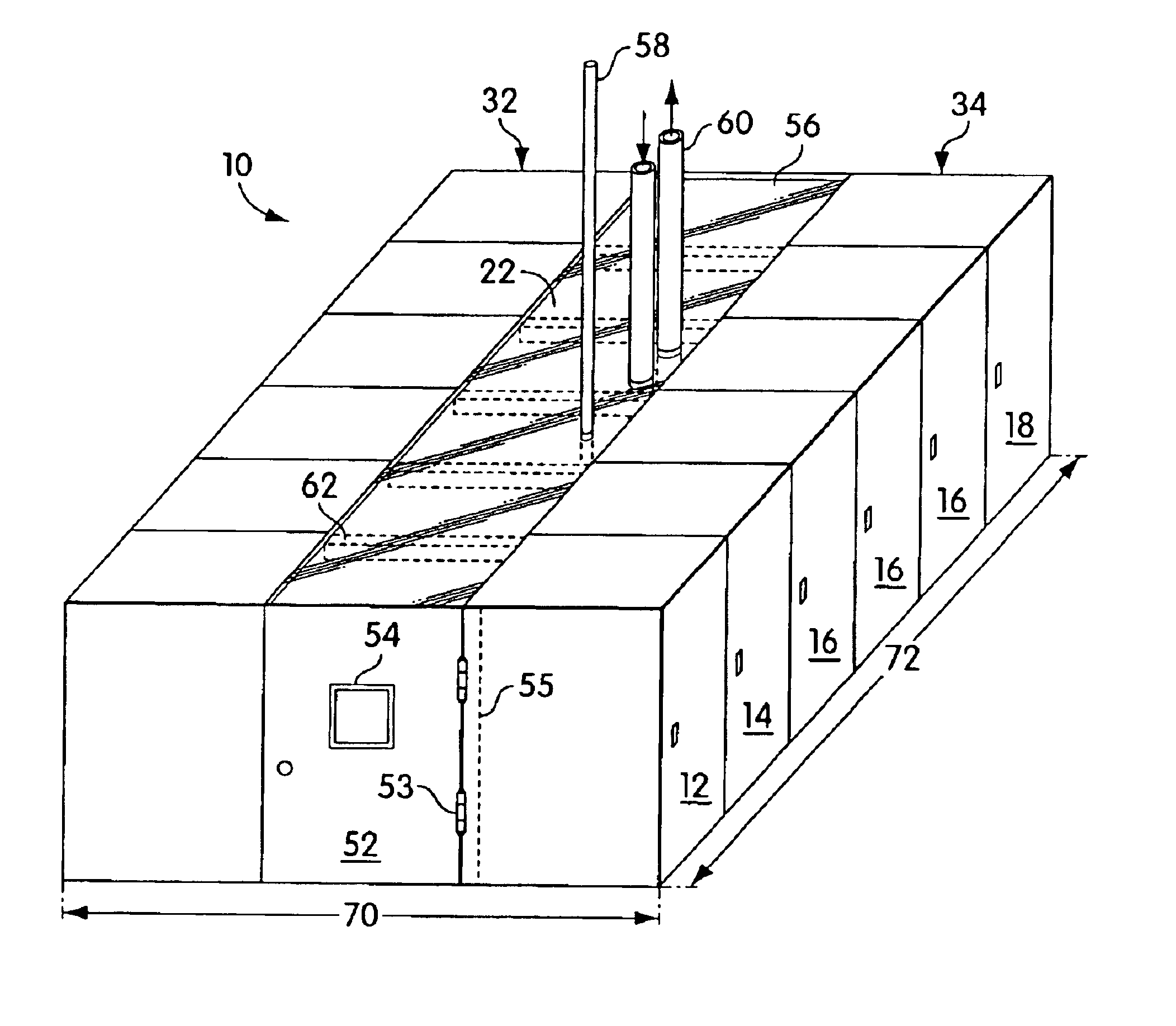

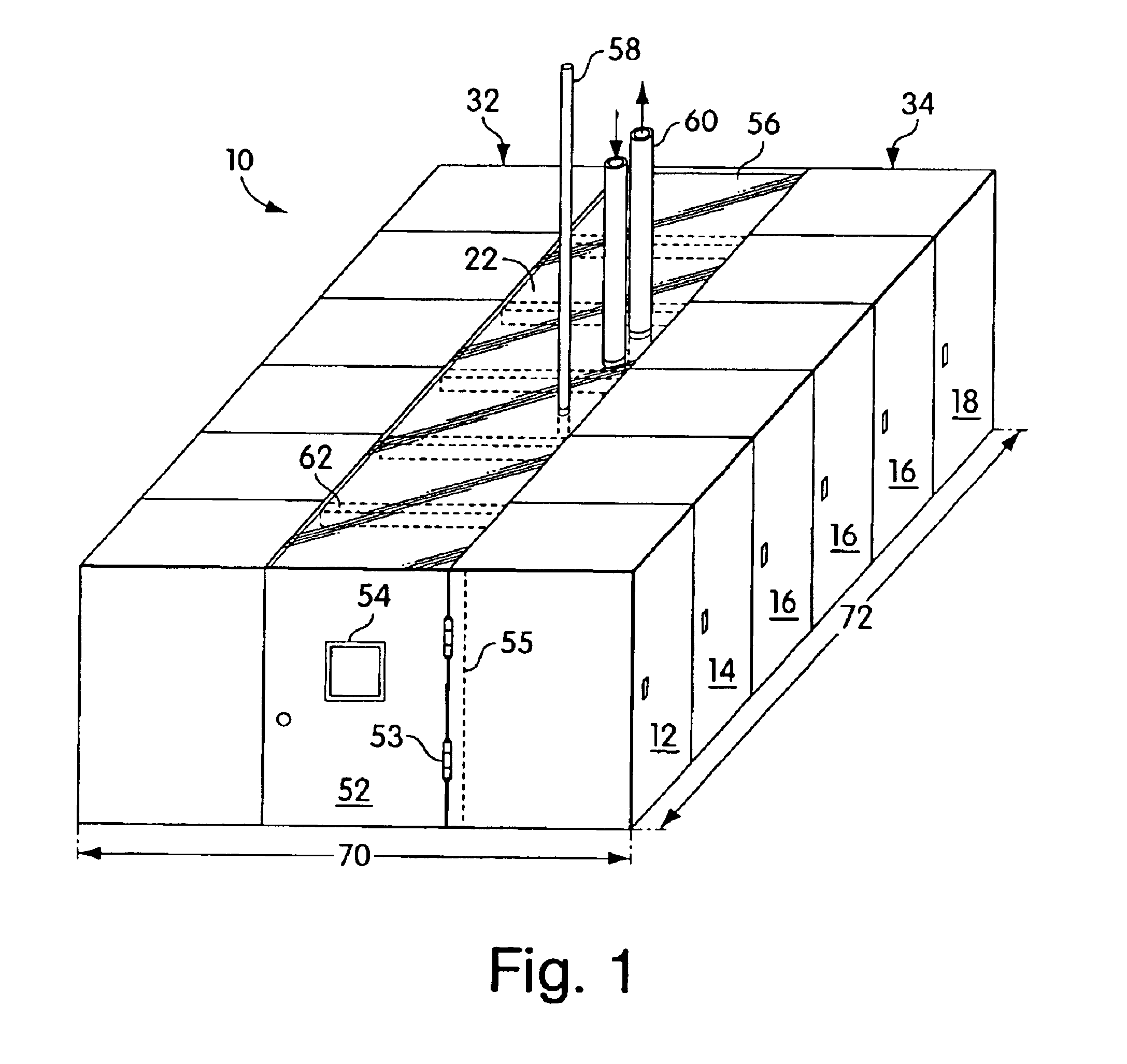

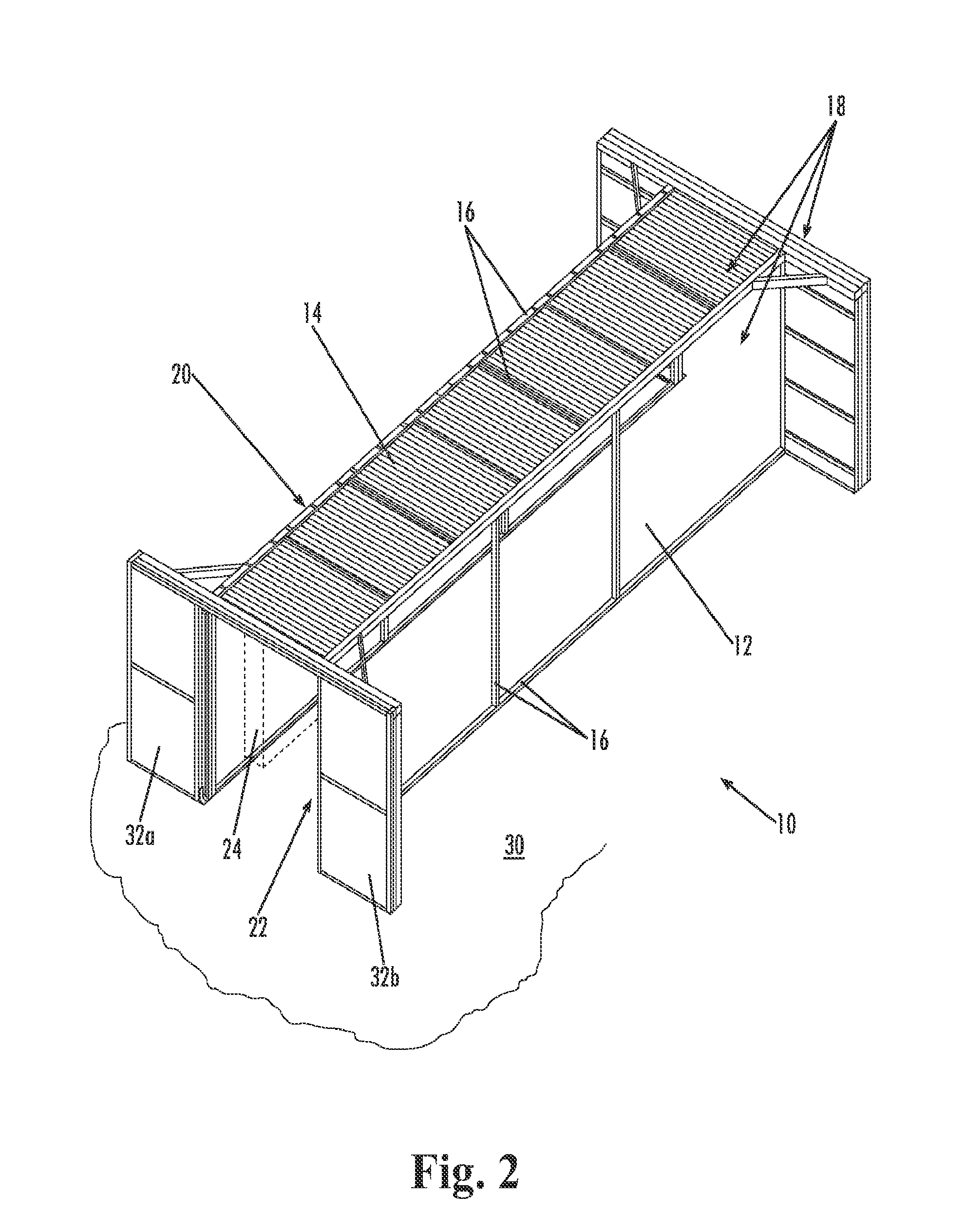

Modular data center

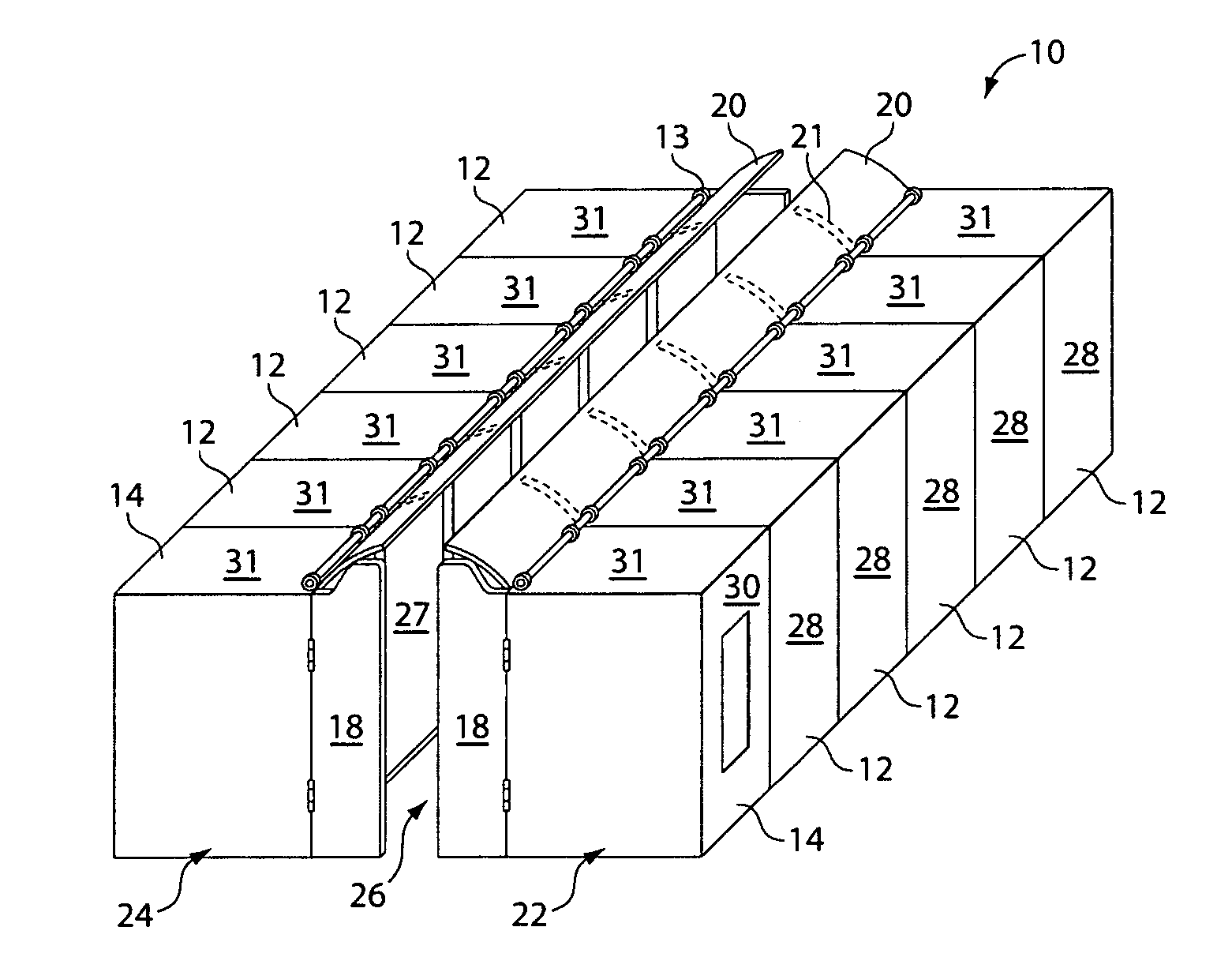

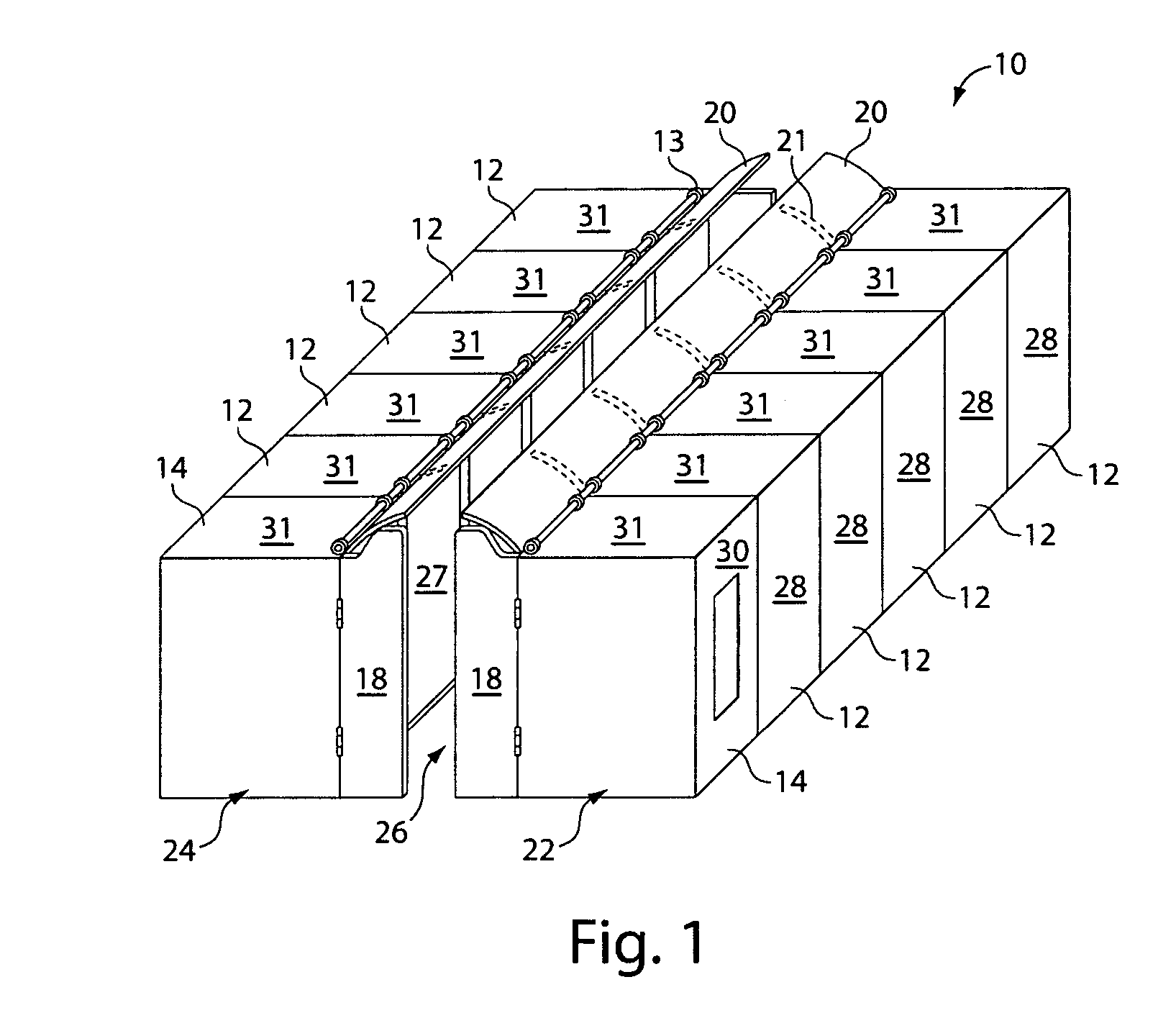

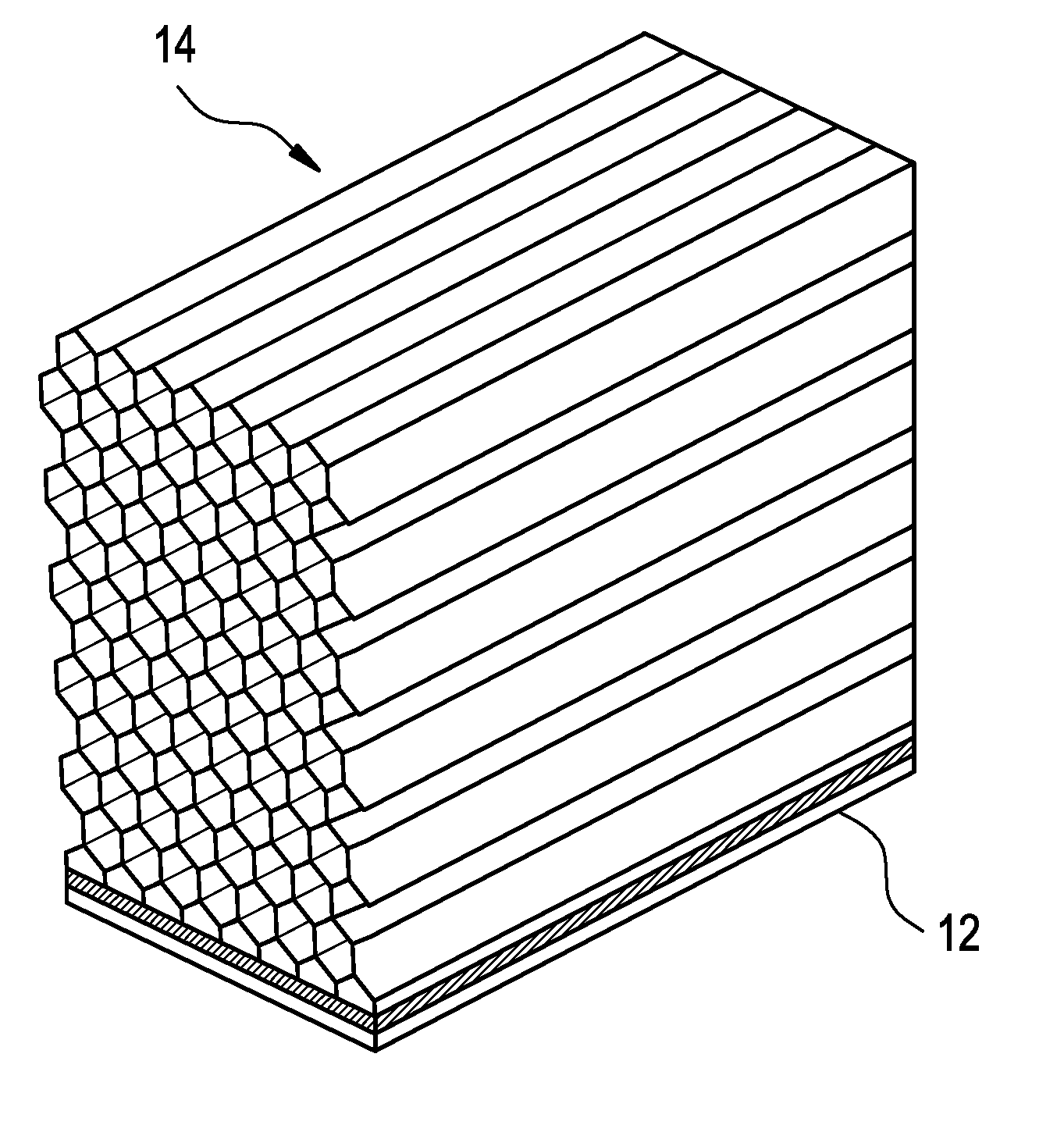

Modular data centers with modular components suitable for use with rack or shelf mount computing systems, for example, are disclosed. The modular center generally includes a modular computing module including an intermodal shipping container and computing systems mounted within the container and configured to be shipped and operated within the container and a temperature control system for maintaining the air temperature surrounding the computing systems. The intermodal shipping container may be configured in accordance to International Organization for Standardization (ISO) container manufacturing standards or otherwise configured with respect to height, length, width, weight, and / or lifting points of the container for transport via an intermodal transport infrastructure. The modular design enables the modules to be cost effectively built at a factory and easily transported to and deployed at a data center site.

Owner:GOOGLE LLC

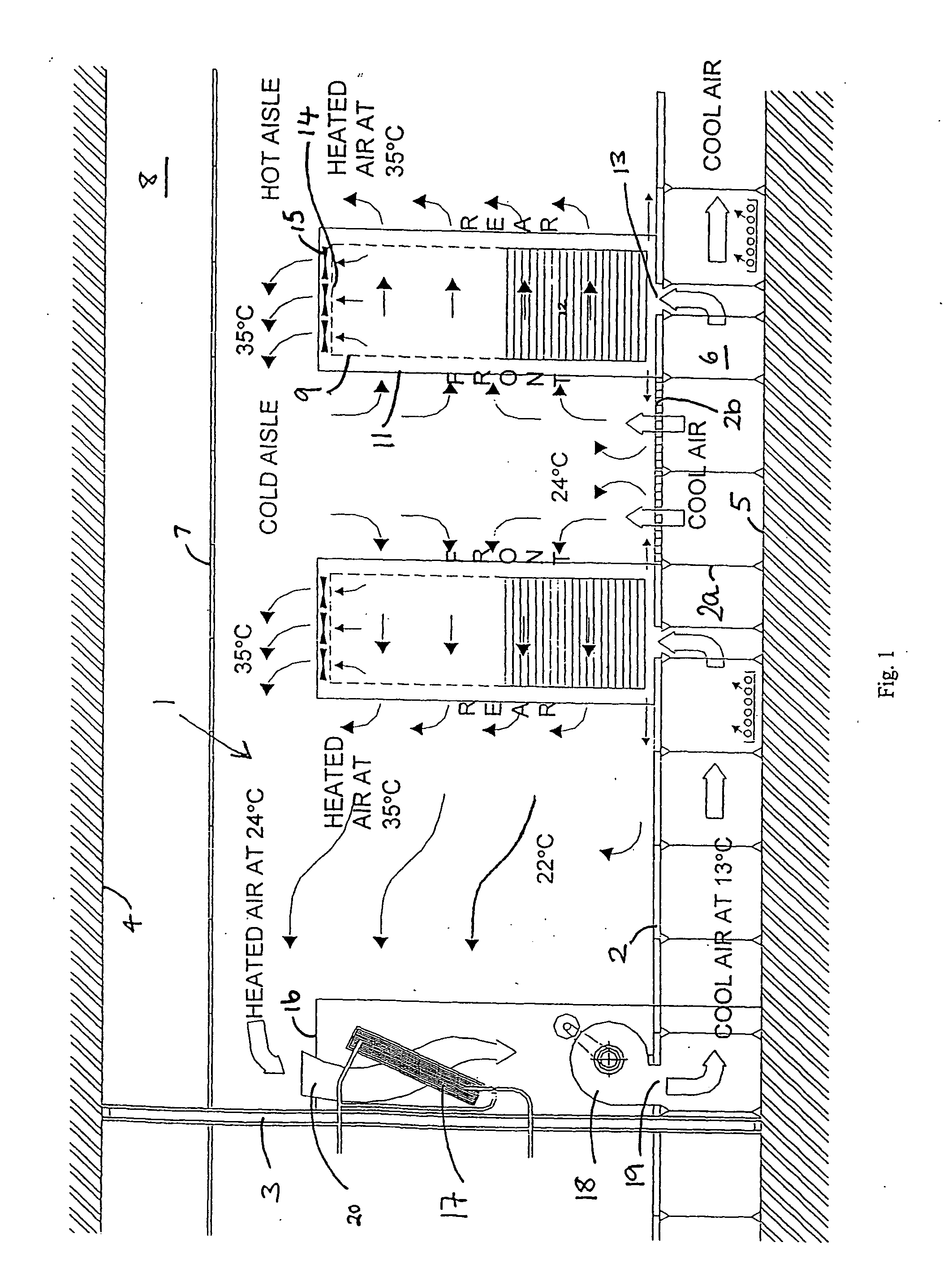

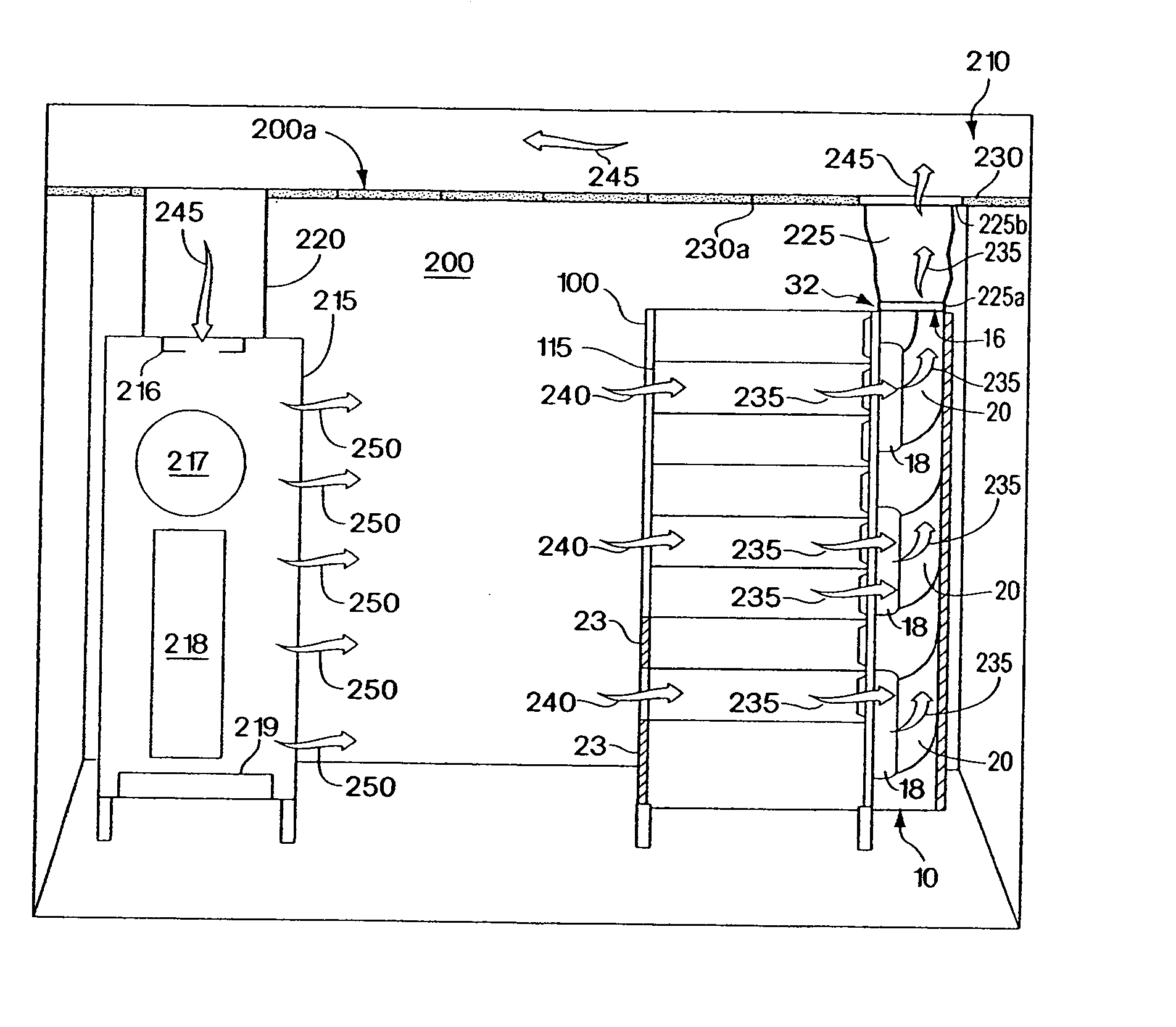

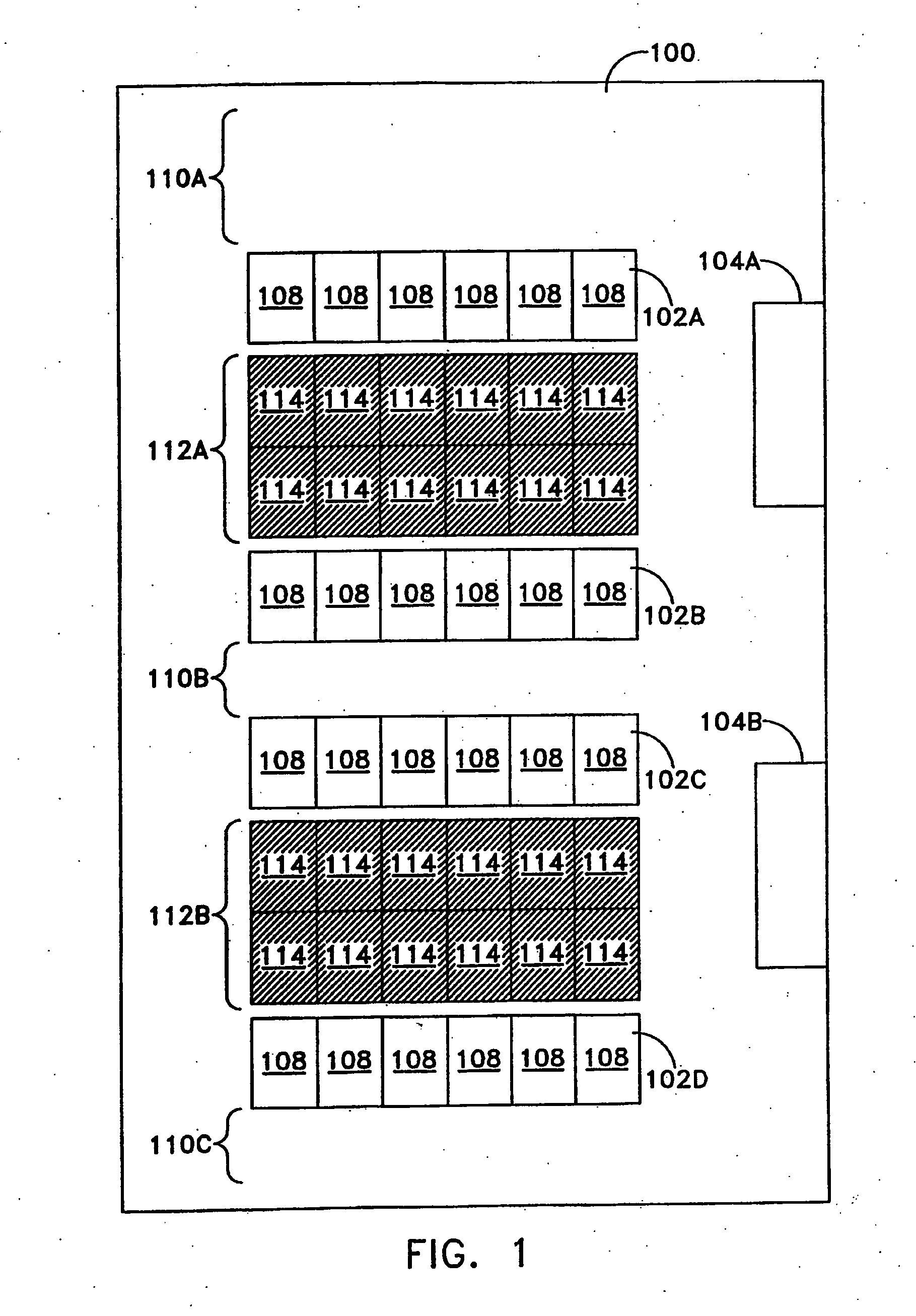

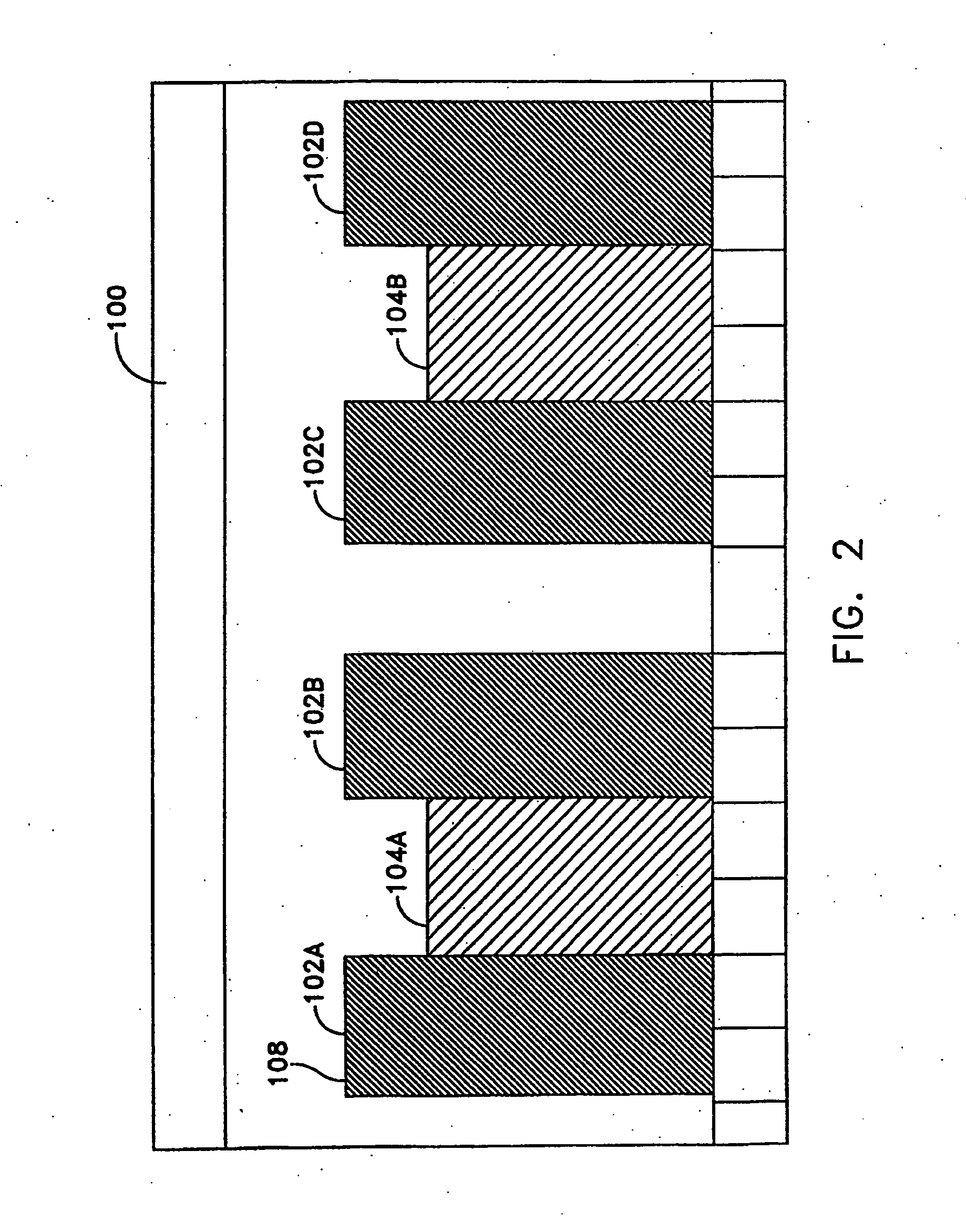

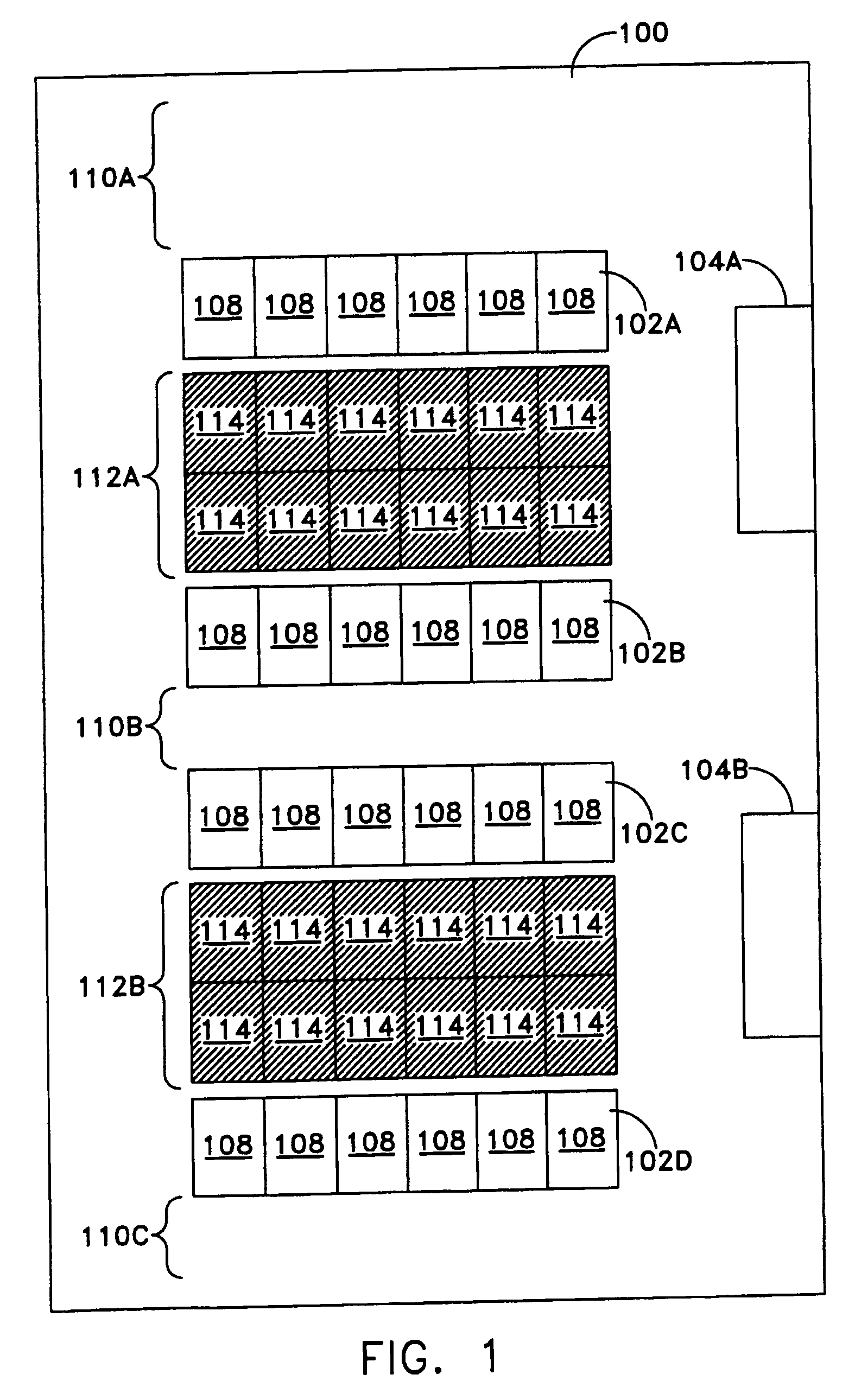

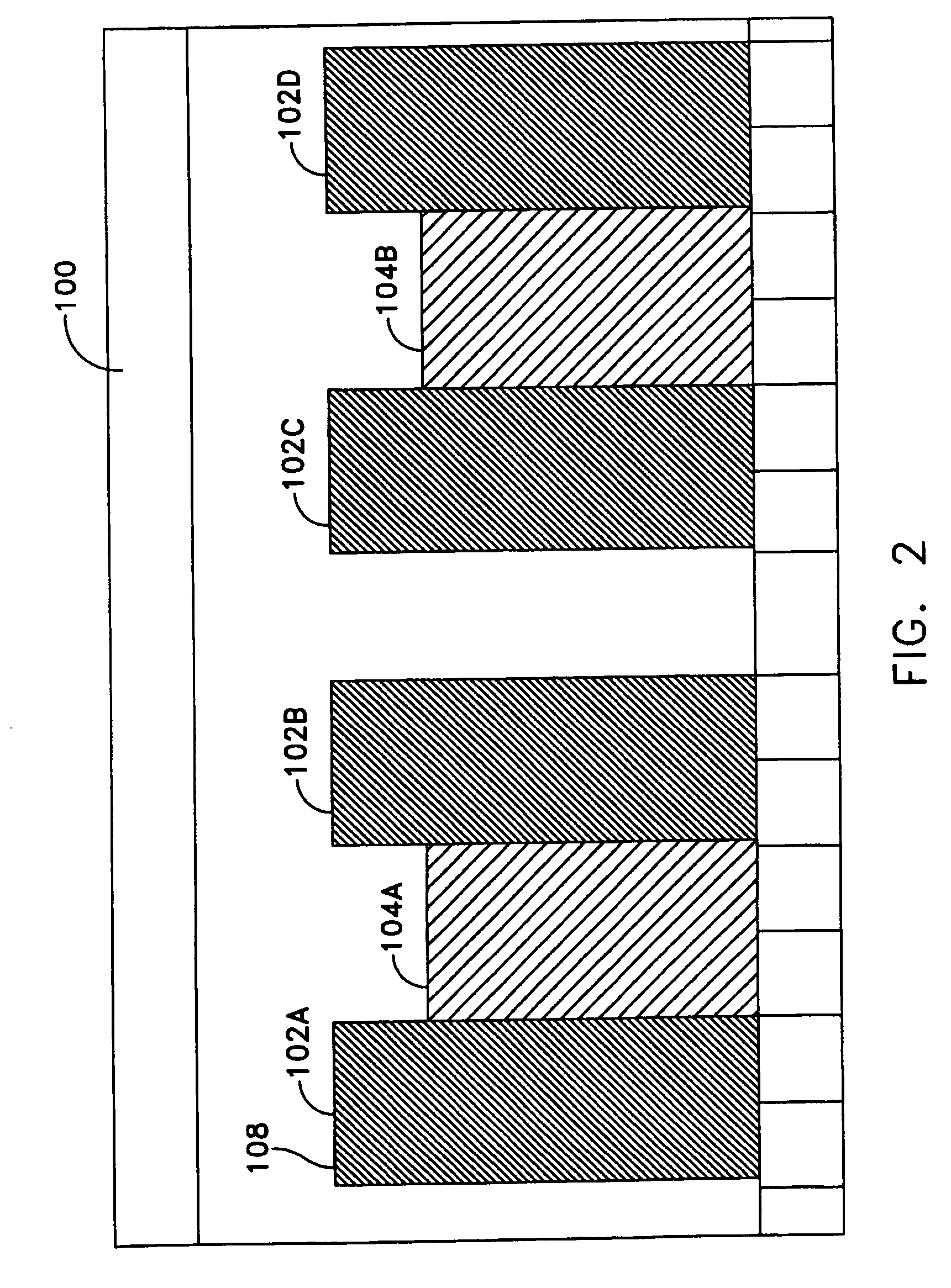

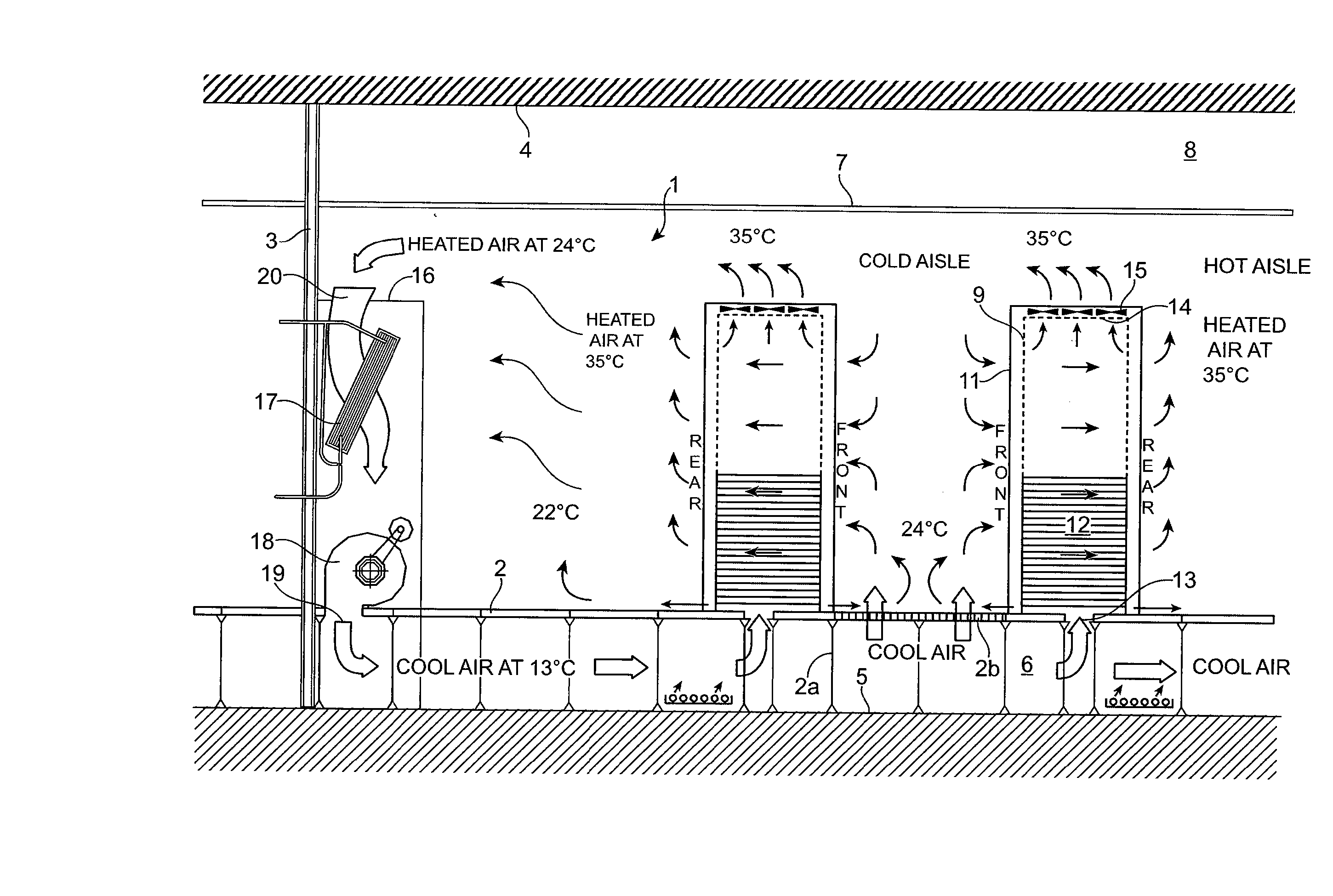

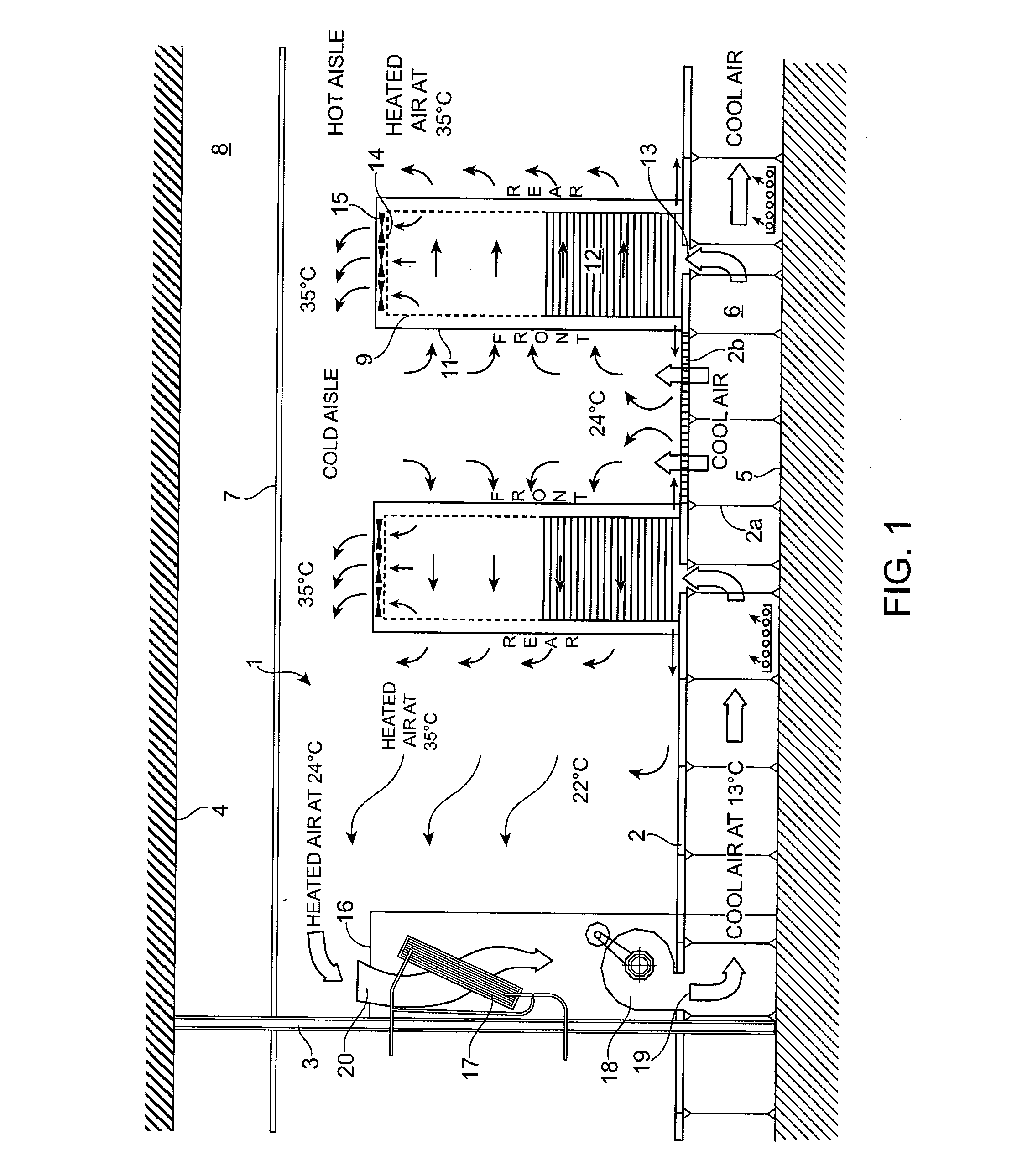

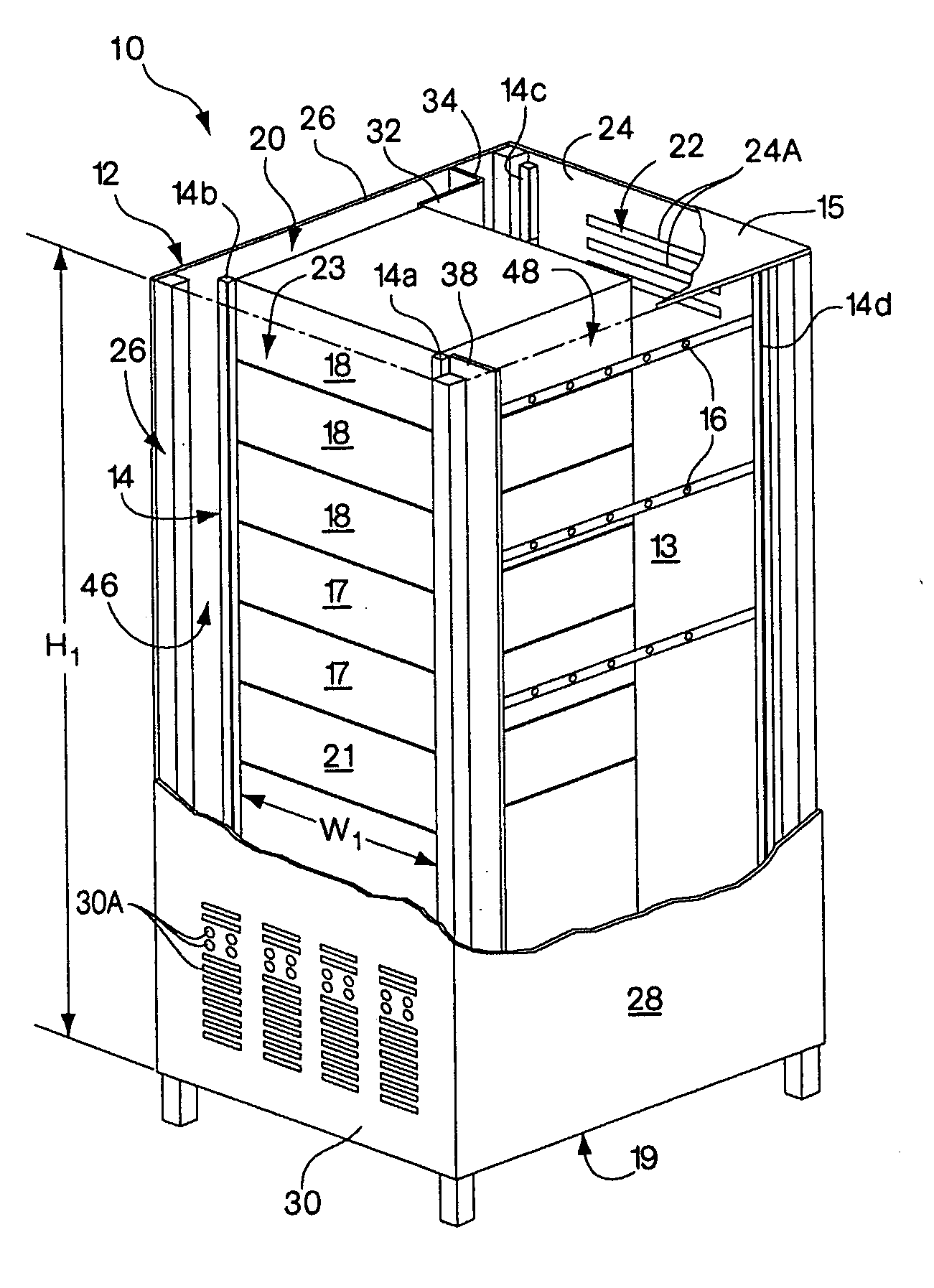

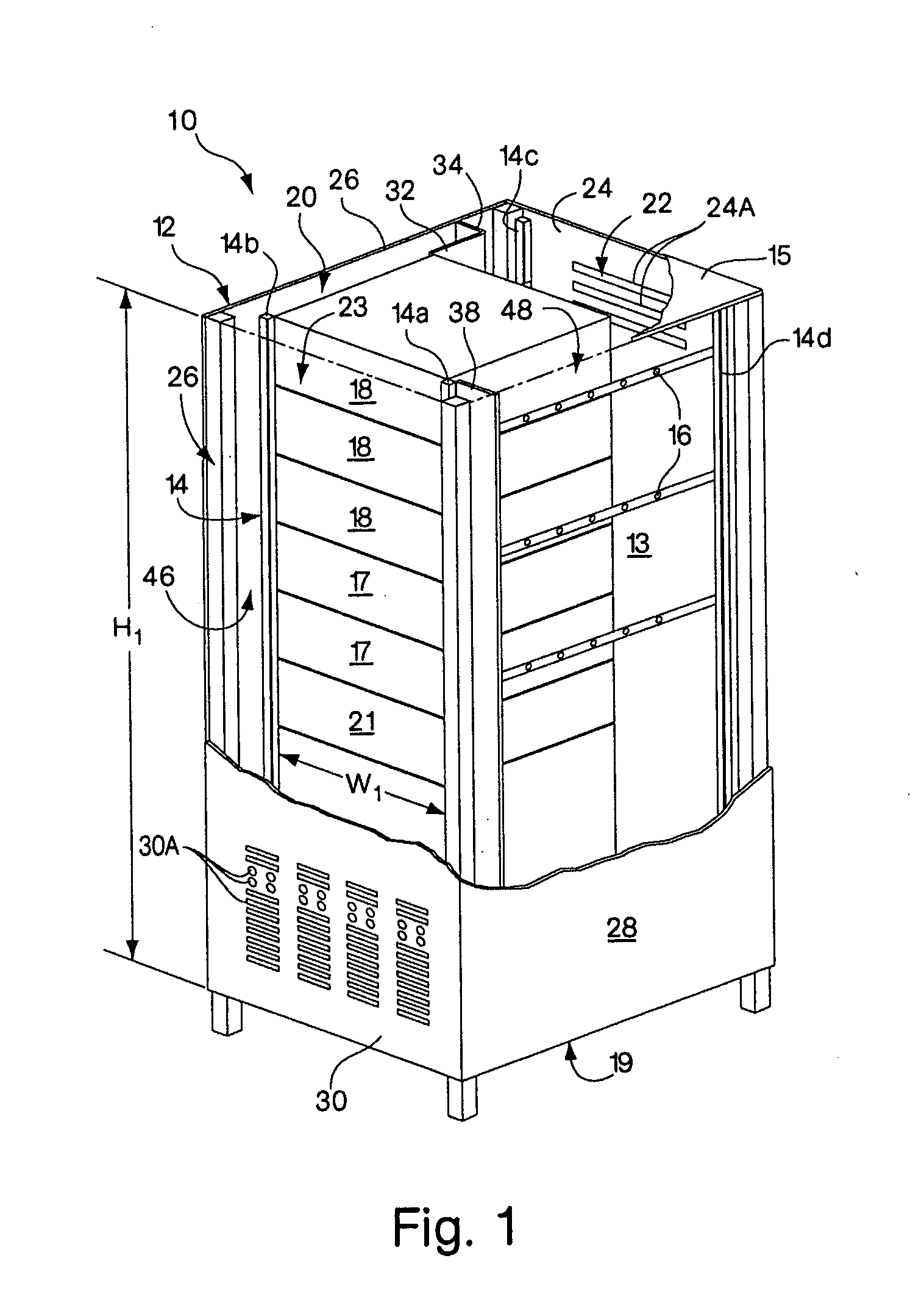

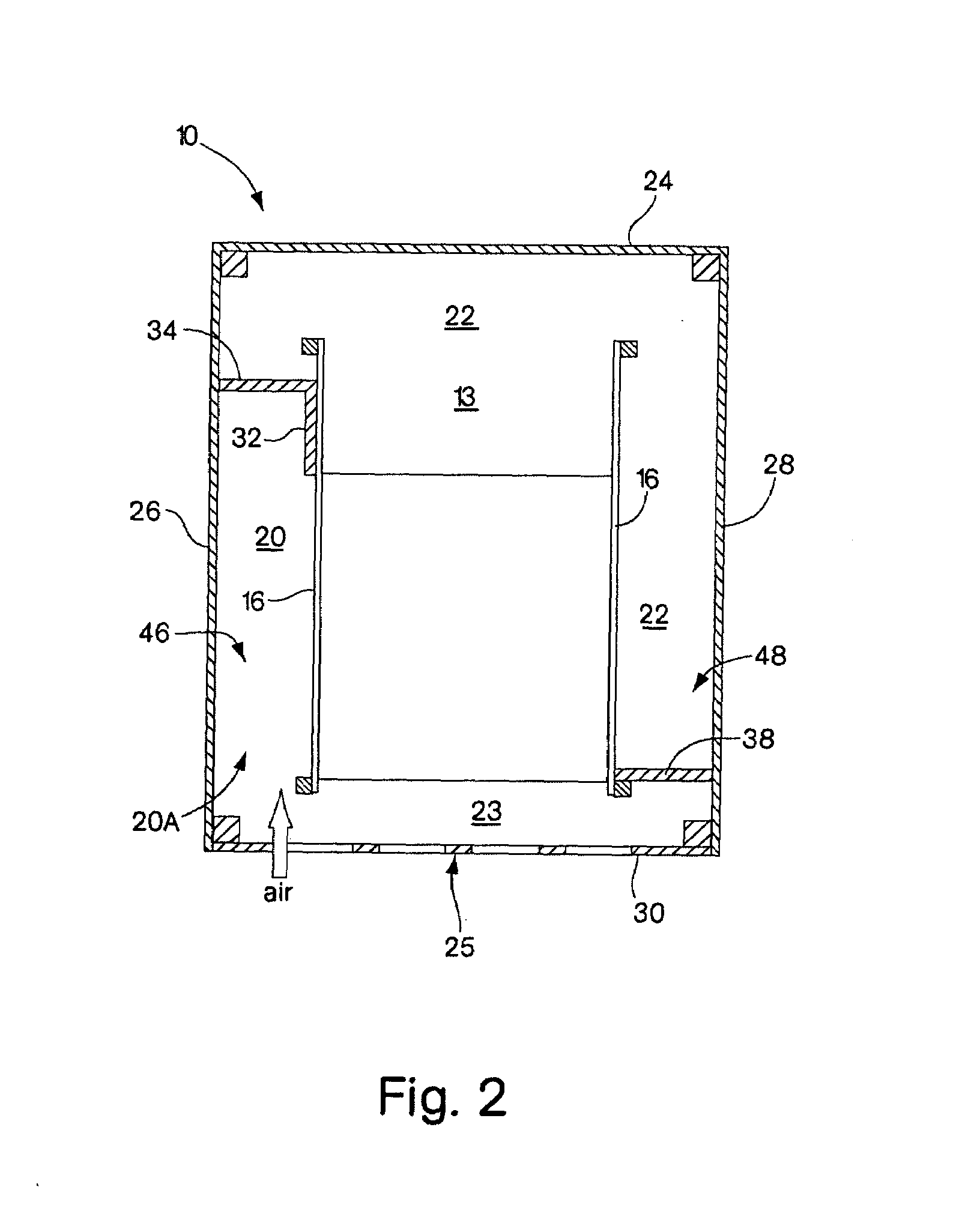

Cooling of a data centre

InactiveUS20050225936A1Improve availabilityHigh fault toleranceLighting and heating apparatusDigital data processing detailsData centerVertical array

Owner:SCHNEIDER ELECTRIC IT CORP

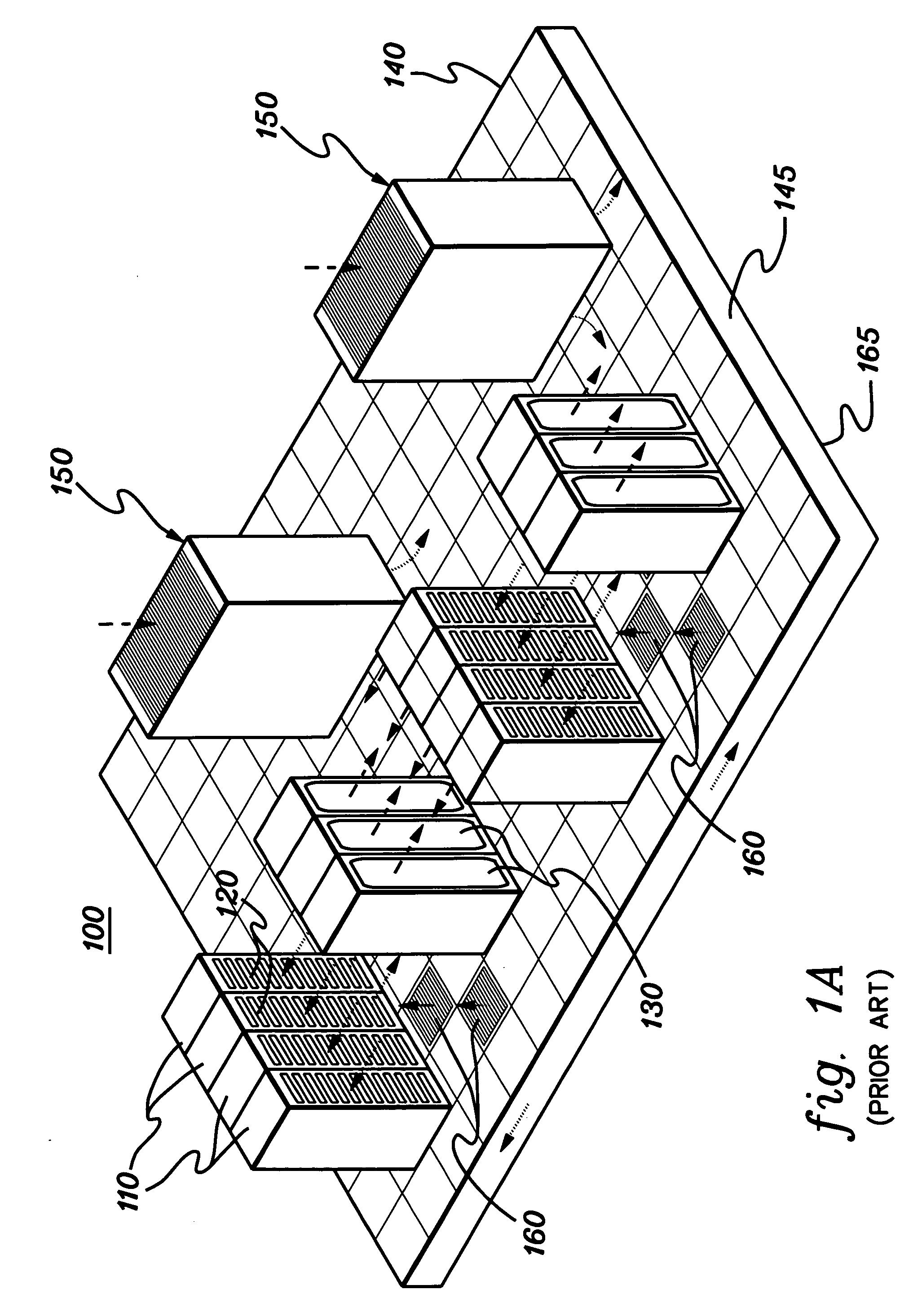

Data center cooling system

InactiveUS6859366B2Reduce mixProduce cool airSemiconductor/solid-state device detailsSolid-state devicesData centerEngineering

A cooling solution is provided for a modular data center. The modular data center includes a plurality of racks, each of the racks having a front face and a back face, wherein the plurality of racks is arranged in a first row and a second row, such that the back faces of racks of the first row are facing the second row, and the back faces of the racks of the second row are facing the first row, a first end panel coupled between a first rack of the first row and a first rack of the second row, the first end panel having a bottom edge and a tope edge, a second end panel coupled between a second rack of the first row and a second rack of the second row, the second end panel having a top edge and a bottom edge, and a roof panel coupled between the top edge of the first panel and the top edge of the second panel. Cooling equipment within at least one of the equipment racks draws hot air from between the rows of racks and delivers cooled air out of the front face of one of the racks.

Owner:SCHNEIDER ELECTRIC IT CORP

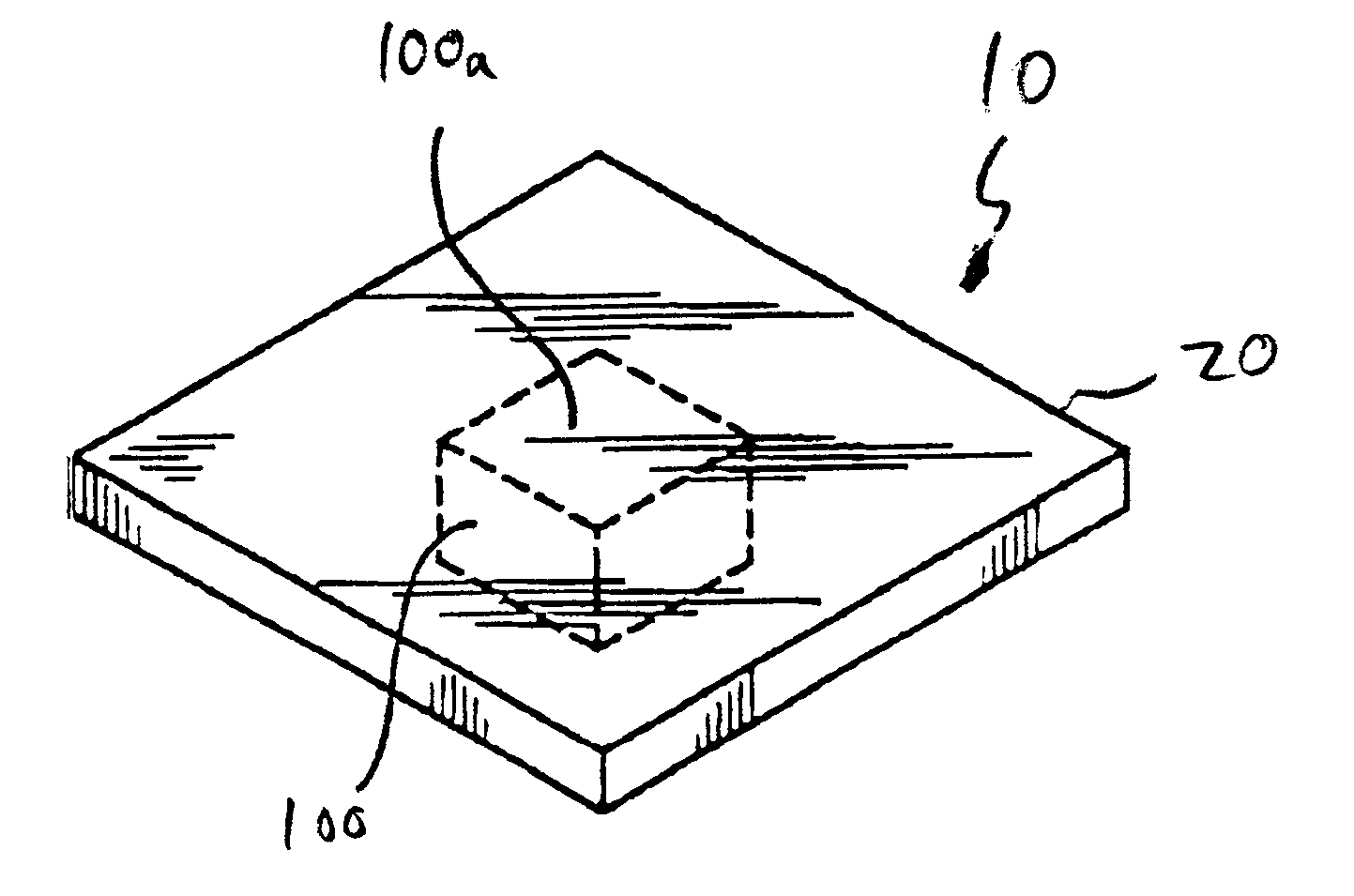

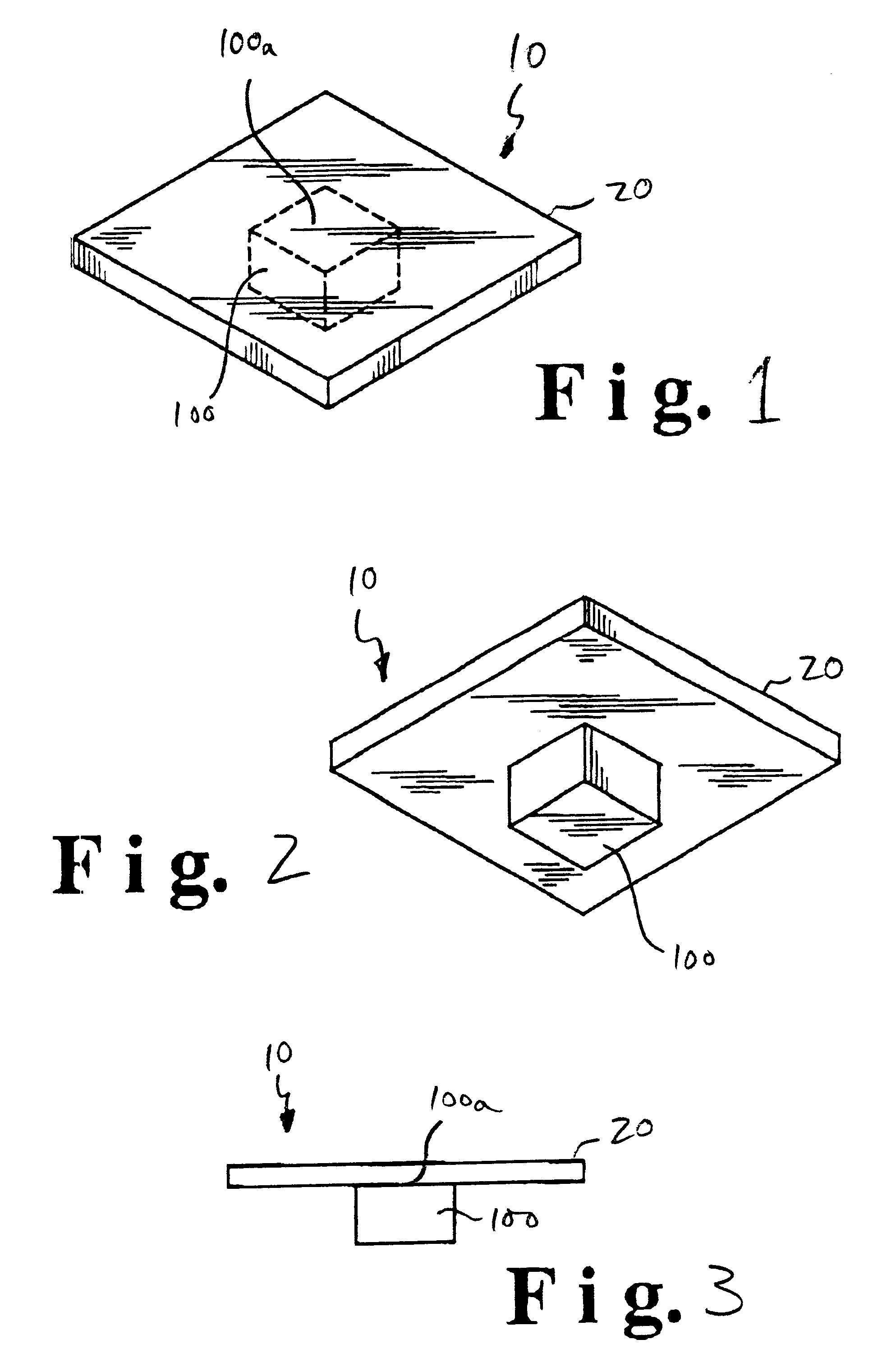

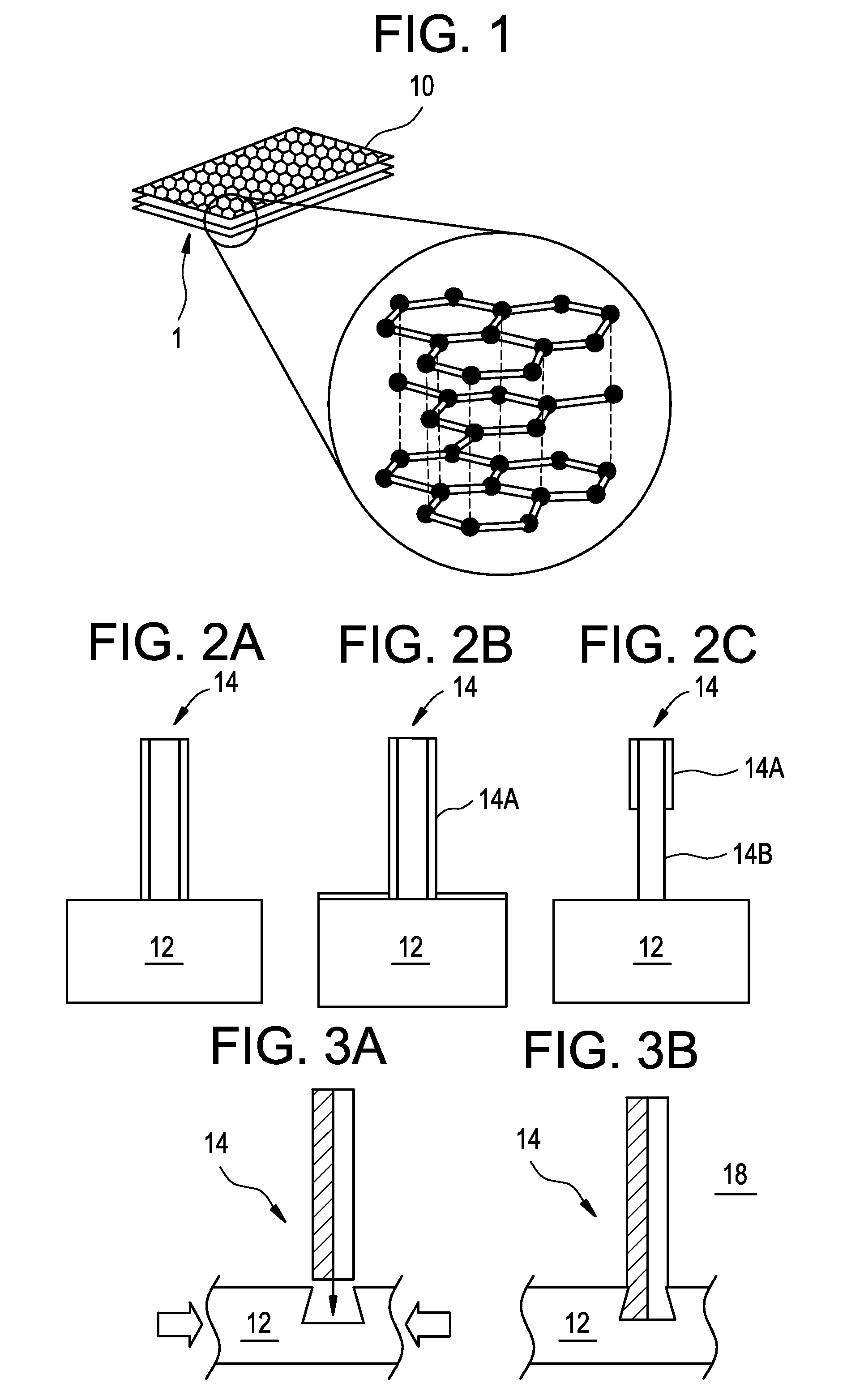

Thermal management system

InactiveUS6482520B1Improve cooling effectIncreased anisotropyLayered productsSemiconductor/solid-state device detailsEngineeringThermal management system

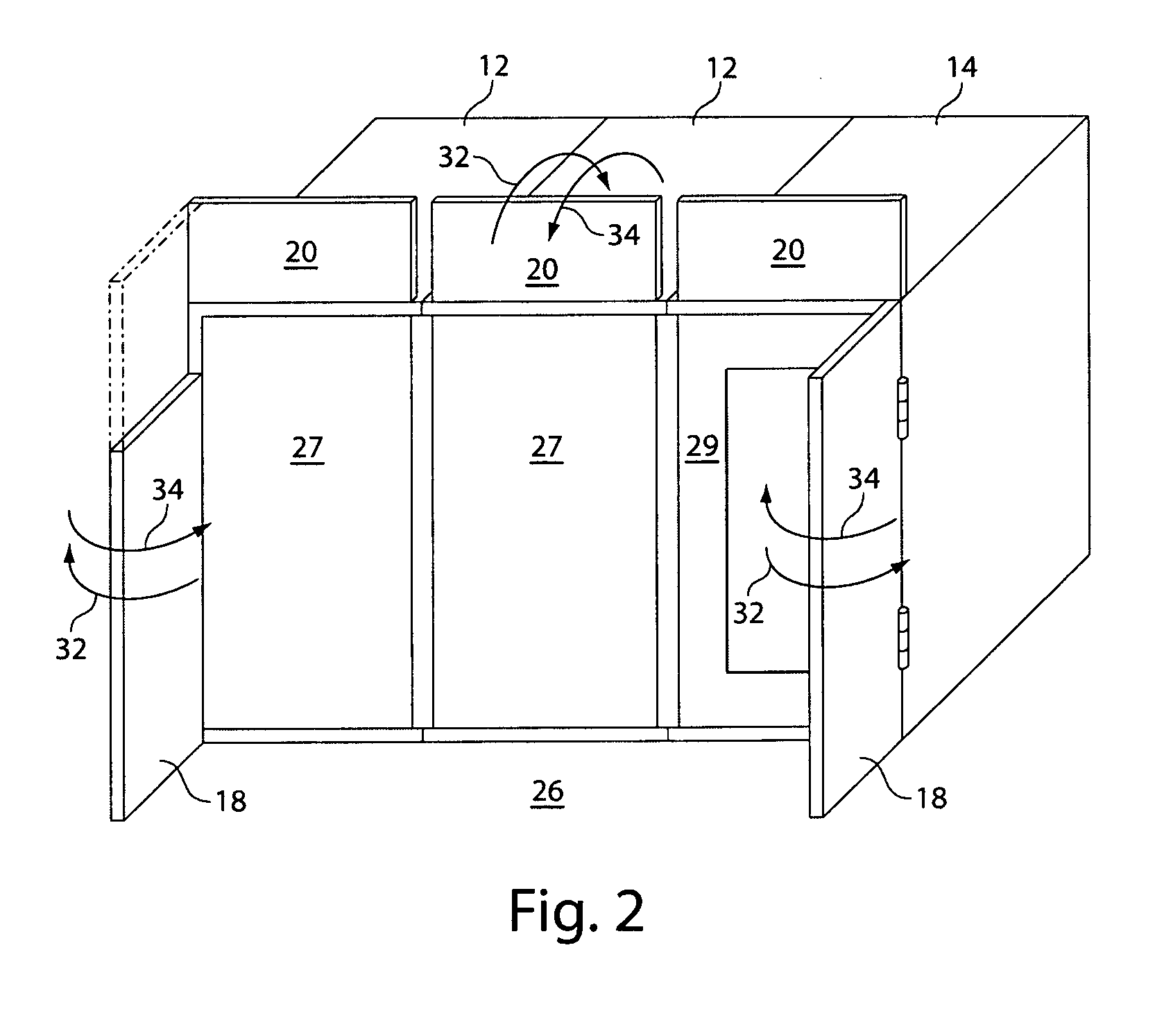

The present invention relates to a system for managing the heat from a heat source like an electronic component. More particularly, the present invention relates to a system effective for dissipating the heat generated by an electronic component using a thermal management system that includes a thermal interface formed from a flexible graphite sheet and / or a heat sink formed from a graphite article.

Owner:NEOGRAF SOLUTIONS LLC

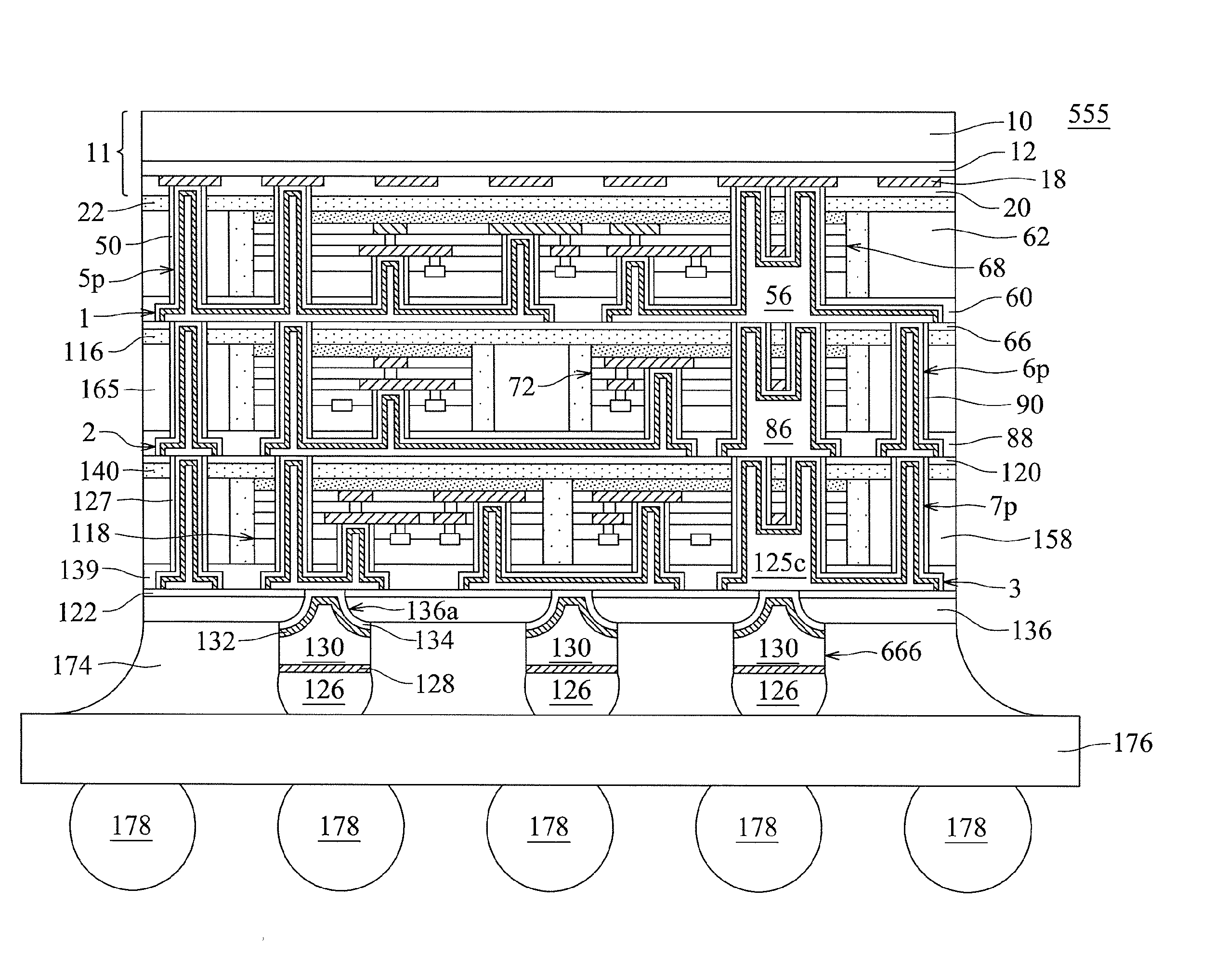

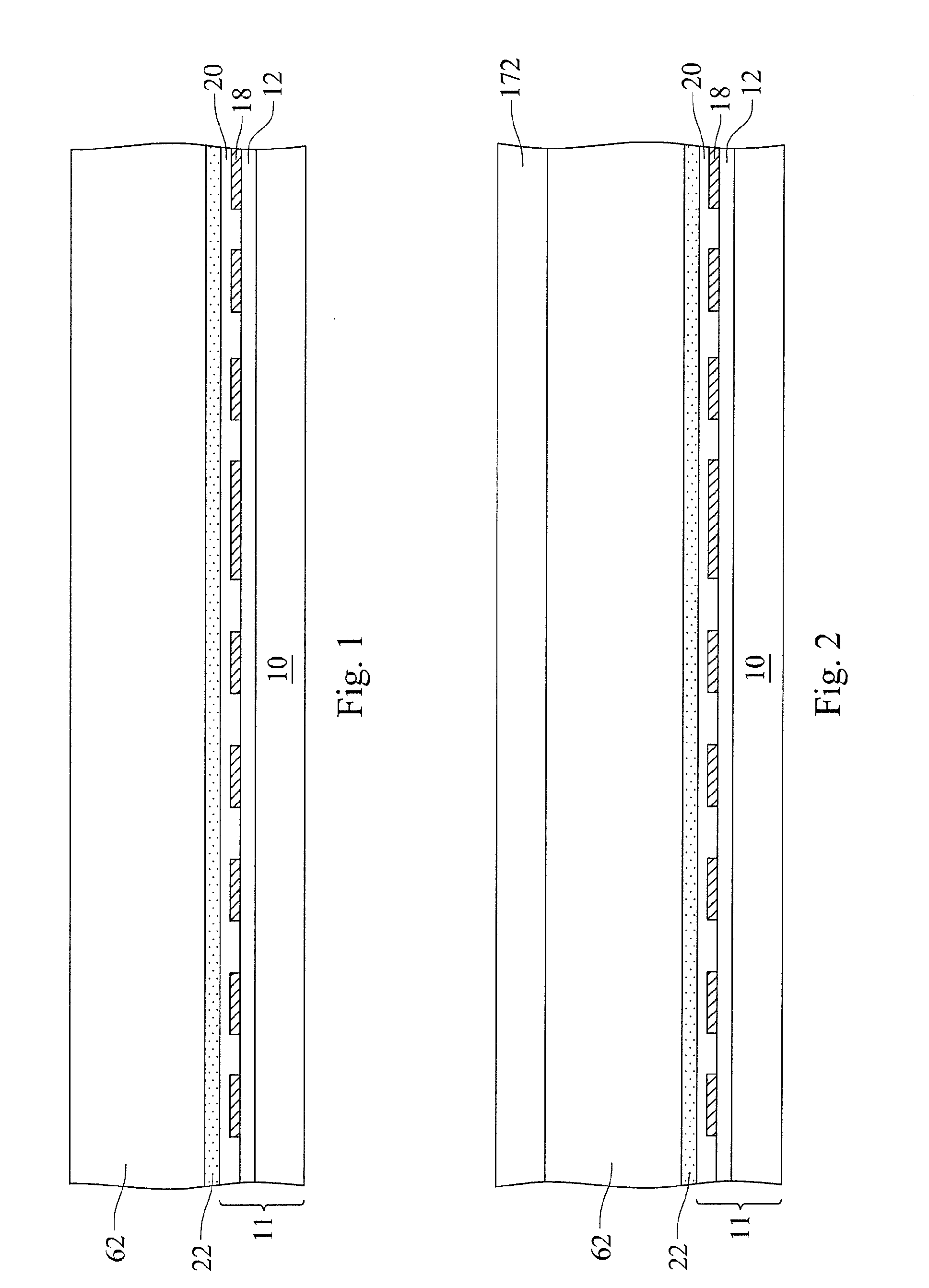

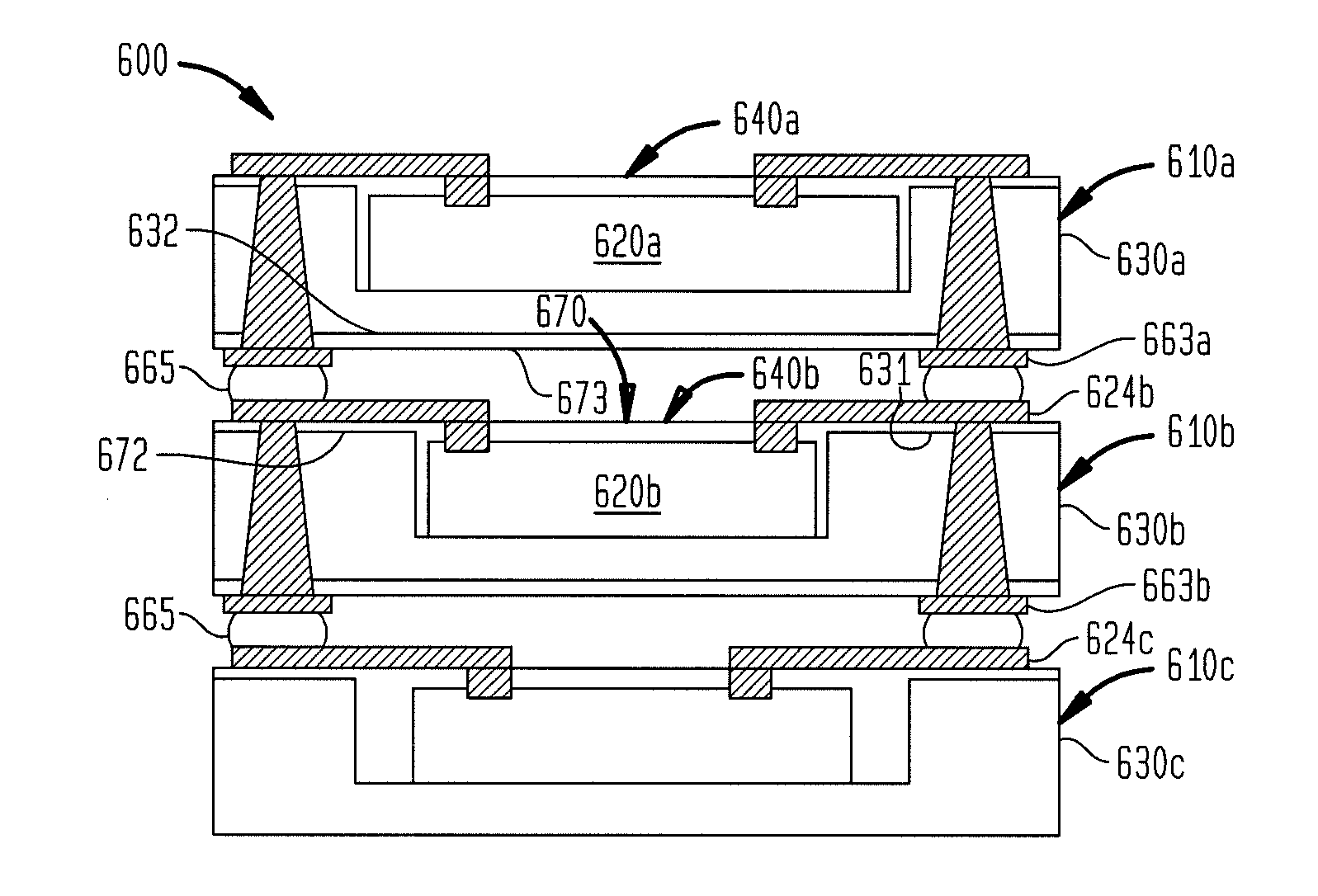

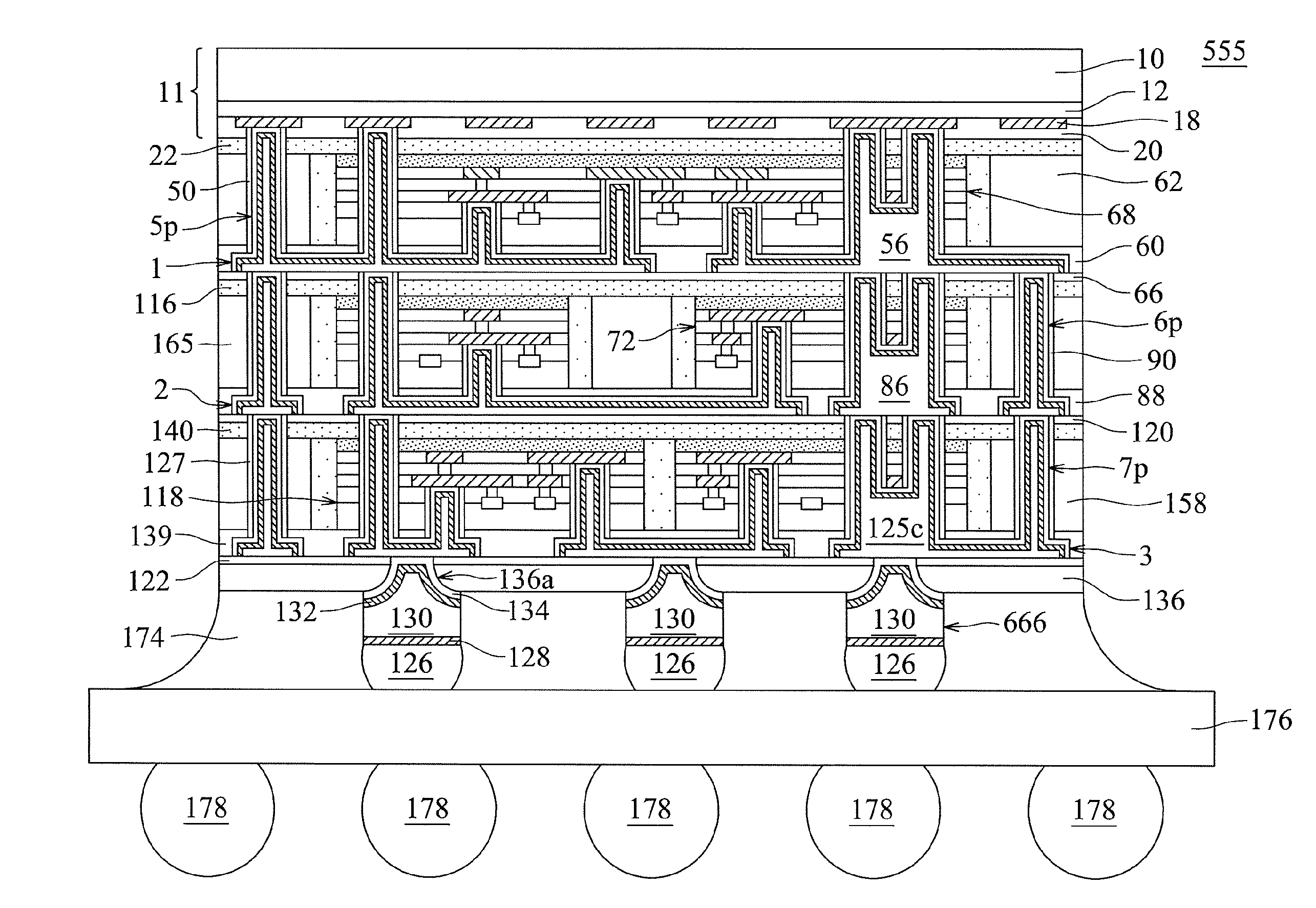

System-in packages

ActiveUS20110026232A1Improve uniformitySemiconductor/solid-state device detailsCircuit arrangements on support structuresMetal interconnectSystem in package

System-in packages, or multichip modules, are described which can include multi-layer chips and multi-layer dummy substrates over a carrier, multiple through vias blindly or completely through the multi-layer chips and completely through the multi-layer dummy substrates, multiple metal plugs in the through vias, and multiple metal interconnects, connected to the metal plugs, between the multi-layer chips. The multi-layer chips can be connected to each other or to an external circuit or structure, such as mother board, ball grid array (BGA) substrate, printed circuit board, metal substrate, glass substrate, or ceramic substrate, through the metal plugs and the metal interconnects.

Owner:QUALCOMM INC

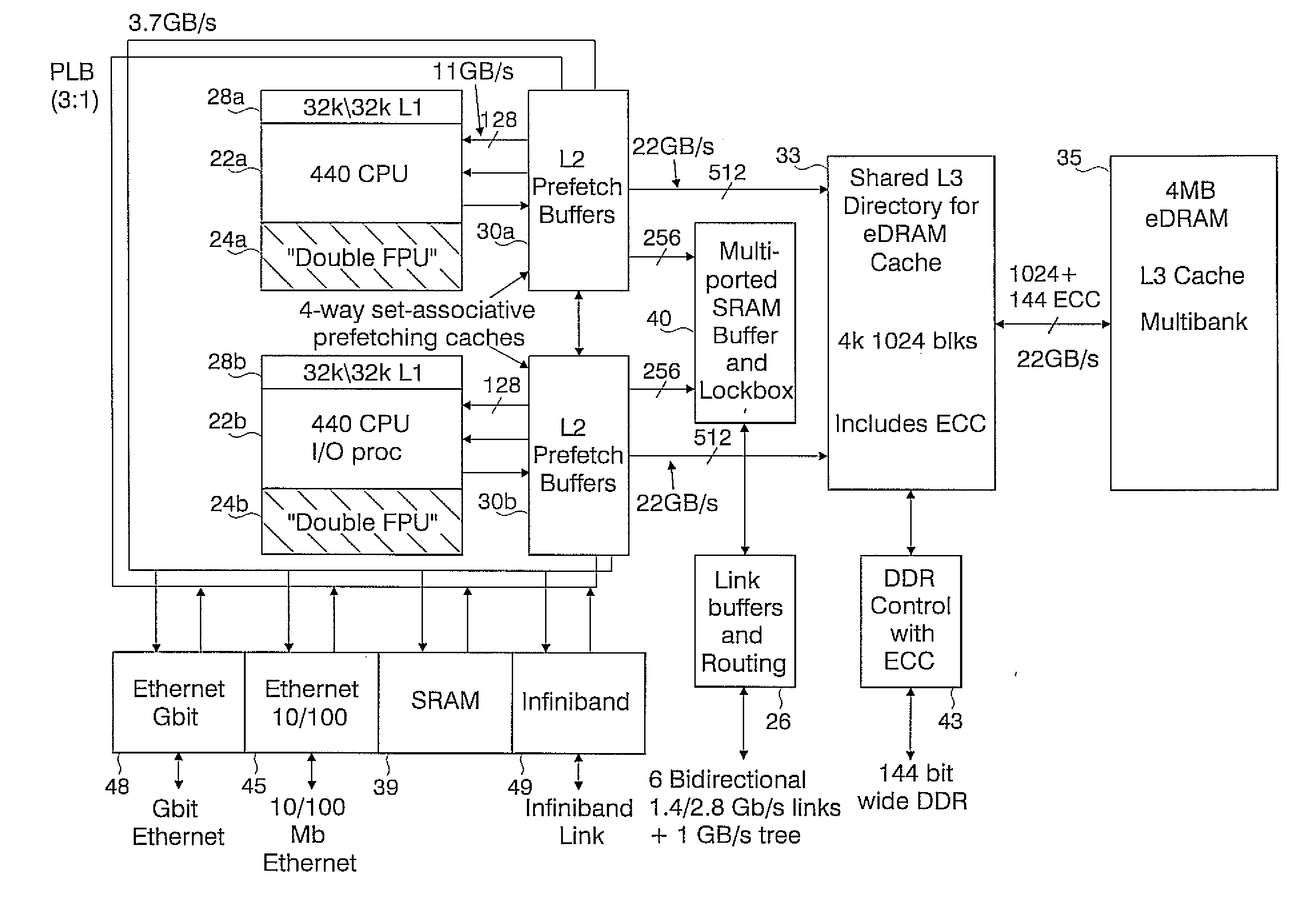

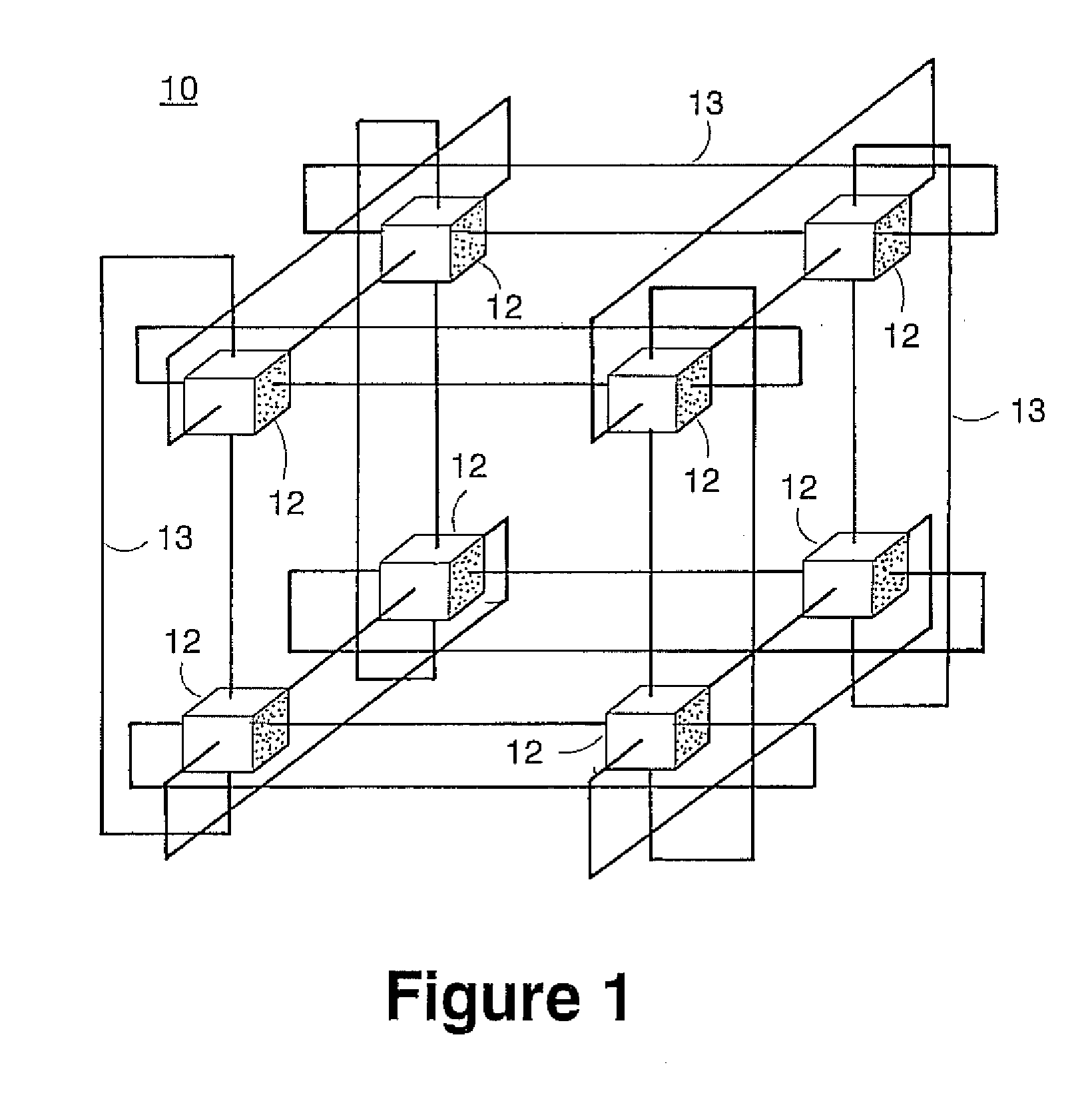

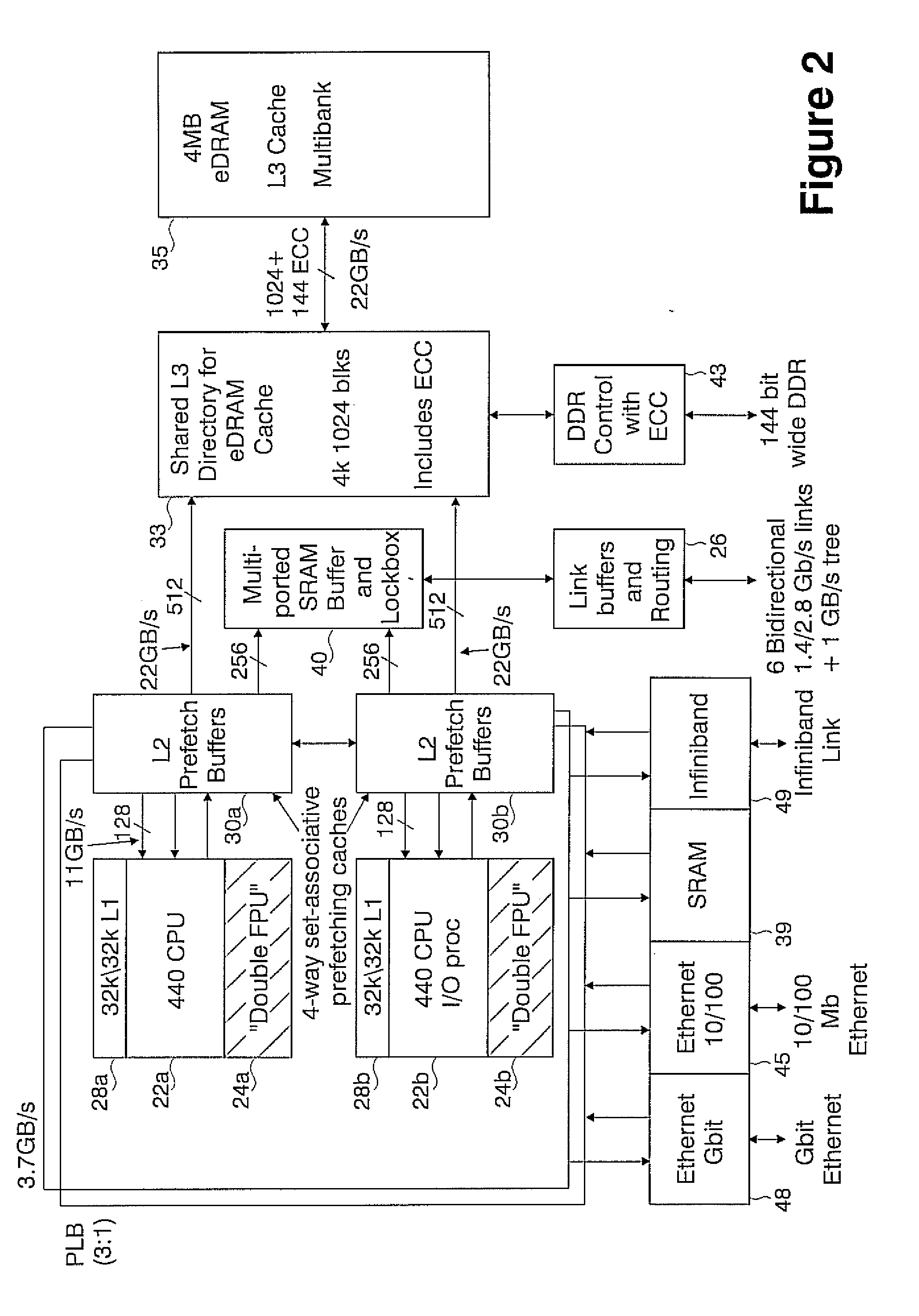

Novel massively parallel supercomputer

InactiveUS20090259713A1Low costReduced footprintError preventionProgram synchronisationSupercomputerPacket communication

Owner:INT BUSINESS MASCH CORP

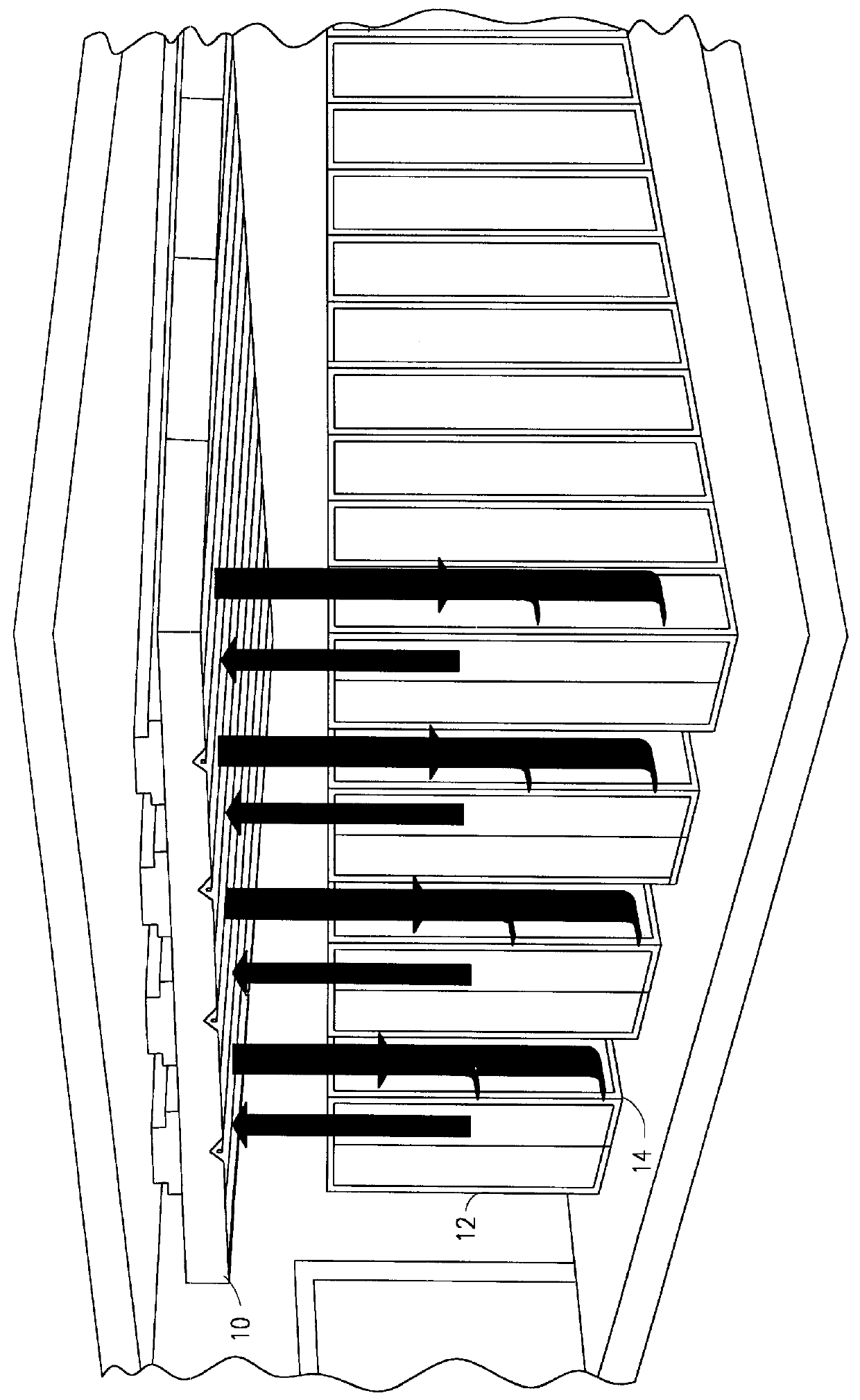

Exhaust air removal system

InactiveUS20050170770A1Mixing with airMeet the requirementsIndirect heat exchangersCooling/ventilation/heating modificationsExhaust fumesBack door

An exhaust air removal system and method for use with a rack or enclosure containing equipment is provided. The system and method are configured for removal of exhaust air vented from equipment during operation to thereby remove heat from the equipment. In one aspect, the system includes a fan unit preferably configured to serve as a back door of an equipment rack or enclosure and configured to provide access to an interior of the rack or enclosure. The fan unit provides multiple fans coupled to internal exhaust ducts that are arranged to draw and to remove exhaust air vented from rack-mounted equipment. The fan unit is further configured to vent exhaust air to an area external to a rack or enclosure, such as an external exhaust duct or plenum. Removal of hot and warm exhaust air vented from rack-mounted equipment enables the equipment to operate effectively, drawing sufficient amounts of cooling air to meet its cooling requirements. The fan unit is constructed for portability and for easy attachment to and removal from a rack or enclosure, providing flexibility in handling equipment exhaust needs.

Owner:SCHNEIDER ELECTRIC IT CORP

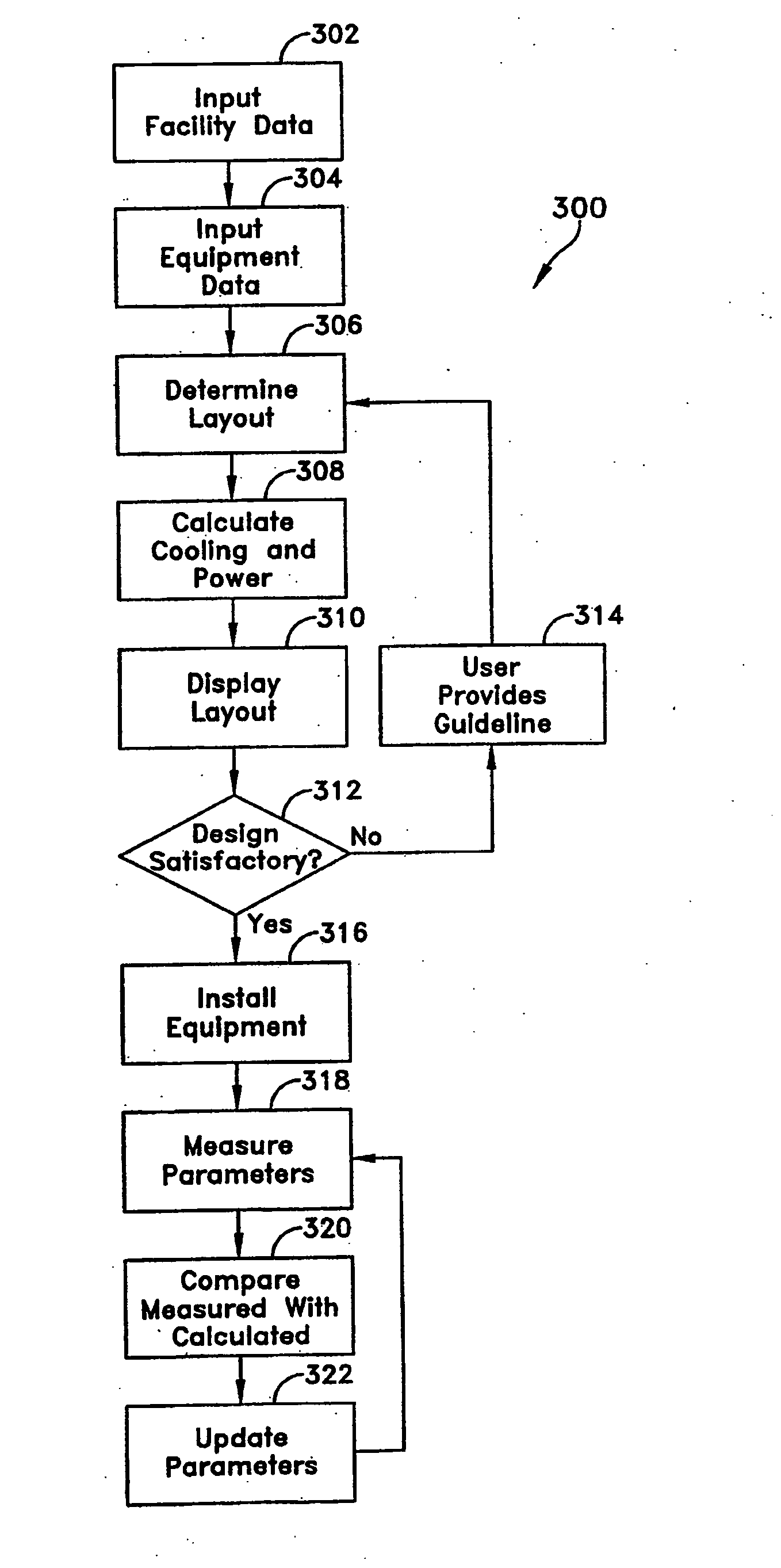

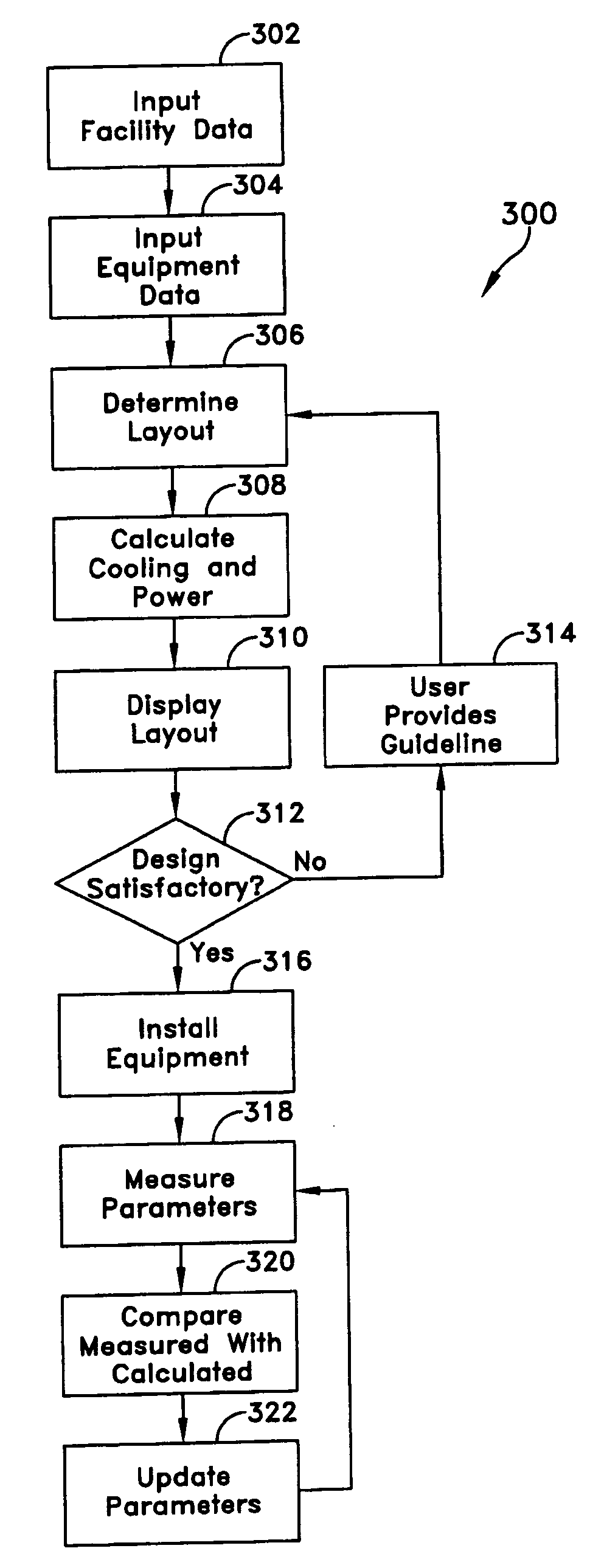

Methods and systems for managing facility power and cooling

Systems and methods are provided for determining data center cooling and power requirements and for monitoring performance of cooling and power systems in data centers. At least one aspect provides a system and method that enables a data center operator to determine available power and cooling at specific areas and enclosures in a data center to assist in locating new equipment in the data center.

Owner:SCHNEIDER ELECTRIC IT CORP

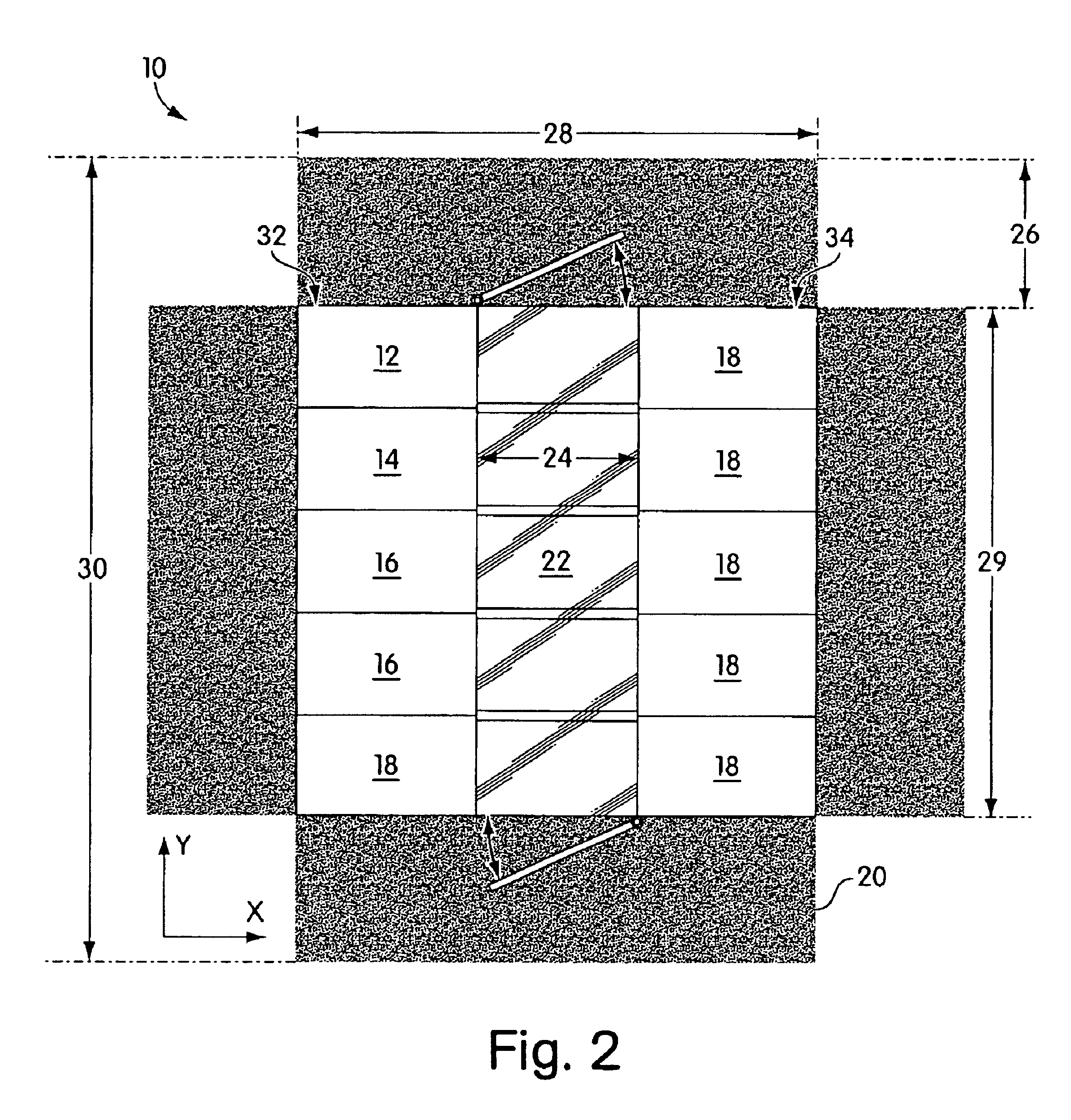

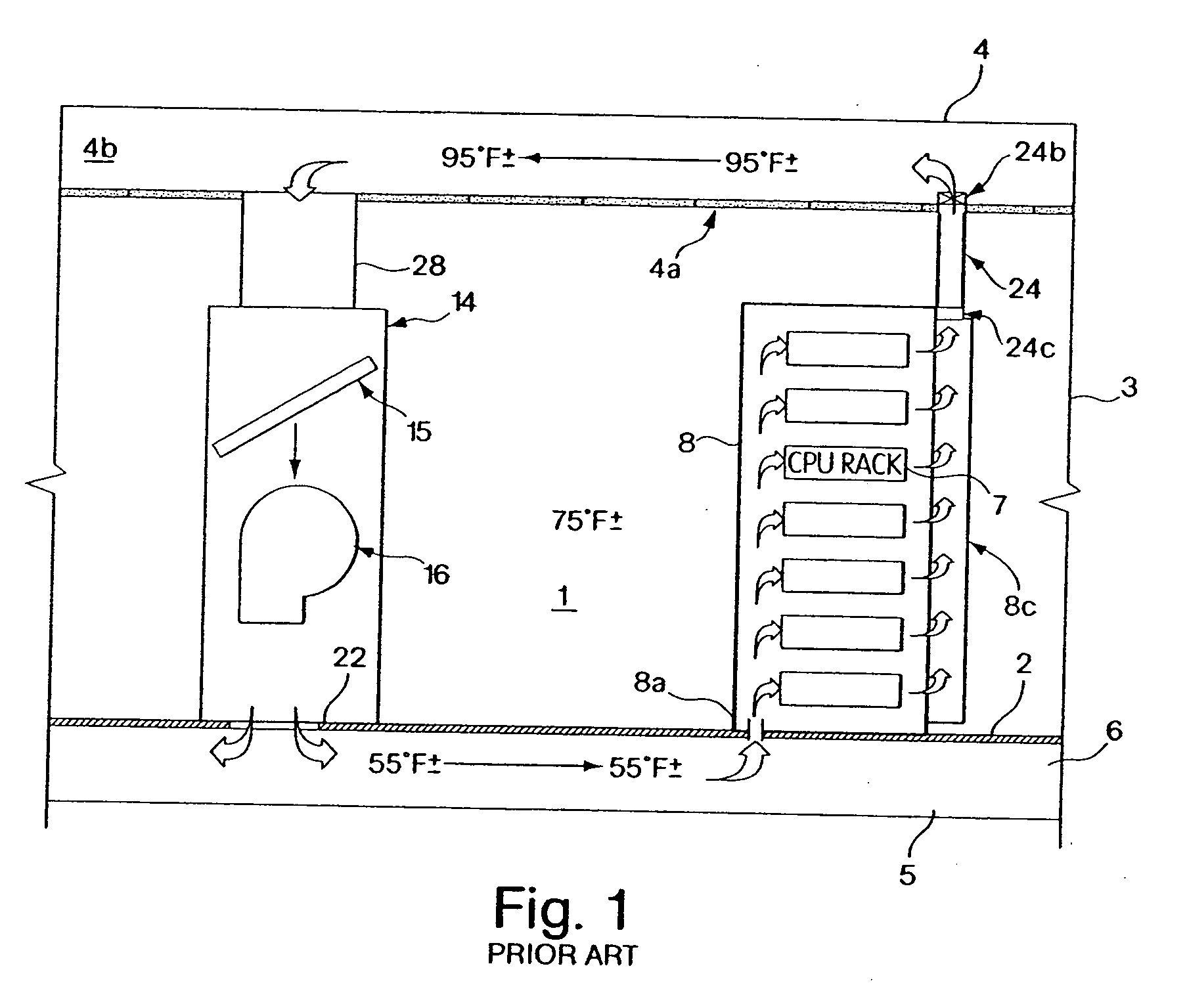

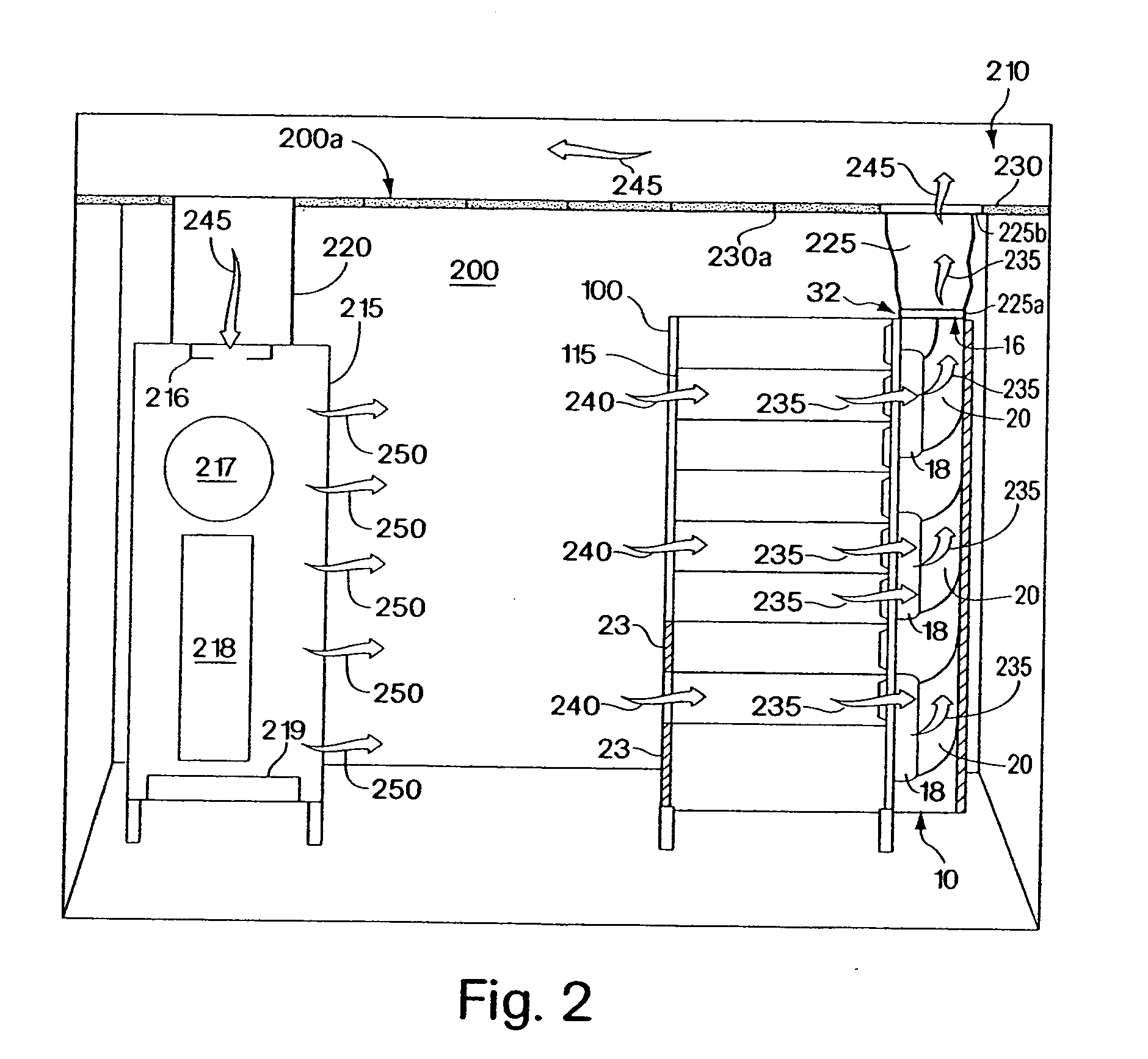

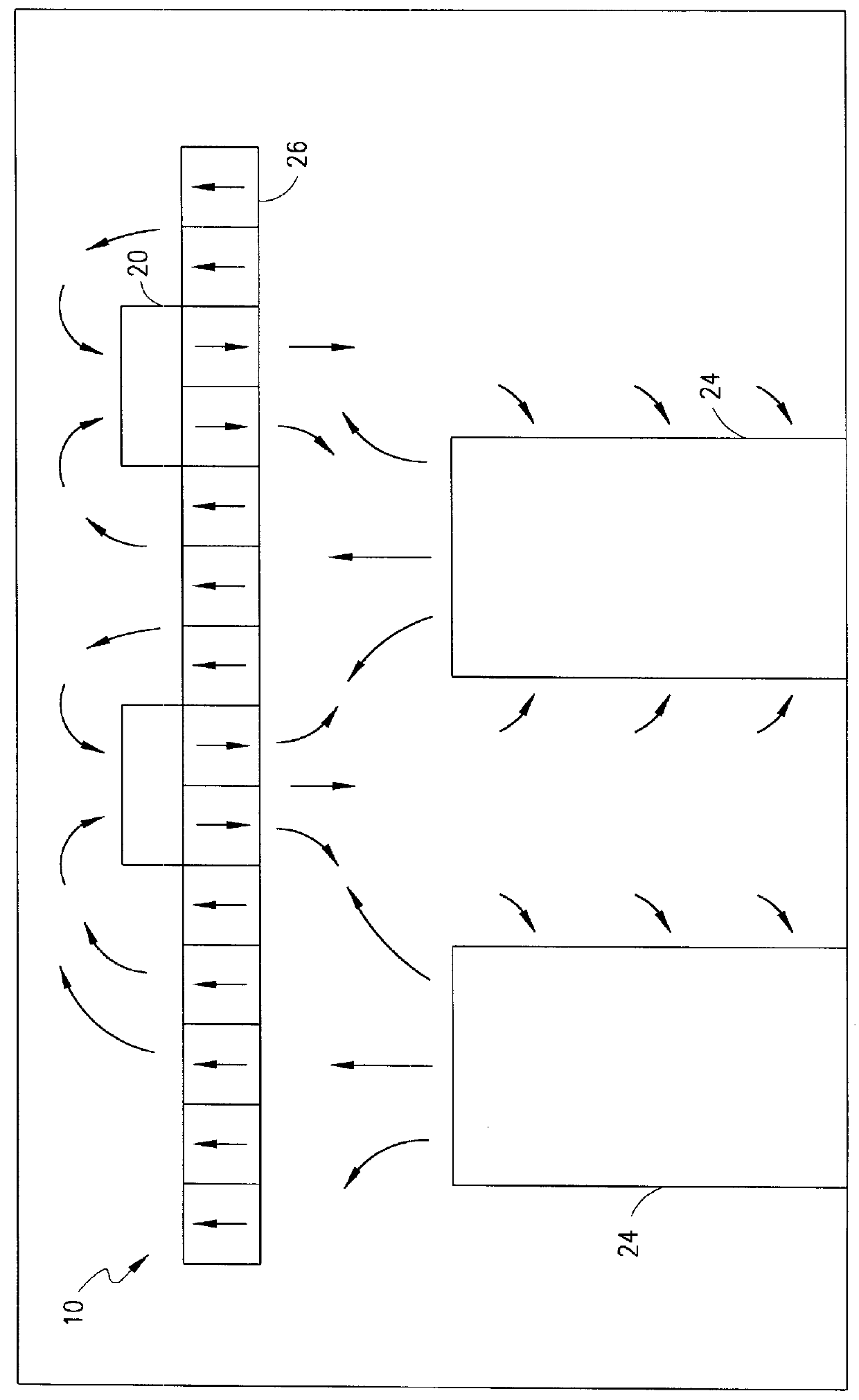

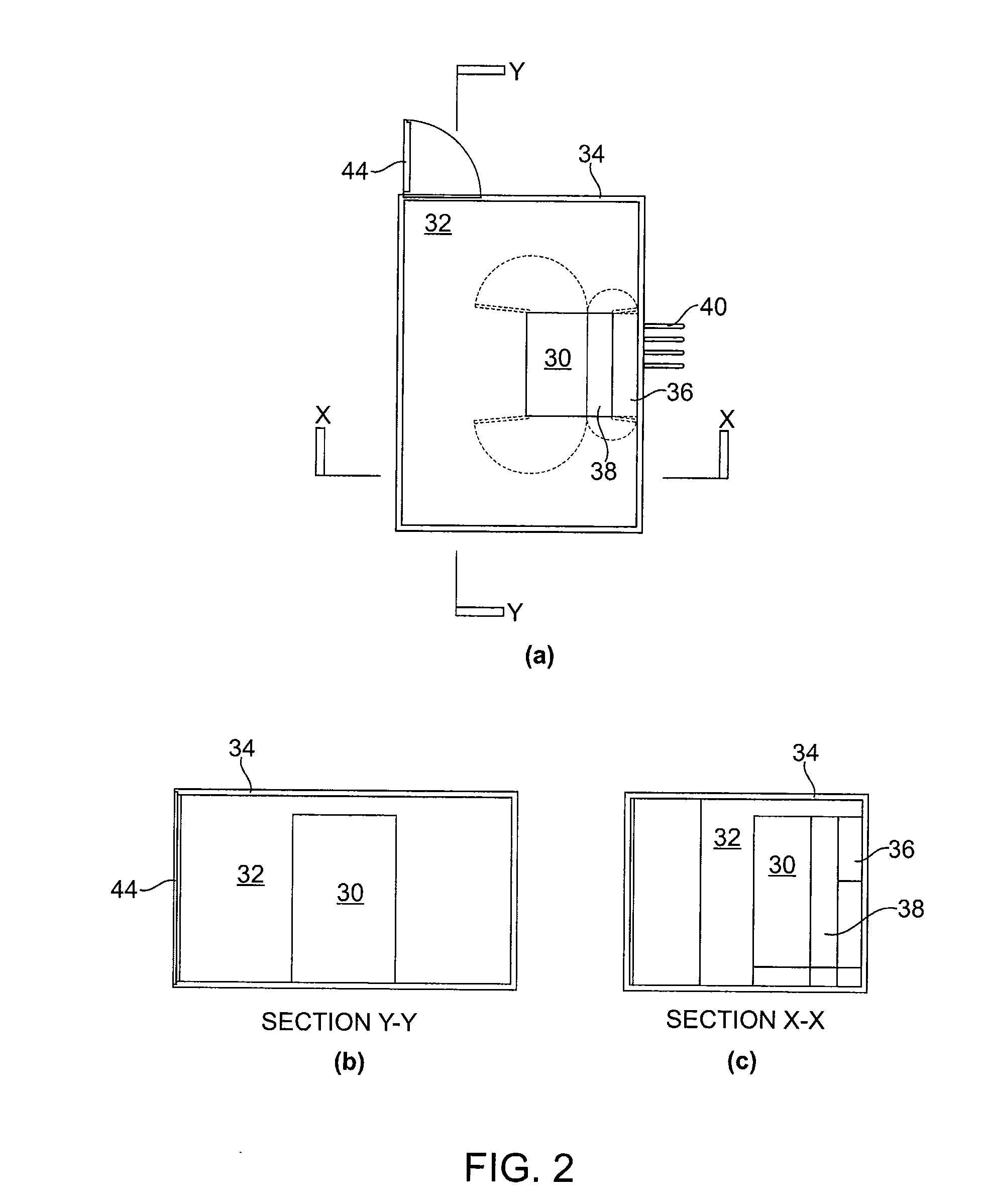

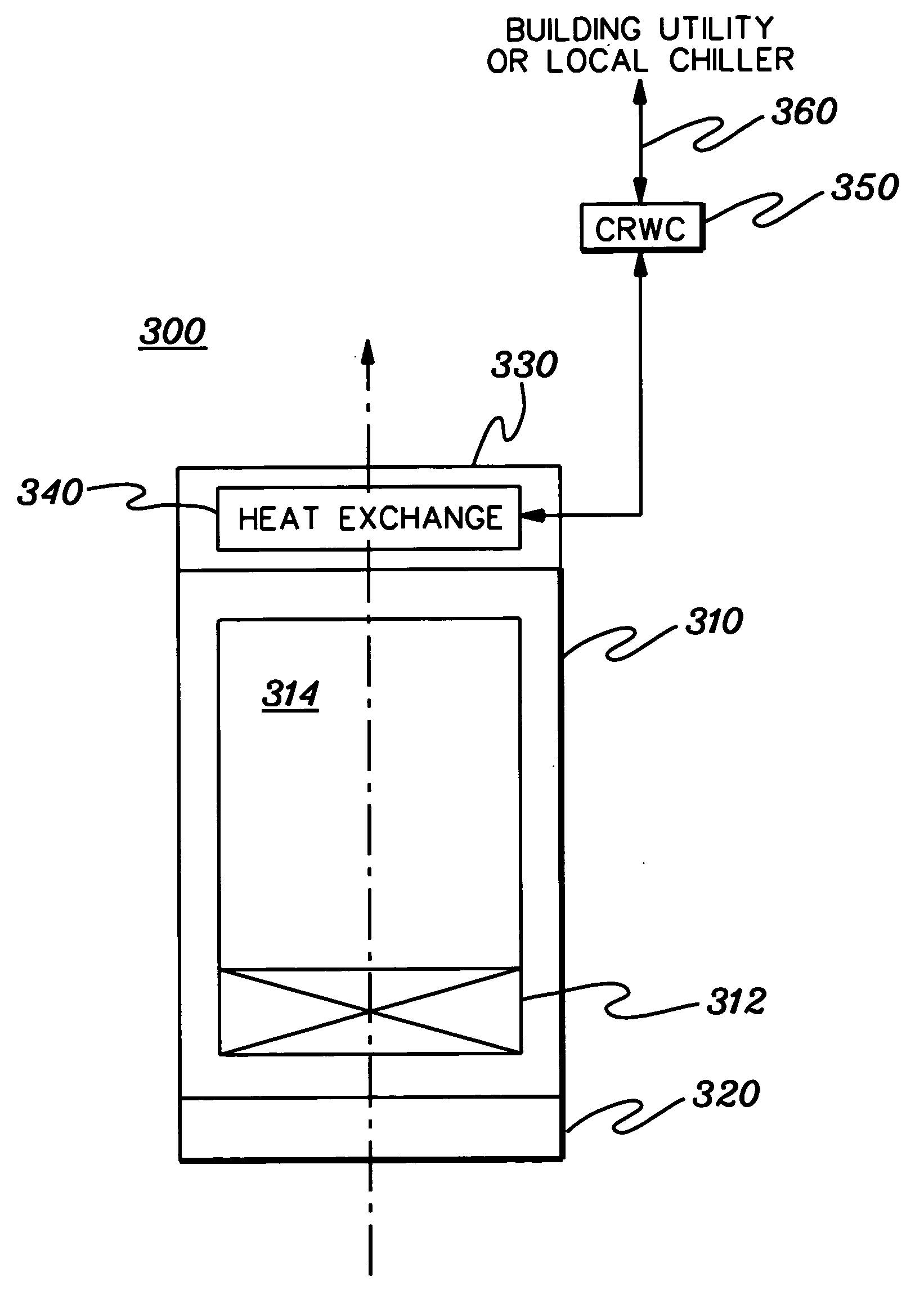

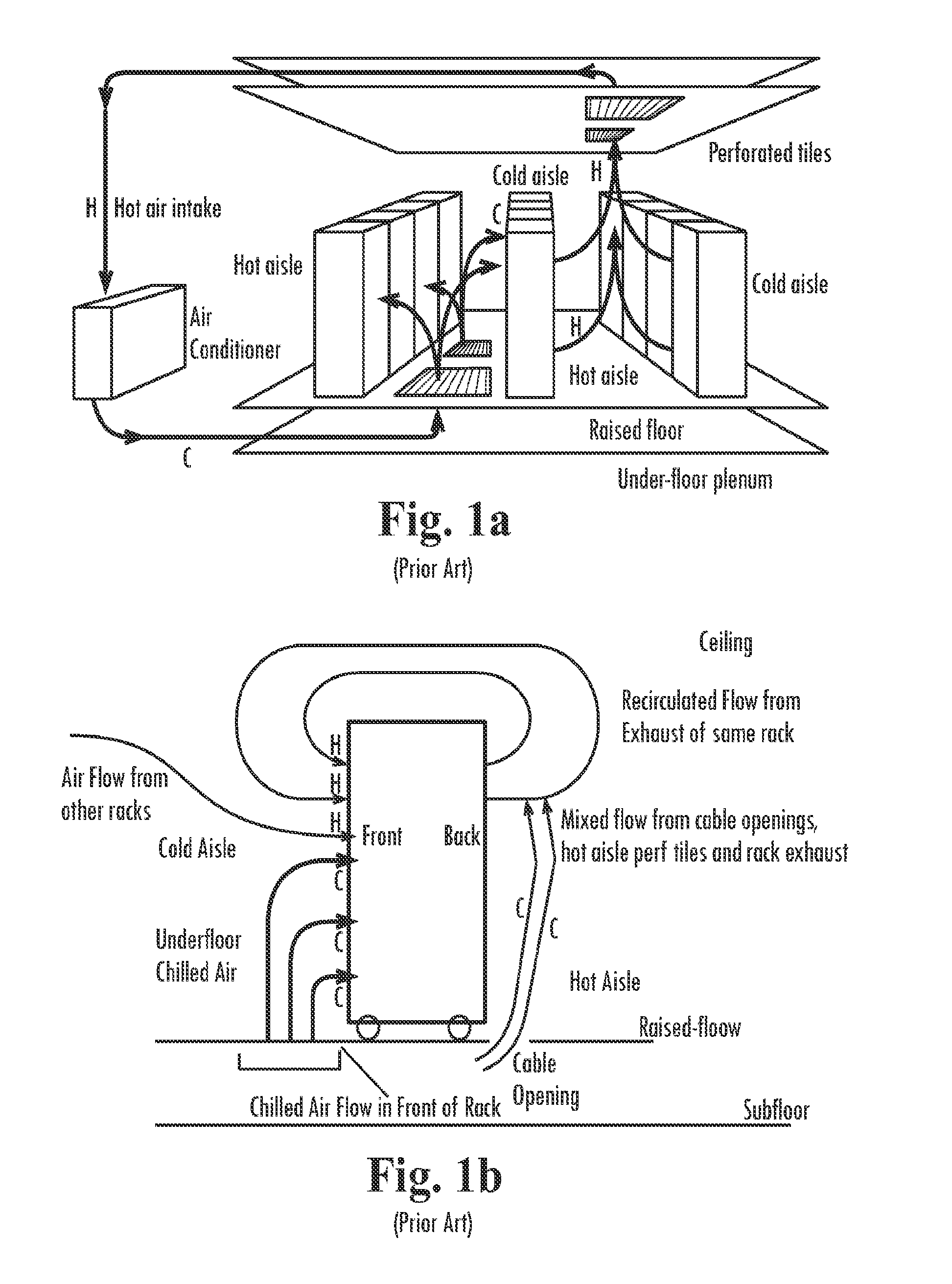

System and method for separating air flows in a cooling system

InactiveUS6034873AGreat and great efficiencyImprove efficiencyHeat exchange apparatusCooling/ventilation/heating modificationsMulti materialEngineering

A cooling system and method employing separation chutes and baffles is disclosed. The separation chutes separate the cooled air descending from a heat exchanger positioned above heat-generating equipment in an equipment room from heated air ascending from the heat-generating equipment. Separation of the airflows reduces turbulence and increases cooling efficiencies. The separation chutes are made of a variety of materials, both rigid and flexible, for a variety of applications.

Owner:VERTIV CORP

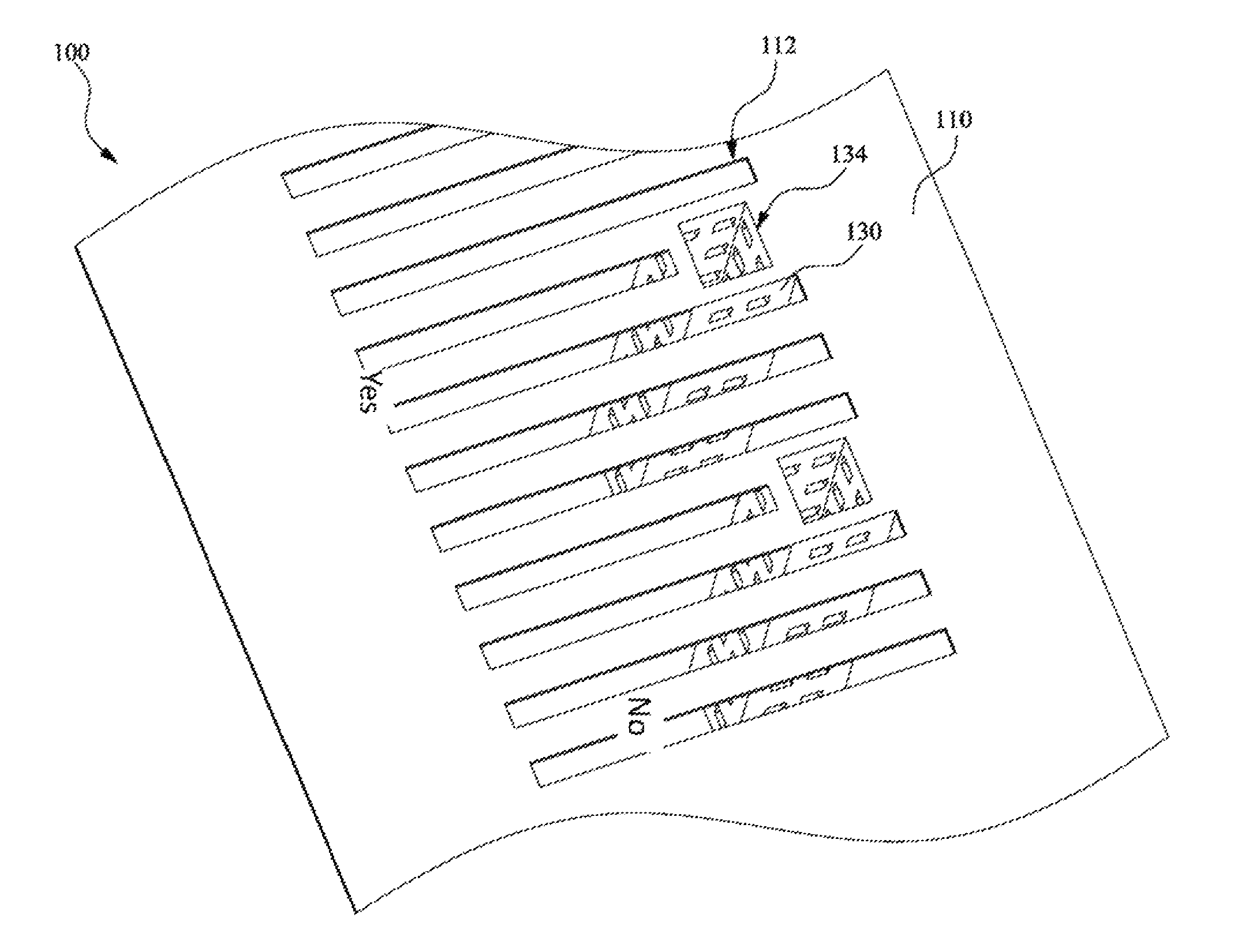

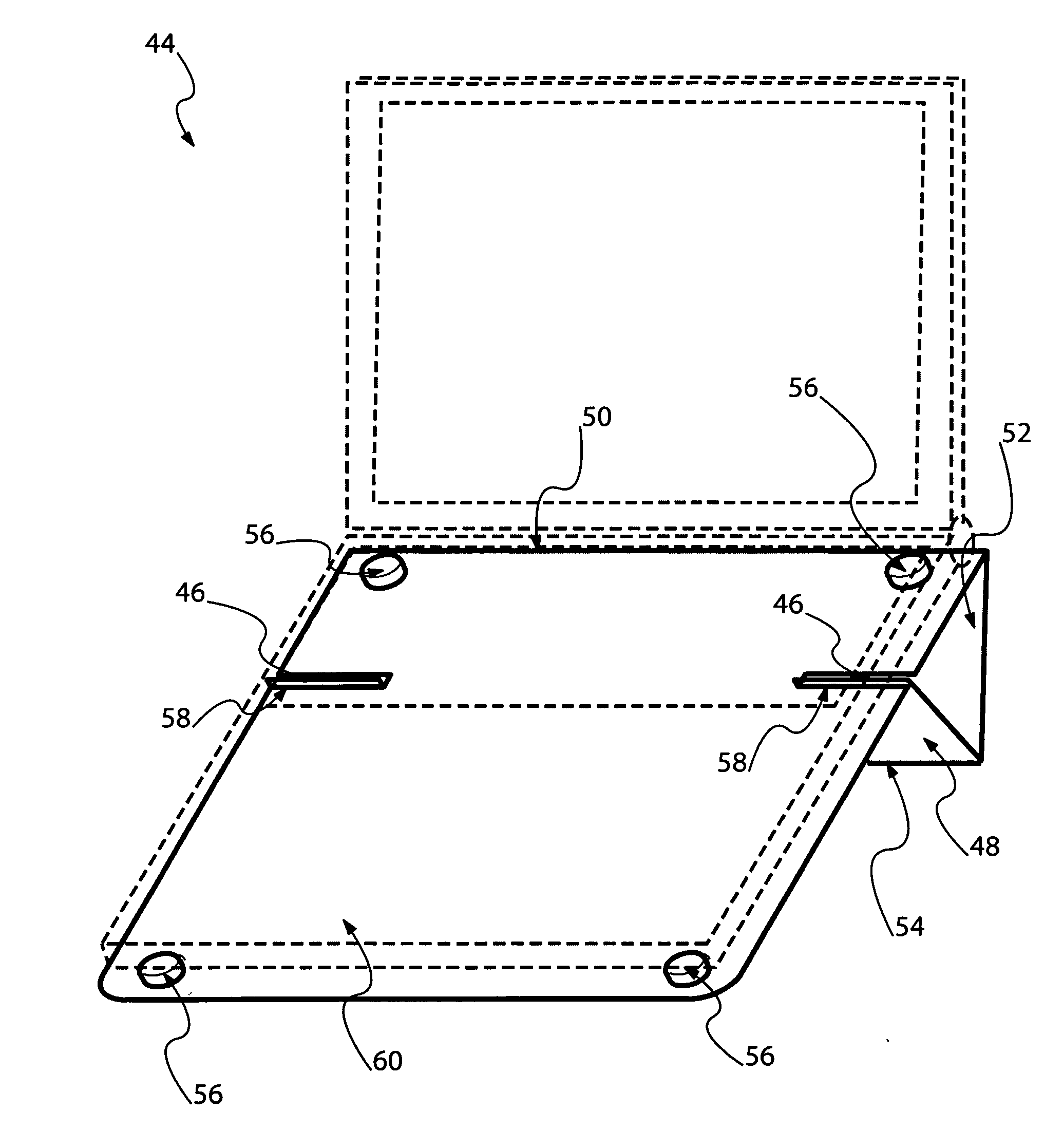

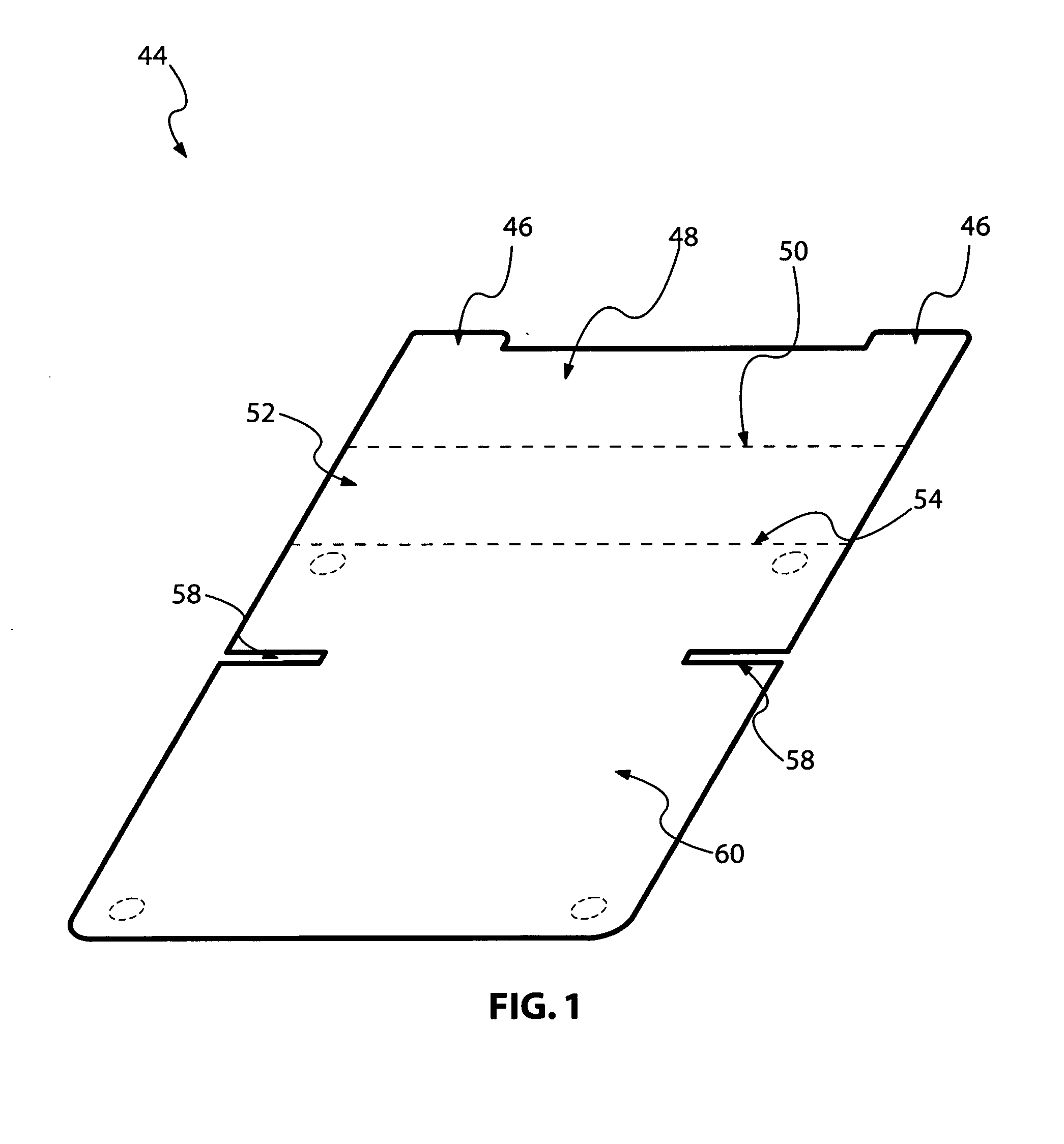

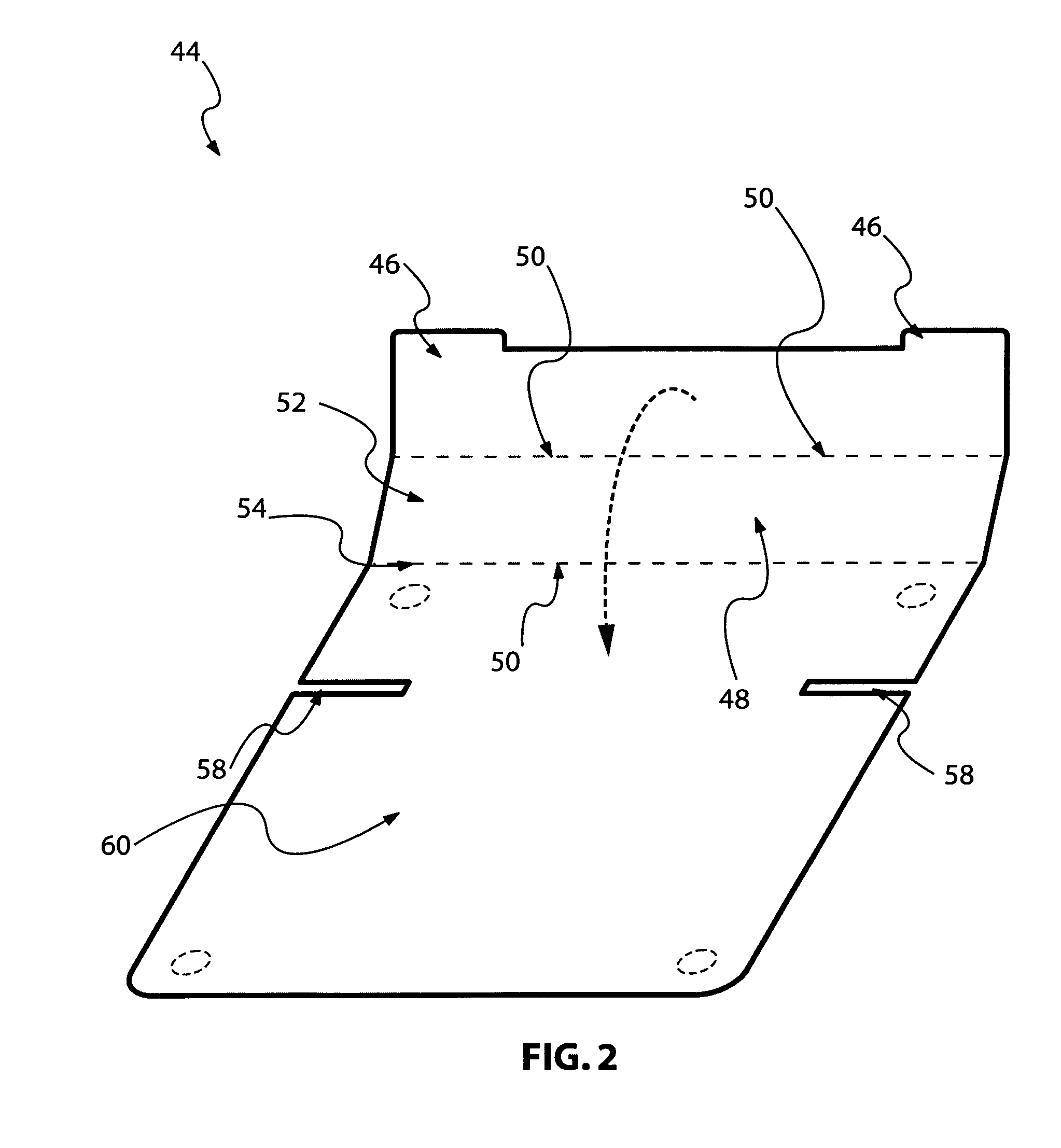

Portable laptop stand

InactiveUS20090159763A1Reduce manufacturing costEasy to operateBook-restsDetails for portable computersEngineeringFlat panel

A portable laptop stand comprising a generally rectangular flat board having a longitudinal axis perpendicular to a width of the board; said board having a distal end; said board having a proximal end; said board having a first portion, a second portion pivotably coupled to the first portion, and a main body pivotably coupled to the second portion; wherein the first portion has a longitudinal axis that is perpendicular to the longitudinal axis of the board; wherein the second portion has a longitudinal axis that is perpendicular to the longitudinal axis of the board; wherein said first portion is capable of folding back towards the main body and contact the main body. The board having a first attachment means disposed on the first portion; and a second attachment means disposed on the main body to detachably attach to said first attachment means.

Owner:KIM SANG KWON

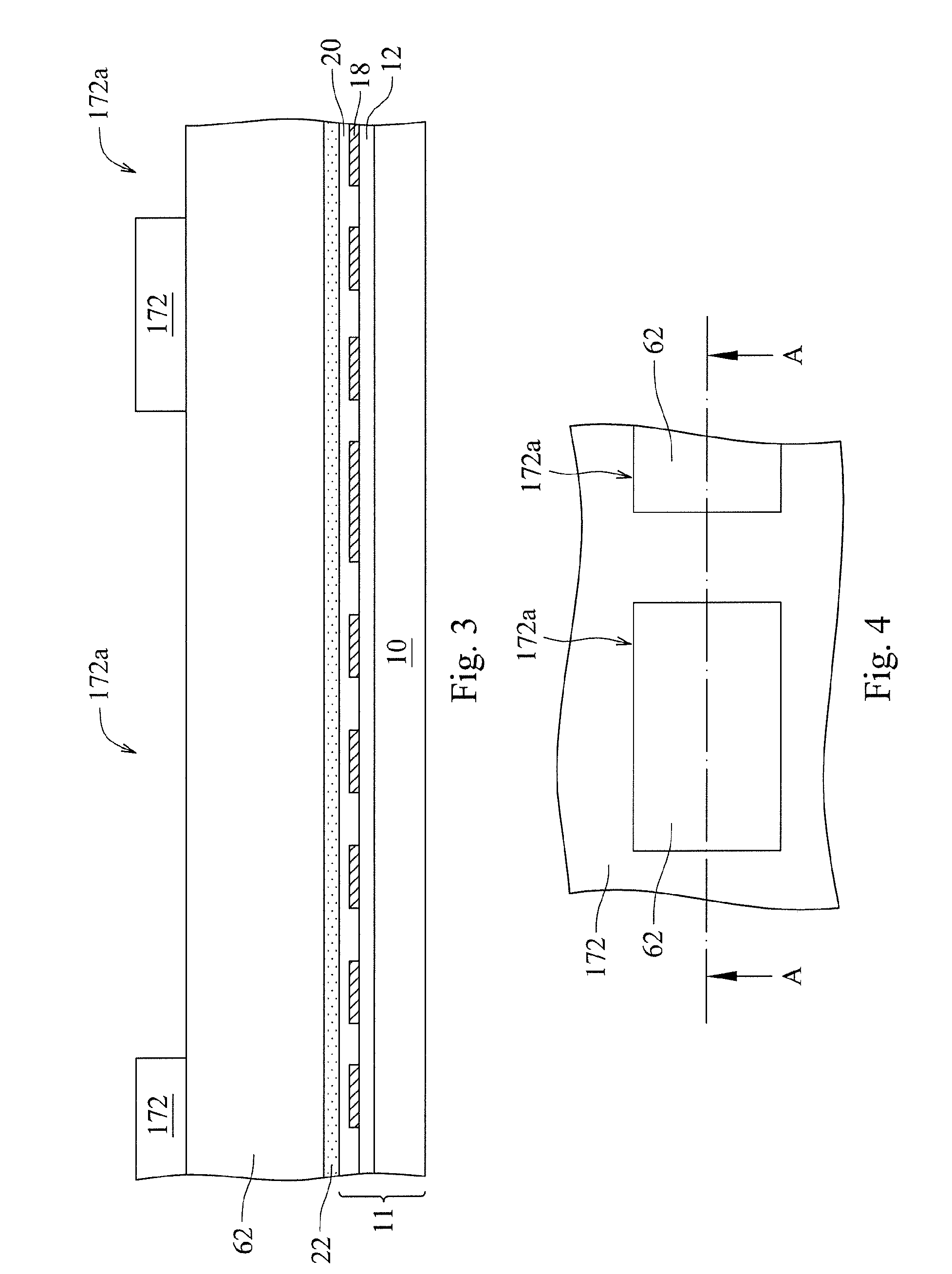

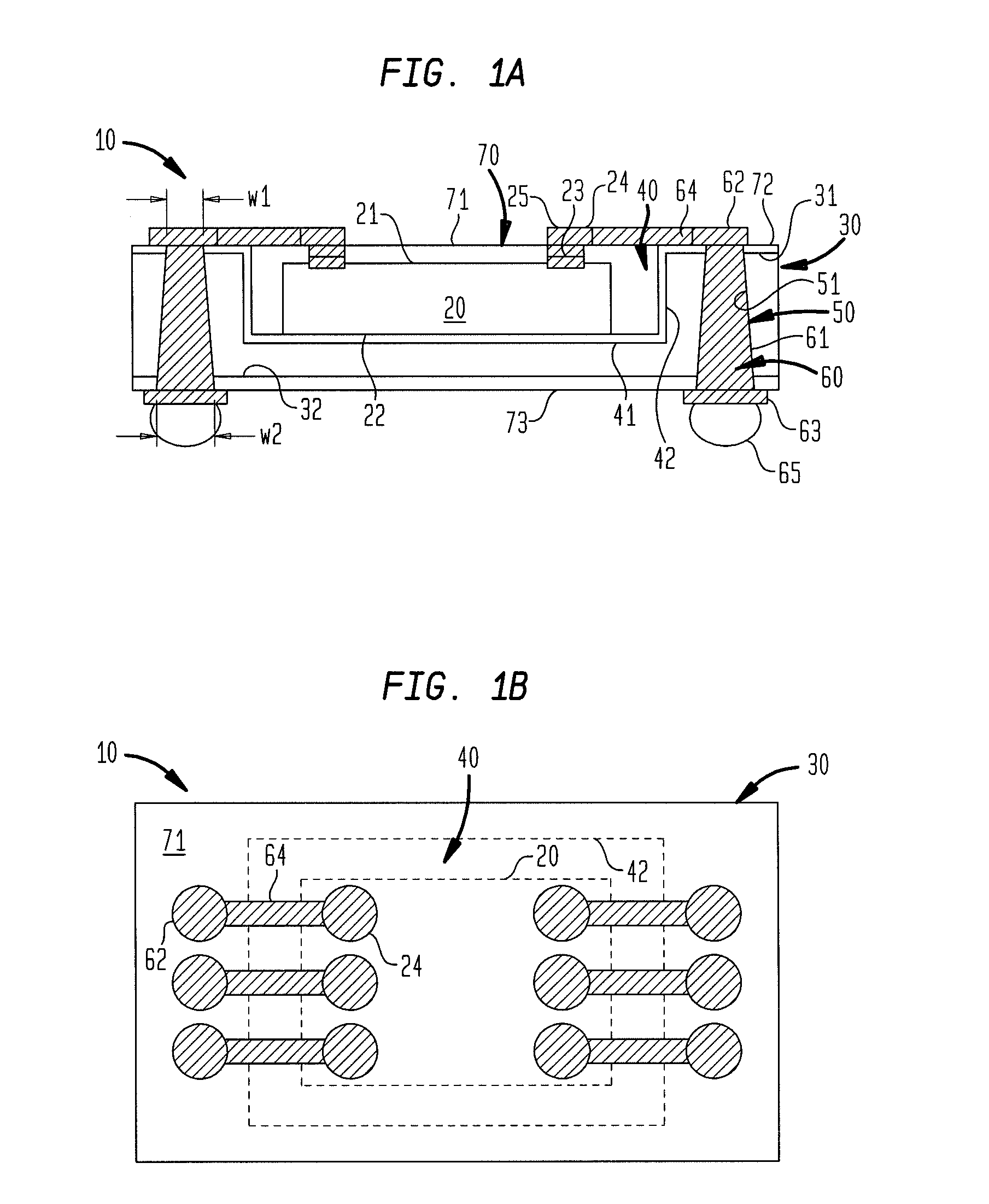

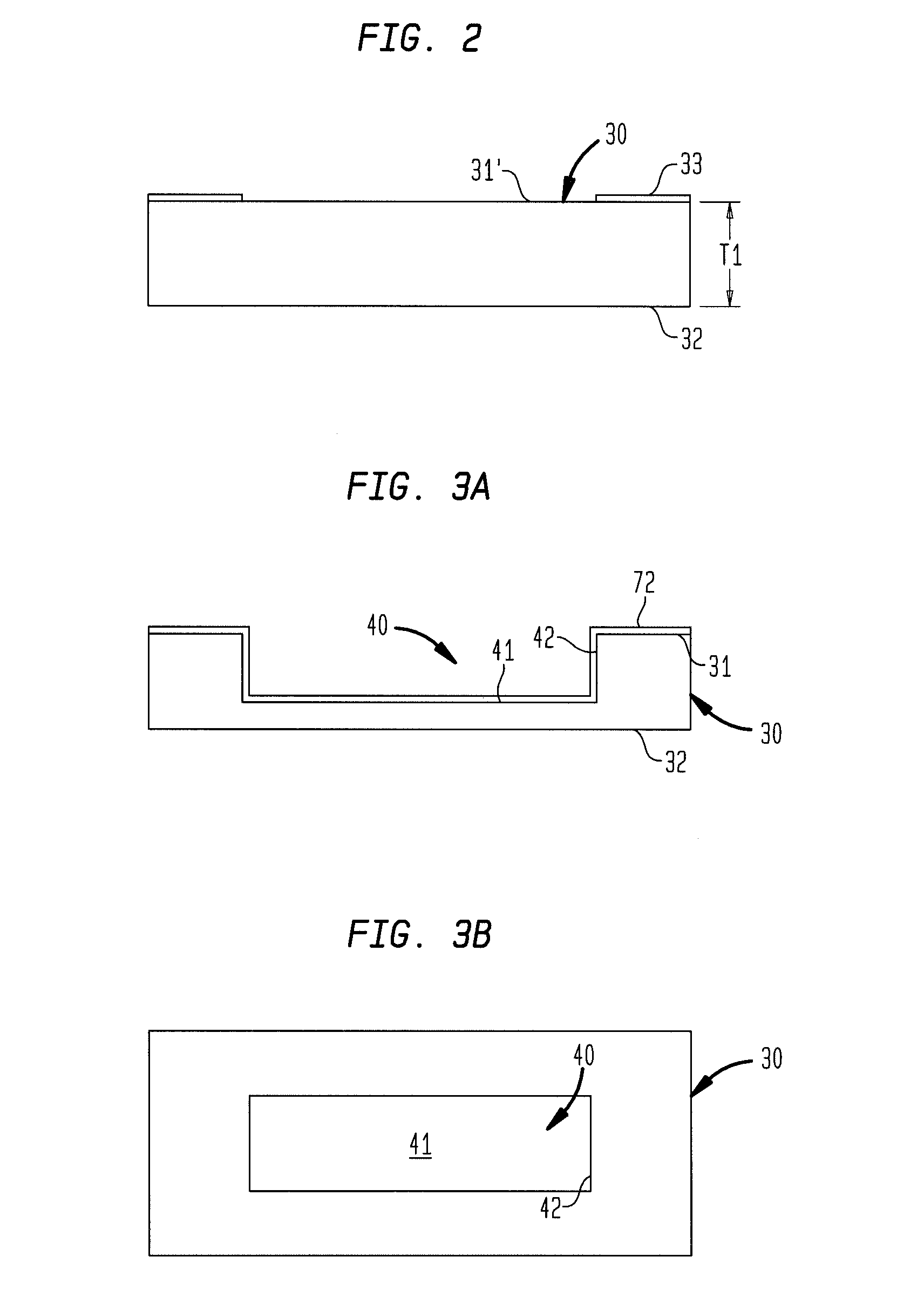

Microelectronic elements with post-assembly planarization

ActiveUS20120020026A1Wave amplification devicesSemiconductor/solid-state device detailsDielectricEngineering

A microelectronic unit includes a carrier structure having a front surface, a rear surface remote from the front surface, and a recess having an opening at the front surface and an inner surface located below the front surface of the carrier structure. The microelectronic unit can include a microelectronic element having a bottom surface adjacent the inner surface, a top surface remote from the bottom surface, and a plurality of contacts at the top surface. The microelectronic element can include terminals electrically connected with the contacts of the microelectronic element. The microelectronic unit can include a dielectric region contacting at least the top surface of the microelectronic element. The dielectric region can have a planar surface located coplanar with or above the front surface of the carrier structure. The terminals can be exposed at the surface of the dielectric region for interconnection with an external element.

Owner:TESSERA INC

Methods and systems for managing facility power and cooling

Systems and methods are provided for determining data center cooling and power requirements and for monitoring performance of cooling and power systems in data centers. At least one aspect provides a system and method that enables a data center operator to determine available power and cooling at specific areas and enclosures in a data center to assist in locating new equipment in the data center.

Owner:SCHNEIDER ELECTRIC IT CORP

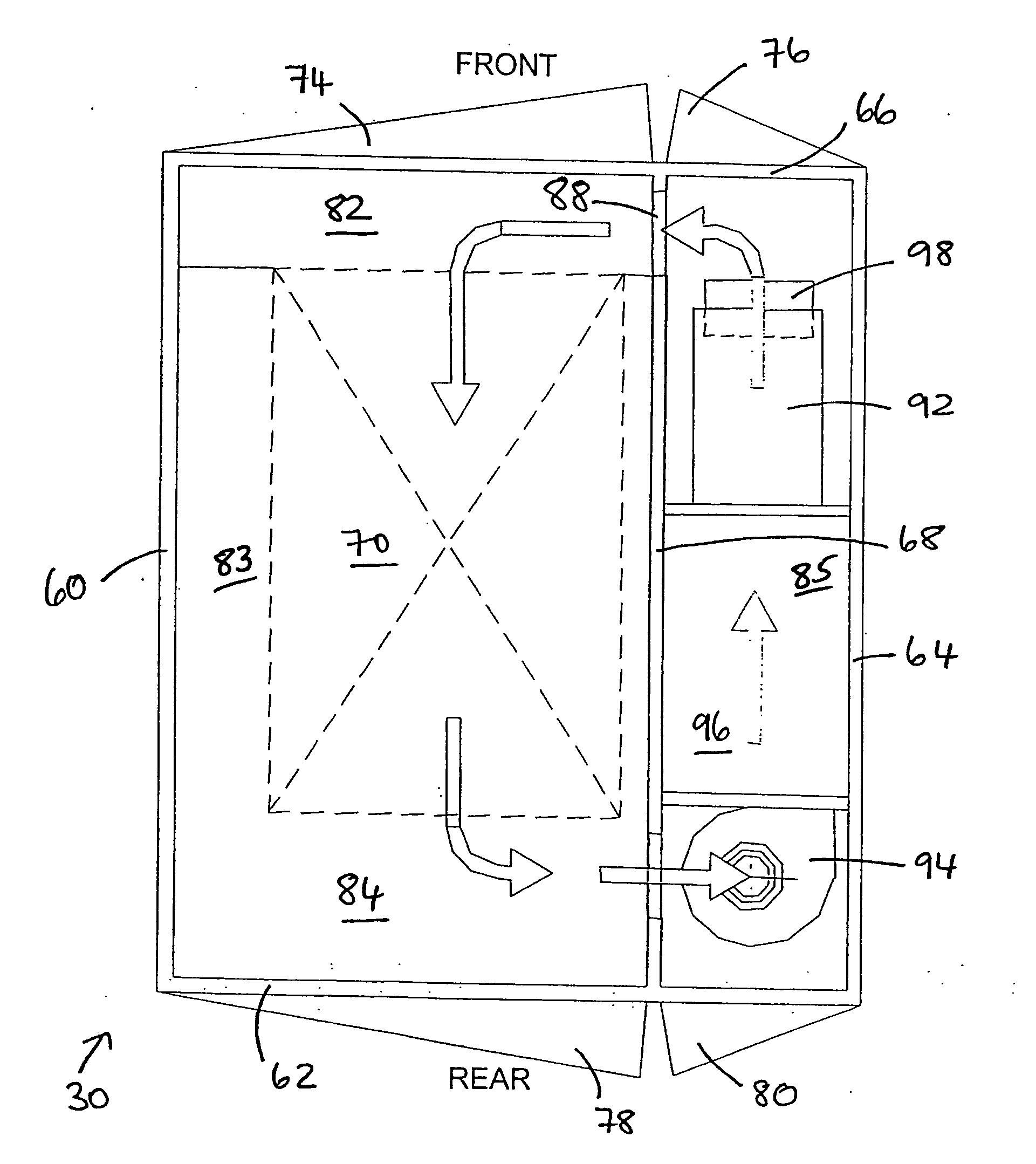

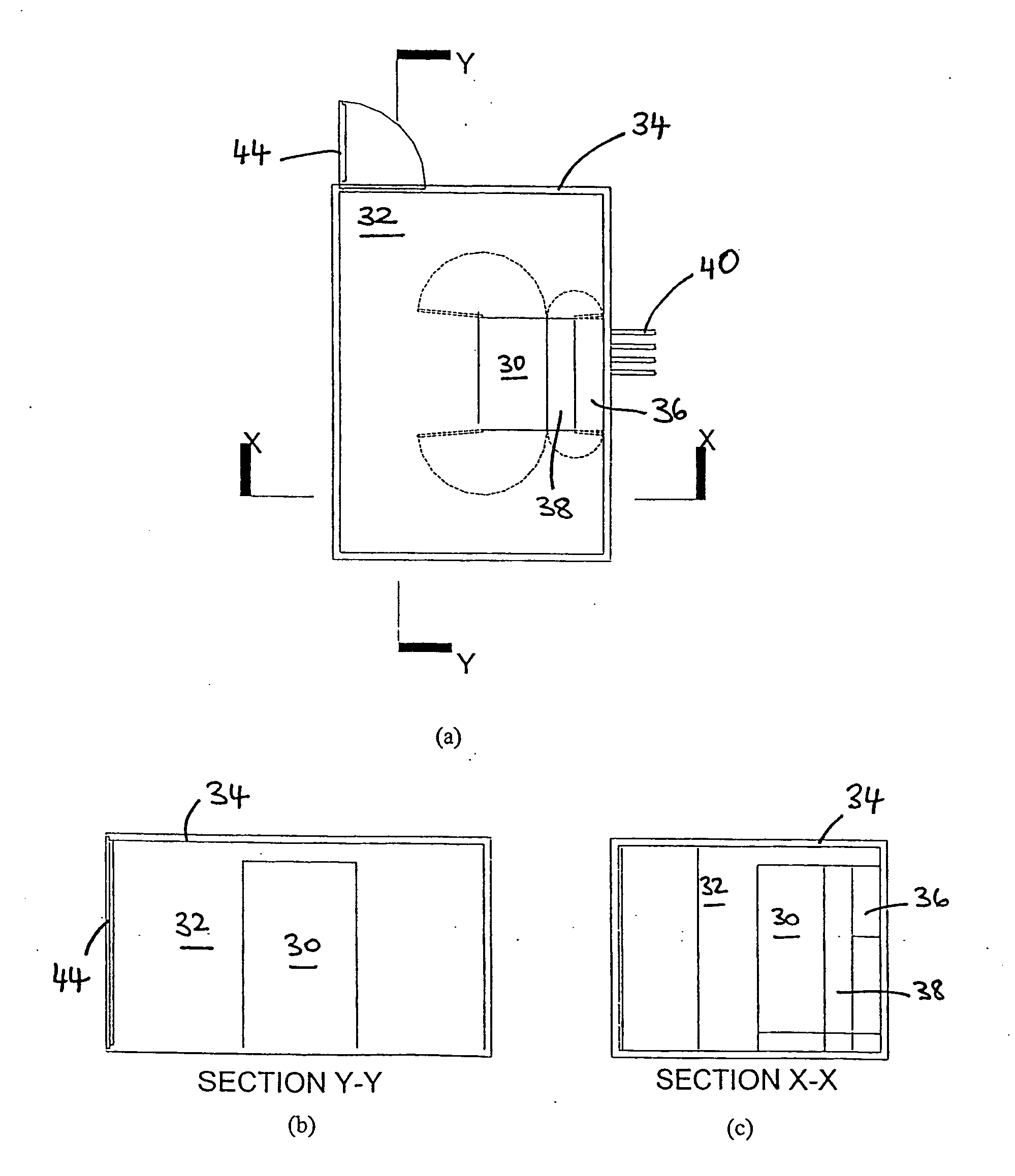

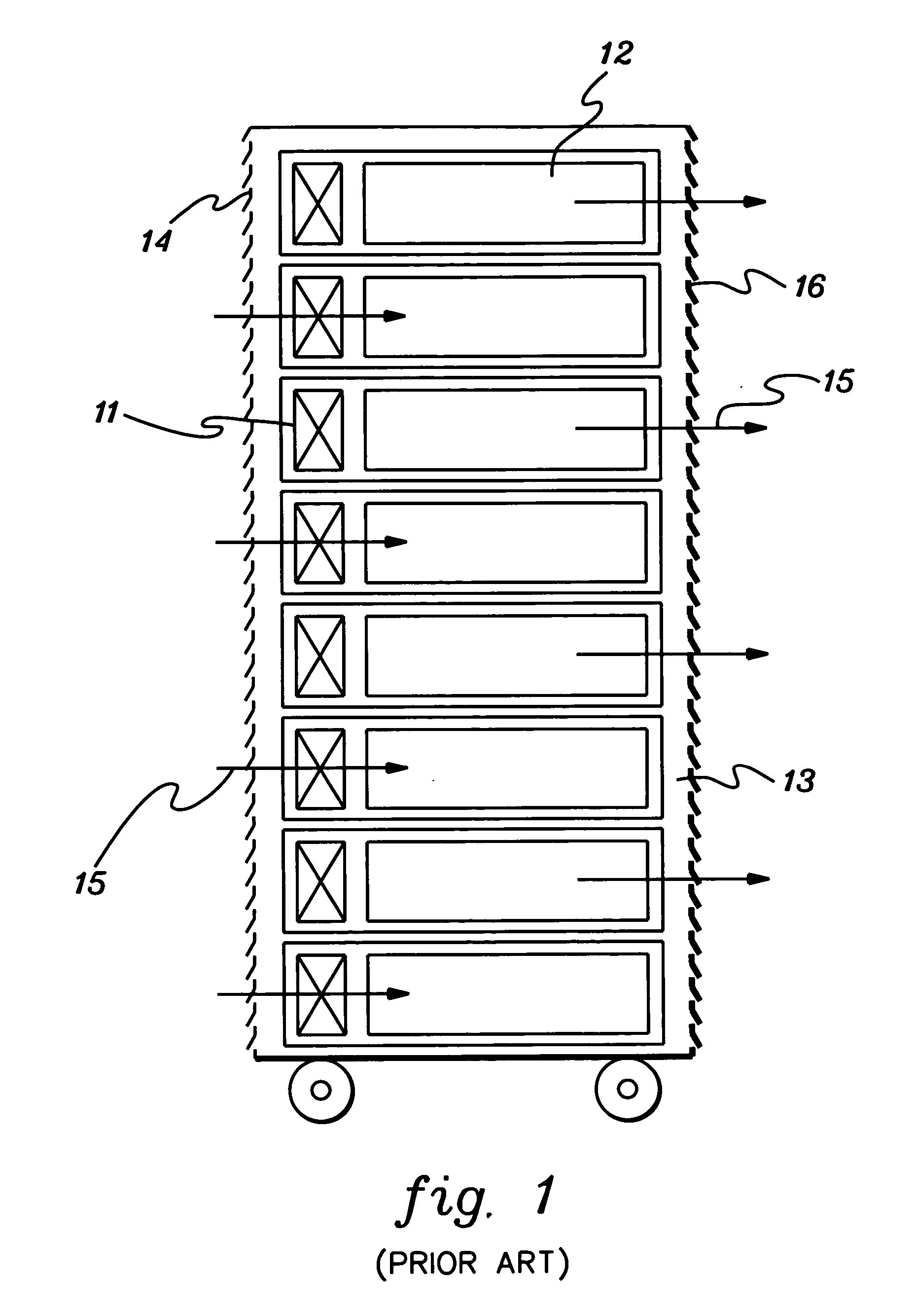

Data Center Cooling

InactiveUS20070213000A1Meet needsDomestic cooling apparatusLighting and heating apparatusData centerEngineering

A system includes a substantially sealed, substantially airtight cabinet sized for housing a vertical array of heat-producing units, the cabinet having an exterior shell and the system including an interior divider wall disposed inside the cabinet, the shell and divider wall providing an equipment chamber adapted to support the array such that the array cooperates with the shell and divider wall in use to define a first plenum, the first plenum having a first inlet defined by the divider wall for receiving a flow of cooling gas and having a first outlet defined by a plurality of openings through the array whereby the first plenum communicates with the openings in use to exhaust substantially all of the flow of cooling fluid through the openings and hence through the array, wherein the divider wall is configured to allow the first inlet to admit the gas to the first plenum in a substantially horizontal direction.

Owner:SCHNEIDER ELECTRIC IT CORP

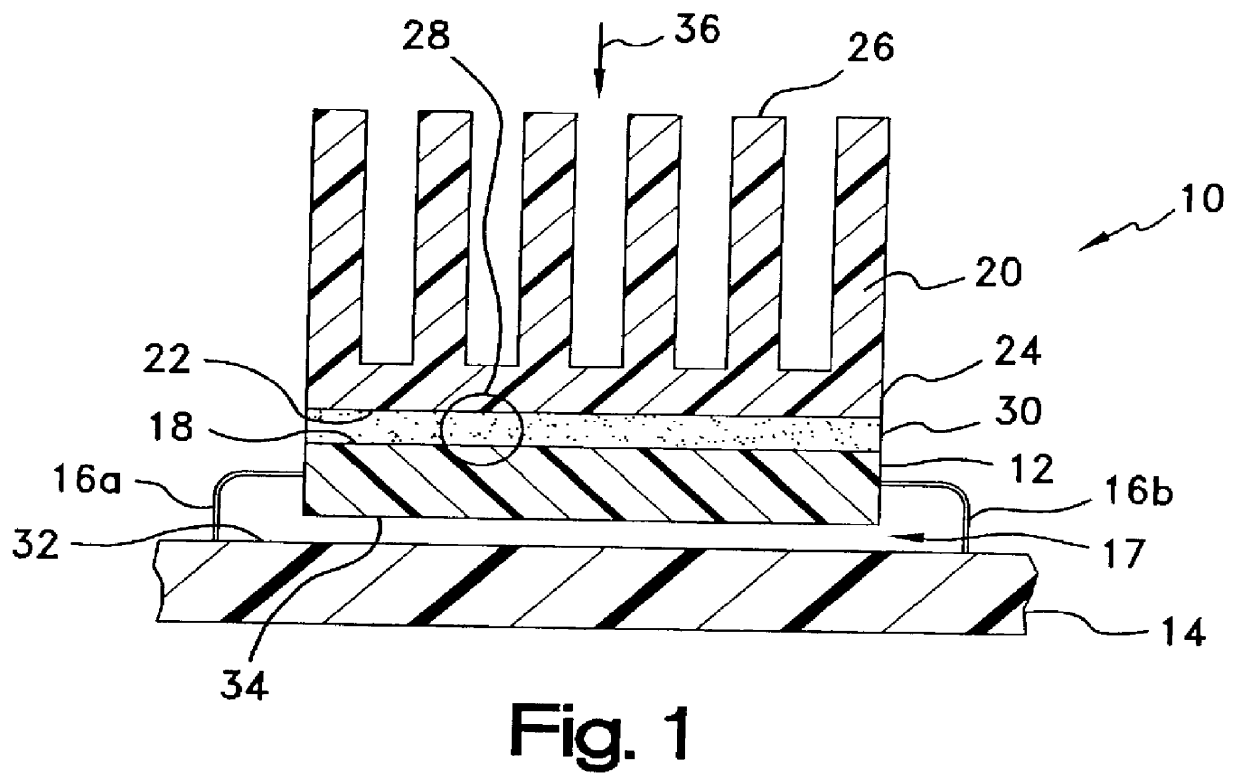

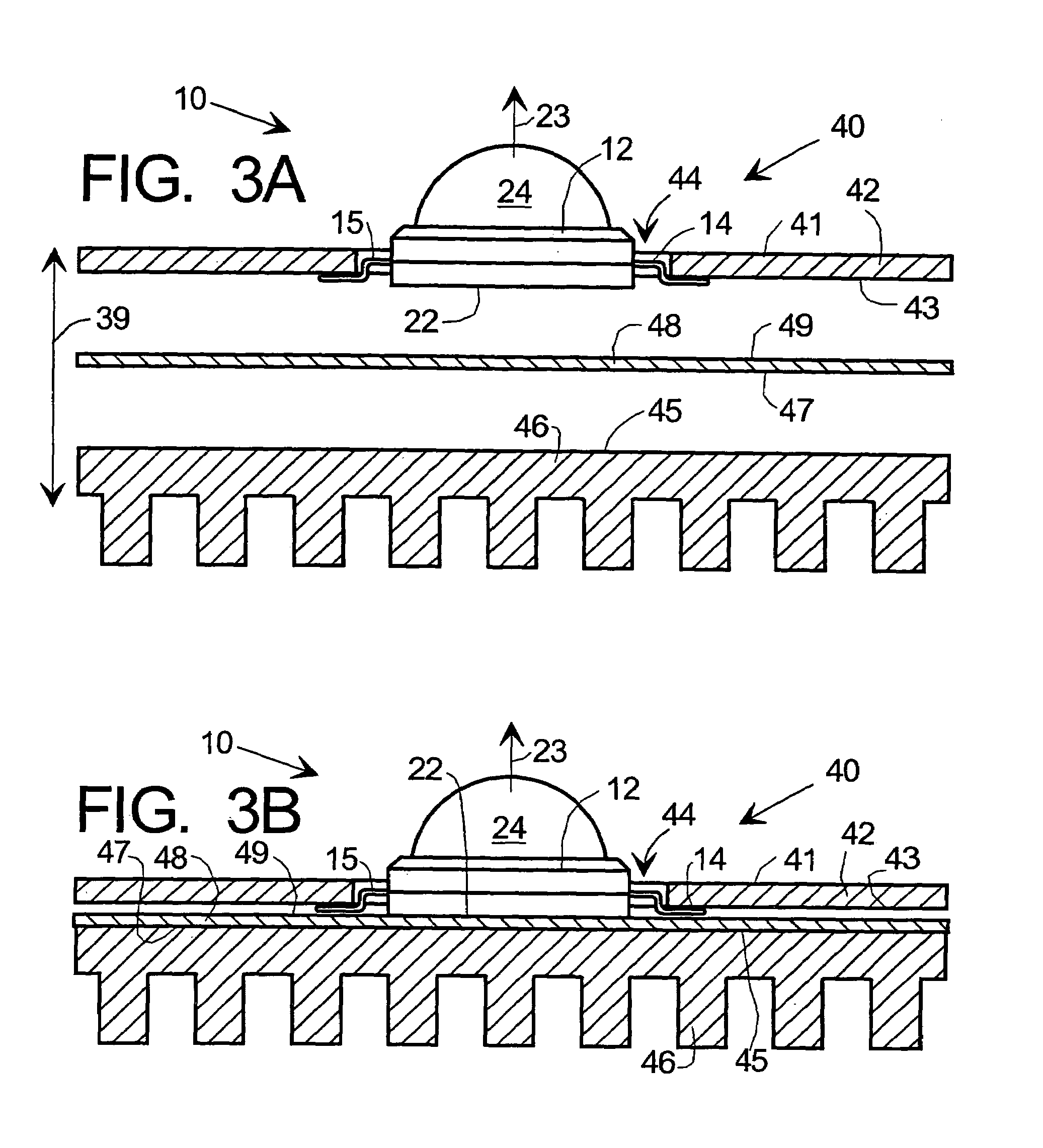

Conformal thermal interface material for electronic components

InactiveUS6054198AOptimize allocationReadily apparentSemiconductor/solid-state device detailsSolid-state devicesRoom temperatureConductive materials

A thermally-conductive interface for conductively cooling a heat-generating electronic component having an associated thermal dissipation member such as a heat sink. The interface is formed as a self-supporting layer of a thermally-conductive material which is form-stable at normal room temperature in a first phase and substantially conformable in a second phase to the interface surfaces of the electronic component and thermal dissipation member. The material has a transition temperature from the first phase to the second phase which is within the operating temperature range of the electronic component.

Owner:PARKER INTANGIBLES LLC

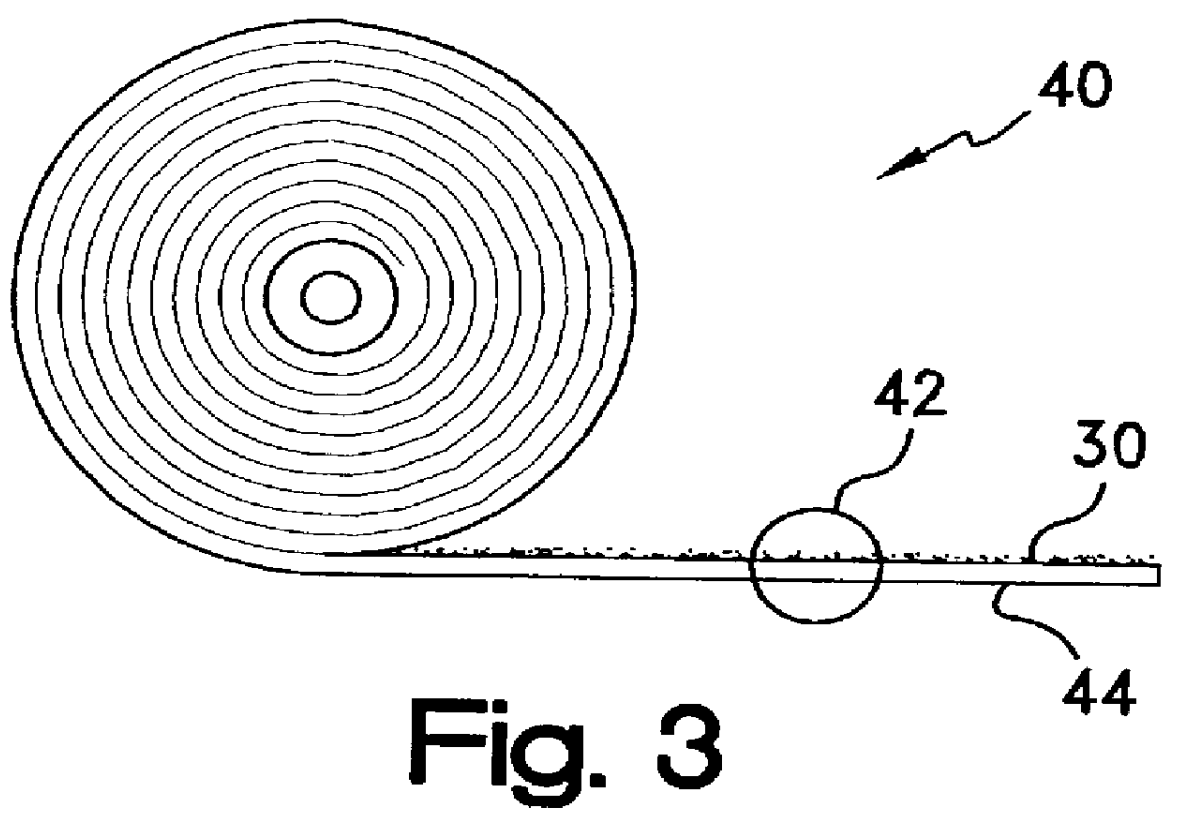

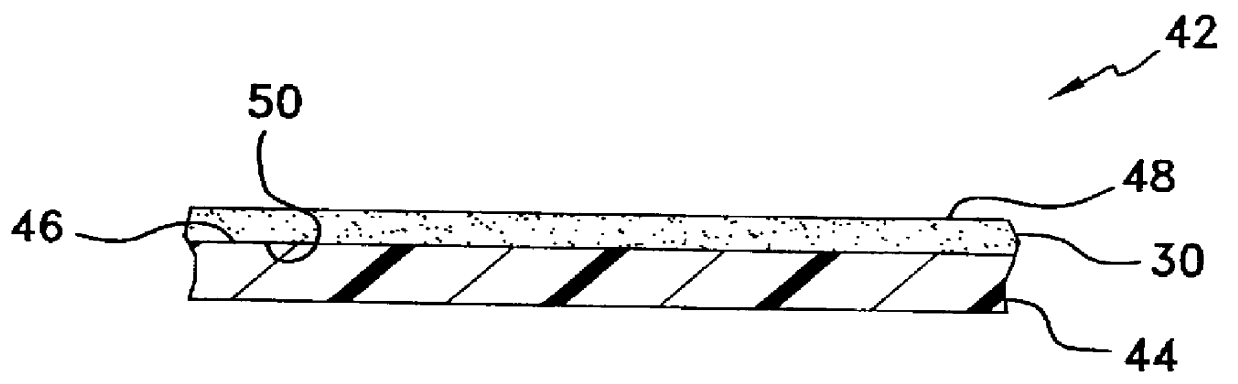

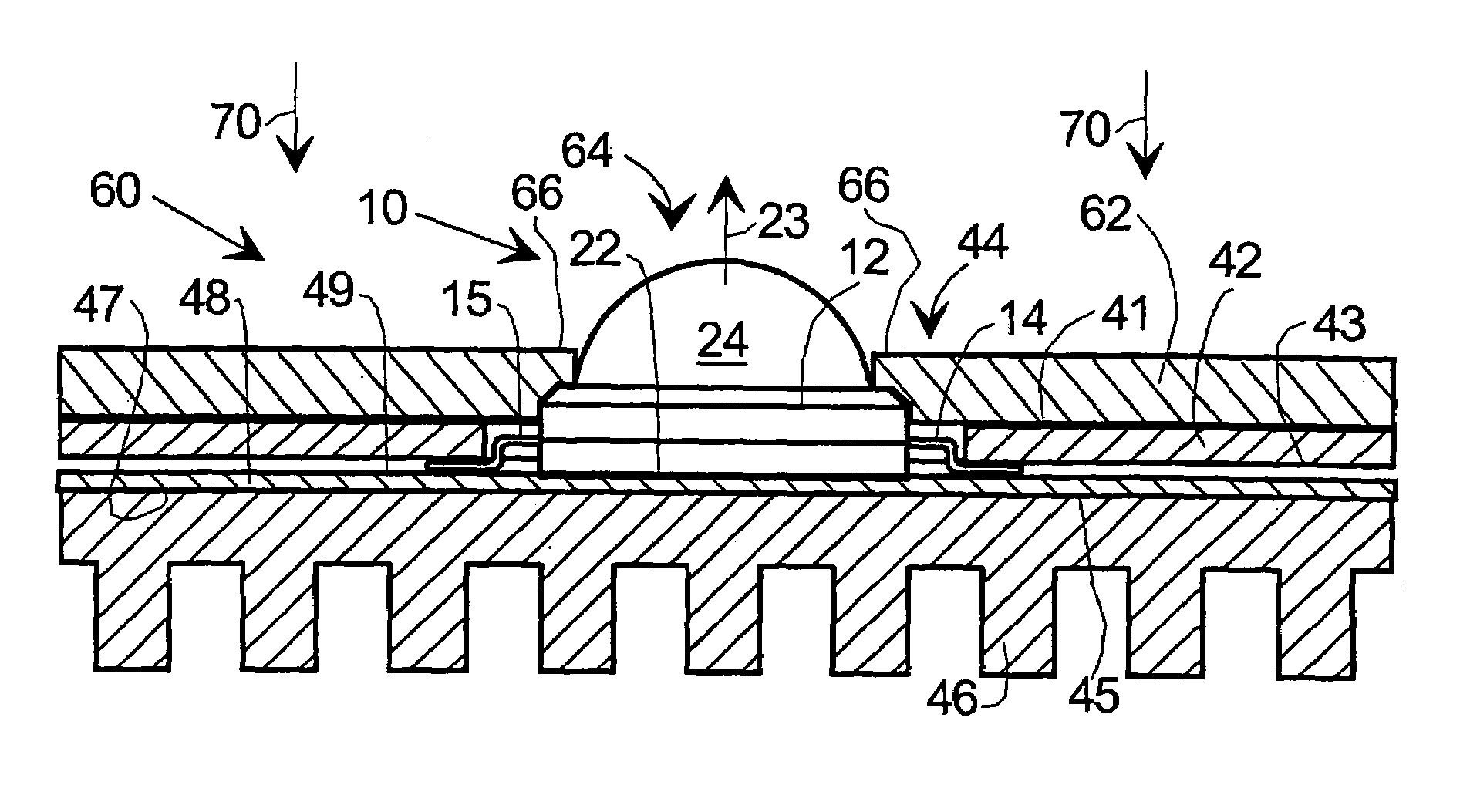

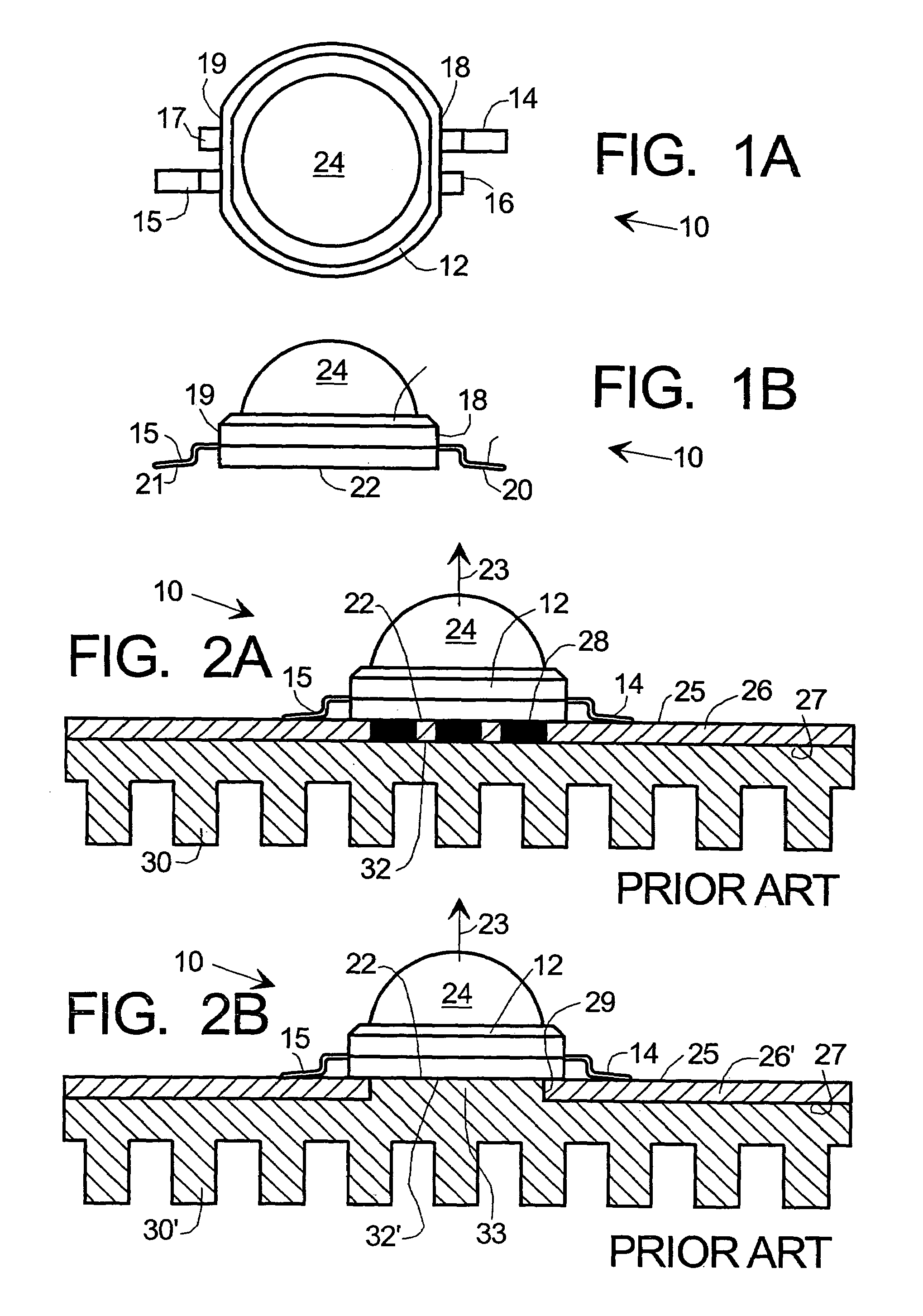

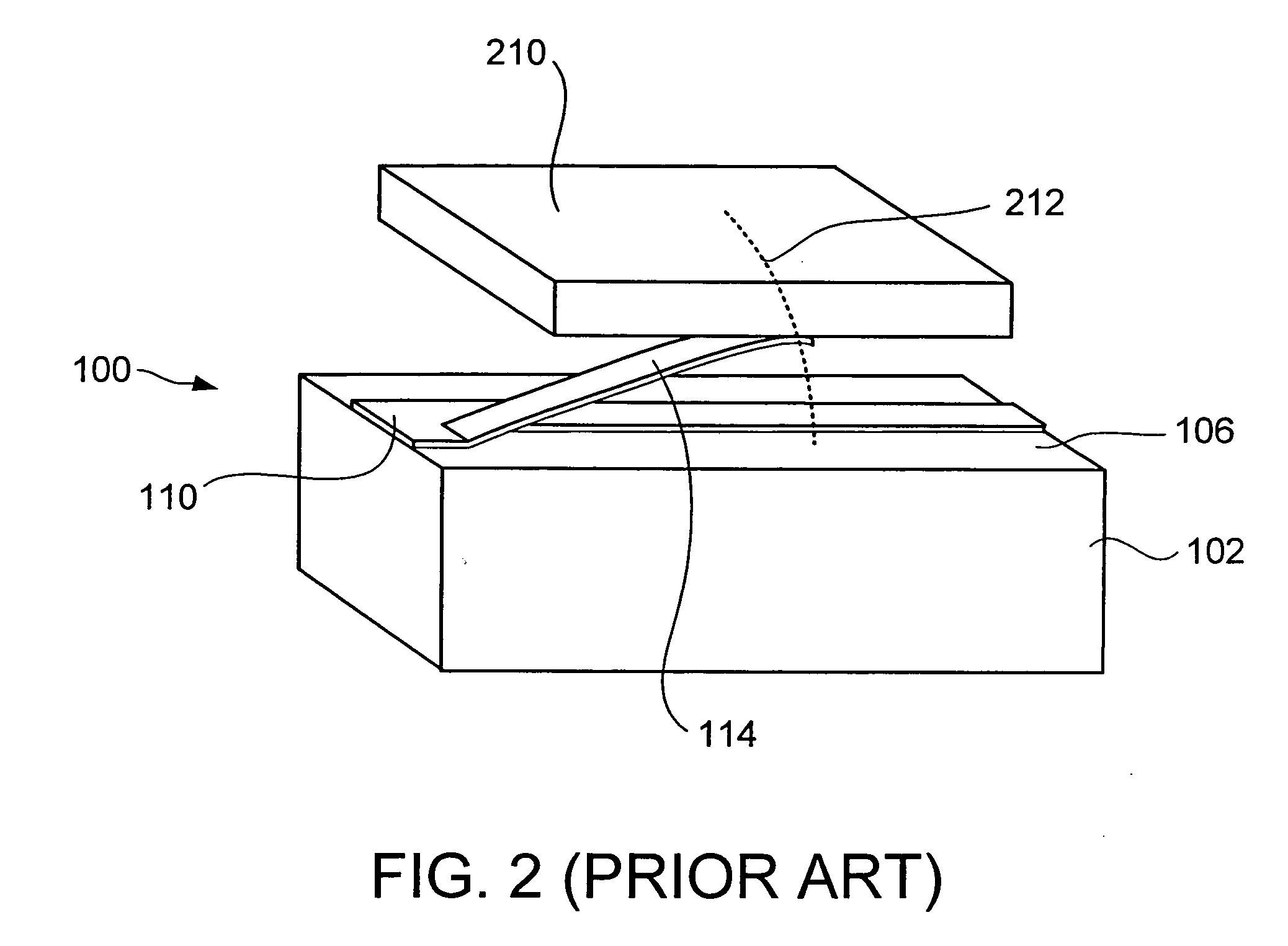

Heatsinking electronic devices

InactiveUS6999318B2Adequate thermal conductionEasy to replacePlanar light sourcesPoint-like light sourceElectricityEngineering

Method and apparatus are provided for thermally coupling one or more electronic devices to a heatsink. The apparatus comprises a heatsink having a substantially planar upper surface, a wiring board (PWB) with a through-hole for receiving the device such that a principal face thereof is in thermal contact with the heatsink, its electrical leads are captured between at least a portion of the wiring board and the heatsink, and a top of the device protrudes through the PWB. The method comprises placing the device in the through-hole with its base exposed on and protruding from the underside of the PWB, attaching its electrical leads to contacts on the wiring board and pressing the PWB toward the heatsink with the leads captured there between. An electrically insulating thermally conducting layer is desirably placed between the wiring board and the heatsink.

Owner:HONEYWELL INT INC

Rack enclosure

ActiveUS7112131B2Avoid overall overheatingPrevent air lossSemiconductor/solid-state device detailsSolid-state devicesData centerTelecommunications equipment

An enclosure is provided for housing electronic equipment that accommodates the different cooling and ventilating requirements of different types of equipment. The enclosure is constructed and arranged to support cooling airflow in a front-to-back configuration through the enclosure and in a side-to-side configuration from one side to an opposite side of the enclosure. The enclosure can thereby provide within a single enclosure means cooling air for components using front-to-back airflow for cooling, such as information technology (IT) equipment, and for components using side-to-side airflow, such as certain types of telecommunications equipment. The enclosure can thereby support a mix of IT and telecommunications equipment, providing flexibility and adaptability in network room and data center configuration. The enclosure is further configured to separate intake air used by equipment for cooling from exhaust air vented by equipment into its interior during operation. As a result, the enclosure promotes sufficient equipment cooling and prevents / minimizes equipment overheating.

Owner:AMERICA POWER CONVERSION CORP

Apparatus and method for facilitating cooling of an electronics rack employing a heat exchange assembly mounted to an outlet door cover of the electronics rack

Apparatus and method are provided for facilitating cooling of an electronics rack employing a heat exchange assembly mounted to an outlet door cover hingedly affixed to an air outlet side of the rack. The heat exchange assembly includes a support frame, an air-to-liquid heat exchanger, and first and second perforated planar surfaces covering first and second main sides, respectively, of the air-to-liquid heat exchanger. The heat exchanger is supported by the support frame and includes inlet and outlet plenums disposed adjacent to the edge of the outlet door cover hingedly mounted to the rack. Each plenum is in fluid communication with a respective connect coupling, and the heat exchanger further includes multiple horizontally-oriented heat exchange tube sections each having serpentine cooling channel with an inlet and an outlet coupled to the inlet plenum and outlet plenum, respectively. Fins extend from the heat exchange tube sections.

Owner:VETTE TECH

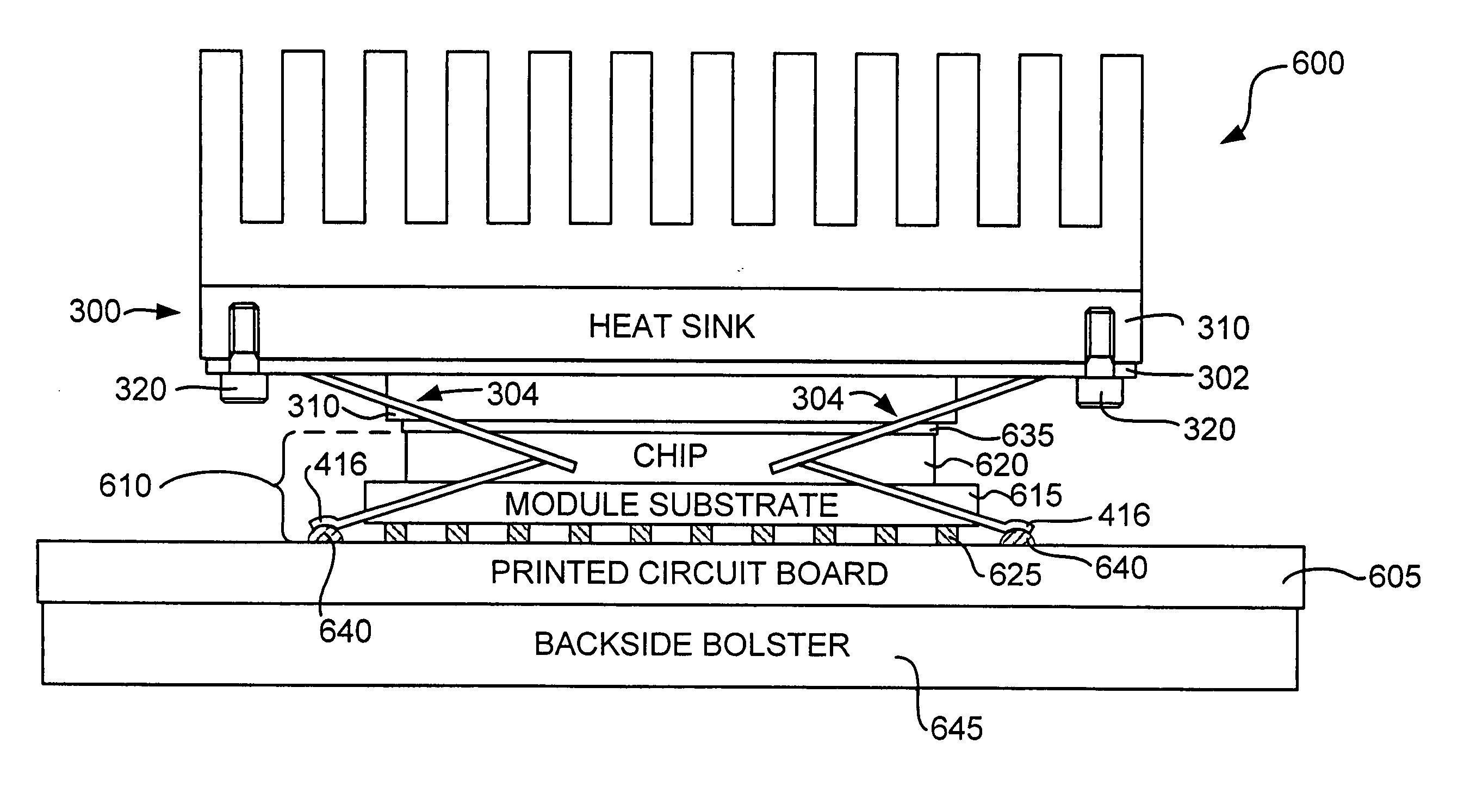

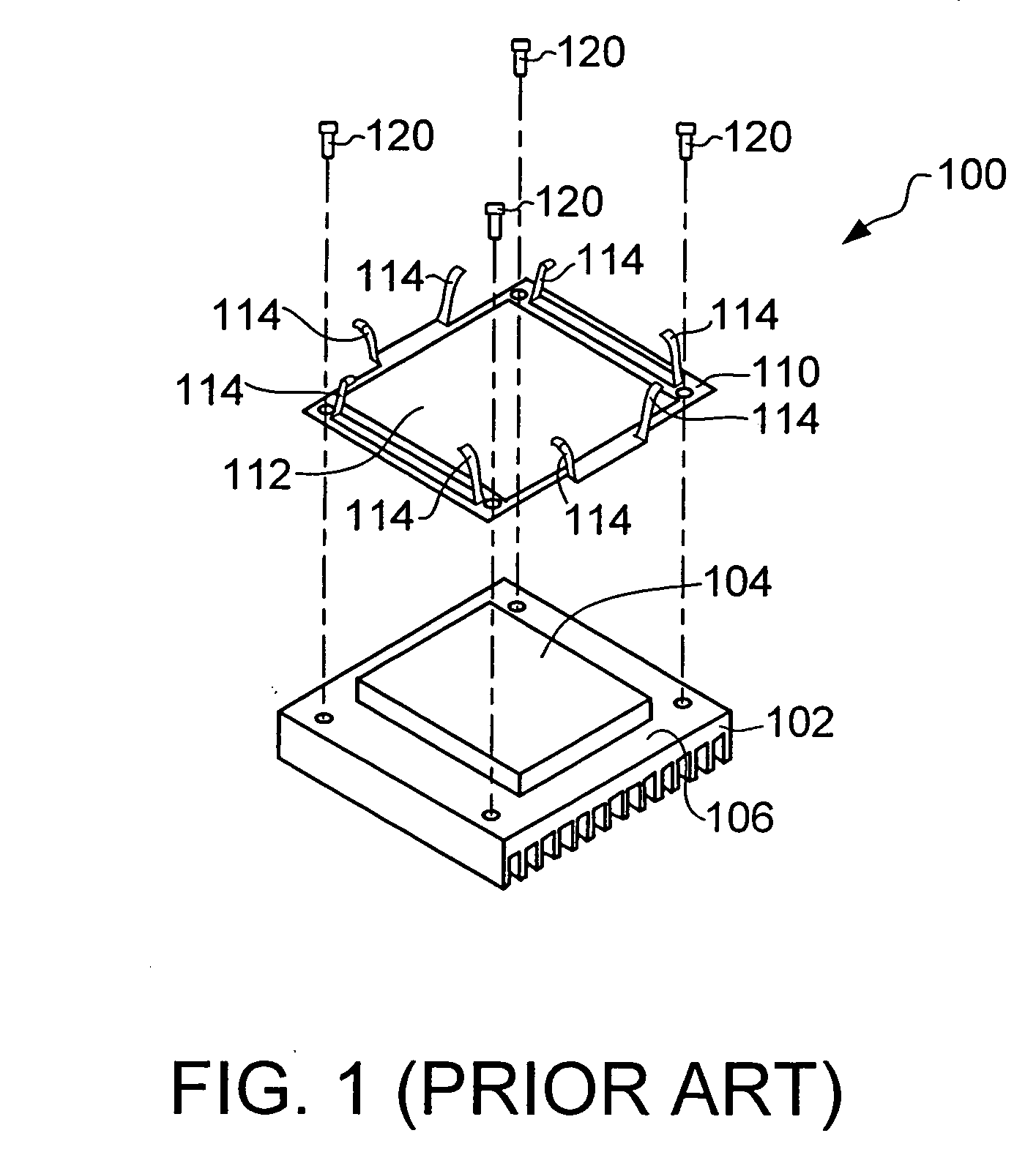

Method and apparatus for grounding a heat sink in thermal contact with an electronic component using a grounding spring having multiple-jointed spring fingers

InactiveUS20070097653A1Not easy to slipRestrict movementSemiconductor/solid-state device detailsSolid-state devicesElectricityElectromagnetic interference

A grounding spring for electromagnetic interference (EMI) suppression is interposed between a heat sink and a printed circuit board (PCB). The grounding spring comprises a conductive material having an opening formed at its base through which the heat sink makes thermal contact with an electronic module mounted on the PCB. The base makes electrical contact with a peripheral surface of the heat sink, and multiple-jointed spring fingers extend from the base to make electrical contact with conductive pads on the PCB. During compression, the movement of each spring finger's tip is substantially limited to the z-axis. Accordingly, the final installed location of the tip can be precisely controlled even when the grounding spring must accommodate a wide variety of installed heights of the heat sink relative to the PCB. Preferably, the spring fingers terminate with a concave tip that is less susceptible to sliding off the conductive pads.

Owner:IBM CORP

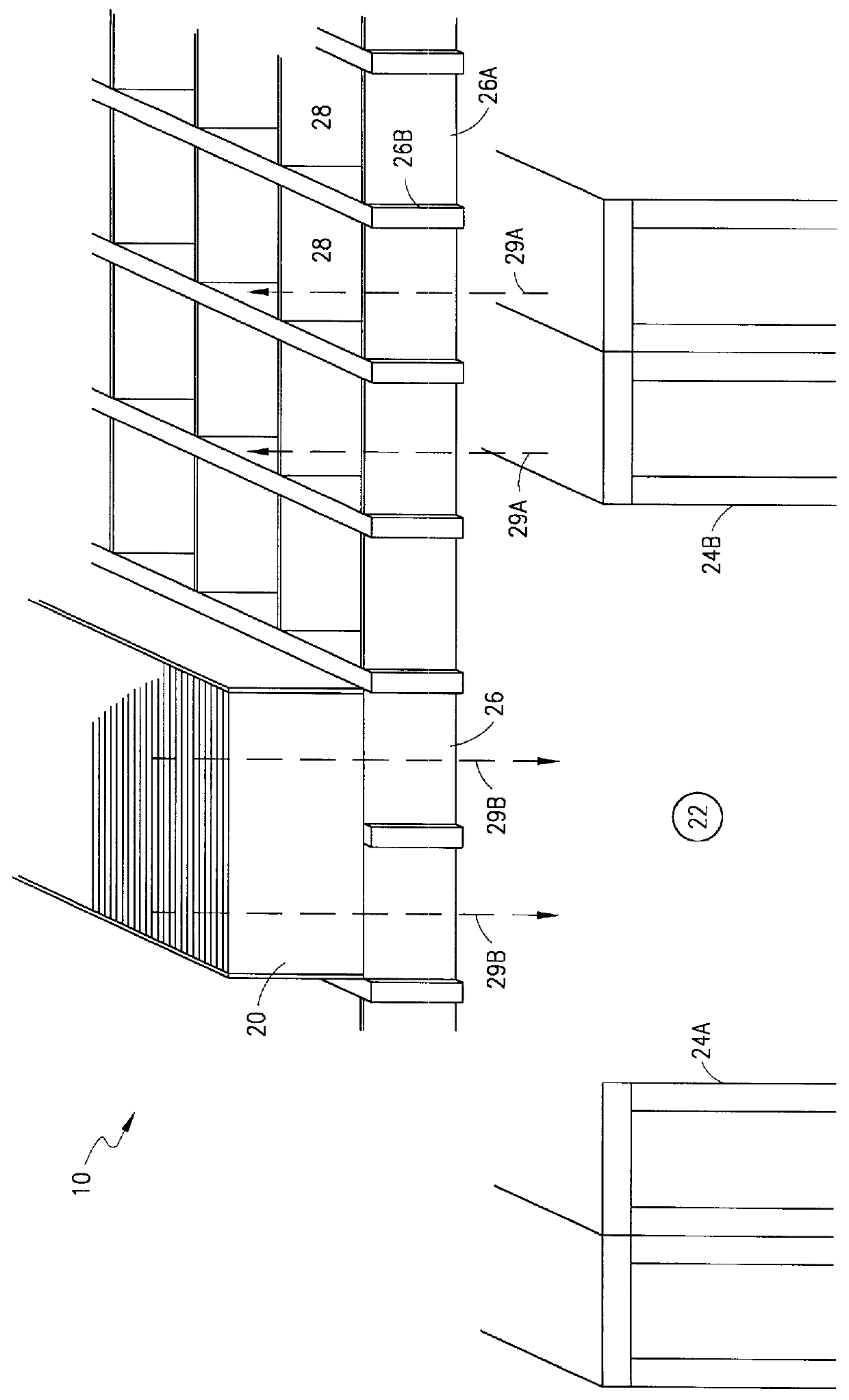

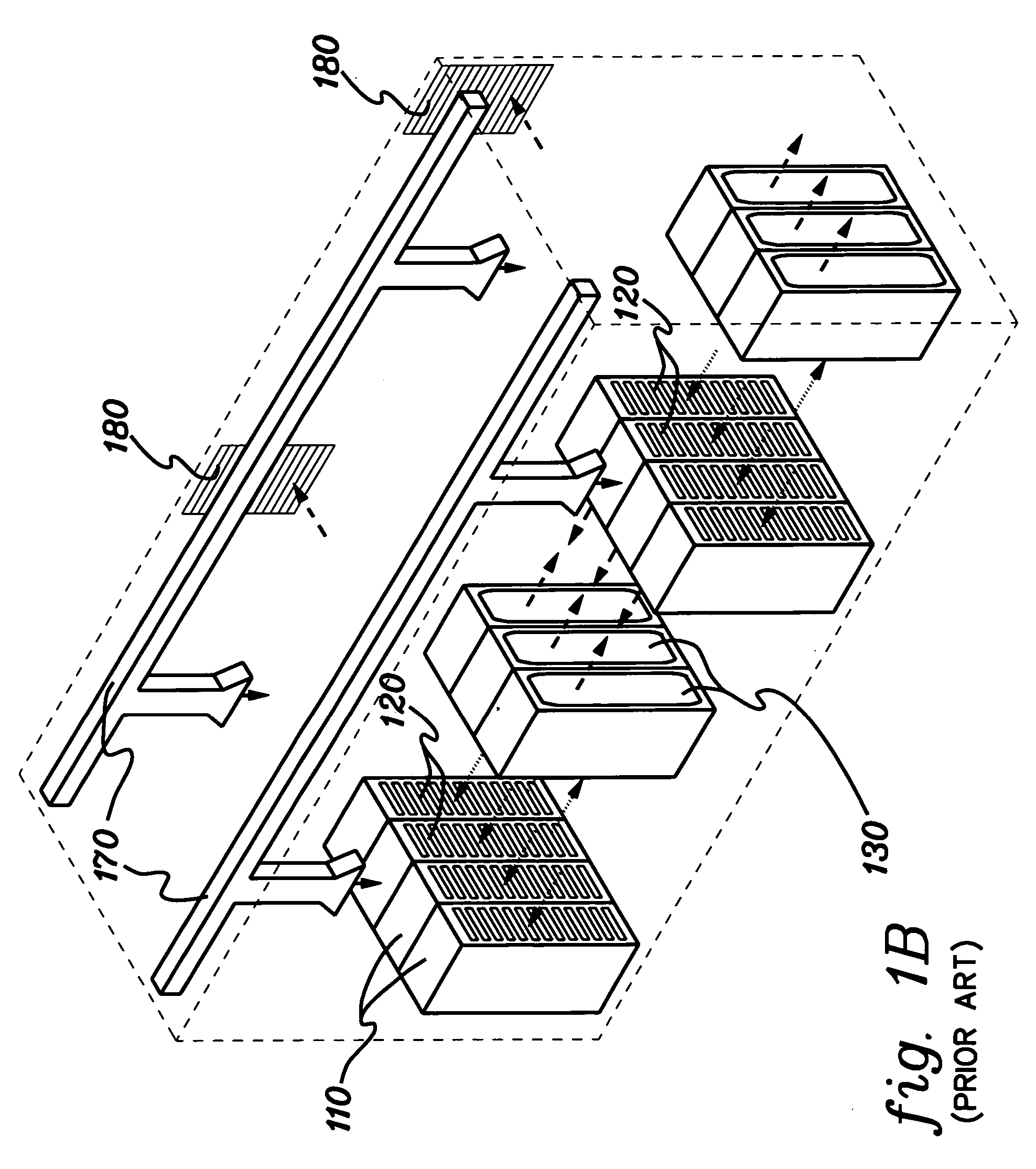

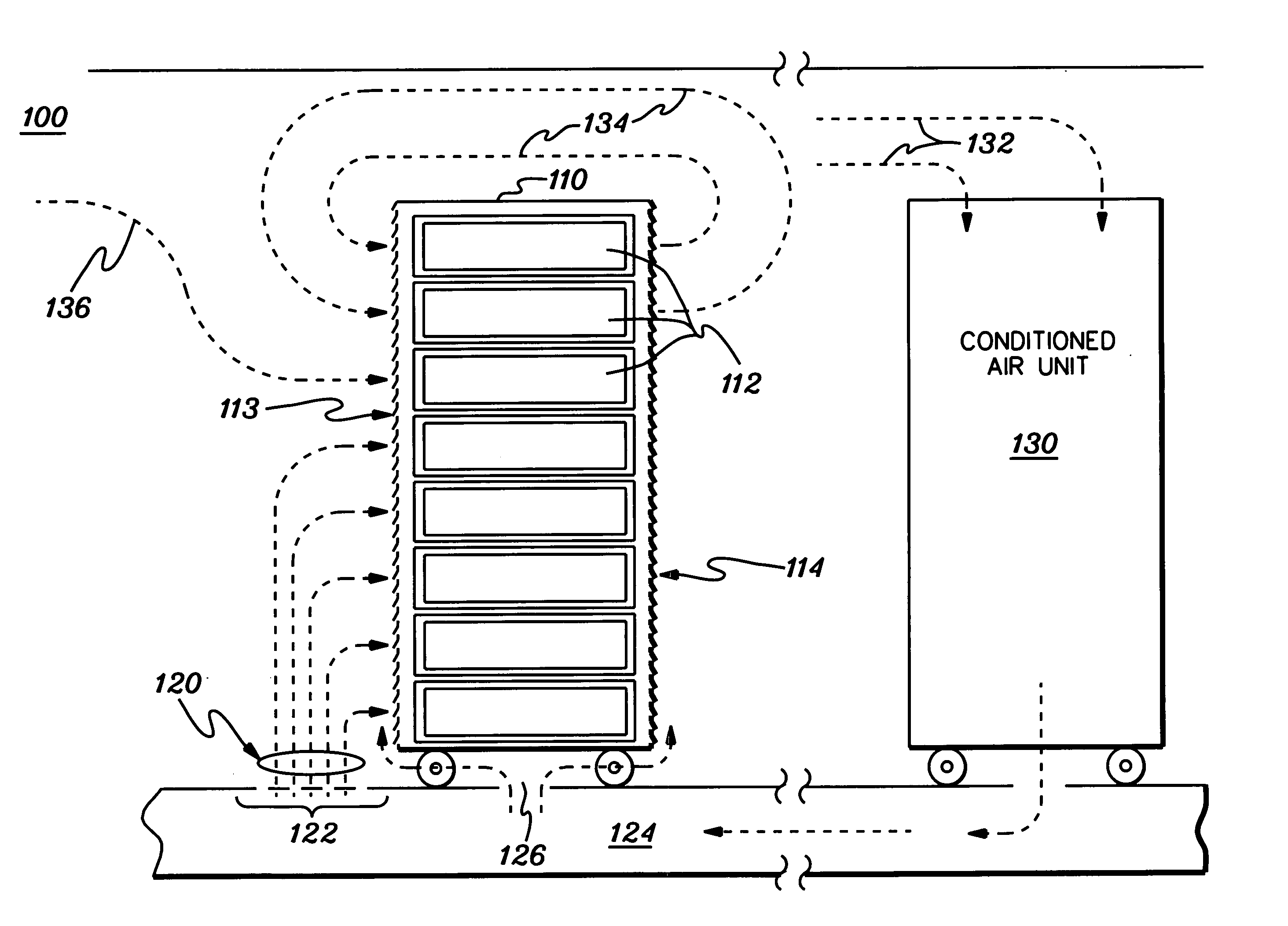

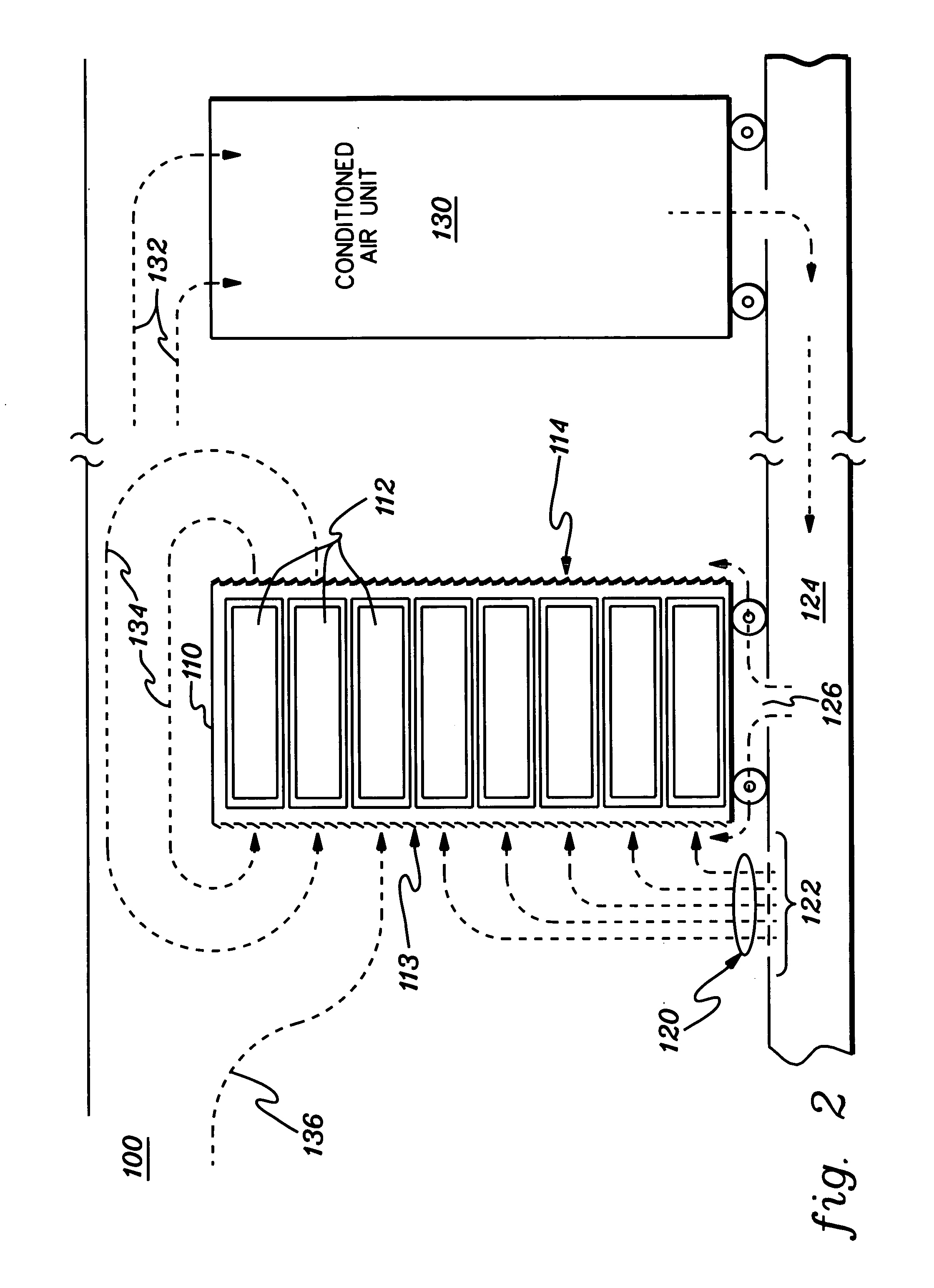

Air flow system and method for facilitating cooling of stacked electronics components

InactiveUS20050237716A1Improve cooling effectWell mixedCooling/ventilation/heating modificationsElectronic componentElectronics

An air flow system and method are provided which include a duct configured to mount either as an inlet or outlet duct to an electronics rack. When mounted to cover an air-intake side of the electronics rack, a supply air flow plenum is defined for directing conditioned air to the air-intake side. The duct includes a first air inlet at a first end for receiving the conditioned air, and is tapered from the first end to a second end thereof, with the supply plenum having a varying air flow cross-section. The duct further includes a second air inlet for providing supplemental room air to the plenum. The second inlet is disposed adjacent to the first inlet, thereby facilitating mixing of conditioned air with room air within the supply air flow plenum prior to delivery thereof to the air-intake side of the electronics rack.

Owner:IBM CORP

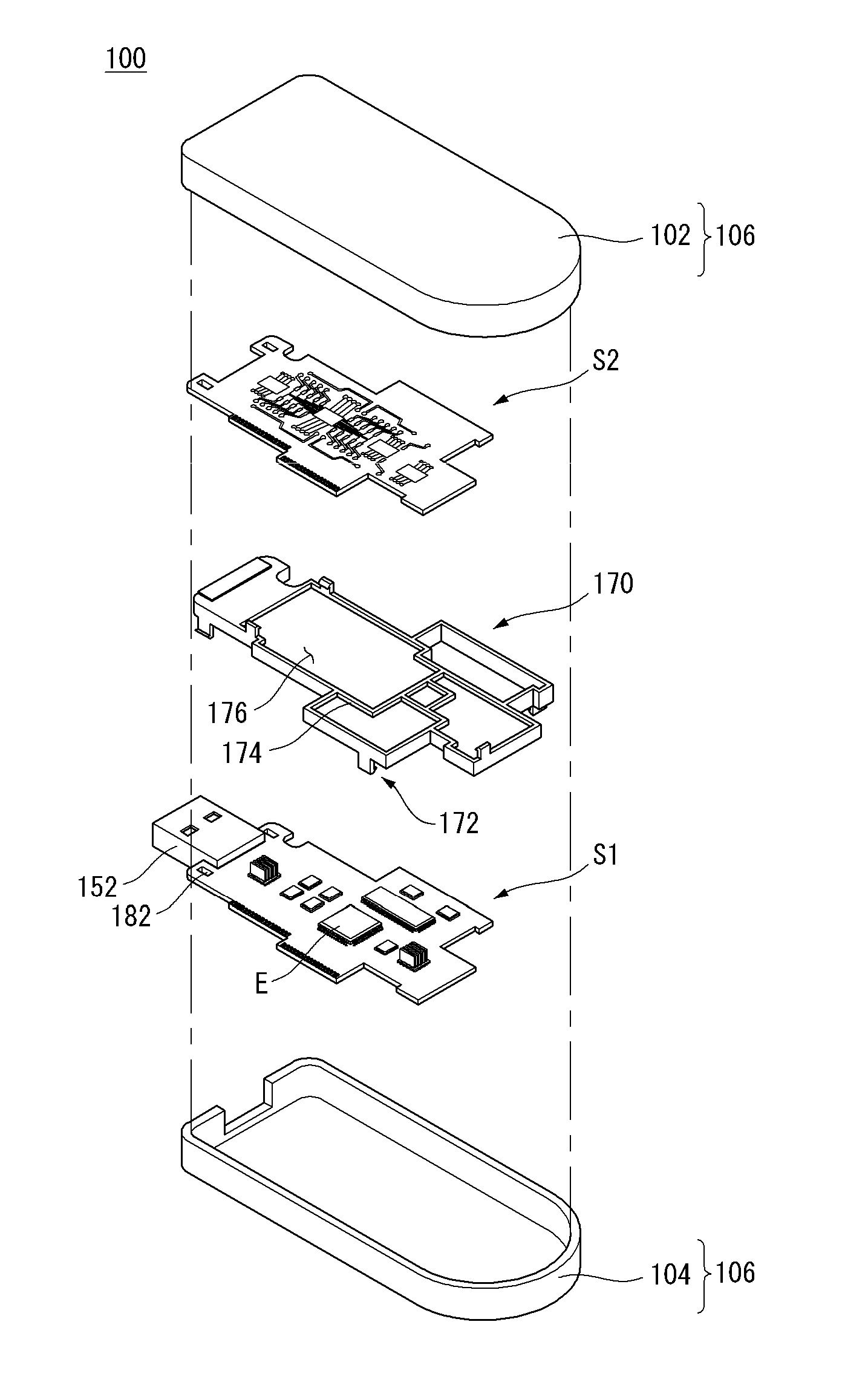

Mobile terminal

InactiveUS20110188207A1Efficient transferMinimized in sizeDigital data processing detailsSemiconductor/solid-state device detailsData interchangeElectrical and Electronics engineering

A mobile terminal is provided. The mobile terminal comprises at least one element, a connector selectively connected to another device to provide a data exchange path between the at least one element and the other device, and a thermal conduction frame having one side coming into contact with the at least one element and the other side coming into contact with the connector to transfer heat generated from the at least one element to the connector. The connector is connected to the element included in the mobile terminal and the other device through the thermal conduction frame to effectively transfer heat generated from the element to the other device through the connector.

Owner:LG ELECTRONICS INC

System-in packages

ActiveUS8503186B2Improve uniformityCircuit arrangements on support structuresSemiconductor/solid-state device detailsMetal interconnectSystem in package

Owner:QUALCOMM INC

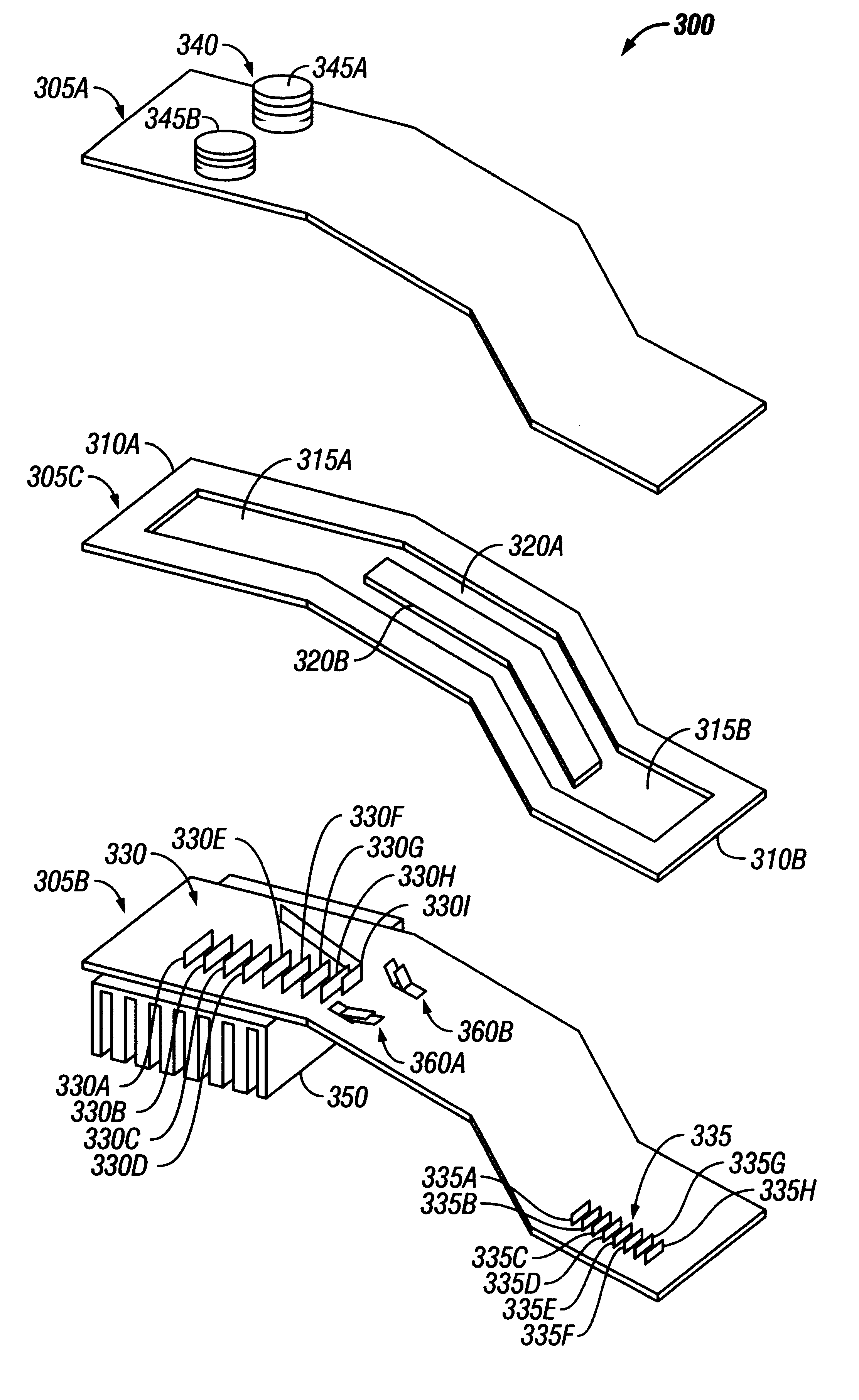

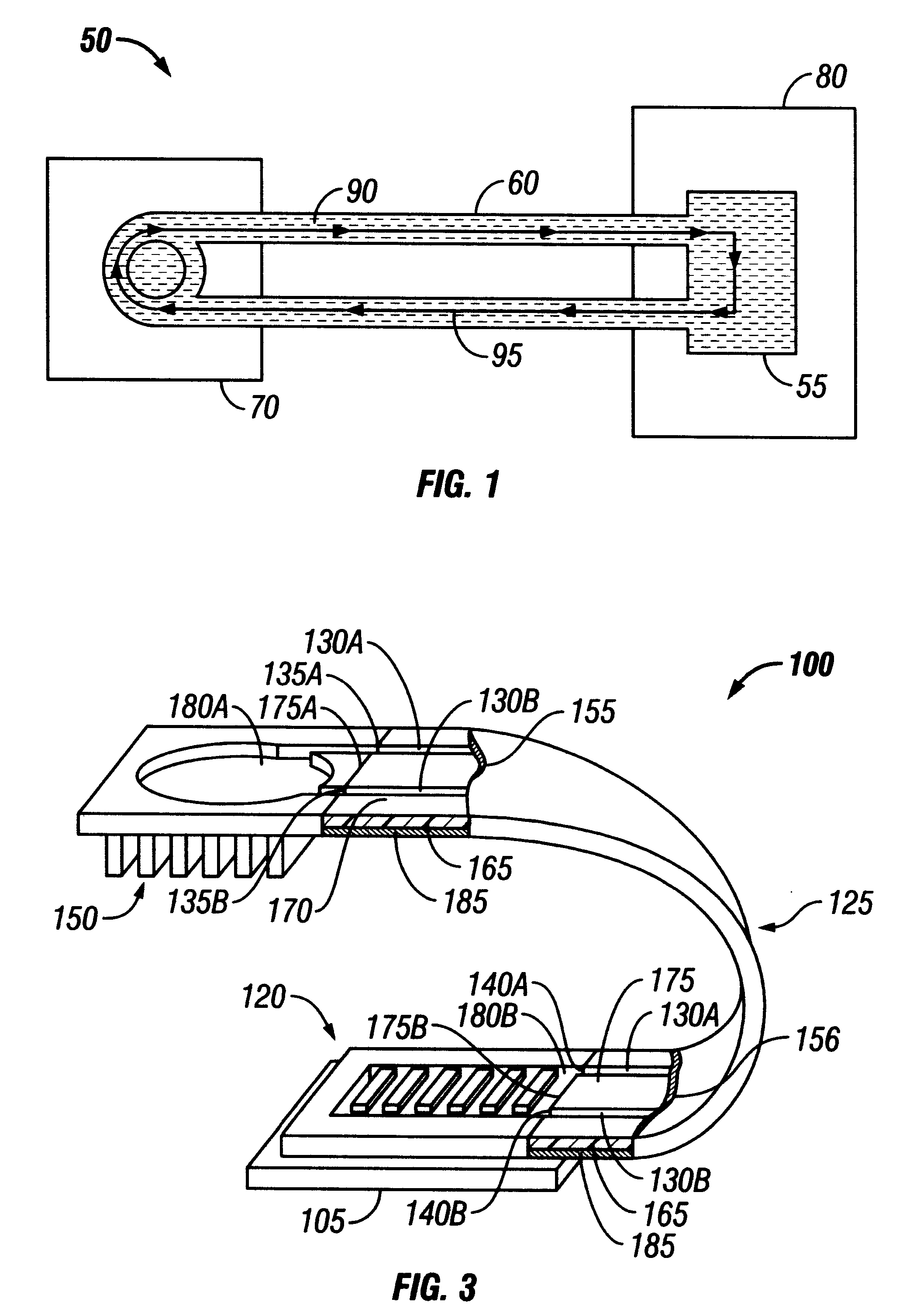

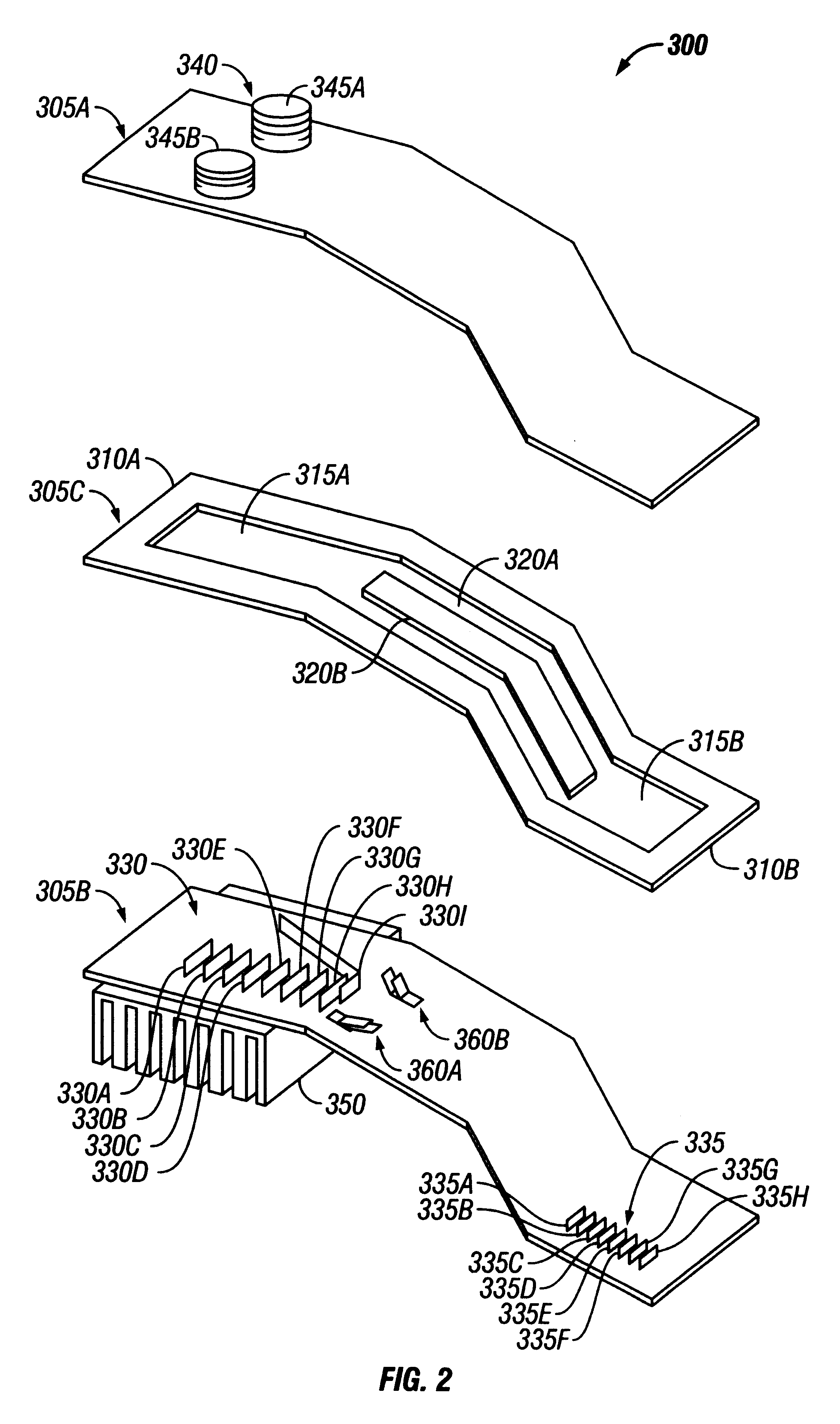

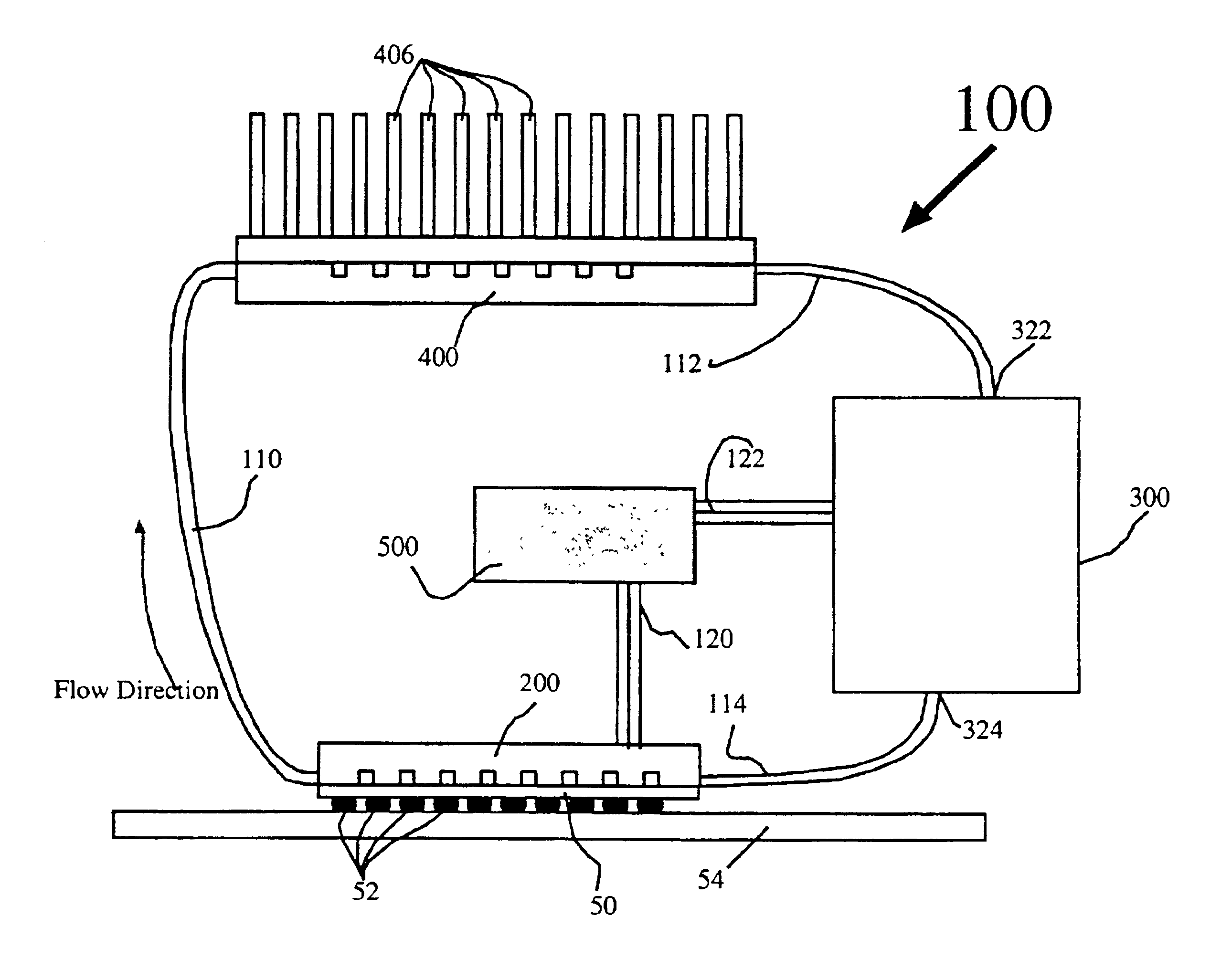

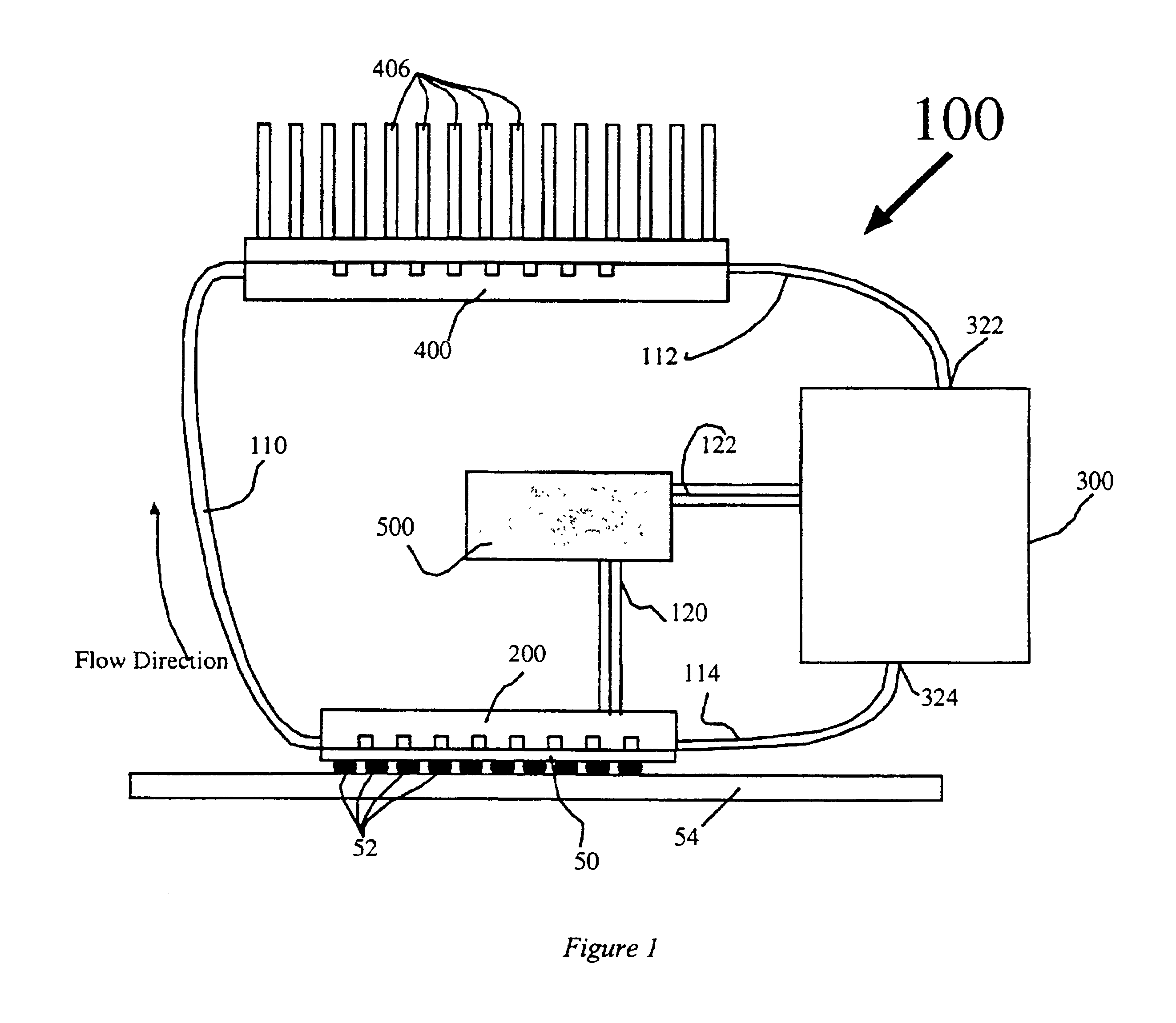

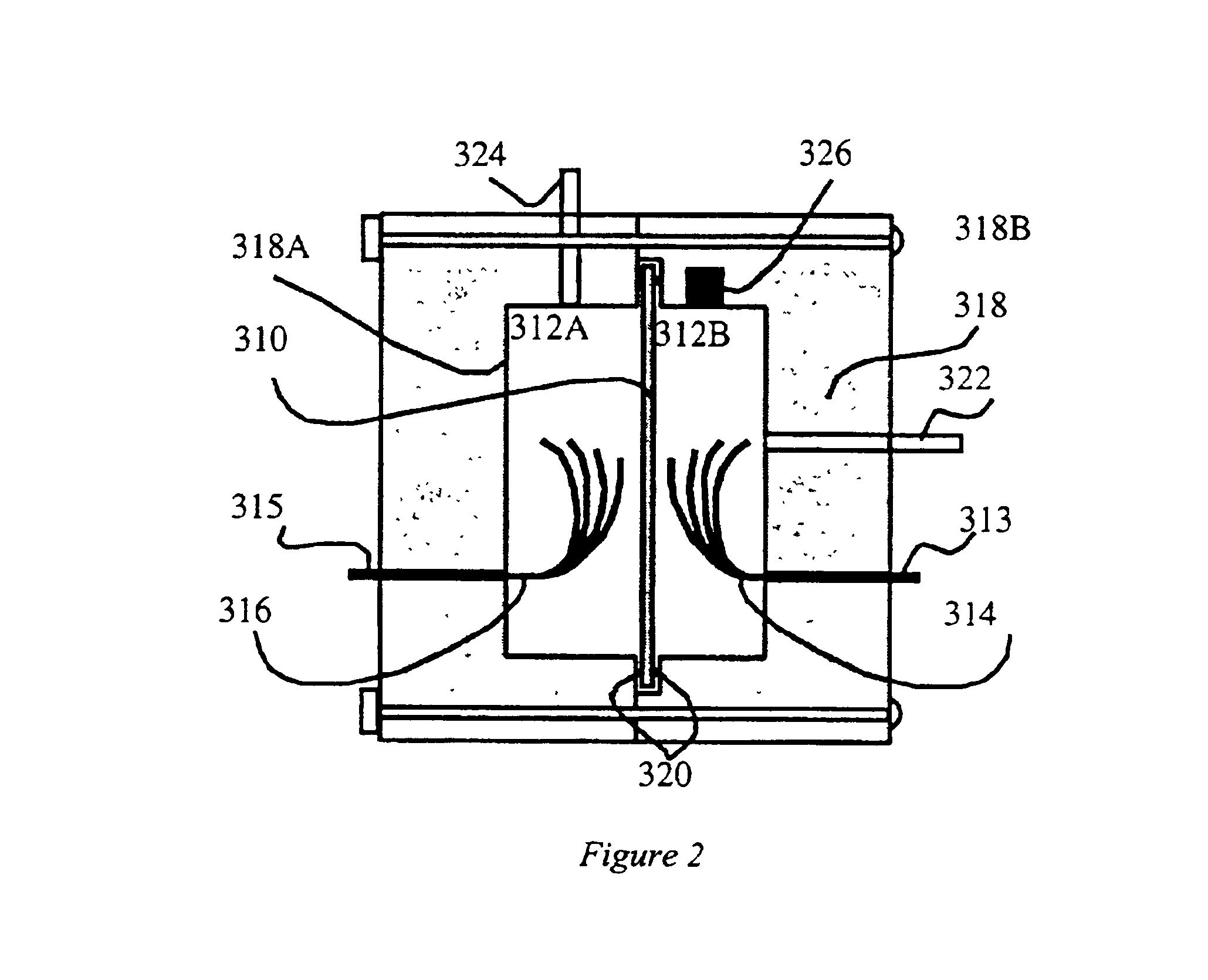

Integrated cooling system

InactiveUS6529377B1Cost effectiveQuality improvementOrganic active ingredientsDigital data processing detailsClosed loopEngineering

Systems and methods are described for integrated cooling system. A method includes: circulating a liquid inside a flexible multi-layer tape; and transporting heat between a heat source that is coupled to the flexible multi-layer tape and a heat sink that is coupled to the flexible multi-layer tape. A method includes installing a flexible multi-layer tape in an electrical system, wherein the flexible multi-layer tape includes a top layer; an intermediate, layer coupled to the top layer; and a bottom layer coupled to the intermediate layer, the intermediate layer defining a closed loop circuit for a circulating fluid. An apparatus includes a flexible multi-layer tape, including: a top layer; an intermediate layer coupled to the top layer; and a bottom layer coupled to the intermediate layer, wherein the intermediate layer defines a closed loop circuit for a circulating fluid.

Owner:STOVOKOR TECH

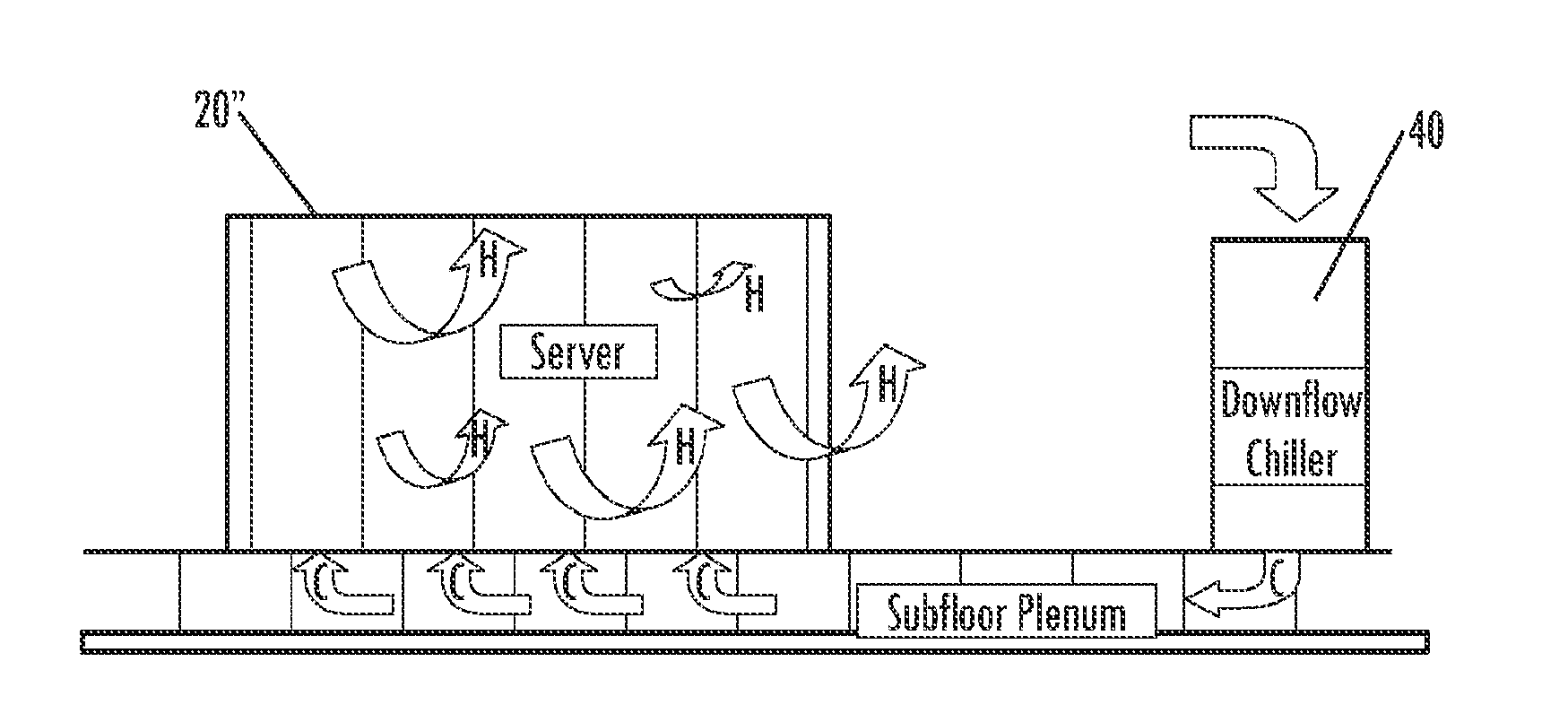

Energy saving system and method for cooling computer data center and telecom equipment

ActiveUS20090168345A1Avoid thermal failureEfficient cooling and heatingMechanical apparatusSpace heating and ventilation safety systemsElectricityData center

A system and method of reducing consumption of electricity used to cool electronic computer data center, networking, and telecommunications equipment, and to reduce the incidence of thermal failure of electronic components, includes provision of one or more partitions to reduce the volume of the cooled environment supplying coldest possible cooled air from air conditioning systems to a chamber adjacent to racks containing the electronic components, preventing dilution of the supplied cooling airflow by warmer air from outside of the reduced volume environment, and controlling the delivery of cooling air flow through the reduced volume of the cooled environment.

Owner:MARTINI VALAN R

Electroosmotic microchannel cooling system

InactiveUS6942018B2High heat fluxIncrease powerFixed microstructural devicesSemiconductor/solid-state device detailsElectricityClosed loop

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Rack height cooling

InactiveUS20060139877A1Improve efficiencyLess opportunityCooling/ventilation/heating modificationsElectrical apparatus casings/cabinets/drawersCooling UnitsEngineering

A data center includes an electronic equipment rack having a front face and a back face and a cooling unit positioned adjacent to the rack, the cooling unit having a front face and a back face, the cooling unit being configured to exhaust cooled air from the front face of the cooling unit to cool the rack. The cooling unit is configured to release the cooled air along a substantial portion of a height of the front face of the rack.

Owner:AMERICA POWER CONVERSION CORP

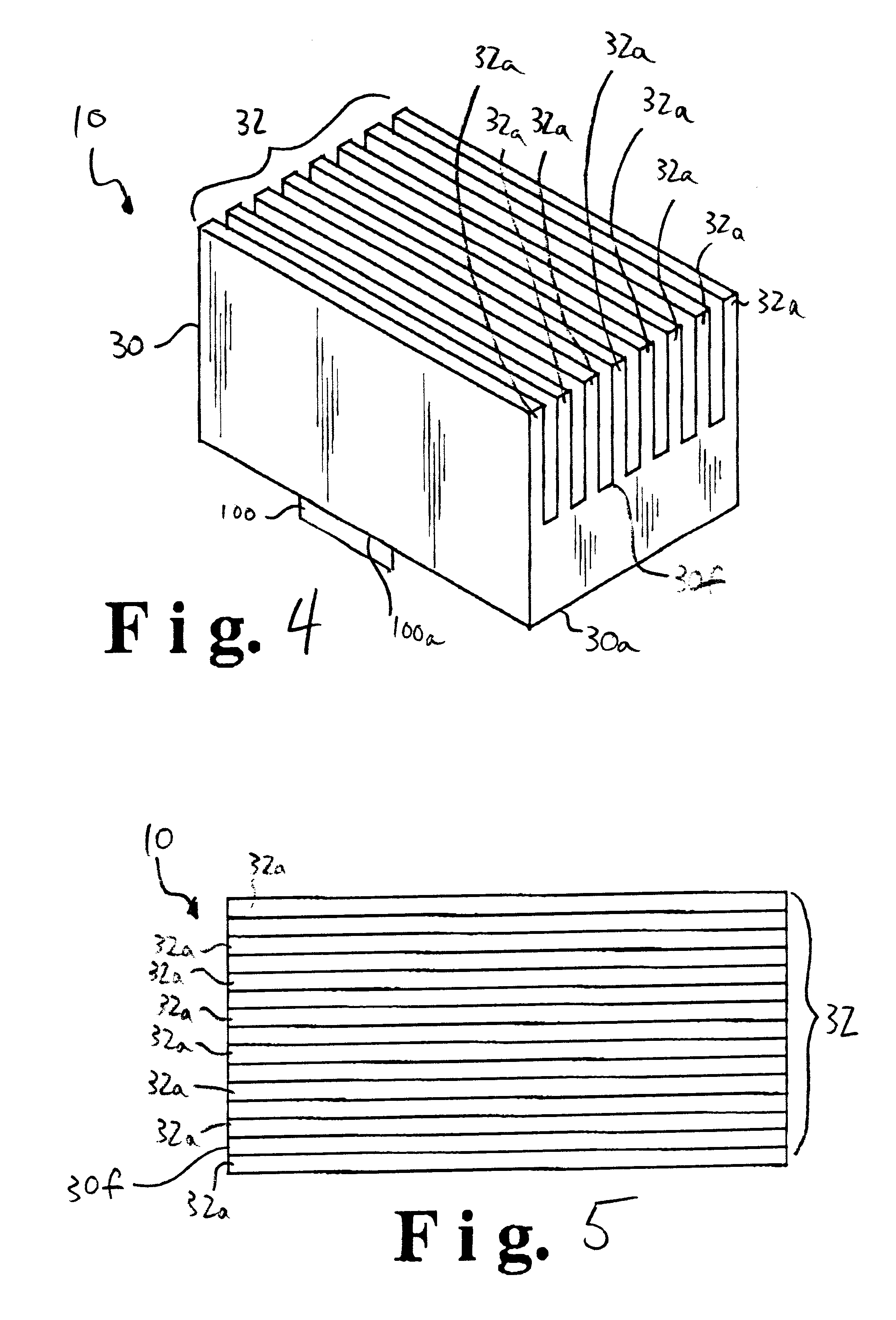

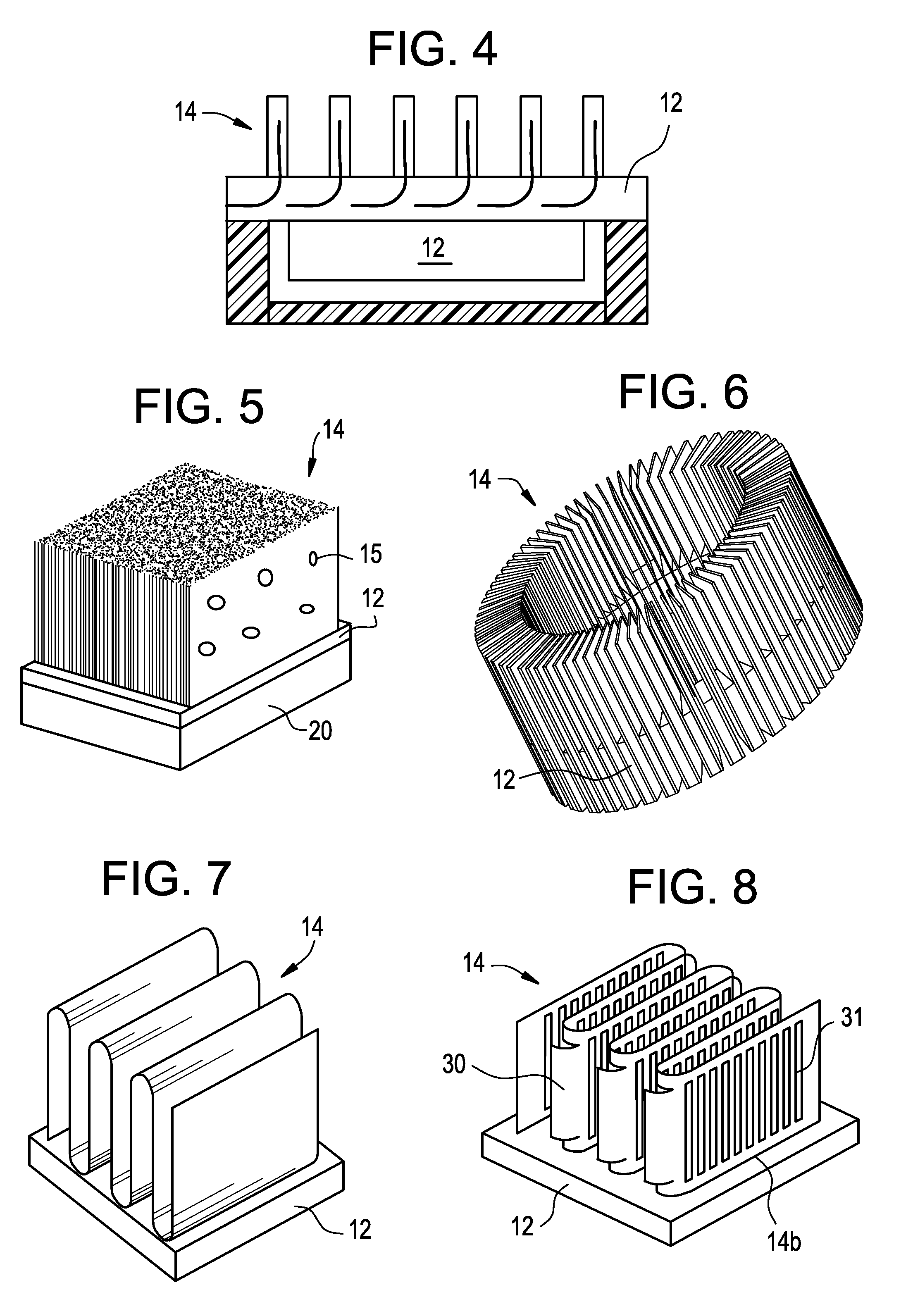

Advanced heat sinks and thermal spreaders

InactiveUS20070053168A1Material nanotechnologyDigital data processing detailsGraphiteMaterials science

A heat sink assembly for an electronic device or a heat generating device(s) is constructed from an ultra-thin graphite layer. The ultra-thin graphite layer exhibits thermal conductivity which is anisotropic in nature and is greater than 500 W / m° C. in at least one plane and comprises at least a graphene layer. The ultra-thin graphite layer is structurally supported by a layer comprising at least one of a metal, a polymeric resin, a ceramic, and a mixture thereof, which is disposed on at least one surface of the graphite layer.

Owner:GENERAL ELECTRIC CO