Patents

Literature

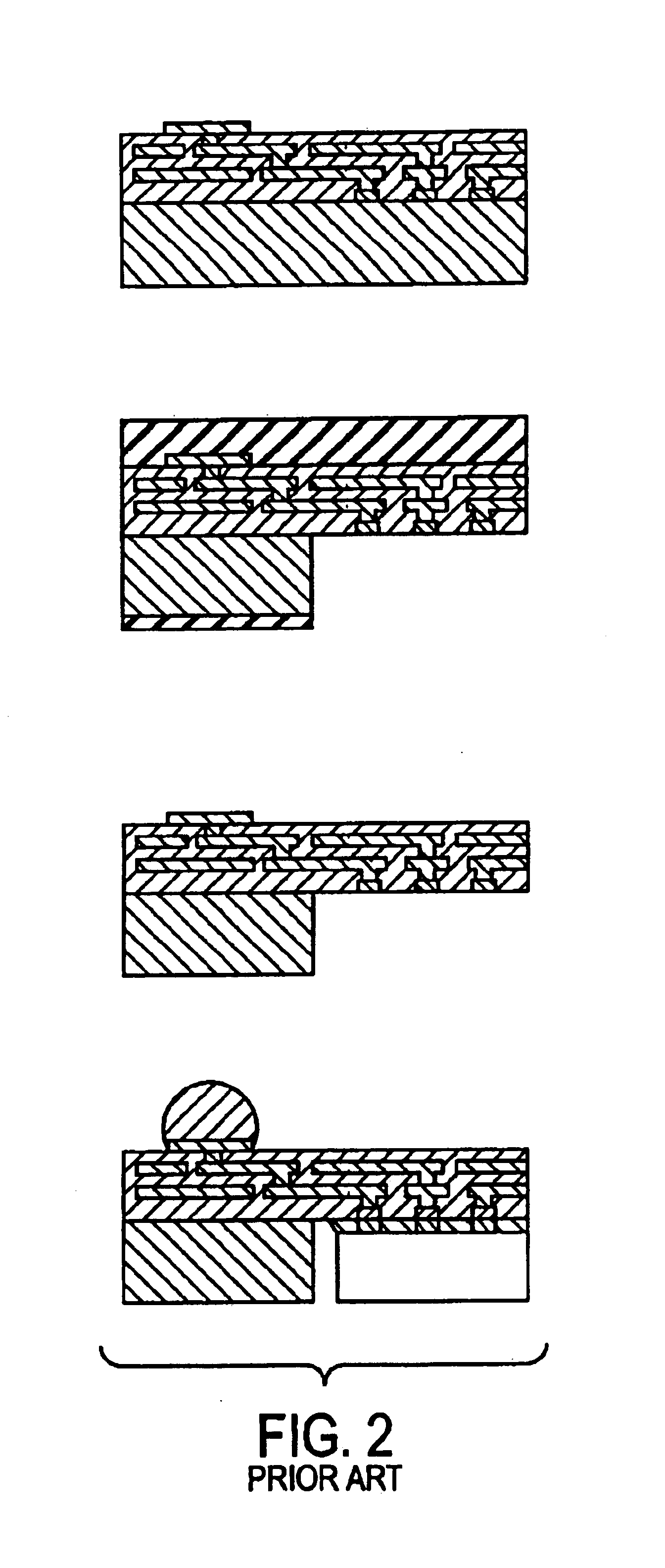

778 results about "System in package" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

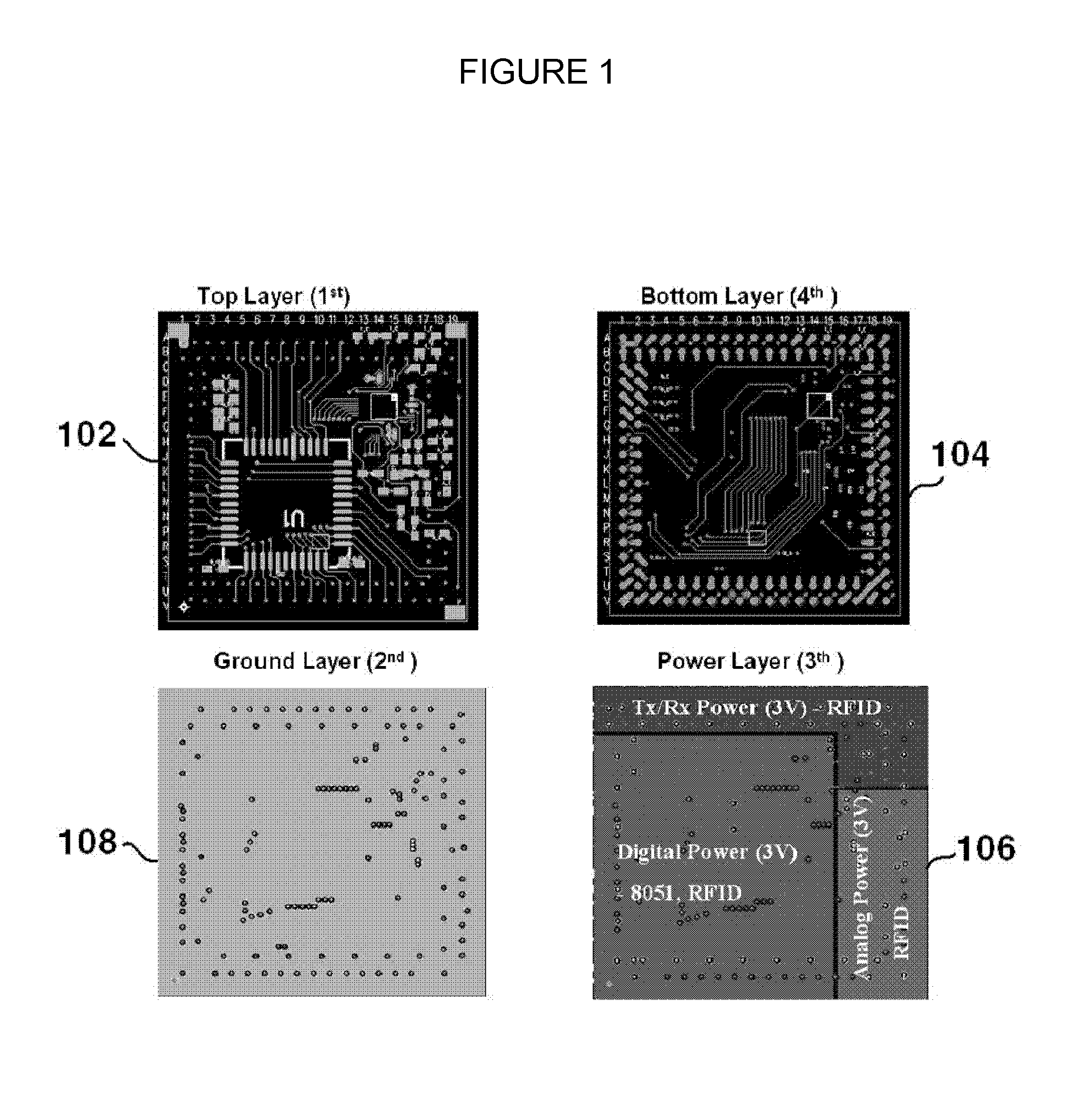

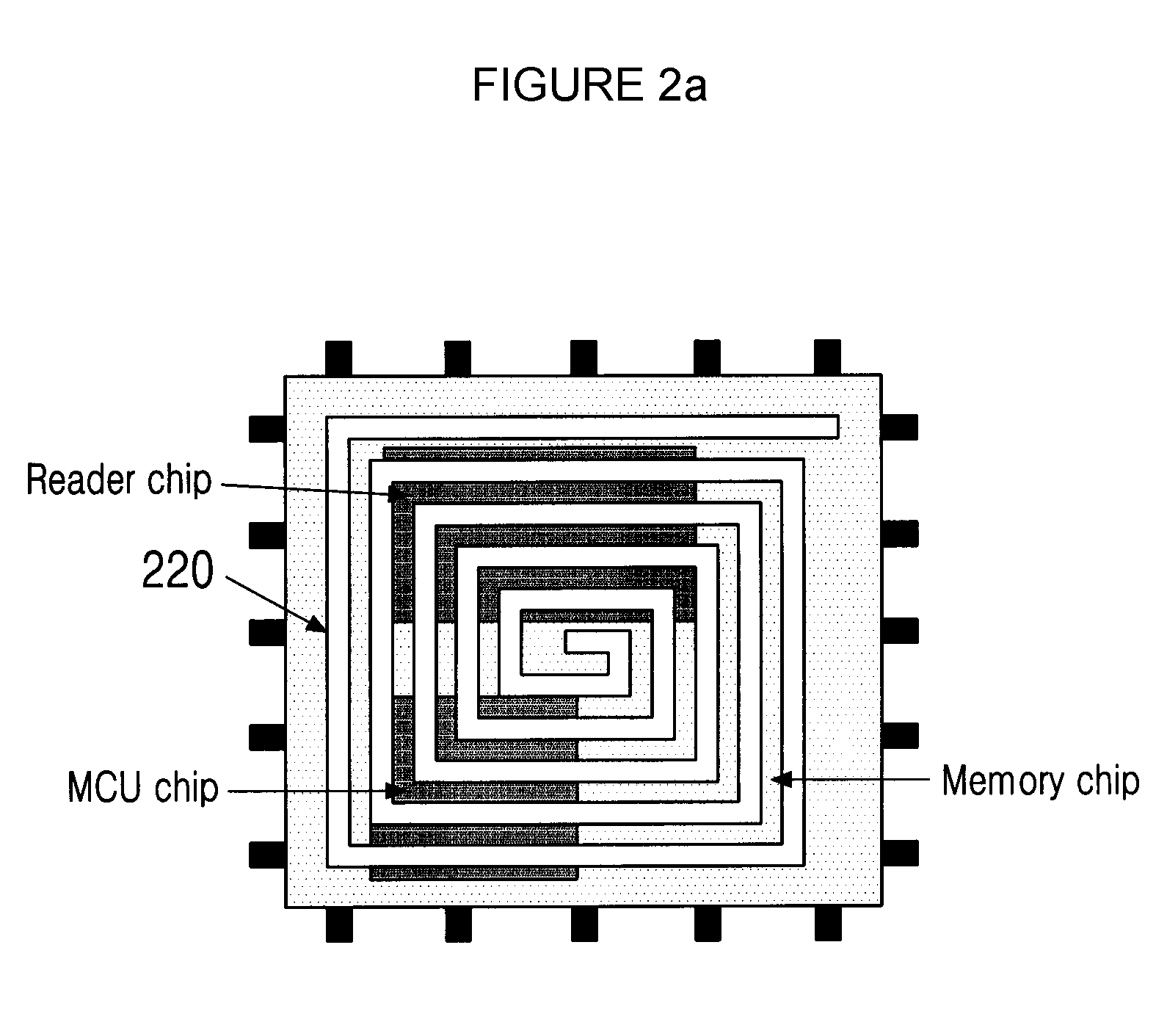

A system in package (SiP) or system-in-a-package is a number of integrated circuits enclosed in a single chip carrier package. The SiP performs all or most of the functions of an electronic system, and is typically used inside a mobile phone, digital music player, etc. Dies containing integrated circuits may be stacked vertically on a substrate. They are internally connected by fine wires that are bonded to the package. Alternatively, with a flip chip technology, solder bumps are used to join stacked chips together. Systems-in-package are like systems-on-chip (SoC) but less tightly integrated and not on a single semiconductor die.

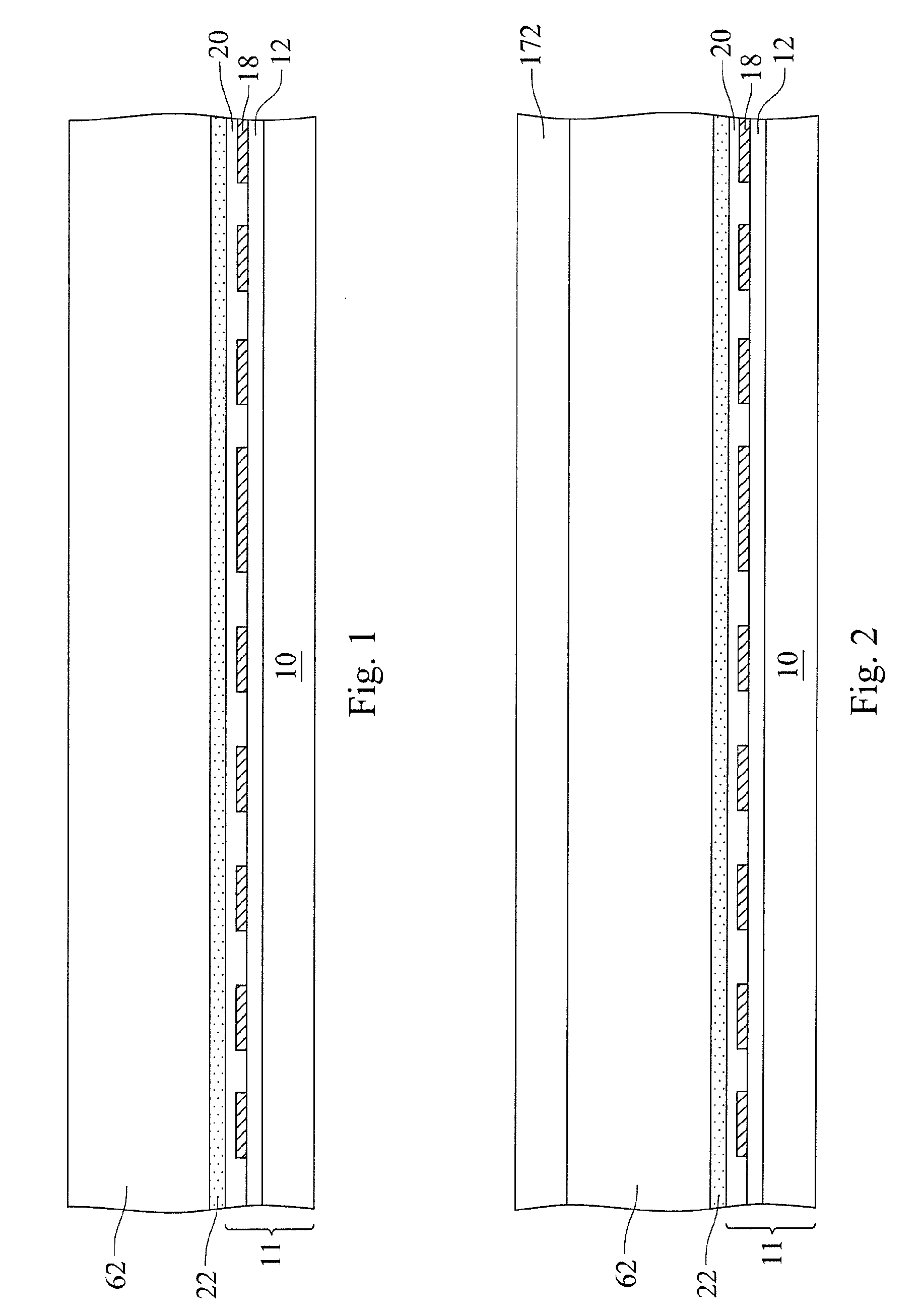

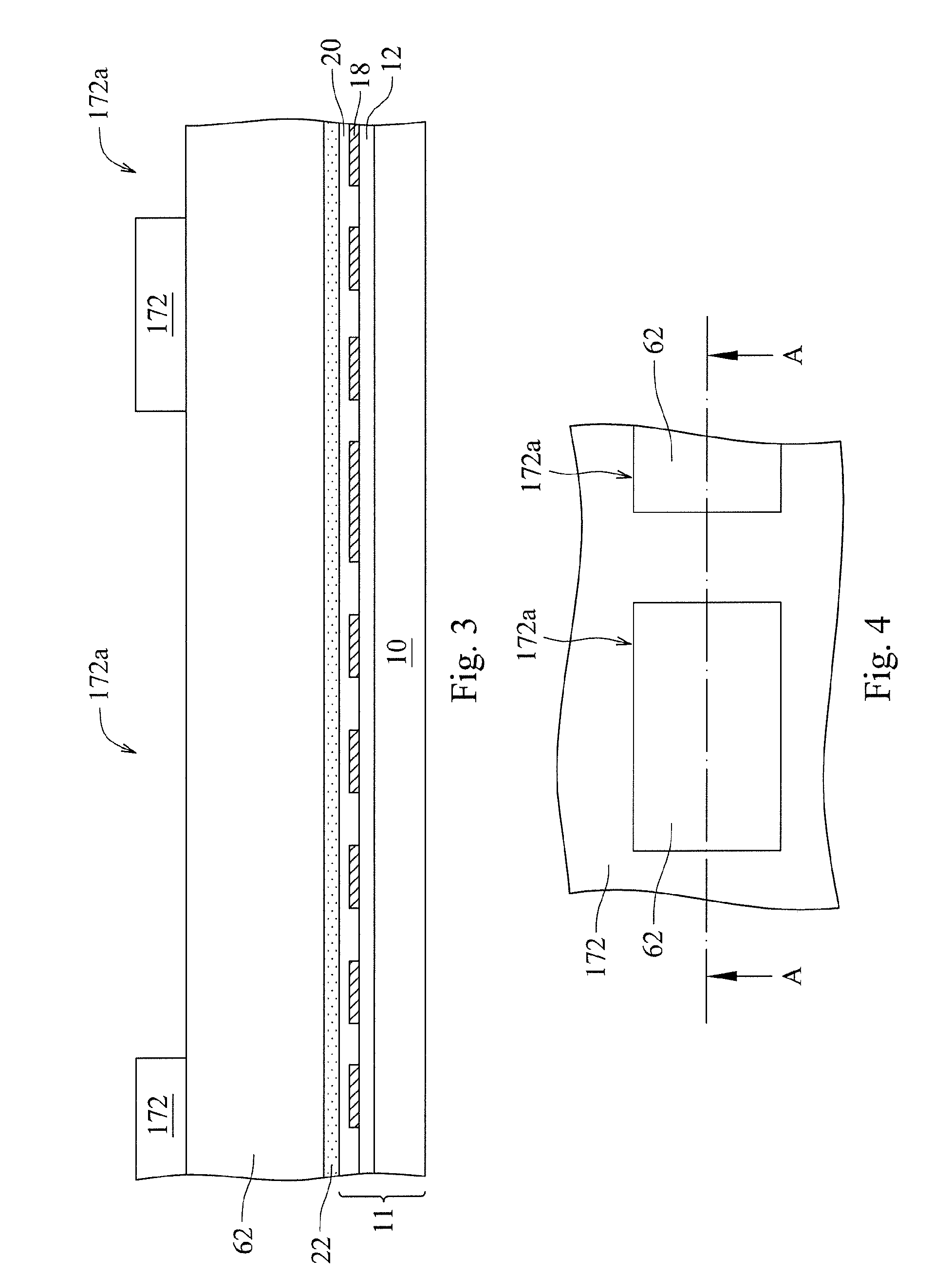

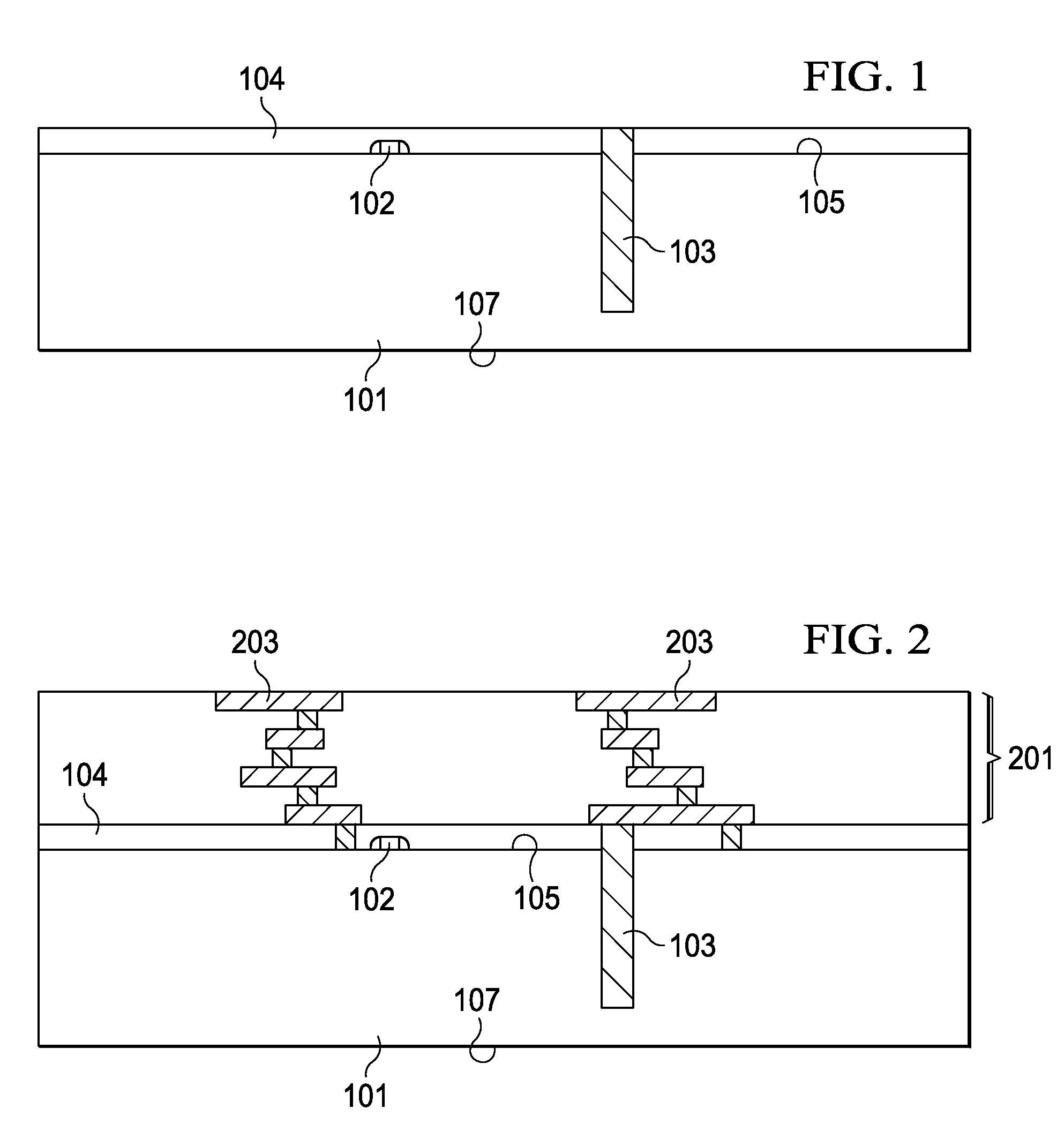

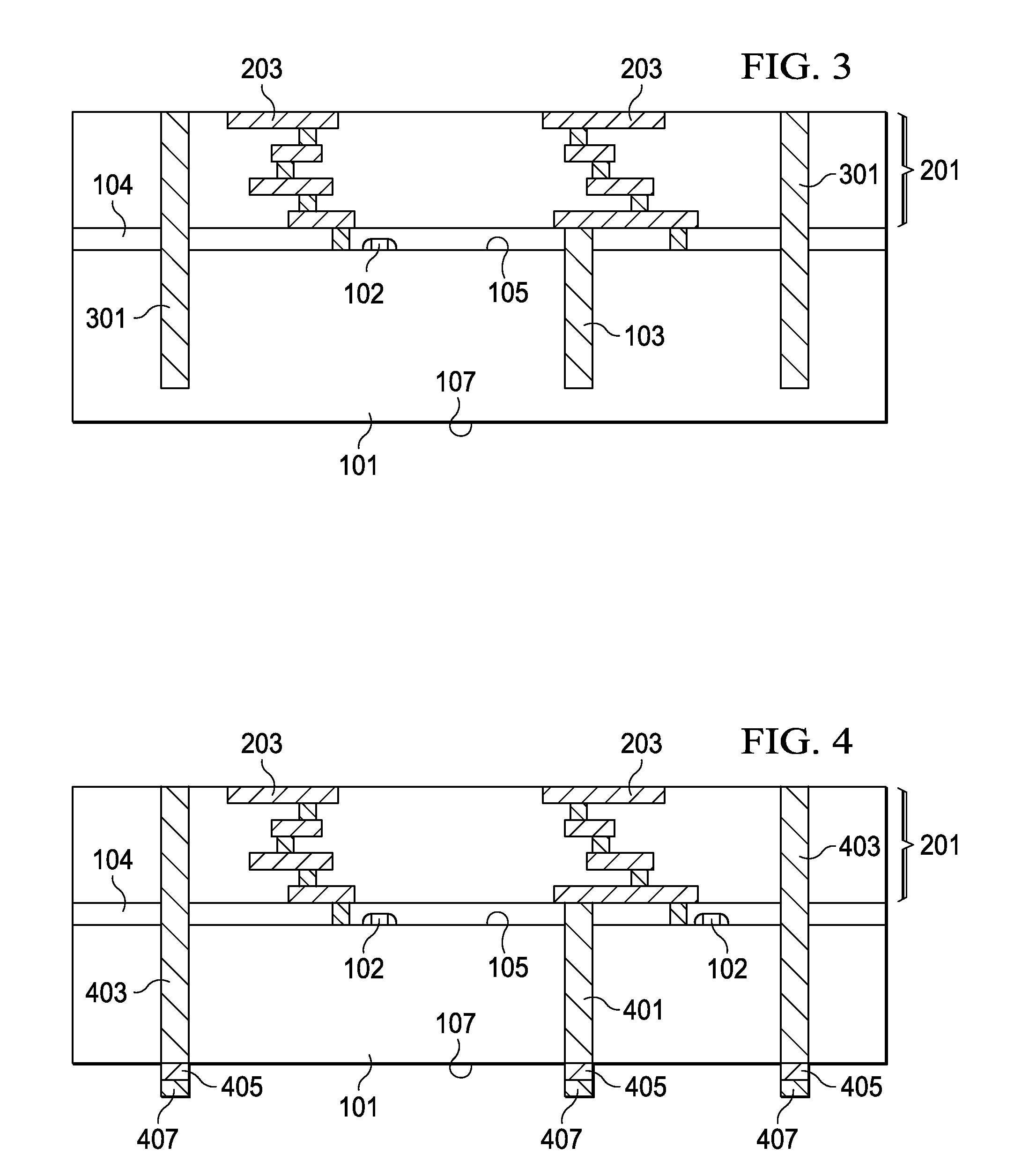

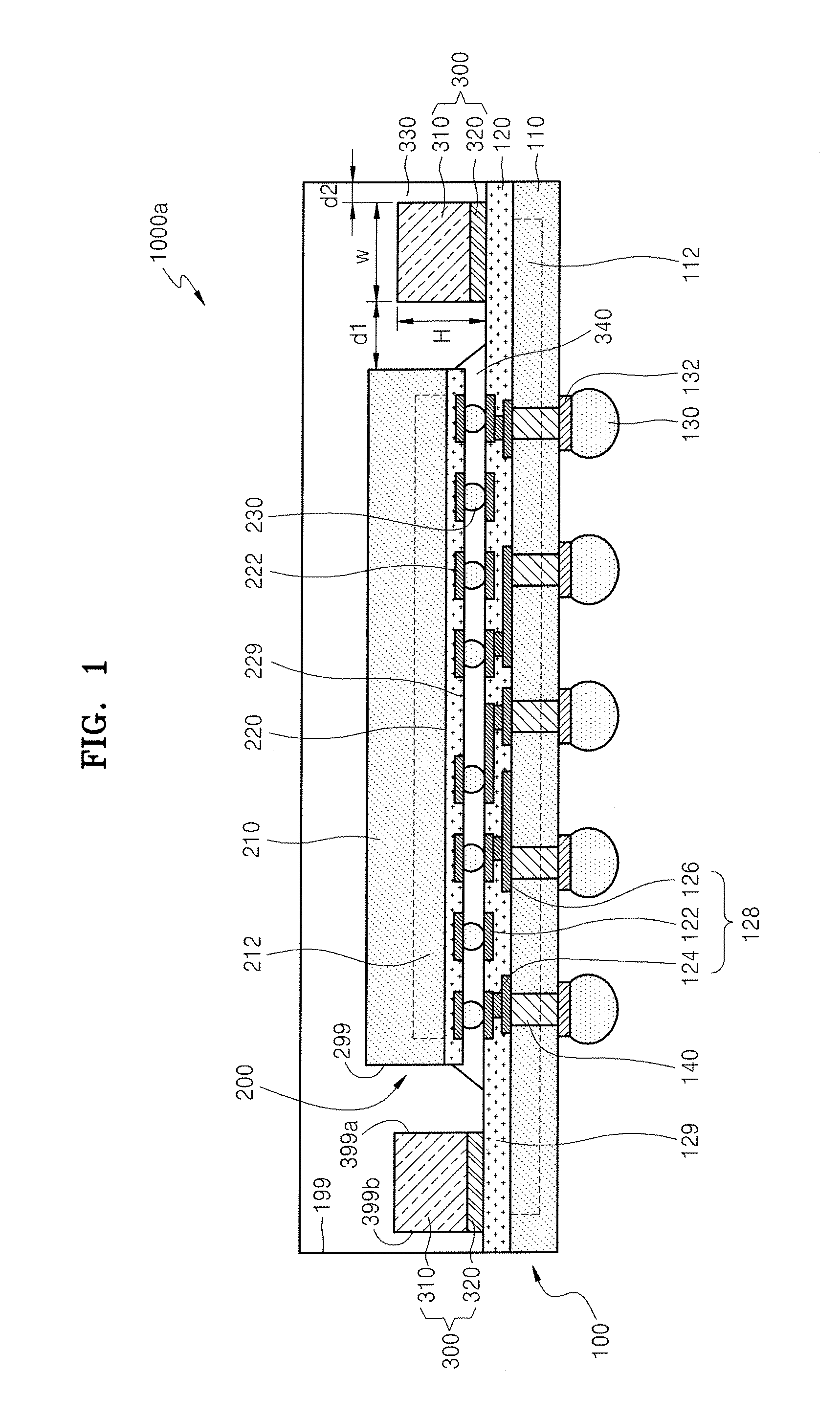

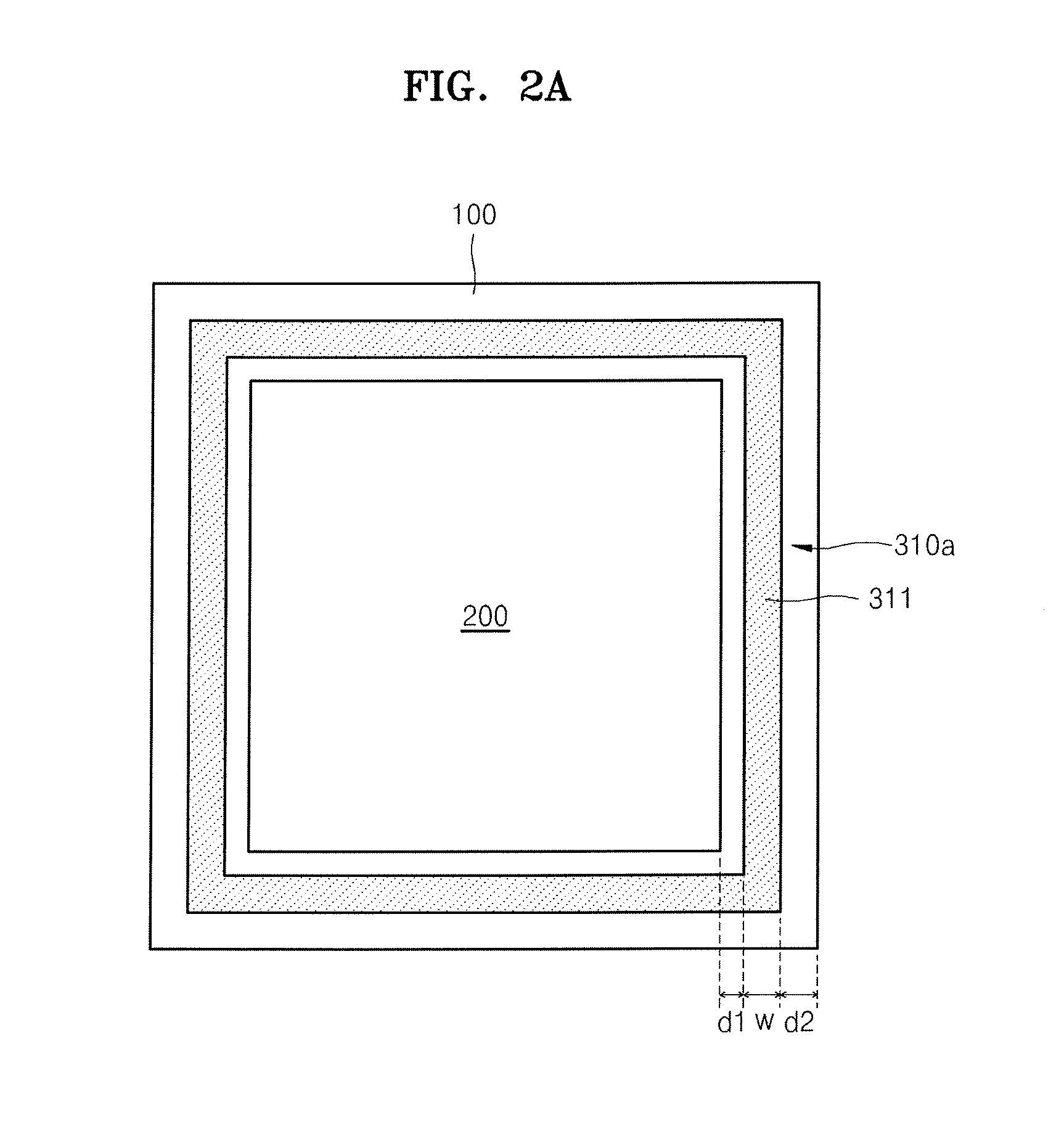

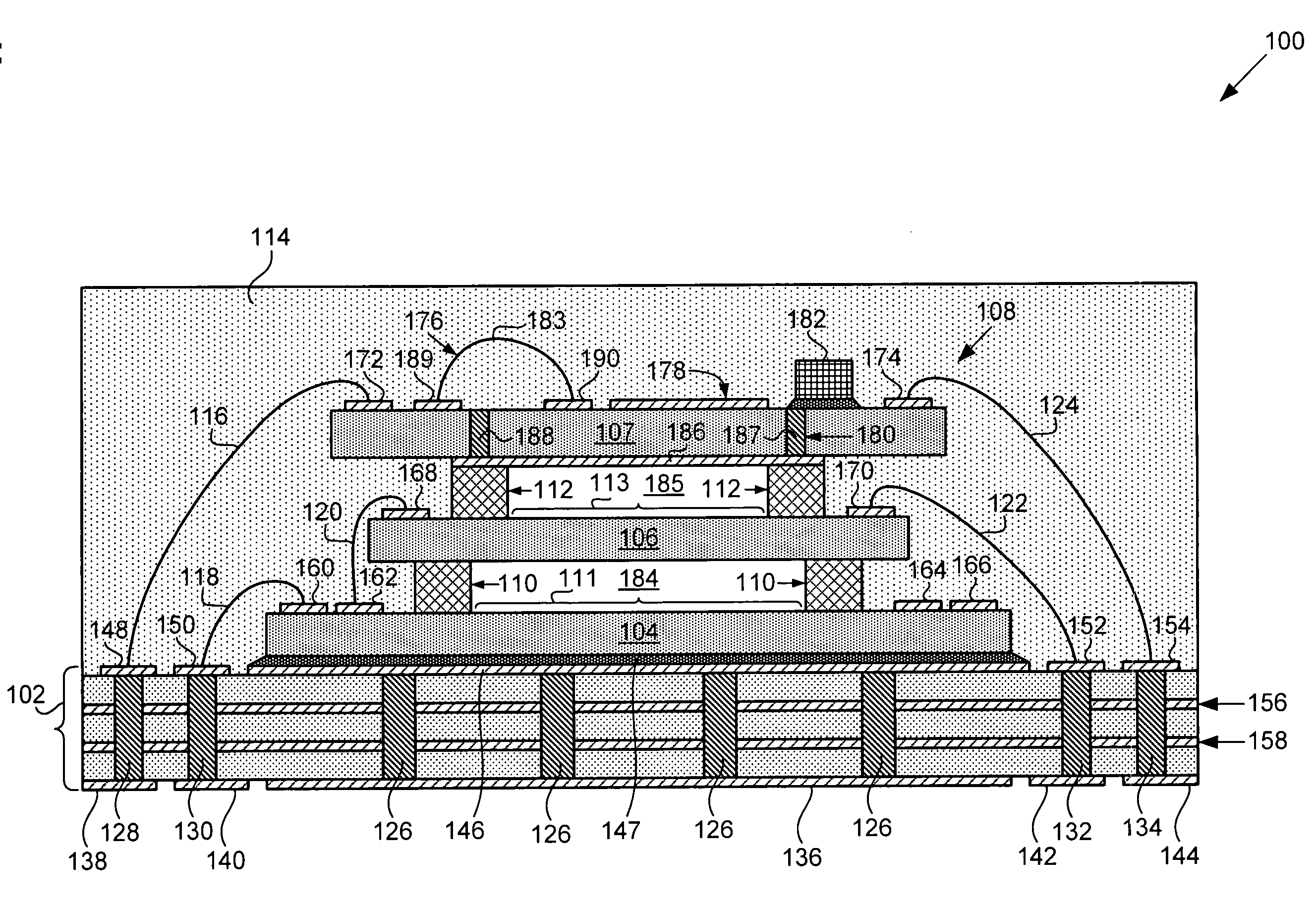

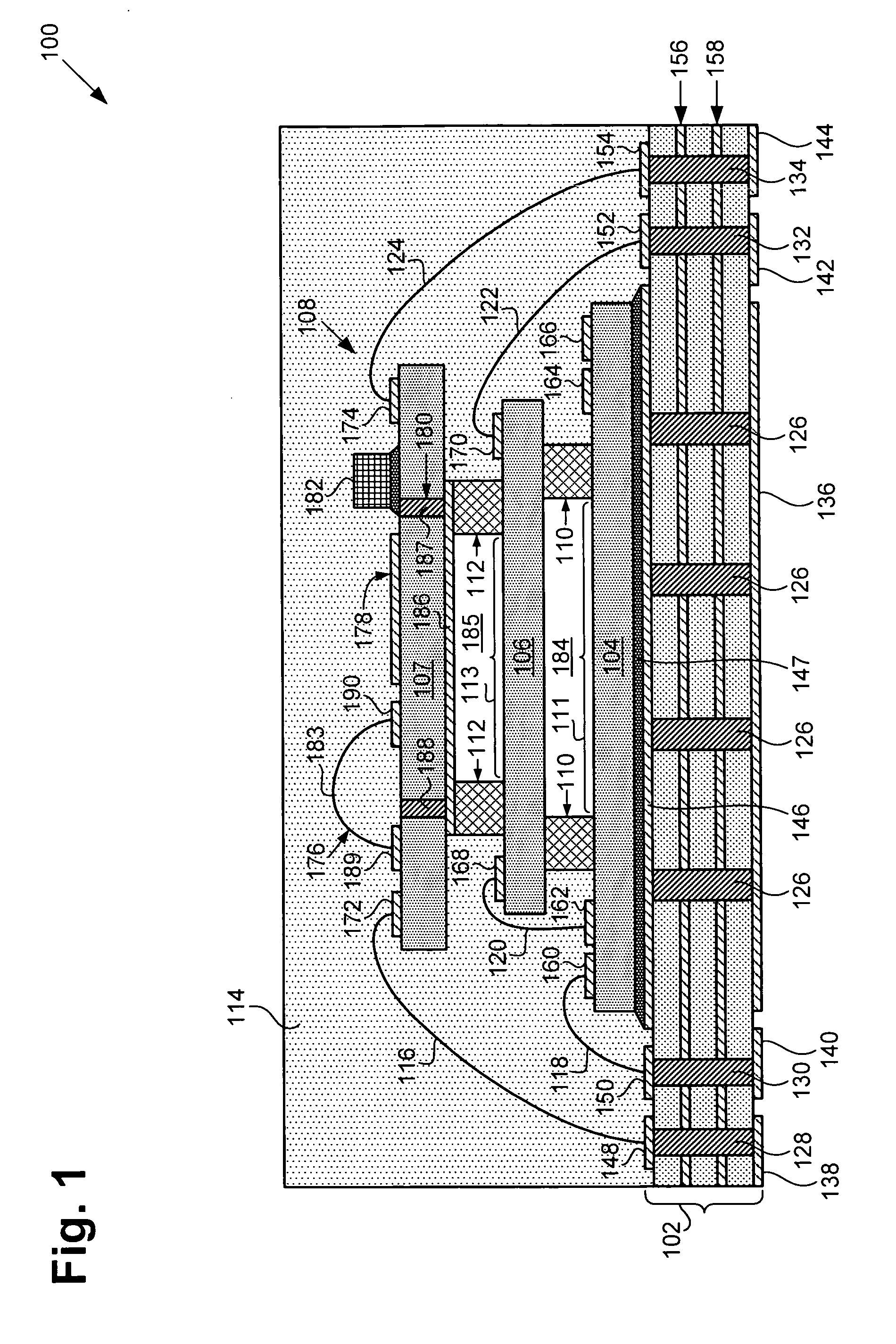

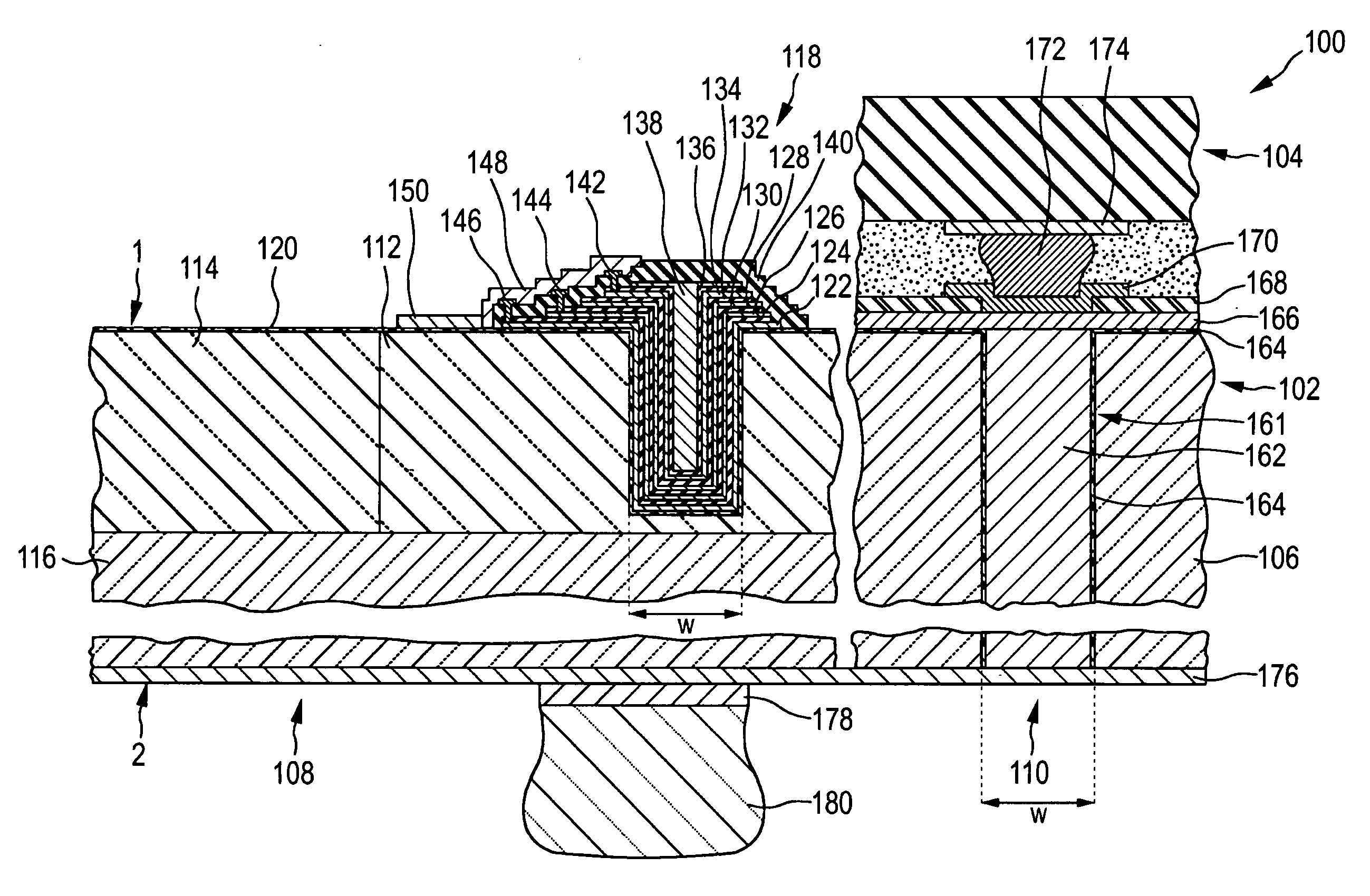

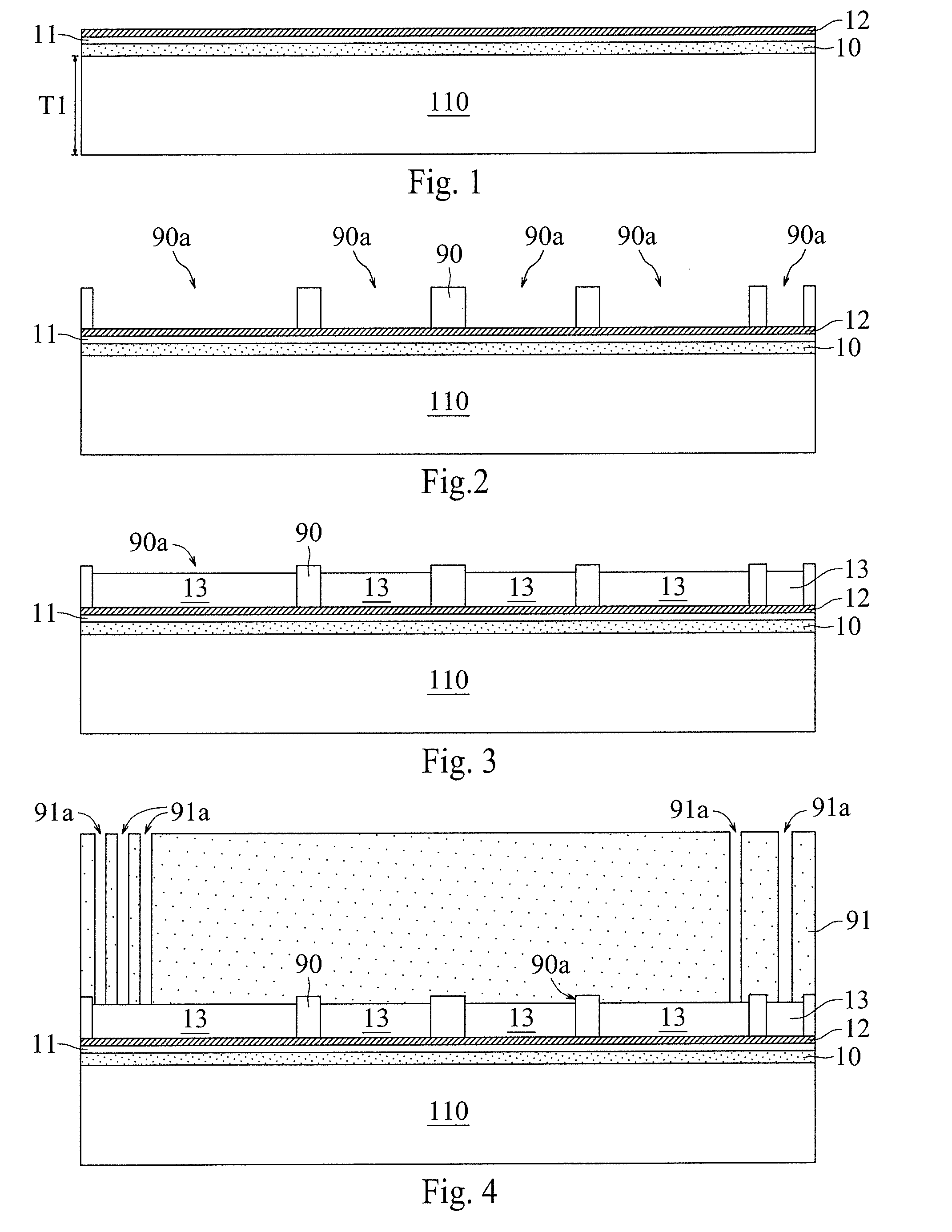

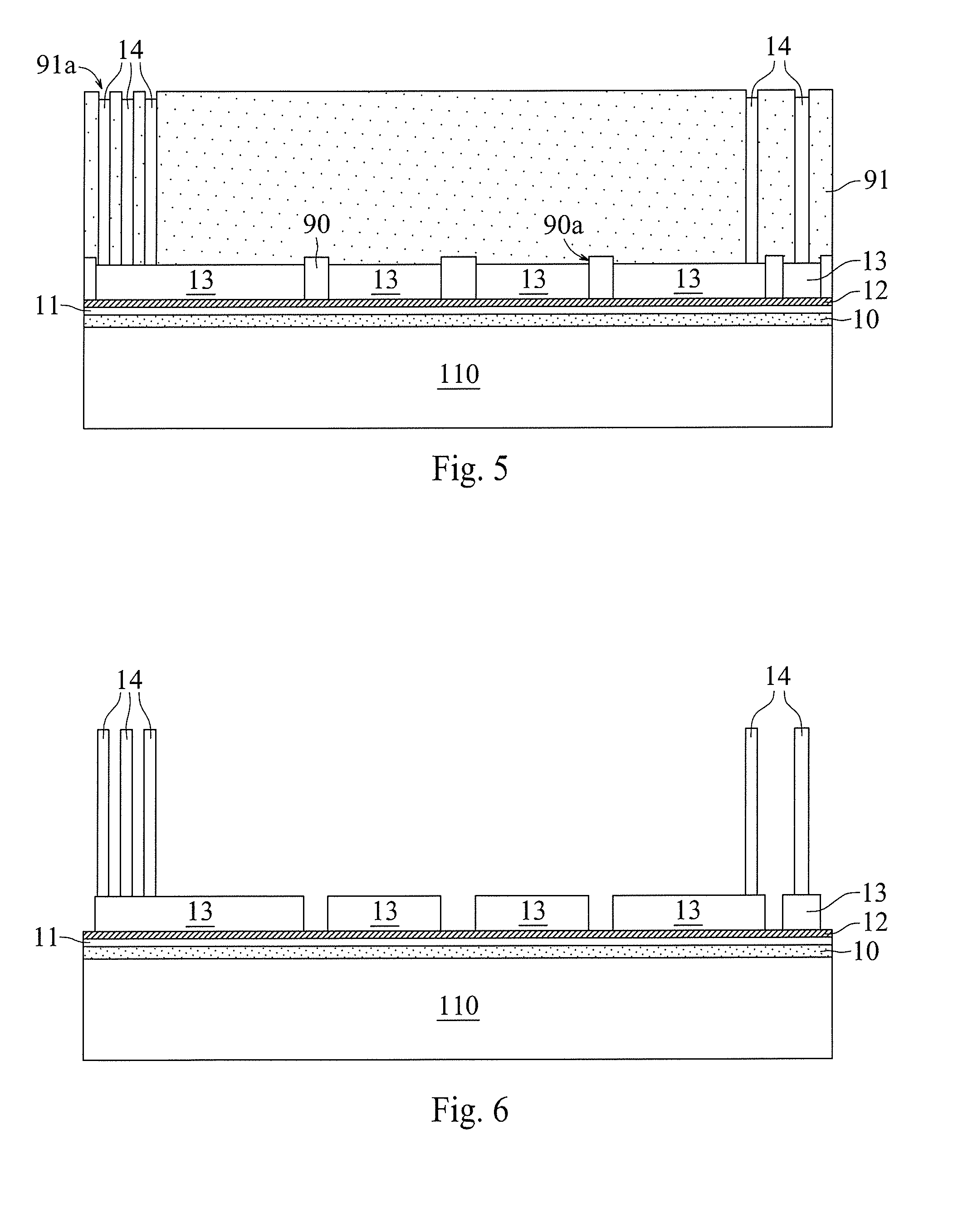

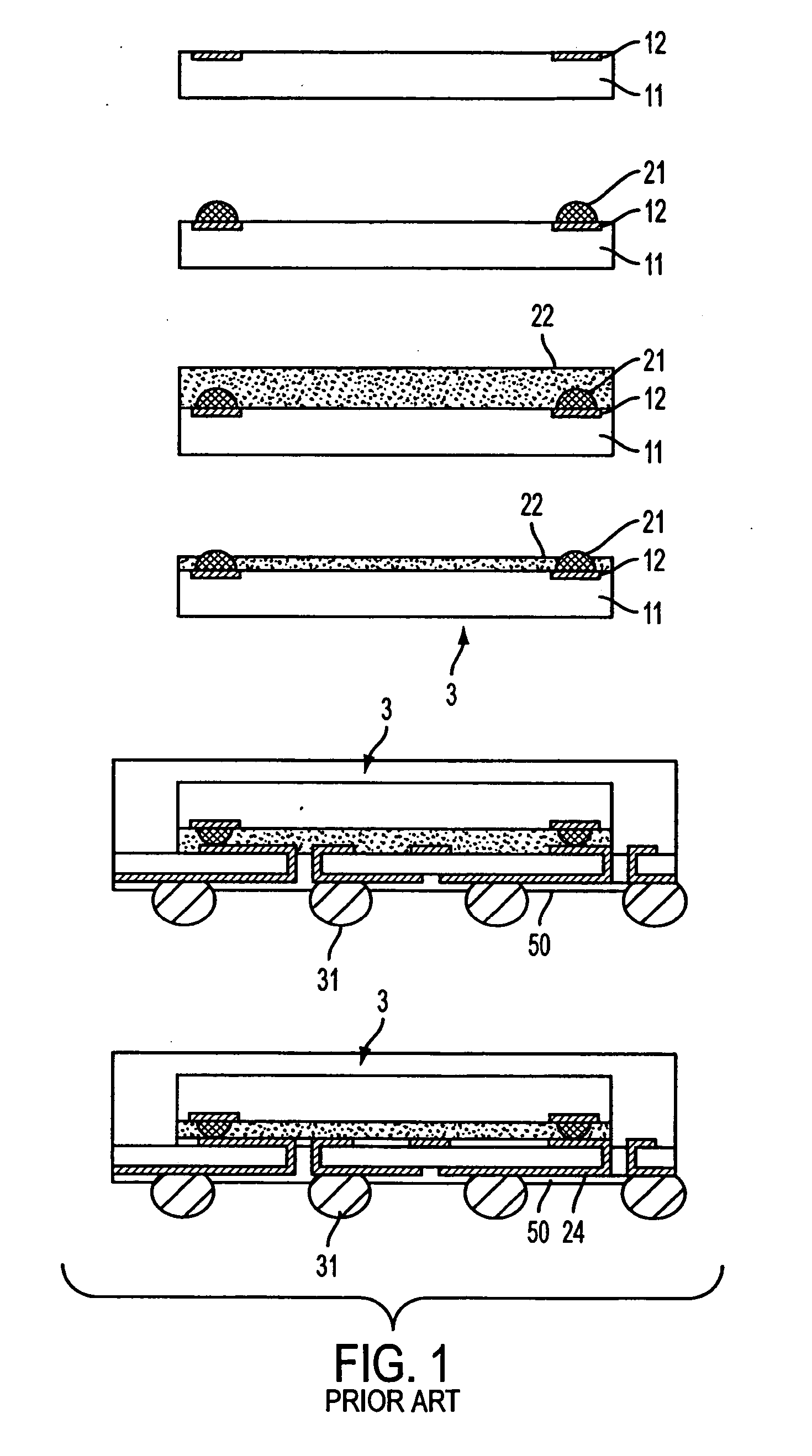

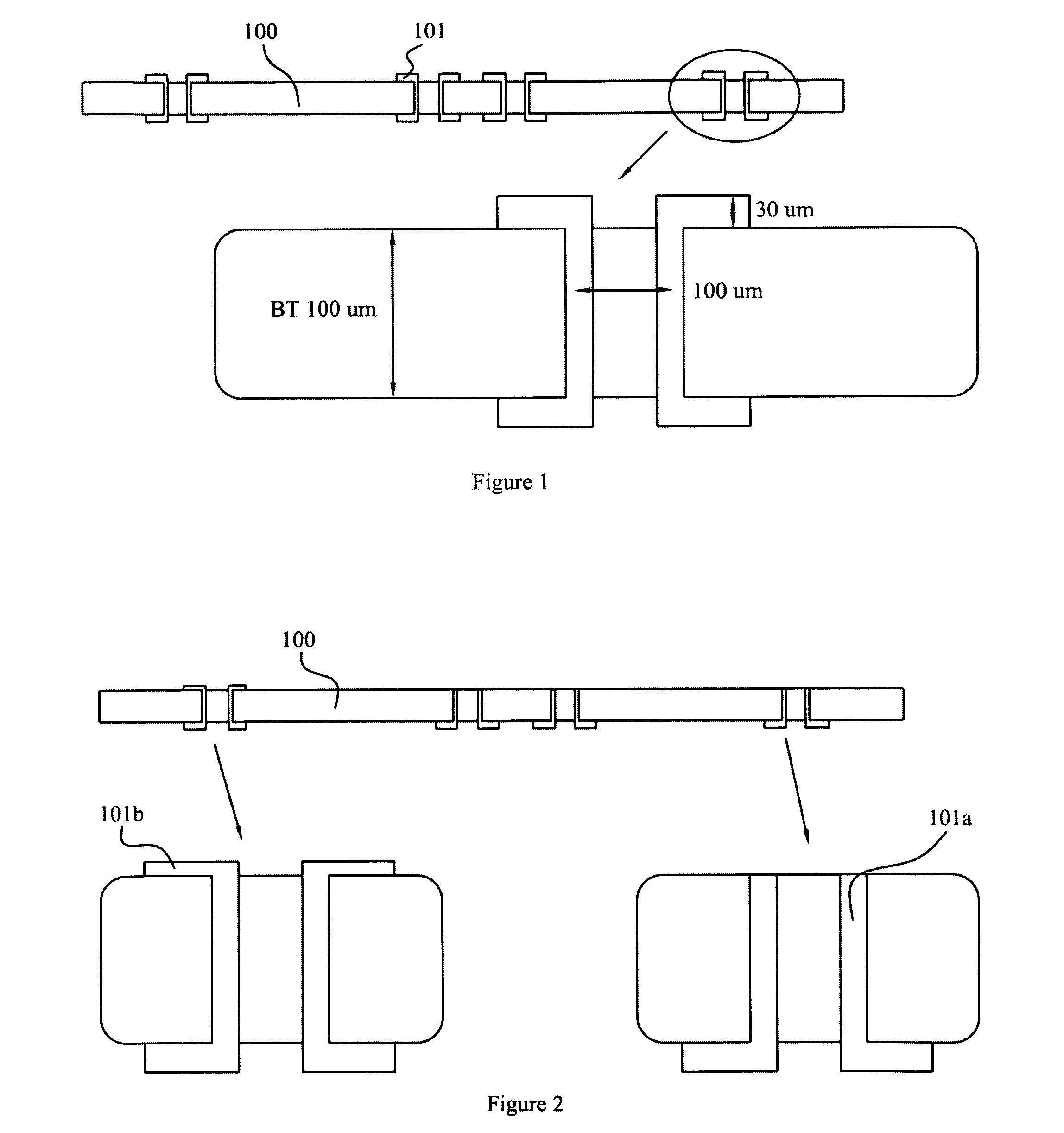

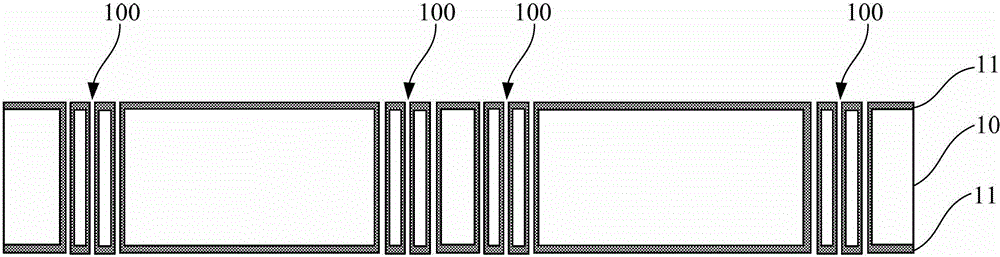

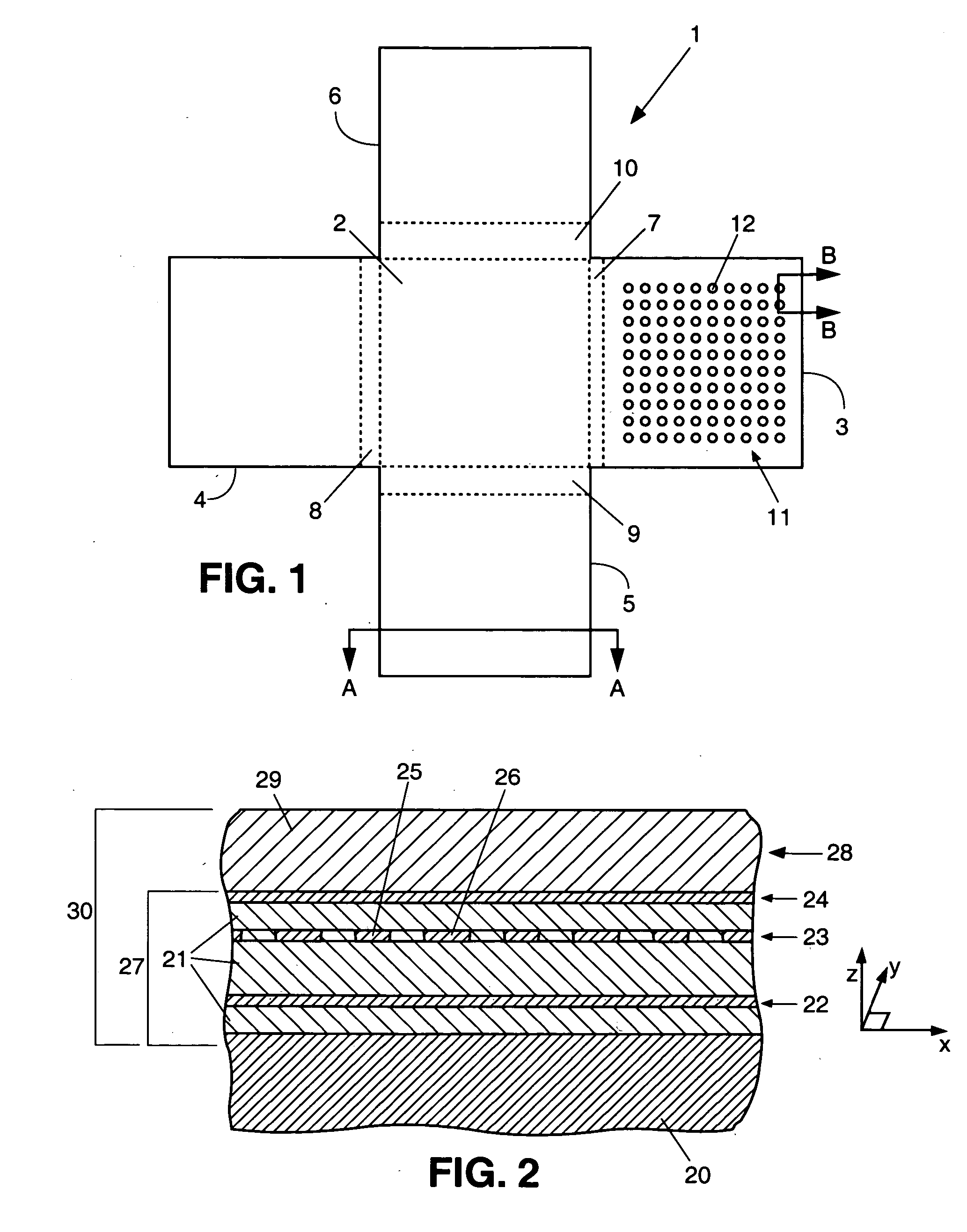

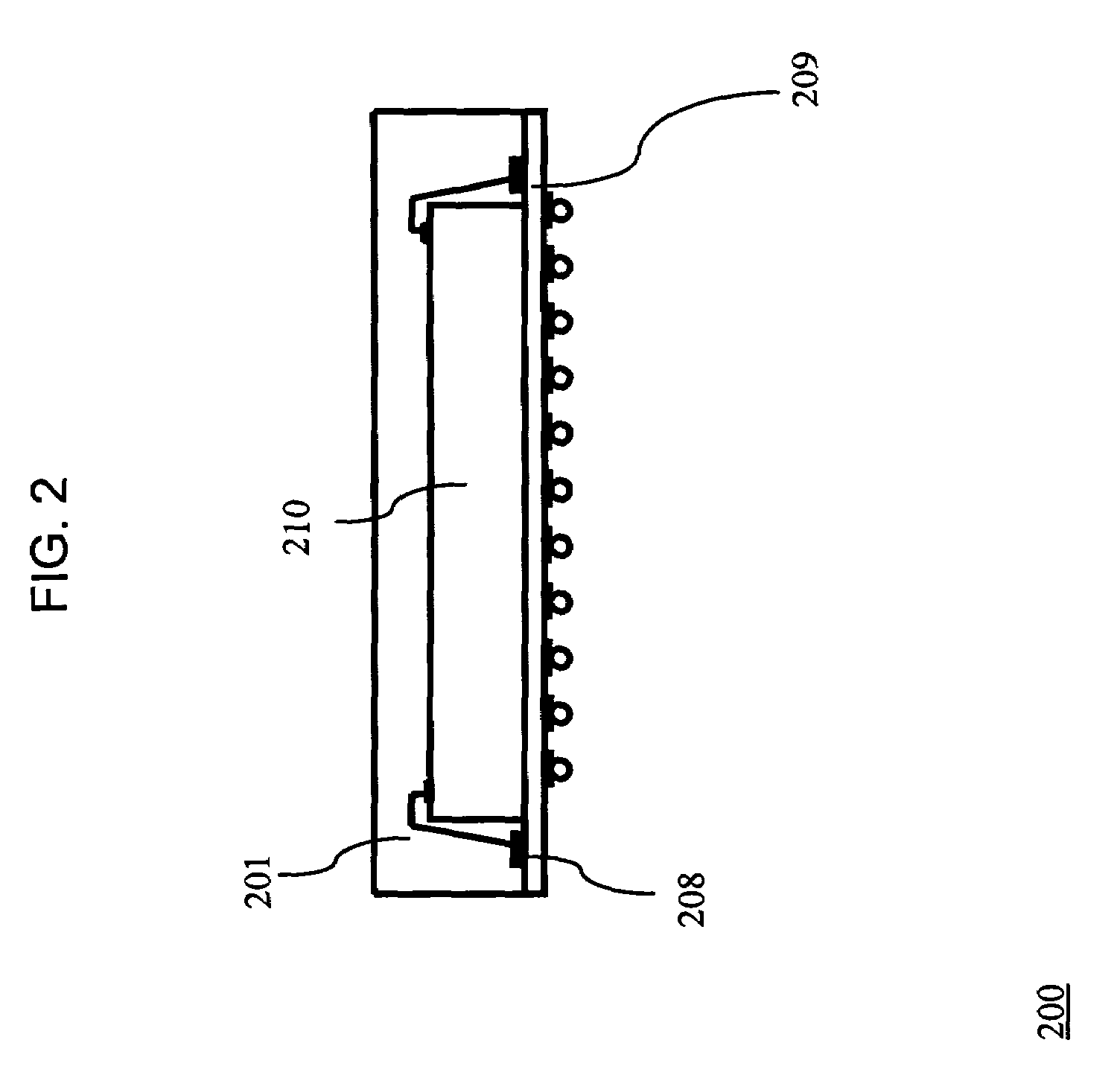

Wafer level stack structure for system-in-package and method thereof

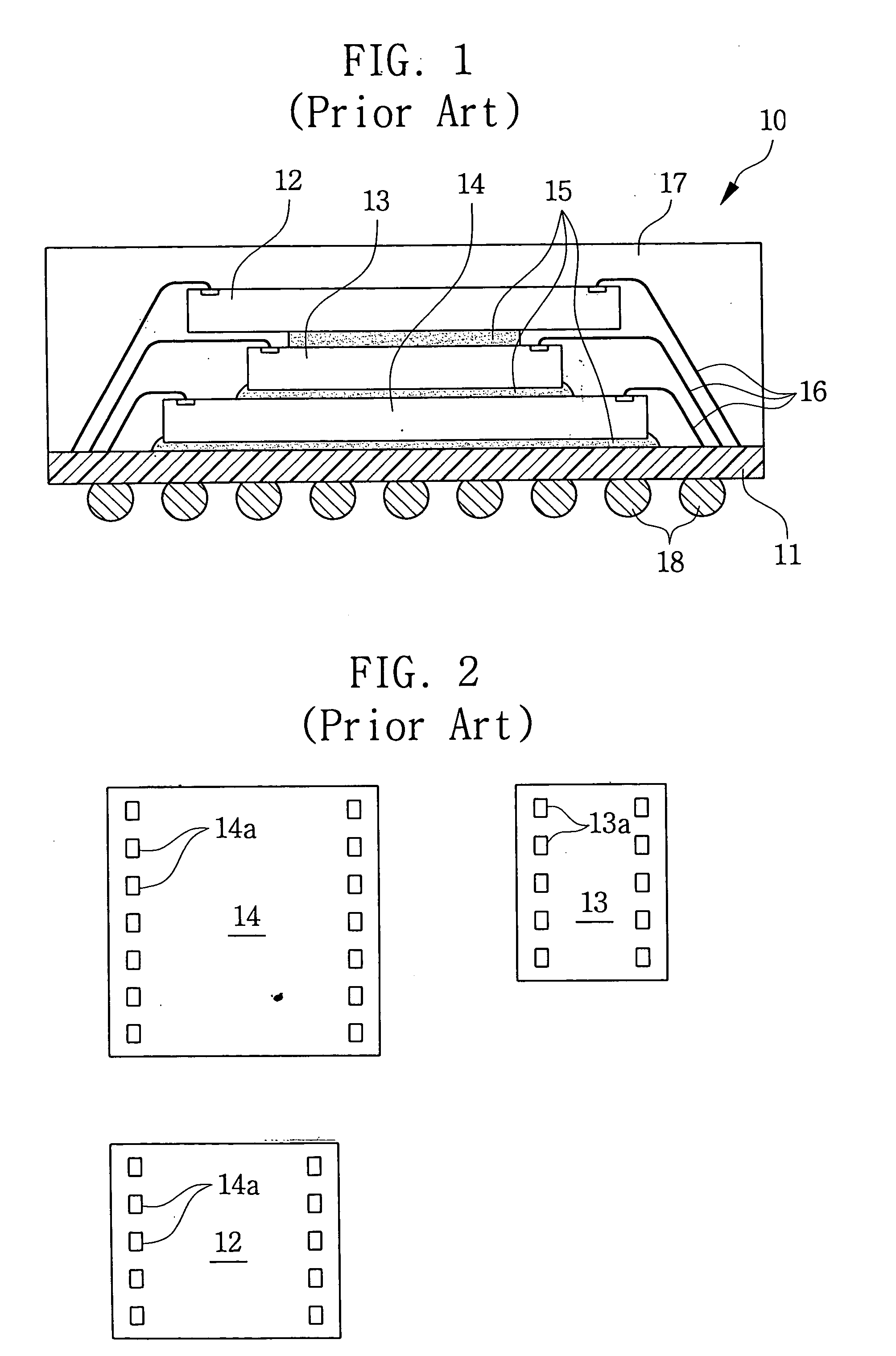

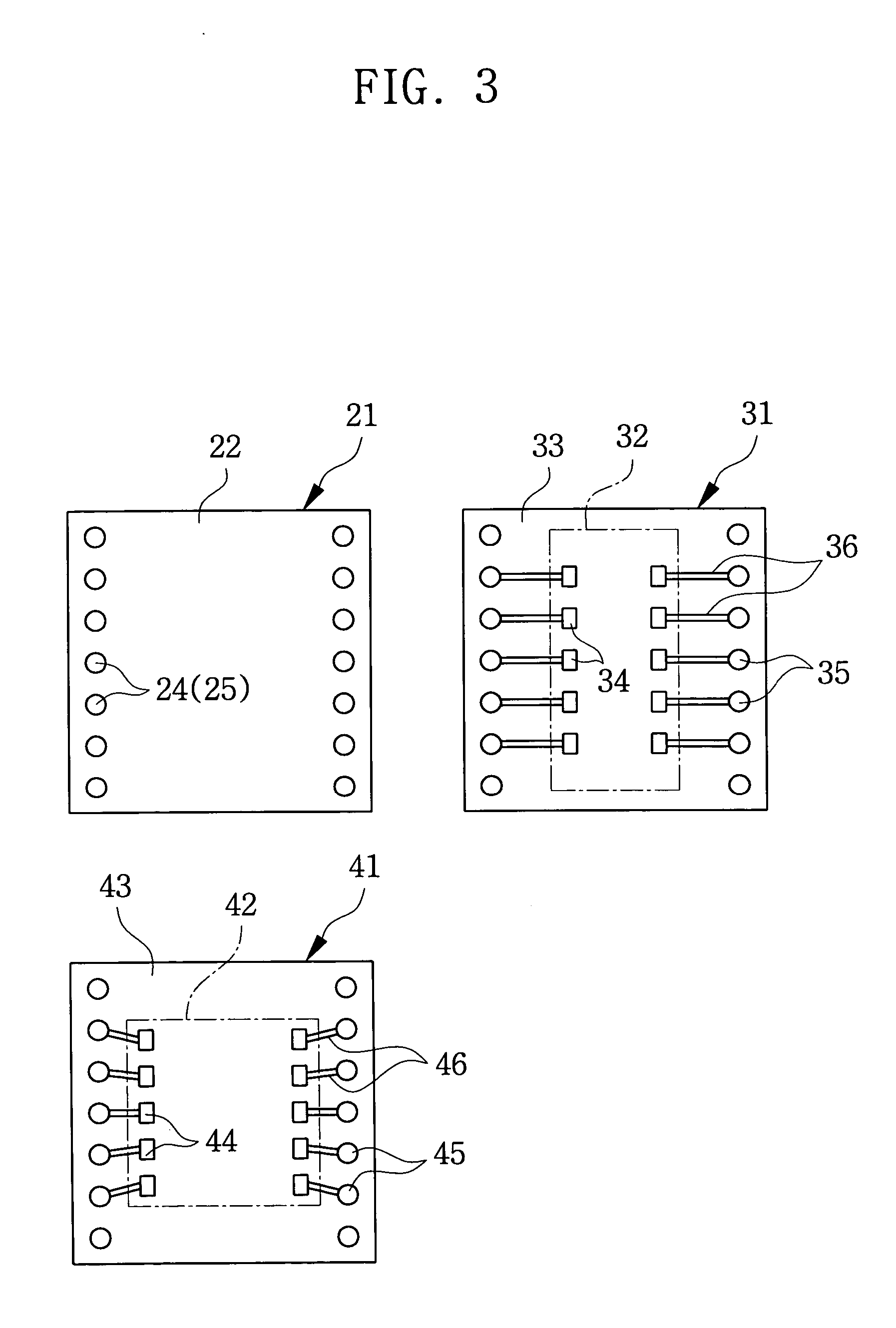

ActiveUS7215033B2Semiconductor/solid-state device detailsSolid-state devicesChip sizeSystem in package

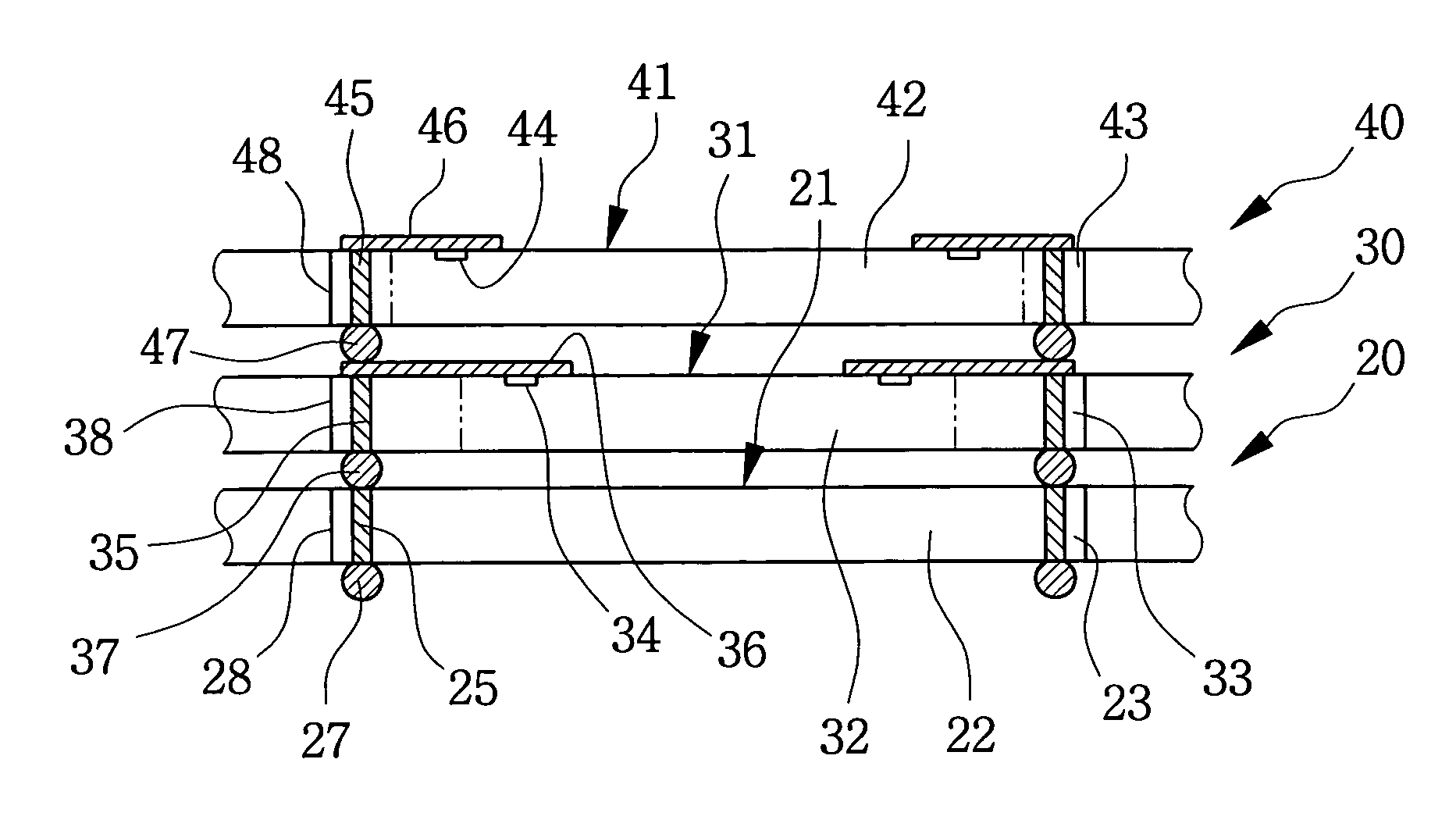

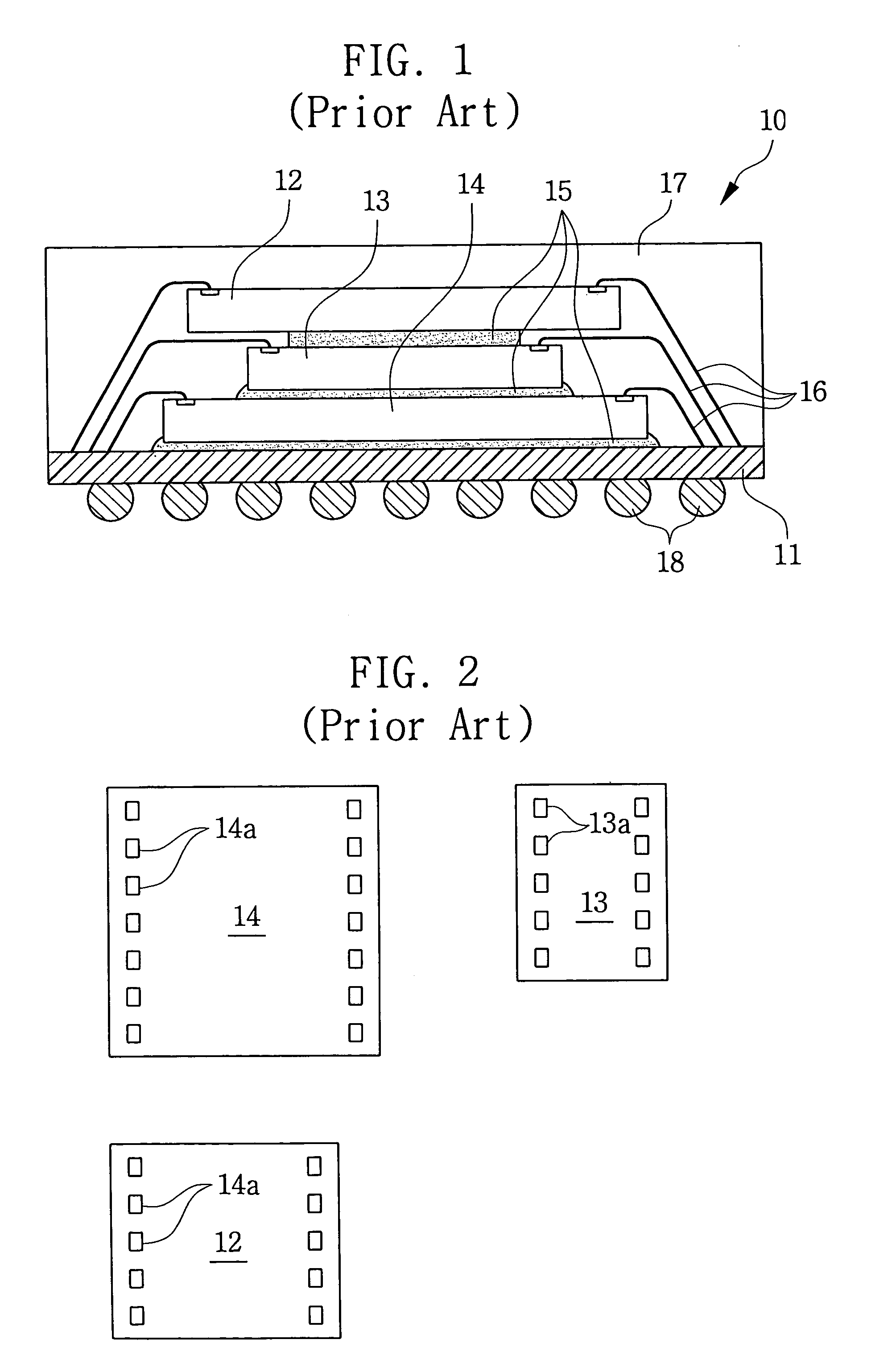

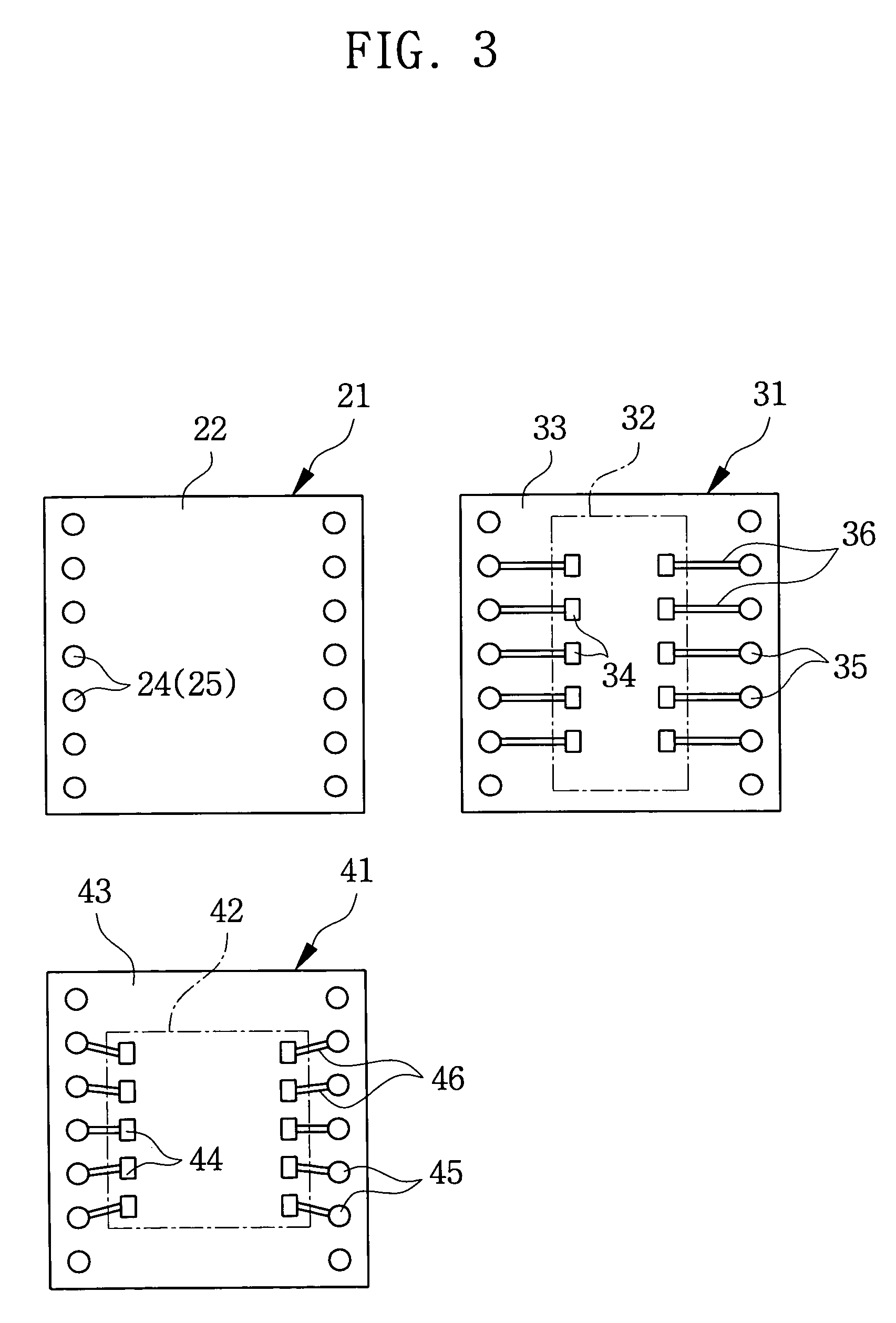

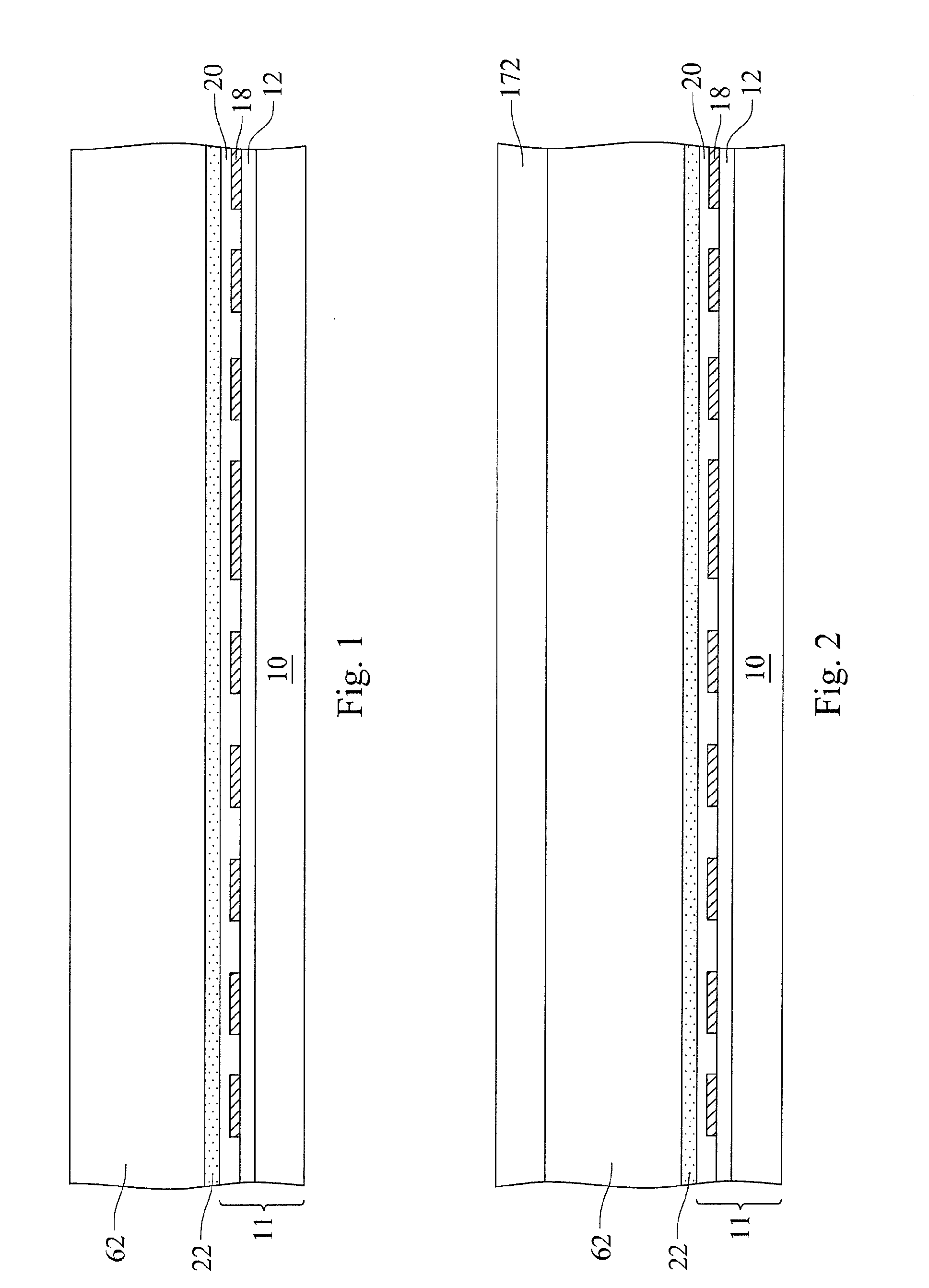

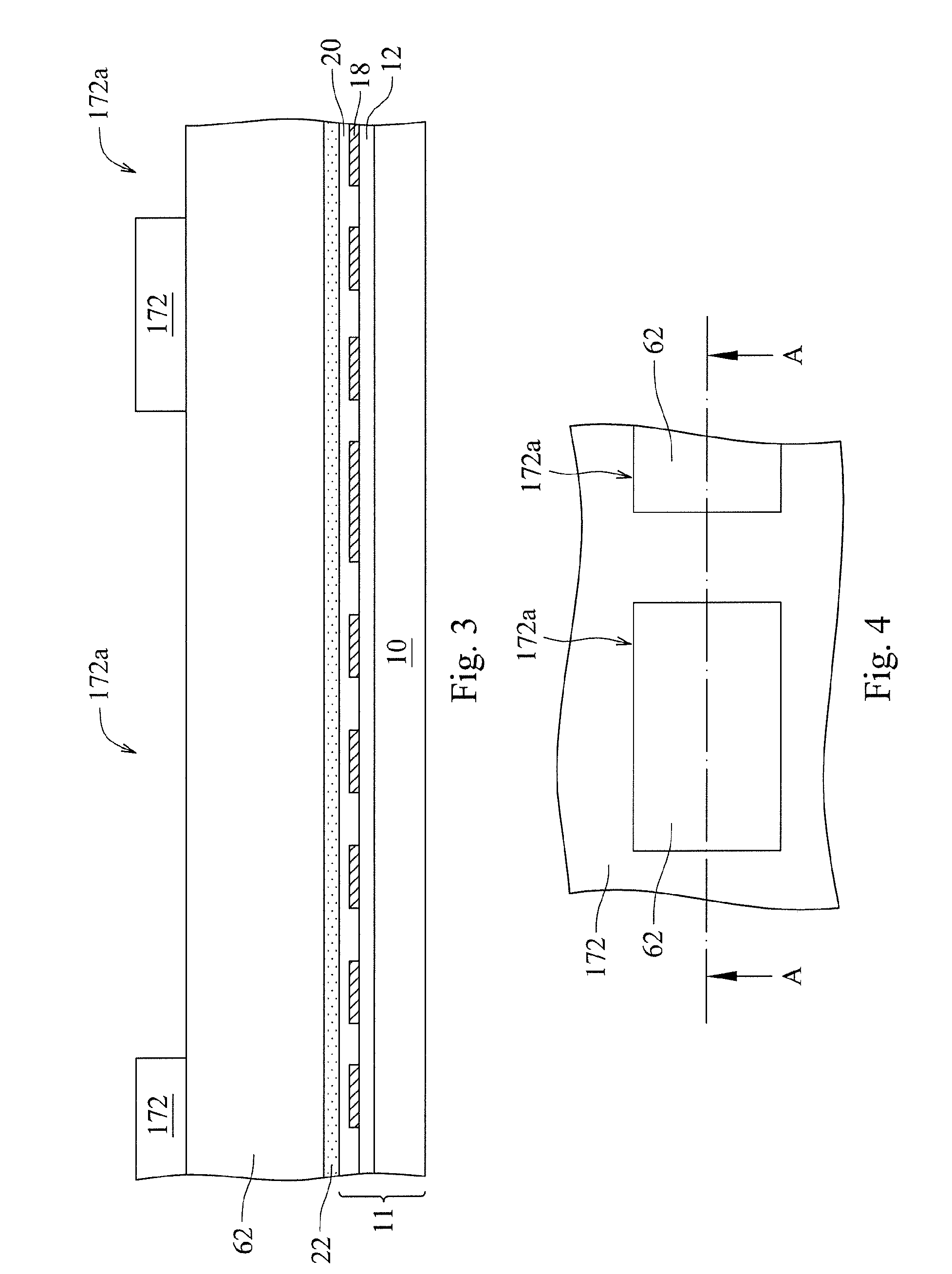

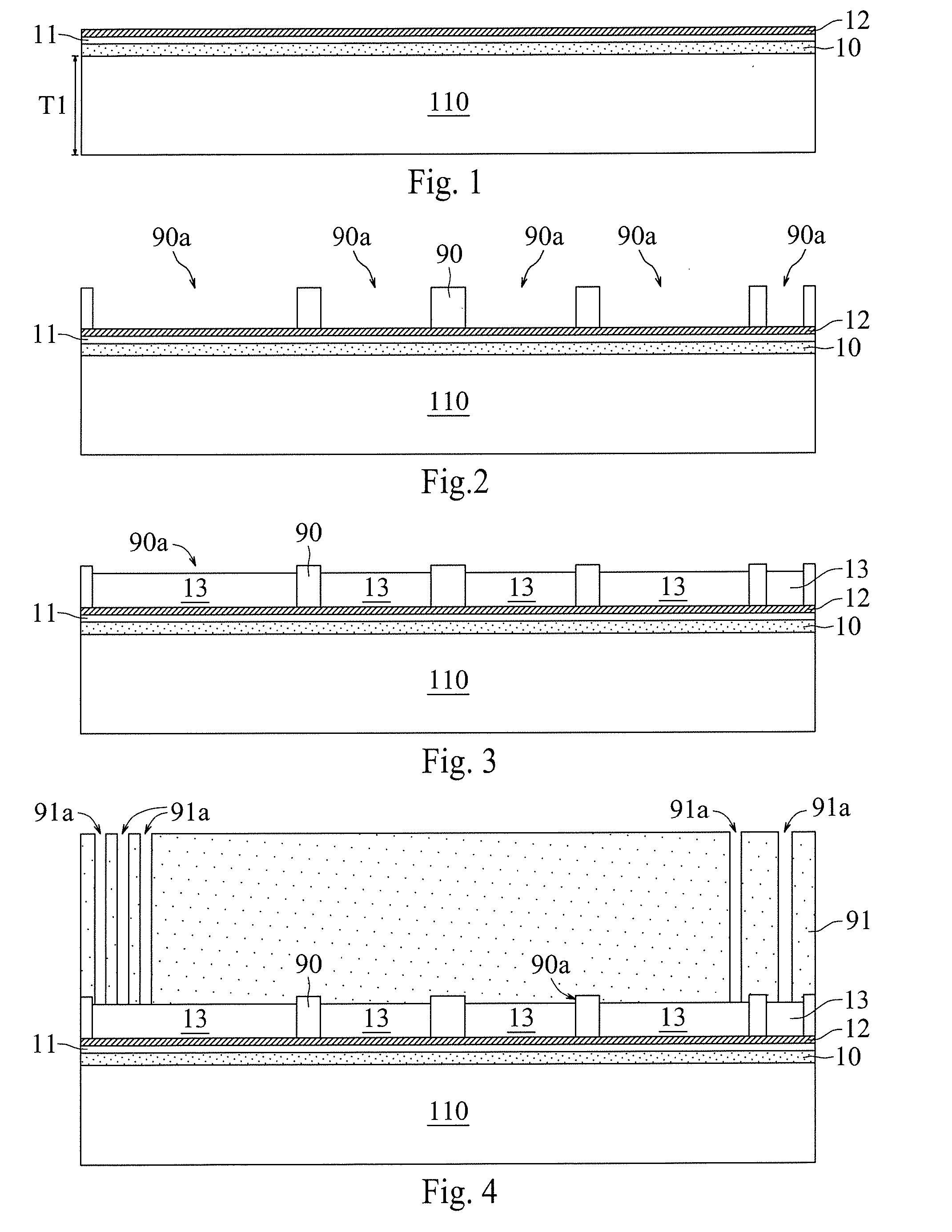

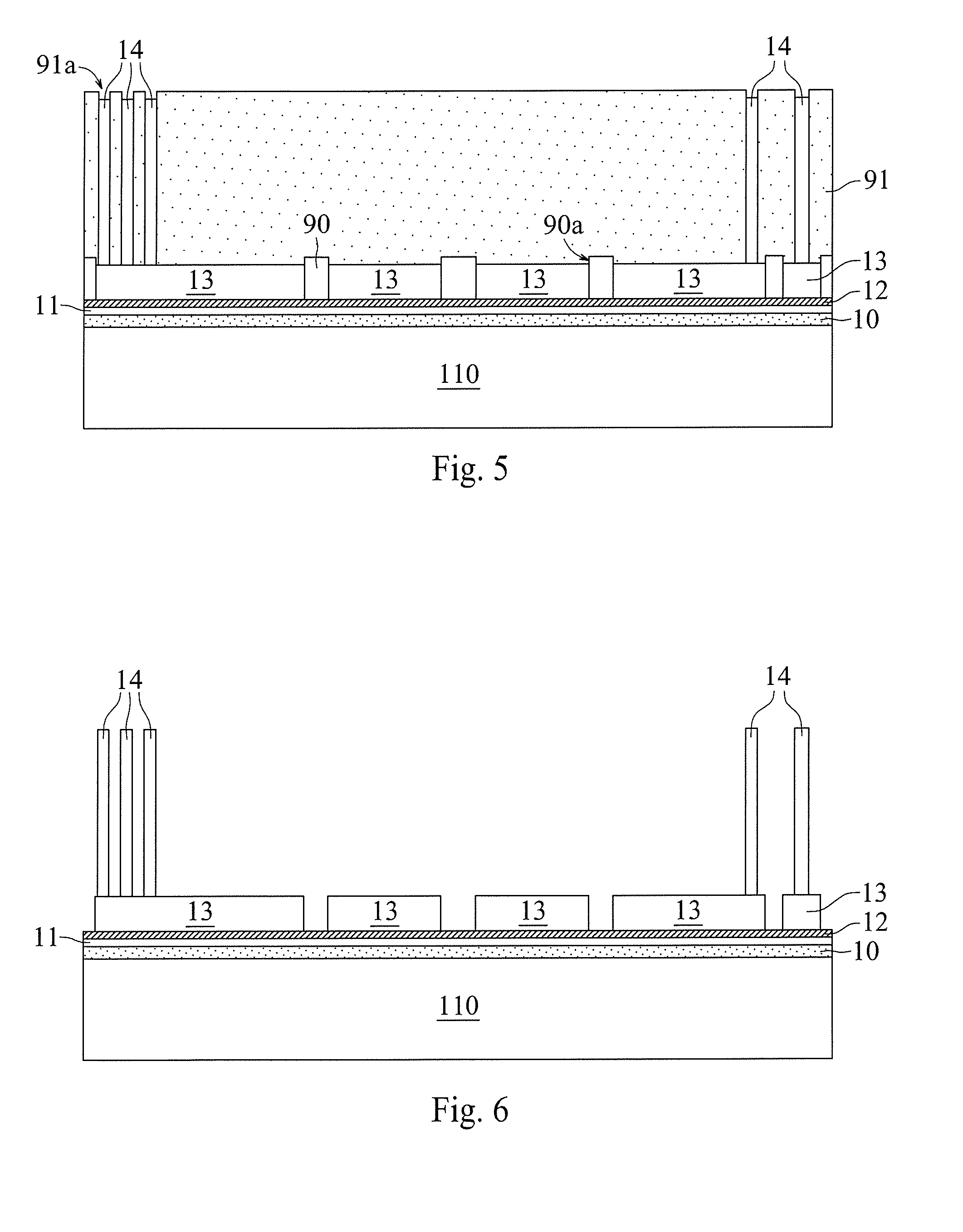

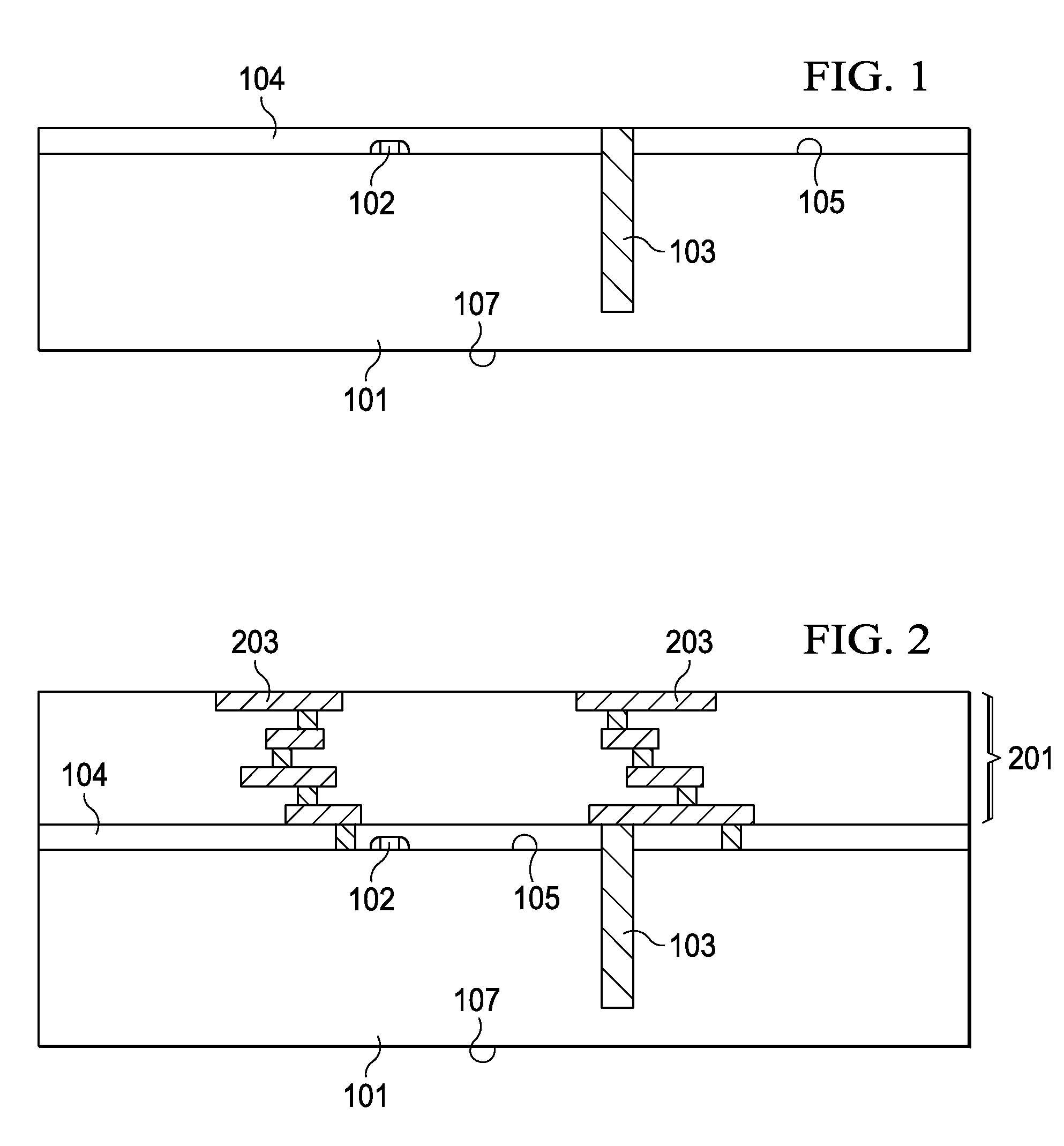

A wafer level stack structure, including a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, wherein the first wafer and the second wafer are stacked, and wherein the first wafer and the second wafer are coupled to each other. A method of forming a wafer level stack structure, including forming a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, forming a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, stacking the first wafer and the second wafer, and coupling the first wafer and the second wafer to each other. A system-in-package, including a wafer level stack structure including at least one first device chip with a first plurality of input / output (I / O) pads and at least one second device chip with a second plurality of I / O pads, and a common circuit board to which the wafer level stack structure is connected.

Owner:SAMSUNG ELECTRONICS CO LTD

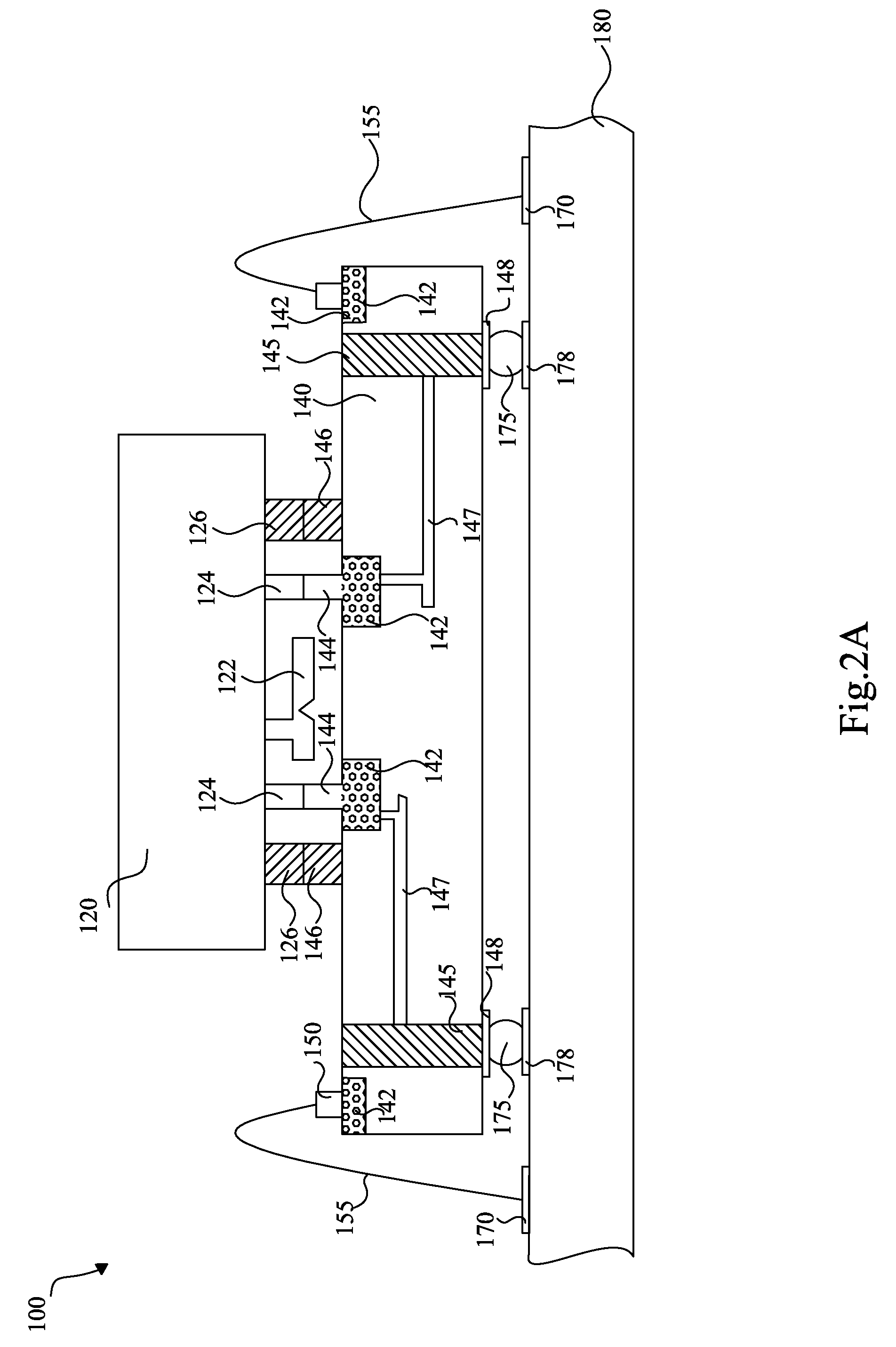

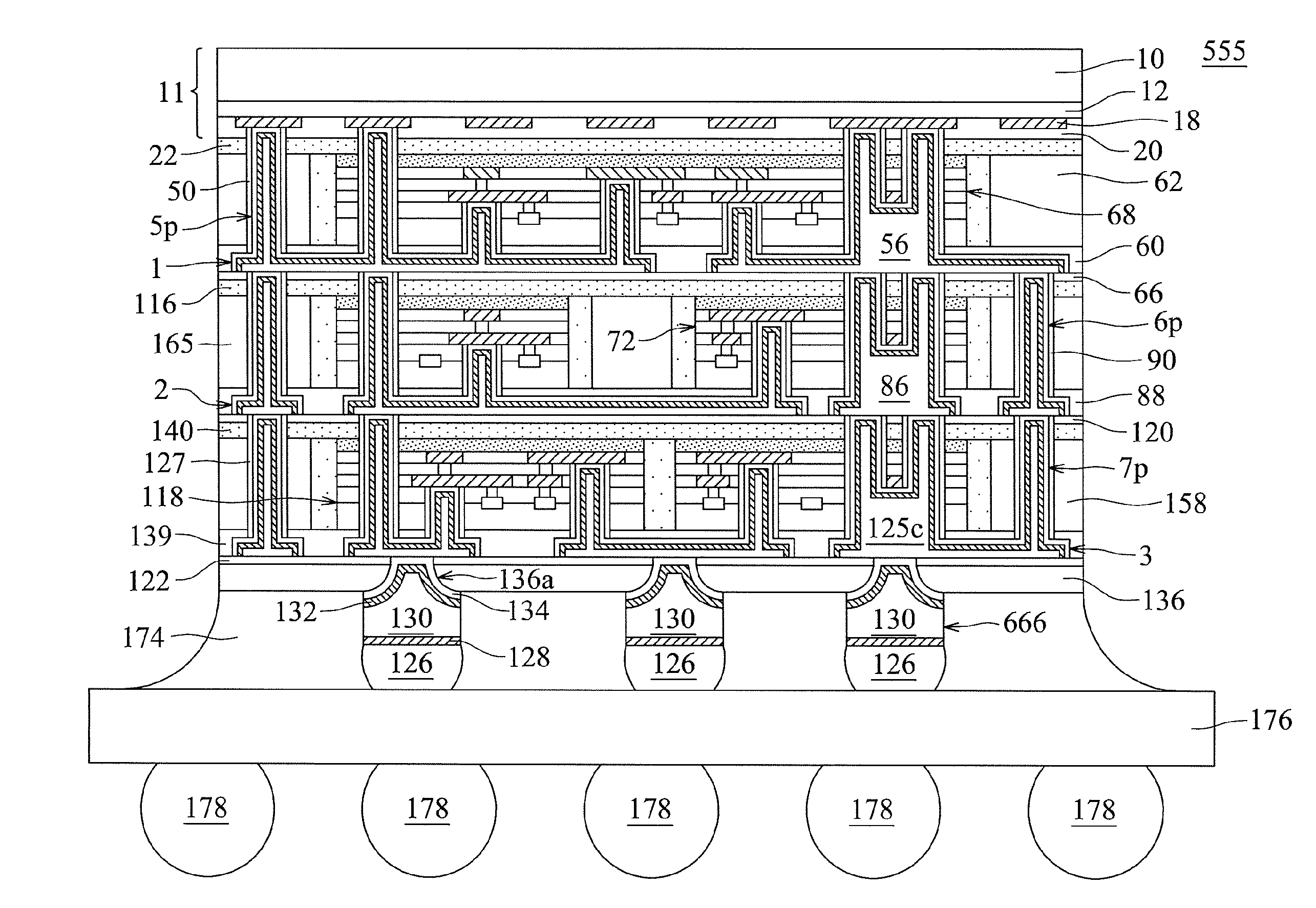

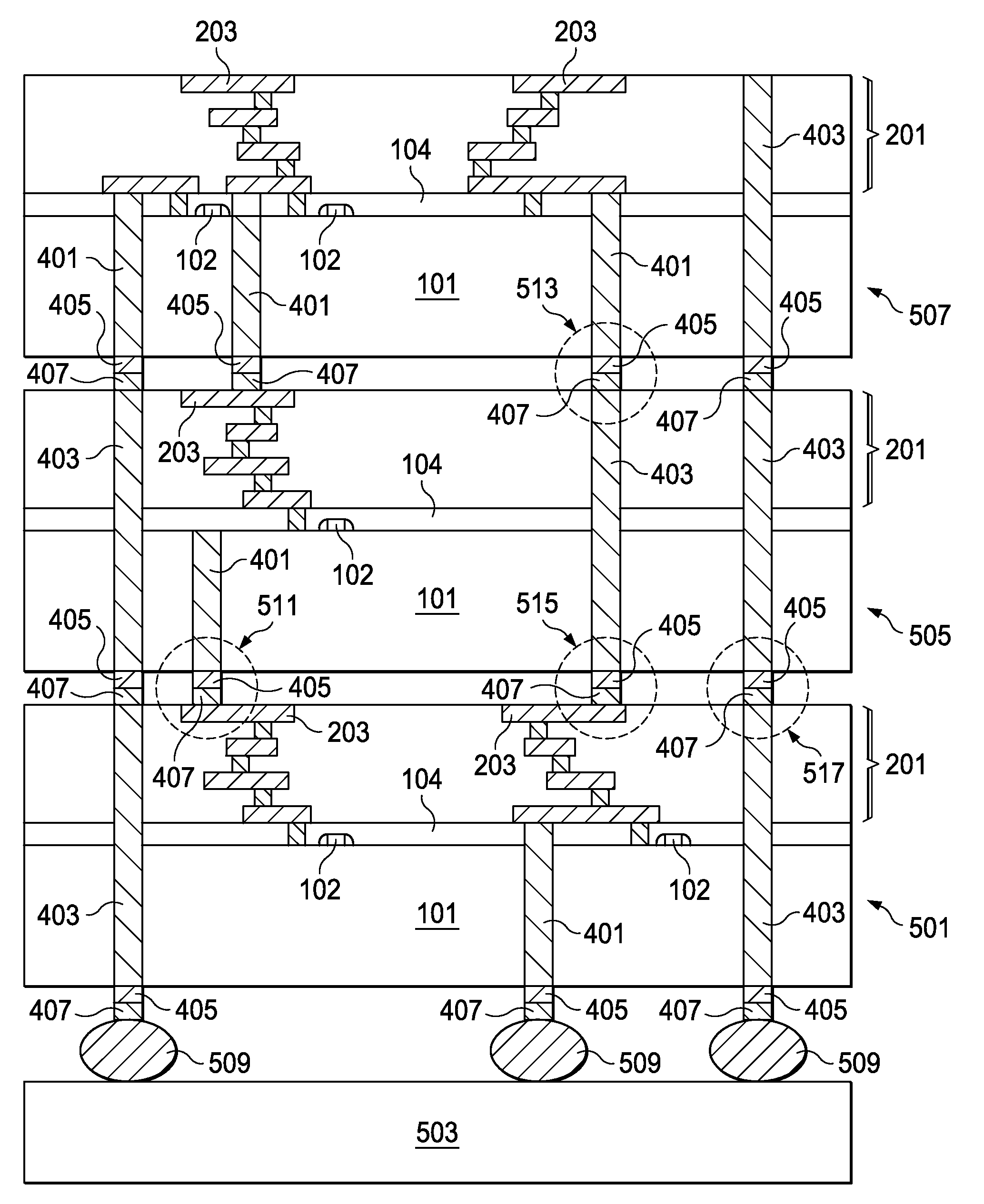

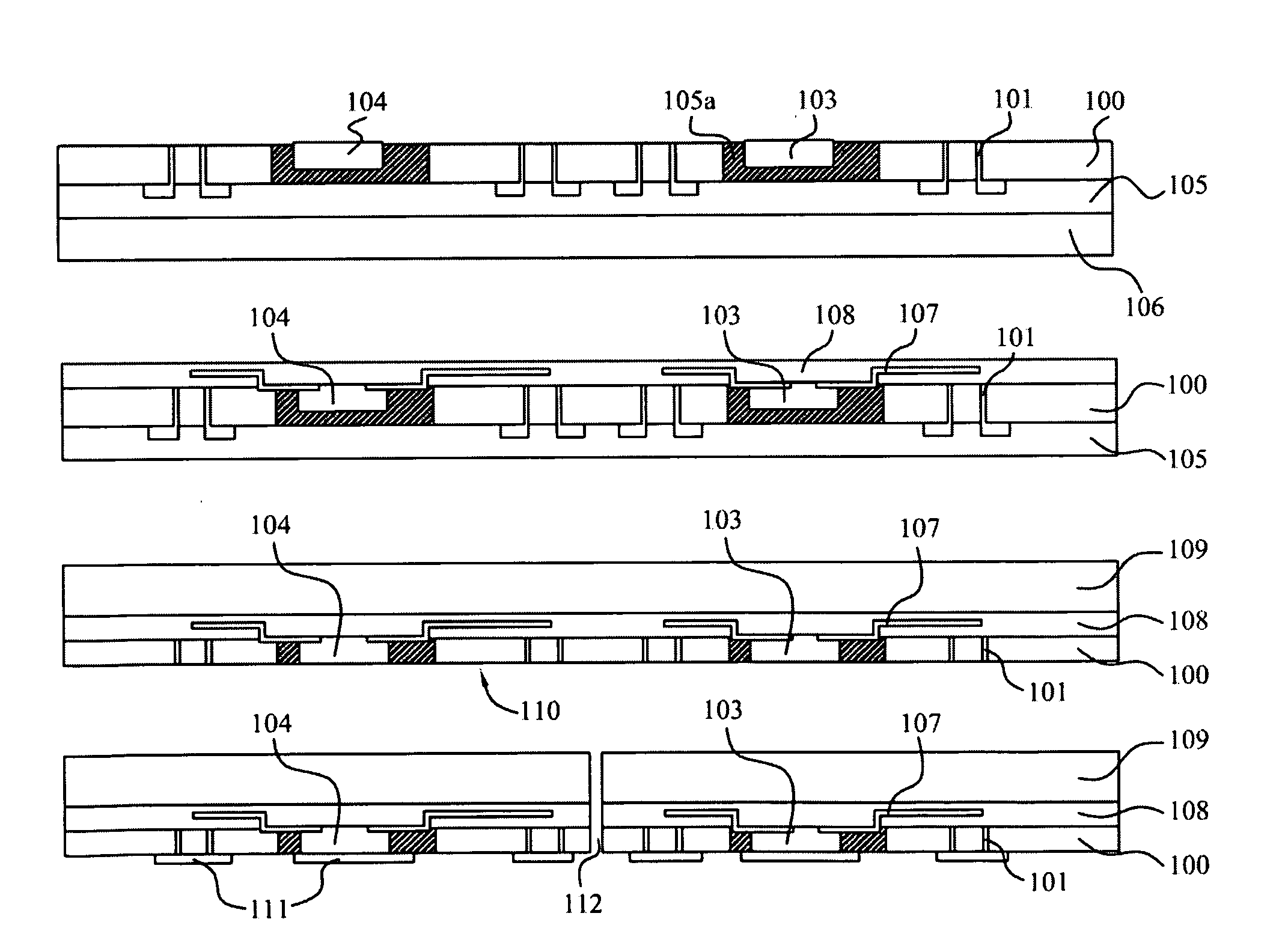

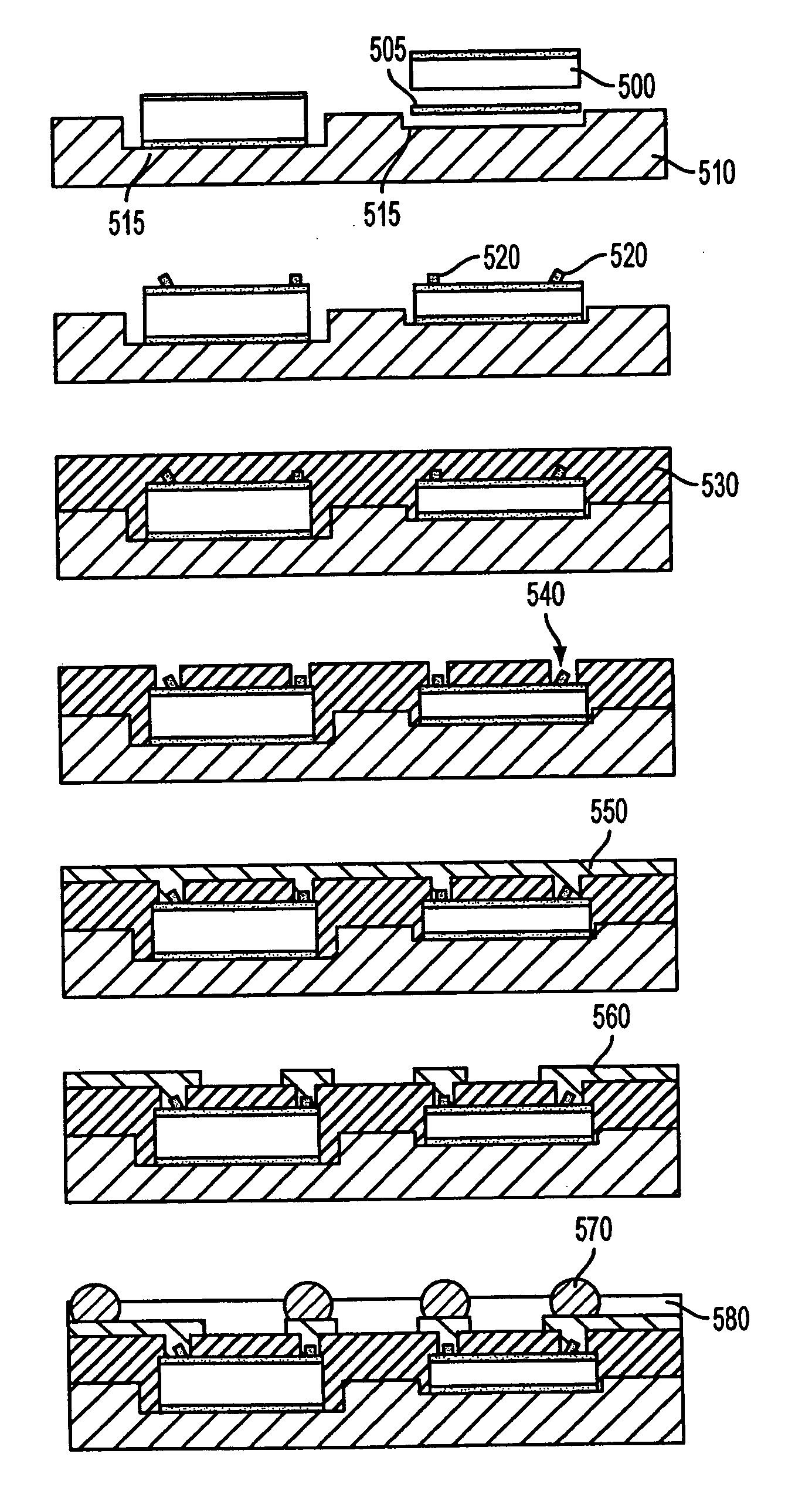

System-in packages

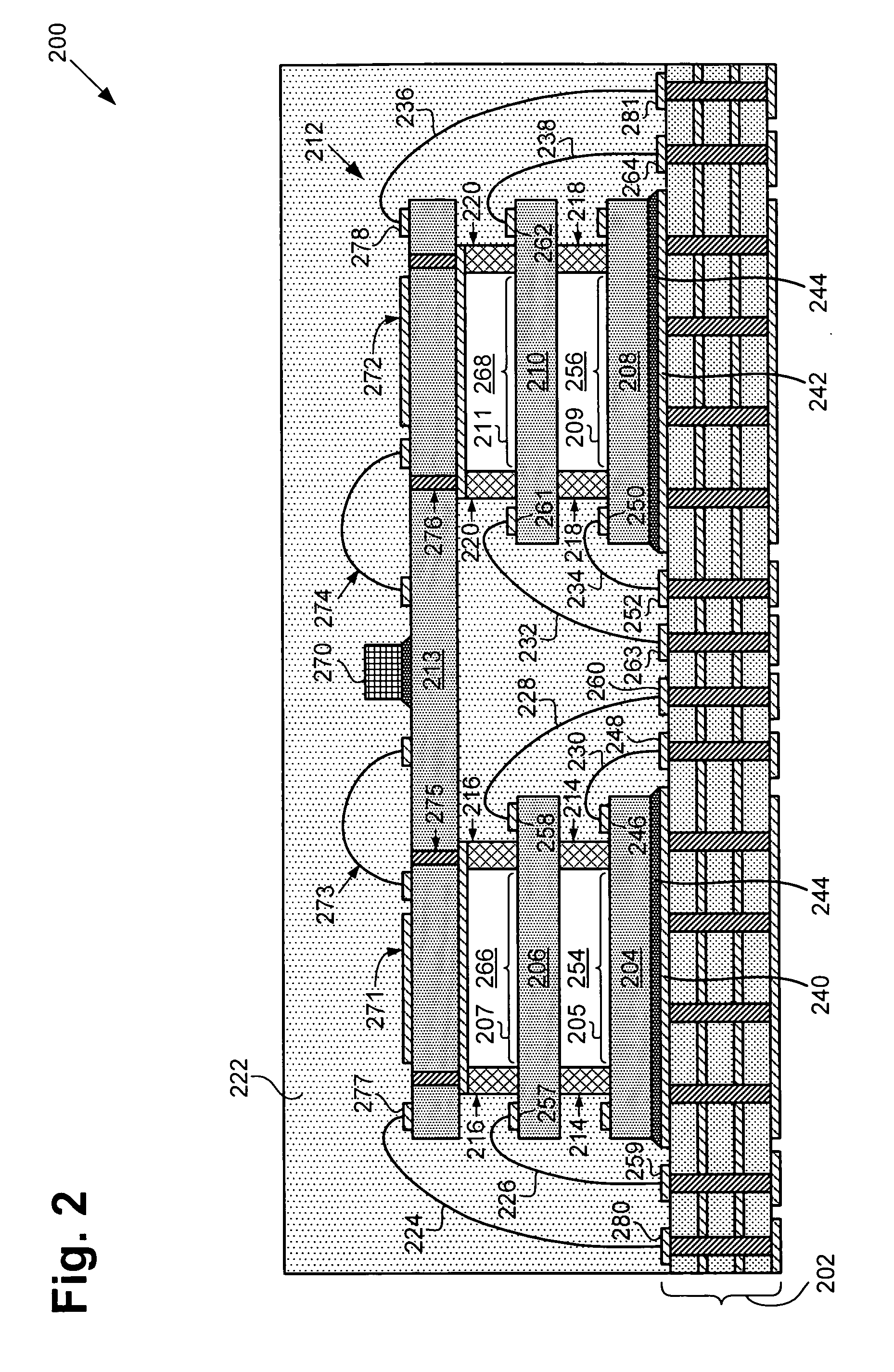

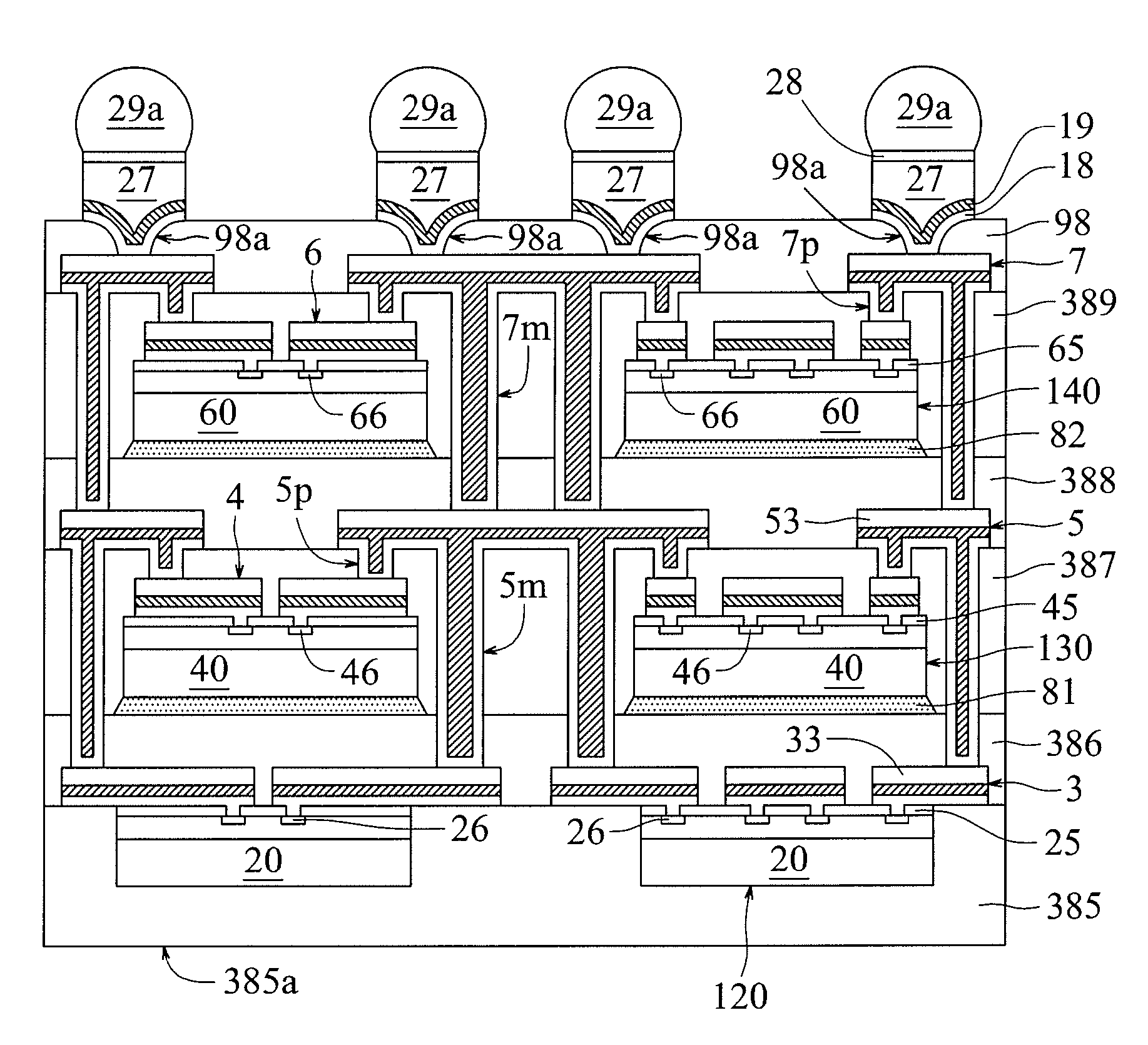

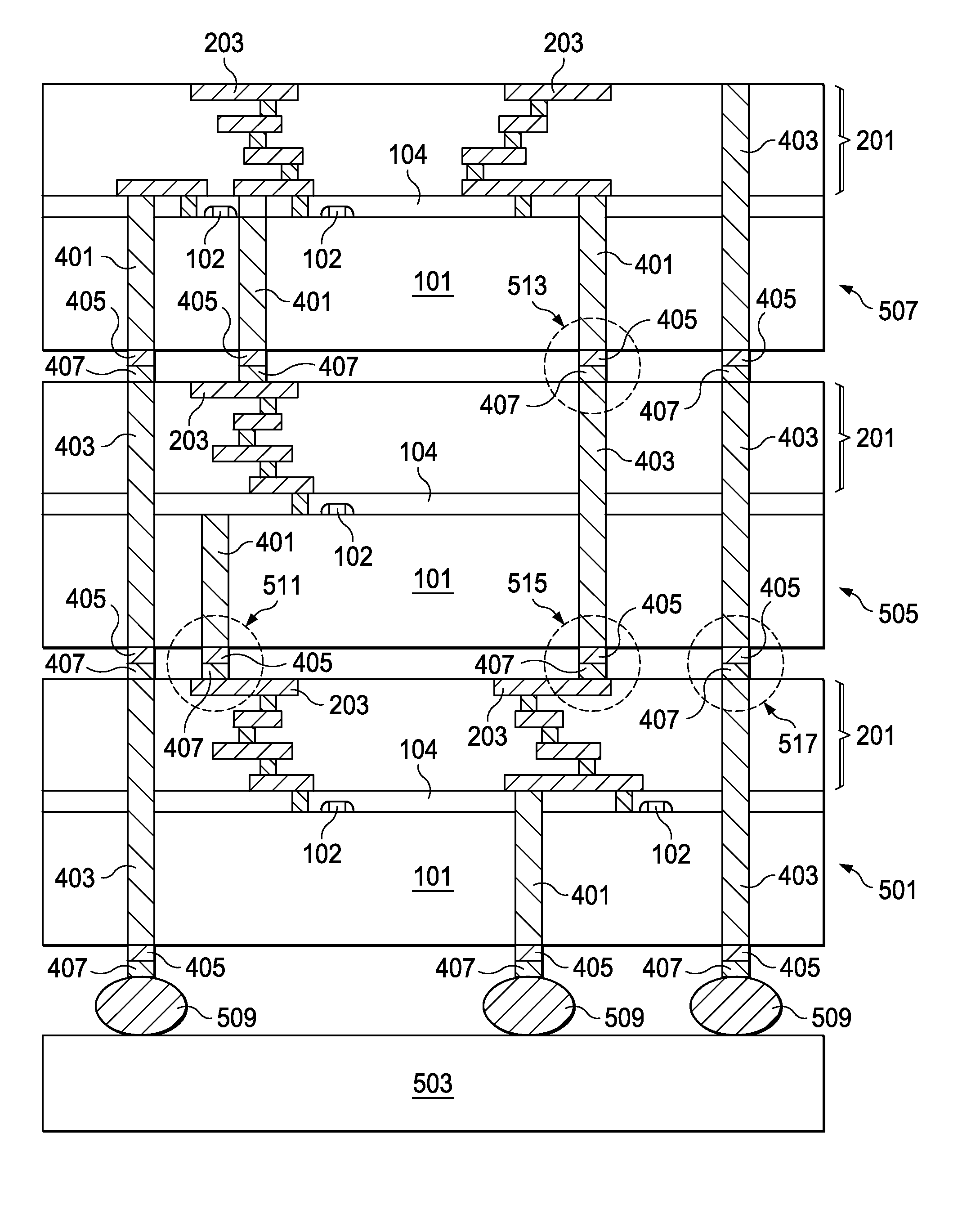

ActiveUS20110026232A1Improve uniformitySemiconductor/solid-state device detailsCircuit arrangements on support structuresMetal interconnectSystem in package

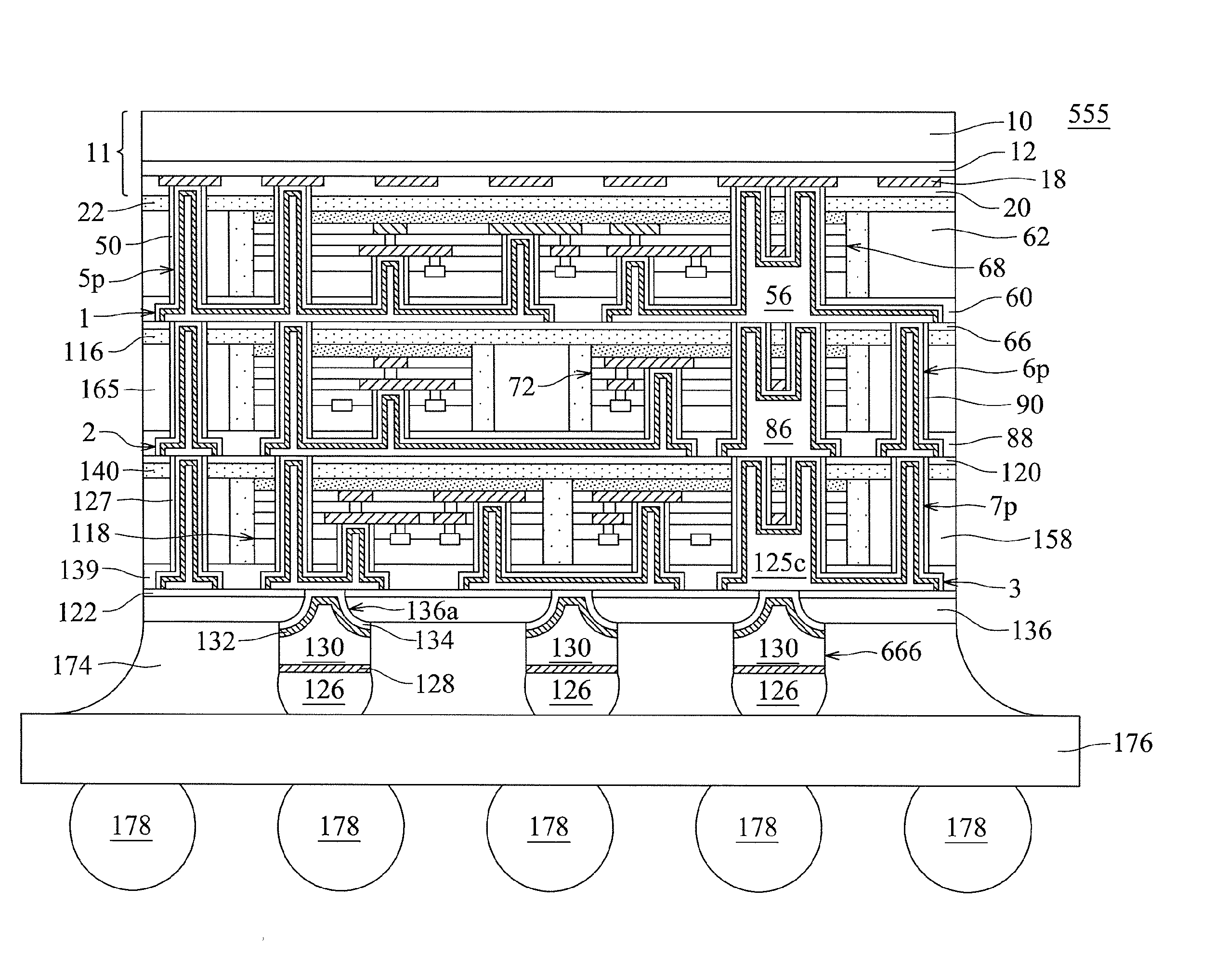

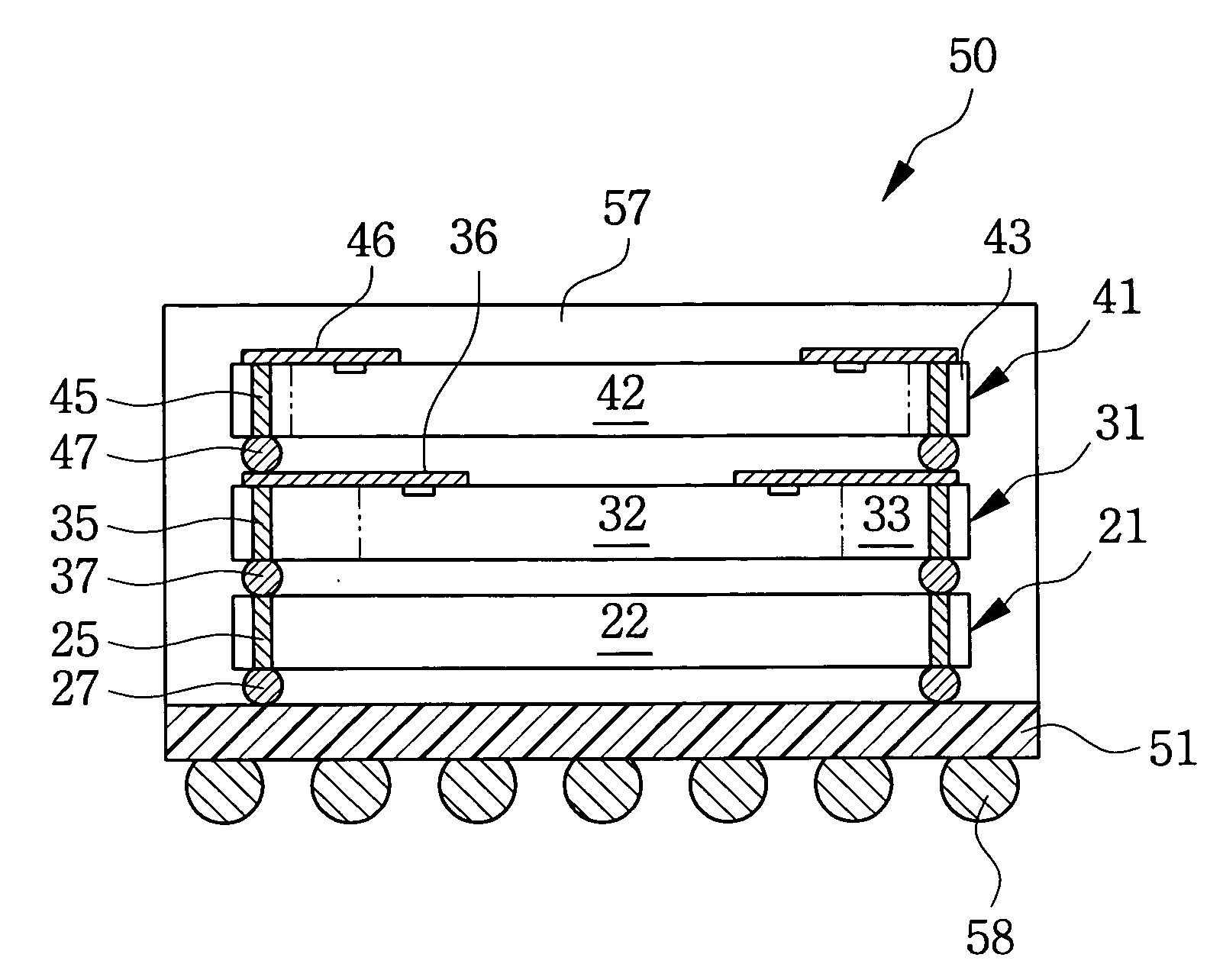

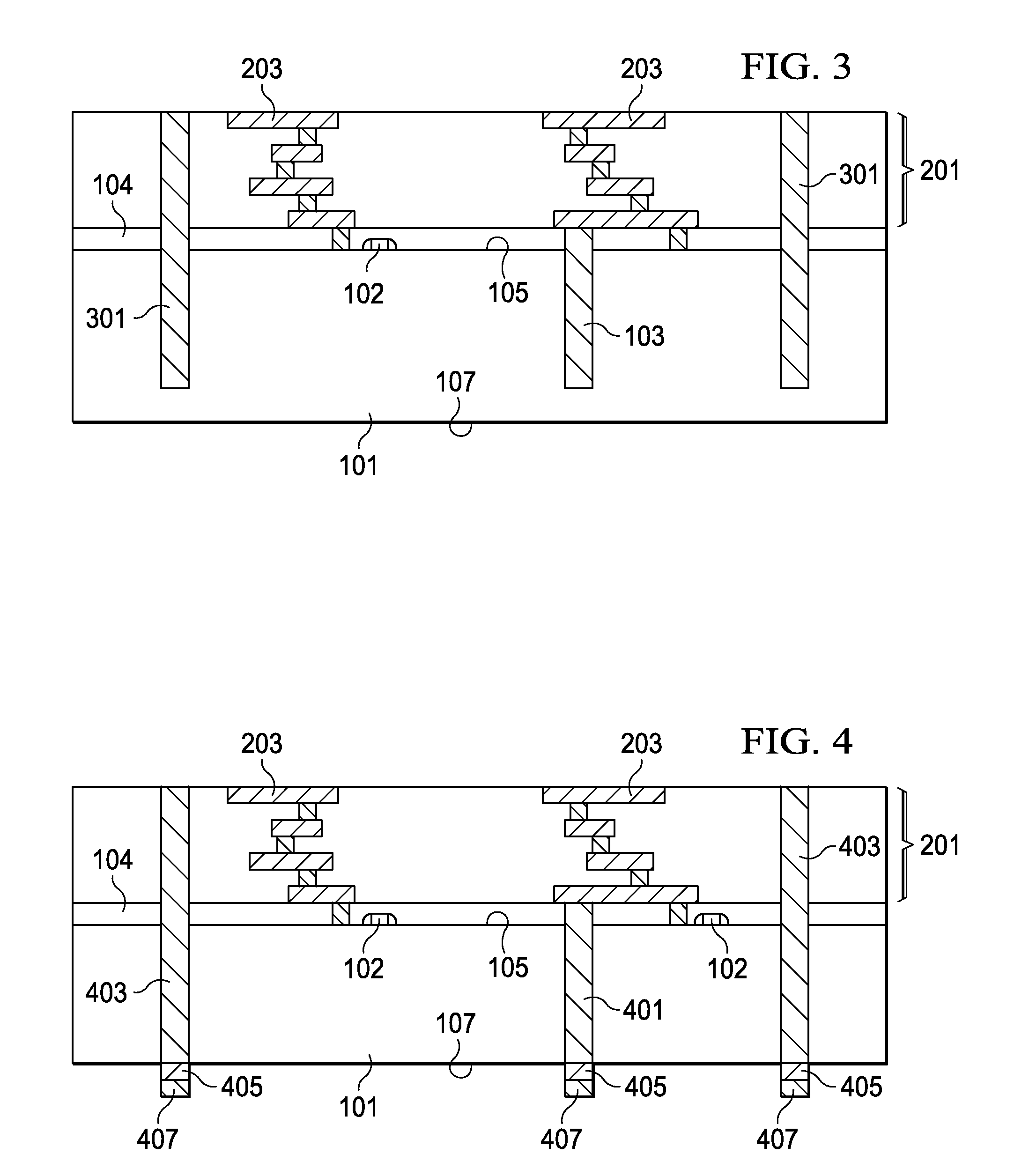

System-in packages, or multichip modules, are described which can include multi-layer chips and multi-layer dummy substrates over a carrier, multiple through vias blindly or completely through the multi-layer chips and completely through the multi-layer dummy substrates, multiple metal plugs in the through vias, and multiple metal interconnects, connected to the metal plugs, between the multi-layer chips. The multi-layer chips can be connected to each other or to an external circuit or structure, such as mother board, ball grid array (BGA) substrate, printed circuit board, metal substrate, glass substrate, or ceramic substrate, through the metal plugs and the metal interconnects.

Owner:QUALCOMM INC

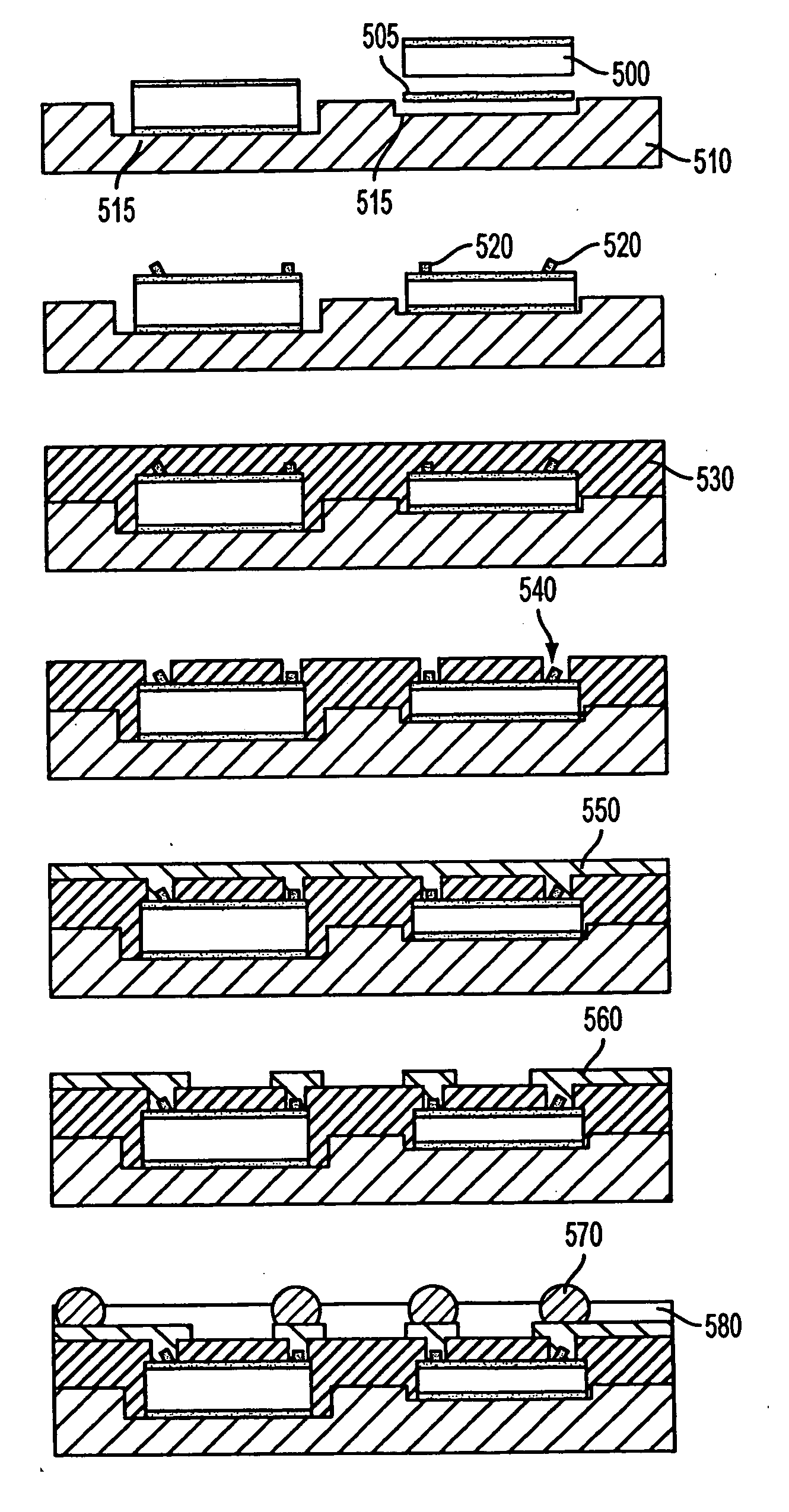

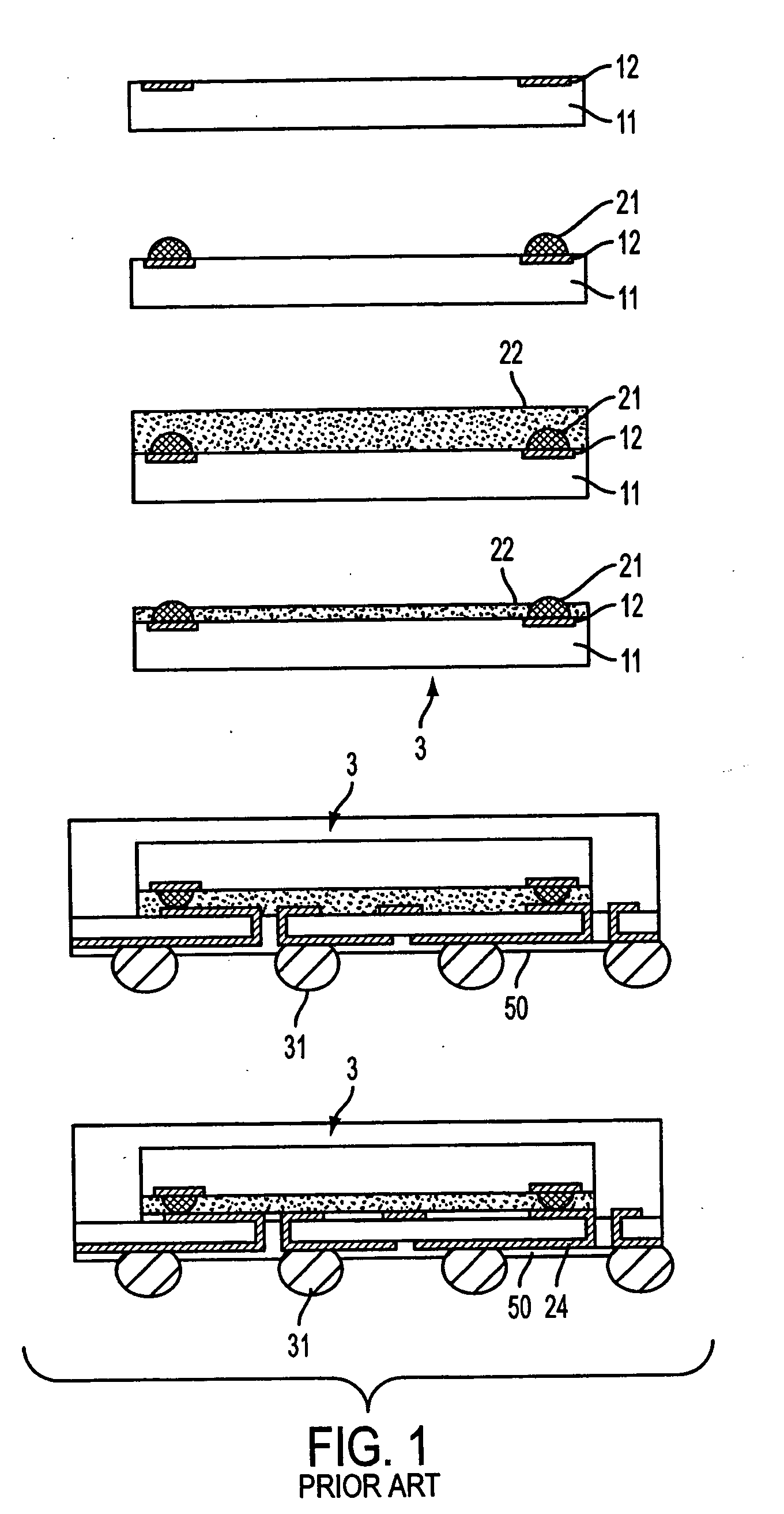

MEMS Packaging Including Integrated Circuit Dies

InactiveUS20090194829A1Highly integratedReduced package footprintSemiconductor/solid-state device detailsSolid-state devicesOn boardElectrical connection

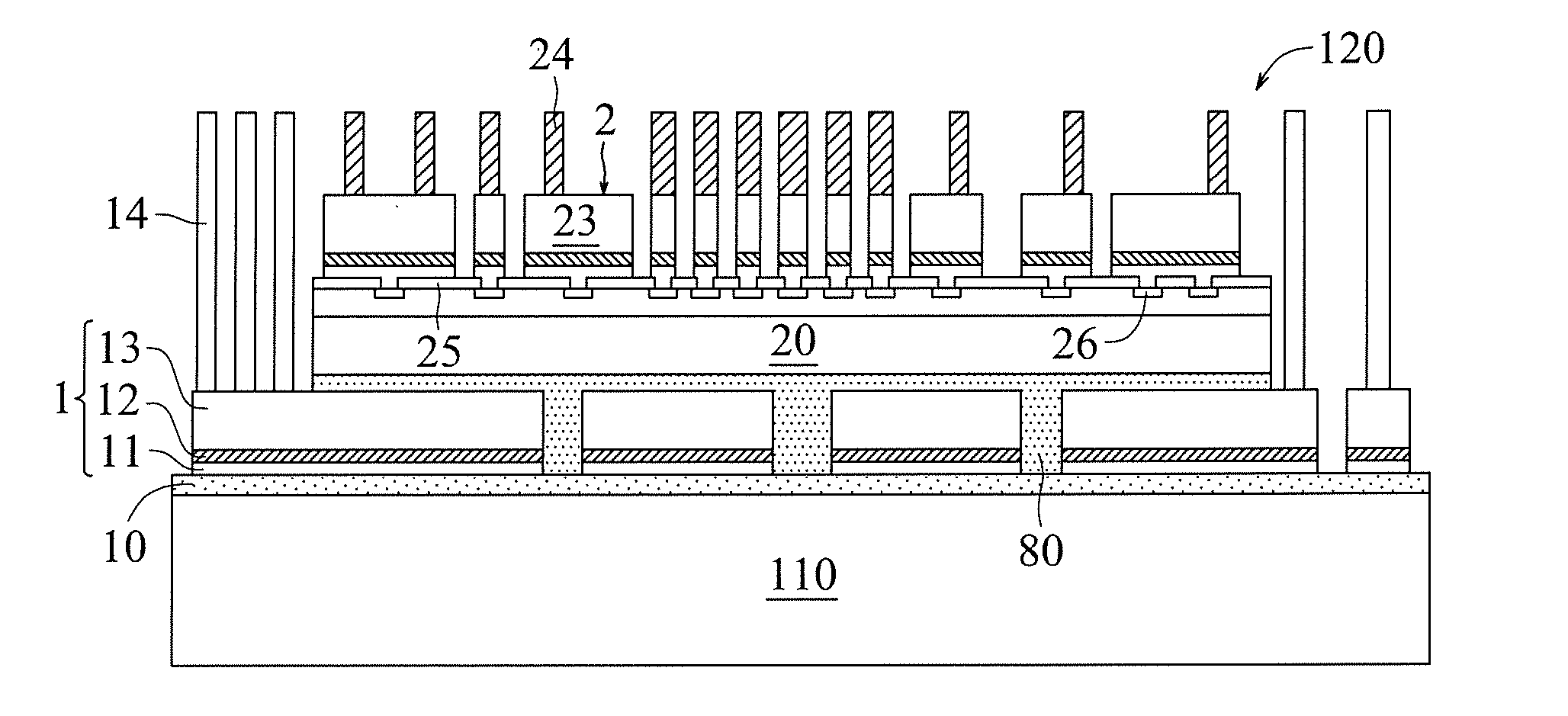

MEMS packaging schemes having a system-on-package (SOP) configuration and a system-on-board (SOB) configuration are provided. The MEMS package comprises one or more MEMS dies, a cap section having one or more integrated circuit (IC) dies, and a packaging substrate or a printed circuit board (PCB) arranged in a stacking manner. Vertical connectors, such as through-silicon-vias (TSVs), are formed to provide short electrical connections between the various components. The MEMS packaging schemes enable higher integration density, reduced MEMS package footprints, reduced RC delays and power consumption.

Owner:TAIWAN SEMICON MFG CO LTD

System-in packages

ActiveUS8503186B2Improve uniformityCircuit arrangements on support structuresSemiconductor/solid-state device detailsMetal interconnectSystem in package

Owner:QUALCOMM INC

Three-Dimensional System-in-Package Architecture

ActiveUS20100225002A1Reduce resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSystem in package

A system and method for making semiconductor die connections with through-silicon vias (TSVs) are disclosed. A semiconductor die is manufactured with both via-first TSVs as well as via-last TSVs in order to establish low resistance paths for die connections between adjacent dies as well as for providing a low resistance path for feedthrough channels between multiple dies.

Owner:TAIWAN SEMICON MFG CO LTD

Stack package and semiconductor package including the same

ActiveUS20120018871A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A stack package usable in a three-dimensional (3D) system-in-package (SIP) includes a first semiconductor chip, a second semiconductor chip, and a supporter. The first semiconductor chip includes a through silicon via (TSV), and the second semiconductor chip is stacked on the first semiconductor chip and is electrically connected to the first semiconductor chip through the TSV of the first semiconductor chip. The supporter is attached onto the first semiconductor chip so as to be spaced apart from an edge of the second semiconductor chip.

Owner:SAMSUNG ELECTRONICS CO LTD

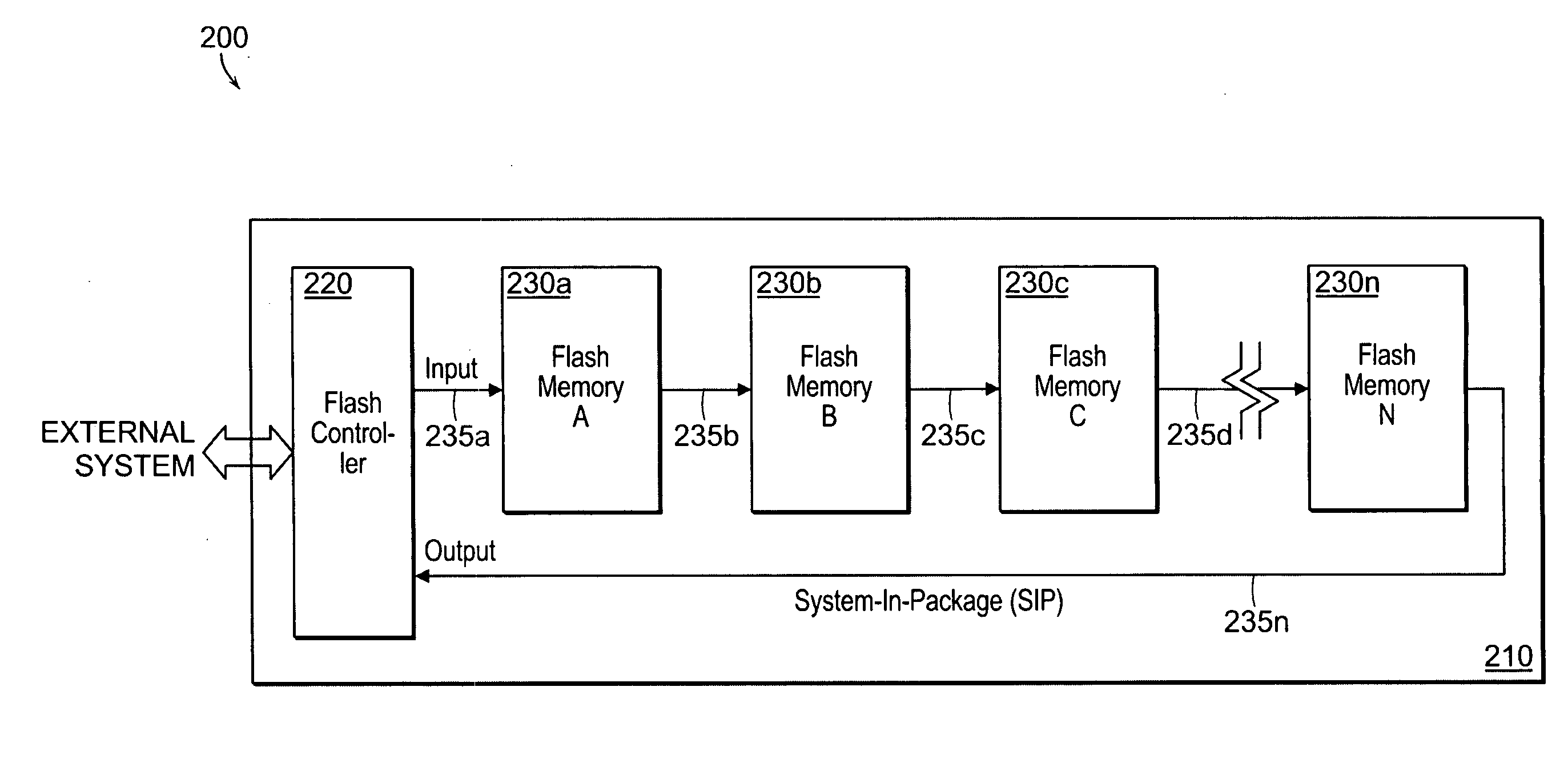

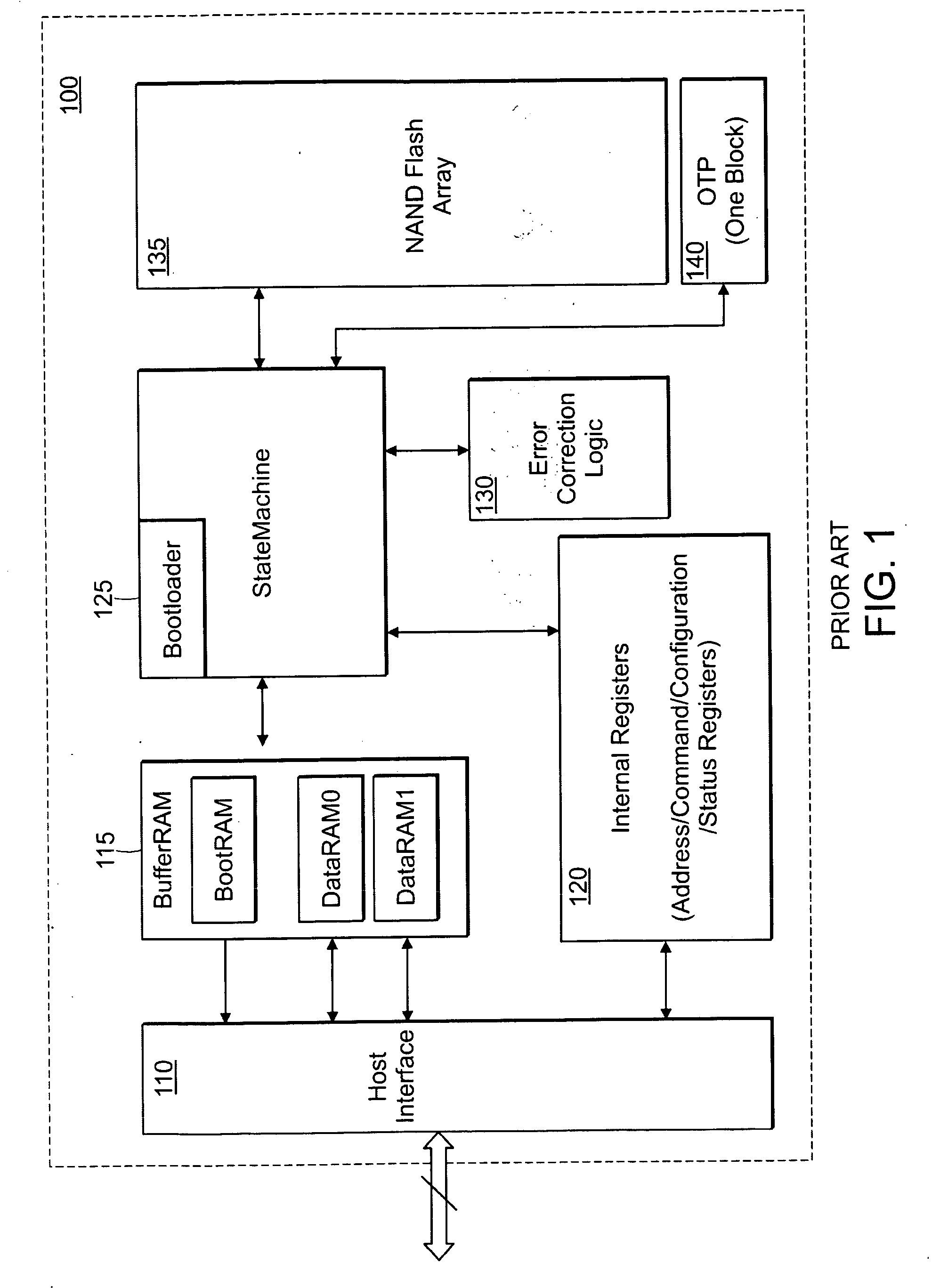

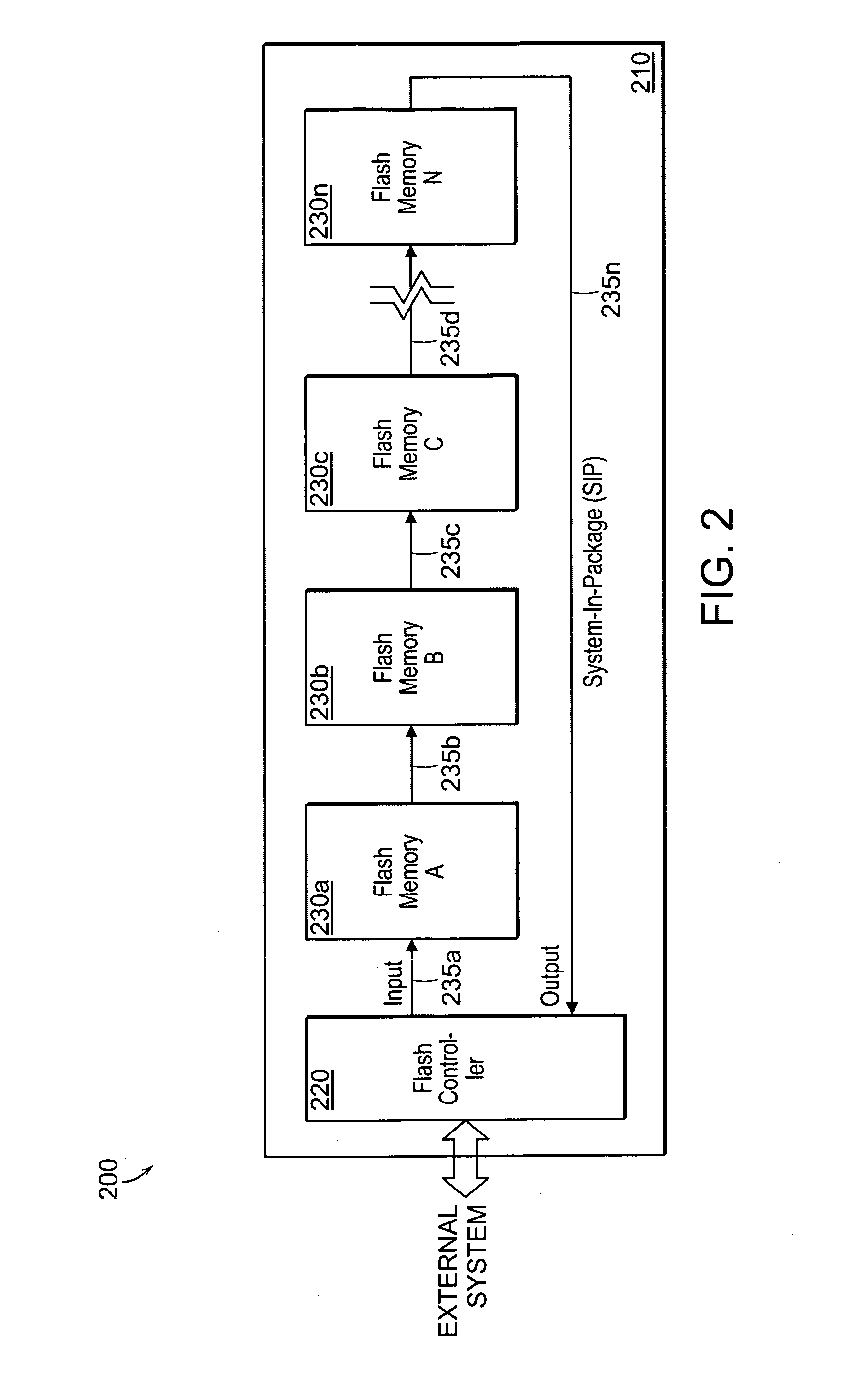

Nonvolatile memory system

InactiveUS20070165457A1Increase memory capacitySignificant overheadSolid-state devicesRead-only memoriesDaisy chainFlash memory controller

A Flash memory system is implemented in a system-in-package (SIP) enclosure, the system comprising a Flash memory controller and a plurality Flash memory devices. An SIP relates to a single package or module comprising a number of integrated circuits (chips). The Flash memory controller is configured to interface with an external system and a plurality of memory devices within the SIP. The memory devices are configured in a daisy chain cascade arrangement, controlled by the Flash memory controller through commands transmitted through the daisy chain cascade.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Integrated passive cap in a system-in-package

InactiveUS20080217708A1Impedence networksSemiconductor/solid-state device detailsEngineeringSystem in package

According to an exemplary embodiment, a system-in-package includes at least one semiconductor die situated over a package substrate. The system-in-package further includes a wall structure situated on the at least one semiconductor die. The system-in-package further includes an integrated passive cap situated over the wall structure, where the integrated passive cap includes at least one passive component. The wall structure and the integrated passive cap form an air cavity over the at least one semiconductor die. The system-in-package can further include at least one bond pad situated on a cap substrate. The at least one bond pad on the cap substrate of the integrated passive cap can be electrically connected to a substrate bond pad on the package substrate.

Owner:SKYWORKS SOLUTIONS INC

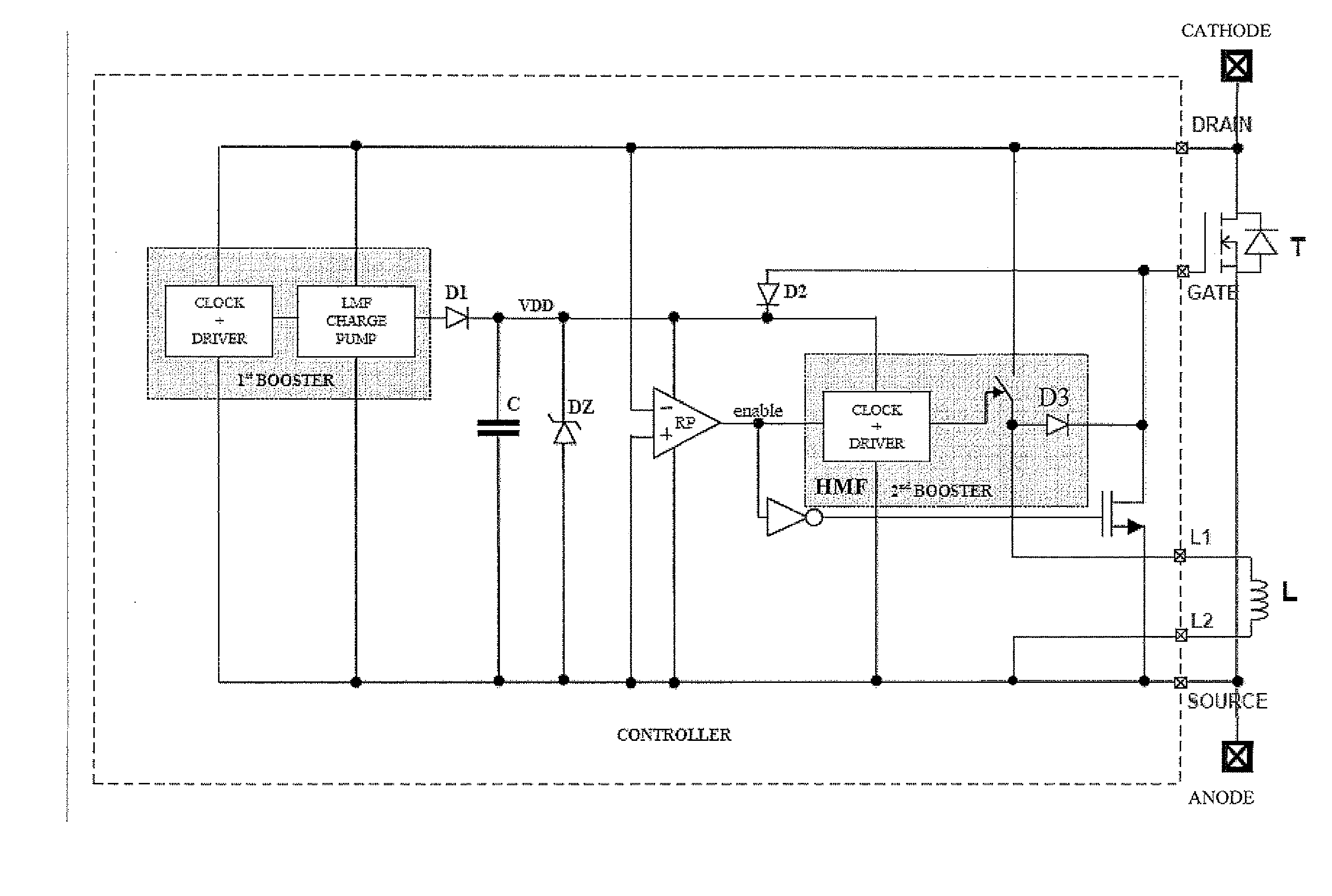

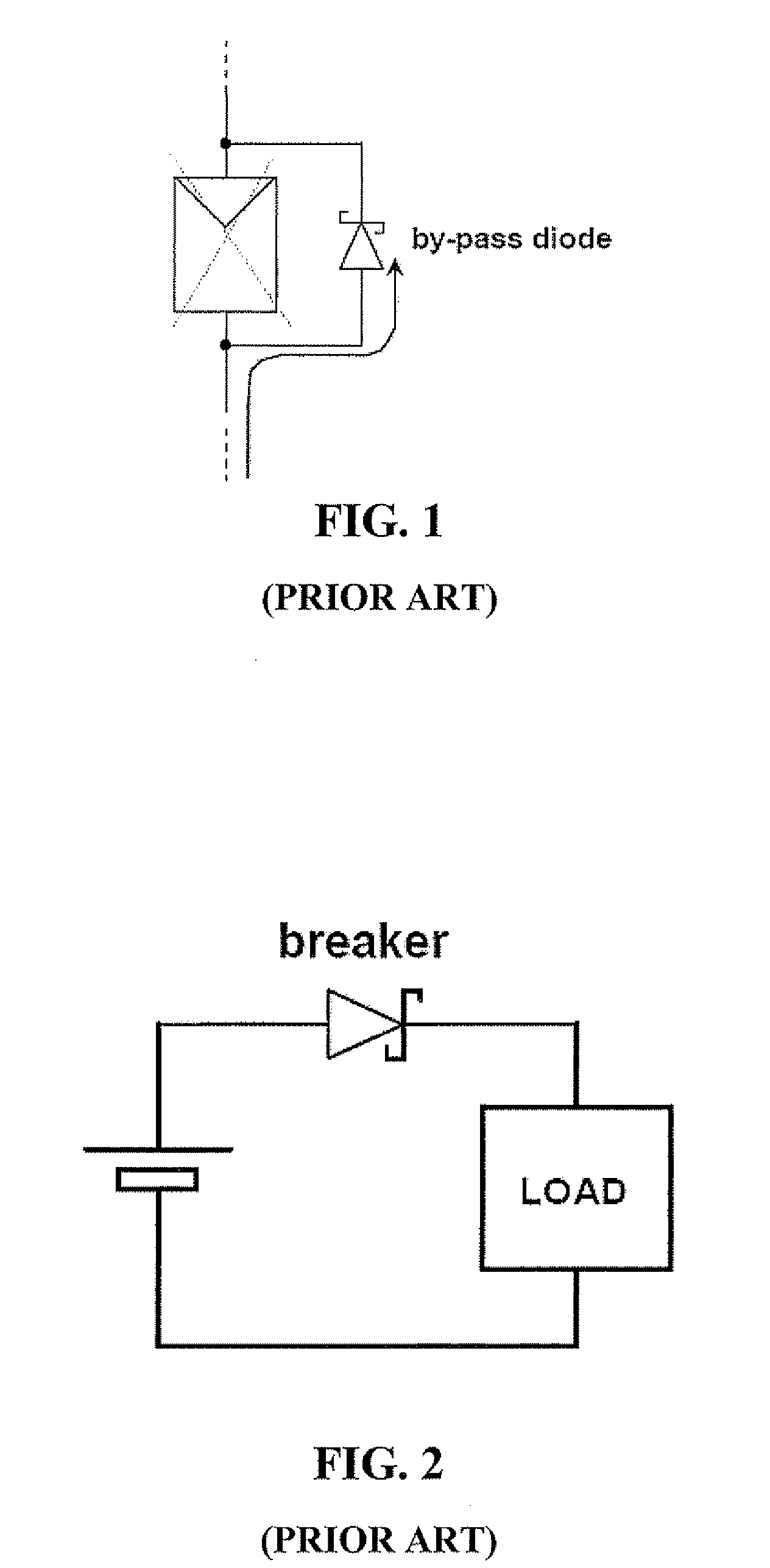

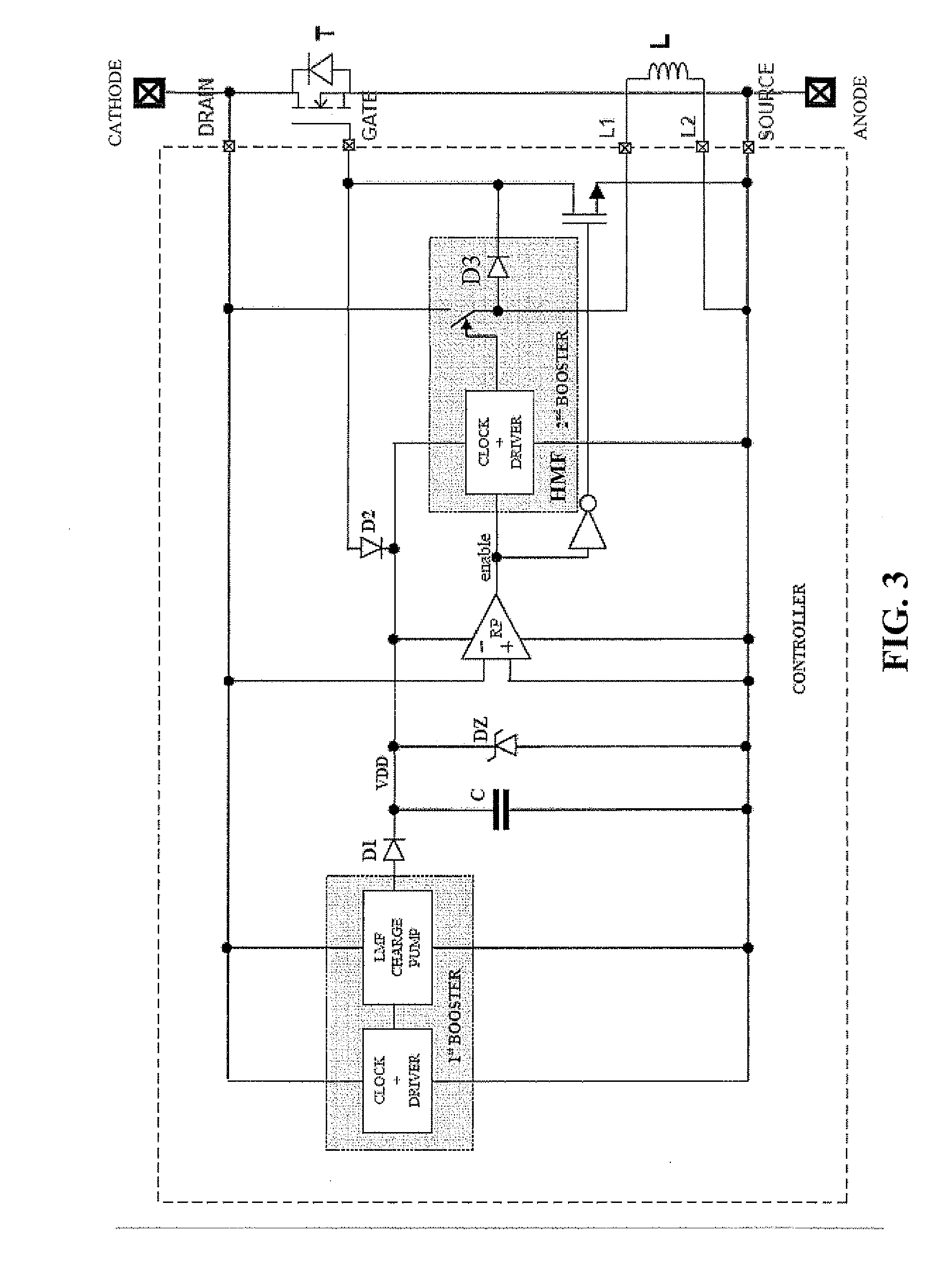

Low on-resistance mosfet implemented, by-pass diode or circuit breaker and related self-powering and control circuit

A MOSFET implemented self-powered current by-pass or circuit breaker device is based on the use of a high multiplication factor (HMF) inductive voltage booster, adapted to boost a voltage as low as few tens of mV up to several Volts, assisted by a start-up low multiplication factor (LMF) charge pump made with low threshold transistors for providing a supply voltage to a polarity inversion detecting comparator of the drain-to-source voltage difference of a power MOSFET connected in parallel to a DC source or string of series connected DC sources or battery, in series to other DC sources during normal operation of the parallel connected DC source or string of series connected DC sources or battery. The inductance for the high multiplication factor, inductive voltage booster for most of the considered power applications is on the order of a few pH and such a relatively send inductor may be included as a discrete component in a compact package or “system-in-package” of monolithically integrated circuits.

Owner:STMICROELECTRONICS SRL

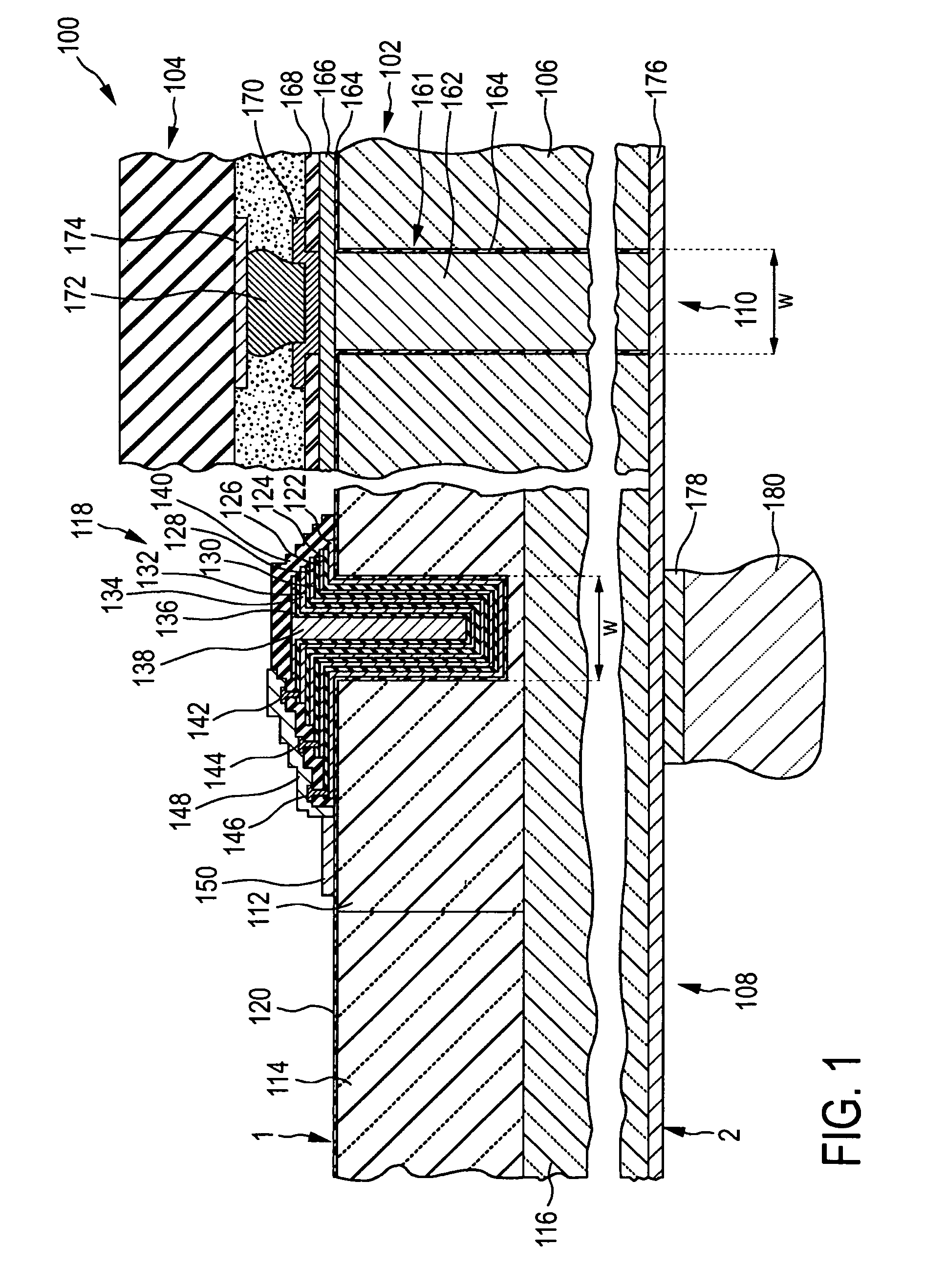

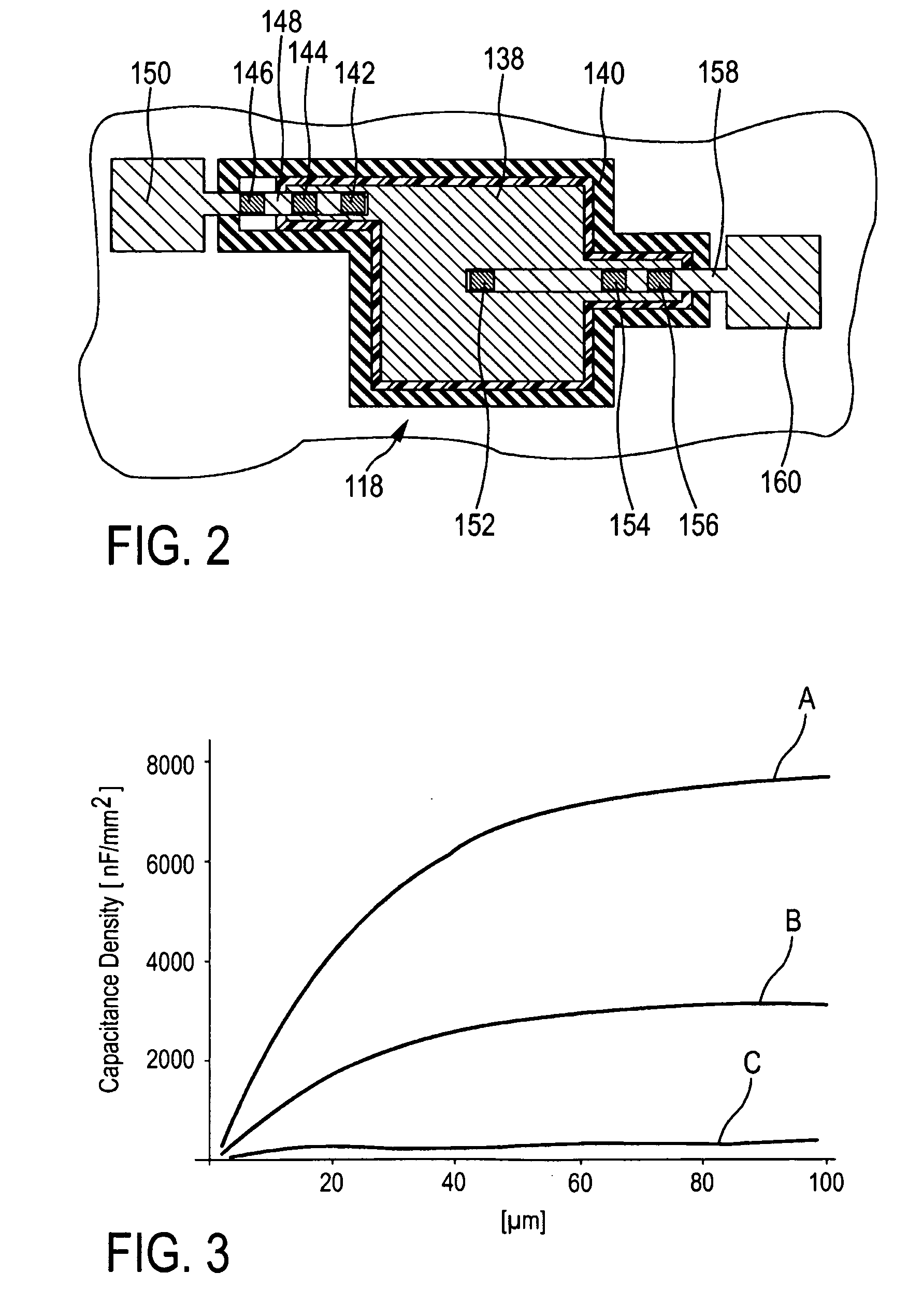

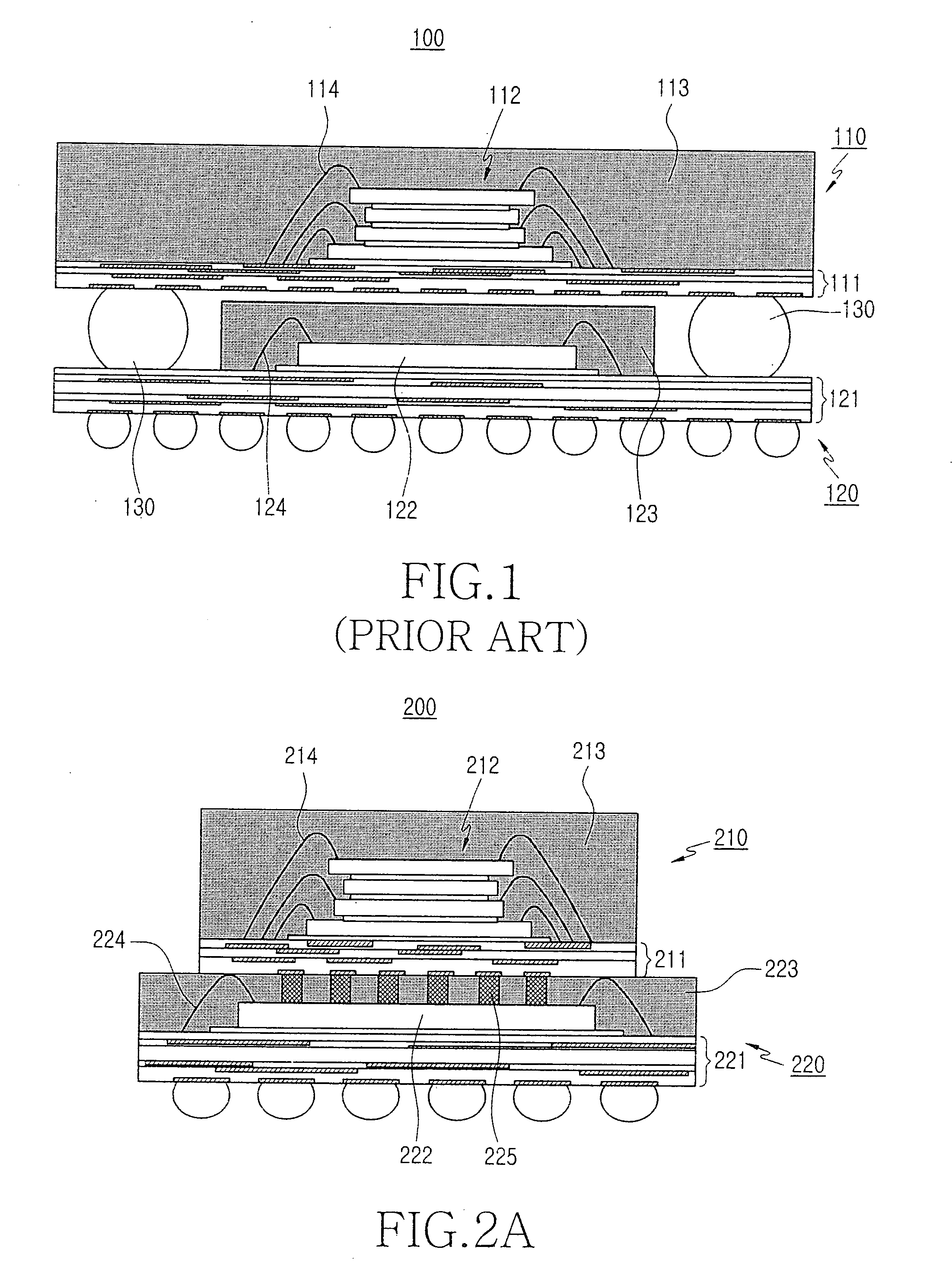

Integration substrate with a ultra-high-density capacitor and a through-substrate via

ActiveUS20100244189A1Simple to introduce into existing production lineIncrease capacitance densitySemiconductor/solid-state device detailsSolid-state devicesMicrometerEngineering

An integration substrate for a system in package comprises a through-substrate via and a trench capacitor wherein with a trench filling that includes at least four electrically conductive capacitor-electrode layers in an alternating arrangement with dielectric layers. —The capacitor-electrode layers are alternatingly connected to a respective one of two capacitor terminals provided on the first or second substrate side. The trench capacitor and the through-substrate via are formed in respective trench openings and via openings in the semiconductor substrate, which have an equal lateral extension exceeding 10 micrometer. This structure allows, among other advantages, a particularly cost-effective fabrication of the integration substrate because the via openings and the trench openings in the substrate can be fabricated simultaneously.

Owner:MURATA INTEGRATED PASSIVE SOLUTIONS

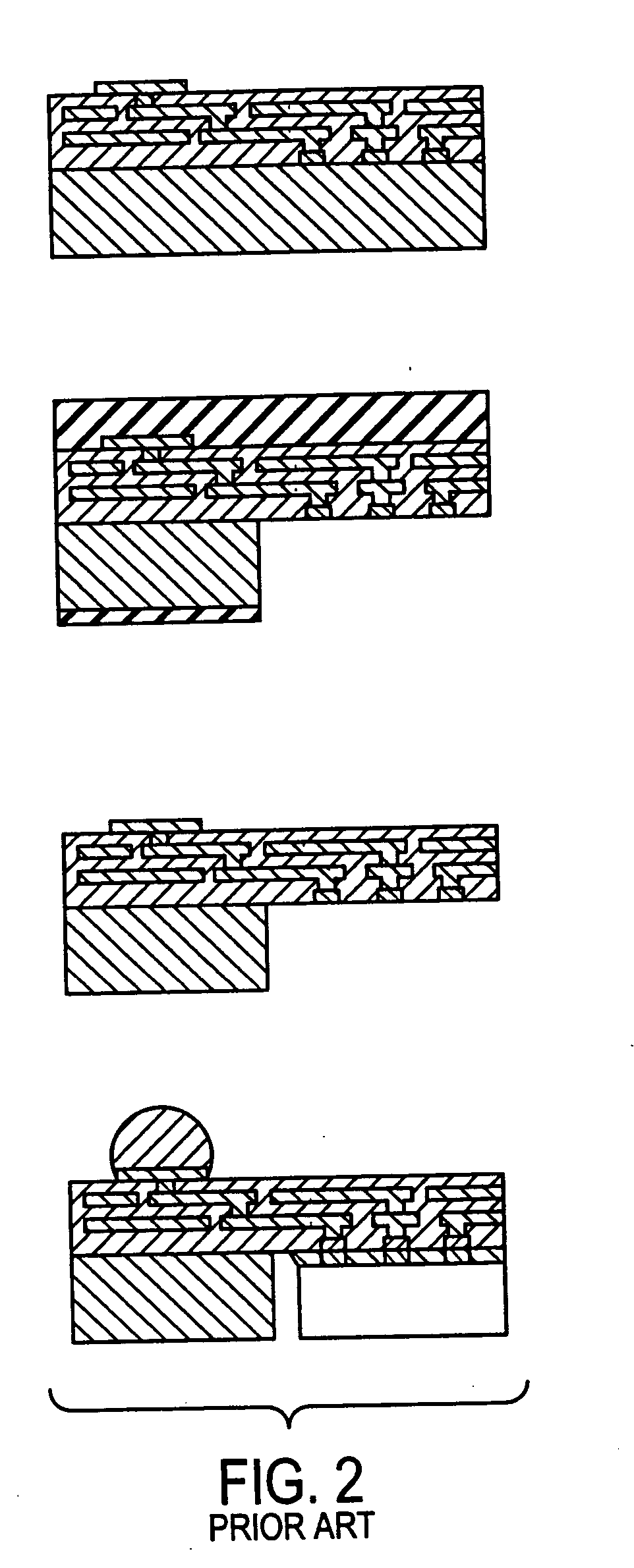

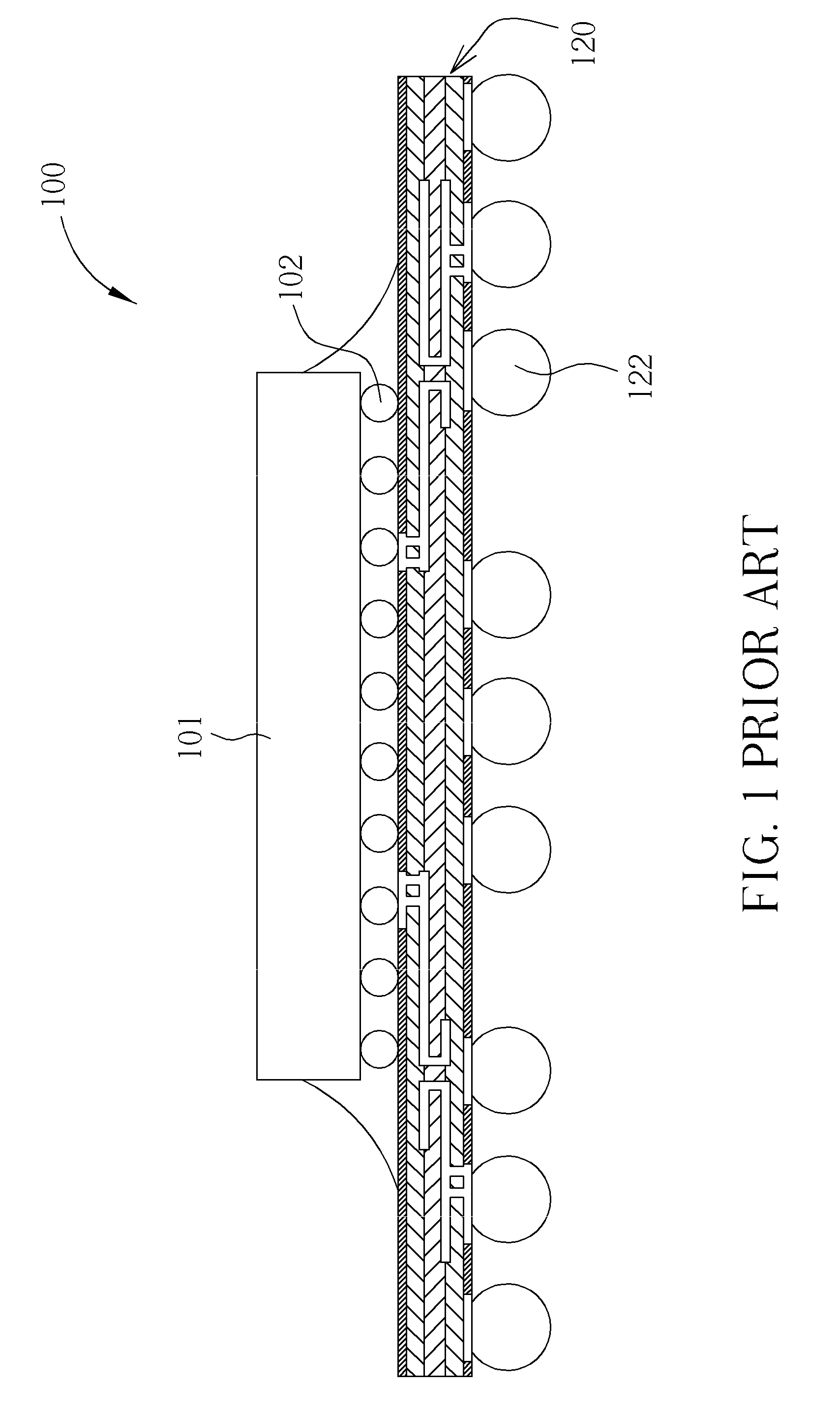

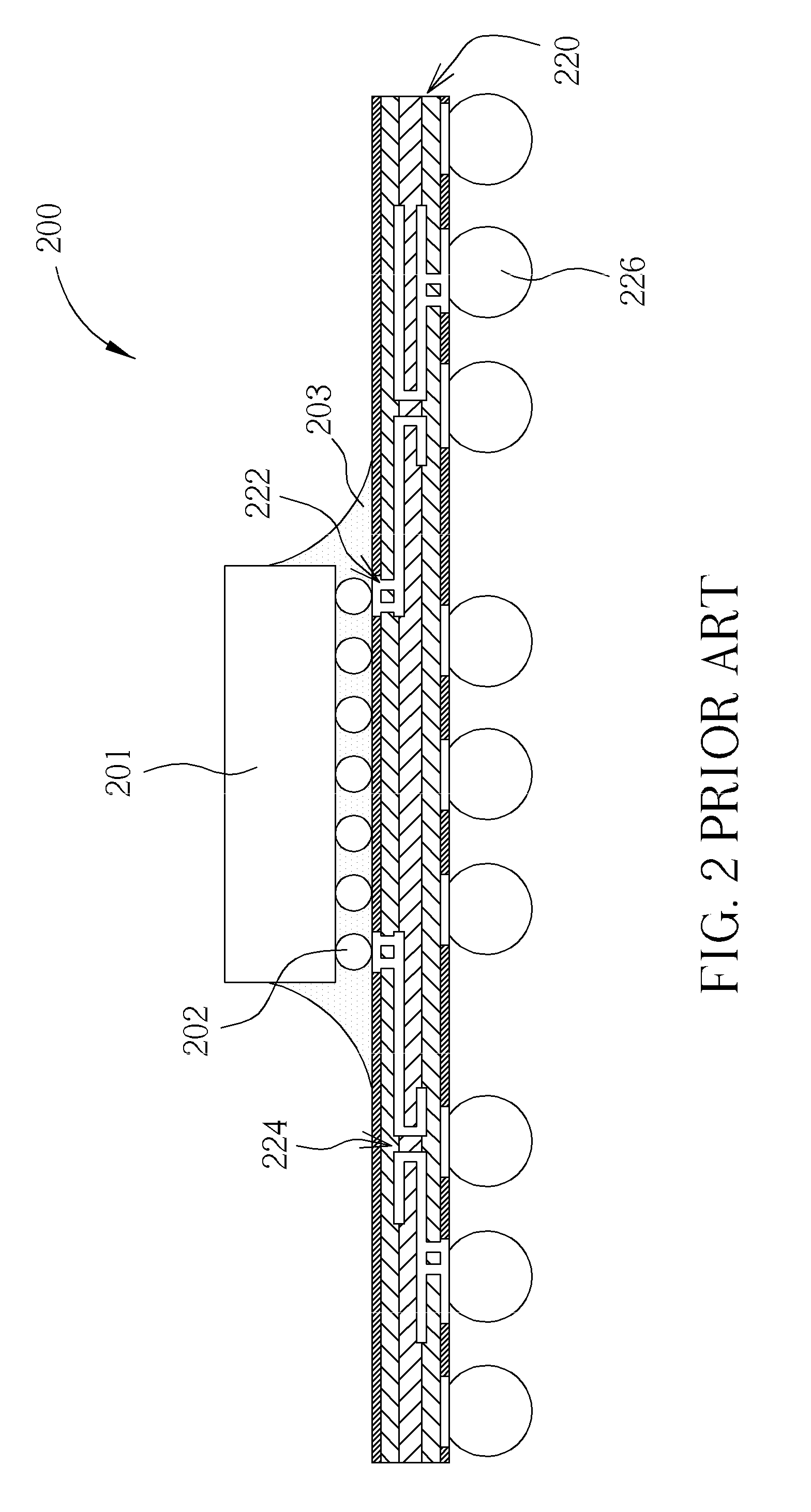

Semiconductor package and semiconductor system in package using the same

InactiveUS20080073771A1Lower the volumeEnhanced advantageSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageSystem in package

Disclosed are a semiconductor package and semiconductor system in package using the same. The semiconductor package includes: a printed circuit board (PCB); a semiconductor die disposed on the PCB and having conductive posts formed on an upper surface of the semiconductor die; and a molding formed on the PCB to cover the semiconductor die, wherein the conductive posts have a surface exposed out of an upper surface of the molding. The semiconductor system in package includes: a first semiconductor package having a semiconductor die on which conductive posts are formed, and a molding formed so that upper surfaces of the conductive posts are exposed; and a second semiconductor package disposed on the first semiconductor package and electrically connected to the conductive posts.

Owner:SAMSUNG ELECTRONICS CO LTD

System-in packages

ActiveUS20100290191A1Good electromagnetic field shieldImprove routing densitySemiconductor/solid-state device detailsSolid-state devicesSystem in packageExternal circuit

System-in packages, or multichip modules, are described which can include multi-layer chips in a multi-layer polymer structure, on-chip metal bumps on the multi-layer chips, intra-chip metal bumps in the multi-layer polymer structure, and patterned metal layers in the multi-layer polymer structure. The multi-layer chips in the multi-layer polymer structure can be connected to each other or to an external circuit through the on-chip metal bumps, the intra-chip metal bumps and the patterned metal layers. The system-in packages can be connected to external circuits through solder bumps, meal bumps or wirebonded wires.

Owner:QUALCOMM INC

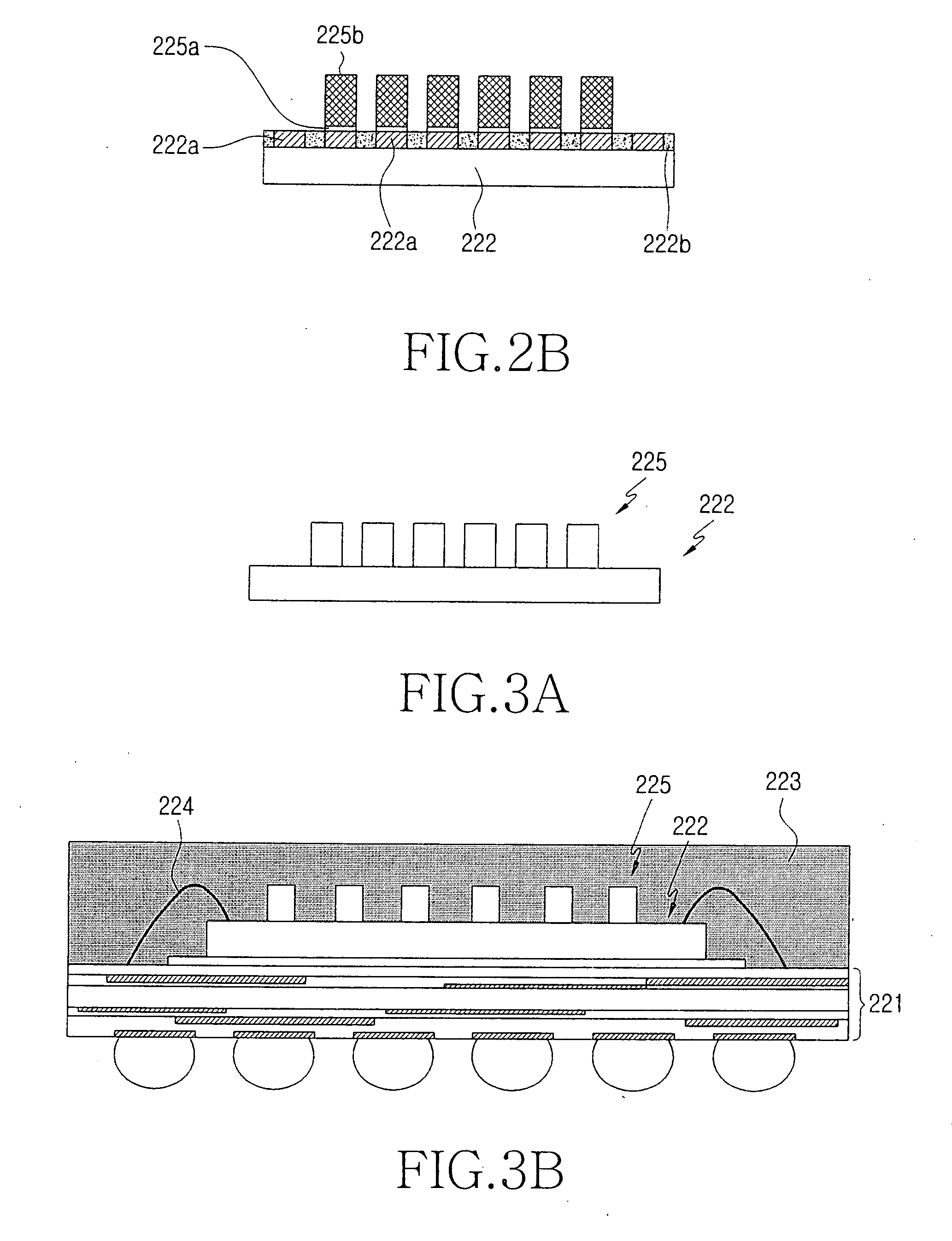

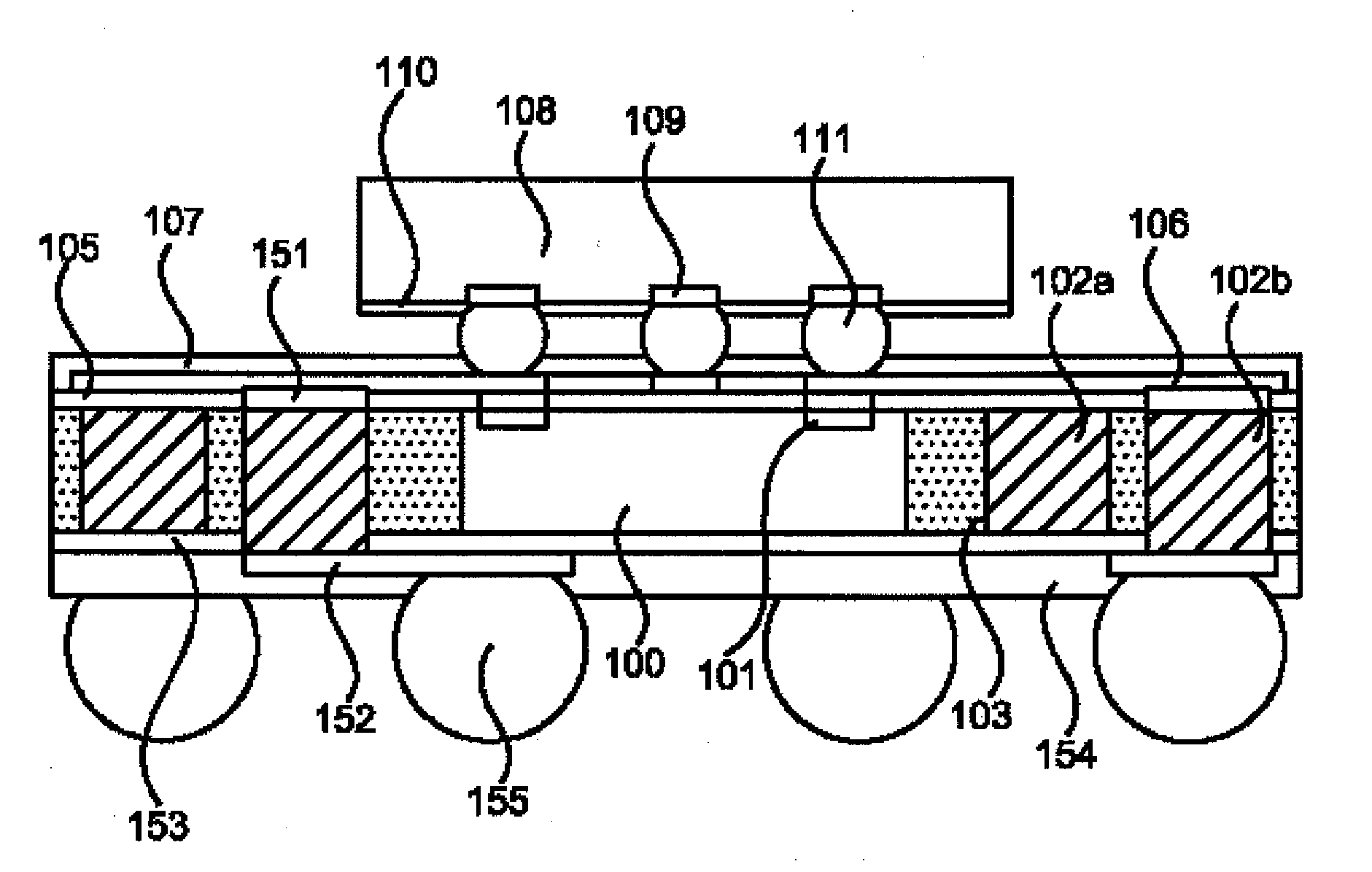

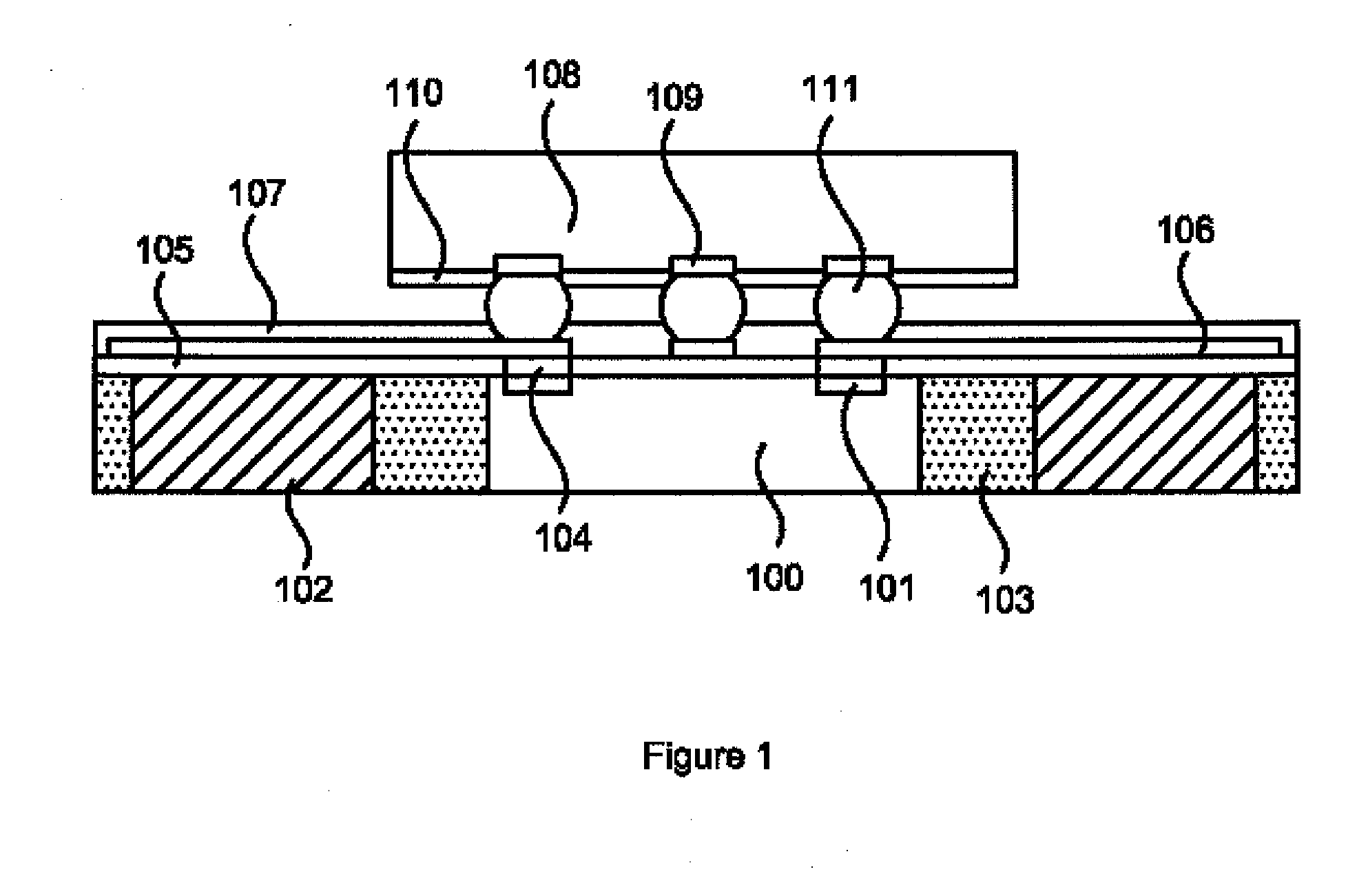

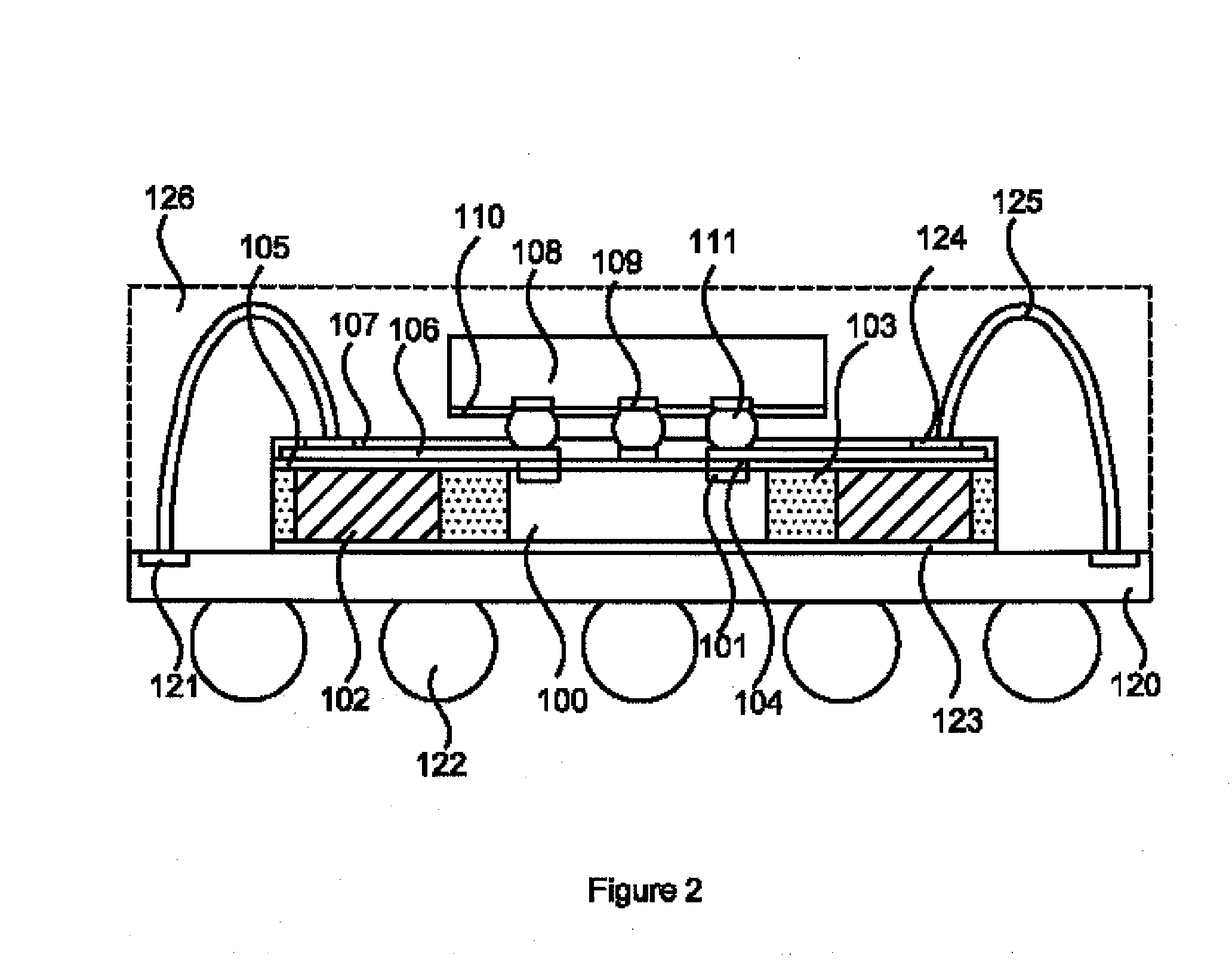

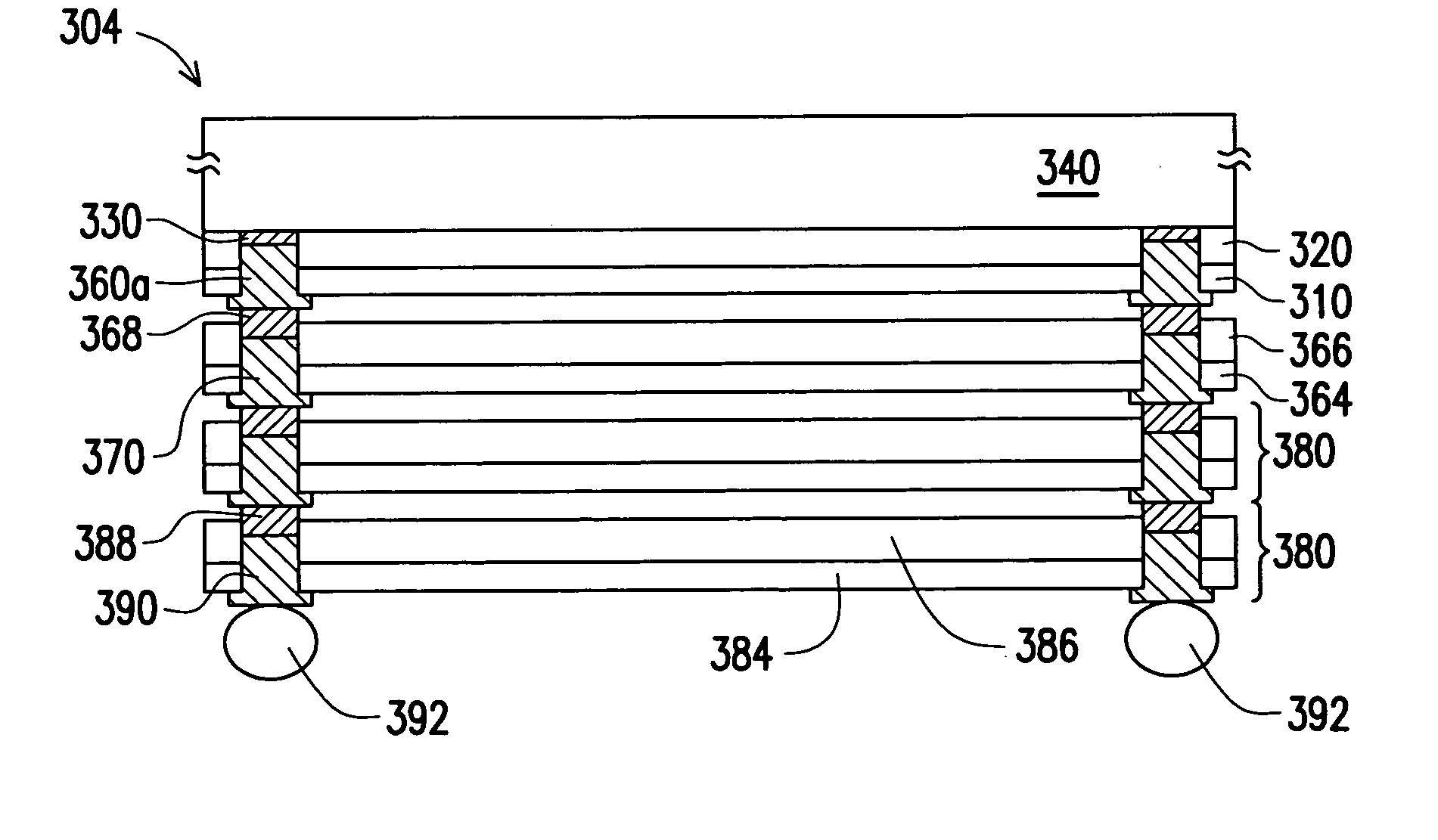

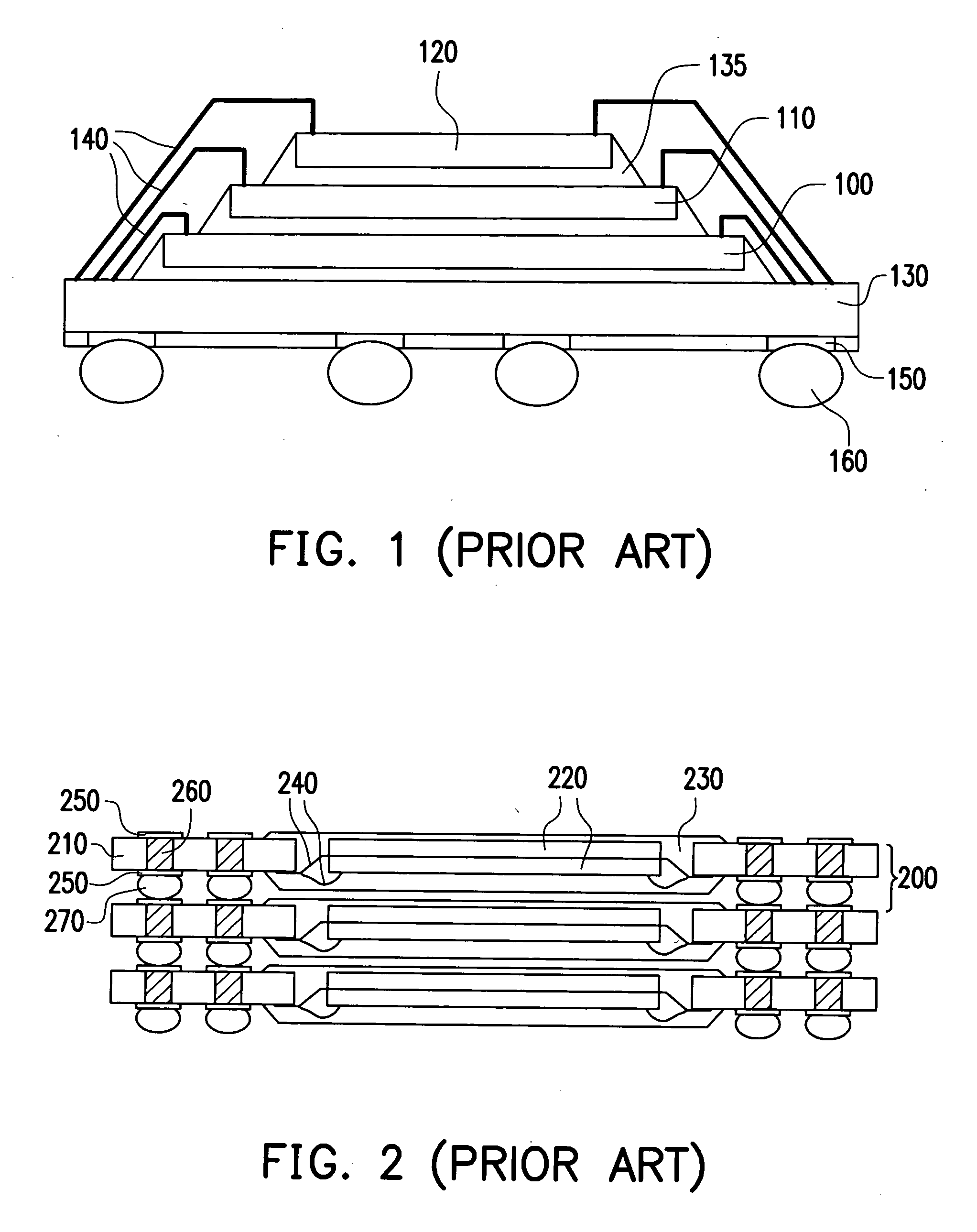

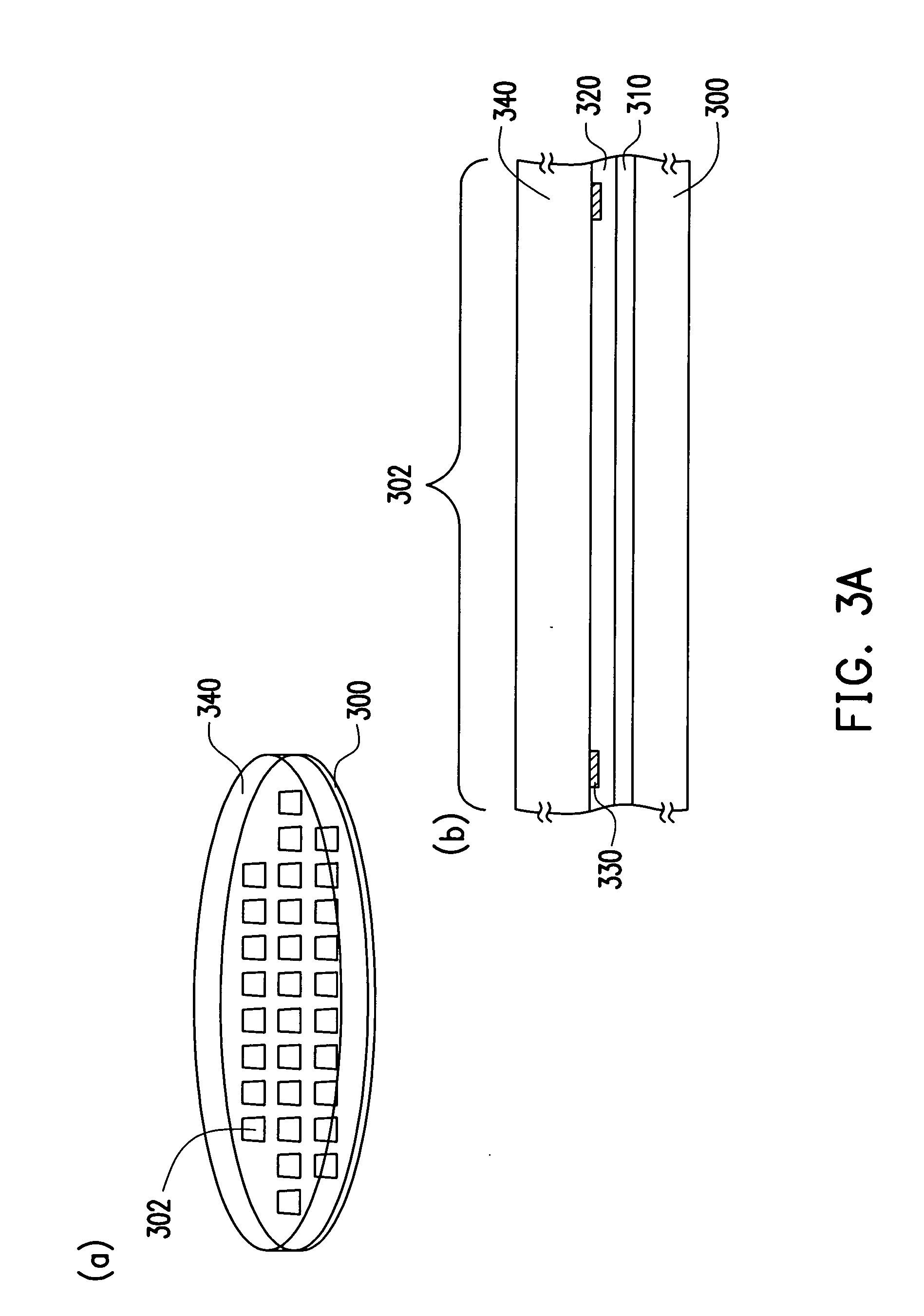

Wafer level stack structure for system-in-package and method thereof

ActiveUS20050104181A1Semiconductor/solid-state device detailsSolid-state devicesChip sizeSystem in package

A wafer level stack structure, including a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, wherein the first wafer and the second wafer are stacked, and wherein the first wafer and the second wafer are coupled to each other. A method of forming a wafer level stack structure, including forming a first wafer including at least one first device chip of a first chip size, wherein each first device chip contains a first plurality of input / output (I / O) pads, forming a second wafer including at least one second device chip of a second chip size smaller than the first chip size, wherein each second device chip contains a second plurality of I / O pads, wherein the at least one second device chip is increased to the first chip size, stacking the first wafer and the second wafer, and coupling the first wafer and the second wafer to each other. A system-in-package, including a wafer level stack structure including at least one first device chip with a first plurality of input / output (I / O) pads and at least one second device chip with a second plurality of I / O pads, and a common circuit board to which the wafer level stack structure is connected. A method of forming a system-in-package for containing a wafer level stack structure, including forming a wafer level stack structure including at least one first device chip having a first plurality of input / output (I / O) pads and at least one second device chip having a second plurality of I / O pads, and forming a common circuit board to which the wafer level stack structure is connected.

Owner:SAMSUNG ELECTRONICS CO LTD

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

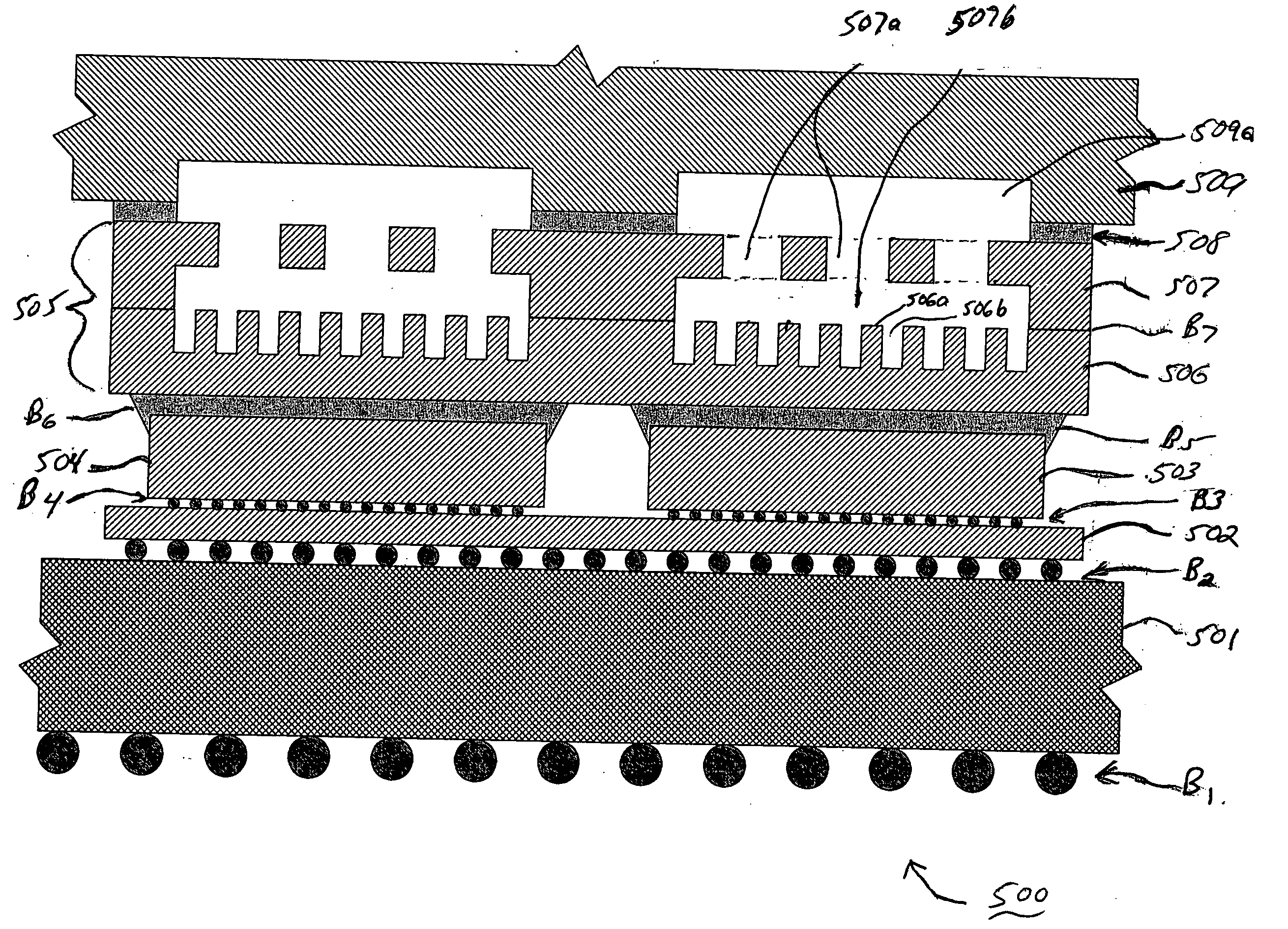

InactiveUS6919508B2Improve performanceIncrease speedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmCopper interconnect

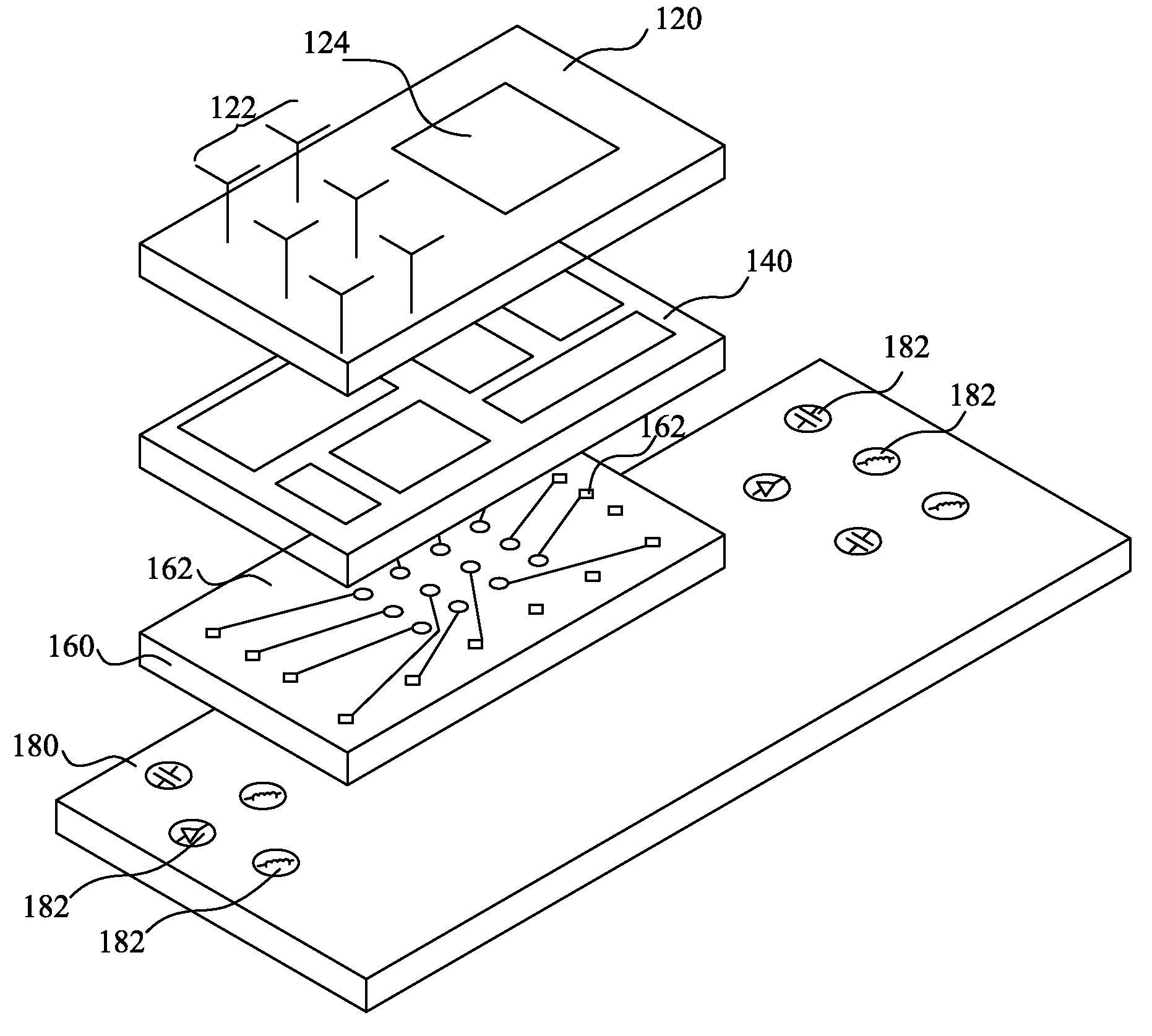

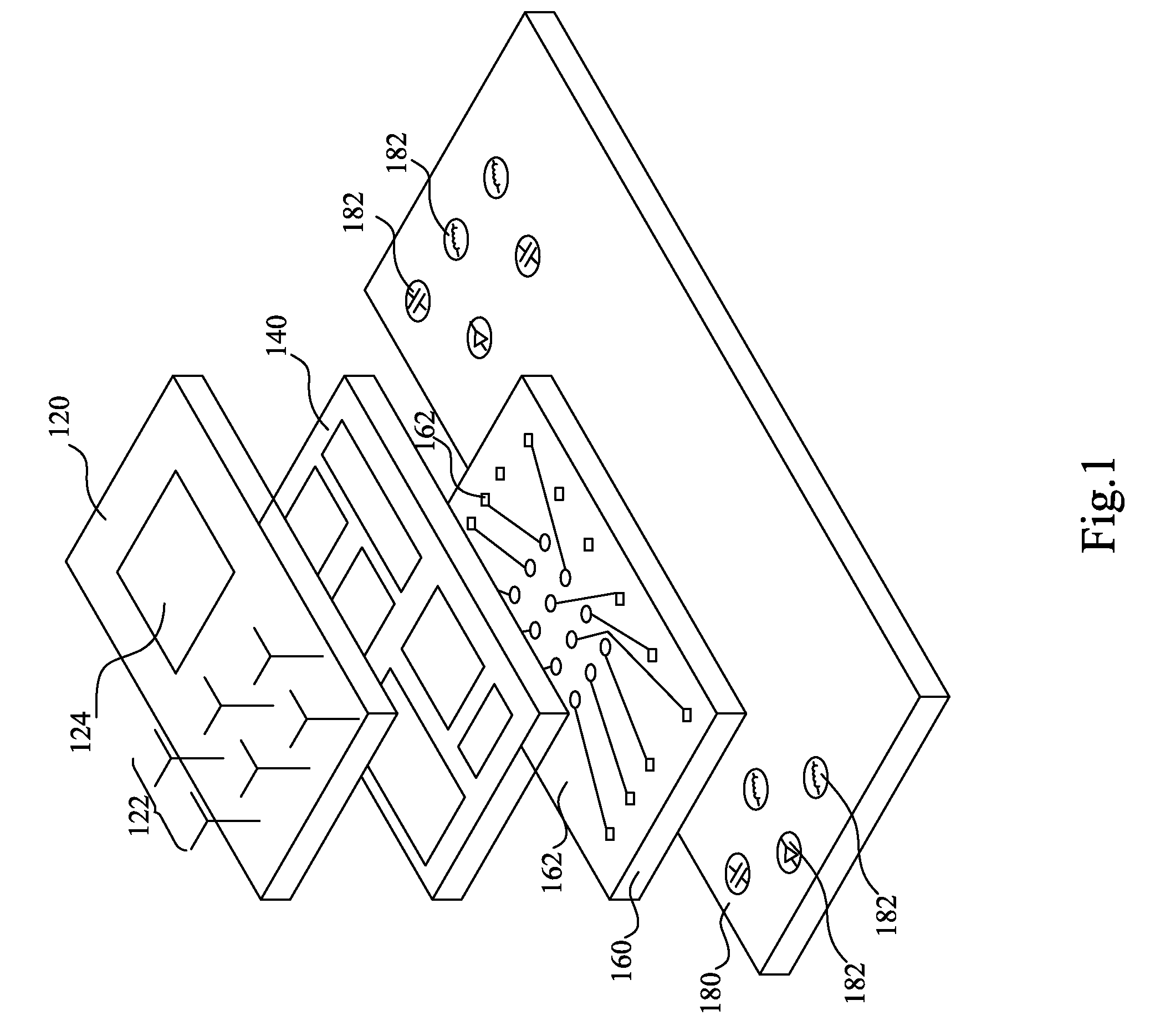

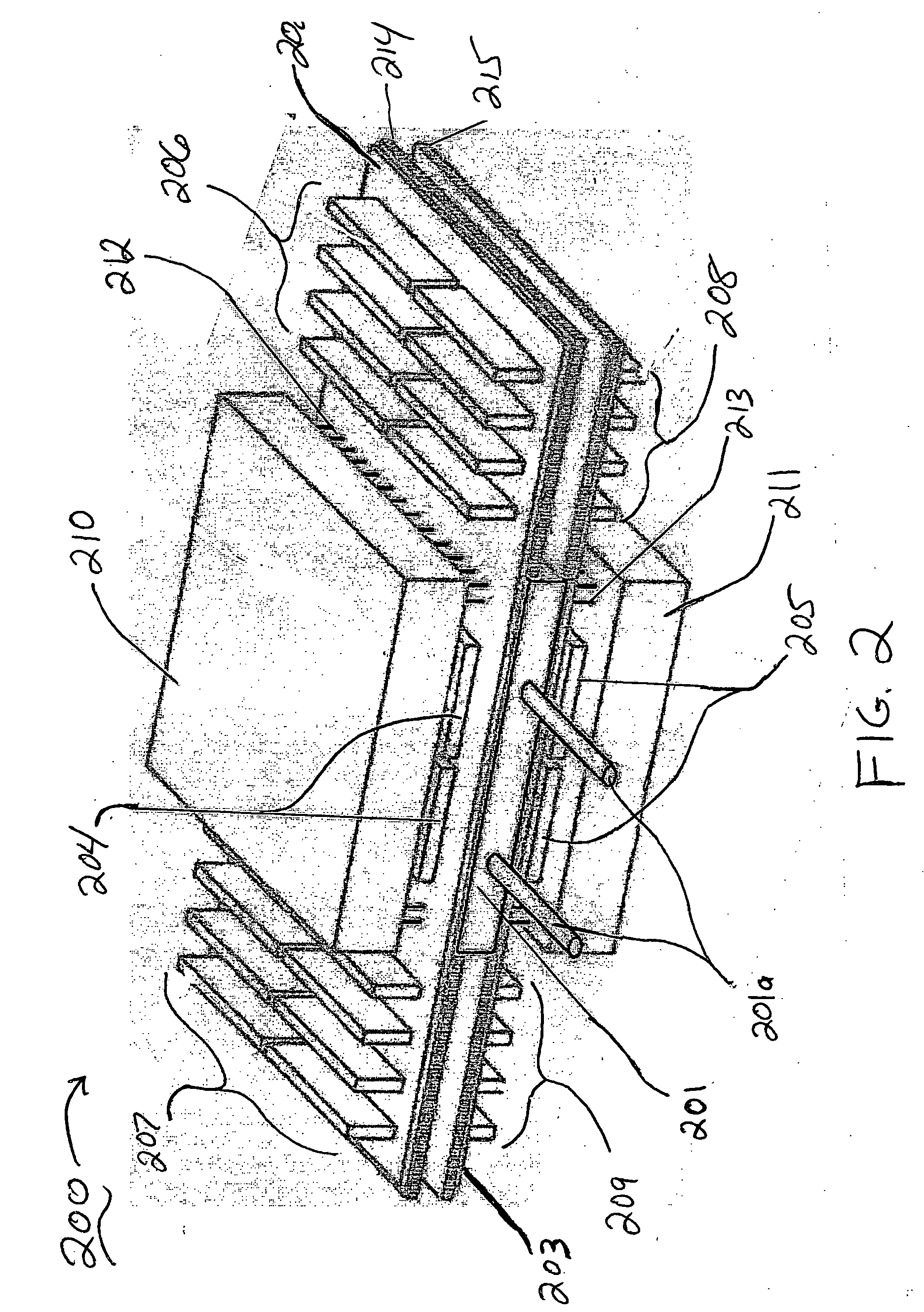

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

System-in packages

ActiveUS8164171B2Improve routing densityGood electromagnetic field shieldSemiconductor/solid-state device detailsSolid-state devicesSystem in packageExternal circuit

System-in packages, or multichip modules, are described which can include multi-layer chips in a multi-layer polymer structure, on-chip metal bumps on the multi-layer chips, intra-chip metal bumps in the multi-layer polymer structure, and patterned metal layers in the multi-layer polymer structure. The multi-layer chips in the multi-layer polymer structure can be connected to each other or to an external circuit through the on-chip metal bumps, the intra-chip metal bumps and the patterned metal layers. The system-in packages can be connected to external circuits through solder bumps, meal bumps or wirebonded wires.

Owner:QUALCOMM INC

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS20050087356A1Enhanced signalReduce in quantityTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmEngineering

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

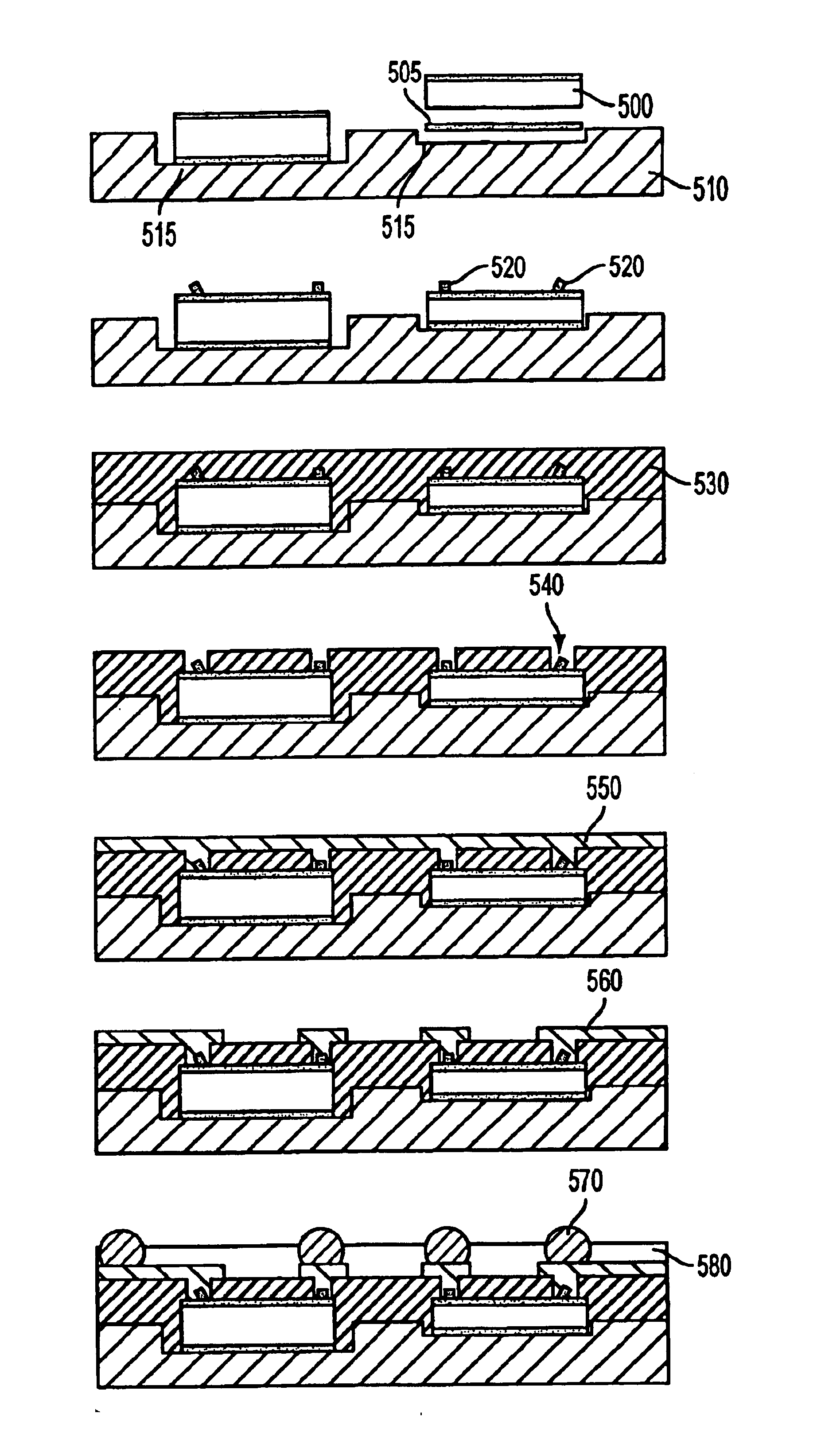

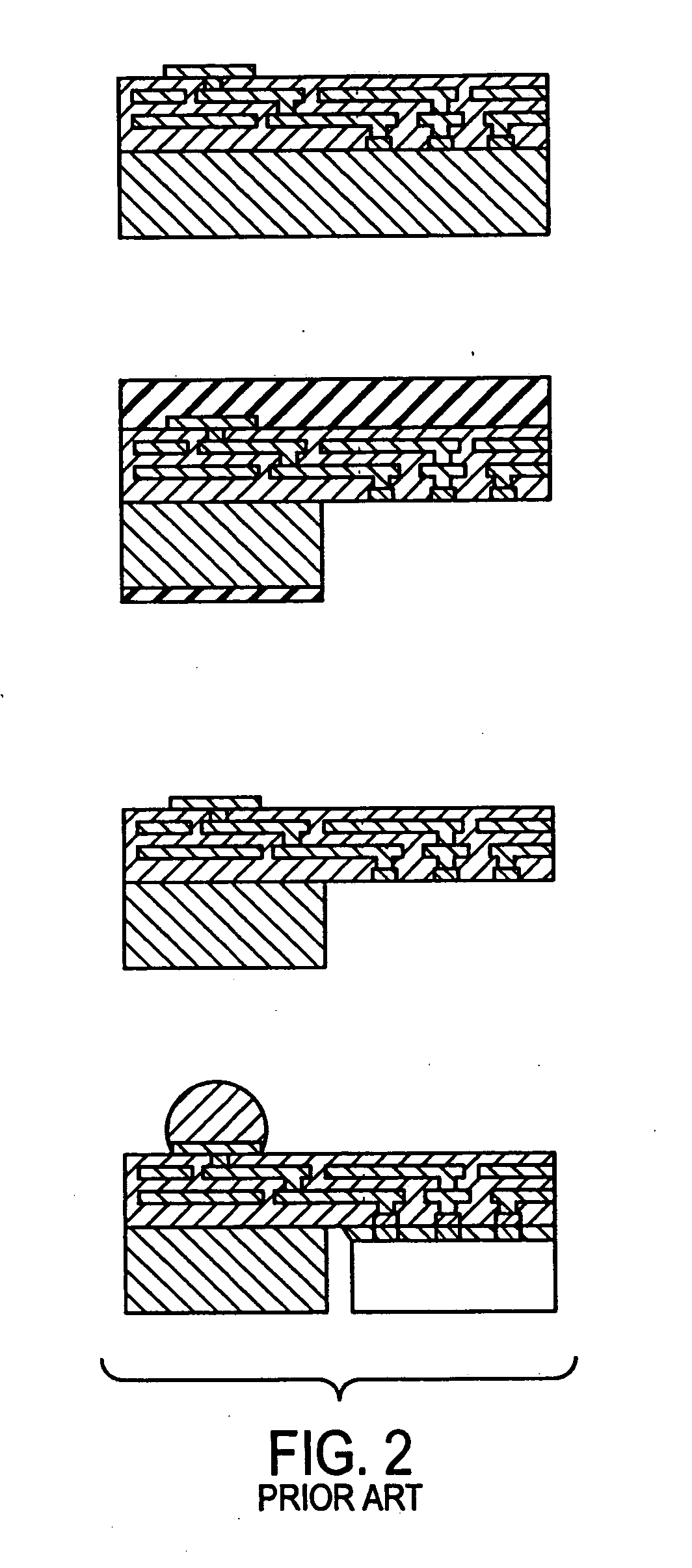

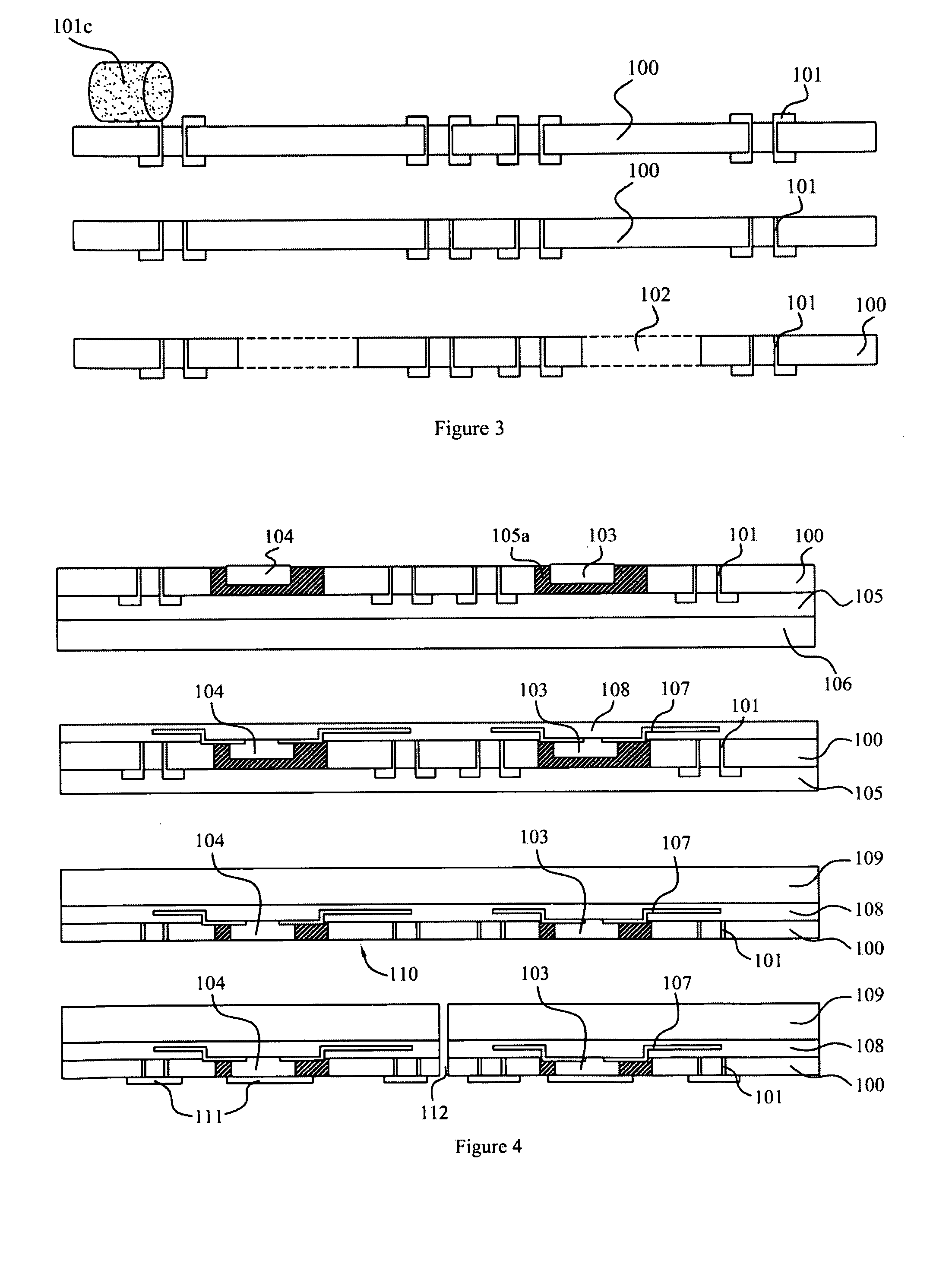

System-in-package and manufacturing method of the same

ActiveUS20090321915A1Reduce thicknessImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesContact padProtection layer

The present invention discloses a structure of package comprising: a substrate with a die receiving through hole and a contact conductive via formed therein, a die disposed within the die receiving through hole, a surrounding material filled in the gap except the die area of the die receiving though hole, a re-distribution layer formed on the substrate and coupled to the contact conductive via, a protection layer formed over the re-distribution layer, a cover material formed over the protection layer; and a terminal contact pad formed on the lower surface of the substrate and under the contact conductive via and the die to couple the contact conductive via.

Owner:ADL ENERGY CORP

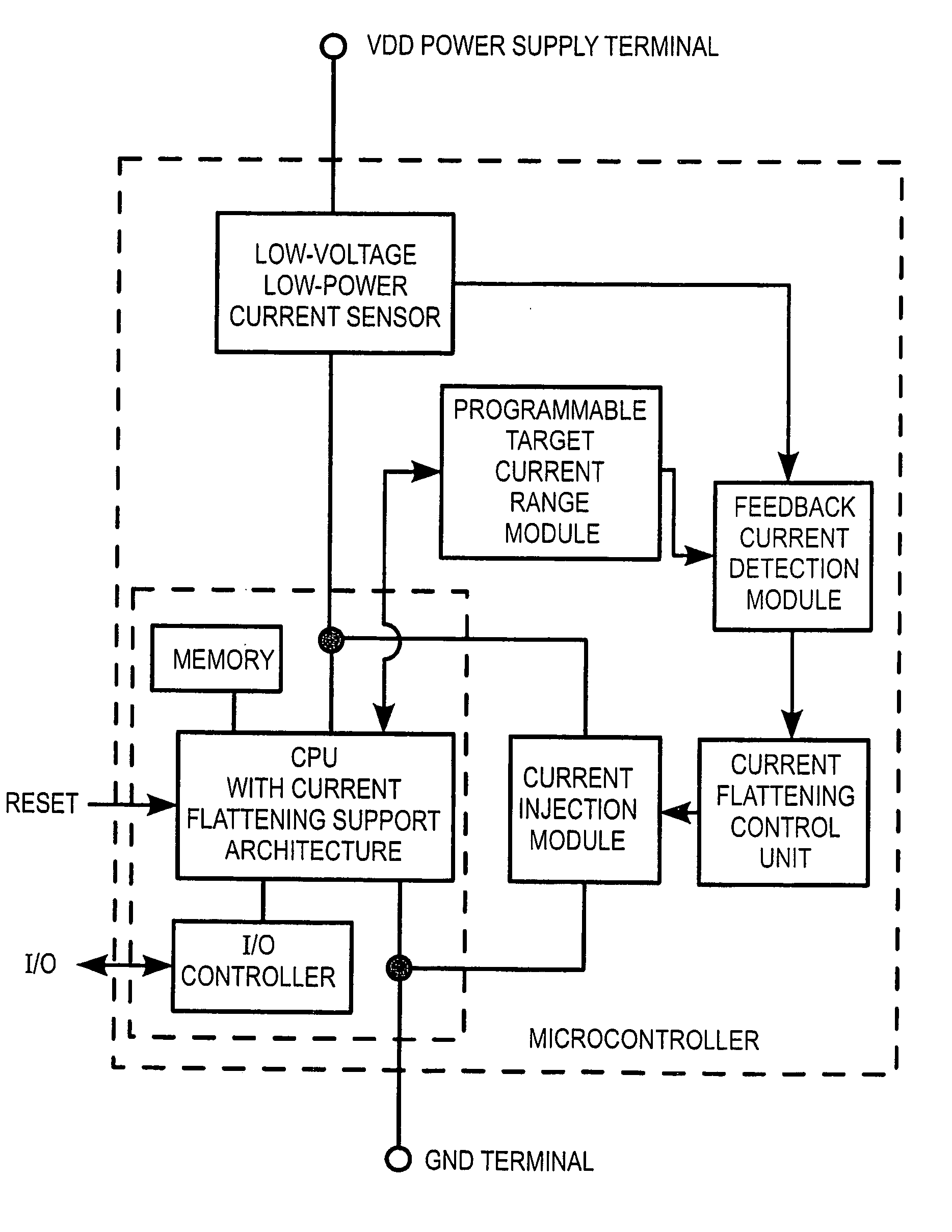

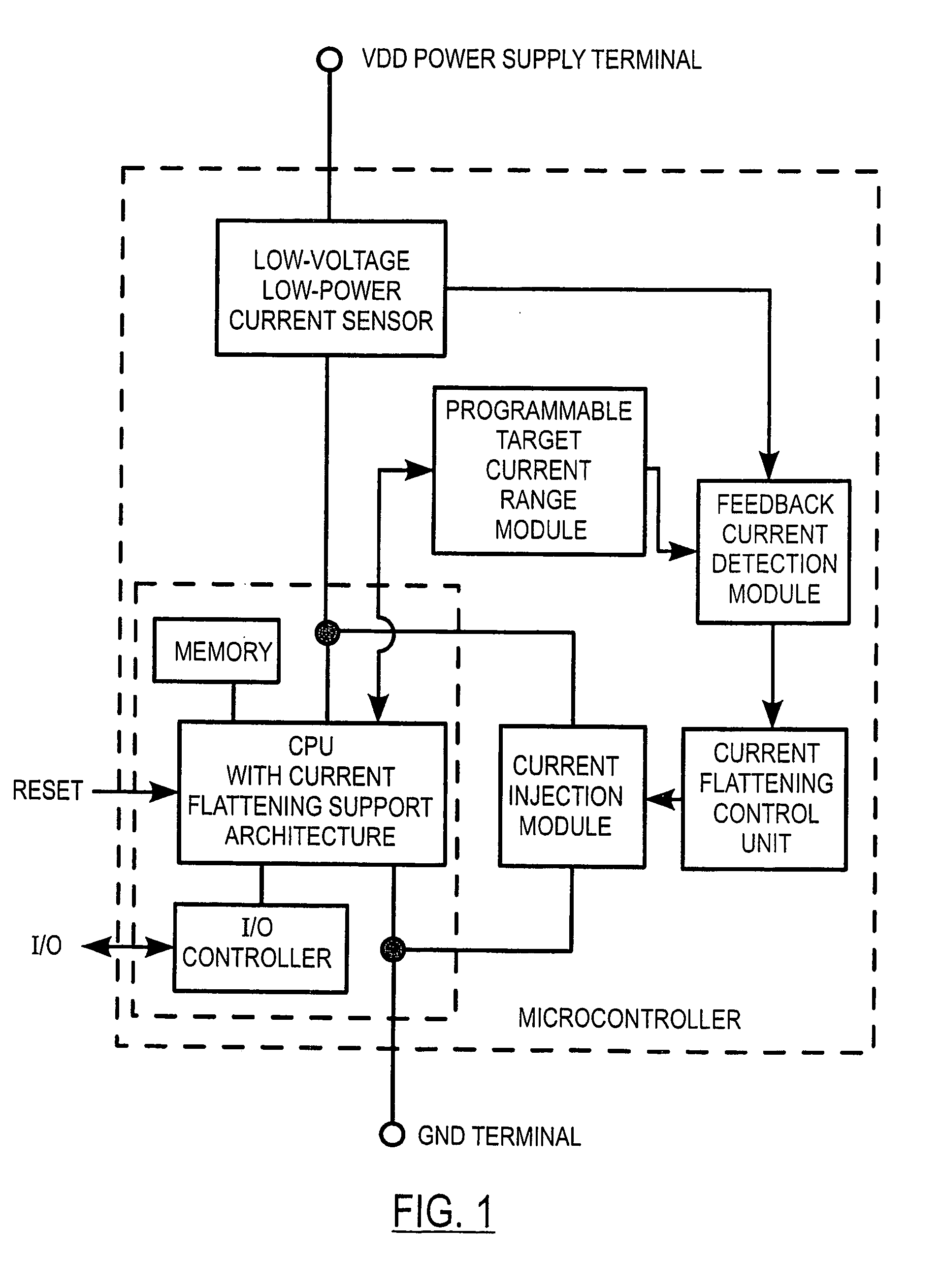

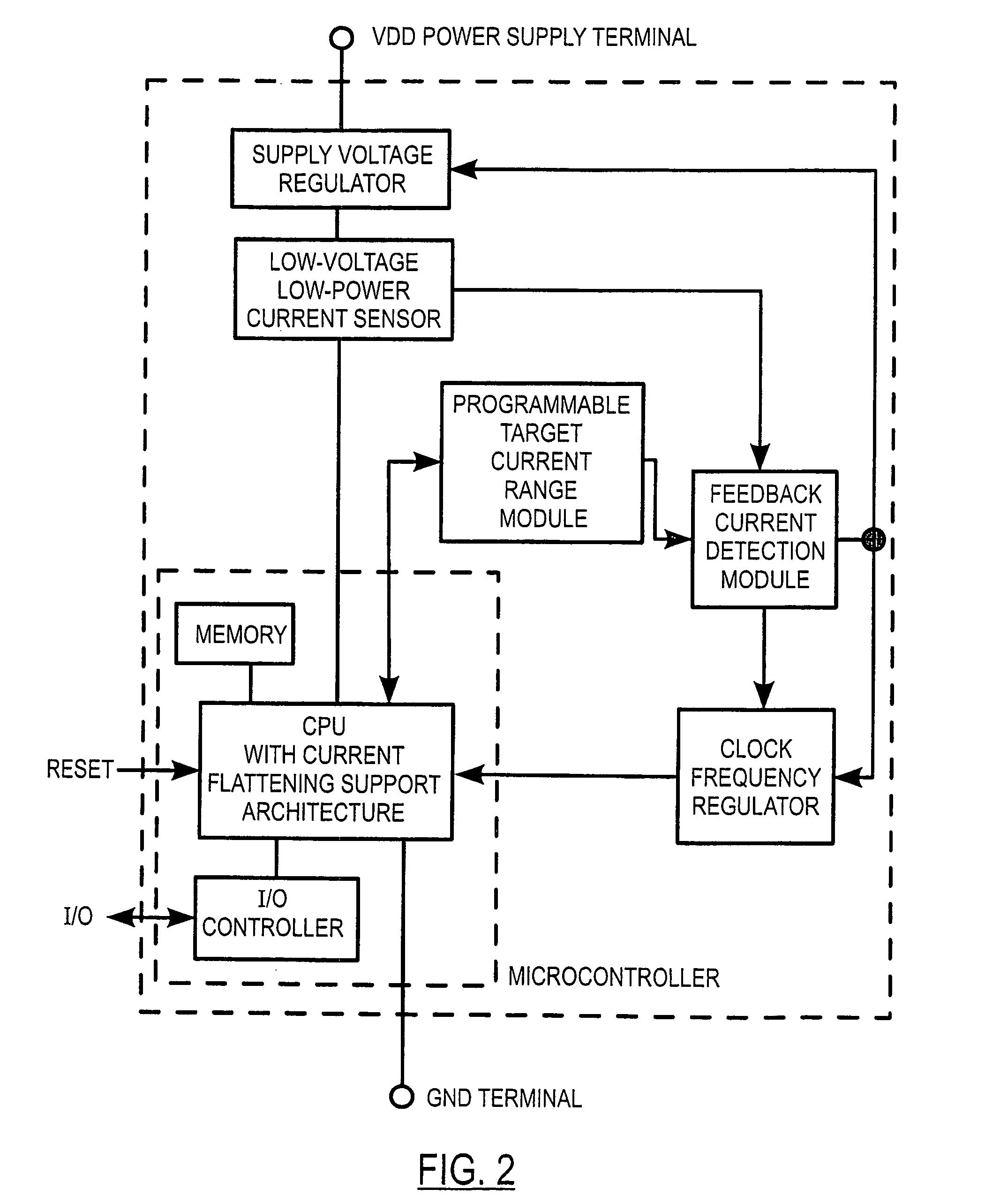

Current flattening and current sensing methods and devices

InactiveUS20070076890A1Flattening total current consumptionCurrent consumptionDigital data processing detailsHardware monitoringReference currentCurrent sensor

Flattening total current consumption of system having processing core and power supply input by current sensing within system at power supply input and controlling system current consumption such that system current is reduced if over reference current threshold, and increased if below reference current threshold. Inject additional current through digital injections cells working higher frequencies, by increasing switching activity, by increasing voltage supply to core, and by increasing operating frequency of processor core. Feedback signal indicates current consumption of system. Current consumption similarly decreased. Current sensed by mirroring input current inline with power supply input and compensating for voltage drop introduced by mirroring using opposing field effect transistors and maintaining outputs at same voltage through feedback control loop. Processor core may be general purpose processor core or cryptographic processor core. System may be system-on-chip or system-on-package. System includes processor core and current flattening device based on method. Also, current flattening device and current sensor. On chip current sensor sensing current draw of processor core.

Owner:GREGORI STEFANO +1

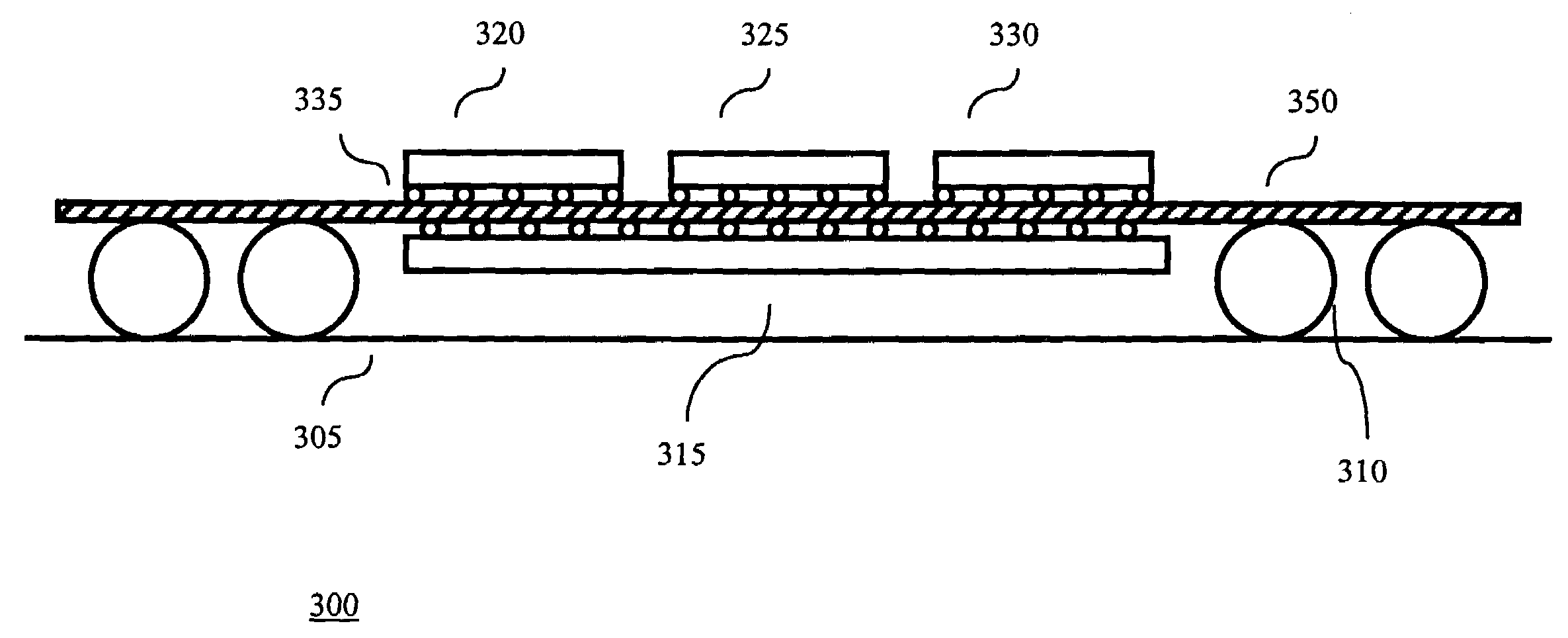

Three-dimensional system-in-package package-on-package structure

ActiveUS20120161315A1Reduce CTE mismatchMinimize size of deviceSemiconductor/solid-state device detailsSolid-state devicesFilling materialsEngineering

The present invention provides a three-dimensional System-In-Package (SIP) Package-On-Package (POP) structure comprising a support element formed around a first electronic device. A filling material is filled between the first electronic device and the support element. Signal channels are coupled to first die pads of the first electronic device. Conductive elements form signal connection between the first end of the signal channels and the second die pads of a second electronic device.

Owner:ADL ENERGY CORP

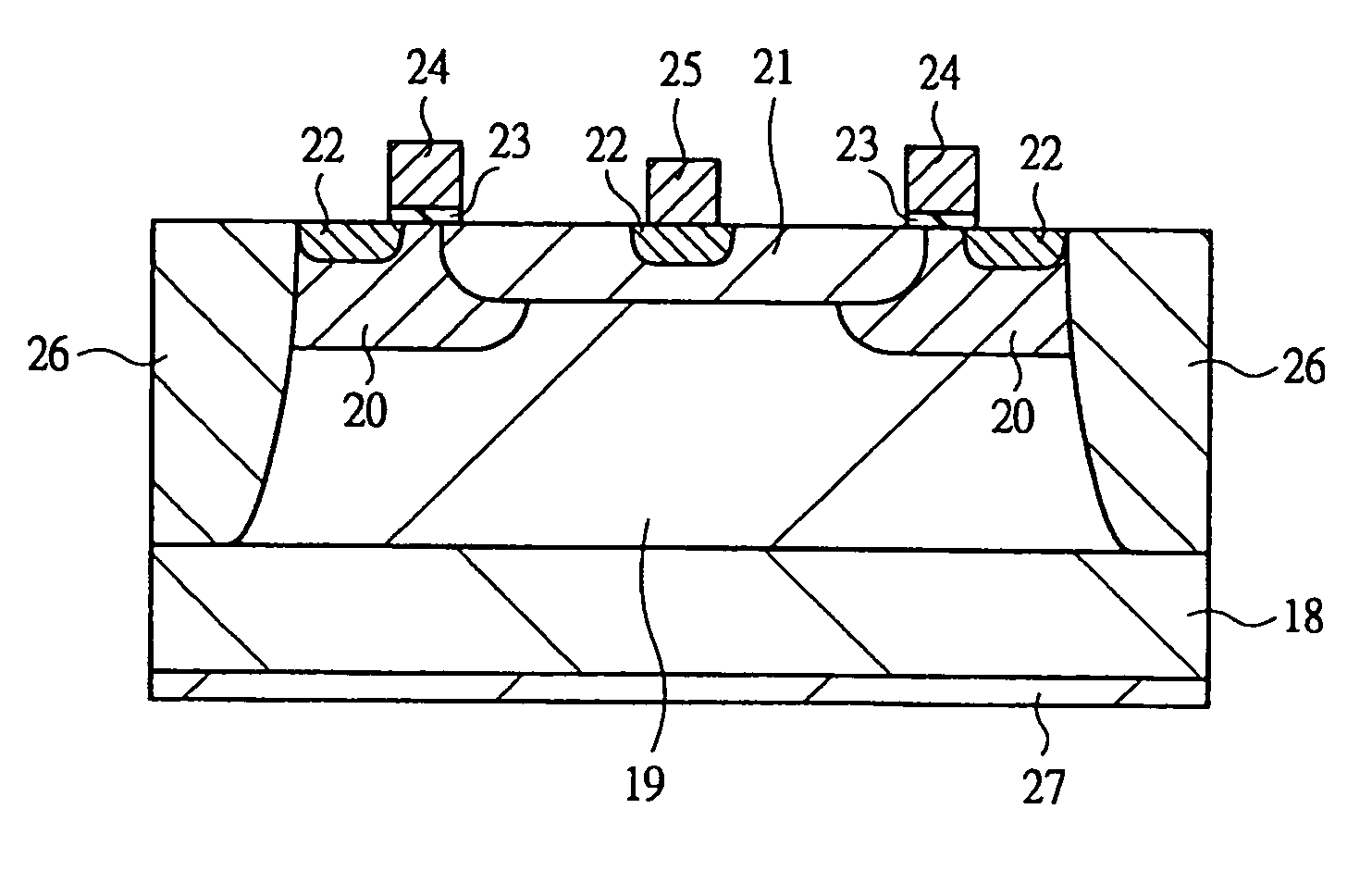

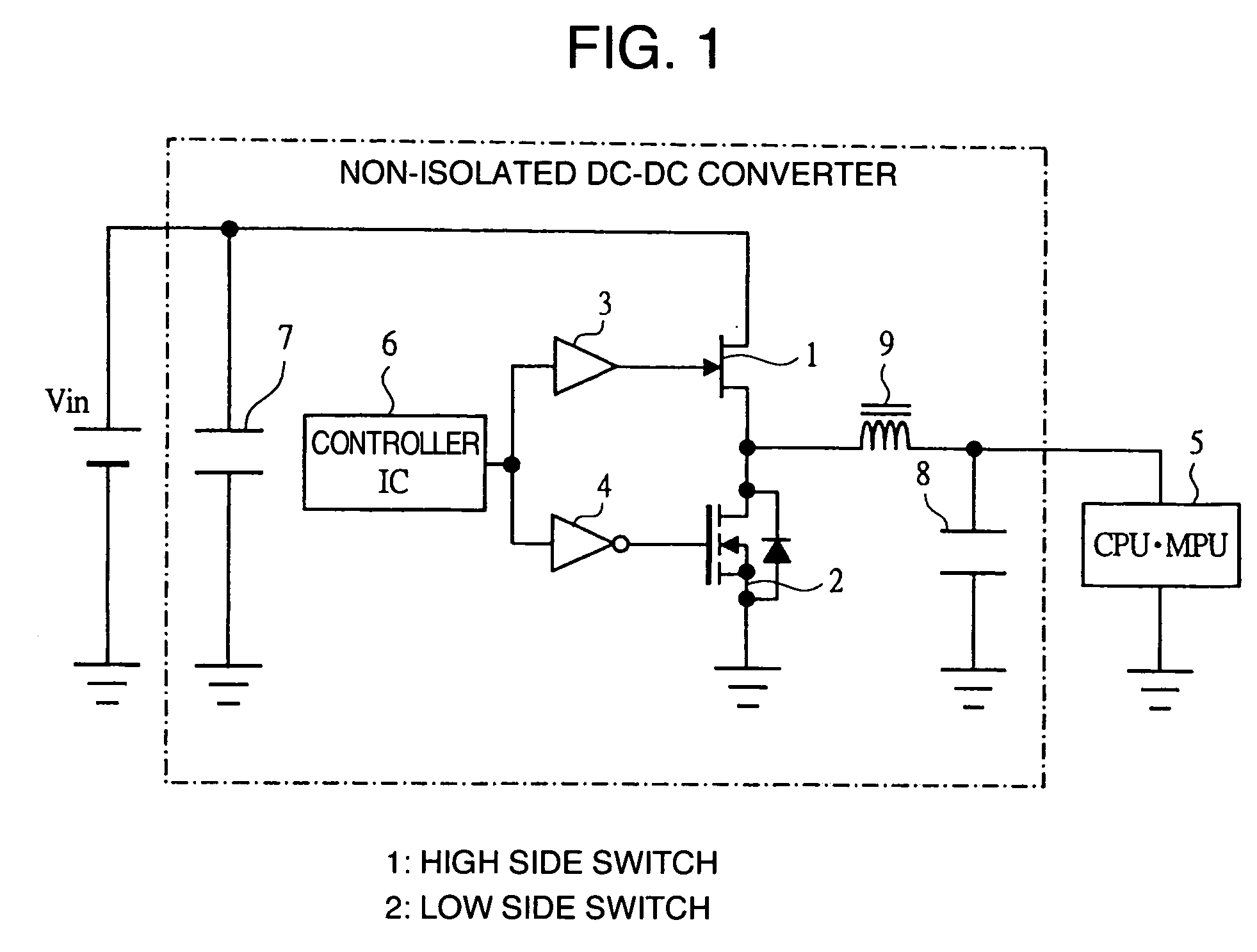

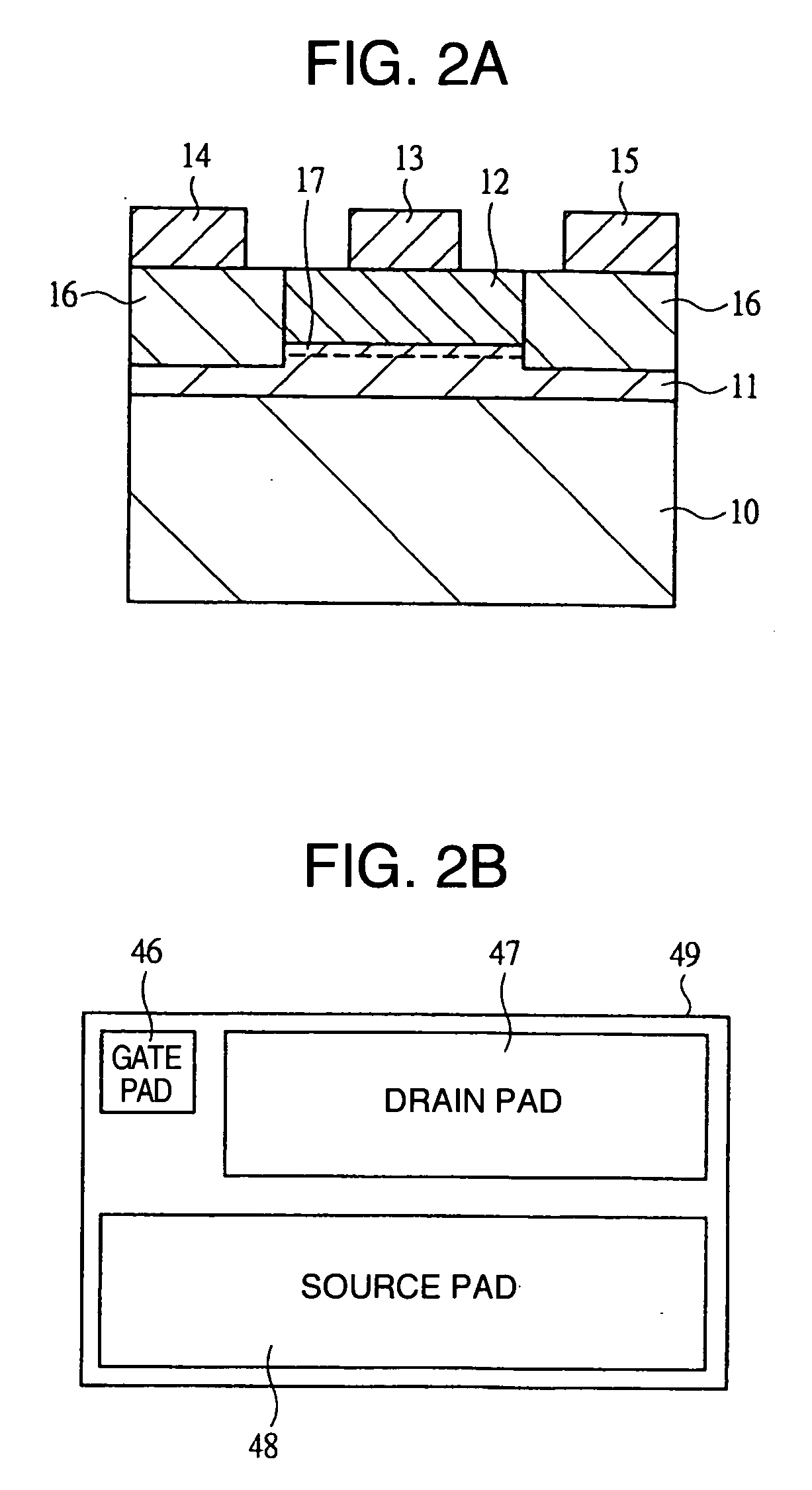

Power supply, multi chip module, system in package and non-isolated DC-DC converter

InactiveUS20060175627A1Reduce capacityLower on-resistanceEfficient power electronics conversionSemiconductor/solid-state device detailsDc dc converterComputer module

A power supply includes a non-isolated DC-DC converter for use in a power source system having a high side switch and a low side switch, in which HEMT or HFET or gallium nitride device with low capacity and low on-resistance is used for the high side switch and a vertical power MOSFET of silicon device with low on-resistance is used for the low side switch.

Owner:RENESAS TECH CORP

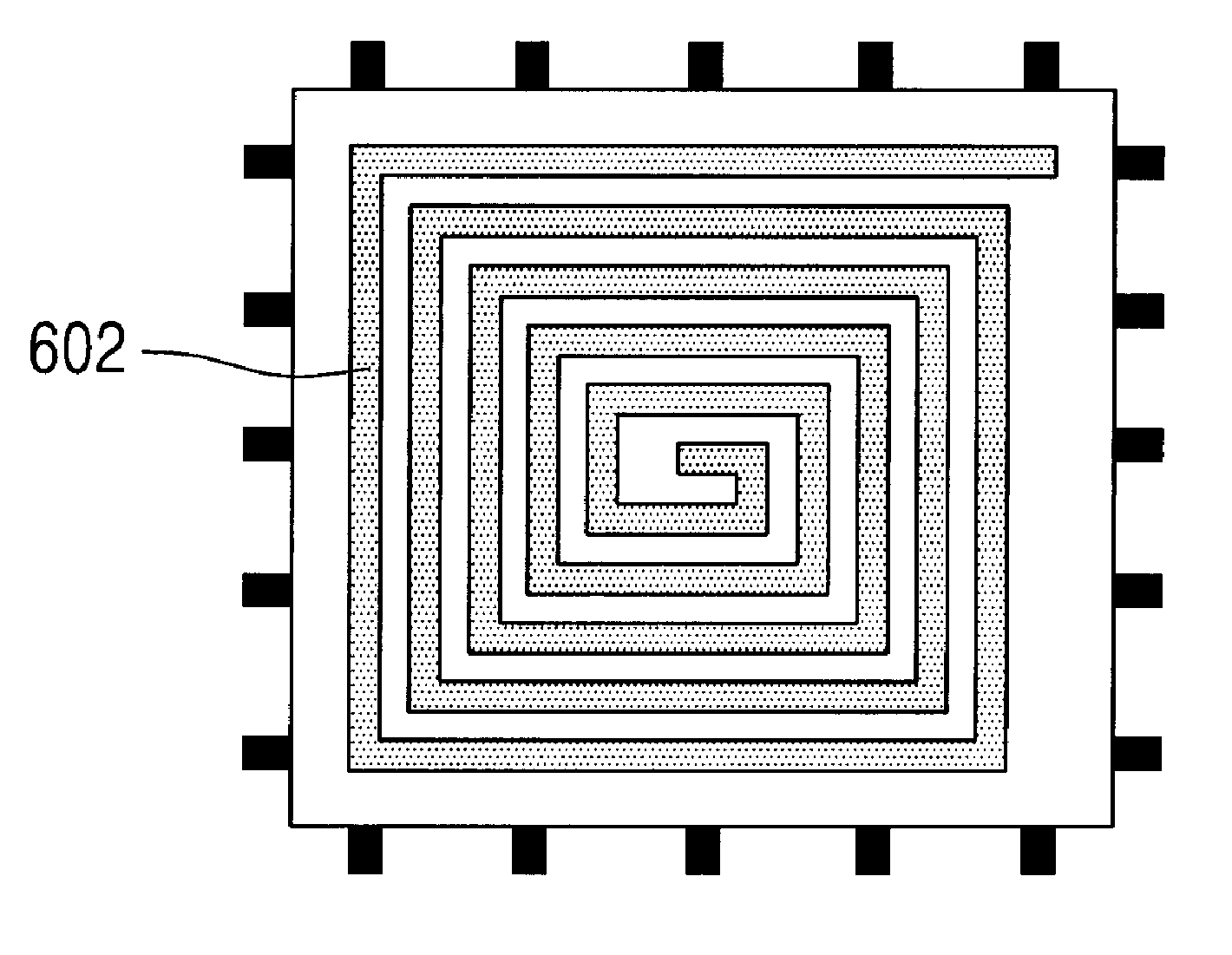

System-in-package having reduced influence between conductor and antenna and method of designing the same

InactiveUS20080149736A1MinimizeReduce the impactSolid-state devicesAntenna feed intermediatesElectrical conductorElectromagnetic field

The present invention relates to a SiP having reduced influence between a conductor and an antenna, and a method of designing the SiP. The SiP includes an antenna configured to function to transmit or receive data and mounted in the SiP to be integrated in the SiP, and a first planar conductor having at least one slit formed therein. Therefore, the present invention minimizes the amount of current or electromagnetic field induced on the conductor by the current or electromagnetic field of the antenna, thus reducing the influence of the conductor on the operating characteristics of the antenna.

Owner:KOREA ADVANCED INST OF SCI & TECH

Microwave multi-chip packaging structure using silicon through hole and manufacture method thereof

ActiveCN102723306AReduce lossIncrease packing densitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSystem in package

The invention provides a microwave multi-chip packaging structure using a silicon through hole and a manufacture method thereof. The method uses a temperature safety valve (TSV) to achieve two-sided integrated system-stage packaging structure, when a monolithic microwave integrated circuit (MMIC) chip needs integrating, a user does not need embed a substrate before wiring, and performance, reliability and rate of finished products of the packaging structure are improved. Simultaneously, processes such as injection, corrosion, release and high temperature annealing in a manufacture process can be used before integration of the MMIC, and components needing special processes can be assembled and integrated in advance on the other side of the substrate. Therefore, the substrate comprising active and passive devices, micro-electromechanical systems (MEMS), photoelectric devices and the like can be conveniently manufactured in a large scale before integration of the MMIC, and the manufacture method is simple in process, reduces cost, and is advanced and reliable at present.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Build-up structures with multi-angle vias for chip to chip interconnects and optical bussing

InactiveUS20050269687A1Improve performanceIncrease speedTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesAnisotropic conductive filmEngineering

A build-up structure for chip to chip interconnects and System-In-Package utilizing multi-angle vias for electrical and optical routing or bussing of electronic information and controlled CTE dielectrics including mesocomposites to achieve optimum electrical and optical performance of monolithic structures. Die, multiple die, Microelectromechanical Machines (MEMs) and / or other active or passive components such as transducers or capacitors can be accurately positioned on a substrate such as a copper heatsink and multi-angle stud bumps can be placed on the active sites of the components. A first dielectric layer is preferably placed on the components, thereby embedding the components in the structure. Through various processes of photolithography, laser machining, soft lithography or anisotropic conductive film bonding, escape routing and circuitry is formed on the first metal layer. Additional dielectric layers and metal circuitry are formed utilizing multi-angle vias to form escape routing from tight pitch bond pads on the die to other active and passive components. Multi-angle vias can carry electrical or optical information in the form of digital or analog electromagnetic current, or in the form of visible or non-visible optical bussing and interconnections.

Owner:CAPITALSOURCE FINANCE

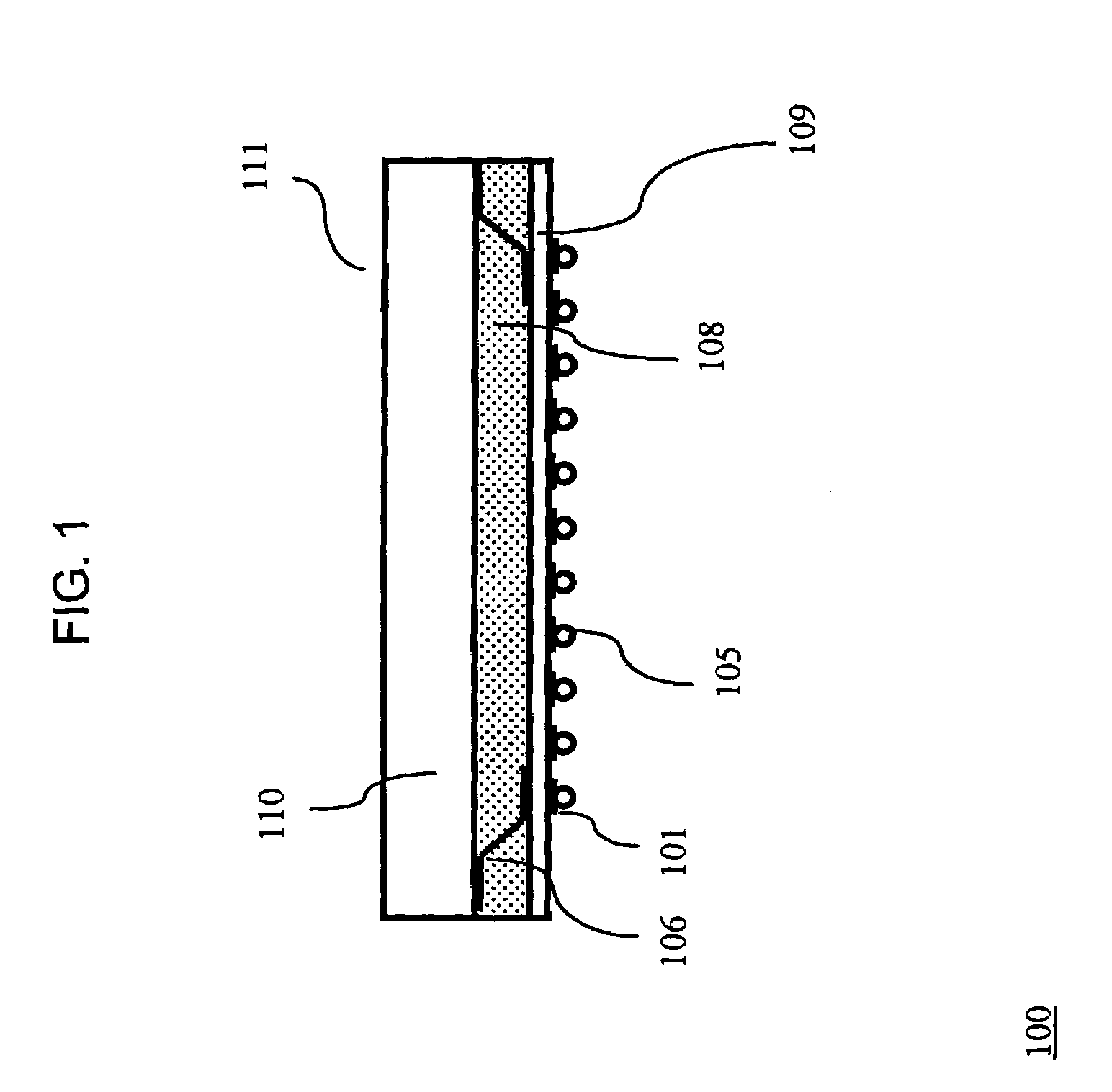

System-in-package (SIP) structure and fabrication thereof

InactiveUS20050269680A1Reduce thicknessLess bumpSemiconductor/solid-state device detailsSolid-state devicesEngineeringSoi substrate

A system-in-package (SIP) structure is described, including stacked circuit / insulator composite layers, bumps and a cover plate. Each circuit / insulator composite layer is lifted off from a semiconductor-on-insulator (SOI) substrate, including the insulator of the SOI substrate and a circuit layer based on the semiconductor of the SOI substrate. The circuit layer of a circuit / insulator composite layer is electrically coupled with the circuit layer of the underlying circuit / insulator composite layer. The bumps are disposed on the lower surface of the bottom circuit / insulator composite layer, electrically coupled with the circuit layer of the bottom circuit / insulator composite layer. The cover plate is disposed on the top circuit / insulator composite layer.

Owner:UNITED MICROELECTRONICS CORP

Three-dimensional system-in-package architecture

ActiveUS8487444B2Reduce resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSystem in package

Owner:TAIWAN SEMICON MFG CO LTD

Apparatus and methods for cooling semiconductor integrated circuit chip packages

ActiveUS20060103011A1Improves Structural IntegrityReduce mechanical stressSemiconductor/solid-state device detailsSolid-state devicesHigh densityEngineering

Apparatus and methods are provided for integrating microchannel cooling modules within high-density electronic modules (e.g., chip packages, system-on-a-package modules, etc.,) comprising multiple high-performance IC chips. Electronic modules are designed such that high-performance (high power) IC chips are disposed in close proximity to the integrated cooling module (or cooling plate) for effective heat extraction. Moreover, electronic modules which comprise large surface area silicon carriers with multiple chips face mounted thereon are designed such that integrated silicon cooling modules are rigidly bonded to the back surfaces of such chips to increase the structural integrity of the silicon carriers.

Owner:GLOBALFOUNDRIES US INC

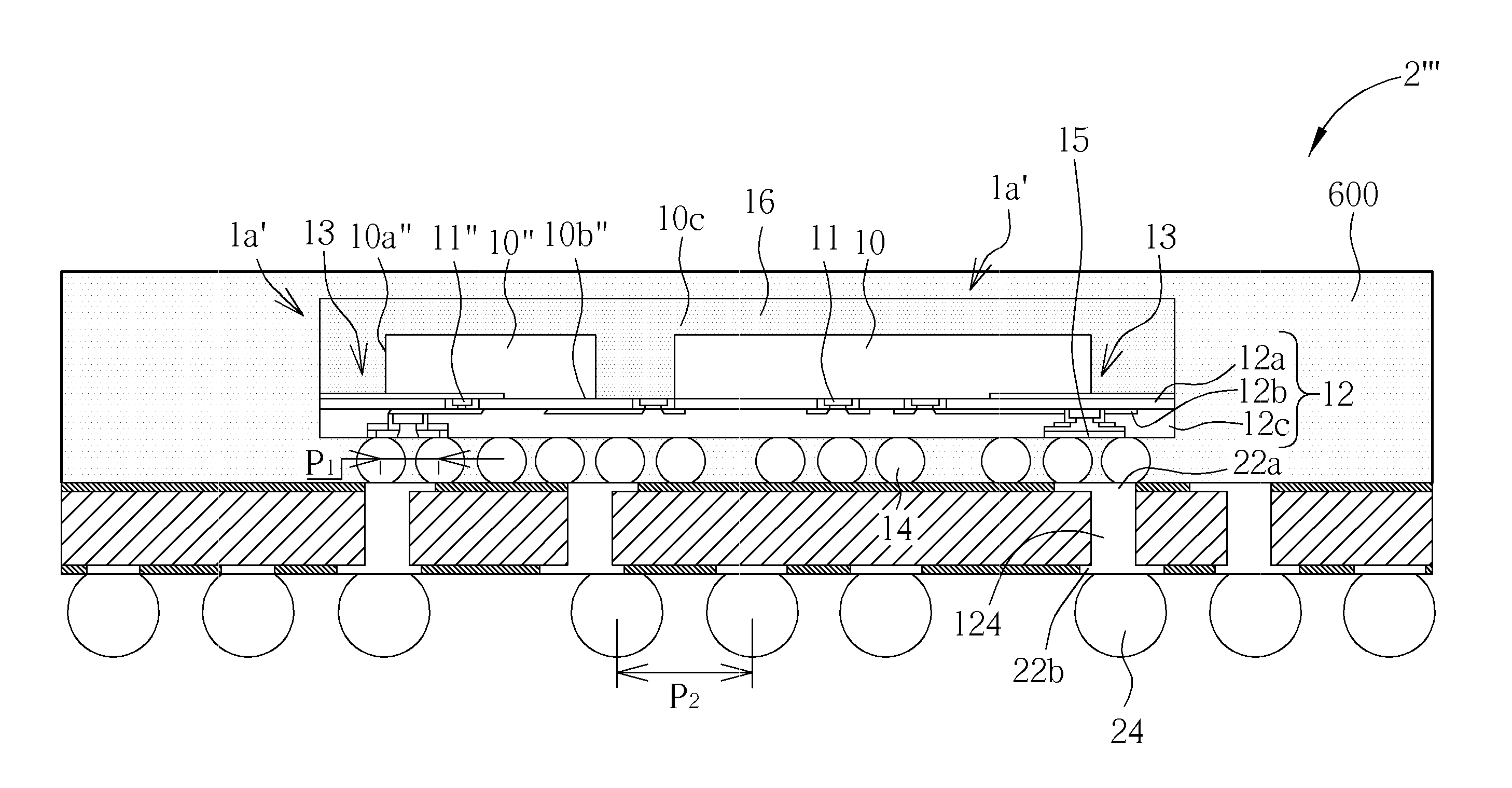

System-in-package with fan-out WLCSP

ActiveUS8093722B2Overcome limitationsCost-effectiveSemiconductor/solid-state device detailsSolid-state devicesEngineeringSystem in package

A system-in-package includes a package carrier; a first semiconductor die having a die face and a die edge, the first semiconductor die being assembled face-down to a chip side of the package carrier; a second semiconductor die mounted alongside of the first semiconductor die; a rewiring laminate structure comprising a re-routed metal layer between the first semiconductor die and the package carrier. At least a portion of the re-routed metal layer projects beyond the die edge. A plurality of bumps are arranged on the rewiring laminate structure for electrically connecting the first semiconductor die with the package carrier.

Owner:MEDIATEK INC

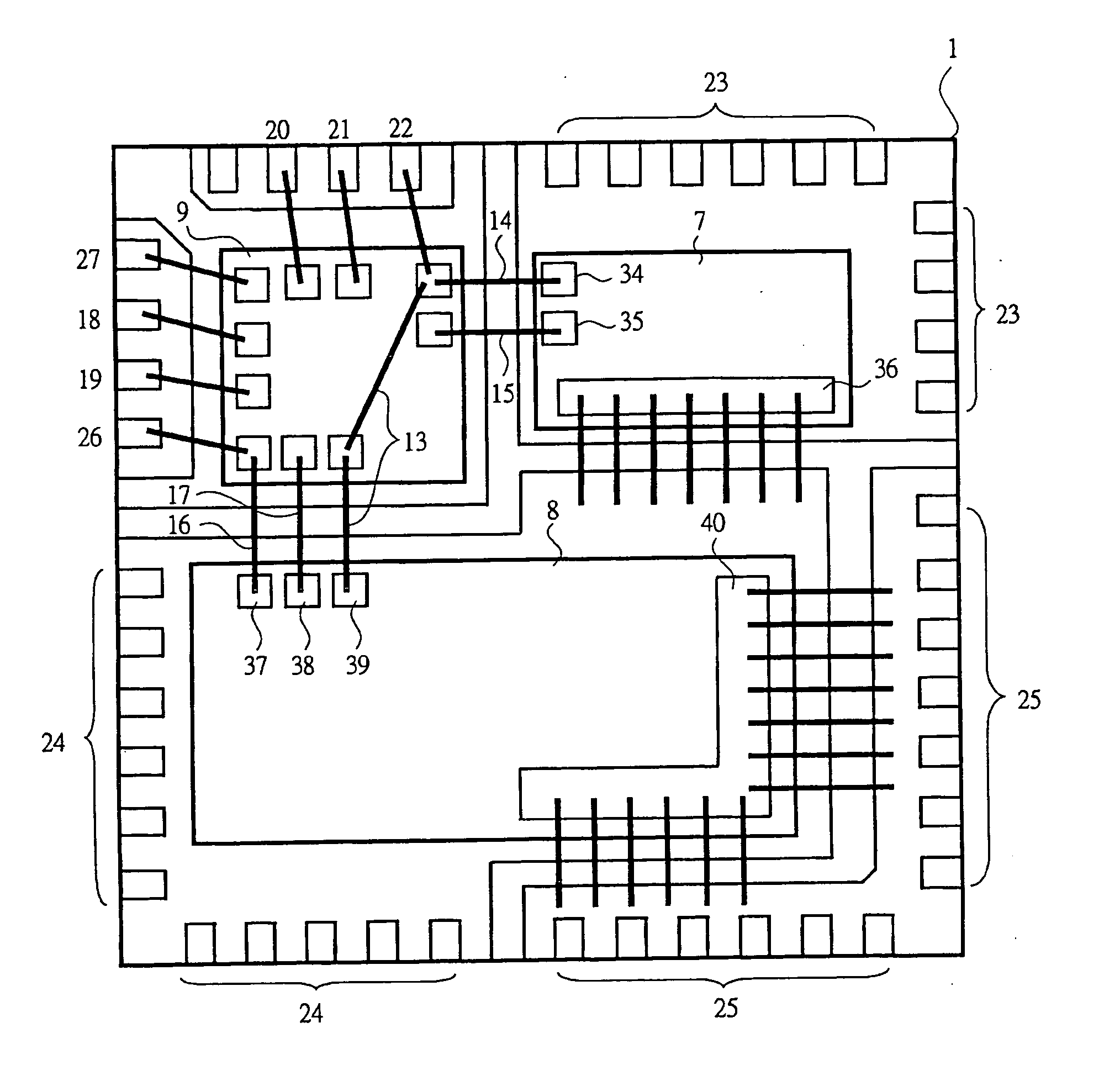

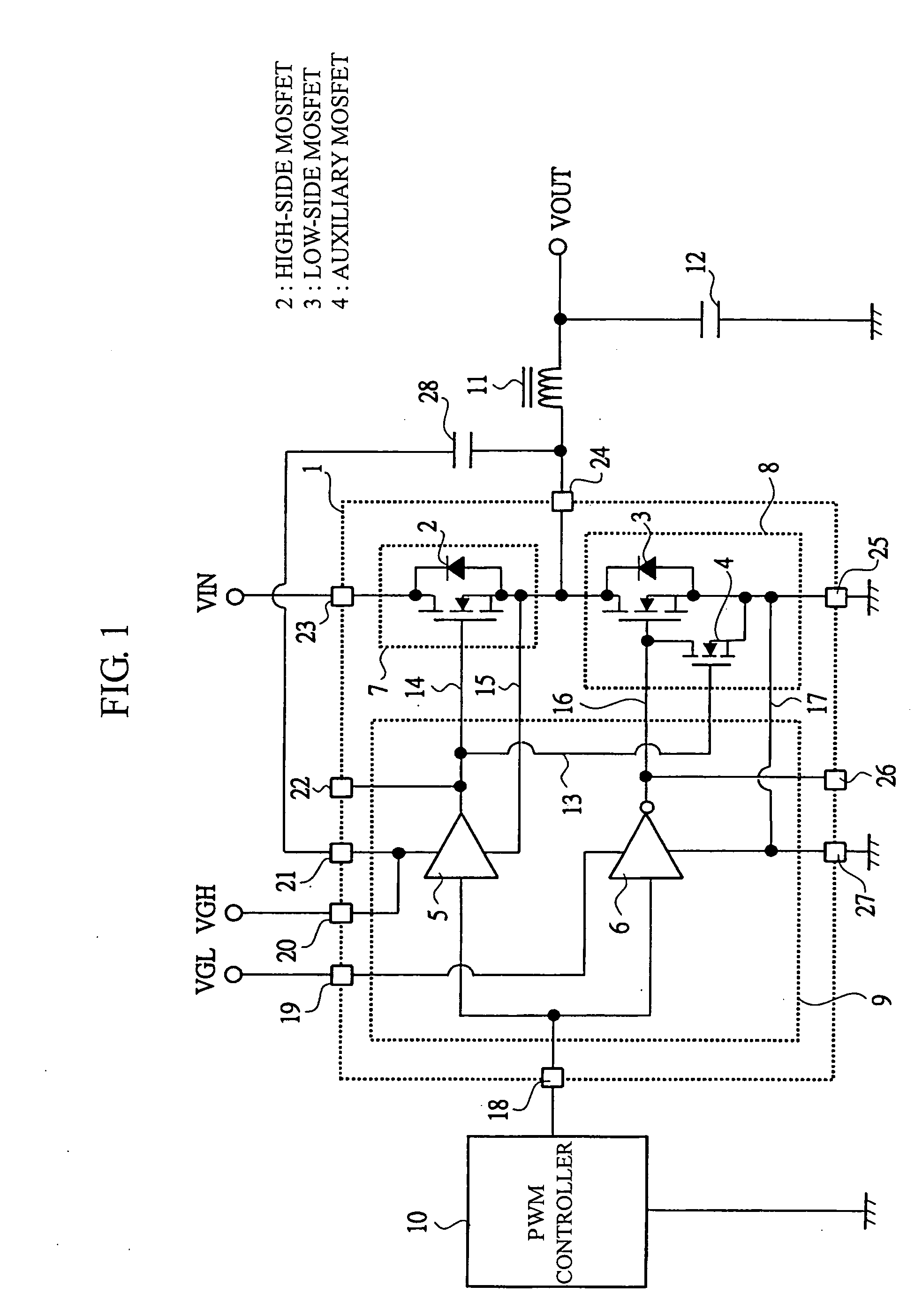

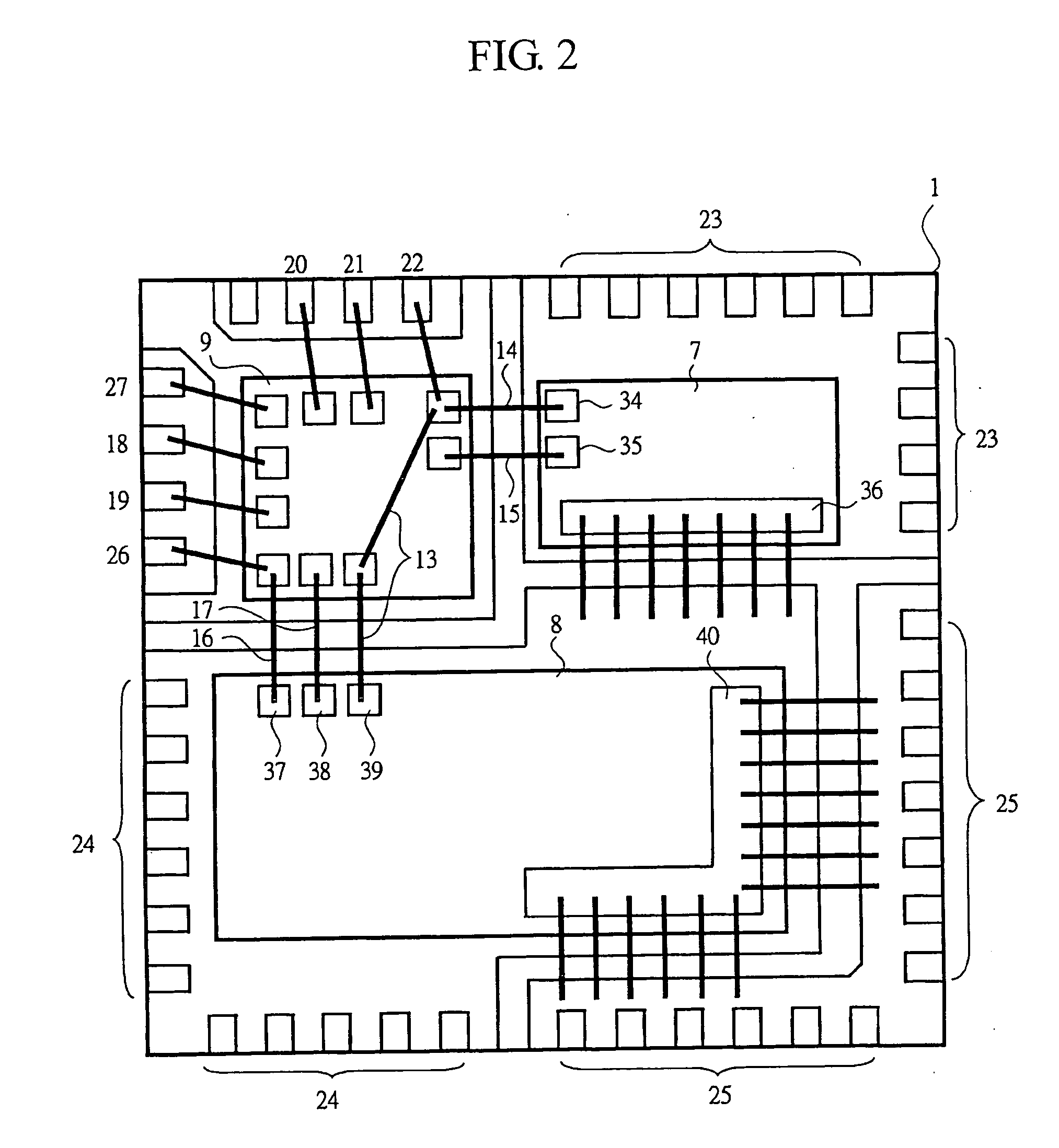

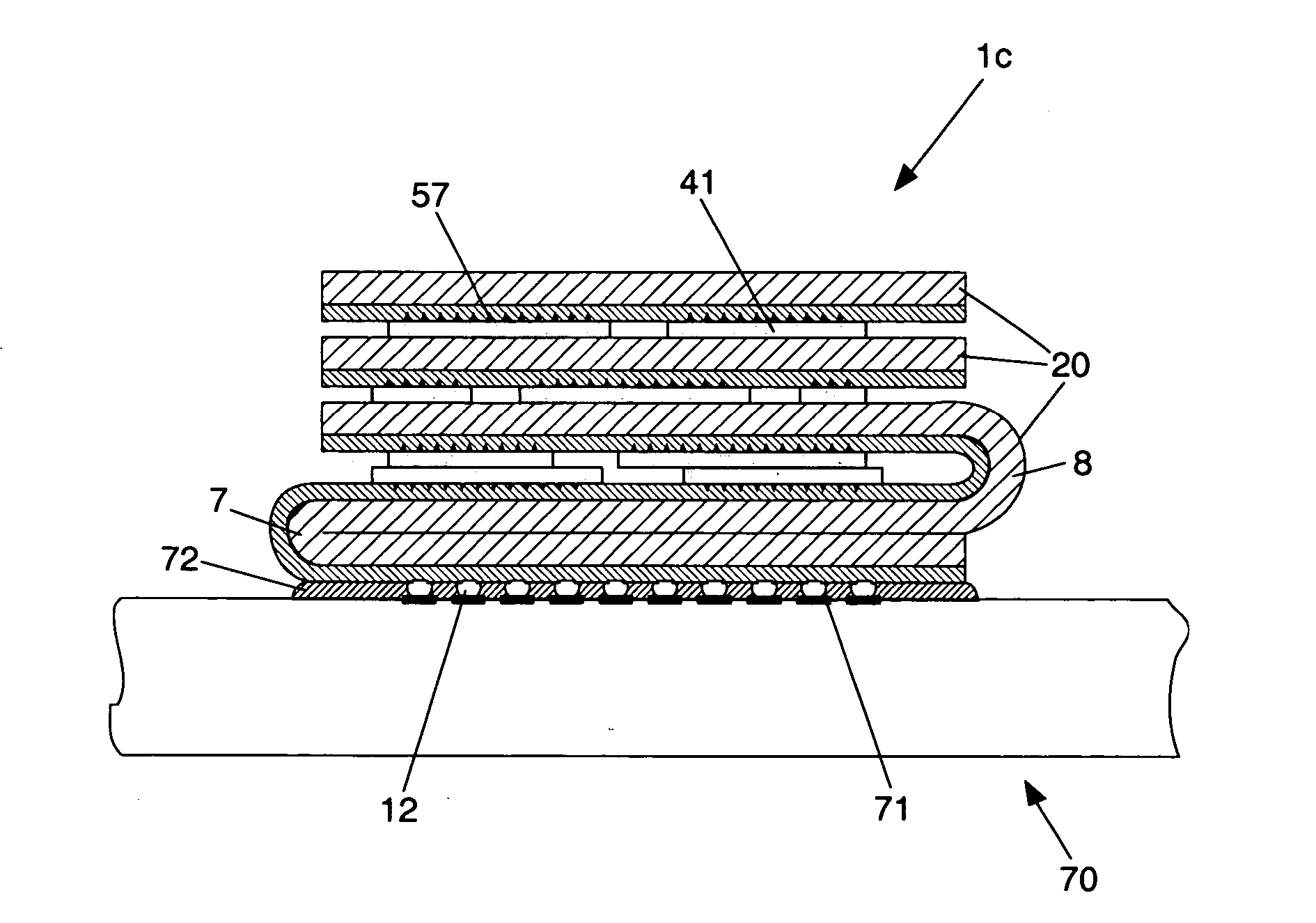

Semiconductor devices, DC/DC converter and power supply

ActiveUS20060006432A1Improve conversion efficiencyTransistorEfficient power electronics conversionMOSFETPower semiconductor device

A semiconductor device in which the self-turn-on phenomenon is prevented that can significantly improve power conversion efficiency. The semiconductor device is a system-in-package for power supply applications in which a high-side switch, a low-side switch, and two drivers are included in a single package. The device includes an auxiliary switch disposed between the gate and source of said low-side switch, and a low-side MOSFET 3 for the low-side switch and an auxiliary MOSFET 4 for the auxiliary switch are disposed on the same chip. In this way, the self-turn-on phenomenon can be prevented, allowing the mounting of a low-side MOSFET 3 with a low threshold voltage and thereby significantly improving power conversion efficiency. The gate of the auxiliary MOSFET 4 is driven by the driver for the high-side MOSFET 2, thereby eliminating the need for a new drive circuit and realizing the same pin configuration as existing products, which facilitates easy replacement.

Owner:RENESAS ELECTRONICS CORP

System in package

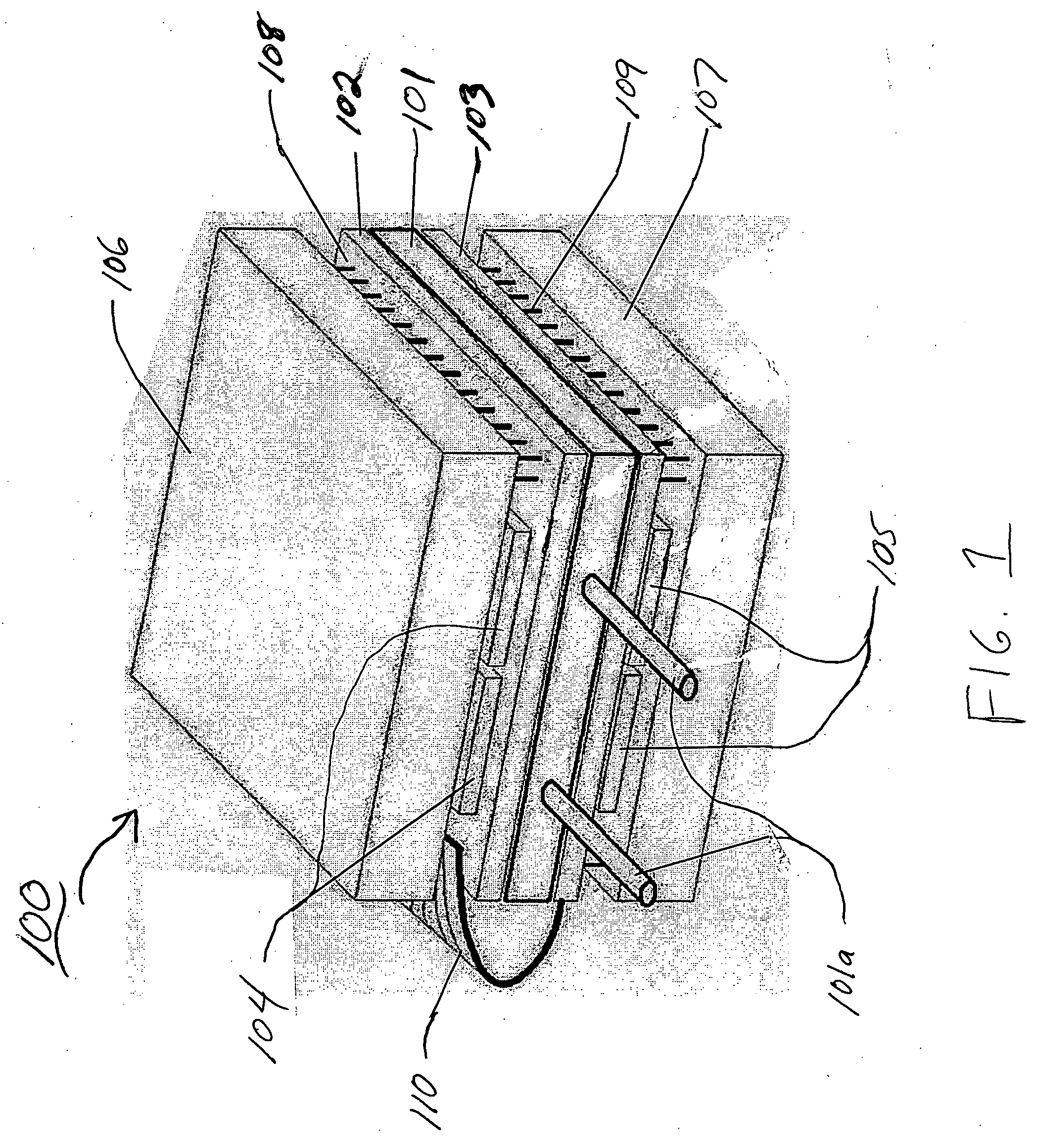

InactiveUS20050184376A1Improve cooling effectIncrease speedSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCopper conductorBand shape

A system in package (SIP) is fabricated on a sheet of copper foil. An interconnection circuit is fabricated on the foil using copper conductors and a dual damascene structure for each conductive layer. The preferred dielectric material is an amorphous fluorinated polymer called Cytop. Input / output traces of the interconnection circuit terminate in wells filled with solder. Chips are bumped and direct attached by inserting the bumps into the wells. The preferred bumps are gold stud bumps, and the preferred wells contain solder paste to a depth of approximately 15 microns. Imprinting is the preferred method for patterning; it enables 6-micron wide traces, 6-micron diameter vias, and a cost per well of around 0.02 cents. Stripline structures are described for a 4-layer stackup that can support operating frequencies of at least 10 GHz. New methods are proposed for testing the completed assembly and for rework of any chips that prove defective. After the assembly is fully tested and reworked in sheet form the copper foil is folded to form a stacked die package or system in package. 5-high and 9-high stacks are illustrated. The copper foil provides a low impedance thermal path for cooling every chip in the SIP.

Owner:SALMON TECH

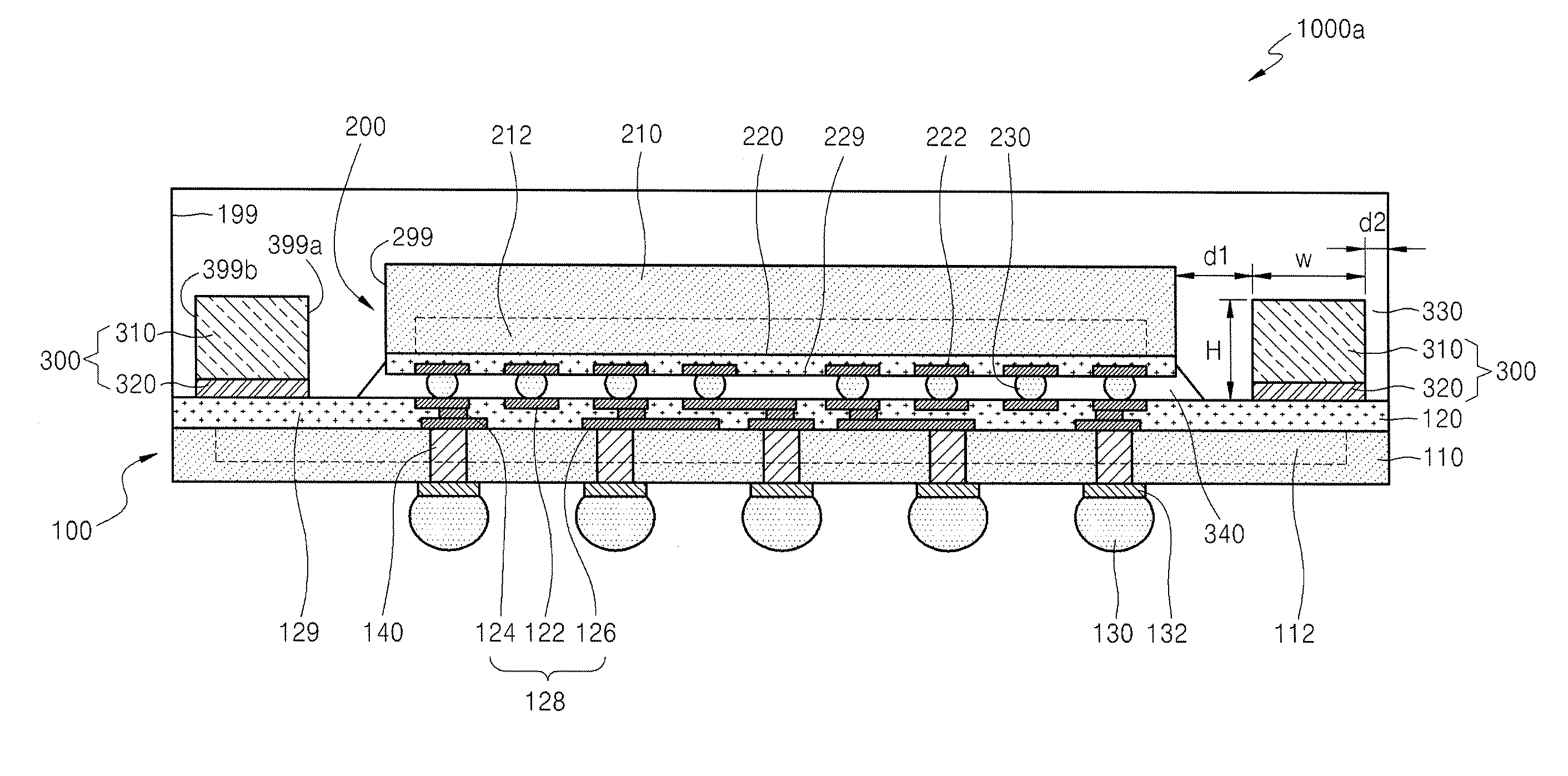

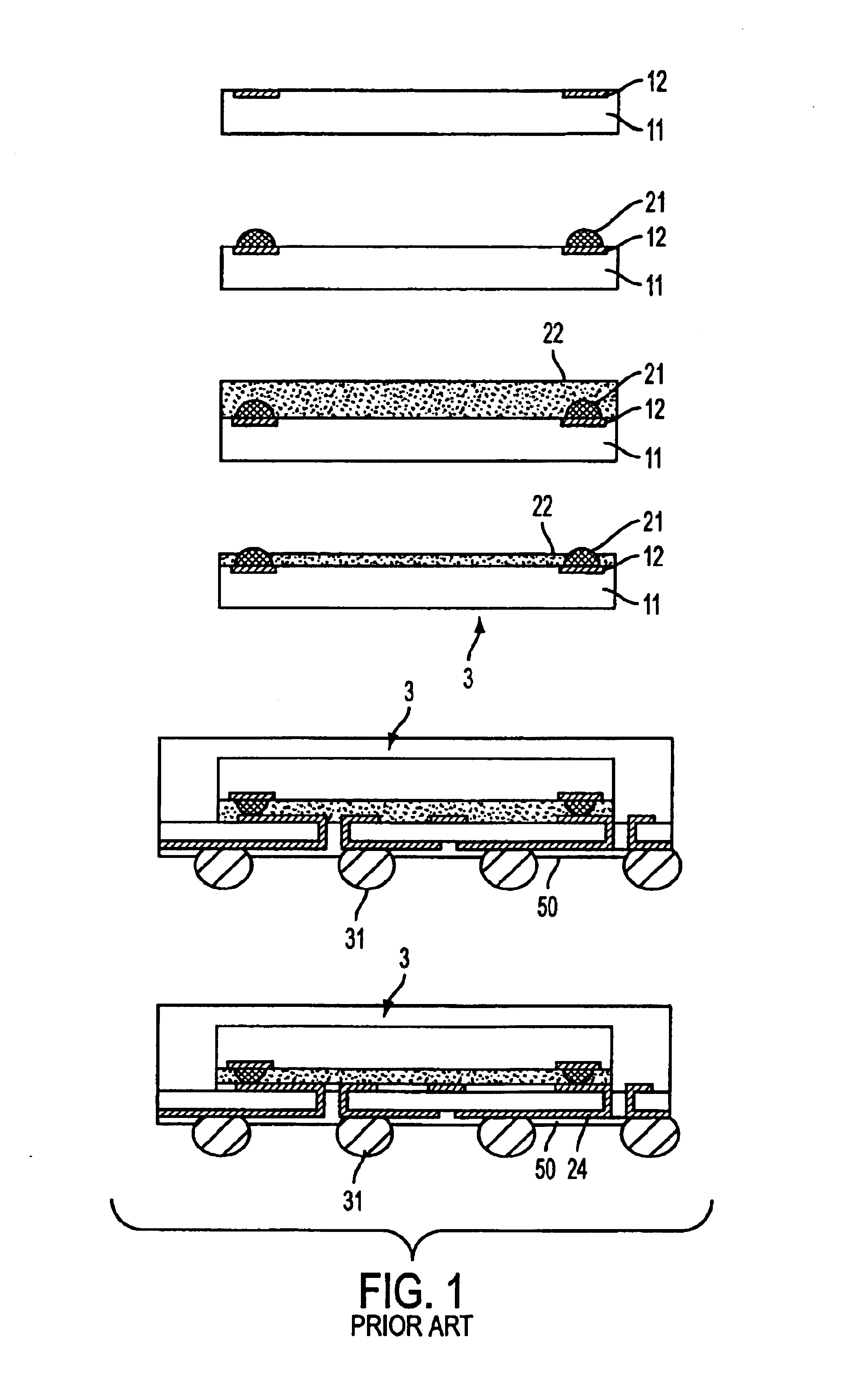

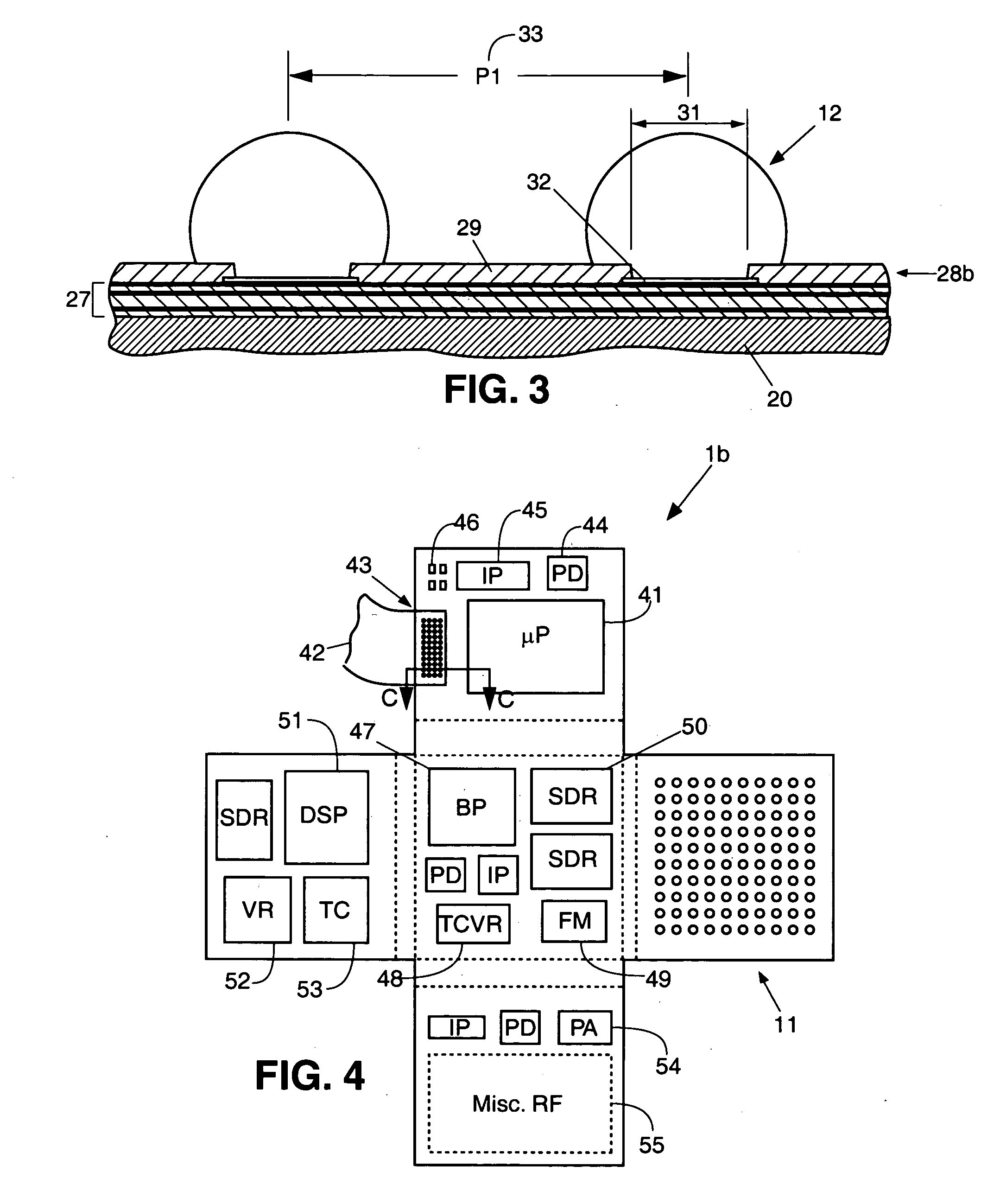

Components, methods and assemblies for multi-chip packages

ActiveUS7061122B2Reduce the overall heightImprove repair capabilityPrinted circuit assemblingSemiconductor/solid-state device detailsSemiconductor chipSystem in package

Owner:TESSERA INC