Patents

Literature

318results about How to "Improve routing density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

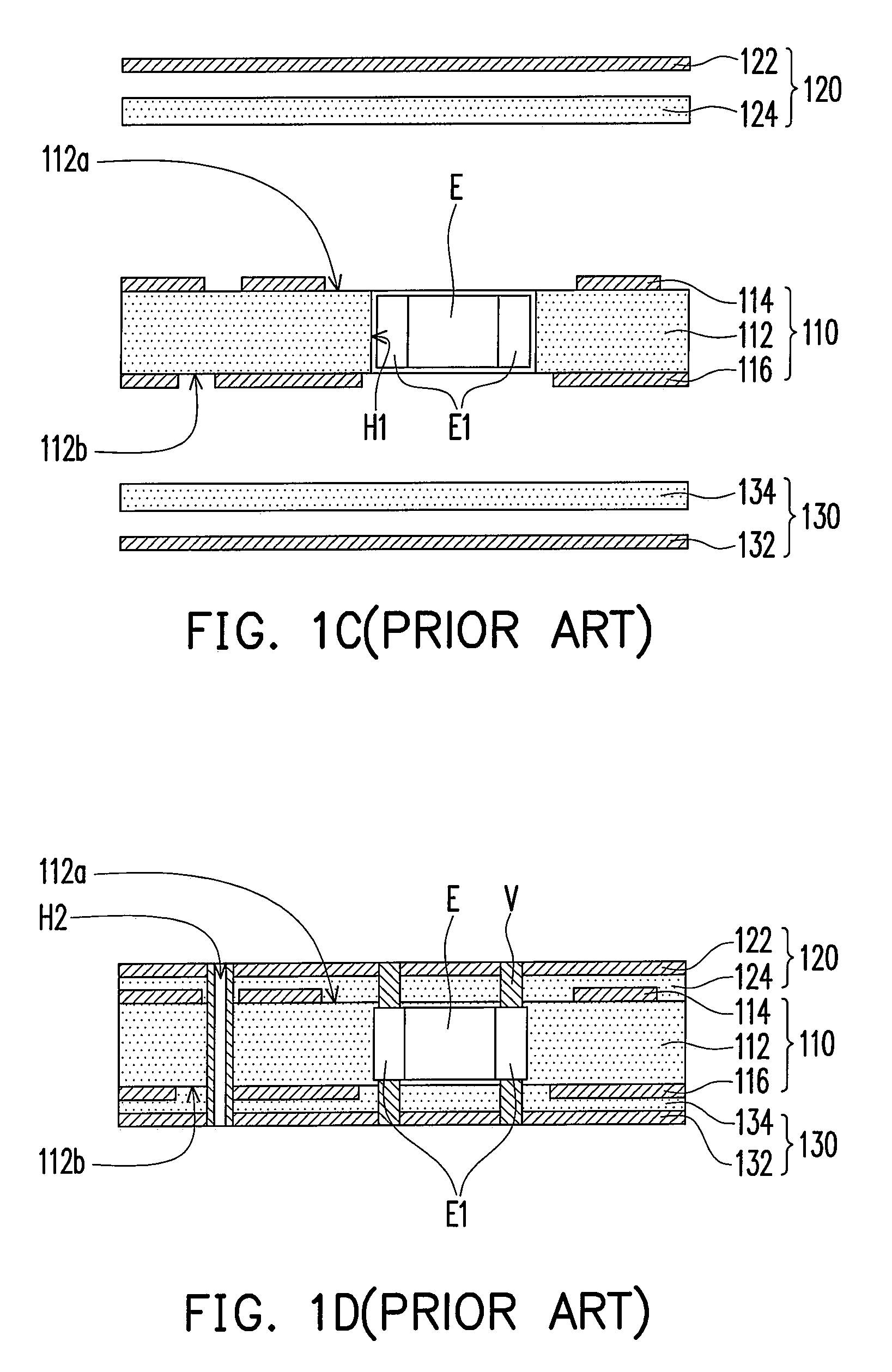

System-in packages

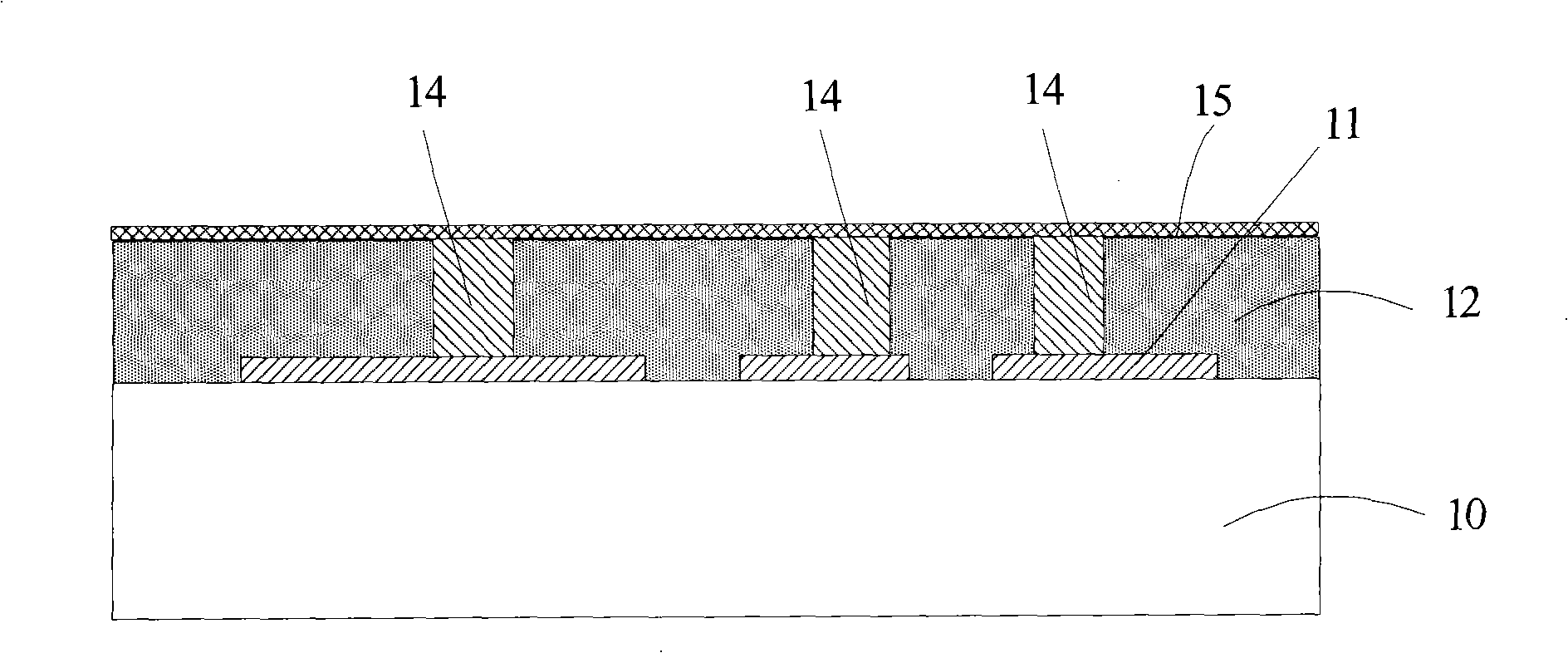

ActiveUS8164171B2Improve routing densityGood electromagnetic field shieldSemiconductor/solid-state device detailsSolid-state devicesSystem in packageExternal circuit

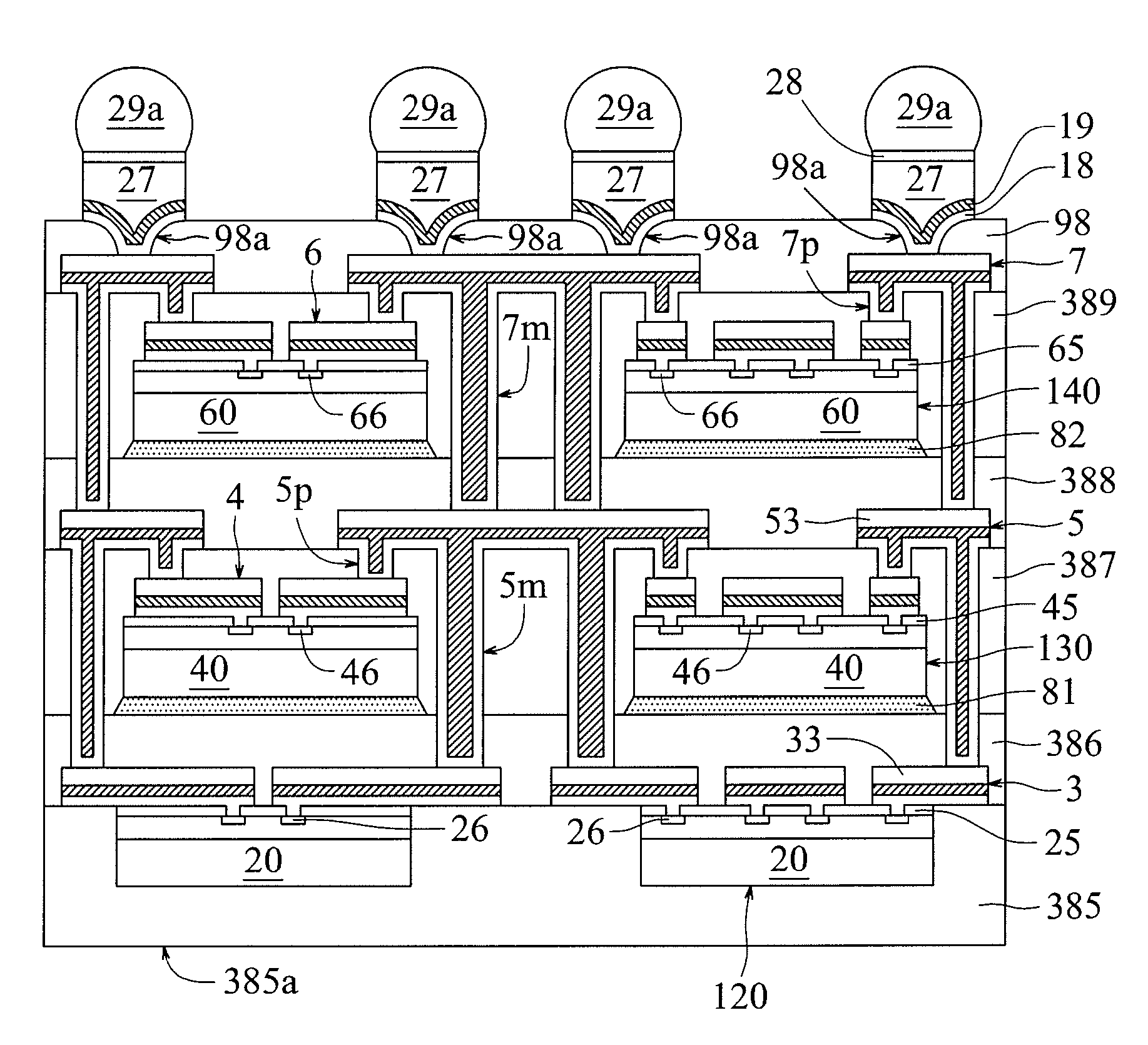

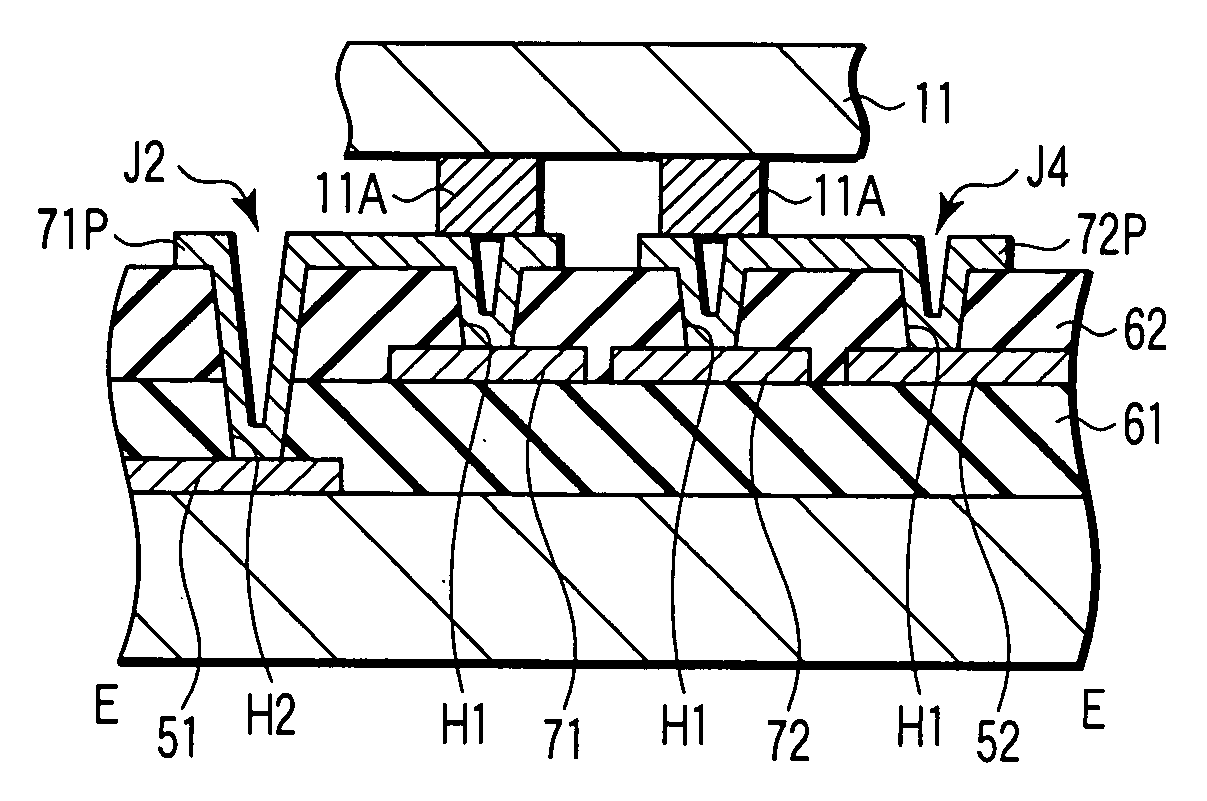

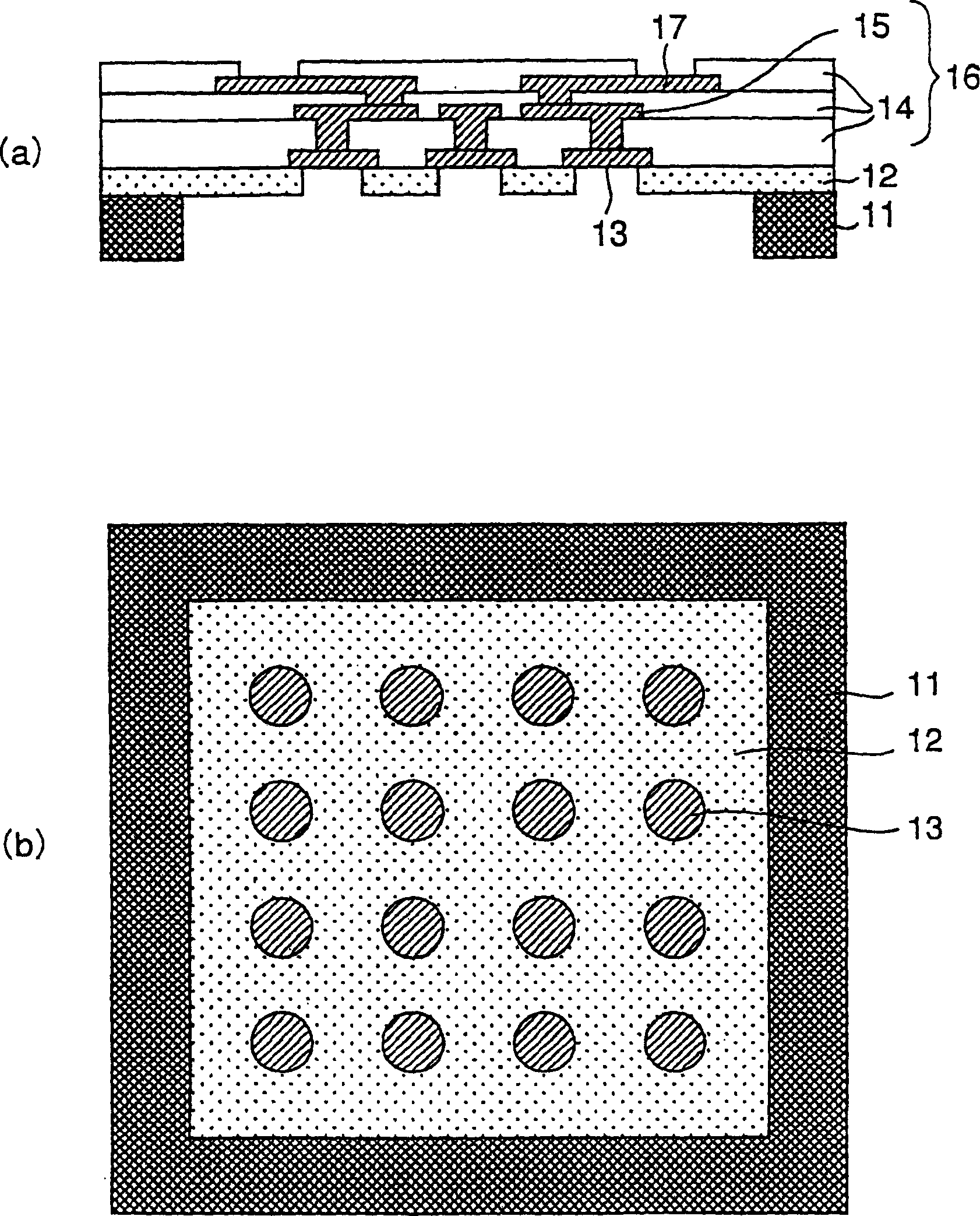

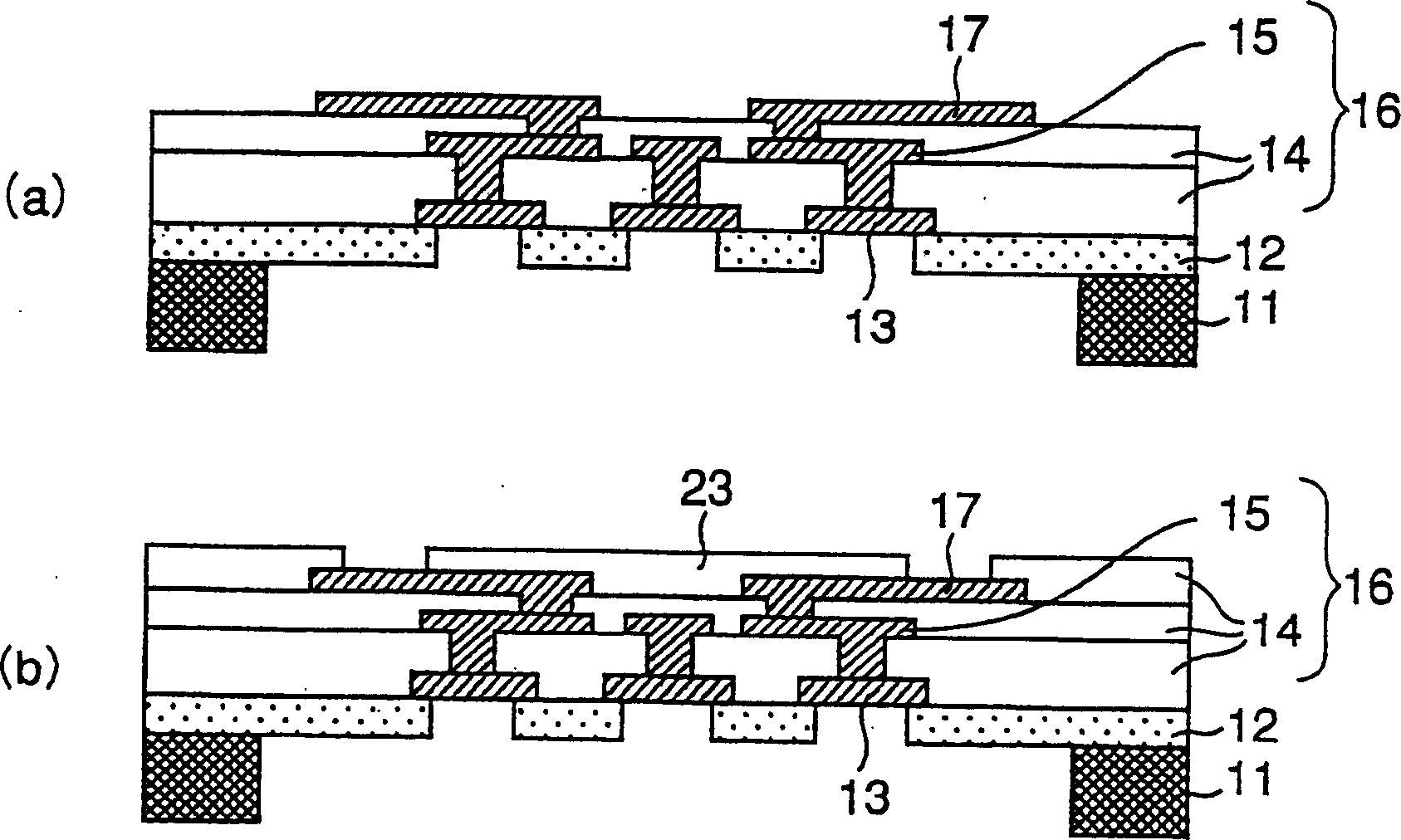

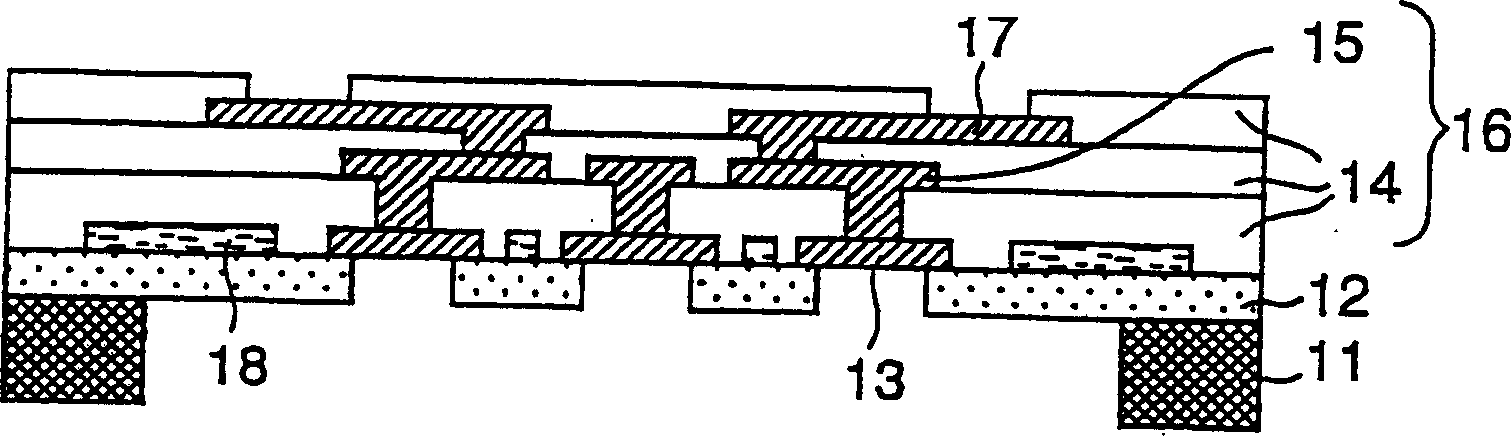

System-in packages, or multichip modules, are described which can include multi-layer chips in a multi-layer polymer structure, on-chip metal bumps on the multi-layer chips, intra-chip metal bumps in the multi-layer polymer structure, and patterned metal layers in the multi-layer polymer structure. The multi-layer chips in the multi-layer polymer structure can be connected to each other or to an external circuit through the on-chip metal bumps, the intra-chip metal bumps and the patterned metal layers. The system-in packages can be connected to external circuits through solder bumps, meal bumps or wirebonded wires.

Owner:QUALCOMM INC

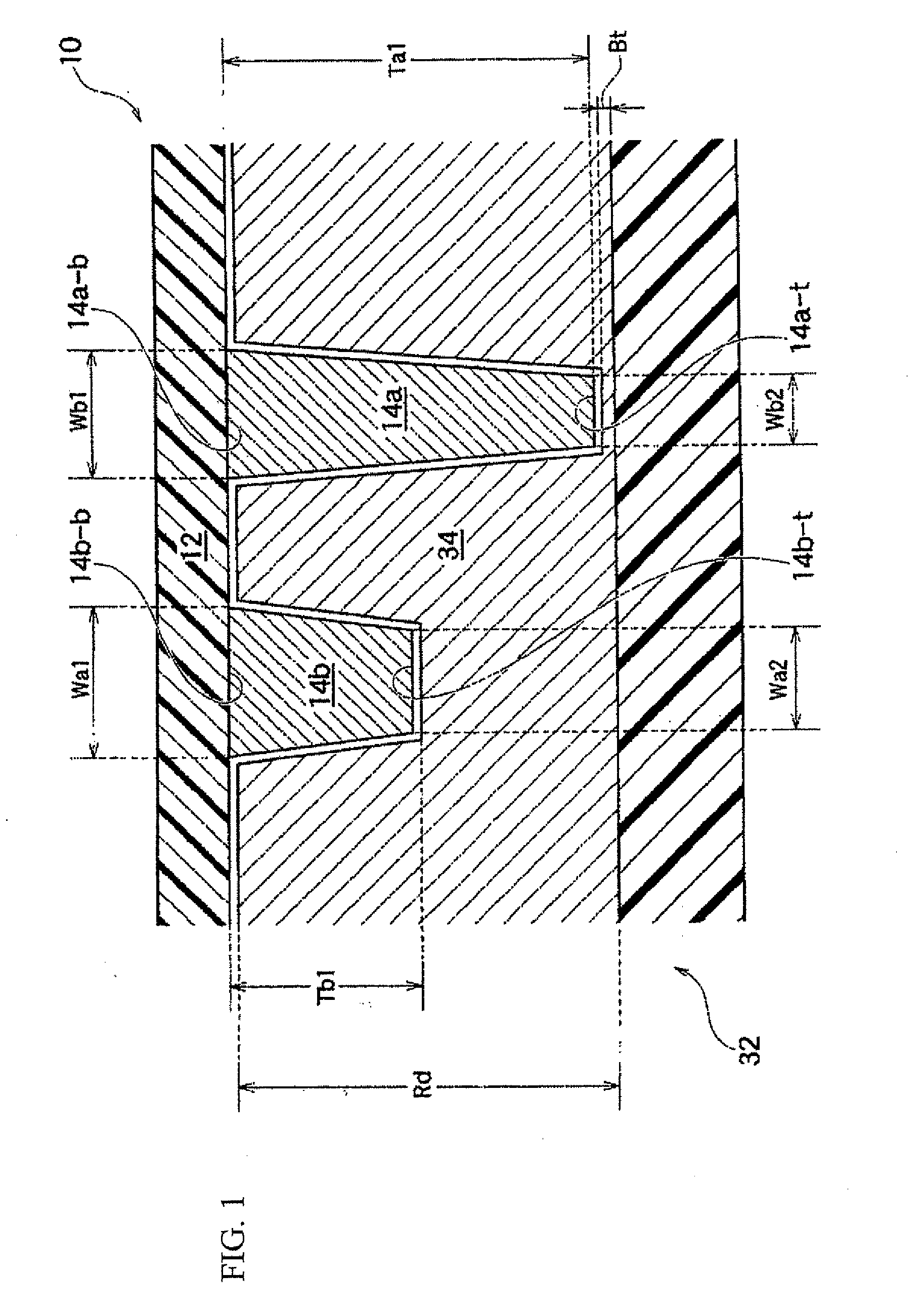

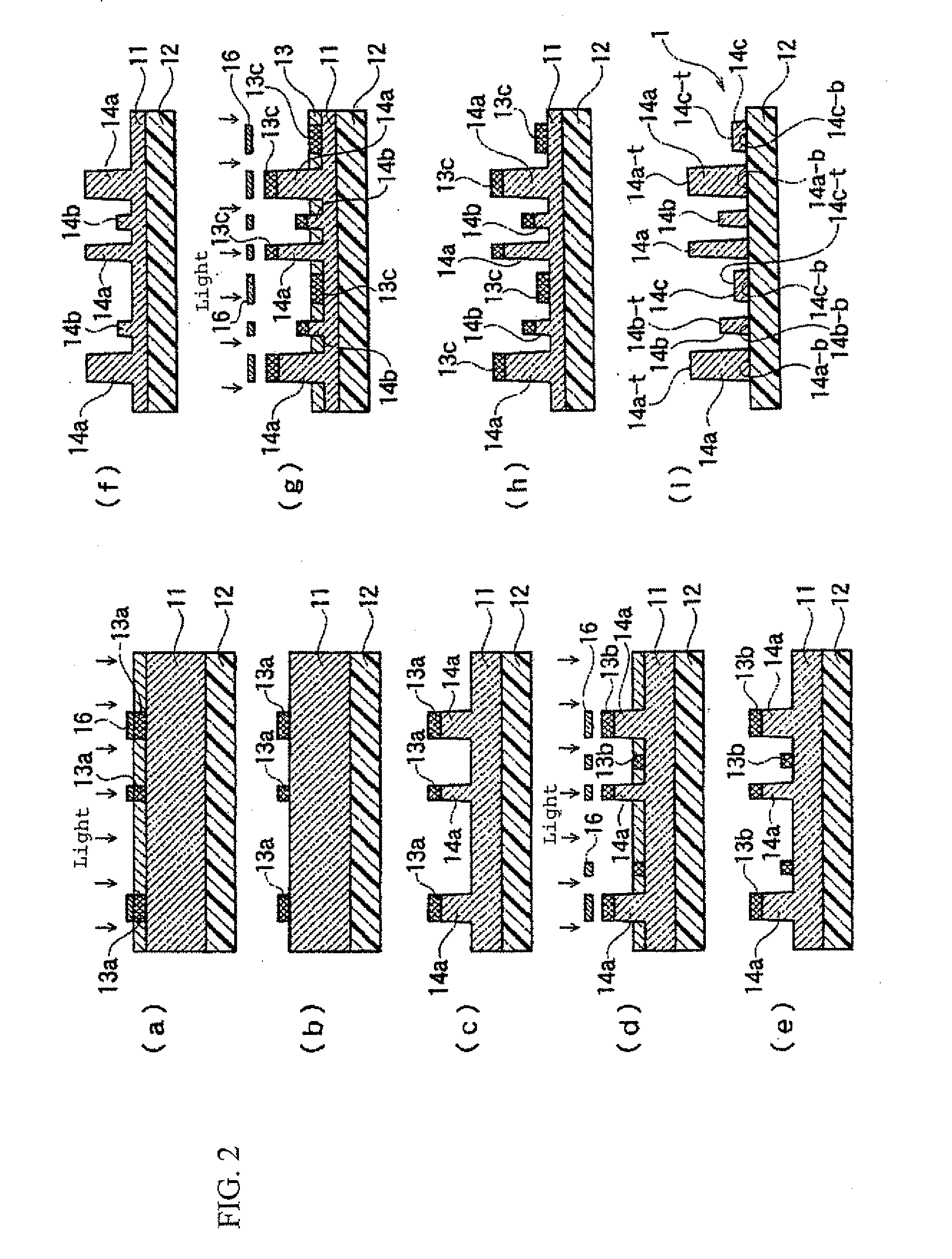

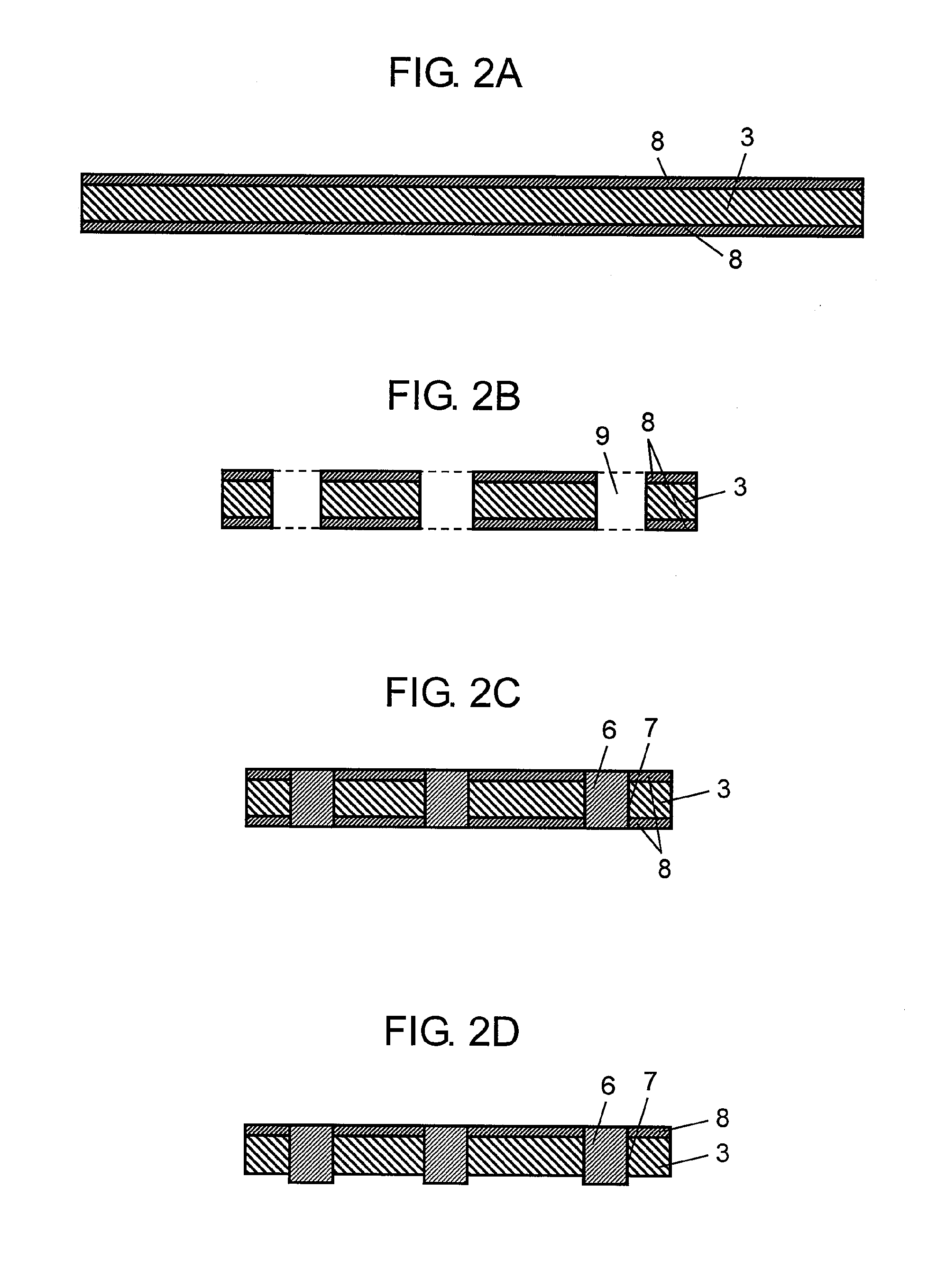

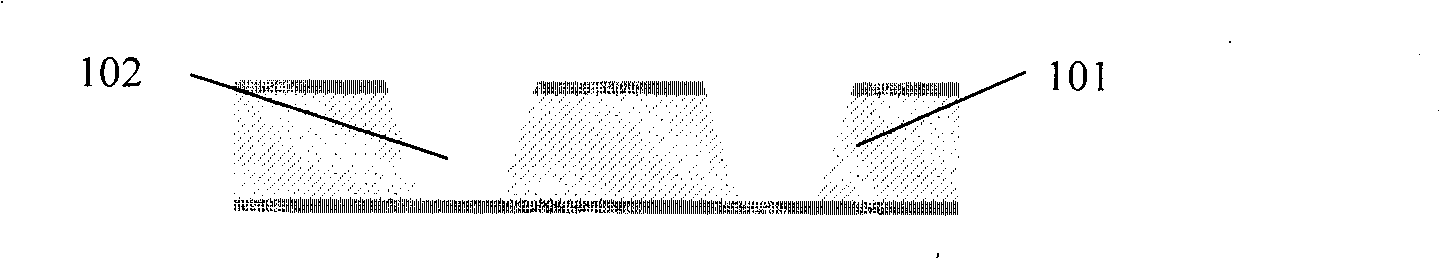

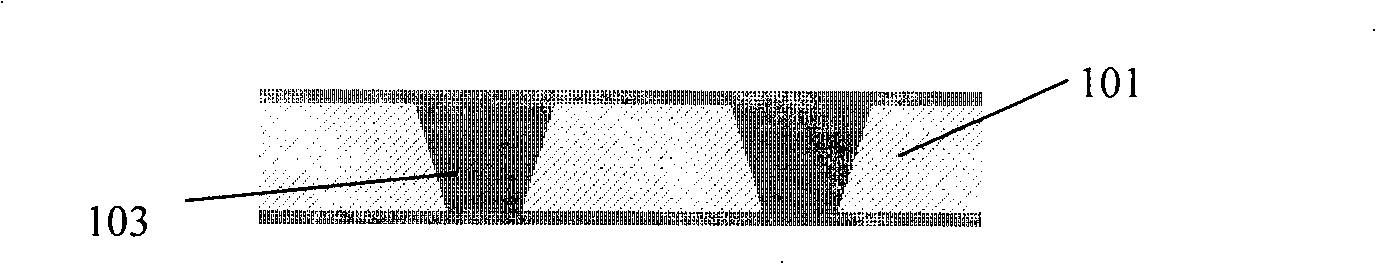

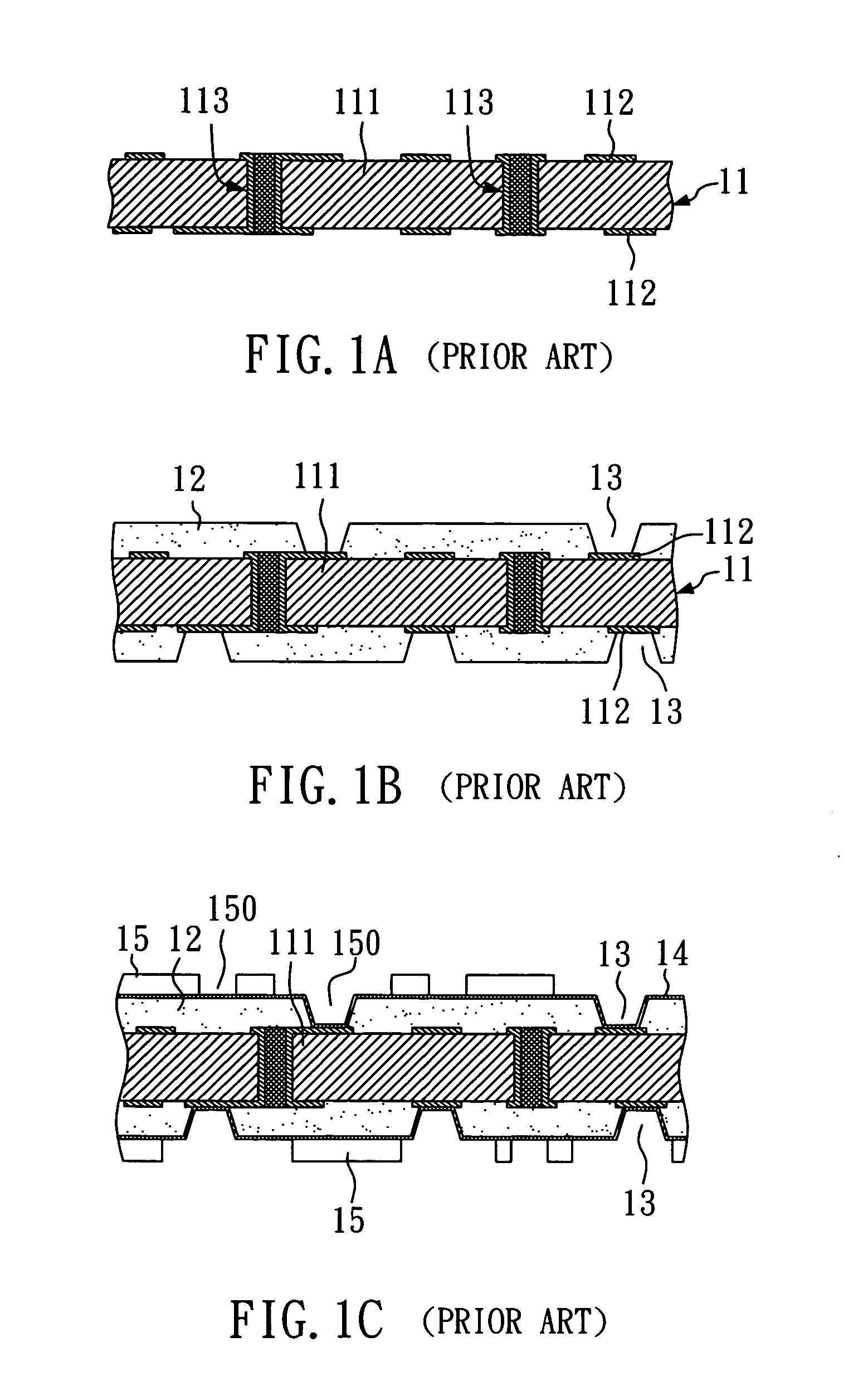

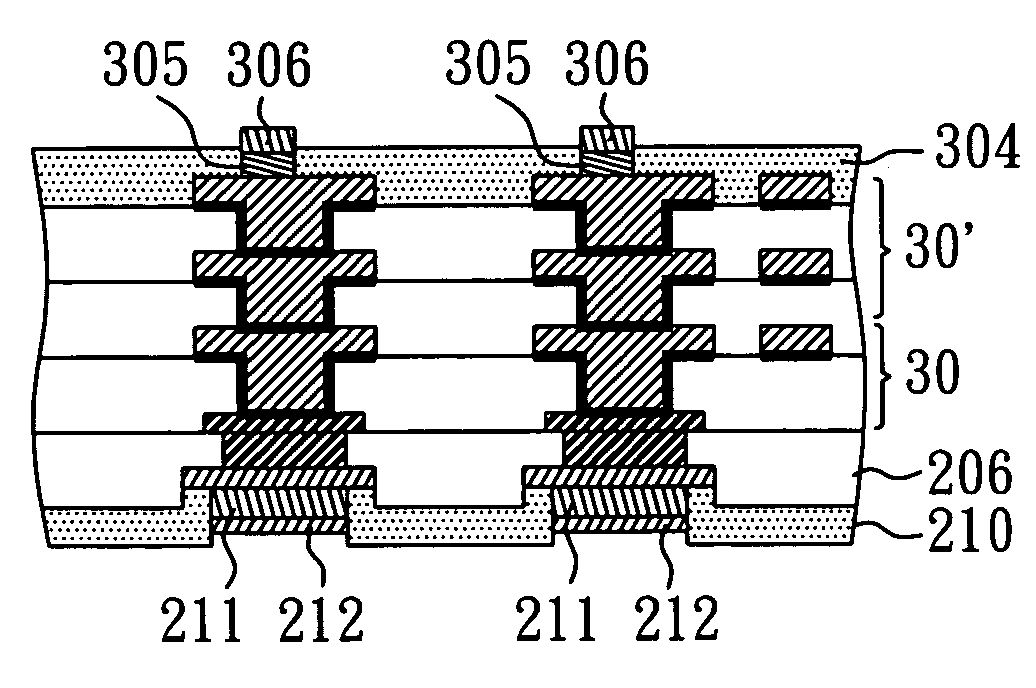

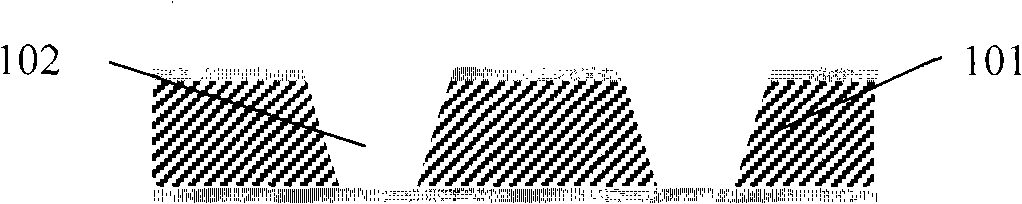

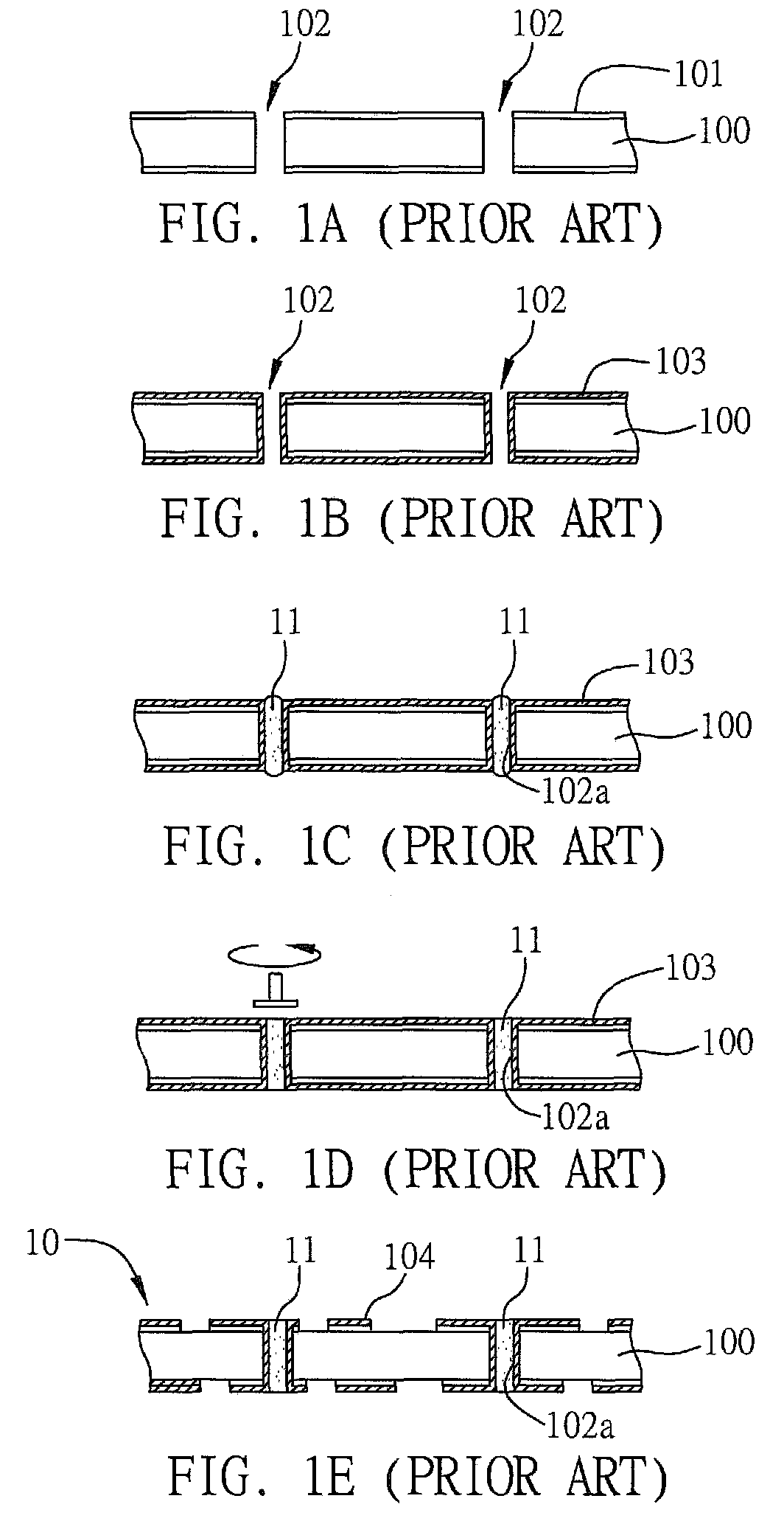

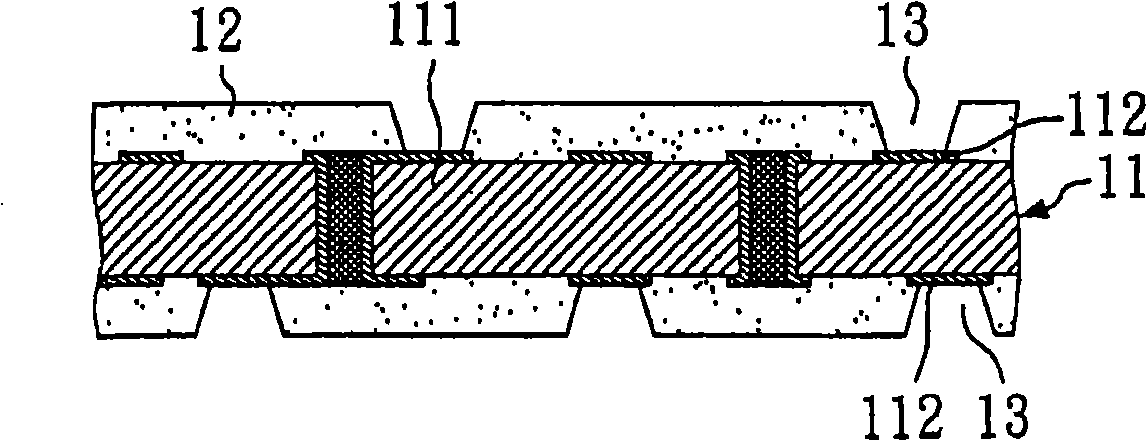

Mold for Wiring Substrate Formation and Process for Producing the Same, Wiring Substrate and Process for Producing the Same, Process for Producing Multilayered Laminated Wiring Substrate and Method for Viahole Formation

InactiveUS20090314525A1Large widthFacilitated releaseContact member manufacturingTransparent dielectricsEngineeringMultiple layer

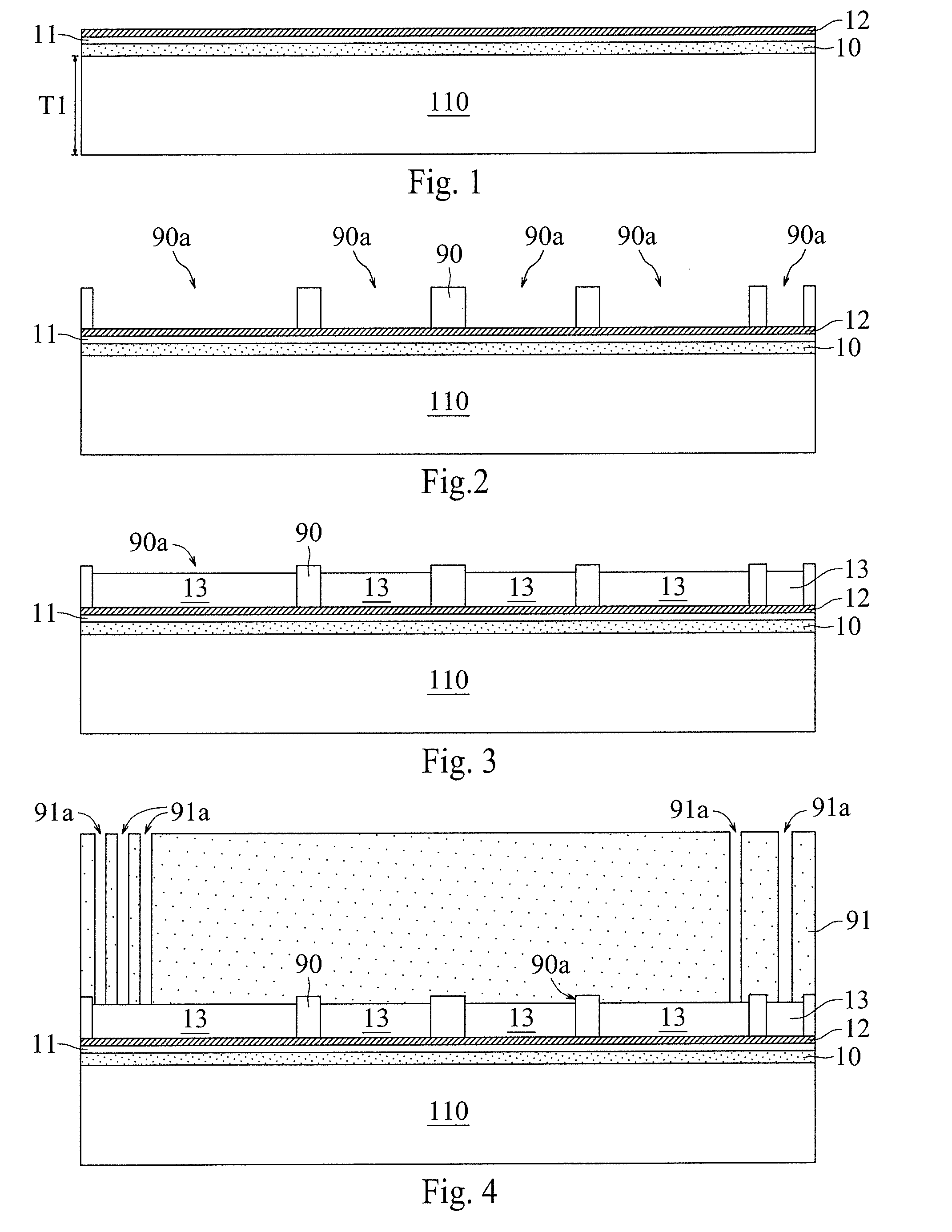

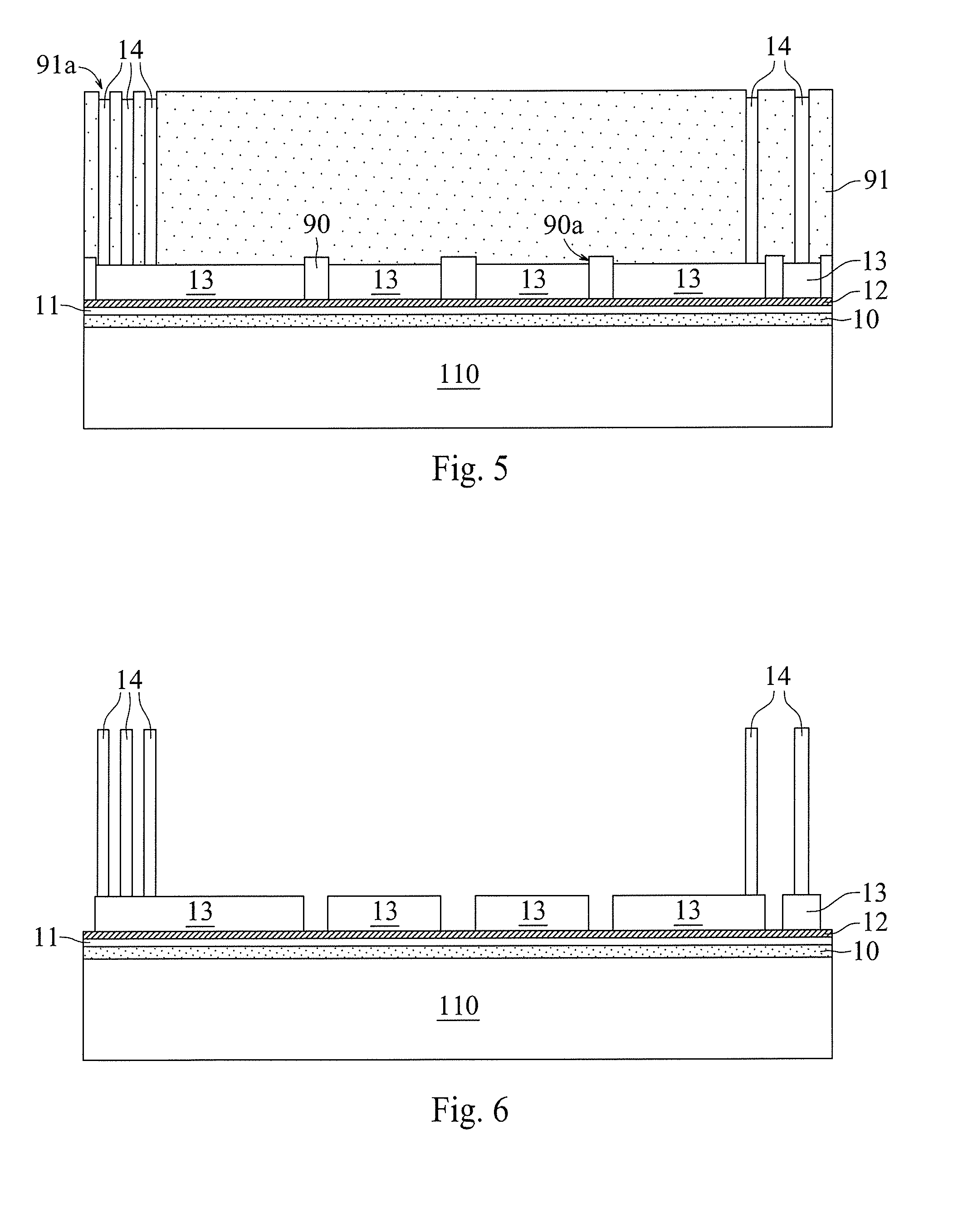

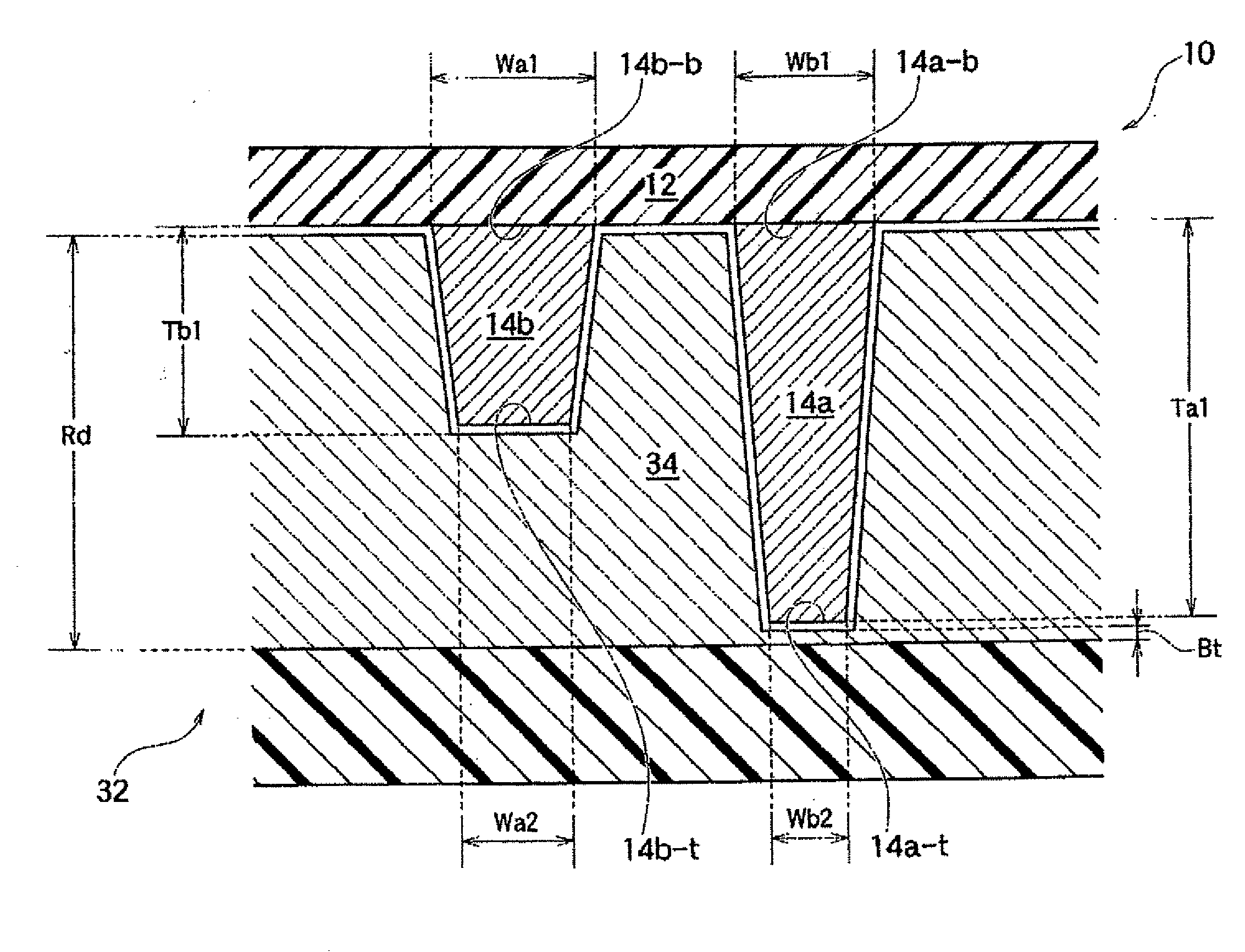

A process for producing a wiring board is provided, comprising allowing a wiring board-forming mold, which comprises a support base and a mold pattern that is formed in a protruded shape on one surface of the support base wherein the sectional width of the mold pattern on the support base side is larger than the sectional width thereof on the tip side in the same section of the mold pattern, to penetrate into a curing resin layer to transfer the mold pattern, curing the curing resin layer, releasing the laminate from the mold, depositing a conductive metal, and polishing the deposited metal layer that to form a depressed wiring pattern, and a wiring board produced by this process. Further, described is a process for producing a wiring board, comprising bringing a precision mold having a mold pattern on a surface of a mold base into contact with a surface of a metal thin film formed on an organic insulating base, pressing the mold to form a depression having a shape corresponding to the mold pattern of the precision mold in the organic insulating base, thereafter forming a metal plating layer having a thickness larger than the depth of the depression to fill the plating metal in the depression, and then polishing the metal plating layer until the organic insulating base is exposed, to form a wiring pattern, and a wiring pattern produced by this process.

Owner:MITSUI MINING & SMELTING CO LTD

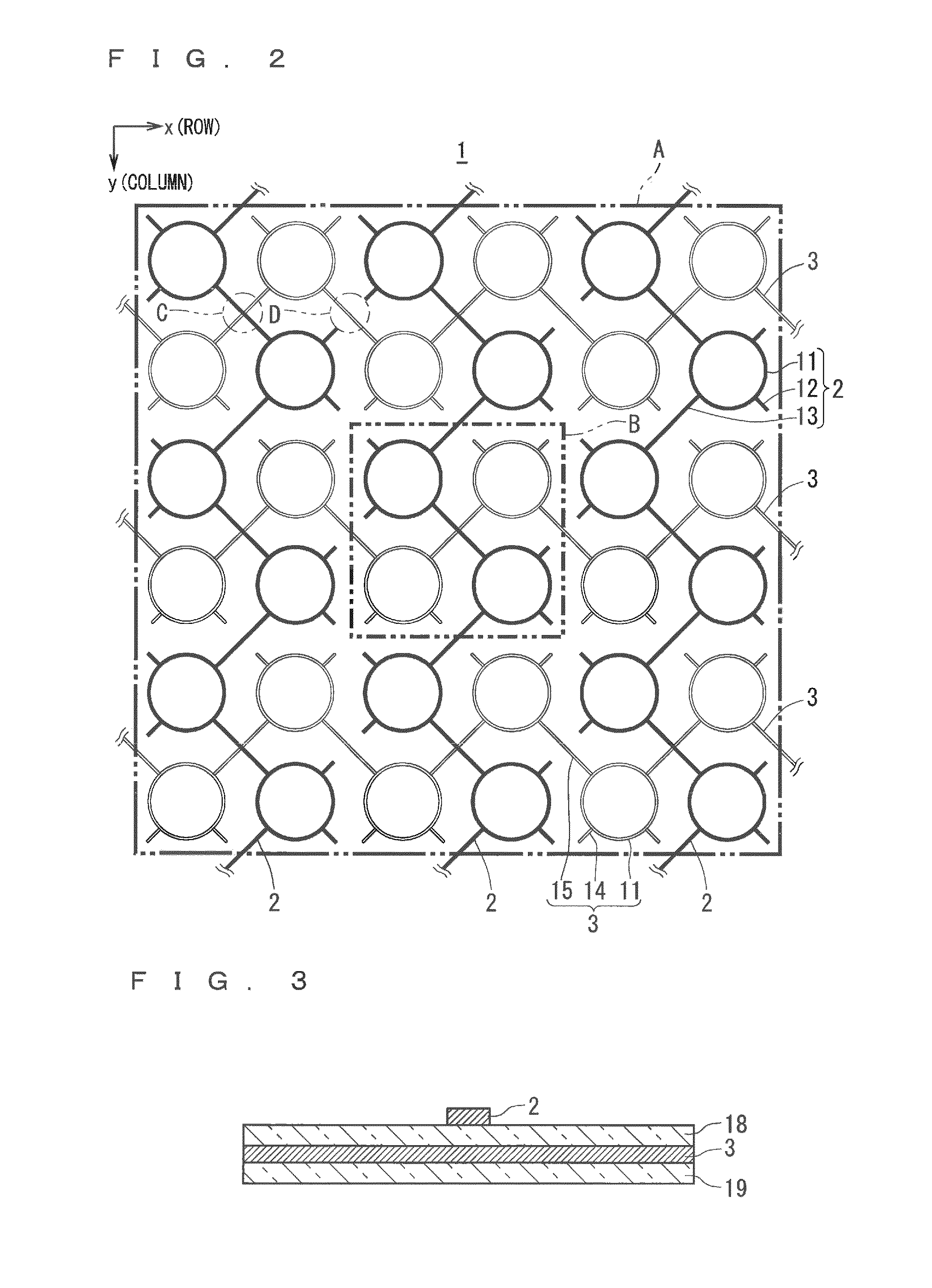

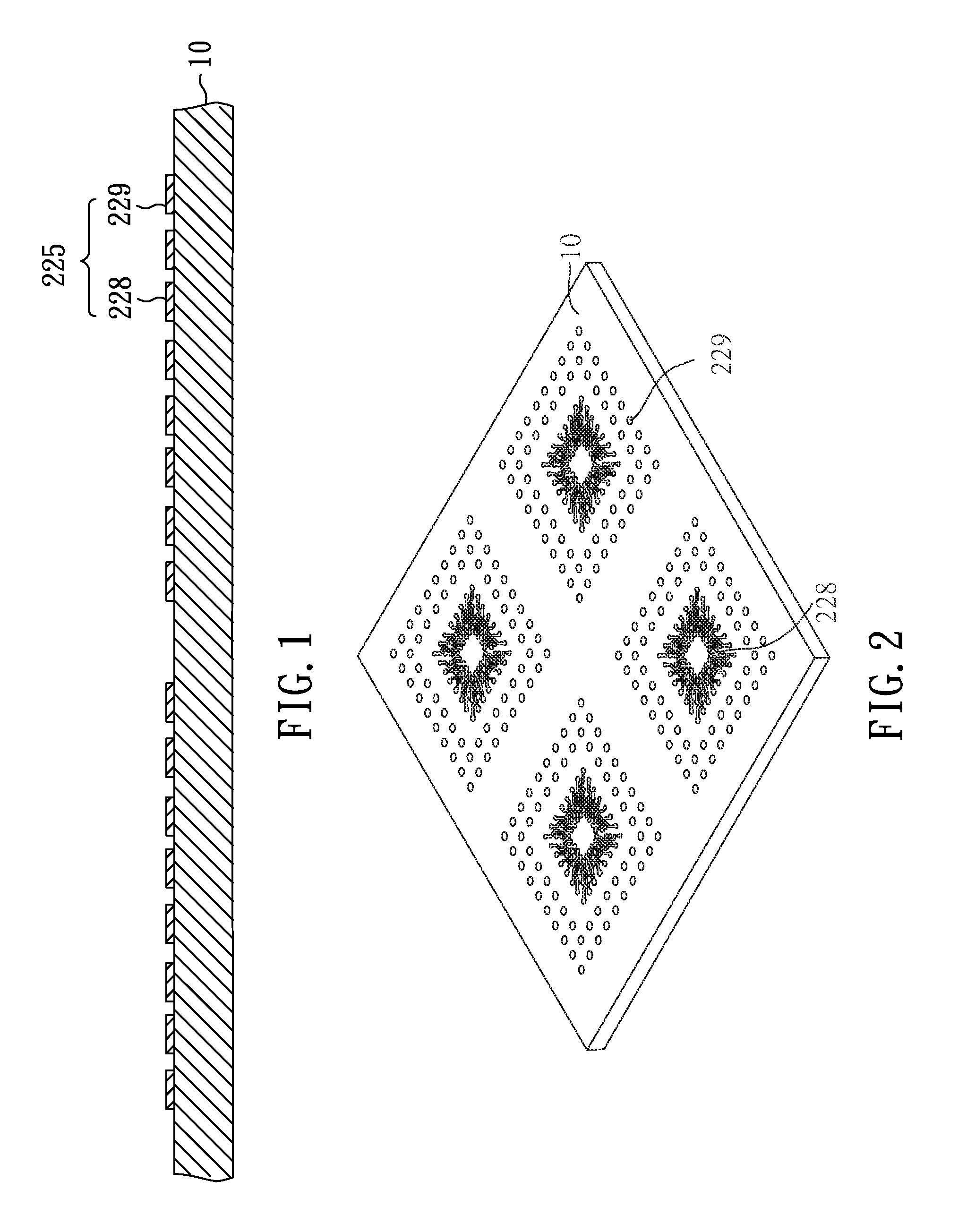

Touch screen, touch panel, display device and electronic device

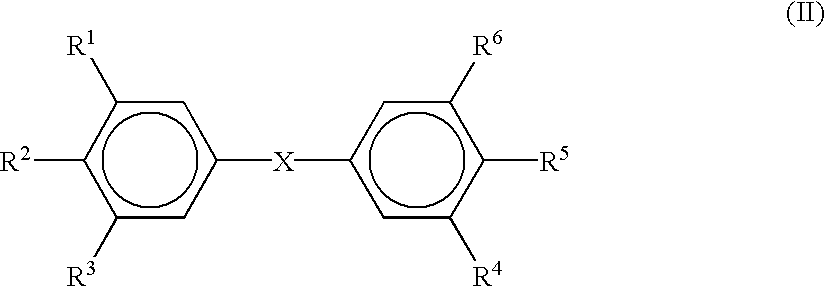

ActiveUS20150002464A1Solve the broken effect is not goodReduce display unevennessCircuit optical detailsPrinted circuit aspectsDisplay deviceAlloy

Detection column wires and detection row wires are configured of thin wires made of a conductive material having light reflectivity, such as a metal or alloy including silver and aluminum. A predetermined plural number of detection column wires are electrically connected to form a plurality of column-direction bundle wires. A predetermined plural number of detection row wires are electrically connected to form a plurality of row-direction bundle wires. A reflected-light distribution pattern is further provided. When viewed in a direction vertical to the surface of the touch screen, the reflected-light distribution pattern includes a curved portion, and the normal lines of the curved portion head for all directions.

Owner:TRIVALE TECH LLC

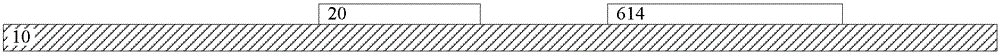

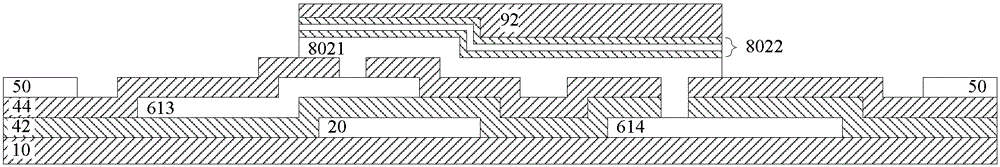

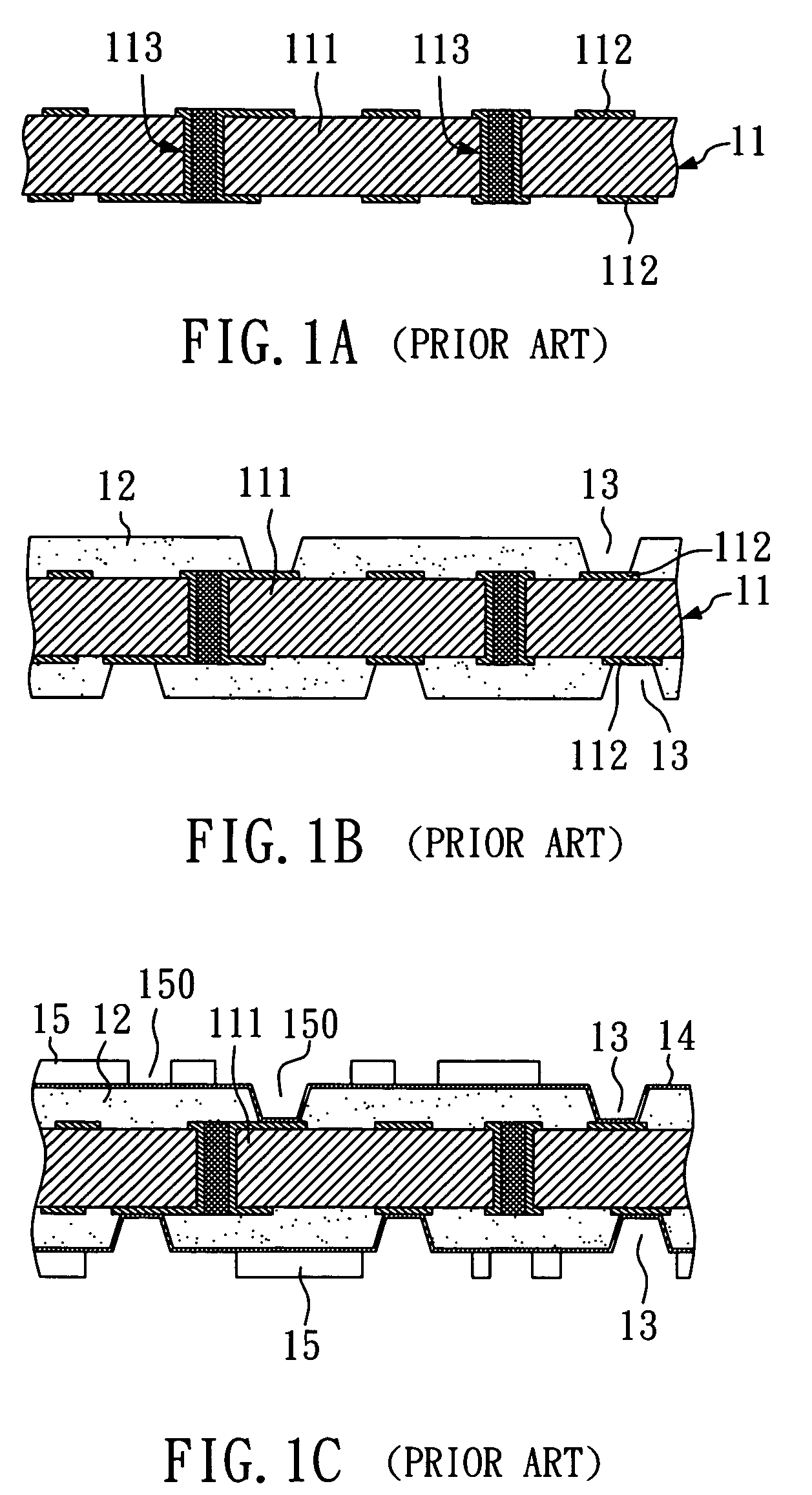

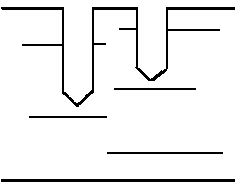

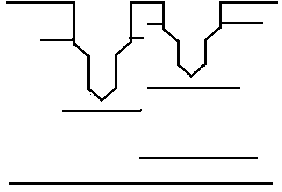

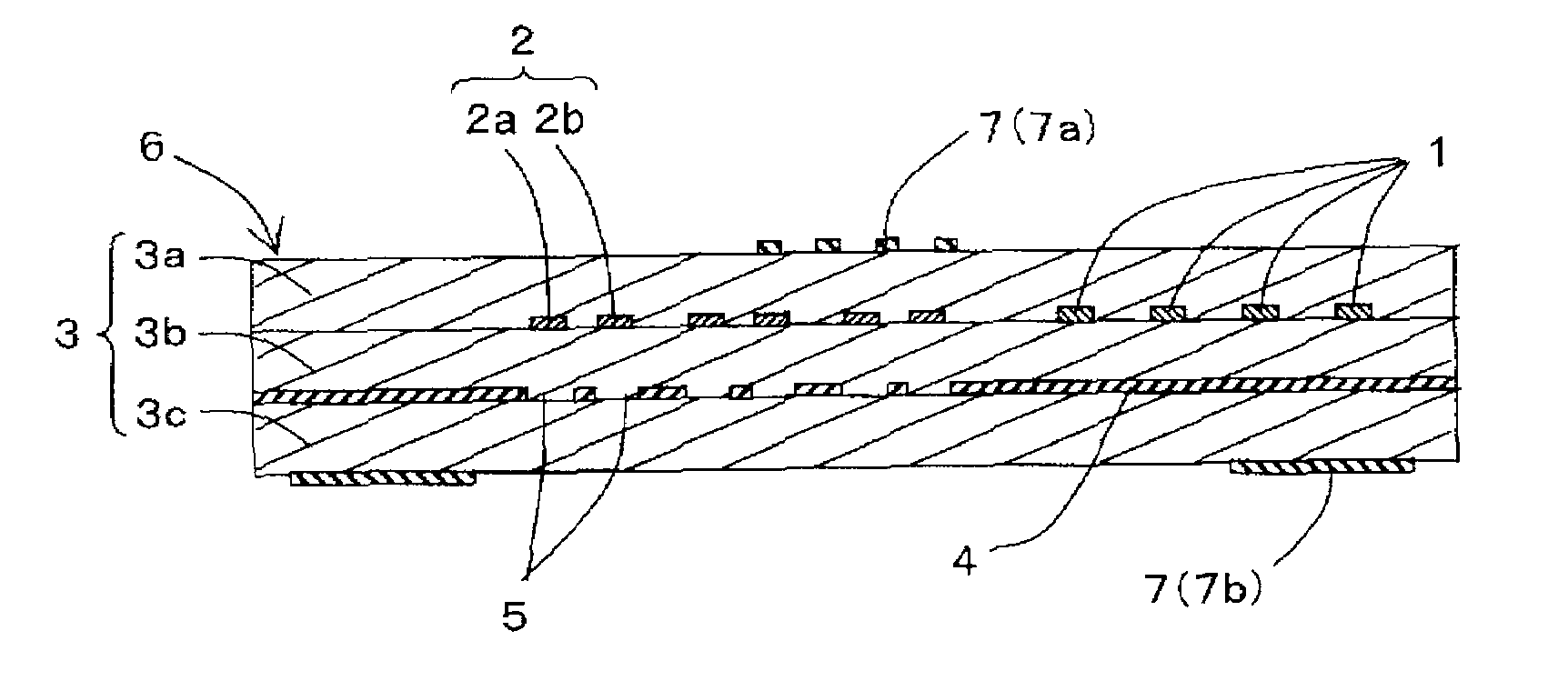

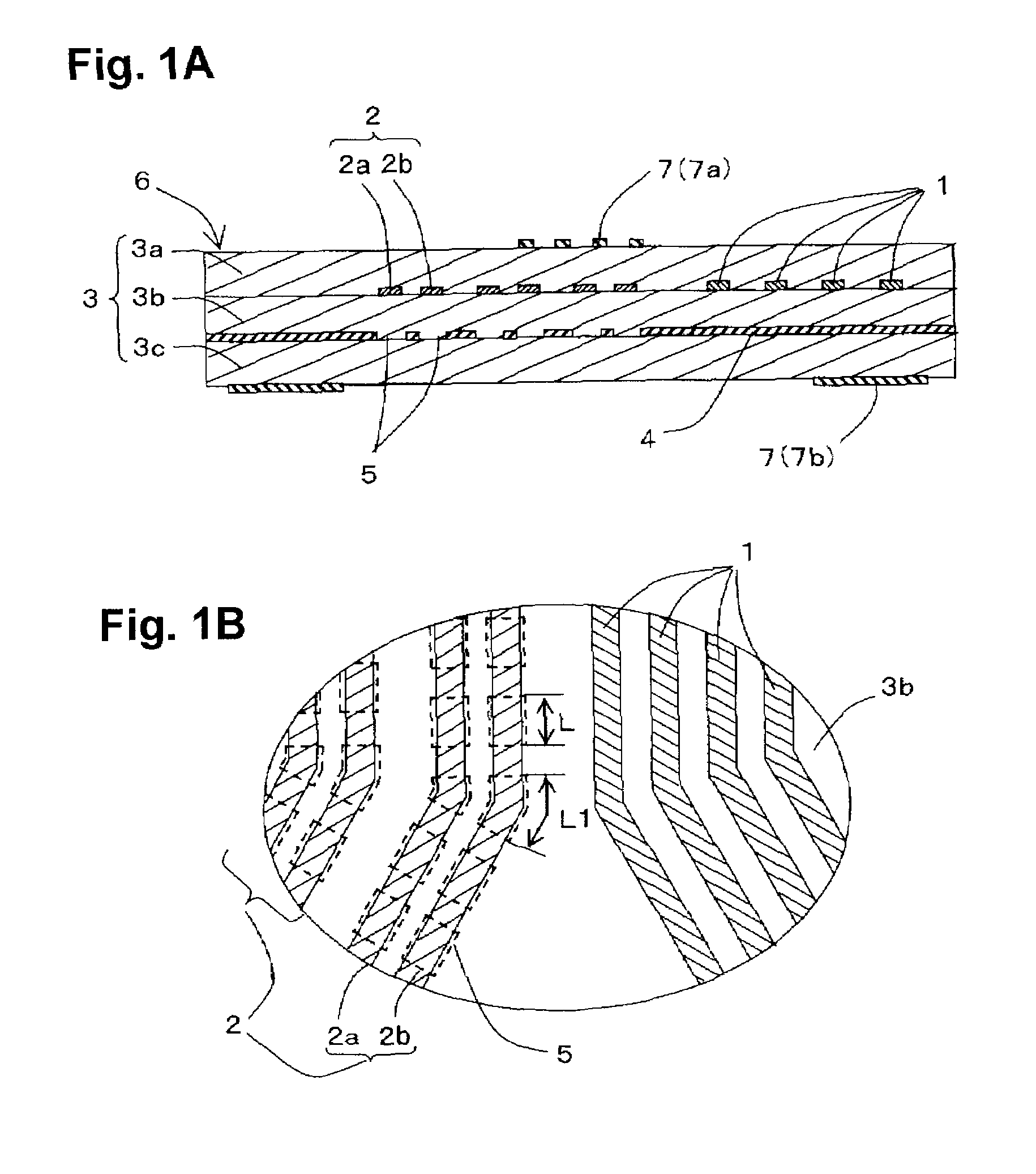

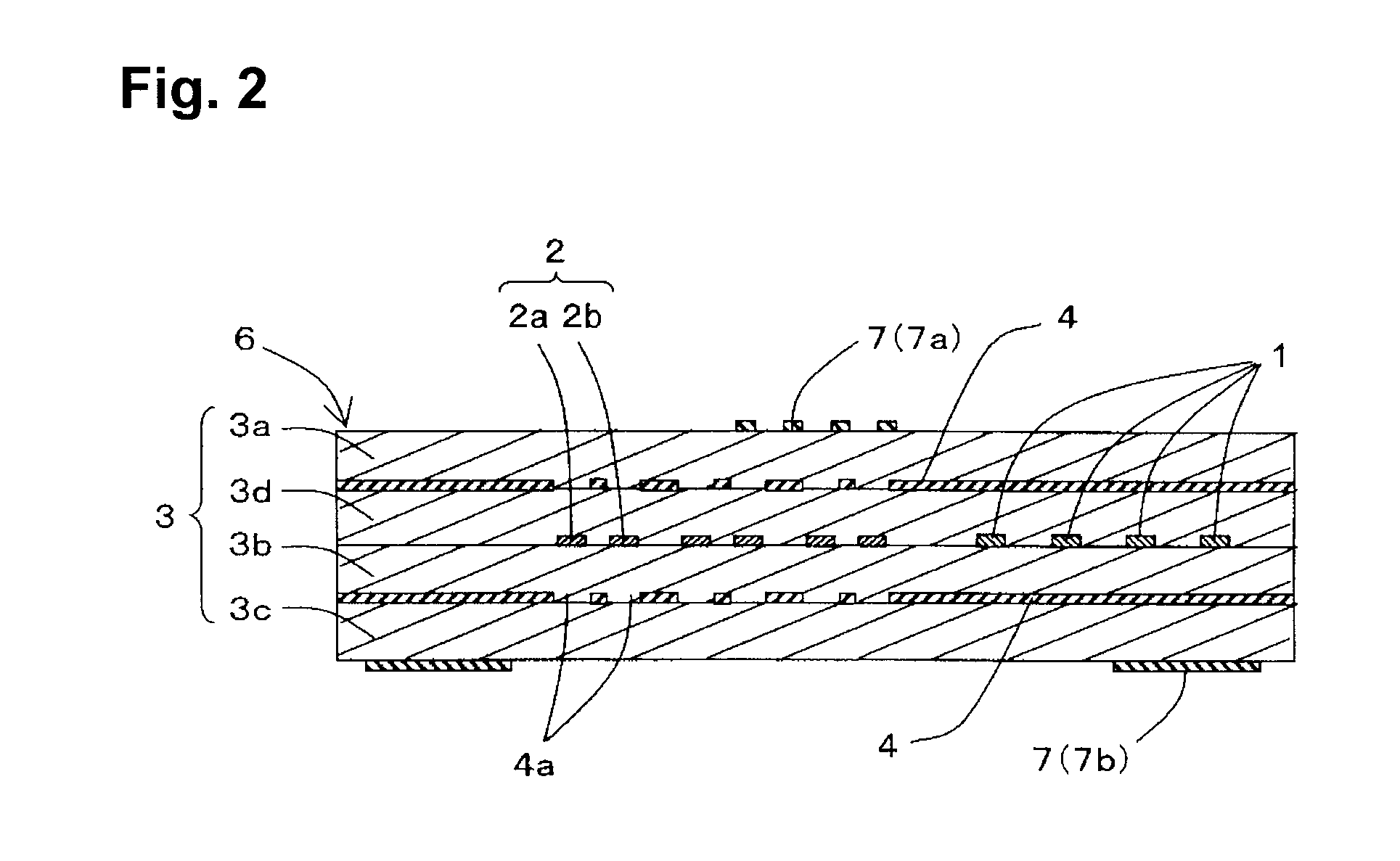

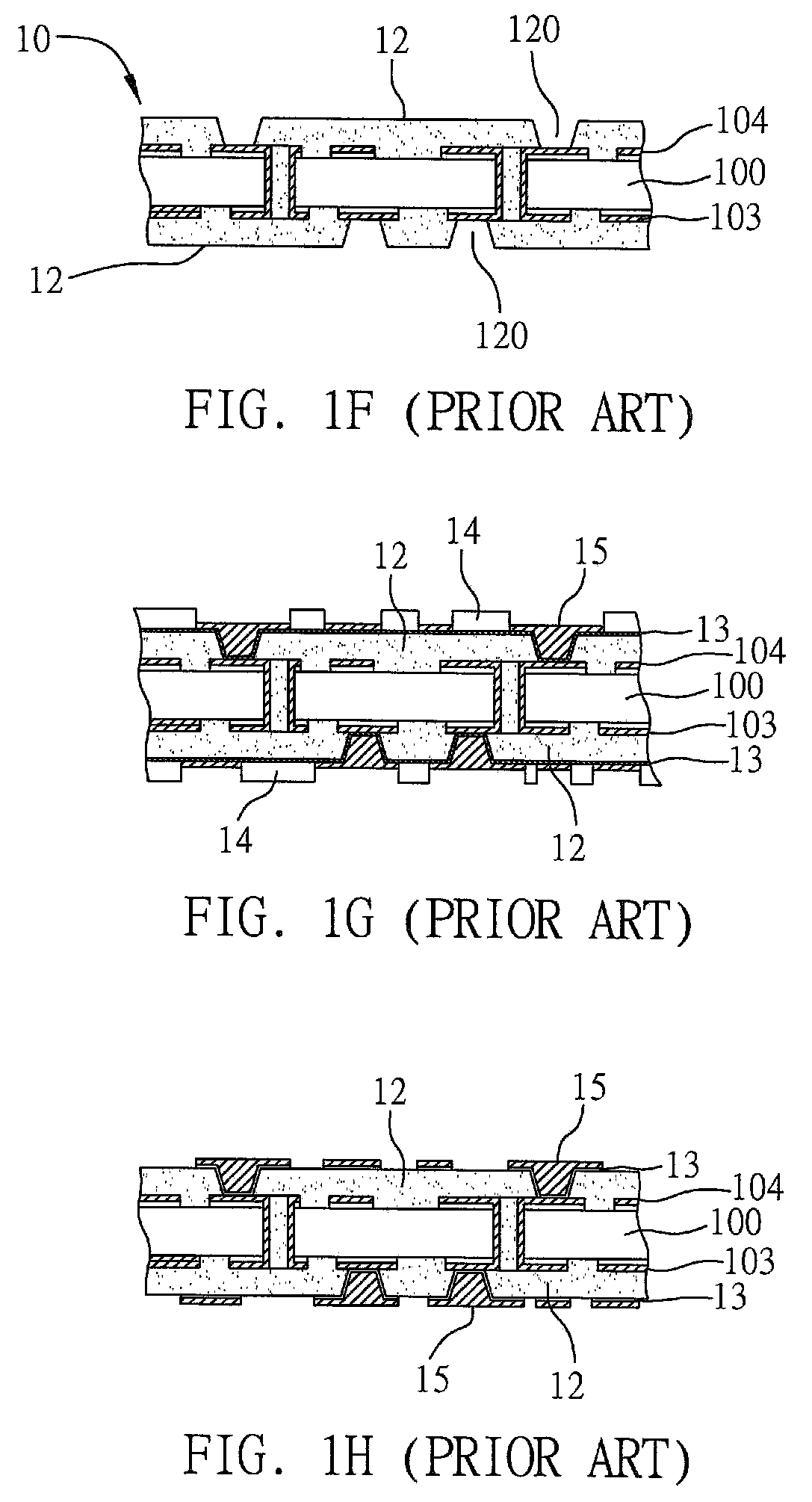

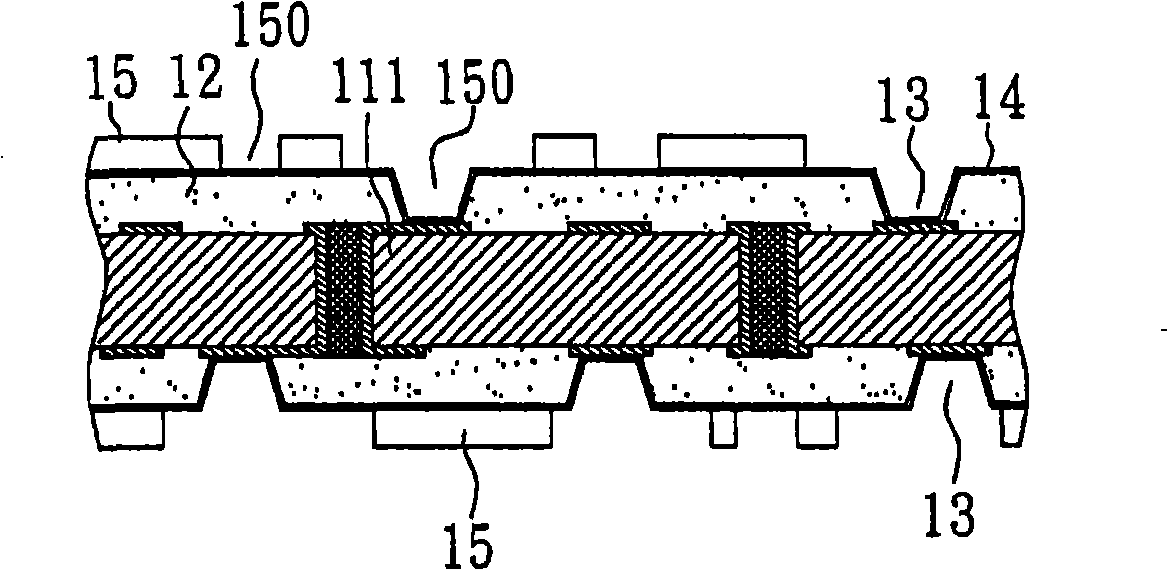

Solid printed circuit board and method of manufacturing the same

InactiveUS20100170700A1Improve routing densityLow profilePrinted electric component incorporationPrinted circuit aspectsConductive pasteEngineering

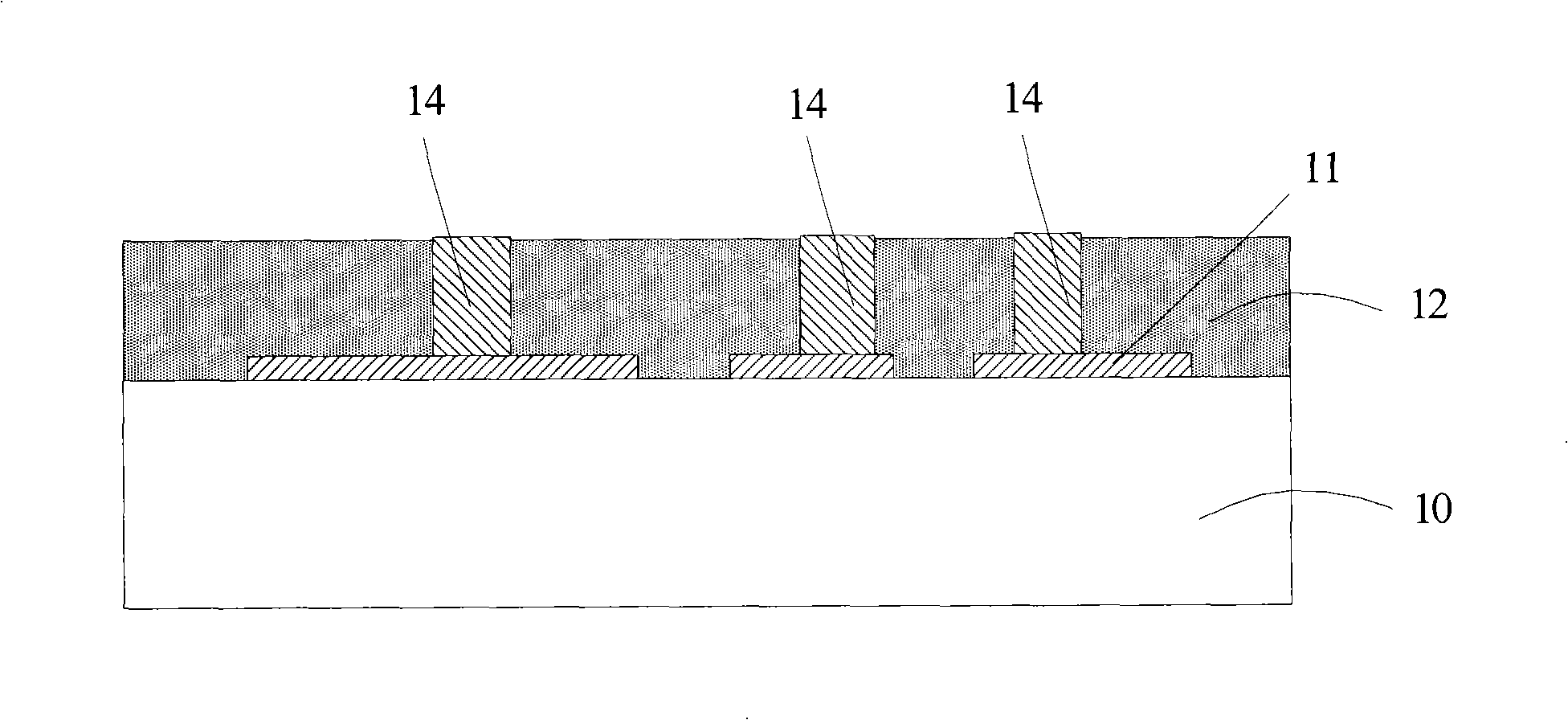

A solid printed circuit board is manufactured by bonding upper and lower printed circuit boards having different shapes and provided with wirings formed on surfaces thereof. A bonding layer is made of insulating material containing thermosetting resin and inorganic filler dispersed therein, and has a via-conductor made of conductive paste filling a through-hole perforated in a predetermined position of the bonding layer. This circuit board provides a packaging configuration achieving small size and thickness and three-dimensional mounting suitable for semiconductors of high performance and multiple-pin structure.

Owner:PANASONIC CORP

Printed circuit board and producing method of encapsulation base of integrated circuit

ActiveCN101286454AFinely craftedAvoid production capacity constraintsPrinted circuit aspectsSemiconductor/solid-state device manufacturingEngineeringInterconnection

The invention relates to a manufacturing method of a printed circuit board and an integrated circuit packaging substrate; based on the interconnection of electroplating pore filling and a semi-additive forming layer and a fine circuit, the method comprises the following steps: (1) a dielectric layer is manufactured on the substrate; (2) blind hole structure is manufactured on the dielectric layer; (3) after the blind hole structure is completed, a first conductive seed layer is manufactured; (4) a solid conductive via hole is manufactured by adopting the method of electroplating pore filling, and a copper layer grows and covers on the first seed layer in the process of electroplating pore filling; (5) the copper layer and the first seed layer are removed, and a solid copper cylinder in the solid conductive via hole is retained; (6) a second seed layer of semi-additive manufacturing circuit is manufactured; (7) a photosensitive thin film is glued, an anti-plating layer is formed by transferring diagram and the circuit diagram is exposed: (8) the circuit in the circuit diagram is thickened; (9) the photosensitive thin film and the exposed second seed layer are removed, the thickened circuit is retained, and a needed conductive diagram is formed; (10) all the steps from (1) to (9) are repeated on the new circuit surface, and the manufacture of fine circuits of following circuit layers and the connection of the solid conductive via holes in the layers are completed.

Owner:SHANGHAI MEADVILLE SCI & TECH

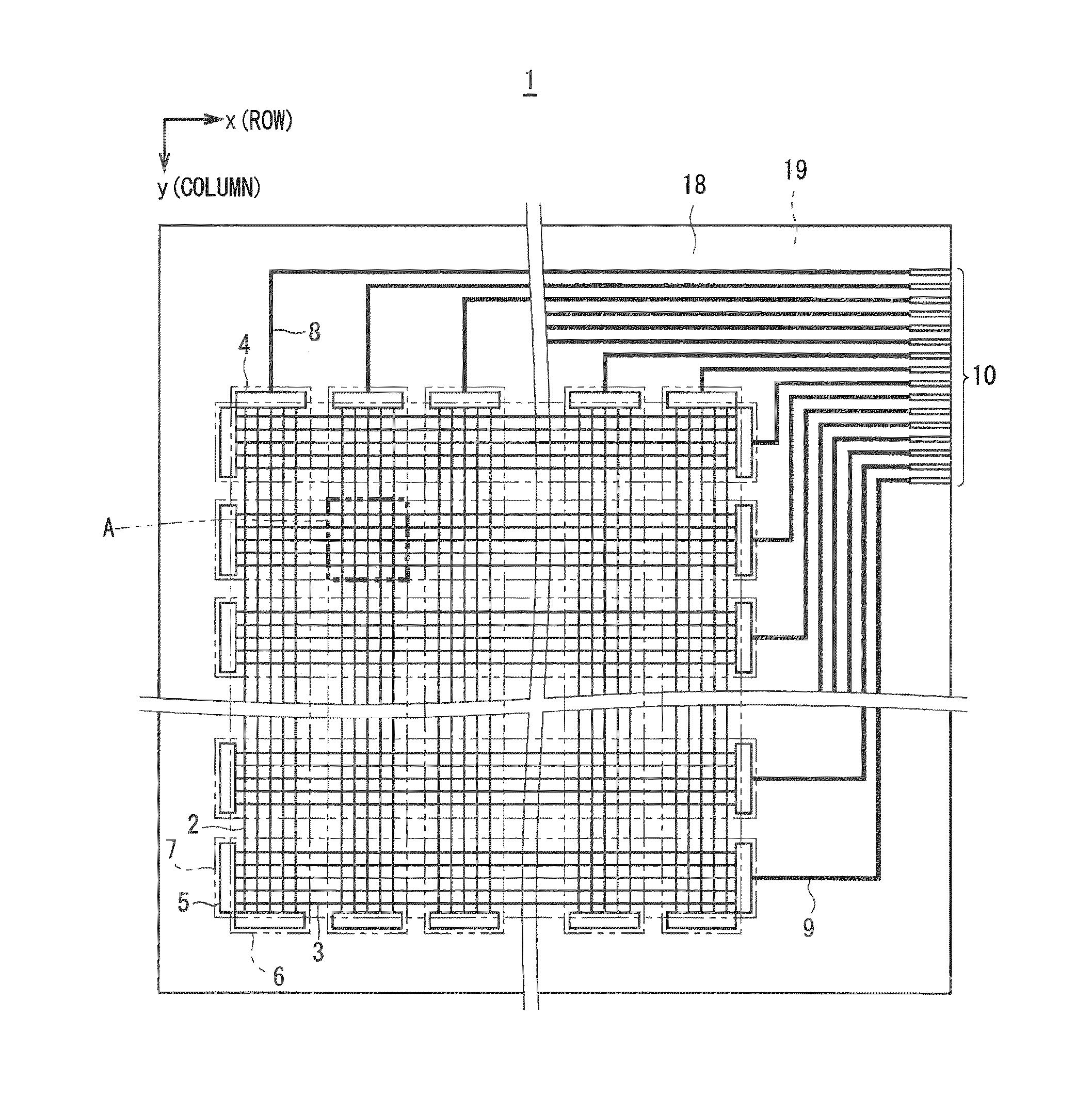

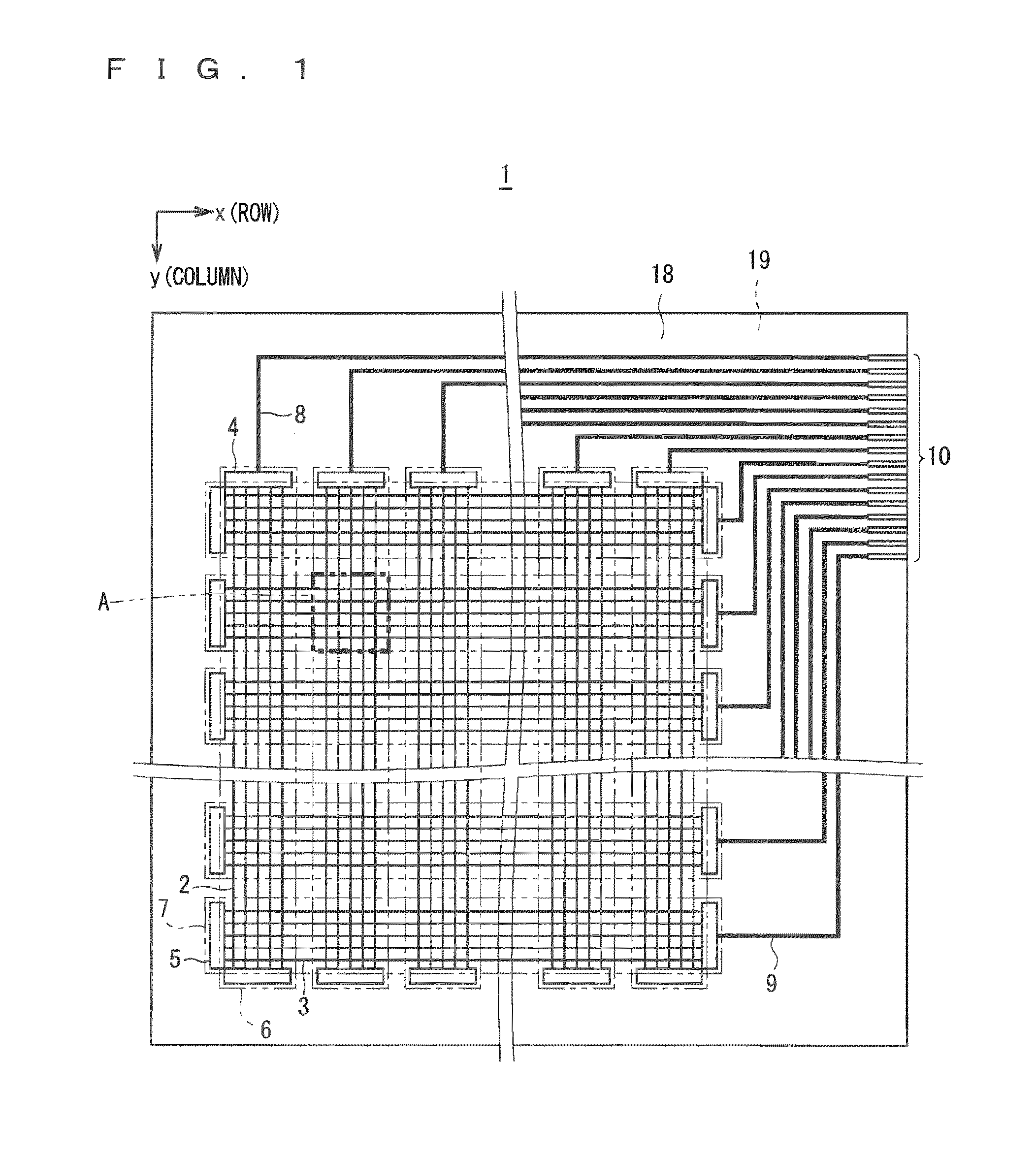

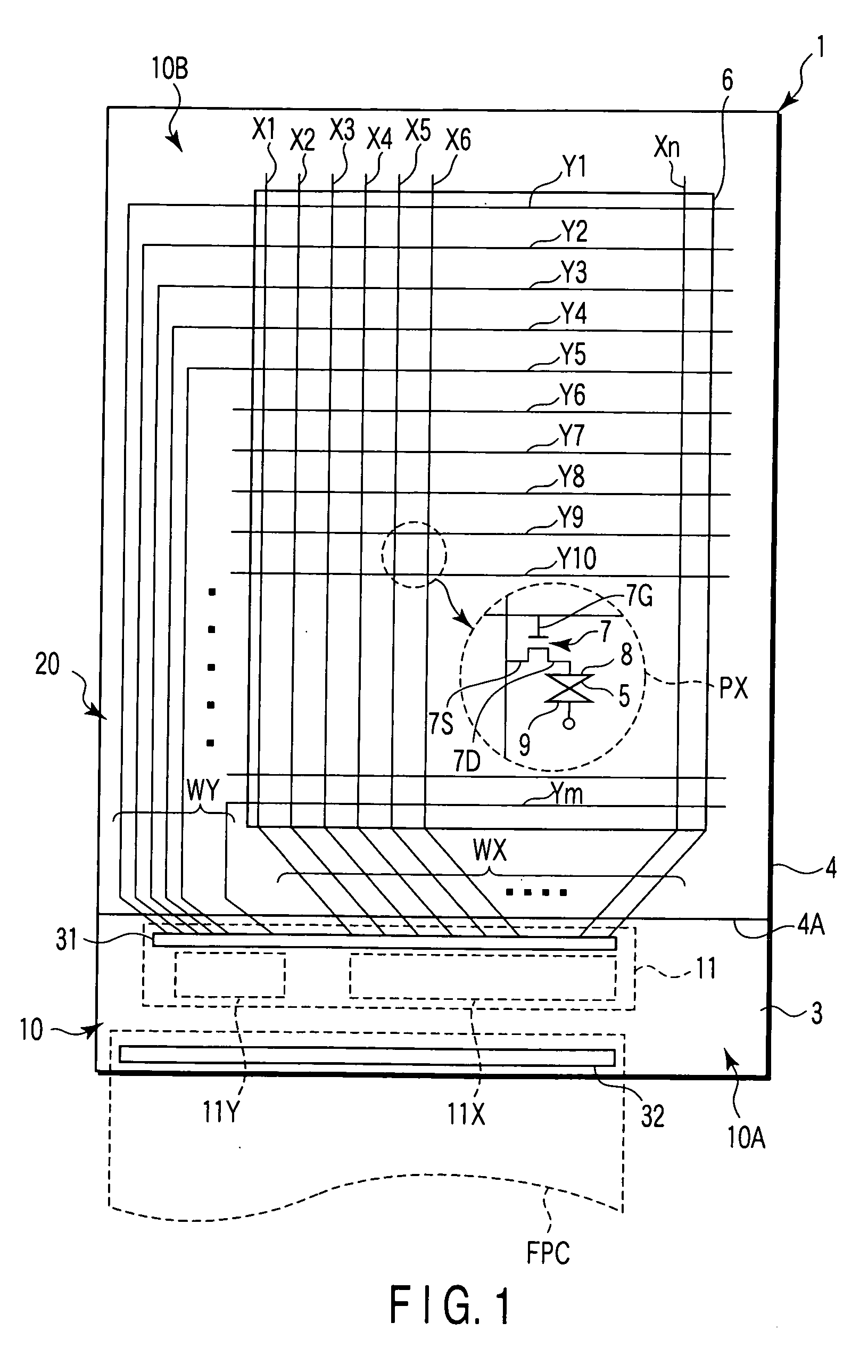

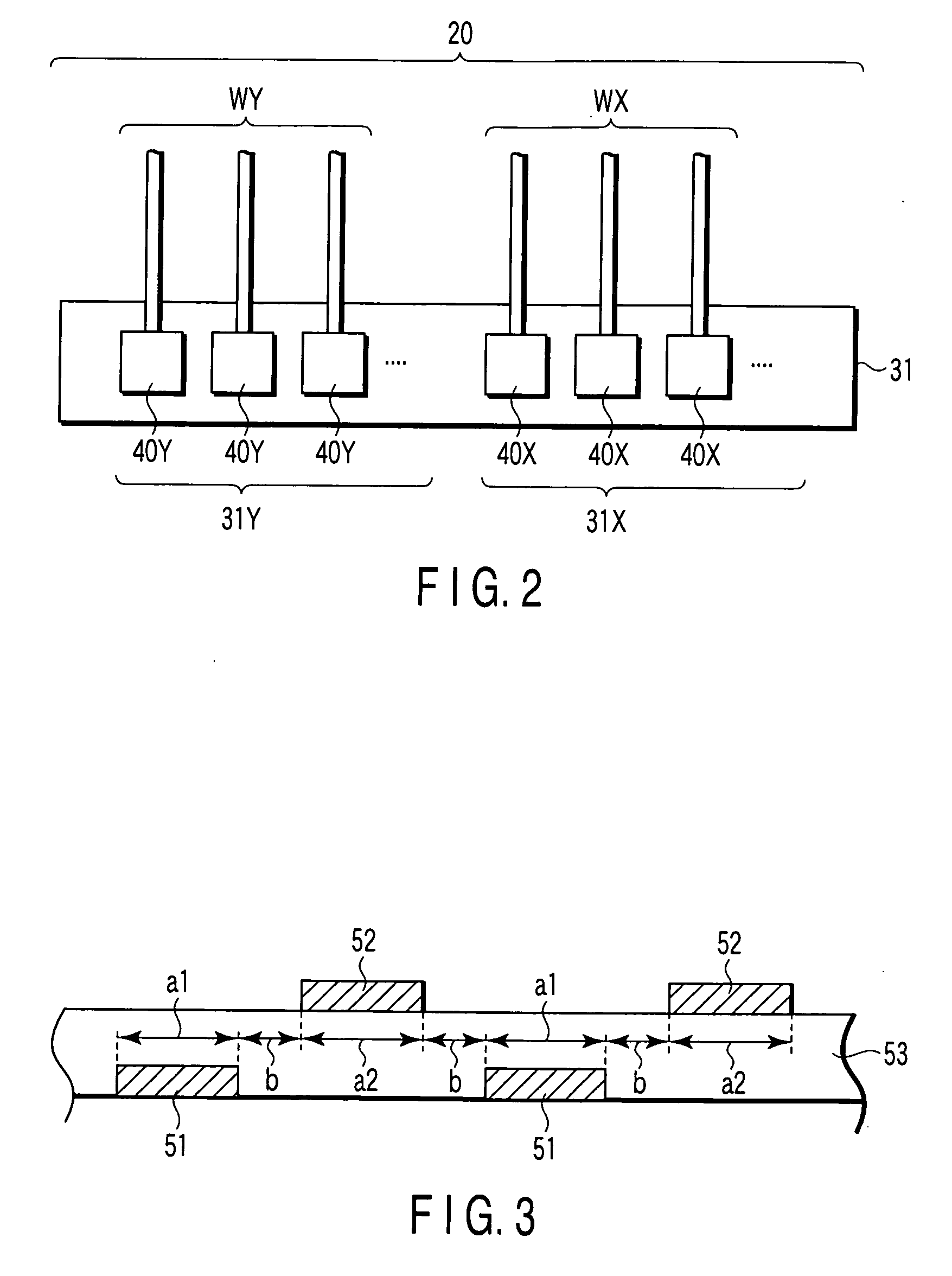

Display device

A display device includes an active area that is composed of a plurality of pixels and a plurality of signal supply wiring lines that supply driving signals to the pixels, a plurality of input sections that are disposed outside the active area and function to input the driving signals that are to be supplied to the signal supply wiring lines, and a plurality of connection wiring lines that connect the signal supply wiring lines and the input sections. Mutually neighboring first connection wiring line and second connection wiring line of the connection wiring lines are disposed in different layers via an insulating layer.

Owner:TOSHIBA MATSUSHITA DISPLAY TECH

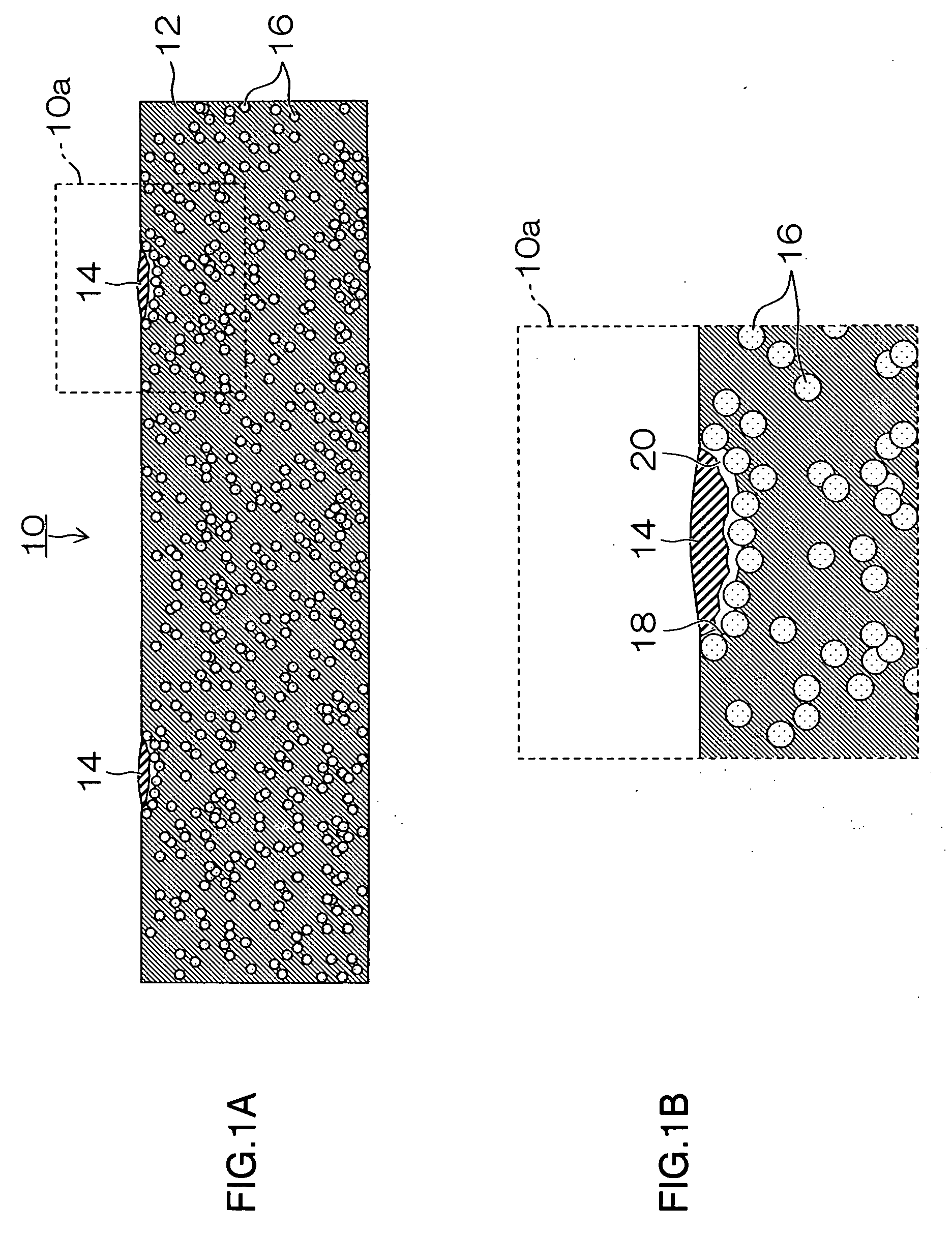

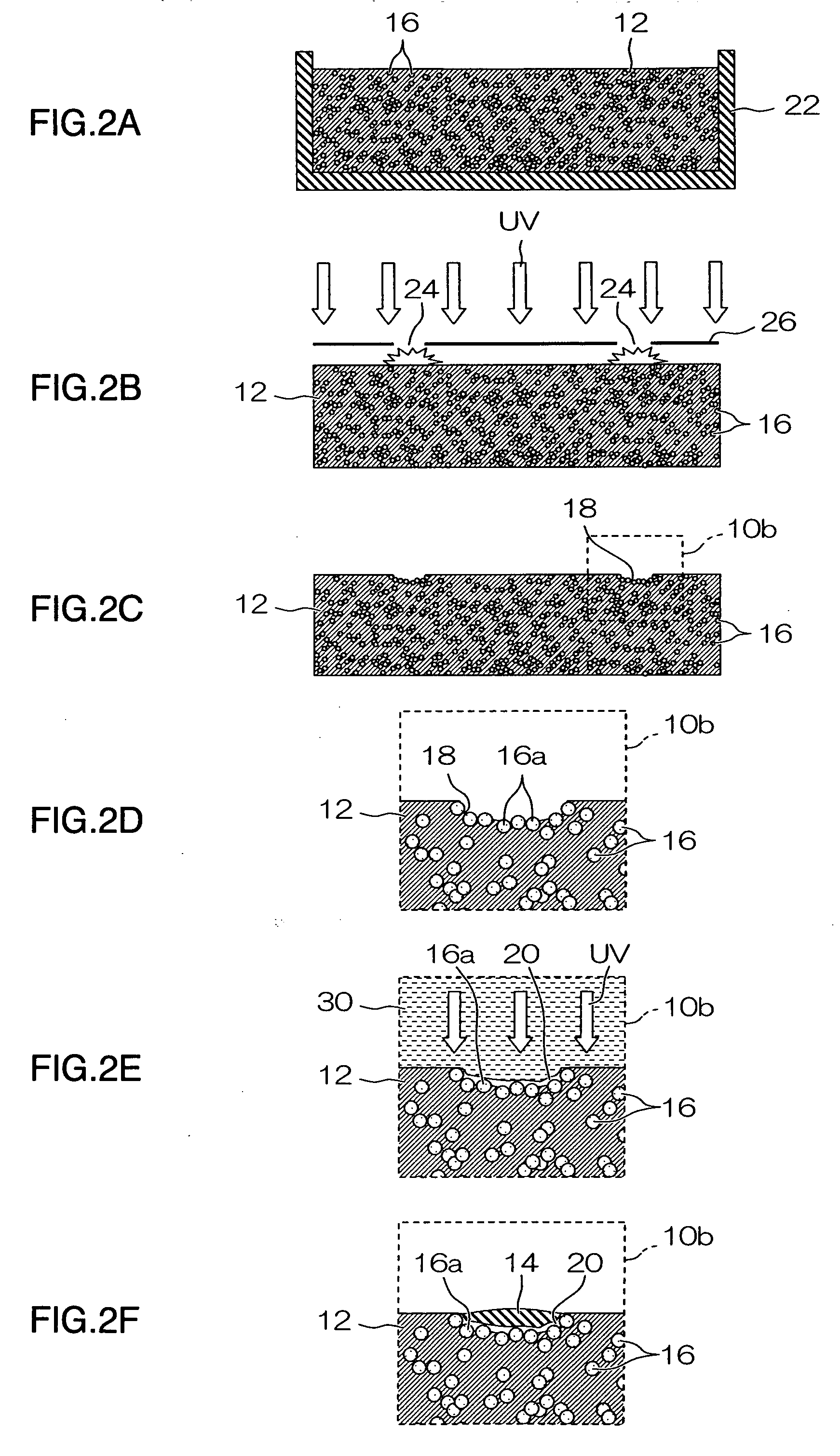

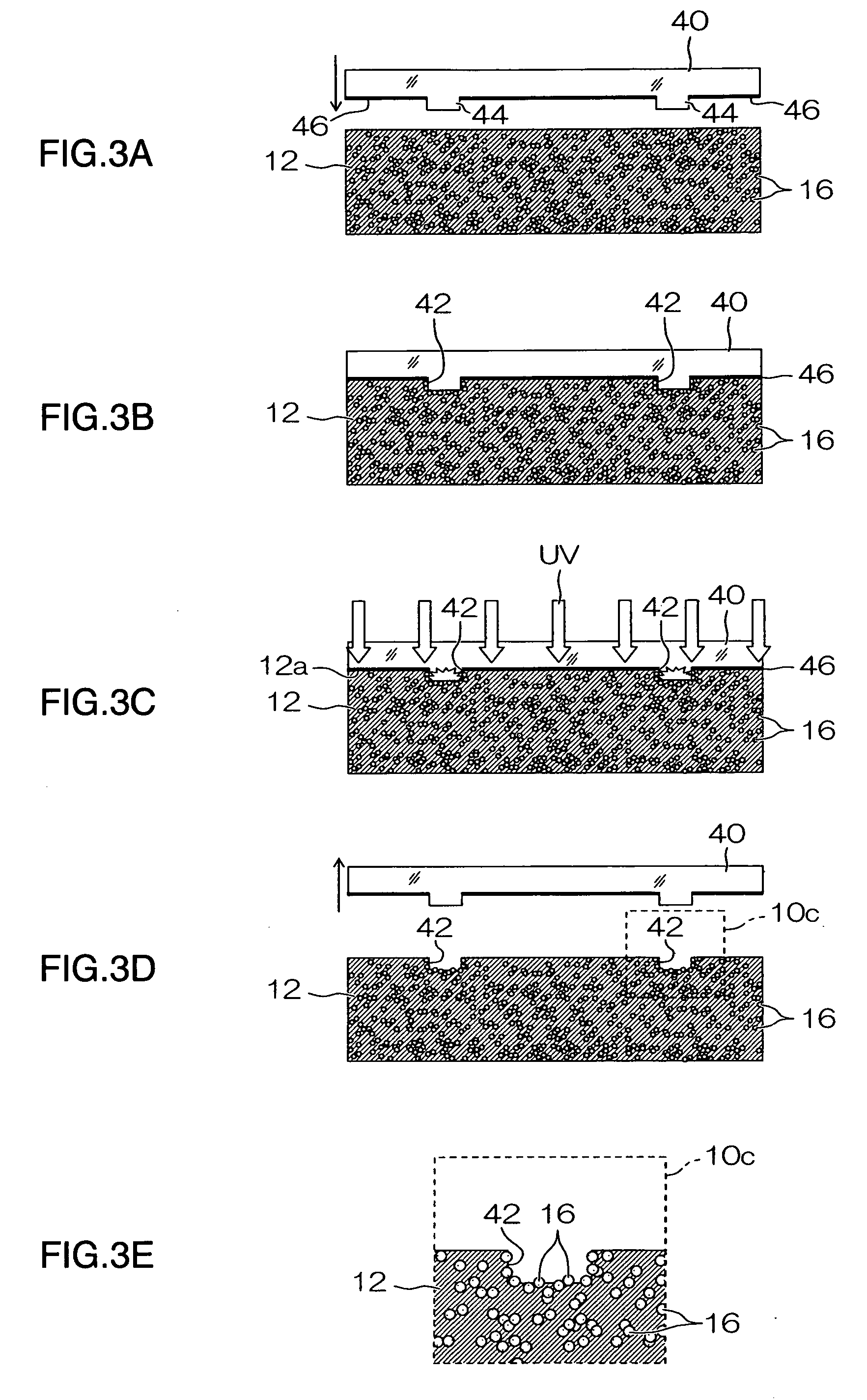

Method of manufacturing wiring substrate, and wiring substrate

InactiveUS20070014975A1Improve adhesionHigh bonding strengthPretreated surfacesTransparent dielectricsOptoelectronicsRadiation exposure

The method of manufacturing a wiring substrate comprises the steps of: performing a pattern exposure of a resin layer containing photocatalyst particles, in a shape of a desired wiring pattern so that the photocatalyst particles are exposed at a surface of the resin layer; performing irradiation of radiation to the resin layer having the exposed photocatalyst particles while the resin layer having the exposed photocatalyst particles is immersed in an aqueous solution of a metallic salt so that a photochemical reduction and precipitating of a metal film onto the exposed photocatalyst particles are performed; and forming a conducting layer on the metal film.

Owner:FUJIFILM CORP

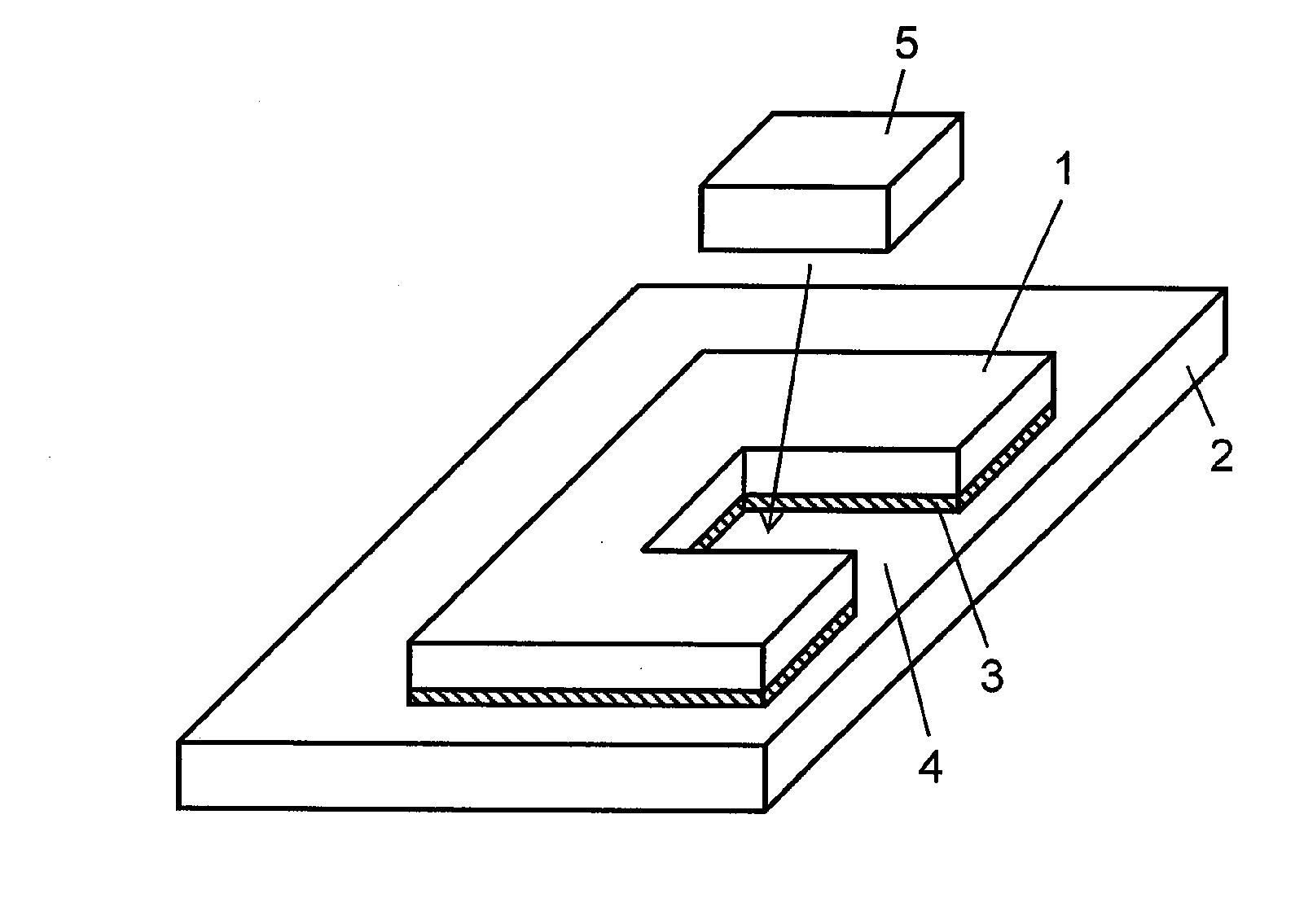

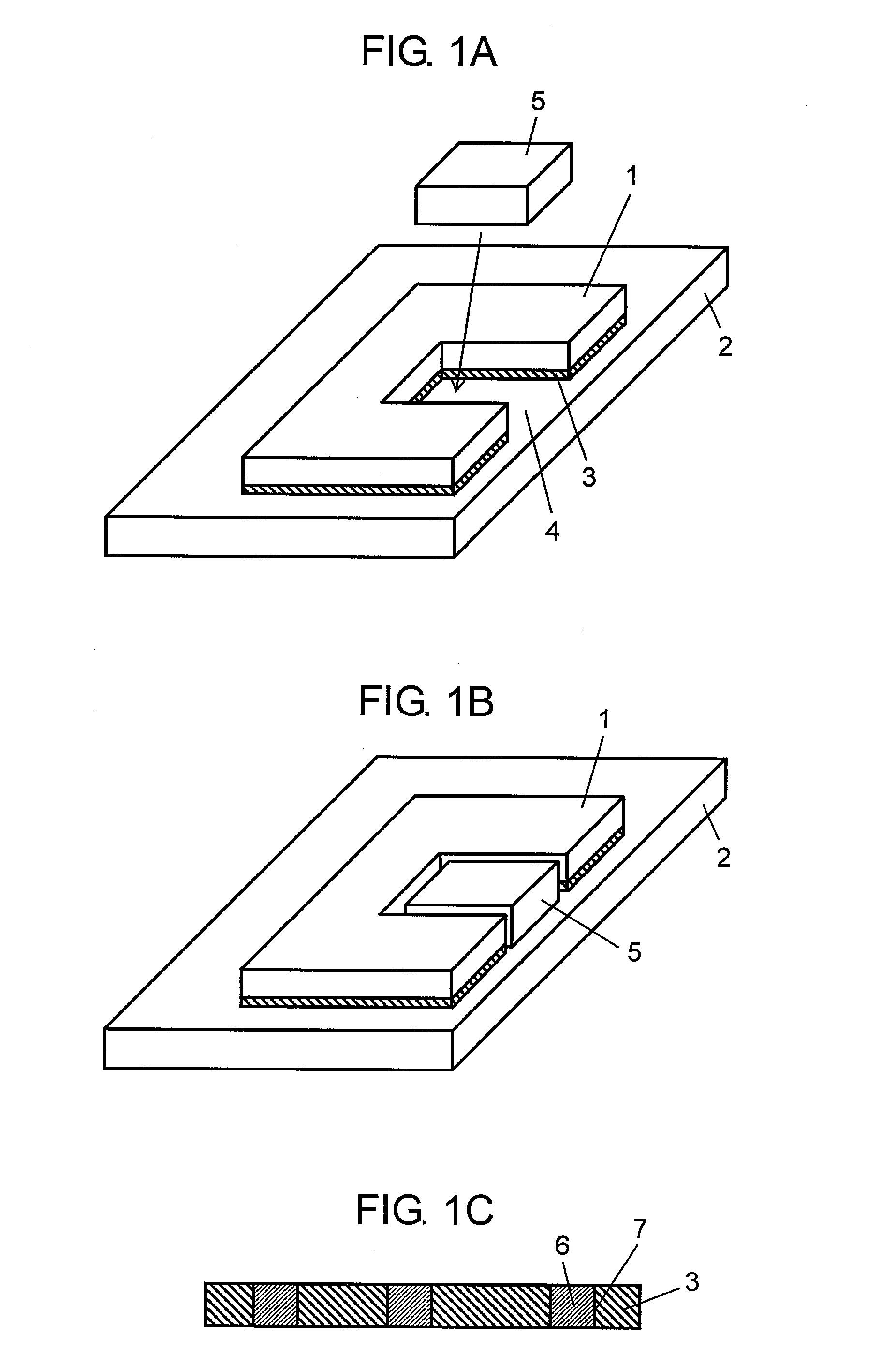

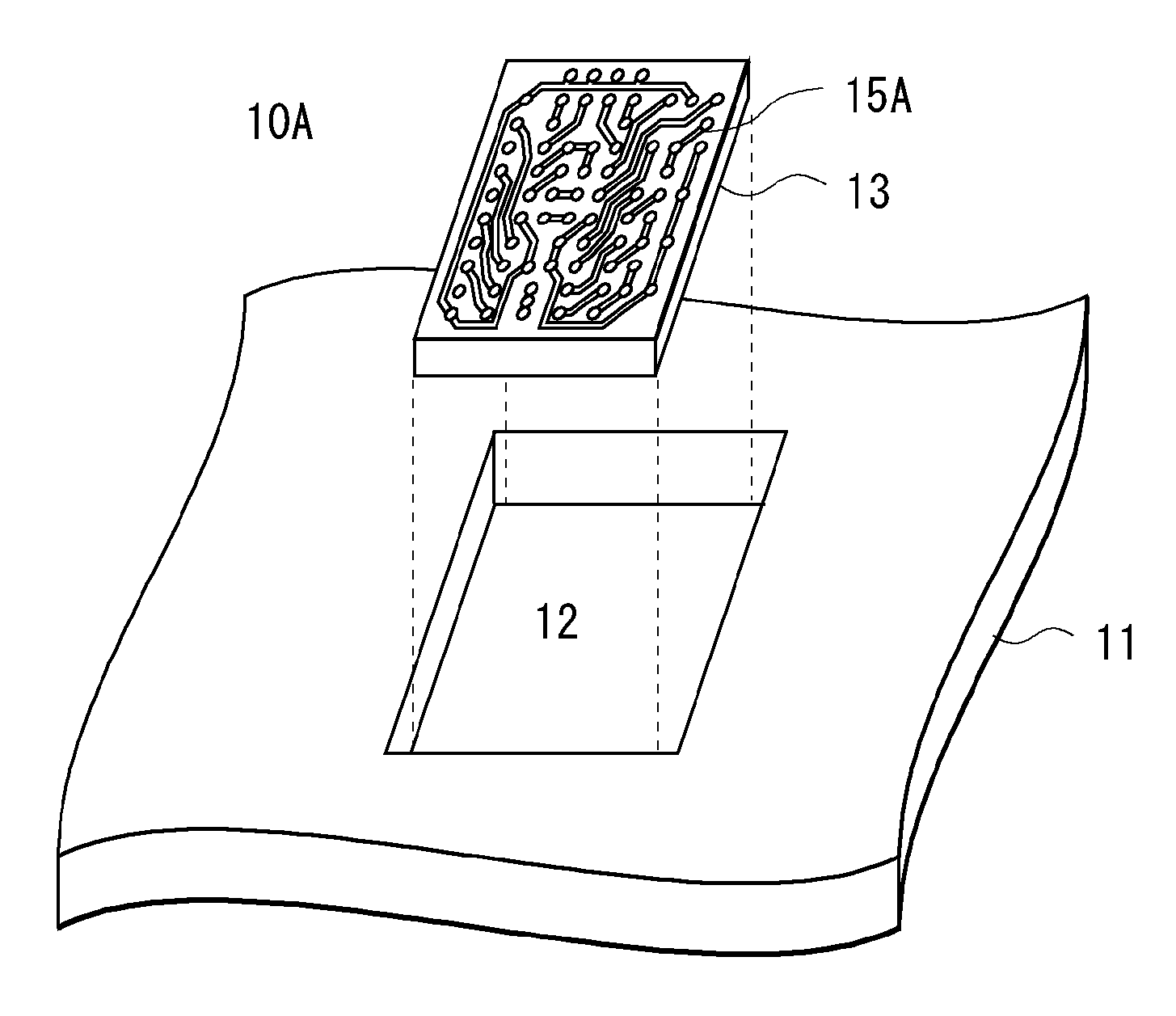

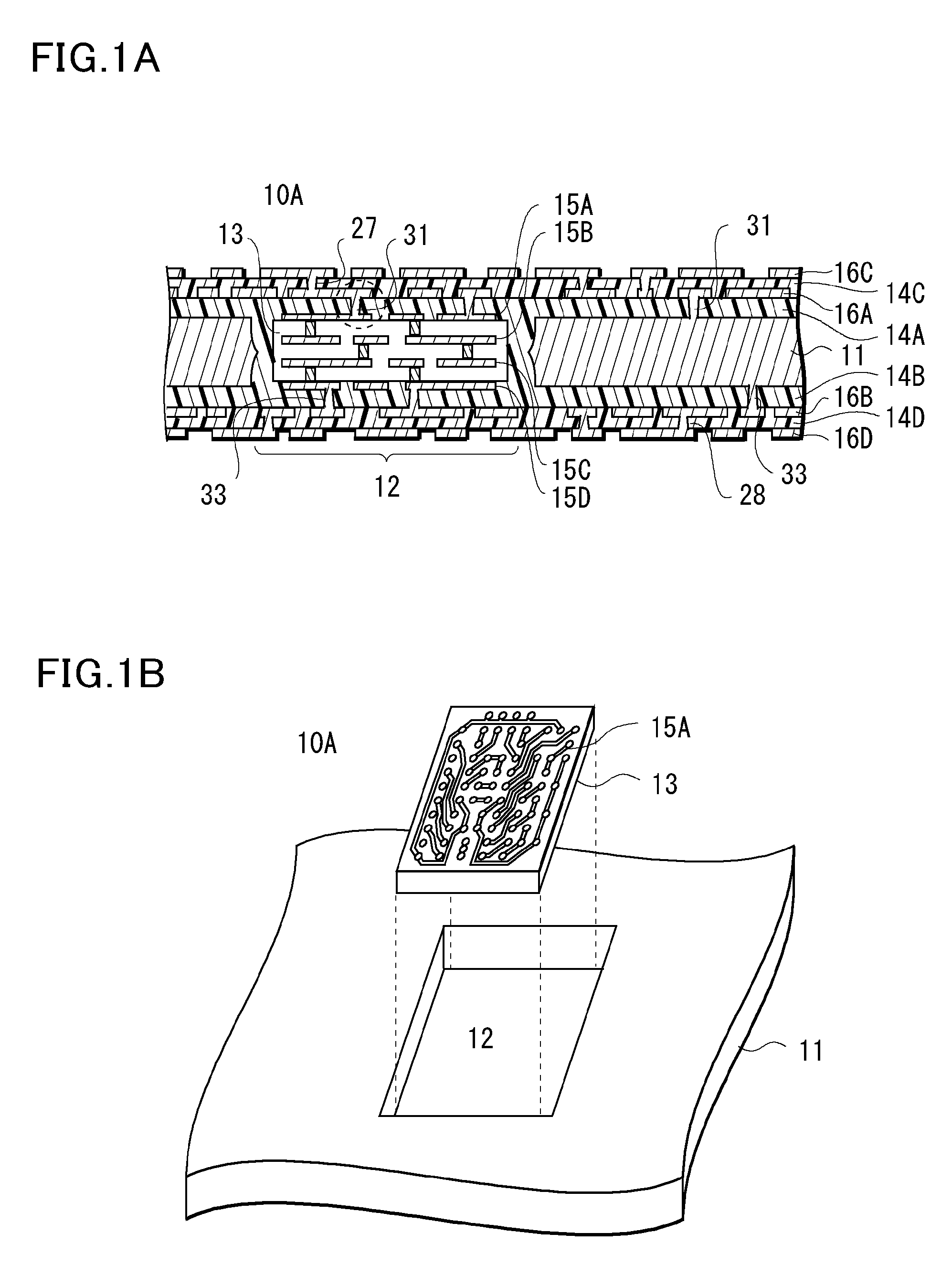

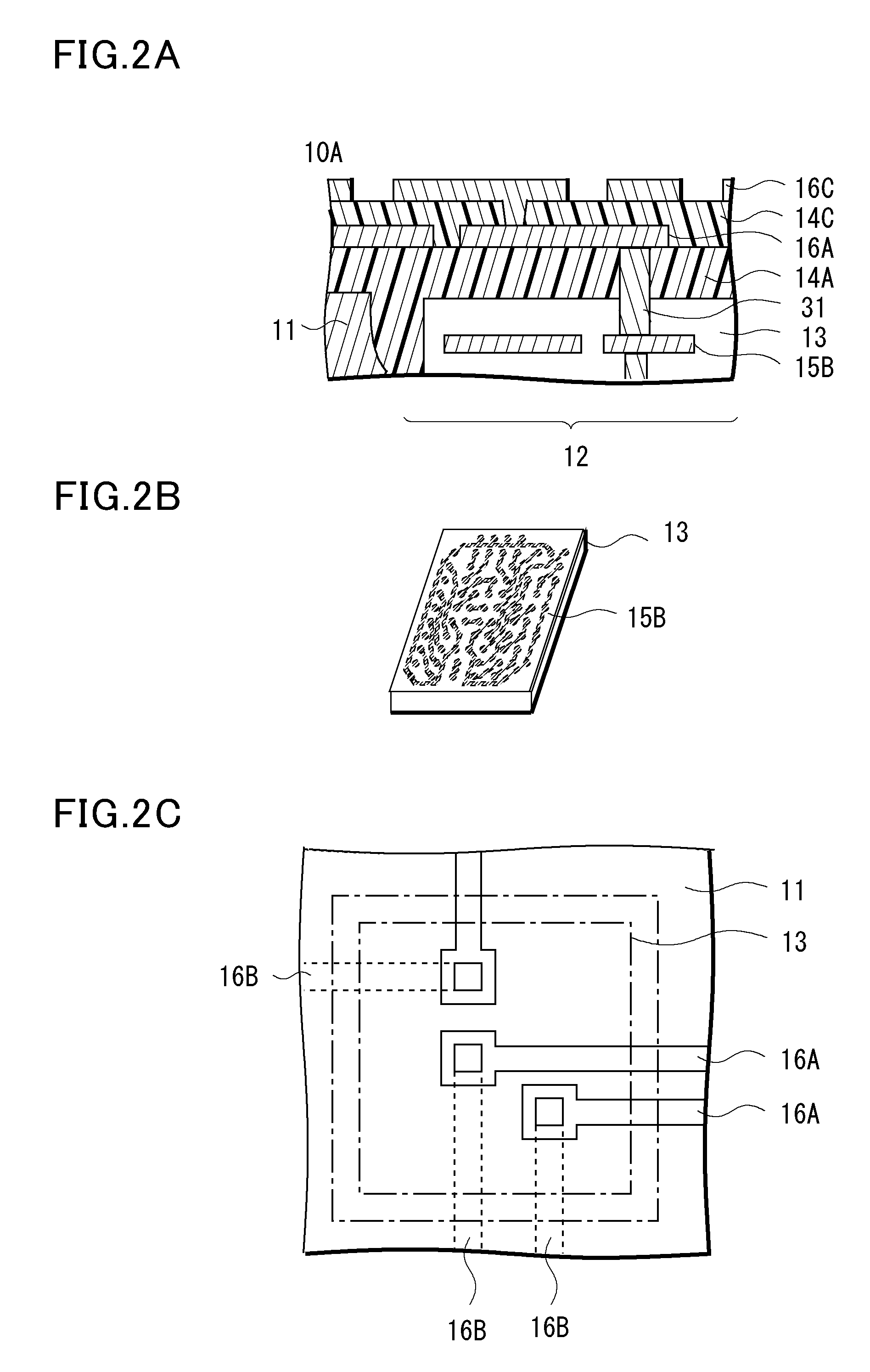

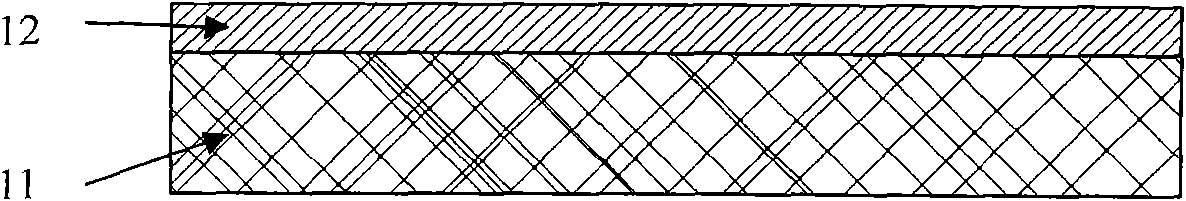

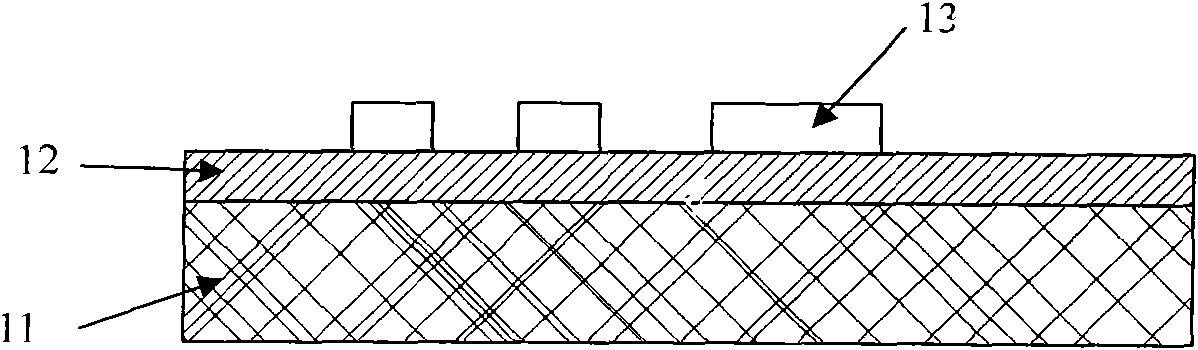

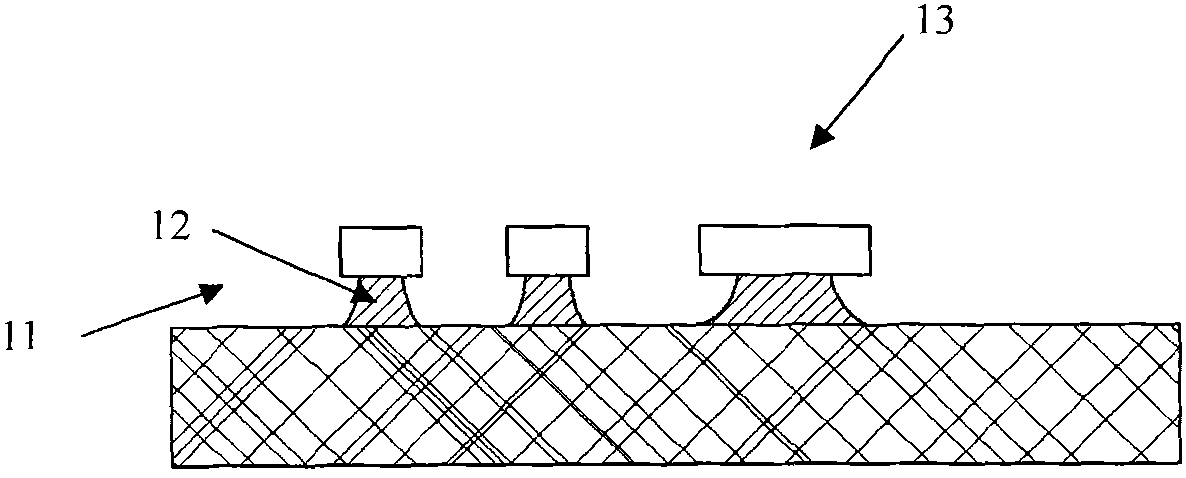

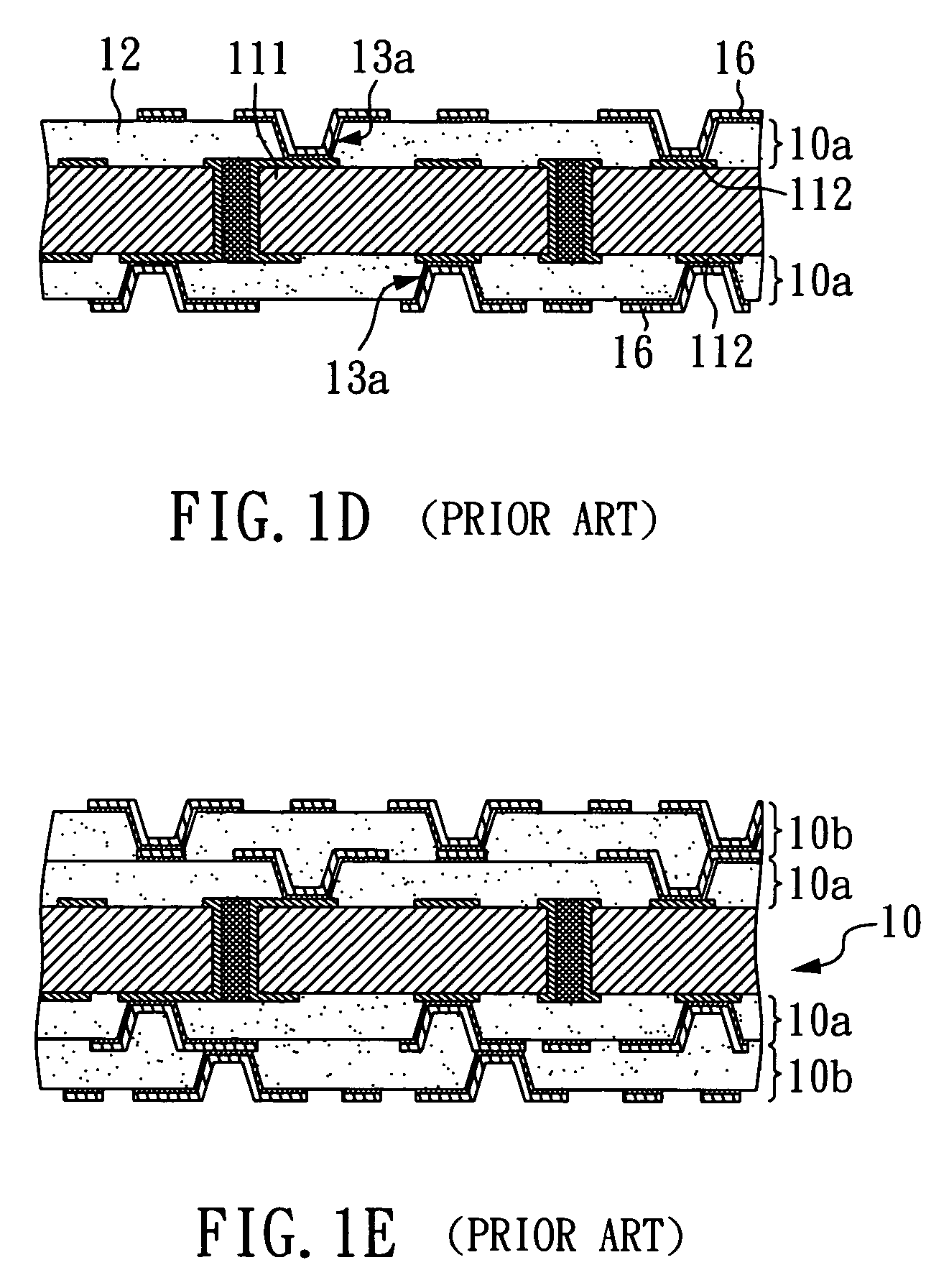

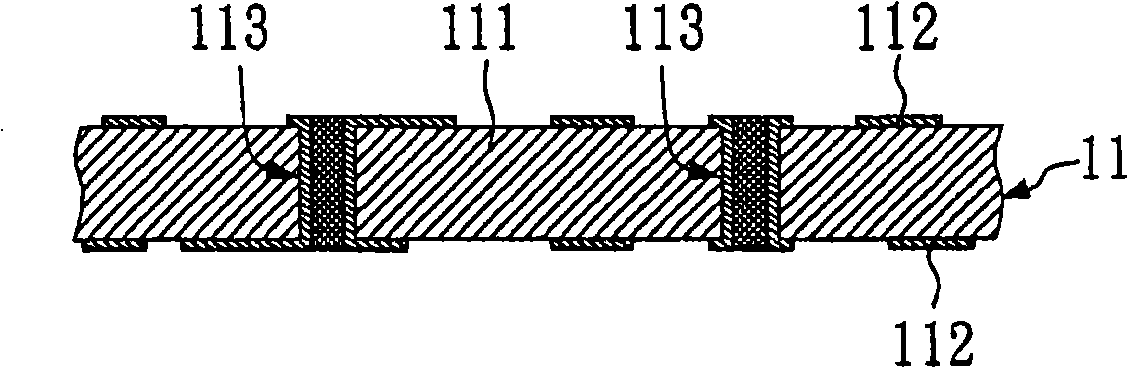

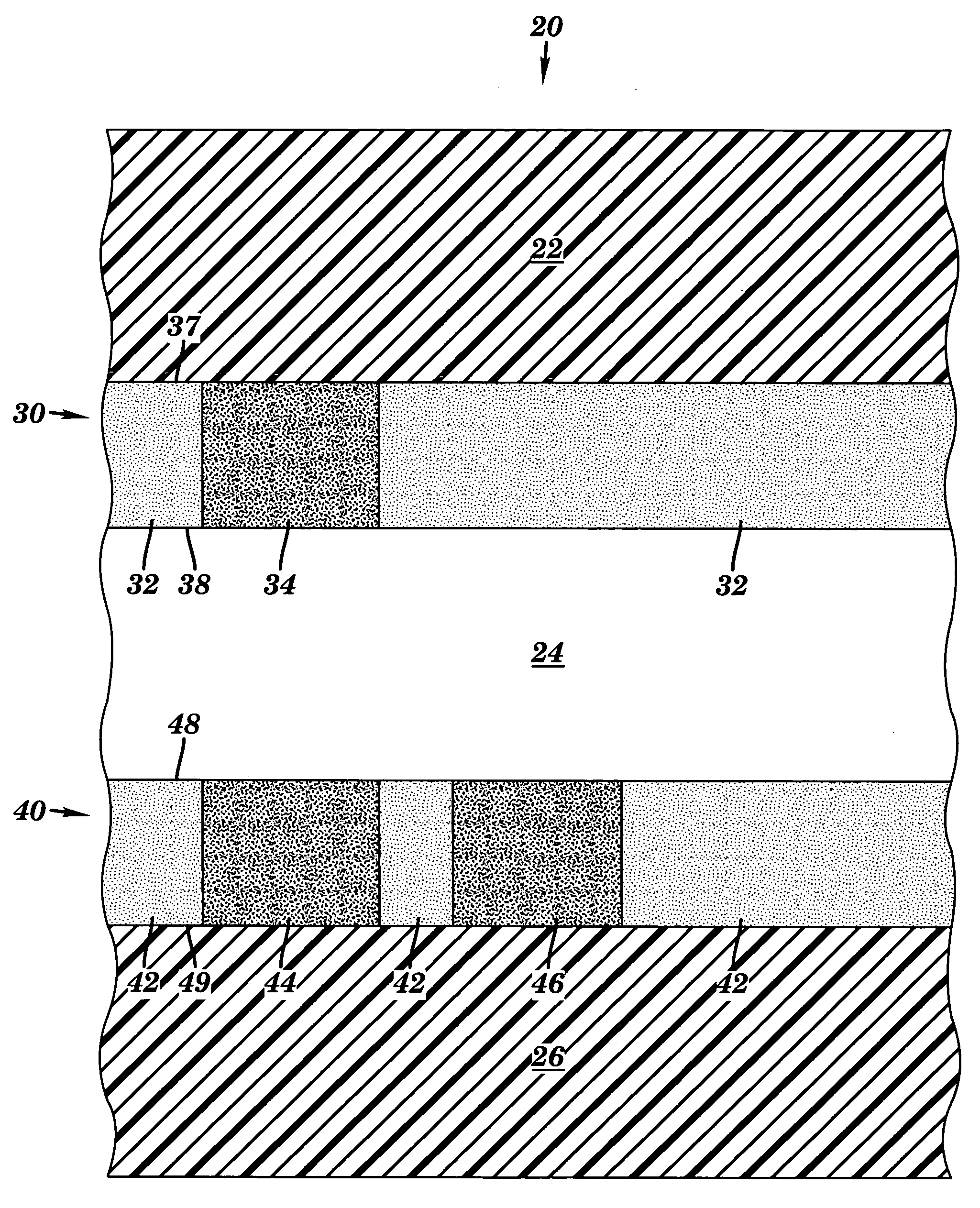

Multilayer printed circuit board and manufacturing method therefor

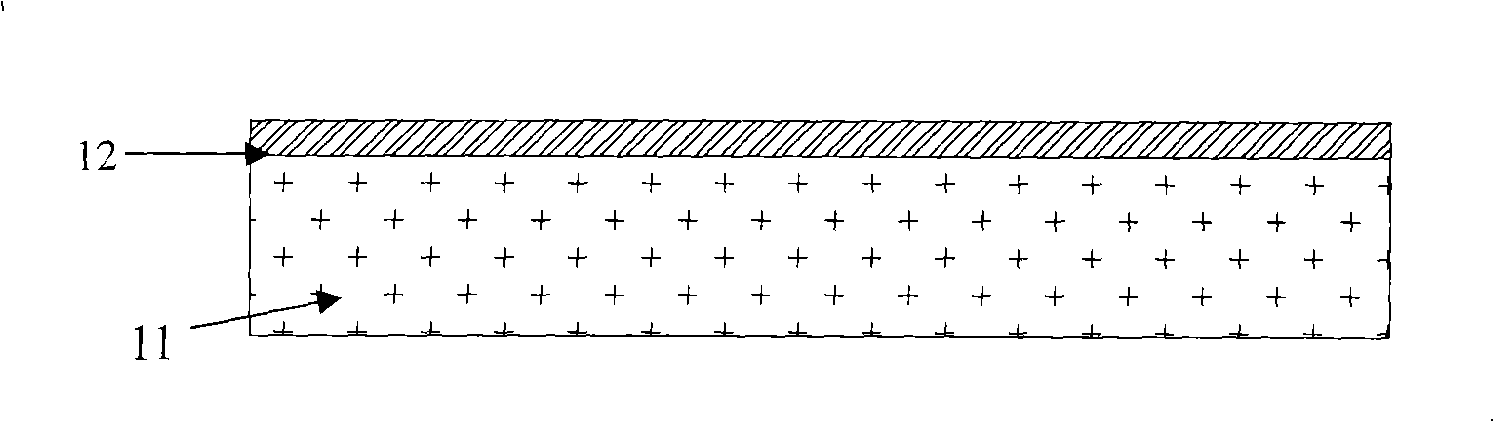

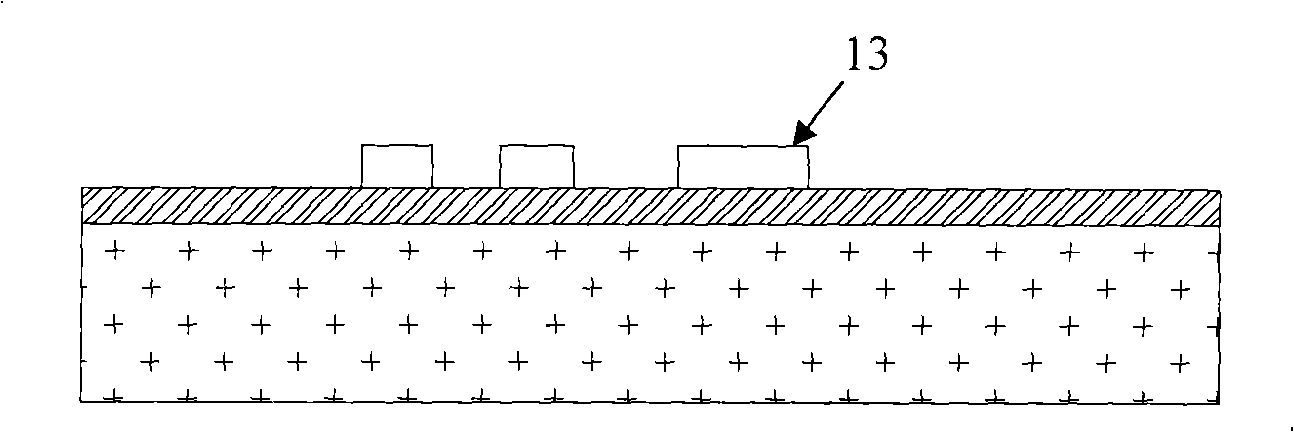

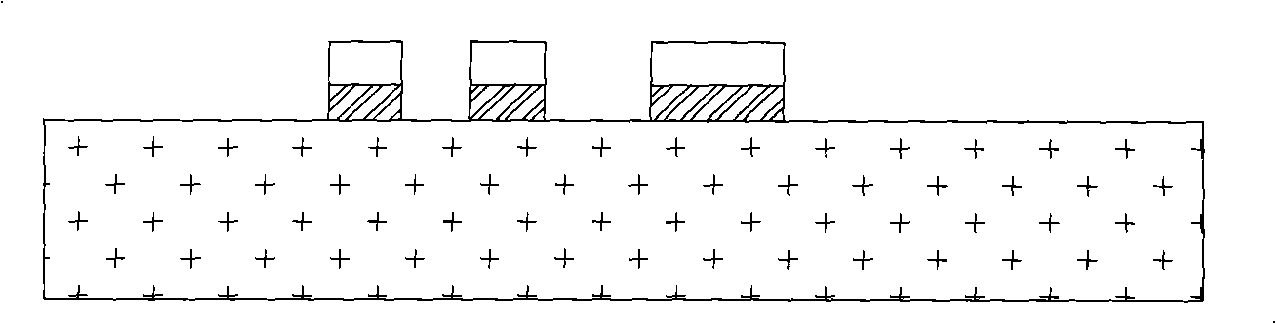

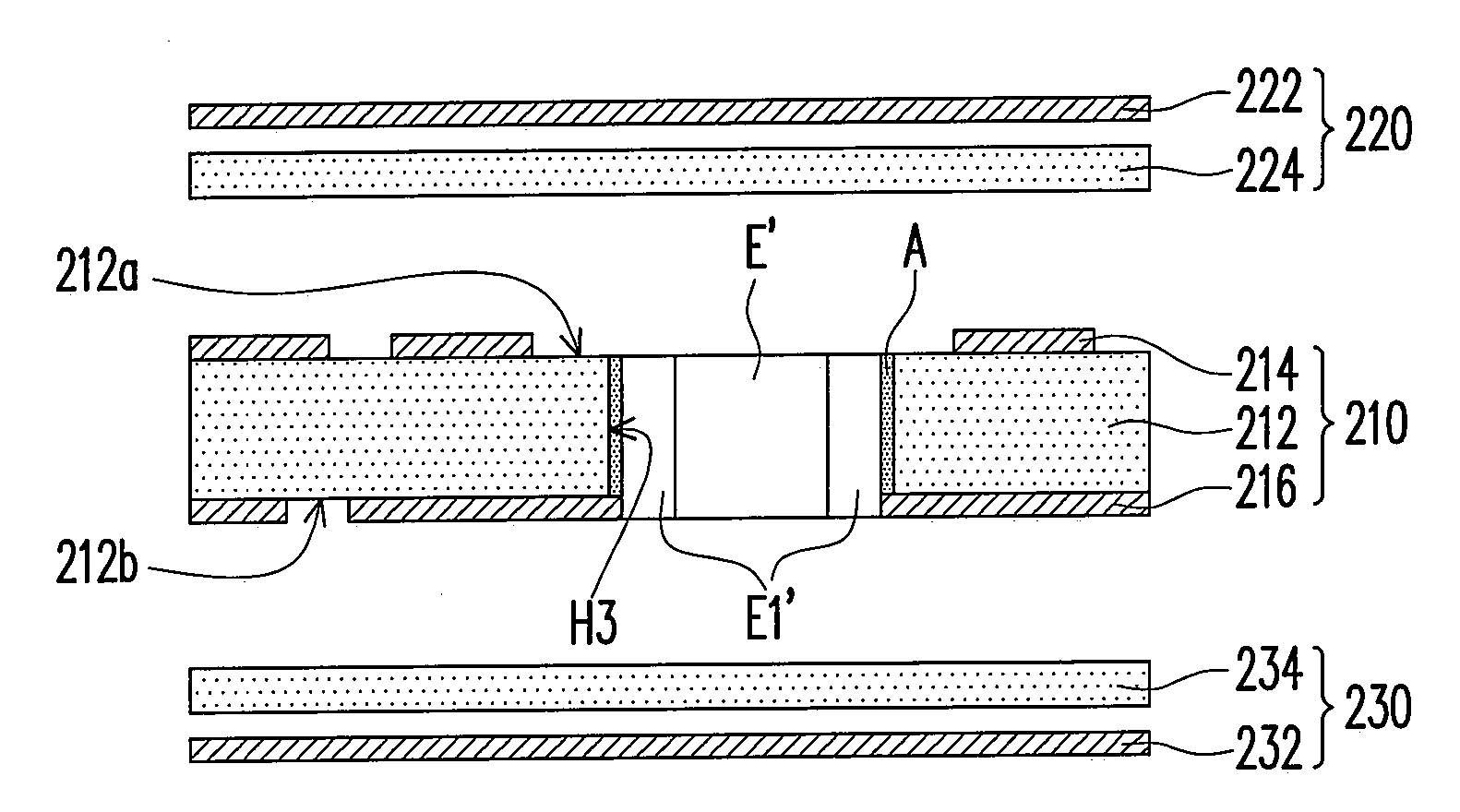

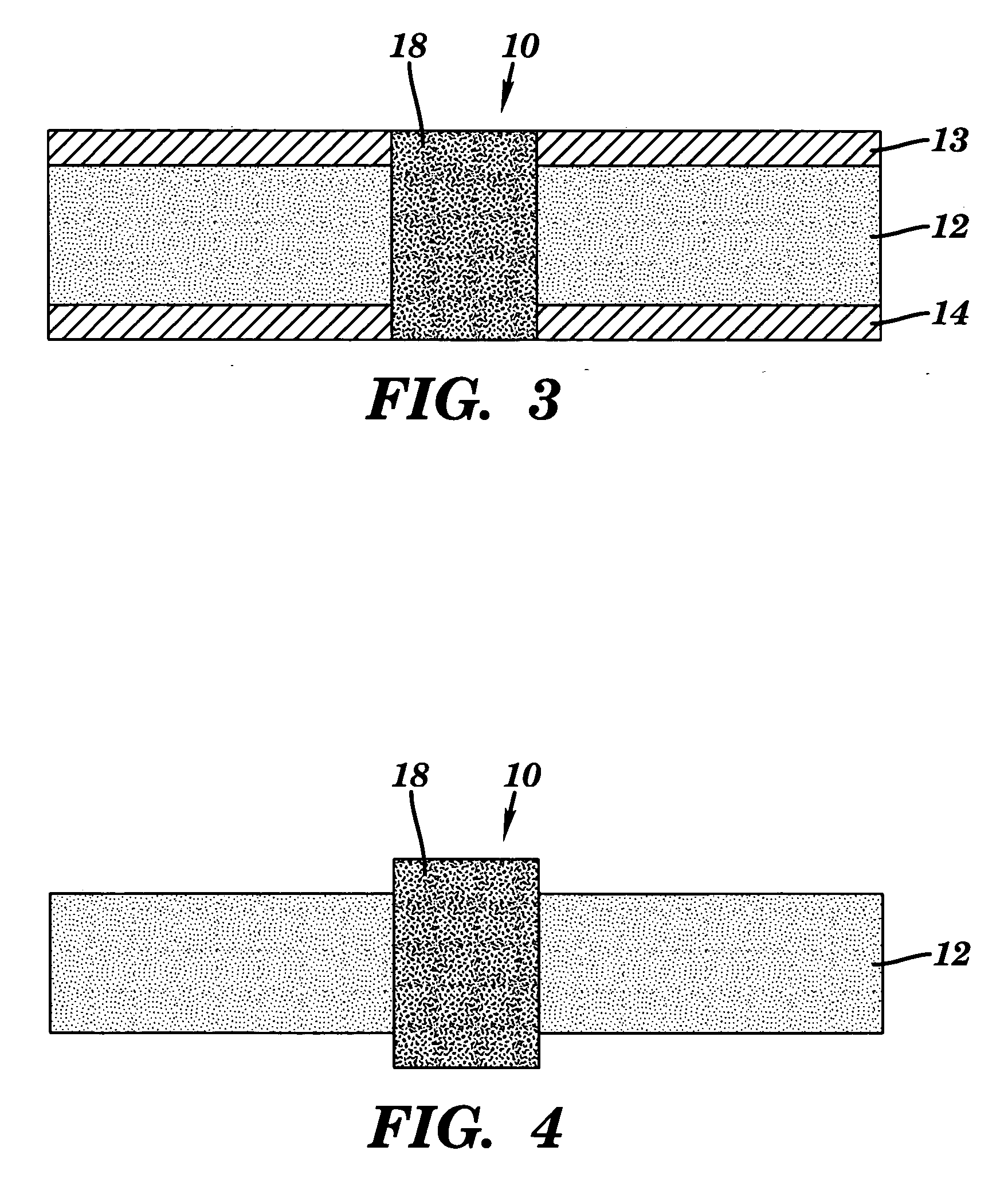

InactiveUS20130003314A1Reduce manufacturing costImprove routing densitySemiconductor/solid-state device detailsPrinted circuit aspectsSmall form factorEngineering

Provided is a substrate wherein wiring layers laminated onto the top and bottom surfaces of a core layer are connected to each other by a simple means. Also provided is a method for manufacturing said substrate. In the provided substrate (10A), a connection substrate (13) is placed in a removed region (12) which goes all the way through a part of a thick core layer (11). Said connection substrate (13) electrically connects a first wiring layer (16A) laminated onto the top surface of the core layer (11) to a second wiring layer (16B) laminated onto the bottom surface of the core layer (11). This eliminates the requirement of providing a through-hole through the core layer (11) for each connection, resulting in a small form-factor substrate (10A) with a high wiring density.

Owner:SANYO ELECTRIC CO LTD

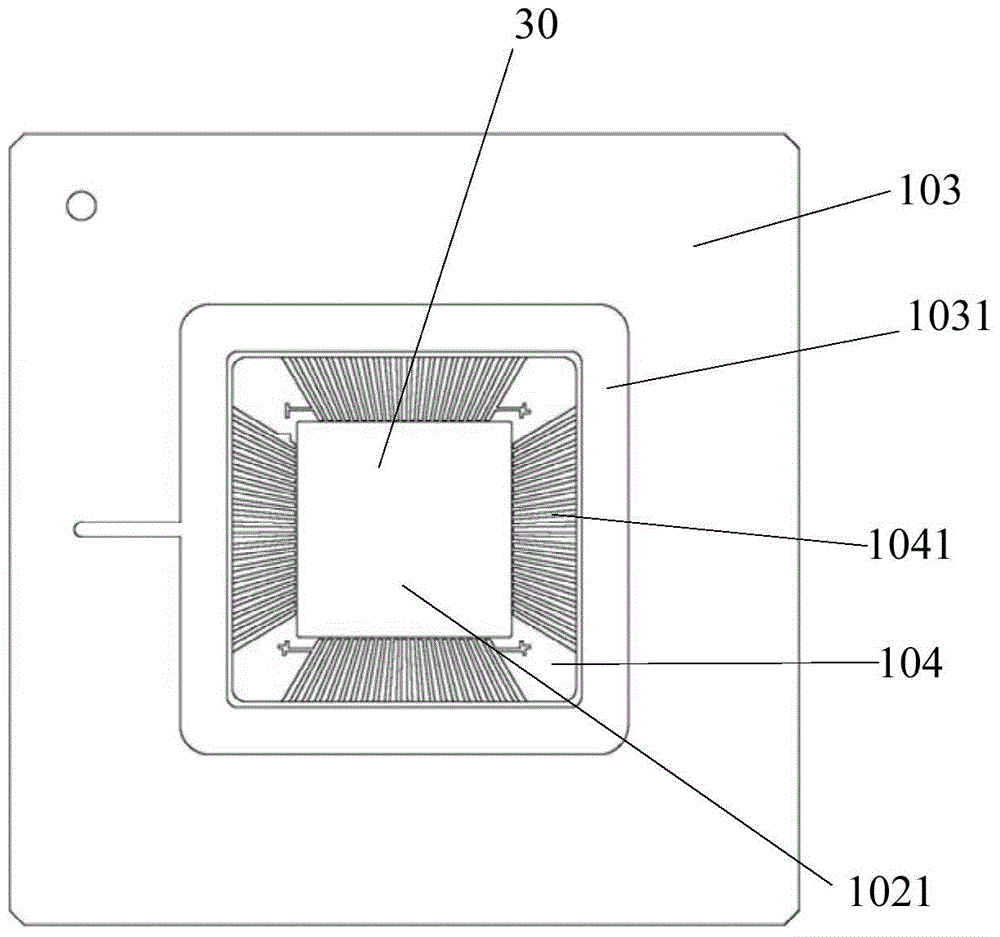

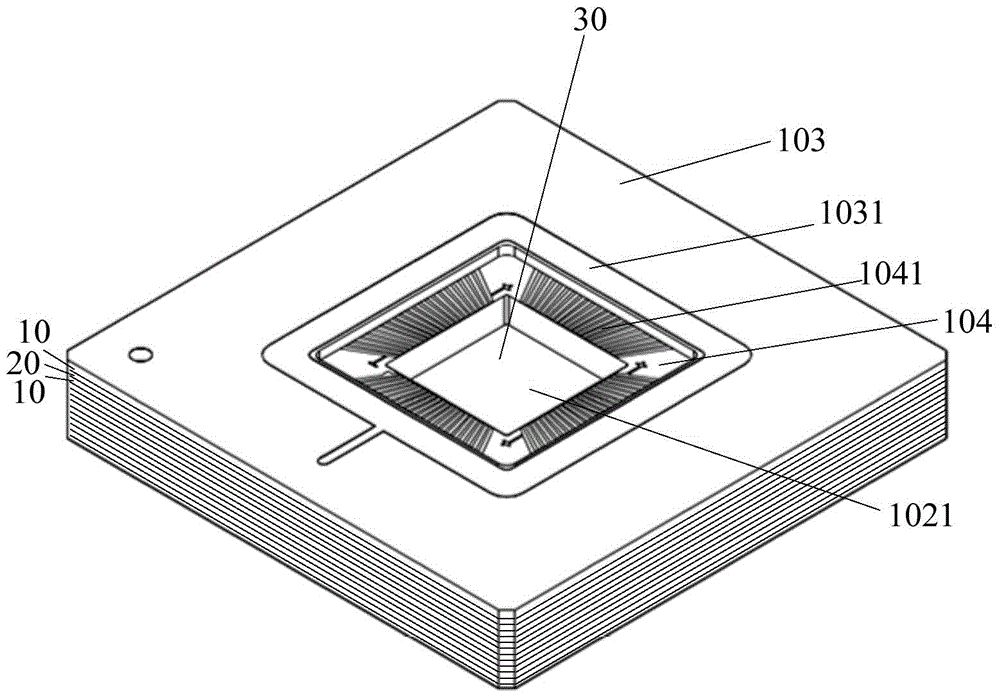

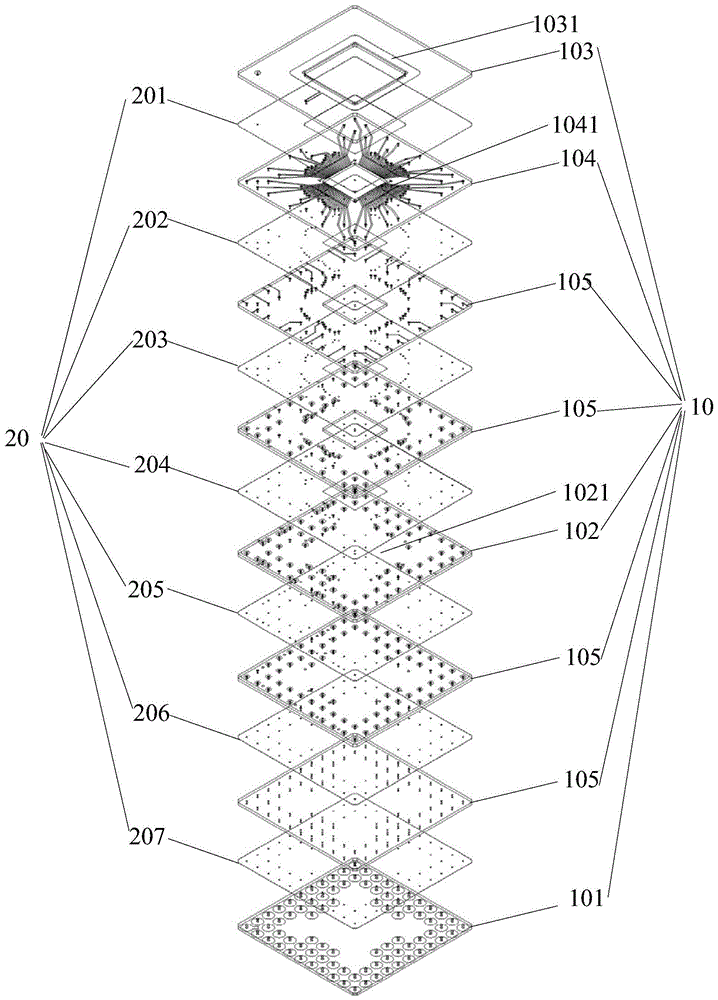

Packaging shell and preparation method based on lcp substrate

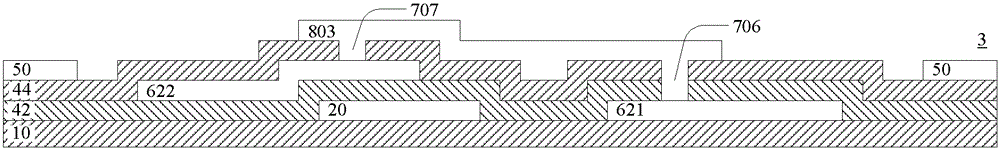

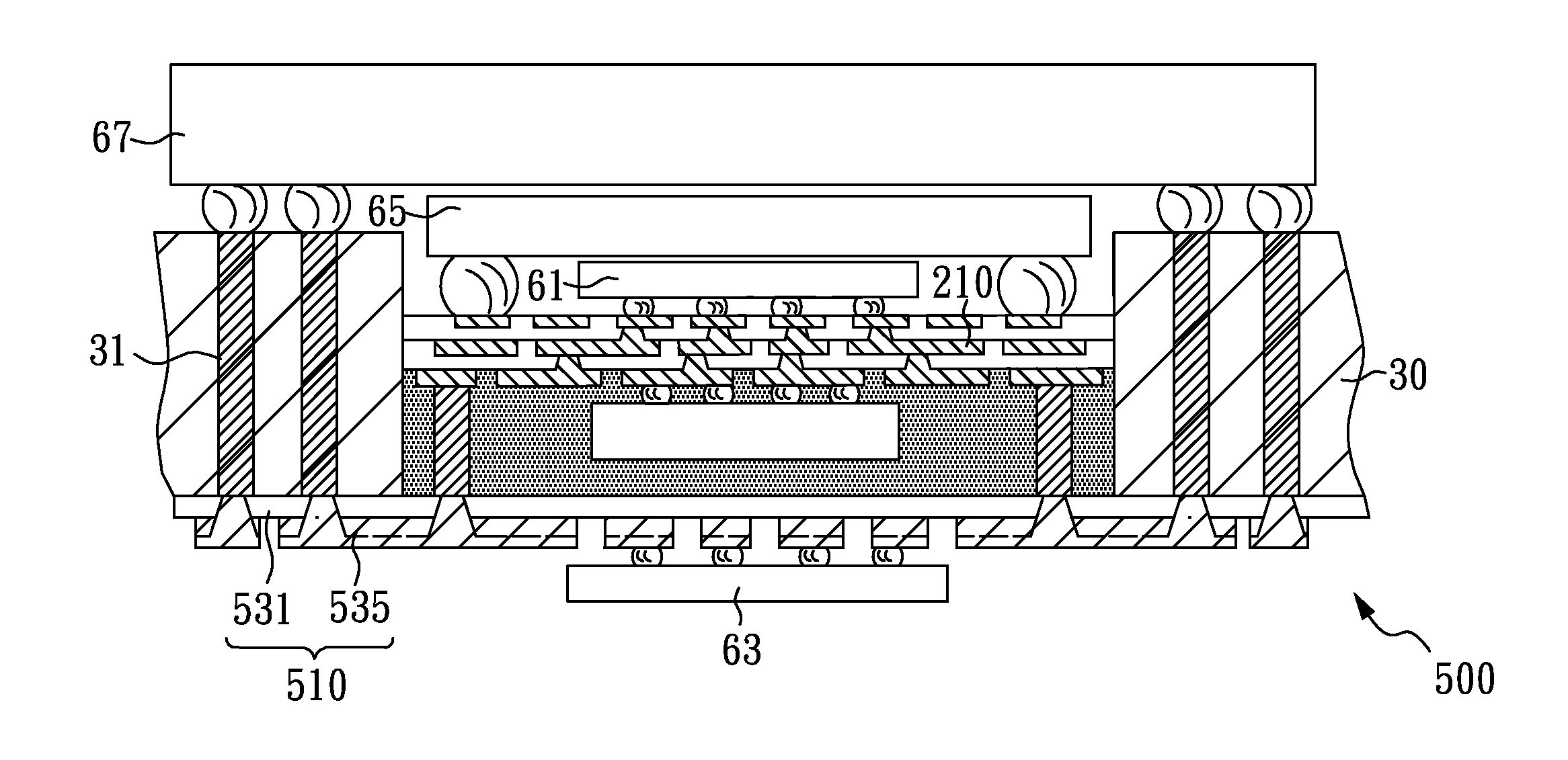

ActiveCN104282632BLow dielectric constantImprove routing densitySemiconductor/solid-state device detailsSolid-state devicesEngineeringInterconnection

The invention provides a packaging shell based on an LCP substrate. The packaging shell comprises a lamination structure formed by laminating multiple LCP substrate composition layers; adjacent LCP substrate composition layers are combined through intermediate bonding layers; each LCP substrate composition layer comprises a bottom bonding pad layer located on the bottommost layer of the lamination structure, a chip mounting layer located in the middle of the lamination structure, a sealing layer located on the top layer of the lamination structure and a keying layer under the sealing layer; each LCP substrate composition layer further comprises at least one wiring interconnection layer arranged between the bottom bonding pad layer and the chip mounting layer and at least one wiring interconnection layer arranged between the keying layer and the chip mounting layer; all the layers of the lamination structure are electrically connected through via holes; each chip mounting layer is provided with a chip adhesion region, the positions, corresponding to the chip adhesion regions, of all the other layers above the chip mounting layers are provided with openings, and all the layers are stacked together to form a cavity used for containing a chip. The packaging shell has excellent high-frequency characteristics and air tightness.

Owner:WUXI ZHONGWEI GAOKE ELECTRONICS

Processing method of ultra-thin core board in manufacturing of printed circuit board or integrated circuit package substrate

ActiveCN101541145ALow costIncrease productivitySemiconductor/solid-state device manufacturingMultilayer circuit manufactureElectrical conductorEngineering

A processing method of thin core board in manufacturing of printed circuit board or integrated circuit package substrate comprises the followings: copper foil and bonding sheet, two core boards are used for laminating and thermocompression bonding to obtain a processing board with periphery being bonded, and the thickness and strength thereof can satisfy the processing requirements of conventional devices; pattern conversion processing is carried out on the bonded processing board; laminating method is carried out on newly formed conductor line pattern surface, insulating medium and conductor line are formed through laminating, laser beam drilling, plating and pattern conversion technology; the previous processes are repeated to form multilayer processing boards; when two sides of multilayer processing boards reaches certain thickness and strength, the multilayer processing boards are incised at the bonding joint to form two processing boards; conventional laminating, drilling, plating and pattern conversion technologies are adopted to process the two processing boards respectively until the manufacturing of the needed circuit board and package substrate is finished. The invention needs no special device or processing tool to process thin core board, thus greatly reducing cost and improving productivity and yield of the product.

Owner:SHANGHAI MEADVILLE SCI & TECH

Array substrate, display panel, display device and manufacturing method of array substrate

InactiveCN105068349AAvoid crosstalkIncrease opening ratioSolid-state devicesSemiconductor/solid-state device manufacturingData linesDisplay device

The invention relates to the technical field of display and provides an array substrate, a display panel, a display device and a manufacturing method of the array substrate. The array substrate comprises grid lines and data lines insulated from one another on a lining substrate intersecting with each other to limit a plurality of sub pixel units. A thin film transistor and a pixel electrode are formed in each sub pixel unit. Each data line comprises a first data line body and a second data line body arranged between two columns of the corresponding adjacent sub pixel units side by side. In every two columns of the adjacent sub pixel units, the sub pixel units on the odd number line are connected with the corresponding first data line bodies, the sub pixel units on the even number line are connected with the corresponding second data line bodies, and at least part of first data line bodies and the adjacent second data line bodies are arranged on different layers between every two adjacent sub pixel units. According to the array substrate, the display panel, the display device and the manufacturing method of the array substrate, at least part of the first data lines and the adjacent corresponding second data lines are arranged on the different layers, and the short circuit between double data lines is solved.

Owner:BOE TECH GRP CO LTD +1

Manufacturing method of novel printed circuit board

ActiveCN101790288AAvoid the problem of low binding forceImprove routing densityPrinted element electric connection formationElectrical conductorInterconnection

The invention relates to a manufacturing method of a novel printed circuit board, which can form fine circuits and laminated interconnection based on the improved semi-additive process and the process of pore filling under pattern plating. The specific steps of the method are as follows: a) preparing a dielectric layer and laminating a conductive layer on the dielectric layer, thereby forming a substrate of a composite structure with the dielectric layer and the conductive layer; b) manufacturing conduction blind holes on the dielectric layer and the conductive layer; c) carrying out conduction treatment for the conductive layer and the walls of the conduction blind holes, thereby forming a seed layer; d) adhering a light-sensitive film to the surface of the substrate and forming a plated blocking layer on the substrate through pattern transfer; e) plating the substrate with the plated blocking layer, forming a conductor pattern, and filling the conduction blind holes through plating, thereby forming a solid conductive pole; f) removing the plated blocking layer; g) removing the exposed seed layer and the conductive layer below the seed layer, and reserving the conductor pattern and circuits formed through plating, thereby forming a circuit board; and h) repeating the steps from Step a) to Step g) on the circuit board, so as to realize the multi-layer superposition.

Owner:SHANGHAI MEADVILLE SCI & TECH

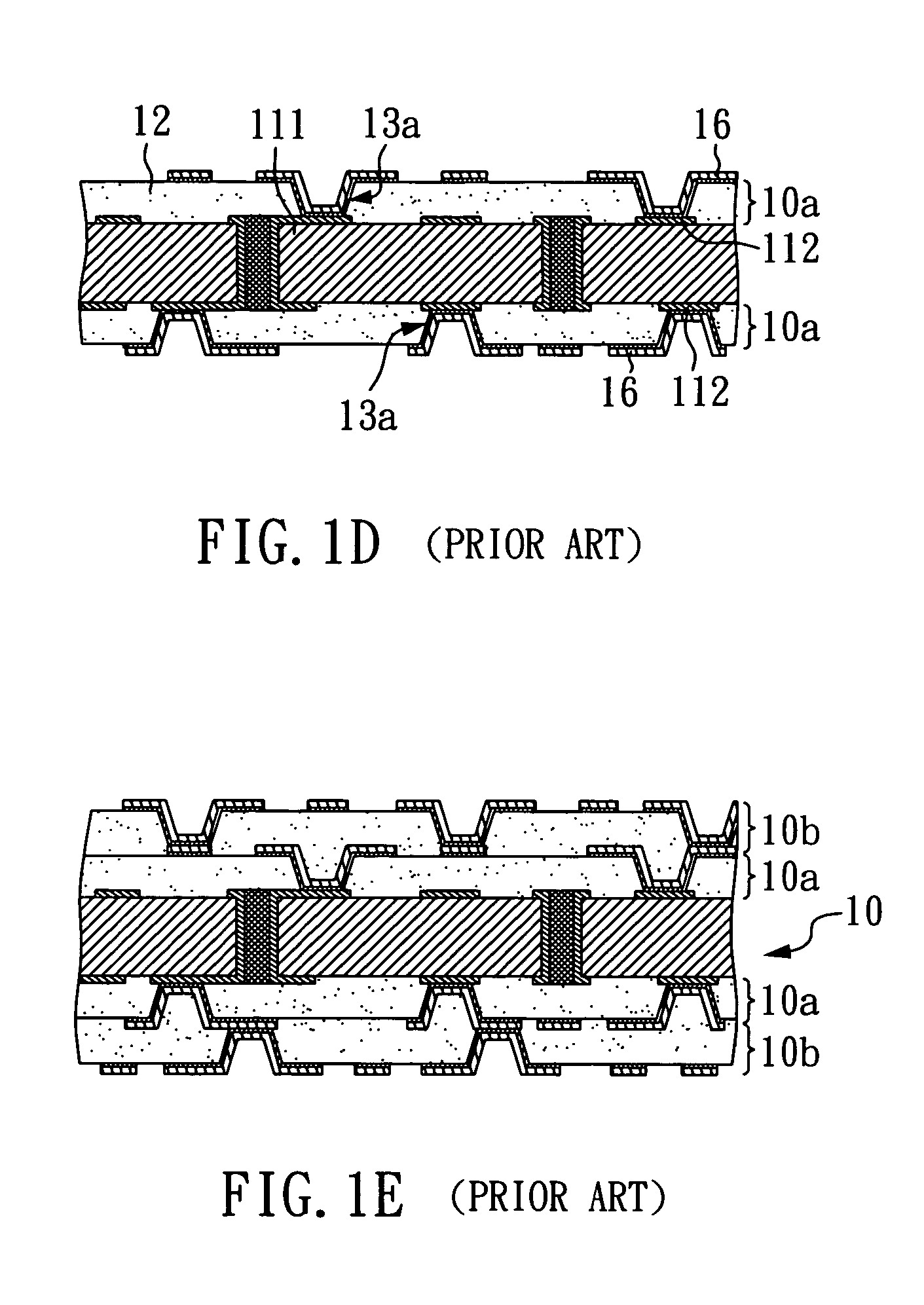

Method of manufacturing a coreless package substrate and conductive structure of the substrate

InactiveUS20070246744A1Reduce thicknessImprove routing densitySemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskHigh density

A method of manufacturing a coreless package substrate together with a conductive structure of the substrate is disclosed. The method can produce a coreless package substrate which comprises: at least a built-up structure having a first solder mask and a second solder mask, wherein a plurality of openings are formed in the first and second solder mask to expose the conductive pads of the built-up structure; and a plurality of solder bumps as well as solder layers formed on the conductive pads. Therefore, the invention can produce the coreless package substrate with high density of circuit layout, less manufacturing steps, and small size.

Owner:PHOENIX PRECISION TECH CORP

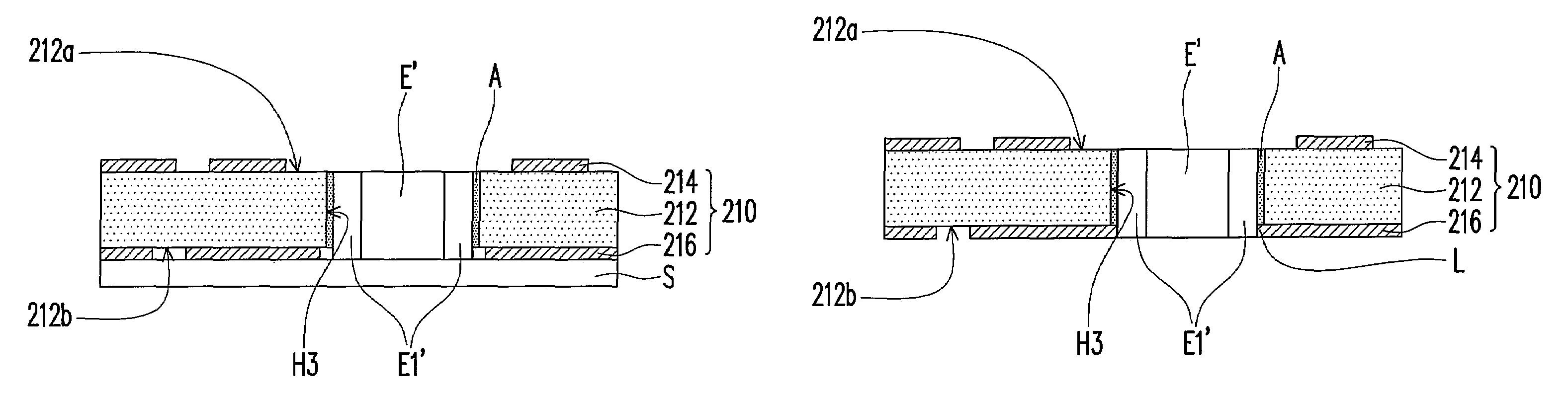

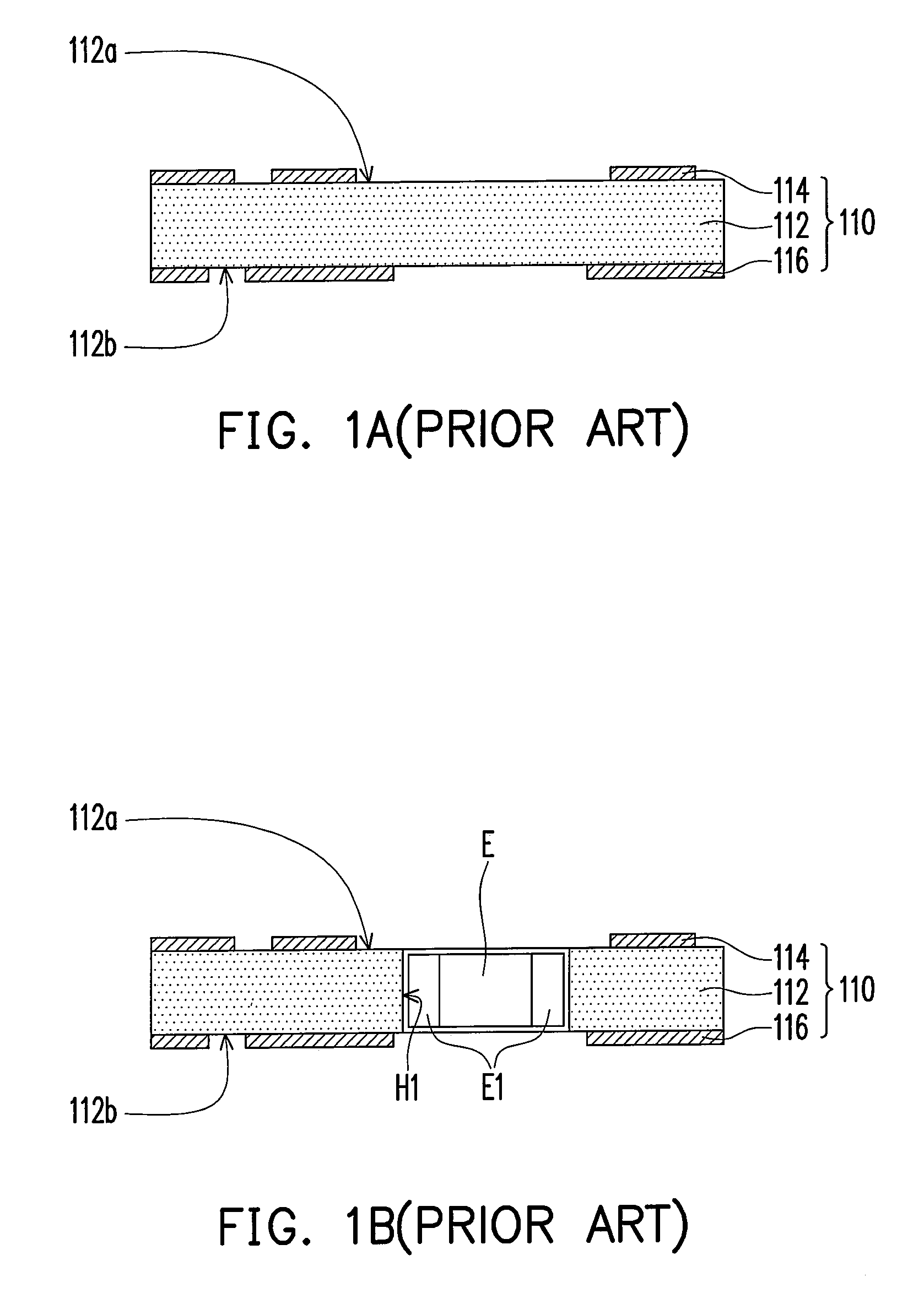

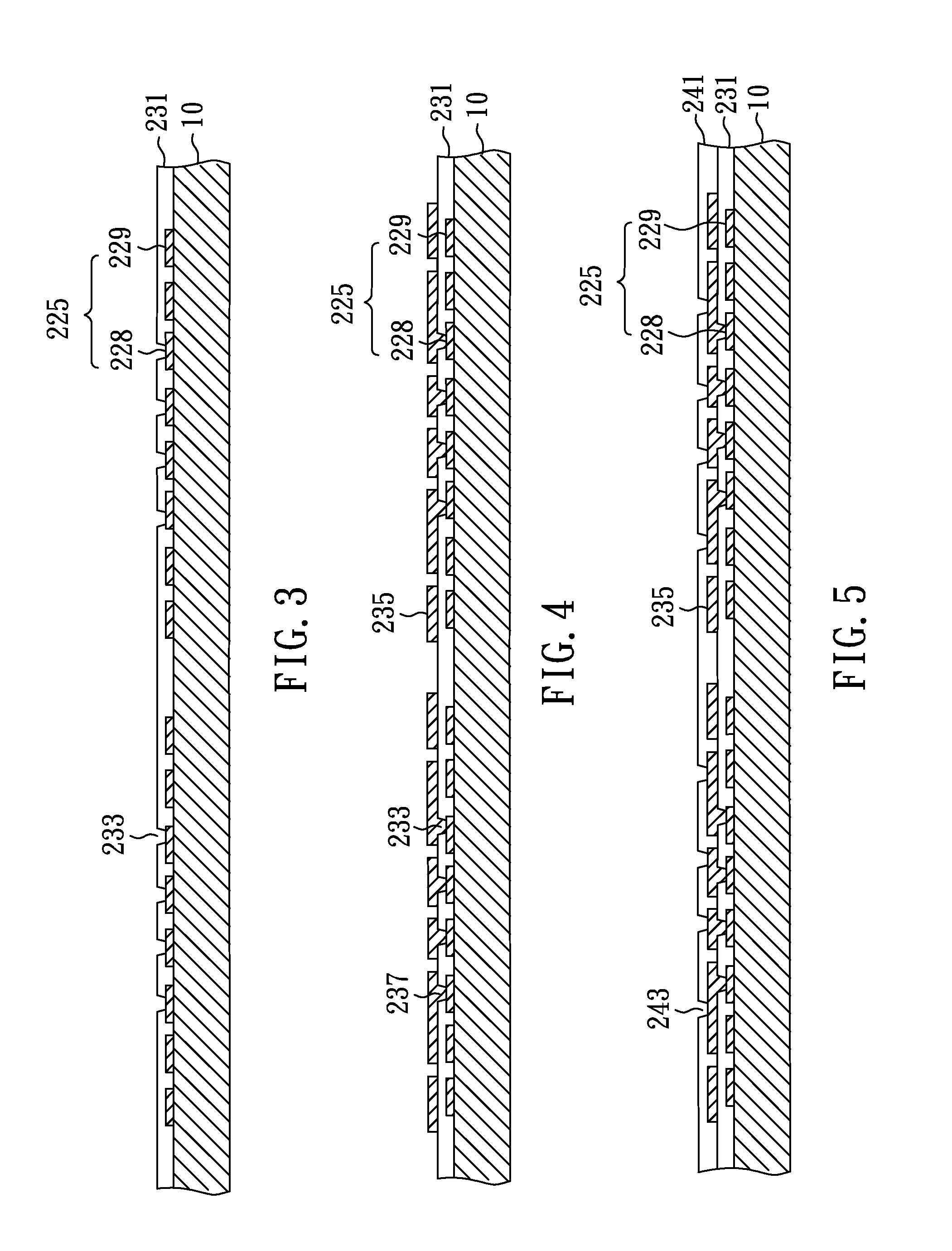

Method of fabricating substrate with embedded component therein

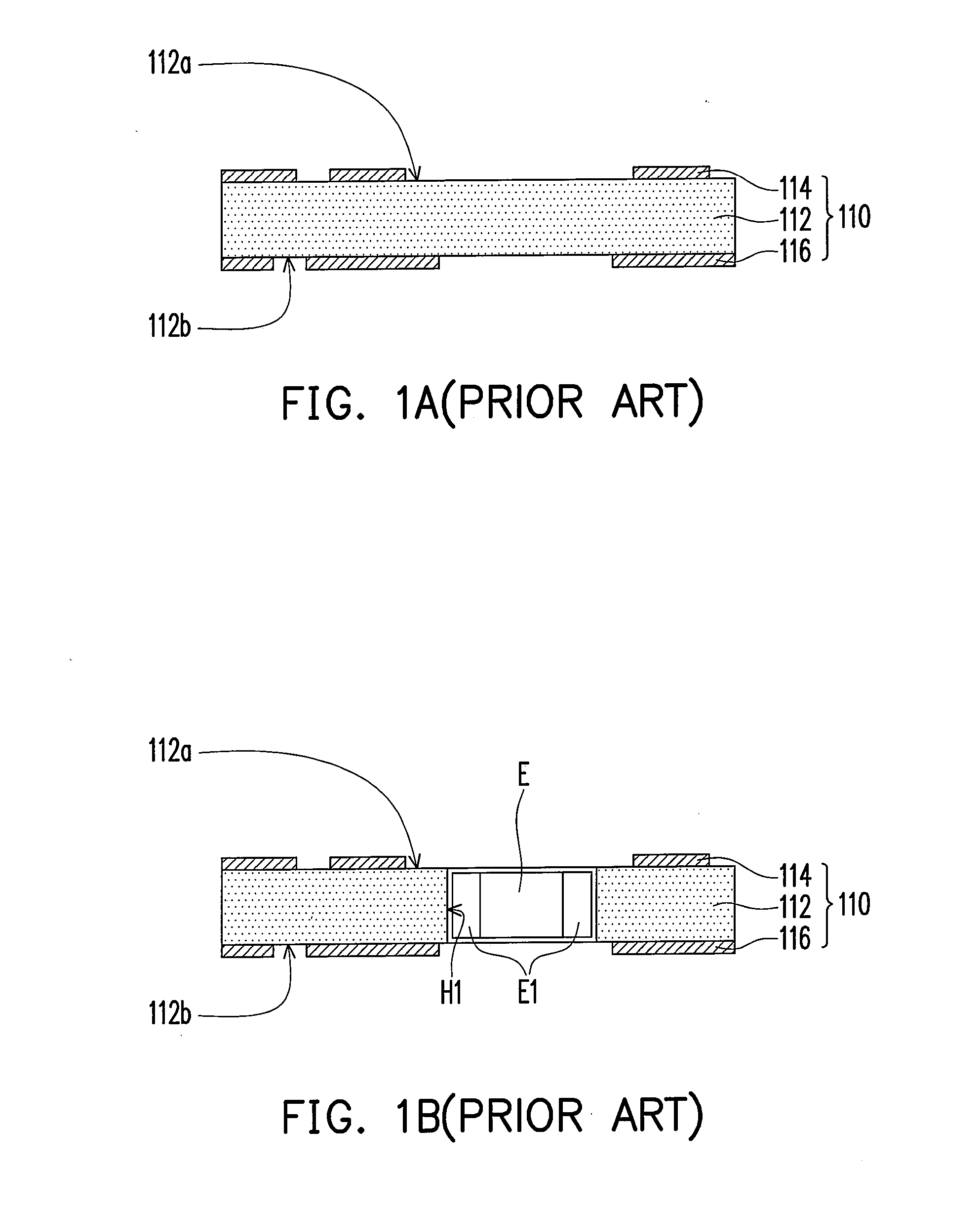

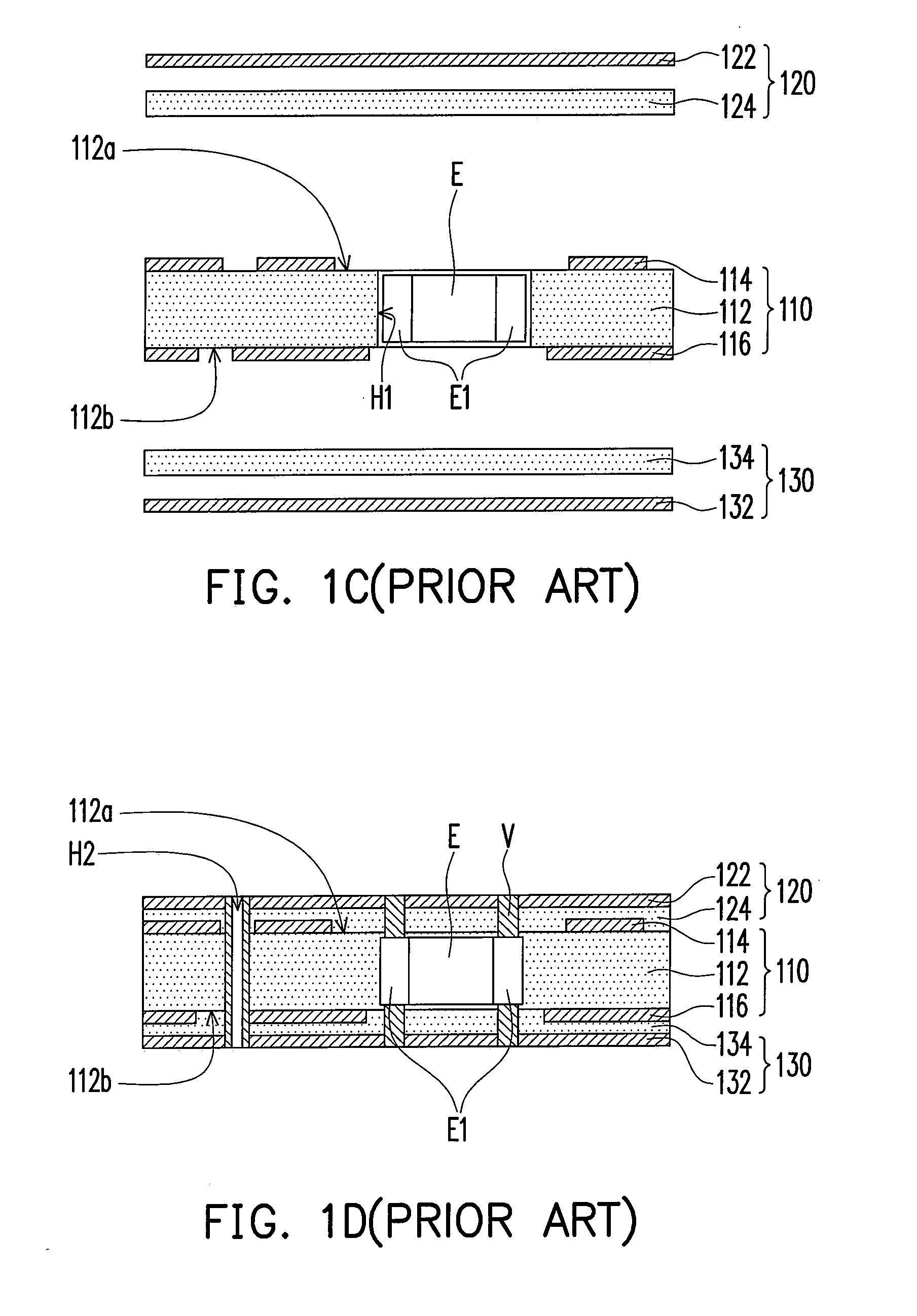

ActiveUS7550320B2Reduce thicknessImprove routing densityFinal product manufacturePrinted circuit aspectsDielectric layerMaterials science

A method of fabricating a substrate with an embedded component therein including the following steps is provided. First, a core layer having a first dielectric layer, a first patterned circuit layer, and a second patterned circuit layer is provided. The first patterned circuit layer and the second patterned circuit layer are disposed on an upper surface and a lower surface of the first dielectric layer, respectively. Then, a through hole is formed in the core layer. Next, the core layer is arranged on a supporting board and an embedded component having at least one electrode is disposed in the through hole. Afterward, a process of filling glue is carried out, such that the embedded component is fixed in the through hole. Thereafter, the supporting board is removed. Finally, the electrode of the embedded component is electrically connected to the second patterned circuit layer.

Owner:ADVANCED SEMICON ENG INC

Coreless package substrate with conductive structures

InactiveUS7626270B2Reduce thicknessImprove routing densitySemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskHigh density

A method of manufacturing a coreless package substrate together with a conductive structure of the substrate is disclosed. The method can produce a coreless package substrate which comprises: at least a built-up structure having a first solder mask and a second solder mask, wherein a plurality of openings are formed in the first and second solder mask to expose the conductive pads of the built-up structure; and a plurality of solder bumps as well as solder layers formed on the conductive pads. Therefore, the invention can produce the coreless package substrate with high density of circuit layout, less manufacturing steps, and small size.

Owner:PHOENIX PRECISION TECH CORP

Double-surface pressing connecting through hole structure of printed-circuit board and machining method thereof

ActiveCN103458627AEliminate parasitic capacitanceImprove integrityElectrical connection printed elementsPrinted element electric connection formationTinningCopper plating

The invention discloses a double-surface pressing connecting through hole structure of a printed-circuit board and a machining method of the double-surface pressing connecting through hole structure of the printed-circuit board. The machining method comprises the following steps that a small hole A is drilled in the upper surface of a substrate in a depth-control mode; a pressing connecting hole B is drilled in the same position of the small hole A; the substrate is overturned; a small hole C is drilled in the surface opposite to the small hole A in a depth-control mode and is communicated with the small hole A; a pressing connecting hole D is drilled in the position of the small hole C; electroless copper plating, copper electroplating and tinning are carried out; a hole E is drilled in the position of the small hole A in a depth-control mode; the substrate is overturned; a hole F is drilled in the position of the small hole C in a depth-control mode; alkaline etching and tin stripping are carried out; part of a copper layer at each pressing connecting hole is thickened in a plating mode until the design requirement of a finished product is met, and finally the double-surface pressing connecting through hole structure is obtained. The double-surface pressing connecting through hole structure of the printed-circuit board and the machining method of the double-surface pressing connecting through hole structure of the printed-circuit board completely eliminate the stray capacitance among pressing connecting elements, facilitates the integrality of signal transmission and improves wire distribution density; the process is reasonable, the difficulty that plating layers of the middle small holes are eliminated in a drilling mode is largely lowered, and the diameter of the pressing connecting holes is made to be the smallest; the completeness of the plating layers on the walls of the pressing connecting holes is guaranteed, and the non-metallic middle small holes are achieved; copper wire defects in the holes are avoided.

Owner:SHANTOU ULTRASONIC PRINTED BOARD NO 2 FACTORY +1

Method of fabricating substrate with embedded component therein

ActiveUS20070190686A1Increase wiring densityReduce thicknessFinal product manufacturePrinted circuit aspectsMaterials scienceDielectric layer

A method of fabricating a substrate with an embedded component therein including the following steps is provided. First, a core layer having a first dielectric layer, a first patterned circuit layer, and a second patterned circuit layer is provided. The first patterned circuit layer and the second patterned circuit layer are disposed on an upper surface and a lower surface of the first dielectric layer, respectively. Then, a through hole is formed in the core layer. Next, the core layer is arranged on a supporting board and an embedded component having at least one electrode is disposed in the through hole. Afterward, a process of filling glue is carried out, such that the embedded component is fixed in the through hole. Thereafter, the supporting board is removed. Finally, the electrode of the embedded component is electrically connected to the second patterned circuit layer.

Owner:ADVANCED SEMICON ENG INC

Flowable compositions and use in filling vias and plated through-holes

InactiveUS6427325B1Improve routing densityCleanliness or solderability of the unfilled plated through-hole barrelsCeramic layered productsGlass/slag layered productsEngineeringPrinted circuit board

A printed circuit board or card having plated through-holes is provided wherein plated through-holes are filled with a photocured polymerized composition. Also, a method for fabricating these printed circuit boards or cards is provided. Also provided are compositions and methods of providing carrier films coated with the compositions for use in filling vias or plated through-holes.

Owner:INT BUSINESS MASCH CORP

Two-board-in-one processing method for substrate manufacture of printed circuit board or integrated circuit package

InactiveCN101359601ALow costIncrease productivitySemiconductor/solid-state device manufacturingMultilayer circuit manufactureElectrical conductorProcess patterns

Disclosed is a method for combining two plates in the fabrication process of an enclosure baseplate of a printed circuit or an integrated circuit. The method includes the following steps: splicing two chip plates through a bonding sheet so as to make a machining plate which is big in thickness, higher in rigidity and can satisfy common equipment machining requirements; processing pattern transfer to the spliced machining plate and developing a necessary circuit diagram of a conductor on the surface of the machining plate; developing an insulating medium layer and a conducting copper layer on the surface of the newly developed circuit diagram of the conductor through the method of lamination; repeating above processes so as to form a multilayer machining plate; separating the machining plate at two sides of the splicing sheet from the splicing sheet after the machining plate reaches certain thickness and rigidity, thus forming two machining plates; and respectively processing the two machining plates through regular lamination, boring, electroplating and pattern transfer techniques until the necessary circuit board and the enclosure baseplate are finished. The method requires no special equipment or machining tools and can reduce cost by a large margin and improve production efficiency and yield.

Owner:SHANGHAI MEADVILLE SCI & TECH +2

Wiring structure, multilayer wiring board, and electronic device

InactiveUS20070222052A1Facilitates impedance matchingHigh wiring densitySemiconductor/solid-state device detailsHigh frequency circuit adaptationsWave shapeSignal lines

A wiring structure includes a general signal line, a differential signal line having a pair of signal wiring lines and a reference potential layer. The signal wiring lines respectively transmit differential signals of which waveforms are inverted from each other. The reference potential layer is arranged to have a distance from the general signal line and the differential signal line, and has a non-formed portion in a region to be electromagnetically coupled to the differential signal line.

Owner:KYOCERA CORP

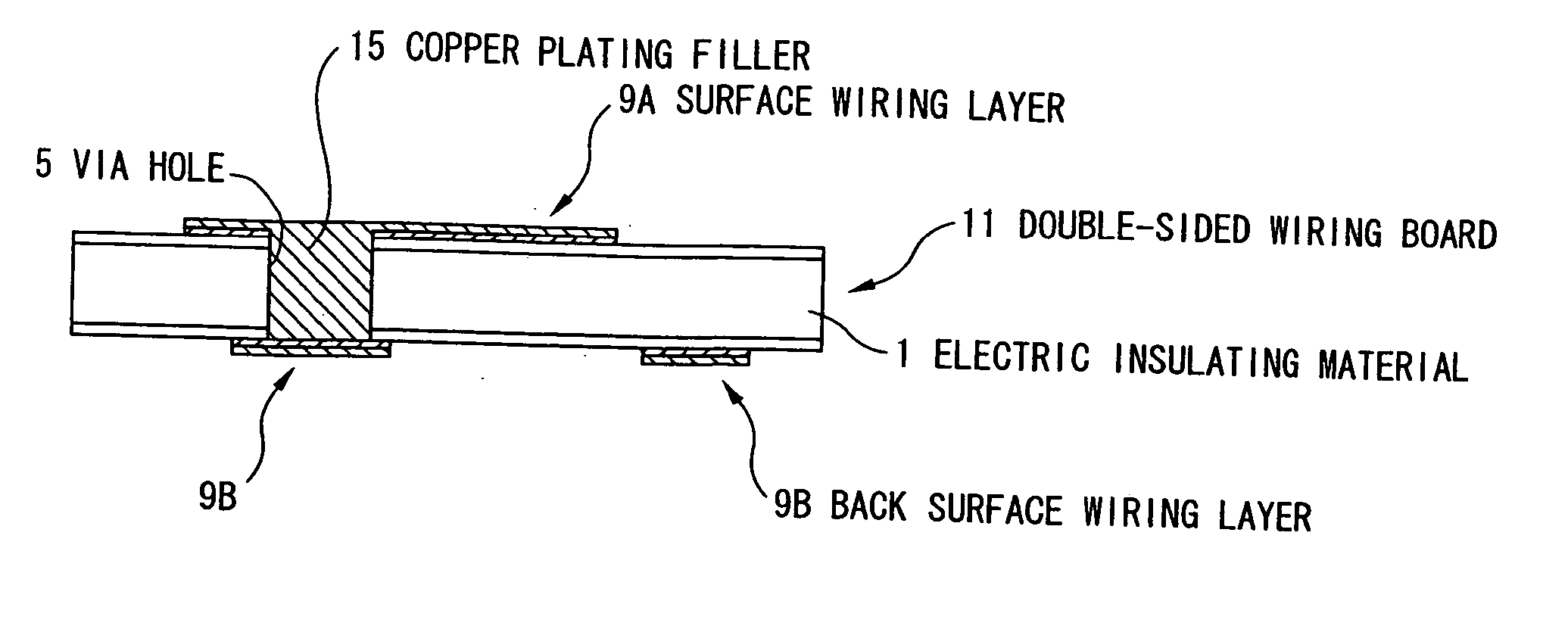

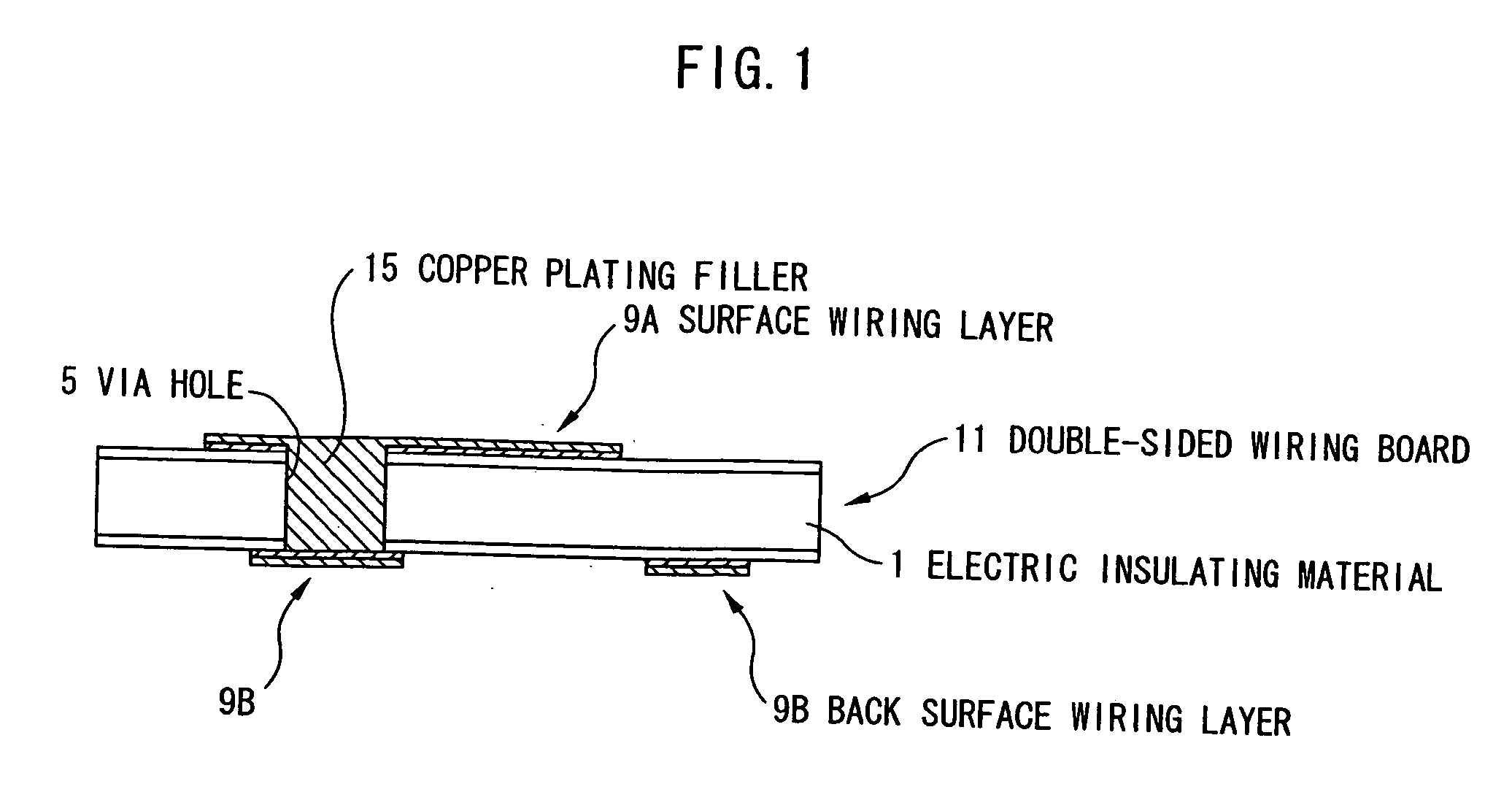

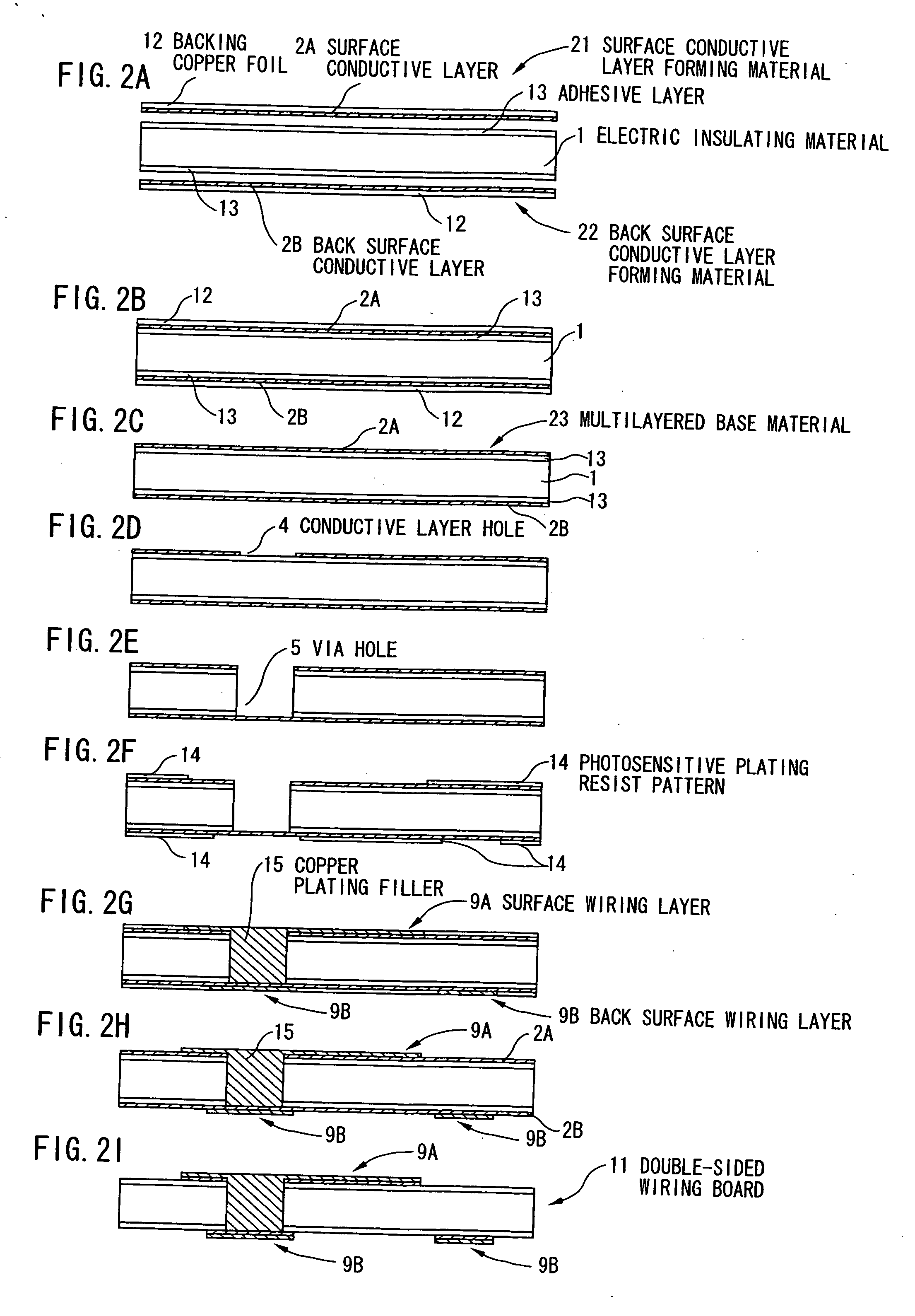

Method for fabricating a multilayer wiring board, multilayer wiring board, and electronic device using the same

InactiveUS20070034519A1Improve routing densityReduce manufacturing costPrinted circuit aspectsSolid-state devicesResistCopper plating

On both surfaces of an electric insulating material 1, a surface conductive layer 2A and a back surface conductive layer 2B are formed by transcription. Further, a via hole 5 penetrating through the surface conductive layer 2A and the electric insulating material 1 is provided. After forming a photosensitive plating resist pattern 14, the via hole 5 is filled with a copper plating filler 15, and the surface wiring layer 9A and the back surface wiring layer 9B are formed. Thereafter, the photosensitive plating resist pattern 14 as well as the surface conductive layer 2A and the back surface conductive layer 2B provided under the photosensitive plating resist pattern 14 are removed to fabricate a double-sided wiring board 11.

Owner:HITACHI CABLE +1

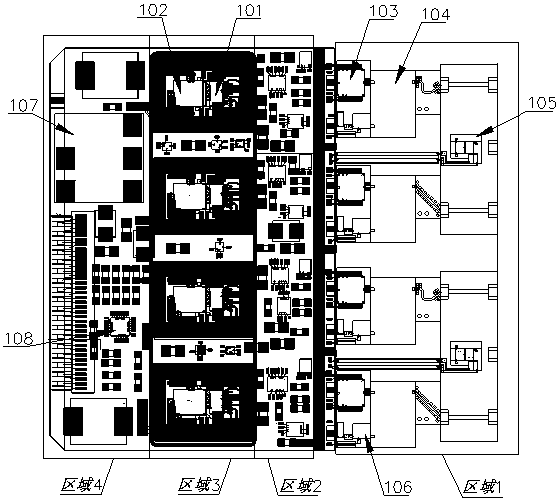

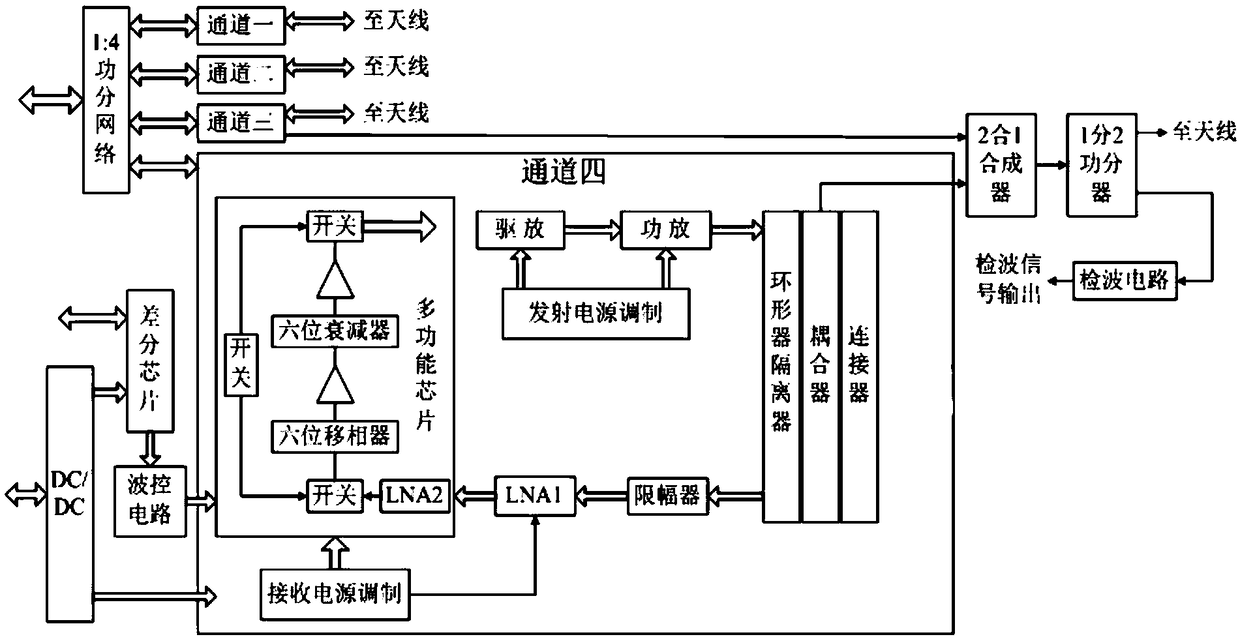

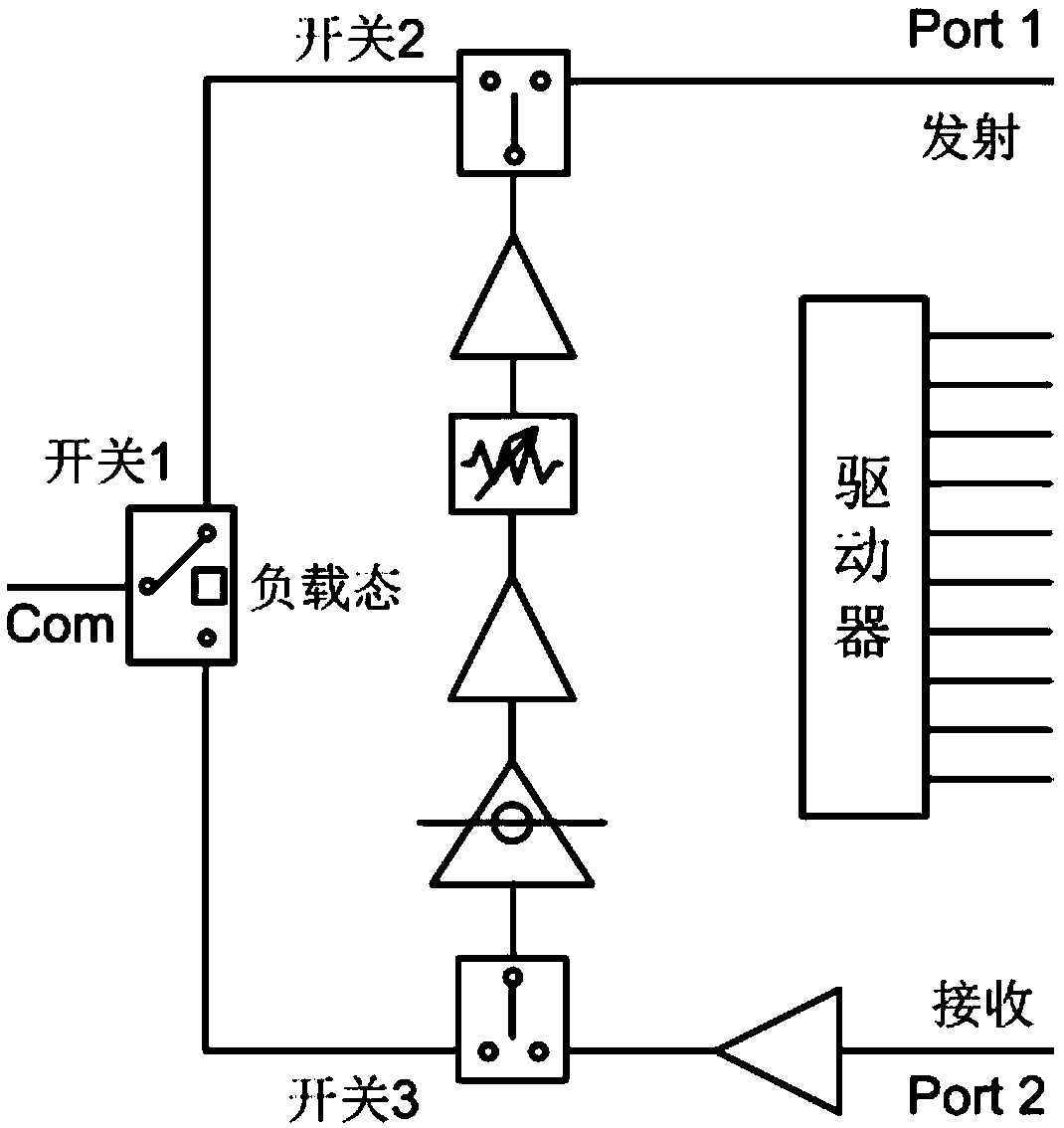

Four-channel microwave T/R module

The invention discloses a four-channel microwave T / R module. The four-channel microwave T / R module has a common cavity structure consisting of the same four independent T / R channels, wherein all the components are MMICs (Monolithic Microwave Integrated Circuits) being integrally fabricated on the same multilayer circuit board. The four-channel microwave T / R module is characterized in that a microwave device is a multifunctional MMIC bare chip integrated with a phase shifter, an attenuator, a working state switch, an amplitude limiting low noise amplifier and a driver; and the multi-layer circuit board is an HTCC multi-layer circuit board. The four-channel microwave T / R module has the advantages of compact structure, small size, high wiring density, low material cost, high mechanical strength, stable chemical performance, corrosion resistance, high temperature resistance, multiple channels, high performance, high reliability, high integration degree, light weight, low power consumptionand high heat dissipation characteristic, and can monitor the transmission and reception phases of each T / R channel. Compared with an existing microwave T / R module, the four-channel microwave T / R module has the advantages that the weight and volume of the microwave T / R module are reduced by 30 percent or more under the same function and index conditions. The four-channel microwave T / R module can be widely used in airborne, shipborne, spaceborne phased array radar and communication fields.

Owner:南京吉凯微波技术有限公司

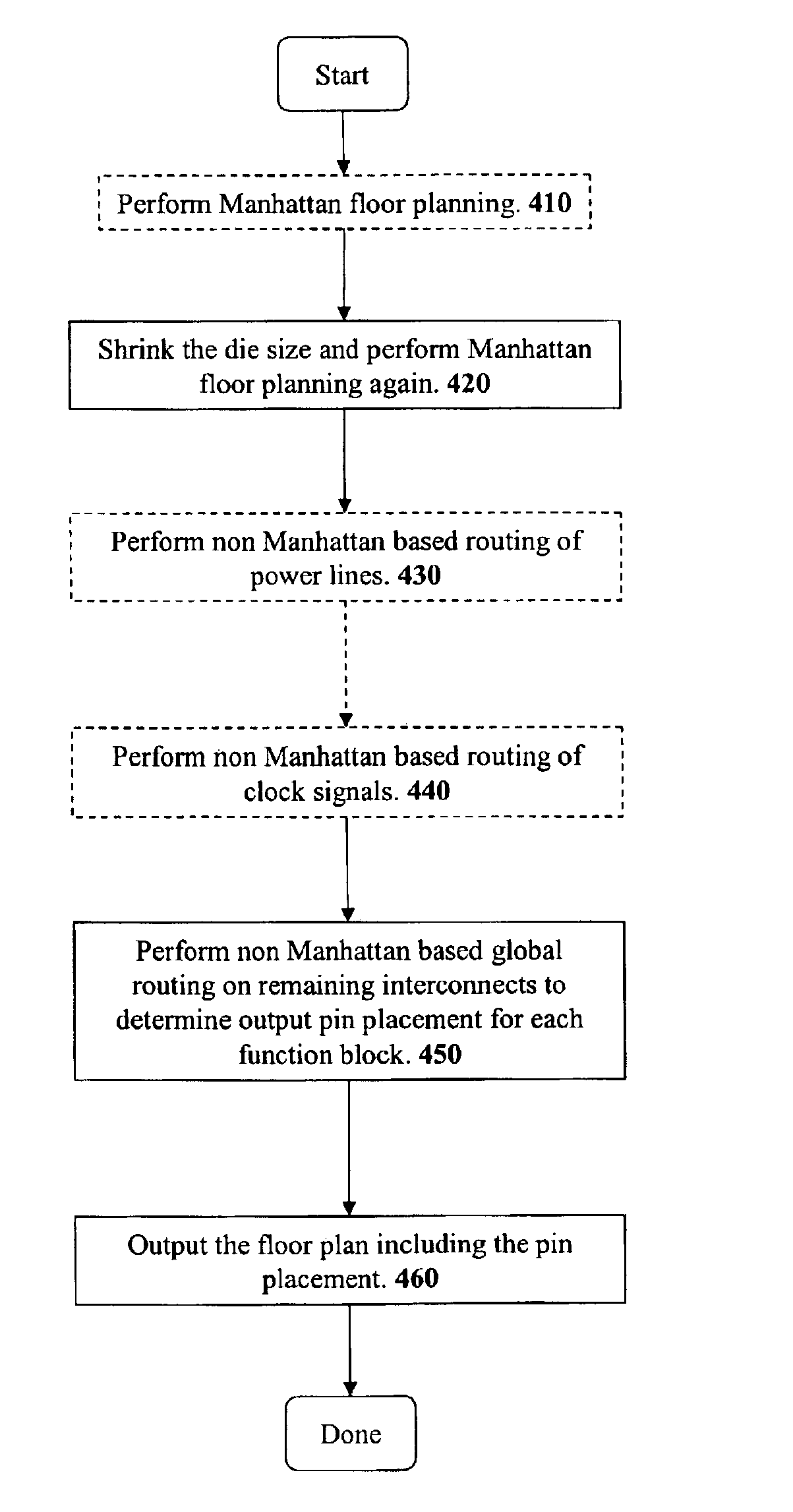

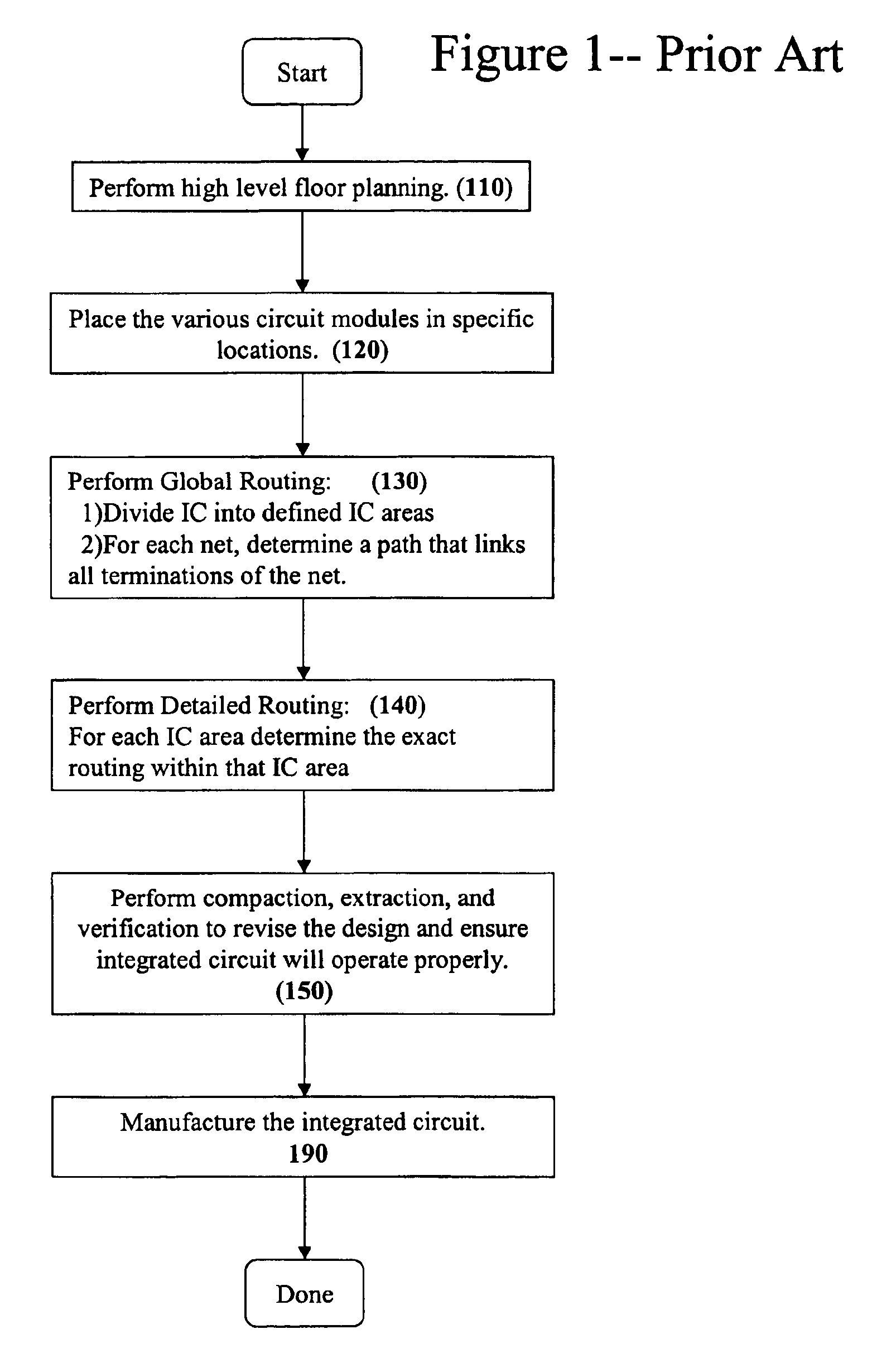

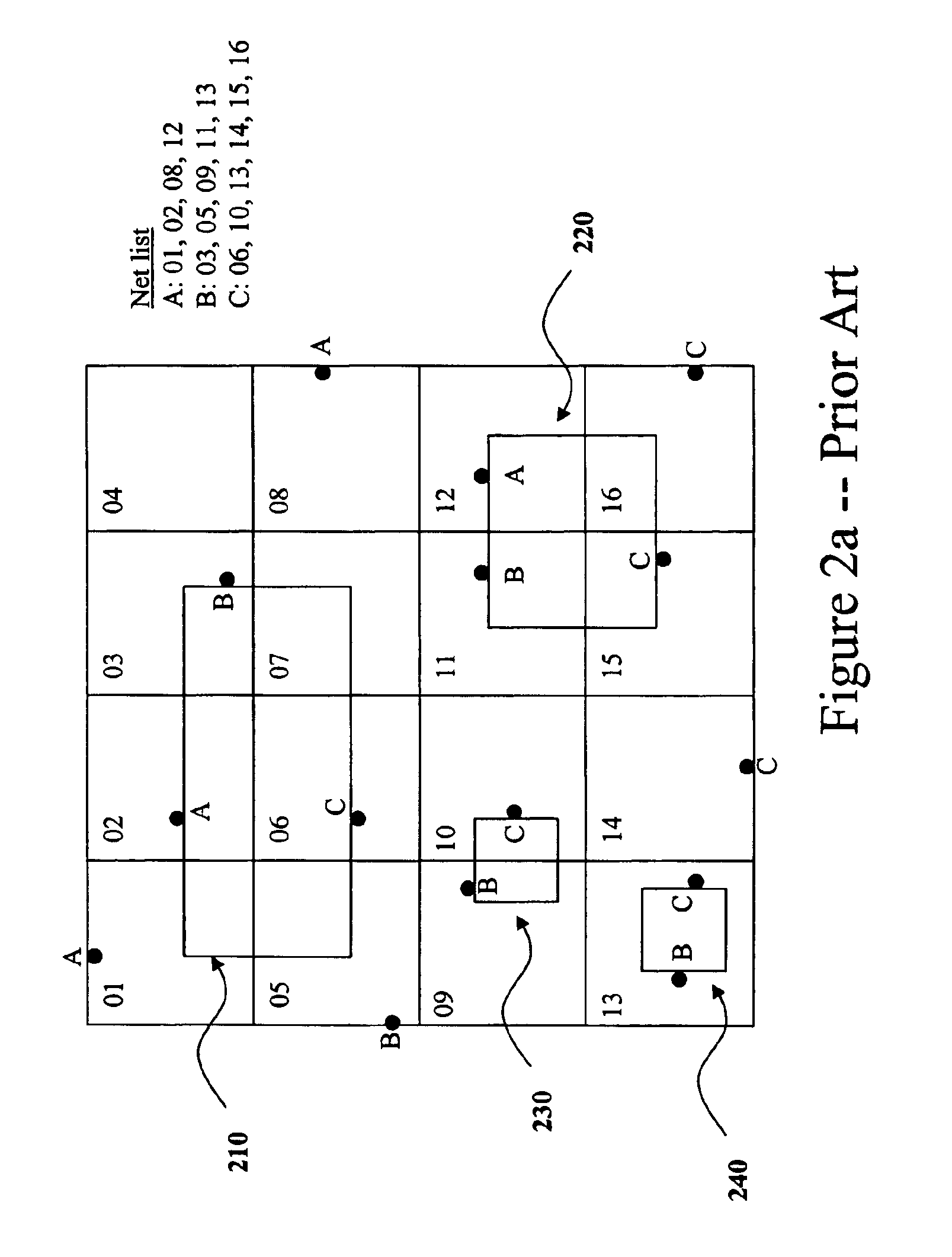

Method and system for floor planning non Manhattan semiconductor integrated circuits

InactiveUS6912704B1Improve routing densityDie sizeComputer aided designSoftware simulation/interpretation/emulationFloor planPost processor

The present invention introduces methods of creating floor plans and placements for non Manhattan integrated circuits with existing electronic design automation tools. To create a floor plan, an existing Manhattan based floor planning tool is used. The die size for the floor plan is reduced to take into account the improved wiring density of non Manhattan wiring. A non Manhattan global router is then used on the floor plan to create pin placements. The floor plan may create a floor plan having circuit modules with beveled corners to take advantage of diagonal wiring. To create a placement, an existing Manhattan based placer is first used to create an initial placement. The initial placement is then processed by a non Manhattan aware post processor. The post processor performs local optimizations on the initial placement to improve the placement for a non Manhattan routed integrated circuit.

Owner:CADENCE DESIGN SYST INC

Structure of circuit board and method for fabricating same

ActiveUS7906850B2Reduce thicknessImprove routing densitySemiconductor/solid-state device detailsSolid-state devicesBoard structureDielectric layer

Owner:UNIMICRON TECH CORP

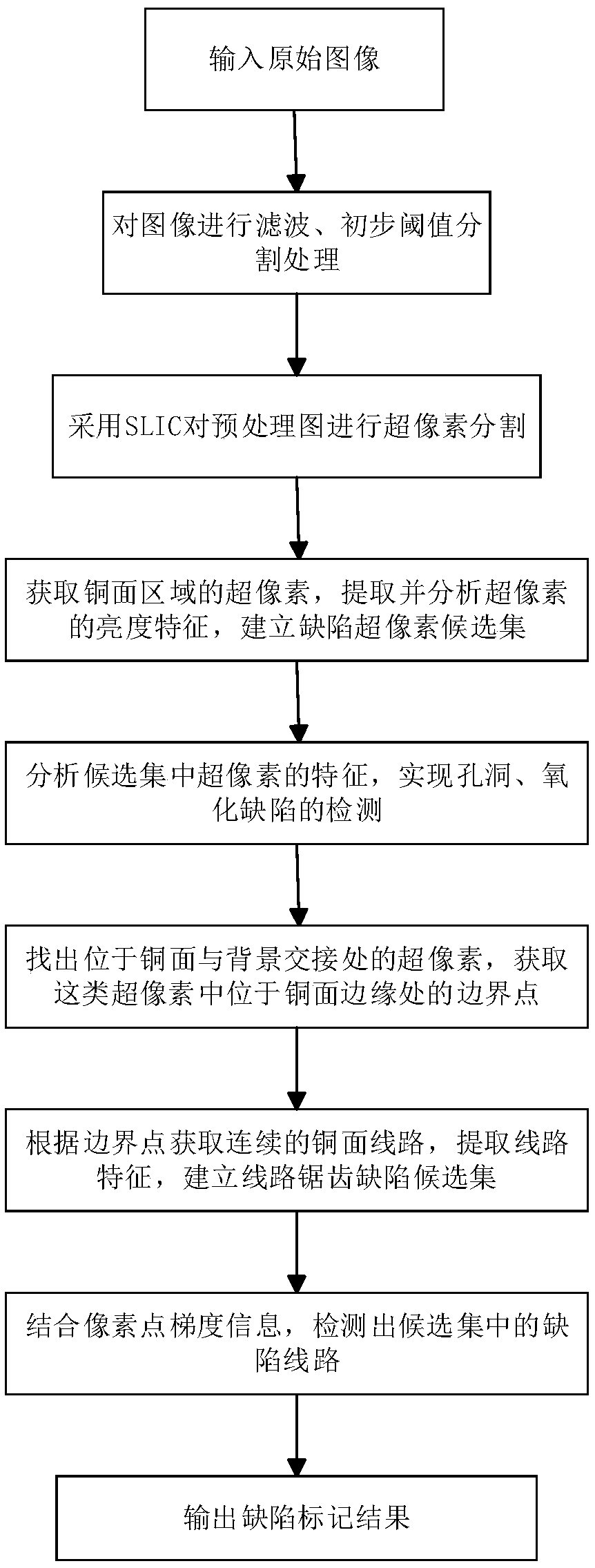

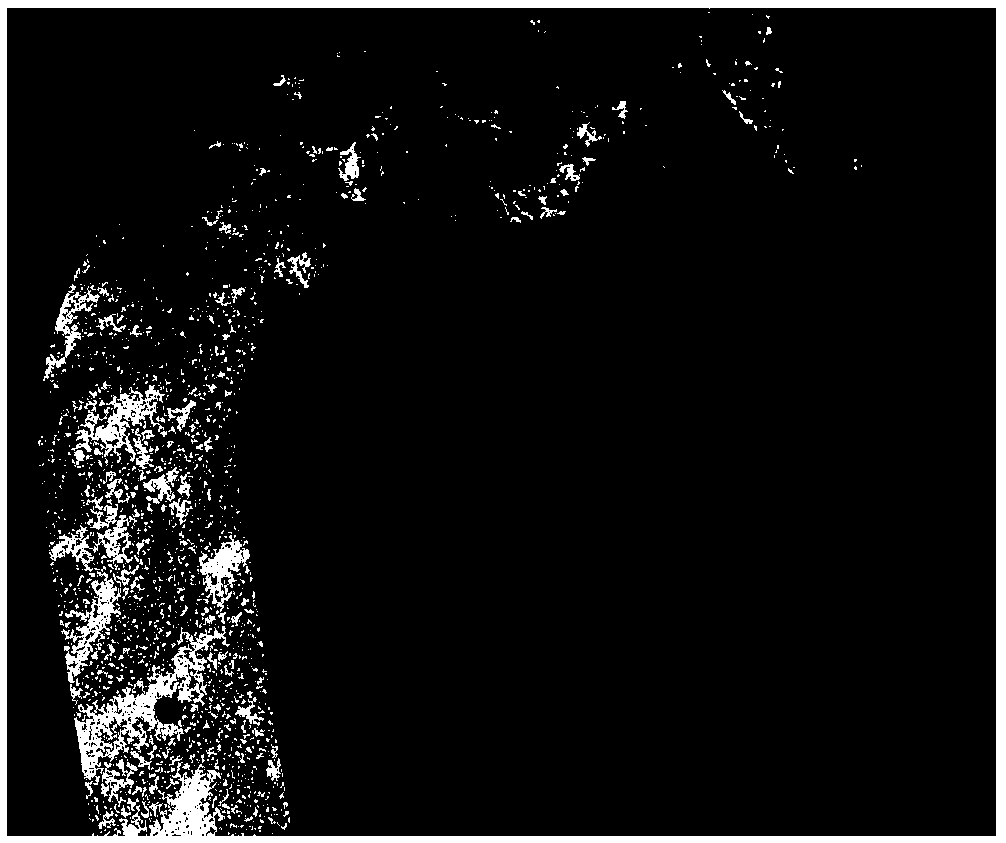

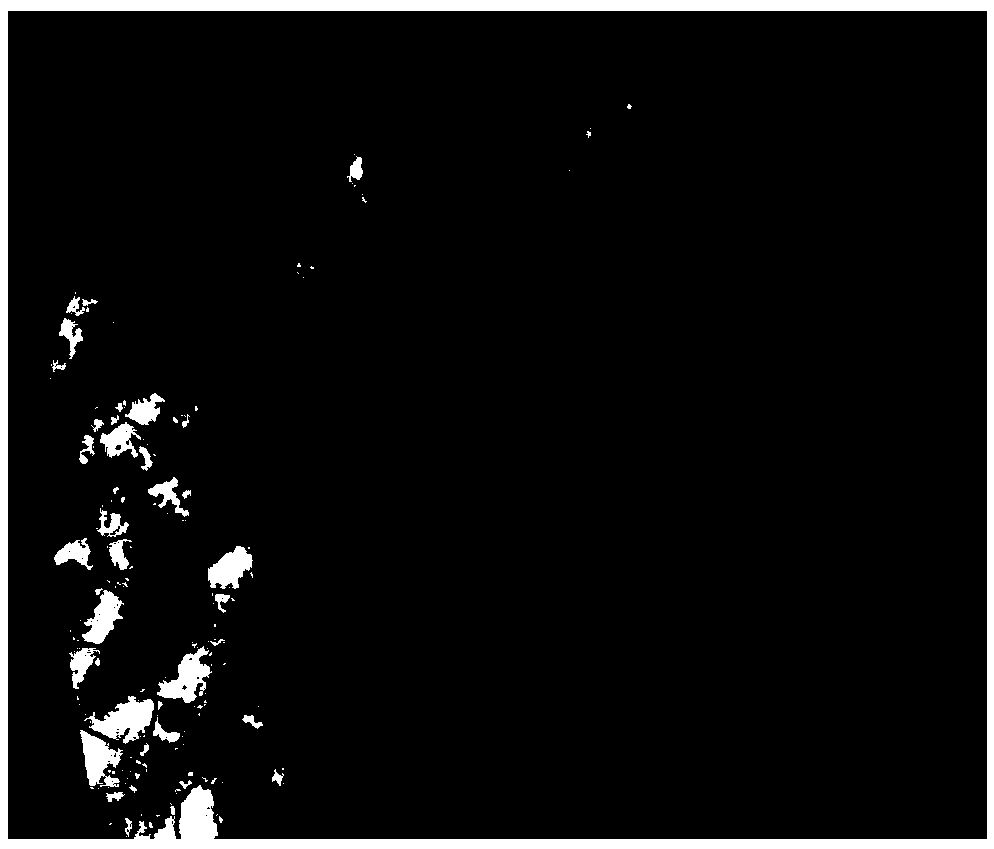

superpixel-based copper surface defect detection method for a flexible IC packaging substrate

ActiveCN109658381AImprove routing densityImprove detection accuracyImage enhancementImage analysisCopperFeature extraction

The invention discloses a superpixel-based copper surface defect detection method for a flexible IC packaging substrate, and the method comprises the steps: carrying out the filtering and preliminarythreshold segmentation of an original color image, and obtaining a superpixel segmentation image through employing a simple linear iterative clustering method; Selecting a superpixel of the copper surface area according to the brightness characteristic, extracting the characteristic of the superpixel of the copper surface area by combining the global characteristic of the image, calculating the brightness difference degree of pixel points in the superpixel, finding out a hole in the copper surface, and oxidizing a defect area; Secondly, finding out a superpixel located at the joint of the copper surface and the background according to the gradient and neighborhood information of the pixel, obtaining boundary pixel points located at the edge of the copper surface, obtaining a continuous copper surface line by scanning the neighborhood of the boundary pixel points, and performing feature extraction and analysis on the edge pixel points on the copper surface line to find out the line sawtooth defect. Defects such as holes, oxidation and circuit sawteeth of a copper surface can be accurately positioned.

Owner:SOUTH CHINA UNIV OF TECH

Method for preparing seedless layer package substrate

InactiveCN101409238AImprove routing densityReduce thicknessPrinted circuit detailsSemiconductor/solid-state device detailsSolder maskEngineering

The invention relates to a method for manufacturing a package substrate without a core layer and a conductive structure of the package substrate. The structure manufactured by the method comprises a storey-adding structure which is provided with a first solder mask layer and a second solder mask layer, wherein, a plurality of openings are formed at the first solder mask layer and the second solder mask layer to expose an electric connection gasket of the storey-adding structure, and the structure also comprises a plurality of solder projections formed on the electric connection gasket and a solder layer. Therefore, the package substrate without the core layer manufactured by the invention can provide a shorter conductive path, improves the wiring density of a circuit and reduces the manufacturing procedures, and the thickness of a whole product is reduced to achieve the light, thin and small function.

Owner:PHOENIX PRECISION TECH CORP

Formation of multisegmented plated through holes

InactiveUS20050079289A1Improve routing densityPrinted circuit assemblingPrinted circuit aspectsDielectric layerElectroplating

A method and structure relating to multisegmented plated through holes. A substrate includes a dielectric layer sandwiched between a first laminate layer and a second laminate layer. A through hole is formed through the substrate. The through hole passes through nonplatable dielectric material within the dielectric layer. As a result, subsequent seeding and electroplating of the through hole results in a conductive metal plating forming at a wall of the through hole on a segment of the first laminate layer and on a segment of the second laminate layer, but not on the nonplatable dielectric material of the dielectric layer. Thus, the conductive metal plating is not continuous from the first laminate layer to the second laminate layer.

Owner:IBM CORP

Wiring board with embedded component and integrated stiffener and method of making the same

InactiveUS20170018505A1Serious problemImprove reliabilityFinal product manufactureSemiconductor/solid-state device detailsDevice materialElectrical connection

A wiring board with embedded component and integrated stiffener is characterized in that an embedded semiconductor device, a first routing circuitry, an encapsulant and an array of vertical connecting elements are integrated as an electronic component disposed within a through opening of a stiffener, and a second routing circuitry is disposed beyond the through opening of the stiffener and extends over the stiffener. The mechanical robustness of the stiffener can prevent the wiring board from warping. The embedded semiconductor device is electrically coupled to the first routing circuitry and surrounded by the vertical connecting elements in electrical connection with the first and second routing circuitries. The first routing circuitry provides primary fan-out routing for another semiconductor device to be assembled on the wiring board, whereas the second routing circuitry not only provides further fan-out wiring structure, but also mechanically binds the electronic component with the stiffener.

Owner:BRIDGE SEMICON

Semiconductor device mounting board, method of manufacturing the same, method of inspecting the same, and semiconductor package

InactiveCN1656611AEfficient manufacturingReduce the numberSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor package

A semiconductor device mounting board in which high density packaging and fining can be realized in response to smaller pitches while ensuring excellent reliability of package by improving a conventional wiring board, its producing method and inspecting method, and a semiconductor package. The semiconductor device mounting board in characterized by comprising a wiring structure film consisting of an insulation layer and a wiring layer, a first electrode pattern provided on one surface of the wiring structure film such that at least the side circumference thereof touches the insulation layer but at least the lower surface thereof does not touch the insulation layer and the surface of the insulation layer provided with the first electrode pattern is coplanar with the lower surface of the first electrode pattern, a second electrode pattern formed on the surface opposite to the first electrode pattern, an insulator film provided with an opening pattern being confined in the first electrode pattern, and a metal support provided on the surface of the insulator film.

Owner:NEC CORP

Manufacturing method for multi-layer high-density interconnected printed circuit board

ActiveCN101312619AFast manufacturingSimple processElectrical connection printed elementsMultilayer circuit manufactureHigh densityConductive materials

The invention relates to a production method of multilayer high-density interconnection printed circuit board, wherein one or two circuit faces of the baseboard are provided with a first wiring layer, the first wiring layer is formed with a first conductive block for interconnecting the wiring layers. The production method comprises: forming an insulated medium layer covering the first wiring layer and a first conductive block on the baseboard, forming a conductive layer on the insulated medium layer, forming a first insulated layer on the conductive layer and forming a second wiring layer picture on the first insulated layer, depositing conductive material to form a second wiring layer, forming a second insulated layer on the second wiring layer and the first insulated layer, etching the second insulated layer to form an opening exposing the second wiring layer, depositing the second conductive block in the opening, deleting the second insulated layer, the first insulated layer and the conductive layer under the first insulated layer, repeating aforementioned processes to form a multilayer high-density interconnection printed circuit board. The method simplifies the production.

Owner:JIANGNAN INST OF COMPUTING TECH