Method for preparing seedless layer package substrate

A technology of packaging substrate and coreless layer, which is applied in the direction of multilayer circuit manufacturing, semiconductor/solid-state device manufacturing, electrical components, etc. Thickness etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

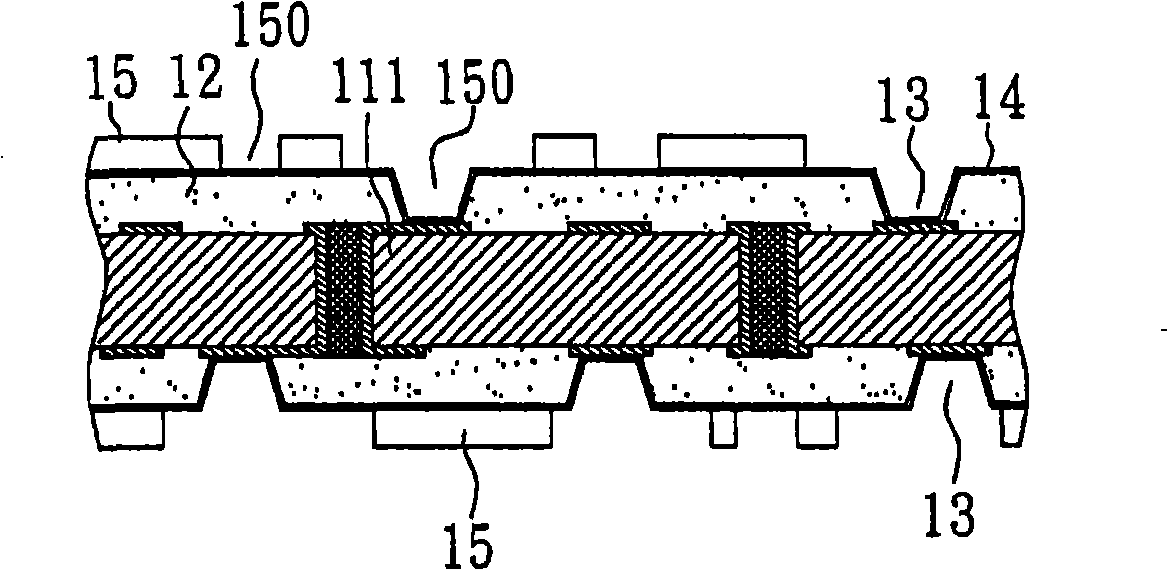

[0051] see Figures 2A to 2Q A schematic cross-sectional view of a coreless layer packaging substrate in a preferred embodiment of the present invention. First, if Figure 2A As shown, a carrier board 201 made of metal is provided. Next, if Figure 2B As shown, a first resist layer 202 of high photosensitive polymer material is pressed on the carrier 201 . Another example Figure 2C As shown, a plurality of first openings 202a are formed on the first resist layer 202 by means of exposure and development to expose the carrier 201 thereunder. Next, if Figure 2D ,and Figure 2E As shown, an etch stop layer 204 of nickel metal and a first metal layer 205 of copper metal are sequentially electroplated in the first openings 202a. In this embodiment, the first resist layer 202 is a dry film photoresist layer.

[0052] see Figure 2F , stripping and removing the first resistance layer 202 . Another example Figure 2G As shown, a dielectric layer 206 of an ABF (Ajinomoto Bu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More