Patents

Literature

34668 results about "Insulation layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

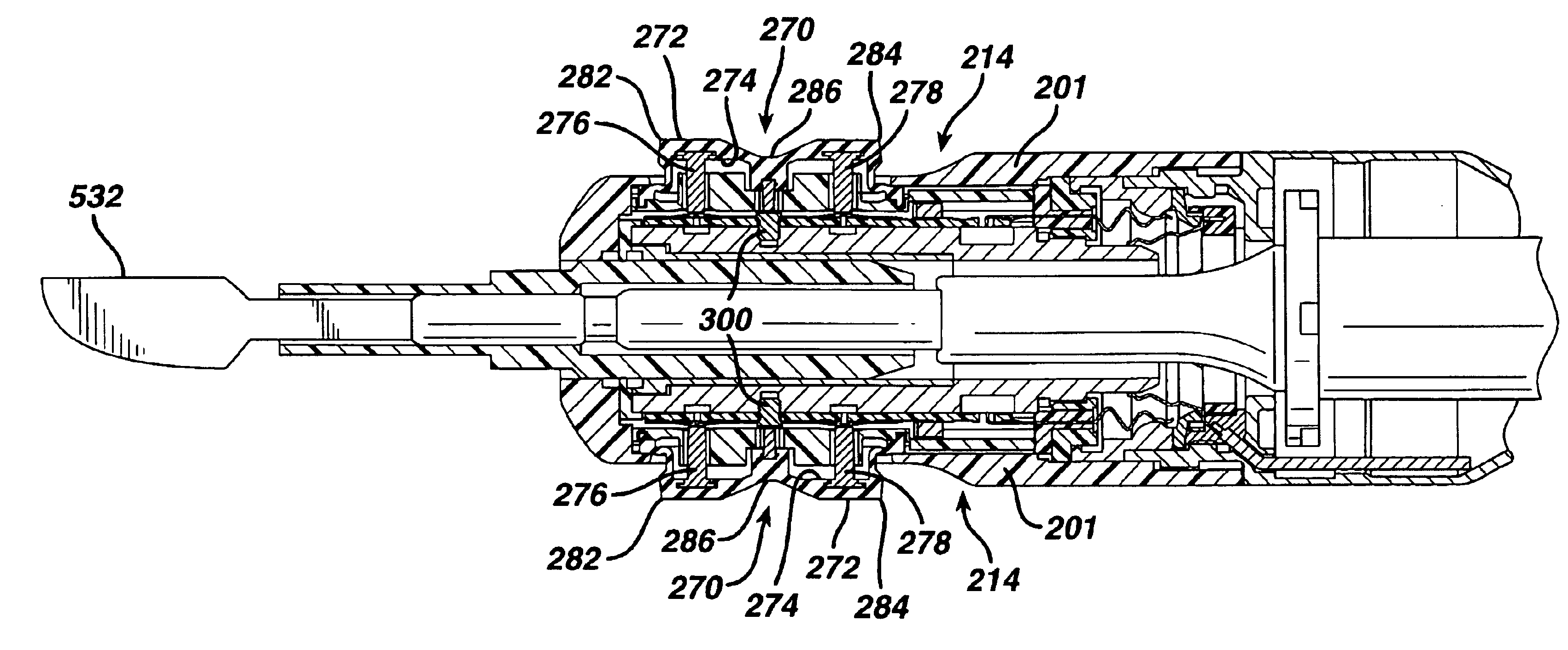

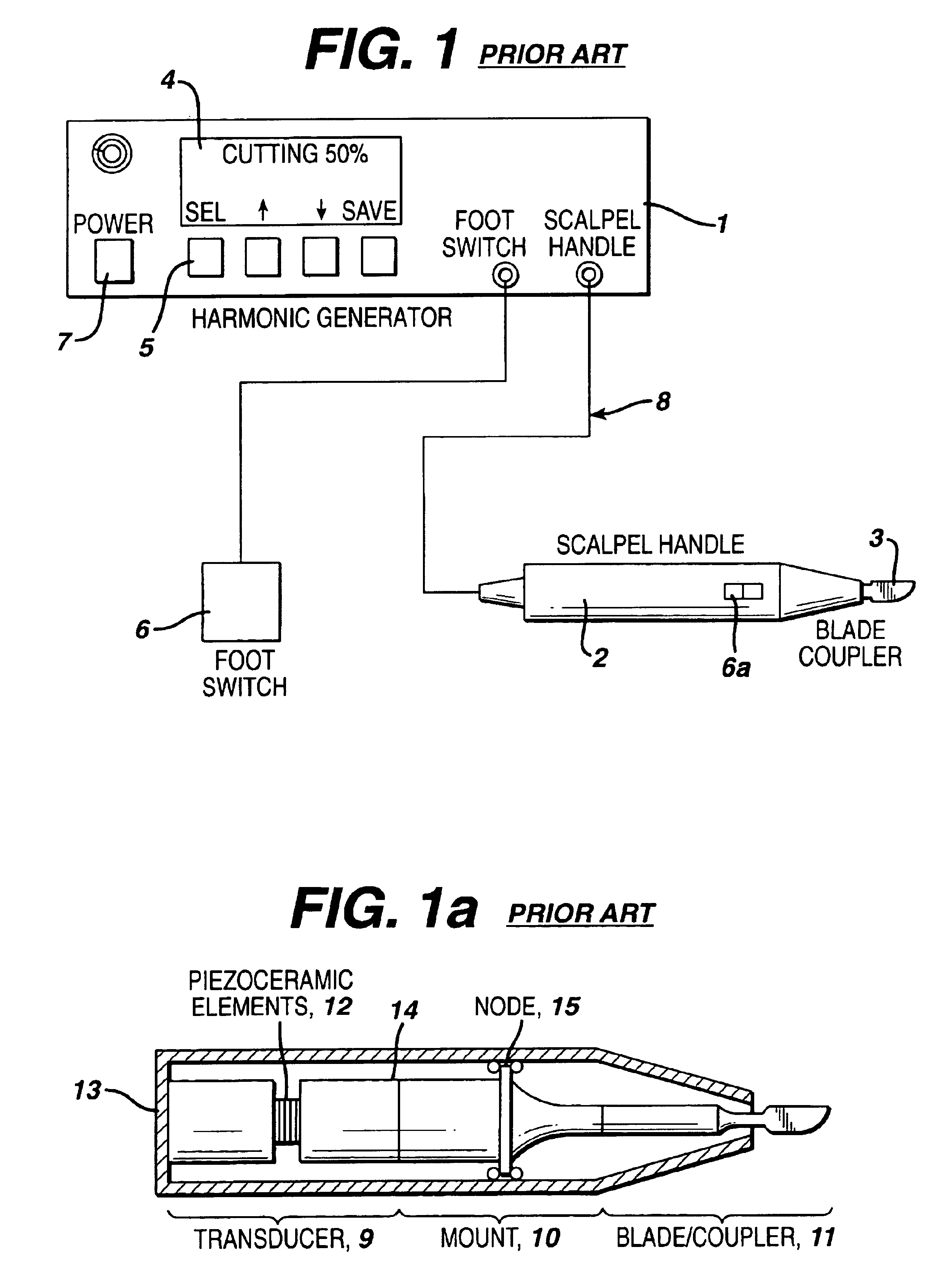

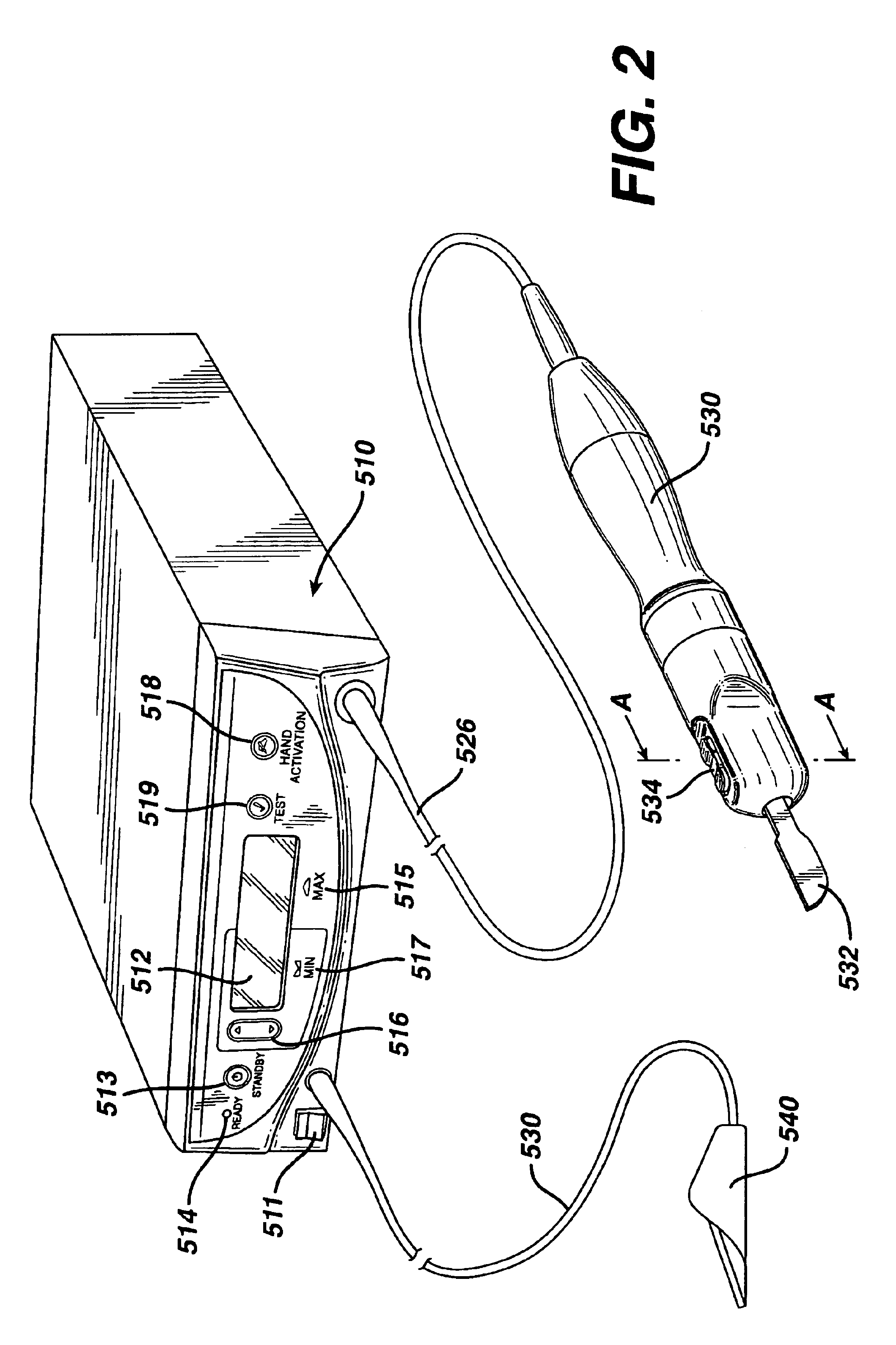

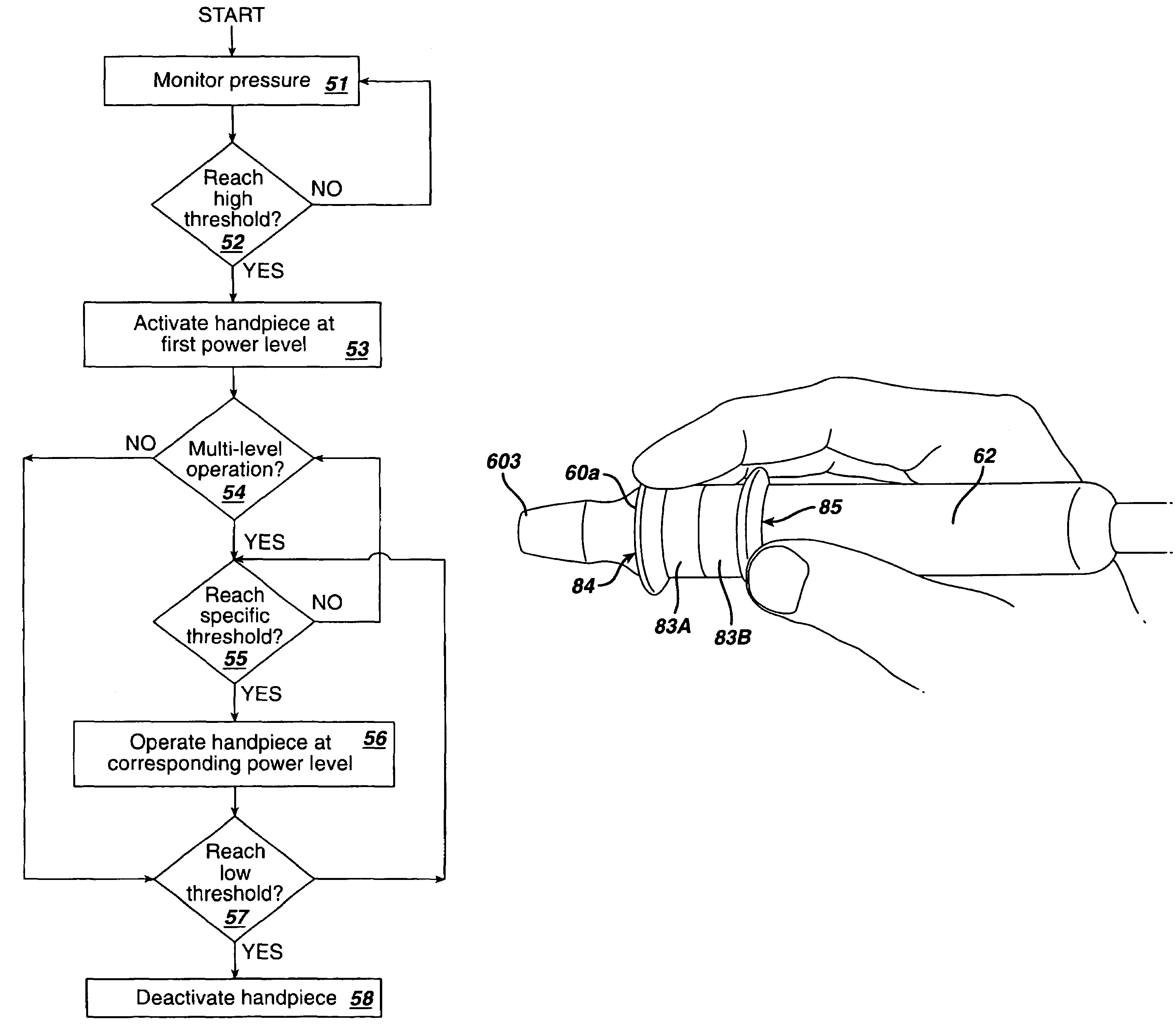

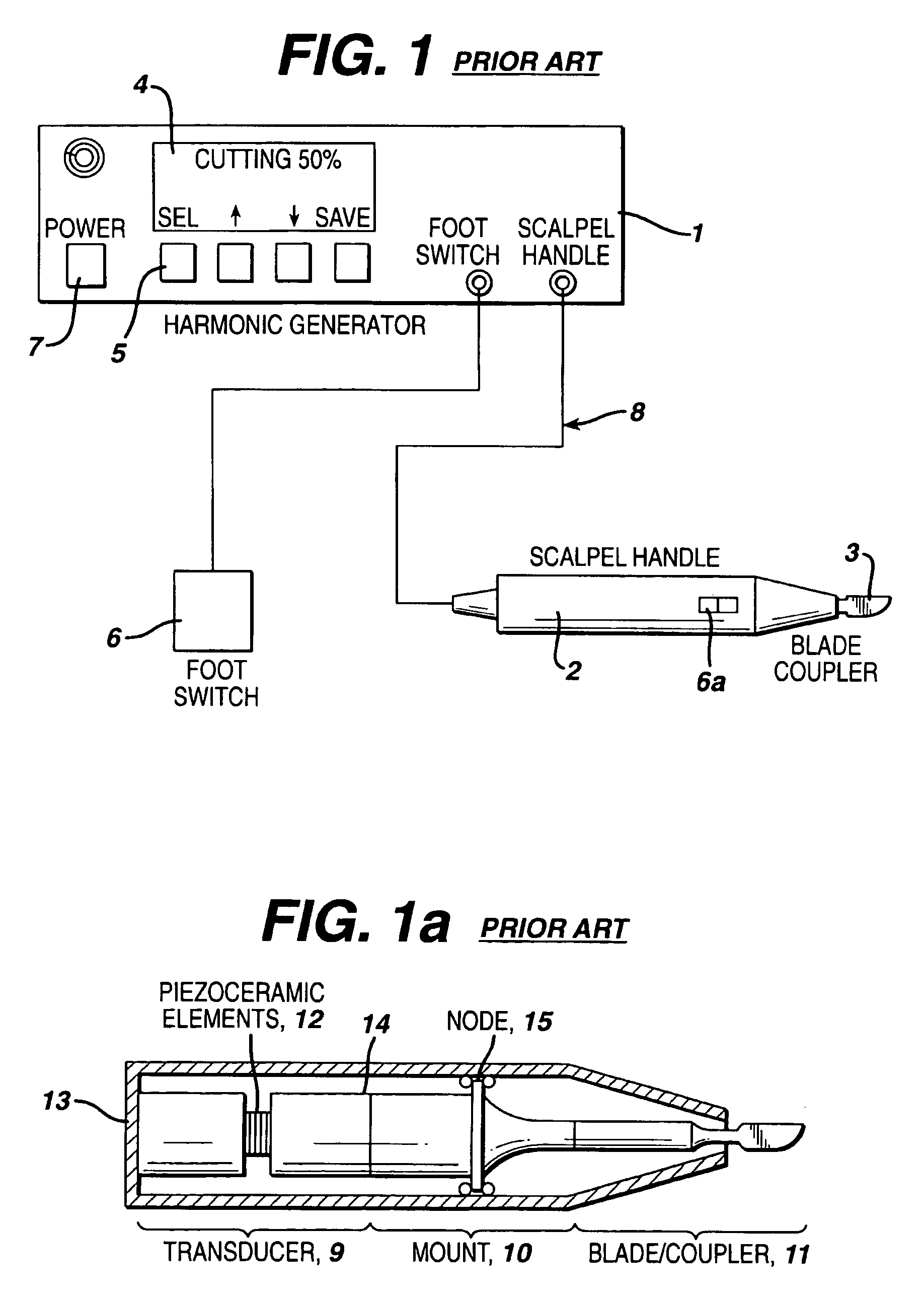

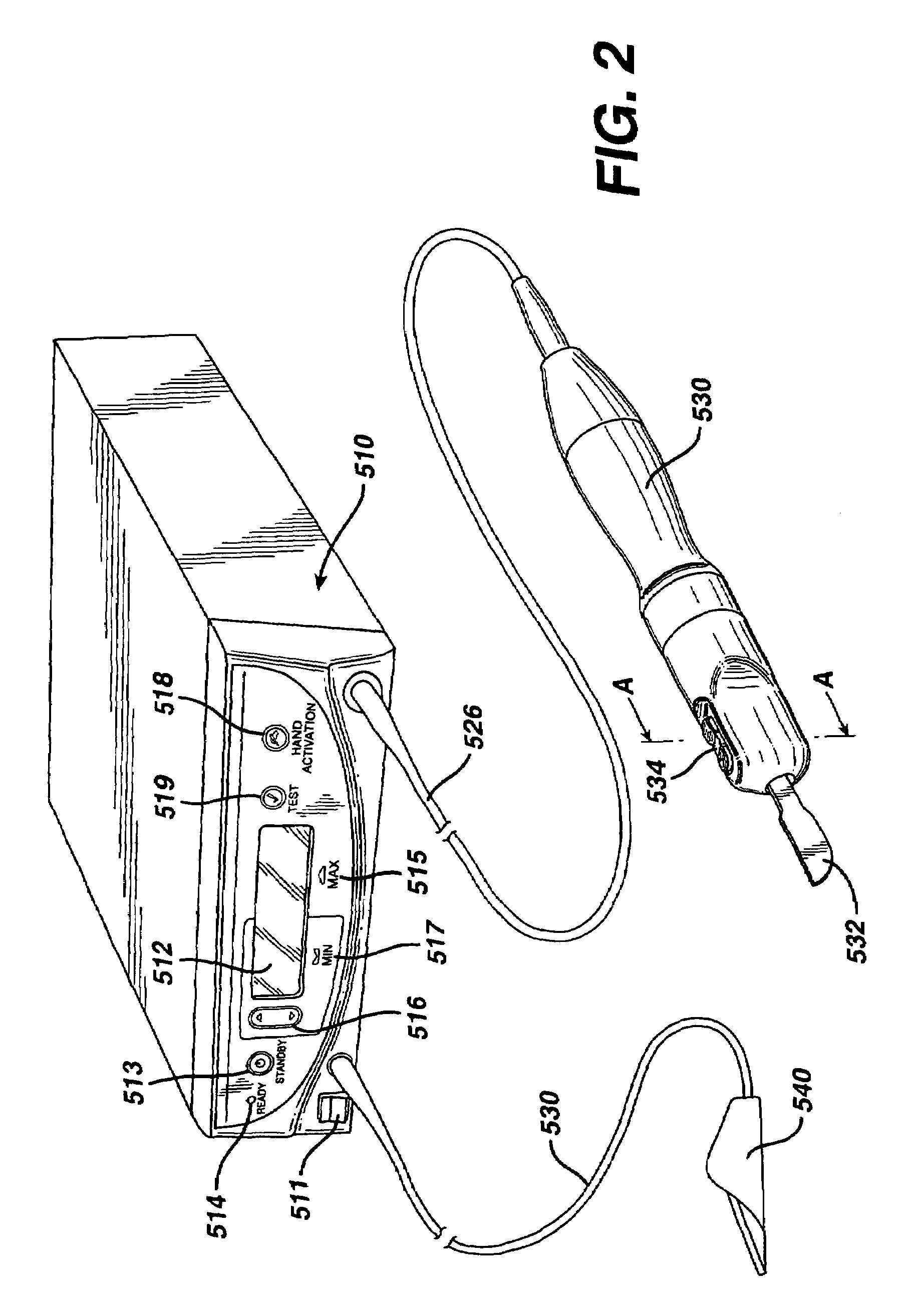

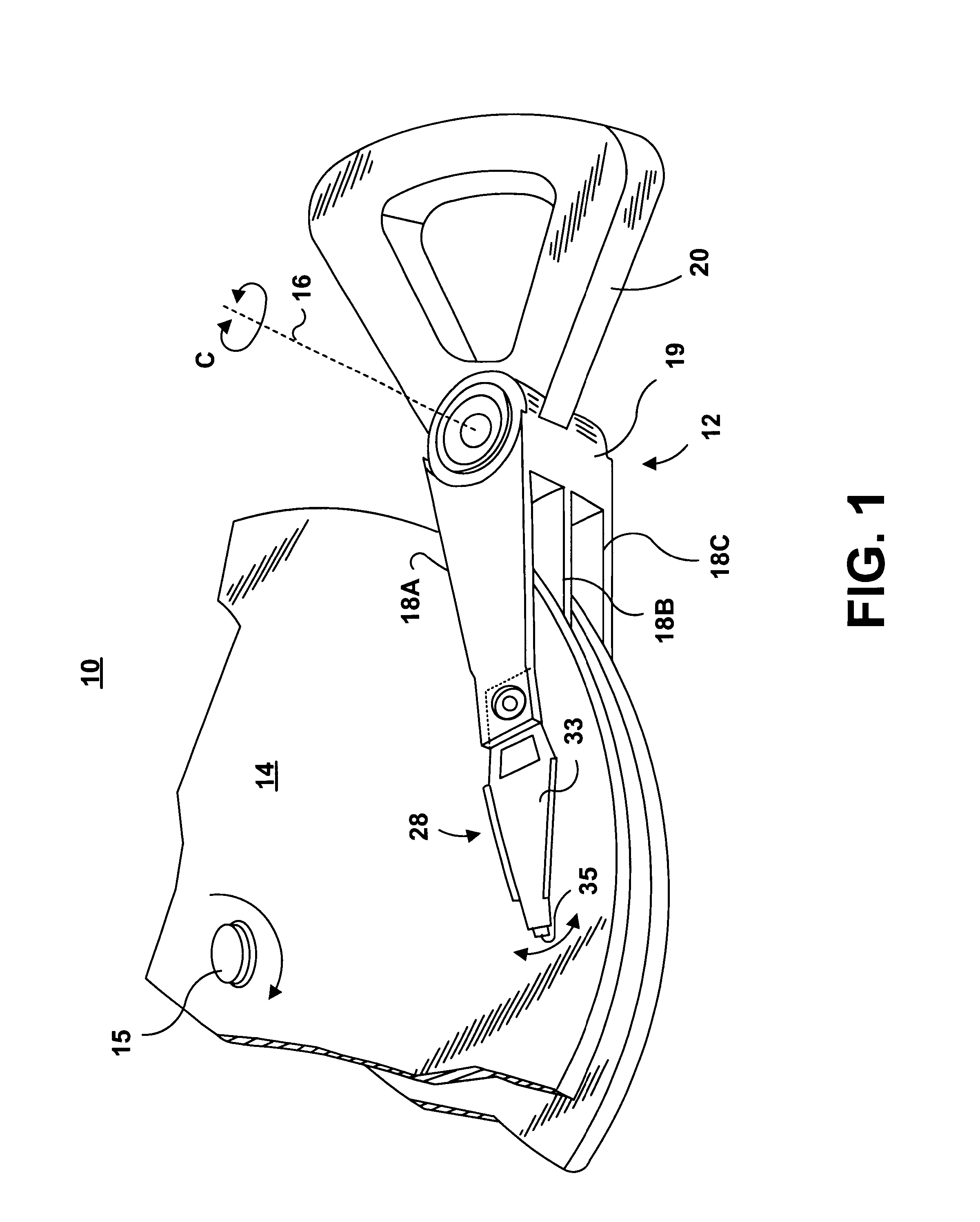

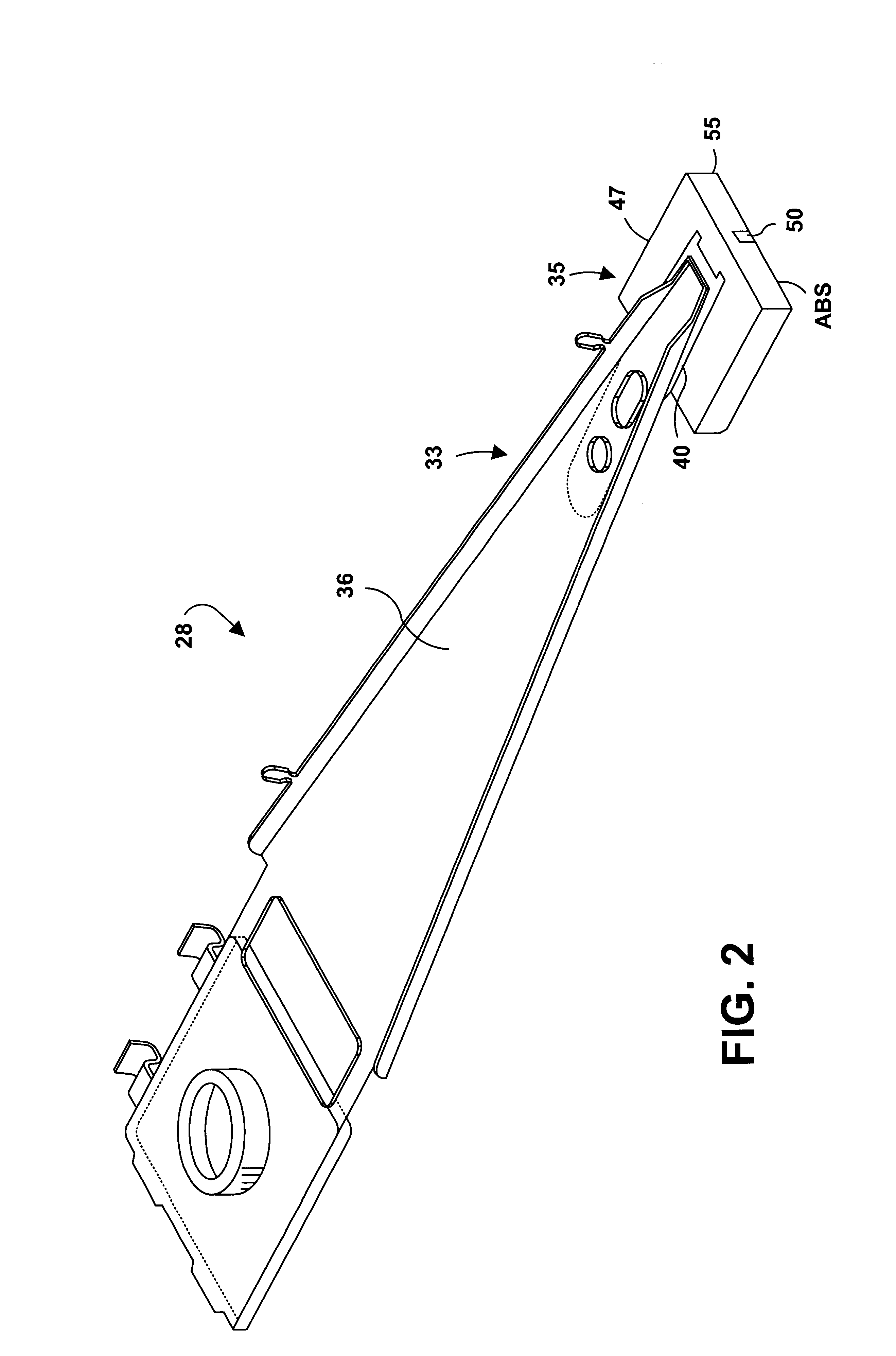

Finger operated switch for controlling a surgical handpiece

According to the invention, a finger-operated switch for activating and operating an ultrasonic surgical handpiece is provided. The power output of the surgical handpiece is responsive and proportional to the pressure applied to the finger-operated switch. The finger-operated switch includes, but not limited to, force sensitive resistors whose resistance is proportional to the force applied by the finger of the human operator of the surgical handpiece, force sensitive capacitors whose capacitance is proportional to the pressure, deflection or compression of the insulation layer between two electrodes or is proportional to the spacing between the two conductive layers, strain gauges mounted underneath or integral to the housing of the surgical handpiece such that the pressure applied thereto results in an output change in the strain gauges, magnets or ferromagnets encased or embedded in an elastomer with a sensor inside the surgical handpiece that detects the field strength of the magnet and monitors changes relative to the force applied to the handpiece housing, and piezo film or piezo ceramic whose charge or voltage is proportional to the force applied.

Owner:ETHICON ENDO SURGERY INC

Finger operated switch for controlling a surgical handpiece

ActiveUS7883465B2Ultrasonic/sonic/infrasonic diagnosticsSurgical instrument detailsElastomerCapacitance

According to the invention, a finger-operated switch for activating and operating an ultrasonic surgical handpiece is provided. The power output of the surgical handpiece is responsive and proportional to the pressure applied to the finger-operated switch. The finger-operated switch includes, but not limited to, force sensitive resistors whose resistance is proportional to the force applied by the finger of the human operator of the surgical handpiece, force sensitive capacitors whose capacitance is proportional to the pressure, deflection or compression of the insulation layer between two electrodes or is proportional to the spacing between the two conductive layers, strain gauges mounted underneath or integral to the housing of the surgical handpiece such that the pressure applied thereto results in an output change in the strain gauges, magnets or ferromagnets encased or embedded in an elastomer with a sensor inside the surgical handpiece that detects the field strength of the magnet and monitors changes relative to the force applied to the handpiece housing, and piezo film or piezo ceramic whose charge or voltage is proportional to the force applied.

Owner:ETHICON ENDO SURGERY INC

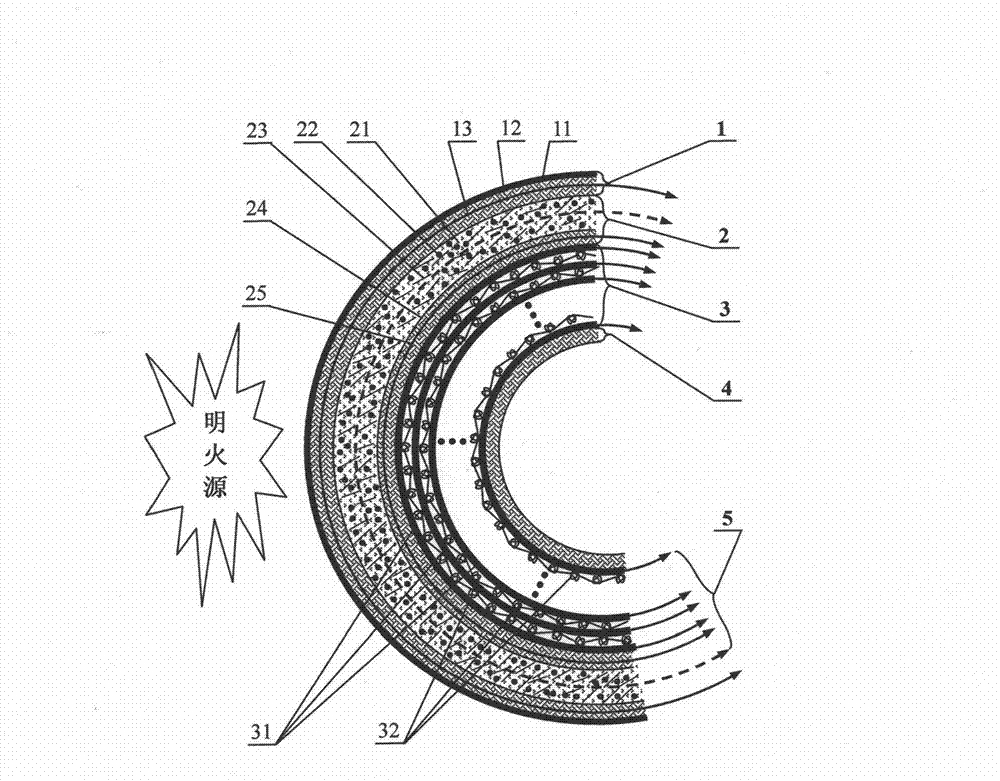

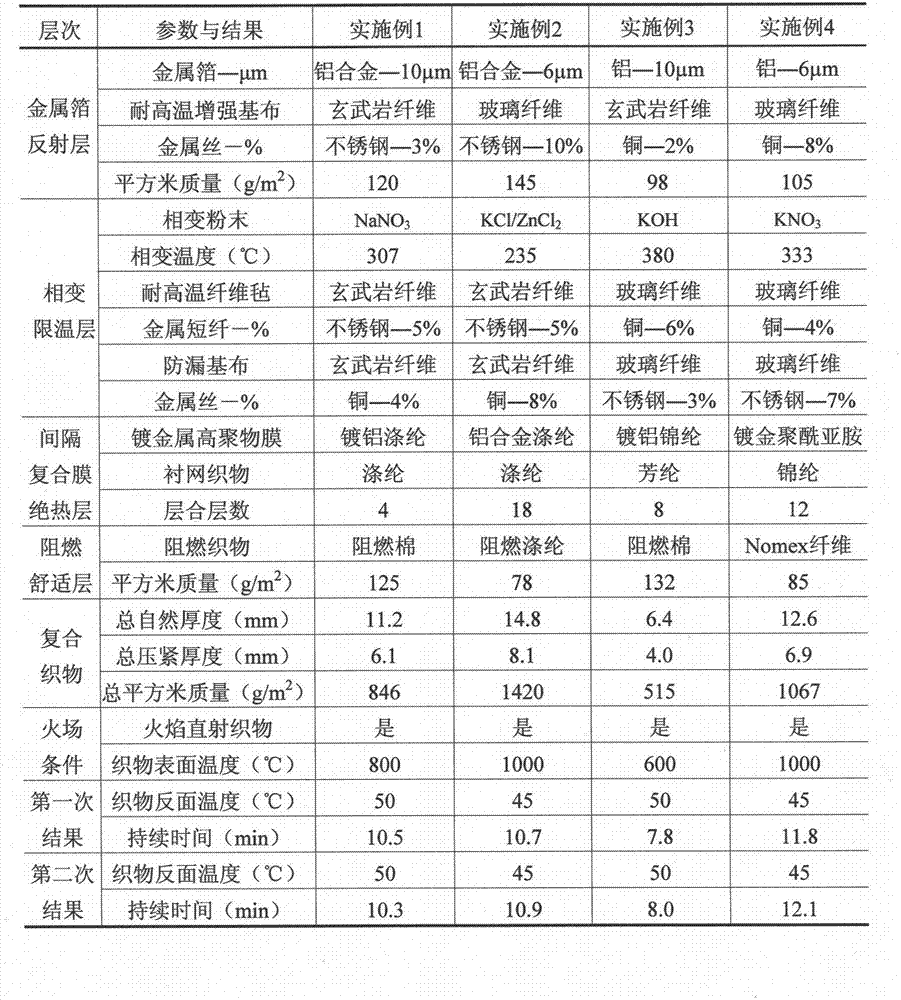

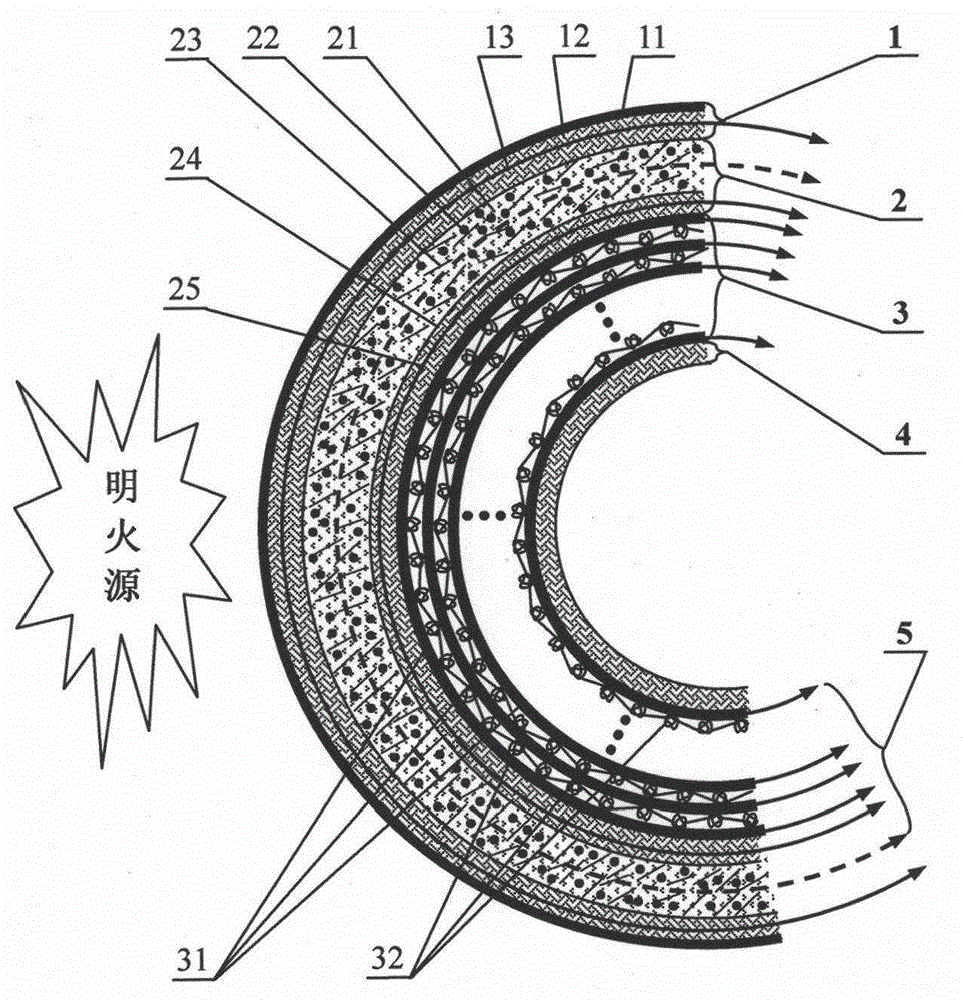

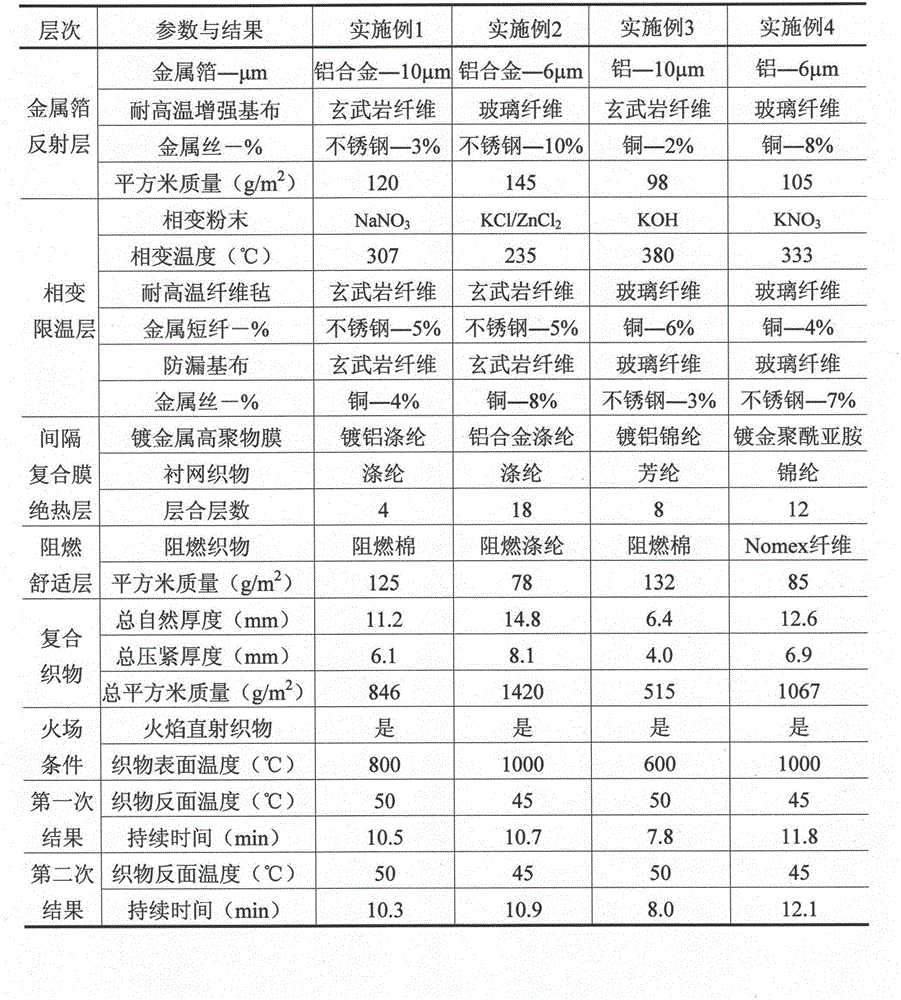

Multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric, preparation method and application

ActiveCN102783741AImprove permeabilityPromote absorptionLaminationLamination apparatusInsulation layerMetal foil

The invention relates to a preparation method and an application of multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric. The multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric is formed by successively arranging and laminating a metal foil reflection layer, a phase change temperature limitation layer, an interval composite membrane heat-insulation layer and a flame-retardant comfortable layer, wherein the metal foil reflection layer has high reflectivity and an enhanced heat-dissipation function; the phase change temperature limitation layer has functions of high energy consumption absorption and evenly-distributed heat conduction; the interval composite membrane heat-insulation layer has the functions of reflection insulation and even distribution of heat; and the flame-retardant comfortable layer has the functions of low-contact heat conduction, heat insulation and comfort. When the front side of the multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric is under the action of open fire and strong heat flow environment, the back side of the multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric can be kept below 50DEG C which is near the safe temperature state of the human skin, and the integral structural form and the mechanical property are stable. The natural thickness of the composite fabric is 5-15mm, the compression thickness of the composite fabric is 3-8mm, and the square meter quality of the composite fabric is 400-1500g / m<2>. The composite fabric is fire-proof heat-insulation material which is totally sealed, stuck and sewn and can be used for individual protection and environment heat insulation in special high-temperature occasions, such as fire control, military, exploration, safe escape and industry and the like.

Owner:DONGHUA UNIV

Fire-proof and heat-insulating composite fabric with multi-stage expansion and heat dissipation, preparation method and application

ActiveCN102783741BImprove permeabilityPromote absorptionLaminationLamination apparatusInsulation layerMetal foil

The invention relates to a preparation method and an application of multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric. The multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric is formed by successively arranging and laminating a metal foil reflection layer, a phase change temperature limitation layer, an interval composite membrane heat-insulation layer and a flame-retardant comfortable layer, wherein the metal foil reflection layer has high reflectivity and an enhanced heat-dissipation function; the phase change temperature limitation layer has functions of high energy consumption absorption and evenly-distributed heat conduction; the interval composite membrane heat-insulation layer has the functions of reflection insulation and even distribution of heat; and the flame-retardant comfortable layer has the functions of low-contact heat conduction, heat insulation and comfort. When the front side of the multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric is under the action of open fire and strong heat flow environment, the back side of the multistage-spreading heat-dissipation fire-proof heat-insulation composite fabric can be kept below 50DEG C which is near the safe temperature state of the human skin, and the integral structural form and the mechanical property are stable. The natural thickness of the composite fabric is 5-15mm, the compression thickness of the composite fabric is 3-8mm, and the square meter quality of the composite fabric is 400-1500g / m<2>. The composite fabric is fire-proof heat-insulation material which is totally sealed, stuck and sewn and can be used for individual protection and environment heat insulation in special high-temperature occasions, such as fire control, military, exploration, safe escape and industry and the like.

Owner:DONGHUA UNIV

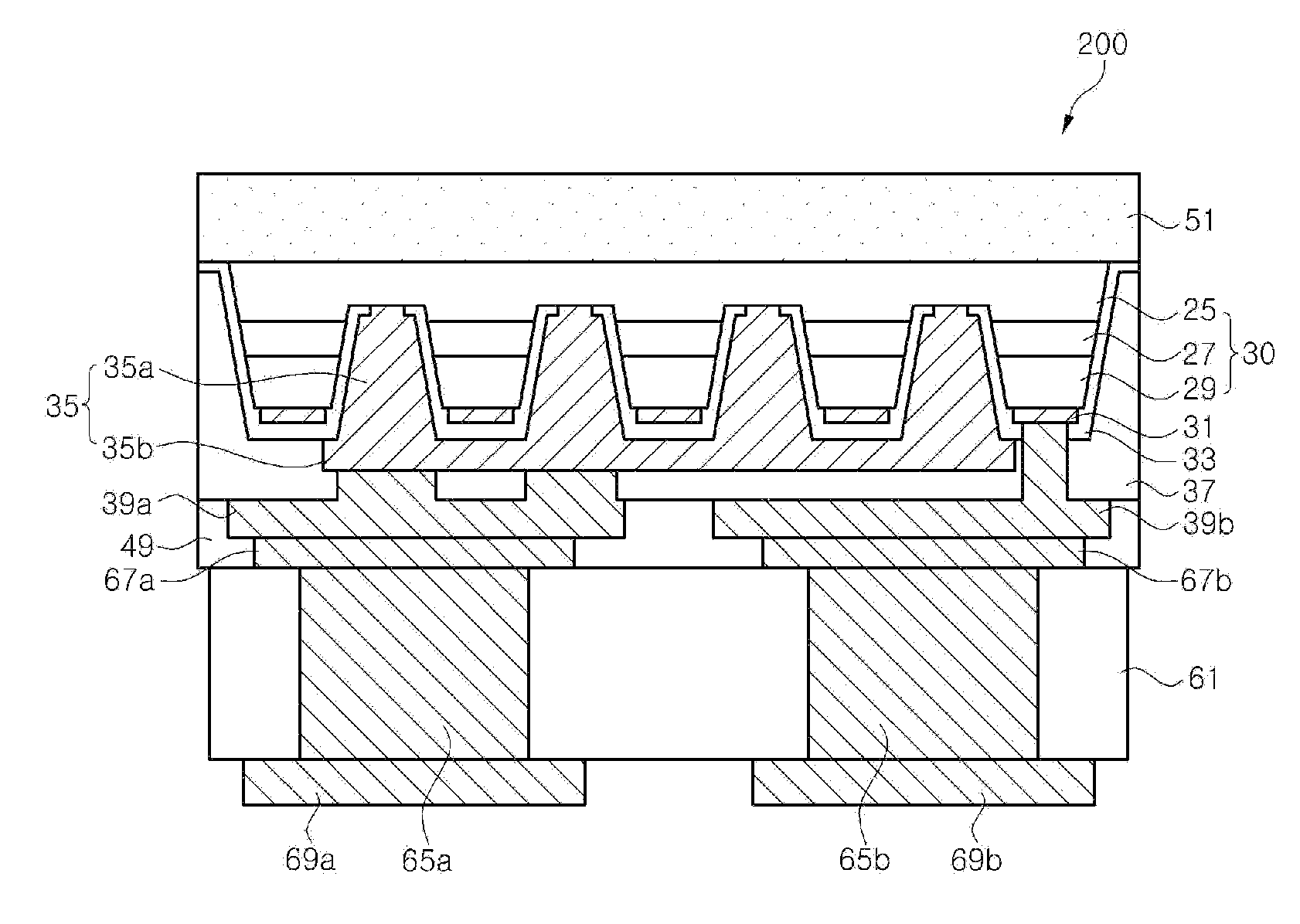

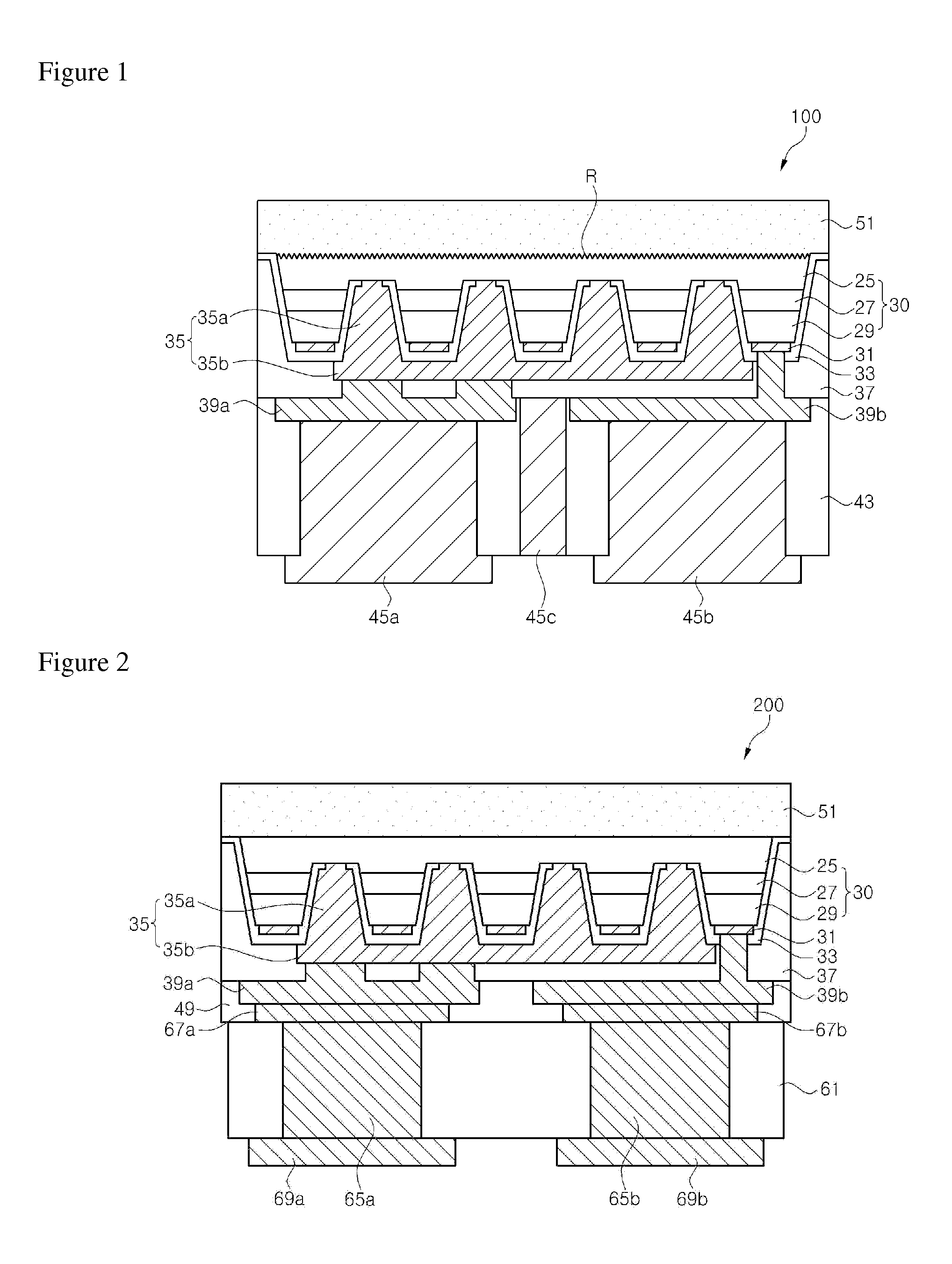

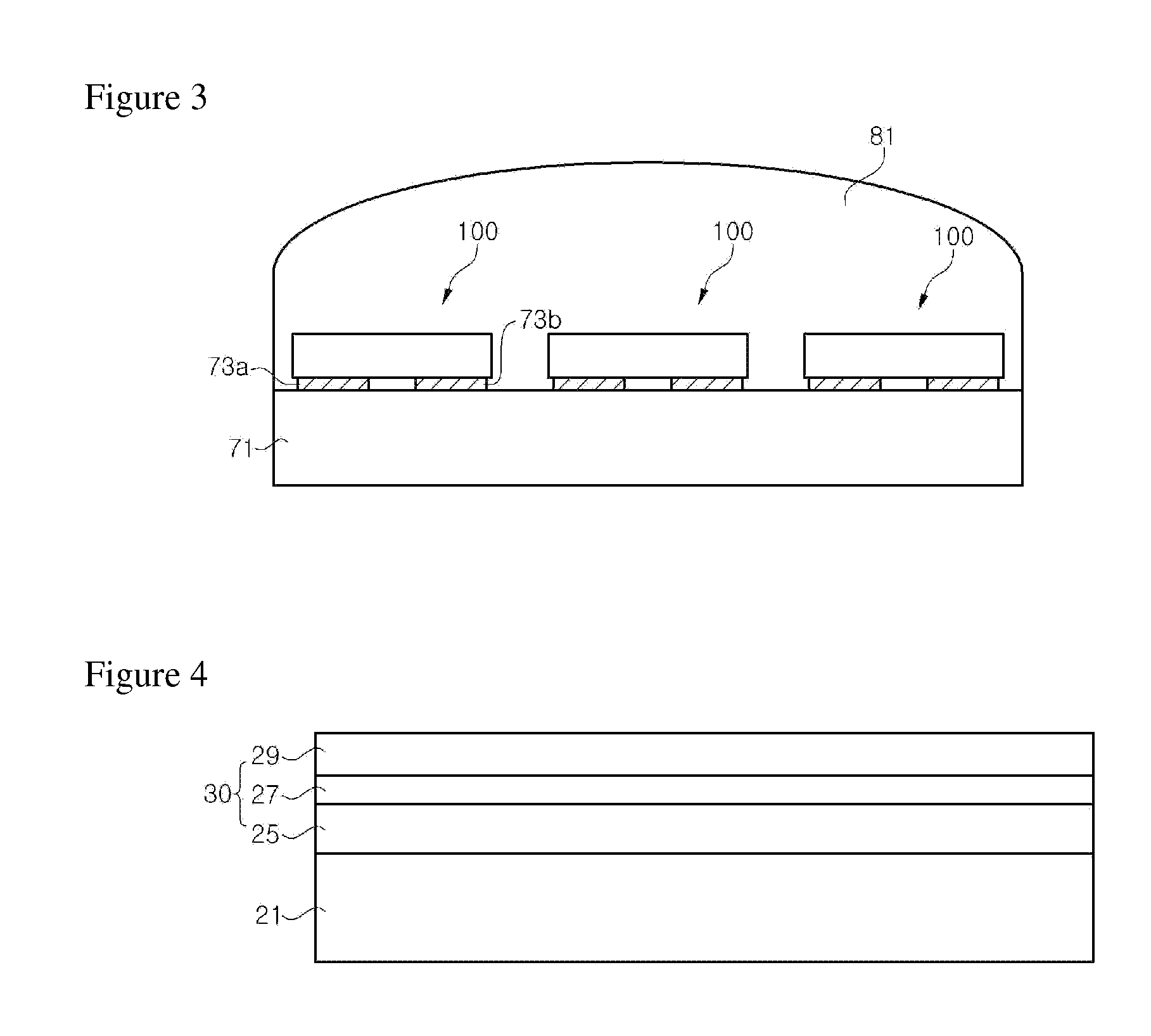

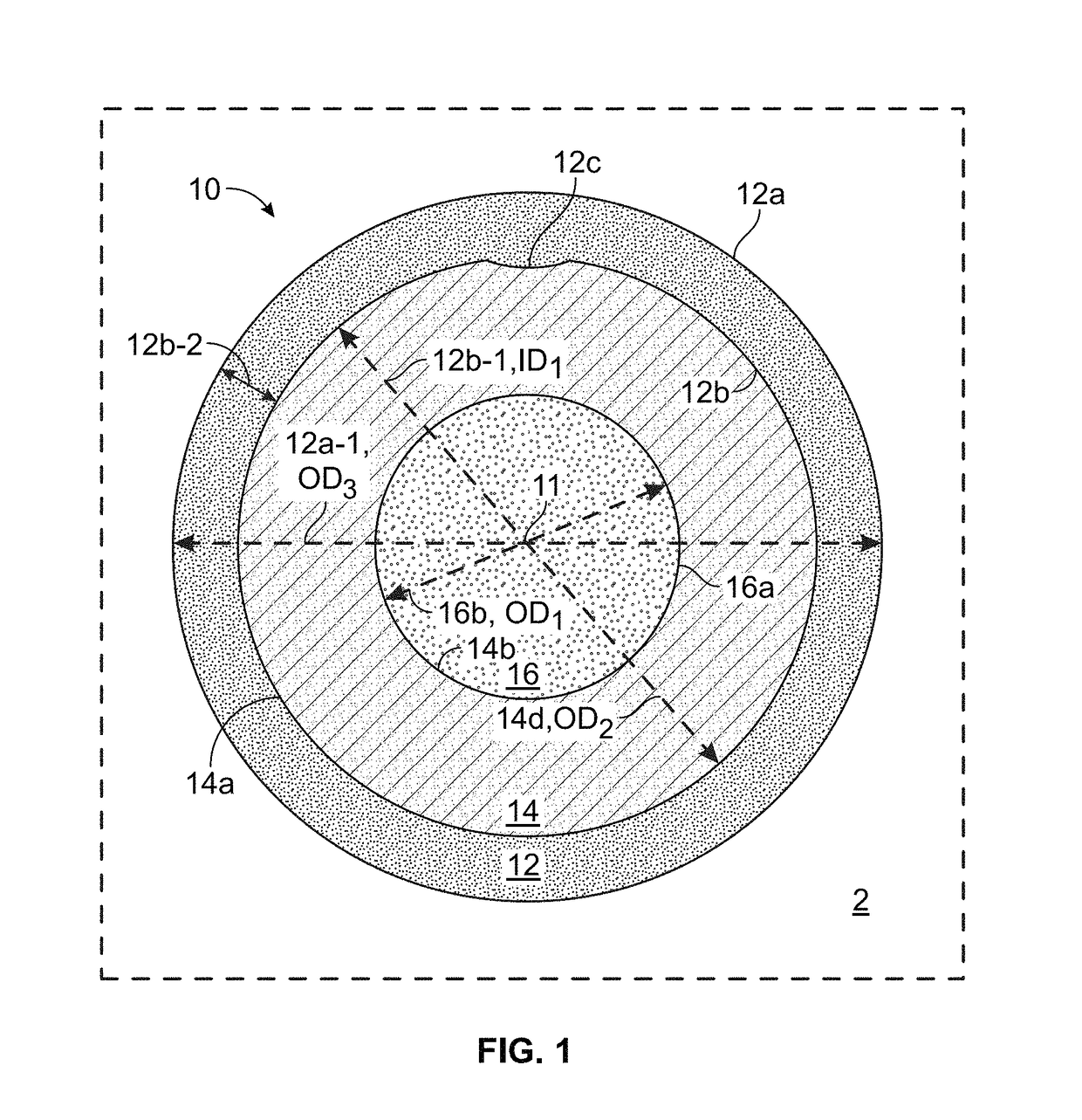

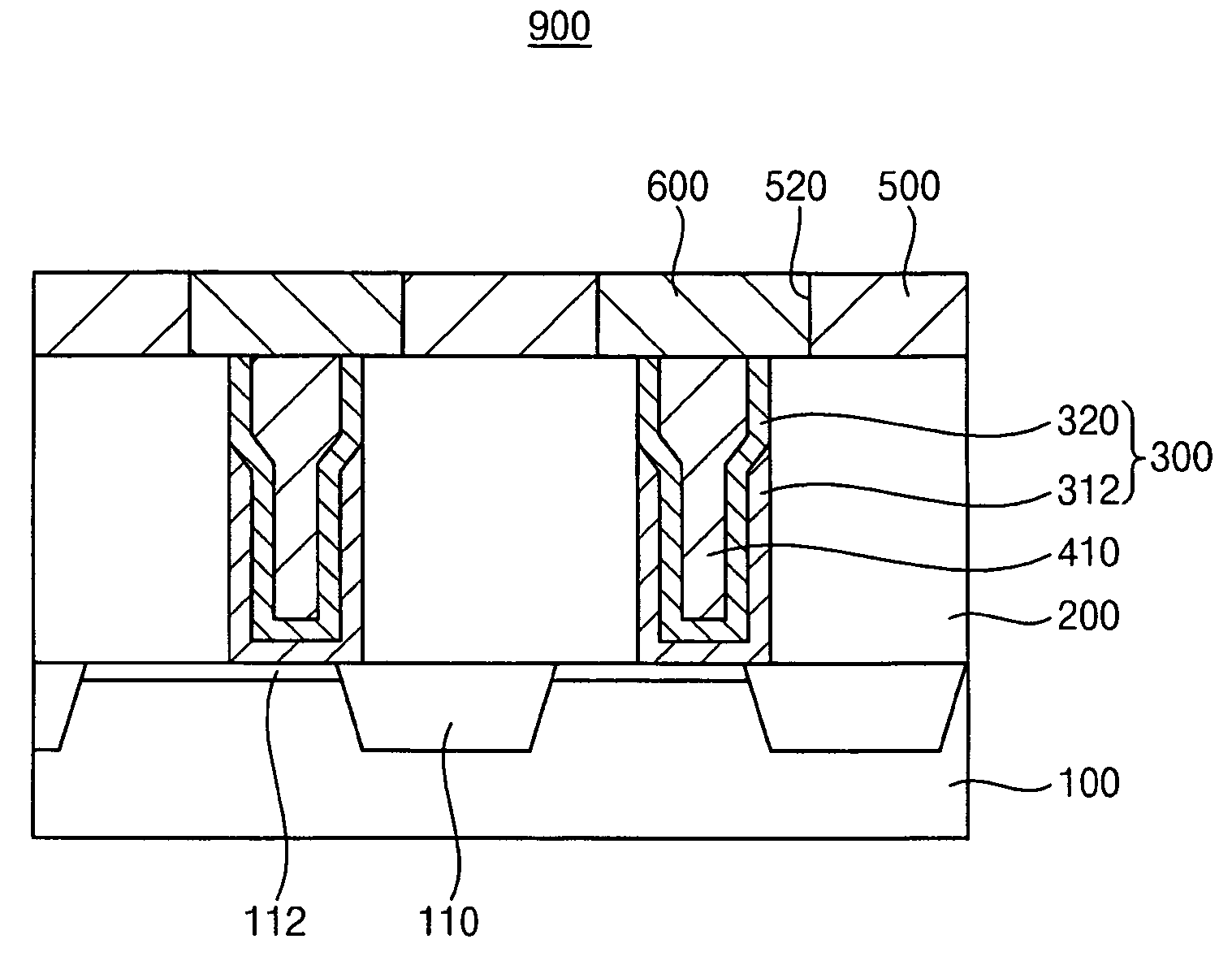

Wafer-level light emitting diode package and method of fabricating the same

ActiveUS20120074441A1Improve efficiencyImprove cooling effectSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

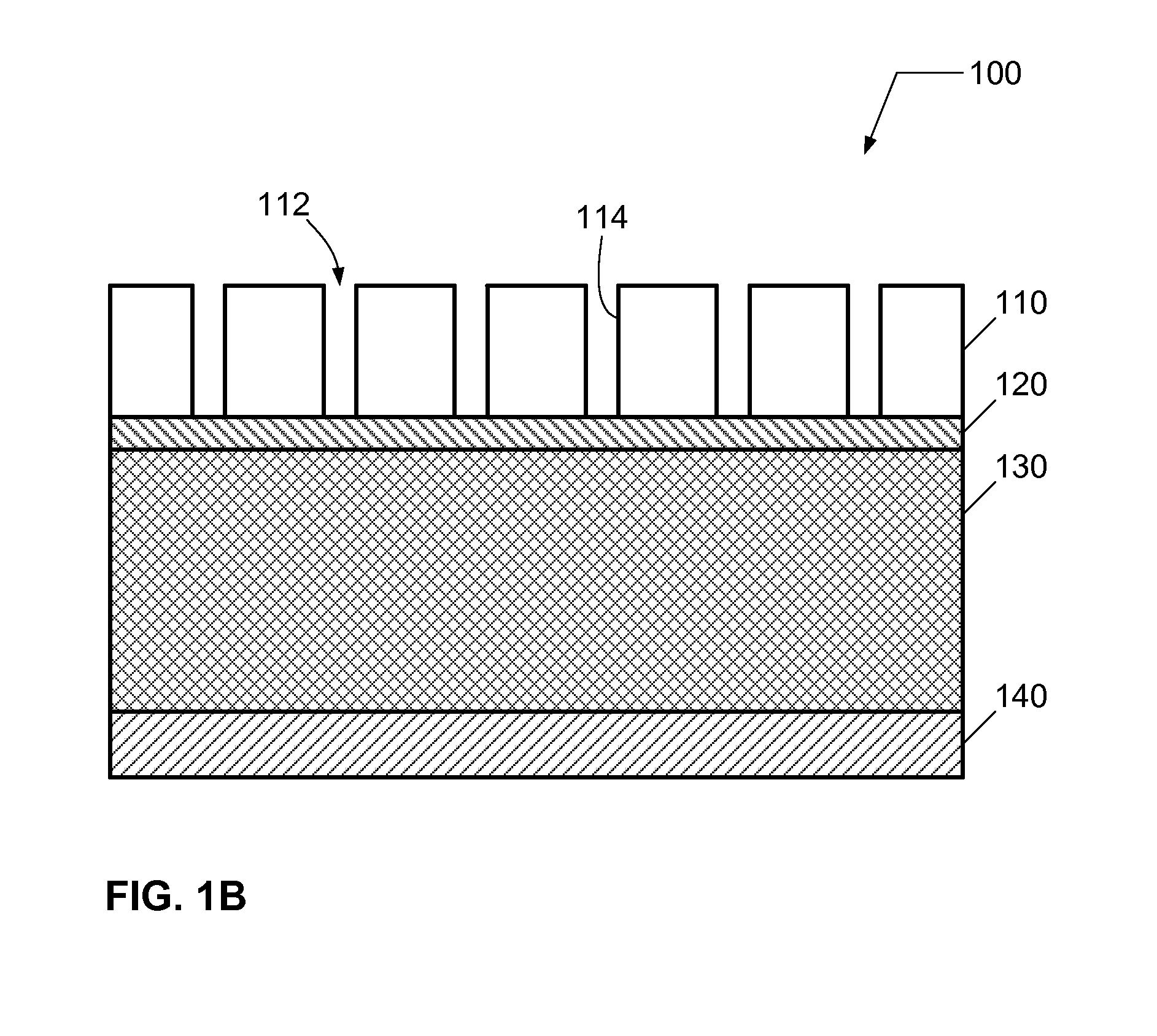

Exemplary embodiments of the present invention provide a wafer-level light emitting diode (LED) package and a method of fabricating the same. The LED package includes a semiconductor stack including a first conductive type semiconductor layer, an active layer, and a second conductive type semiconductor layer; a plurality of contact holes arranged in the second conductive type semiconductor layer and the active layer, the contact holes exposing the first conductive type semiconductor layer; a first bump arranged on a first side of the semiconductor stack, the first bump being electrically connected to the first conductive type semiconductor layer via the plurality of contact holes; a second bump arranged on the first side of the semiconductor stack, the second bump being electrically connected to the second conductive type semiconductor layer; and a protective insulation layer covering a sidewall of the semiconductor stack.

Owner:SEOUL SEMICONDUCTOR

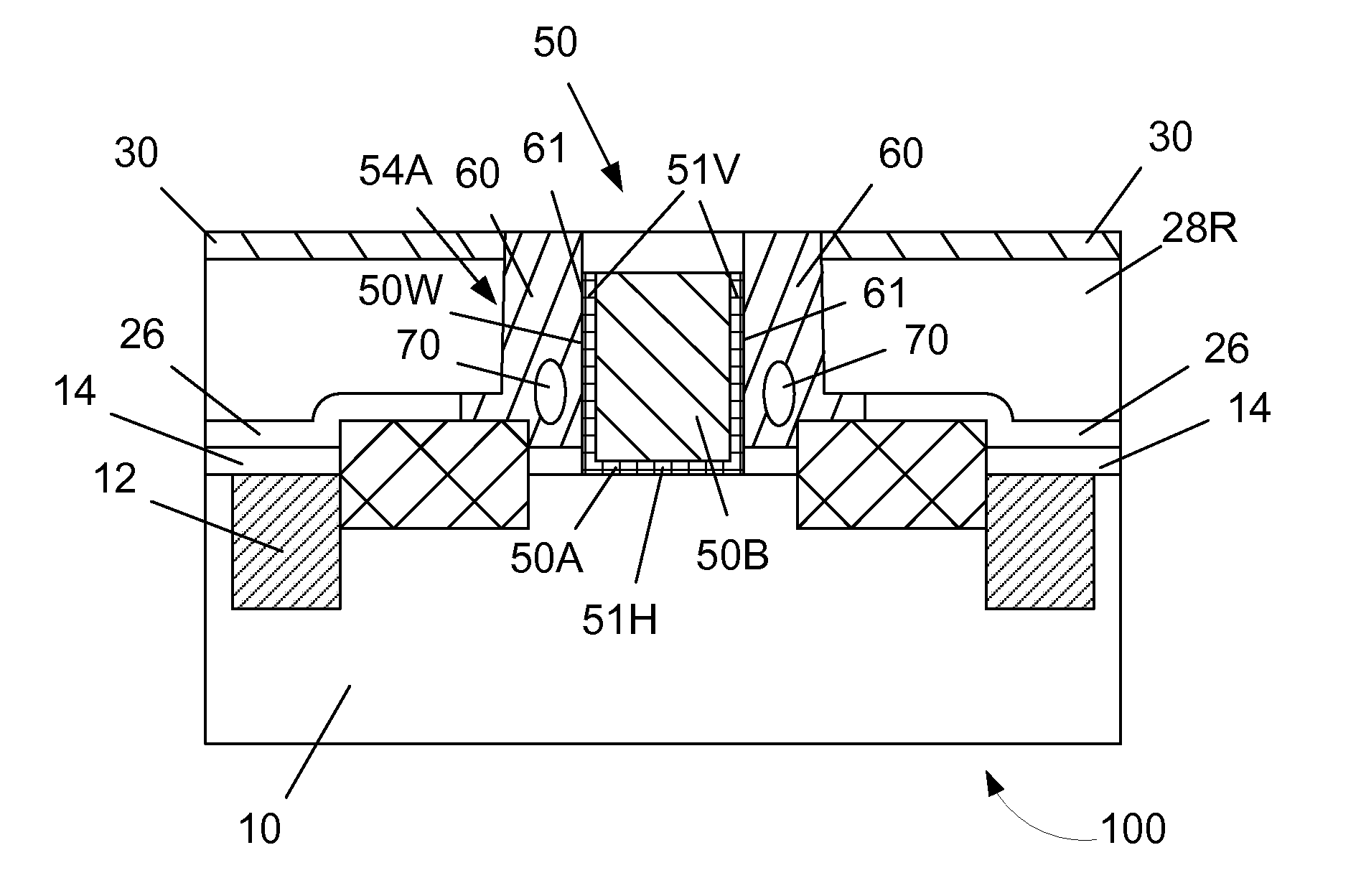

Methods of forming a semiconductor device with low-k spacers and the resulting device

ActiveUS20140110798A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerEngineering

One method disclosed herein includes forming at least one sacrificial sidewall spacer adjacent a sacrificial gate structure that is formed above a semiconducting substrate, removing at least a portion of the sacrificial gate structure to thereby define a gate cavity that is laterally defined by the sacrificial spacer, forming a replacement gate structure in the gate cavity, removing the sacrificial spacer to thereby define a spacer cavity adjacent the replacement gate structure, and forming a low-k spacer in the spacer cavity. A novel device disclosed herein includes a gate structure positioned above a semiconducting substrate, wherein the gate insulation layer has two upstanding portions that are substantially vertically oriented relative to an upper surface of the substrate. The device further includes a low-k sidewall spacer positioned adjacent each of the vertically oriented upstanding portions of the gate insulation layer.

Owner:GLOBALFOUNDRIES US INC

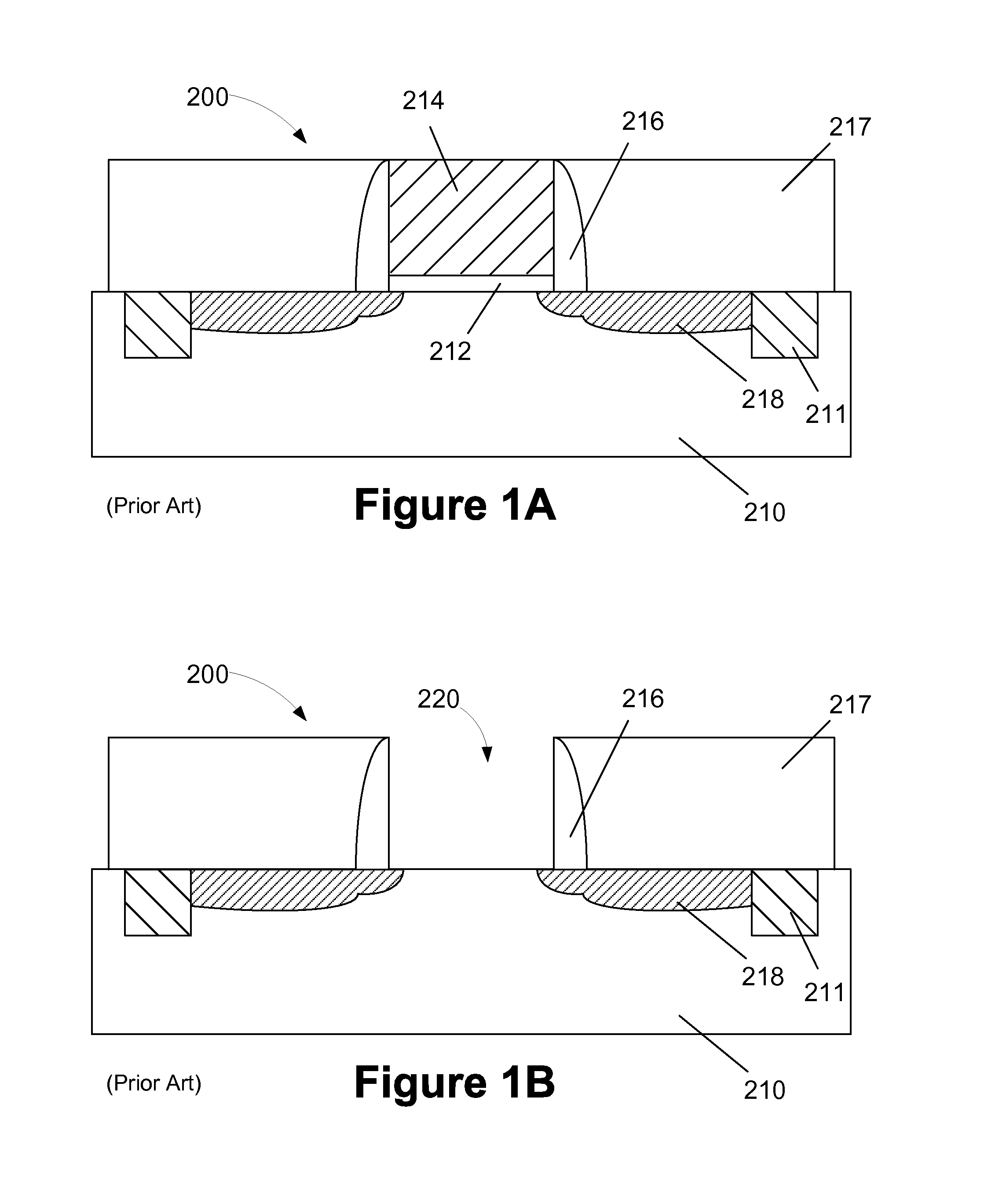

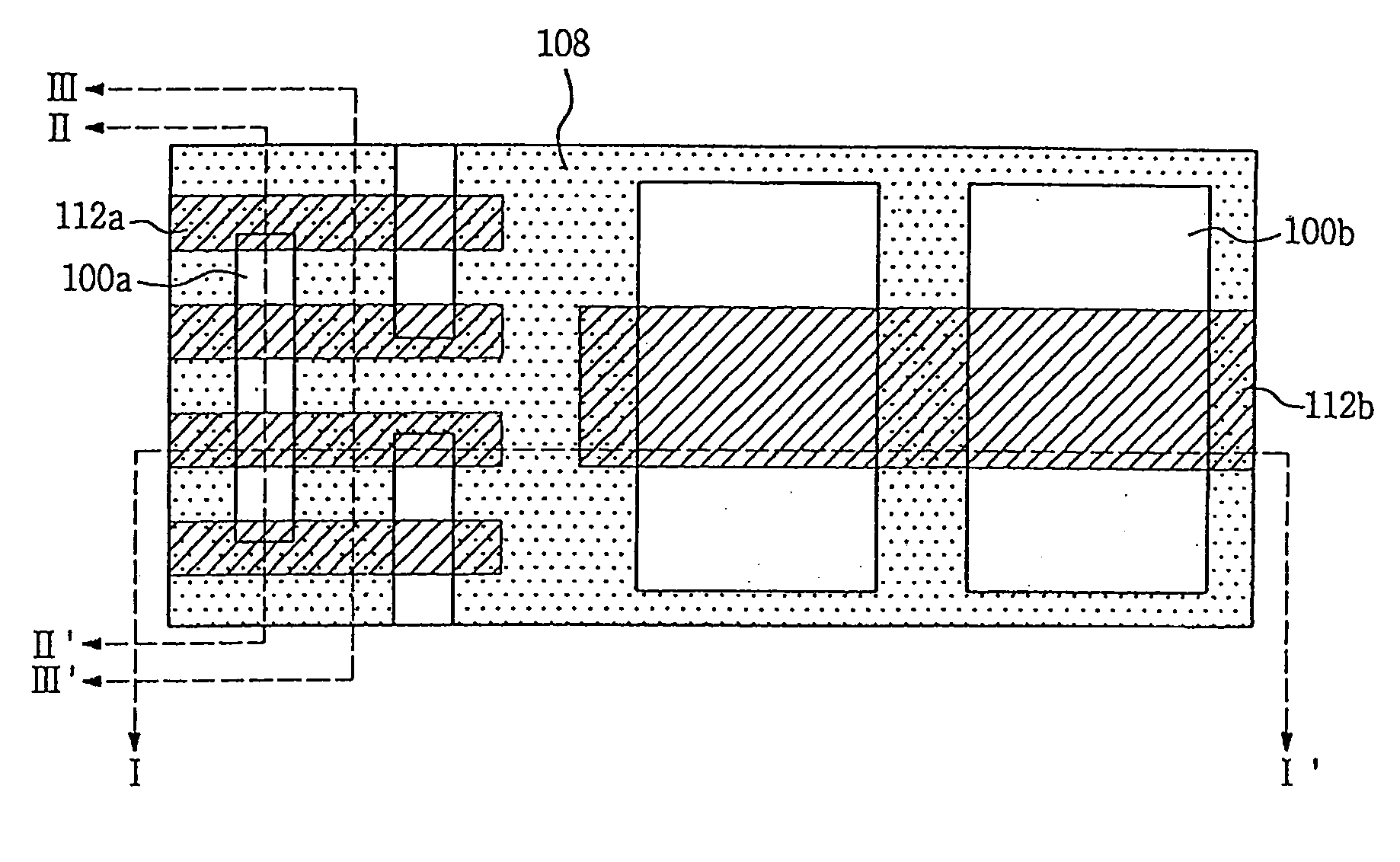

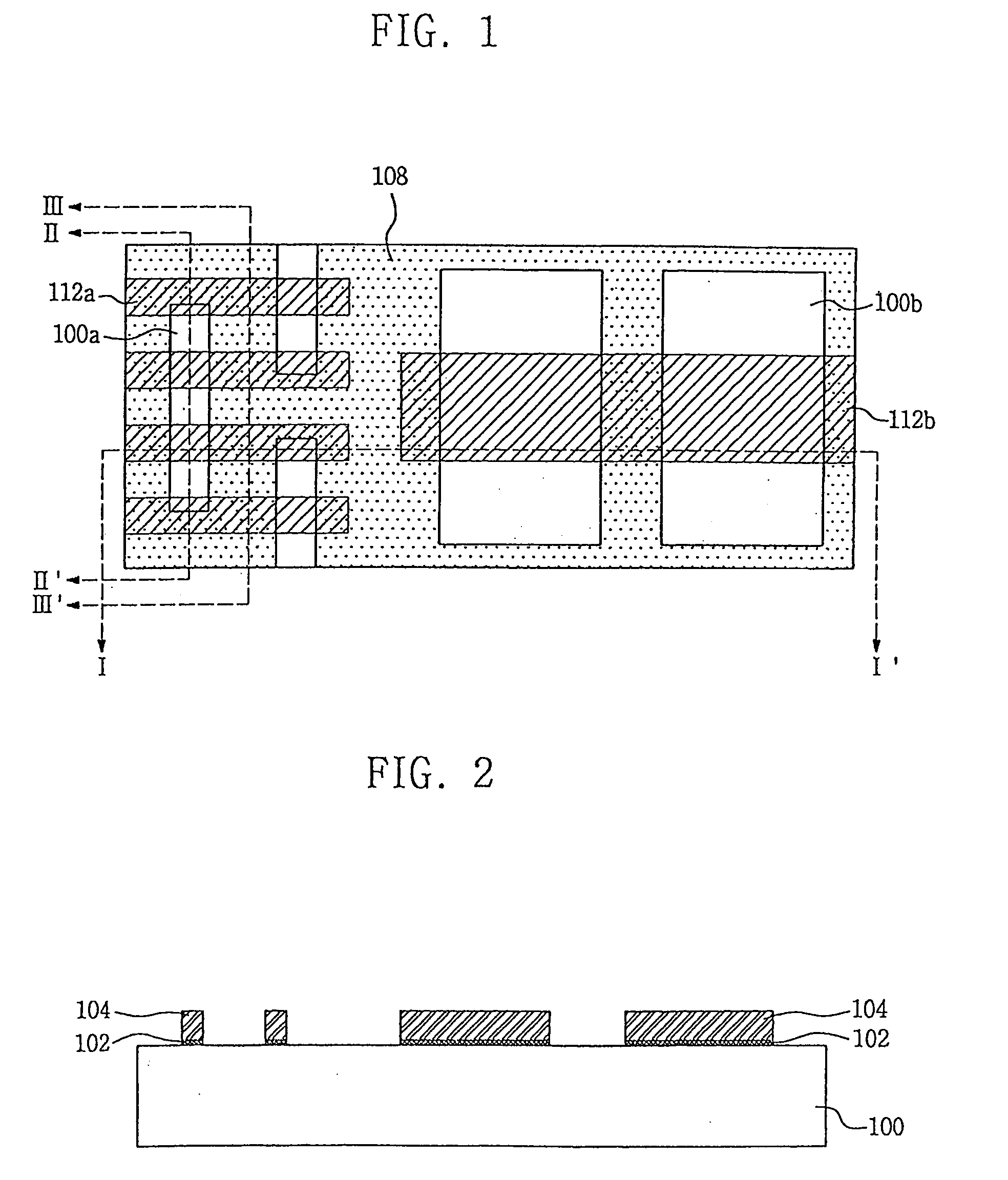

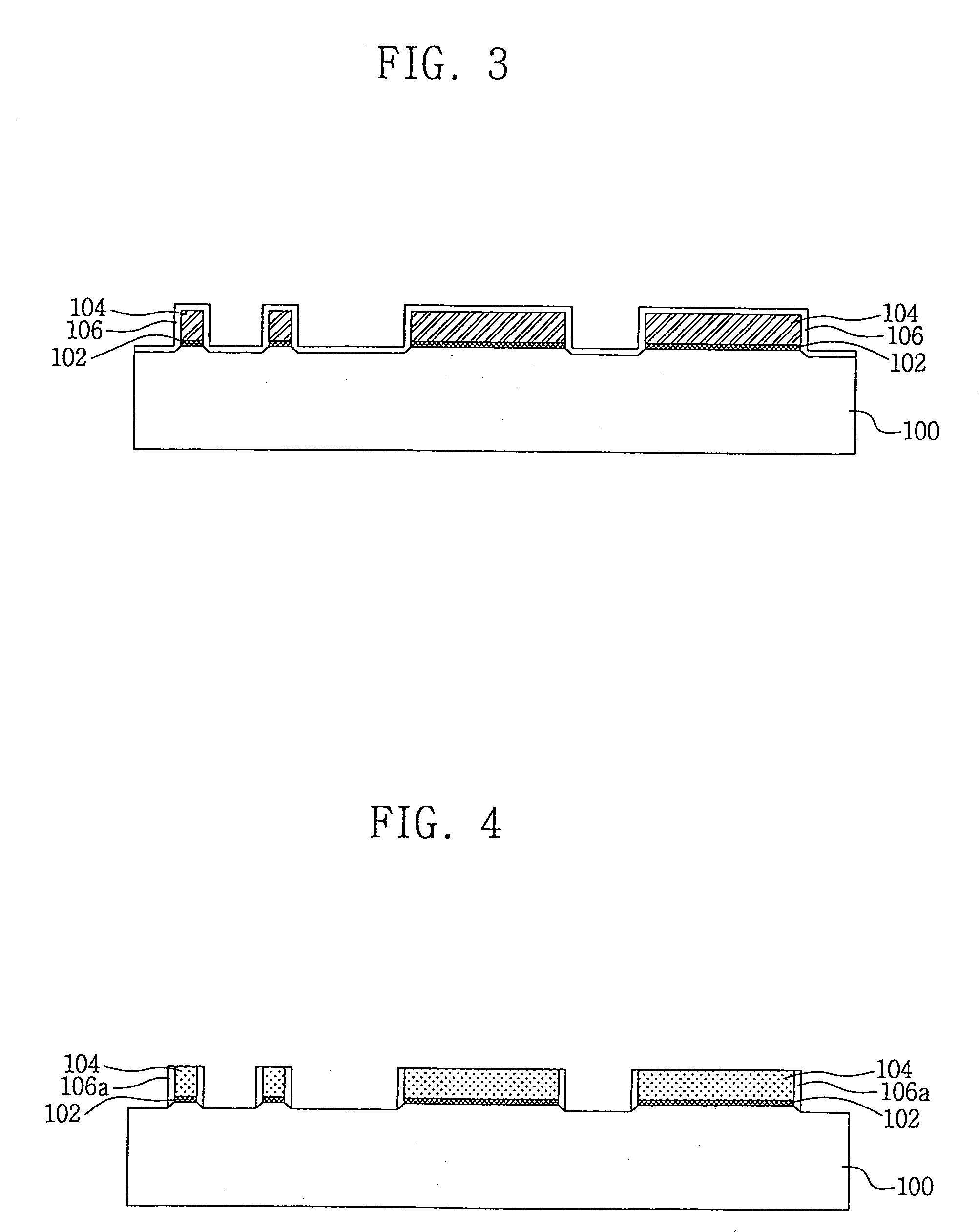

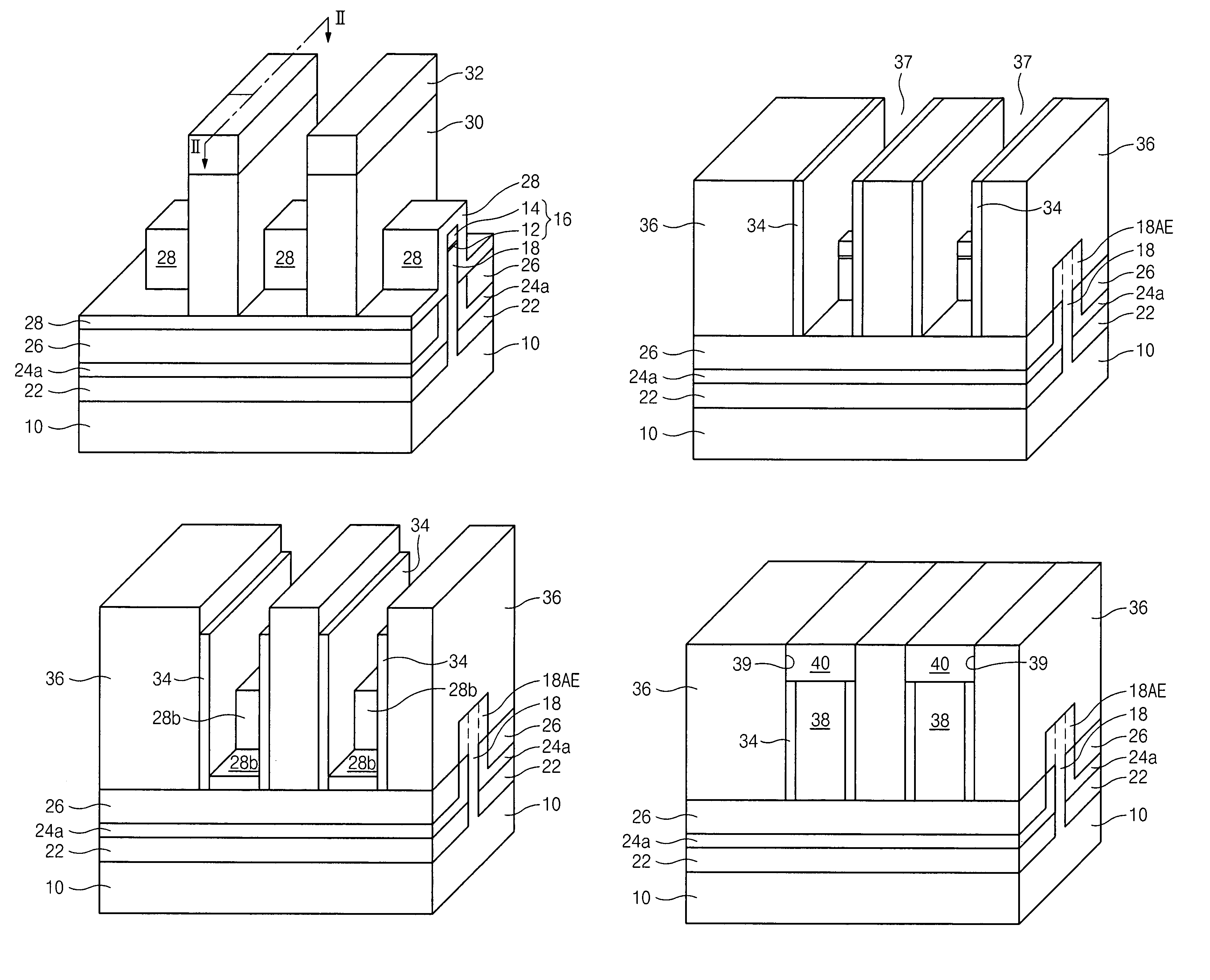

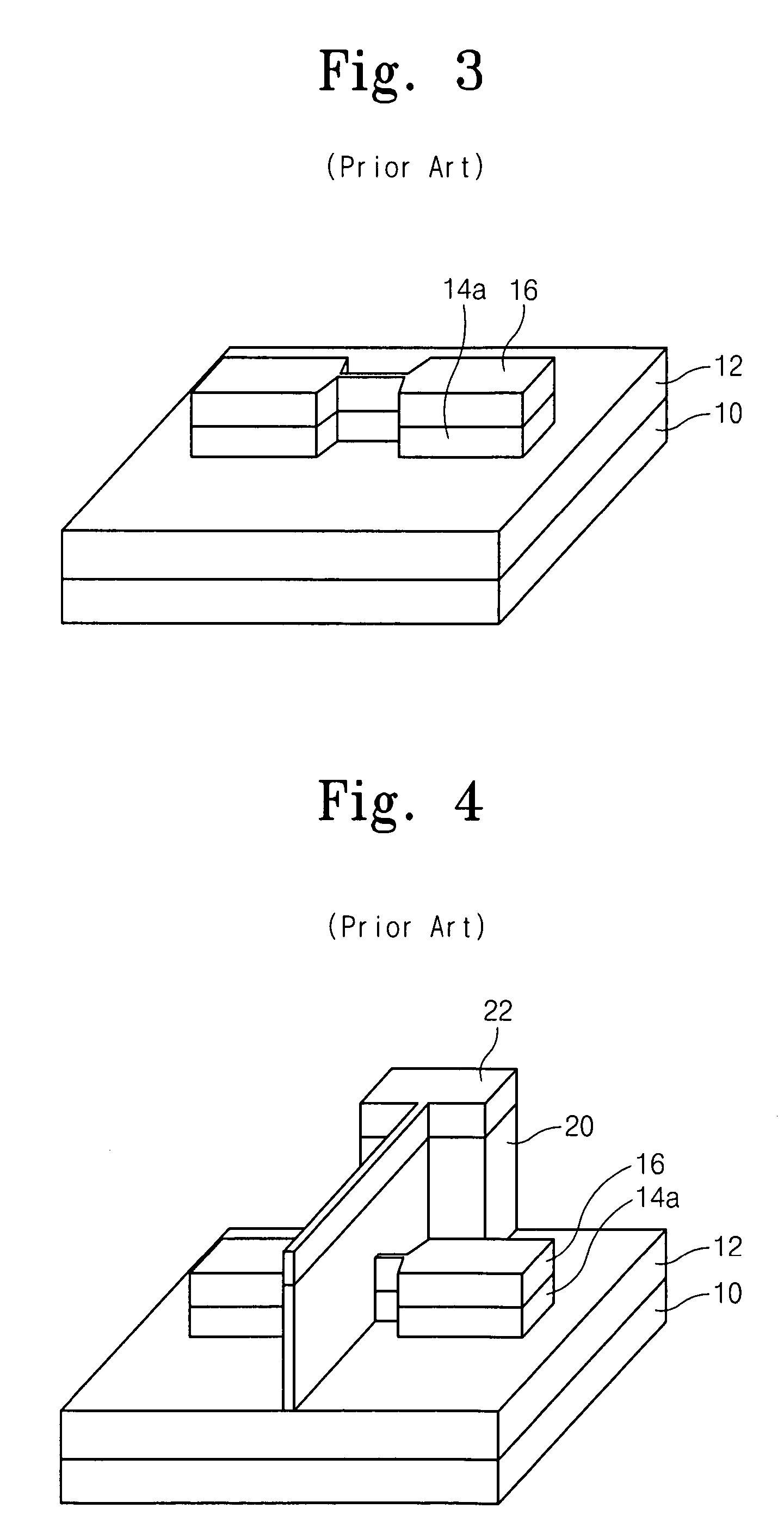

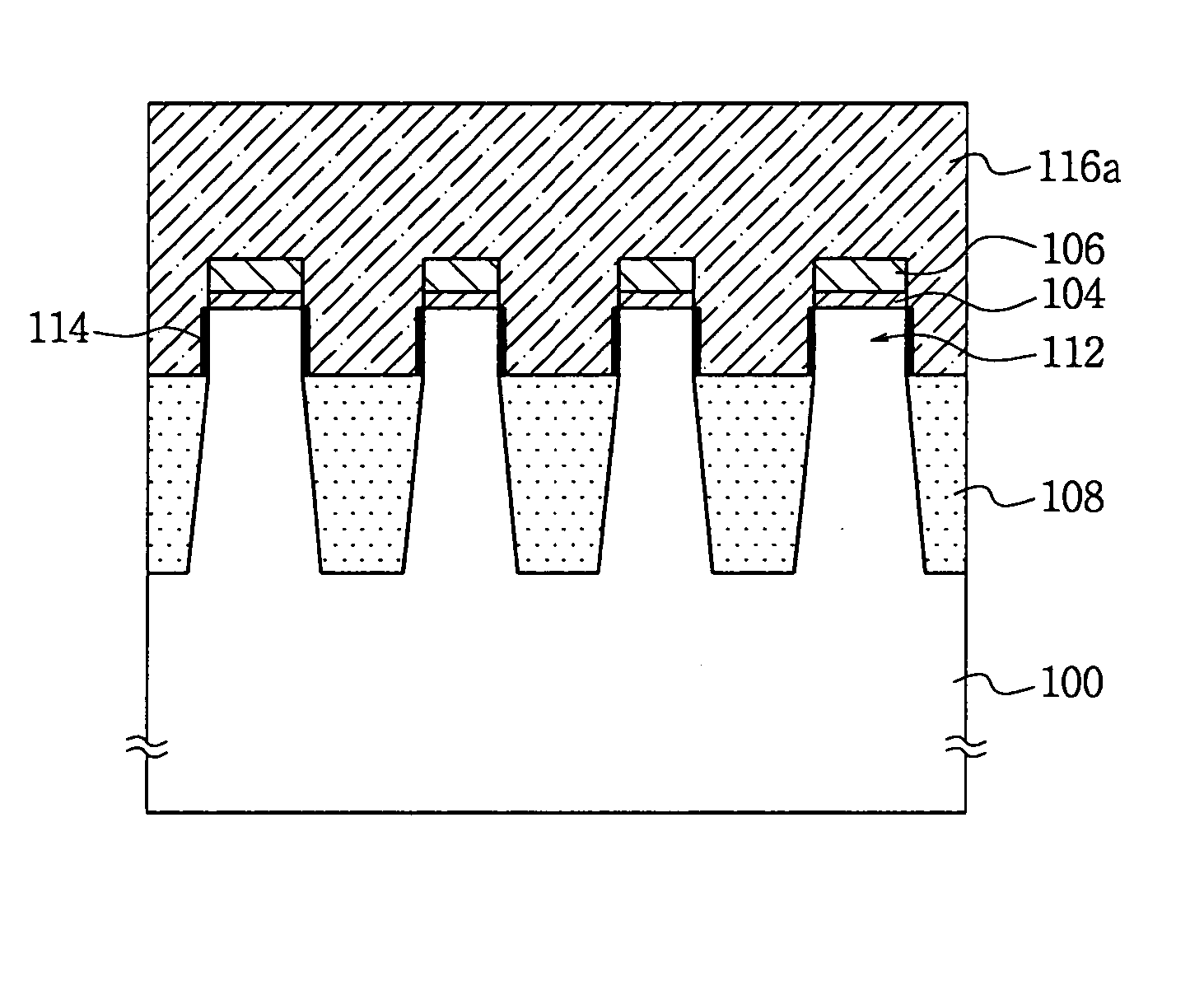

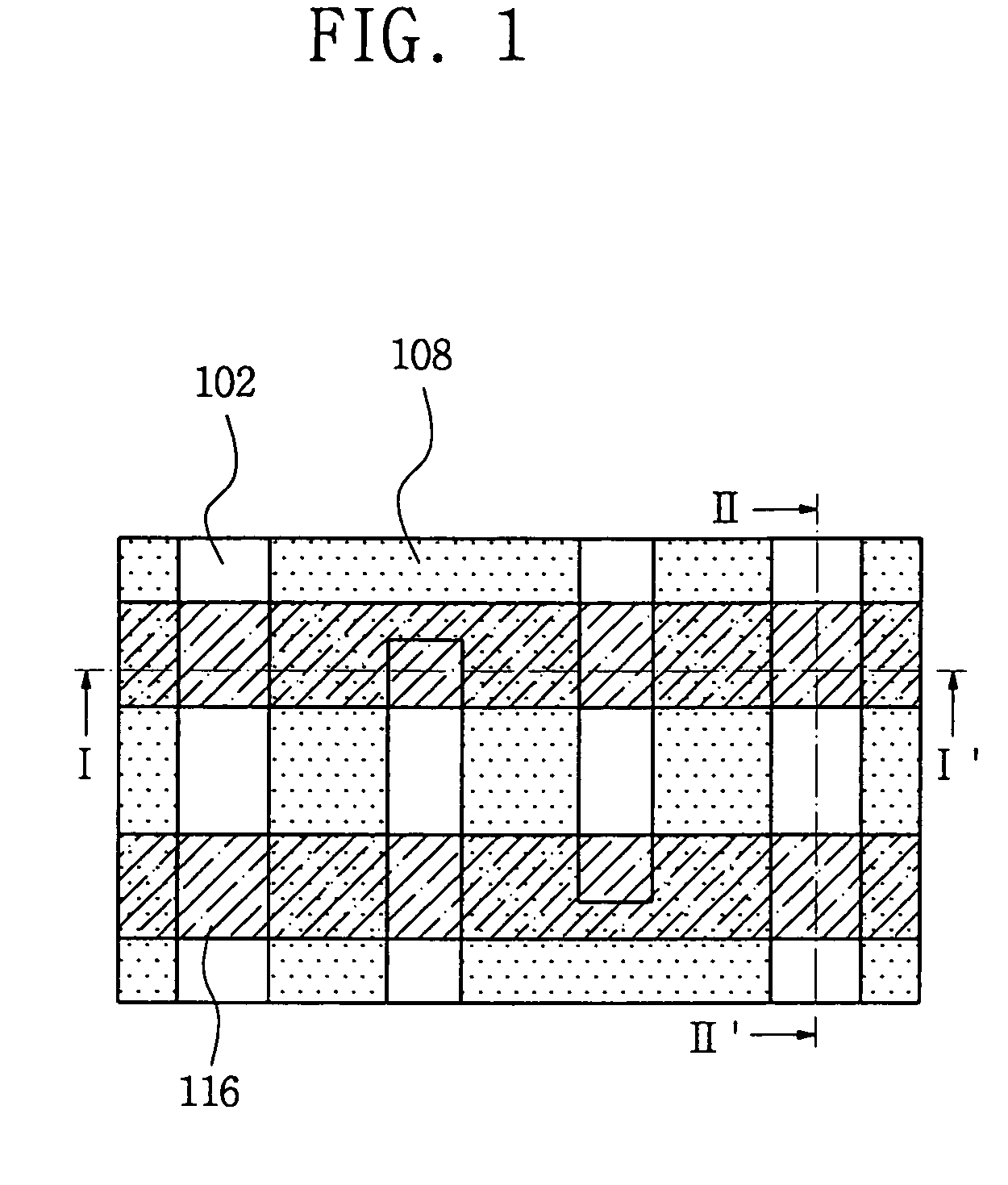

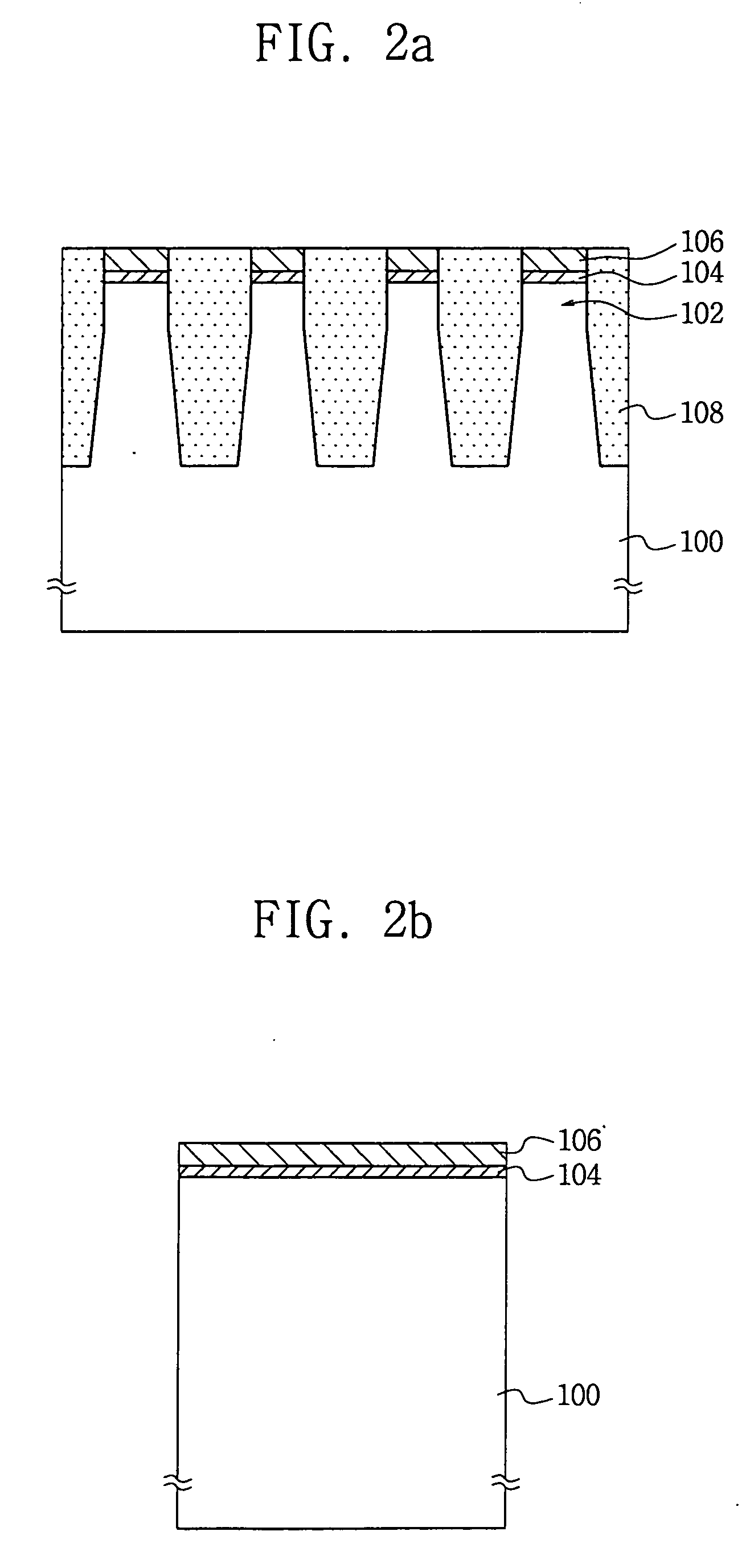

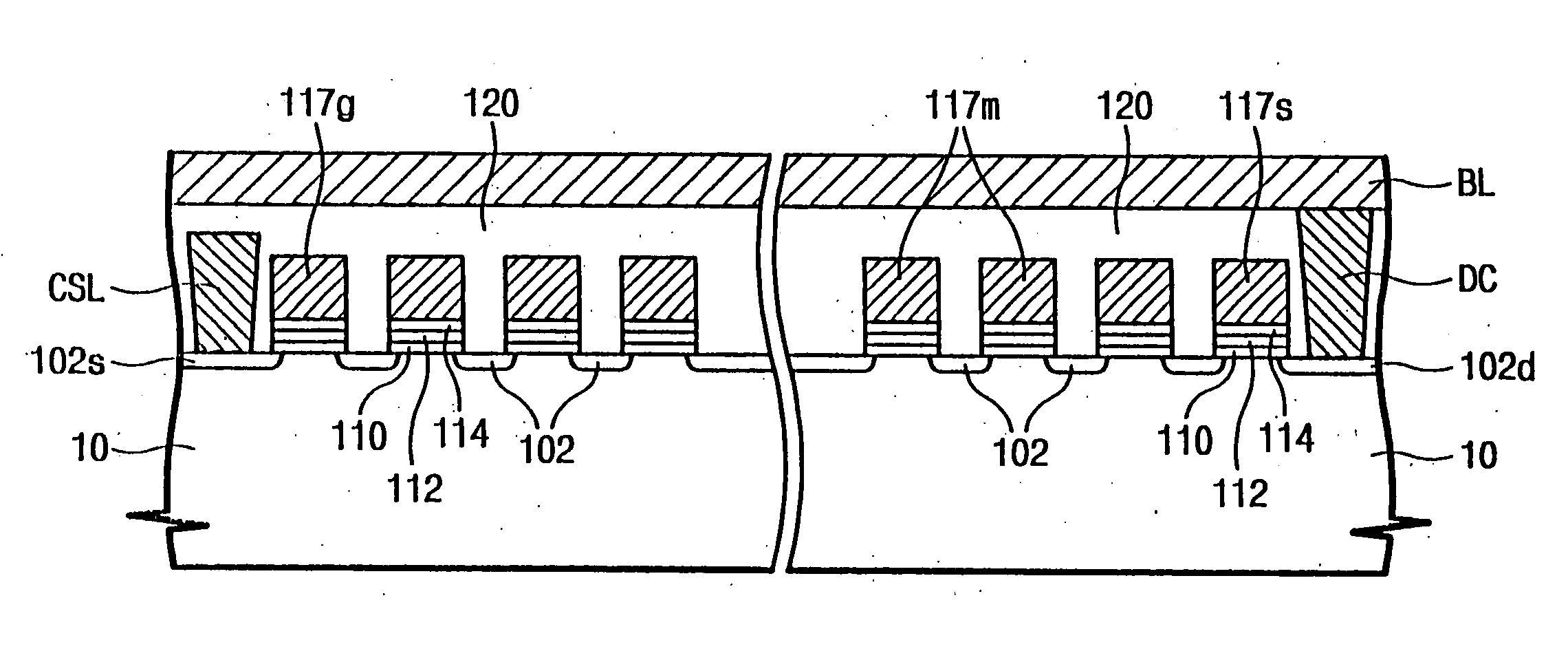

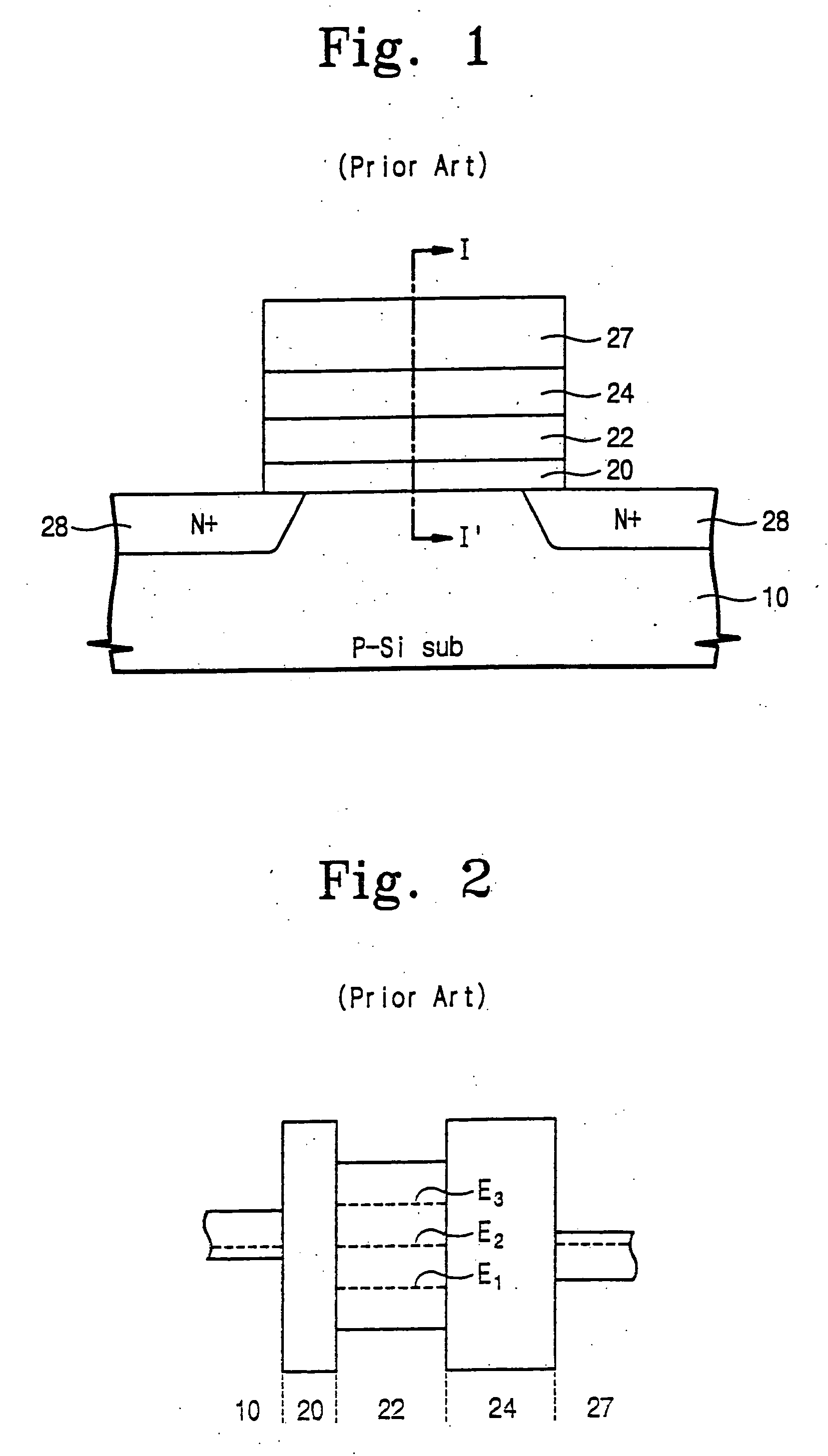

Method of forming fin field effect transistor

ActiveUS20050153490A1Prevent and substantially reduce leakage currentElectrode can be separatedTransistorSolid-state devicesInsulation layerDrain current

According to some embodiments, a fin type active region is formed under an exposure state of sidewalls on a semiconductor substrate. A gate insulation layer is formed on an upper part of the active region and on the sidewalls, and a device isolation film surrounds the active region to an upper height of the active region. The sidewalls are partially exposed by an opening part formed on the device isolation film. The opening part is filled with a conductive layer that partially covers the upper part of the active region, forming a gate electrode. Source and drain regions are on a portion of the active region where the gate electrode is not. The gate electrode may be easily separated and problems causable by etch by-product can be substantially reduced, and a leakage current of channel region and an electric field concentration onto an edge portion can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

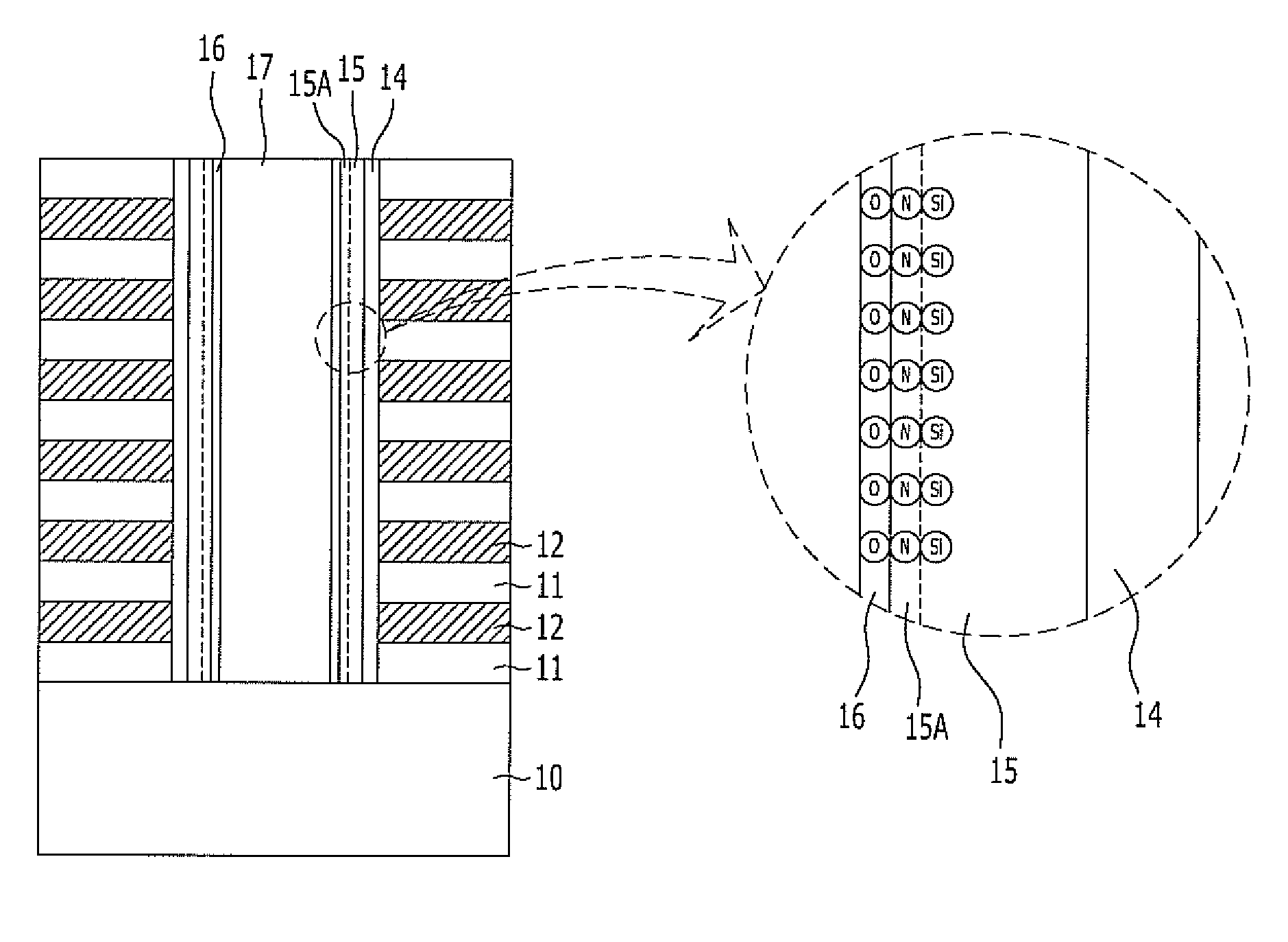

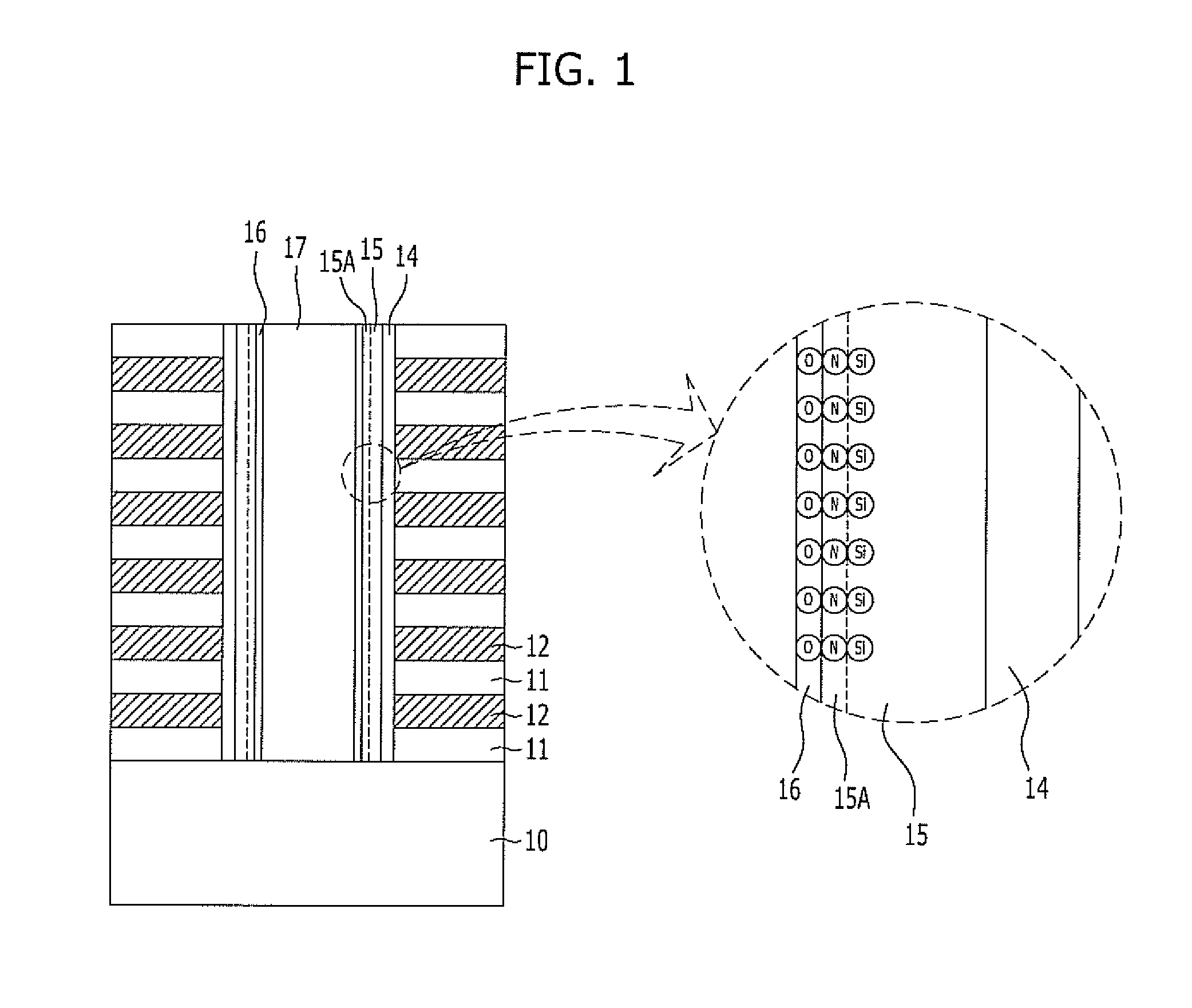

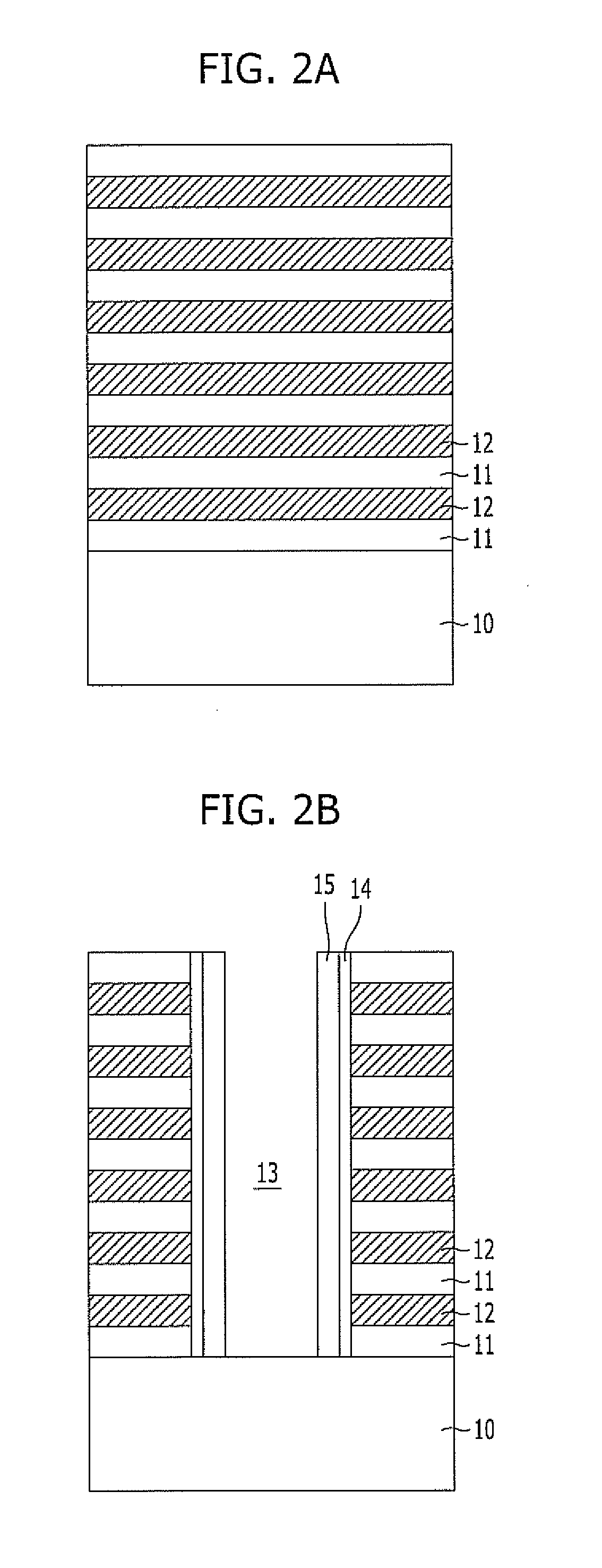

Vertical channel type nonvolatile memory device and method for fabricating the same

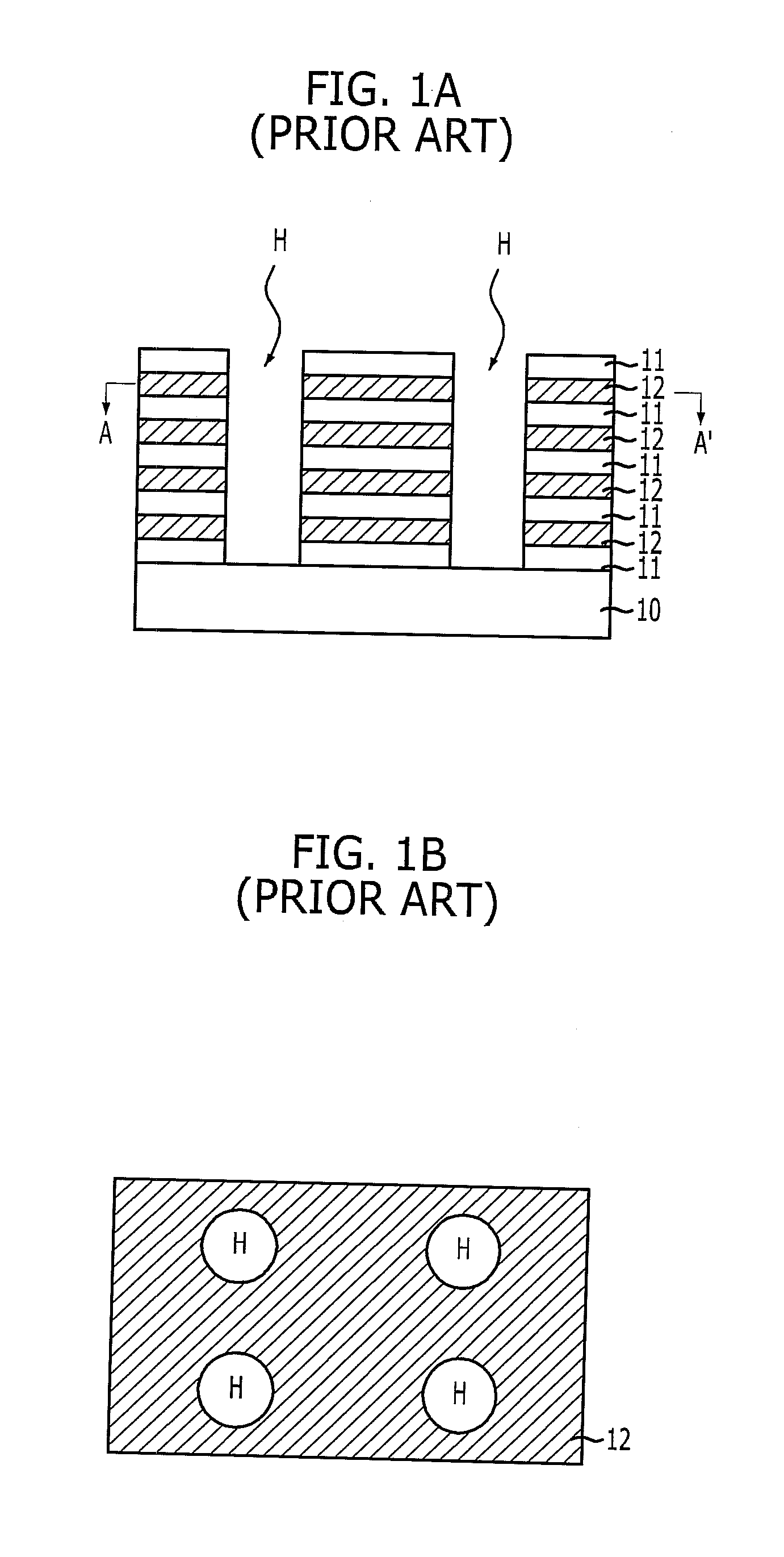

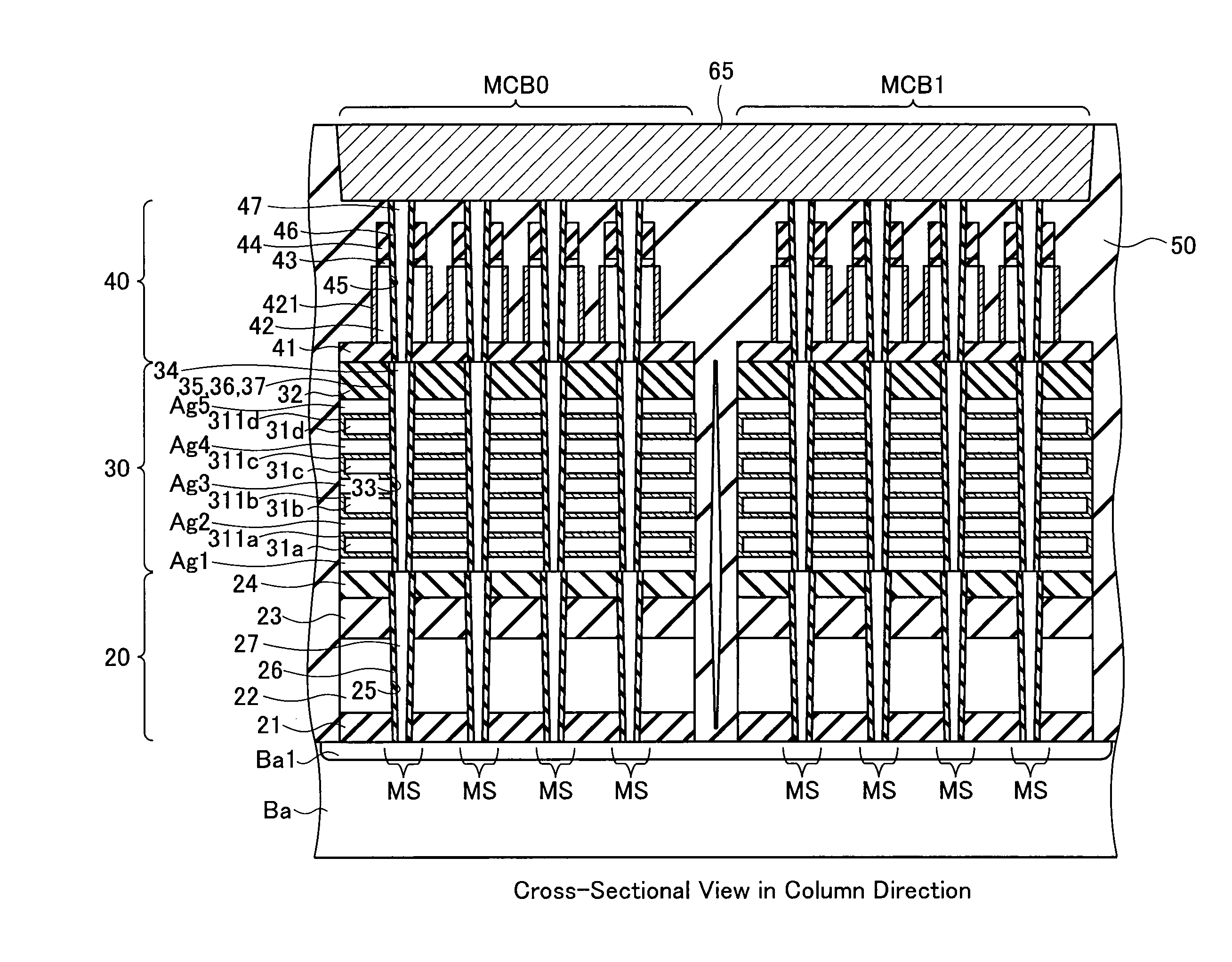

A method for fabricating, a vertical channel type nonvolatile memory device includes: alternately forming a plurality of sacrificial layers and a plurality of interlayer dielectric layers over a semiconductor substrate; etching the sacrificial layers and the interlayer dielectric layers to form a plurality of first openings for channel each of which exposes the substrate; filling the first openings to form a plurality of channels protruding from the semiconductor substrate; etching the sacrificial layers and the interlayer dielectric layers to form second openings for removal of the sacrificial layers between the channels; exposing sidewalls of the channels by removing the sacrificial layers exposed by the second openings; and forming a tunnel insulation layer, a charge trap layer, a charge blocking layer, and a conductive layer for gate electrode on the exposed sidewalls of the channels.

Owner:SK HYNIX INC

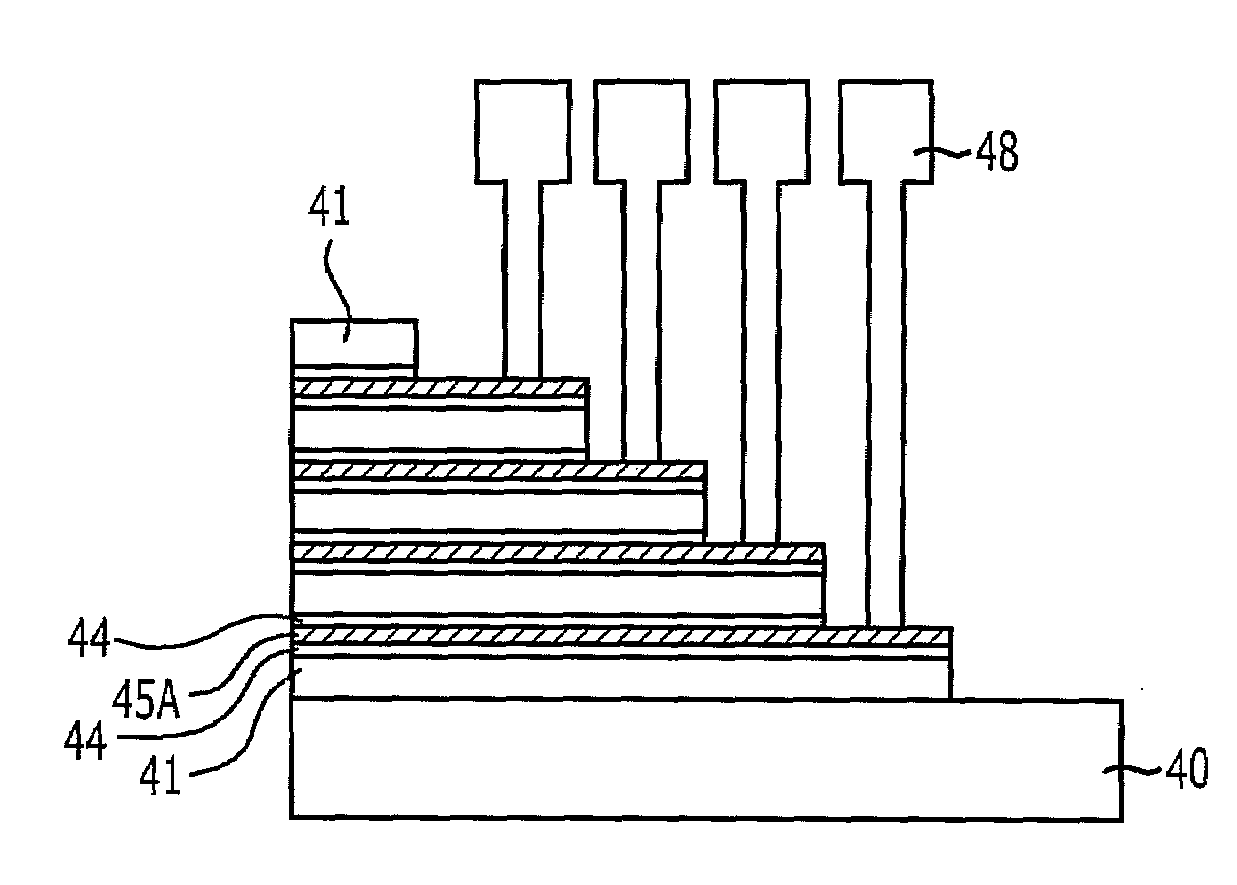

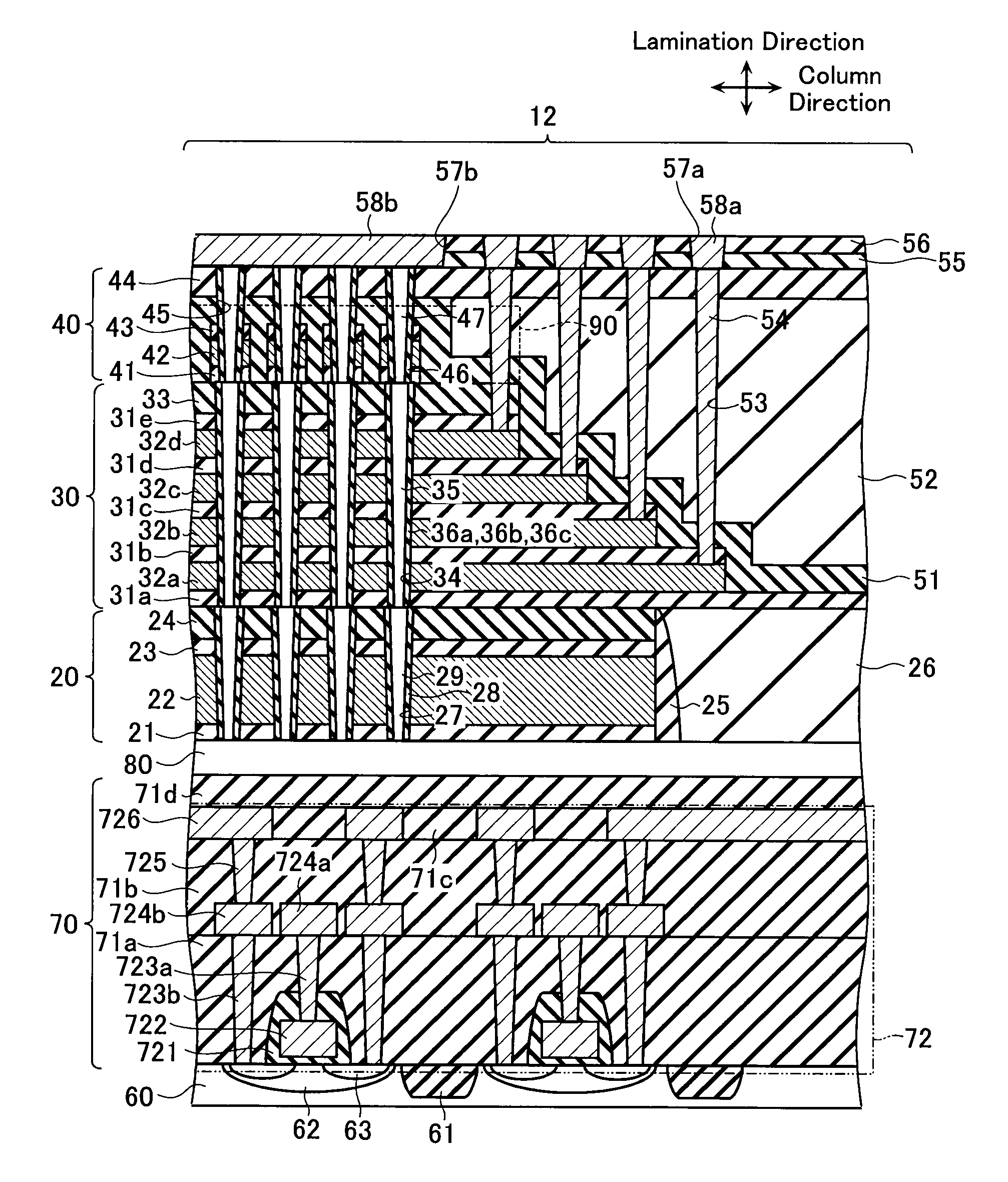

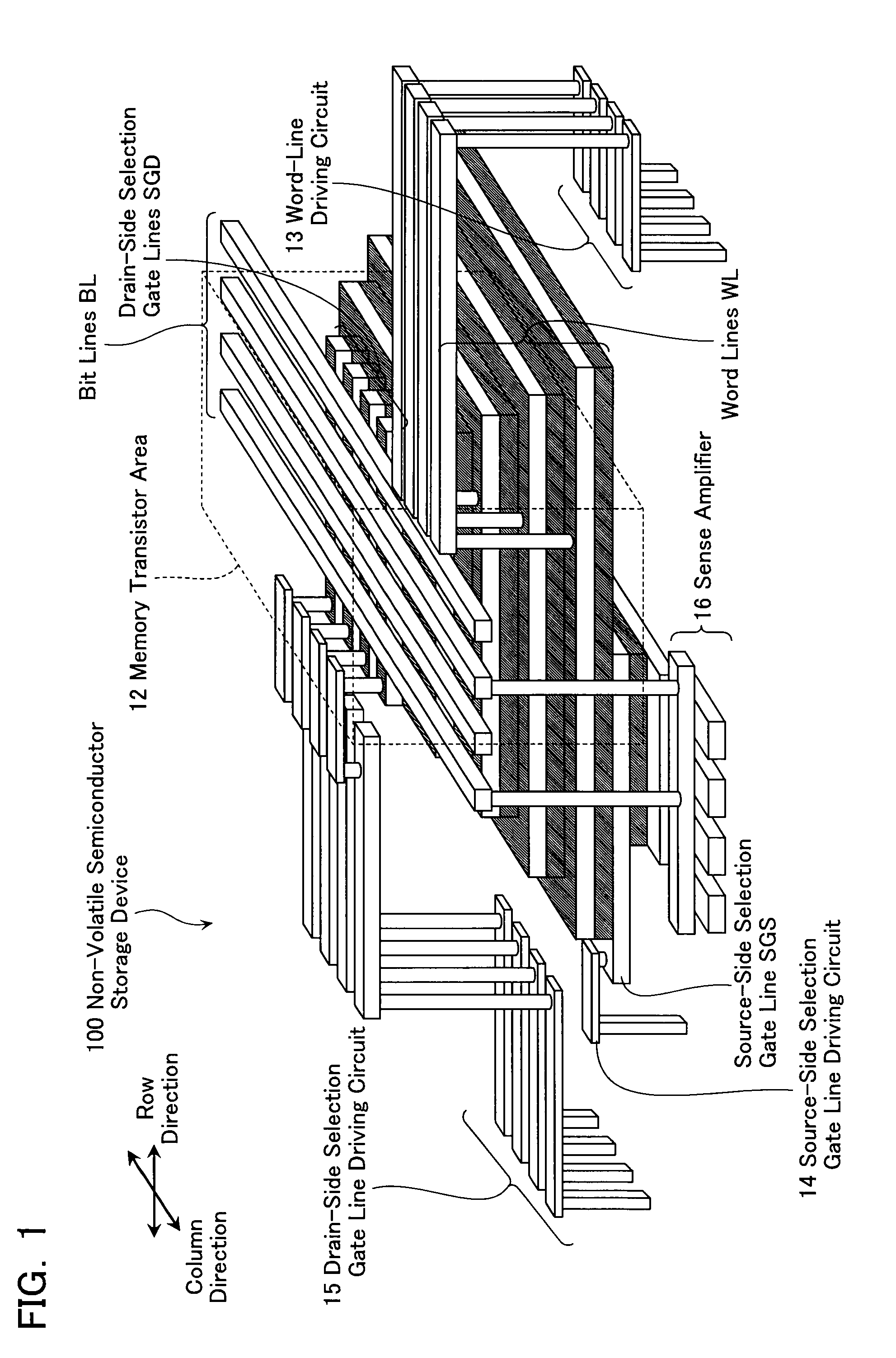

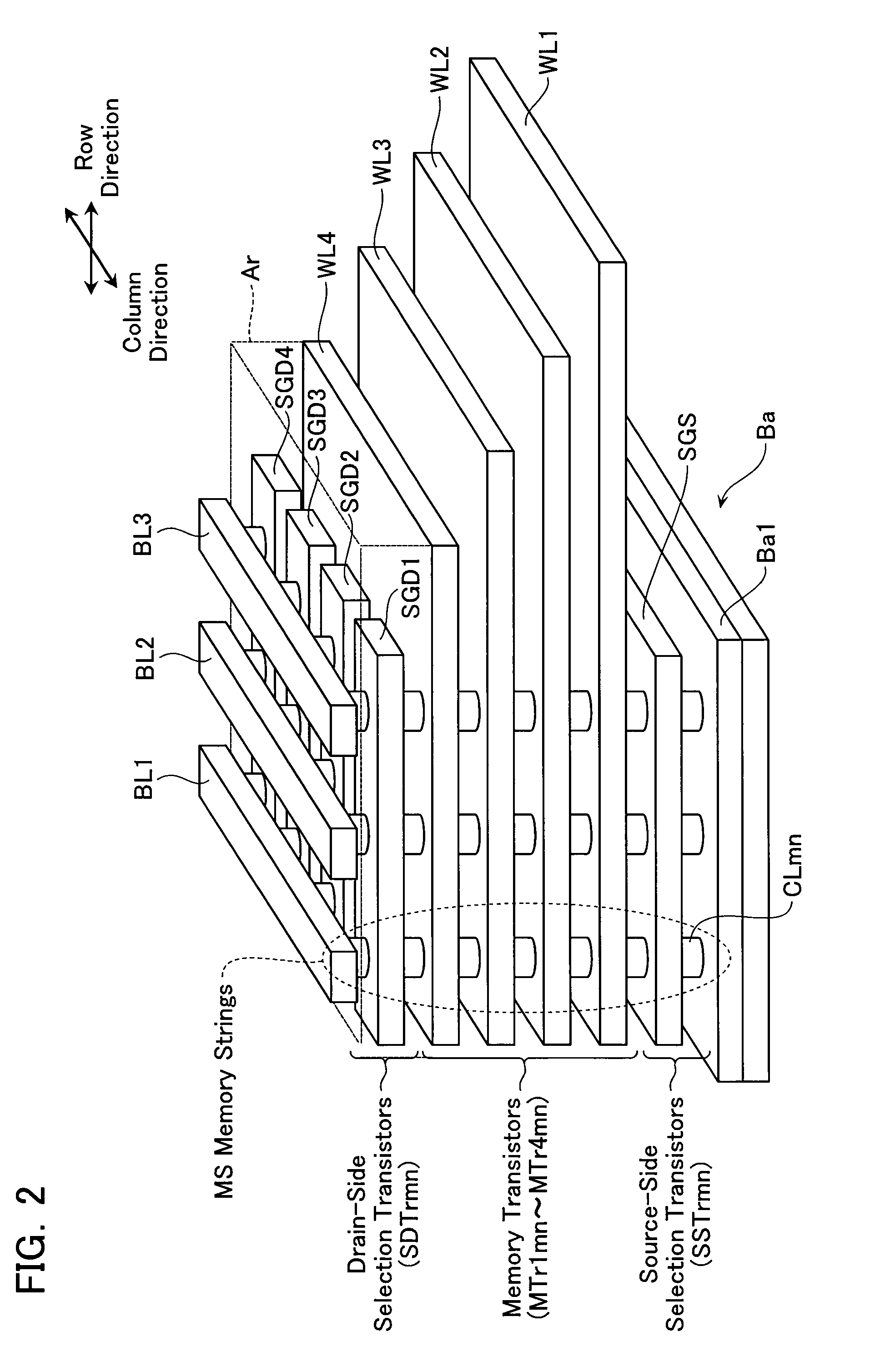

Non-volatile semiconductor storage device and method of manufacturing the same

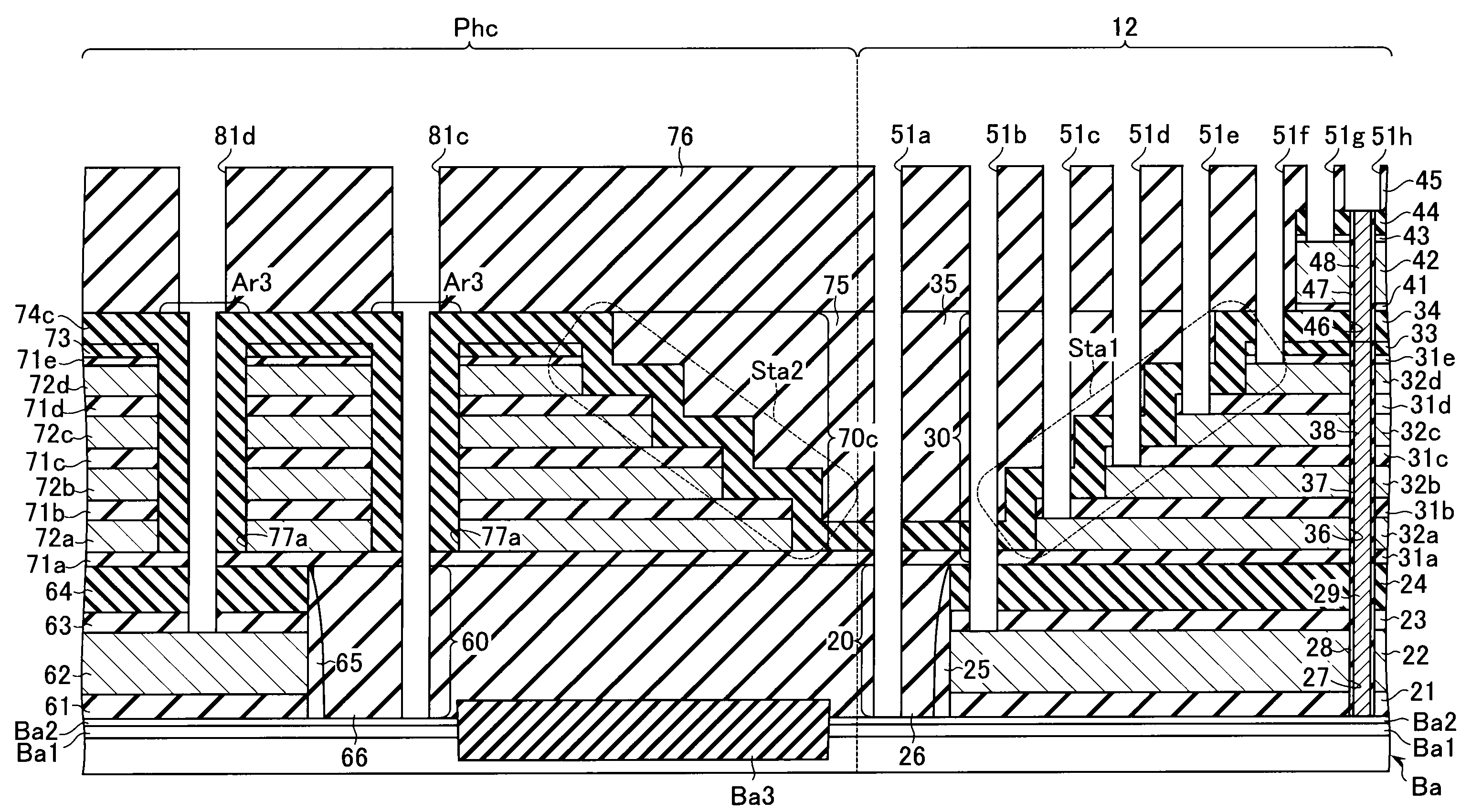

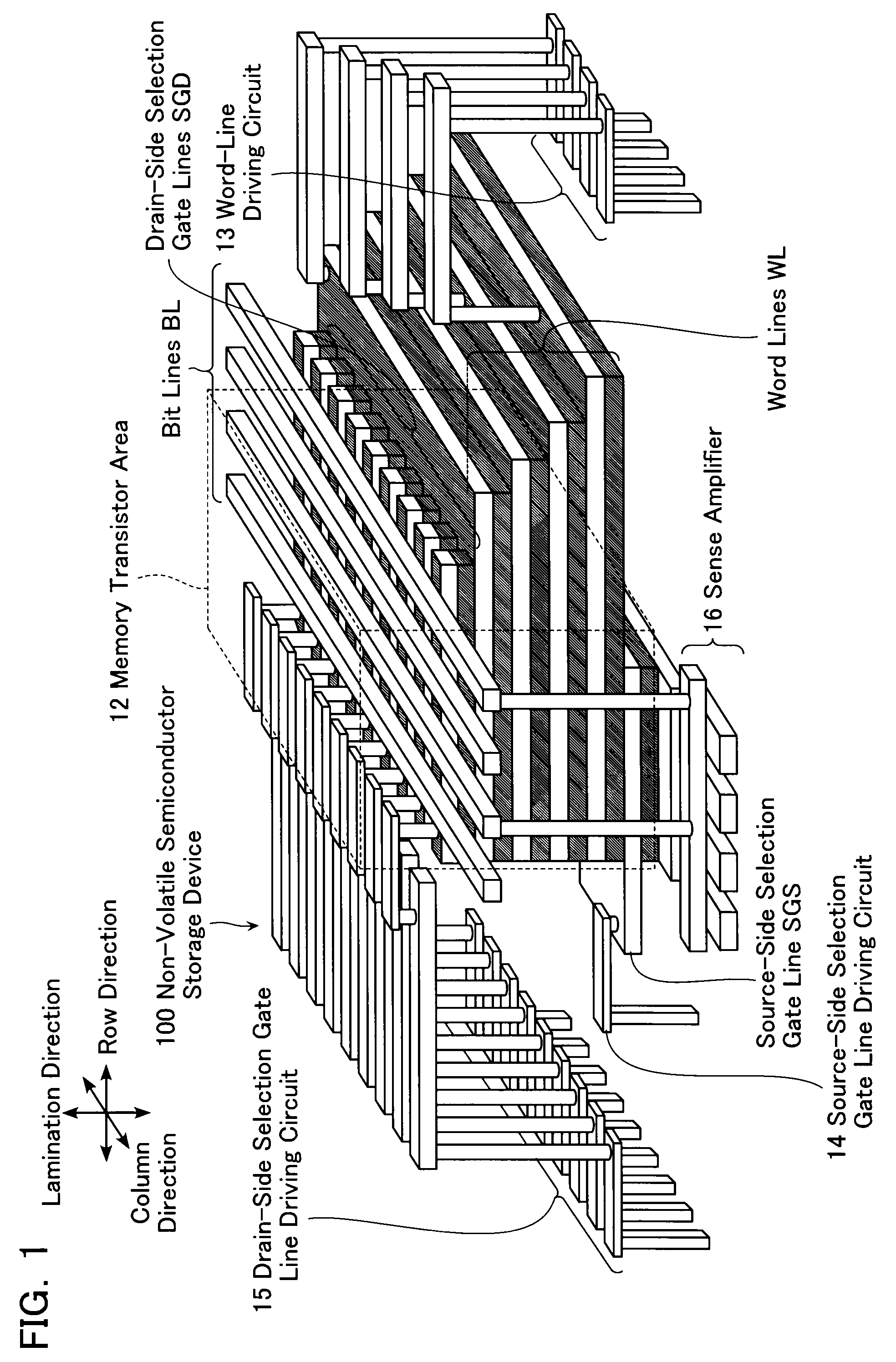

ActiveUS20090267135A1Solid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorInsulation layer

A non-volatile semiconductor storage device includes a first layer and a second layer. The first layer includes: a plurality of first conductive layers extending in parallel to a substrate and laminated in a direction perpendicular to the substrate; a first insulation layer formed on an upper layer of the plurality of first conductive layers; a first semiconductor layer formed to penetrate the plurality of first conductive layers; and a charge accumulation layer formed between the first conductive layers and the first semiconductor layer. Respective ends of the first conductive layers are formed in a stepwise manner in relation to each other in a first direction. The second layer includes: a plurality of second conductive layers extending in parallel to the substrate and laminated in a direction perpendicular to the substrate, the second conductive layers being formed in the same layer as the plurality of first conductive layers; and a second insulation layer formed on an upper layer of the plurality of second conductive layers. Respective ends of the second conductive layers are formed to align along a straight line extending in a direction substantially perpendicular to the substrate at a predetermined area.

Owner:KIOXIA CORP

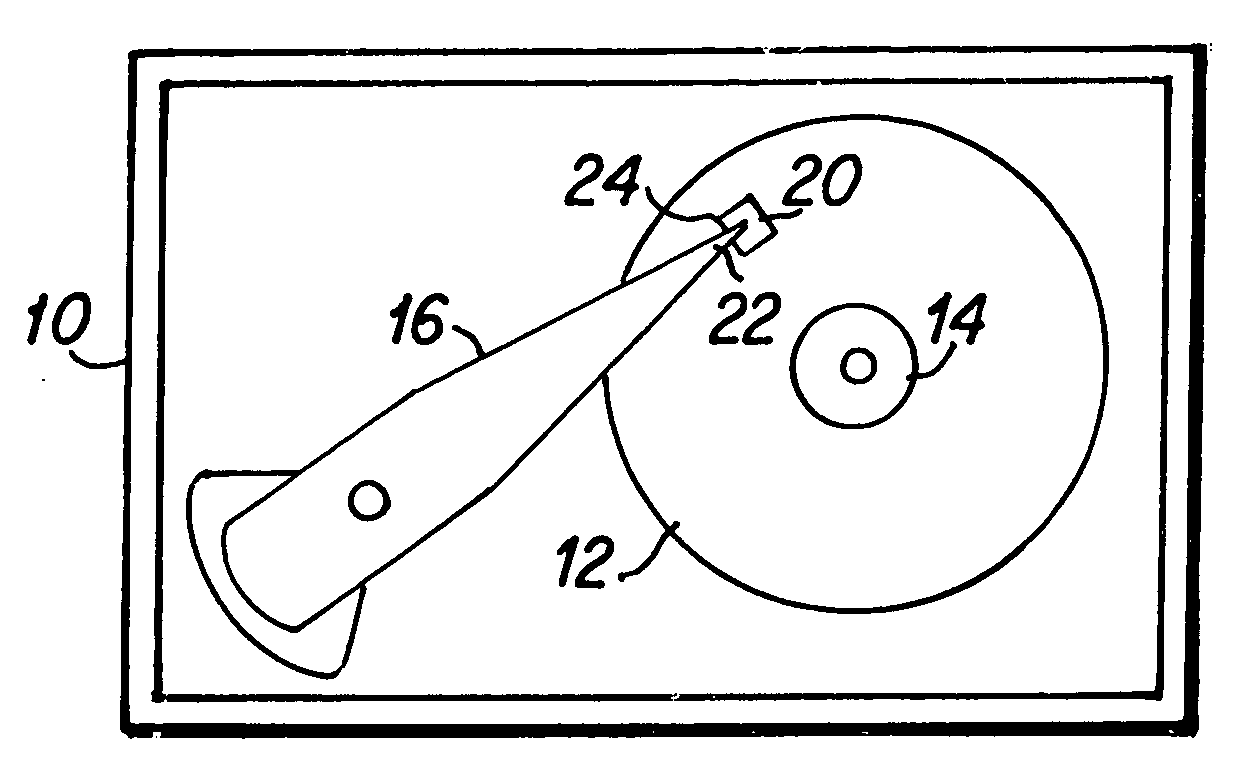

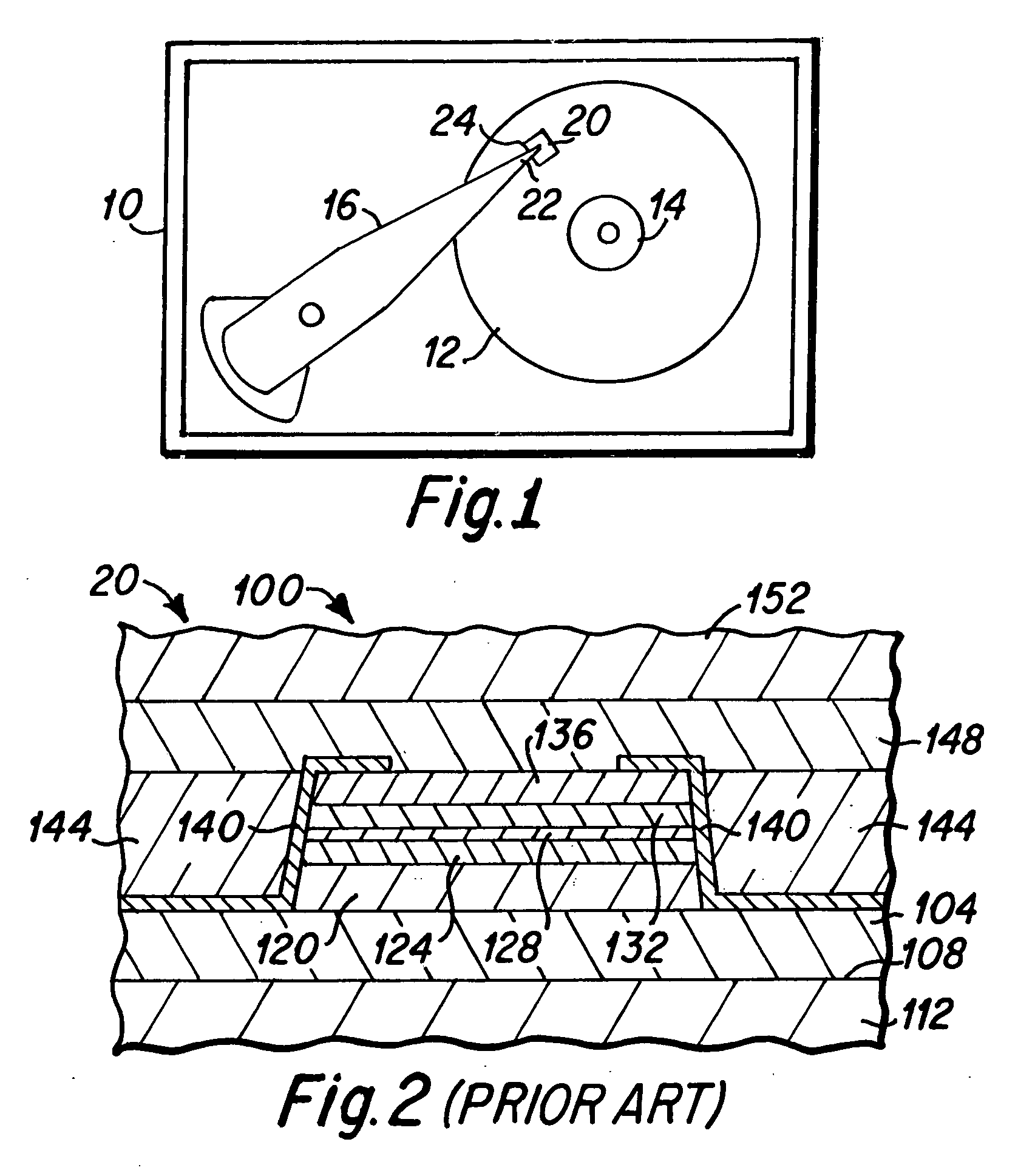

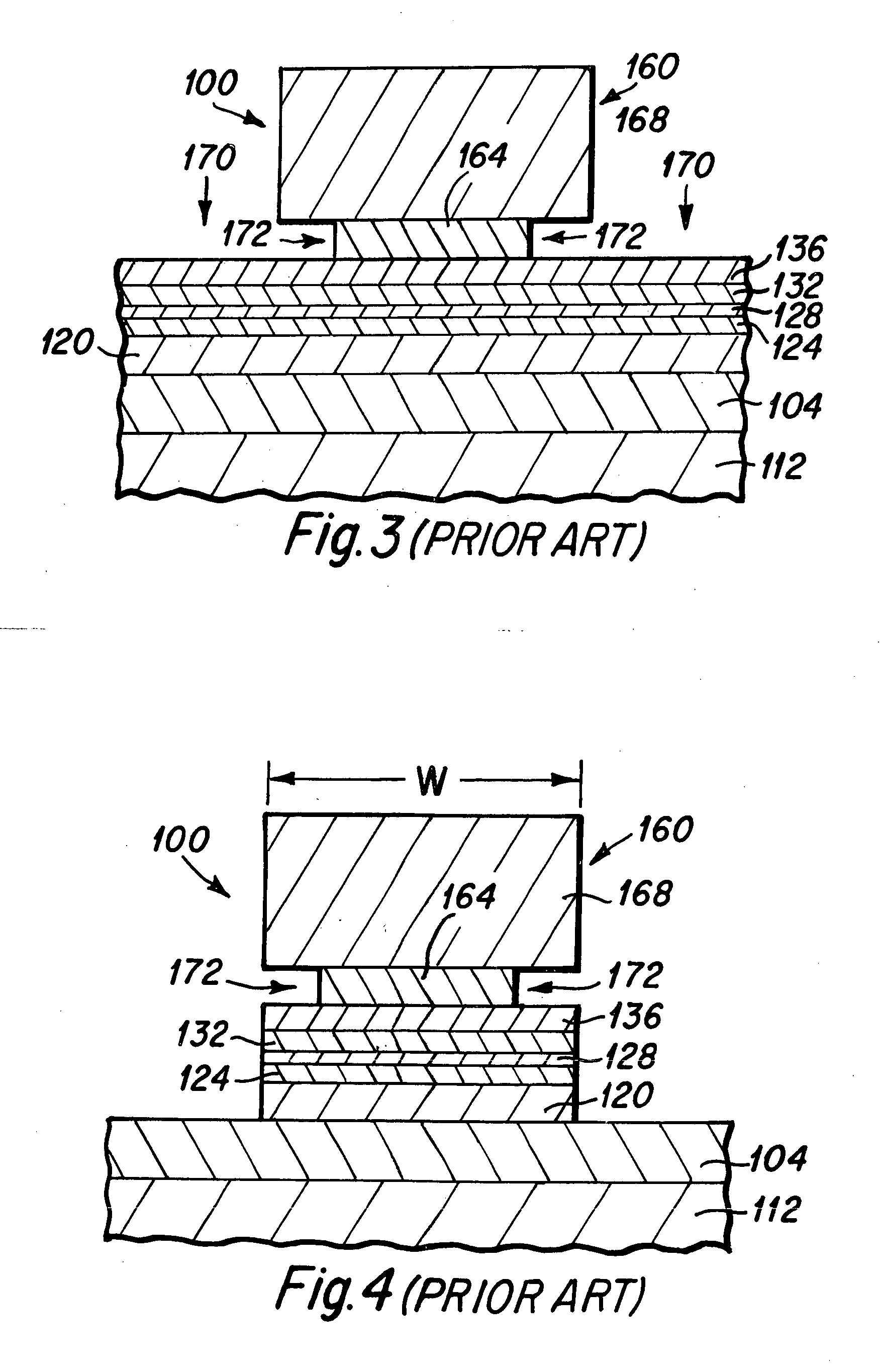

Method to fabricate side shields for a magnetic sensor

InactiveUS20060256482A1Reduce widthElectrical transducersDecorative surface effectsInsulation layerCompound (substance)

A method for fabricating magnetic side shields for an MR sensor of a magnetic head. Following the deposition of MR sensor layers, a first DLC layer is deposited. Milling mask layers are then deposited, and outer portions of the milling mask layers are removed such that a remaining central portion of the milling mask layers is formed having straight sidewalls and no undercuts. Outer portions of the sensor layers are then removed such that a relatively thick remaining central portion of the milling mask resides above the remaining sensor layers. A thin electrical insulation layer is deposited, followed by the deposition of magnetic side shields. A second DLC layer is deposited and the remaining mask layers are then removed utilizing a chemical mechanical polishing (CMP) liftoff step. Thereafter, the first DLC layer and the second DLC layer are removed and a second magnetic shield layer is then fabricated thereabove.

Owner:WESTERN DIGITAL TECH INC

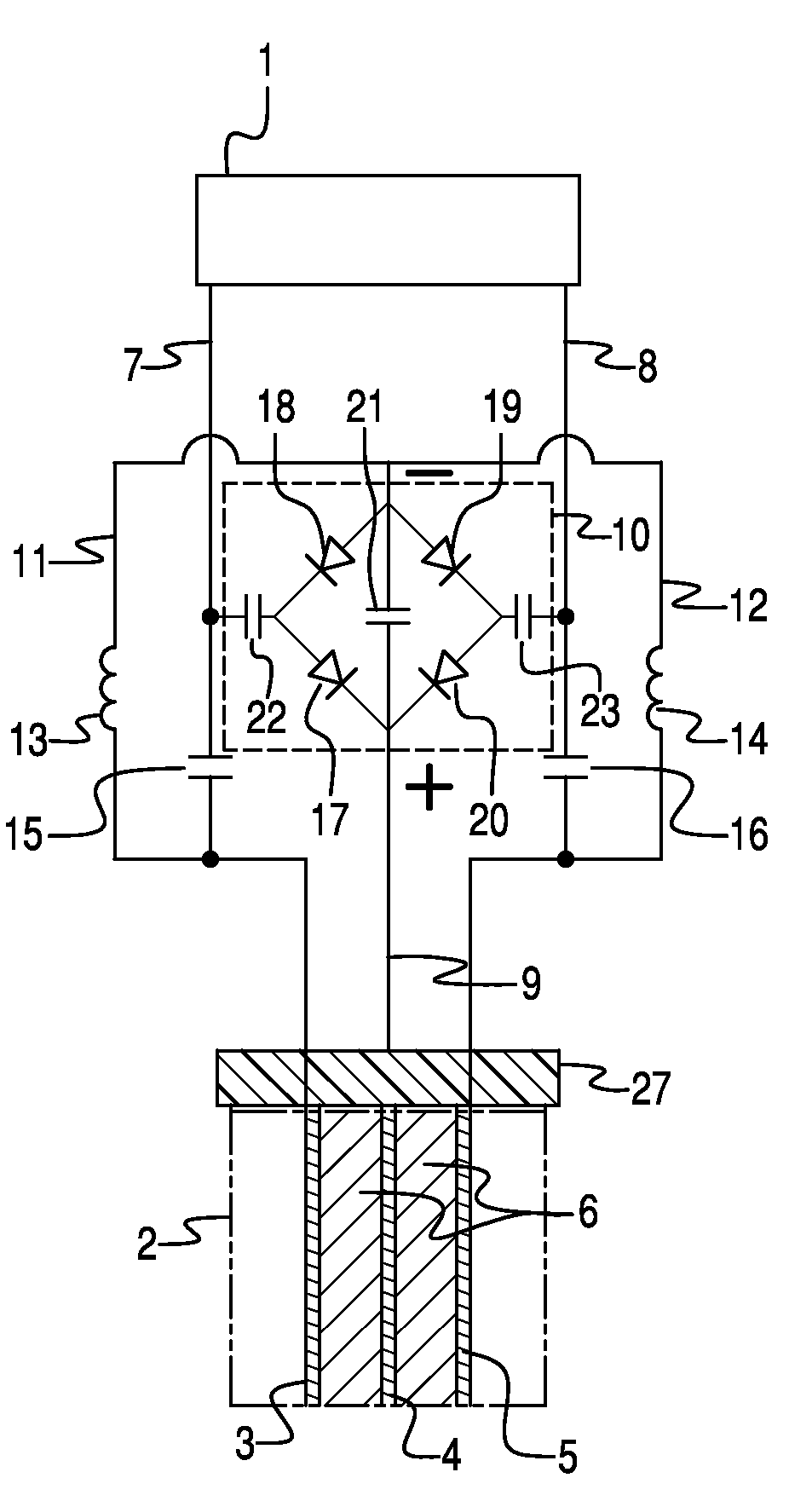

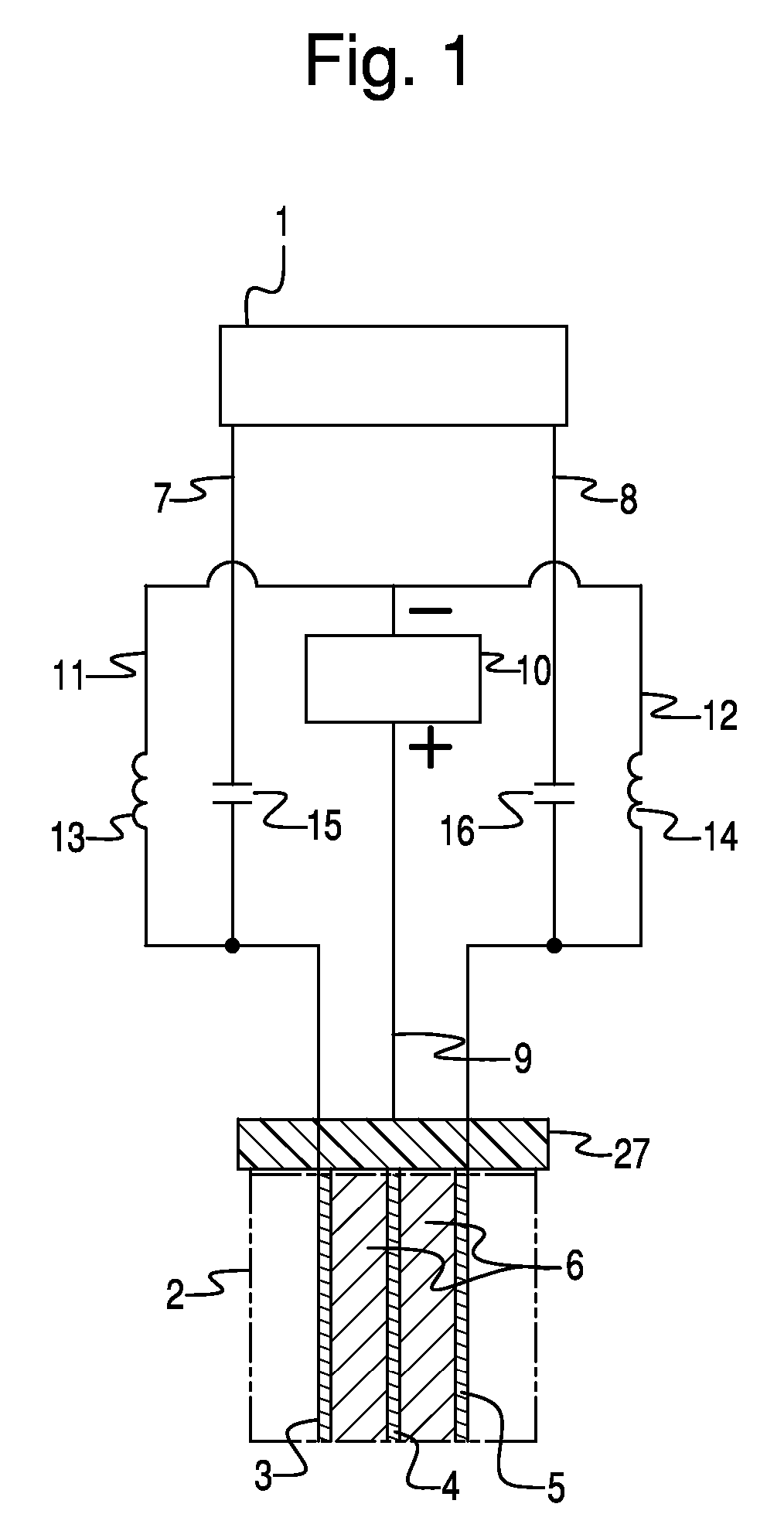

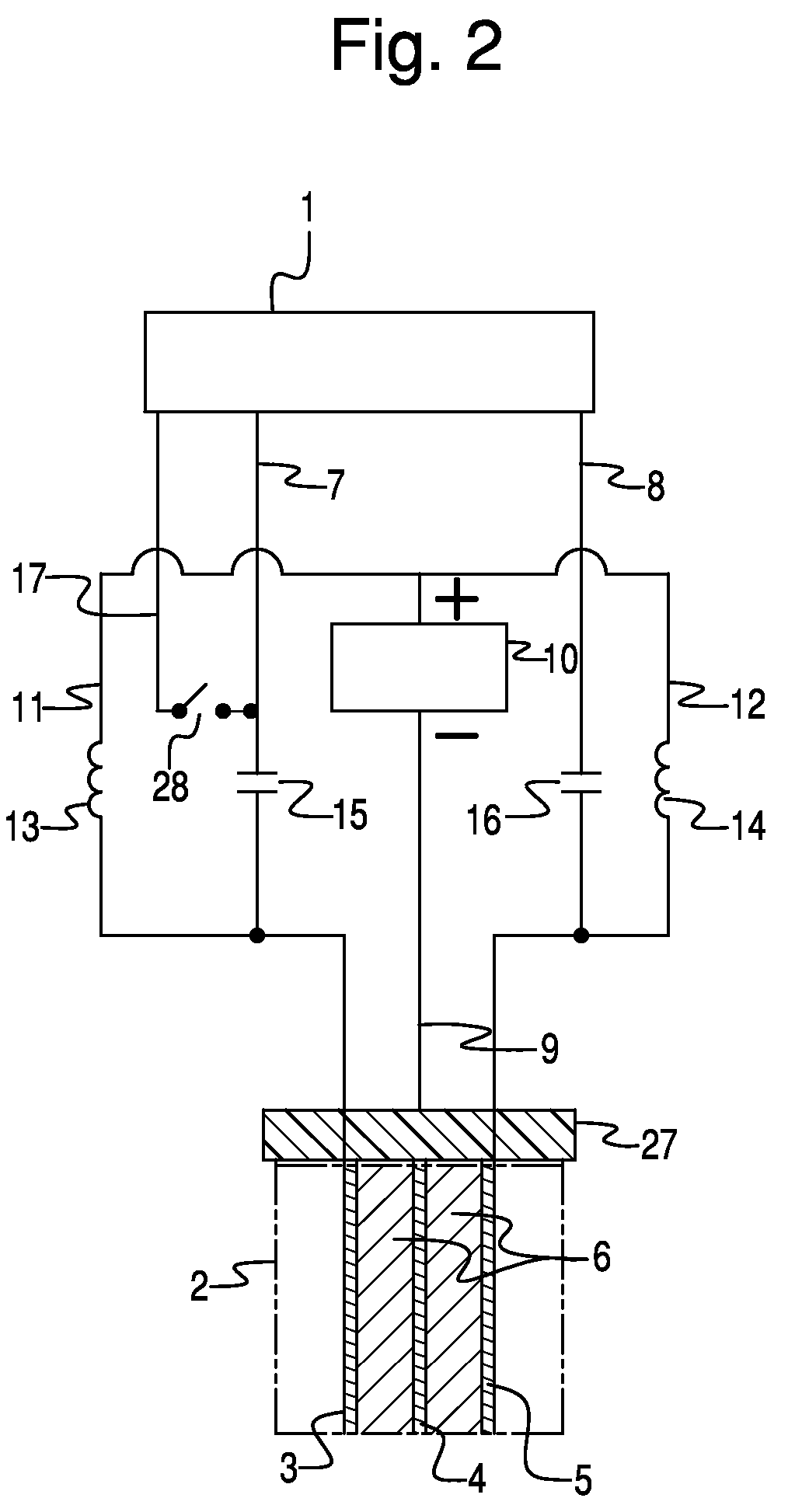

Battery powered electrosurgical system

ActiveUS7896875B2Avoid excessive accumulationMinimize durationSurgical instruments for heatingCoatingsInsulation layerElectrical conductor

An battery-powered electrosurgical instrument includes a blade having a conductor edge portion and insulation layer with geometric shapes and composition that concentrate electrosurgical energy and reduce or eliminate the production of smoke and eschar and reduce tissue damage, thereby providing more efficient application of electrosurgical energy. The more efficient use of electrosurgical energy permits configuring the system to be battery-powered. The system may be portable or configured as a battery-backup powered system.

Owner:SURGINETICS

Stress control cones for downhole electrical power system tubing encapsulated power cables

ActiveUS20190089143A1Reduce electrical stressElectrically conductive connectionsDrilling rodsInsulation layerPower cable

A stress cone for reducing electrical stresses is disclosed for use on terminated ends of tubing encapsulated power cable used in surface applications in a subsurface well power system employing electric submersible pumps (ESPs). The stress cone comprises an annular section about a longitudinal axis for receiving a terminated end of the TEPC in its first end and for abutting the terminated metal TEPC end against a metal shoulder at its second end therein, and an insulation chamber axially aligned with and connected to the annular section. The chamber comprises a metal interior surface symmetrical about the axis. The insulated TEPC core (without outer metal sheath) passes through the insulation chamber along the axis and then exits. The ID of the TEPC metal sheath and the inside metal surface of the chamber form a smooth ground plane transition surface. Insulation material surrounds the TEPC insulation layer within the insulation chamber.

Owner:ARTIFICIAL ELEVATOR

Method to remove capping layer of insulation dielectric in interconnect structures

ActiveUS20110143542A1Semiconductor/solid-state device detailsSolid-state devicesSelf limitingInsulation layer

A method for patterning an insulation layer and selectively removing a capping layer overlying the insulation layer is described. The method utilizes a dry non-plasma removal process. The dry non-plasma removal process may include a self-limiting process.

Owner:TOKYO ELECTRON LTD

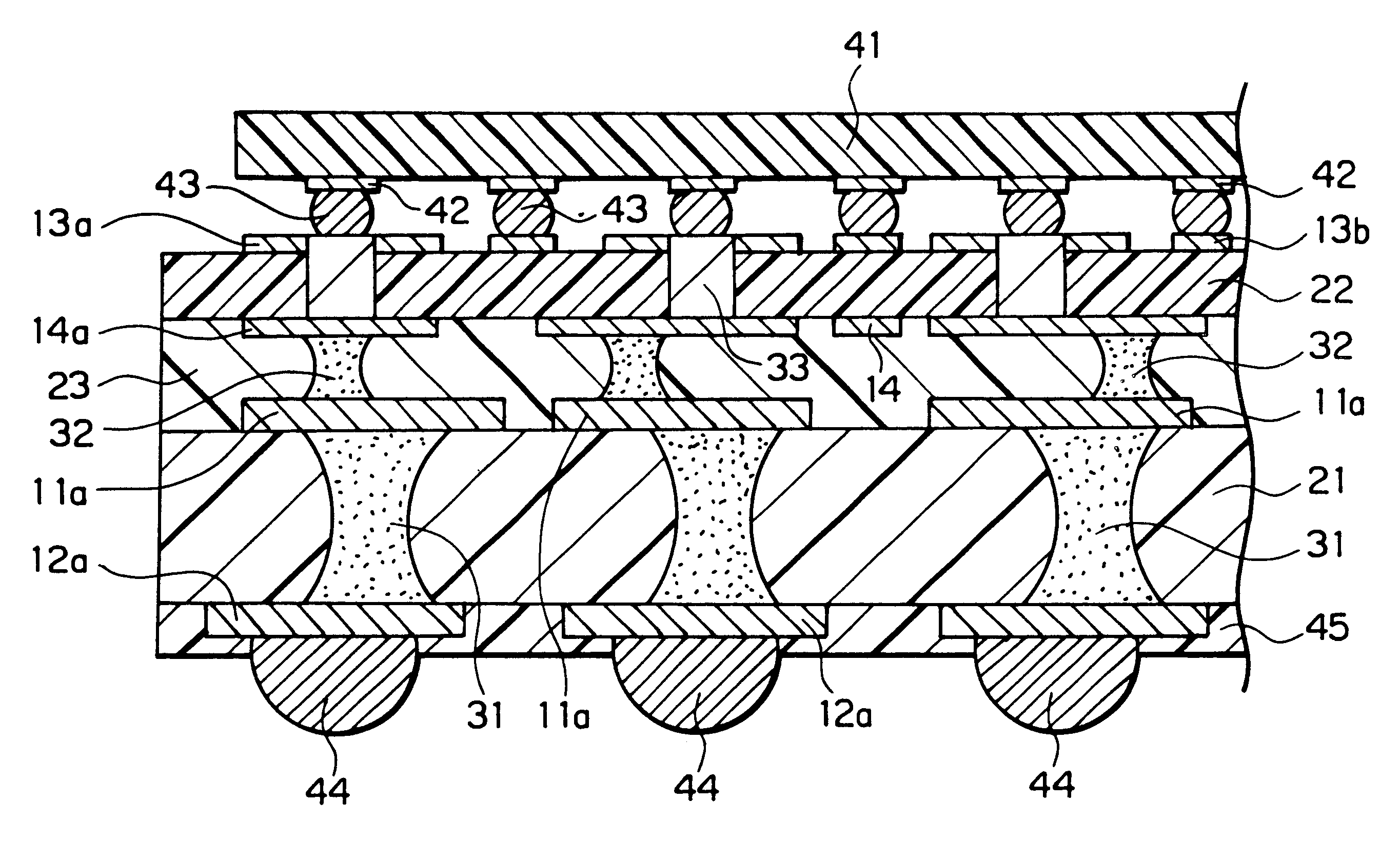

Hybrid wiring board, semiconductor apparatus, flexible substrate, and fabrication method of hybrid wiring board

InactiveUS6329610B1Semiconductor/solid-state device detailsPrinted electric component incorporationInsulation layerEngineering

A first via land of a wiring layer on a first surface of a first insulation layer that is a rigid layer and a second via land of a wiring layer on a second surface of a second insulation layer that is a flexible layer are electrically and mechanically connected with a conductive pillar pierced through a third insulation layer disposed between the first insulation layer and the second insulation layer. In such a structure, a wiring board that can mount a highly integrated semiconductor device, that is small and thin, and that has high reliability can be accomplished.

Owner:KK TOSHIBA

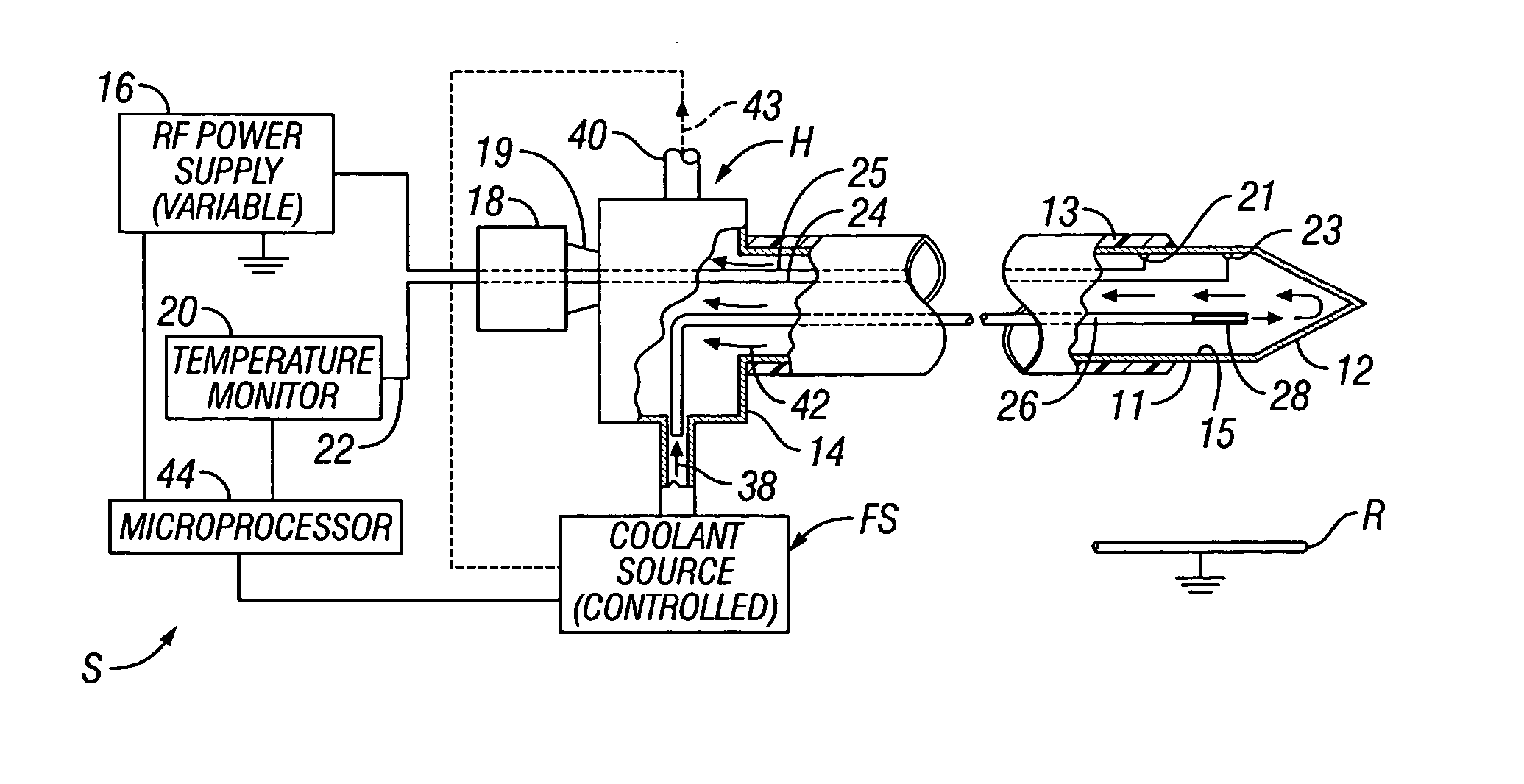

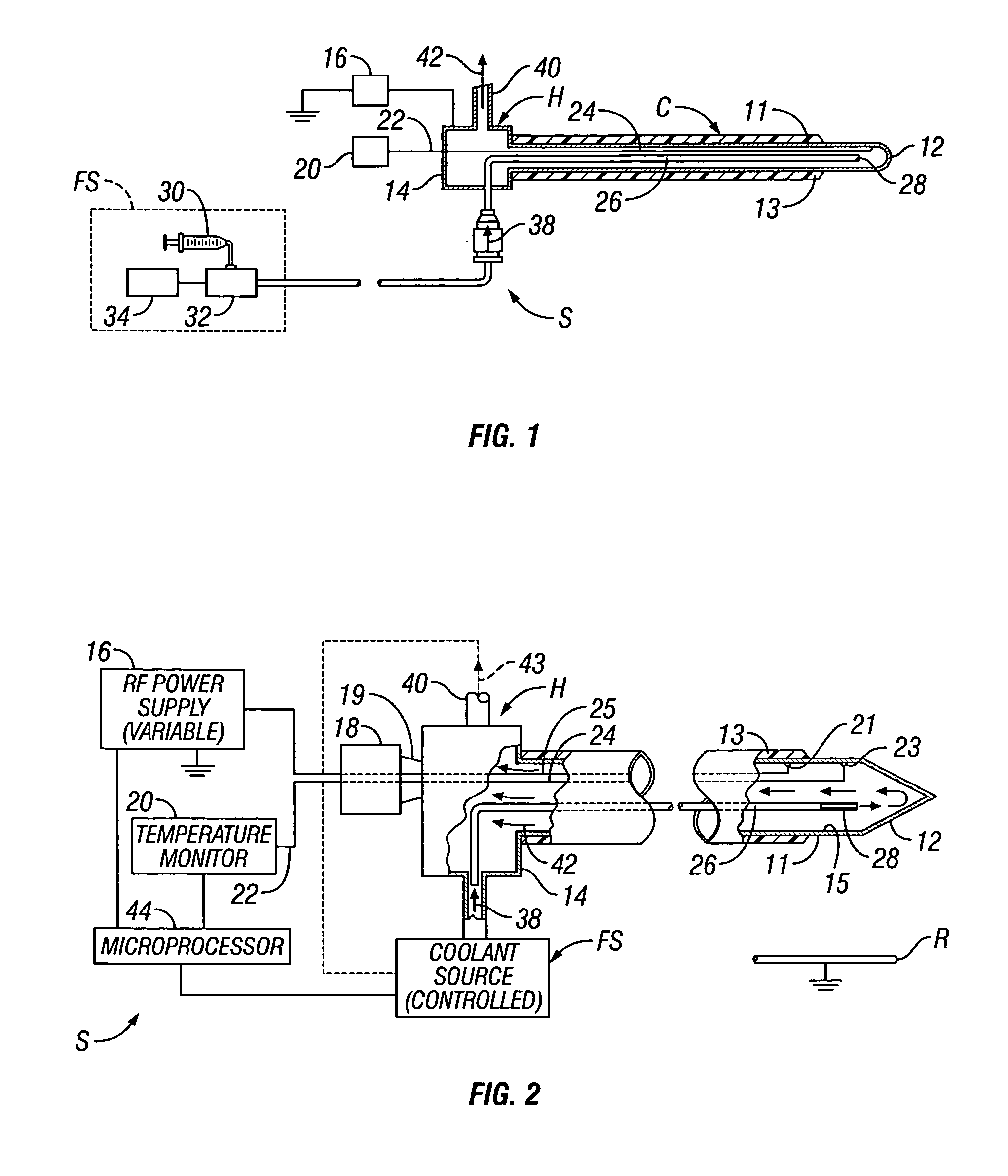

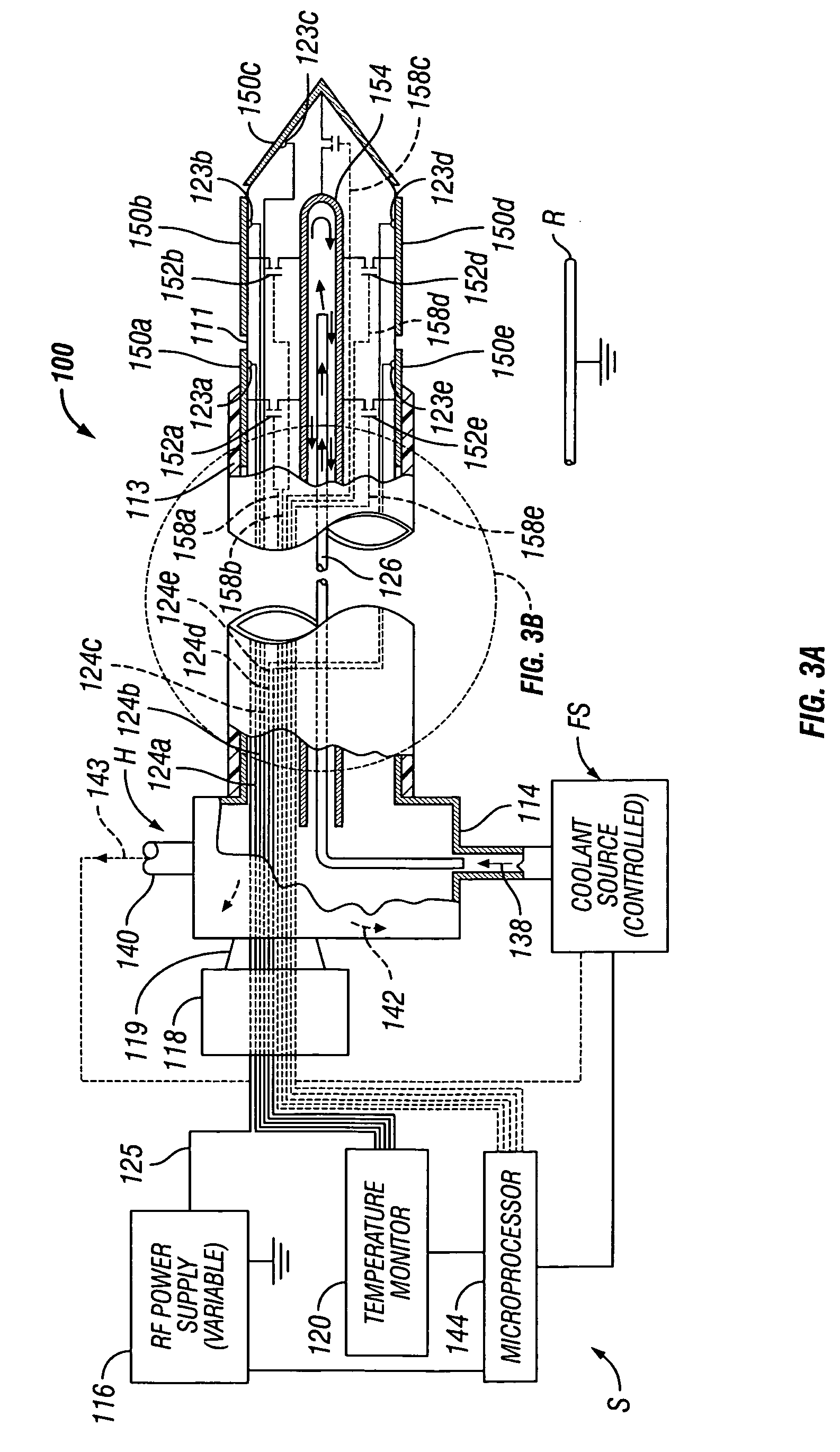

Apparatus and method for electrode thermosurgery

InactiveUS20070260235A1Maximize formation of lesionSurgical needlesSurgical instruments for heatingInsulation layerBiomedical engineering

An electrosurgical instrument for use with a source of electrical energy to ablate tissue in a living subject is provided. The instrument includes an elongated tissue-penetrating electrode including a rigid tubular member having a closed distal end defining an interior cavity extending from the closed distal end to a proximal end of the rigid tubular member. The rigid tubular member defines an electrically conductive surface capable of receiving electrical energy from the source of electrical energy. The instrument further includes at least one electrically conductive segment located on the electrode, the segment being configured to receive locally controlled electrosurgical energy from the rigid tubular member. An insulation layer is disposed upon the elongated tissue-penetrating electrode. The layer defines an exposed portion of the electrode at the distal end. The instrument also includes at least one sensor that detects a temperature during ablation and at least one transistor that connects the rigid tubular member with the at least one electrically conductive segment.

Owner:COVIDIEN AG

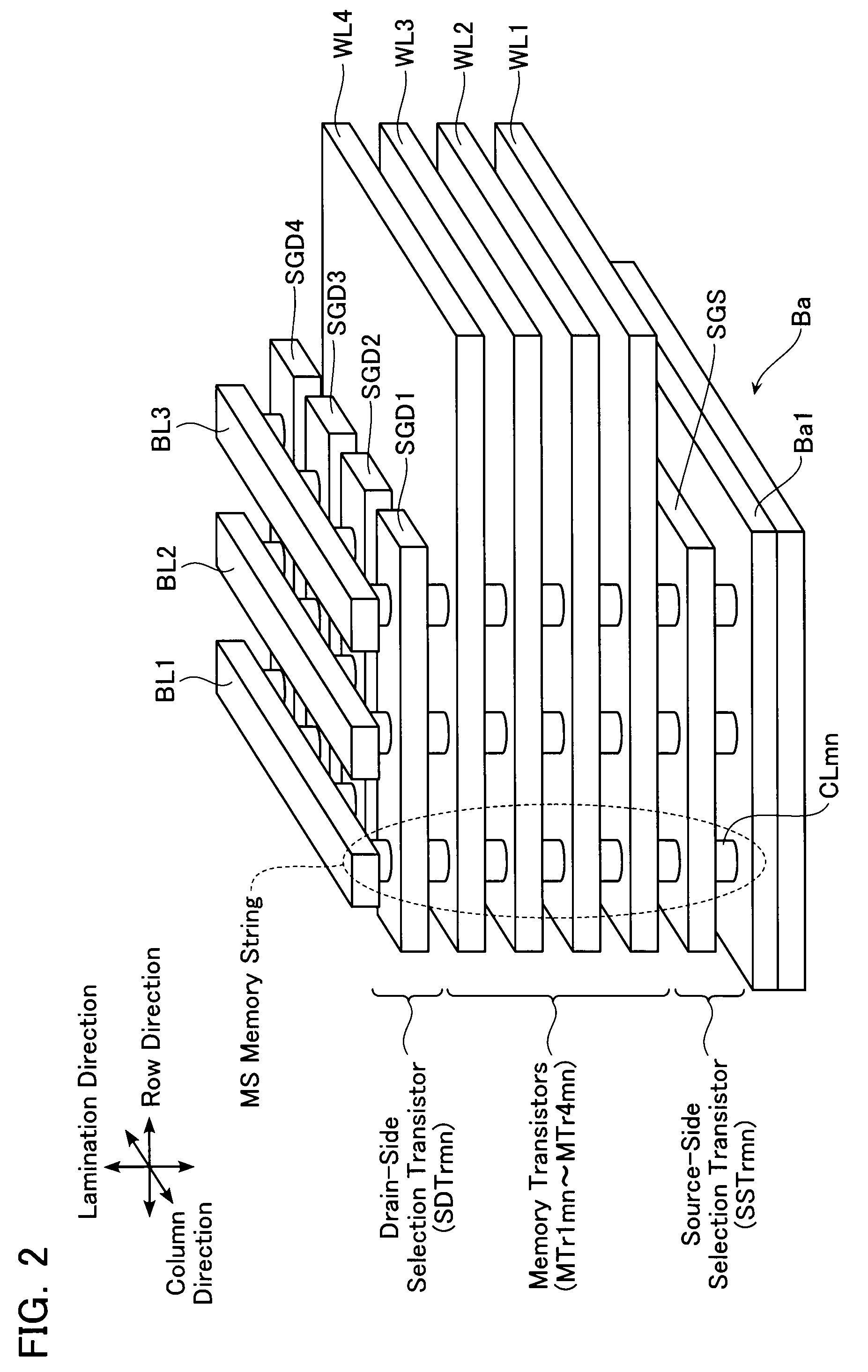

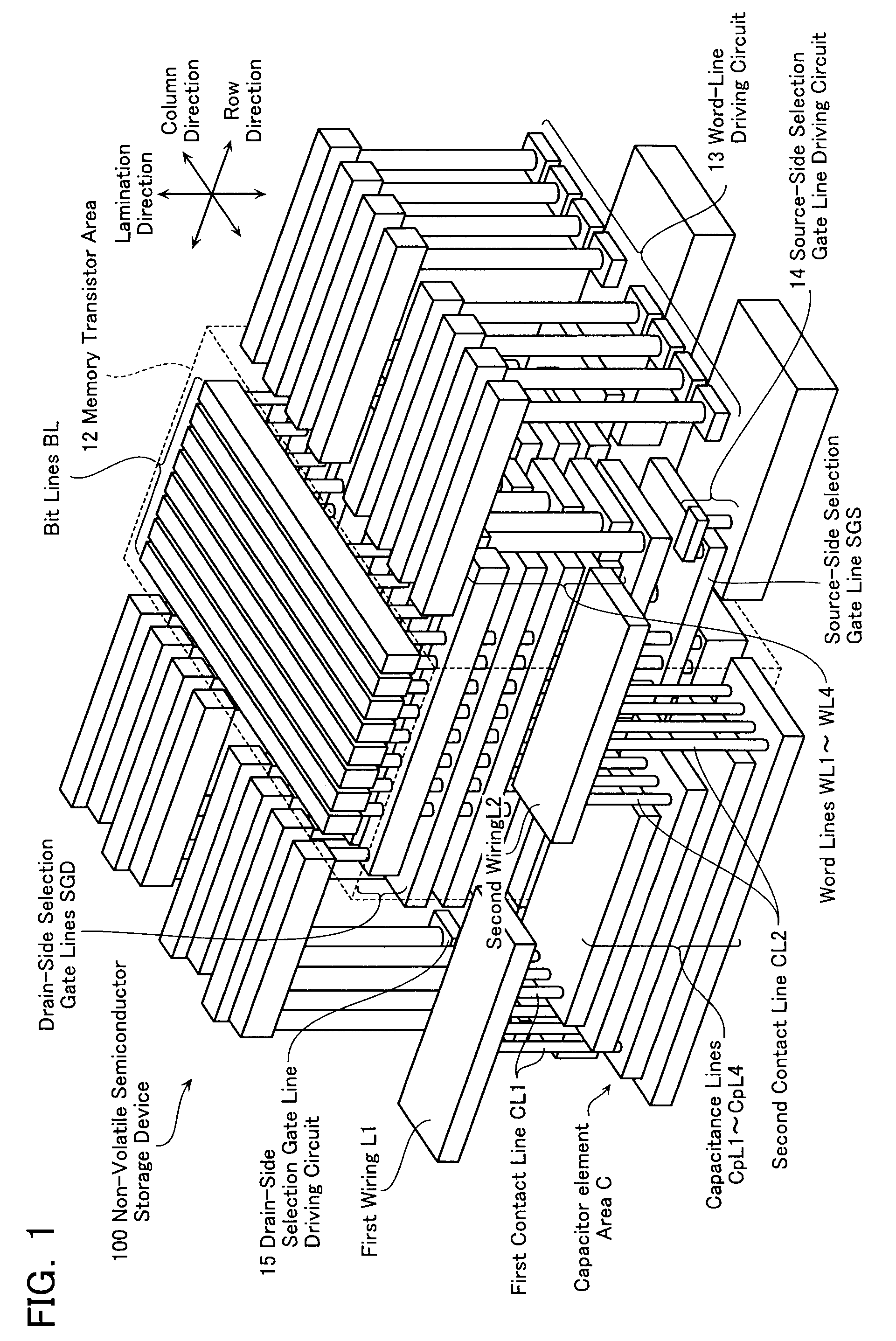

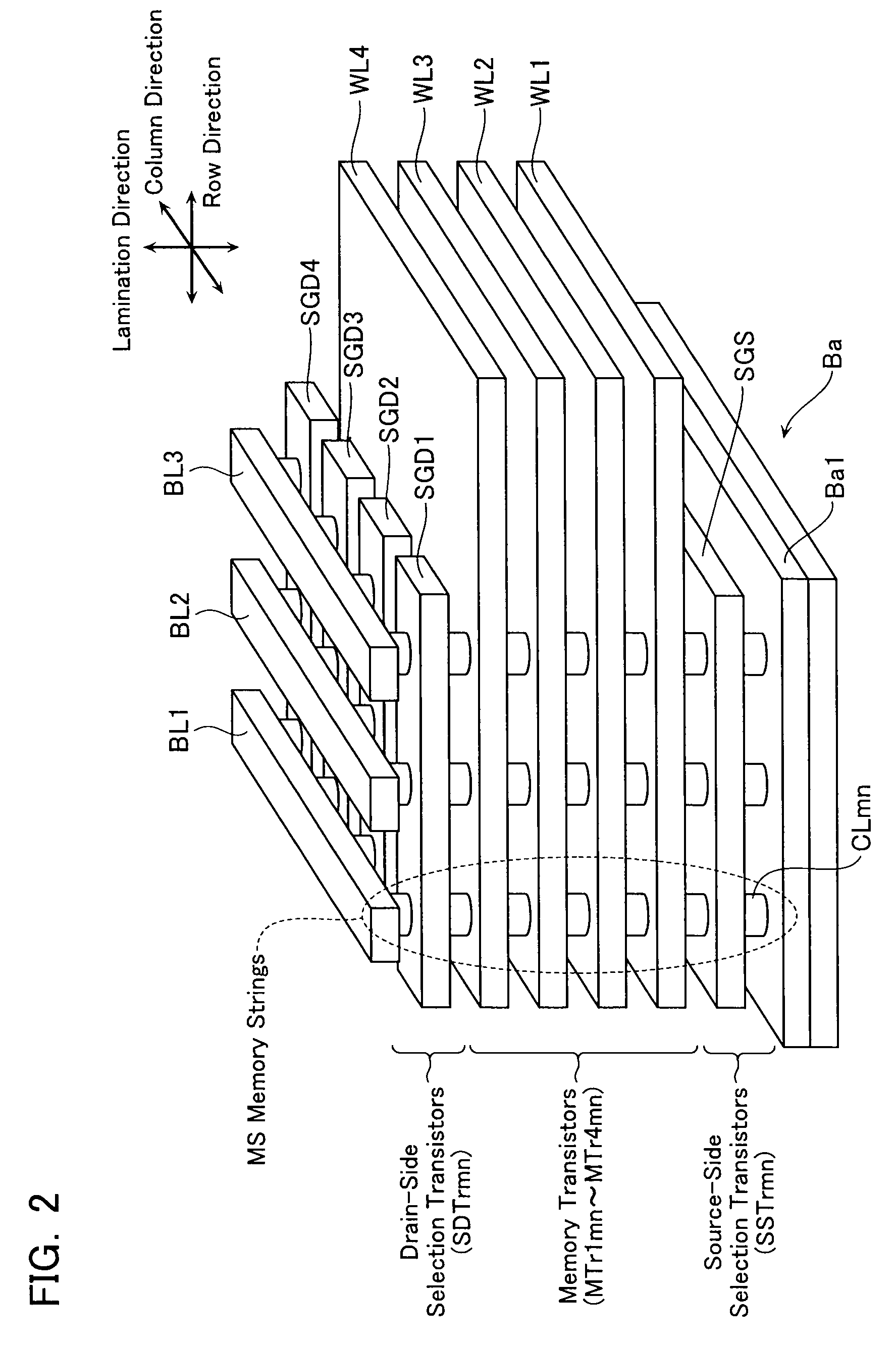

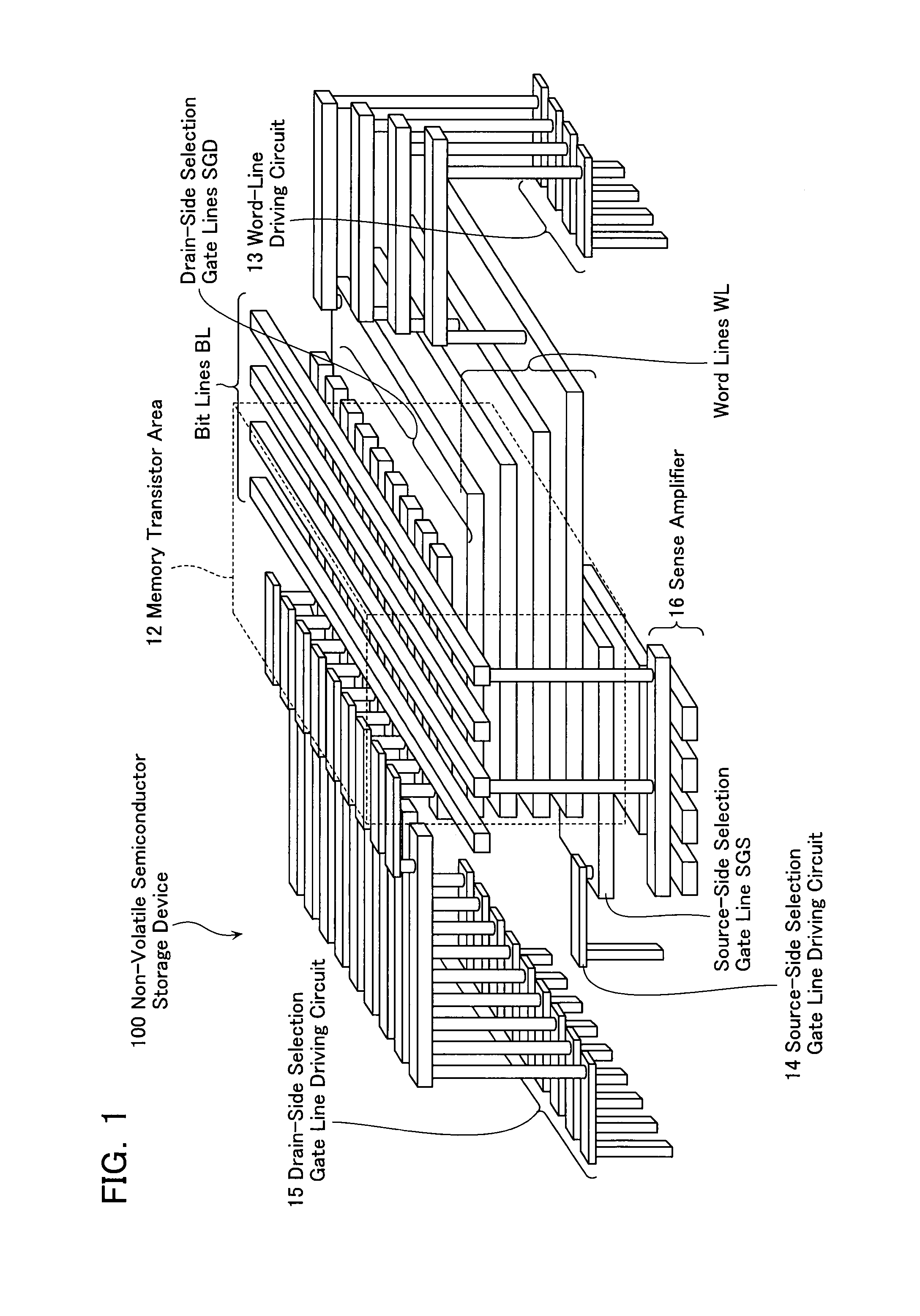

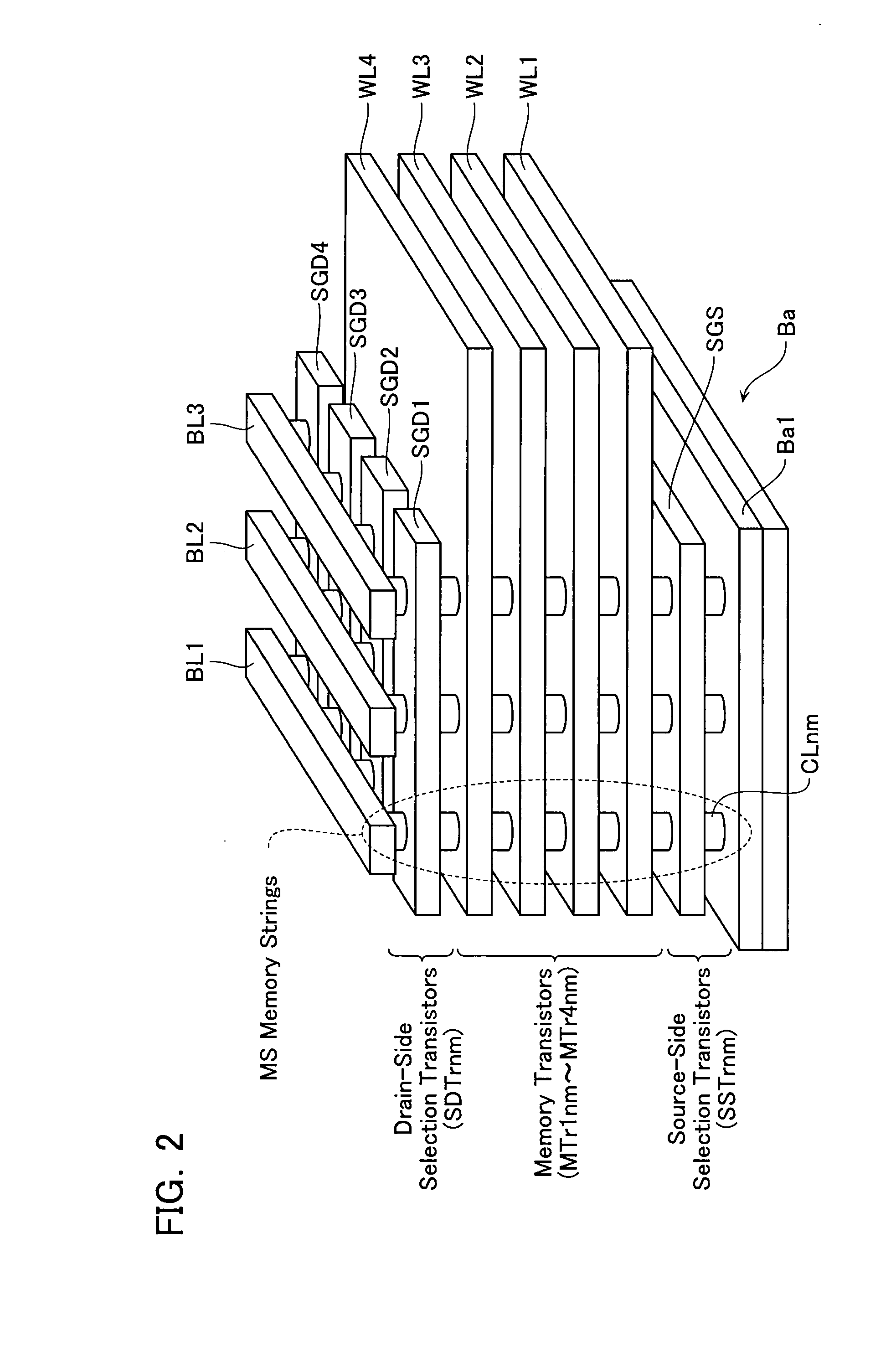

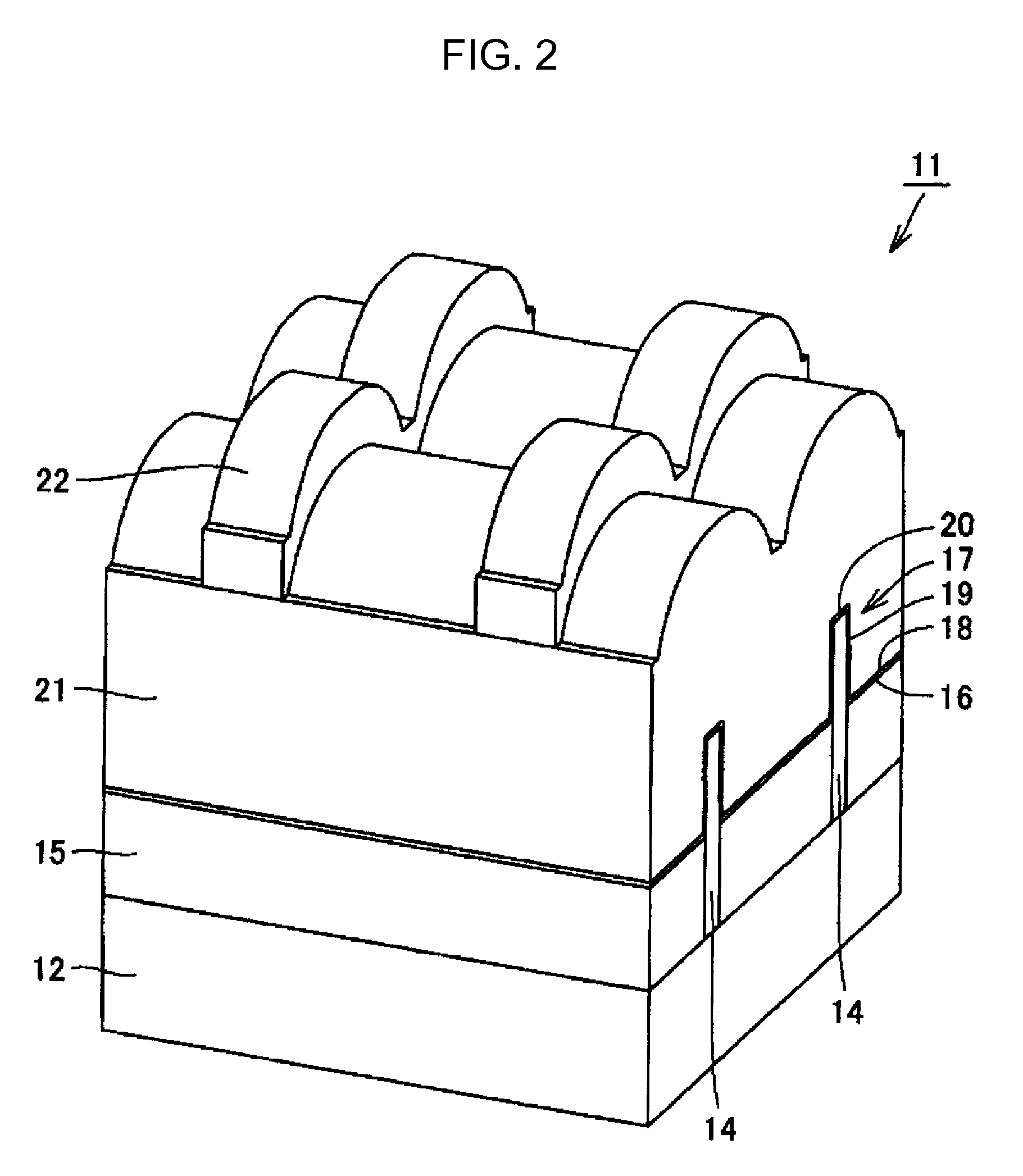

Semiconductor storage device

A non-volatile semiconductor storage device has: a plurality of memory strings with a plurality of electrically rewritable memory cells connected in series; and a capacitor element area including capacitor elements. Each of the memory strings includes: a plurality of first conductive layers laminated on a substrate; and a plurality of first interlayer insulation layers formed between the plurality of first conductive layers. The capacitor element area includes: a plurality of second conductive layers laminated on a substrate and formed in the same layer as the first conductive layers; and a plurality of second interlayer insulation layers formed between the plurality of second conductive layers and formed in the same layer as the first interlayer insulation layers. A group of the adjacently-laminated second conductive layers is connected to a first potential, while another group thereof is connected to a second potential.

Owner:KK TOSHIBA

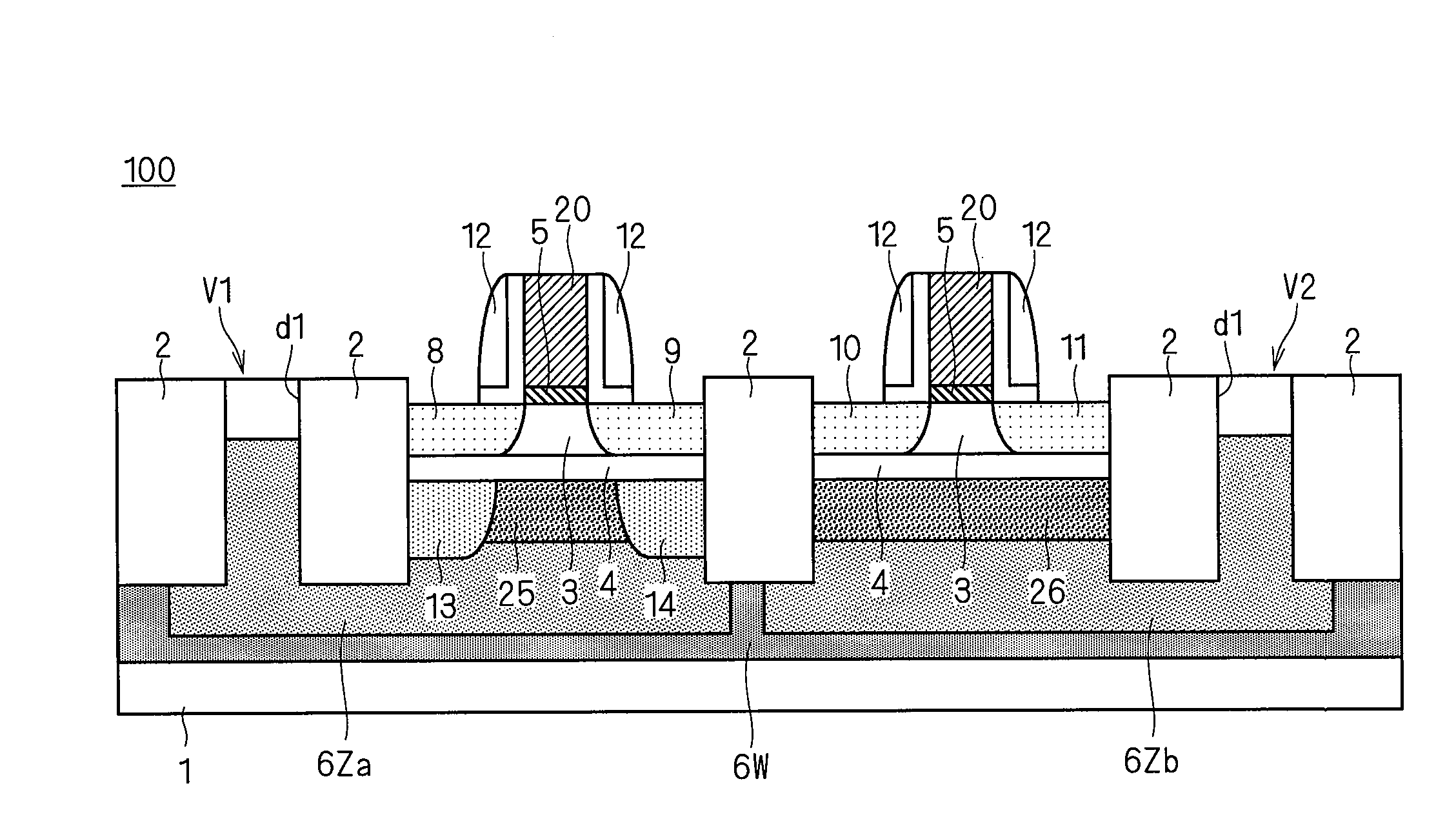

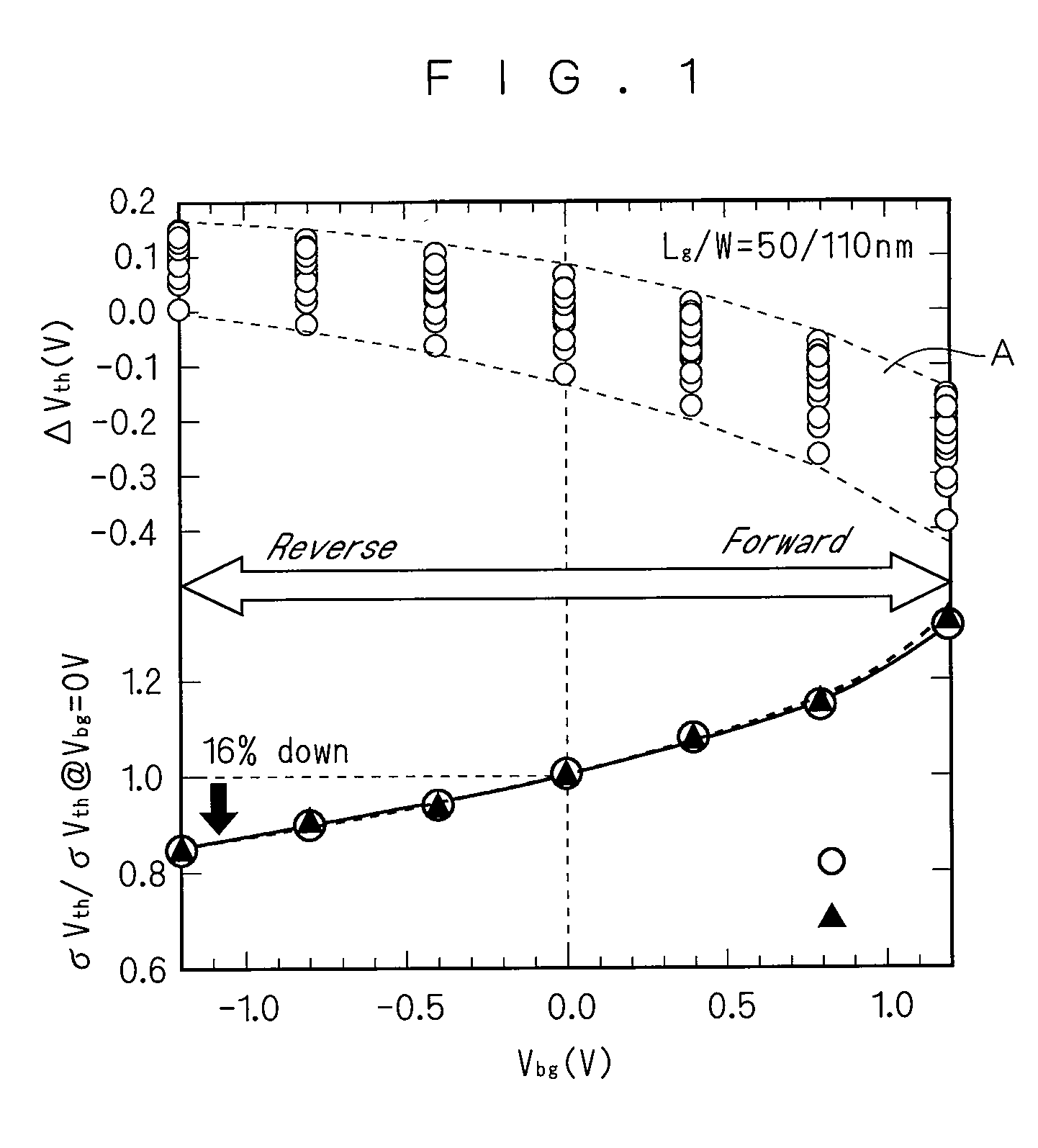

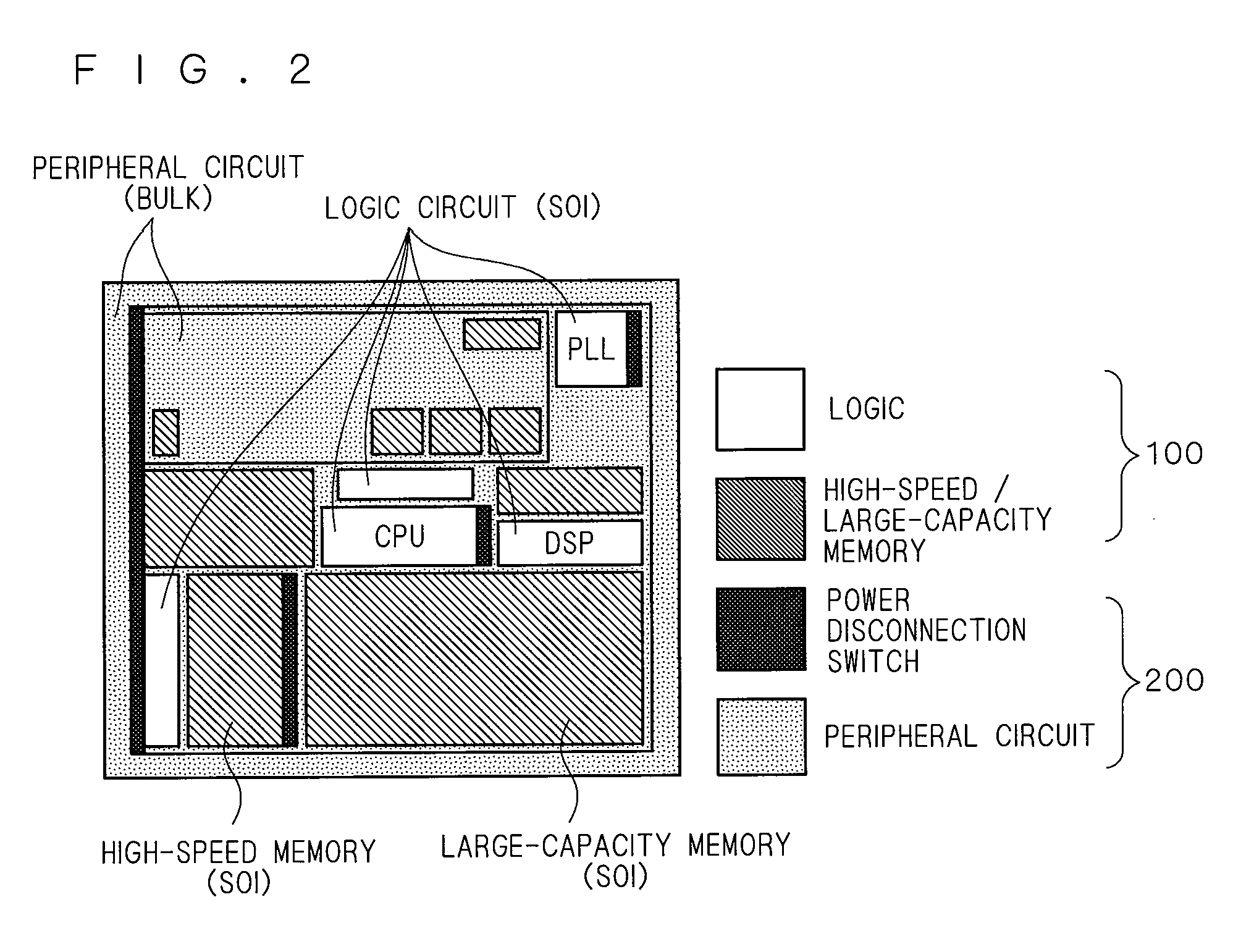

Semiconductor device and method for controlling semiconductor device

ActiveUS20090134468A1Meet high-speed operationGuaranteed uptimeTransistorSolid-state devicesInsulation layerMemory circuits

To provide a semiconductor device having a thin-film BOX-SOI structure and capable of realizing a high-speed operation of a logic circuit and a stable operation of a memory circuit. A semiconductor device according to the present invention includes a semiconductor support substrate, an insulation layer having a thickness of at mast 10 nm, and a semiconductor layer. In an upper surface of the semiconductor layer, a first field-effect transistor including a first gate electrode and constituting a logic circuit is formed. Further, in the upper surface of the semiconductor layer, a second field-effect transistor including a second gate electrode and constituting a memory circuit is formed. At least three well regions having different conductivity types are formed in the semiconductor support substrate. In the presence of the well regions, a region of the semiconductor support substrate below the first gate electrode and a region of the semiconductor support substrate below the second gate electrode are electrically separated from each other.

Owner:RENESAS ELECTRONICS CORP

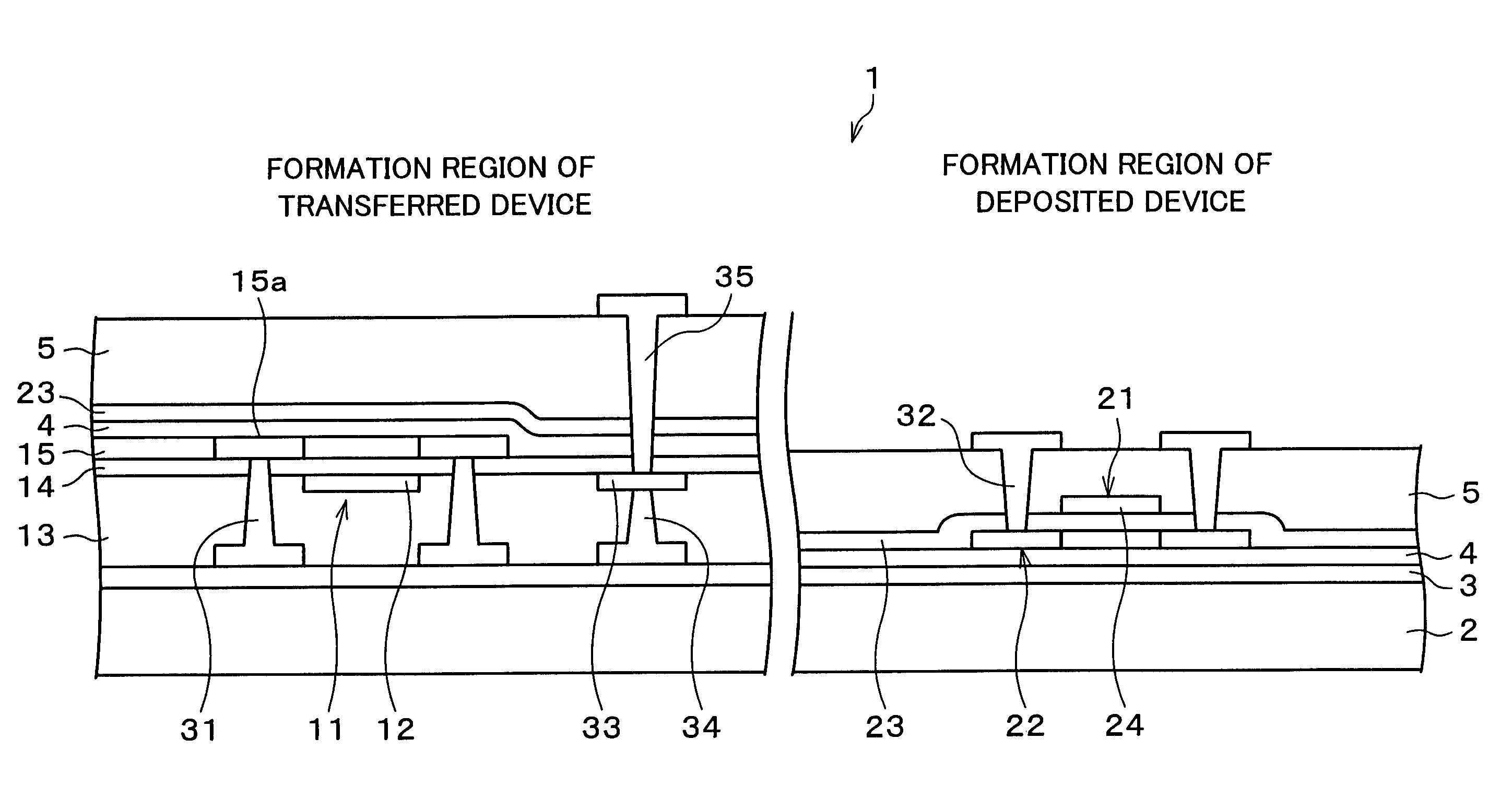

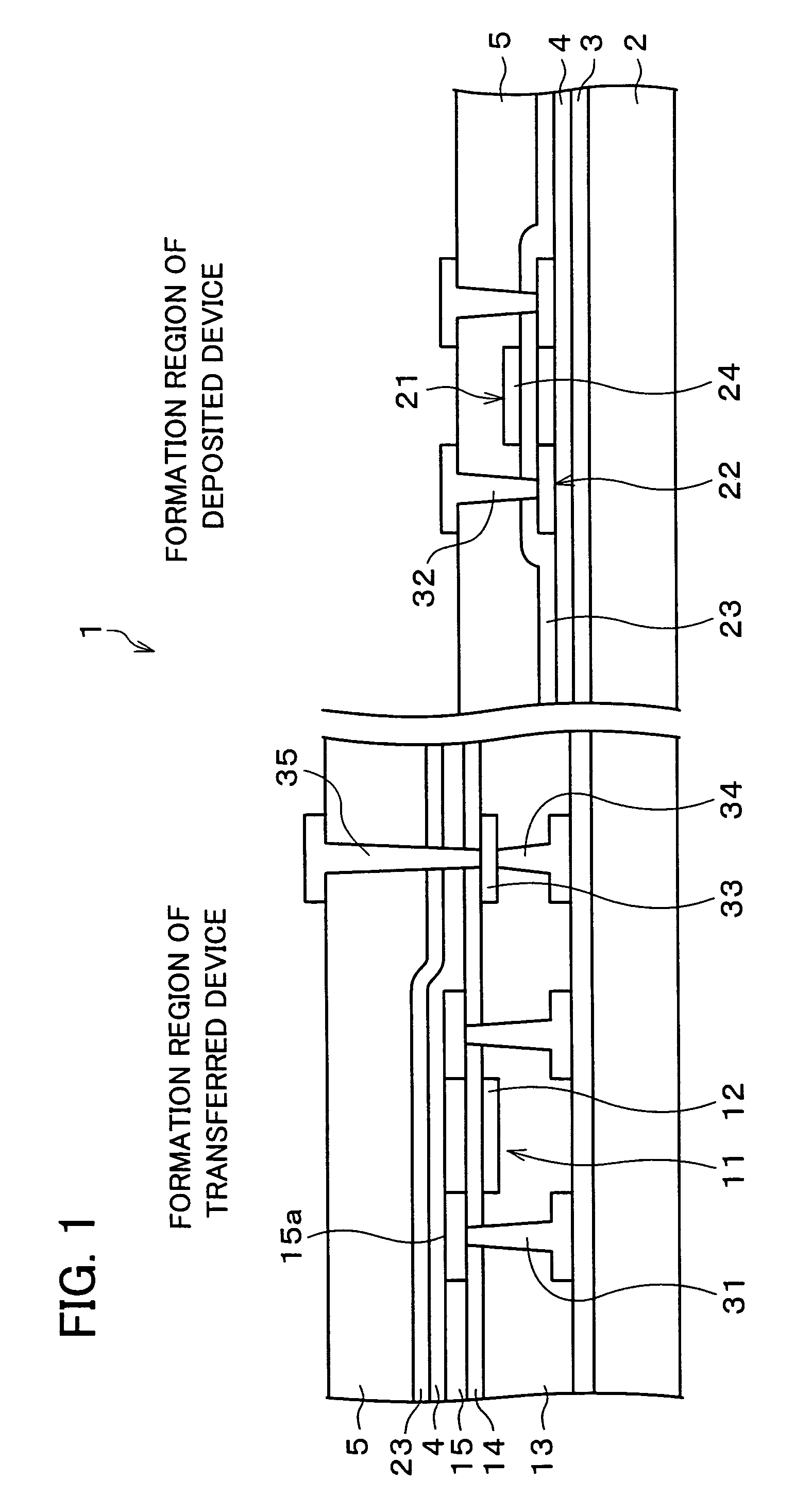

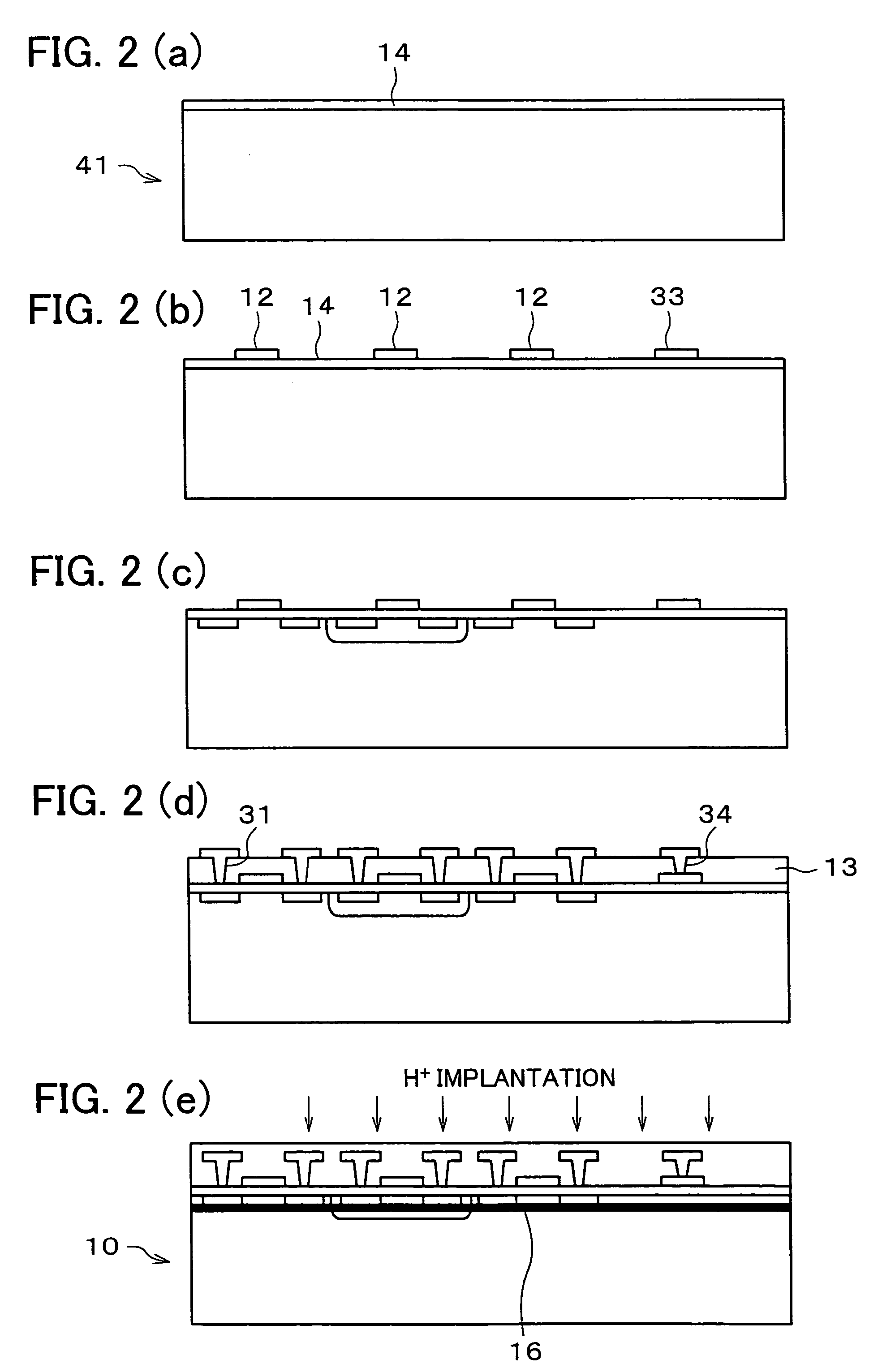

Thin film semiconductor device and fabrication method therefor

InactiveUS7488980B2Restraining aspect ratioSmall sizeTransistorSemiconductor/solid-state device detailsInsulation layerEngineering

A relaying pad is formed in a predetermined portion in an insulation layer of the single-crystal thin film device, in a region where the single-crystal thin film device is formed. The relaying pad is for providing connection wiring through the insulator substrate. With this configuration it is possible to prevent an increase in an aspect ratio of a contact hole formed in an insulation layer in a region in which a transferred device is formed, the semiconductor device including a substrate on which the transferred device and a deposited device coexist.

Owner:SHARP KK

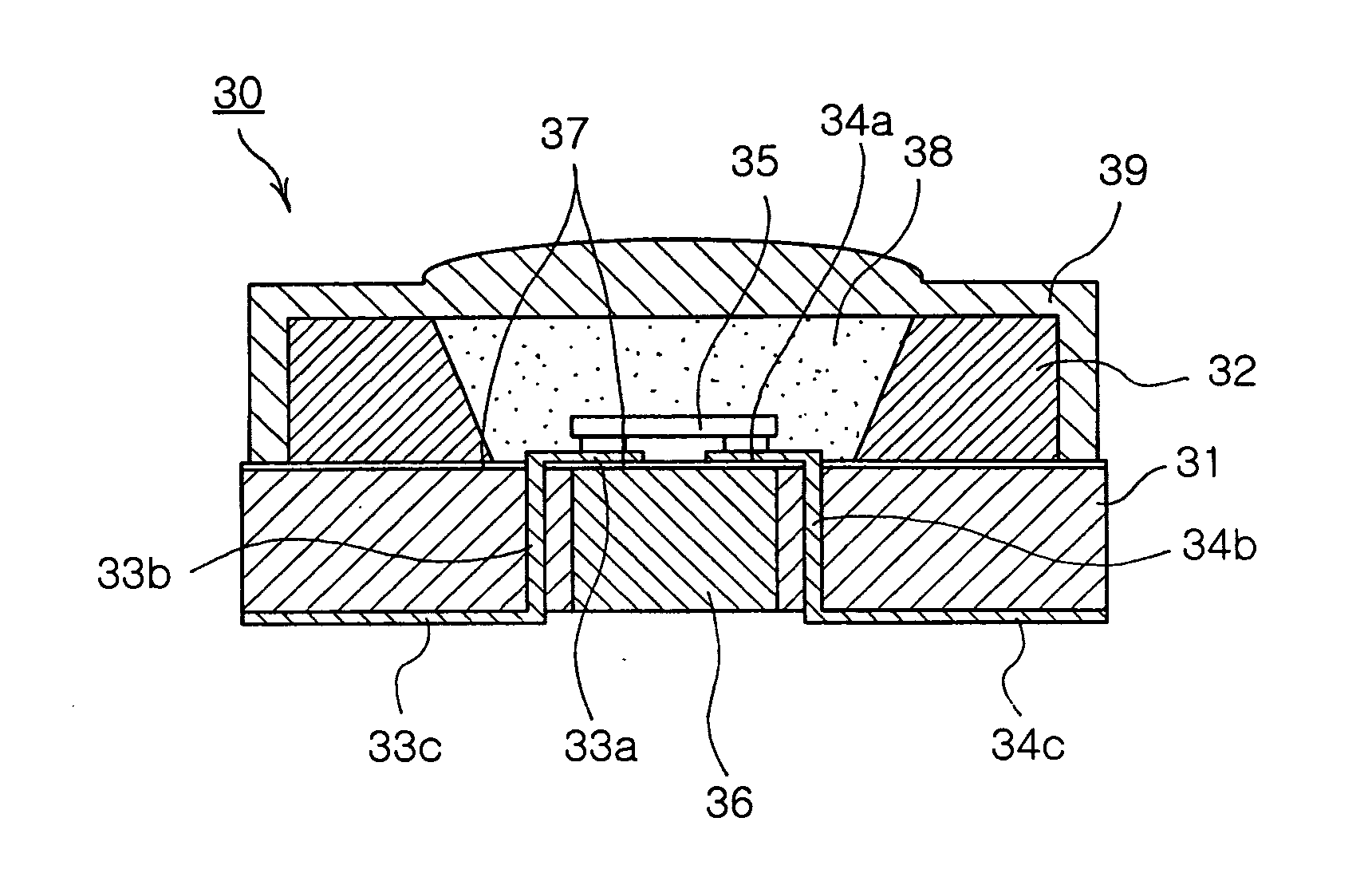

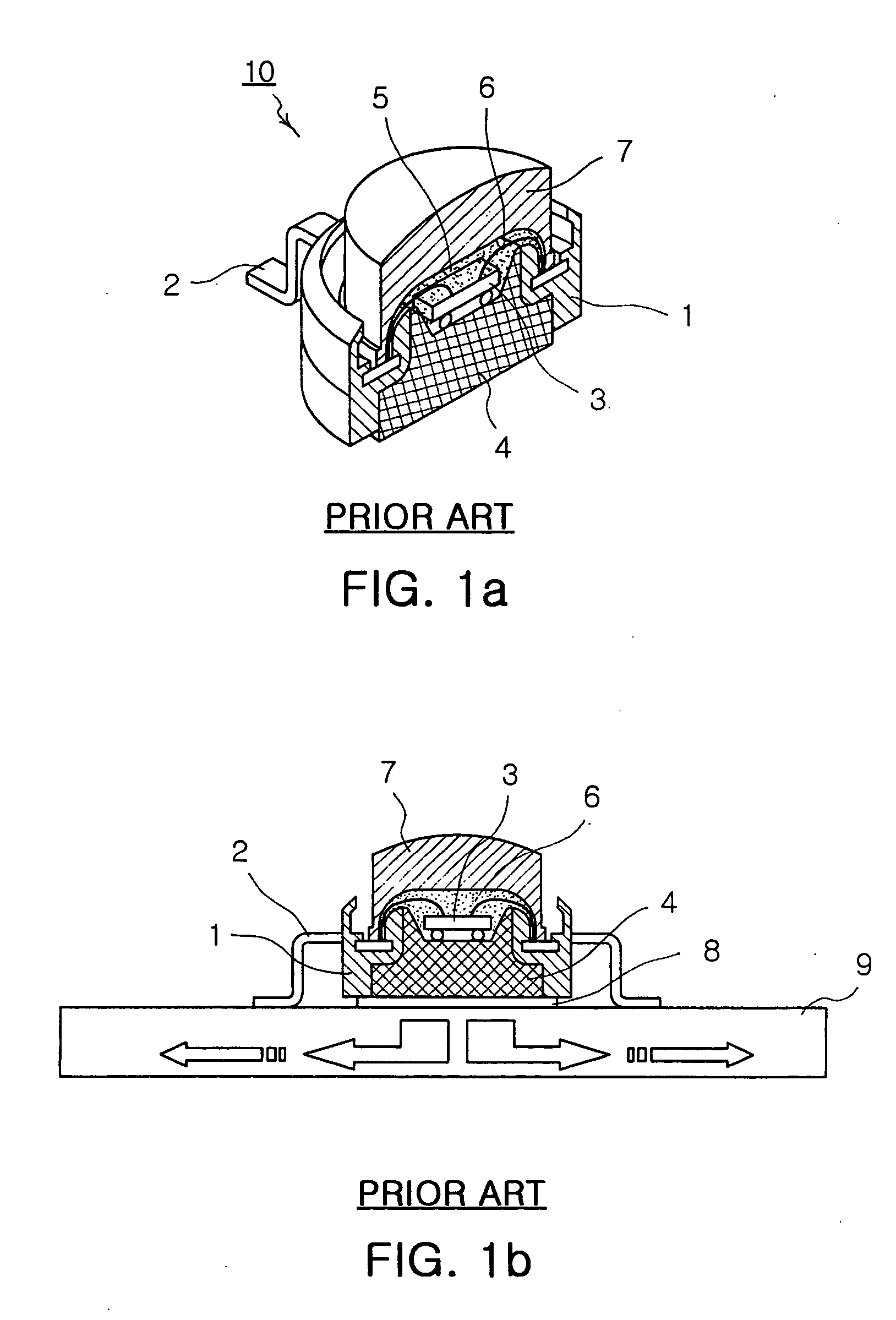

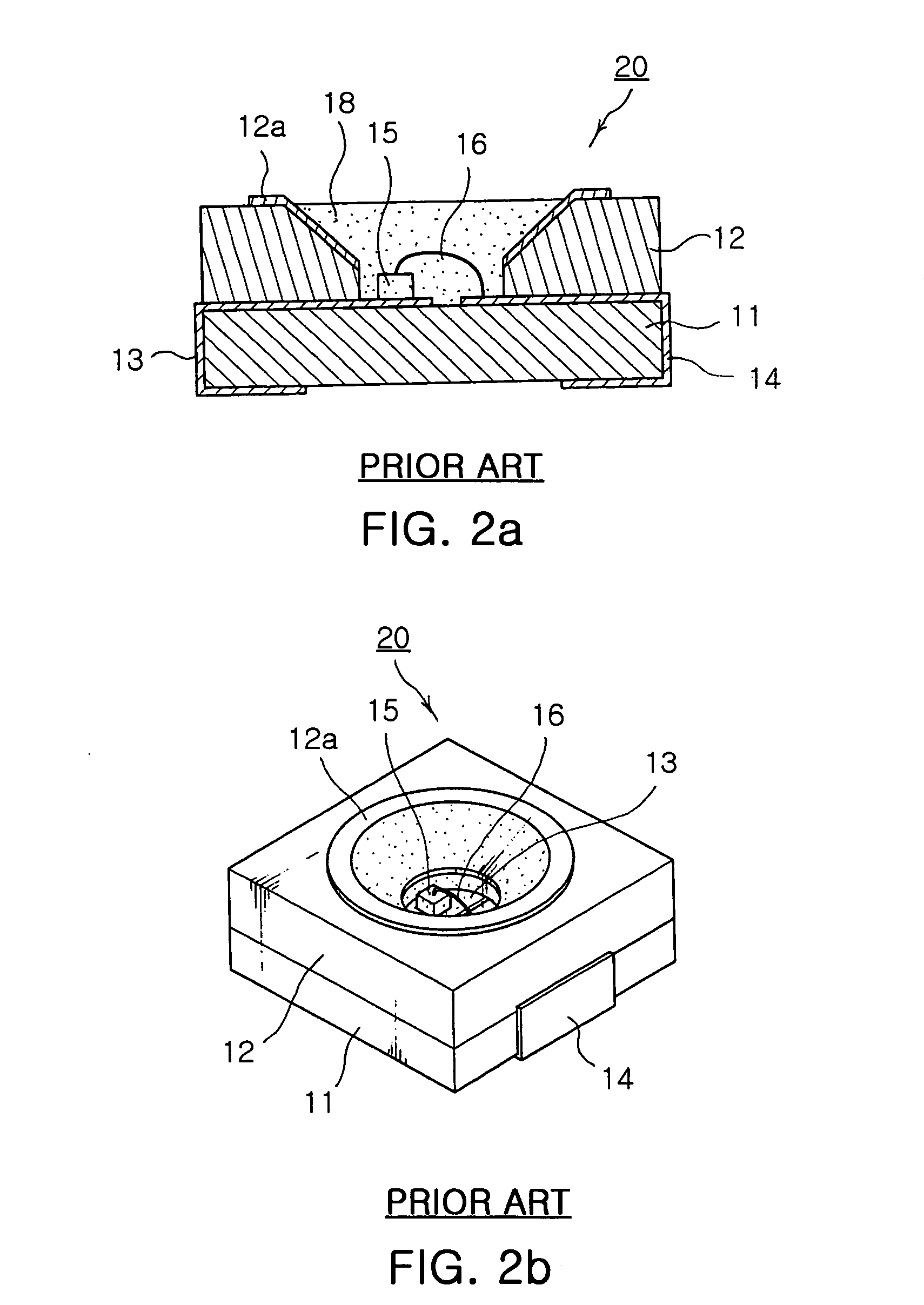

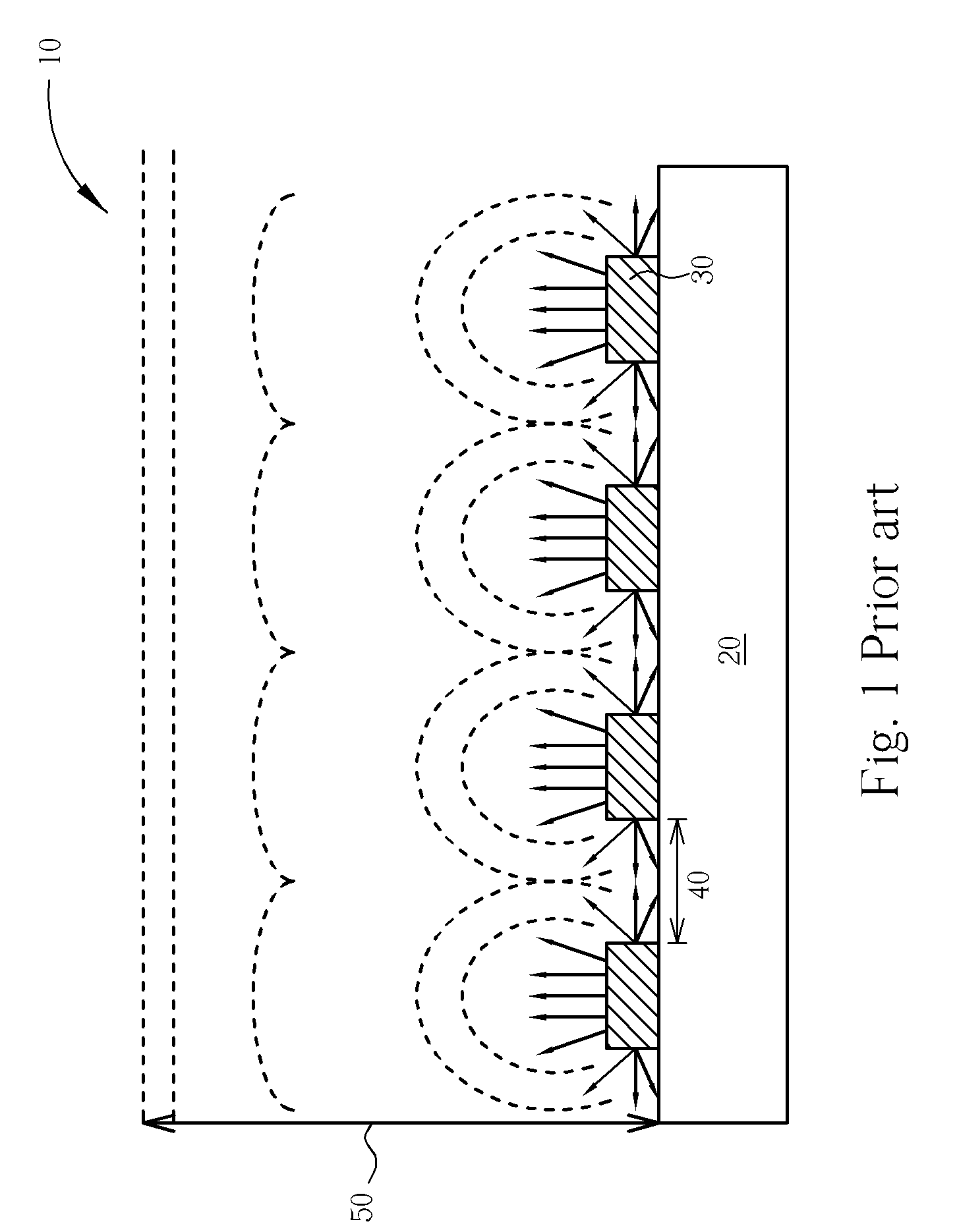

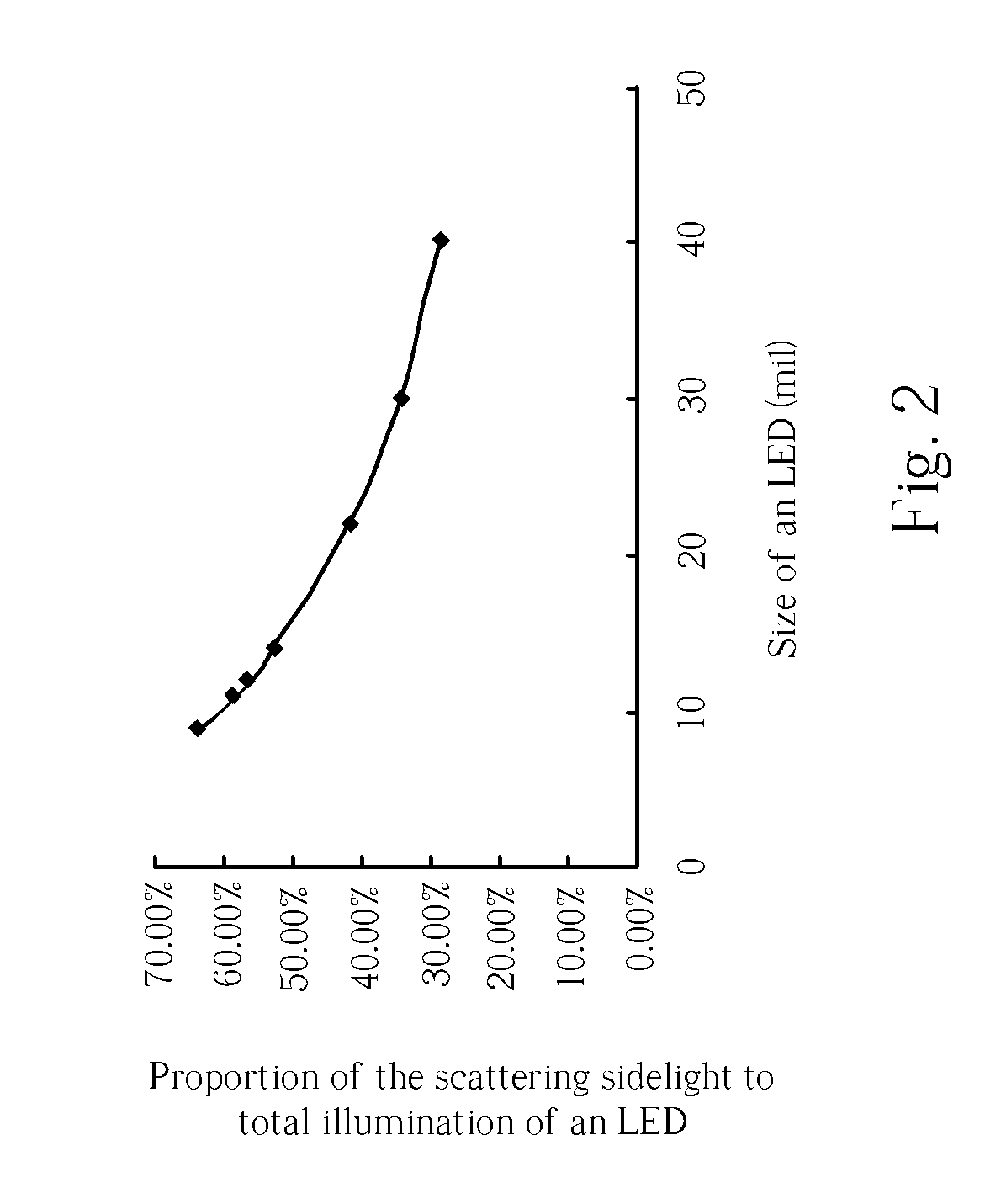

High power light emitting diode package and fabrication method thereof

InactiveUS20050139846A1Improve cooling effectSimple structureSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

Disclosed is a high power LED package. In the LED package, a lower board has a heat radiation member in an LED mounting area and at least one via hole around the heat radiation member. First and second bottom electrodes are formed in the underside of the lower board, and connected to the heat radiation member and the via hole. An insulation layer is formed on the lower board to cover the heat radiation member. First and second electrode patterns on the insulation layer are connected to the first and second bottom electrodes through the via hole.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS20090014879A1Semiconductor/solid-state device detailsSolid-state devicesInsulation layerDevice material

In a method of forming a wiring structure for a semiconductor device, an insulation layer is formed on a semiconductor substrate on which a plurality of conductive structures is positioned. An upper surface of the insulation layer is planarized and spaces between the conductive structures are filled with the insulation layer. The insulation layer is partially removed from the substrate to form at least one opening through which the substrate is partially exposed. A residual metal layer is formed on a bottom and a lower portion of the sidewall of the at least one opening and a metal nitride layer is formed on the residual metal layer and an upper sidewall of the opening with a metal material. Accordingly, an upper portion of the barrier layer can be prevented from being removed in a planarization process for forming the metal plug.

Owner:SAMSUNG ELECTRONICS CO LTD

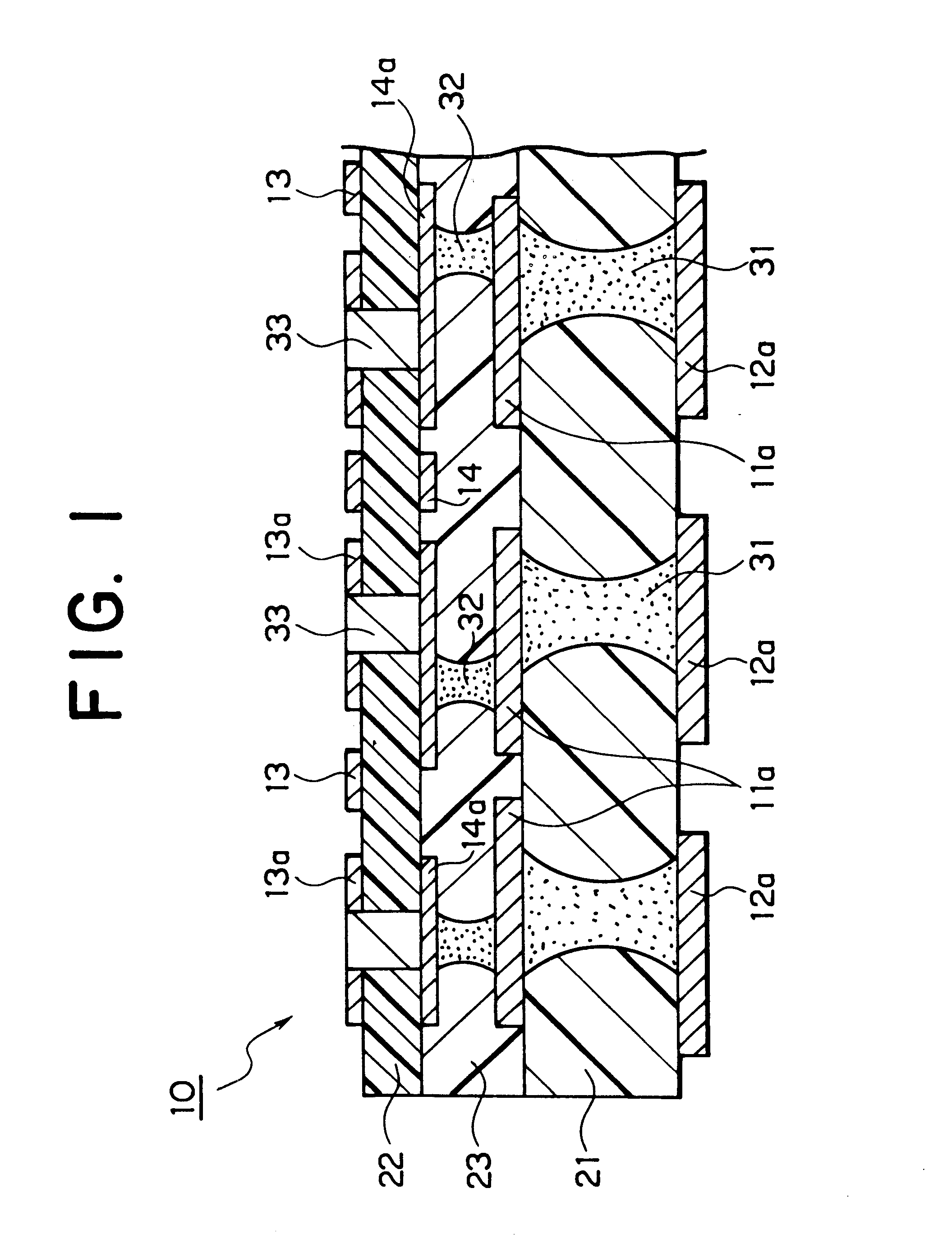

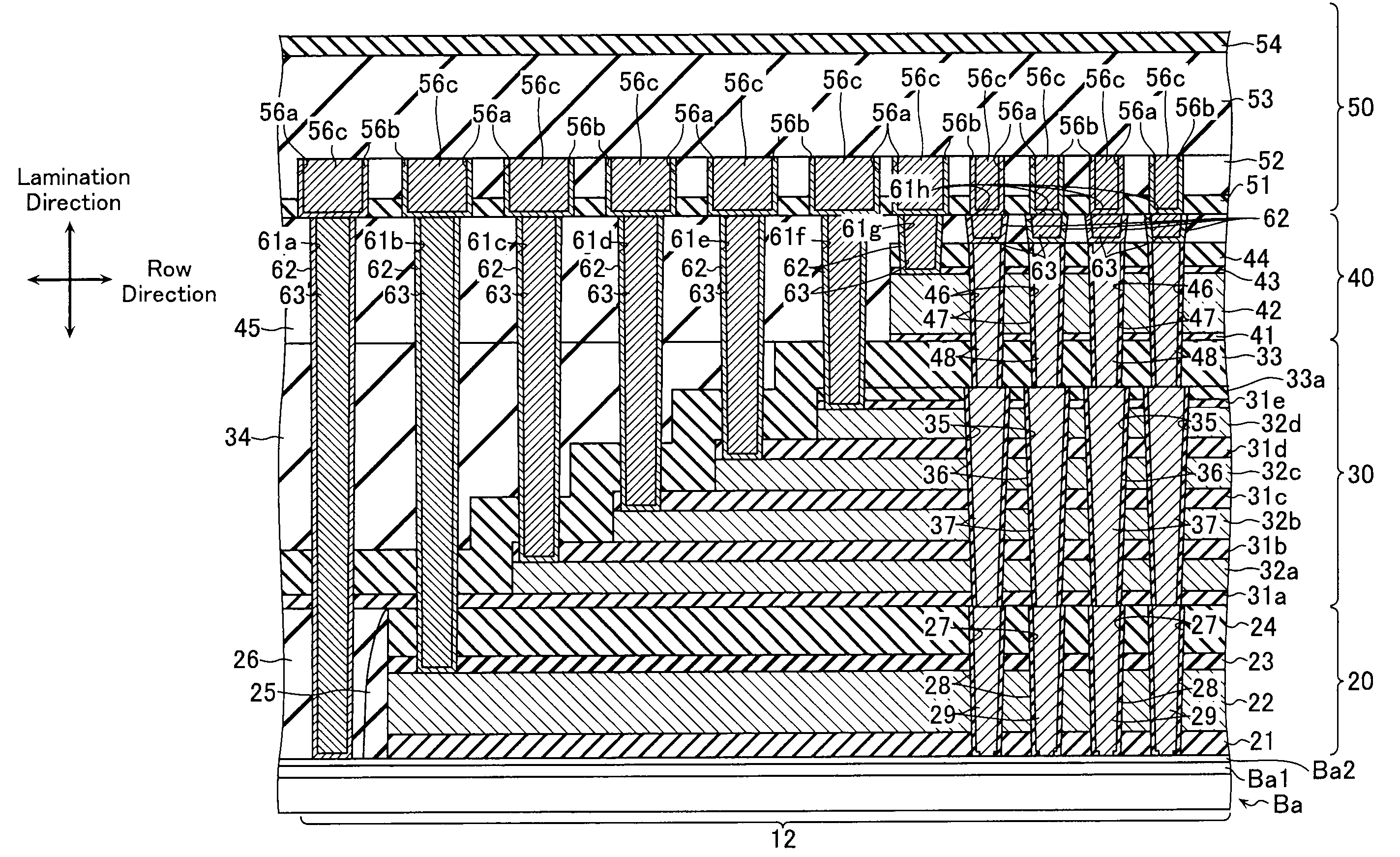

Non-volatile semiconductor storage device and method of manufacturing the same

ActiveUS20090242967A1Solid-state devicesSemiconductor/solid-state device manufacturingInsulation layerSemiconductor storage devices

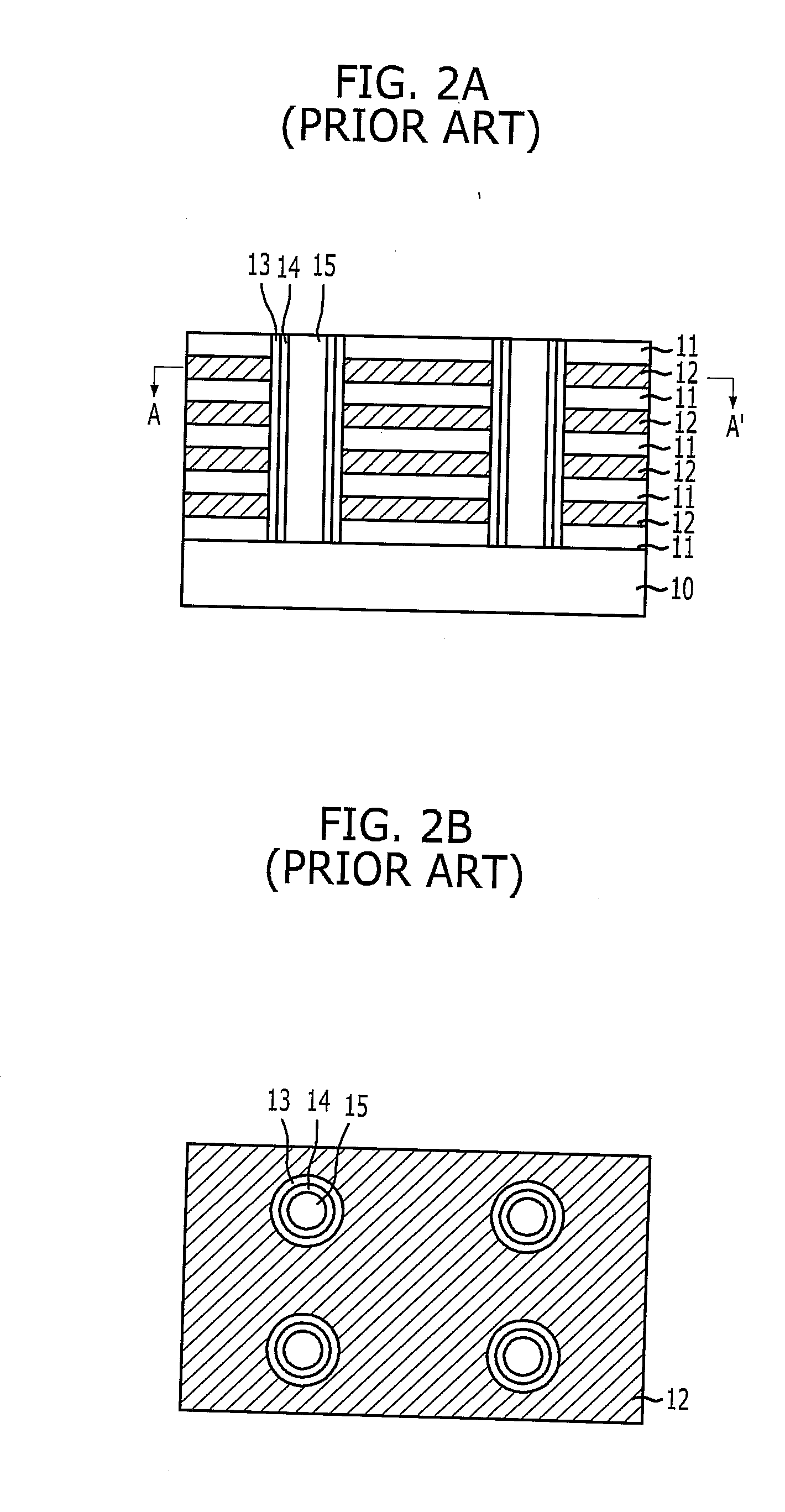

A non-volatile semiconductor storage device has a plurality of memory strings with a plurality of electrically rewritable memory cells connected in series. Each of the memory strings comprises: a first columnar semiconductor layer extending in a vertical direction to a substrate; a charge accumulation layer formed around the first columnar semiconductor layer via a first insulation layer; and a first conductive layer formed around the charge accumulation layer via a second insulation layer. Each of the first conductive layers is formed to expand in a two-dimensional manner, and air gaps are formed between the first conductive layers located there above and there below.

Owner:KIOXIA CORP

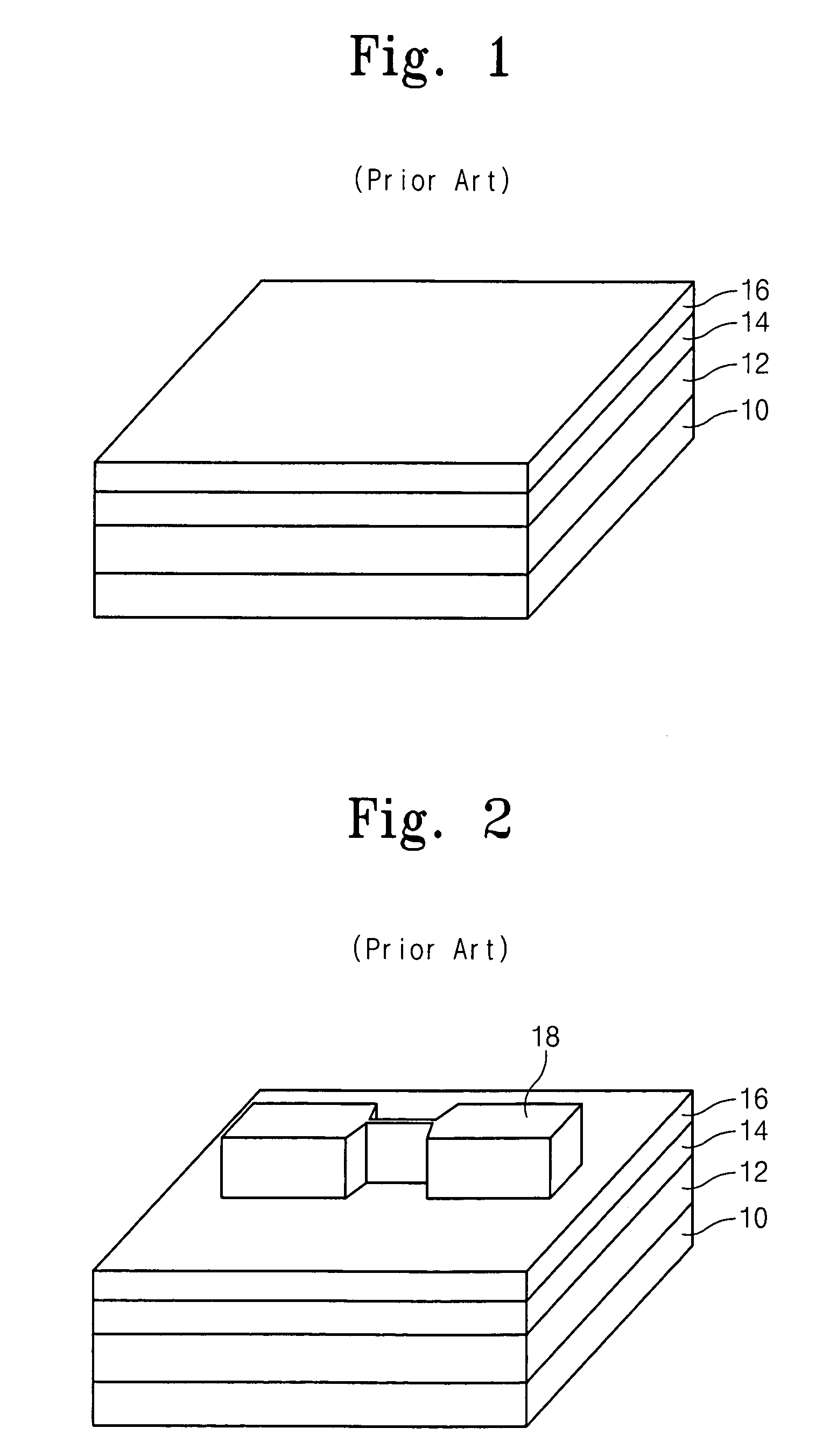

Nonvolatile memory device and method for fabricating the same

InactiveUS20110266611A1Excellent characteristicsIncrease speedSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerDielectric layer

A nonvolatile memory device includes a plurality of interlayer dielectric layers and conductive layers for gate electrodes alternately stacked over a substrate, a channel trench passing through the interlayer dielectric layers and the conductive layers and exposing the substrate, a charge blocking layer and a charge trap or charge storage layer formed on sidewalls of the trench, a coupling prevention layer formed at the surface of the charge trap or charge storage layer, and a tunnel insulation layer formed over the coupling prevention layer.

Owner:SK HYNIX INC

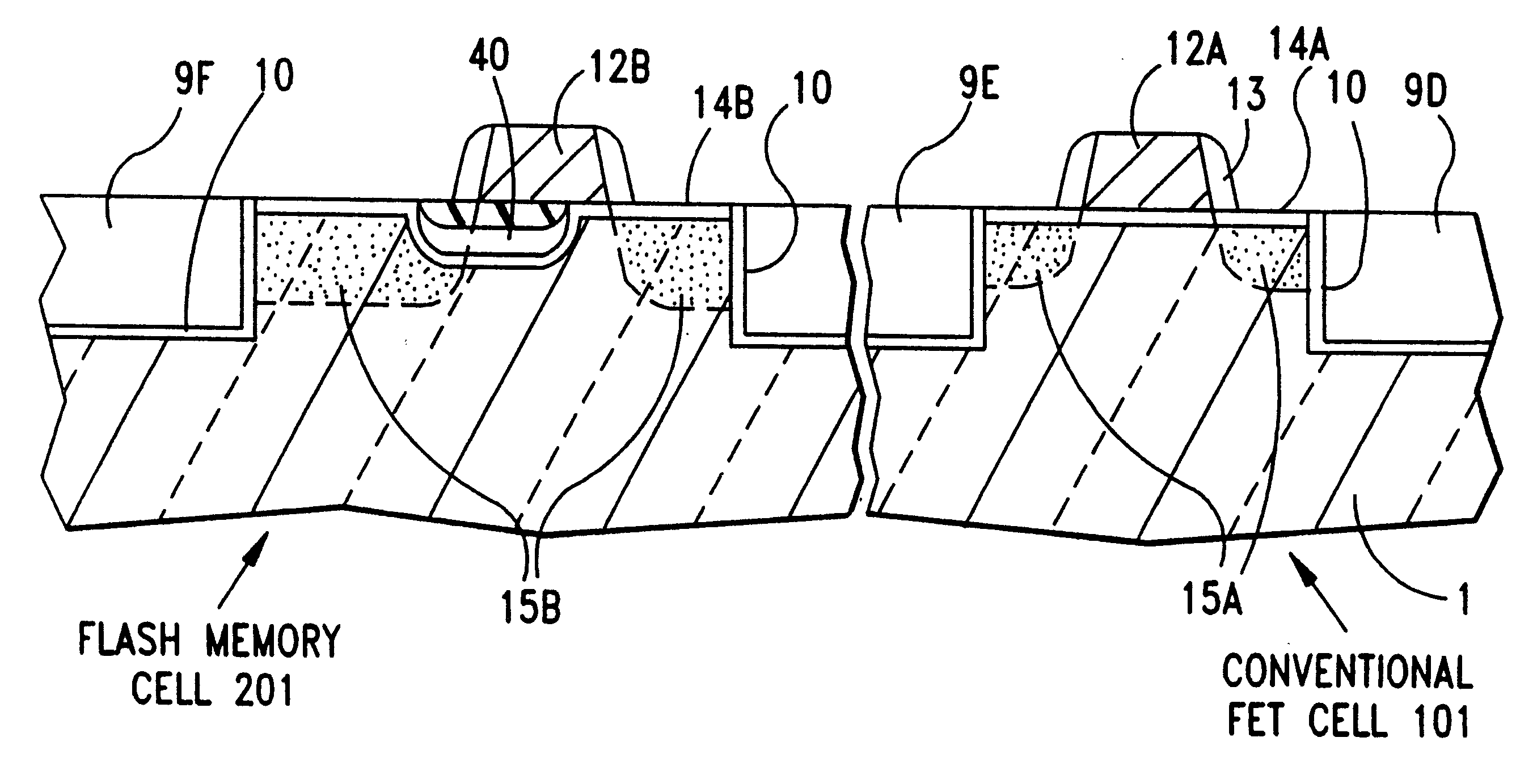

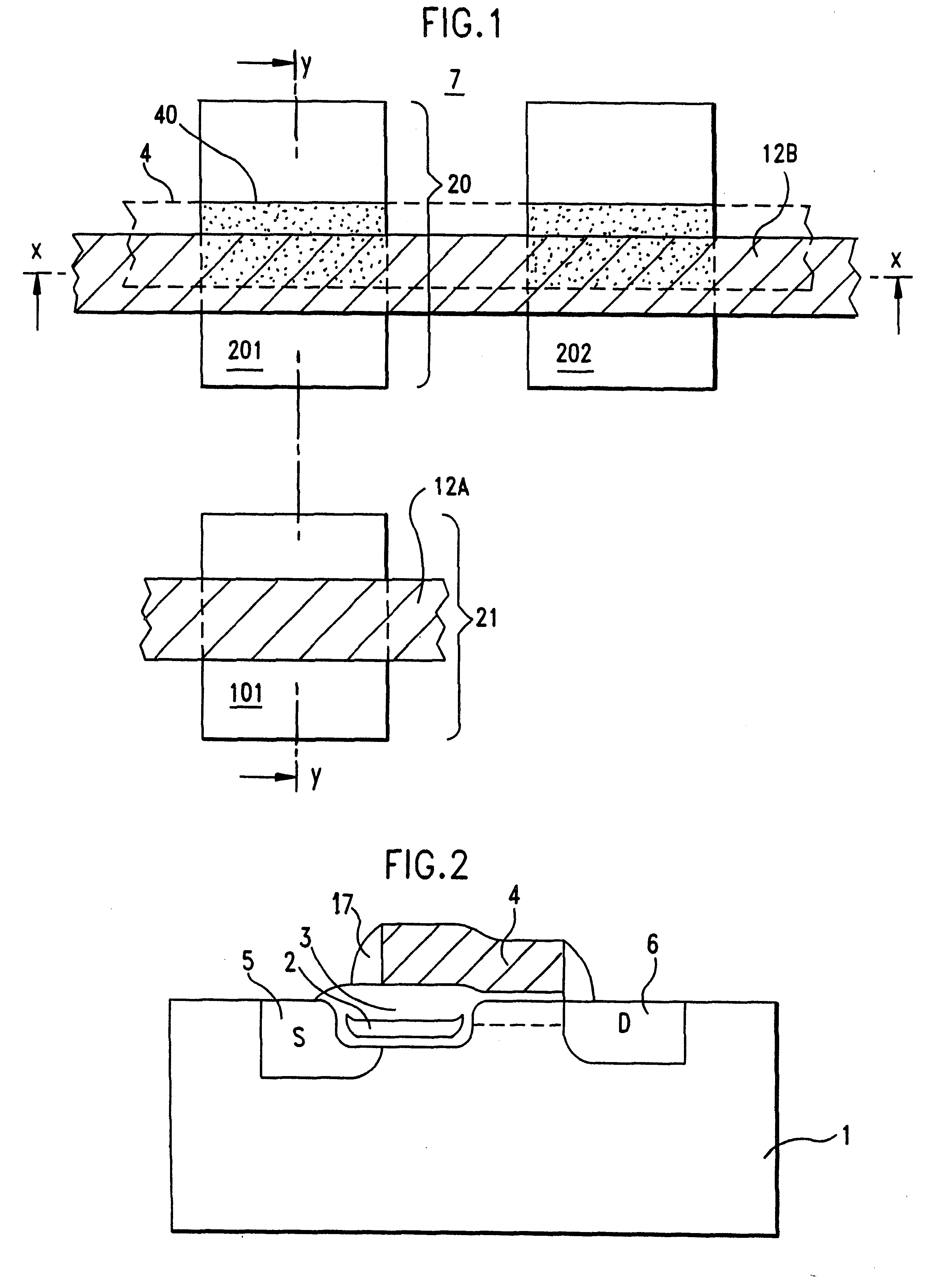

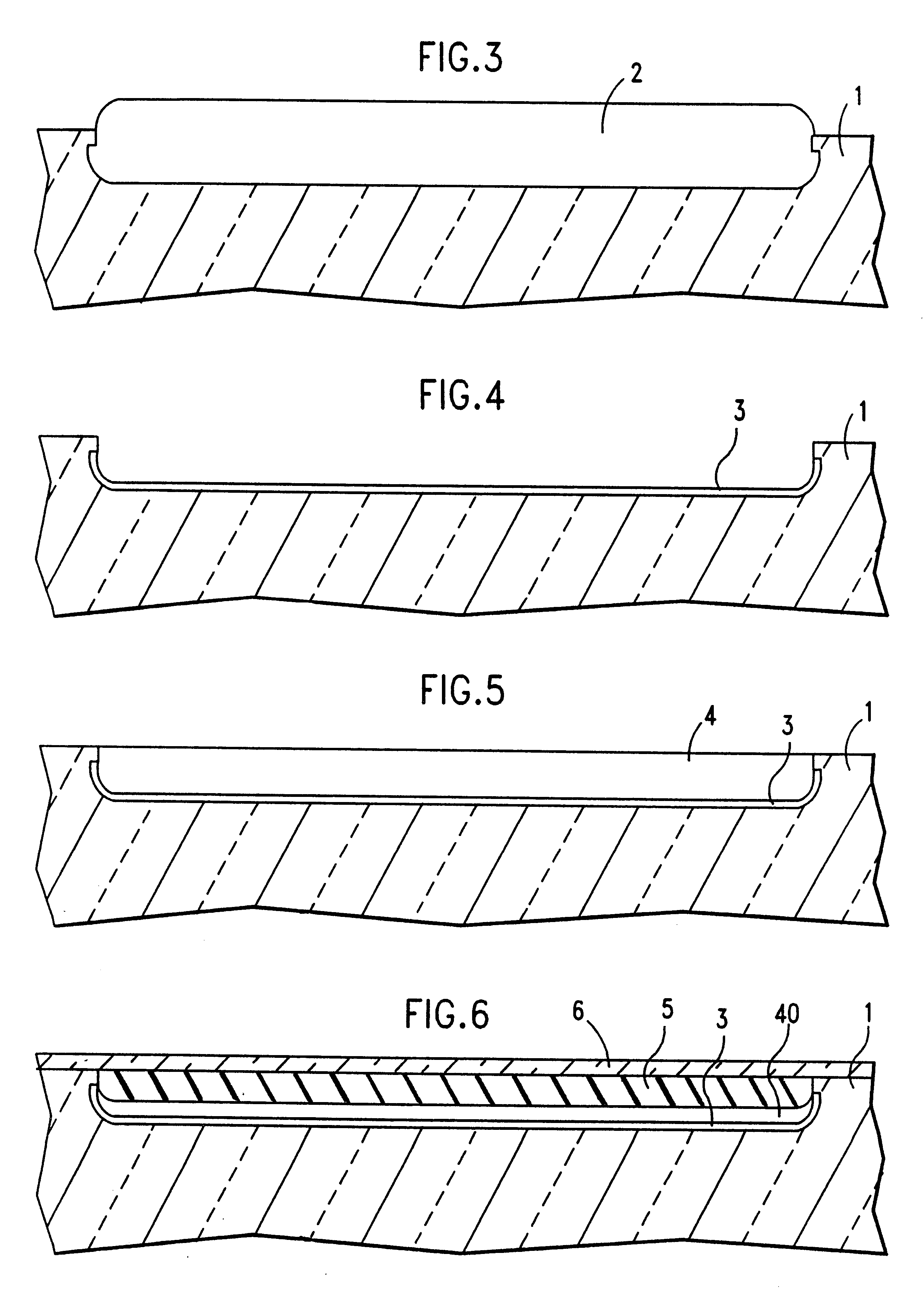

Field effect transistor having a floating gate

InactiveUS6245613B1Solid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A field effect transistor which comprises a semiconductor substrate having a source region and a drain region separated by a channel region; a conductive floating gate formed over a first portion of the channel region adjacent to the doped source region and recessed into the semiconductor substrate; and being separated from the first portion of the channel region by a first insulation layer; and a conductive control gate formed substantially over but electrically isolated from the floating gate and formed over the entire channel region; along with a method for fabricating such is provided.

Owner:GLOBALFOUNDRIES INC

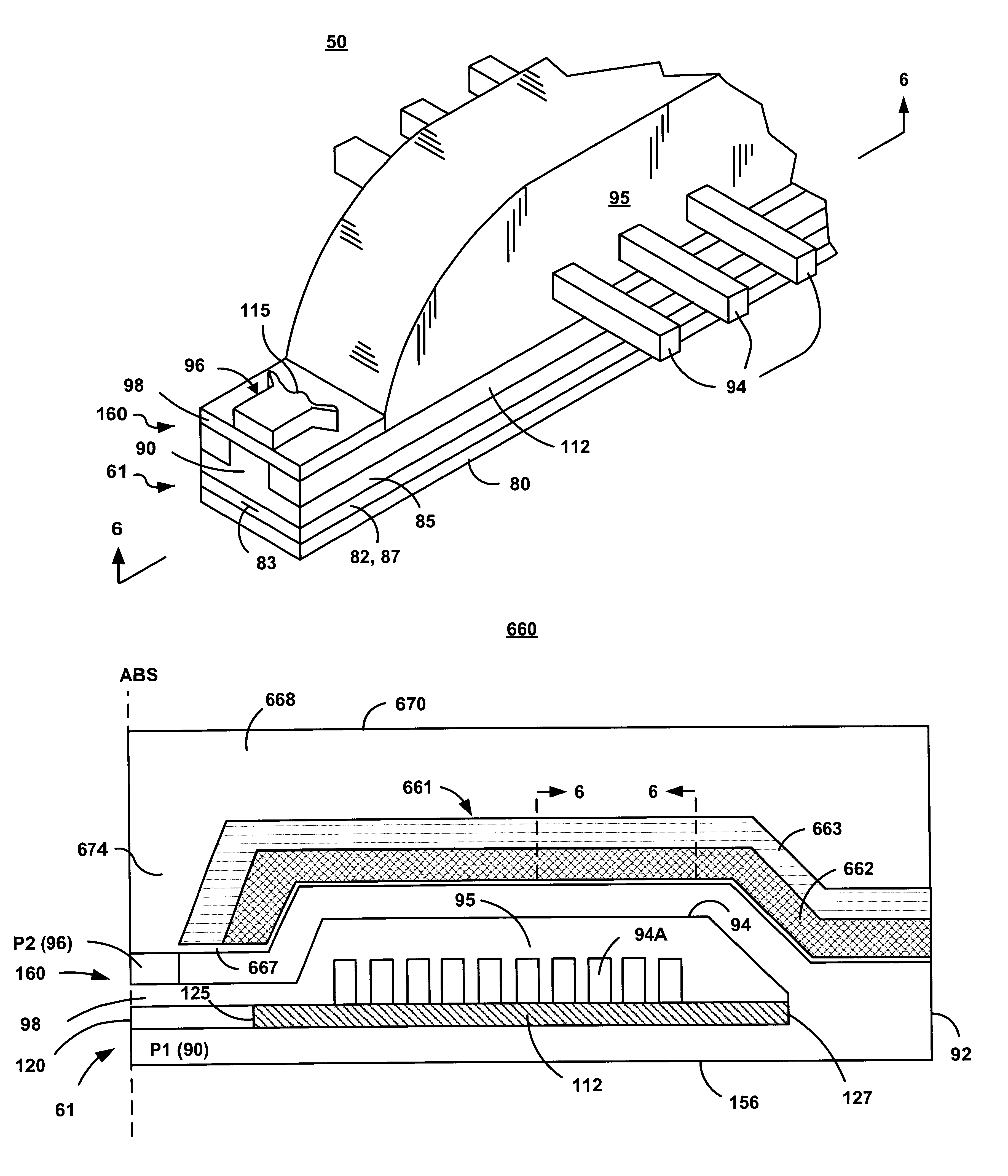

Hybrid diffuser for minimizing thermal pole tip protrusion and reader sensor temperature

InactiveUS6859343B1Reduces reader sensor temperatureImprove thermal conductivityManufacture head surfaceRecord information storageInvarInsulation layer

An enchance recording head design provides conduction and mechanical restraint control in order to minimize the pole tip protrusion and the head temperature resulting from the thermal heating of the magnetic recording head during operation. In one embodiment, the recording head includes a hybrid diffuser formed within an insulation layer, at a predetermined distance from the head write section. The hybrid diffuser is comprised of a thermal conduction layer with high thermal conductivity, such as gold or copper, and a mechanical restraint layer having near zero CTE, such as a 60-80% face-centered-cubic NiFe (Invar) material. The hybrid diffuser is recessed from the ABS to prevent the delamination of the hybrid diffuser due to the otherwise displacement incompatibility between the inner insulating layer and the hybrid diffuser at the ABS.

Owner:WESTERN DIGITAL TECH INC

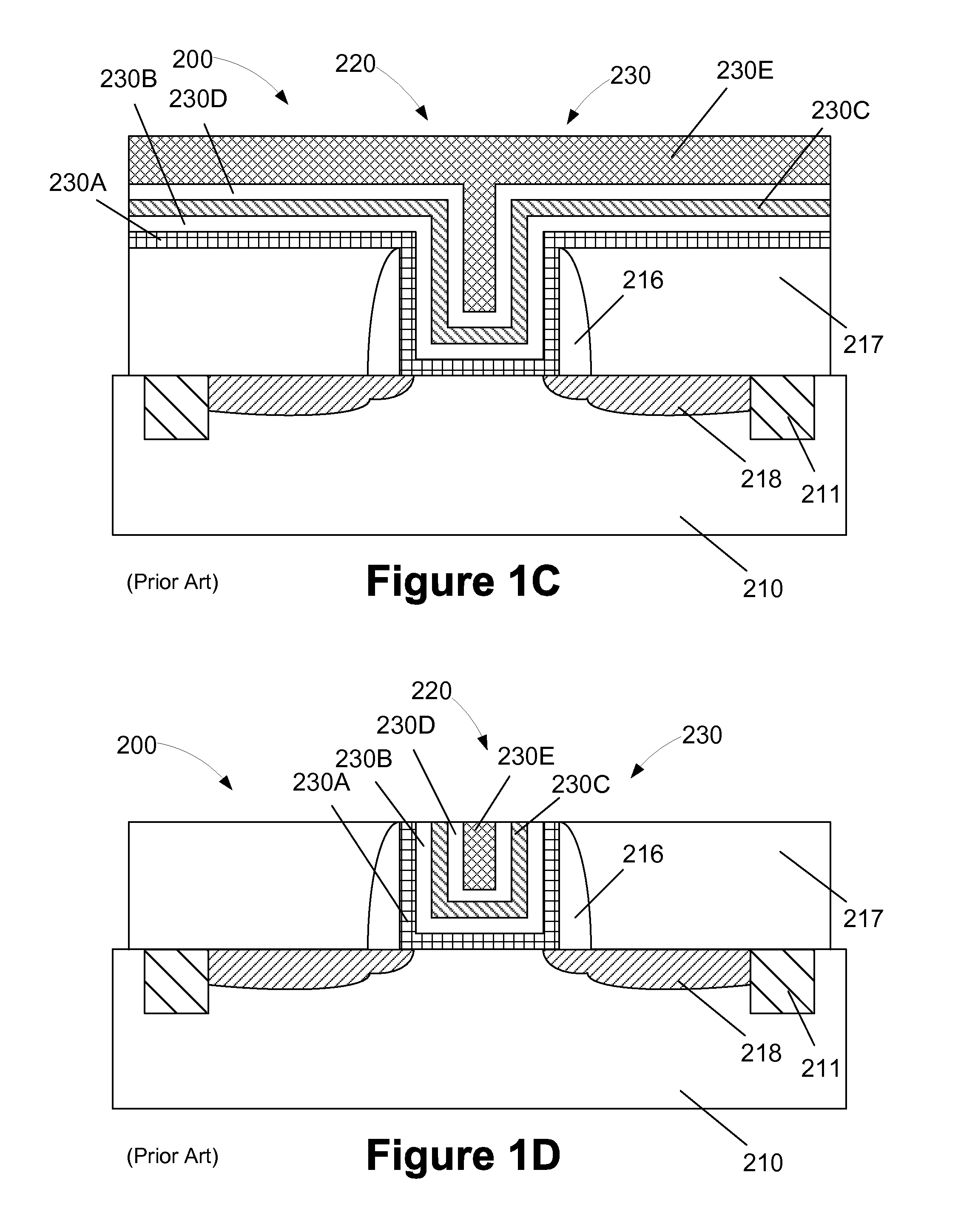

Methods for fabricating fin field effect transistors using a protective layer to reduce etching damage

A method of forming a fin field effect transistor on a semiconductor substrate includes forming a vertical fin protruding from the substrate. A buffer oxide liner is formed on a top surface and on sidewalls of the fin. A trench is then formed on the substrate, where at least a portion of the fin protrudes from a bottom surface of the trench. The trench may be formed by forming a dummy gate on at least a portion of the fin, forming an insulation layer on the fin surrounding the dummy gate, and then removing the dummy gate to expose the at least a portion of the fin, such that the trench is surrounded by the insulation layer. The buffer oxide liner is then removed from the protruding portion of the fin, and a gate is formed in the trench on the protruding portion of the fin.

Owner:SAMSUNG ELECTRONICS CO LTD

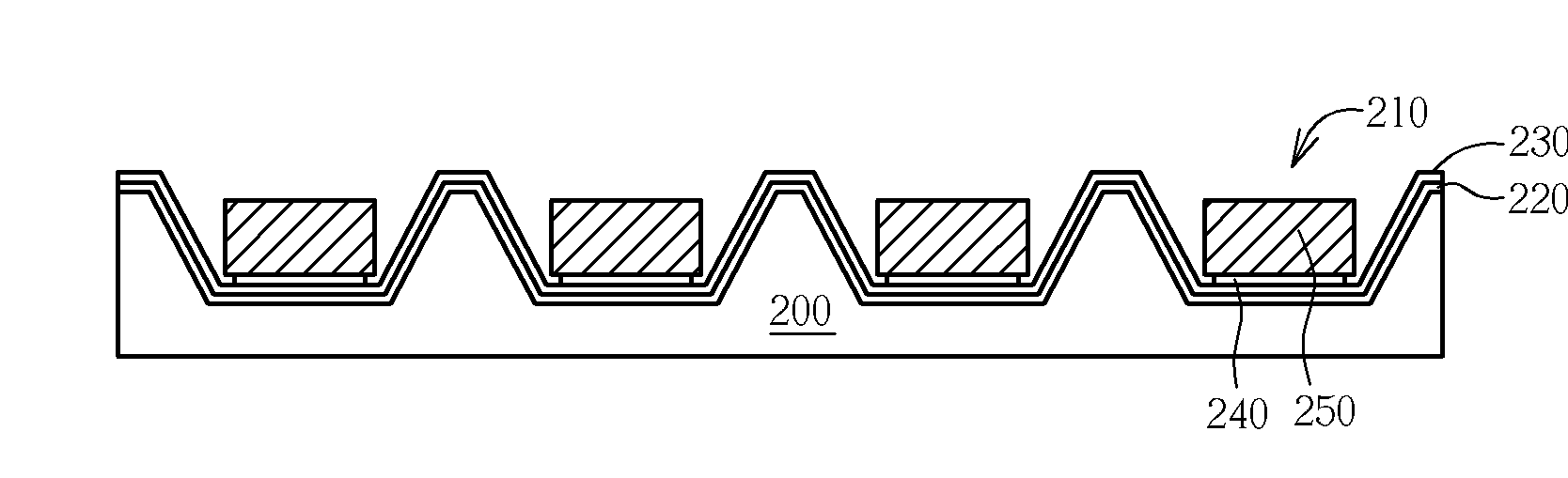

LED array package structure having silicon substrate and method of making the same

InactiveUS20080194054A1Improve light utilizationReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerLed array

An LED array package structure having a silicon substrate is disclosed. The LED array package structure comprises a silicon substrate having a plurality of cup-structures thereon, a reflective layer disposed on the silicon substrate, a transparent insulation layer disposed on the reflective layer, a conductive layer disposed on the transparent insulation layer and a plurality of LEDs disposed respectively on the conductive layer in each cup-structures.

Owner:TOUCH MICRO SYST TECH

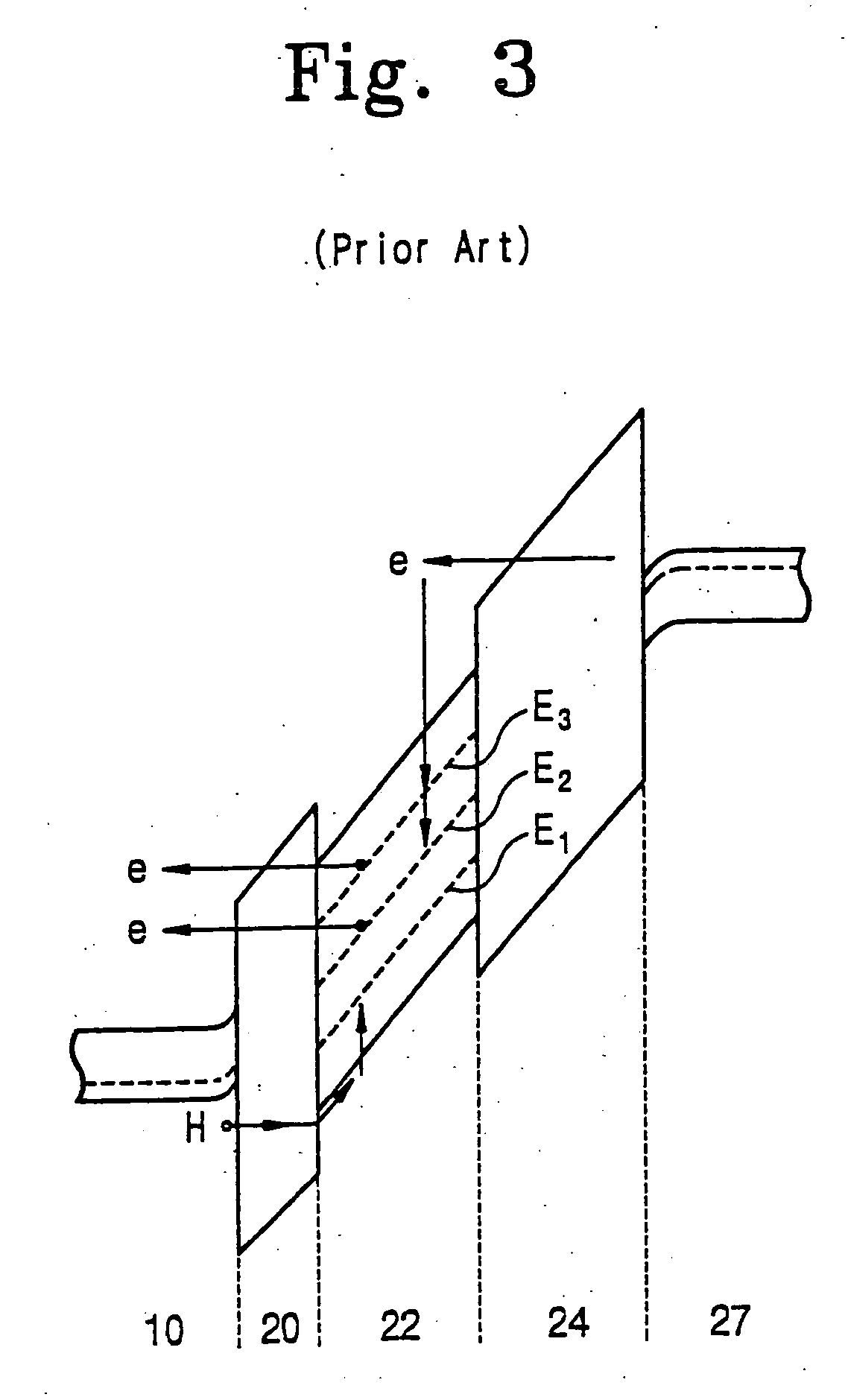

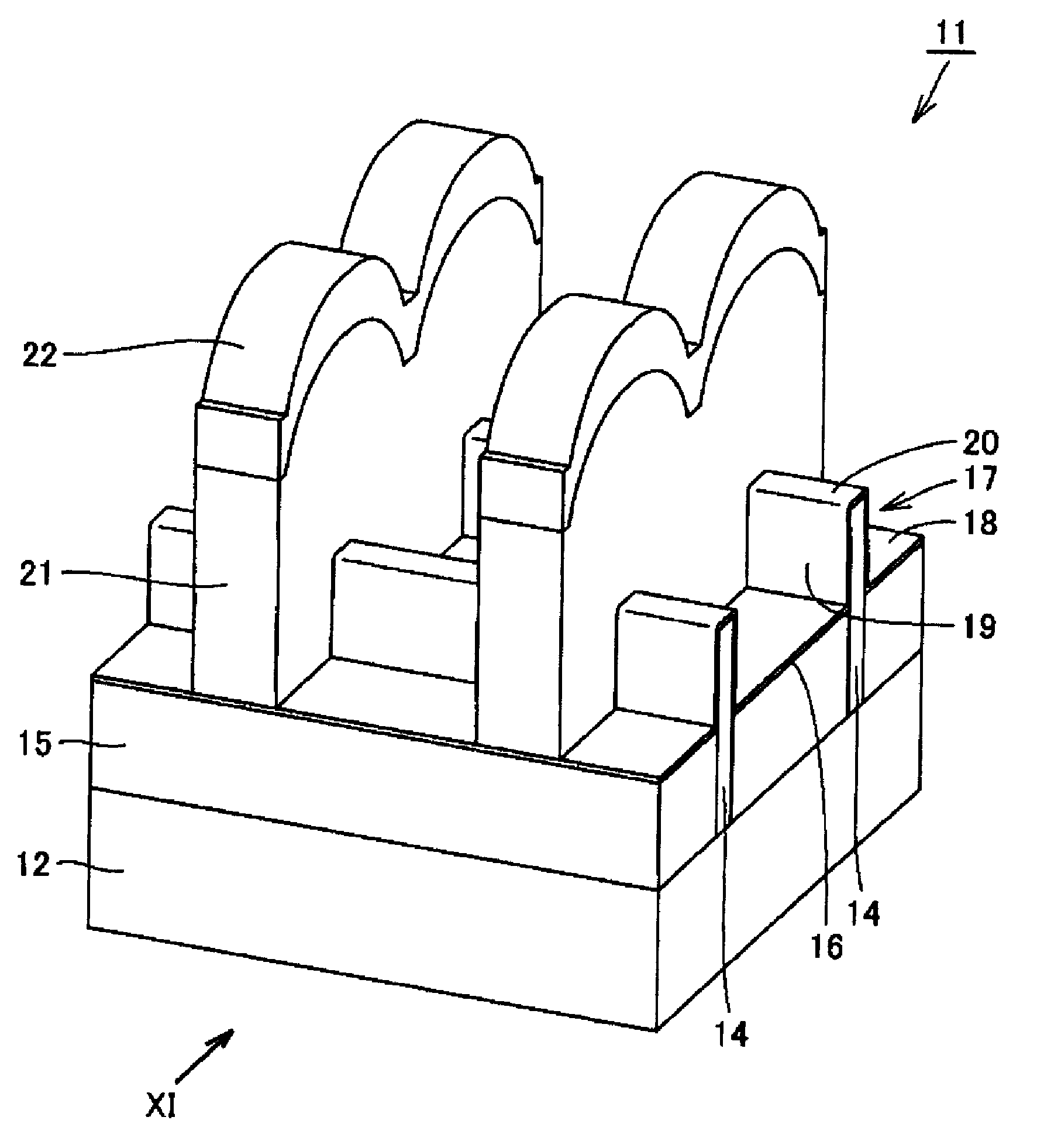

Method for forming a FinFET by a damascene process

ActiveUS20050170593A1Low costAvoid shortingTransistorBrushesManufacturing cost reductionInsulation layer

A device isolation film and an active region are formed on a semiconductor substrate, using a first mask pattern to expose only a formation region of the device isolation film. Only the device isolation film is selectively etched by using the first mask pattern and a second mask pattern as an etch mask, to form a fin only on a gate formation region, the second mask pattern to expose only a gate electrode formation region. A gate insulation layer is formed on both sidewalls of the fin and a gate electrode covering the first mask pattern and the gate insulation layer is formed. Source and drain regions are formed on the remaining portion of the active region where the gate electrode was not formed. Gate electrode separation becomes adequate and manufacturing costs can be reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

Non-volatile memory devices and methods of operating the same

Non-volatile memory devices and methods of operating the same are disclosed. A non-volatile memory device includes a semiconductor substrate. A tunnel insulating layer and a gate electrode are on the semiconductor substrate. A multiple tunnel insulation layer with a plurality of layers, a charge storage insulation layer, and a multiple blocking insulation layer with a plurality of layers are sequentially stacked between the gate electrode and the tunnel insulating layer. A first diffusion region and a second diffusion region in the semiconductor substrate are adjacent to opposite respective sides of the gate electrode. When a voltage is applied to the gate electrode and the semiconductor substrate to form a voltage level difference therebetween, a minimum field in the tunnel insulation layer is stronger than a minimum field in the blocking insulation layer. A minimum field established at a blocking insulation layer can be stronger than a minimum field established at a tunnel insulation layer, and the migration probability of charges through the tunnel insulation layer can be higher than that of charges through the blocking insulation layer. Therefore, it may be possible to use lower operation voltages, obtain higher program and erase speeds, and / or obtain a greater difference between threshold values of a program threshold voltage and an erase threshold voltage. As a result, a multi-valued non-volatile memory device may be formed therefrom.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device manufacturing method

InactiveUS20110039407A1Appropriately and efficiently manufacturingAppropriatelySemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerDevice material

A semiconductor device manufacturing method, the method including: forming an insulation layer having a protruding portion, the insulation layer having a surface and a rising surface that protrudes upward from the surface, on a semiconductor substrate; forming a conductive layer to cover the insulation layer having the protruding portion; and removing a predetermined region of the conductive layer by patterning the predetermined region according to an etching process using microwave plasma, which uses a microwave as a plasma source, while applying bias power of 70 mW / cm2 or above on the semiconductor substrate, under a high pressure condition of 85 mTorr or above.

Owner:TOKYO ELECTRON LTD

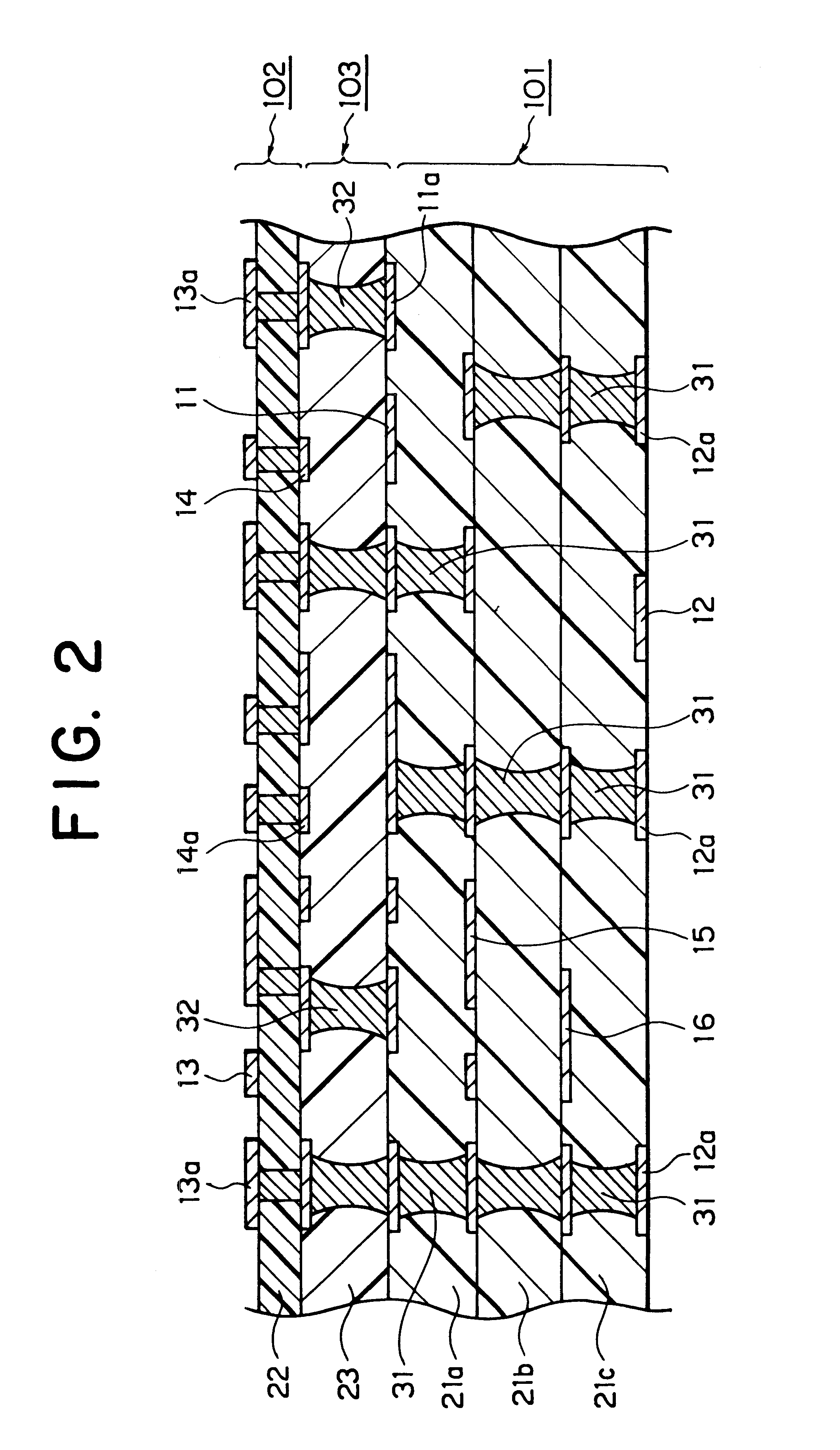

Non-volatile semiconductor storage device and method of manufacturing the same

ActiveUS7910432B2Solid-state devicesSemiconductor/solid-state device manufacturingInsulation layerSemiconductor storage devices

Each of the memory strings includes: a first columnar semiconductor layer extending in a vertical direction to a substrate; a plurality of first conductive layers formed to sandwich an insulation layer with a charge trap layer and expand in a two-dimensional manner; a second columnar semiconductor layer formed in contact with the top surface of the first columnar semiconductor layer and extending in a vertical direction to the substrate; and a plurality of second conductive layers formed to sandwich an insulation layer with the second columnar semiconductor layer and formed in a stripe pattern extending in a first direction orthogonal to the vertical direction. Respective ends of the plurality of first conductive layers in the first direction are formed in a stepwise manner in relation to each other, entirety of the plurality of the second conductive layers are formed in an area immediately above the top layer of the first conductive layers, and the plurality of first conductive layers and the plurality of second conductive layers are covered with a protection insulation layer that is formed continuously with the plurality of first conductive layers and the second conductive layers.

Owner:KIOXIA CORP