Patents

Literature

1353 results about "Vertical channel" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In vertical marketing channels, all levels of the channel are controlled by one entity. This happens when a corporation acquires or holds the key assets at all levels of the channel. It may also be done through contractual agreement or cooperative structure.

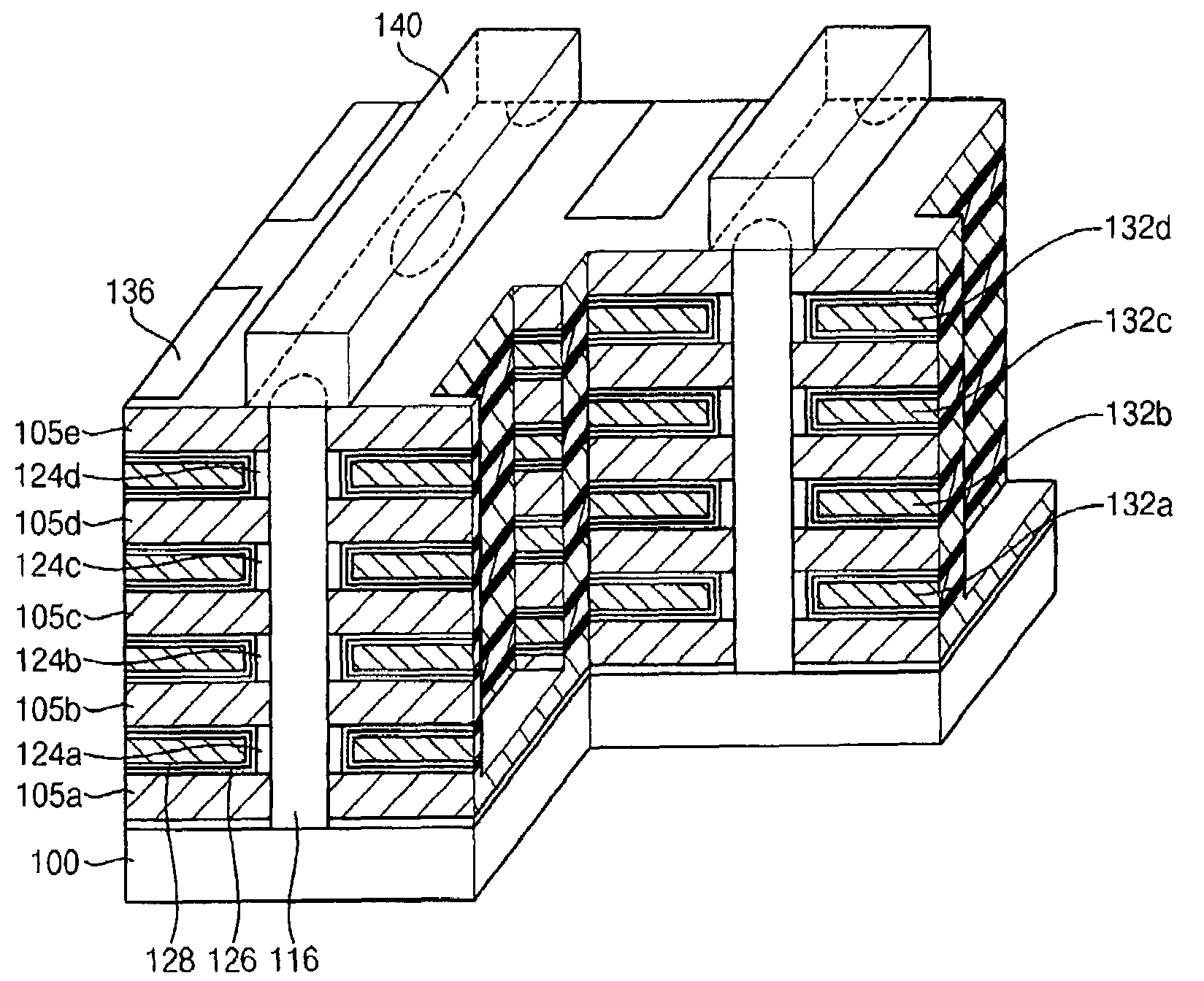

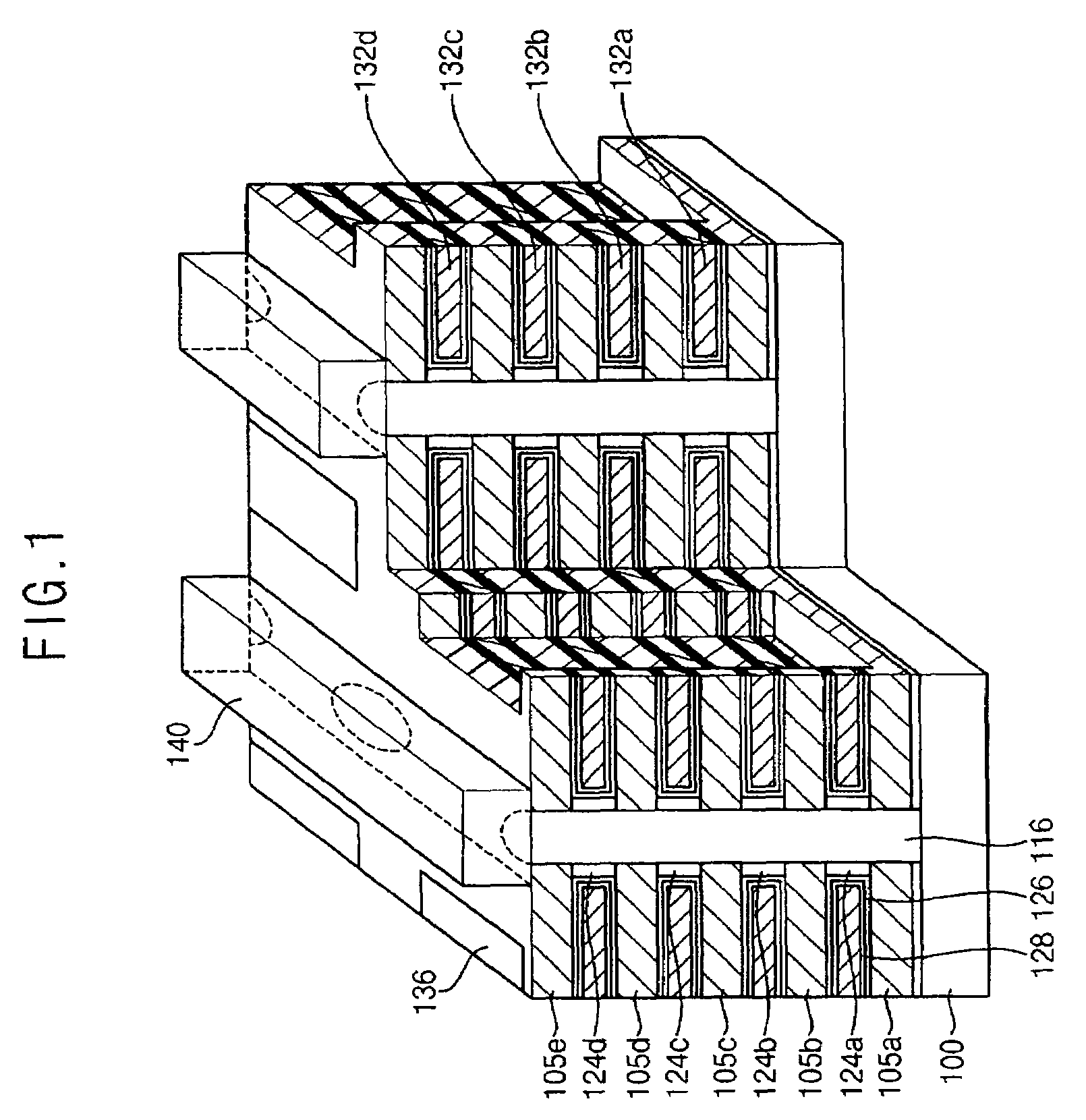

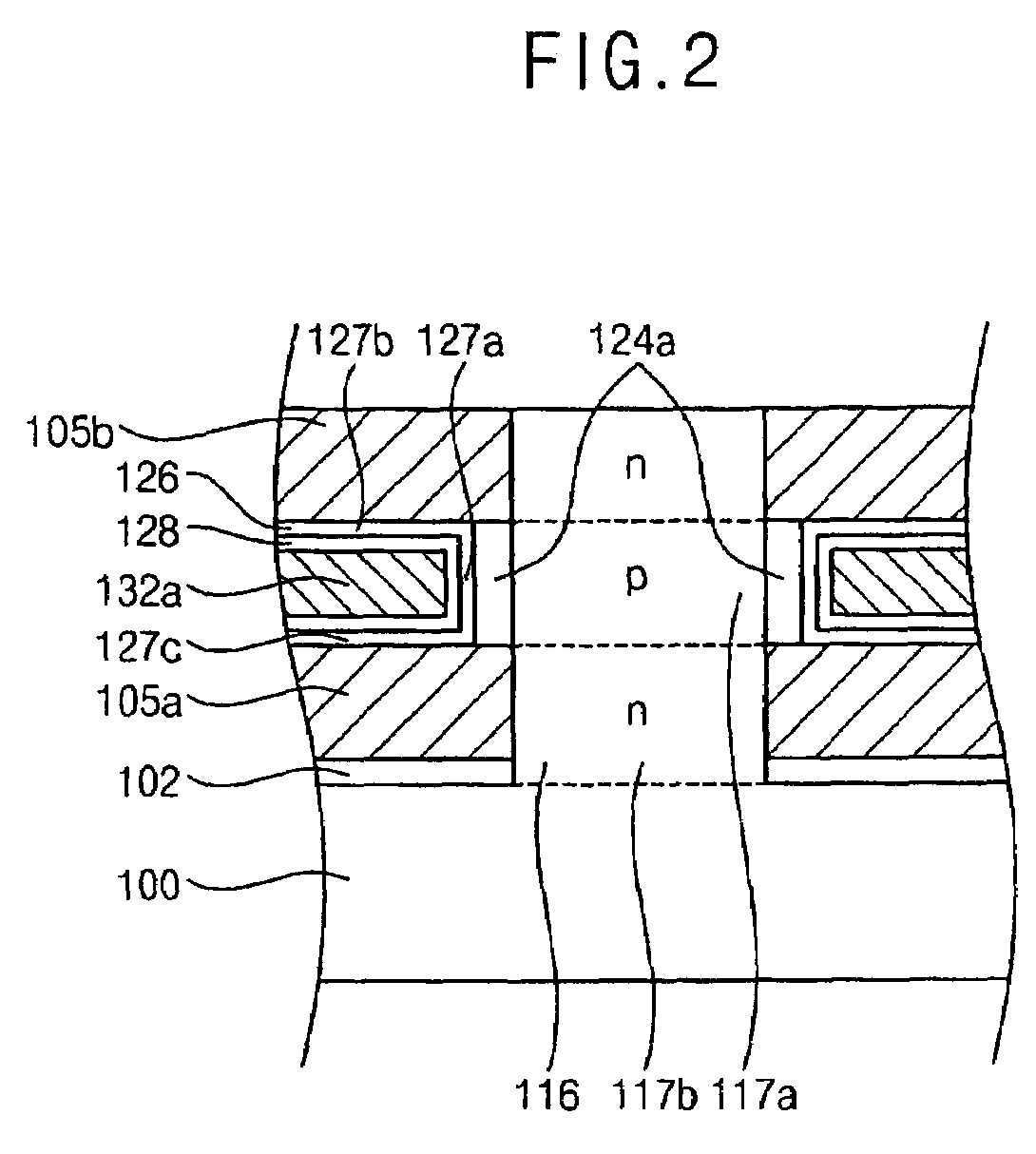

Vertical-type non-volatile memory devices

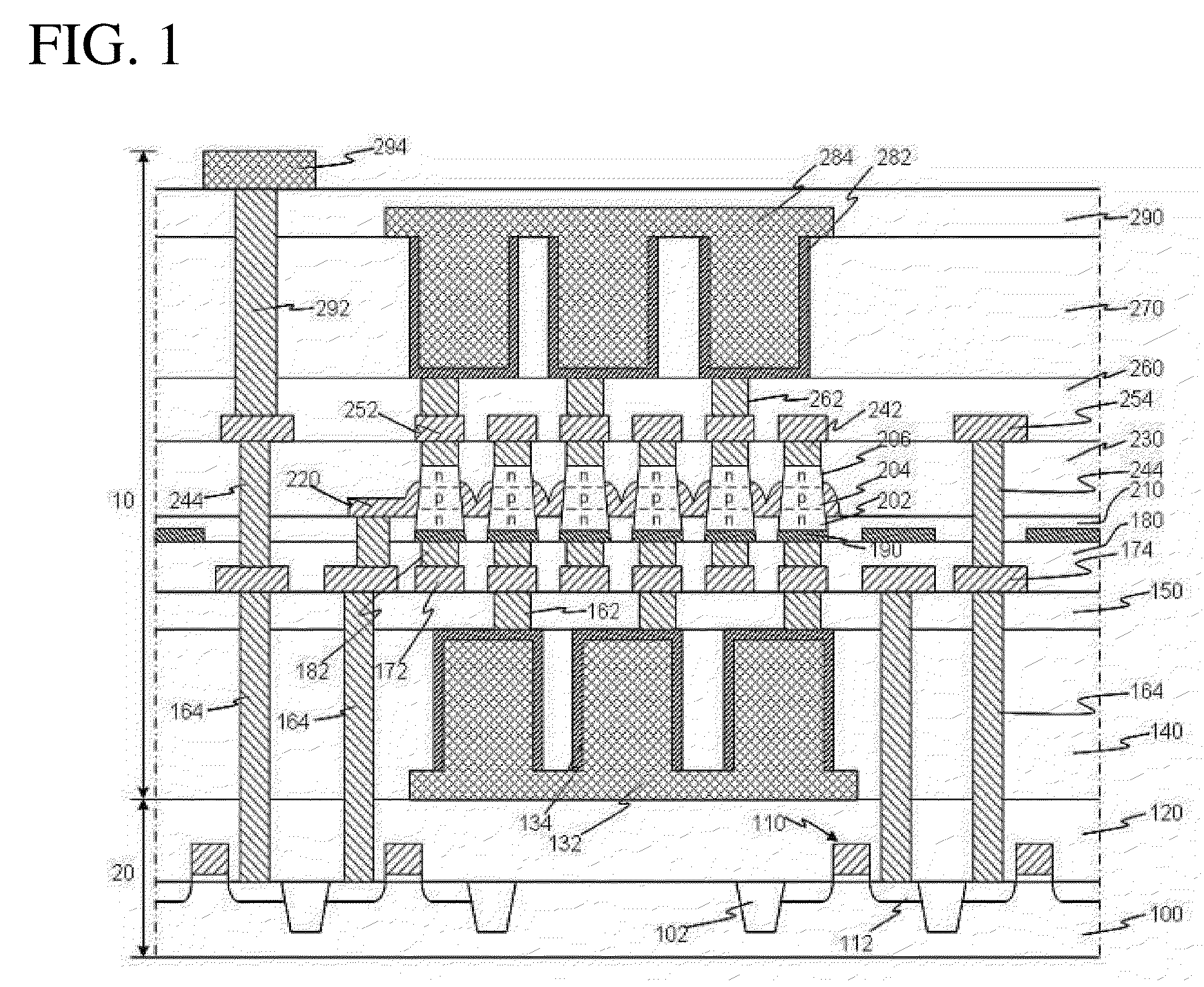

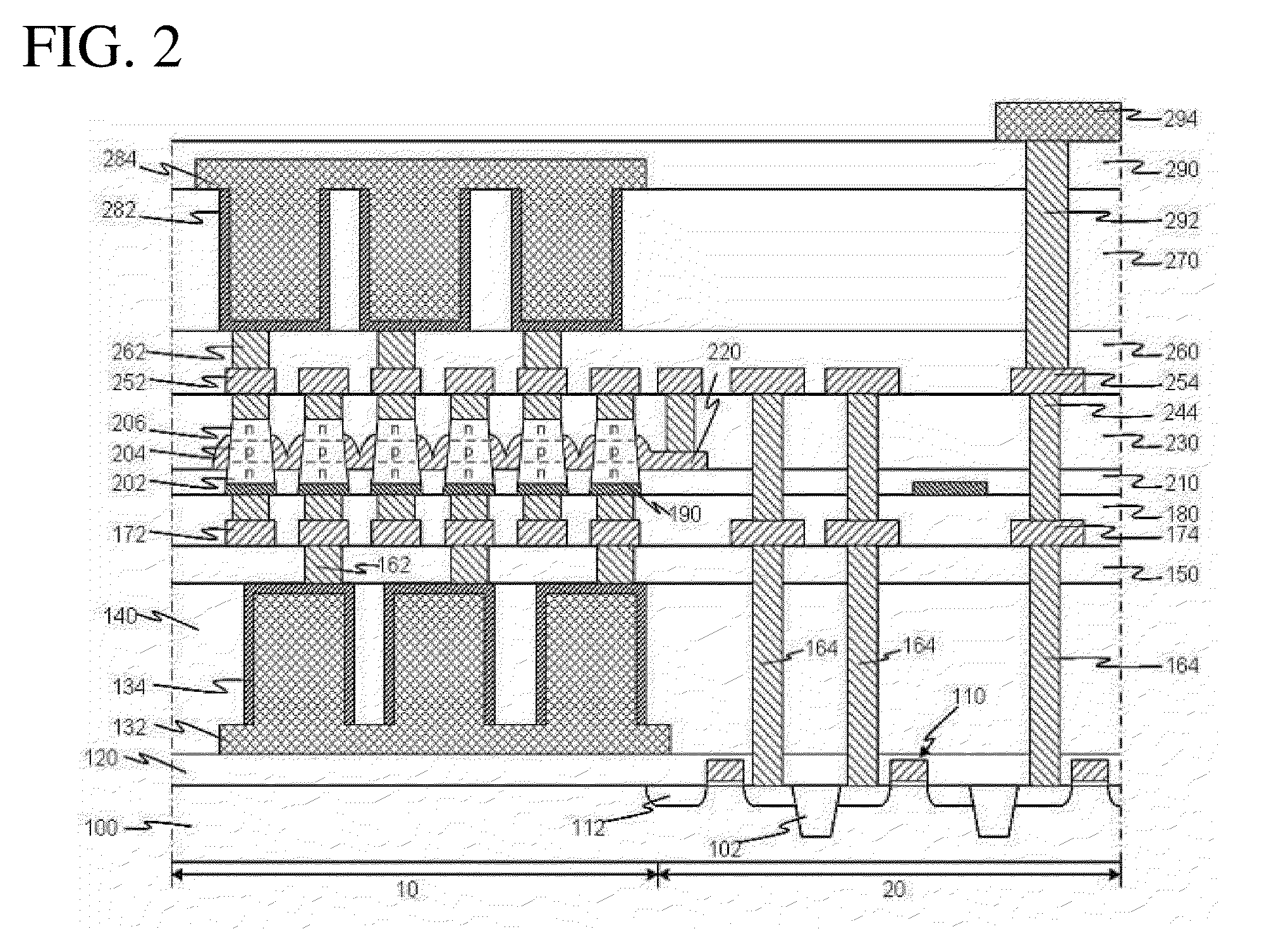

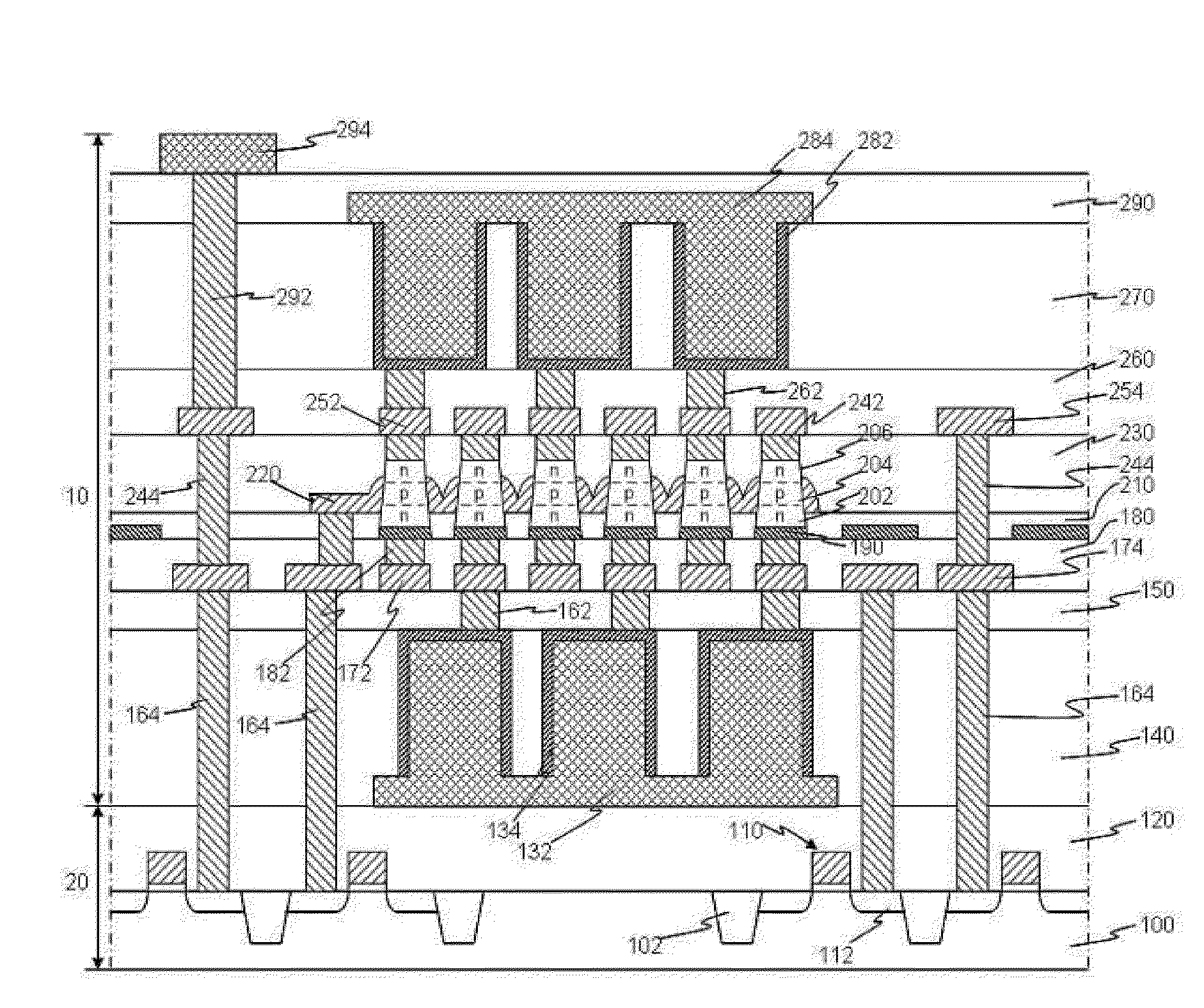

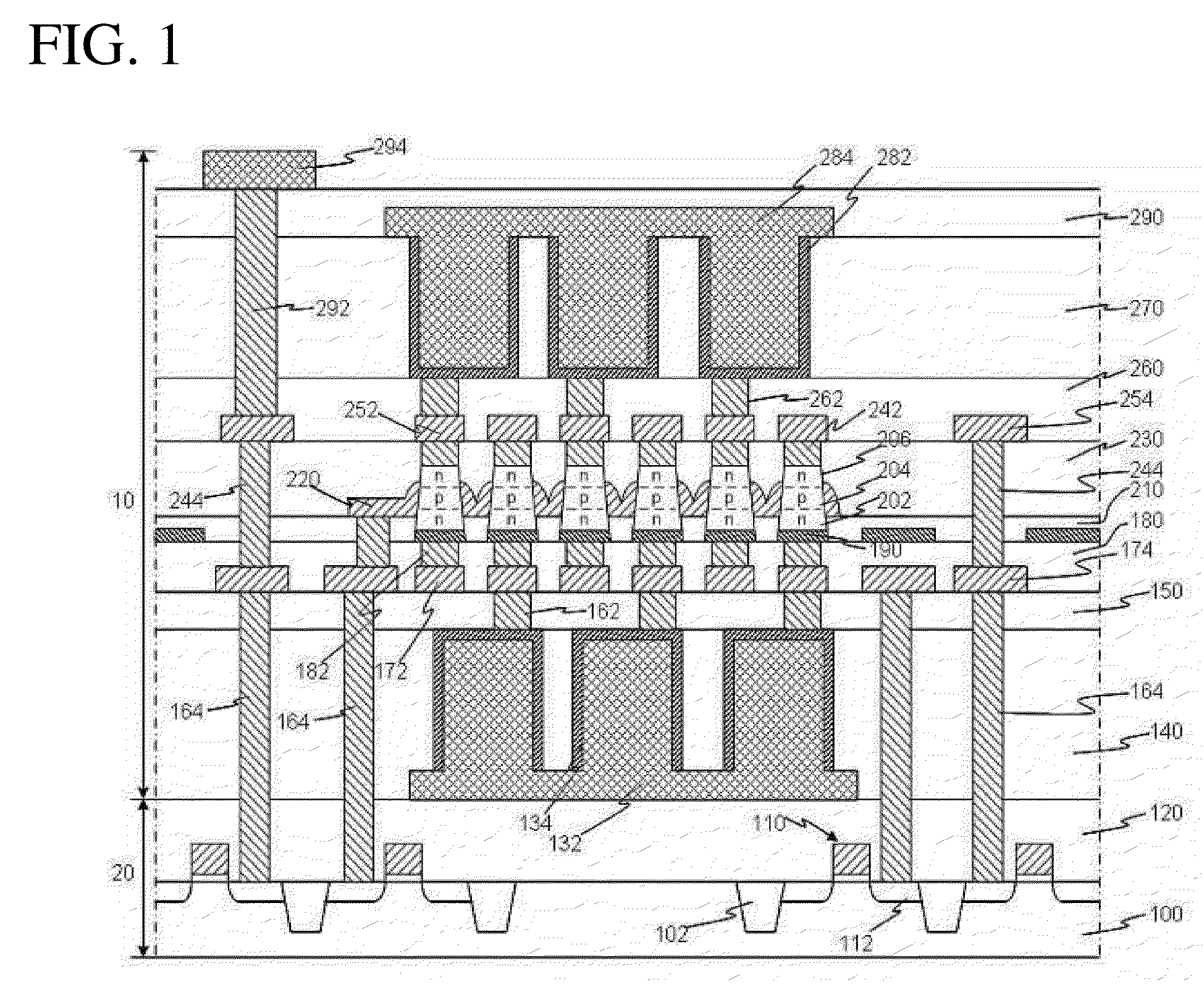

ActiveUS7679133B2Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

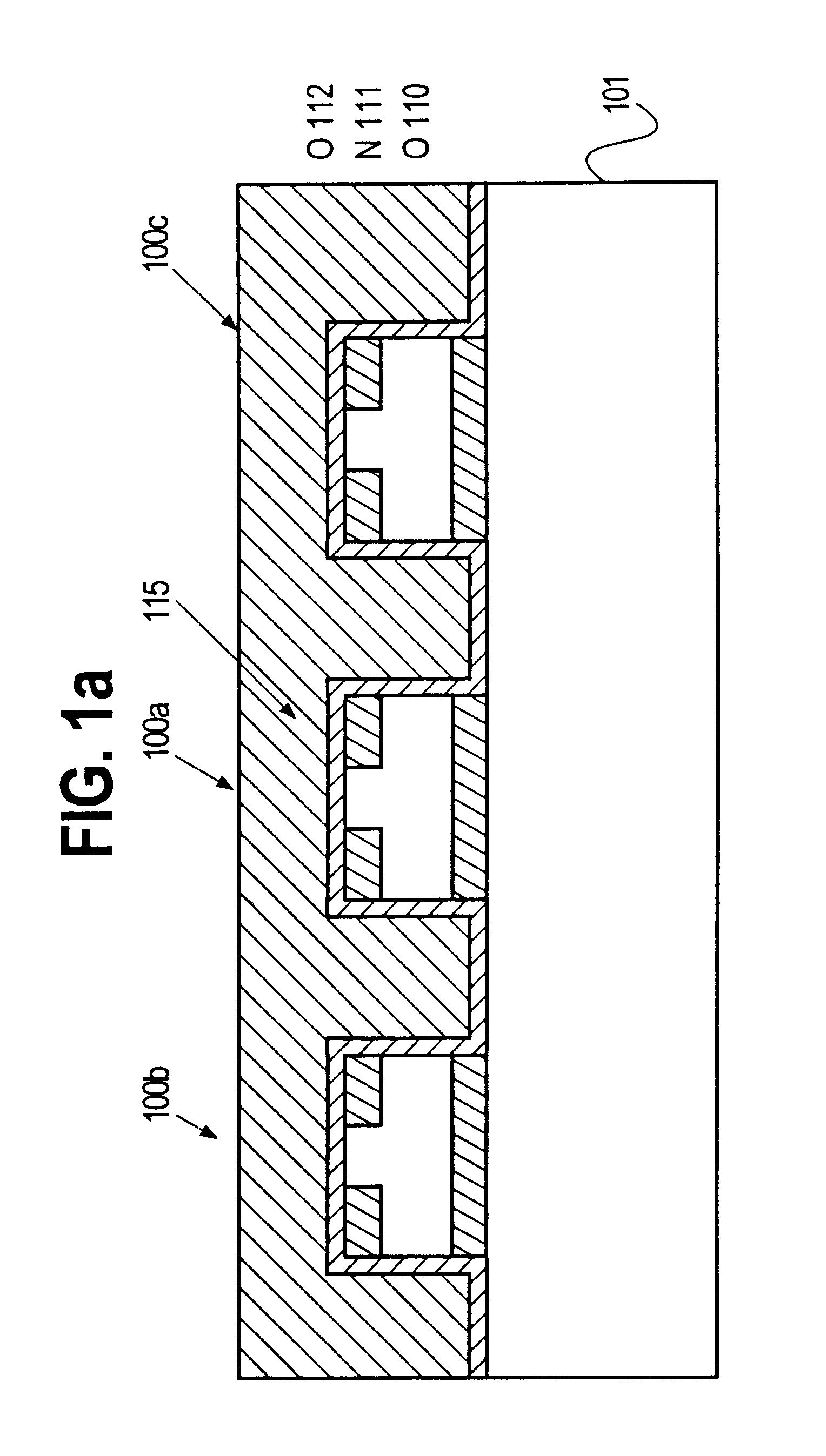

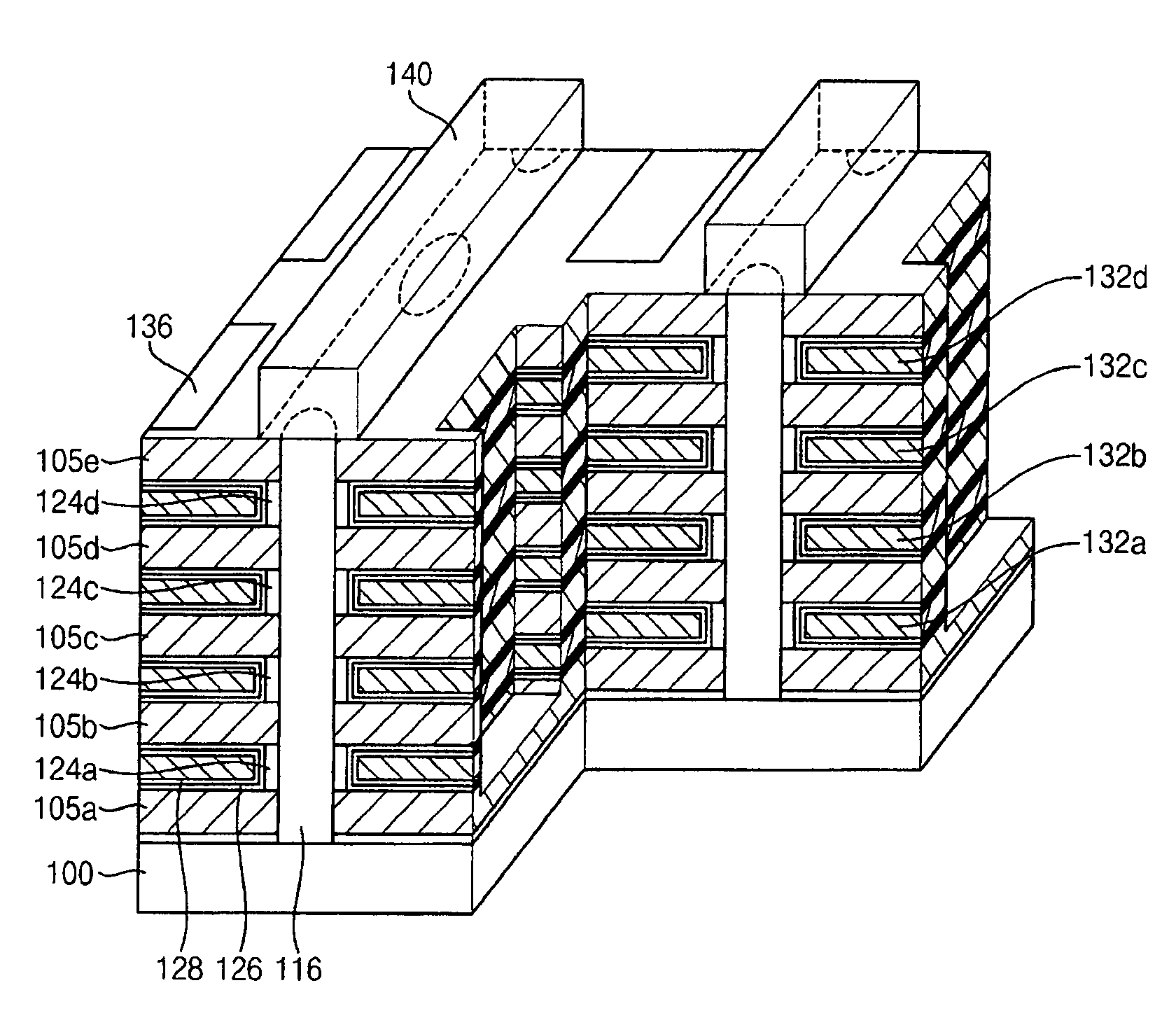

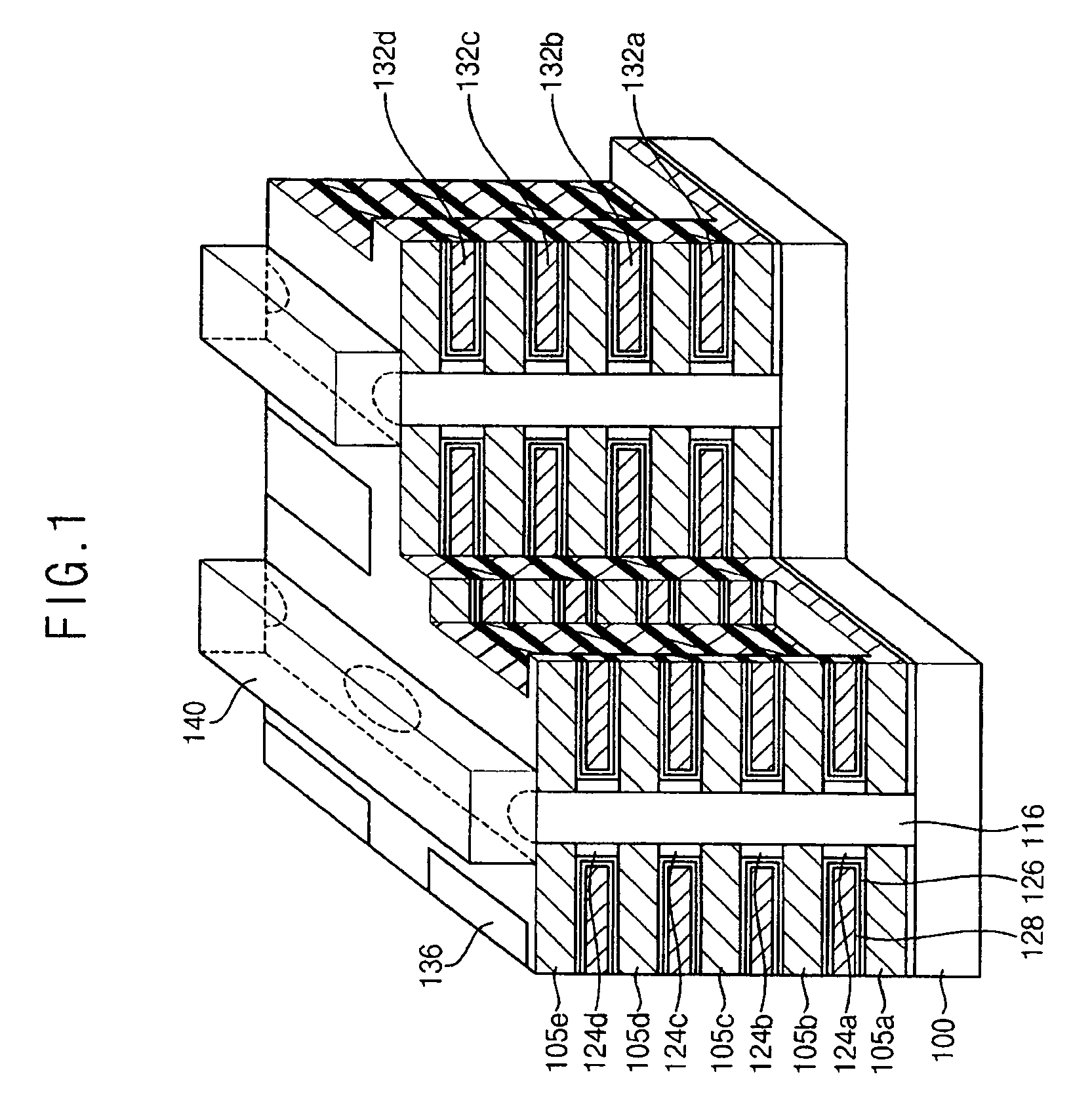

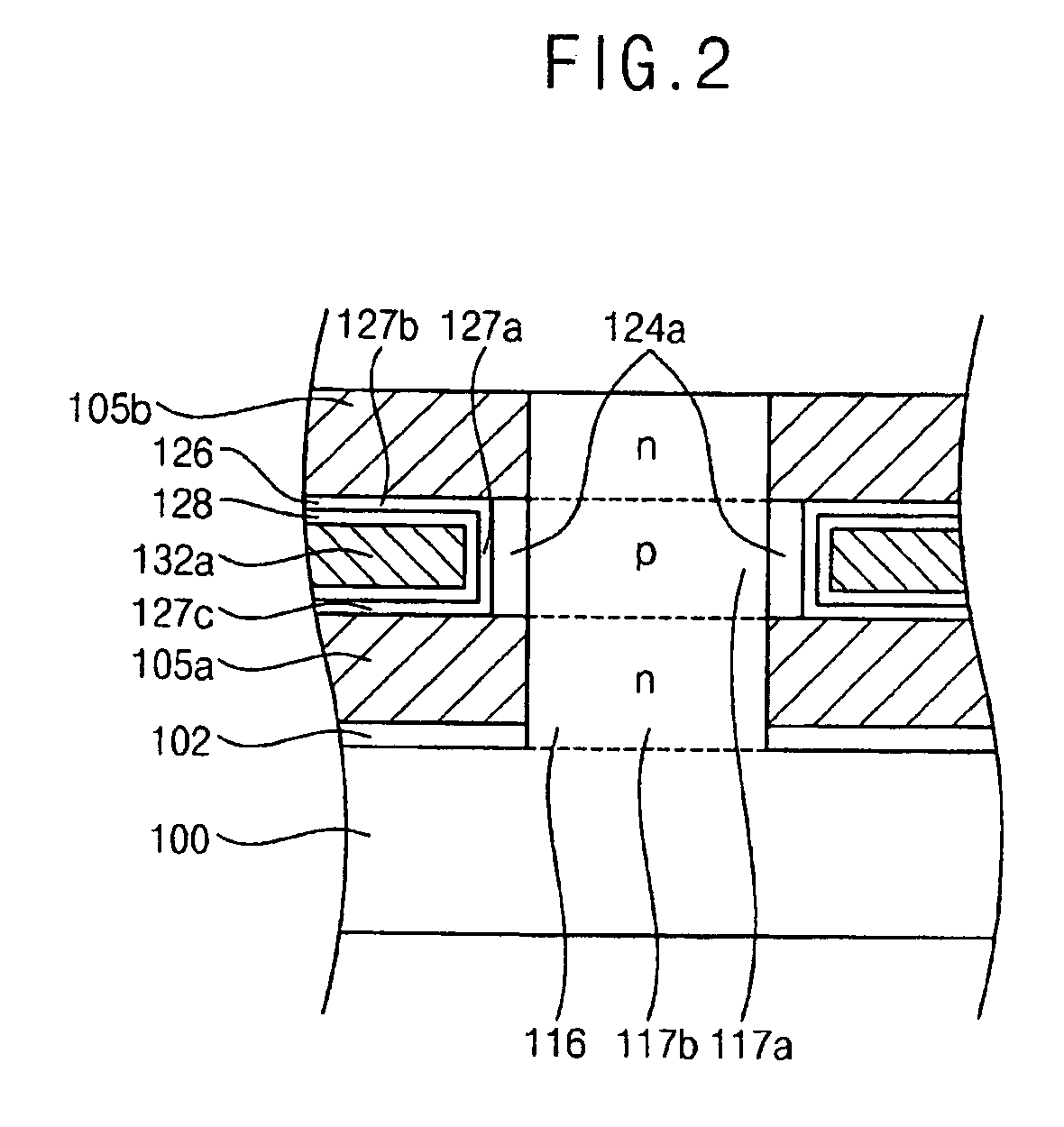

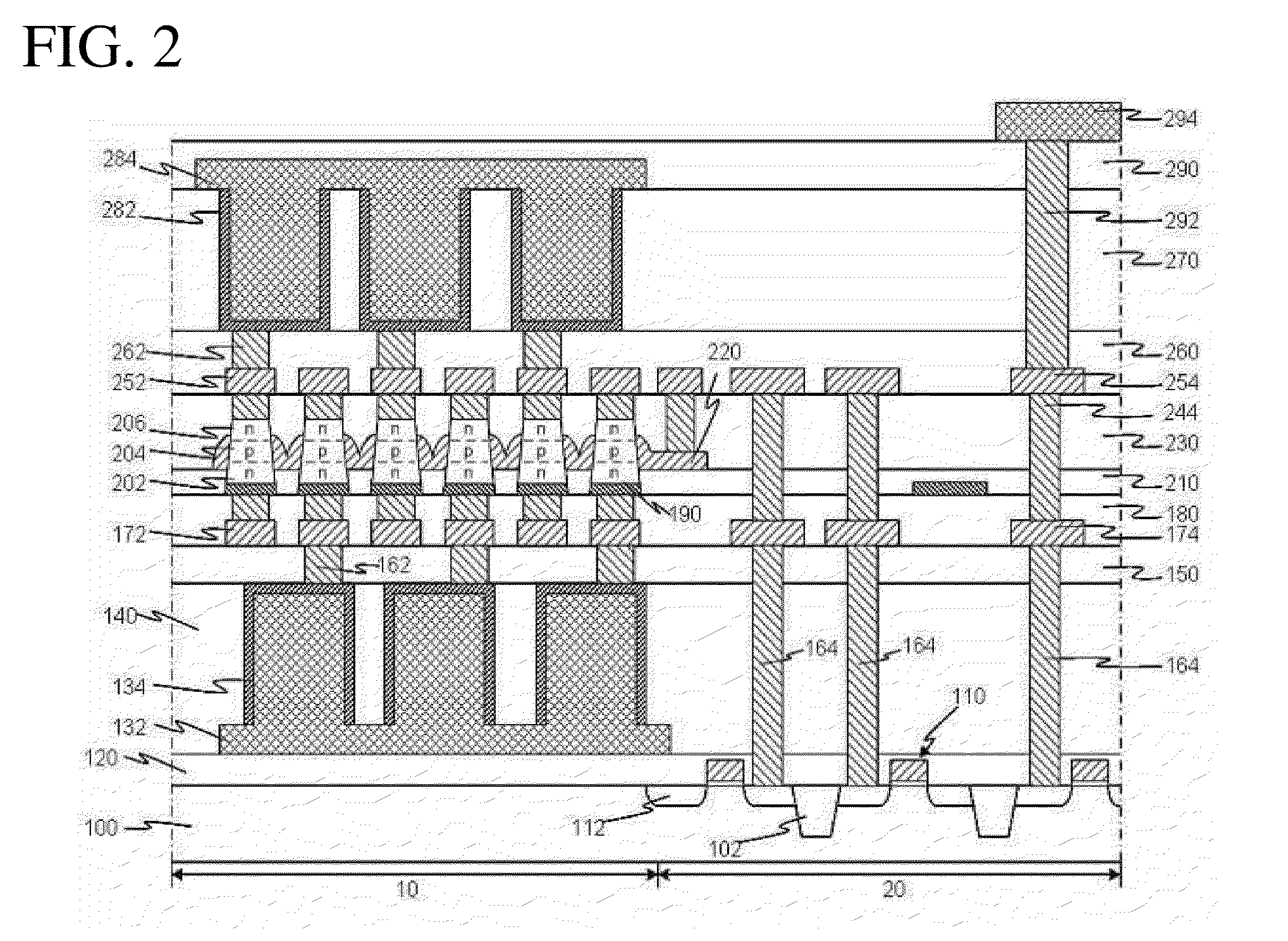

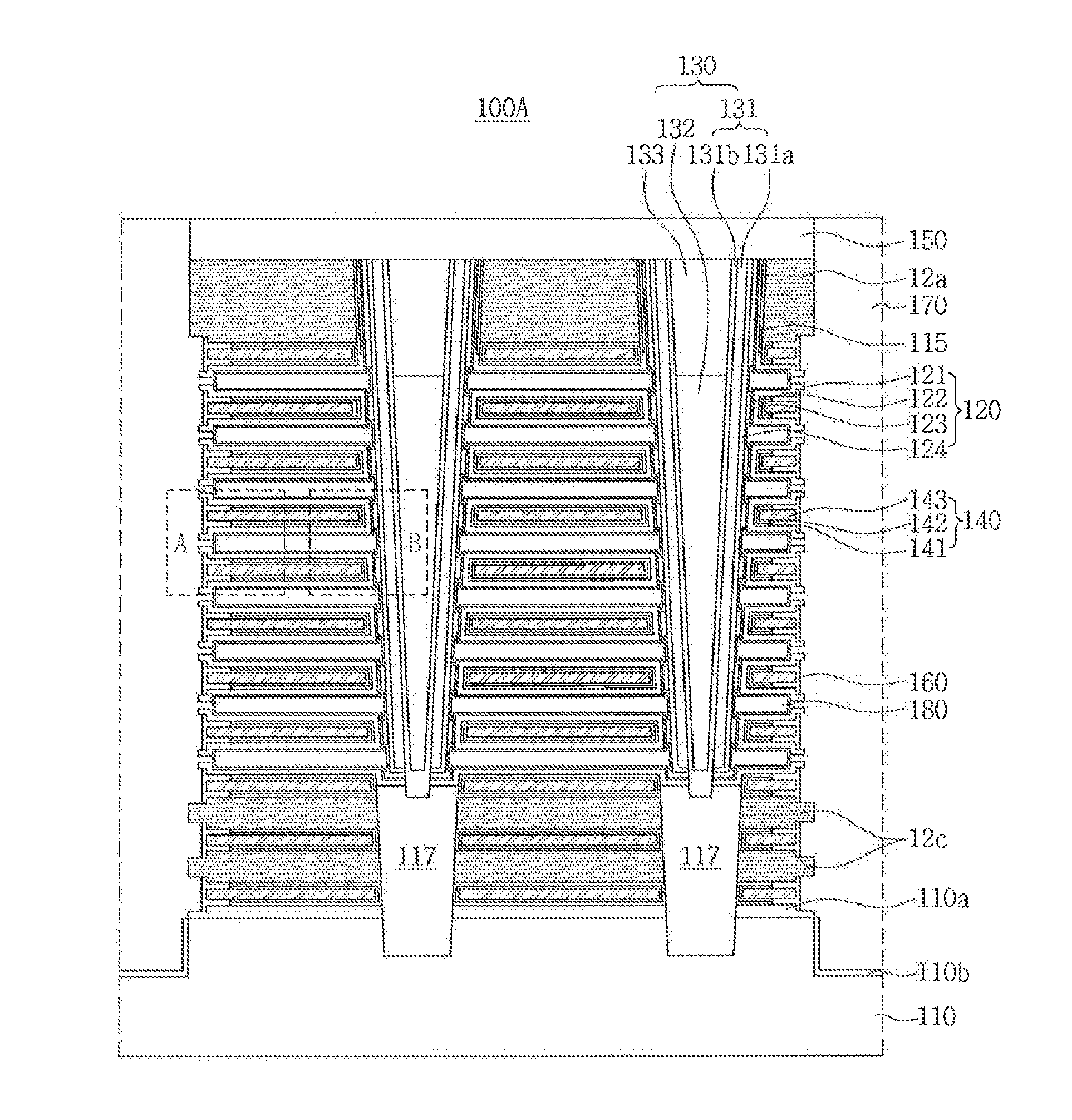

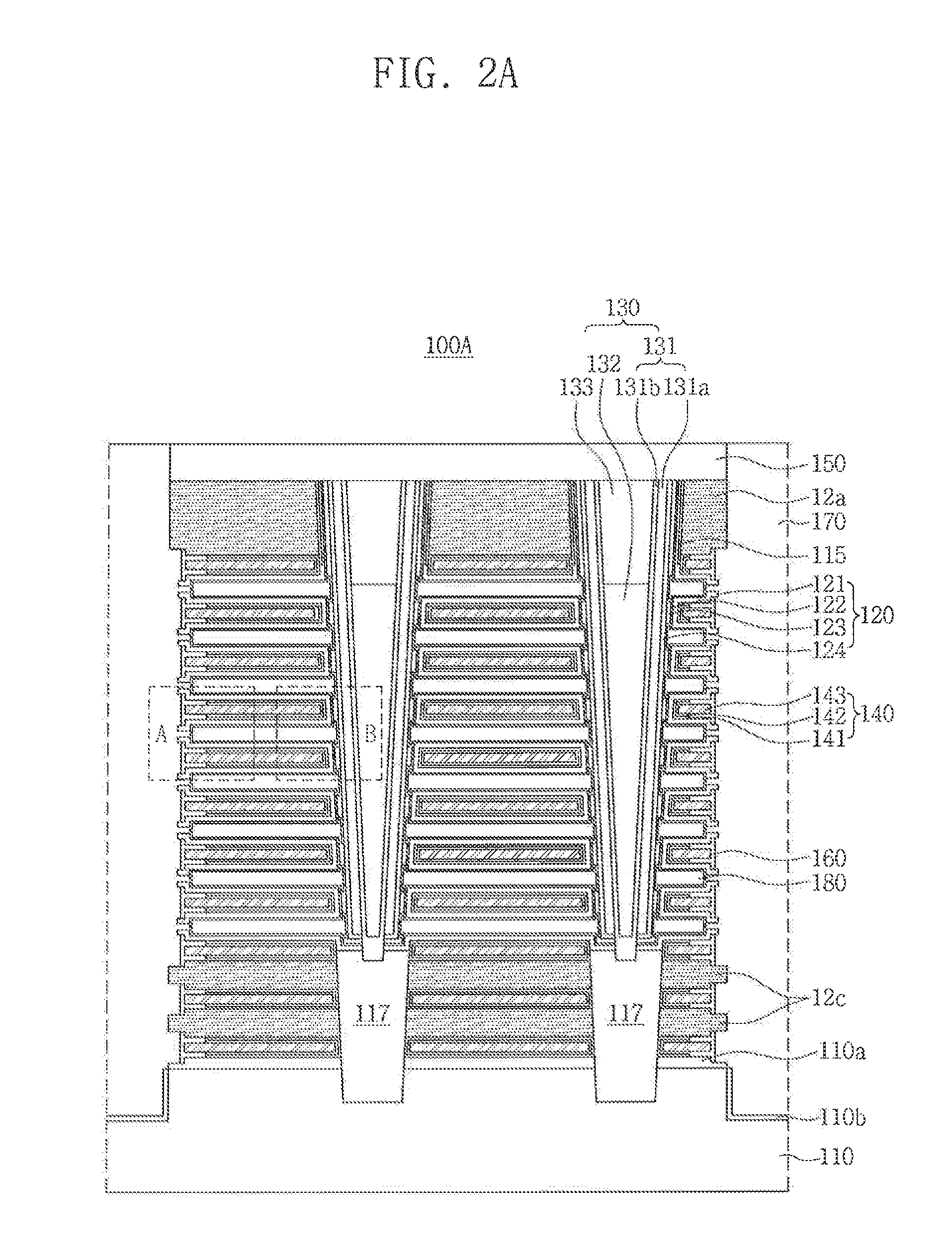

In a semiconductor device, and a method of manufacturing thereof, the device includes a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

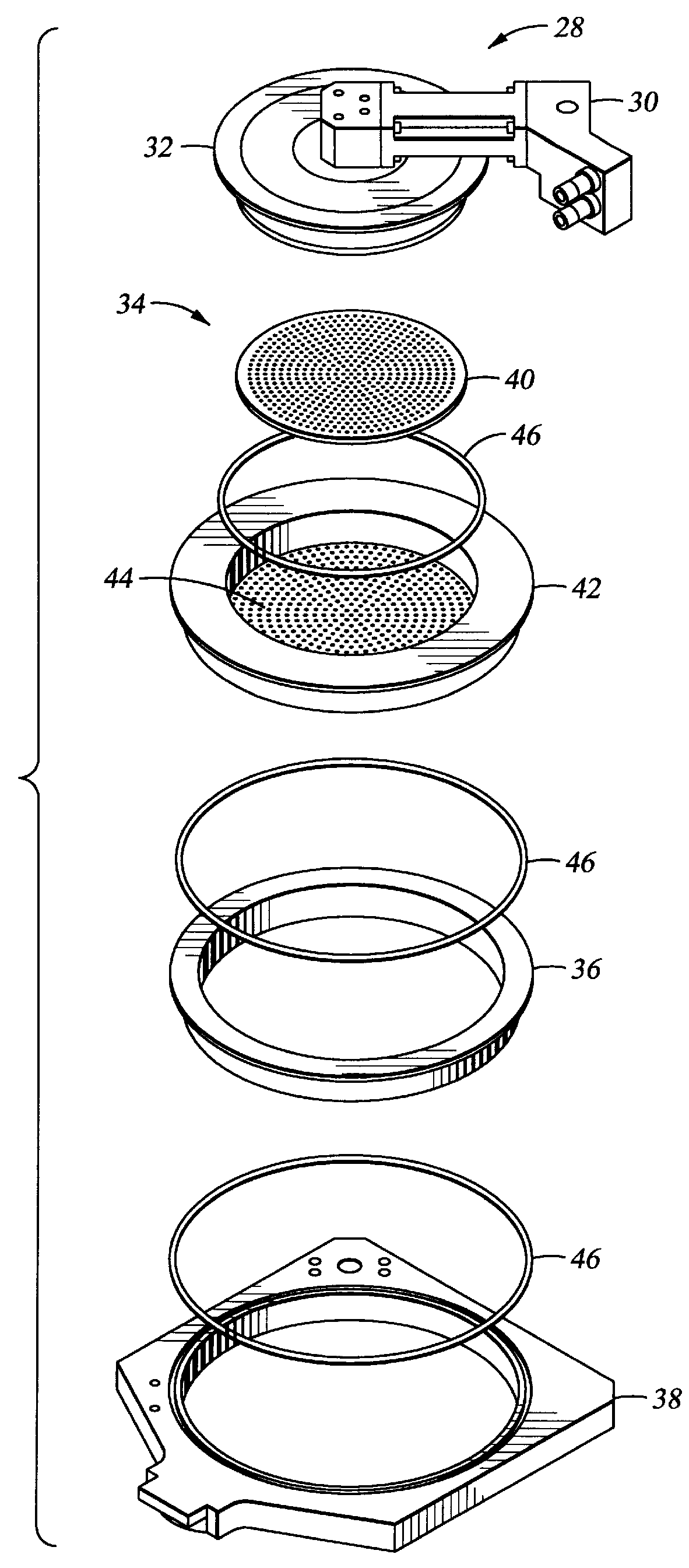

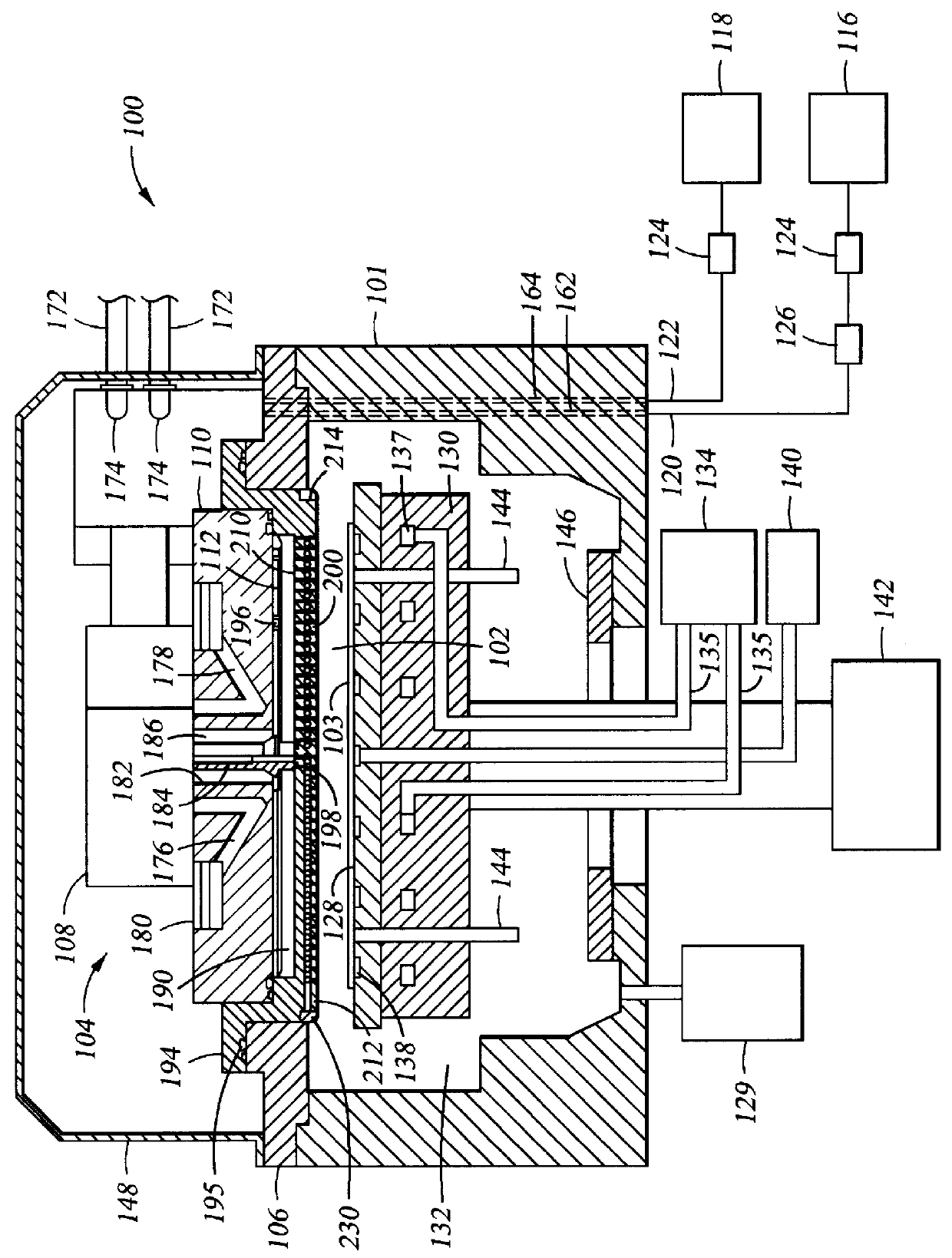

Dual channel gas distribution plate

InactiveUS6148761ASemiconductor/solid-state device manufacturingChemical vapor deposition coatingVertical channelDelivery system

A multi-channel faceplate 200, that in some embodiments is monolithic, is provided as a portion of a gas delivery system to a process chamber 100. At least two sets of gas pathways are disposed through a faceplate and allow for independent delivery of separate gases into a process chamber 100. In one embodiment, a first gas pathway, which includes a first set of vertical channels 226, is formed through the faceplate 200. A second gas pathway includes a second set of vertical channels 228, which is formed through a portion of the faceplate and connected to a set of interconnecting horizontal channels 222 in the faceplate 200, where the second gas pathway maintains fluidic separation from the first gas pathway, prior to the gases entering the process chamber 100.

Owner:APPLIED MATERIALS INC

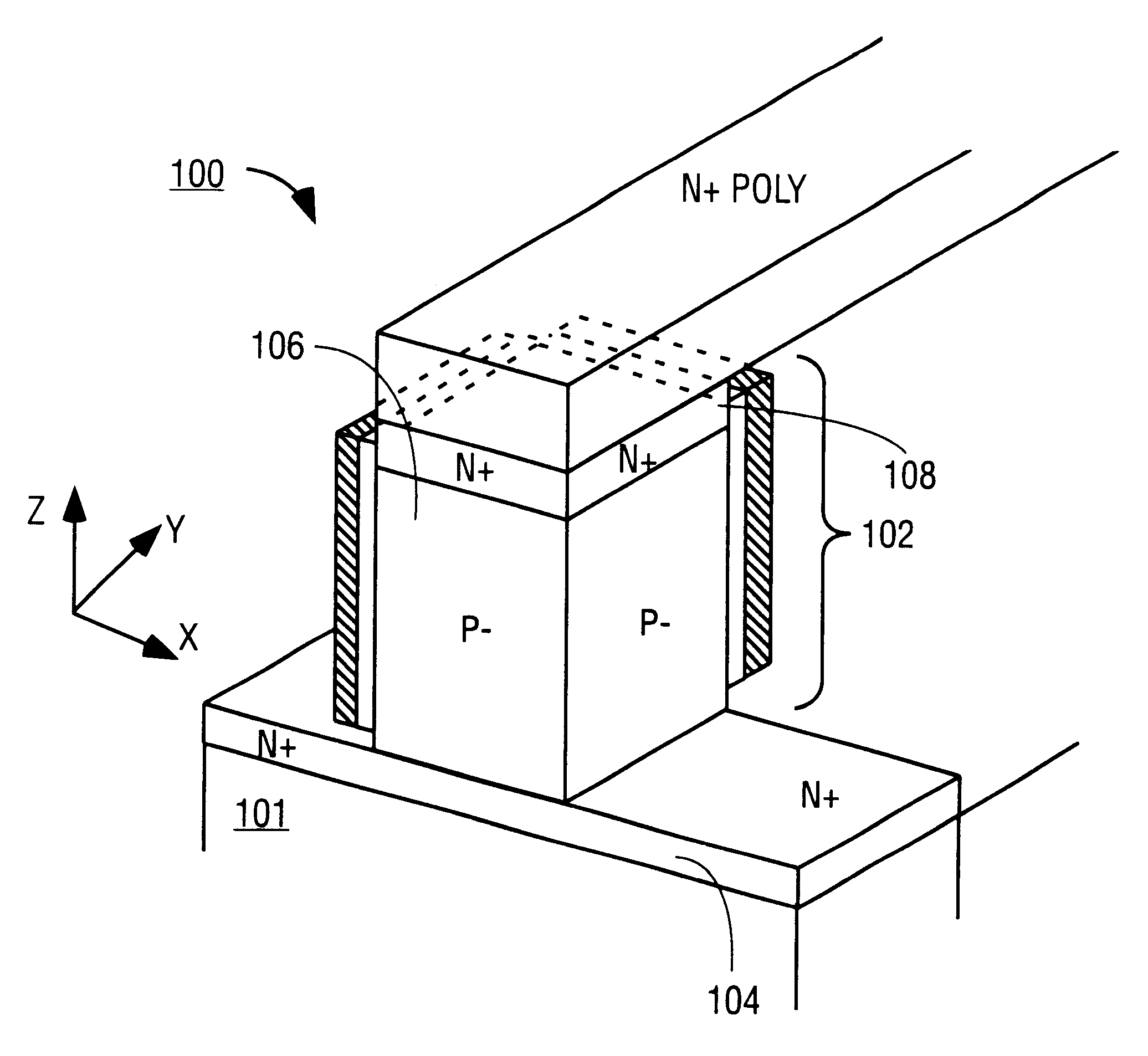

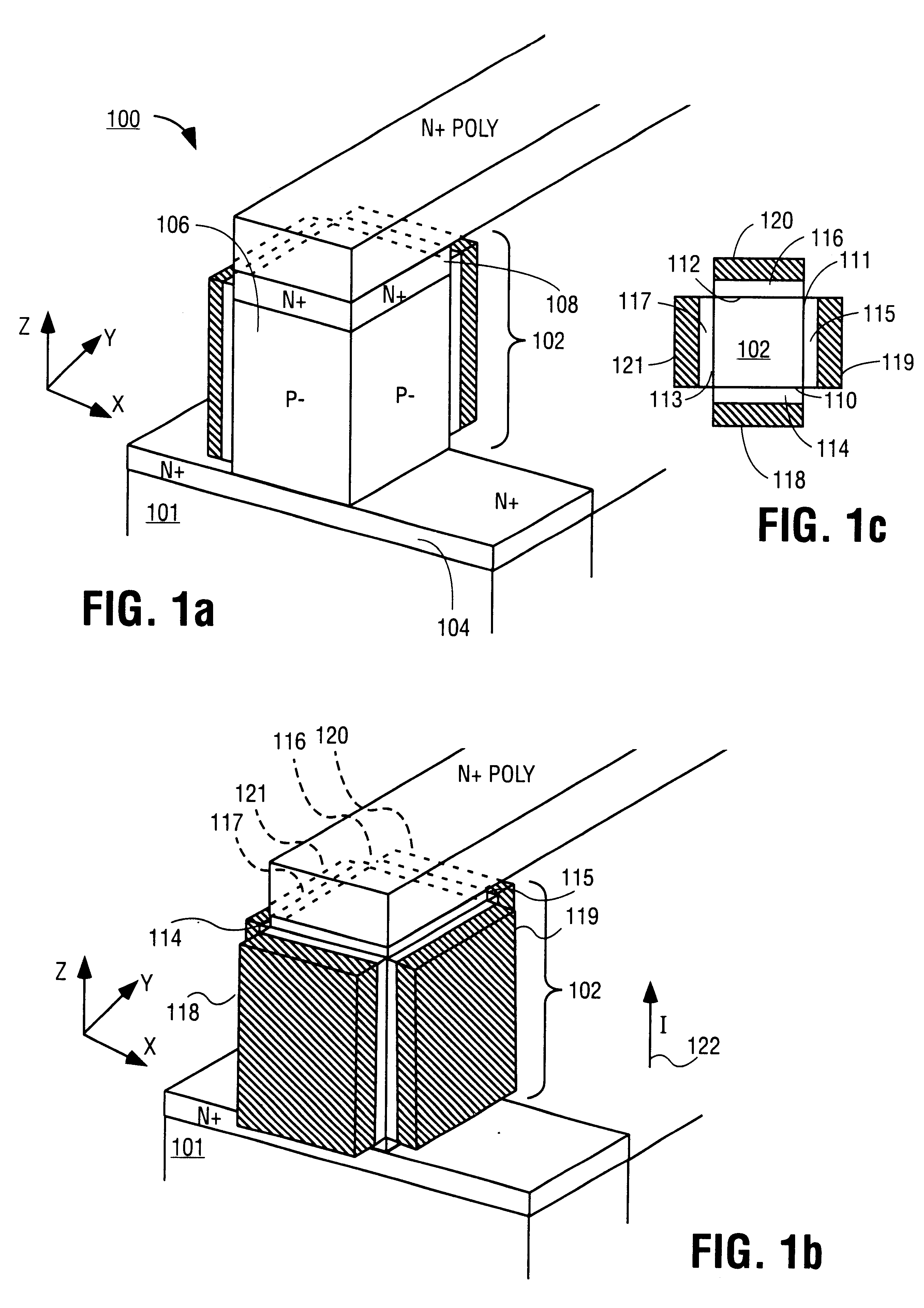

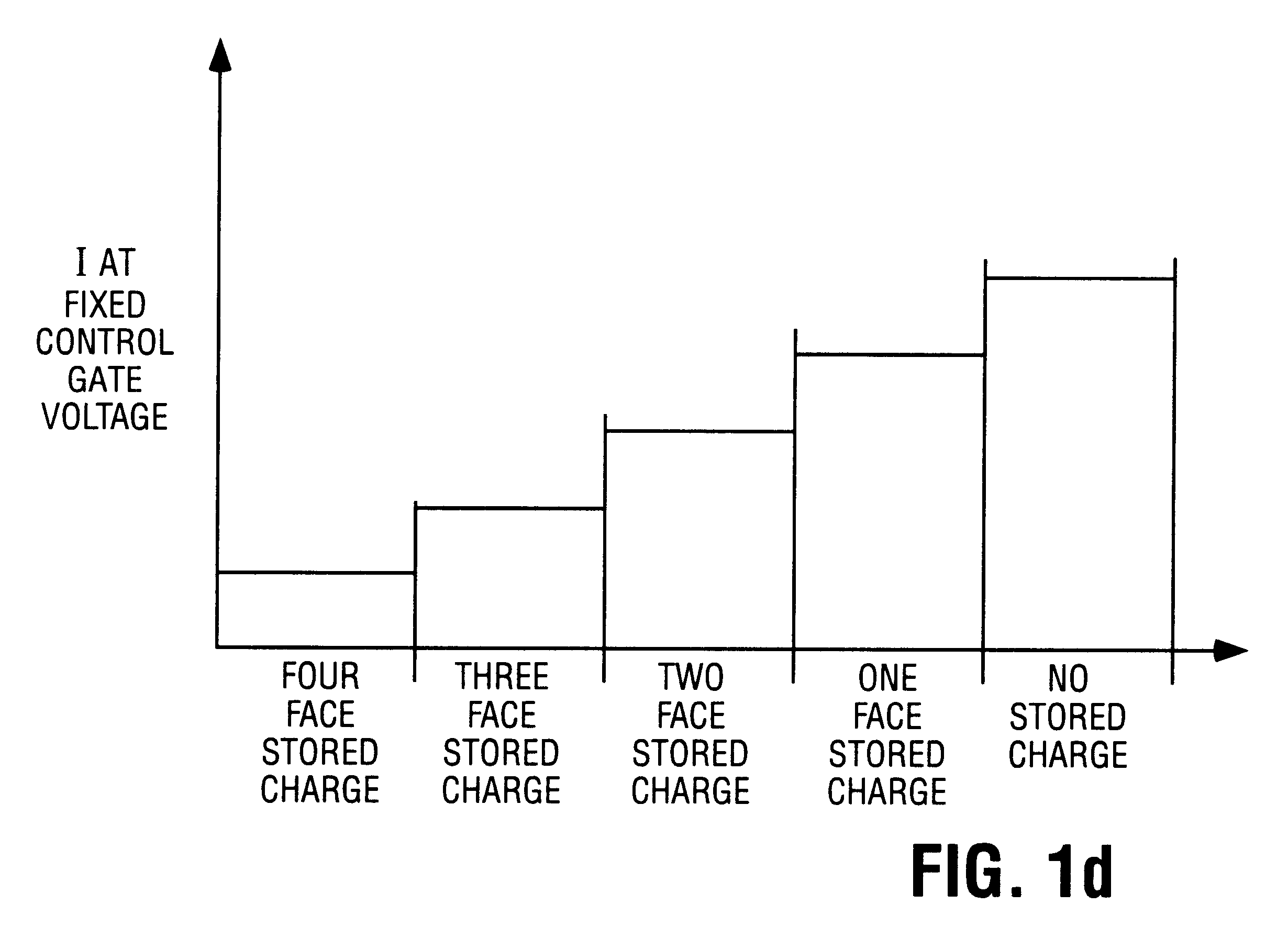

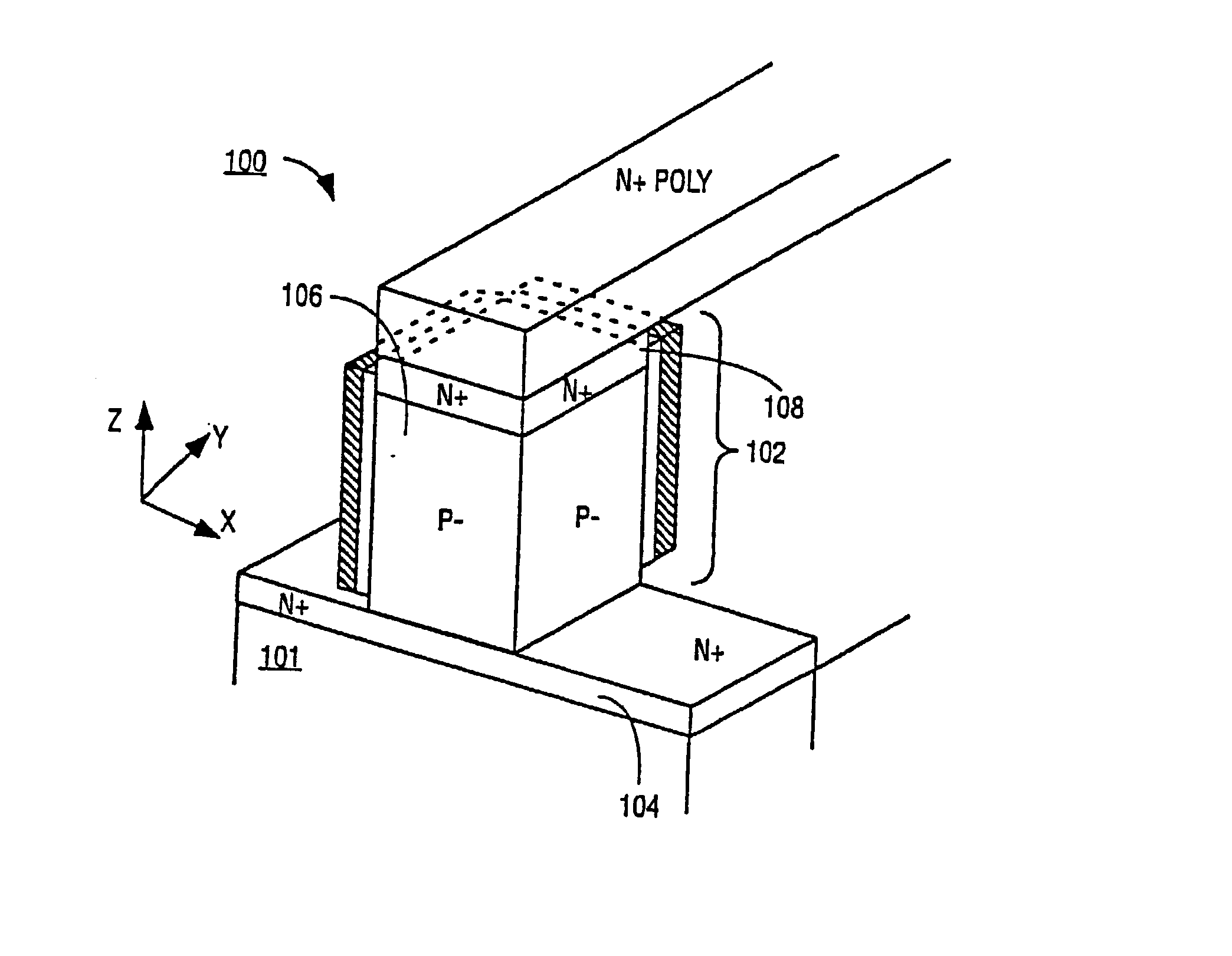

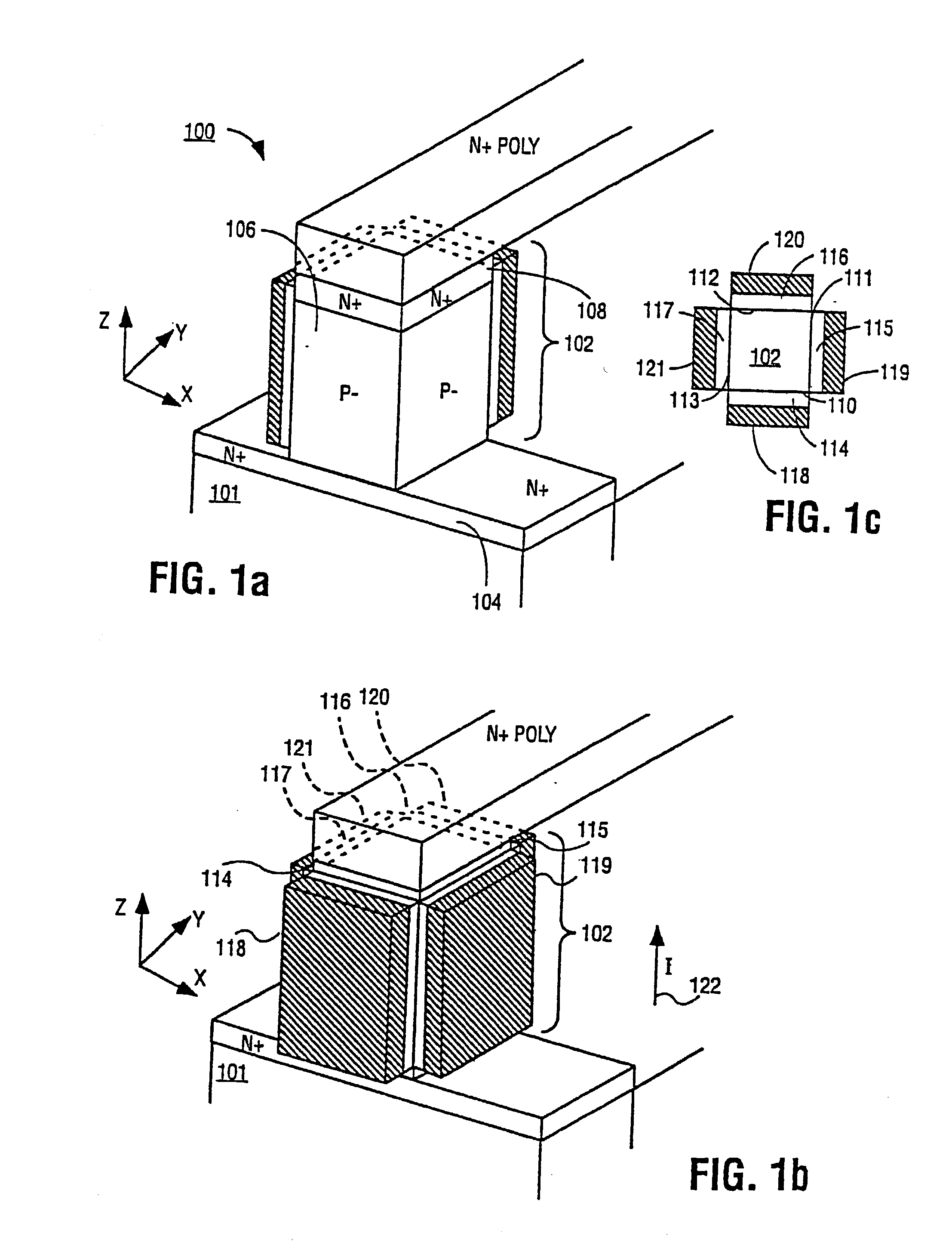

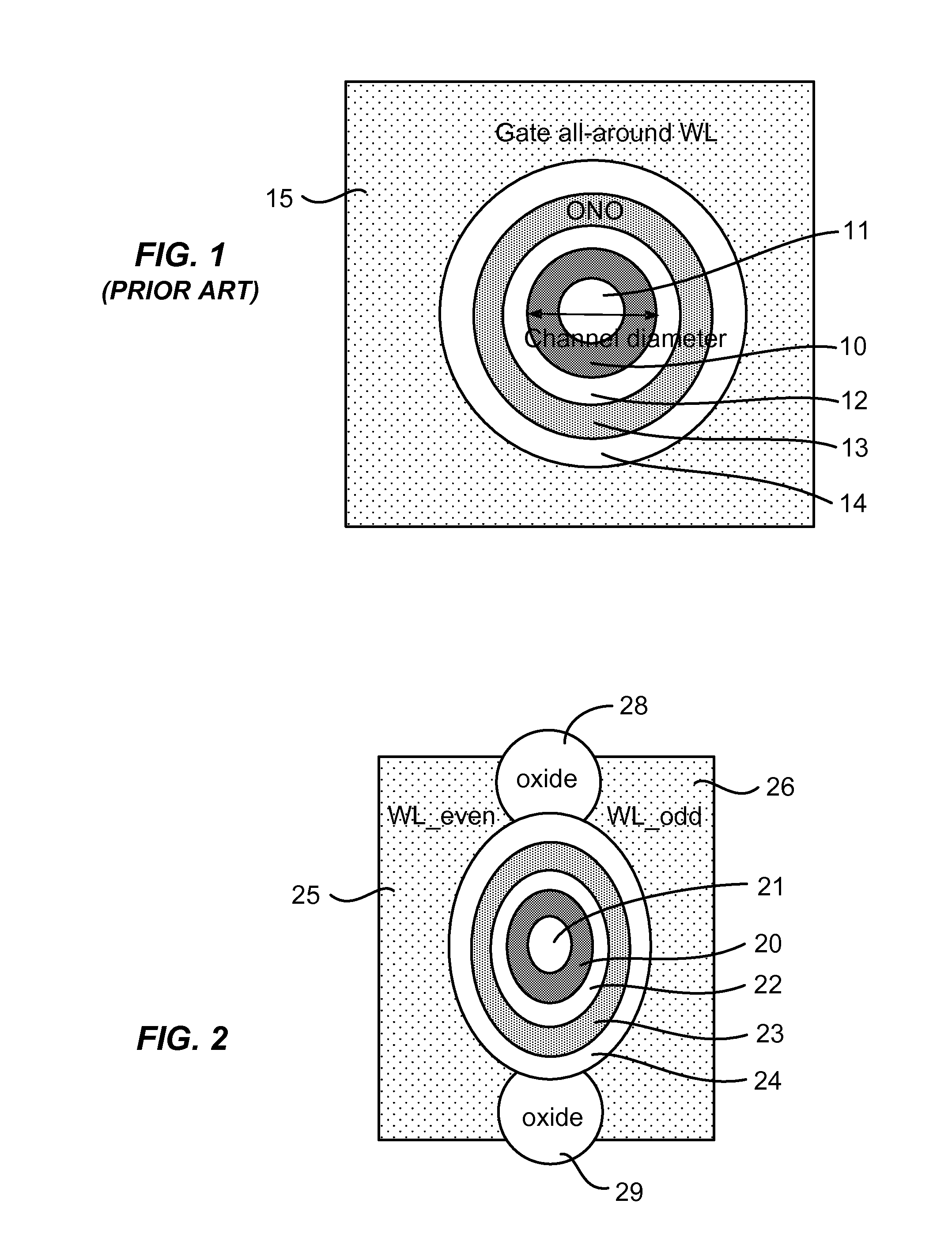

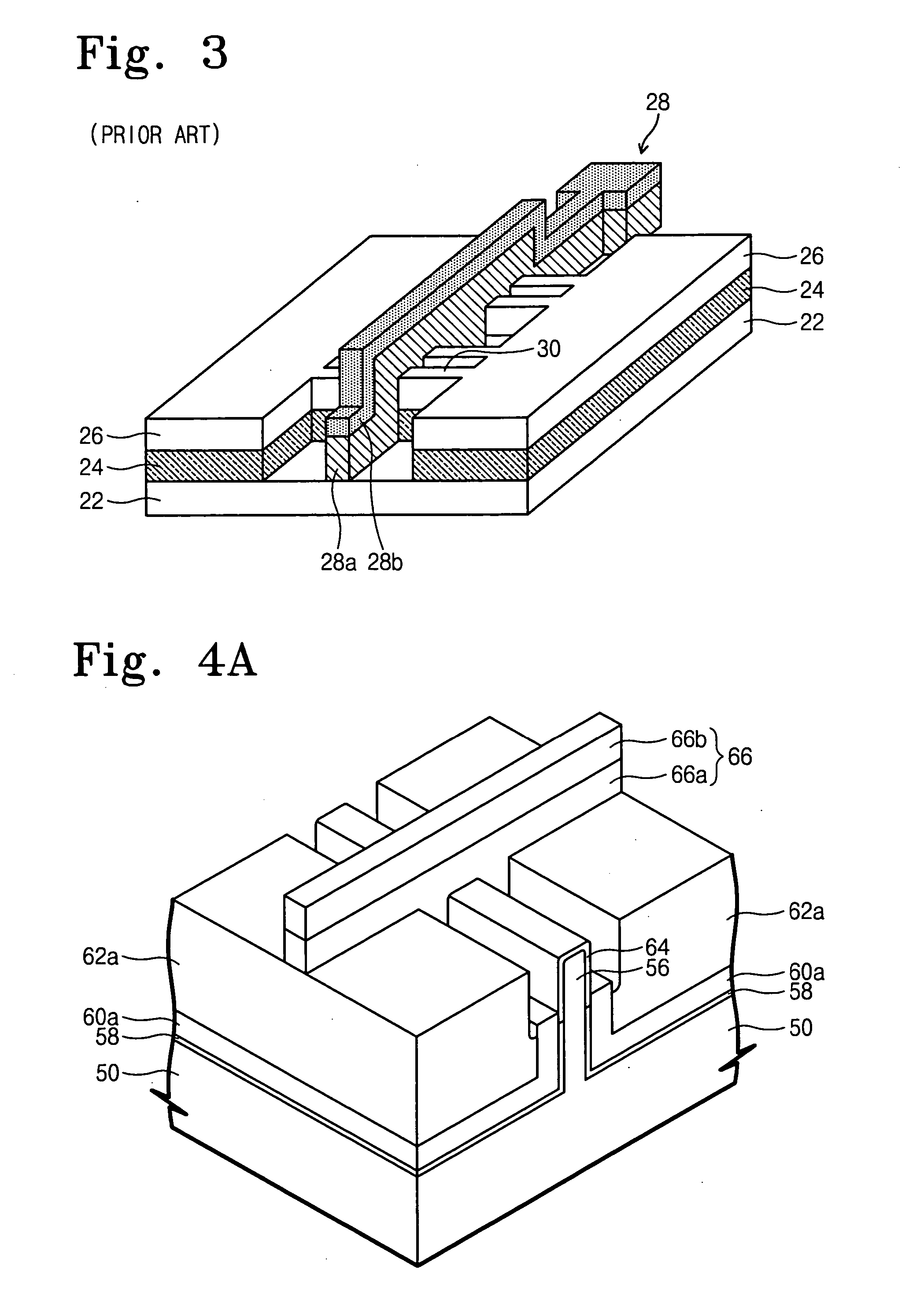

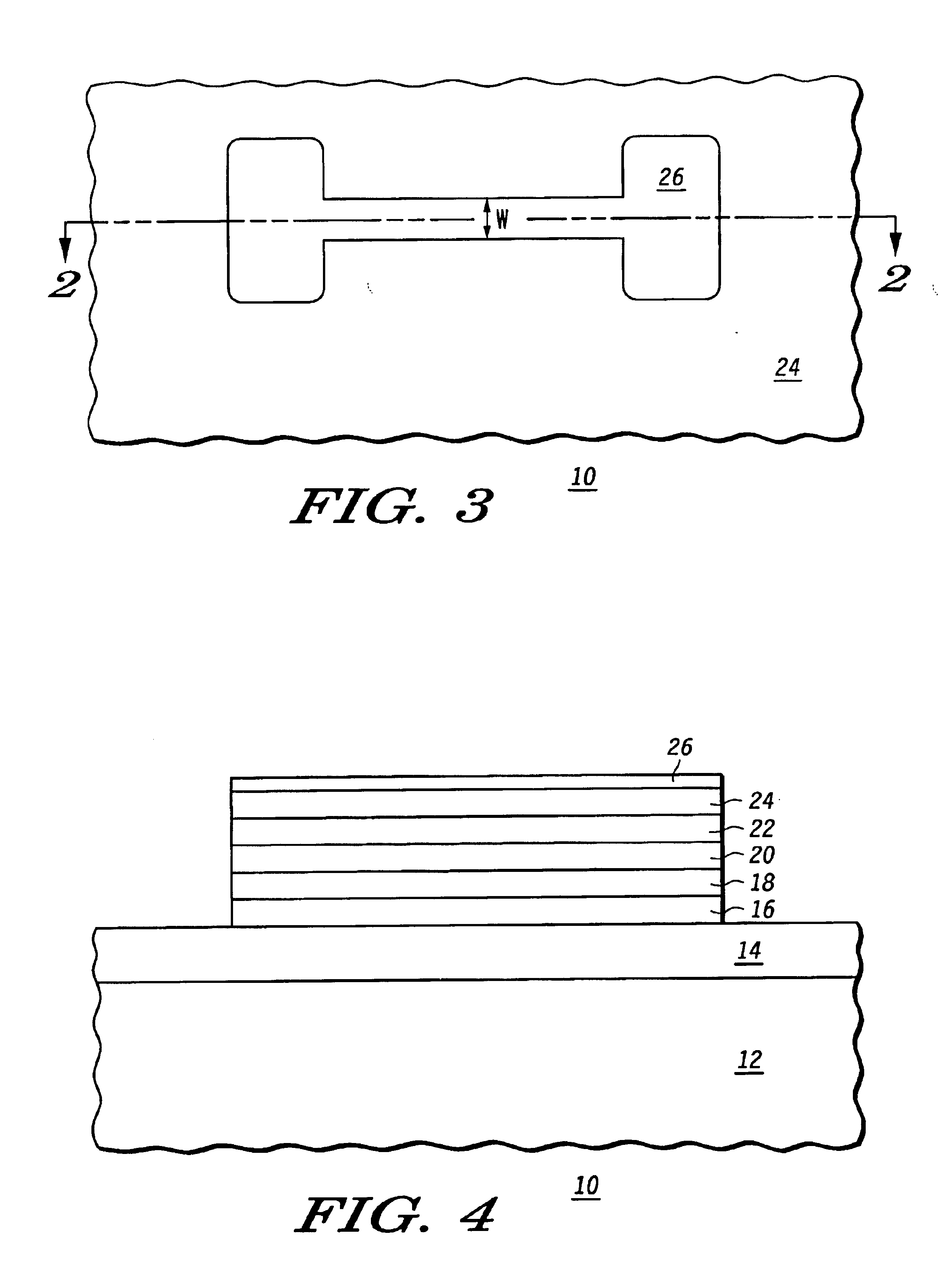

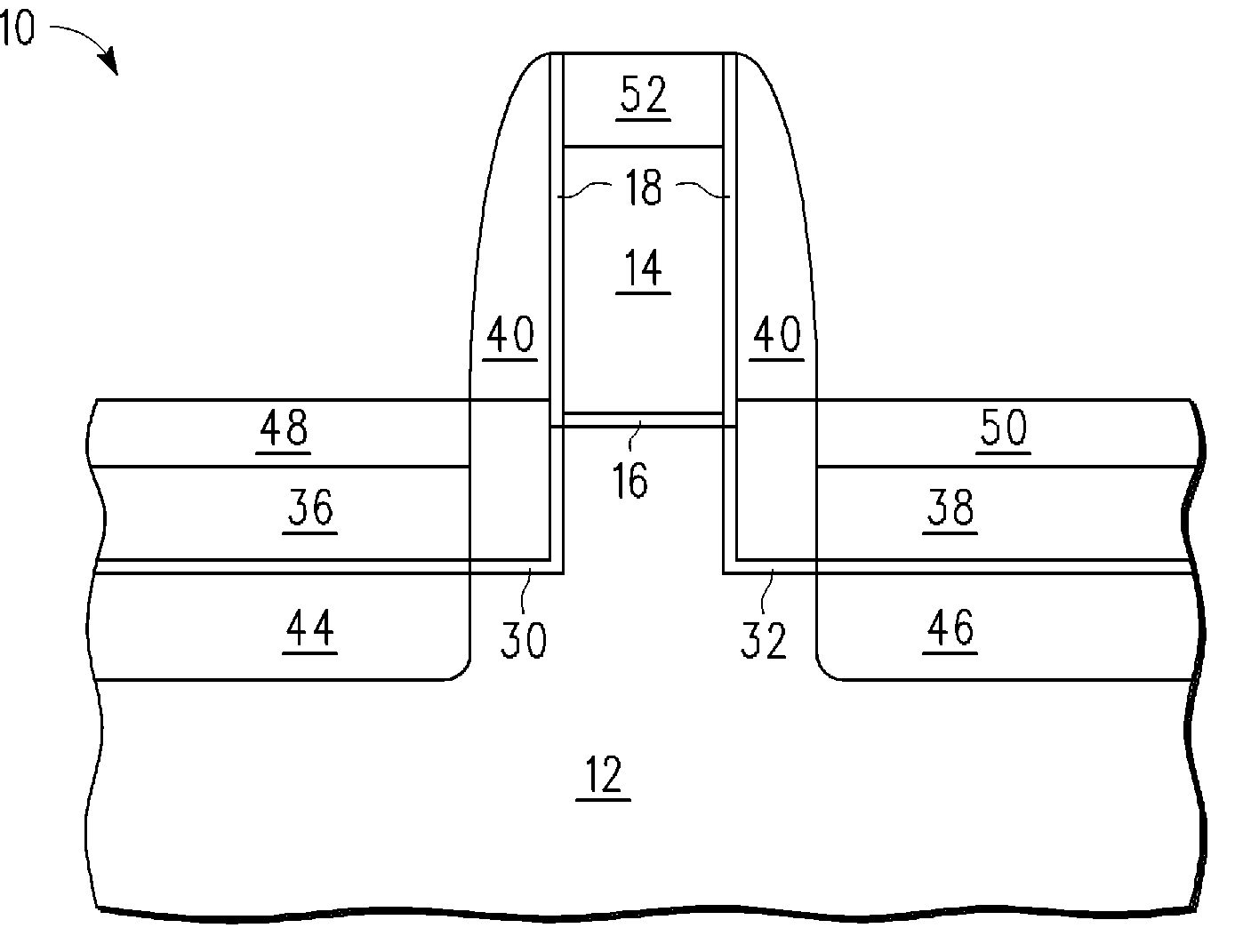

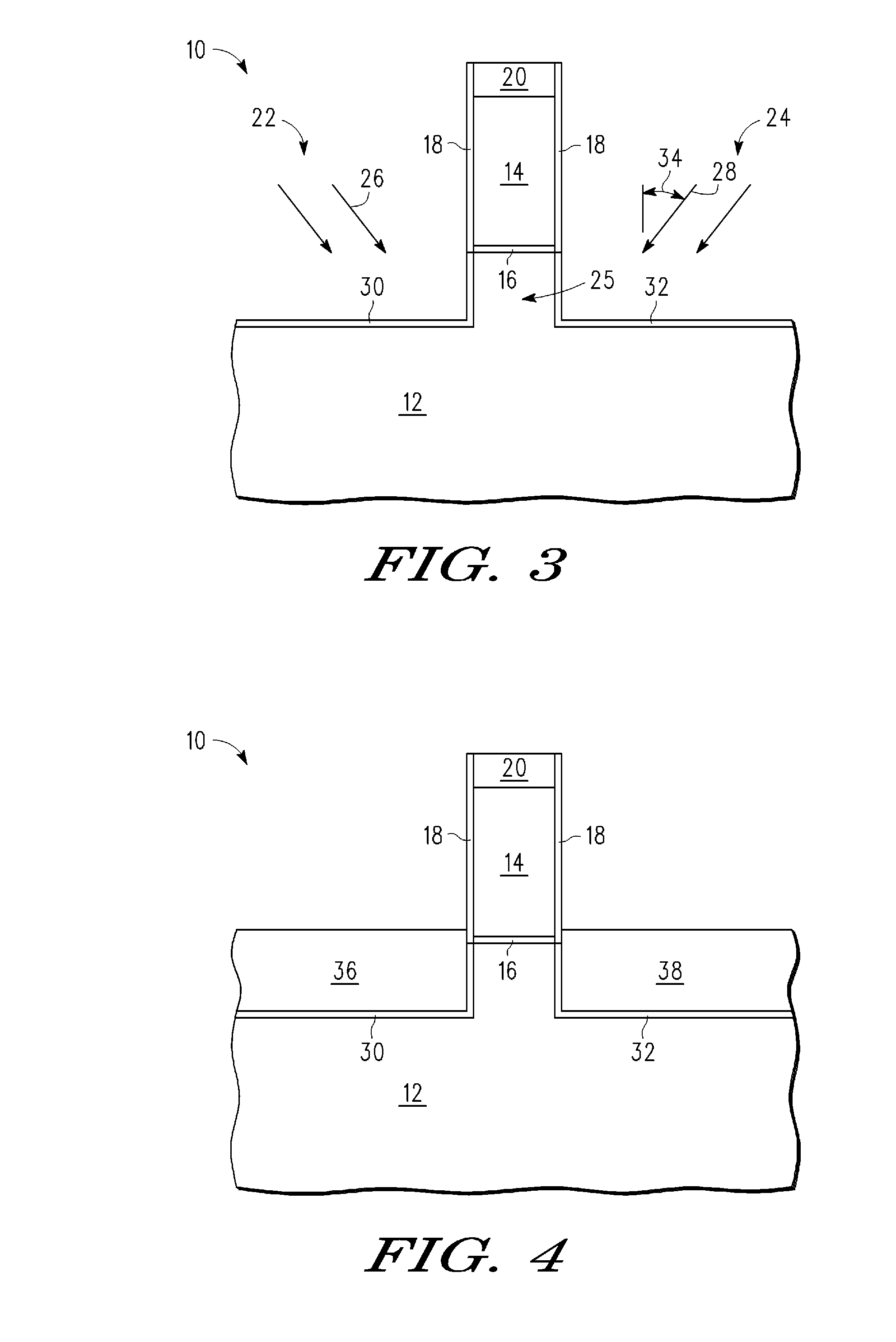

Charge storage structure formation in transistor with vertical channel region

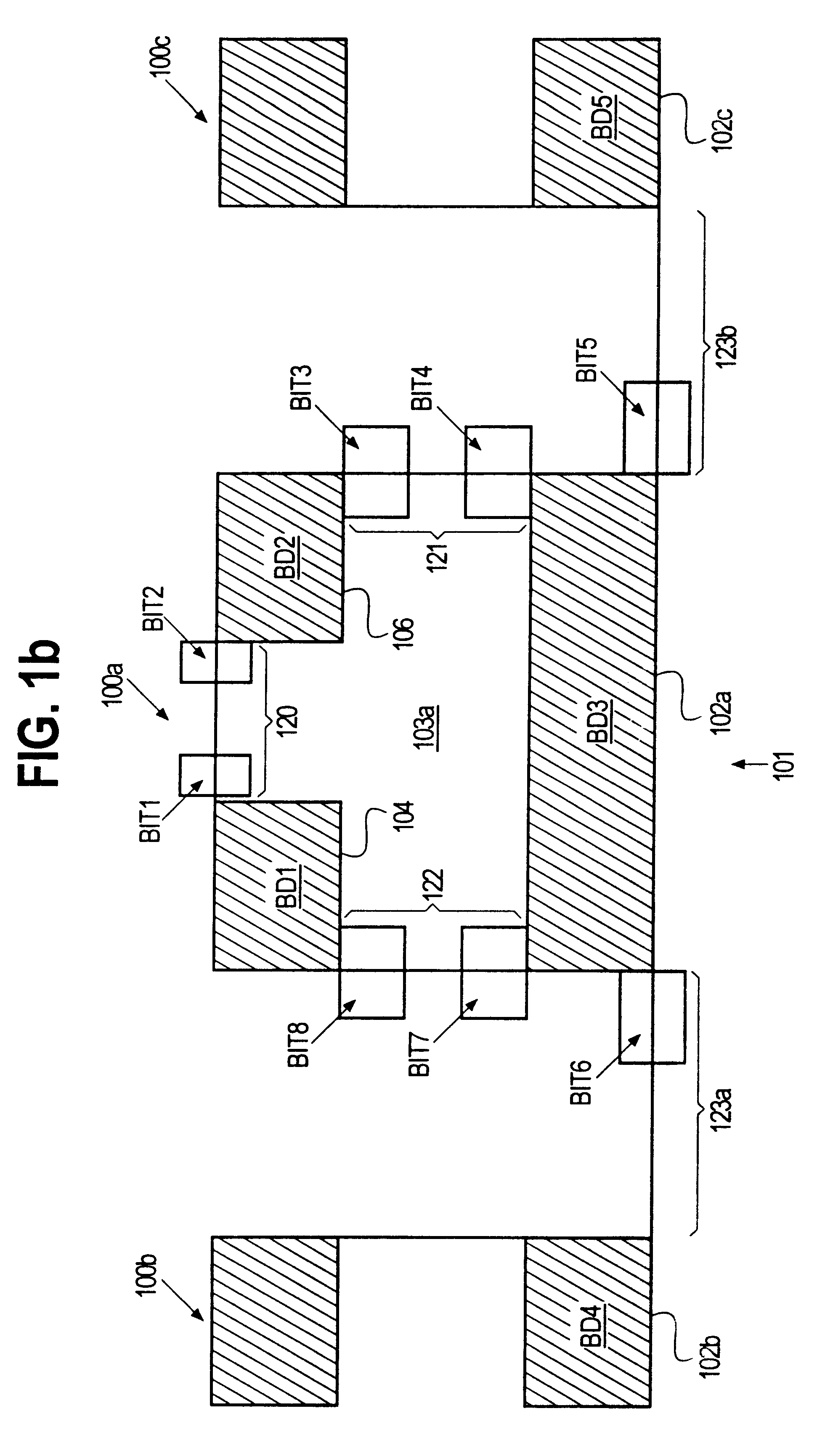

A semiconductor device includes a semiconductor structure having a first sidewall. A vertical channel region is formed in the semiconductor structure along the first sidewall between a first current electrode region and a second current electrode region. First and second charge storage structures are formed adjacent to the first sidewall in openings of a dielectric layer. The first and second charge storage structures are electrically isolated from each other and from the semiconductor structure. A control electrode is formed adjacent to the first sidewall. In another embodiment, third and fourth charge storage structures may be formed adjacent to a second sidewall of the semiconductor structure in openings of a dielectric layer.

Owner:NXP USA INC

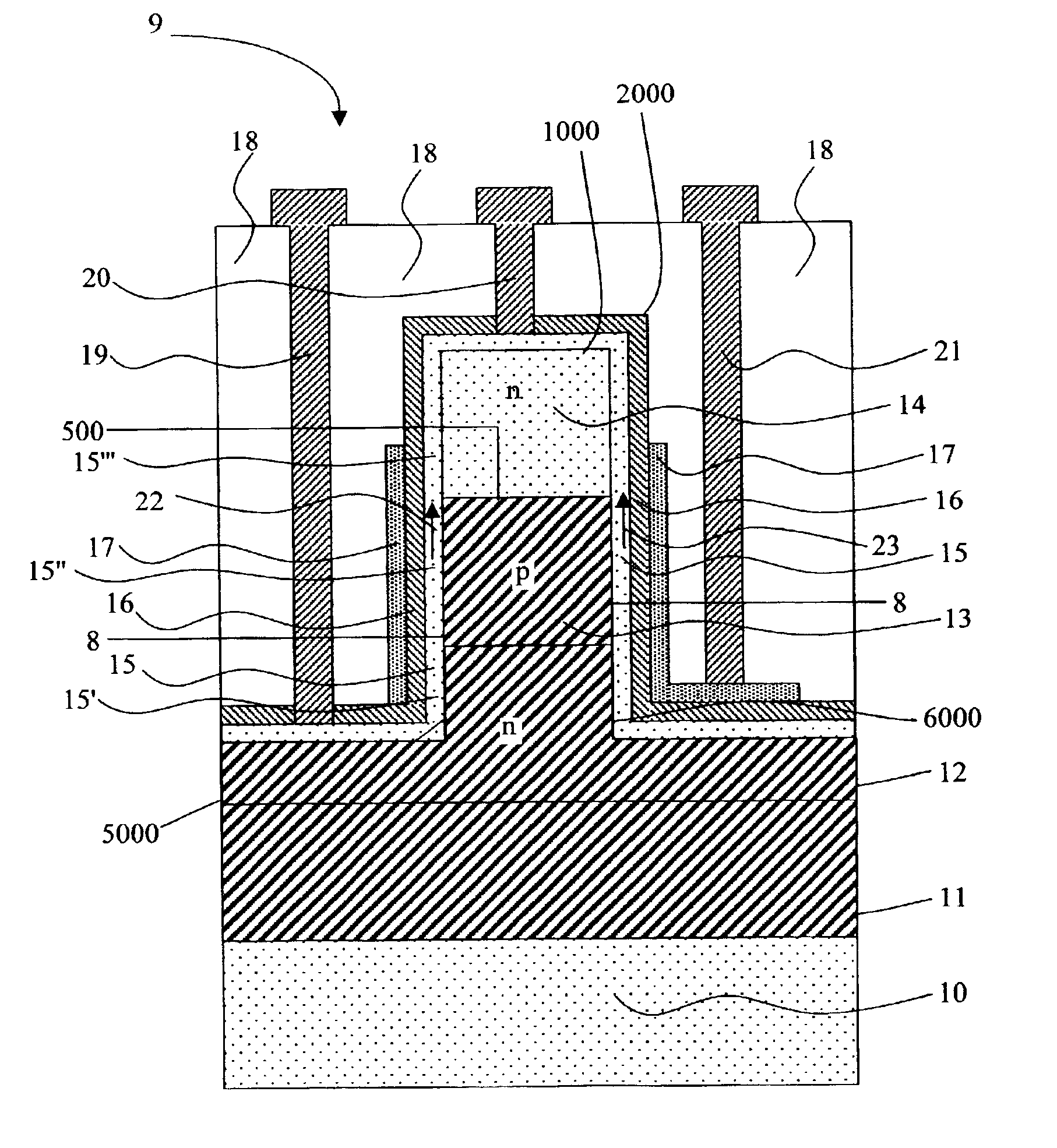

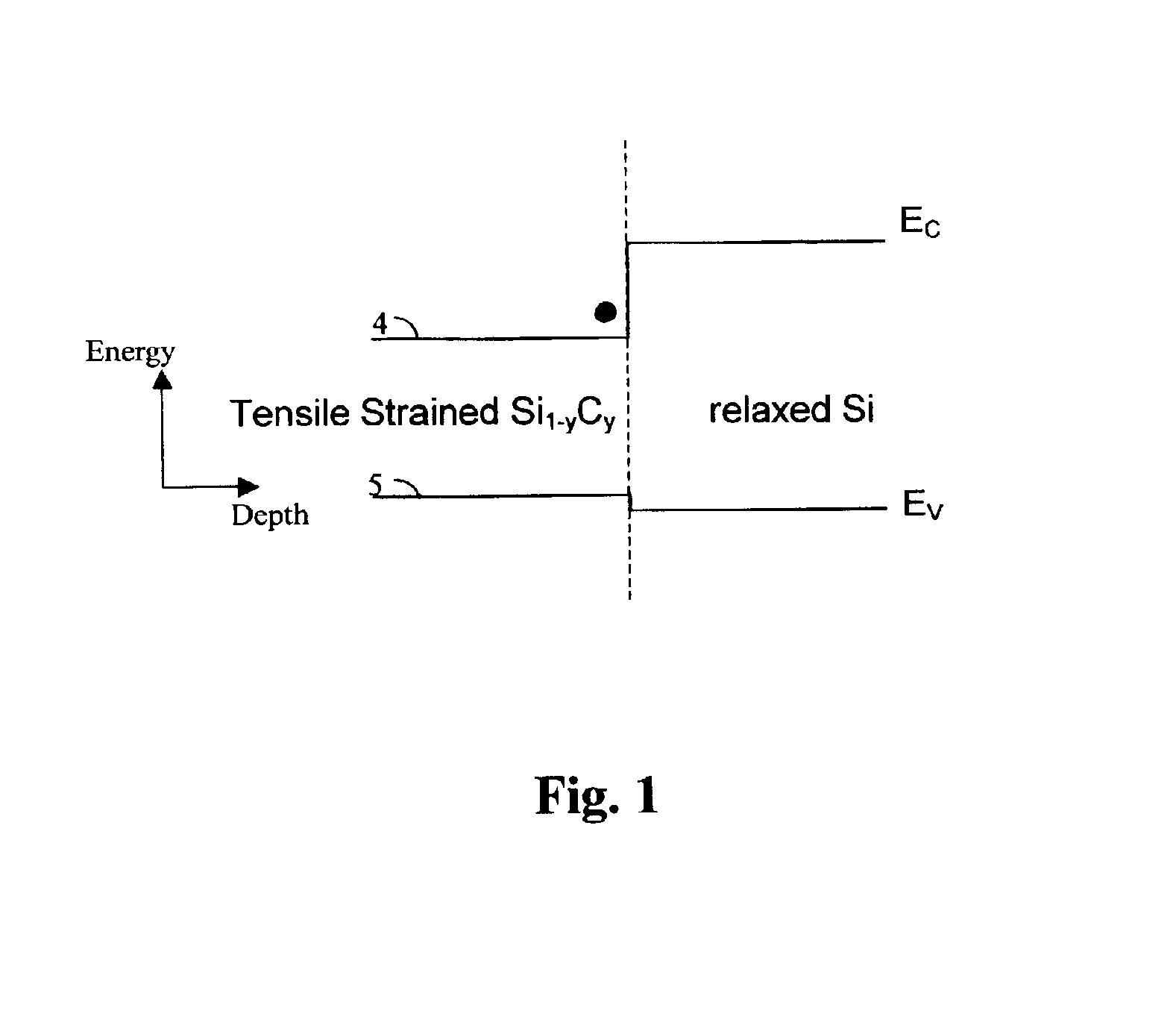

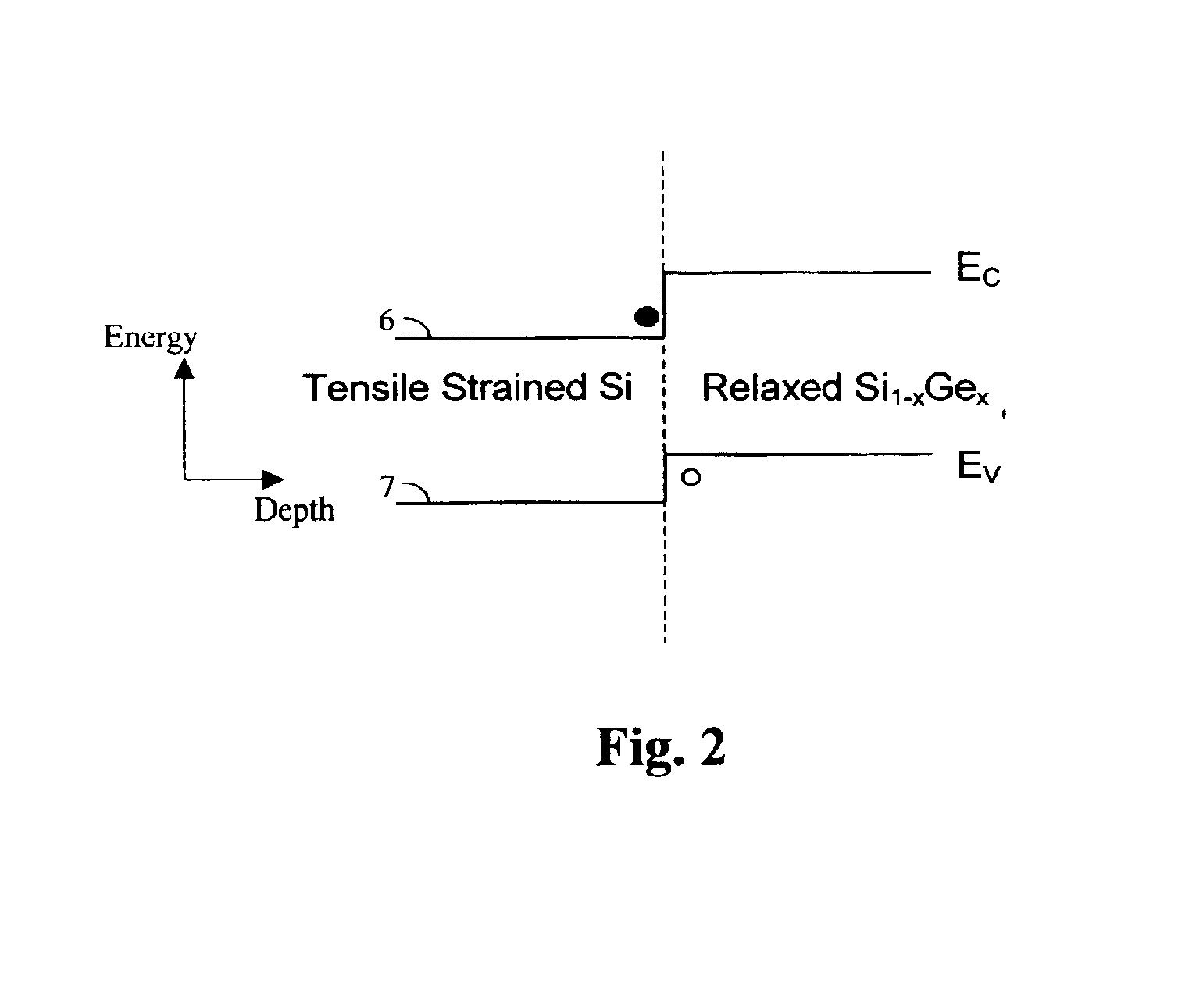

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

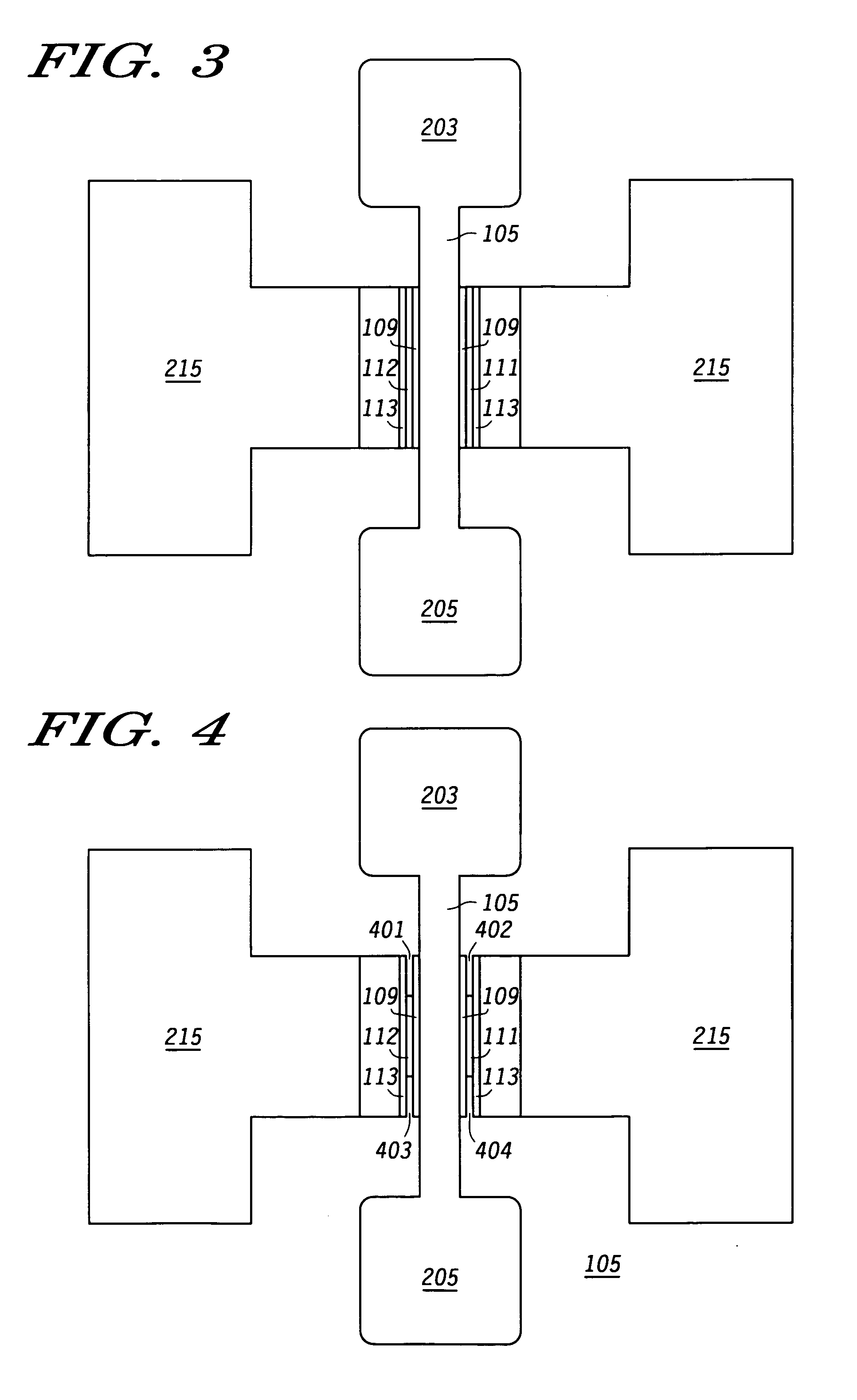

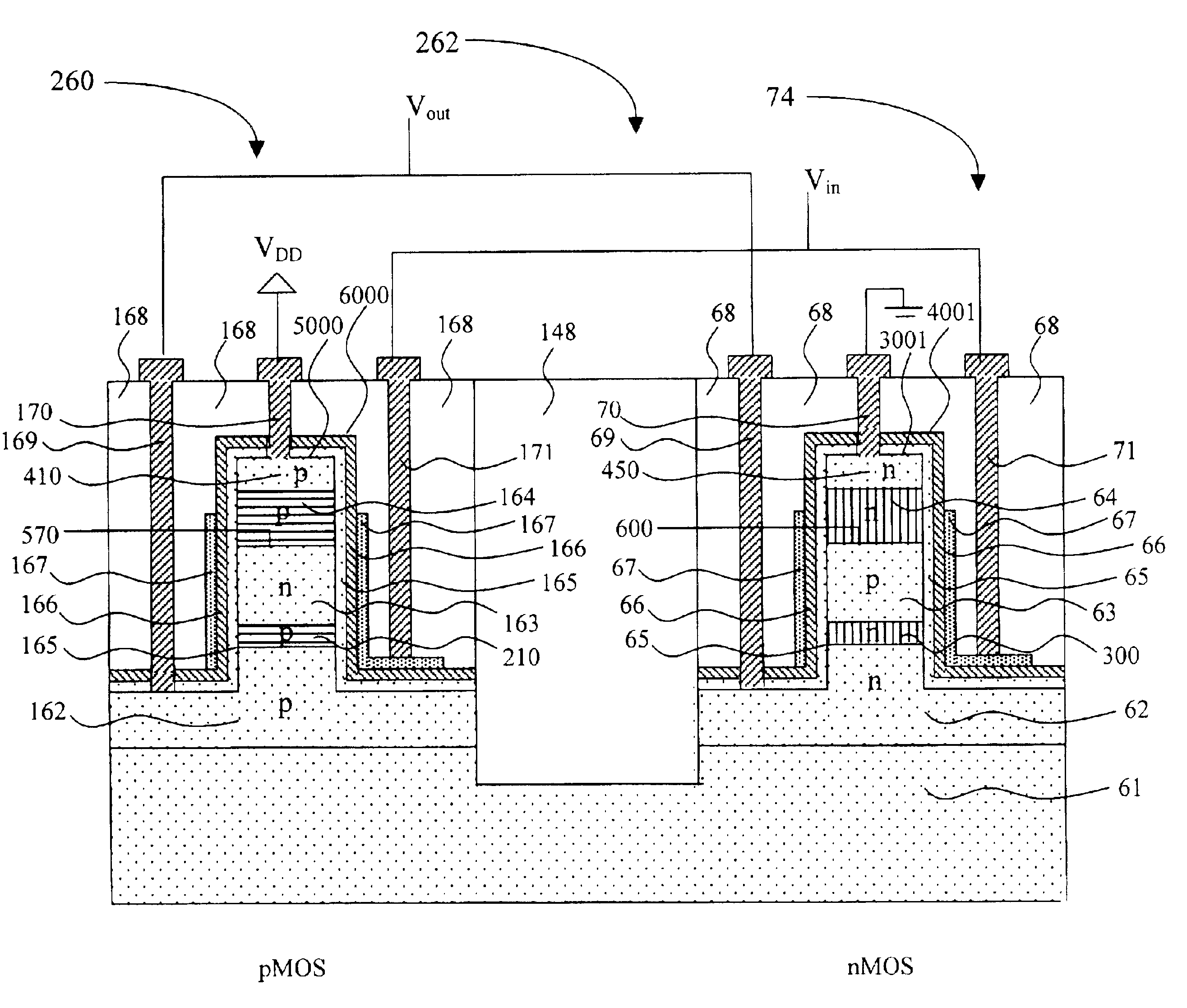

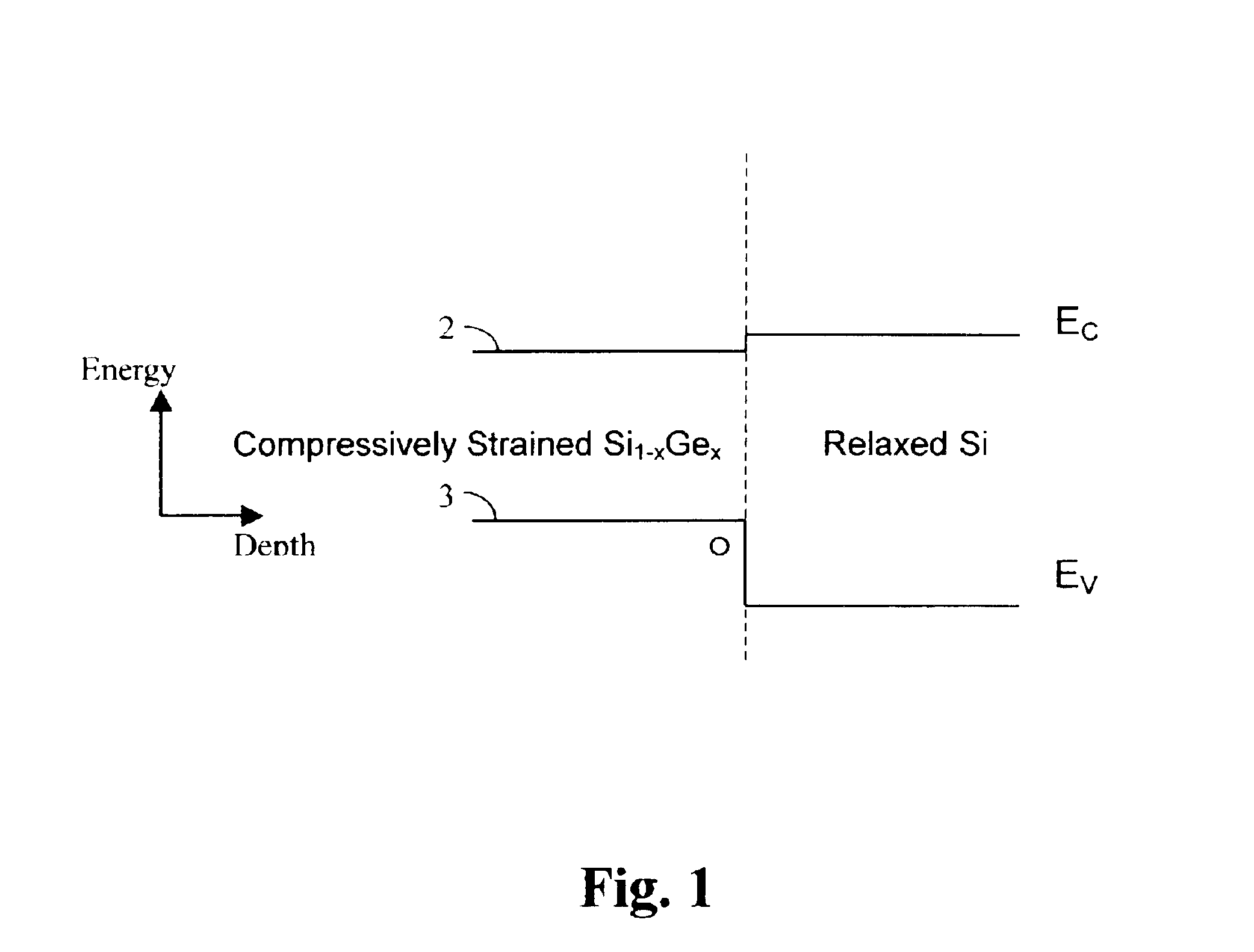

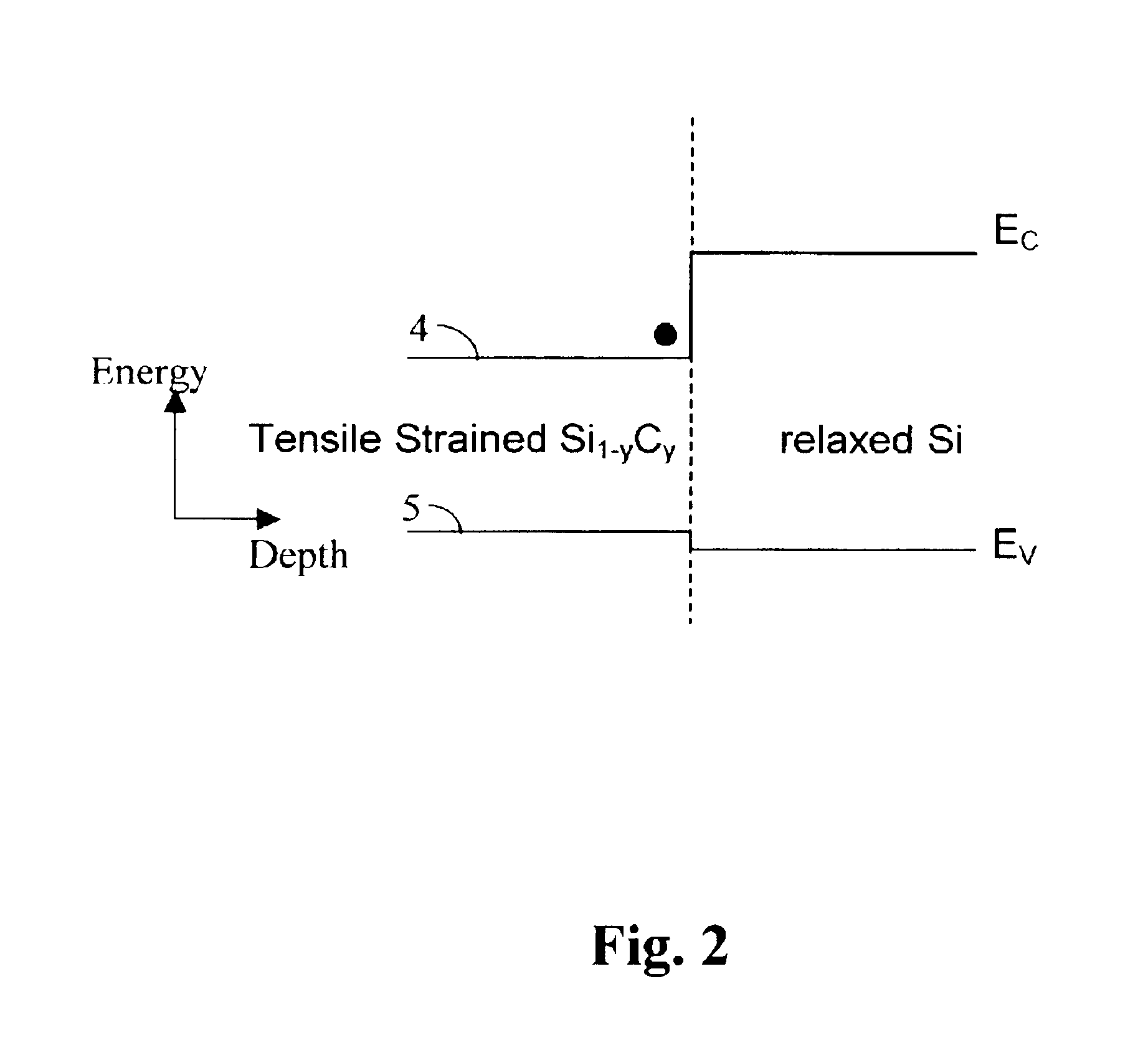

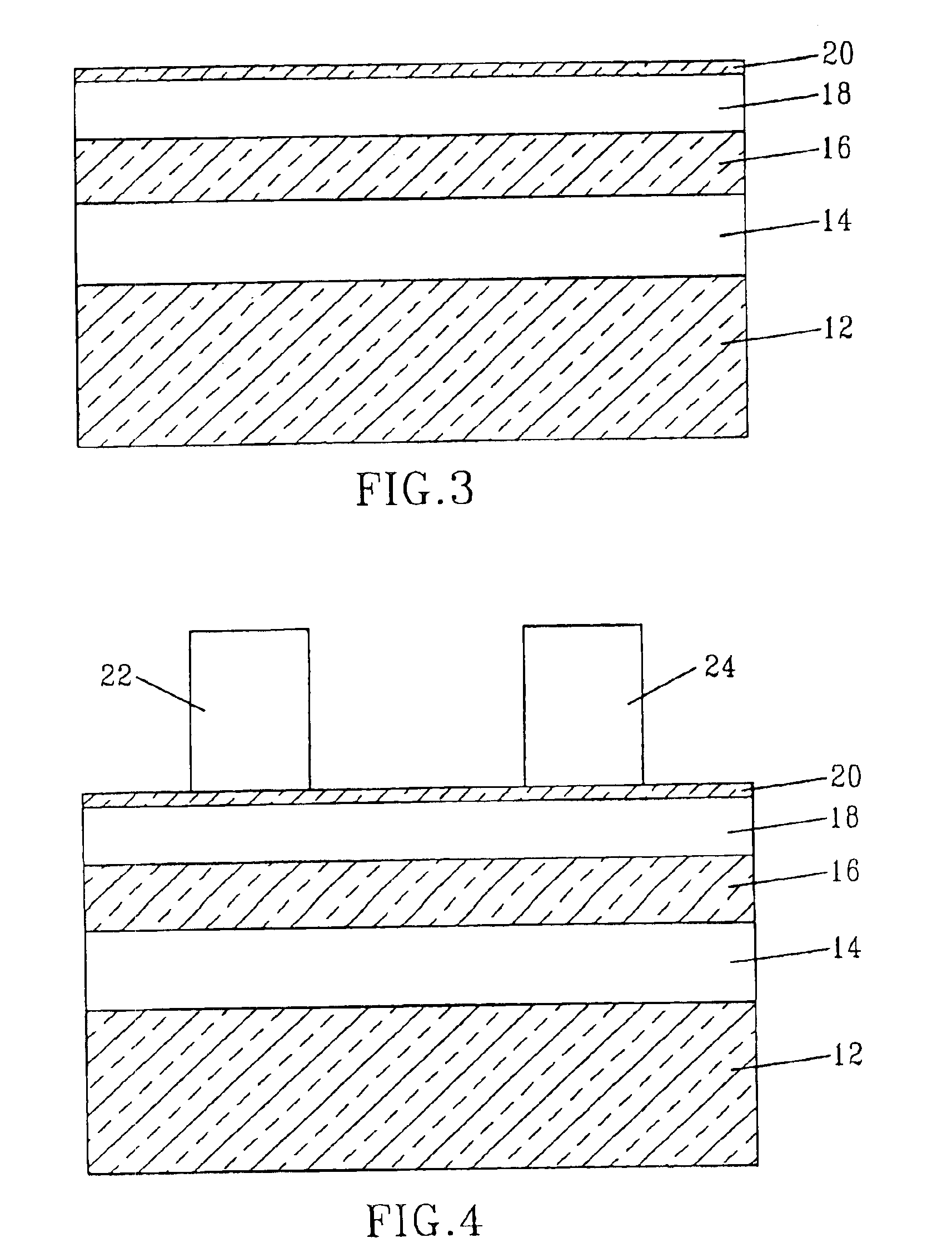

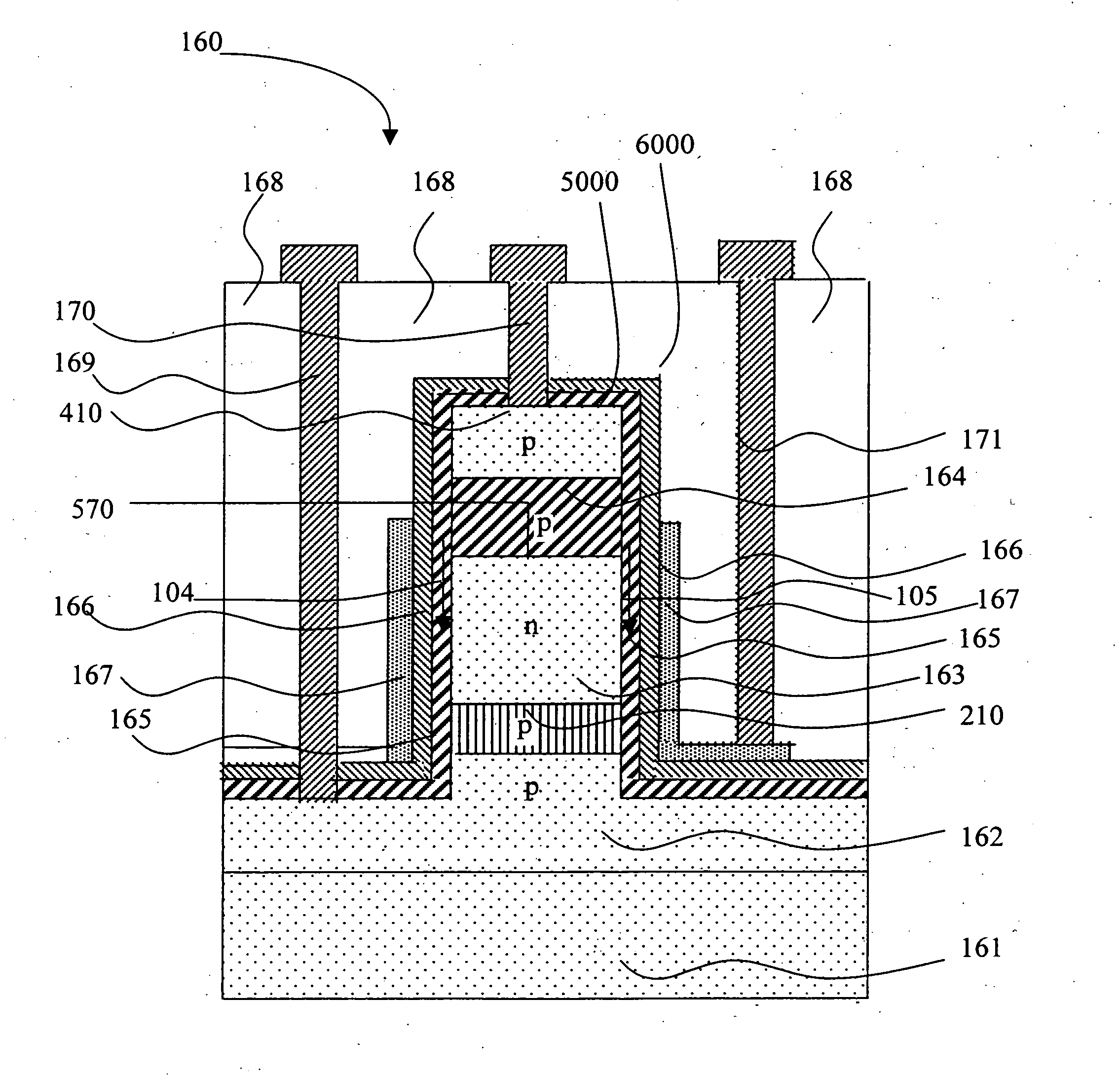

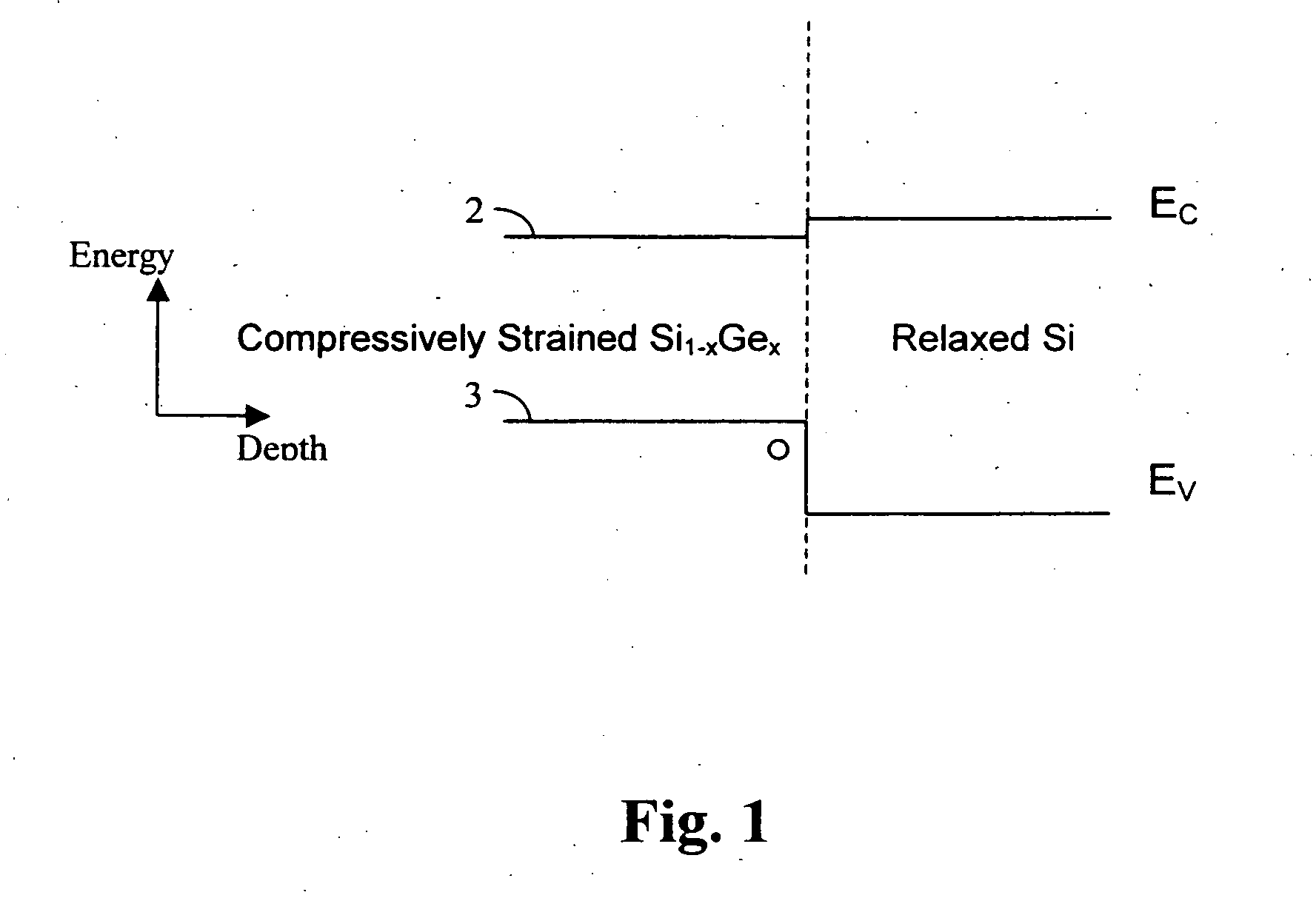

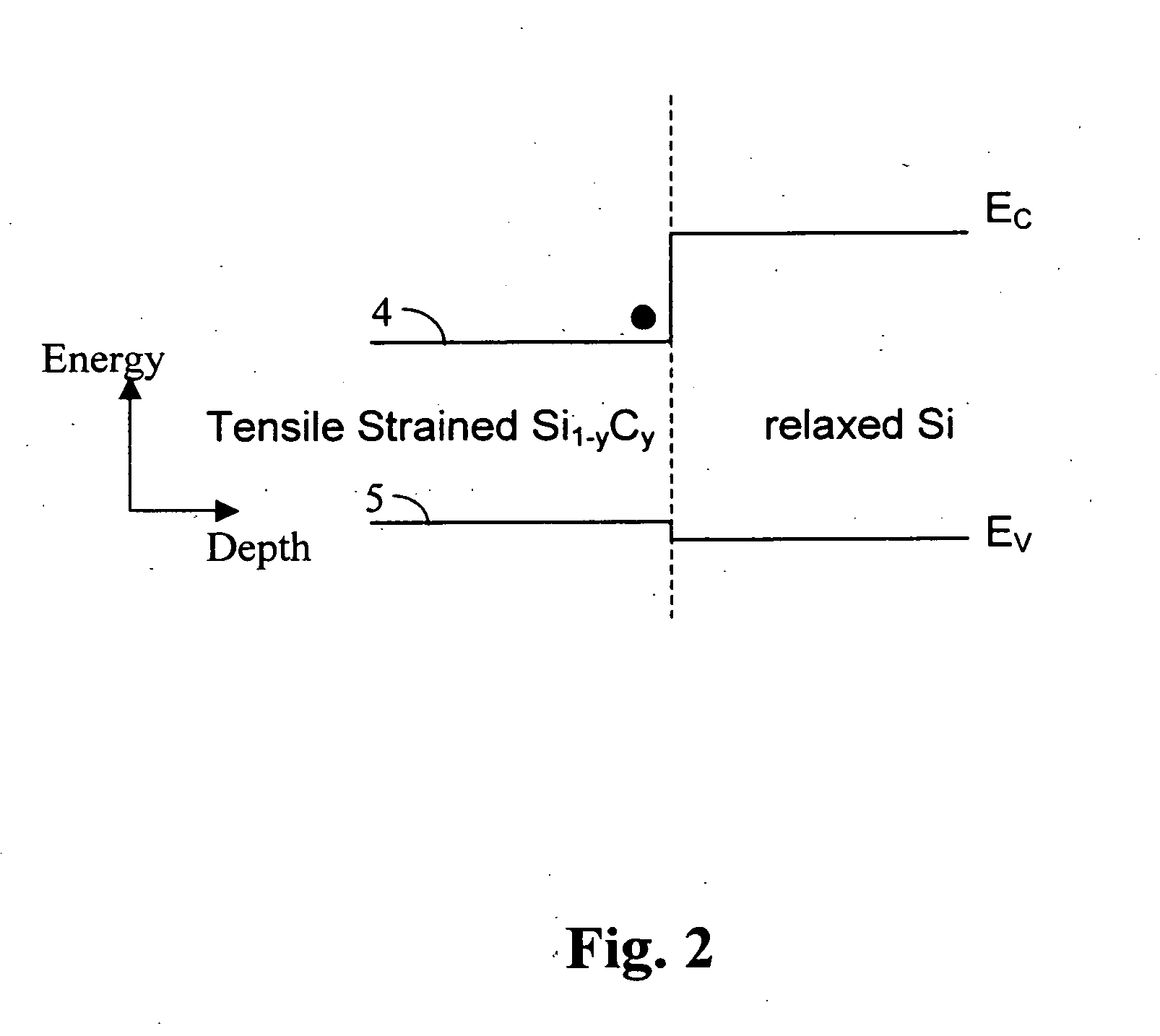

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

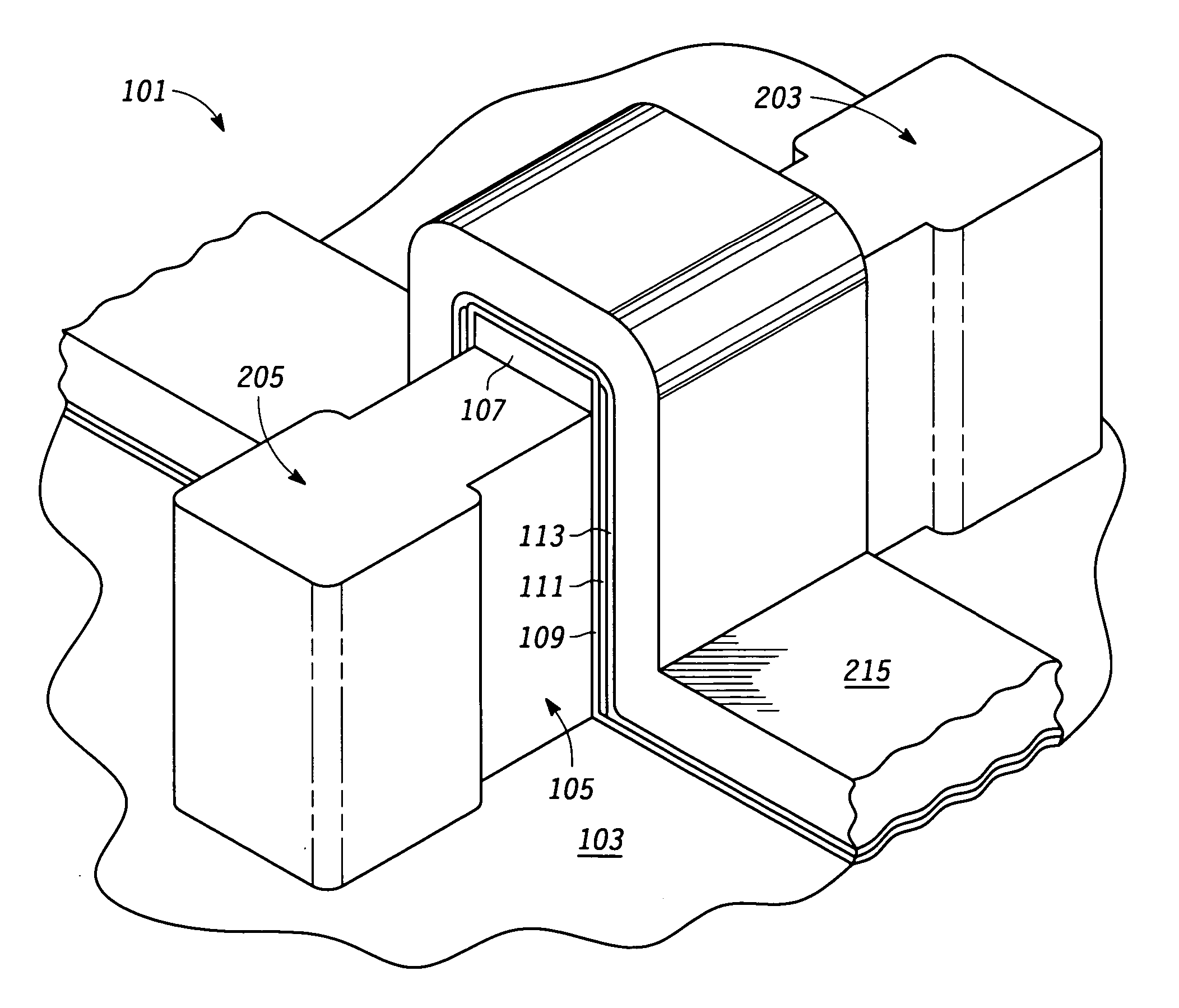

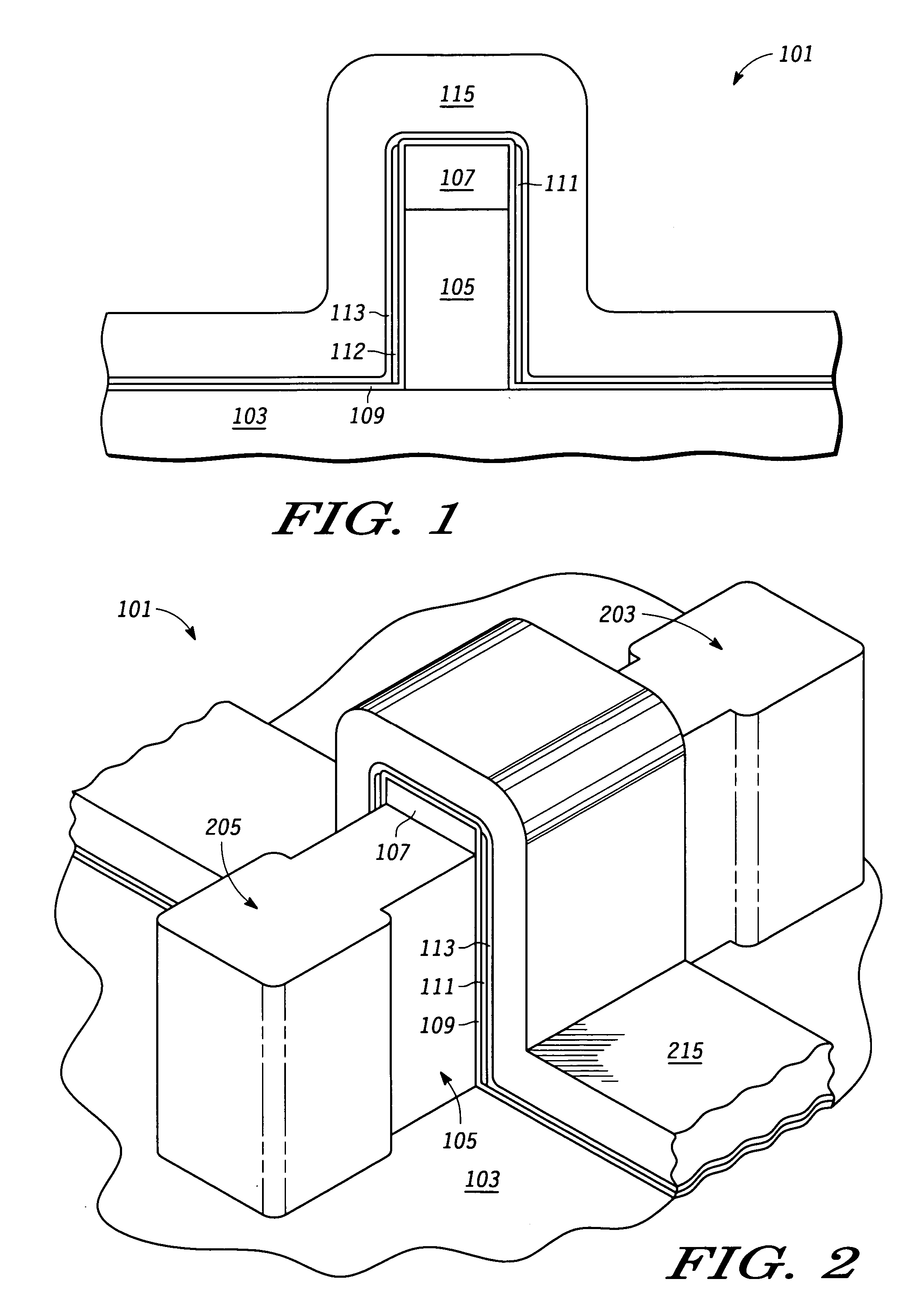

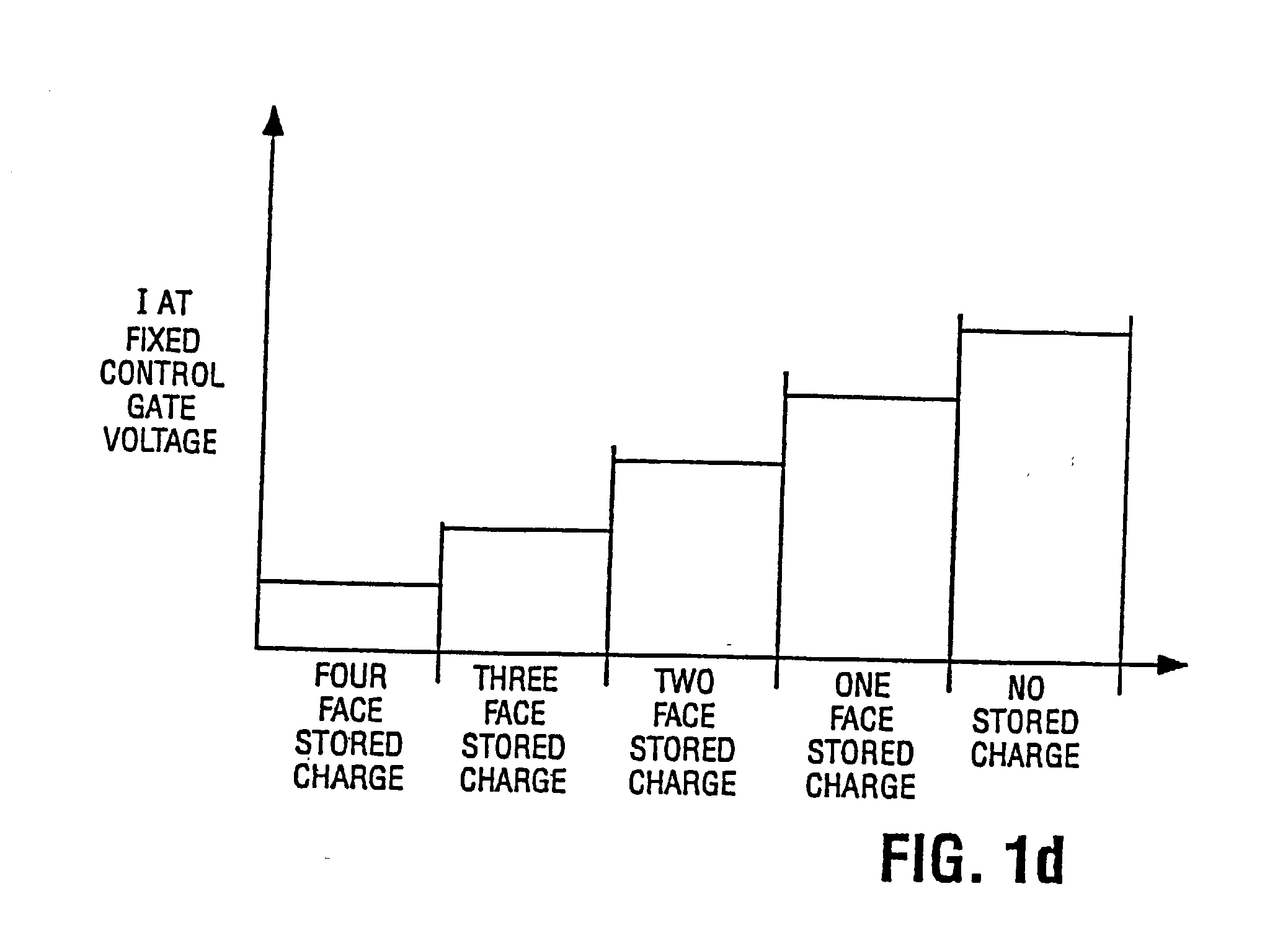

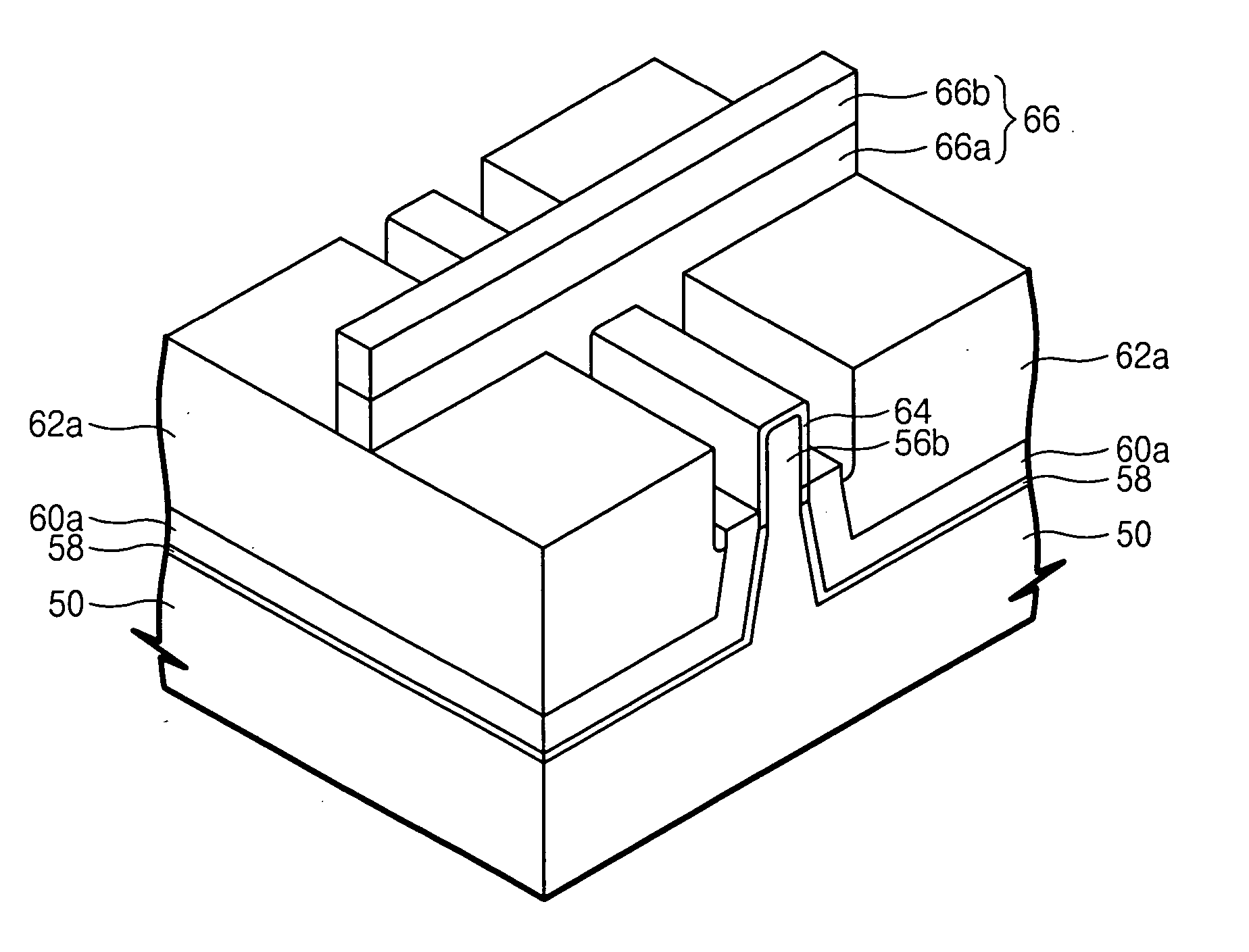

Multigate semiconductor device with vertical channel current and method of fabrication

The present invention is a multibit nonvolatile memory and its method of fabrication. According to the present invention a silicon channel body having a first and second channel surface is formed. A charge storage medium is formed adjacent to the first channel surface and a second charge storage medium is formed adjacent to the second channel surface. A first control gate is formed adjacent to the first charge storage medium adjacent to the first channel surface and a second control gate is formed adjacent to the second charge storage medium adjacent to the second surface.

Owner:SANDISK TECH LLC

8 bit per cell non-volatile semiconductor memory structure utilizing trench technology and dielectric floating gate

The present application discloses a non-volatile semiconductor memory device for storing up to eight-bits of information. The device has a semiconductor substrate of one conductivity type, a central bottom diffusion region on top of a portion of the semiconductor substrate, a second semiconductor layer on top of the bottom diffusion region, and left and right diffusion regions formed in the second semiconductor layer apart from the central bottom diffusion region thus forming a first vertical channel between the right and central bottom diffusion regions. The device further includes a trapping dielectric layer formed over exposed portions of the semiconductor substrate, left, central and right bottom diffusion regions and second semiconductor layer and a wordline formed over the trapping dielectric layer. A methods of fabricating this novel cell using trench technology is also disclosed.

Owner:MACRONIX INT CO LTD

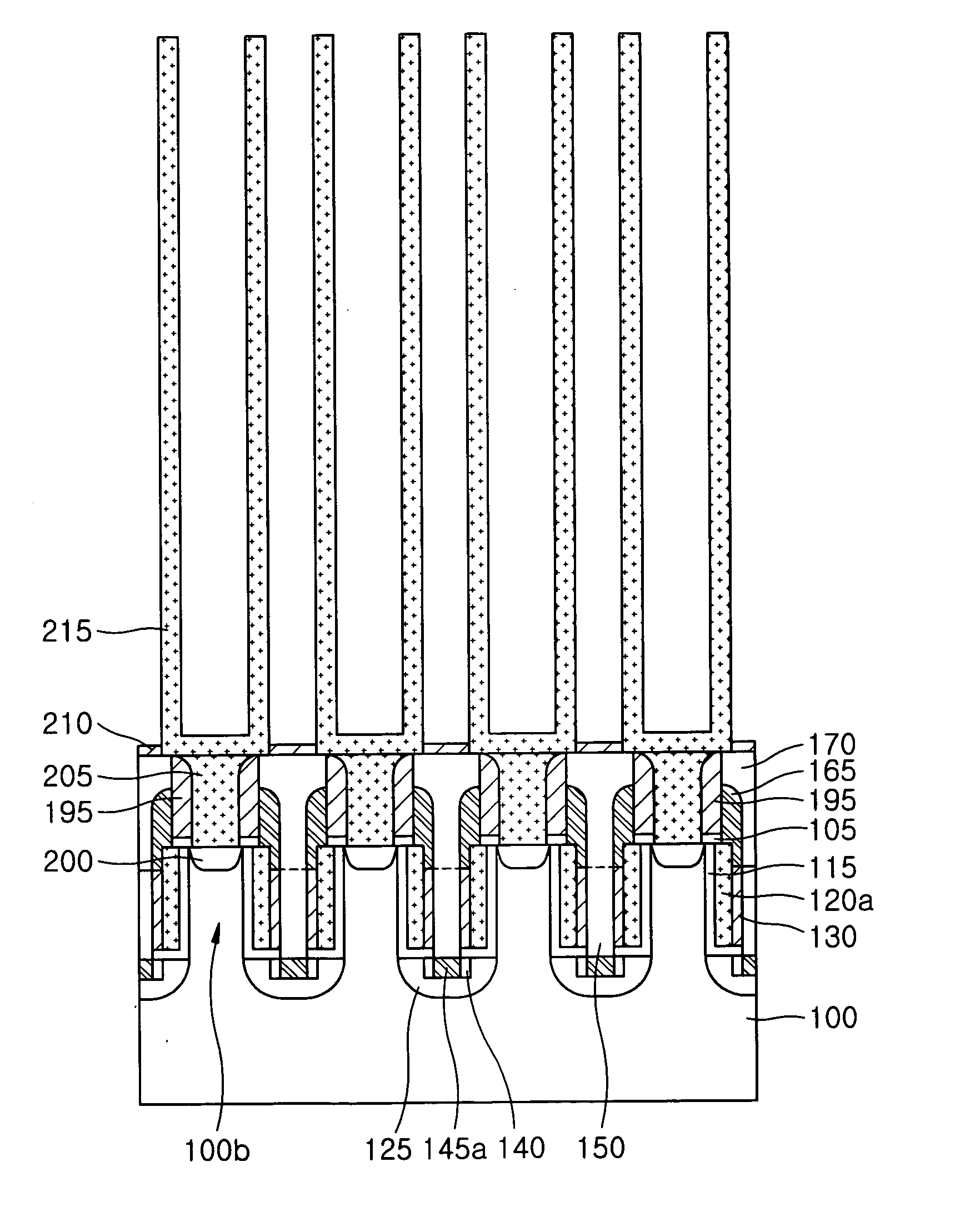

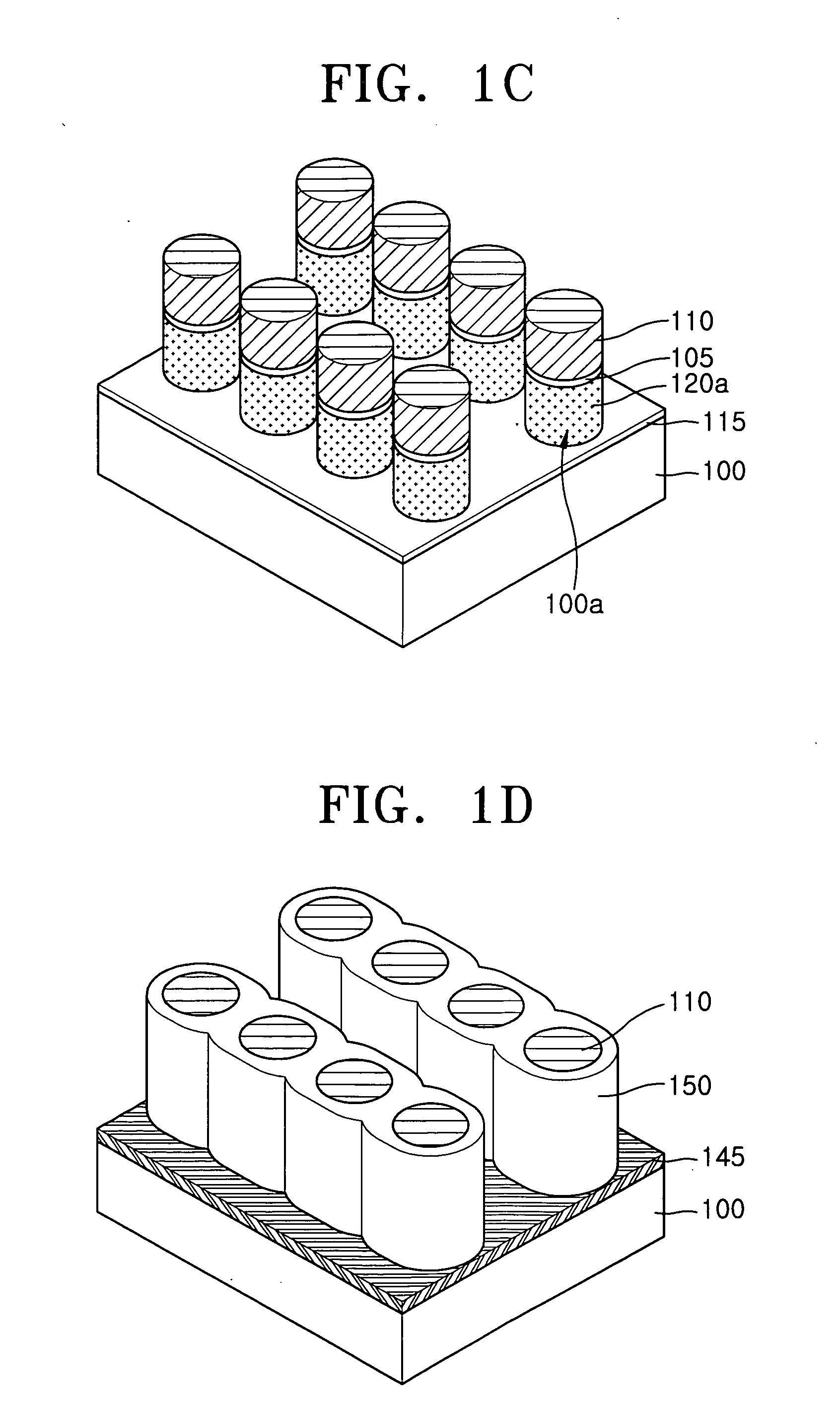

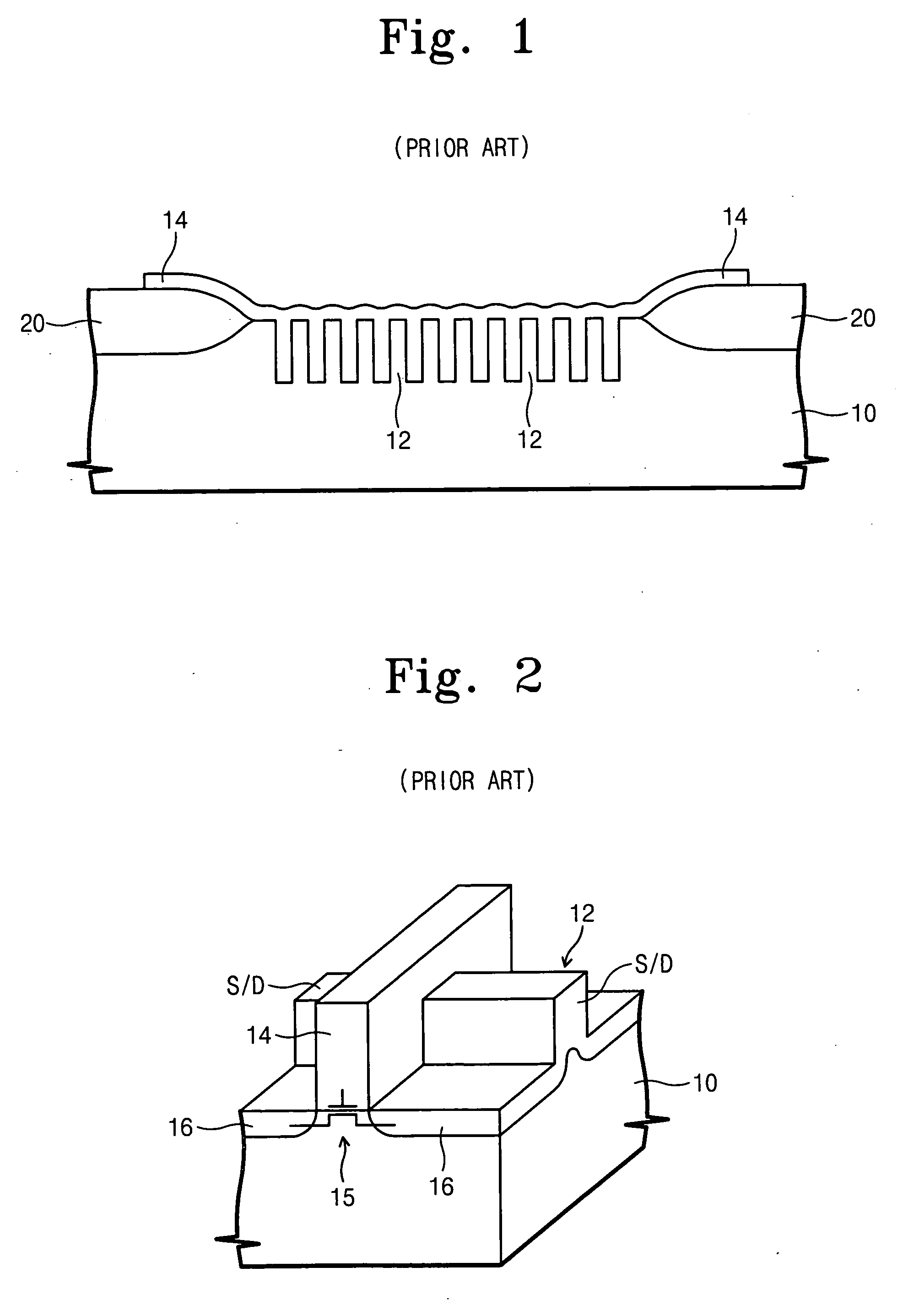

Vertical channel type nonvolatile memory device and method for fabricating the same

A method for fabricating, a vertical channel type nonvolatile memory device includes: alternately forming a plurality of sacrificial layers and a plurality of interlayer dielectric layers over a semiconductor substrate; etching the sacrificial layers and the interlayer dielectric layers to form a plurality of first openings for channel each of which exposes the substrate; filling the first openings to form a plurality of channels protruding from the semiconductor substrate; etching the sacrificial layers and the interlayer dielectric layers to form second openings for removal of the sacrificial layers between the channels; exposing sidewalls of the channels by removing the sacrificial layers exposed by the second openings; and forming a tunnel insulation layer, a charge trap layer, a charge blocking layer, and a conductive layer for gate electrode on the exposed sidewalls of the channels.

Owner:SK HYNIX INC

Vertical-type non-volatile memory devices

ActiveUS20090121271A1Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

In a semiconductor device, and a method of manufacturing thereof, the device comprises a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

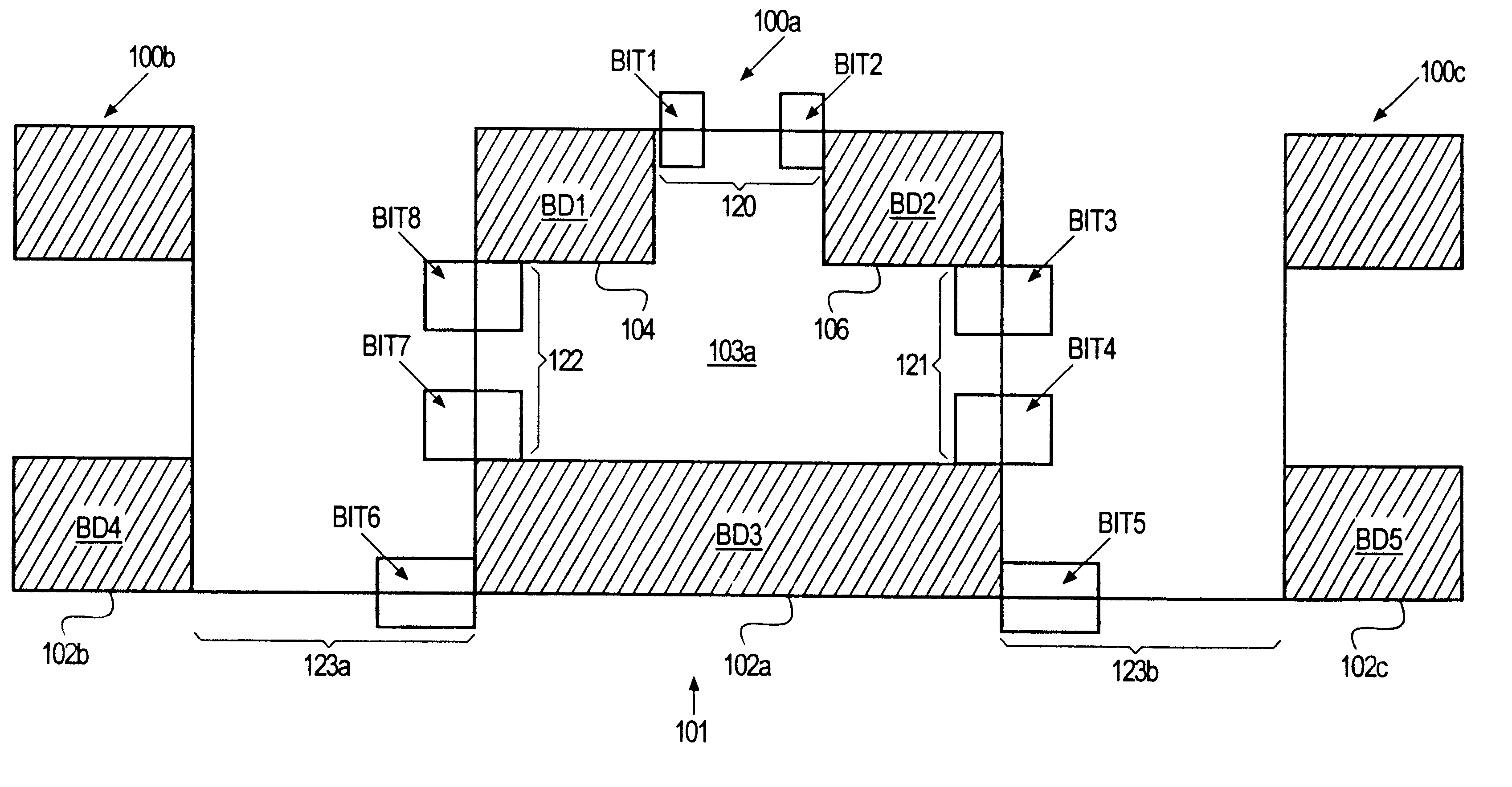

Multigate semiconductor device with vertical channel current and method of fabrication

The present invention is a multibit nonvolatile memory and its method of fabrication. According to the present invention a silicon channel body having a first and second channel surface is formed. A charge storage medium is formed adjacent to the first channel surface and a second charge storage medium is formed adjacent to the second channel surface. A first control gate is formed adjacent to the first charge storage medium adjacent to the first channel surface and a second control gate is formed adjacent to the second charge storage medium adjacent to the second surface. According to the second aspect of the present invention, a transistor is provided that has a source, a channel, a drain, and a plurality of gates where the channel current flows vertically between the source and drain. According to a third embodiment of the present invention, a memory element is formed using a transistor that has a read current that flows in a direction perpendicular to a substrate in or over which the transistors form. The transistor has a charge storage medium for storing its state. Multiple control gates address the transistor.

Owner:SANDISK TECH LLC

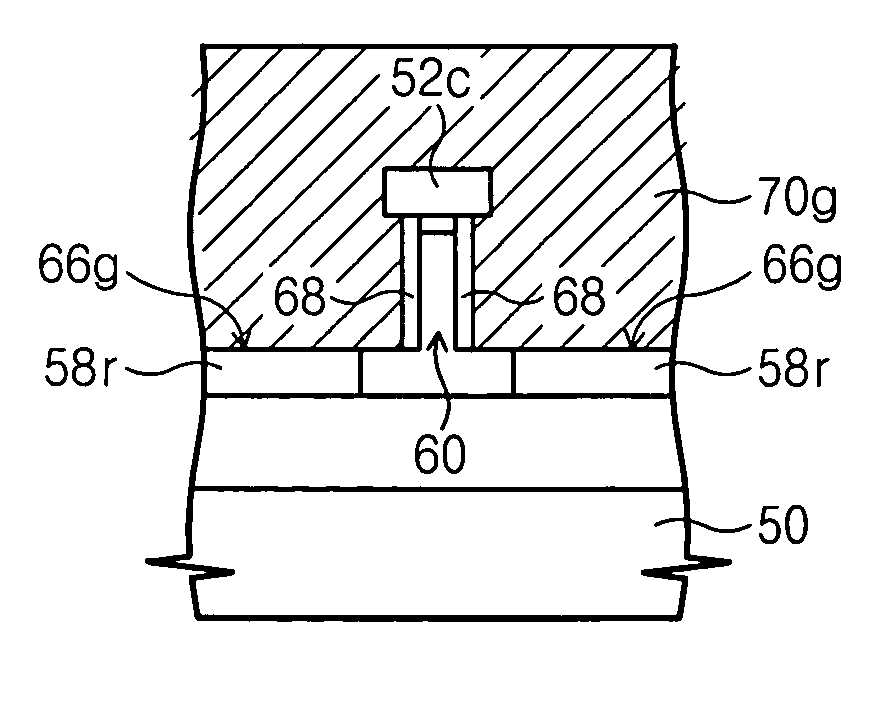

Semiconductor memory device

InactiveUS20100112753A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringVertical channel

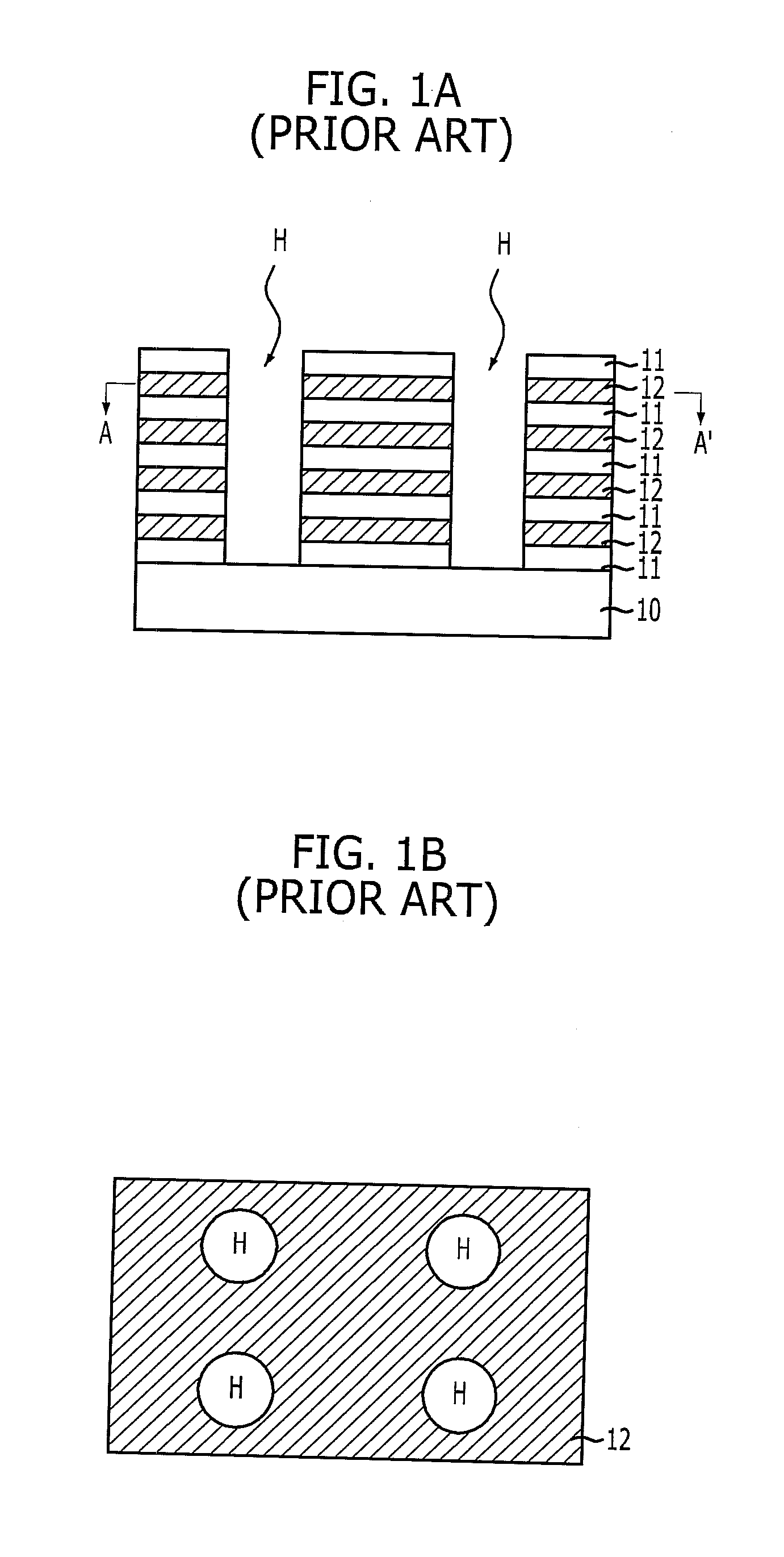

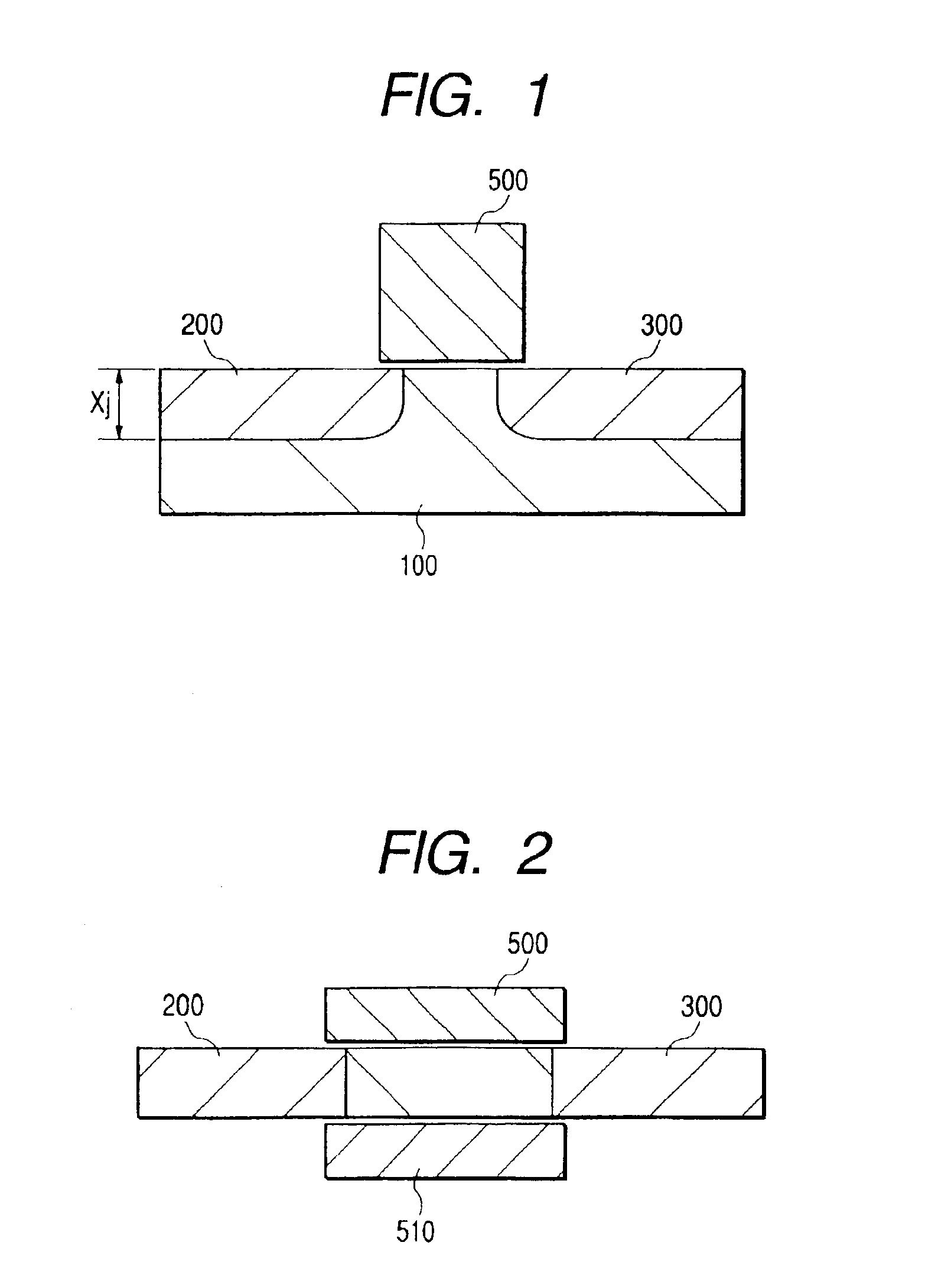

A method includes forming a switching device which includes a vertical channel spaced apart from a semiconductor substrate, and forming a storage device which is positioned on opposed sides of the switching device. The storage device includes a cylindrically shaped storage node, a plate electrode coupled to the storage node, and a dielectric film which is formed between the storage node and plate electrode, the storage nodes being electrically connected to the switching device.

Owner:BESANG

Semiconductor memory device

InactiveUS7867822B2Solid-state devicesSemiconductor/solid-state device manufacturingVertical channelSemiconductor

A method includes forming a switching device which includes a vertical channel spaced apart from a semiconductor substrate, and forming a storage device which is positioned on opposed sides of the switching device. The storage device includes a cylindrically shaped storage node, a plate electrode coupled to the storage node, and a dielectric film which is formed between the storage node and plate electrode, the storage nodes being electrically connected to the switching device.

Owner:BESANG

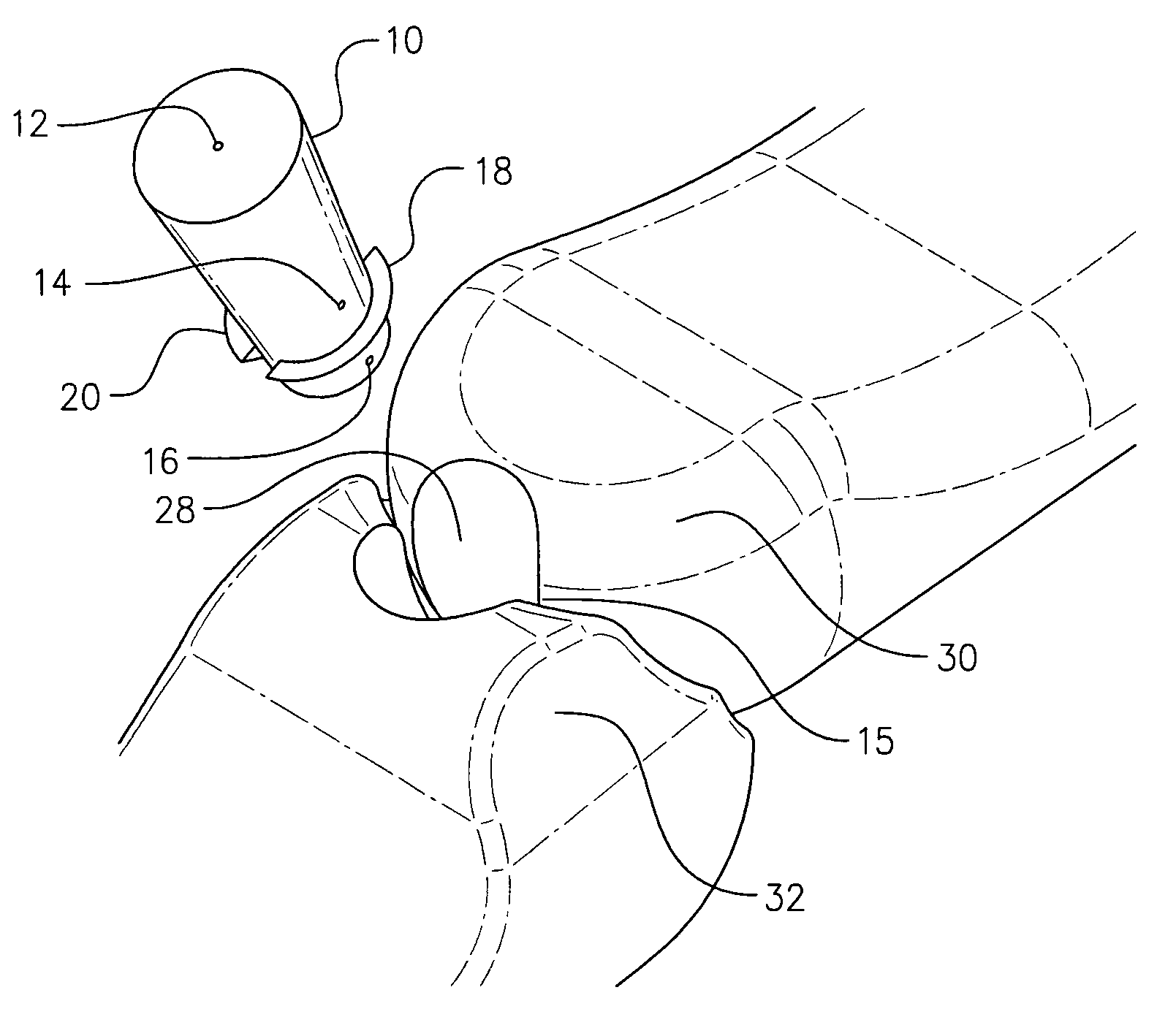

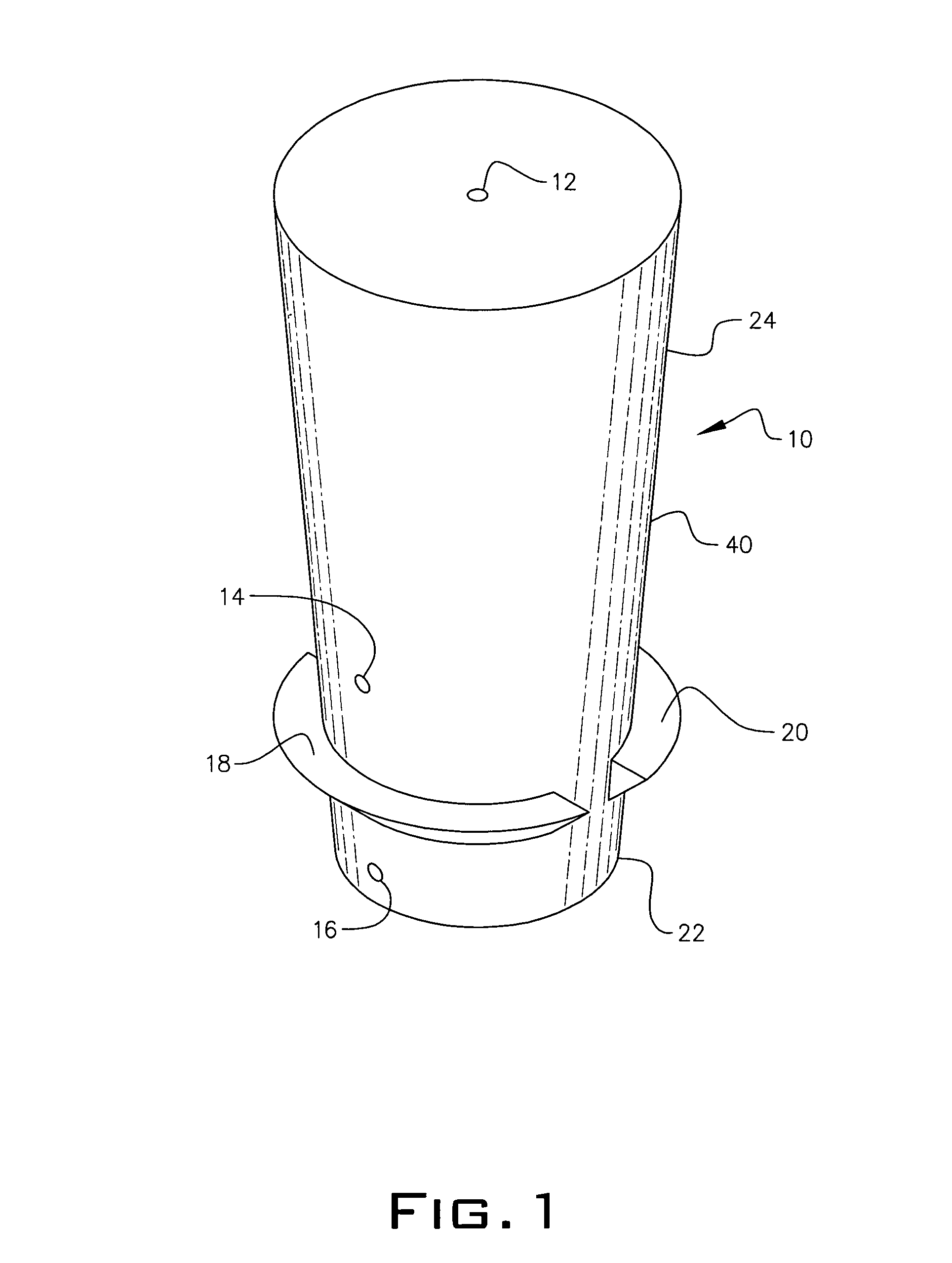

Spinal plug for a minimally invasive facet joint fusion system

InactiveUS7708761B2Strong and unique and superior fusionReduce riskInternal osteosythesisBone implantSpinal columnDetent

A frustum shaped body has an aperture in a top surface and a pair of first and second opposed apertures in a side surface, first and second horizontal internal channels connect both the first and second opposed apertures. A vertical channel from the top aperture connects with the first and second channels. After the body is inserted into a hole in a facet joint, compatible synthetic or biologic material is inserted into the vertical channel until the material exits from the first and second apertures in the side surface. At least one pair of flanges on a portion of an exterior side surface of the body acts as a detent to hold the body in place within the facet joint hole.

Owner:MINSURG INT INC

Method for forming active pillar of vertical channel transistor

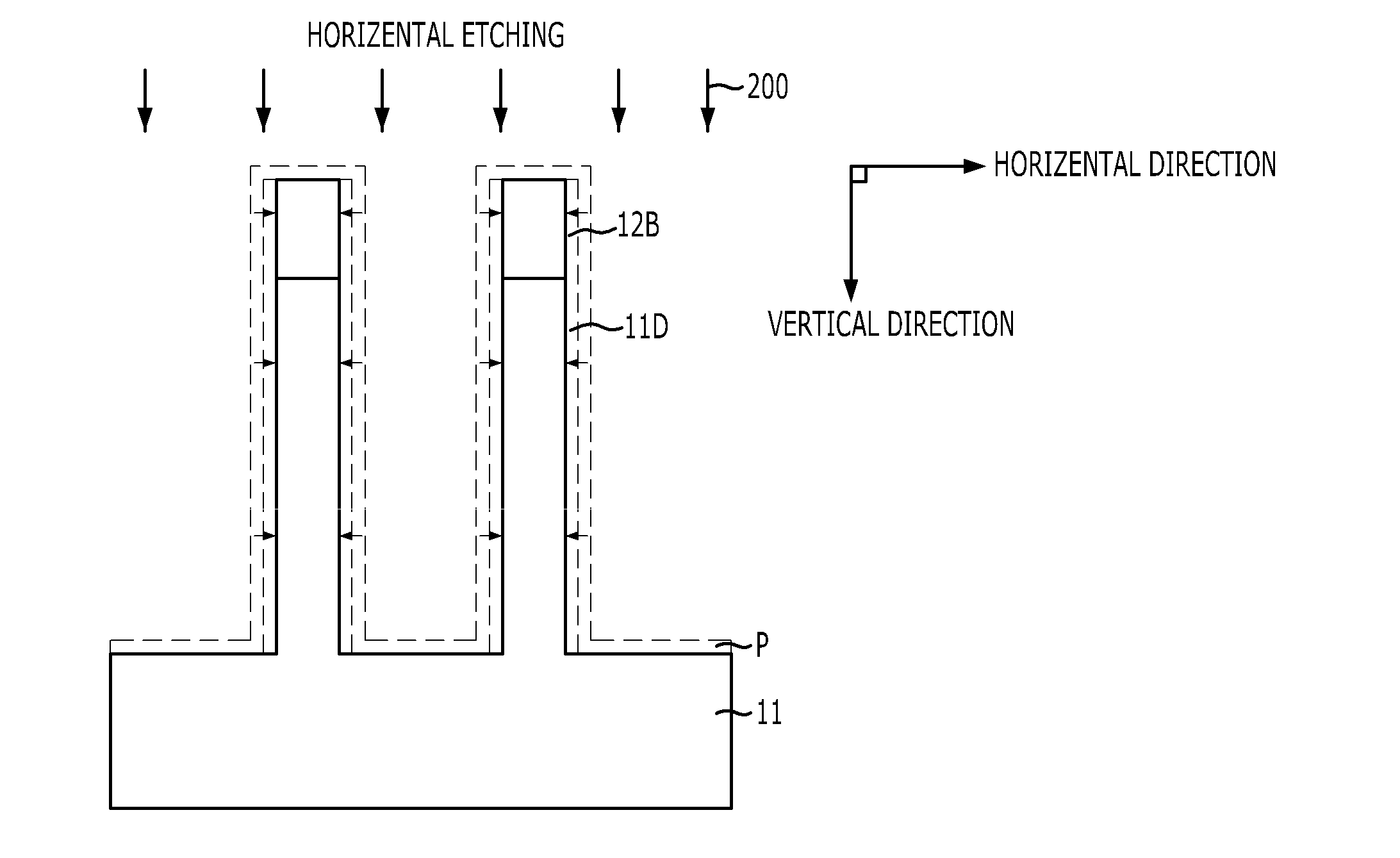

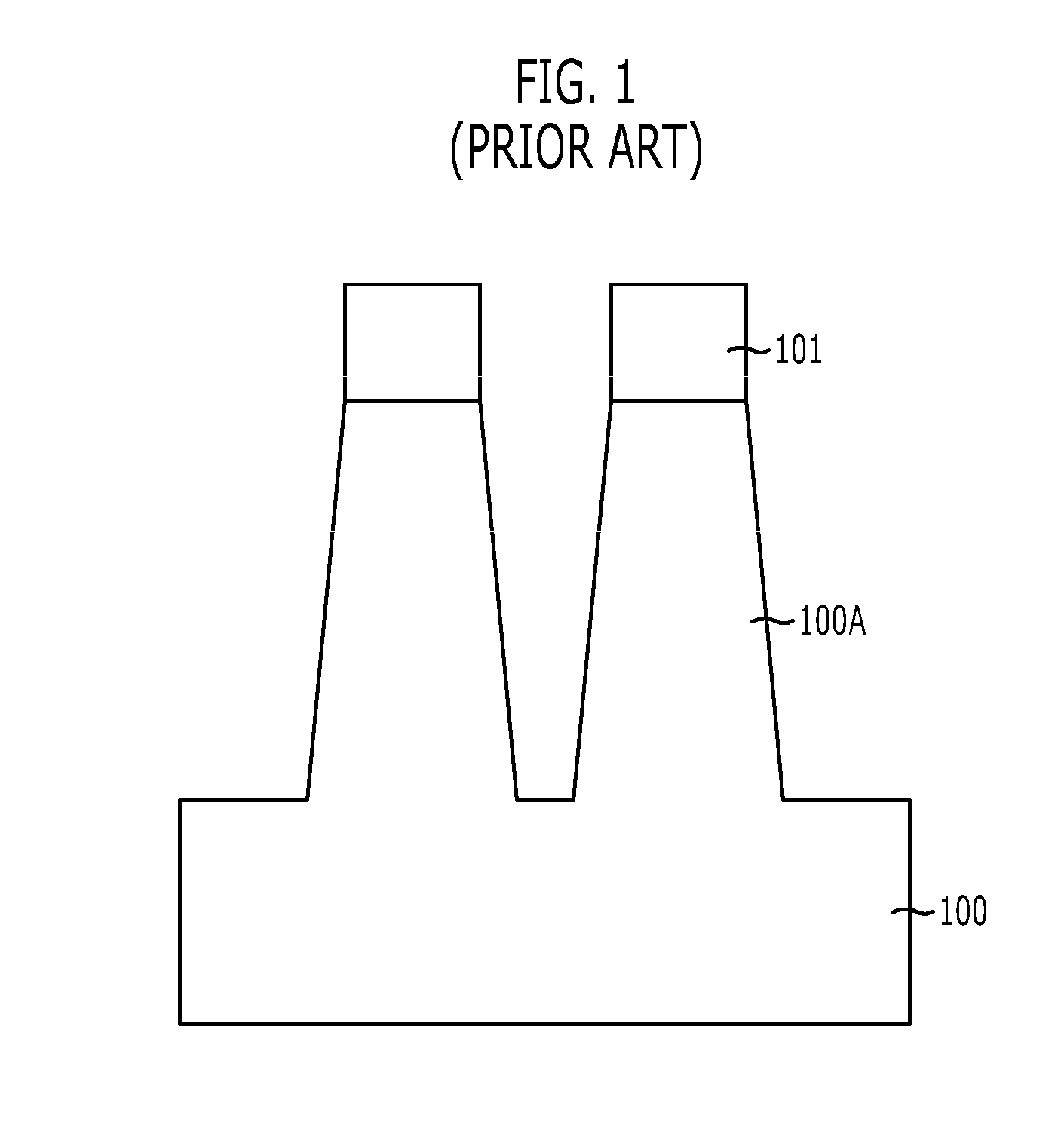

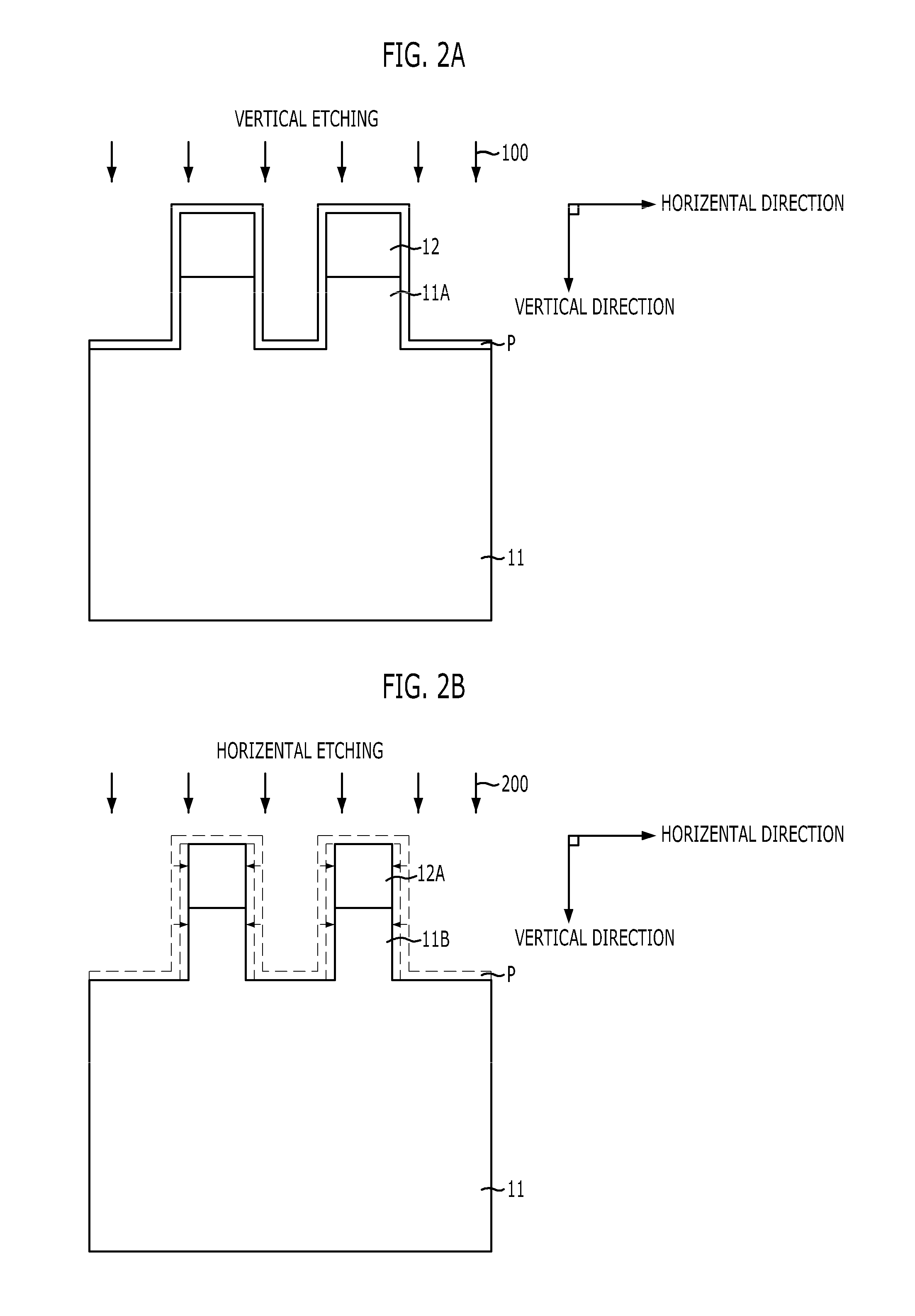

ActiveUS20100055917A1Reduce horizontal widthOvercome limitationsSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLine width

A method for forming an active pillar of a vertical channel transistor includes forming a hard mask pattern on a substrate, etching vertically the substrate using the hard mask pattern as an etch barrier to form an active pillar, and etching horizontally to remove by-product remaining on the exposed substrate, the hard mask pattern and the active pillar and at the same time to reduce line width of the hard mask pattern and the active pillar, wherein a unit cycle in which the vertical etching and the horizontal etching are each performed subsequently once, respectively, is performed repeatedly at least two times or more. According to the present invention, an active pillar having vertical profiles on its sidewalls and having height and line width (or diameter) required in a highly integrated vertical channel transistor can be provided.

Owner:SK HYNIX INC

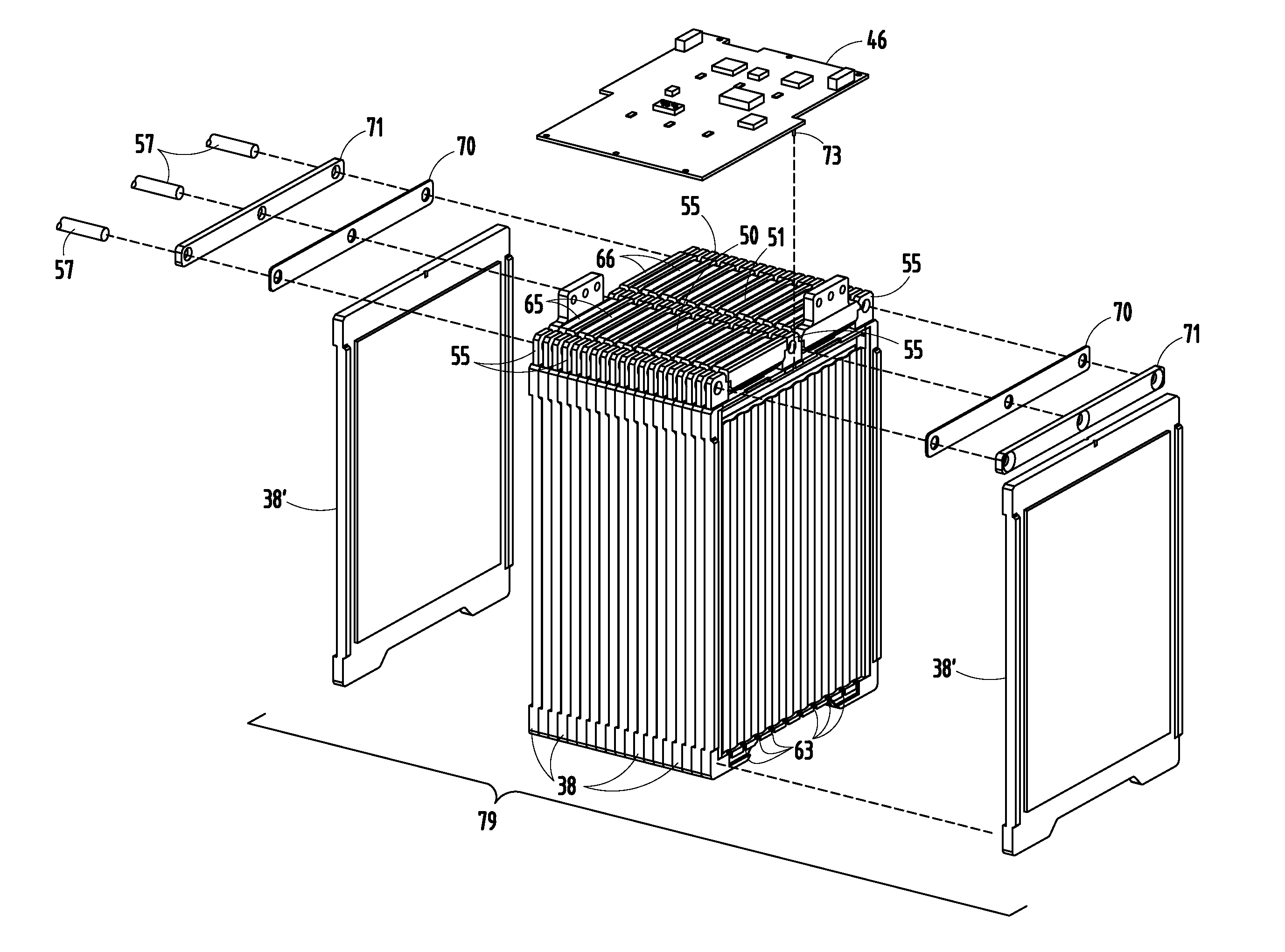

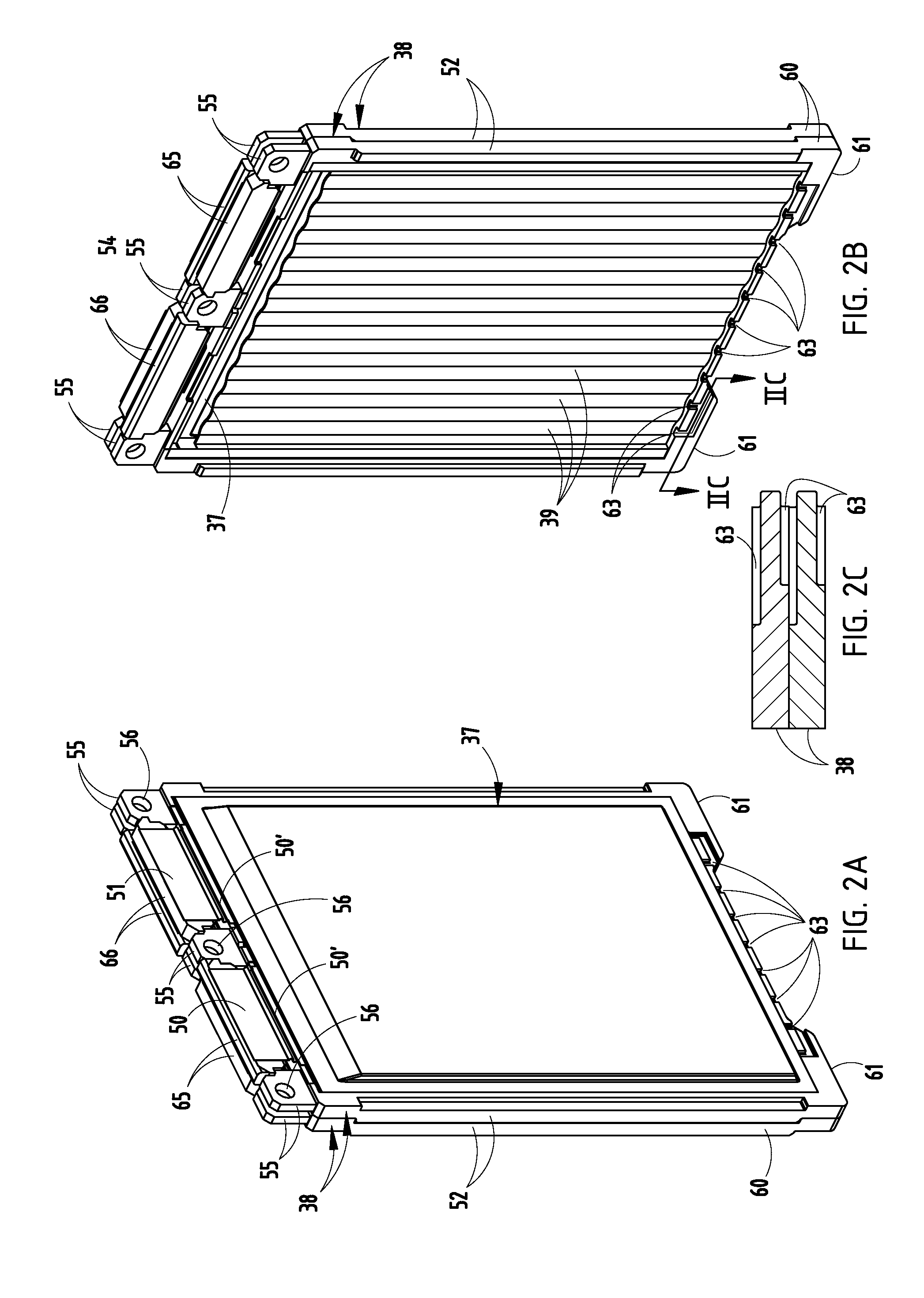

Temperature-controlled battery configuration

A vehicle includes a body adapted to carry passengers or cargo, an electric engine / motor, and a temperature-controlled battery configuration. The battery configuration includes a casing, and a plurality of alternating Lithium-ion cell packs and spacers defining vertical channels, the spacers supporting the cell packs in a hanging manner in the casing. The casing is flooded with a thermally-conductive electrically-insulating fluid flowing from the inlet under the cell packs, upwardly across the cell packs and out an outlet to a heat exchanger for controlling a temperature of the cell packs. A fluid pump connected to the engine / motor and a heat exchanger pumps the liquid through the system. A controller is provided for controlling the pump and fluid flow to control a temperature of the battery configuration to maintain the temperature in a desired temperature range.

Owner:EDGEWATER AUTOMATION

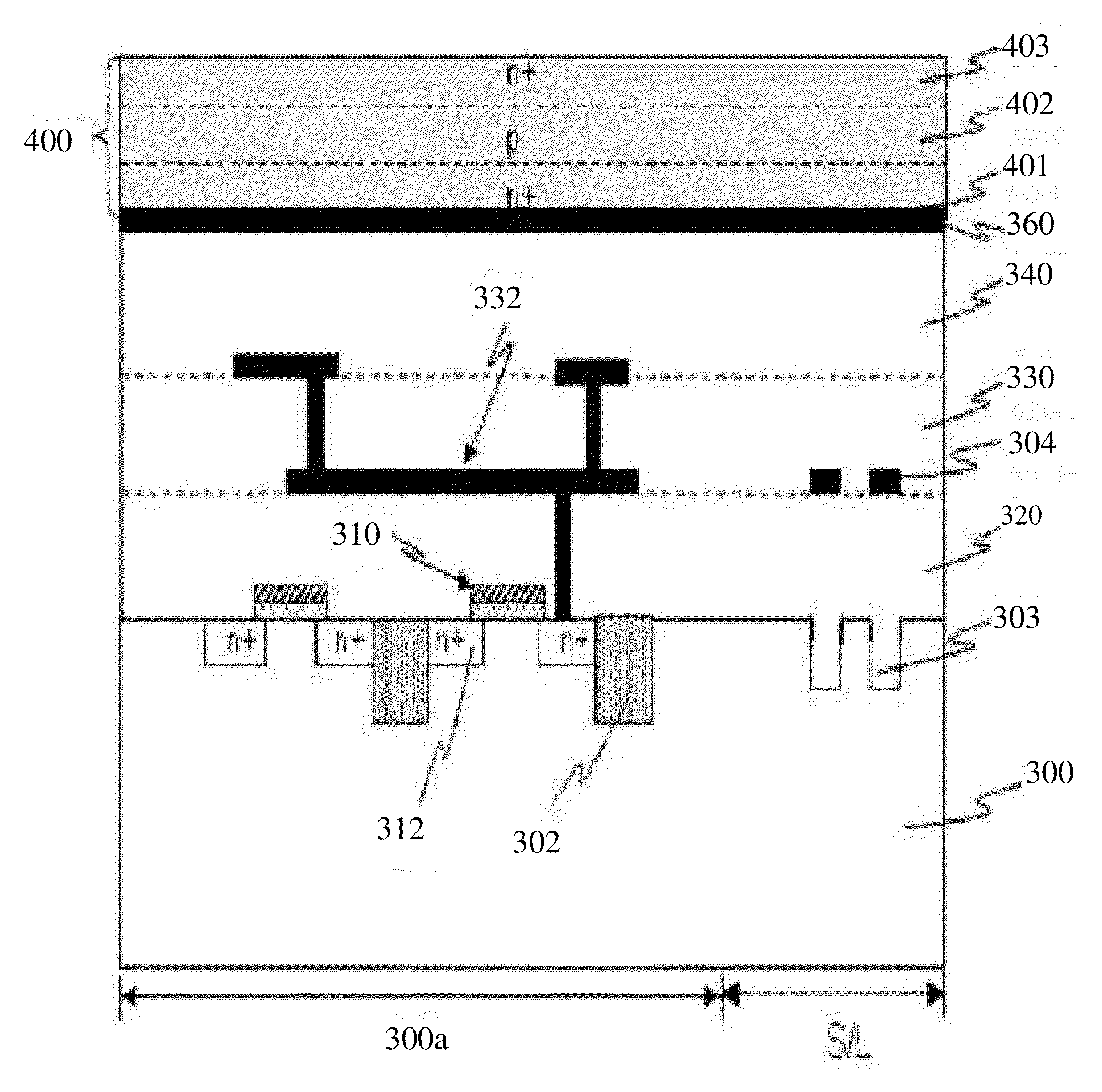

Three-Dimensional Semiconductor Device and Manufacturing Method Therefor

InactiveUS20170154895A1Improve control characteristicsReduce off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEtching

A three-dimensional semiconductor device, comprising a plurality of memory cell transistors and a plurality of select transistors at least partially overlapped in the vertical direction, wherein each select transistor comprises a first drain, an active region and a common source formed in the substrate, distributed along the vertical direction, as well as a metal gate distributed around the active region; wherein each memory cell transistor comprises a channel layer distributed perpendicularly to the substrate surface, a plurality of inter-layer insulating layers and a plurality of gate stack structures alternately stacked along the sidewalls of said channel layer, a second drain located on top of said channel layer; wherein said channel layer and said the first drain are electrically connected. In accordance with the three-dimensional semiconductor memory device and manufacturing method of the present invention, the multi-gate MOSFET is formed beneath the stack structure of the memory cell string including vertical channel to serve as the select transistor, this can improve the control characteristics of the gate threshold voltage, reduce the off-state leakage current, prevent the substrate from over-etching, and effectively improve the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor device having vertical channel and air gap, and method of manufacturing thereof

ActiveUS20150380431A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringVertical channel

A semiconductor device is provided. Word lines are formed on a substrate. An air gap is interposed between two adjacent word lines. A channel structure penetrates through the word lines and the air gap. A memory cell is interposed between each word line and the channel structure. The memory cell includes a blocking pattern, a charge trap pattern and a tunneling insulating pattern. The blocking pattern conformally covers a top surface, a bottom surface, and a first side surface of each word line. The first side surface is adjacent to the channel structure. The charge trap pattern is interposed only between the first side surface and the channel structure.

Owner:SAMSUNG ELECTRONICS CO LTD

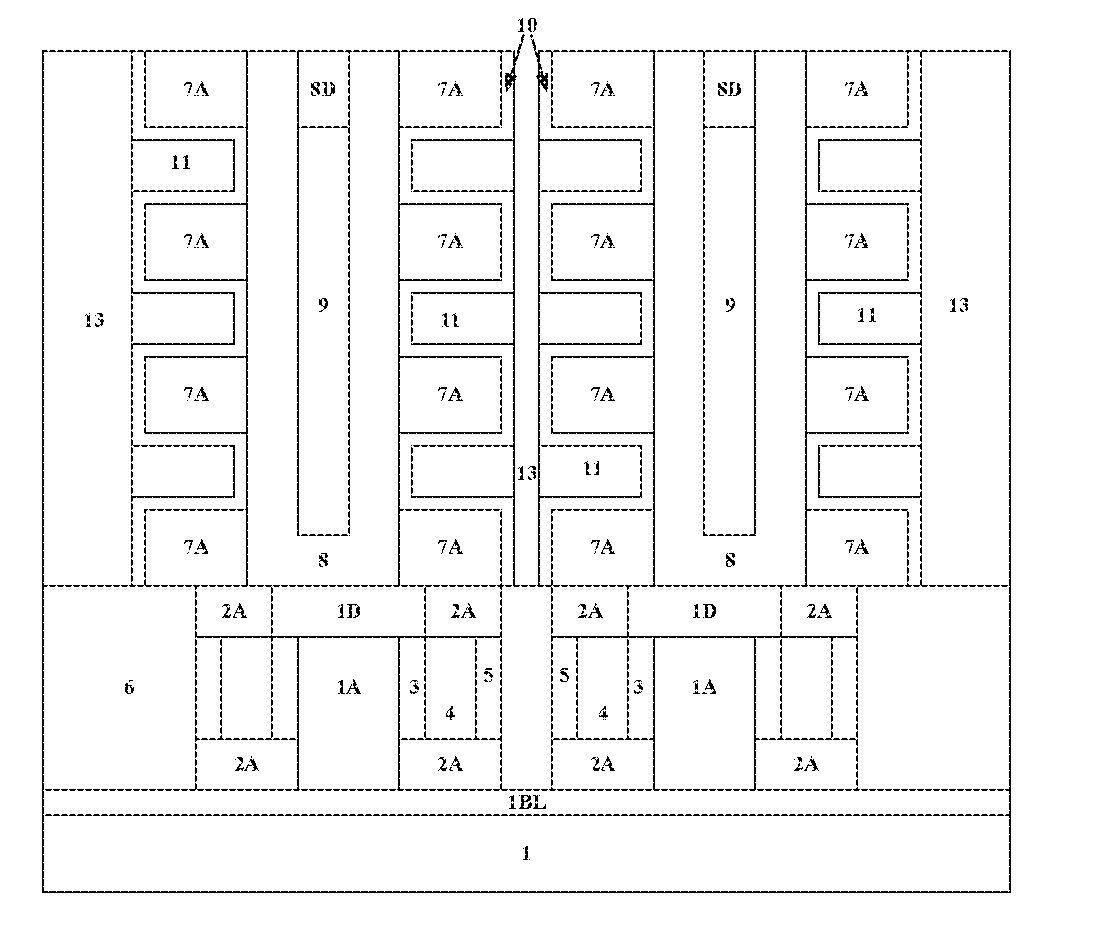

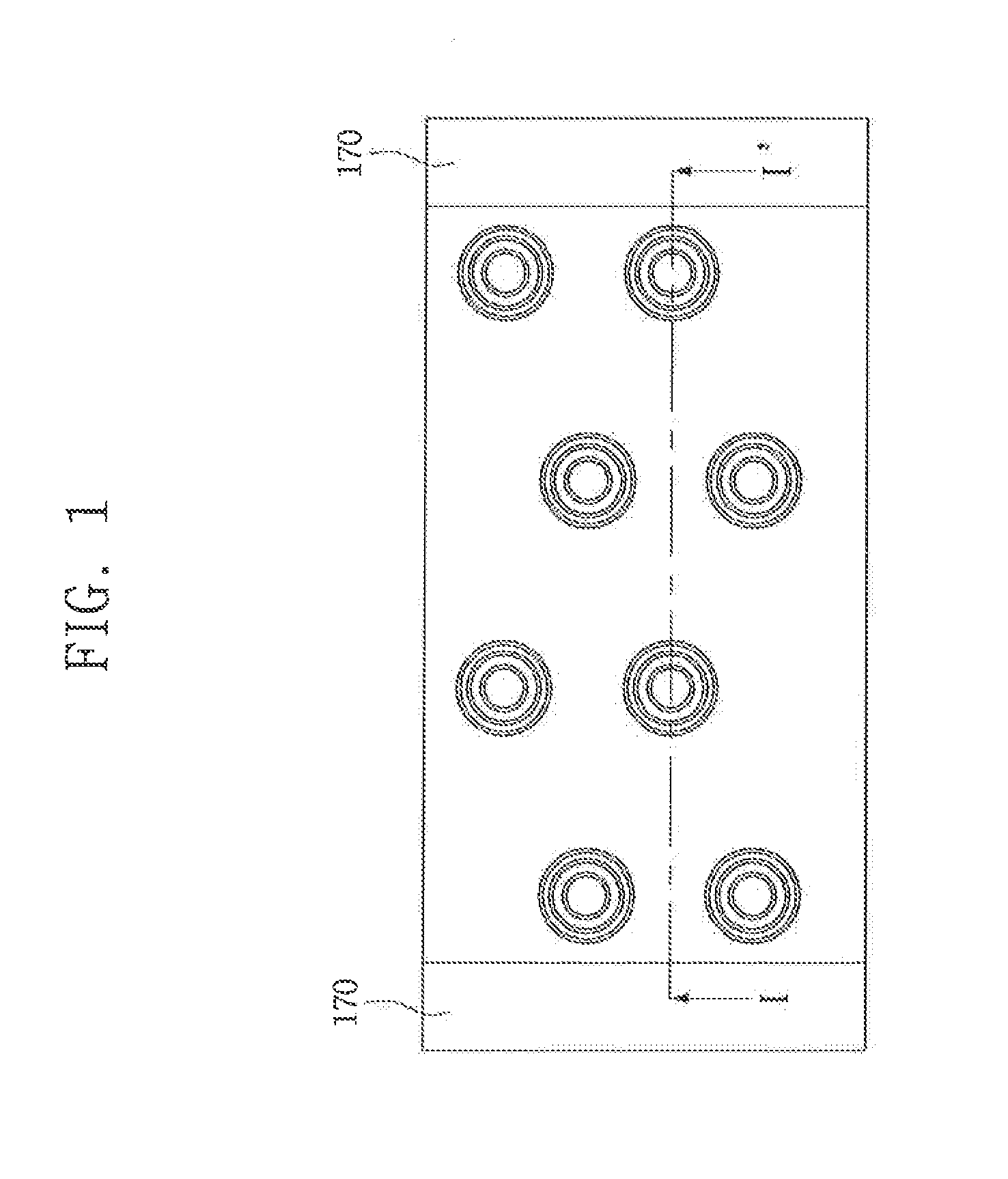

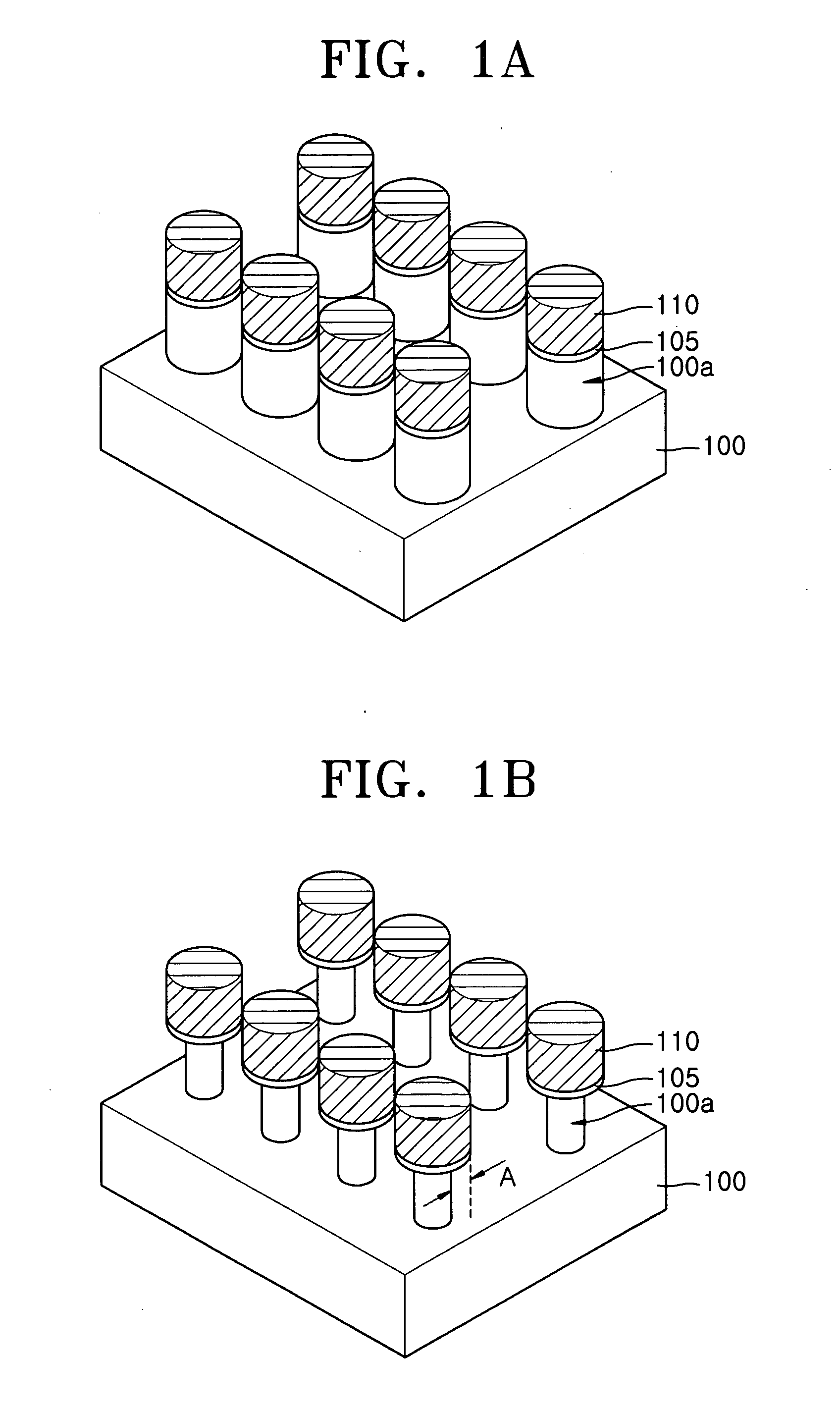

Semiconductor devices having transistors with vertical channels and method of fabricating the same

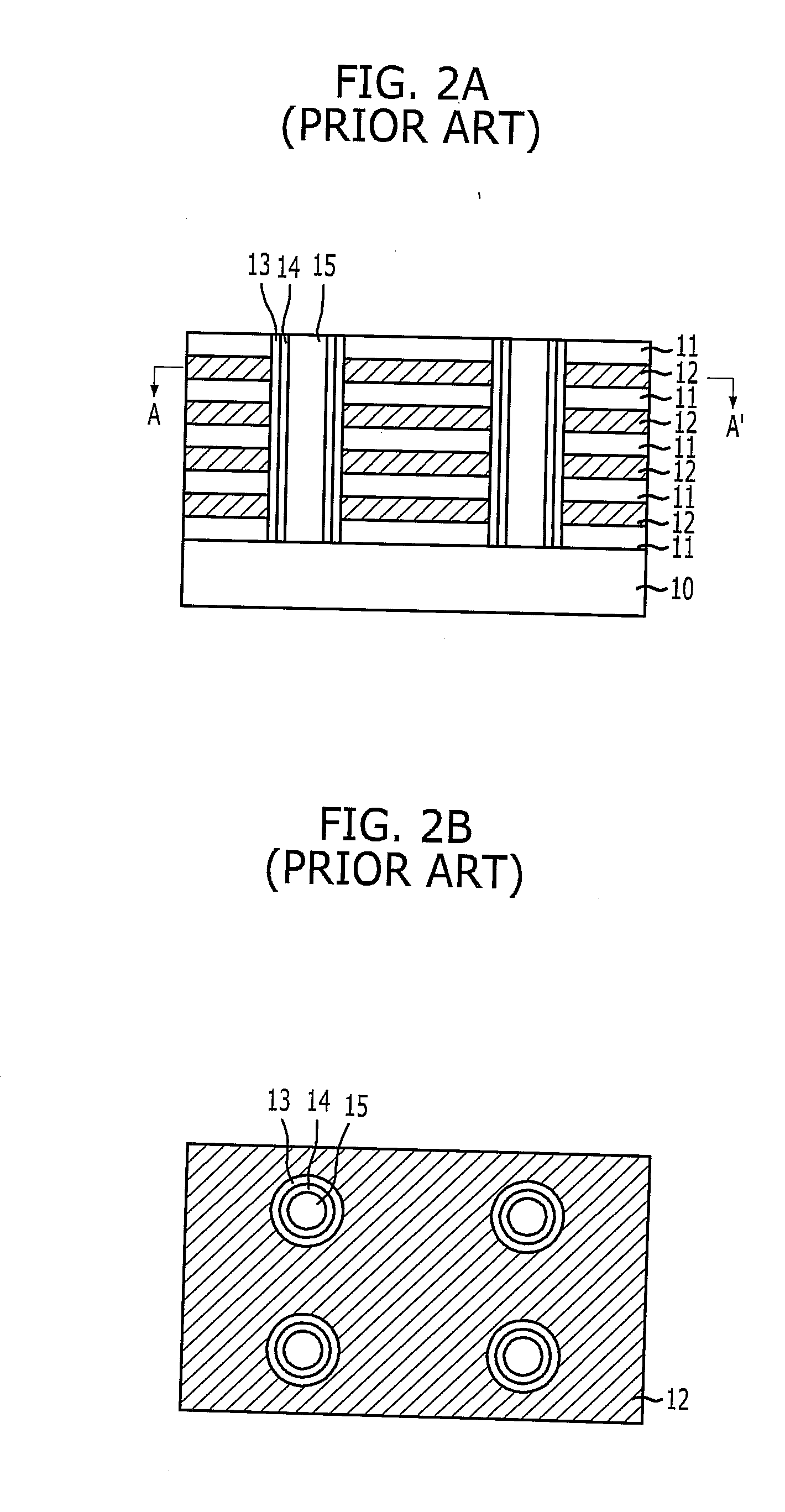

InactiveUS20070082448A1Overcome limitationsSolid-state devicesSemiconductor/solid-state device manufacturingBit lineDevice material

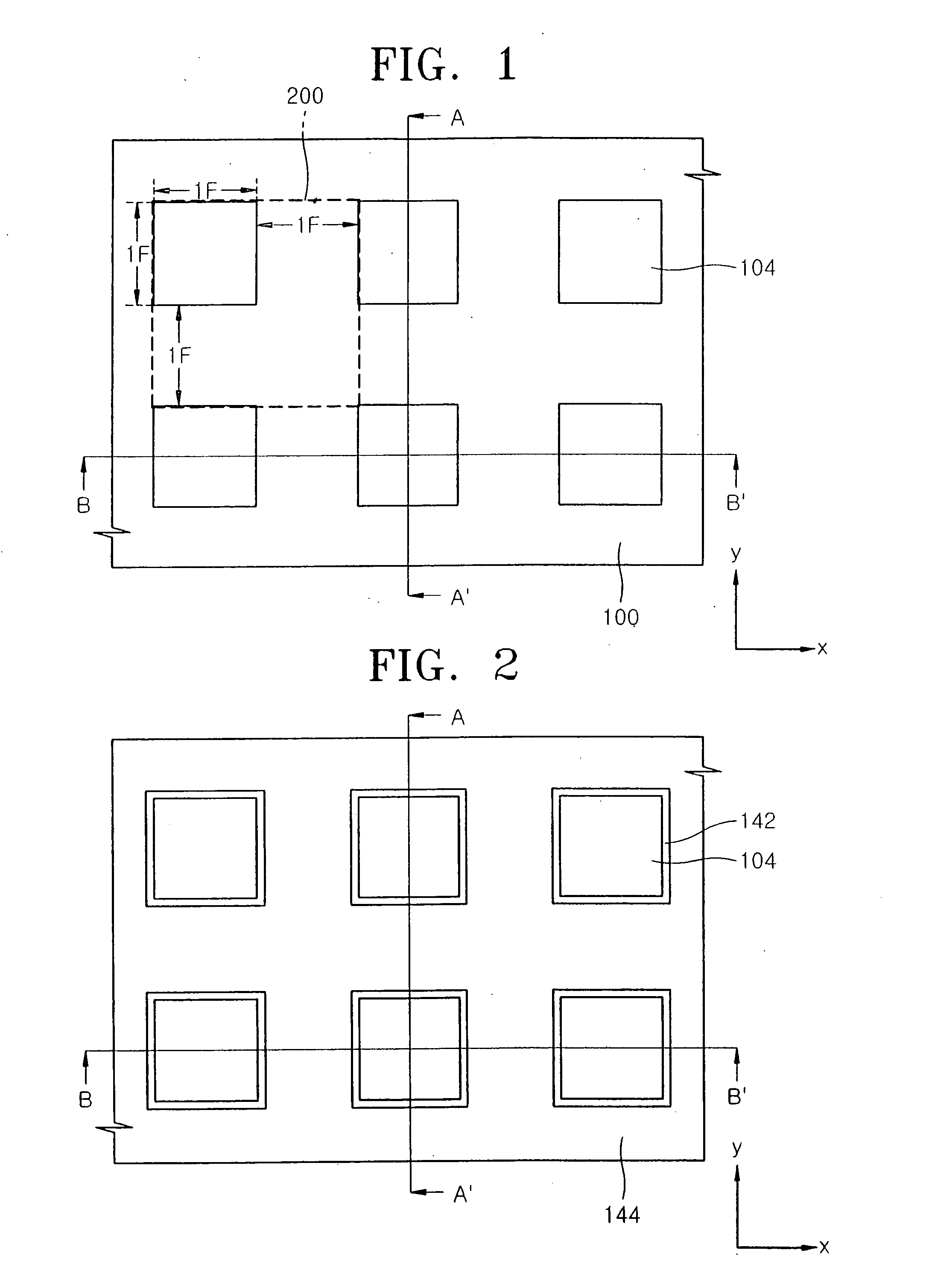

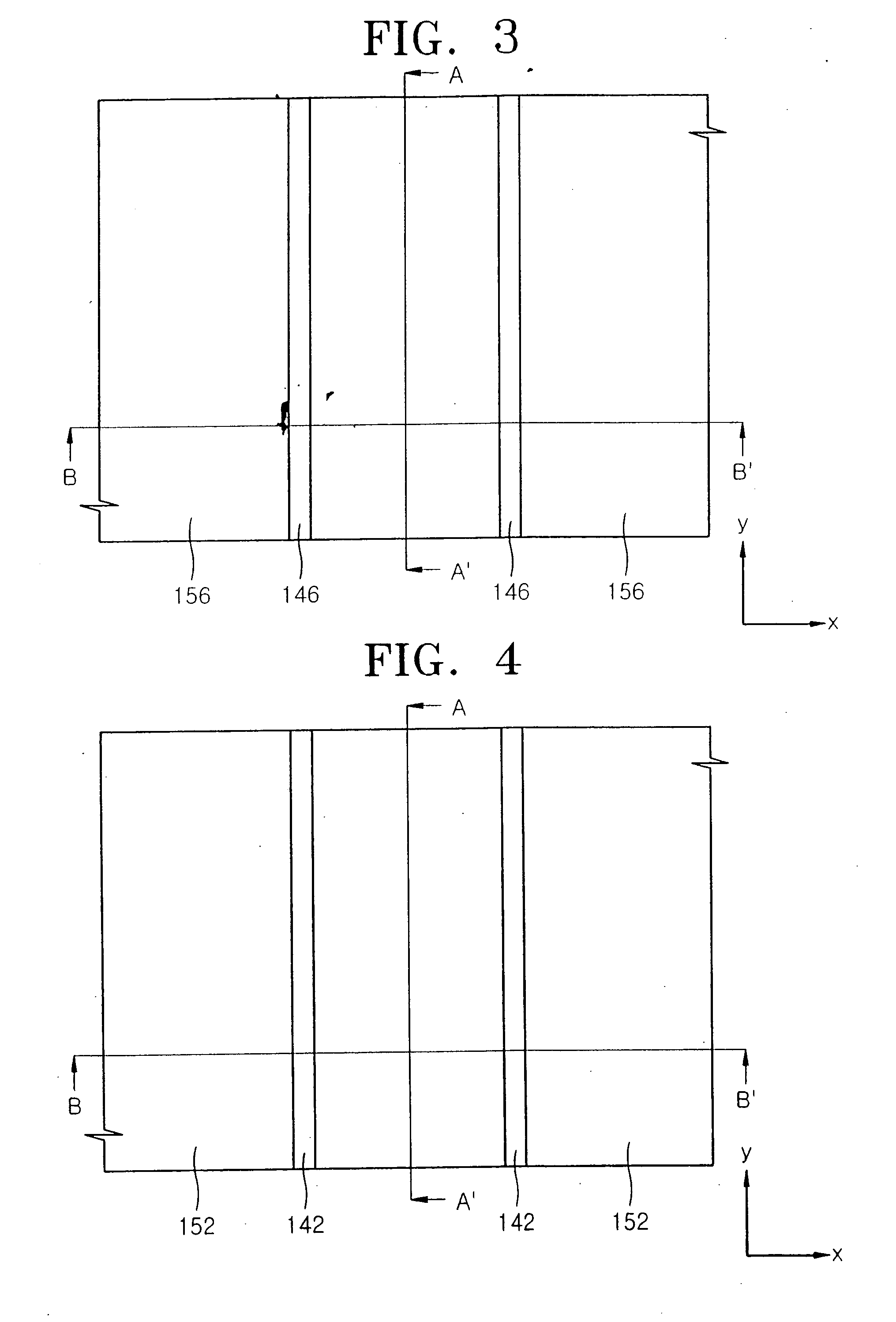

In a semiconductor device and a method of fabricating the same, a vertical channel transistor has a cell occupation area of 4 F2. The semiconductor device comprises: a cell array region having a plurality of unit cells, each unit cell having a cell occupation area, repeatedly aligned along a first direction and along a second direction, the first and second directions being perpendicular to each other in a horizontal direction along a primary surface of a semiconductor substrate, wherein each unit cell has a uniform first pitch in the first direction and in the second direction; an active pillar vertically extending from an active region of each unit cell integrally with the semiconductor substrate in a vertical direction that is perpendicular with respect to the primary surface of the semiconductor substrate, wherein widths of at least a portion of the active pillar in the first direction and in the second direction are equal to a first width 1 F as a minimum feature size in the cell array region; a ring-shaped gate surrounding a sidewall of the active pillar; a channel region formed to extend along the active pillar in the vertical direction; a buried bit line formed below the active pillar in the semiconductor substrate; and a word line extending in the horizontal direction perpendicular to the buried bit line, and electrically connected to the ring-shaped gate, wherein a distance from the active pillar of any one unit cell of the plurality of unit cells to each of the active pillars of nearest neighboring unit cells in the first direction and the second direction is equal to the first width of the active pillar of one unit cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Vertical semiconductor device with tunnel insulator in current path controlled by gate electrode

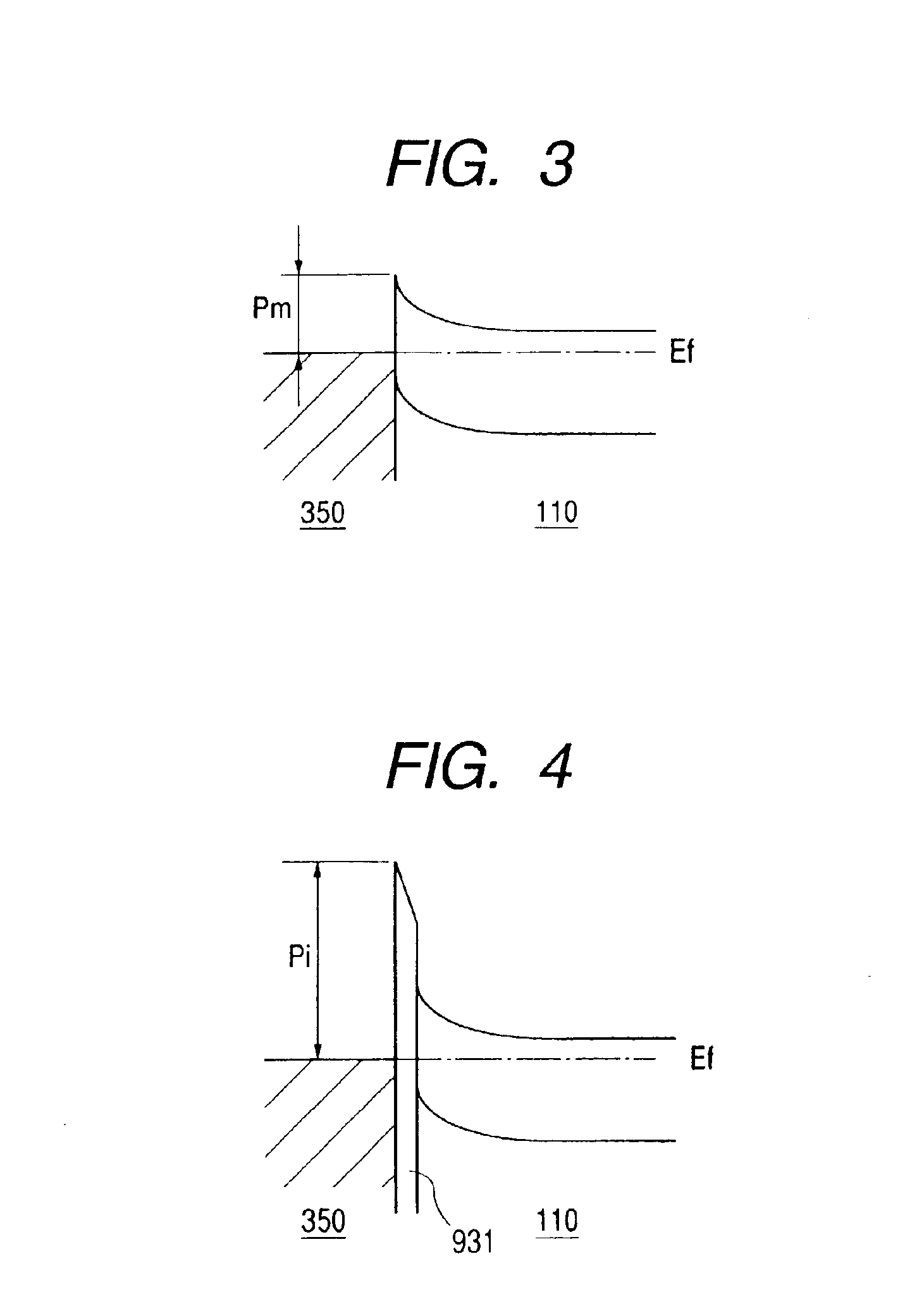

InactiveUS6873009B2Suppress lowering of driving forceLower average currentTransistorSolid-state devicesGate leakage currentJunction leakage

It is an object of the present invention to provides a field effect transistor with extremely low leakage current. It is another object of the invention to provide a semiconductor memory device having an excellent information holding characteristic. It is a further object of the invention to provide a method for manufacturing in a simple manner a novel field effect transistor or semiconductor memory device with extremely low leakage current. According to a typical basic configuration of the present invention, a thin insulating film is inserted in a vertically disposed Schottky junction to form source and drain electrodes and a tunnel of the insulating film in the junction is controlled by a gate electrode. The gate electrode is disposed on each of both sides of a vertical channel, permitting a field effect to be exerted effectively on the junction, whereby a junction leakage in an OFF state can be made extremely low.

Owner:HITACHI LTD

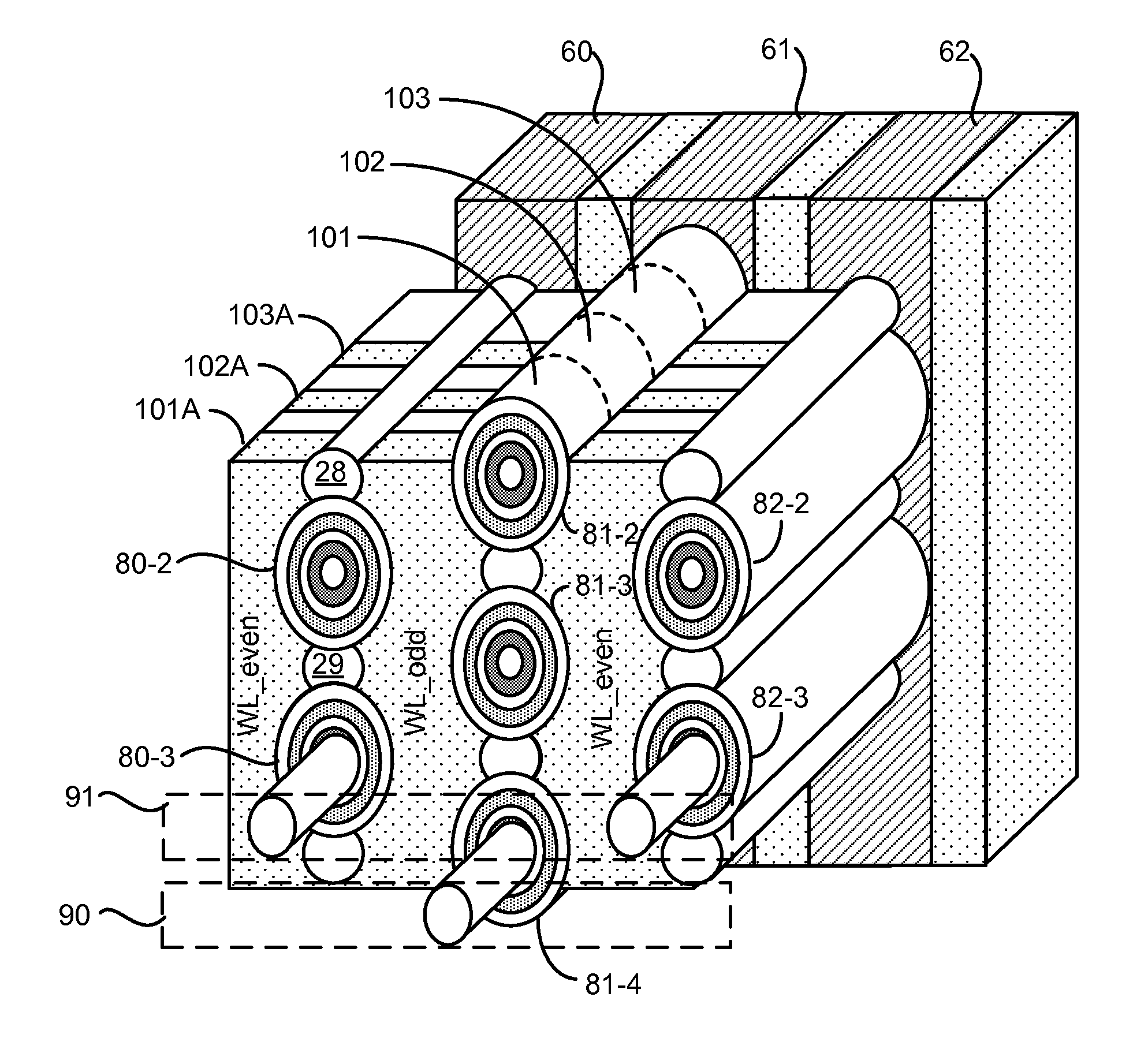

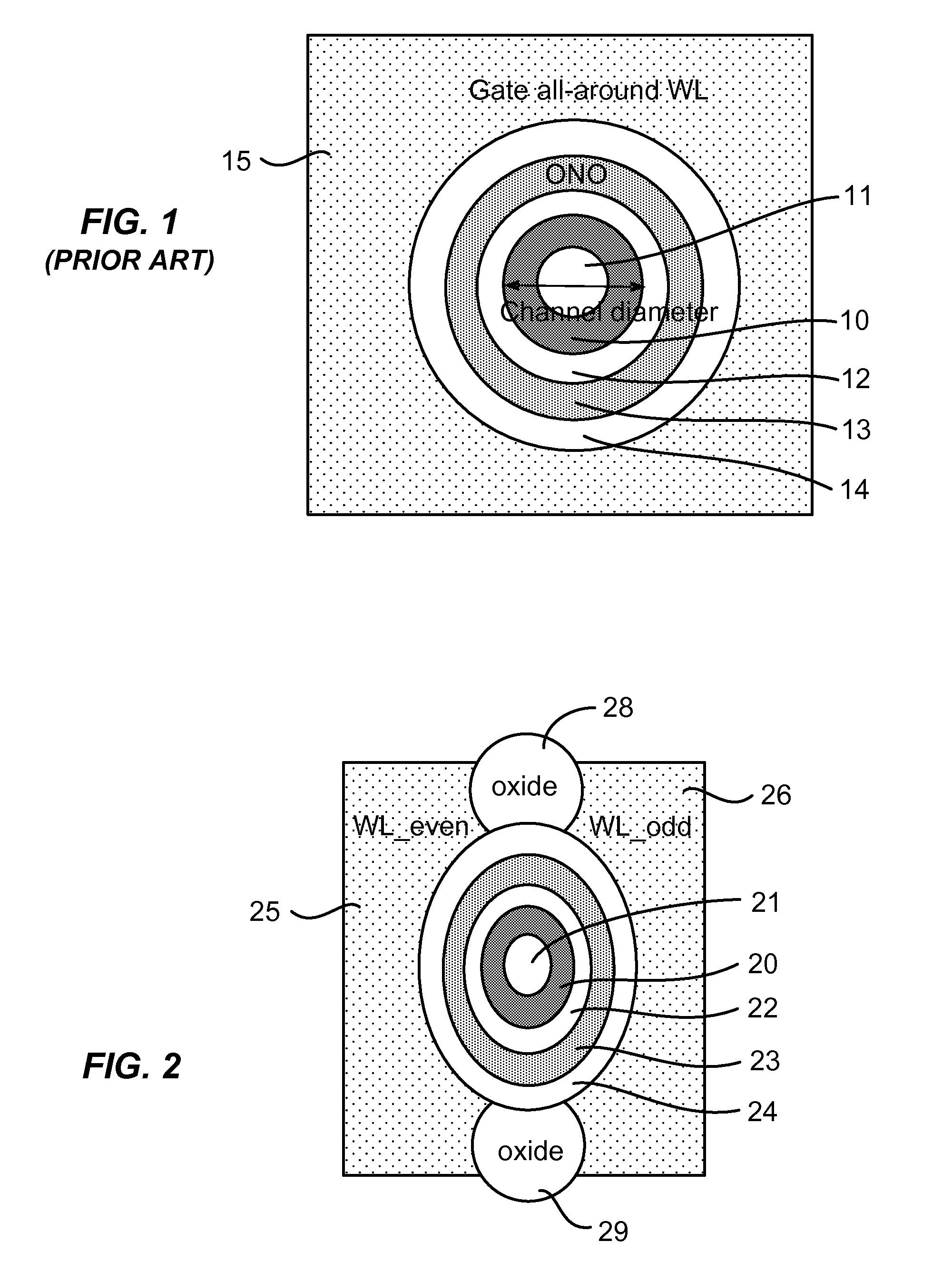

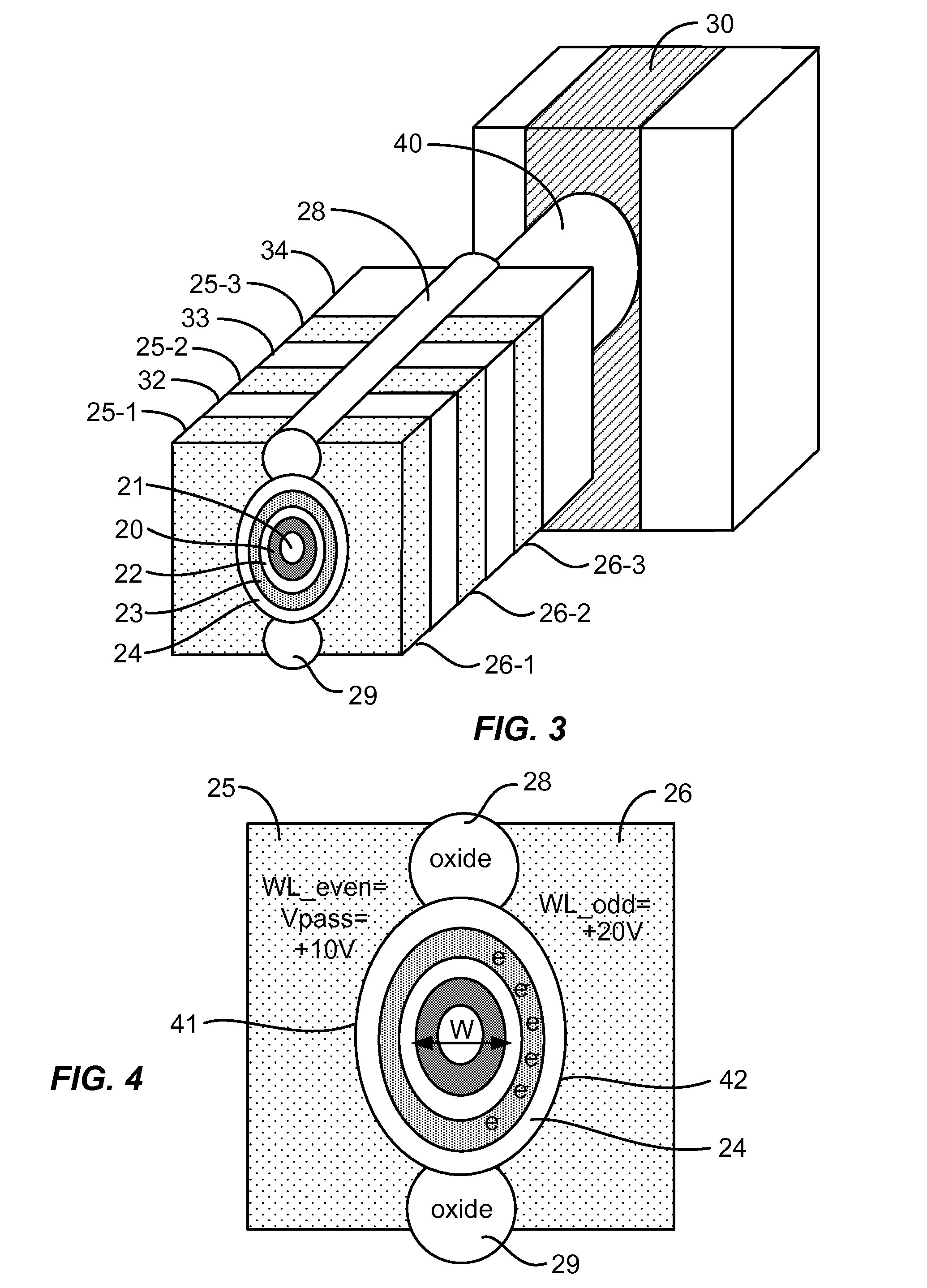

3D independent double gate flash memory

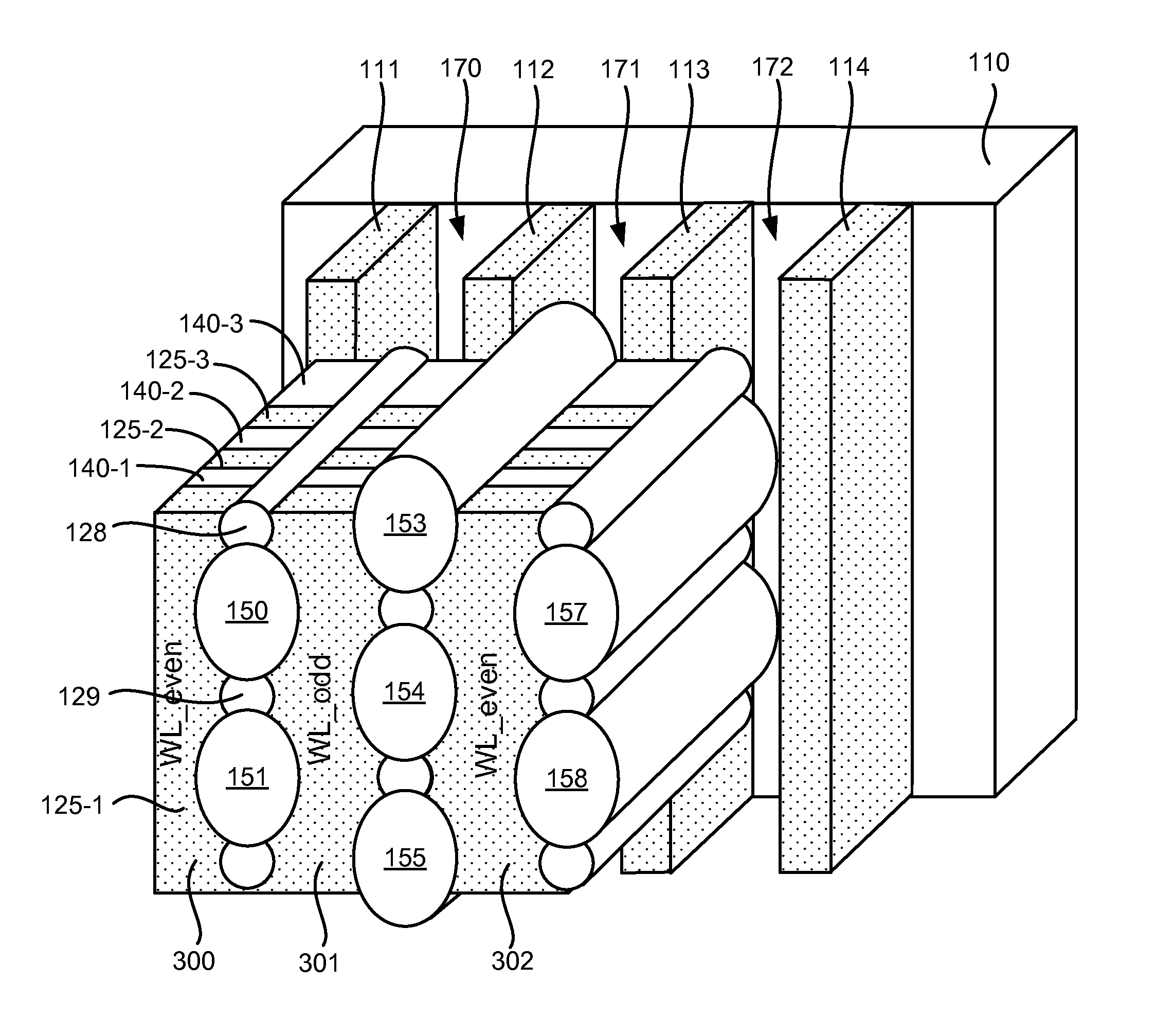

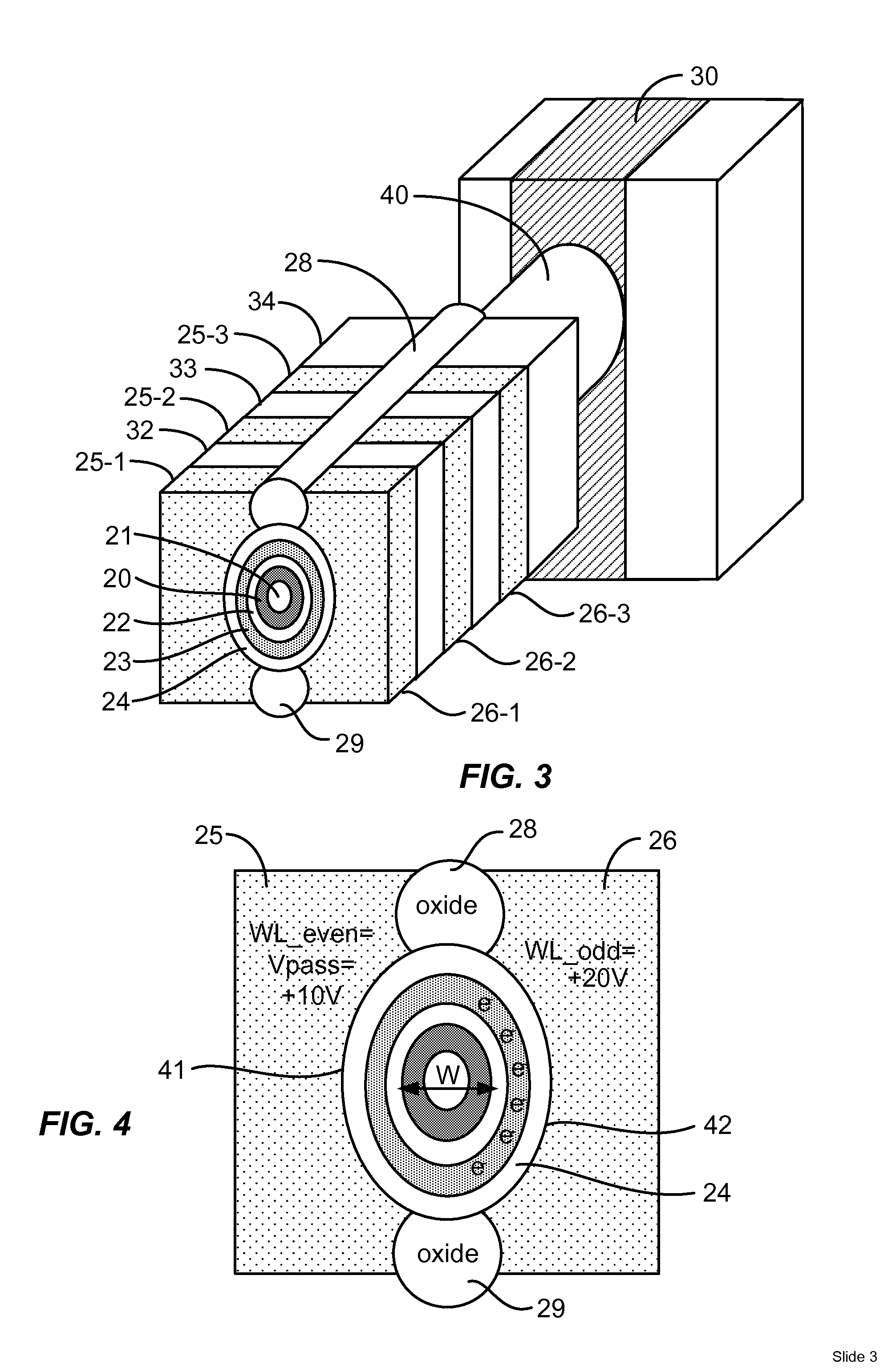

ActiveUS20150340369A1High density data storageIncrease data storageSolid-state devicesRead-only memoriesVertical channelDouble gate

A memory device configurable for independent double gate cells, storing multiple bits per cell includes multilayer stacks of conductive strips configured as word lines. Active pillars are disposed between pairs of first and second stacks, each active pillar comprising a vertical channel structure, a charge storage layer and an insulating layer. The insulating layer in a frustum of an active pillar contacts a first arcuate edge of a first conductive strip in a layer of the first stack and a second arcuate edge of a second conductive strip in a same layer of the second stack. A plurality of insulating columns serve, with the active pillars, to divide the stacks of word lines into even and odd lines contacting opposing even and odd sides of each active pillar. The active pillar can be generally elliptical with a major axis parallel with the first and second conductive strips.

Owner:MACRONIX INT CO LTD

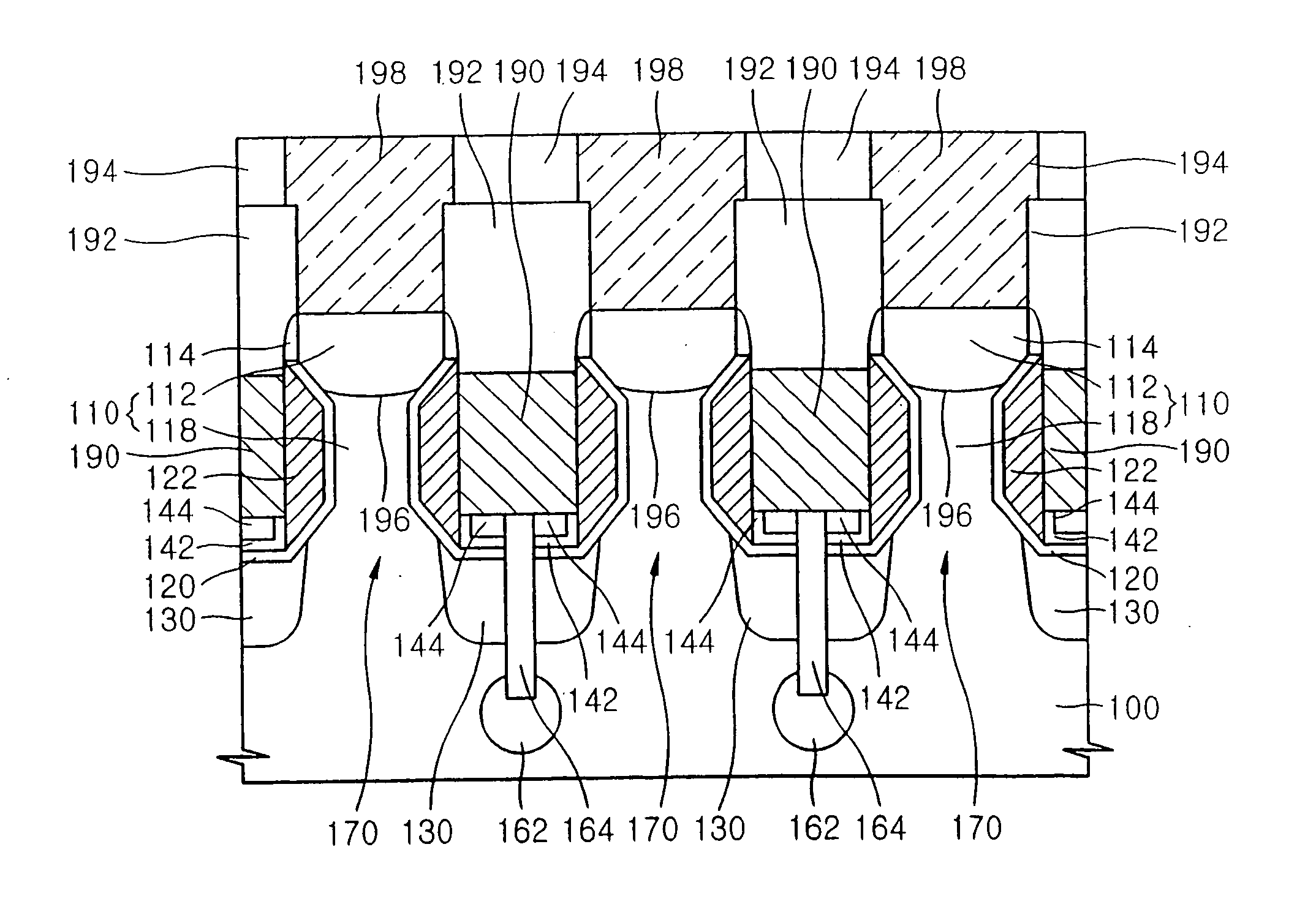

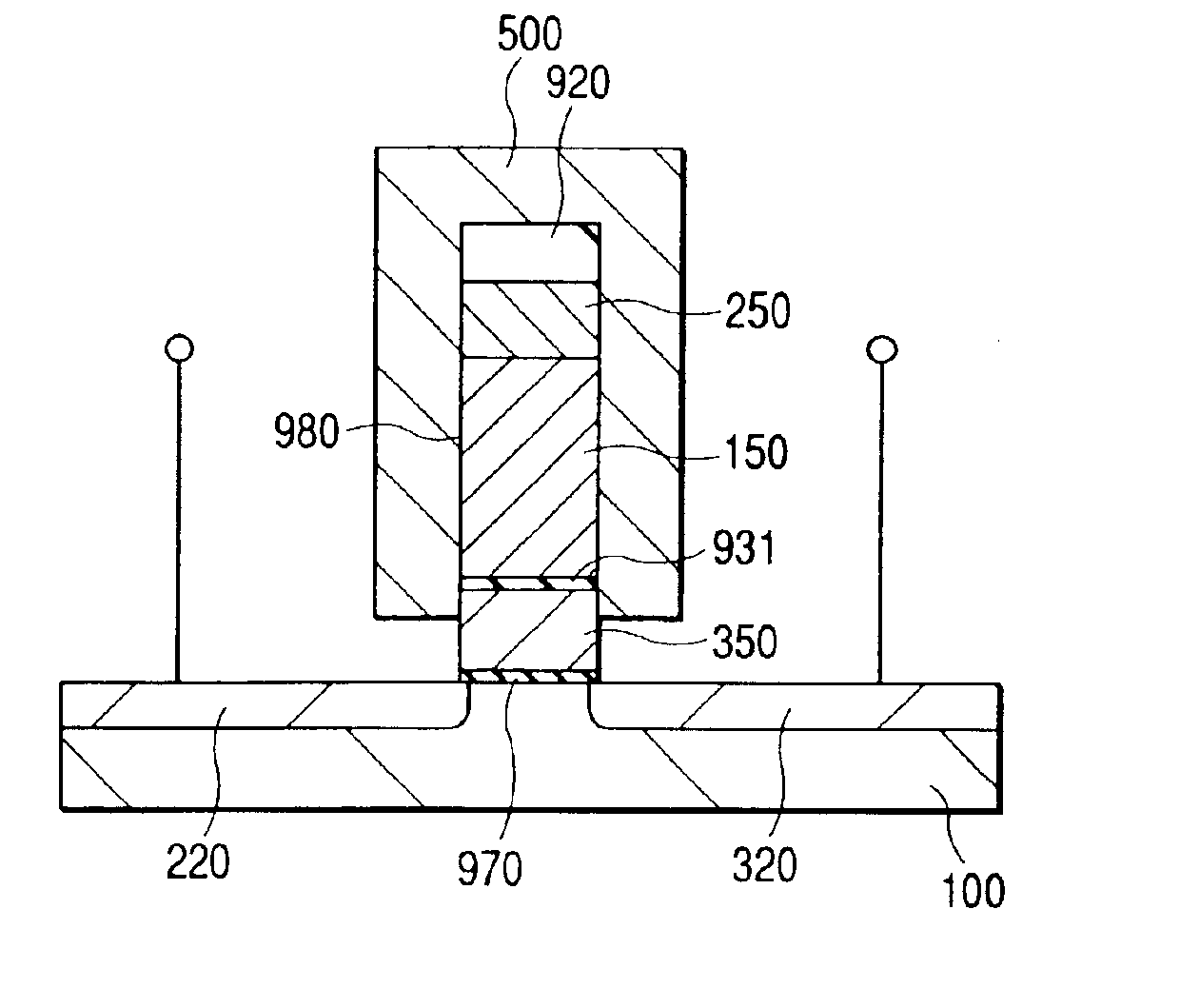

Semiconductor memory devices including a vertical channel transistor and methods of manufacturing the same

Semiconductor memory devices include a semiconductor substrate and a plurality of semiconductor material pillars in a spaced relationship on the semiconductor substrate. Respective surrounding gate electrodes surround ones of the pillars. A first source / drain region is in the semiconductor substrate between adjacent ones of the pillars and a second source / drain region is in an upper portion of at least one of the adjacent pillars. A buried bit line is in the first source / drain region and electrically coupled to the first source / drain region and a storage node electrode is on the upper portion of the at least one of the adjacent pillars and electrically contacting with the second source / drain region.

Owner:SAMSUNG ELECTRONICS CO LTD

3D independent double gate flash memory on bounded conductor layer

ActiveUS20150340371A1High density data storageIncrease data storageSolid-state devicesRead-only memoriesElectrical conductorVertical channel

A memory device configurable for independent double gate cells, storing multiple bits per cell, includes multilayer stacks of conductive strips configured as word lines. Active pillars are disposed between pairs of first and second stacks, each active pillar comprising a vertical channel structure extending from an underlying bounded conductive layer, a charge storage layer and an insulating layer. The insulating layer in a frustum of an active pillar contacts a first arcuate edge of a first conductive strip in a layer of the first stack and a second arcuate edge of a second conductive strip in a same layer of the second stack. The conductive strips can comprise a metal. The active pillar can be generally elliptical with a major axis parallel with the first and second conductive strips.

Owner:MACRONIX INT CO LTD

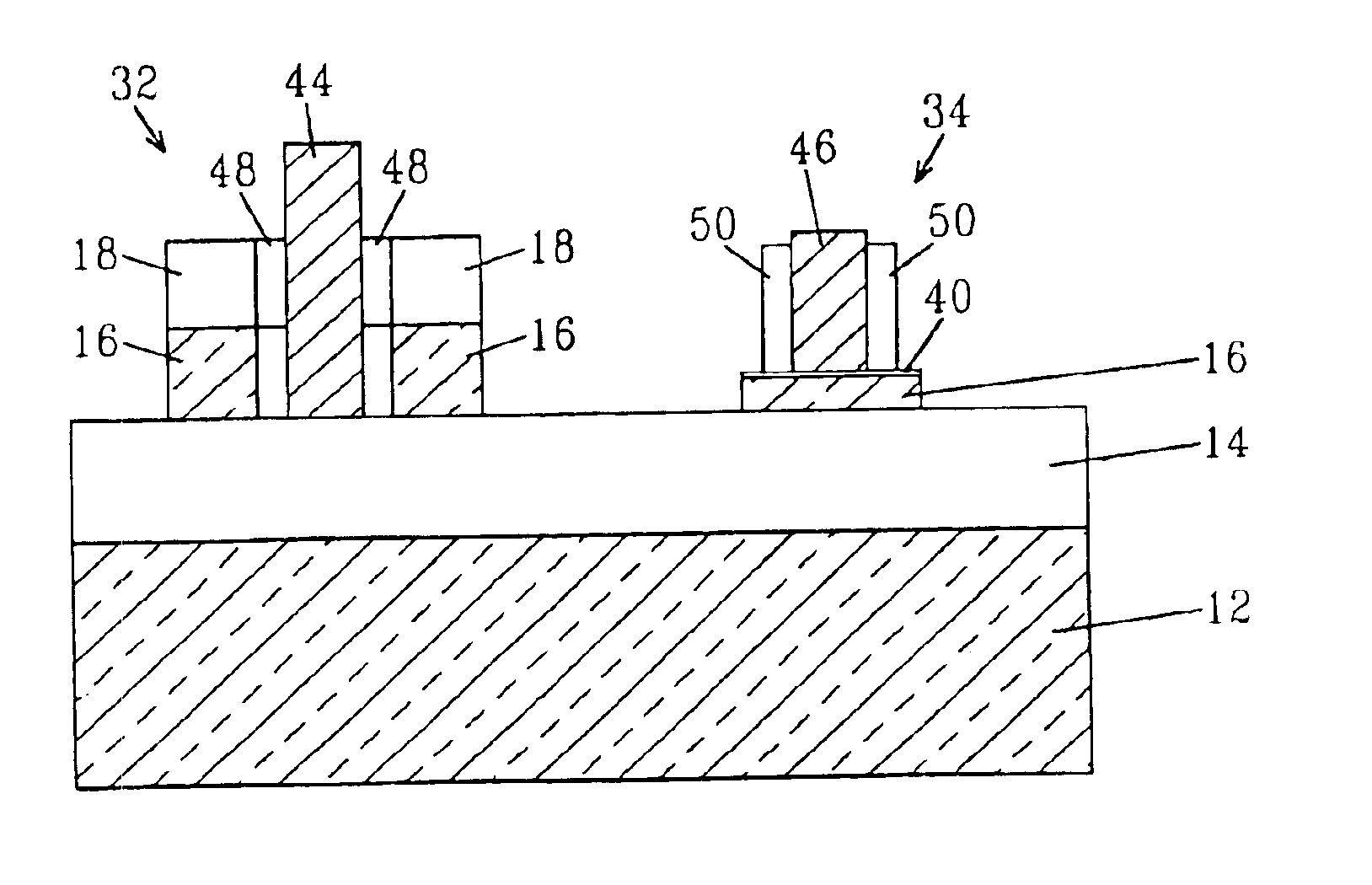

Hybrid planar and finFET CMOS devices

The present invention provides an integrated semiconductor circuit containing a planar single gated FET and a FinFET located on the same SOI substrate. Specifically, the integrated semiconductor circuit includes a FinFET and a planar single gated FET located atop a buried insulating layer of an silicon-on-insulator substrate, the planar single gated FET is located on a surface of a patterned top semiconductor layer of the silicon-on-insulator substrate and the FinFET has a vertical channel that is perpendicular to the planar single gated FET. A method of forming a method such an integrated circuit is also provided. In the method, resist imaging and a patterned hard mask are used in trimming the width of the FinFET active device region and subsequent resist imaging and etching are used in thinning the thickness of the FET device area. The trimmed active FinFET device region is formed such that it lies perpendicular to the thinned planar single gated FET device region.

Owner:AURIGA INNOVATIONS INC

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS20070148939A1Superb performanceSuperb scalabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

Ultra scalable high speed heterojunction vertical n-channel MISFETs and methods thereof

ActiveUS7205604B2Superb performanceSuperb scalabilityTransistorDiagnosticsHeterojunctionSemiconductor materials

A method for forming and the structure of a strained vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a heterojunction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect to the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (boron) into the body. The invention reduces the problem of leakage current from the source region via the heterojunction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials.

Owner:GLOBALFOUNDRIES US INC

Vertical channel field effect transistors having insulating layers thereon and methods of fabricating the same

ActiveUS20050145932A1Improve driving abilityTransistorSolid-state devicesEngineeringVertical channel

A field effect transistor can include a vertical channel protruding from a substrate including a source / drain region junction between the vertical channel and the substrate, and an insulating layer extending on a side wall of the vertical channel toward the substrate to beyond the source / drain region junction. The transistor can also include a nitride layer extending on the side wall away from the substrate to beyond the insulating layer, a second insulating layer extending on the side wall that is separated from the channel by the nitride layer, and a gate electrode extending on the side wall toward the substrate to beyond the source / drain region junction. Related methods are also disclosed.

Owner:HONDA MOTOR CO LTD +1

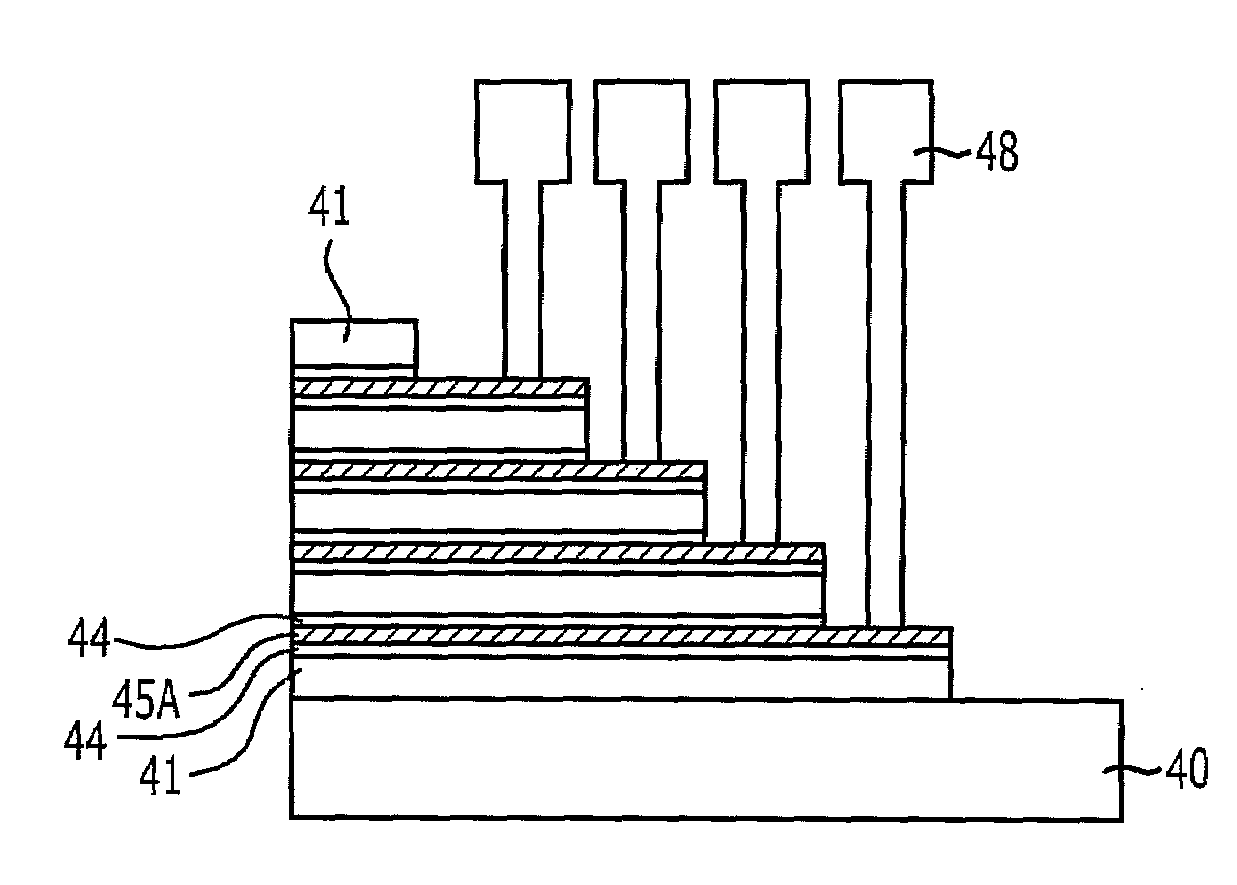

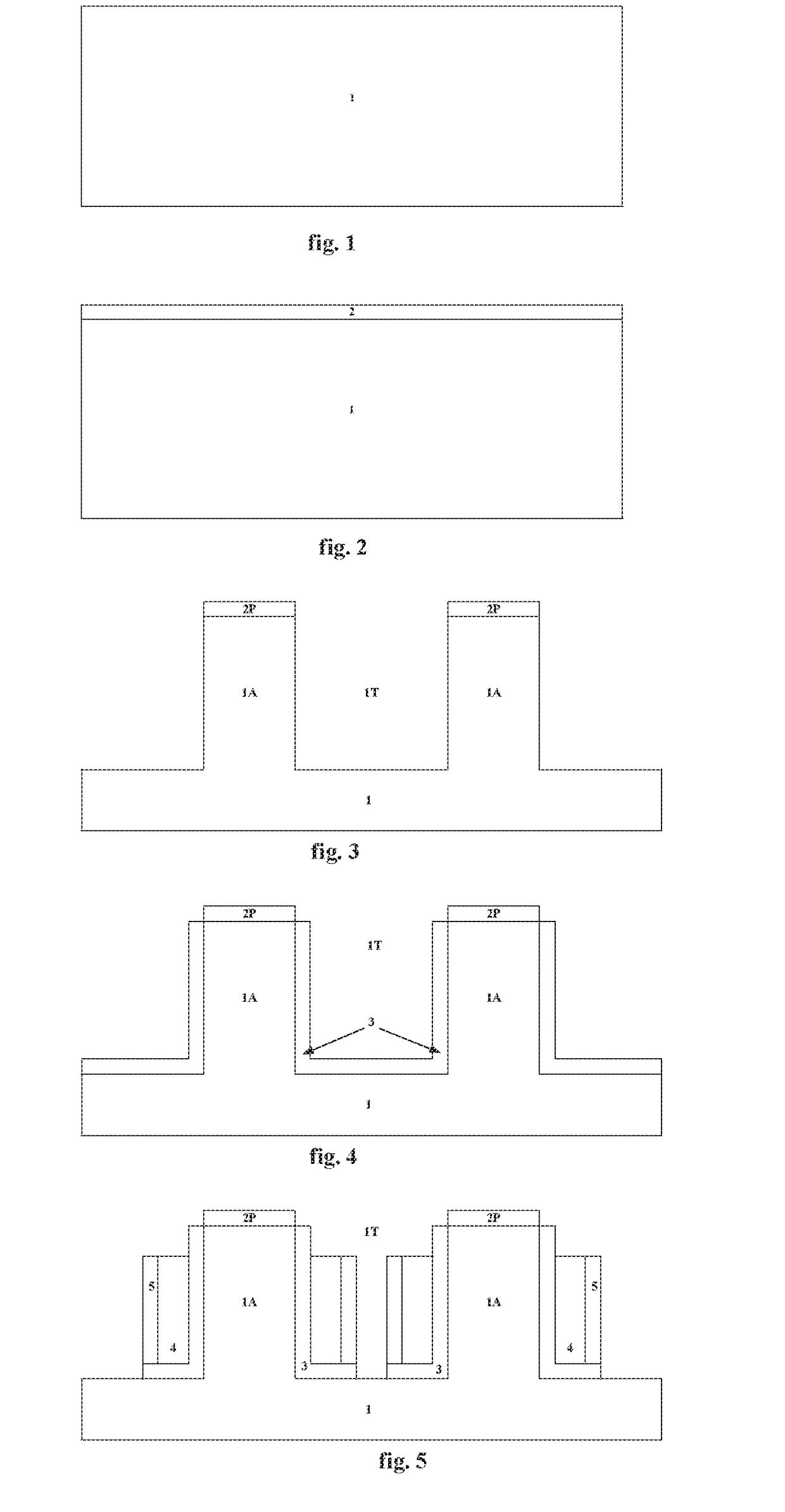

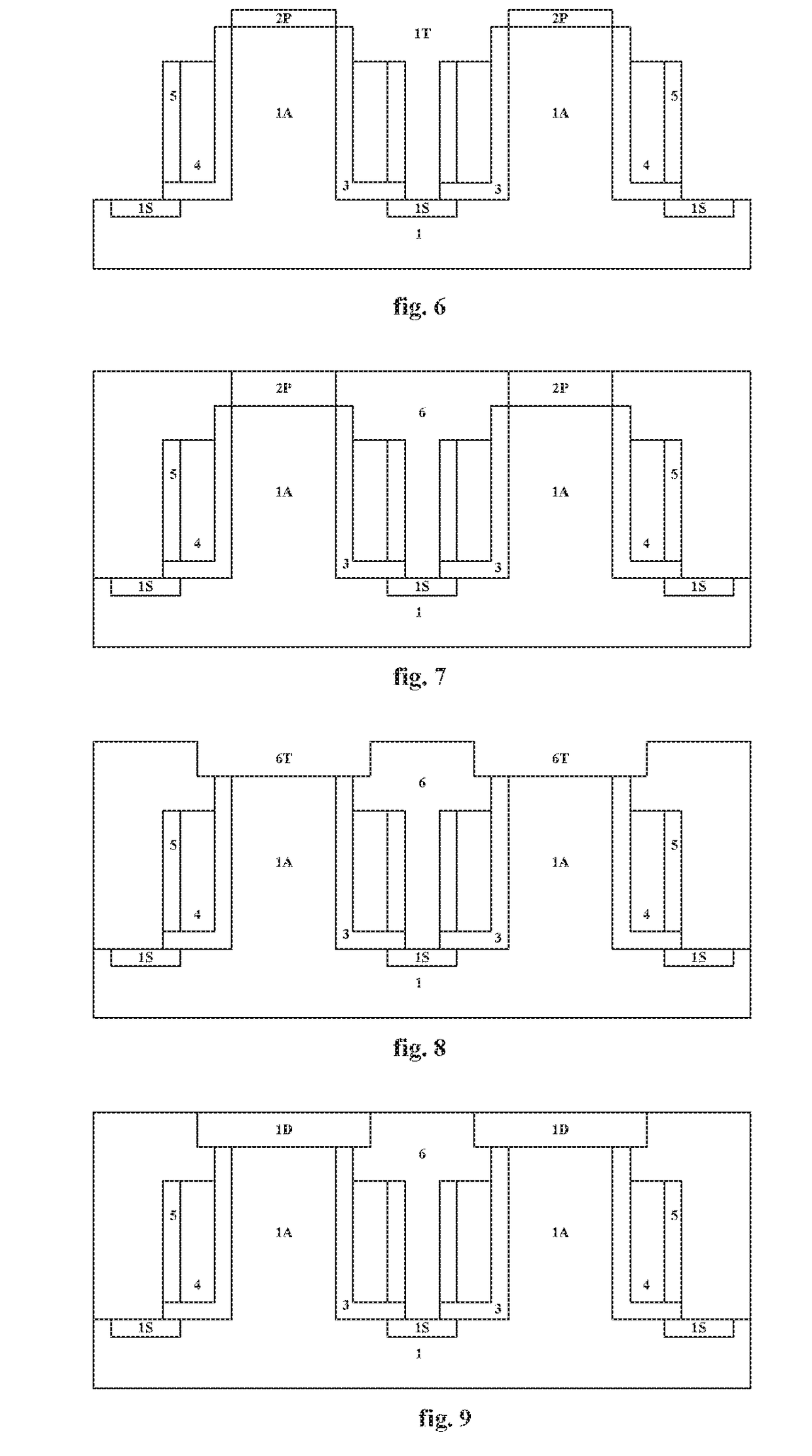

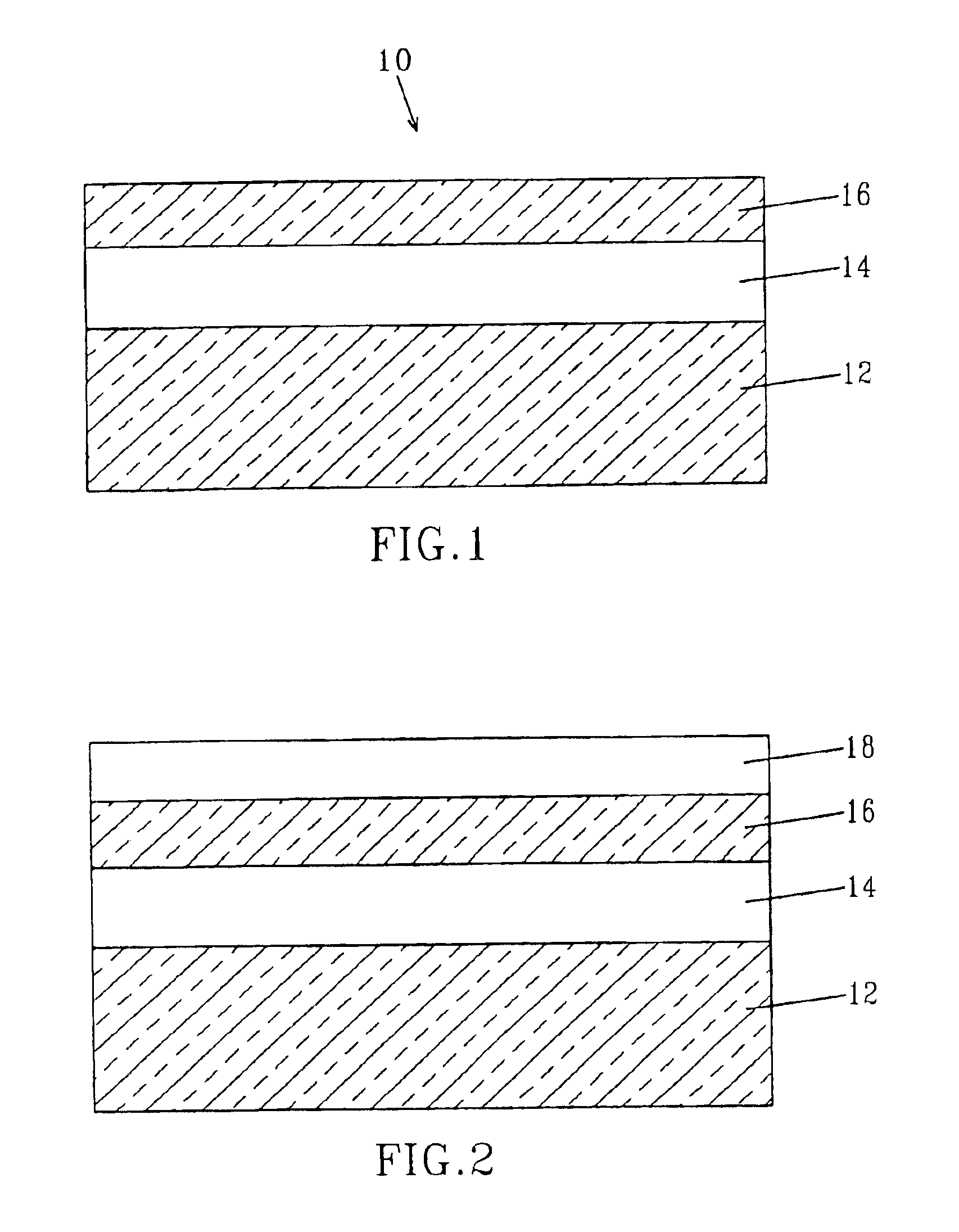

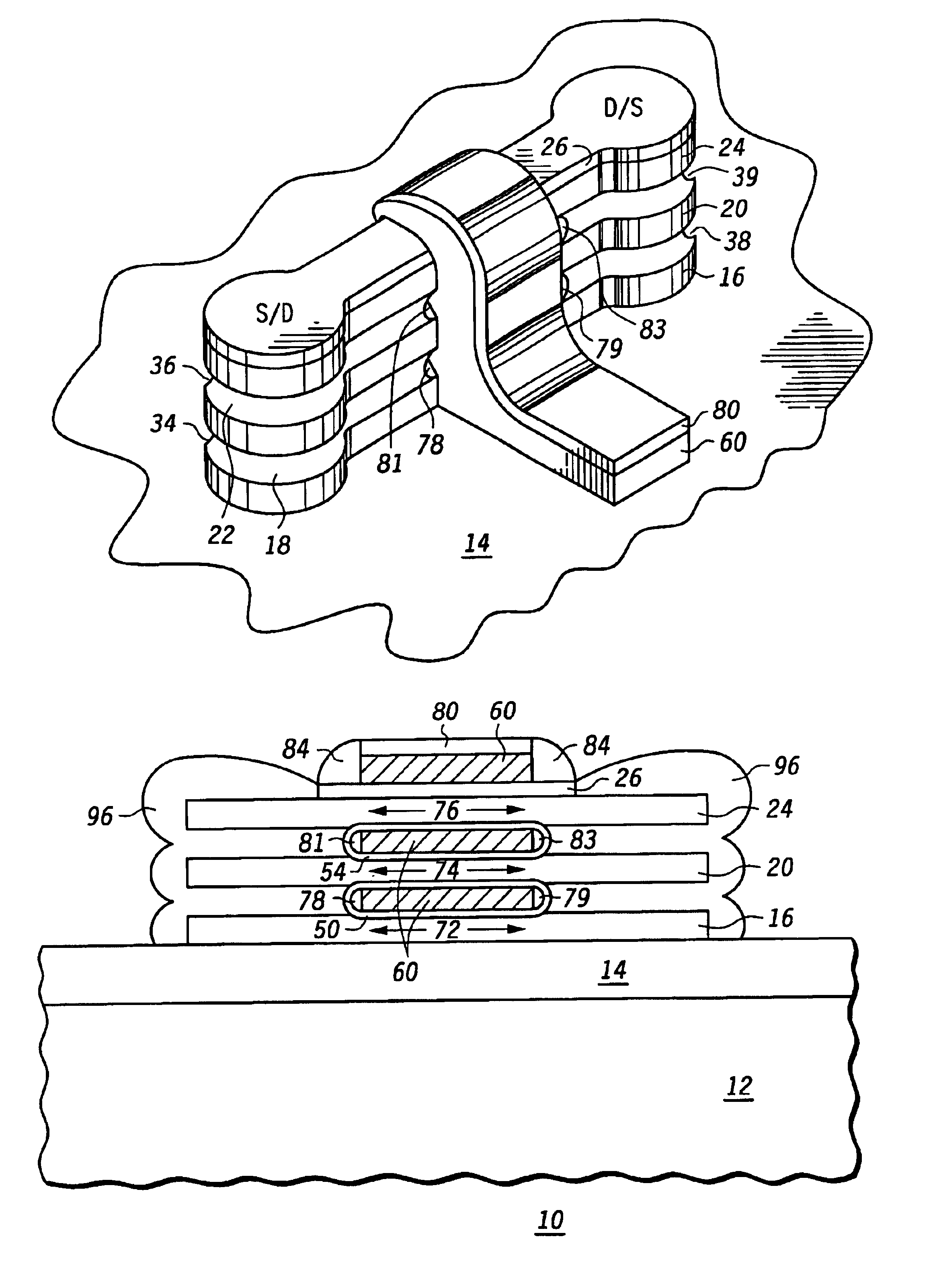

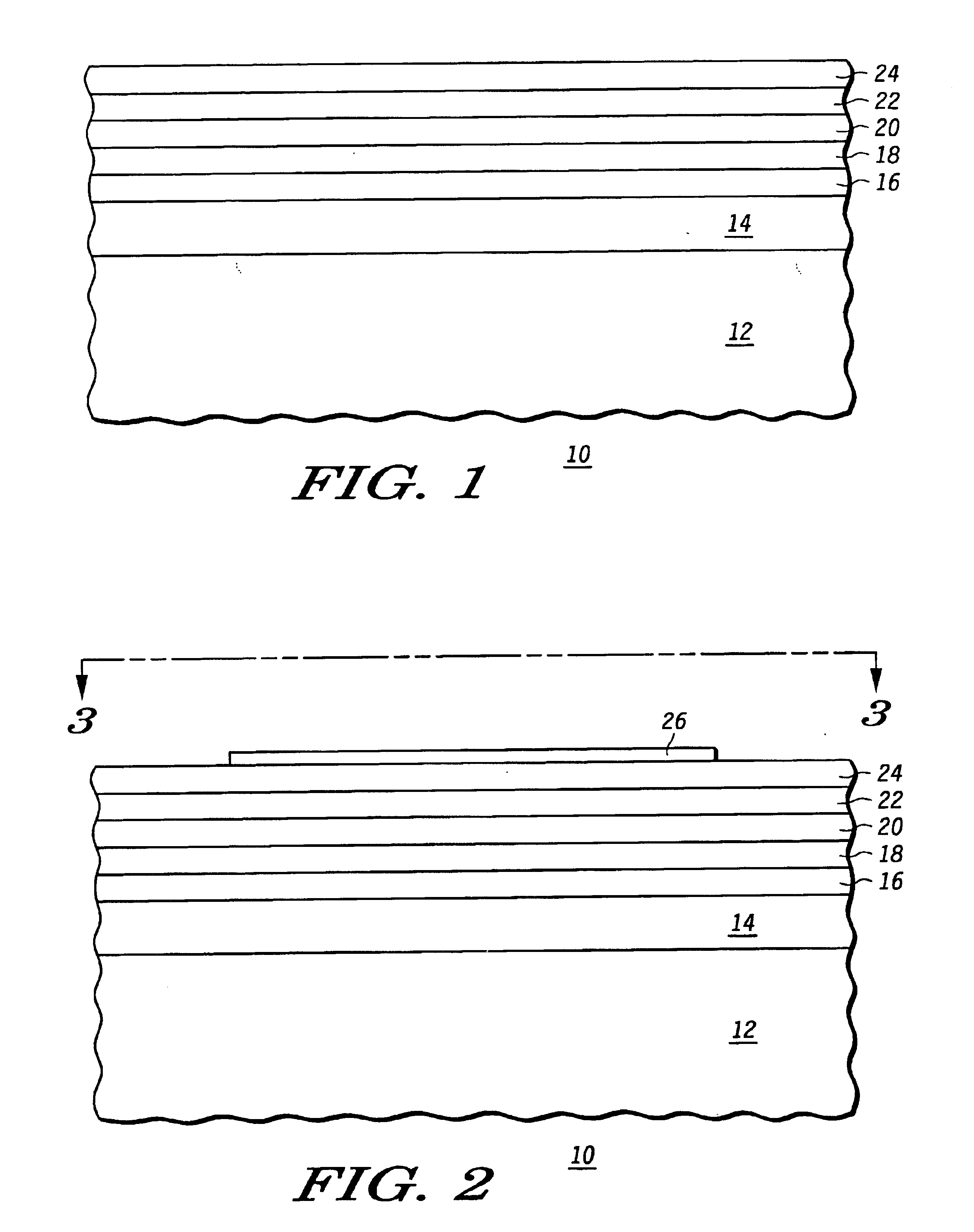

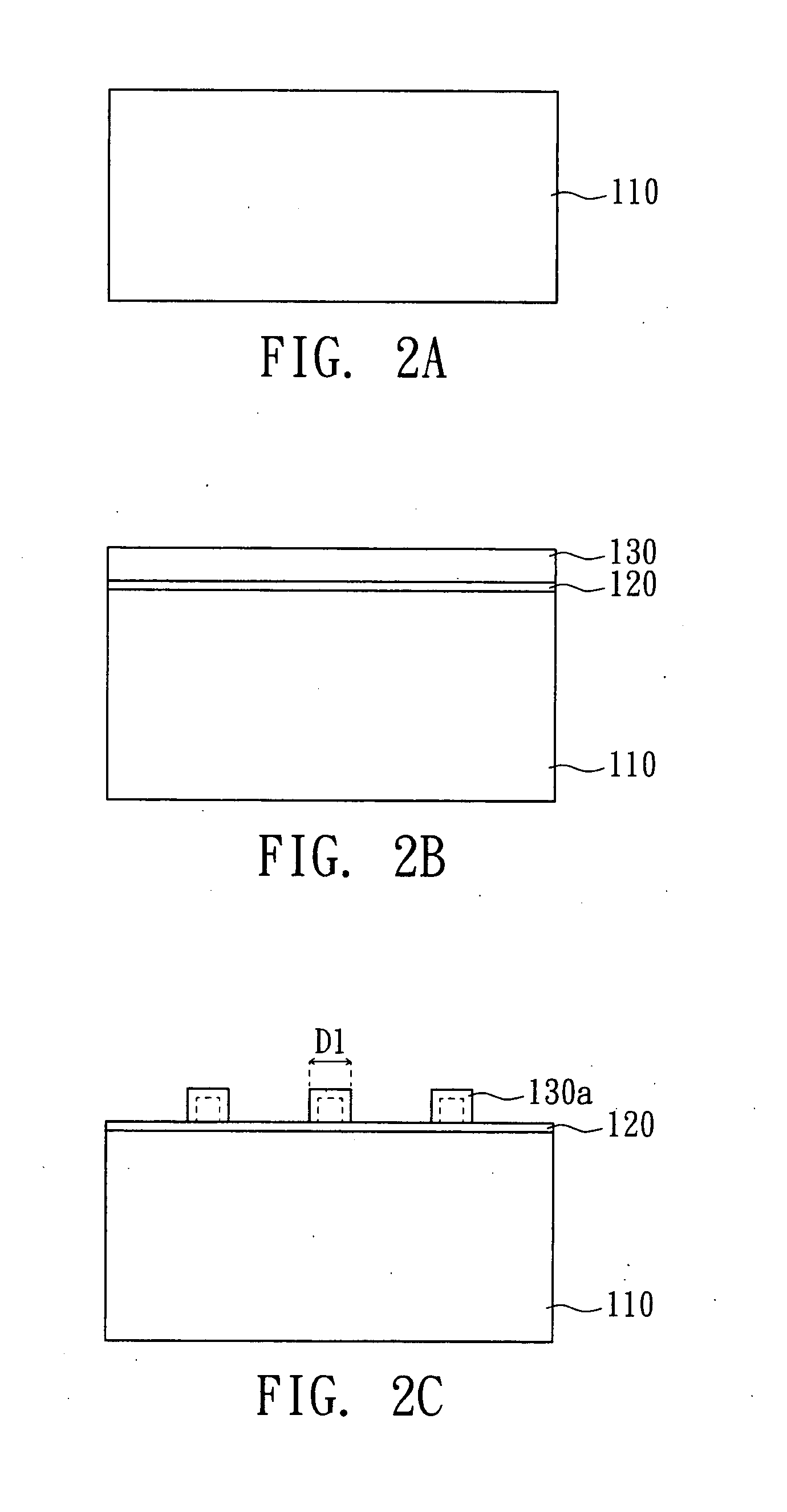

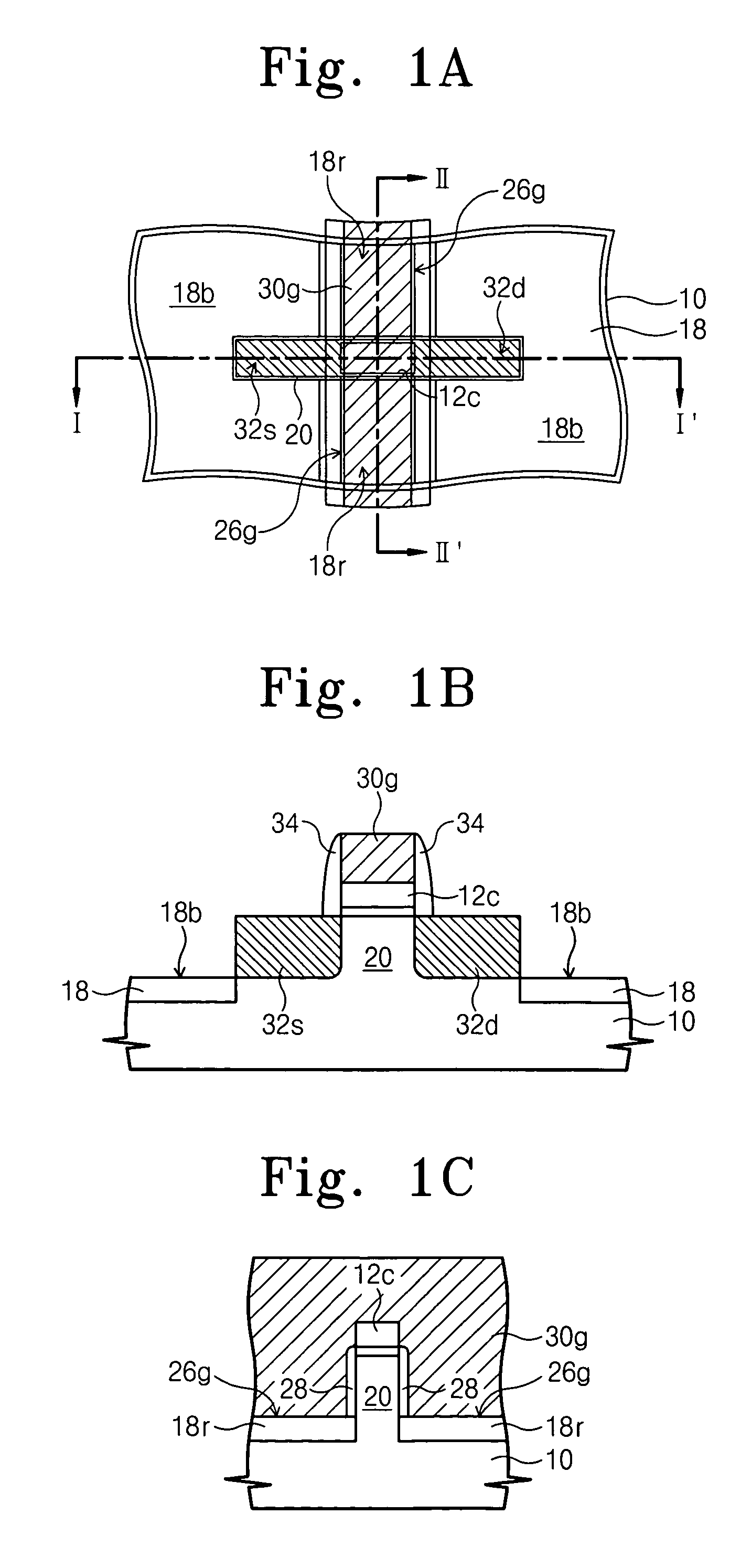

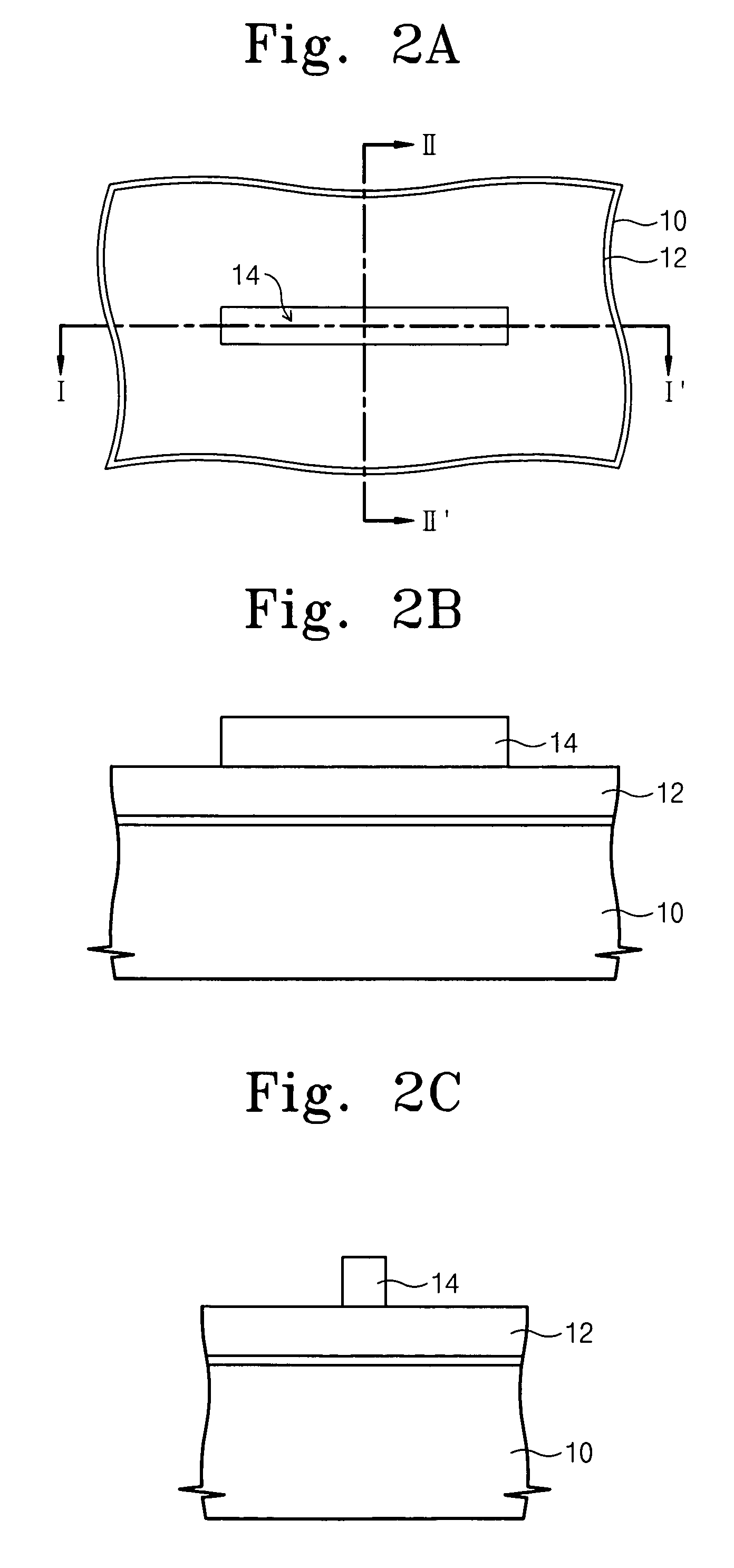

Method of forming a transistor having multiple channels

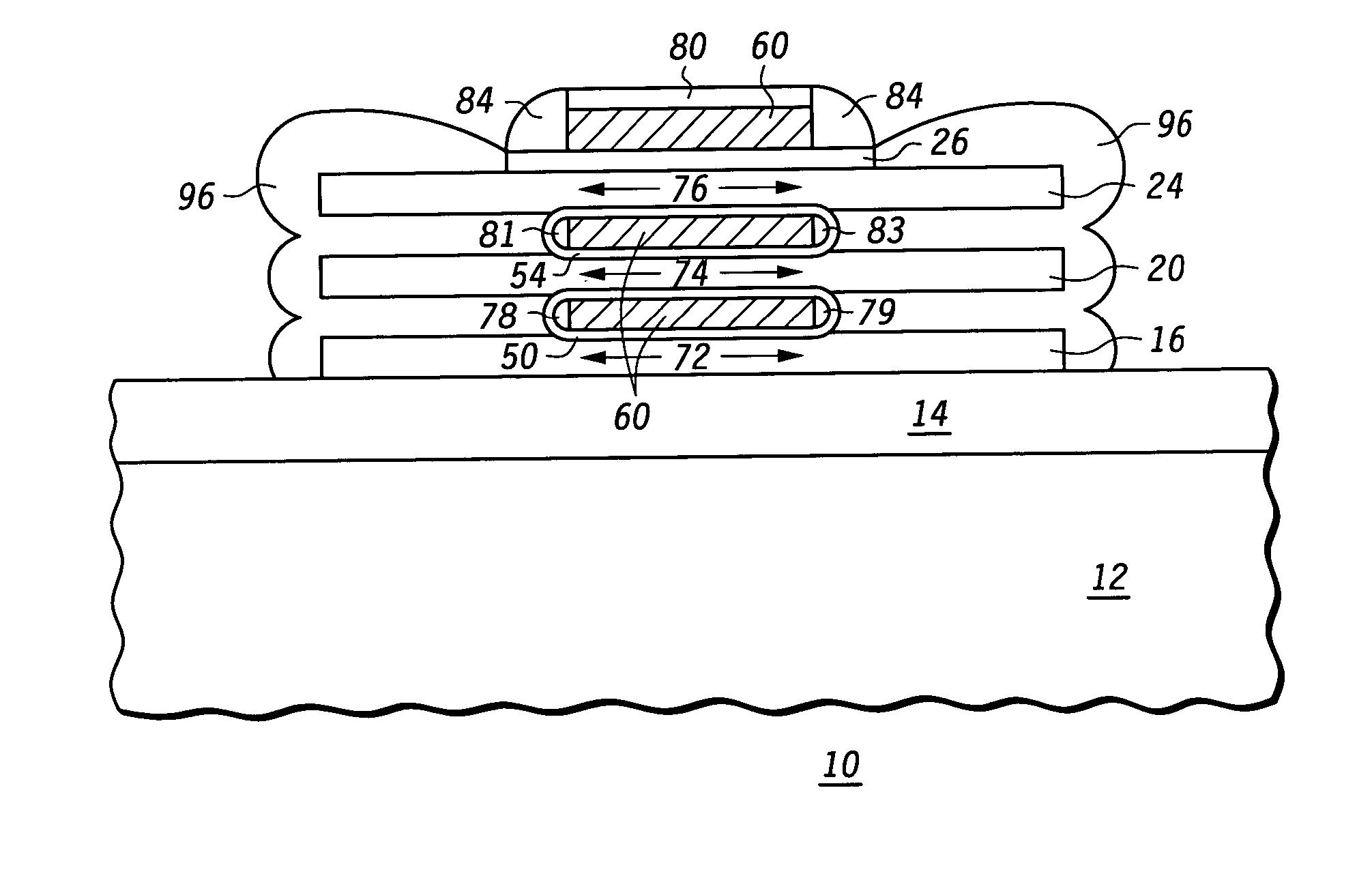

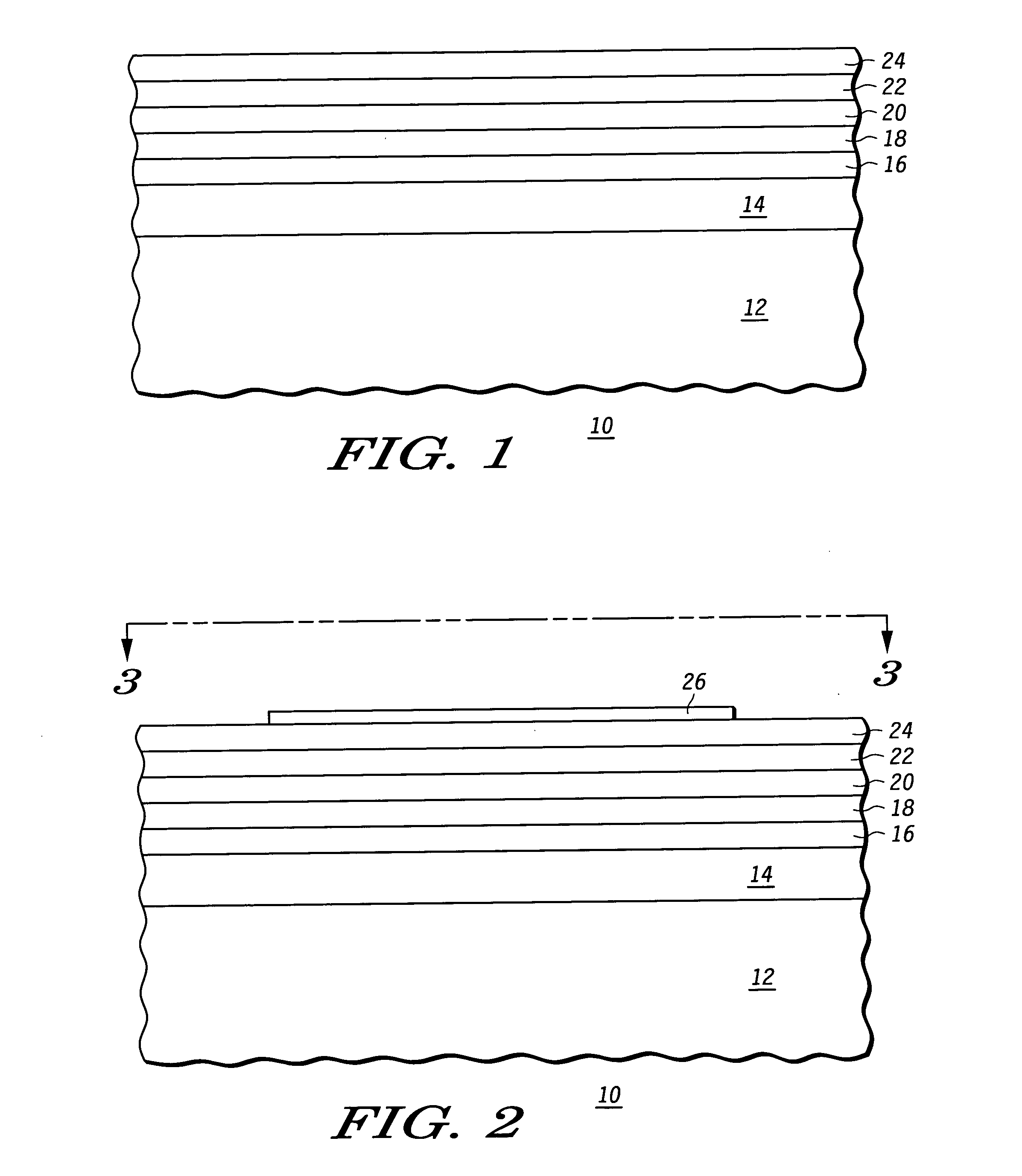

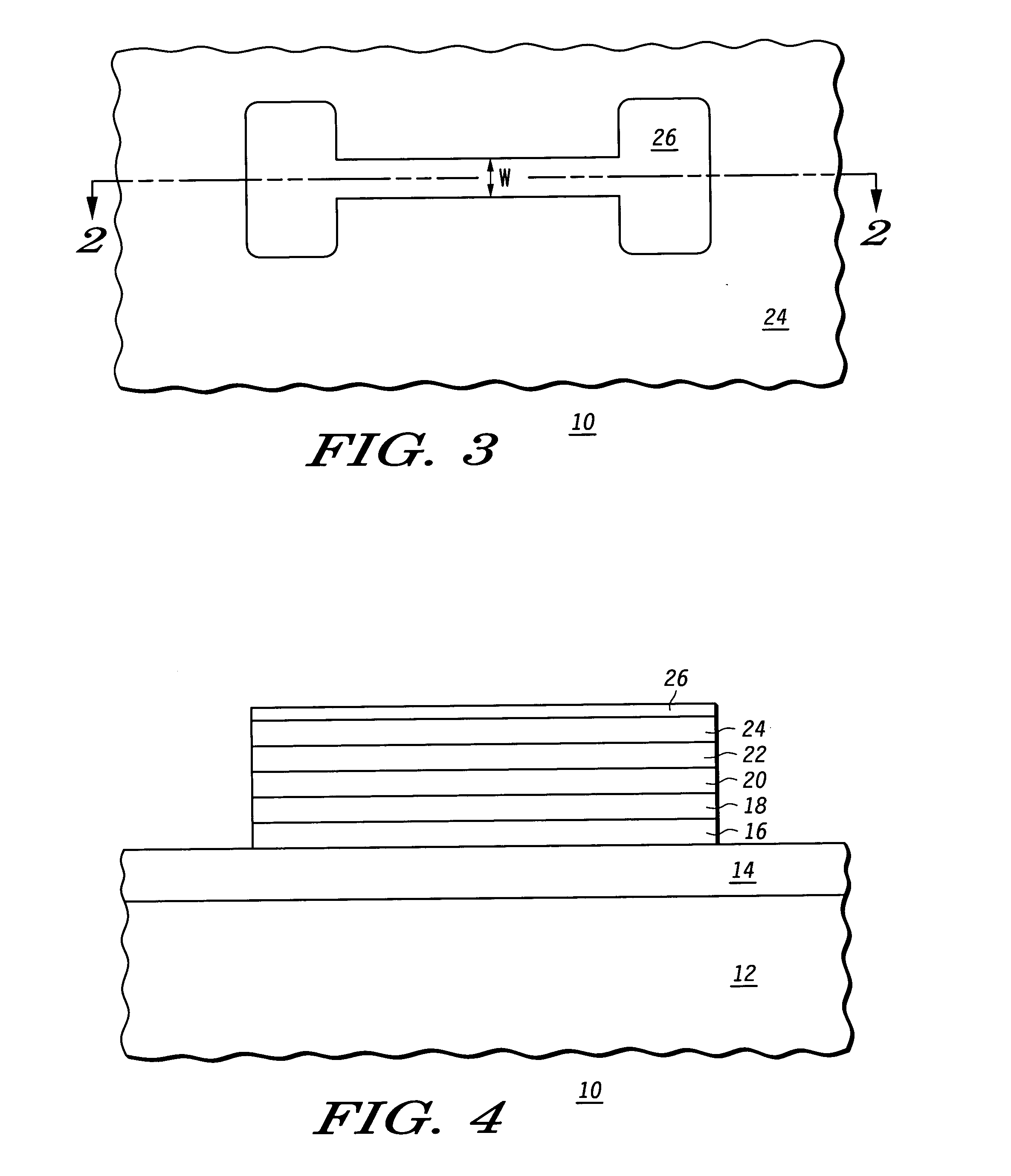

A transistor (10) overlies a substrate (12) and has a plurality of overlying channels (72, 74, 76) that are formed in a stacked arrangement. A continuous gate (60) material surrounds each of the channels. Each of the channels is coupled to source and drain electrodes (S / D) to provide increased channel surface area in a same area that a single channel structure is conventionally implemented. A vertical channel dimension between two regions of the gate (60) are controlled by a growth process as opposed to lithographical or spacer formation techniques. The gate is adjacent all sides of the multiple overlying channels. Each channel is formed by growth from a common seed layer and the source and drain electrodes and the channels are formed of a substantially homogenous crystal lattice.

Owner:TAIWAN SEMICON MFG CO LTD

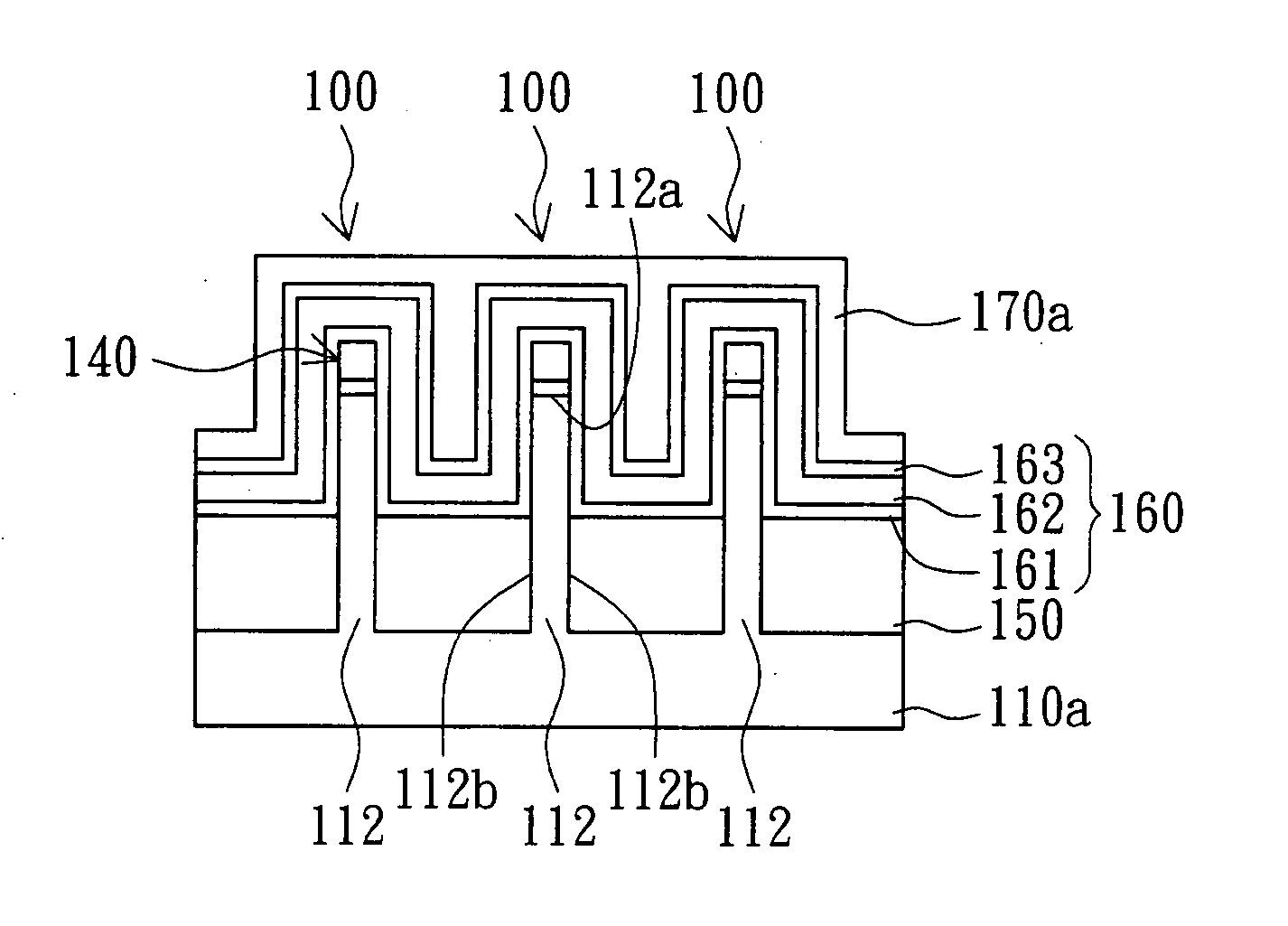

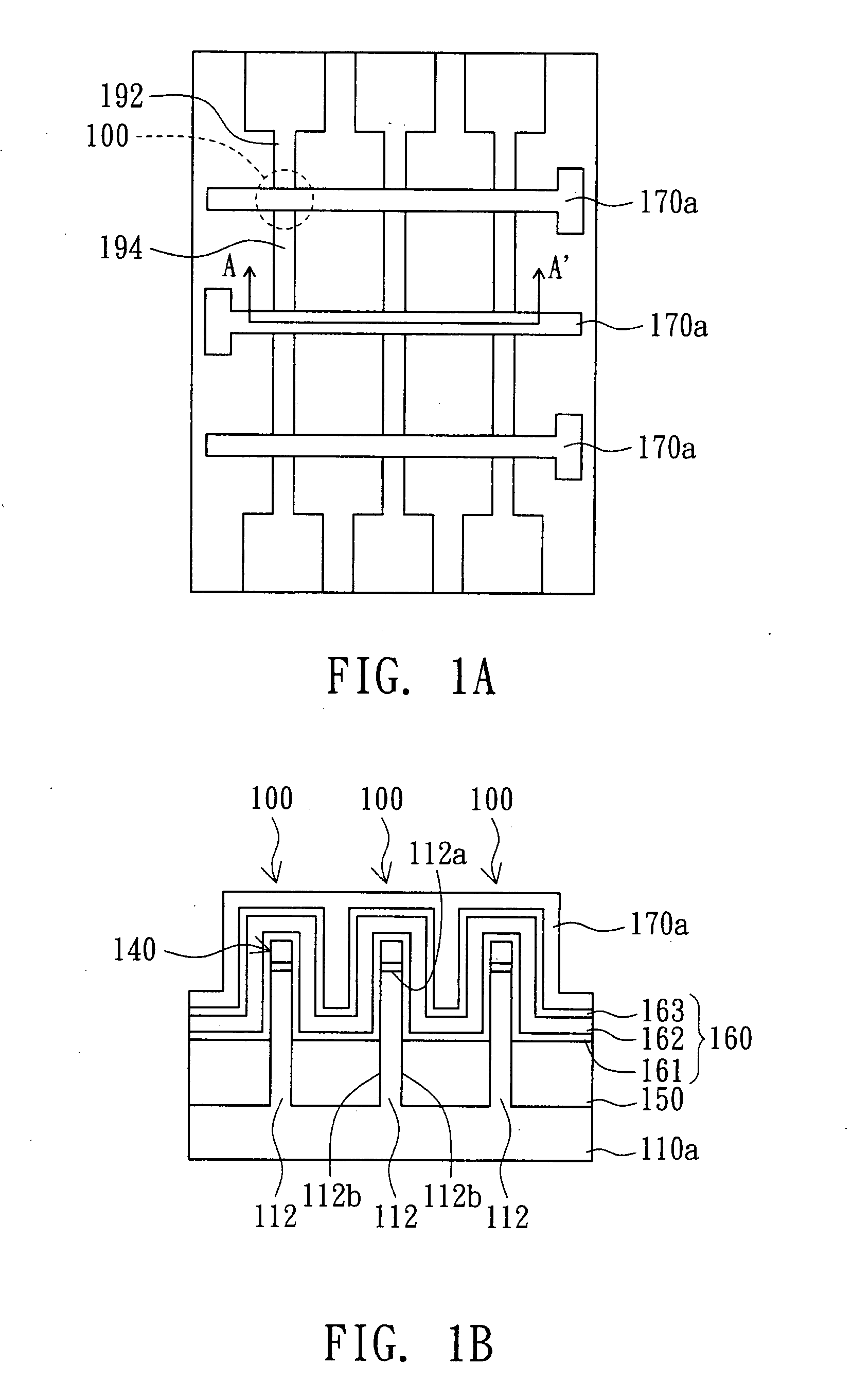

Vertical channel memory and manufacturing method thereof and operating method using the same

ActiveUS20080087942A1Increase currentSmall dimensionSolid-state devicesRead-only memoriesEngineeringVertical channel

A vertical channel memory including a substrate, a channel, a multi-layer structure, a gate, a first terminal and a second terminal is provided. The channel is protruded from the substrate and has a top surface and two vertical surfaces. The multi-layer structure is disposed on the two vertical surfaces of the channel. The gate straddling multi-layer structure is positioned above the two vertical surfaces of the channel. The first terminal and the second terminal are respectively positioned at two sides of the channel opposing to the gate.

Owner:MACRONIX INT CO LTD

Method of forming a transistor having multiple channels and structure thereof

A transistor (10) overlies a substrate (12) and has a plurality of overlying channels (72, 74, 76) that are formed in a stacked arrangement. A continuous gate (60) material surrounds each of the channels. Each of the channels is coupled to source and drain electrodes (S / D) to provide increased channel surface area in a same area that a single channel structure is conventionally implemented. A vertical channel dimension between two regions of the gate (60) are controlled by a growth process as opposed to lithographical or spacer formation techniques. The gate is adjacent all sides of the multiple overlying channels. Each channel is formed by growth from a common seed layer and the source and drain electrodes and the channels are formed of a substantially homogenous crystal lattice.

Owner:TAIWAN SEMICON MFG CO LTD

Method for forming a transistor having gate dielectric protection and structure

A transistor structure is formed by providing a semiconductor substrate and providing a gate above the semiconductor substrate. The gate is separated from the semiconductor substrate by a gate insulating layer. A source and a drain are provided adjacent the gate to define a transistor channel underlying the gate and separated from the gate by the gate insulating layer. A barrier layer is formed by applying nitrogen or carbon on opposing outer vertical sides of the transistor channel between the transistor channel and each of the source and the drain. In each of the nitrogen and the carbon embodiments, the vertical channel barrier retards diffusion of the source / drain dopant species into the transistor channel. There are methods for forming the transistor structure.

Owner:NORTH STAR INNOVATIONS

Vertical channel fin field-effect transistors having increased source/drain contact area and methods for fabricating the same

InactiveUS20050186742A1TransistorSemiconductor/solid-state device manufacturingContact formationEngineering

A fin field-effect transistor (FinFET) device includes a fin-shaped active region having first and second source / drain regions therein and a channel region therebetween vertically protruding from a semiconductor substrate. A gate electrode is formed on an upper surface and sidewalls of the channel region. First and second source / drain contacts are formed on respective upper surfaces and sidewalls of the first and second source / drain regions of the fin-shaped active region at opposite sides of the gate electrode. The channel region may be narrower than the first and second source / drain regions of the fin-shaped active region.

Owner:SAMSUNG ELECTRONICS CO LTD