Patents

Literature

749 results about "Carbon doped" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

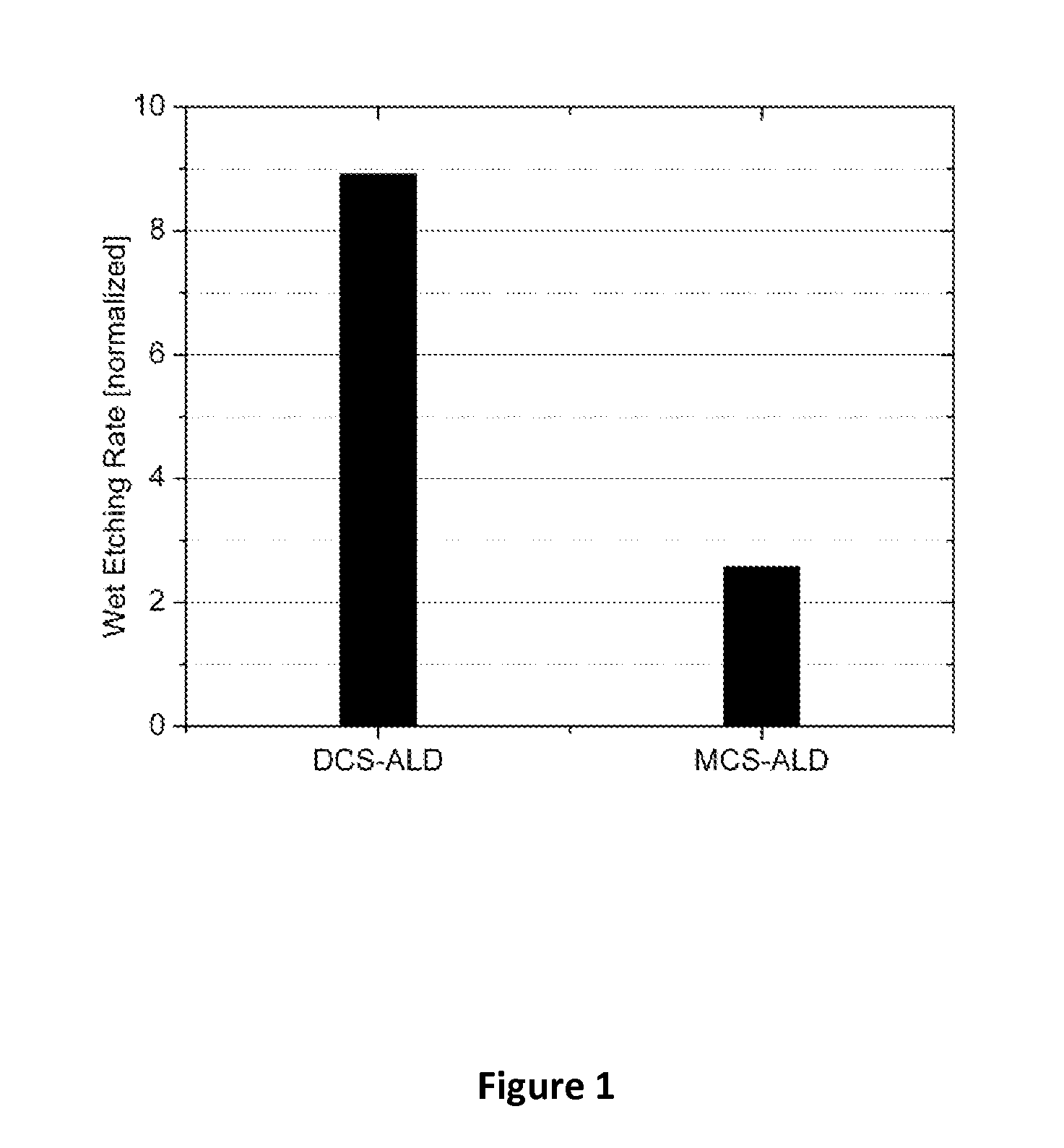

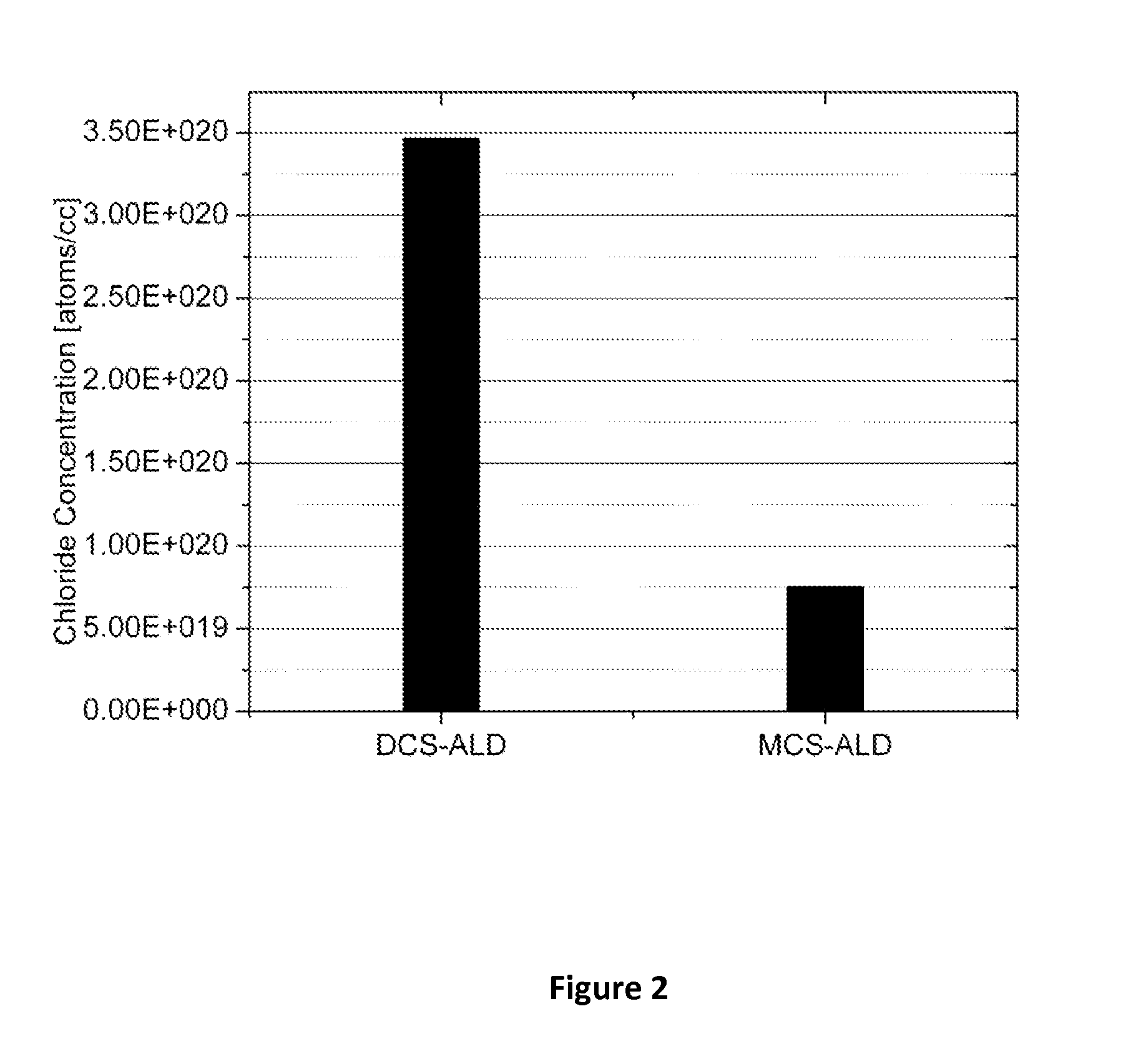

Low Temperature Deposition of Silicon-Containing Films

ActiveUS20100304047A1Low deposition temperatureSemiconductor/solid-state device manufacturingSpecial surfacesLow temperature depositionDeposition temperature

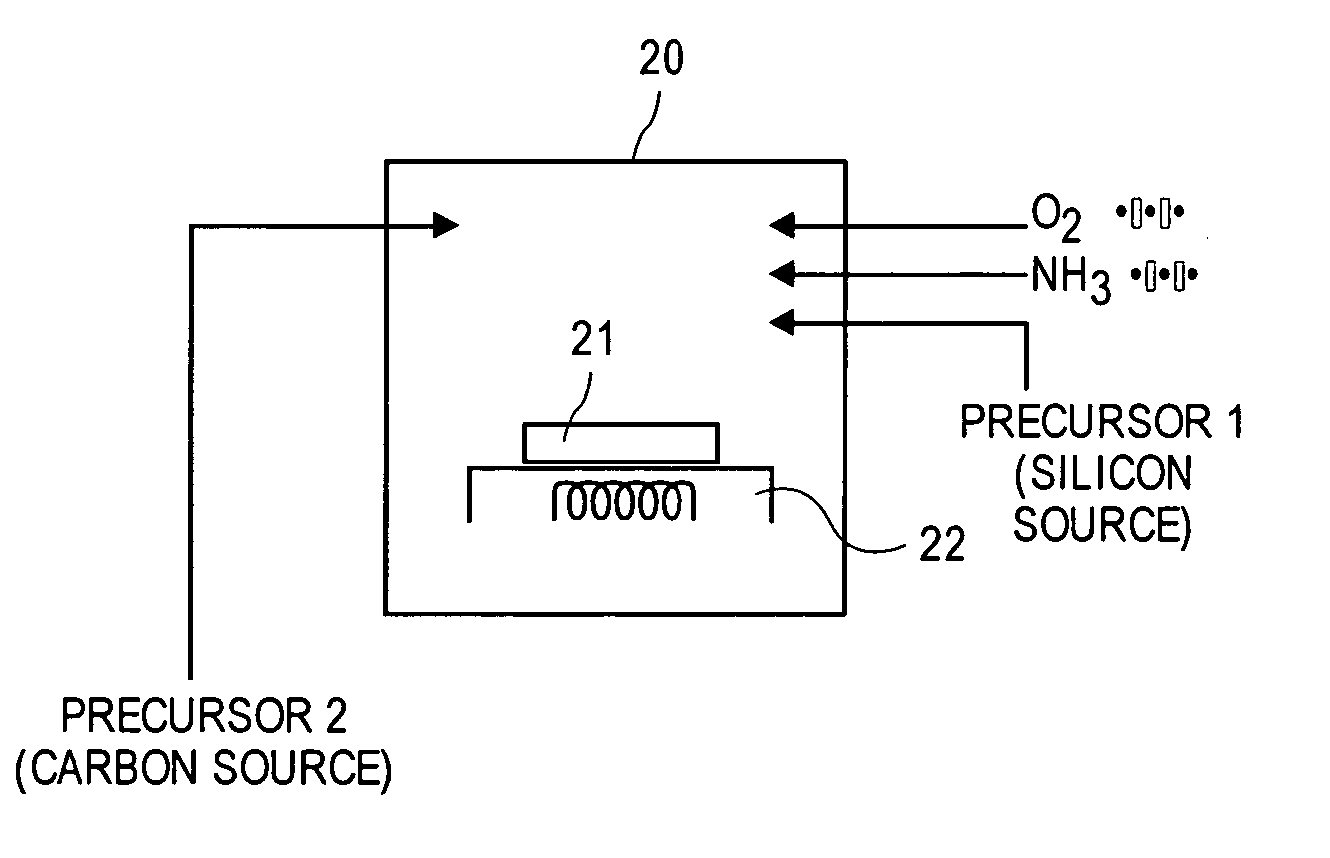

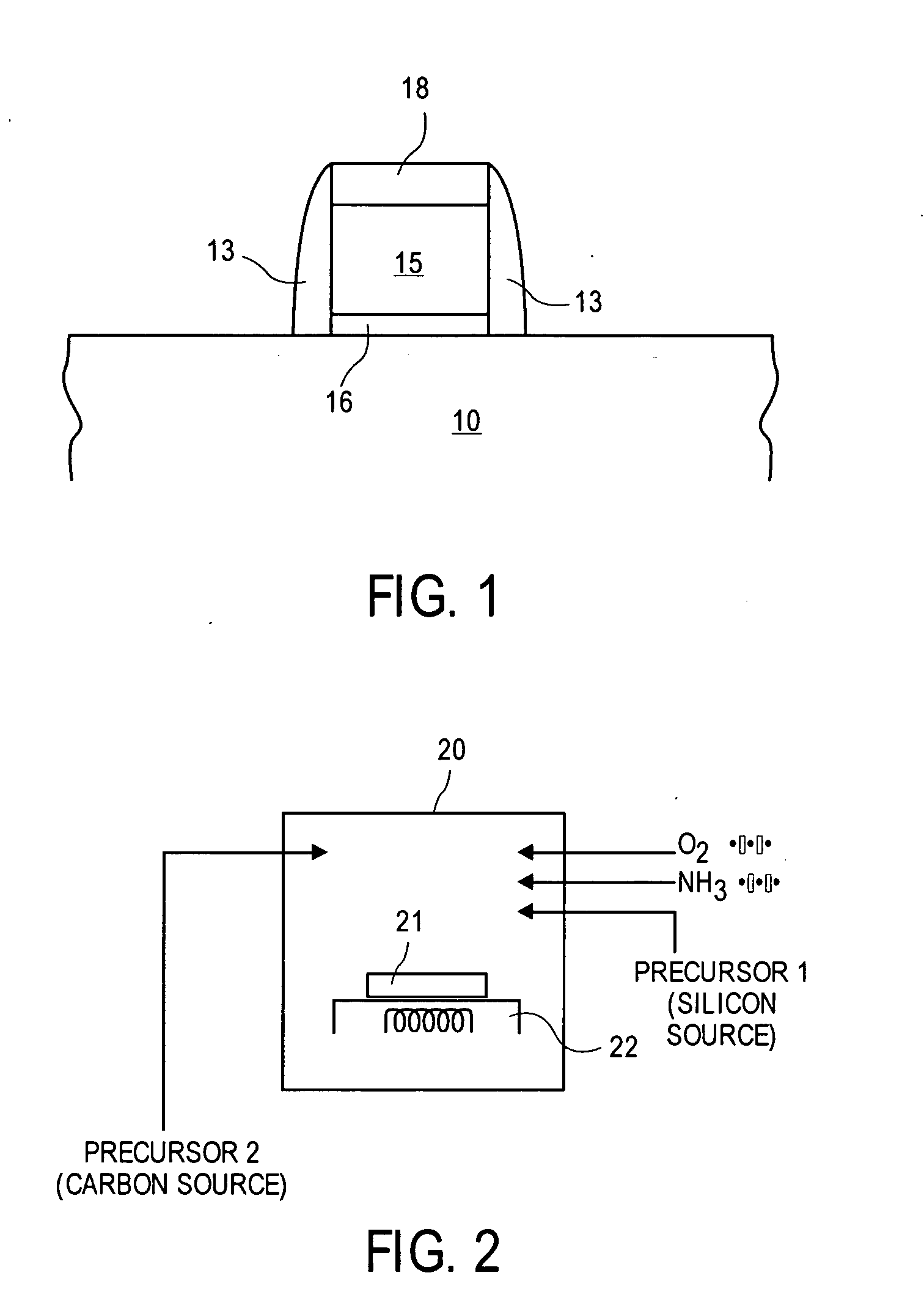

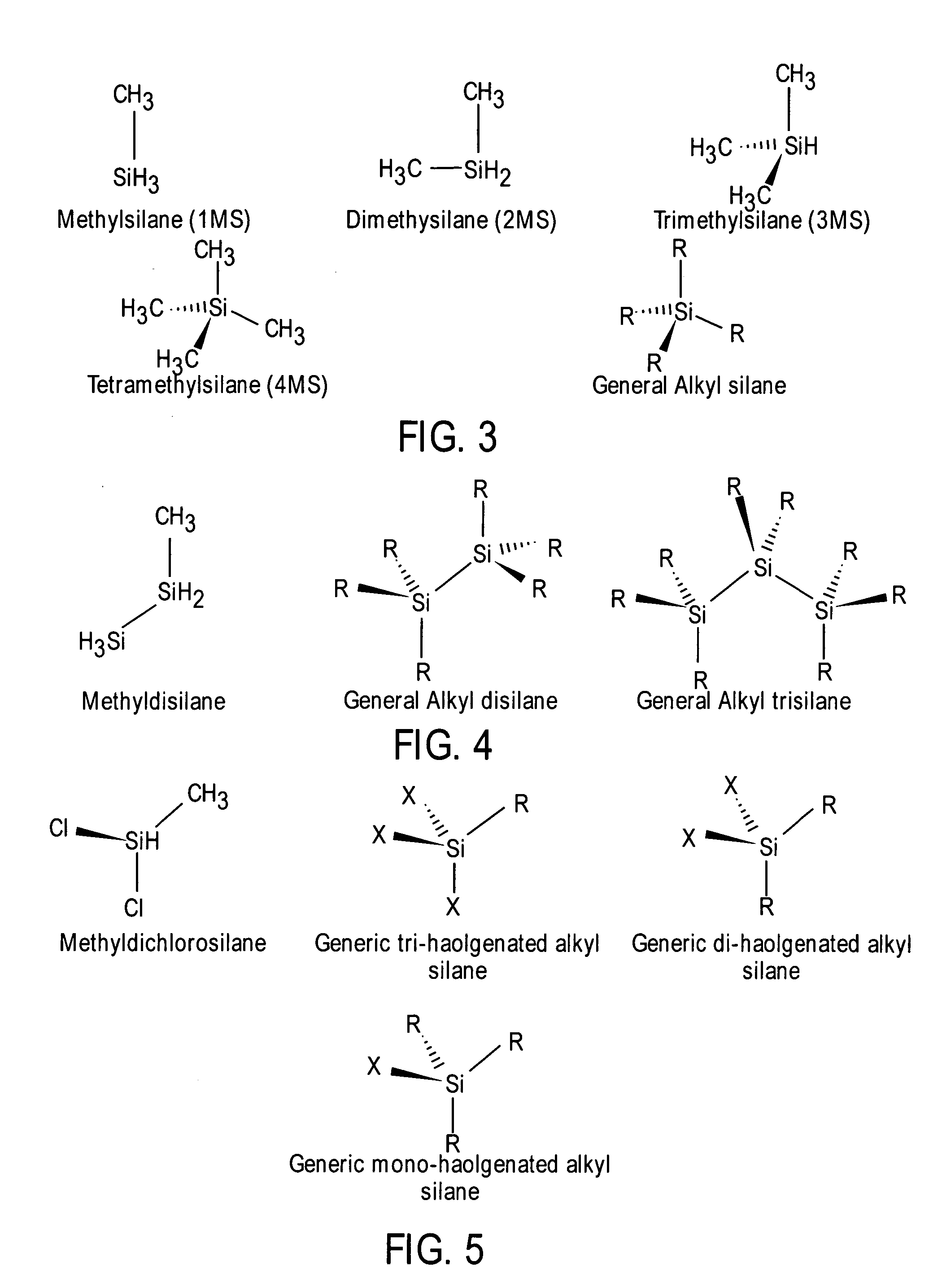

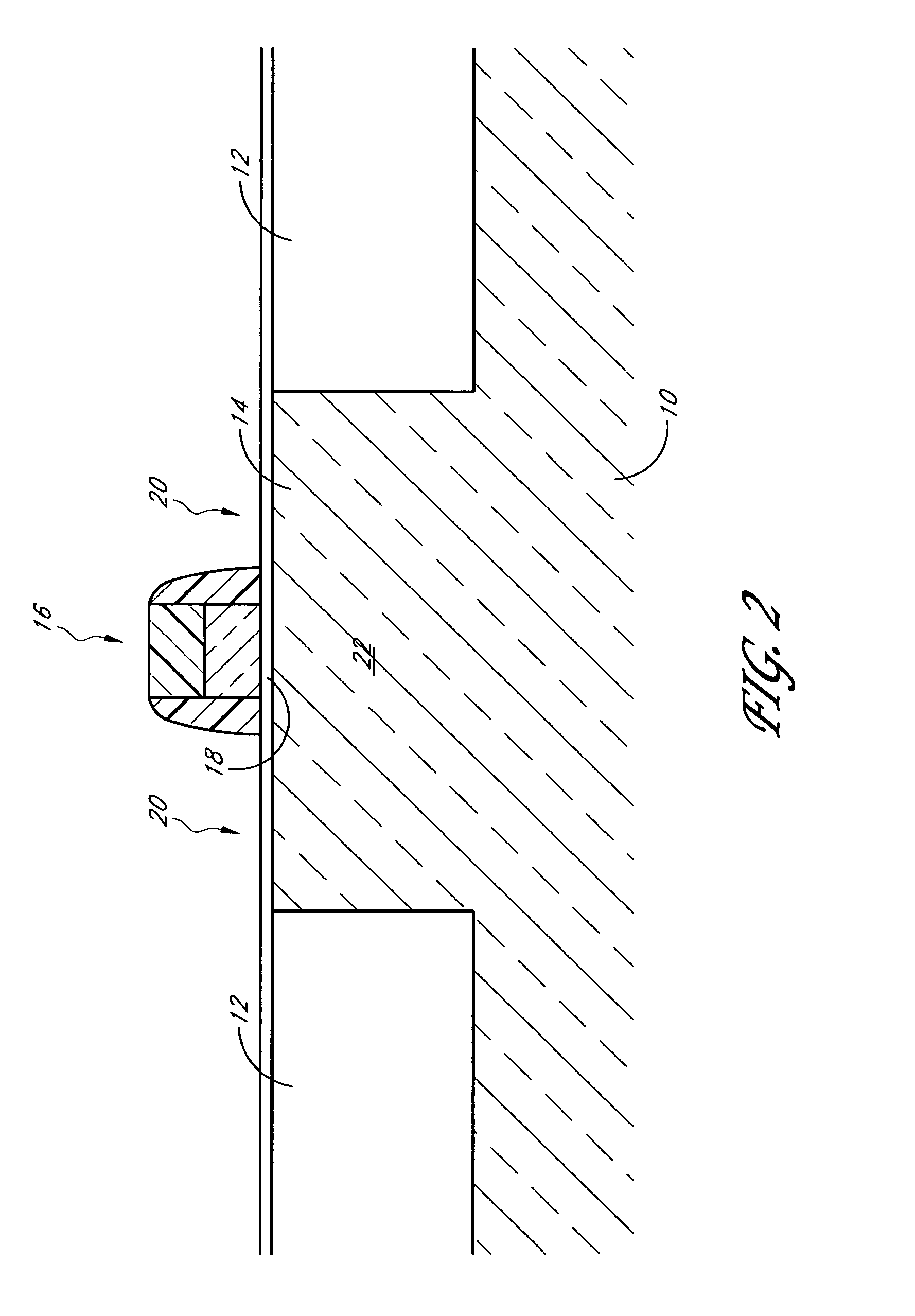

This invention discloses the method of forming silicon nitride, silicon oxynitride, silicon oxide, carbon-doped silicon nitride, carbon-doped silicon oxide and carbon-doped oxynitride films at low deposition temperatures. The silicon containing precursors used for the deposition are monochlorosilane (MCS) and monochloroalkylsilanes. The method is preferably carried out by using plasma enhanced atomic layer deposition, plasma enhanced chemical vapor deposition, and plasma enhanced cyclic chemical vapor deposition.

Owner:TOKYO ELECTRON LTD +1

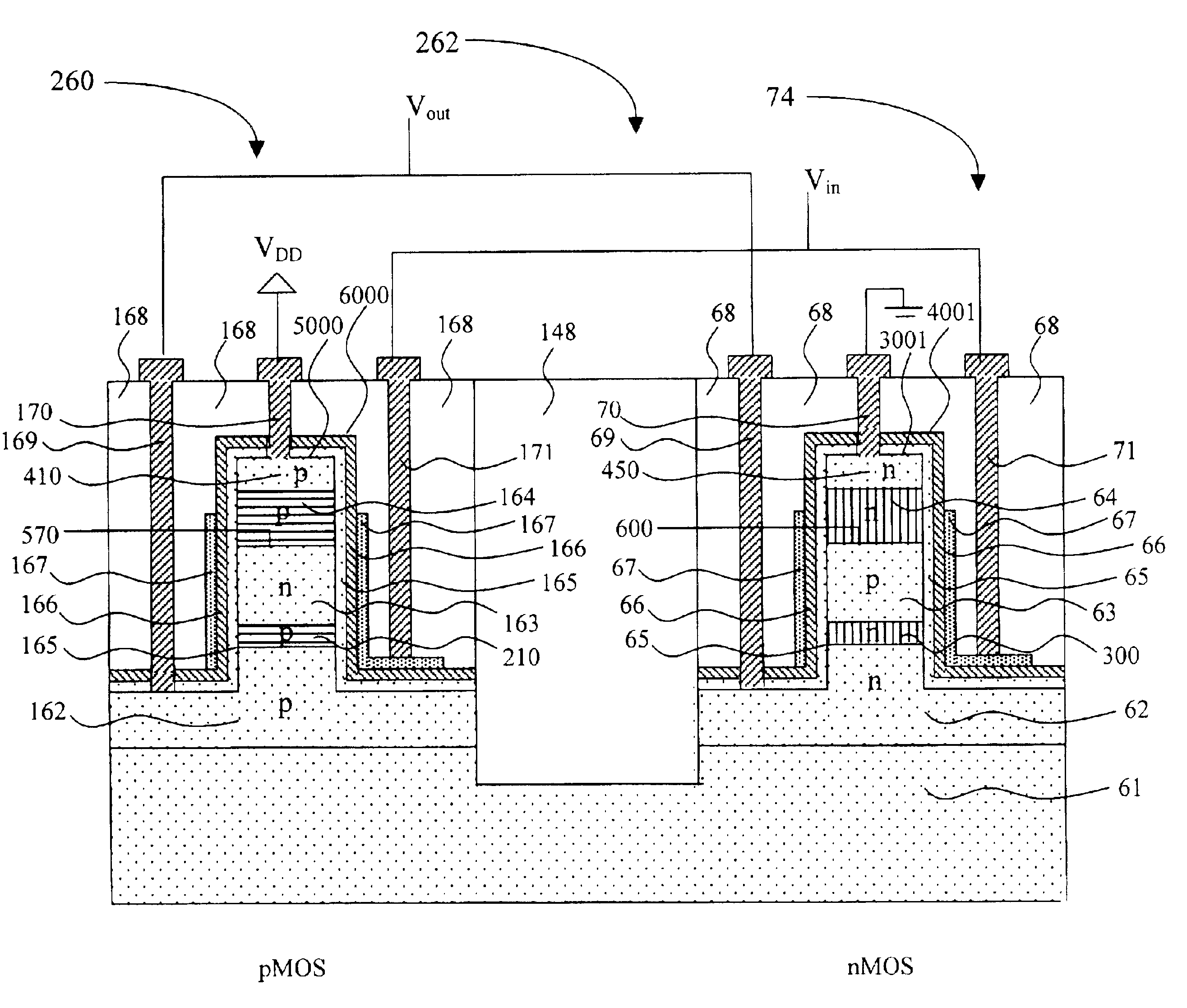

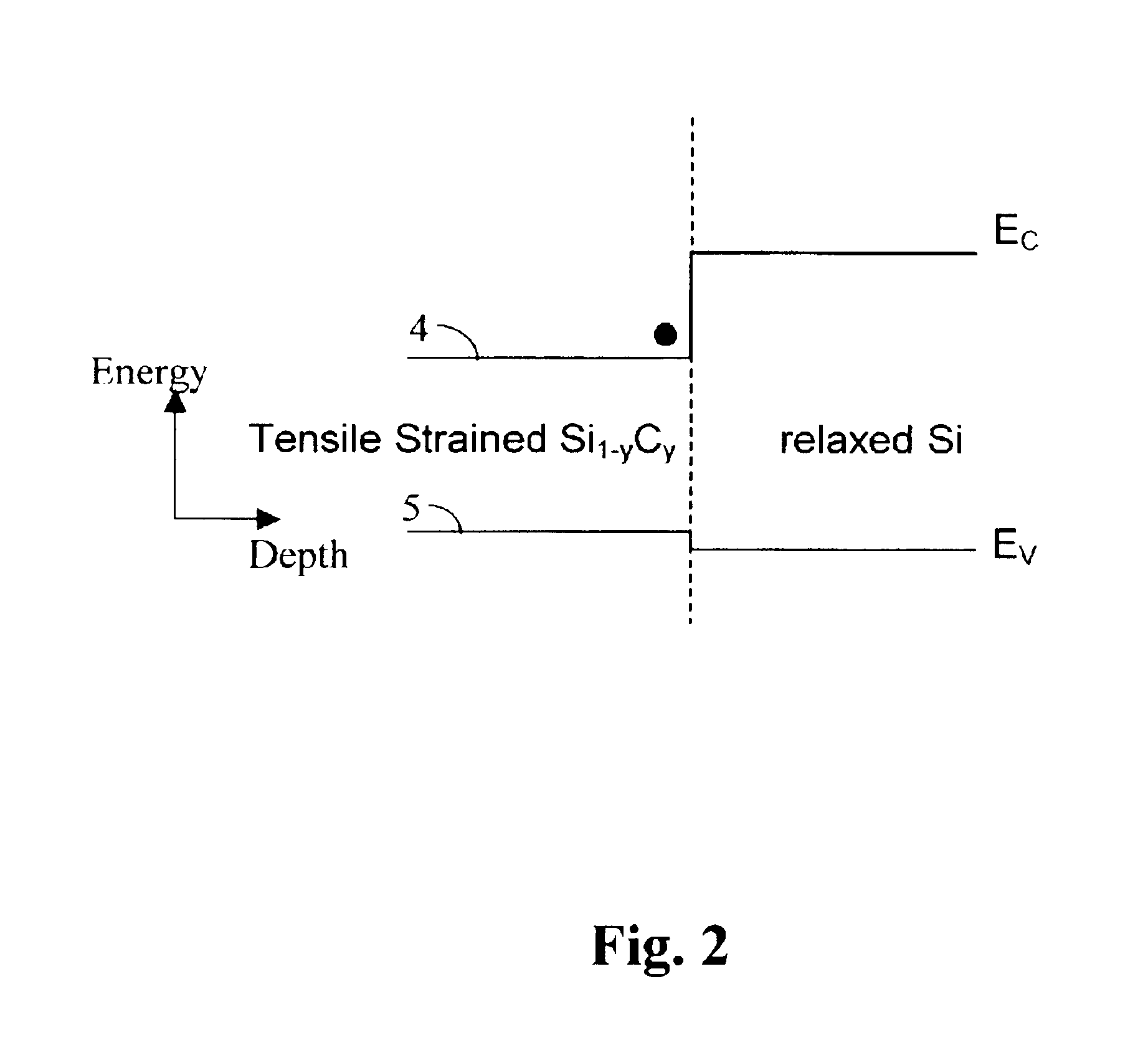

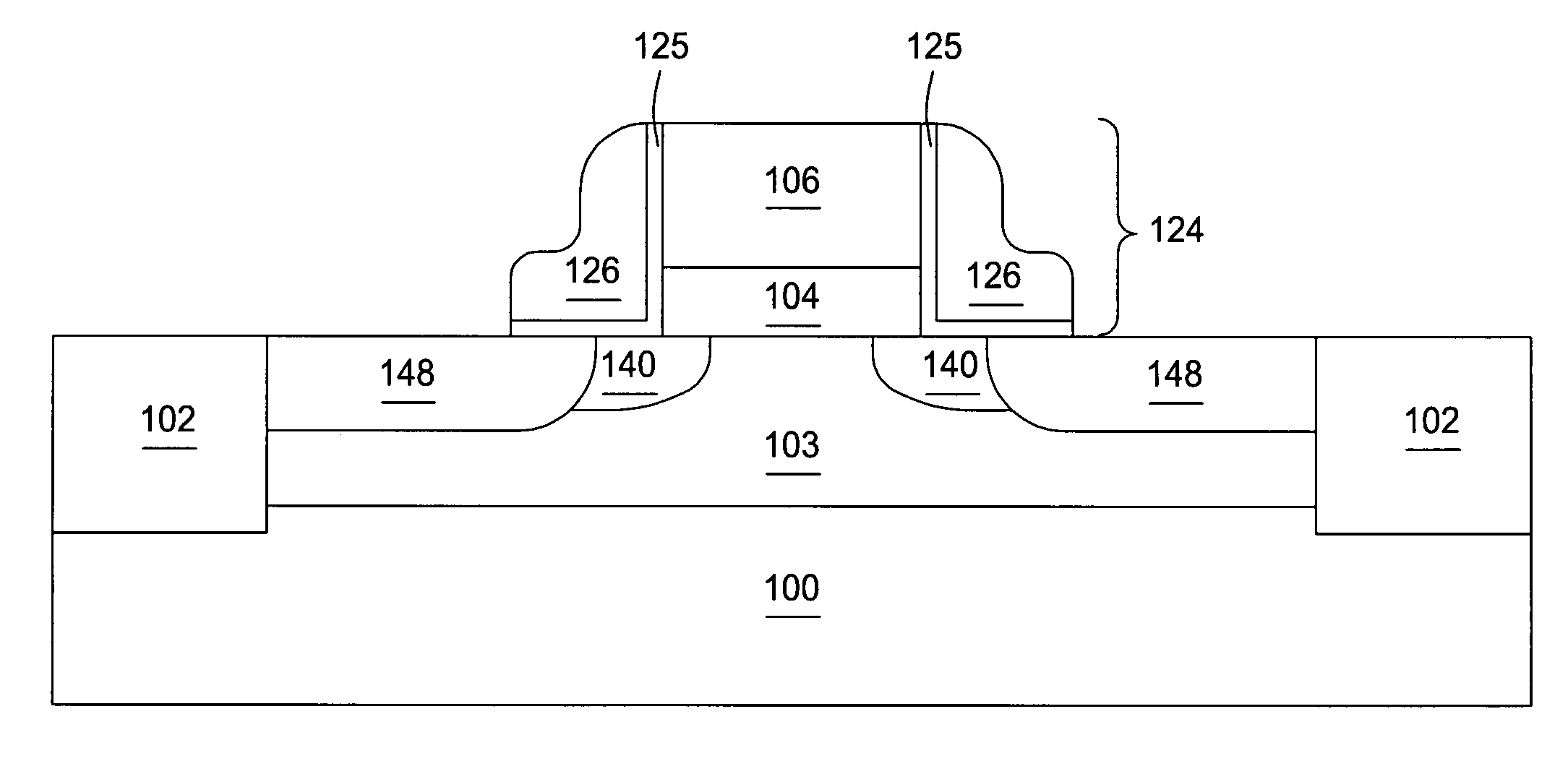

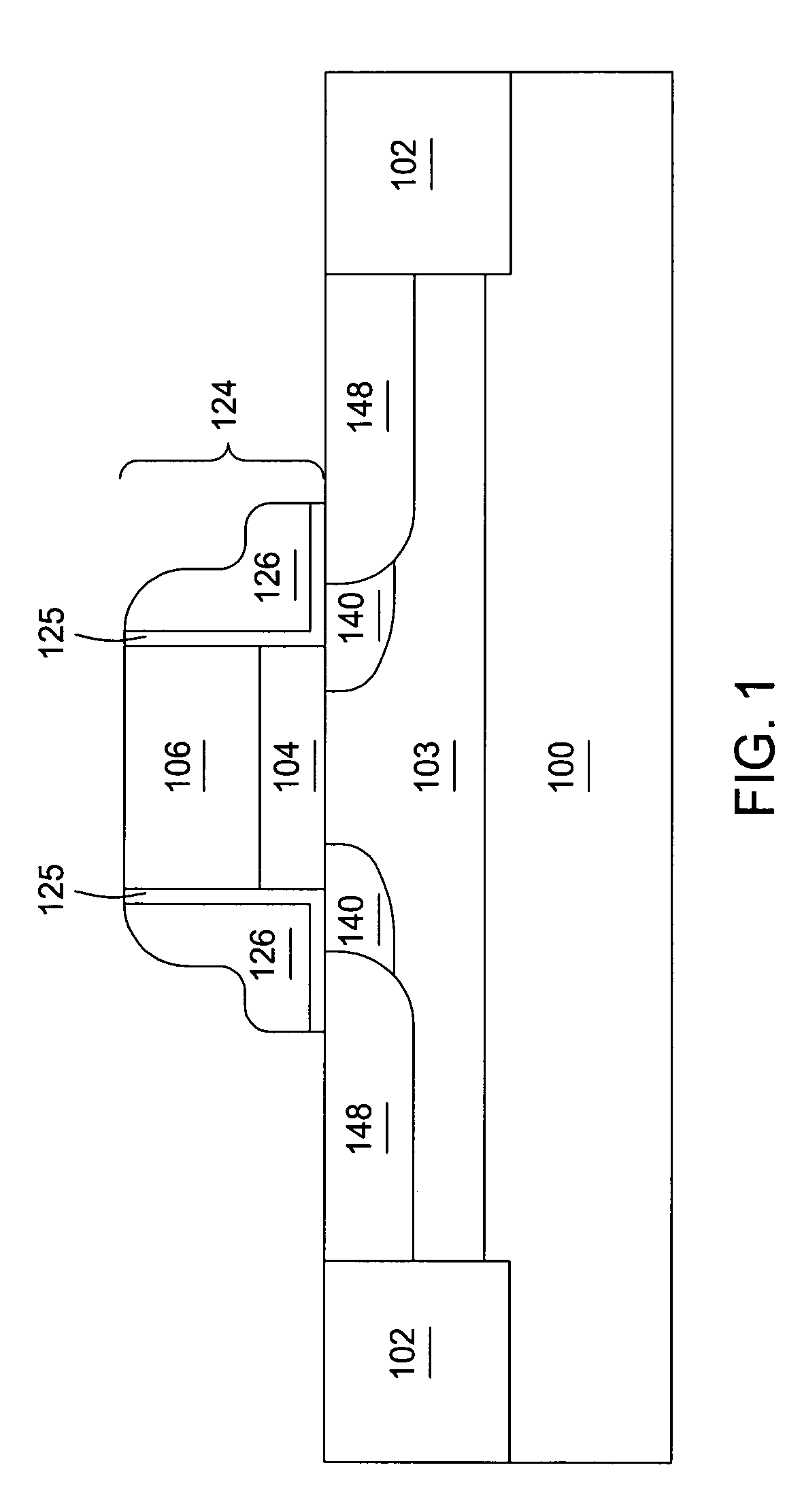

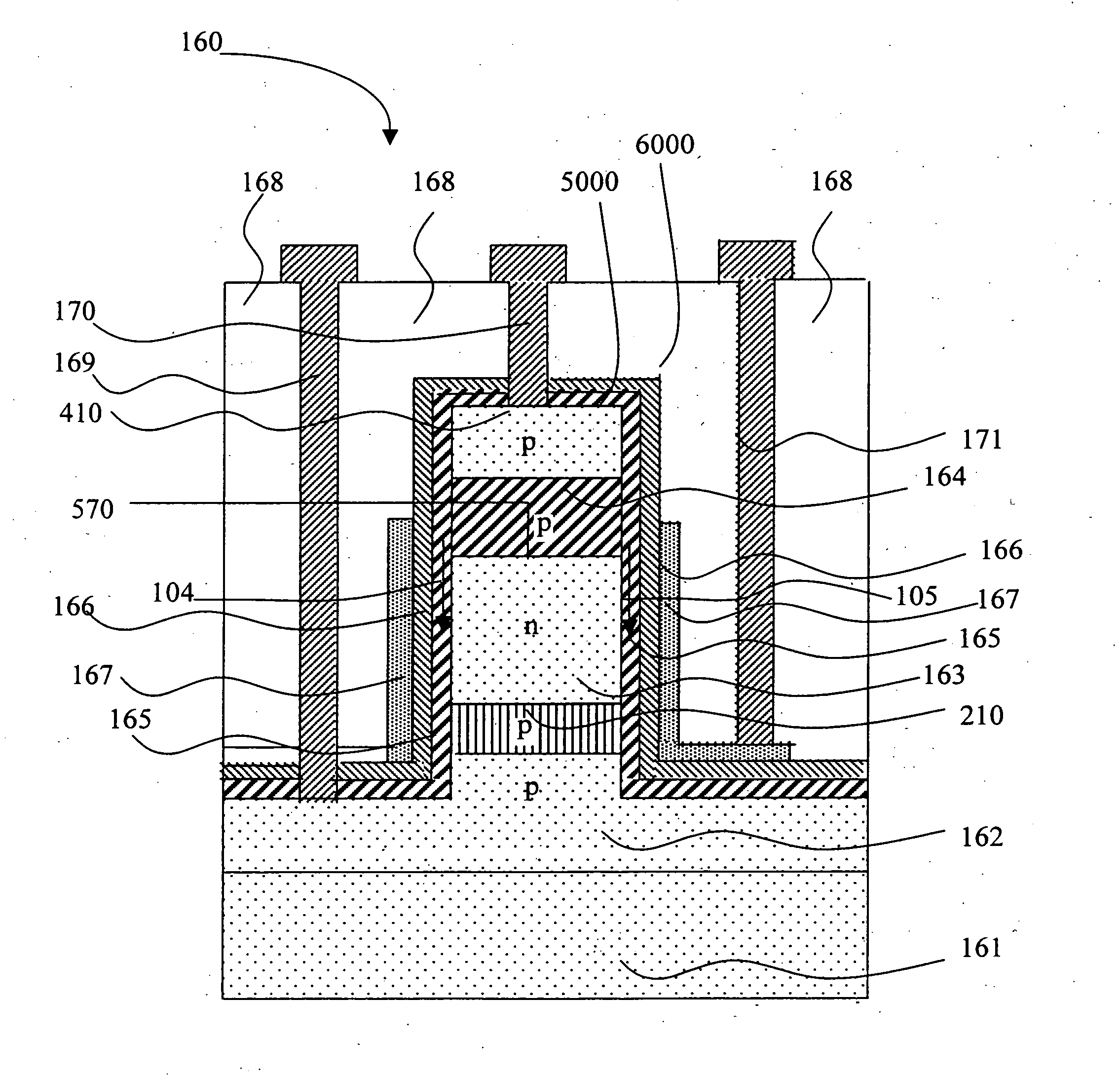

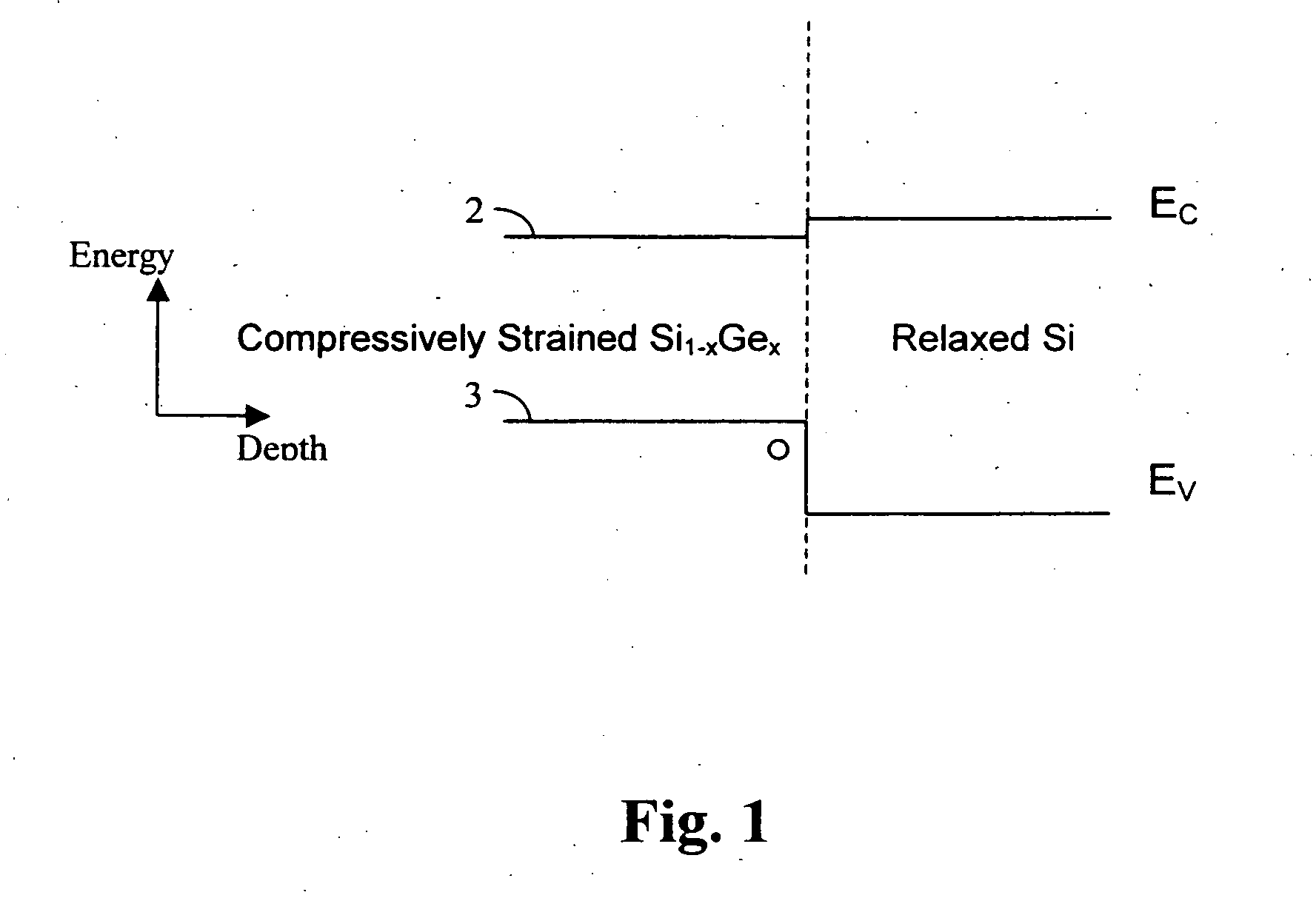

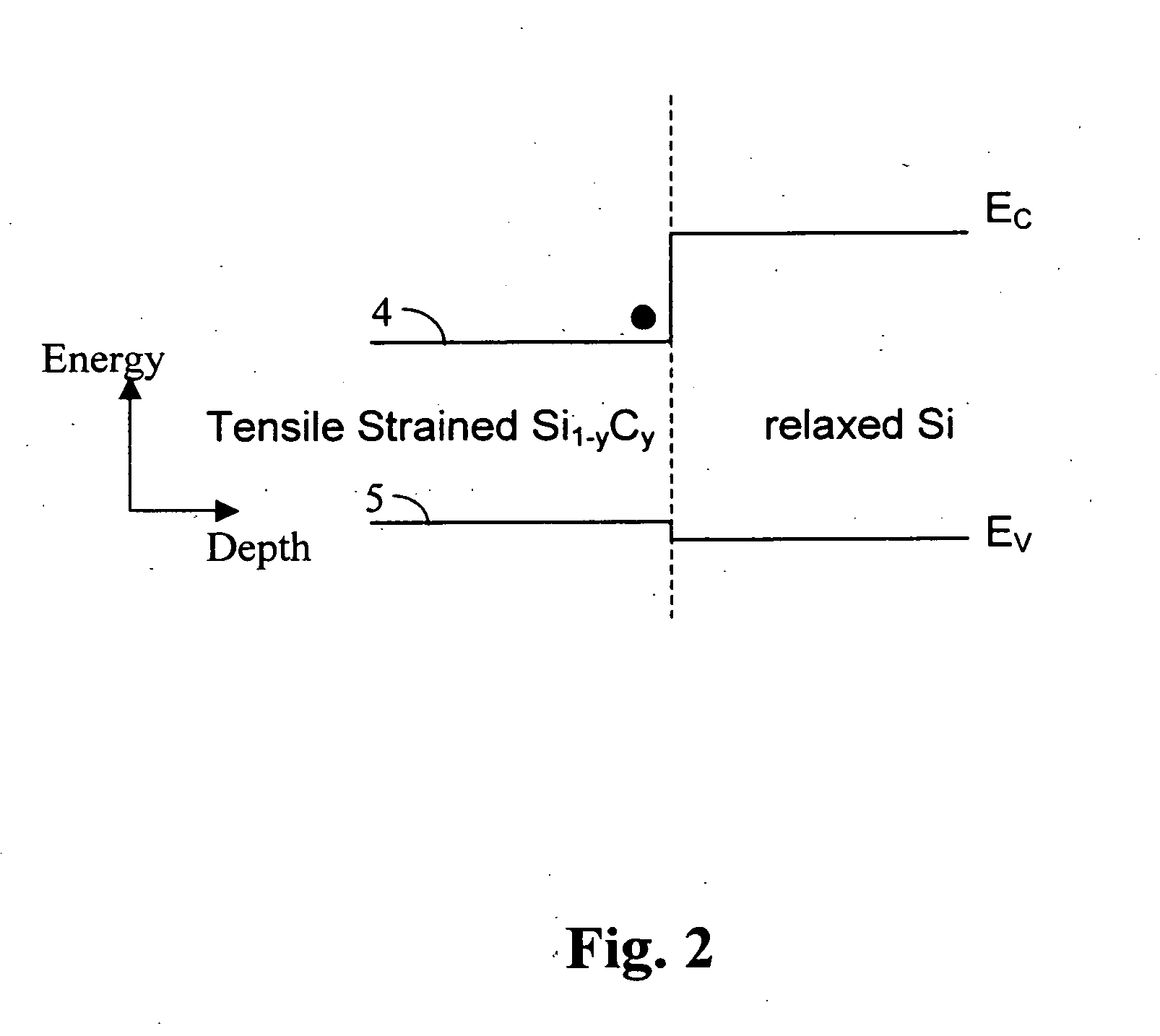

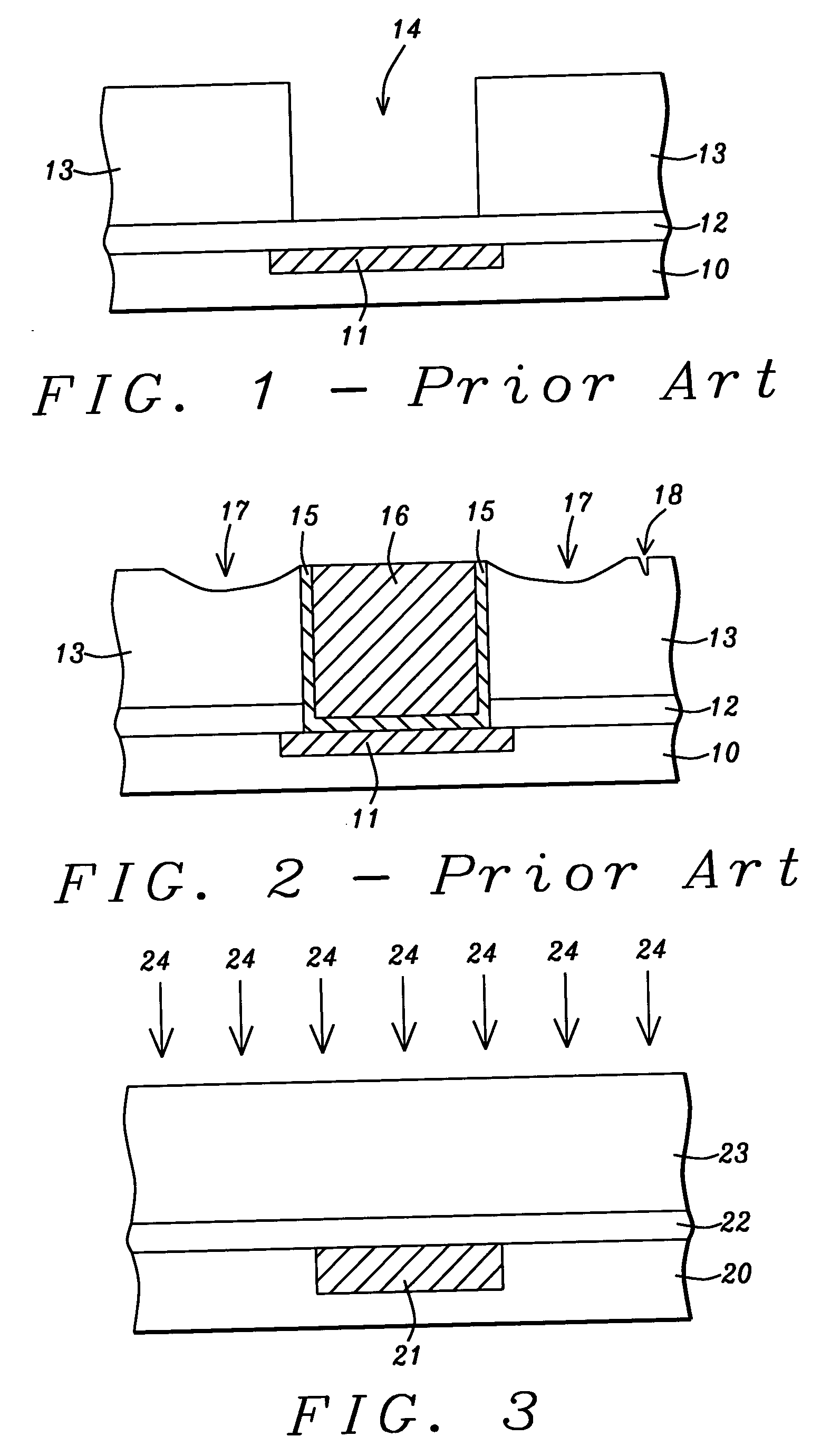

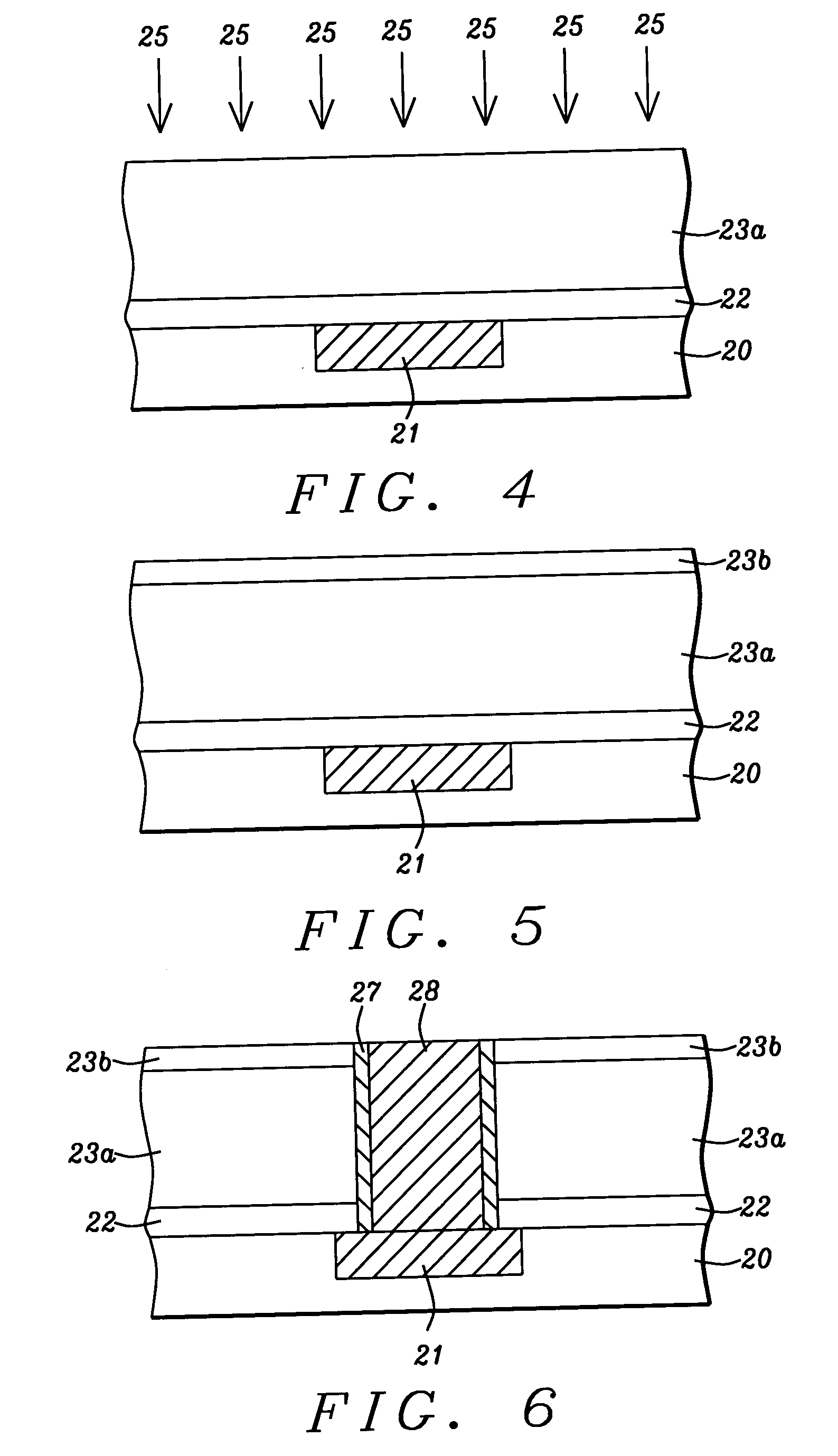

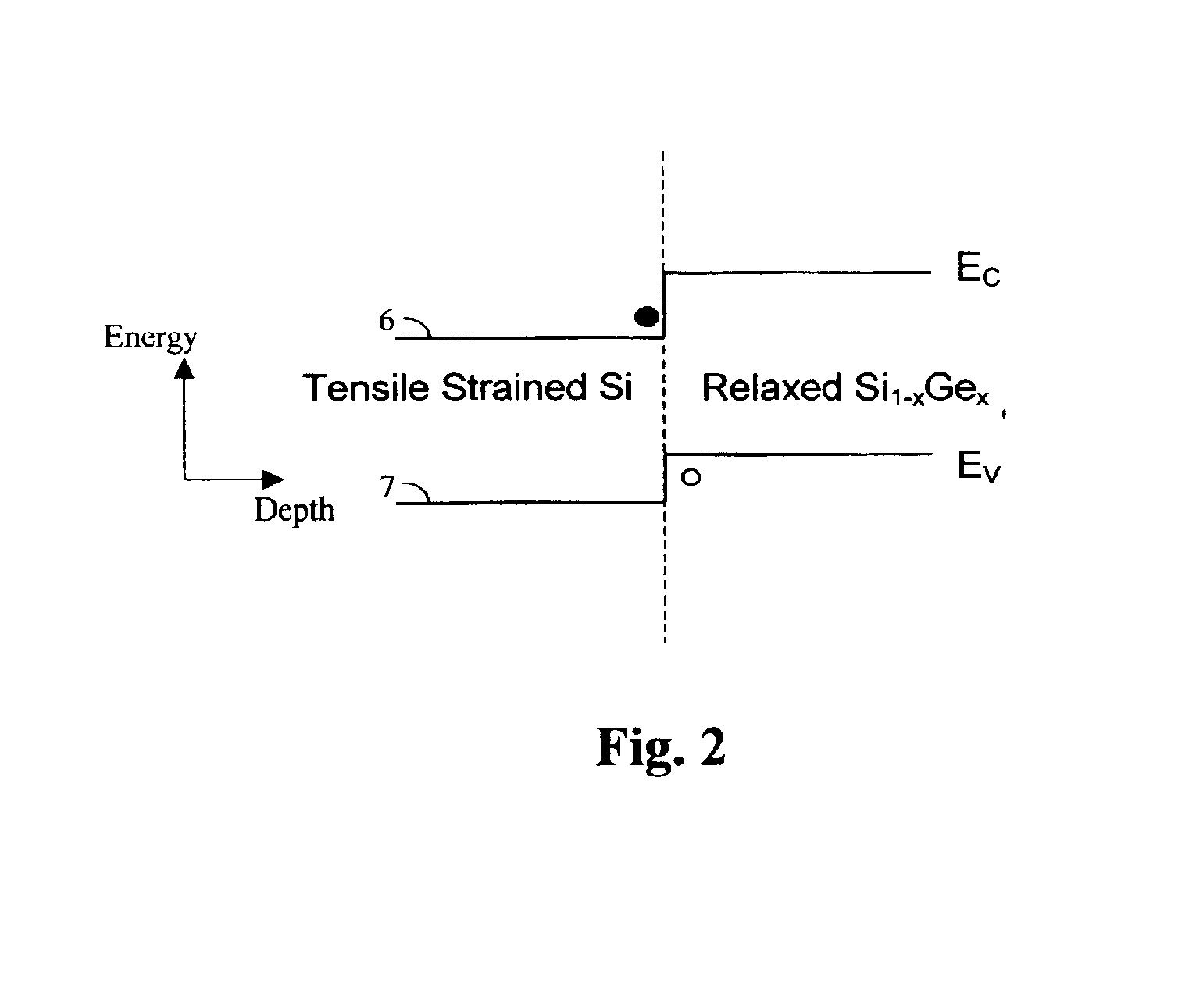

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS6943407B2Superb performanceSuperb scalabilityTransistorSolid-state devicesReverse short-channel effectHeterojunction

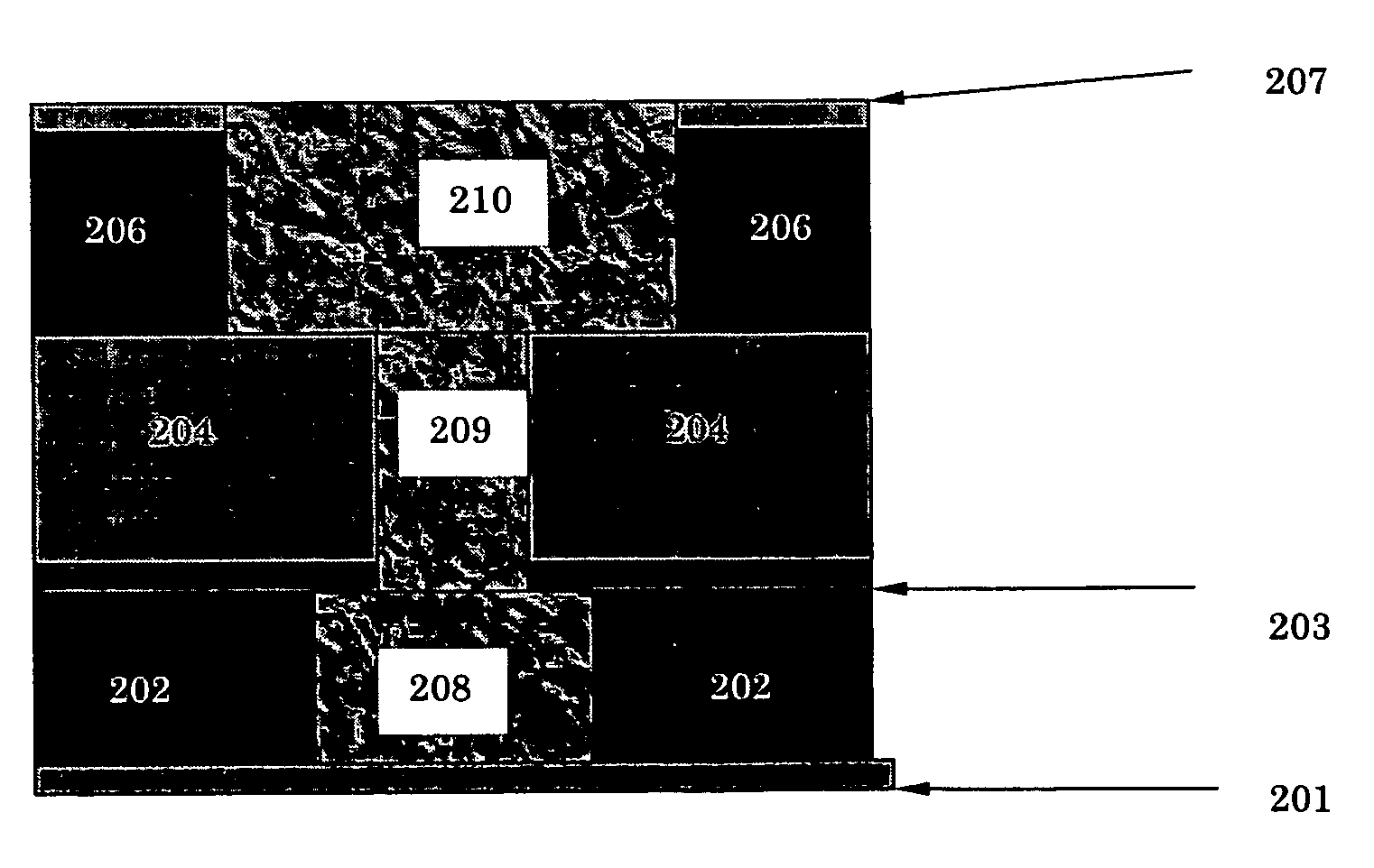

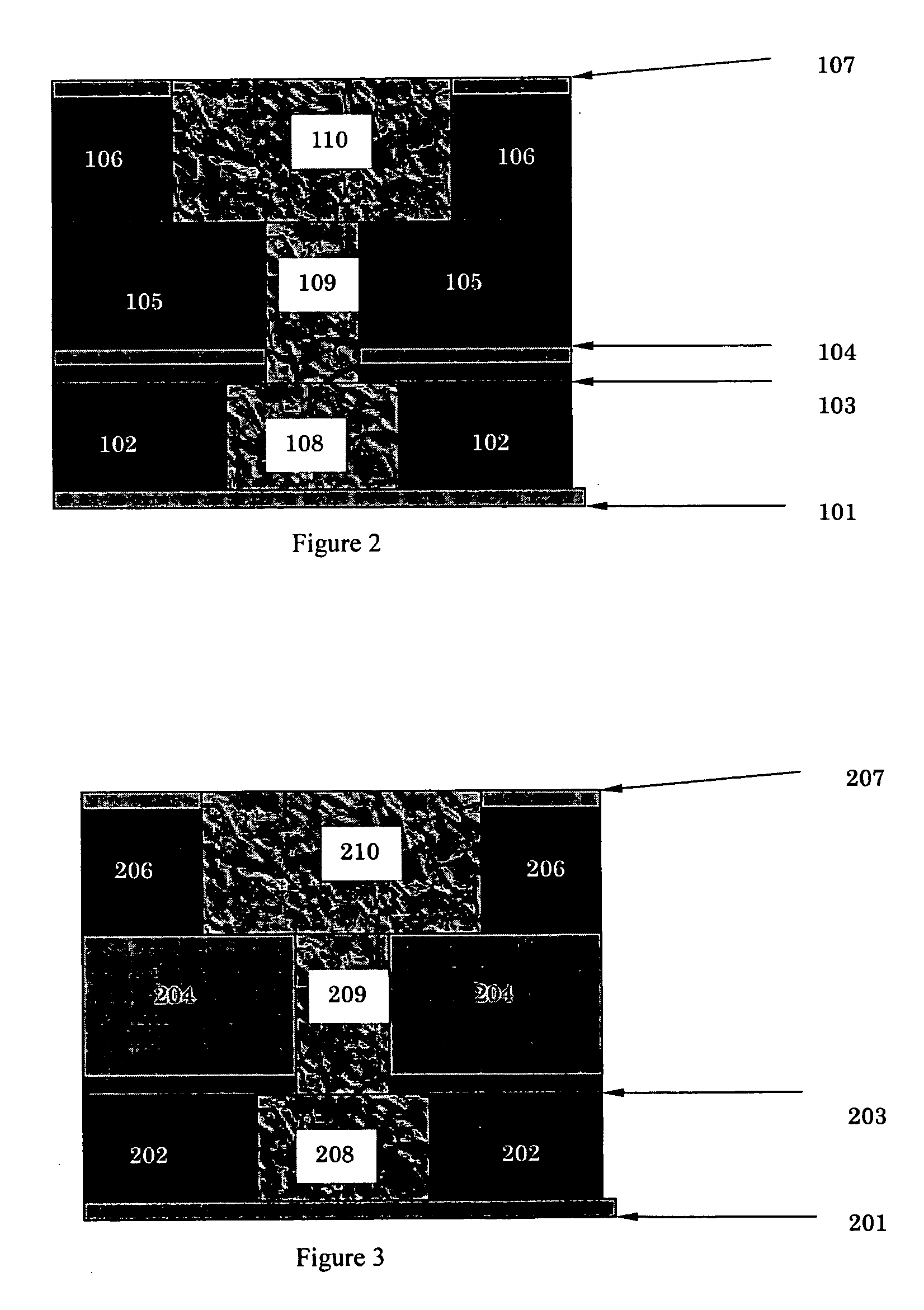

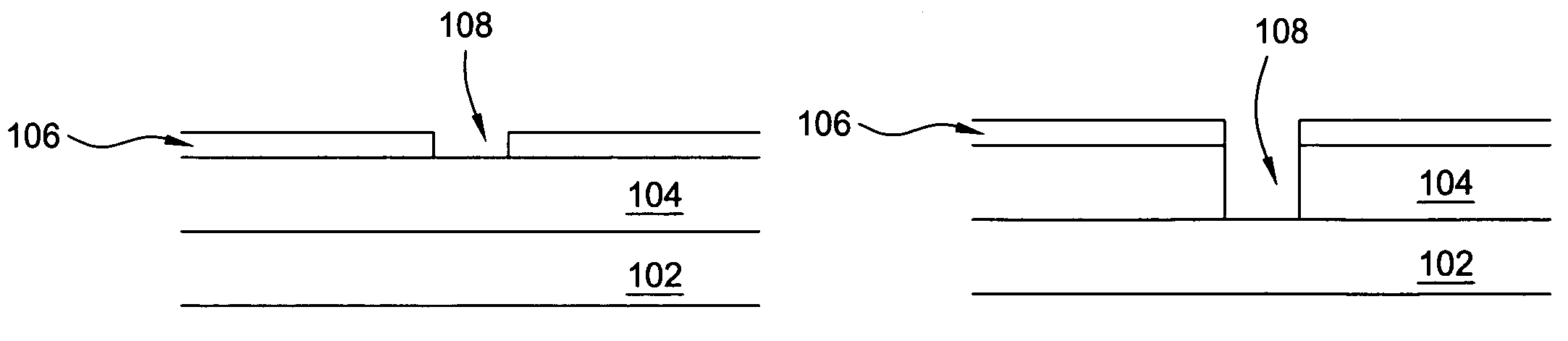

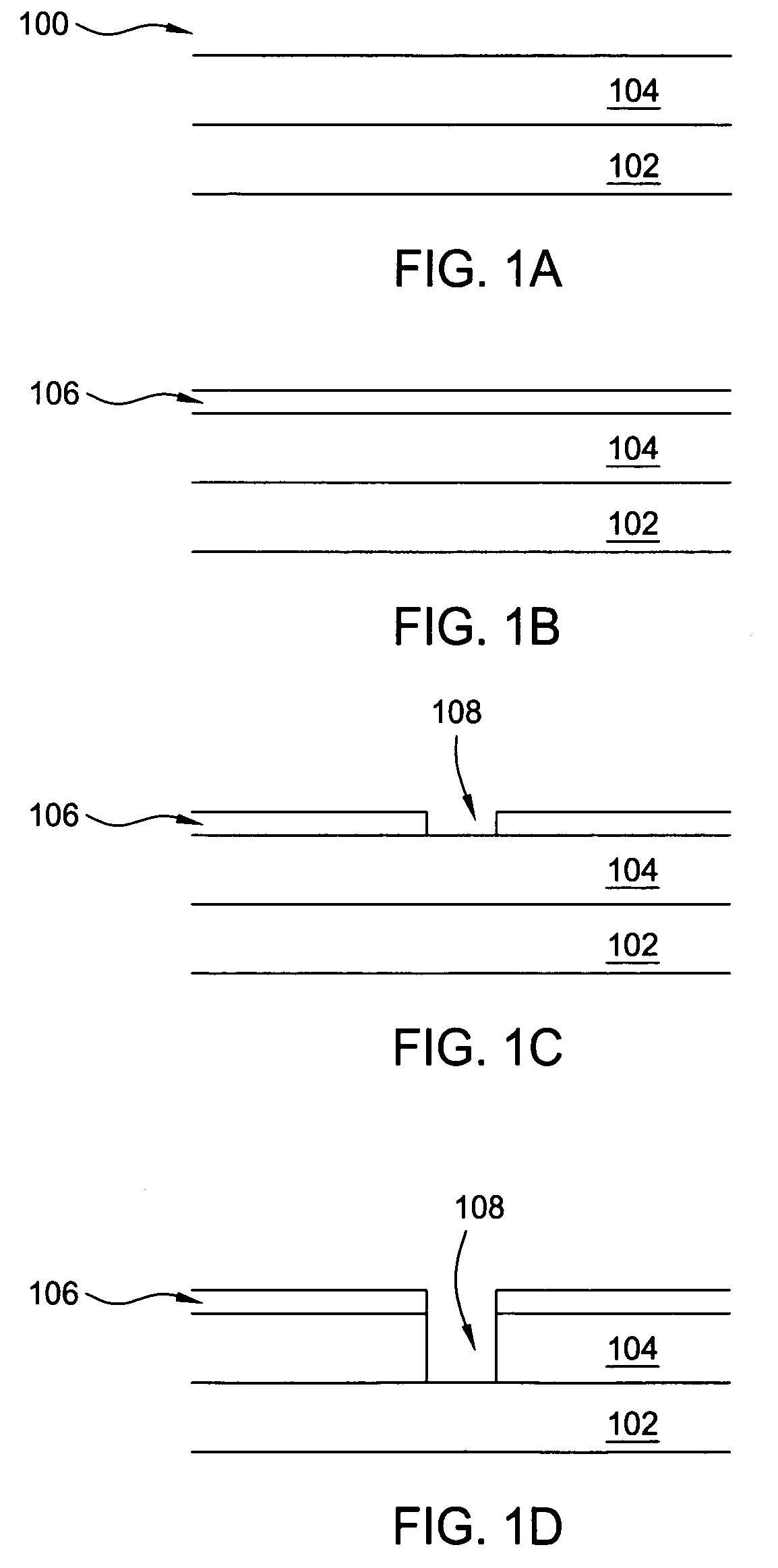

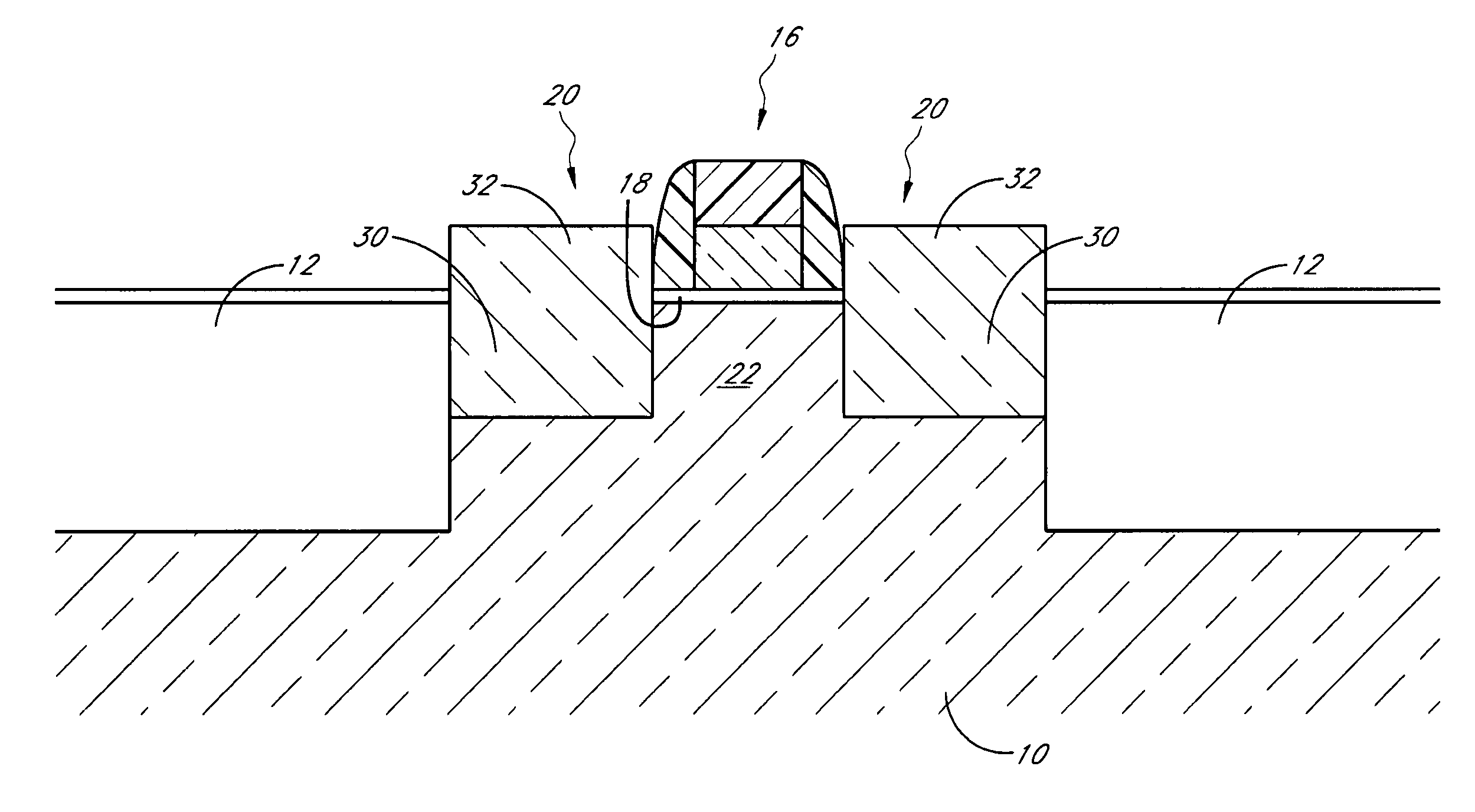

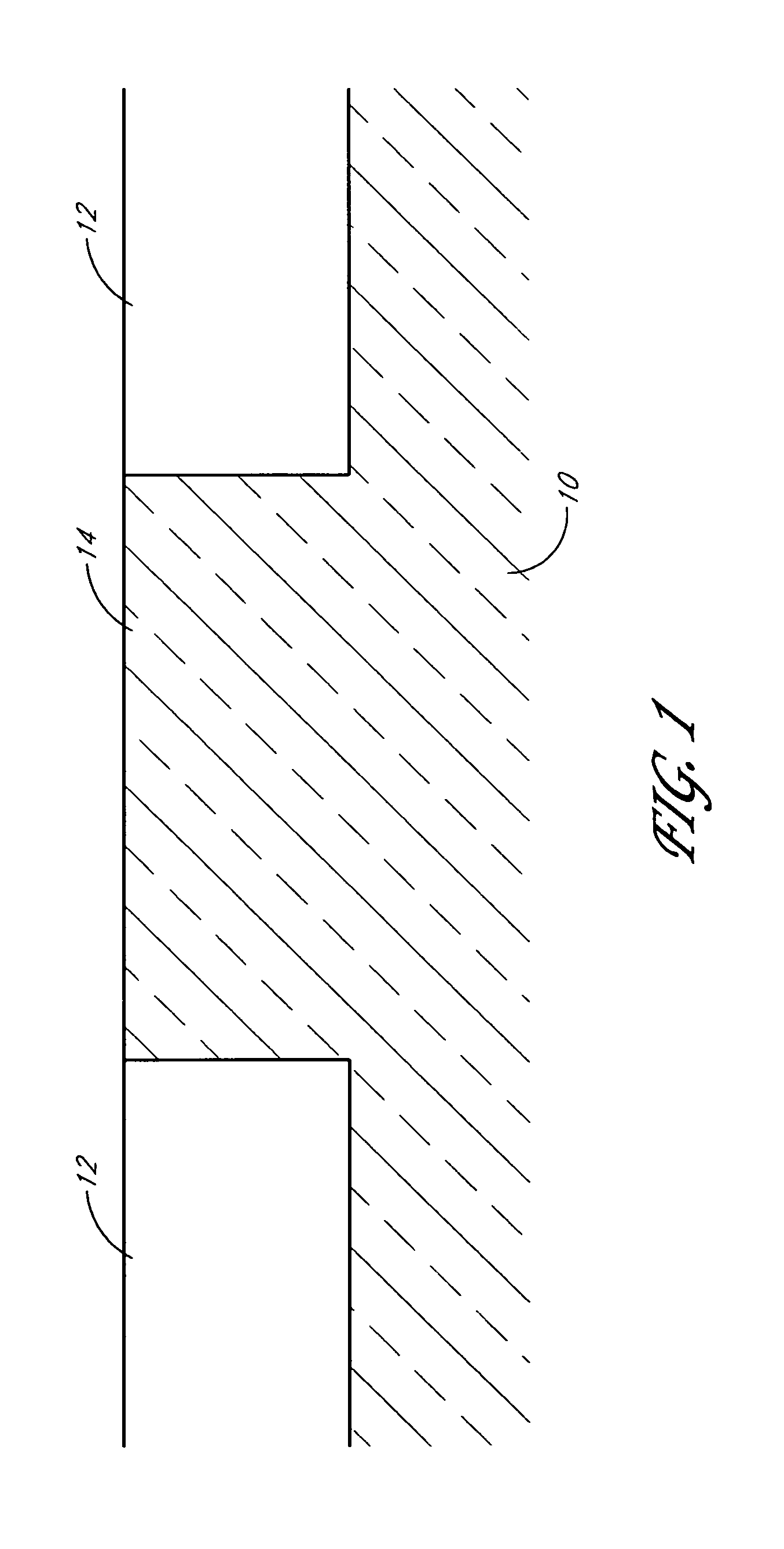

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

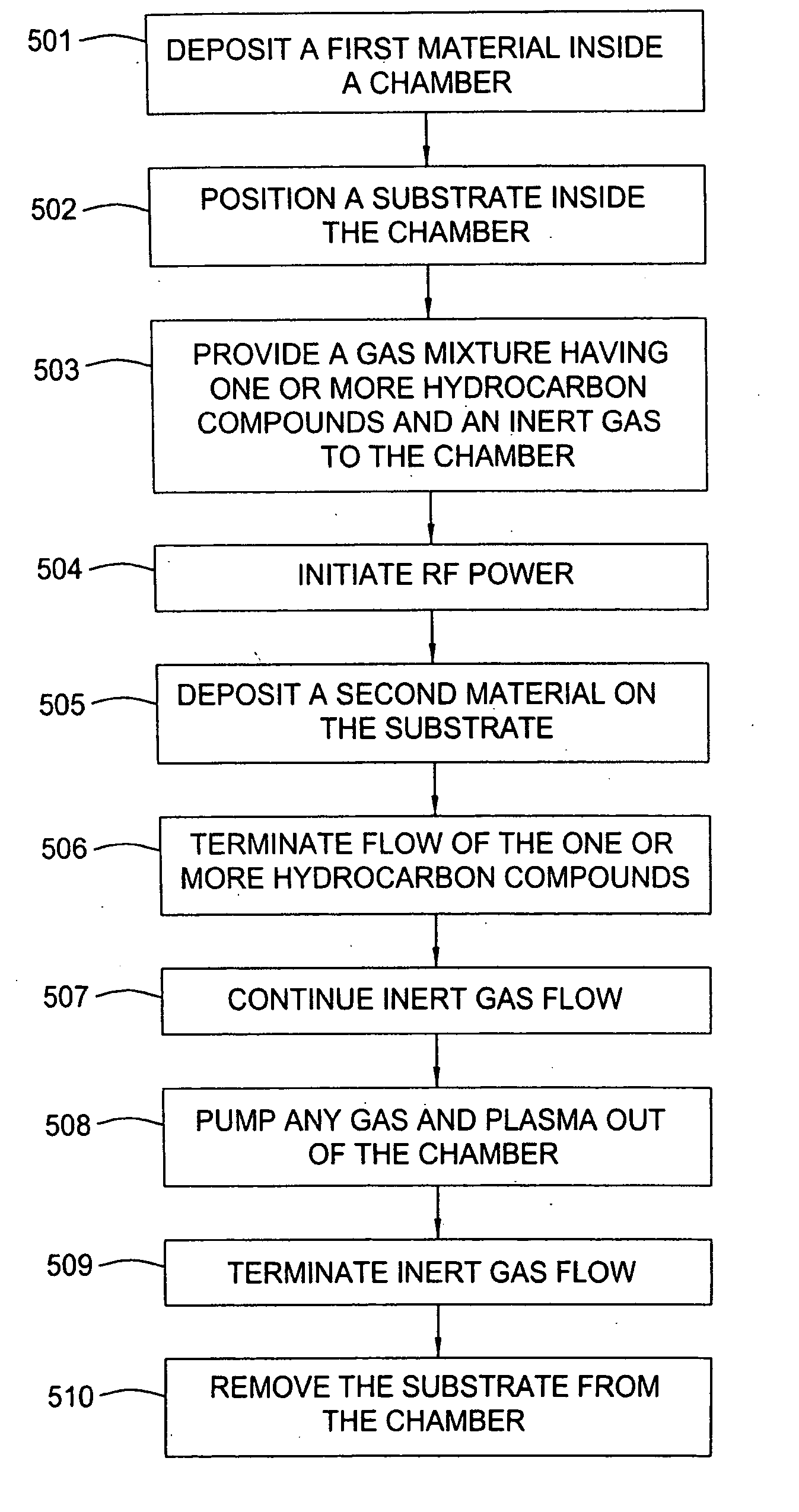

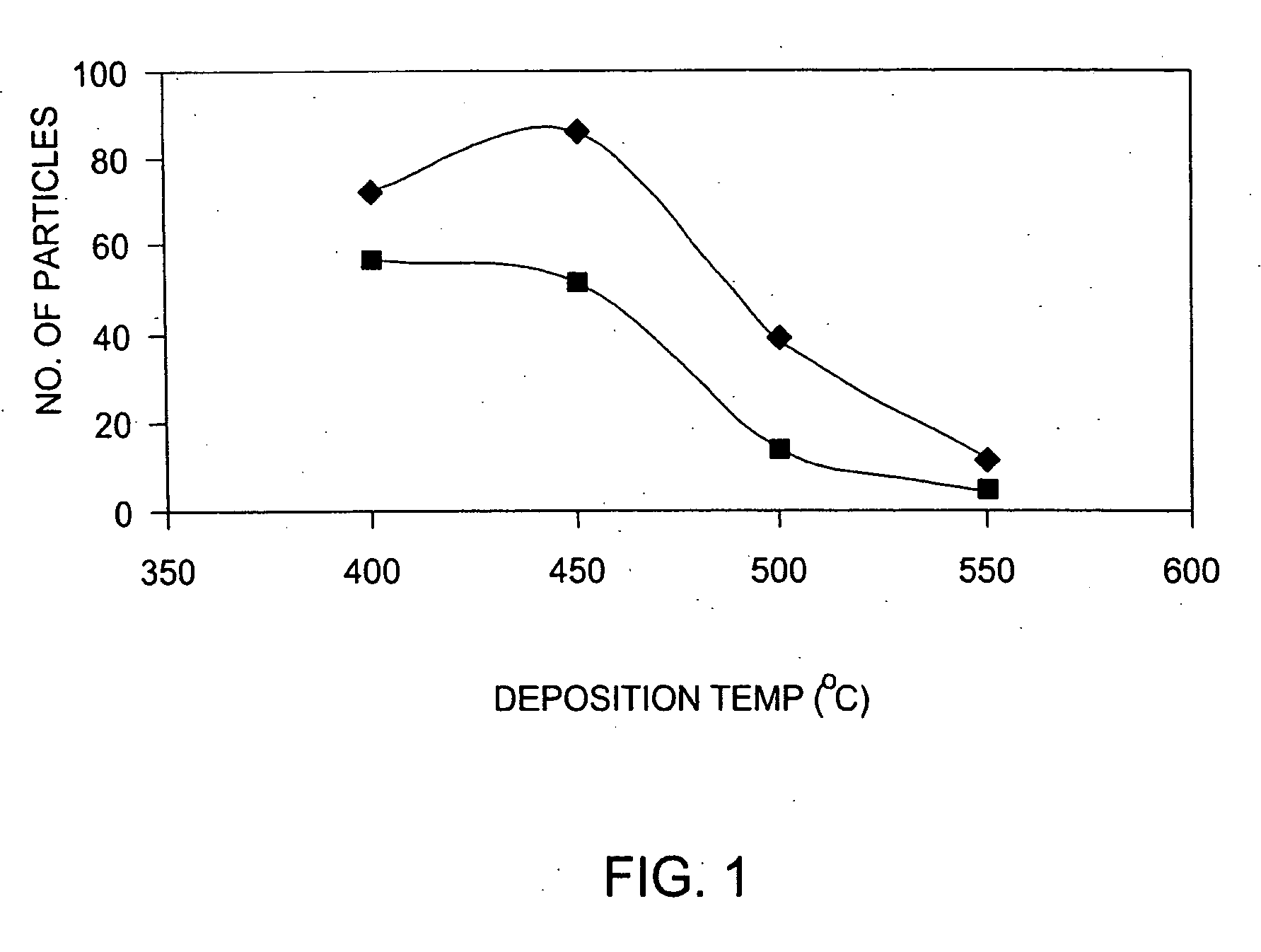

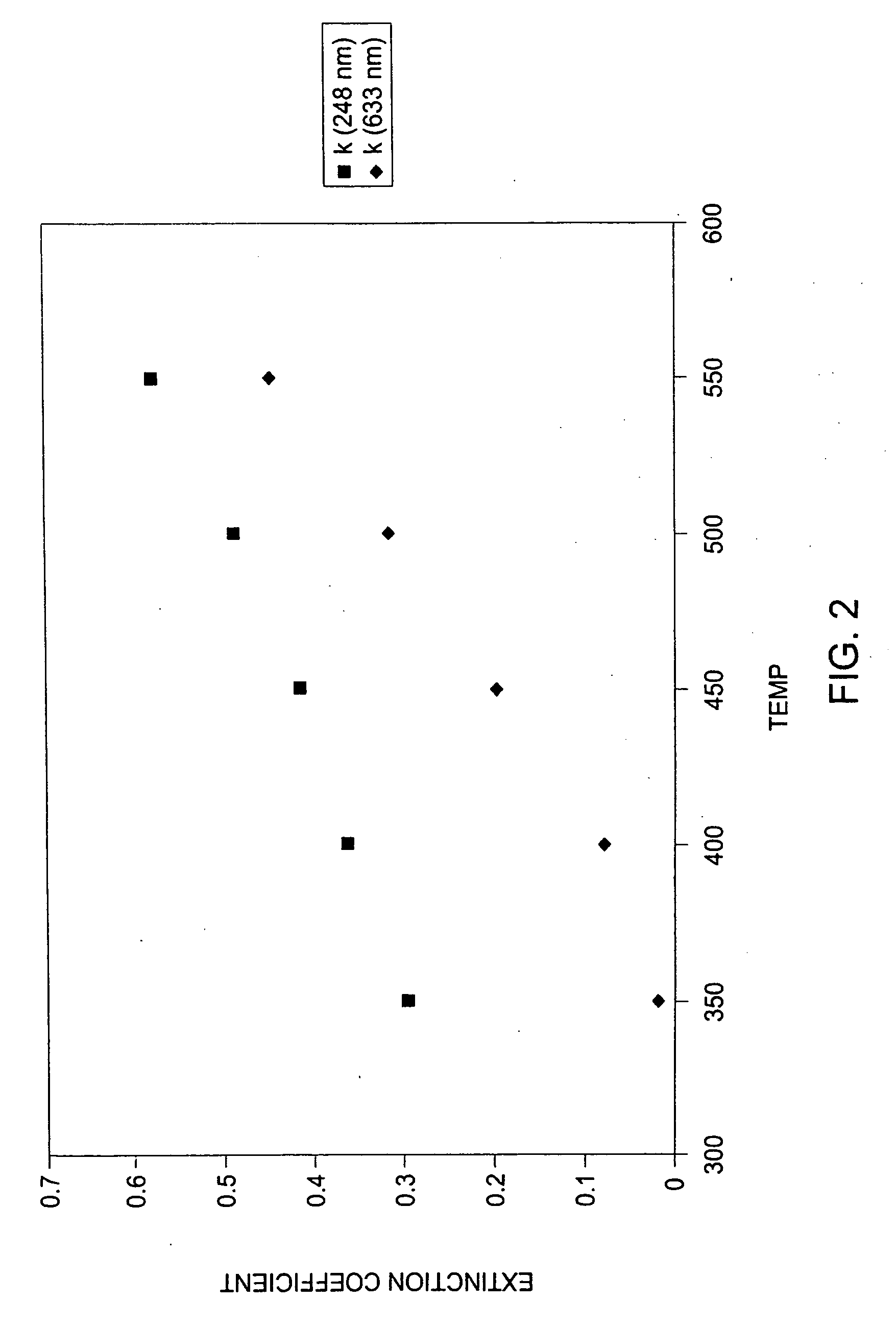

Methods for the reduction and elimination of particulate contamination with CVD of amorphous carbon

InactiveUS20060014397A1Minimal defect formationReduce particle pollutionSemiconductor/solid-state device manufacturingSpecial surfacesVariable thicknessMicroparticle

A method is provided for forming an amorphous carbon layer, deposited on a dielectric material such as oxide, nitride, silicon carbide, carbon doped oxide, etc., or a metal layer such as tungsten, aluminum or poly-silicon. The method includes the use of chamber seasoning, variable thickness of seasoning film, wider spacing, variable process gas flows, post-deposition purge with inert gas, and post-deposition plasma purge, among others, to make the deposition of an amorphous carbon film at low deposition temperatures possible without any defects or particle contamination.

Owner:APPLIED MATERIALS INC +1

Low-carbon-doped silicon oxide film and damascene structure using same

ActiveUS20050260850A1Reduce electrical circuit lifetimeEnhance moisture intakeSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectDevice material

A method of forming an interconnect for a semiconductor device using triple hard layers, comprises: forming a first hard layer serving as an etch stop layer on a metal interconnect-formed dielectric layer; forming a second hard layer on the first hard layer; forming a dielectric layer on the second hard layer; forming a third hard layer on the dielectric layer; forming a hole through the third and second hard layers, the dielectric layer, and the first hard layer; and filling the hole with metal to establish an interconnect. The second and third hard layers are each made of carbon-doped silicon oxide formed from a source gas and a redox gas, while controlling the carbon content in the second hard layer as a function of a flow rate of the redox gas.

Owner:ASM JAPAN

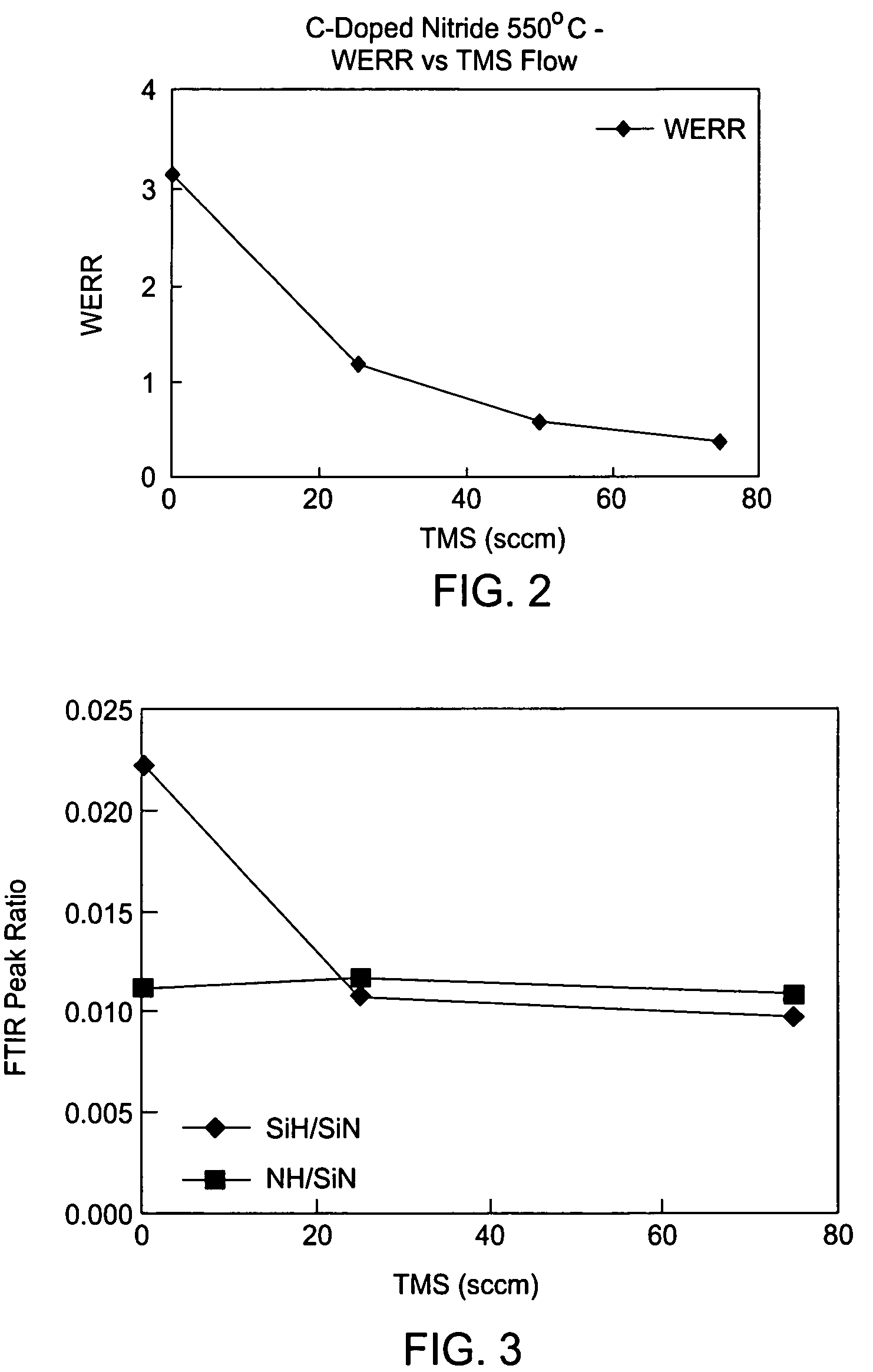

Decreasing the etch rate of silicon nitride by carbon addition

Methods for forming silicon nitride hard masks are provided. The silicon nitride hard masks include carbon-doped silicon nitride layers and undoped silicon nitride layers. Carbon-doped silicon nitride layers that are deposited from a mixture comprising a carbon source compound, a silicon source compound, and a nitrogen source in the presence of RF power are provided. Also provided are methods of UV post-treating silicon nitride layers to provide silicon nitride hard masks. The carbon-doped silicon nitride layers and UV post-treated silicon nitride layers have desirable wet etch rates and dry etch rates for hard mask layers.

Owner:APPLIED MATERIALS INC

Selective etching of carbon-doped low-k dielectrics

InactiveUS20050026430A1High selectivityReducing micro-loadingDecorative surface effectsVacuum evaporation coatingPlasma etchingChemistry

The present invention includes a process for selectively etching a low-k dielectric material formed on a substrate using a plasma of a gas mixture in a plasma etch chamber. The gas mixture comprises a fluorine-rich fluorocarbon or hydrofluorocarbon gas, a nitrogen-containing gas, and one or more additive gases, such as a hydrogen-rich hydrofluorocarbon gas, an inert gas and / or a carbon-oxygen gas. The process provides a low-k dielectric to a photoresist mask etching selectivity ratio greater than about 5:1, a low-k dielectric to a barrier / liner layer etching selectivity ratio greater about 10:1, and a low-k dielectric etch rate higher than about 4000 Å / min.

Owner:APPLIED MATERIALS INC

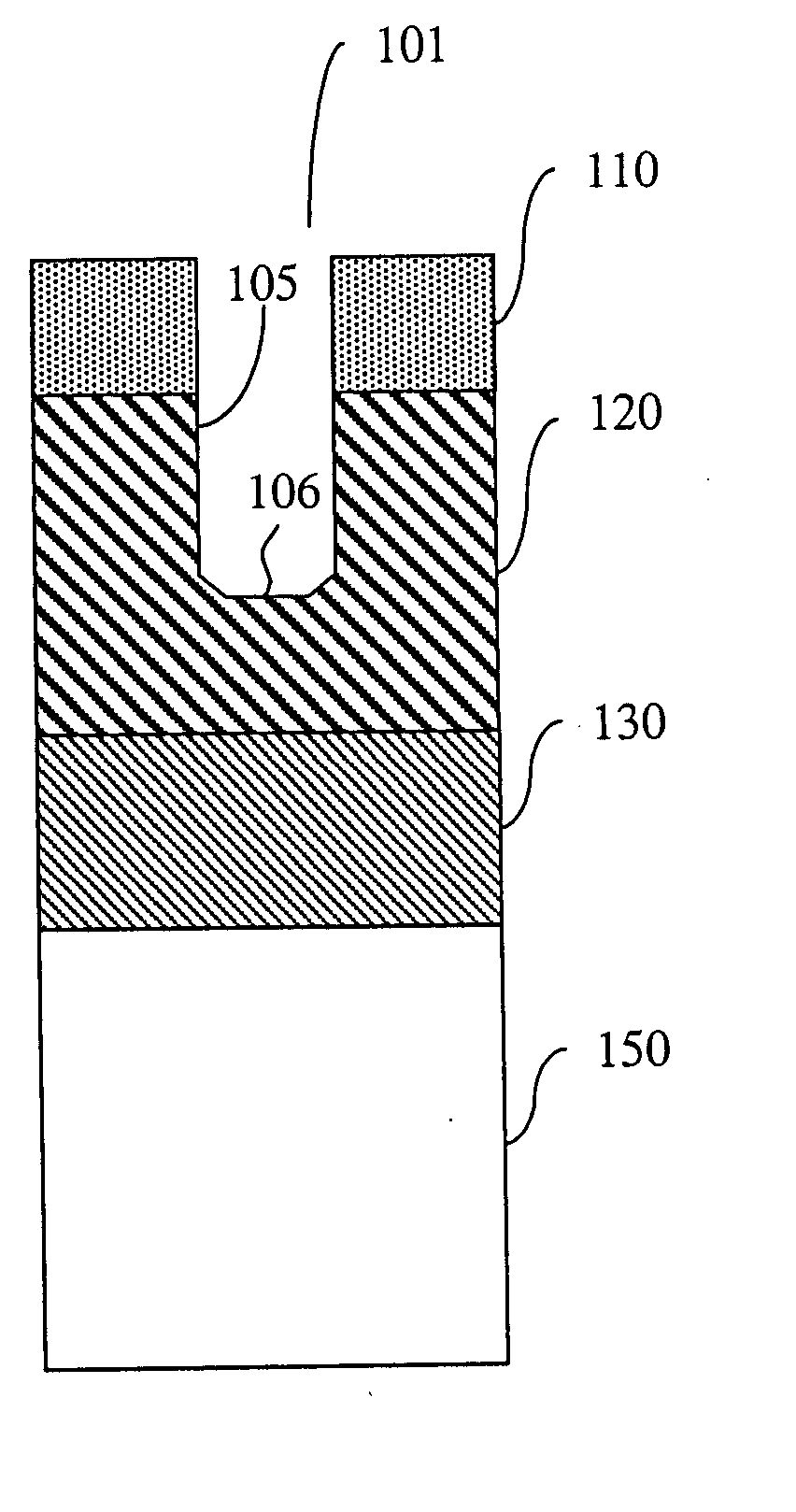

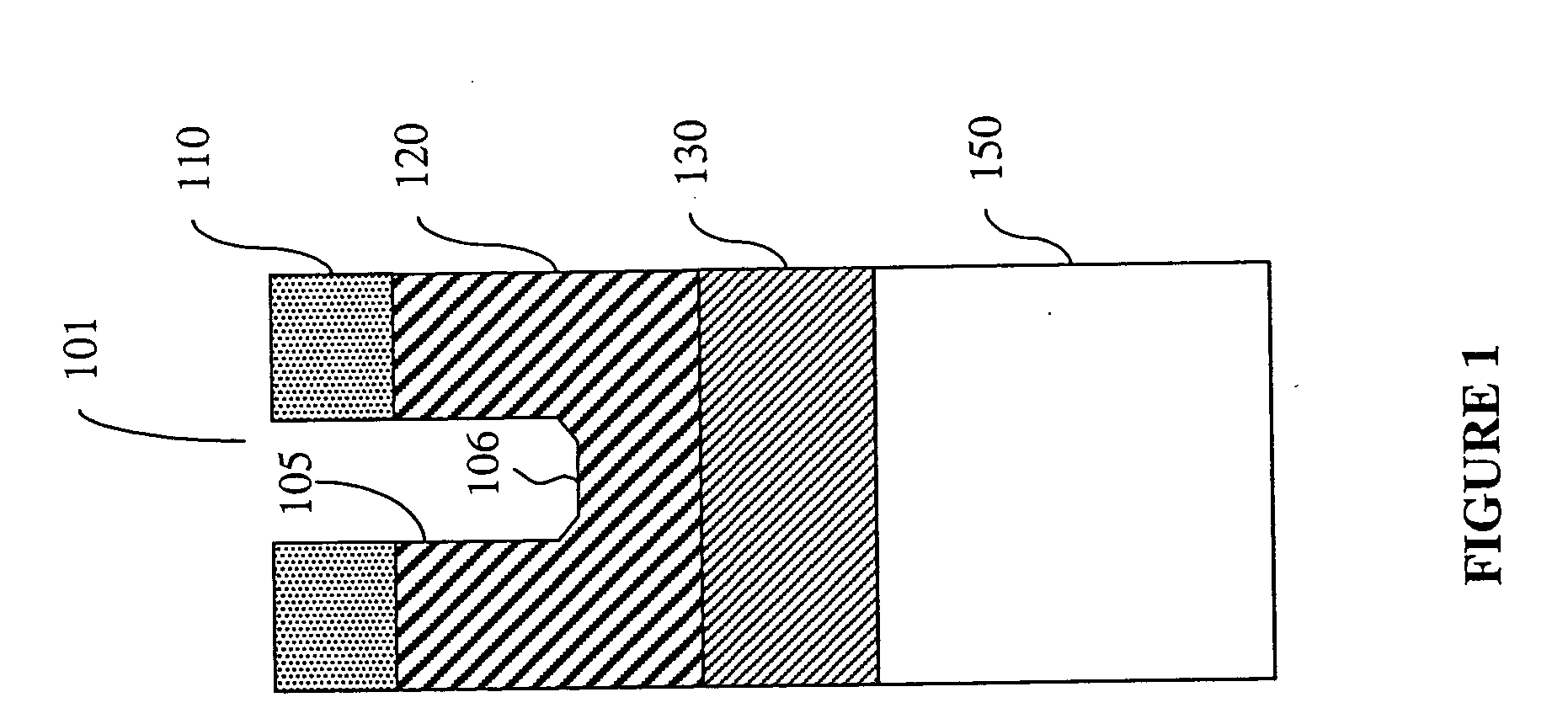

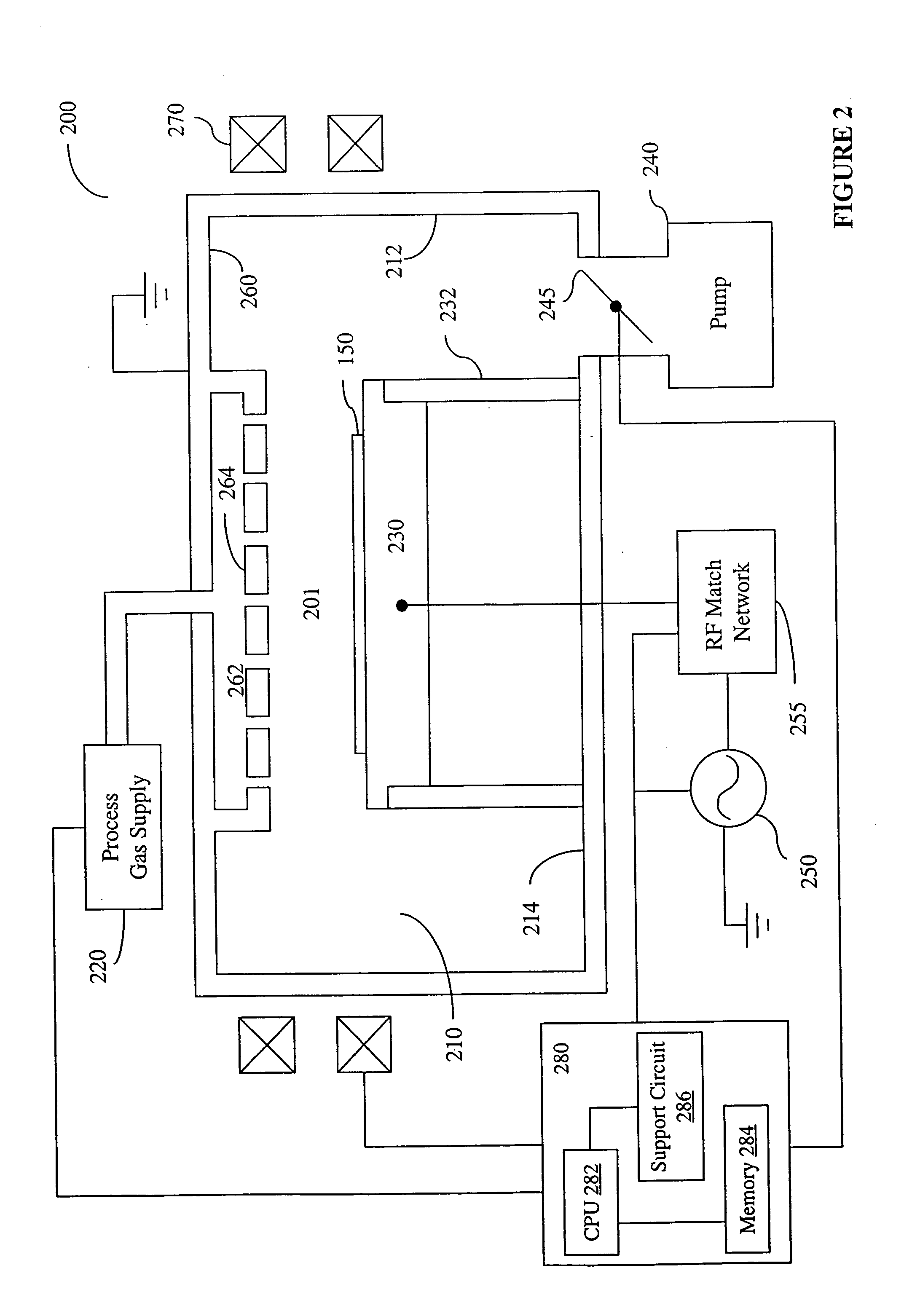

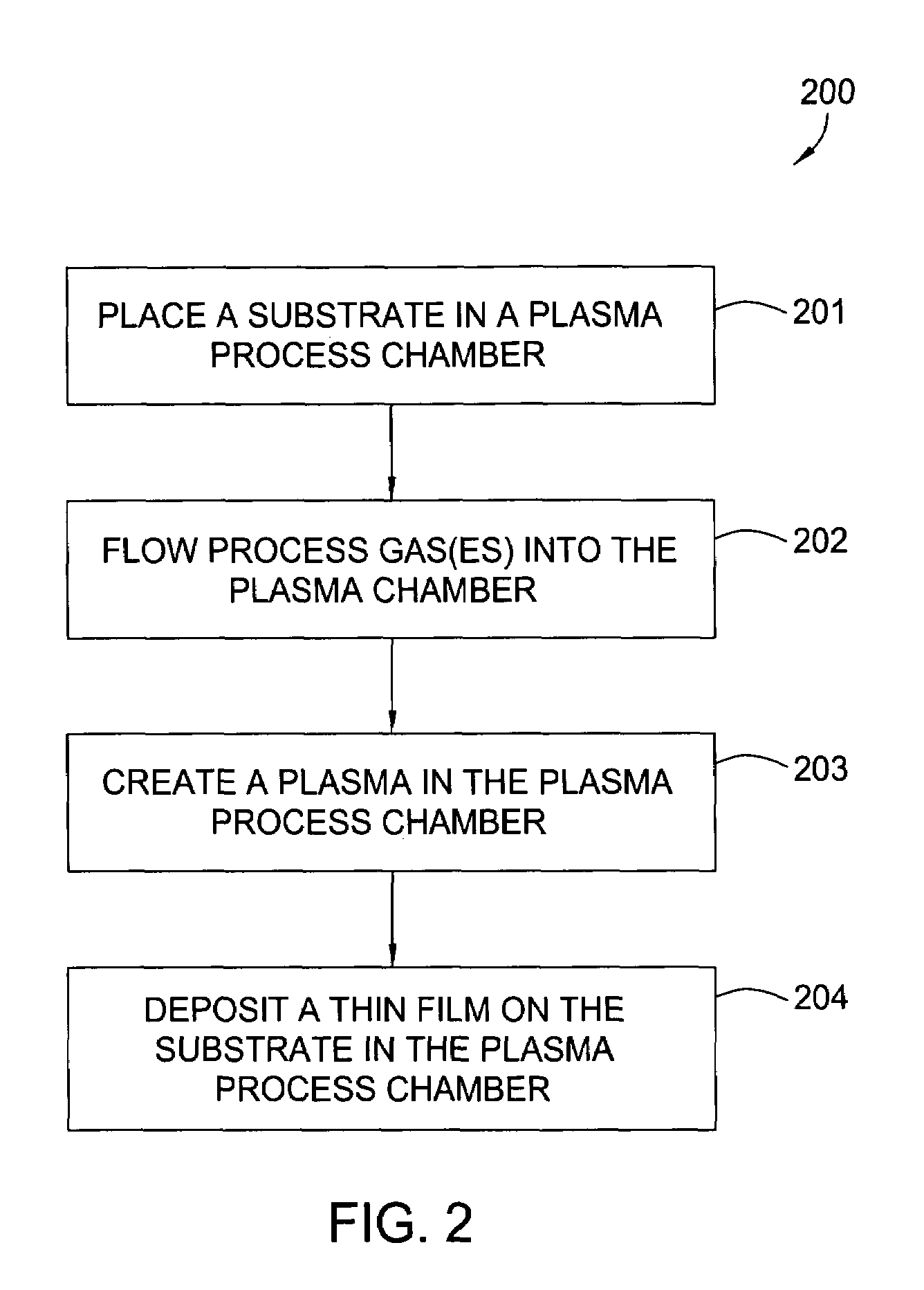

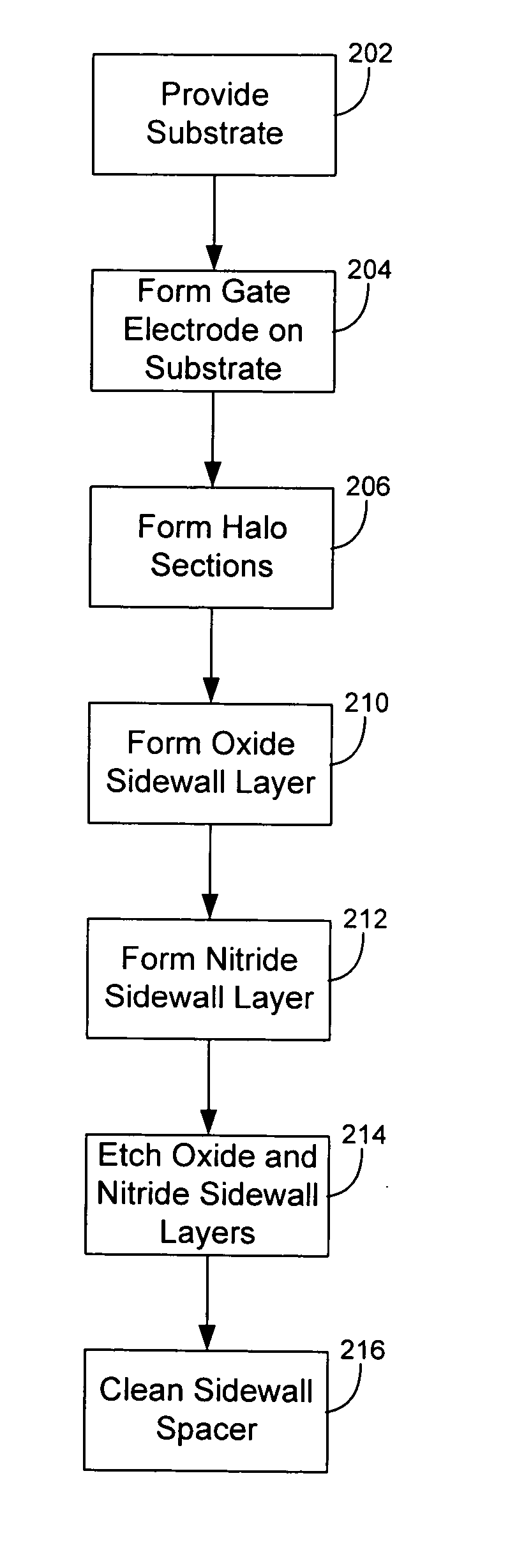

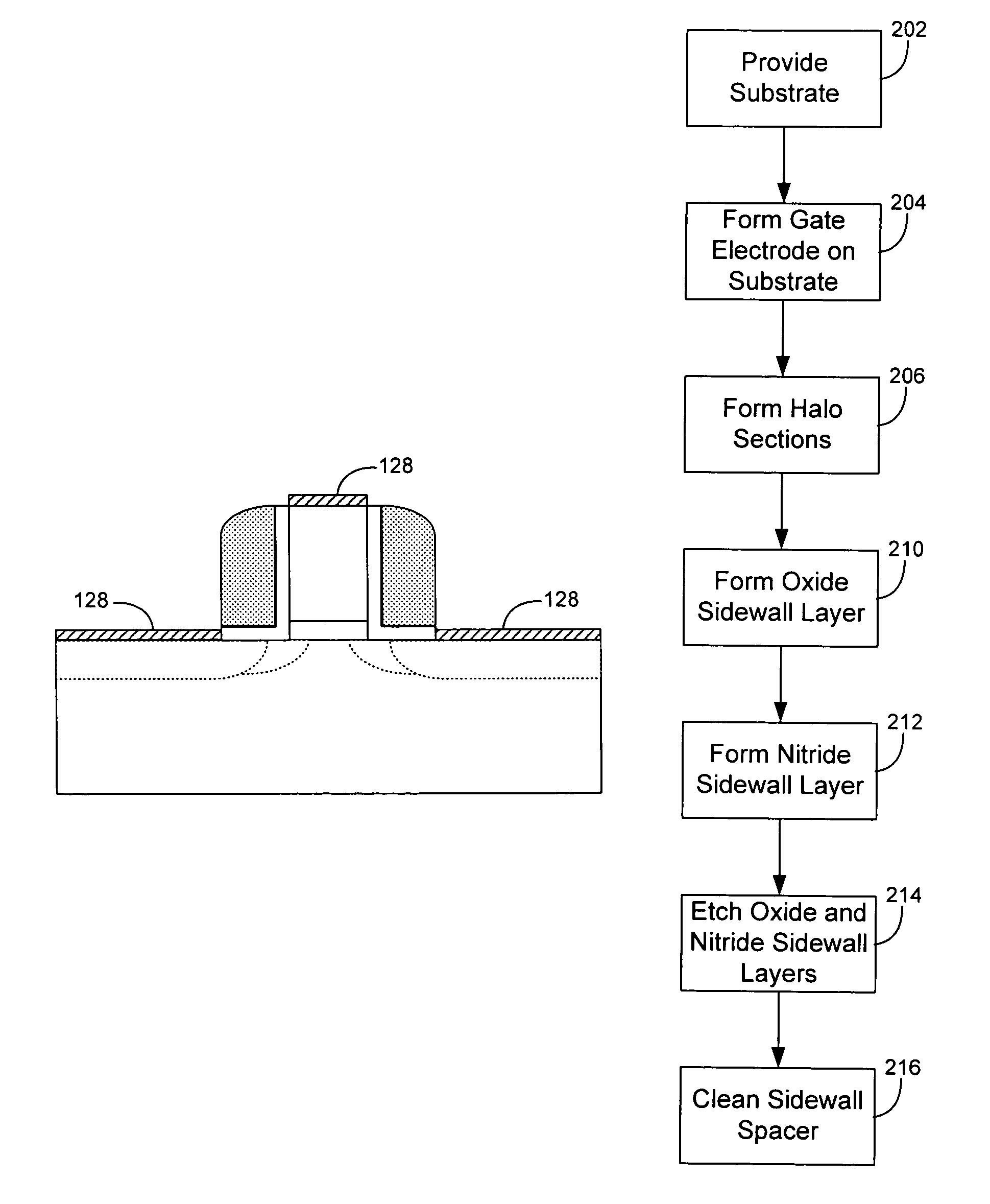

Method for producing gate stack sidewall spacers

A method for forming sidewall spacers on a gate stack by depositing one or more layers of silicon containing materials using PECVD process(es) on a gate structure to produce a spacer having an overall k value of about 3.0 to about 5.0. The silicon containing materials may be silicon carbide, oxygen doped silicon carbide, nitrogen doped silicon carbide, carbon doped silicon nitride, nitrogen doped silicon oxycarbide, or combinations thereof. The deposition is performed in a plasma enhanced chemical vapor deposition chamber and the deposition temperature is less than 450° C. The sidewall spacers so produced provide good capacity resistance, as well as excellent structural stability and hermeticity.

Owner:APPLIED MATERIALS INC

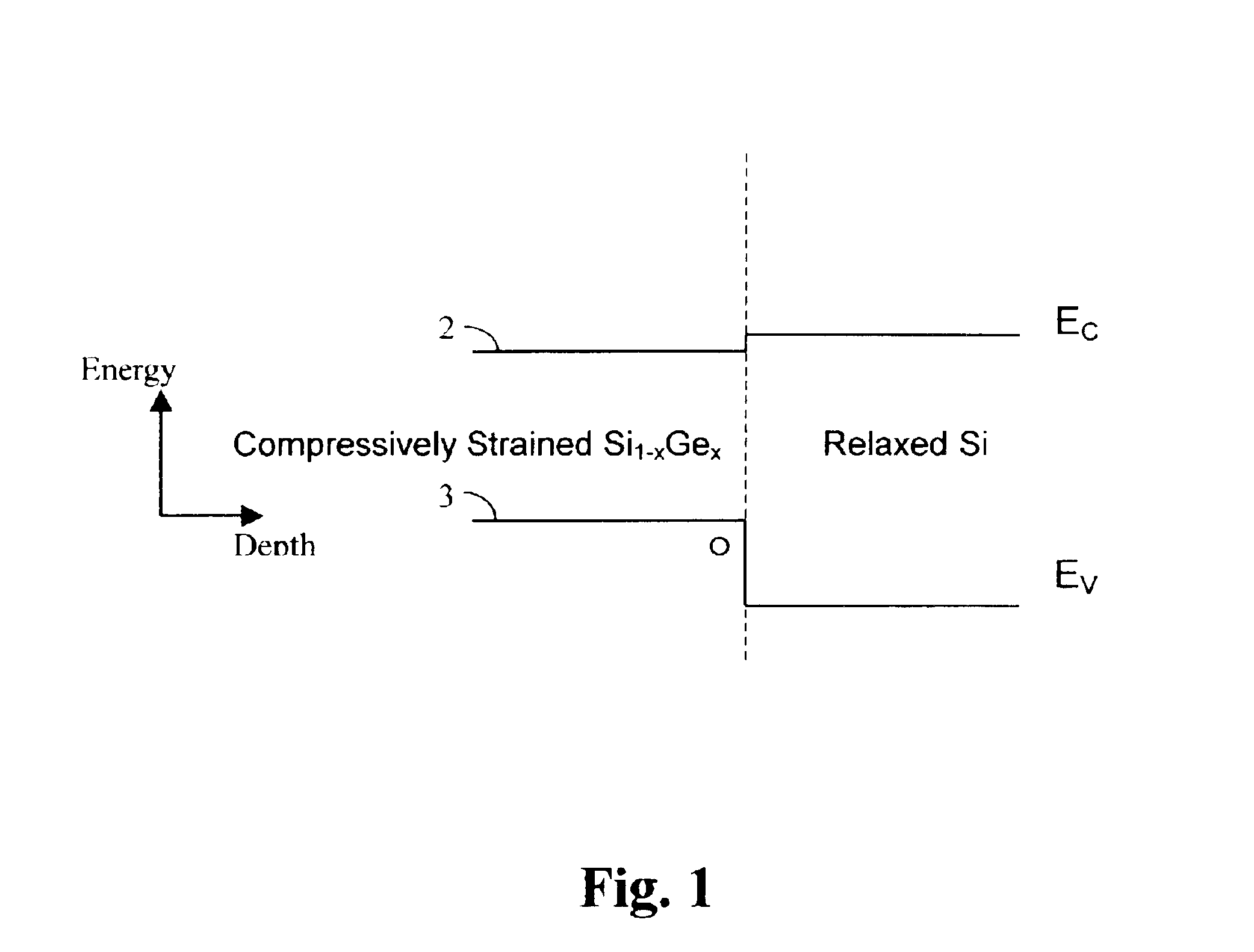

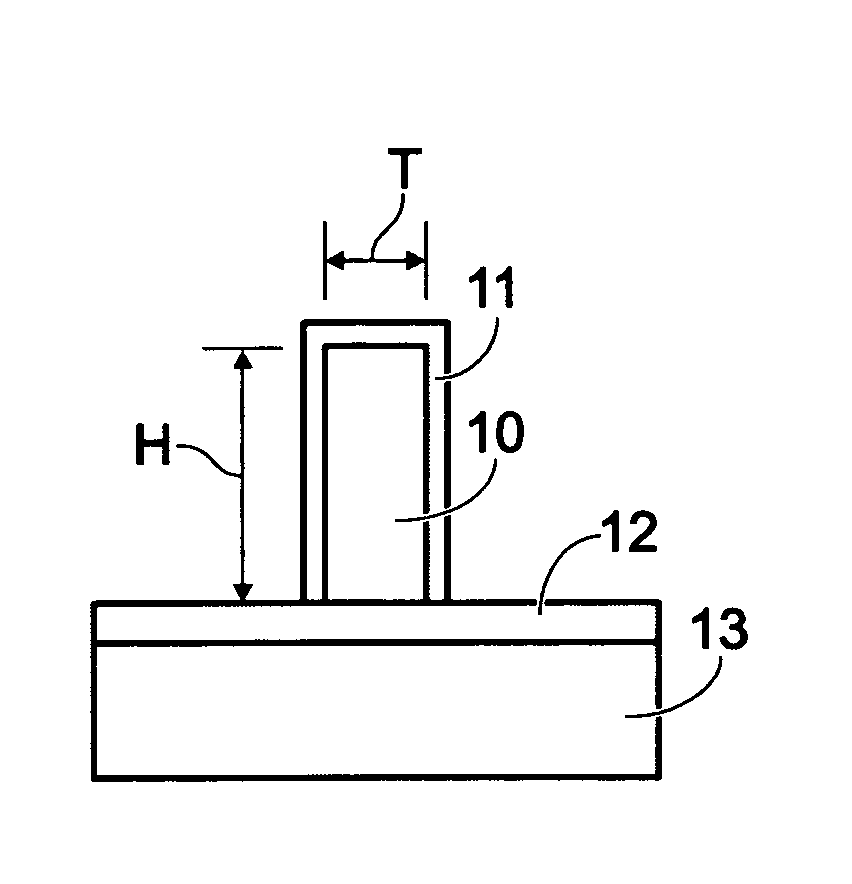

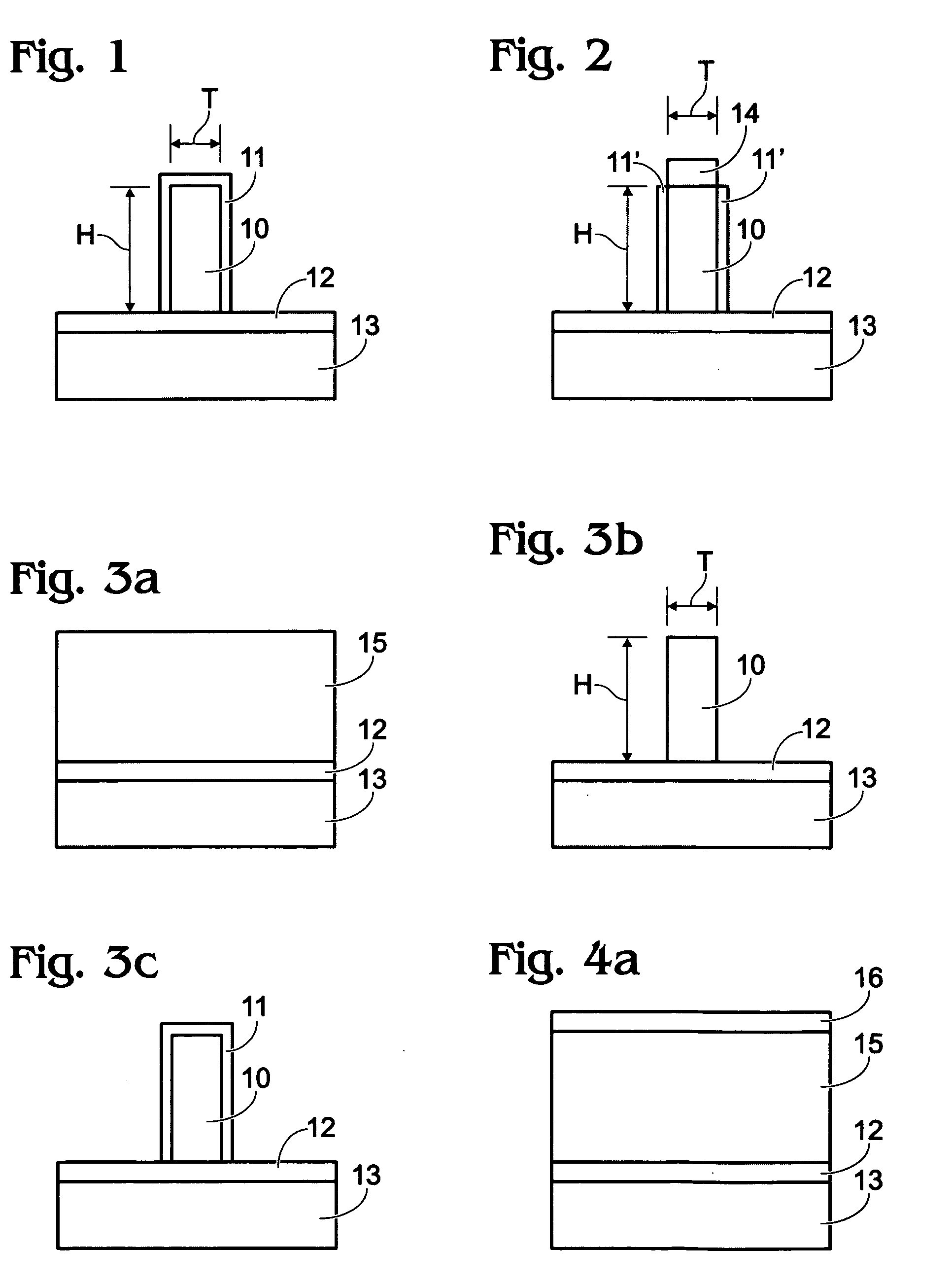

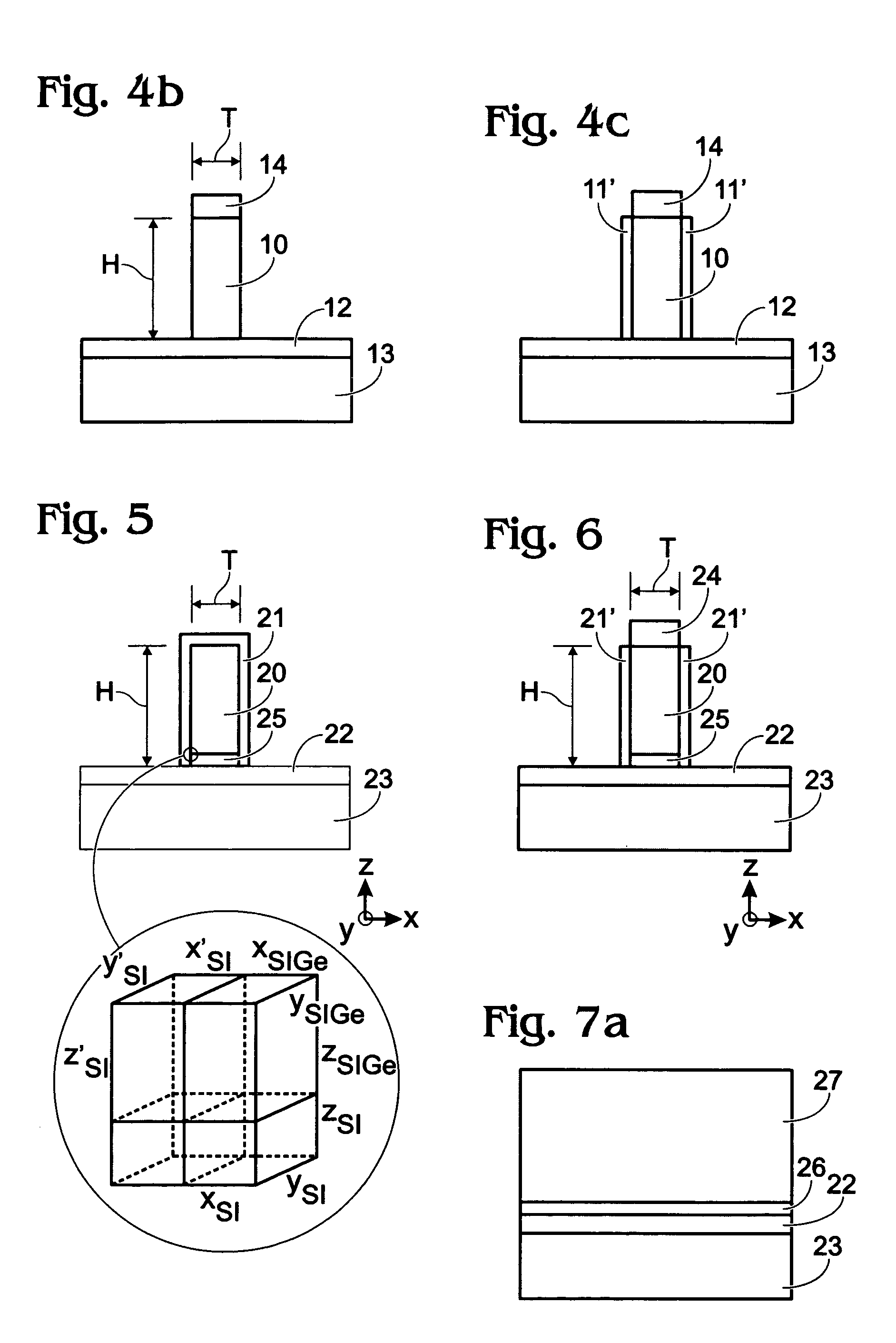

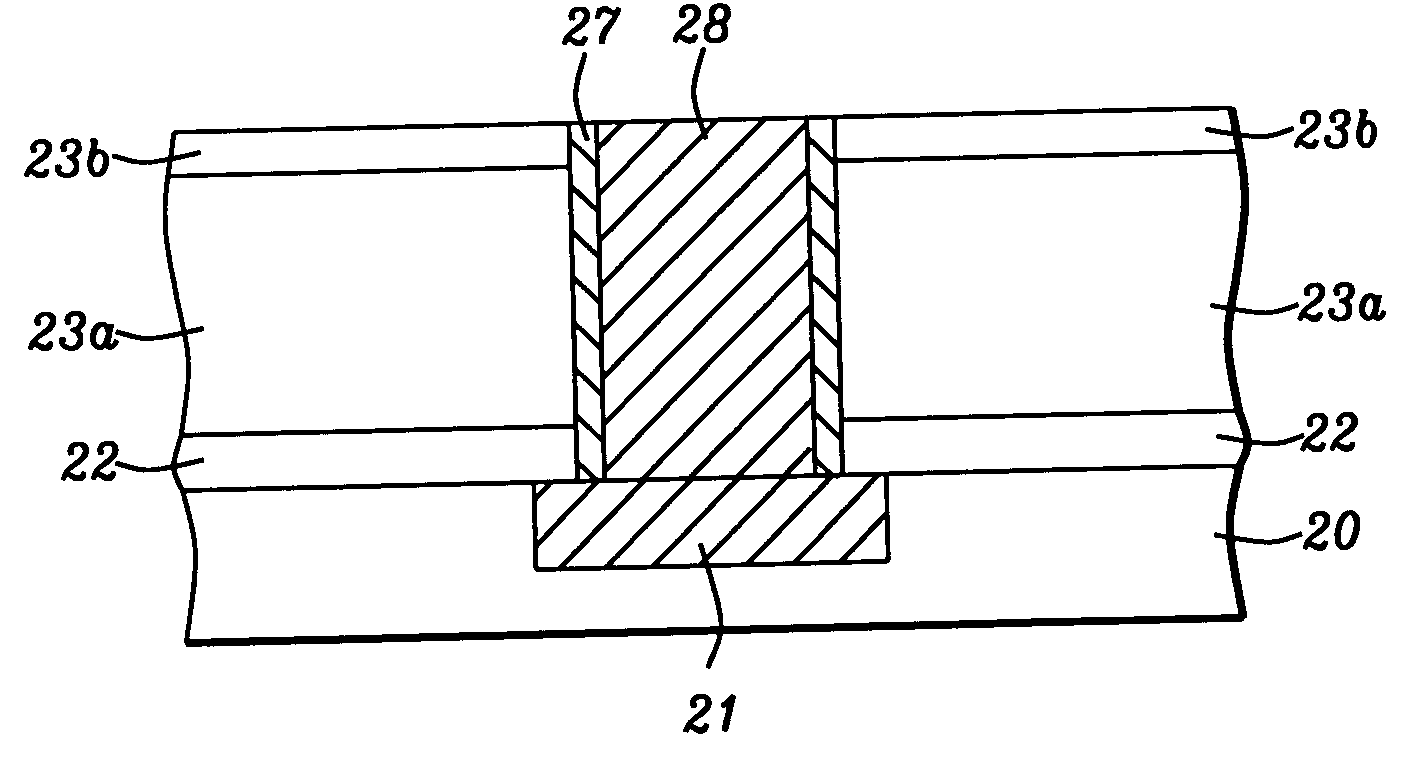

Strained silicon fin structure

InactiveUS20060113522A1Suppression of short channel effectsIncrease currentTransistorSemiconductor/solid-state device manufacturingDriving currentLattice mismatch

Disclosing is a strained silicon finFET device having a strained silicon fin channel in a double gate finFET structure. The disclosed finFET device is a double gate MOSFET consisting of a silicon fin channel controlled by a self-aligned double gate for suppressing short channel effect and enhancing drive current. The silicon fin channel of the disclosed finFET device is a strained silicon fin channel, comprising a strained silicon layer deposited on a seed fin having different lattice constant, for example, a silicon layer deposited on a silicon germanium seed fin, or a carbon doped silicon layer deposited on a silicon seed fin. The lattice mismatch between the silicon layer and the seed fin generates the strained silicon fin channel in the disclosed finFET device to improve hole and electron mobility enhancement, in addition to short channel effect reduction characteristic inherently in a finFET device.

Owner:MICROSOFT TECH LICENSING LLC +1

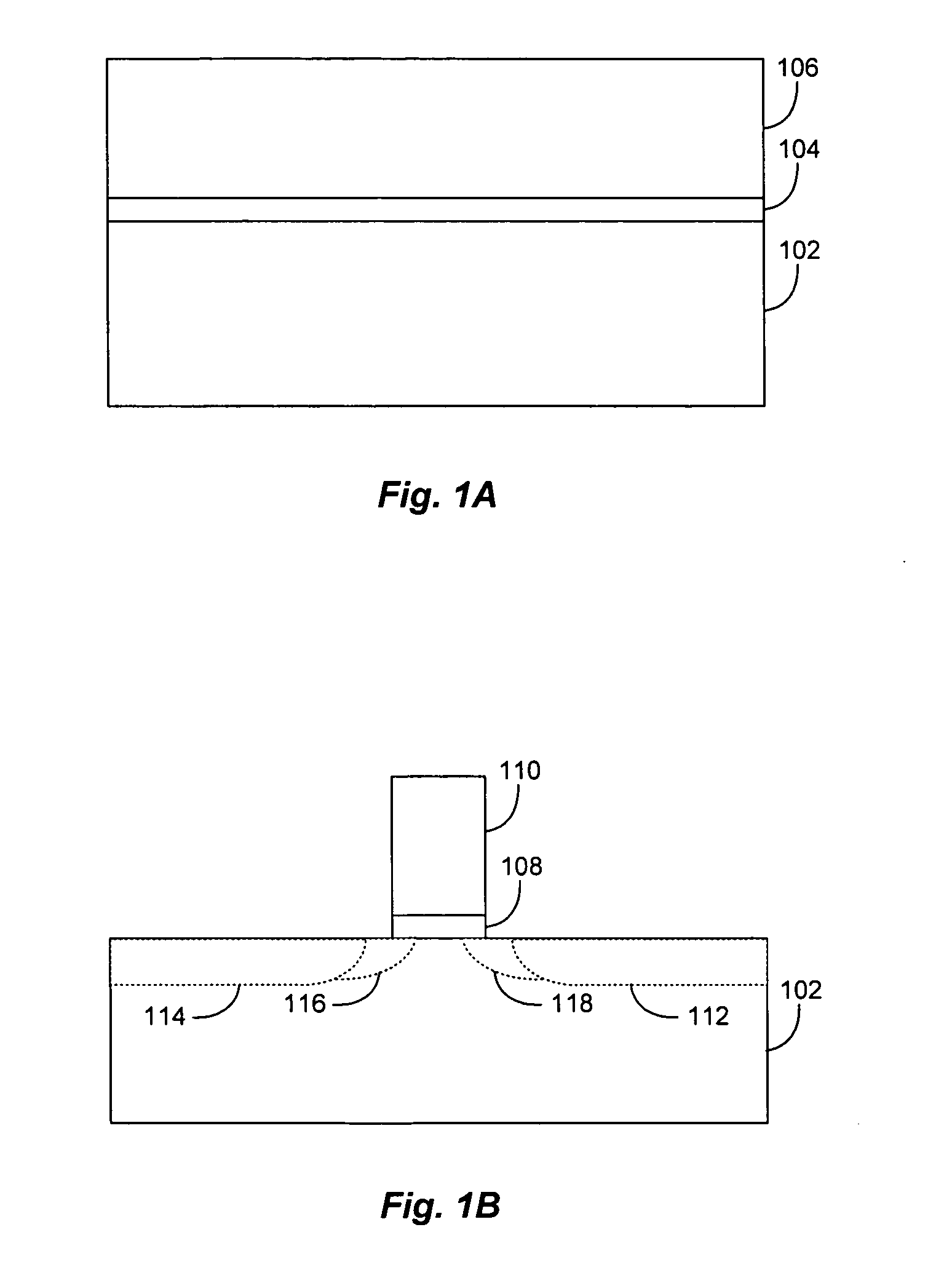

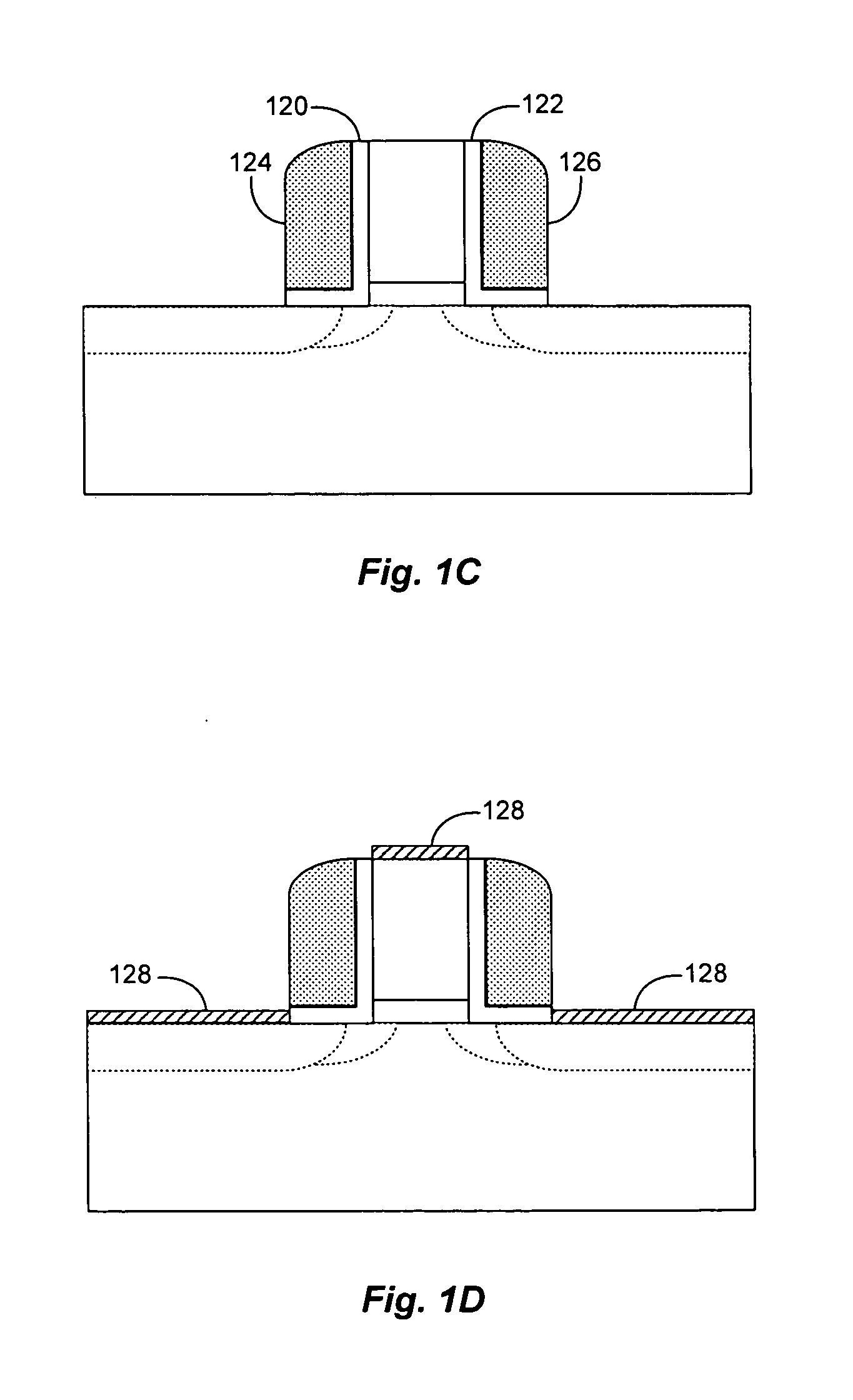

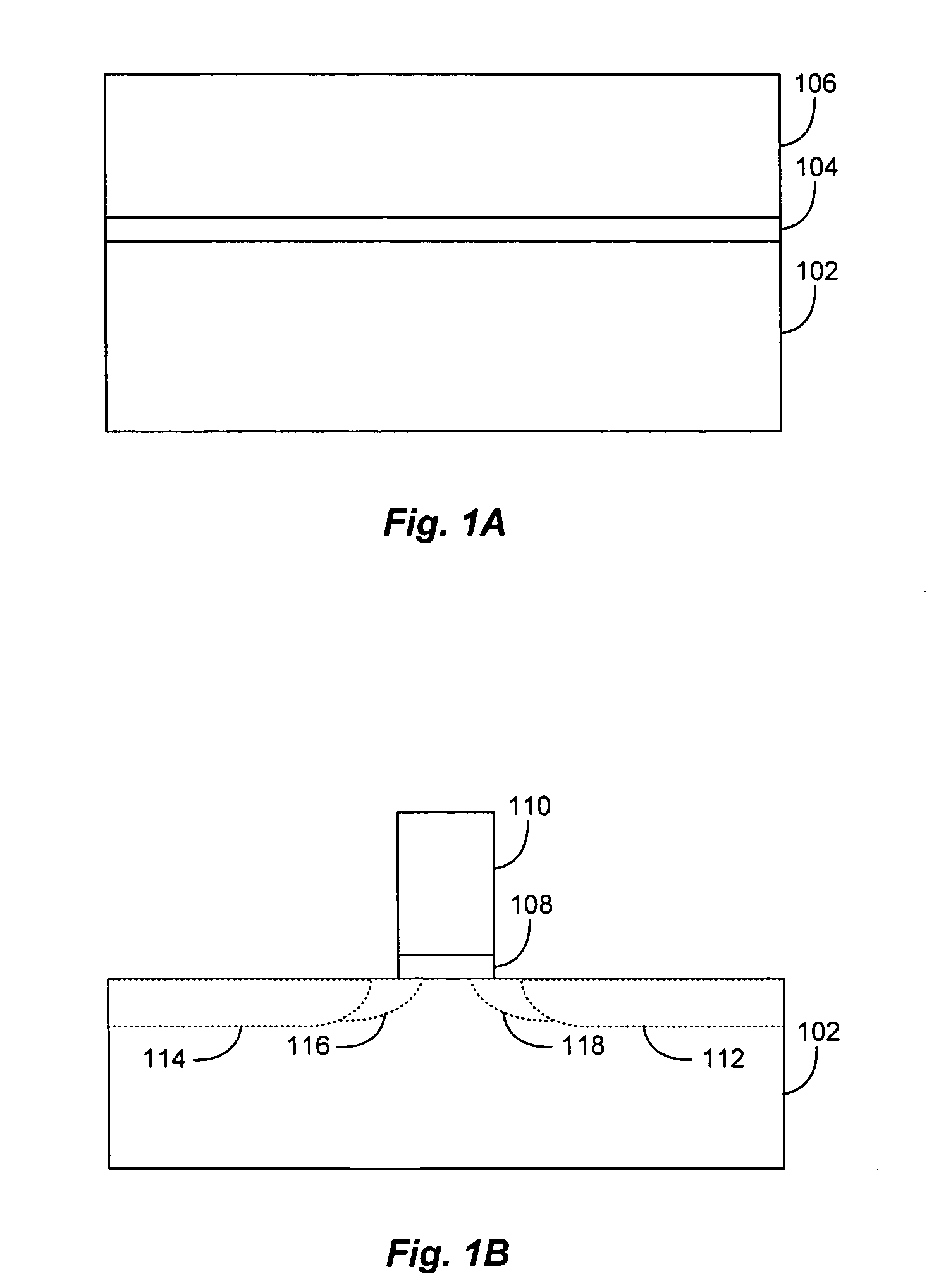

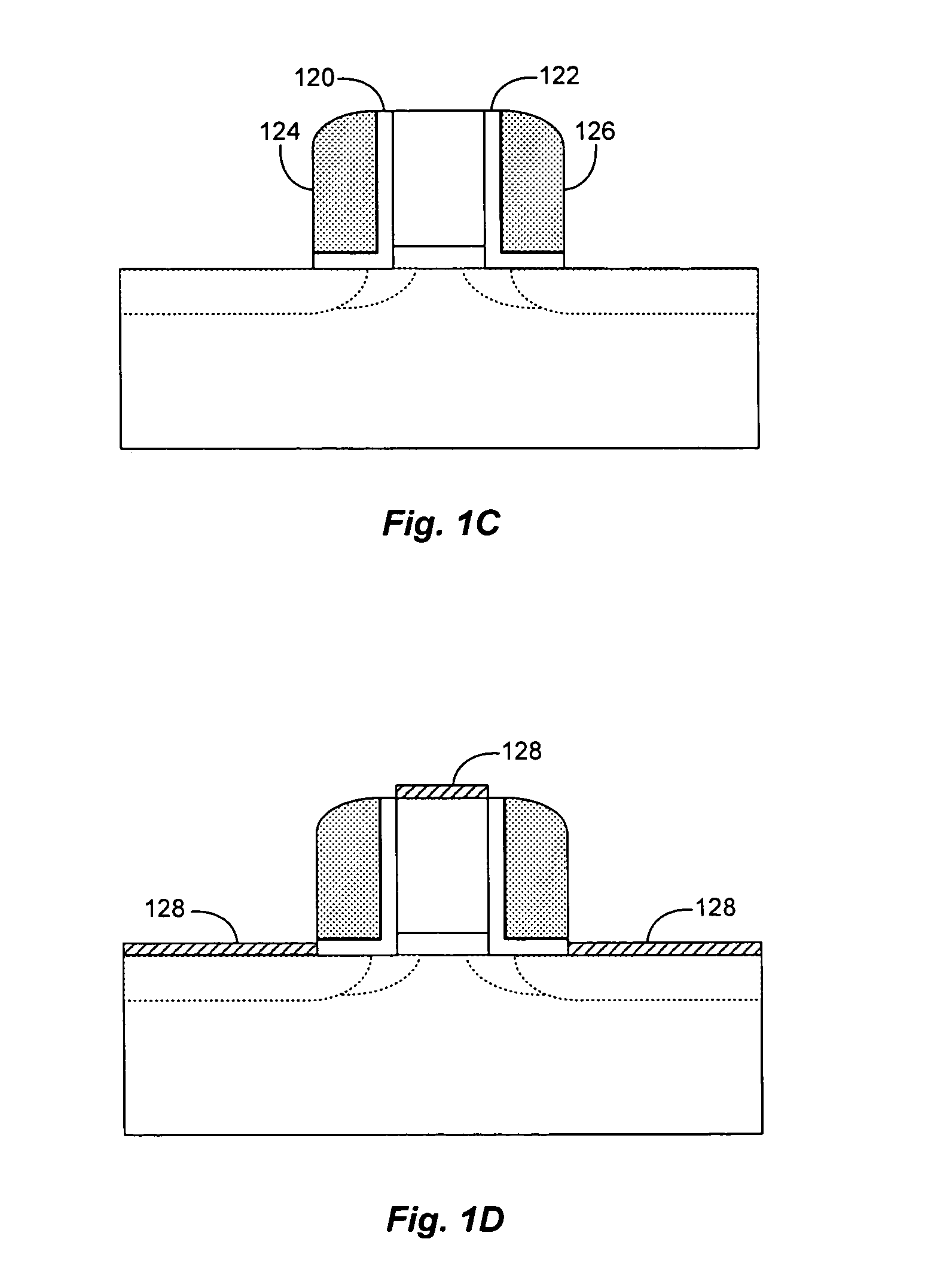

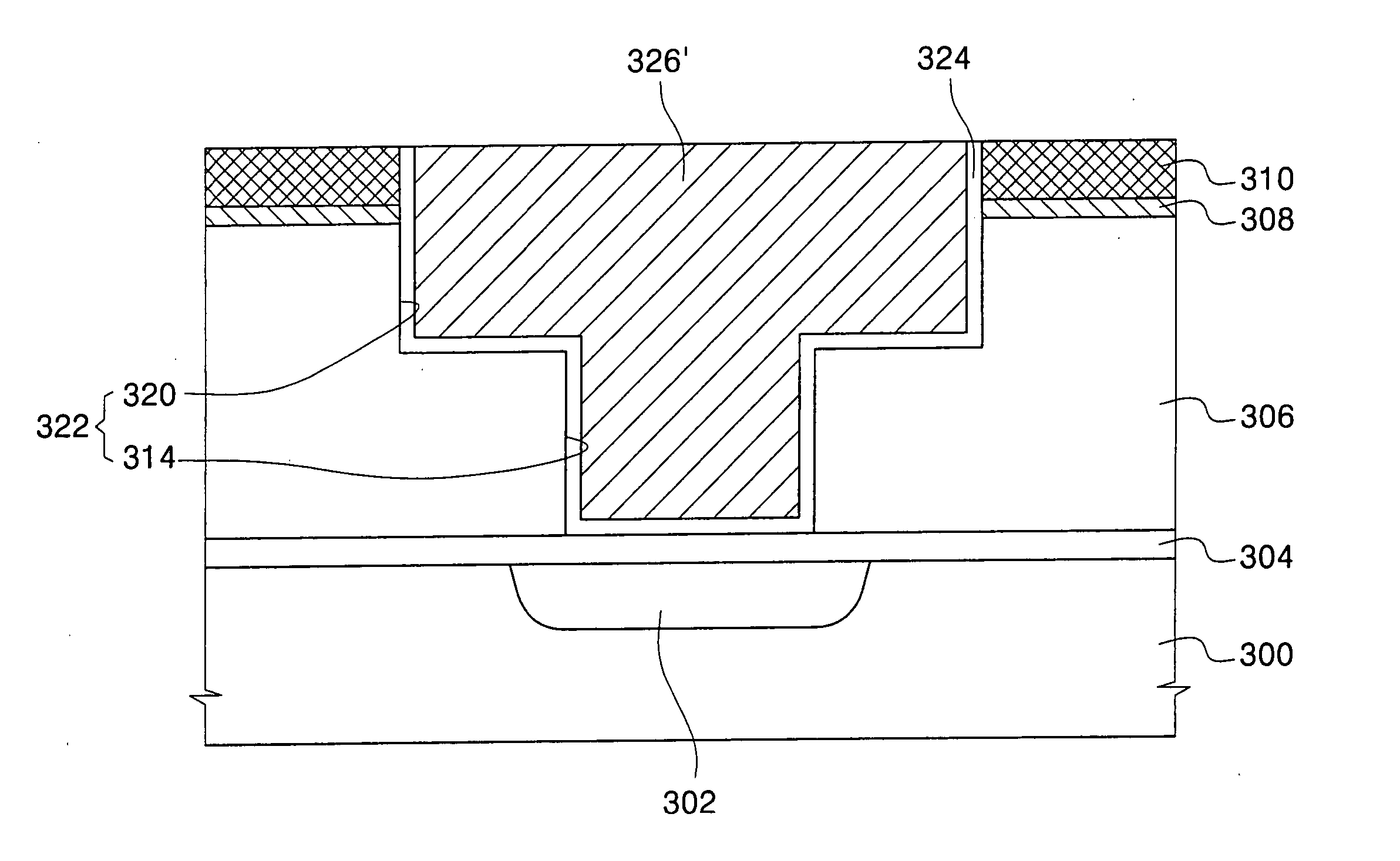

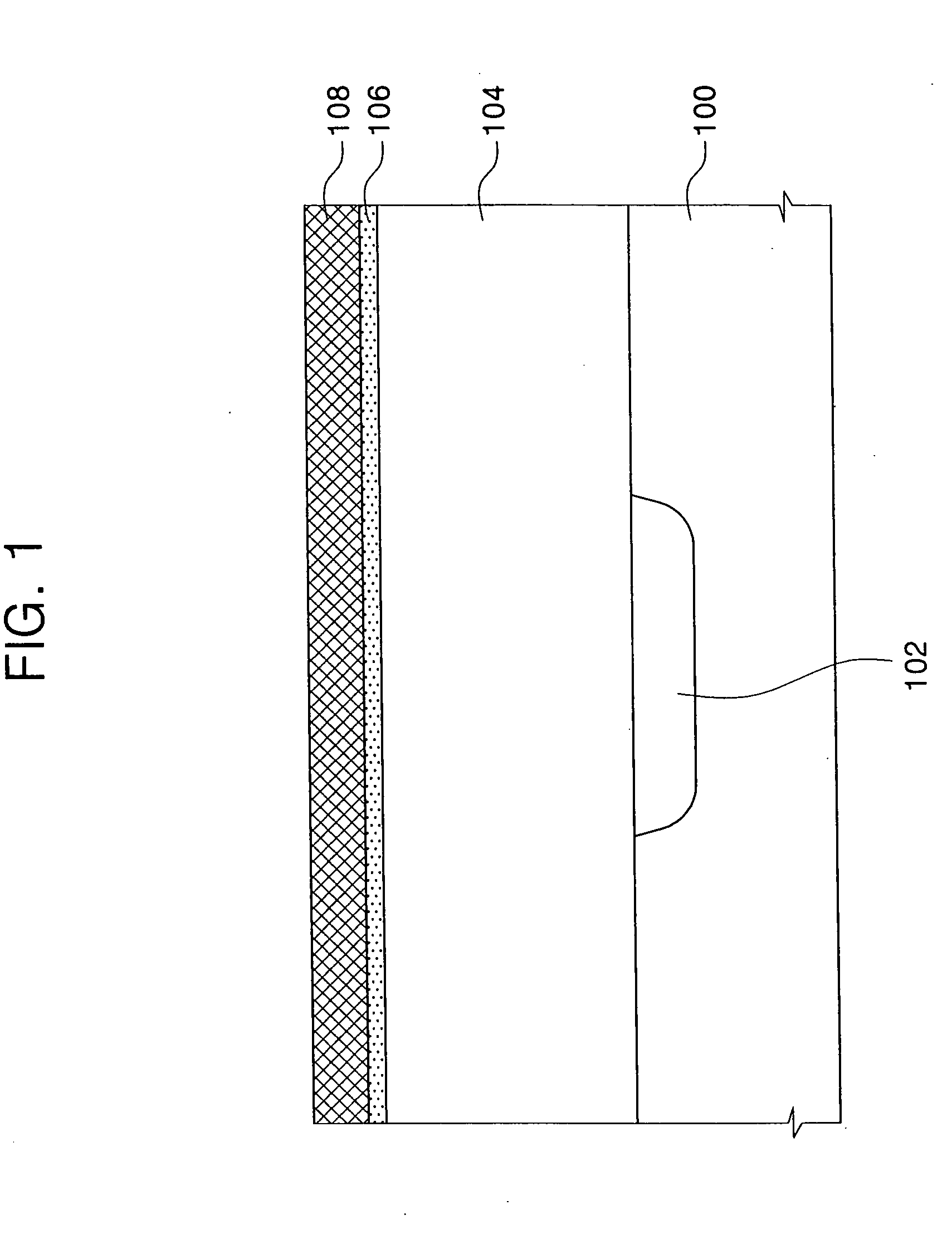

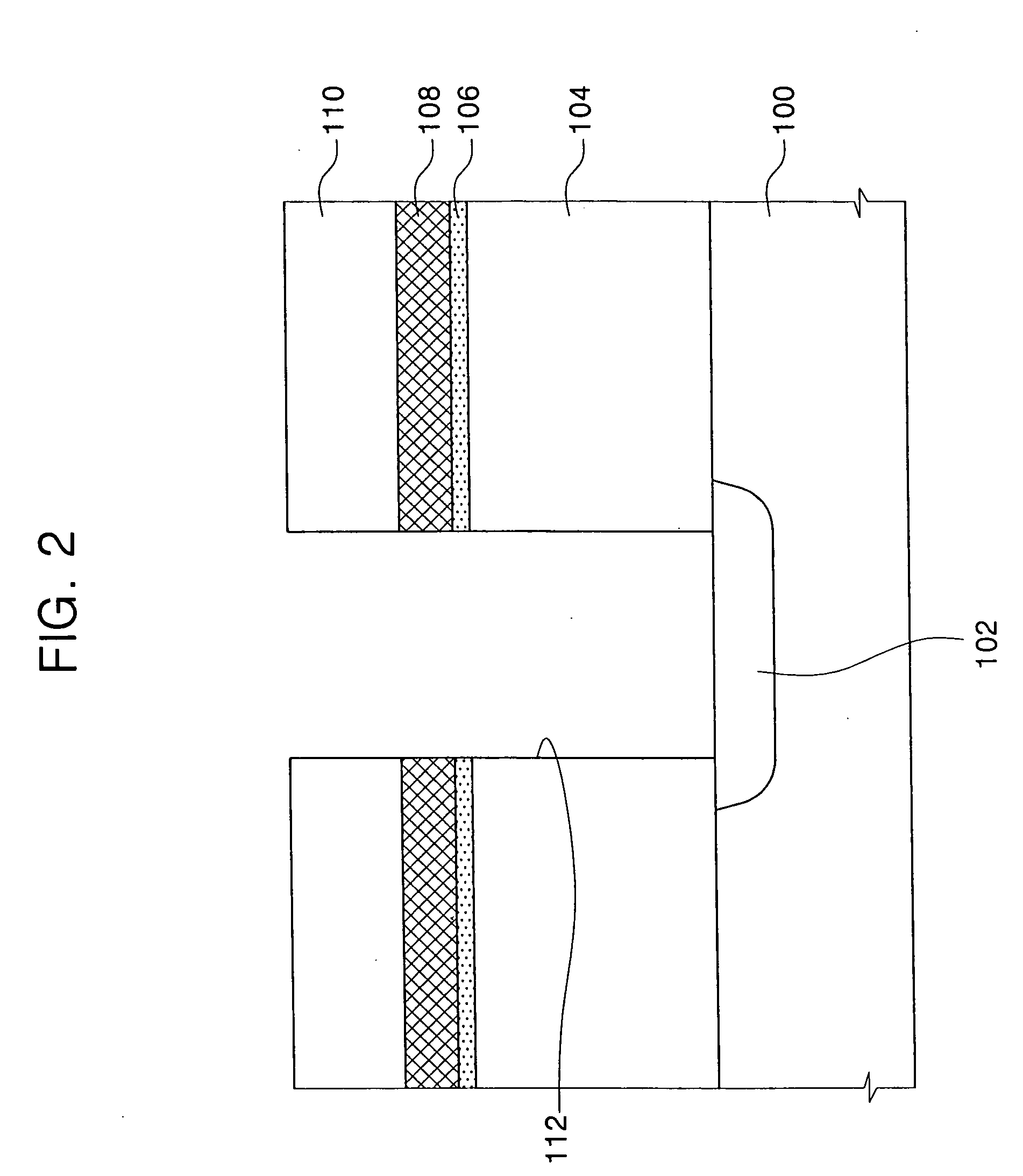

Method for forming a low thermal budget spacer

InactiveUS20050266622A1Semiconductor/solid-state device manufacturingSemiconductor devicesSilanesNitride

A method of forming a sidewall spacer on a gate electrode of a metal oxide semiconductor device that includes striking a first plasma to form an oxide layer on a side of the gate electrode, where the first plasma is generated from a oxide gas that includes O3 and bis-(tertiarybutylamine)silane, and striking a second plasma to form a carbon-doped nitride layer on the oxide layer, where the second plasma may be generated from a nitride gas that includes NH3 and the bis-(tertiarybutylamine)silane. The first and second plasmas may be formed using plasma CVD and the bis-(tertiarybutylamine)silane flows uninterrupted between the striking of the first plasma and the striking of the second plasma.

Owner:APPLIED MATERIALS INC

Method for forming a low thermal budget spacer

InactiveUS7049200B2Semiconductor/solid-state device manufacturingSemiconductor devicesSilanesNitride

A method of forming a sidewall spacer on a gate electrode of a metal oxide semiconductor device that includes striking a first plasma to form an oxide layer on a side of the gate electrode, where the first plasma is generated from a oxide gas that includes O3 and bis-(tertiarybutylamine)silane, and striking a second plasma to form a carbon-doped nitride layer on the oxide layer, where the second plasma may be generated from a nitride gas that includes NH3 and the bis-(tertiarybutylamine)silane. The first and second plasmas may be formed using plasma CVD and the bis-(tertiarybutylamine)silane flows uninterrupted between the striking of the first plasma and the striking of the second plasma.

Owner:APPLIED MATERIALS INC

Ultra-conformal carbon film deposition layer-by-layer deposition of carbon-doped oxide films

ActiveUS20160005596A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMetallurgyCarbon doped

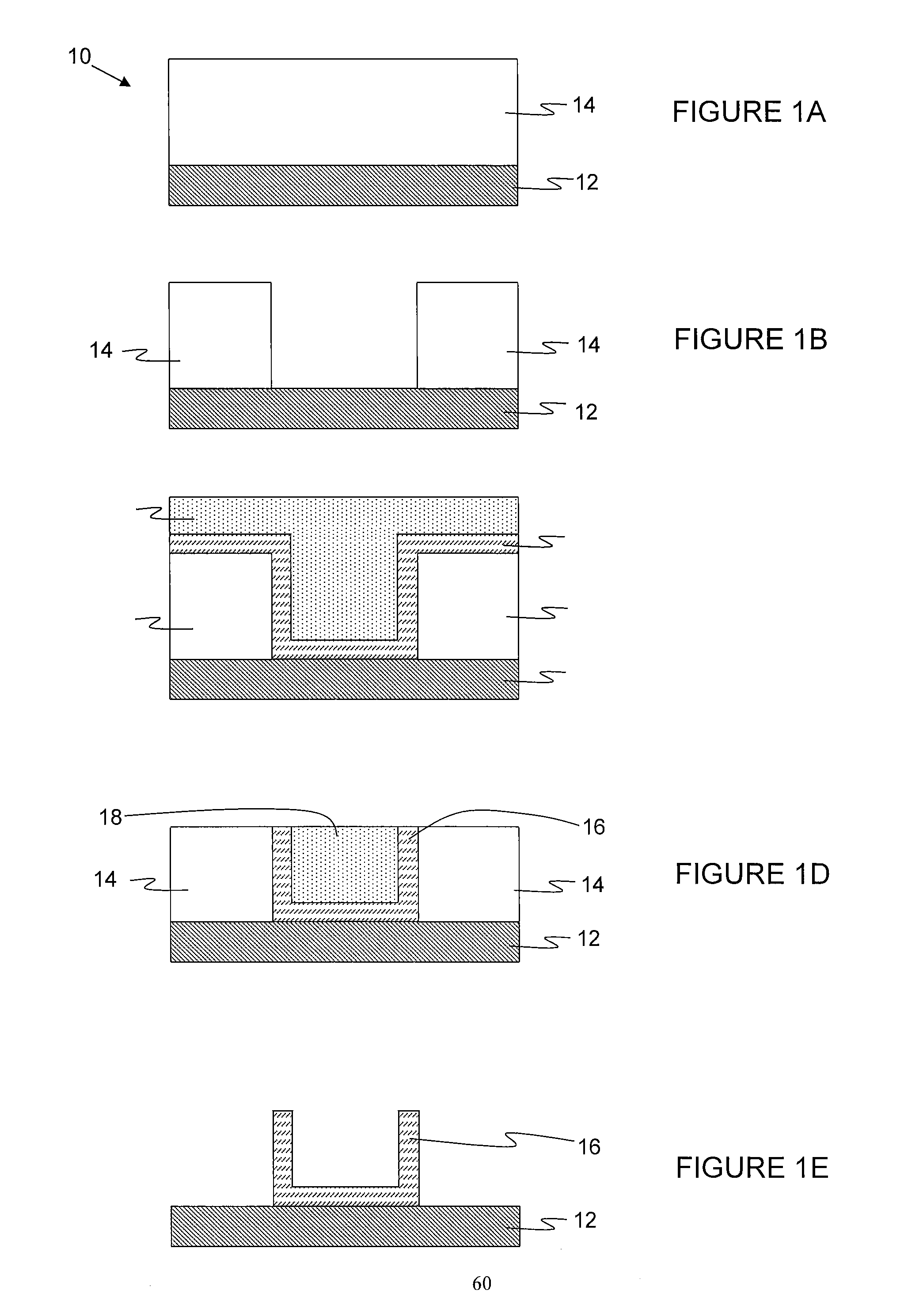

Embodiments of the invention relate to deposition of a conformal carbon-based material. In one embodiment, the method comprises depositing a sacrificial dielectric layer with a predetermined thickness over a substrate, forming patterned features on the substrate by removing portions of the sacrificial dielectric layer to expose an upper surface of the substrate, introducing a hydrocarbon source, a plasma-initiating gas, and a dilution gas into the processing chamber, wherein a volumetric flow rate of hydrocarbon source: plasma-initiating gas: dilution gas is in a ratio of 1:0.5:20, generating a plasma at a deposition temperature of about 300 C to about 500 C to deposit a conformal amorphous carbon layer on the patterned features and the exposed upper surface of the substrate, selectively removing the amorphous carbon layer from an upper surface of the patterned features and the upper surface of the substrate, and removing the patterned features.

Owner:APPLIED MATERIALS INC

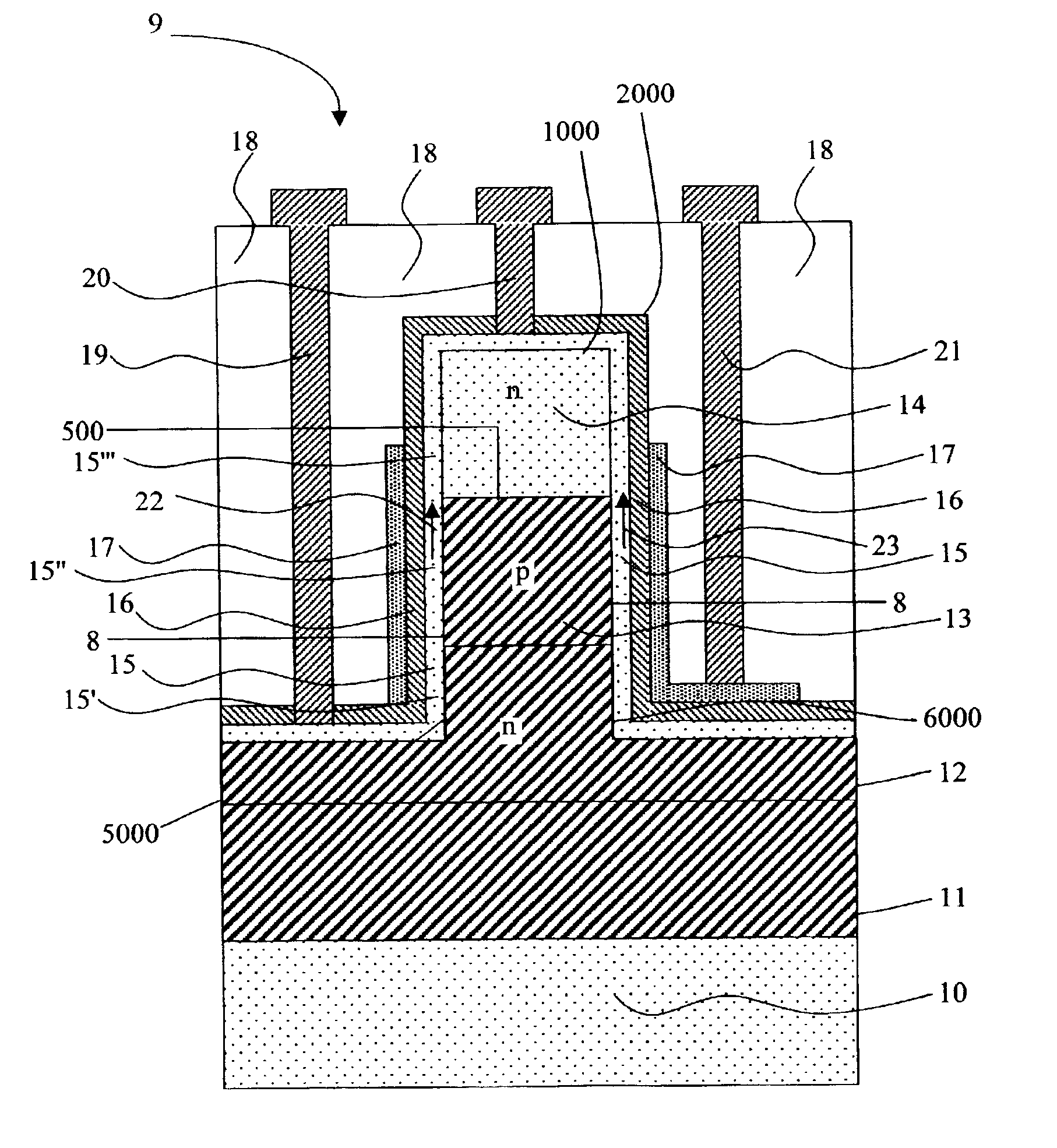

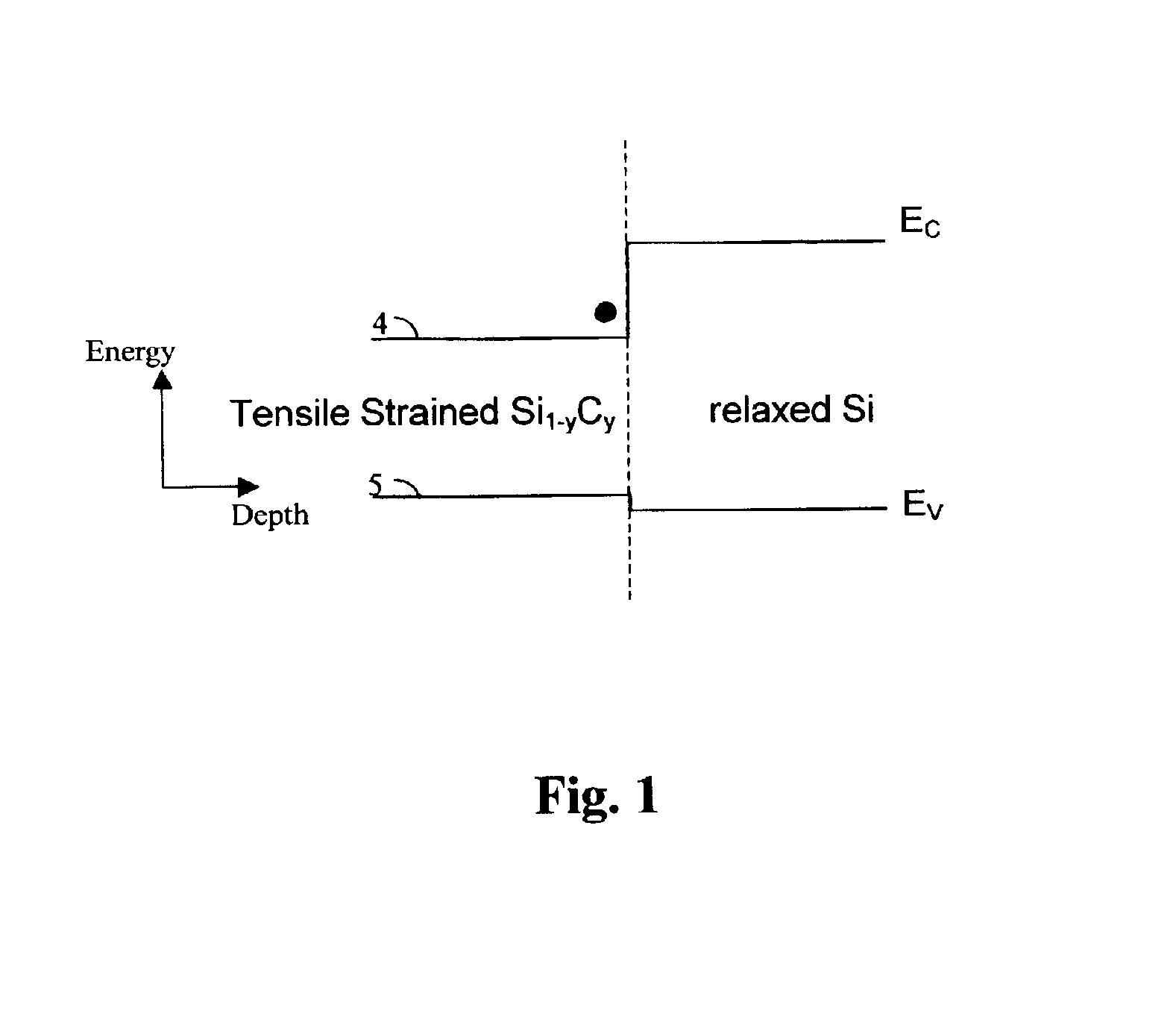

Patterned strained semiconductor substrate and device

ActiveUS20060019462A1Semiconductor/solid-state device manufacturingSemiconductor devicesLattice constantSemiconductor

A method that includes forming a pattern of strained material and relaxed material on a substrate; forming a strained device in the strained material; and forming a non-strained device in the relaxed material is disclosed. In one embodiment, the strained material is silicon (Si) in either a tensile or compressive state, and the relaxed material is Si in a normal state. A buffer layer of silicon germanium (SiGe), silicon carbon (SiC), or similar material is formed on the substrate and has a lattice constant / structure mis-match with the substrate. A relaxed layer of SiGe, SiC, or similar material is formed on the buffer layer and places the strained material in the tensile or compressive state. In another embodiment, carbon-doped silicon or germanium-doped silicon is used to form the strained material. The structure includes a multi-layered substrate having strained and non-strained materials patterned thereon.

Owner:TAIWAN SEMICON MFG CO LTD

Precursors for the deposition of carbon-doped silicon nitride or silicon oxynitride films

InactiveUS20060228903A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingEtchingMetallurgy

Owner:INTEL CORP

Epitaxial deposition of doped semiconductor materials

ActiveUS7863163B2Polycrystalline material growthSemiconductor/solid-state device manufacturingSemiconductor materialsSingle crystal

A method for depositing a carbon doped epitaxial semiconductor layer comprises maintaining a pressure of greater than about 700 torr in a process chamber housing a patterned substrate having exposed single crystal material. The method further comprises providing a flow of a silicon source gas to the process chamber. The silicon source gas comprises dichlorosilane. The method further comprises providing a flow of a carbon precursor to the process chamber. The method further comprises selectively depositing the carbon doped epitaxial semiconductor layer on the exposed single crystal material.

Owner:ASM IP HLDG BV

Low leakage heterojunction vertical transistors and high performance devices thereof

InactiveUS20070148939A1Superb performanceSuperb scalabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

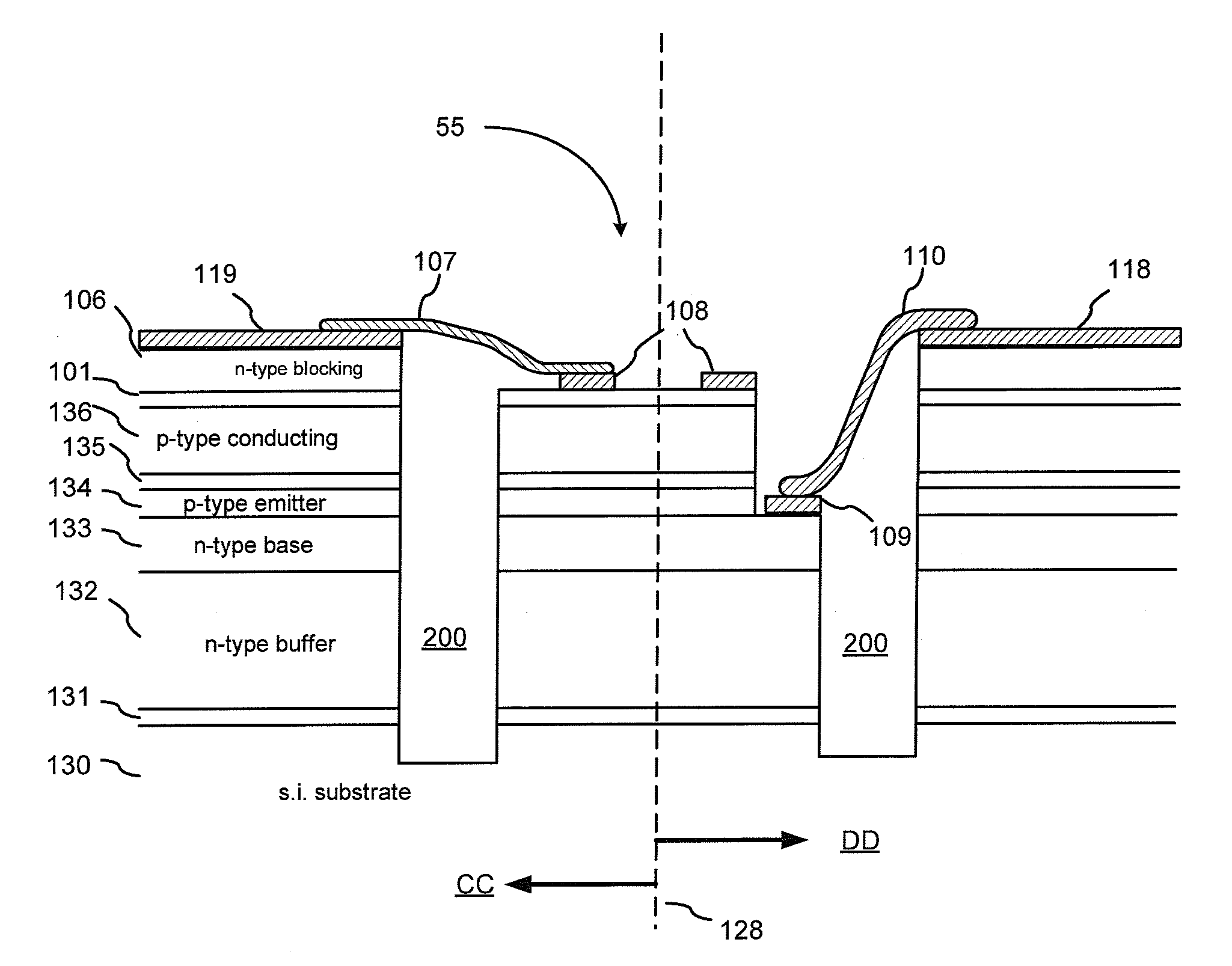

A method for forming and the structure of a vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry are described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a hetero-junction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (i.e., B and P) into the body. The invention reduces the problem of short channel effects such as drain induced barrier lowering and the leakage current from the source to drain regions via the hetero-junction and while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials. The problem of scalability of the gate length below 100 nm is overcome by the heterojunction between the source and body regions.

Owner:GLOBALFOUNDRIES INC

Two step post-deposition treatment of ILD layer for a lower dielectric constant and improved mechanical properties

InactiveUS20050064698A1Increase resistanceImprove the immunityDecorative surface effectsSemiconductor/solid-state device detailsMoistureMechanical property

A method of lowering the dielectric constant of an organosilicon low k dielectric layer while improving the hardness and thermal stability is provided. A deposited layer of carbon doped oxide, HSQ, or MSQ is cured and treated with a He plasma which improves hardness for a subsequent CMP step and lowers the dielectric constant. There is no loss of H2O or CH4 during the He treatment. The low k dielectric layer is then treated with a H2 plasma which converts some of the Si—O and Si—CH3 bonds near the surface to Si—H bonds, thereby further lowering the dielectric constant and increasing thermal stability that improves breakdown resistance. Moisture uptake is also reduced. The method is especially useful for interconnect schemes with deep sub-micron ground rules. Surprisingly, the k value obtained from two different plasma treatments is lower than when two He treatments or two H2 treatment are performed.

Owner:TAIWAN SEMICON MASNUFACTURING

Ultra scalable high speed heterojunction vertical n-channel MISFETs and methods thereof

ActiveUS7205604B2Superb performanceSuperb scalabilityTransistorDiagnosticsHeterojunctionSemiconductor materials

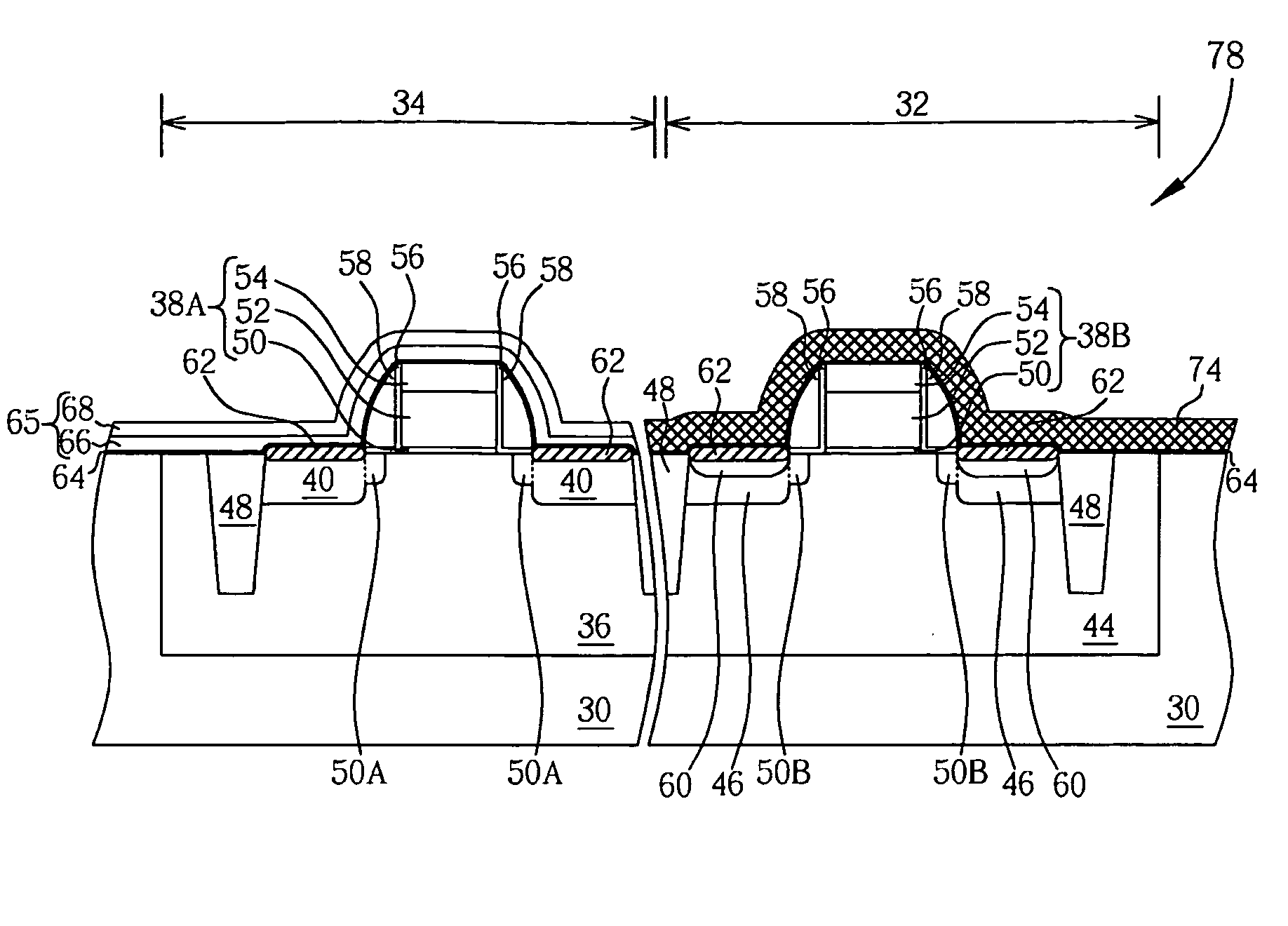

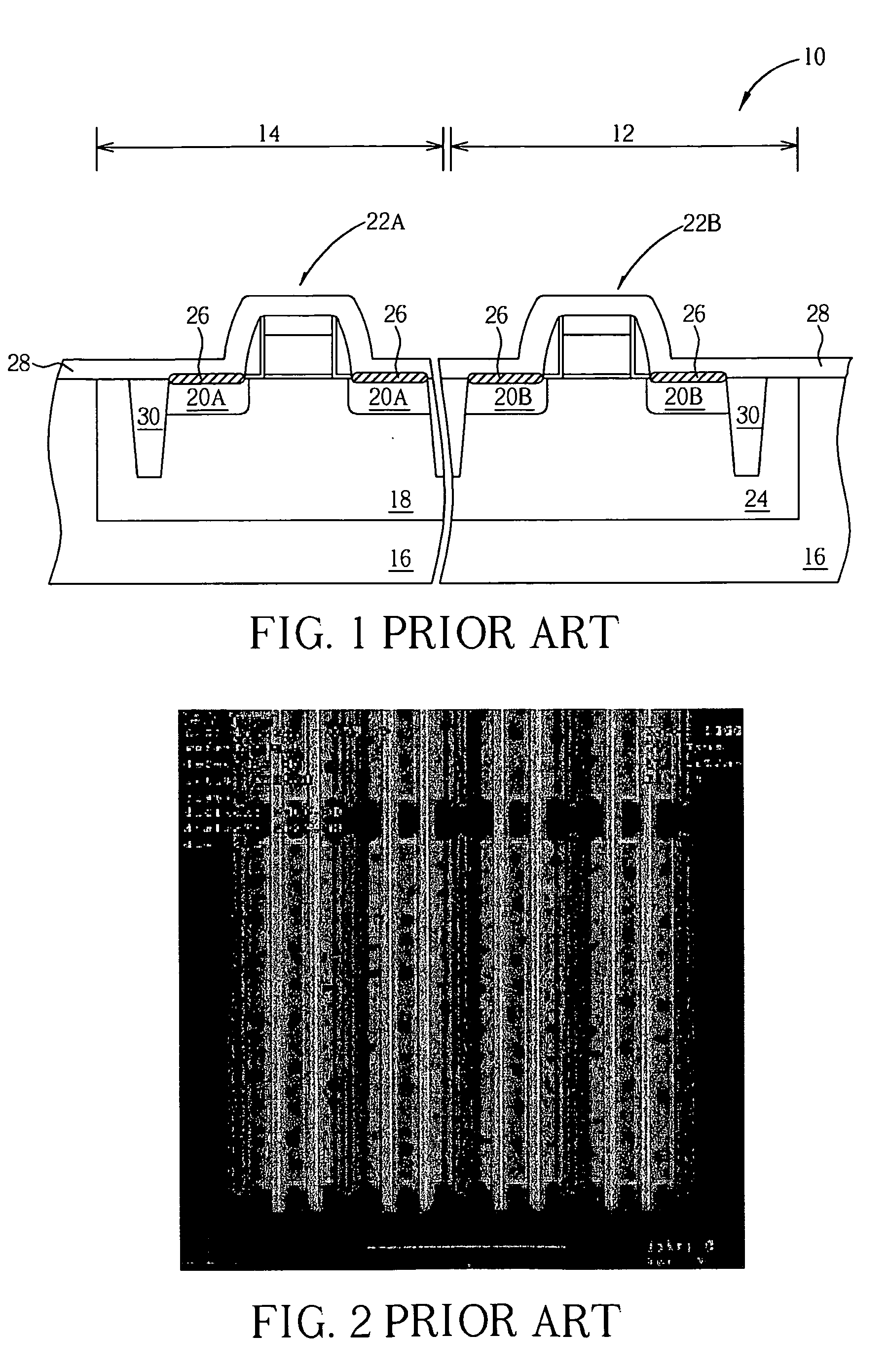

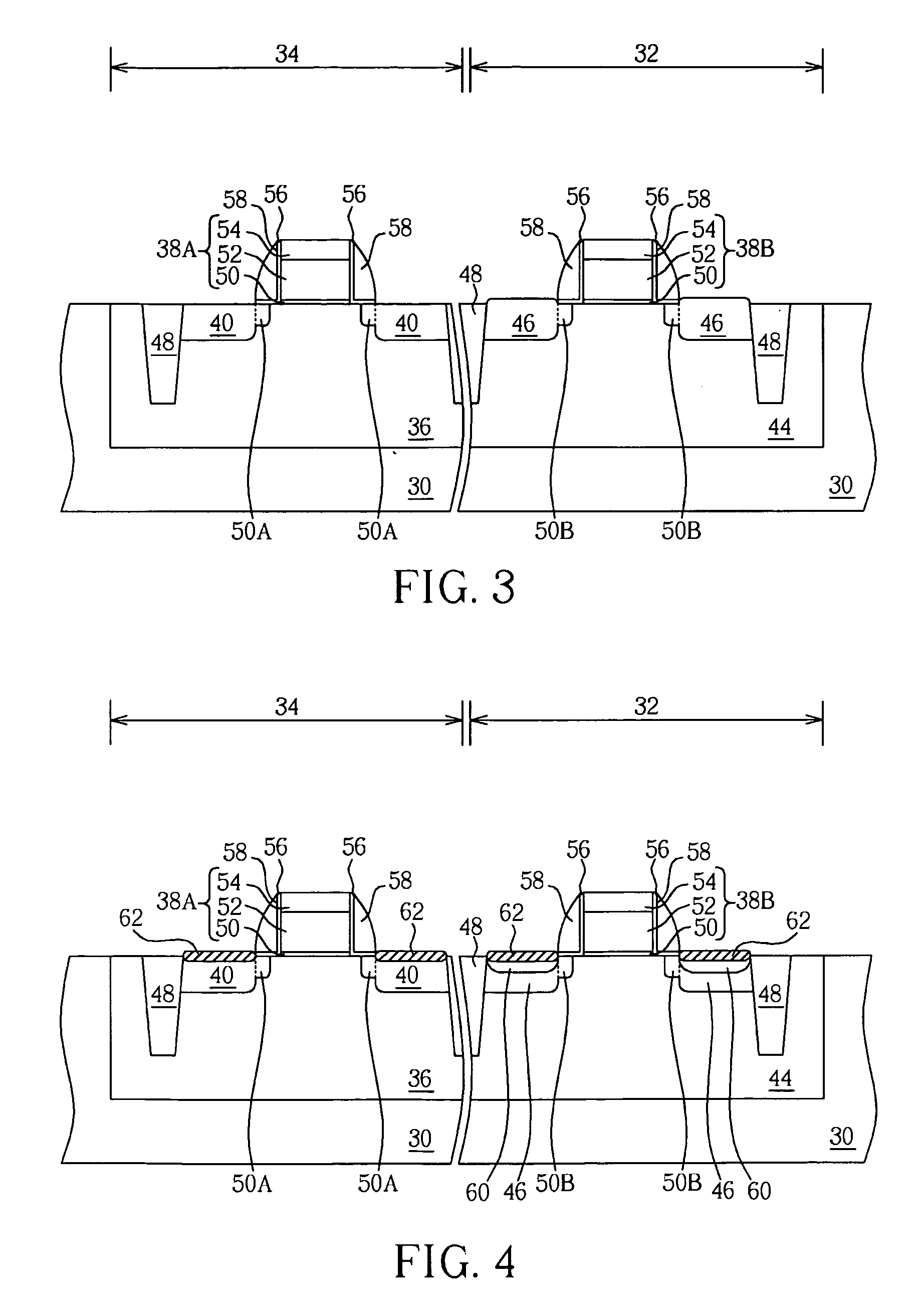

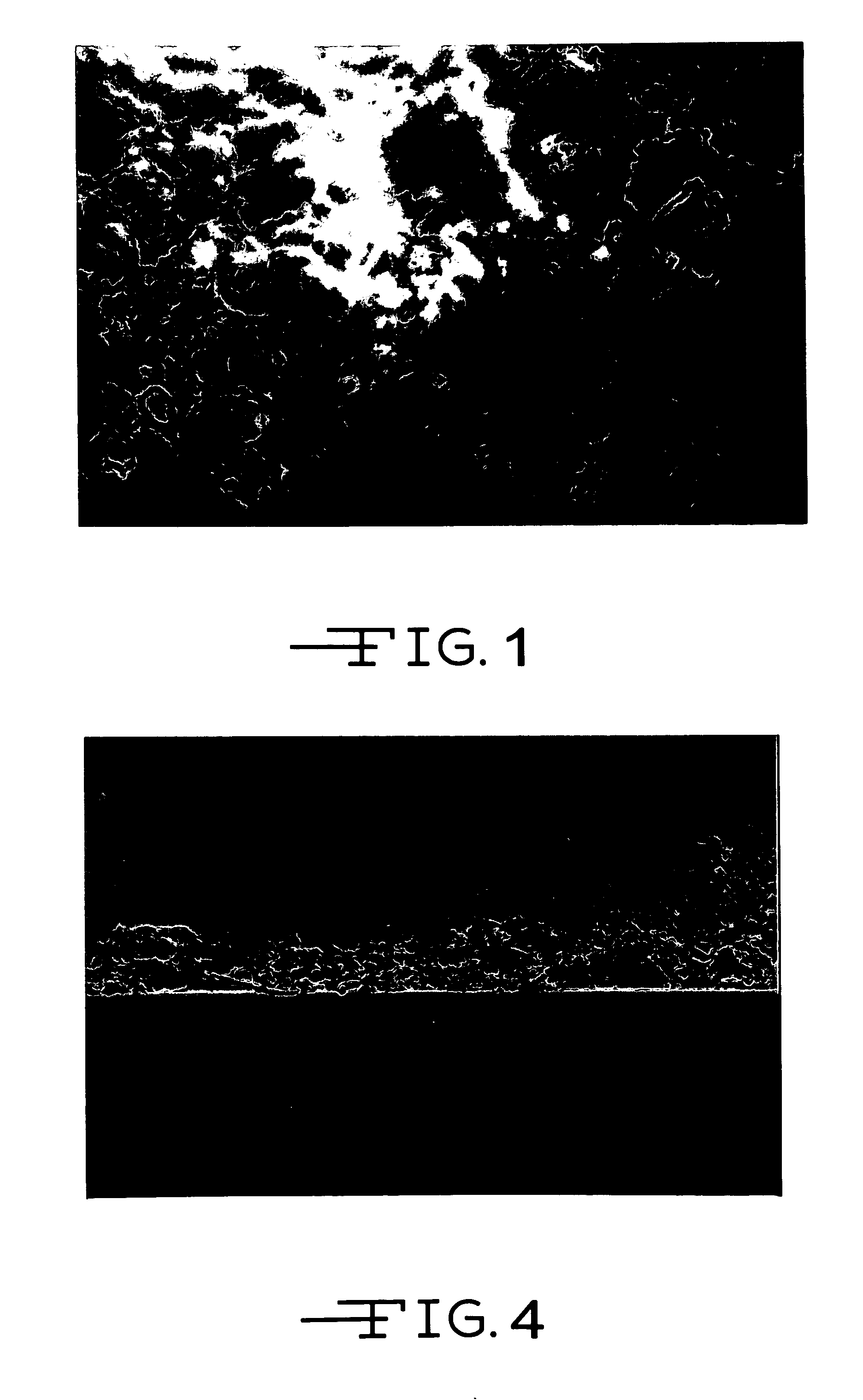

A method for forming and the structure of a strained vertical channel of a field effect transistor, a field effect transistor and CMOS circuitry is described incorporating a drain, body and source region on a sidewall of a vertical single crystal semiconductor structure wherein a heterojunction is formed between the source and body of the transistor, wherein the source region and channel are independently lattice strained with respect to the body region and wherein the drain region contains a carbon doped region to prevent the diffusion of dopants (boron) into the body. The invention reduces the problem of leakage current from the source region via the heterojunction and lattice strain while independently permitting lattice strain in the channel region for increased mobility via choice of the semiconductor materials.

Owner:GLOBALFOUNDRIES US INC

High-strength and high-toughness reactive powder concrete of carbon doped nano-tube and preparation method of high-strength and high-toughness reactive powder concrete

The invention provides high-strength and high-toughness reactive powder concrete of a carbon doped nano-tube. The high-strength and high-toughness reactive powder concrete is prepared by taking cement, a carbon nano-tube, silica fume, a water reducing agent, silica sand, coal ash, quartz powder, steel fiber and water as raw materials, wherein all the components in the mixture are calculated in parts by mass: 1000-1200 parts of cement, 250-350 parts of silica fume, 250-350 parts of slag powder, 40-50 parts of water reducing agent, 1200-1400 parts of silica sand, 180-230 parts of water, 190-230 parts of steel fiber, 180-250 parts of coal ash, 80-120 parts of quartz powder, 0.1-5 parts of carbon-nano-tube dispersing agent and 1-10 parts of carbon nano-tube powder. The invention also provides a preparation method of the high-strength and high-toughness reactive powder concrete. The reactive powder concrete obtained by the invention has the high compression strength of 250-300MPa and breaking strength of 45-60MPa, which are higher than the 200-level related performances of the traditional RPC (Reactive Powder Concrete). Meanwhile, the initial cracking strength of the reactive powder concrete material prepared by using the carbon nano-tube is greatly improved and is up to 10MPa in a direct stretching state, and the tensile strain corresponding to peak stress is up to more than 0.5%, so that the toughness and strength of the traditional RPC material are greatly improved.

Owner:浙江固邦新材料有限公司

Formulations for cleaning memory device structures

InactiveUS20080125342A1Inorganic/elemental detergent compounding agentsOrganic detergent compounding agentsBorophosphosilicate glassSilicon oxide

A removal composition and process for removing silicon-containing layers from a microelectronic device having said layers thereon. The removal composition selectively removes layers including, but not limited to, silicon oxide, plasma enhanced tetraethyl orthosilicate (P-TEOS), borophosphosilicate glass (BPSG), plasma enhanced oxide (PEOX), high density plasma oxide (HDP), phosphosilicate glass (PSG), spin-on-dielectrics (SOD), thermal oxide, updoped silicate glass, sacrificial oxides, silicon-containing organic polymers, silicon-containing hybrid organic / inorganic materials, organosilicate glass (OSG), TEOS, fluorinated silicate glass (FSG), hemispherical grain (HSQ), carbon-doped oxide (CDO) glass, and combinations thereof, relative to lower electrode, device substrate, and / or etch stop layer materials.

Owner:ADVANCED TECH MATERIALS INC

Photovoltaic Power Converter

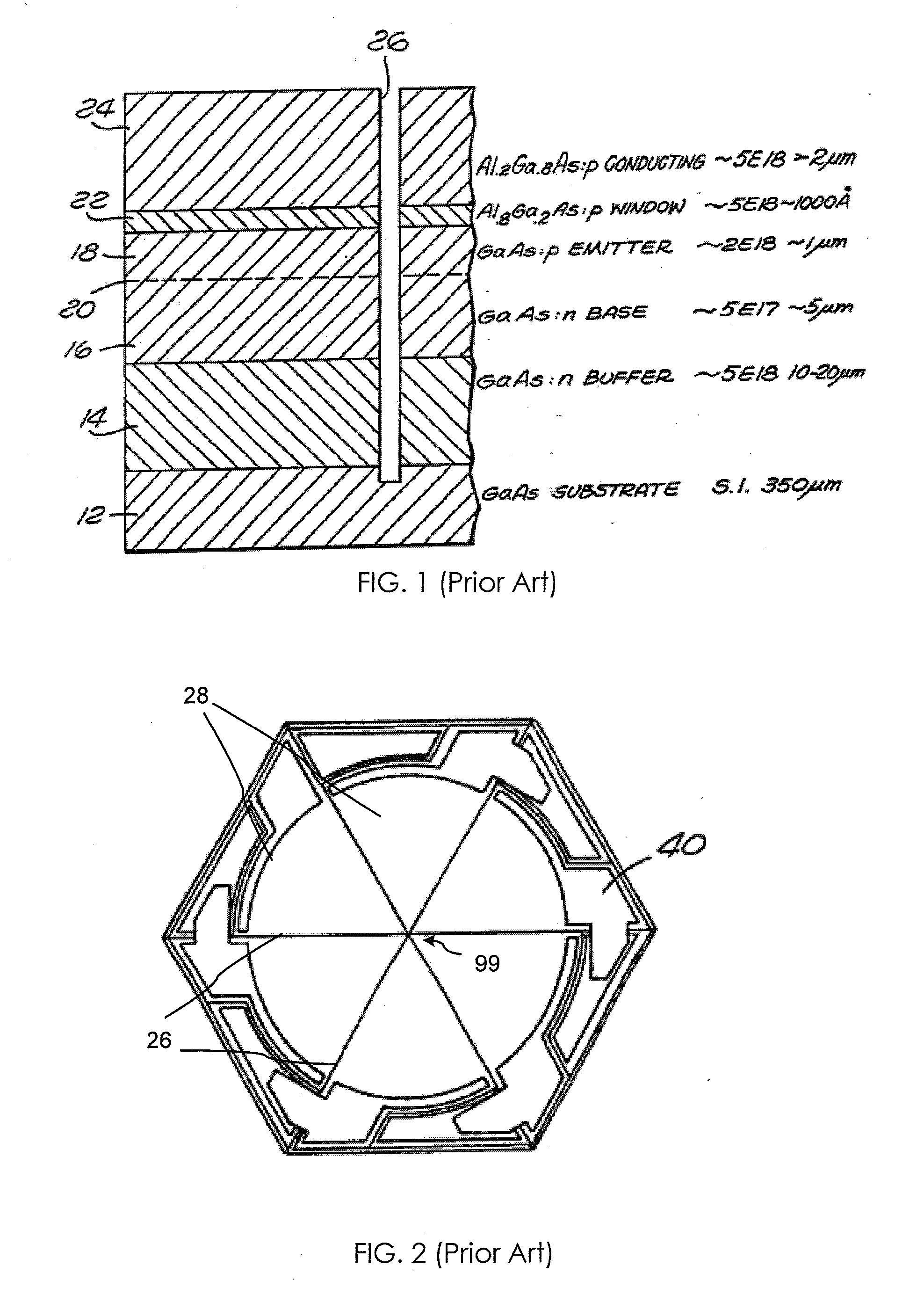

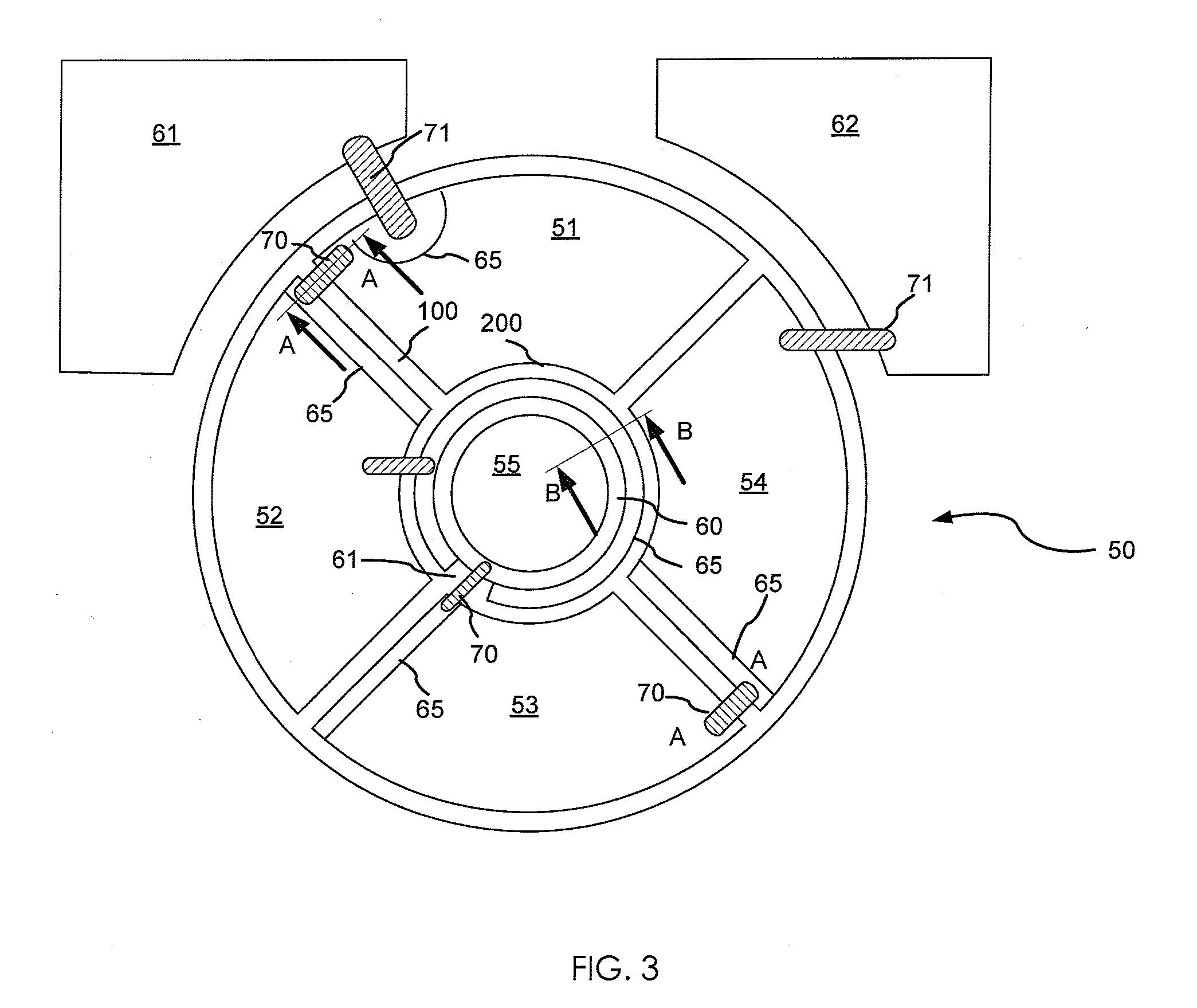

InactiveUS20110108081A1PV power plantsPhotovoltaic energy generationSemiconductor materialsOptoelectronics

The invention provides a photovoltaic power converter that includes a multilayer structure supported by a substrate having a base layer of a semiconductor material of a first conductivity type and a first emitter layer of a semiconductor material of a second conductivity type opposite said first conductivity type forming a p-n junction region therebetween, and a first current blocking layer of a semiconductor material of the second conductivity type interposed between the substrate and the first multilayer structure. The emitter layer is carbon doped.

Owner:JDS UNIPHASE CORP

CMOS transistor and the method for manufacturing the same

InactiveUS20100001317A1Preventing Ge-out diffusionTransistorSemiconductor/solid-state device manufacturingCMOSSemiconductor

A CMOS transistor and a method for manufacturing the same are disclosed. A semiconductor substrate having at least a PMOS transistor and an NMOS transistor is provided. The source / drain of the PMOS transistor comprises SiGe epitaxial layer. A carbon implantation process is performed to form a carbon-doped layer in the top portion of the source / drain of the PMOS transistor. A silicide layer is formed on the source / drain. A CESL is formed on the PMOS transistor and the NMOS transistor. The formation of the carbon-doped layer is capable of preventing Ge out-diffusion.

Owner:UNITED MICROELECTRONICS CORP

Nanotube coatings for implantable electrodes

ActiveUS7162308B2Reduce polarizationIncrease surface areaSpinal electrodesMaterial nanotechnologyImplantable ElectrodesBoron nitride

Coatings for implantable electrodes consisting of single- or multi-walled nanotubes, nanotube ropes, carbon whiskers, and a combination of these are described. The nanotubes can be carbon or other conductive nanotube-forming materials such as a carbon-doped boron nitride. The nanotube coatings are grown “in situ” on a catalytic substrate surface from thermal decomposition, or they are bonded to the substrate using a metal or conductive metal oxide thin film binder deposited by means of a metal compound precursor in liquid form. In the latter case, the precursor / nanotube coating is then converted to a pure metal or conductive metal oxide, resulting in the desired surface coating with imbedded nanotubes.

Owner:WILSON GREATBATCH LTD

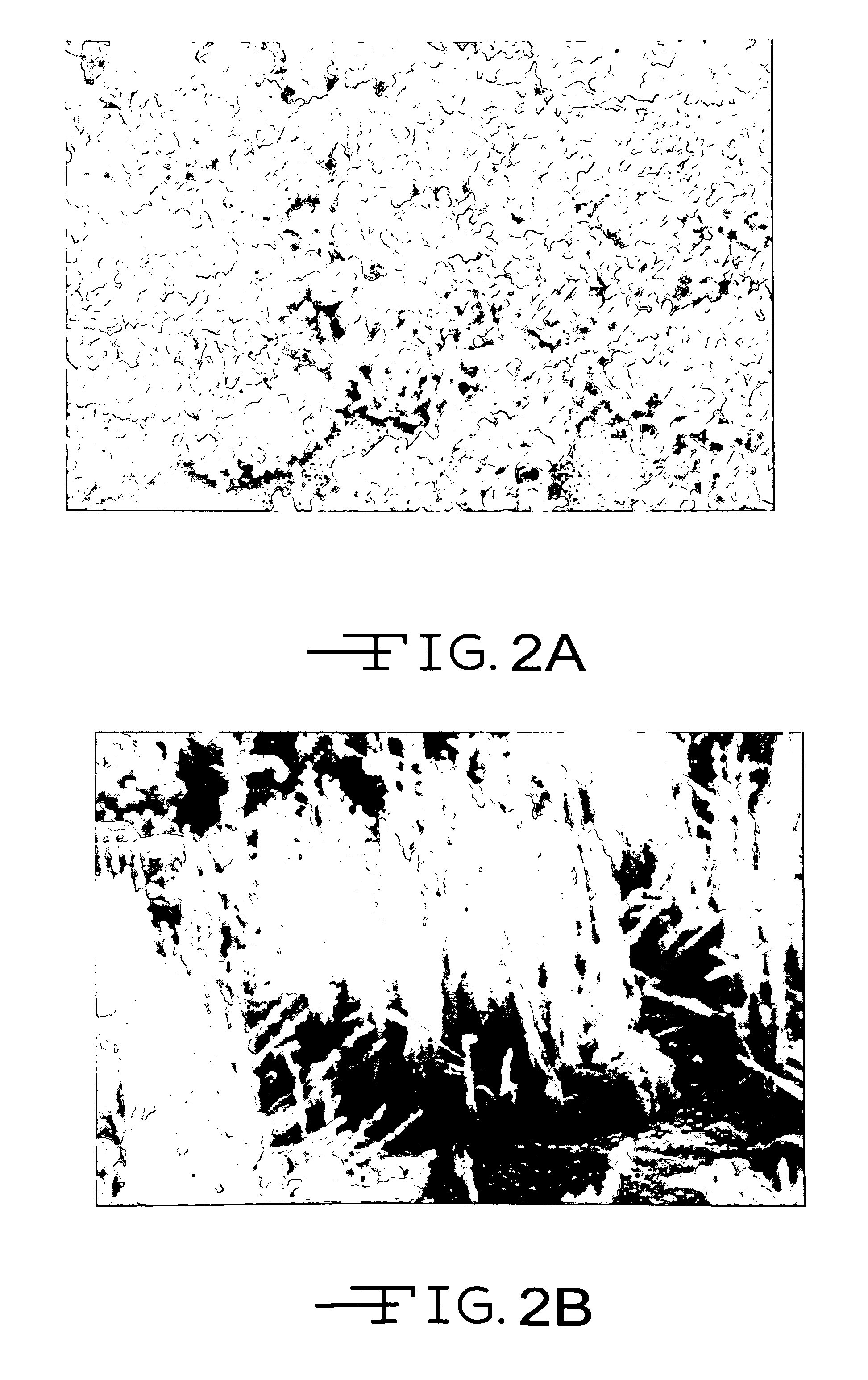

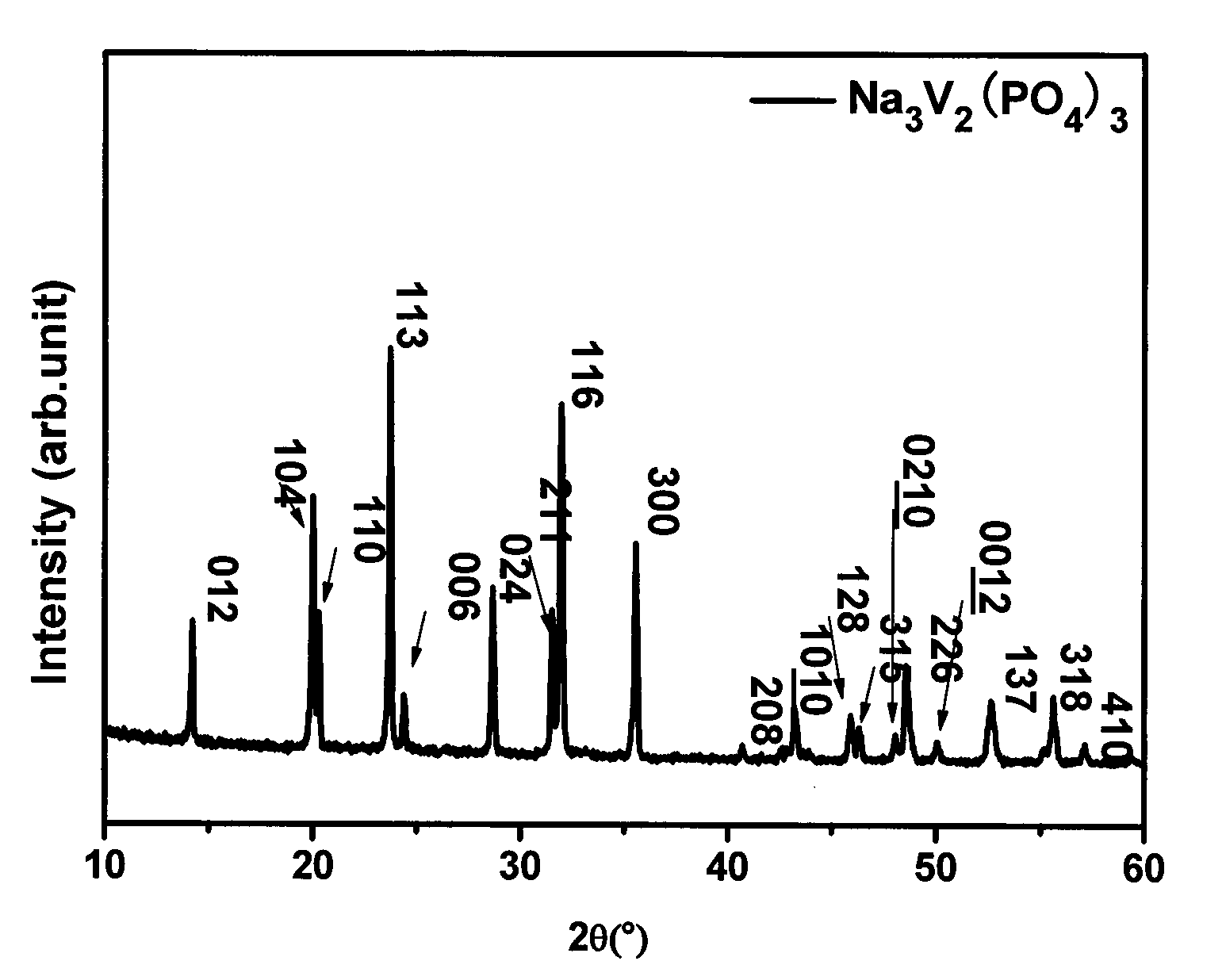

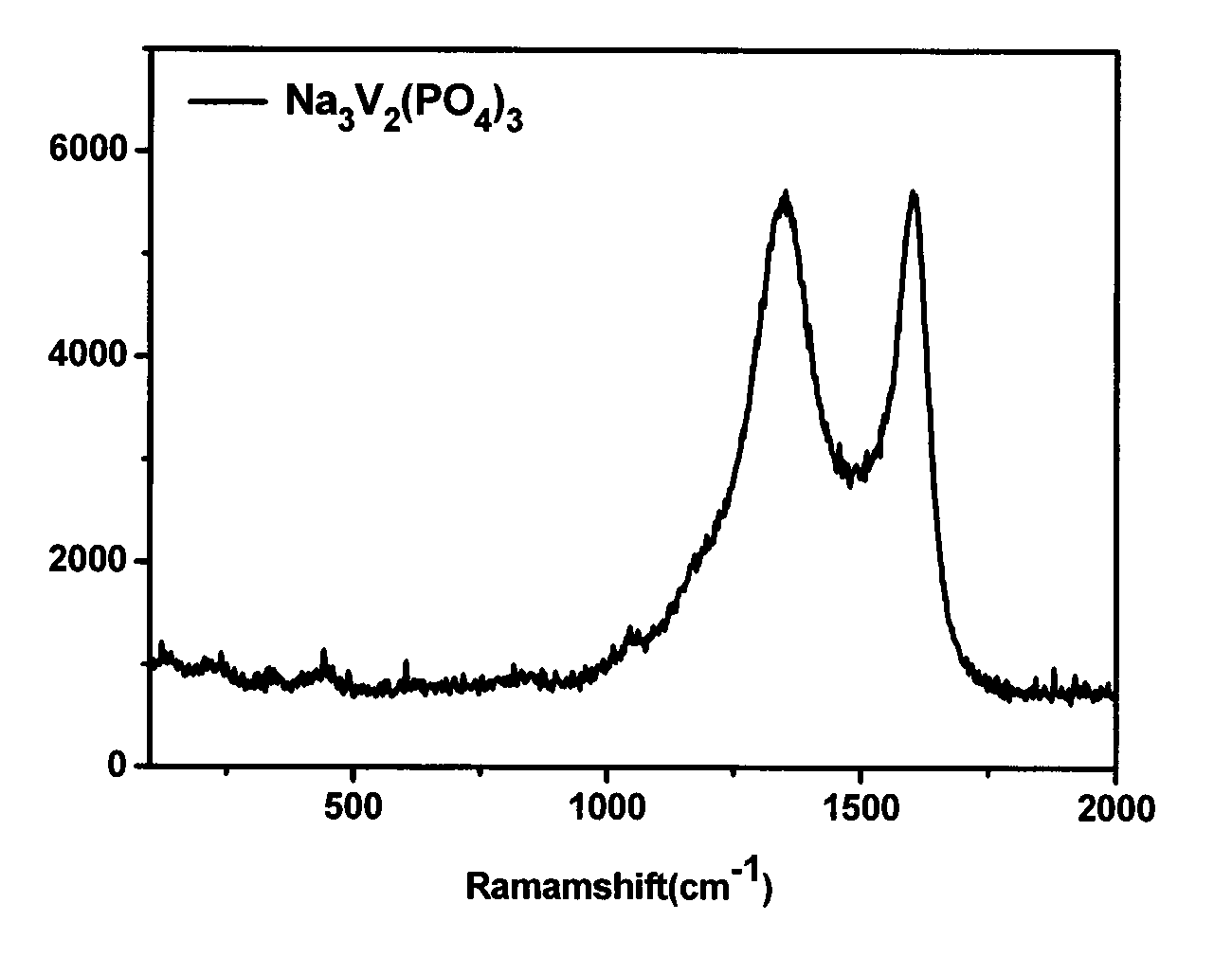

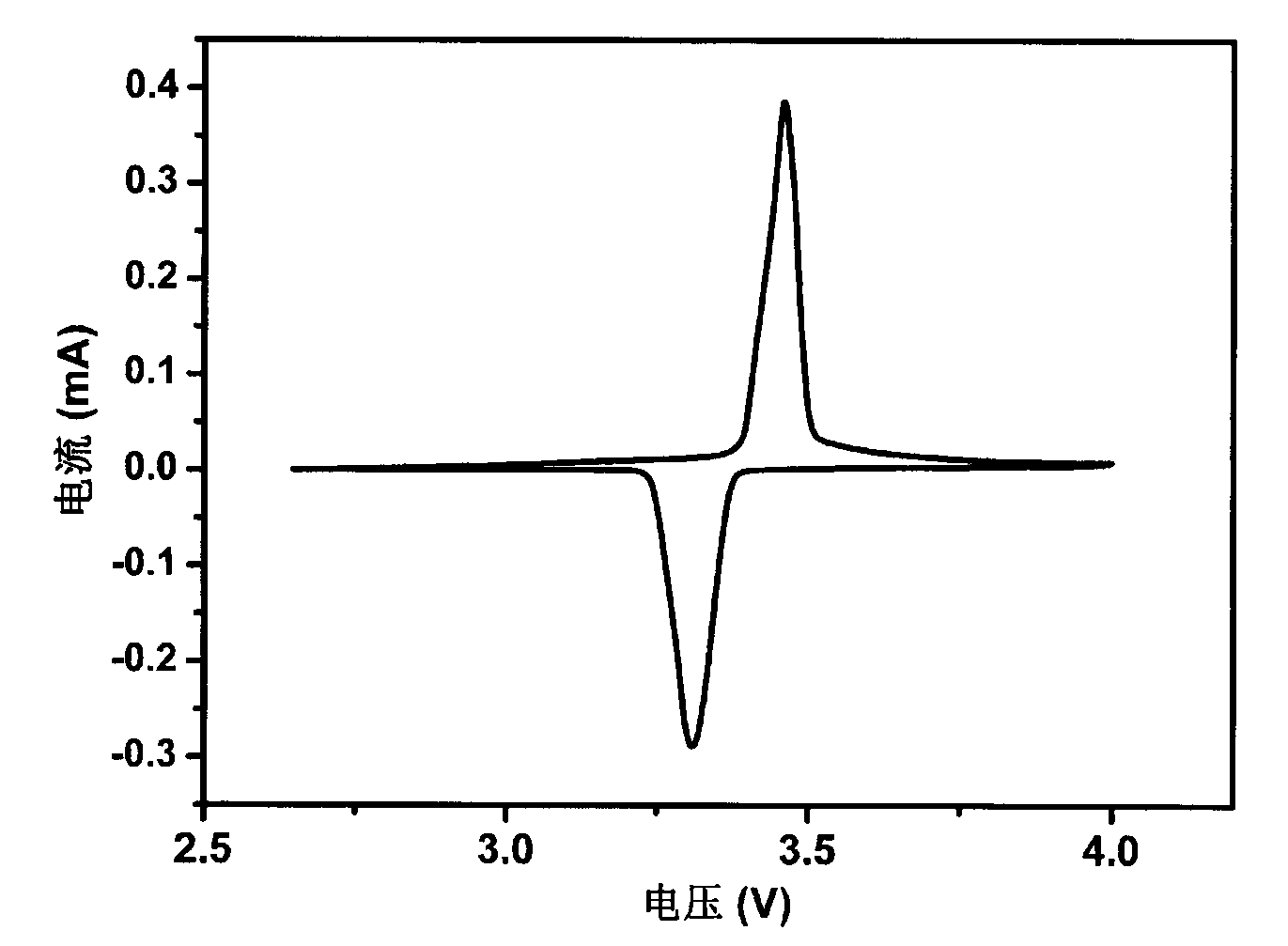

Vanadium sodium phosphate composite material as well as preparation method and application thereof

InactiveCN103000884AImprove cycle performanceImprove securityCell electrodesSodium phosphatesNitrogen

The invention relates to a vanadium sodium phosphate composite material as well as a preparation method and an application thereof. The general formula of the composite material provided by the invention is C1-xNx-LaNabMcVd(PO4)3, wherein C1-xNx is carbon or carbon doped with nitrogen, L is one or two selected from Li and K; M is one or more than one selected from Mg, B, Al, Ca, Ti, Cr, Mn, Fe, Co, Ni, Cu, Zn, Ce, Y, Zr, Nb, Mo, Sn, La, Ta and W; and x, a, b, c and d are mol percents, wherein x is more than or equal to 0 and less than 1, a is more than or equal to 0 and less than 2, b is more than 1 and less than or equal to 3, c is more than or equal to 0 and less than or equal to 1, and d is more than or equal to 1 and less than or equal to 2. The invention also provides a preparation method and an application of the composite material. The vanadium sodium phosphate composite material can be taken as cathode or anode material of a secondary sodium-ion battery, especially vanadium sodium phosphate composite material coated with carbon and nitrogen has higher coulombic efficiency and ion and electron conductivity and better cycling performance, is high in safety, low in price, simple in process and wide in application range and can be applied to energy storage equipment, a backup power supply, a spare power supply and the like.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

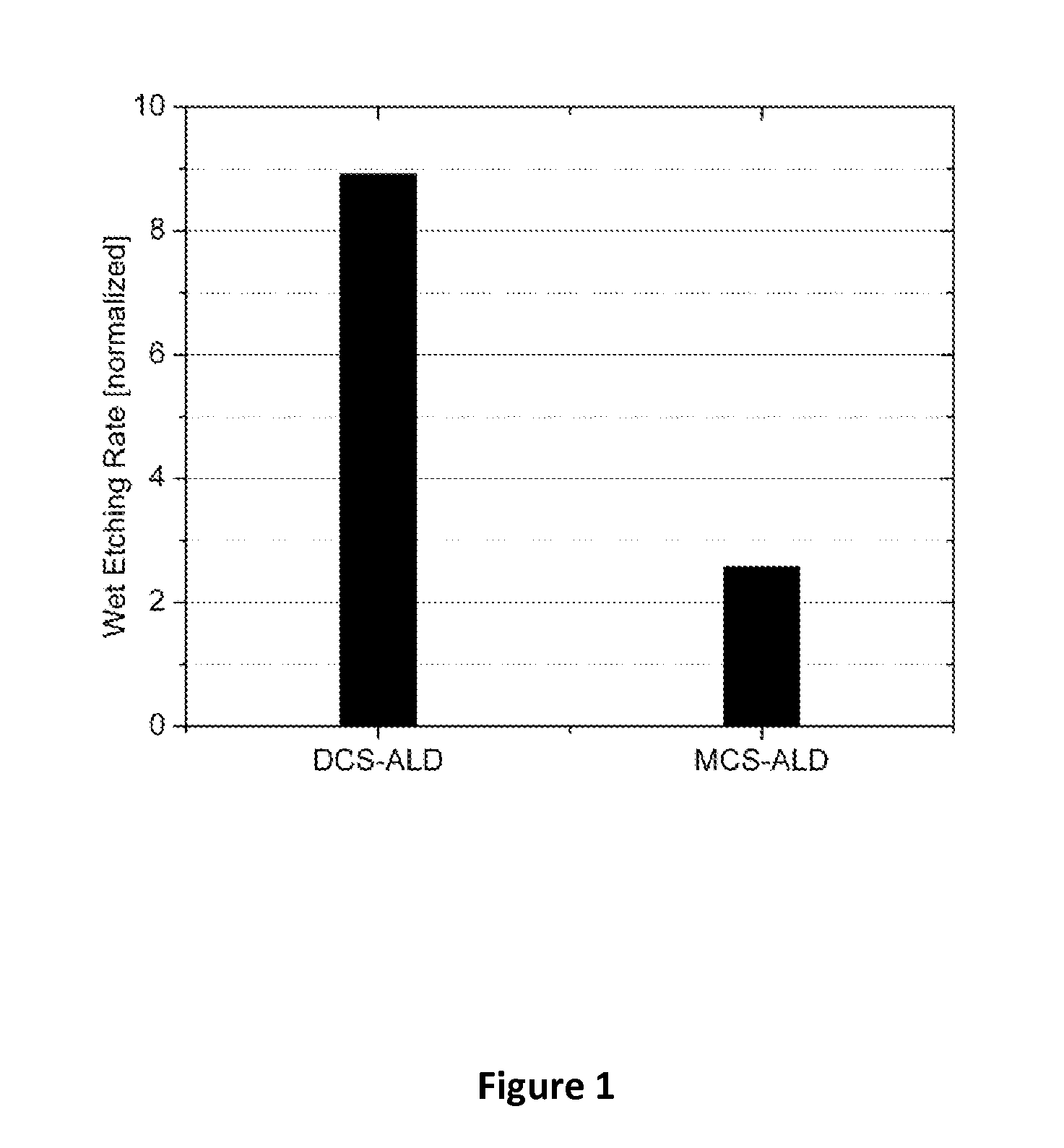

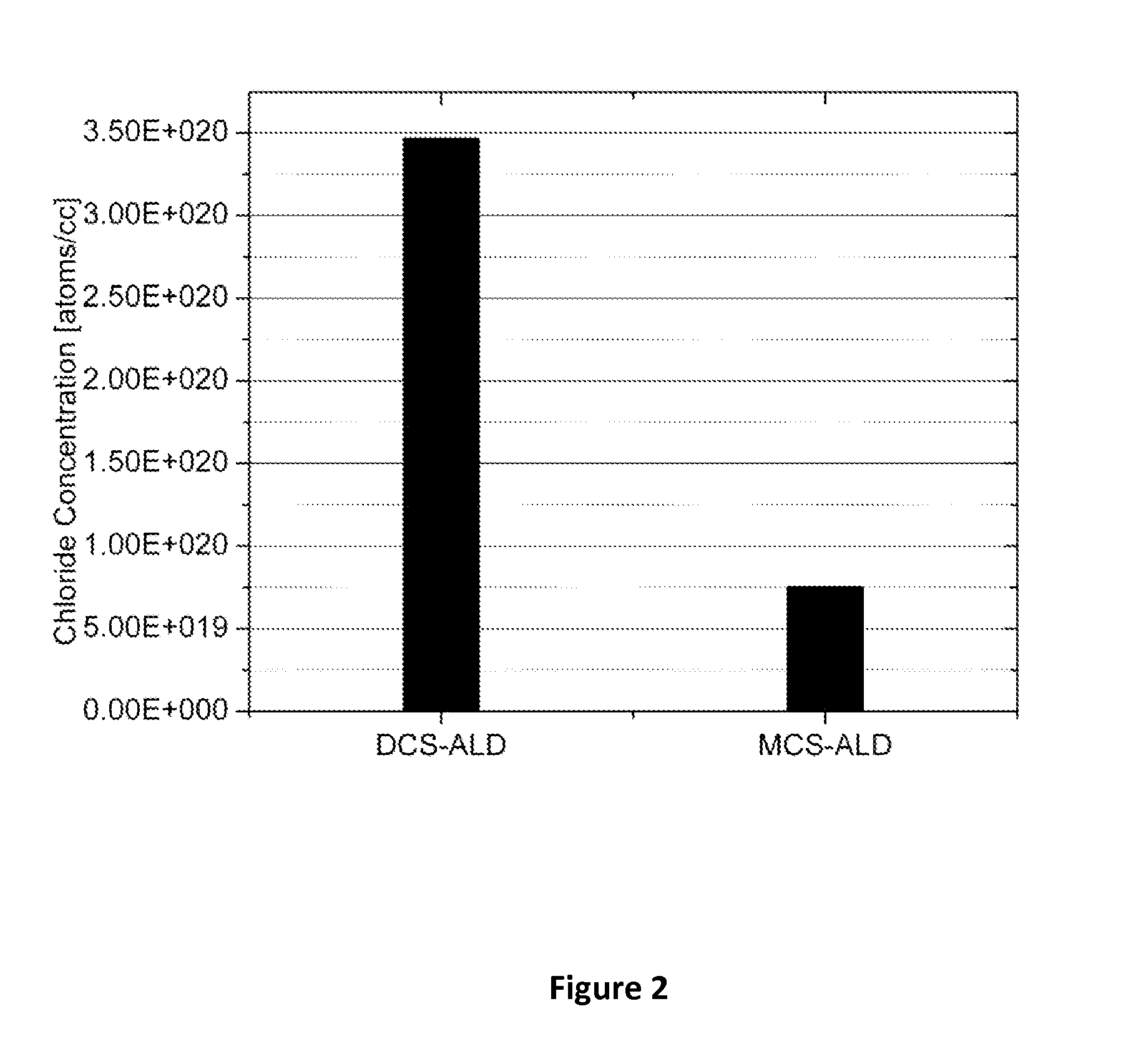

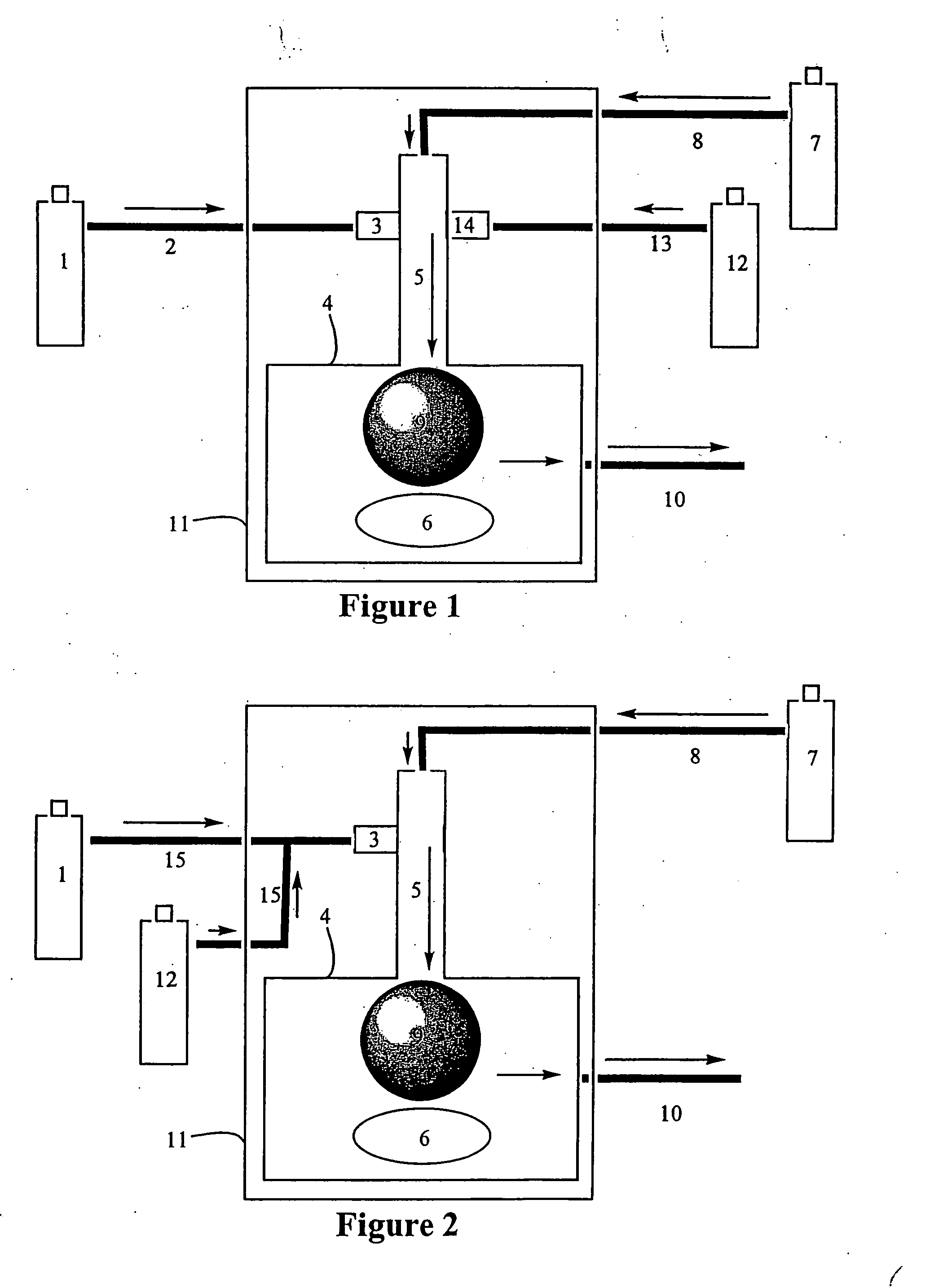

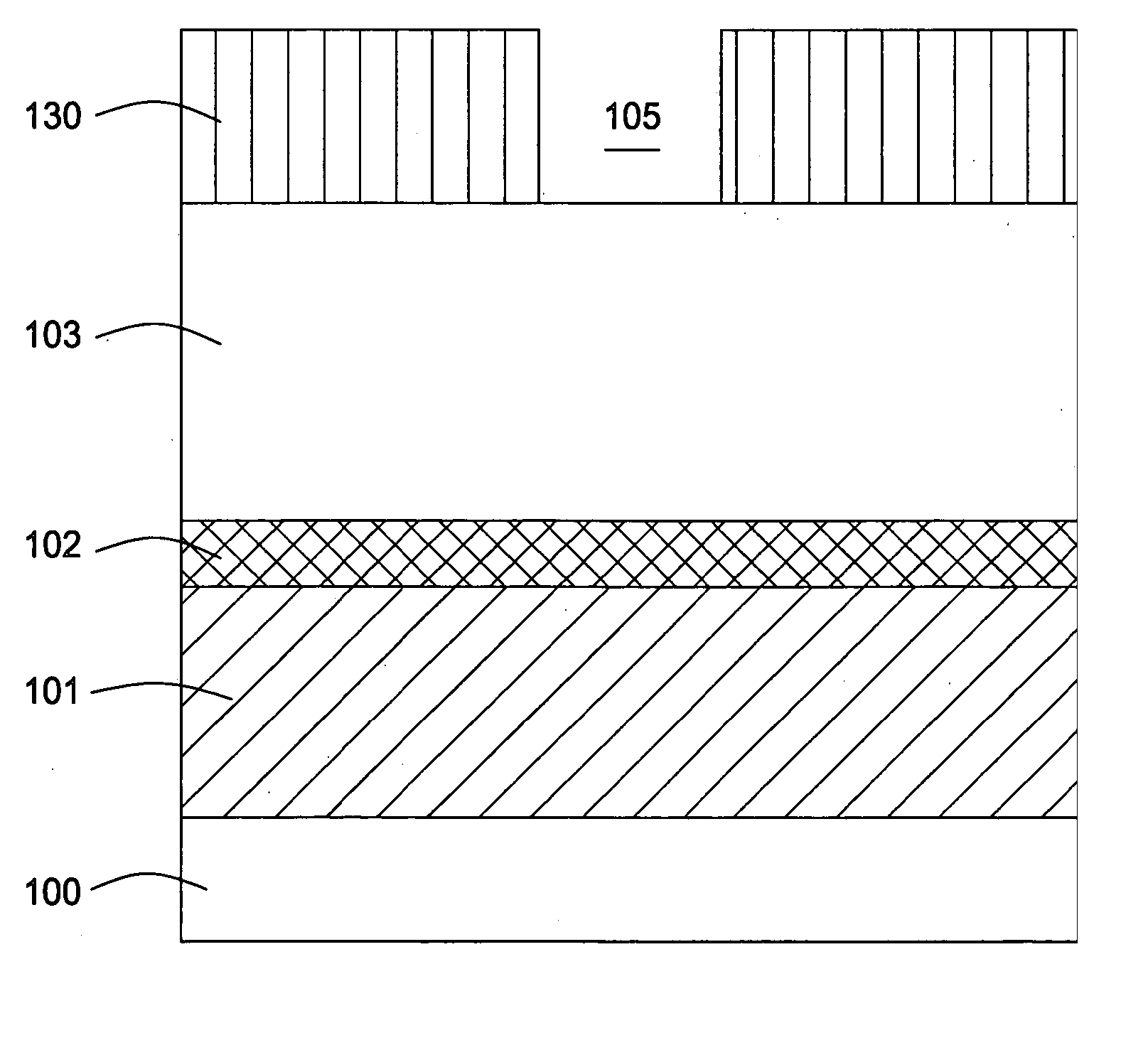

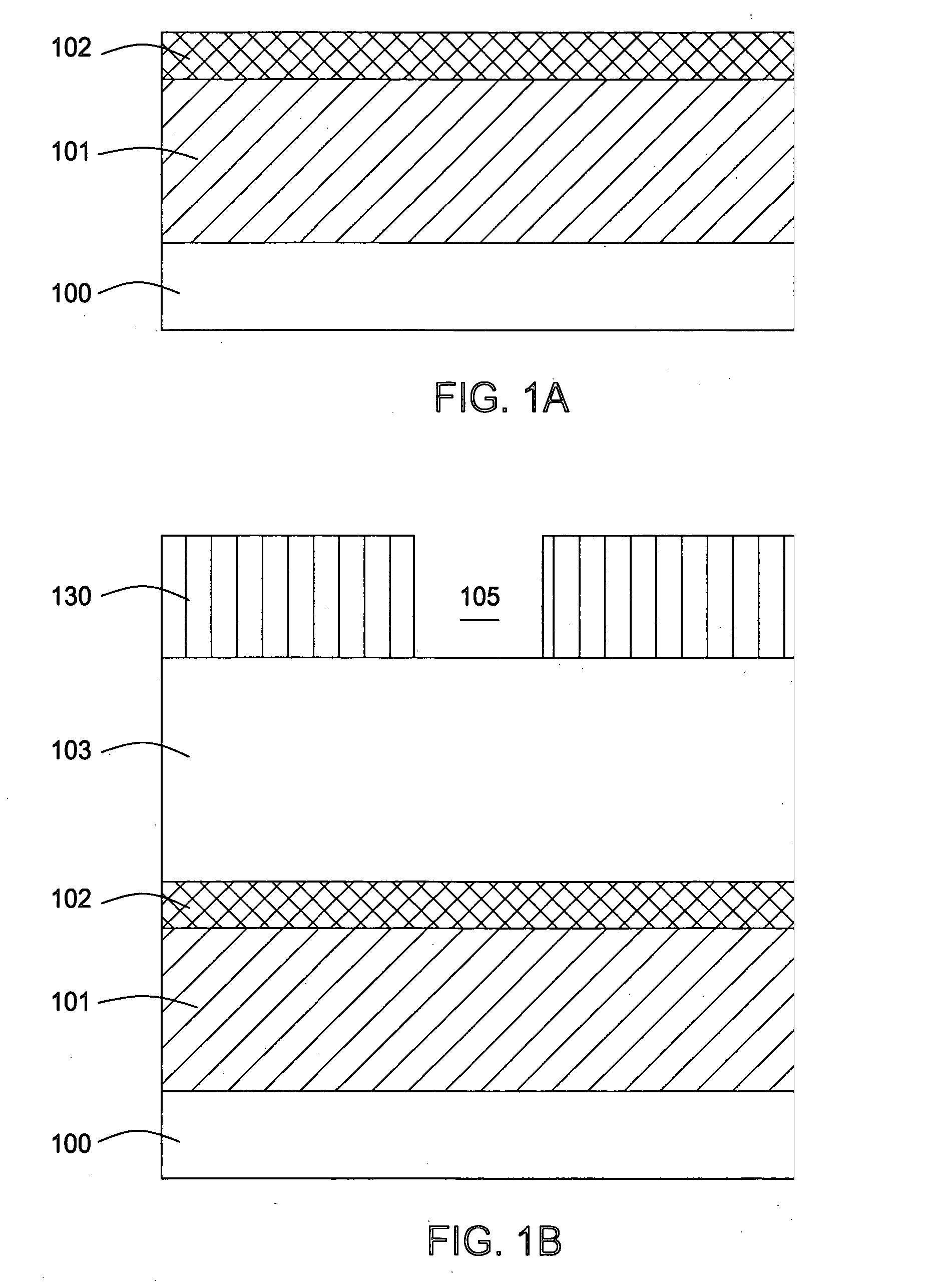

Low temperature deposition of silicon-containing films

ActiveUS8298628B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingLow temperature depositionDeposition temperature

This invention discloses the method of forming silicon nitride, silicon oxynitride, silicon oxide, carbon-doped silicon nitride, carbon-doped silicon oxide and carbon-doped oxynitride films at low deposition temperatures. The silicon containing precursors used for the deposition are monochlorosilane (MCS) and monochloroalkylsilanes. The method is preferably carried out by using plasma enhanced atomic layer deposition, plasma enhanced chemical vapor deposition, and plasma enhanced cyclic chemical vapor deposition.

Owner:TOKYO ELECTRON LTD +1

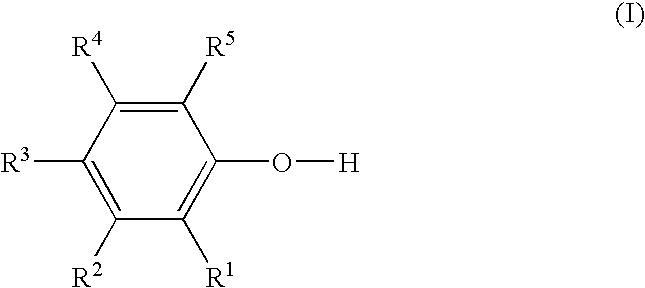

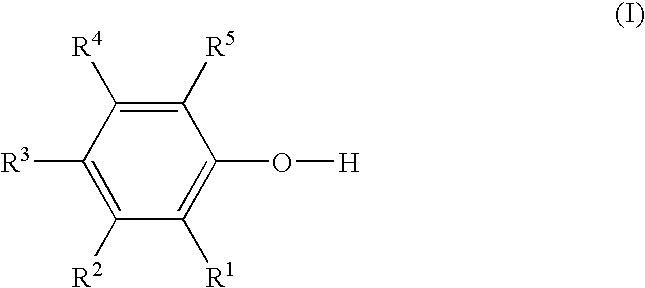

Additives to prevent degradation of cyclic alkene derivatives

A stabilized cyclic alkene composition comprising one or more cyclic alkenes, and at least one antioxidant compound having the formula (I), wherein R1 through R5 can each independently be H, OH, C1-C8 linear, branched, or cyclic alkyl, C1-C8 linear, branched, or cyclic alkoxy or substituted or unsubstituted aryl, and wherein the antioxidant compound is present in an amount between 1 ppm and 200 ppm and has a boiling point lower than 265° C. A method for forming a layer of carbon-doped silicon oxide on a substrate, which uses the stabilized alkene composition and a silicon containing compound.

Owner:FUJIFILM ELECTRONICS MATERIALS US

Selective etch process of a sacrificial light absorbing material (SLAM) over a dielectric material

InactiveUS20050029229A1Decorative surface effectsSemiconductor/solid-state device manufacturingHydrogenNitrogen gas

A process of selectively etching a sacrificial light absorbing material (SLAM) over a dielectric material, such as carbon doped oxide, on a substrate using a plasma of a gas mixture in a plasma etch chamber. The gas mixture comprises a hydrofluorocarbon gas, an optional hydrogen-containing gas, an optional fluorine-rich fluorocargon gas, a nitrogen gas, an oxygen gas, and an inert gas. The process could provide a SLAM to a dielectric material etching selectivity ratio greater than 10:1.

Owner:APPLIED MATERIALS INC

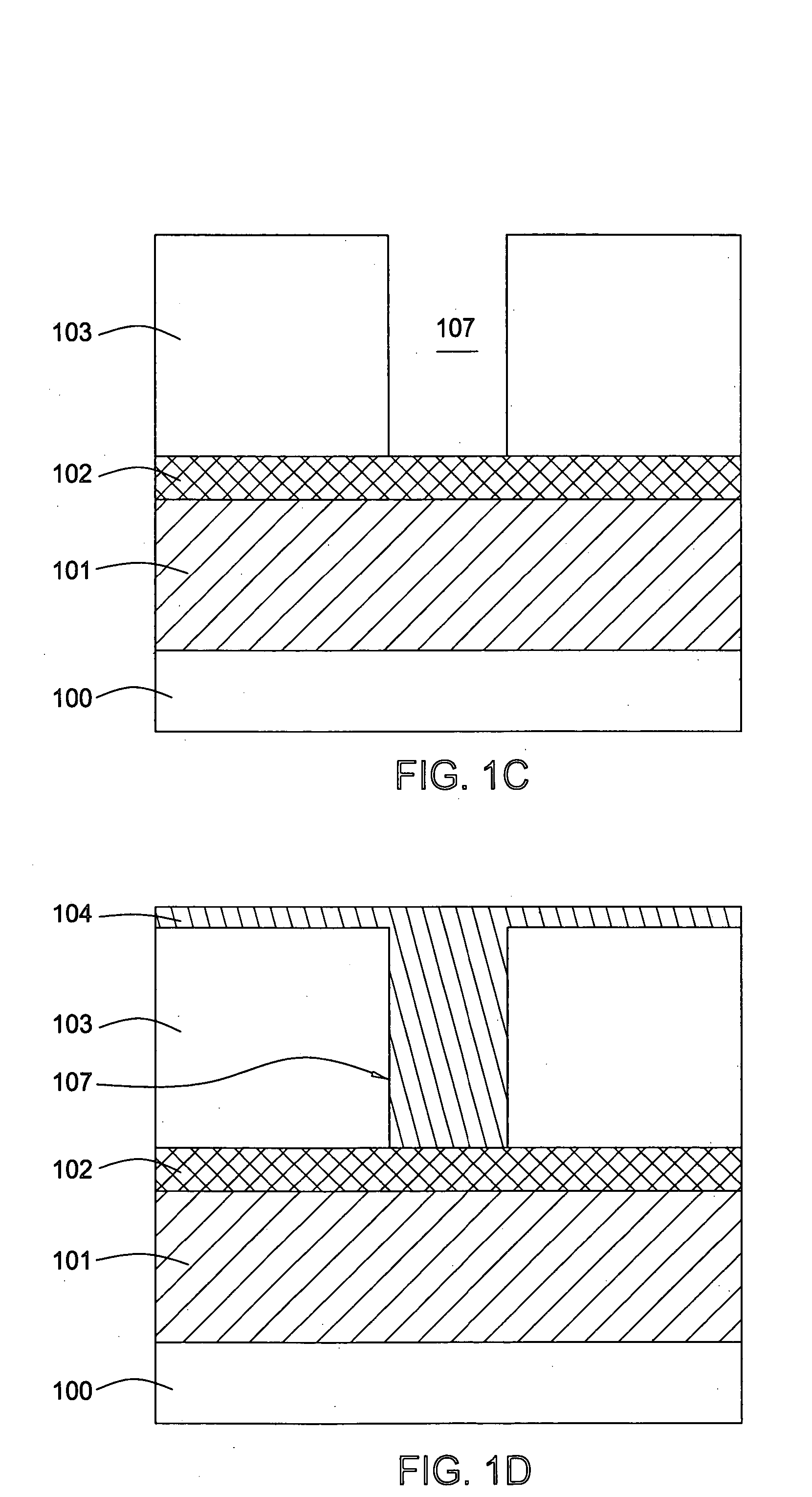

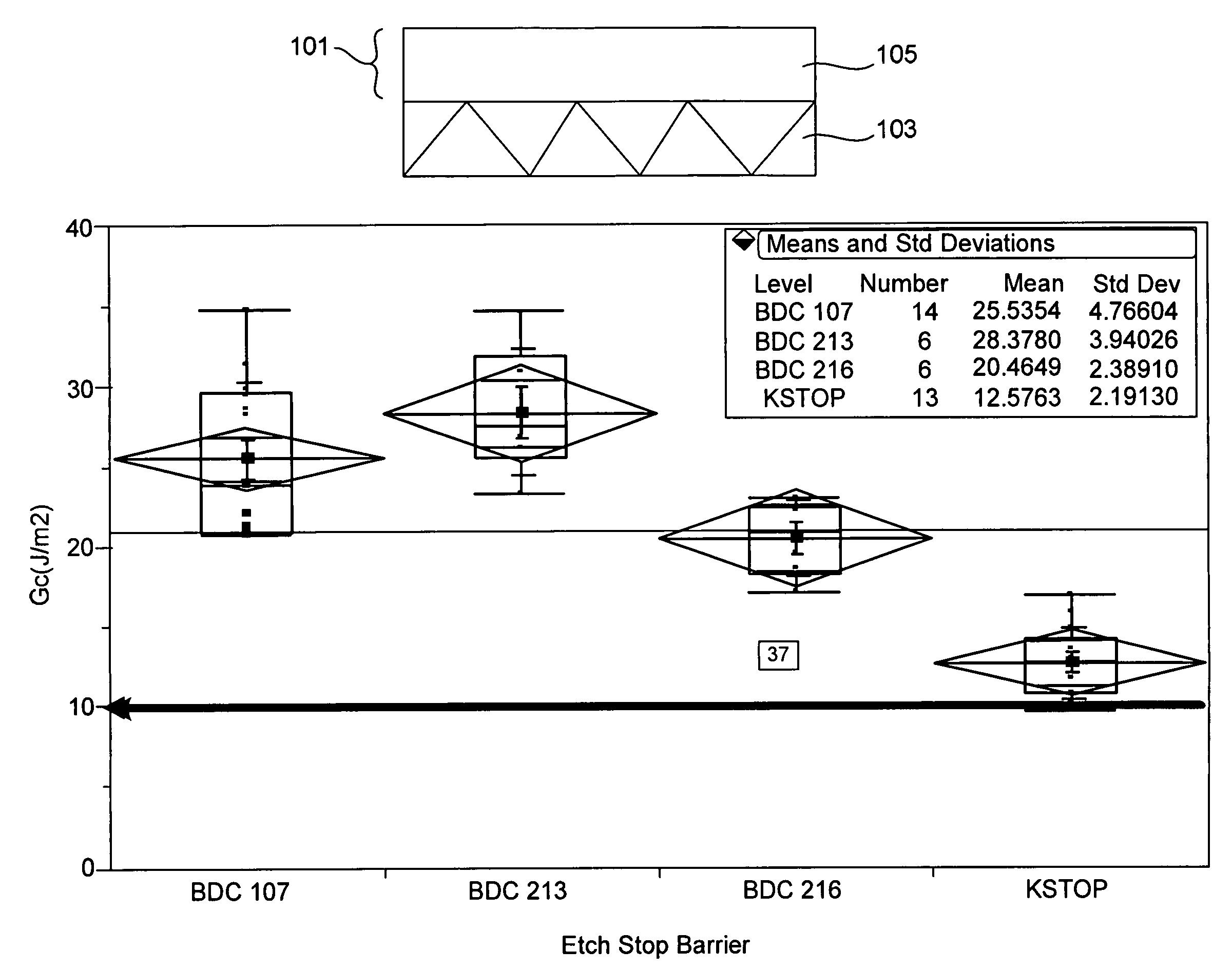

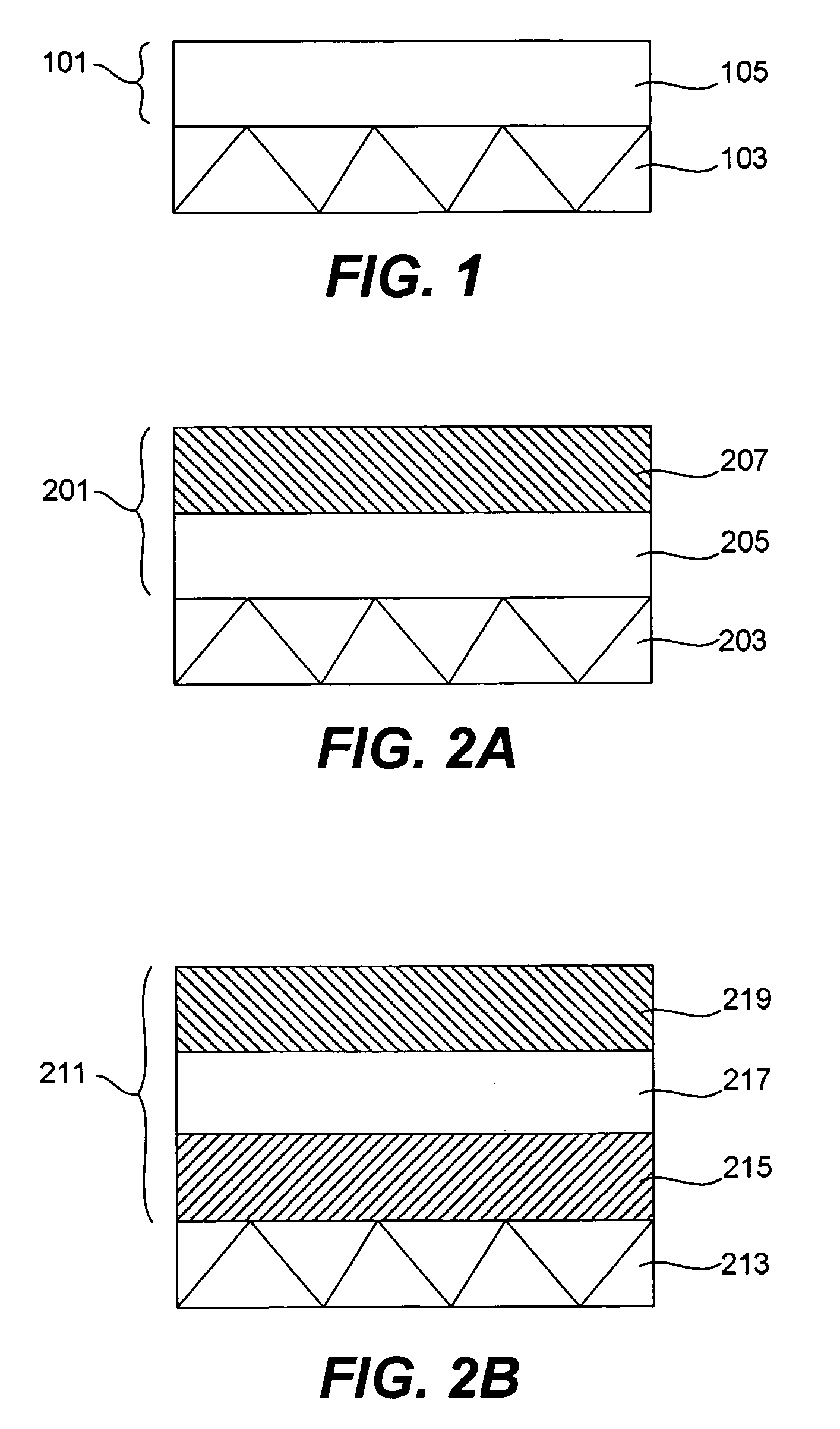

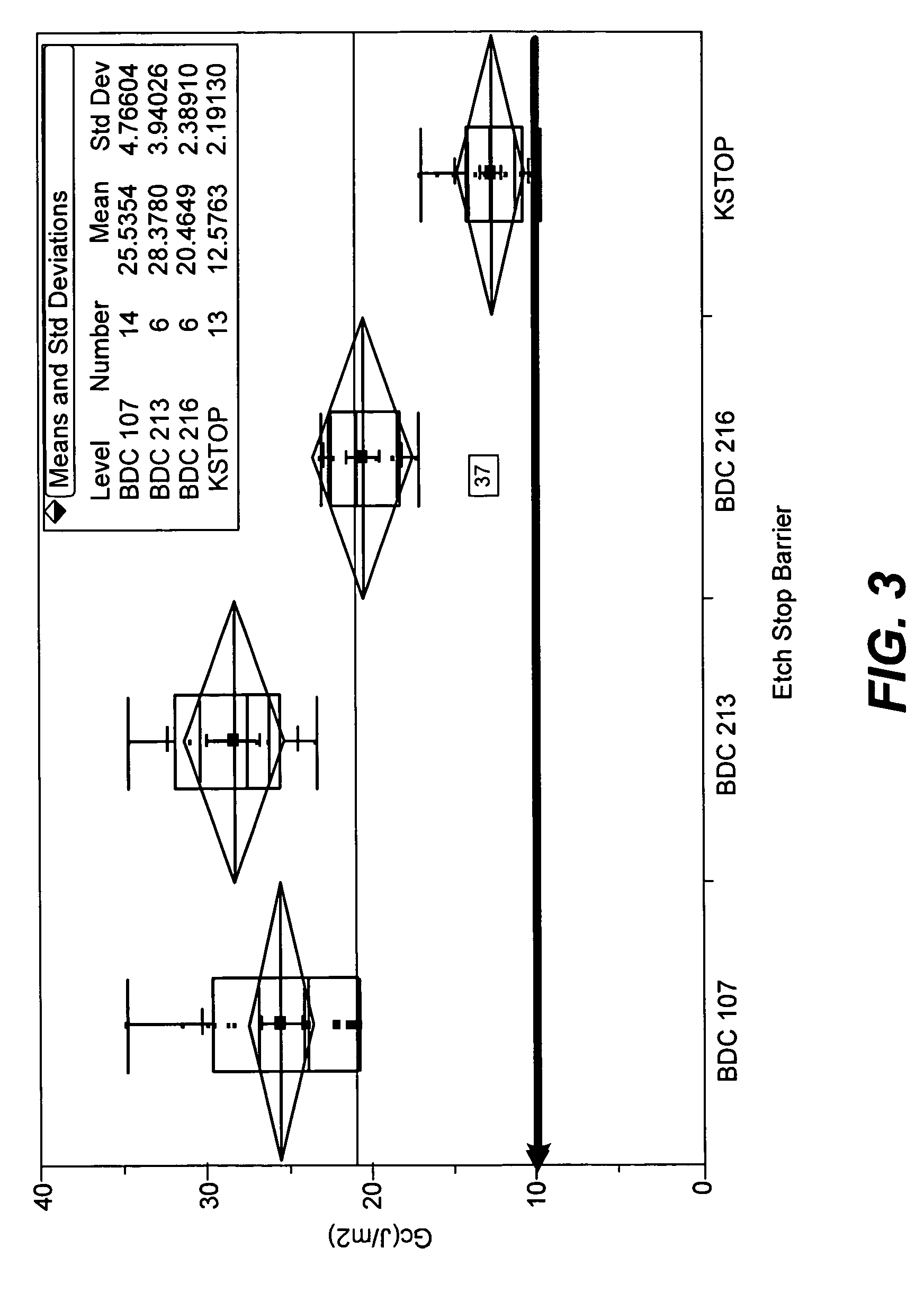

Boron-doped SIC copper diffusion barrier films

ActiveUS7420275B1Improve etch selectivityEnhanced copper adhesionSemiconductor/solid-state device detailsSolid-state devicesDiffusion barrierCopper

Copper diffusion barrier films having a boron-doped silicon carbide layer with at least 25% boron by atomic weight of the layer composition have advantages for semiconductor device integration schemes. The films have an integration worthy etch selectivity to carbon doped oxide of at least 10 to 1, can adhere to copper with an adhesion energy of at least 20 J / m2, and can maintain an effective dielectric constant of less than 4.5 in the presence of atmospheric moisture. The films are suitable for use in a wide range of VLSI and ULSI structures and devices.

Owner:NOVELLUS SYSTEMS

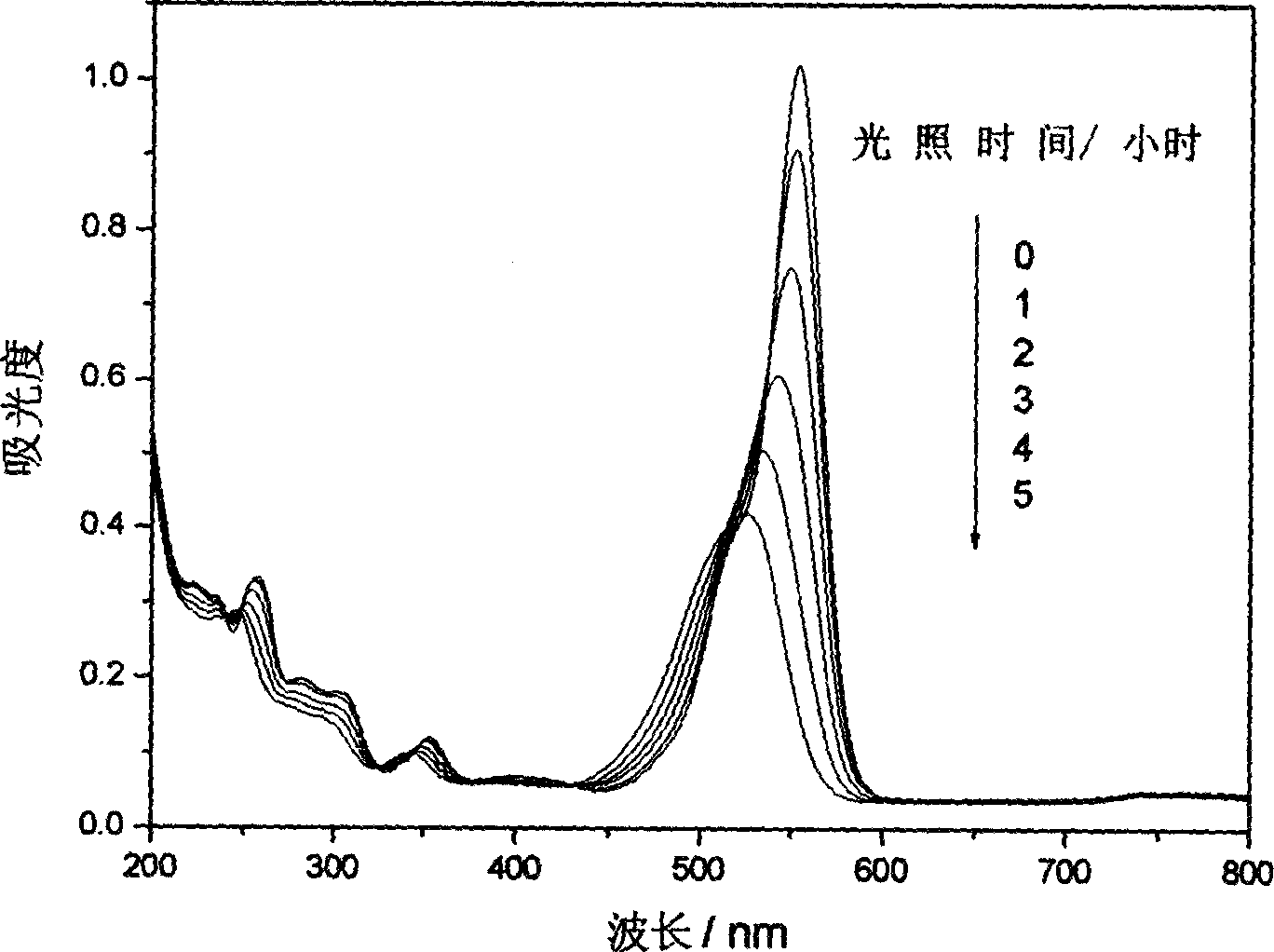

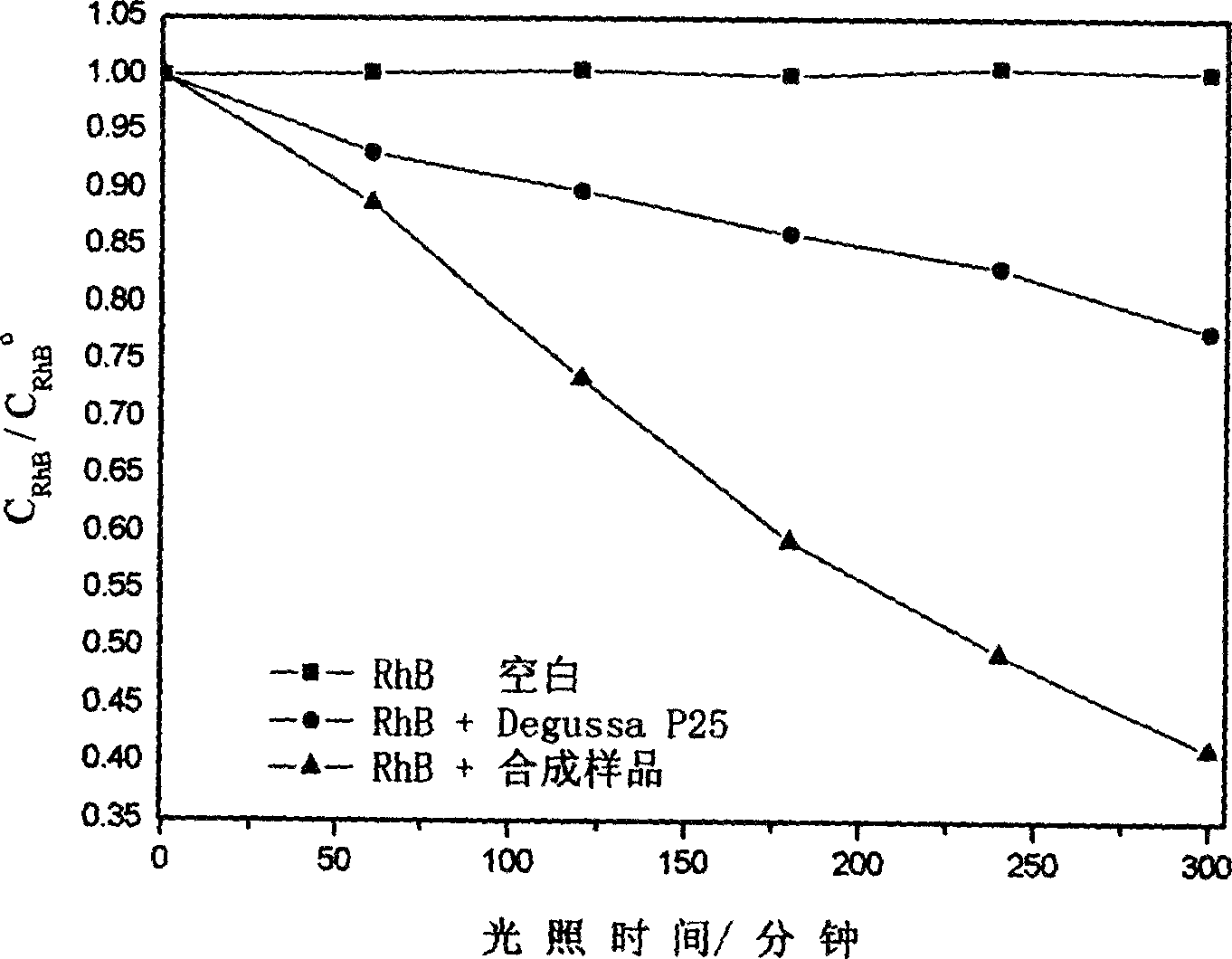

Low temperature process of preparing carbon-doped mesoporous TiO2 visible light catalyst

InactiveCN1857769ALarge specific surface areaUniform pore size distributionPhysical/chemical process catalystsTitaniumSolvent

The present invention relates to preparation process of carbon-doped mesoporous TiO2 visible light catalyst, and belongs to the field of nanometer catalyst material technology. The present invention features that amorphous titania powder prepared with titanium containing compound through hydrolysis and used as the titanium source and saccharide compound as carbon source are produced into the carbon-doped mesoporous TiO2 visible light catalyst through heat treatment in water or solvent, suction filtering, washing and drying. The carbon-doped mesoporous TiO2 visible light catalyst has specific surface area up to 126 sq m / g, homogeneous pore size of about 8 nm, high visible light catalytic activity, simple synthesis path and easy control of the technological process.

Owner:HUAZHONG NORMAL UNIV

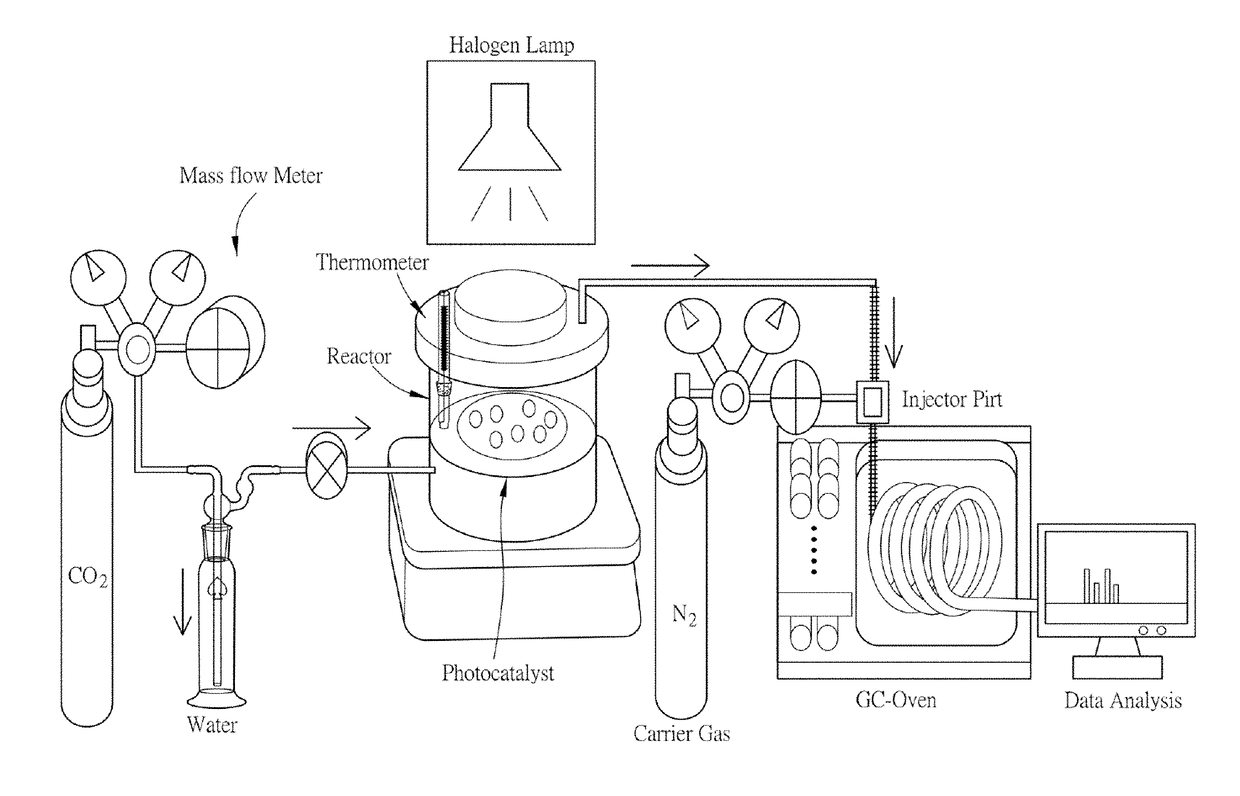

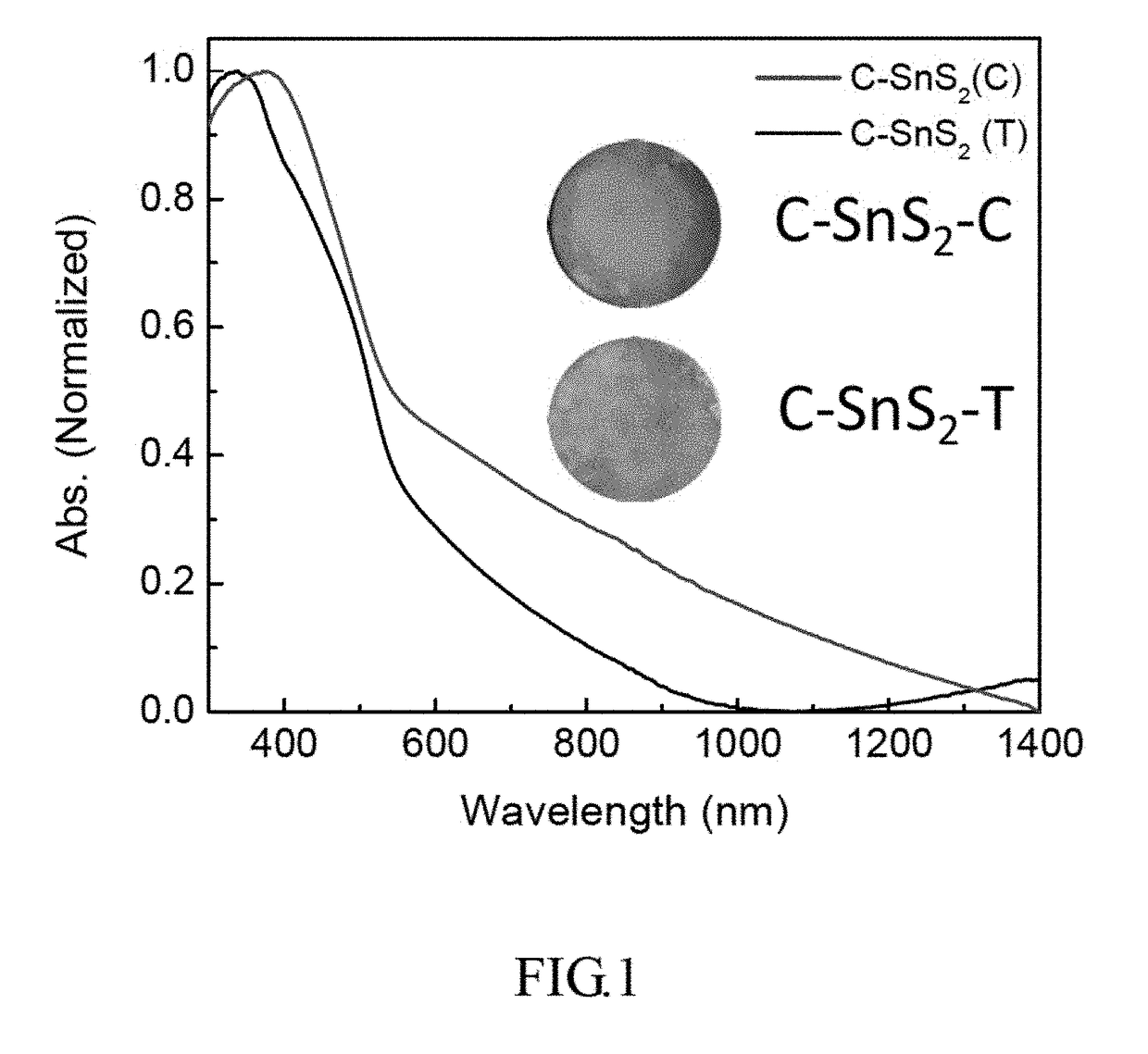

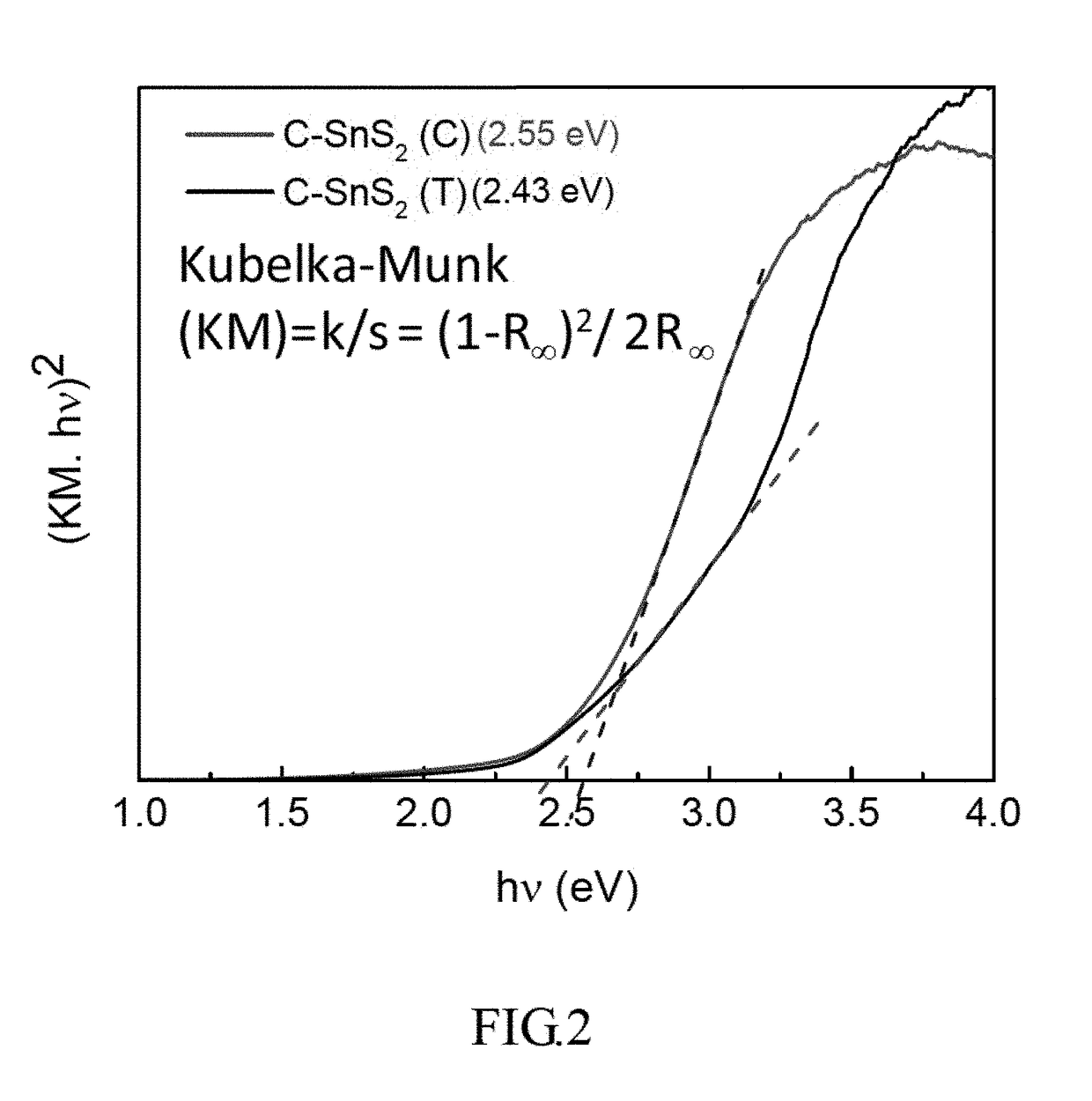

Carbon doped tin disulphide and methods for synthesizing the same

ActiveUS20180280942A1Hydrocarbon from carbon oxidesOrganic compound preparationVisible light photocatalyticMaterials science

Disclosed herein are carbon doped tin disulphide (C—SnS2) and other SnS2 composites as visible light photocatalyst for CO2 reduction to solar fuels. The in situ carbon doped SnS2 photocatalyst provide higher efficiency than the undoped pure SnS2. Also disclosed herein are methods for preparing the catalysts.

Owner:ACAD SINIC +1

Method for forming interconnection line in semiconductor device and interconnection line structure

ActiveUS20050161821A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialInterconnection

Methods for forming an interconnection line and interconnection line structures are disclosed. The method includes forming an interlayer insulating layer on a semiconductor substrate, wherein the interlayer insulating layer is formed of a carbon-doped low-k dielectric layer. An oxidation barrier layer is formed on the interlayer insulating layer. An oxide capping layer is formed on the oxidation barrier layer. A via hole is in the oxide capping layer, the oxidation barrier, and the interlayer insulating layer. A conductive layer pattern is formed within the via hole.

Owner:SAMSUNG ELECTRONICS CO LTD