CMOS transistor and the method for manufacturing the same

a transistor and cmos technology, applied in the field of cmos transistors, can solve the problems of silicide agglomeration that increases resistance, and the method has encountered difficulties with high-expense and technical bottlenecks, and achieve the effect of preventing ge-out diffusion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

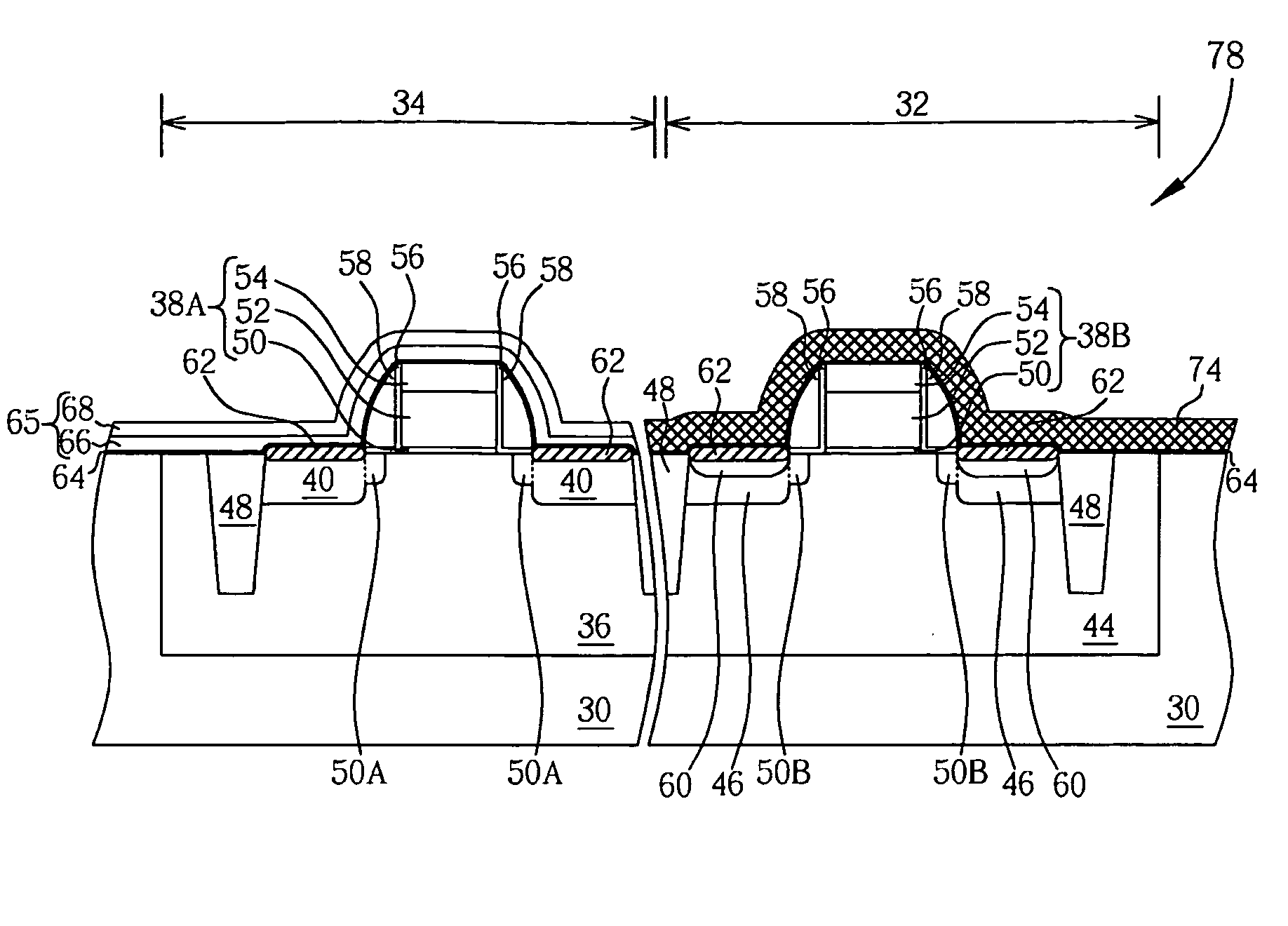

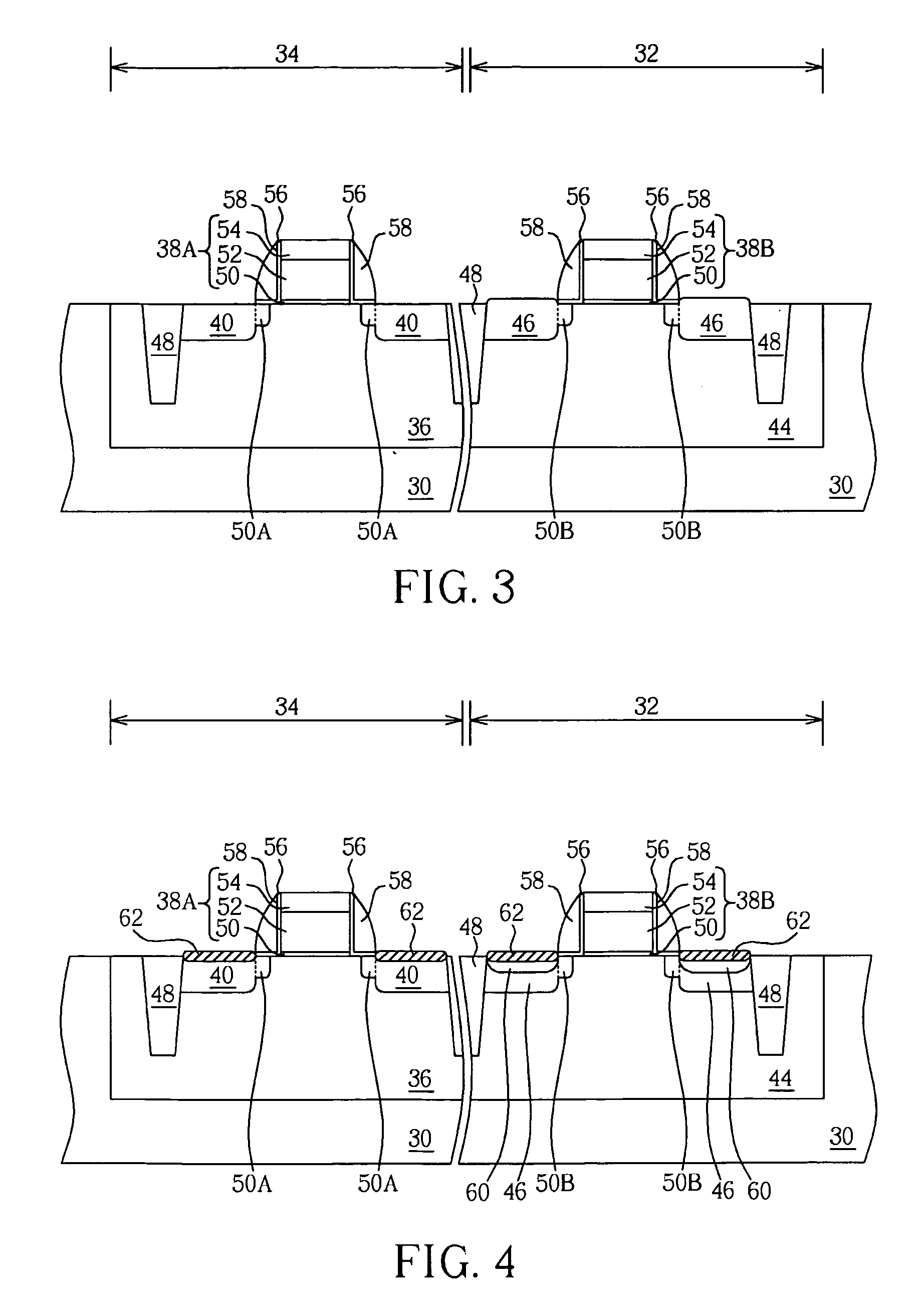

[0017]Please refer to FIG. 3 through FIG. 10. FIG. 3 to FIG. 9 are schematic diagrams illustrating a method for manufacturing a CMOS transistor according to a preferred embodiment of the present invention. FIG. 10 is a flow diagram of the method of the present invention to manufacture the CMOS transistor for preventing Ge-out diffusion. Please refer to FIG. 3. A semiconductor substrate 30 is provided, in which the semiconductor substrate 30 has at least a PMOS transistor 32 and an NMOS transistor 34 disposed thereon. The NMOS transistor 34 is formed in a P well 36 disposed in the semiconductor substrate 30. The NMOS transistor 34 includes a gate structure 38A formed on the surface of the semiconductor substrate 30 and a source / drain 40 disposed beside the gate structure 38A. The PMOS transistor 32 is formed in an N well 44. The PMOS transistor 32 includes a gate structure 38B formed on the surface of the semiconductor substrate 30 and a source / drain 46 disposed beside the gate struc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More