Patents

Literature

55 results about "Borophosphosilicate glass" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

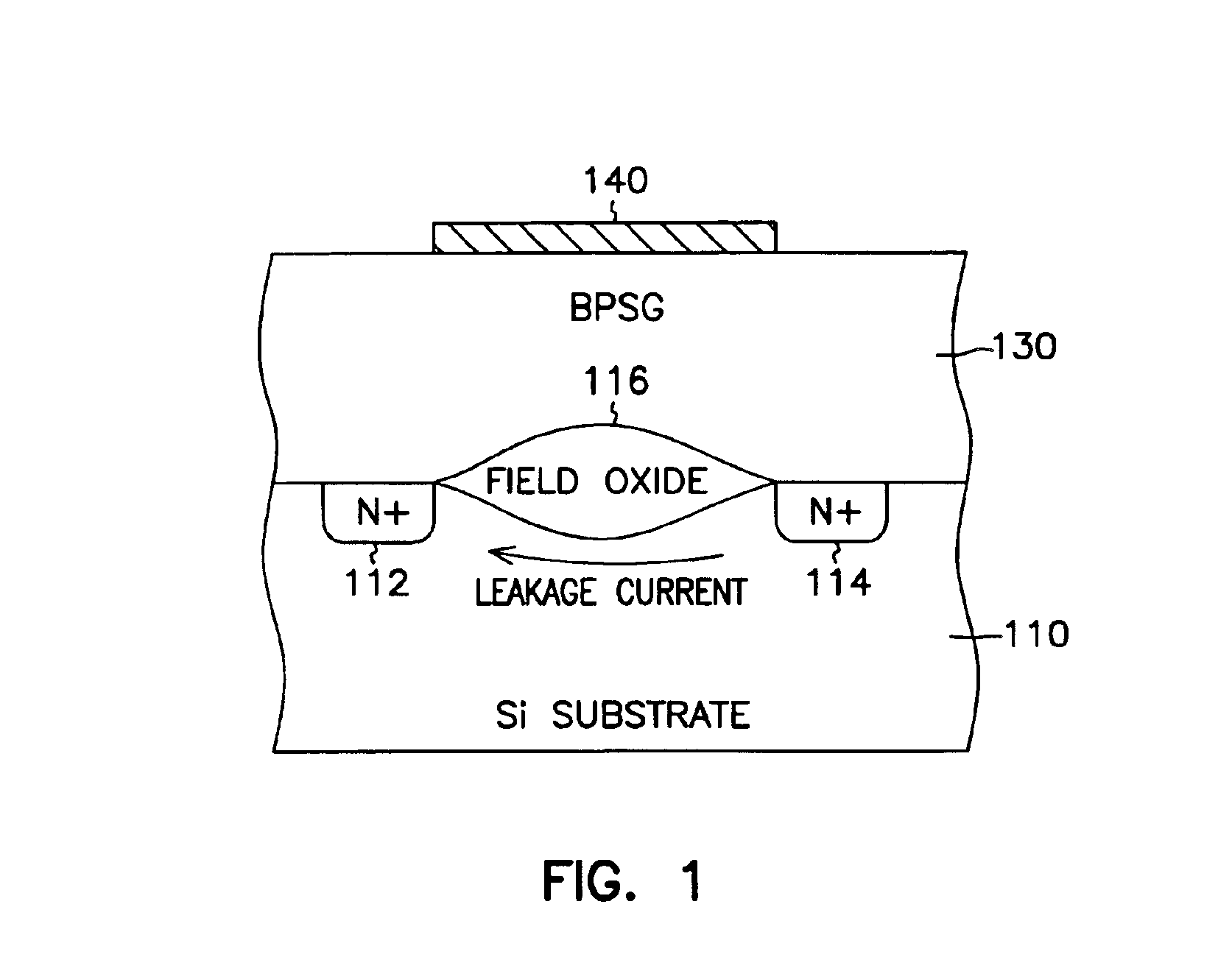

Borophosphosilicate glass, commonly known as BPSG, is a type of silicate glass that includes additives of both boron and phosphorus. Silicate glasses such as PSG and borophosphosilicate glass are commonly used in semiconductor device fabrication for intermetal layers, i.e., insulating layers deposited between succeedingly higher metal or conducting layers.

Formulations for cleaning memory device structures

InactiveUS20080125342A1Inorganic/elemental detergent compounding agentsOrganic detergent compounding agentsBorophosphosilicate glassSilicon oxide

A removal composition and process for removing silicon-containing layers from a microelectronic device having said layers thereon. The removal composition selectively removes layers including, but not limited to, silicon oxide, plasma enhanced tetraethyl orthosilicate (P-TEOS), borophosphosilicate glass (BPSG), plasma enhanced oxide (PEOX), high density plasma oxide (HDP), phosphosilicate glass (PSG), spin-on-dielectrics (SOD), thermal oxide, updoped silicate glass, sacrificial oxides, silicon-containing organic polymers, silicon-containing hybrid organic / inorganic materials, organosilicate glass (OSG), TEOS, fluorinated silicate glass (FSG), hemispherical grain (HSQ), carbon-doped oxide (CDO) glass, and combinations thereof, relative to lower electrode, device substrate, and / or etch stop layer materials.

Owner:ADVANCED TECH MATERIALS INC

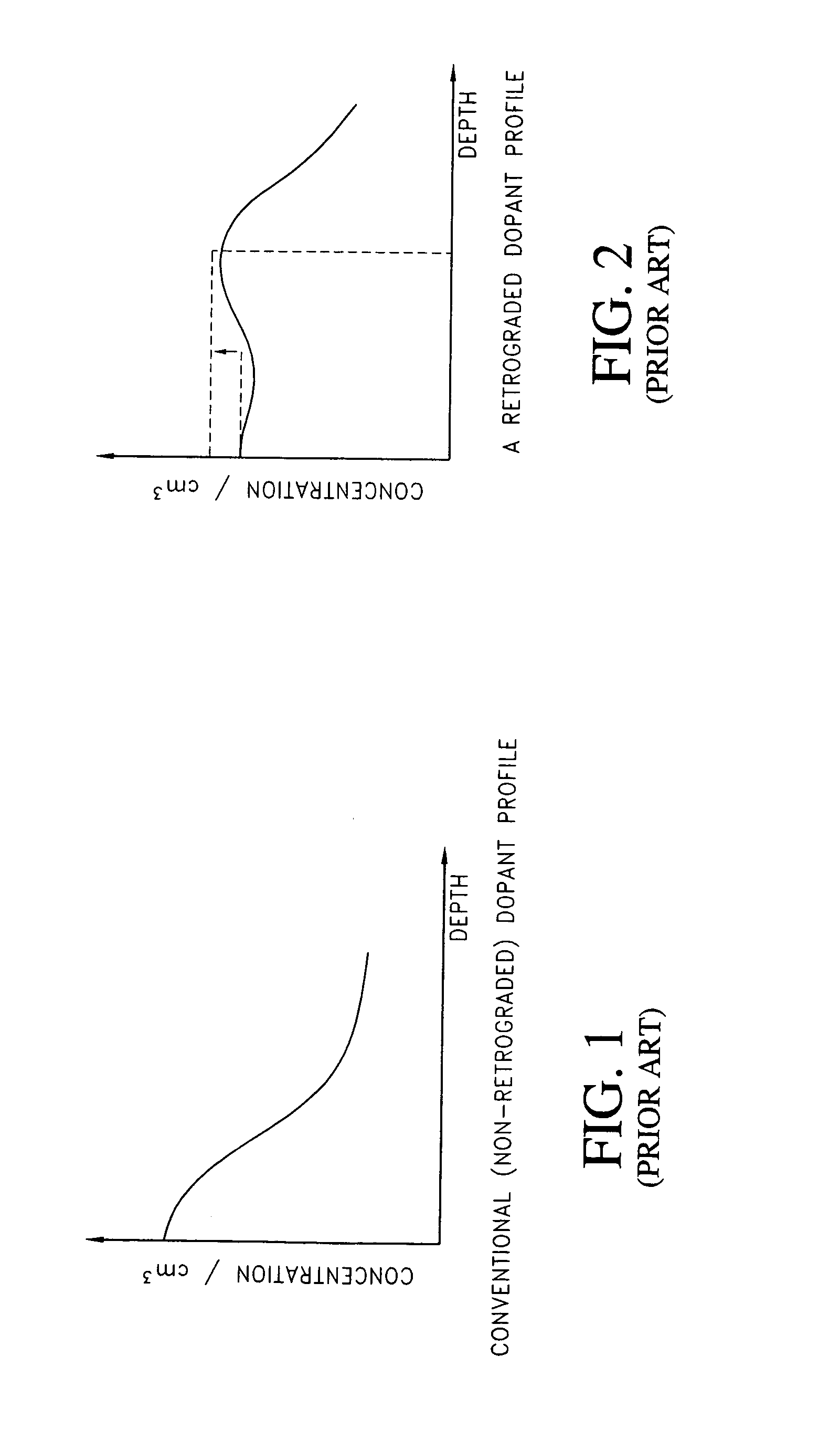

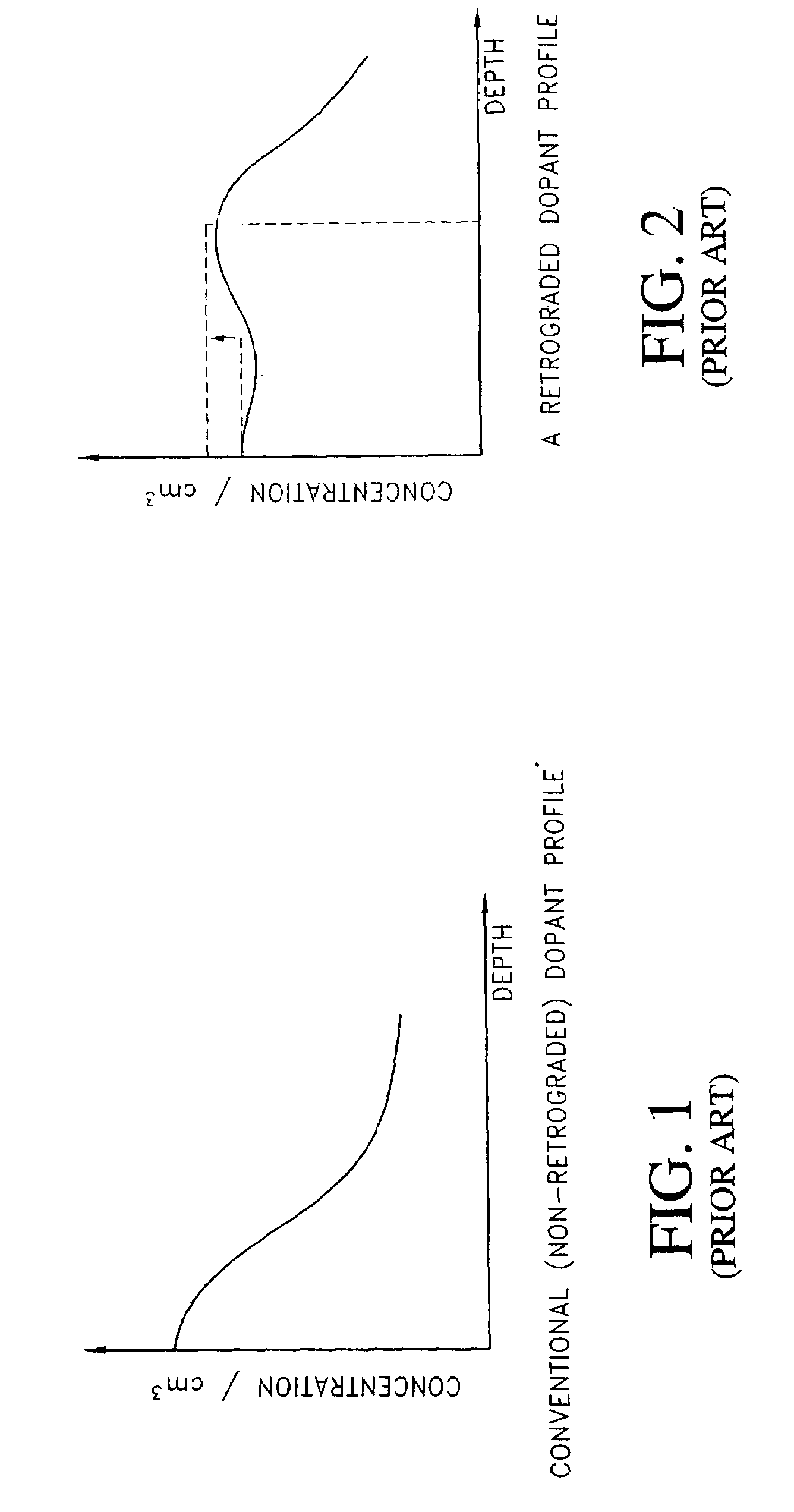

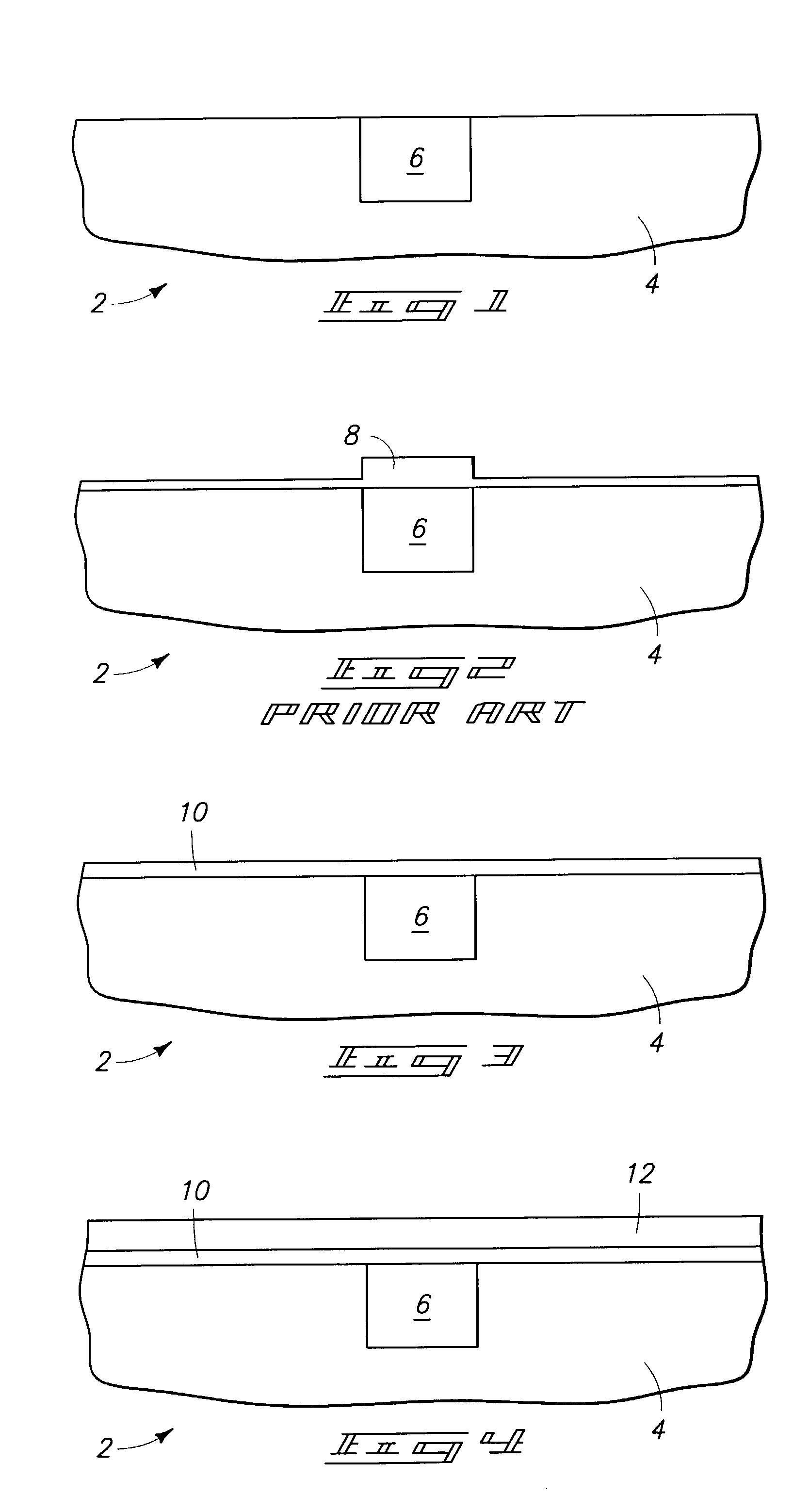

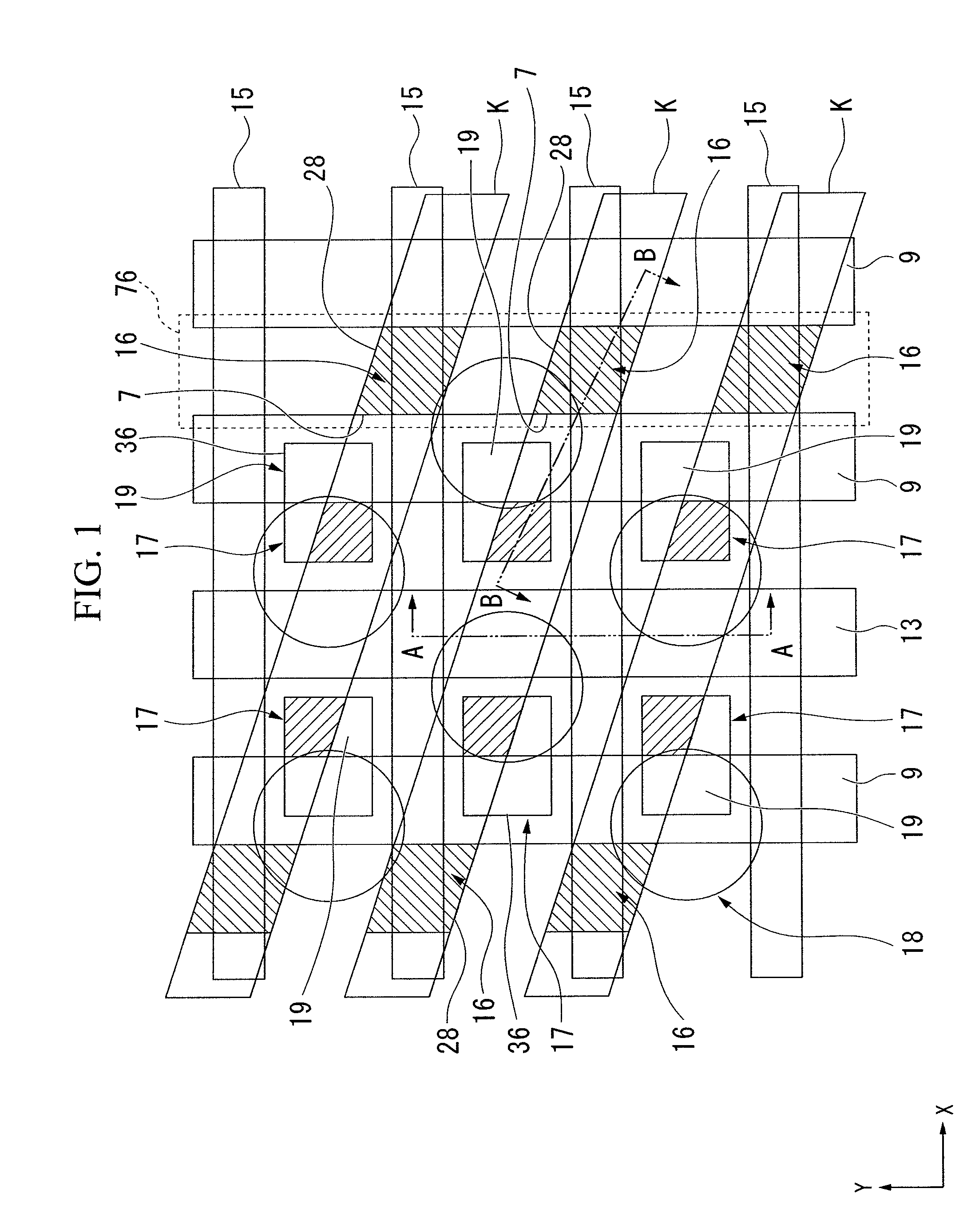

SOI CMOS device with reduced DIBL

ActiveUS6872640B1Prevent penetrationSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosDopant

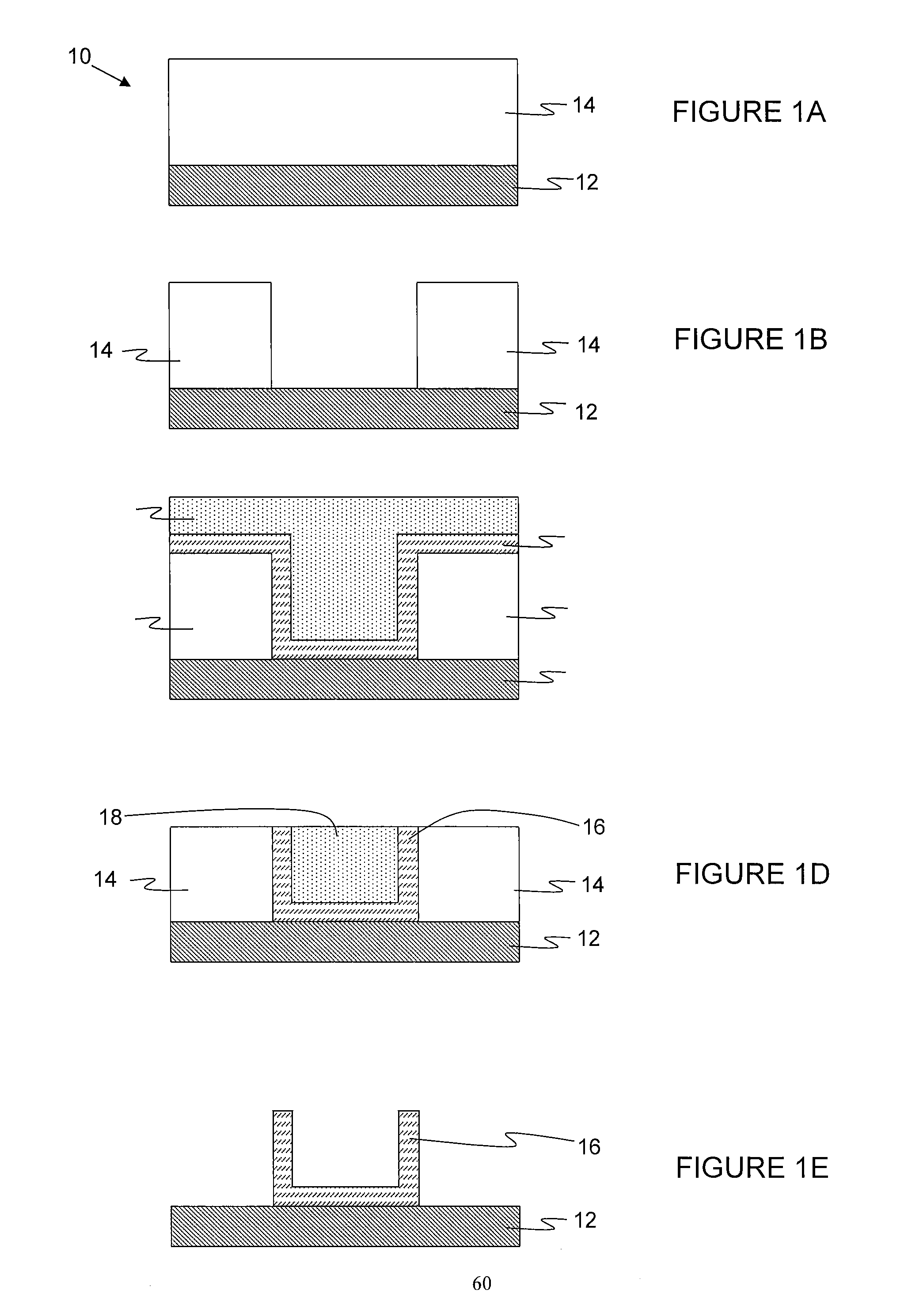

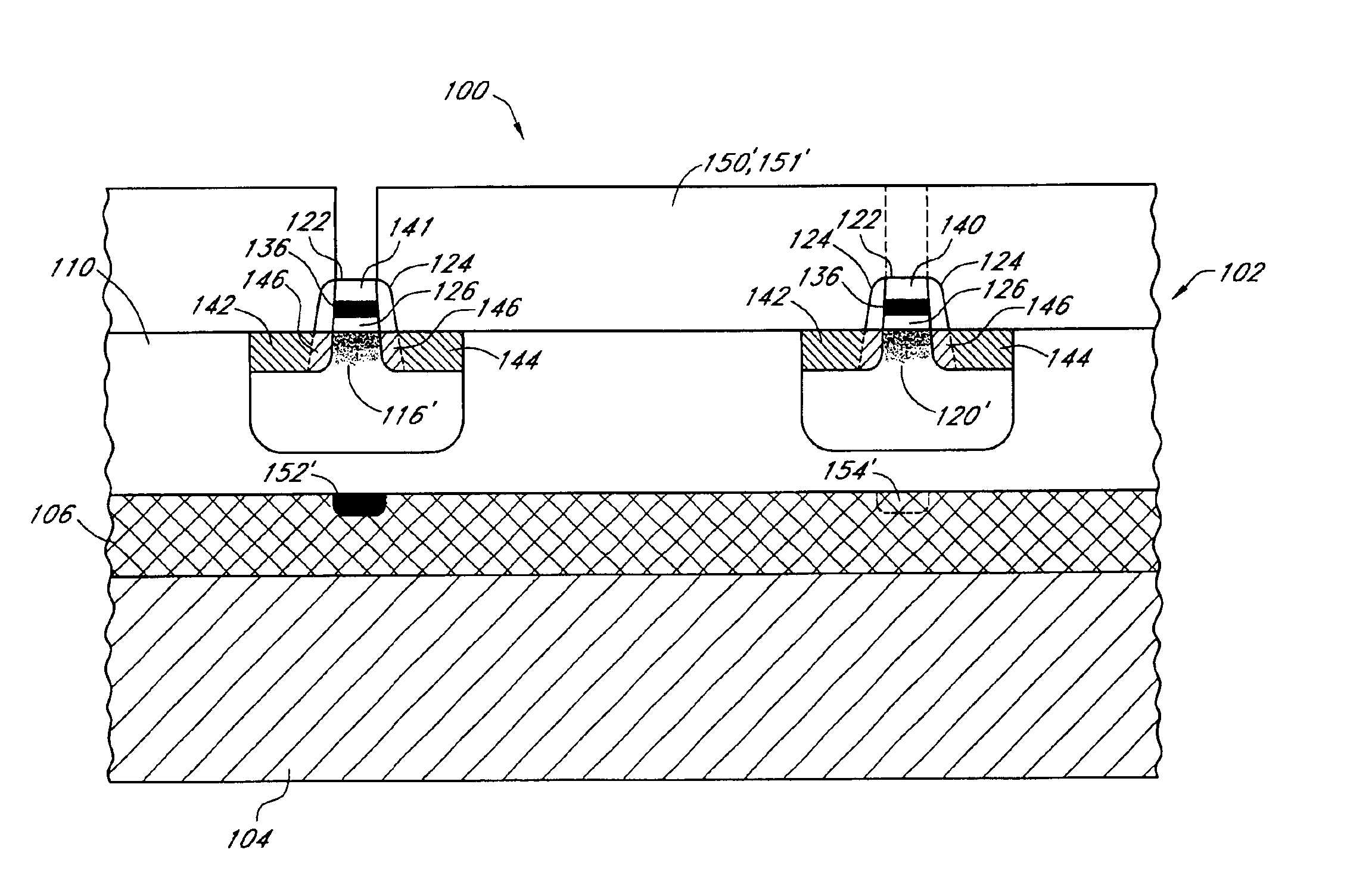

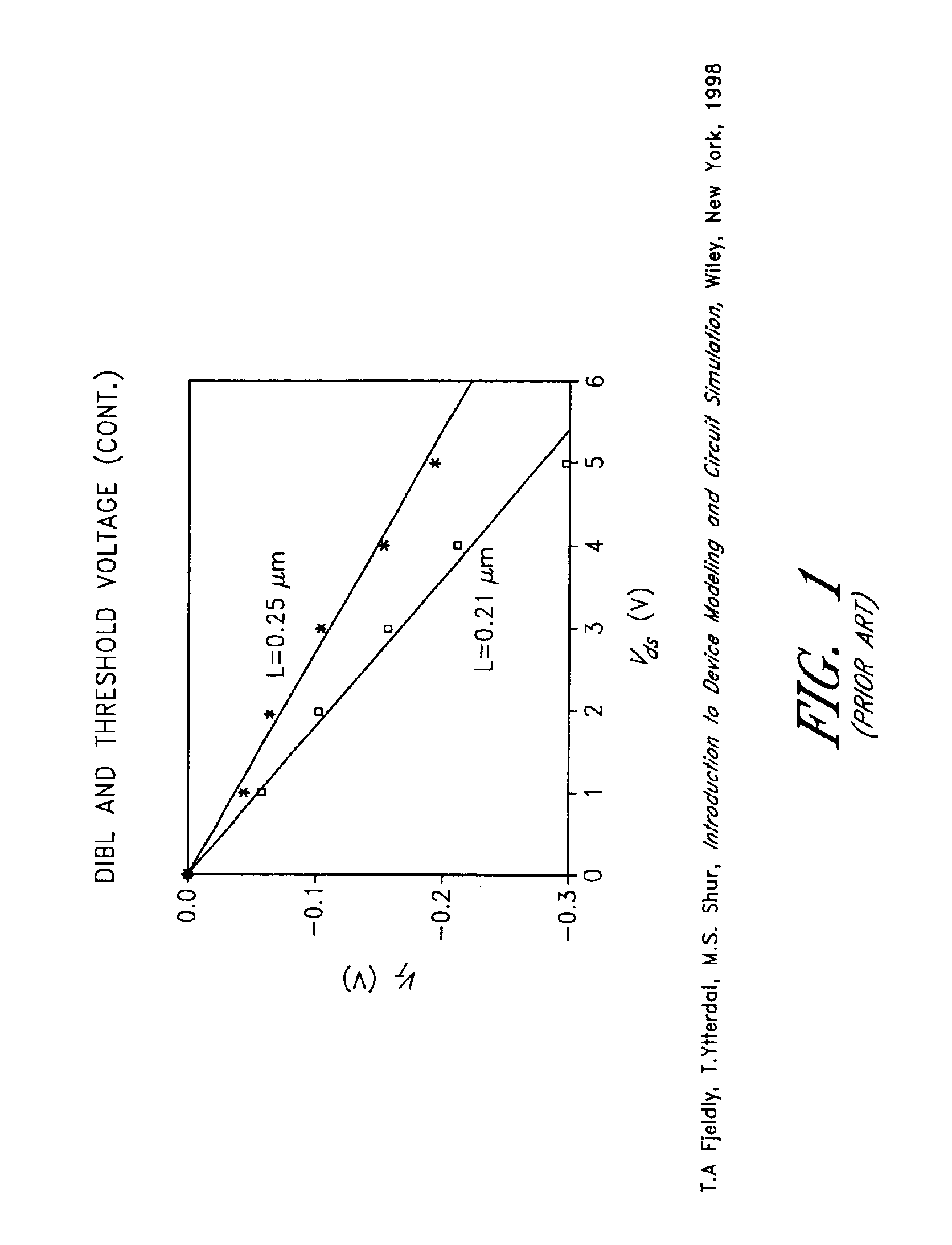

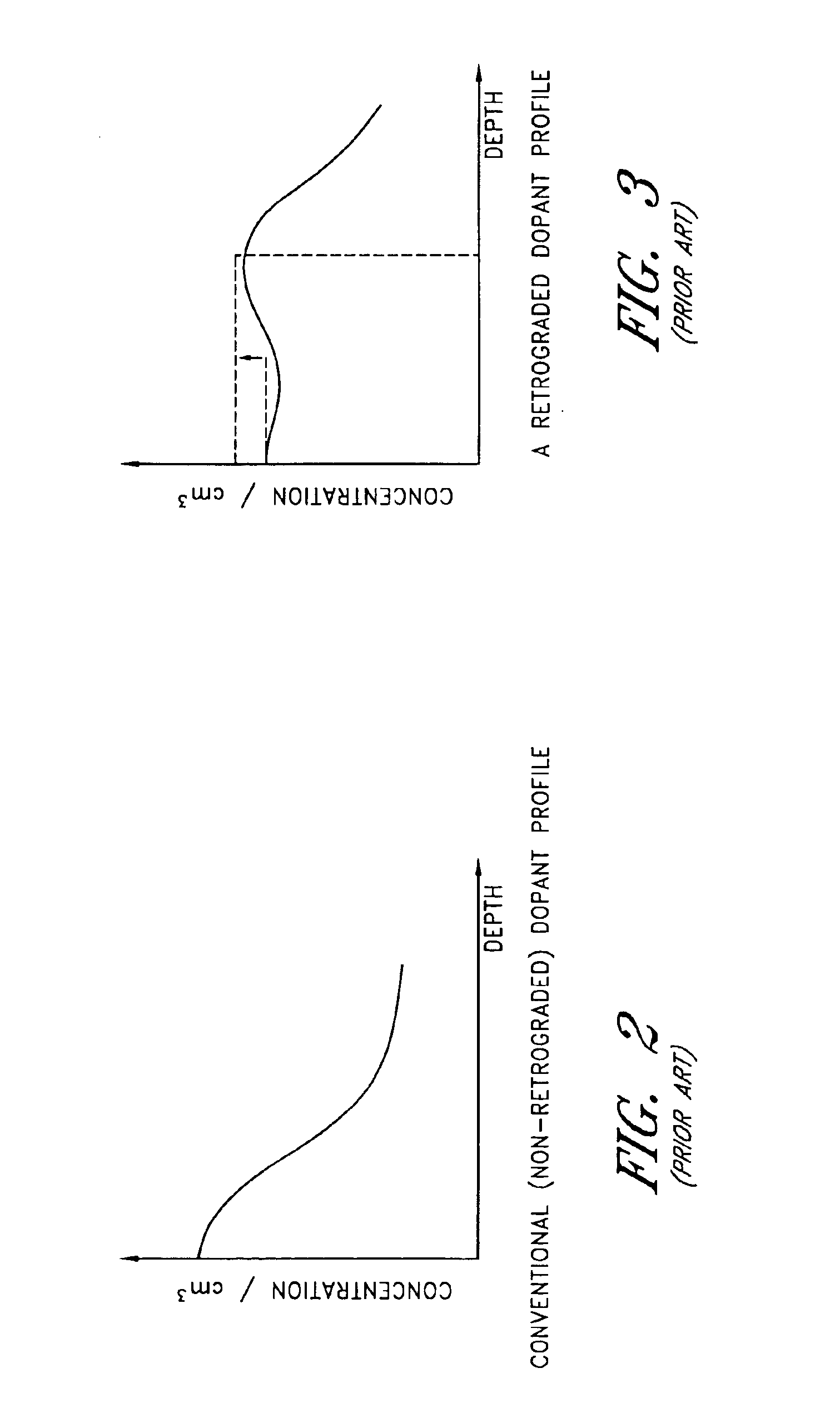

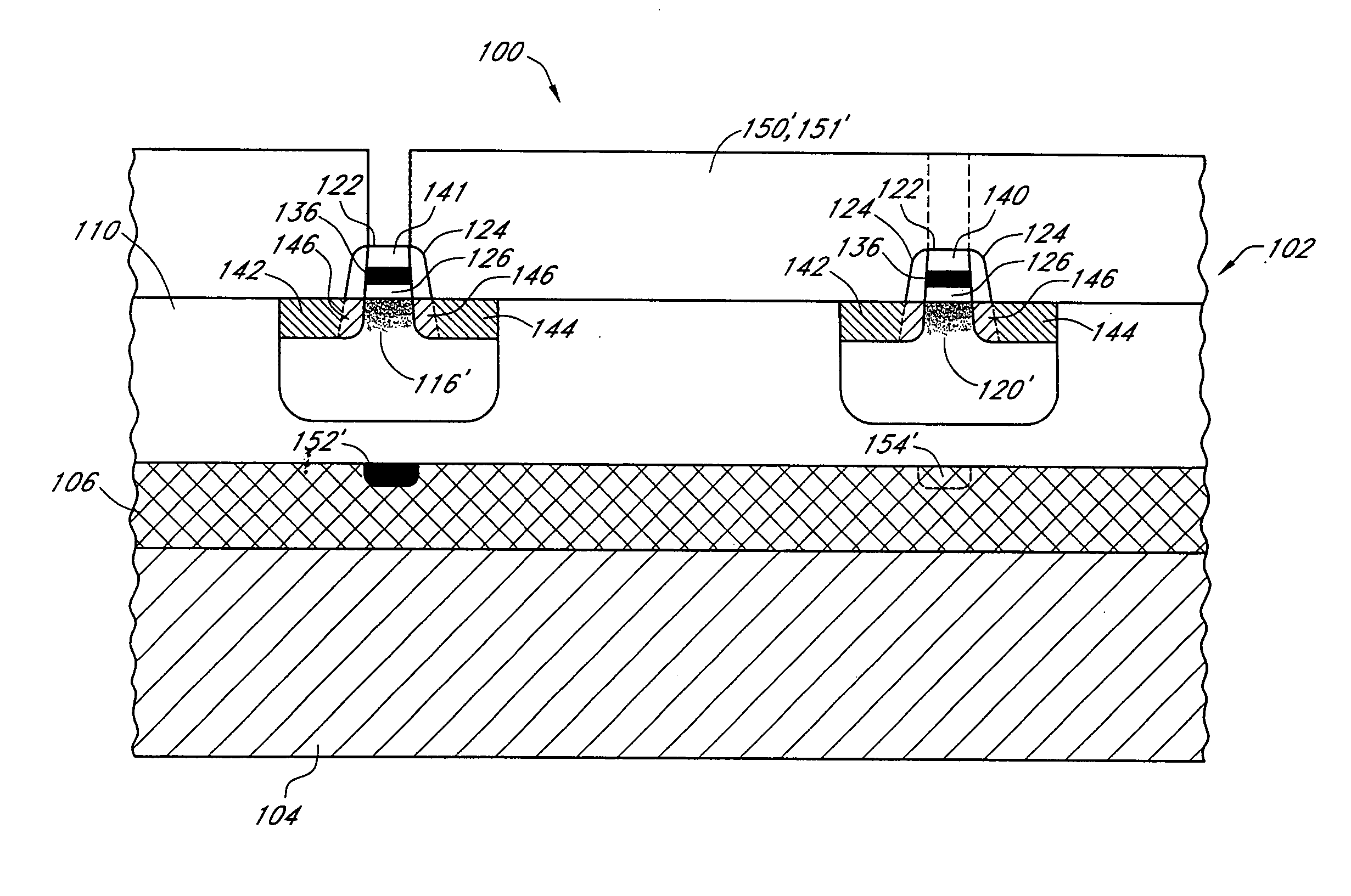

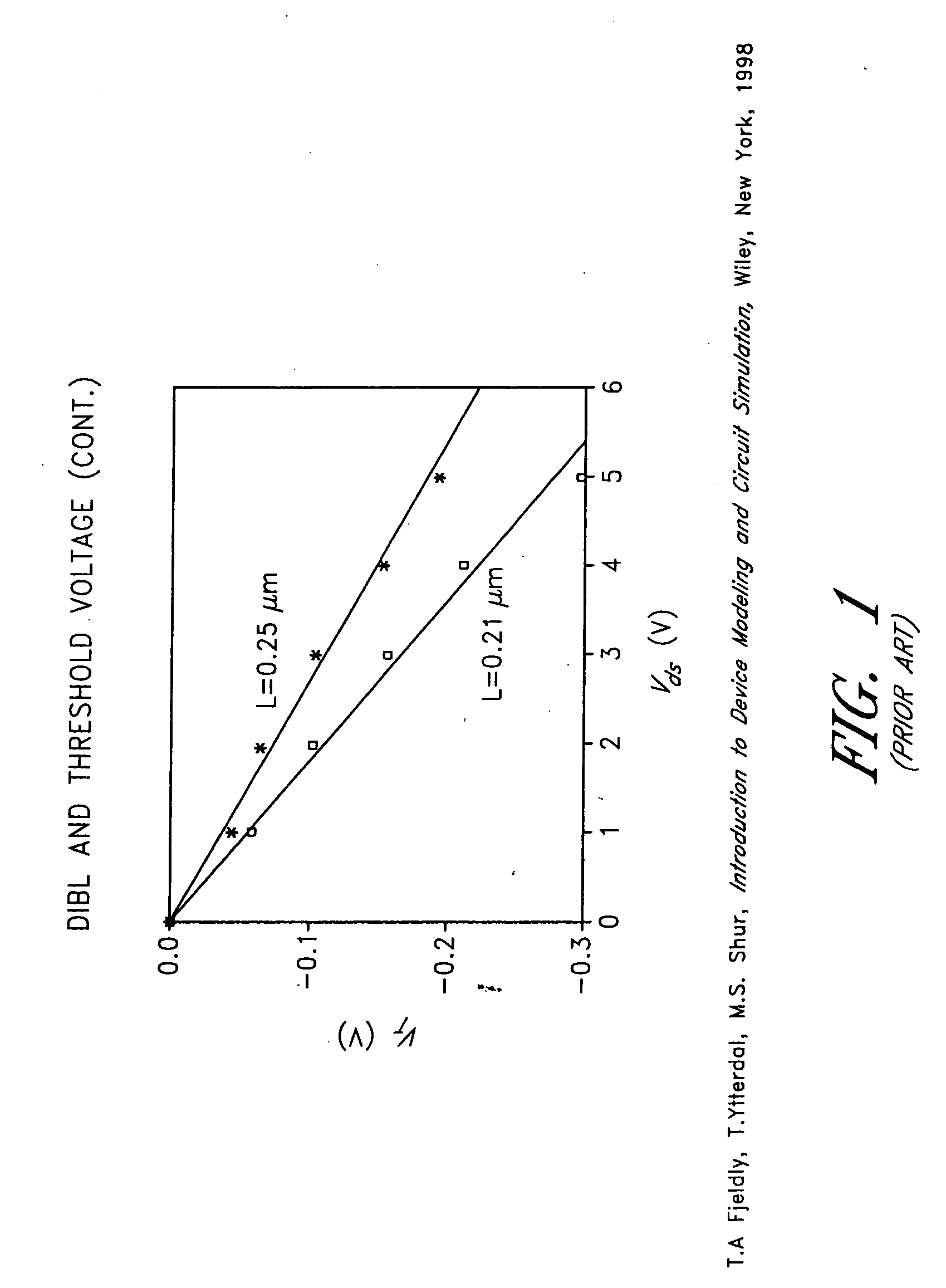

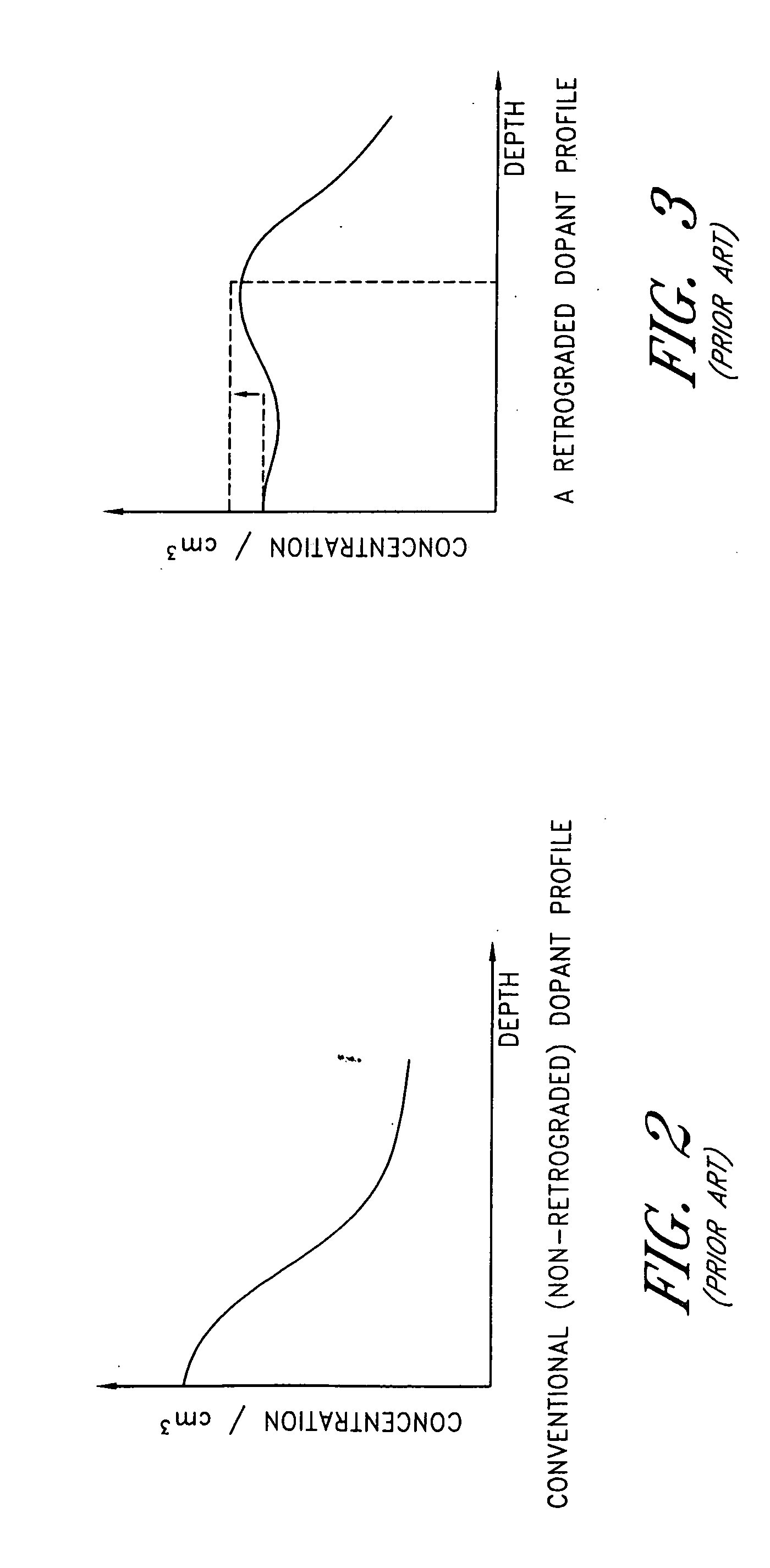

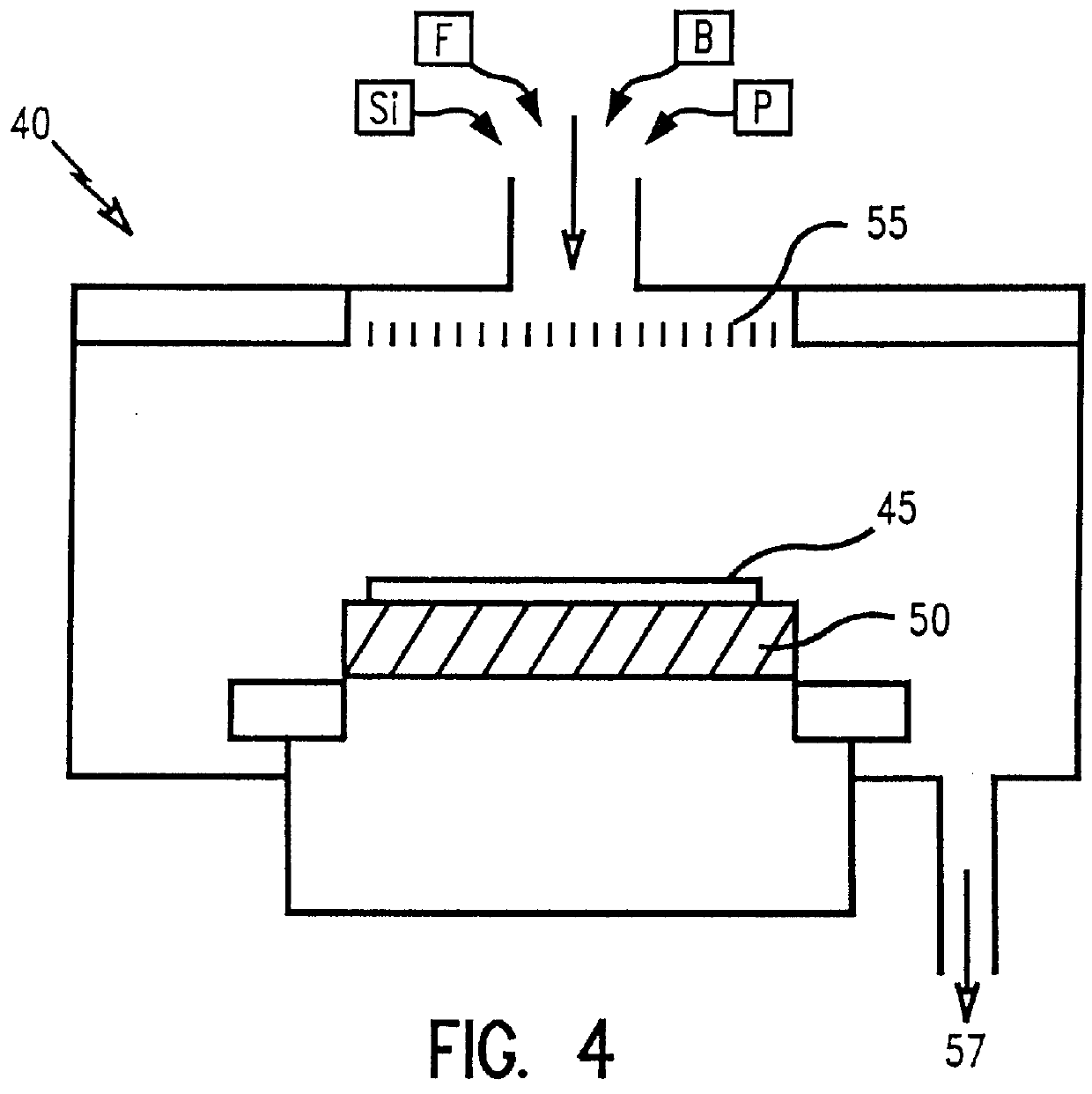

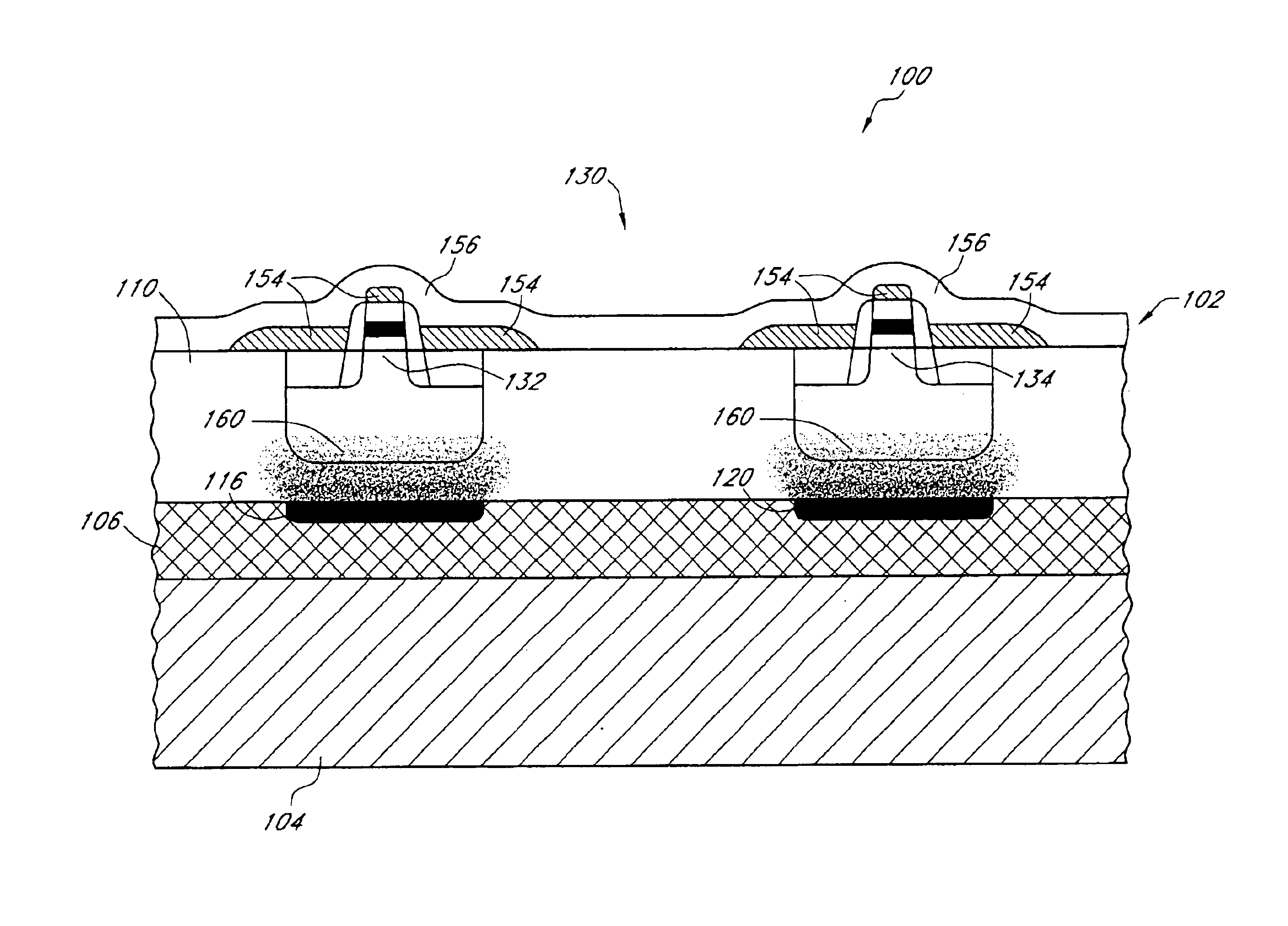

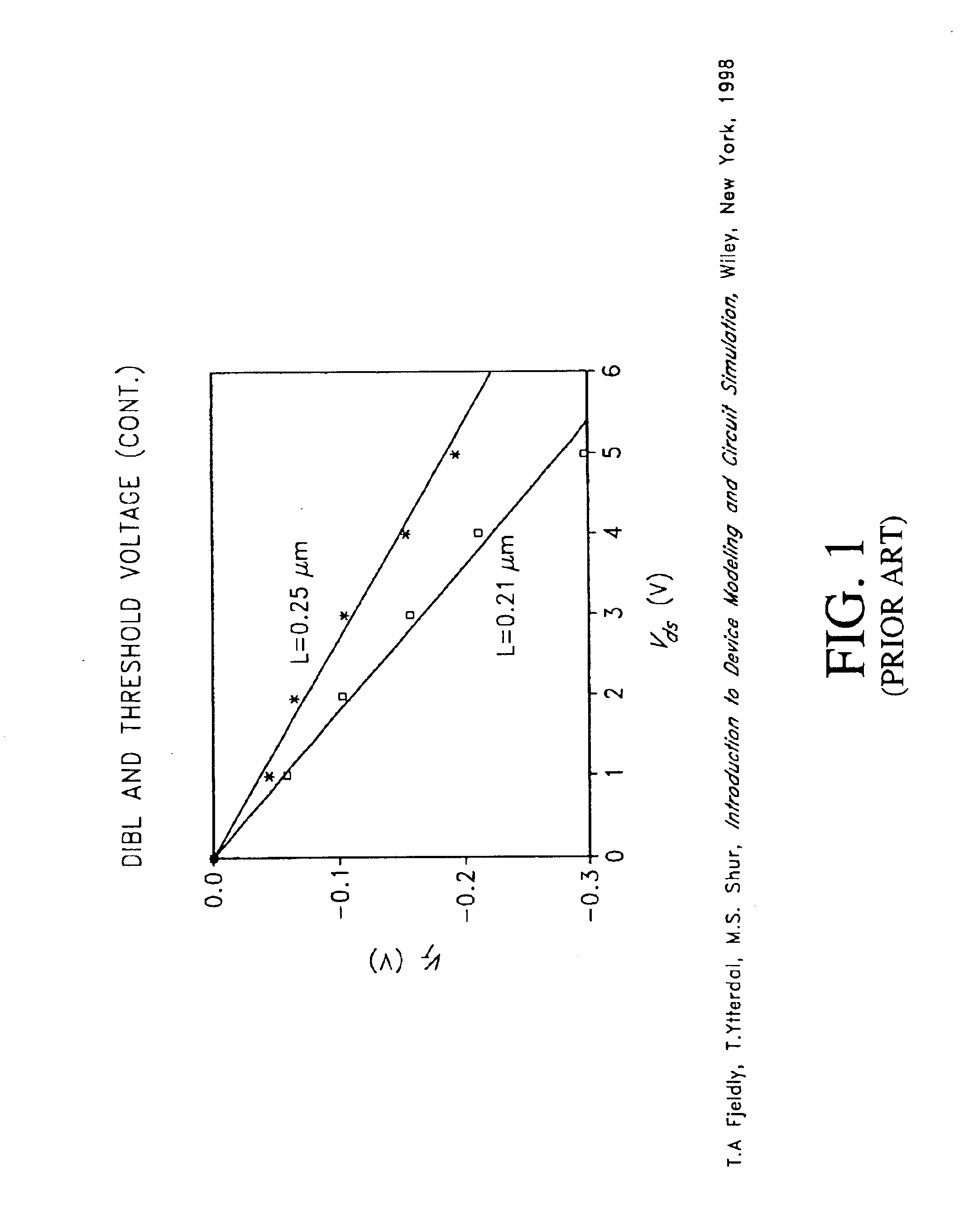

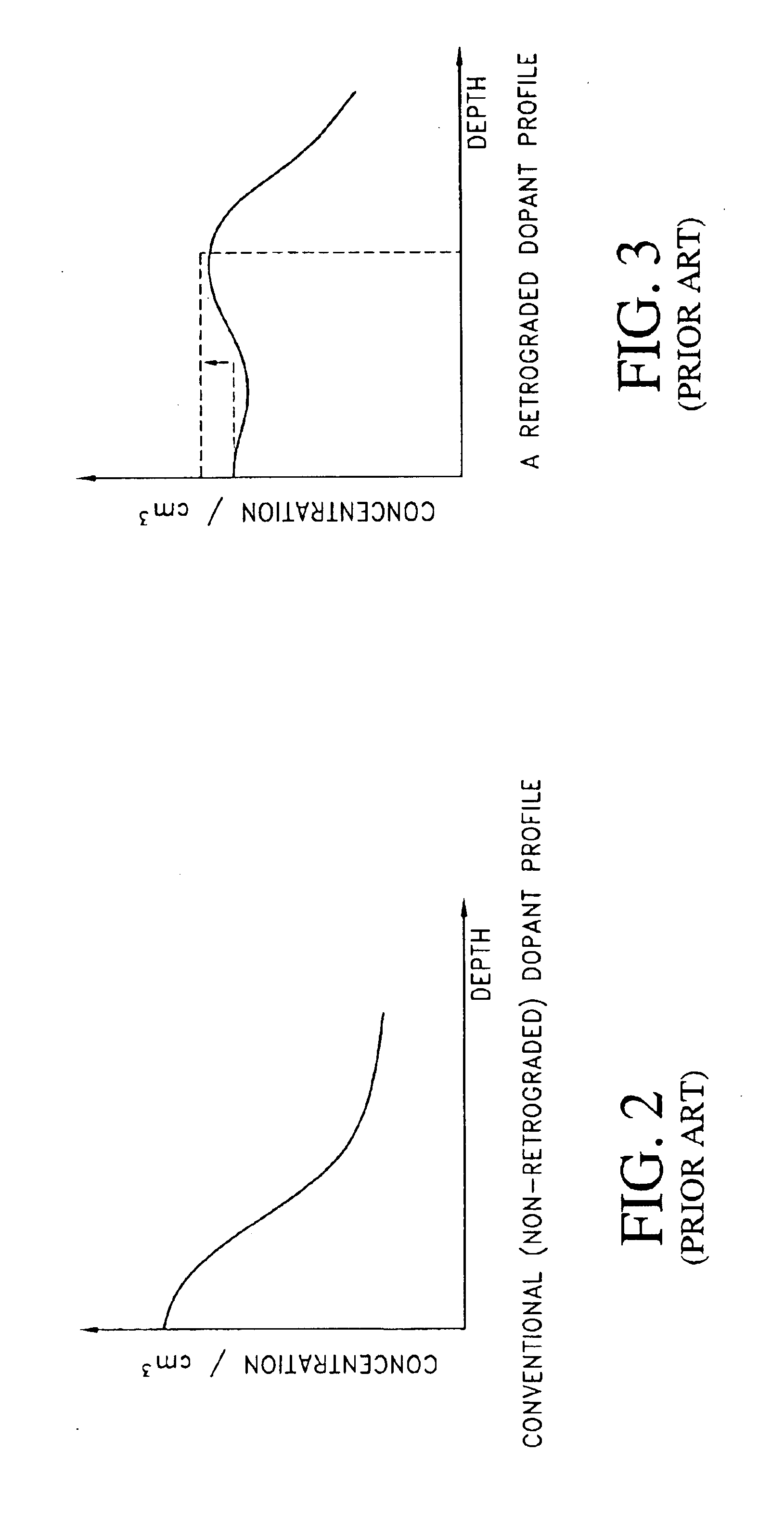

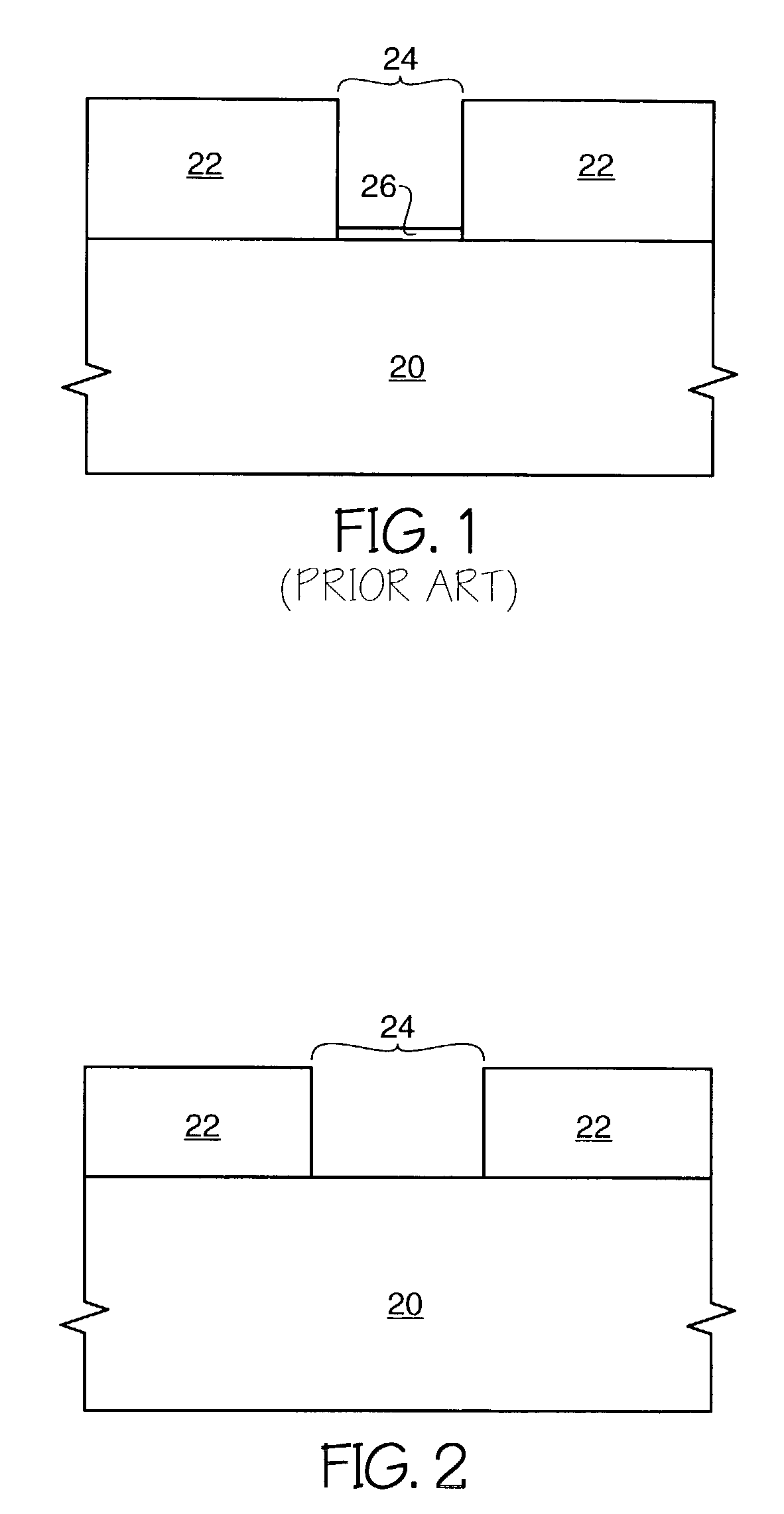

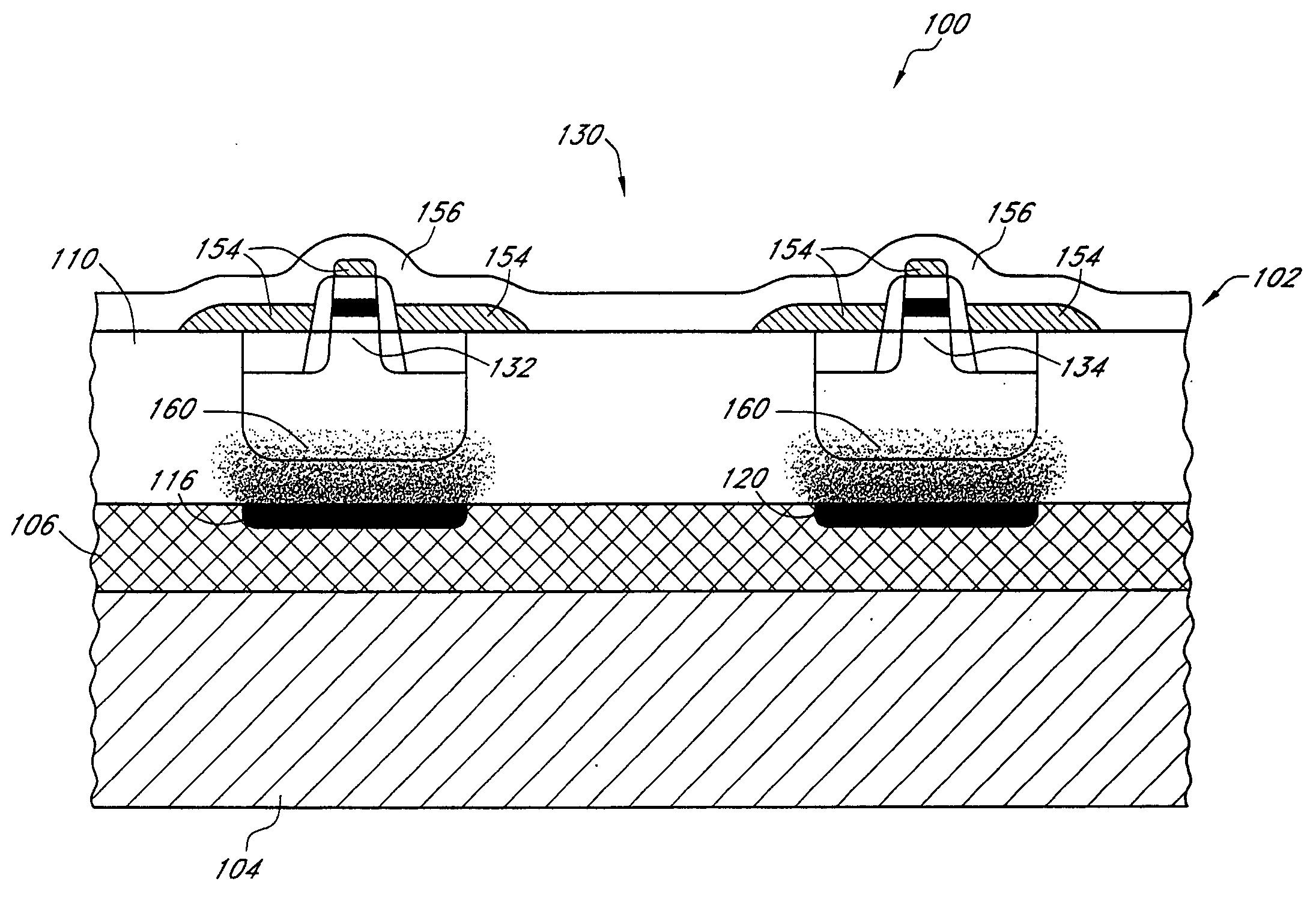

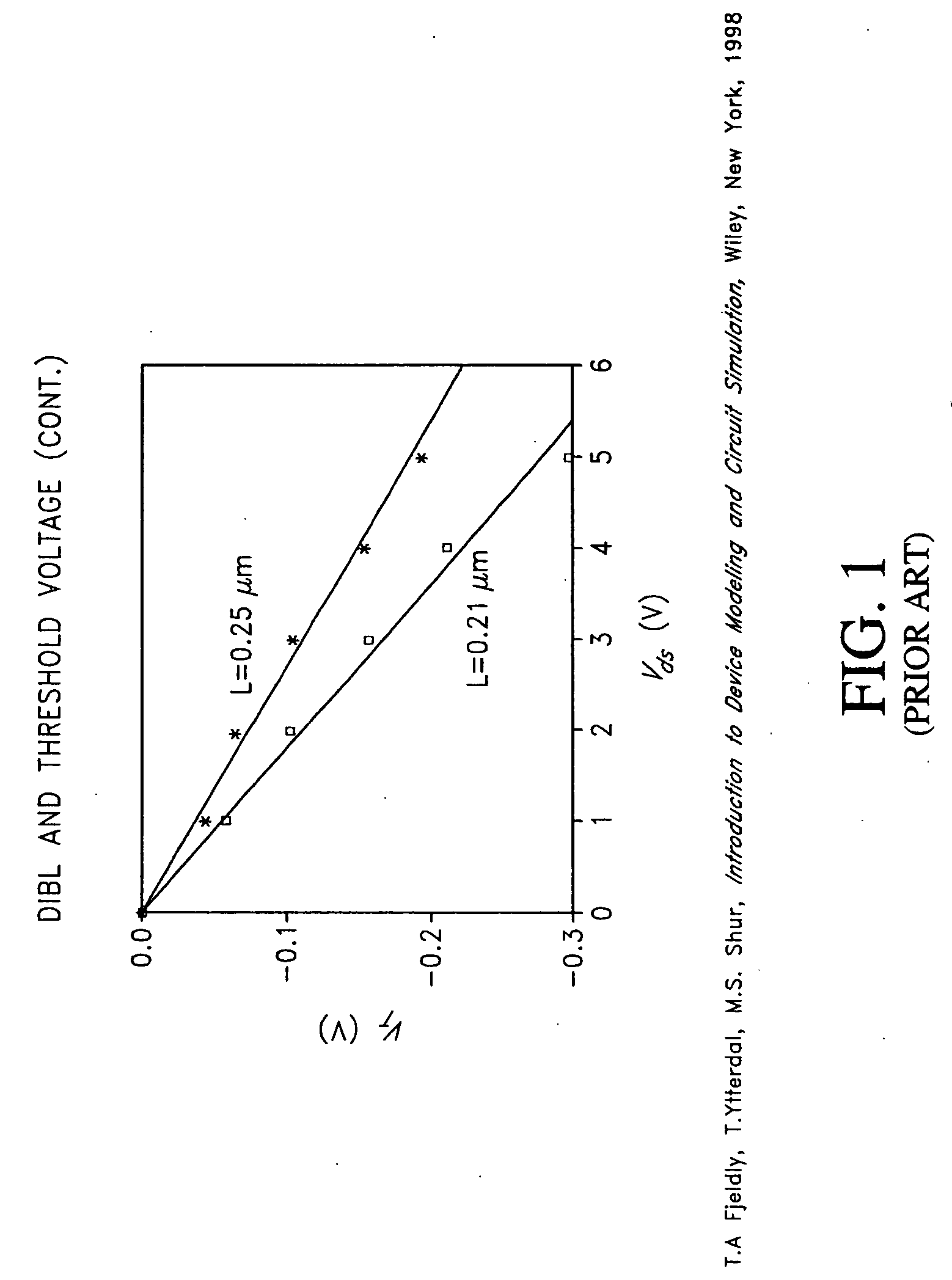

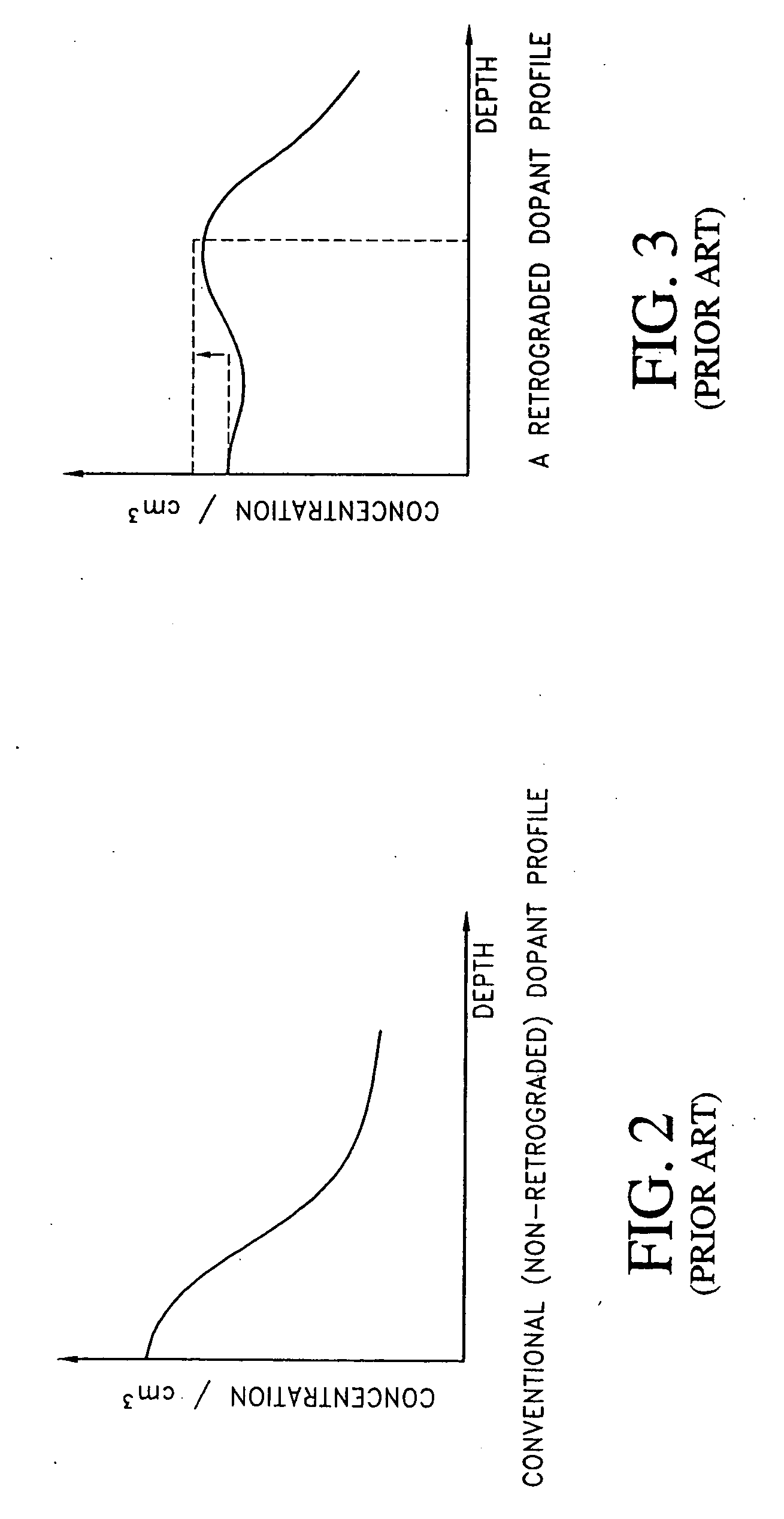

CMOS devices formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and a method for producing the same. The method involves a high energy, high dose implant through openings in a masking layer and through channel regions of the p- and n-wells, into the insulator layer, thereby creating a borophosphosilicate glass (BPSG) diffusion source within the insulation layer underlying the gate regions of the SOI wafer substantially between the source and drain. Backend high temperature processing steps induce diffusion of the dopants contained in the diffusion source into the p- and n-wells, thereby forming asymmetric retrograde dopant profiles in the channel under the gate. The method can be selectively applied to selected portions of a wafer to tailor device characteristics, such as for memory cells.

Owner:APTINA IMAGING CORP

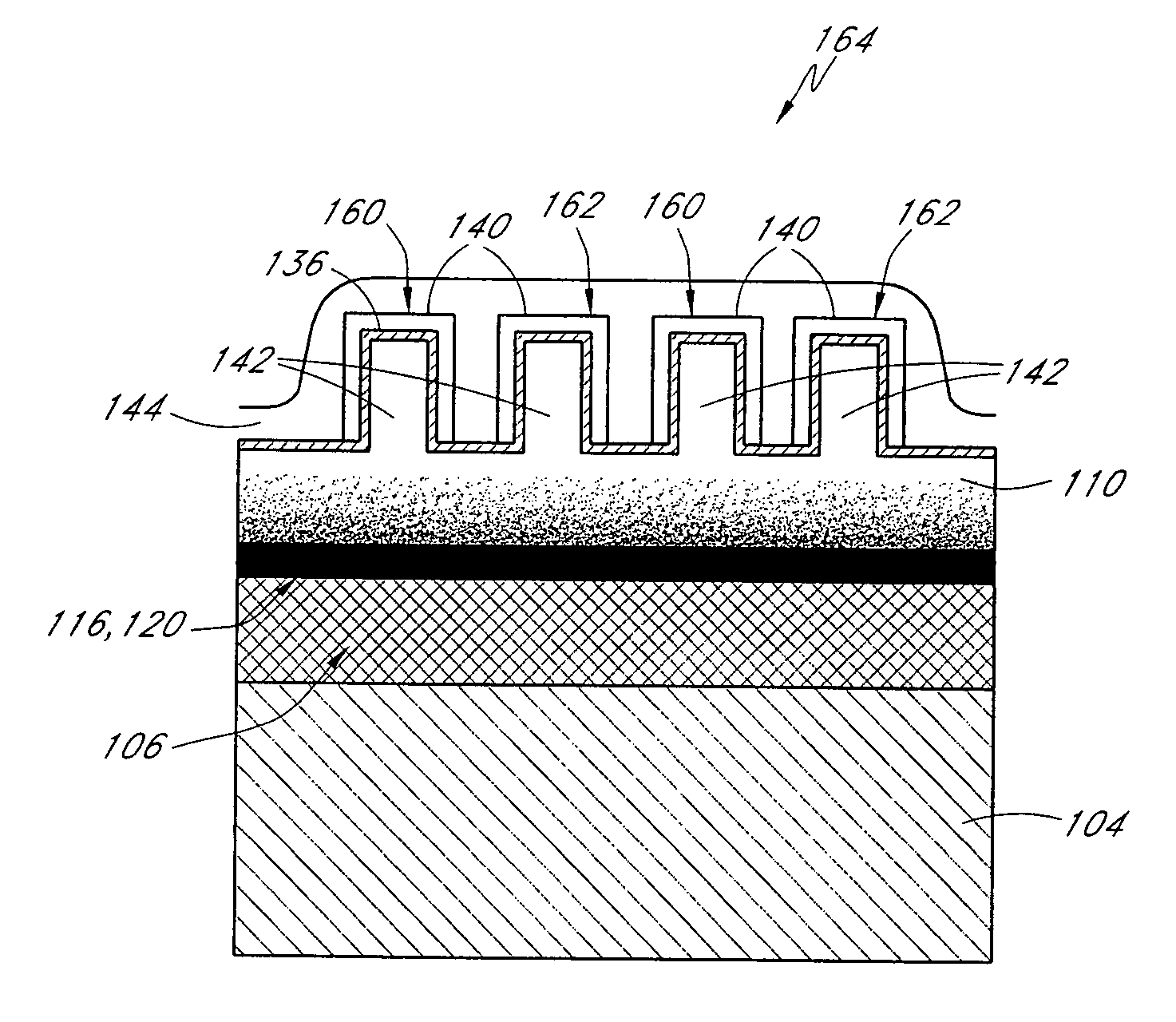

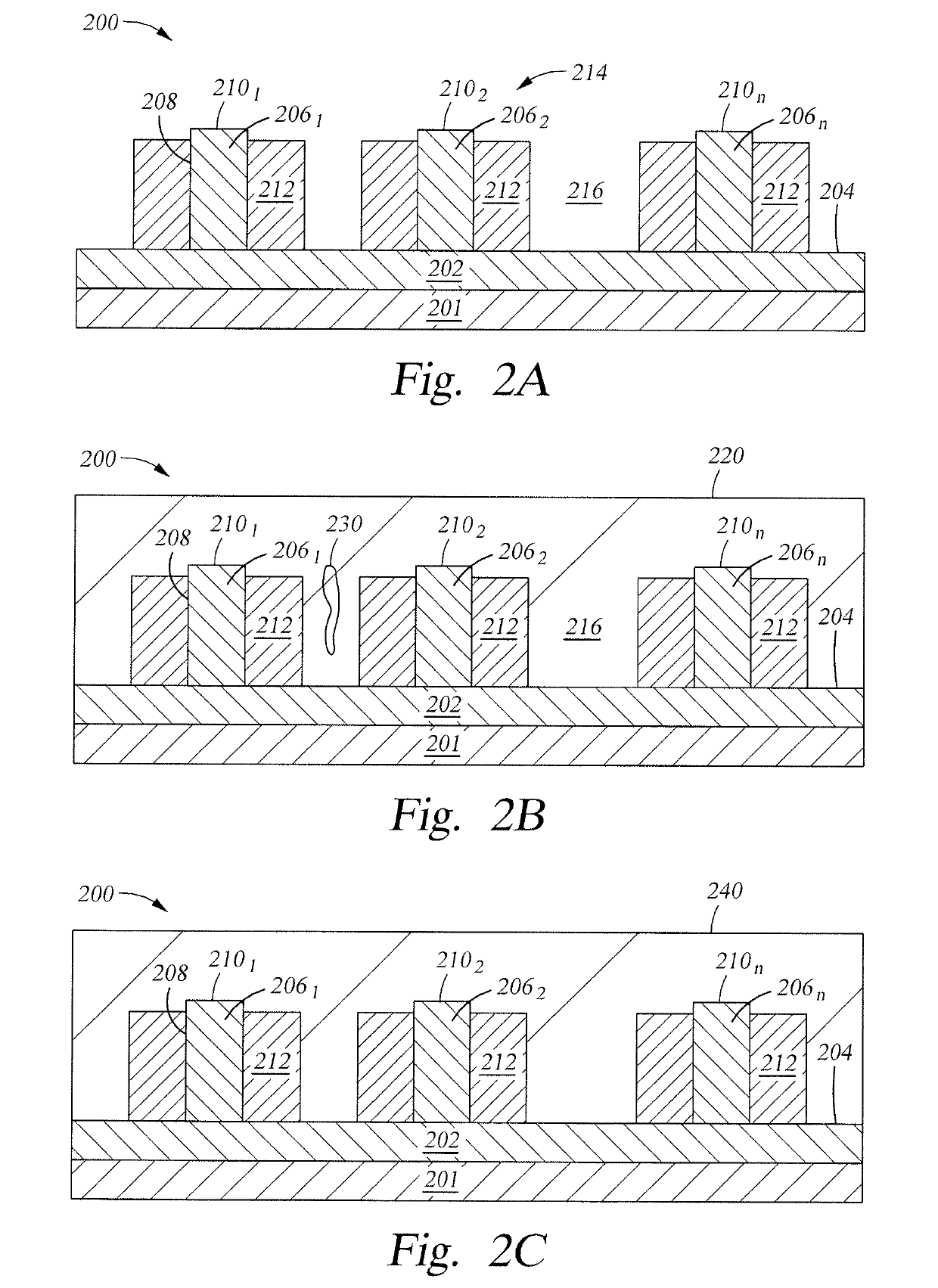

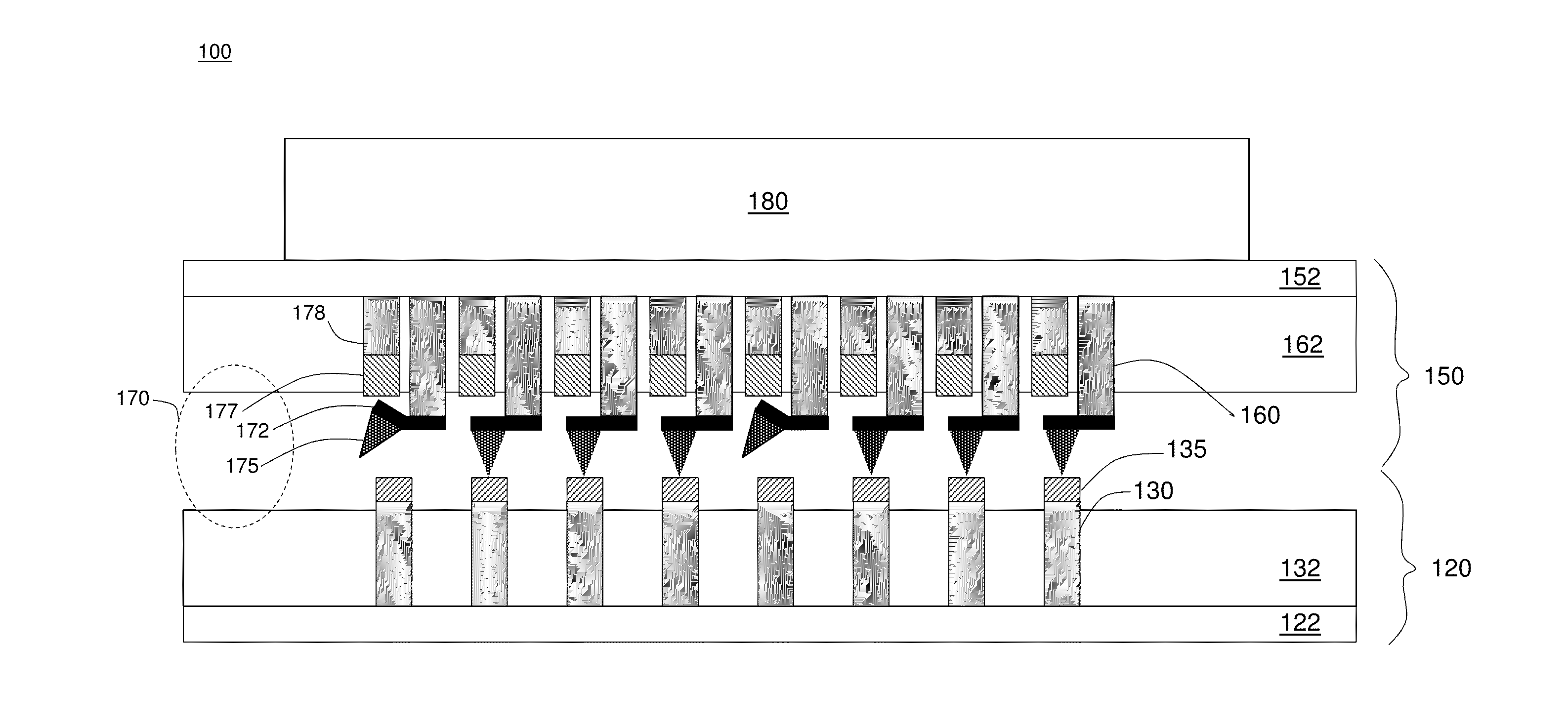

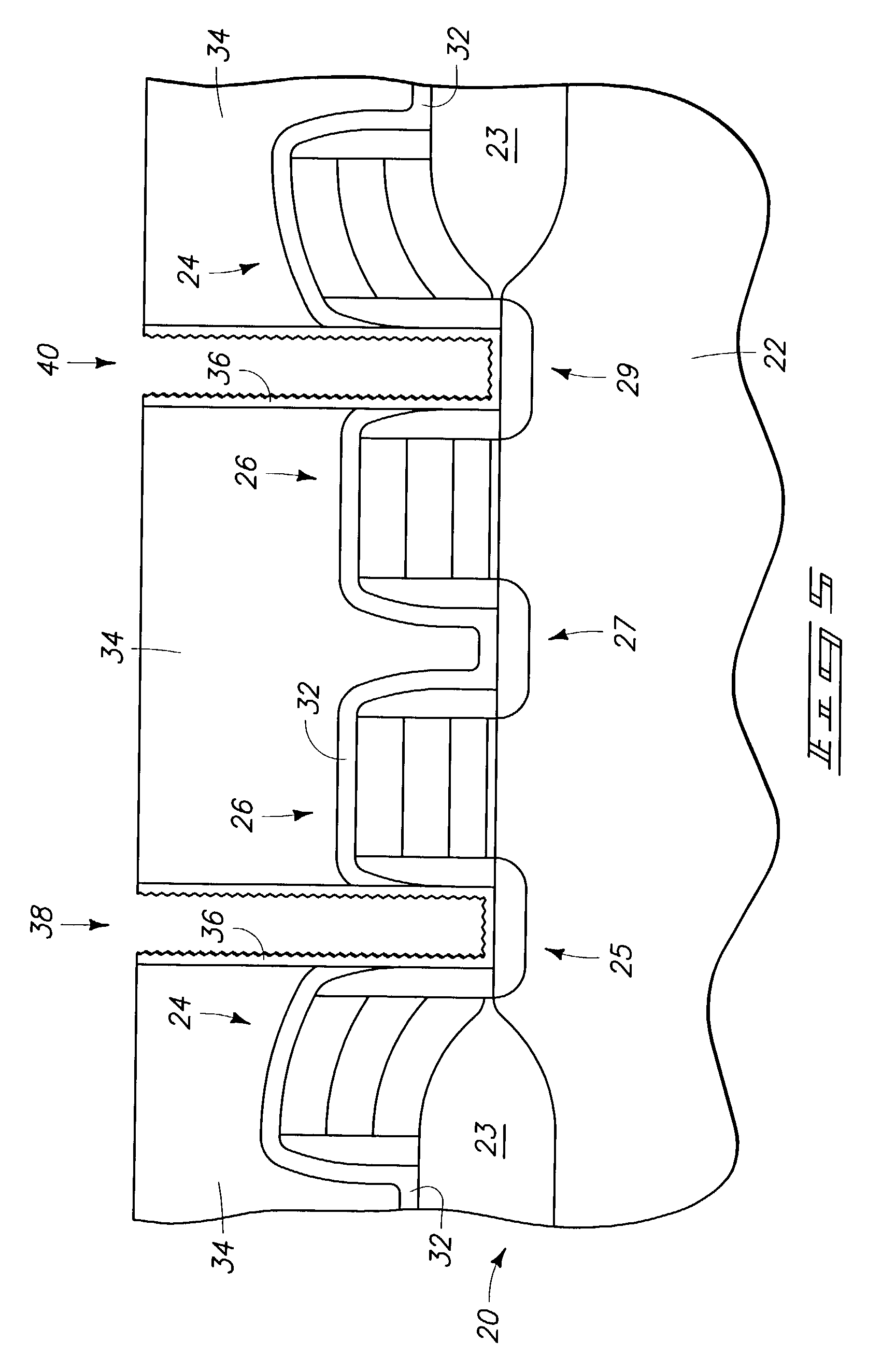

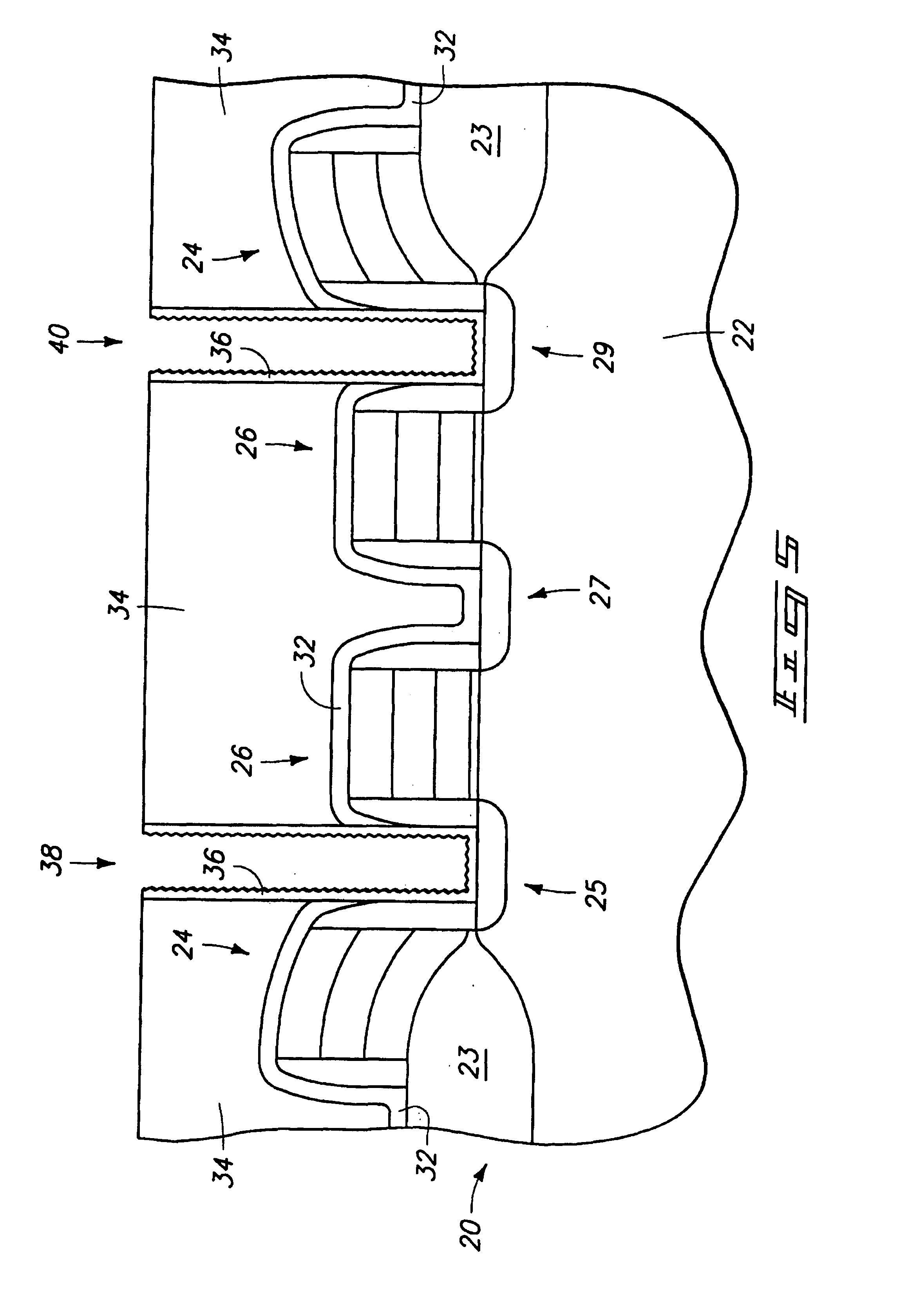

FinFET device with reduced DIBL

ActiveUS7009250B1Reduce resistanceSuppression of floating body effectSolid-state devicesSemiconductor/solid-state device manufacturingBorophosphosilicate glassEngineering

FinFET devices formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and methods for producing the same. The methods involve dopant implants into the insulator layer, thereby creating borophosphosilicate glass (BPSG) diffusion sources within the insulation layer underlying the active regions of the SOI wafer. Backend high temperature processing steps induce diffusion of the dopants contained in the diffusion source into the active regions, thereby forming a retrograde dopant profile extending towards the channel region. The method can be selectively applied to selected portions of a wafer to tailor device characteristics, such as for memory cells.

Owner:MICRON TECH INC

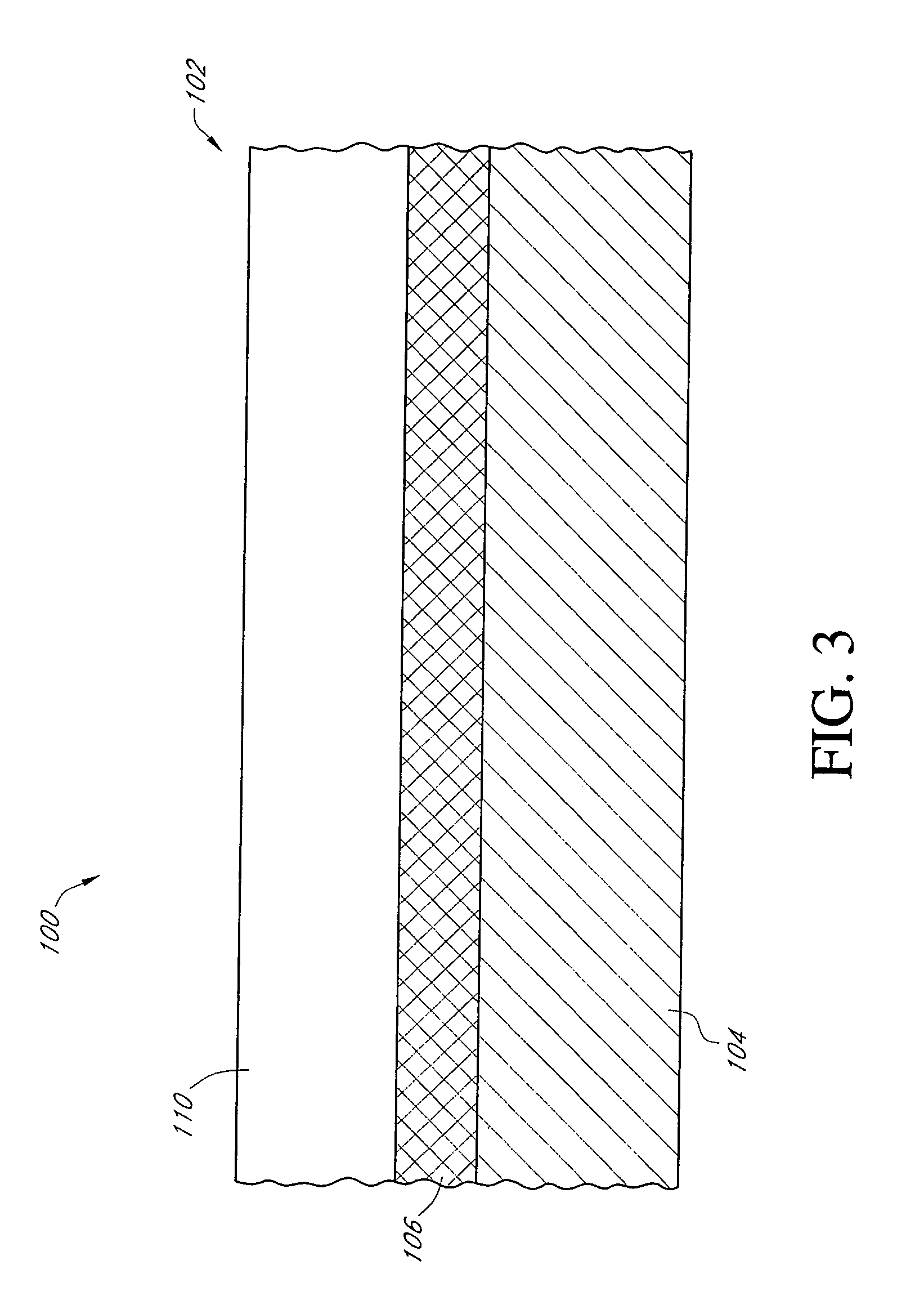

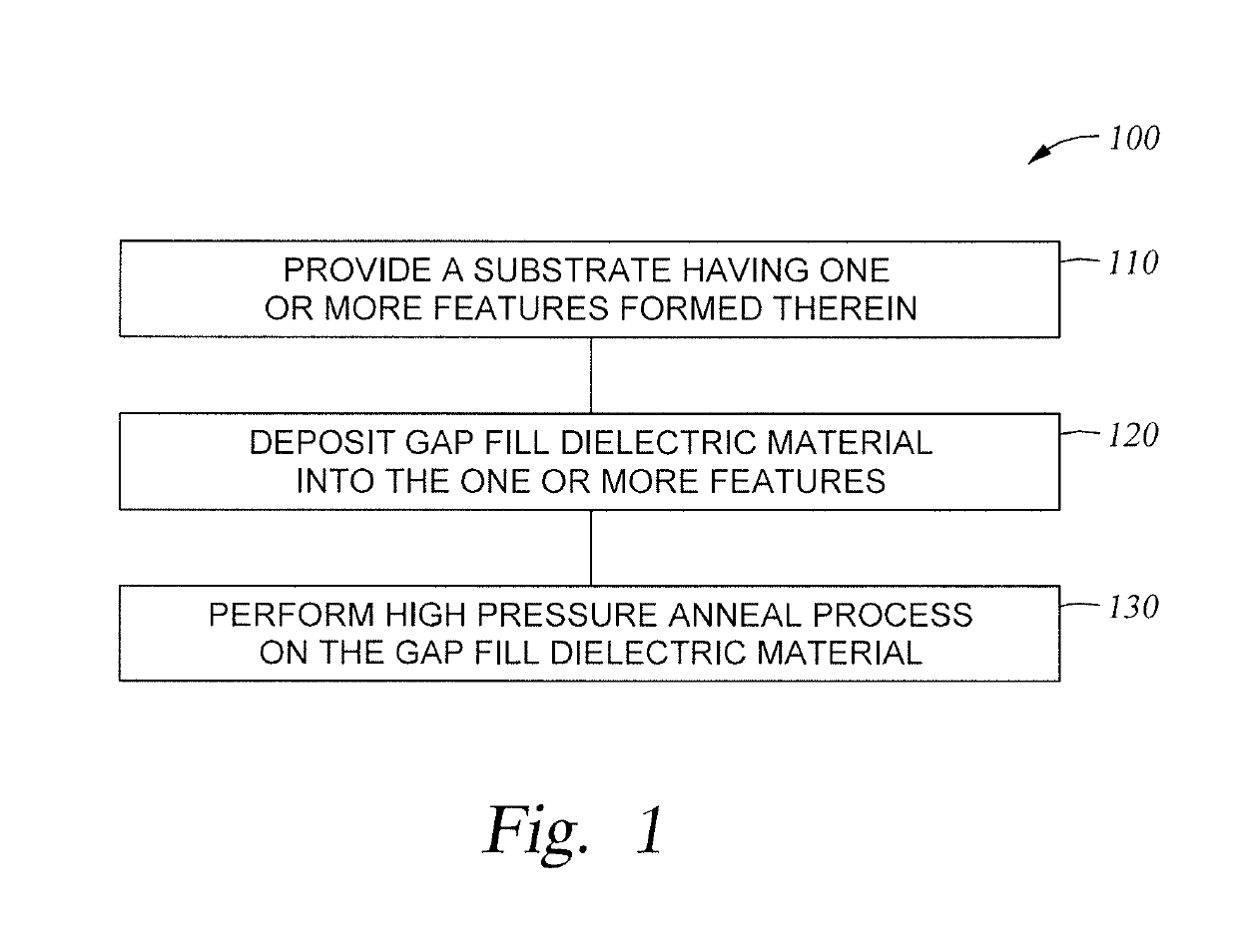

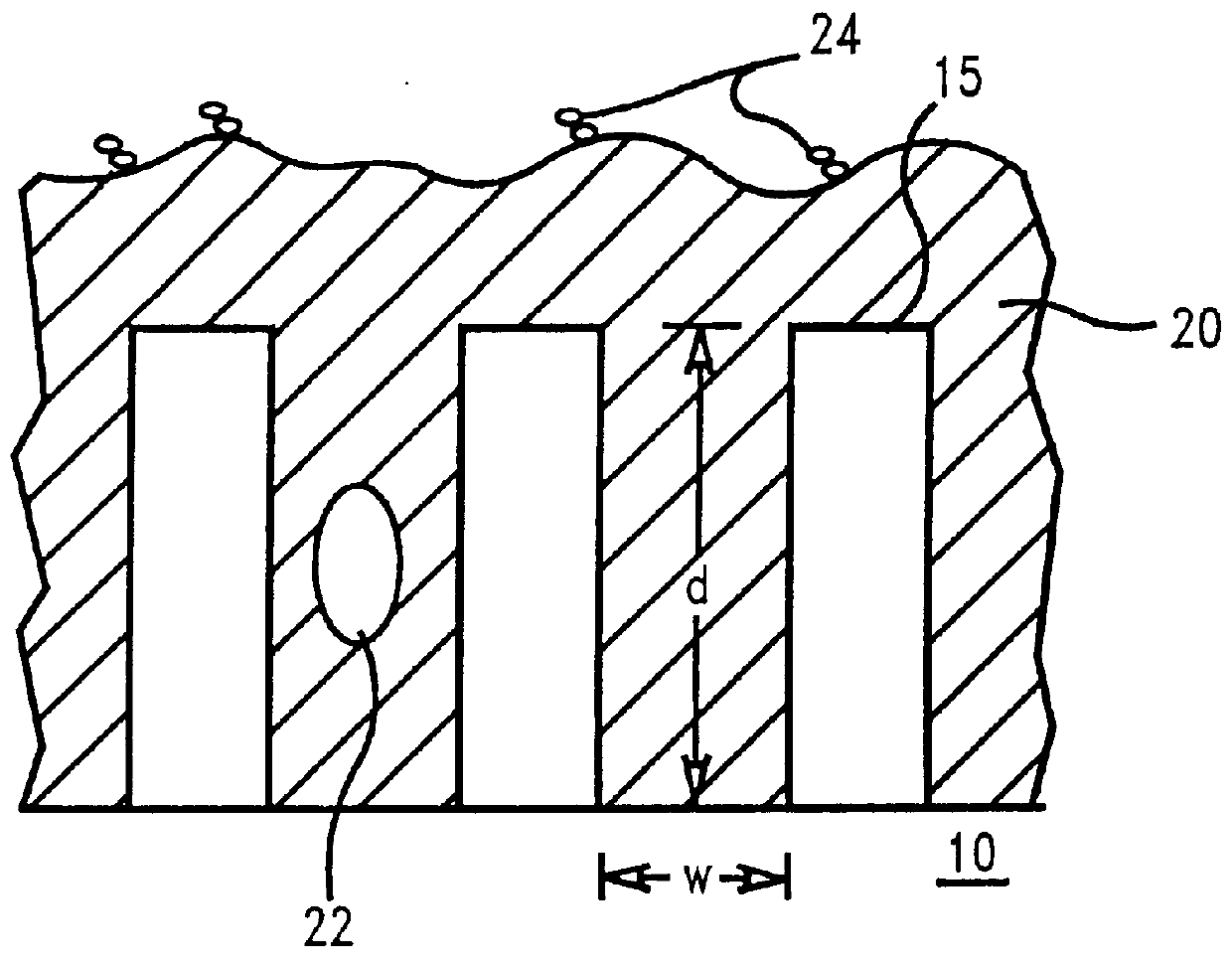

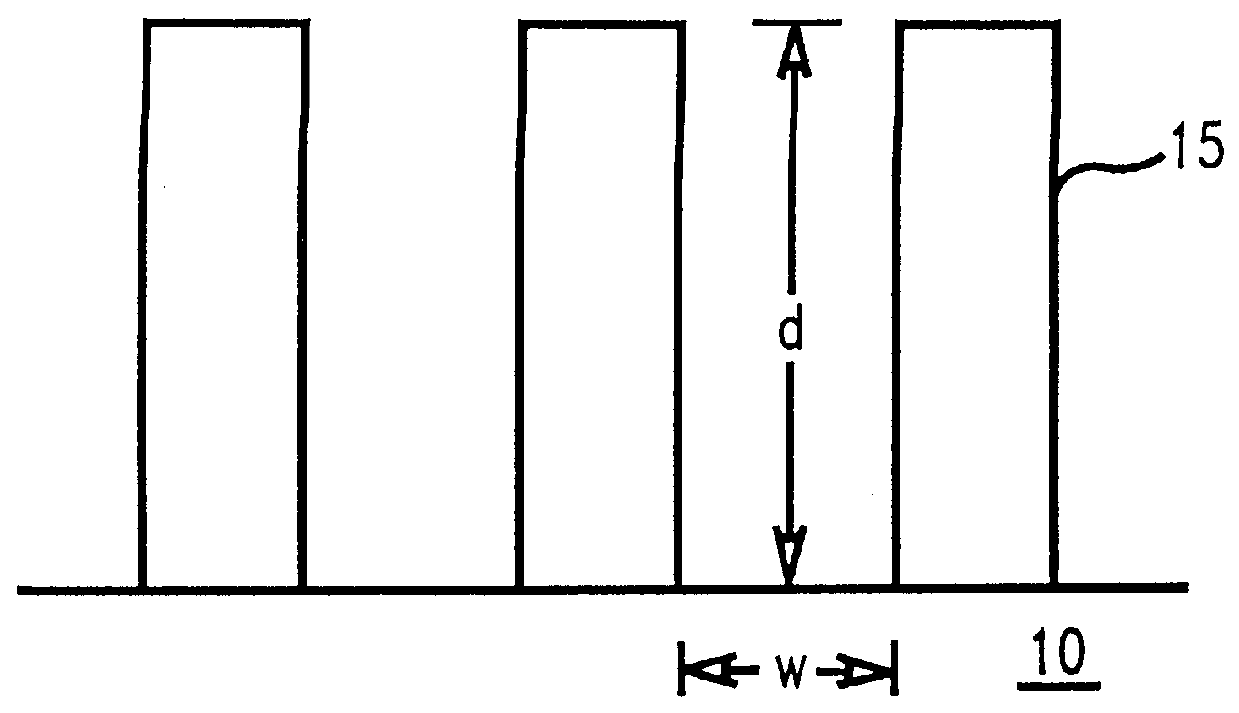

Method for depositing and reflow of a high quality etch resistant gapfill dielectric film

ActiveUS20190259625A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicate glassBorophosphosilicate glass

Methods for depositing a gapfill dielectric film that may be utilized for multi-colored patterning processes are provided. In one implementation, a method for processing a substrate is provided. The method comprises filling the one or more features of a substrate with a dielectric material. The dielectric material is a doped silicate glass selected from borophosphosilicate glass (BPSG), phosphosilicate glass (PSG), and borosilicate glass (BSG). The method further comprises treating the substrate with a high-pressure anneal in the presence of an oxidizer to heal seams within the dielectric material. The high-pressure anneal comprises supplying an oxygen-containing gas mixture on a substrate in a processing chamber, maintaining the oxygen-containing gas mixture in the processing chamber at a process pressure at greater than 2 bar and thermally annealing the dielectric material in the presence of the oxygen-containing gas mixture.

Owner:MICROMATERIALS LLC

FinFET device with reduced DIBL

ActiveUS7235468B1Suppression of short channel effectsReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantInsulation layer

Owner:MICRON TECH INC

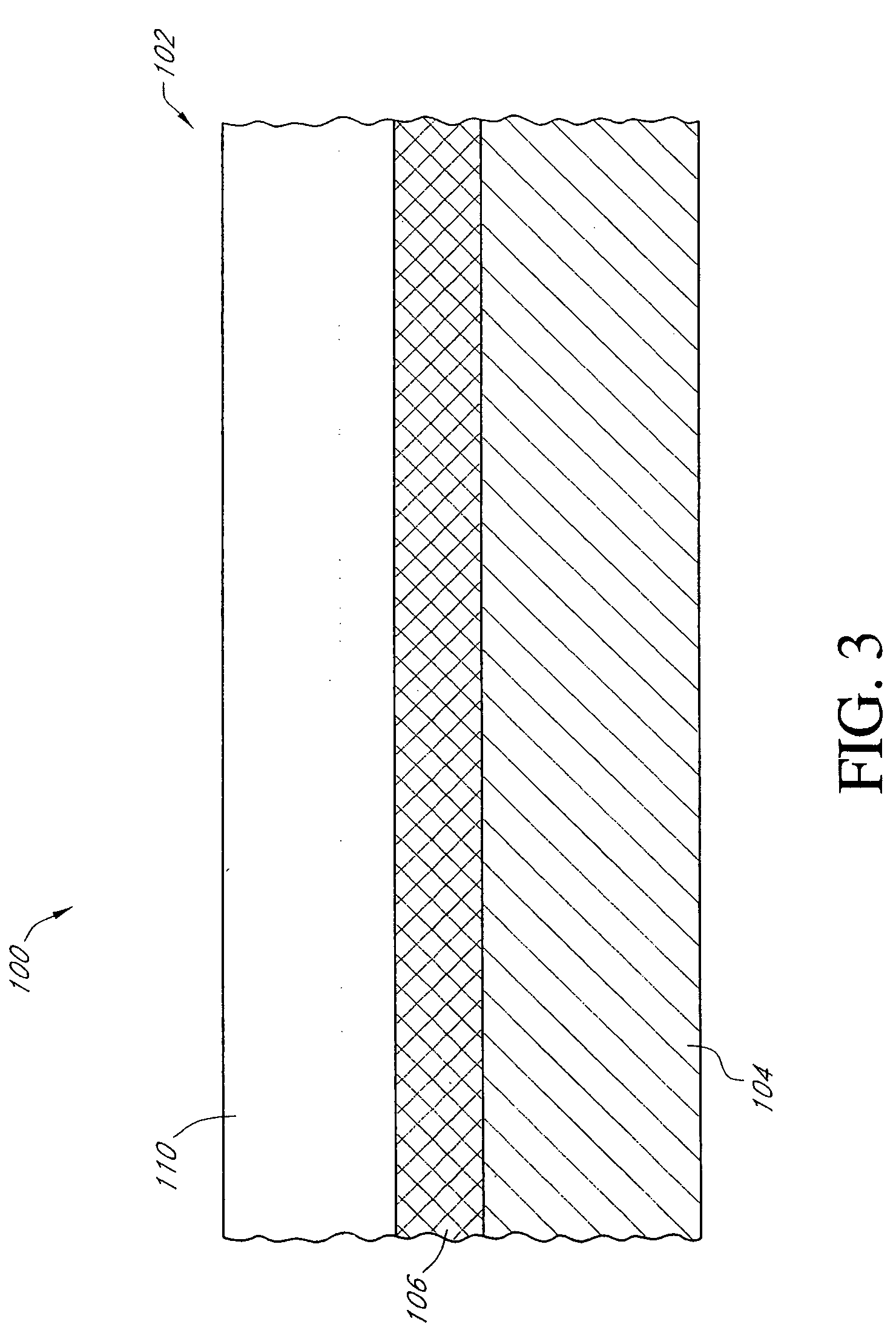

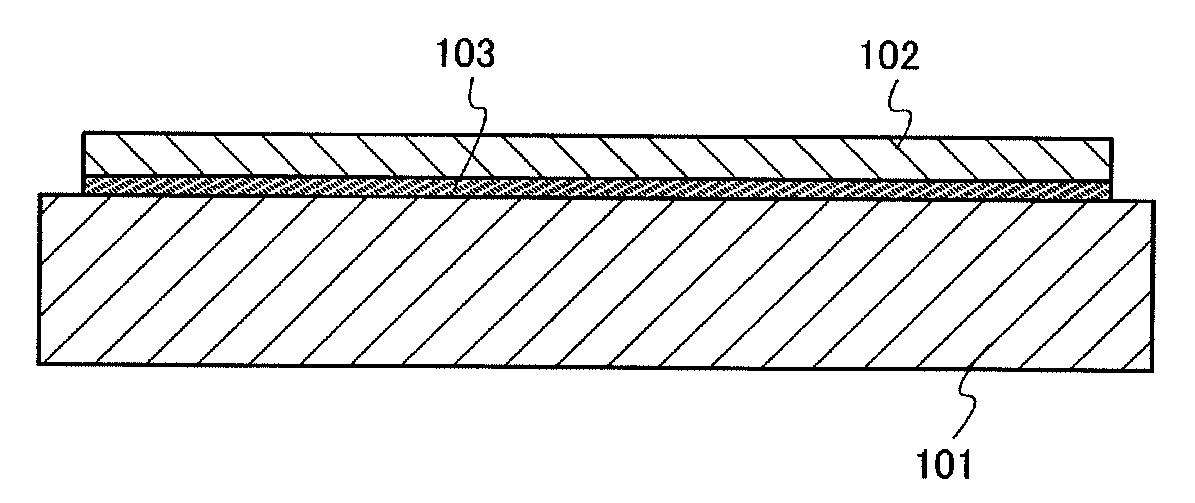

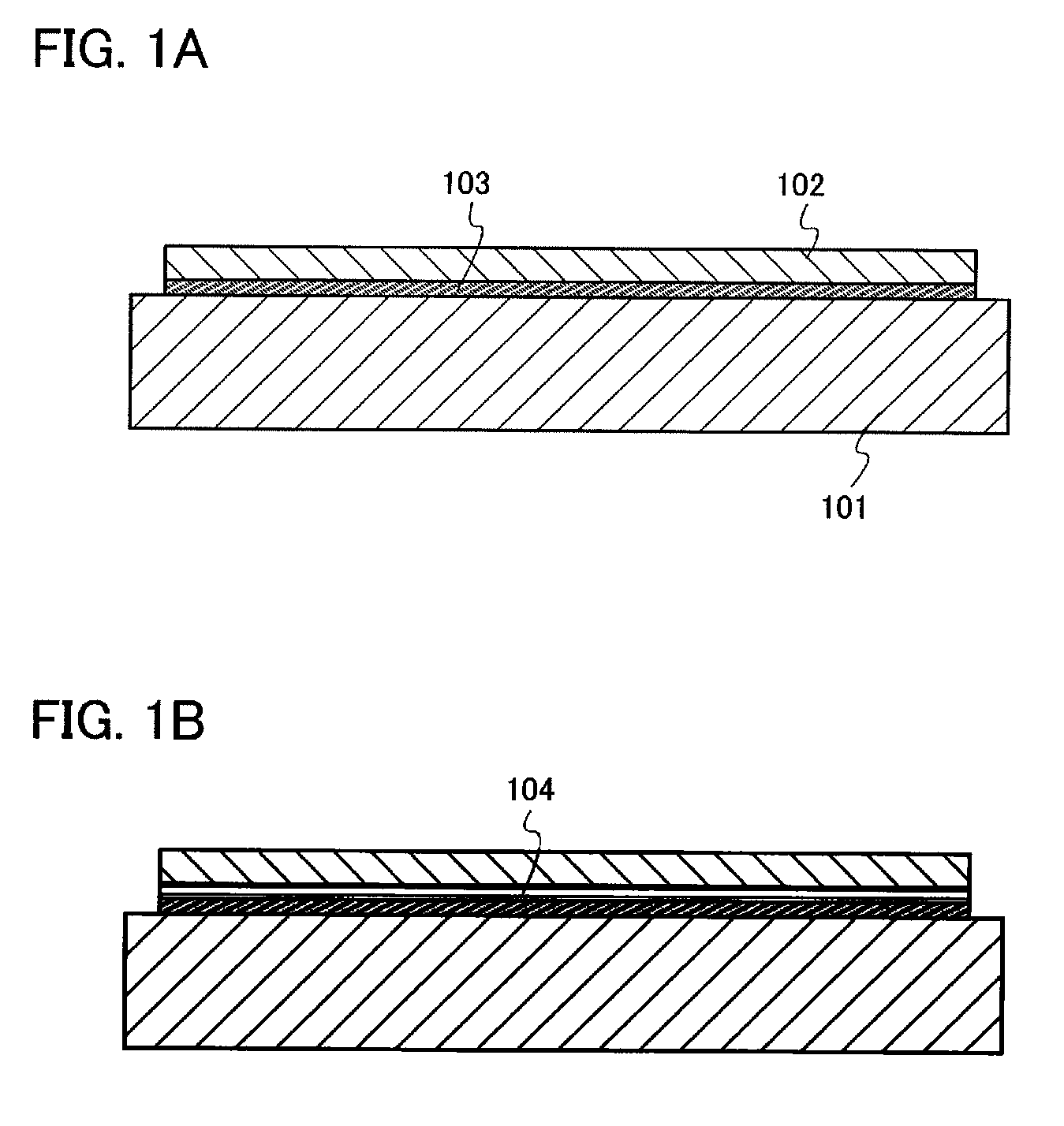

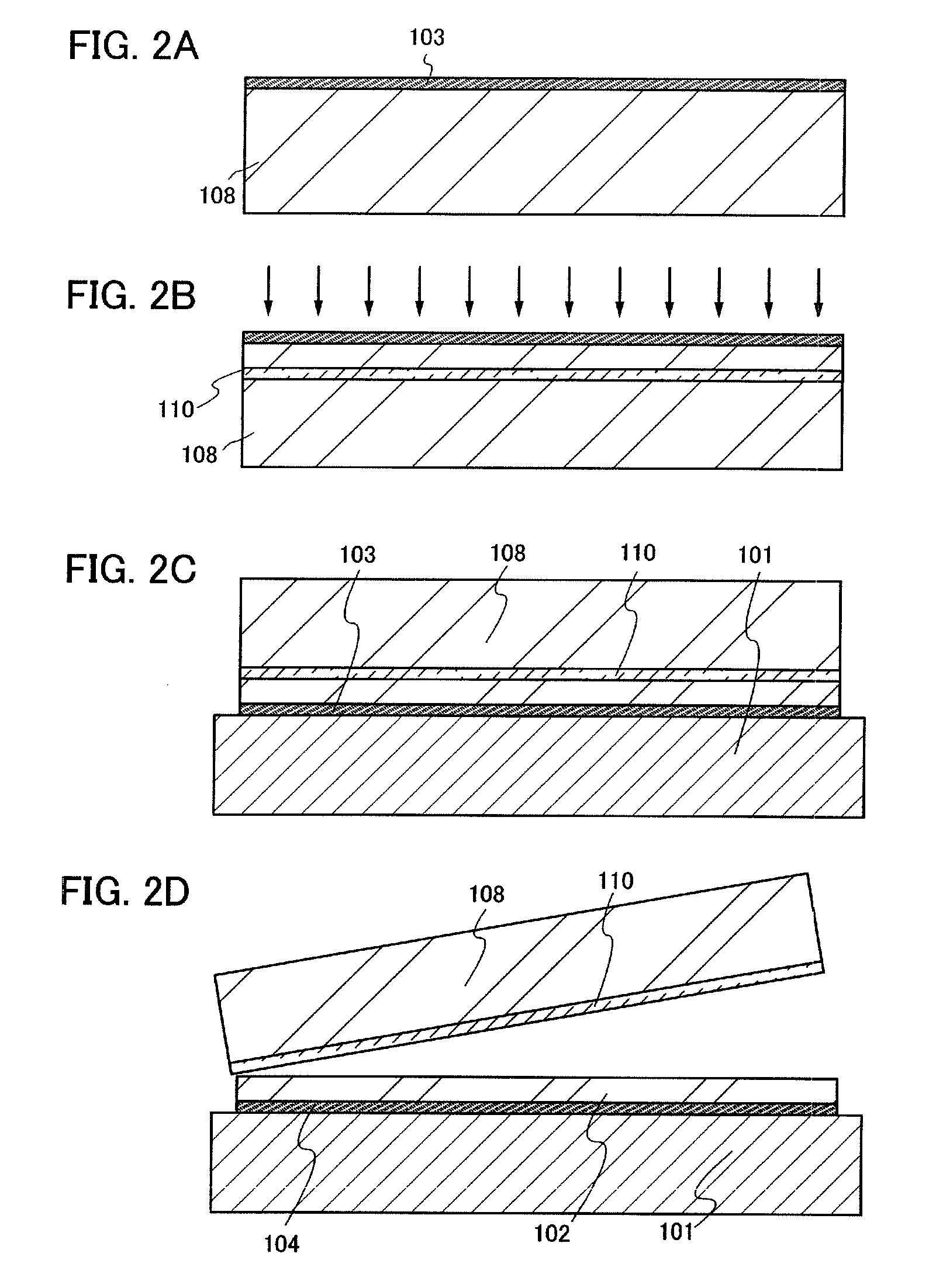

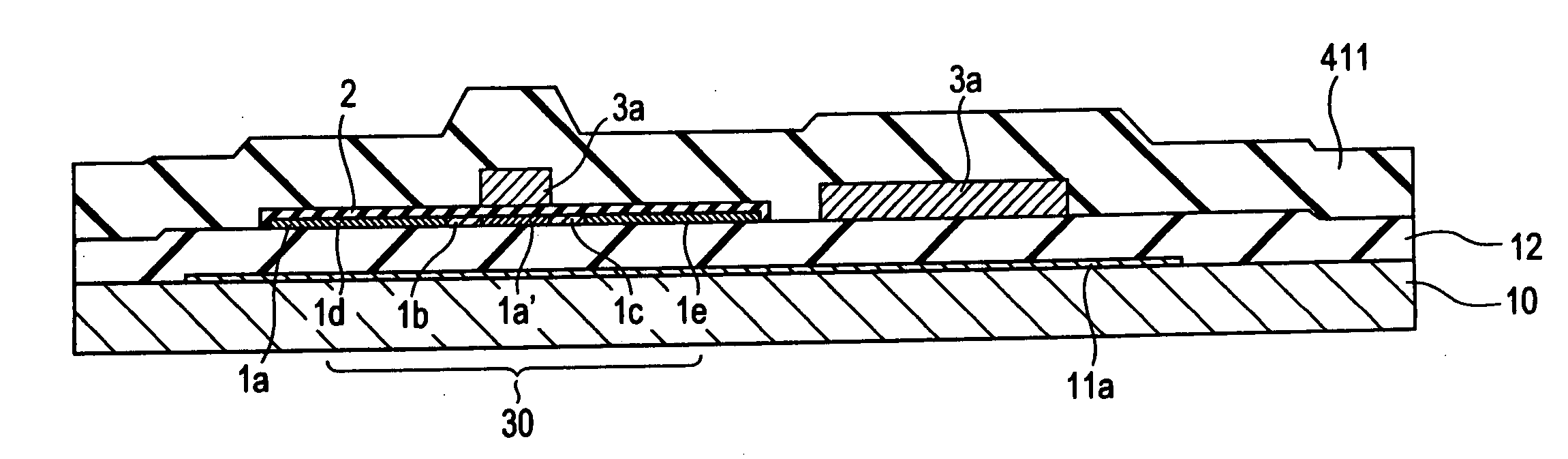

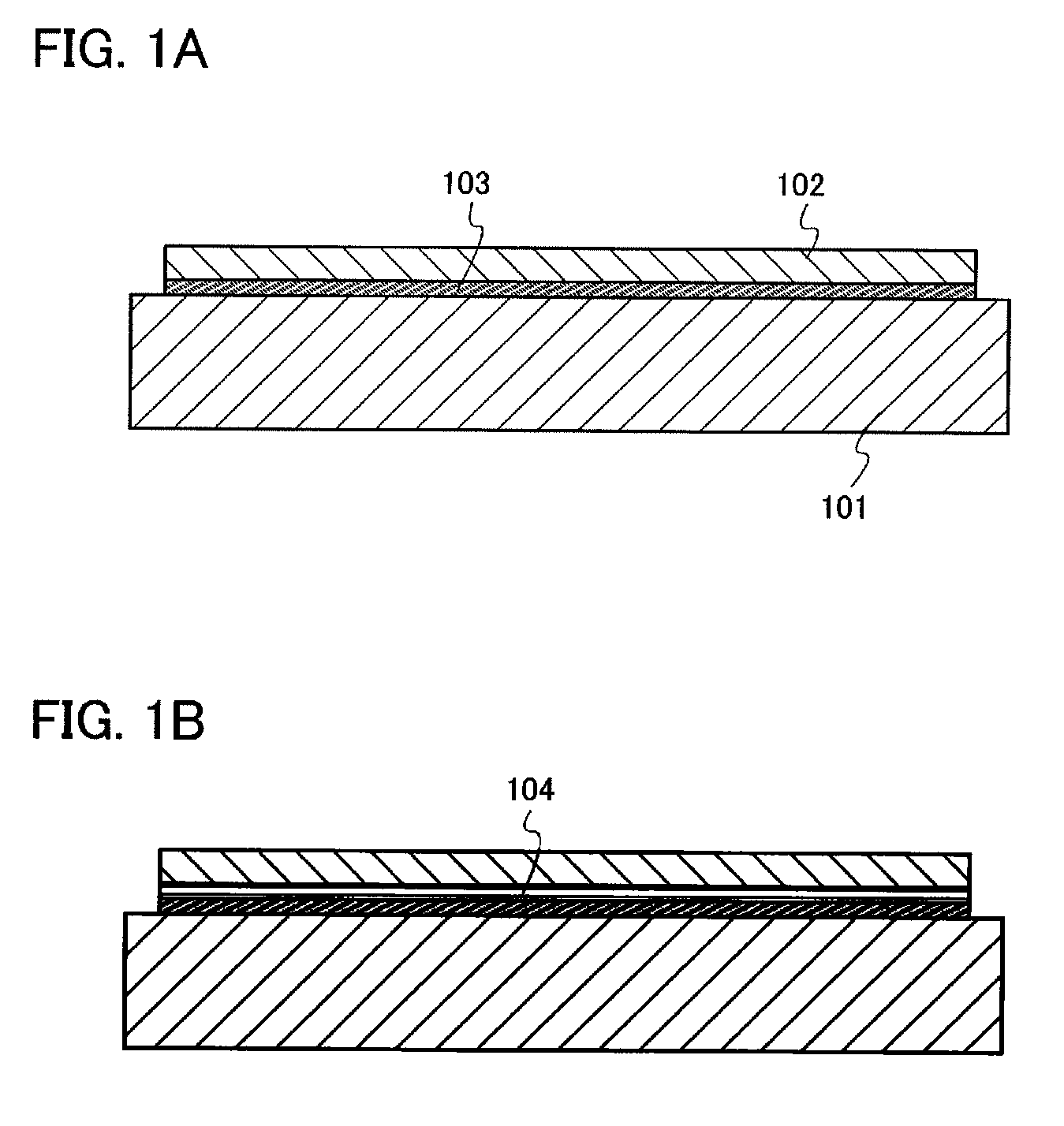

Semiconductor substrate and semiconductor device and manufacturing method of the same

InactiveUS20090102008A1Guaranteed uptimeEasily increased in areaSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSilicate glass

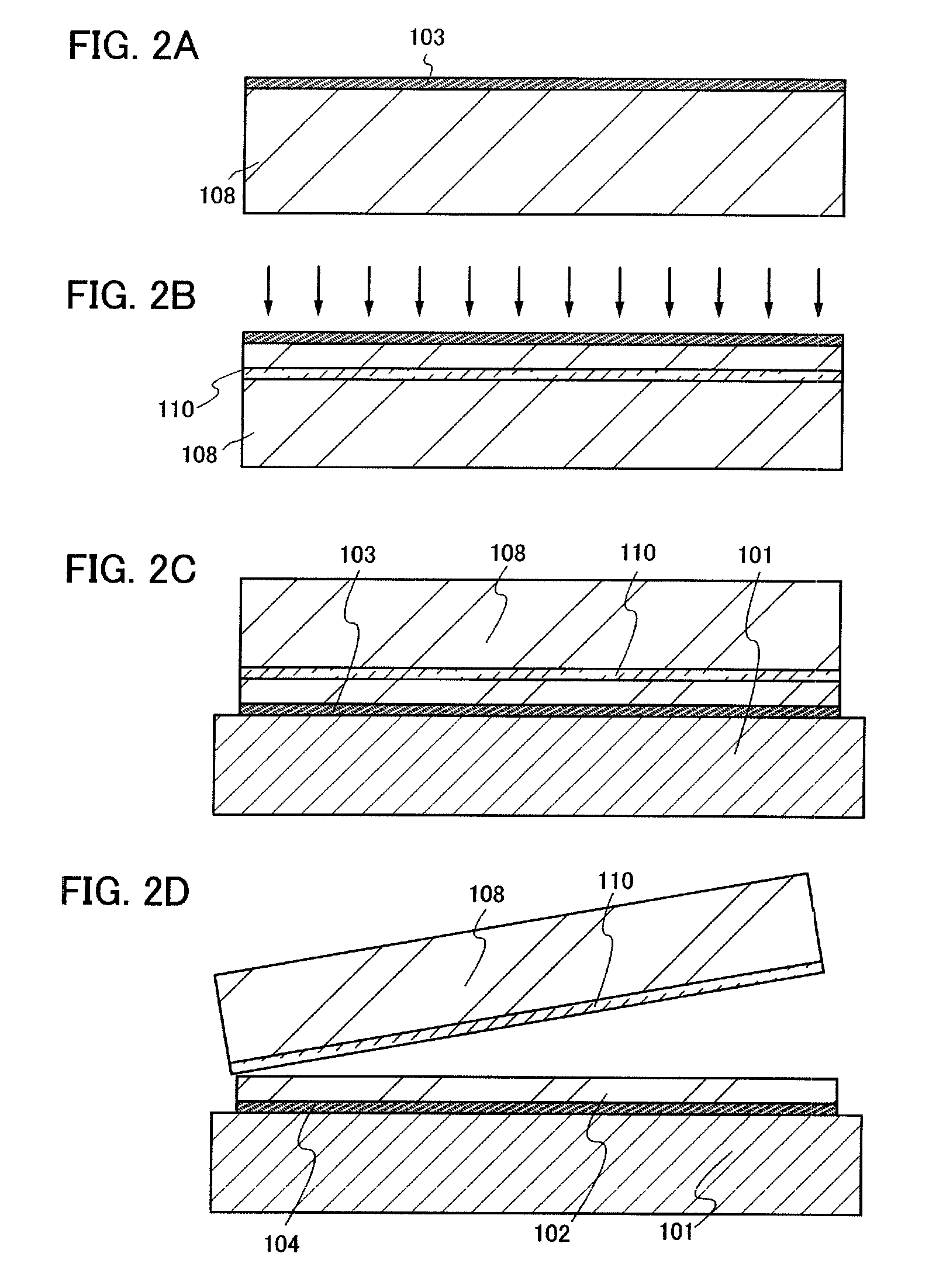

A semiconductor substrate having an SOI layer is provided. Between an SOI layer and a glass substrate, a bonding layer is provided which is formed of one layer or a plurality of layers of phosphosilicate glass, borosilicate glass, and / or borophosphosilicate glass, using organosilane as one material by a thermal CVD method at a temperature of 500° C. to 800° C.

Owner:SEMICON ENERGY LAB CO LTD

SOI CMOS device with reduced DIBL

InactiveUS20050205931A1Solid-state devicesSemiconductor/solid-state device manufacturingSoi cmosDopant

CMOS devices formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and a method for producing the same. The method involves a high energy, high dose implant through openings in a masking layer and through channel regions of the p- and n-wells, into the insulator layer, thereby creating a borophosphosilicate glass (BPSG) diffusion source within the insulation layer underlying the gate regions of the SOI wafer substantially between the source and drain. Backend, high temperature processing steps induce diffusion of the dopants contained in the diffusion source into the p- and n-wells, thereby forming asymmetric retrograde dopant profiles in the channel under the gate. The method can be selectively applied to selected portions of a wafer to tailor device characteristics, such as for memory cells.

Owner:SEMICON COMPONENTS IND LLC

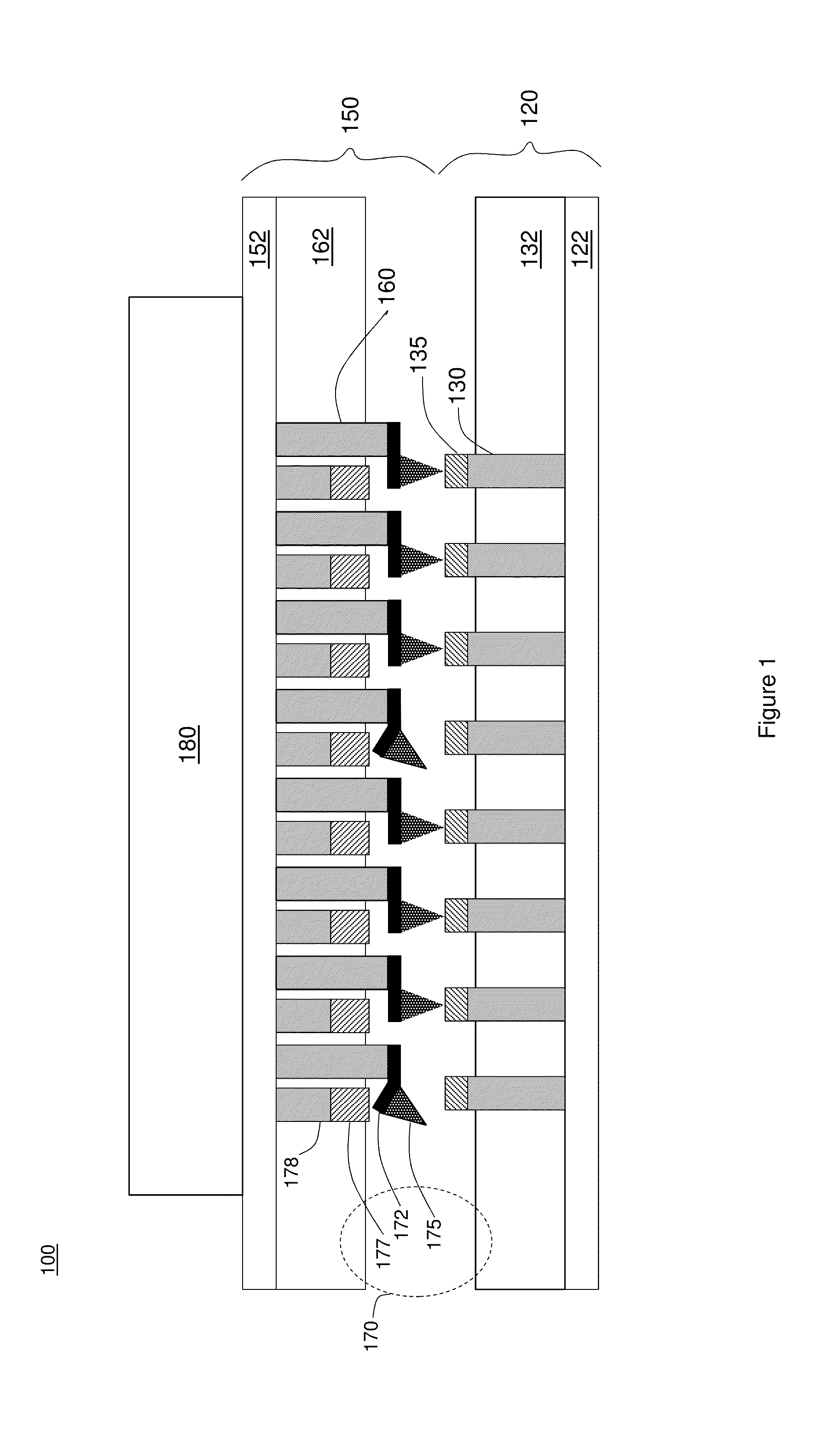

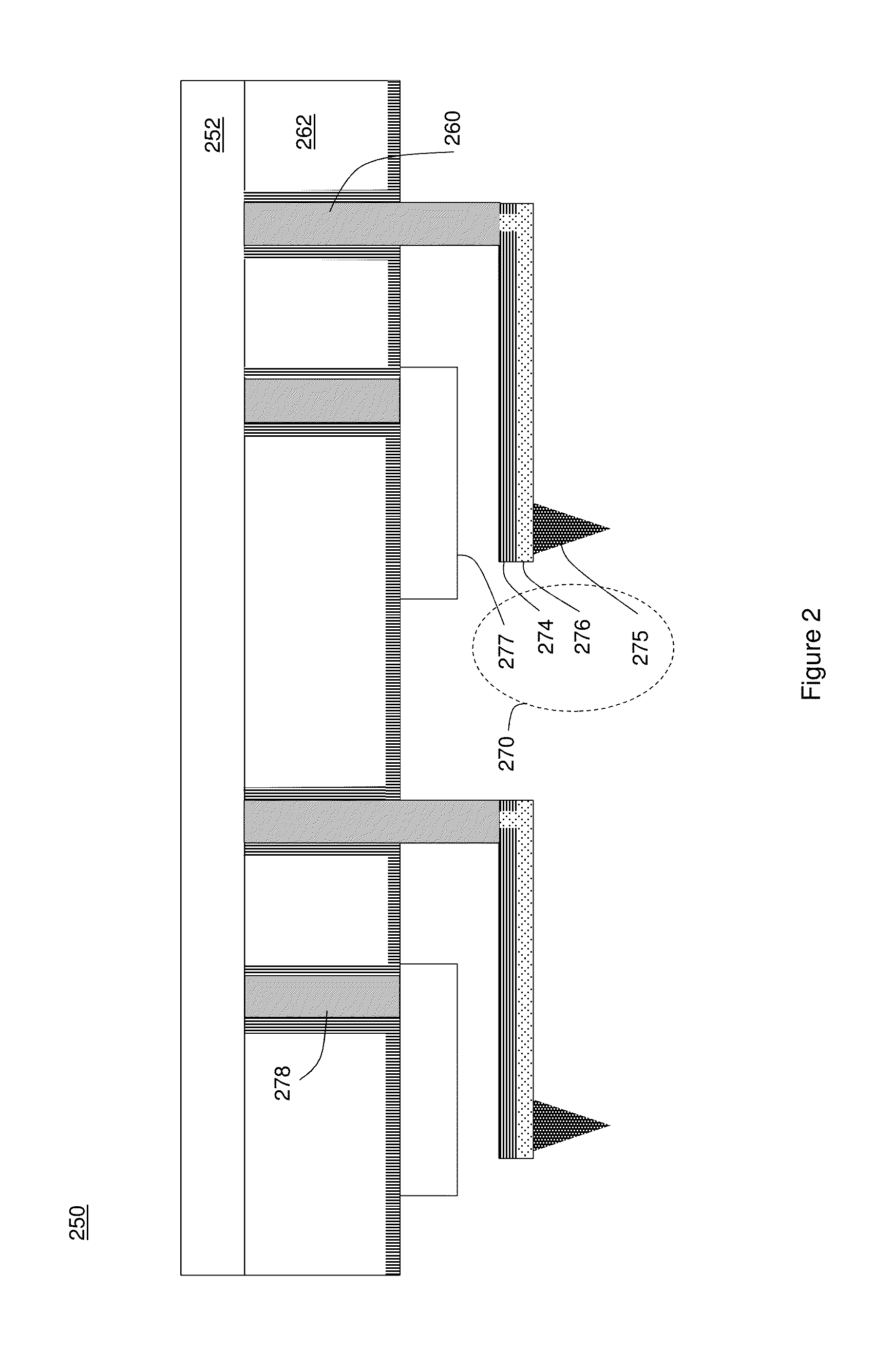

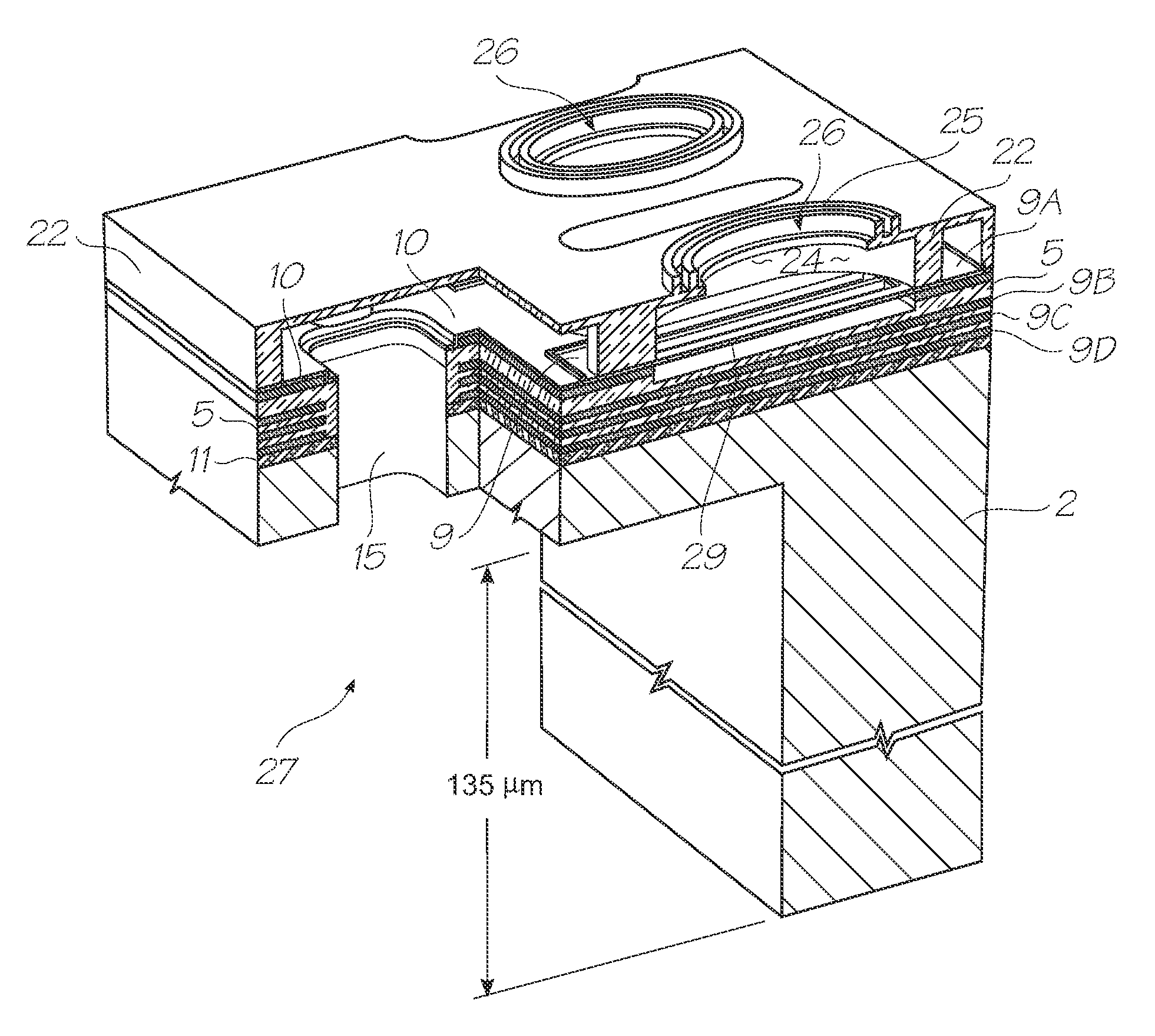

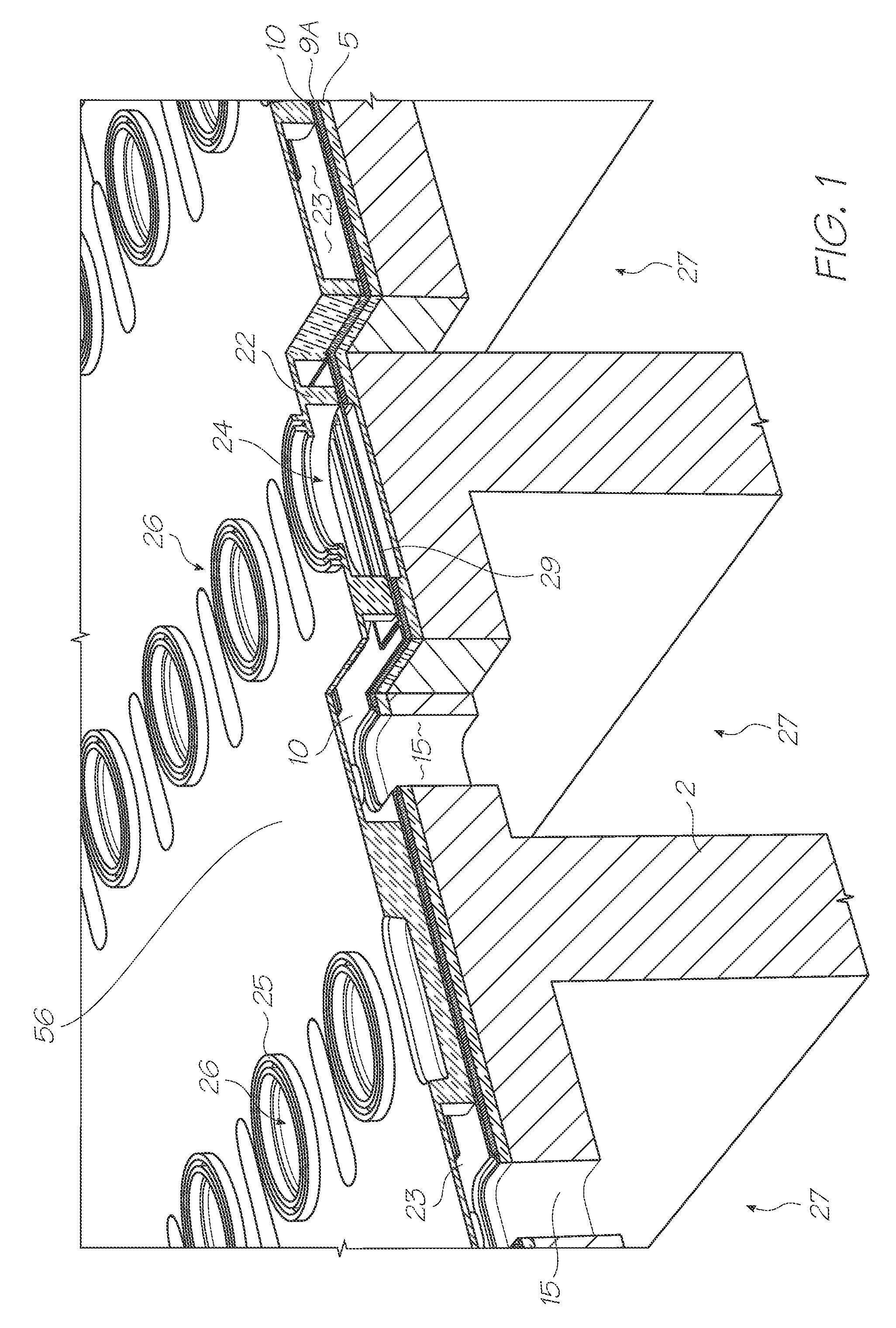

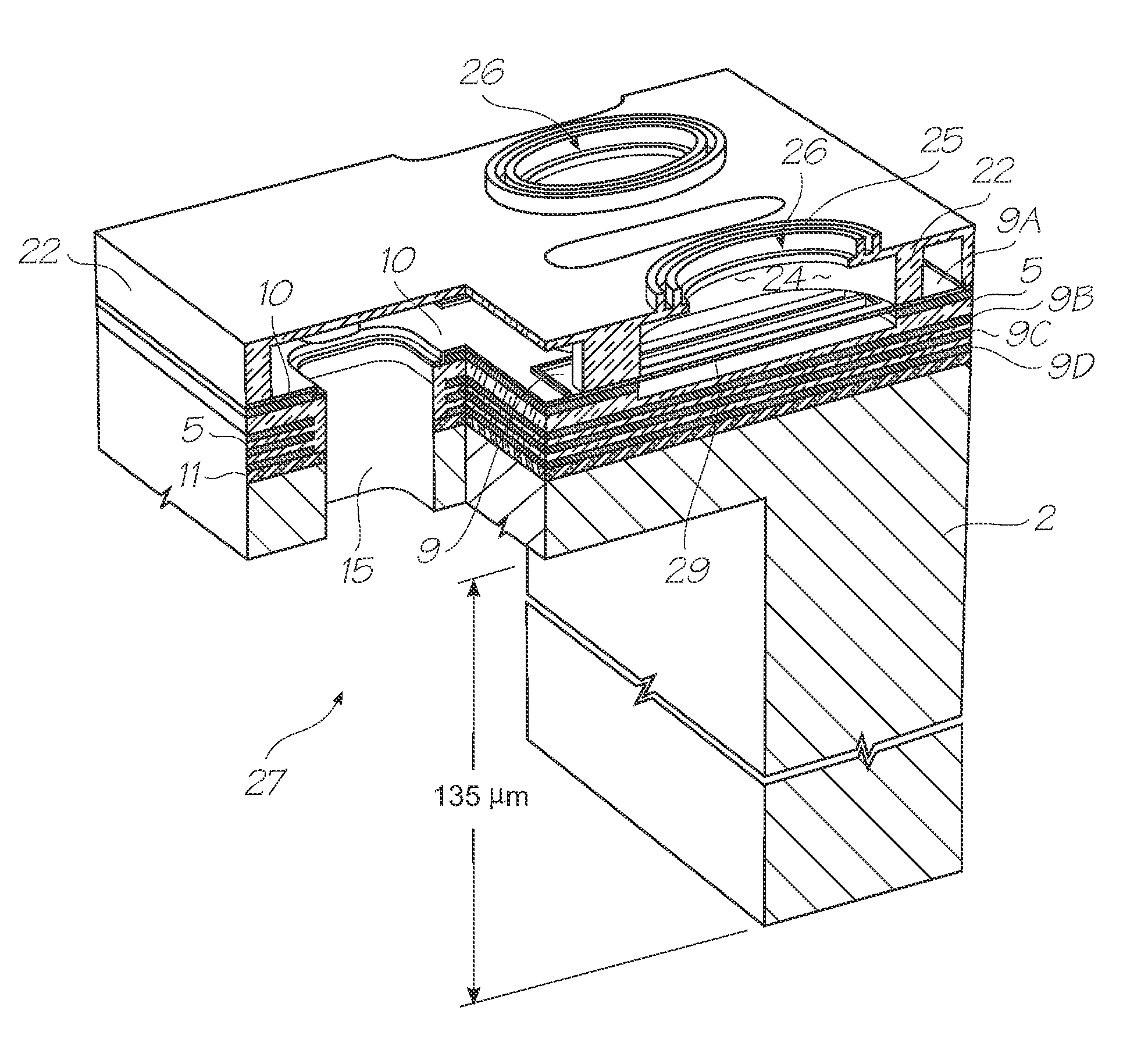

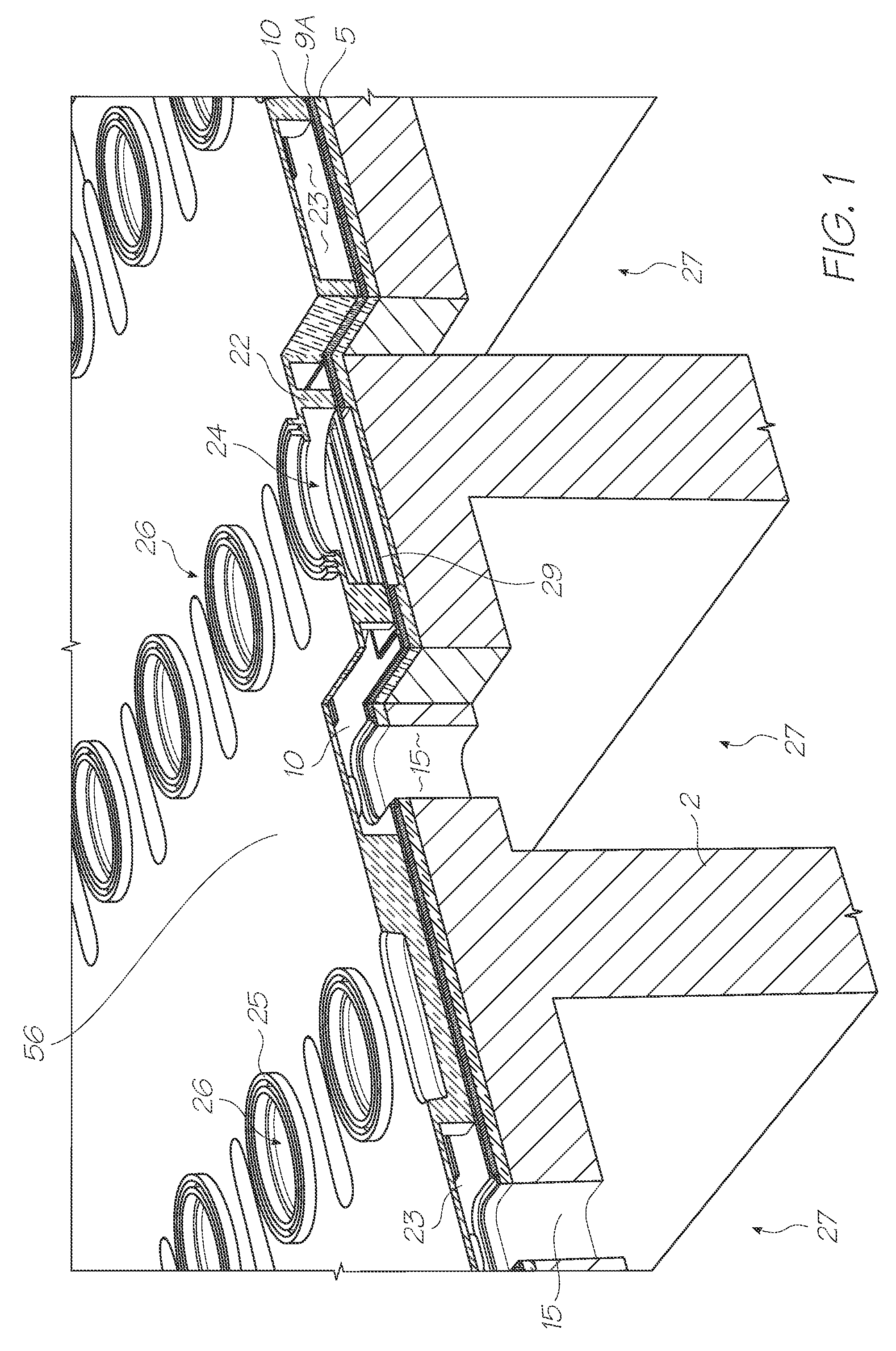

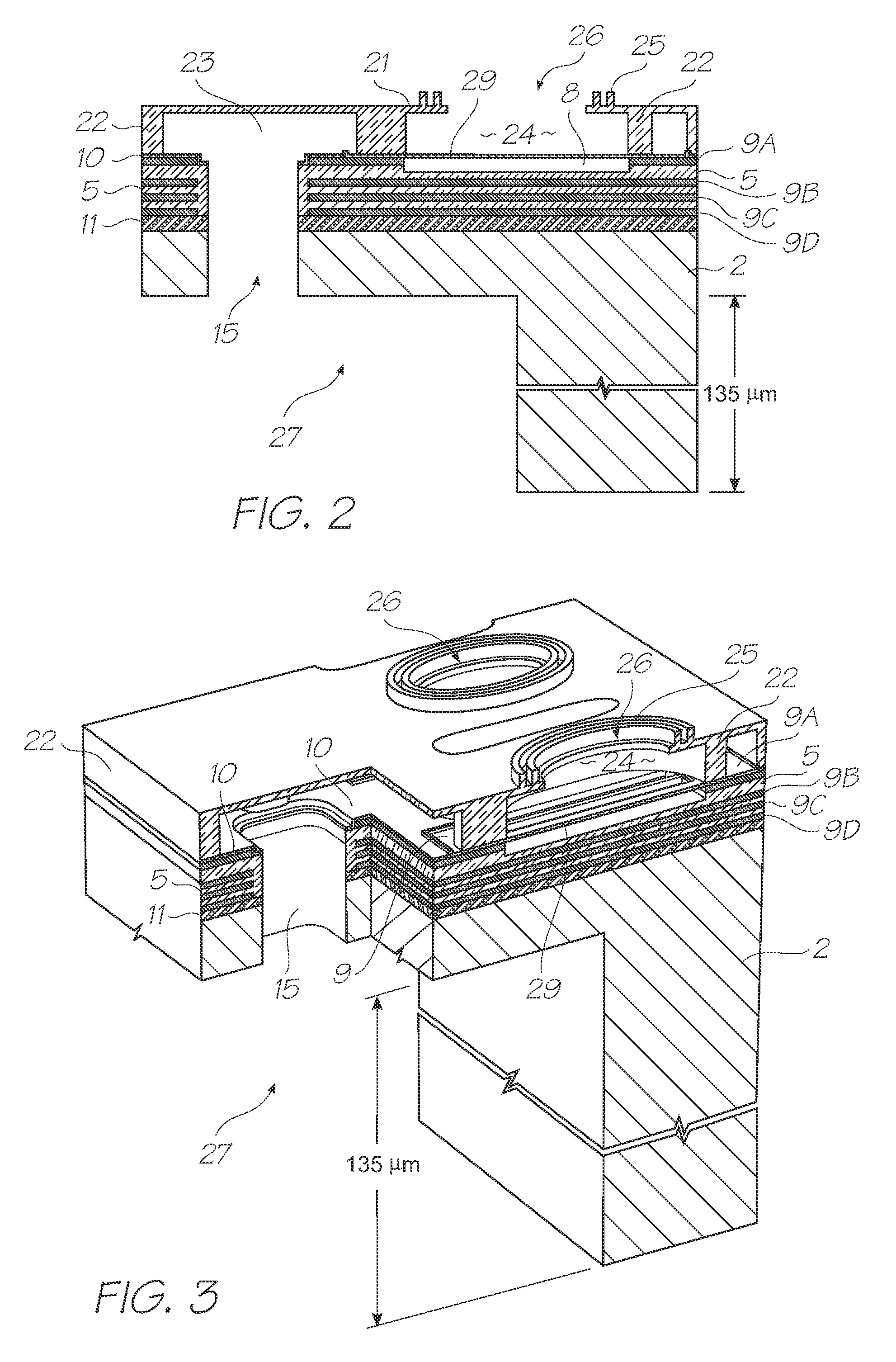

3-dimensional integrated circuit testing using MEMS switches with tungsten cone contacts

InactiveUS20130200910A1Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsBorophosphosilicate glassEngineering

A test system for testing a multilayer 3-dimensional integrated circuit (IC), where two separate layers of IC circuits are temporarily connected in order to achieve functionality, includes a chip under test with a first portion of the 3-dimensional IC, and a test probe chip with a second portion of the 3-dimensional IC and micro-electrical-mechanical system (MEMS) switches that selectively complete functional circuits between the first portion of the 3-dimensional IC in a first IC layer to circuits within the second portion of the 3-dimensional IC in a second IC layer. The MEMS switches include tungsten (W) cone contacts, which make the selective electrical contacts between circuits of the chip under test and the test probe chip and which are formed using a template of graded borophosphosilicate glass (BPSG).

Owner:IBM CORP

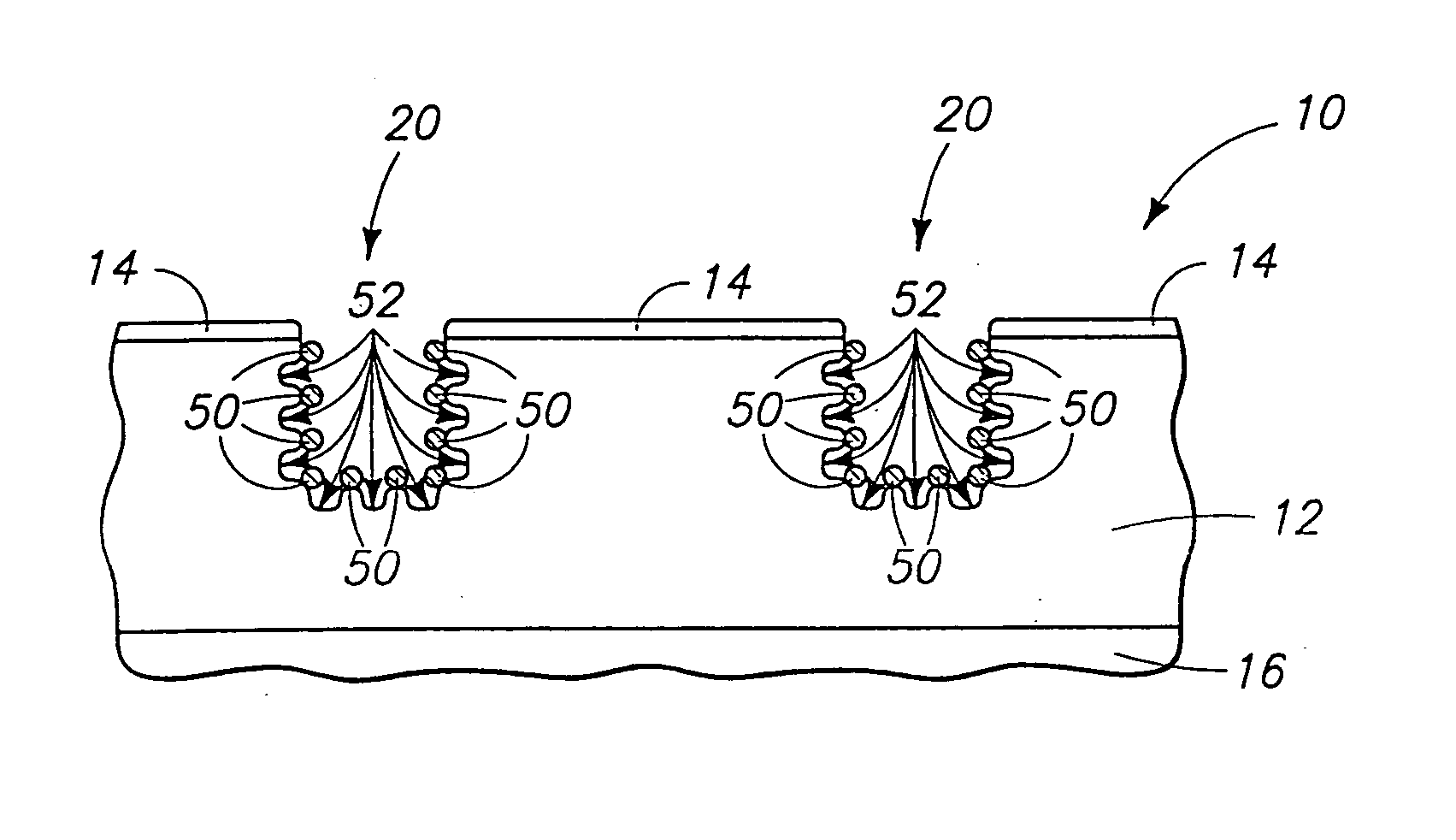

Borophosphosilicate glass incorporated with fluorine for low thermal budget gap fill

InactiveUS6159870AStrong Gap Filling CapabilityHigh aspect ratio gapsSemiconductor/solid-state device manufacturingBorophosphosilicate glassChemistry

A method of depositing a fluorinated borophosphosilicate glass (FBPSG) on a semiconductor device as either a final or interlayer dielectric film. Gaps having aspect ratios greater than 6:1 are filled with a substantially void-free FBPSG film at a temperature of about 480 DEG C. at sub-atmospheric pressures of about 200 Torr. Preferably, gaseous reactants used in the method comprise TEOS, FTES, TEPO and TEB with an ozone / oxygen mixture. Dopant concentrations of boron and phosphorus are sufficiently low such that surface crystallite defects and hygroscopicity are avoided. The as-deposited films at lower aspect ratio gaps are substantially void-free such that subsequent anneal of the film is not required. Films deposited into higher aspect ratio gaps are annealed at or below about 750 DEG C., well within the thermal budget for most DRAM, logic and merged logic-DRAM chips. The resultant FBPSG layer contains less than or equal to about 5.0 wt % boron, less than about 4.0 wt % phosphorus, and about 0.1 to 2.0 wt % fluorine.

Owner:IBM CORP

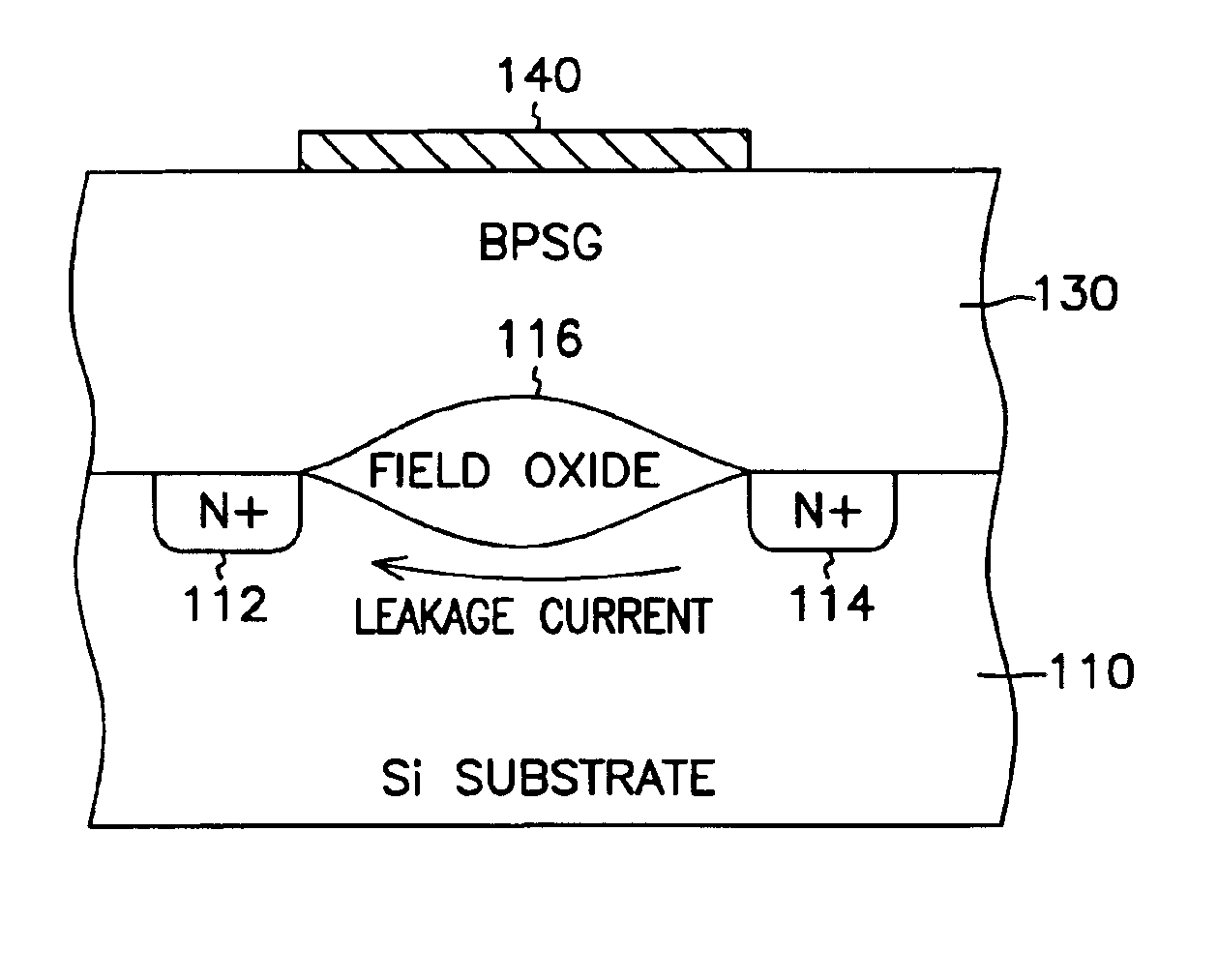

SOI device with reduced drain induced barrier lowering

InactiveUS6905918B2Reduce resistanceEliminate the effects ofSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectInsulation layer

A CMOS device formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and a method for producing the same. The method involves a high energy, high dose implant of boron and phosphorus through the p- and n-wells, into the insulator layer, thereby creating a borophosphosilicate glass (BPSG) structure within the insulation layer underlying the p- and n-wells of the SOI wafer. Backend high temperature processing steps induce diffusion of the boron and phosphorus contained in the BPSG into the p- and n-wells, thereby forming a retrograde dopant profile in the wells. The retrograde dopant profile reduces DIBL and also provides recombination centers adjacent the insulator layer and the active layer to thereby reduce floating body effects for the CMOS device.

Owner:MICRON TECH INC

Low selectivity deposition methods

InactiveUS6987073B2Reduce rateLow selectivitySemiconductor/solid-state device manufacturingCapacitorsChemisorptionNitrogen

A deposition method includes forming a nucleation layer over a substrate, forming a layer of a first substance at least one monolayer thick chemisorbed on the nucleation layer, and forming a layer of a second substance at least one monolayer thick chemisorbed on the first substance. The chemisorption product of the first and second substance may include silicon and nitrogen. The nucleation layer may comprise silicon nitride. Further, a deposition method may include forming a first part of a nucleation layer on a first surface of a substrate and forming a second part of a nucleation layer on a second surface of the substrate. A deposition layer may be formed on the first and second parts of the nucleation layer substantially non-selectively on the first part of the nucleation layer compared to the second part. The first surface may be a surface of a borophosphosilicate glass layer. The second surface may be a surface of a rugged polysilicon layer. The first and second part of the nucleation layer may be formed simultaneously.

Owner:MICRON TECH INC

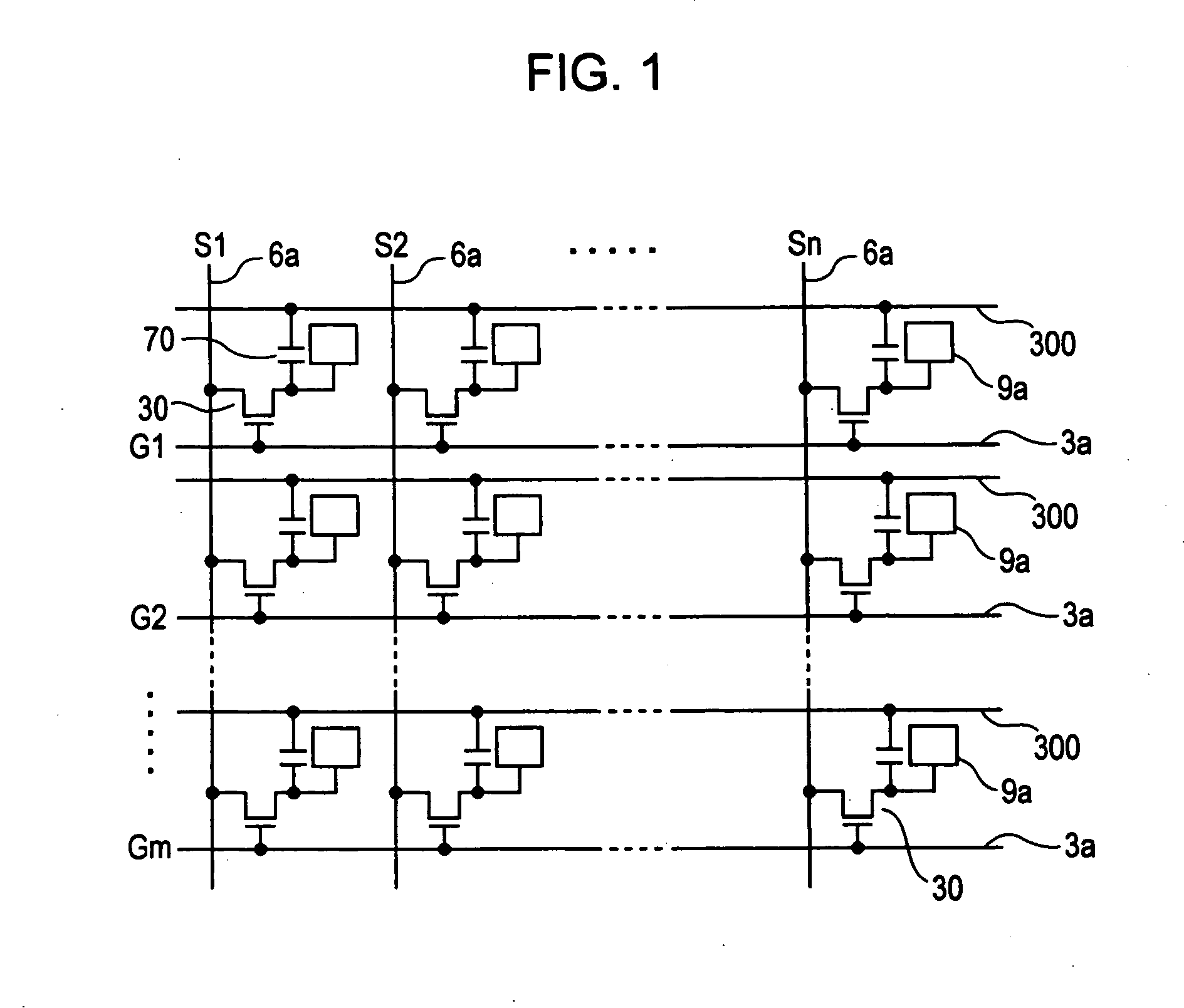

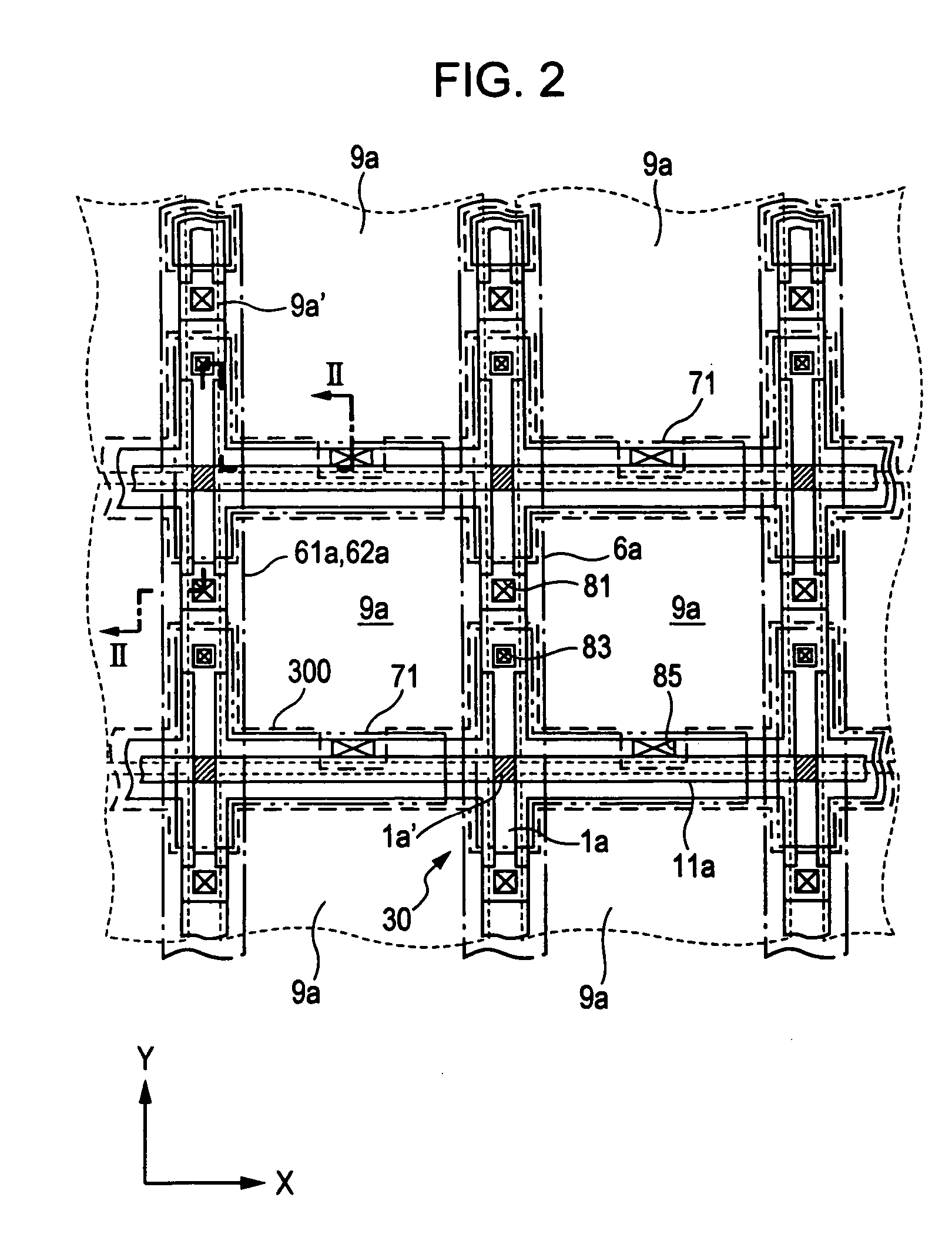

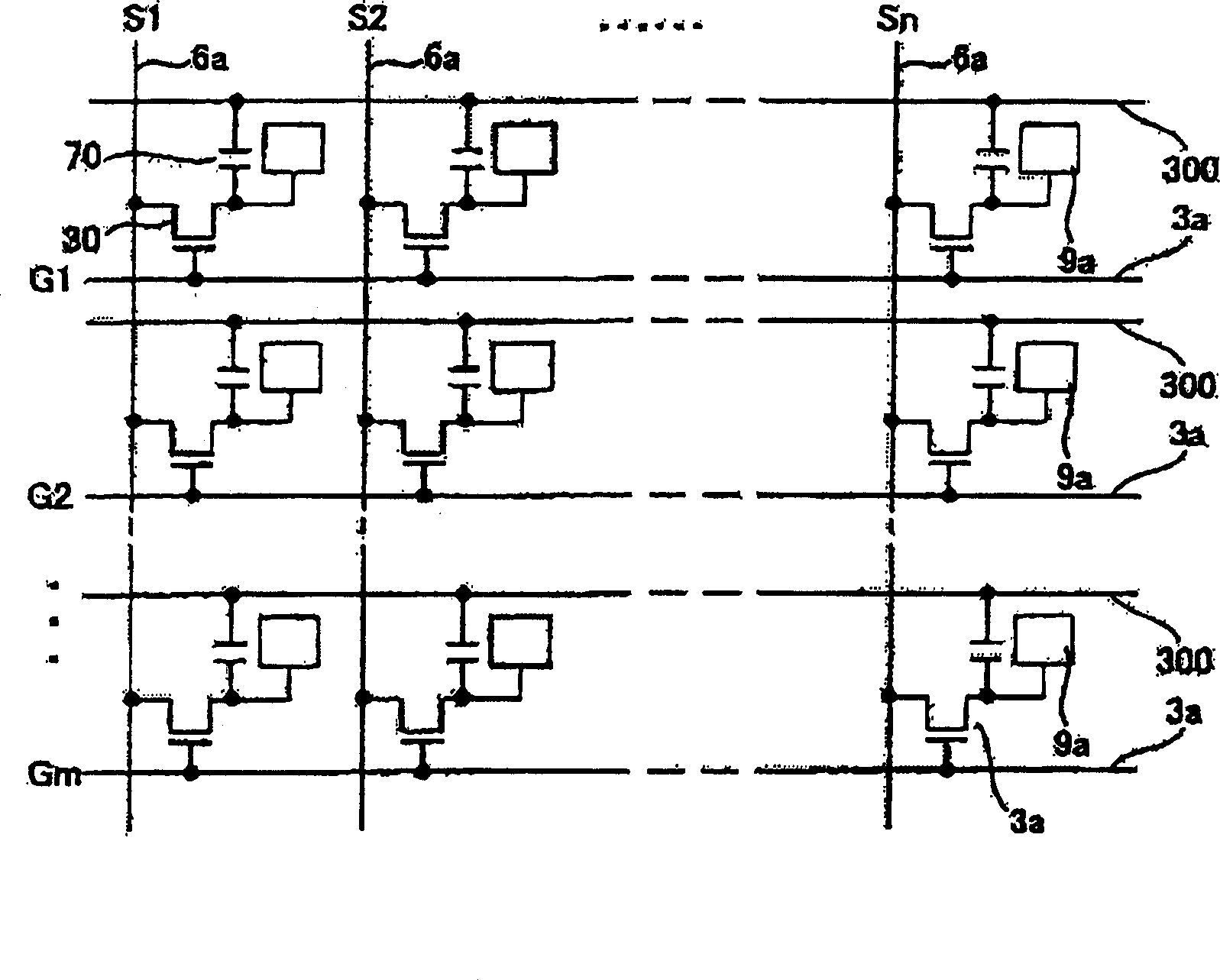

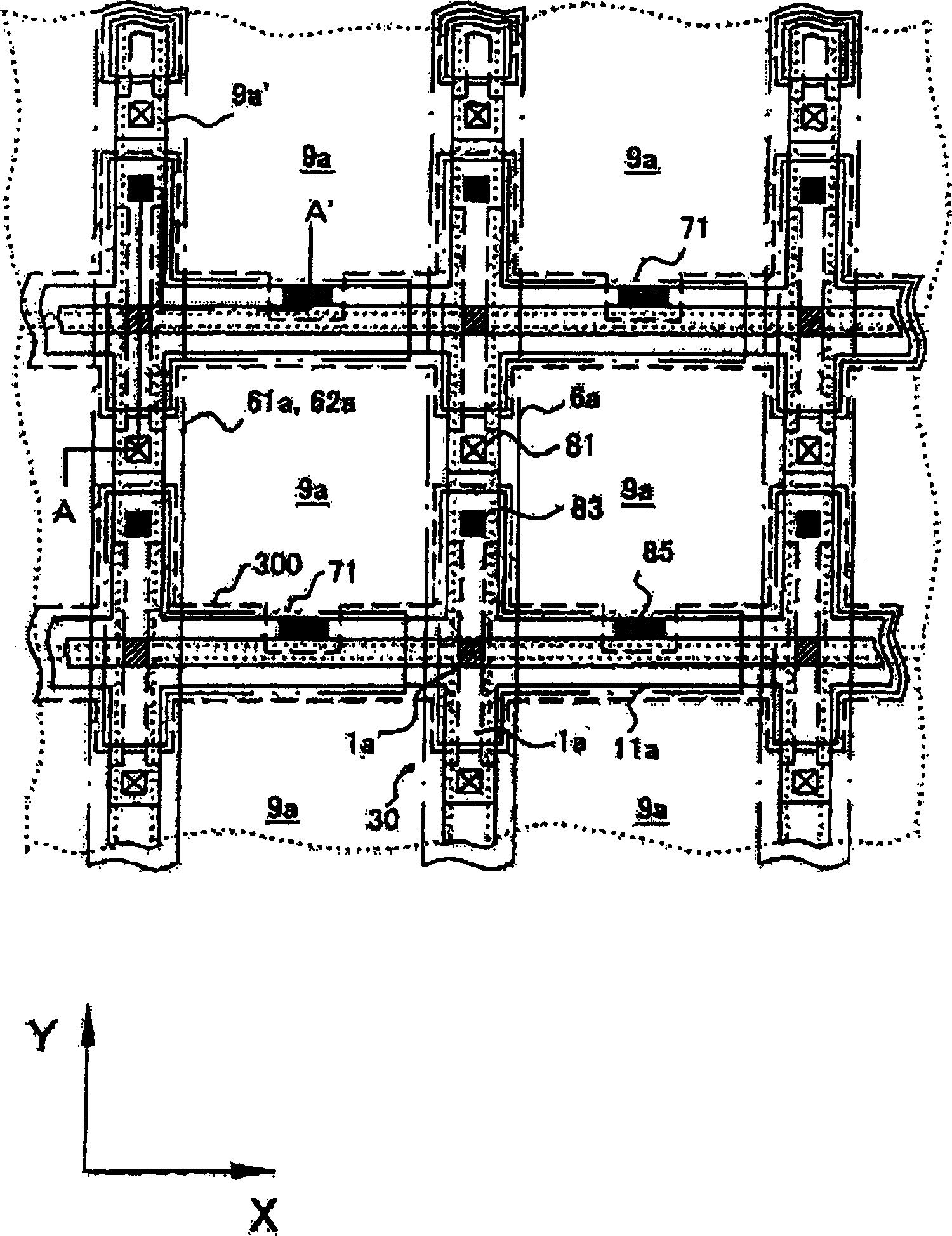

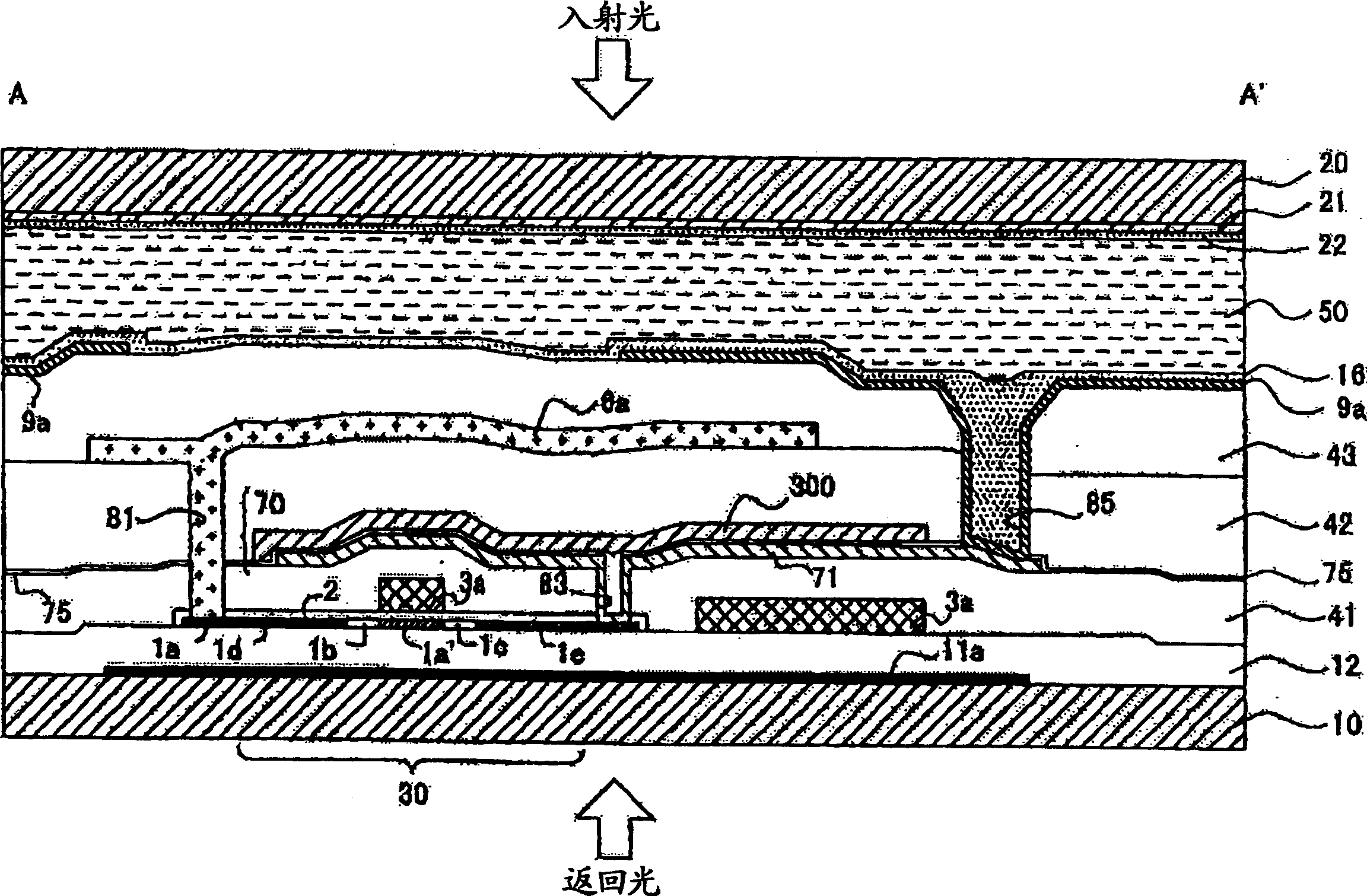

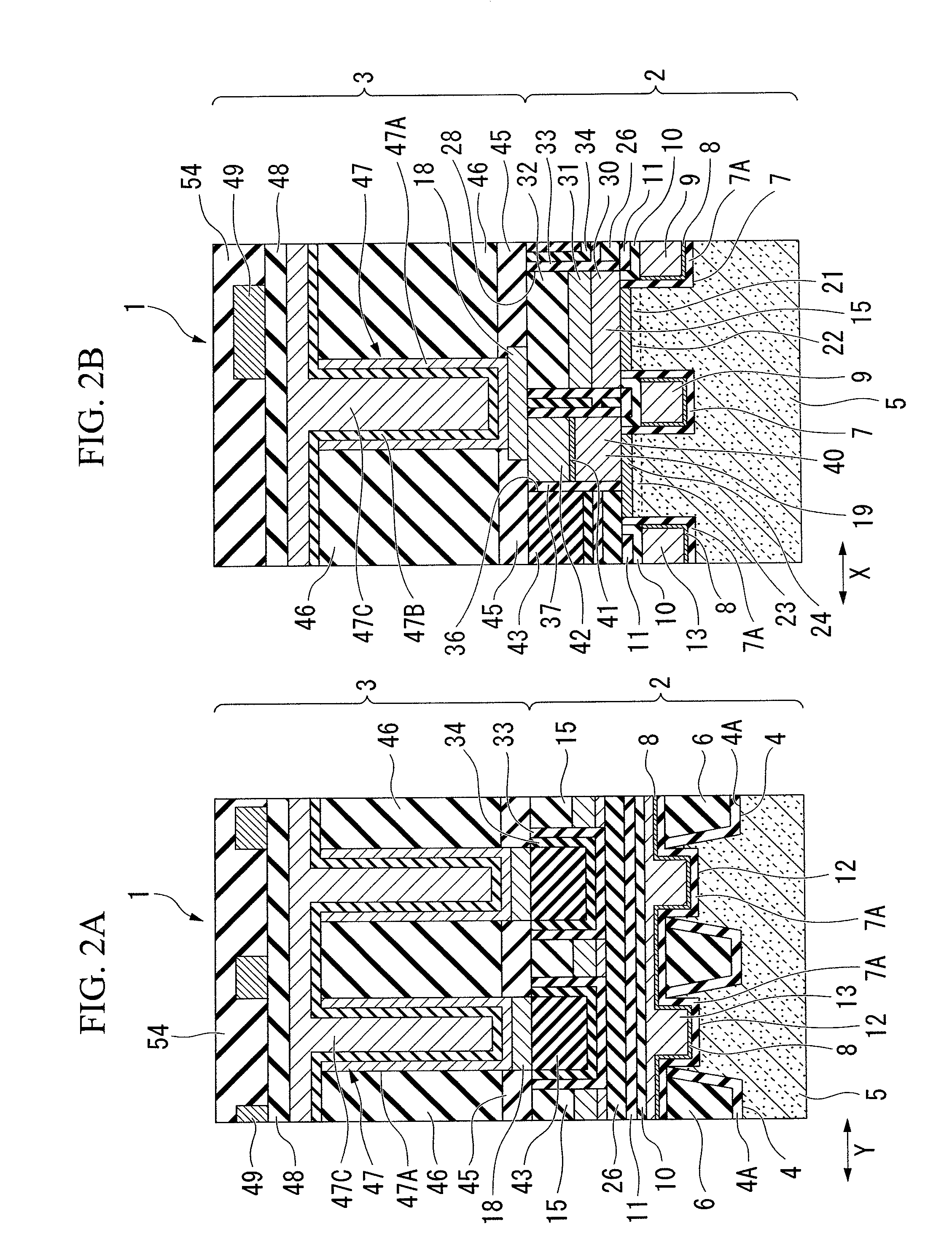

Method of manufacturing electro-optical device, electro-optical device, and electronic apparatus comprising the same

InactiveUS20050127810A1Reduce spotsEasy to controlTransistorDischarge tube luminescnet screensElectricitySilicate glass

To provide an electro-optical device, which has a high manufacturing yield and high quality display, the electro-optical device includes above a substrate, display electrodes, at least one of wiring lines and electronic elements that drive the display electrodes, and interlayer insulating films provided below the display electrodes to electrically insulate the display electrodes and at least one of the wiring lines and electronic elements from each other. At least one of the interlayer insulating films includes a boron phosphorus silicate glass film and has its top face subjected to planarizing treatment by being put into a fluidized state.

Owner:SEIKO EPSON CORP

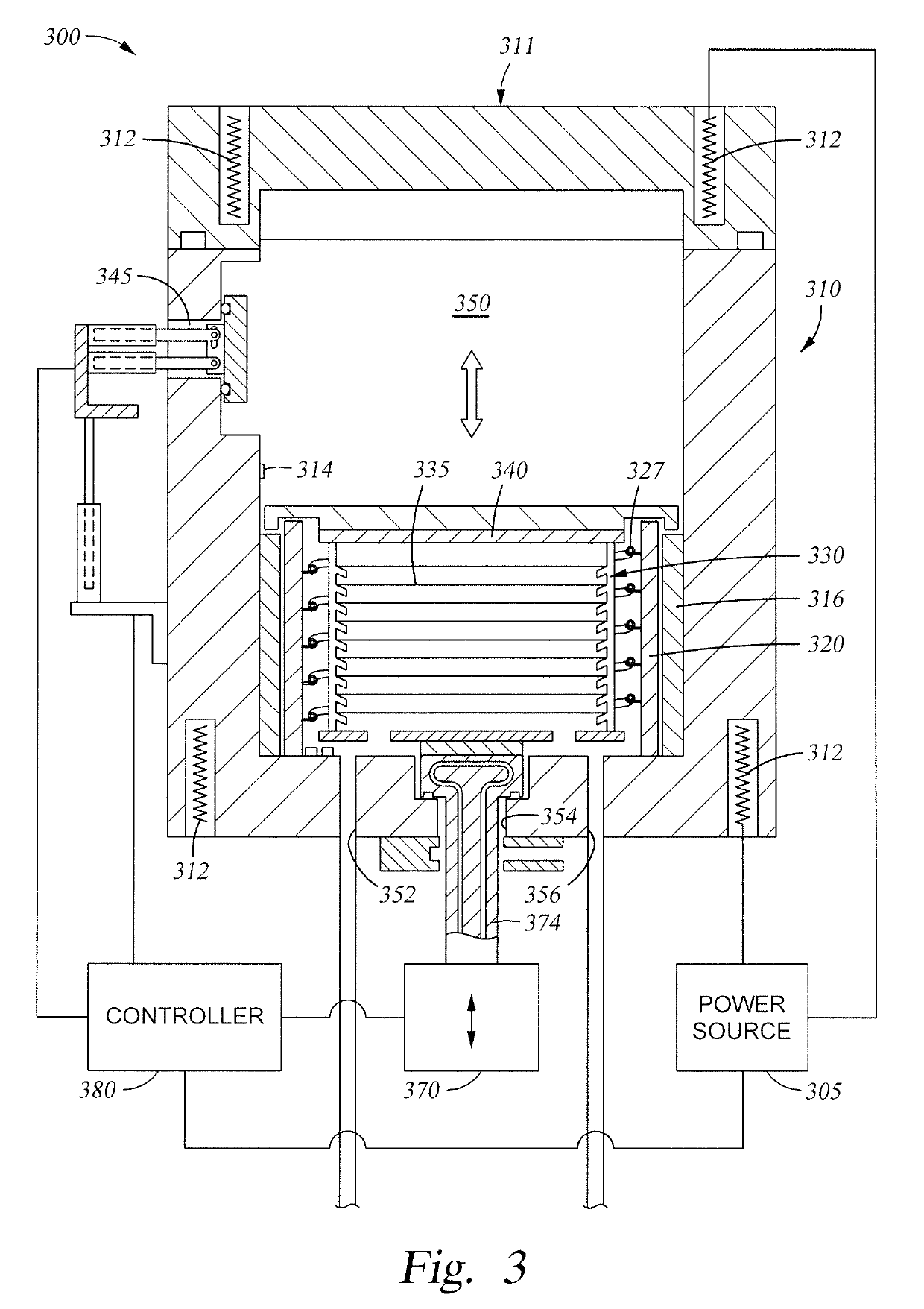

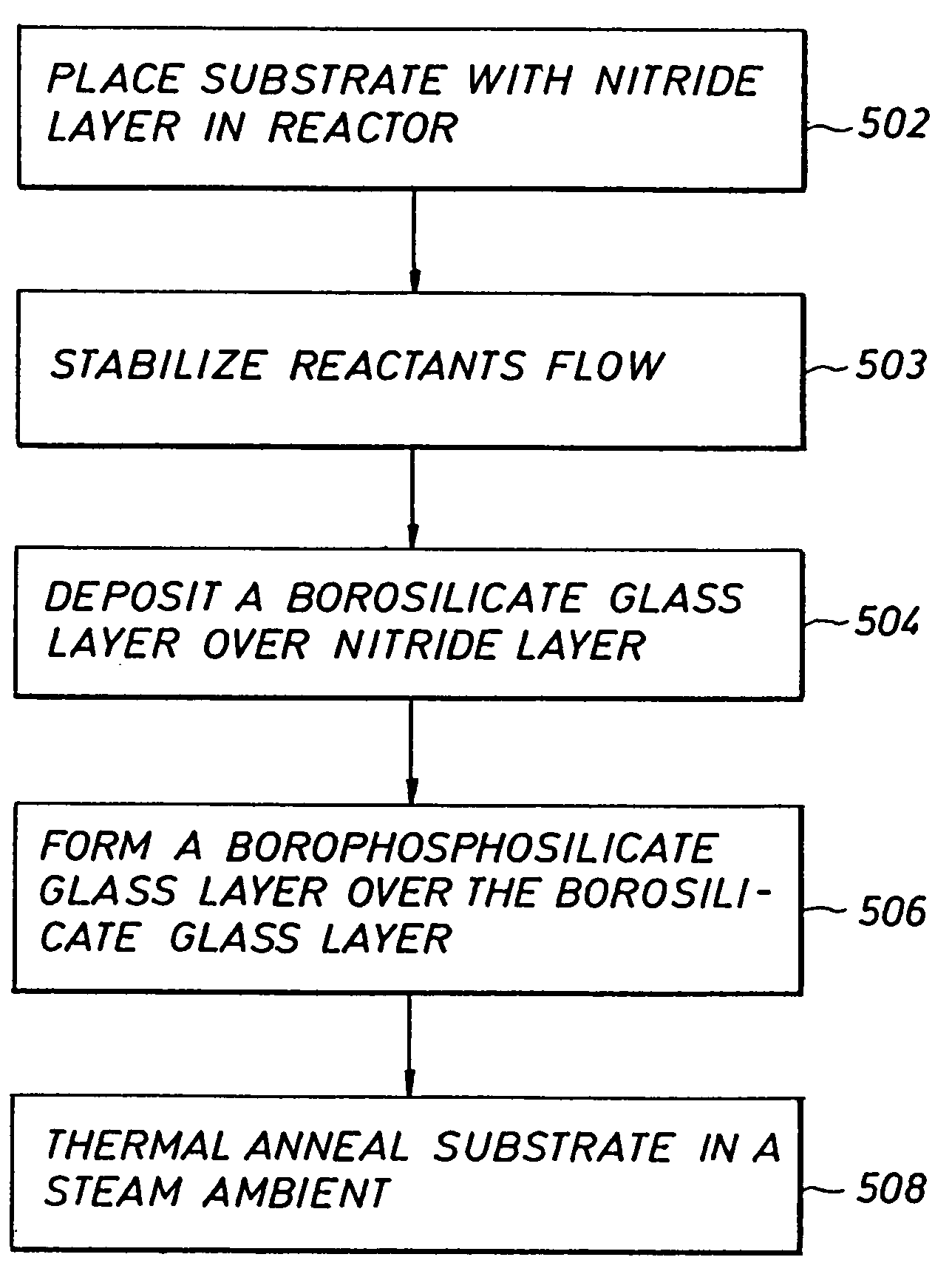

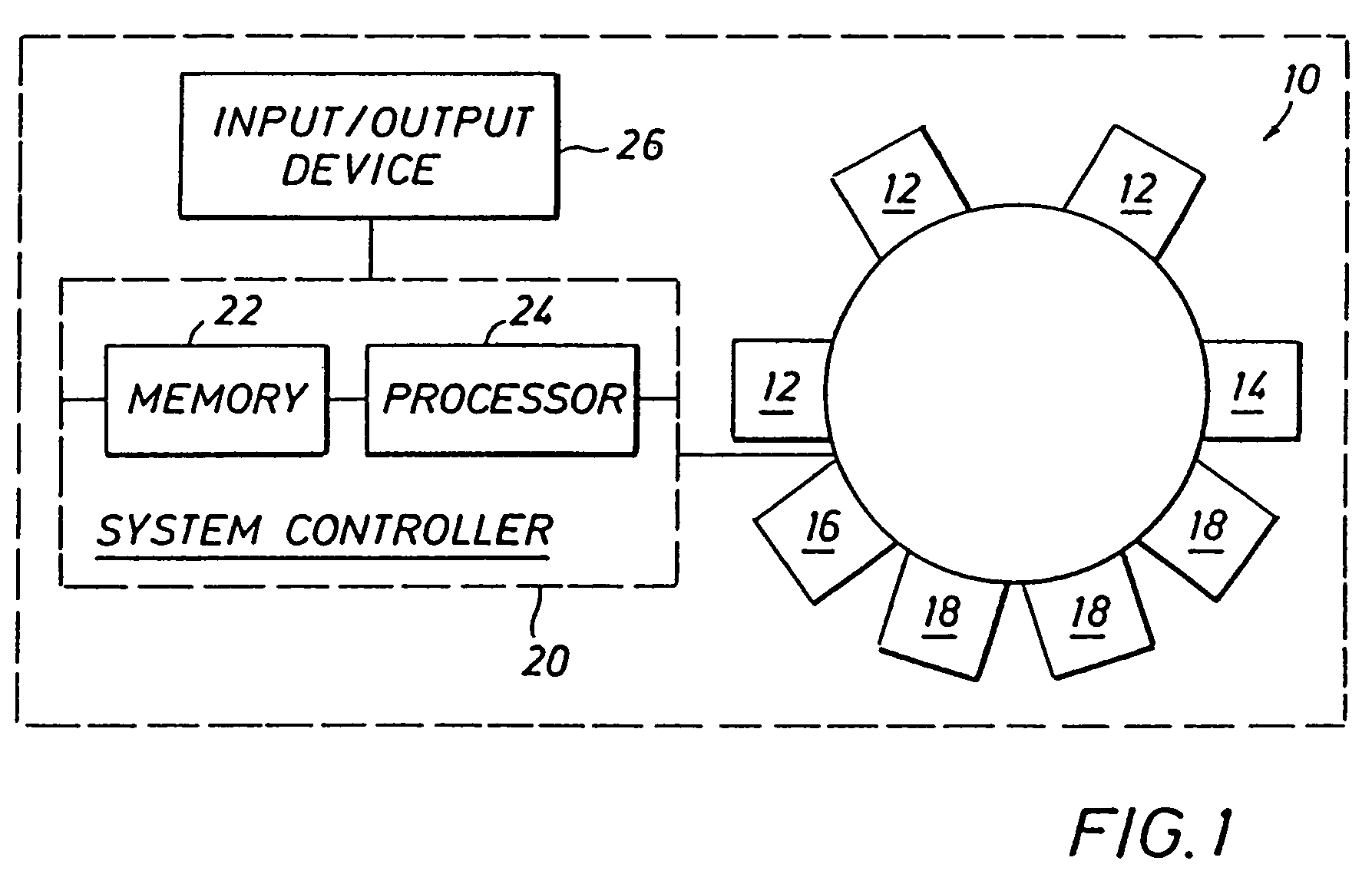

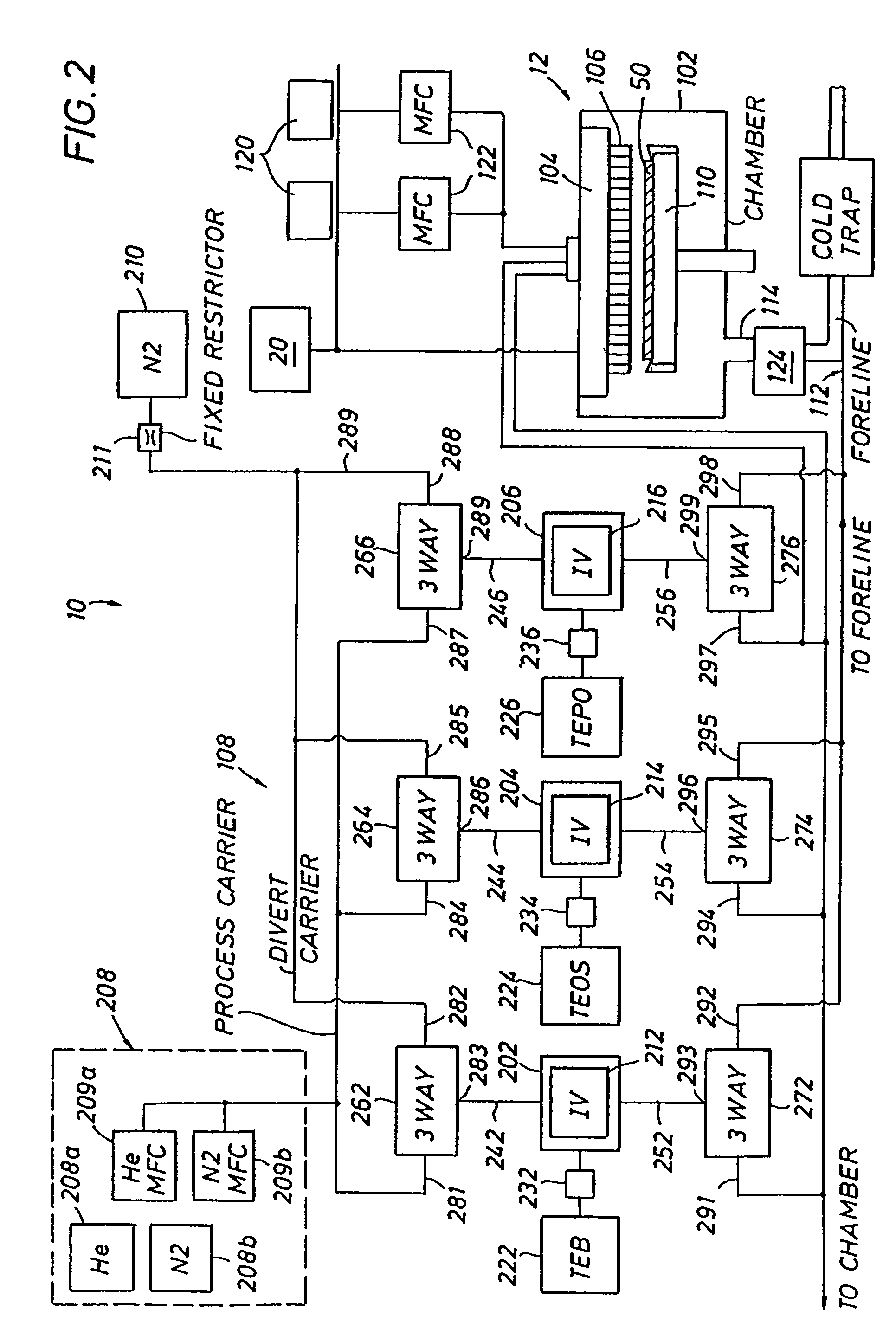

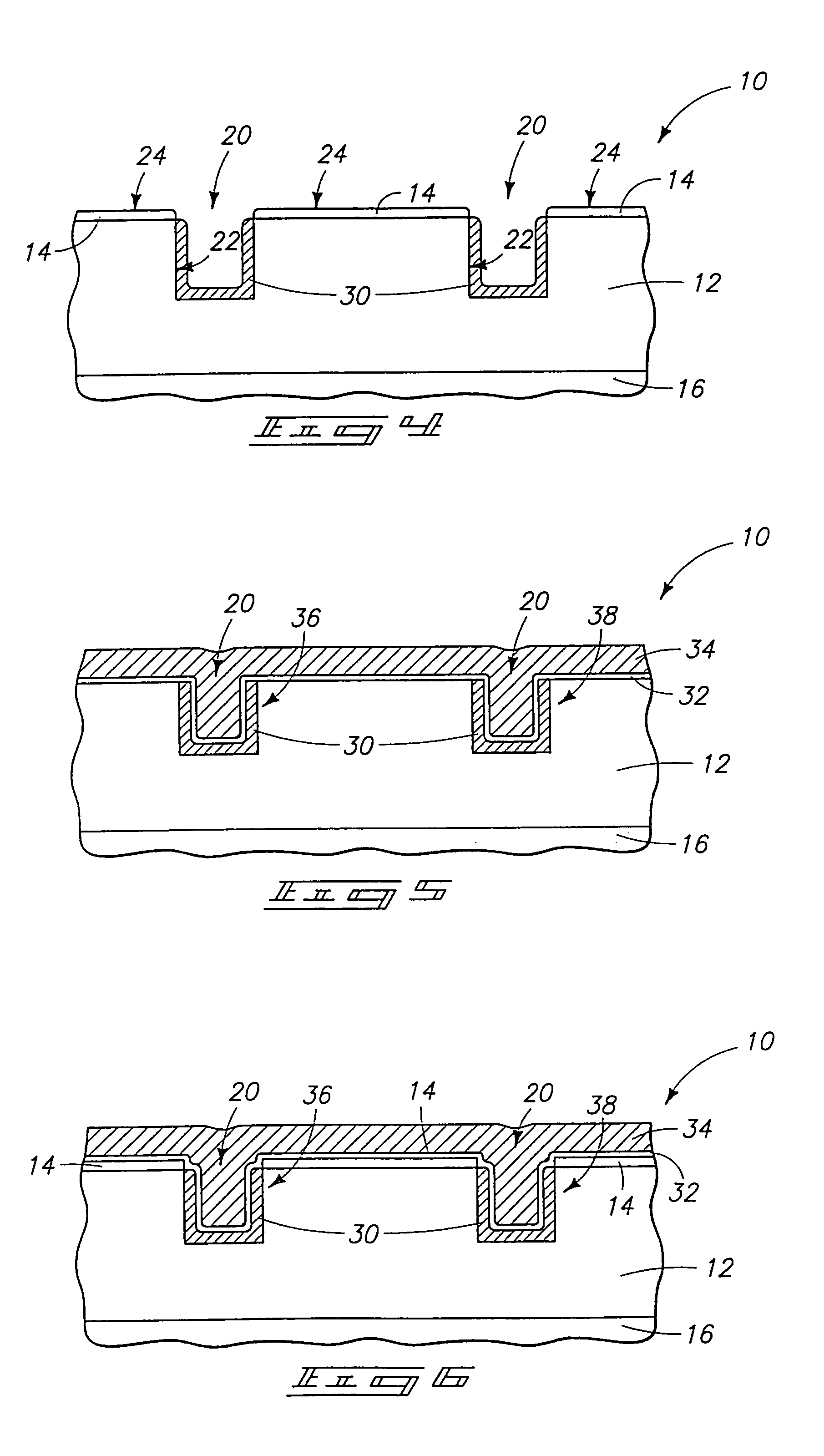

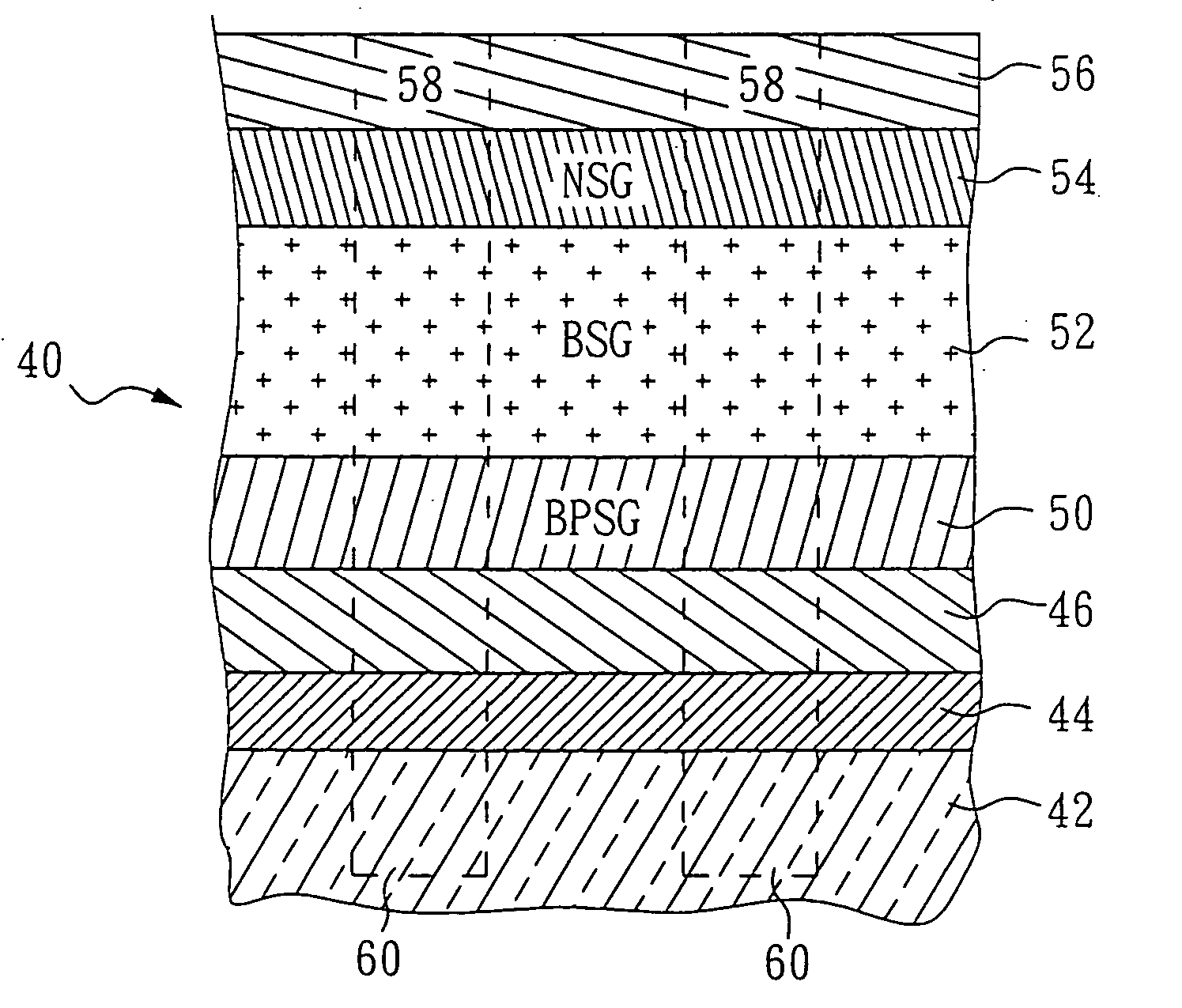

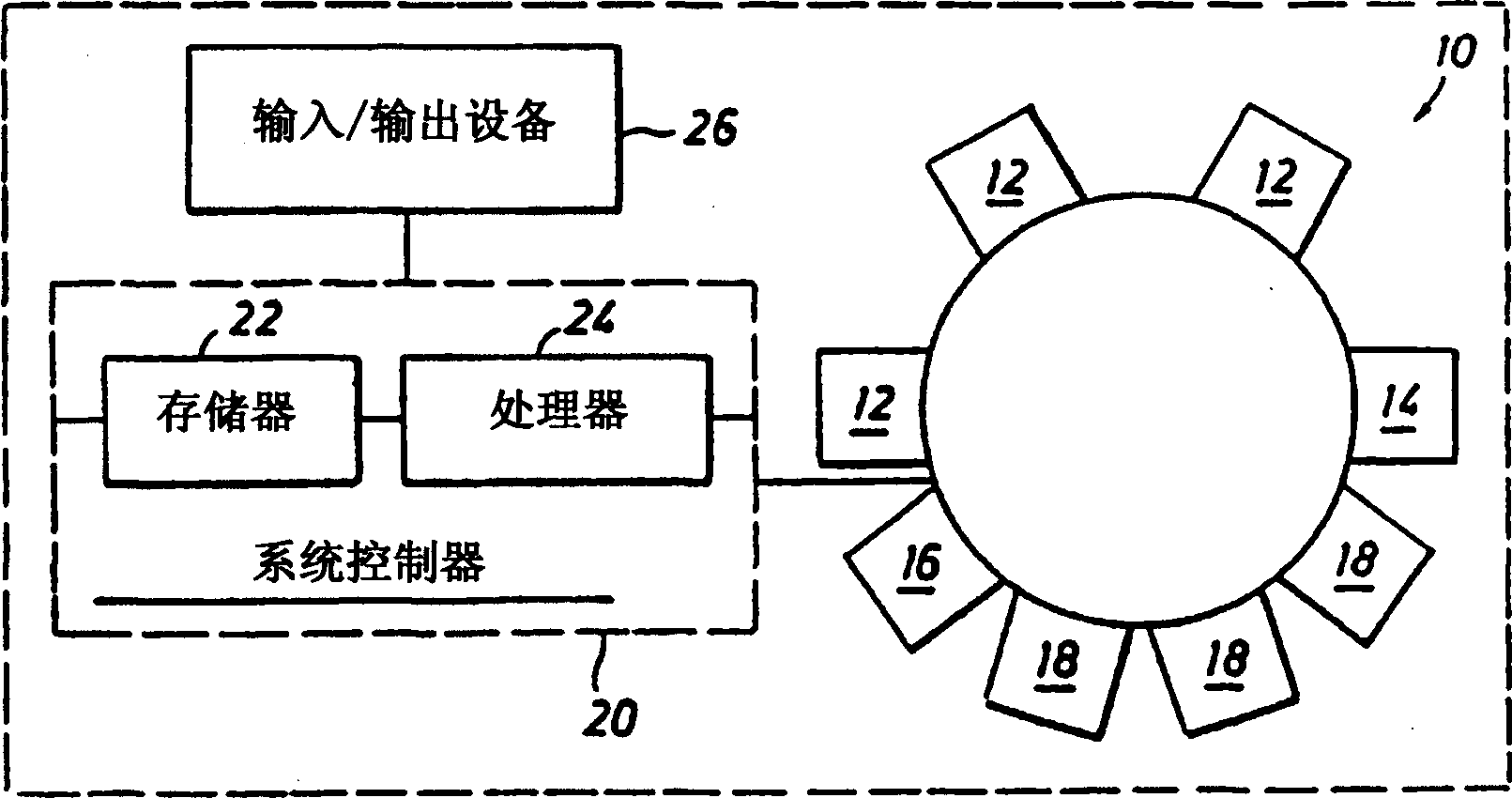

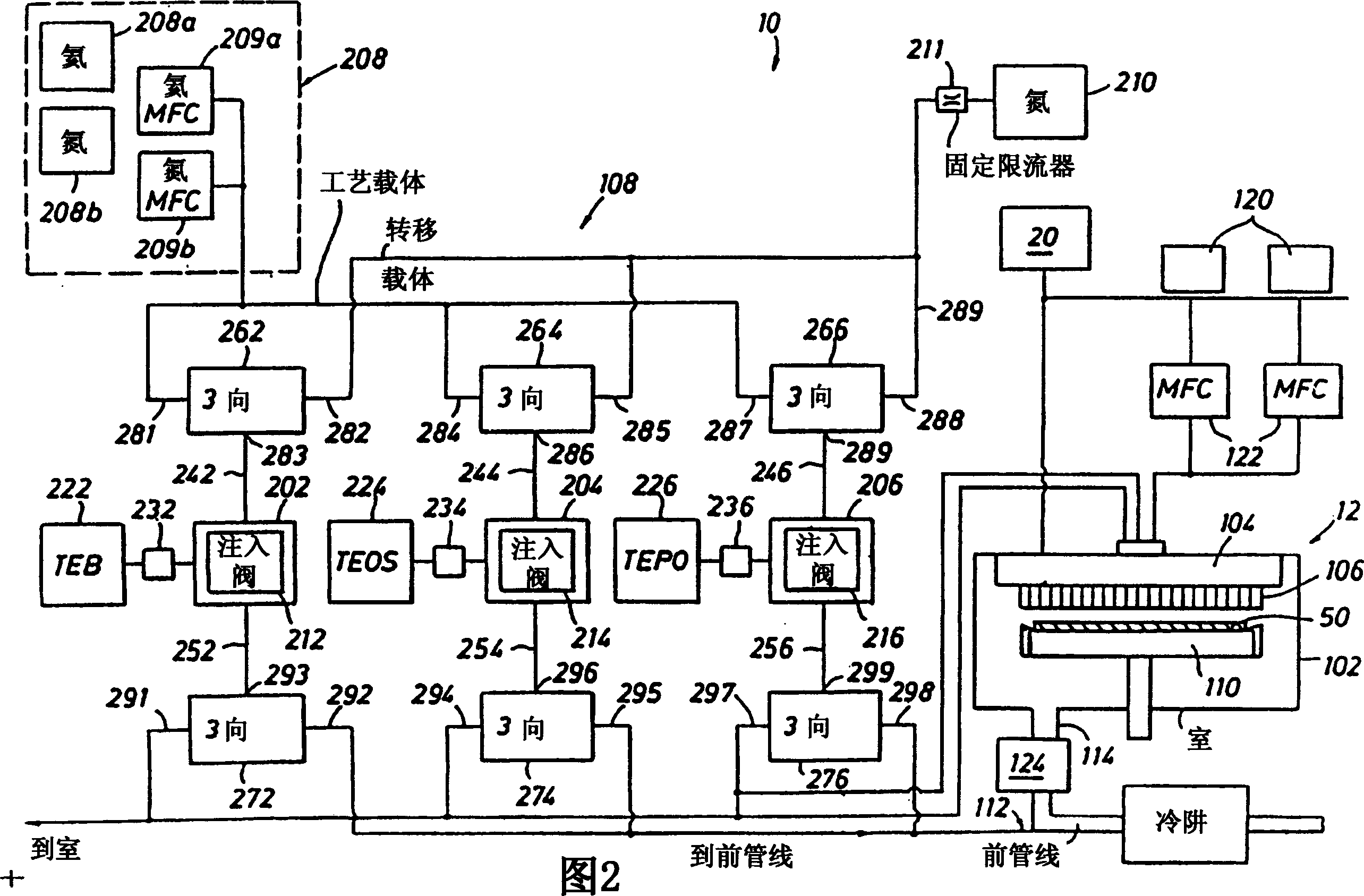

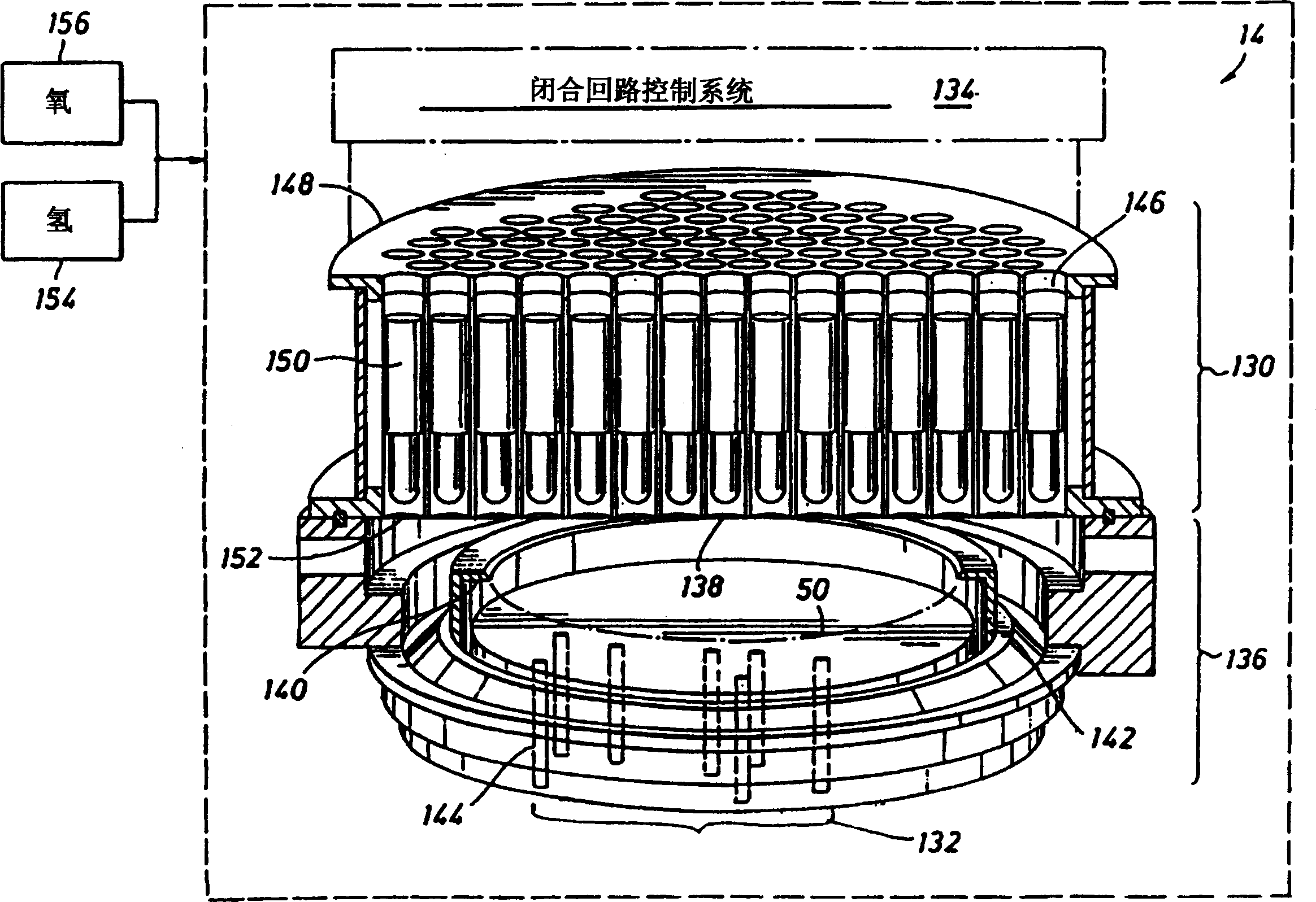

Method and apparatus for controlling dopant concentration during BPSG film deposition to reduce nitride consumption

InactiveUS7638161B2Reduce consumptionVacuum evaporation coatingSputtering coatingDopantSilicate glass

A method and apparatus for controlling dopant concentration during borophosphosilicate glass film deposition on a semiconductor wafer to reduce consumption of nitride on the semiconductor wafer. In one embodiment of the invention, the method starts by placing a substrate having a nitride layer in a reaction chamber and providing a silicon source, an oxygen source and a boron source into the reaction chamber while delaying providing a phosphorous source into the reaction chamber to form a borosilicate glass layer over the nitride layer. The method continues by providing the silicon, oxygen, boron and phosphorous sources into the reaction chamber to form a borophosphosilicate film over the borosilicate glass layer.

Owner:APPLIED MATERIALS INC

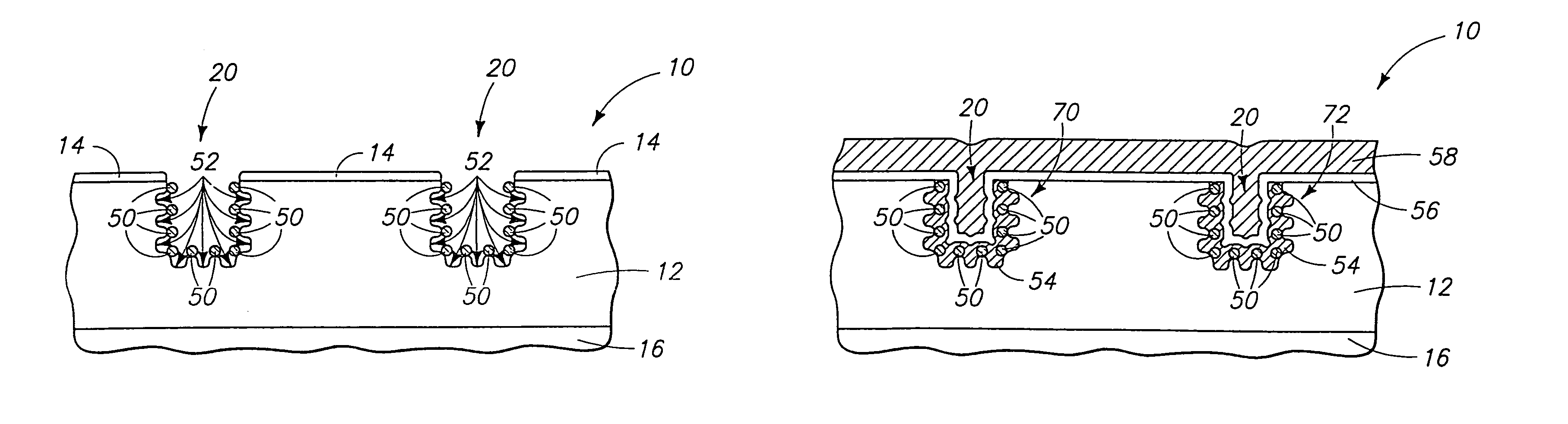

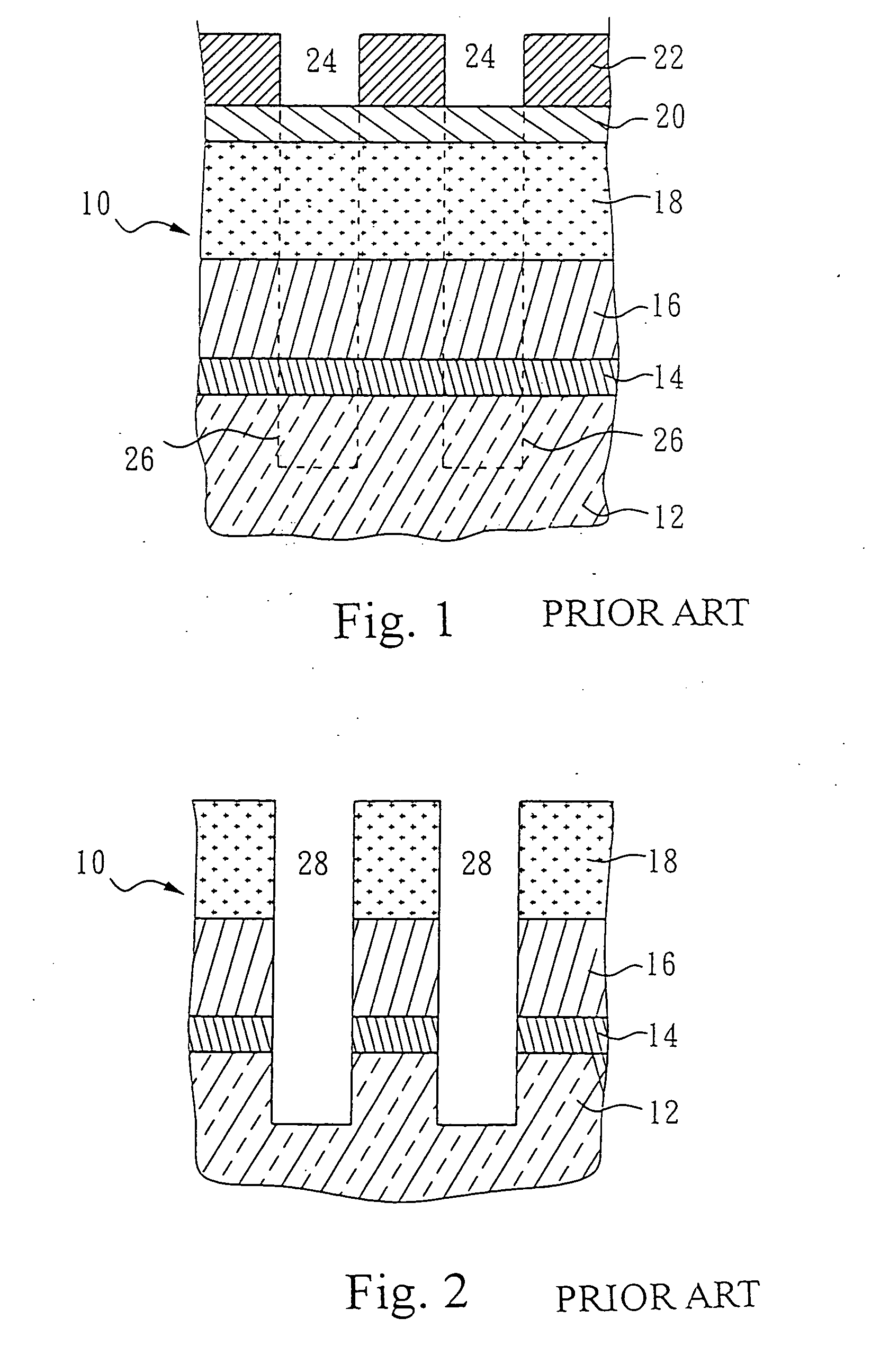

DRAM constructions, memory arrays and semiconductor constructions

InactiveUS20050104111A1TransistorSolid-state devicesSemiconductor structureBorophosphosilicate glass

The invention includes a method of depositing a noble metal. A substrate is provided. The substrate has a first region and a second region. The first and second regions are exposed to a mixture comprising a precursor of a noble metal and an oxidant. During the exposure, a layer containing the noble metal is selectively deposited onto the first region relative to the second region. In particular applications, the first region can comprise borophosphosilicate glass, and the second region can comprise either aluminum oxide or doped non-oxidized silicon. The invention also includes capacitor constructions and methods of forming capacitor constructions.

Owner:MICRON TECH INC

DRAM constructions, memory arrays and semiconductor constructions

The invention includes a method of depositing a noble metal. A substrate is provided. The substrate has a first region and a second region. The first and second regions are exposed to a mixture comprising a precursor of a noble metal and an oxidant. During the exposure, a layer containing the noble metal is selectively deposited onto the first region relative to the second region. In particular applications, the first region can comprise borophosphosilicate glass, and the second region can comprise either aluminum oxide or doped non-oxidized silicon. The invention also includes capacitor constructions and methods of forming capacitor constructions.

Owner:MICRON TECH INC

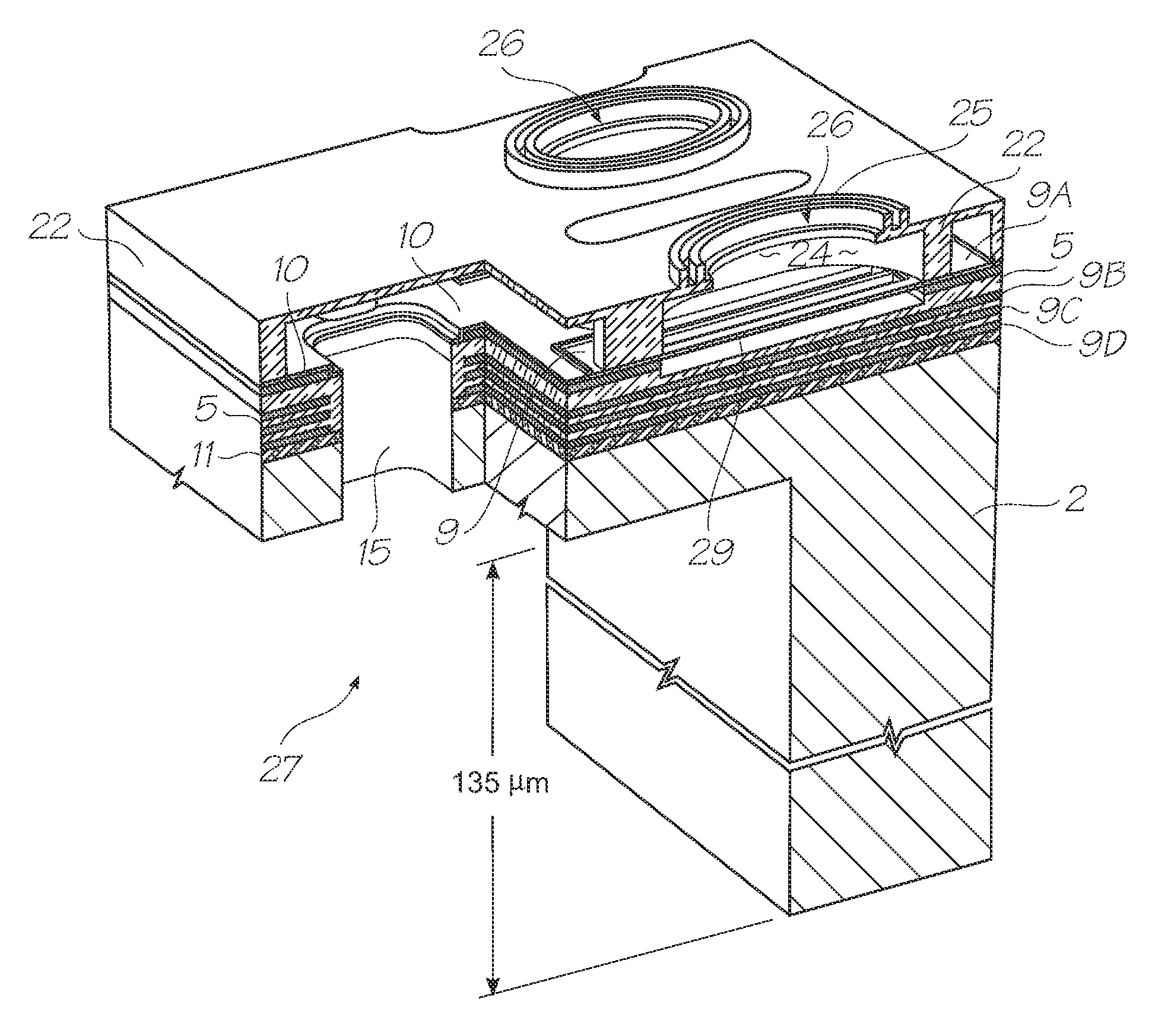

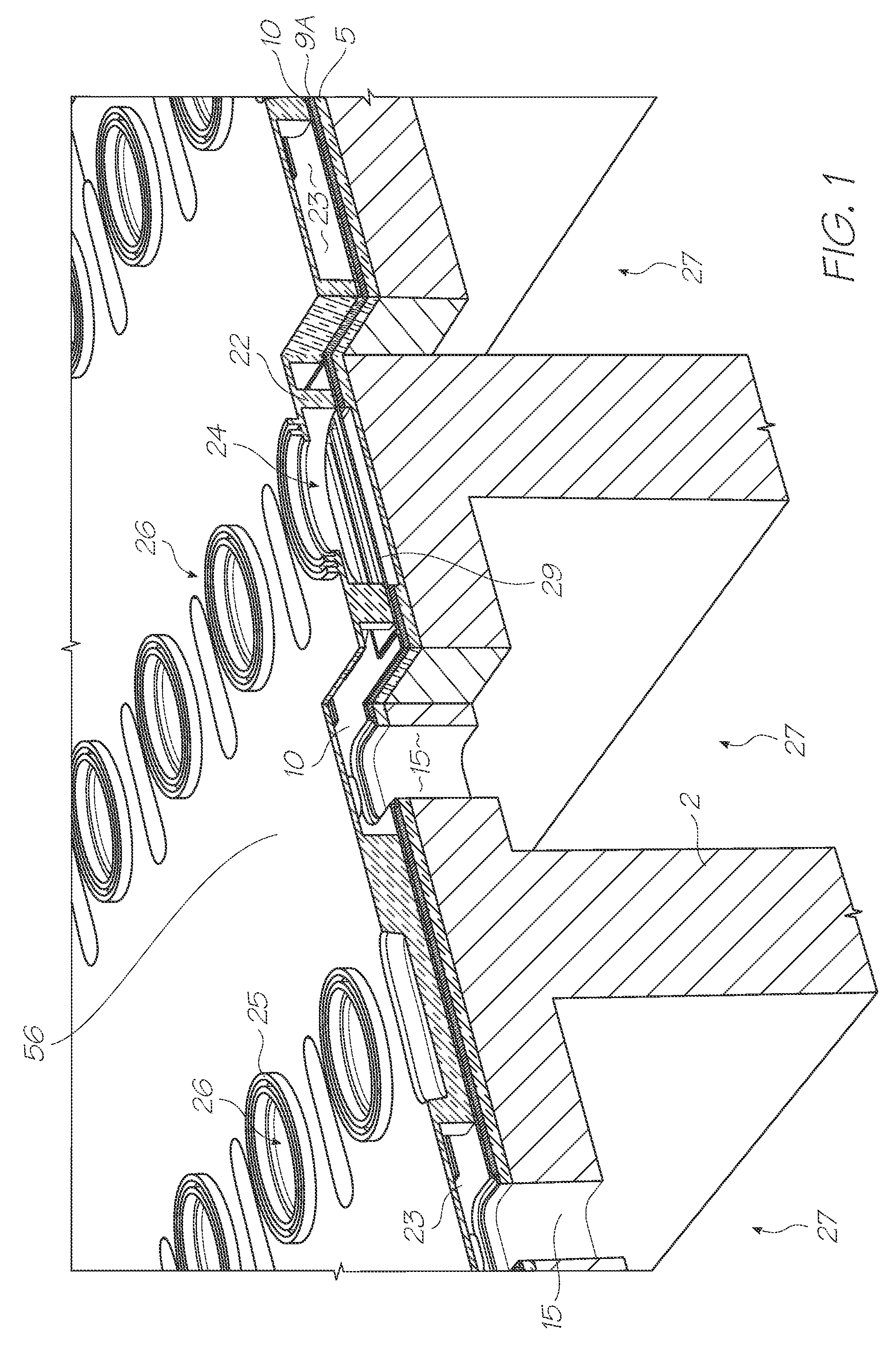

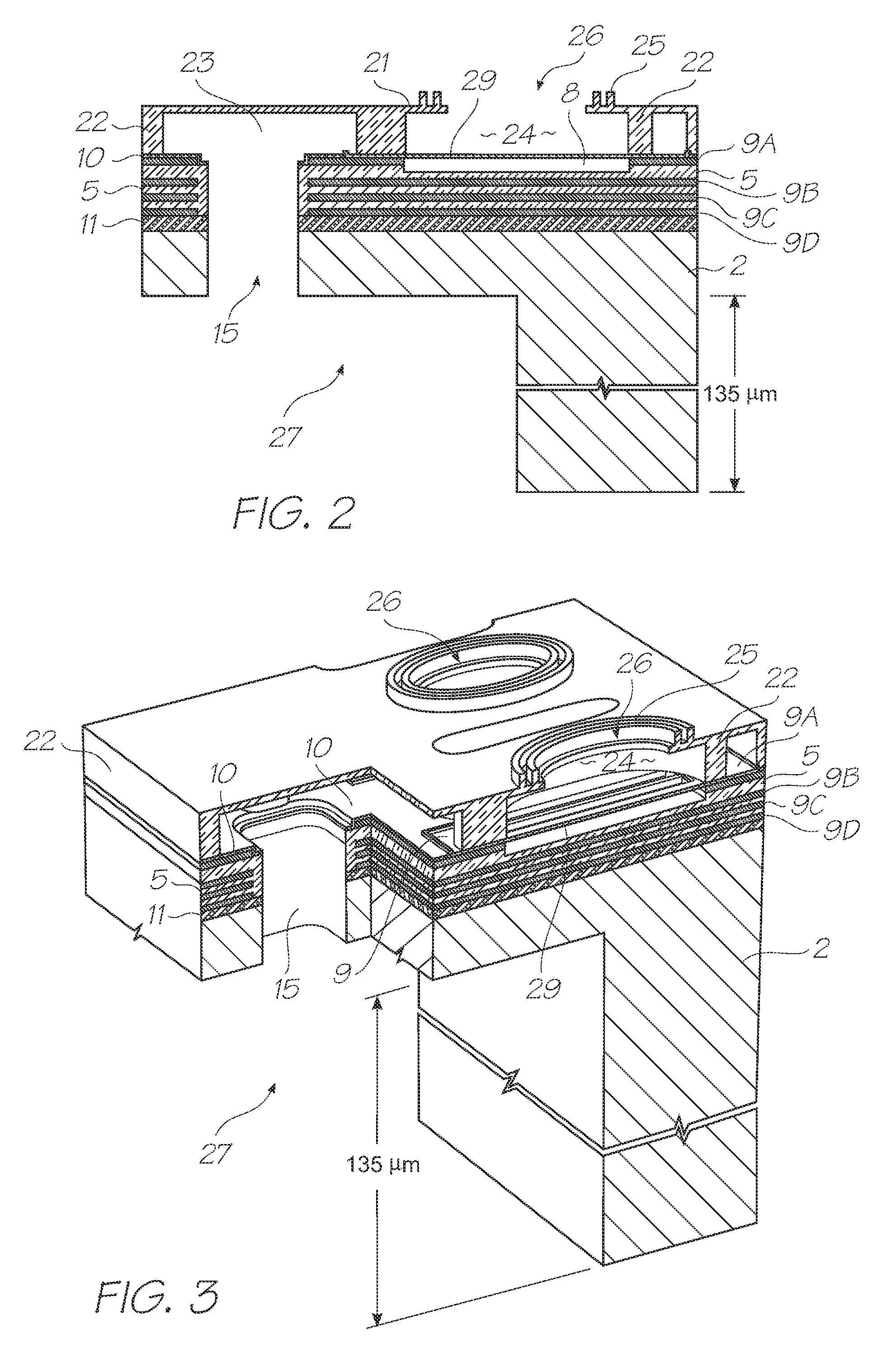

Inkjet printer having printhead and ink for minimizing corrosion of exposed corrodible structures within printhead

InactiveUS20120287206A1Corrosion minimizationMinimizing corrosionInking apparatusInksEngineeringBorophosphosilicate glass

An inkjet printer includes: an inkjet printhead having an exposed corrodible structure containing silicon nitride, borophosphosilicate glass (BPSG) or silicon oxide; and an ink reservoir containing said ink which is in fluid communication with said printhead. The ink includes: water; a dye; and a metal additive for minimizing corrosion of the exposed structure.

Owner:ZAMTEC

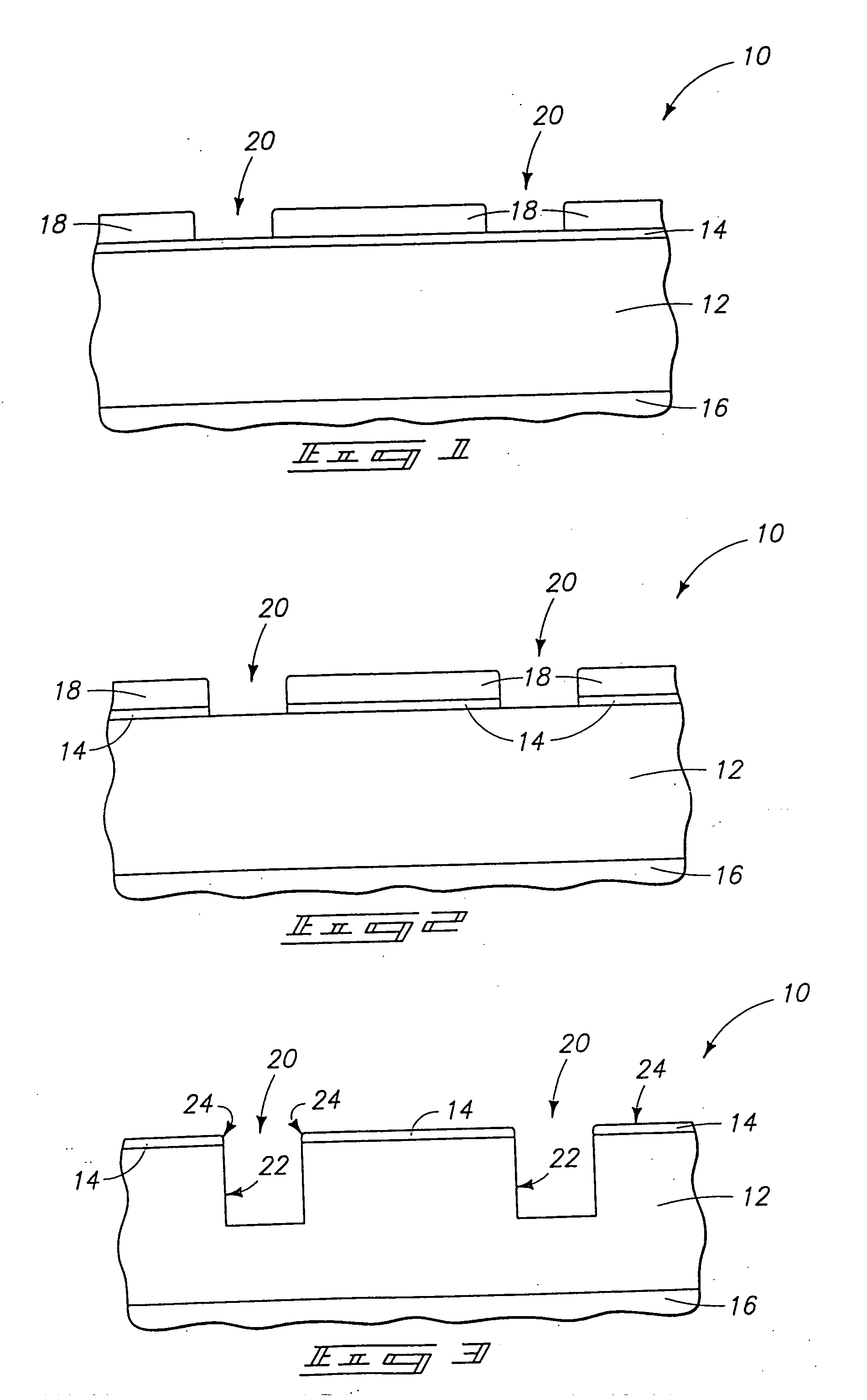

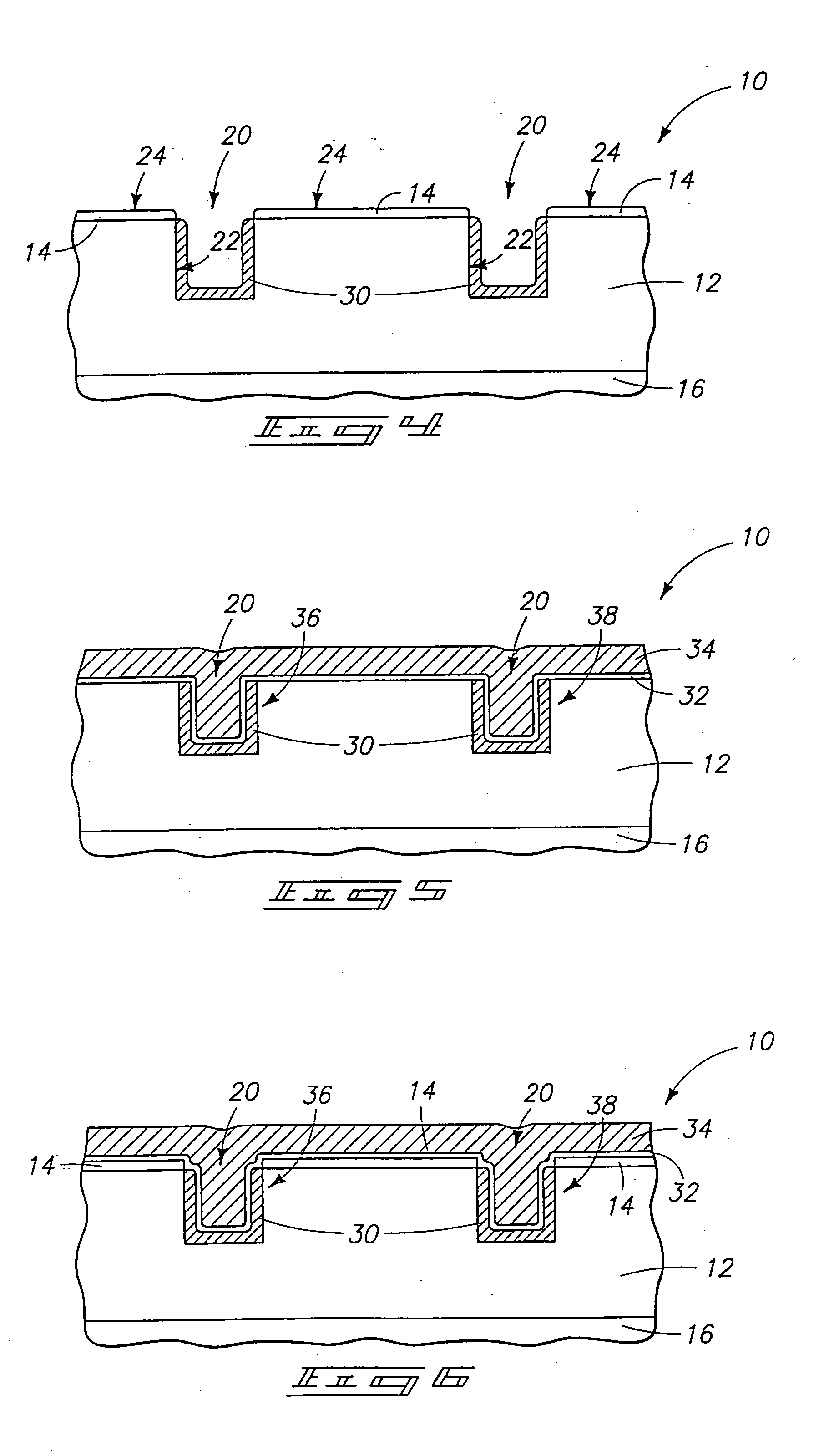

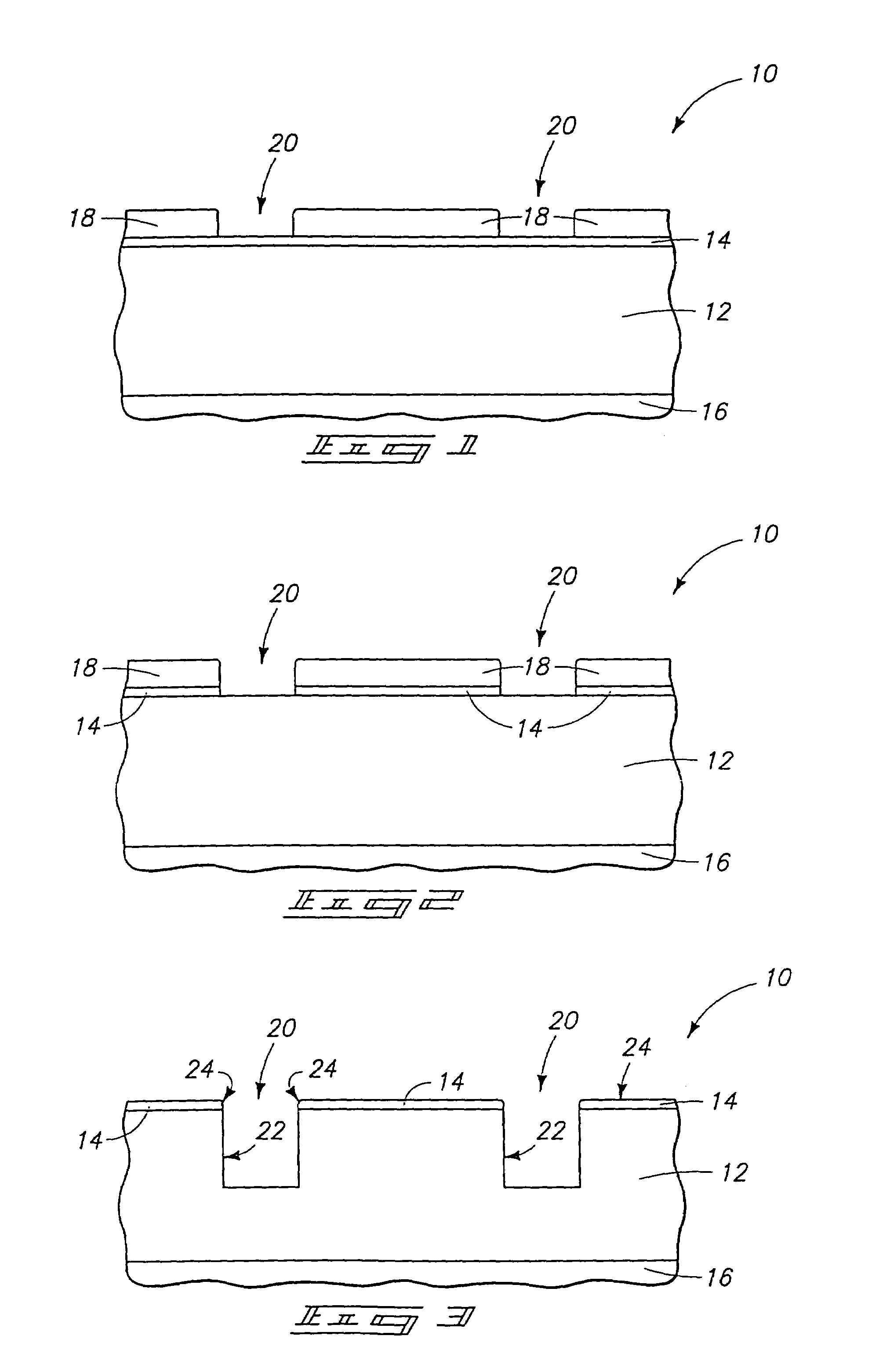

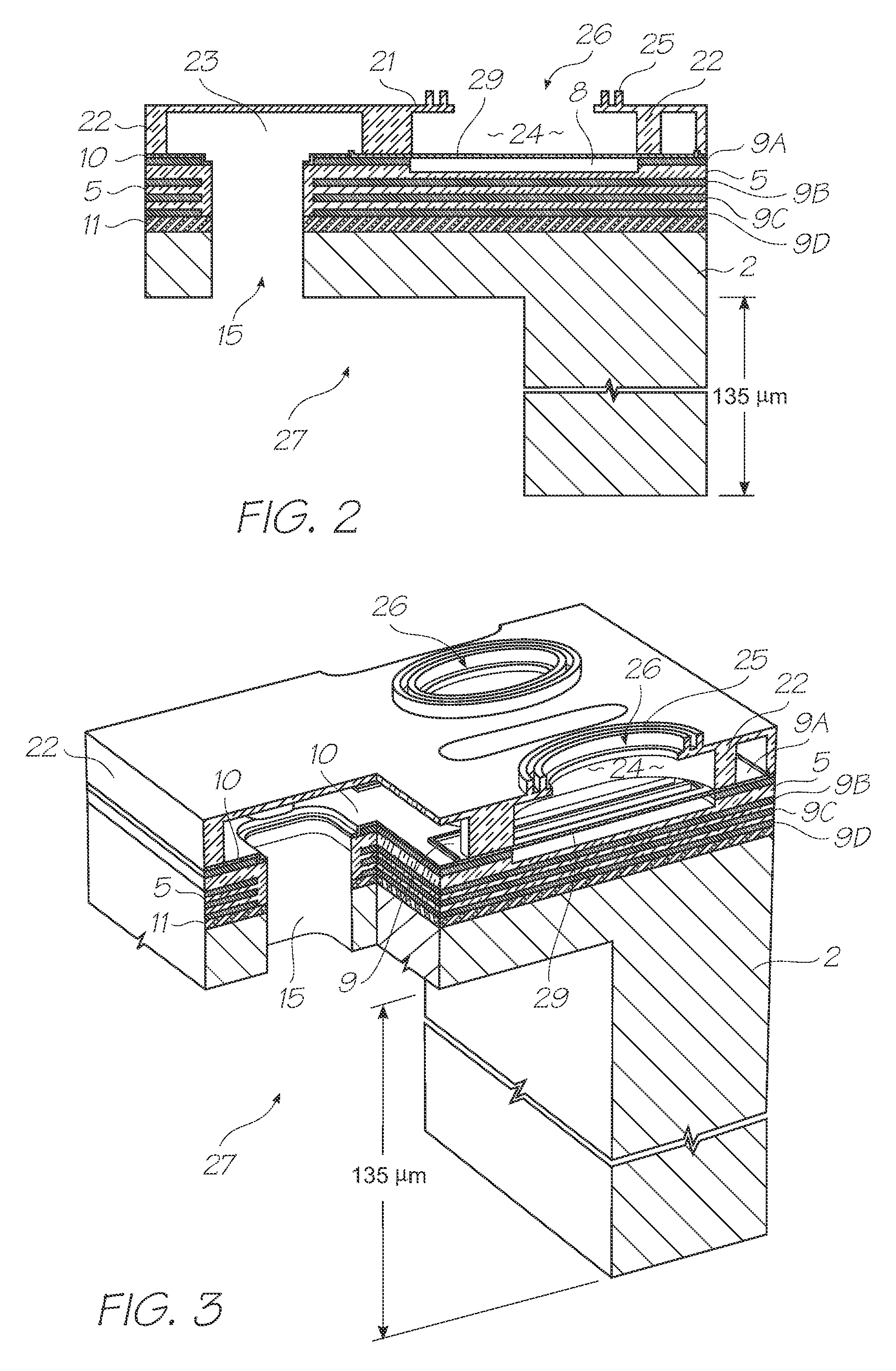

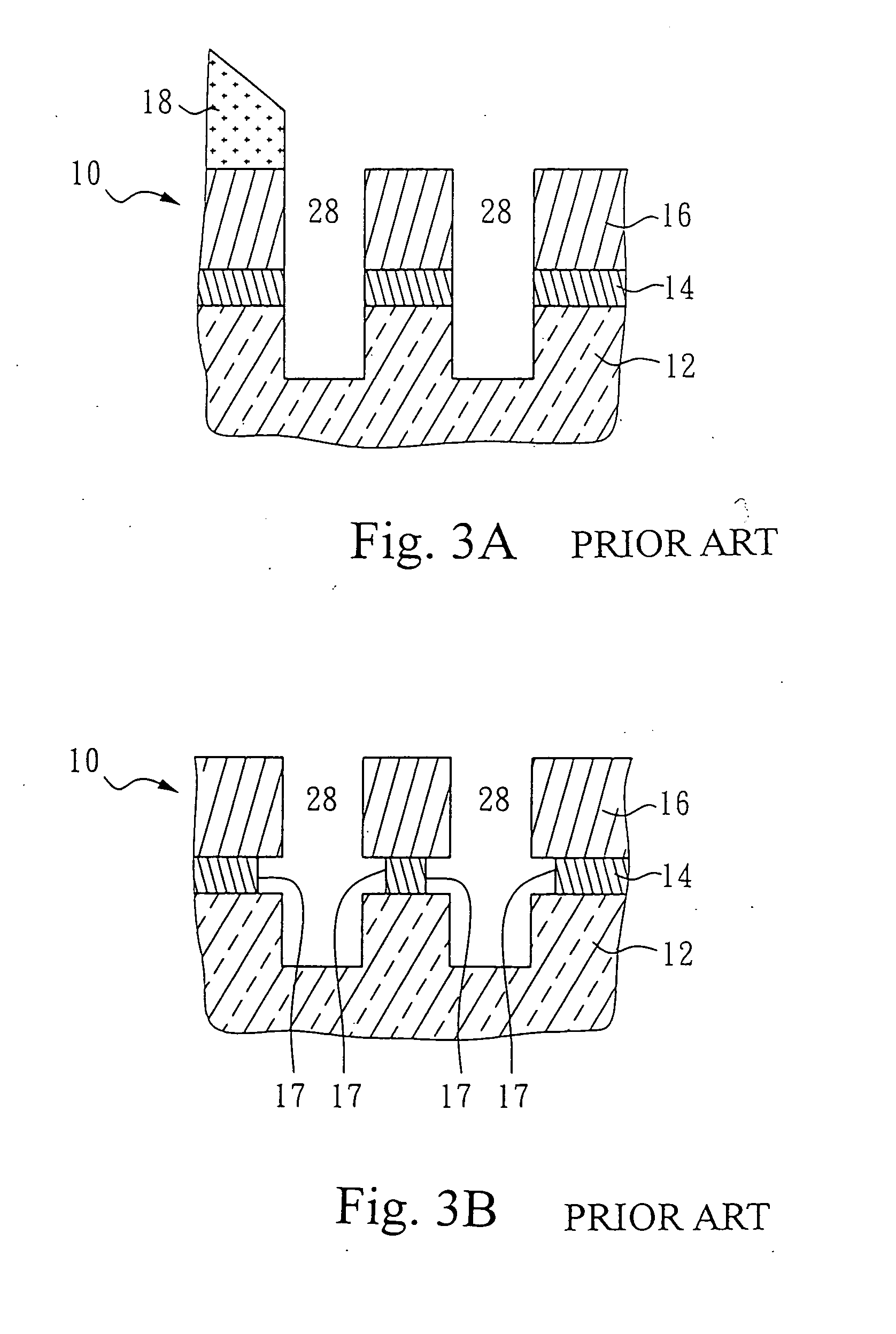

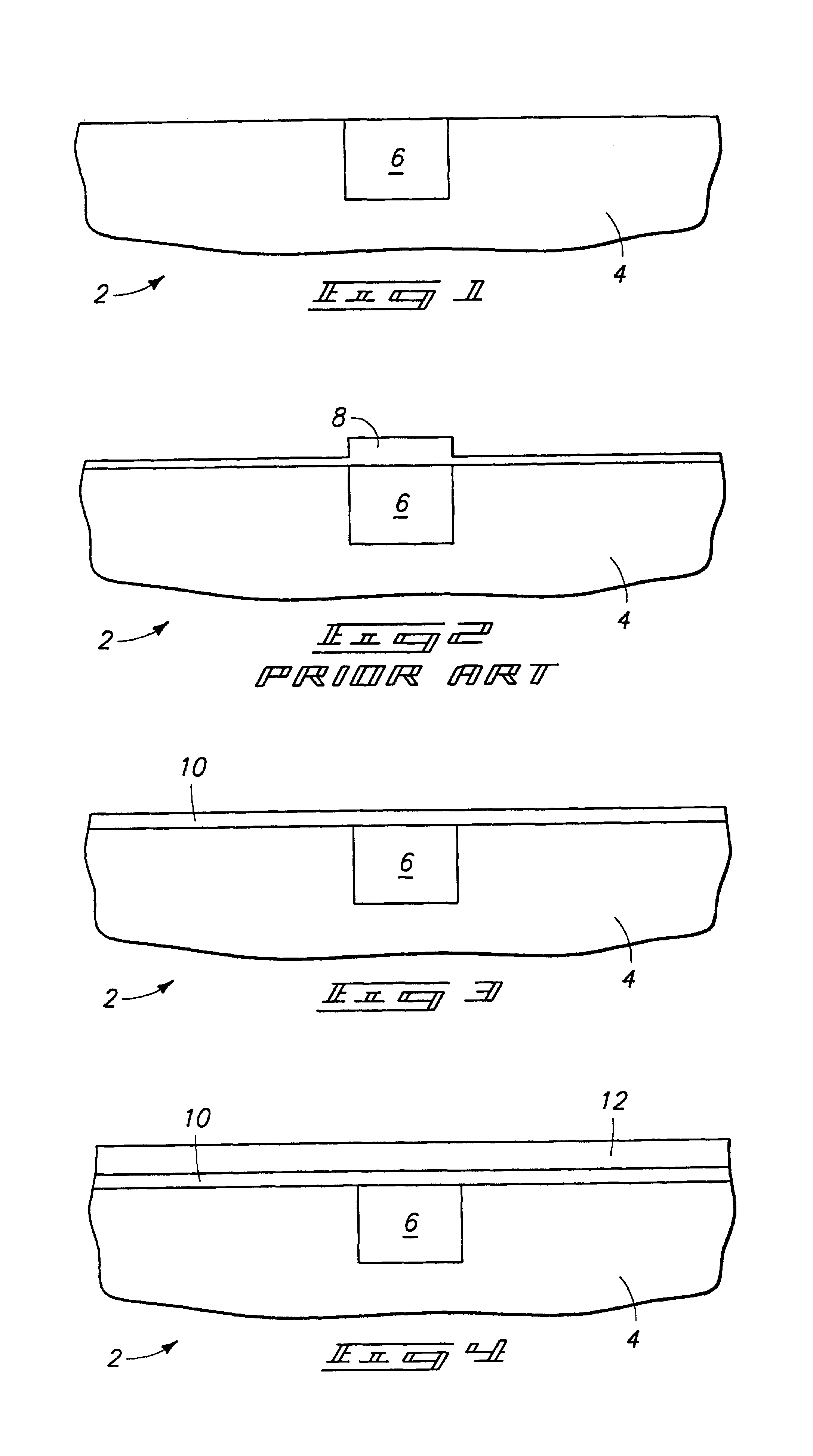

Method and composite hard mask for forming deep trenches in a semiconductor substrate

ActiveUS20050215061A1Easily and completely removedTransistorSolid-state devicesHydrogen fluorideBorophosphosilicate glass

A method and structure for forming deep trenches in a semiconductor substrate is provided. The method comprises: providing a semiconductor substrate; forming a pad oxide layer on the semiconductor substrate; forming a pad nitride layer on the pad oxide layer; forming a borophosphosilicate glass layer on the pad nitride layer; forming a borosilicate glass layer on the borophosphosilicate glass layer; and forming deep trenches through the borosilicate glass layer, through the borophosphosilicate glass layer, through the pad nitride, through the pad oxide, and into the semiconductor substrate. The borosilicate glass layer and the borophosphosilicate glass layer function as a composite hard mask in forming the deep trenches. With the borophosphosilicate glass layer, the composite hard mask can be easily removed by dry etch process using hydrogen fluoride vapor after the deep trenches have been formed.

Owner:NAN YA TECH

Method and apparatus for deposition of boron-phosphorus silicate glass

InactiveCN1553968AReduce consumptionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingWaferingSilicate glass

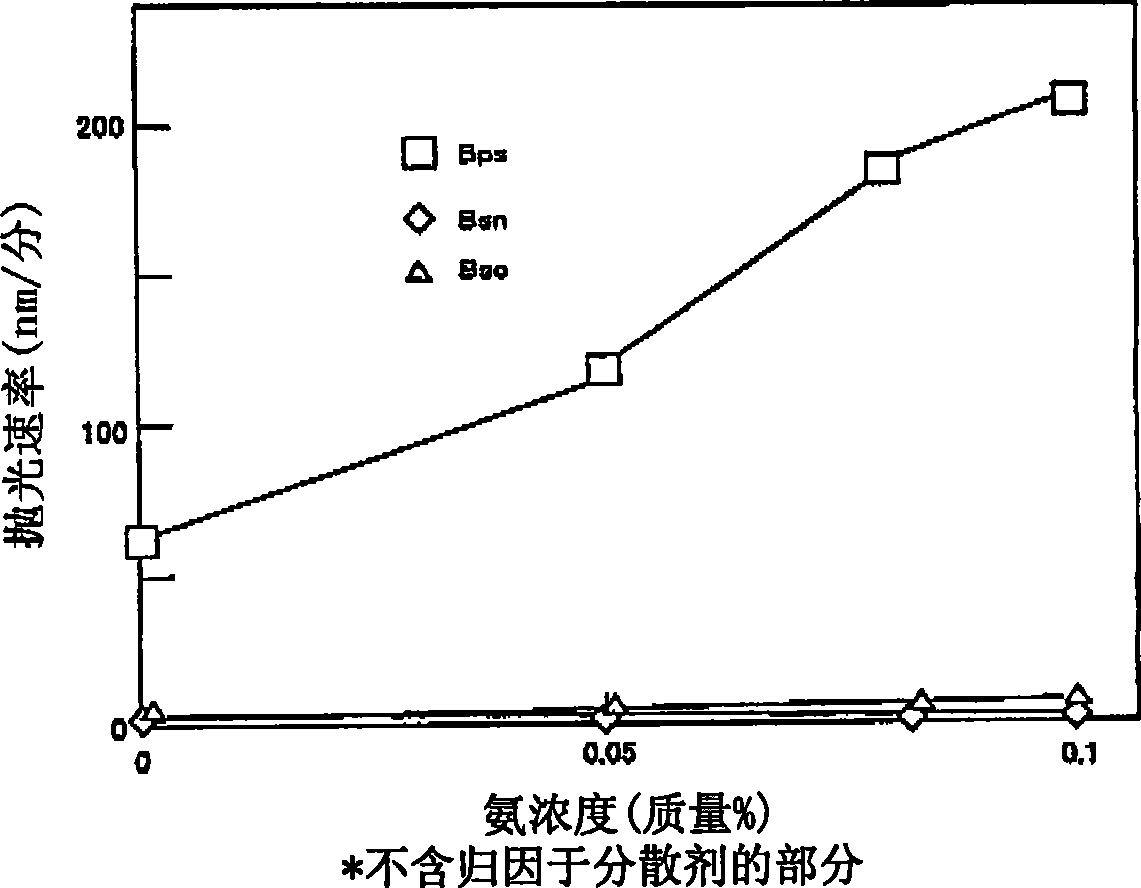

In a process of deposition of boron-phosphorus silicate glass film on a semiconductor wafer, a method and apparatus for controlling the adulteration thickness to reduce consumption of nitride on said semiconductor wafer. In an embodiment of the invention, at first, said method arranges substrate having nitride layer in a reaction chamber (502), and supplies silicon resource, oxide resource and boron resource, but delays the supply of phosphor resource to the reaction chamber, in order to form borosilicate glass layer (504) on said nitride layer. Then said method forms boron-phosphor-silicate film on the borosilicate glass film by supplying said silicon resource, oxide resource and boron resource to the reaction chamber.

Owner:APPLIED MATERIALS INC

Inkjet printer having printhead and ink for minimizing corrosion of exposed corrodible structures within printhead

ActiveUS8757779B2Minimizing corrosionAvoid corrosionInking apparatusMeasurement apparatus componentsSilicon oxideBorophosphosilicate glass

An inkjet printer includes: an inkjet printhead having an exposed corrodible structure containing silicon nitride, borophosphosilicate glass (BPSG) or silicon oxide; and an ink reservoir containing said ink which is in fluid communication with said printhead. The ink includes: water; a dye; and a metal additive for minimizing corrosion of the exposed structure.

Owner:MEMJET TECH LTD

Method and apparatus for reducing fixed charge in semiconductor device layers

InactiveUS6864561B2Semiconductor/solid-state device detailsSolid-state devicesBorophosphosilicate glassFixed charge

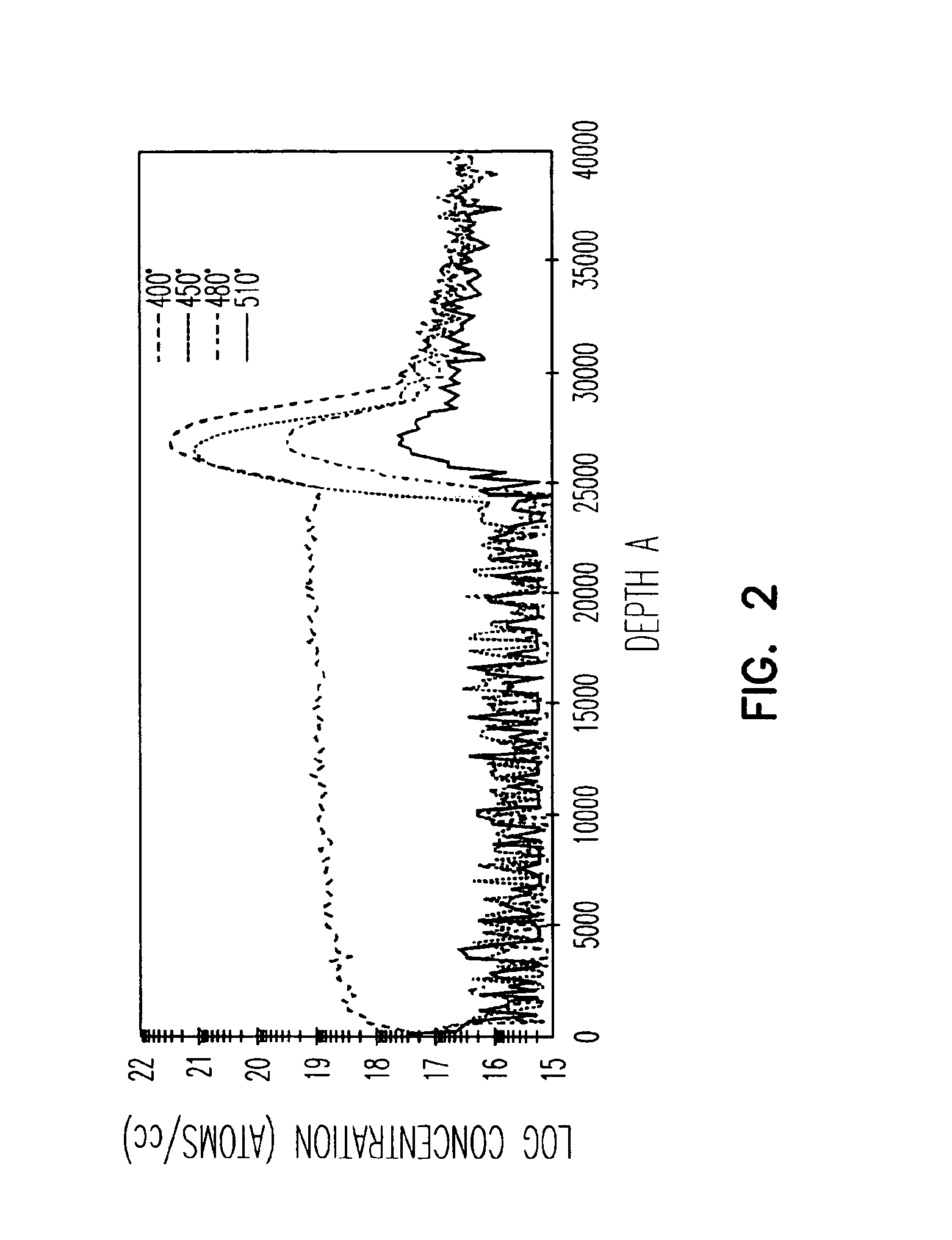

The fixed charge in a borophosphosilicate glass insulating film deposited on a semiconductor device is reduced by reacting an organic precursor such as TEOS with O3. When done at temperatures higher than approximately 480 degrees C., the carbon level in the resulting film appears to be reduced, resulting in a higher threshold voltage for field transistor devices.

Owner:MICRON TECH INC

Passivation for cleaning a material

InactiveUS7544622B2Decorative surface effectsNon-surface-active detergent compositionsBorophosphosilicate glassProcess design

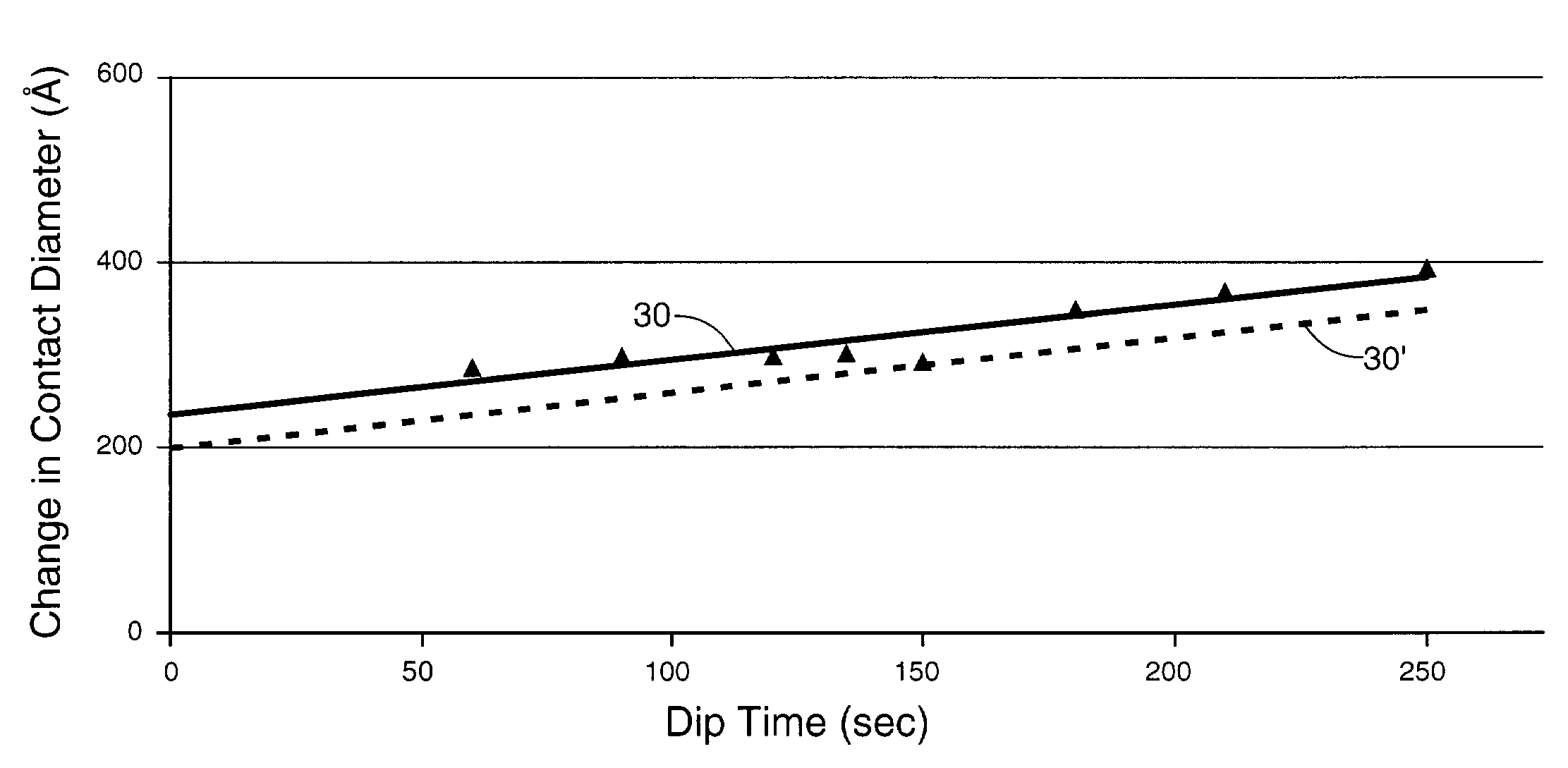

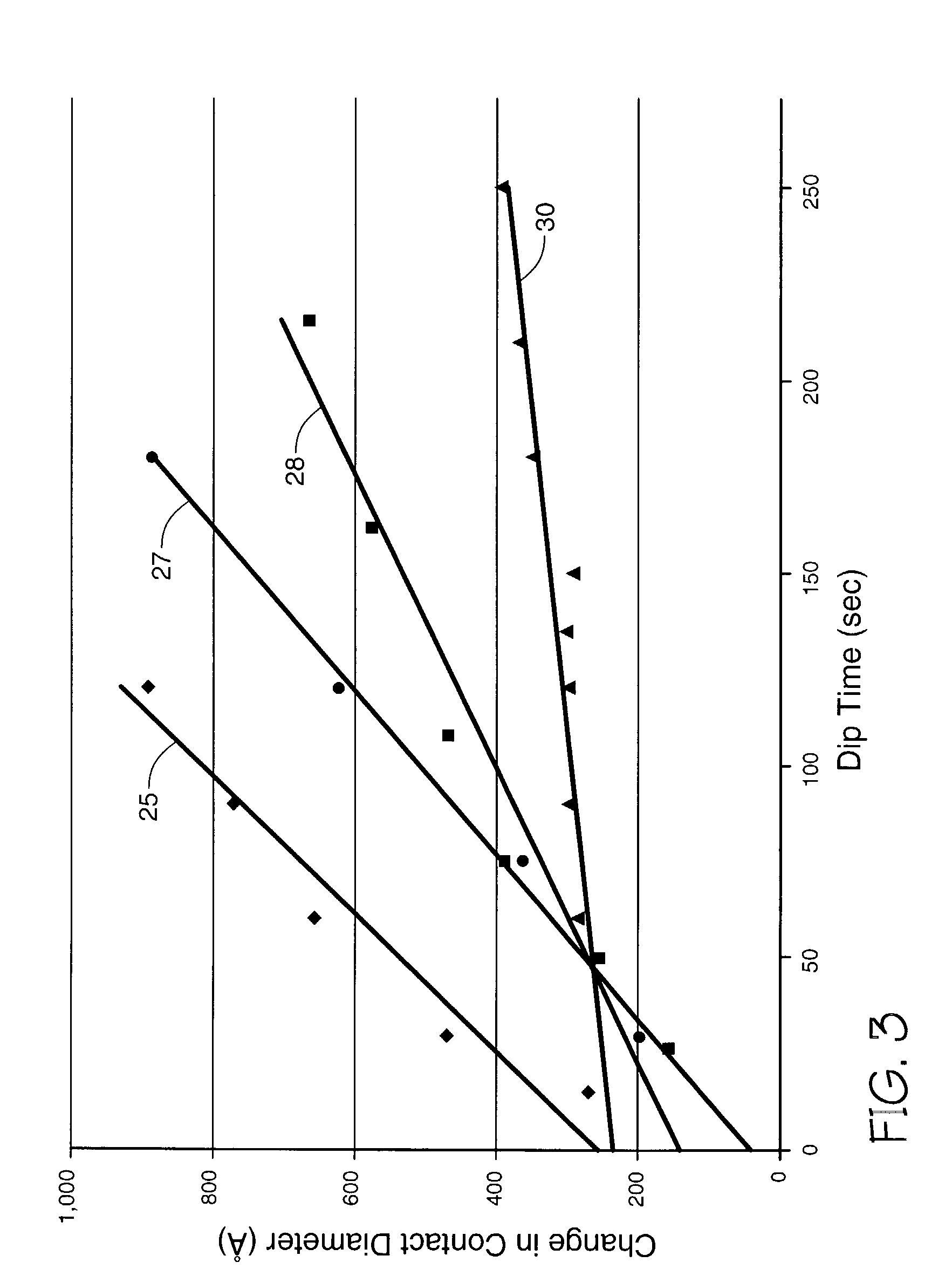

A contact is defined by an opening etched into borophosphosilicate glass (BPSG) down to a silicon substrate. In a contact cleaning process designed to remove native oxide at the bottom of the contact with little effect on the BPSG, the contact is dipped in an etch retardant before being dipped in a cleaning solution containing both the etch retardant and an etchant. The dip in etch retardant modifies the surface of the BPSG, thereby lessening the enhanced etching experienced during the initiation of the dip into the etchant / etch retardant cleaning solution. Results of a etchant / etch retardant clean, both with and without the prepassivation, can be illustrated on a graph depicting the change in contact diameter as a function of dip time. Specifically, the results define “best fit” lines on that graph. For a given dip time, a first line representing the prepassivation+etchant / etch retardant clean is 30 to 40 Angstroms lower than a second line representing the prior art clean using the etchant / etch retardant without prepassivation. Accordingly, the first line's Y-axis intercept, representing the “zero dip time,” is also 30 to 40 Angstroms lower than the second line's zero dip time.

Owner:MICRON TECH INC

Polishing agent for semiconductor integrated circuit device, polishing method, and method for manufacturing semiconductor integrated circuit device

InactiveCN101512733AAchieve a high degree of planarizationSuitable polishing rate ratioOther chemical processesSemiconductor/solid-state device manufacturingWater solubleEngineering

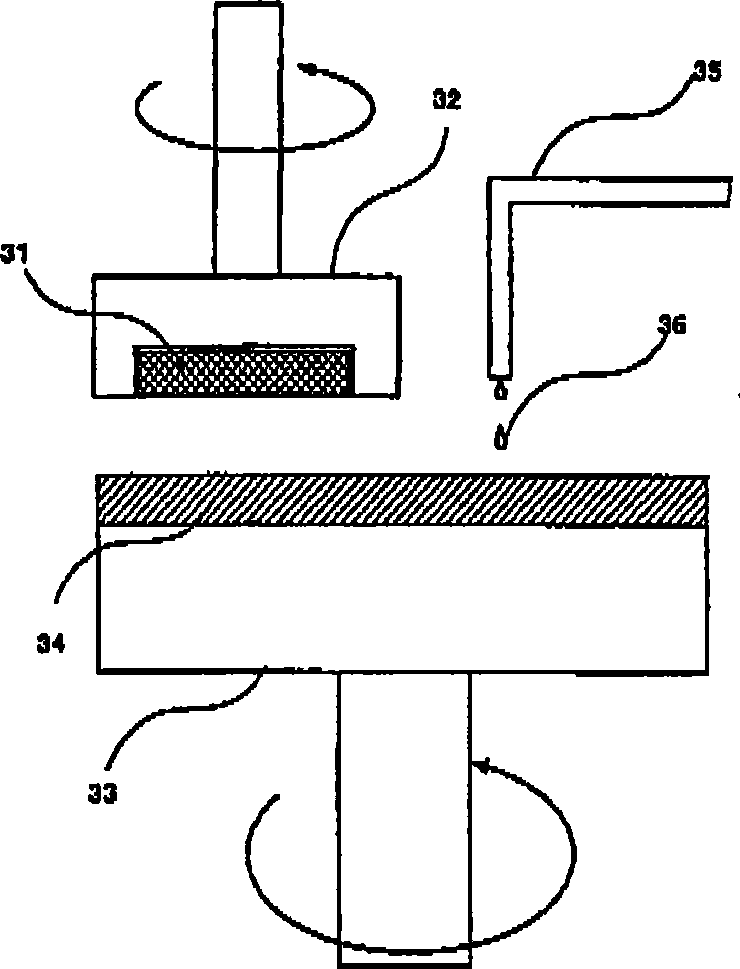

The present invention is to provide a polishing technique ensuring that when polishing a to-be-polished surface in the production of a semiconductor integrated circuit device, appropriate polishing rate ratios can be obtained between a borophosphosilicate glass material layer and other materials and high planarization of the to-be-polished surface containing a borophosphosilicate glass material layer can be thereby realized. The present invention relates to a polishing agent for chemical mechanical polishing, containing a cerium oxide particle, a water-soluble polyamine, one or more basic compounds selected from the group consisting of monoethanolamine, ethylethanolamine, diethanolamine and ammonia, and water, wherein the polishing agent has a pH of from 10 to 13 and wherein the basic compound is contained in an amount of more than 0.01 mass%.

Owner:ASAHI GLASS CO LTD

Photoelectronic device and its producing method and electronic device with said photoelectronic device

InactiveCN1617032AReduce precipitationPrevent precipitationTransistorCathode ray tubes/electron beam tubesSilicate glassBorophosphosilicate glass

The present invention provides electro-optical devices that can be manufactured with high yield and display high quality. In this electro-optical device, the substrate has electrodes for display, at least one of wirings for driving the electrodes for display, and electronic components, and at least one of the electrodes for display, wirings, and electronic components for electrically connecting each other with each other. An interlayer insulating film provided on the lower layer of the display electrode for insulation. At least one of the interlayer insulating films is composed of a borophosphosilicate glass film and has been subjected to a planarization process in a fluidized state.

Owner:SEIKO EPSON CORP

Low selectivity deposition methods

A deposition method includes forming a nucleation layer over a substrate, forming a layer of a first substance at least one monolayer thick chemisorbed on the nucleation layer, and forming a layer of a second substance at least one monolayer thick chemisorbed on the first substance. The chemisorption product of the first and second substance may include silicon and nitrogen. The nucleation layer may comprise silicon nitride. Further, a deposition method may include forming a first part of a nucleation layer on a first surface of a substrate and forming a second part of a nucleation layer on a second surface of the substrate. A deposition layer may be formed on the first and second parts of the nucleation layer substantially non-selectively on the first part of the nucleation layer compared to the second part. The first surface may be a surface of a borophosphosilicate glass layer. The second surface may be a surface of a rugged polysilicon layer. The first and second part of the nucleation layer may be formed simultaneously.

Owner:MICRON TECH INC

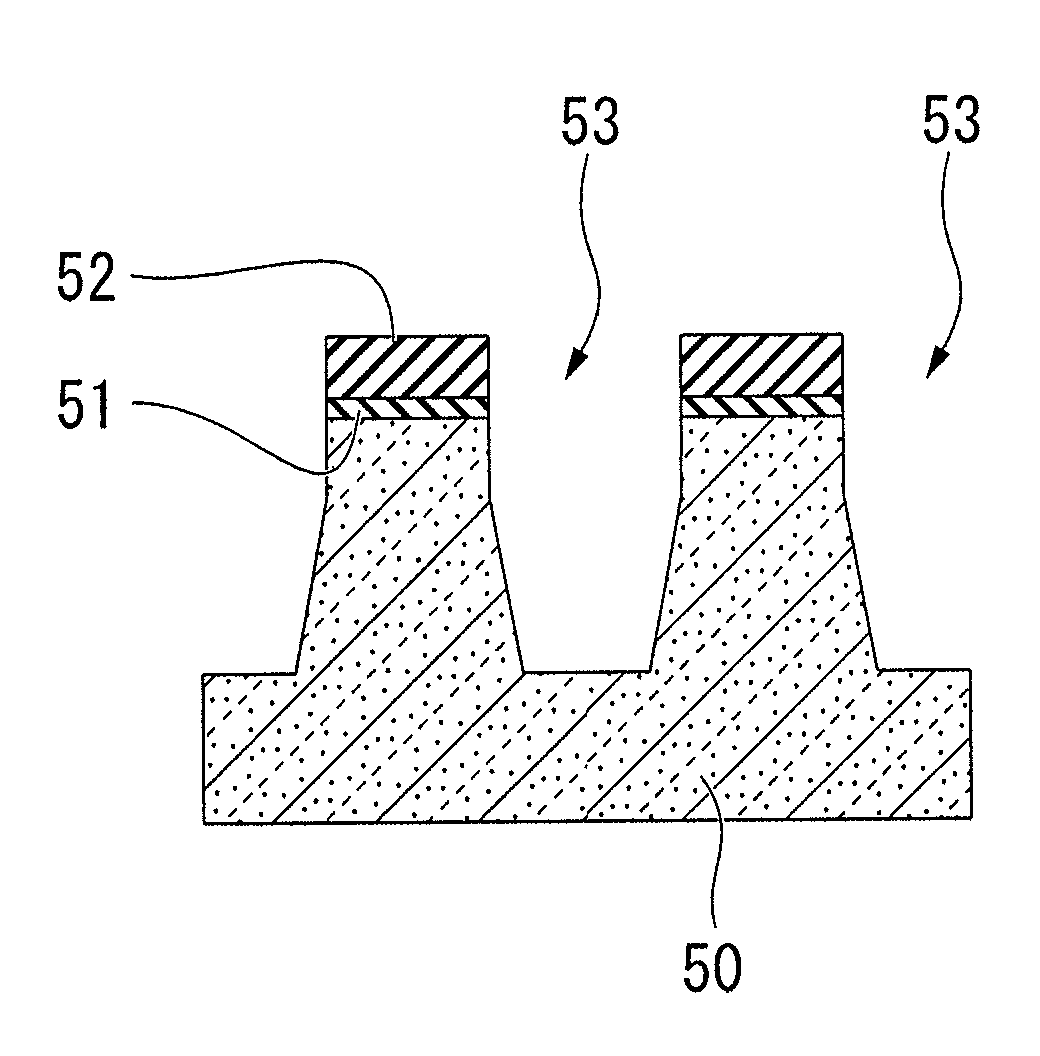

Semiconductor device and method of fabricating the same

InactiveUS20110151656A1Prevent removalSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSilicate glass

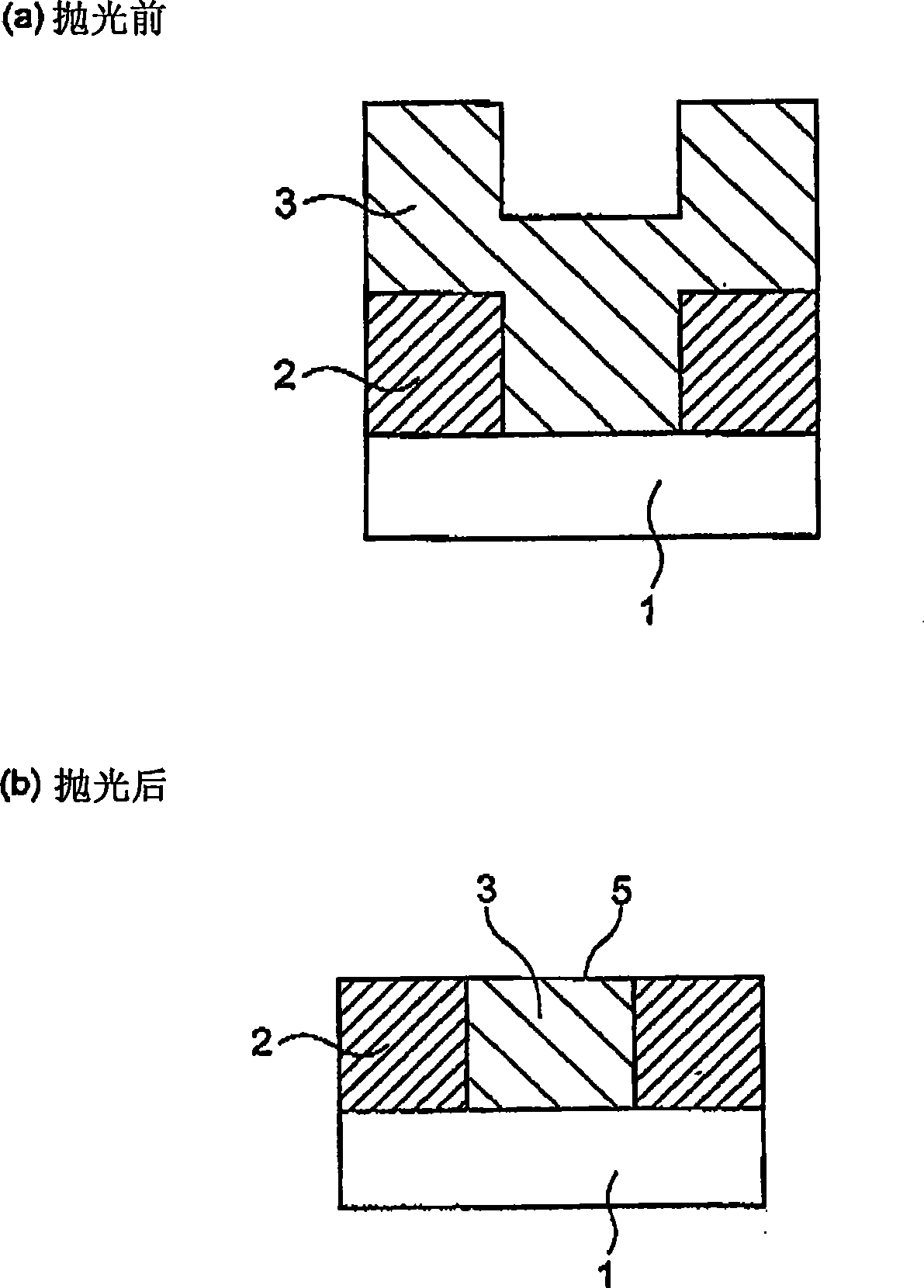

A method of forming a semiconductor device, the method including the following processes. A groove is formed in a semiconductor substrate. A gate electrode is formed in the groove. A boron-phosphorus silicate glass film is formed over the gate electrode. An etching process is performed using the boron-phosphorus silicate glass film as an etching stopper for preventing the gate electrode from being removed.

Owner:ELPIDA MEMORY INC

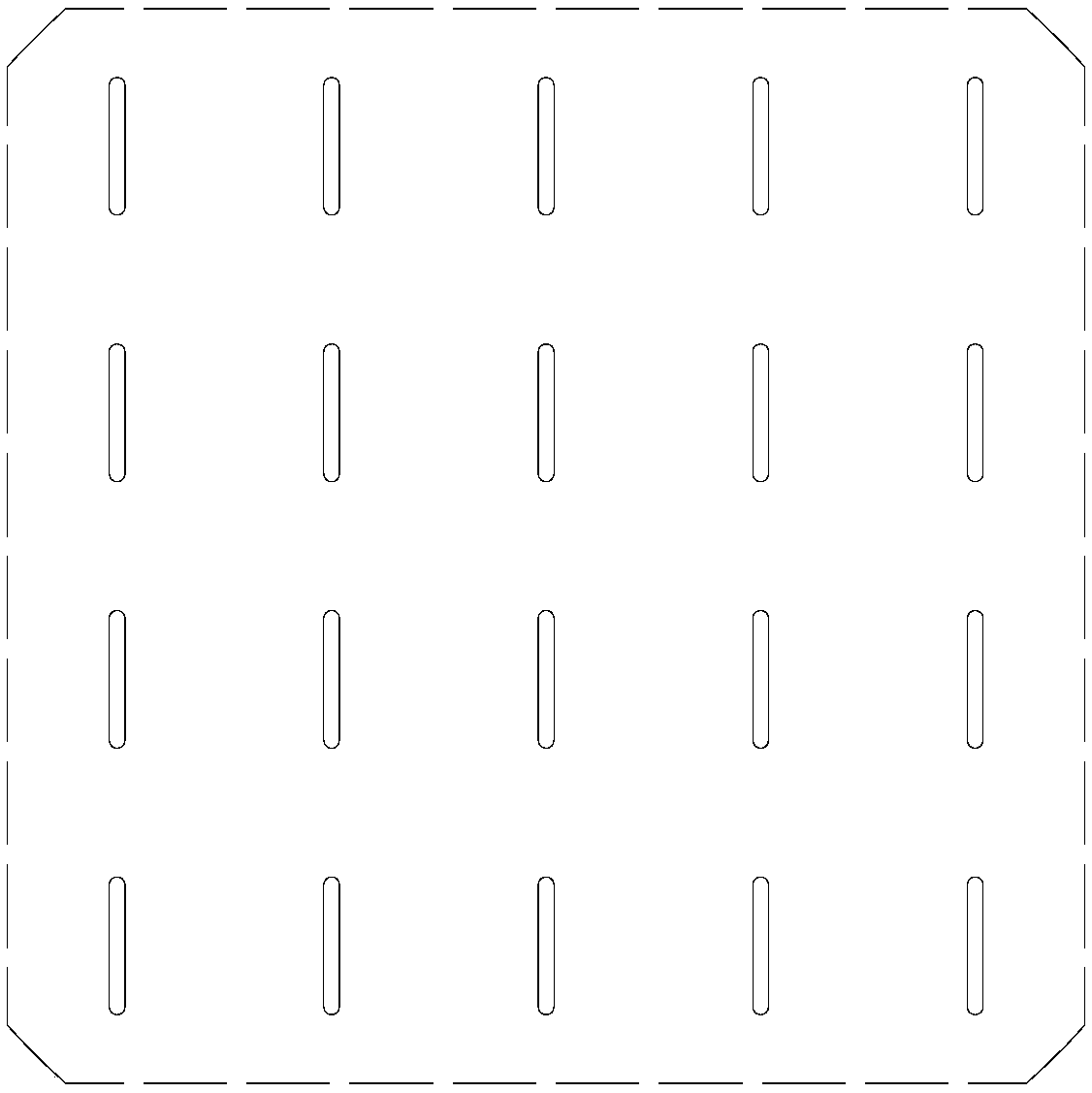

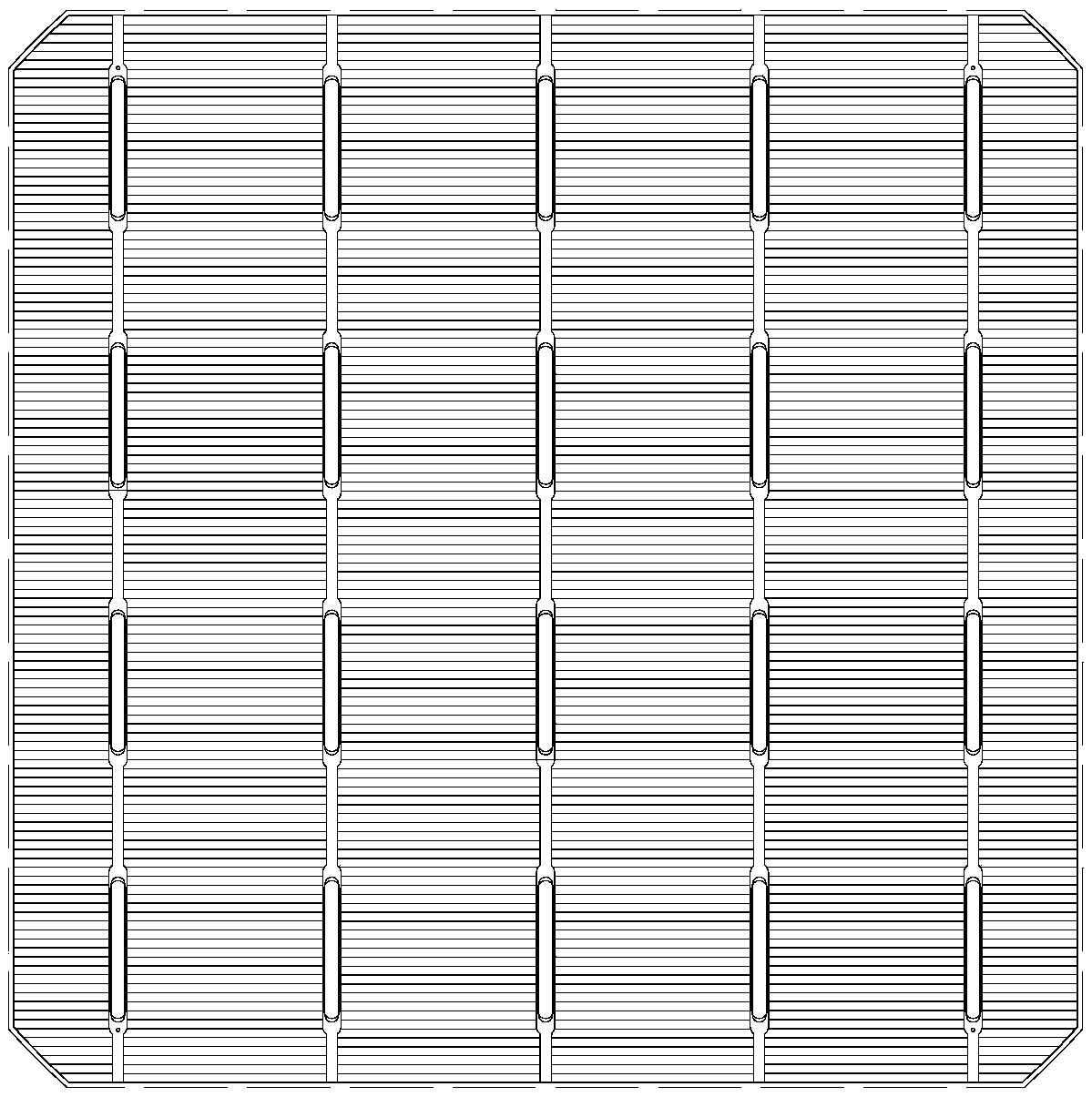

Method for manufacturing double-sided PERC high-efficiency crystalline silicon solar cell

InactiveCN109585600AIncrease power generationImprove conversion efficiencyFinal product manufacturePhotovoltaic energy generationGrid patternLine width

The invention discloses a method for manufacturing a double-sided PERC high-efficiency crystalline silicon solar cell. The method comprises the following steps of (1) texturing, (2) diffusion including crystalline silicon diffusion, (3) laser doping including the laser doping of a diffused crystalline silicon, (4) etching including the removal of diffused borophosphosilicate glass, (5) back passivation including the production of a SiO2-Al2O3-SiNx:H laminated passivation film with a thickness of 80-100 nm, (6) front side film coating including the generation of a SiO2-SiNx anti-reflection filmwith thickness of 80-90 nm by using the PECVD technology, (7) Backside laser doping and trenching including the formation of a corresponding P++ layer, wherein the line width of each of 120 laser doped region sub-gate lines is 40-45 micrometers, and composite 1.6 mm main grids are set, and (8) backside printing including the formation of a back aluminum grid pattern, the collection of current andsintering to form the double-sided PERC high-efficiency crystalline silicon solar energy battery.

Owner:RENESOLA JIANGSU LTD

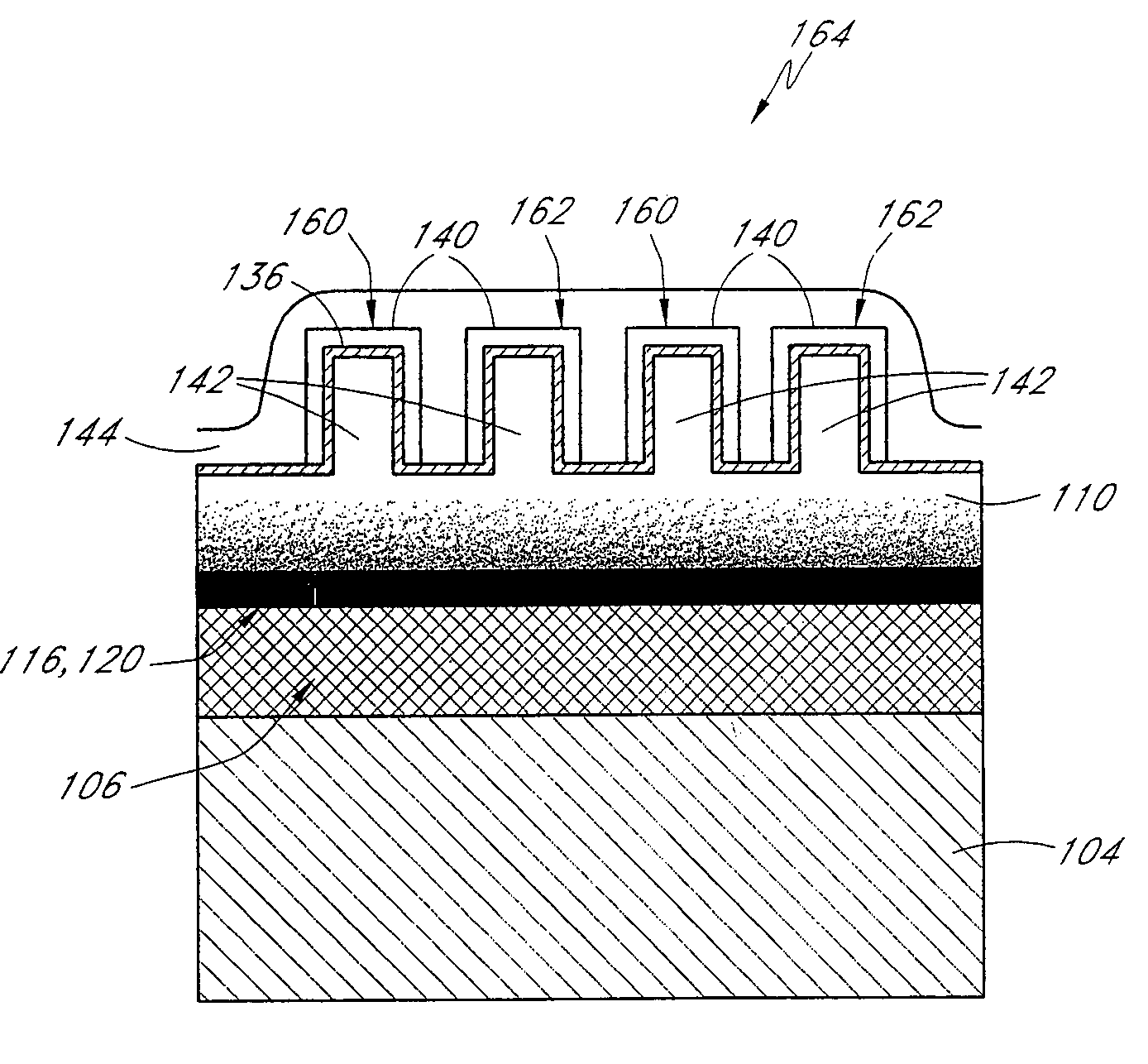

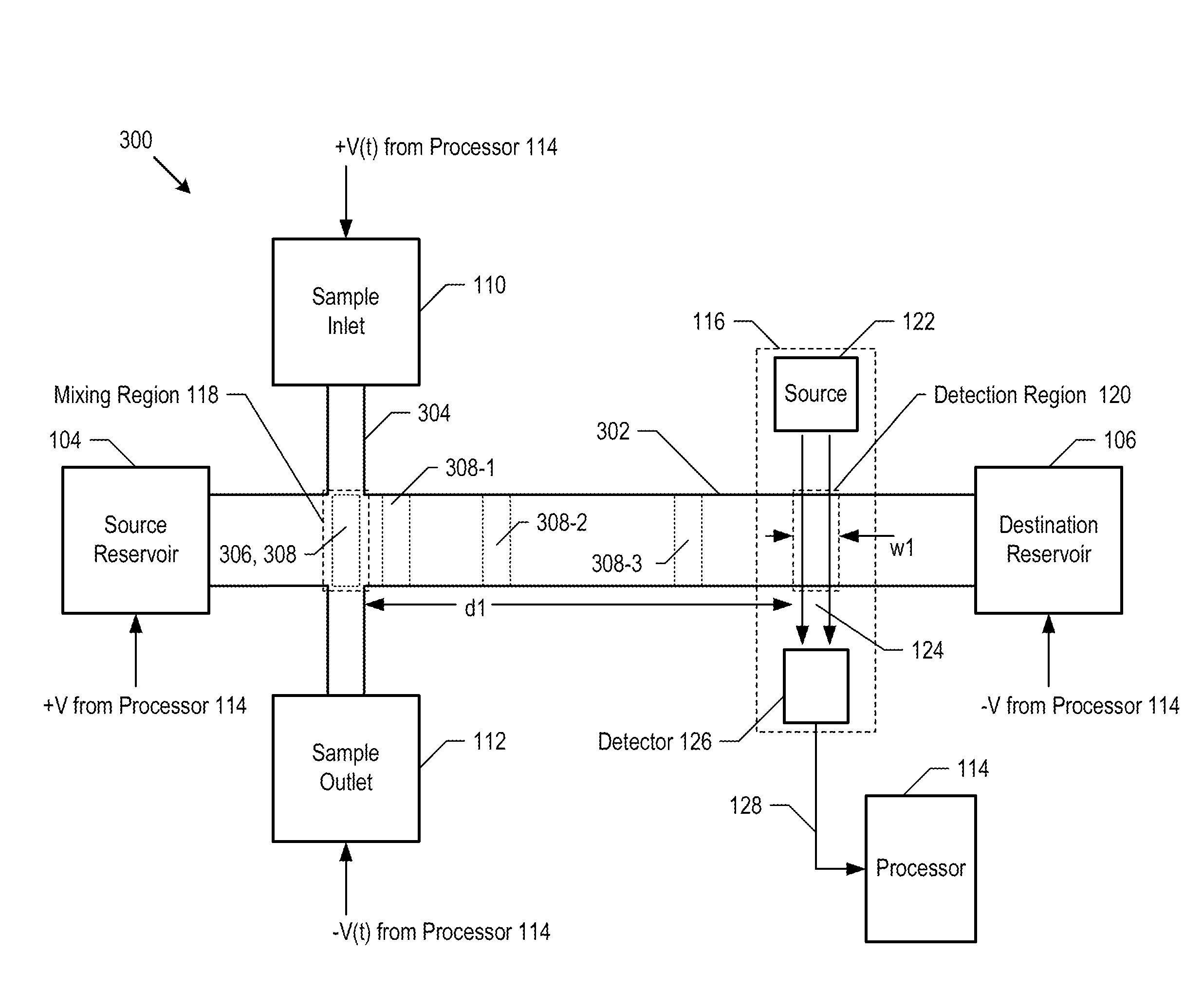

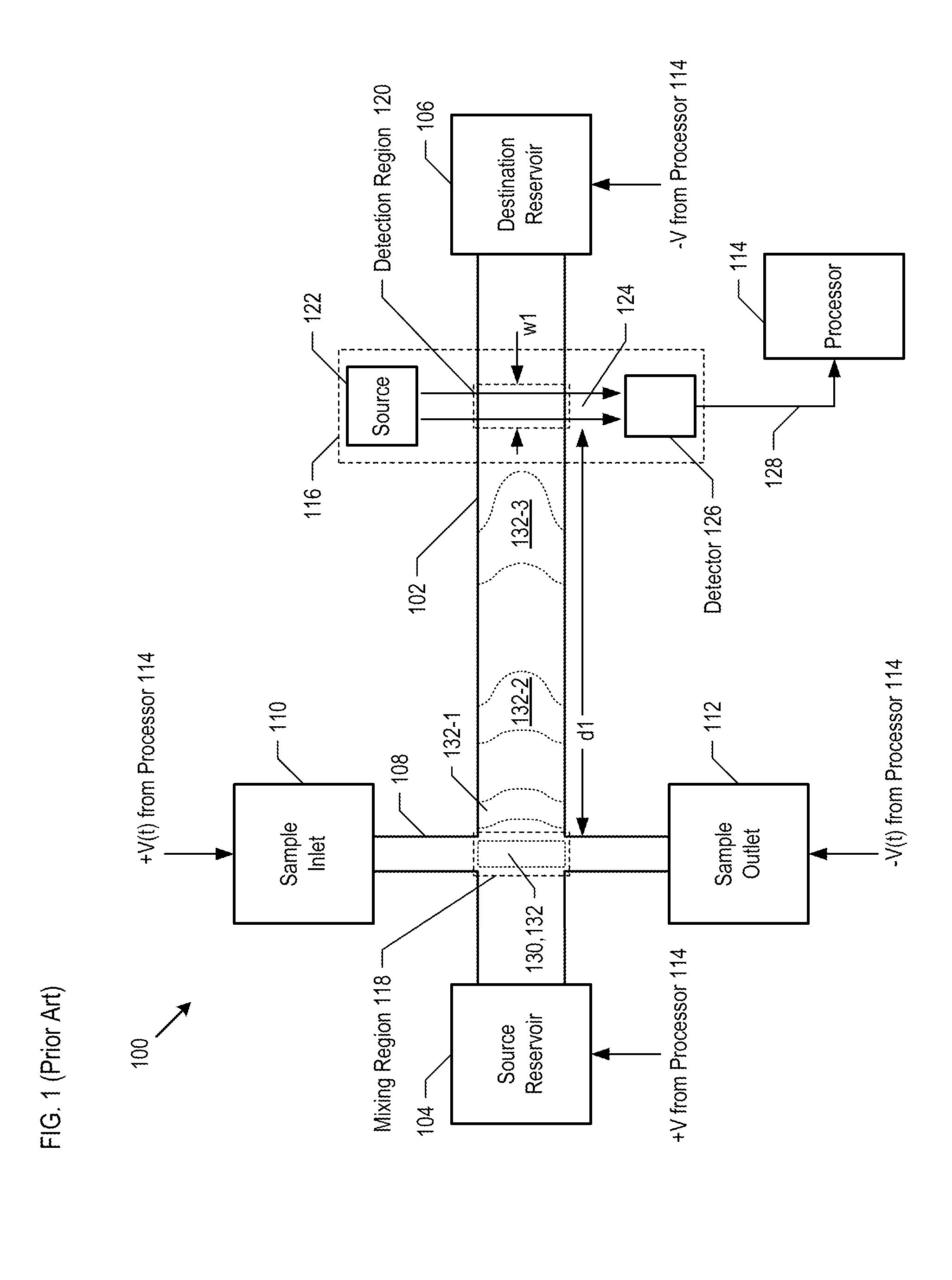

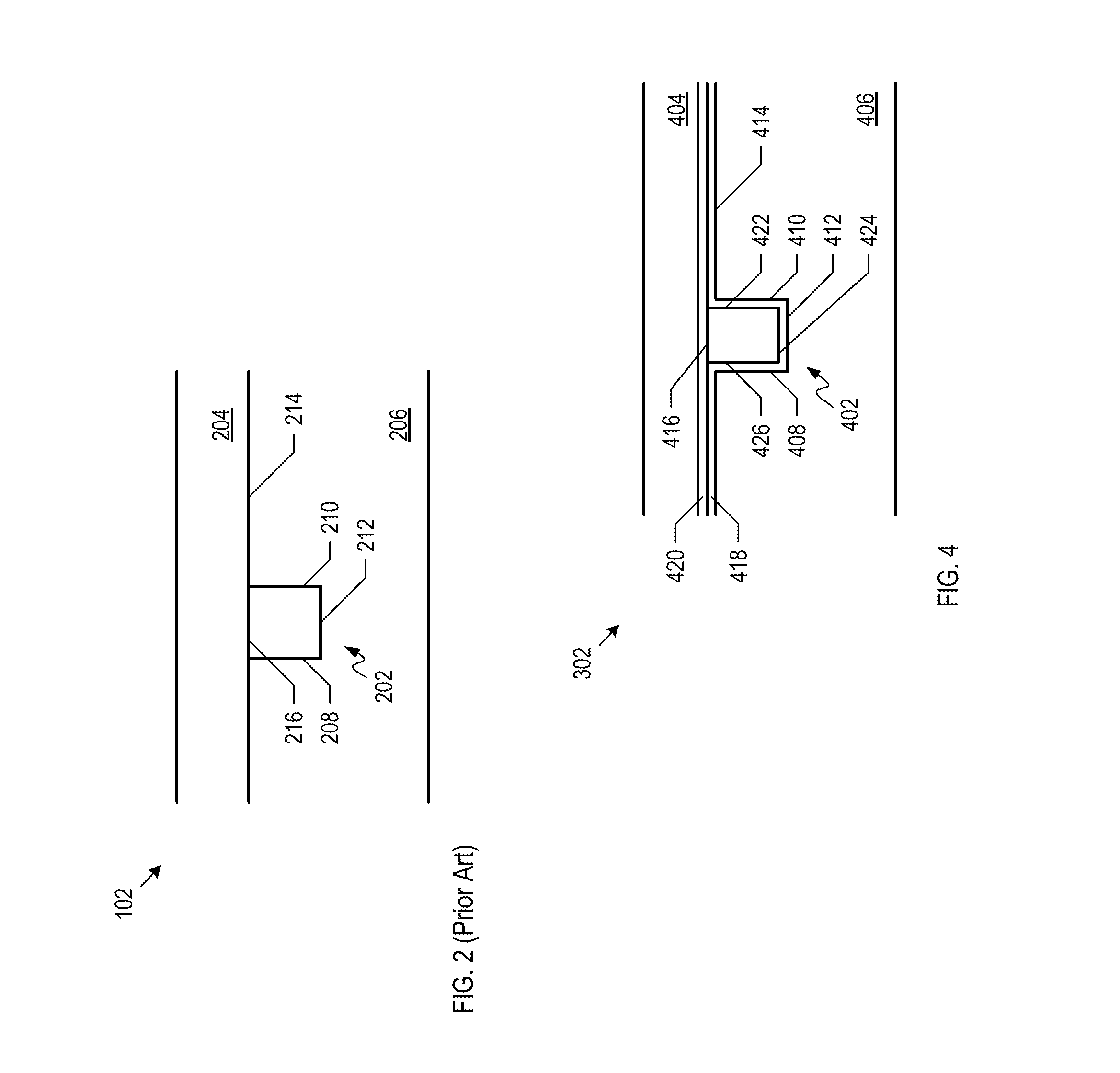

Microfluidic system

InactiveUS20130256138A1Low costAvoid disadvantagesSludge treatmentVolume/mass flow measurementMicrofluidic channelBorophosphosilicate glass

A method for forming a microfluidic channel with improved flow characteristics for one or more analytes is disclosed. A microfluidic channel having modified surfaces is formed in a glass layer or glass substrate. The glass surfaces of the microfluidic channel are modified by the addition of a layer of borophosphosilicate glass. The addition of the borophosphosilicate glass results in an improved flow velocity profile of the analyte. As a result, control over the position and movement of analytes within the solution is improved.

Owner:OCTROLIX

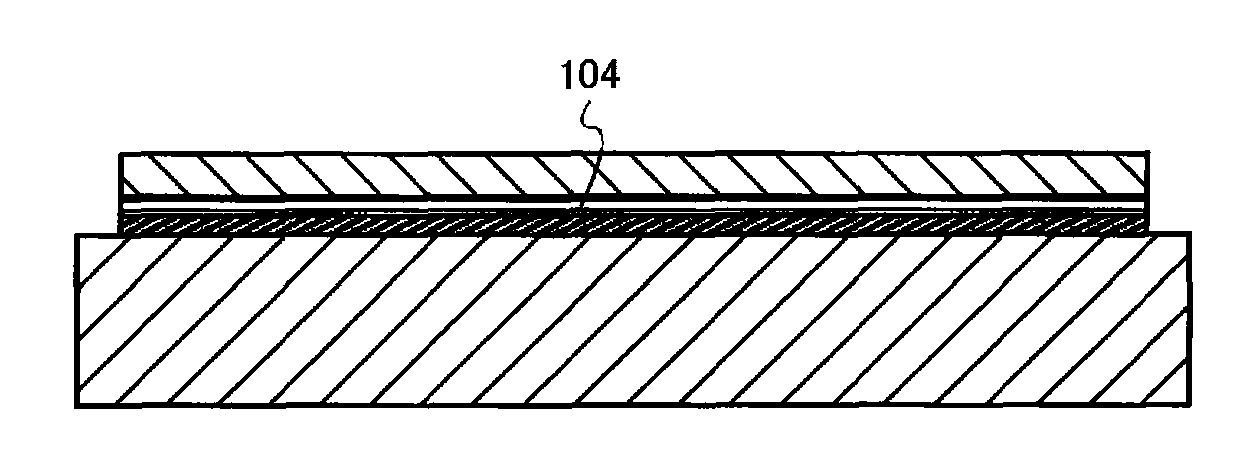

Semiconductor substrate and semiconductor device and manufacturing method of the same

InactiveUS7994022B2Good adhesionHigh bonding strengthSolid-state devicesSemiconductor/solid-state device manufacturingSilicate glassOptoelectronics

A semiconductor substrate having an SOI layer is provided. Between an SOI layer and a glass substrate, a bonding layer is provided which is formed of one layer or a plurality of layers of phosphosilicate glass, borosilicate glass, and / or borophosphosilicate glass, using organosilane as one material by a thermal CVD method at a temperature of 500° C. to 800° C.

Owner:SEMICON ENERGY LAB CO LTD

Inkjet printer having printhead and ink for minimizing corrosion of exposed corrodible structures within printhead

ActiveUS20120287207A1Corrosion minimizationMinimizing corrosionInking apparatusInksBorophosphosilicate glassEngineering

An inkjet printer includes: an inkjet printhead having an exposed corrodible structure containing silicon nitride, borophosphosilicate glass (BPSG) or silicon oxide; and an ink reservoir containing said ink which is in fluid communication with said printhead. The ink includes: water; a dye; and a metal additive for minimizing corrosion of the exposed structure.

Owner:MEMJET TECH LTD

SOI device with reduced drain induced barrier lowering

InactiveUS20050020041A1Reduce resistanceEliminate the effects ofSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectInsulation layer

A CMOS device formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and a method for producing the same. The method involves a high energy, high dose implant of boron and phosphorus through the p- and n-wells, into the insulator layer, thereby creating a borophosphosilicate glass (BPSG) structure within the insulation layer underlying the p- and n-wells of the SOI wafer. Backend high temperature processing steps induce diffusion of the boron and phosphorus contained in the BPSG into the p- and n-wells, thereby forming a retrograde dopant profile in the wells. The retrograde dopant profile reduces DIBL and also provides recombination centers adjacent the insulator layer and the active layer to thereby reduce floating body effects for the CMOS device.

Owner:MICRON TECH INC