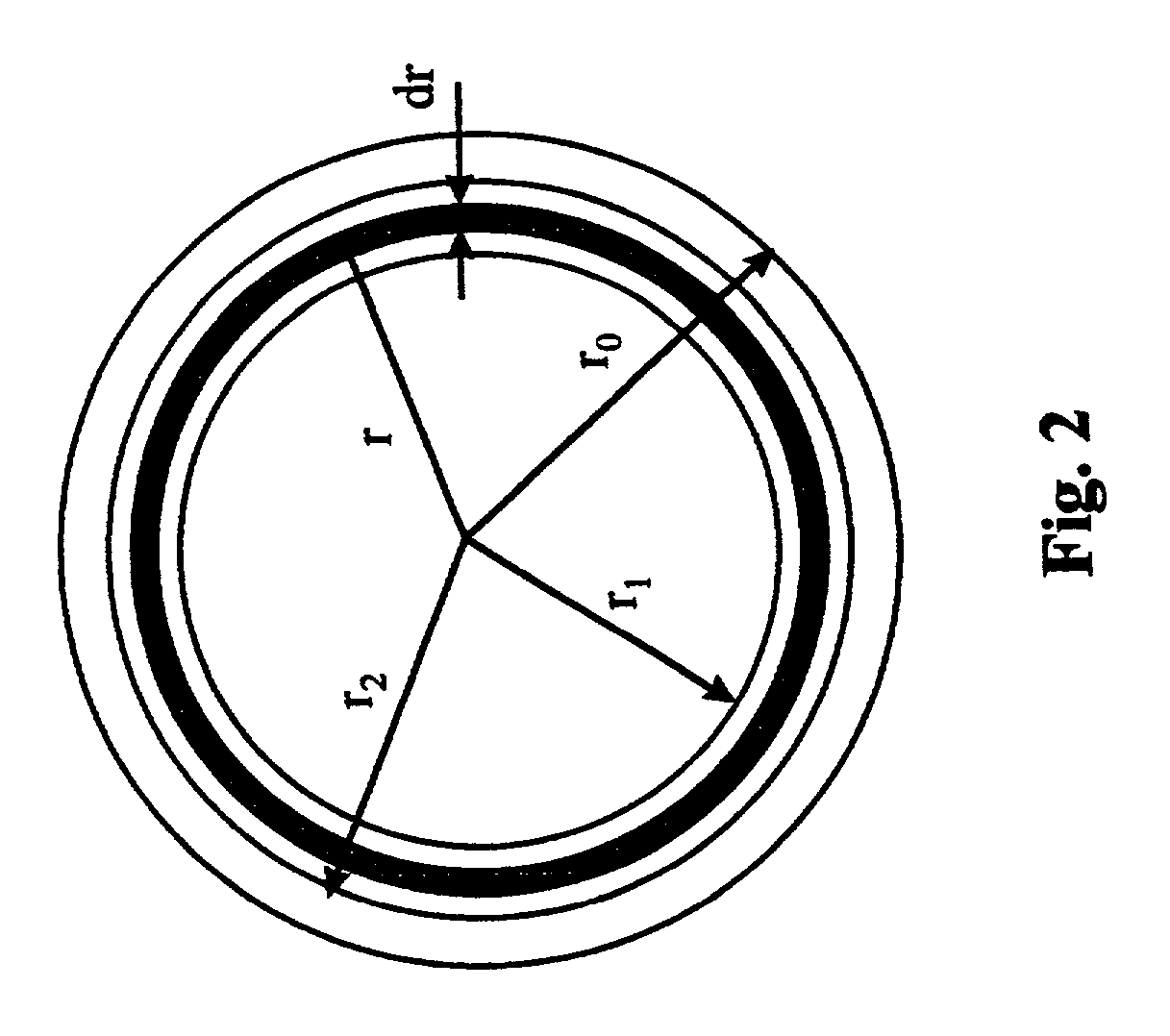

Patents

Literature

57results about How to "Strong Gap Filling Capability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Hydrogen assisted undoped silicon oxide deposition process for HDP-CVD

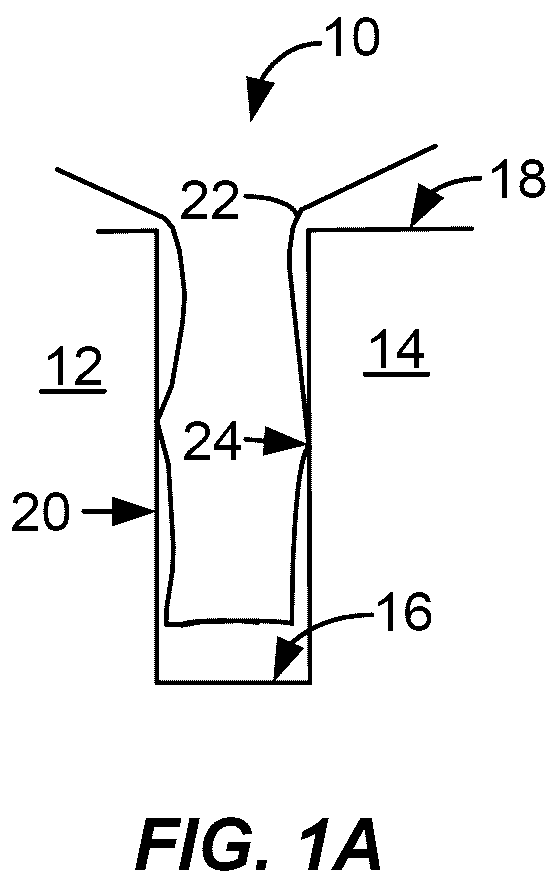

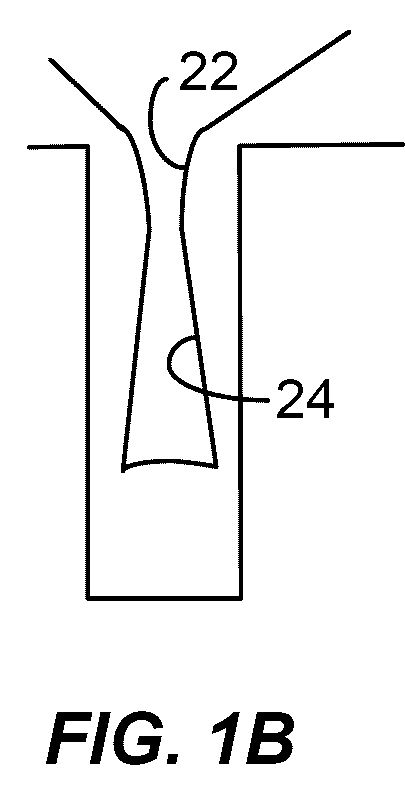

InactiveUS6929700B2Improve gap fill capabilityStrong Gap Filling CapabilityLiquid surface applicatorsSemiconductor/solid-state device manufacturingDistribution systemEngineering

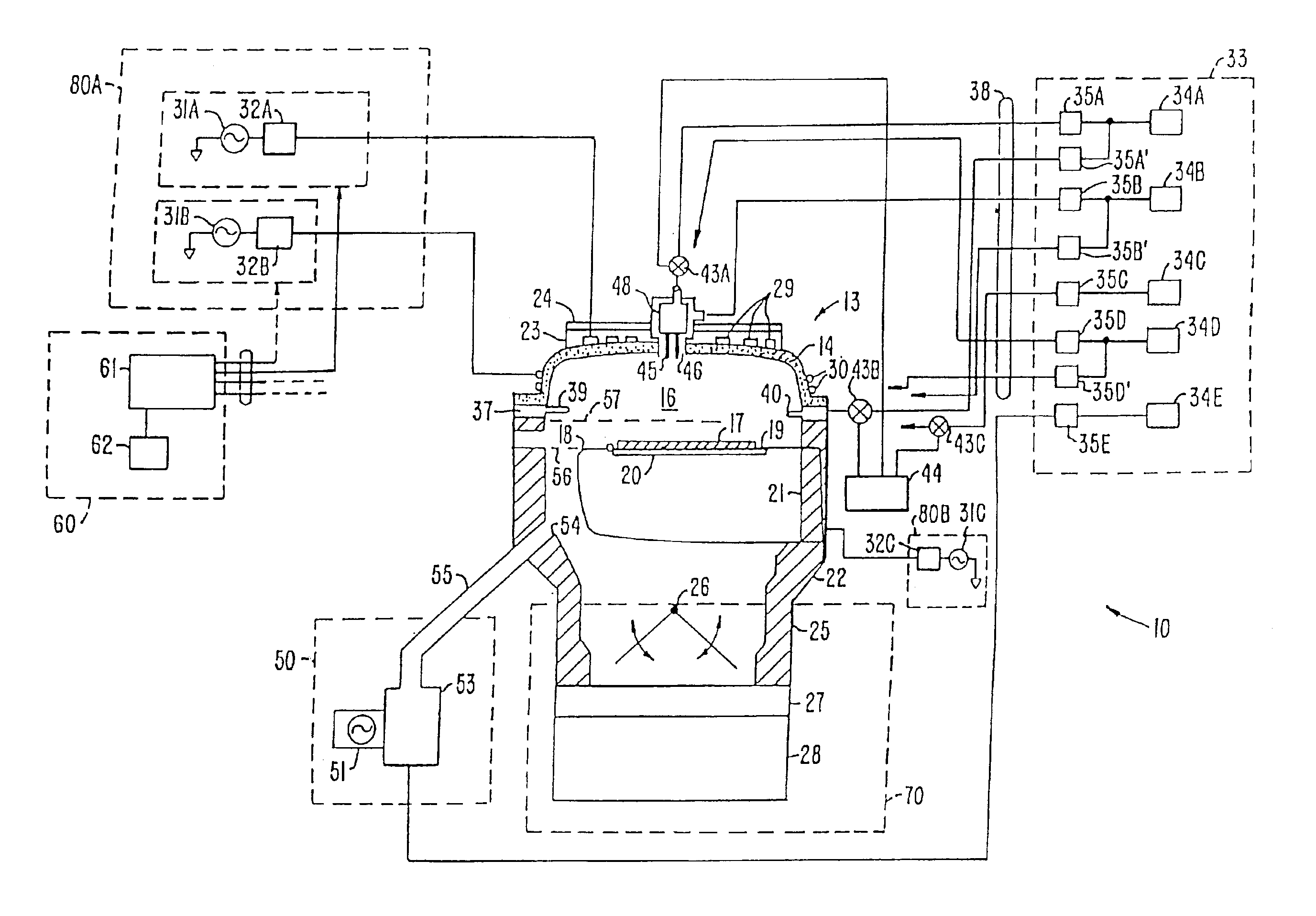

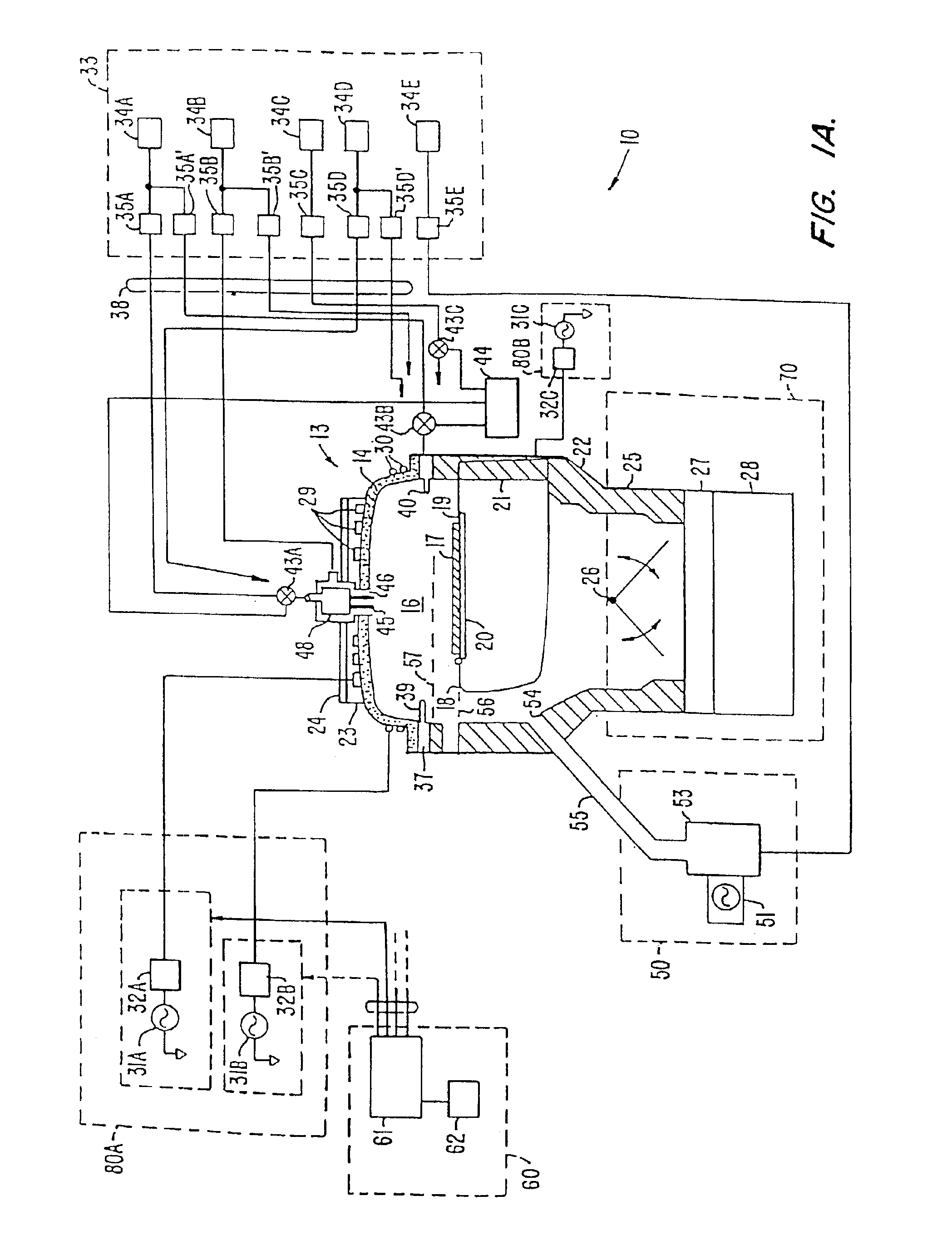

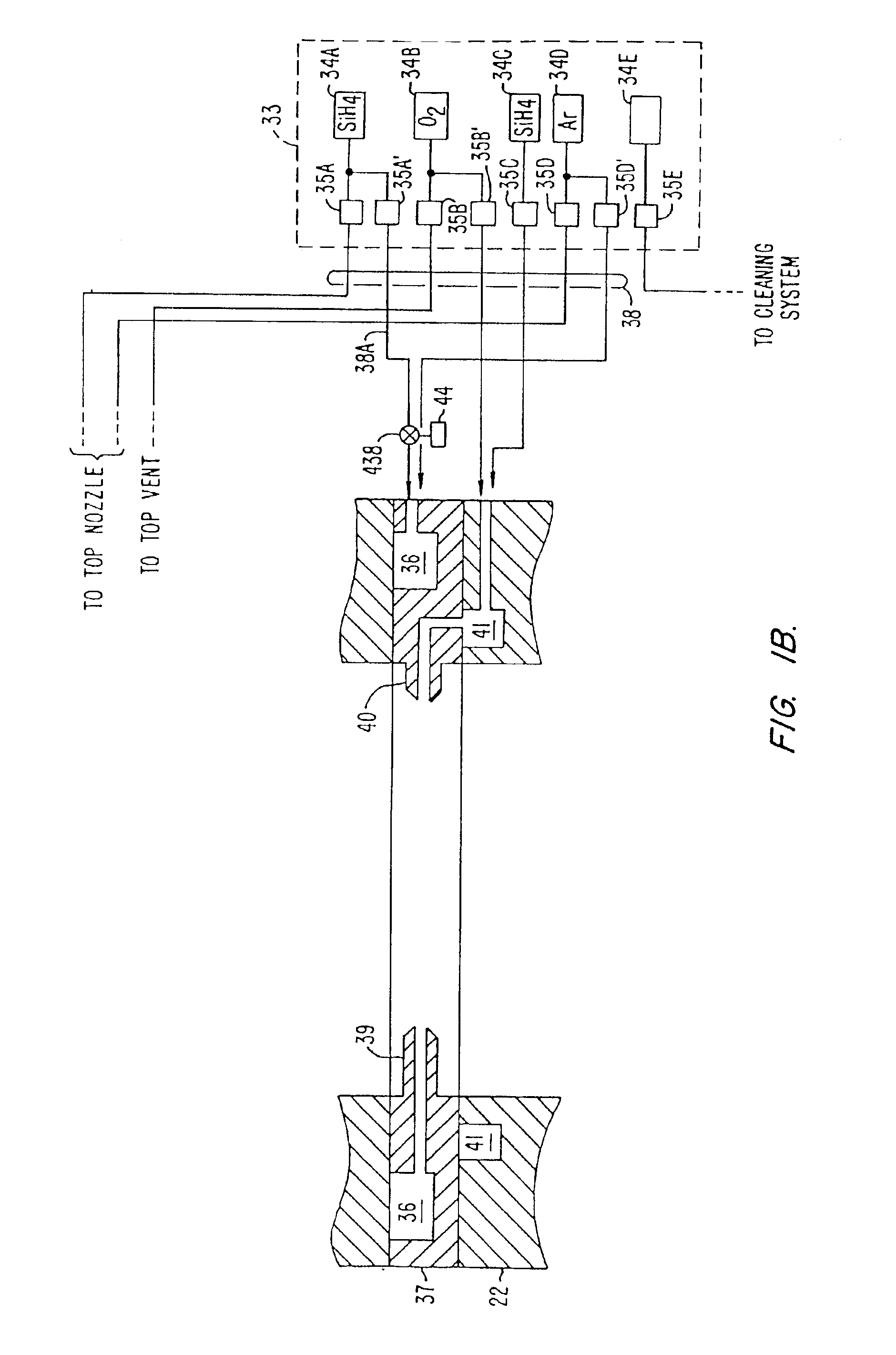

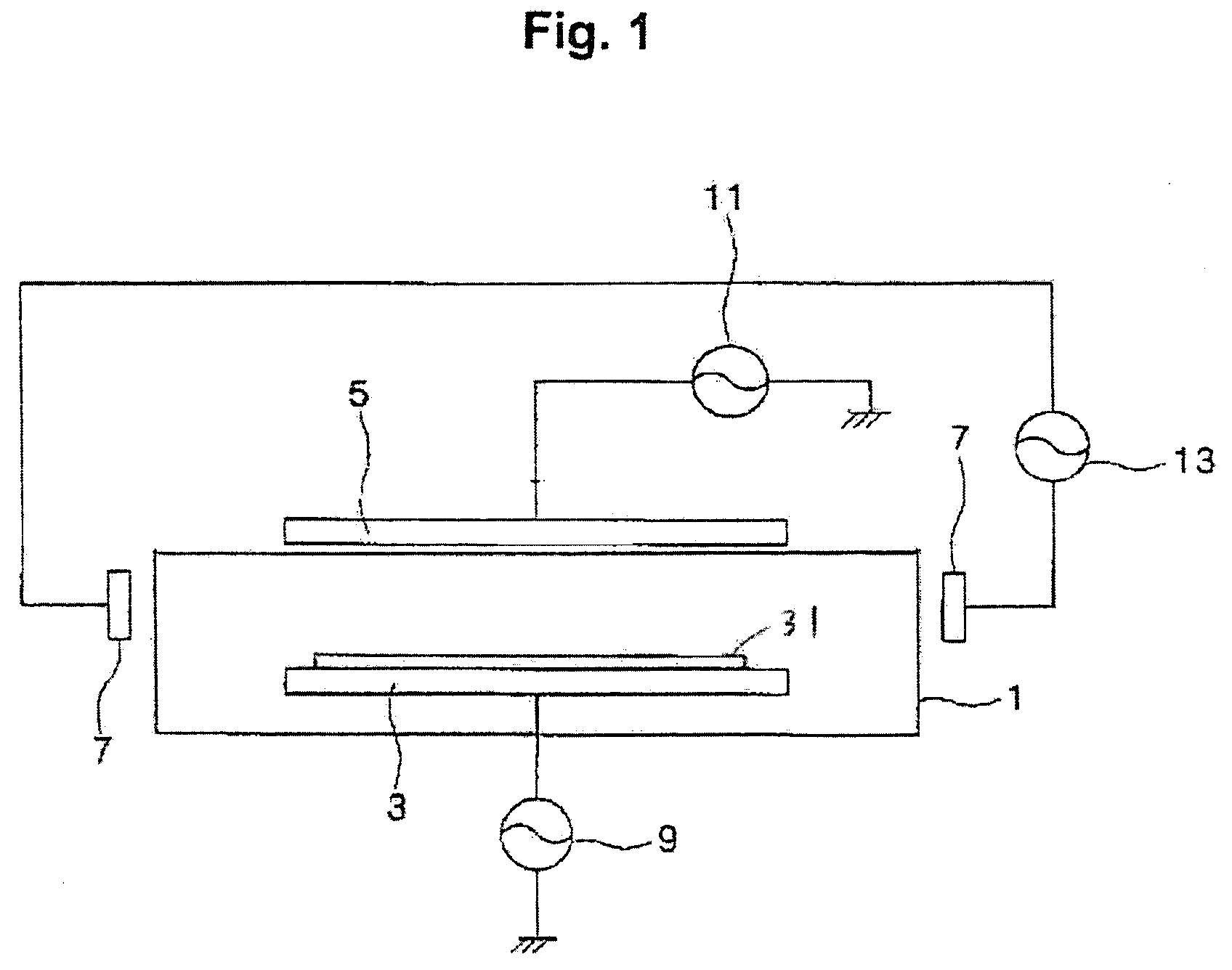

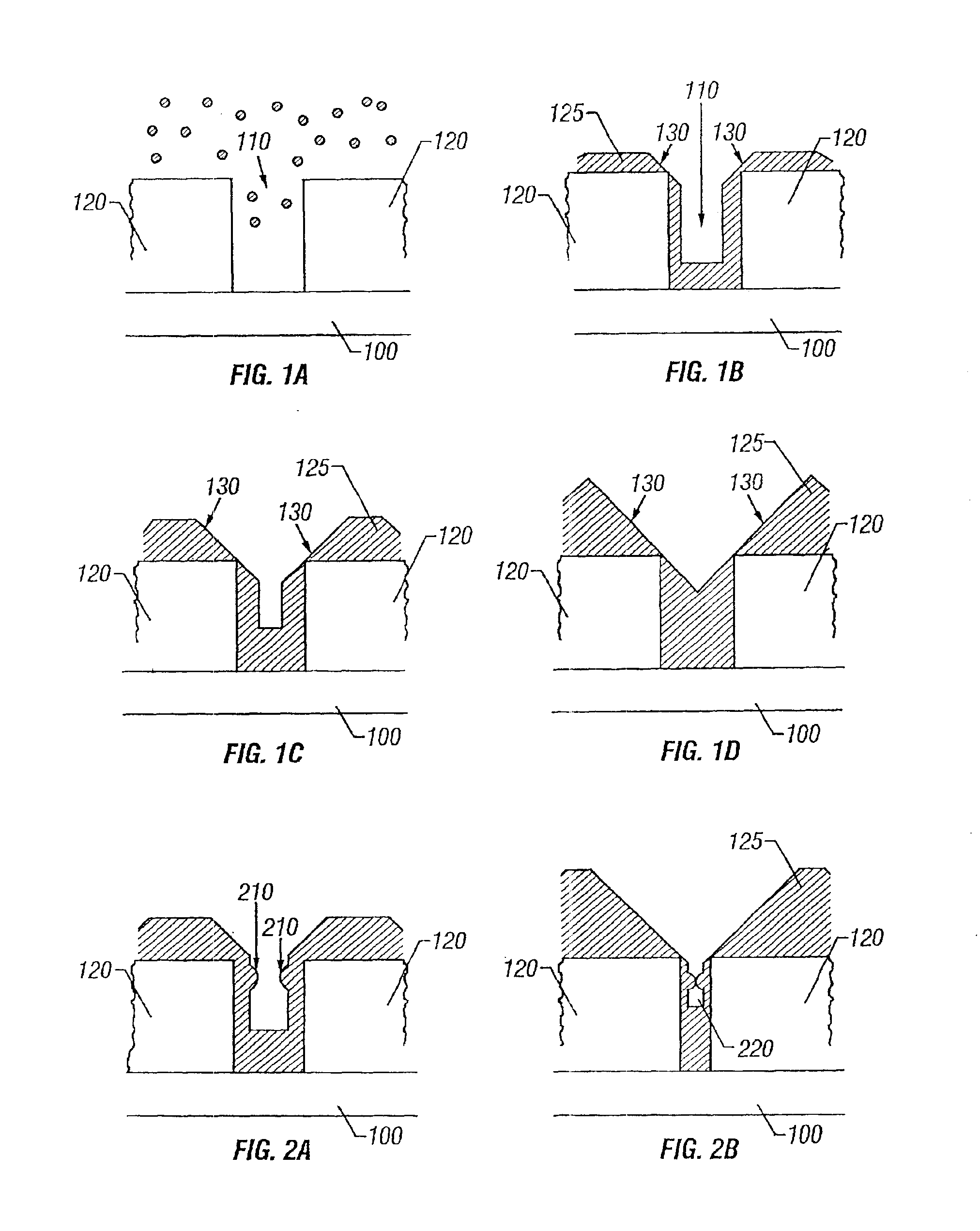

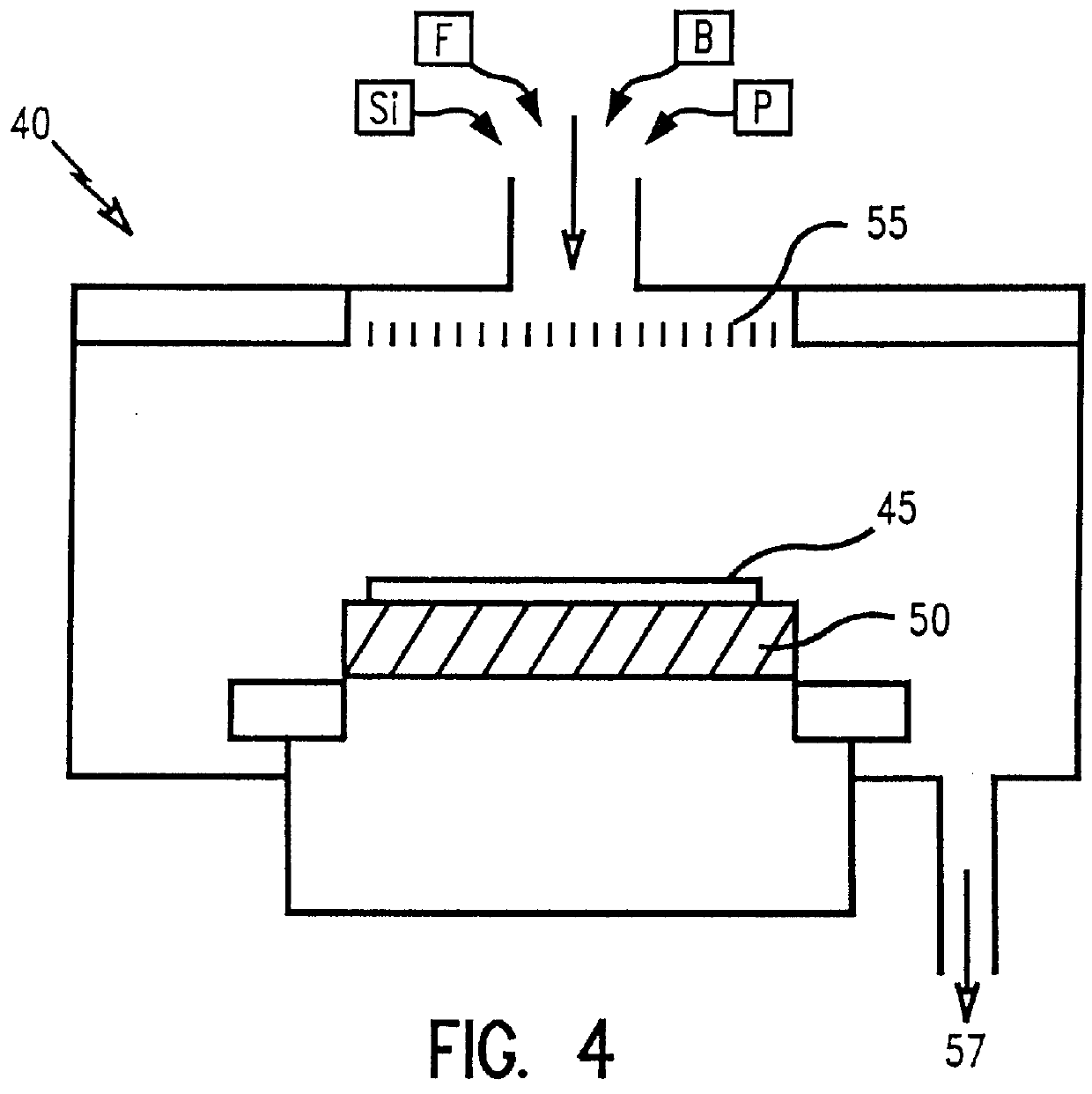

A substrate processing apparatus comprising a substrate processing chamber, a gas distribution system operatively coupled to the chamber, a high density plasma power source, a controller operatively coupled to the gas distribution system and the high density plasma power source and a memory coupled to the controller. The memory includes computer instructions embodied in a computer-readable format. The computer instructions comprise (i) instructions that control the gas distribution system to flow a process gas comprising a silane gas, an oxygen-containing source, an inert gas and a hydrogen-containing source that is either molecular hydrogen or a hydride gas that does not include silicon, boron or phosphorus and (ii) instructions that control the high density plasma source to form a plasma having an ion density of at least 1×1011 ions / cm3 from the process gas to deposit the silicon oxide layer over the substrate.

Owner:APPLIED MATERIALS INC

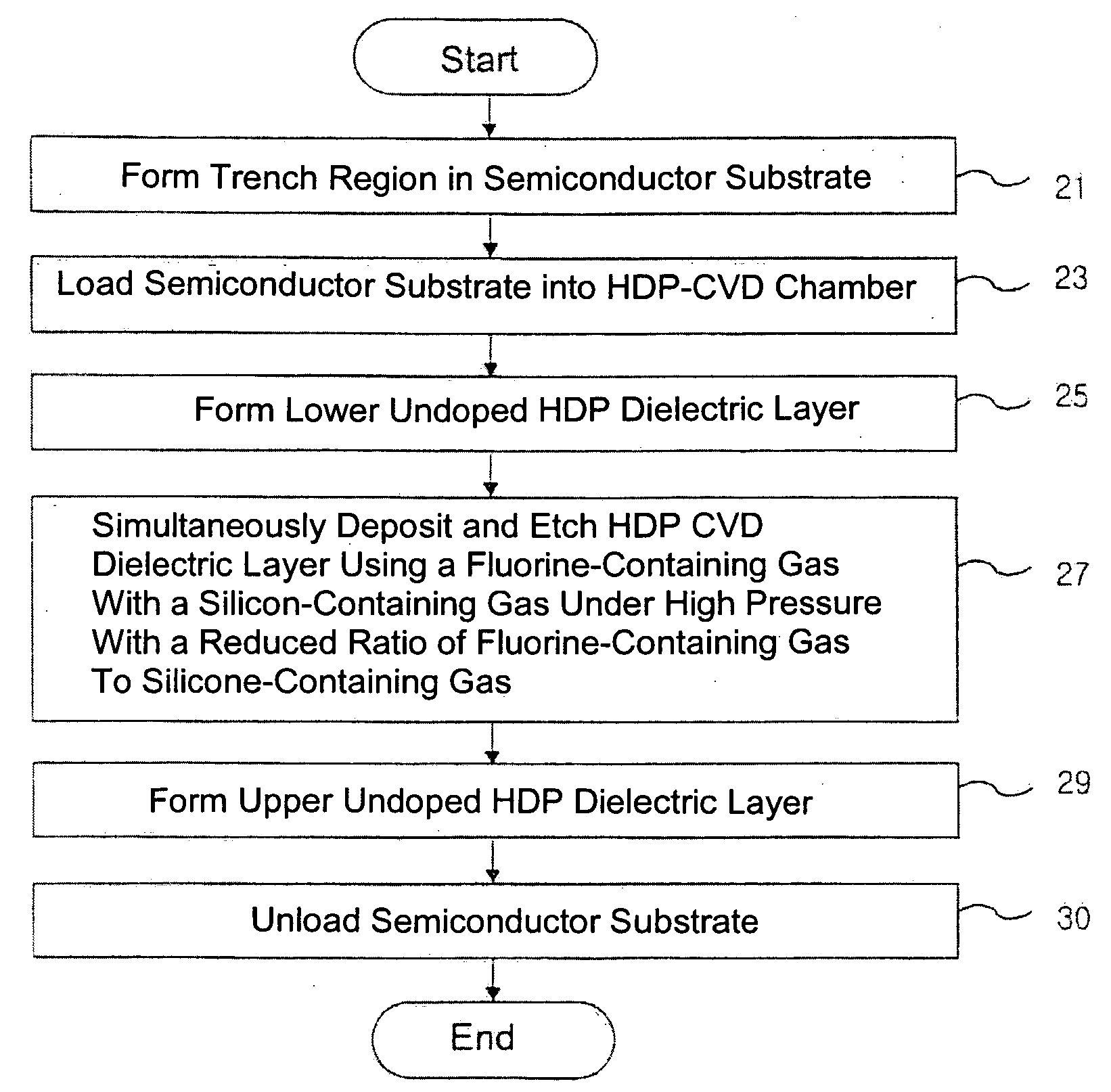

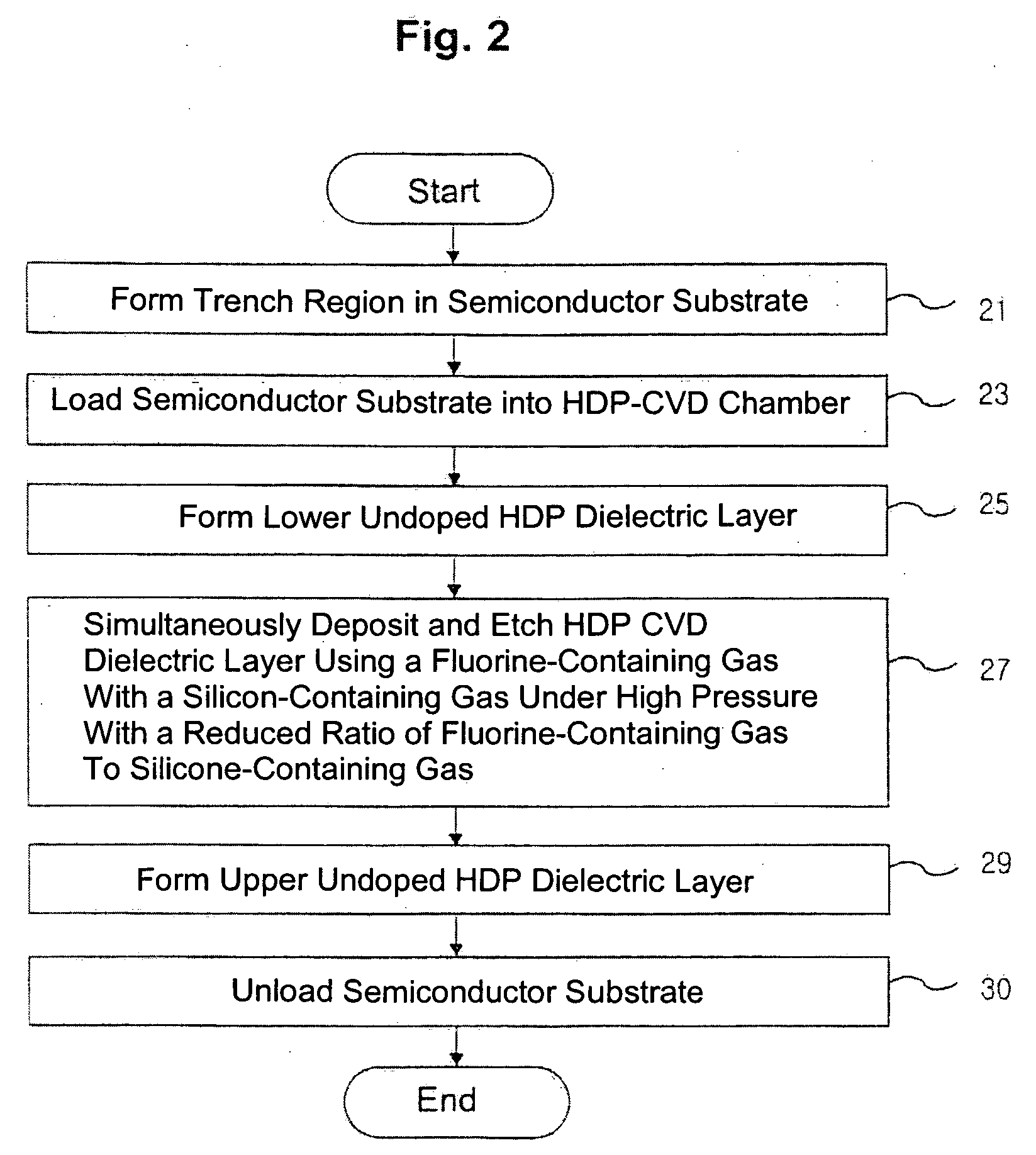

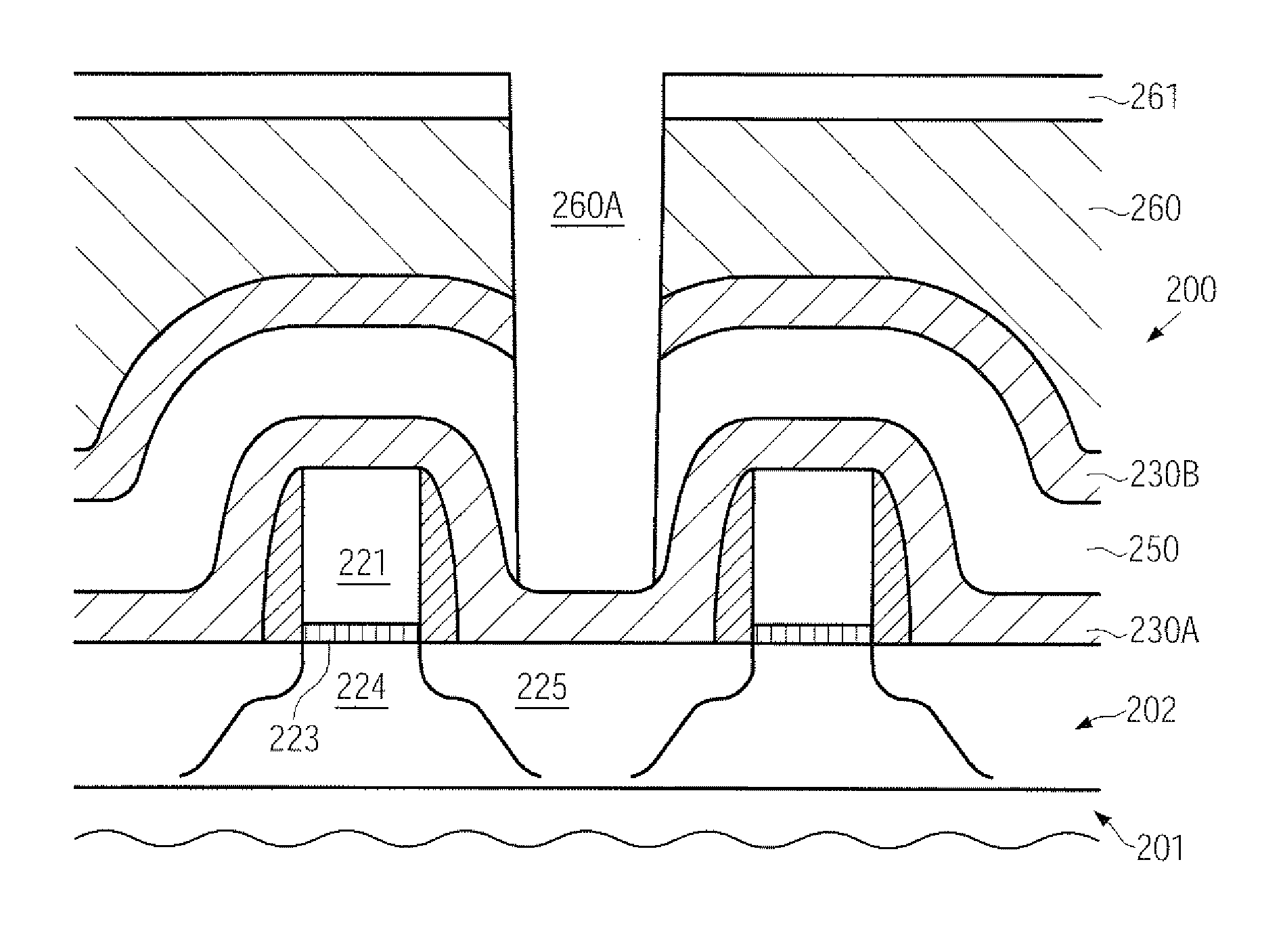

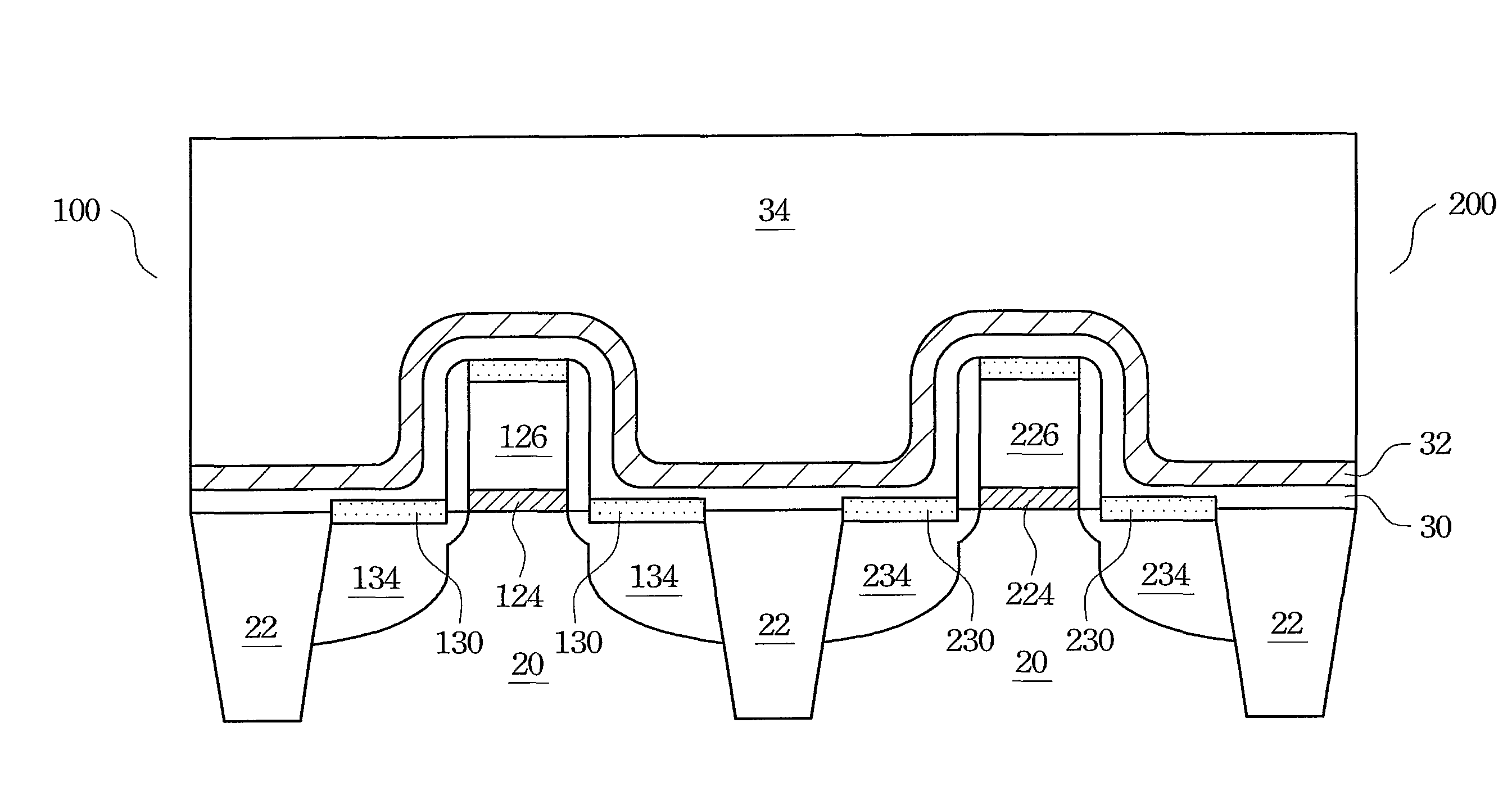

High-density plasma (HDP) chemical vapor deposition (CVD) methods and methods of fabricating semiconductor devices employing the same

InactiveUS7183214B2Reduce amountStrong Gap Filling CapabilitySemiconductor/solid-state device manufacturingPackaging toiletriesGas phaseDevice material

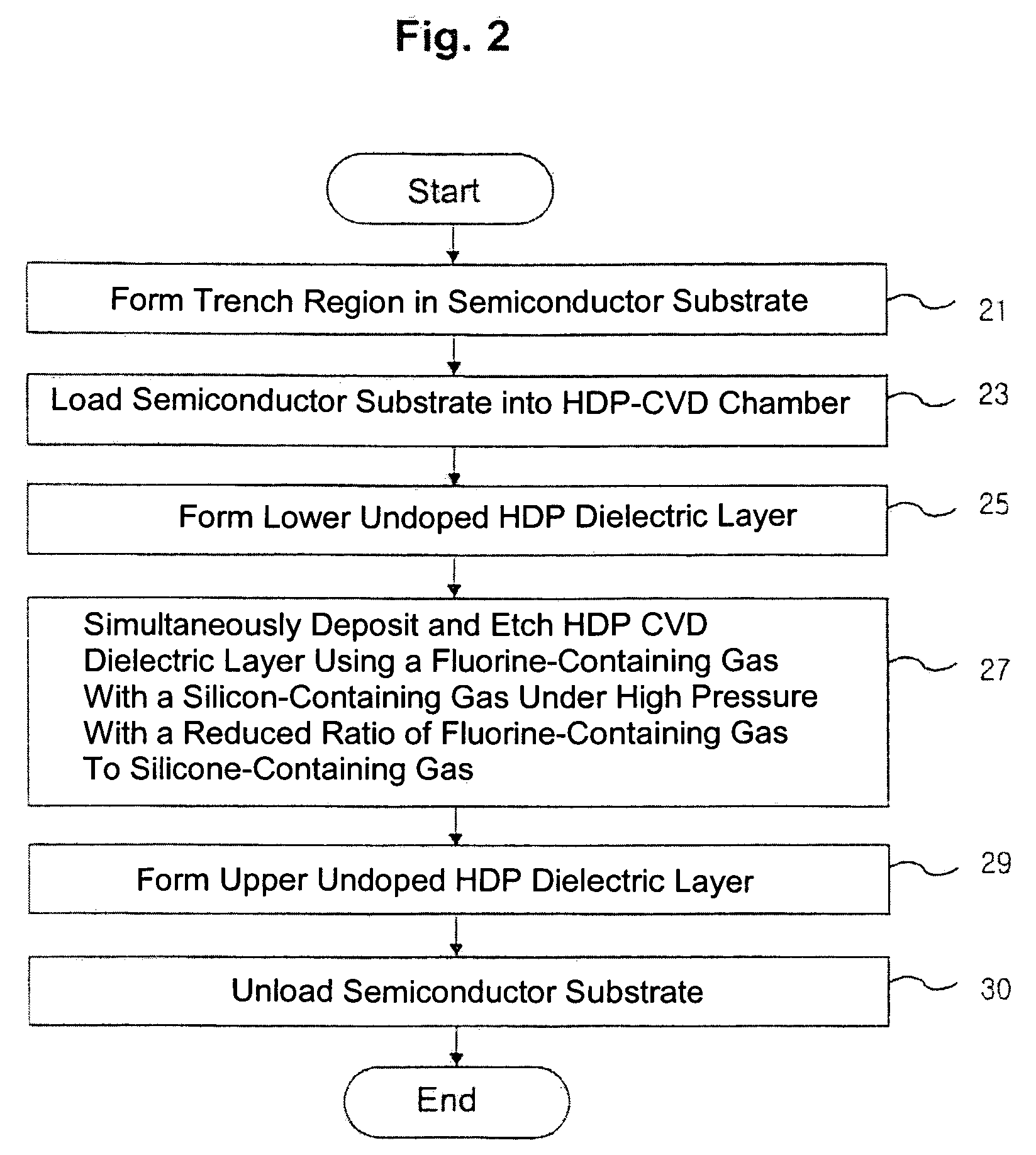

In one embodiment, a semiconductor substrate is placed into a process chamber. A gas mixture including a silicon-containing gas, a fluorine-containing gas, an inert gas, and an oxygen gas is introduced into the chamber at a pressure range of from about 30 mTorr to about 90 mTorr. During this time, deposition and etching processes are concurrently performed using a plasma to form a high-density plasma (HDP) insulating layer on the semiconductor substrate. A ratio of deposition to etching is from about 3:1 to about 10:1. A ratio of a flow rate of the fluorine-containing gas to a flow rate of the silicon-containing gas is less than about 0.9.

Owner:SAMSUNG ELECTRONICS CO LTD

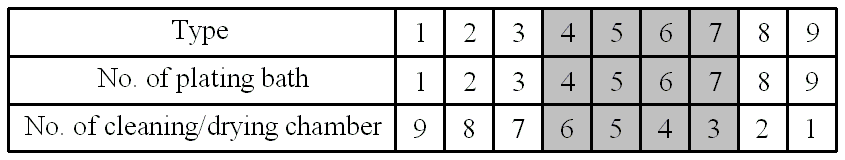

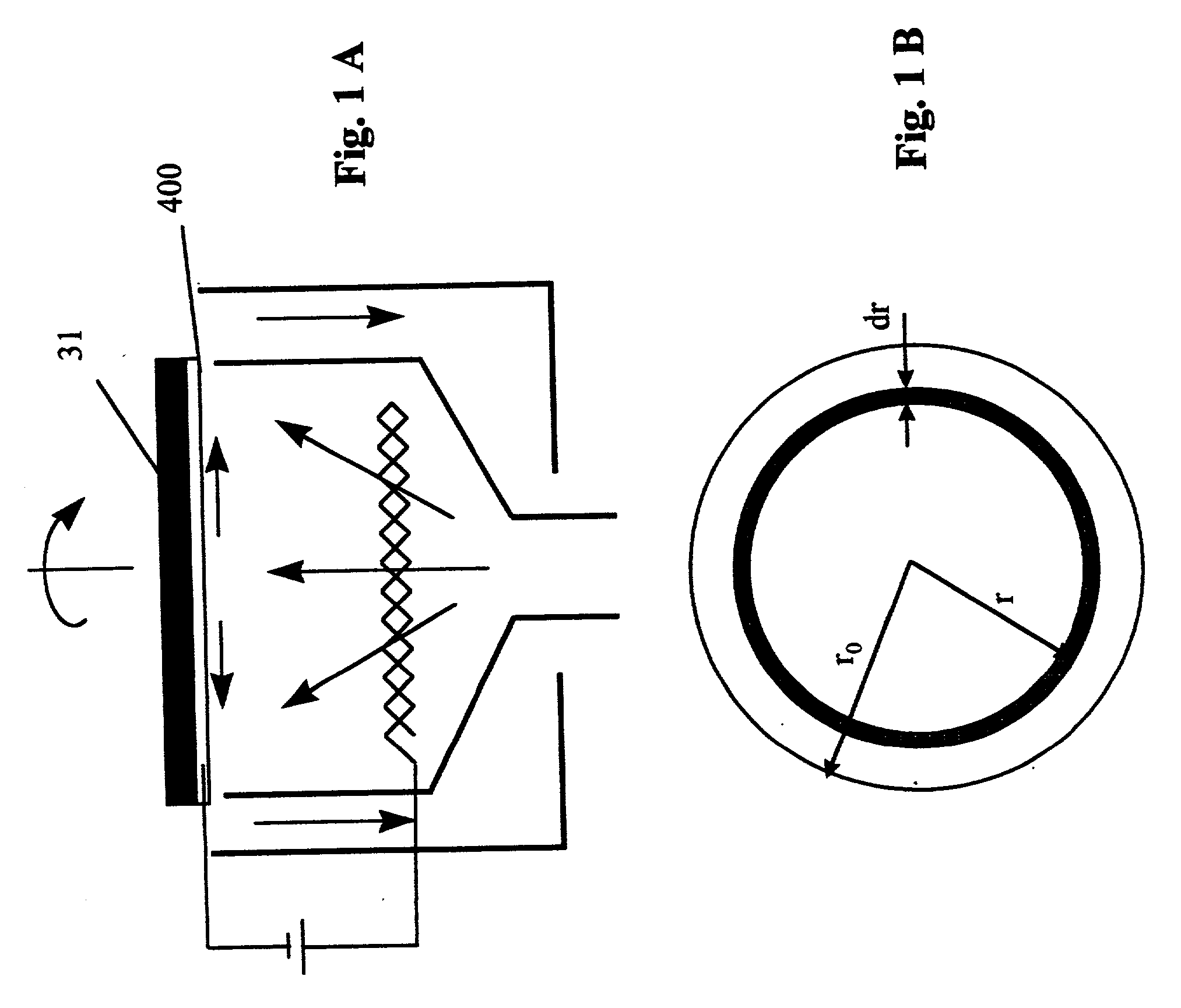

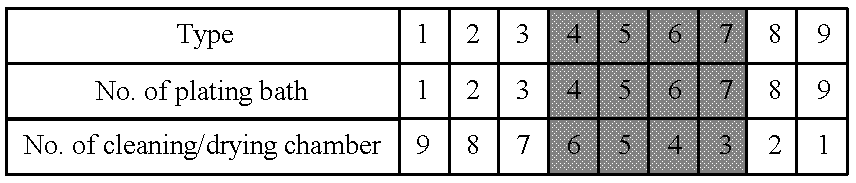

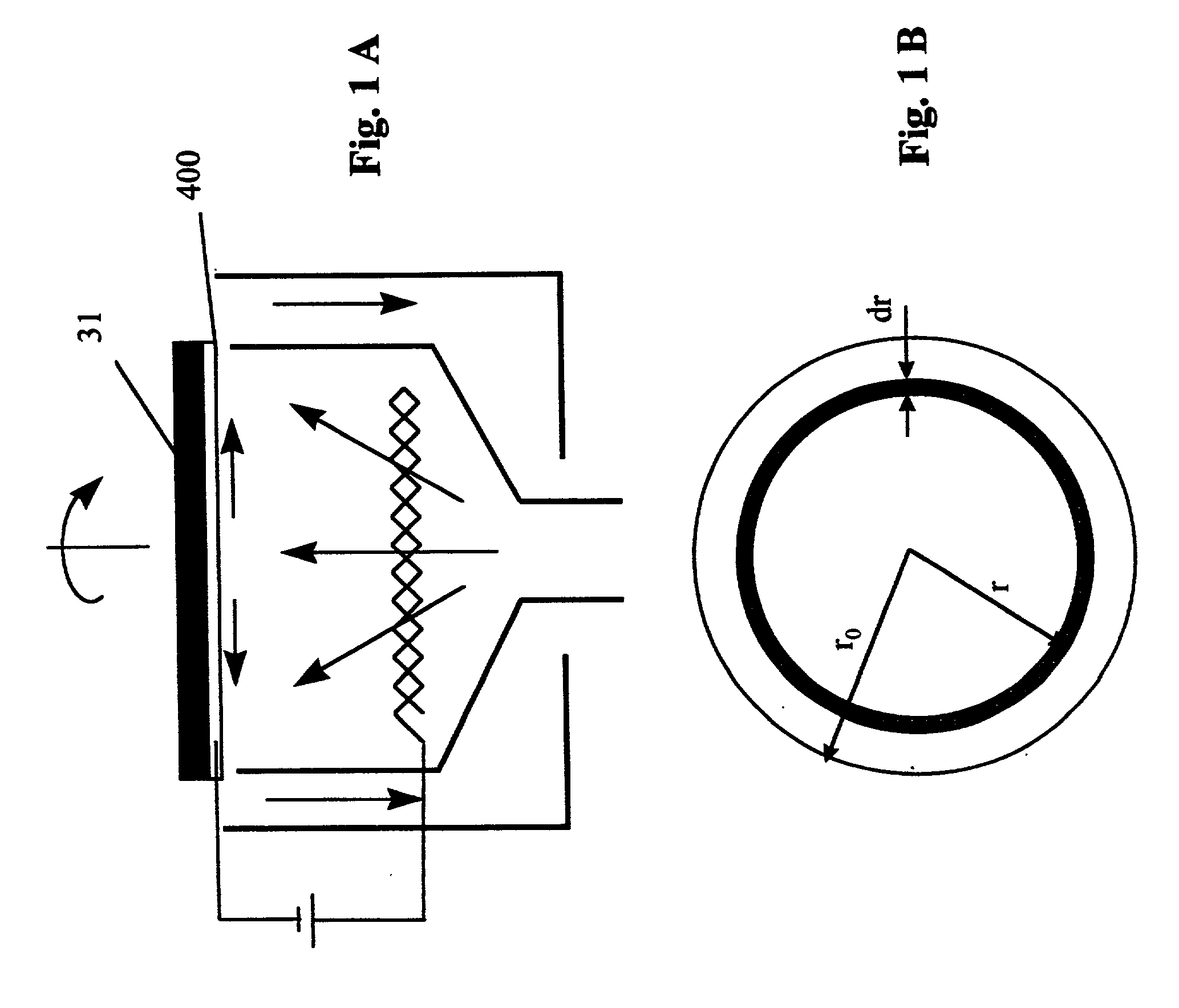

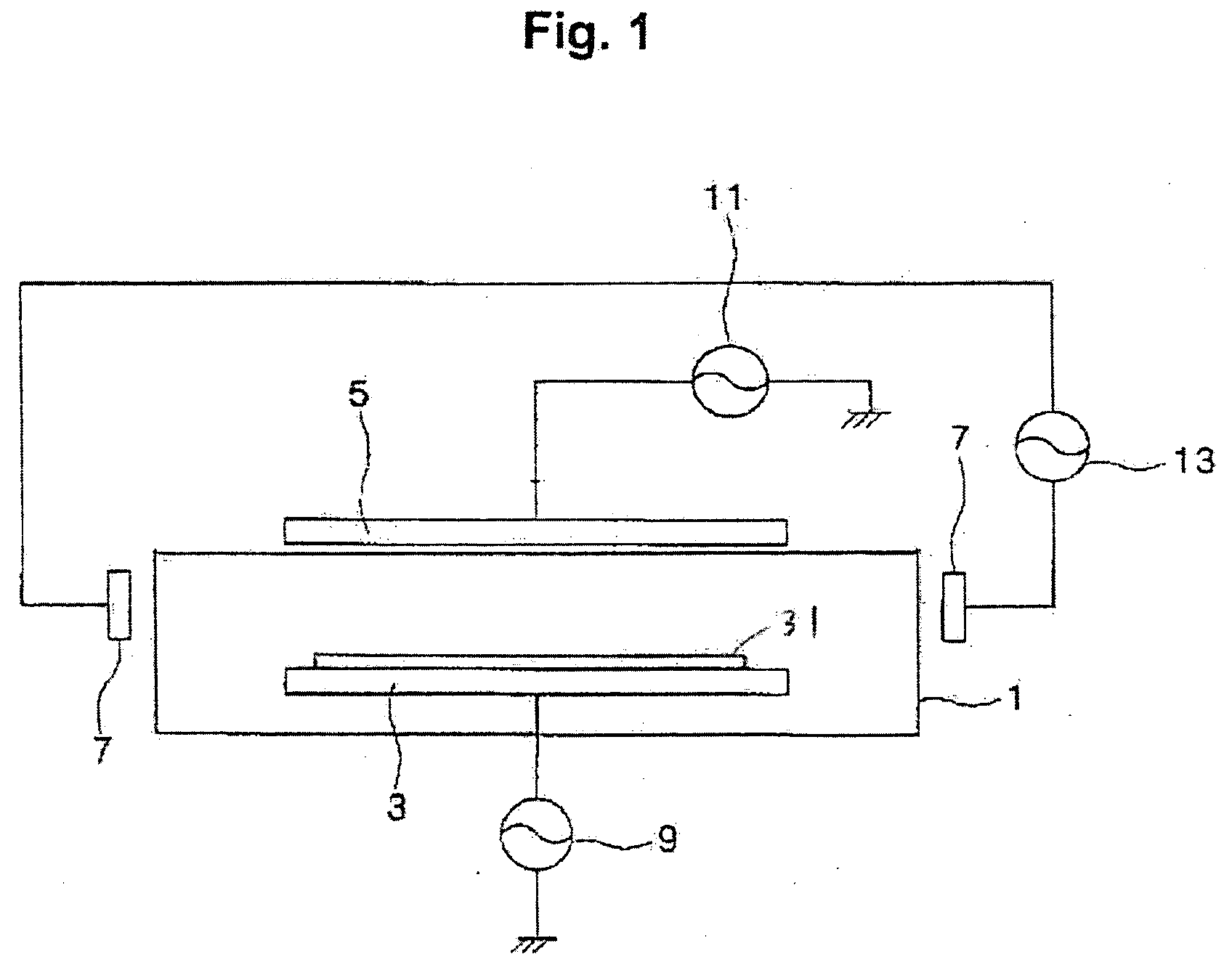

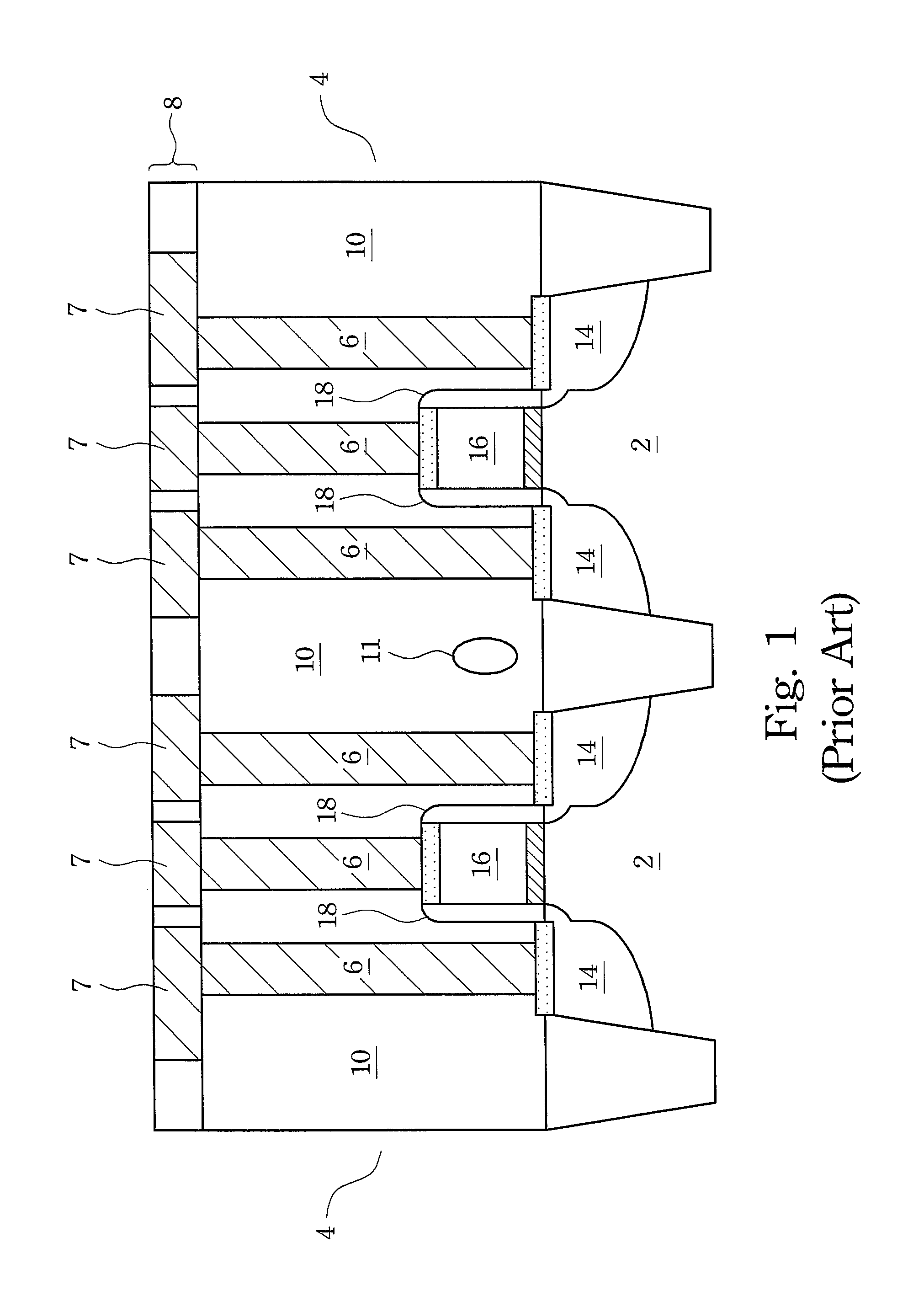

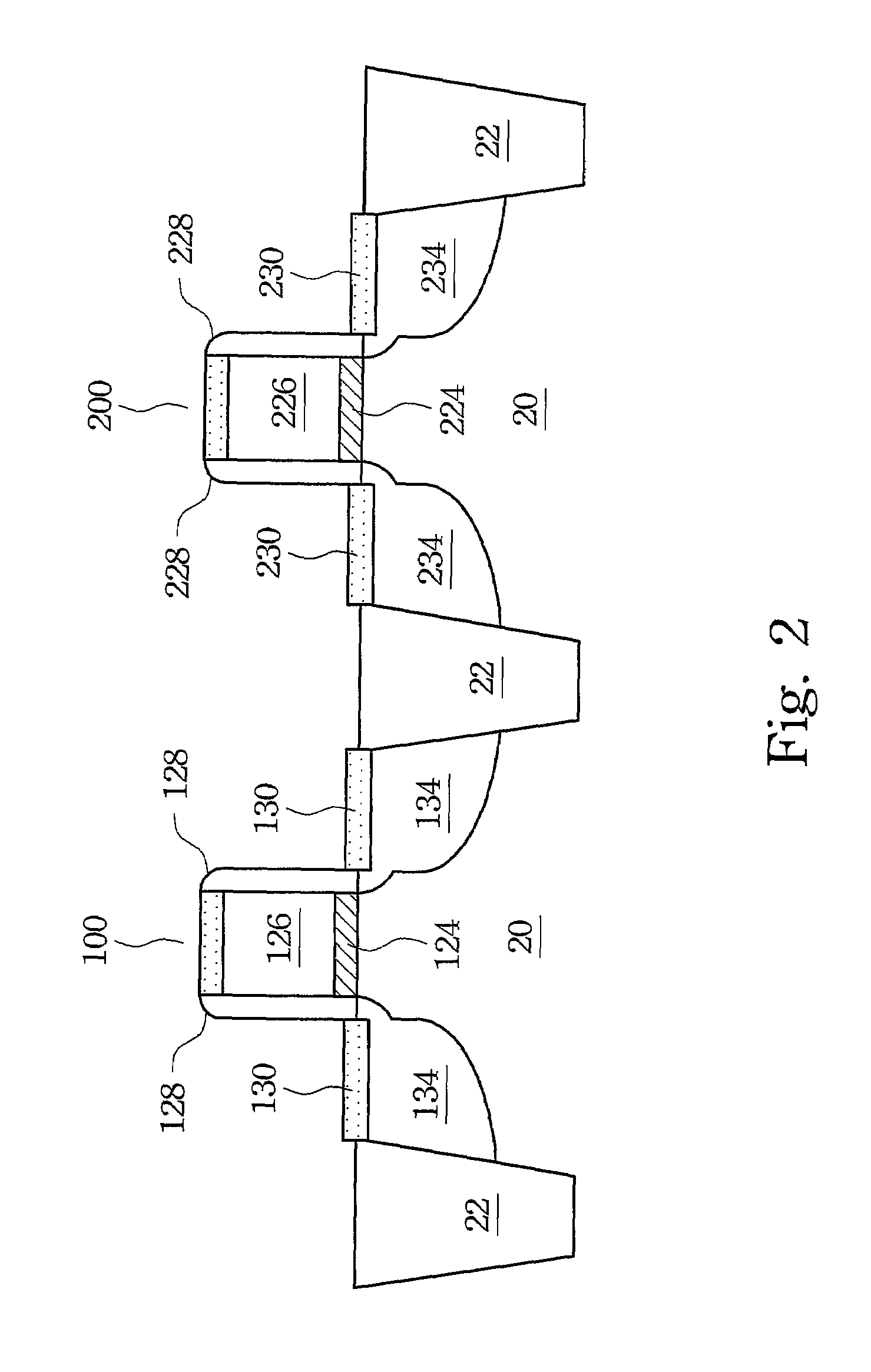

Plating apparatus and method

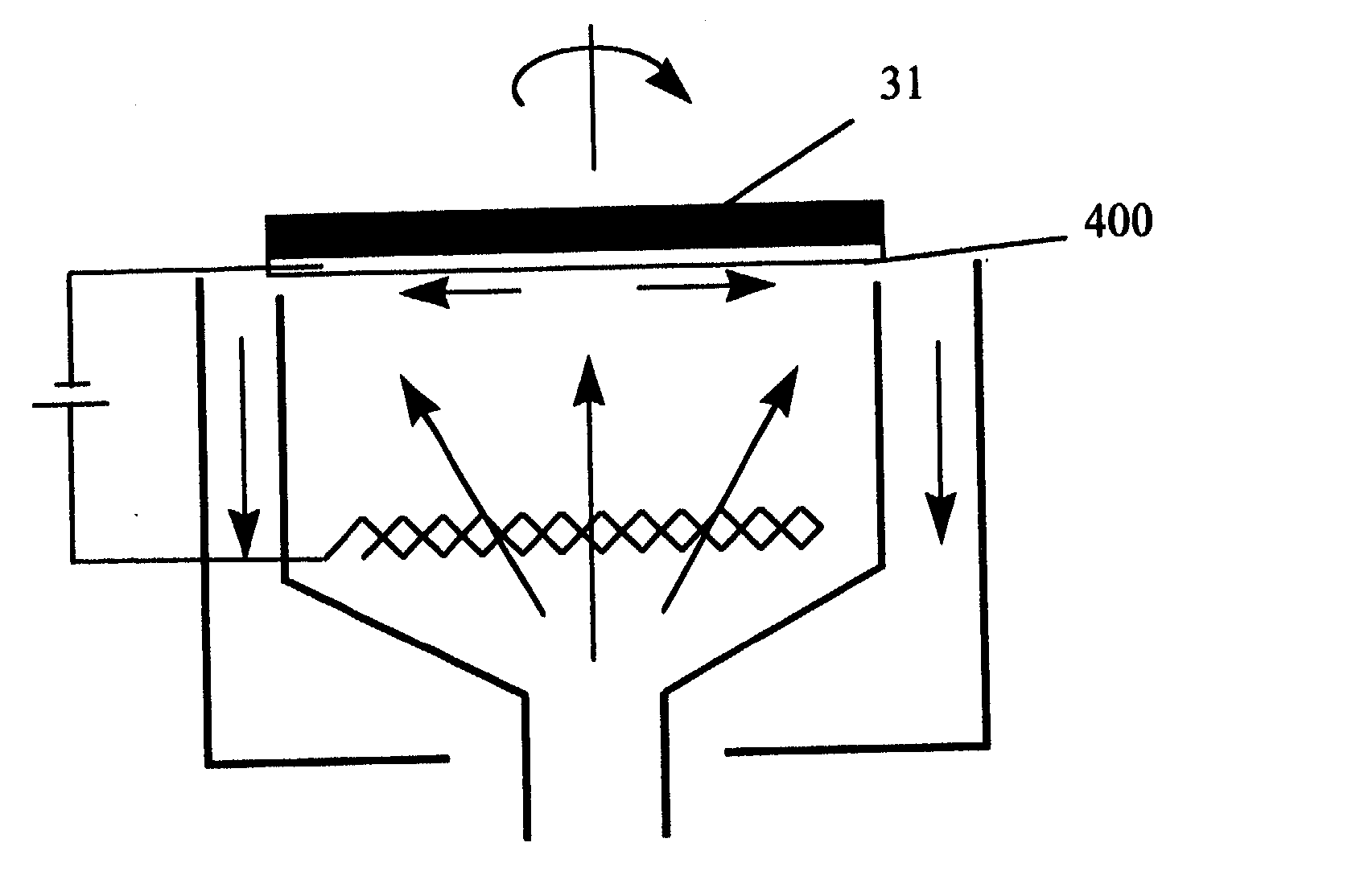

InactiveUS20020008036A1Strong Gap Filling CapabilityReduce stressCellsSemiconductor/solid-state device manufacturingElectrolyte leakageEngineering

An apparatus for plating a conductive film directly on a substrate with a barrier layer on top includes anode rod (1) placed in tube (109), and anode rings (2), and (3) placed between cylindrical walls (107) and (105), (103) and (101), respectively. Anodes (1), (2), and (3) are powered by power supplies (13), (12), and (11), respectively. Electrolyte (34) is pumped by pump (33) to pass through filter (32) and reach inlets of liquid mass flow controllers (LMFCs) (21), (22), and (23). Then LMFCs (21), (22) and (23) deliver electrolyte at a set flow rate to sub-plating baths containing anodes (3), (2) and (1), respectively. After flowing through the gap between wafer (31) and the top of the cylindrical walls (101), (103), (105), (107) and (109), electrolyte flows back to tank (36) through spaces between cylindrical walls (100) and (101), (103) and (105), and (107) and (109), respectively. A pressure leak valve (38) is placed between the outlet of pump (33) and electrolyte tank (36) to leak electrolyte back to tank (36) when LMFCs (21), (22), (23) are closed. A wafer (31) held by wafer chuck (29) is connected to power supplies (11), (12) and (13). A drive mechanism (30) is used to rotate wafer (31) around the z axis, and oscillate the wafer in the x, y, and z directions shown. Filter (32) filters particles larger than 0.1 or 0.2 mum in order to obtain a low particle added plating process.

Owner:ACM RES

Plating apparatus and method

InactiveUS20010040100A1Uniform thicknessStrong Gap Filling CapabilityCellsSemiconductor/solid-state device manufacturingElectrolyte leakageEngineering

An apparatus for plating a conductive film directly on a substrate with a barrier layer on top includes anode rod (1) placed in tube (109), and anode rings (2), and (3) placed between cylindrical walls (107) and (105), (103) and (101), respectively. Anodes (1), (2), and (3) are powered by power supplies (13), (12), and (11), respectively. Electrolyte (34) is pumped by pump (33) to pass through filter (32) and reach inlets of liquid mass flow controllers (LMFCs) (21), (22), and (23). Then LMFCs (21), (22) and (23) deliver electrolyte at a set flow rate to sub-plating baths containing anodes (3), (2) and (1), respectively. After flowing through the gap between wafer (31) and the top of the cylindrical walls (101), (103), (105), (107) and (109), electrolyte flows back to tank (36) through spaces between cylindrical walls (100) and (101), (103) and (105), and (107) and (109), respectively. A pressure leak valve (38) is placed between the outlet of pump (33) and electrolyte tank (36) to leak electrolyte back to tank (36) when LMFCs (21), (22), (23) are closed. A wafer (31) held by wafer chuck (29) is connected to power supplies (11), (12) and (13). A drive mechanism (30) is used to rotate wafer (31) around the z axis, and oscillate the wafer in the x, y, and z directions shown. Filter (32) filters particles larger than 0.1 or 0.2 mum in order to obtain a low particle added plating process.

Owner:ACM RES

Hydrogen assisted hdp-cvd deposition process for aggressive gap-fill technology

InactiveUS20040146661A1Excellent gap fillingStrong Gap Filling CapabilityElectric discharge tubesVacuum evaporation coatingHigh densityHydrogen

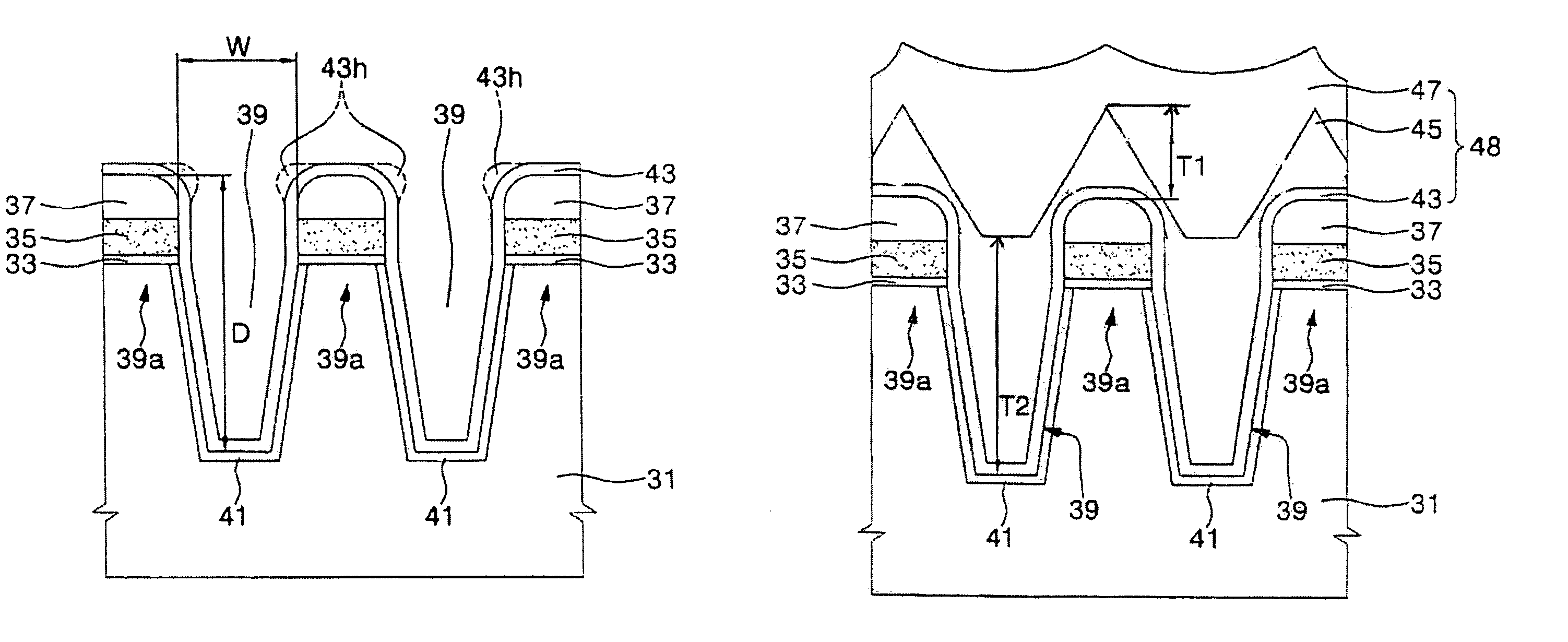

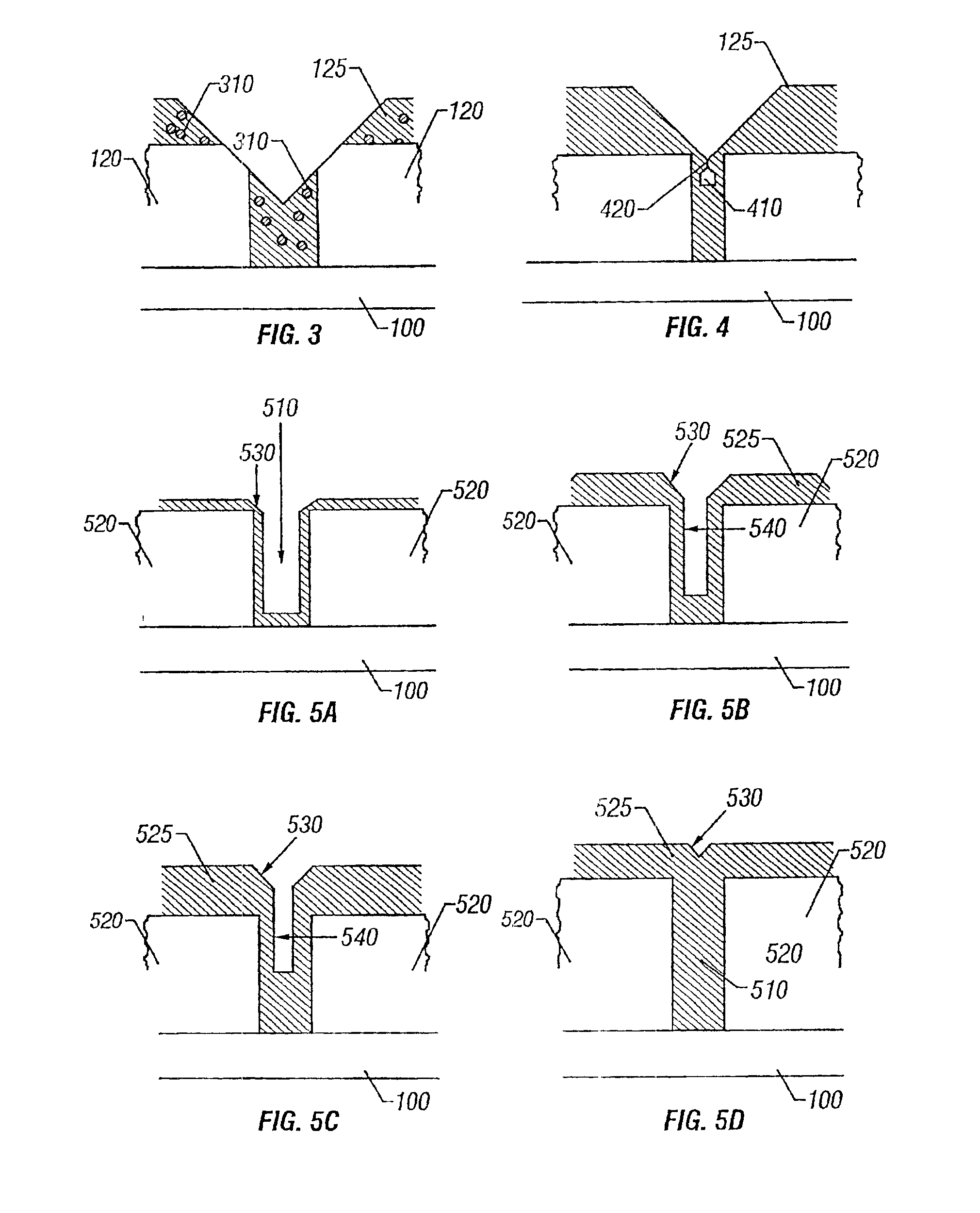

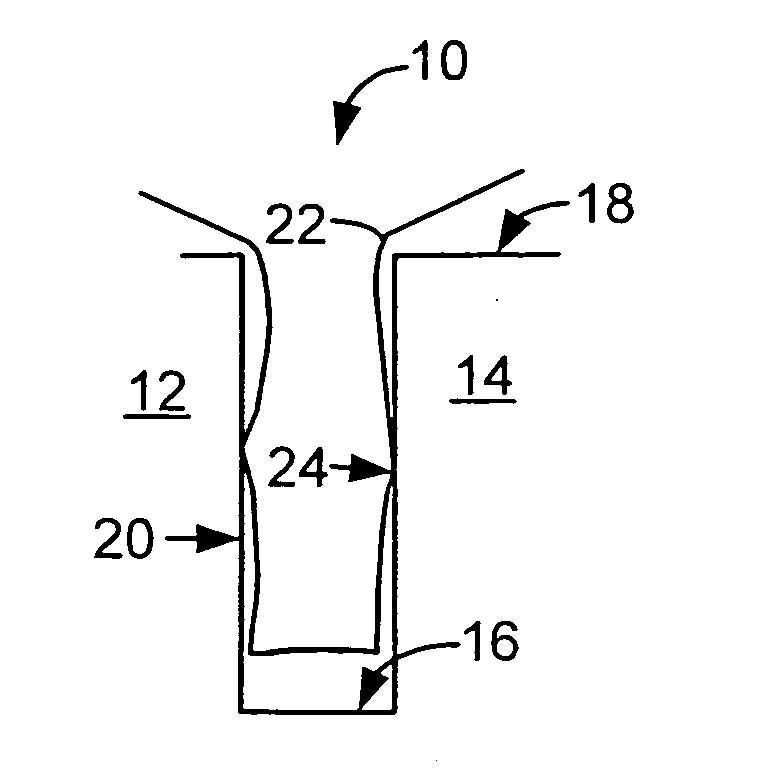

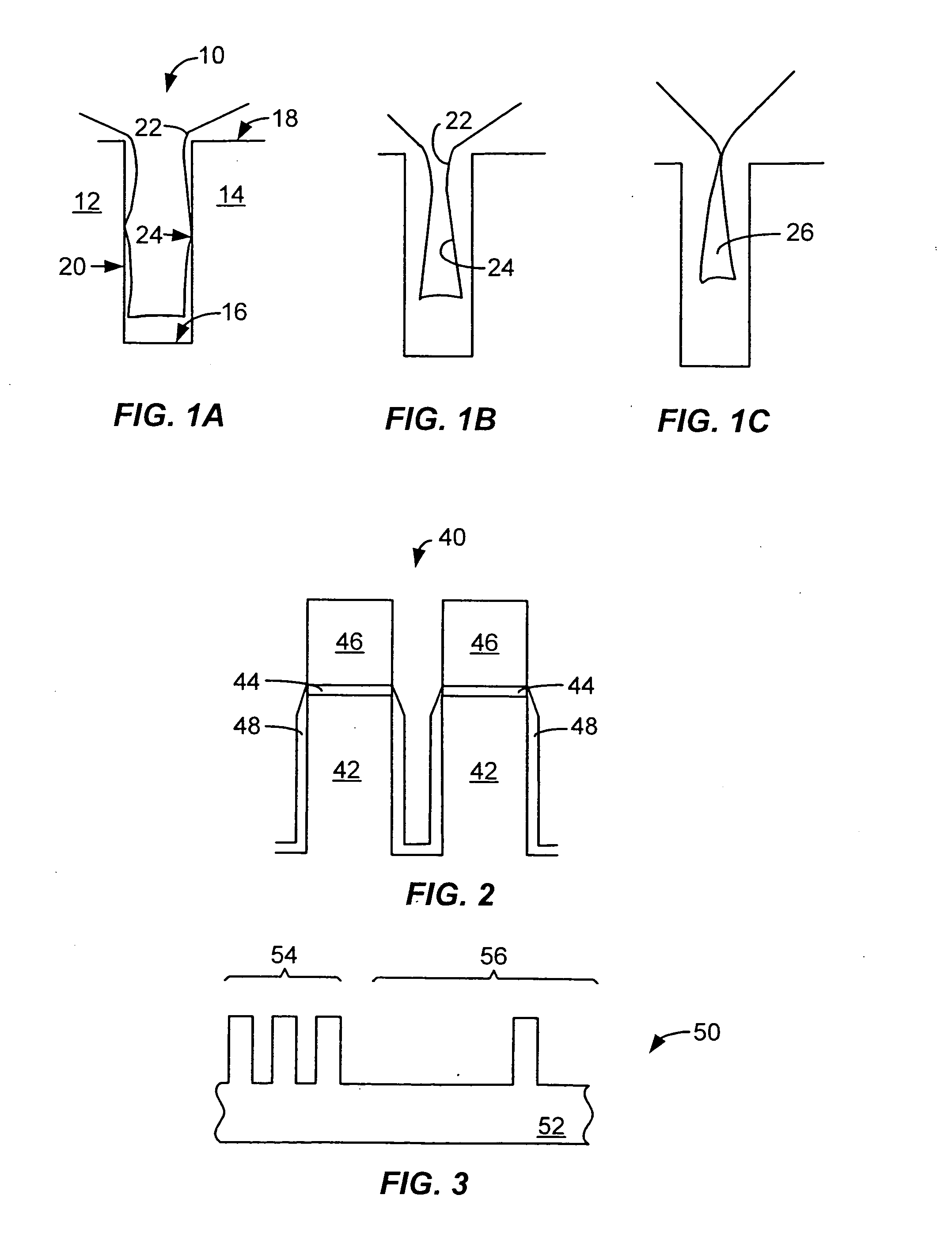

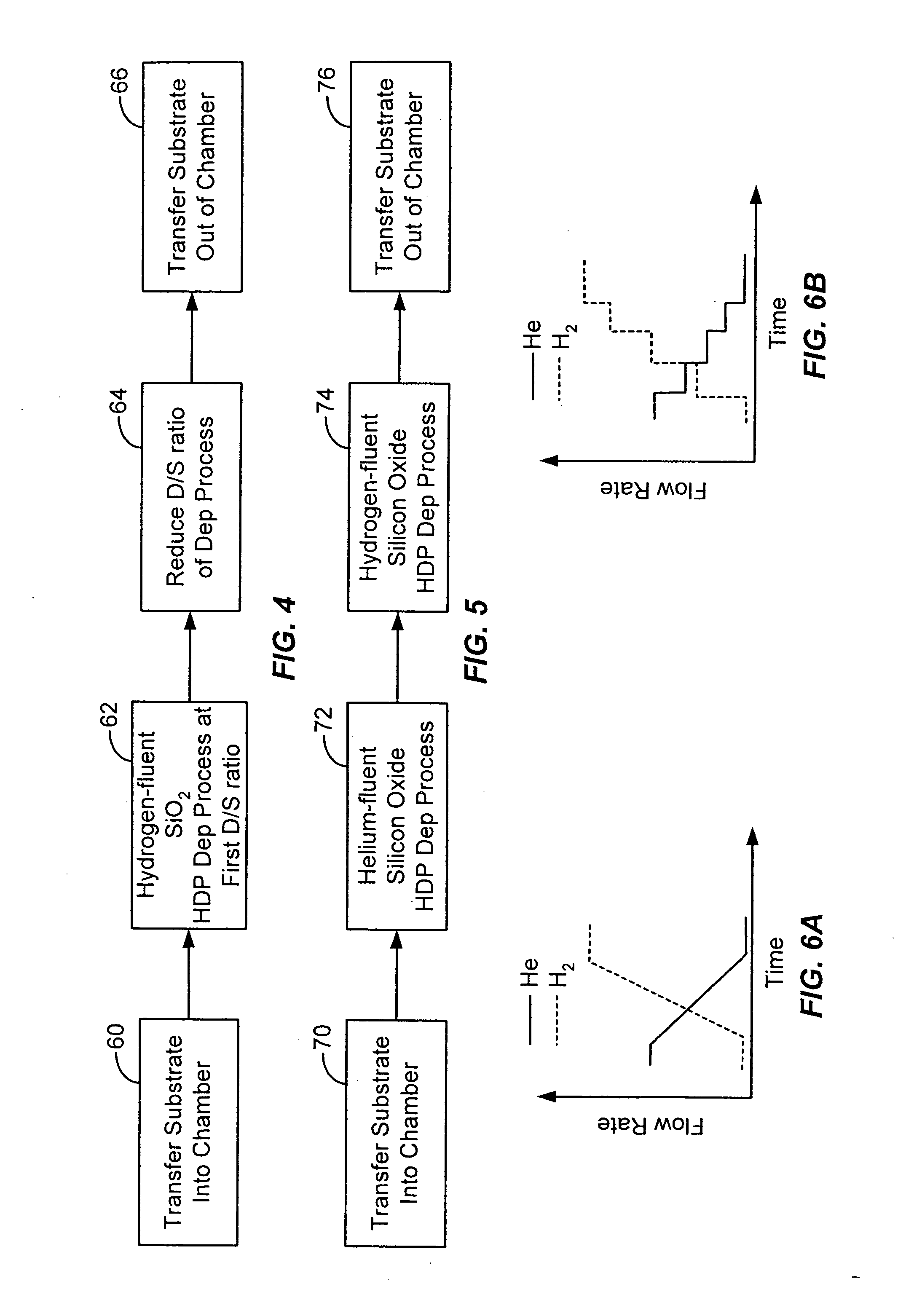

Abstract of the Disclosure A method of depositing a silicon oxide layer over a substrate having a trench formed between adjacent raised surfaces. In one embodiment the silicon oxide layer is formed in a multistep process that includes depositing a first portion of layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a first process gas comprising a silicon source, an oxygen source and helium and / or molecular hydrogen with high D / S ratio, for example, 10-20 and, thereafter, depositing a second portion of the silicon oxide layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a second process gas comprising a silicon source, an oxygen source and molecular hydrogen with a lower D / S ratio of, for example, 3-10.

Owner:APPLIED MATERIALS INC

Process for depositing F-doped silica glass in high aspect ratio structures

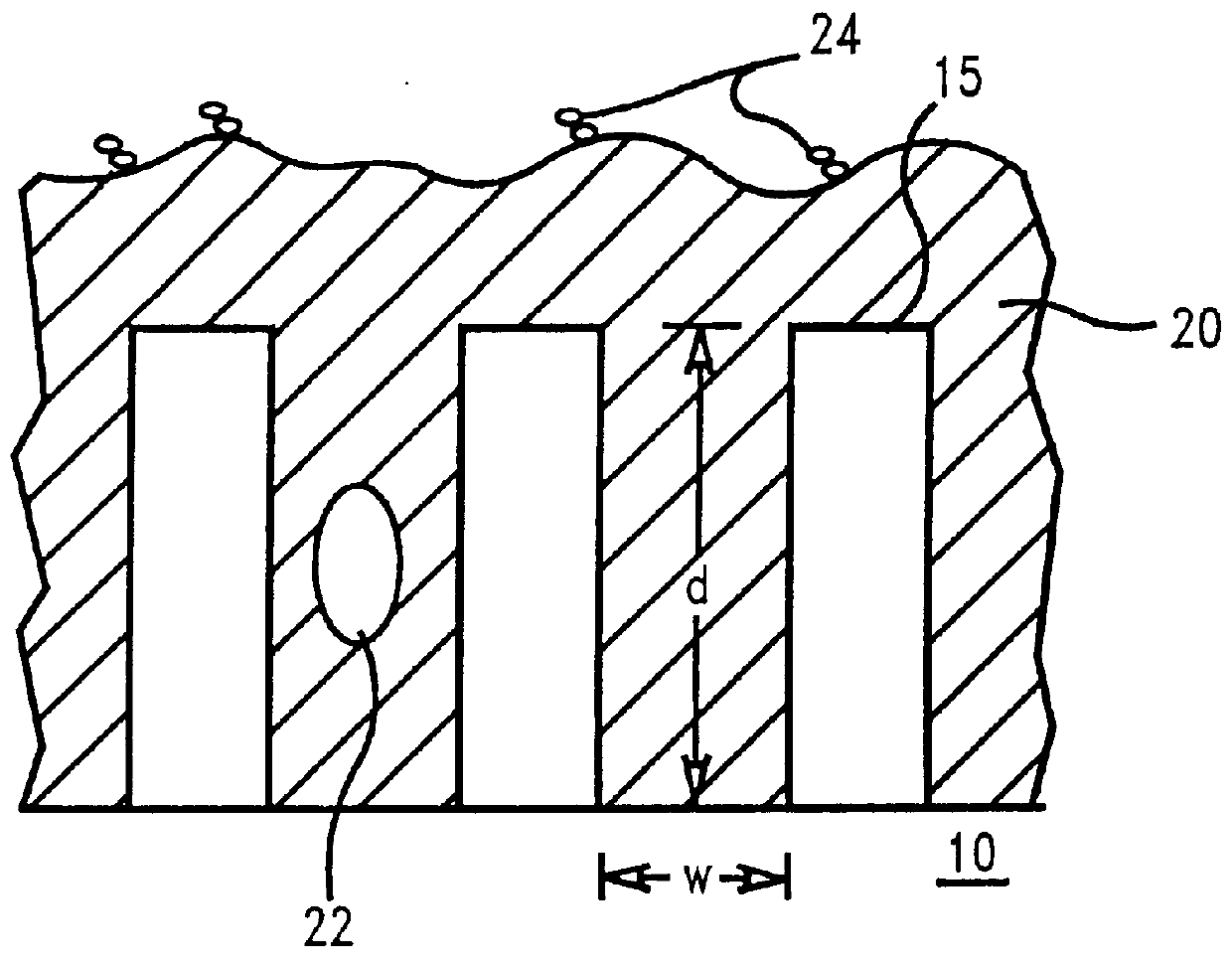

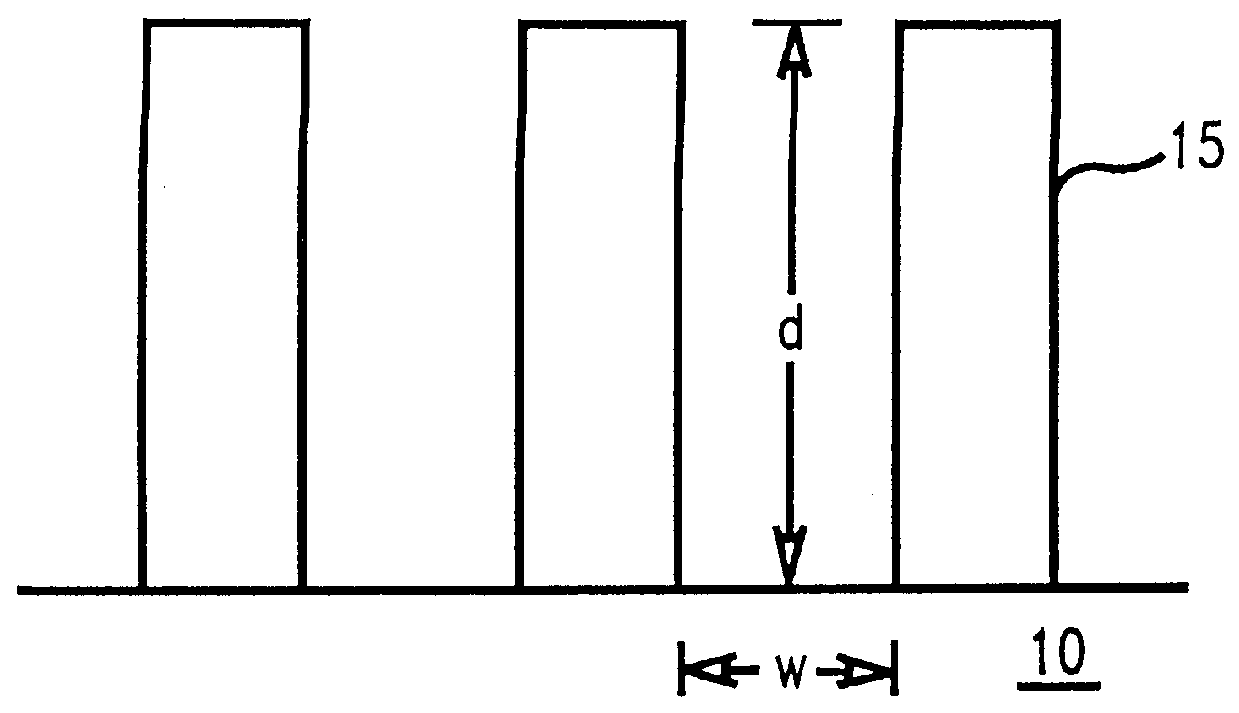

InactiveUS6846391B1Reduce effect of sputteringHigh aspect ratio gapDecorative surface effectsVacuum evaporation coatingHigh densityHydrogen

A process for filling high aspect ratio gaps on substrates uses conventional high density plasma deposition processes to deposit fluorine-doped films, with an efficient sputtering inert gas, such as Ar, replaced or reduced with an inefficient sputtering inert gas such as He and / or hydrogen. By reducing the sputtering component, sidewall deposition from the sputtered material is reduced. Consequently, gaps with aspect ratios greater than 3.0:1 and spacings between lines less than 0.13 microns can be filled with low dielectric constant films without the formation of voids and without damaging circuit elements.

Owner:NOVELLUS SYSTEMS

Borophosphosilicate glass incorporated with fluorine for low thermal budget gap fill

InactiveUS6159870AStrong Gap Filling CapabilityHigh aspect ratio gapsSemiconductor/solid-state device manufacturingBorophosphosilicate glassChemistry

A method of depositing a fluorinated borophosphosilicate glass (FBPSG) on a semiconductor device as either a final or interlayer dielectric film. Gaps having aspect ratios greater than 6:1 are filled with a substantially void-free FBPSG film at a temperature of about 480 DEG C. at sub-atmospheric pressures of about 200 Torr. Preferably, gaseous reactants used in the method comprise TEOS, FTES, TEPO and TEB with an ozone / oxygen mixture. Dopant concentrations of boron and phosphorus are sufficiently low such that surface crystallite defects and hygroscopicity are avoided. The as-deposited films at lower aspect ratio gaps are substantially void-free such that subsequent anneal of the film is not required. Films deposited into higher aspect ratio gaps are annealed at or below about 750 DEG C., well within the thermal budget for most DRAM, logic and merged logic-DRAM chips. The resultant FBPSG layer contains less than or equal to about 5.0 wt % boron, less than about 4.0 wt % phosphorus, and about 0.1 to 2.0 wt % fluorine.

Owner:IBM CORP

Hydrogen assisted HDP-CVD deposition process for aggressive gap-fill technology

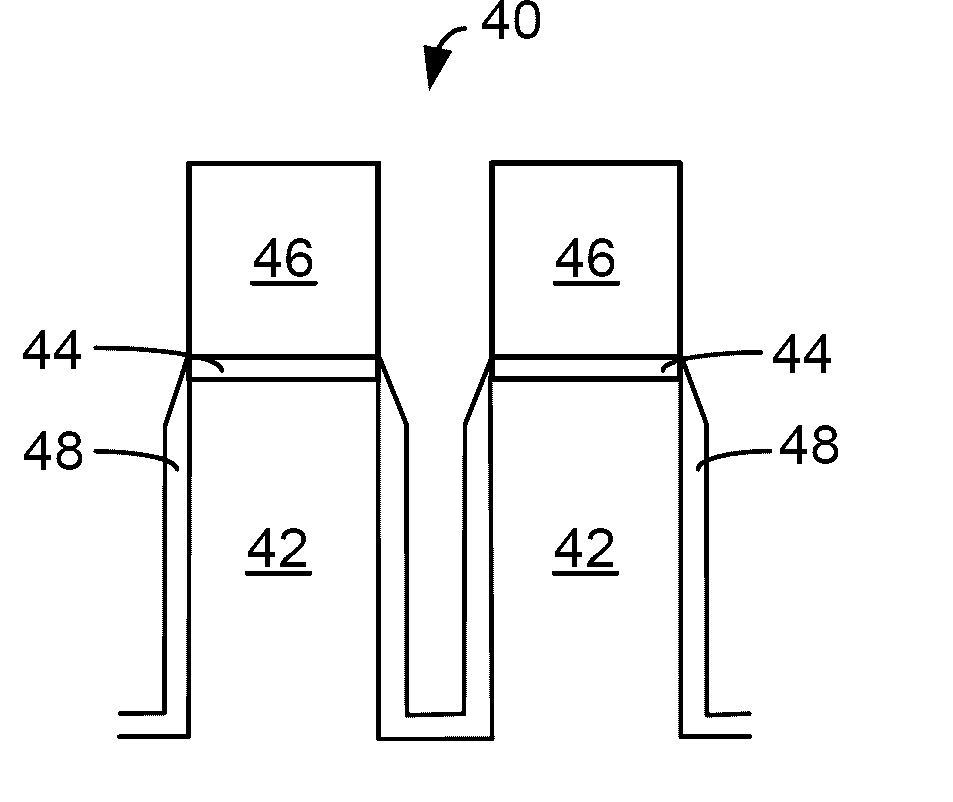

InactiveUS20050008790A1Strong Gap Filling CapabilityReduce the overall heightElectric discharge tubesSemiconductor/solid-state device manufacturingHigh densityHydrogen

A method of depositing a silicon oxide layer over a substrate having a trench formed between adjacent raised surfaces. In one embodiment the silicon oxide layer is formed in a multistep process that includes depositing a first portion of layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a first process gas comprising a silicon source, an oxygen source and helium and / or molecular hydrogen with highD / S ratio, for example, 10-20 and, thereafter, depositing a second portion of the silicon oxide layer over the substrate and within the trench by forming a high density plasma process that has simultaneous deposition and sputtering components from a second process gas comprising a silicon source, an oxygen source and molecular hydrogen with a lowerD / S ratio of, for example, 3-10.

Owner:APPLIED MATERIALS INC

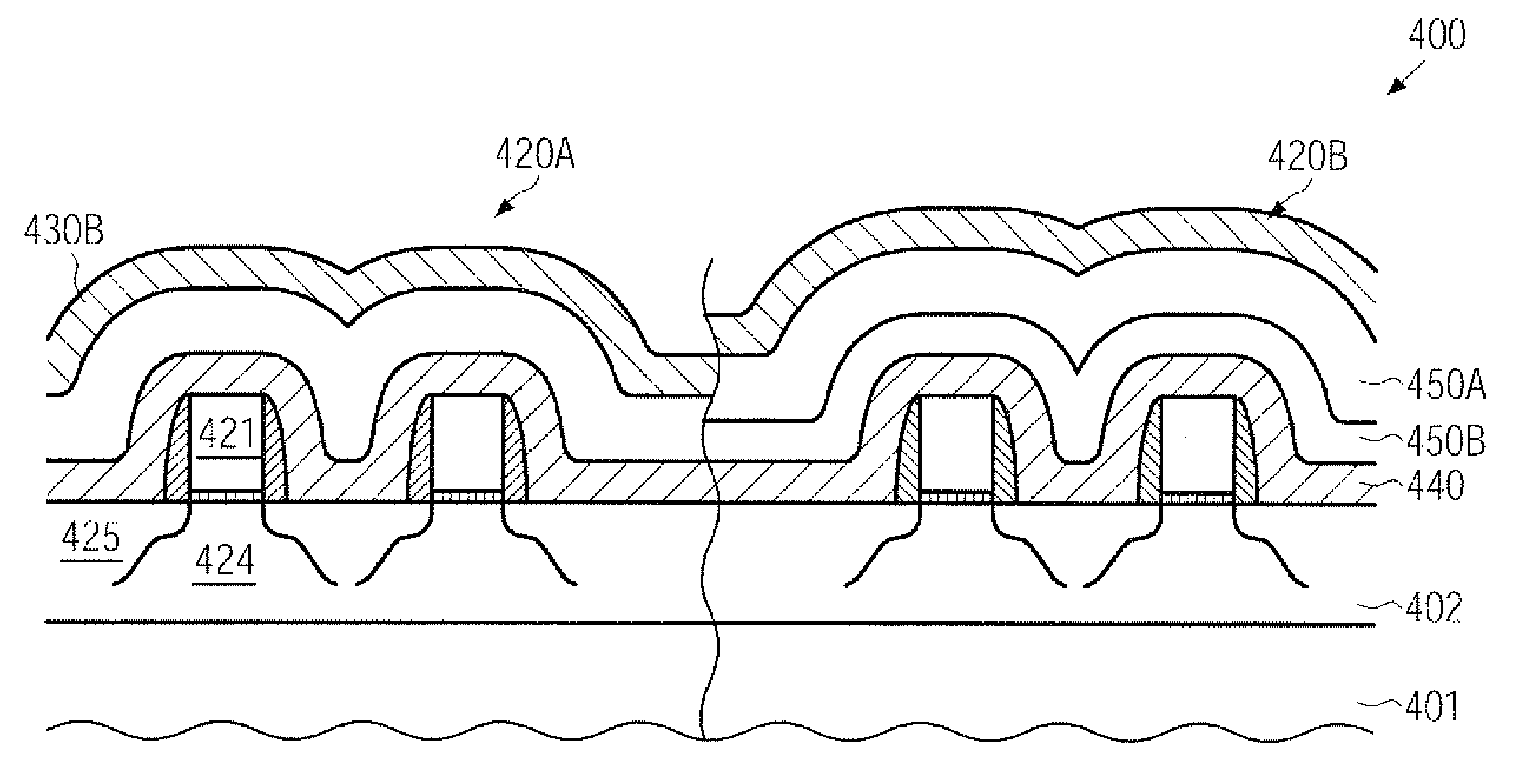

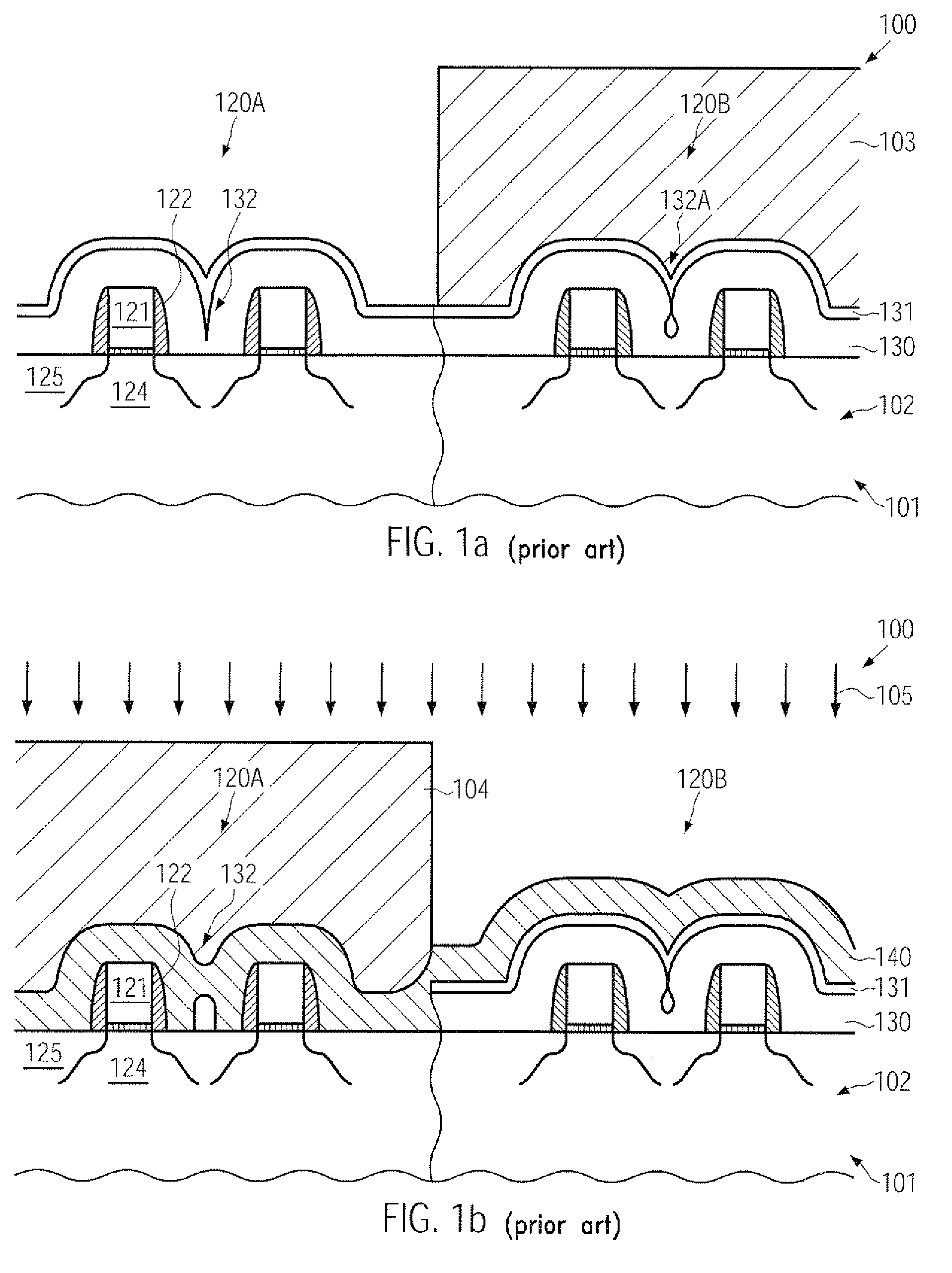

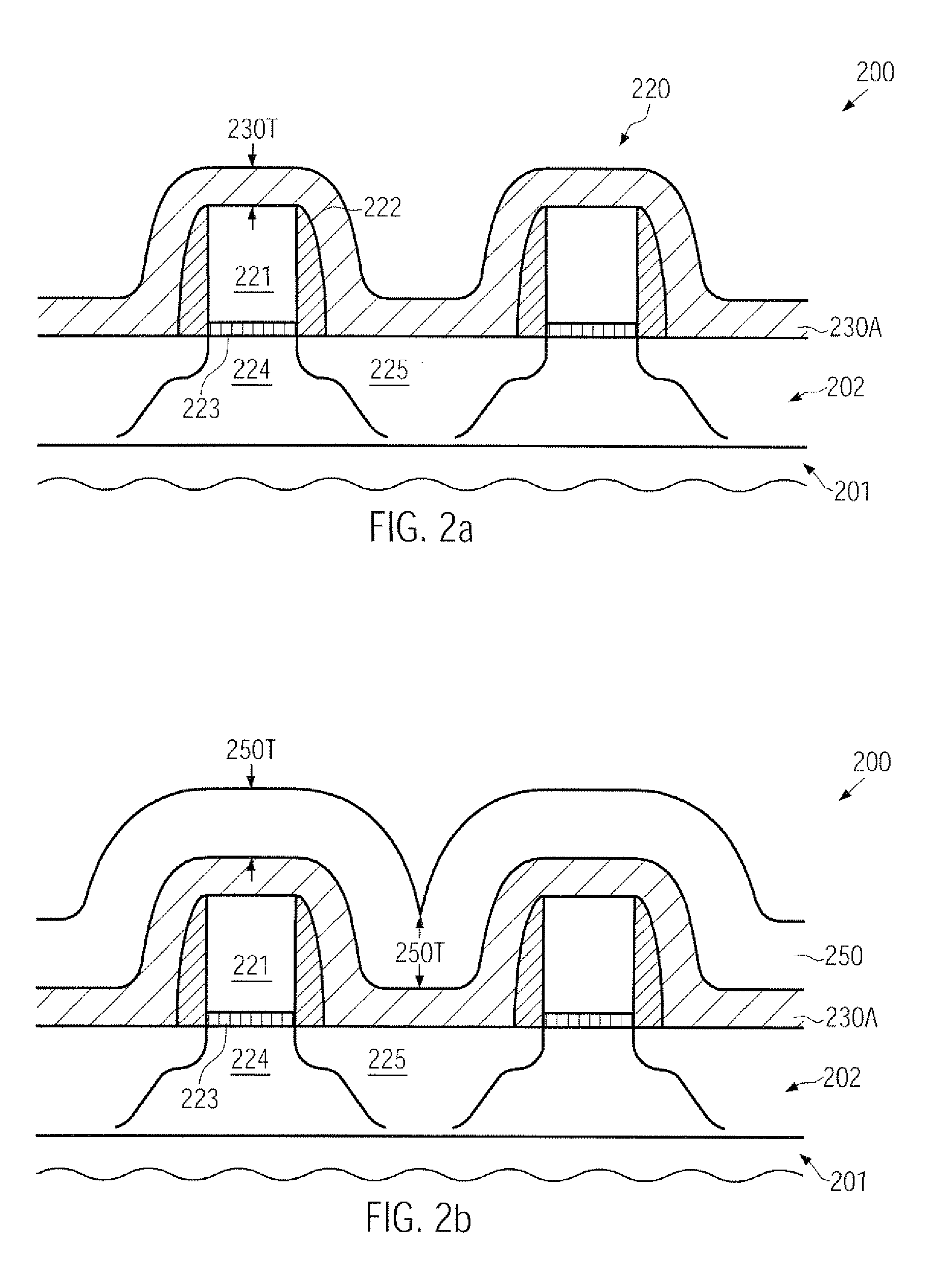

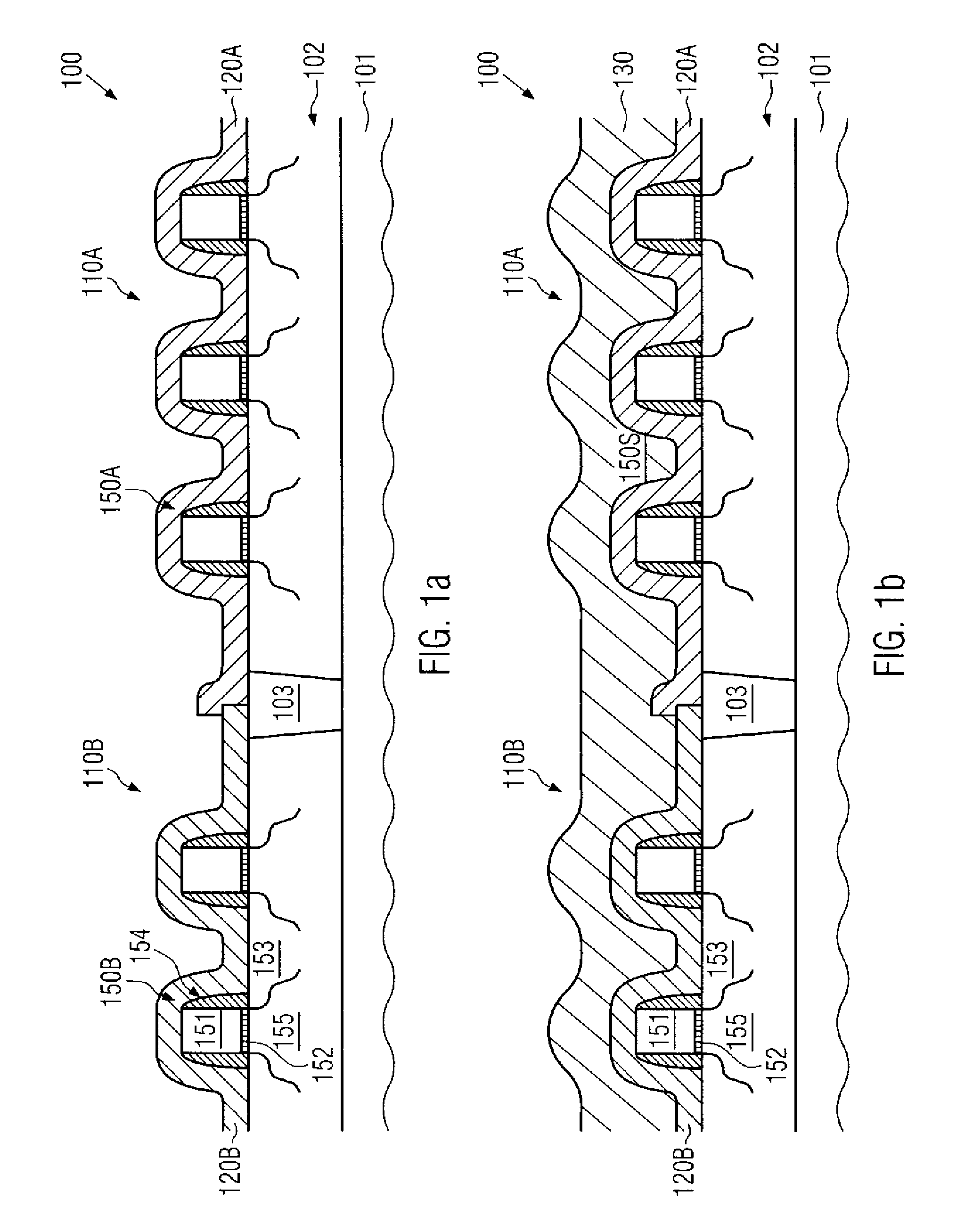

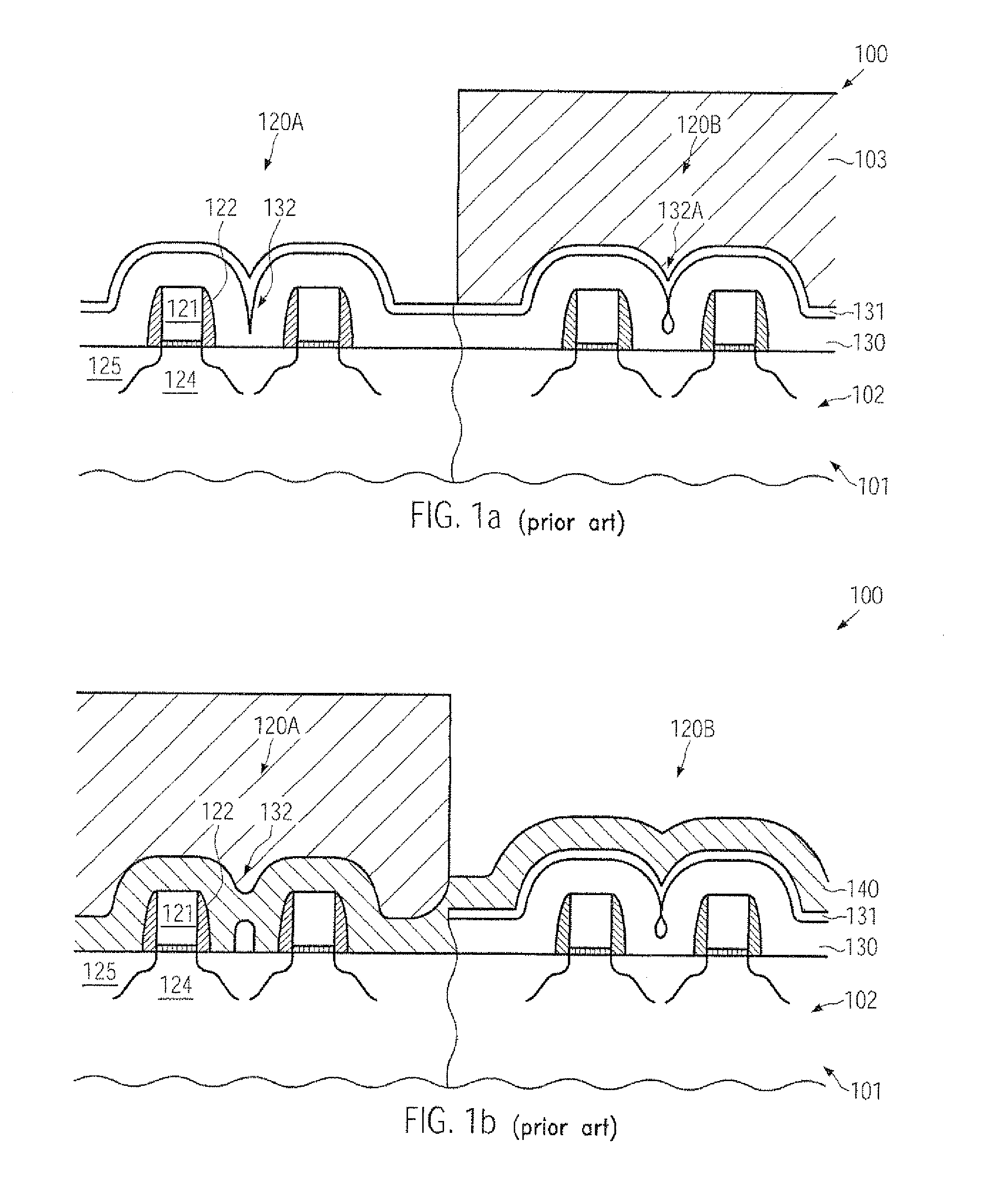

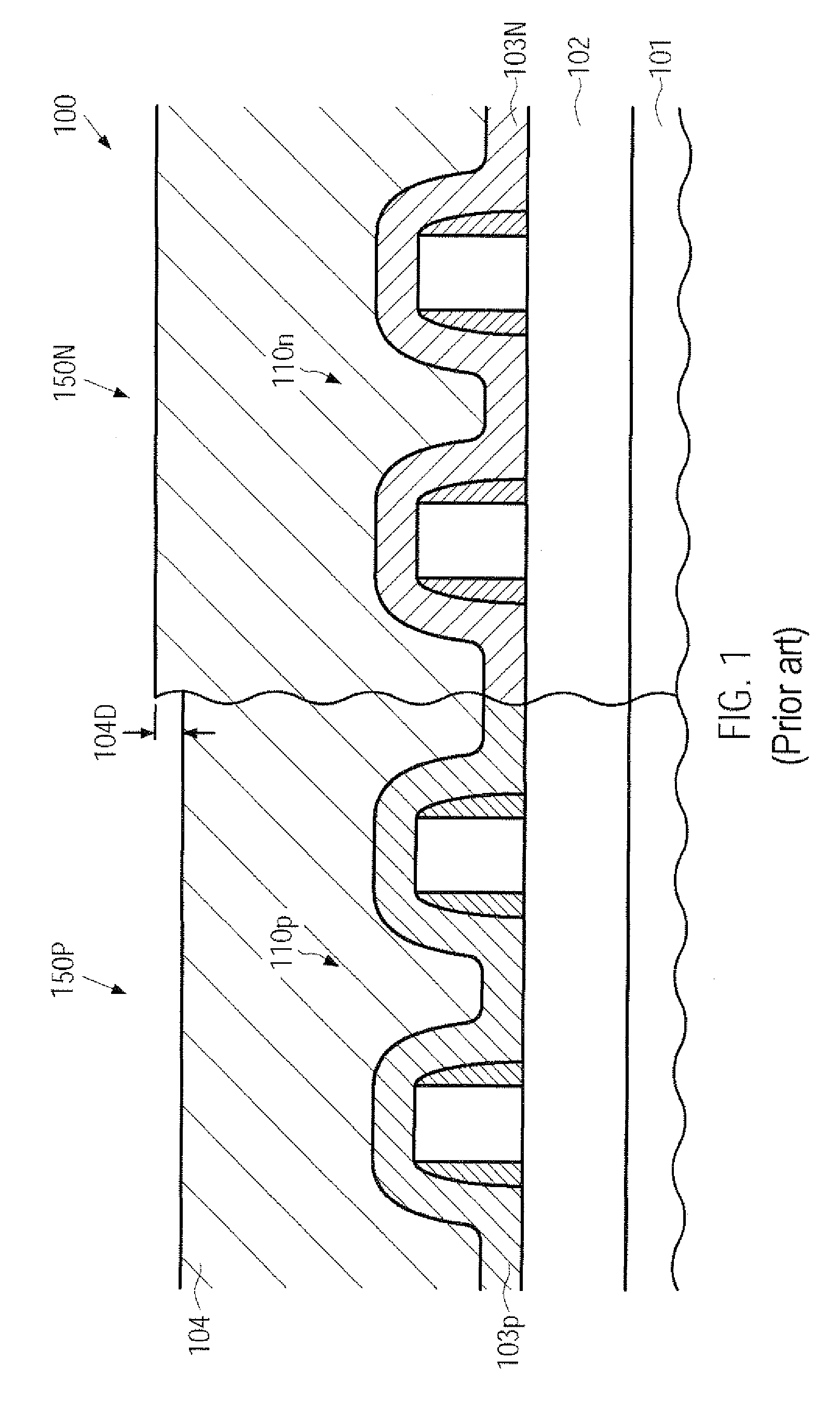

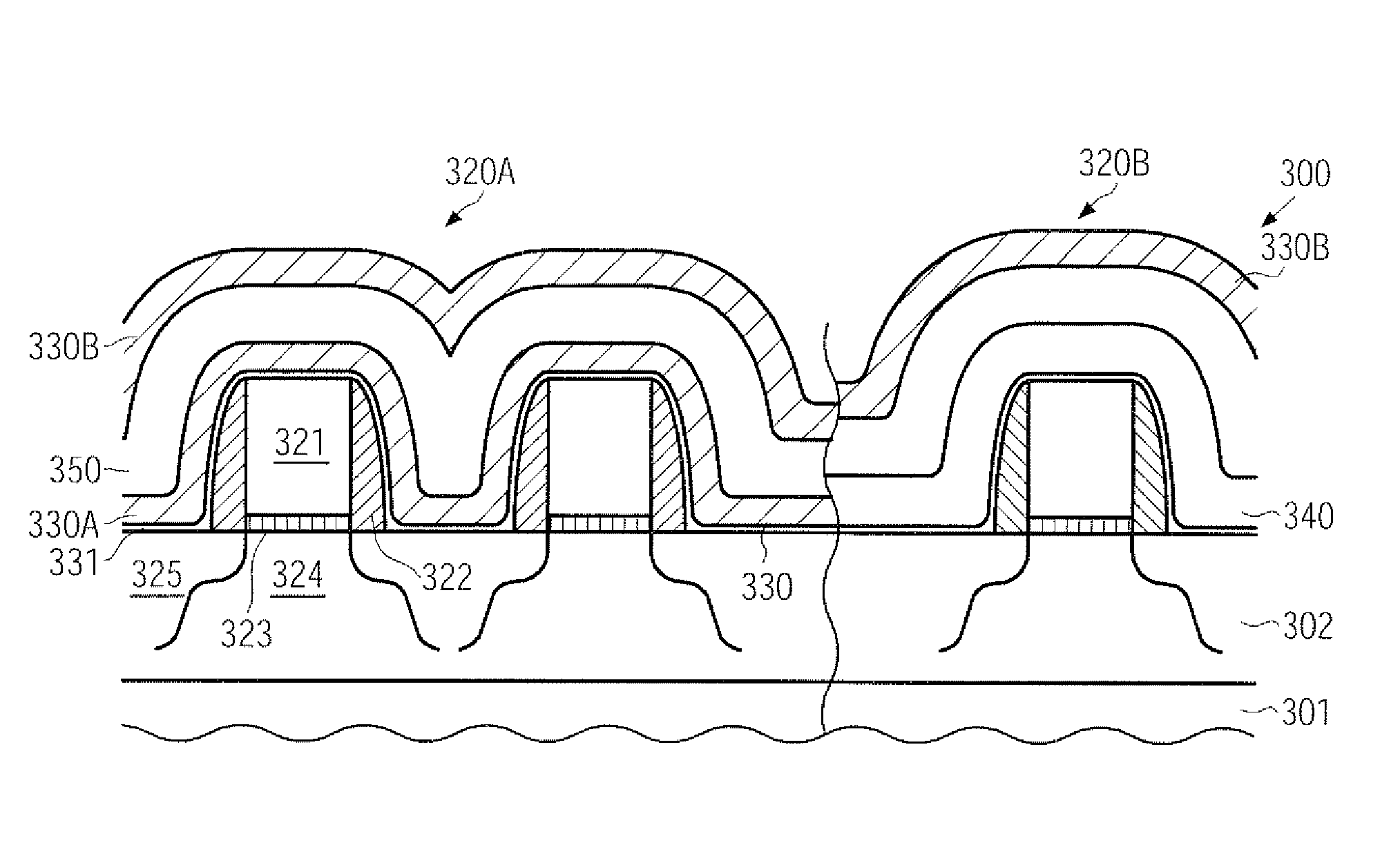

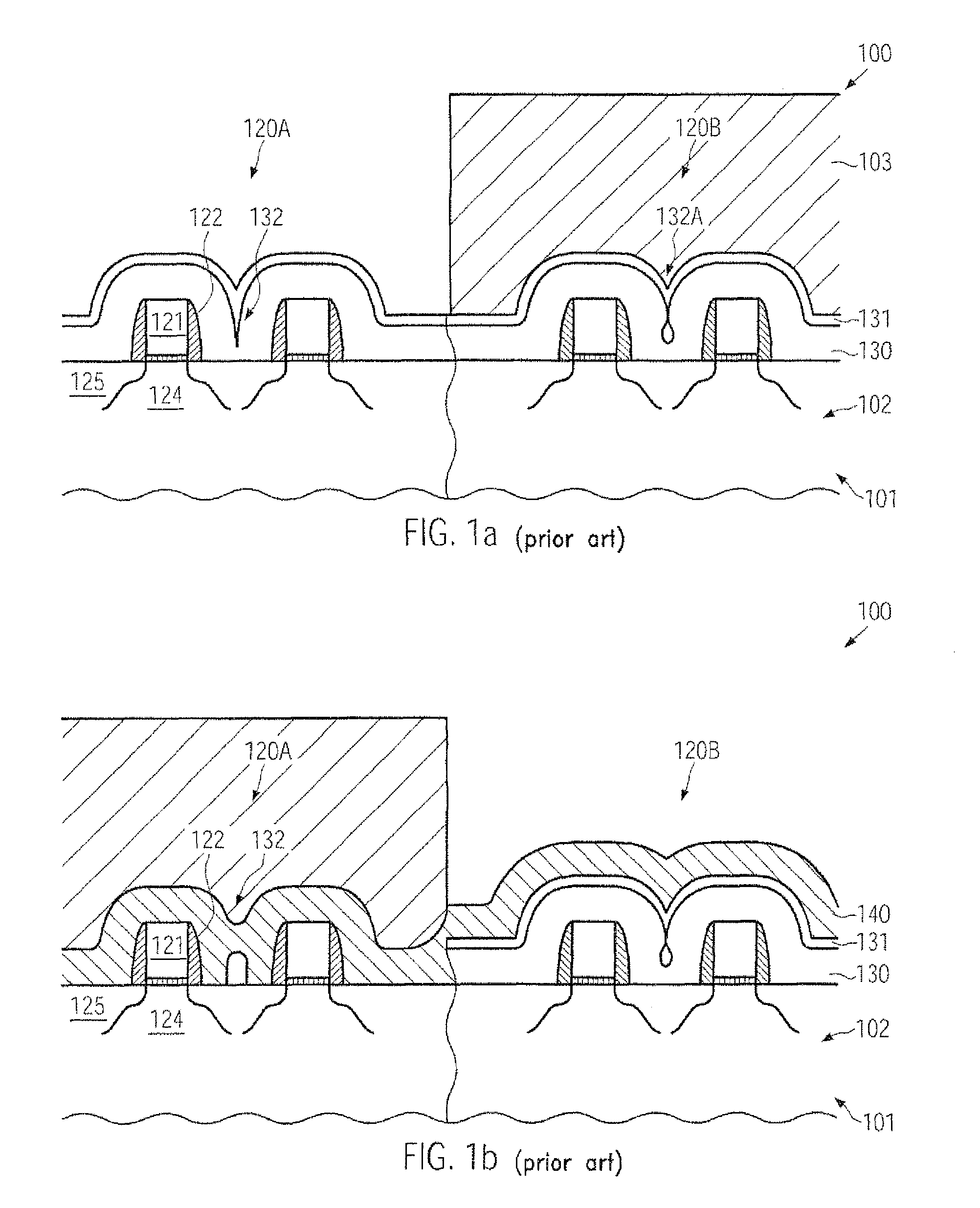

Interlayer dielectric material in a semiconductor device comprising stressed layers with an intermediate buffer material

InactiveUS20090166814A1Low efficiencyReduce probabilitySemiconductor/solid-state device detailsSolid-state devicesDielectricStress induced

A highly stressed dielectric material, such as a tensile stressed material, may be deposited in a conformal manner so as to respect any deposition constraints caused by pronounced surface topography of highly scaled semiconductor devices, followed by the deposition of a buffer material having enhanced gap-filling capabilities. Thereafter, a further stress-inducing layer is deposited to form a doublet structure, which acts on the transistor elements, thereby enhancing overall performance, without increasing the probability of creating deposition-related irregularities. Hence, production yield as well as performance of highly scaled semiconductor devices may be increased.

Owner:ADVANCED MICRO DEVICES INC

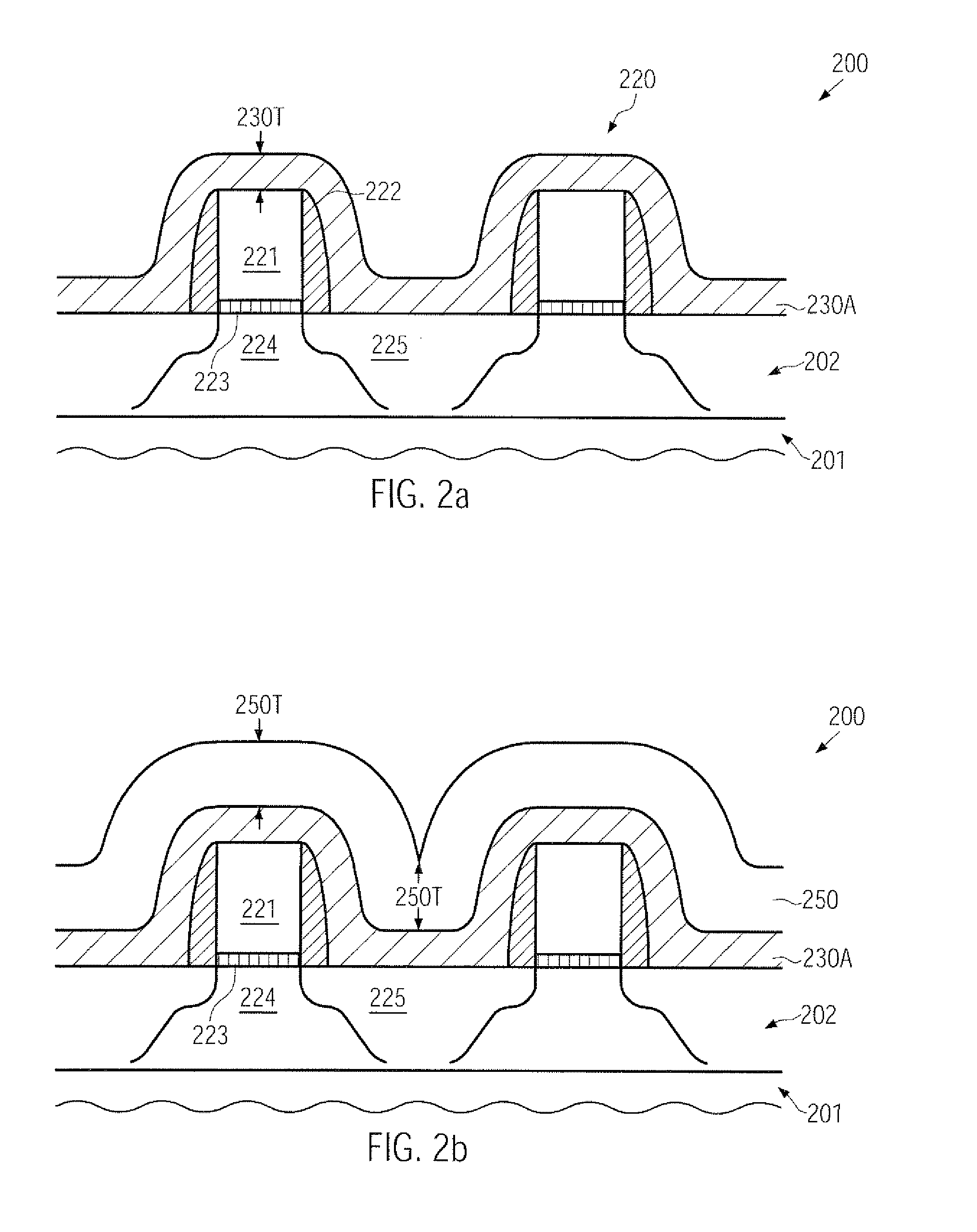

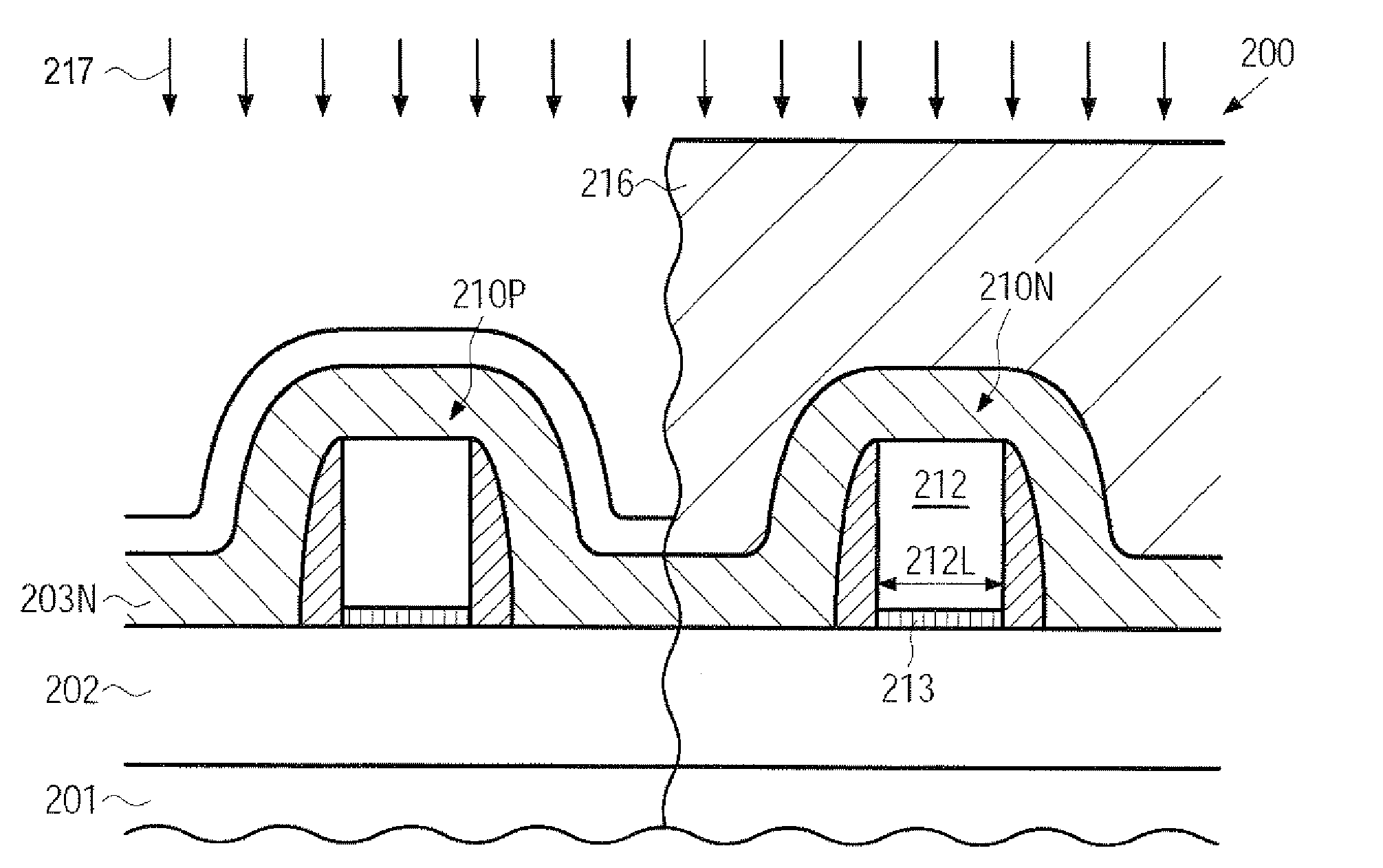

Semiconductor device including field effect transistors laterally enclosed by interlayer dielectric material having increased intrinsic stress

ActiveUS20090061645A1Increased charge carrier mobilityImproved mechanismTransistorSemiconductor/solid-state device manufacturingDielectricField-effect transistor

By appropriately treating an interlayer dielectric material above P-channel transistors, the compressive stress may be significantly enhanced, which may be accomplished by expanding the interlayer dielectric material, for instance, by providing a certain amount of oxidizable species and performing an oxidation process.

Owner:ADVANCED MICRO DEVICES INC

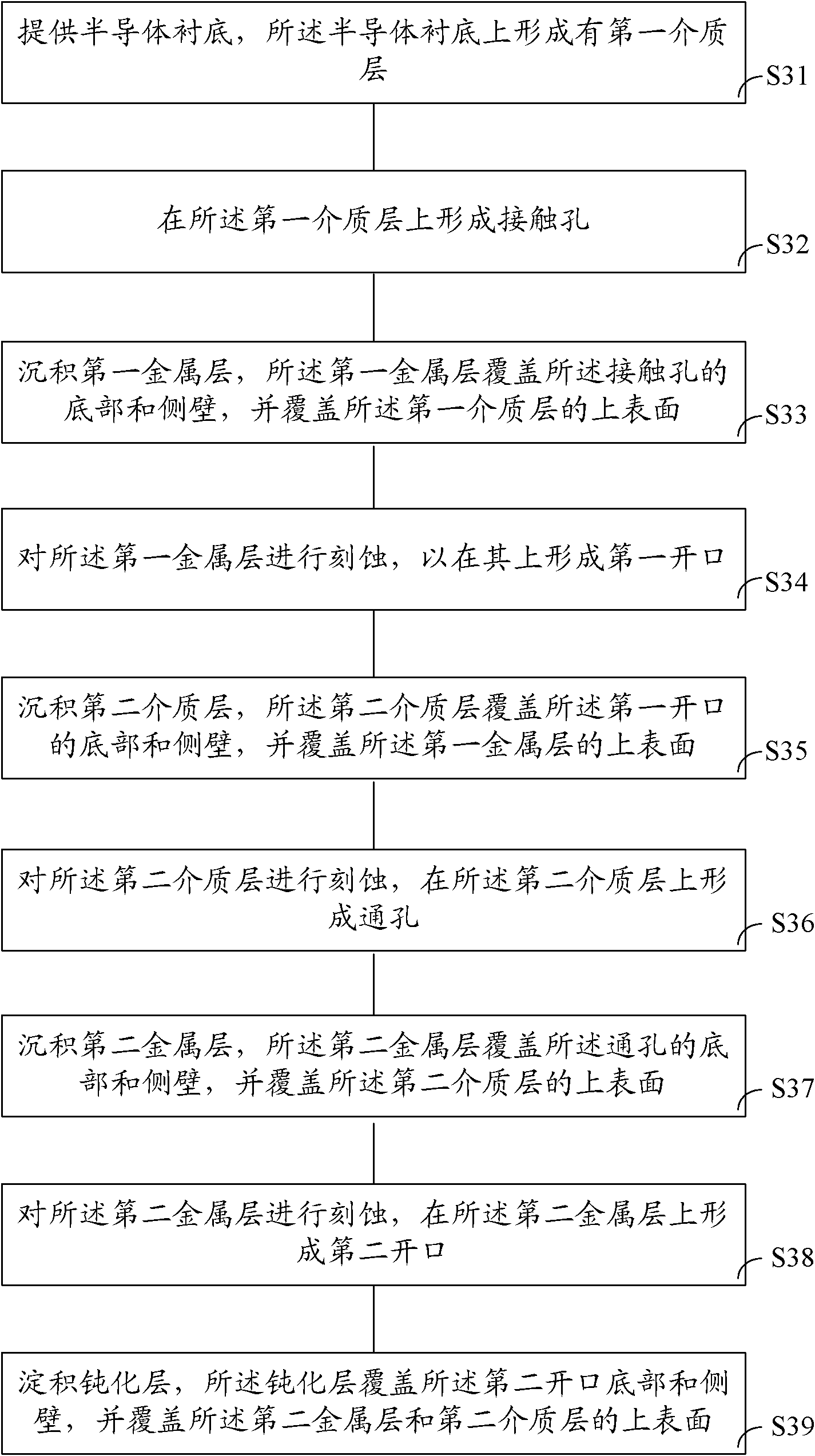

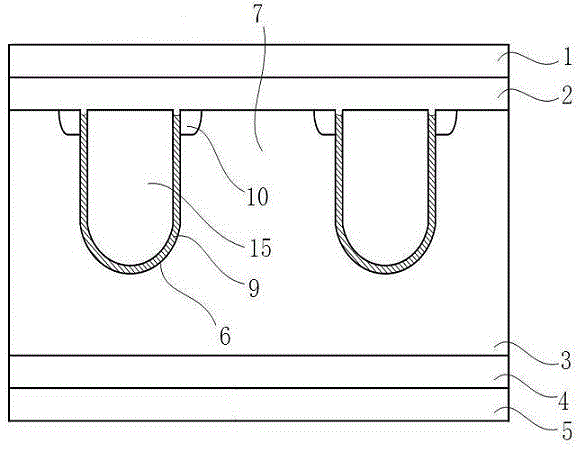

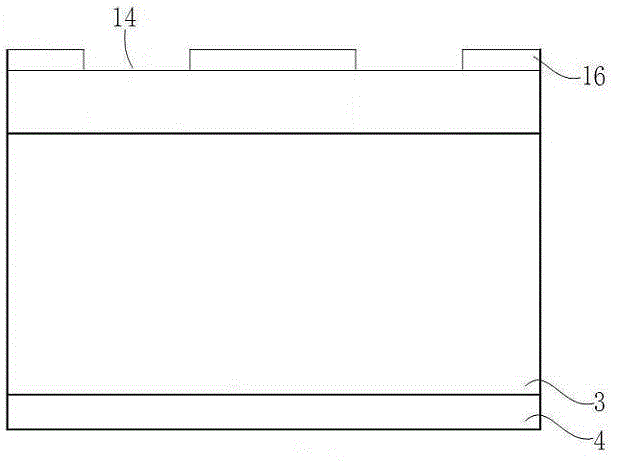

Wiring structure forming method

InactiveCN102354684AImprove the shape of the stepsPromote formationSemiconductor/solid-state device manufacturingEngineeringMedia layer

The invention provides a wiring structure forming method which comprises the following steps of: providing a semiconductor substrate, and forming a first medium layer thereon; forming a contact hole on the first medium layer; depositing a first metal layer, covering the bottom and side wall of the contact hole and covering the upper surface of the first medium layer; etching the first metal layer with a wet method, and etching with a dry method to form a bowl-mouth first opening; depositing a second medium layer, covering the bottom and side wall of the first opening and covering the upper surface of the first metal layer; etching the second medium layer to form an inverted trapezoidal through hole; depositing a second metal layer, covering the bottom and side wall of the through hole and covering the upper surface of the second medium layer; and etching the second metal layer with a wet method, and etching with a dry method to form a bowl-mouth second opening. Through the invention, the requirement on planarization of a process platform of near or below 1.5 microns is met without adopting SOG planarization, glue back-etching SOG planarization and the like.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

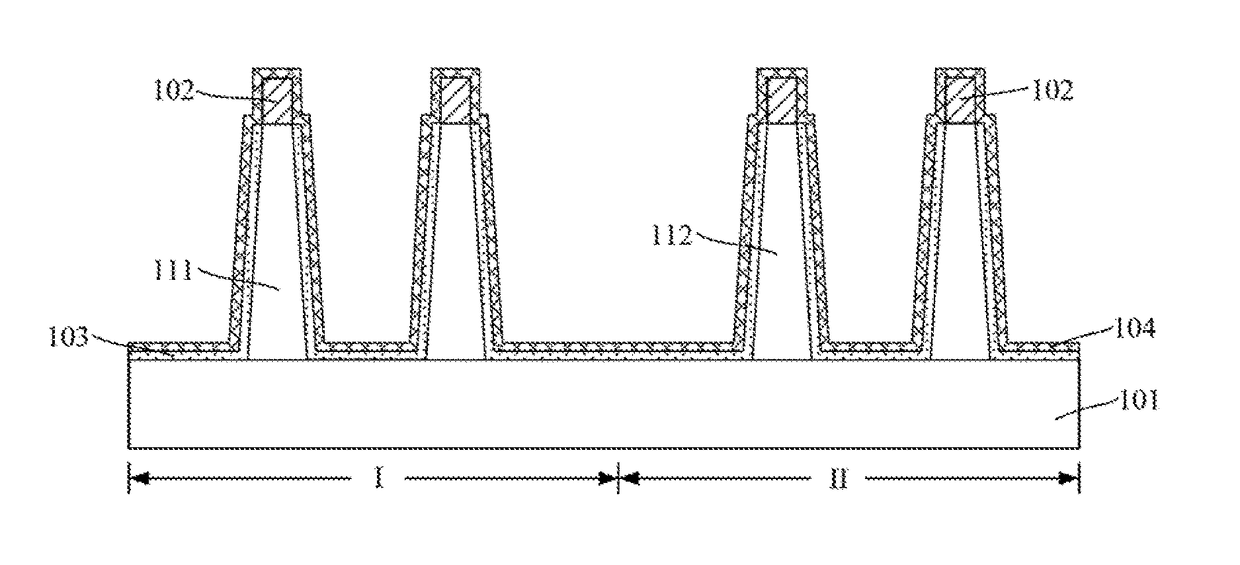

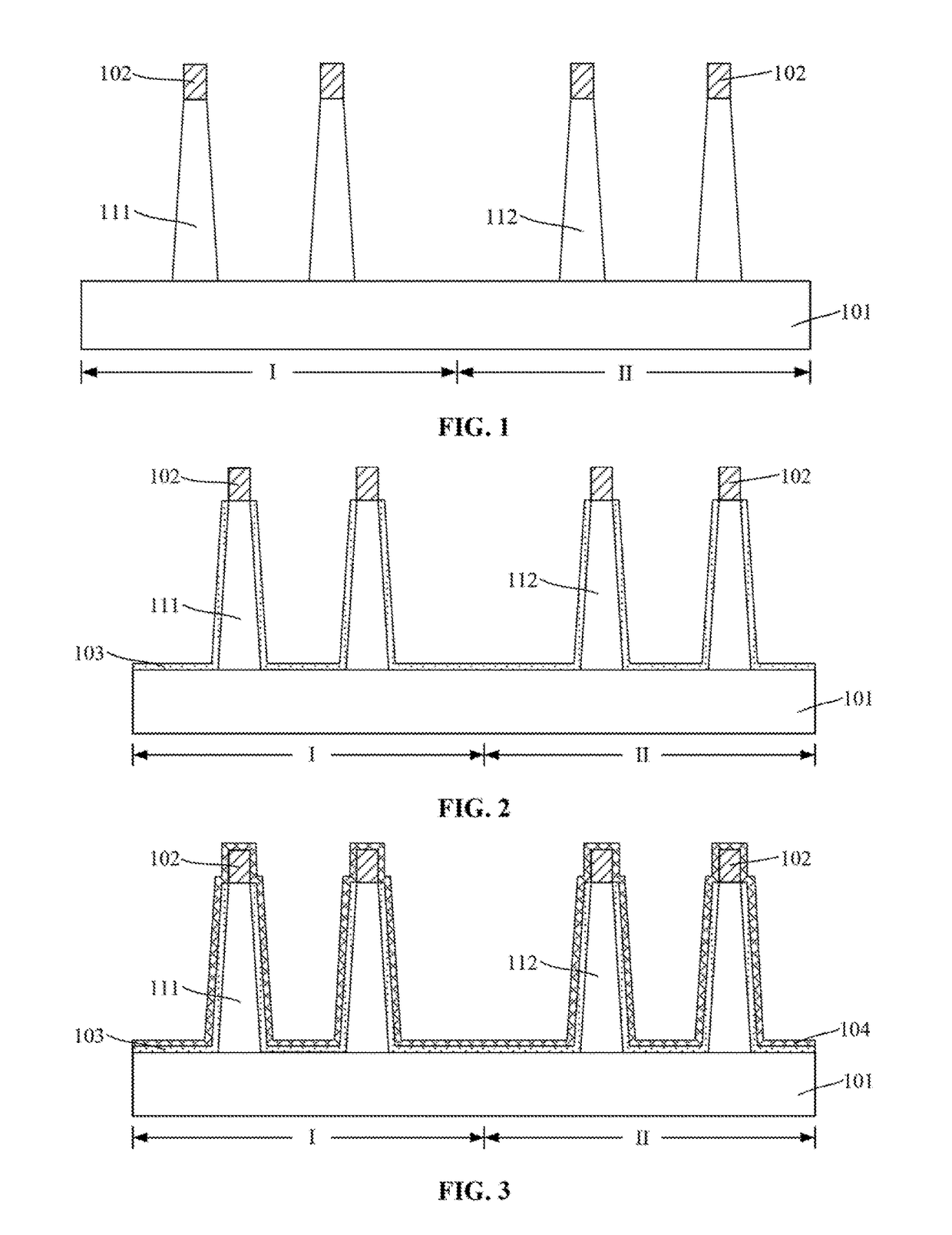

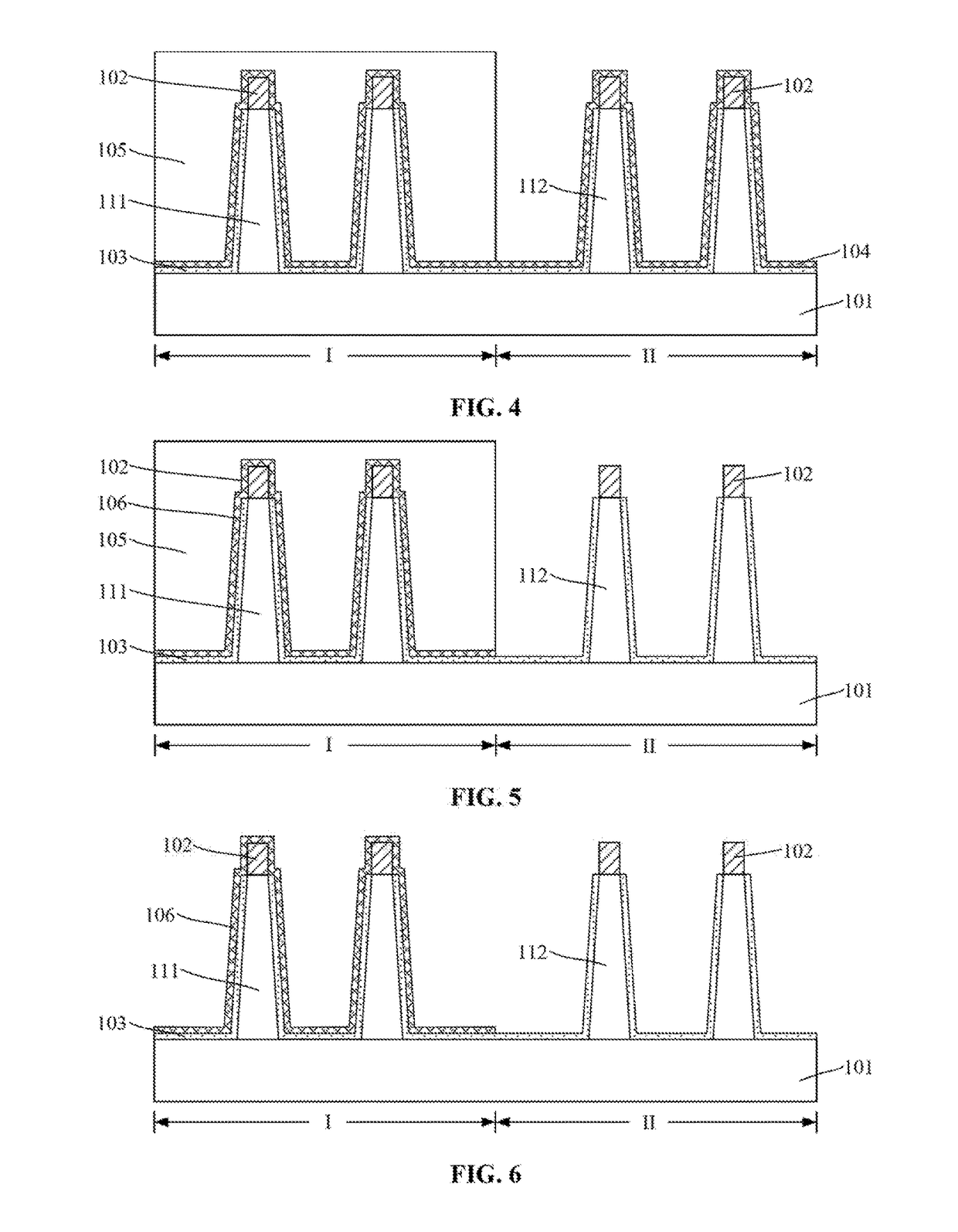

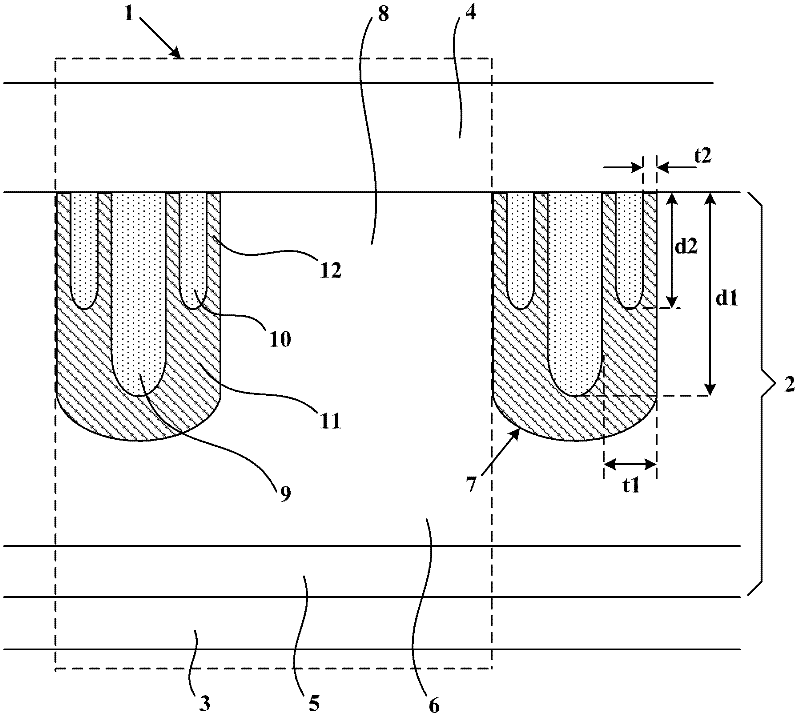

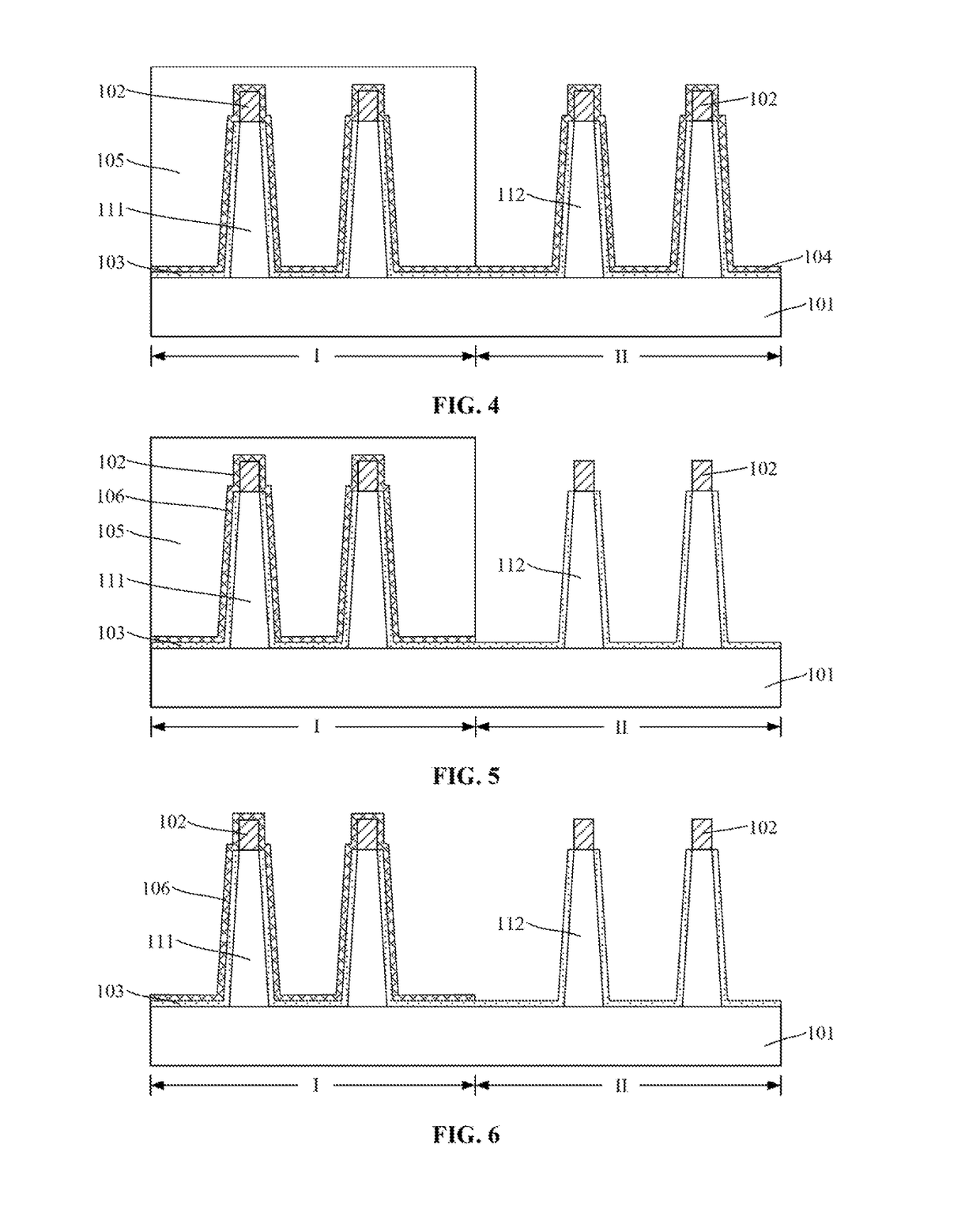

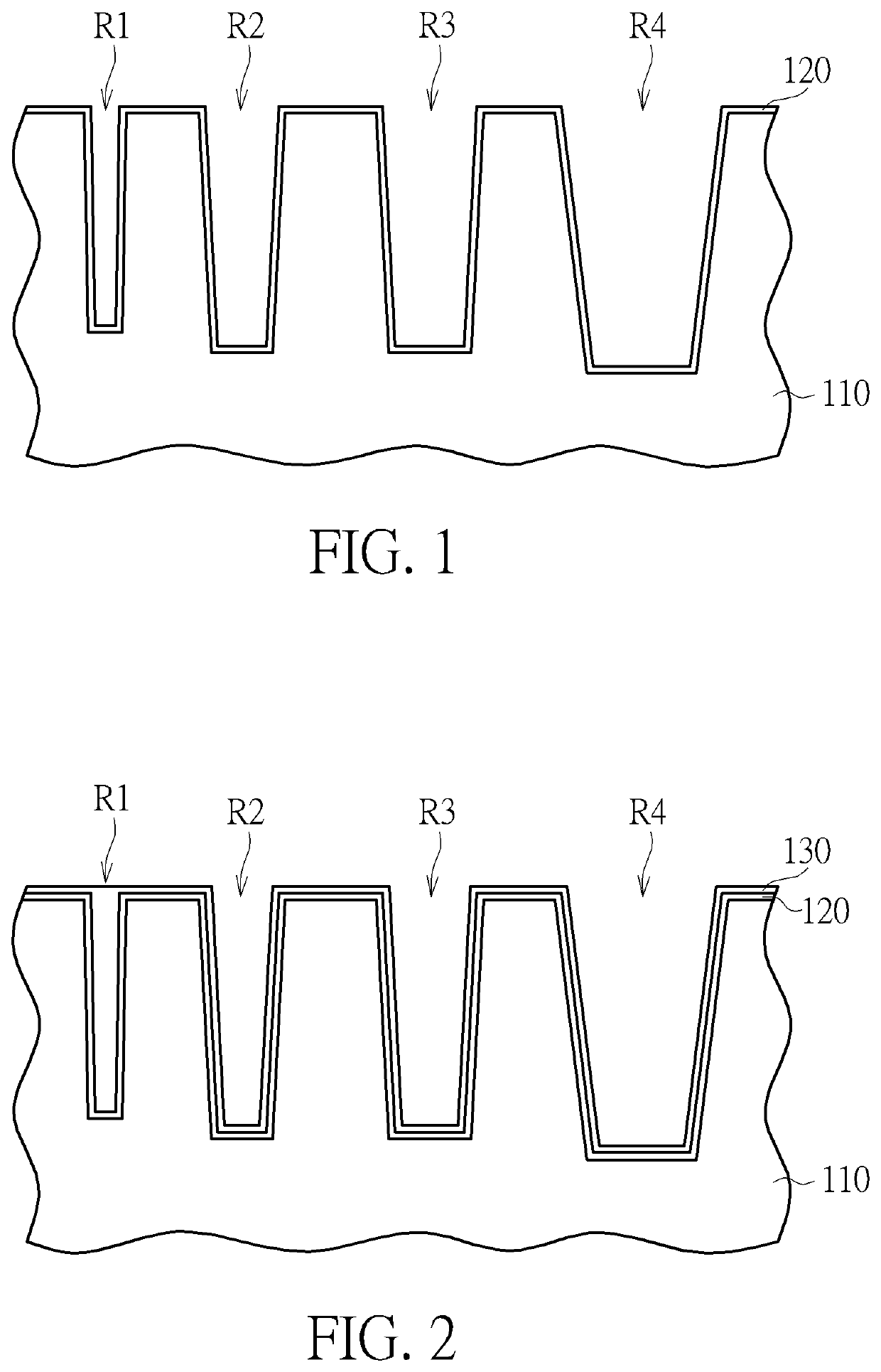

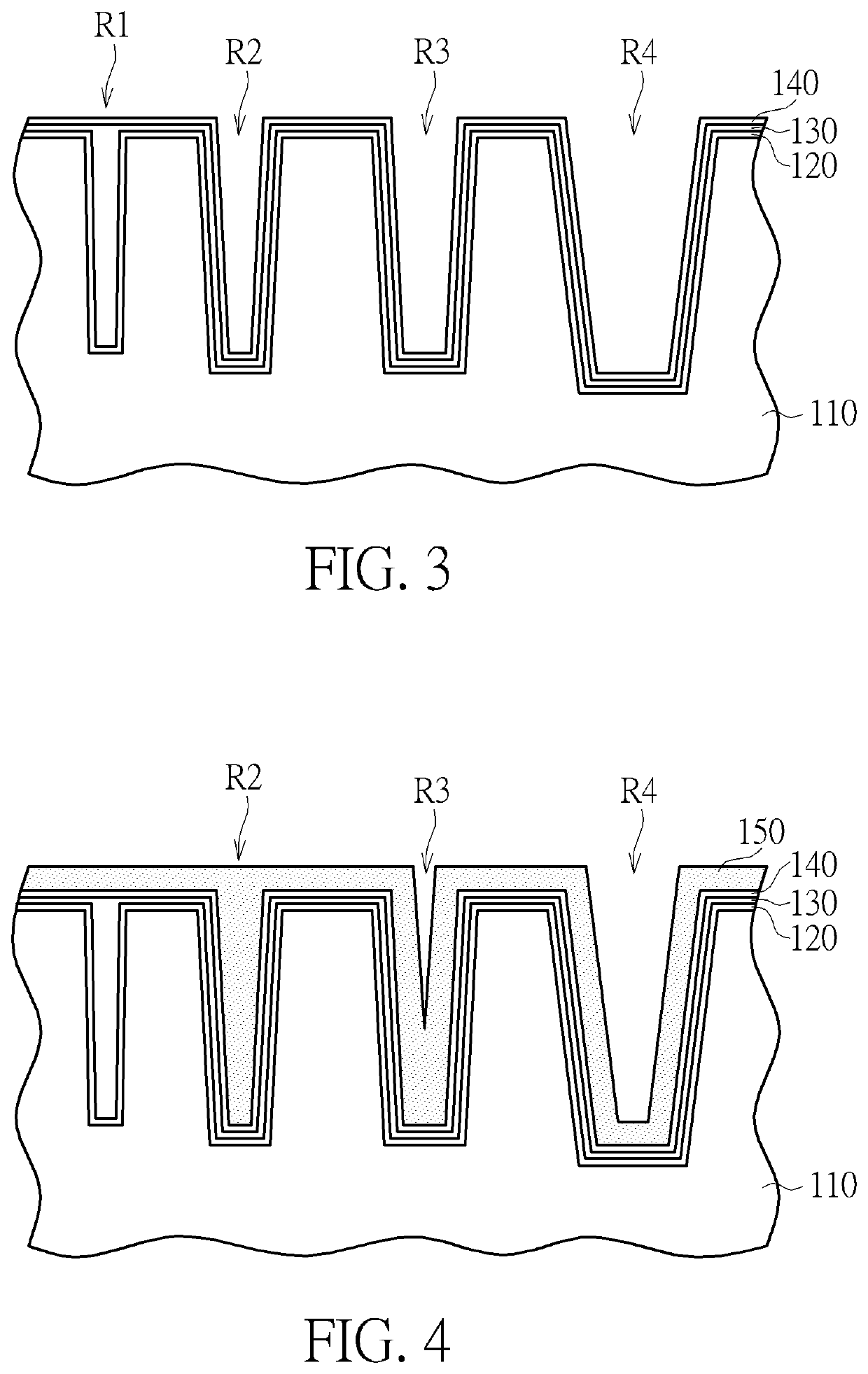

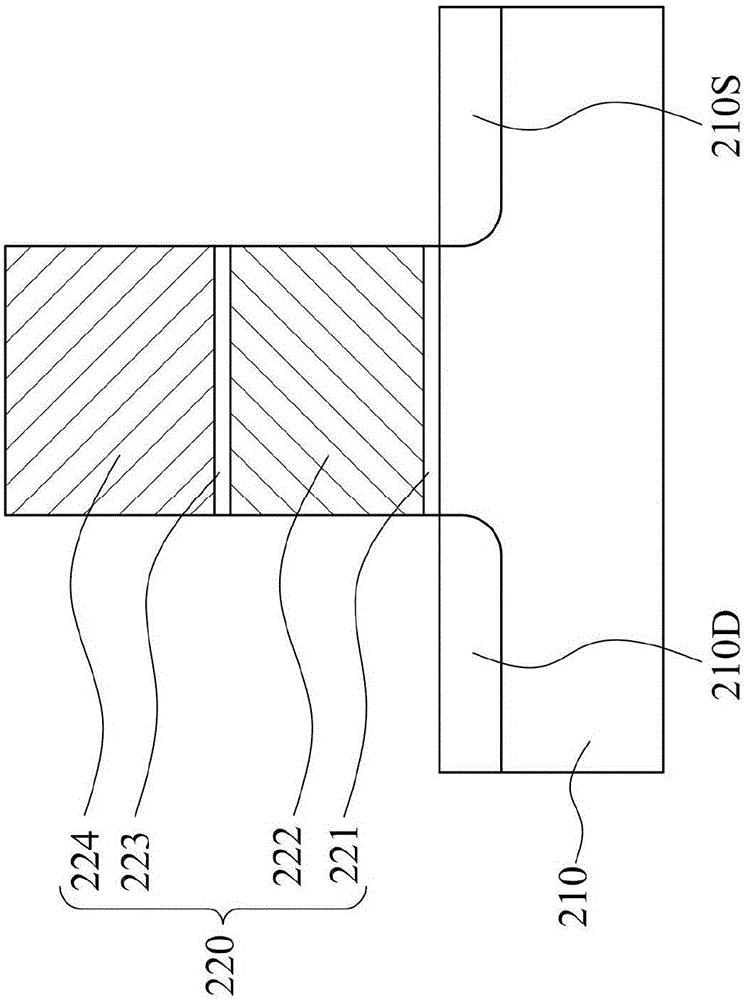

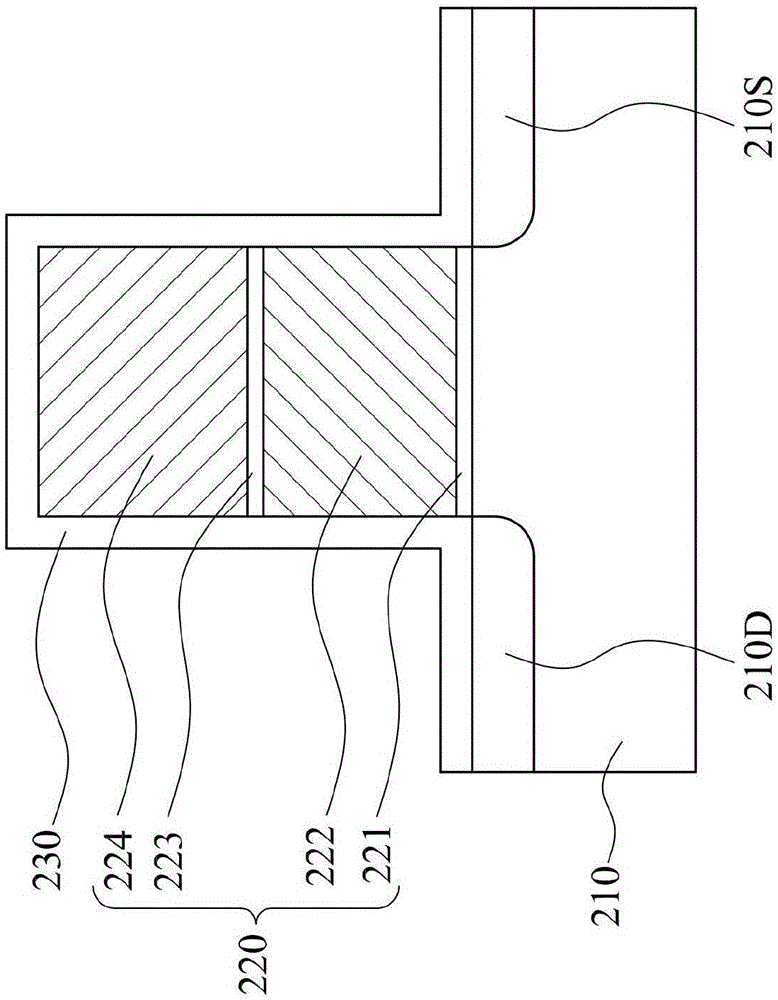

Fin field-effect transistor and fabrication method thereof

ActiveUS20170200810A1Strong preventive abilityStrong Gap Filling CapabilitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

The present disclosure provides fin field-effect transistors and fabrication methods thereof. An exemplary fabrication process includes providing a substrate having a first region and a second region; forming first fins in the first region and second fins in the second region; forming a liner oxide layer on side surfaces of the first fins, the second fins and a surface of the substrate; forming an insulating barrier layer on the liner oxide layer in the first region; forming a precursor material layer on the insulating barrier layer in the first region and on the liner oxide layer in the second region; performing a curing annealing process to convert the precursor material into an insulation layer; and removing a top portion of the insulation layer to form an isolating layer and removing portions of the liner oxide layer, the insulating barrier layer, the first oxide layer and the second oxide layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

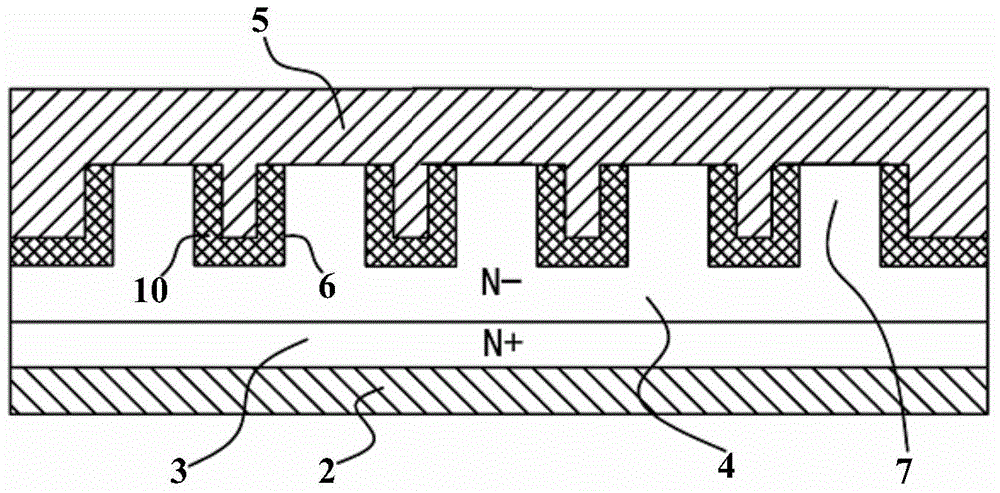

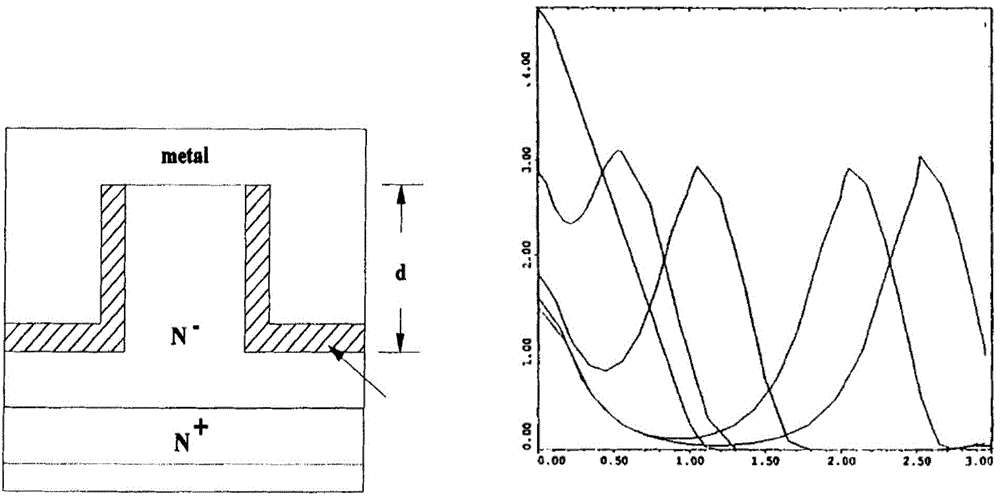

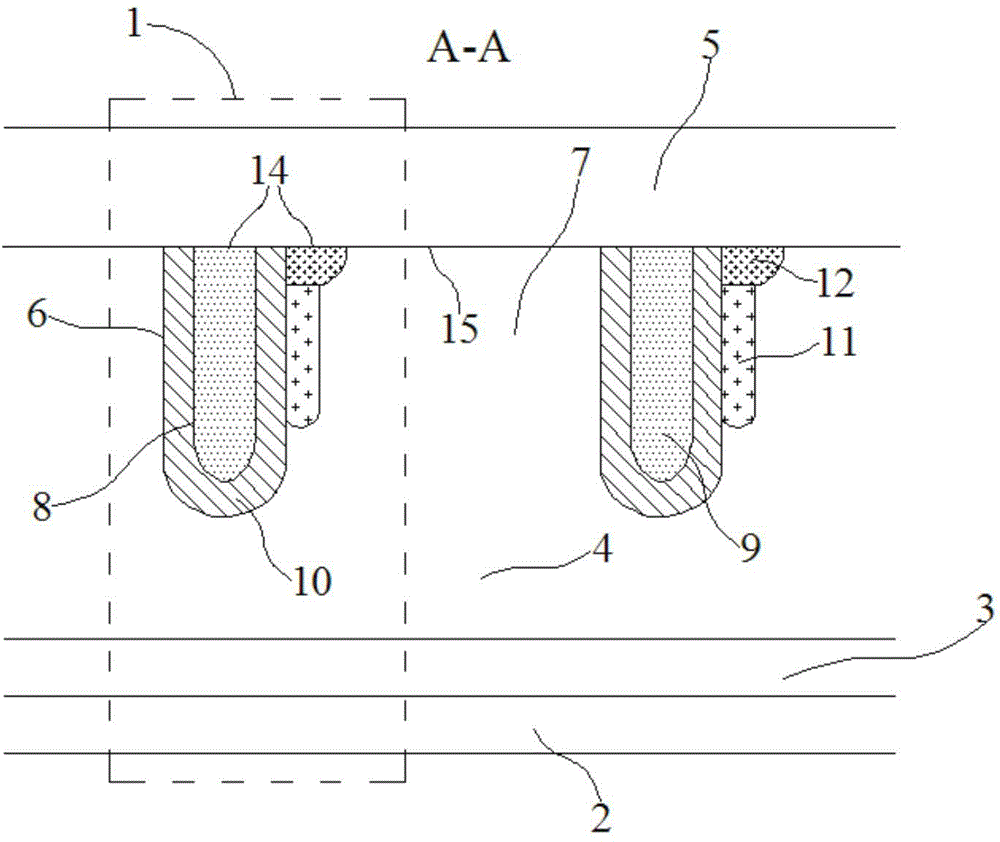

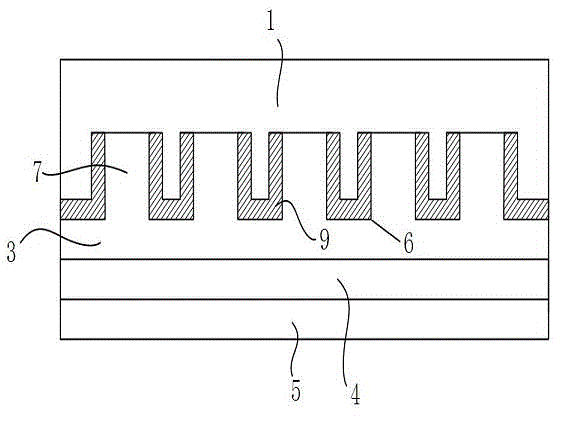

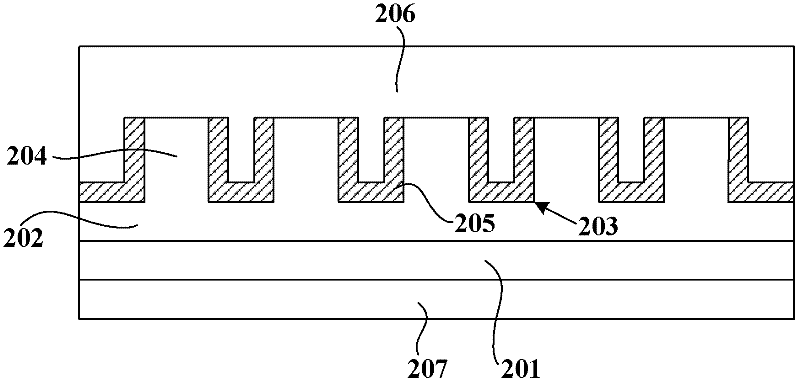

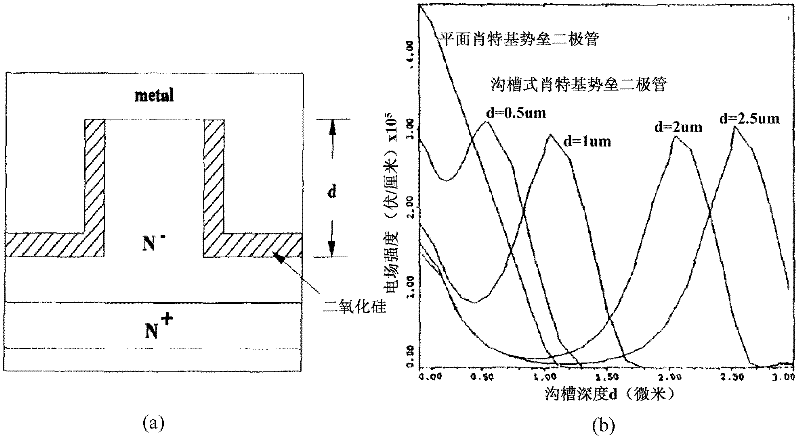

Enhanced grooved Schottky diode rectification device and fabrication method thereof

InactiveCN104134702AEnhanced reverse voltage blocking capabilityStrong Gap Filling CapabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierOhmic contact

The invention discloses an enhanced grooved Schottky diode rectification device. Grooves extend from the upper surface of an epitaxial layer to a middle part of the epitaxial layer, a monocrystalline silicon boss of a first conductive type is formed at the region of the epitaxial layer between the adjacent grooves, Schottky barrier contact is formed between the top surface of the monocrystalline silicon boss and an upper metal layer, a gate groove is arranged in the grooves and filled with conductive polycrystalline silicon, ohmic contact is formed between the conductive polycrystalline silicon and the upper metal layer, the gate groove and the epitaxial layer are isolated by silicon dioxide, a doped region of a second conductive type is arranged in the monocrystalline silicon boss and attached to the side surface of the groove, the heavily-doped region of the second conductive type is arranged between the top of the doped region of the second conductive type and the upper surface of the epitaxial layer, both the doped region of the second conductive type and the heavily-doped region of the second conductive type form a pn junction interface with the epitaxial layer. The device of the invention modulates electric field distribution of a device during reverse bias, enhances a reverse voltage blocking capacity of the device, and provides more flexibility for performance adjustment of the device.

Owner:SUZHOU SILIKRON SEMICON CO LTD

Trenched Schottky-barrier diode and manufacturing method thereof

ActiveCN102916055ALower doping concentration is lowReduce reverse leakageSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierOhmic contact

The invention discloses a trenched Schottky-barrier diode, and solves the problems that a conventional trenched Schottky-barrier diode is lower in performance and reliability, high in reverse current leakage and poor in reverse blocking capability. The doping density of an epilayer gradually increases from the top to bottom, a second conduction type non-uniformly doped conductive polycrystalline silicon of which the doping density gradually decreases from the top to bottom is filled in trenches, second conduction type heavily doped lug boss apex angle protection areas are formed at the apex angles on two sides of lug bosses, and a Schottky-barrier metal layer in ohmic contact with the top surfaces of both the conductive polycrystalline silicon and the lug boss apex angle protection areas is added to the bottom surface of an anodal metal layer. The trenched Schottky-barrier diode provided by the invention has the advantages of low reverse current leakage, good voltage reverse blocking capability and excellent reliability. The invention also provides a manufacturing method of the trenched Schottky-barrier diode, which has the advantages of less steps and low manufacturing cost and can effectively isolate areas from damage by the technological process and contamination of impurities due to local impairment of isolating layers.

Owner:HANGZHOU LION MICROELECTRONICS CO LTD

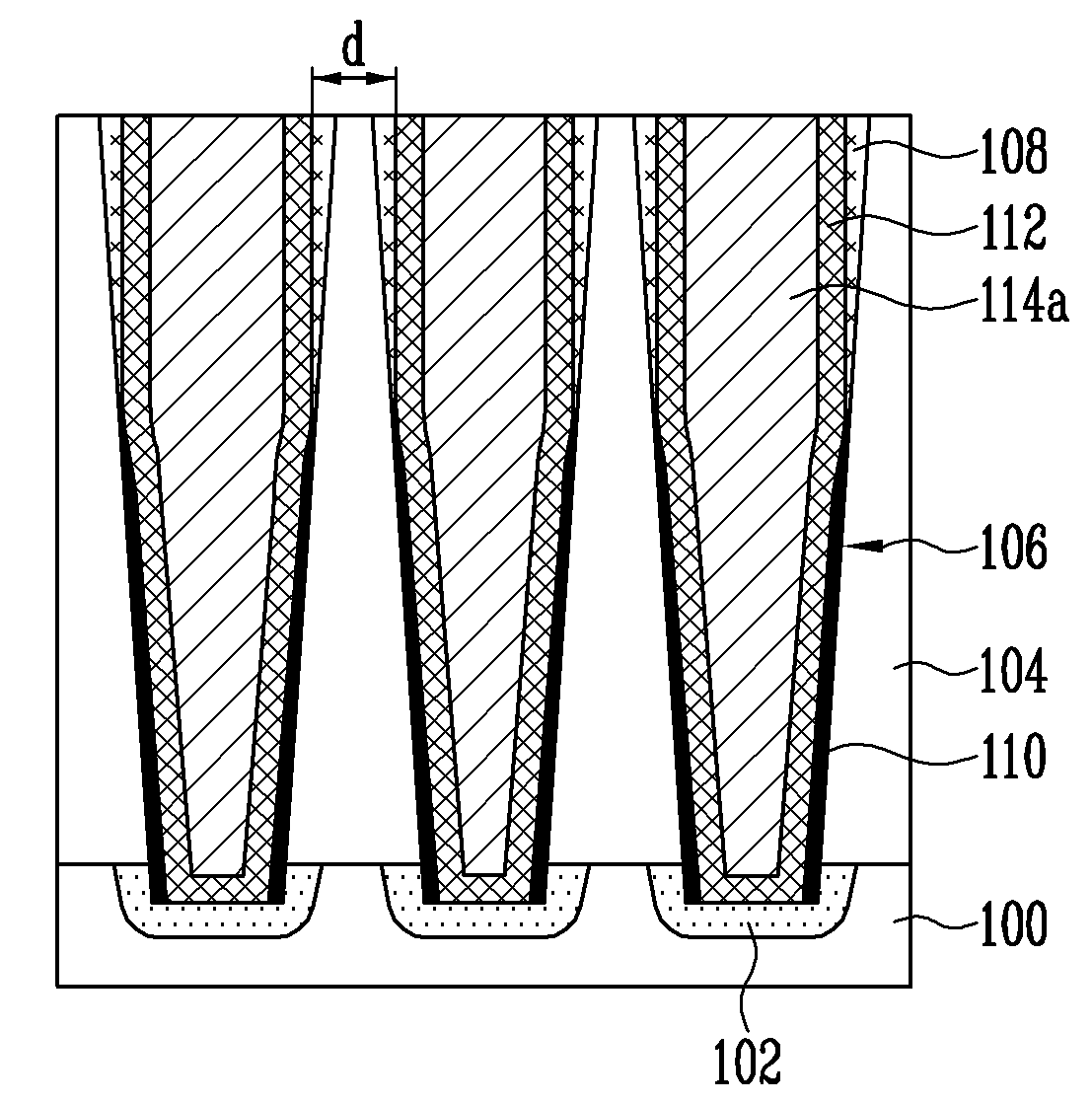

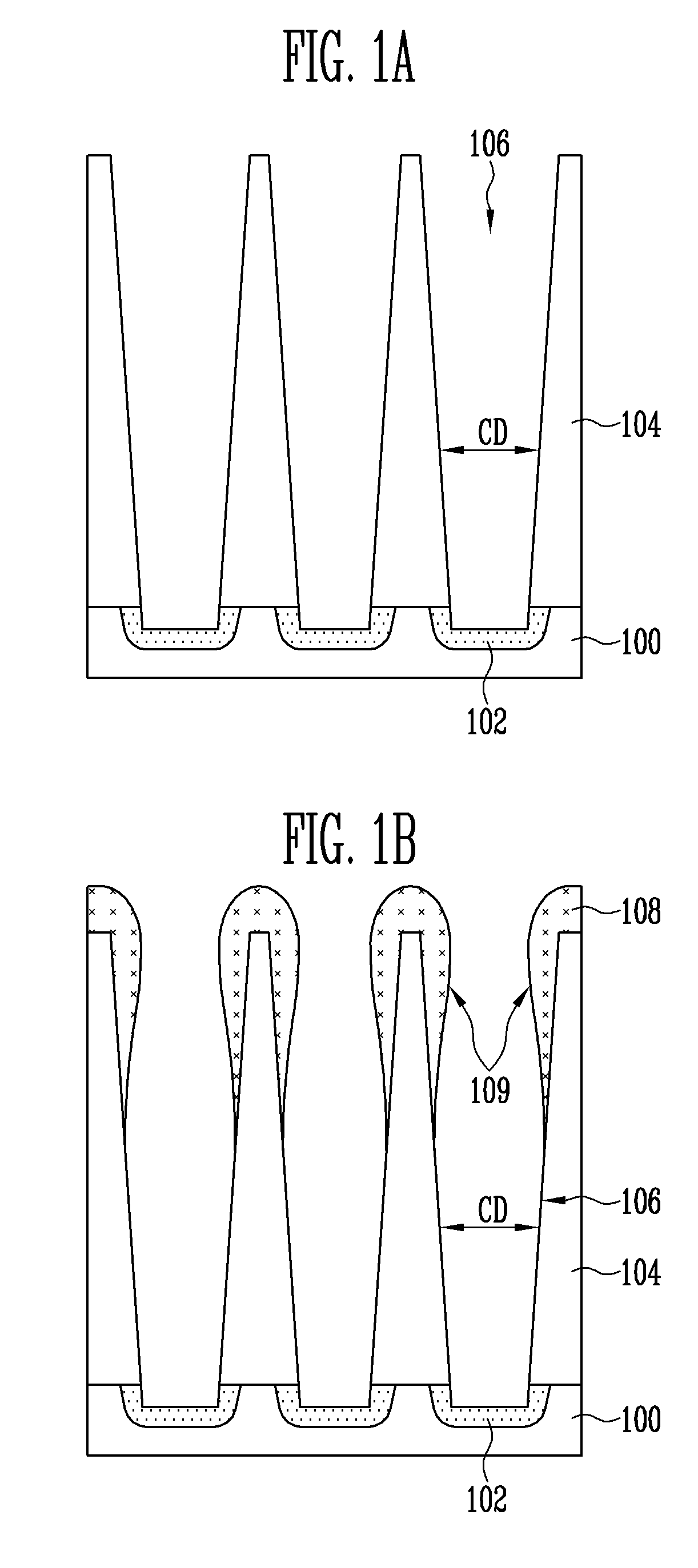

Method of forming contact plug in semiconductor device

InactiveUS20090004856A1Enhance contact gap-fill capabilityAvoid seamsSemiconductor/solid-state device manufacturingCritical dimensionSemiconductor

A method of forming a contact plug in a semiconductor device comprising etching an interlayer insulating layer to form a patterned interlayer insulating layer having contact holes such that a distance between upper portions of the contact holes is minimized; forming a first insulating layer including a overhang portion for wrapping an upper portion of the patterned interlayer insulating layer; forming a liner-shaped second insulating layer on the patterned interlayer insulating layer including the first insulating layer, the second insulating layer being formed from material having a selectivity which differs from that of the first insulating layer; and at least partially removing the second insulating layer to increase a bottom critical dimension of the contact hole and removing the overhang portion of the first insulating layer. The invention can secure the bottom critical dimension of the contact hole as well as a distance between the upper portions of the contact holes when the contact plug is formed in a trench in a subsequent process so that the subsequent process margin can be secured. Also, the invention can inhibit an overhang or seam from being formed on the contact plug to enhance contact gap-fill capability and improve contact resistance.

Owner:SK HYNIX INC

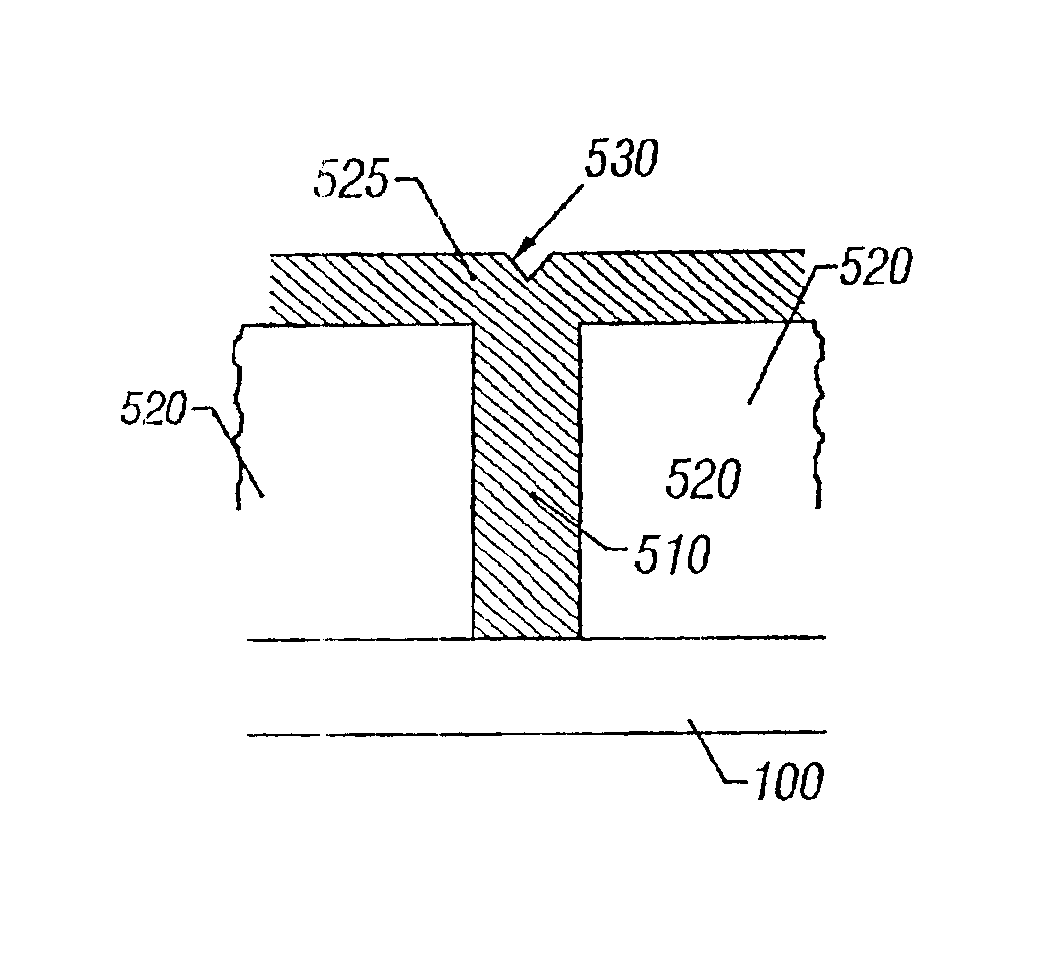

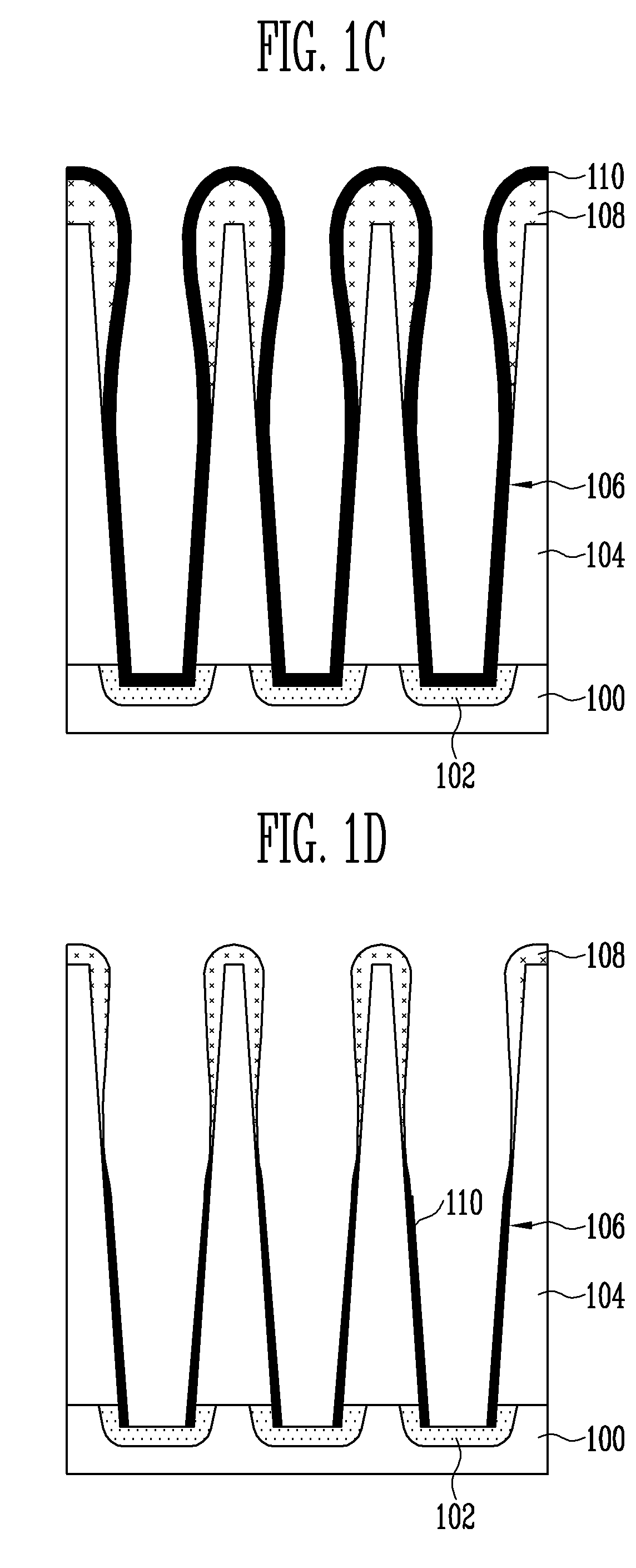

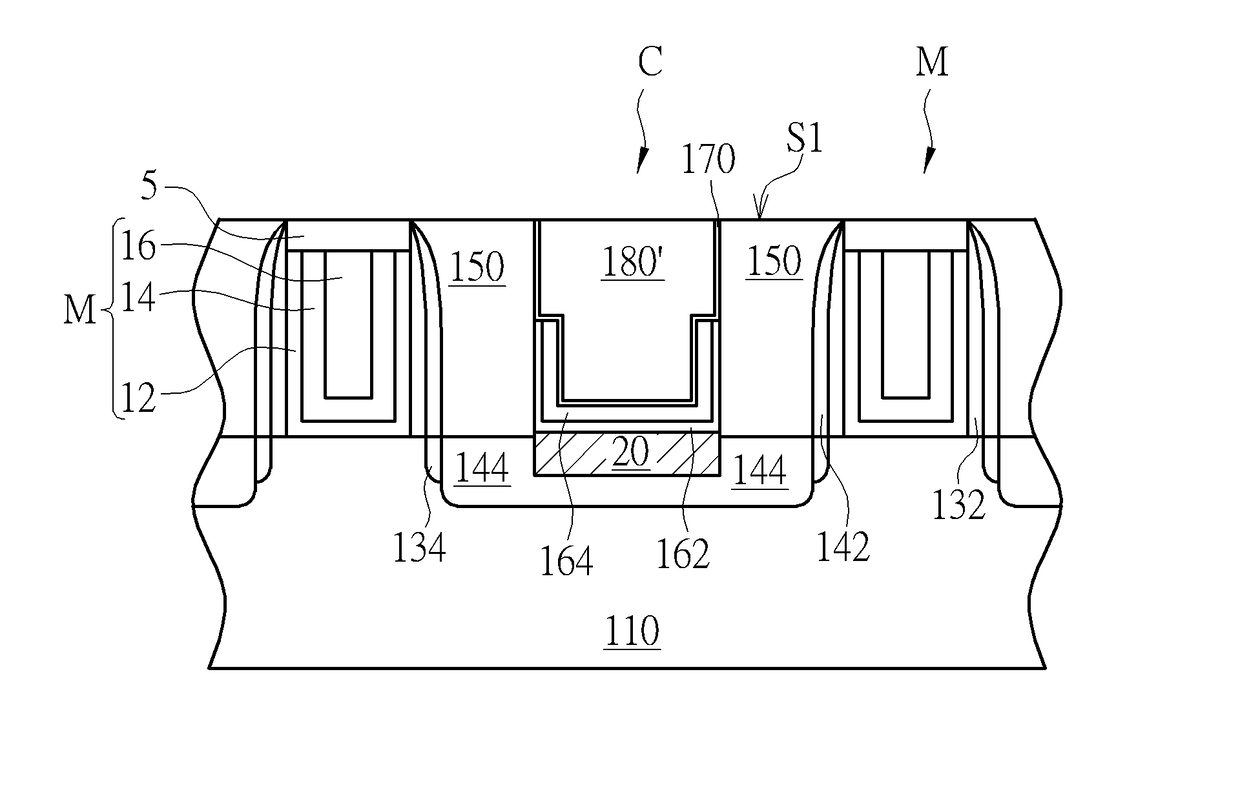

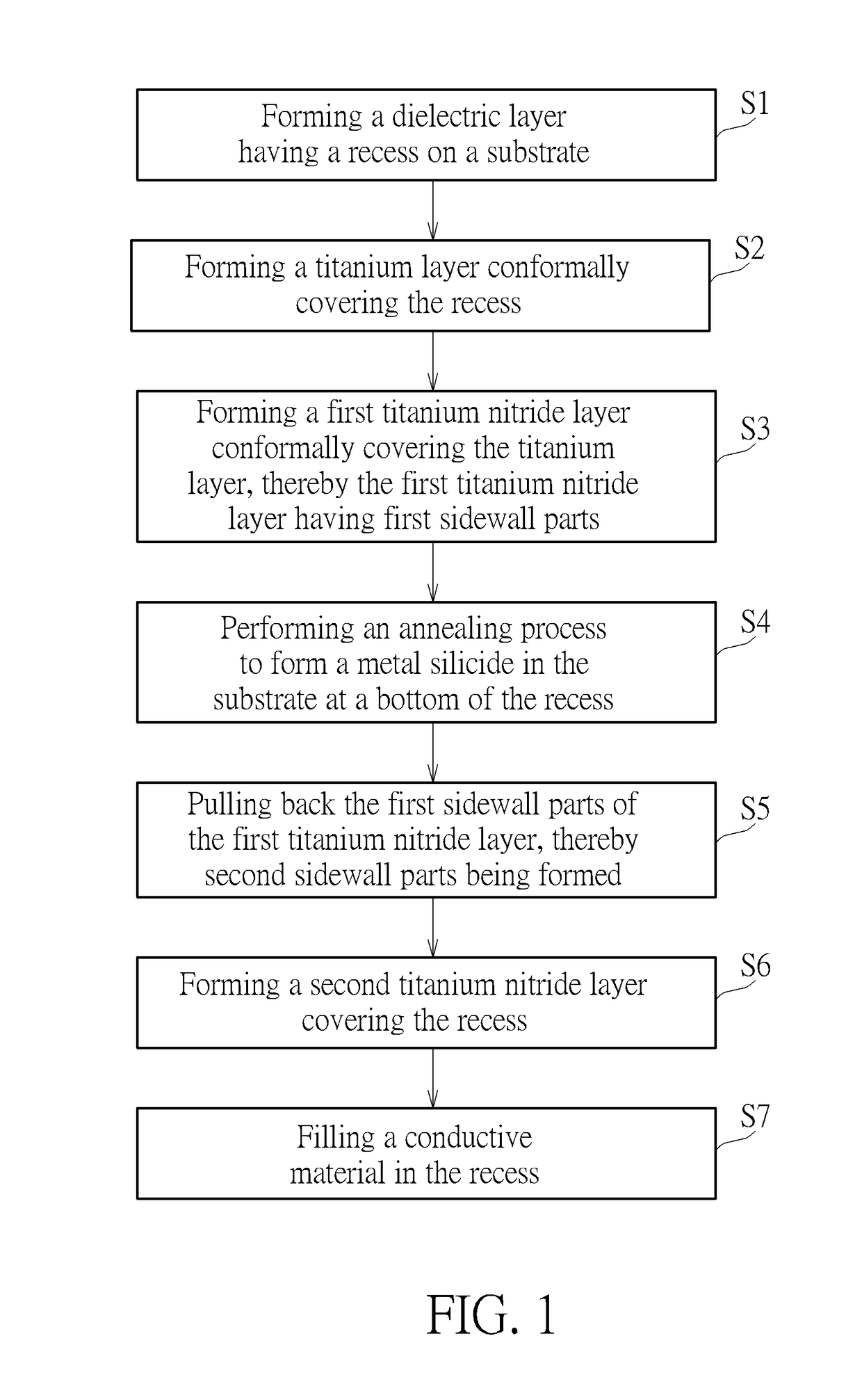

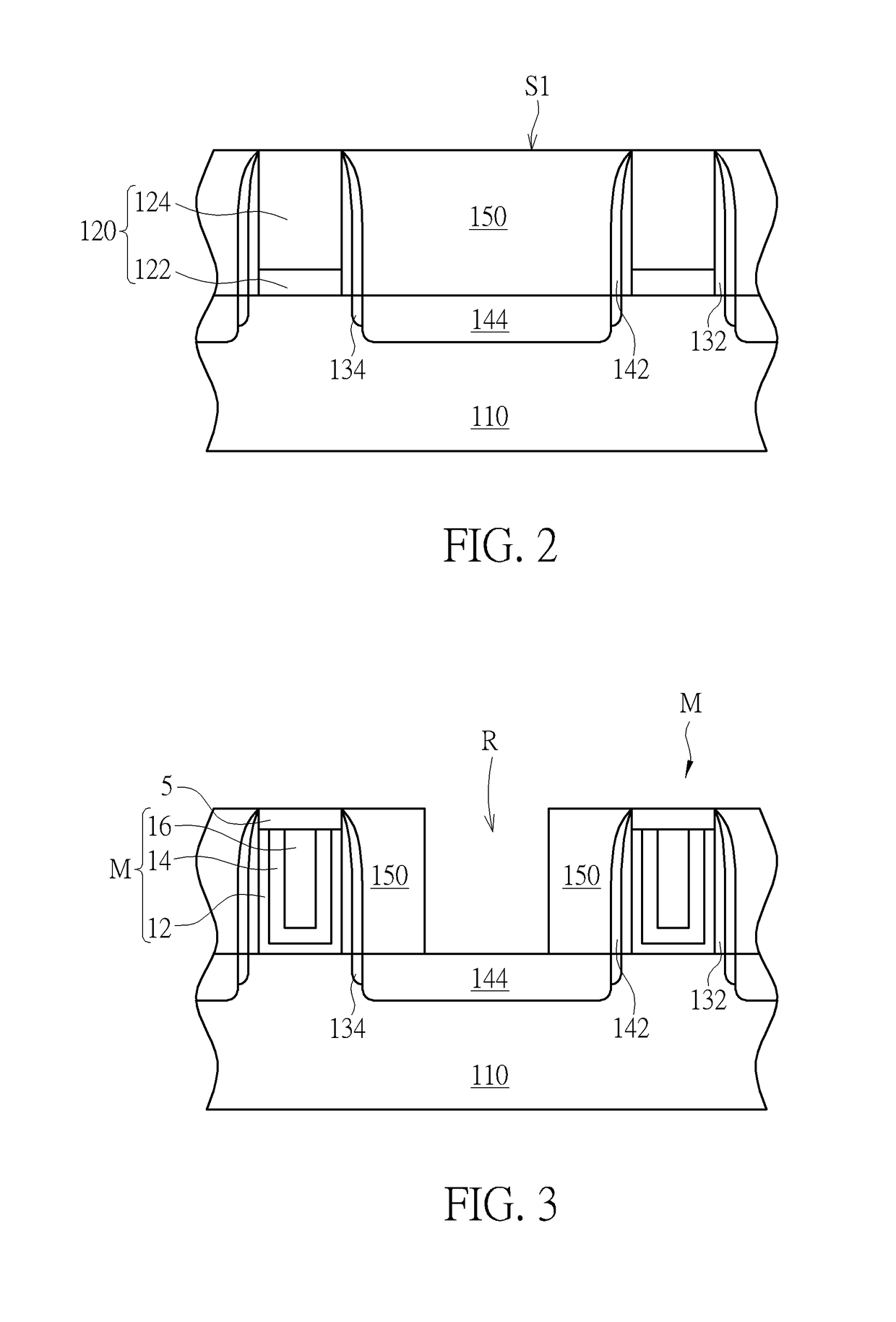

Semiconductor structure and process for forming plug including layer with pulled back sidewall part

ActiveUS9679813B2Strong Gap Filling CapabilityOpening of the recess can be increasedSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureTitanium nitride

Owner:UNITED MICROELECTRONICS CORP

High-density plasma (HDP) chemical vapor deposition (CVD) methods and methods of fabricating semiconductor devices employing the same

InactiveUS20060223321A1Reducing fluorine atomReduce amountSemiconductor/solid-state device manufacturingPackaging toiletriesPressure rangeSemiconductor

In one embodiment, a semiconductor substrate is placed into a process chamber. A gas mixture including a silicon-containing gas, a fluorine-containing gas, an inert gas, and an oxygen gas is introduced into the chamber at a pressure range of from about 30 mTorr to about 90 mTorr. During this time, deposition and etching processes are concurrently performed using a plasma to form a high-density plasma (HDP) insulating layer on the semiconductor substrate. A ratio of deposition to etching is from about 3:1 to about 10:1. A ratio of a flow rate of the fluorine-containing gas to a flow rate of the silicon-containing gas is less than about 0.9.

Owner:SAMSUNG ELECTRONICS CO LTD

Interlayer dielectric material in a semiconductor device comprising stressed layers with an intermediate buffer material

ActiveUS20100276790A1Low efficiencyReduce probabilitySemiconductor/solid-state device detailsSolid-state devicesStress inducedDielectric

A highly stressed dielectric material, such as a tensile stressed material, may be deposited in a conformal manner so as to respect any deposition constraints caused by pronounced surface topography of highly scaled semiconductor devices, followed by the deposition of a buffer material having enhanced gap-filling capabilities. Thereafter, a further stress-inducing layer is deposited to form a doublet structure, which acts on the transistor elements, thereby enhancing overall performance, without increasing the probability of creating deposition-related irregularities. Hence, production yield as well as performance of highly scaled semiconductor devices may be increased.

Owner:TAIWAN SEMICON MFG CO LTD

Brazing rare earth magnesium alloy brazing filler metal and preparation method and brazing process

ActiveCN106077994AUniform compositionGood wetting and spreadingWelding/cutting media/materialsSoldering mediaRare earthFiller metal

The invention discloses brazing rare earth magnesium alloy brazing filler metal and a preparation method and a brazing process. The brazing rare earth magnesium alloy brazing filler metal comprises the following element components in percentage by weight: 13-19% of Zn, 1.0-3.0% of Ni, 1.8-4.4% of Al, 0.4-1.0% of Ti, 5.1-7.0% of Cu, 0.3-0.8% of Mn, 0.004-0.01% of La, 0.004-0.01% of Nd, and the balance of Mg. The magnesium alloy brazing filler metal reaches the brazing temperature of 420-460 DEG C, and is proper in melting temperature and uniform in components; and a magnesium alloy brazing filler metal foil piece facilitates acceleration of dispersion and interface reaction of all alloy elements in the brazing connecting process, so that the wetting spreadability and the gap filling performance of the brazing filler metal in a rare earth magnesium alloy are improved, the grains are refined, the residual stress is reduced, and the joint bonding strength is improved.

Owner:JIANGSU YANGMING SHIP EQUIP MFG TECH

Heat-conducting material

InactiveCN106366583AStrong Gap Filling CapabilityGood shapeHeat-exchange elementsAntioxidantGraphite

The invention relates to a heat-conducting material which comprises the following components in parts by weight: 20-50 parts of PBT (polybutylene terephthalate), 2-4 parts of PET (polyethylene terephthalate), 3-4 parts of polyurethane, 2-5 parts of nylon, 2-5 parts of heat-conducting filler, 2-5 parts of polyethyleneglycol, 20-30 parts of silicone rubber, 0.5-0.9 part of vulcanizing agent, 0.33-0.9 part of antioxidant, 0.3-0.5 part of lubricant, 2-3 parts of graphite, 3-4 parts of silicone rubber and 1-2 parts of combustion improver. The heat-conducting material has favorable gap filling capacity and moldability, can perform favorable heat transfer functions, is convenient for assembly and disassembly, and has favorable heat-conducting effects.

Owner:裴寿益

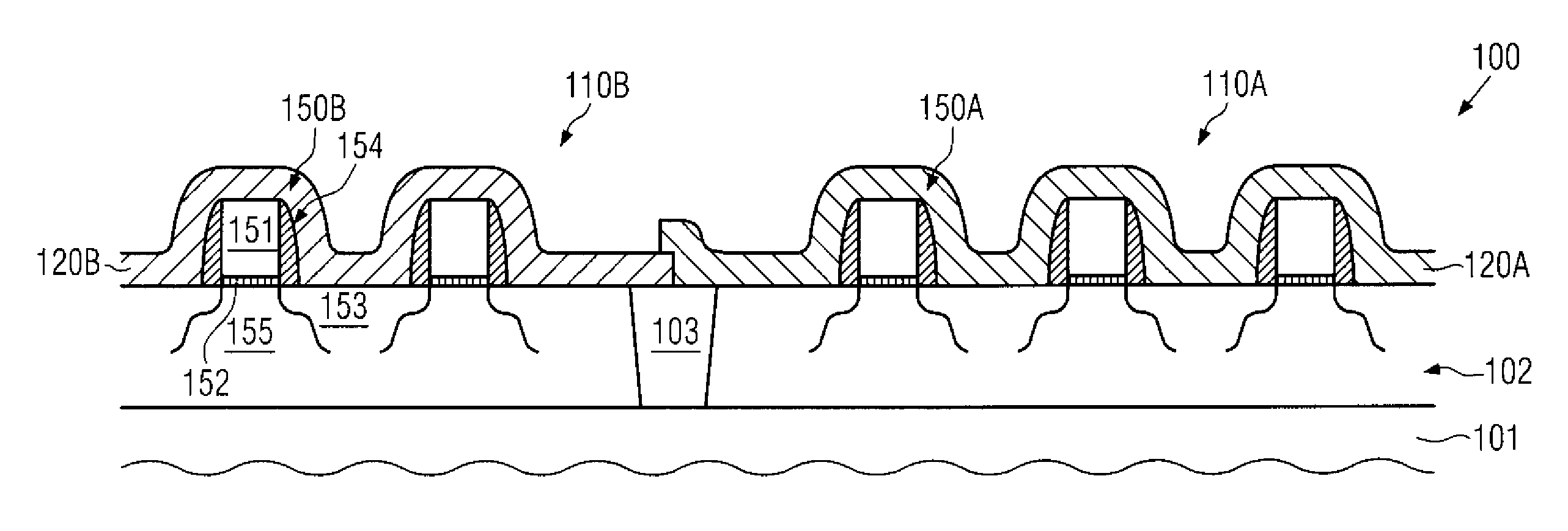

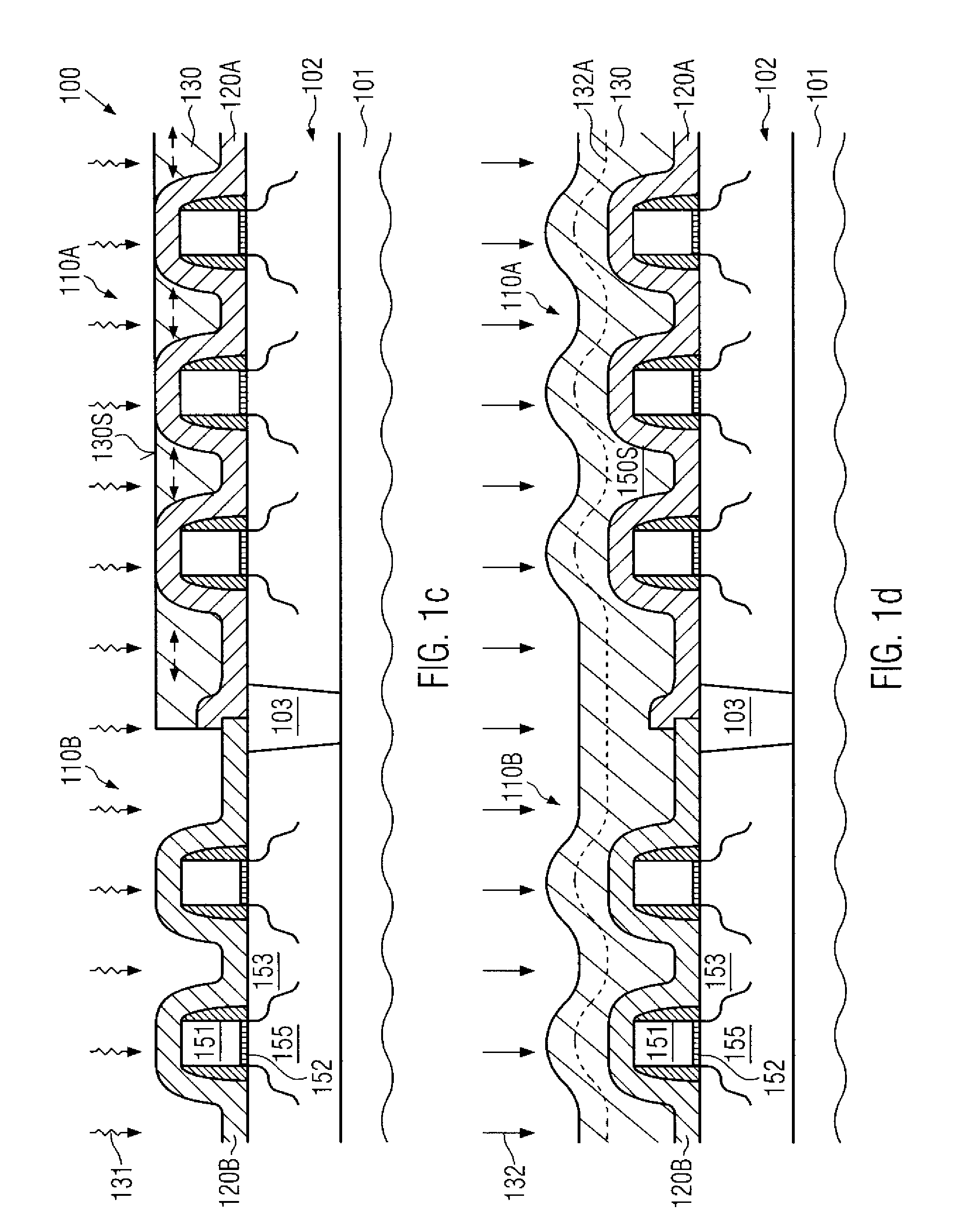

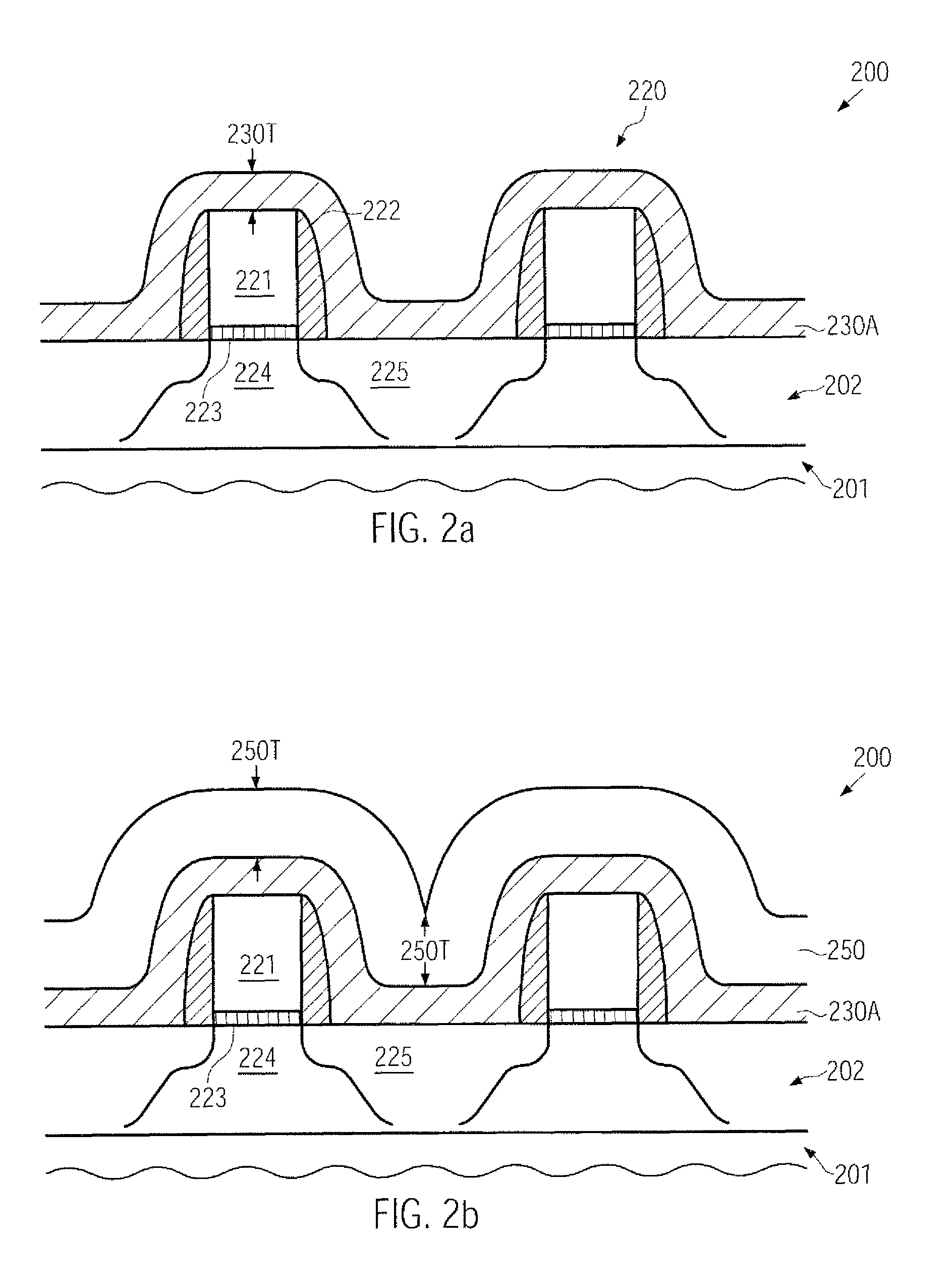

Technique for compensating for a difference in deposition behavior in an interlayer dielectric material

ActiveUS20090087999A1Reduce height differenceStrong Gap Filling CapabilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingOptoelectronicsHeight difference

By selectively providing a buffer layer having an appropriate thickness, height differences occurring during the deposition of an SACVD silicon dioxide may be reduced during the formation of an interlayer dielectric stack of advanced semiconductor devices. The buffer material may be selectively provided after the deposition of contact etch stop layers of both types of internal stress or may be provided after the deposition of one type of dielectric material and may be used during the subsequent patterning of the other type of dielectric stop material as an efficient etch stop layer.

Owner:ADVANCED MICRO DEVICES INC

Schottky barrier diode rectifying device and manufacture method thereof

InactiveCN102522431AIncrease the enclosing areaStrong Gap Filling CapabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSilicon chipMonocrystalline silicon

The invention discloses a Schottky barrier diode rectifying device and a manufacture method thereof. According to the device, an active region is formed by parallel connection of a plurality of Schottky barrier diode unit cells; each unit cell comprises a first conductive light dope monocrystalline silicon epitaxial layer which is connected with an upper part of a silicon chip and an upper metal layer, grooves which are at an upper part of the epitaxial layer and whose openings are at upper surface of the epitaxial layer, and a boss which is formed between adjacent grooves in an epitaxial layer area; a lower metal layer and a substrate form ohmic contact; the upper metal layer is connected with upper surfaces of a first conductive polysilicon zone and a second conductive polysilicon zone to form ohmic contact; the upper metal layer is connected with an upper surface of the boss to form Schottky barrier contact; lower bottom depth of the first conductive polysilicon zone is larger than lower bottom depth of the second conductive polysilicon zone; and thickness of a first isolation oxidation layer is larger than thickness of the second isolation oxidation layer. According to the device and the method of the invention, reverse voltage blockout capability of the device is enhanced substantially, slit filling capability is improved, thus much flexibility is provided for device structure design, and device reliability is reinforced.

Owner:SUZHOU SILIKRON SEMICON CO LTD

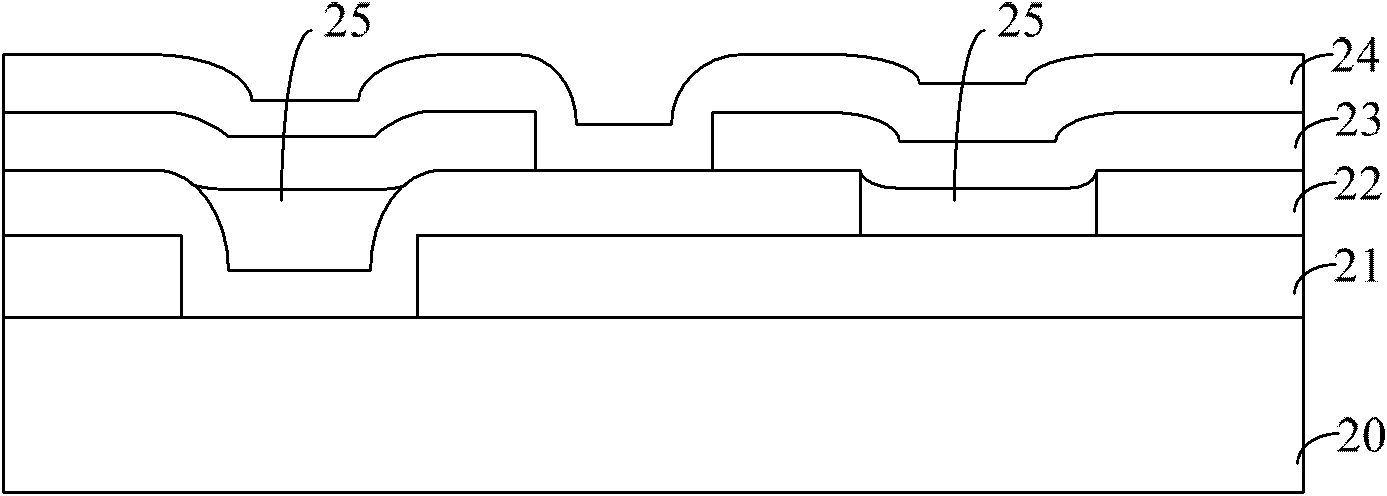

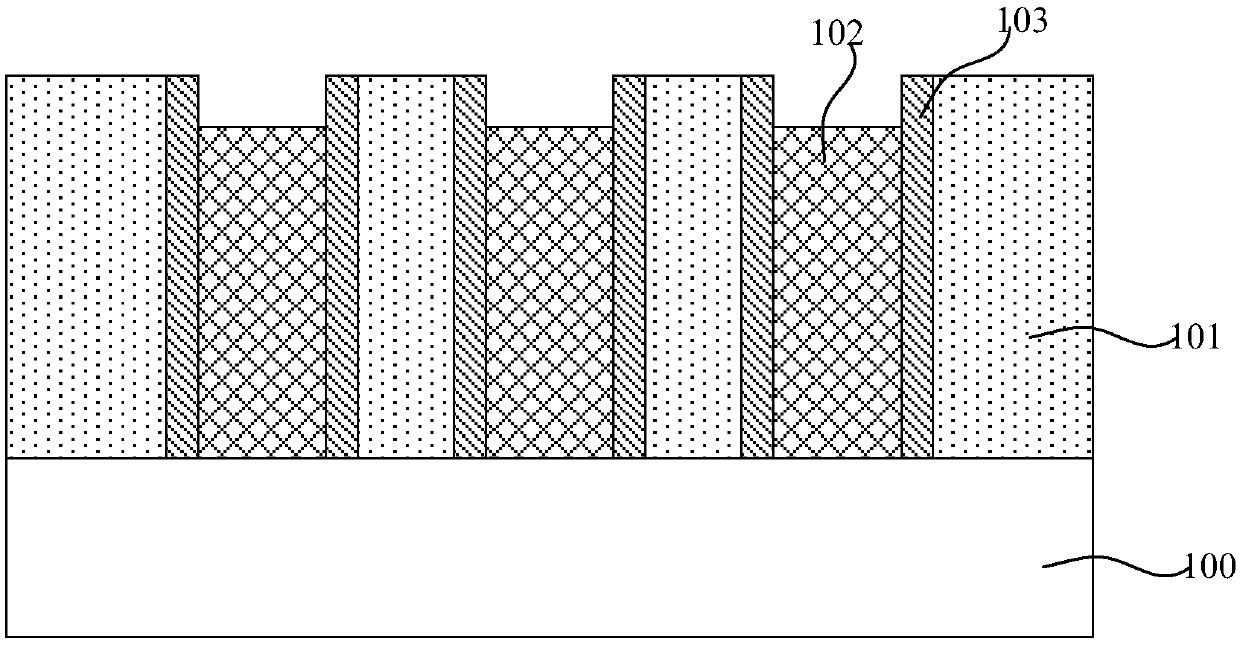

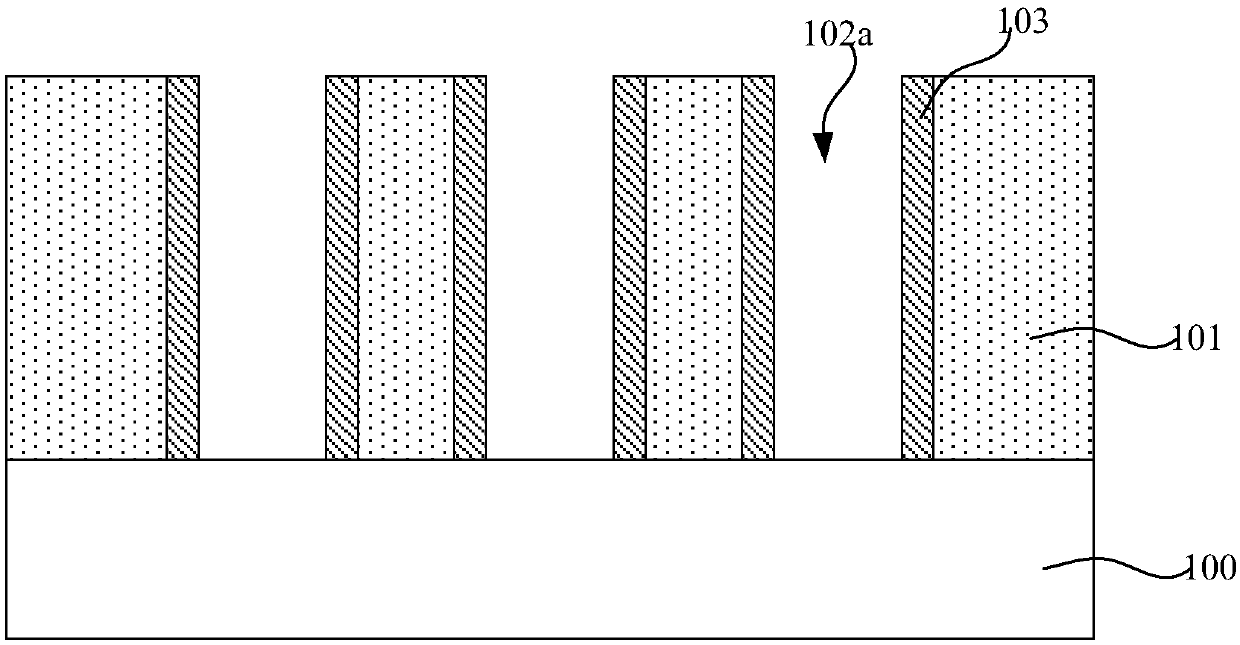

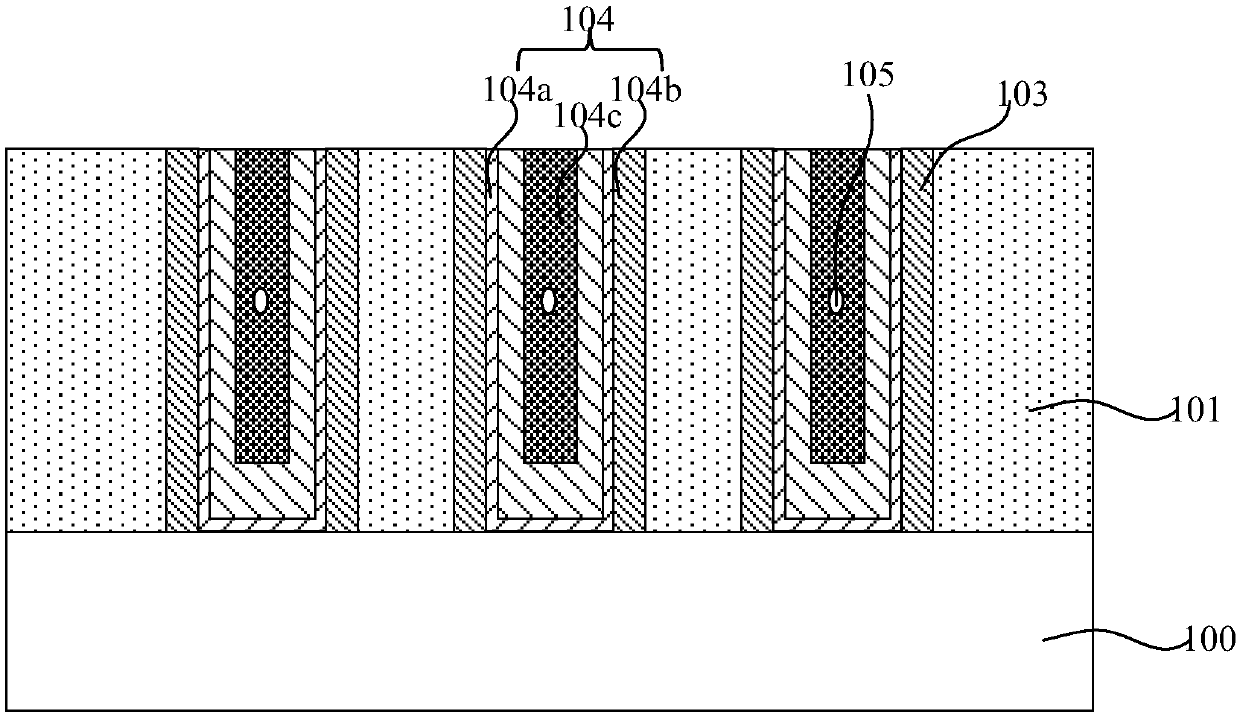

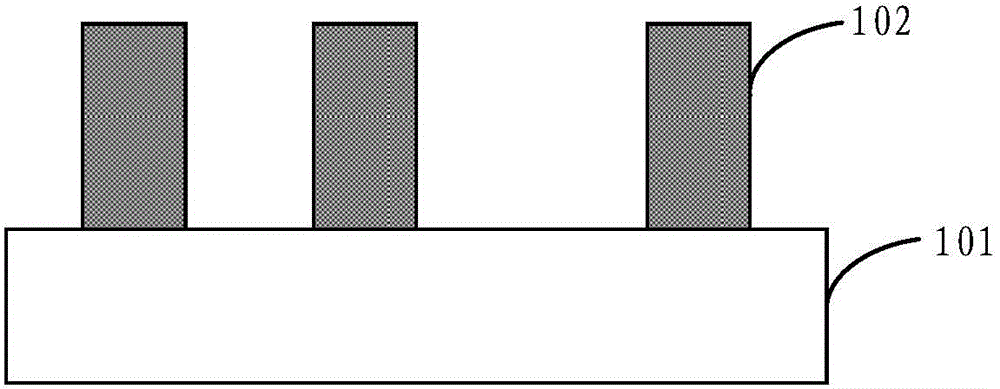

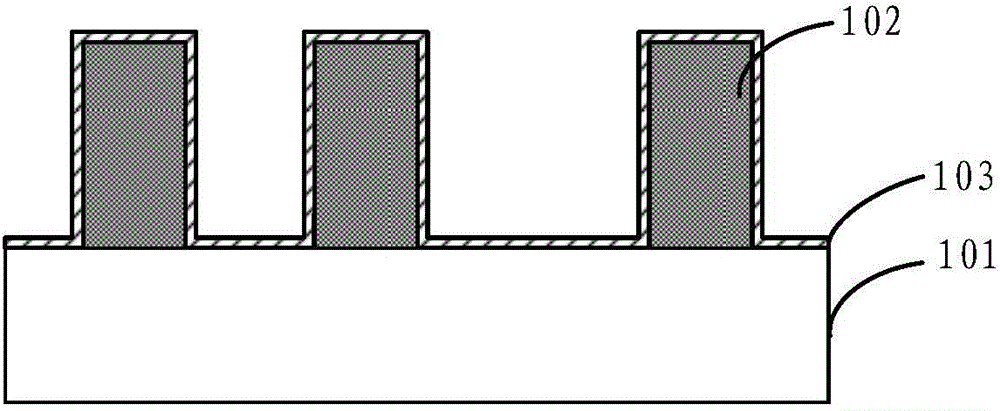

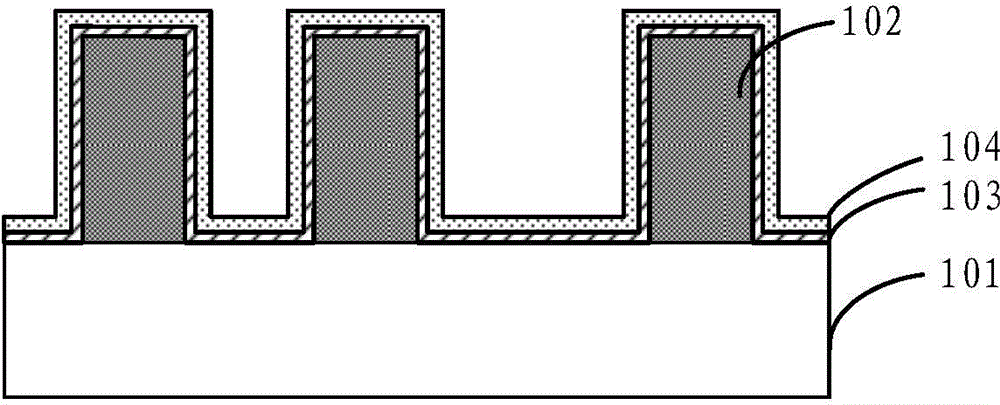

Method for manufacturing metal gate and method for manufacturing semiconductor device

ActiveCN110571141AStrong Gap Filling CapabilityReduce filling voidsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringWidth ratio

The invention provides a method for manufacturing a metal gate and a method for manufacturing a semiconductor device. Before a dummy gate is removed to form an opening for filling metal gate, a portion of an initial spacer on the sidewall of the dummy gate is firstly subjected to material modification in order that the initial spacer is transformed into a first spacer not subjected to material modification and a second spacer located on the first spacer and subjected to material modification. Thus, all or part of the second spacer can be removed simultaneously while the virtual gate is removed, so that the opening having an wide top and a narrow bottom and for filling the metal gate can be formed after the process of removing the virtual gate ends. The depth-to-width ratio of the opening is reduced so as to improve the subsequent gap filling capability of the metal gate, and reduce defects such as filling voids and gaps of the metal gate, thereby improving the performance of the finally manufactured semiconductor device.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

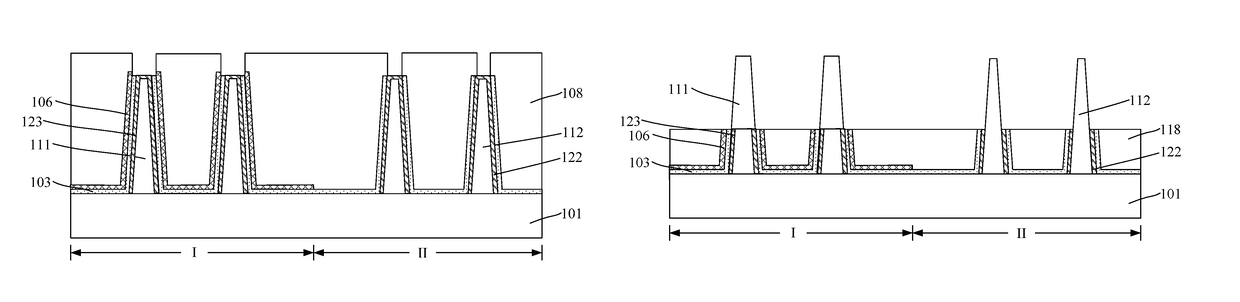

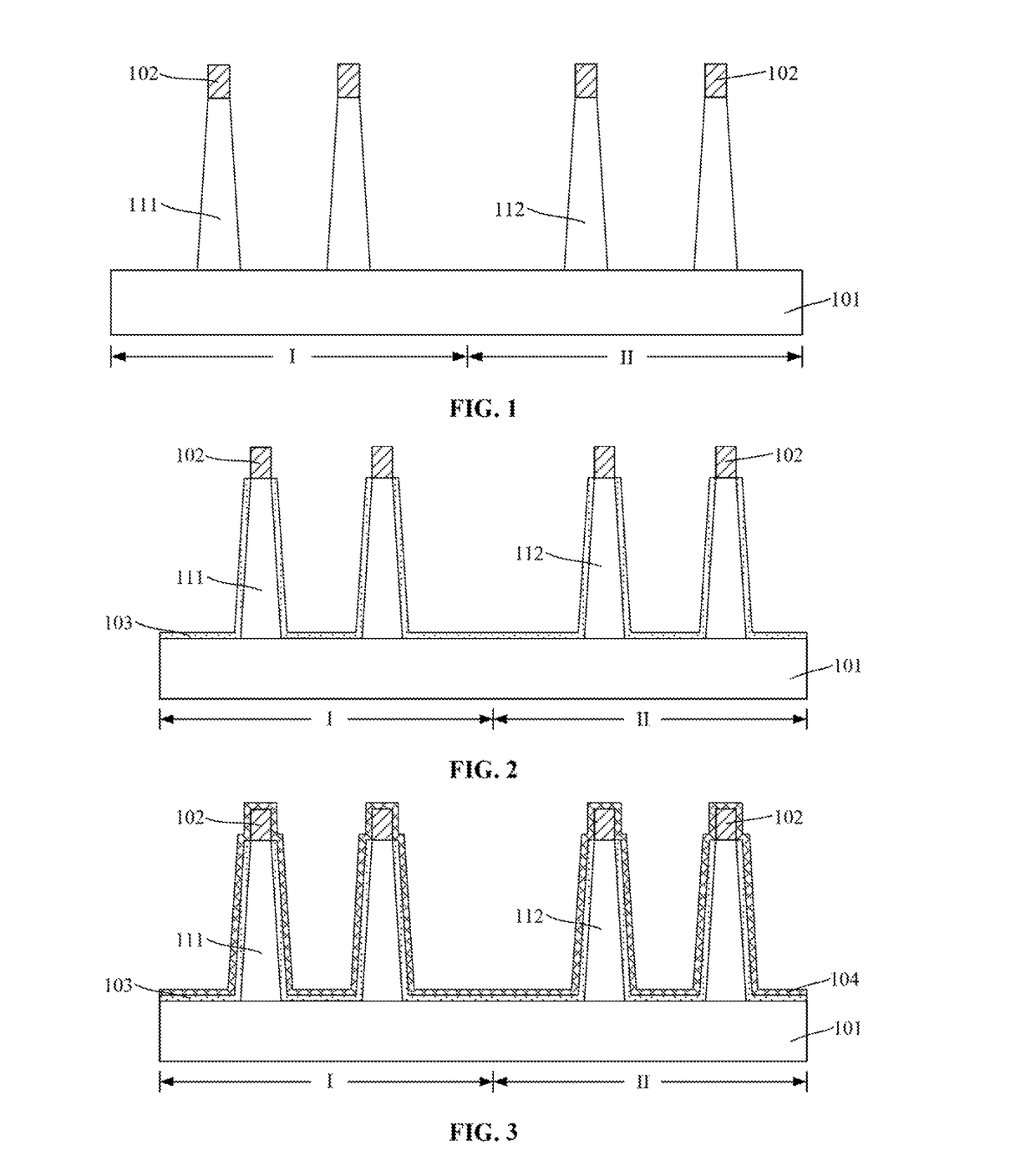

Fin field-effect transistor and fabrication method thereof

ActiveUS10121880B2Strong preventive abilityStrong Gap Filling CapabilityTransistorSolid-state devicesInsulation layerManufacturing technology

The present disclosure provides fin field-effect transistors and fabrication methods thereof. An exemplary fabrication process includes providing a substrate having a first region and a second region; forming first fins in the first region and second fins in the second region; forming a liner oxide layer on side surfaces of the first fins, the second fins and a surface of the substrate; forming an insulating barrier layer on the liner oxide layer in the first region; forming a precursor material layer on the insulating barrier layer in the first region and on the liner oxide layer in the second region; performing a curing annealing process to convert the precursor material into an insulation layer; and removing a top portion of the insulation layer to form an isolating layer and removing portions of the liner oxide layer, the insulating barrier layer, the first oxide layer and the second oxide layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Oxygen-rich layers underlying BPSG

ActiveUS7741171B2Strong Gap Filling CapabilityReduced lateral etchingSemiconductor/solid-state device detailsSolid-state devicesSilicate glassSilicon oxide

An integrated circuit structure and a method of forming the same are provided. The method includes providing a surface; performing an ionized oxygen treatment to the surface; forming an initial layer comprising silicon oxide using first process gases comprising a first oxygen-containing gas and tetraethoxysilane (TEOS); and forming a silicate glass over the initial layer. The method may further include forming a buffer layer using second process gases comprising a second oxygen-containing gas and TEOS, wherein the first and the second process gases have different oxygen-to-TEOS ratio.

Owner:TAIWAN SEMICON MFG CO LTD

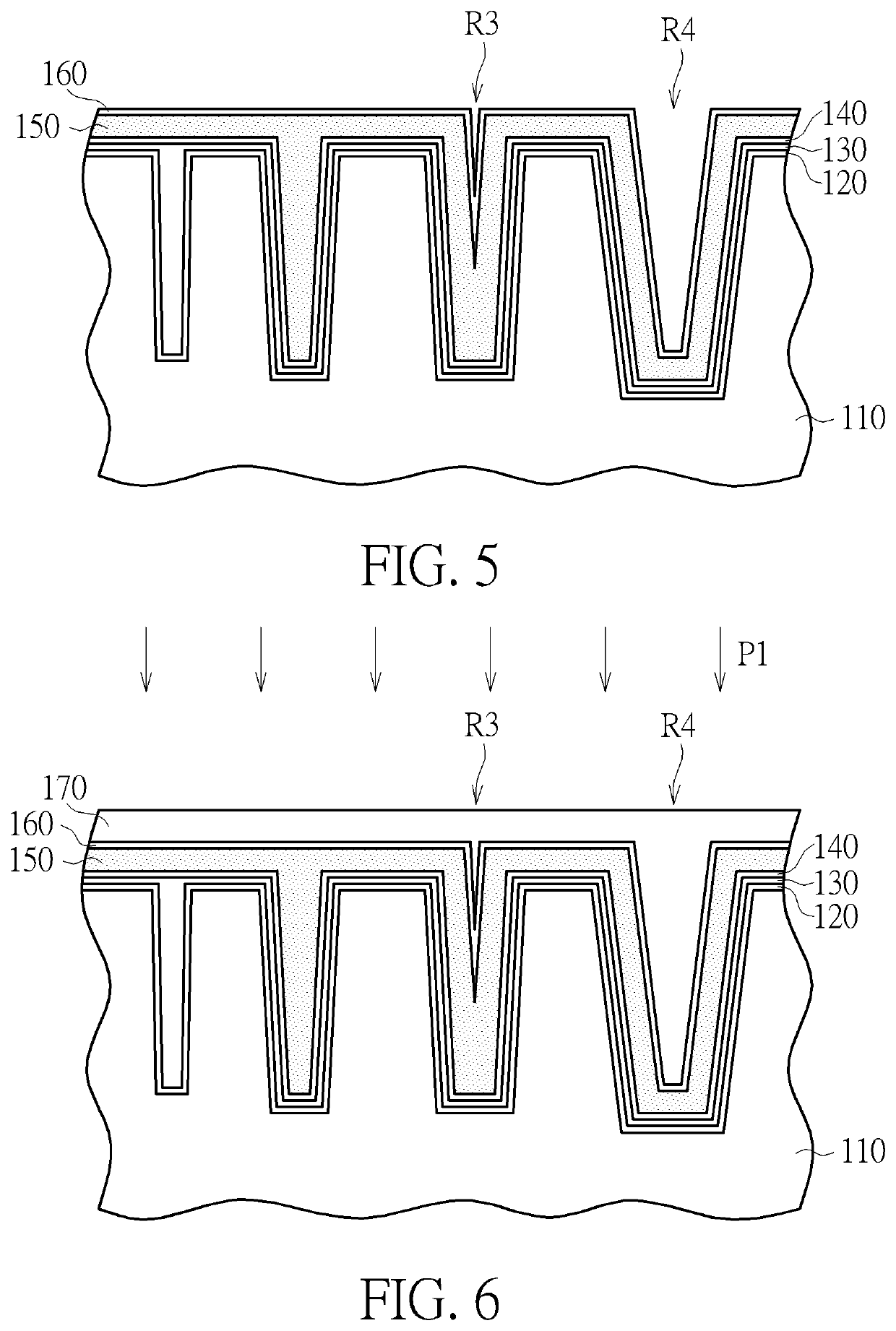

Method of forming isolation structure

ActiveUS20200075397A1Avoid uneven stressStrong Gap Filling CapabilitySemiconductor/solid-state device manufacturingEngineering physicsAtomic layer deposition

A method of forming an isolation structure includes the following steps. A substrate having a first trench, a second trench and a third trench is provided, wherein the opening of the third trench is larger than the opening of the second trench, and the opening of the second trench is larger than the opening of the first trench. A first oxide layer is formed to conformally cover the first trench, the second trench and the third trench by an atomic layer deposition (ALD) process. A second oxide layer fills up the first trench by an in-situ steam generation (ISSG) process.

Owner:UNITED MICROELECTRONICS CORP +1

Interlayer dielectric material in a semiconductor device comprising stressed layers with an intermediate buffer material

InactiveUS7875561B2Low efficiencyReduce probabilitySemiconductor/solid-state device detailsSolid-state devicesElectricityPower semiconductor device

A highly stressed dielectric material, such as a tensile stressed material, may be deposited in a conformal manner so as to respect any deposition constraints caused by pronounced surface topography of highly scaled semiconductor devices, followed by the deposition of a buffer material having enhanced gap-filling capabilities. Thereafter, a further stress-inducing layer is deposited to form a doublet structure, which acts on the transistor elements, thereby enhancing overall performance, without increasing the probability of creating deposition-related irregularities. Hence, production yield as well as performance of highly scaled semiconductor devices may be increased.

Owner:ADVANCED MICRO DEVICES INC

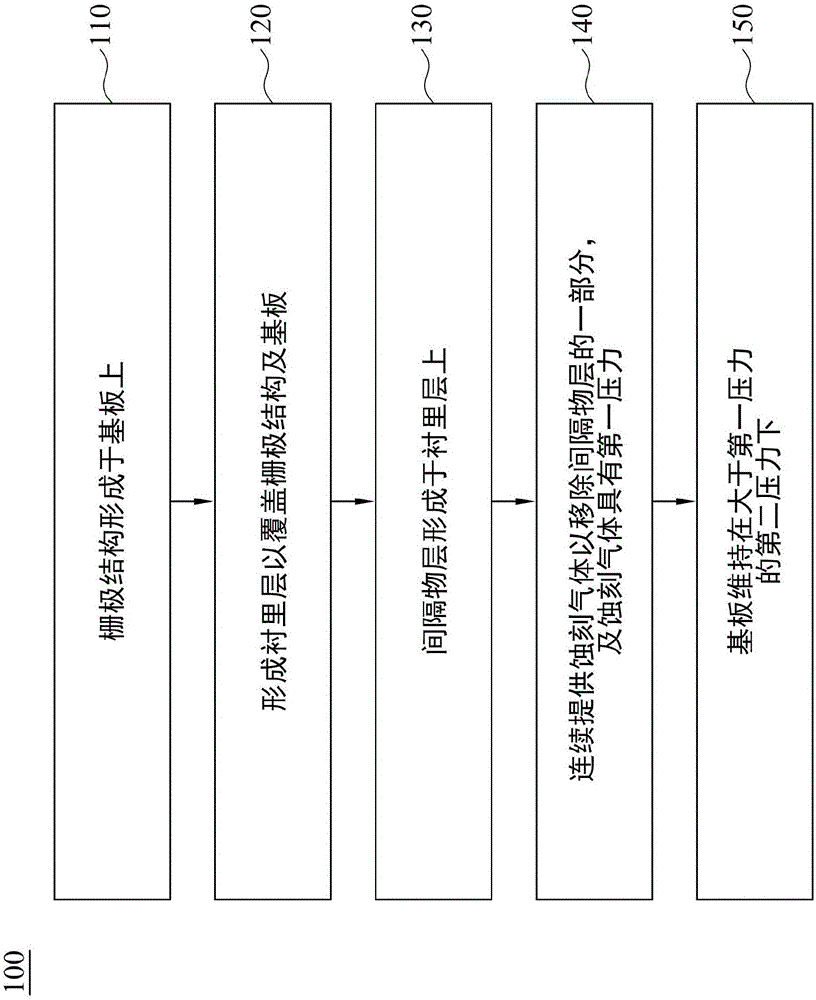

Method of fabricating semiconductor structure

ActiveCN106816469AHigh yieldStrong Gap Filling CapabilityTransistorSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The present disclosure provides a method of fabricating a semiconductor structure, and the method includes following steps. A gate structure is formed on a substrate, and a liner layer is formed to cover the gate structure and the substrate. A spacer layer is formed on the liner layer, and an etching gas is continuously provided to remove a portion of the spacer layer while maintaining the substrate at a second pressure, which the etching gas has a first pressure. The second pressure is greater than the first pressure.

Owner:TAIWAN SEMICON MFG CO LTD

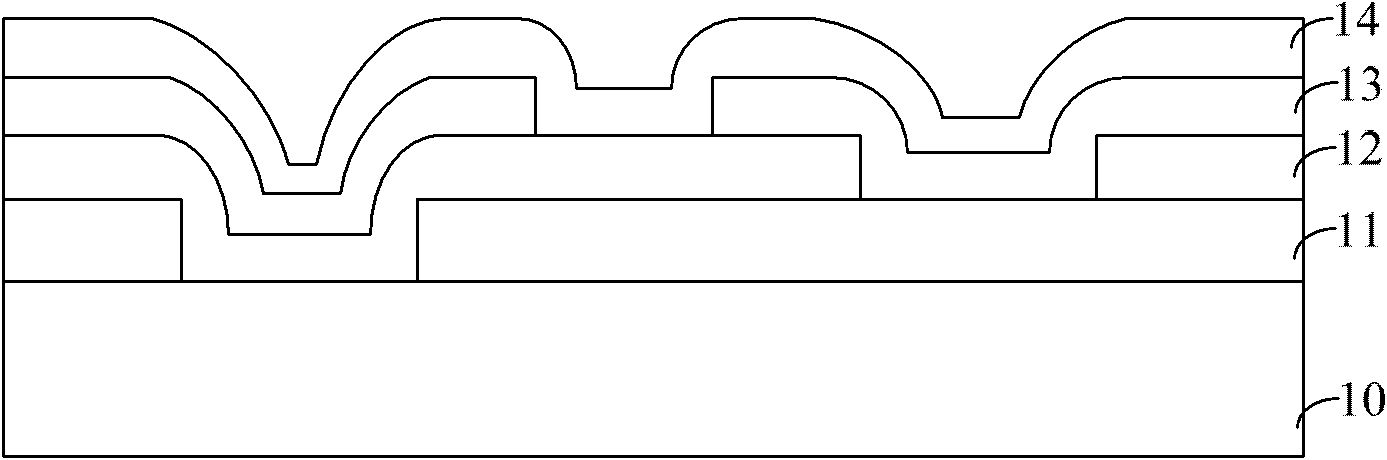

Semiconductor device and manufacturing method therefore, and electronic apparatus

ActiveCN105489605AEasy to changeAvoid stayingSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceInter layer

The invention provides a semiconductor device and a manufacturing method therefore, and an electronic apparatus. The manufacturing method comprises the steps of providing a semiconductor substrate, wherein a grid electrode structure is formed in the semiconductor substrate; forming an oxygen-rich laying layer on the top and side wall of the grid electrode structure and the semiconductor substrate; performing operations of disposition and curing treatment on a flowable dielectric material circularly on the oxygen-rich laying layer to form an inter-layer dielectric layer; and performing annealing treatment. According to the manufacturing method for the semiconductor device, due to the adoption of the oxygen-rich laying layer, the conversion of the flowable dielectric material can be promoted, and voids in the inter-layer dielectric layer are avoided; a high-temperature thermal annealing treatment step is not required to improve the gap filling of the dielectric layer; and therefore, the manufacturing method can improve the gap filling capability of the dielectric layer, and can improve the quality of the dielectric layer without increasing thermal budget.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Magnesium alloy brazing filler metal based on rare earth magnesium alloy braze as well as preparation method and brazing technology of magnesium alloy brazing filler metal

ActiveCN106001984AUniform compositionGood wetting and spreadingWelding/cutting media/materialsSoldering mediaInterfacial reactionAdditive ingredient

The invention discloses a magnesium alloy brazing filler metal based on rare earth magnesium alloy braze as well as a preparation method and a brazing technology of the magnesium alloy brazing filler metal. The magnesium alloy brazing filler metal comprises the following elements in percentage by weight: 8.8%-11.5% of Zn, 8.2%-9.3% of Al, 3.8%-5.5% of Ni, 1.0%-3.0% of Ag, 1.0%-2.0% of Ti, 0.8%-2.2% of Cu, 0.5%-1.0% of Mn and the balance of Mg. The rotary feeding device is moderate in melting temperature and uniform in ingredients; application of a magnesium alloy brazing filler metal chaff facilitates diffusion and interfacial reaction of all alloy elements during the brazed connection process, improves wetting spreadability and gap filling performance of the brazing filler metal in rare earth magnesium alloy, refines grain, reduces residual stress, and improves the bonding strength of joints.

Owner:JIANGSU YANGMING SHIP EQUIP MFG TECH