Method for manufacturing metal gate and method for manufacturing semiconductor device

A metal gate and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components and other directions, can solve problems such as affecting device performance, easy to generate voids, gaps, etc., to improve performance, improve gap filling capability, Reduce the effect of filling voids

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

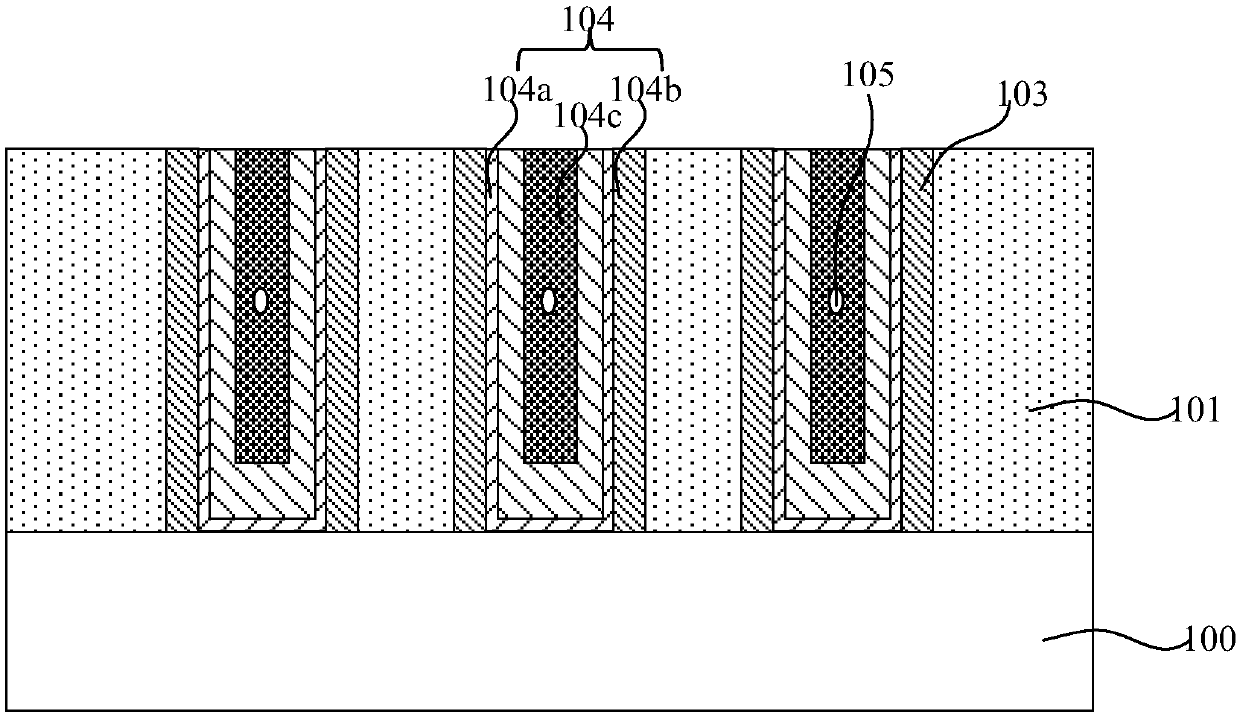

[0036] A method for manufacturing a high-K metal gate, comprising the following steps:

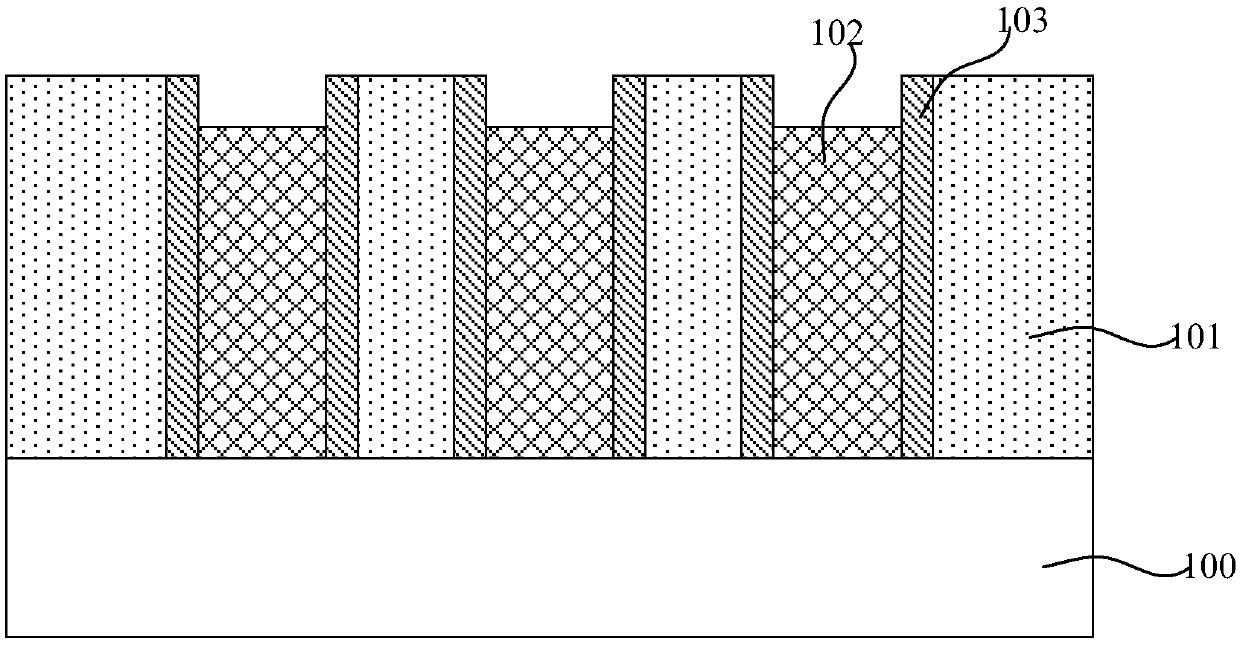

[0037] First, please refer to Figure 1A , providing a semiconductor substrate 100, forming a polysilicon gate 102 on the semiconductor substrate 100 as a dummy gate replaced by a subsequent metal gate, and forming sidewalls 103 on the sidewall of the polysilicon gate 102;

[0038] Next, please continue to refer to Figure 1A , depositing an interlayer dielectric layer 101, and performing chemical mechanical planarization on the top of the deposited interlayer dielectric layer 101 until the top surface of the polysilicon gate 102 is exposed;

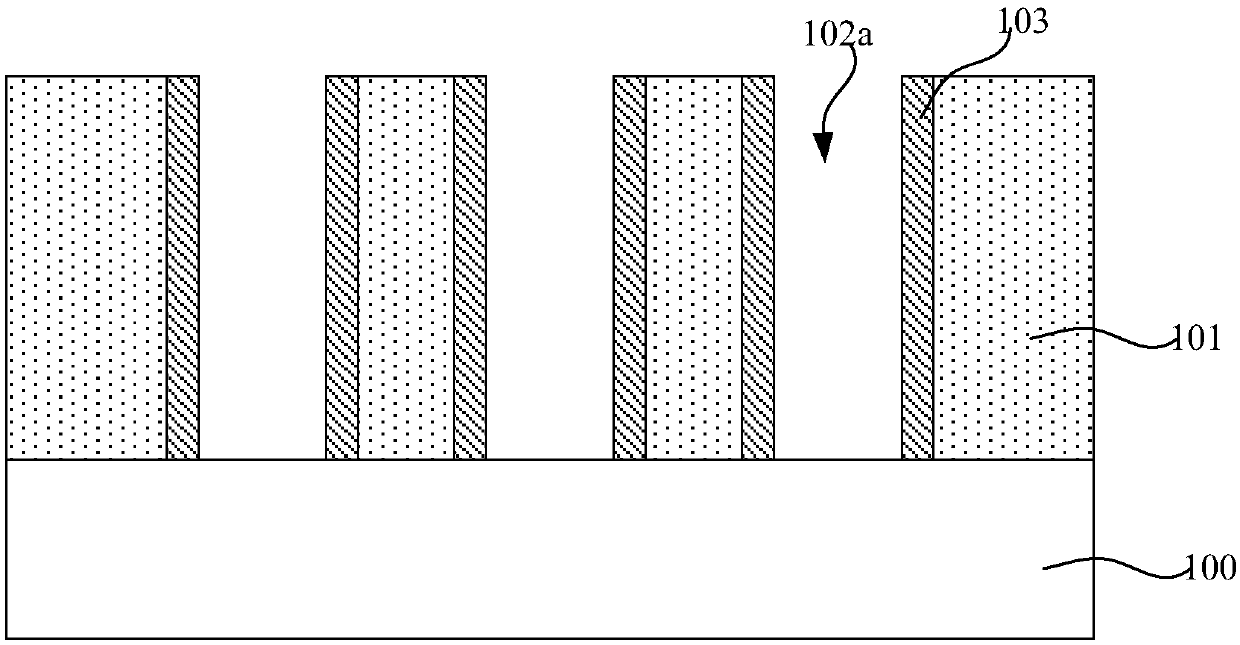

[0039] Then, refer to Figure 1A and Figure 1B , first using a dry etching process to partially etch the exposed polysilicon gate 102 to provide an etching solution storage area for subsequent wet etching to improve the effect of subsequent wet etching; then use tetramethyl Ammonium hydroxide solution (THMA) completely removes the remaining poly...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More