Patents

Literature

17723 results about "Engineering physics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Engineering physics or engineering science refers to the study of the combined disciplines of physics, mathematics and engineering, particularly computer, nuclear, electrical, electronic, materials or mechanical engineering. By focusing on the scientific method as a rigorous basis, it seeks ways to apply, design, and develop new solutions in engineering.

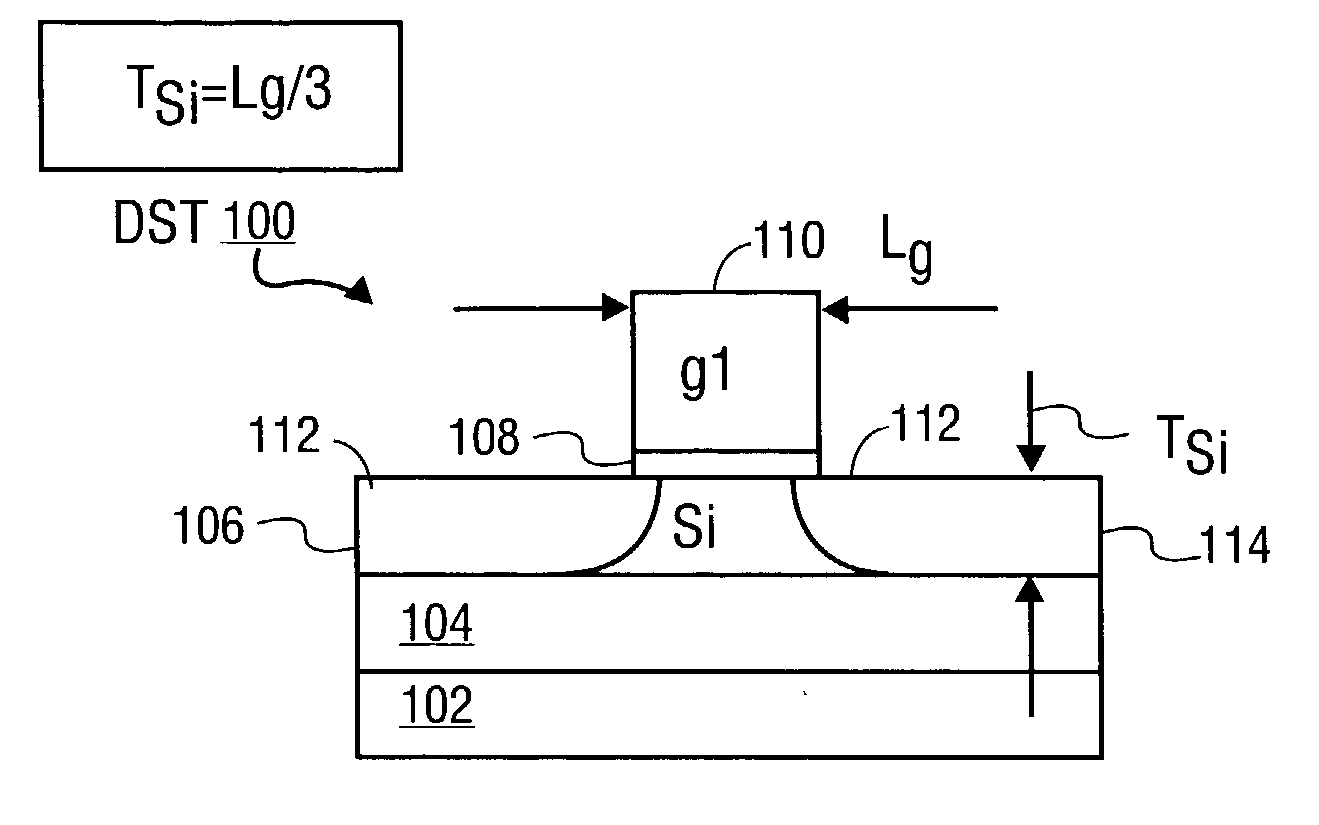

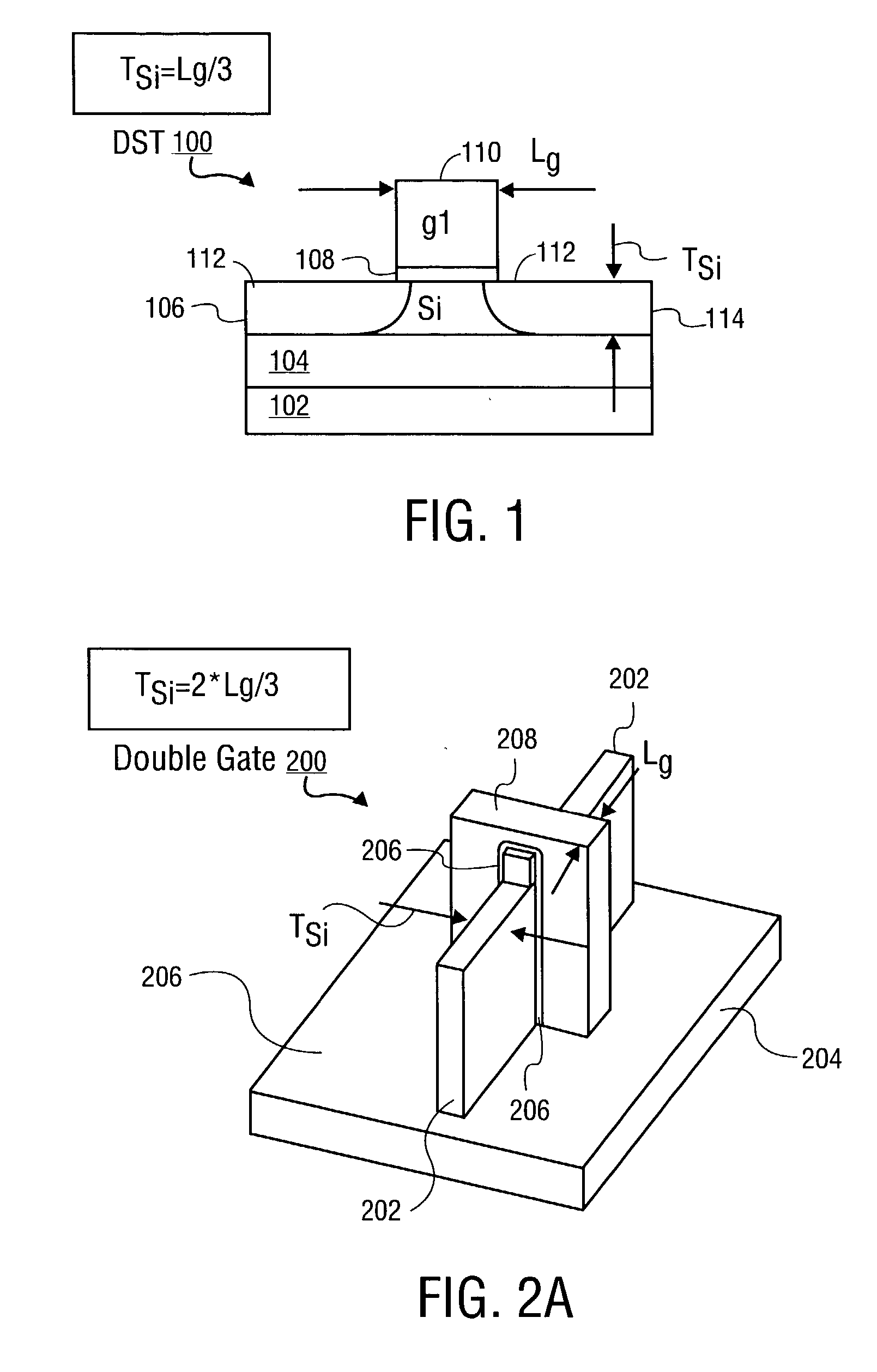

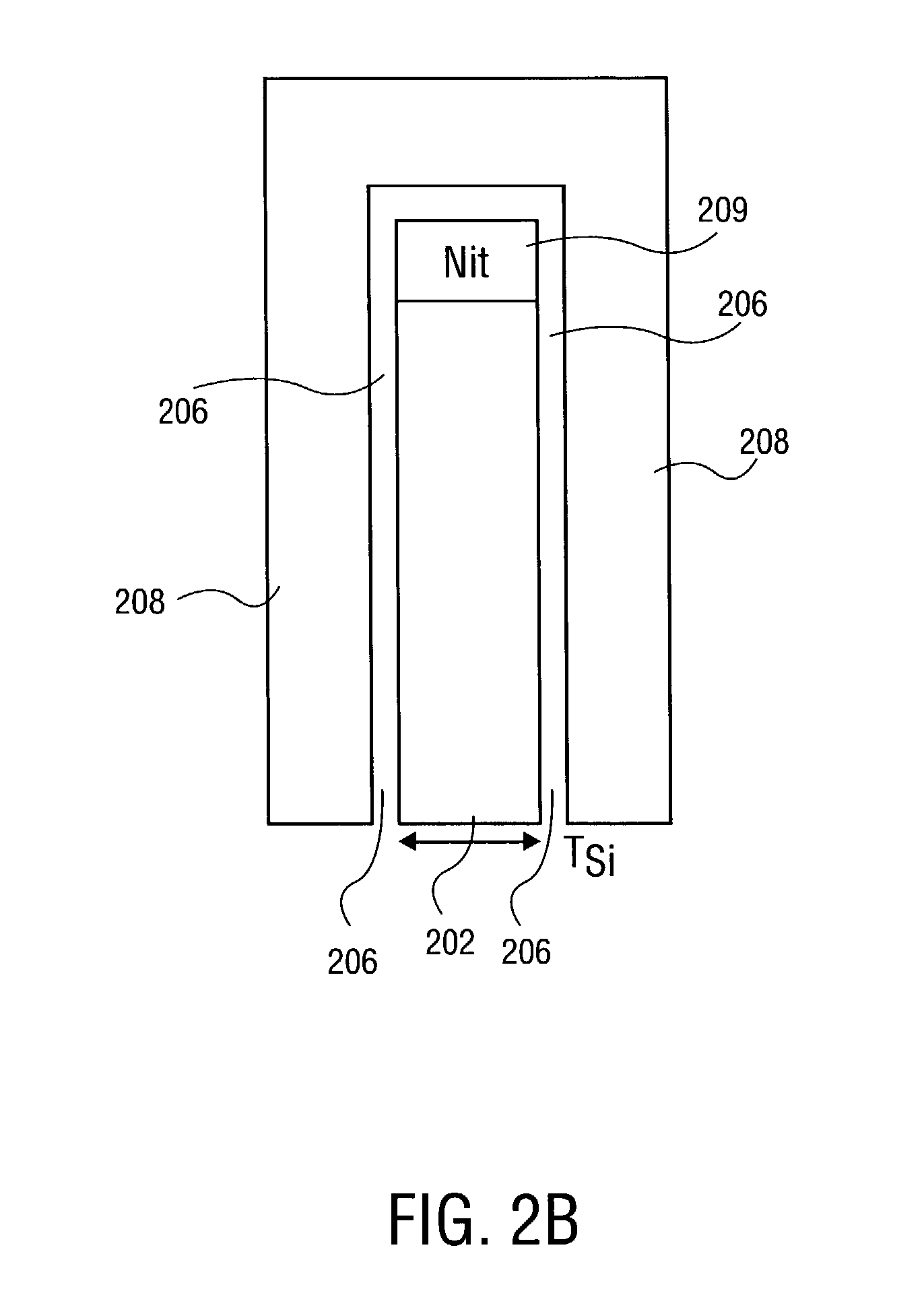

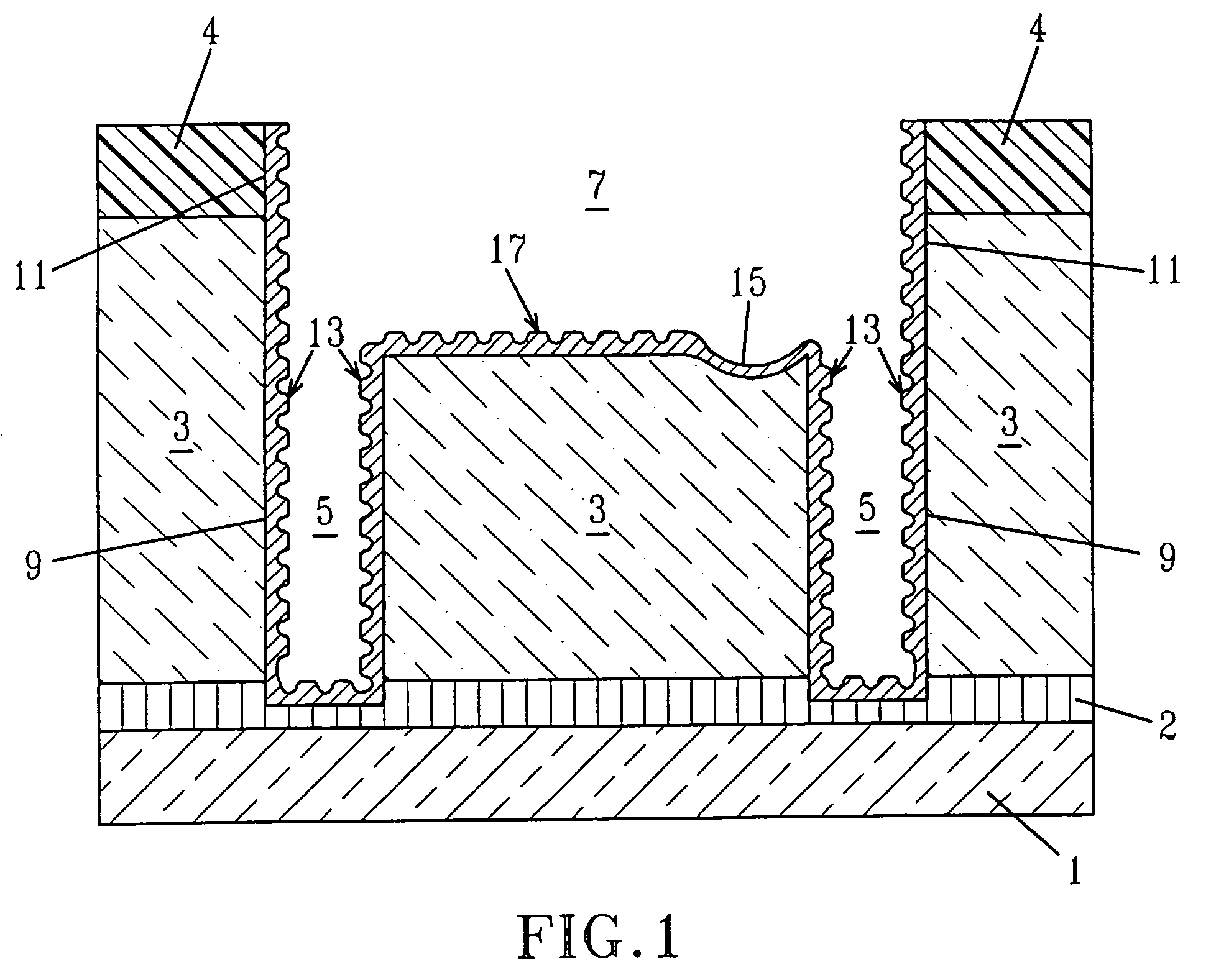

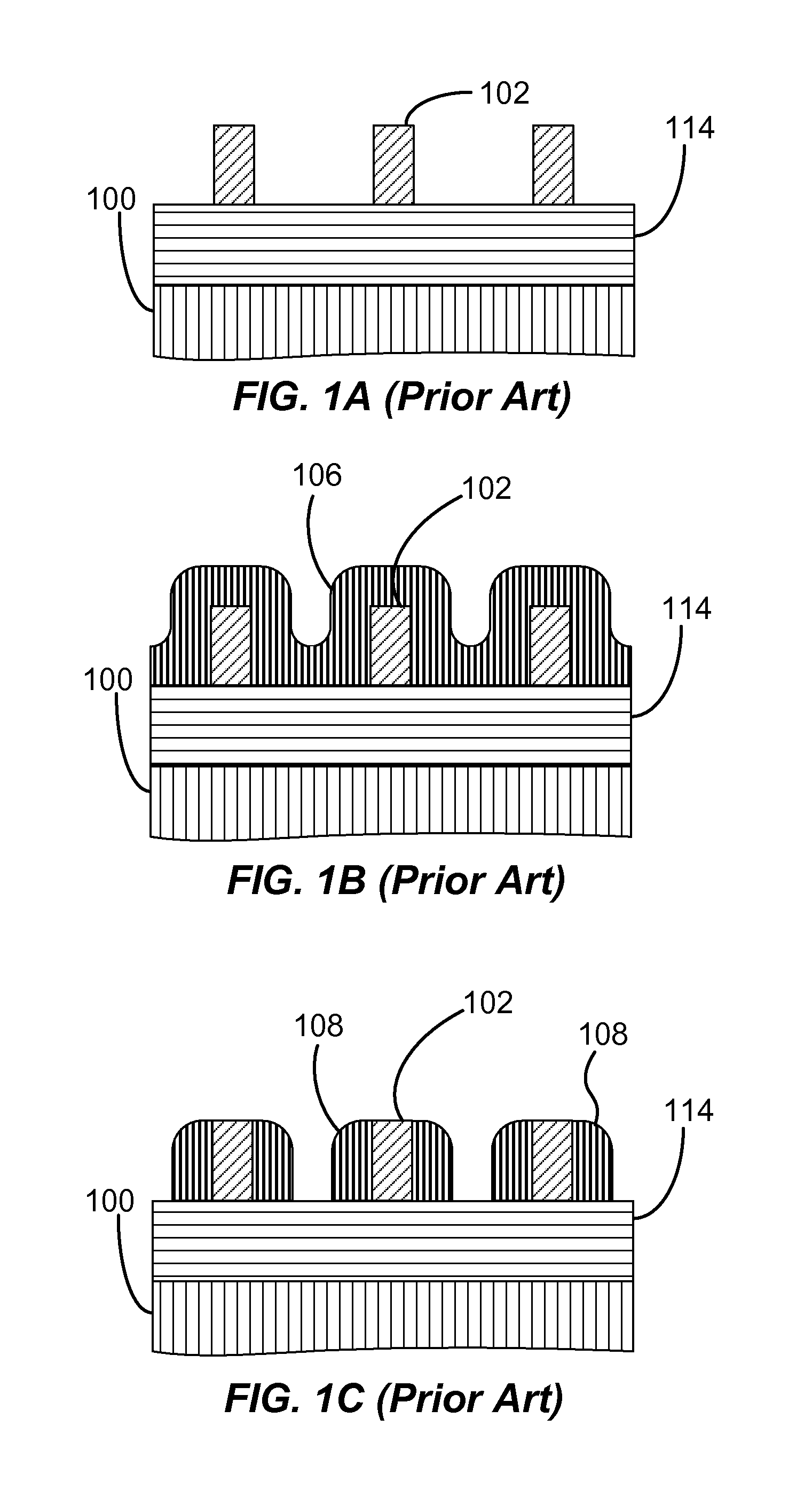

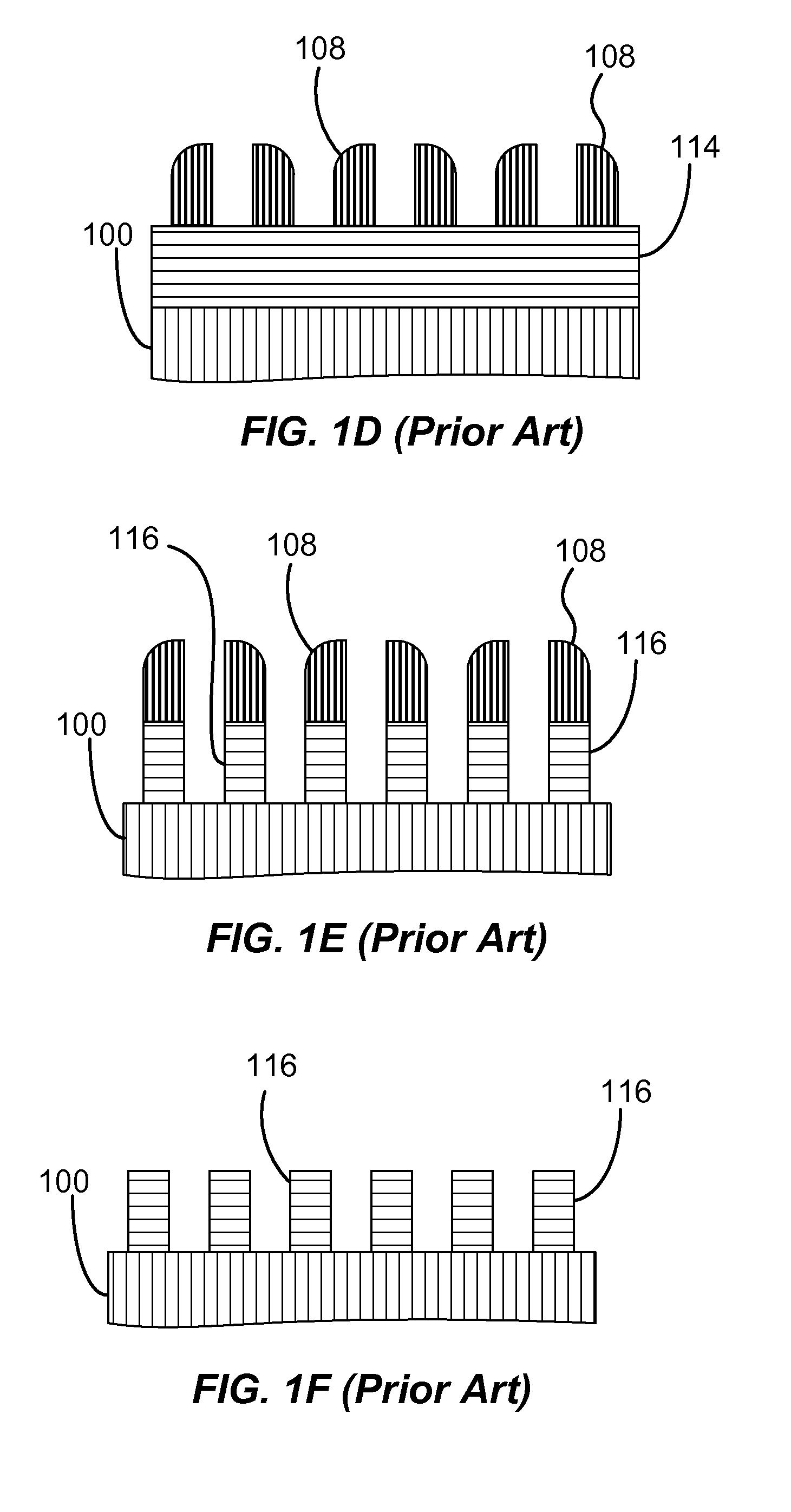

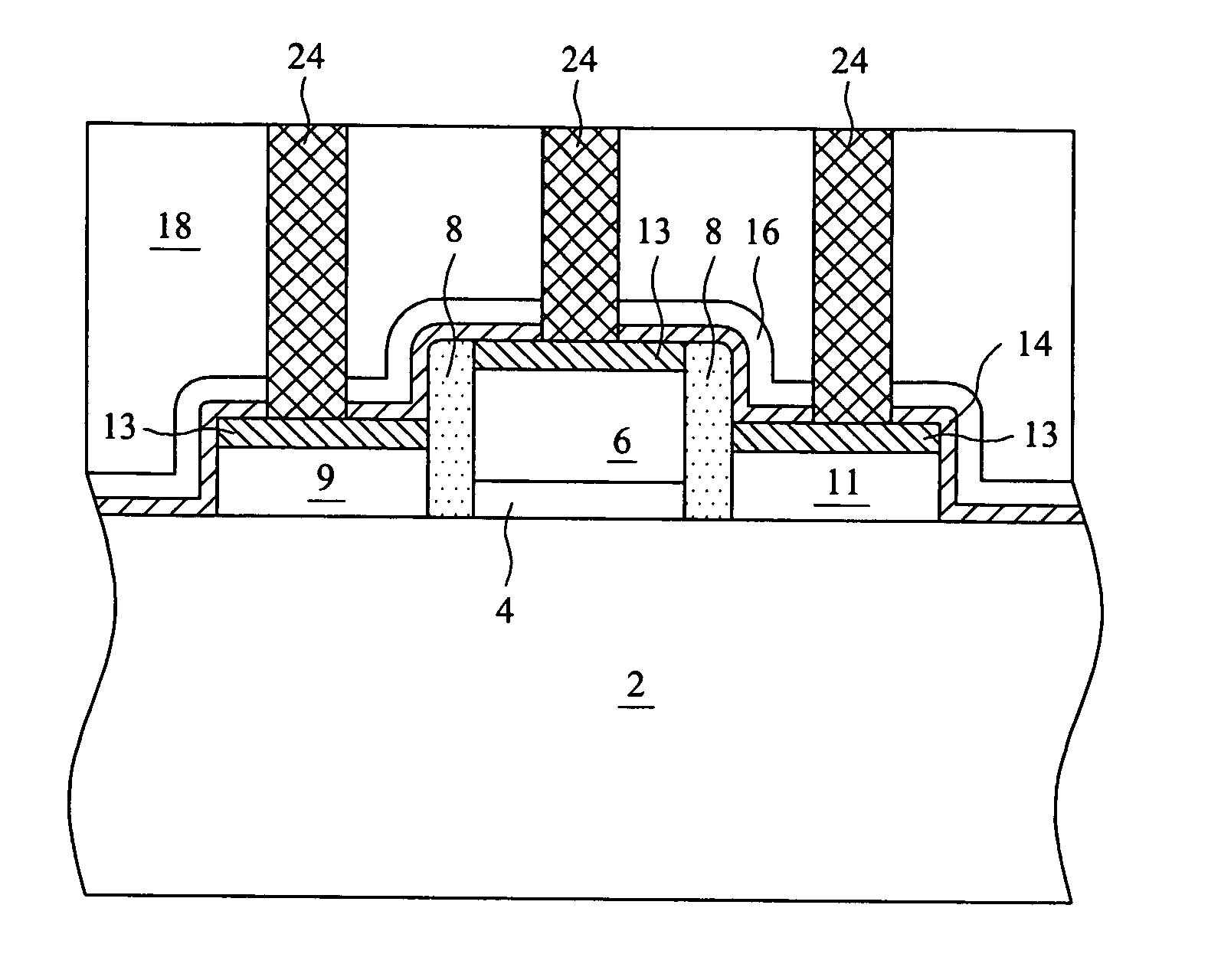

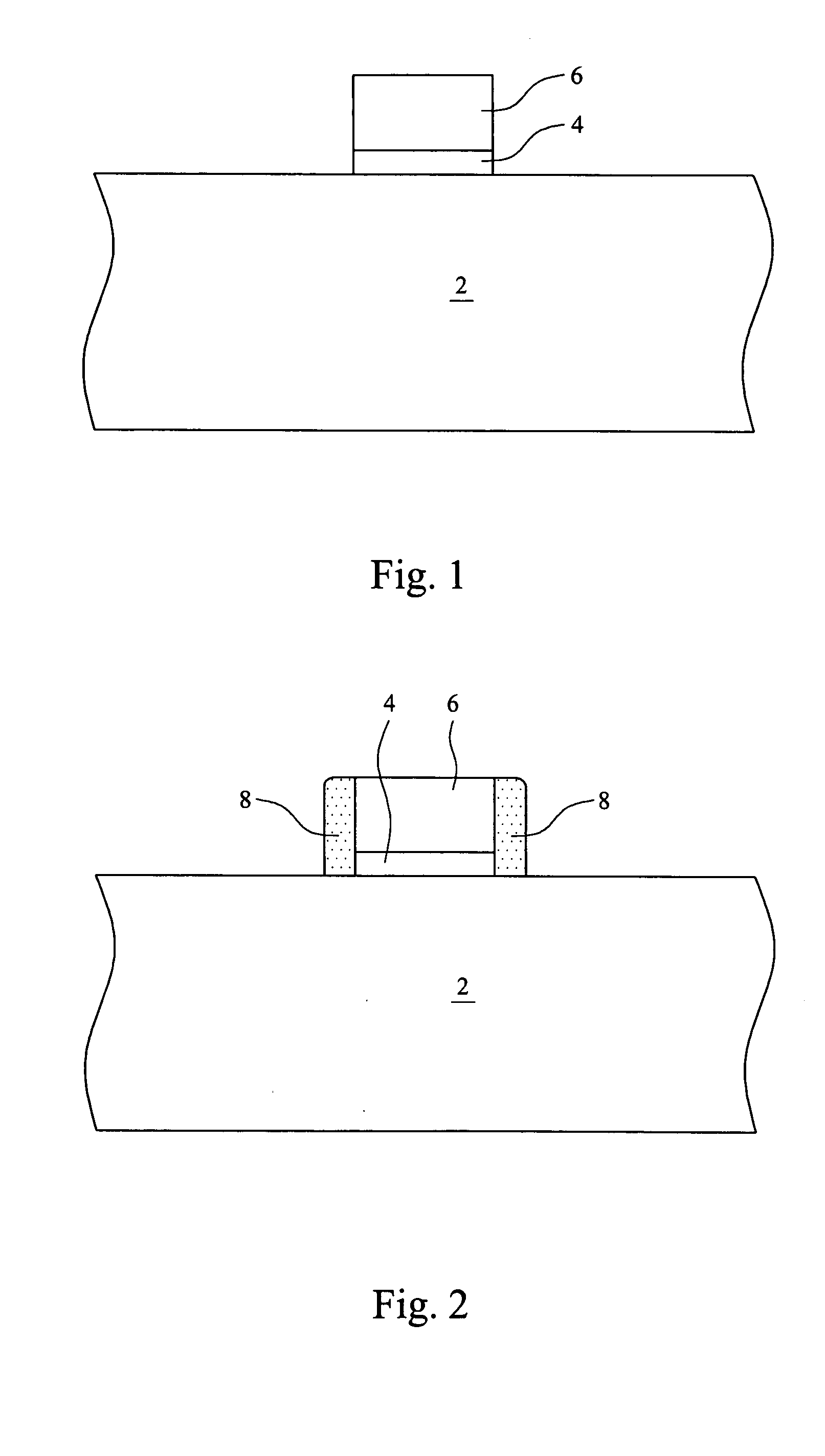

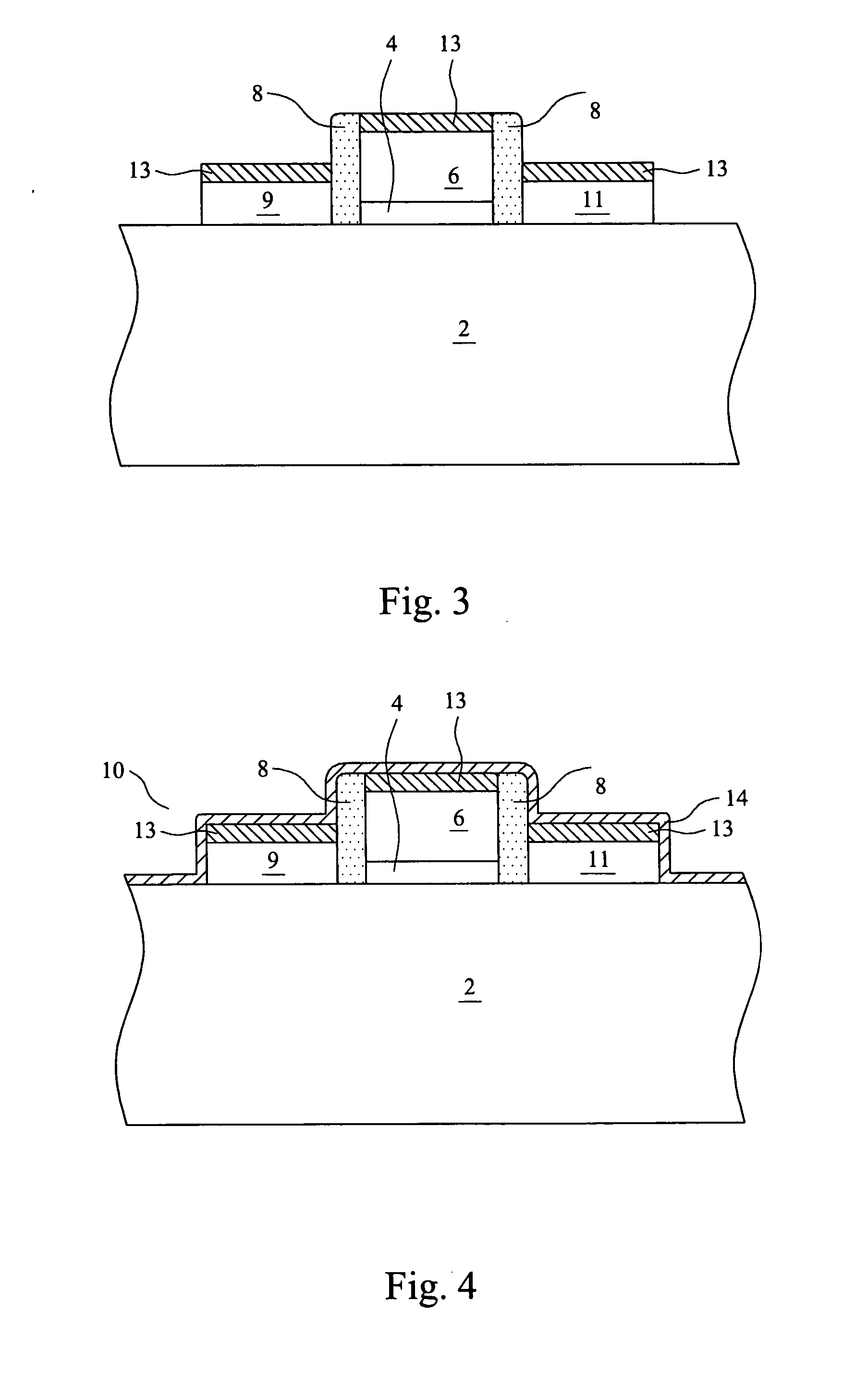

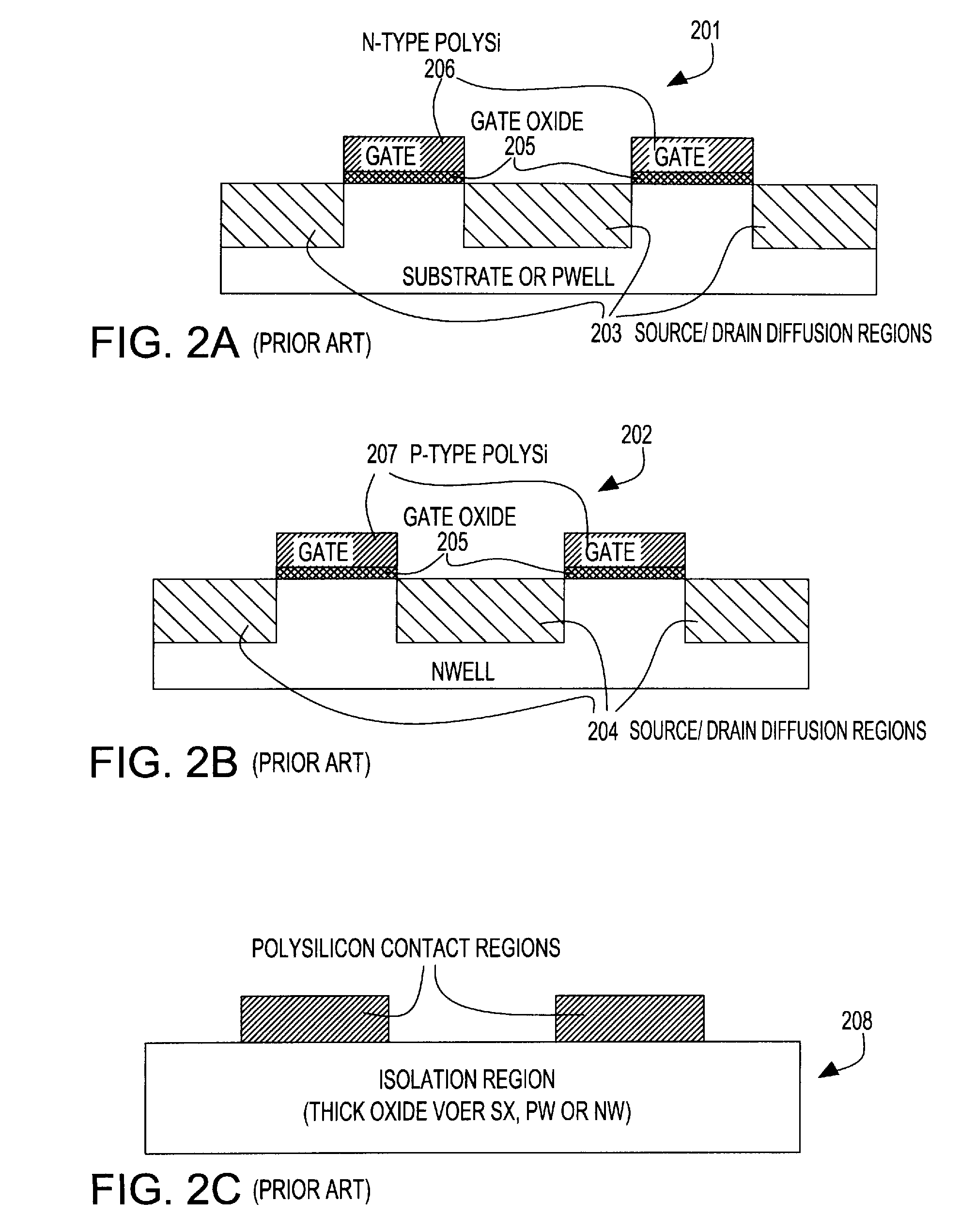

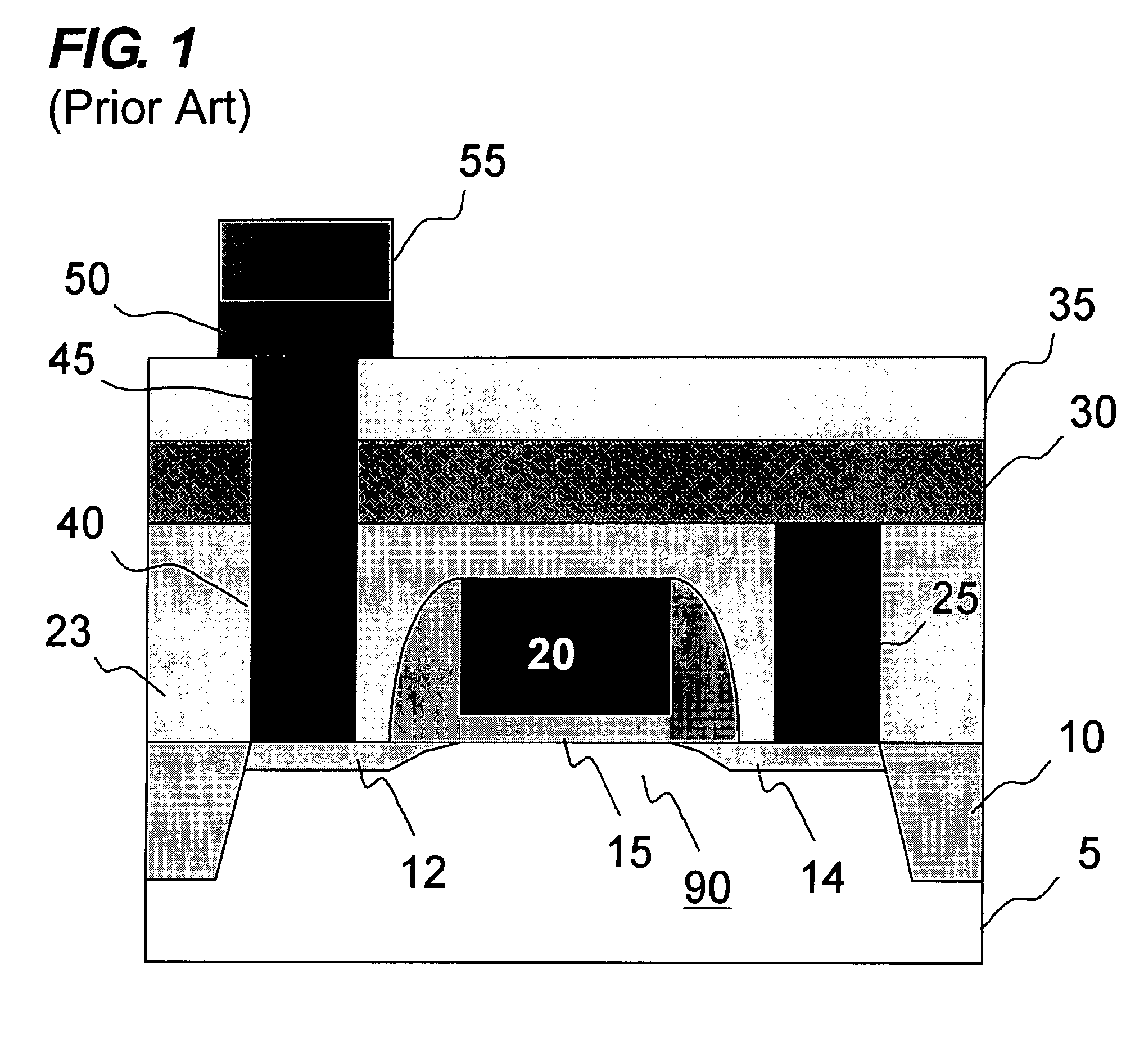

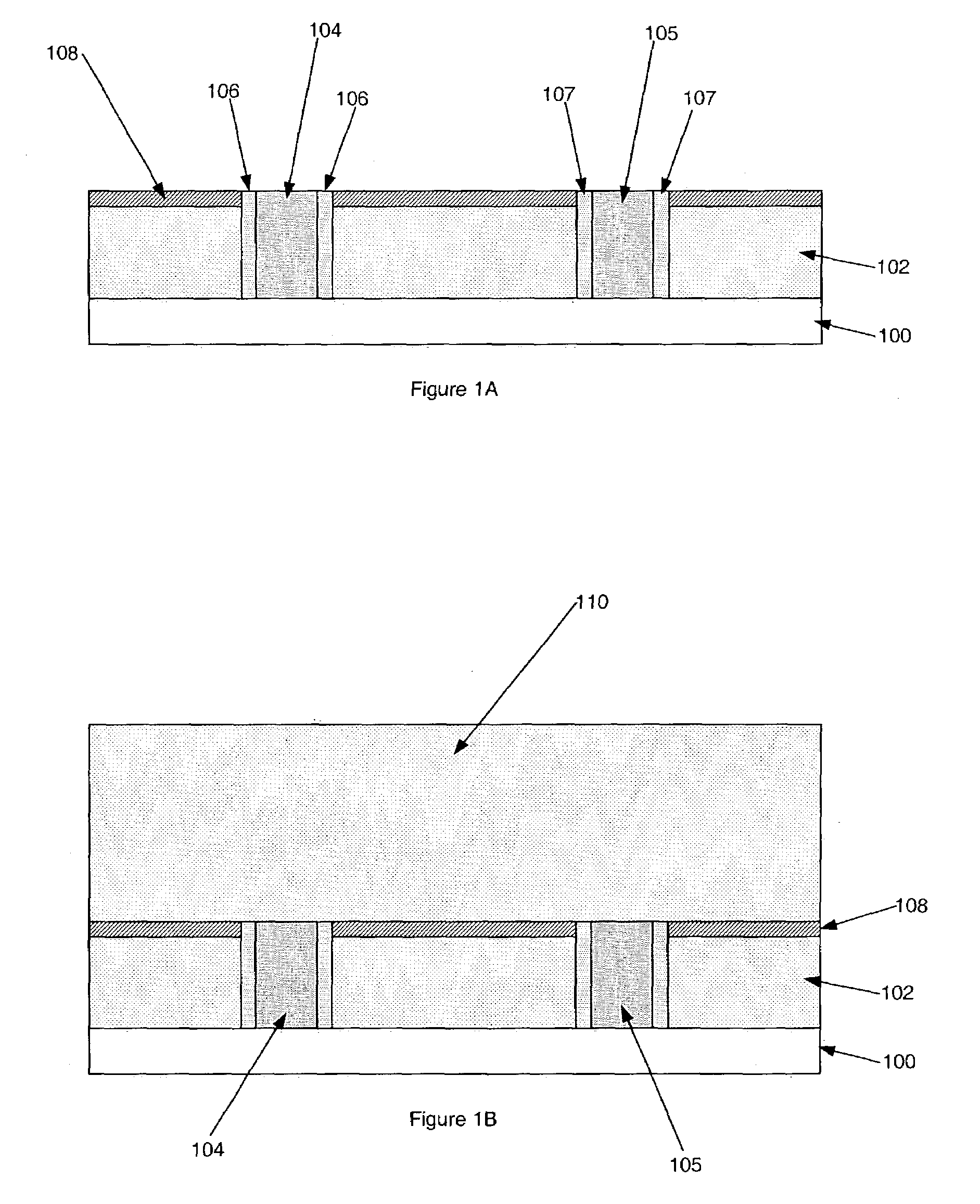

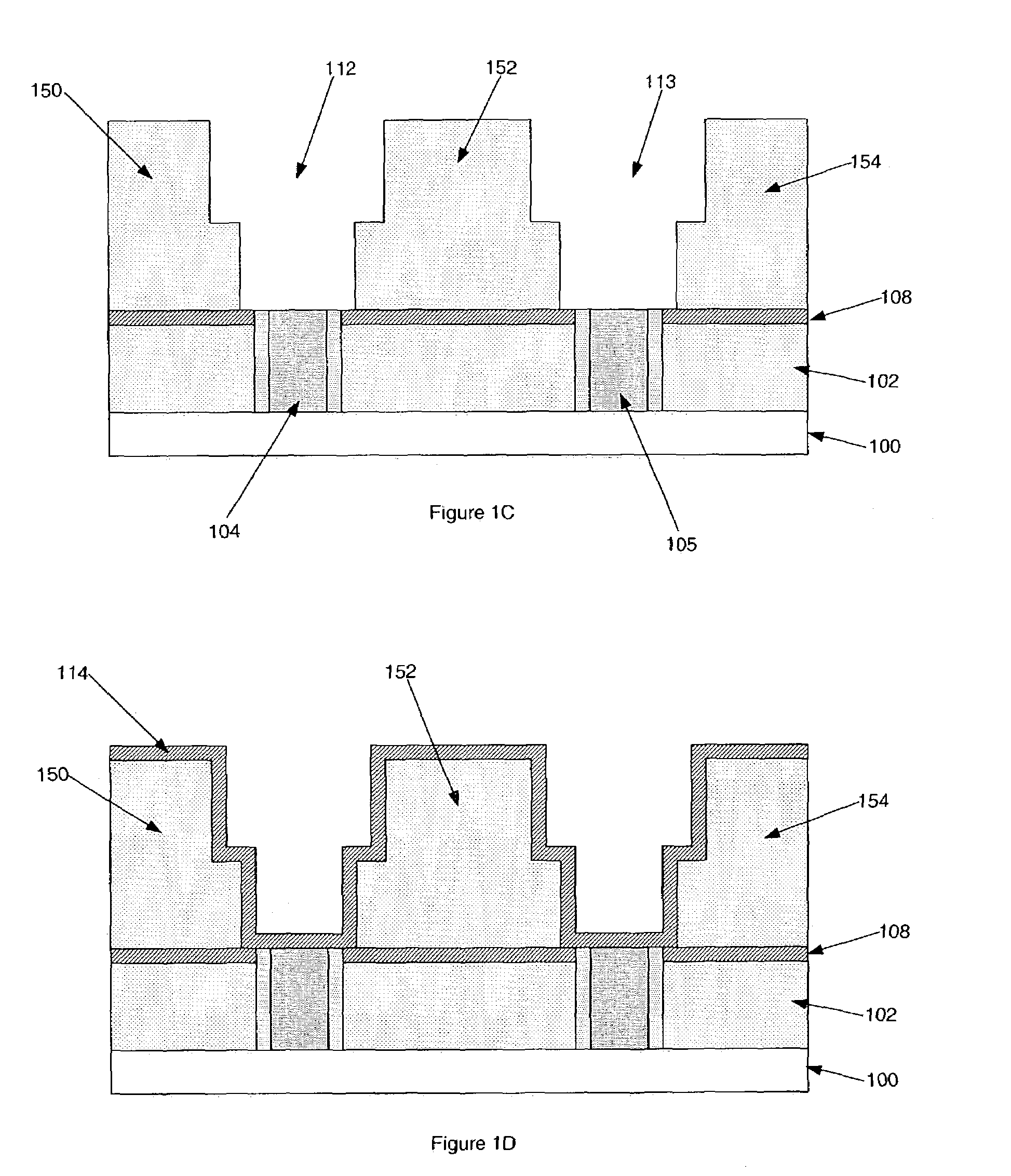

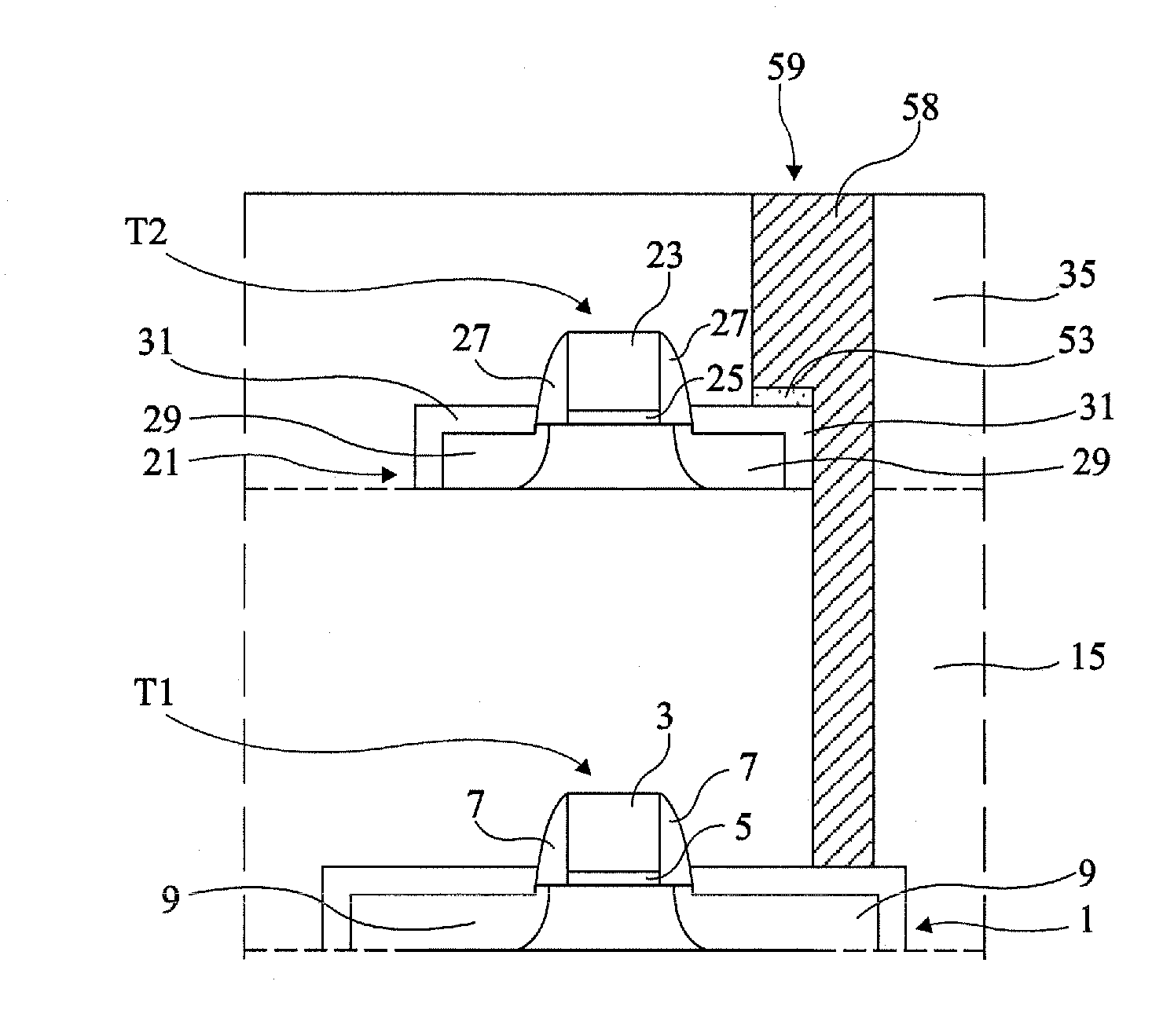

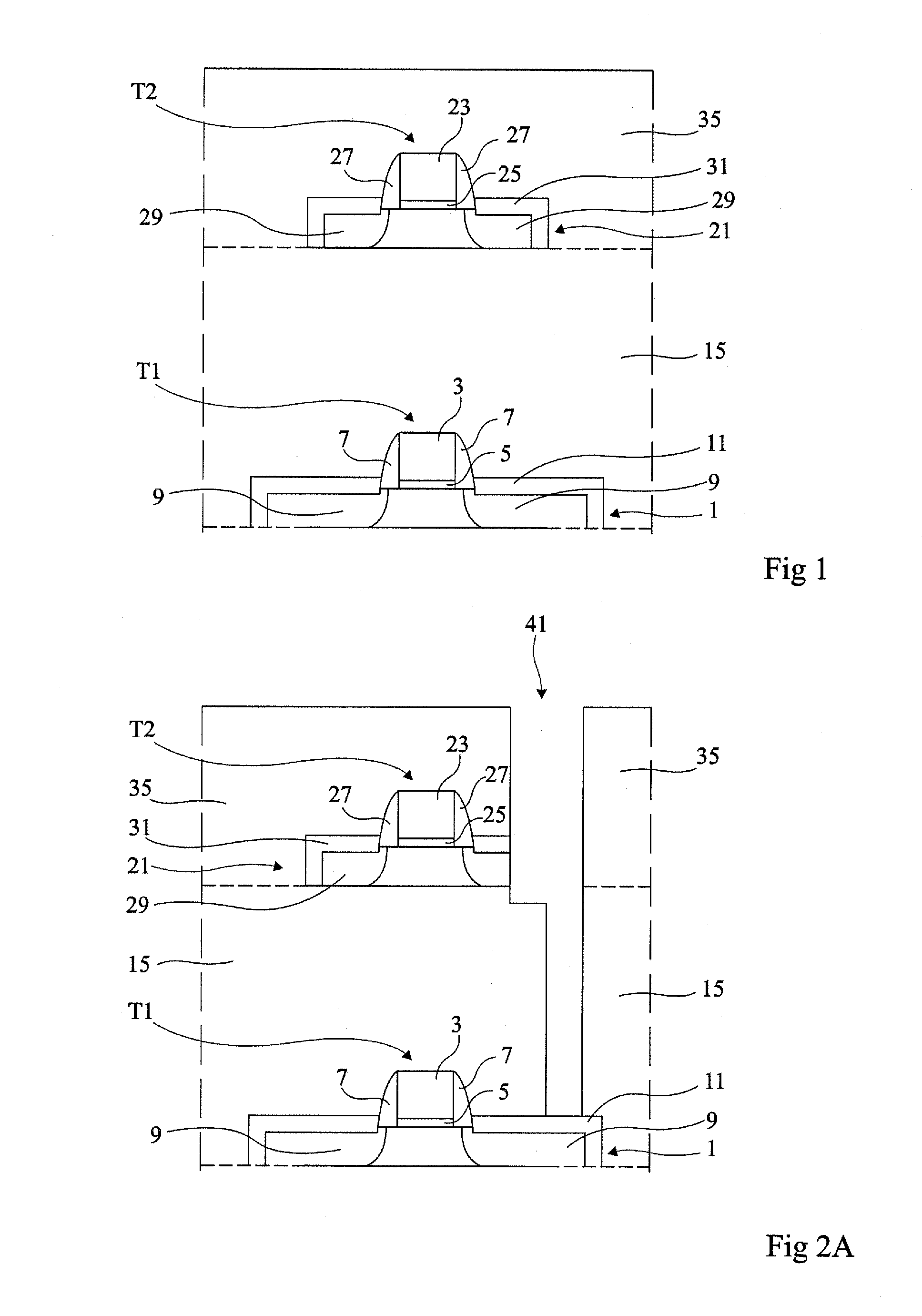

Tri-gate devices and methods of fabrication

The present invention is a semiconductor device comprising a semiconductor body having a top surface and laterally opposite sidewalls formed on a substrate. A gate dielectric layer is formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body.

Owner:INTEL CORP

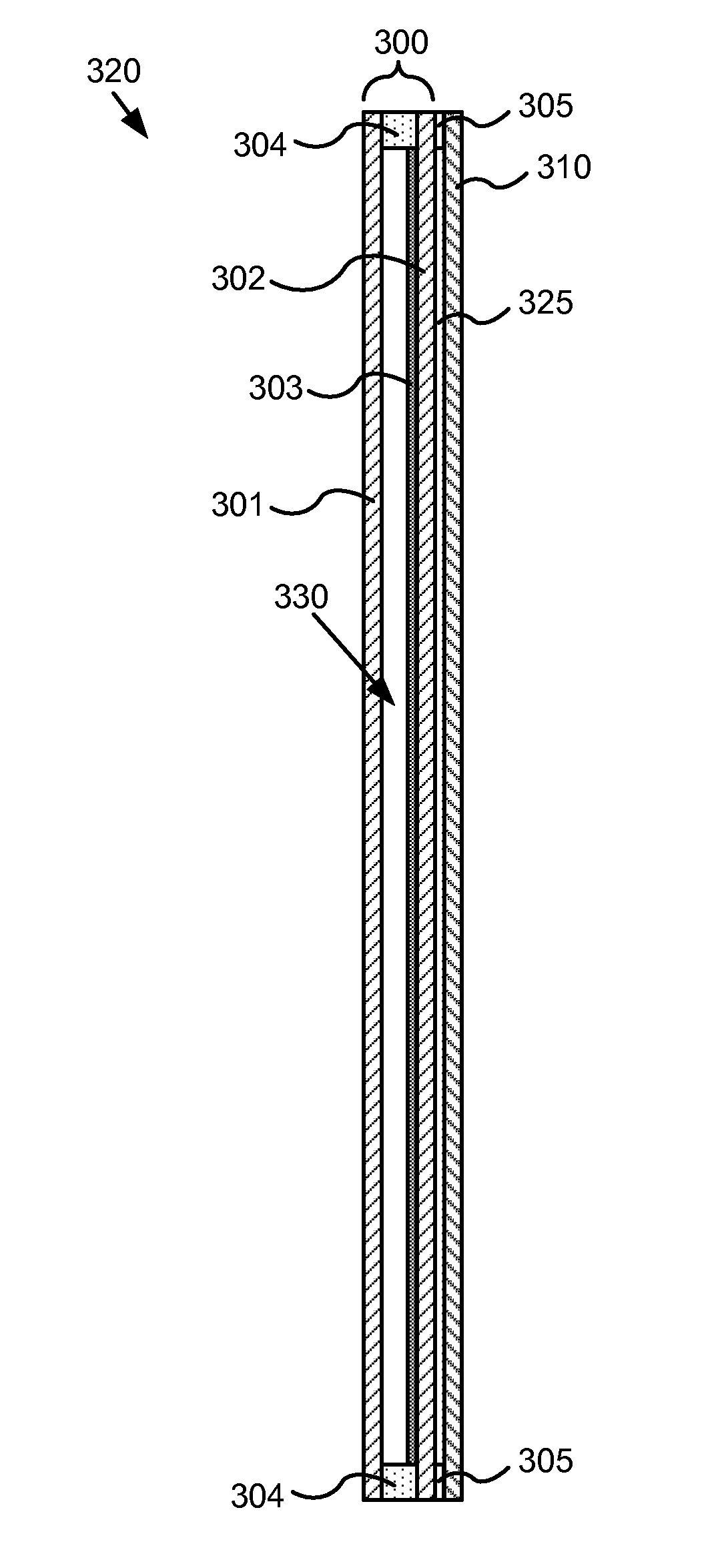

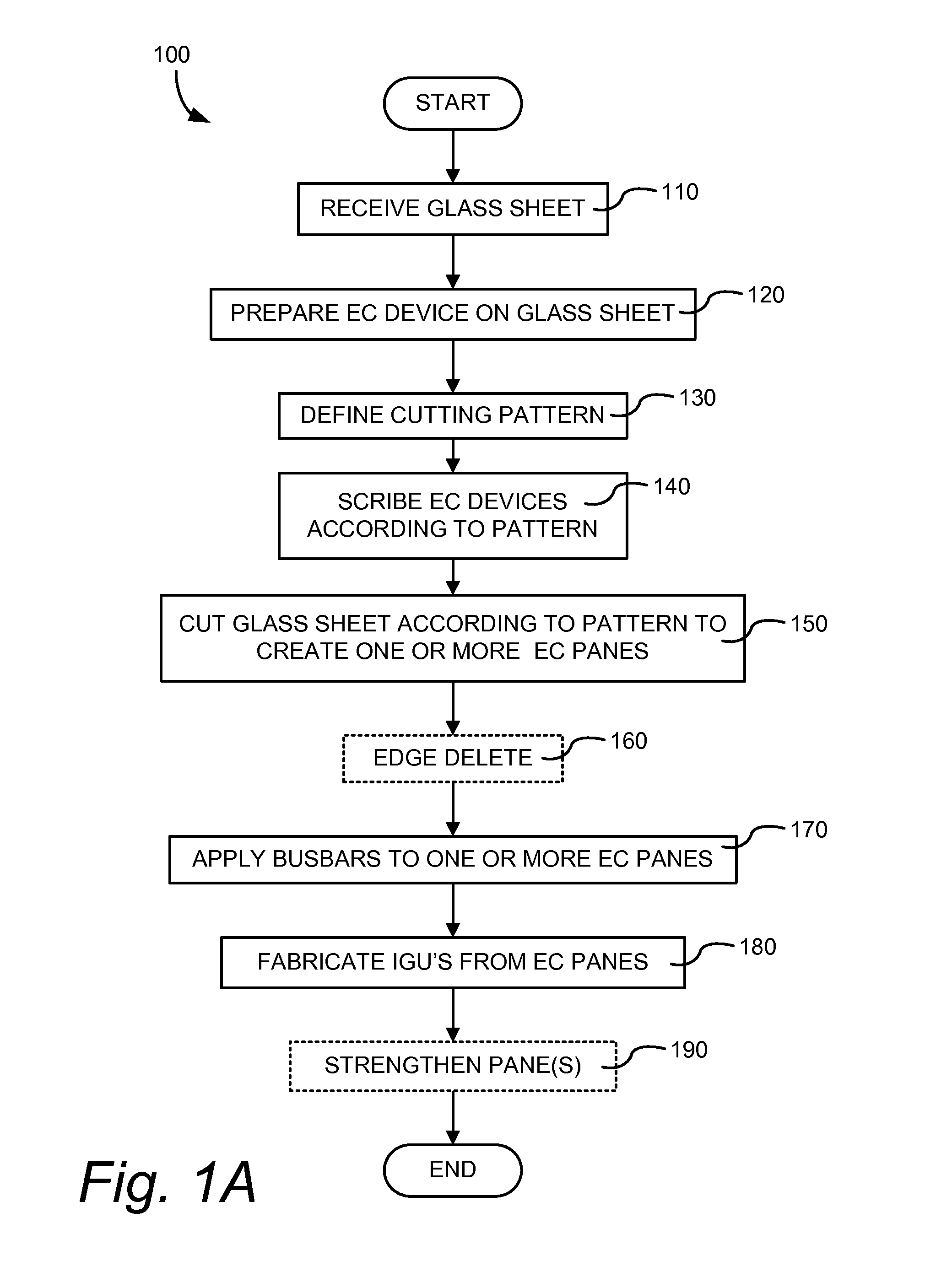

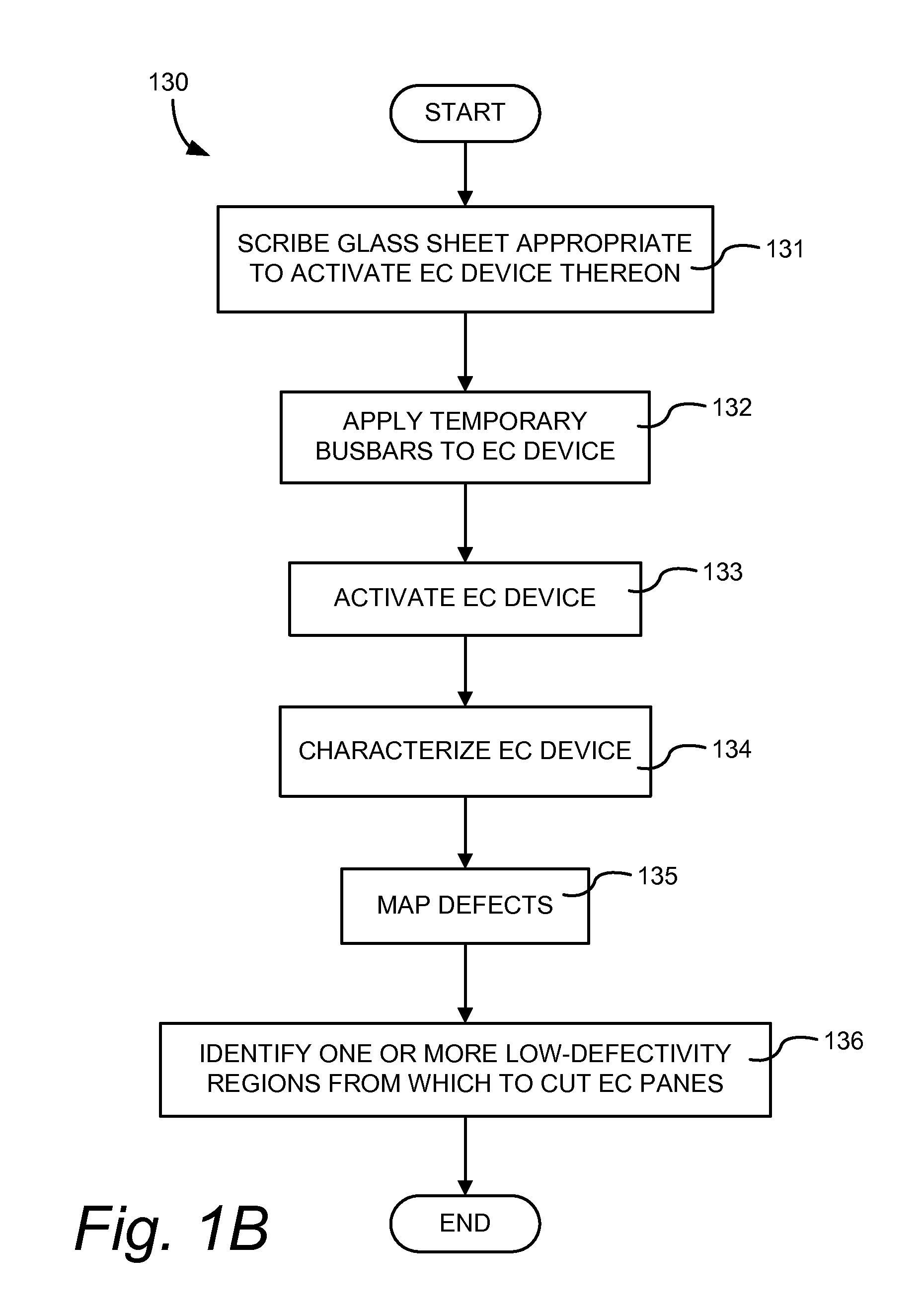

Electrochromic window fabrication methods

ActiveUS20120026573A1Maximize effective useLamination ancillary operationsLaminationEngineeringElectrochromism

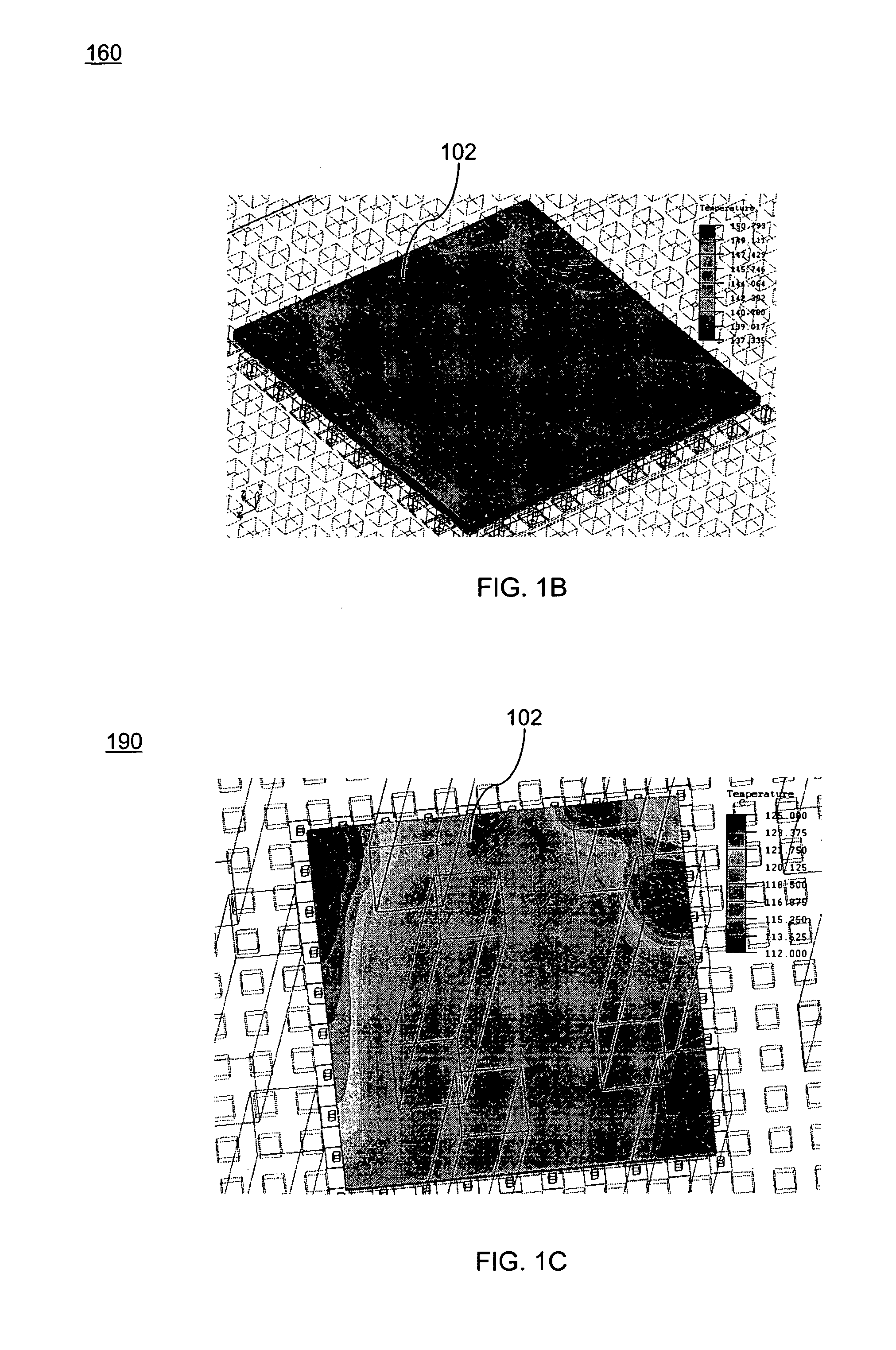

Methods of manufacturing electrochromic windows are described. An electrochromic device is fabricated to substantially cover a glass sheet, for example float glass, and a cutting pattern is defined based on one or more low-defectivity areas in the device from which one or more electrochromic panes are cut. Laser scribes and / or bus bars may be added prior to cutting the panes or after. Edge deletion can also be performed prior to or after cutting the electrochromic panes from the glass sheet. Insulated glass units (IGUs) are fabricated from the electrochromic panes and optionally one or more of the panes of the IGU are strengthened.

Owner:VIEW INC

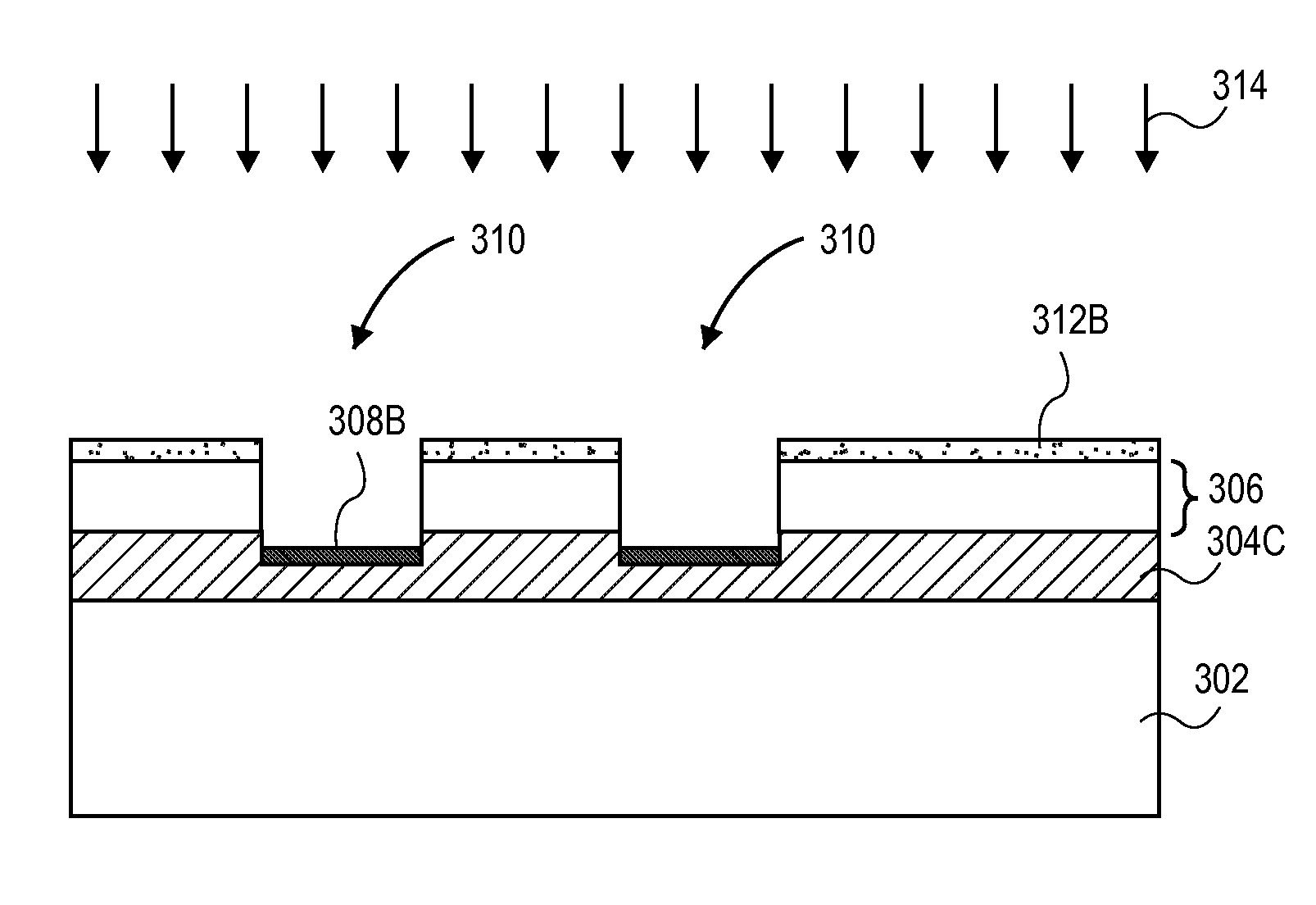

Structures and methods for integration of ultralow-k dielectrics with improved reliability

ActiveUS7088003B2Semiconductor/solid-state device detailsSolid-state devicesBiological activationDielectric layer

An improved back end of the line (BEOL) interconnect structure comprising an ultralow k (ULK) dielectric is provided. The structure may be of the single or dual damascene type and comprises a dense thin dielectric layer (TDL) between a metal barrier layer and the ULK dielectric. Disclosed are also methods of fabrication of BEOL interconnect structures, including (i) methods in which a dense TDL is provided on etched opening of a ULK dielectric and (ii) methods in which a ULK dielectric is placed in a process chamber on a cold chuck, a sealing agent is added to the process chamber, and an activation step is performed.

Owner:GLOBALFOUNDRIES U S INC

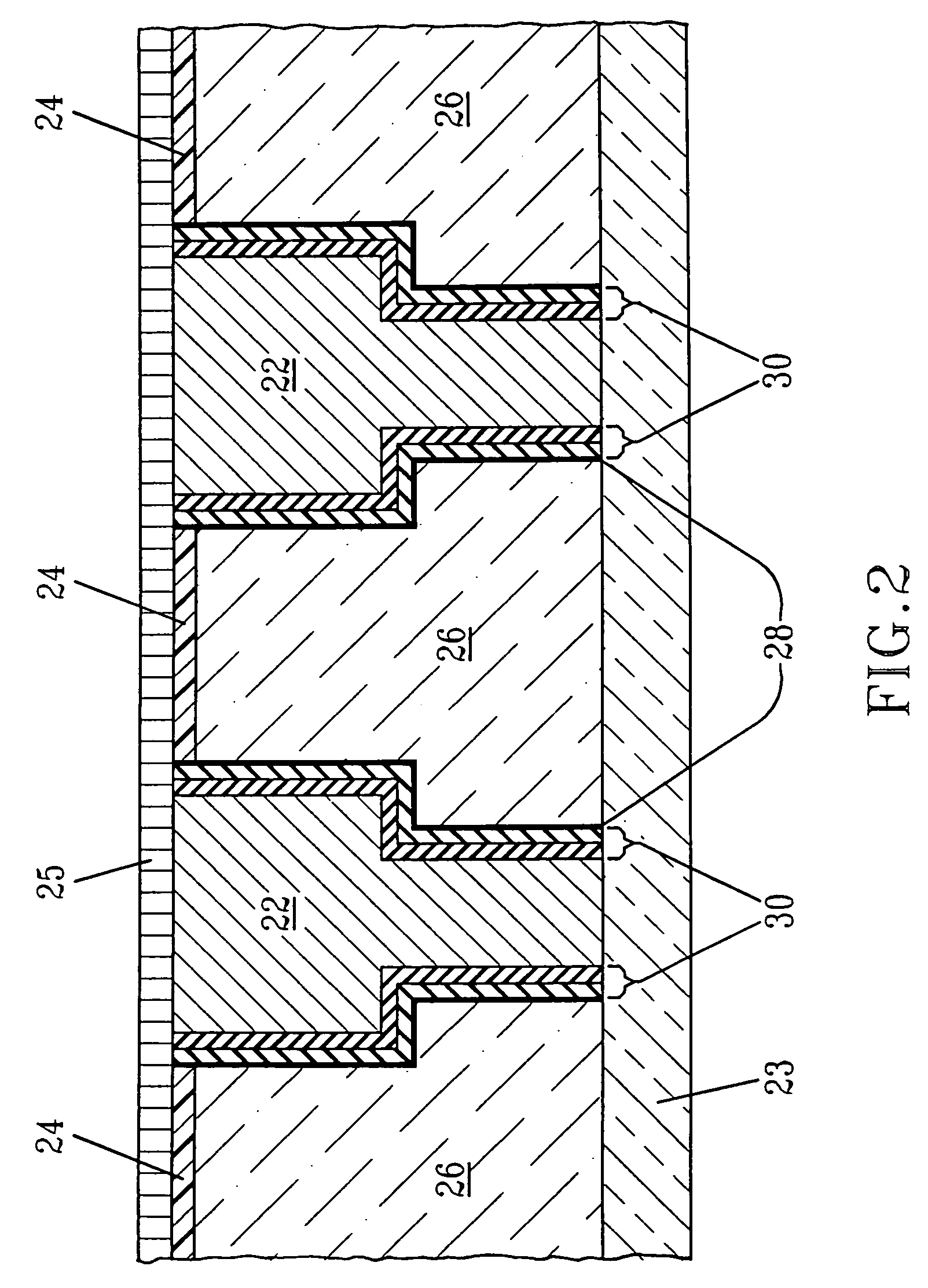

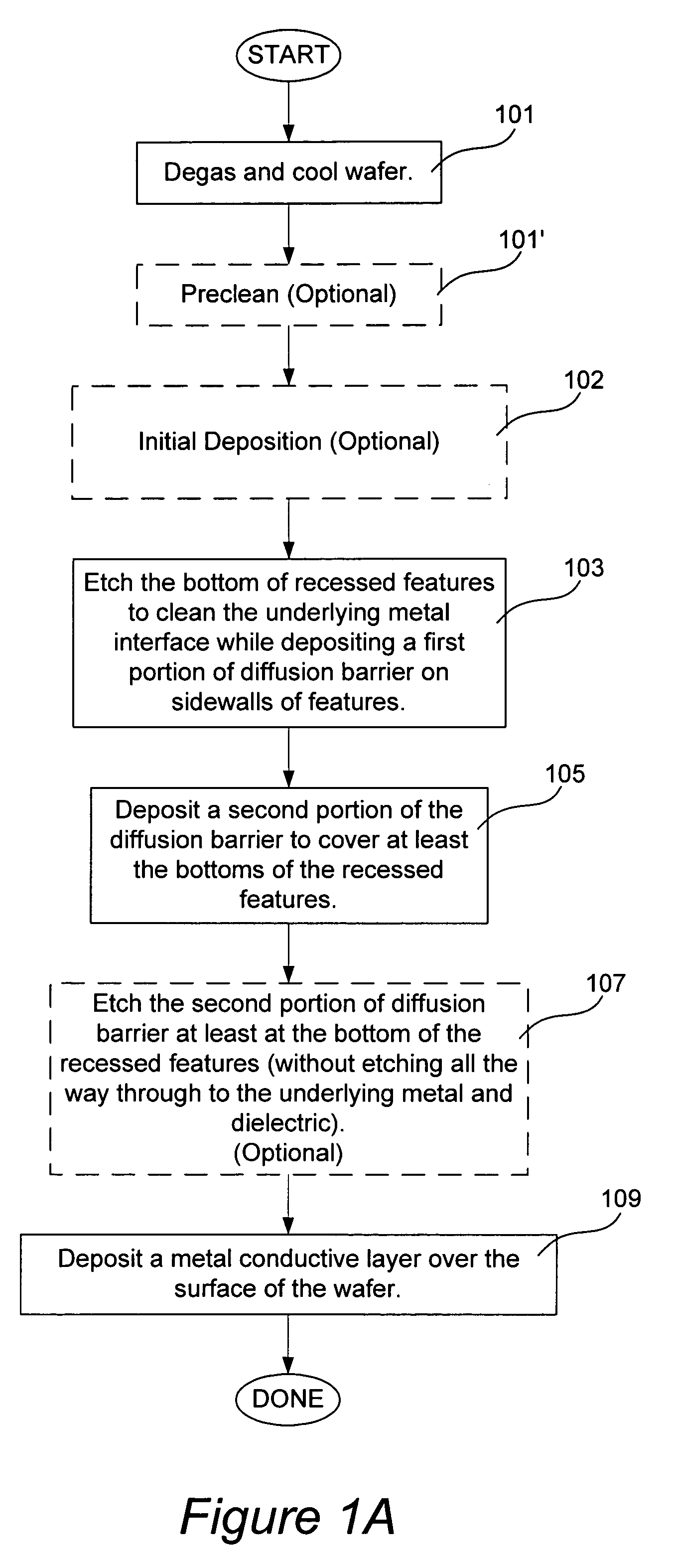

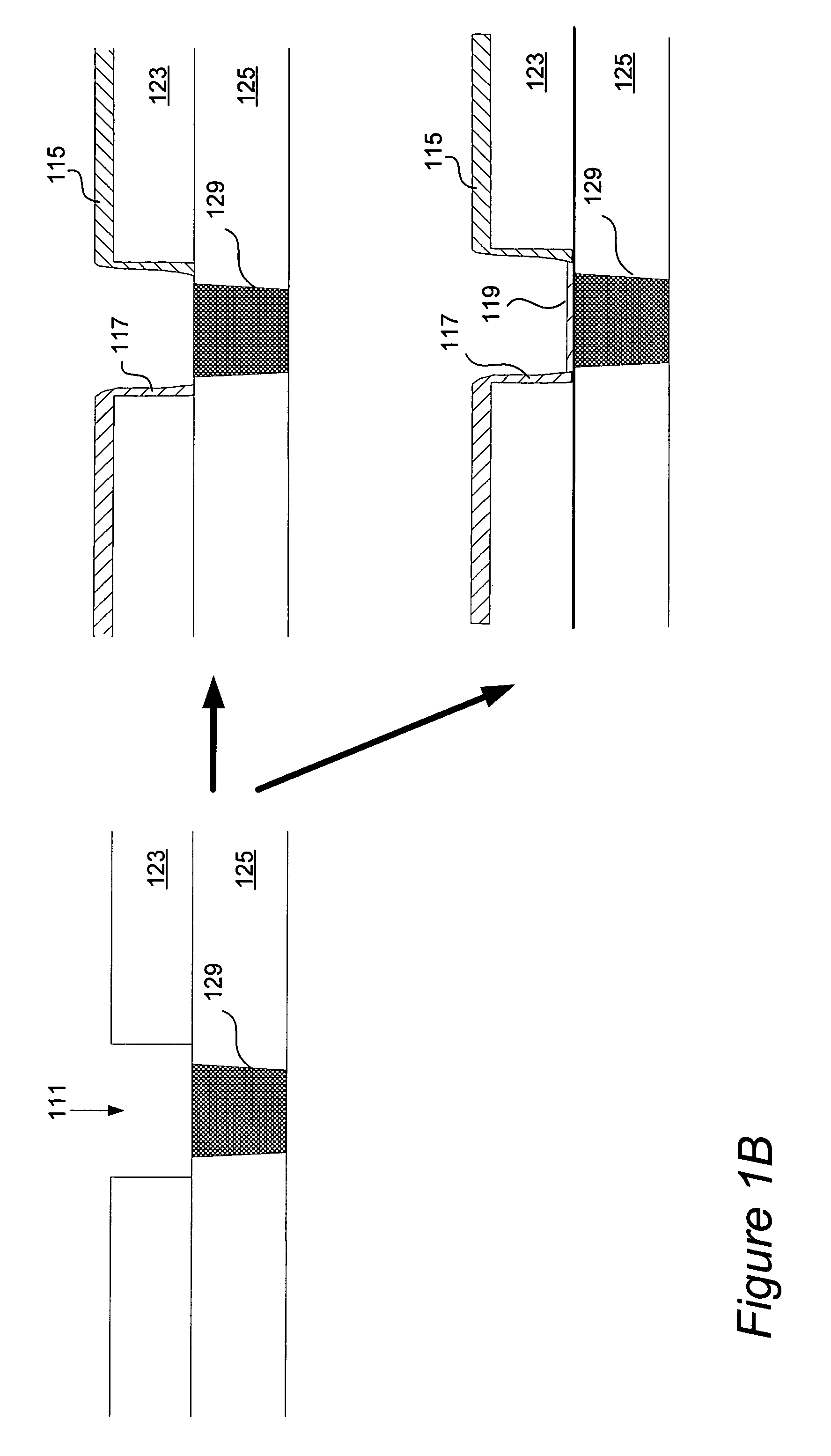

Barrier first method for single damascene trench applications

InactiveUS7186648B1Increase throughputHigh throughputSemiconductor/solid-state device manufacturingMetal interconnectEtching

Methods for forming a diffusion barrier on low aspect features of an integrated circuit include at least three operations. The first operation deposits a barrier material and simultaneously etches a portion of an underlying metal at the bottoms of recessed features of the integrated circuit. The second operation deposits barrier material to provide some minimal coverage over the bottoms of the recessed features. The third operation deposits a metal conductive layer. Controlled etching is used to selectively remove barrier material from the bottom of the recessed features, either completely or partially, thus reducing the resistance of subsequently formed metal interconnects.

Owner:NOVELLUS SYSTEMS

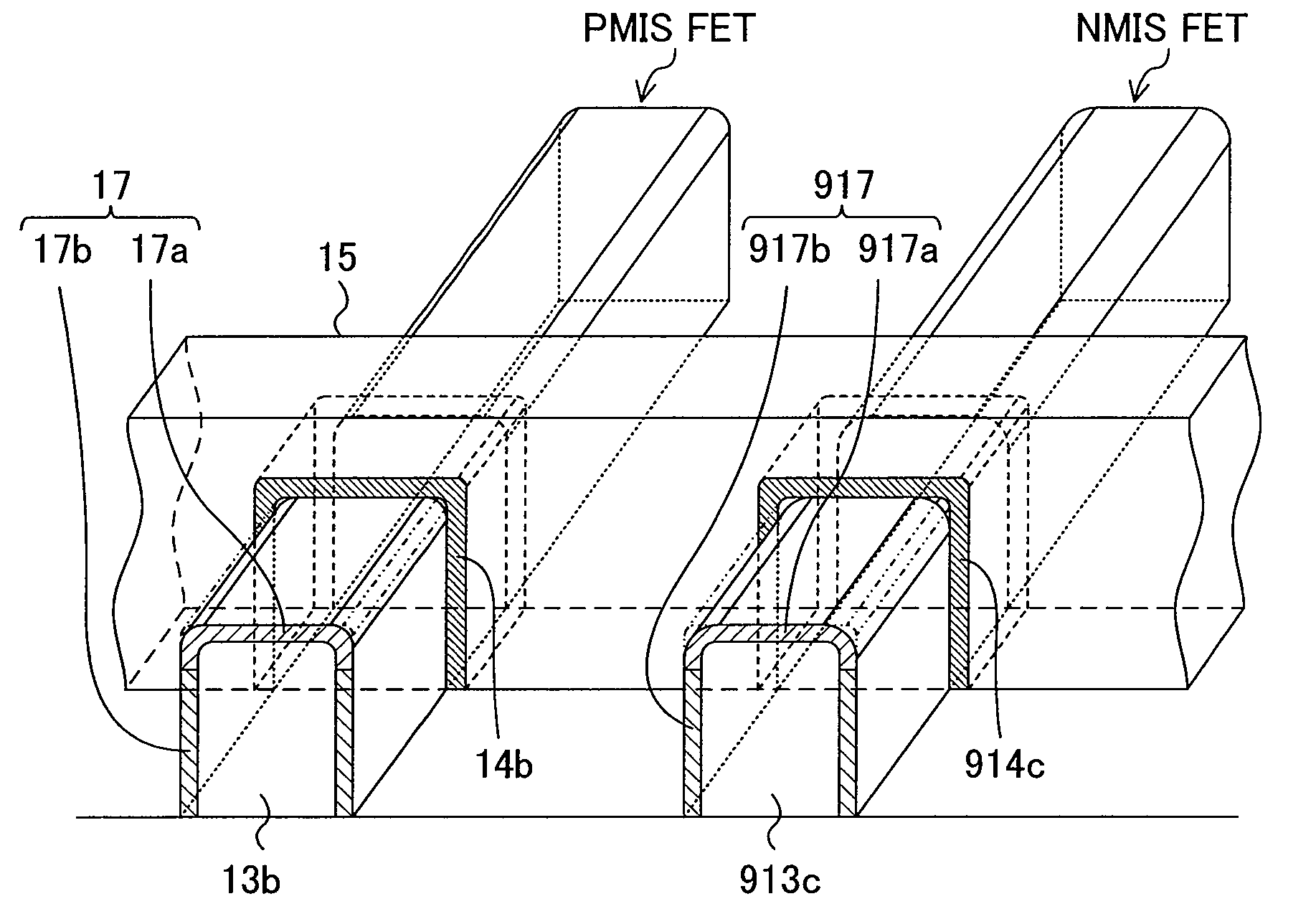

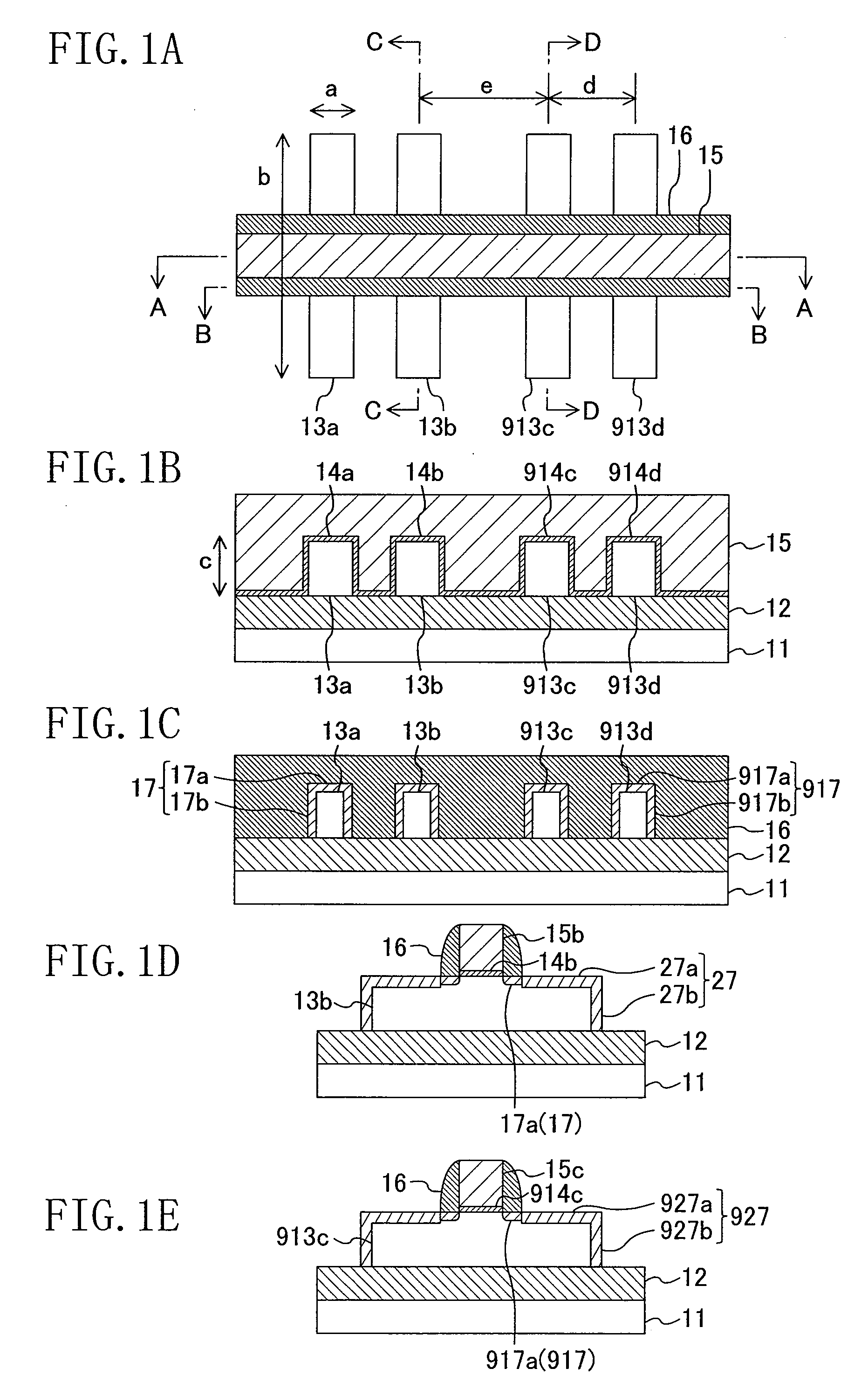

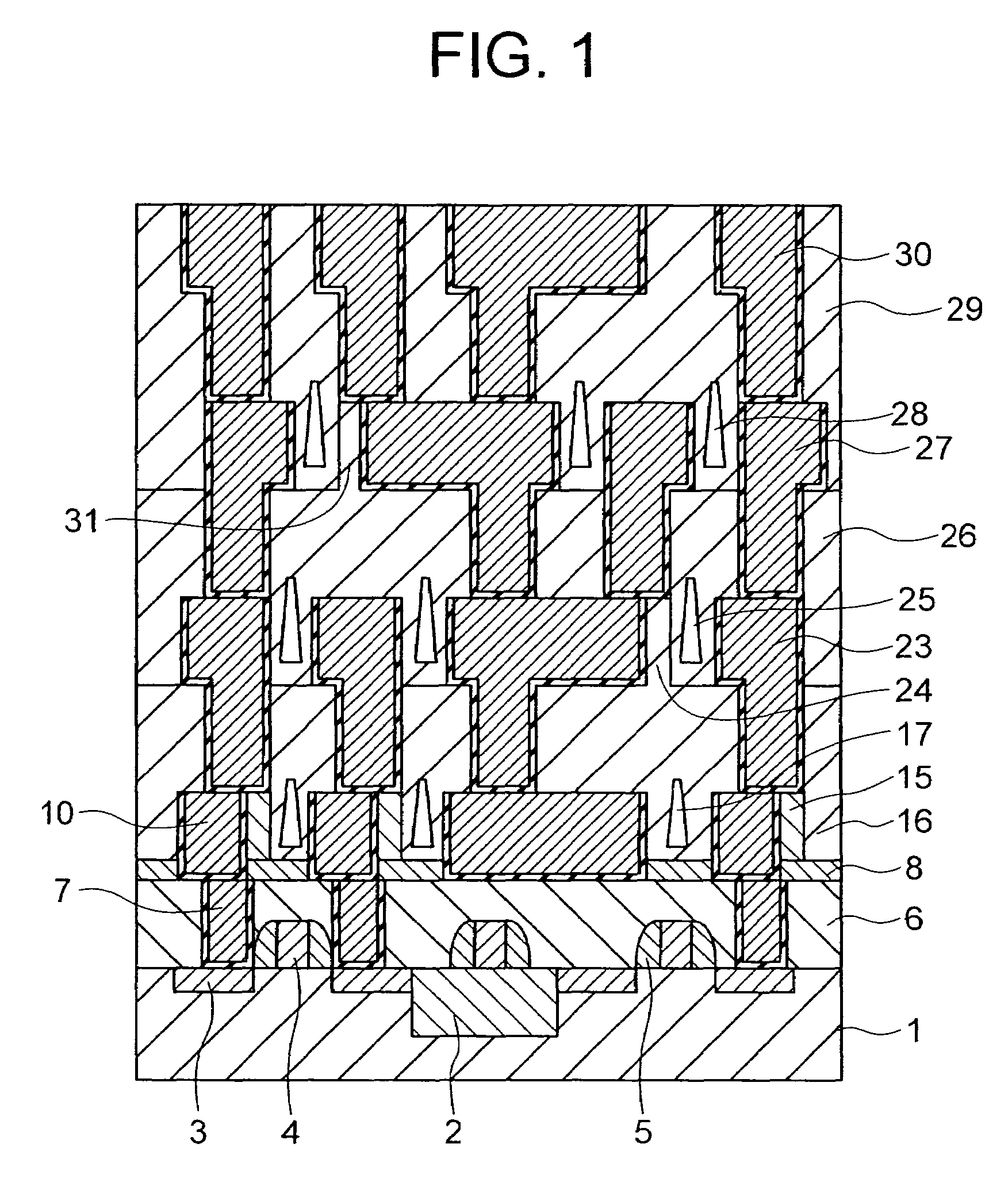

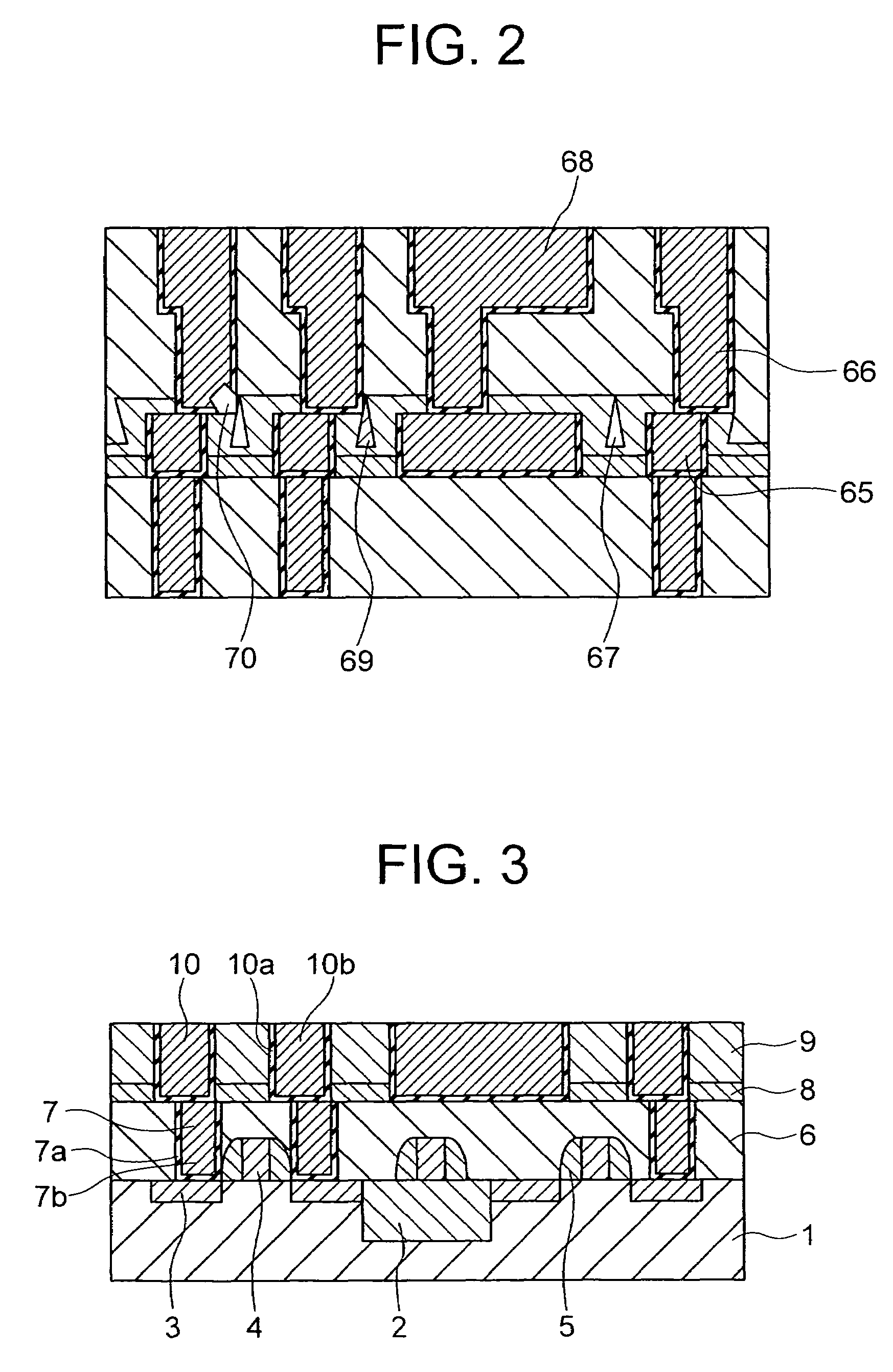

Semiconductor device and method for producing the same

ActiveUS20090289300A1Low ion densityReduce pressureTransistorSolid-state devicesEngineeringSemiconductor

First and second gate insulating films are formed so as to cover at least the upper corner of first and second fin-shaped semiconductor regions. The radius of curvature r1′ of the upper corner of the first fin-shaped semiconductor region located outside the first gate insulating film is greater than the radius of curvature r1 of the upper corner of the first fin-shaped semiconductor region located under the first gate insulating film and is less than or equal to 2×r1. The radius of curvature r2′ of the upper corner of the second fin-shaped semiconductor region located outside the second gate insulating film is greater than the radius of curvature r2 of the upper corner of the second fin-shaped semiconductor region located under the second gate insulating film and is less than or equal to 2×r2.

Owner:GK BRIDGE 1

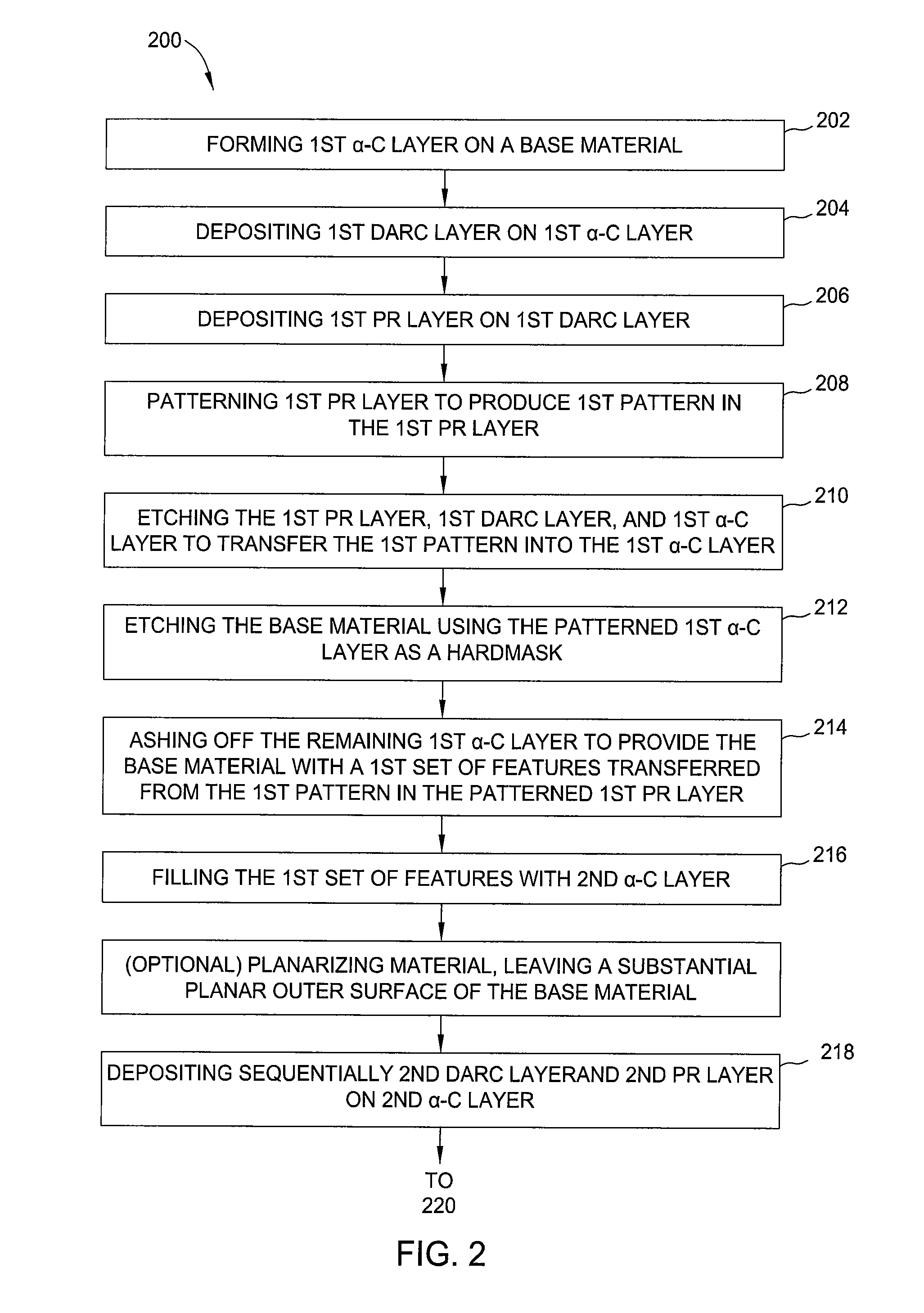

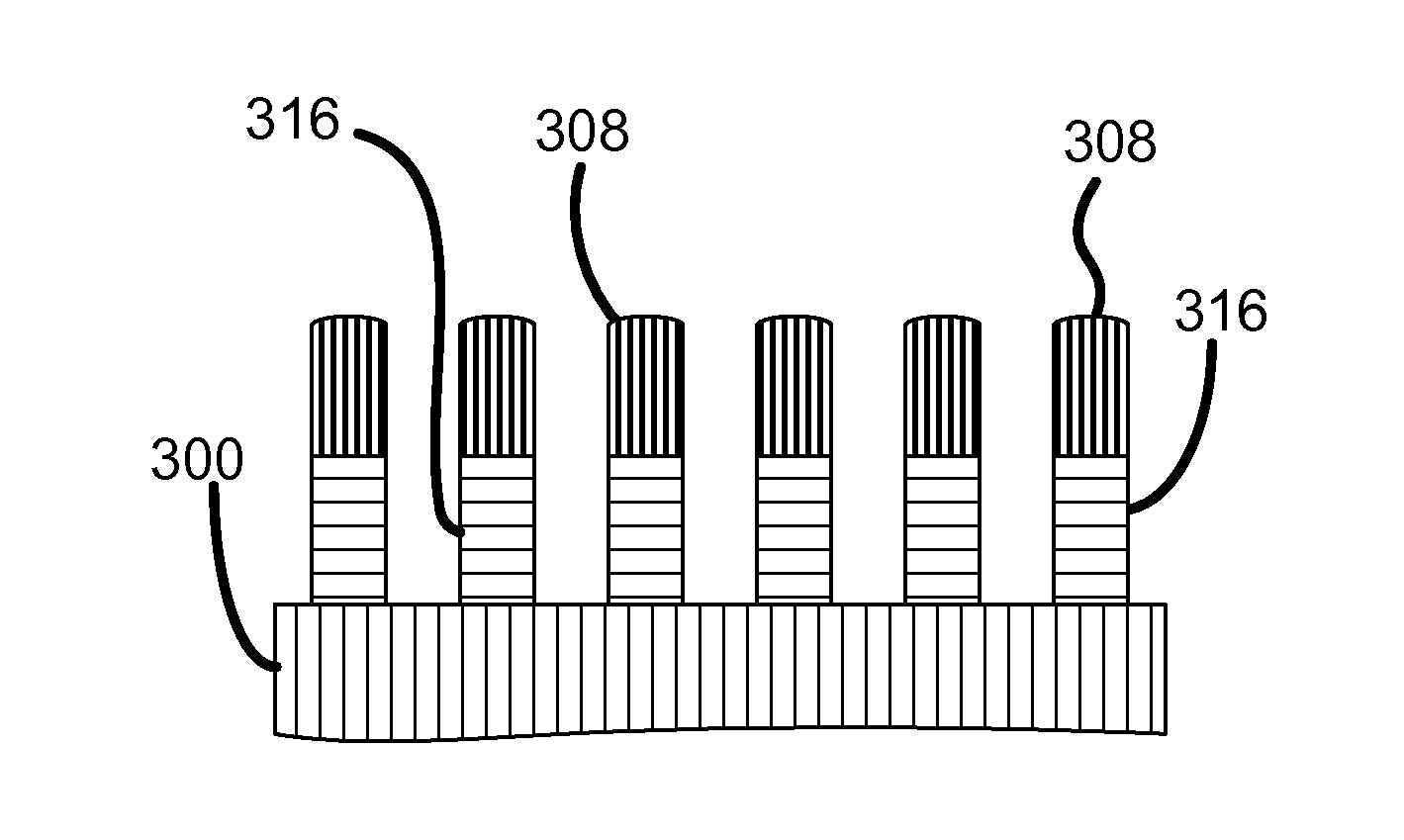

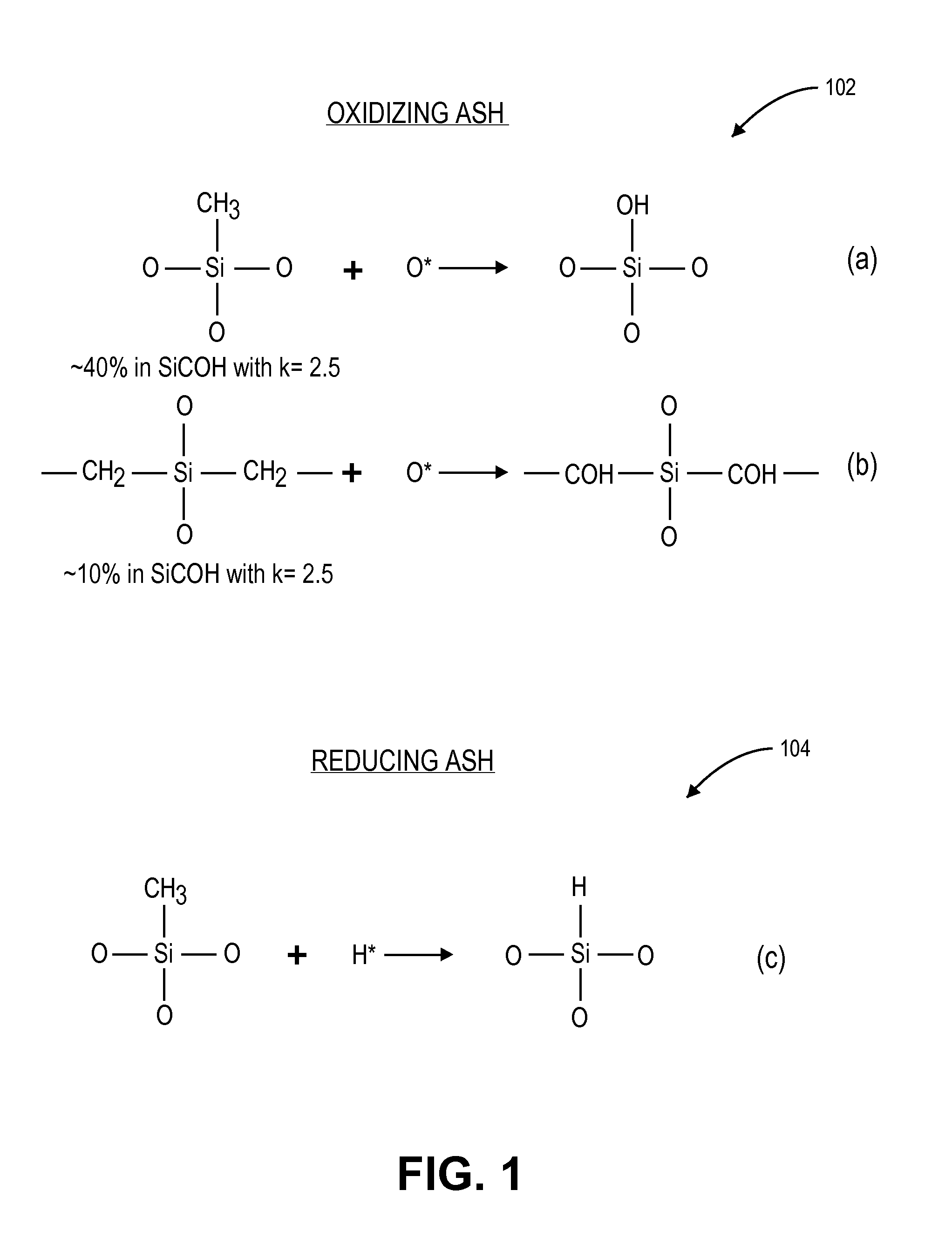

Planarizing etch hardmask to increase pattern density and aspect ratio

InactiveUS20110291243A1Easy to disassembleAdd depthSemiconductor/solid-state device detailsSolid-state devicesAnti-reflective coatingEngineering

Methods for manufacturing a semiconductor device in a processing chamber are provided. In one embodiment, a method includes depositing over a substrate a first base material having a first set of interconnect features, filling an upper portion of the first set of interconnect features with an ashable material to an extent capable of protecting the first set of interconnect features from subsequent processes while being easily removable when desired, planarizing an upper surface of the first base material such that an upper surface of the ashable material filled in the first set of interconnect features is at the same level with the upper surface of the first base material, providing a substantial planar outer surface of the first base material, depositing a first film stack comprising a second base material on the substantial planar outer surface of the first base material, forming a second set of interconnect features in the second base material, wherein the second set of interconnect features are aligned with the first set of interconnect features, and removing the ashable material from the first base material, thereby extending a feature depth of the semiconductor device by connecting the second set of interconnect features to the first set of interconnect features. In another embodiment, a method includes providing a base material having a first film stack deposited thereon, wherein the base material is formed over the substrate and having a first set of interconnect features filled with an amorphous carbon material, the first film stack comprising a first amorphous carbon layer deposited on a surface of the base material, a first anti-reflective coating layer deposited on the first amorphous carbon layer, and a first photoresist layer deposited on the first anti-reflective coating layer, and patterning a portion of the first photoresist layer by shifting laterally a projection of a mask on the first photoresist layer relative to the substrate a desired distance, thereby introducing into the first photoresist layer a first feature pattern to be transferred to the underlying base material, wherein the first feature pattern is not aligned with the first set of interconnect features.

Owner:APPLIED MATERIALS INC

Spacer formation

ActiveUS20150287612A1Semiconductor/solid-state device manufacturingImage resolutionOptical resolution

Embodiments of the present invention pertain to methods of forming more symmetric spacers which may be used for self-aligned multi-patterning processes. A conformal spacer layer of spacer material is formed over mandrels patterned near the optical resolution of a photolithography system using a high-resolution photomask. A carbon-containing layer is further formed over the conformal spacer layer. The carbon-containing layer is anisotropically etched to expose the high points of the conformal spacer layer while retaining carbon side panels. The conformal spacer layer may then be etched to form spacers without the traditional skewing of the profile towards one side or the other.

Owner:APPLIED MATERIALS INC

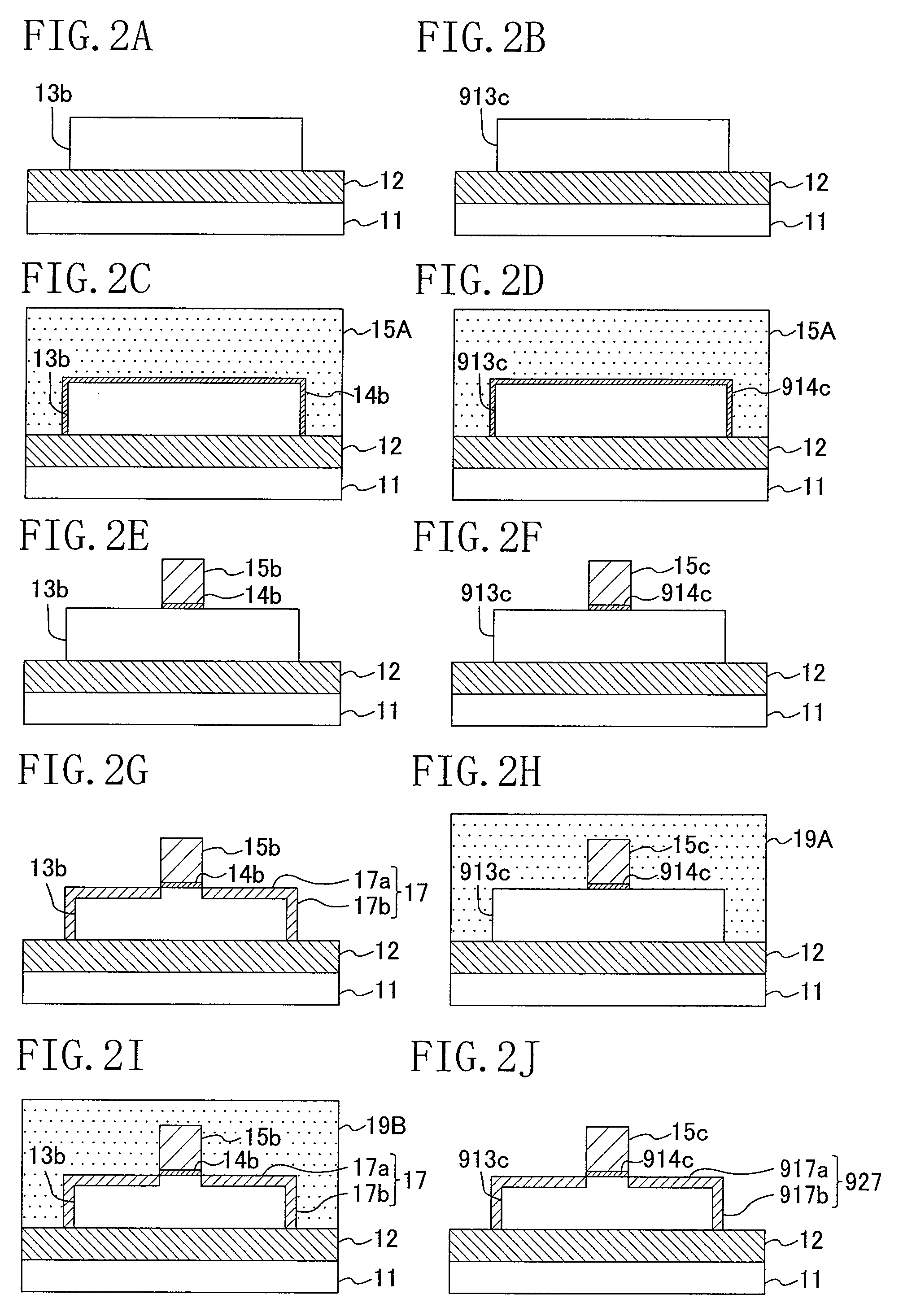

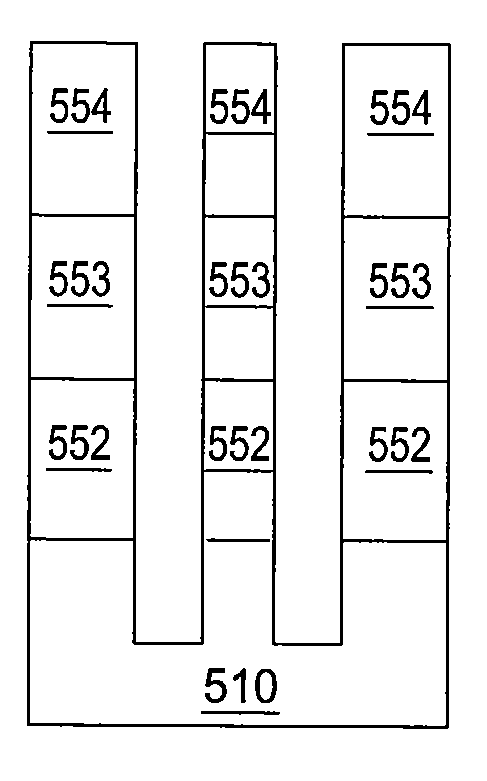

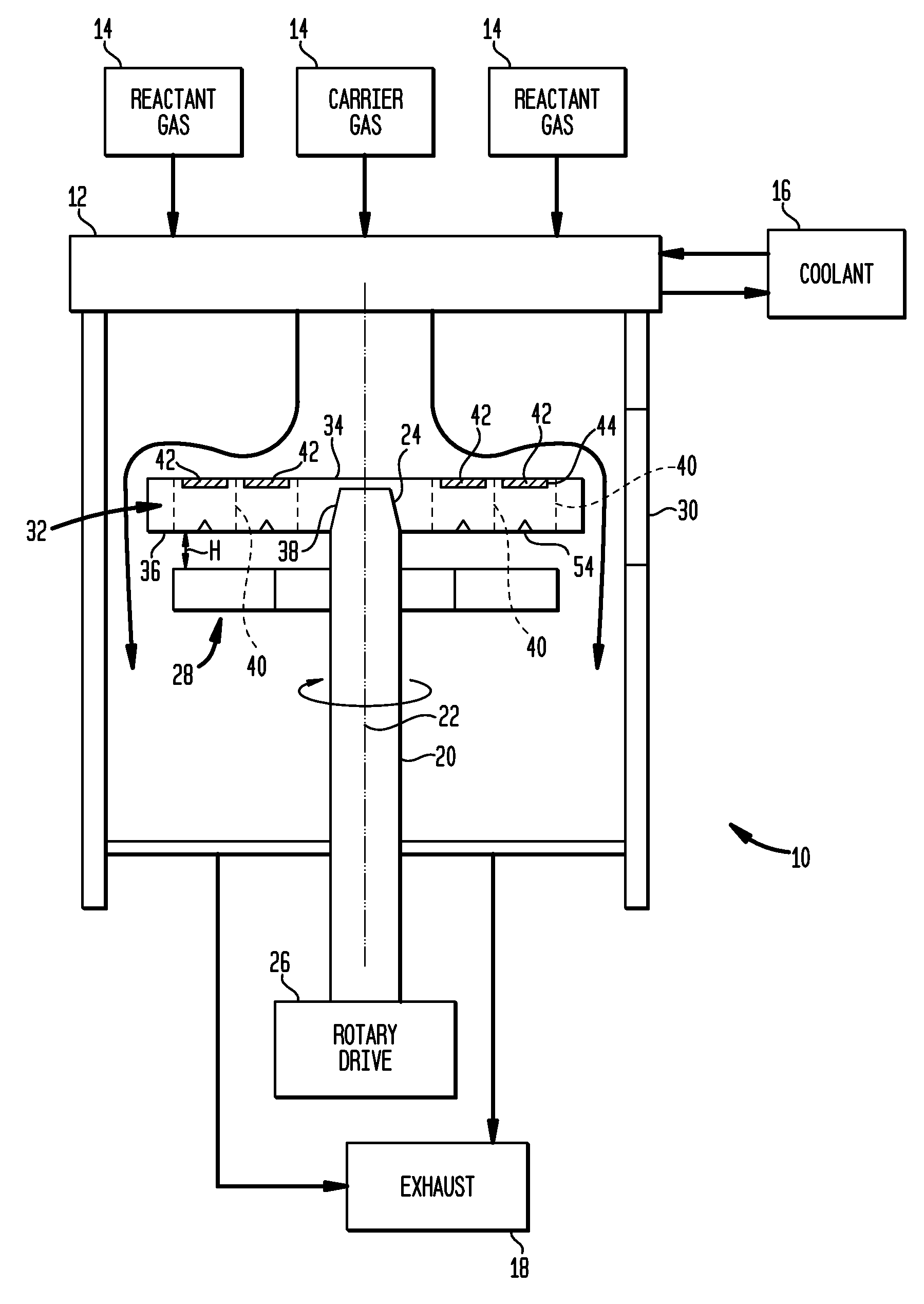

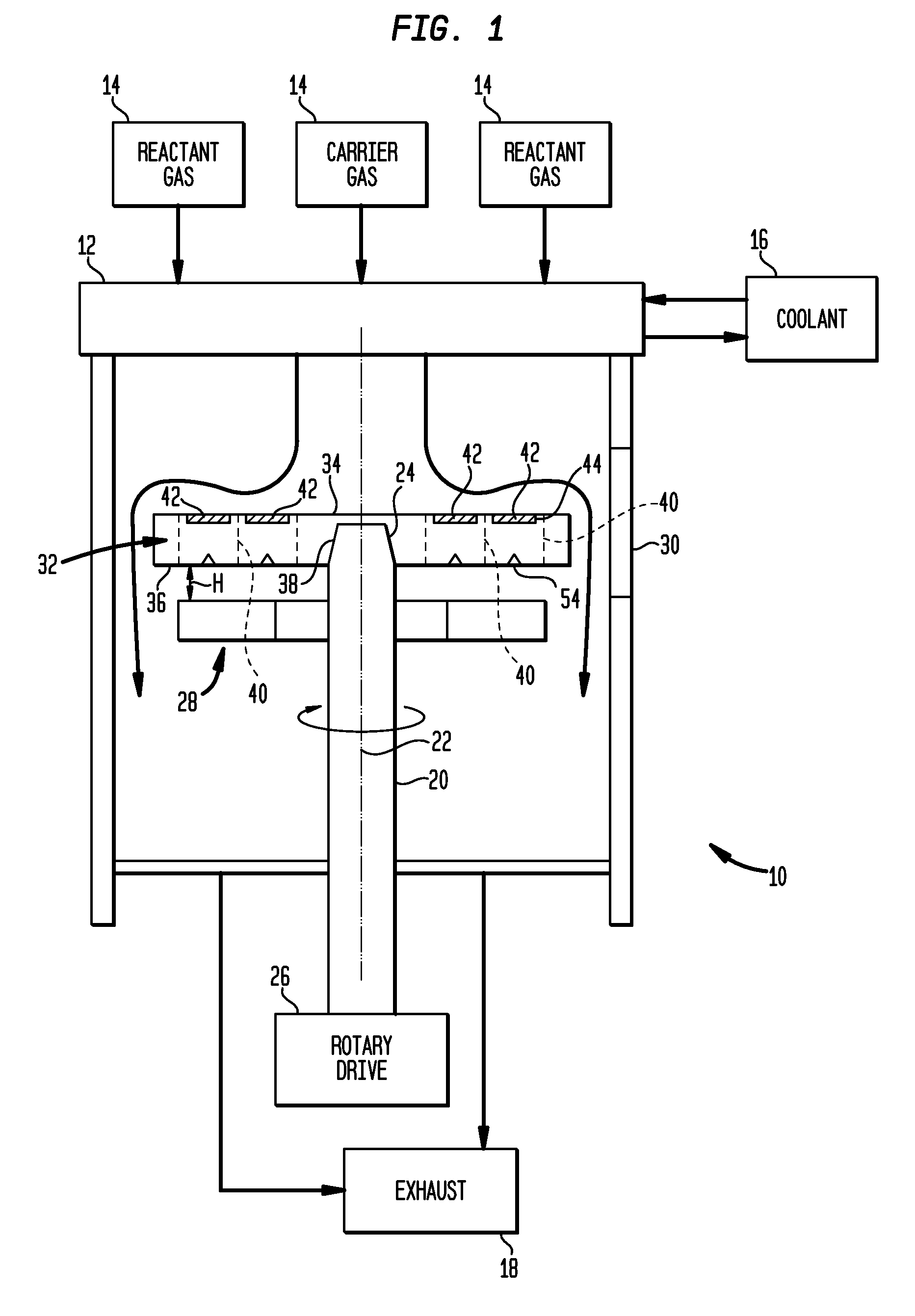

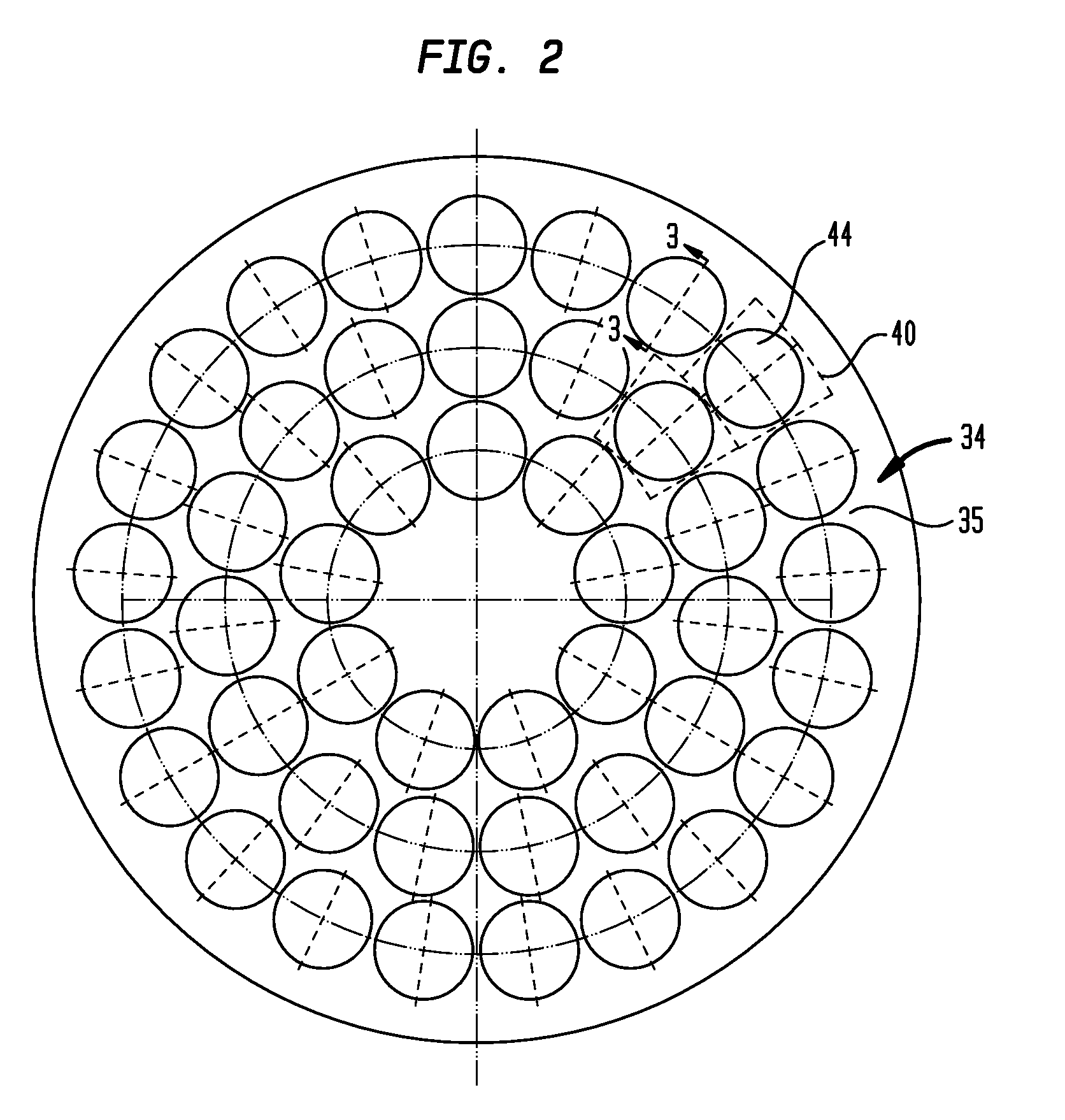

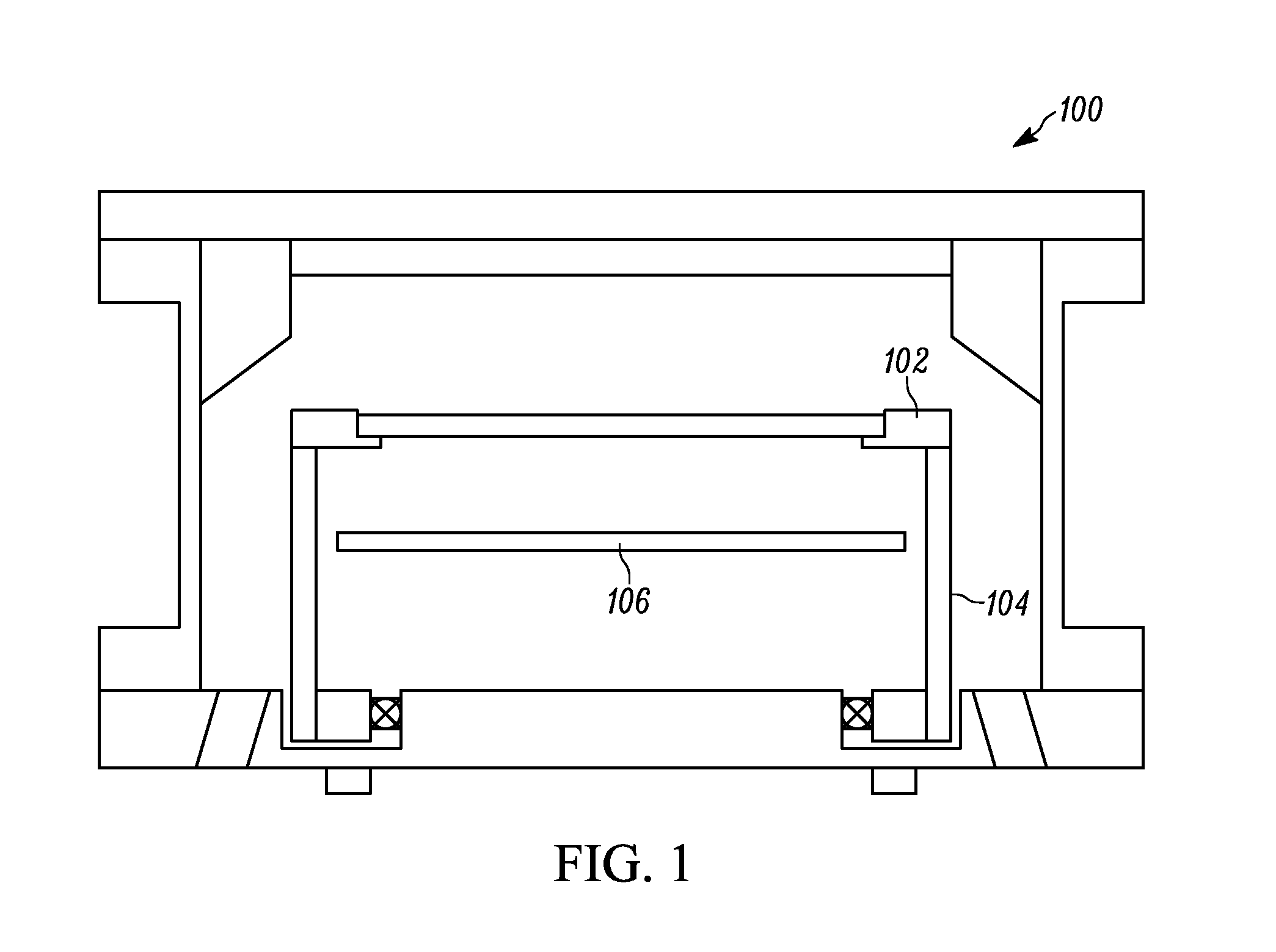

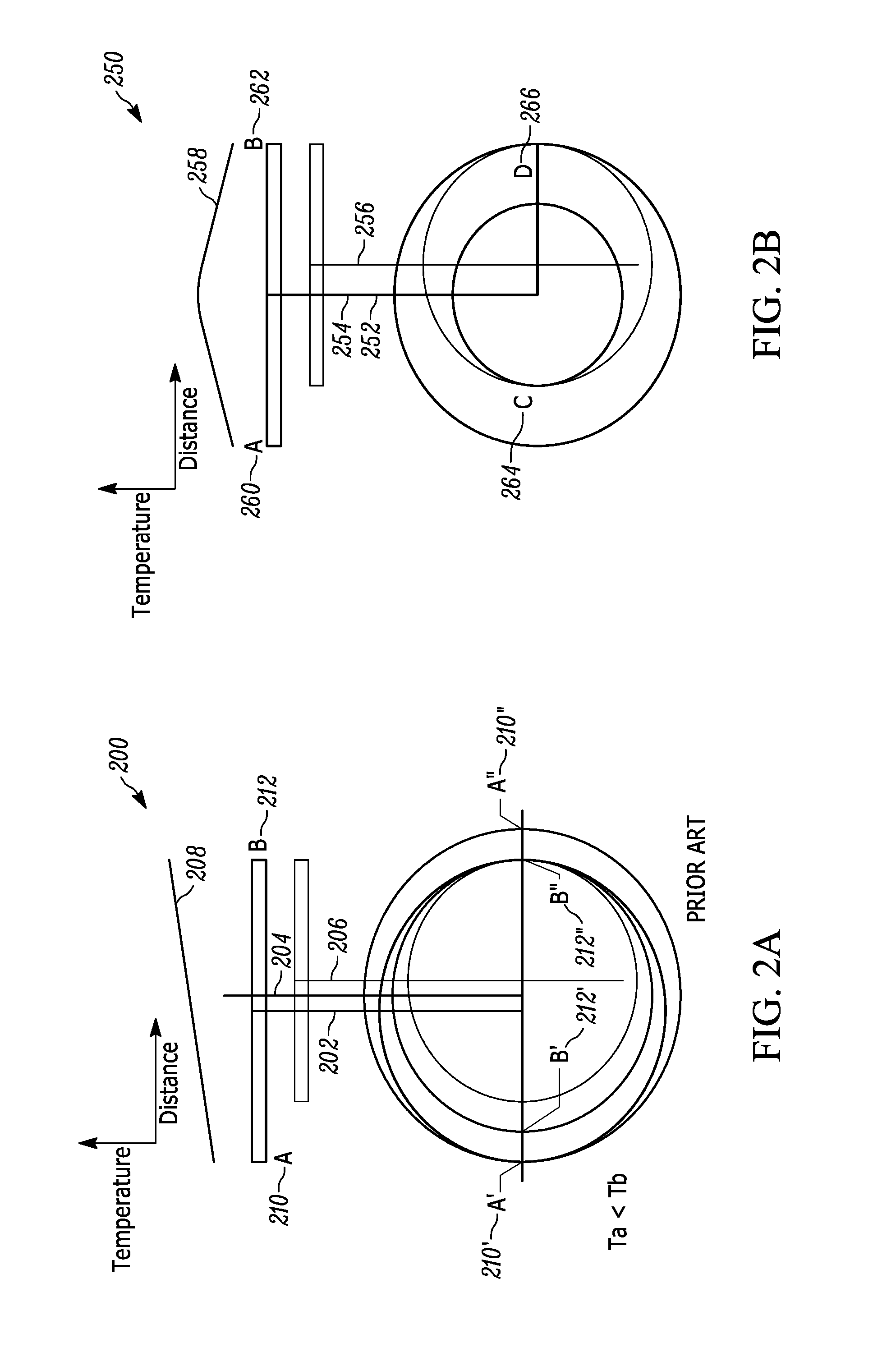

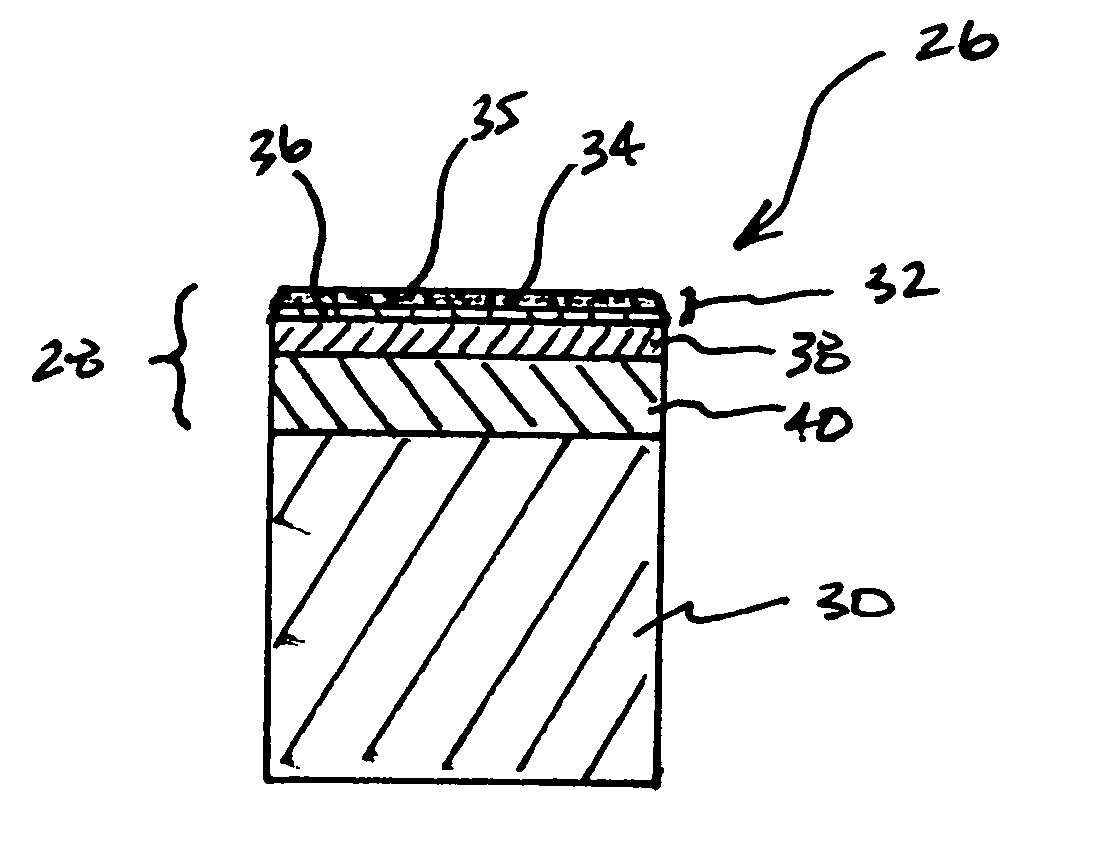

Wafer carrier with varying thermal resistance

InactiveUS20100055318A1Minimize contactImprove temperature uniformityLiquid surface applicatorsSemiconductor/solid-state device manufacturingEngineeringRadiant heat transfer

In chemical vapor deposition apparatus, a water carrier (32) has a top surface (34) holding the wafers and a bottom surface (36) heated by radiant heat transfer from a heating element (28). The bottom surface (36) of the wafer carrier is non-planar due to features such as depressions (54) so that the wafer carrier has different thickness at different locations. The thicker portions of the wafer carrier have higher thermal resistance. Differences in thermal resistance at different locations counteract undesired non-uniformities in heat transfer to the wafer. The wafer carrier may have pockets with projections (553, 853) for engaging spaced-apart locations on the edges of the wafer.

Owner:VEECO INSTR

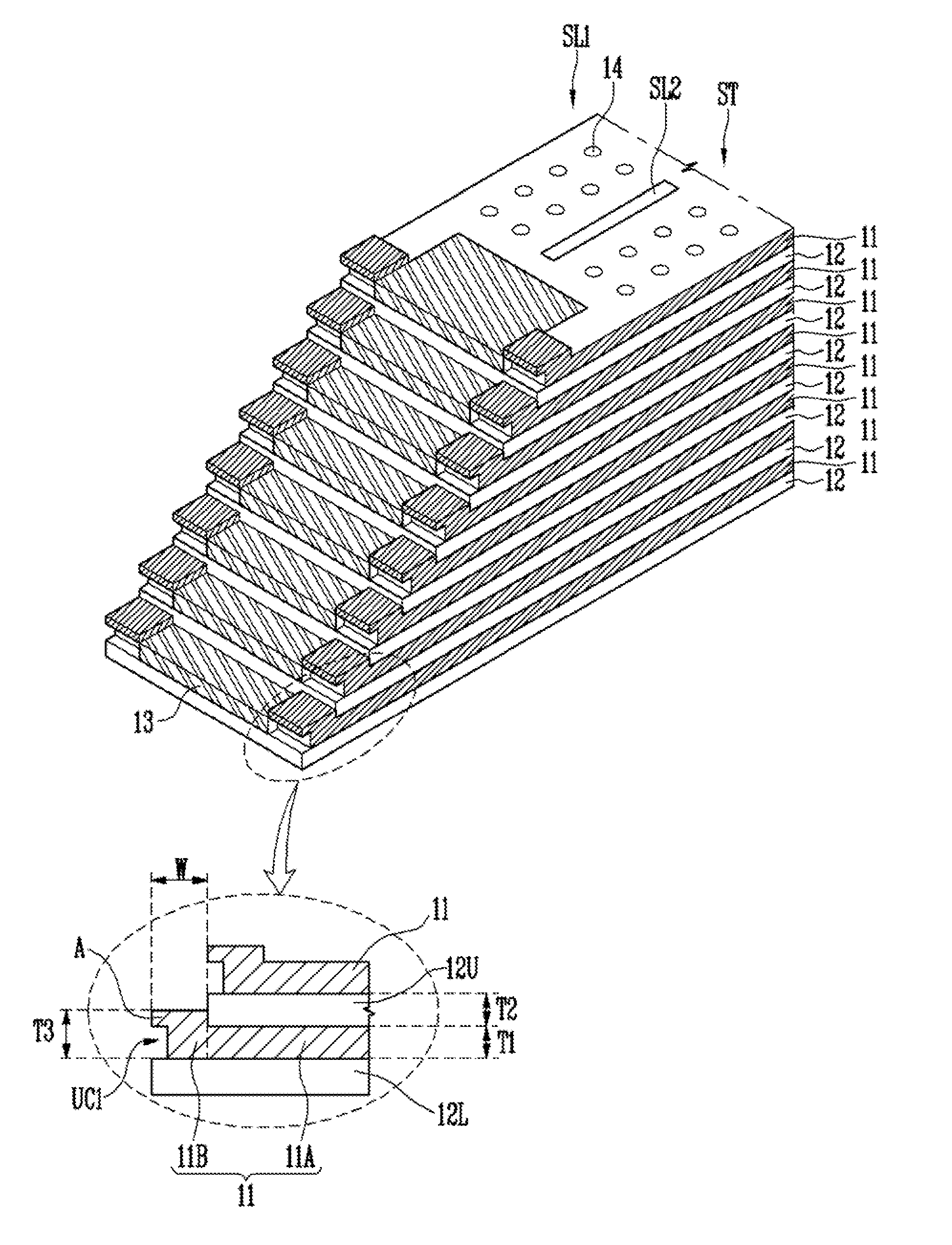

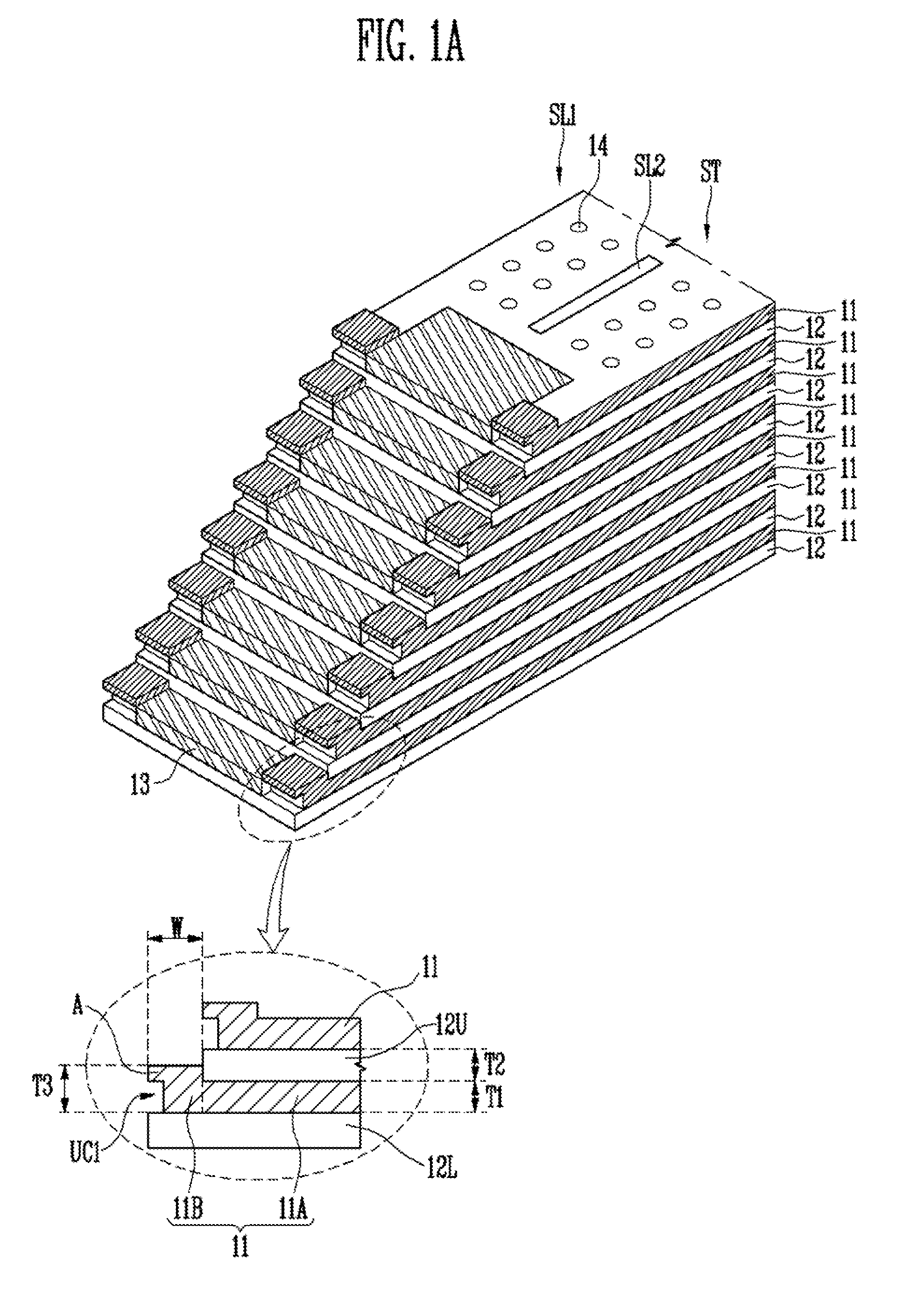

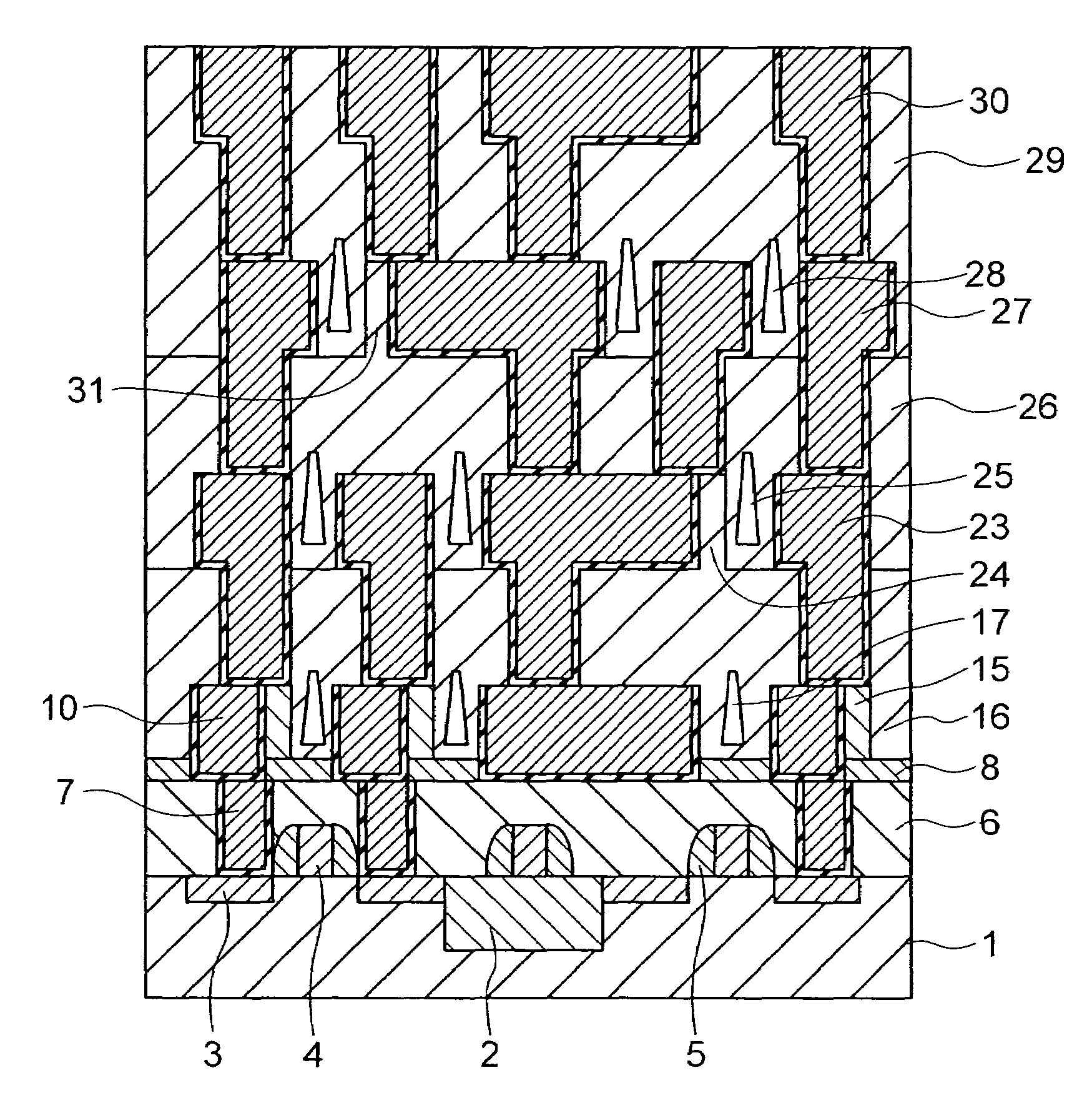

Semiconductor device and method of fabricating the same

ActiveUS20150255385A1Simplified method of fabricatingSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering physics

A semiconductor device and a method of fabricating the same are provided. The semiconductor device includes insulating layers stacked in the shape of stairs, and conductive layers alternately stacked with the insulating layers, wherein the conductive layers each include a first region interposed between upper and lower insulating layers thereof, among the insulating layers, and a second region which extends from the first region and protrudes between the upper and lower insulating layers, and wherein a protruding part formed on a sidewall or an upper surface of the second region.

Owner:SK HYNIX INC

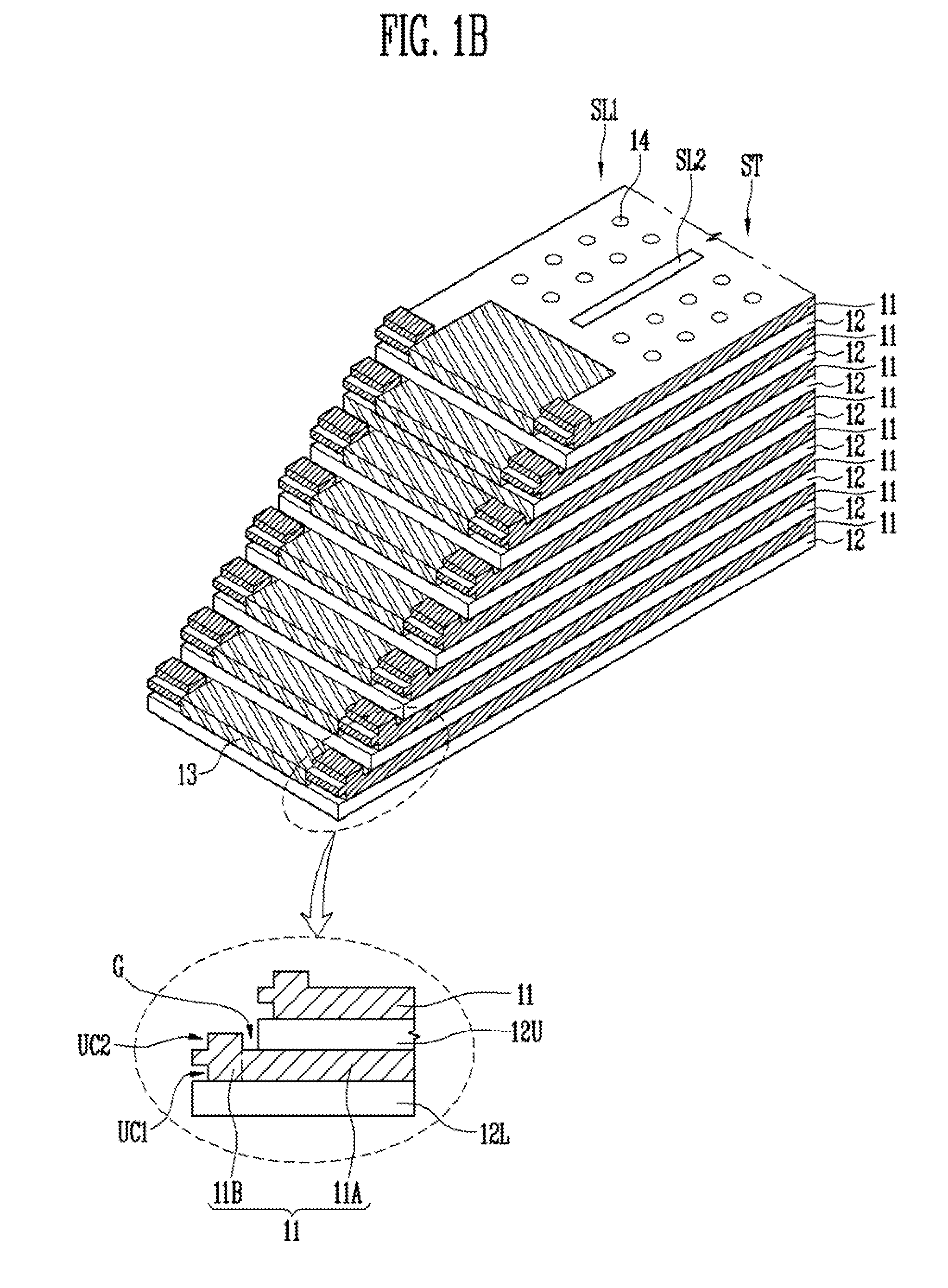

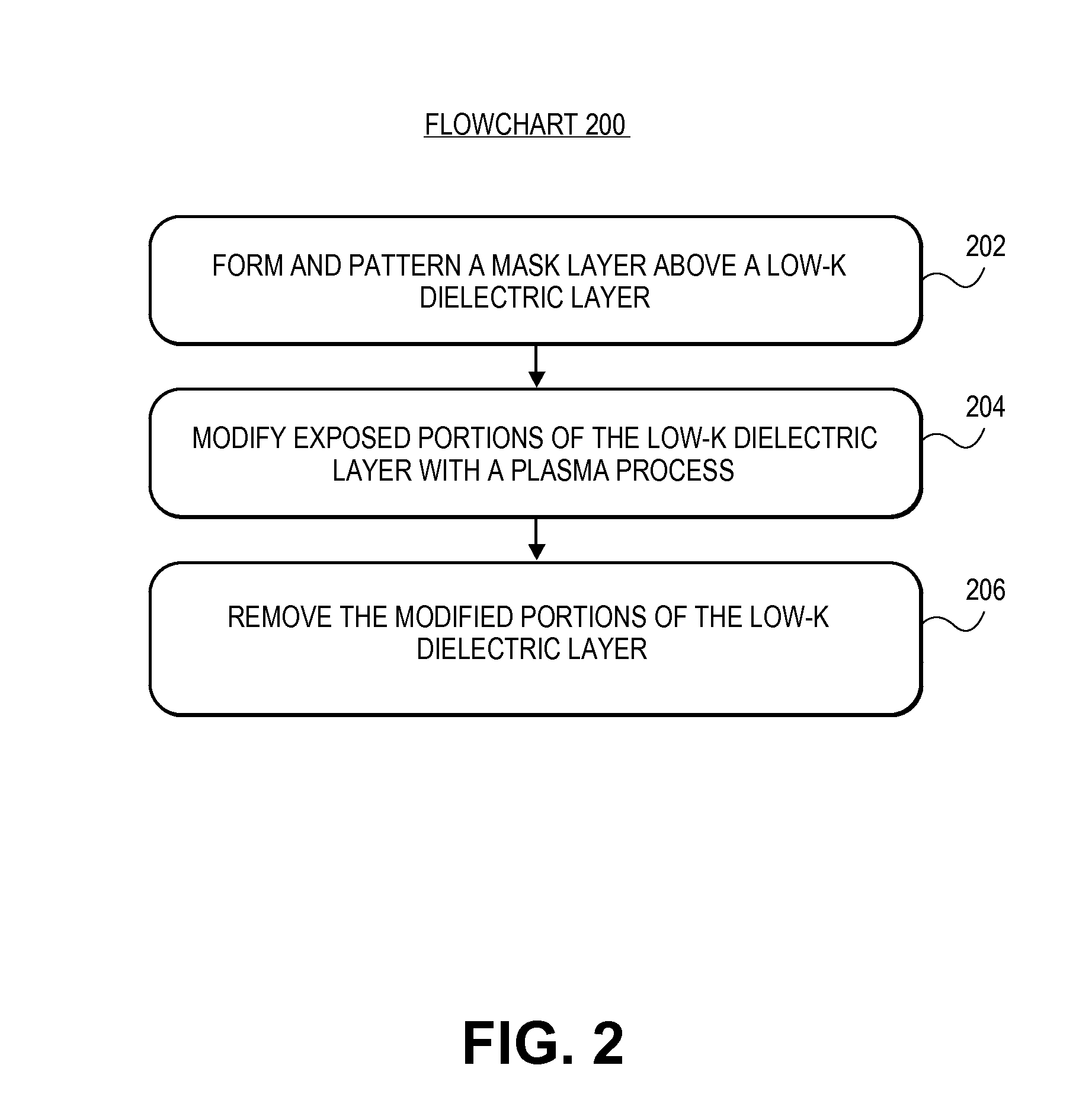

Method of patterning a low-k dielectric film

Methods of patterning low-k dielectric films are described. For example, a method includes forming and patterning a mask layer above a low-k dielectric layer, the low-k dielectric layer disposed above a substrate. Exposed portions of the low-k dielectric layer are modified with a plasma process. The modified portions of the low-k dielectric layer are removed selective to the mask layer and unmodified portions of the low-k dielectric layer.

Owner:APPLIED MATERIALS INC

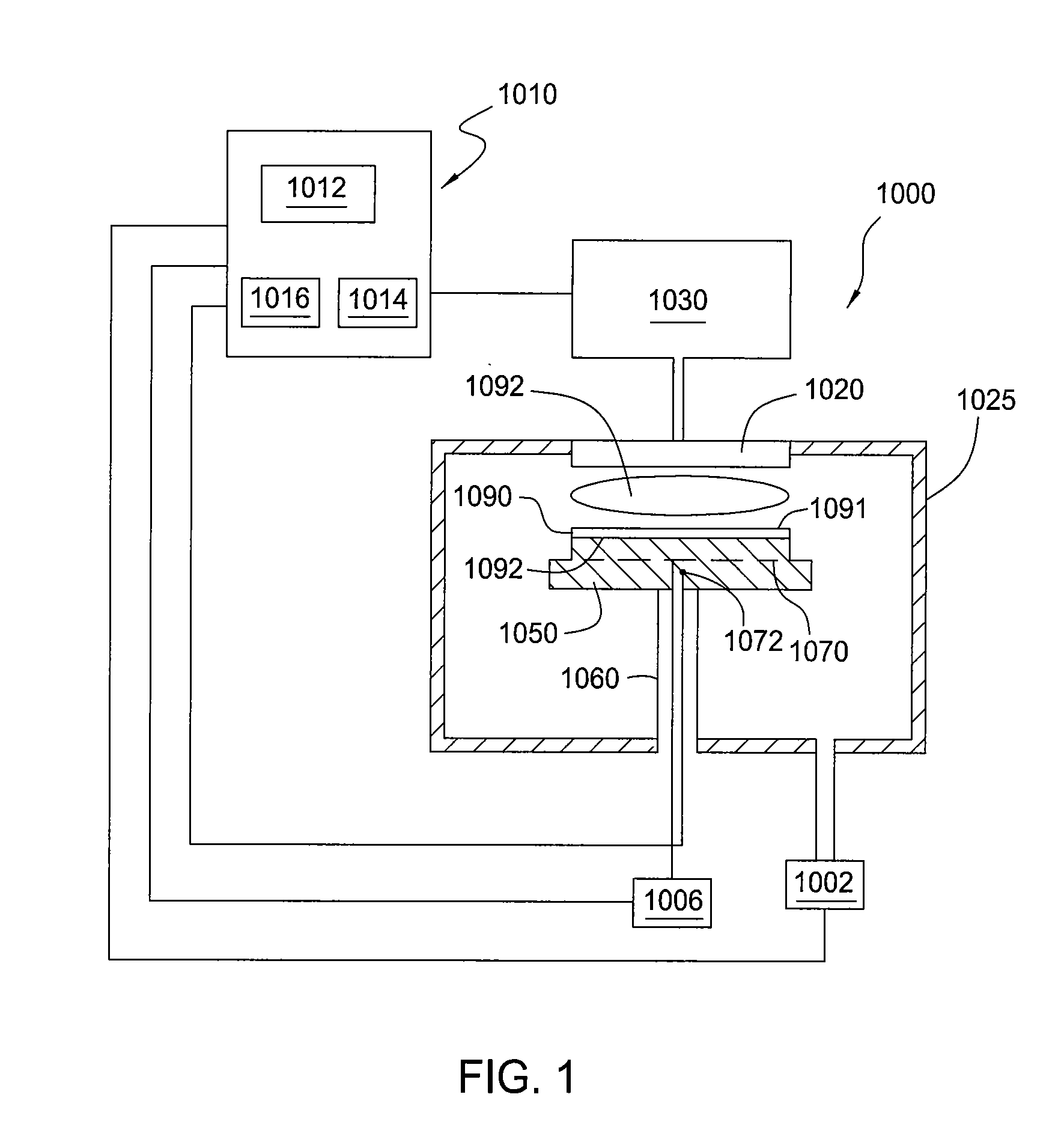

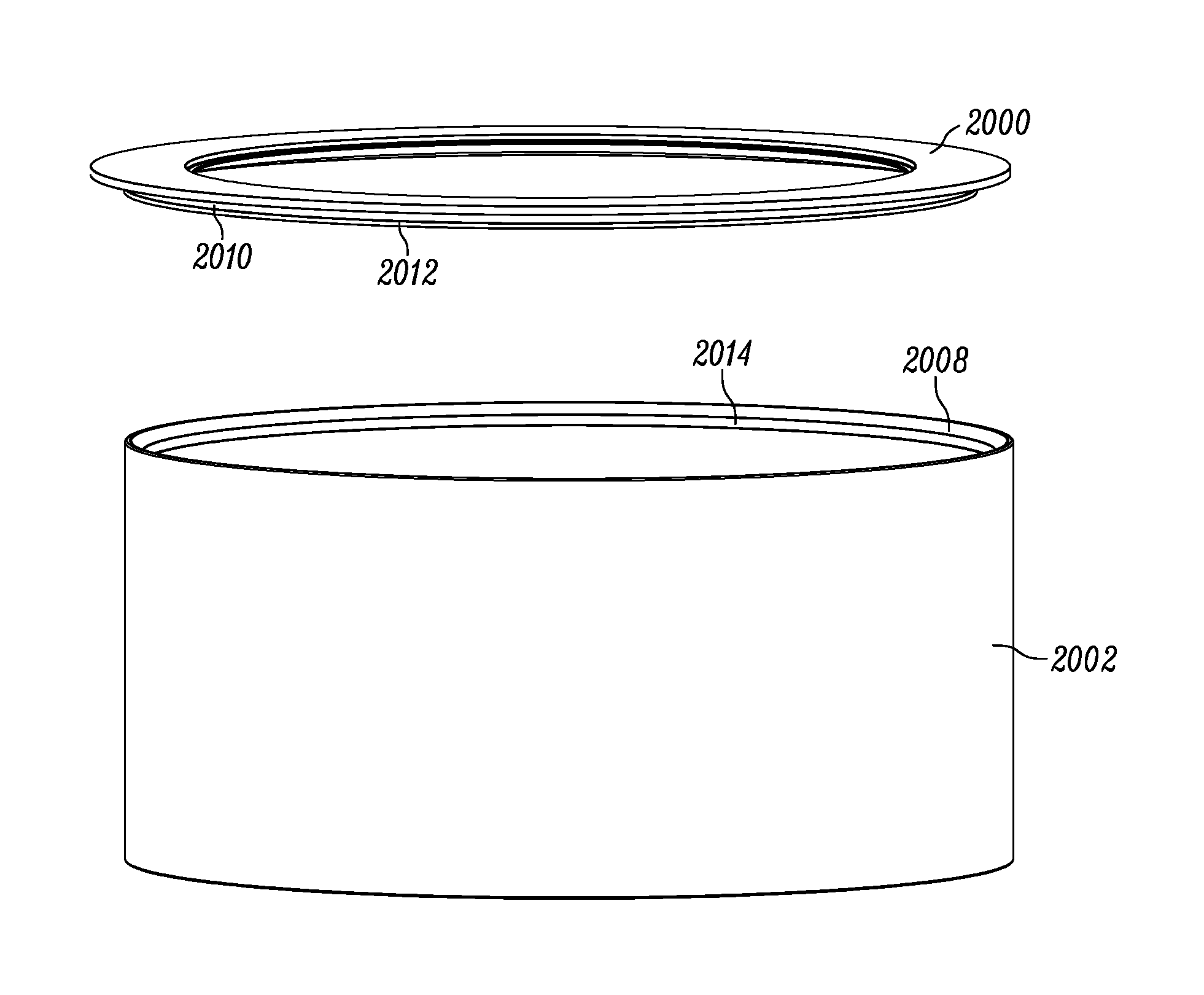

Self-Centering Wafer Carrier System For Chemical Vapor Deposition

ActiveUS20160372321A1Increase probabilityQuality improvementSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingGas phaseCarrier system

A self-centering wafer carrier system for a chemical vapor deposition (CVD) reactor includes a wafer carrier comprising an edge. The wafer carrier at least partially supports a wafer for CVD processing. A rotating tube comprises an edge that supports the wafer carrier during processing. An edge geometry of the wafer carrier and an edge geometry of the rotating tube being chosen to provide a coincident alignment of a central axis of the wafer carrier and a rotation axis of the rotating tube during process at a desired process temperature.

Owner:VEECO INSTR

Silicon oxycarbide and silicon carbonitride based materials for MOS devices

ActiveUS20050236694A1Lower the K valueIncrease deposition rateSemiconductor/solid-state device detailsSolid-state devicesGate dielectricMaterials science

In the preferred embodiment, a gate dielectric and an electrode are formed on a substrate. A pair of spacers is formed along opposite sidewalls of the gate electrode and the gate dielectric. Spacers are preferably formed of SiCO based material or SiCN based material. The source and drain are then formed. A contact etch stop (CES) layer is formed on the source / drain regions and the spacers. The CES layer is preferably formed of SiCO based material or SiCN based material. An Inter-Level Dielectric (ILD) is then formed on the CES layer.

Owner:TAIWAN SEMICON MFG CO LTD

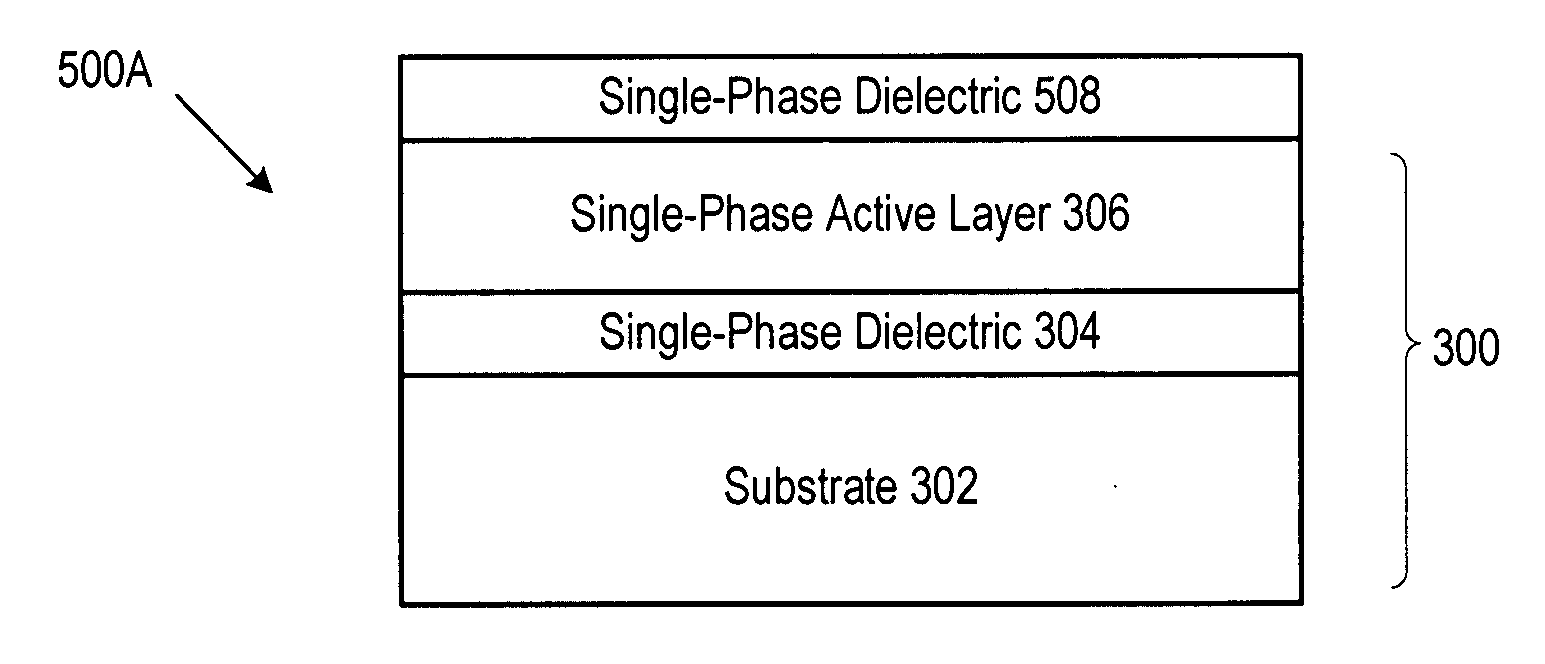

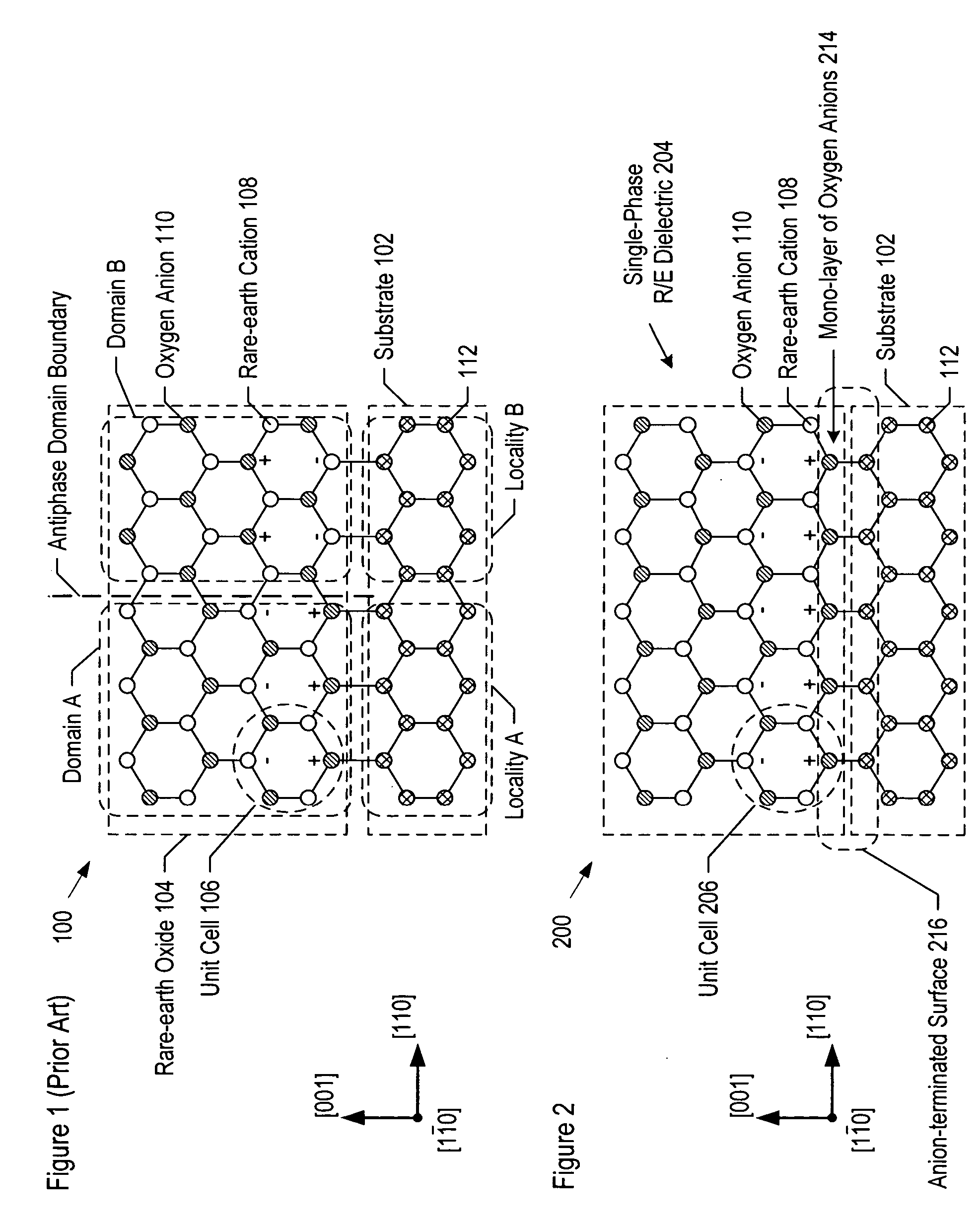

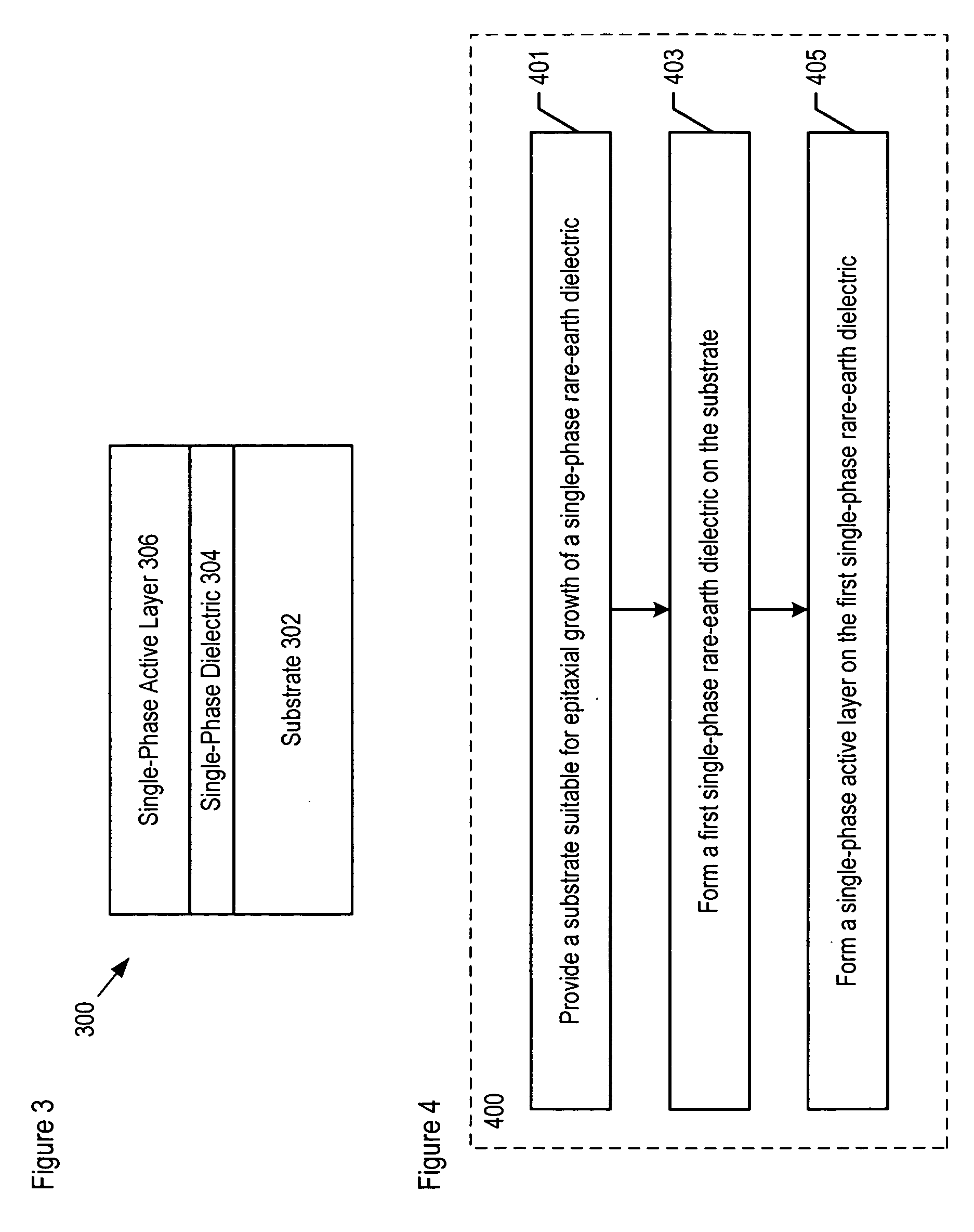

Method of forming a rare-earth dielectric layer

ActiveUS20060060131A1Quality improvementPolycrystalline material growthLaser detailsSemiconductor structureRare earth

Methods for forming compositions comprising a single-phase rare-earth dielectric disposed on a substrate are disclosed. In some embodiments, the method forms a semiconductor-on-insulator structure. Compositions and structures that are formed via the method provide the basis for forming high-performance devices and circuits.

Owner:IQE

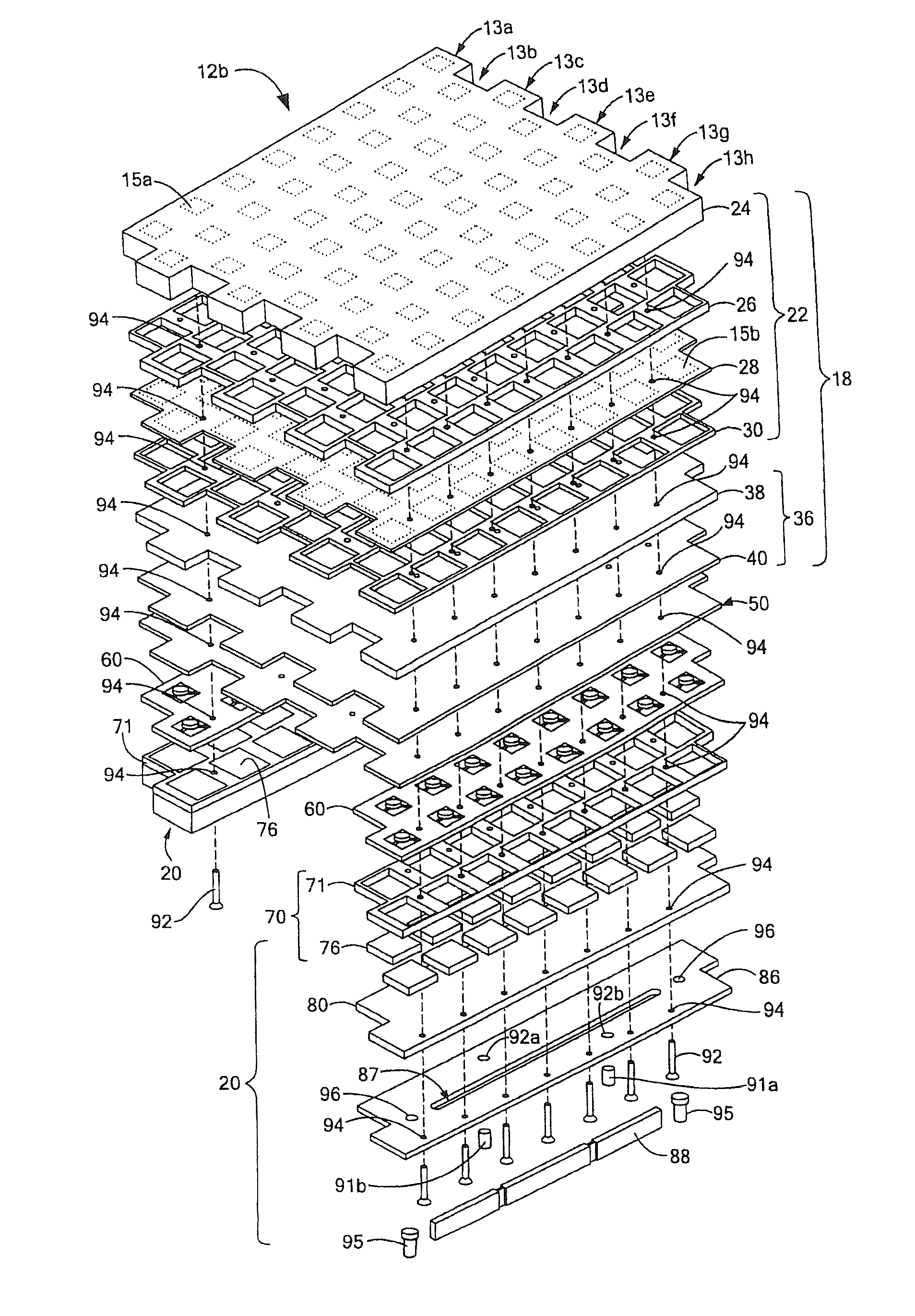

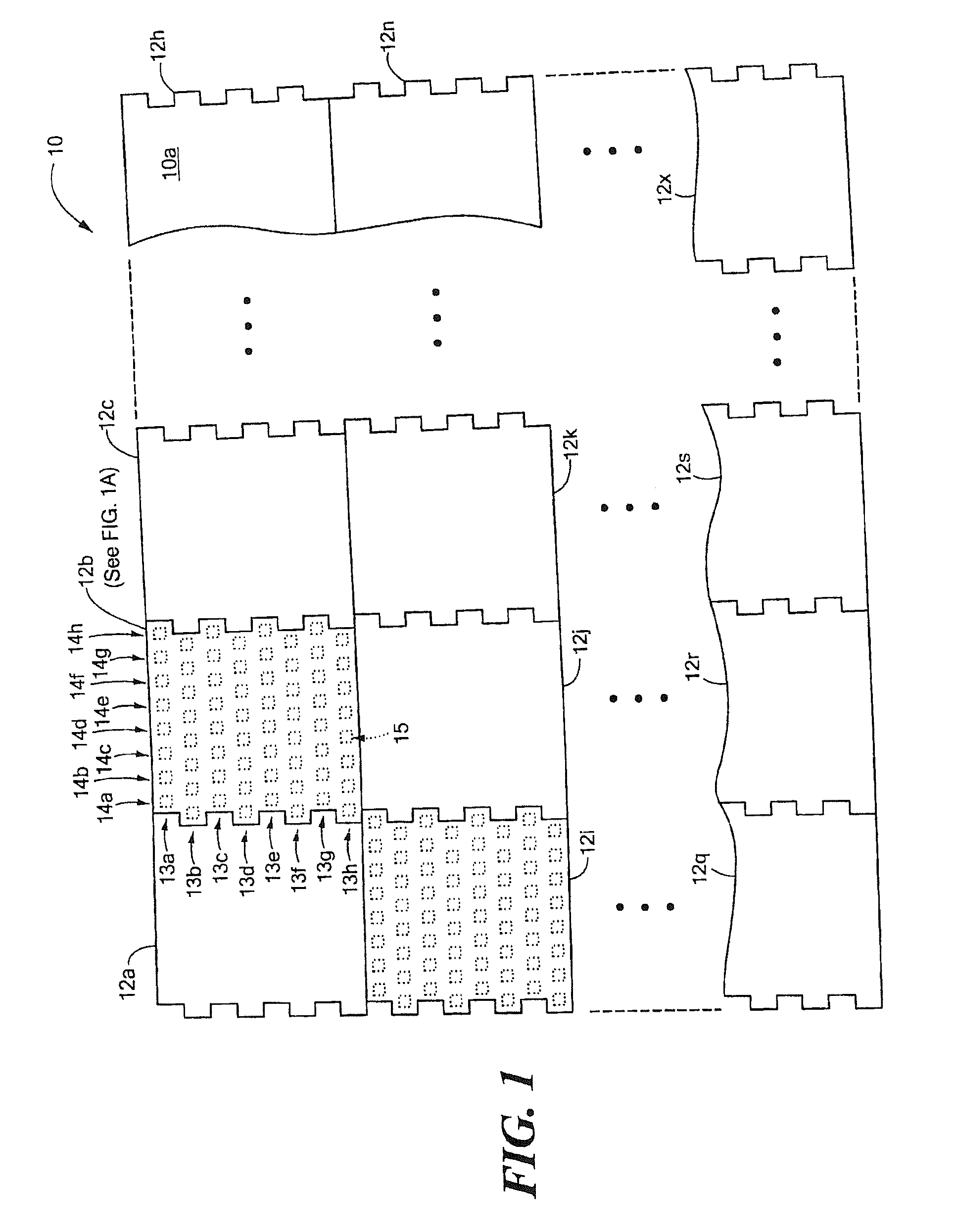

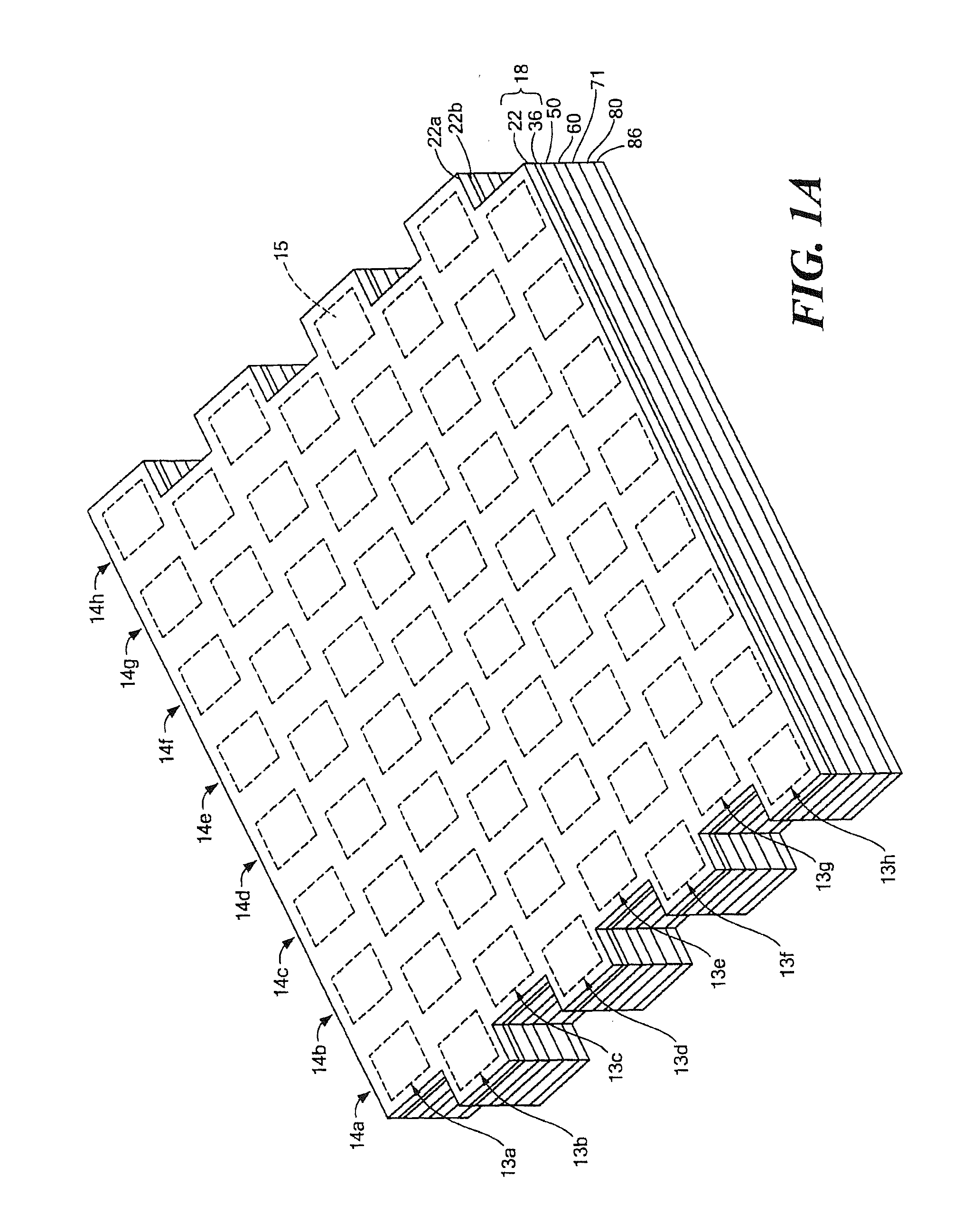

Panel Array

ActiveUS20100066631A1Low insertion lossEliminate needAntenna arrays manufactureModular arraysHemt circuitsChipset

A mixed-signal, multilayer printed wiring board fabricated in a single lamination step is described. The PWB includes one or more radio frequency (RF) interconnects between different circuit layers on different circuit boards which make up the PWB. The PWB includes a number of unit cells with radiating elements and an RF cage disposed around each unit cell to isolate the unit cell. A plurality of flip-chip circuits are disposed on an external surface of the PWB and a heat sink can be disposed over the flip chip components.

Owner:RAYTHEON CO

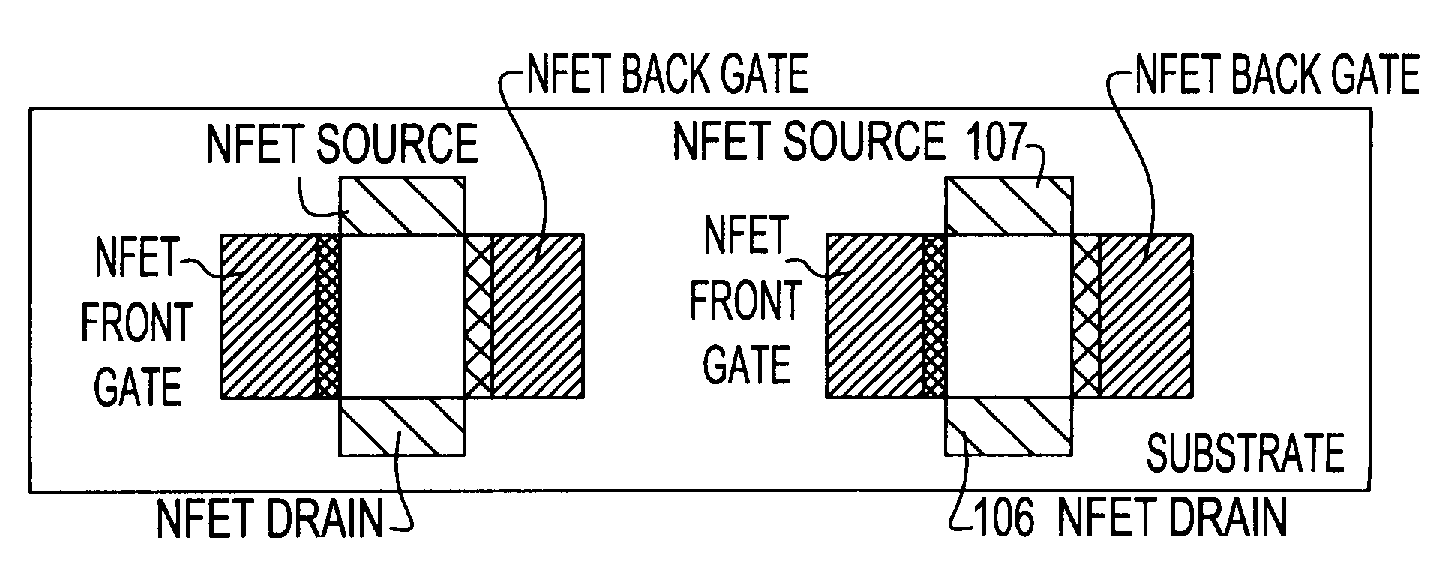

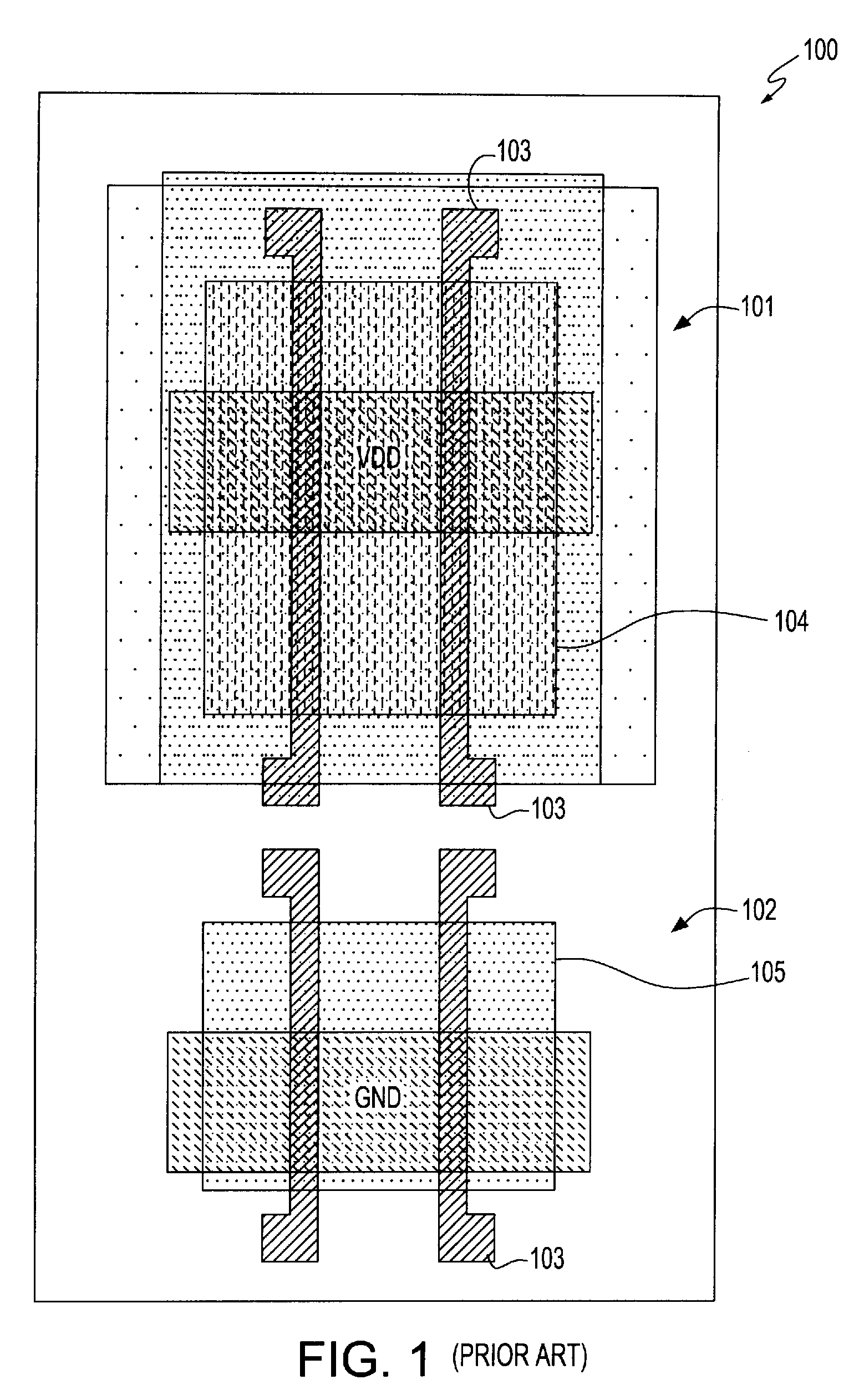

Dual gate fet structures for flexible gate array design methodologies

InactiveUS20090101940A1Easy to operateSolid-state devicesSemiconductor/solid-state device manufacturingGate arrayStandard cell

A gate array cell adapted for standard cell design methodology or programmable gate array that incorporates a dual gate FET device to offer a range of performance options within the same unit cell area. The conductivity and drive strength of the dual gate device may be selectively tuned through independent processing of manufacturing parameters to provide an asymmetric circuit response for the device or a symmetric response as dictated by the circuit application.

Owner:GLOBALFOUNDRIES INC

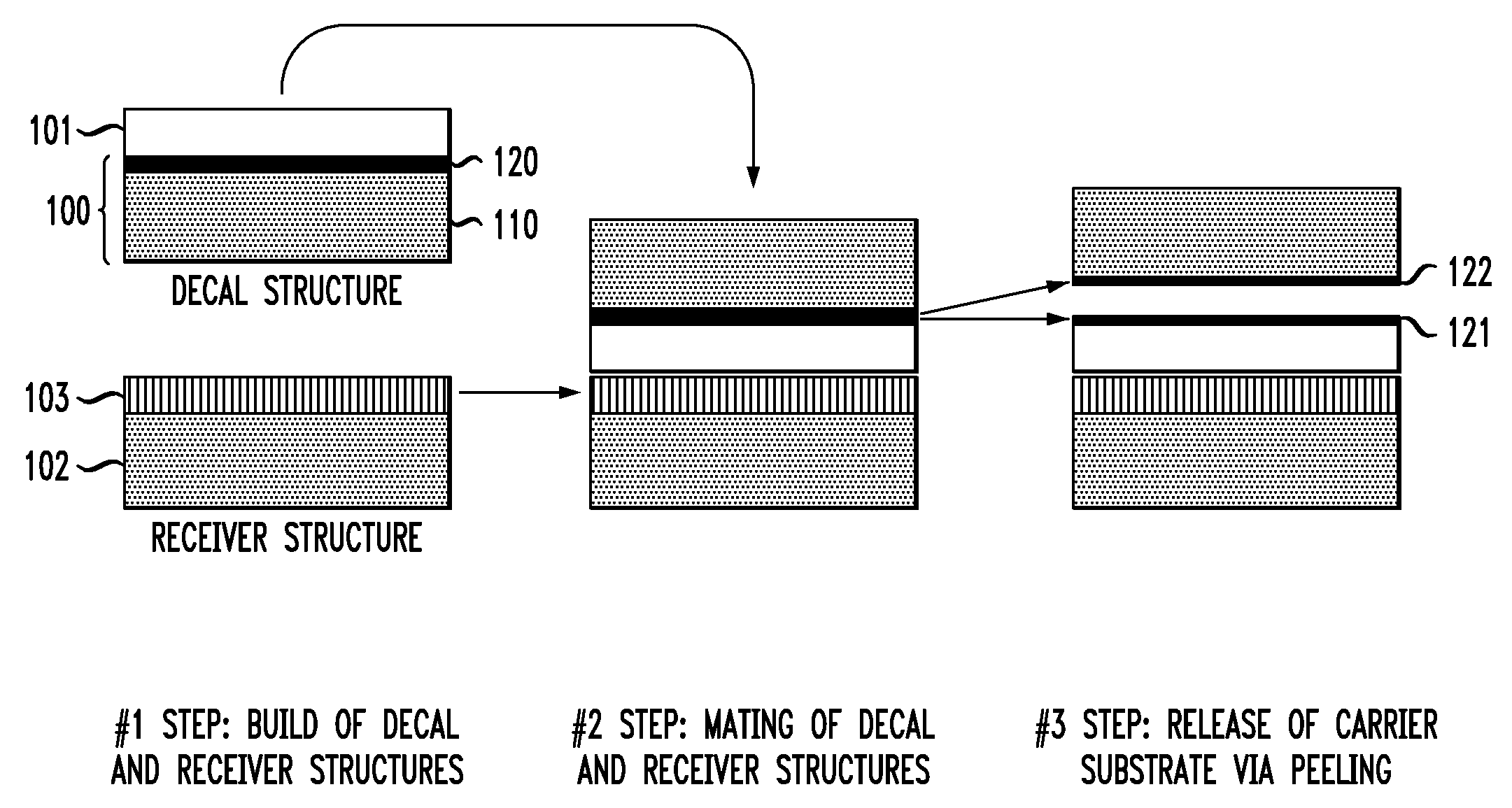

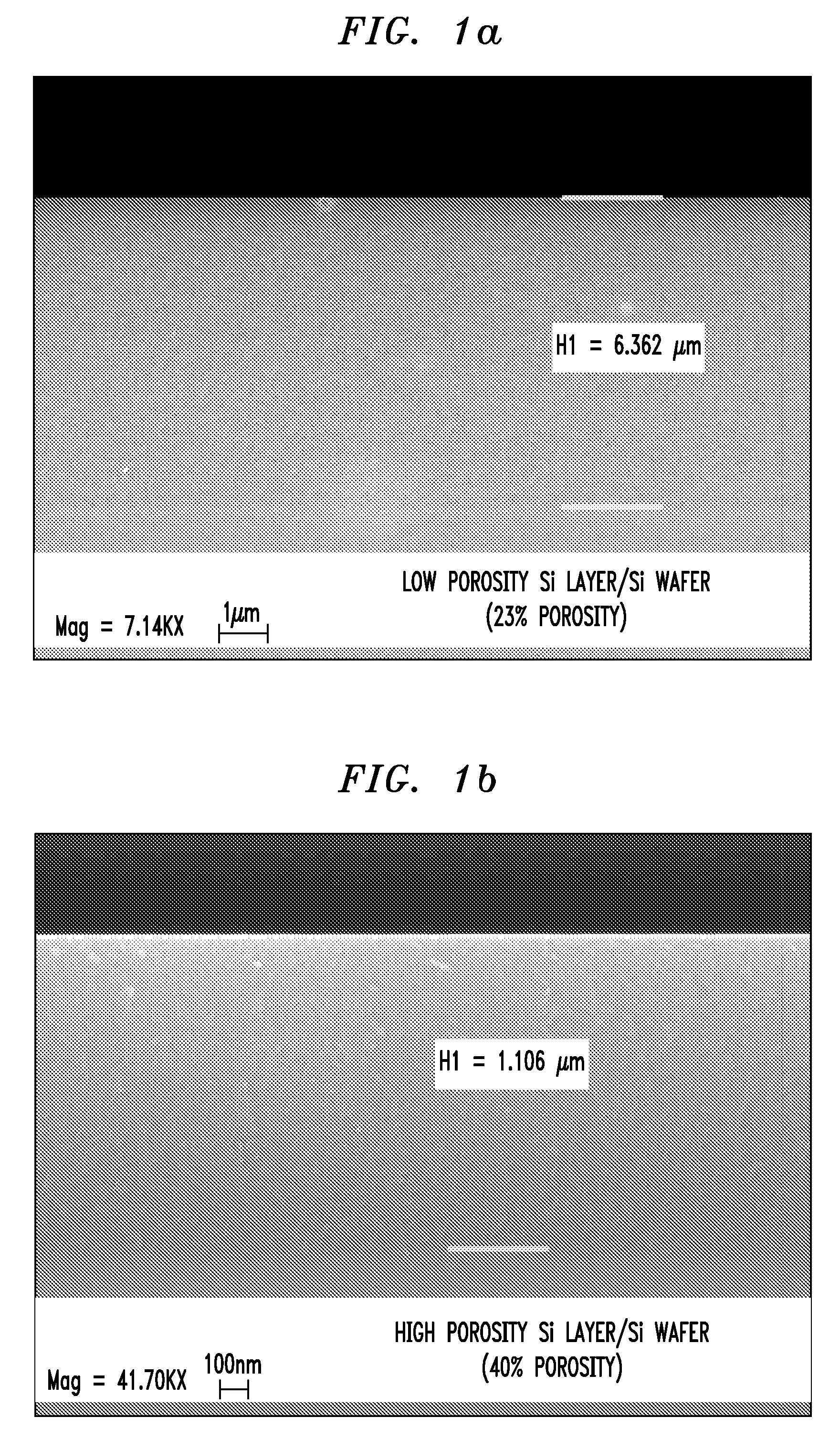

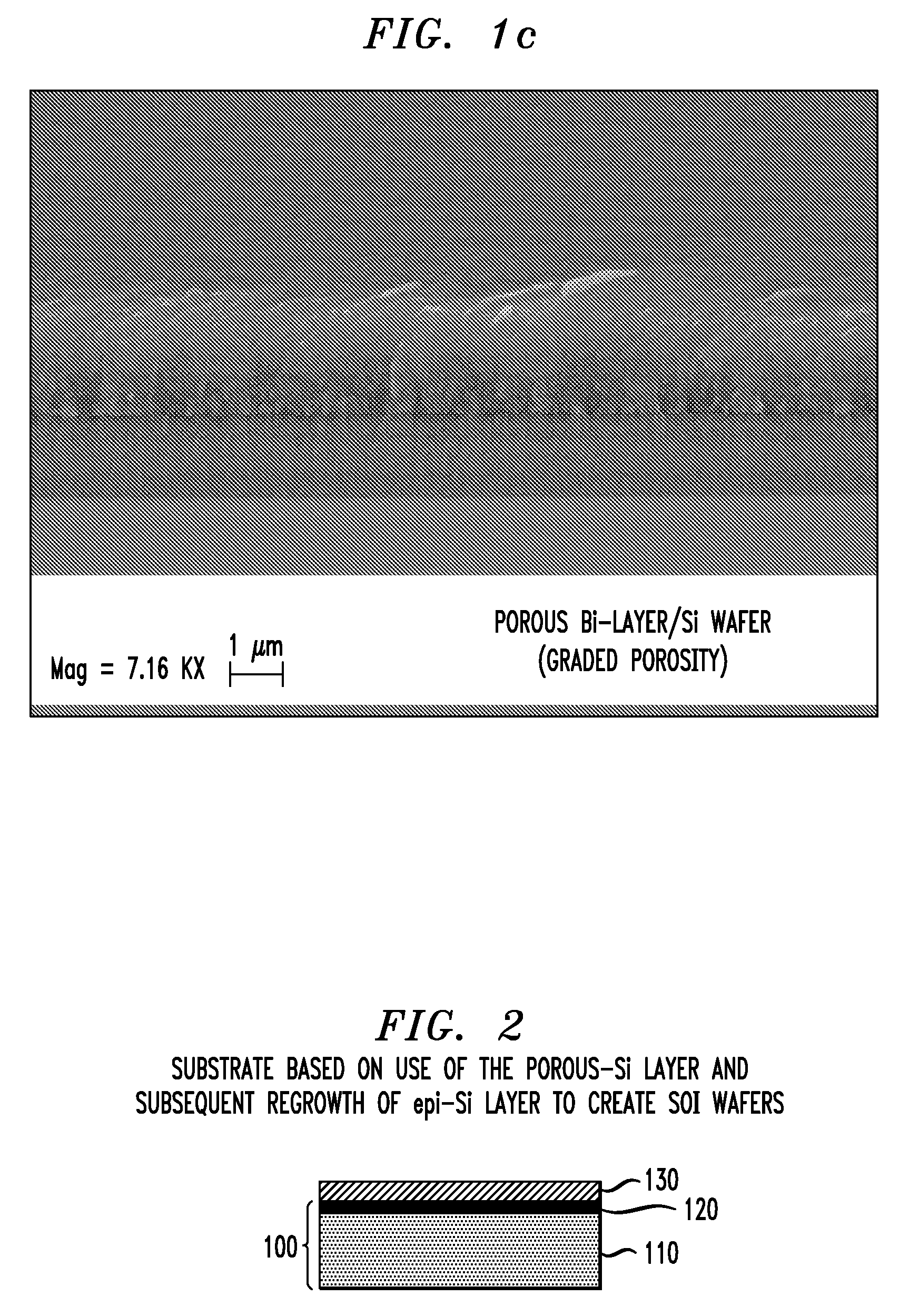

Techniques for Layer Transfer Processing

InactiveUS20070281439A1Semiconductor/solid-state device manufacturingThin material handlingDevice materialEngineering physics

Techniques for the fabrication of semiconductor devices are provided. In one aspect, a layer transfer structure is provided. The layer transfer structure comprises a carrier substrate having a porous region with a tuned porosity in combination with an implanted species defining a separation plane therein In another aspect, a method of forming a layer transfer structure is provided. In yet another aspect, a method of forming a thee dimensional integrated structure is provided.

Owner:GLOBALFOUNDRIES INC

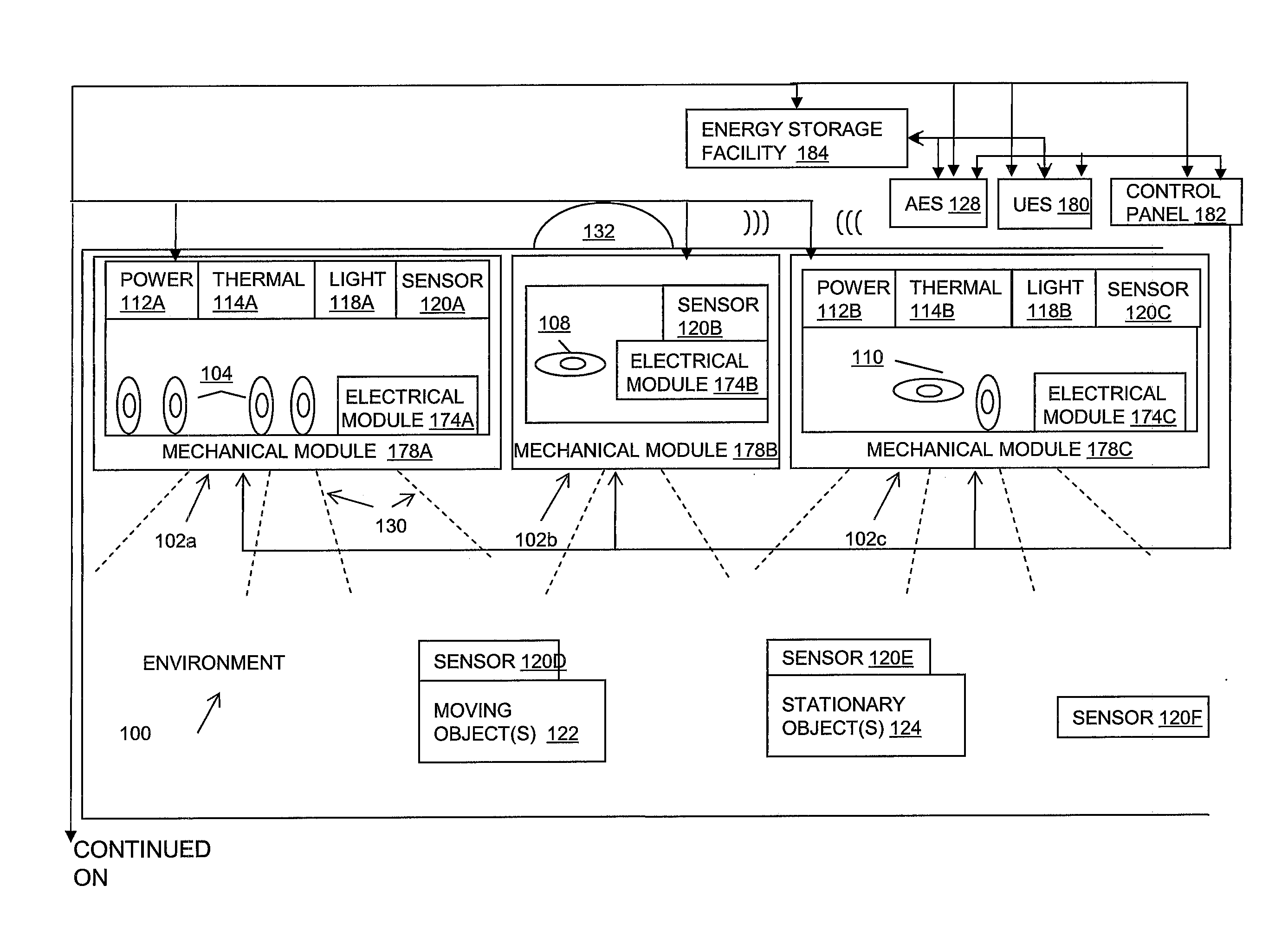

Power Management Unit with Temperature Protection

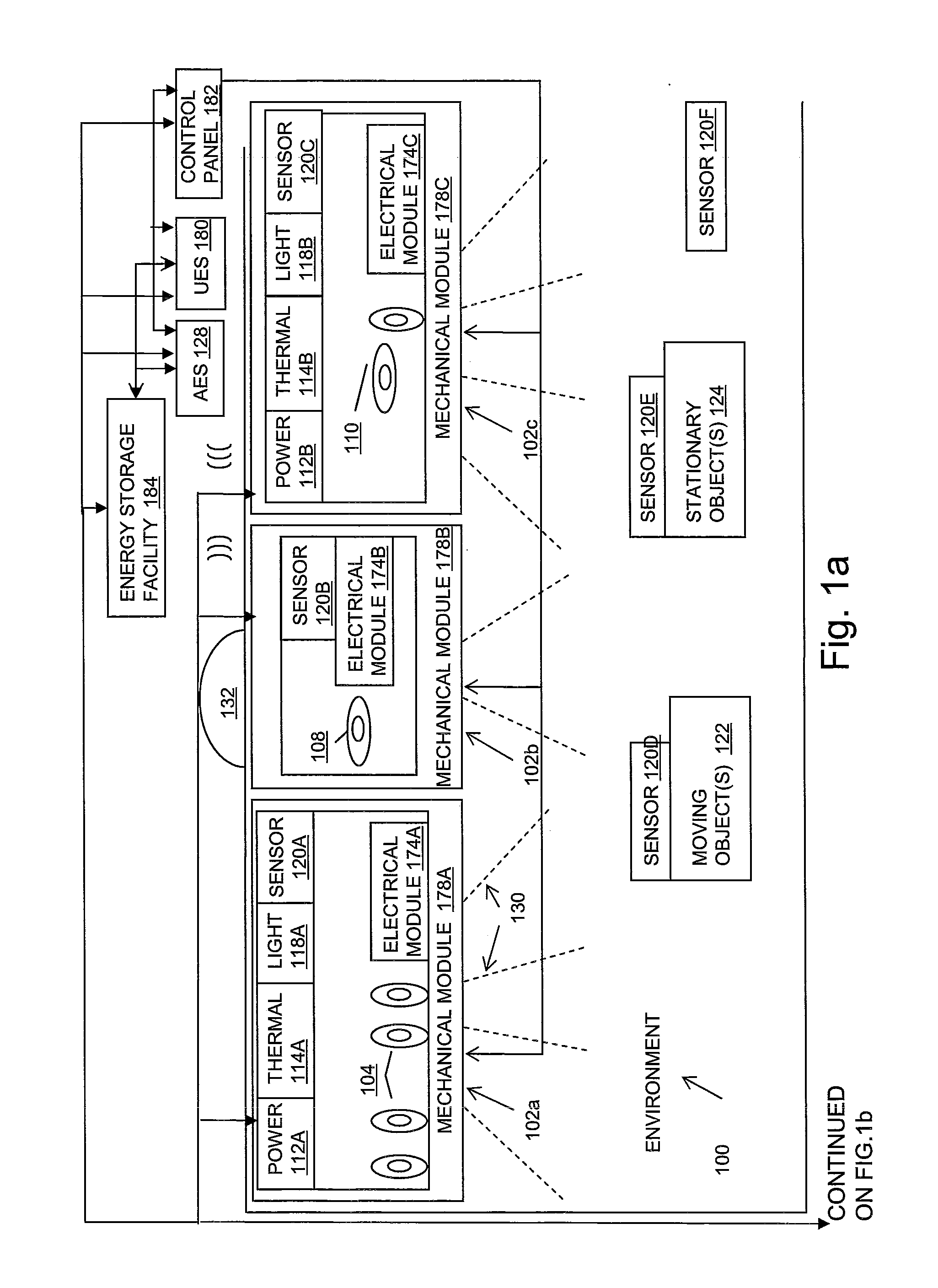

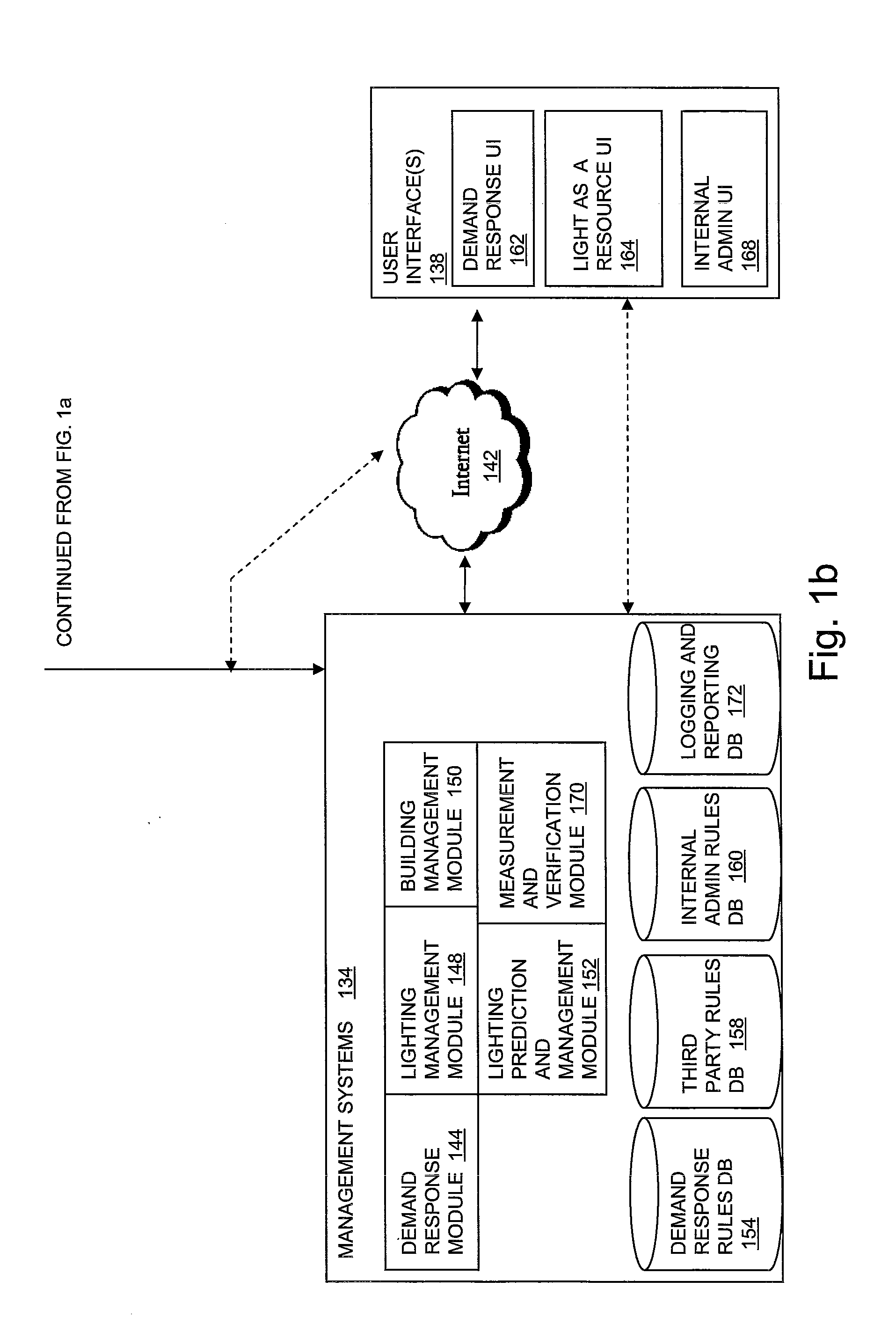

ActiveUS20110001438A1Failure to compensateMaintain lightElectrical apparatusElectric light circuit arrangementIntelligent lightingPower Management Unit

In embodiments of the present invention, a method and system is provided for designing improved intelligent, LED-based lighting systems. The LED based lighting systems may include fixtures with one or more of rotatable LED light bars, integrated sensors, onboard intelligence to receive signals from the LED light bars and control the LED light bars, and a mesh network connectivity to other fixtures.

Owner:OSRAM SYLVANIA INC

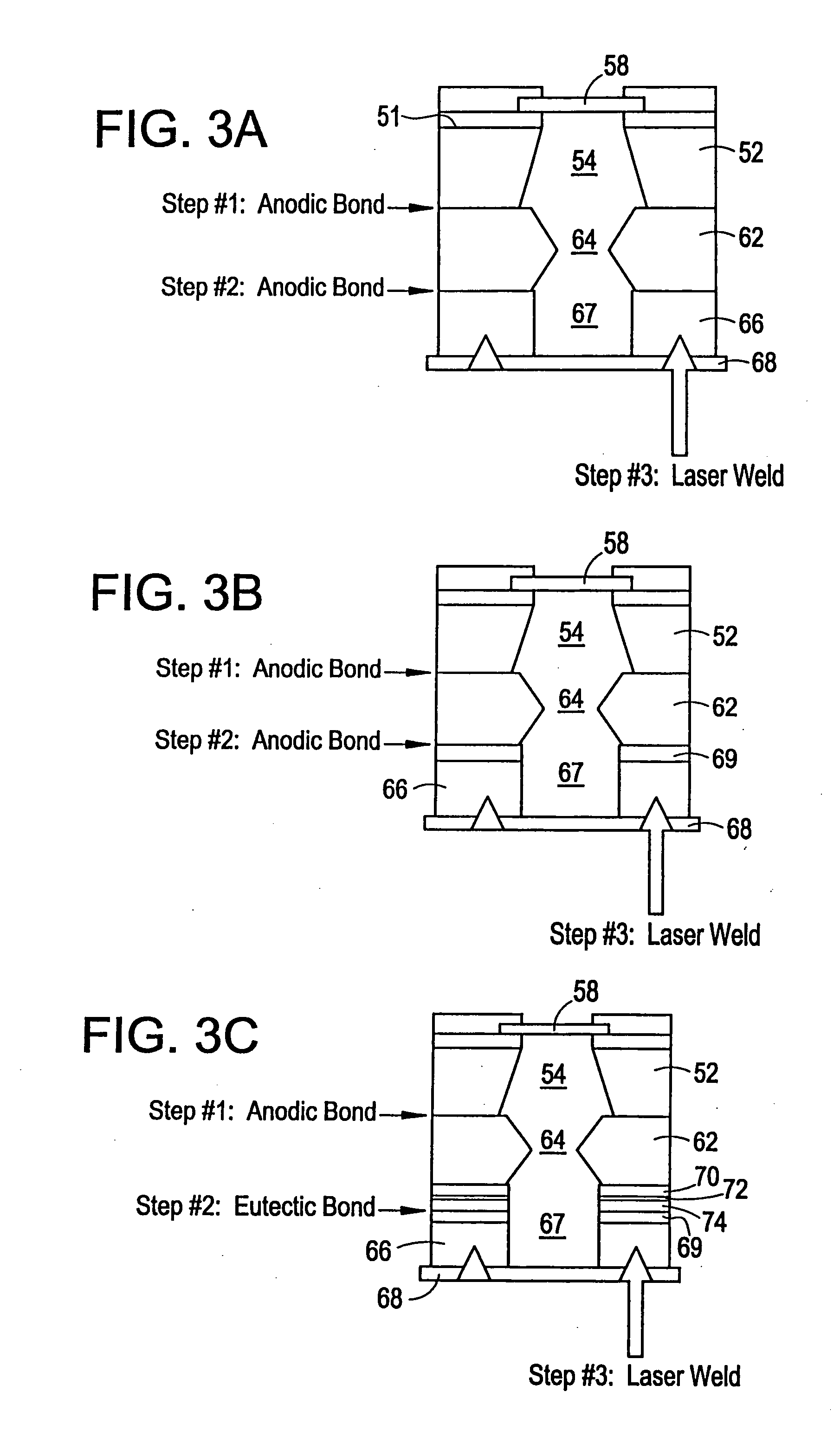

Hermetically sealed microchip reservoir devices

InactiveUS20050077584A1Fixed microstructural devicesVolume/mass flow measurementGlucose sensorsHermetic seal

Devices are provided for the controlled exposure or release of contents stored in hermetically sealed reservoirs. The devices comprise a primary substrate having a front side and a back side, and including one or more hermetic sealing materials; a plurality of reservoirs in the primary substrate positioned between the front side and the back side; reservoir contents, which comprise chemical molecules (such as drugs) or a secondary device (such as a glucose sensor), located inside the reservoirs; a hermetic sealing substrate having a surface composed of one or more hermetic sealing materials; and a hermetic seal formed between and joining the primary substrate and the hermetic sealing substrate, wherein the hermetic seal independently seals the reservoirs.

Owner:MICROCHIPS BIOTECH INC

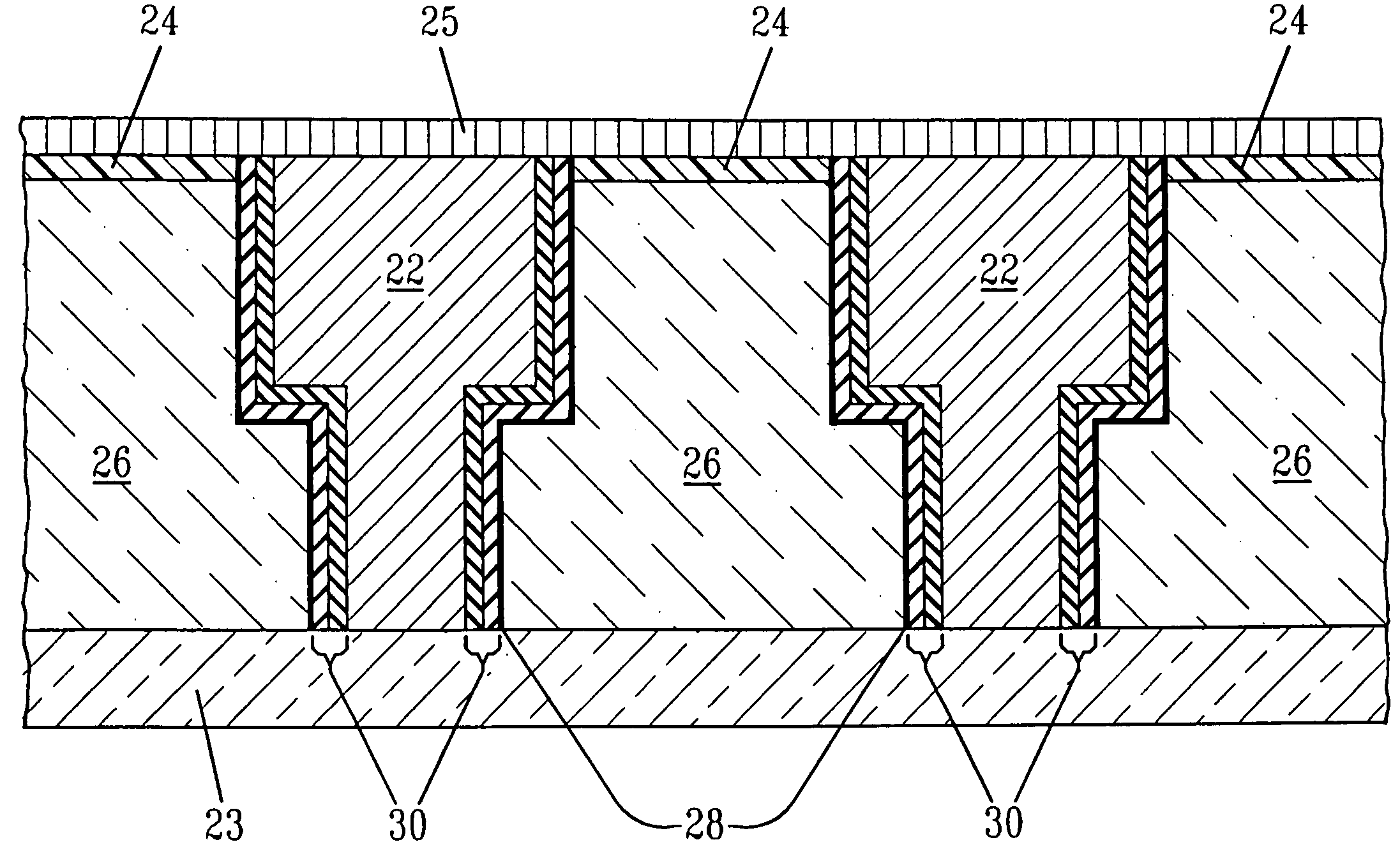

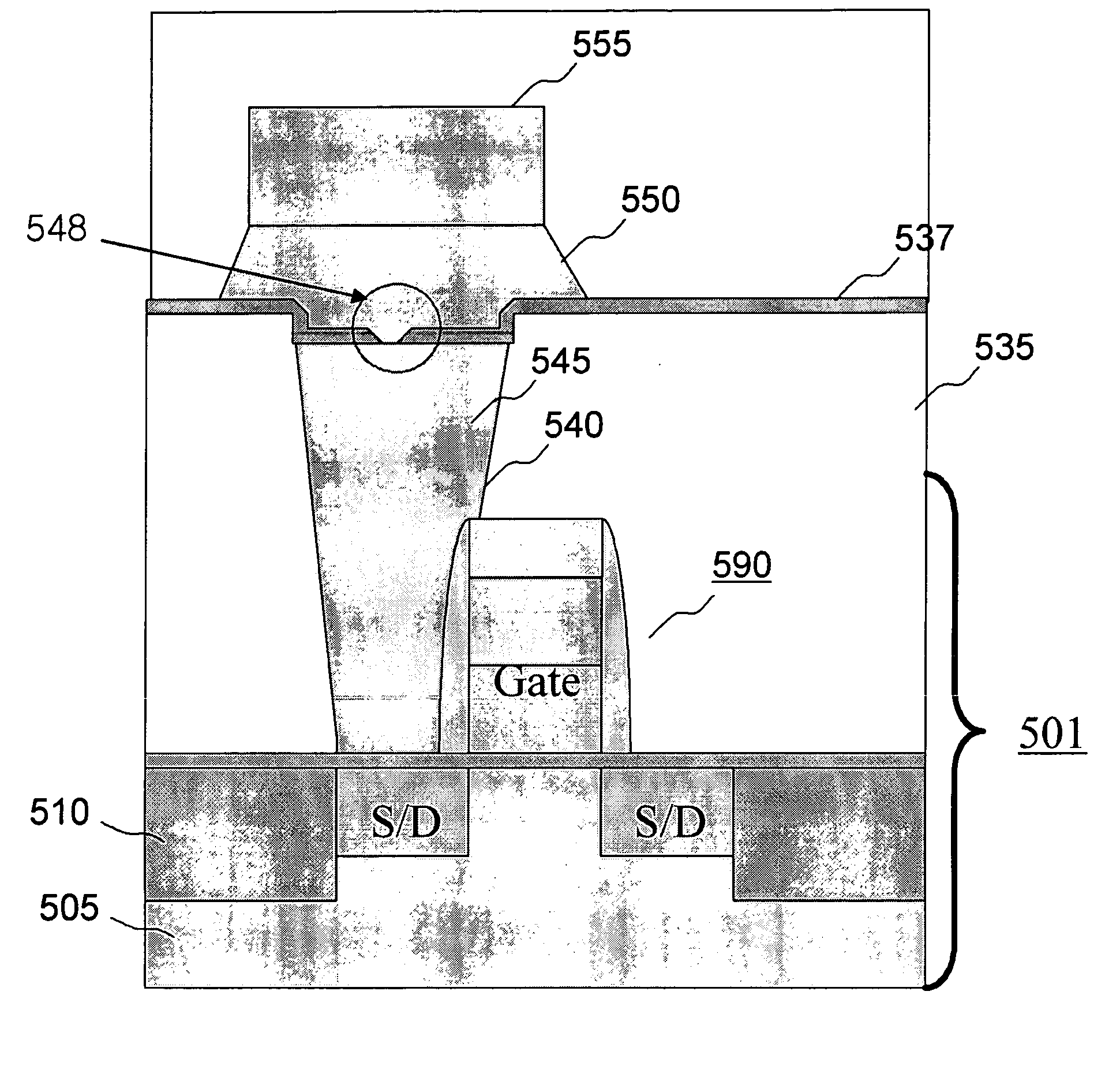

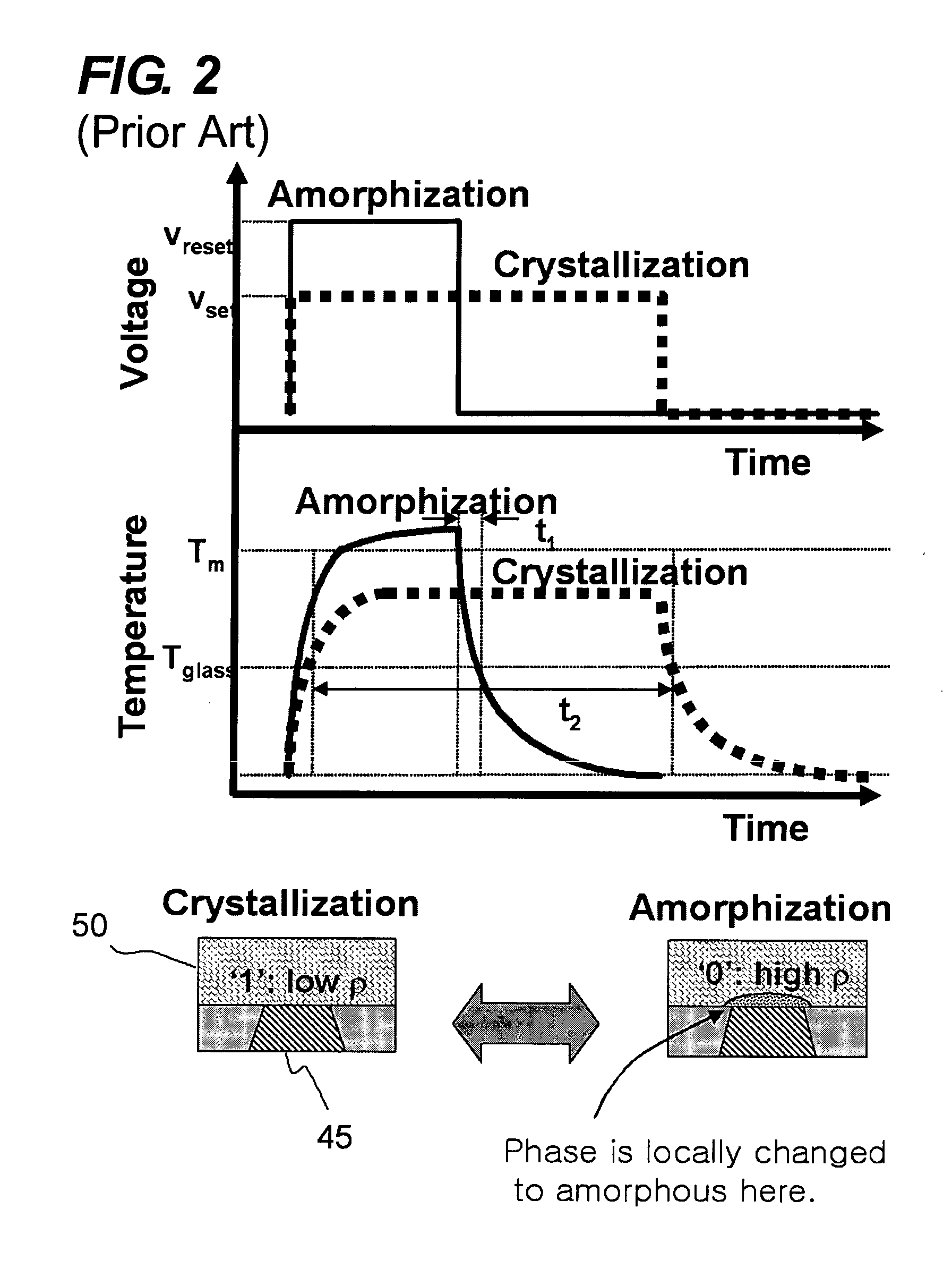

Phase-change memory device and manufacturing method thereof

InactiveUS20050018526A1Easy to manufactureHigh yield rateSolid-state devicesDigital storagePhase-change memoryDielectric layer

The present invention is to provide a phase change memory device having a new structure which can be easily manufactured by mass-production with a high yield rate, therefore, reducing the cost of process and providing reliable device characteristics, and a manufacturing method thereof. The present invention provides a phase-change memory device comprising: a lower dielectric layer; a lower electrode, at least a part of the lateral surface of the lower electrode being surrounded by the lower dielectric layer; a thin dielectric layer including a pore having smaller area than the top surface of the lower electrode, aligned to the top surface of the lower electrode and extending to the top surface of the lower electrode; and a phase-change resistor filling the pore and formed on the thin dielectric layer. In the proposed structure of the present invention, the pores or local damaged spots can provide a micro path of current and localize the phase-changing volume in the phase-change resistor. Thus, the phase-change memory device can be operated with very low power.

Owner:LEE HEON

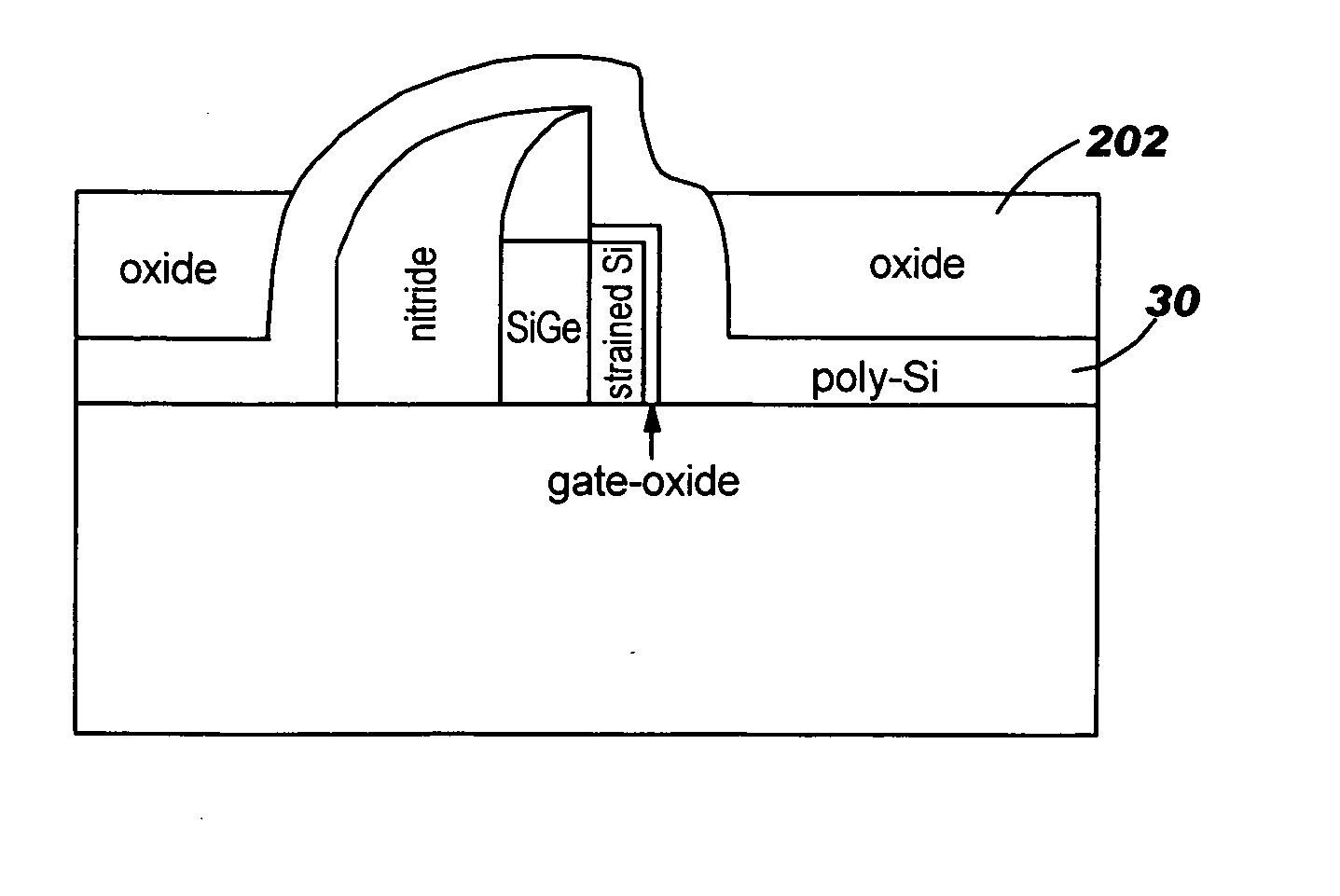

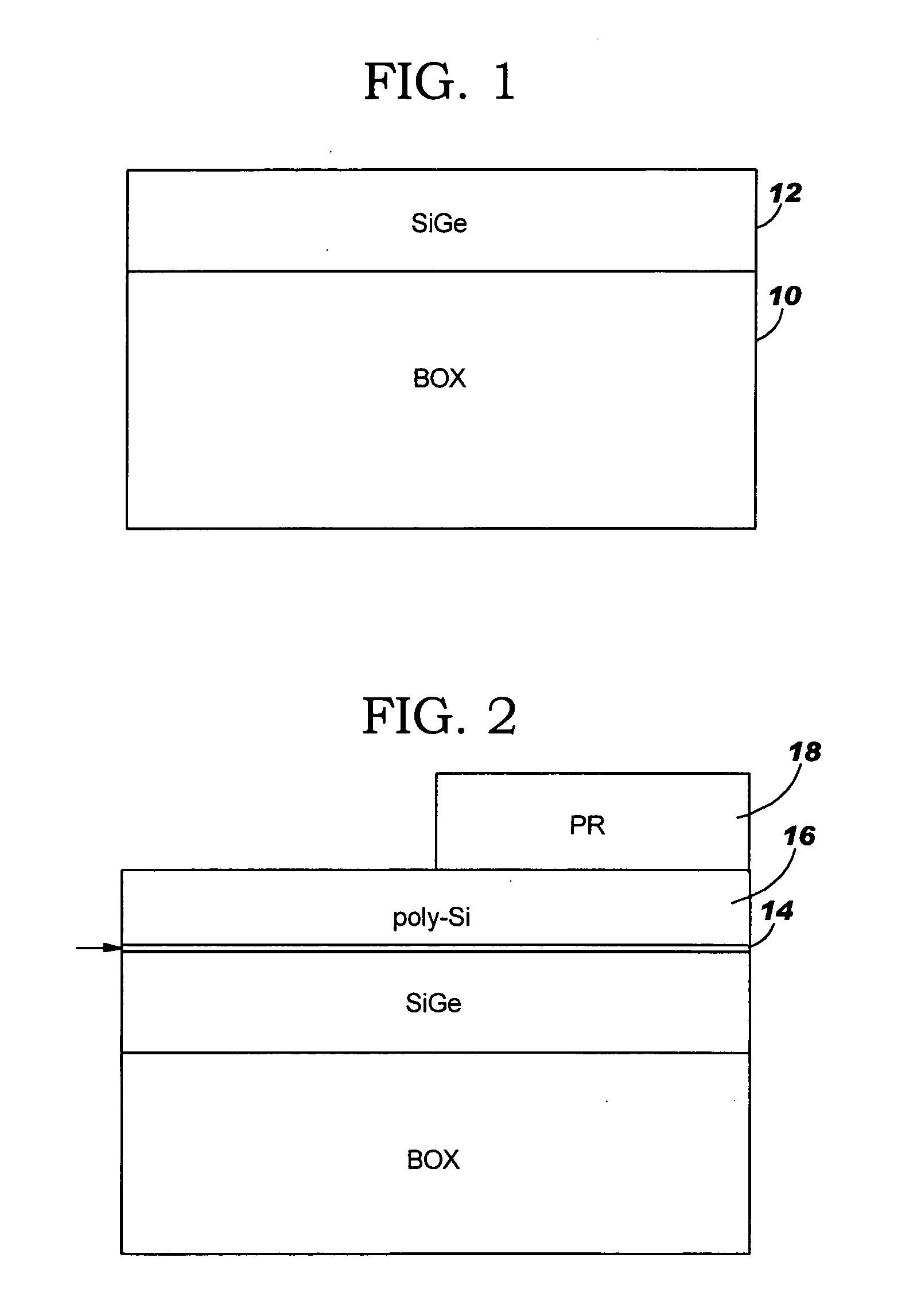

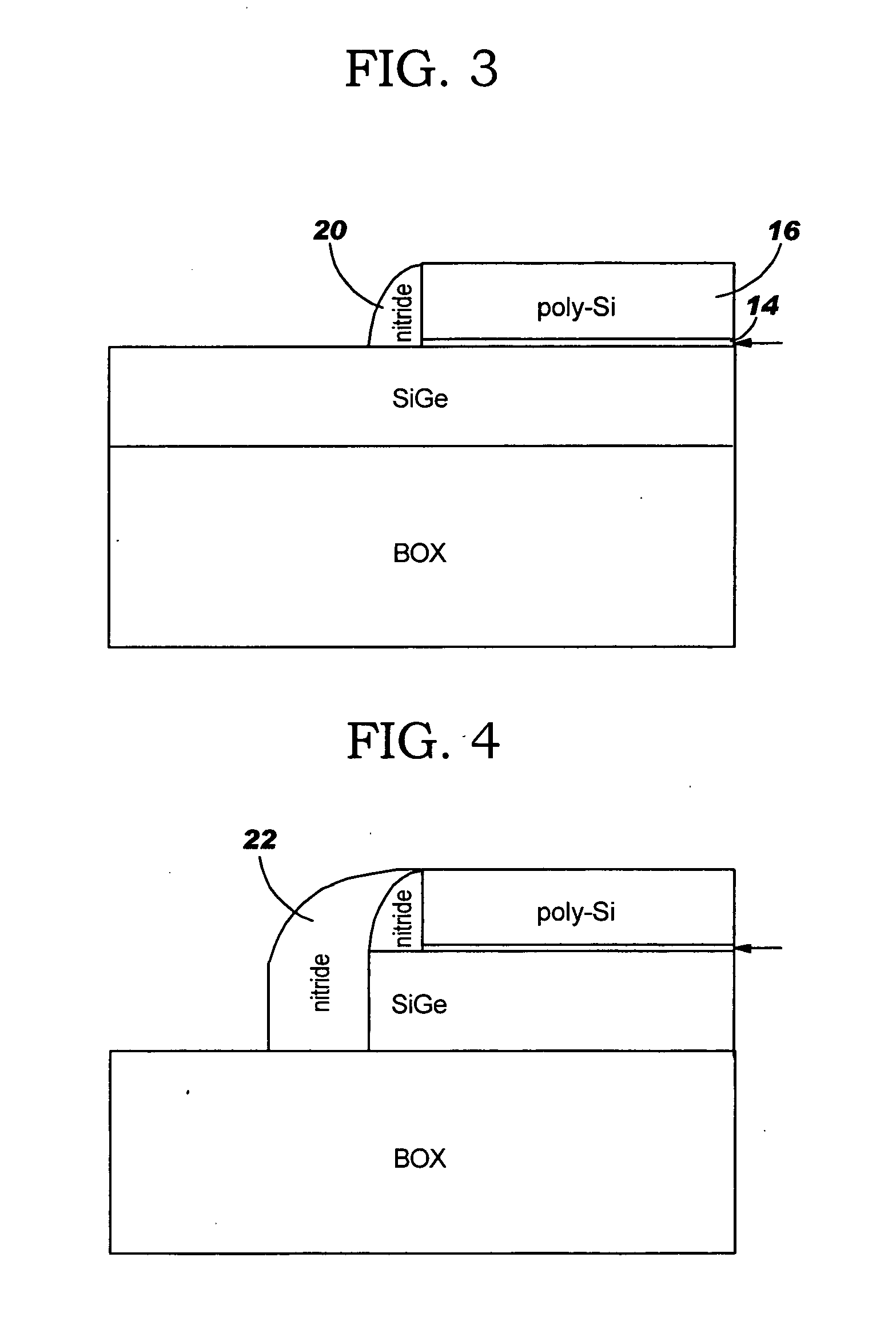

Structures and methods for making strained mosfets

A method and device providing a strained Si film with reduced defects is provided, where the strained Si film forms a fin vertically oriented on a surface of a non-conductive substrate. The strained Si film or fin may form a semiconductor channel having relatively small dimensions while also having few defects. The strained Si fin is formed by growing Si on the side of a relaxed SiGe block. A dielectric gate, such as, for example, an oxide, a high “k” material, or a combination of the two, may be formed on a surface of the strained Si film. Additionally, without substantially affecting the stress in the strained Si film, the relaxed SiGe block may be removed to allow a second gate oxide to be formed on the surface previously occupied by the relaxed SiGe block. Accordingly, a semiconductor device having a strained Si fin vertically oriented on a non-conductive substrate may be formed where the strained Si film is oriented such that it may form a channel of small dimensions allowing access to both sides and top in order to from single gate, double gate, or more gate MOSFETs and finFETs with a channel having a reduced number of defects and / or reduced dimensions.

Owner:GLOBALFOUNDRIES US INC

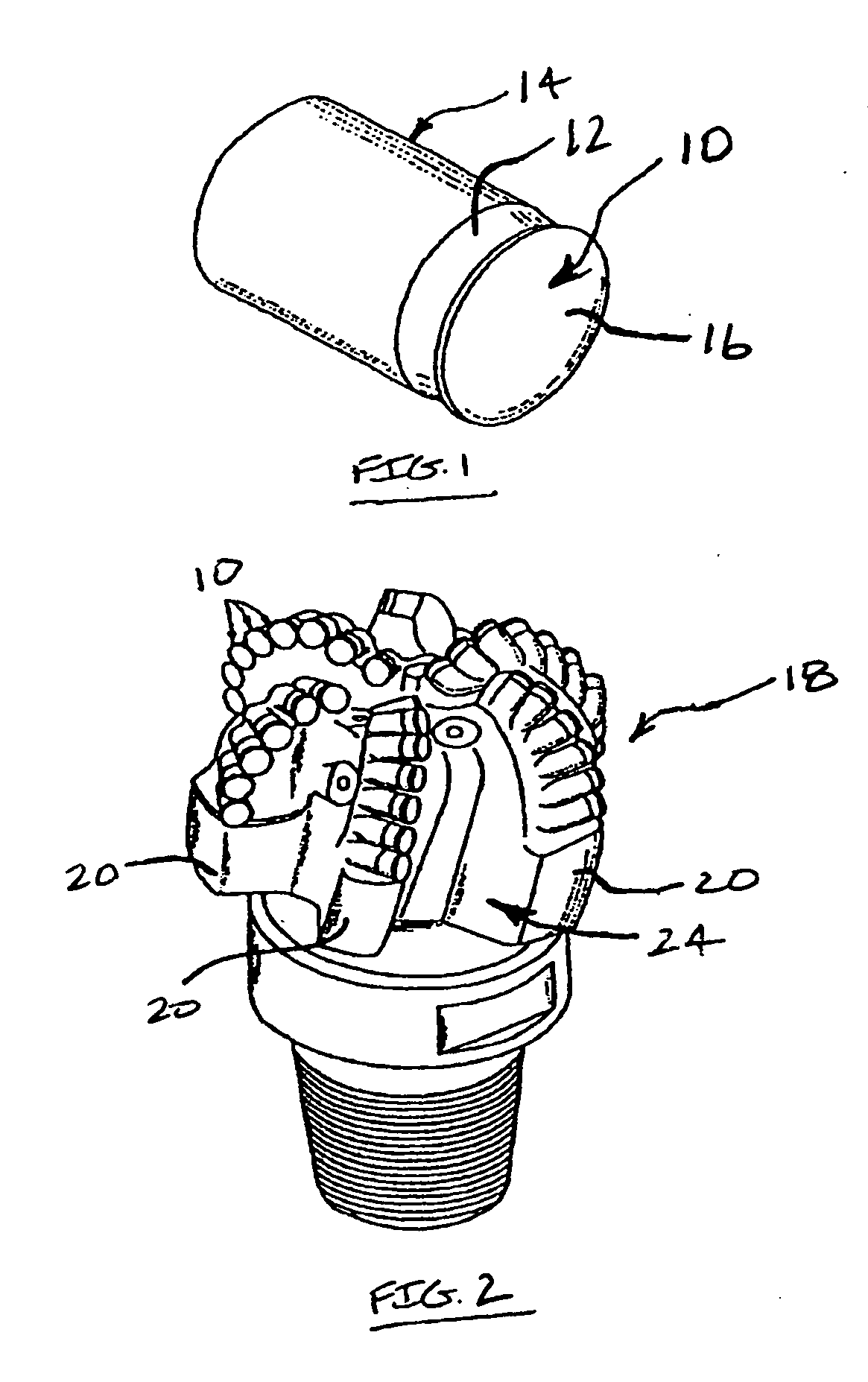

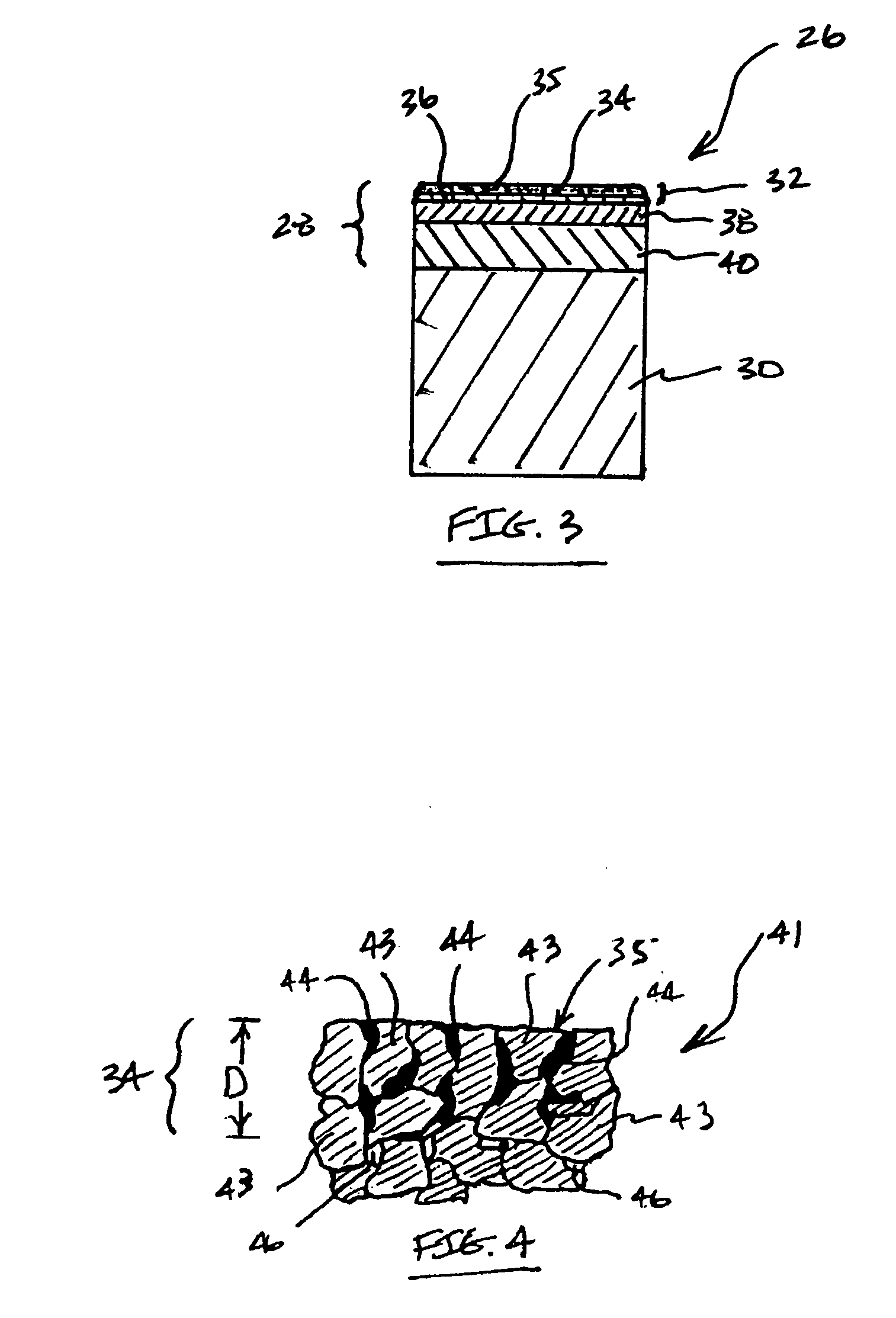

Cutting elements formed from ultra hard materials having an enhanced construction

InactiveUS20060162969A1Eliminate or resist any cracking during useDifferential wear resistanceDrill bitsConstructionsSuperhard materialInter layer

Cutting elements of this invention include an ultra hard body joined with a metallic substrate. The body includes an uppermost layer comprising a plurality of bonded ultra hard crystals and interstitial regions, and that defines a body working surface. The uppermost layer includes an outer region that is relatively more thermally stable than a remaining portion of the uppermost layer. The body further includes an intermediate layer joined to the uppermost layer, comprising a plurality of bonded ultra hard crystals, and having a wear resistance less than that of the uppermost layer remaining region. The body may additionally include a lowermost PCD layer that is interposed between and attached to the intermediate layer and the substrate.

Owner:SMITH INT INC

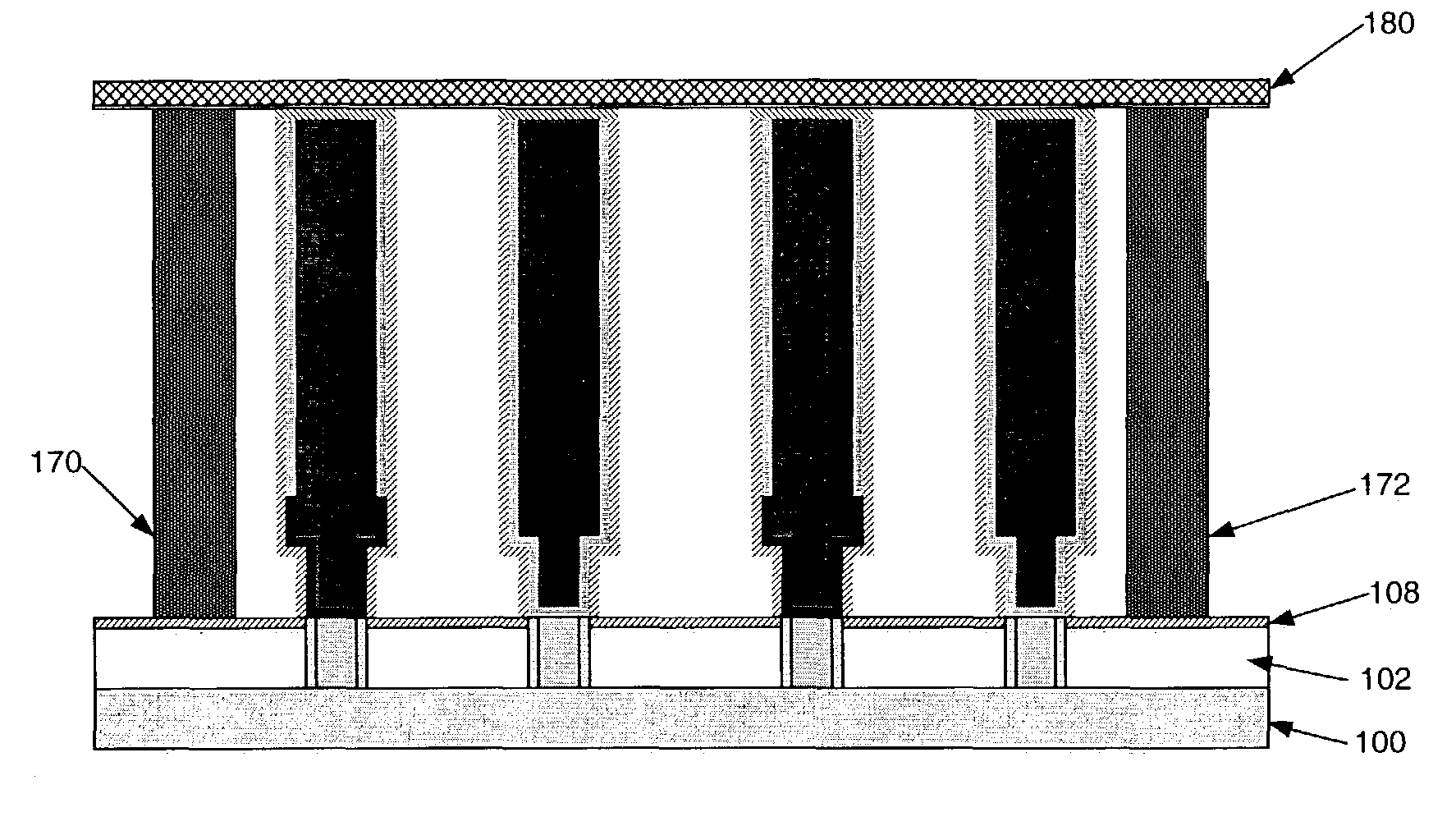

Air gap integration

InactiveUS6995073B2Semiconductor/solid-state device detailsSolid-state devicesEngineering physicsDielectric layer

Method and structure for integrating conductive and dielectric materials in a microelectronic structure having air gaps are disclosed. Certain embodiments of the invention comprise isolating dielectric layers from conductive layers using an etch stop layer to facilitate controlled removal of portions of the dielectric layers and formation of air gaps or voids. Capping and peripheral structural layers may be incorporated to increase the structural integrity of the integration subsequent to removal of sacrificial material.

Owner:TAHOE RES LTD

Process for producing semiconductor integrated circuit device

InactiveUS7553756B2High reliable via connectionReduce parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesParasitic capacitorEngineering physics

Owner:HITACHI LTD

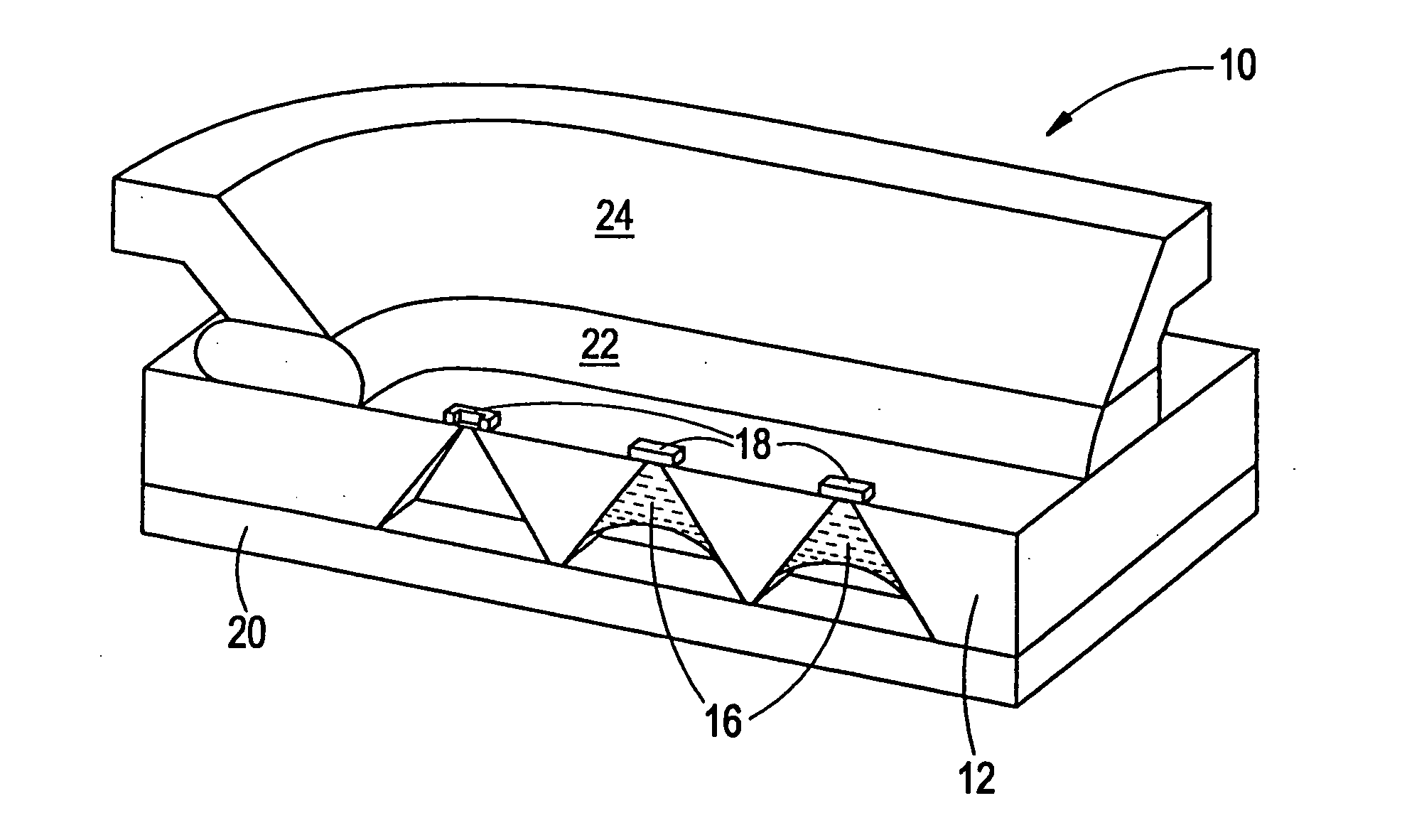

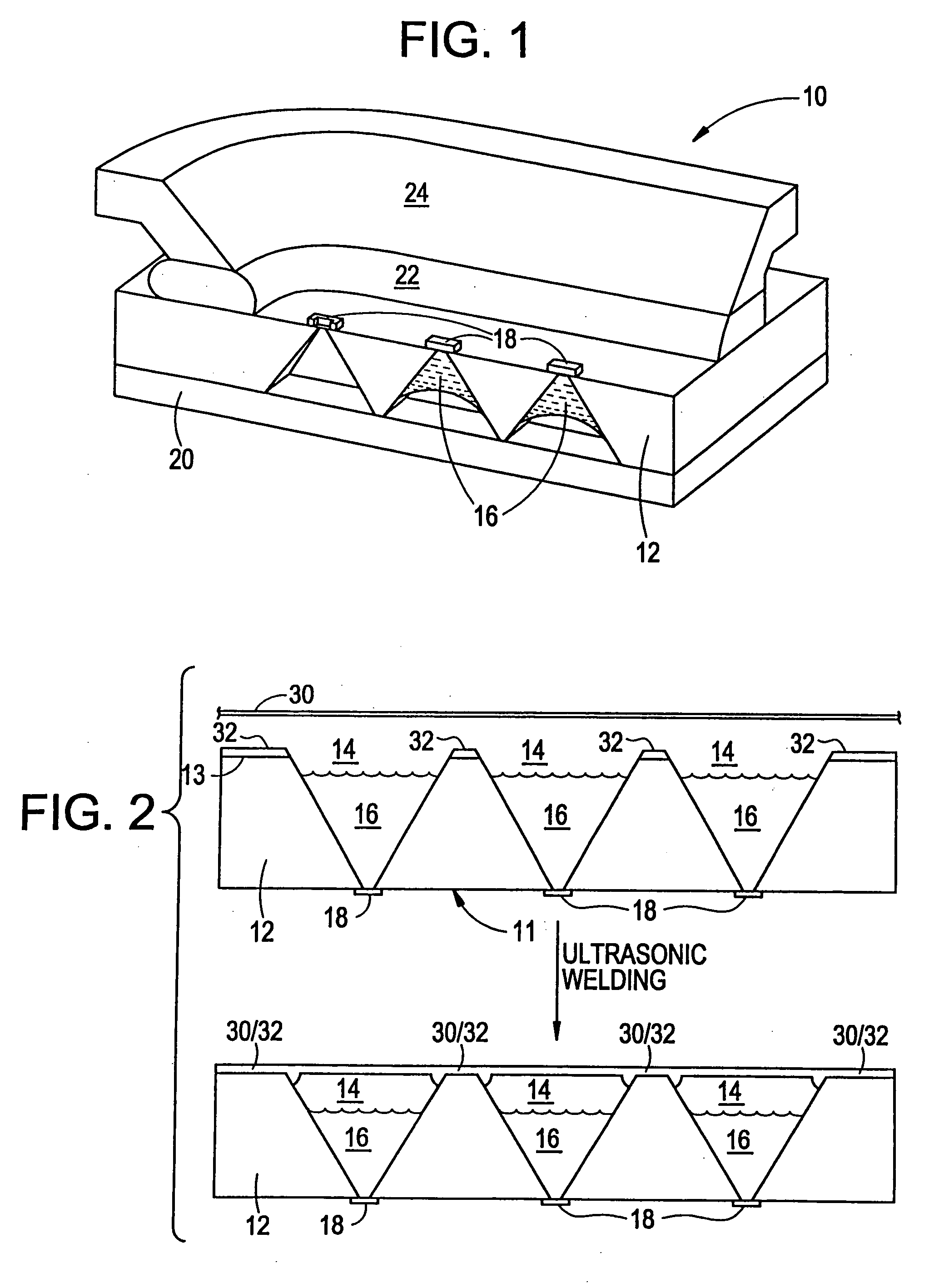

Low temperature co-fired ceramic (LTCC) tape compositions, light emitting diode (LED) modules, lighting devices and method of forming thereof

The present invention provides LTCC (low temperature co-fired ceramic) tape compositions and demonstrates the use of said LTCC tape(s) in the formation of Light-Emitting Diode (LED) chip carriers and modules for various lighting applications. The present invention also provides for the use of (LTCC) tape and LED modules in the formation of lighting devices including, but not limited to, LED devices, High Brightness (HB) LED backlights, display-related light sources, automotive lighting, decorative lighting, signage and advertisement lighting, and information display lighting.

Owner:EI DU PONT DE NEMOURS & CO

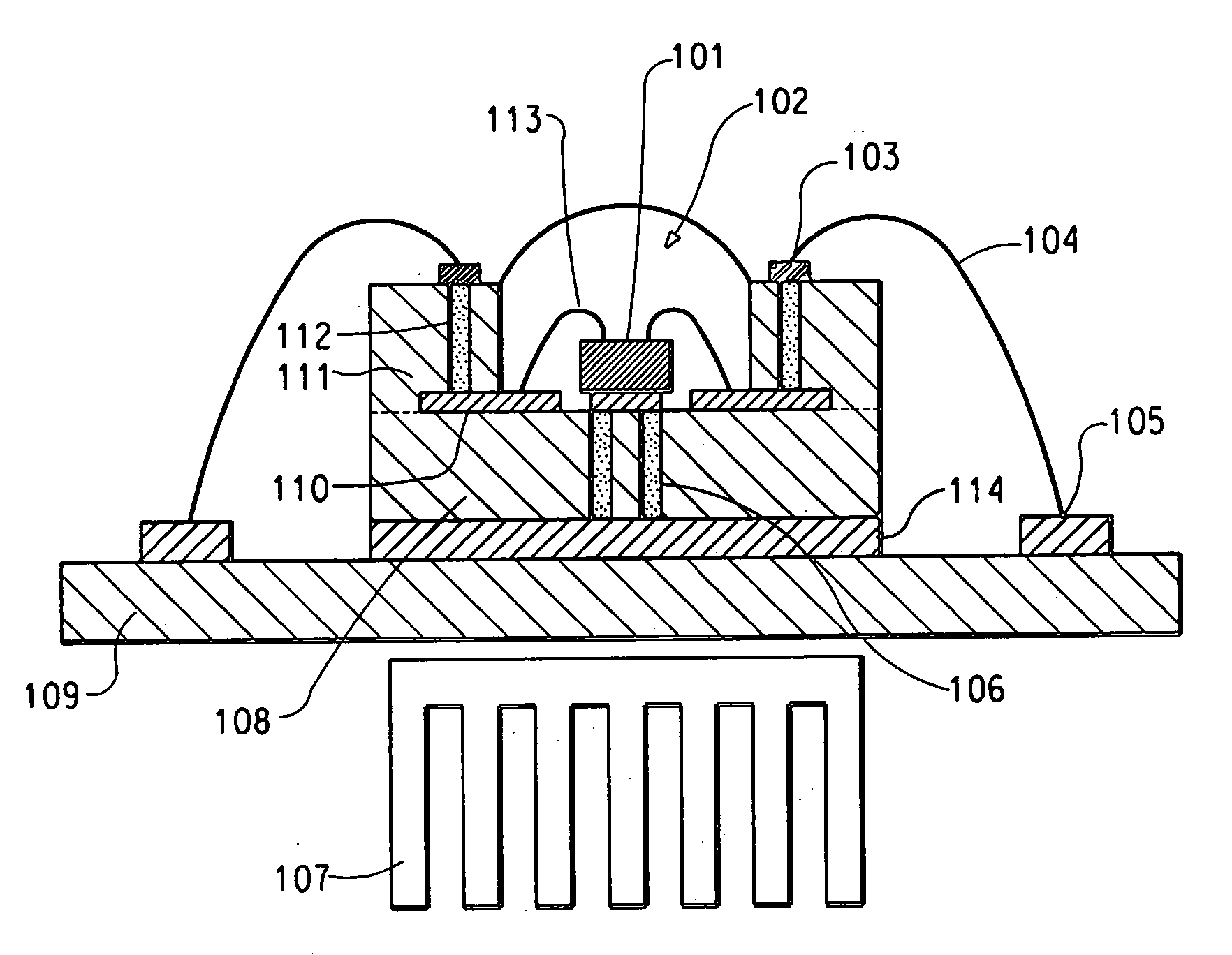

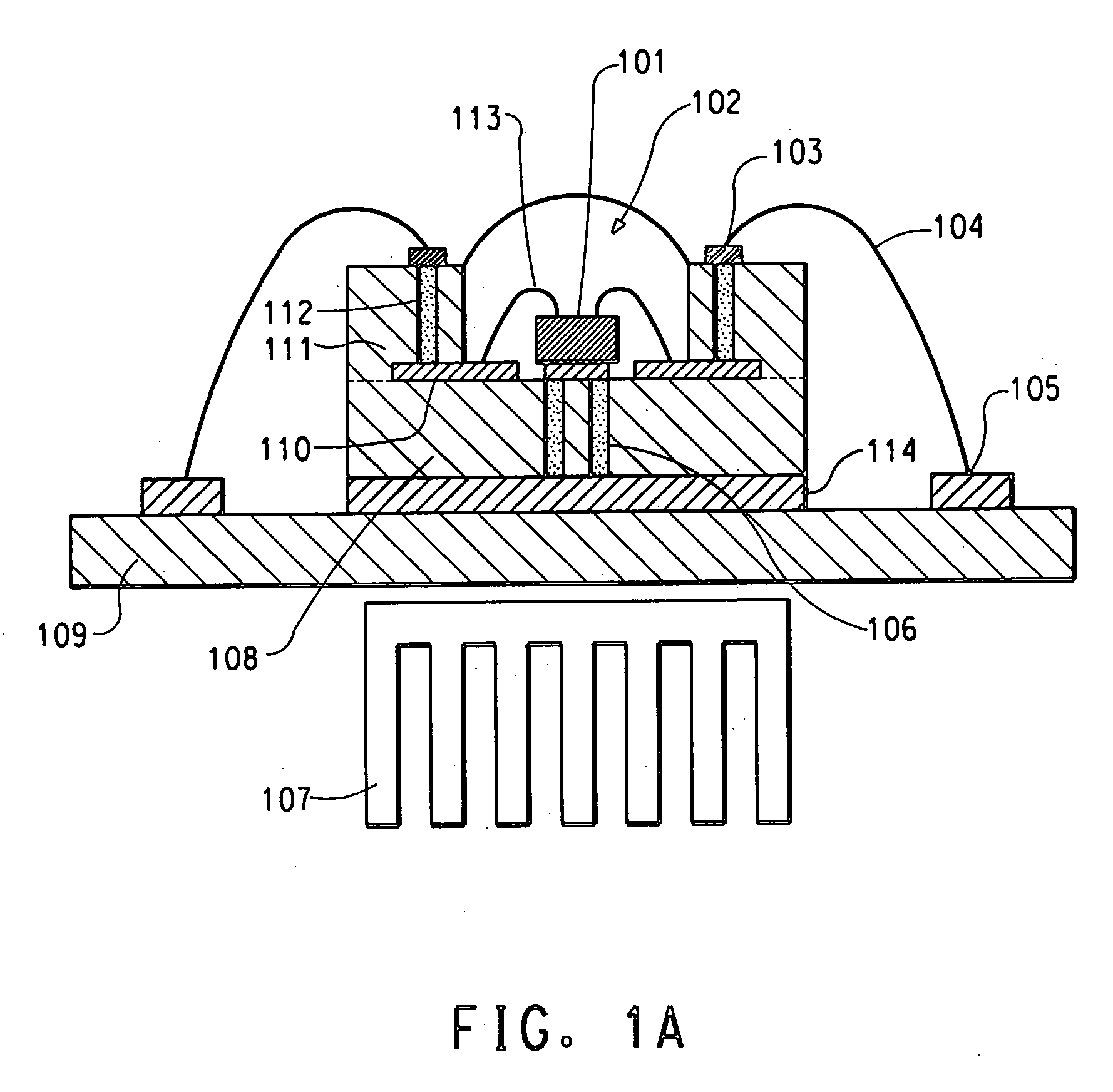

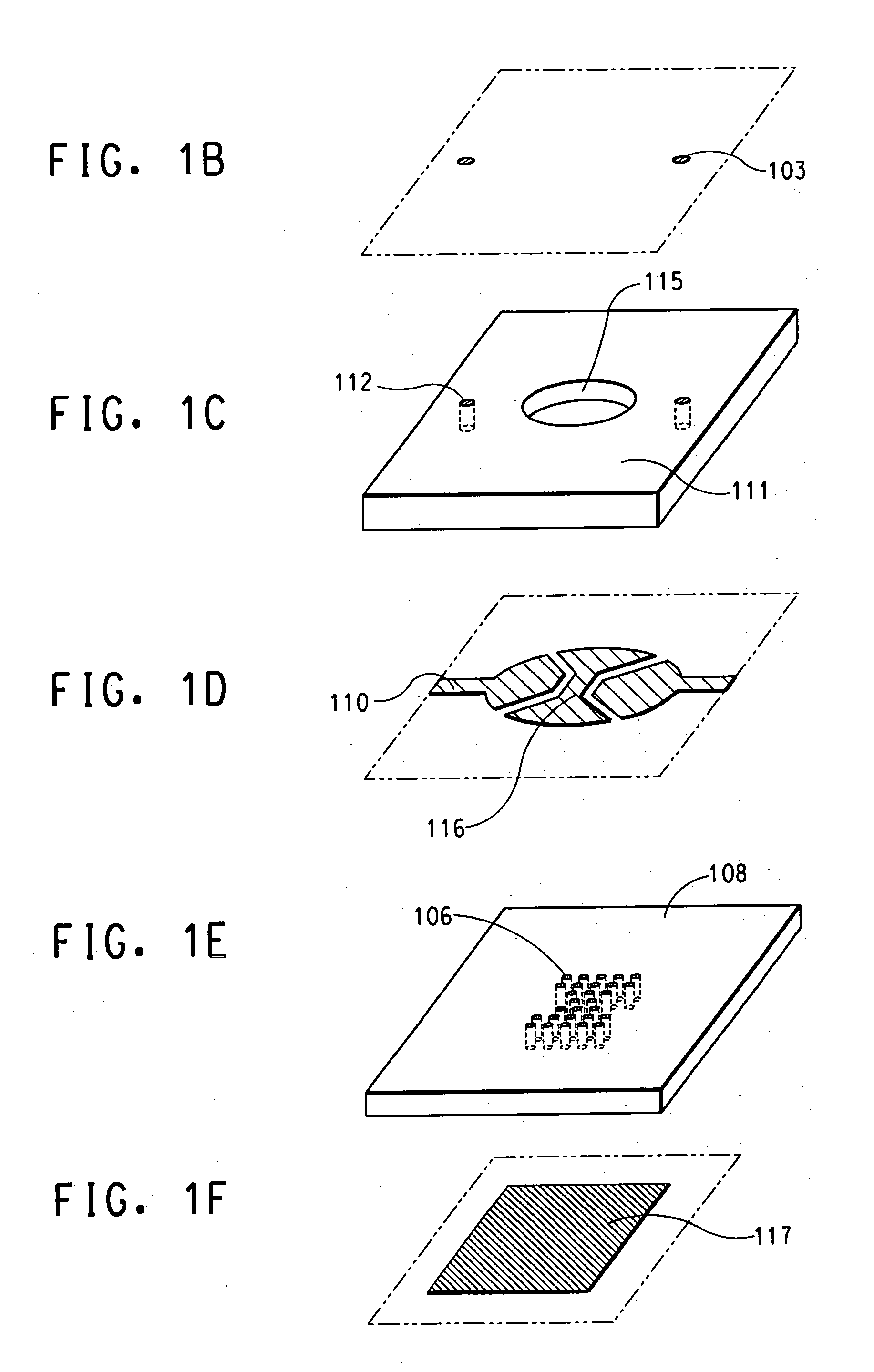

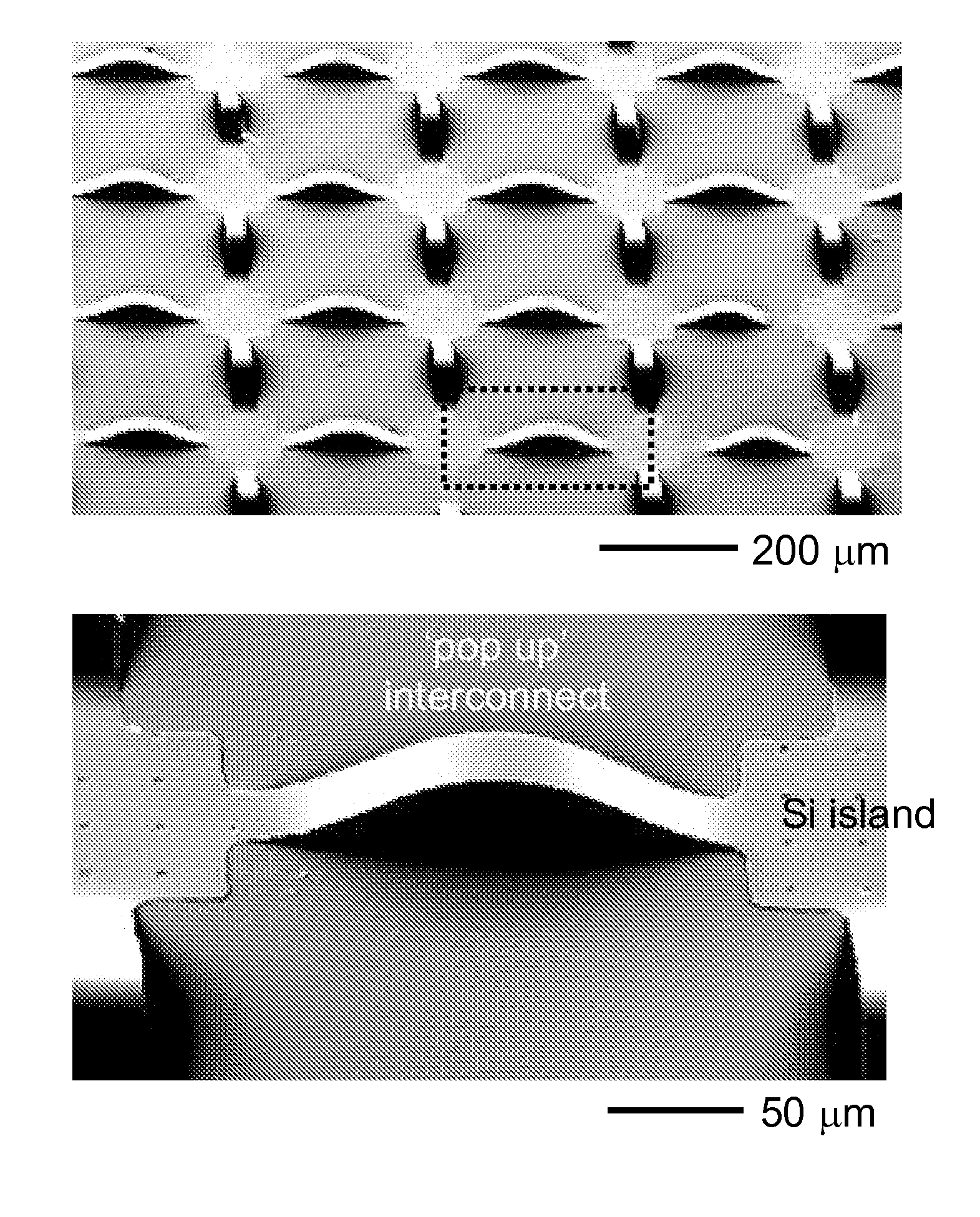

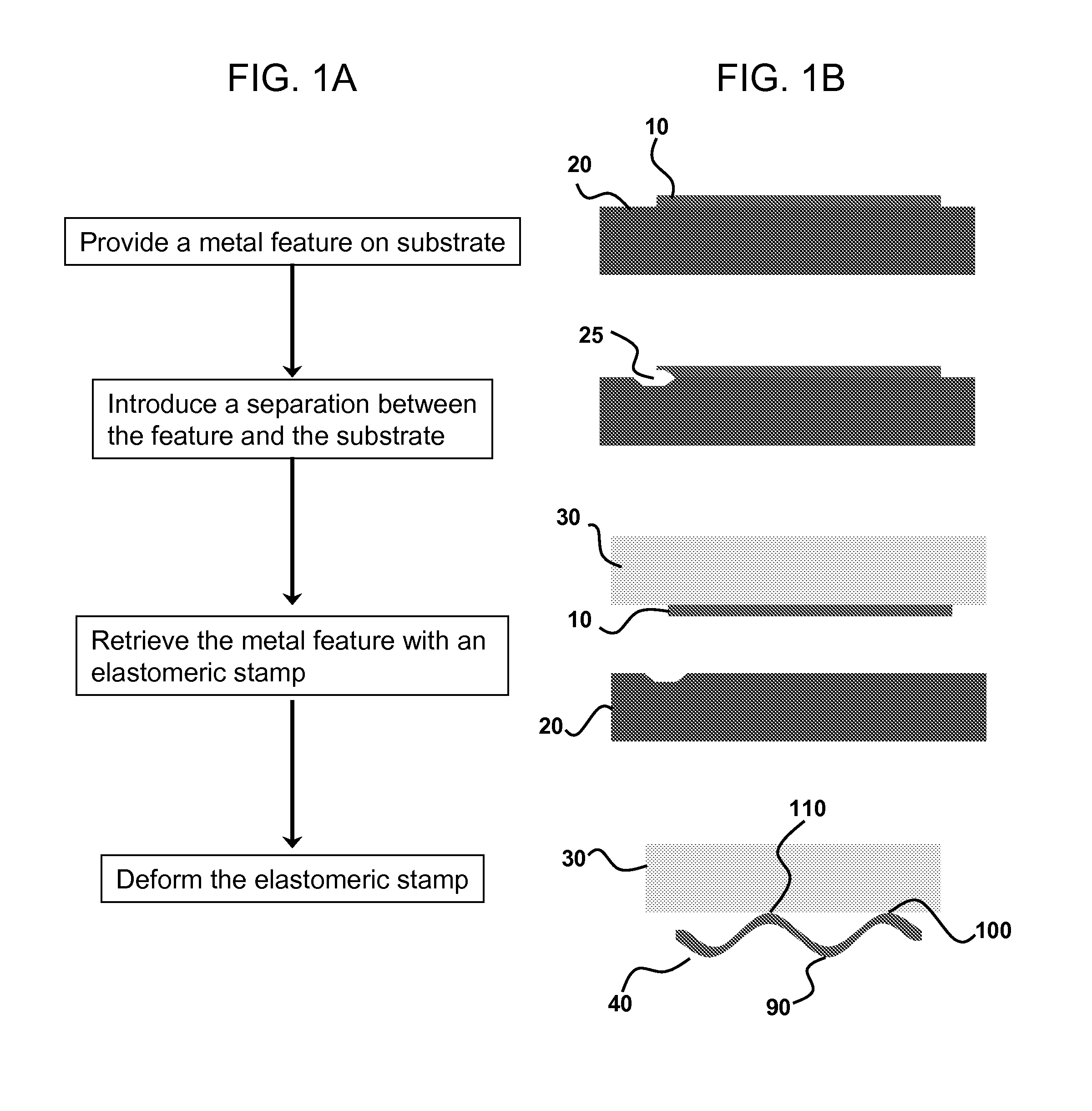

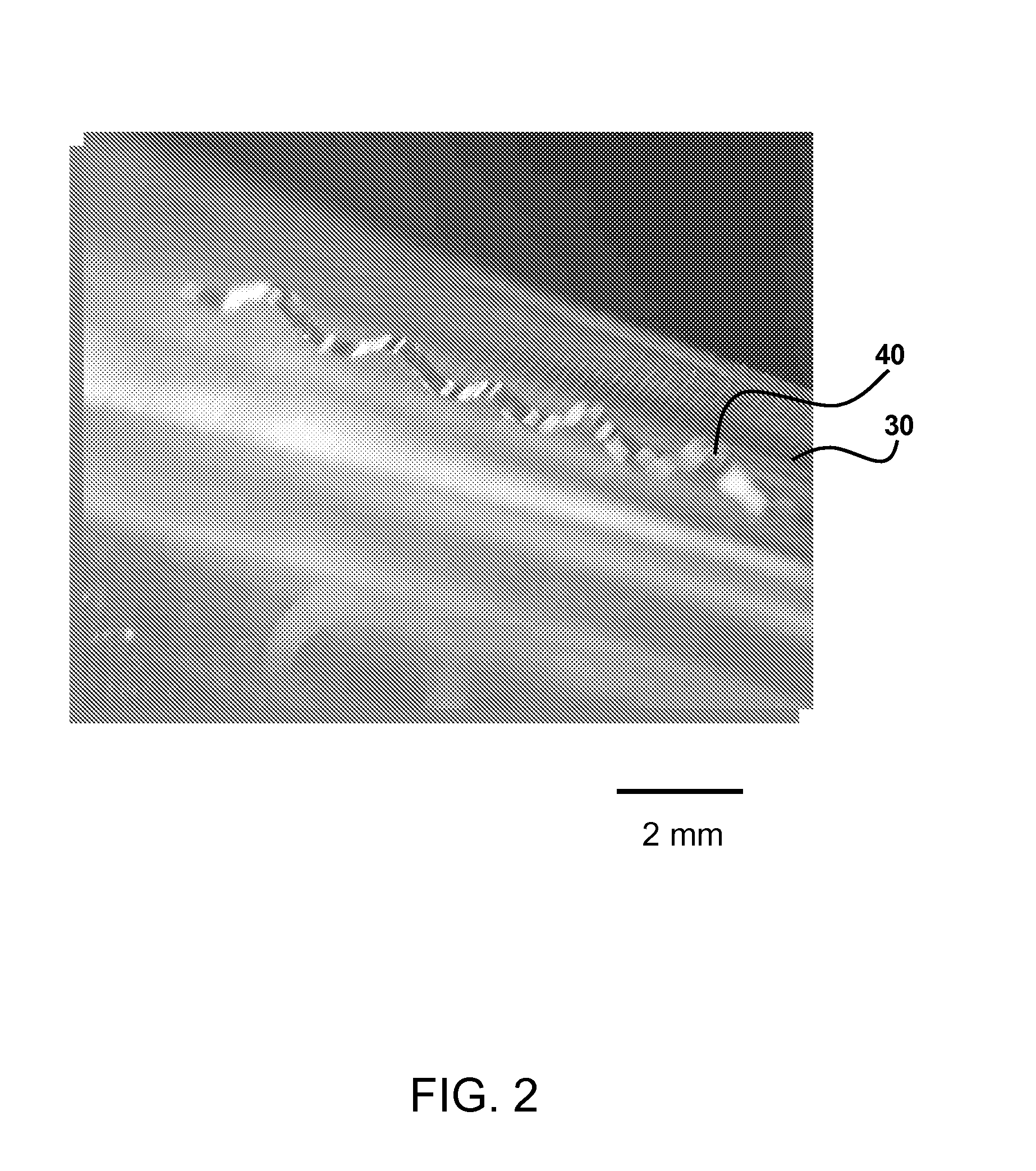

Controlled buckling structures in semiconductor interconnects and nanomembranes for stretchable electronics

ActiveUS8217381B2Without adversely impacting performanceFlexibilityTransistorCircuit bendability/stretchabilityStretchable electronicsEngineering

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

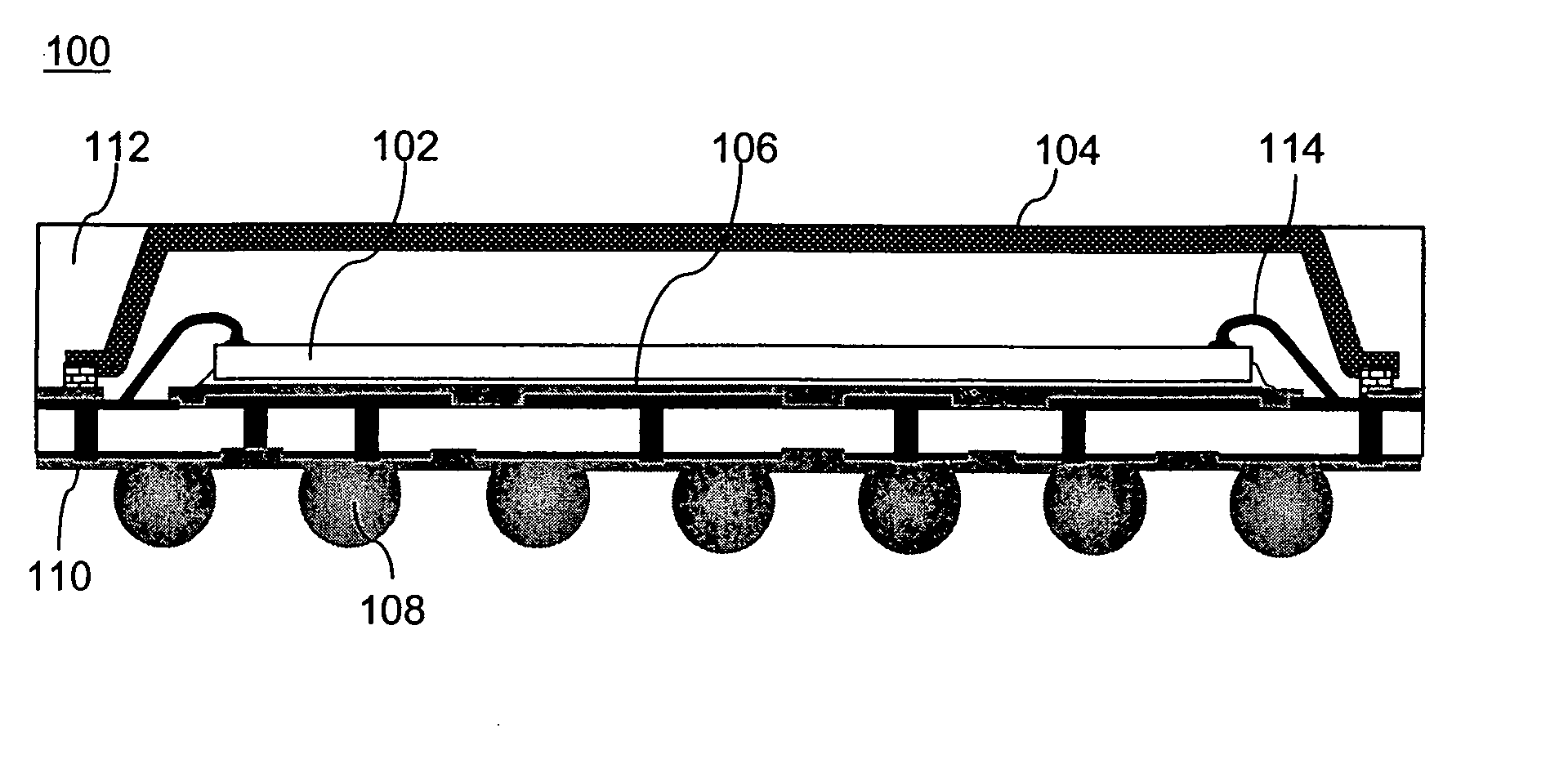

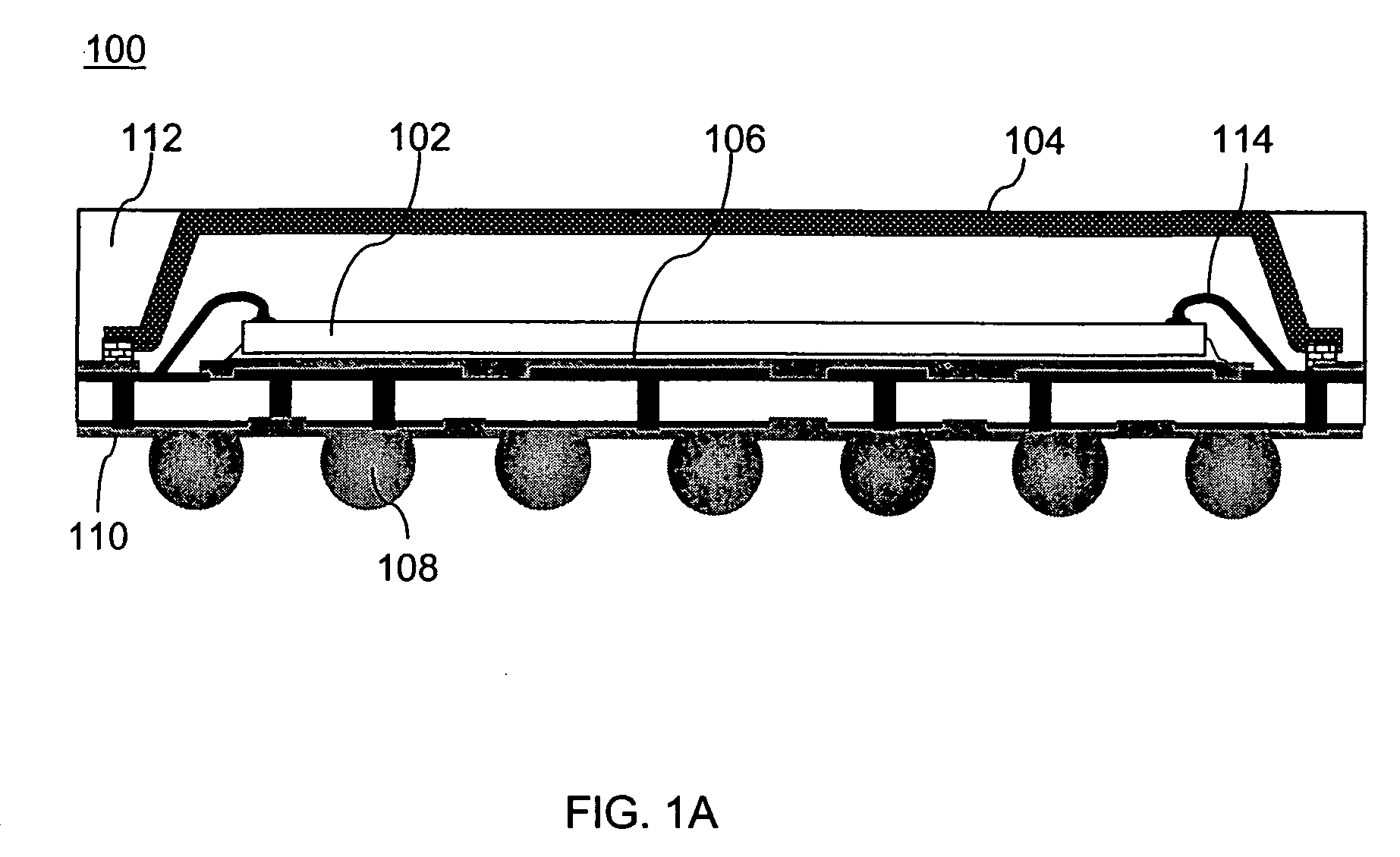

Thermal improvement for hotspots on dies in integrated circuit packages

ActiveUS20070290322A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsContact padEngineering

Methods and apparatuses for improved integrated circuit (IC) packages are described herein. In an aspect, an IC device package includes an IC die having a contact pad, where the contact pad is located on a hotspot of the IC die. The hotspot is thermally coupled to a thermal interconnect member. In an aspect, the package is encapsulated in a mold compound. In a further aspect, a heat spreader is attached to the mold compound, and is thermally coupled to the thermal interconnect member. In another aspect, a thermal interconnect member thermally is coupled between the heat spreader and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

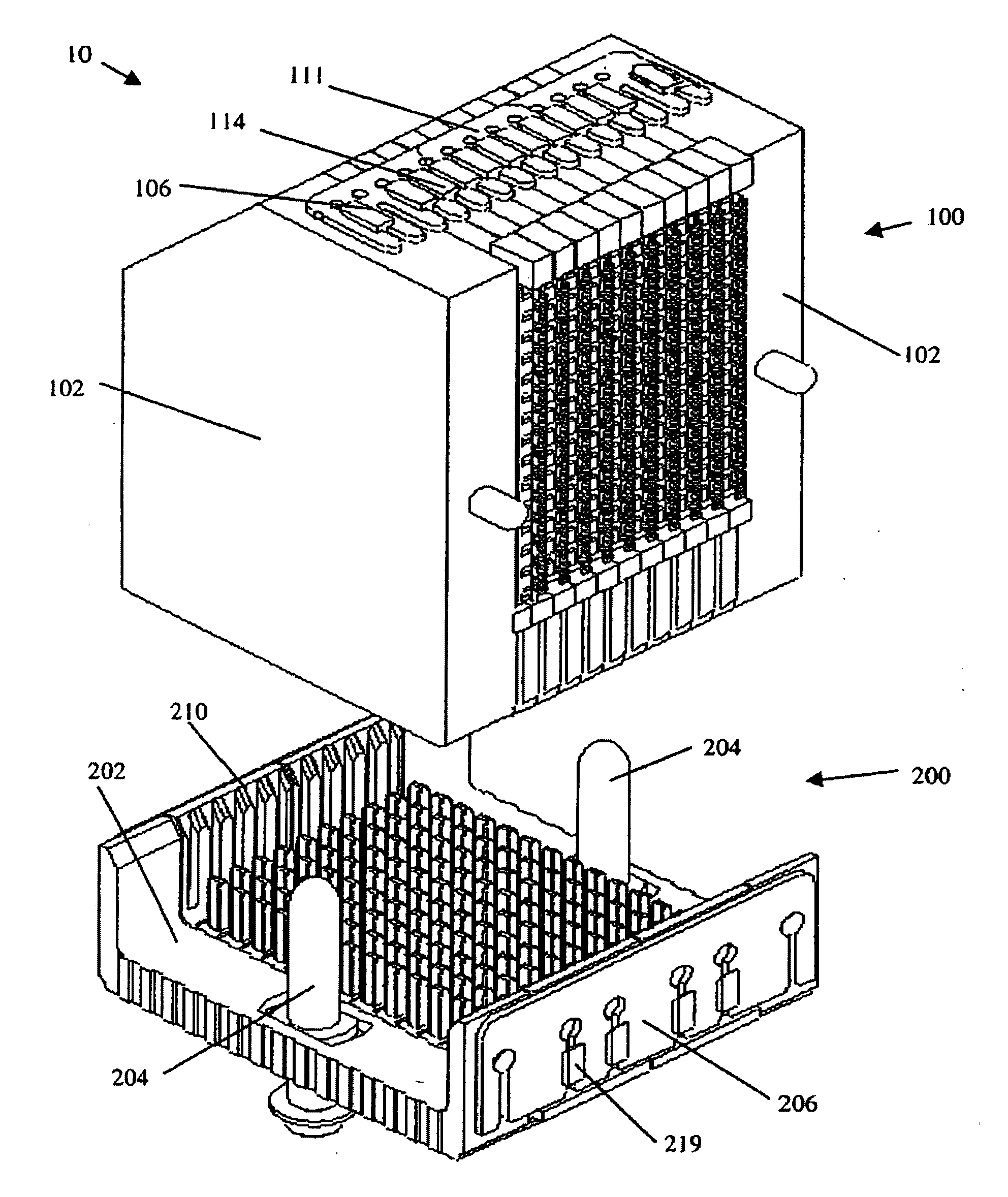

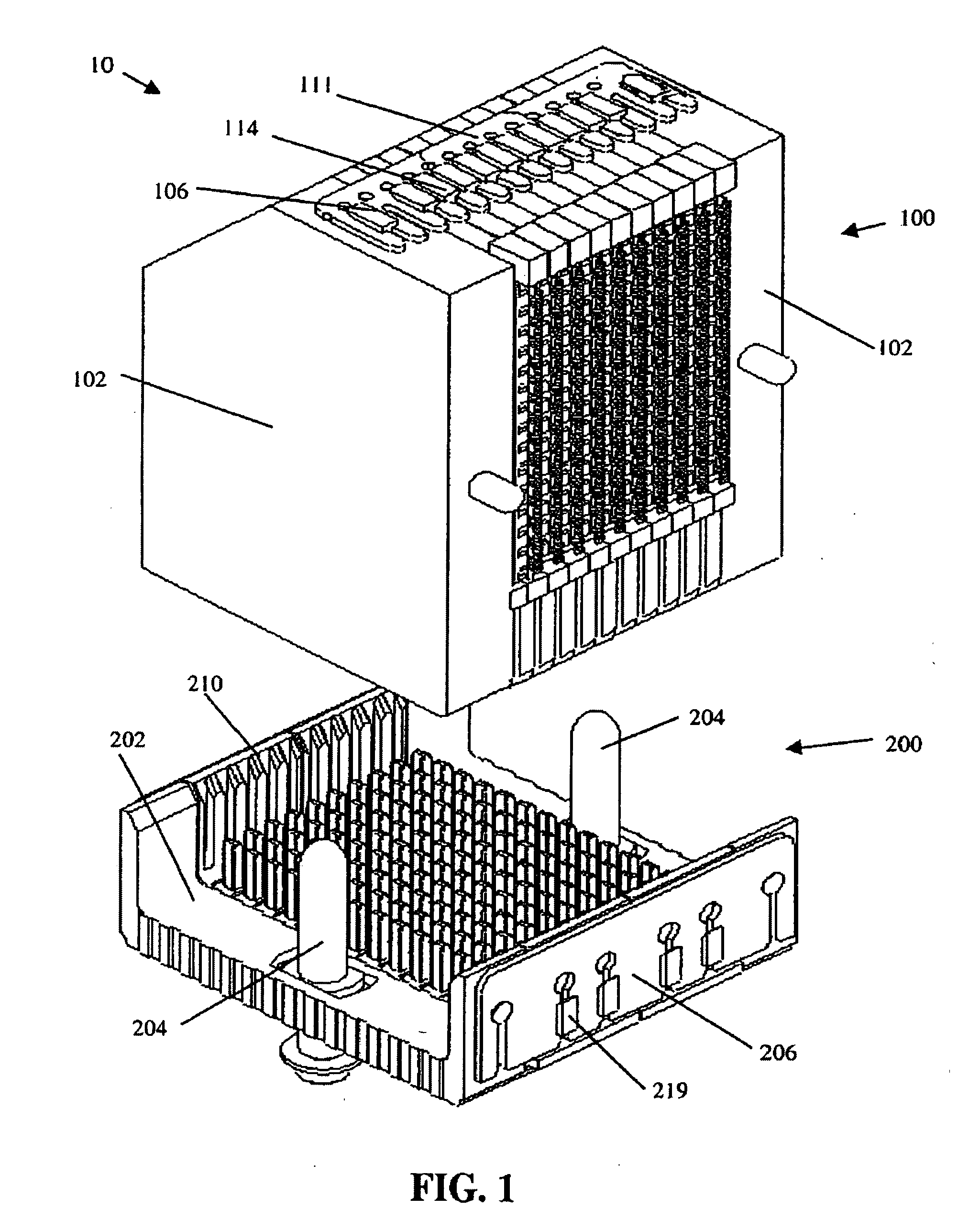

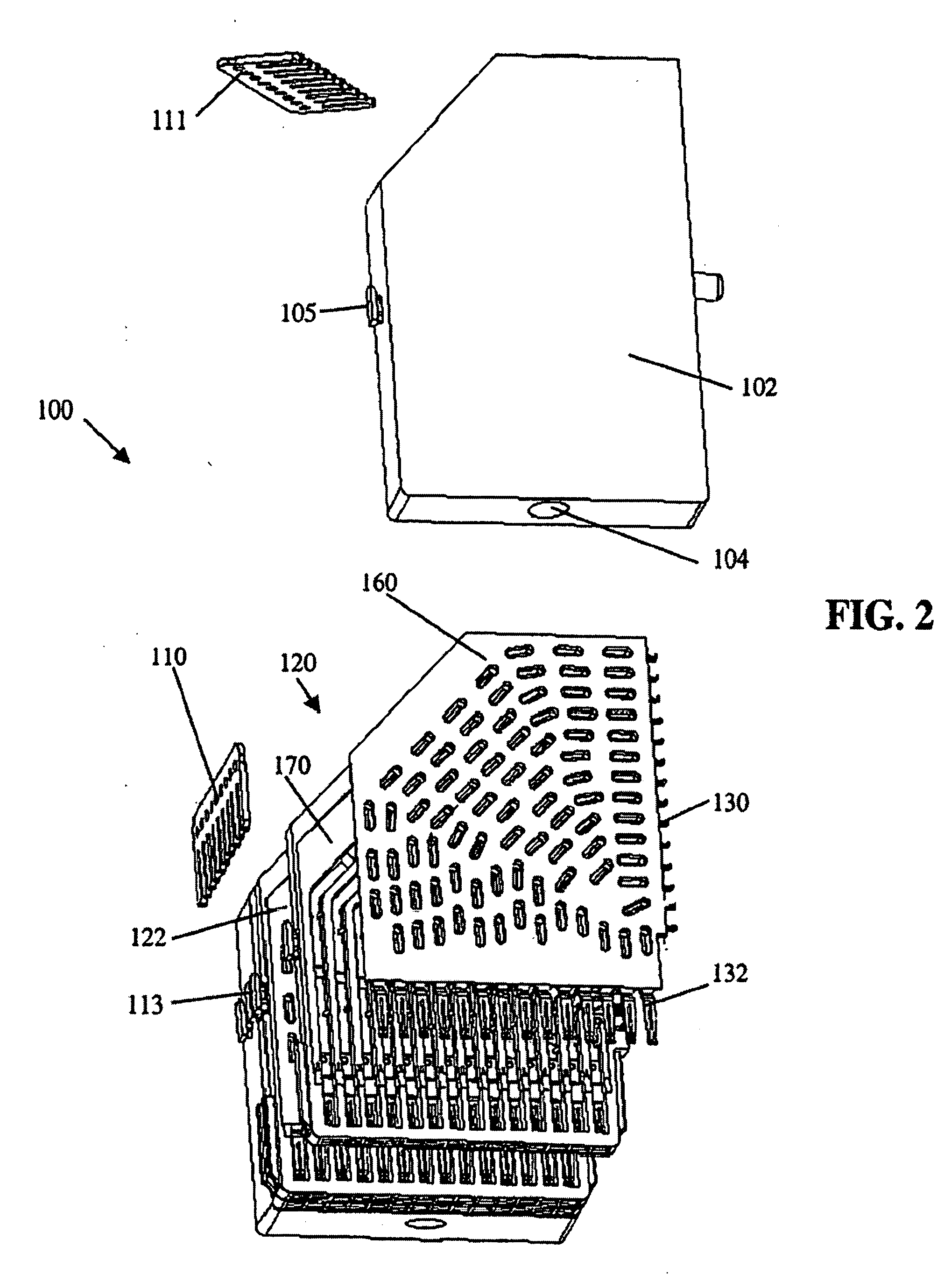

High speed, high density electrical connector

ActiveUS20060068640A1Contact member manufacturingCoupling for high frequencyHigh densityElectrical conductor

An electrical connector with electrically lossy materials bridging ground members. The lossy conductive members may be formed by filling a settable binder with conductive particles, allowing the partially conductive members to be formed through an insert molding process. Connectors assembled from wafers that contain signal conductors held within an insulative housing may incorporate lossy conductive members by having filled thermal plastic molded onto the insulatative housing. The lossy conductive members may be used in conjunction with magnetically lossy materials. The lossy conductive members reduce ground system do resonance within the connector, thereby increasing the high frequency performance of the connector.

Owner:AMPHENOL CORP

Method for forming a via contacting several levels of semiconductor layers

ActiveUS20130196500A1Overcome disadvantagesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method for forming a via connecting a first upper level layer to a second lower level layer, both layers being surrounded with an insulating material, the method including the steps of: a) forming an opening to reach an edge of the first layer, the opening laterally continuing beyond said edge; b) forming a layer of a protection material on said edge only; c) deepening said opening by selectively etching the insulating material to reach the second lower level layer; and d) filling the opening with at least one conductive contact material.

Owner:STMICROELECTRONICS SRL +1

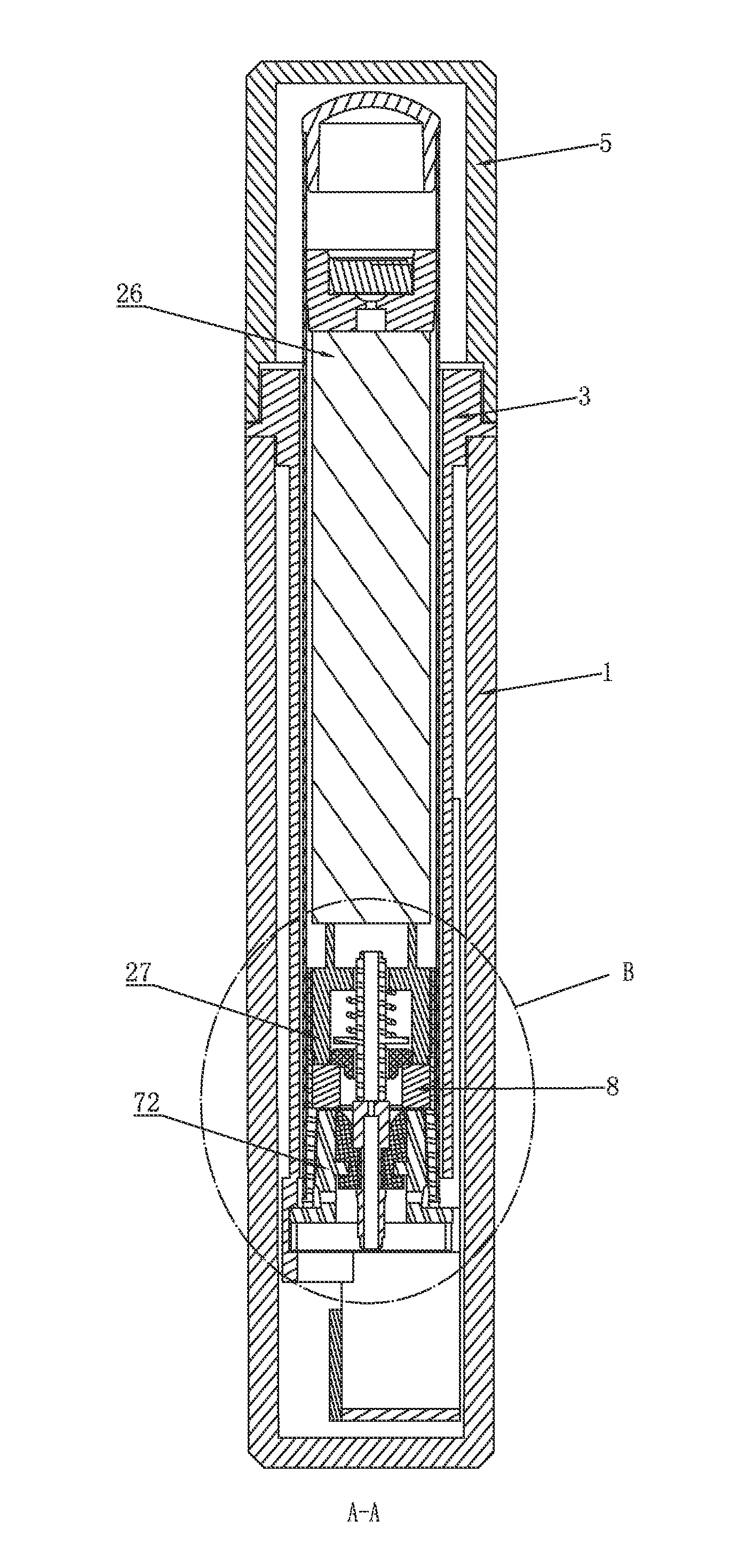

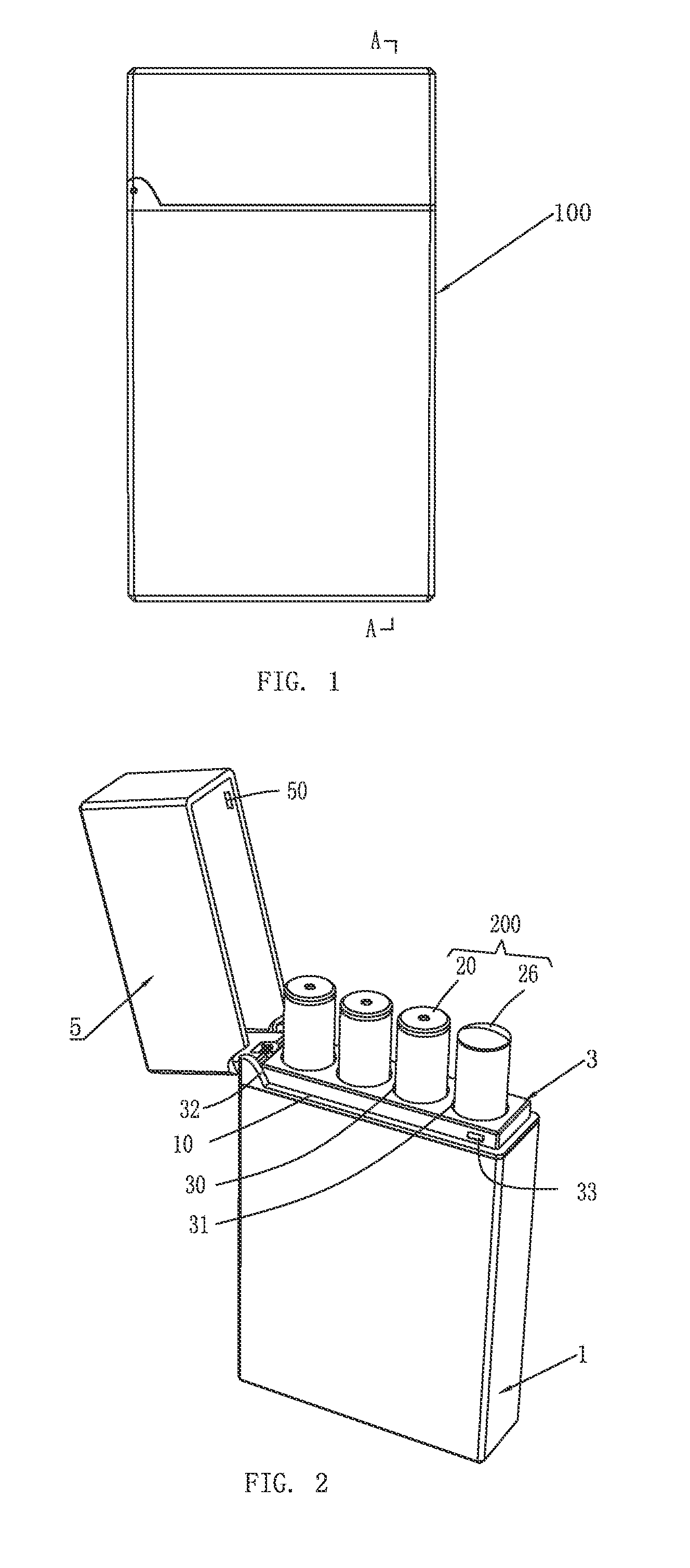

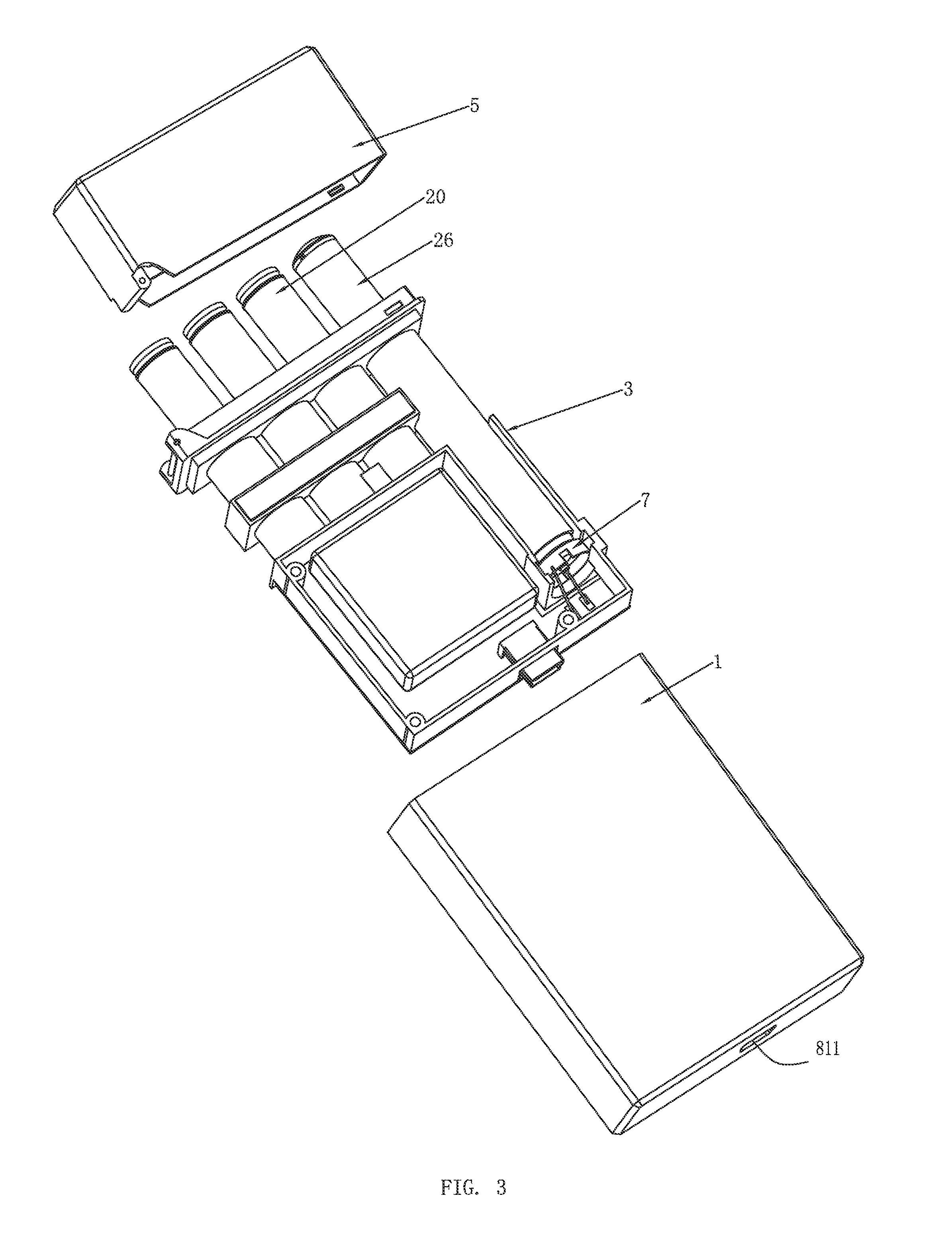

Electronic Cigarette Device

ActiveUS20140053858A1Out of placeBatteries circuit arrangementsTobacco treatmentElectronic cigaretteEngineering physics

An electronic cigarette device includes electronic cigarette and a case for accommodating electronic cigarette. The case has a first magnetic part at a position coupled to electronic cigarette, the electronic cigarette correspondingly has a second magnetic part absorbing the first magnetic part to keep the electronic cigarette and the case firmly engaged. The case has a first connector at a position coupled to electronic cigarette, the first connector comprises a first socket, a first pole in center of the first socket, and first insulating bush inserted between the first socket and first pole. The electronic cigarette includes an inhaling shell and a power shell, the power shell has a battery therein, one end of the power shell has a second connector connected with a second battery and coupled to the first connector. The electronic cigarette device is convenient for placing electronic cigarette into the case or taking it out therefrom.

Owner:HUIZHOU KIMREE TECH

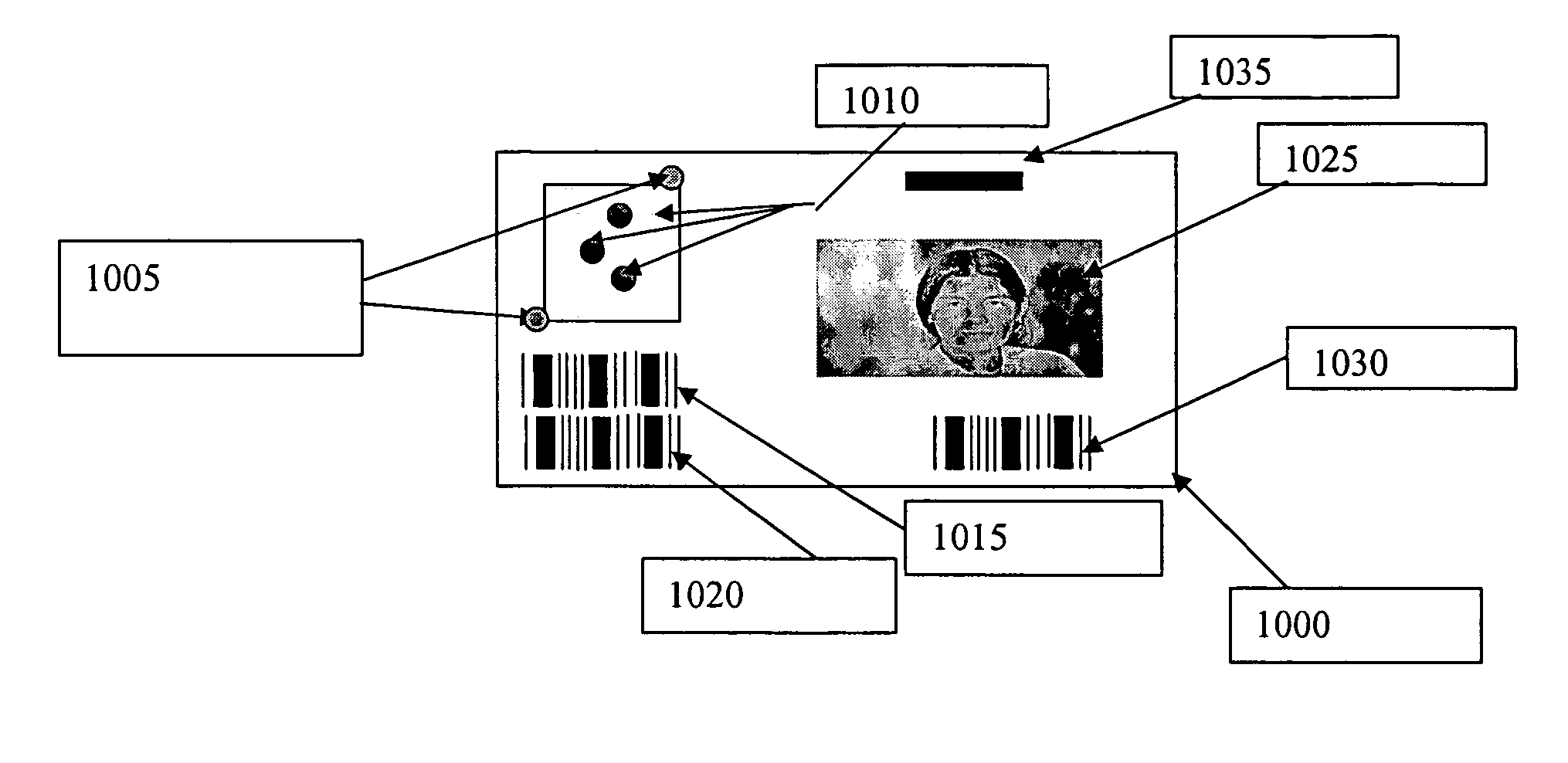

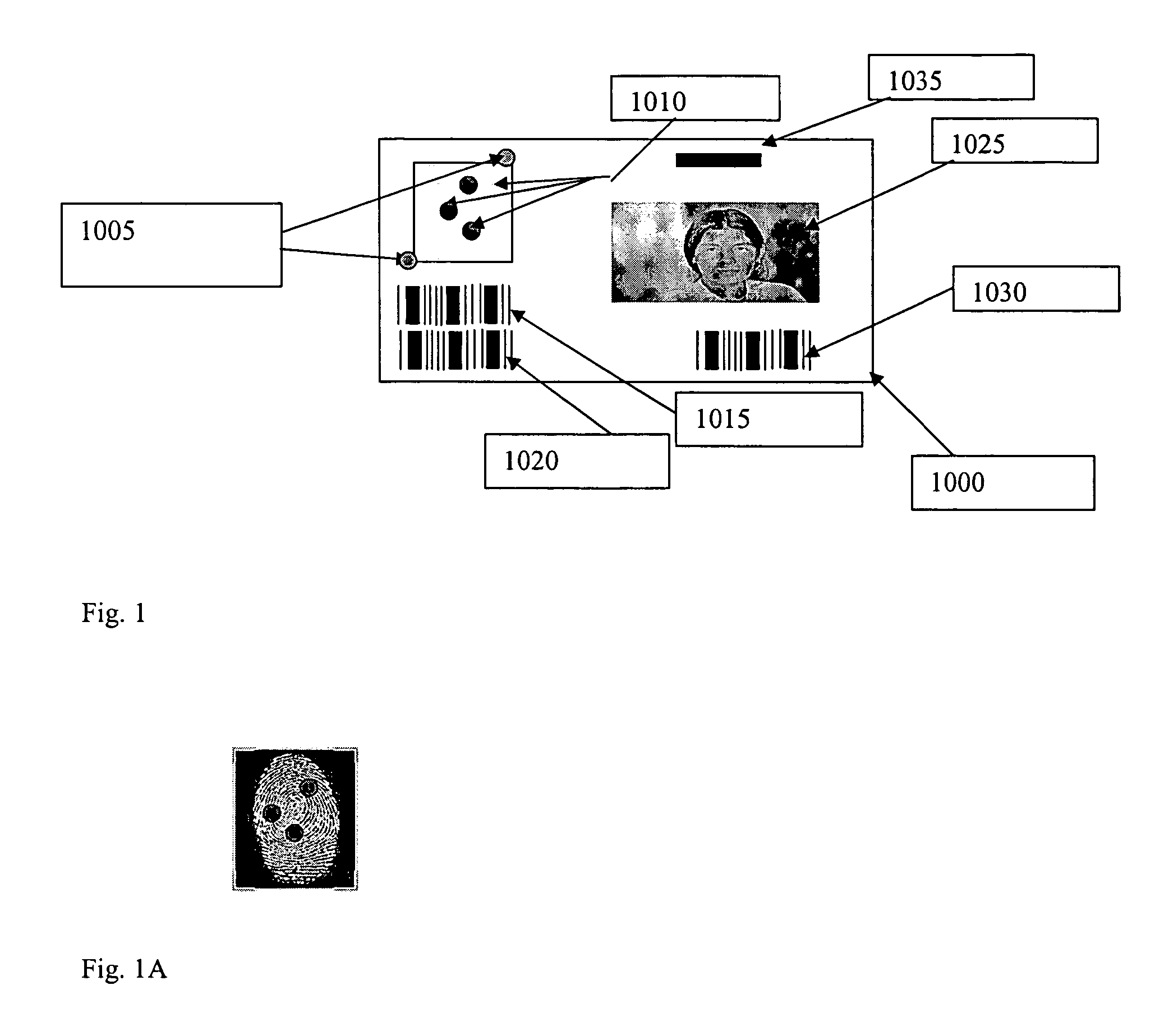

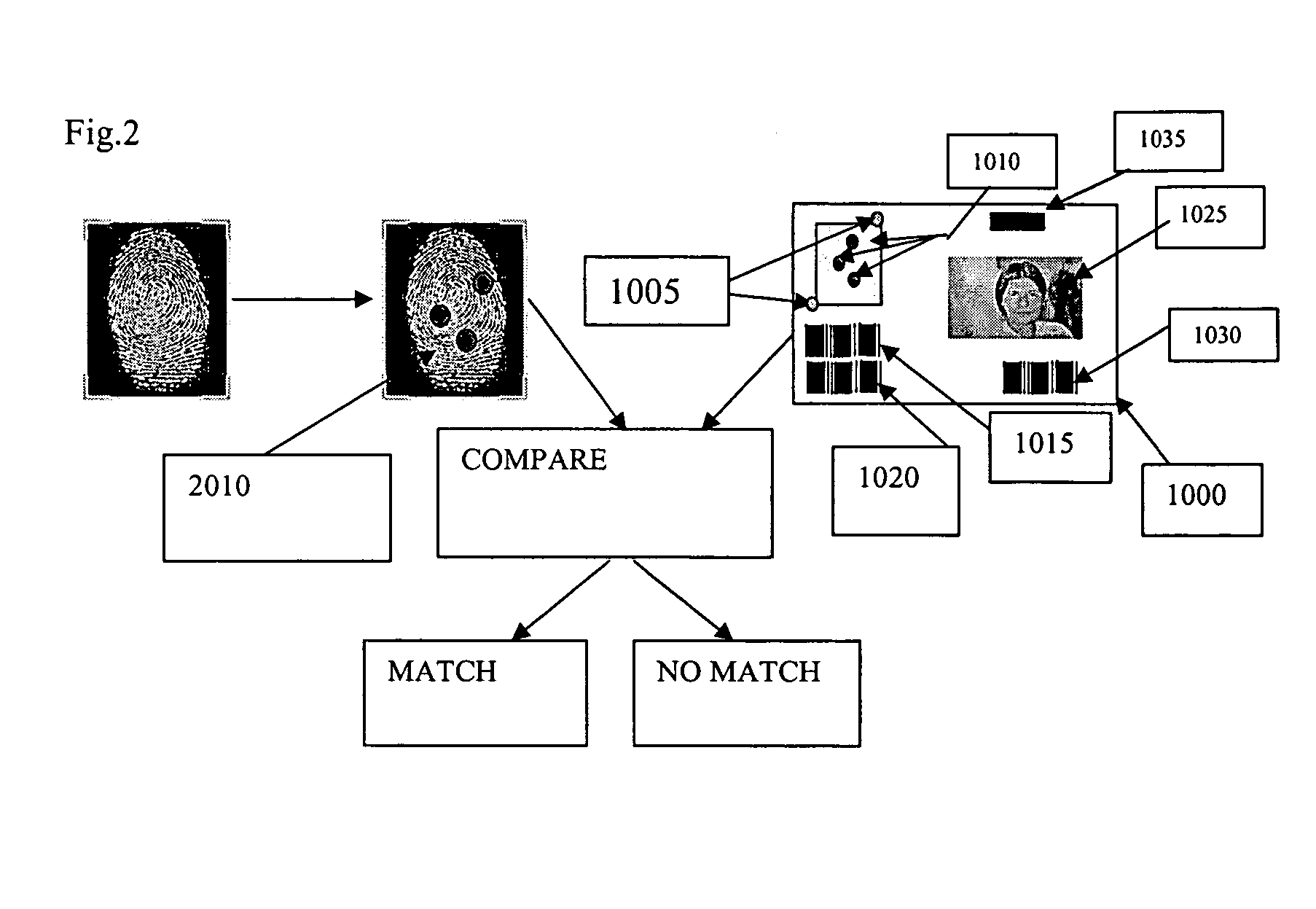

Security marking and security mark

InactiveUS20050156318A1Semiconductor/solid-state device detailsNanoinformaticsPlatinumProduct Identifier

The application discloses a security mark consisting of a plurality of layers, of which the cover layers are highly conductive films and the layers of the card core are films of varying transparency. One layer carries information, which can be read directly, if desired, above a security print, while the transparent conductive layer has an additional security markings, such as biometric or product identifiers marking which can be read conductively only with the aid of a special reader. All the layers consist of polymers, papers or mixtures which can be fused together to form a laminate which is fused together. The conductive layers form conductive traces which may be formed with single-walled or multi walled nano tubes or they can be formed from multiple layers or dispersions containing, carbon nano tubes, carbon nano tubes / antimony tin oxide, carbon nano tubes / platinum, or carbon nano tubes / silver, carbon, silver or carbon nano tubes / silver-cloride. An alternative layer can be formed from a separate conductive layer or suitable dispersion and the encoding accomplished by overlaying a nonconductive trace.

Owner:DOUGLAS JOEL S