Process for producing semiconductor integrated circuit device

a technology of integrated circuits and semiconductors, applied in semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problems of parasitic capacitance that cannot be reduced between adjacent buried wiring lines, signal delay, and increase in resistance of via portions, so as to achieve high reliability of via connections and reduce parasitic capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

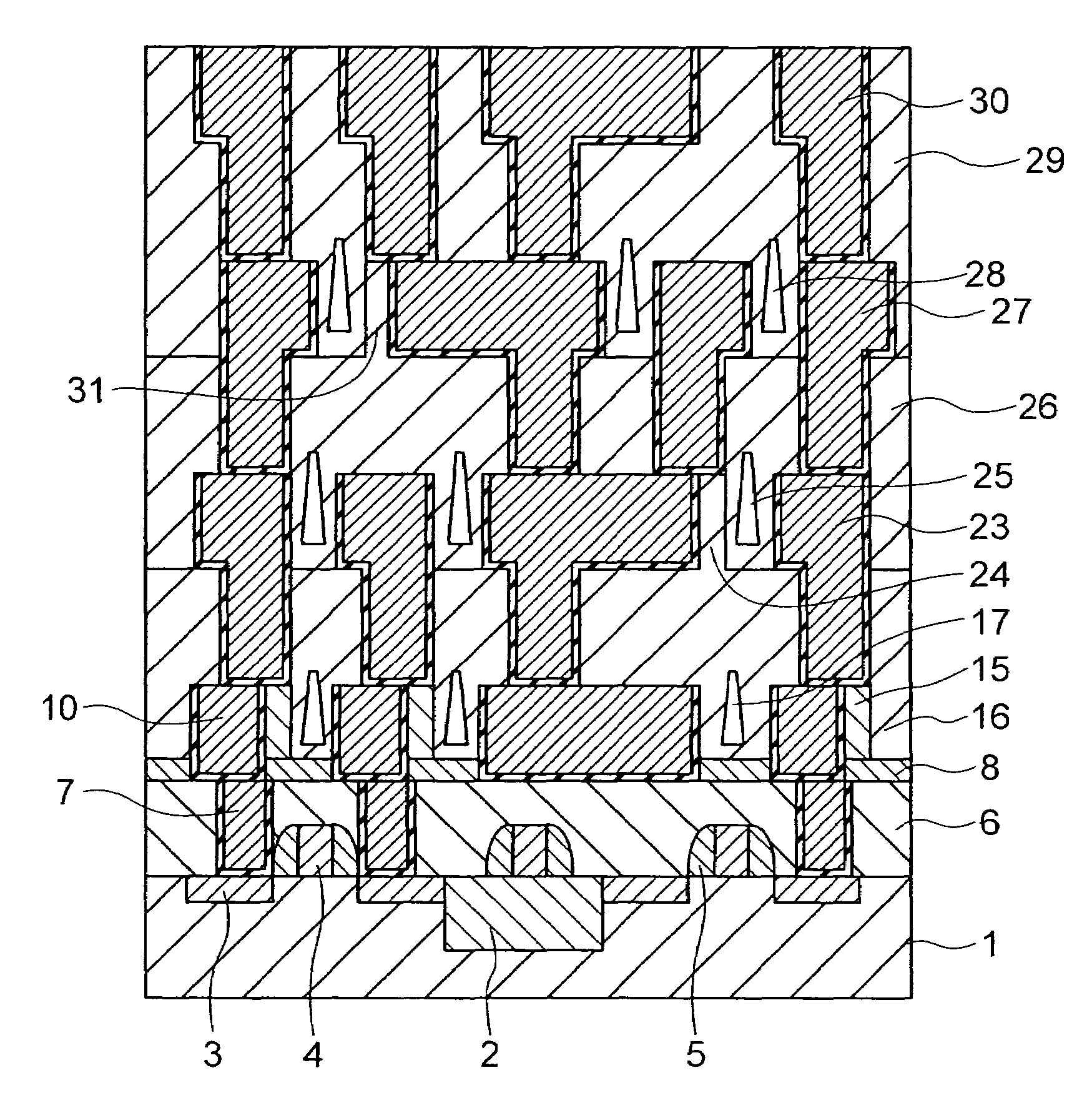

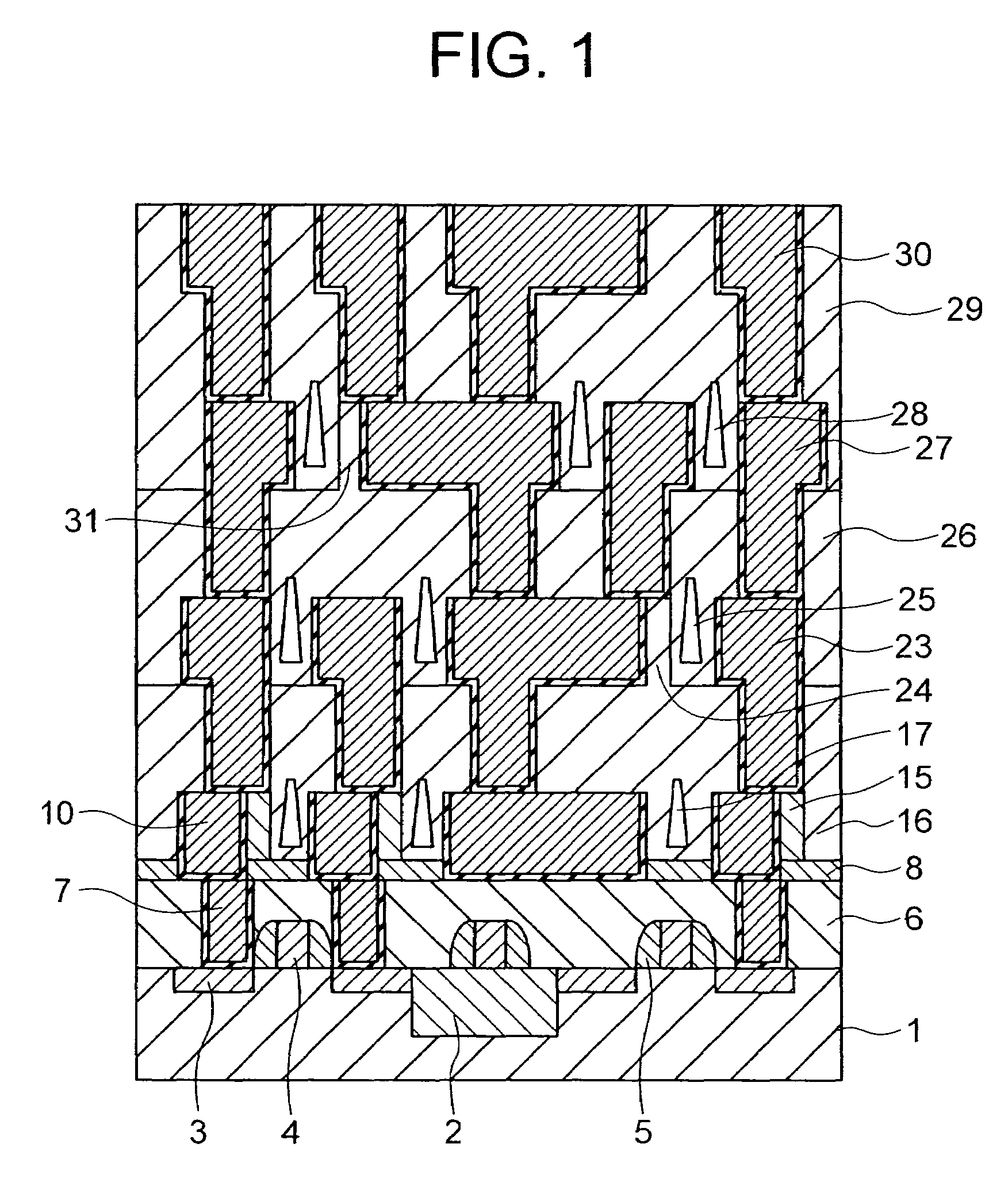

[0133]FIG. 1 is a cross sectional view of a substantial portion of a semiconductor device of an example 1 of the present invention.

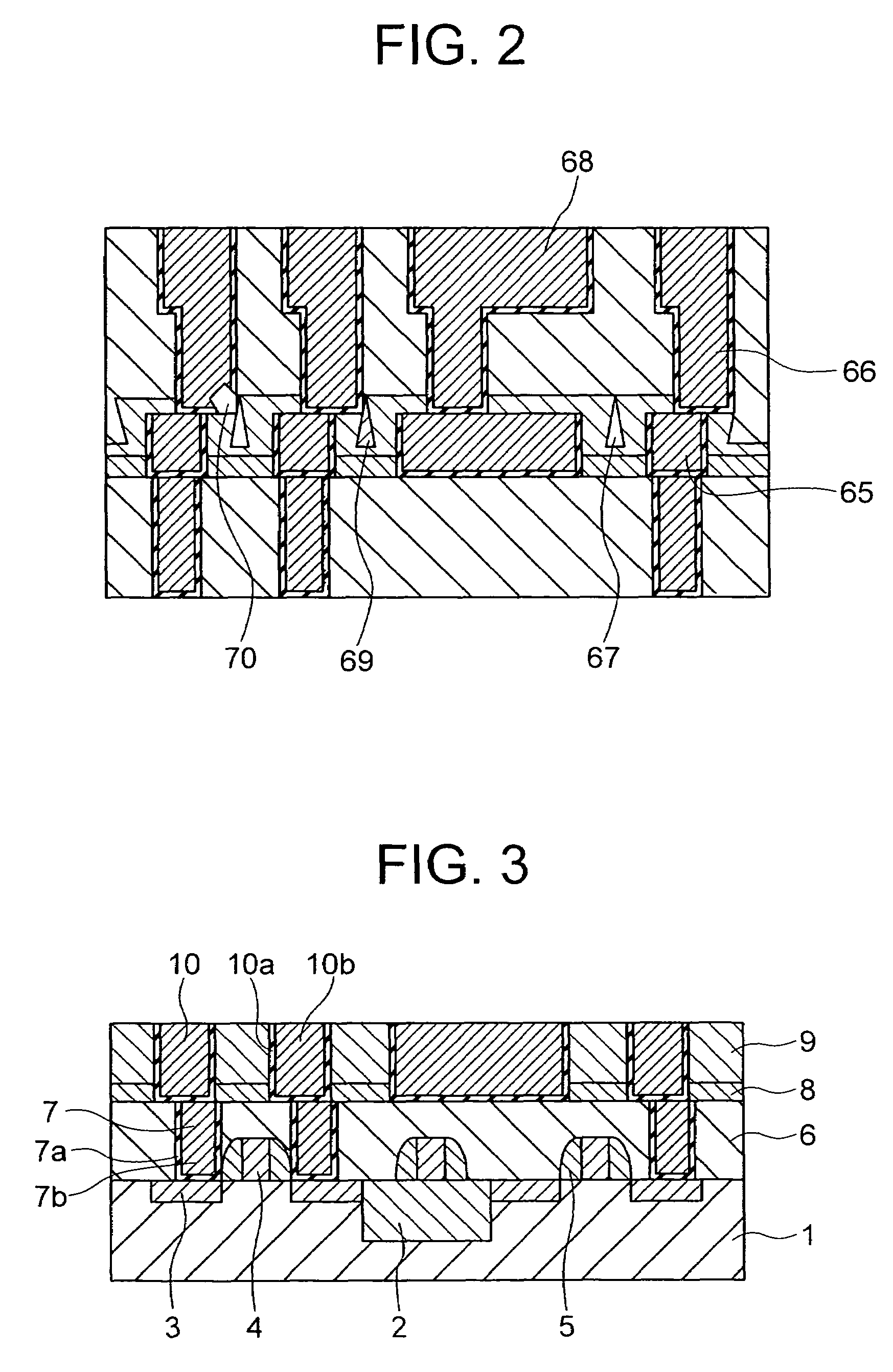

[0134]The main surface of a semiconductor substrate 1 is divided into each of element regions by a field insulating film 2, and a diffusion layer 3 including a source region, drain region and the like is formed in each of the element regions. A gate electrode 4 composed of polycrystalline silicon is formed through a gate insulating film (not shown) between the regions of the source region and drain region 3 on the main surface of the semiconductor substrate 1, and lateral sides of the gate electrode 4 are covered with a side wall insulating film 5.

[0135]The diffusion layer 3 or the gate electrode 4 formed on the main surface of the semiconductor substrate 1 is connected to one end of a plug 7 through an interlayer insulating film 6, and the other end of the plug 7 is connected to a laminated single Damascene wiring portion 10 through the interlayer insul...

example 2

[0164]FIG. 15 is a cross sectional view of a substantial portion of a semiconductor device of an example 2 of the present invention.

[0165]The main surface of a semiconductor substrate 1 is divided into each of element regions by a field insulating film 2, and a diffusion layer 3 including a source region, drain region and the like is formed in each of the element regions. A gate electrode 4 composed of polycrystalline silicon is formed through a gate insulating film (not shown) between the regions of the source region and drain region 3 on the main surface of the semiconductor substrate 1, and lateral sides of the gate electrode 4 are covered with a side wall insulating film 5.

[0166]The diffusion layer 3 or the gate electrode 4 formed on the main surface of the semiconductor substrate 1 is connected to one end of a plug 7 through an interlayer insulating film 6, and the other end of the plug 7 is connected to a laminated single Damascene wiring portion 10 through the interlayer insu...

example 3

[0186]FIG. 20 is a cross sectional view of a substantial portion of a semiconductor device of an example 3 of the present invention.

[0187]The main surface of a semiconductor substrate 1 is divided into each of element regions by a field insulating film 2, and a diffusion layer 3 including a source region, drain region and the like is formed in each of the element regions. A gate electrode 4 composed of polycrystalline silicon is formed through a gate insulating film (not shown) between the regions of the source region and drain region 3 on the main surface of the semiconductor substrate 1, and lateral sides of the gate electrode 4 are covered with a side wall insulating film 5.

[0188]The diffusion layer 3 or the gate electrode 4 formed on the main surface of the semiconductor substrate 1 is connected to one end of a plug 7 through an interlayer insulating film 6, and the other end of the plug 7 is connected to a laminated single Damascene wiring portion 10 through the interlayer insu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More