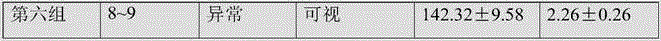

Patents

Literature

63results about How to "Lower the K value" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

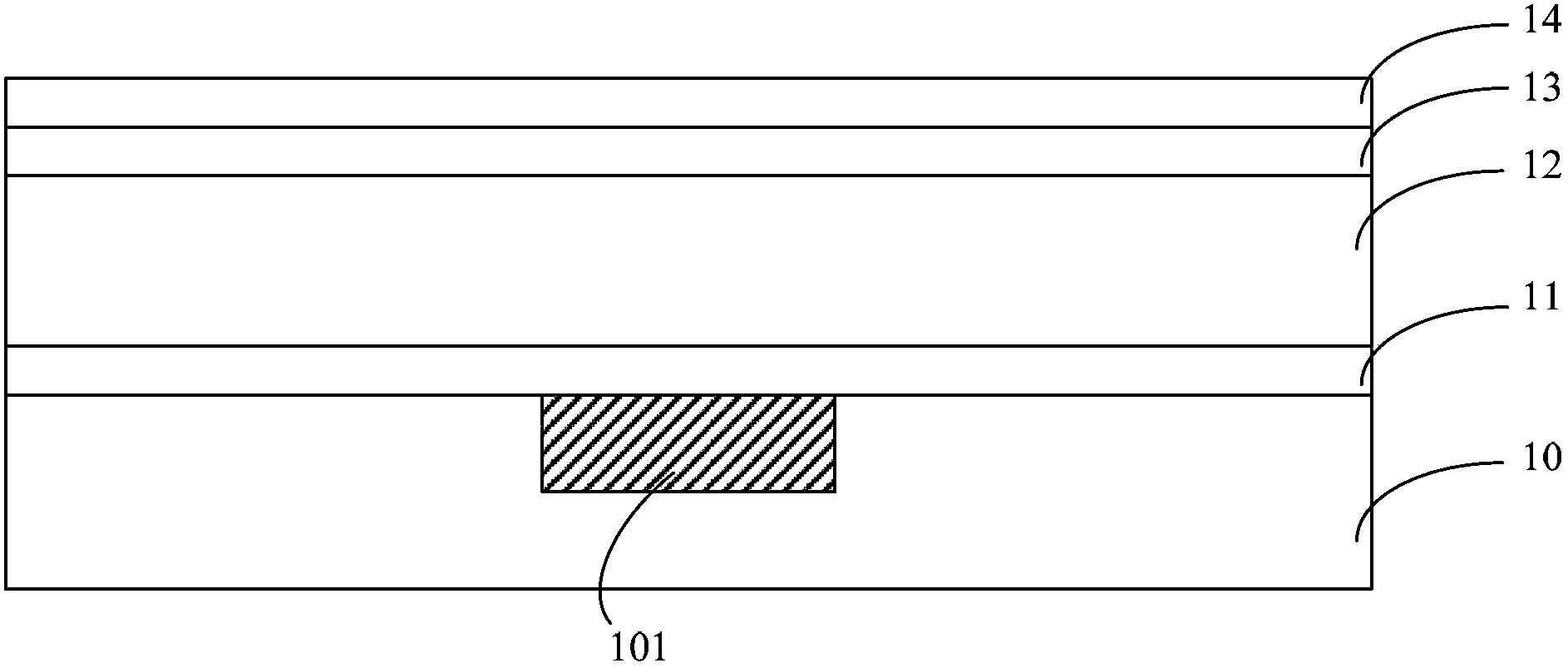

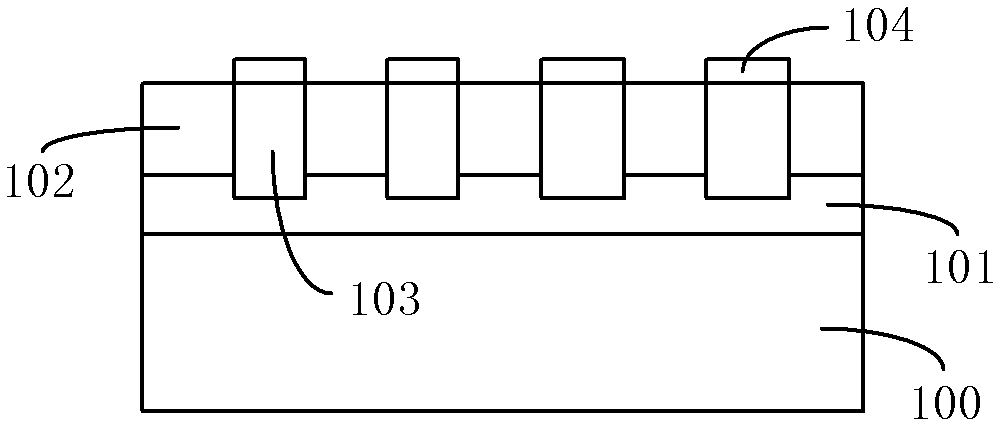

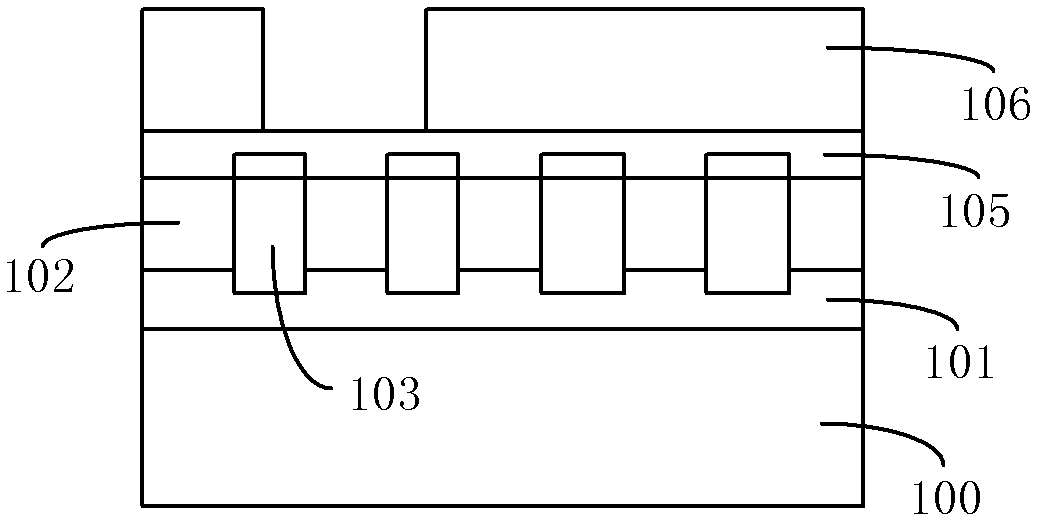

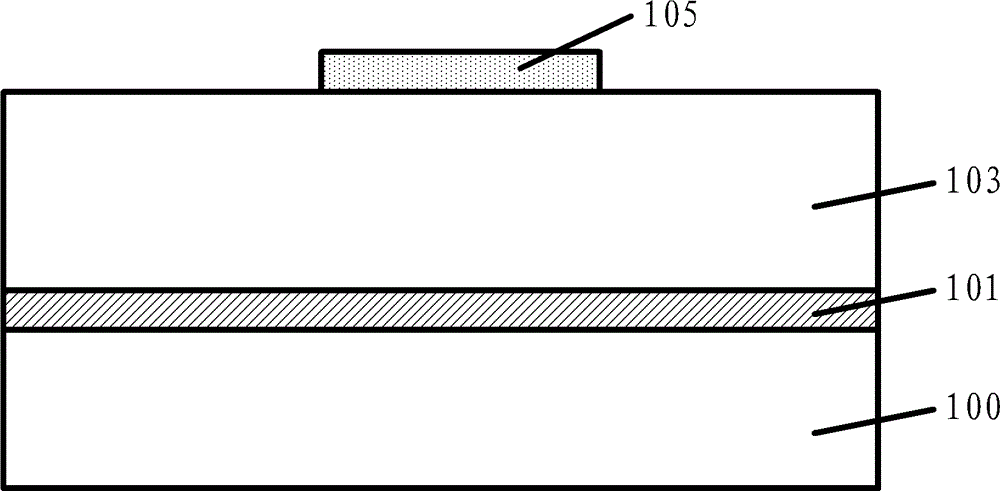

Low-noise avalanche photodetector and preparation method thereof

ActiveCN105576072AImprove quantum efficiencyReduce effective thicknessFinal product manufactureSemiconductor devicesLow noisePhotovoltaic detectors

The invention discloses a low-noise avalanche photodetector and a preparation method thereof. The low-noise avalanche photodetector comprises an N-type ohmic contact layer / P-type ohmic contact layer, a multiplication layer, a charge layer and a P-type ohmic contact layer / N-type ohmic contact layer with different doping types which are formed through diffusion and ion injection, and a substrate is formed at the bottom between the charge layer and the P-type ohmic contact layer / N-type ohmic contact layer; an inverted trapezoidal groove is formed among the charge layer, the P-type ohmic contact layer / N-type ohmic contact layer and the substrate; and an absorbed layer is formed in the inverted trapezoidal groove. A P-type electrode and an N-type electrode are arranged on the P-type ohmic contact layer and the N-type ohmic contact layer respectively. The low-noise avalanche photodetector has the characteristic that a one-dimensional longitudinal avalanche photodetector is of a two-dimensional transverse structure, and the effective thickness of the multiplication layer is reduced to a nanometer size, so that the k value is reduced by using the dead-time effect of a nanometer multiplication area.

Owner:WUHAN IND INST FOR OPTOELECTRONICS

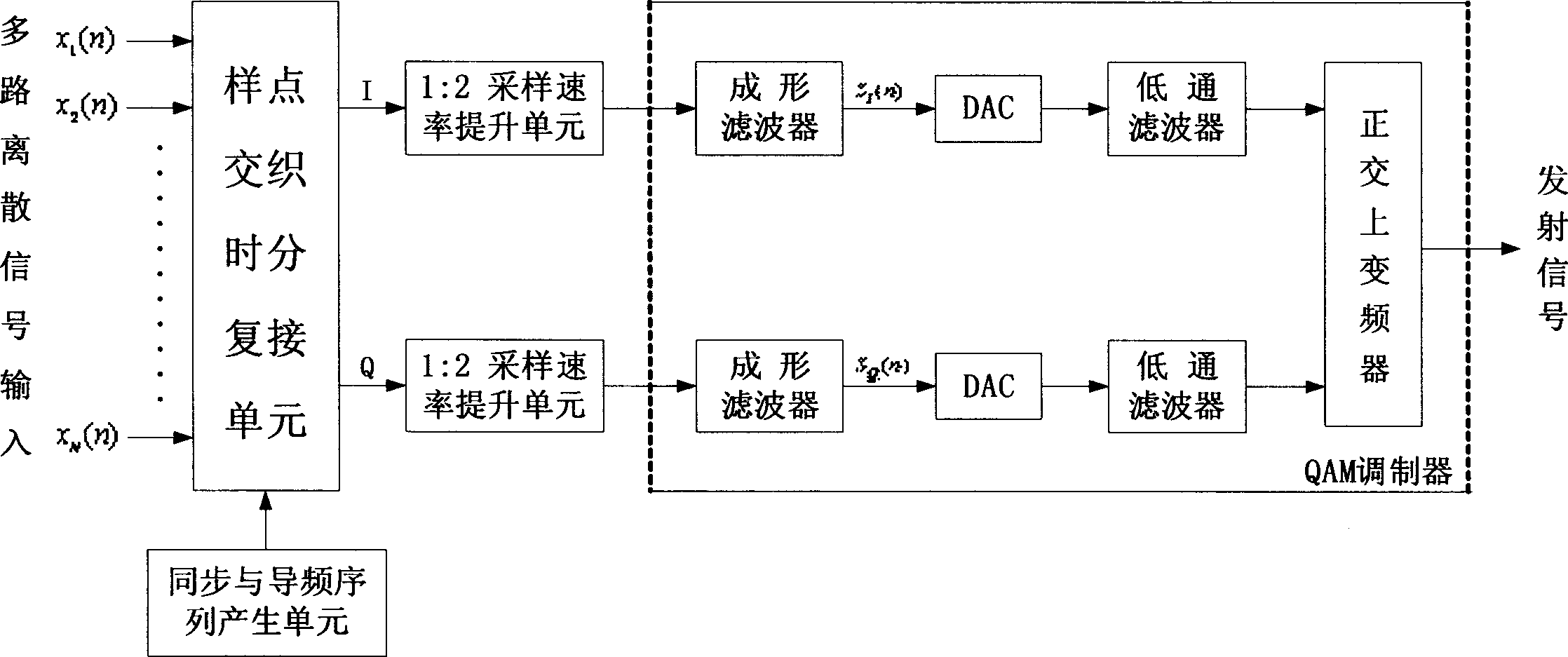

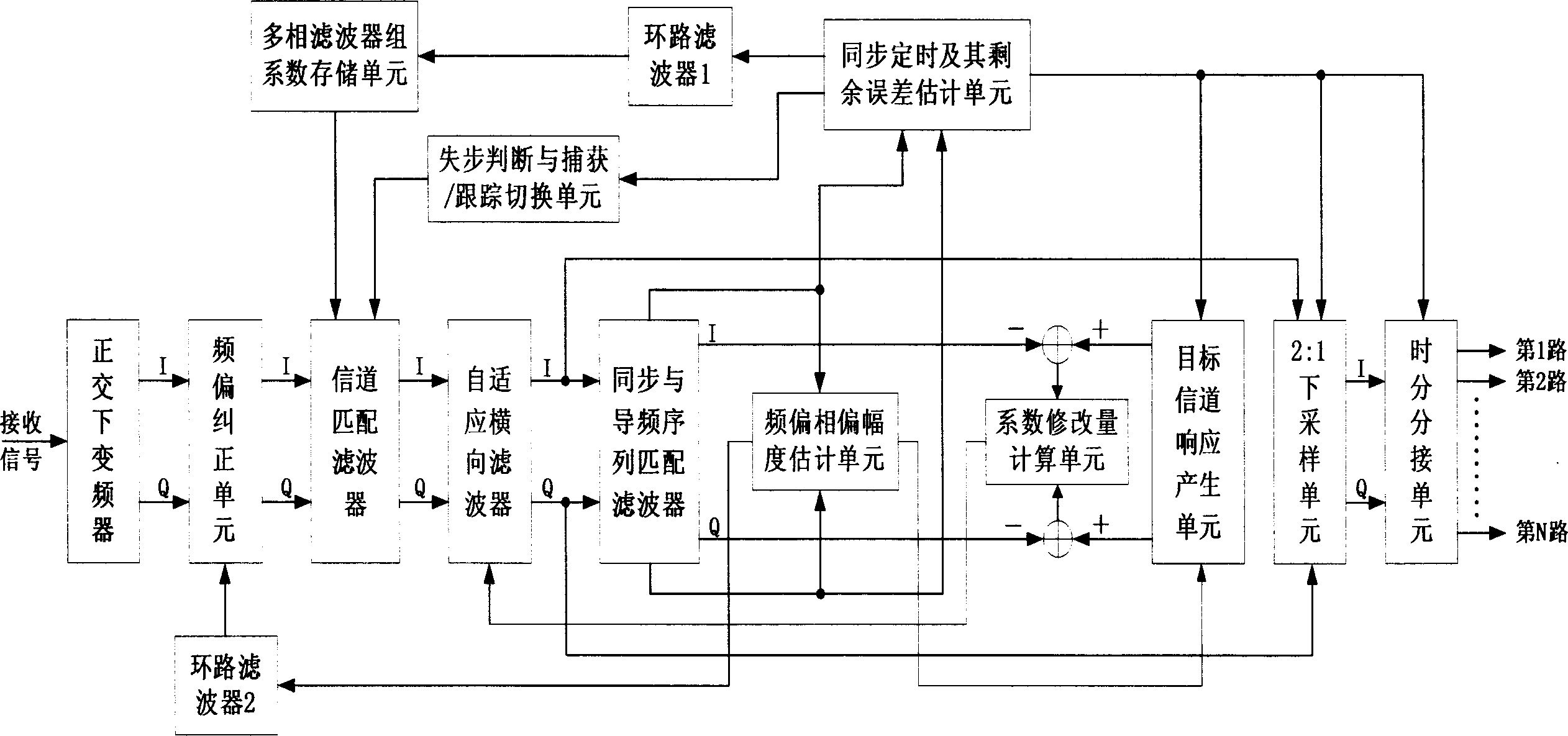

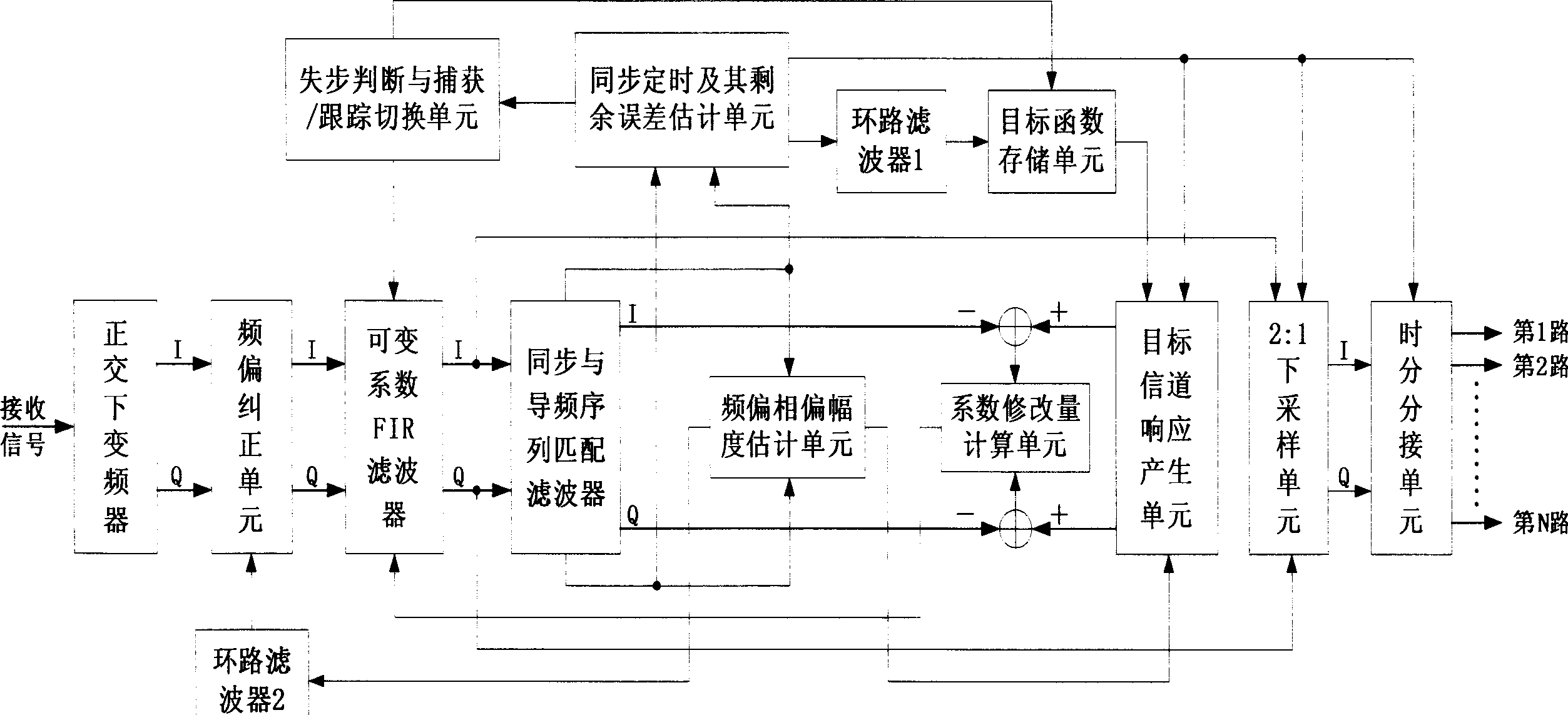

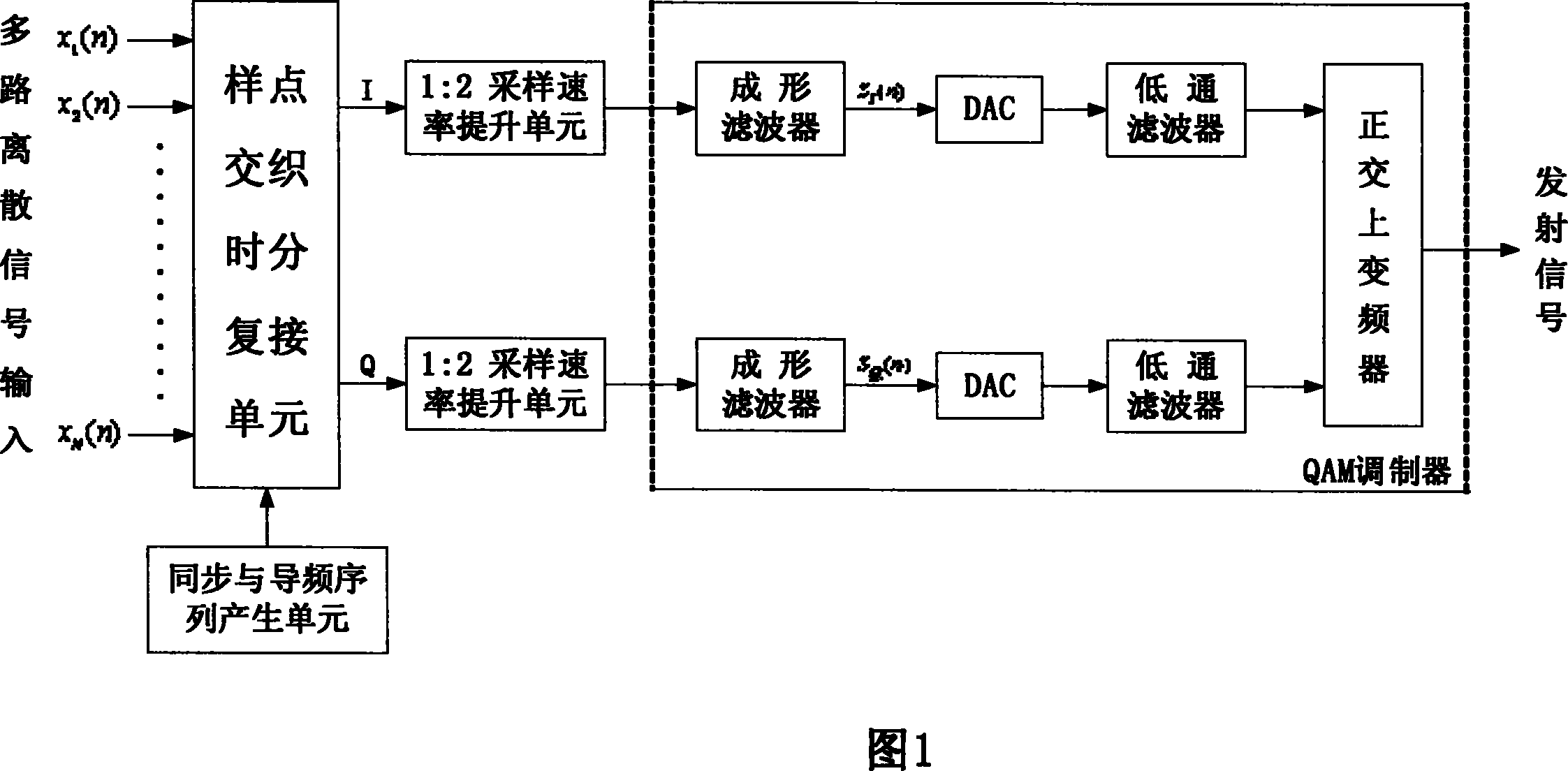

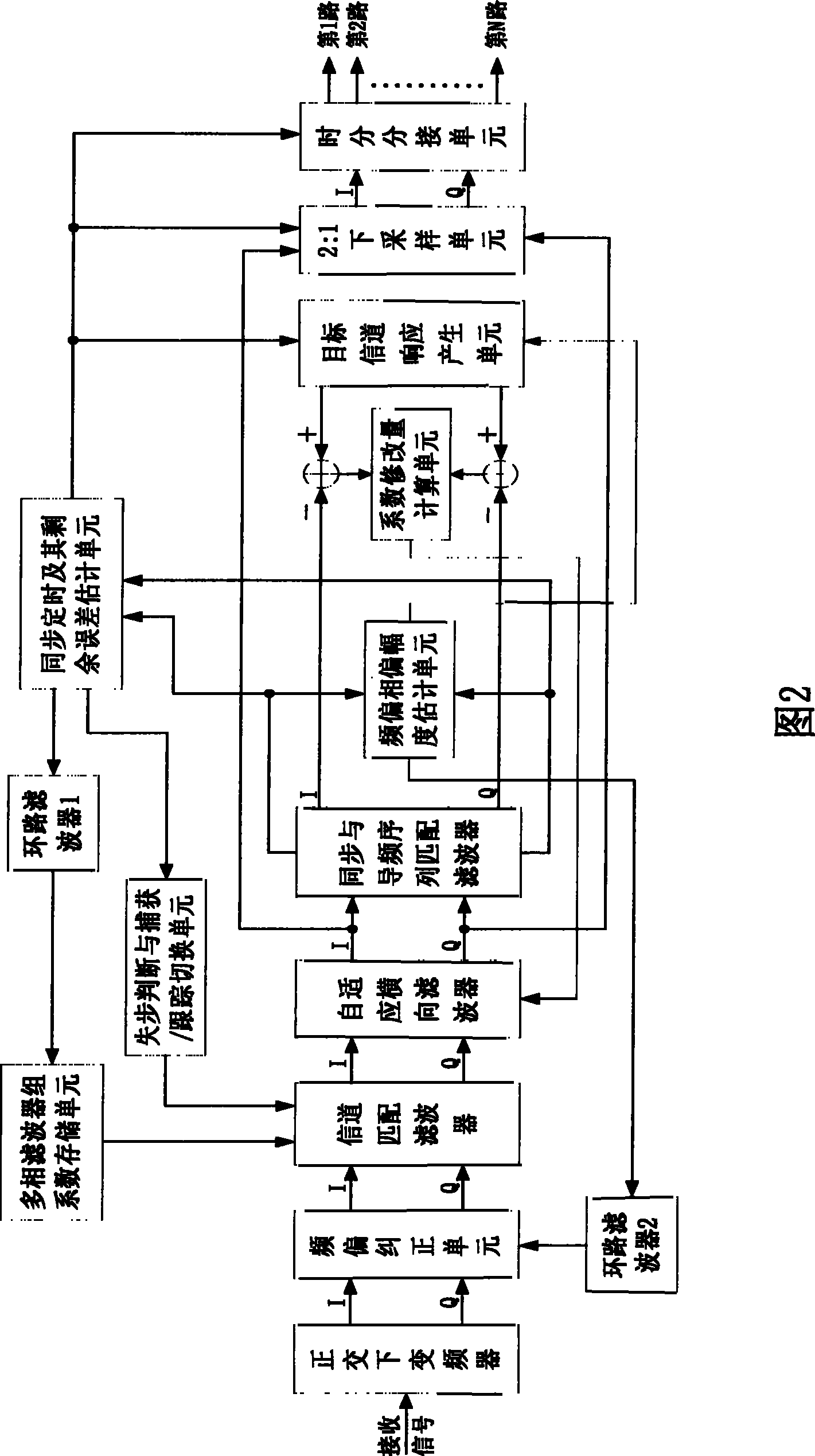

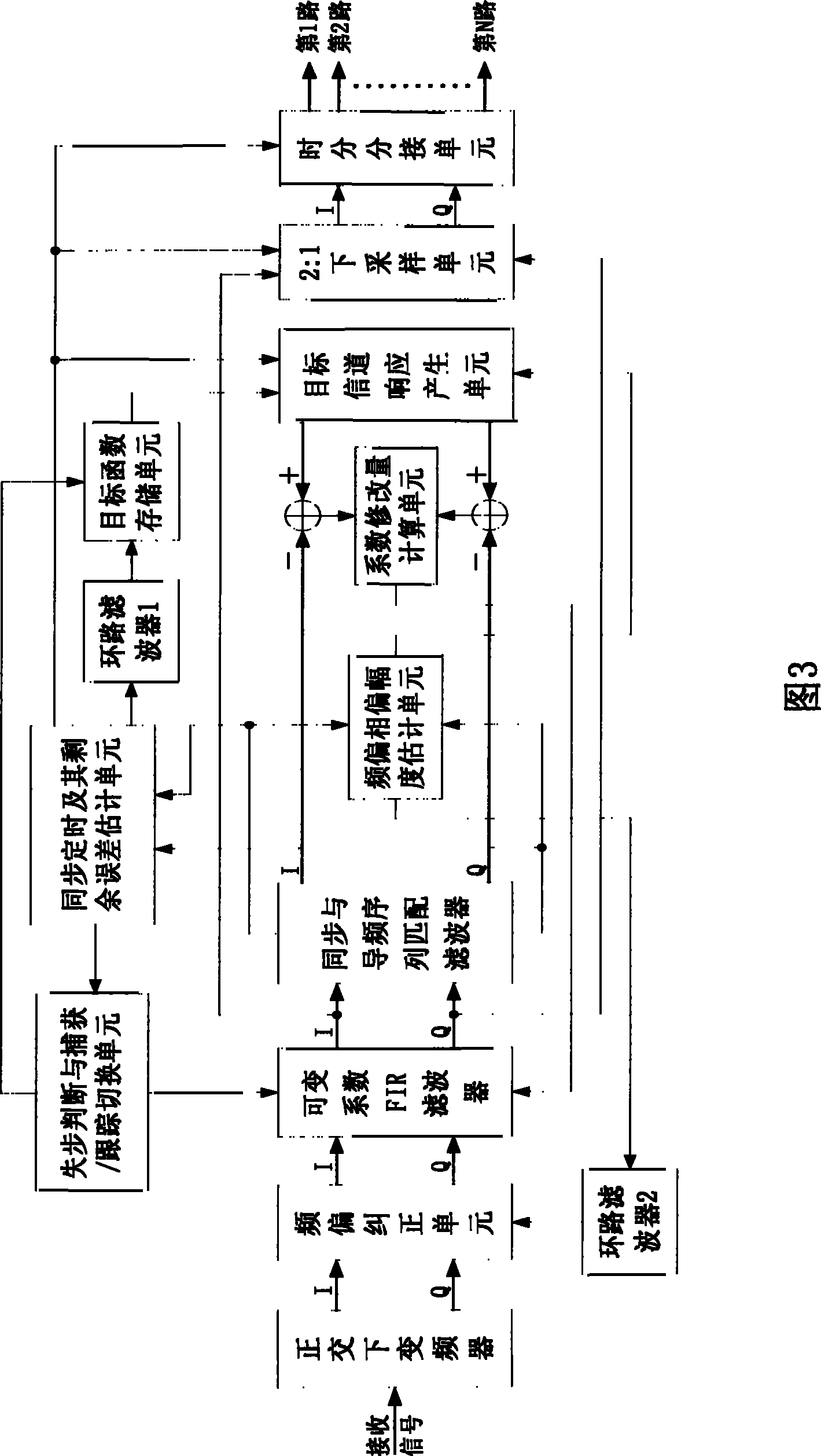

Quasi OTDM transmitting method and system

InactiveCN1845487AThe synchronization accuracy is smallEnsure robustnessMultiple carrier systemsSignal channelsSignal onCarrier signal

The disclosed QOTDM method and system comprise: connecting N continual signals with BHz bandwidth or corresponding sampling sequence into one continual signal to transmit in continual channel; converting the received signal on receive end into a composite zero-IF signal with orthogonal down-conversion and sampling digitalization, connecting frequency deviation by a carrier phase-locking loop; using frame-synchronization loop and adaptive channel balancer for high-precise sampling point synchronization and correction channel distortion; finally, recovering N signals. This invention has well performance for satellite communication system.

Owner:XIDIAN UNIV

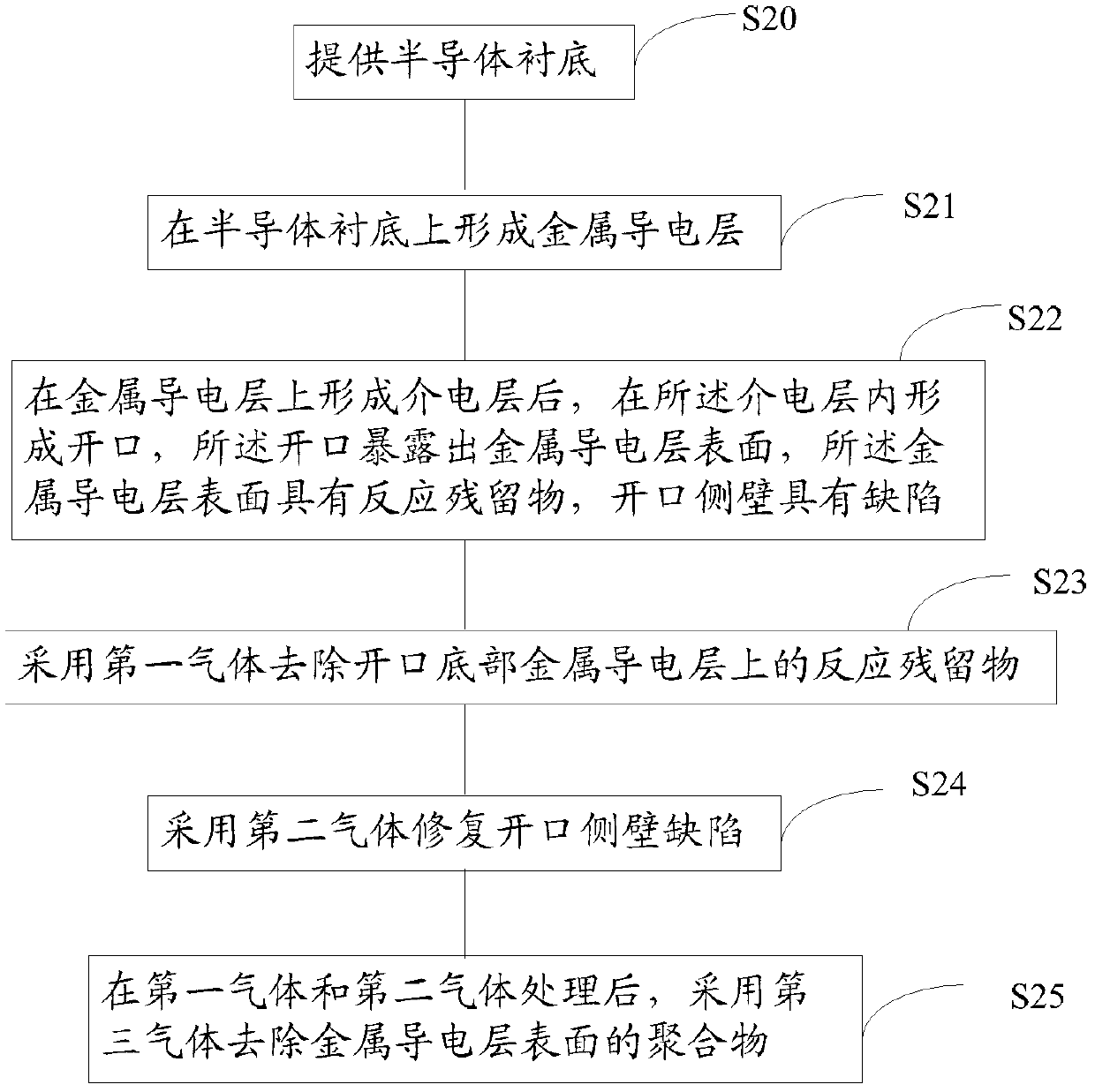

Method of forming opening

ActiveCN103377913AImprove yieldImprove reliabilitySemiconductor/solid-state device manufacturingAfter treatmentDielectric layer

Disclosed is a method of forming an opening. The method comprises the steps of providing a semiconductor substrate; forming a metal conductive layer on the semiconductor substrate; forming a dielectric layer on the metal conductive layer and forming an opening in the dielectric layer with the opening exposing a surface of the metal conductive layer, the surface of the metal conductive layer having a reaction residue and a side wall of the opening having a defect; removing the reaction residue on the metal conductive layer at the bottom of the opening by use of a first gas; repairing the defect on the side wall of the opening by use of a second gas; and removing, after treatment of the first gas and the second gas, a polymer on the surface of the metal conductive layer by use of a third gas. The method of forming the opening is used for improving electrical properties, stability and yield of an integrated circuit.

Owner:SEMICON MFG INT (SHANGHAI) CORP

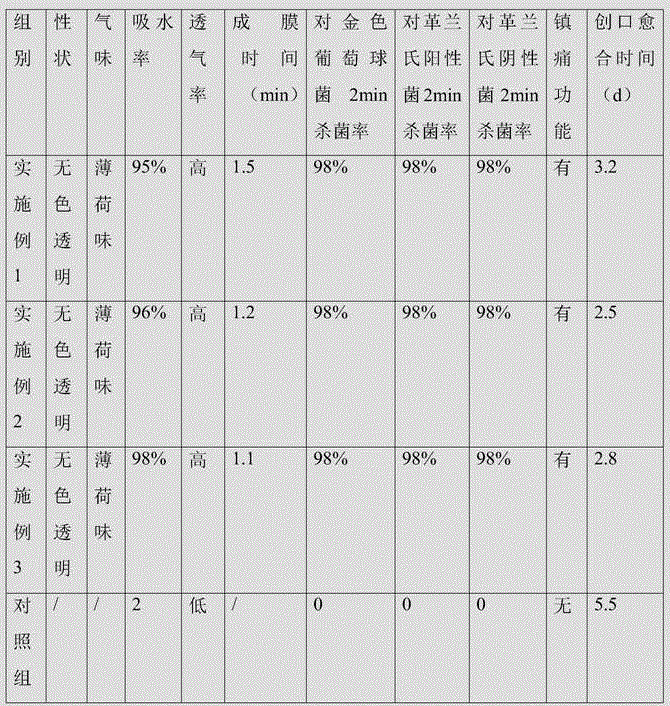

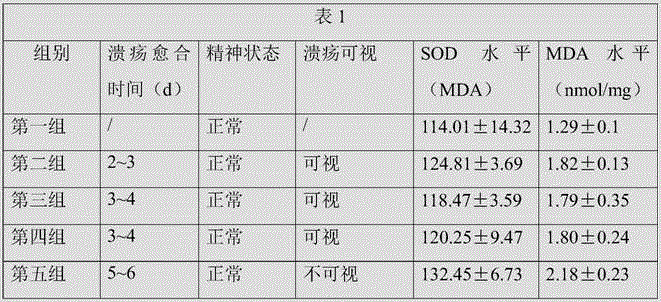

Multifunctional liquid dressing and preparation method thereof

InactiveCN106139239AGood for growth and angiogenesisPromote wound healingSurgical adhesivesBandagesCarrageenanChemistry

The invention relates to the field of medicinal dressings and in particular relates to a multifunctional liquid dressing and a preparation method thereof. The multifunctional liquid dressing comprises the following components in parts by mass: 2-8 parts of polyvinyl butyral, 0.5-0.8 part of sodium alginate-polyvinylpyrrolidone, 0.2-0.6 part of nano-silver-chitosan, 0.1-0.4 part of sodium carboxymethylcellulose, 0.1-0.4 part of carrageenan, 0.1-0.4 part of menthol and 91-97 parts of absolute ethyl alcohol. The multifunctional liquid dressing disclosed by the invention is waterproof, breathable and visible in wound, can prevent infection and contributes to wound healing.

Owner:怡越医疗(广东)有限公司

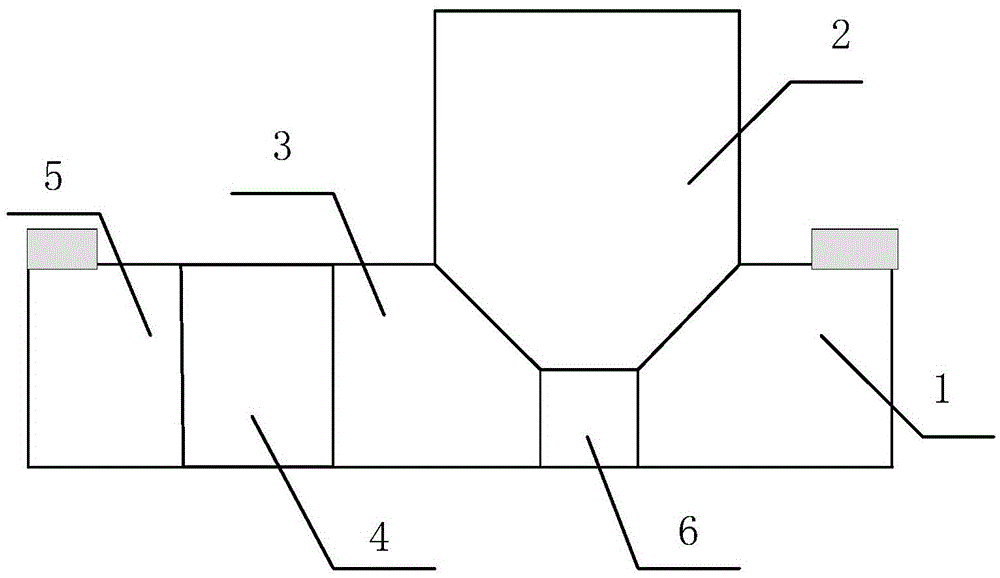

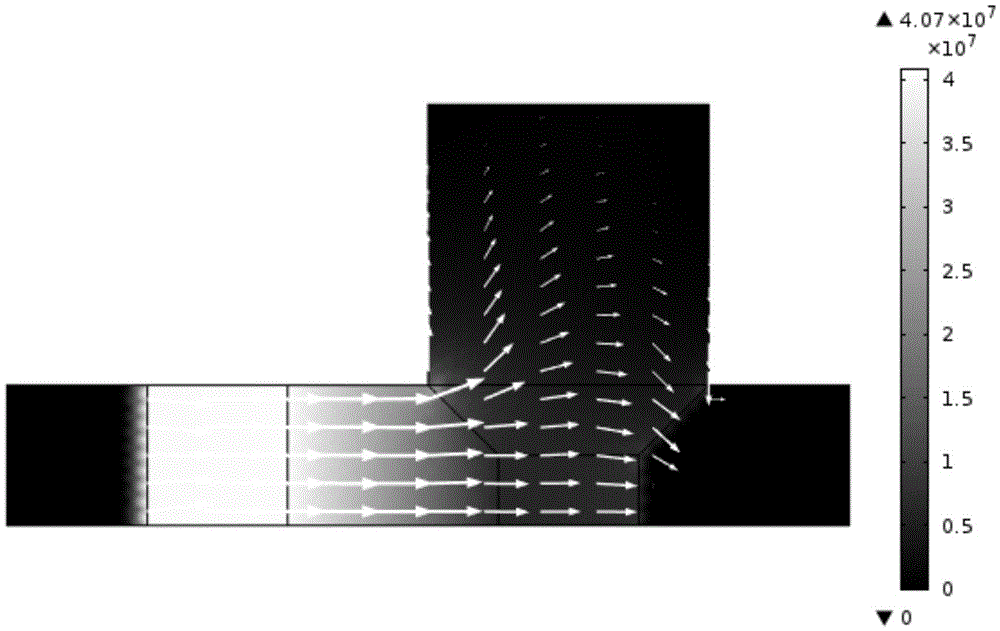

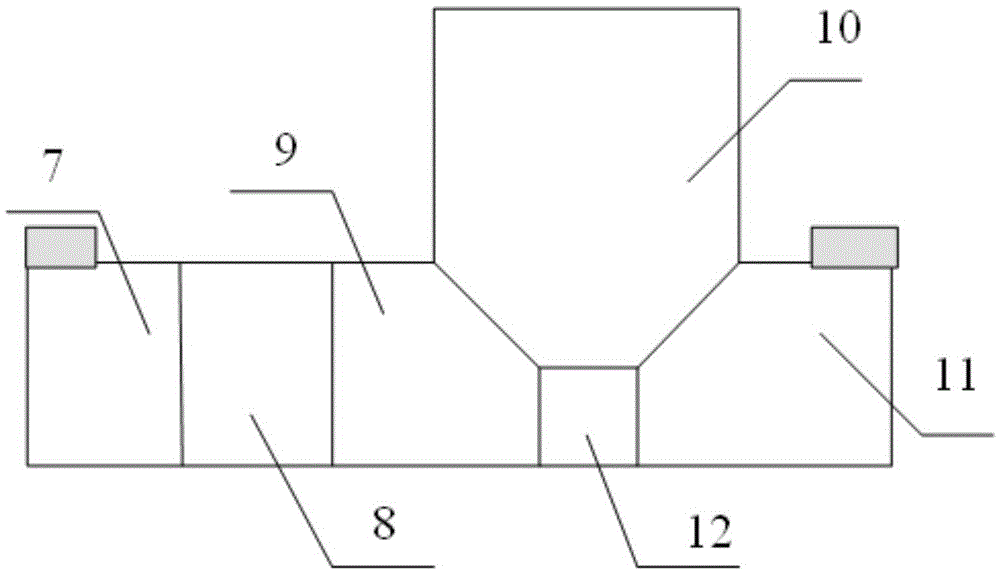

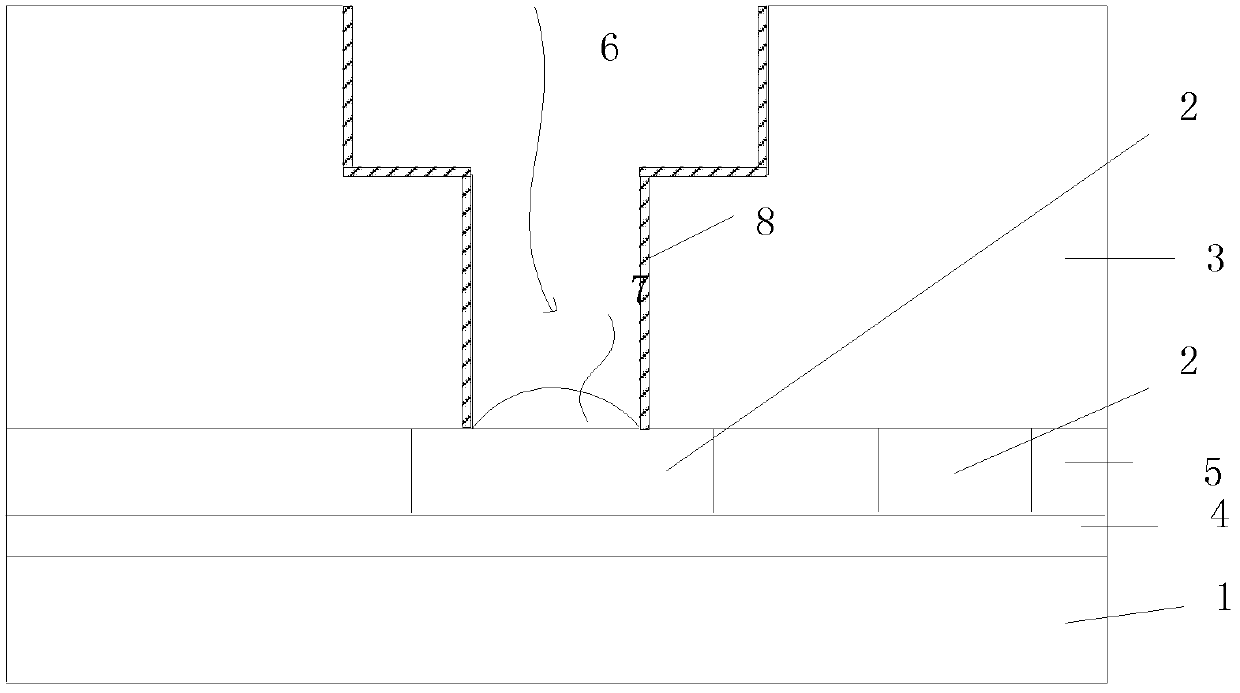

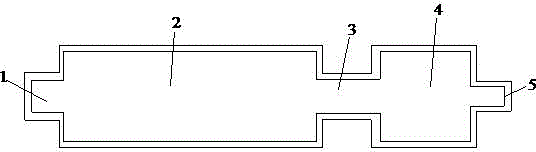

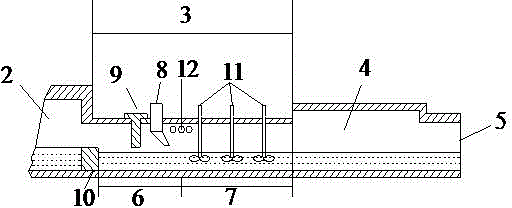

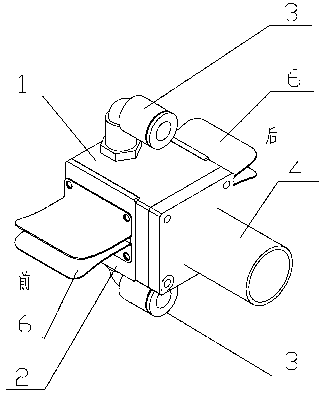

Melting furnace for producing float glass and colorant addition method

The invention relates to a melting furnace for producing float glass and a colorant addition method, belonging to the technical field of glass production. According to the invention, a neck (3) is used as a charging and mixing part; and coloring materials are added into molten glass via a charging channel (8) arranged at the charging area (6) of the neck. Since the melting furnace is filled with colorless basic molten glass, the operation of coloring is performed at the neck, thereby reducing displacement amount of the molten glass and effectively shortening changing time of the molten glass; and the method enables large-size melting furnaces to adapt to features of color glass demand market, and the features of the color glass demand market include demands for various varieties and little demand for a single variety.

Owner:CHINA LUOYANG FLOAT GLASS GROUP

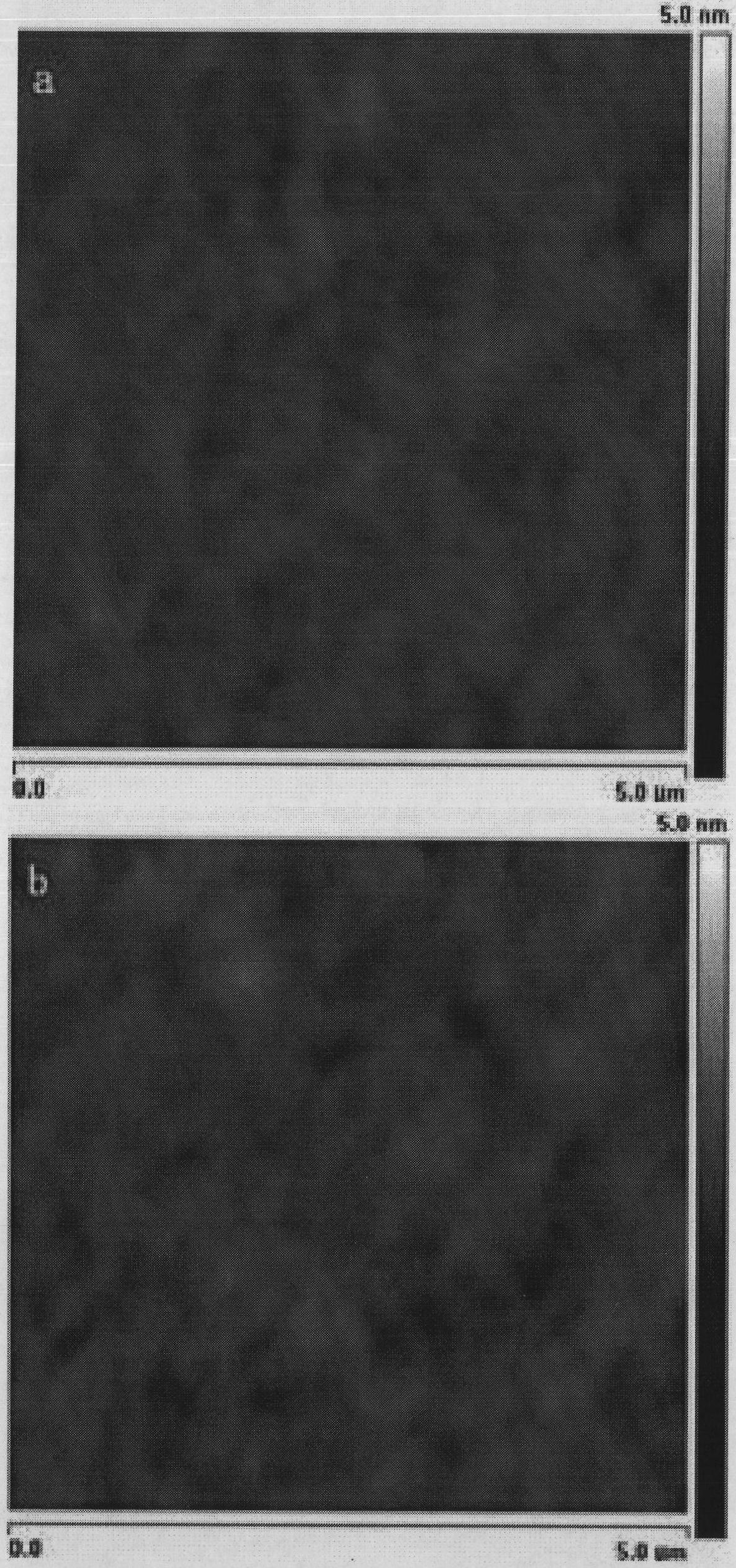

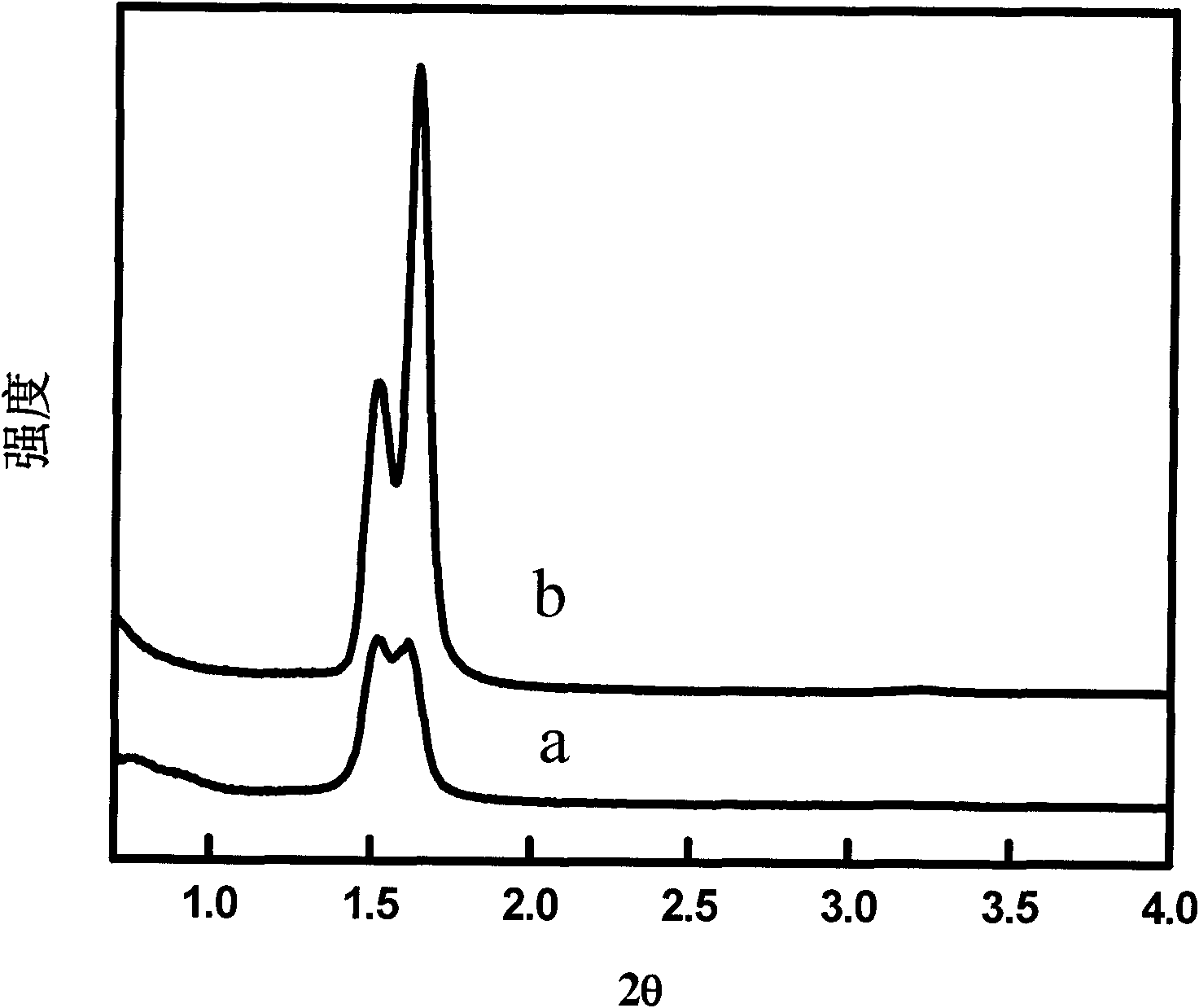

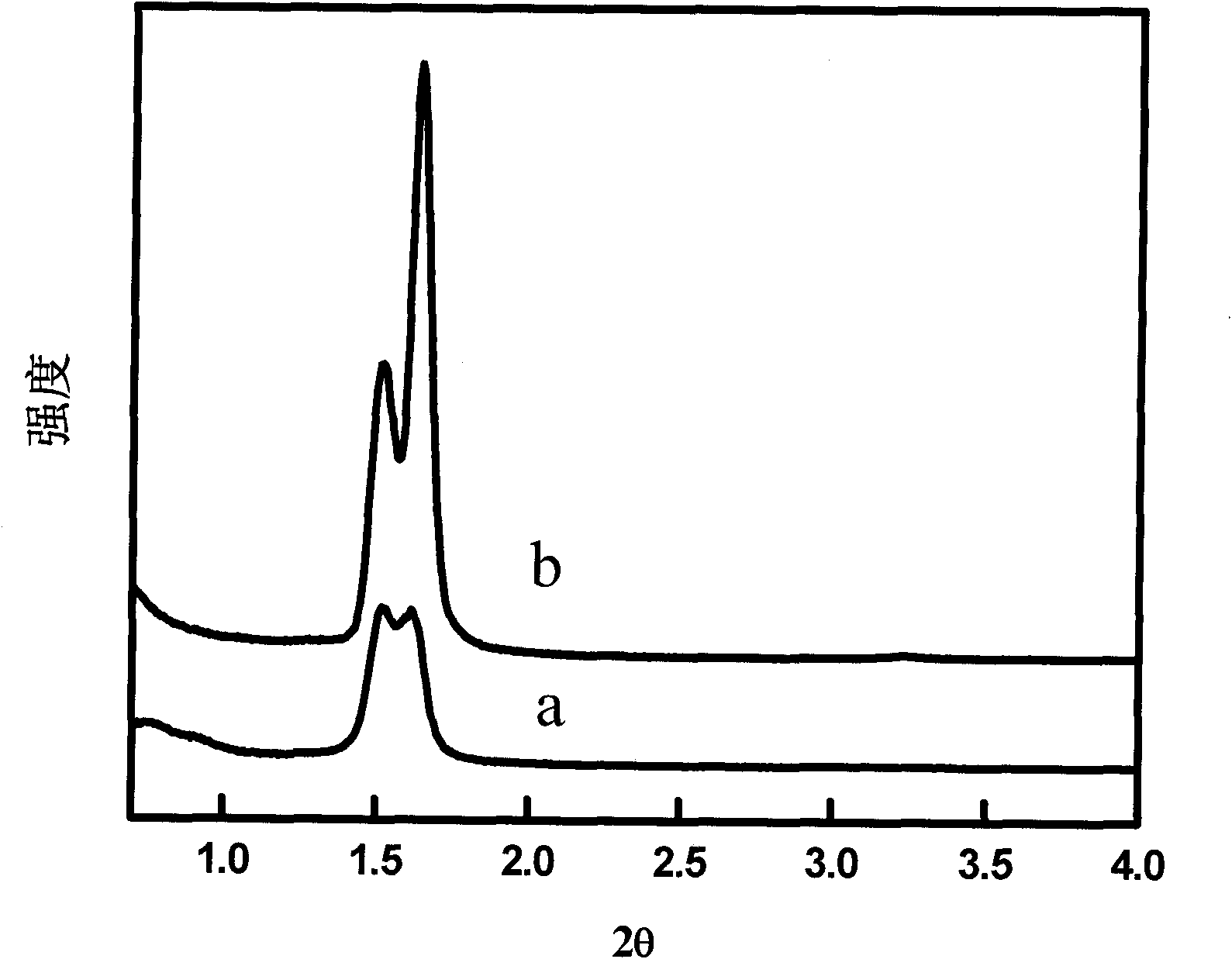

Porous ultra-low dielectric constant material film and preparation method thereof

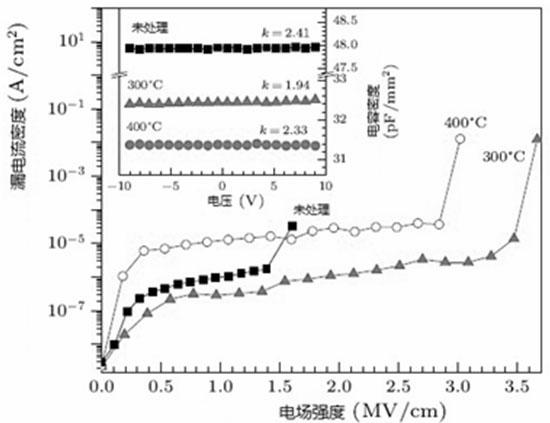

InactiveCN101789418AReduce roughnessLow dielectric constantSemiconductor/solid-state device detailsSolid-state devicesLeakage current densityThermal stability

The invention belongs to the technical field of integrated circuit manufacture, in particular to a porous ultra-low dielectric constant material film and a preparation method thereof. The preparation procedures of the invention are as follows: using the sol-gel process, taking organo-siloxane as a precursor, and preparing the porous ultra-low dielectric constant material by controlling the ratio of the precursor to a pore forming agent, a catalyst and a solvent, the solution concentration, and the synthesis, post-treatment and annealing temperatures and the like. The process has simple procedures, and the prepared film has ordered nano-pores, even surface, low roughness and good thermal stability, the dielectric constant is 1.9-2.0, and the leakage current density is from10-8 to10-9A / cm<2>order of magnitude at 1MV / cm.

Owner:FUDAN UNIV

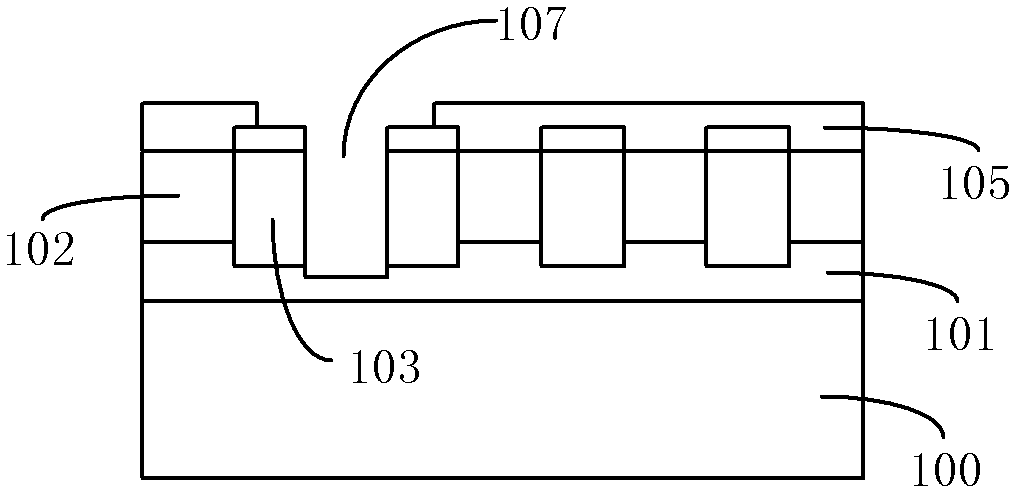

Semiconductor device with dual-mosaic structure and forming method thereof

ActiveCN101740475AGuaranteed forming qualityLower the K valueSemiconductor/solid-state device detailsSolid-state devicesEtchingProcess conditions

The invention discloses a method for forming a semiconductor device with a dual-mosaic structure, which comprises the following steps of: providing a substrate; forming a first dielectric layer on the substrate; forming a through hole pattern on the first dielectric layer; forming an opening of a through hole; detecting the remaining thickness of the first dielectric layer which remains at the bottom of the opening of the through hole; forming a second dielectric layer on the first dielectric layer and in the opening of the through hole; forming a trench pattern on second dielectric layer; forming a trench; removing the second dielectric layer; adjusting process conditions of the third etching according to the remaining thickness; performing the third etching to remove the first dielectric layer which remains at the bottom of the opening of the through hole; and forming the dual-mosaic structure. The invention also discloses the semiconductor device with the dual-mosaic structure. The semiconductor device with the dual-mosaic structure and the forming method thereof of the invention form high-quality dual-mosaic structure below a stop layer without etching and effectively reduce k value of the dual-mosaic structure.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

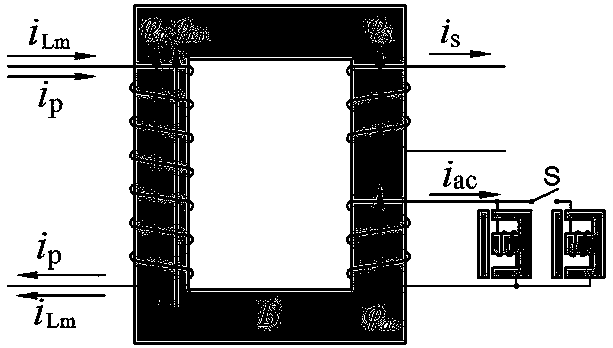

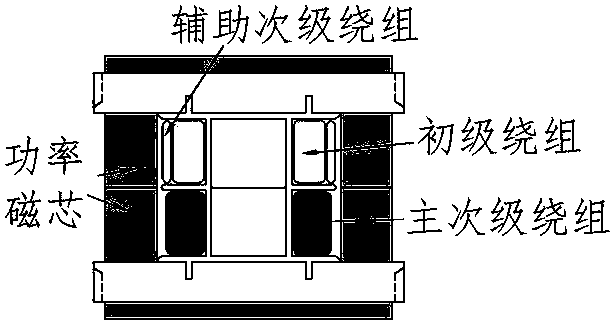

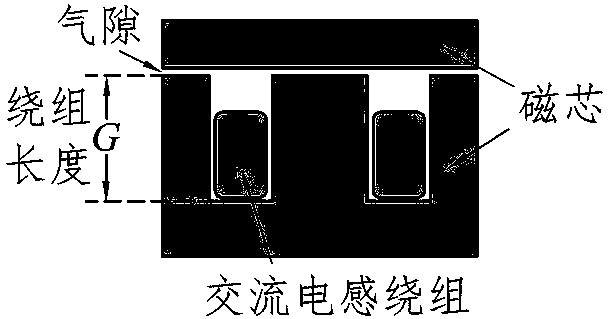

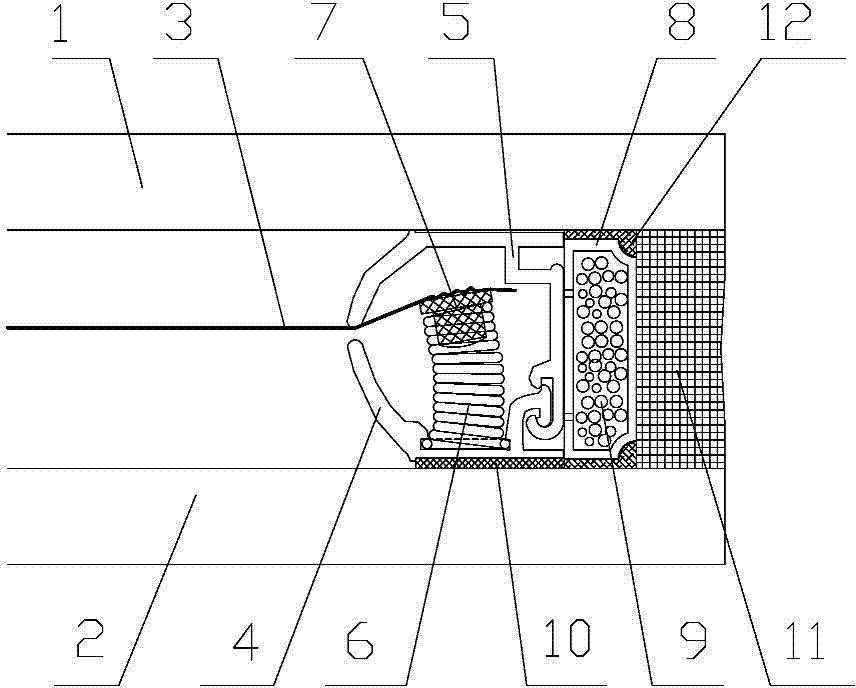

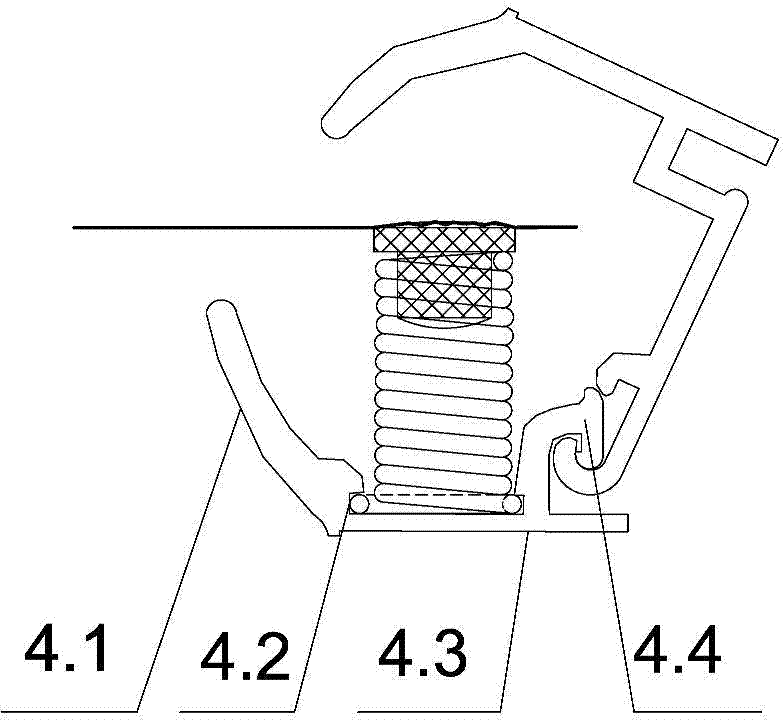

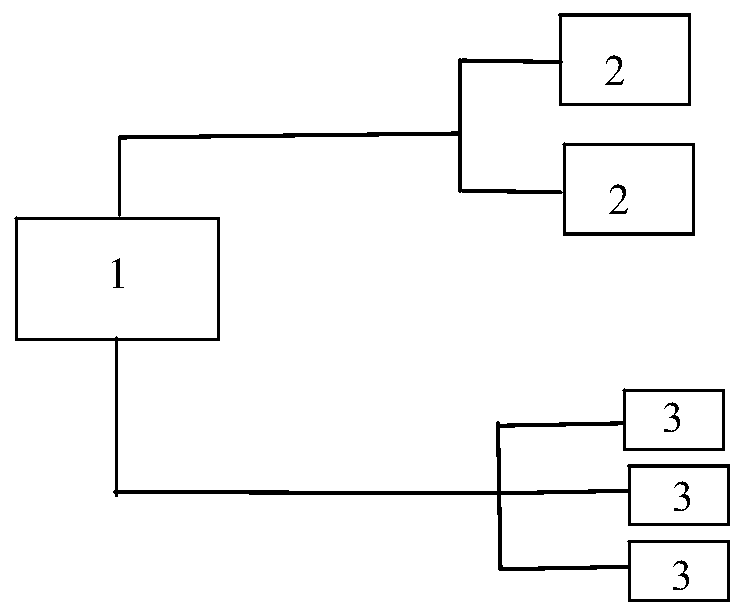

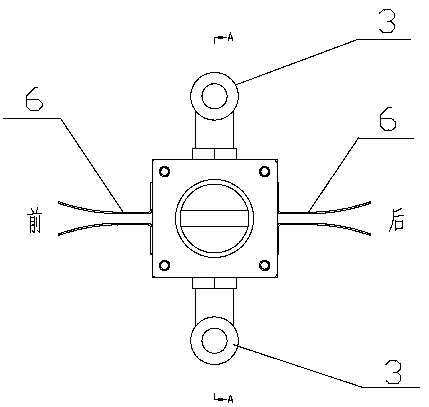

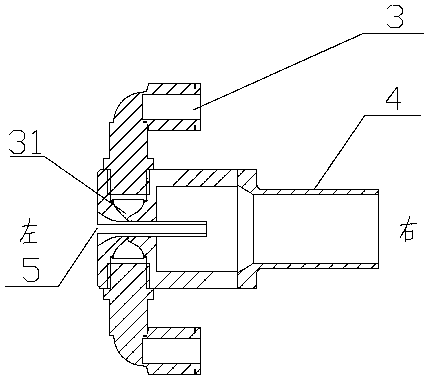

Magnetizing inductance variable LLC resonant transformer

ActiveCN108667300AImprove utilization factorLarge gain adjustment rangeEfficient power electronics conversionTransformers/inductances coils/windings/connectionsEngineeringInductor

The invention discloses a magnetizing inductance variable LLC resonant transformer. The magnetizing inductance variable LLC resonant transformer comprises a primary winding 1, a main secondary winding2, an auxiliary secondary winding 3, a power magnetic core 4, a switch 5, and two alternating current inductors 6 and 7 with air gaps. The two terminals of the alternating current inductor 6 with airgap are respectively connected with the two terminals of the auxiliary secondary winding 3. One terminal of the alternating current inductor 7 with air gap is connected in parallel with the alternating current inductor 6 with air gap through the switch 5. Compared with a traditional LLC transformer, the gain adjustment range of the LLC resonant converter can be wide during heavy load, and the primary loop current is small during light load, so that the output characteristic and light load efficiency of the LLC resonant converter are effectively improved.

Owner:HUNAN INSTITUTE OF ENGINEERING

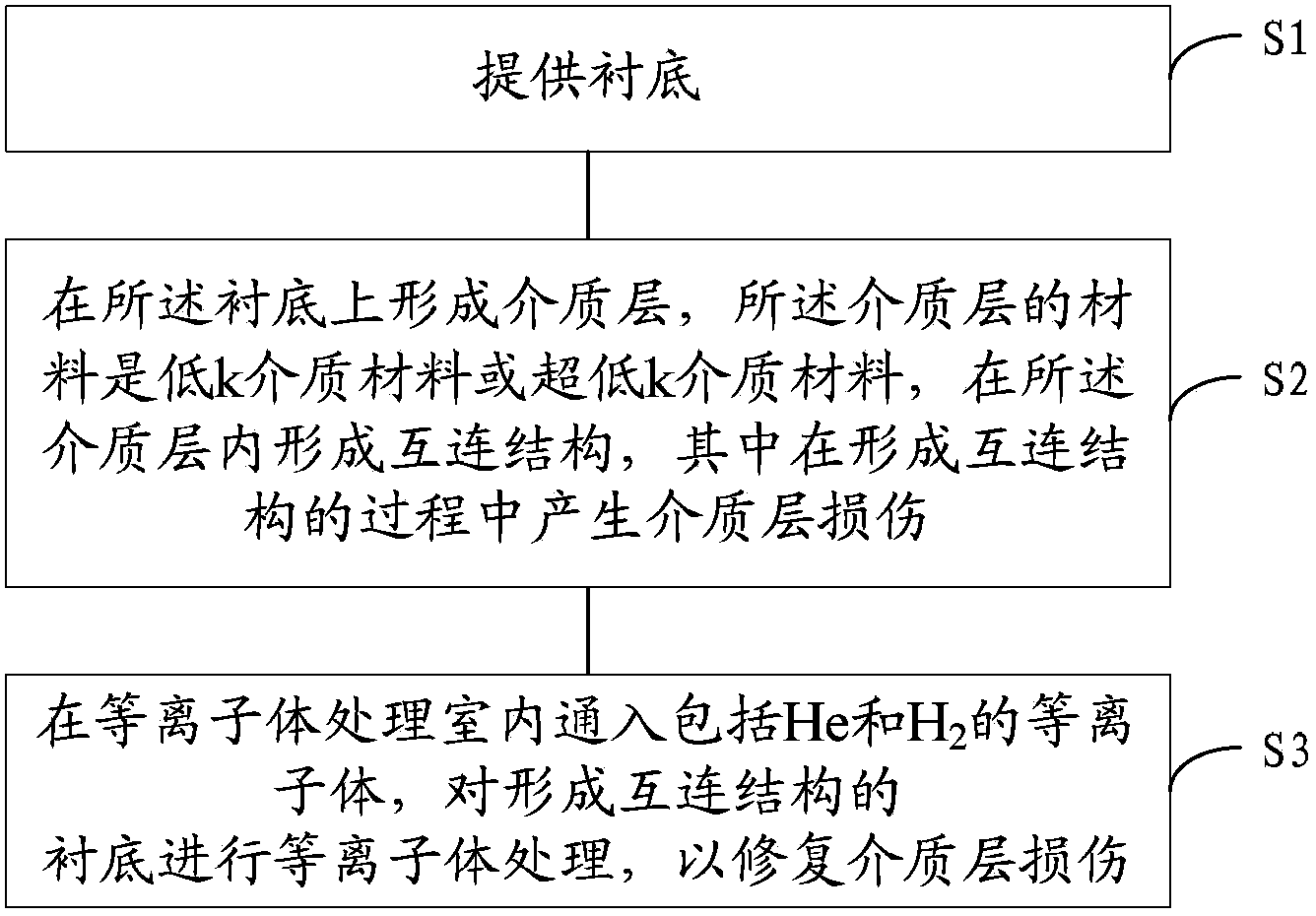

Method for repairing damaged dielectric layer

InactiveCN103474342ARepair damageHigh porositySemiconductor/solid-state device manufacturingPorosityInterconnection

A method for repairing a damaged dielectric layer comprises the following steps: a substrate is provided; a dielectric layer which is a low-k dielectric material or ultralow-k dielectric material is formed on the substrate, and an interconnection structure is formed inside the dielectric layer, wherein the dielectric layer is damaged during the interconnection structure forming process; and plasmas including He and H2 are blown into a plasma processing room, and plasma processing is carried out on the substrate with the formed interconnection structure so as to repair the damaged dielectric layer. According to the invention, the low-k damaged dielectric layer undergoes plasma (He, H2, etc.) processing. Thus, porosity of the dielectric material can be raised, k value of the dielectric material is reduced, and the damaged dielectric layer is repaired so as to reduce RC delay.

Owner:SEMICON MFG INT (SHANGHAI) CORP

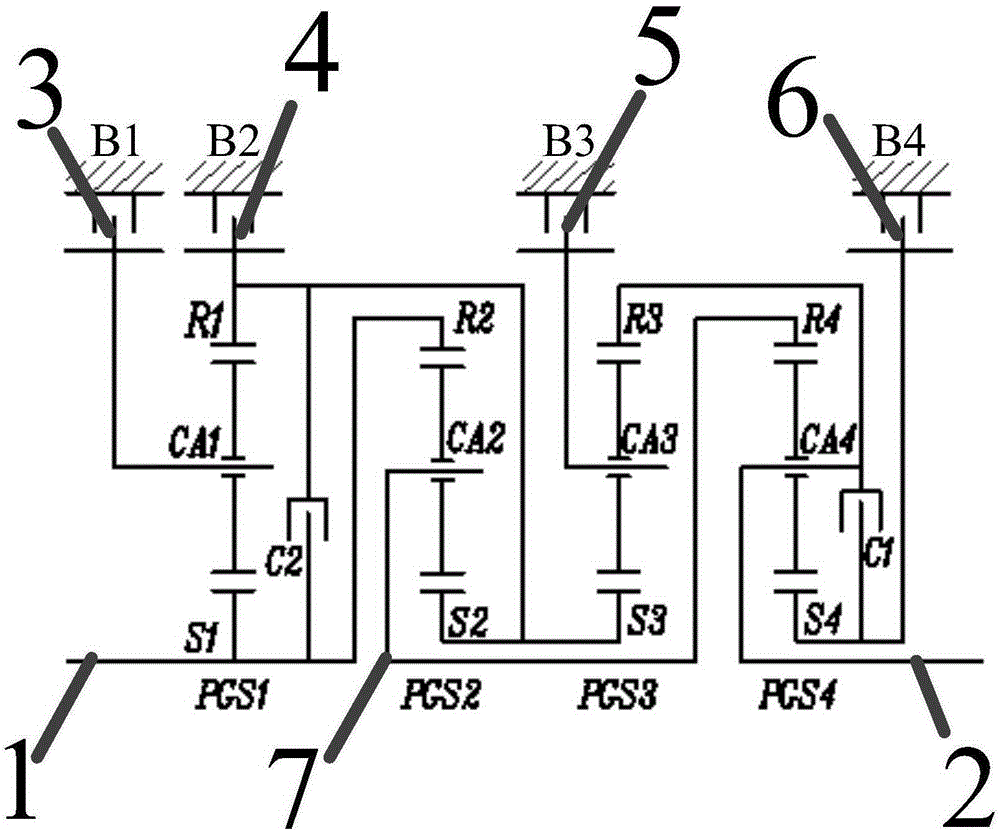

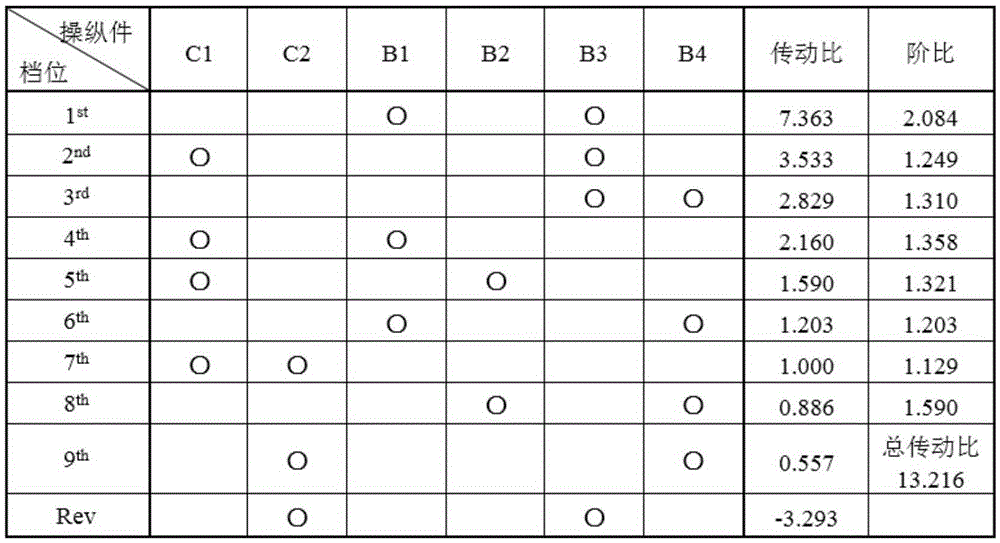

Nine-stage transmission

ActiveCN105299157AImprove fuel economyReduce radial sizeToothed gearingsGearing controlEngineeringClutch

The invention provides a nine-stage transmission which comprises planet rows, an input component, an output component, transmission components, brakes and clutches. The input component and the output component are arranged at the two ends and connected with a corresponding input shaft and a corresponding output shaft respectively. The planet rows comprise the planet row PGS1, the planet row PGS2, the planet row PGS3 and the planet row PGS4. The transmission components comprise the transmission component (3), the transmission component (4), the transmission component (5), the transmission component (6) and the transmission component (7). The brakes comprise the brake B1, the brake B2, the brake B3 and the brake B4. The clutches comprise the clutch C1 and the clutch C2. The transmission has the beneficial effects of having multiple gears and being good in fuel economical efficiency, small in size and light.

Owner:CHINA NORTH VEHICLE RES INST

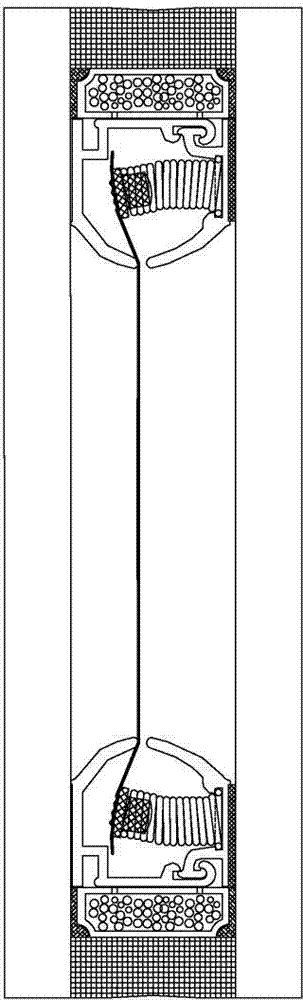

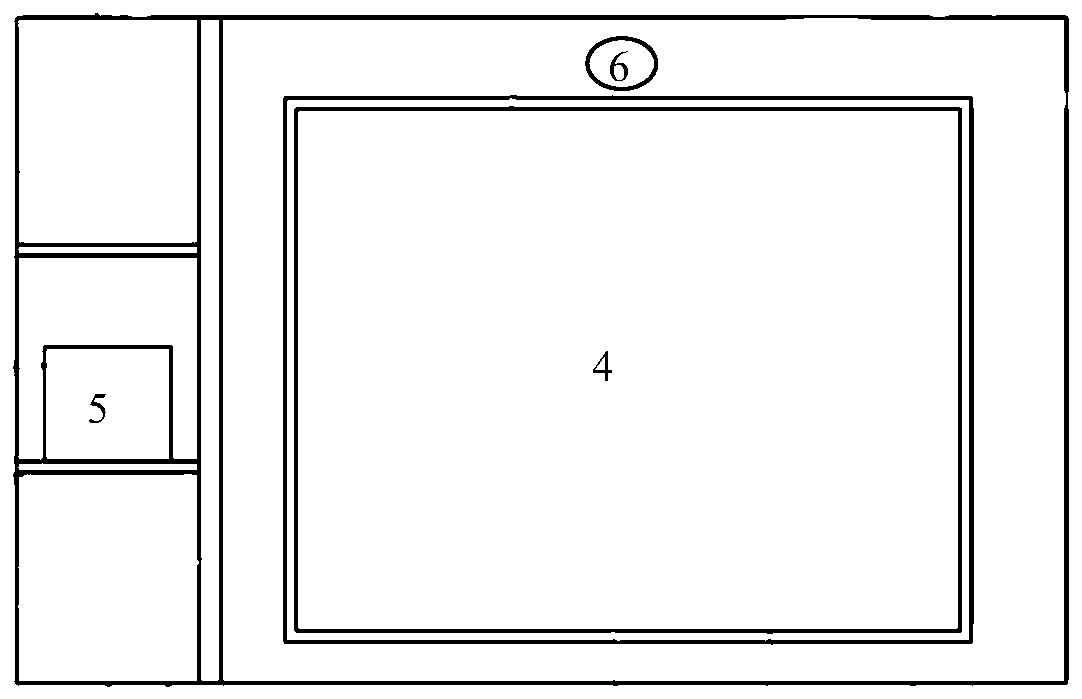

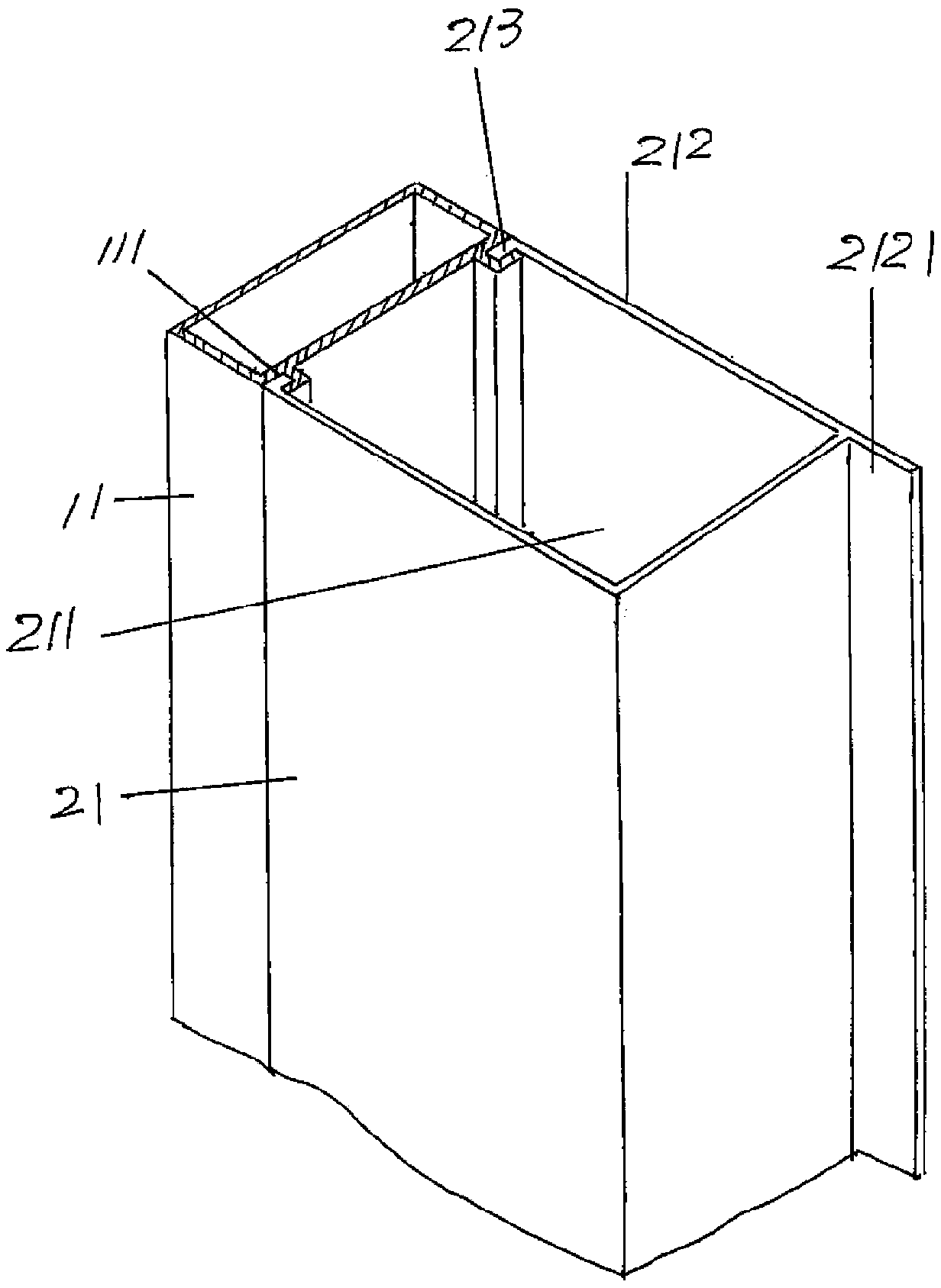

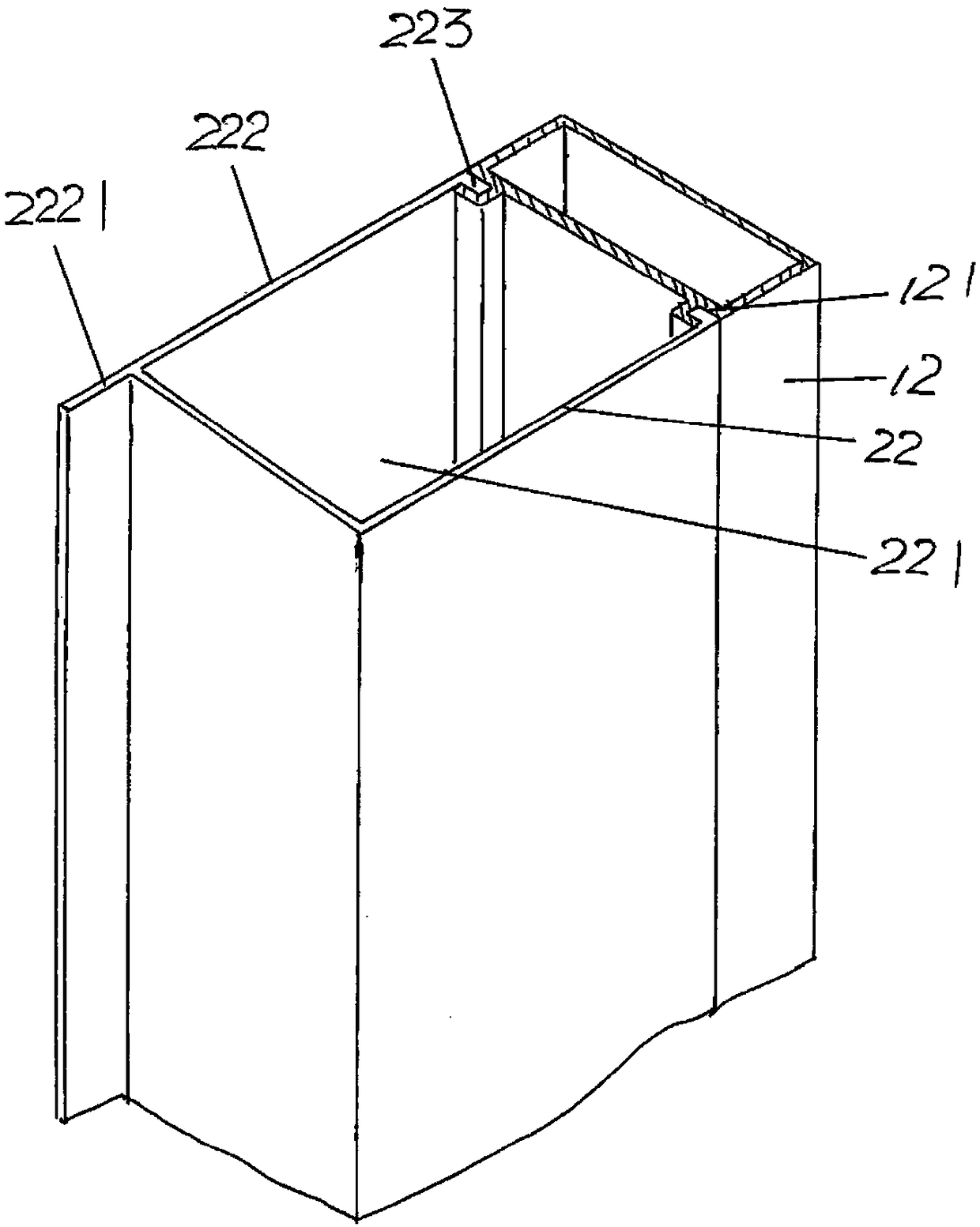

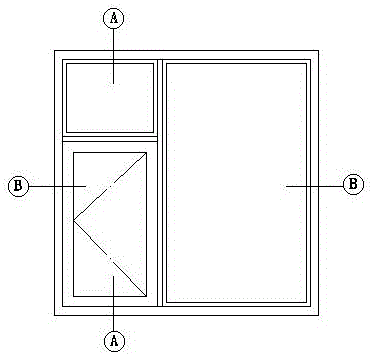

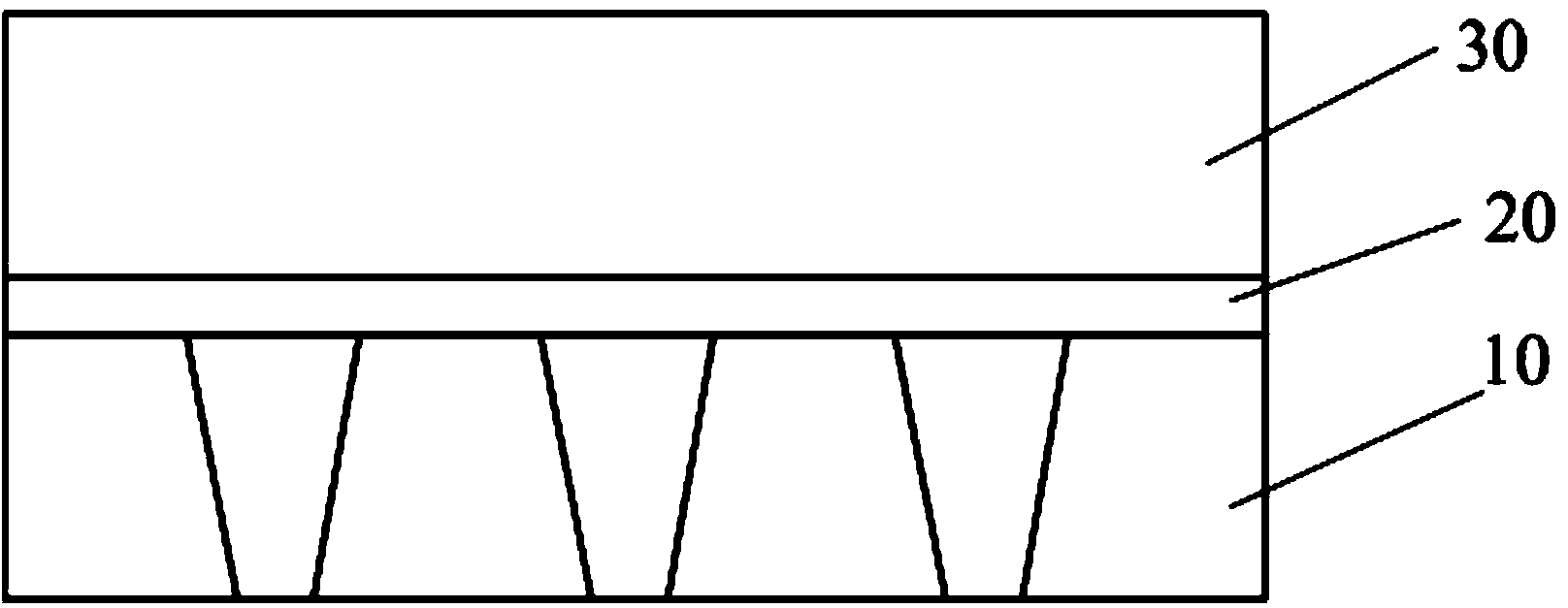

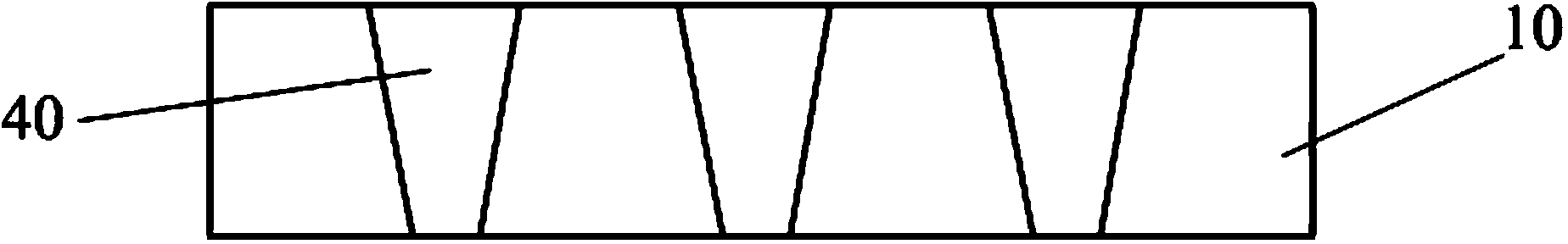

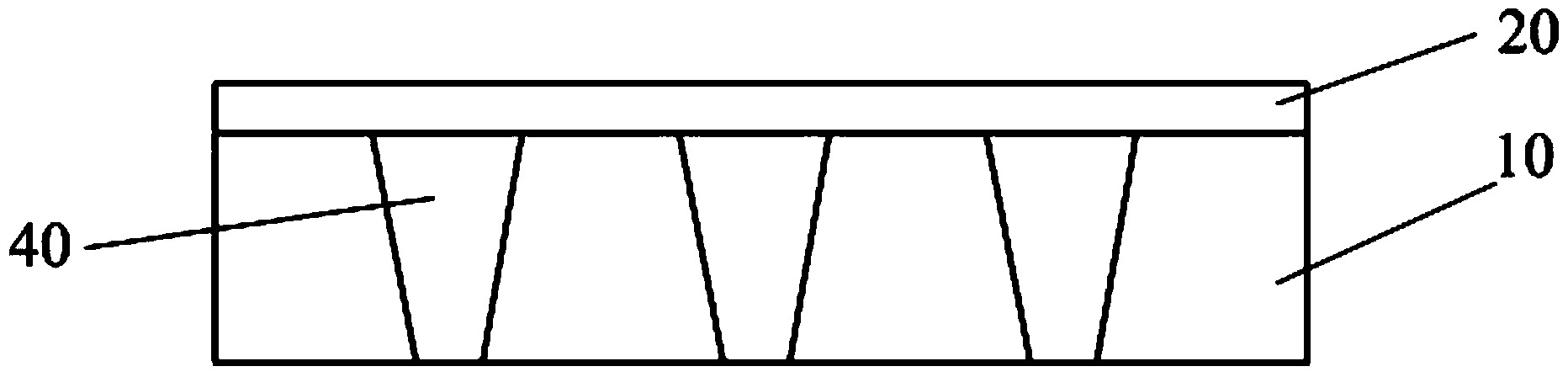

Inner suspension film hollow glass

ActiveCN103498624AGuaranteed thermal deformation effectGuaranteed stabilityWallsUnits with parallel planesPolymer scienceFixed frame

The invention relates to inner suspension film suspension glass. A middle layer formed by an inner suspension film combined frame and an optical plastic film fixed by the inner suspension film combined frame is additionally arranged in an inner cavity of standard hollow glass. The inner suspension film combined frame fixed at the periphery of the inner surface of one side of the glass is composed of a fixing frame and pressing frame, wherein the a spring assembly is previously arranged in the fixing frame to fix the optical plastic film in a welding mode, the pressing frame is buckled with the fixing frame in a lock catch hinge mode to press downwards the optical plastic film fixed on the spring assembly to enable the film to be tensioned, the spring assembly can bend and deform to generate elastic force, and the generated elastic force can enable the film to keep required tension to be adaptive to strain caused by environmental change in use and keep the surface of the film flat all the time. The glass where the inner suspension film middle layer is additionally arranged is of a double hollow structure, the increasing of the total weight of the glass can be ignored, and a packing structure of the glass can completely meet the manufacturing standard of hollow glass.

Owner:伟视幕墙(淮安)有限公司

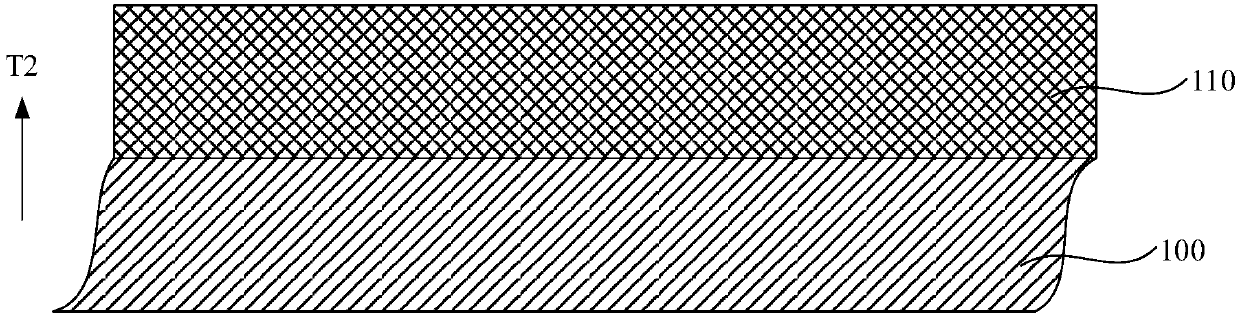

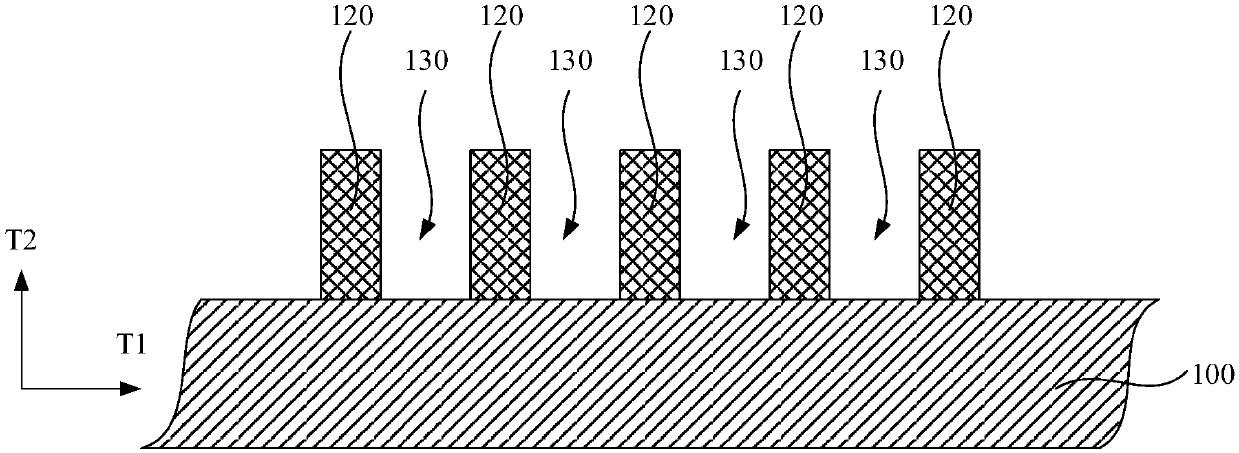

Internal connection structure of semiconductor device and manufacturing method of internal connection structure

PendingCN107895711ALower the K valueEffective isolationSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

The invention provides an internal connection structure of a semiconductor device and a manufacturing method of the internal connection structure. The manufacturing method includes the steps of forming a first medium layer on the substrate structure and covering a first layer interconnecting wire in the process of forming the inner connecting layer, wherein the first medium layer is attached to the side wall of the first layer interconnecting wire and grows in the direction away from the side wall of the first layer interconnecting wire to partially fill the interval region in a non-filling mode, so that a first air gap is formed in the first medium layer in the interval region, and the first air gap is sealed in the first medium layer; opening the first air gap to form a plurality of opengrooves between the first layer interconnecting wires, and expanding the space size of the grooves; forming a second medium layer on the first medium layer, covering the upper notch of the grooves bythe second medium layer to seal the open slot to form a second air gap, wherein the space enclosed by the second air gap is larger than the space enclosed by the first air gap, so that an air gap with a larger size can be formed between every two adjacent interconnecting wires to realize effective and reliable isolation between the interconnecting wires.

Owner:CHANGXIN MEMORY TECH INC

Campus bullying behavior early warning system and method based on artificial intelligence technology

InactiveCN110348754ALower the K valueIncrease K valueResourcesArtificial Intelligence SystemIntelligence analysis

The invention discloses a campus bulwark behavior early warning system and method based on an artificial intelligence technology. The system comprises a processor, a student terminal and a teacher terminal. The processor is used for executing calculation and artificial intelligence analysis; the student terminal is used for students to carry out bulking alarm, the teacher terminal is used for teachers to receive information sent by the processor and carry out subsequent processing according to the sent information, the processor comprises a memory, a basic database is stored in the memory, andthe basic database comprises information of all students. The system can be used for carrying out accurate bulking early warning.

Owner:郭俊雄

Ultra-low dielectric constant material film and preparation method thereof

InactiveCN102157439AWill not cause volatilizationSimple processSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit manufacturingUltraviolet lights

The invention belongs to the technical field of super-large-scale integrated circuit manufacturing, and in particular relates to an ultra-low dielectric constant material film and a preparation method thereof. The preparation method comprises the following steps of: first, taking a single annular 2,4,6,8-tetravinyl-2, 4, 6, 8-tetravinylcyclotetrasiloxane as a precursor; then, forming a precursor film on a silicon substrate by a spin-coating method; next, irradiating the obtained film by using ultraviolet light; later on, performing polyreaction among precursor monomers to form an ultra-low dielectric constant SiOCH film; and finally, performing thermal annealing treatment on the film to further improve the electrical characteristics of the SiOCH film. In the SiOCH film obtained by adopting the method, the dielectric constant can reach 1.94 and the breakdown electric field intensity is greater than 3 MV / cm; and under the external electric field of 1 MV / cm, the film has the leakage current density magnitude order of 10<-7>A / cm2, the young's modulus of greater than 2 GPa, and the hardness of 0.2 GPa.

Owner:FUDAN UNIV

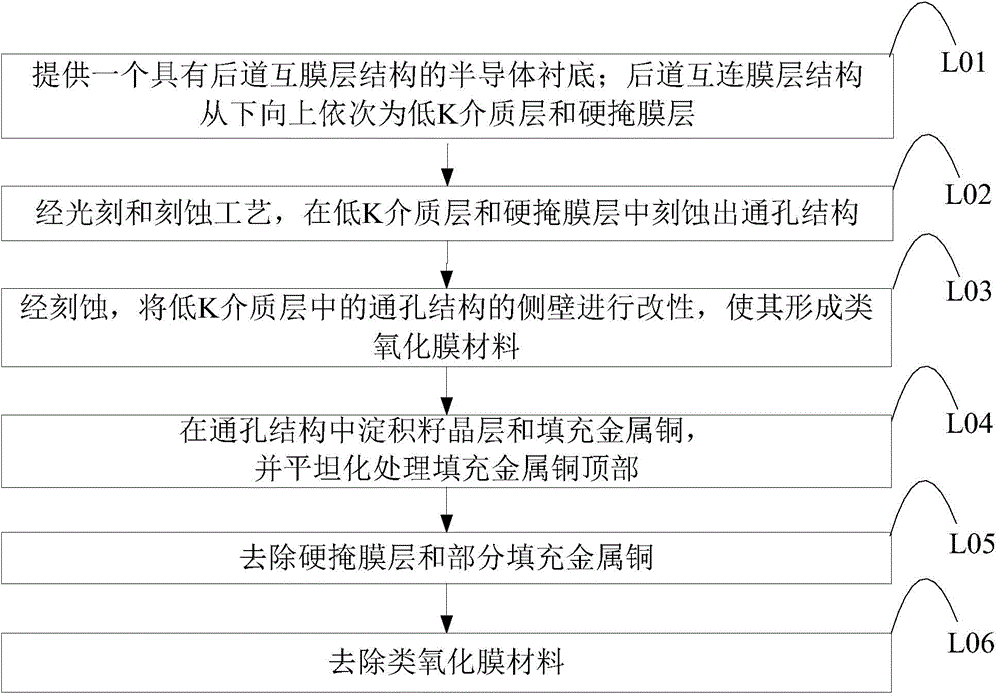

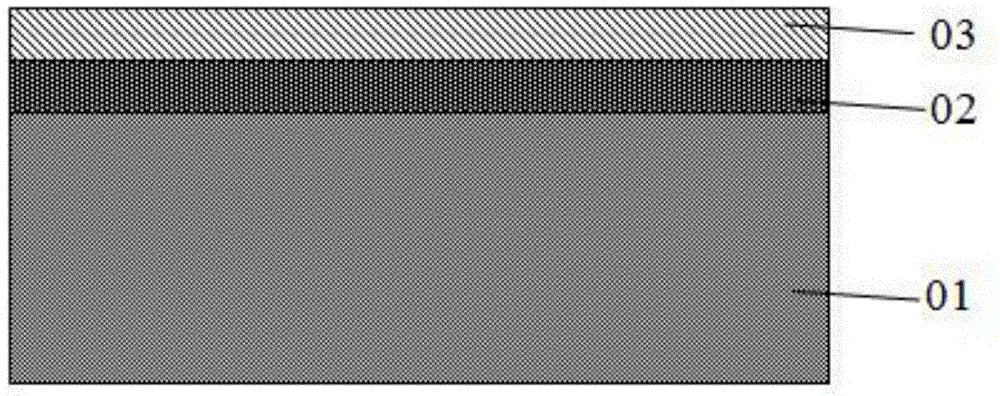

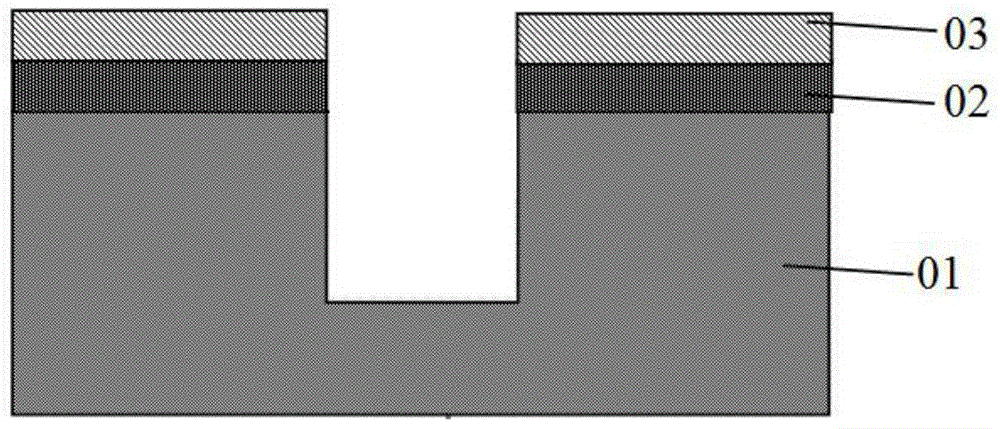

Air gap forming method in back-end-of-line process

ActiveCN104167388AAvoid damageLower the K valueSemiconductor/solid-state device manufacturingSeed crystalLow-k dielectric

The invention provides an air gap forming method in the back-end-of-line process. The method includes the steps that a semiconductor substrate with a back-end-of-line film layer structure is provided; the back-end-of-line film layer structure is sequentially provided with a low-K dielectric layer and a hard mask layer from bottom to top; a through hole structure is respectively etched in the low-K dielectric layer and the hard mask layer through a photoetching process and an etching process; the side wall of the through hole structure in the low-K dielectric layer is modified through etching so as to form class oxidation film type material; the through hole structures are deposited with seed crystal layers and filled with metal copper; the top of the filling metal copper is subjected to planarization; the hard mask layer is subjected to downward reduction; the hard mask layer located at the top of the oxidation film type material is removed, and the top of the oxidation film type material is exposed outside; the oxidation film type material is removed, and the hard mask layer on which reduction has been conducted is removed, so that in the process of removing the oxidation film type material, the low-K dielectric layer is not damaged, damage to the through hole structures is avoided, and the K value of devices prepared in the later processes is further reduced.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

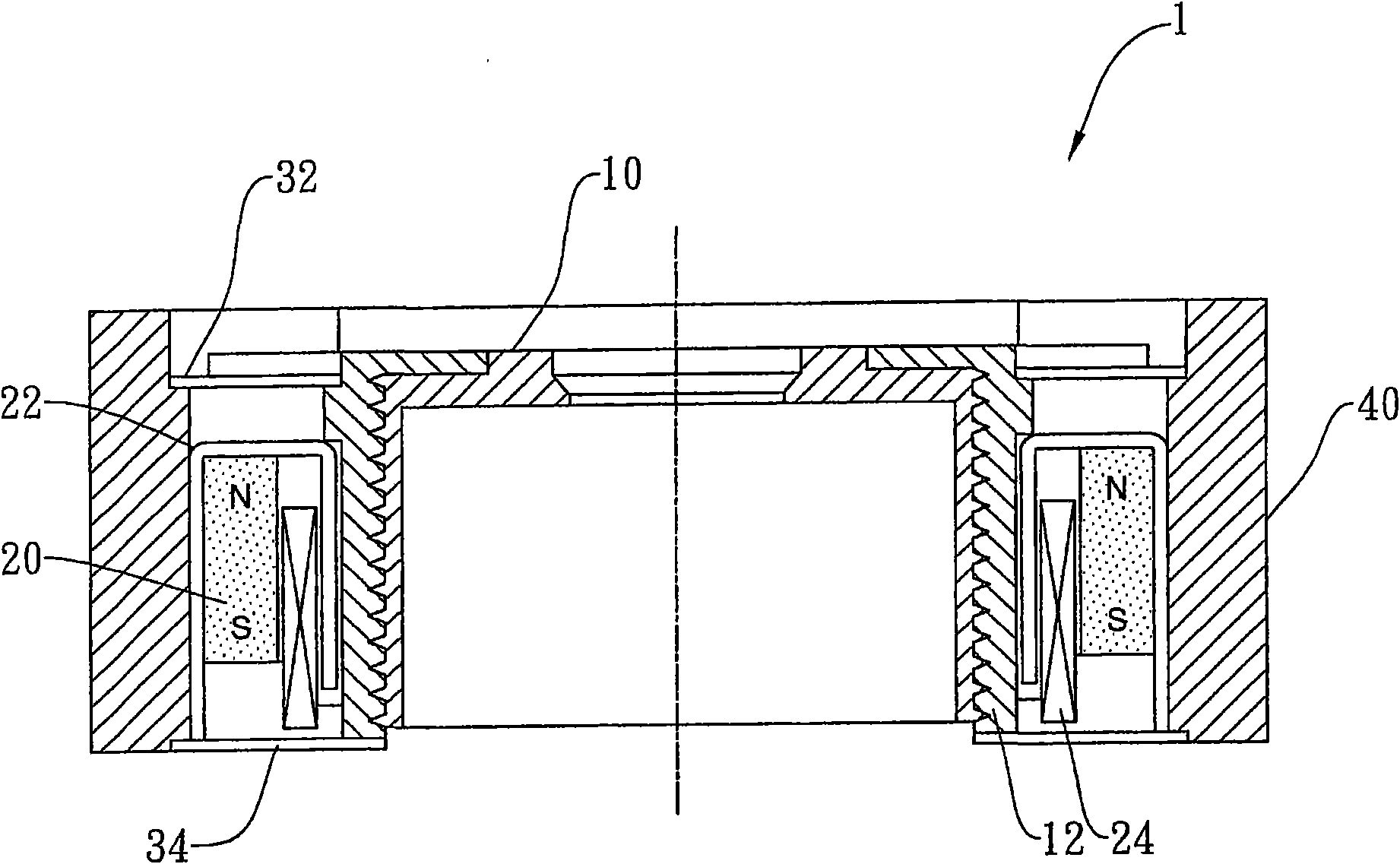

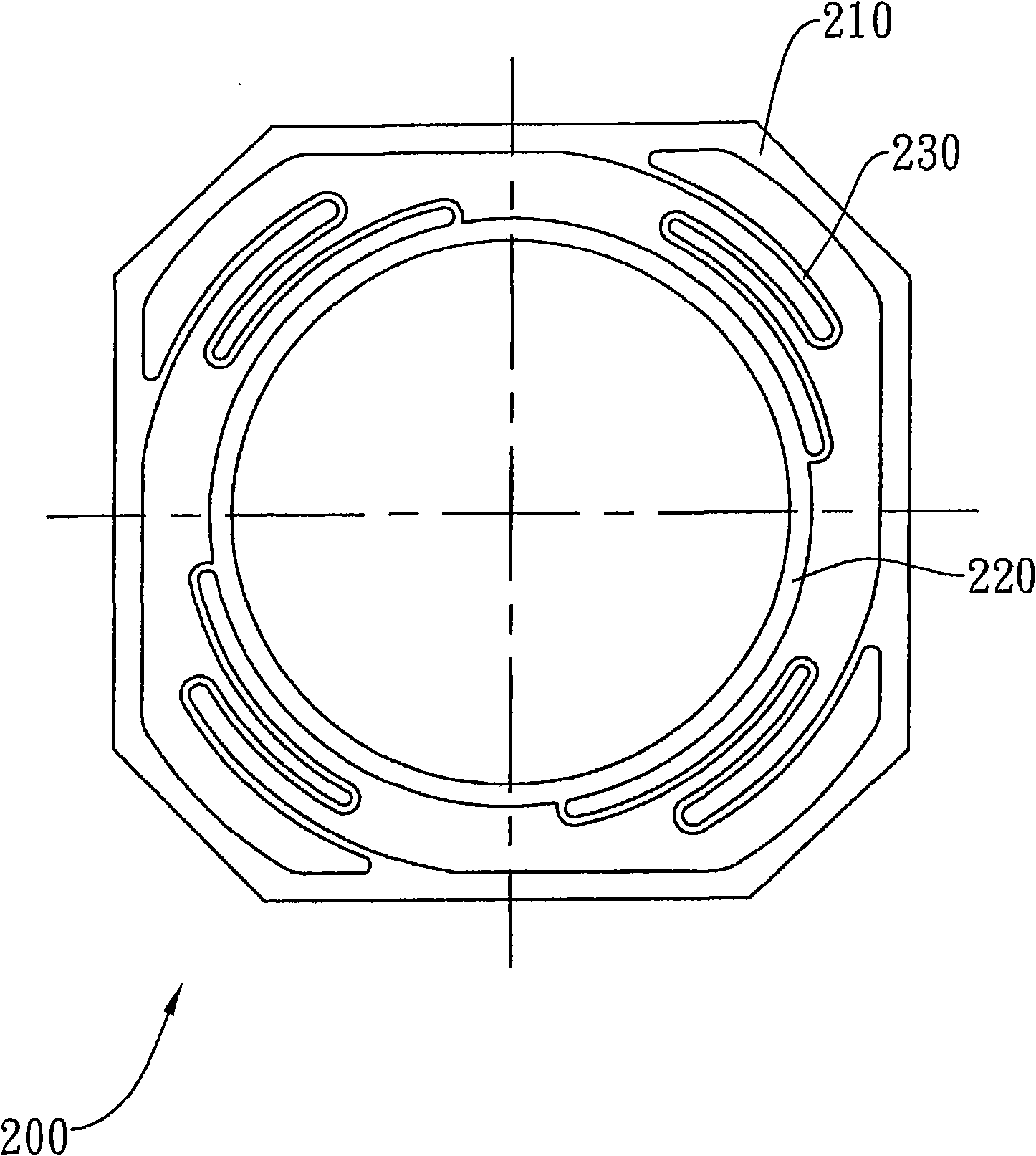

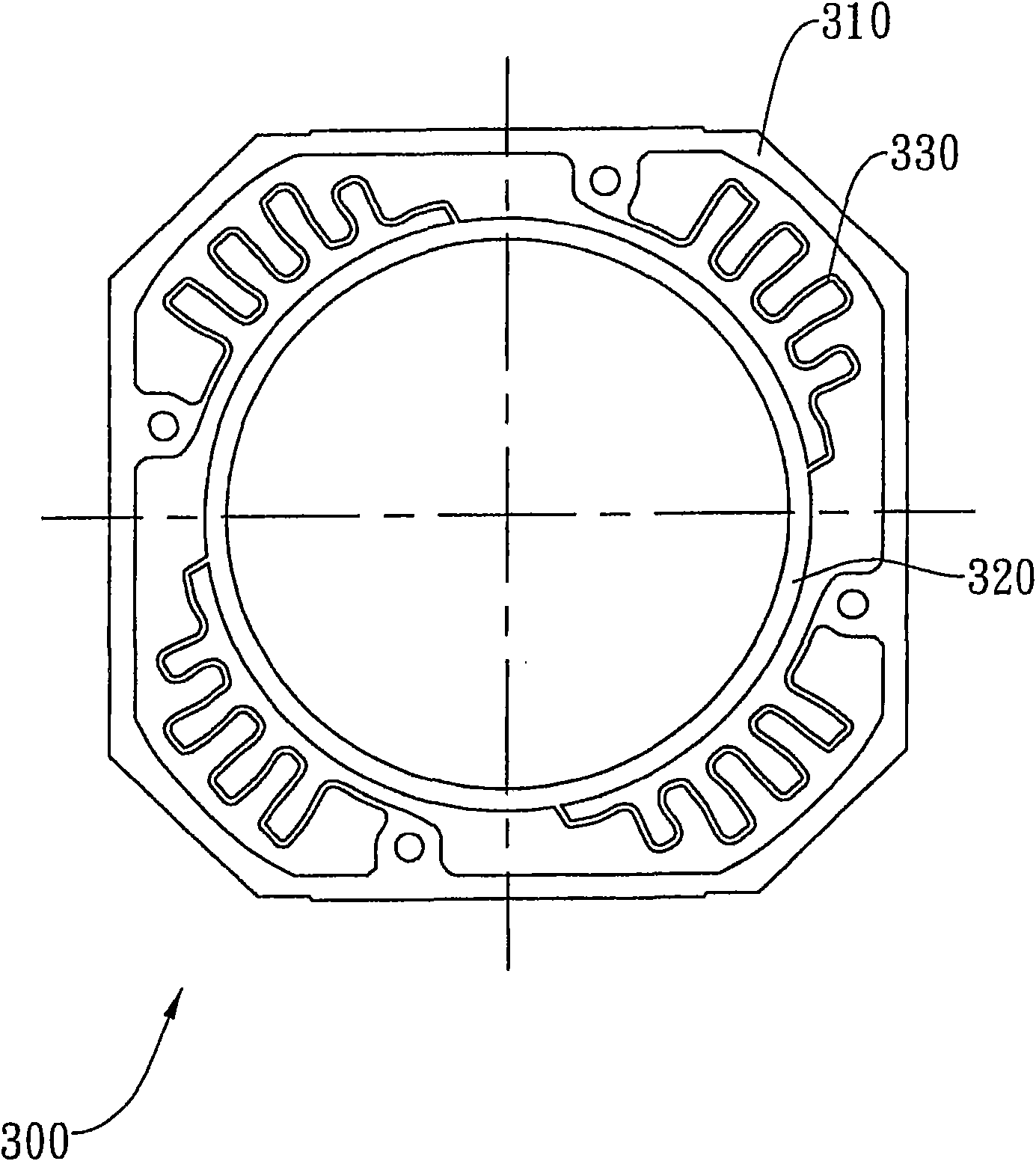

Photography module

The invention provides a photography module which at least comprises a lens, an electric control focusing element, an elastic element, a supporting seat and an optical-sensing element. In the invention, a movable part of the electric control focusing element is electrically driven to lead the lens of a camera module arranged on the movable part to move along an optical axis straight line so as to execute the function of electric control focusing. The elastic element is arranged on the electric control focusing element by the camera module and is equipped with a plurality of elastic force arms; and each elastic force arm is equipped with a plurality of continuous and radial routing bending parts, which can averagely absorb rotating distortion of the lens, plane axial offset and a certain amount of stress accumulated by inclination change, can not cause permanent deformation, can effectively utilize space, increase the length of the force arms, and effectively lower a K value of a spring.

Owner:LARGAN PRECISION

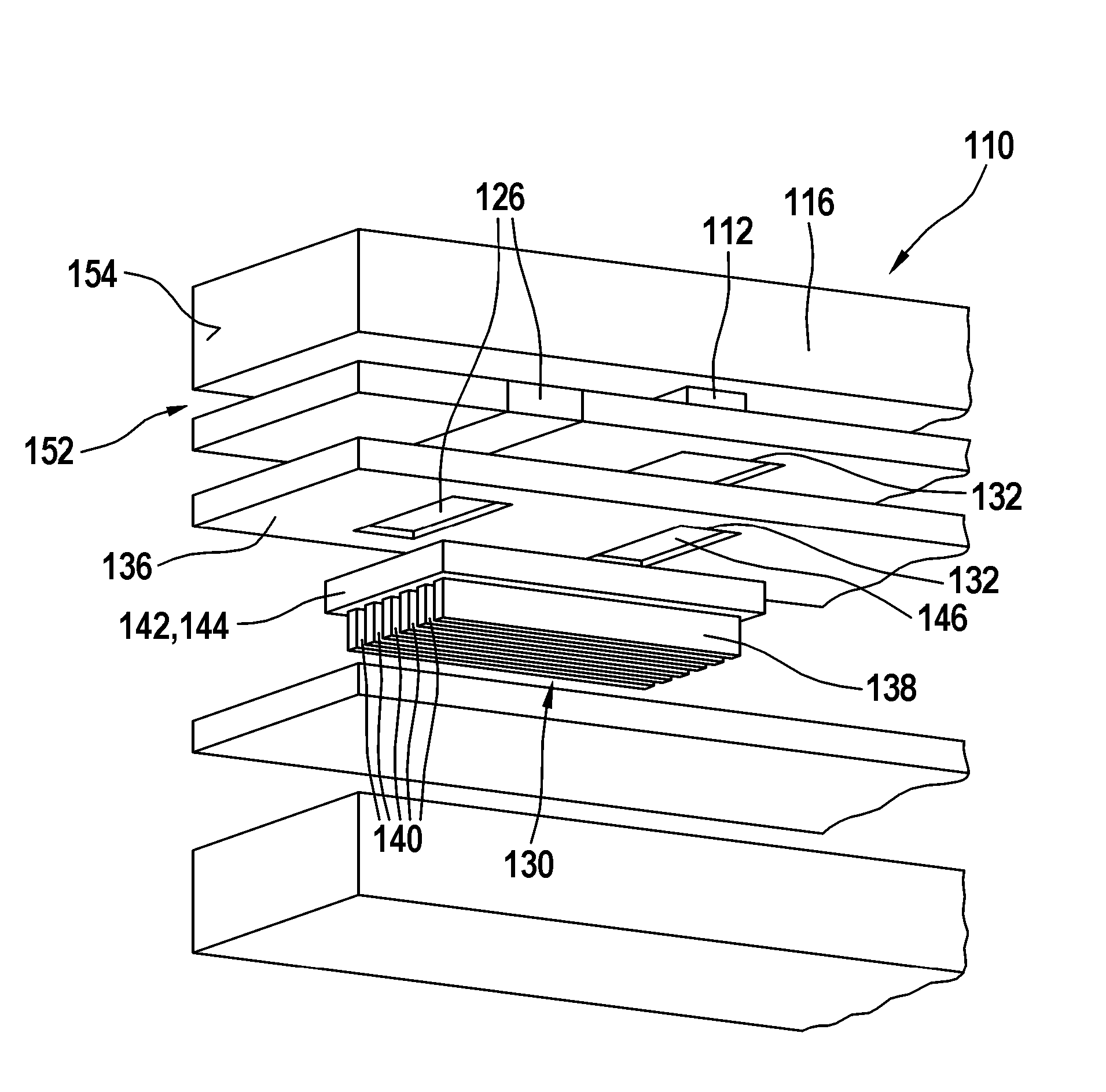

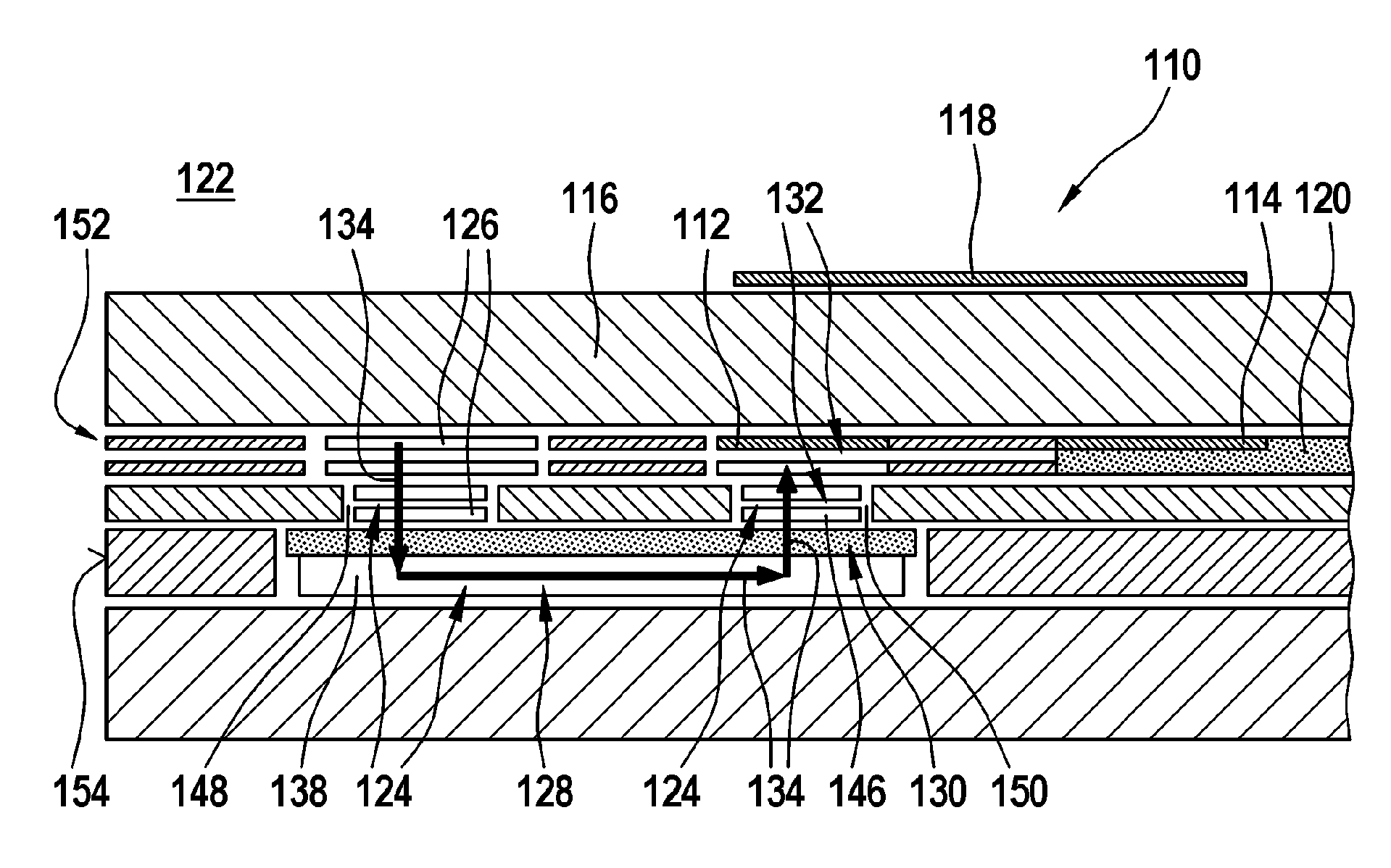

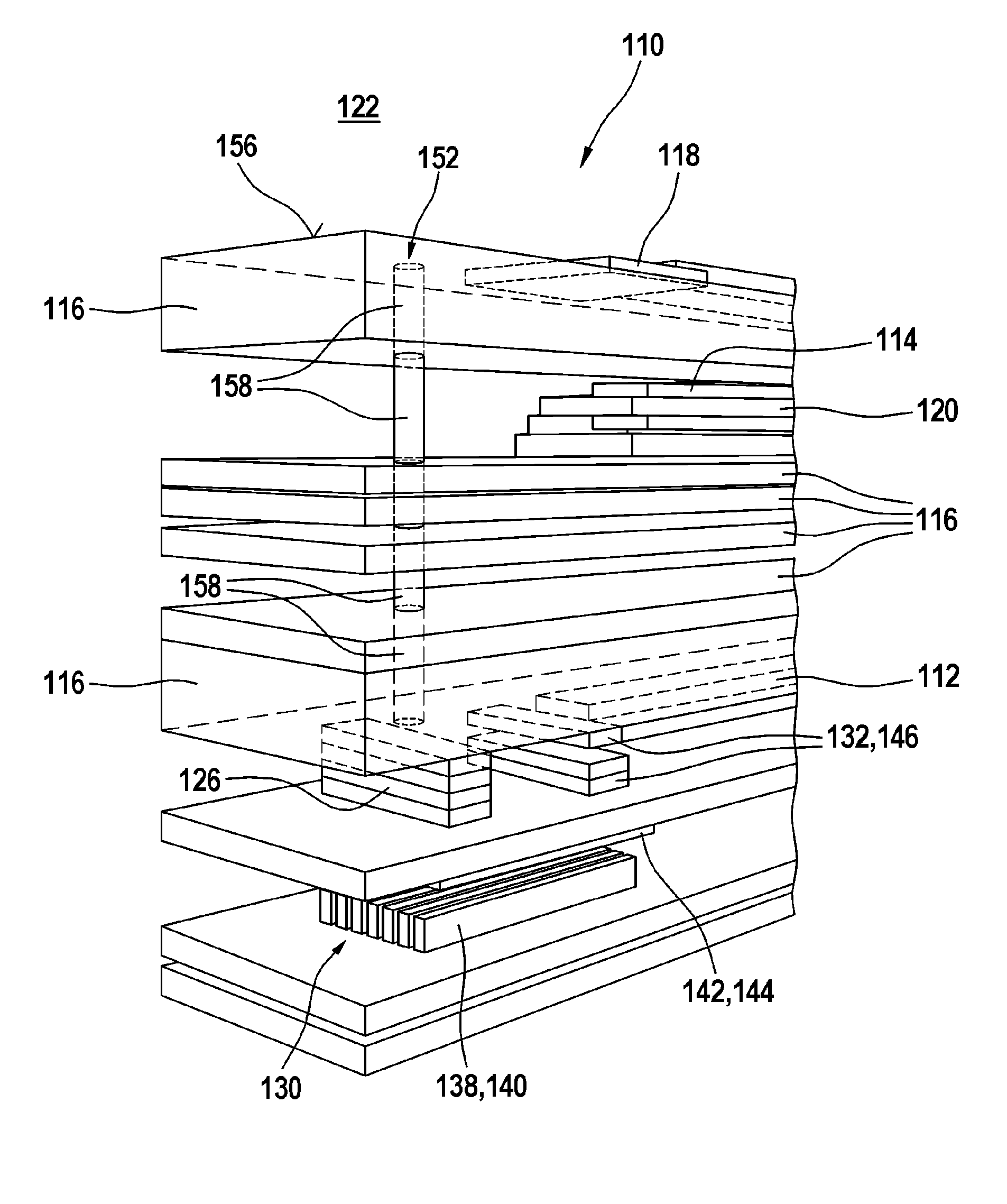

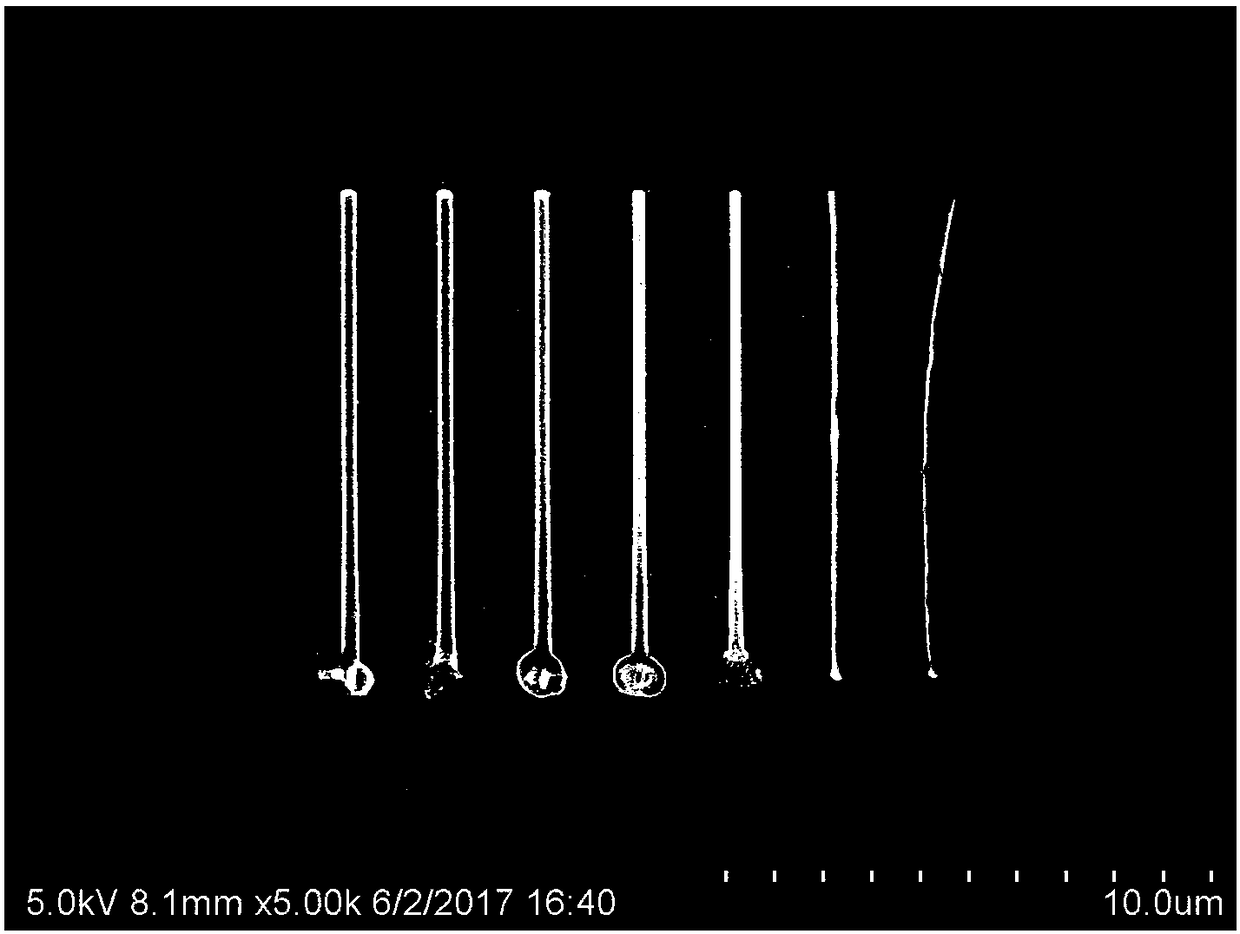

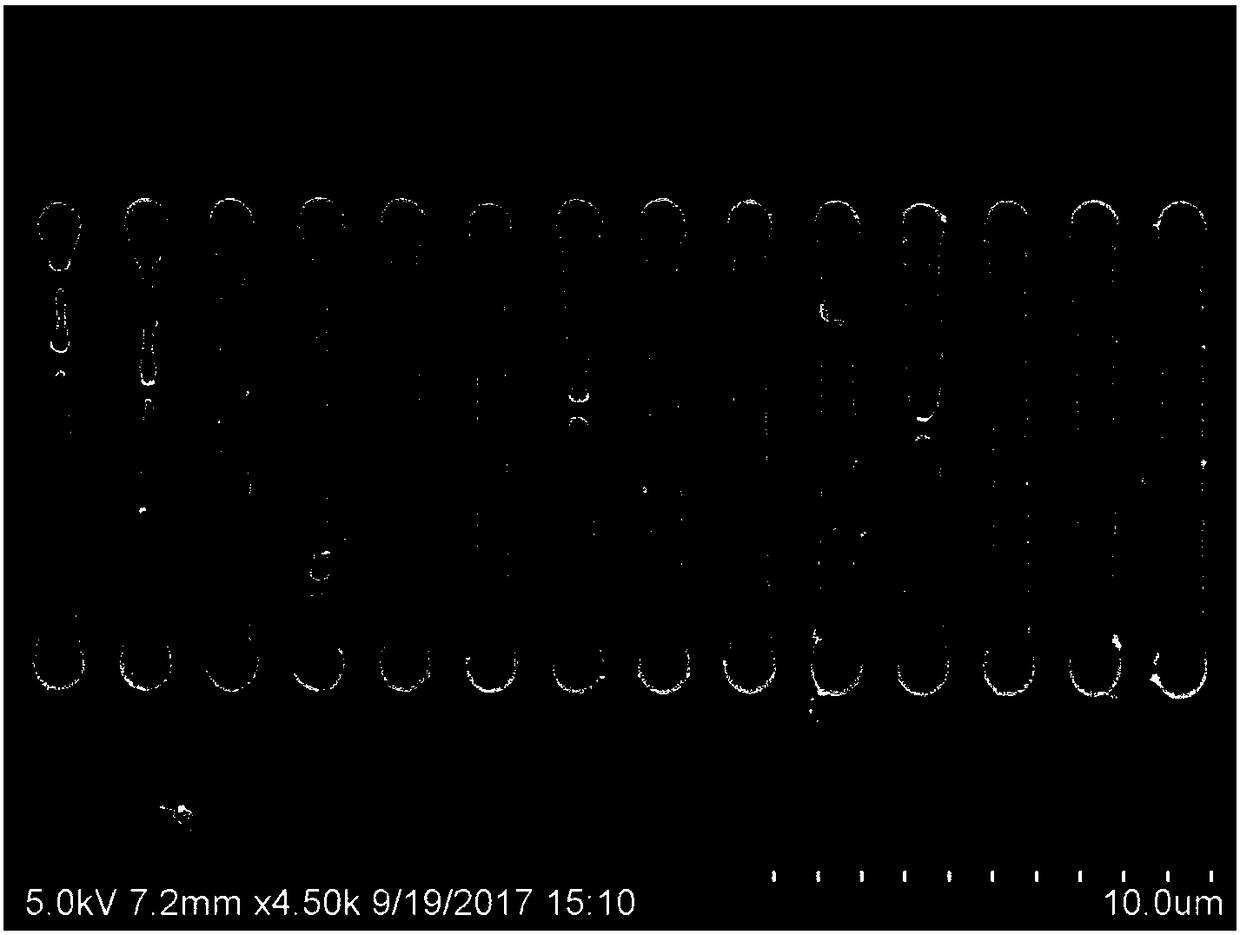

Sensor element having multi-part diffusion barrier

ActiveCN102483389ALower the K valueEvenly loadedMaterial analysis by electric/magnetic meansDiffusion barrierGas chamber

The invention relates to a sensor element (110) for determining at least one property of a gas in a measuring gas chamber (122), in particular for determining a content of a gas component in the measuring gas chamber (122). The sensor element (110) comprises at least one first electrode (112), at least one second electrode (114) and at least one solid electrolyte (116) connecting the first electrode (112) and the second electrode (114). The first electrode (112) can be supplied with gas from the measuring gas chamber (122) via a gas inlet path (124). The gas inlet path (124) comprises at least one diffusion barrier (130), which has at least one first diffusion barrier region (138) and at least one second diffusion barrier region (142). The second diffusion barrier region (142) is designed to be more fine-pored than the first diffusion barrier region (138).

Owner:ROBERT BOSCH GMBH

Insulating film insulating glass

ActiveCN103498624BGuaranteed thermal deformation effectGuaranteed stabilityWallsUnits with parallel planesInter layerFixed frame

The inner hanging film insulating glass of the present invention is to add an inner hanging film combination frame and an optical plastic film fixed by the inner hanging film combination frame to form an intermediate layer in the inner cavity of the standard insulating glass. The inner suspension film combination frame fixed on the inner surface of one side of the glass is composed of a fixed frame and a compression frame. The pre-installed spring assembly in the fixed frame fixes the optical plastic film by welding, and the compression frame is fixed with a lock hinge. The frame is fastened, forming a downward pressure on the optical plastic film fixed on the spring assembly to make the film tense, and the spring assembly also bends and deforms accordingly, and the elastic force generated keeps the film at the required tension to adapt to environmental changes during use. strain and keep the film surface flat all the time. While the glass with the interlayer of the inner suspension film has a double hollow structure, the increase in its total mass is negligible, and the packaging structure is completely in accordance with the manufacturing standards of hollow glass.

Owner:伟视幕墙(淮安)有限公司

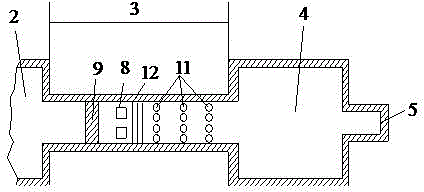

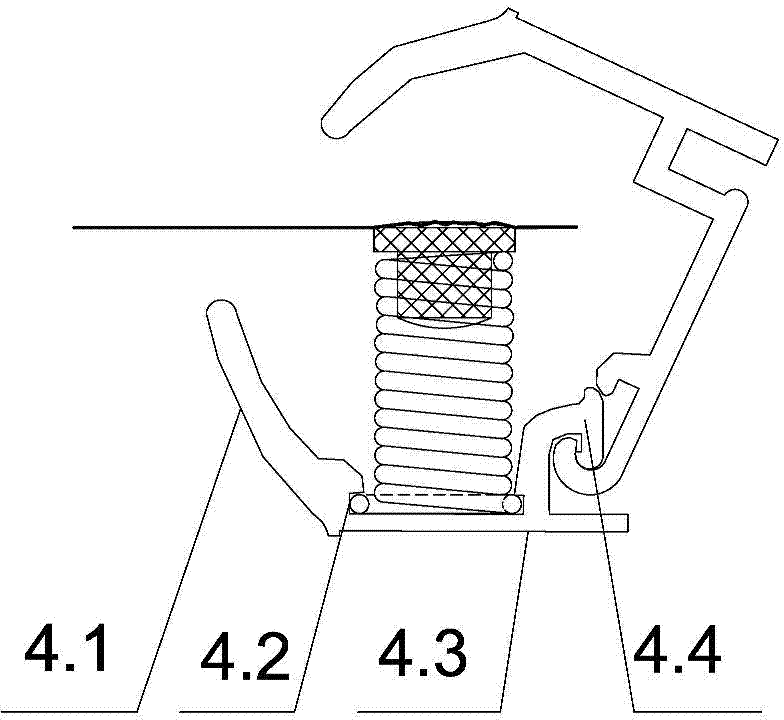

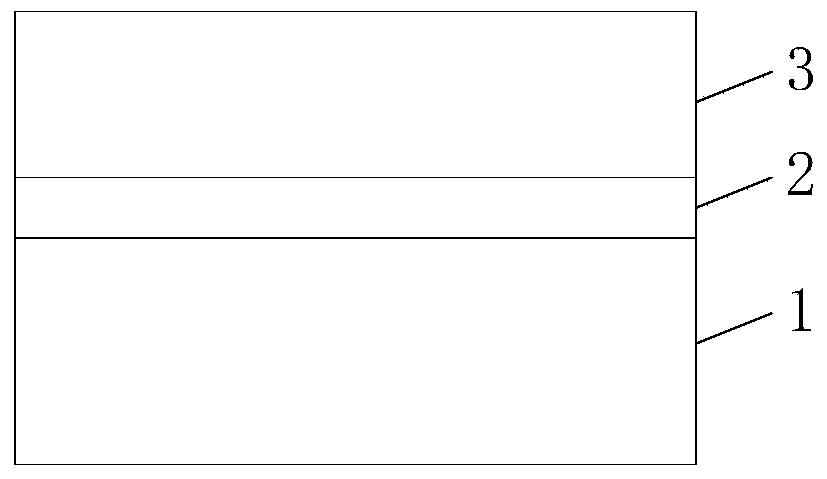

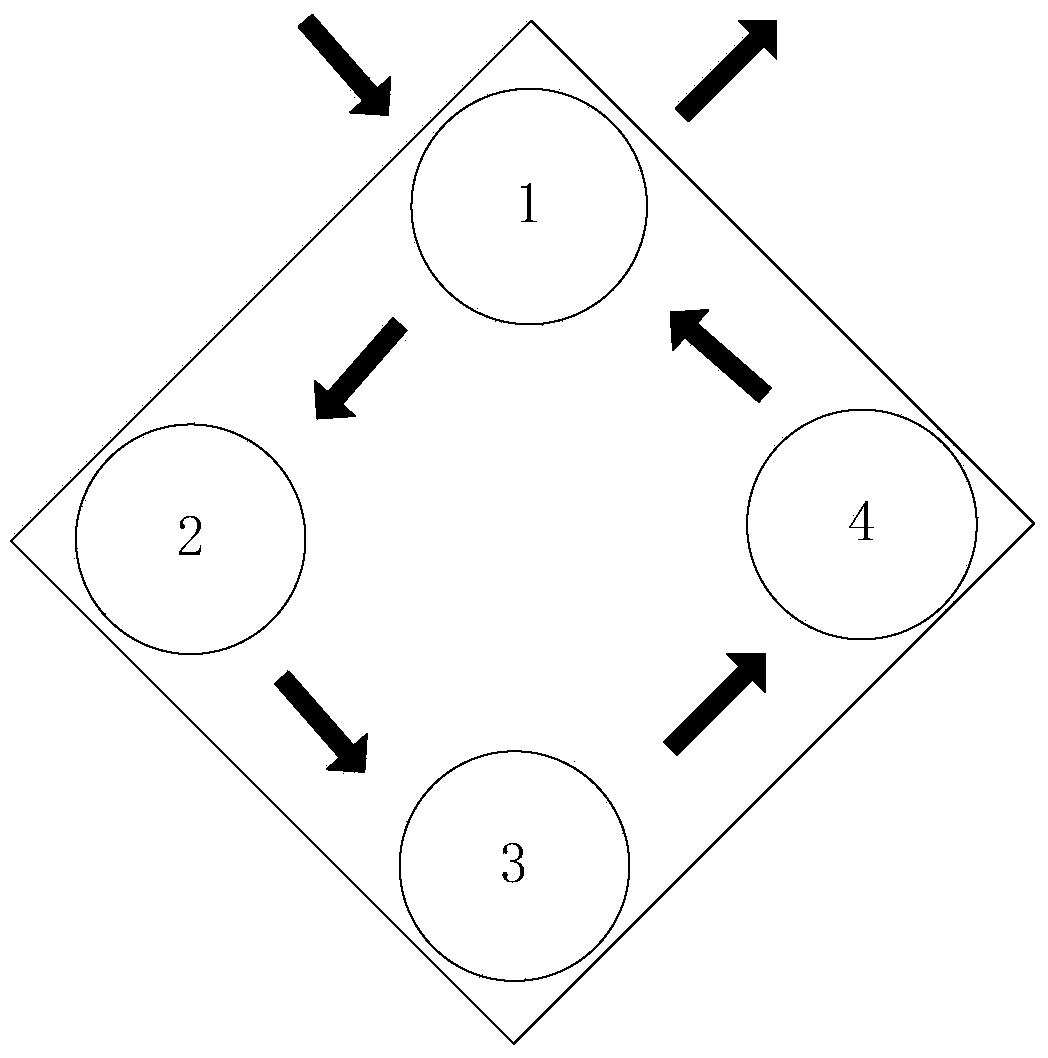

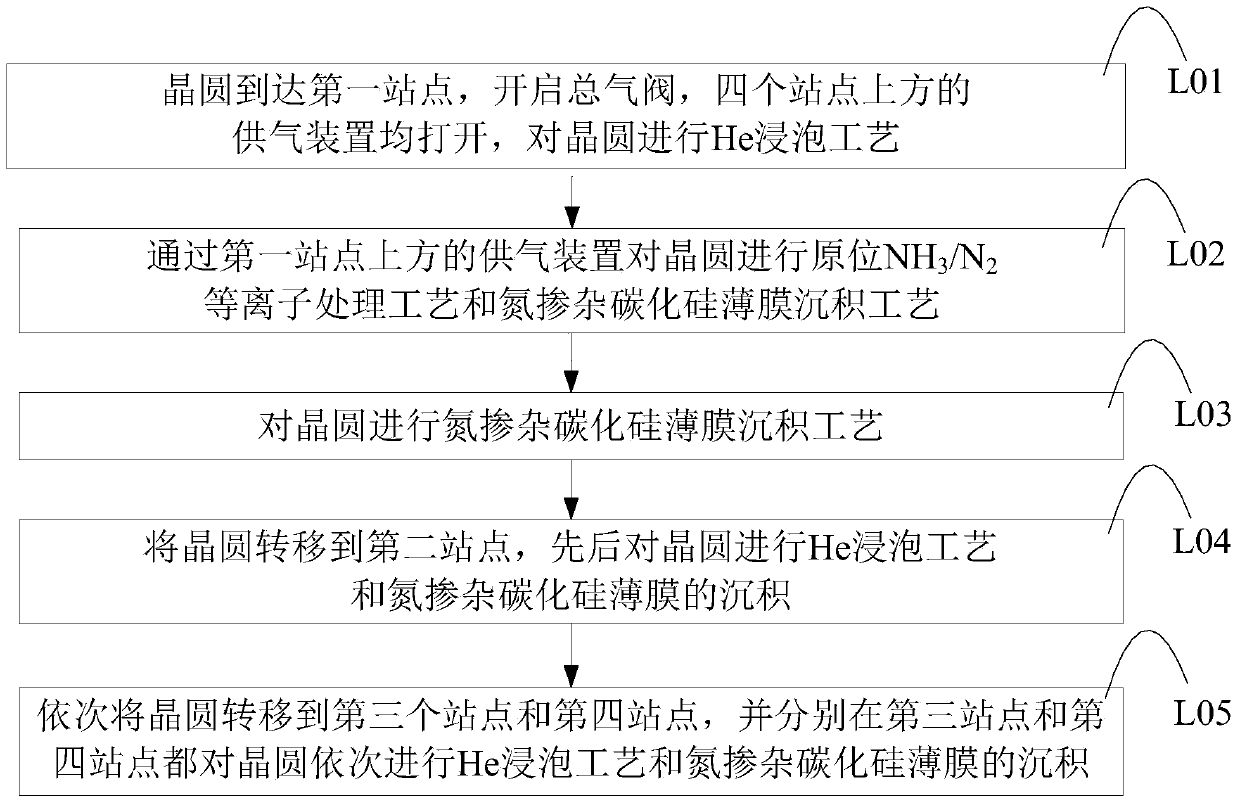

Reaction device and preparation method of nitrogen doped silicon carbide film

InactiveCN104183479AAvoid damageImprove adhesionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingElectricityRemote plasma

The invention provides a reaction device and preparation method of a nitrogen doped silicon carbide film. An air feed device above a first station comprises an independent remote plasma system, for generating remote H2 / He plasma during a preprocessing process or remote NH3 / N2 plasma, for repairing the k value of a low k medium and removing CuO on the surface of Cu so as to enhance the adhesiveness of a low k material and the nitrogen doped silicon carbide film and the adhesiveness of the Cu and the nitrogen doped silicon carbide film; the air feed device above the first station is different from the air feed devices of other three stations and is independently controlled, such that the preprocessing process can be freely adjusted; since the four stations work simultaneously in a reaction cavity of the reaction device, for the purpose of eliminating mutual interference between the preprocessing process and other processes, the four stations are isolated by use of an gas curtain technology, and the technical quality of the preprocessing process is improved; and the reliability and the electrical performance of a final product can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

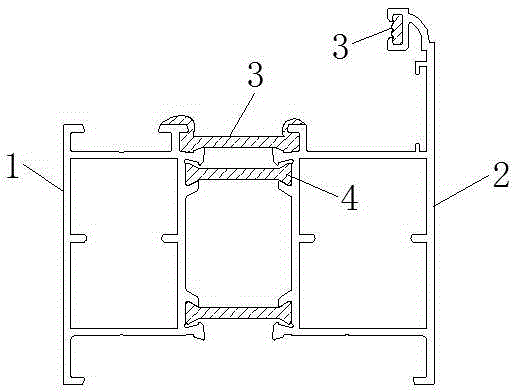

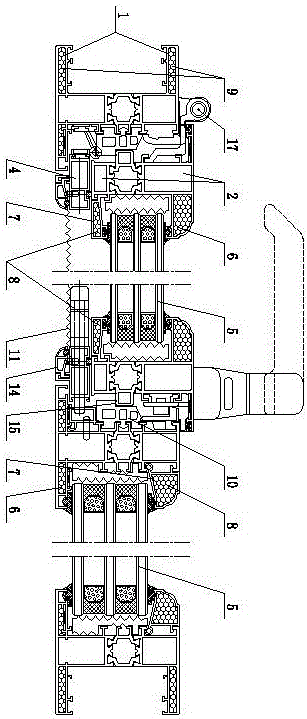

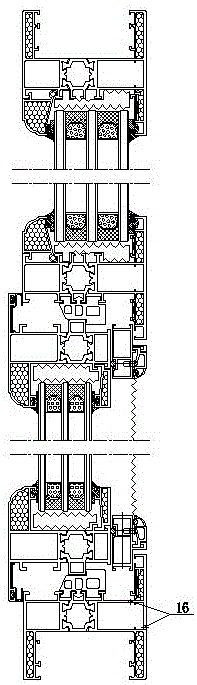

A novel 70-series frame and sash mould and engaged ten-seal rubber strips

InactiveCN106812438AReduce radiationSo as not to damageSealing arrangementsEthylene-propylene-diene-monomerEngineering

The invention discloses a new mold for a 70 series frame and fan and ten sealant strips for occlusion, including a widened indoor side aluminum profile and a widened outdoor side aluminum profile, the widened indoor side aluminum profile and the widened room Ten sealing rubber strips are arranged between the outer aluminum profiles, and inverted triangular protrusions for connecting the widened indoor aluminum profiles and the widened outdoor outdoor aluminum profiles are respectively provided at both ends of the ten sealed rubber profiles. The sealing strip breaks the traditional design limitations of single, double, and triple sealing strips, adding ten sealing strips greatly reduces the K value, greatly improves the effect of cold insulation, heat insulation, sound insulation and noise prevention, and at the same time achieves energy saving and emission reduction effects; widened aluminum alloy profiles Better cooling and heat insulation, sound insulation and noise prevention; the design of ten sealing strips can better meet the needs of sound insulation, anti-drying, anti-cold condensation, and anti-heat transfer; high-quality EPDM sealing strips are not easy to age, It is durable and has better sealing effect, which greatly meets the needs of anti-cold poly and anti-heat transfer.

Owner:中明科技(重庆)有限公司

Quasi OTDM transmitting method and system

InactiveCN1845487BThe synchronization accuracy is smallEnsure robustnessMultiple carrier systemsSignal channelsCommunications systemSignal on

The disclosed QOTDM method and system comprise: connecting N continual signals with BHz bandwidth or corresponding sampling sequence into one continual signal to transmit in continual channel; converting the received signal on receive end into a composite zero-IF signal with orthogonal down-conversion and sampling digitalization, connecting frequency deviation by a carrier phase-locking loop; using frame-synchronization loop and adaptive channel balancer for high-precise sampling point synchronization and correction channel distortion; finally, recovering N signals. This invention has well performance for satellite communication system.

Owner:XIDIAN UNIV

Inorganic photoresist composition patterning method

ActiveCN108089404AImprove universalityLower the K valuePhotomechanical exposure apparatusMicrolithography exposure apparatusUltraviolet lightsVisible near infrared

The invention discloses an inorganic photoresist composition patterning method. A light source is adopted for performing patterning on a photoresist composition, wherein the light source is an ultraviolet light-visible-near infrared light source with wavelength of 250-2,500nm; and the inorganic photoresist composition is hydrogen silsesquioxane. When the inorganic photoresist composition is in exposure, crosslinking of HSQ is caused by the nonlinear interaction between light and the material; the crosslinked hydrogen silsesquioxane HSQ is not dissolved in a developing liquid, while HSQ whichis not crosslinked is dissolved in the developing liquid, so as to form specific a photoresist pattern; and the method for inorganic photoresist HSQ pattering by adopting ultraviolet light, visible and near infrared exposure can be applied to the technical field of microelectronics.

Owner:TECHNICAL INST OF PHYSICS & CHEMISTRY - CHINESE ACAD OF SCI

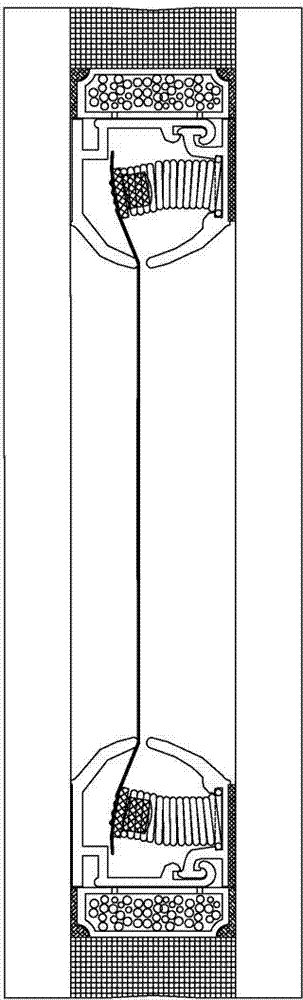

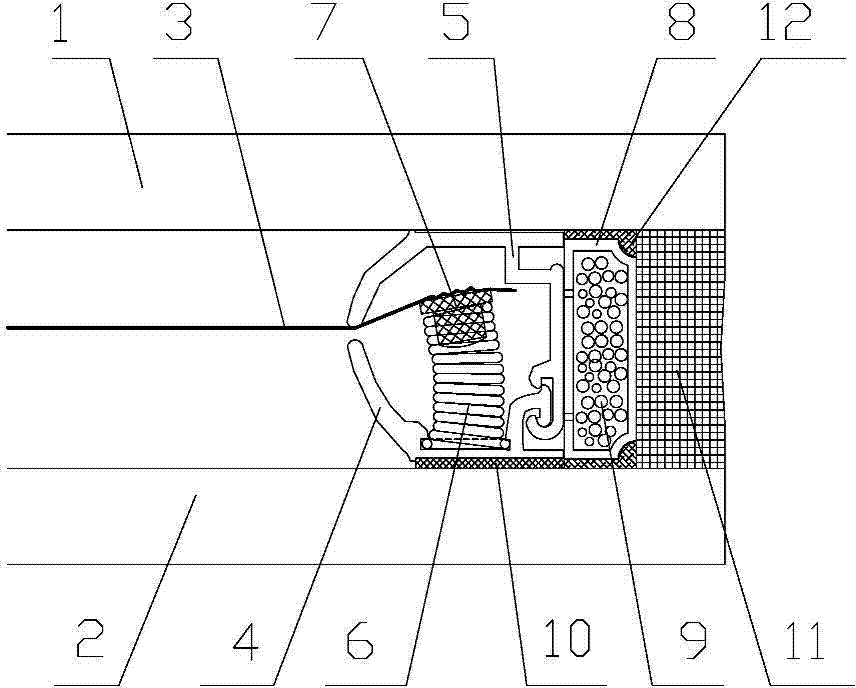

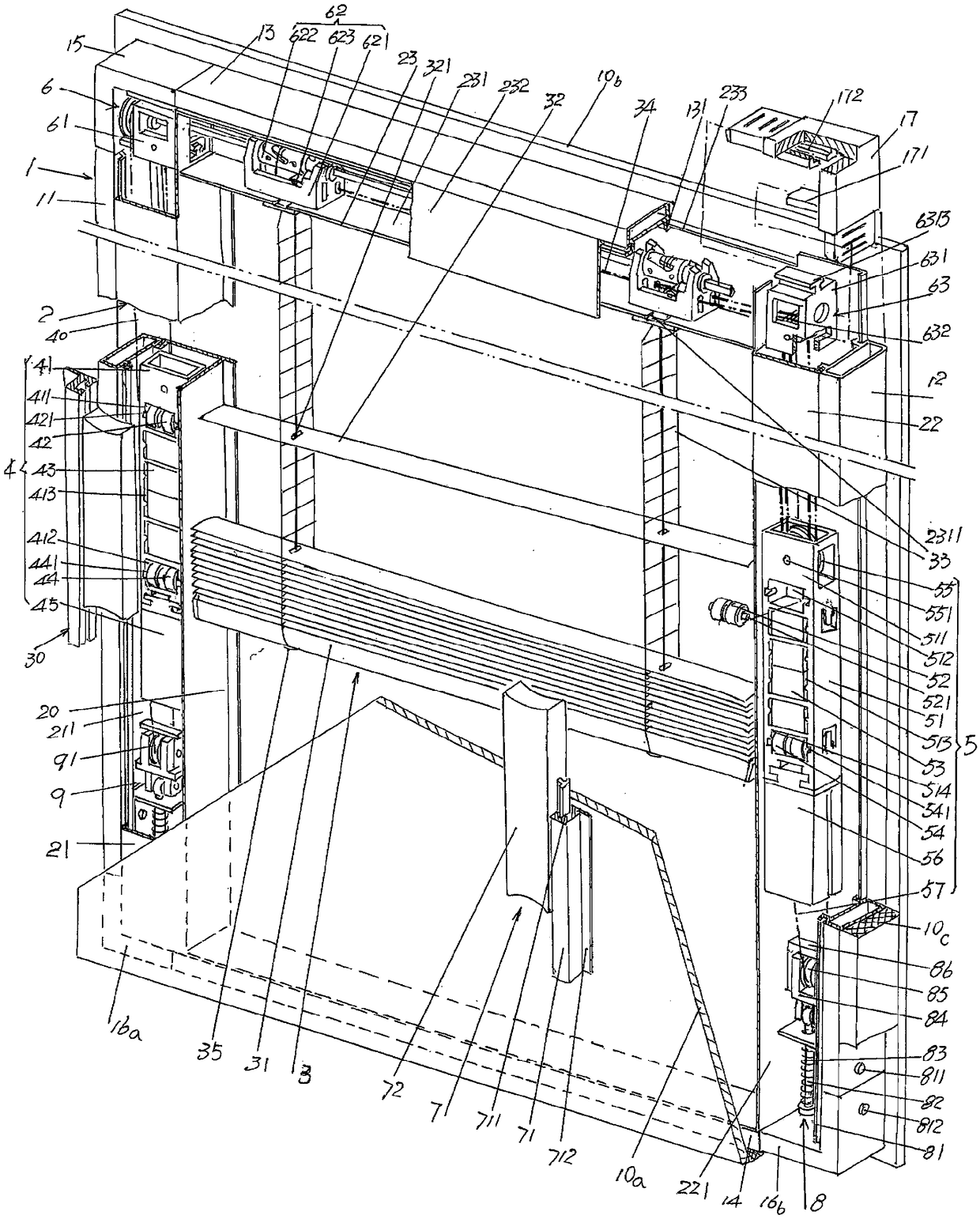

Double control warm frame hollow glass window shade

PendingCN108661525AImprove Flip EffectPrivacy protectionLight protection screensSealing arrangementsWindow shutterVenetian blinds

The invention discloses a double control warm frame hollow glass window shade. The double control warm frame hollow glass window shade comprises a rectangular window body, an inner frame body, front glass and rear glass, a venetian blind, a curtain sheet overturning adjustment control mechanism, a venetian blind lifting adjustment control mechanism, a venetian blind lifting and curtain sheet overturning transition mechanism, a curtain sheet overturning external control mechanism and a venetian blind lifting external control mechanism, wherein the rectangular window body is composed of left andright longitudinal frame strips and upper and lower horizontal frame strips, the inner frame body is composed of left and right inner frame strips and upper inner frame strips, and the venetian blindis arranged in a venetian blind cavity. The double control warm frame hollow glass window shade is characterized in that left inner frame strip lightproof extension edges are arranged on the rear walls of the left inner frame strips and extends to the direction of the venetian blind cavity, right inner frame strip lightproof extension edges are arranged on the rear walls of the right inner framestrips and extends to the direction of the venetian blind cavity, gaps between the left end of the venetian blind and the right side of the left inner frame strips are covered by the left inner framestrip lightproof extension edges, and gaps between the right end of the venetian blind and the left side of the right inner frame strips are covered by the right inner frame strip lightproof extensionedges. Privacy and safety of users are ensured, lifting effect is lasting and stable, and lifting pulling ropes of the venetian blind are not prone to breaking free.

Owner:JIANGSU SDL ENERGY CONSERVATION TECH CO LTD

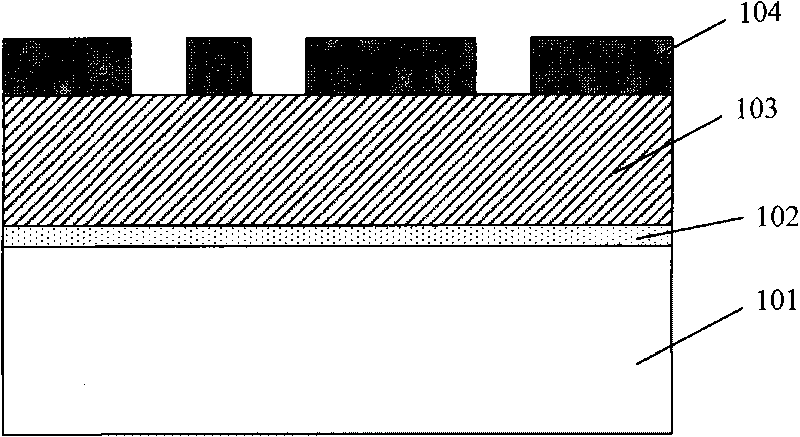

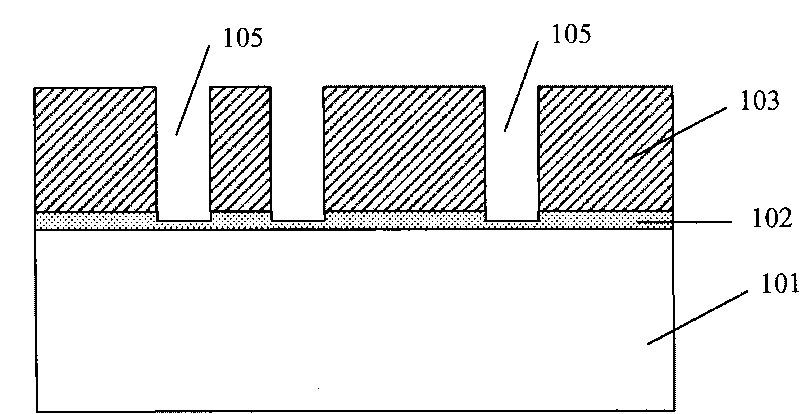

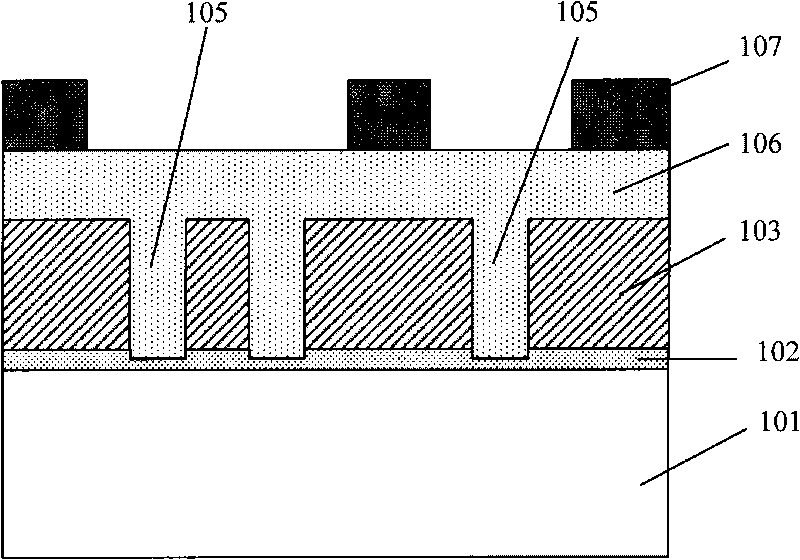

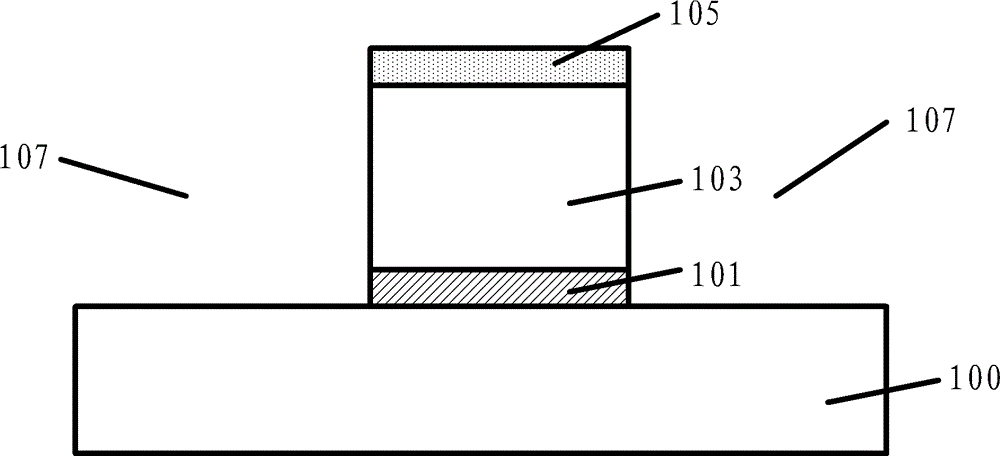

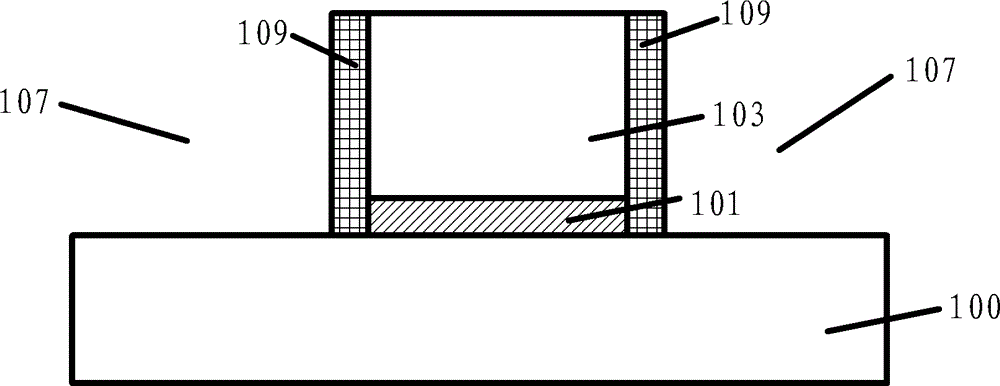

Manufacturing method of semiconductor device

ActiveCN103165519ALower the K valueSemiconductor/solid-state device manufacturingCapacitancePower semiconductor device

The invention provides a manufacturing method of a semiconductor device. The manufacturing method of the semiconductor device comprises providing a semiconductor substrate, forming an etching stop layer and an interlayer dielectric layer on the semiconductor substrate from bottom to up in a sequentially stacked mode, and forming copper metal interconnecting wires in the interlayer dielectric layer; forming a silicon layer on the semiconductor substrate; imaging the silicon layer, and etching the silicon layer and the interlayer dielectric layer in sequence to from a groove between the copper metal interconnecting wires; carrying out oxidation treatment on the silicon layer to narrow a top opening of the groove; carrying out ion implantation on the silicon layer which is processed by the oxidation treatment; and forming the interlayer dielectric layer on the semiconductor substrate to completely seal the top opening of the groove. According to the manufacturing method of the semiconductor device, an air gap with a larger feature size can be formed between copper metal interconnecting structures, and therefore the sizes of interconnecting capacitor is effectively reduced. Meanwhile, a k value of the interlayer dielectric layer can be further reduced through an adopted implantation technology.

Owner:SEMICON MFG INT (SHANGHAI) CORP

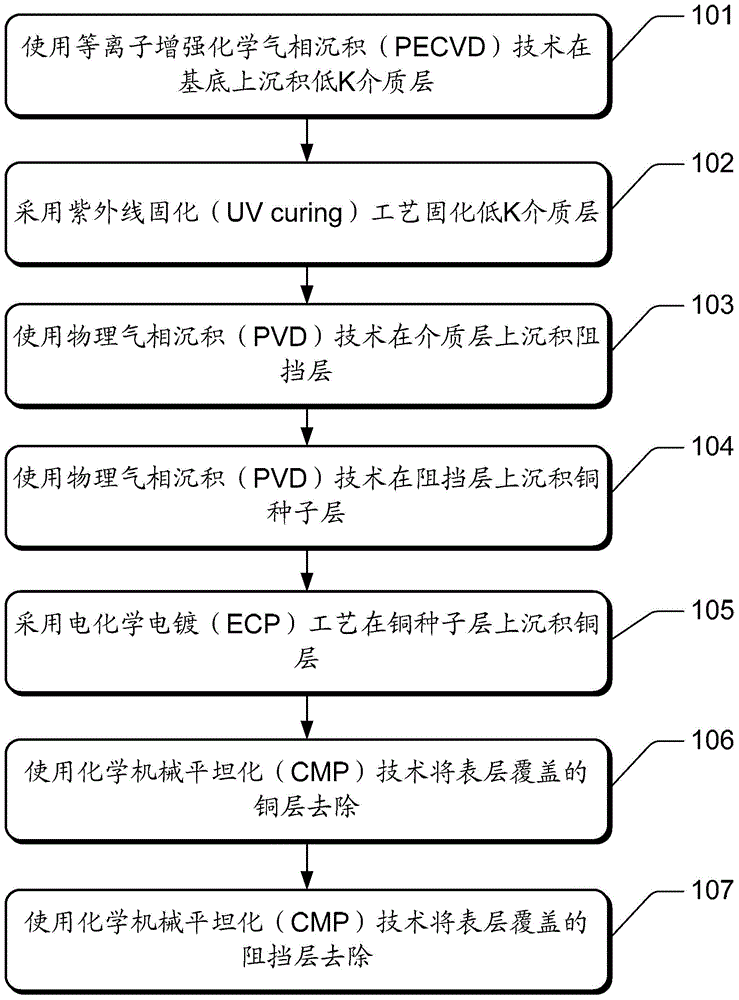

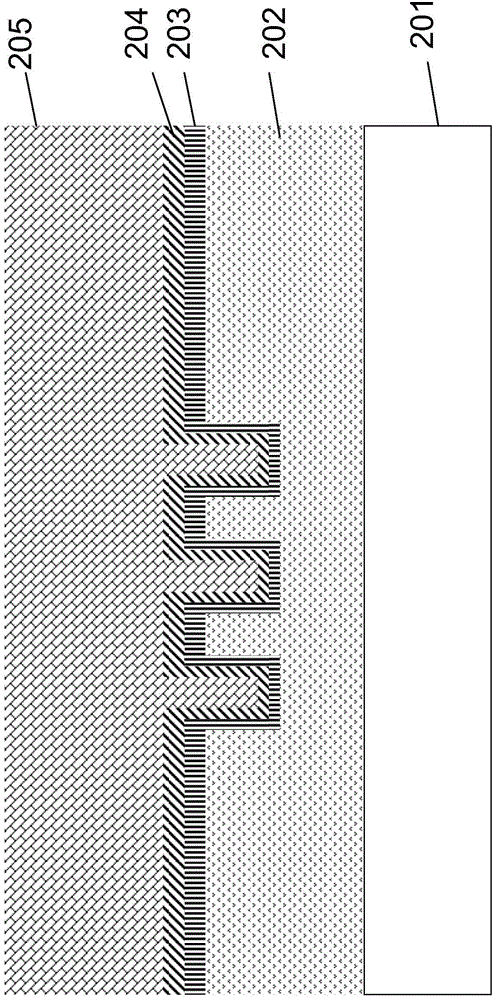

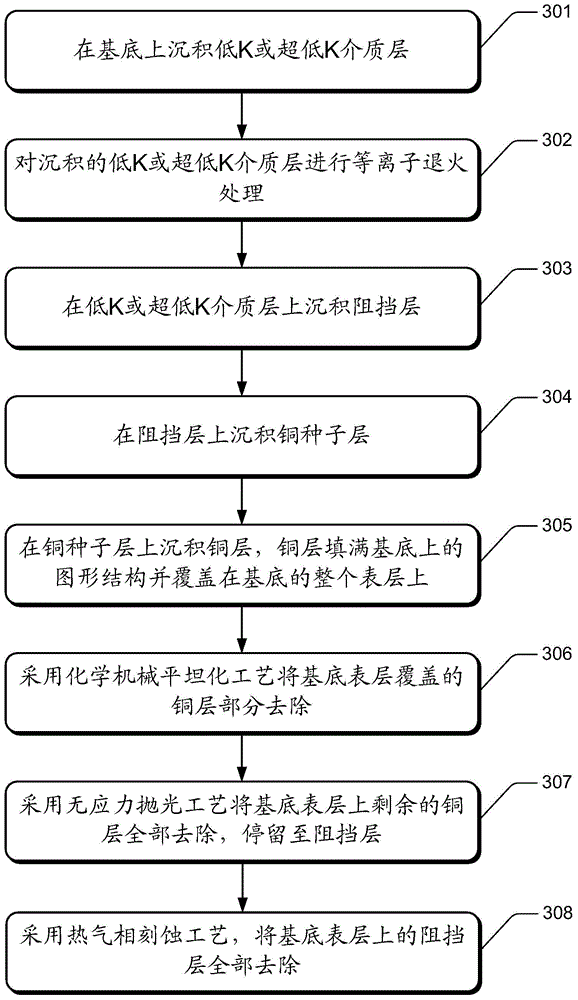

Integration technology of copper and low K dielectric material

InactiveCN105321871ALower the K valueIncrease hole rateSemiconductor/solid-state device manufacturingChemical-mechanical planarizationLow-k dielectric

The invention discloses an integration technology of copper and a low K dielectric material. The method comprises the following steps of depositing a low K or ultralow K dielectric layer on a substrate; carrying out plasma annealing processing on the deposited low K or ultralow K dielectric layer; depositing a barrier layer on the low K or ultralow K dielectric layer; depositing a copper seed layer on the barrier layer; depositing a copper layer on the copper seed layer, wherein the copper layer fills in a graph structure on the substrate and covers a whole surface layer of the substrate; using a chemical mechanical planarization technology to remove a copper layer portion on the substrate surface layer; using a stress-free polishing technology to completely remove the residual copper layer on the substrate surface layer and staying at the barrier layer; using a hot gas phase etching technology to completely remove the barrier layer on the substrate surface layer. By using the technology of the invention, the dielectric material can maintain an enough low K value and integration with copper is realized, and a technical barrier in the prior art is broken through.

Owner:ACM RES SHANGHAI

Double-cavity heat-insulating and temperature-preserving inward casement window structure

InactiveCN105909127ALower the K valueThe heat transfer coefficient K value decreasesInsect protectionWindow/door framesEngineeringLoad capacity

The invention relates to the technical field of processing of combination of casement screen windows and casement windows, in particular to a double-cavity heat-insulating and temperature-preserving inward casement window structure. Specifically, cross sections of a primary frame structure and a secondary frame structure of an original window frame are changed from single-surface contact into double cavities, and the single-surface contact of the cross sections of contact glass of original window sashes is realized as the double cavities; the single-surface contact of a contact glass part of the original window frame is realized as a double-cavity cross section, and the double-cavity cross section is filled with a temperature preserving material, so that the heat preserving property, the load capacity and the wind pressure resistance of a primary frame body and a secondary frame body of a window frame are improved by the cavities of the window frame and a wall surface; the temperature preserving property of the glass contact surfaces of the window sashes is improved, so that the heat-insulating and temperature-preserving effects are improved, and the purpose of reducing a heat transfer coefficient K is achieved. The reasonable arrangement of a combined structure of a screen window and the window frame in a window frame body is realized.

Owner:邸泽勇

Dental ulcer spray and preparation method thereof

InactiveCN106110293AFormula stablePromote regenerationHydroxy compound active ingredientsDipeptide ingredientsFoaming agentAntioxidant

The invention relates to the field of dental ulcer treatment medicine, in particular to a dental ulcer spray and a preparation method thereof. The dental ulcer spray is prepared from, by mass, 1-3 parts of regeneration promoter, 0.3-0.5 part of anti-inflammatory agent, 1-4 parts of film-forming agent, 0.5-2.5 parts of pore-foaming agent, 0.1-0.2 part of suspending agent, 0.1-0.2 part of antioxidant, 0.1-0.2 part of astringent and 92-98 parts of solvent. The dental ulcer spray is good in treatment effect, and meanwhile has the effects of diminishing inflammation, relieving pain and promoting ulcer healing.

Owner:怡越医疗(广东)有限公司

Method for reducing RC delay of integrated circuit

InactiveCN104134629ALower the K valueReduce RC delaySemiconductor/solid-state device detailsSolid-state devicesCopper interconnectCompound (substance)

The invention provides a method for reducing the RC delay of an integrated circuit. The method includes the steps that a copper interconnecting structure is formed in porous low dielectric constant material, and chemical and mechanical grinding flattening processing is performed on the copper interconnecting structure; a copper diffusion dielectric barrier layer grows on the surface of the porous low dielectric constant material for the copper interconnection structure; the portion, outside the copper interconnecting structure, of the copper diffusion dielectric barrier layer is removed through the photoetching and etching process, and the portion, on the copper interconnecting structure, of the copper diffusion dielectric barrier layer is reserved; the low dielectric constant material grows again, and therefore an upper porous low dielectric constant material layer is formed on the reserved copper diffusion dielectric barrier layer and the porous low dielectric constant material; and the surface of the upper porous low dielectric constant material layer is processed in a flattening mode.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Pole piece edge burr cleaning nozzle and device with same

PendingCN110665661ASolve the problem of rough edgesLower the K valueElectrode rolling/calenderingFinal product manufacturePole pieceEngineering

The invention relates to a pole piece edge burr cleaning nozzle and a device with the same, and relates to the technical field of manufacturing of lithium battery equipment. The specific scheme is that the pole piece edge burr cleaning nozzle includes an upper plate, a lower plate, two gas pipes and a vacuum pipe, wherein the upper plate and the lower plate are both horizontally arranged, a gap isreserved between the upper plate and the lower plate, the two gas pipes are installed on the upper plate and the lower plate correspondingly, spraying heads of the two gas pipes are located on the lower surface of the upper plate and the upper surface of the lower plate and are opposite to each other, the two gas pipes are connected to an air pump, one end of the vacuum pipe is connected to the left or right end of the gap, and the other end of the vacuum pipe is connected to a vacuumizer. The pole piece edge burr cleaning nozzle and the device can effectively solve the problem of pole pieceedge burrs of a new process and can remove the edge burrs which cannot be removed by a traditional method; and the K value of a battery cell is reduced, the battery yield is improved, the cost of a single finished battery is reduced, and the battery safety is improved.

Owner:重庆冠宇电池有限公司

Forming method for semiconductor device

ActiveCN103094136BQuality improvementImprove performanceSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

Owner:SEMICON MFG INT (SHANGHAI) CORP