Patents

Literature

390 results about "Charge layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

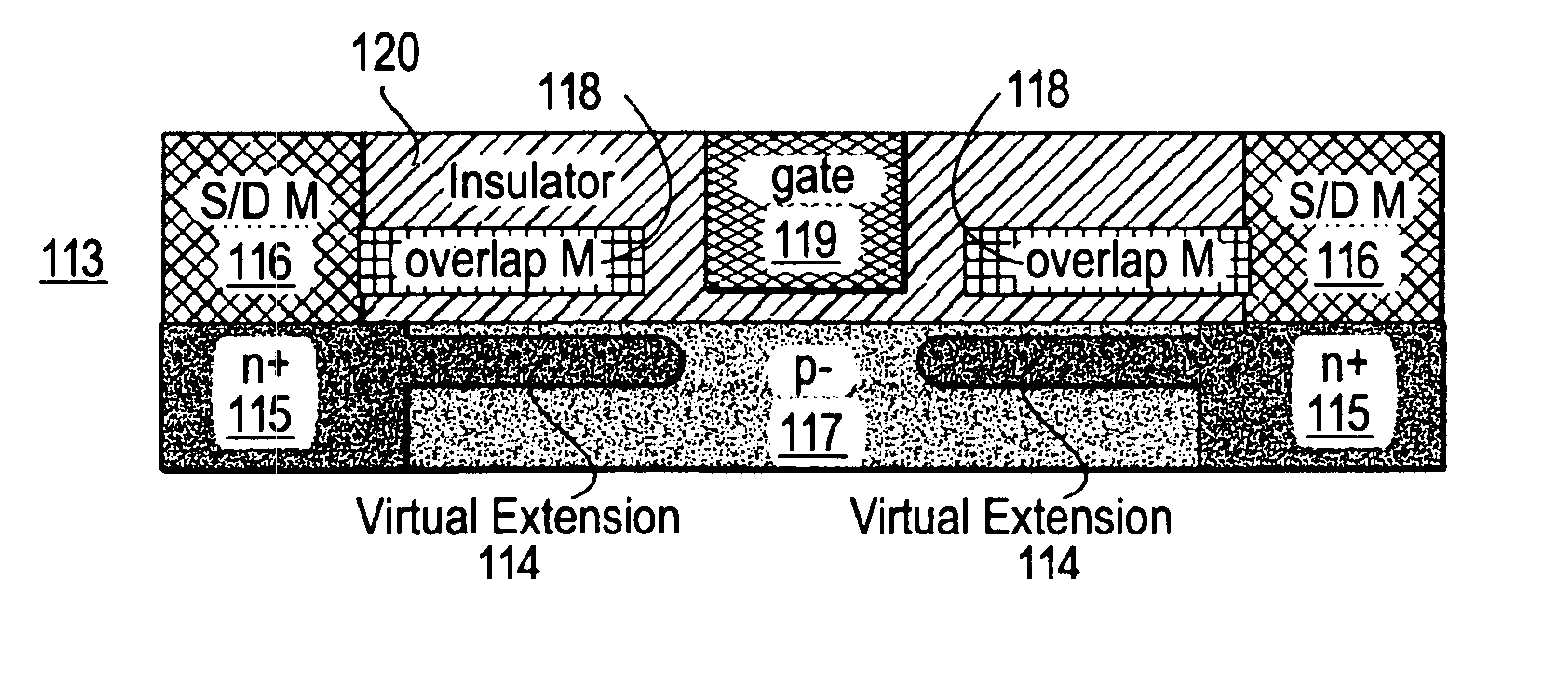

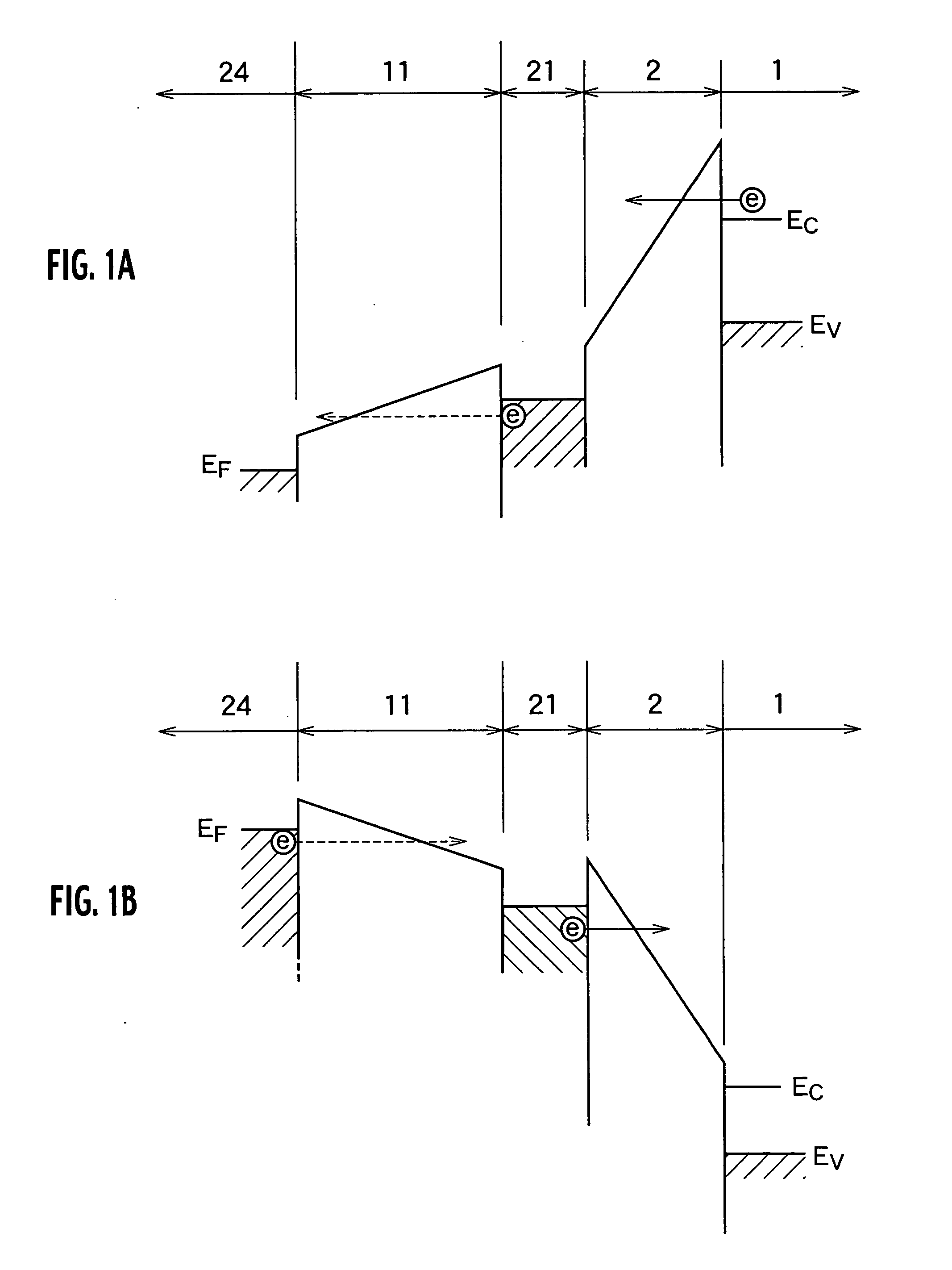

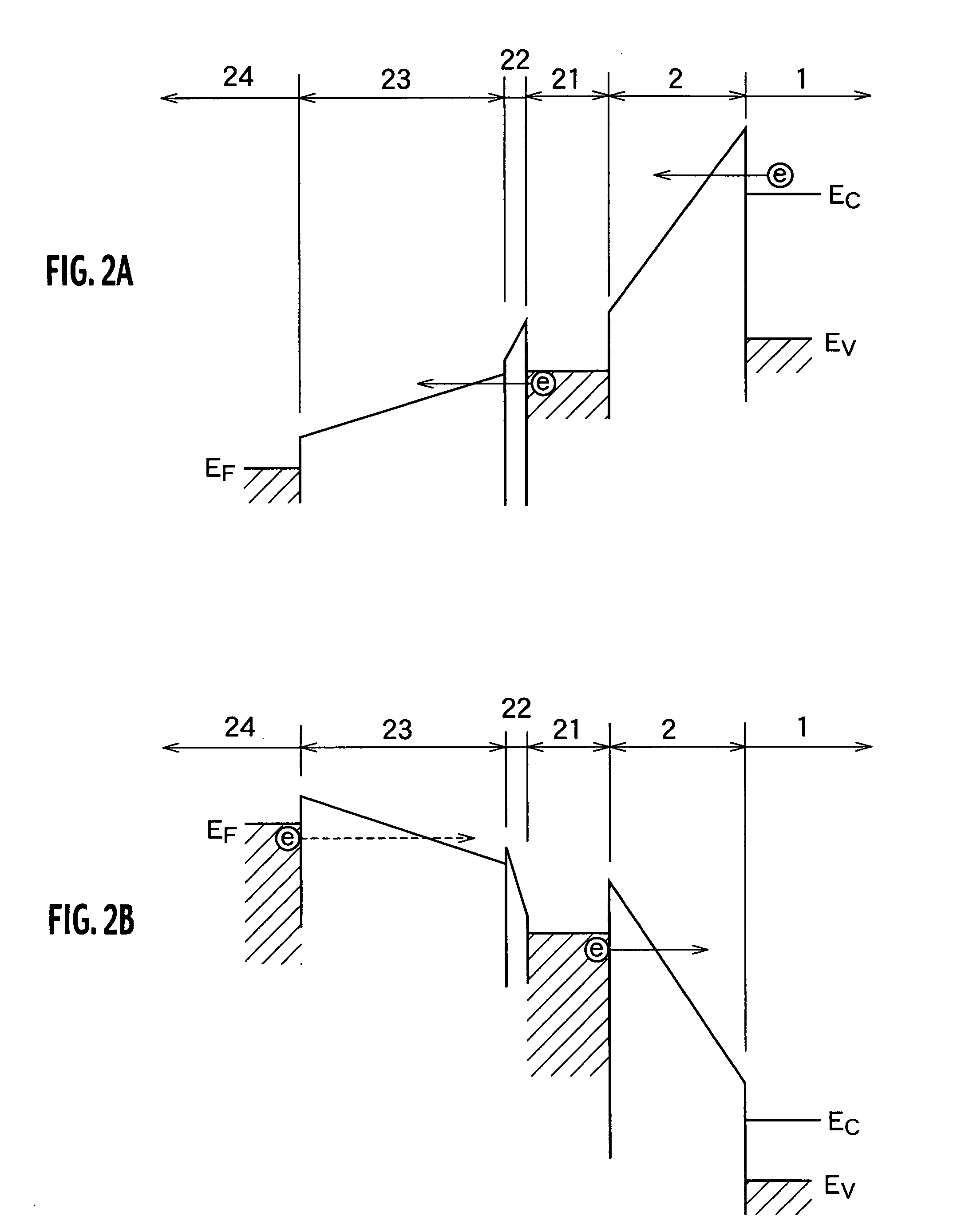

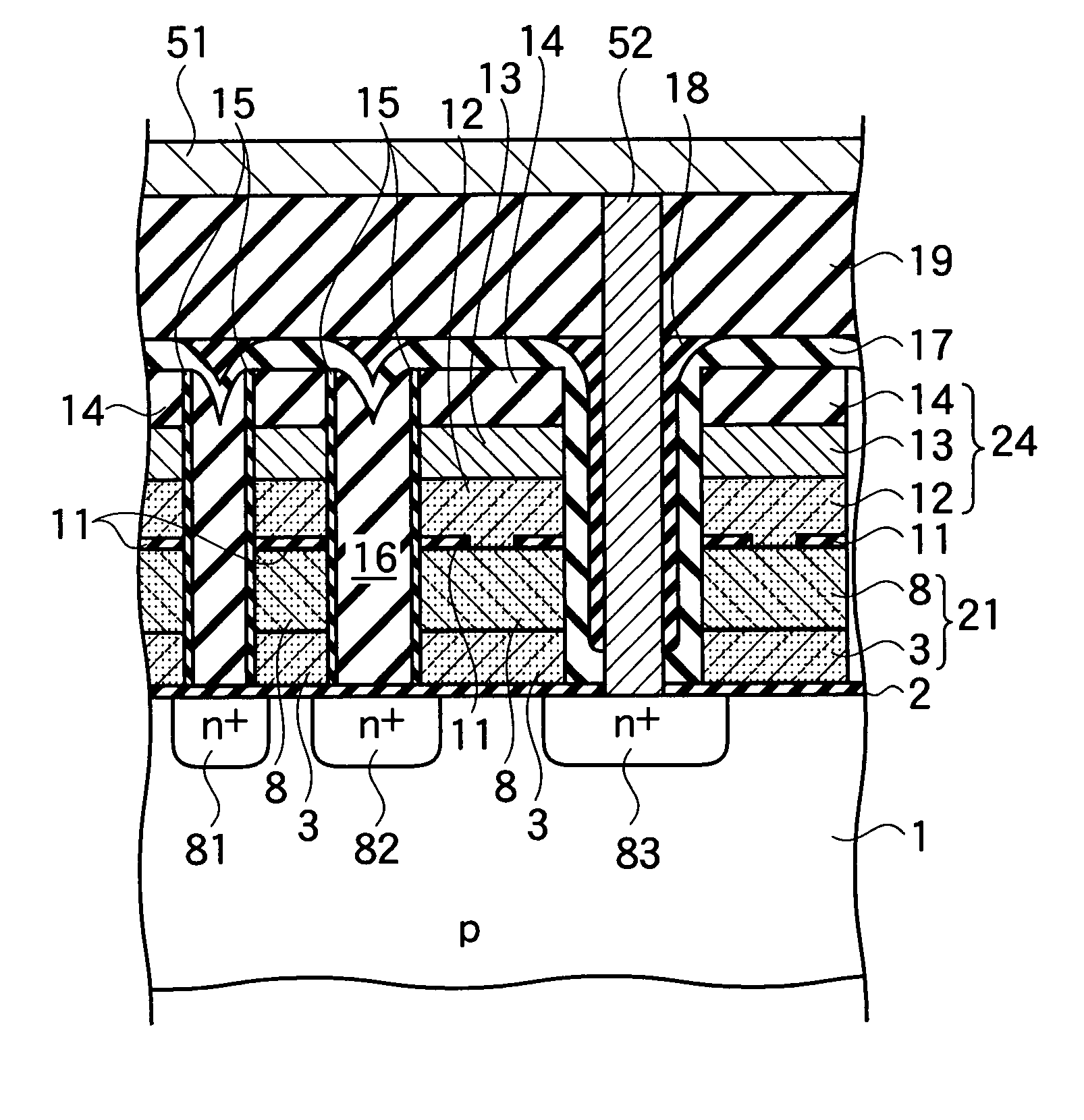

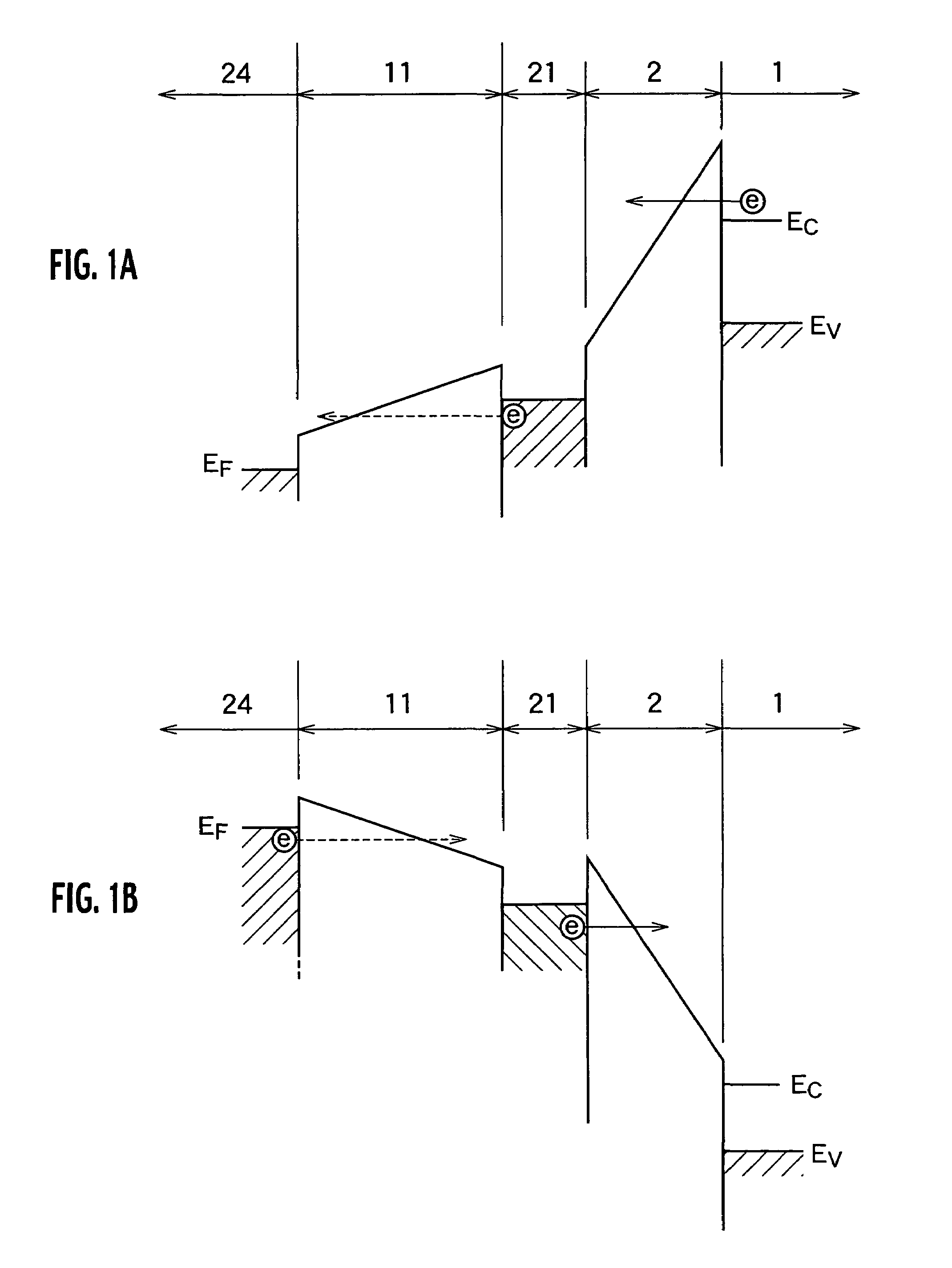

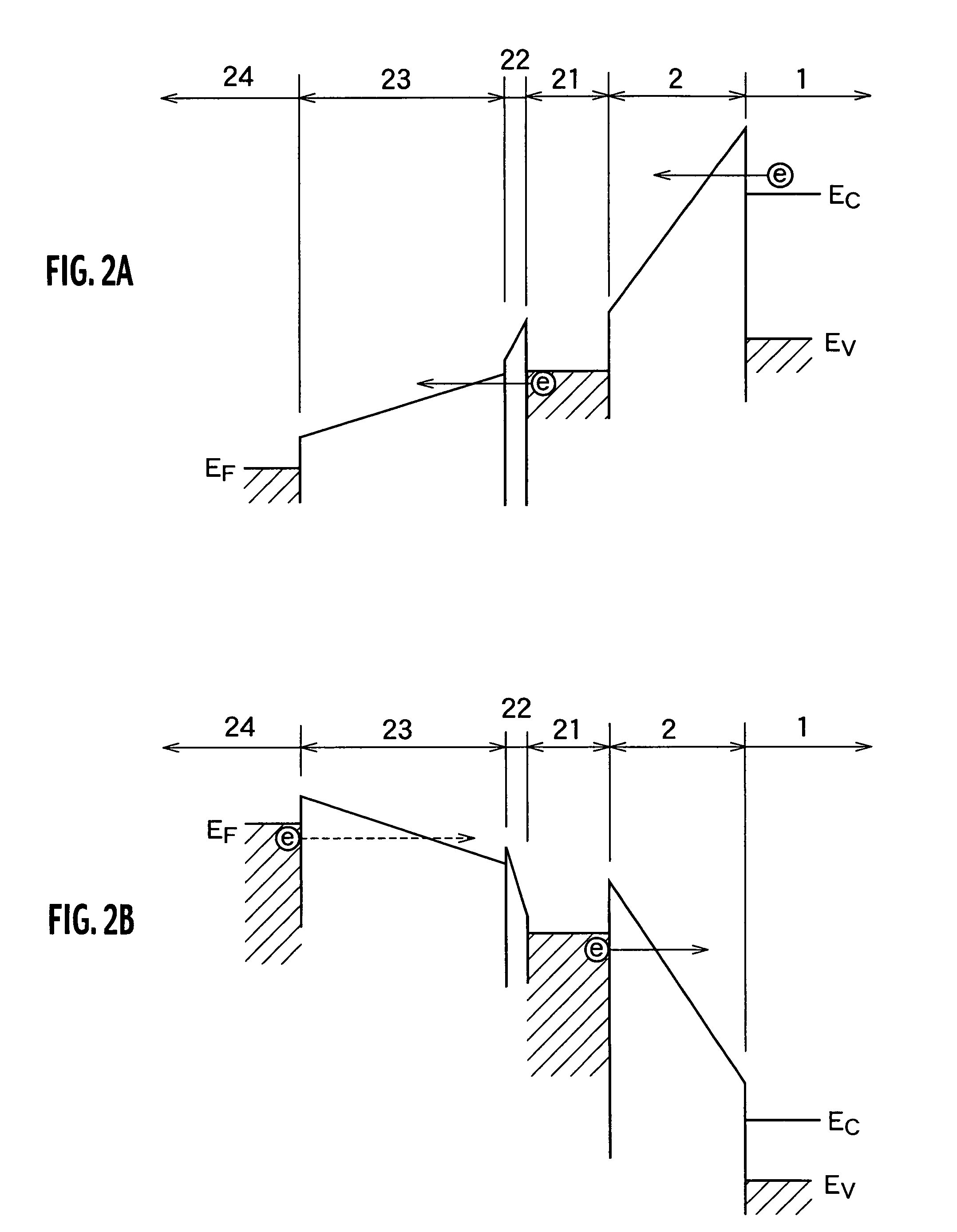

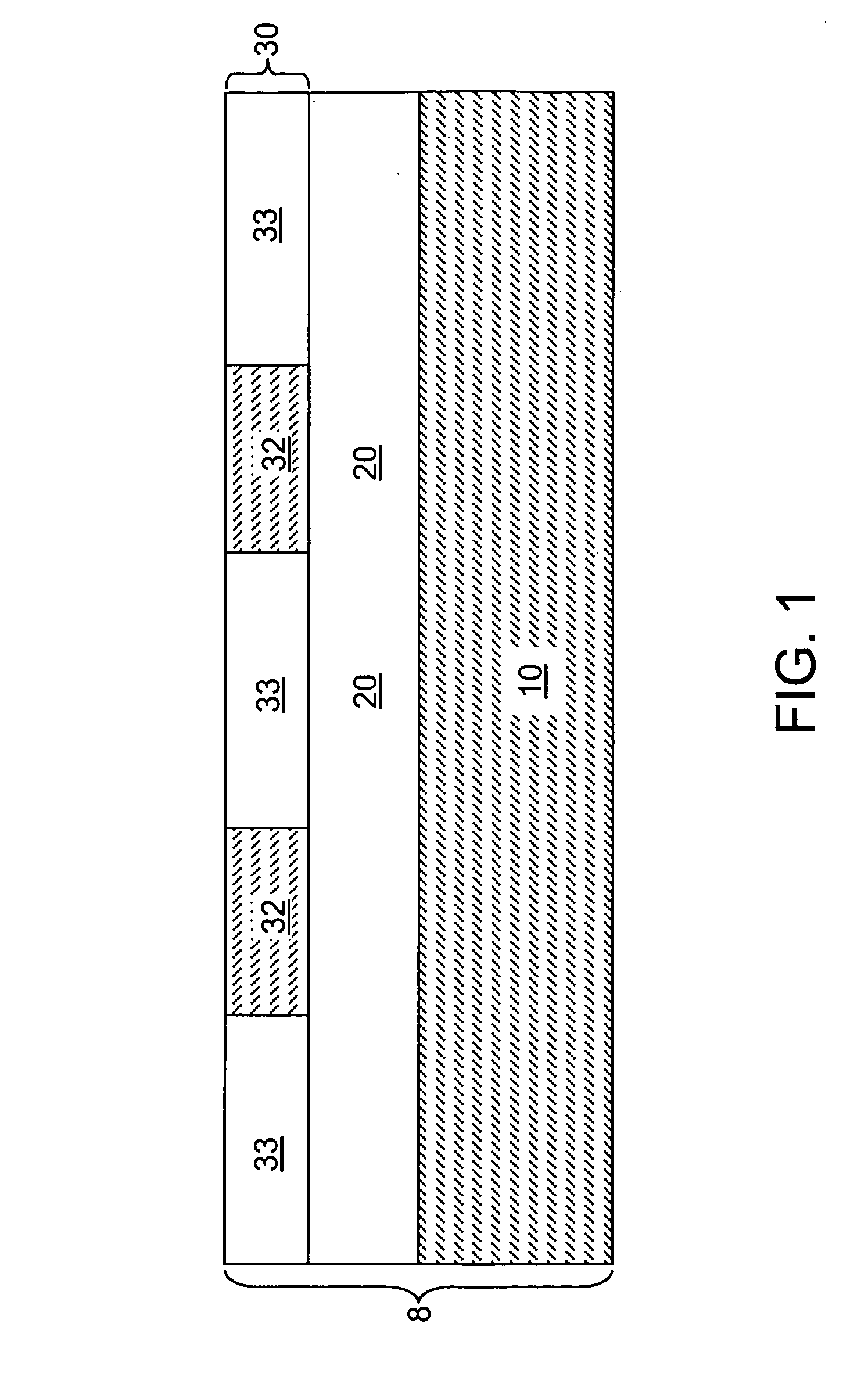

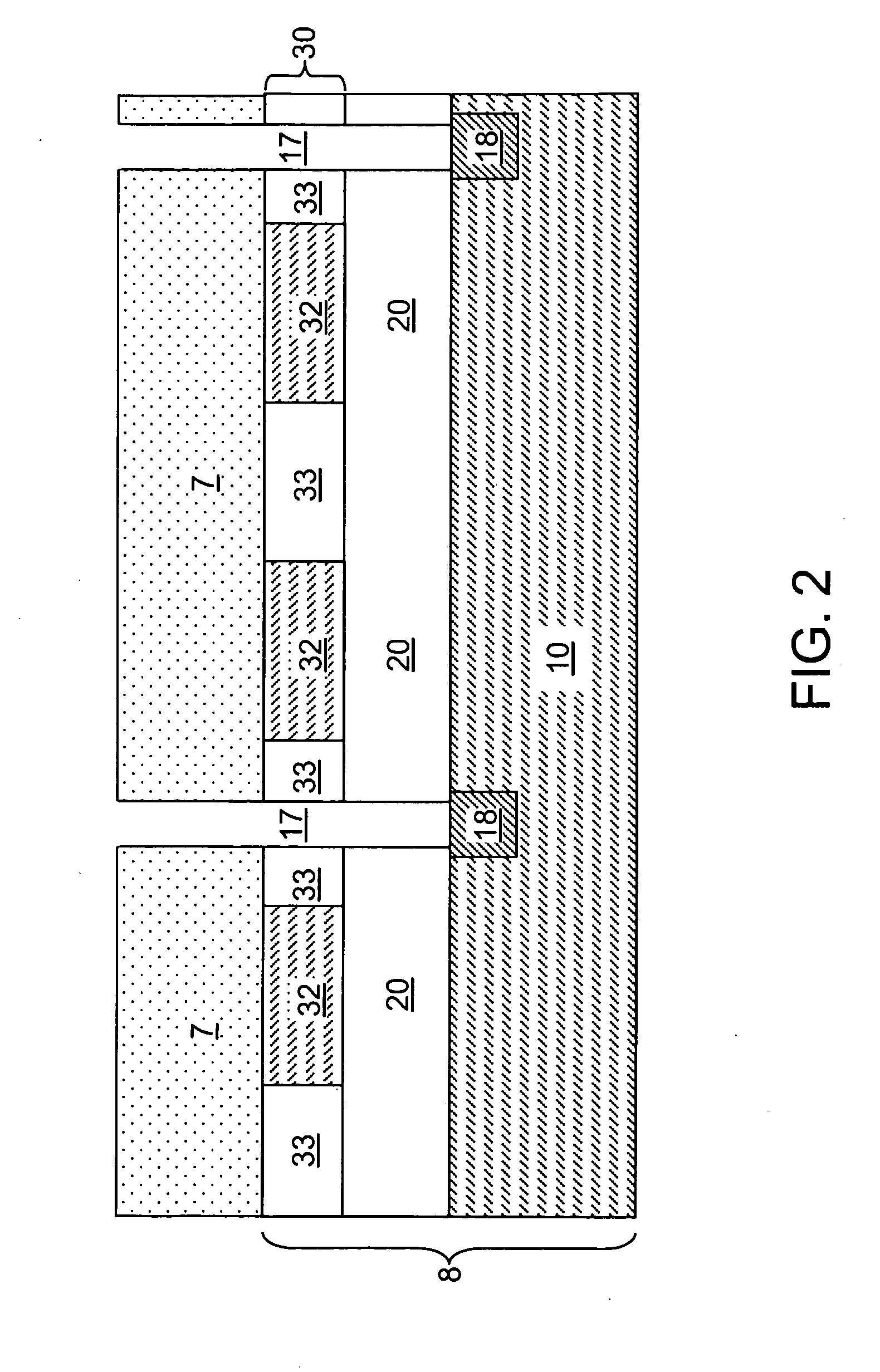

Transistor with workfunction-induced charge layer

ActiveUS6891234B1ConductivityImprove conductivitySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorCharge layer

An electrical switching device includes a semiconductor having a channel therein which is proximate to at least on channel tap in an extension region and also to a gate. A conductor (e.g., a metal) is disposed proximate to the extension region but is electrically isolated from both the extension region and the gate (e.g., through the use of one or more insulators). The conductor has a workfunction outside of the bandgap of a semiconductor in the extension region and therefore includes a layer of charge in the extension region. The magnitude and polarity of this layer of charge is controlled through selection of the metal, the semiconductor, and the insulator.

Owner:ACORN SEMI LLC

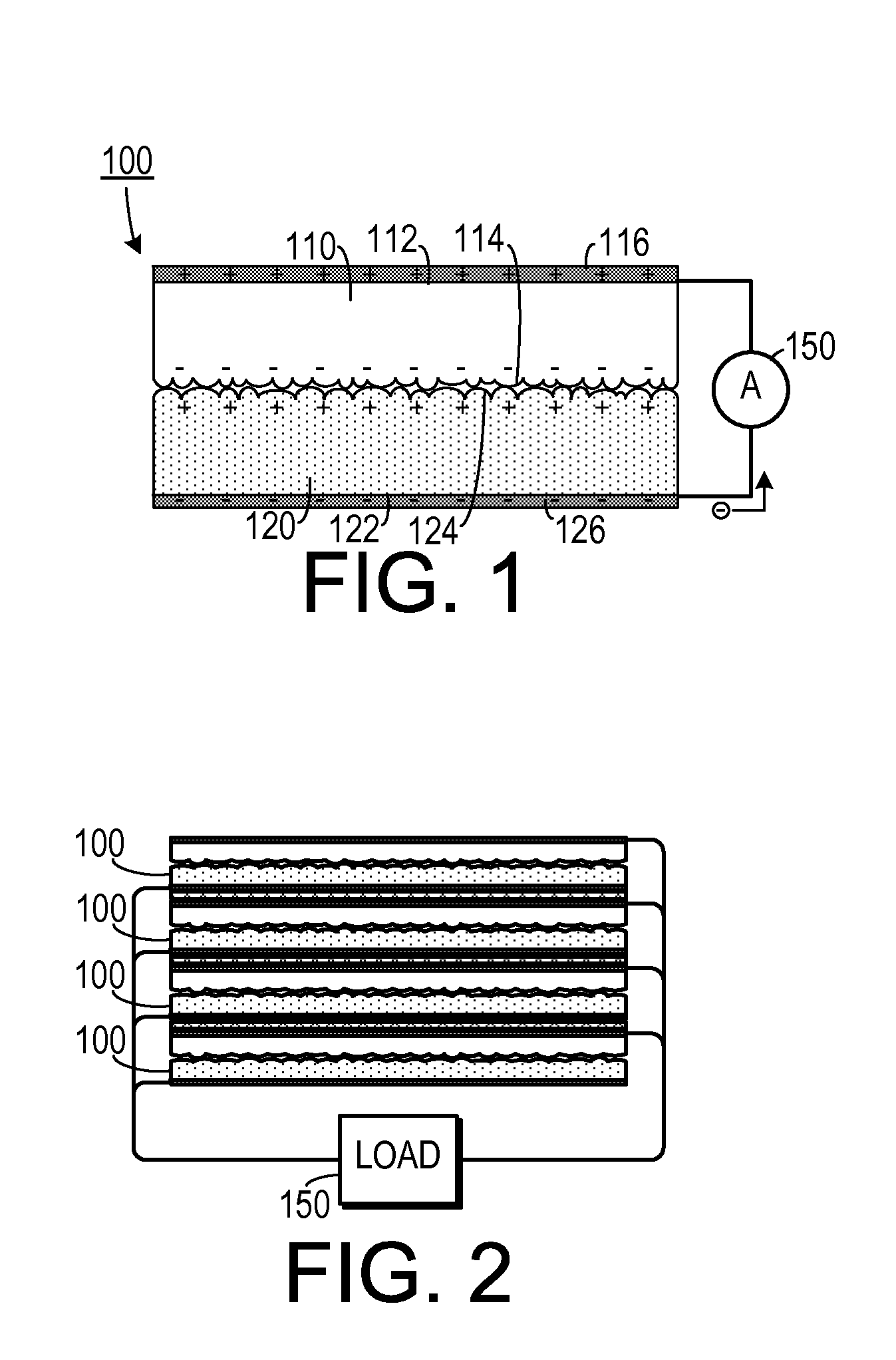

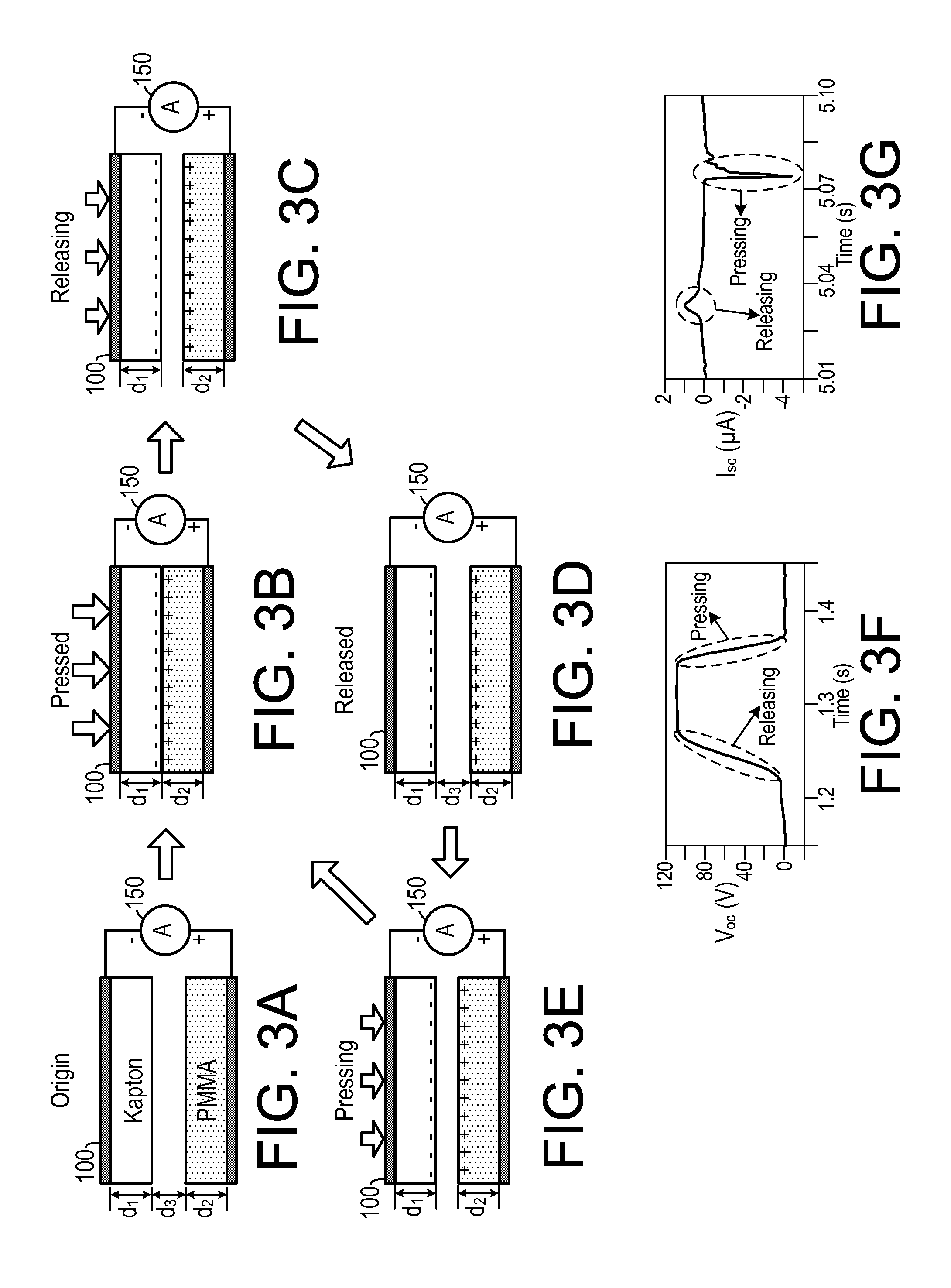

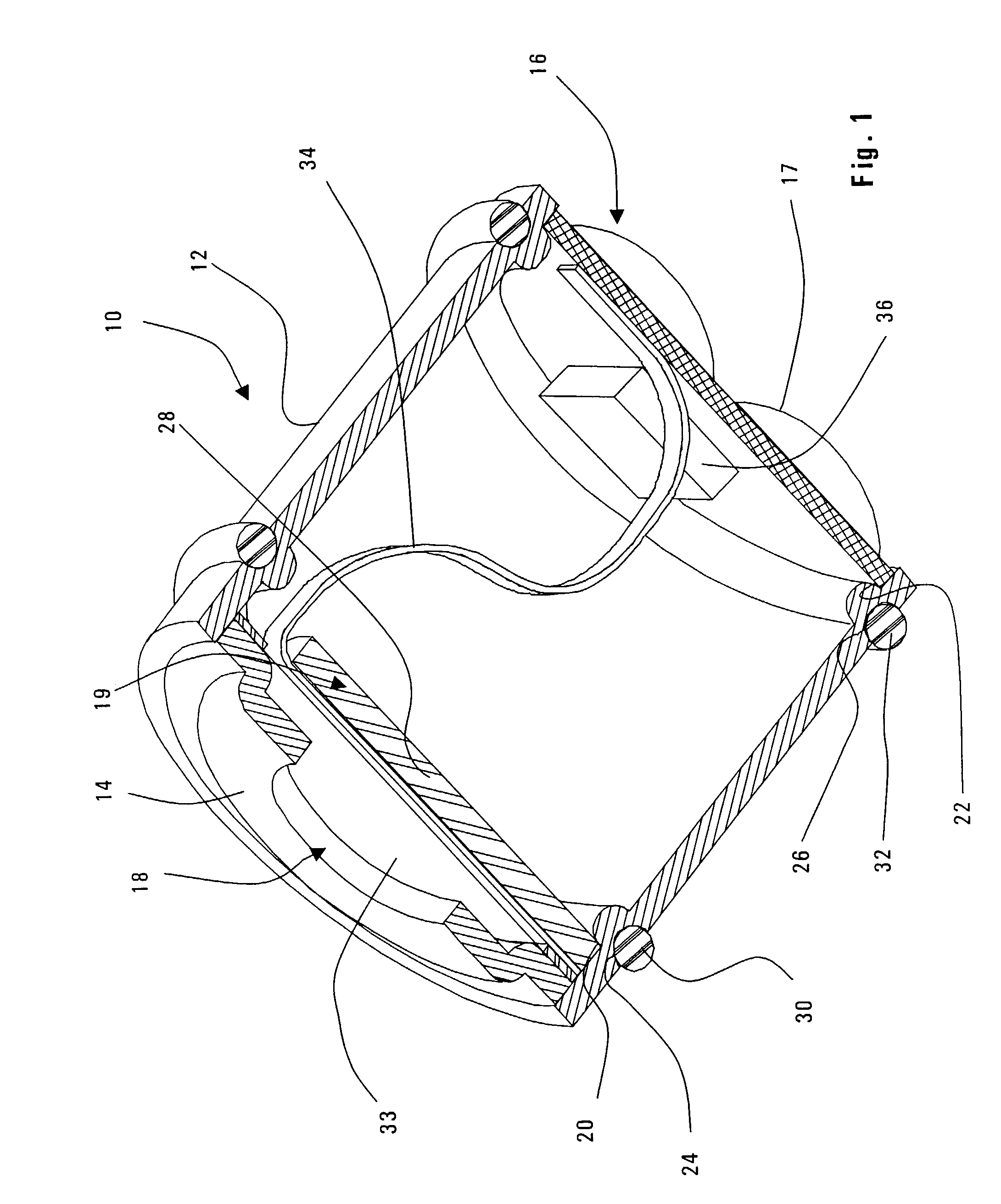

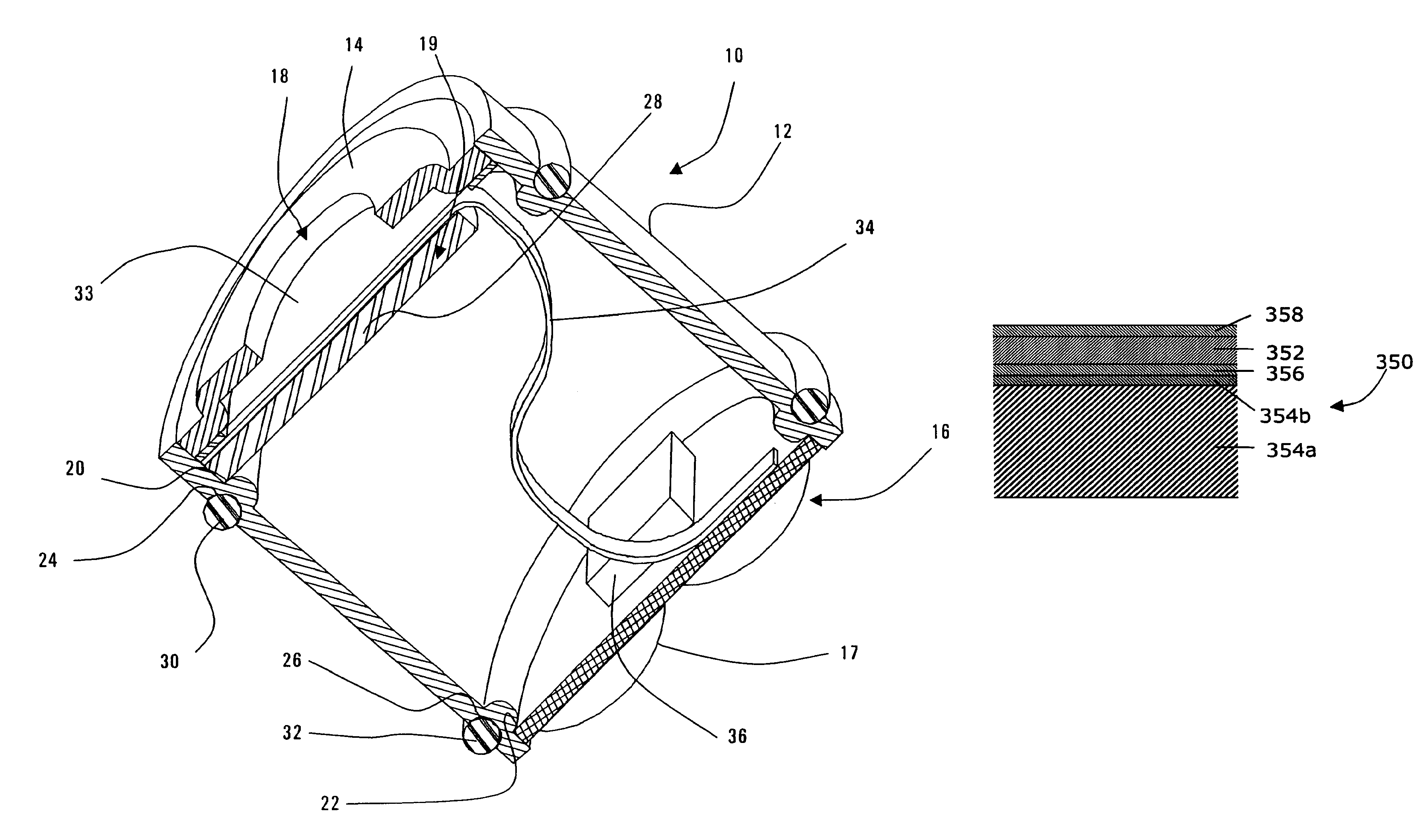

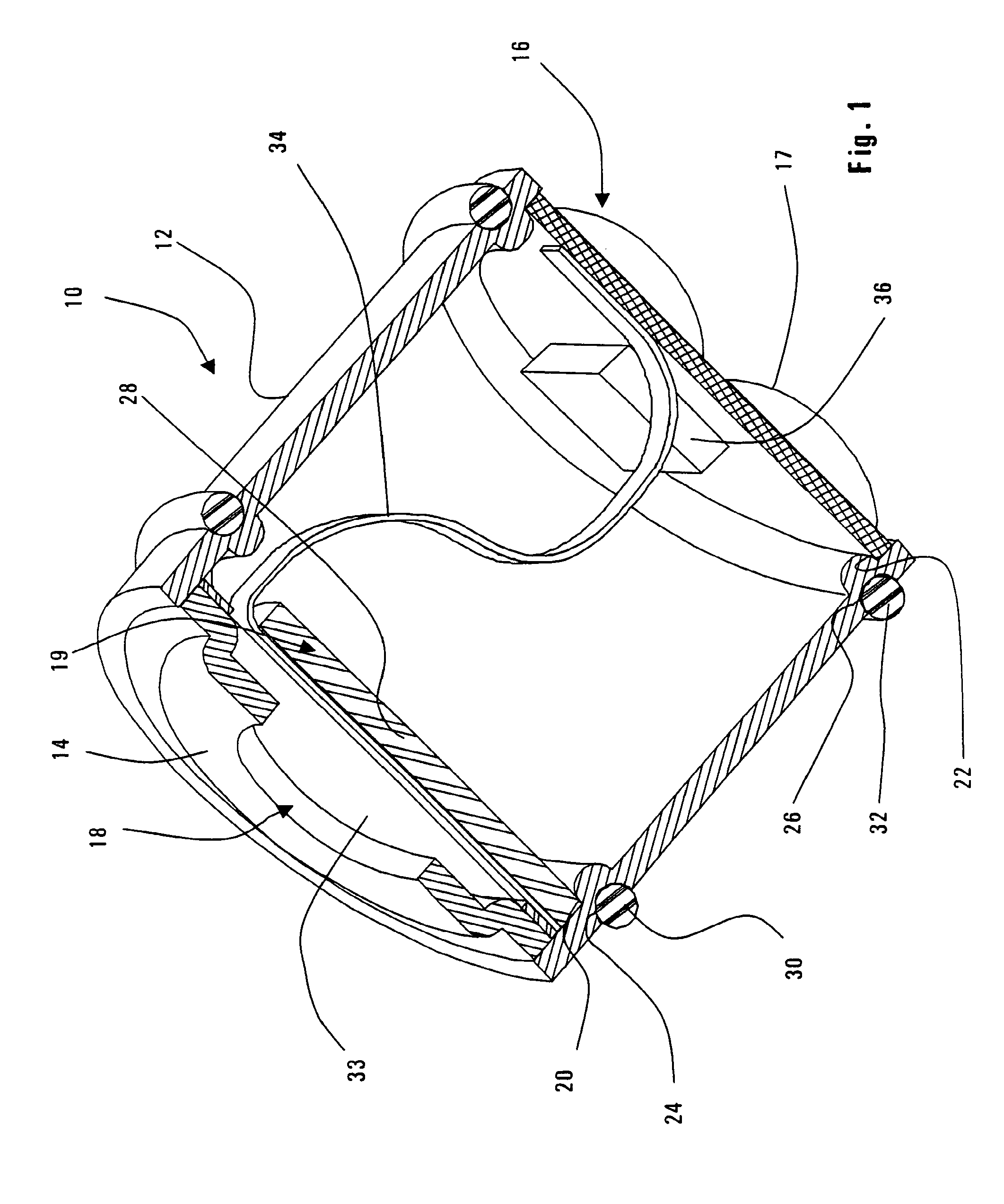

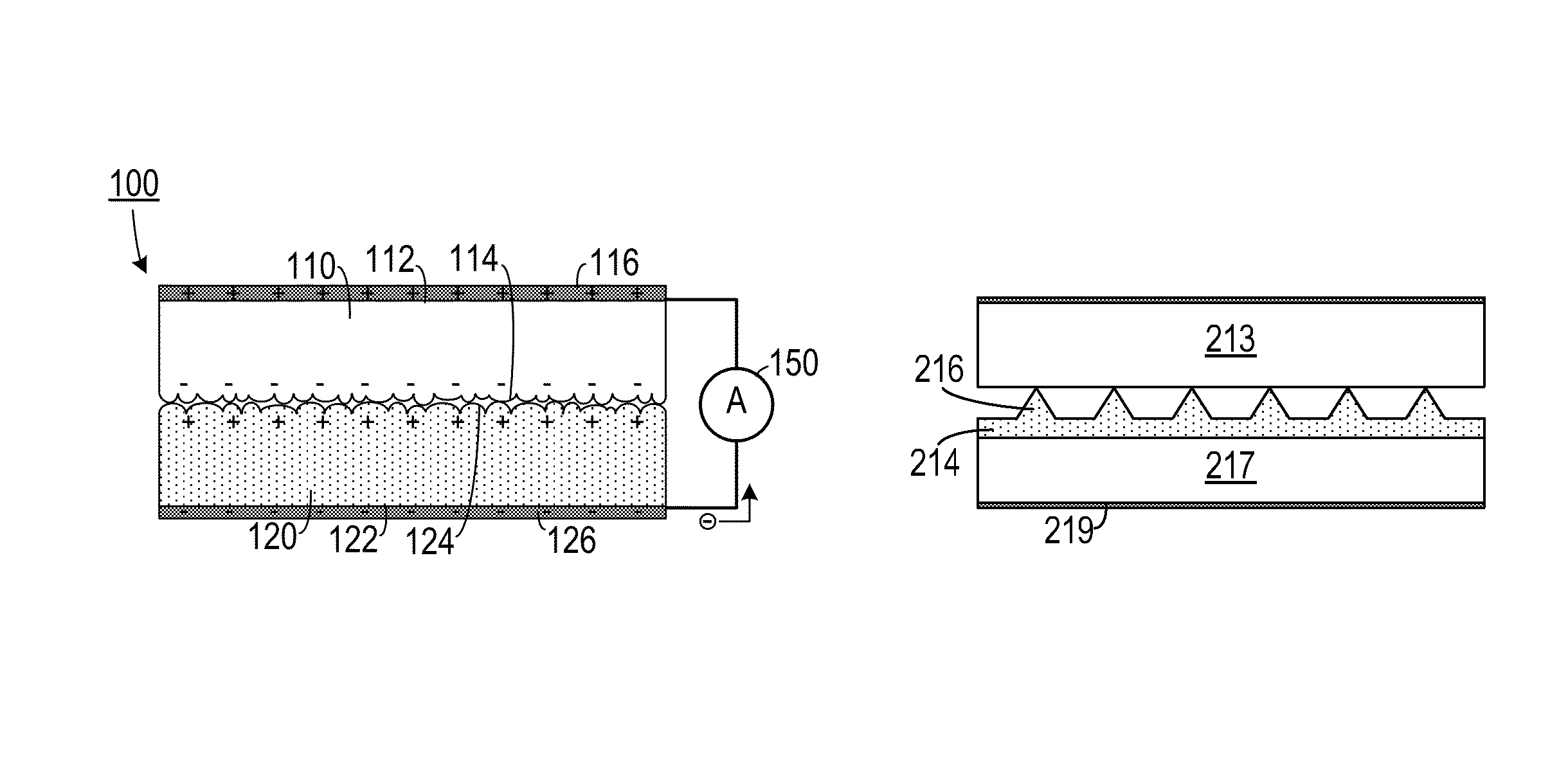

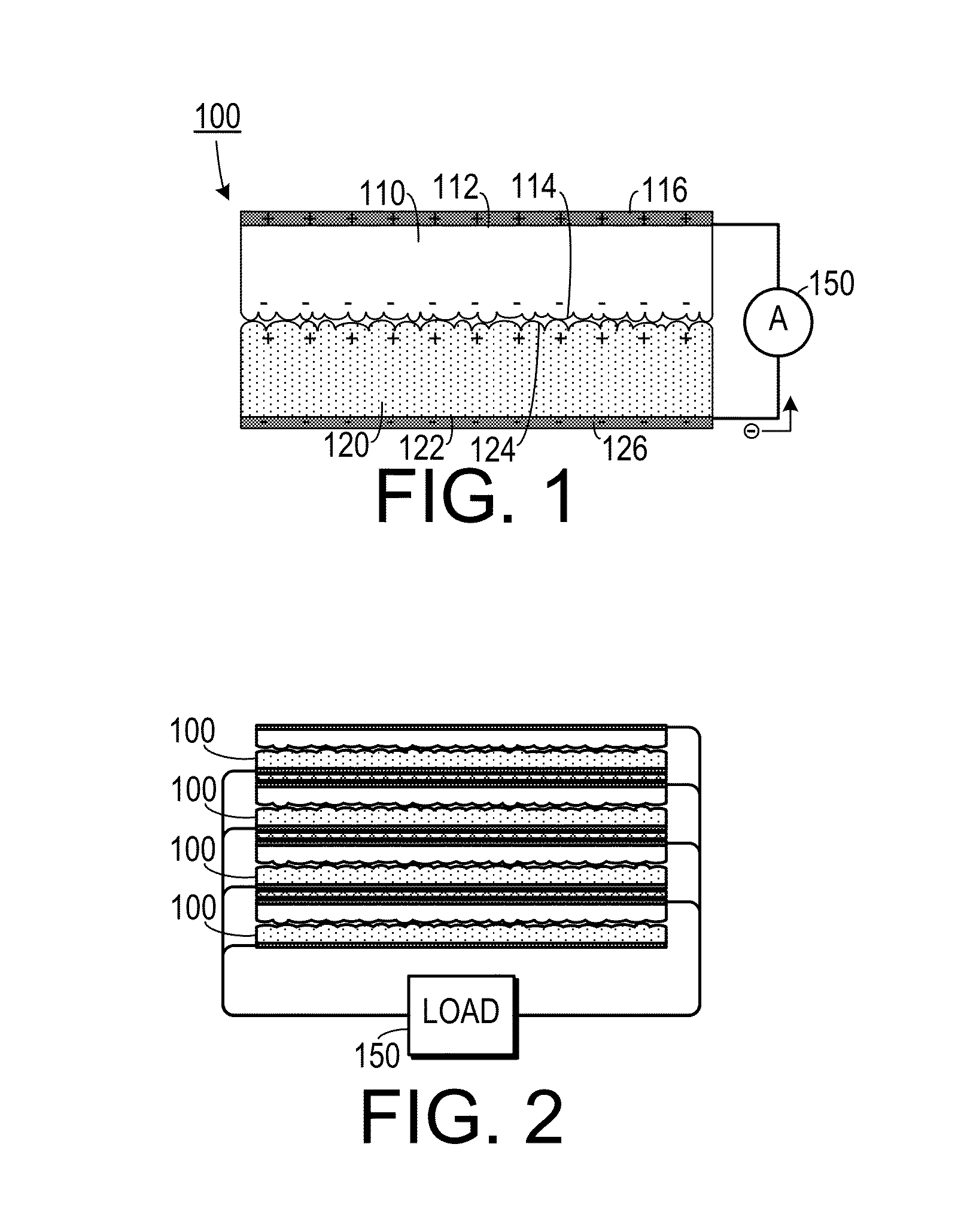

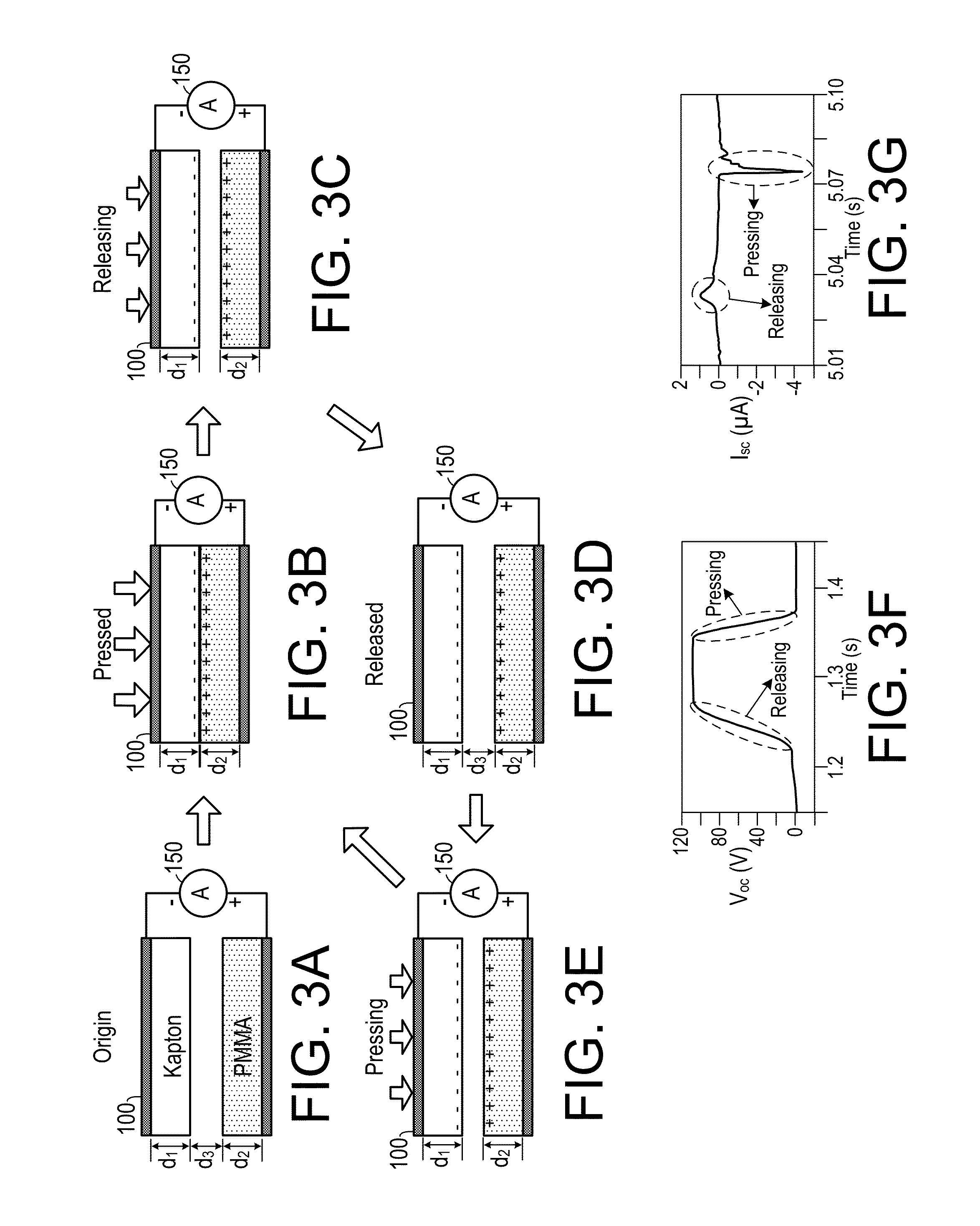

Triboelectric Generator

A generator includes a thin first contact charging layer and a thin second contact charging layer. The thin first contact charging layer includes a first material that has a first rating on a triboelectric series. The thin first contact charging layer has a first side with a first conductive electrode applied thereto and an opposite second side. The thin second contact charging layer includes a second material that has a second rating on a triboelectric series that is more negative than the first rating. The thin first contact charging layer has a first side with a first conductive electrode applied thereto and an opposite second side. The thin second contact charging layer is disposed adjacent to the first contact charging layer so that the second side of the second contact charging layer is in contact with the second side of the first contact charging layer.

Owner:GEORGIA TECH RES CORP

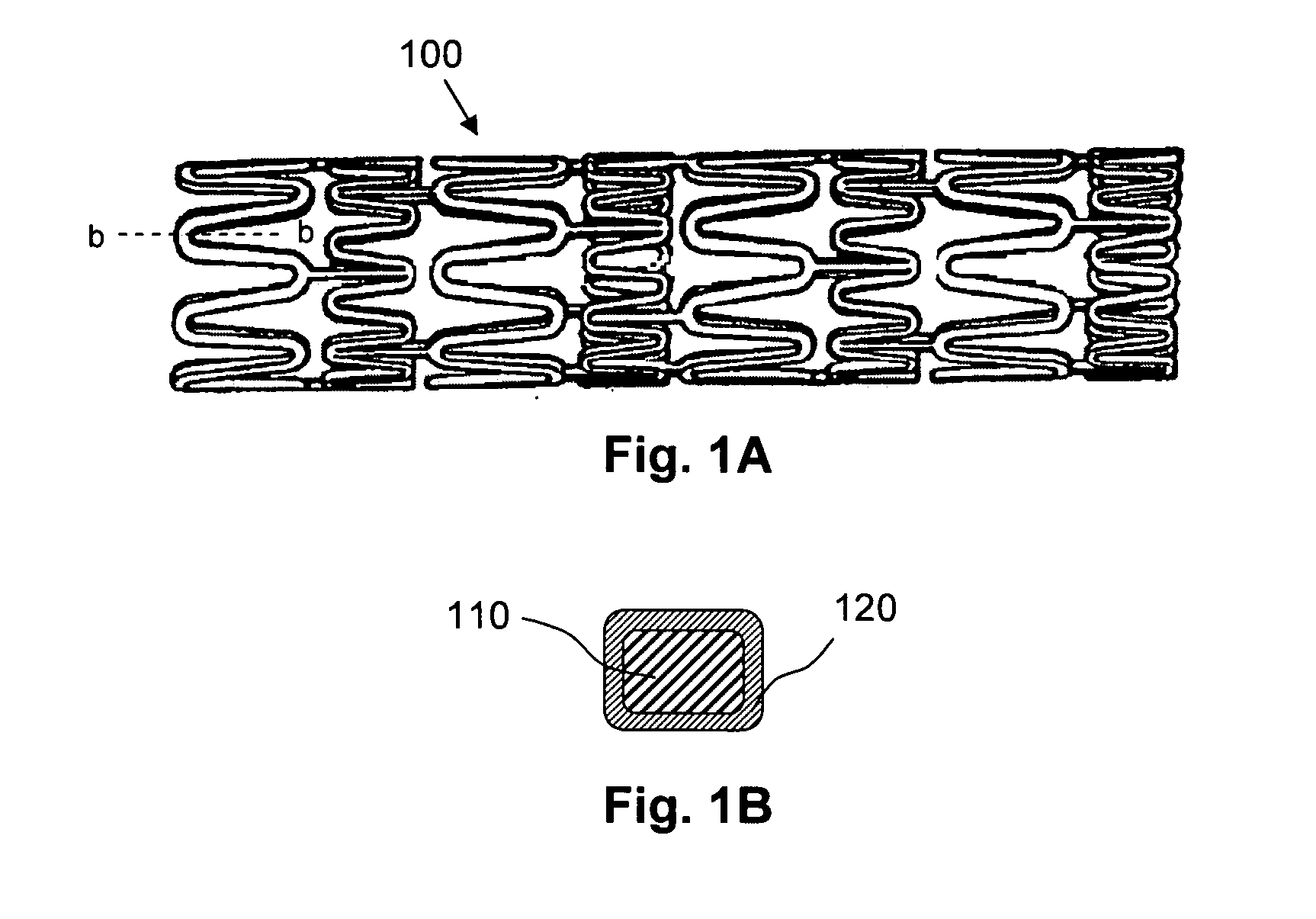

Medical devices having multiple charged layers

InactiveUS20070154513A1Increasing the thicknessGood for uniformity controlStentsSurgeryPolyelectrolyteCharge layer

According to an aspect of the present invention, medical devices are provided, which are adapted for implantation or insertion into a subject and which include at least one multilayer region that contains multiple charged layers of alternating charge. The multiple charged layers, in turn, include the following: (i) at least one charged block copolymer (e.g., a charged block copolymer that contains one or more polyelectrolyte blocks) and (ii) at least one charged therapeutic agent (e.g., a charged therapeutic agent that contains one or more polyelectrolyte blocks).

Owner:BOSTON SCI SCIMED INC

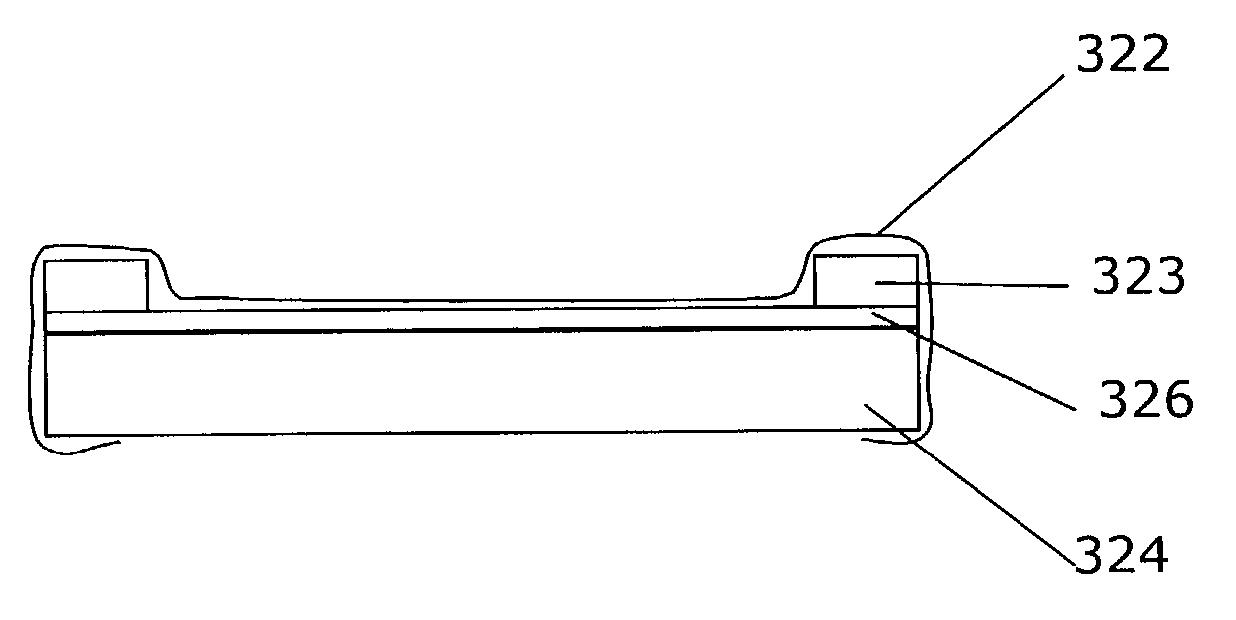

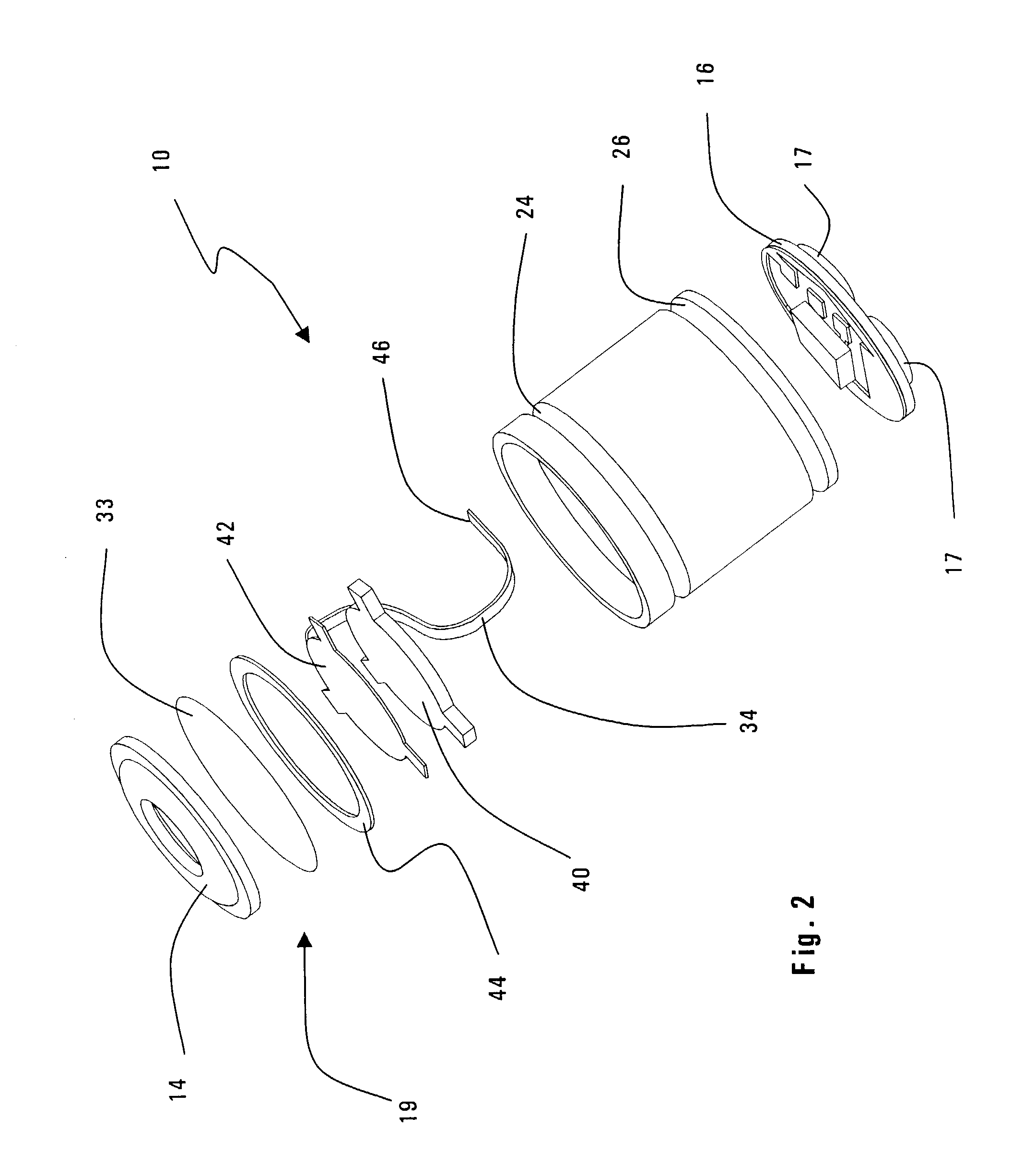

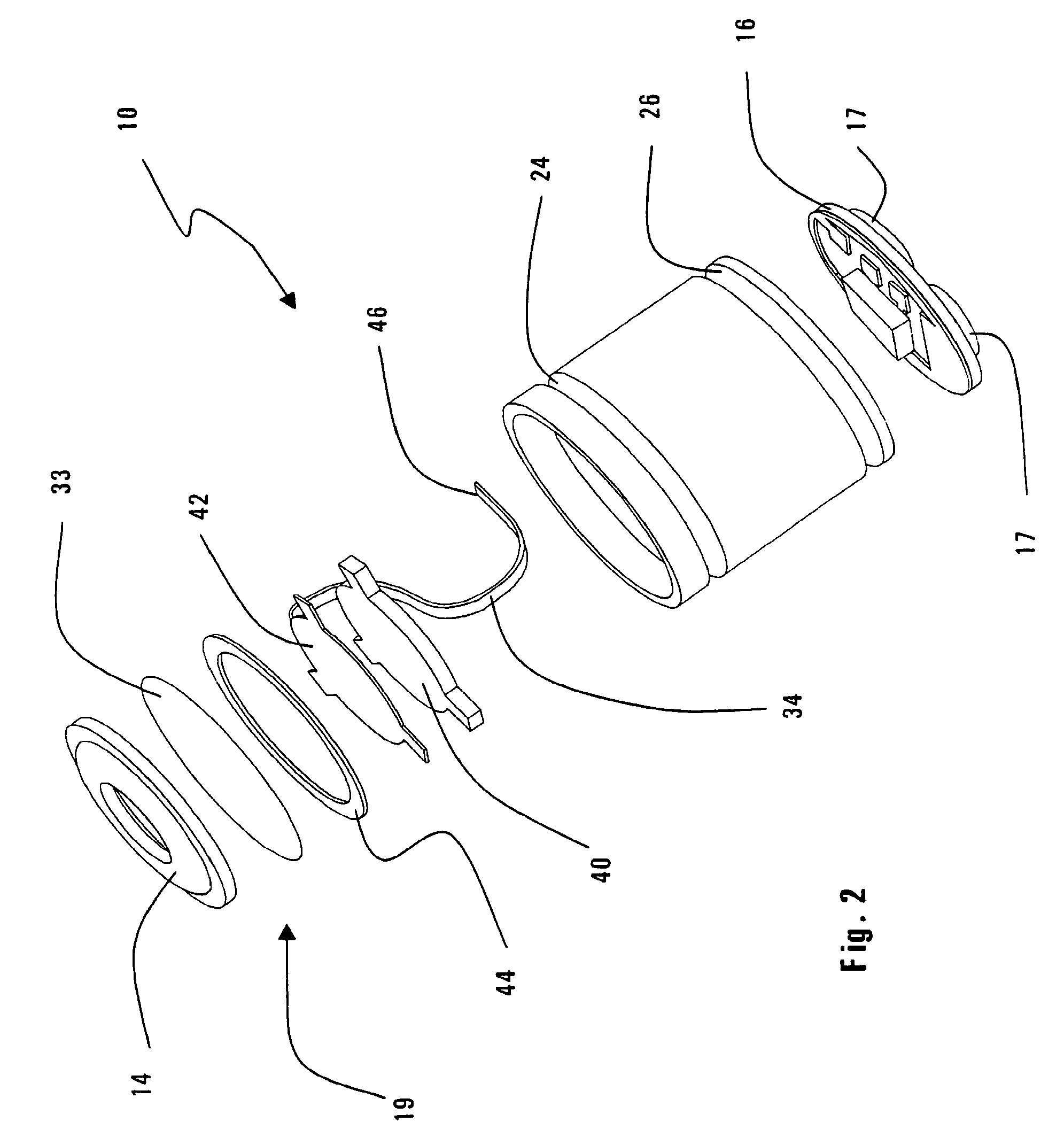

Electret assembly for a microphone having a backplate with improved charge stability

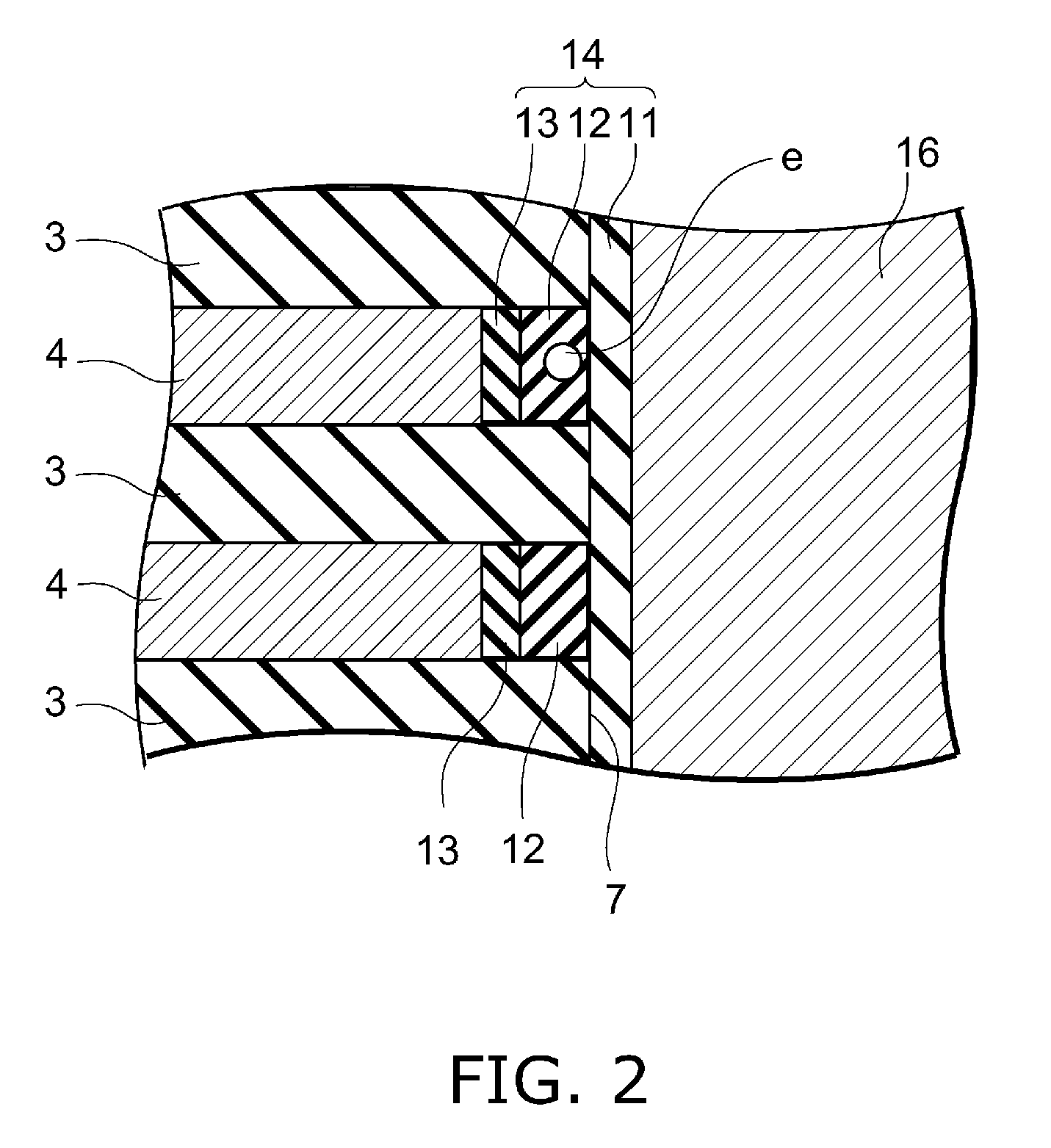

InactiveUS7136496B2Minimize chargeMinimize water absorptionPiezoelectric/electrostrictive microphonesElectrets selectrostatic transducerElectrical conductorCharge layer

The present invention relates to a microphone that includes a housing and a diaphragm and backplate located with the housing. The housing has a sound port for receiving the sound. The diaphragm undergoes movement relative to the backplate, which it opposes, in response to the incoming sound. The backplate has a charged layer with a first surface that is exposed to the diaphragm and a second surface opposite the first surface. The backplate further includes a conductor for transmitting a signal from the backplate to electronics in the housing. The conductor faces the second surface of the charged layer. To minimize the charge degradation created by contact with or infiltration of foreign materials, the first surface, the second surface, or both surfaces of the charged layer includes a protective layer thereon.

Owner:SONION NEDERLAND

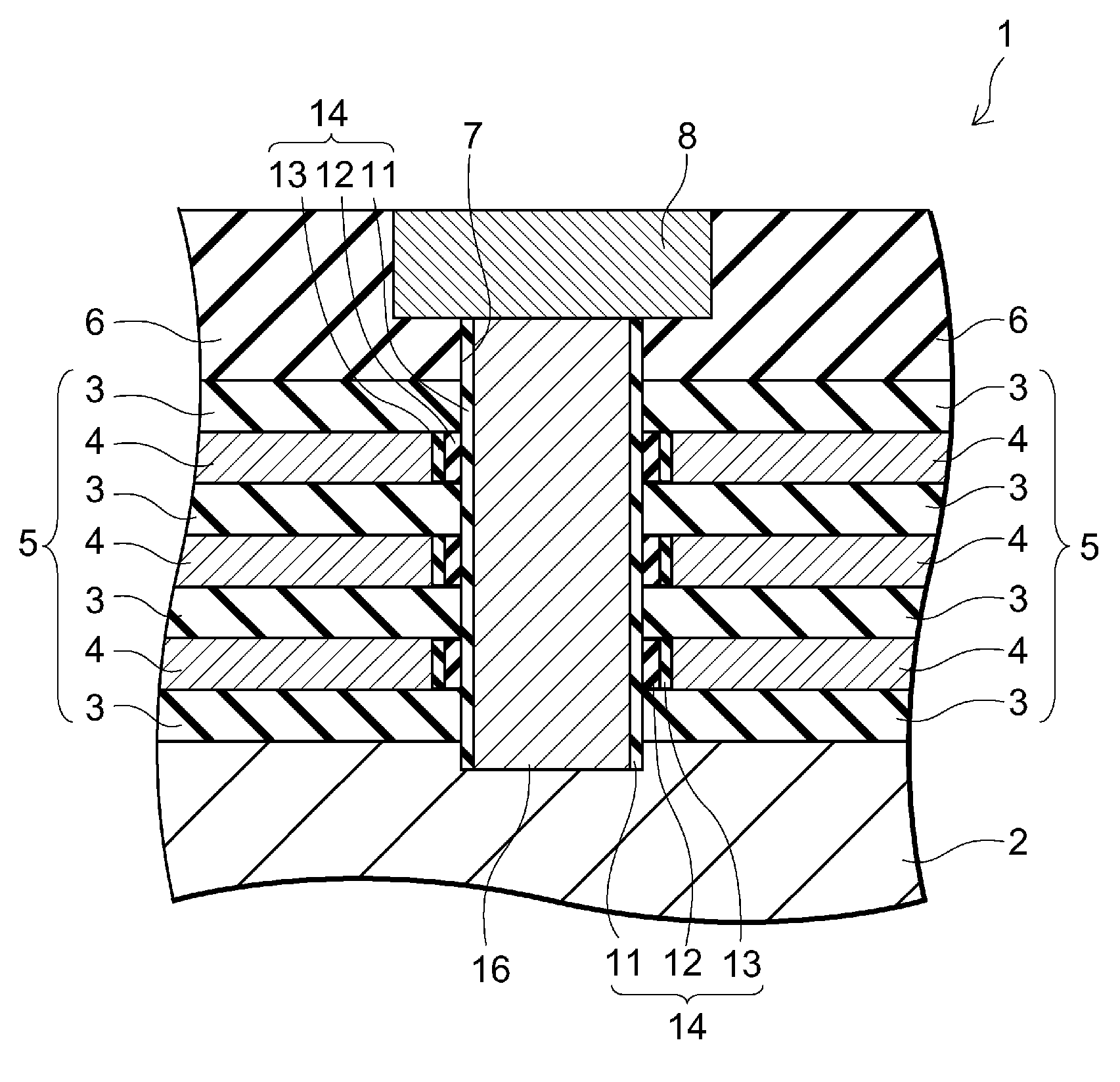

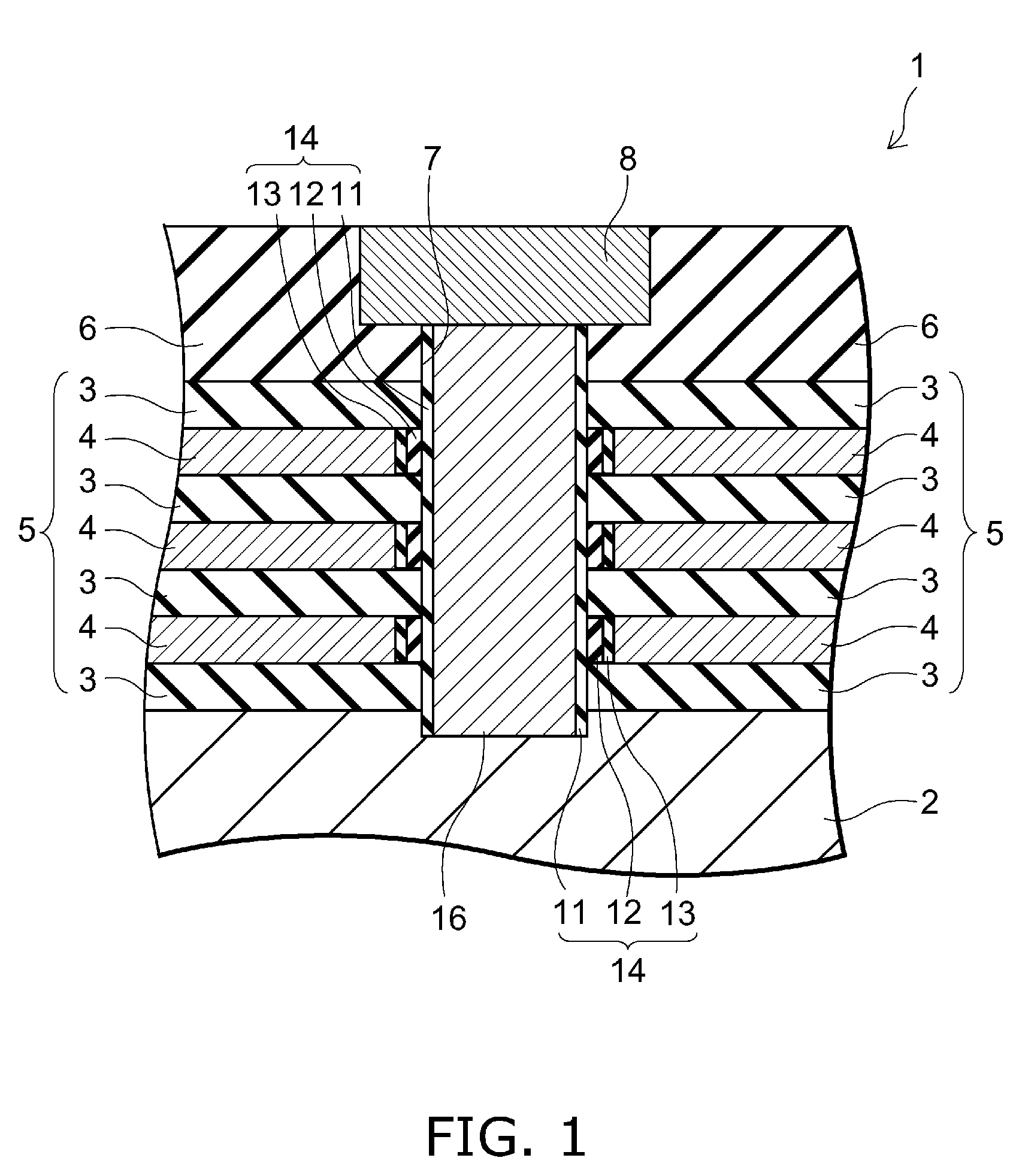

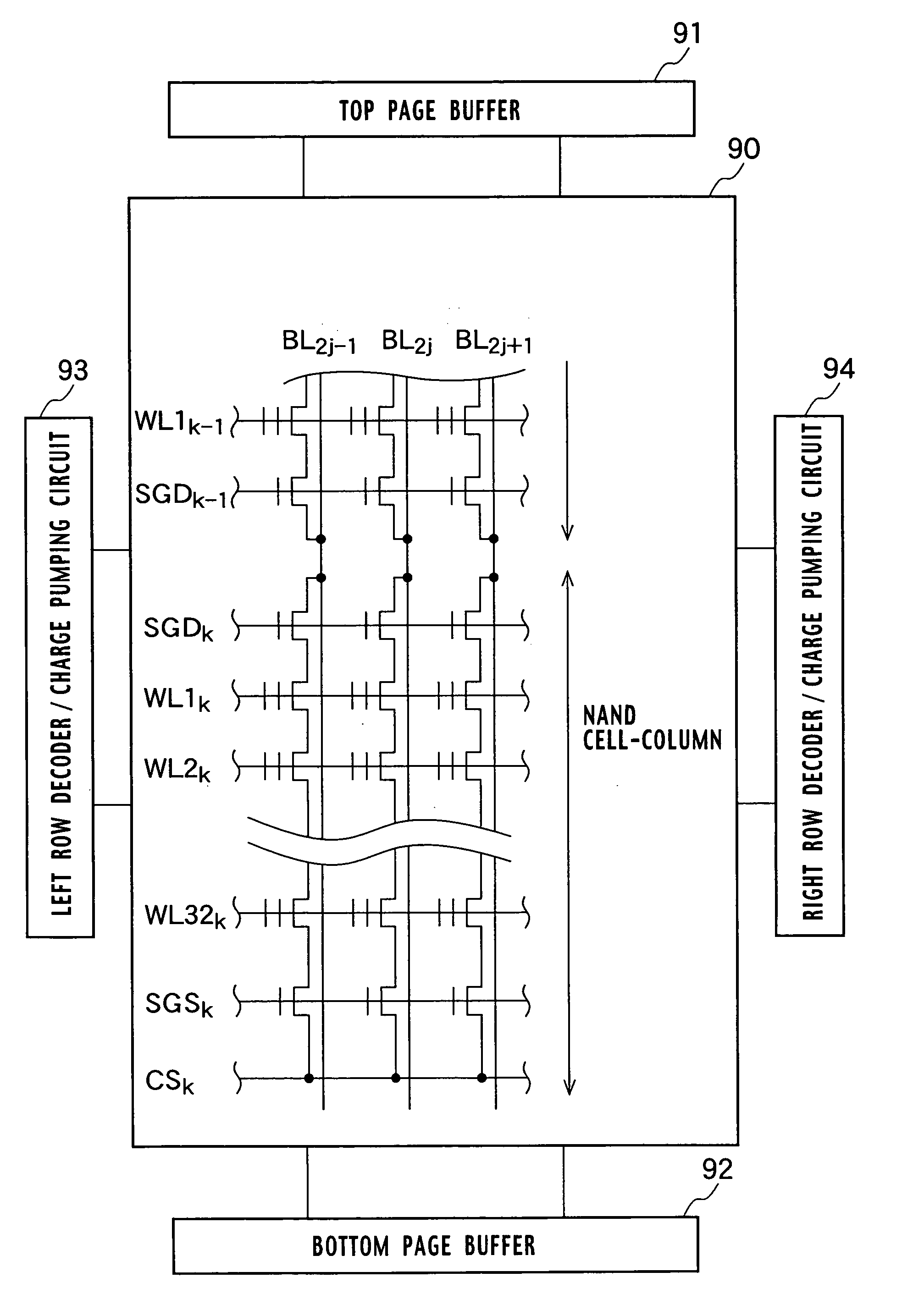

Semiconductor memory device and method for manufacturing same

A laminated body is formed by alternately laminating a plurality of dielectric films and electrode films on a silicon substrate. Next, a through hole extending in the lamination direction is formed in the laminated body. Next, a selective nitridation process is performed to selectively form a charge layer made of silicon nitride in a region of an inner surface of the through hole corresponding to the electrode film. Next, a high-pressure oxidation process is performed to form a block layer made of silicon oxide between the charge layer and the electrode film. Next, a tunnel layer made of silicon oxide is formed on an inner side surface of the through hole. Thus, a flash memory can be manufactured in which the charge layer is split for each electrode film.

Owner:KIOXIA CORP

Electret assembly for a microphone having a backplate with improved charge stability

InactiveUS8280082B2Minimize chargeMinimize water absorptionWave amplification devicesMicrophone structural associationElectrical conductorCharge layer

The present invention relates to a microphone that includes a housing and a diaphragm and backplate located with the housing. The housing has a sound port for receiving the sound. The diaphragm undergoes movement relative to the backplate, which it opposes, in response to the incoming sound. The backplate has a charged layer with a first surface that is exposed to the diaphragm and a second surface opposite the first surface. The backplate further includes a conductor for transmitting a signal from the backplate to electronics in the housing. The conductor faces the second surface of the charged layer. To minimize the charge degradation created by contact with or infiltration of foreign materials, the first surface, the second surface, or both surfaces of the charged layer includes a protective layer thereon.

Owner:SONION NEDERLAND

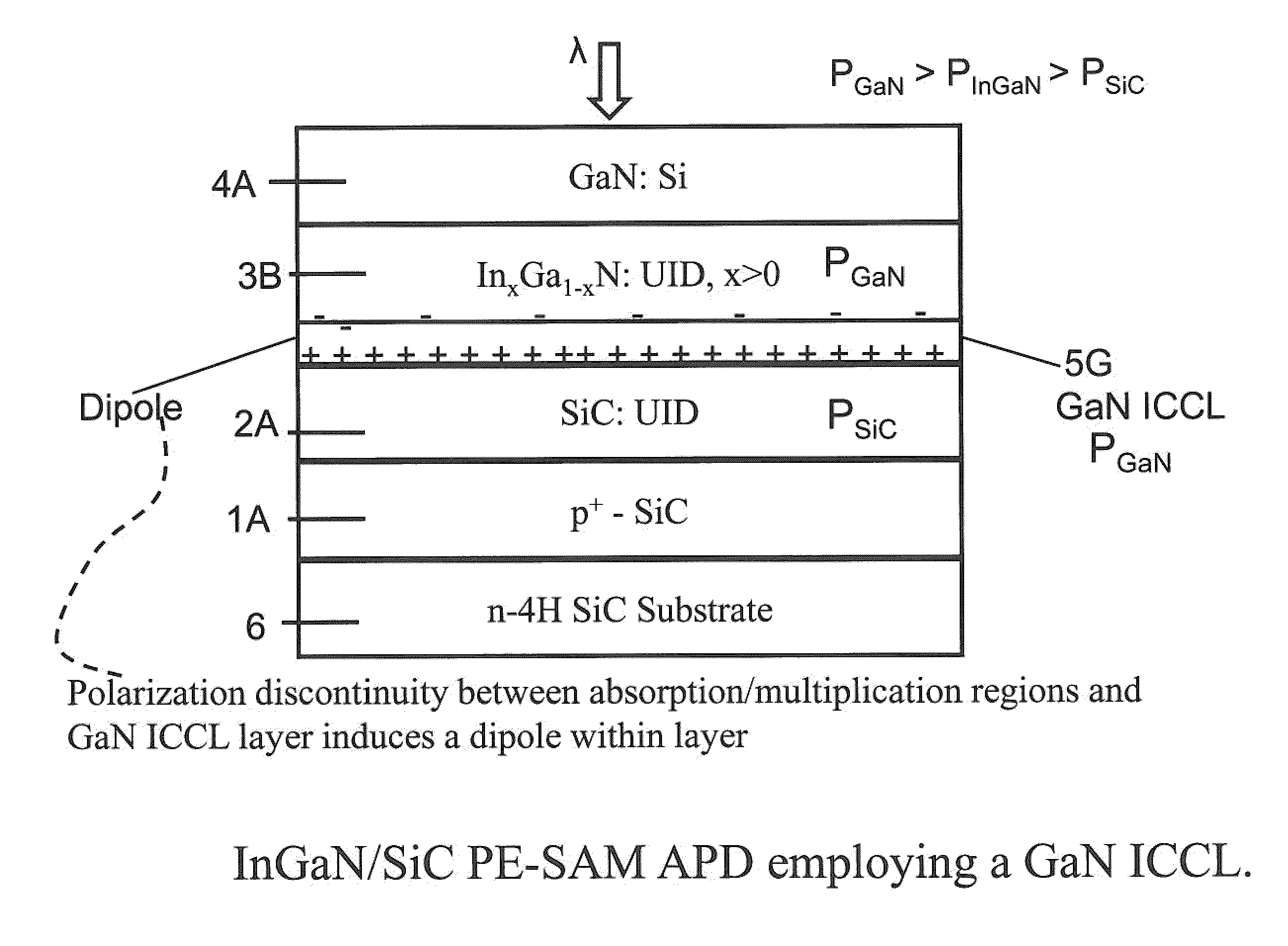

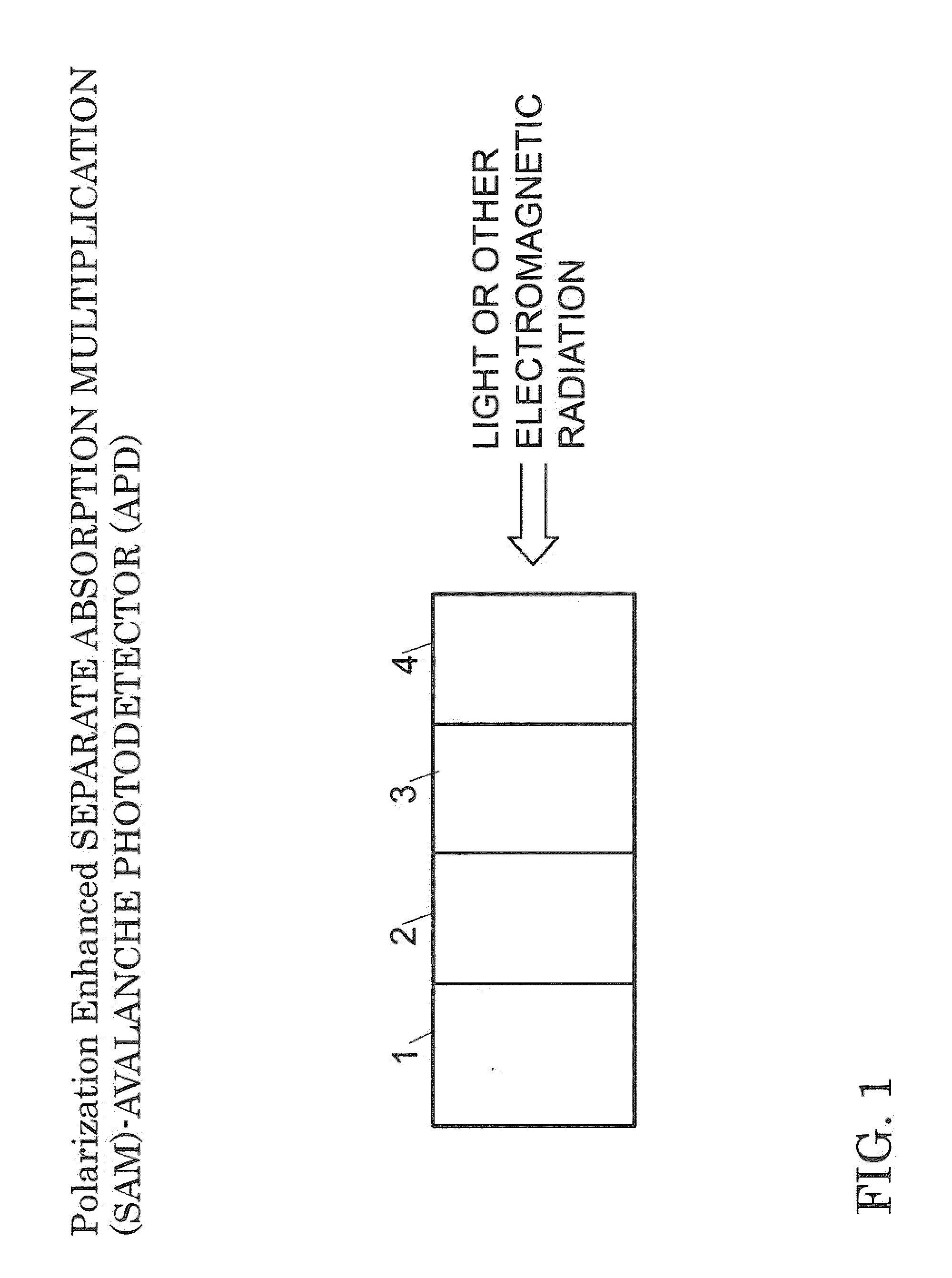

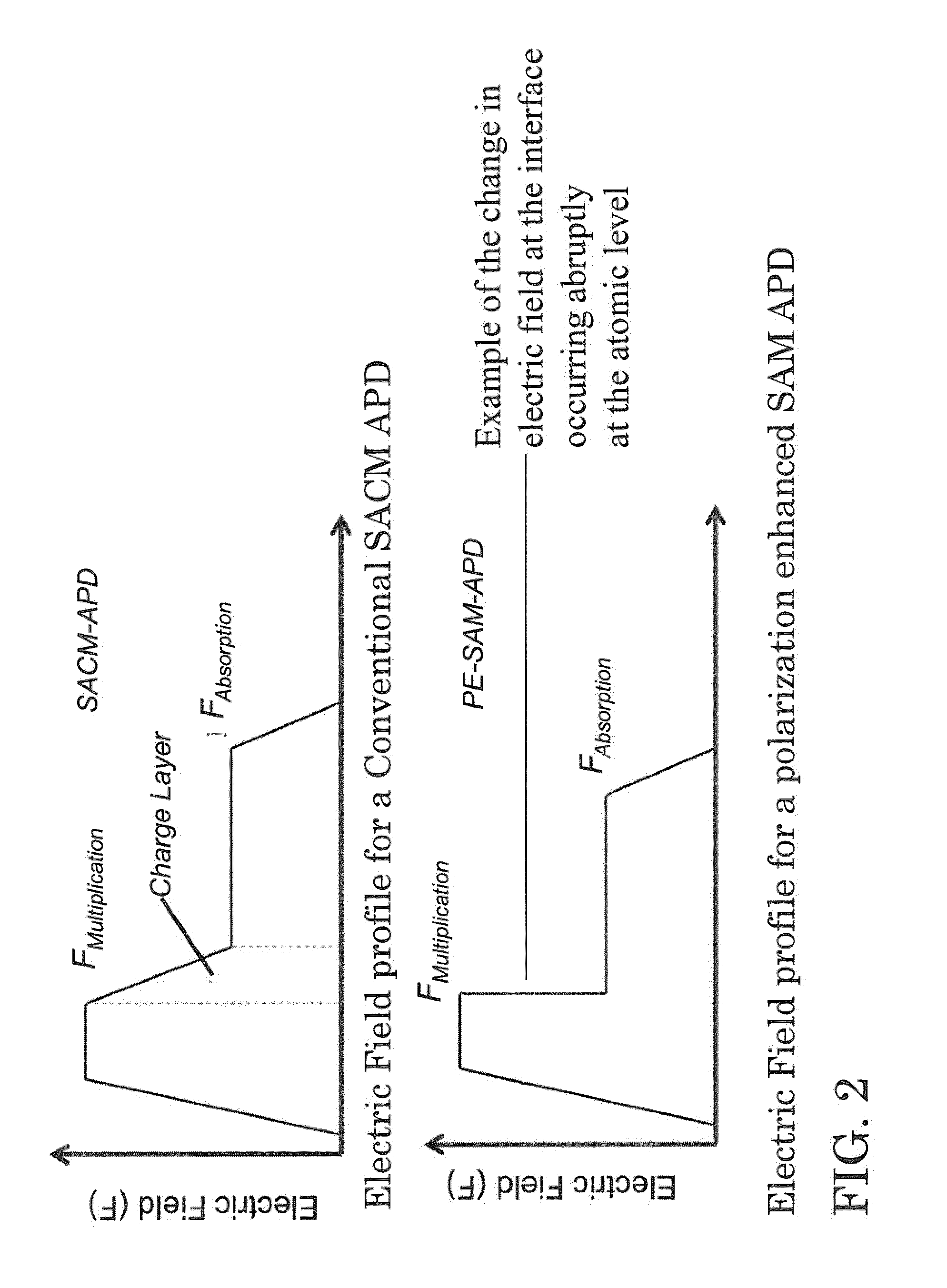

Polarization enhanced avalanche photodetector and method thereof

InactiveUS20110291109A1Efficient collectionLarge gainSemiconductor/solid-state device manufacturingPhotovoltaic energy generationCharge carrierPhotodetector

An avalanche photodetector comprising a multiplication layer formed of a first material having a first polarization; the multiplication layer having a first electric field upon application of a bias voltage; an absorption layer formed of a second material having a second polarization forming an interface with the multiplication layer; the absorption layer having a second electric field upon application of the bias voltage, the second electric field being less than the first electric field or substantially zero, carriers created by light absorbed in the absorption layer being multiplied in the multiplication layer due to the first electric field; the absorption layer having a second polarization which is greater or less than the first polarization to thereby create an interface charge; the interface charge being positive when the first material predominately multiplies holes, the interface charge being negative when the first material predominately multiplies electrons, the change in electric field at the interface occurring abruptly at the atomic level; the interface charge creating electric field discontinuity causing first electric field to attain the breakdown field in the multiplication region and the second electric field to be low or zero in the absorption layer to thereby eliminate the need for a doped charge layer and the associated thickness of the doped charge layer required to transition from the low field to the high field. Also claimed is a method of making.

Owner:ARMY THE UNITED STATES OF AMERICA AS REPREENTED BY THE SECRRETARY OF THE

Stacked gate semiconductor memory and manufacturing method for the same

A semiconductor memory embraces a plurality of memory cell transistors, and each of the memory cell transistors encompasses a substrate; a gate insulator stacked on the substrate, configured to enable tunneling of electrons through the gate insulator; a floating gate electrode stacked on the gate insulator, configured to accumulate electron charges; an inter-electrode dielectric stacked on the floating gate electrode incorporating a positive charge layer, distribution of the positive charge layer being localized in the lower half of the inter-electrode dielectric; and a control gate electrode stacked on the inter-electrode dielectric.

Owner:KK TOSHIBA

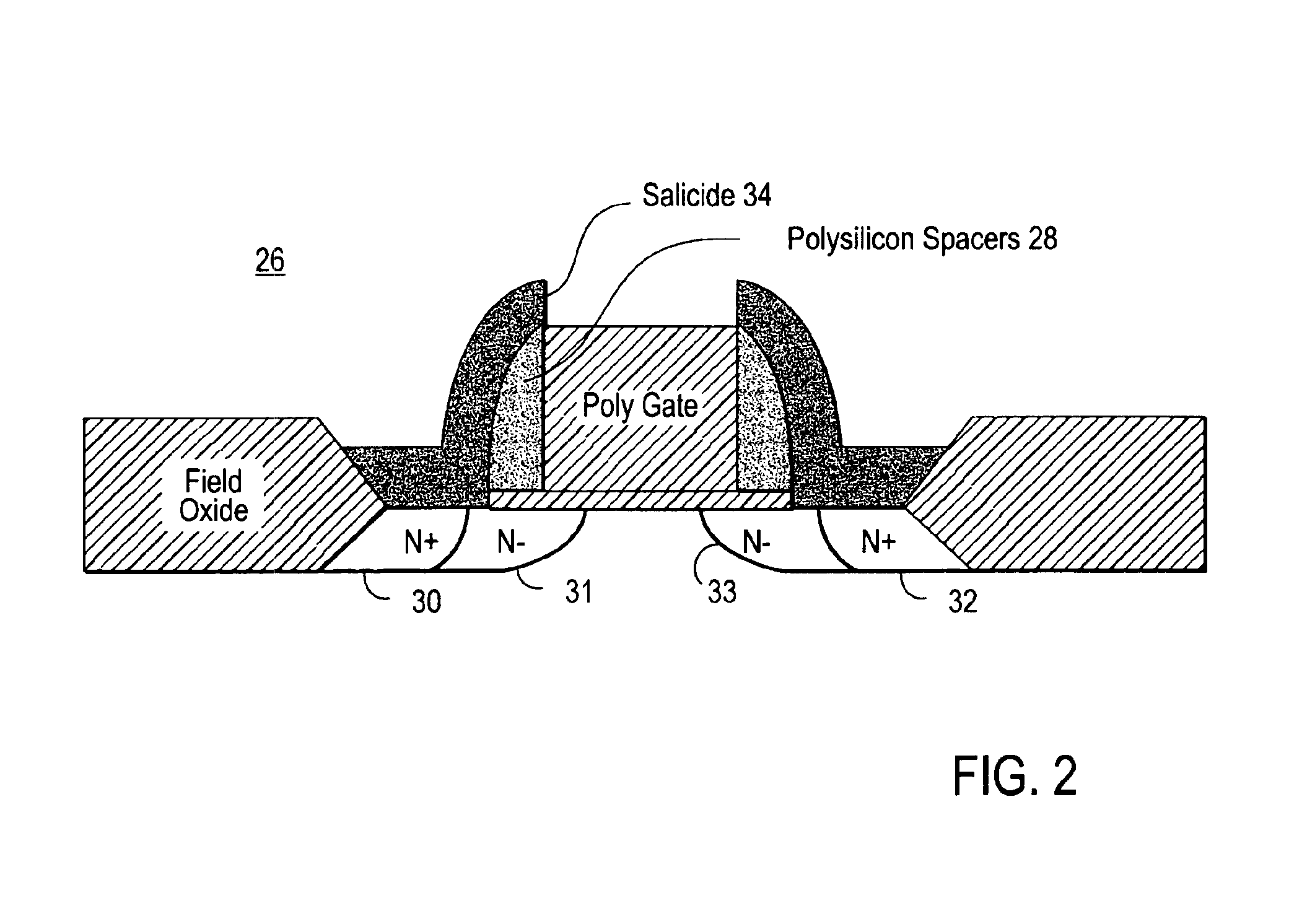

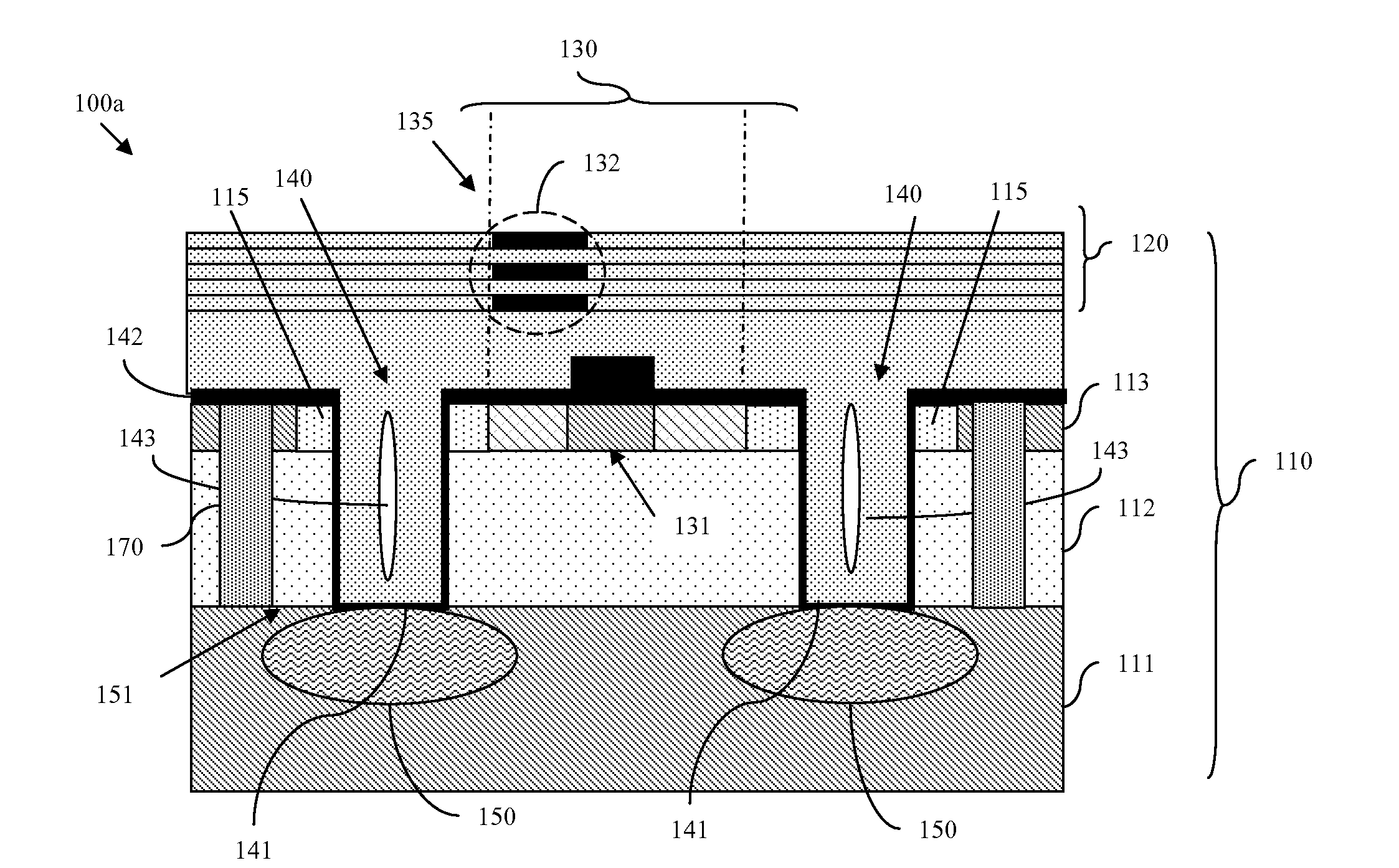

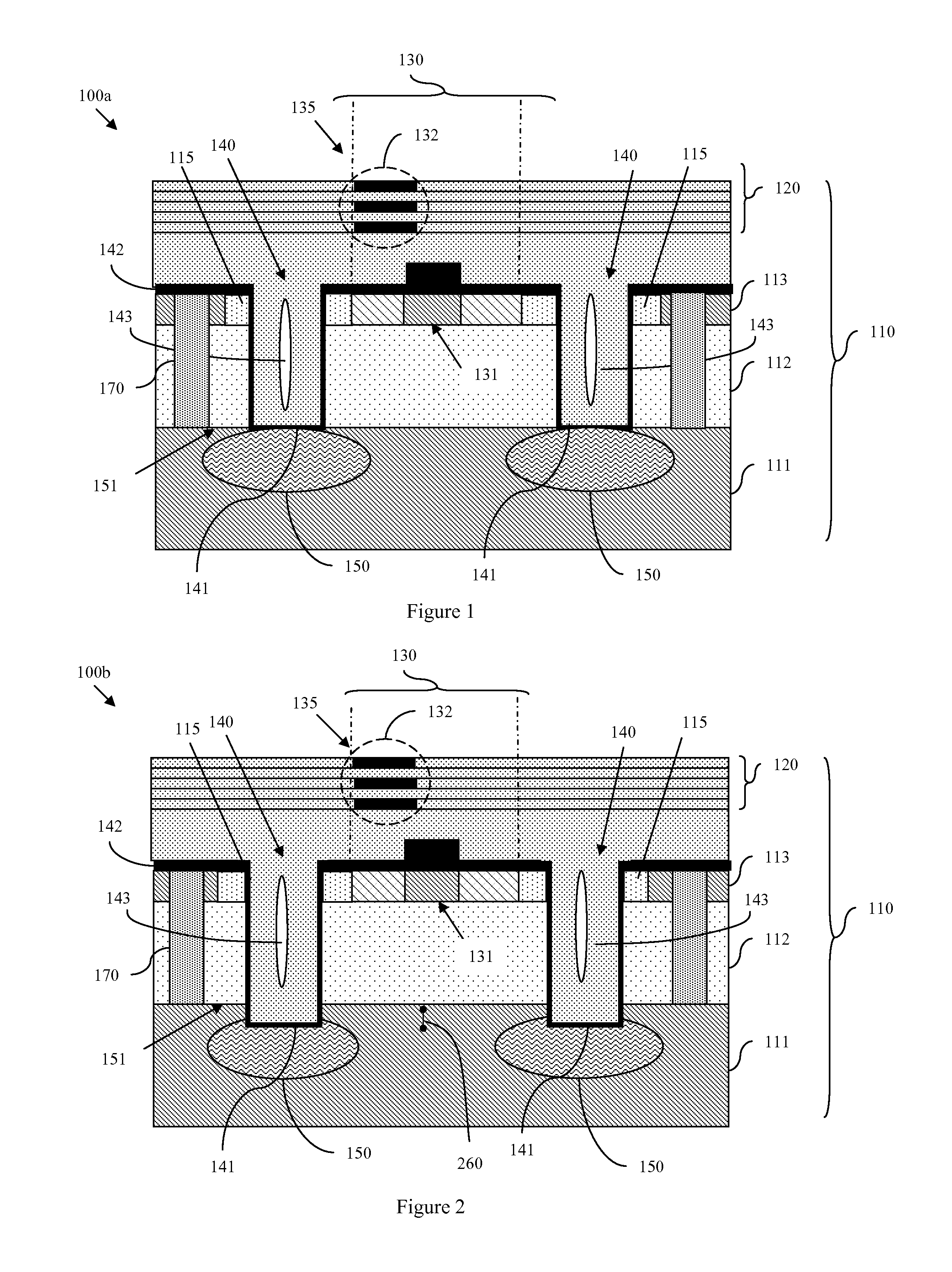

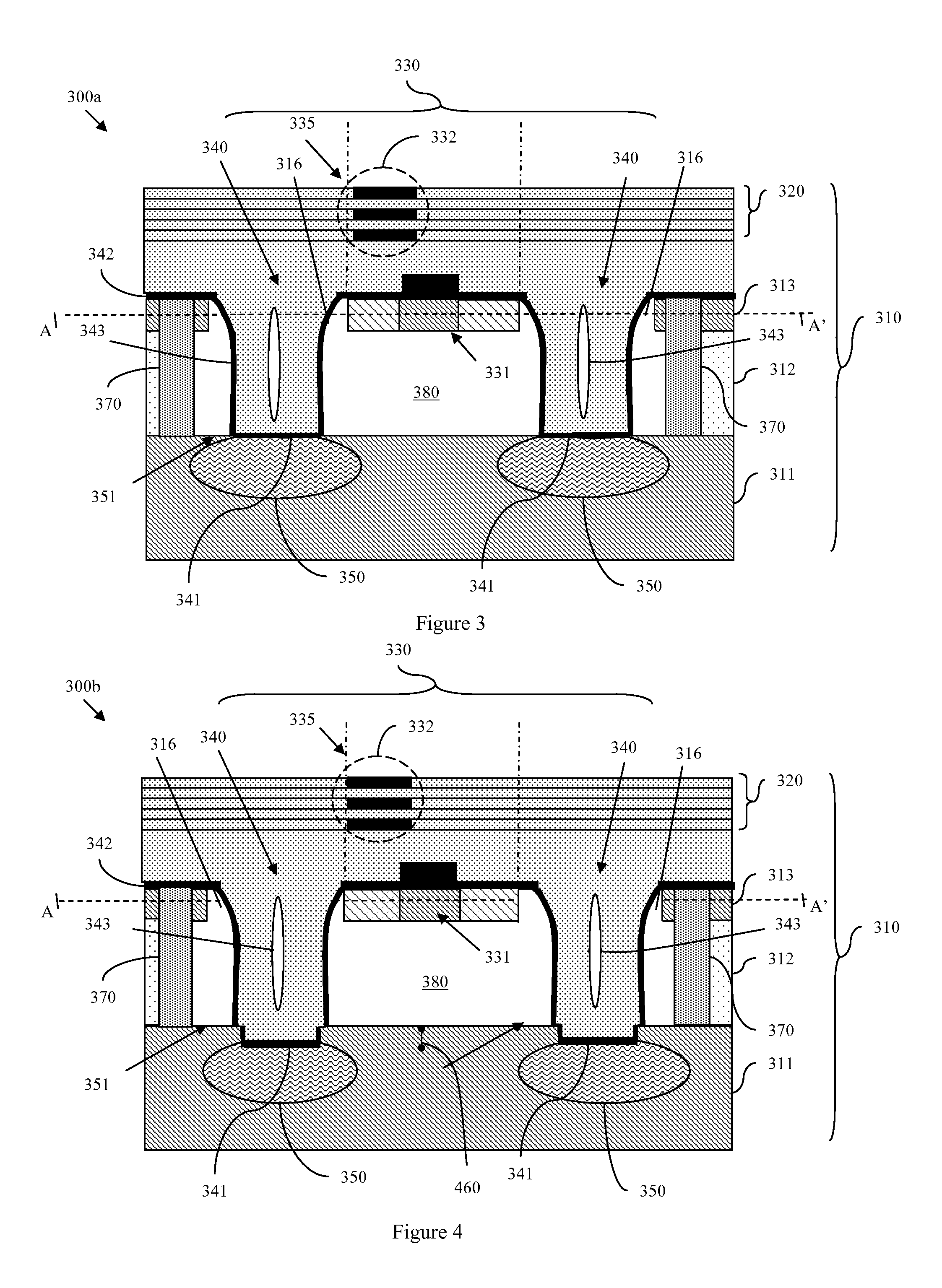

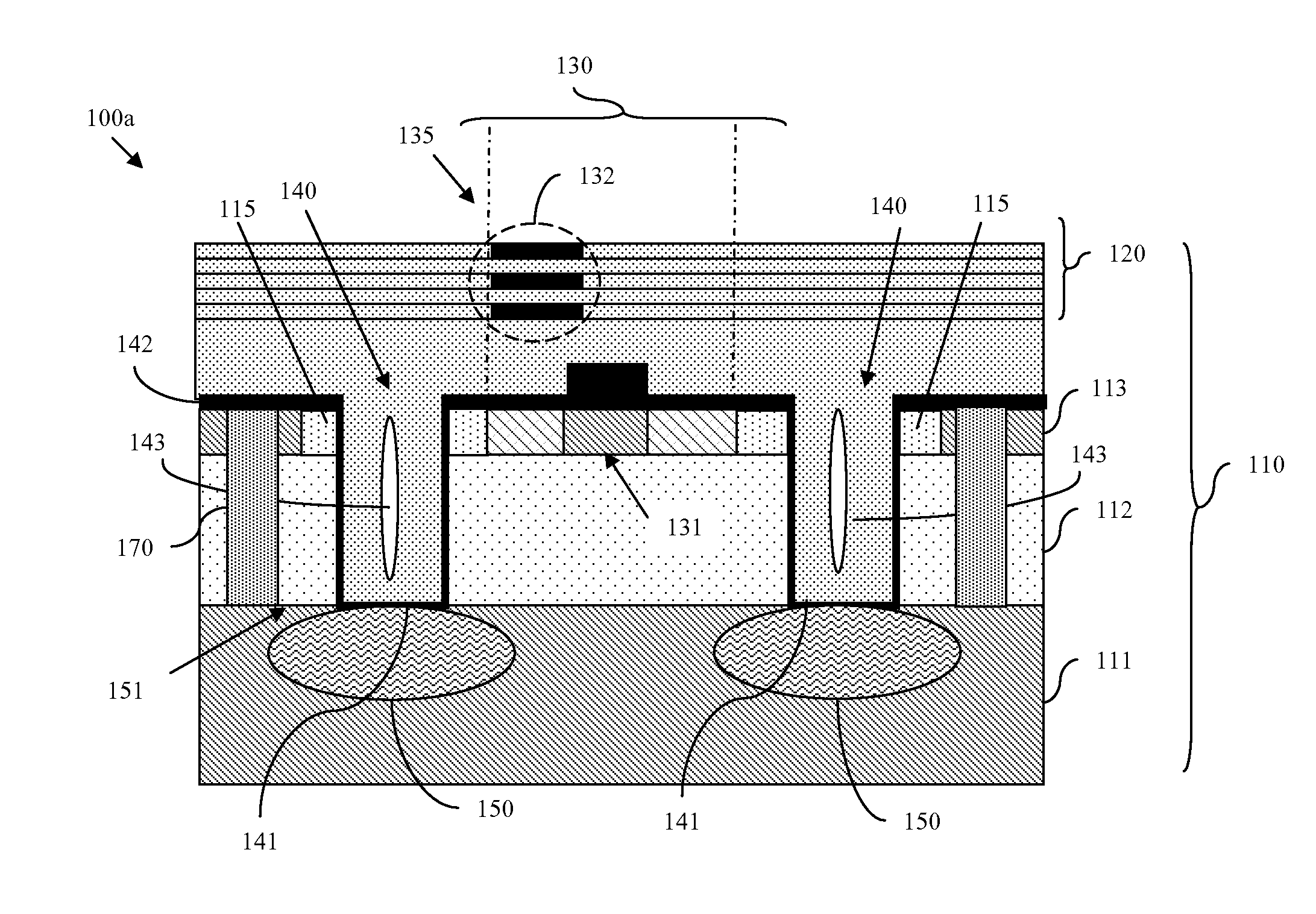

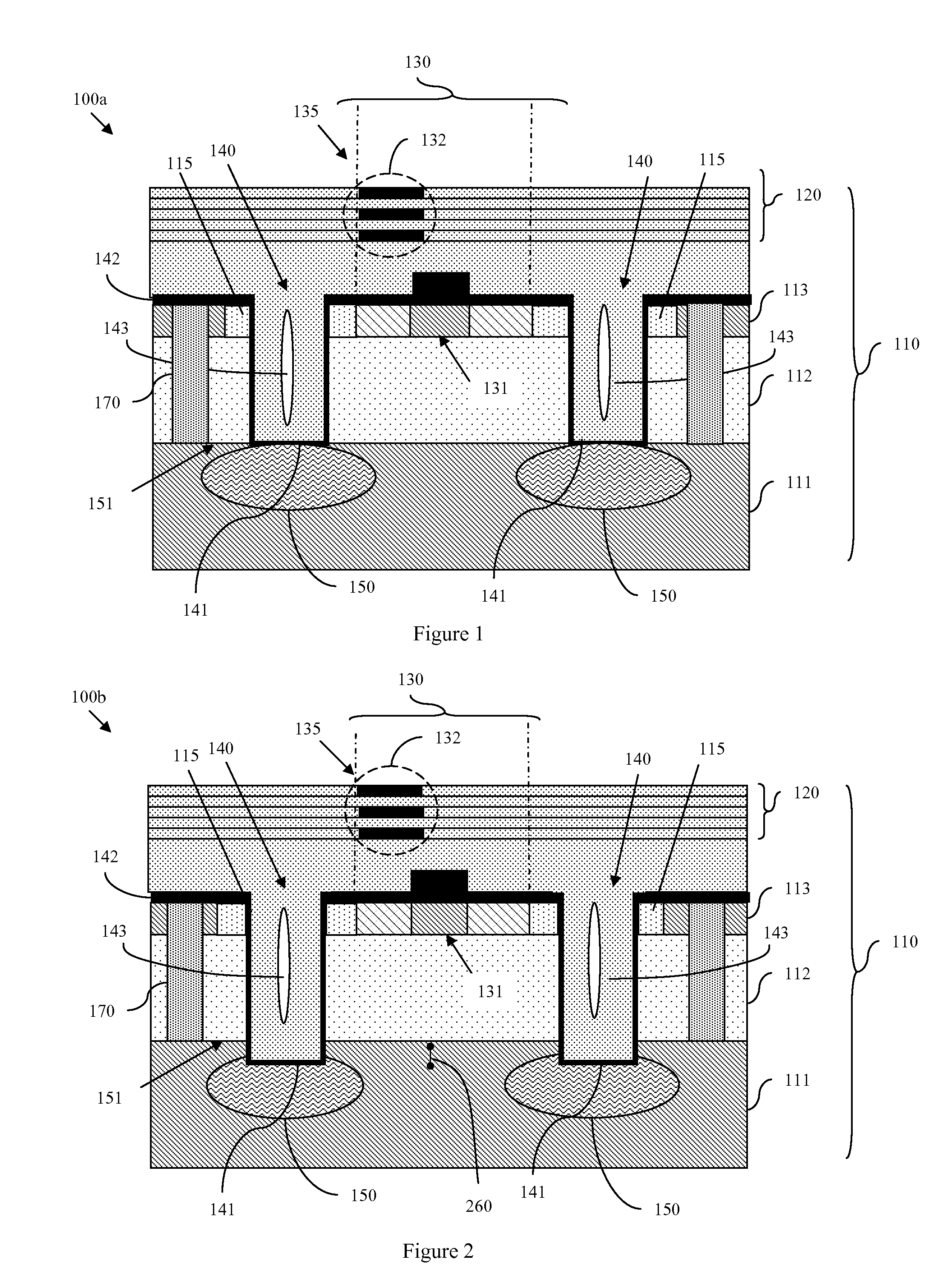

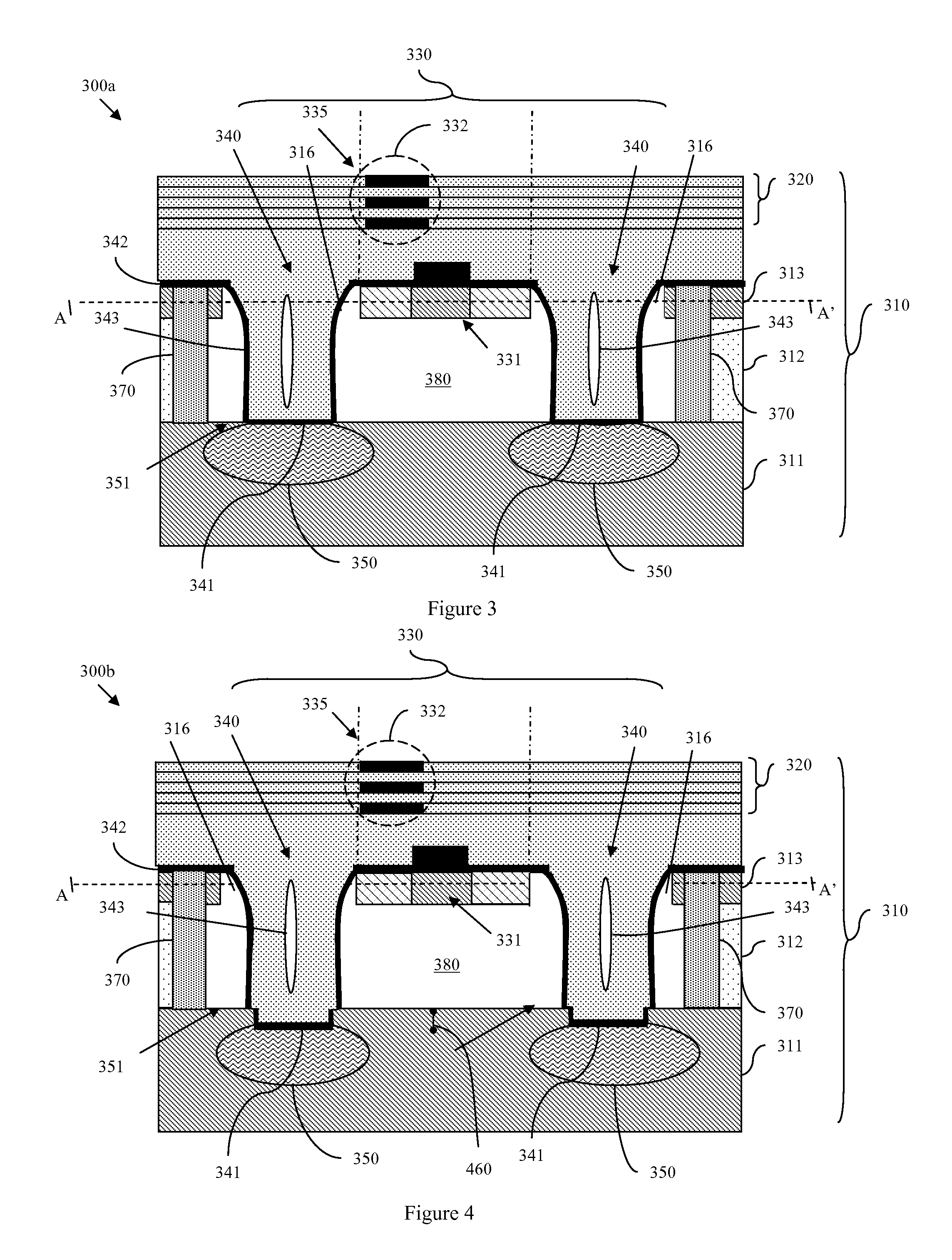

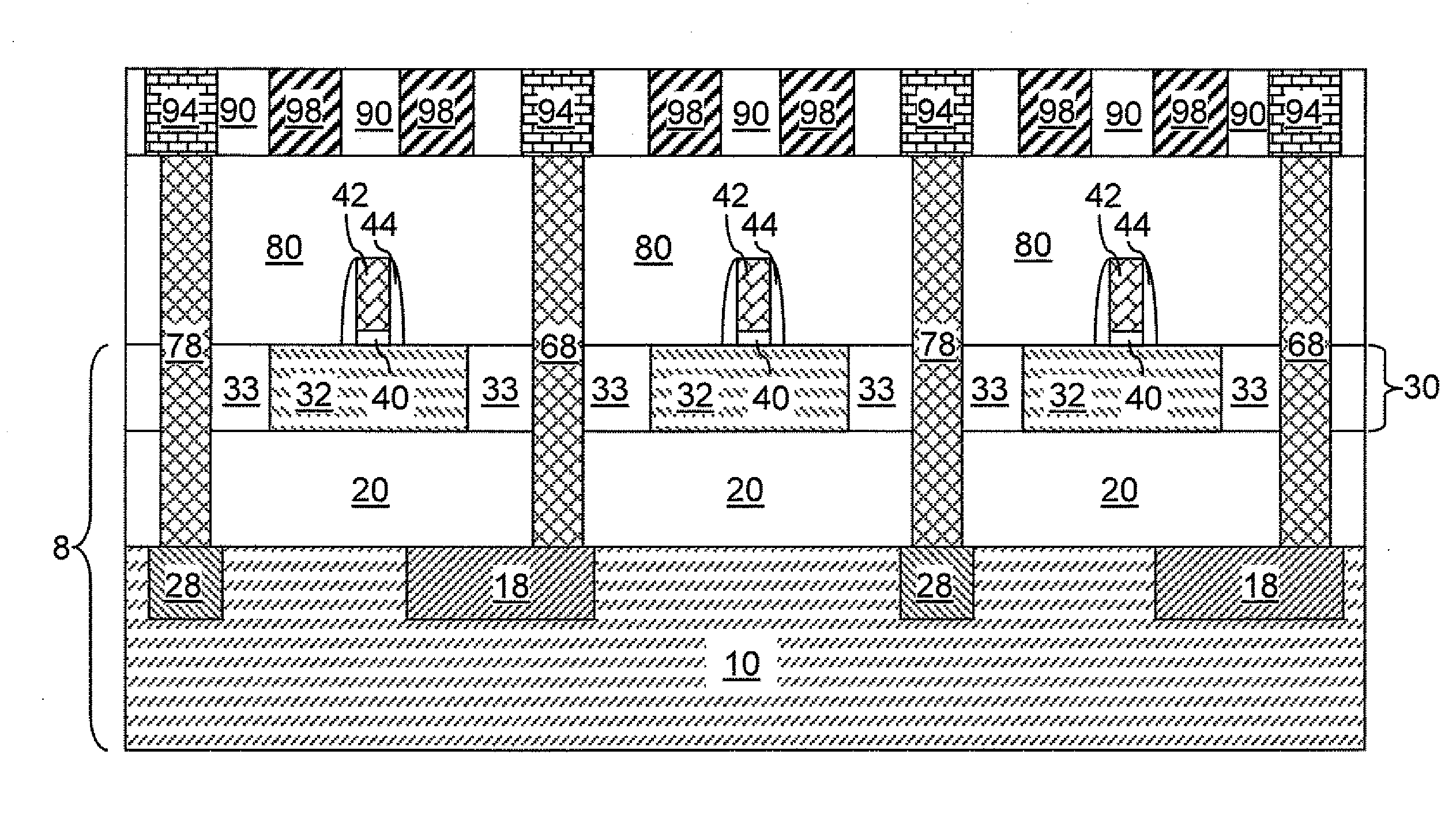

Integrated Circuit Structure, Design Structure, and Method Having Improved Isolation and Harmonics

InactiveUS20100035403A1Harmonic reductionImprove isolationSolid-state devicesSemiconductor/solid-state device manufacturingHarmonicSemiconductor structure

Disclosed are embodiments of a semiconductor structure, a design structure for the semiconductor structure and a method of forming the semiconductor structure. The embodiments reduce harmonics and improve isolation between the active semiconductor layer and the substrate of a semiconductor-on-insulator (SOI) wafer. Specifically, the embodiments incorporate a trench isolation region extending to a fully or partially amorphized region of the wafer substrate. The trench isolation region is positioned outside lateral boundaries of at least one integrated circuit device located at or above the active semiconductor layer of the SOI wafer and, thereby improves isolation. The fully or partially amorphized region of the substrate reduces substrate mobility, which reduces the charge layer at the substrate / BOX interface and, thereby reduces harmonics. Optionally, the embodiments can incorporate an air gap between the wafer substrate and integrated circuit device(s) in order to further improve isolation.

Owner:GLOBALFOUNDRIES INC

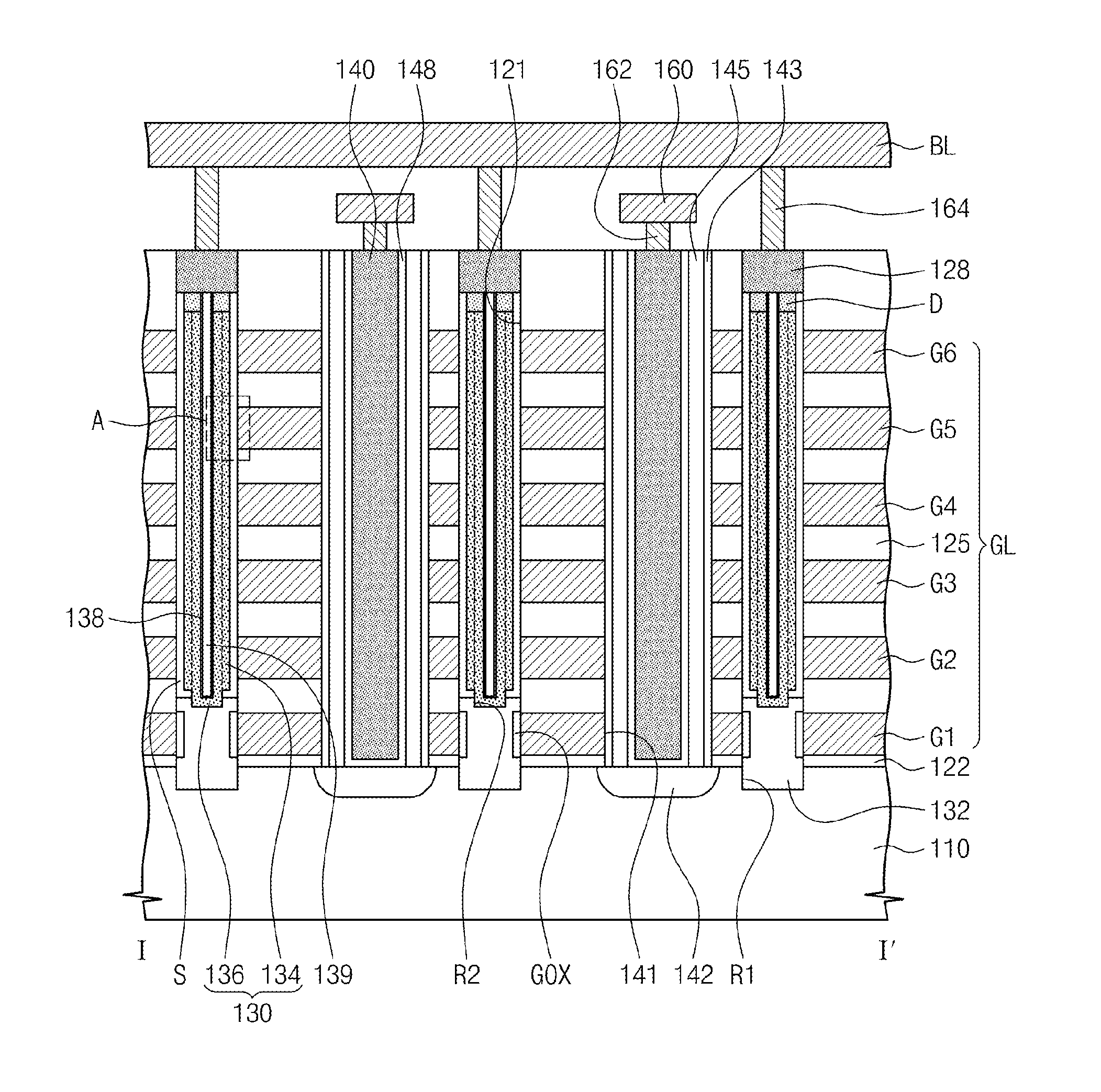

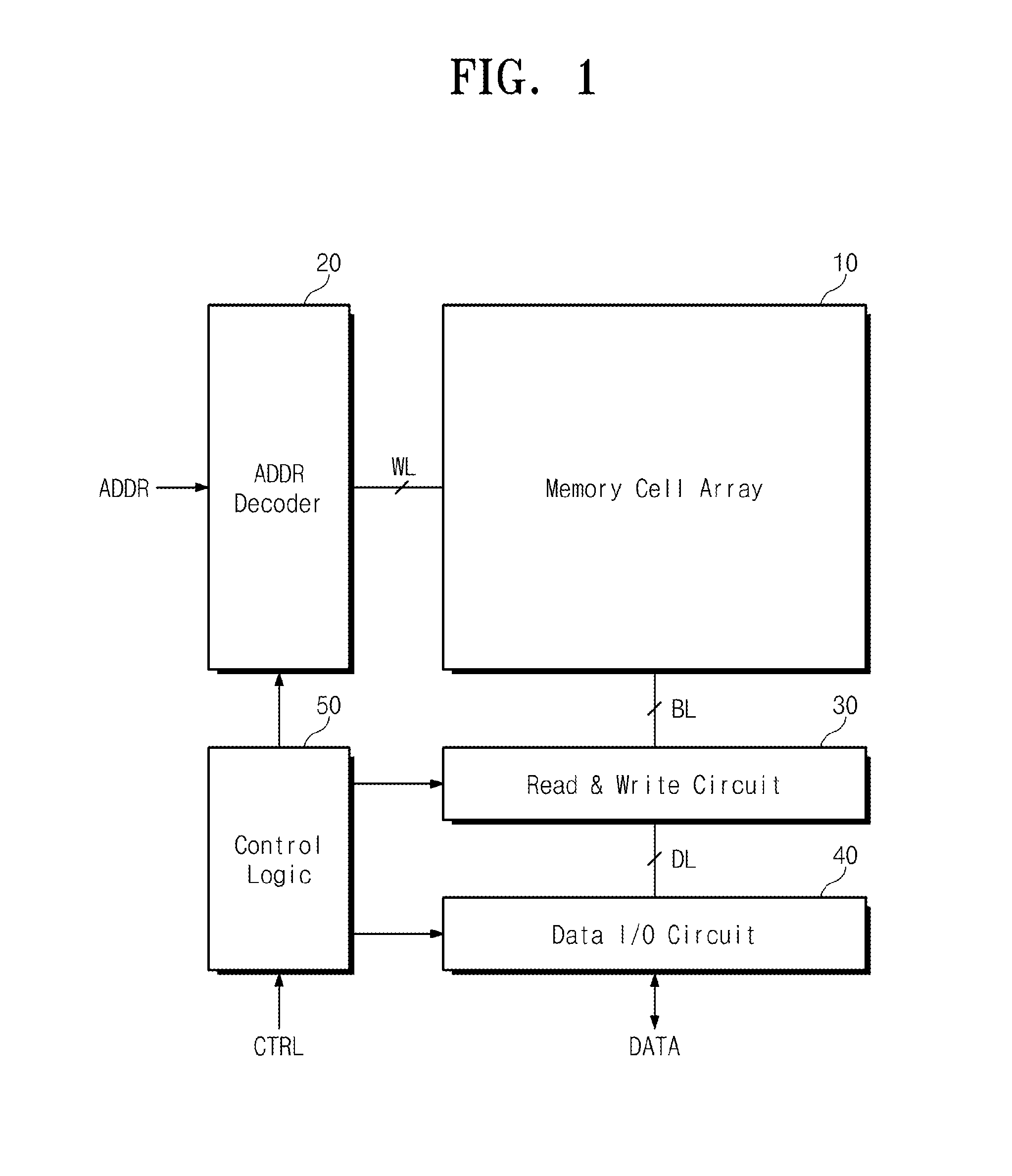

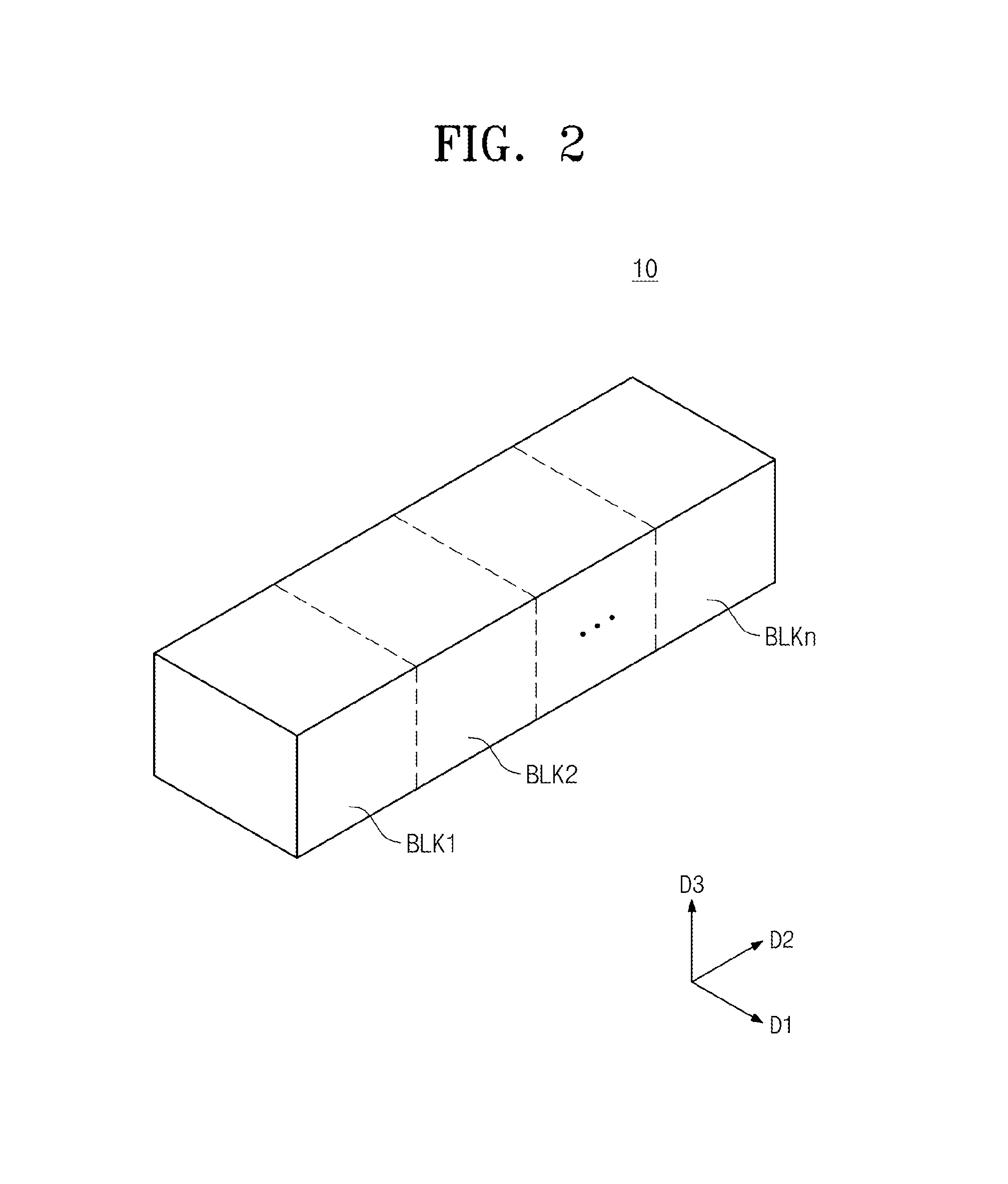

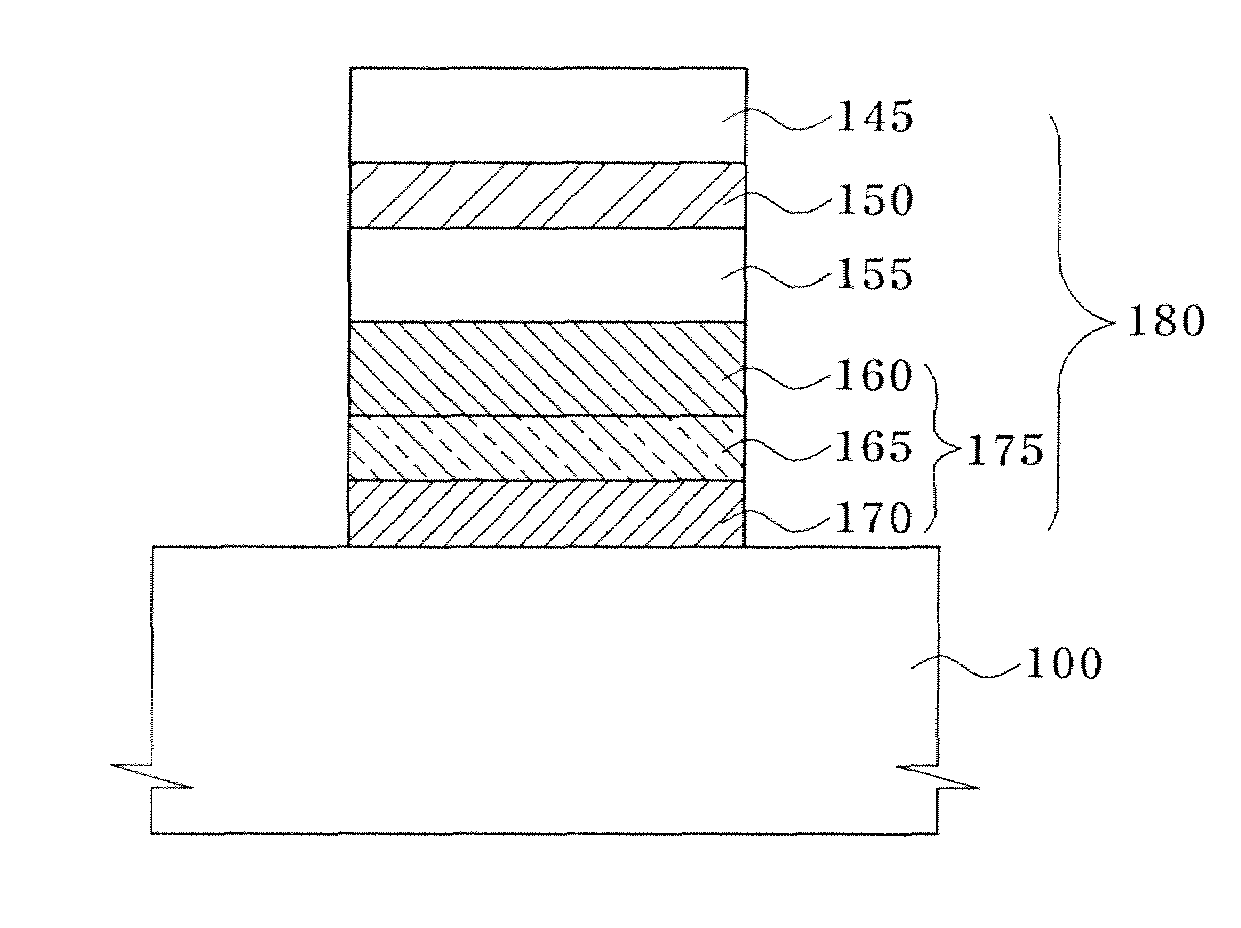

Memory devices and methods of manufacturing the same

A memory device includes a stack including gate electrodes vertically stacked on a substrate and having a vertical hole, an active pillar disposed in the vertical hole and providing a vertical channel, a charge storage section interposed between the active pillar and the gate electrodes, a blocking dielectric interposed between the charge storage section and the gate electrodes, a tunnel dielectric interposed between the charge storage section and the active pillar, insulation filling an inner hole of the active pillar, and a fixed charge layer interposed between the filling insulation and the active pillar. Measures are taken to address phenomena in which current would otherwise be adversely affected near an interface between the vertical channel and the filling insulation.

Owner:SAMSUNG ELECTRONICS CO LTD

Triboelectric generator

A generator includes a thin first contact charging layer and a thin second contact charging layer. The thin first contact charging layer includes a first material that has a first rating on a triboelectric series. The thin first contact charging layer has a first side with a first conductive electrode applied thereto and an opposite second side. The thin second contact charging layer includes a second material that has a second rating on a triboelectric series that is more negative than the first rating. The thin first contact charging layer has a first side with a first conductive electrode applied thereto and an opposite second side. The thin second contact charging layer is disposed adjacent to the first contact charging layer so that the second side of the second contact charging layer is in contact with the second side of the first contact charging layer.

Owner:GEORGIA TECH RES CORP

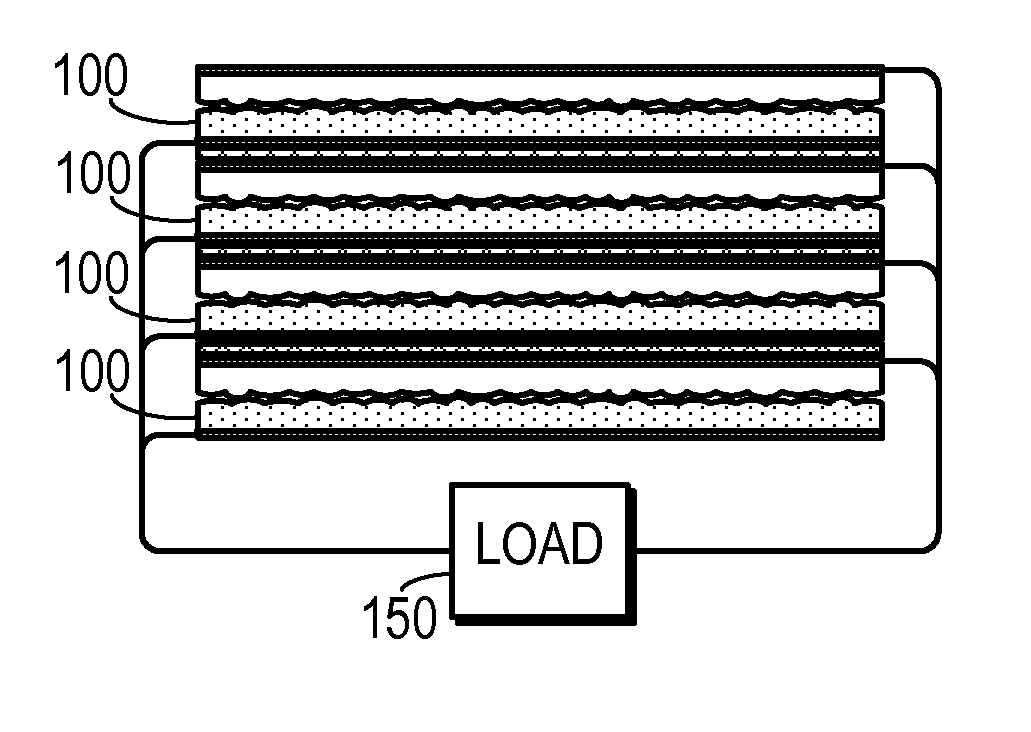

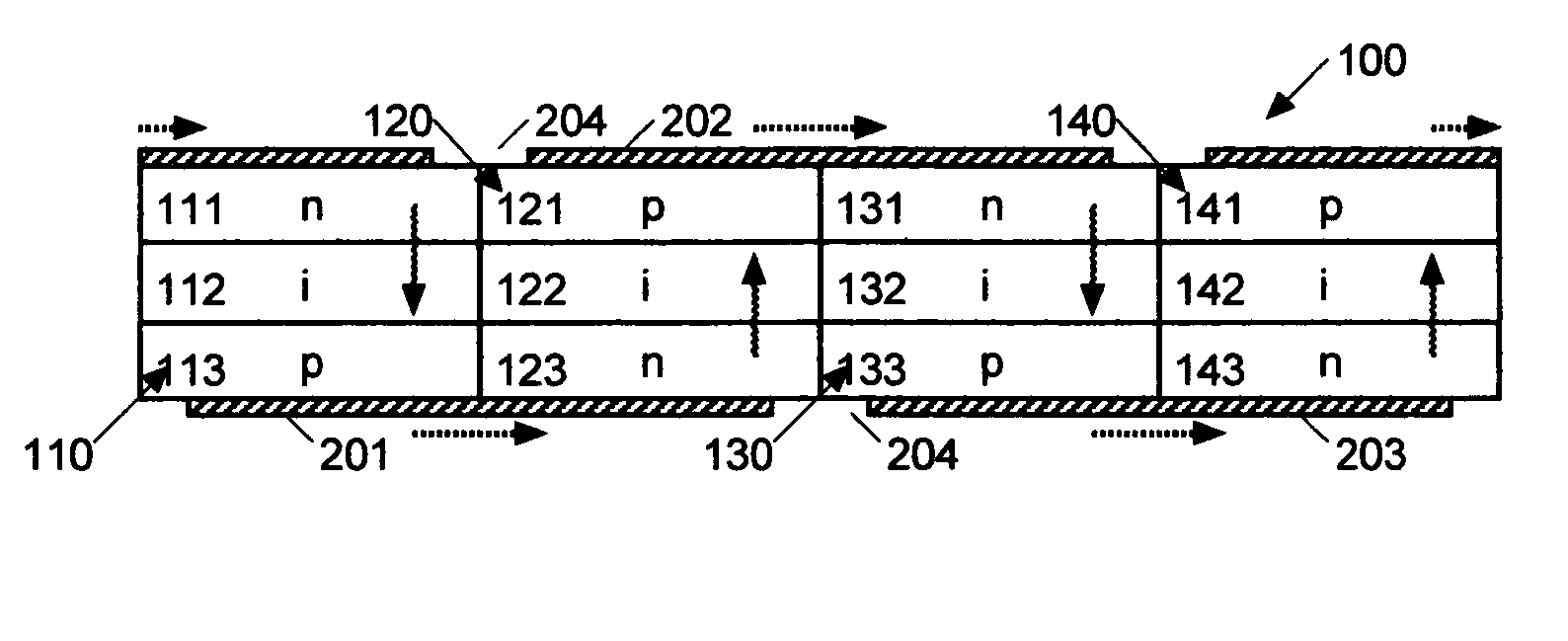

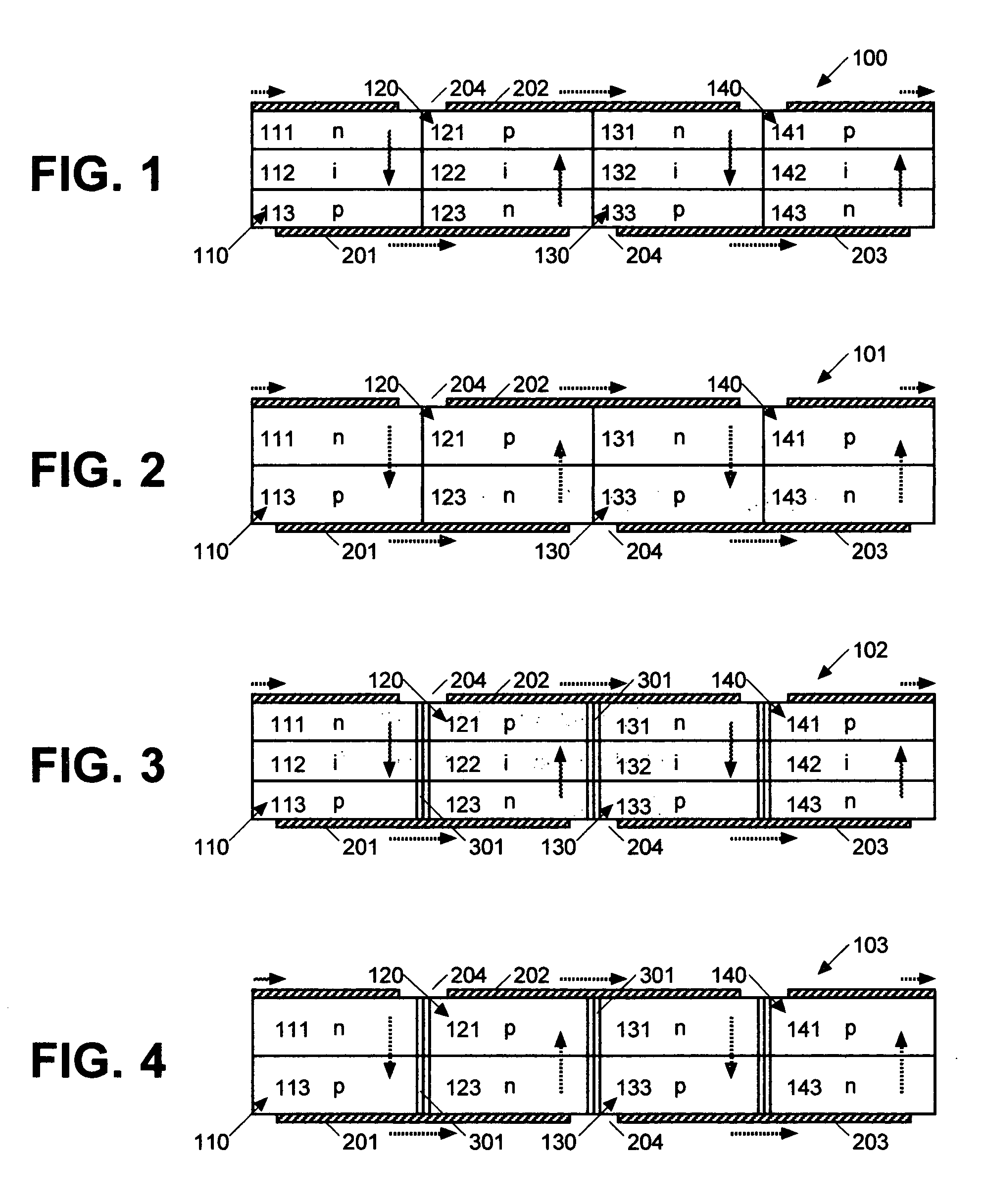

Photovoltaic systems and methods

The present invention generally relates to various photovoltaic systems capable of generating electric energy in response to various electromagnetic waves projected thereupon and, optionally, at least partially transmitting such waves therethrough. More particularly, the present invention relates to planar arrangements and methods of such photovoltaic systems where photovoltaic members are electrically connected in series without employing any conventional vertical interconnects. Therefore, an exemplary photovoltaic system includes multiple photovoltaic members each of which is arranged to include multiple charge layers, where such members are arranged to be disposed laterally and side by side, where the charge layers of each of the members are arranged to be disposed vertically and contacting each other and to have different polarities arranged in a preset order in order to generate voltage in response to said waves, where at least two of the members are arranged to be disposed adjacent to each other, to generate the voltages in opposite vertical direction, and to be connected in series by their top and / or bottom charge layers in order to enable the system to generate the driving voltage greater than each of the voltages generated by such members. Such a present invention also relates to various methods of providing such photovoltaic system and / or members thereof. In addition, the present invention further relates to various process of providing such photovoltaic systems and / or members thereof.

Owner:SHIM YOUNGTACK

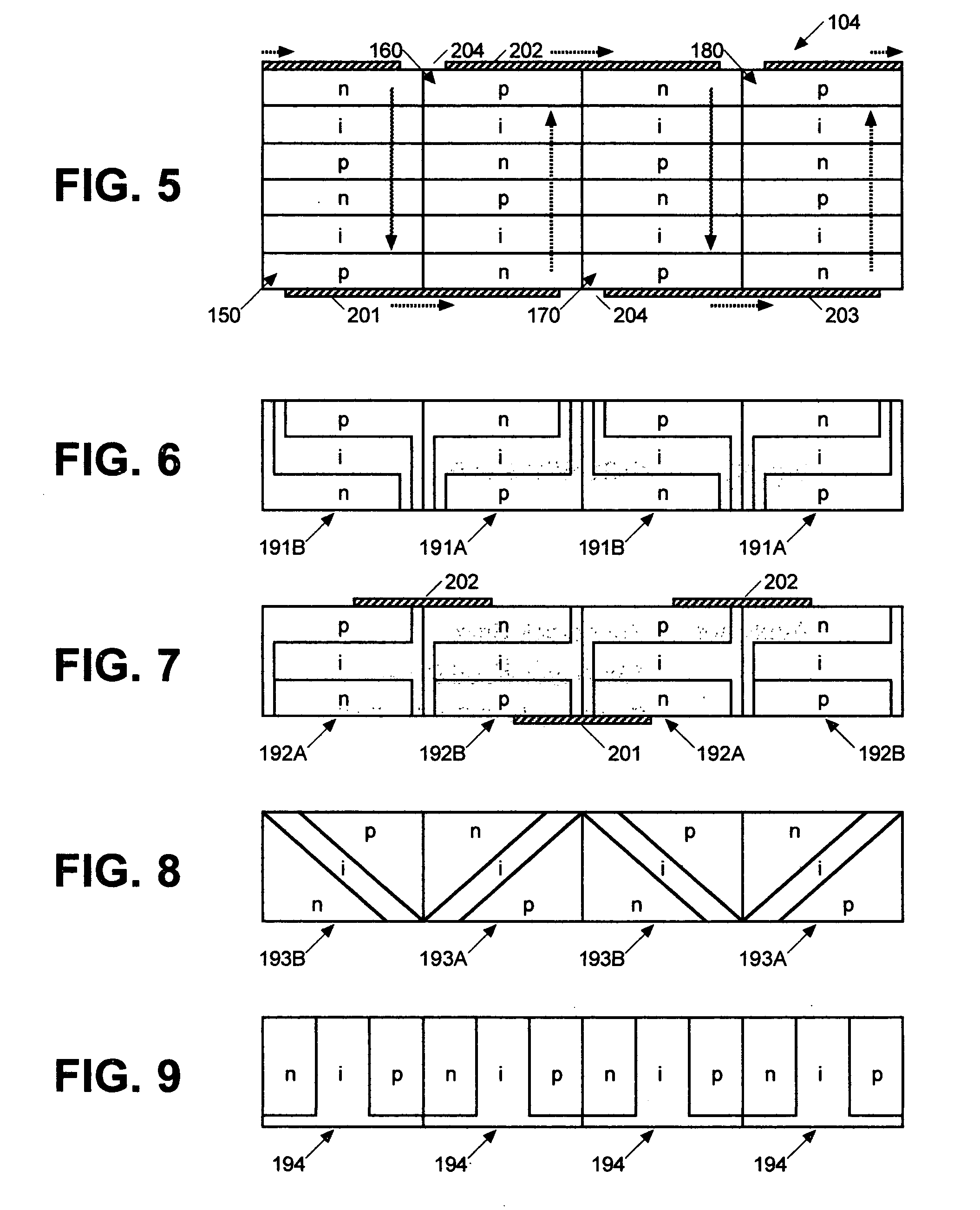

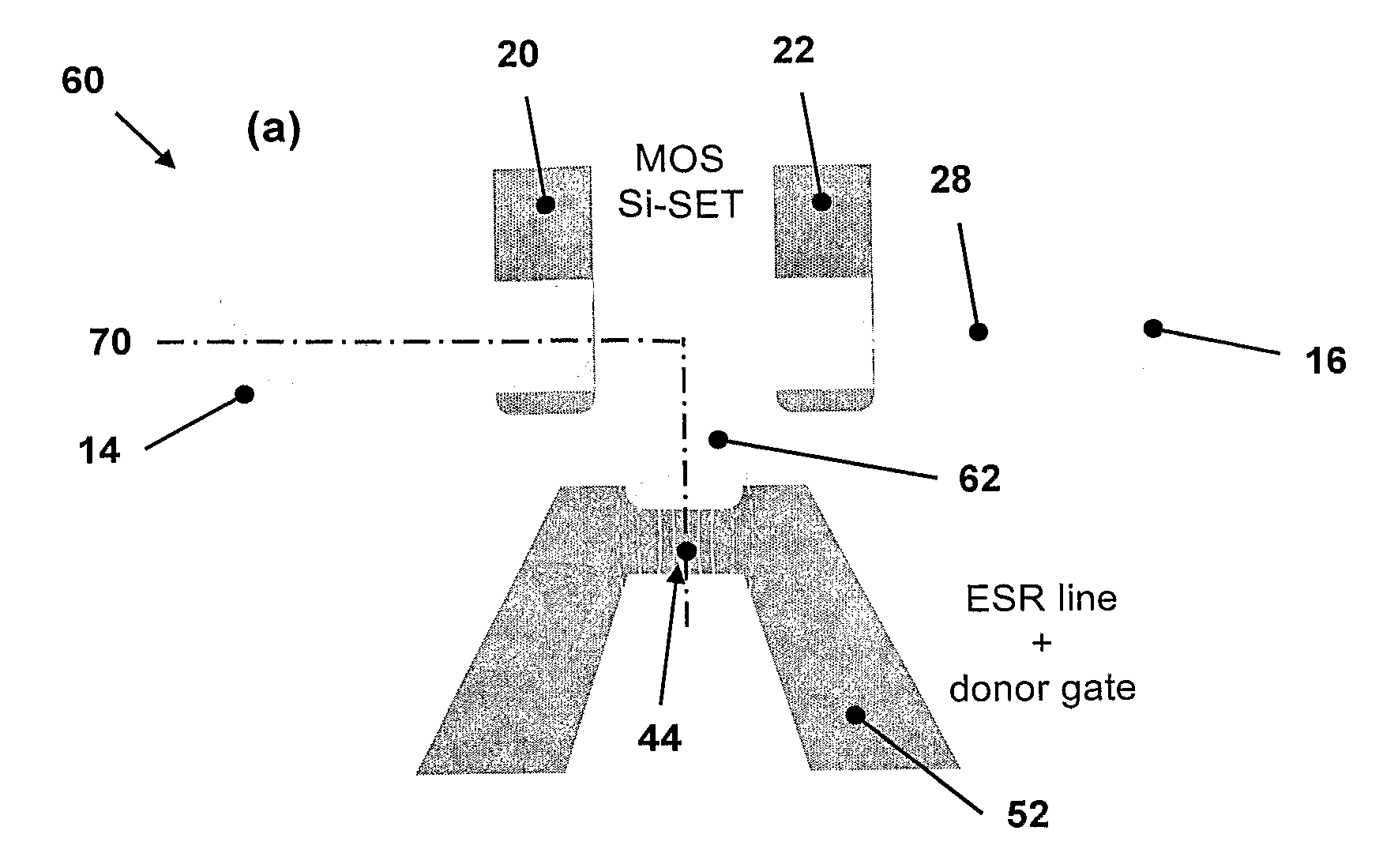

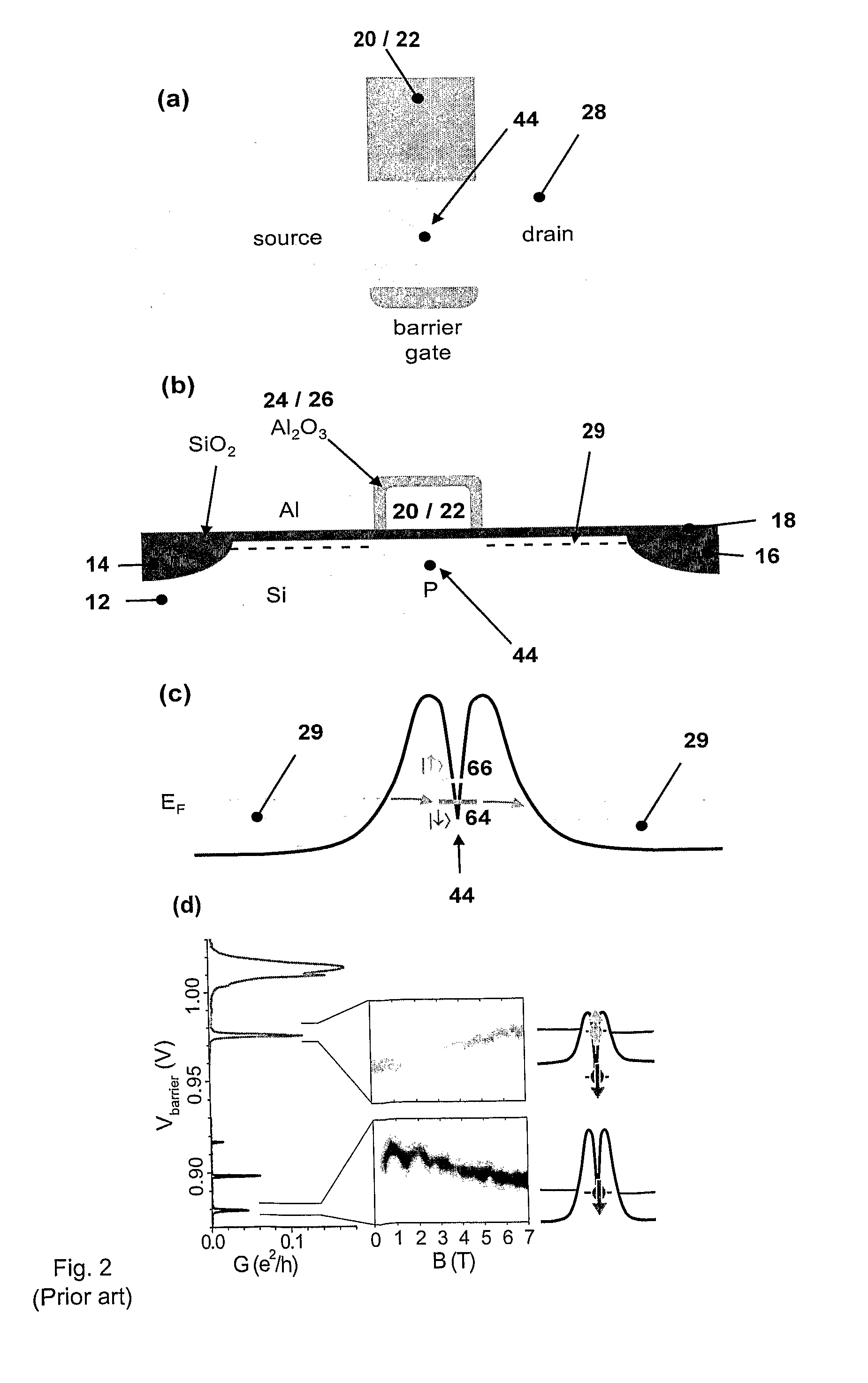

Control and readout of electron or hole spin

This invention concerns an electronic device for the control and readout of the electron or hole spin of a single dopant in silicon. The device comprises a silicon substrate in which there are one or more ohmic contact regions. An insulating region on top of the substrate. First and second barrier gates spaced apart to isolate a small region of charges to form an island of a Single Electron Transistor (SET). A third gate over-lying both the first and second barrier gates, but insulated from them, the third gate being able to generate a gate-induced charge layer (GICL) in the ESR line substrate beneath it. A fourth gate in close proximity to a single dopant donor gate atom, the dopant atom being encapsulated in the substrate outside the region of the GICL but close enough to allow spin-dependent charge tunnelling between the dopant atom and the SET island under the control of gate potentials, mainly the fourth gate. In use either the third or fourth gate also serve as an Electron Spin Resonance (ESR) line to control the spin of the single electron or hole of the dopant atom. In a further aspect it concerns a method for using the device.

Owner:NEWSOUTH INNOVATIONS PTY LTD

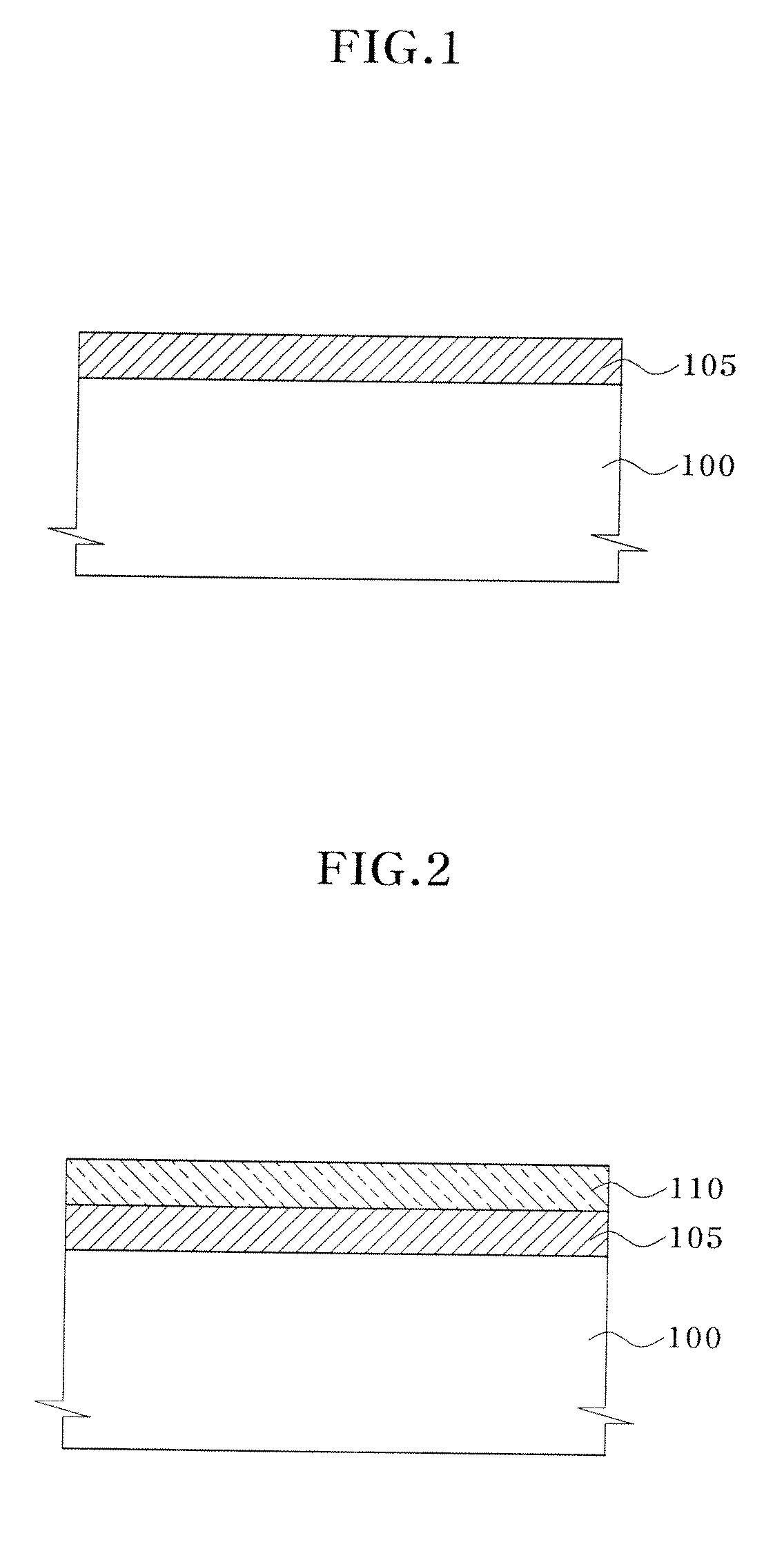

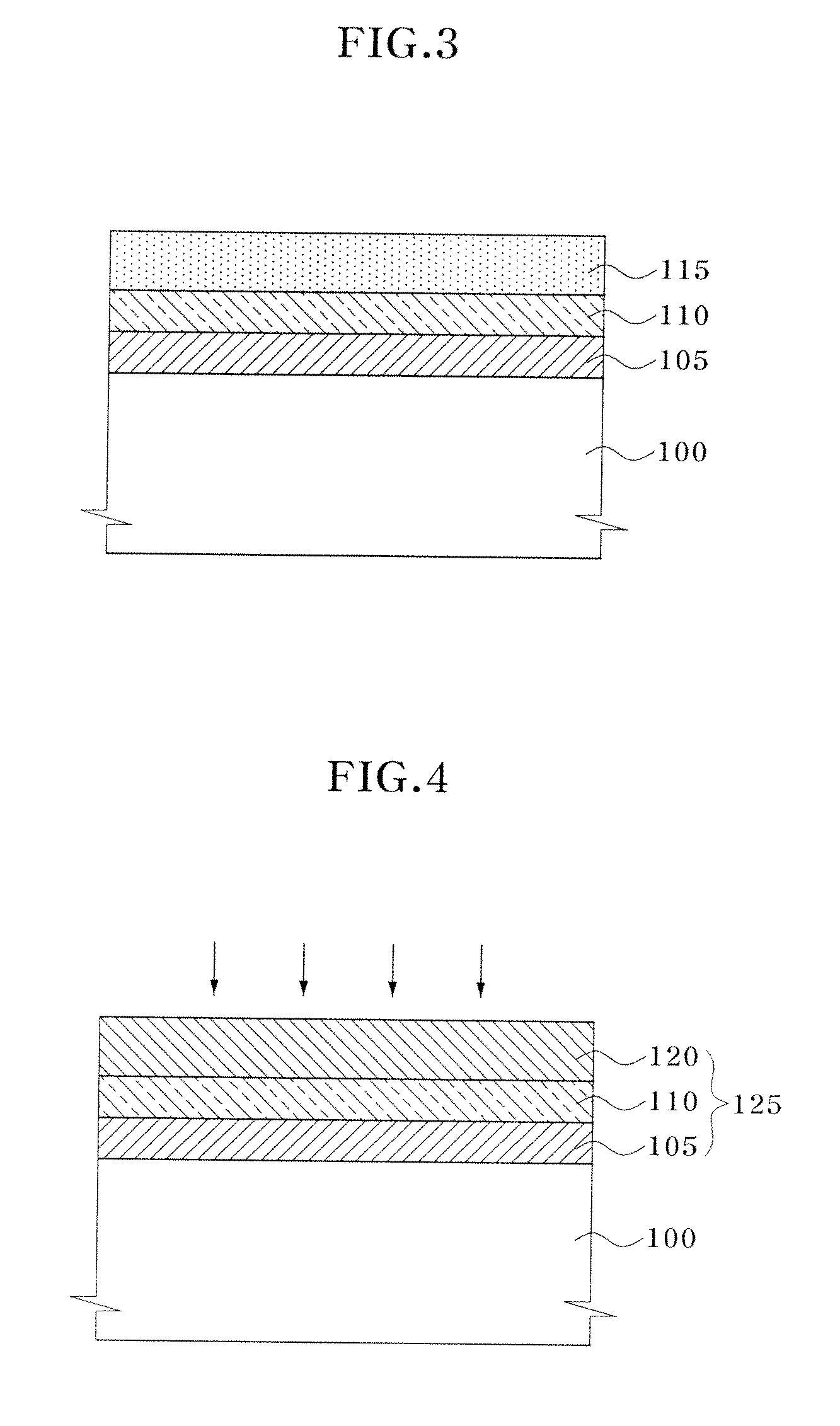

Method for Manufacturing Non-Volatile Memory Device having Charge Trap Layer

InactiveUS20090227116A1Semiconductor/solid-state device manufacturingSemiconductor devicesInterfacial reactionCharge layer

A method for manufacturing a non-volatile memory device having a charge trap layer comprises in one embodiment: forming a first dielectric layer over a semiconductor substrate; forming a second dielectric layer having a higher dielectric constant than that of the first dielectric layer over the first dielectric layer; forming a nitride buffer layer for preventing an interfacial reaction over the second dielectric layer; forming a third dielectric layer by supplying a radical oxidation source onto the nitride buffer layer to oxidize the nitride buffer layer, thereby forming a tunneling layer comprising the first, second, and third dielectric layers; and forming a charge trap layer, a shielding layer, and a control gate electrode layer over the tunneling layer.

Owner:SK HYNIX INC

Stacked gate semiconductor memory

Owner:KK TOSHIBA

Secondary cell

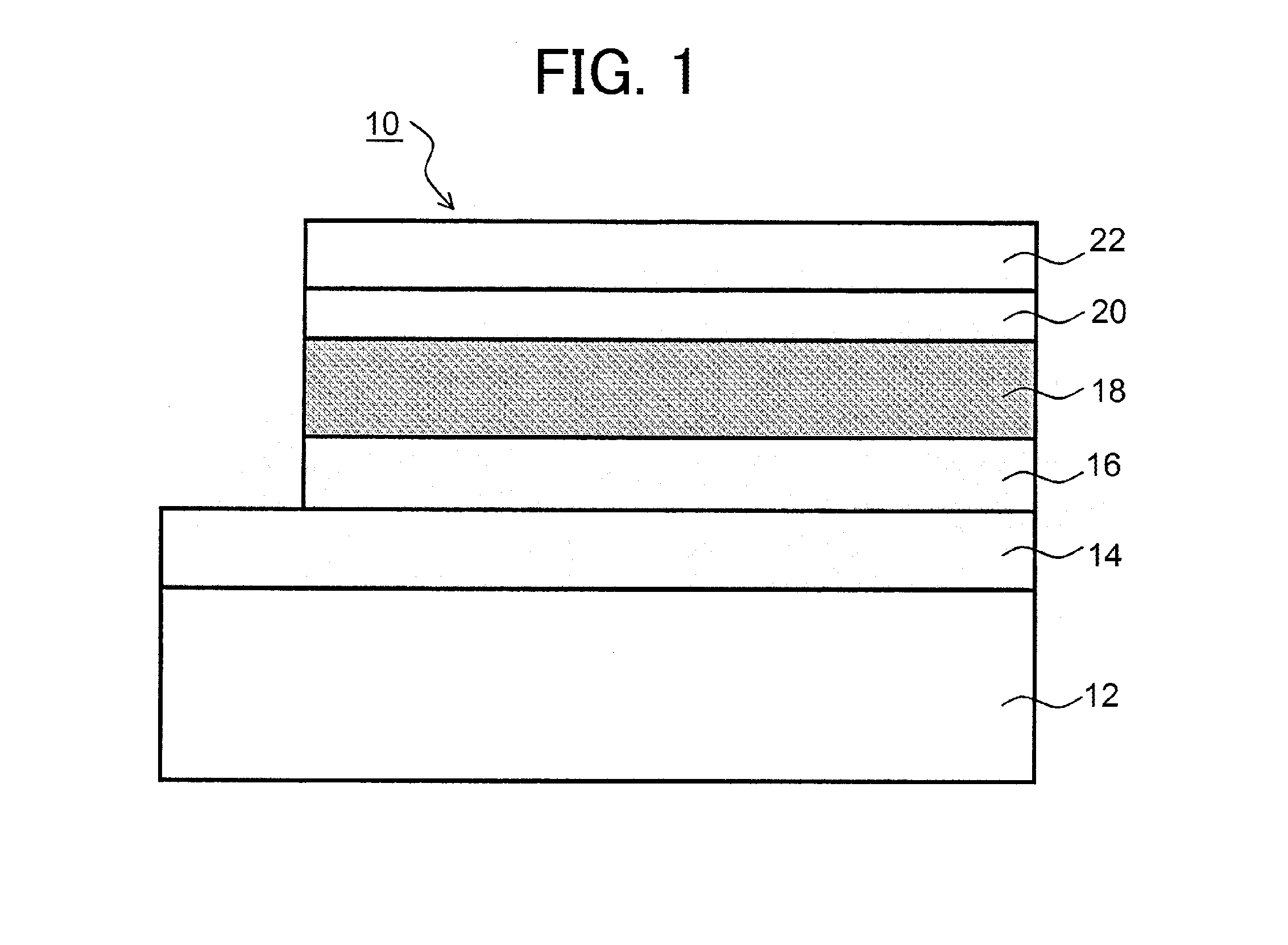

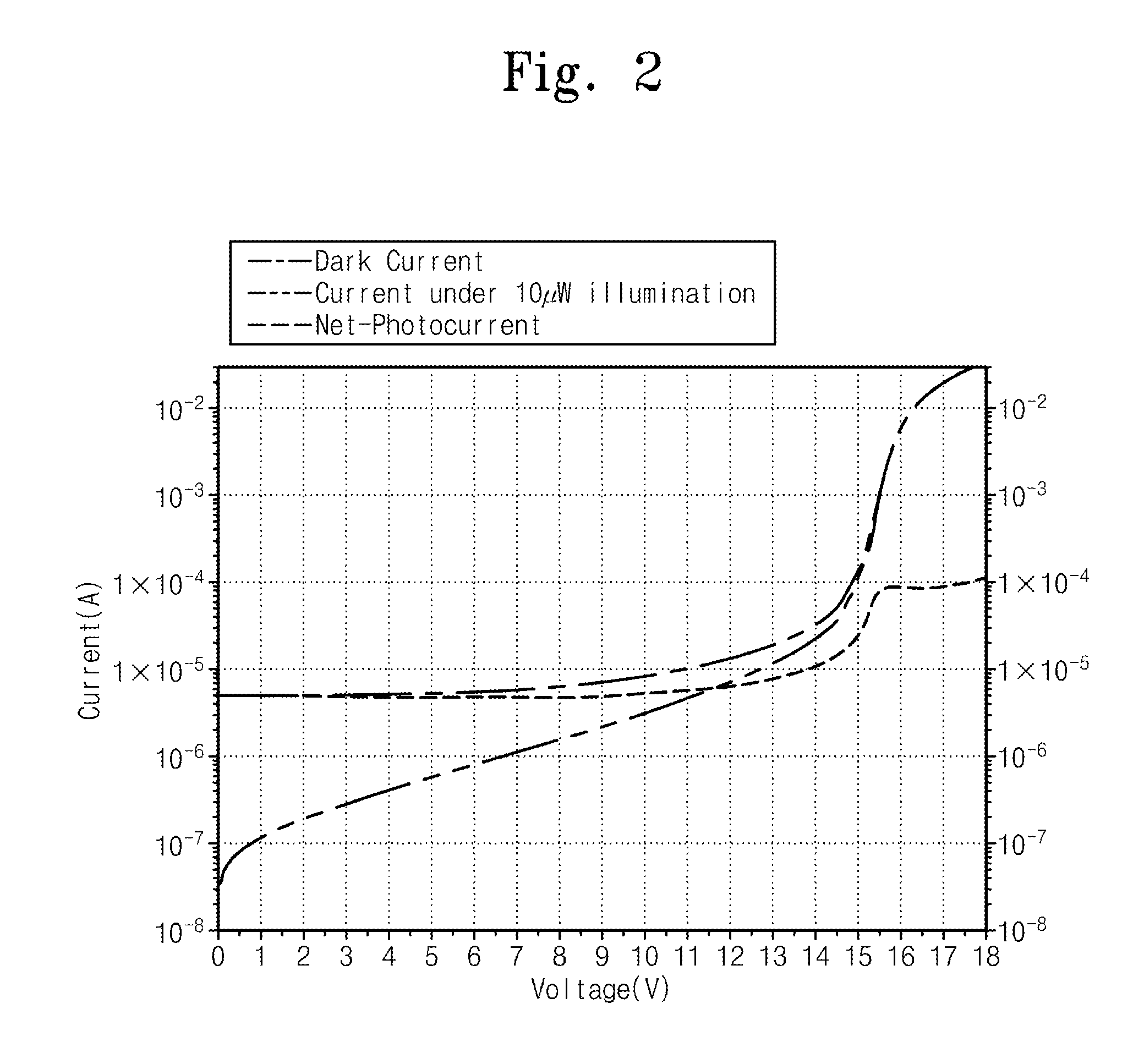

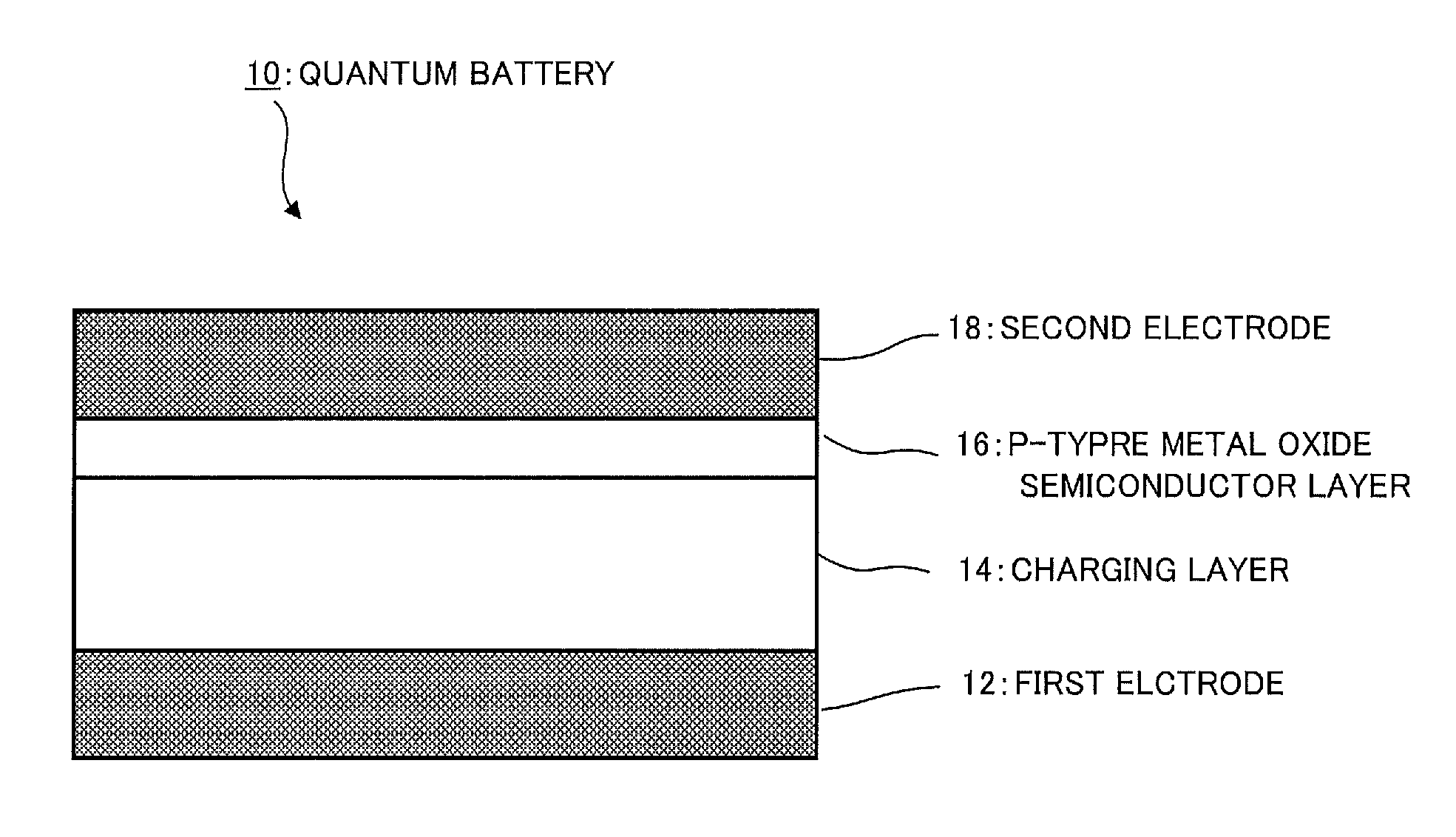

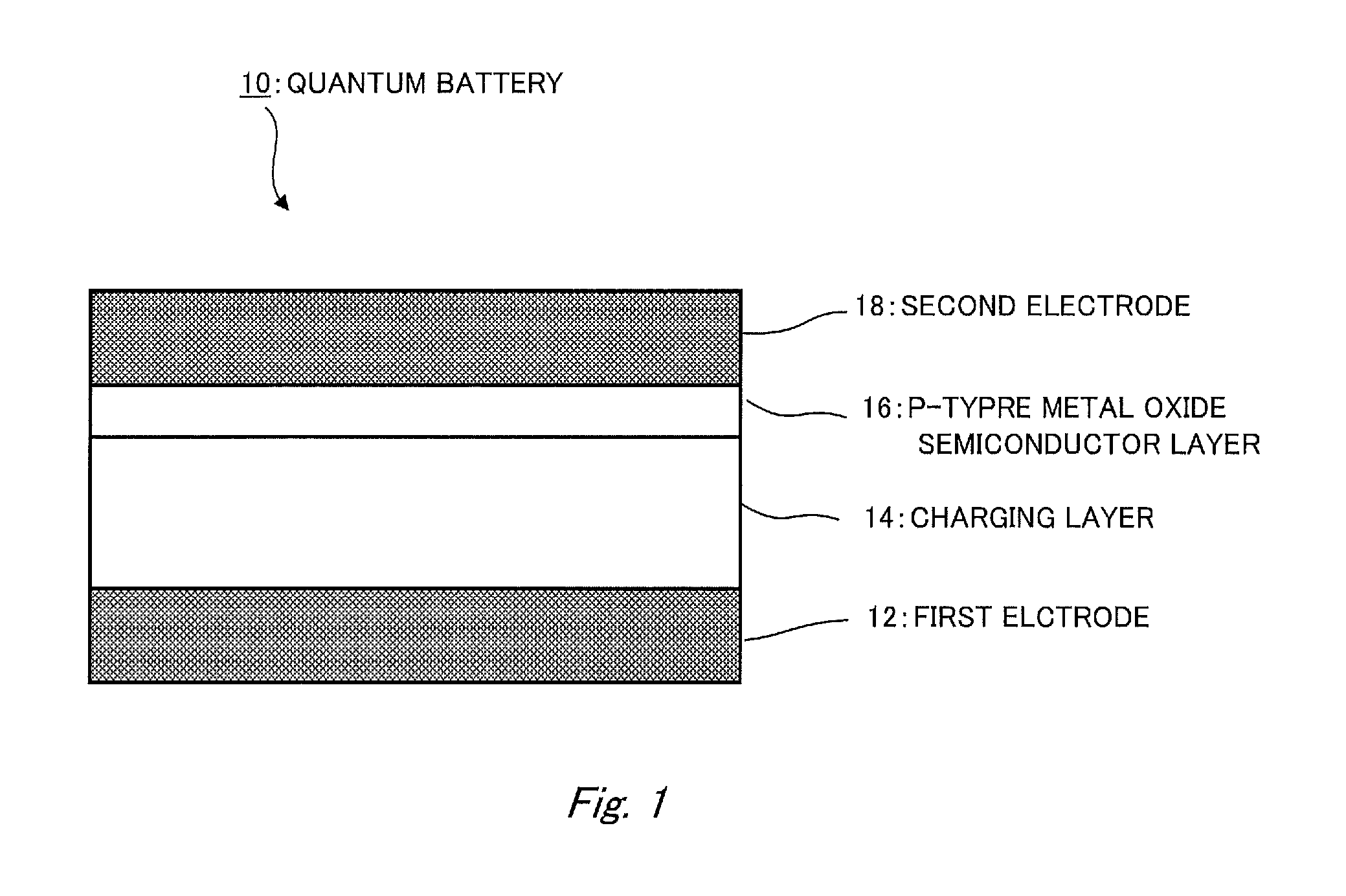

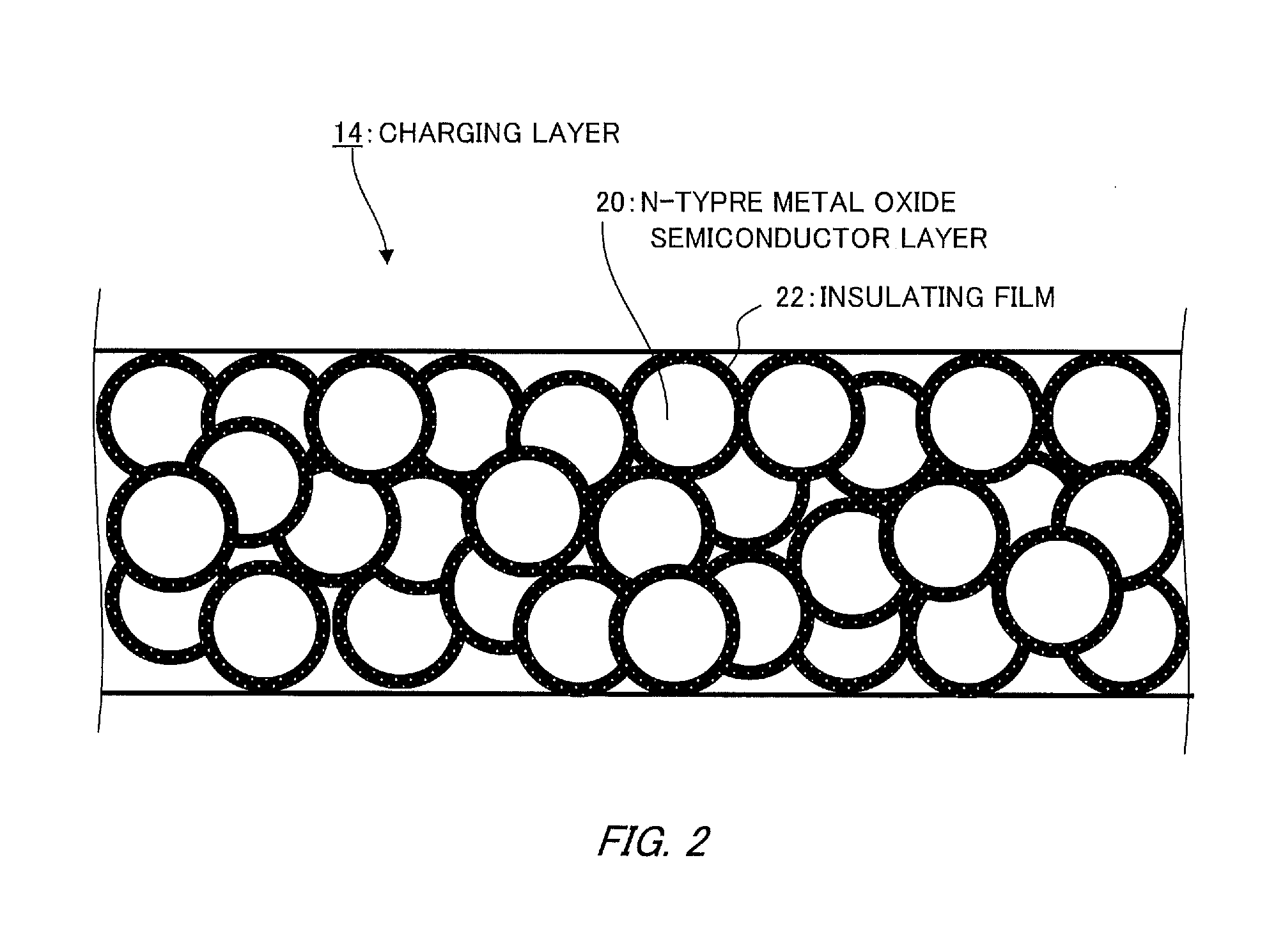

ActiveUS20130224596A1Improve usabilityImprove surface adhesionNon-aqueous electrolyte accumulator electrodesPhotoelectrochemical storage cellsNew energyCharge layer

A secondary cell is provided that enables cost reduction and stable operation with a simple configuration and greatly exceeds the capacity of a lithium-ion cell. In a secondary cell, a conductive first electrode is formed on a substrate. An n-type metal oxide semiconductor layer, a charging layer for charging energy, a p-type metal oxide semiconductor layer, and a second electrode are laminated. The charging layer is filled with an n-type metal oxide semiconductor of fine particles. By a photoexcited structural change phenomenon caused by ultraviolet irradiation, a new energy level is formed in a band gap of the n-type metal oxide semiconductor. An electron is captured at the newly formed energy level, thereby charging energy. The charging layer is charged by connecting a power source between the first electrode and the second electrode. It is also possible to charge energy by light, using a transparent electrode.

Owner:GUALA TECH

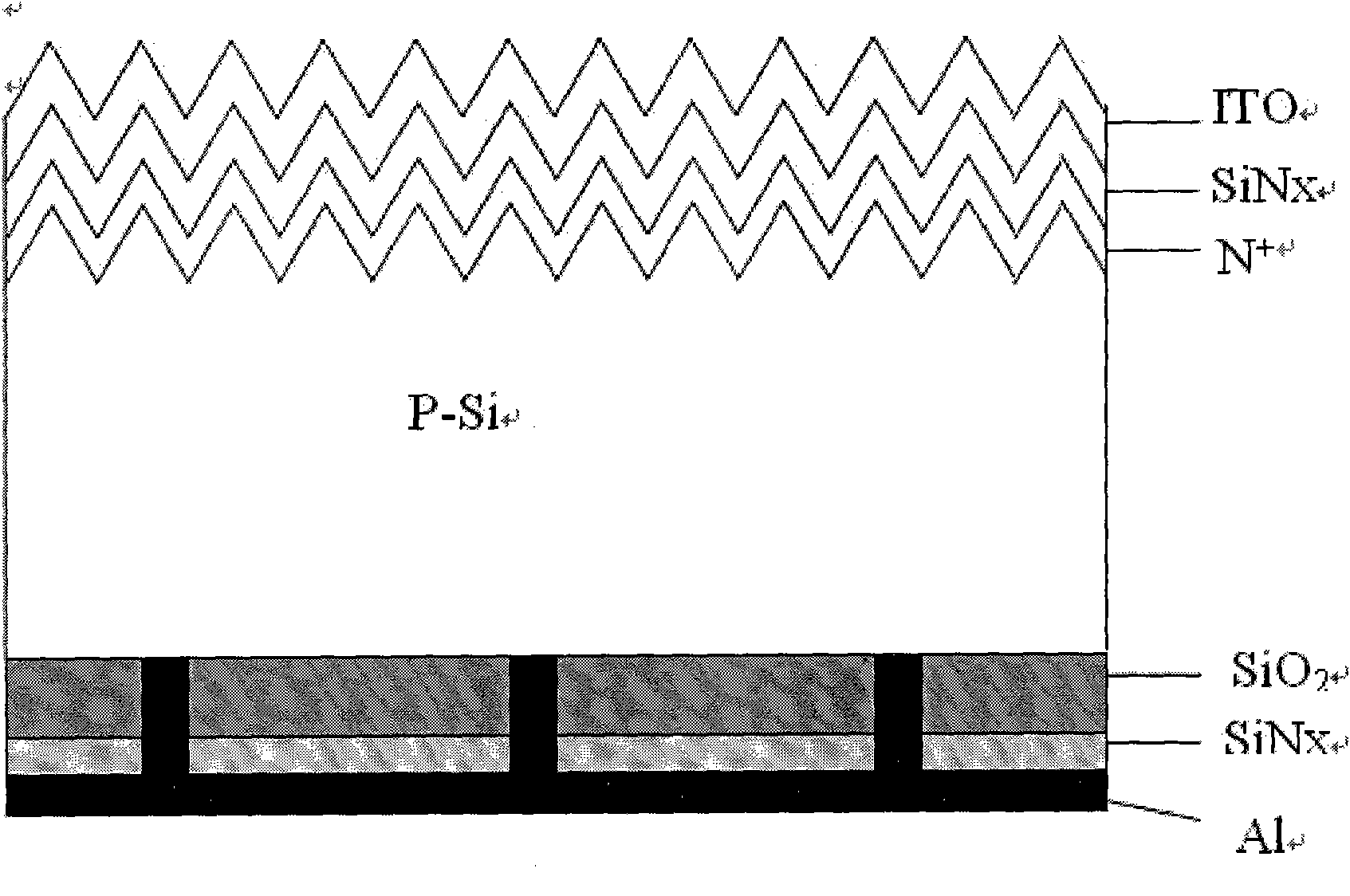

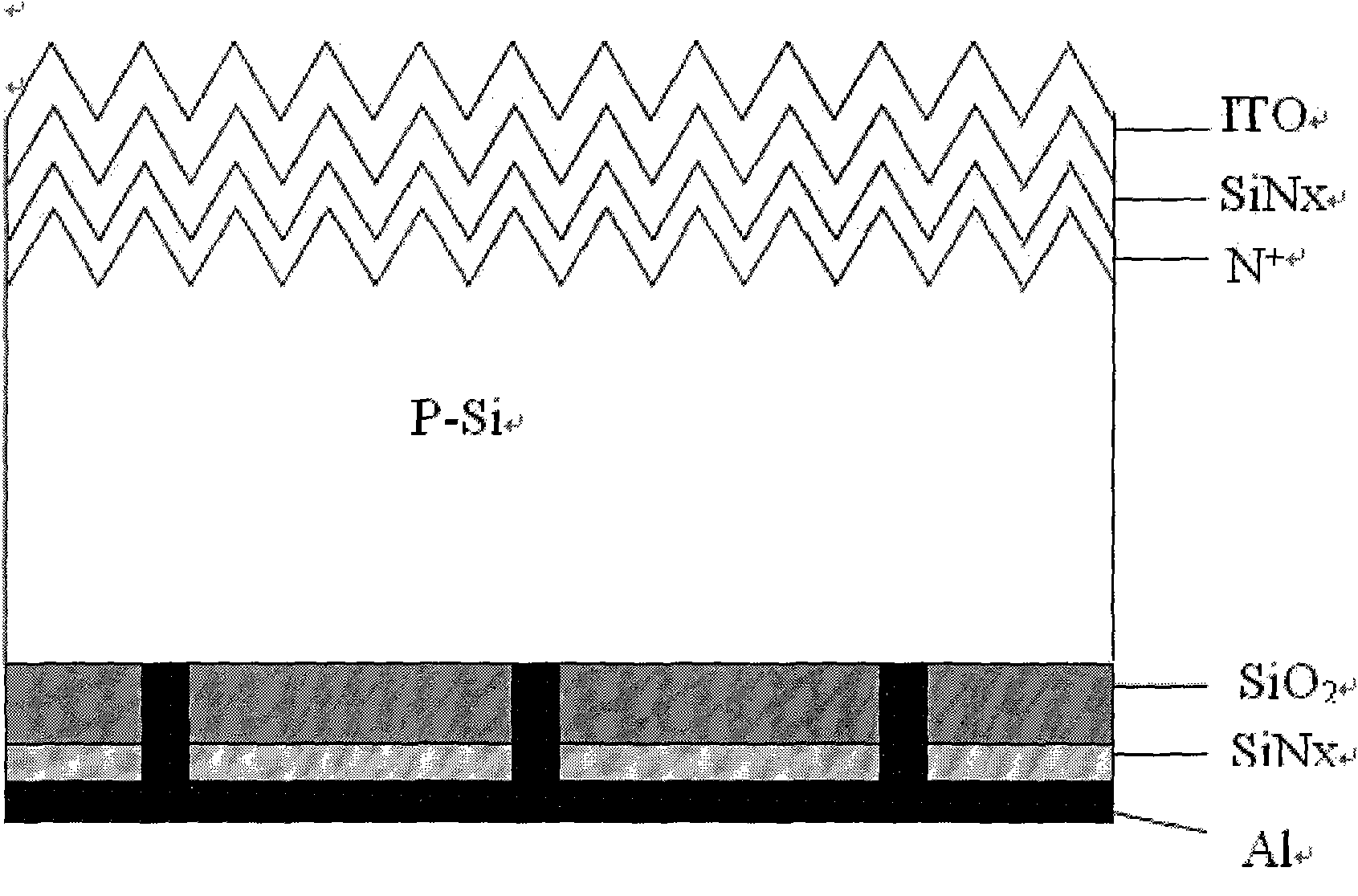

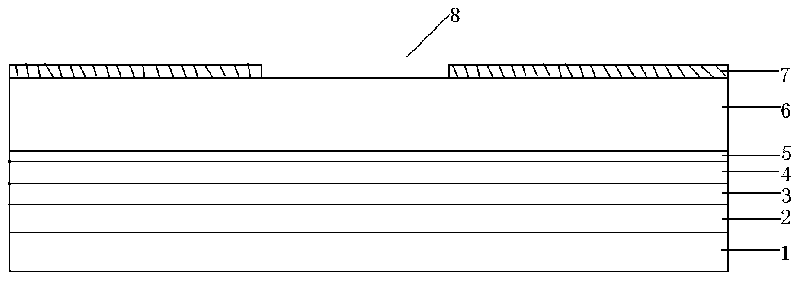

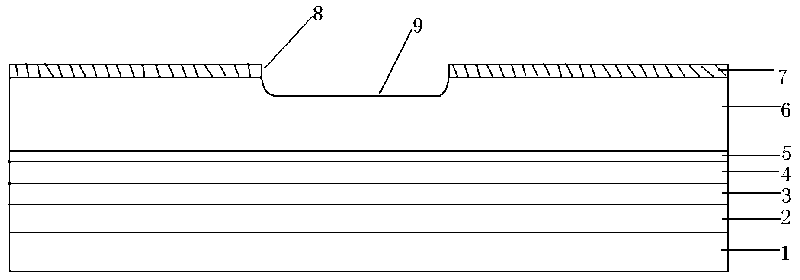

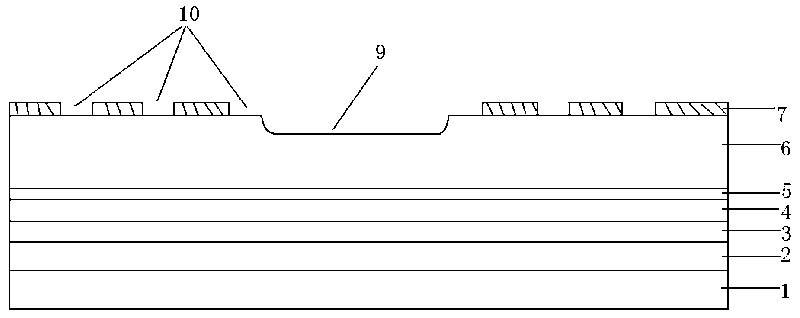

Preparation method of solar cell with buried charge layer

ActiveCN101882650AIncrease short circuit currentAvoid churnFinal product manufactureSemiconductor devicesCharge layerElectrode Contact

The invention relates to a monocrystalline silicon solar cell and a preparation method thereof, in particular to a monocrystalline silicon solar cell with a buried charge layer introduced into a passivating dielectric layer, and belongs to the technical field of the preparation of solar cell devices. The monocrystalline silicon solar cell is developed based on the preparation scheme of the general monocrystalline silicon solar cell and adopts a structure of partial back contact, and the preparation method is characterized by comprising the steps of: growing an SiO2 layer on the back of a solar cell by utilizing a thermal oxidation or atomic layer deposition technology, growing a layer of SiNx thin film by using PECVD (Plasma Enhanced Chemical Vapor Deposition), etching a back electrode contact area by using a laser grooving technology, then injecting electrons with a corona mode, and finally depositing an Al electrode with a vacuum evaporation mode. The invention can effectively improve the solar cell efficiency.

Owner:南通东湖国际商务服务有限公司

Method of and apparatus for manufacturing the metallic iron

InactiveUS20020005089A1Improve heating efficiencyGood effectRetort furnacesManufacturing convertersCombustionSlag

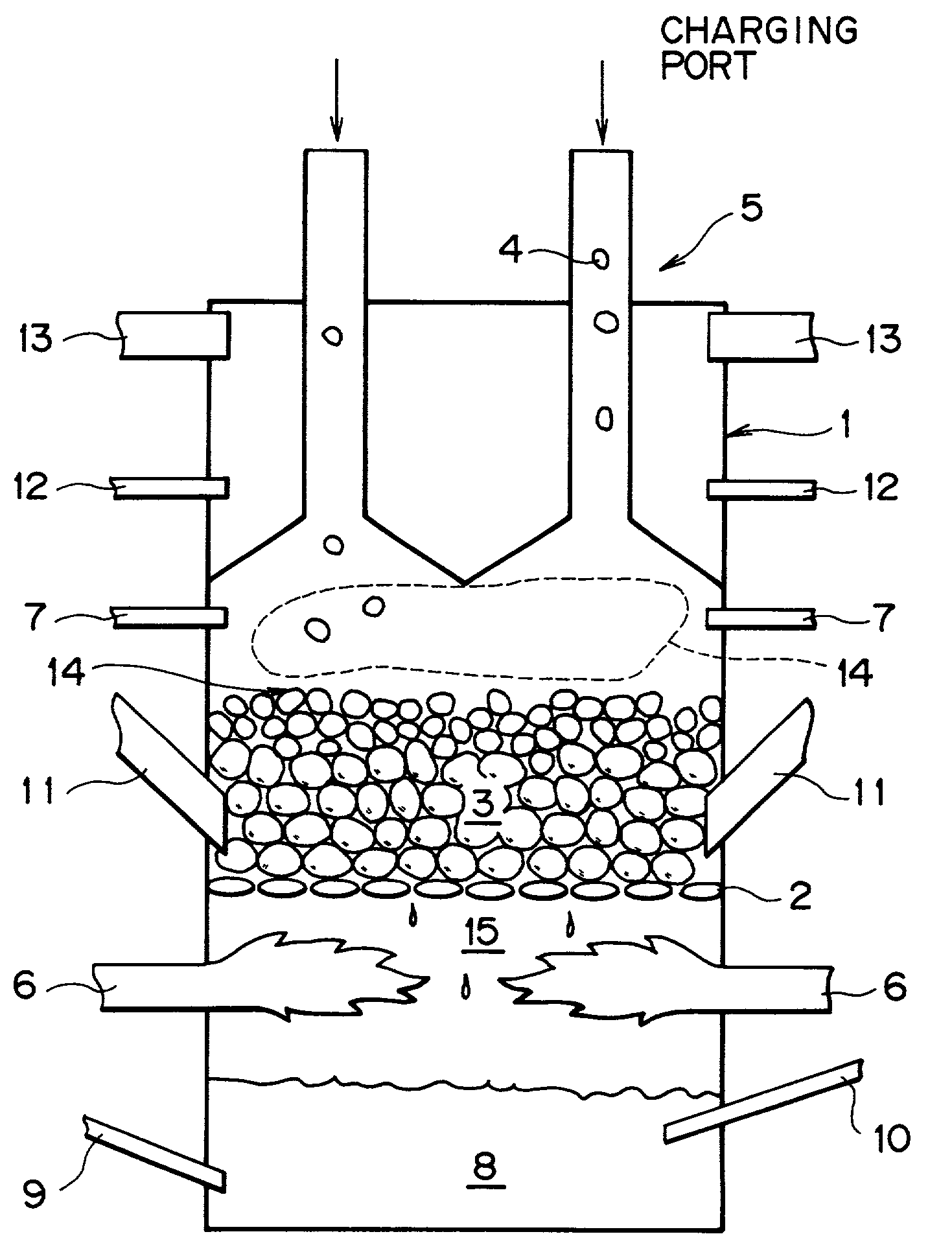

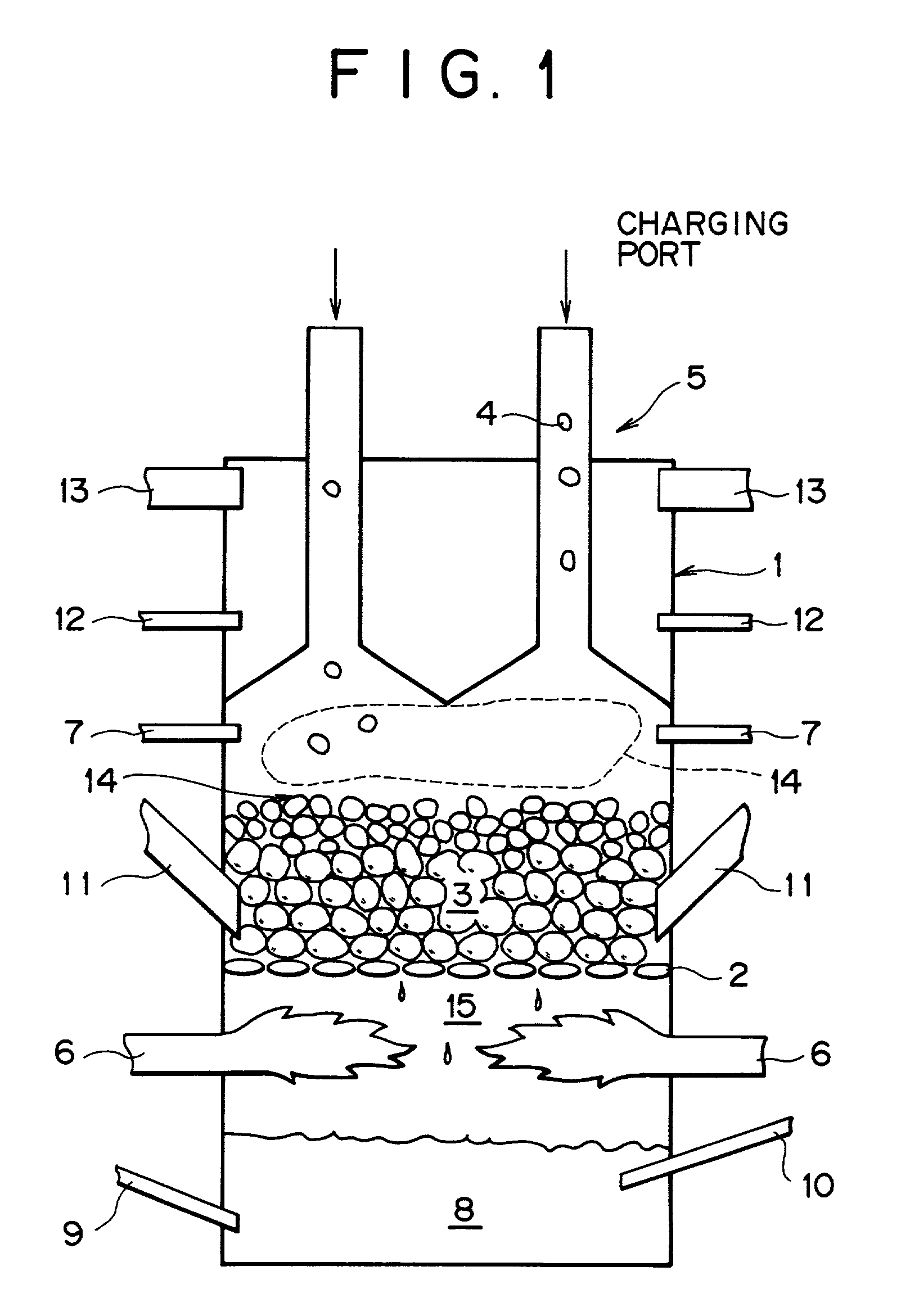

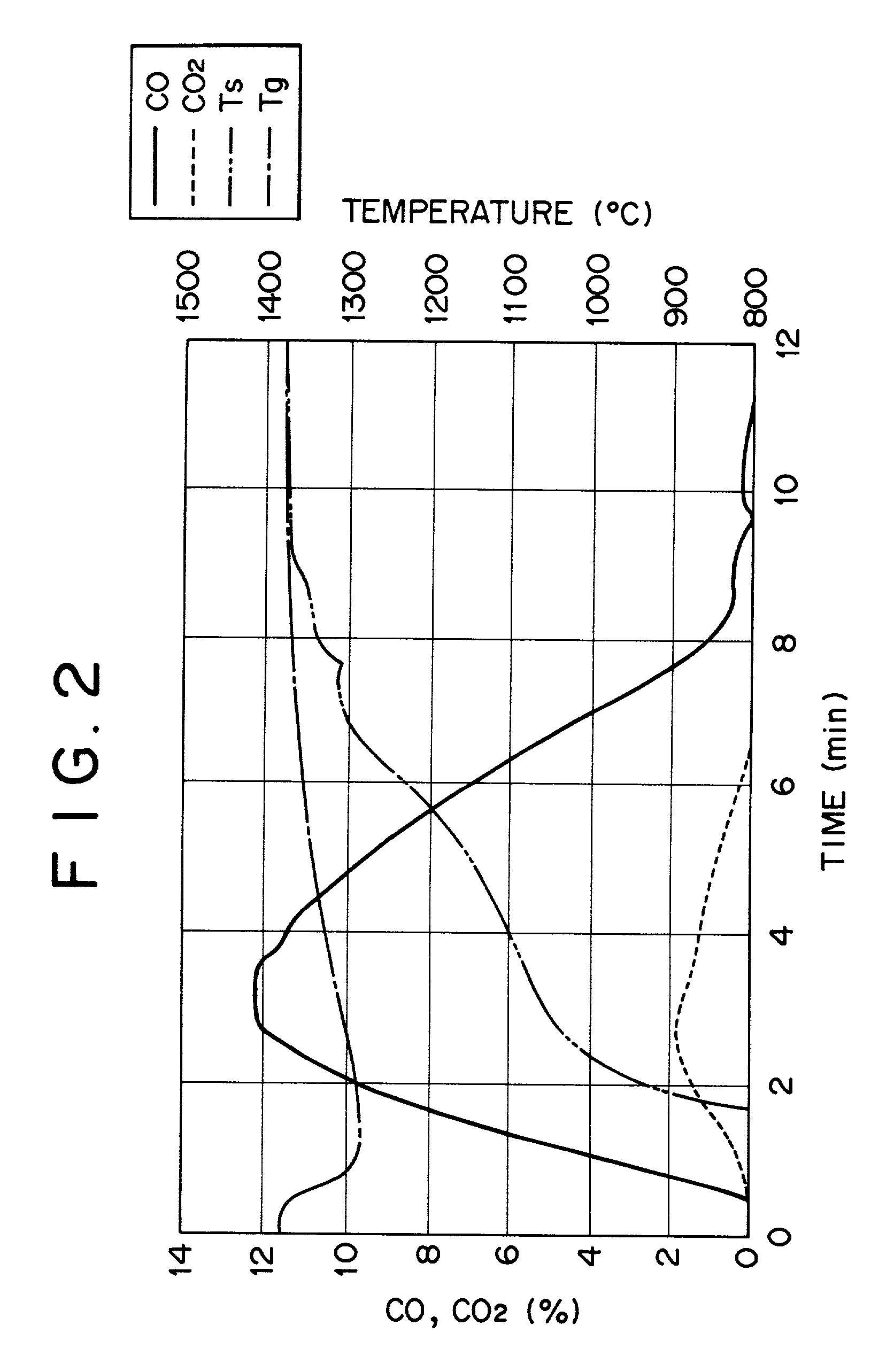

A method of manufacturing reduced iron at high Fe purity efficiently with less intrusion of a slag components using less carbonaceous reducing agent and fuel, comprising charging a compact of the iron oxide containing a carbonaceous reducing agent in a packed bed, reducing the iron oxide to 90% or more while keeping in a solid state by a heat source formed from the lower portion of the furnace and then melting the same, as well as an apparatus for manufacturing the metallic iron, comprising a fire grate disposed in the inside of a packed bed, a compact charged layer on the fire grate, a charging product charging mechanism for supplying the compact and a mechanism for discharging an exhaust gas in the furnace, and a fuel charging mechanism, a fuel combustion space and a molten product stores bath disposed below the fire grate.

Owner:KOBE STEEL LTD

Process for producing sintered ore and sintering machine

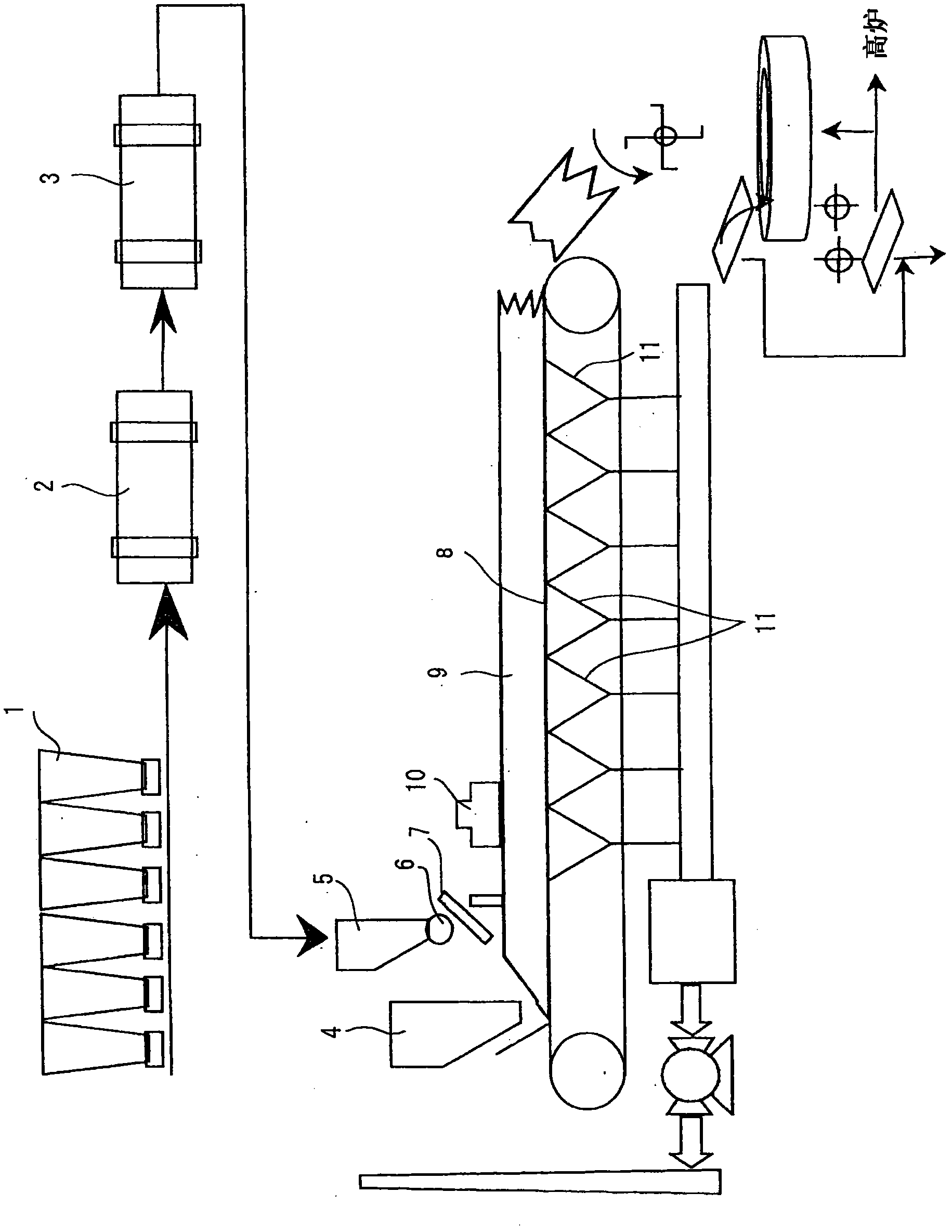

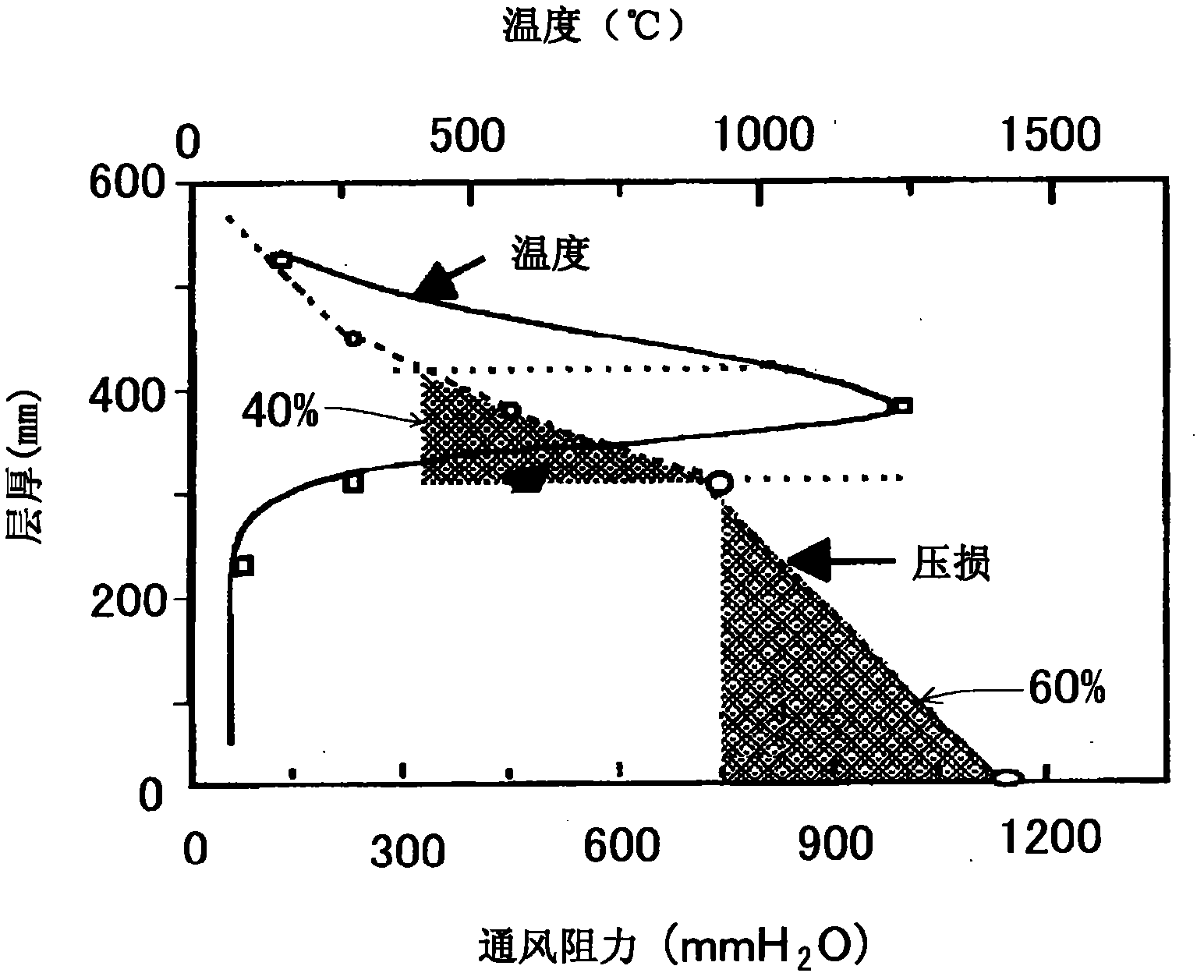

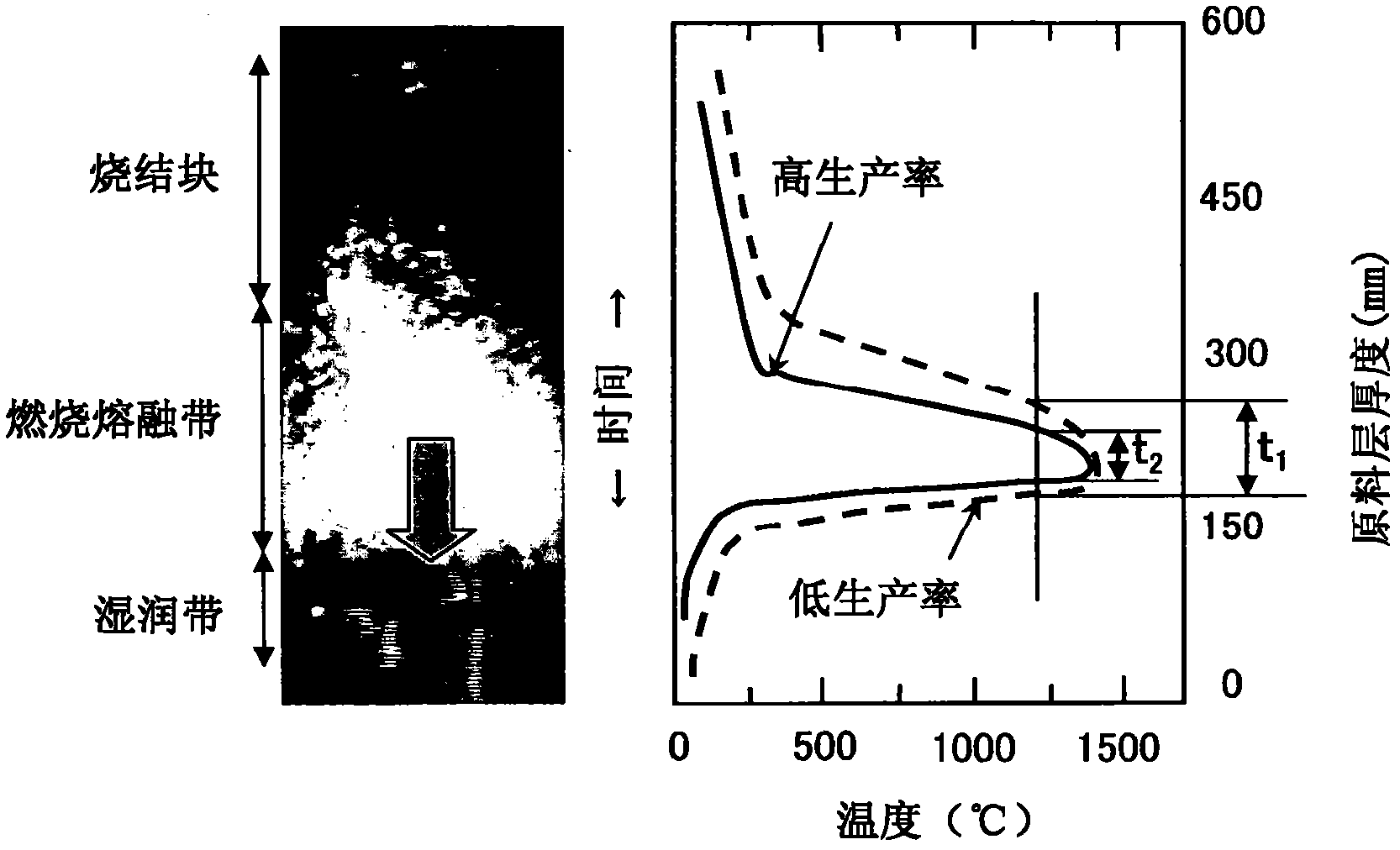

A process for producing a sintered ore which comprises: a charging step in which a pallet traveling cyclically is charged with a raw sintering material comprising a powdery ore and a carbonaceous material to form a charge layer of the raw sintering material on the pallet; an ignition step in which the carbonaceous material present in the surface of the charge layer is ignited with an ignition furnace; a dilute-gaseous-fuel production step in which a gaseous fuel is supplied to the air present over the charge layer to dilute the fuel and thereby obtain a dilute gaseous fuel having a concentration not higher than the lower combustion limit concentration; and a combustion step in which the dilute gaseous fuel and air are sucked into the charge layer by the suction of a wind box disposed beneath the pallet to burn the dilute gaseous fuel in the sinter layer and, at the same time, burn the carbonaceous material contained in the charge layer with the aid of the air sucked into the charge layer, thereby produce a sinter cake.

Owner:JFE STEEL CORP

Integrated Circuit Structure, Design Structure, and Method Having Improved Isolation and Harmonics

ActiveUS20100032796A1Harmonic reductionImprove isolationTransistorSemiconductor/solid-state device detailsSemiconductor structureCharge layer

Disclosed are embodiments of a semiconductor structure, a design structure for the semiconductor structure and a method of forming the semiconductor structure. The embodiments reduce harmonics and improve isolation between the active semiconductor layer and the substrate of a semiconductor-on-insulator (SOI) wafer. Specifically, the embodiments incorporate a trench isolation region extending to a fully or partially amorphized region of the wafer substrate. The trench isolation region is positioned outside lateral boundaries of at least one integrated circuit device located at or above the active semiconductor layer of the SOI wafer and, thereby improves isolation. The fully or partially amorphized region of the substrate reduces substrate mobility, which reduces the charge layer at the substrate / BOX interface and, thereby reduces harmonics. Optionally, the embodiments can incorporate an air gap between the wafer substrate and integrated circuit device(s) in order to further improve isolation.

Owner:GLOBALFOUNDRIES US INC

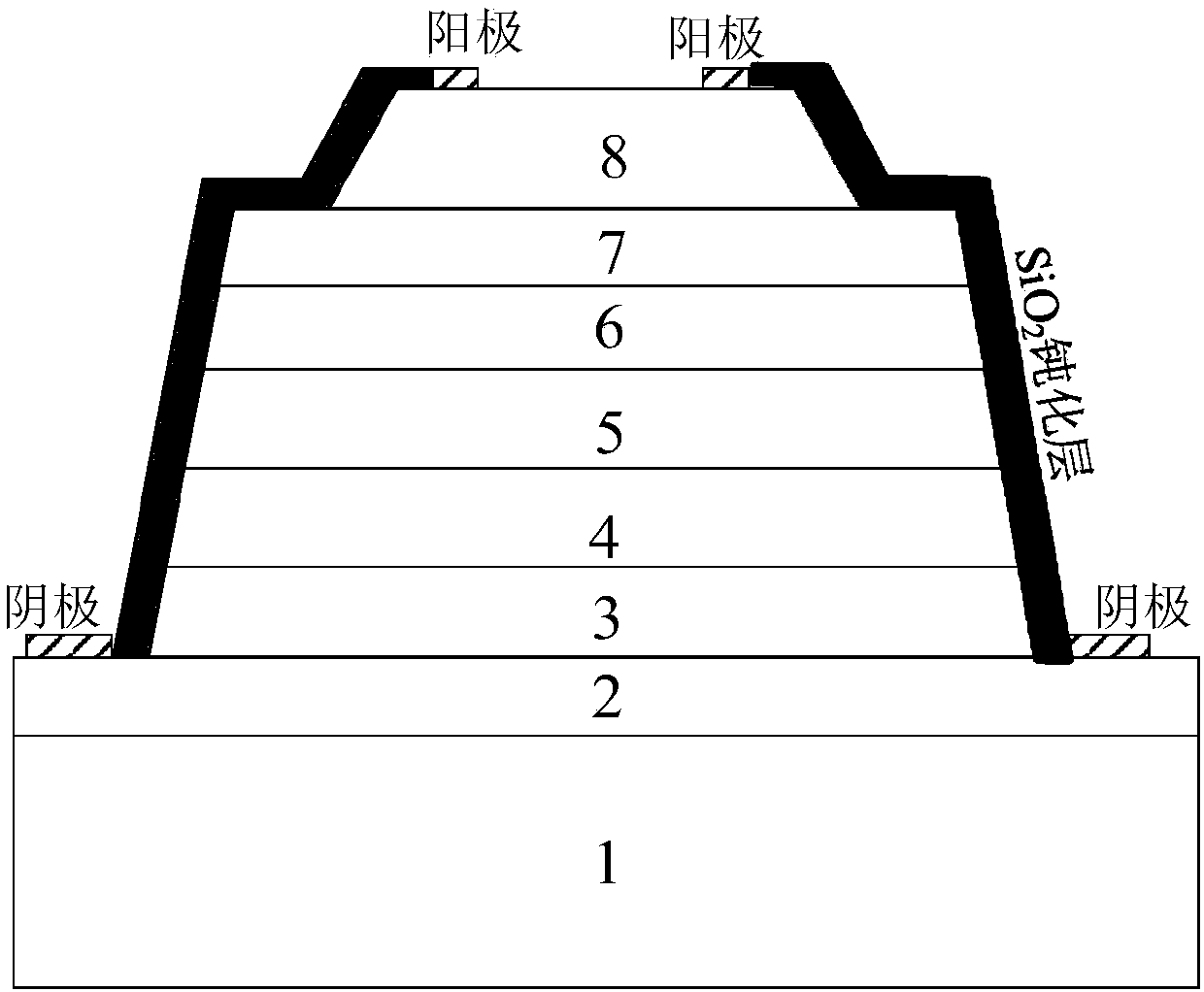

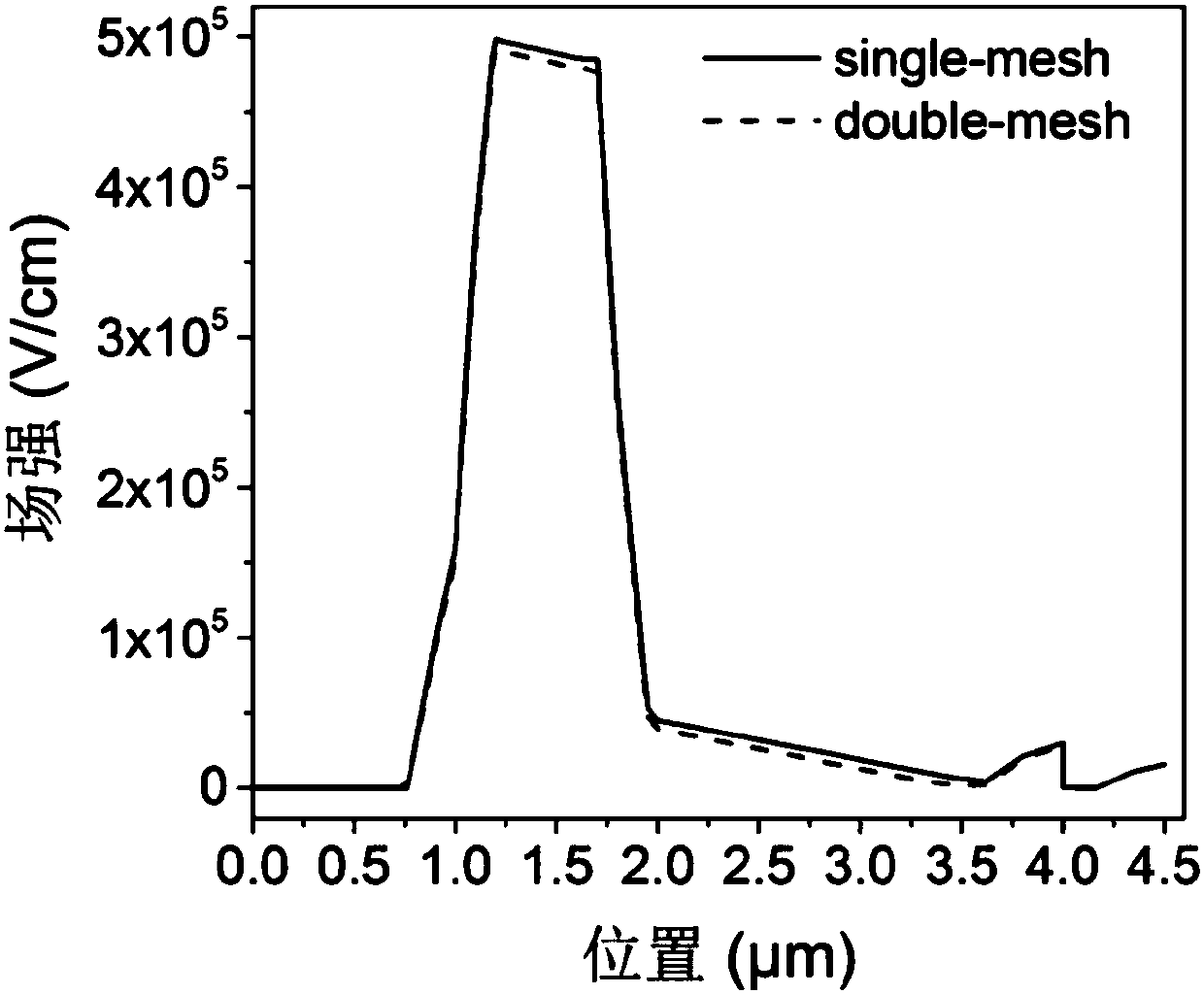

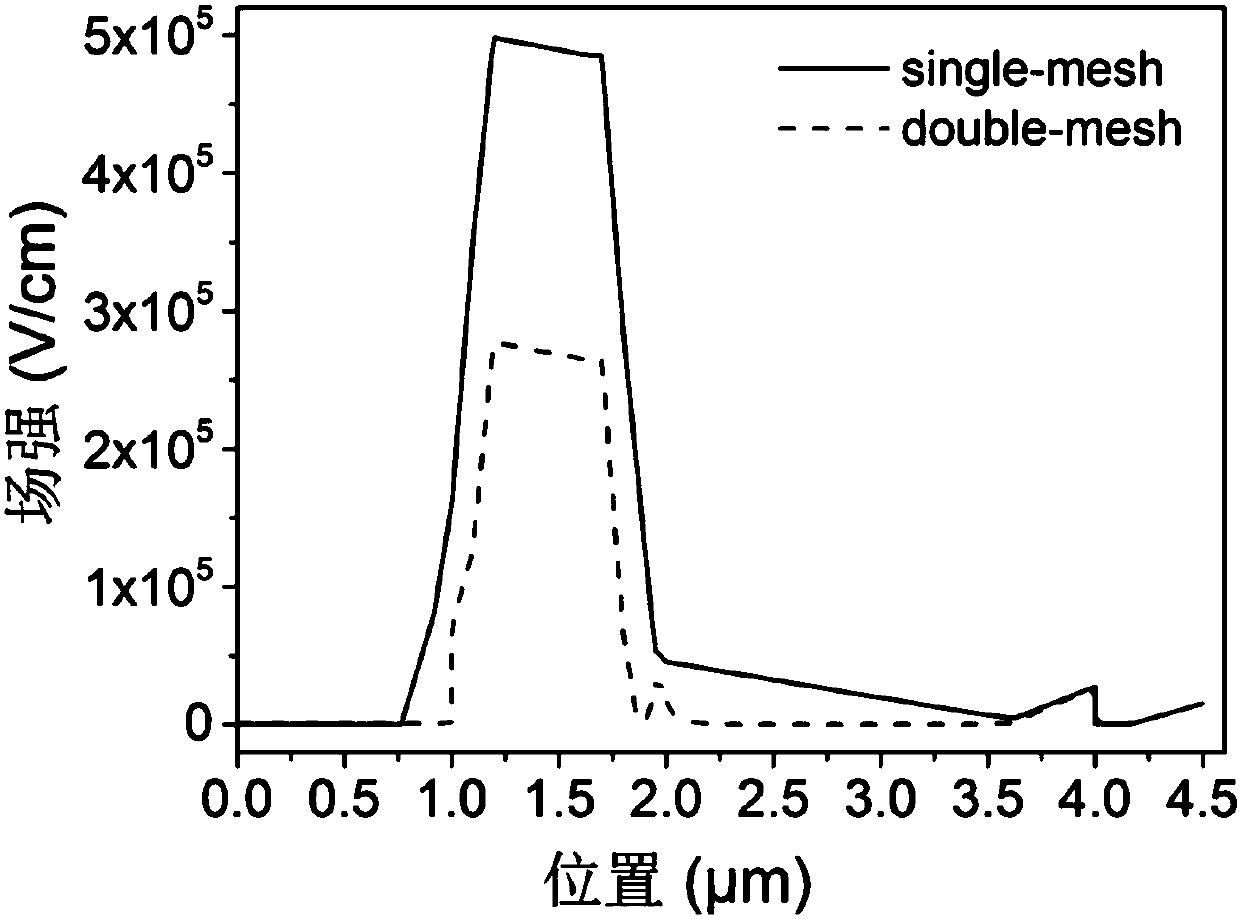

Two-stage table-top InGaAs/InP avalanche photodiode and preparation method thereof

InactiveCN107768462AReduce fringe electric fieldSuppresses edge breakdownSemiconductor devicesCharge layerContact layer

The invention belongs to the fields of photoelectric detection and image sensors, and in order to inhibit fringe field and reduce device dark current while guaranteeing a high field in the central area of the device, reference basis is provided for industrial application. The invention discloses a two-stage table-top InGaAs / InP avalanche photodiode and a preparation method thereof. The structure comprises an N<+>-InP substrate, an N-InP buffer layer, an N<->-InGaAs In0.53Ga0.47As absorbed layer, an N-InGaAsP In(1-x)GaxAsyP(1-y) component gradient layer, an N-InP charge layer, an i-InP multiplying layer, a P-InP field buffer layer and a P<+>-InP contact layer, wherein the P-InP field buffer layer forms a shallow table-top through etching, the N-InP buffer layer forms a deep table-top through etching, and constant impact ionization of photon-generated carriers inside the multiplying layer causes avalanche multiplication. The avalanche photodiode is mainly applied to the design occasionsof photoelectric detection and photoelectric sensors.

Owner:TIANJIN UNIV

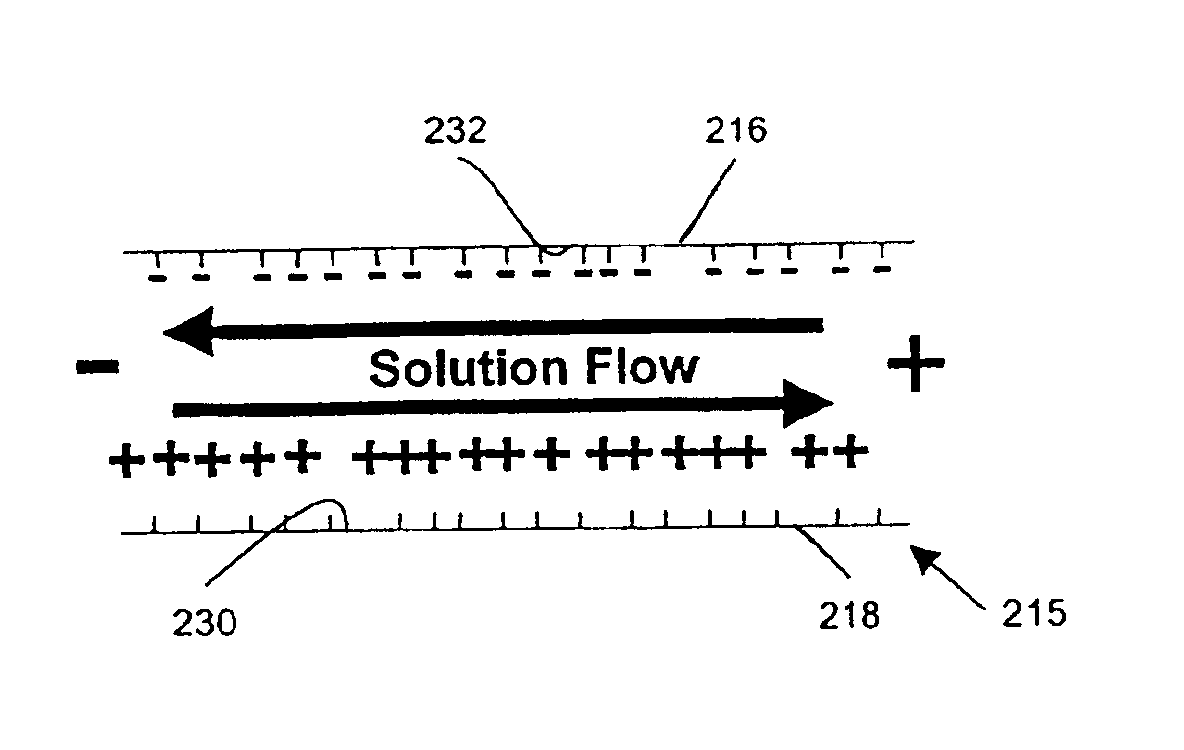

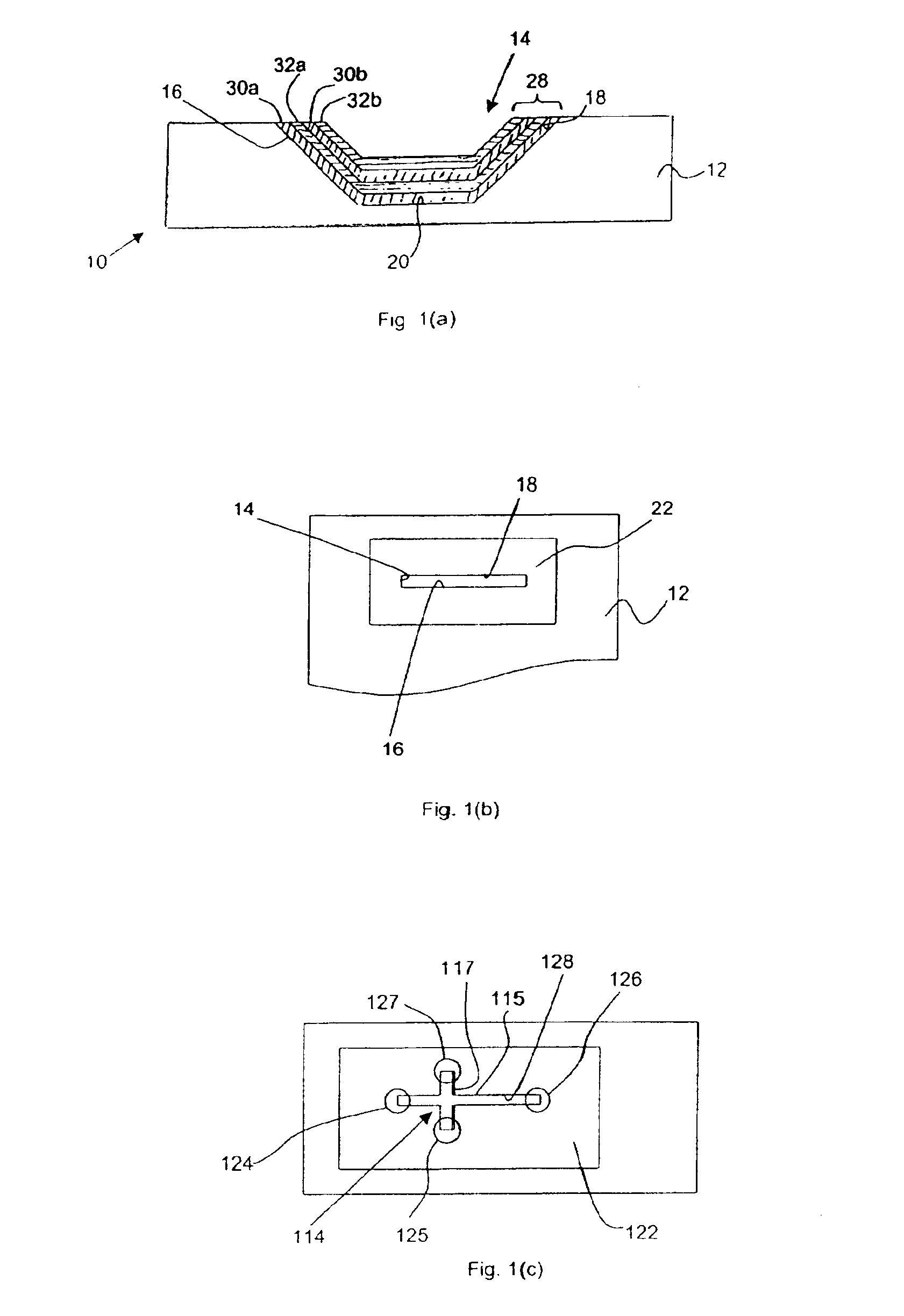

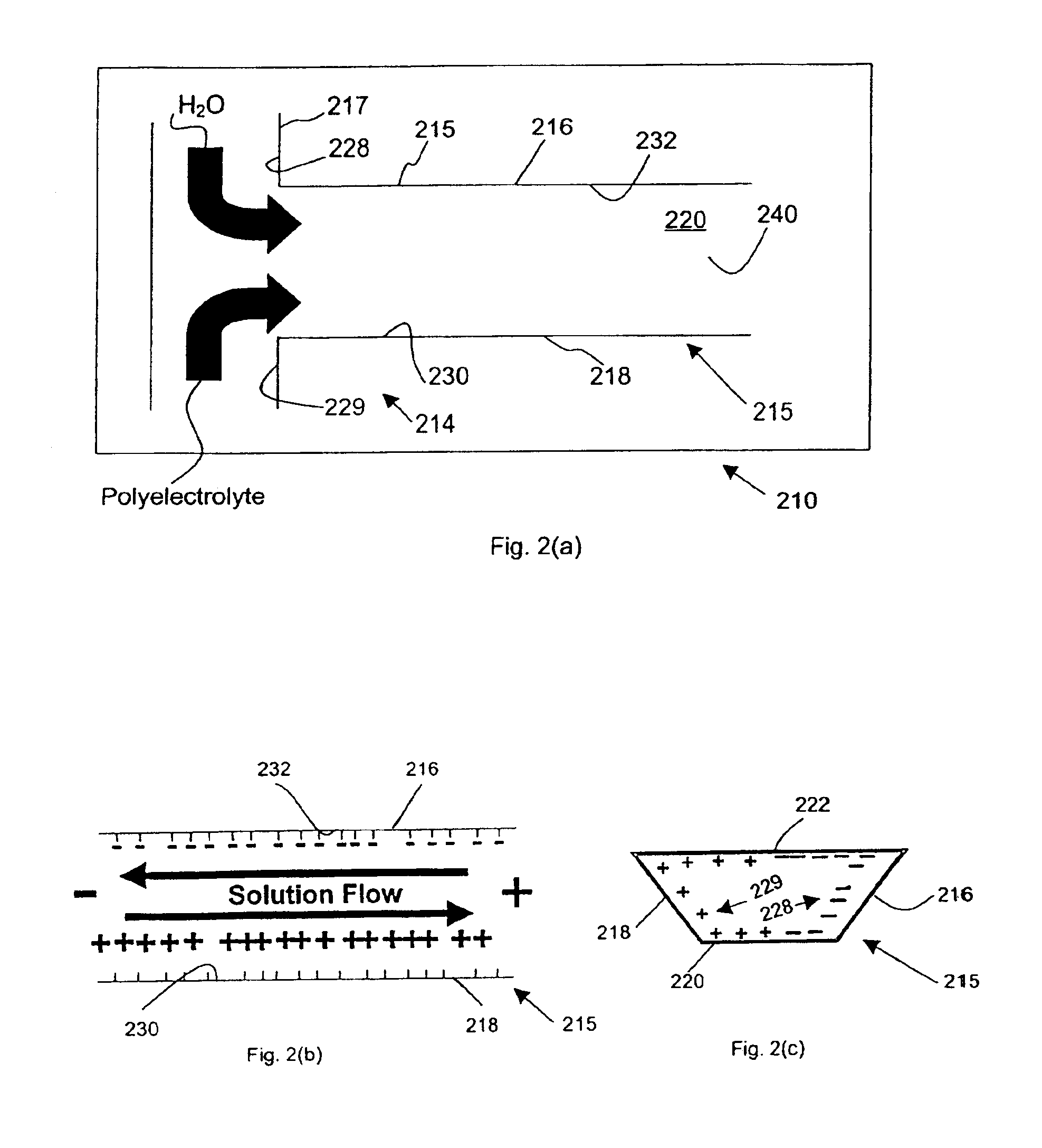

Polyelectrolyte derivatization of microfluidic devices

InactiveUS6860980B2Similar rateGood biocompatibilitySludge treatmentLayered productsPolyelectrolyteCharge layer

A microchannel device is provided with a plastic substrate having a microchannel formed therein. Polyelectrolyte multilayers are disposed along selected surfaces of the microchannel. The polyelectrolyte layers comprise alternating net positively charged layers and net negatively charged layers. A microchannel lid has a surface facing the microchannel. In making the microchannel device, selected surfaces of the microchannel are alternatively exposed to solutions comprising positively charged polyelectrolytes and negatively charged polyelectrolytes to form the desired number of polyelectrolyte layers.

Owner:GOVERNMENT OF THE US REPRESENTED BY THE SEC OF COMMERCE THE

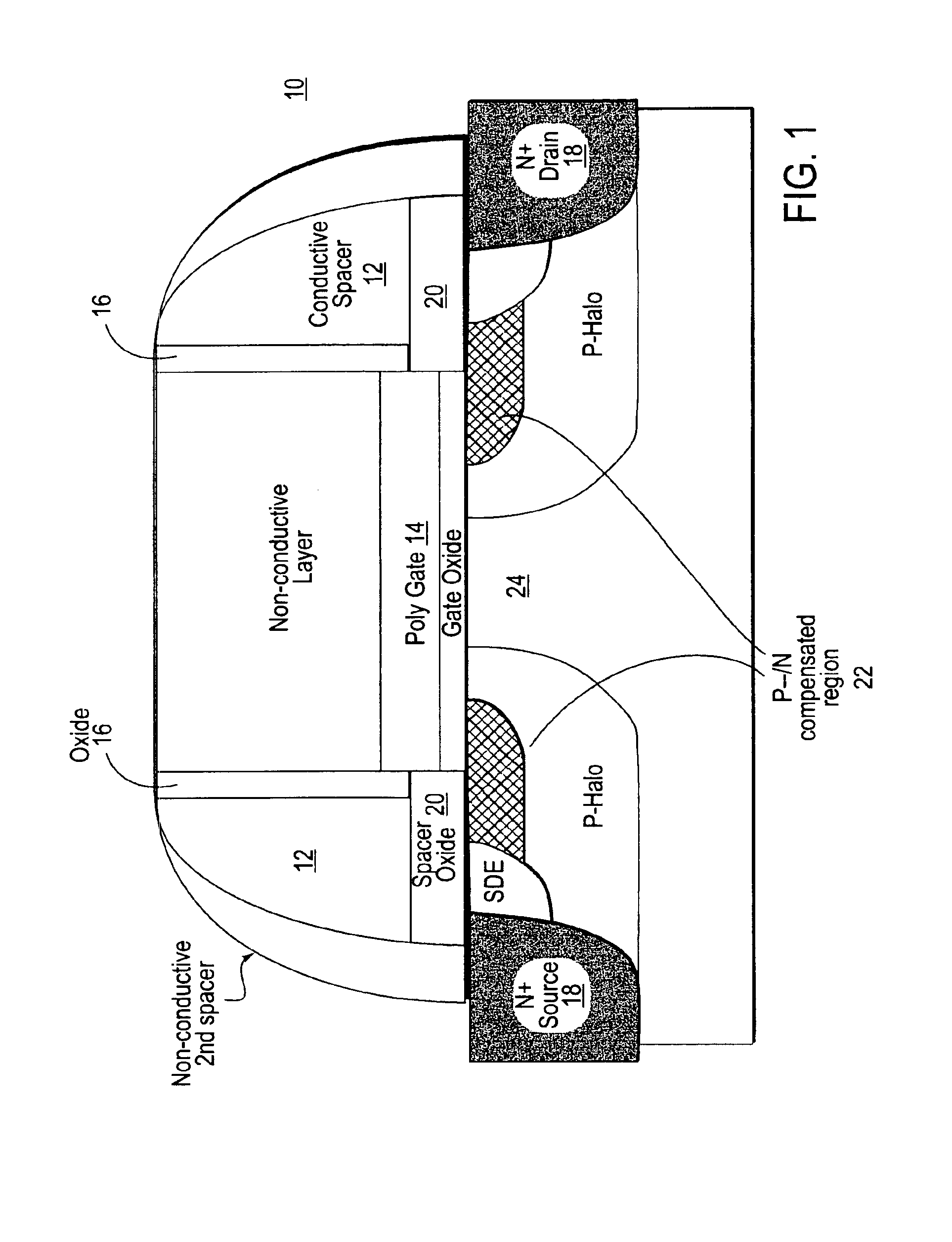

Soi radio frequency switch for reducing high frequency harmonics

First doped semiconductor regions having the same type doping as a bottom semiconductor layer and second doped semiconductor regions having an opposite type doping are formed directly underneath a buried insulator layer of a semiconductor-on-insulator (SOI) substrate. The first doped semiconductor regions and the second doped semiconductor regions are electrically grounded or forward-biased relative to the bottom semiconductor layer at a voltage that is insufficient to cause excessive current due to forward-biased injection of minority carriers into the bottom semiconductor layer, i.e., at a potential difference not exceeding 0.6 V to 0.8V. The electrical charges formed in an induced charge layer by the electrical signal in semiconductor devices on the top semiconductor layer are drained through electrical contacts connected to the first and second doped semiconductor regions, thereby reducing of harmonic signals in the semiconductor devices above and enhancing the performance of the semiconductor devices as a radio-frequency (RF) switch.

Owner:GLOBALFOUNDRIES US INC

Manufacturing method of flat-type avalanche diode detector used for detecting single photon

The invention relates to a manufacturing method of a flat-type avalanche diode detector used for detecting a single photon. The manufacturing method comprises the following steps: sequentially growing an InP buffer layer, an InGaAs absorbing layer, an InGaAsP gradient layer, an N-type InP charge layer and an InP cap layer on an N-type InP substrate; growing an SiO2 protective layer on the InP caplayer; photoengraving a round window at the middle of the SiO2 protective layer; eroding the InP cap layer in the round window through wet-method erosion, thereby forming a round hole; carving a protection ring window on the SiO2 protective layer around the round window; removing surplus SiO2 protective layer by utilizing an HF (hydrogen fluoride) solution in the protection ring window through a diffusion process; regrowing the InP cap layer an SiO2 layer, and caving an electrode window at the periphery of the round hole; forming a top ring electrode on the electrode window through an electron beam evaporation and desquamation process, and preparing a metal electrode at the periphery and one side of the ring electrode; and forming a back electrode at the back of the N-type InP substrate through electron beam evaporation, and preparing a SiNx antireflection layer at the surface of the InP cap layer in the round hole, thereby finishing the manufacture of the avalanche diode detector.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

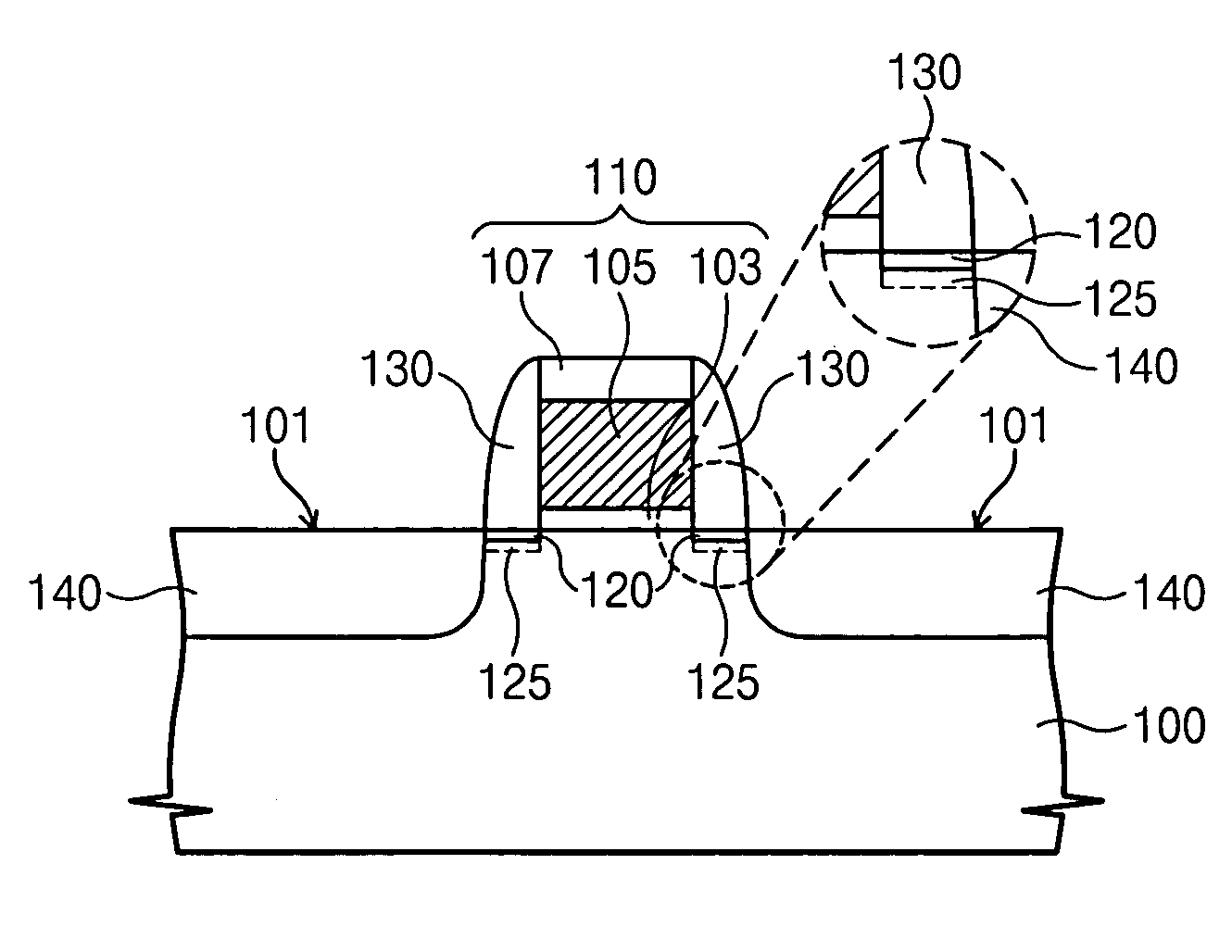

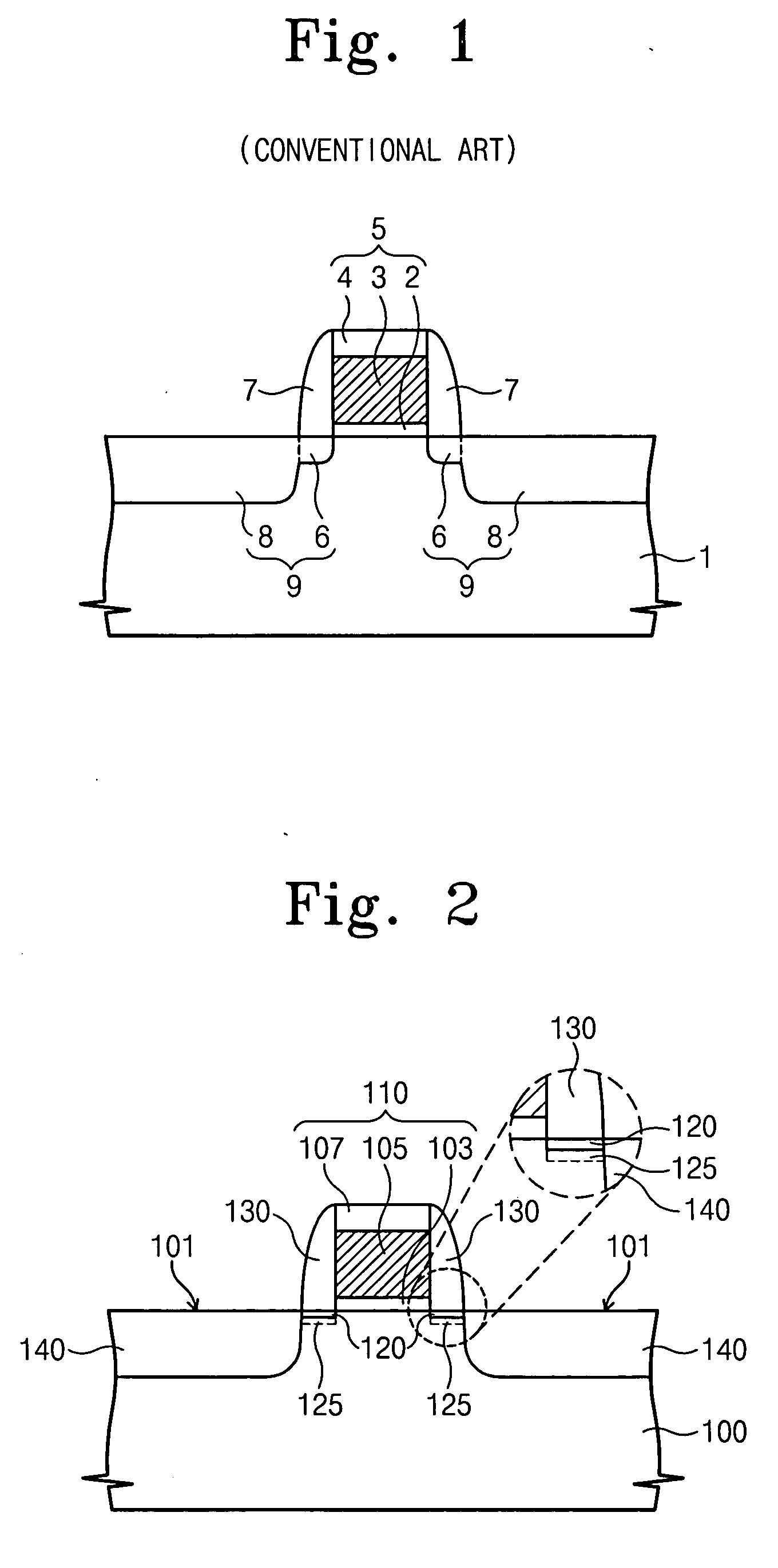

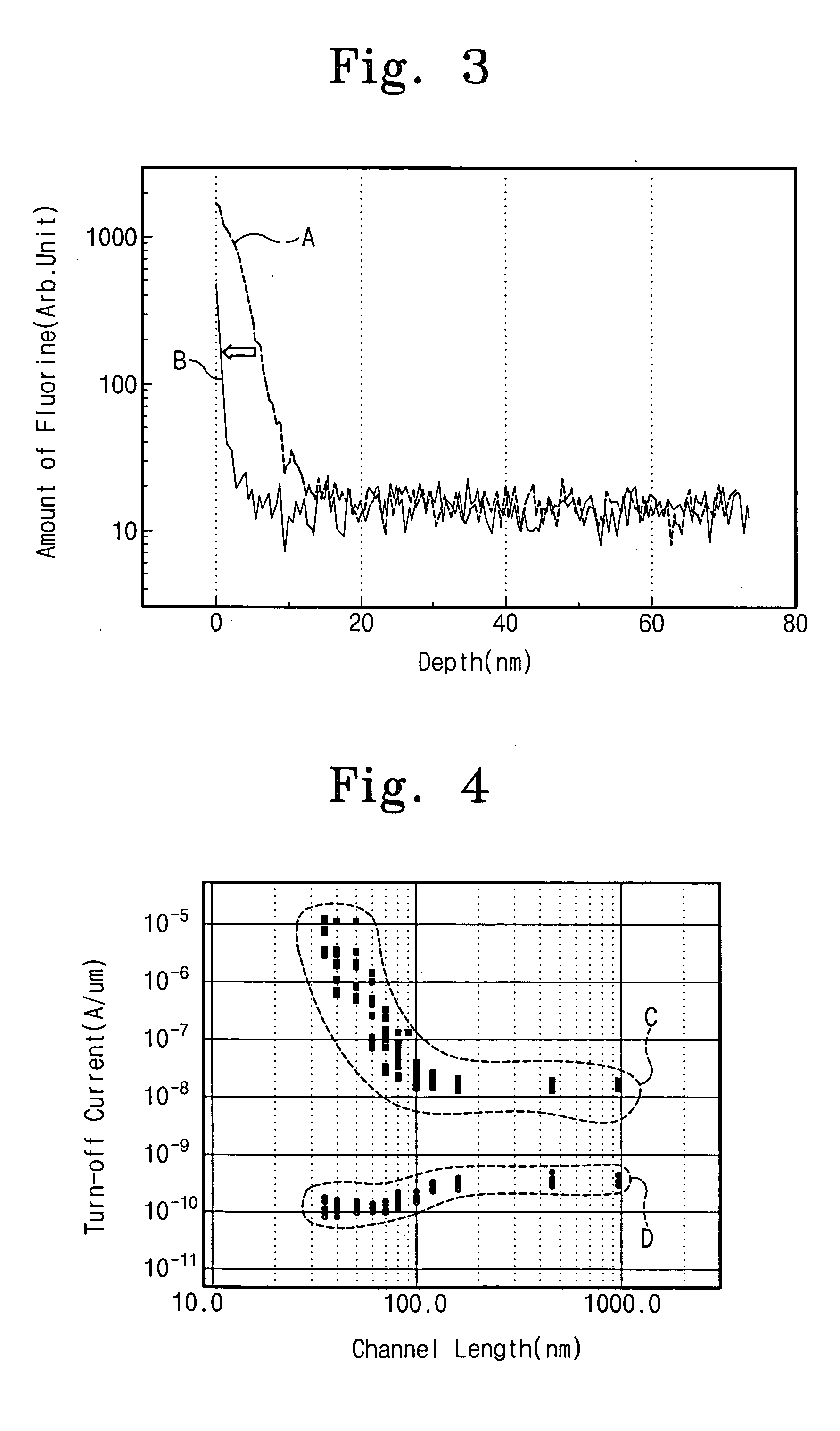

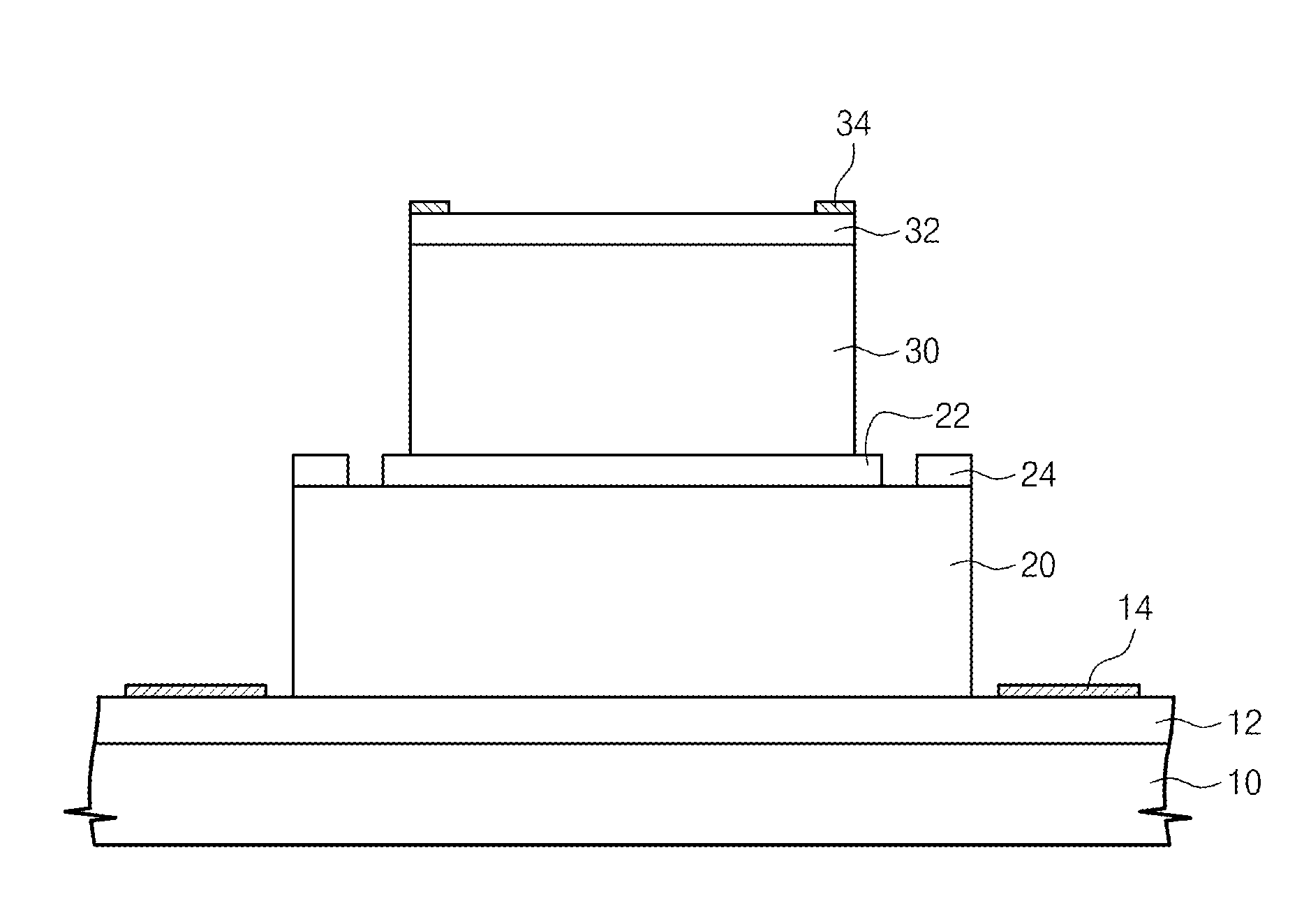

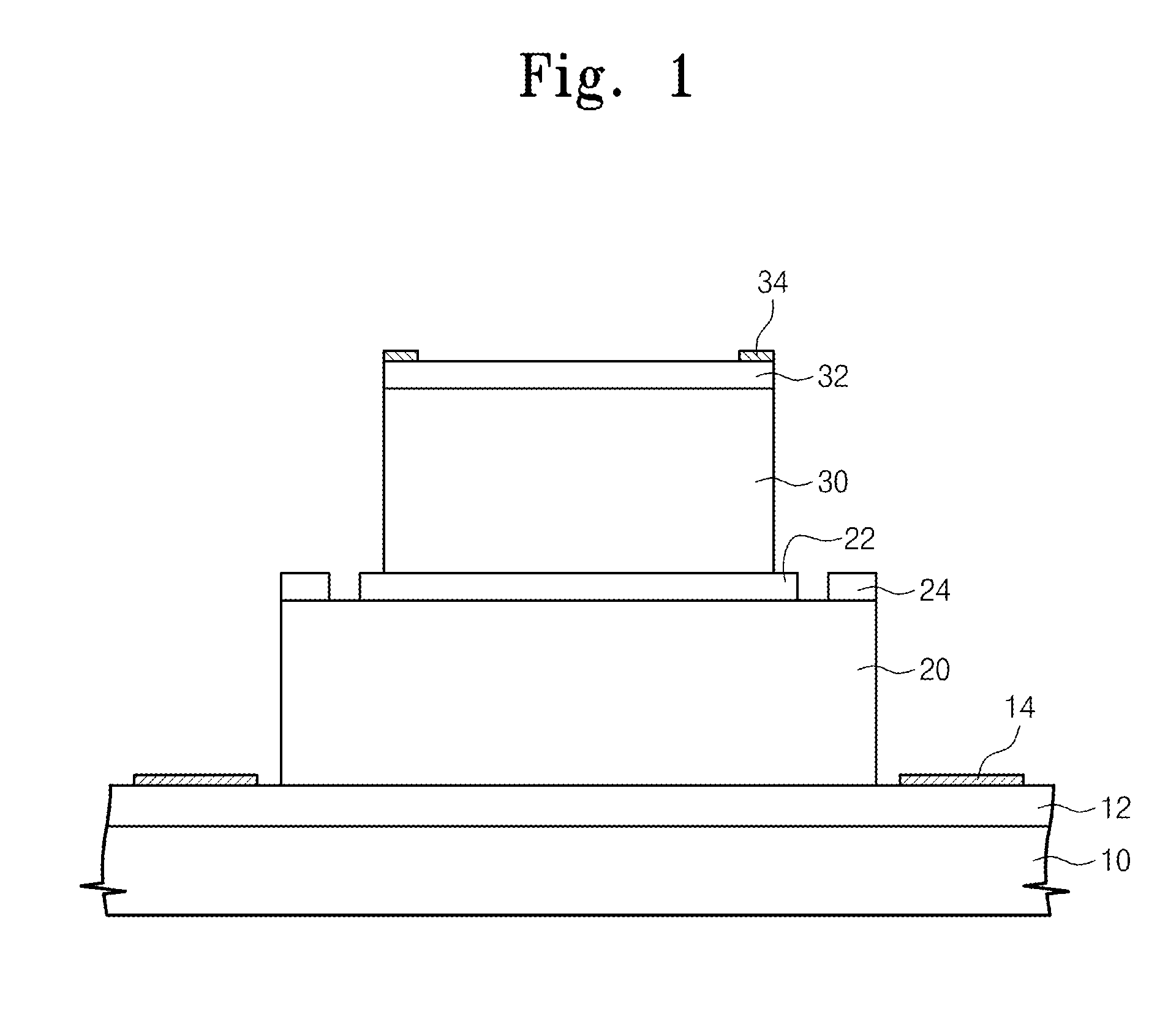

Semiconductor device and method of forming same

A semiconductor device includes a gate pattern disposed on a semiconductor substrate, a gate spacer disposed on both sidewalls of the gate pattern, and a fixed charge layer disposed in the semiconductor substrate below the gate spacer. Elements generating fixed charges are injected into the fixed charge layer. A layer in which carriers induced by the fixed charge layer are accumulated is disposed below the fixed charge layer. The elements are segregated to a substrate of the semiconductor substrate from the inside of the semiconductor substrate by heat.

Owner:SAMSUNG ELECTRONICS CO LTD

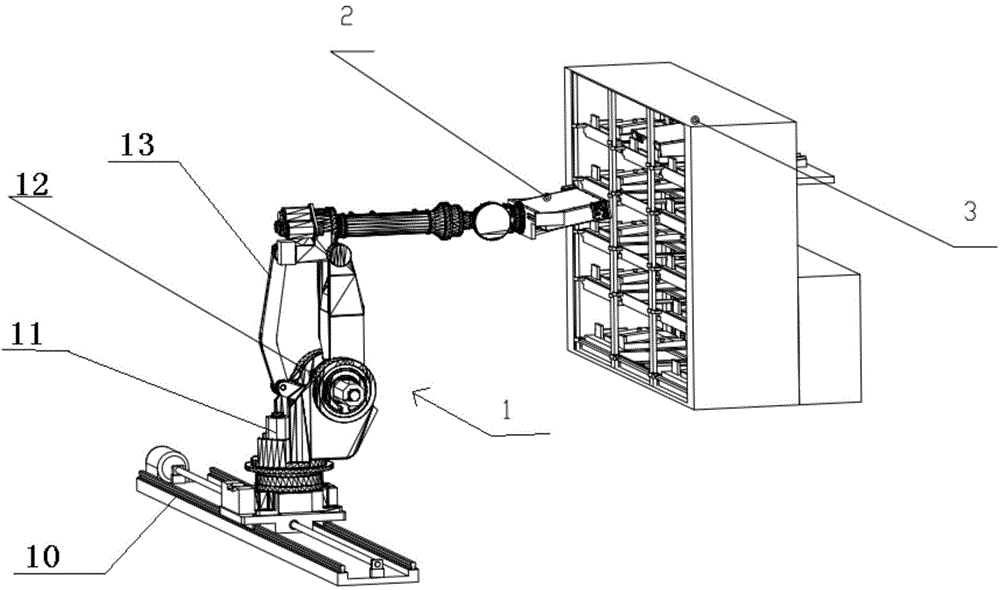

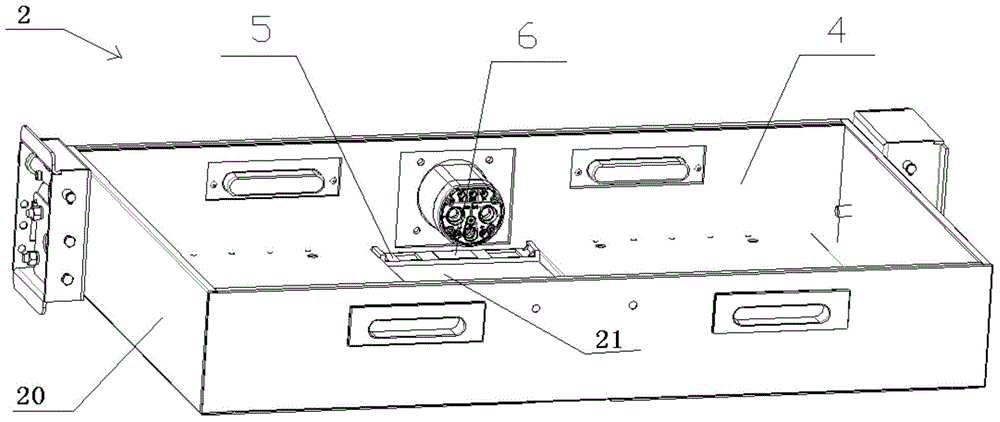

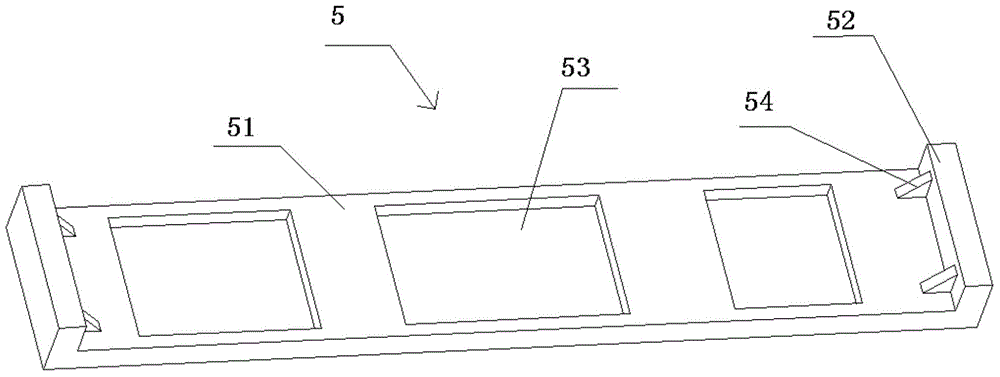

Electric vehicle chassis battery charging and replacing device

ActiveCN103978961AImprove mobile efficiencyGuaranteed positioning accuracyElectric propulsion mountingElectric/fluid circuitElectricityBattery charge

The invention relates to an electric vehicle chassis battery charging and replacing device. The electric vehicle chassis battery charging and replacing device comprises a ground slide guide rail, a mechanical arm, a battery box and a battery frame, wherein the mechanical arm is arranged on the ground slide guide rail; the battery frame is used for placing the battery box; a non-standard clamp used for clamping the battery box is arranged on the mechanical arm; the battery frame comprises a frame body, a charging layer, a working layer and a stored to-be-charged layer; each of the charging layer, the working layer and the stored to-be-charged layer is provided with a lifting table, a moveable guide rail and a tray which are arranged on the frame body; a pressure sensor is arranged on each tray; each lifting table is connected with the frame body through each lifting guide rail; the moveable guide rail is arranged on each lifting table; each tray is arranged on each moveable guide rail of each lifting table. The electric vehicle chassis battery charging and replacing device is convenient and quick in work, clear in labor division, flexible in clamping, precise in positioning, and stable and reliable in the whole working process, the requirement of quickly replacing the battery of a large-mass electric vehicle is better met, the battery charging and replacing efficiency is greatly improved, and the problems of low battery charging and replacing efficiency and the like of the electric vehicle are solved.

Owner:STATE GRID CORP OF CHINA +2

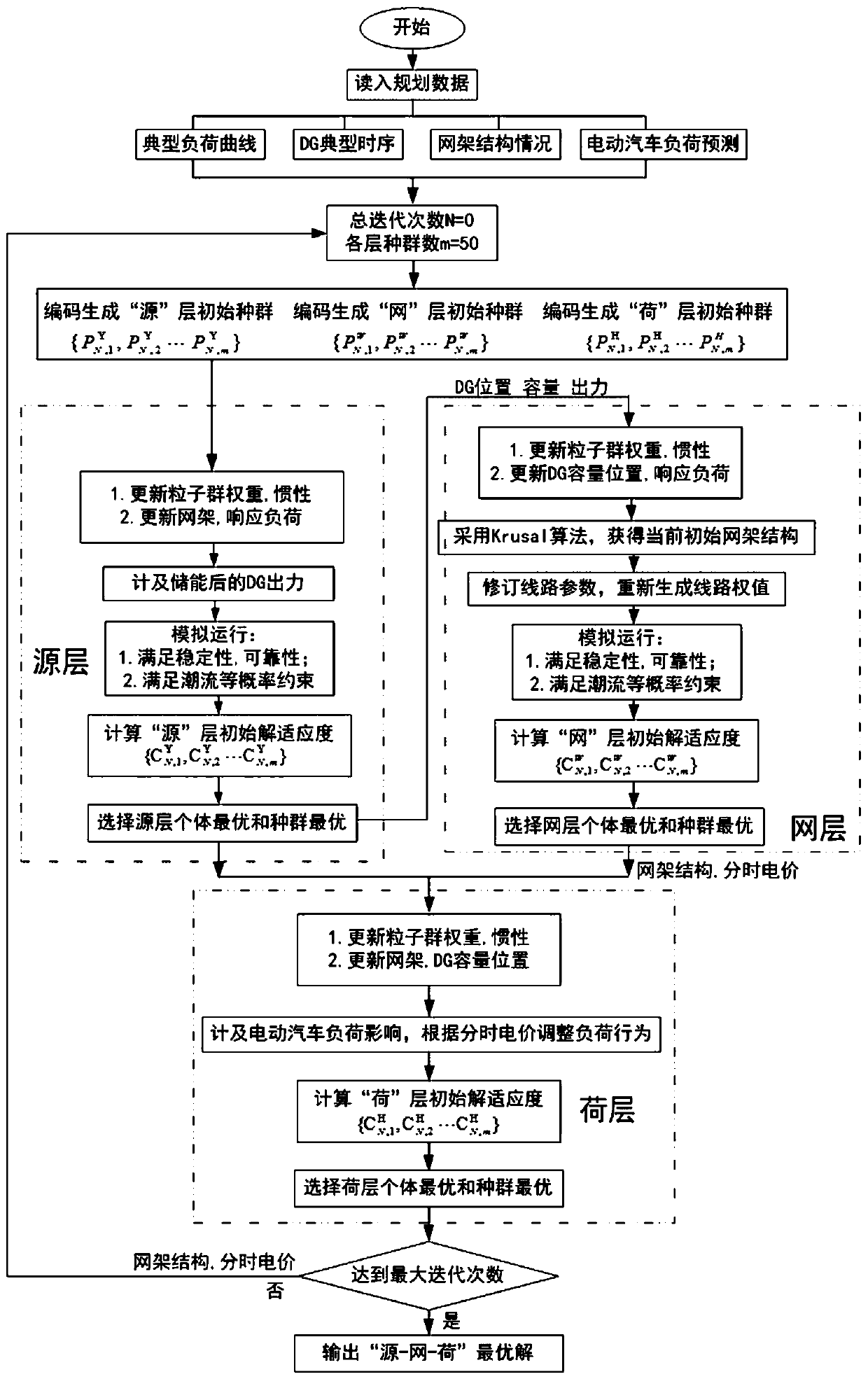

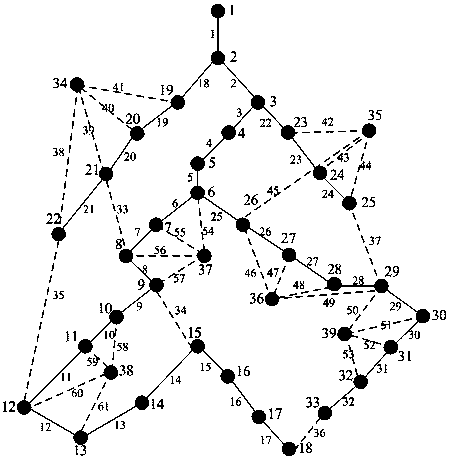

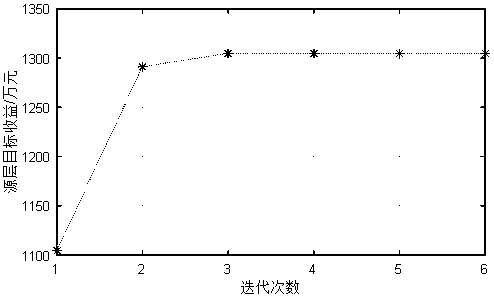

Electric vehicle load demand response-considered network-source-load coordination planning method

InactiveCN108446796ALow investment and operation costEconomic benefit maximizationForecastingCharge layerEngineering

The invention relates to an electric vehicle load demand response-considered network-source-load coordination planning method. According to the method, firstly, during the load forecasting process, the influence of an electric vehicle is considered, and the probability distribution of the first travel time of the electric vehicle is obtained. Meanwhile, the probability distribution calculation iscarried out on the daily running mileage. Through predicting two parameters, the charge load distribution of the electric vehicle for 24 hours of the day is further predicted and the load distributioninformation is improved. After that, under the condition that the interests of three parties, namely the power grid, the power supply and the load, are considered, the network-source-load coordination planning is carried out. According to the invention, the interests of three parties, namely the power grid, the power supply and the load, are coordinated and planned. Meanwhile, the electric vehicle is taken as one of the influence factors of the load response considered in the charge layer planning process, so that the advantages of three parties are complementarily coordinated and developed.The requirement for the planning work of the power distribution network in a new situation is met. The investment and operation cost of a power grid company is saved. Meanwhile, the maximization of economic benefits of operators is guaranteed. The method has important practical value.

Owner:STATE GRID FUJIAN ELECTRIC POWER CO LTD +1

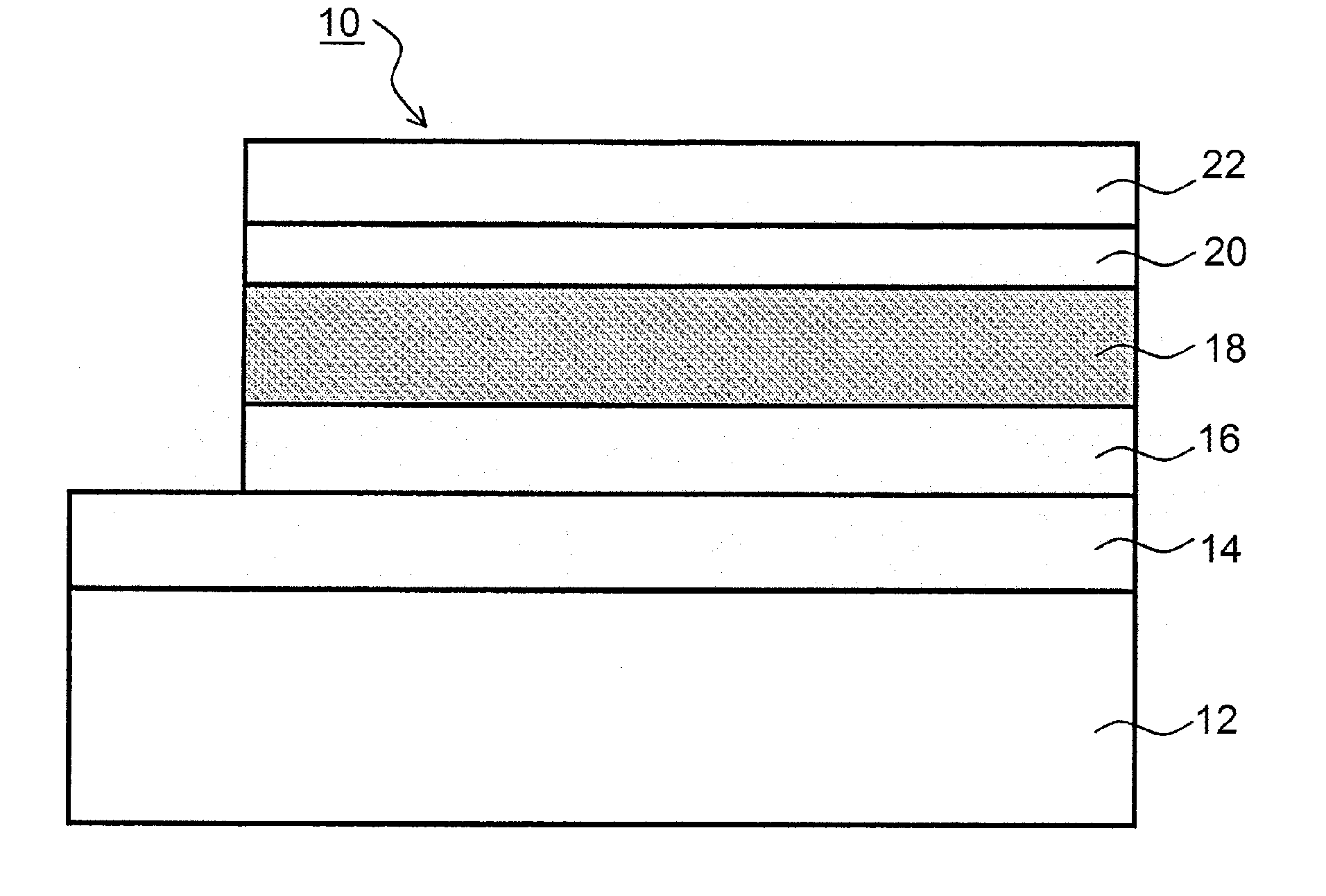

Low-voltage high-gain high-speed germanium photo detector and method of fabricating the same

ActiveUS20140048772A1Semiconductor/solid-state device manufacturingNanoopticsPhotovoltaic detectorsLow voltage

Provided is a silicon-wafer-based germanium semiconductor photodetector configured to be able to provide properties of high gain, high sensitivity, and high speed, at a relatively low voltage. A germanium-based carrier multiplication layer (e.g., a single germanium layer or a germanium and silicon superlattice layer) may be provided on a silicon wafer, and a germanium charge layer may be provided thereon, a germanium absorption layer may be provided on the charge layer, and a polysilicon second contact layer may be provided on the absorption layer. The absorption layer may be configured to include germanium quantum dots or wires.

Owner:ELECTRONICS & TELECOMM RES INST

Repeatedly chargeable and dischargeable quantum battery

InactiveUS20140352775A1Avoid changePreventing deterioration and peelingBatteries circuit arrangementsSolid-state devicesCharge layerMetal electrodes

The purpose of this invention is to provide a repeatedly chargeable and dischargeable quantum battery that is available for a long period of time without an aging change. The quantum battery is charged by causing an n-type metal oxide semiconductor to have a photo-exited structural change, thereby the electrode of quantum battery is prevented from being oxide and a price reduction and stable operation are possible. The repeatedly usable quantum battery is constituted by laminating; a first metal electrode having an oxidation preventing function, charging layer in which an energy level is formed in the band gap by causing an n-type metal oxide semiconductor covered with an insulating material to have a photo-exited structure change and electrons are trapped at the energy level; p-type metal oxide semiconductor layer; and a second metal electrode having the oxidation preventing function, the electrodes are passive metal layers formed of metals having passive characteristics.

Owner:NIHON MICRONICS +1

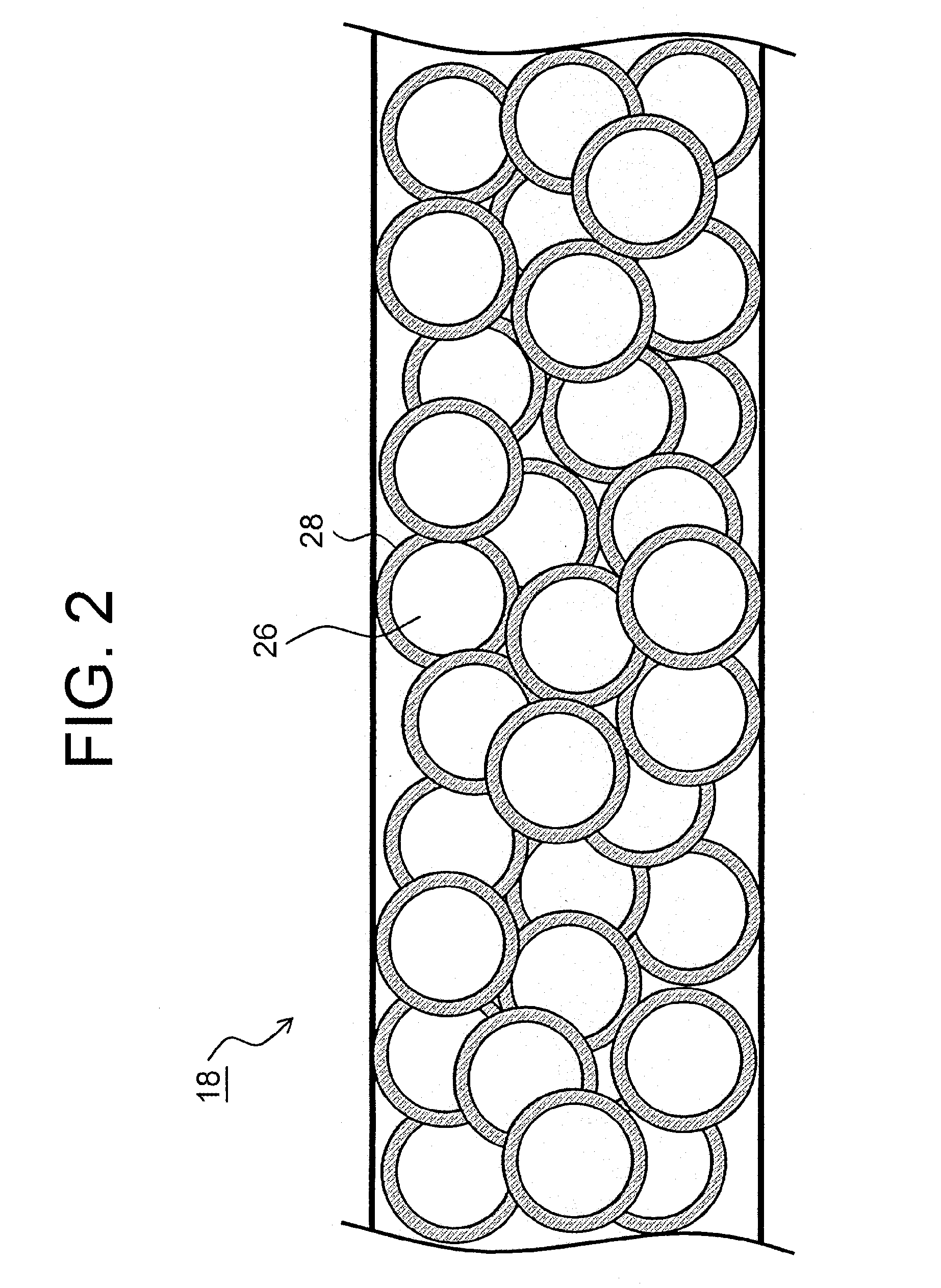

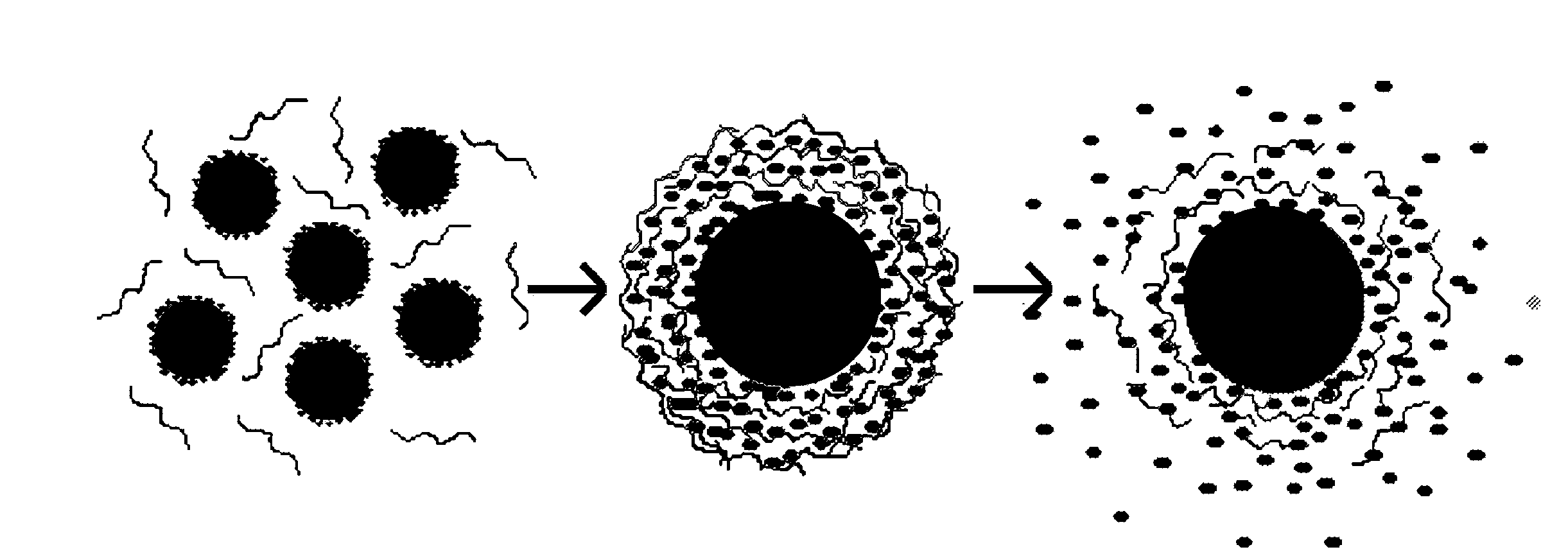

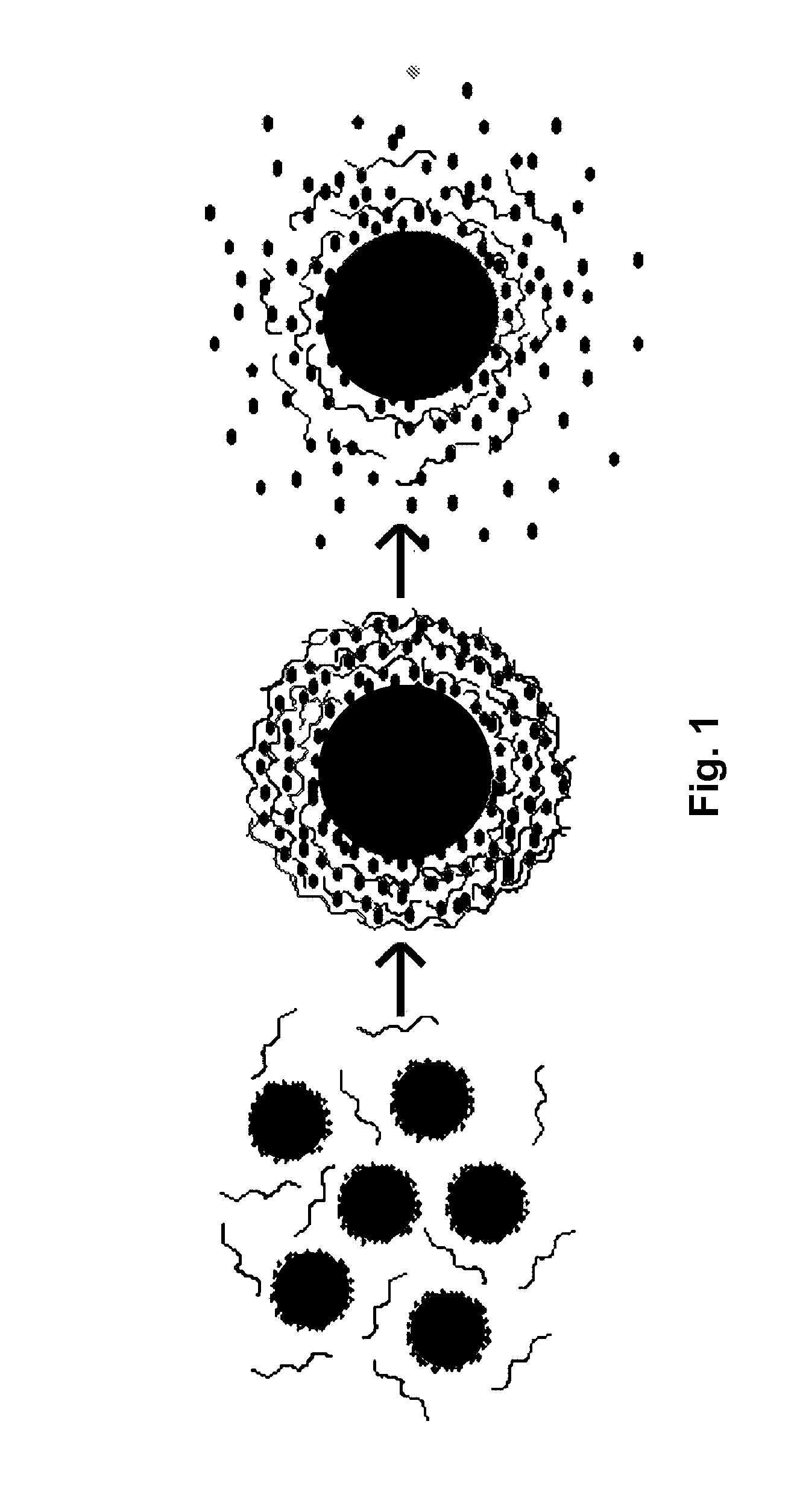

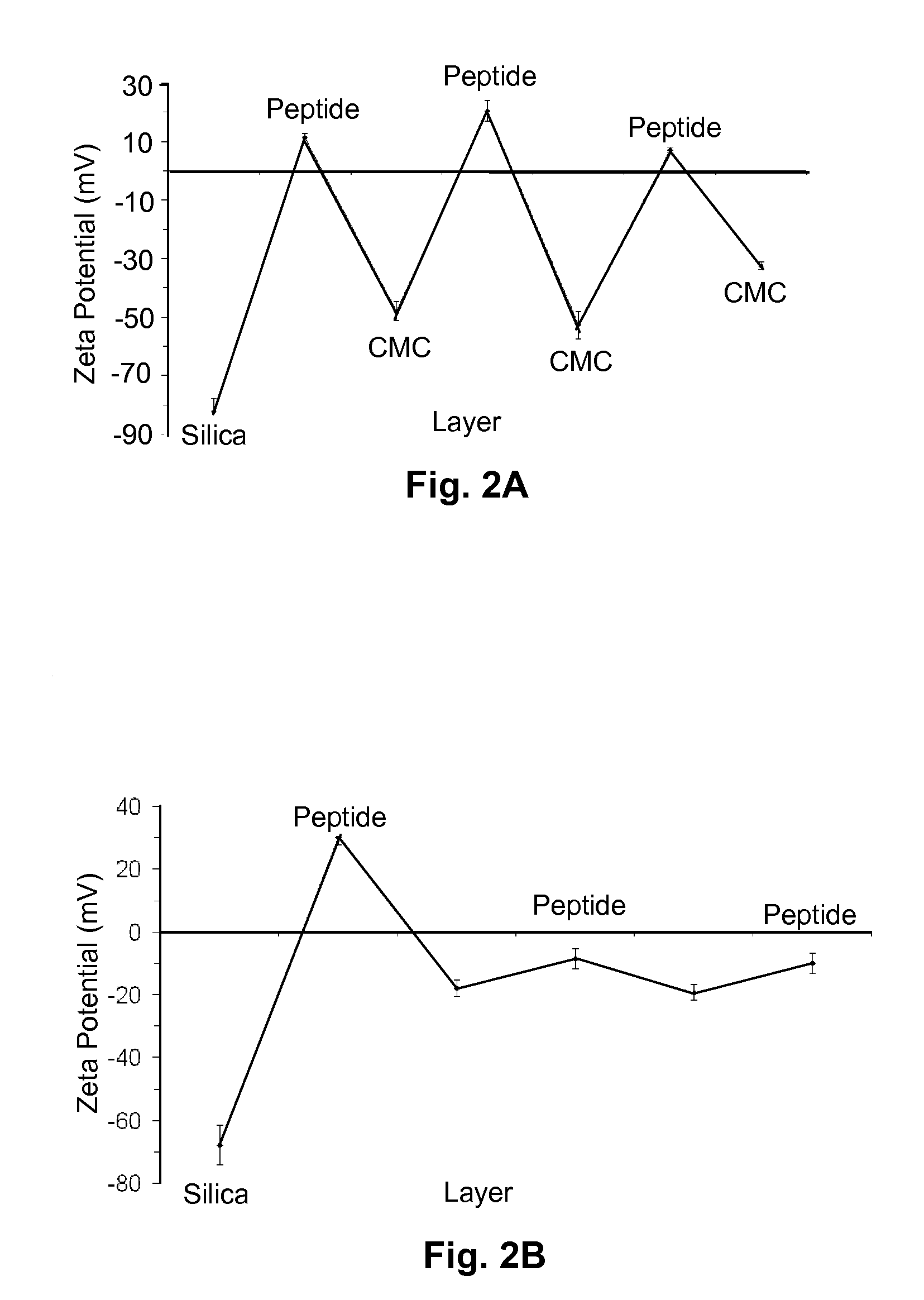

Layered Nanoparticles for Sustained Release of Small Molecules

InactiveUS20090061006A1Strong specificityHigh selectivityPowder deliveryPeptide/protein ingredientsLytic peptideSide effect

Nanoparticle compositions and methods are disclosed for the sustained release of small molecules, such as pharmaceutical compounds in vivo, for example ligand-lytic peptide conjugates. The construction of the nanoparticles helps to prevent self-aggregation of the molecules, and the consequent loss of effectiveness. The system employs layer-by-layer self-assembly of biocompatible polyelectrolyte layers, and layers of charged small molecules such as drug molecules, to form a multilayer nanoparticle in which the drug or other small molecule itself acts as one of the alternating charged layers in the multilayer assembly. The small molecules can then be released over time in a sustained manner. The LbL nano-assemblies can specifically target cancers, metastases, or other diseased tissues, while minimizing side effects.

Owner:BOARD OF SUPERVISORS OF LOUISIANA STATE UNIV & AGRI & MECHANICAL COLLEGE +1