Patents

Literature

54results about How to "Minimize charge" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

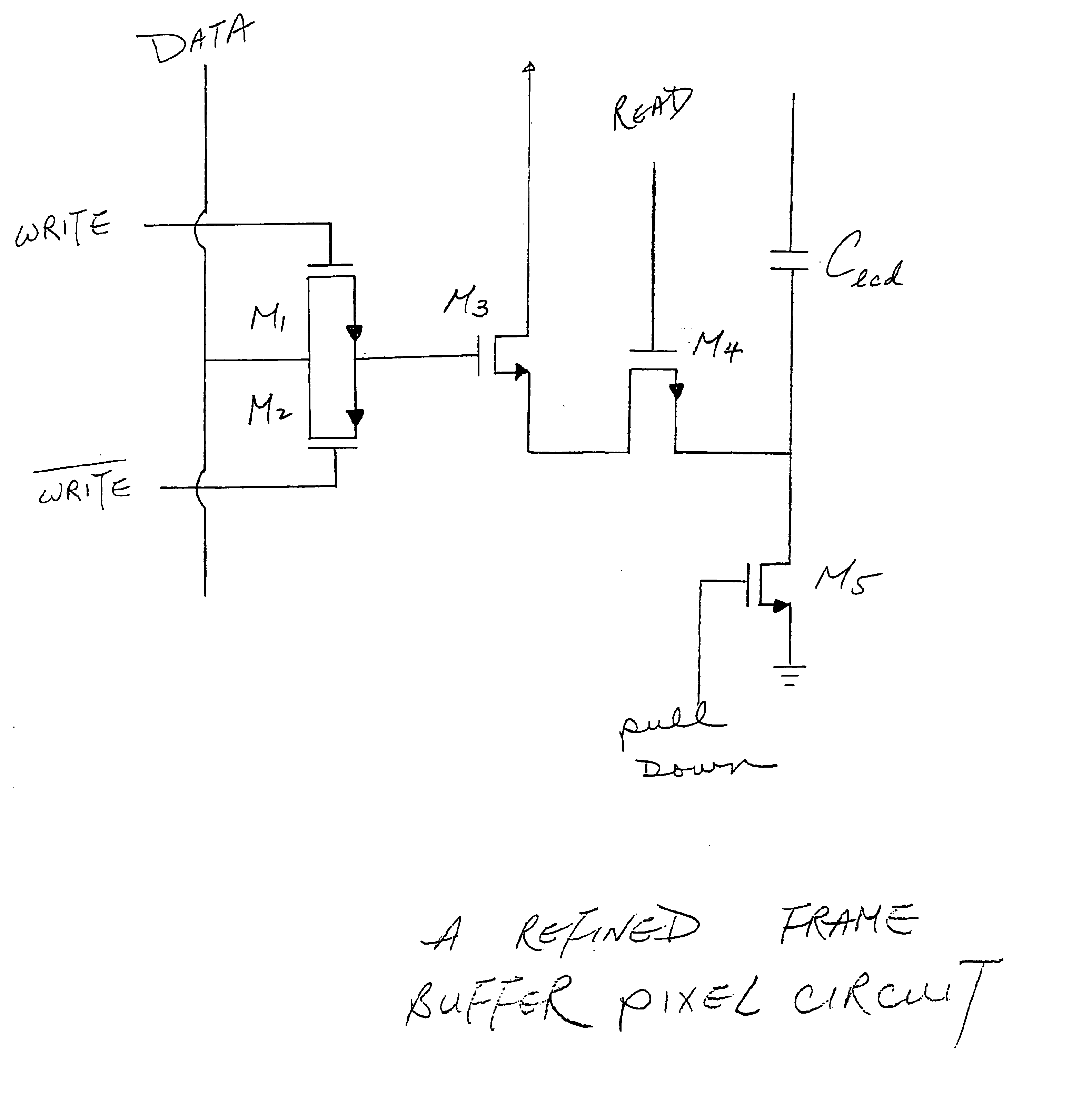

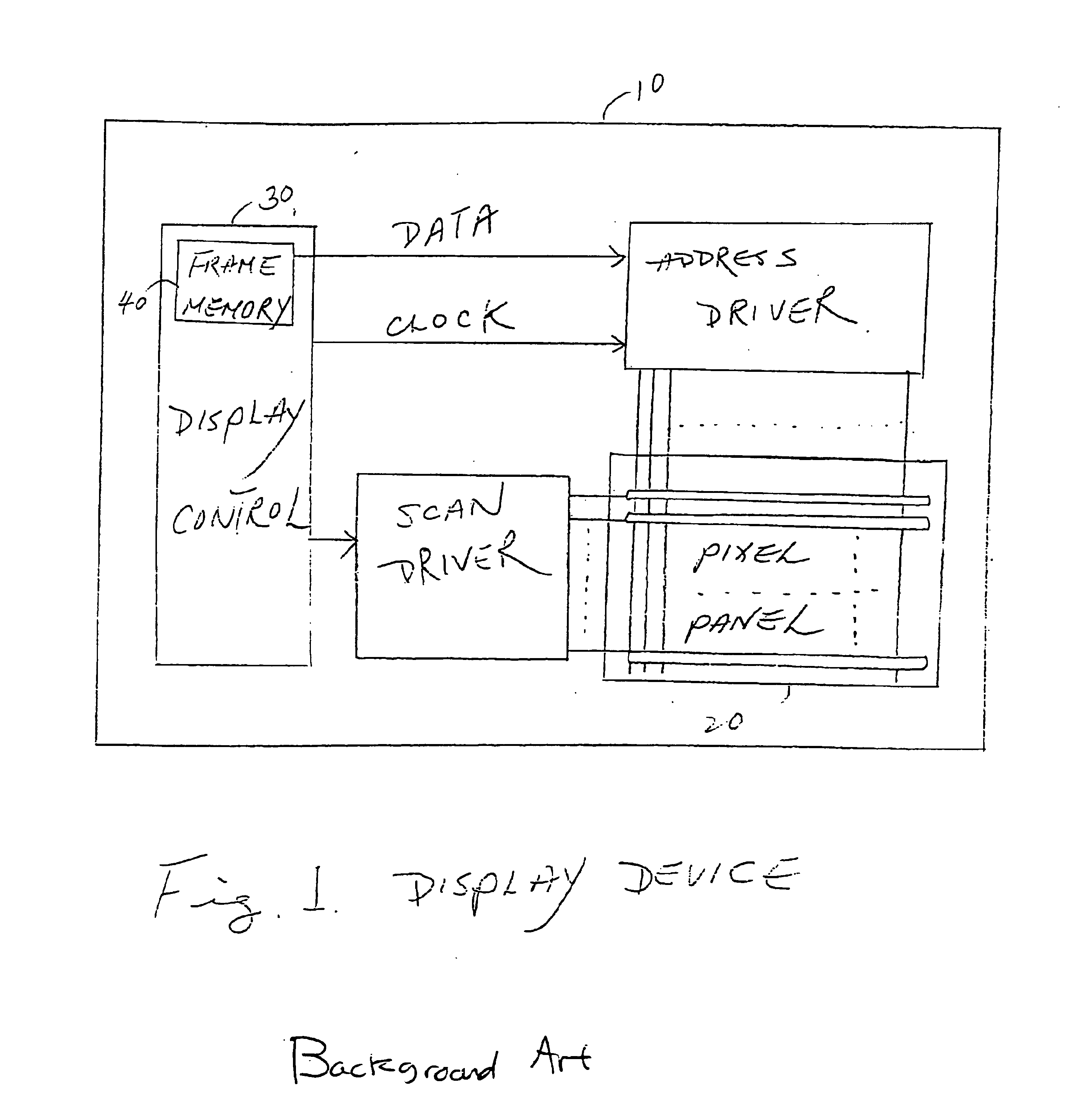

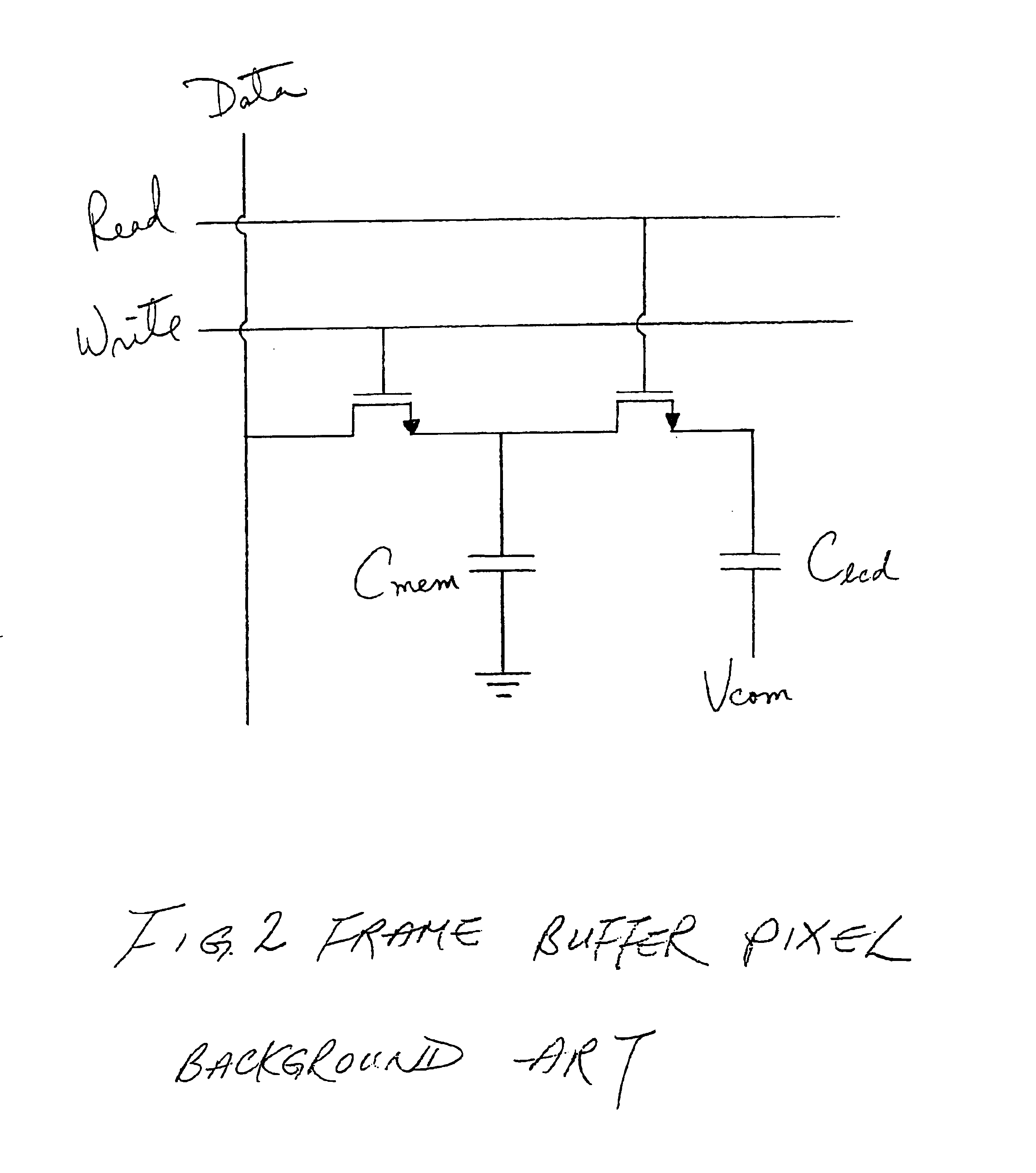

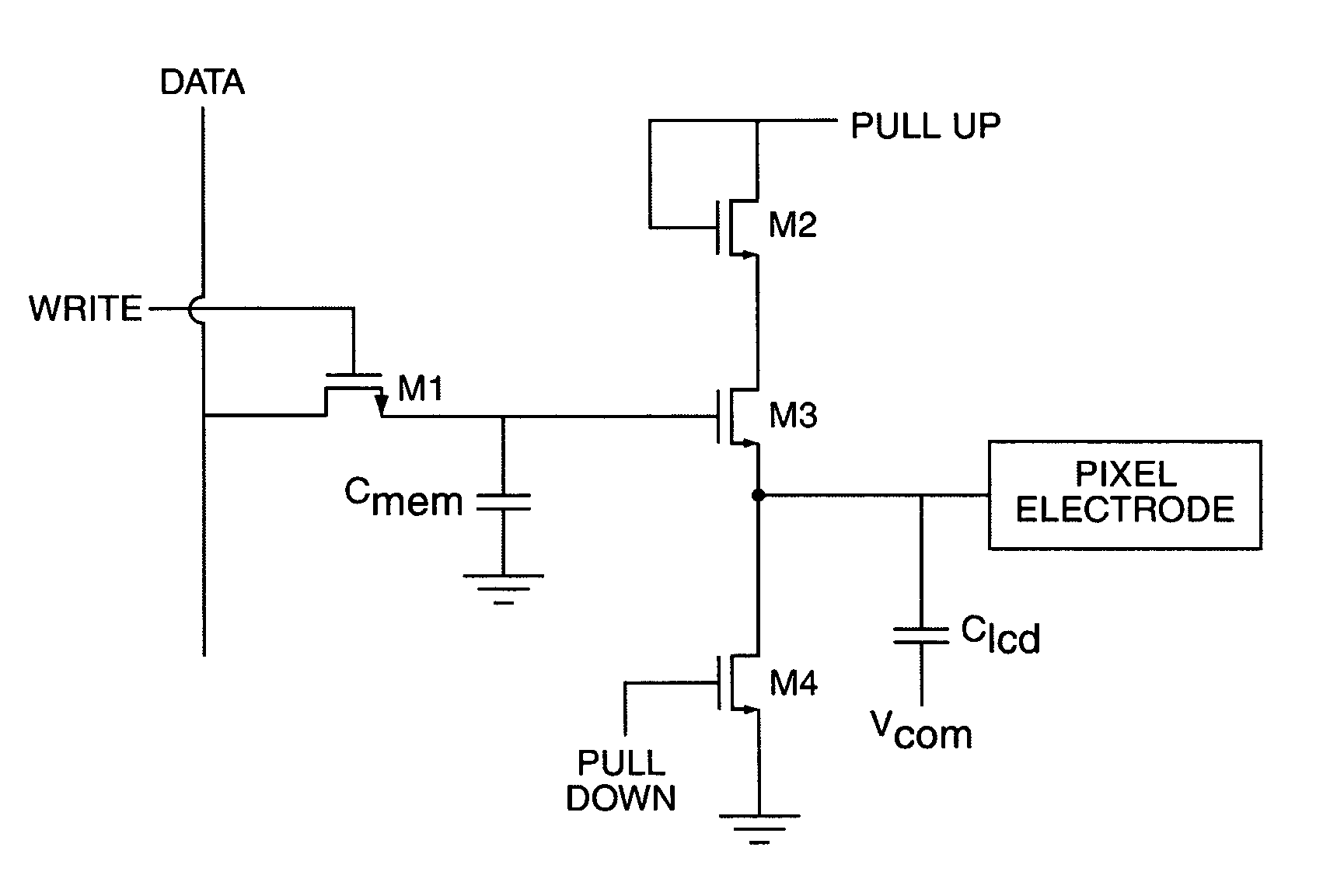

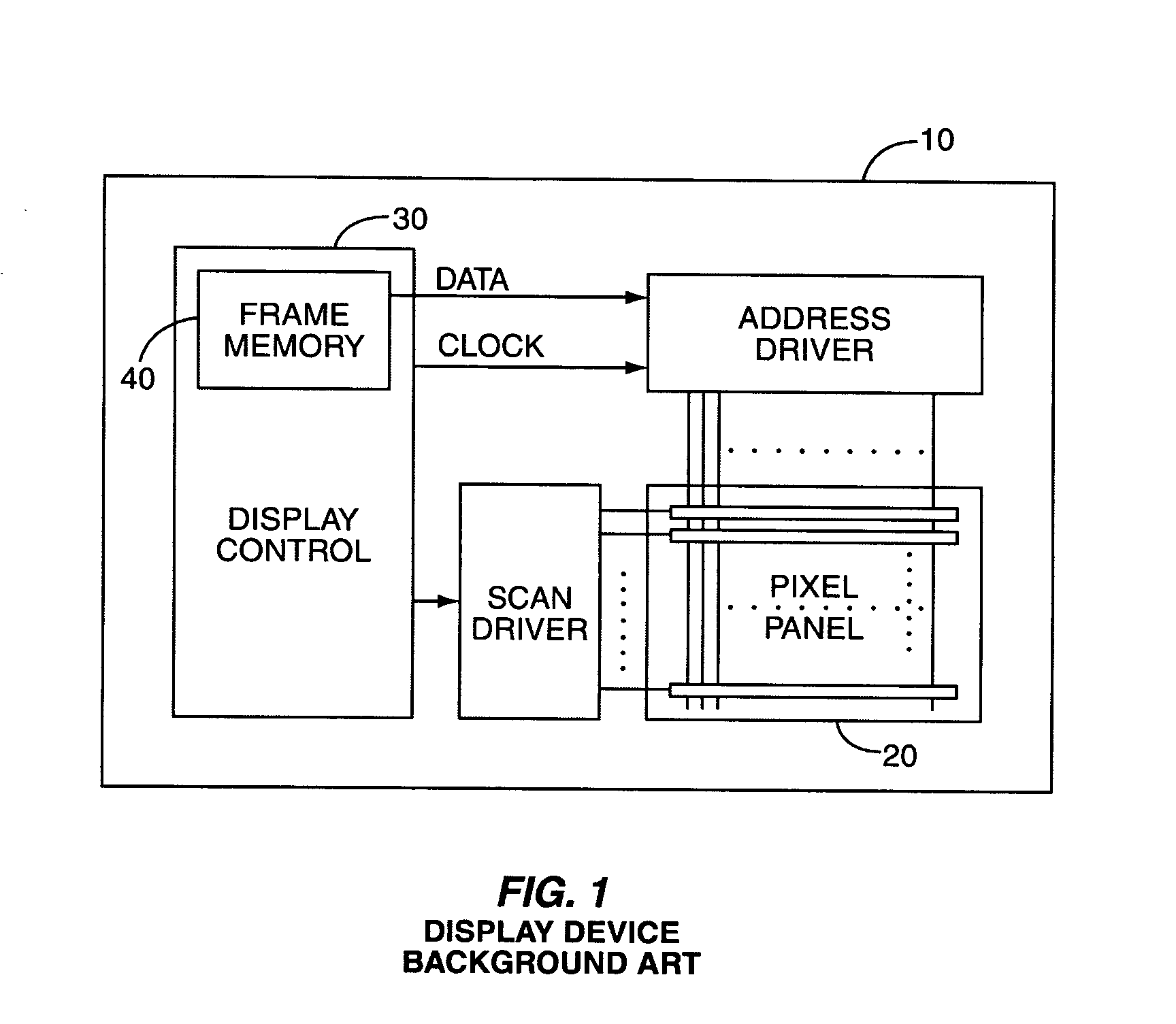

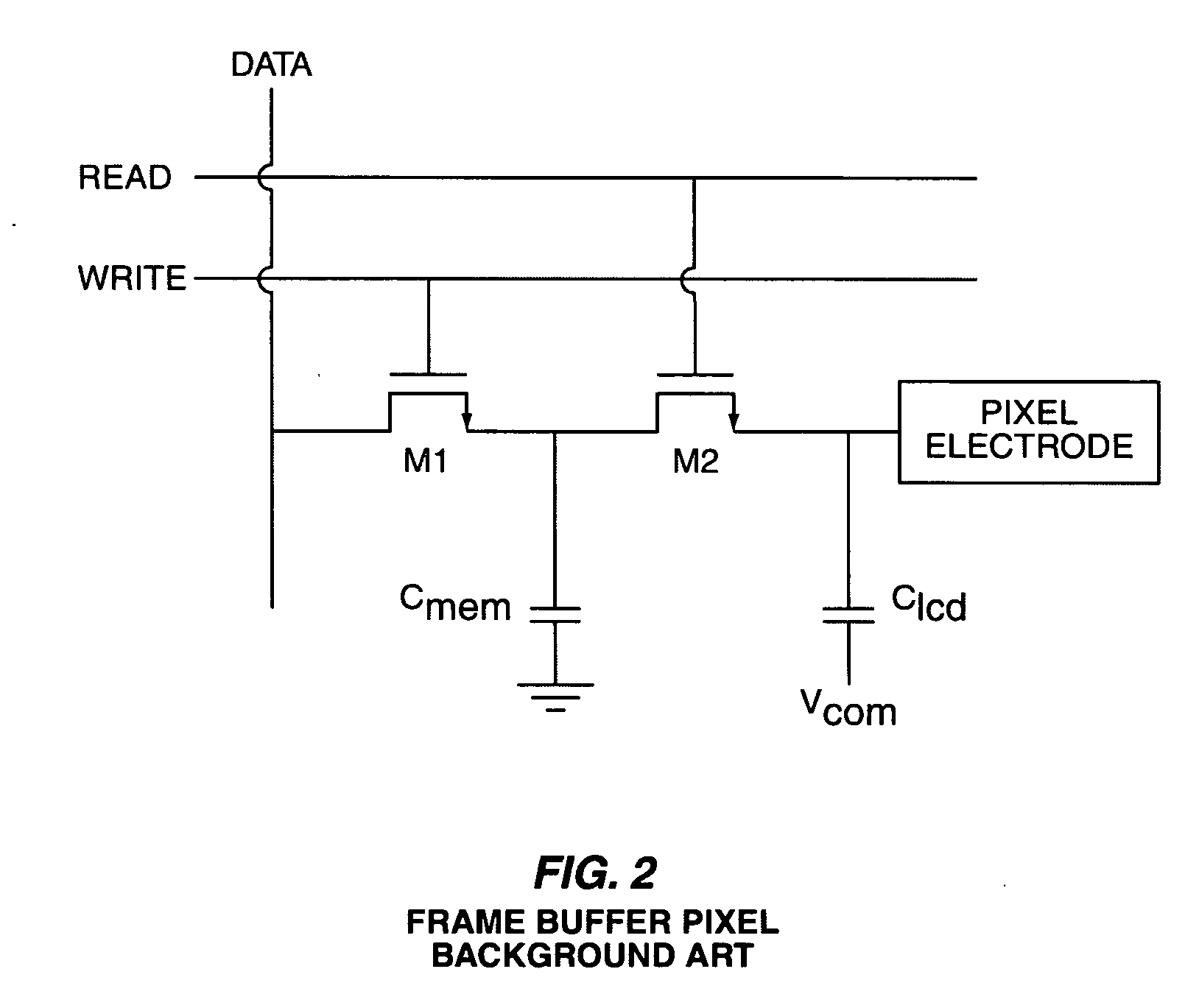

Frame buffer pixel circuit for liquid crystal display

InactiveUS6911964B2Enhanced frame buffer pixelIncrease contrastStatic indicating devicesNon-linear opticsCMOSLiquid-crystal display

An enhanced frame buffer pixel circuit with two control transistors and a separate capacitor put in as a memory capacitor before the memory transistor yields a high contrast ratio by removing induced charge and solving a charge sharing problem between the memory capacitor and the liquid crystal display (LCD) capacitor. The memory transistor may be made of either CMOS or PMOS. The frame buffer pixel can be used to drive binary displays which expresses ON and OFF only if a comparator is put in after the pixel electrode circuit to represent gray levels with reduced sub-frame frequency.

Owner:DUKE UNIV +1

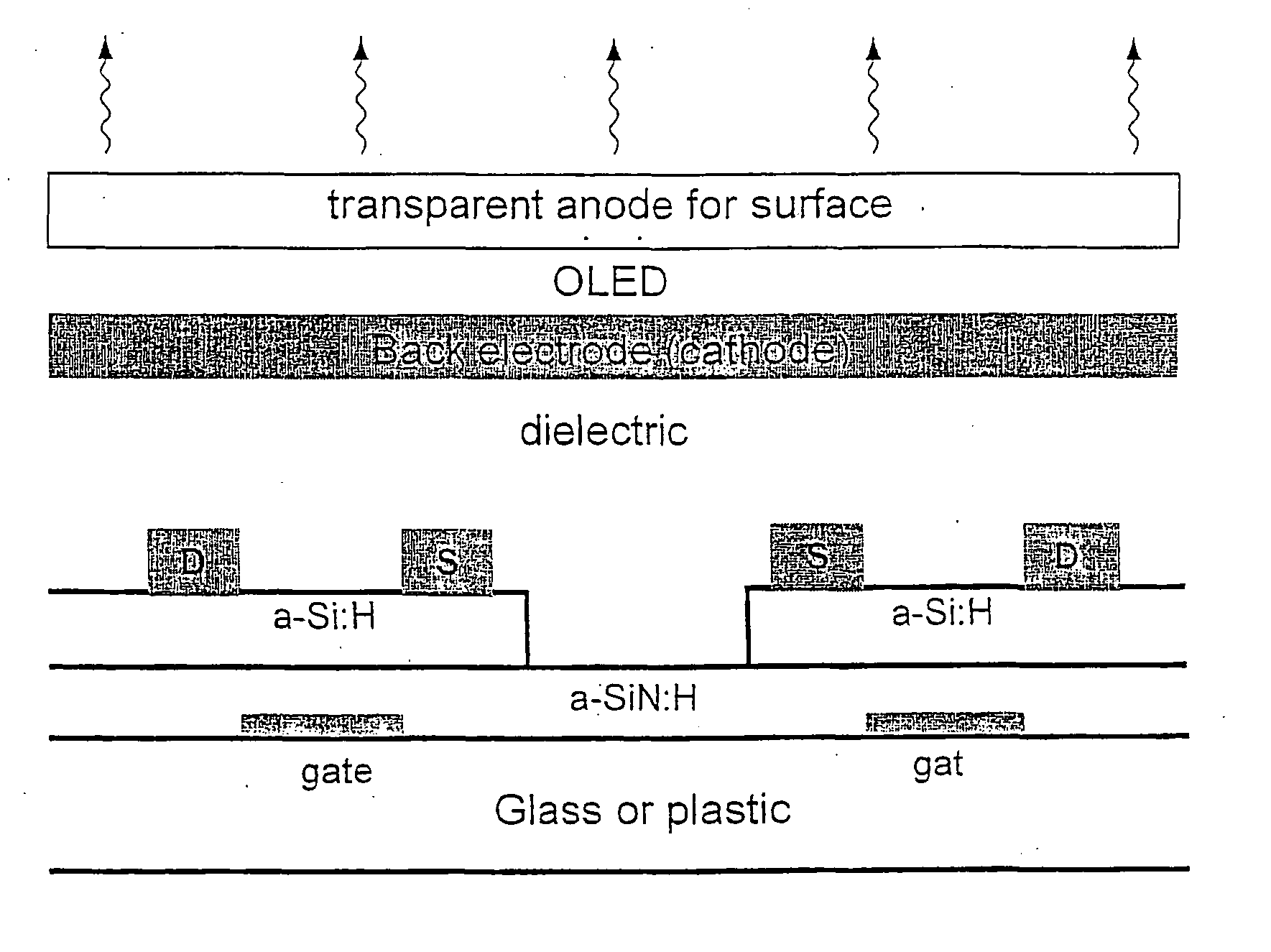

Pixel current driver for organic light emitting diode displays

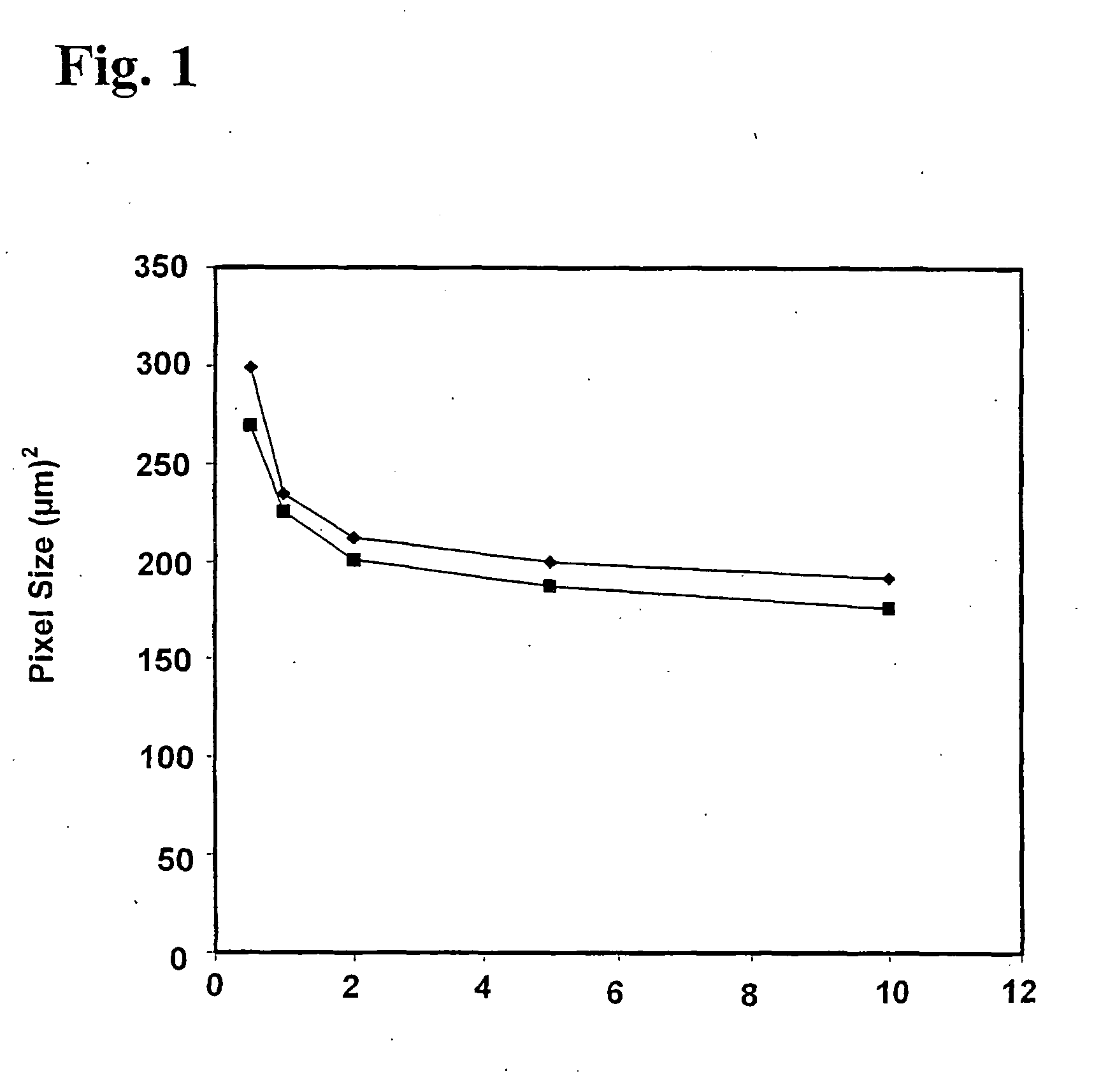

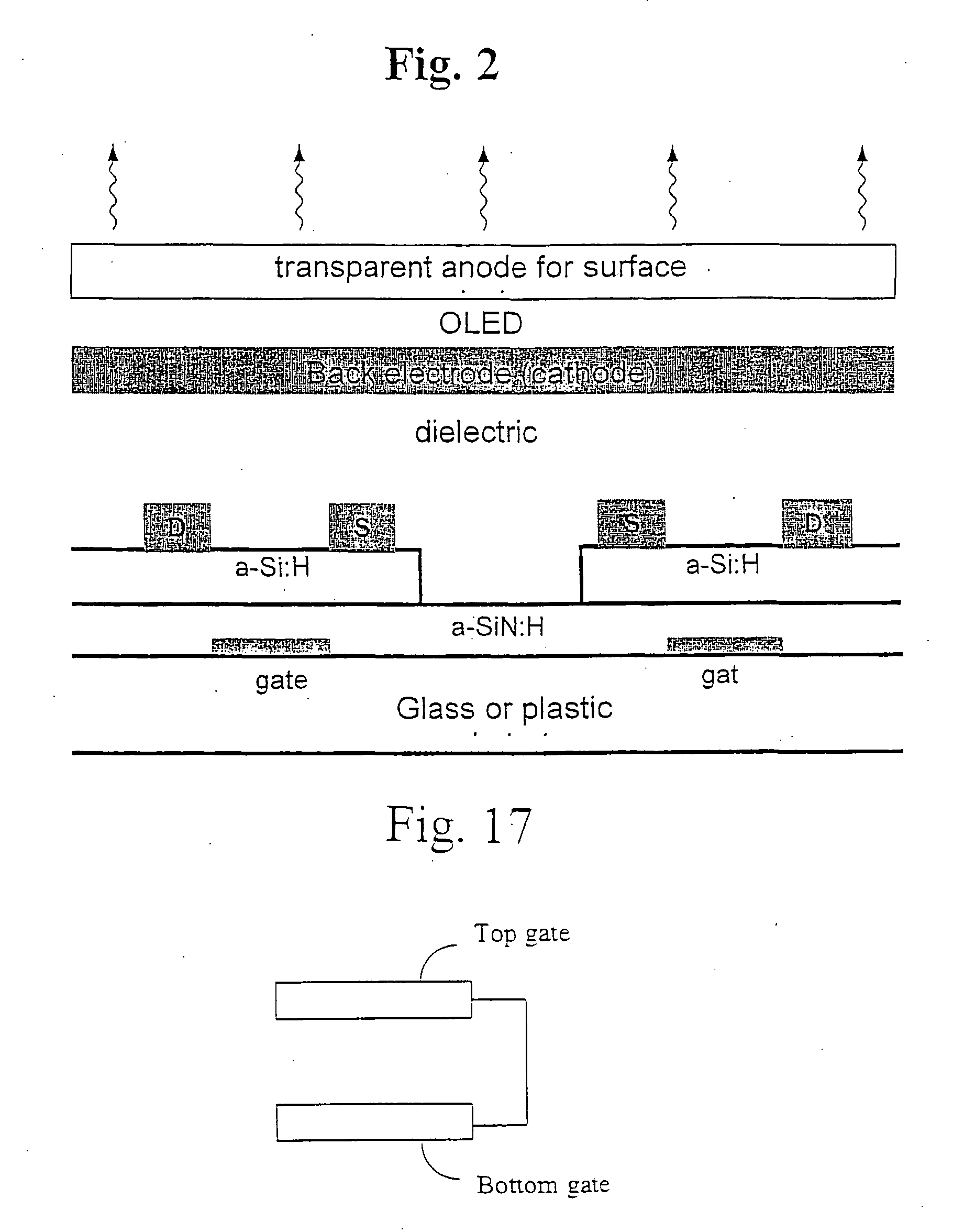

InactiveUS20060027807A1Improve circuit performanceMinimize chargeTransistorStatic indicating devicesBottom gateDisplay device

A pixel current driver comprises a plurality of thin film transistors (TFTs) each having dual gates and for driving OLED layers. A top gate of the dual gates is formed between a source and a drain of each of the thin film transistors, to thereby minimize parasitic capacitance. The top gate is grounded or electrically tied to a bottom gate. The plurality of thin film transistors may be two thin film transistors formed in voltage-programmed manner or five thin film transistors formed in a current-programmed ΔVT-compensated manner. Other versions of the current-programmed circuit with different numbers of thin film transistors are also presented that compensate for δVT. The OLED layer are continuous and vertically stacked on the plurality of thin film transistors to provide an aperture ratio close to 100%.

Owner:IGNIS INNOVATION

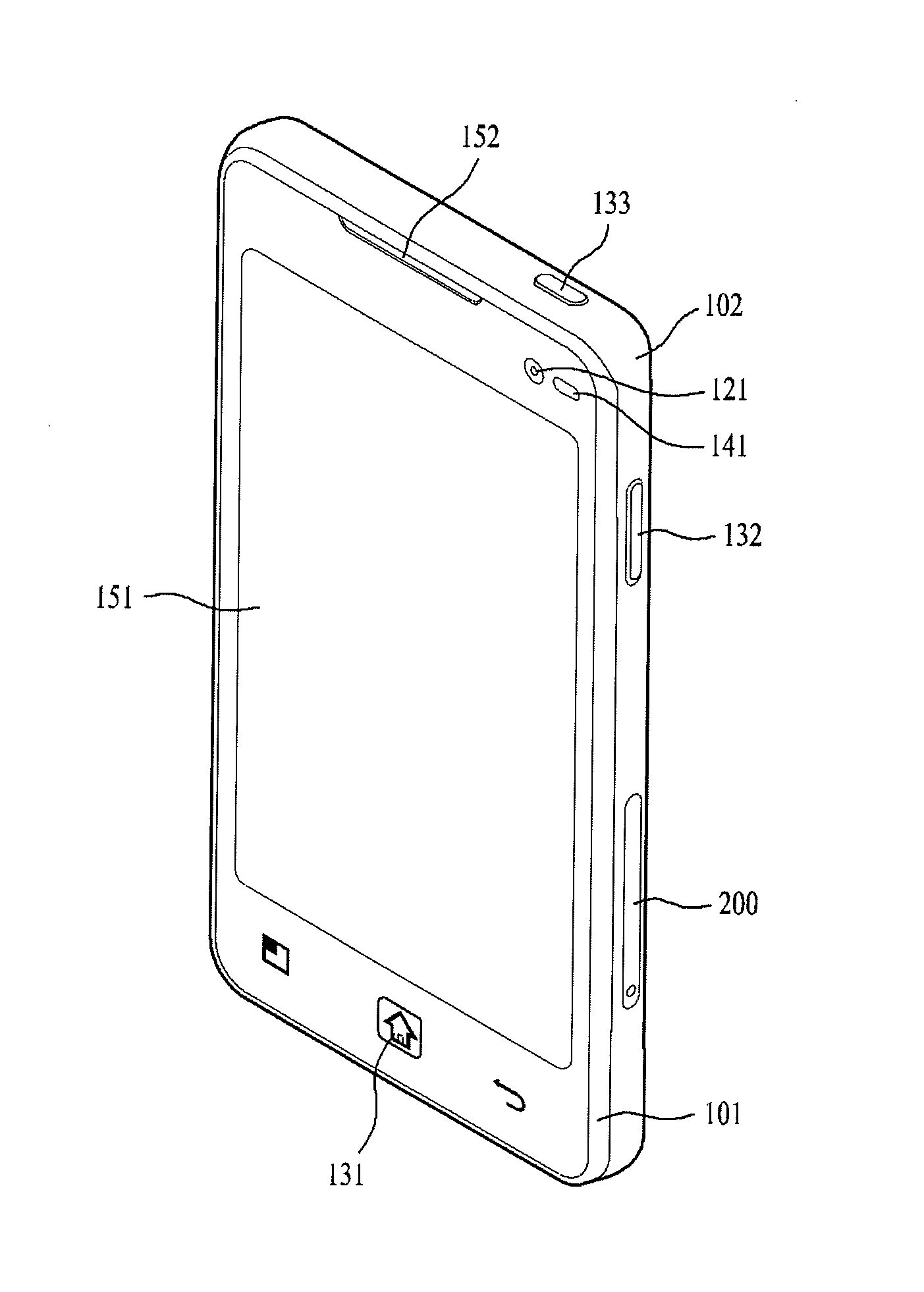

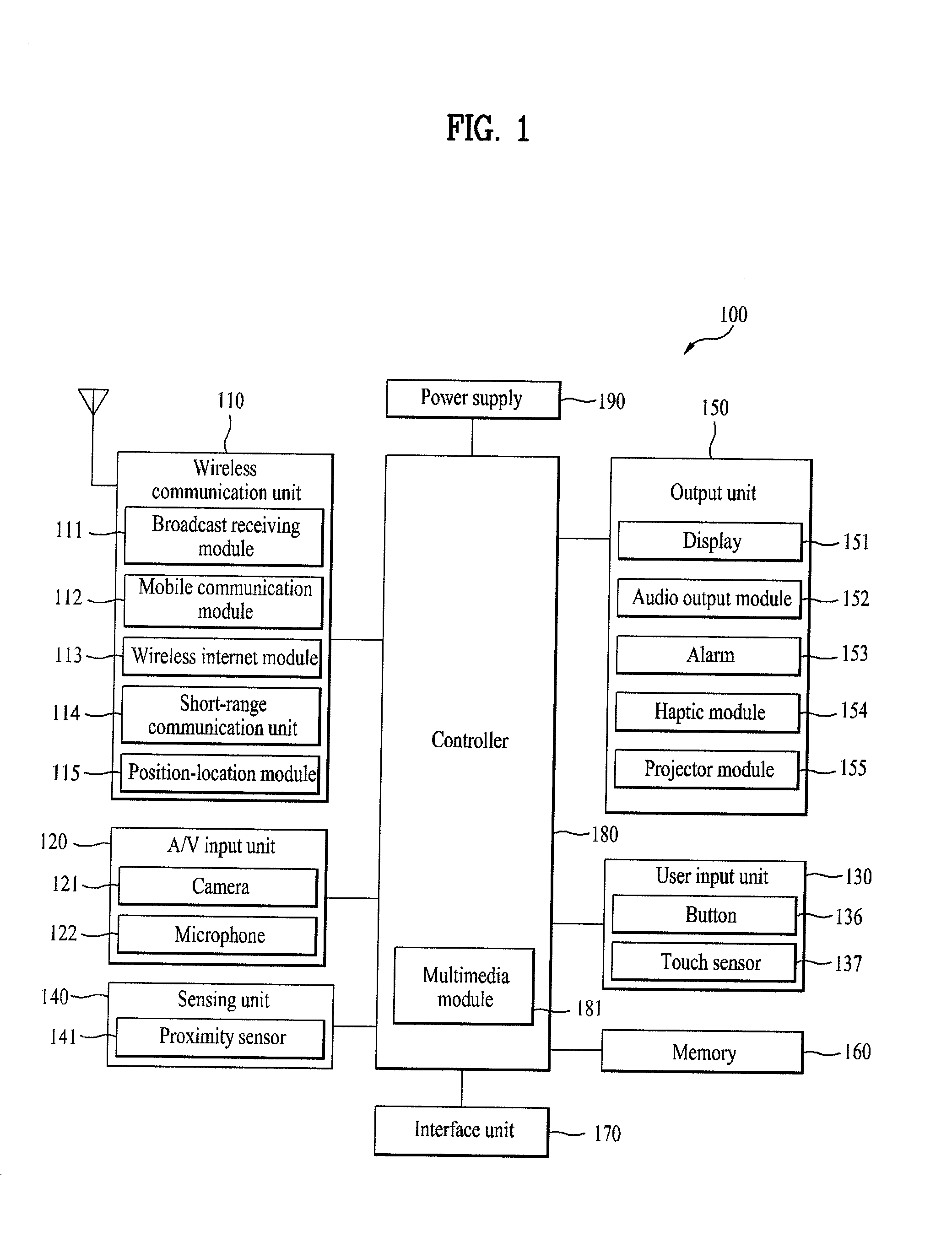

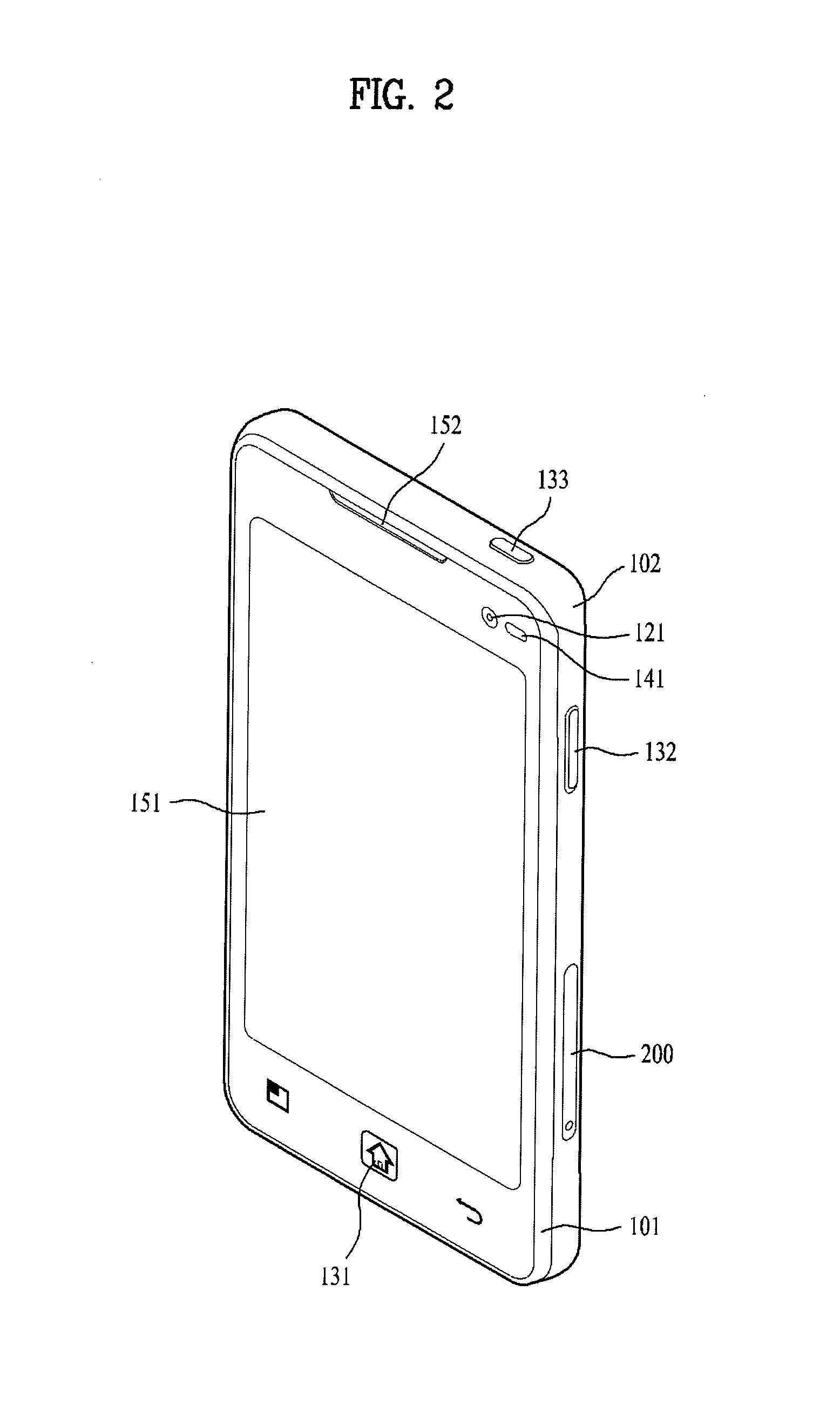

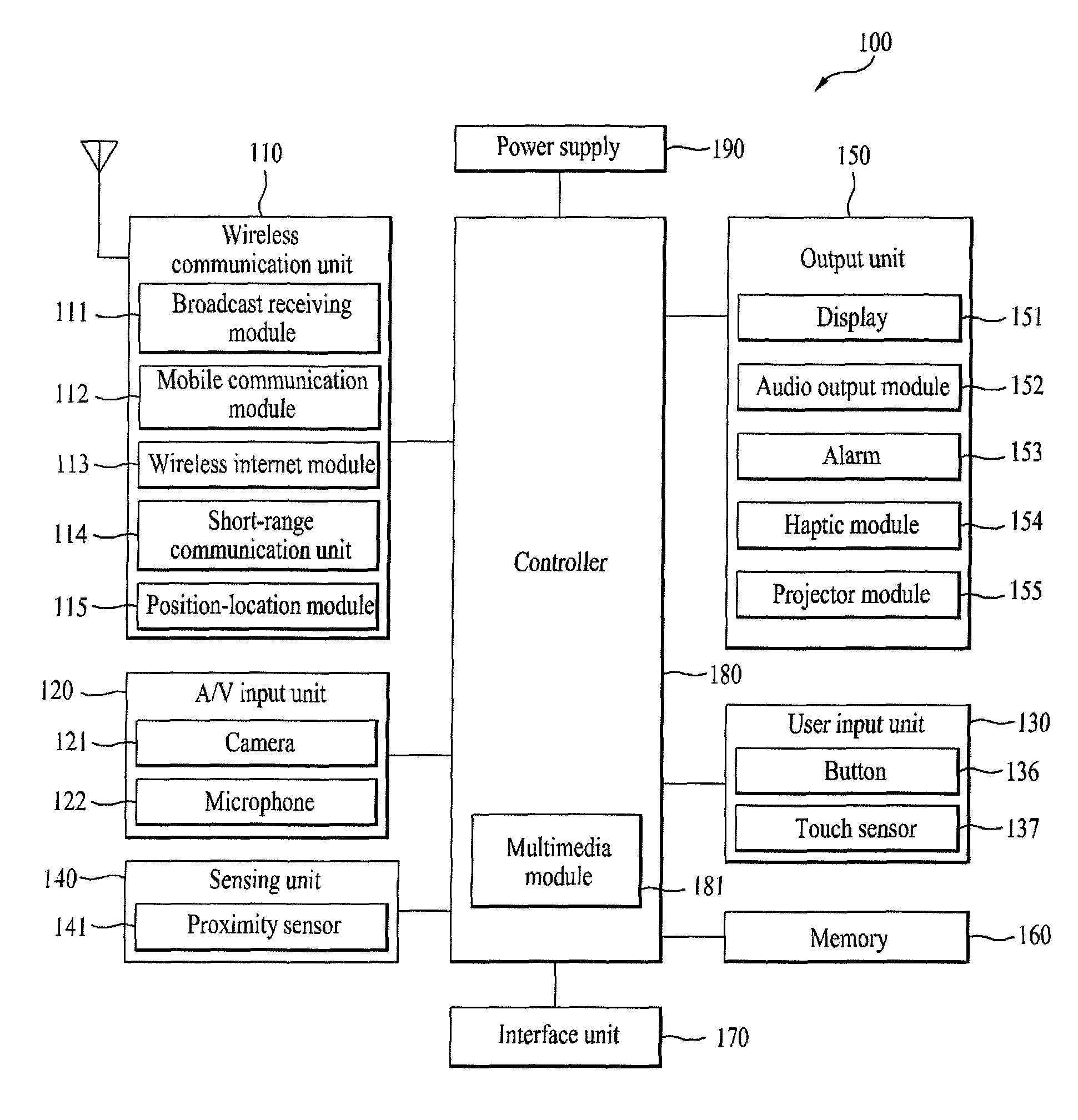

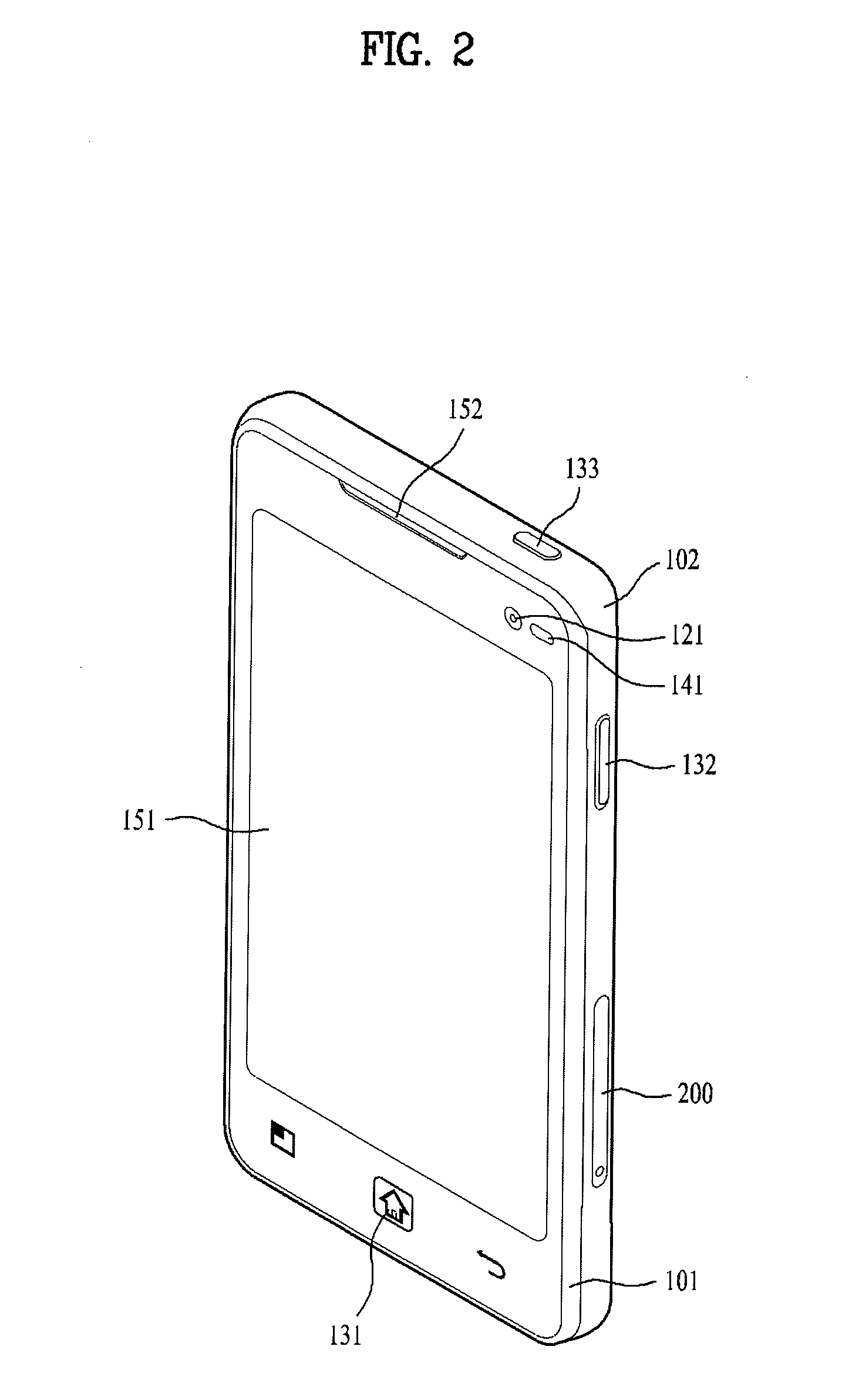

Antenna and mobile terminal having the same

ActiveUS20130267170A1Minimize chargeThickness minimizationLoop antennas with ferromagnetic coreNear-field transmissionPower flowComputer terminal

An antenna and a mobile terminal having the antenna are discussed. According to an embodiment, the antenna can include a flexible board having a first region and a second region; a high frequency antenna pattern formed in the first region of the flexible board to transceive a wireless signal by detecting a magnetic flux; a low frequency antenna pattern formed in the second region of the flexible board to generate an induced current; and a magnetic sheet stacked on one surface of the flexible board to simultaneously cover both of the high frequency antenna pattern and the low frequency antenna pattern, the magnetic sheet having a high magnetic permeability for both a high frequency and a low frequency.

Owner:ROVI GUIDES INC

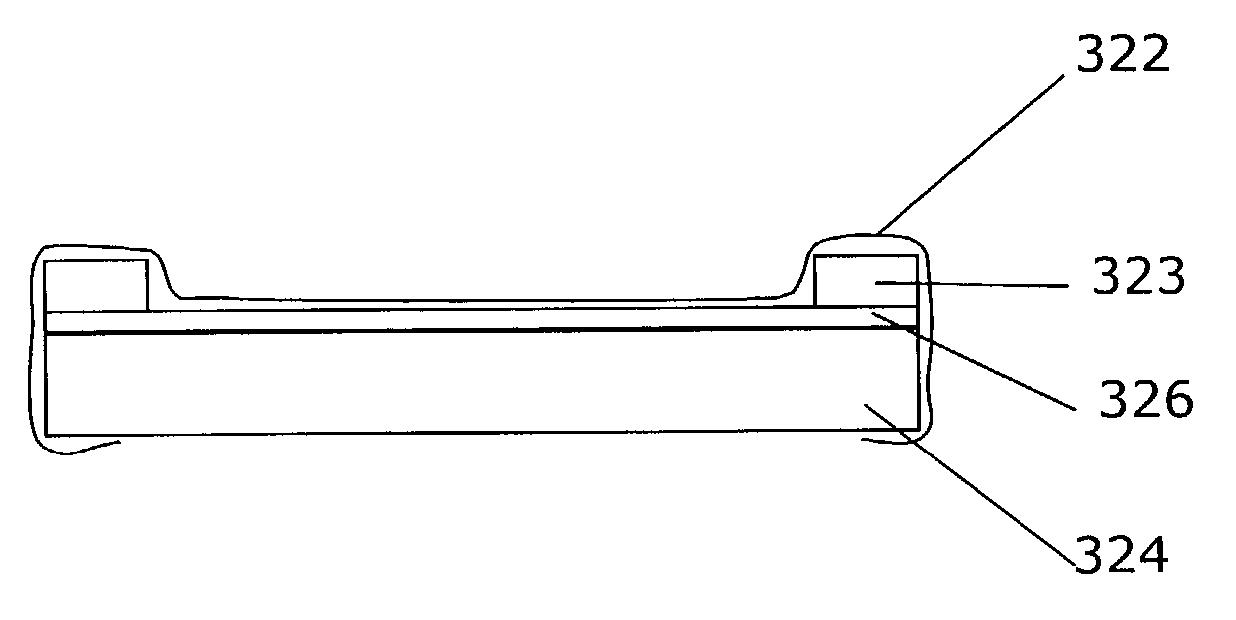

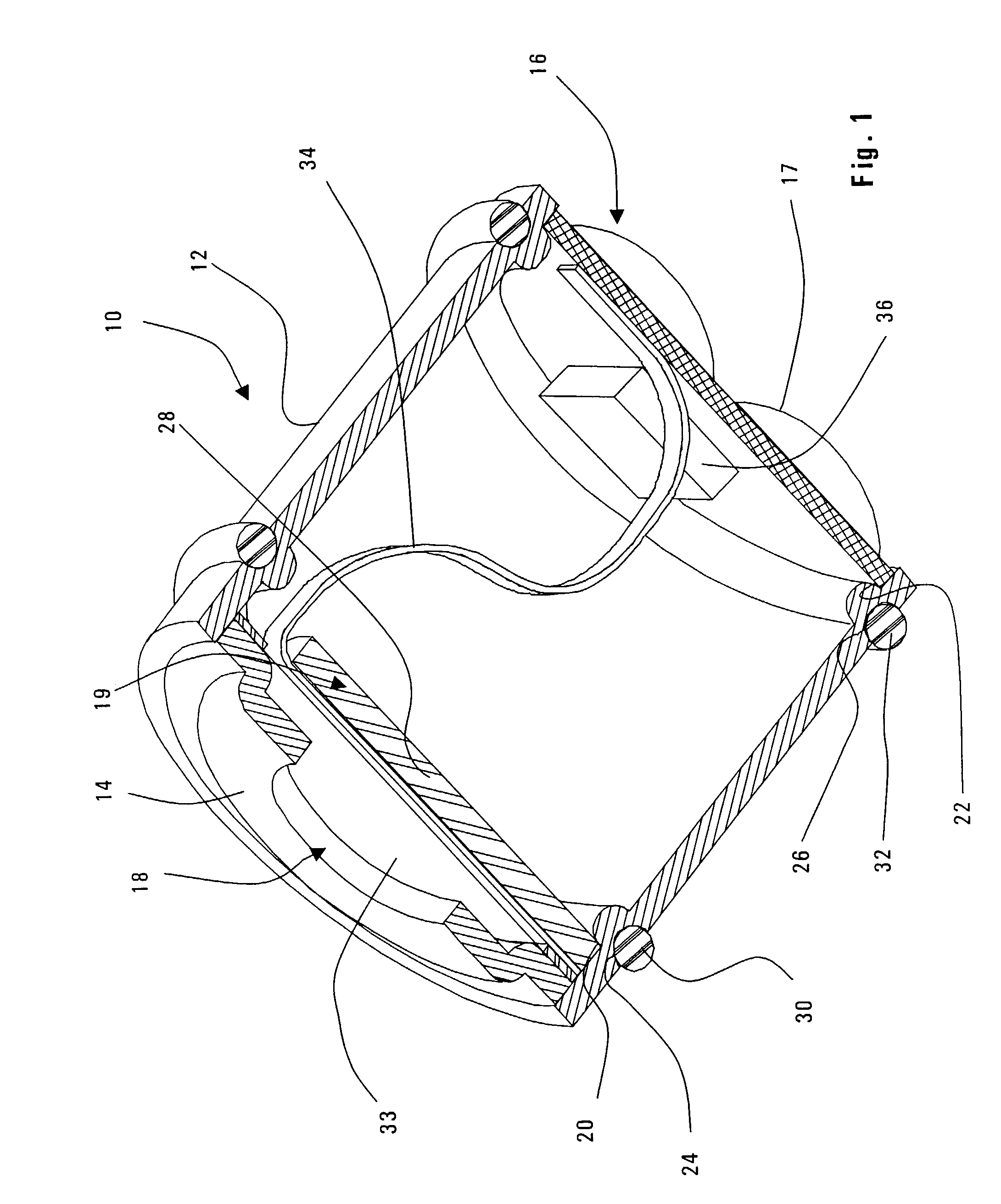

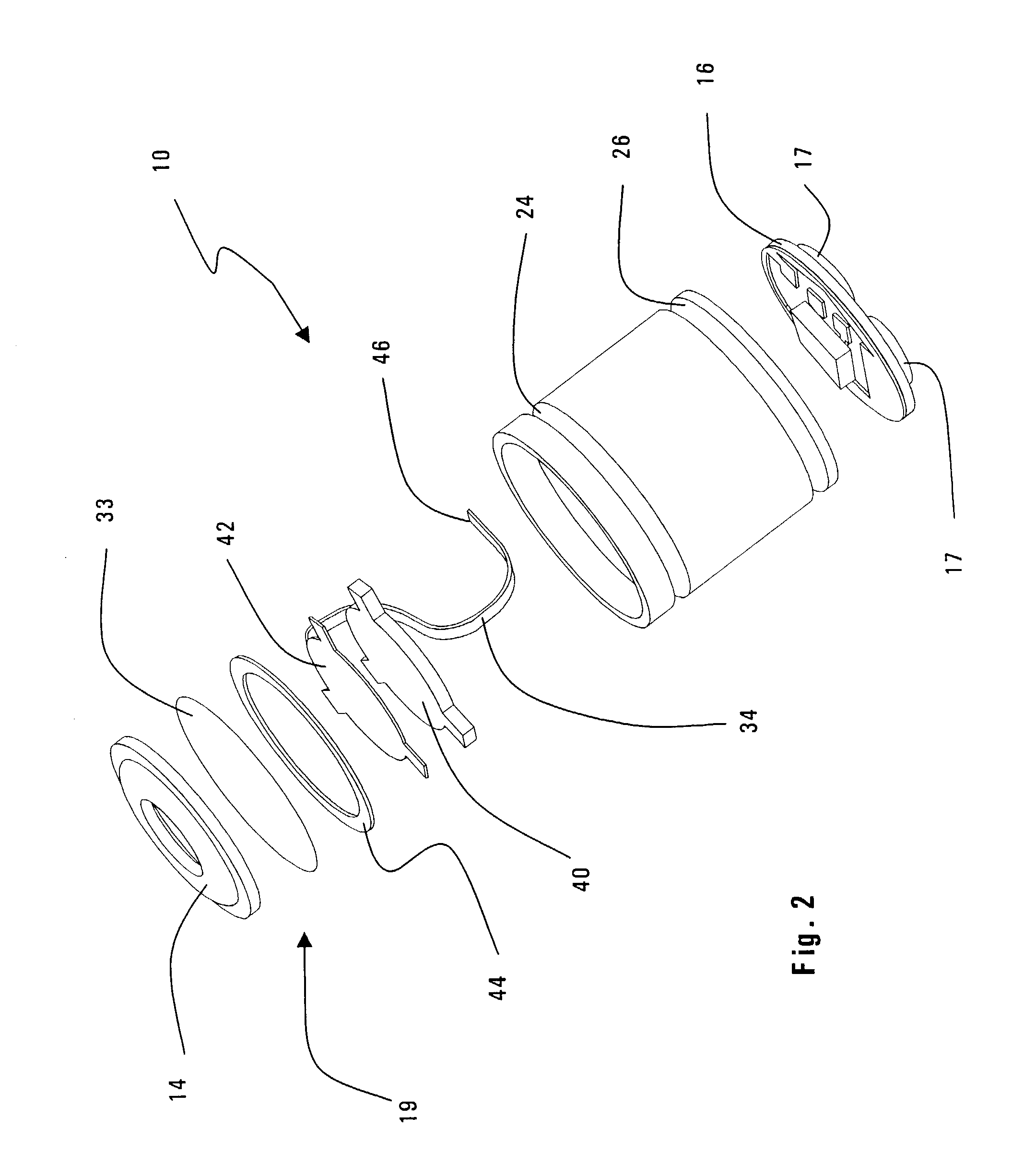

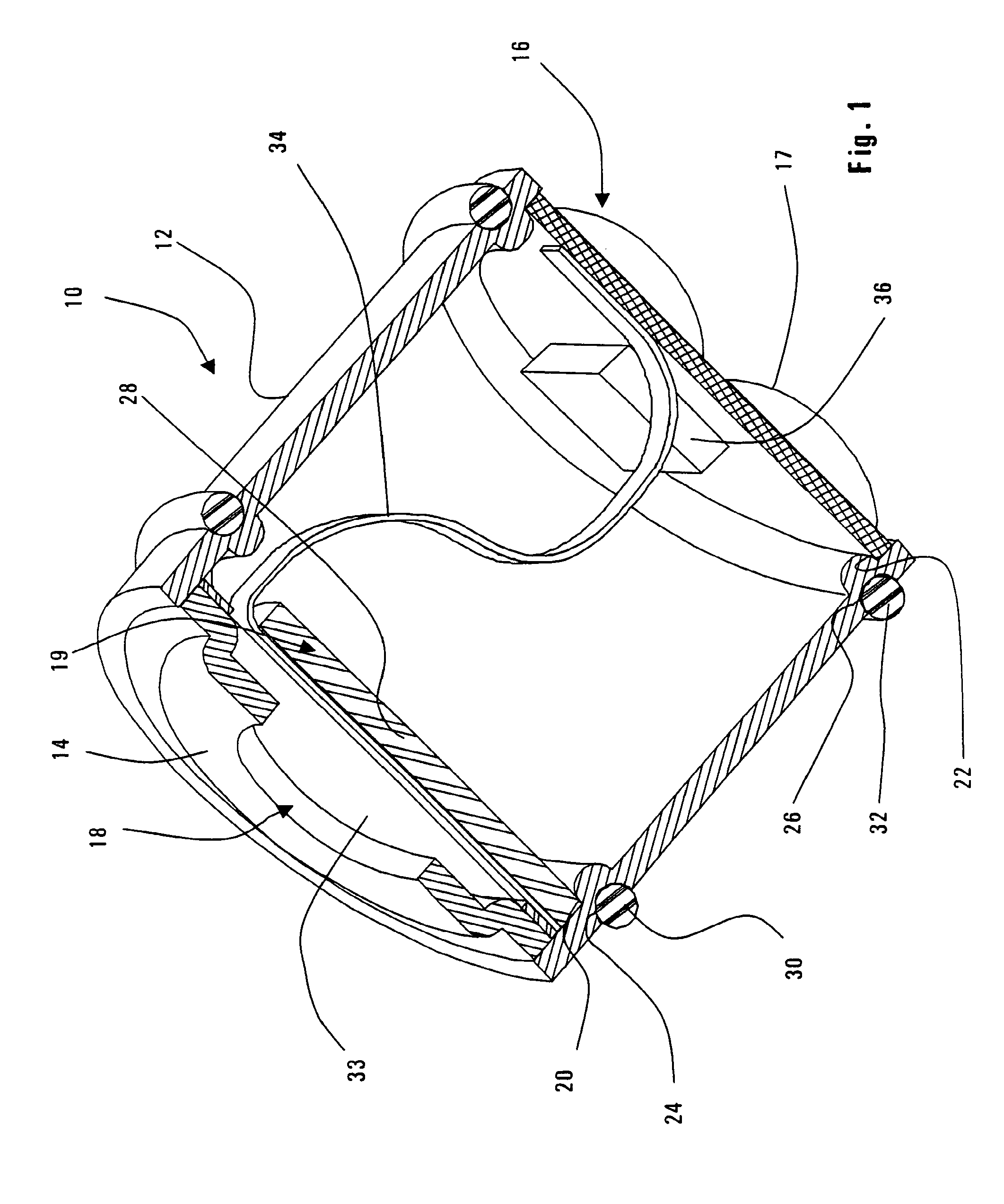

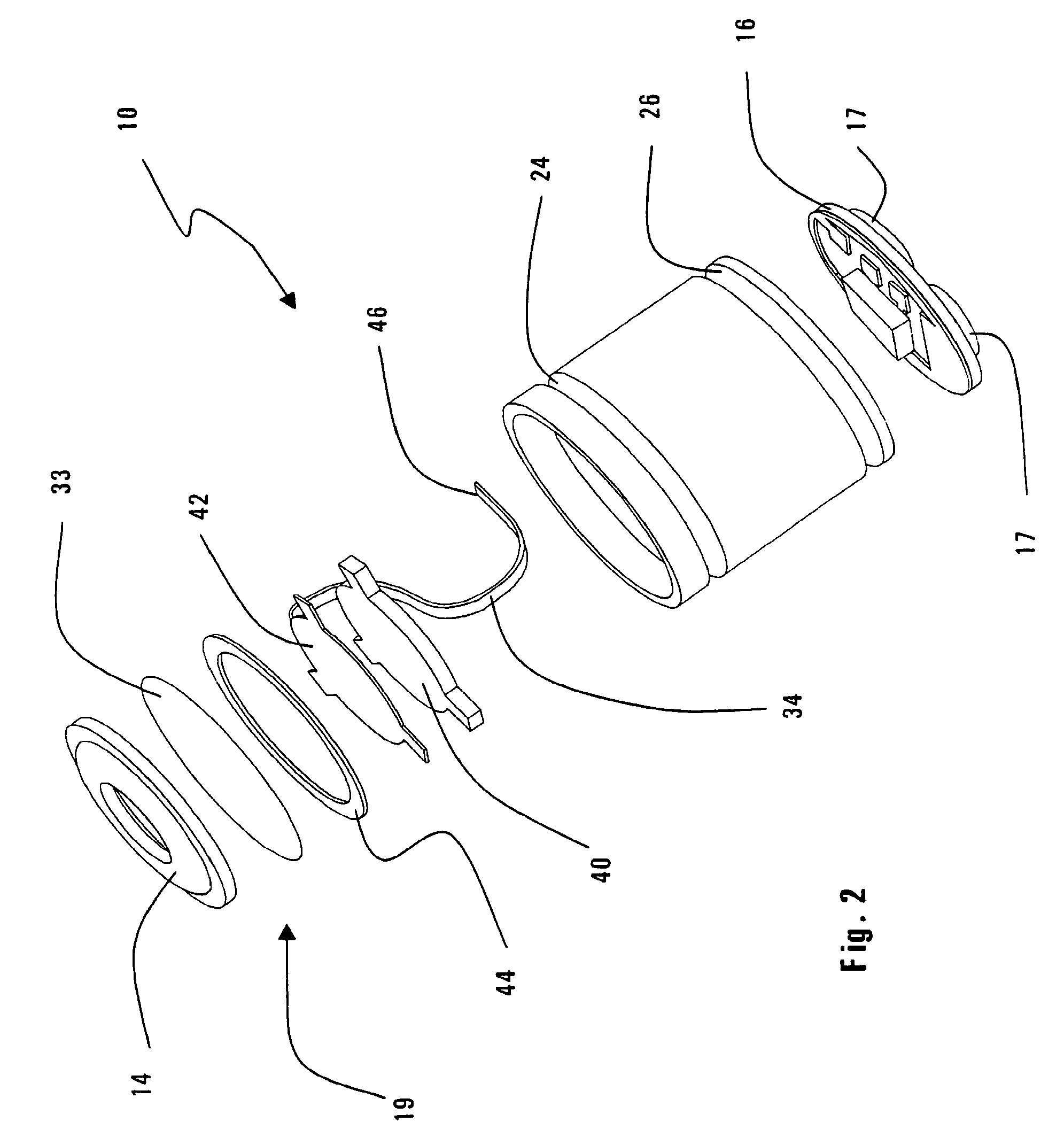

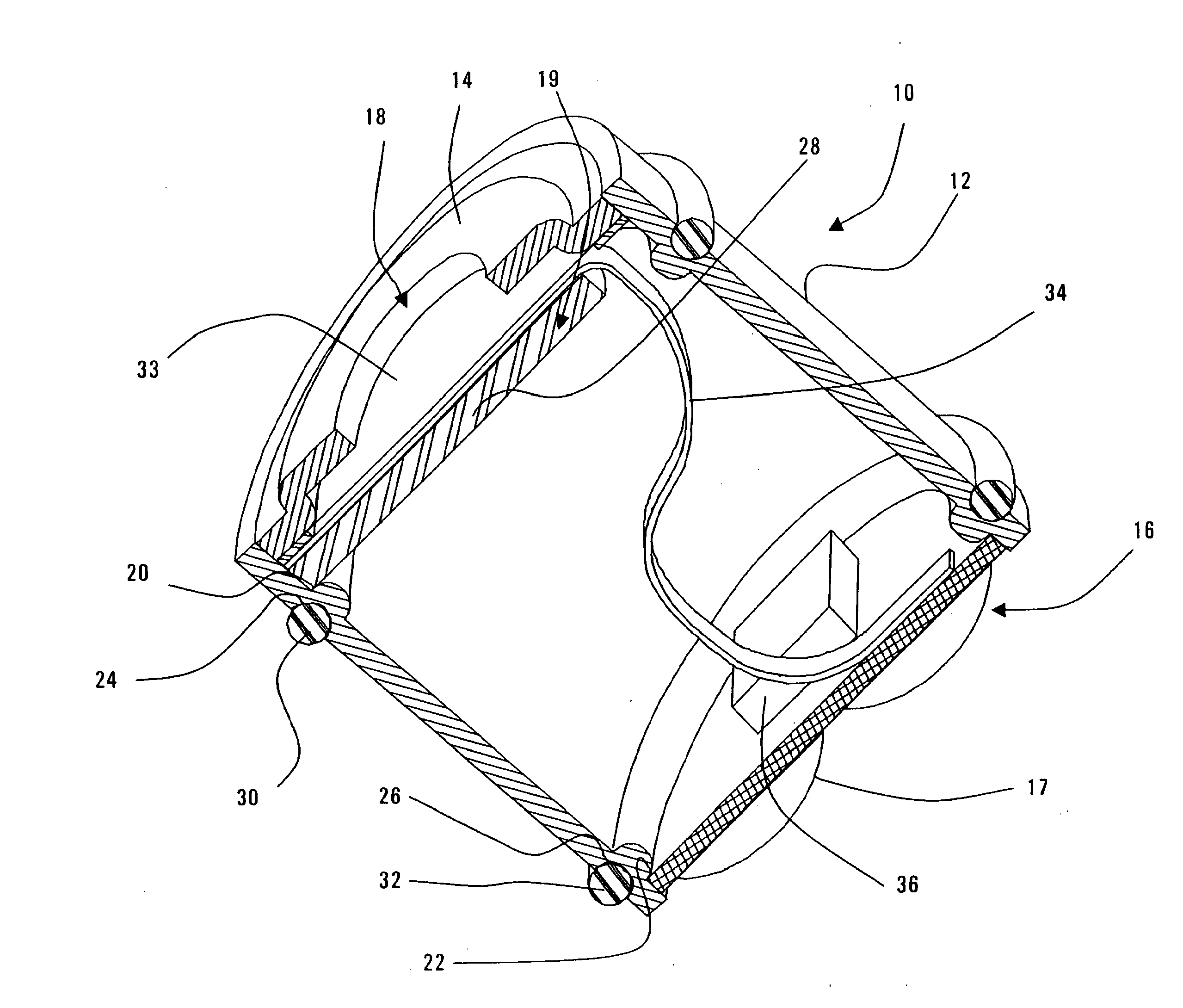

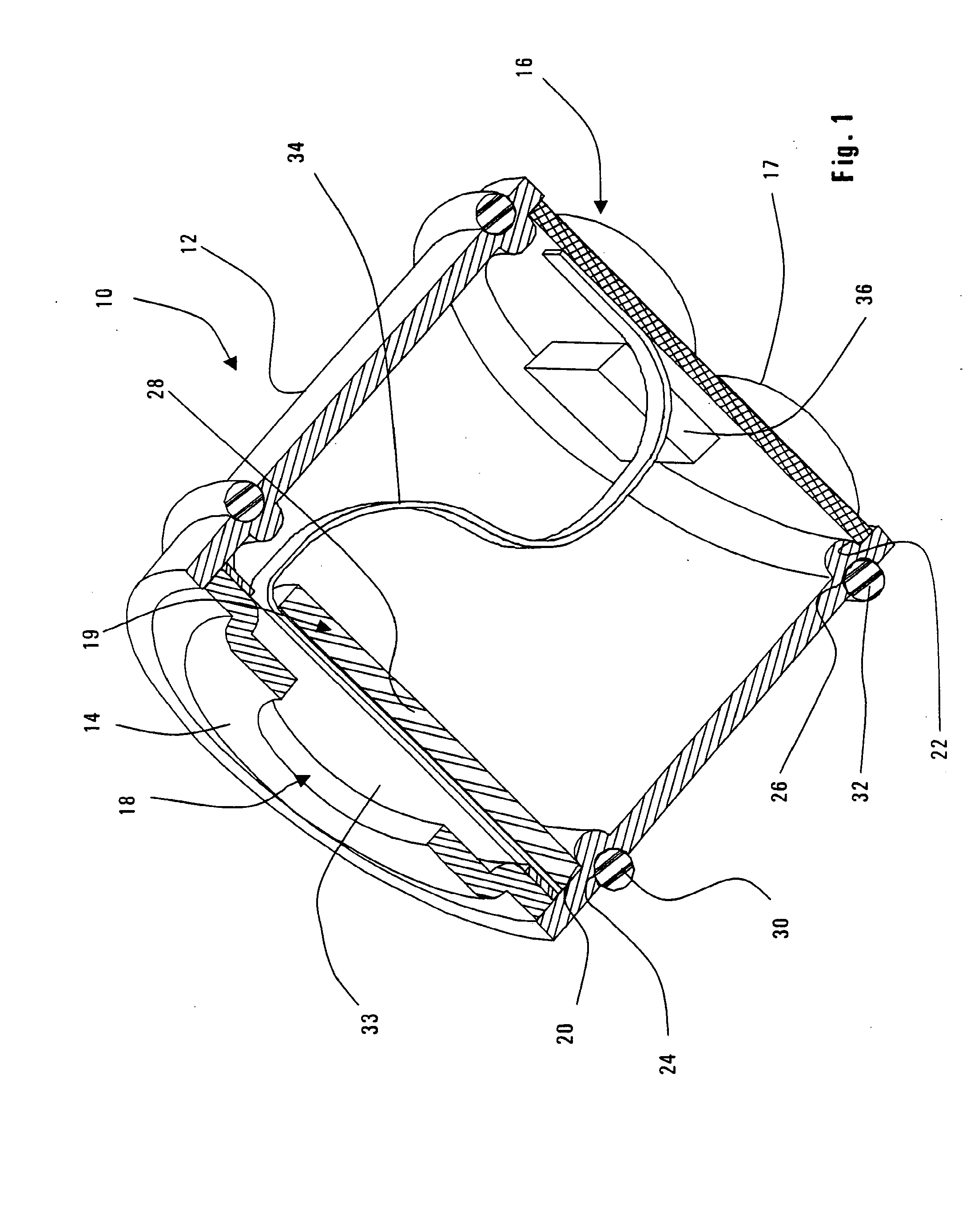

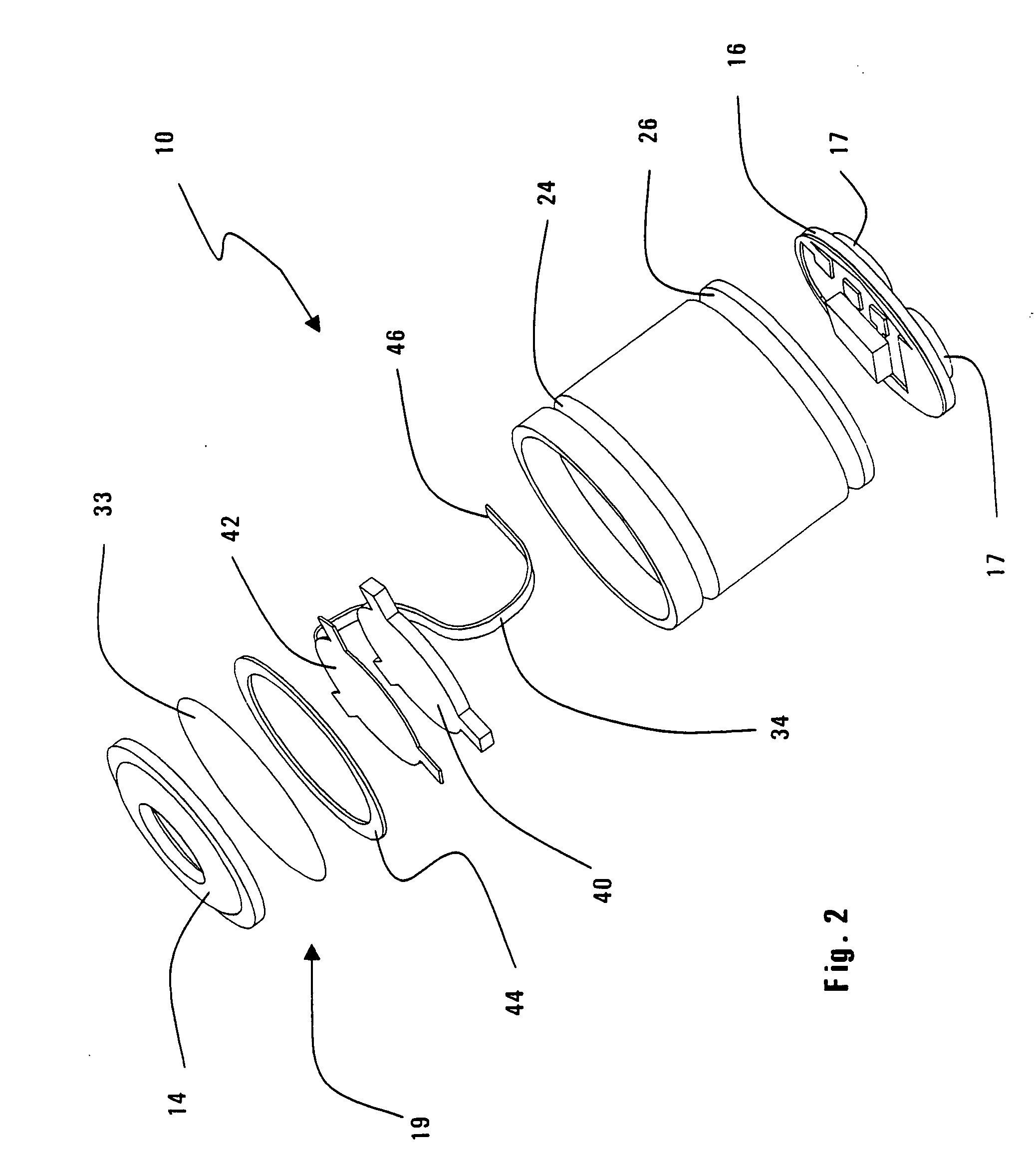

Electret assembly for a microphone having a backplate with improved charge stability

InactiveUS7136496B2Minimize chargeMinimize water absorptionPiezoelectric/electrostrictive microphonesElectrets selectrostatic transducerElectrical conductorCharge layer

The present invention relates to a microphone that includes a housing and a diaphragm and backplate located with the housing. The housing has a sound port for receiving the sound. The diaphragm undergoes movement relative to the backplate, which it opposes, in response to the incoming sound. The backplate has a charged layer with a first surface that is exposed to the diaphragm and a second surface opposite the first surface. The backplate further includes a conductor for transmitting a signal from the backplate to electronics in the housing. The conductor faces the second surface of the charged layer. To minimize the charge degradation created by contact with or infiltration of foreign materials, the first surface, the second surface, or both surfaces of the charged layer includes a protective layer thereon.

Owner:SONION NEDERLAND

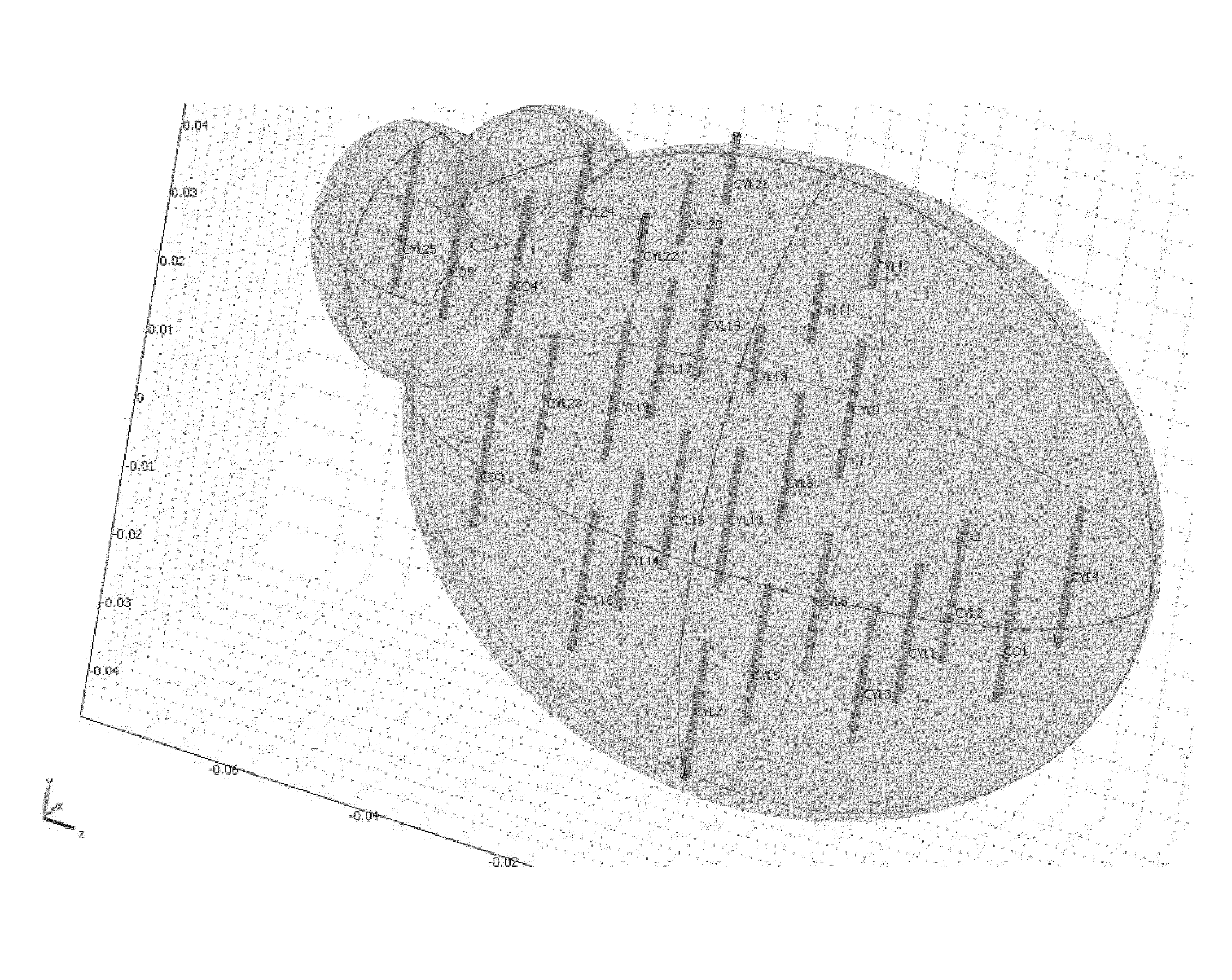

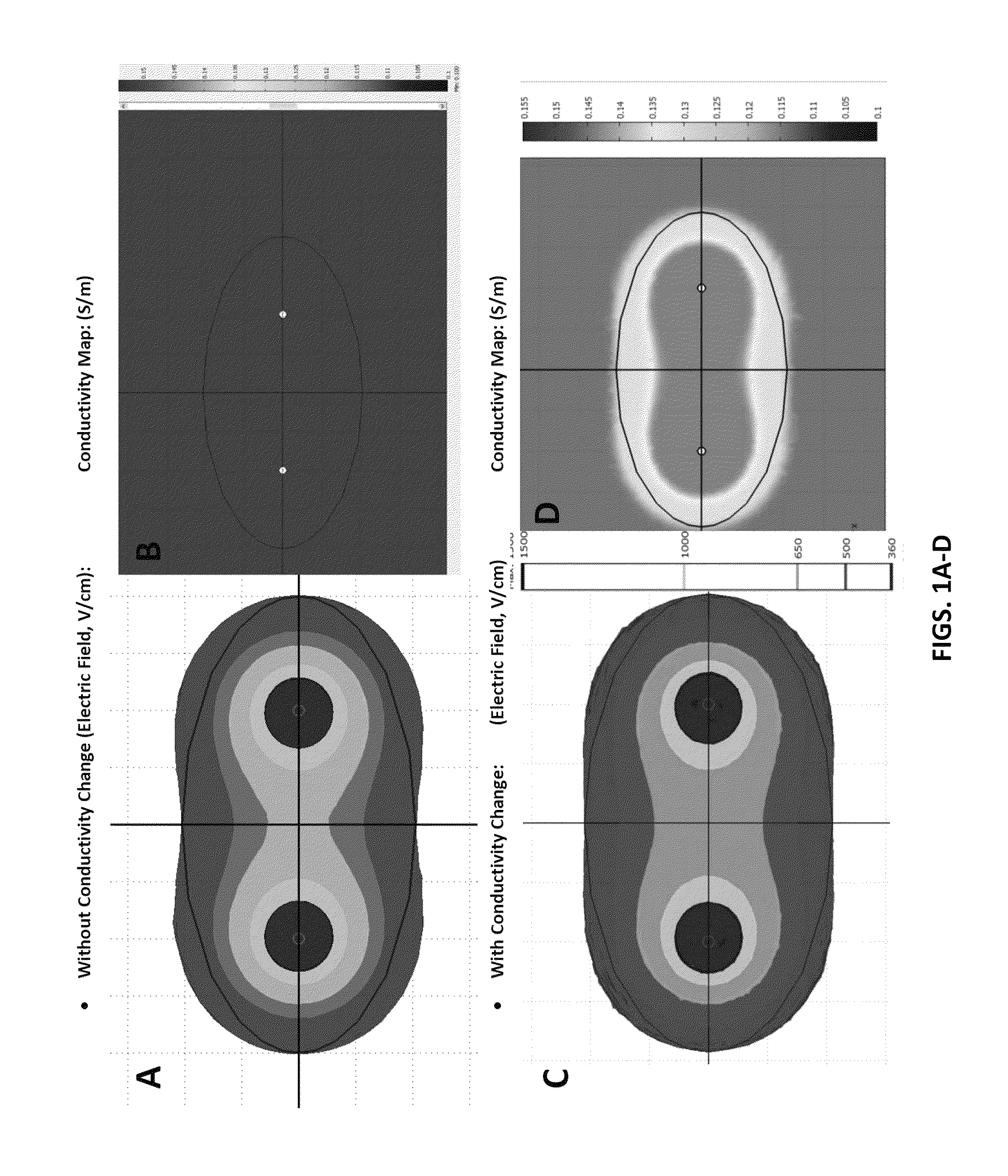

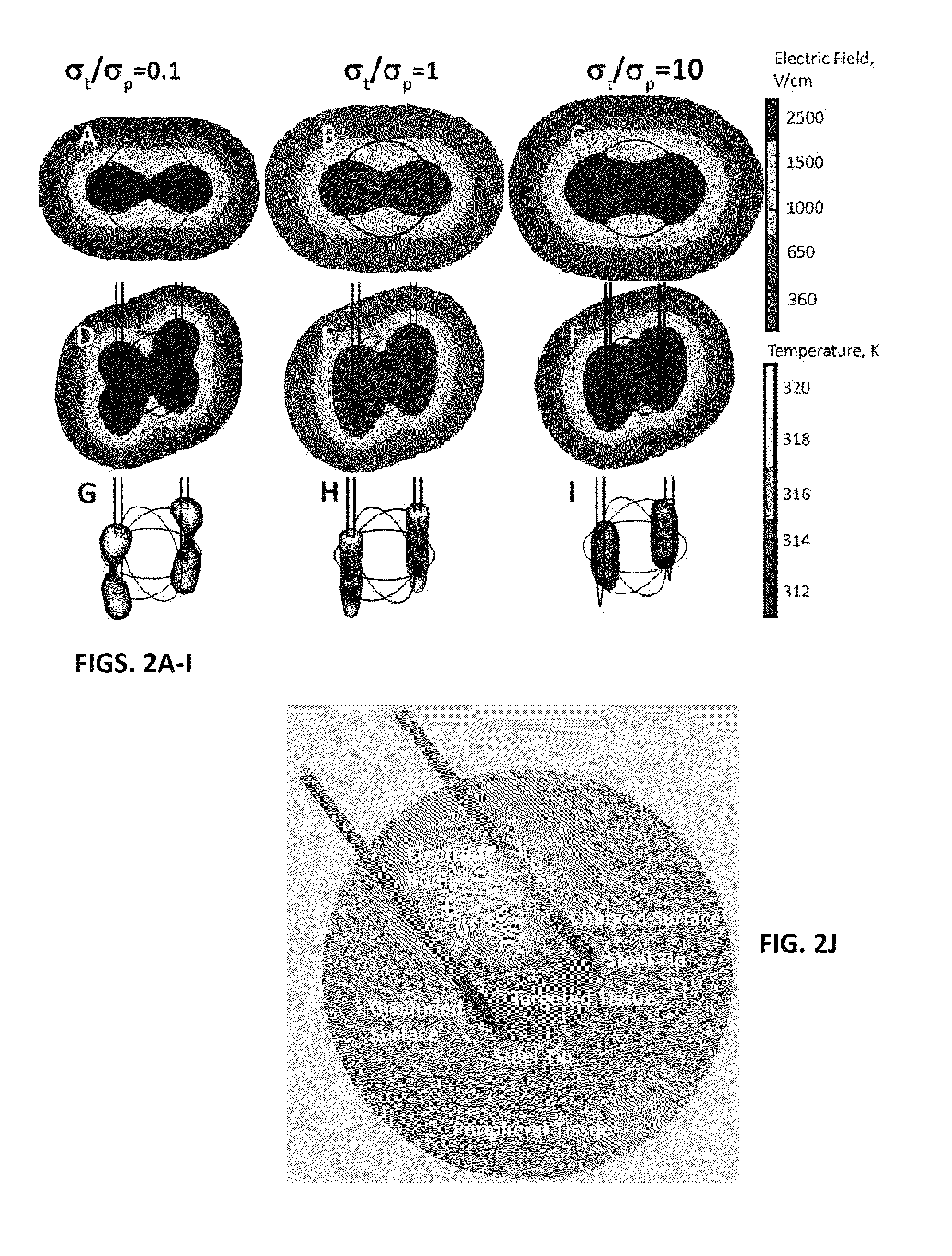

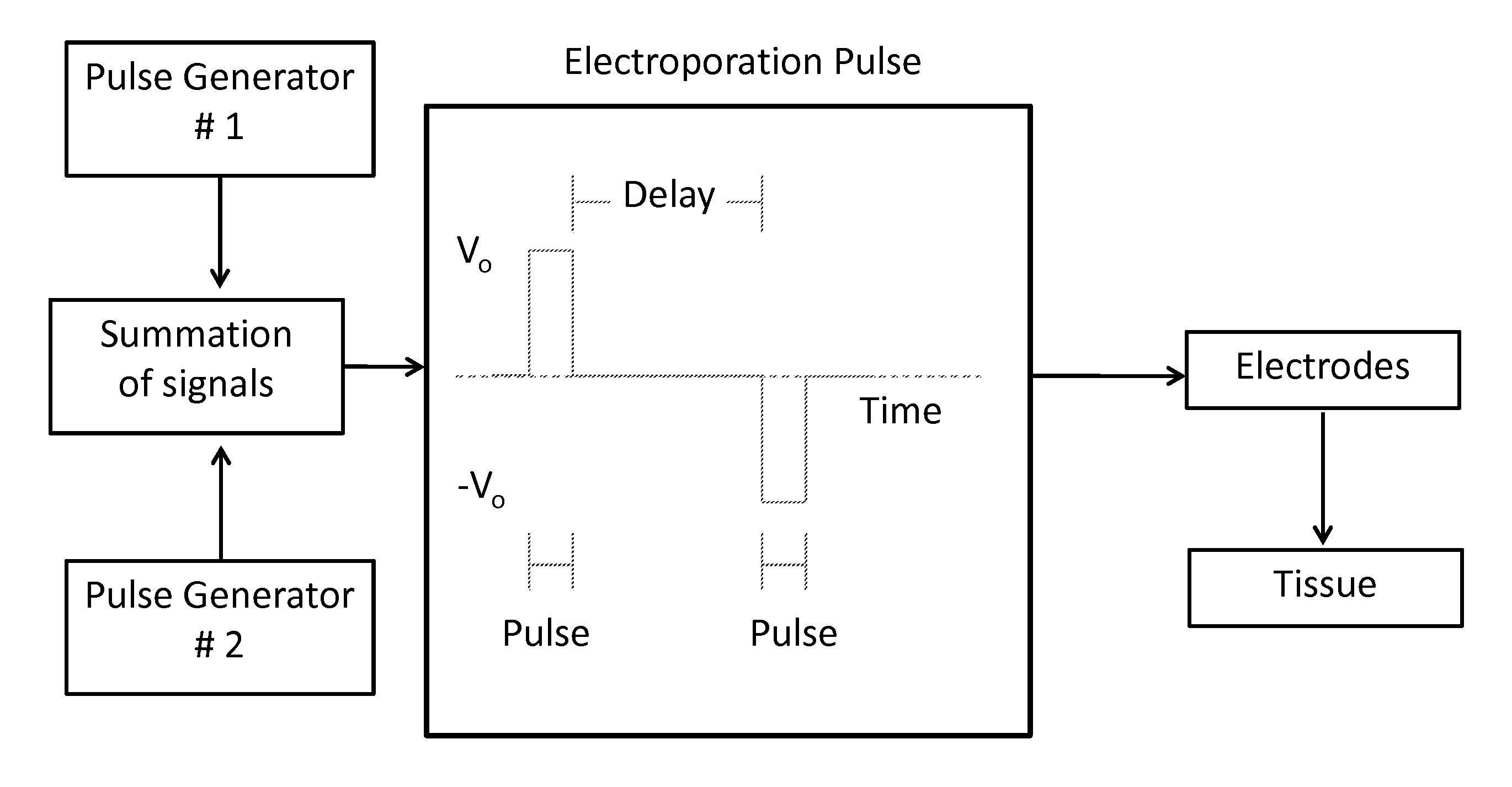

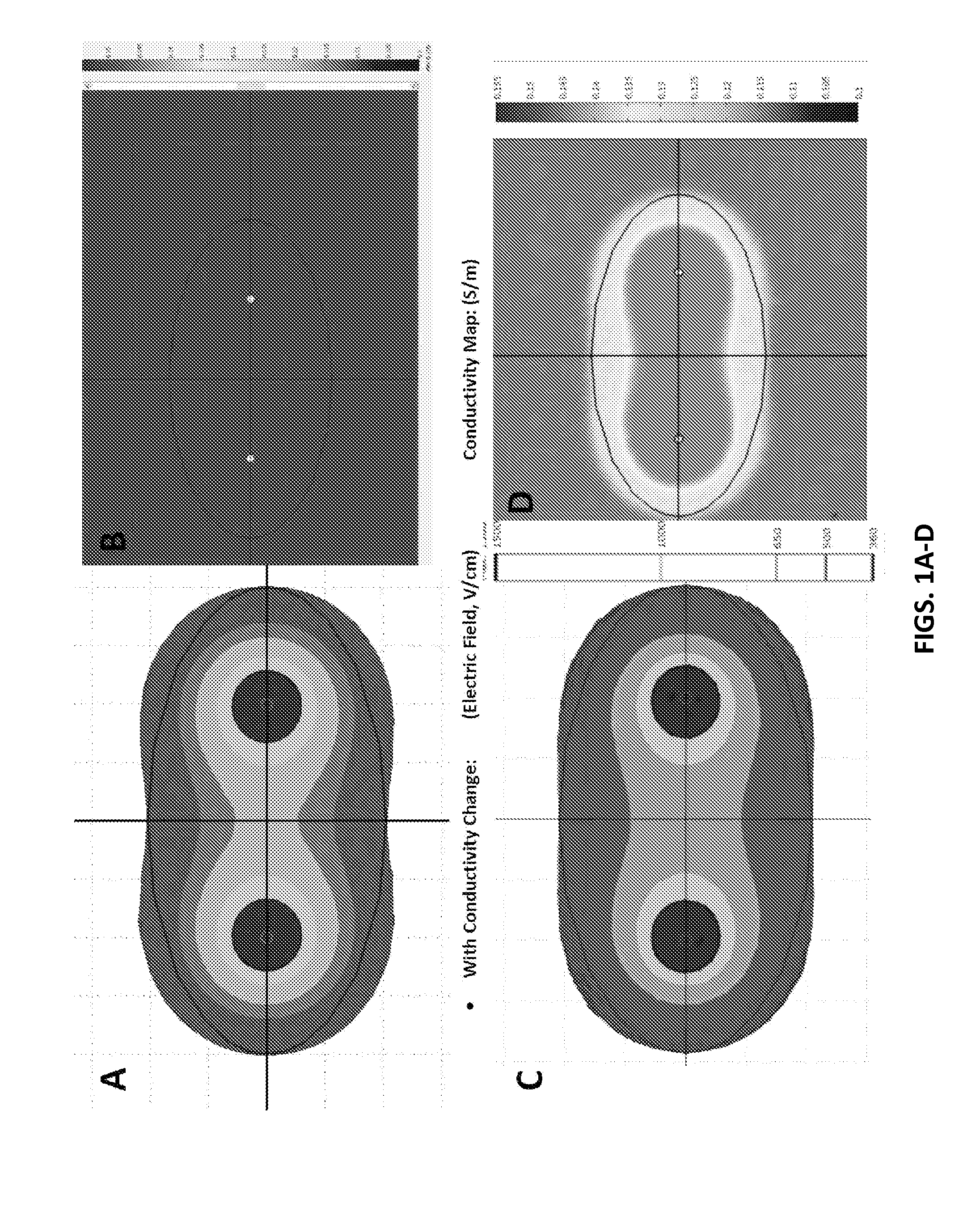

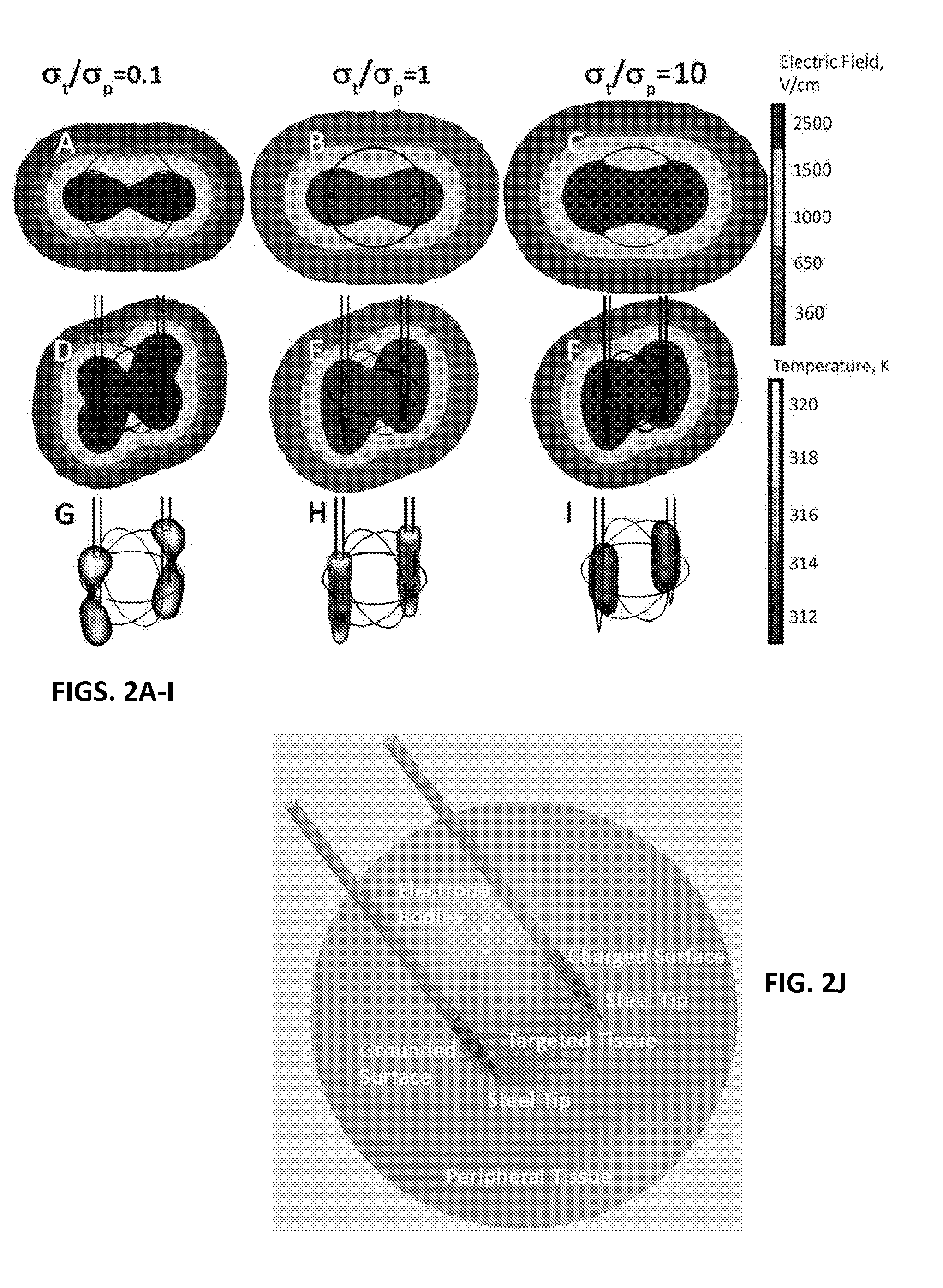

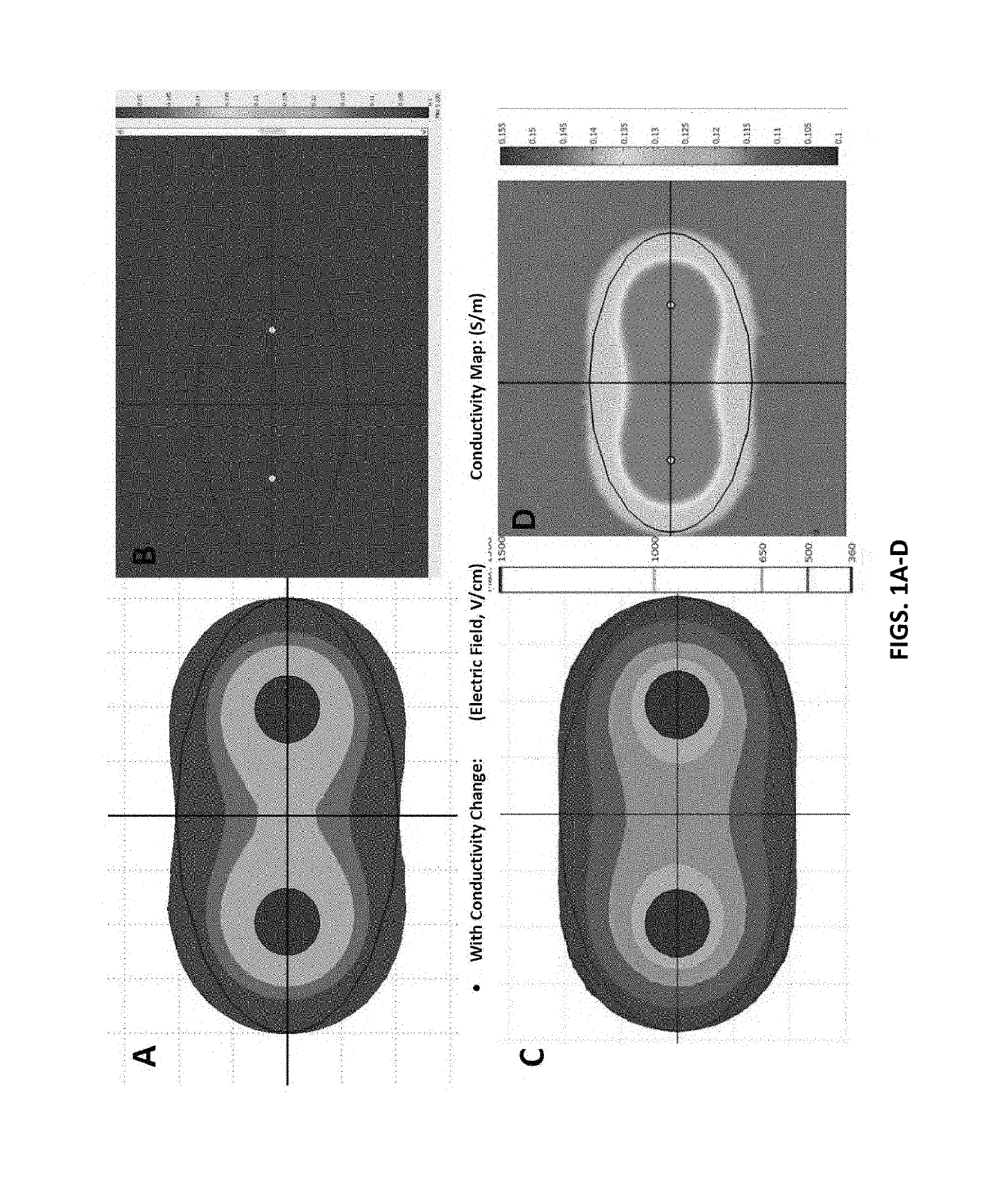

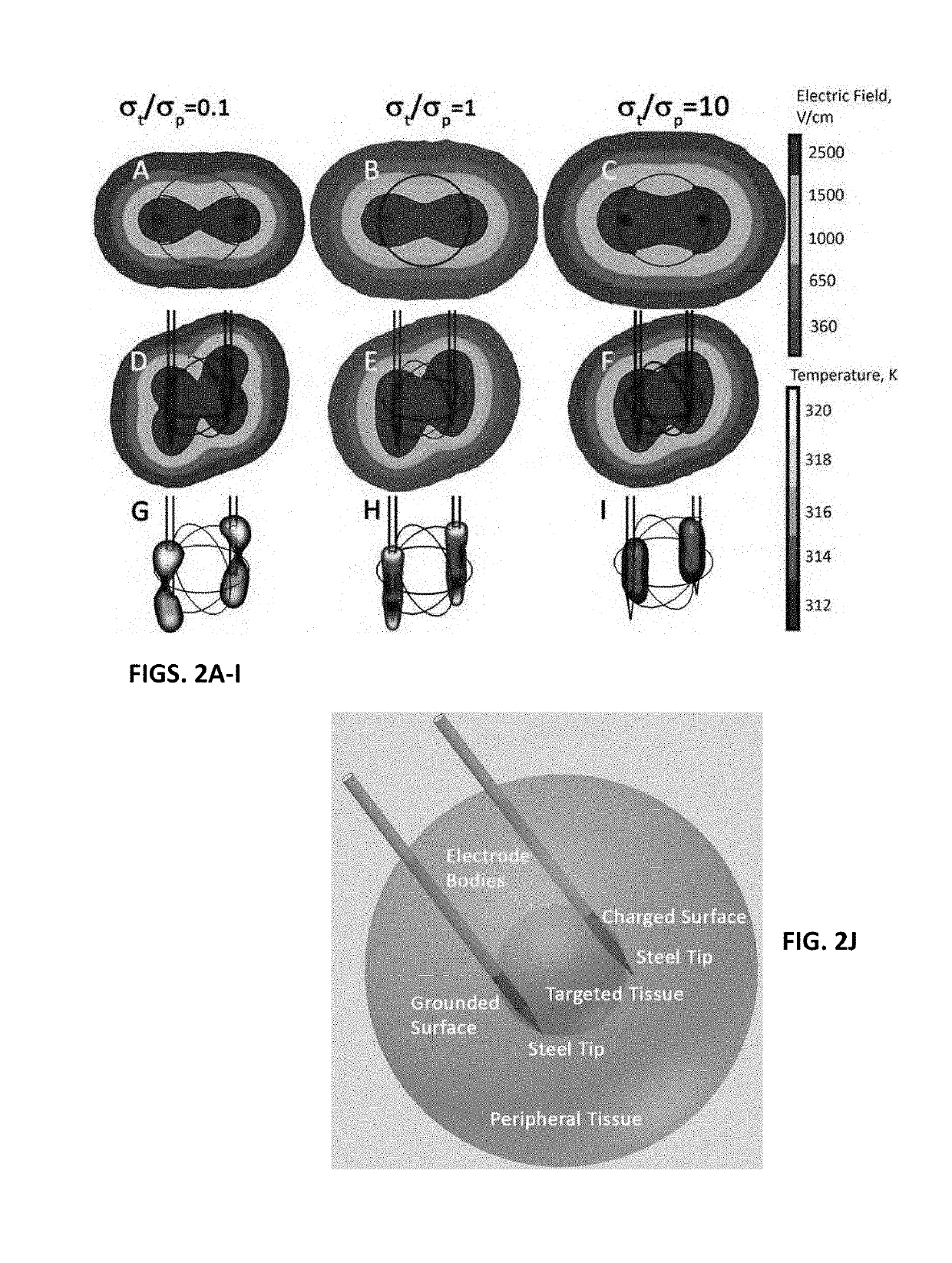

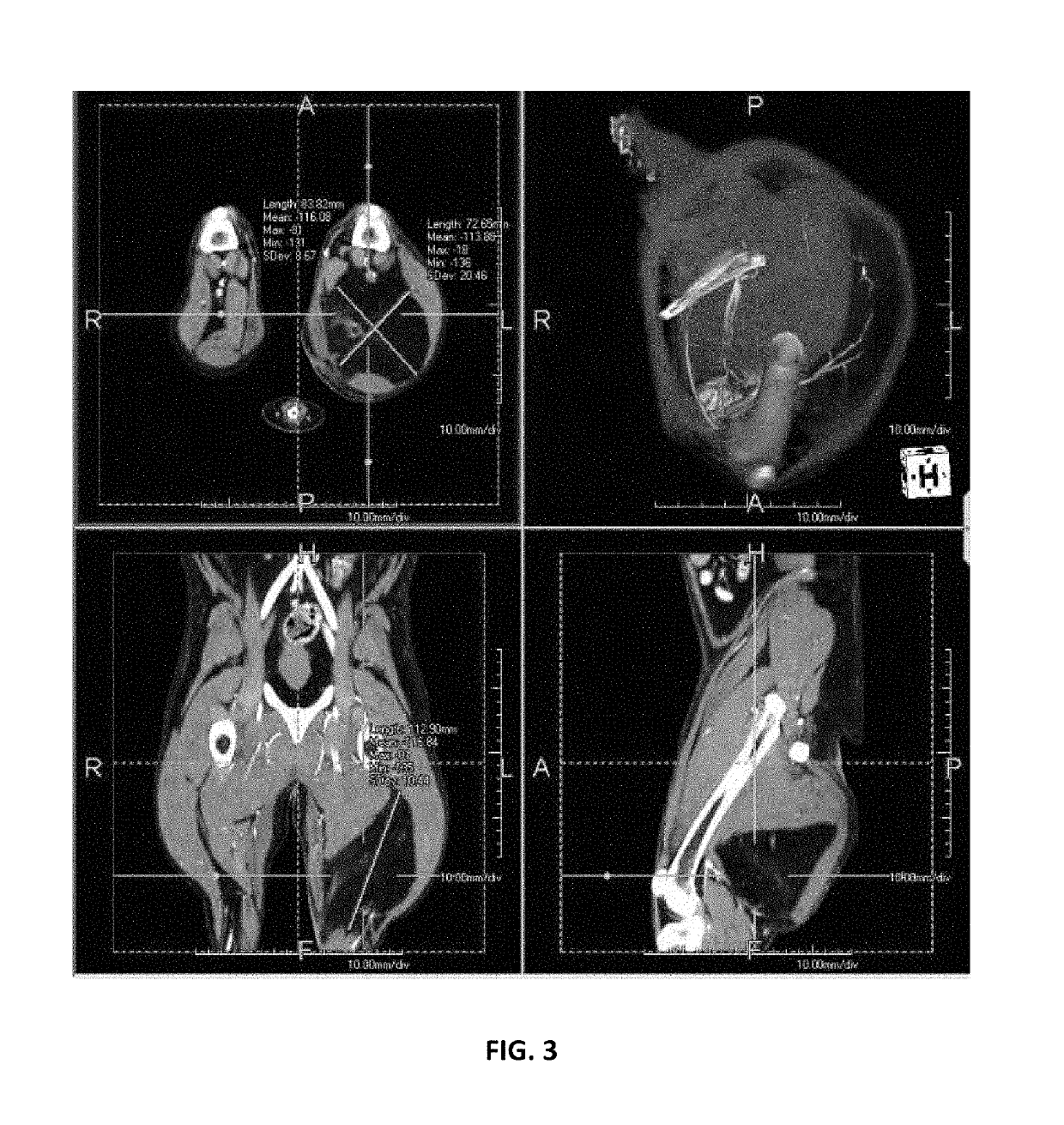

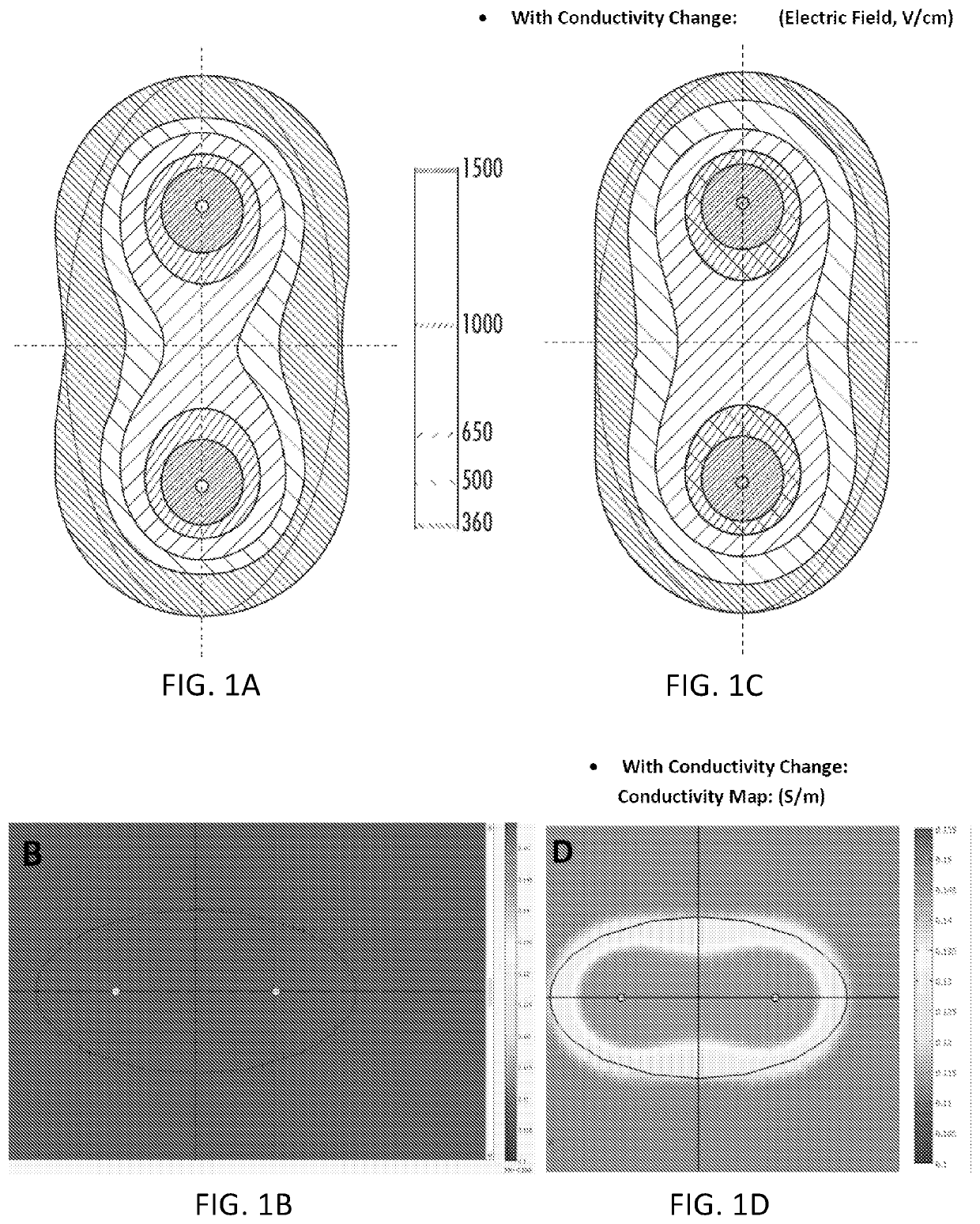

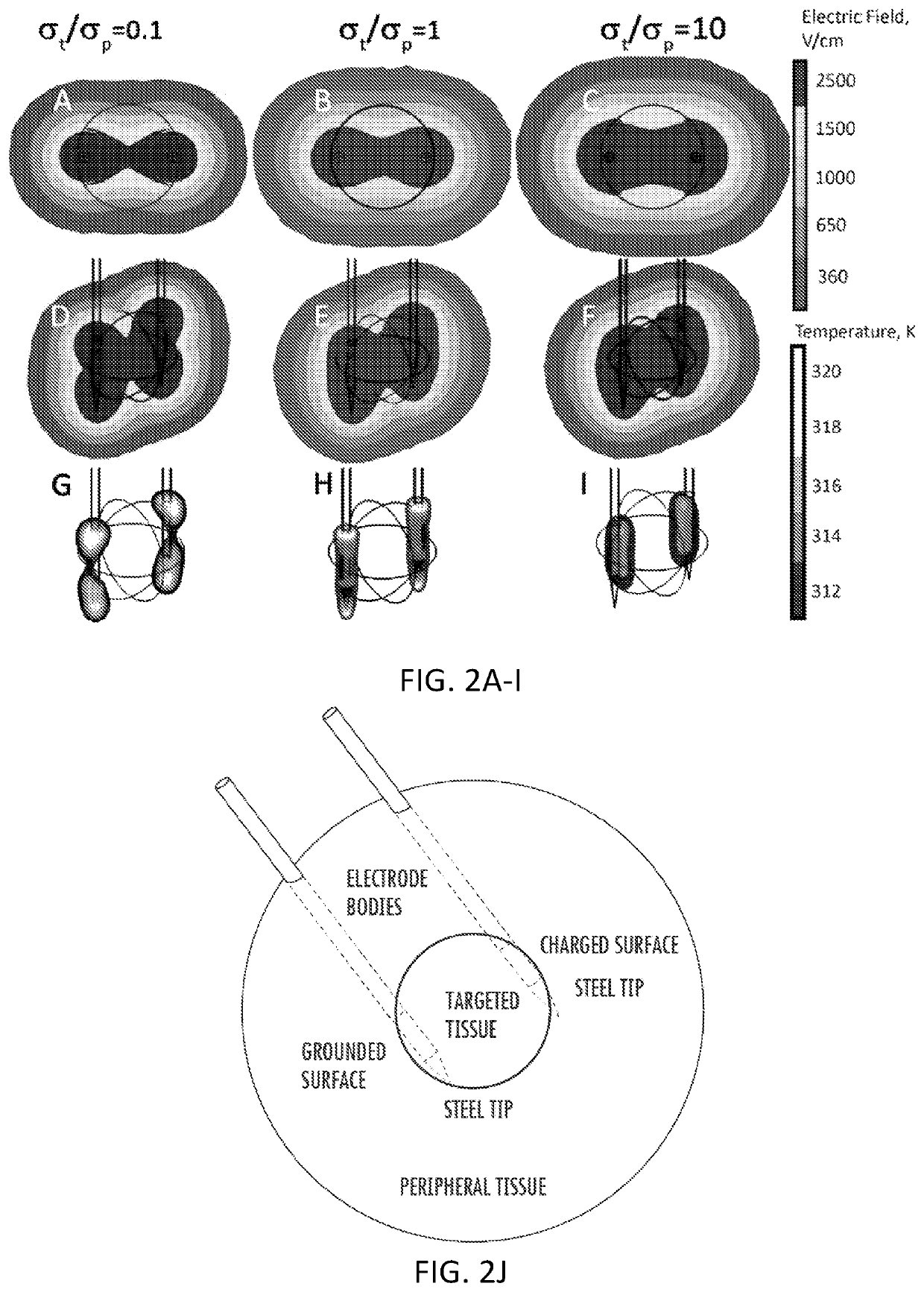

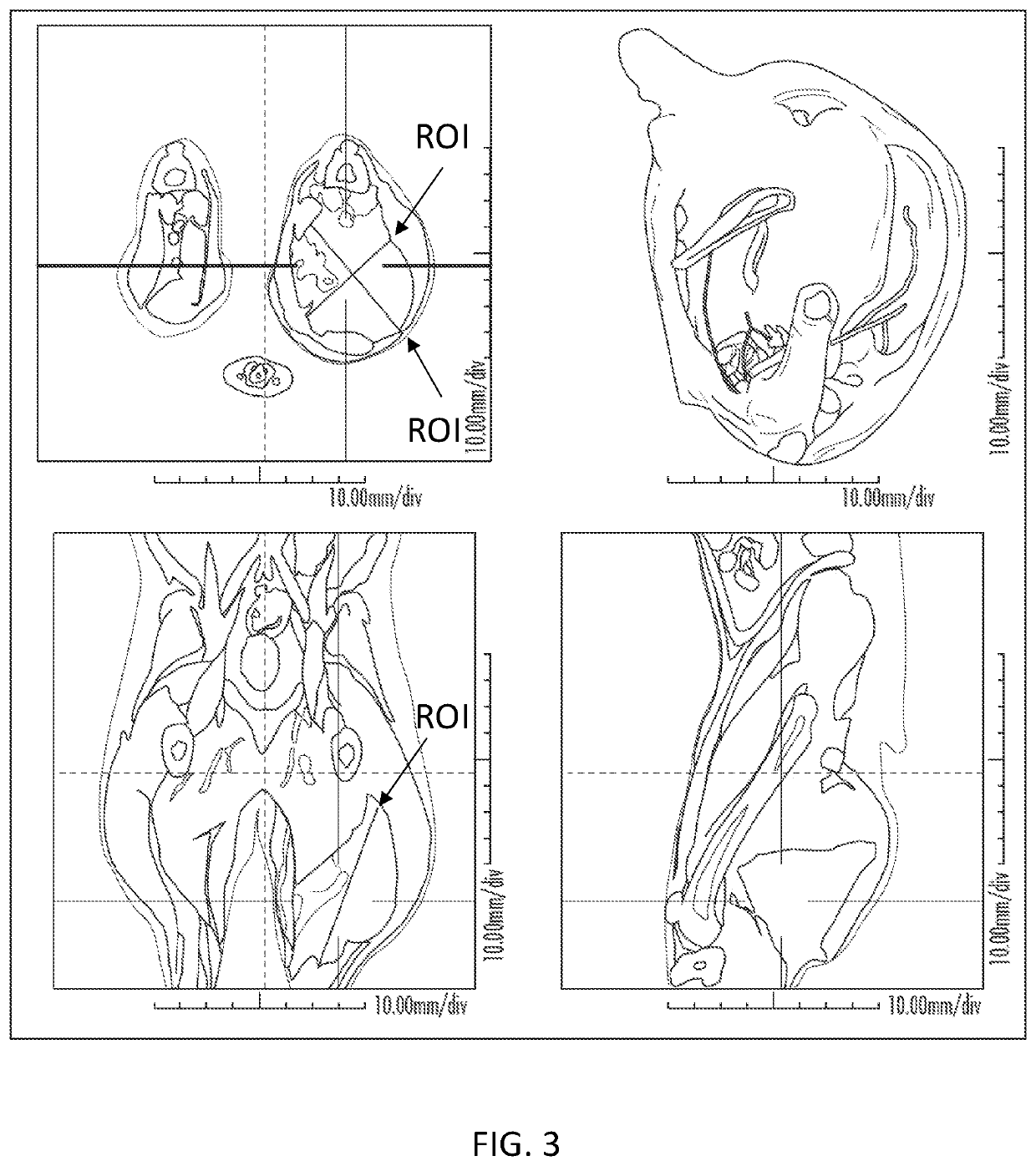

Treatment planning for electroporation-based therapies

ActiveUS9198733B2Reduce adverse effectsMinimize charge buildupMedical simulationDiagnosticsElectroporation therapyElectrical impulse

The present invention provides systems, methods, and devices for electroporation-based therapies (EBTs). Embodiments provide patient-specific treatment protocols derived by the numerical modeling of 3D reconstructions of target tissue from images taken of the tissue, and optionally accounting for one or more of physical constraints or dynamic tissue properties. The present invention further relates to systems, methods, and devices for delivering bipolar electric pulses for irreversible electroporation exhibiting reduced or no damage to tissue typically associated with an EBT-induced excessive charge delivered to the tissue.

Owner:VIRGINIA TECH INTPROP INC

Electret assembly for a microphone having a backplate with improved charge stability

InactiveUS8280082B2Minimize chargeMinimize water absorptionWave amplification devicesMicrophone structural associationElectrical conductorCharge layer

The present invention relates to a microphone that includes a housing and a diaphragm and backplate located with the housing. The housing has a sound port for receiving the sound. The diaphragm undergoes movement relative to the backplate, which it opposes, in response to the incoming sound. The backplate has a charged layer with a first surface that is exposed to the diaphragm and a second surface opposite the first surface. The backplate further includes a conductor for transmitting a signal from the backplate to electronics in the housing. The conductor faces the second surface of the charged layer. To minimize the charge degradation created by contact with or infiltration of foreign materials, the first surface, the second surface, or both surfaces of the charged layer includes a protective layer thereon.

Owner:SONION NEDERLAND

Treatment planning for electroporation-based therapies

ActiveUS20150327944A1Reduce adverse effectsMinimize charge buildupMedical simulationDiagnosticsElectroporation therapyElectrical impulse

The present invention provides systems, methods, and devices for electroporation-based therapies (EBTs). Embodiments provide patient-specific treatment protocols derived by the numerical modeling of 3D reconstructions of target tissue from images taken of the tissue, and optionally accounting for one or more of physical constraints or dynamic tissue properties. The present invention further relates to systems, methods, and devices for delivering bipolar electric pulses for irreversible electroporation exhibiting reduced or no damage to tissue typically associated with an EBT-induced excessive charge delivered to the tissue.

Owner:VIRGINIA TECH INTPROP INC

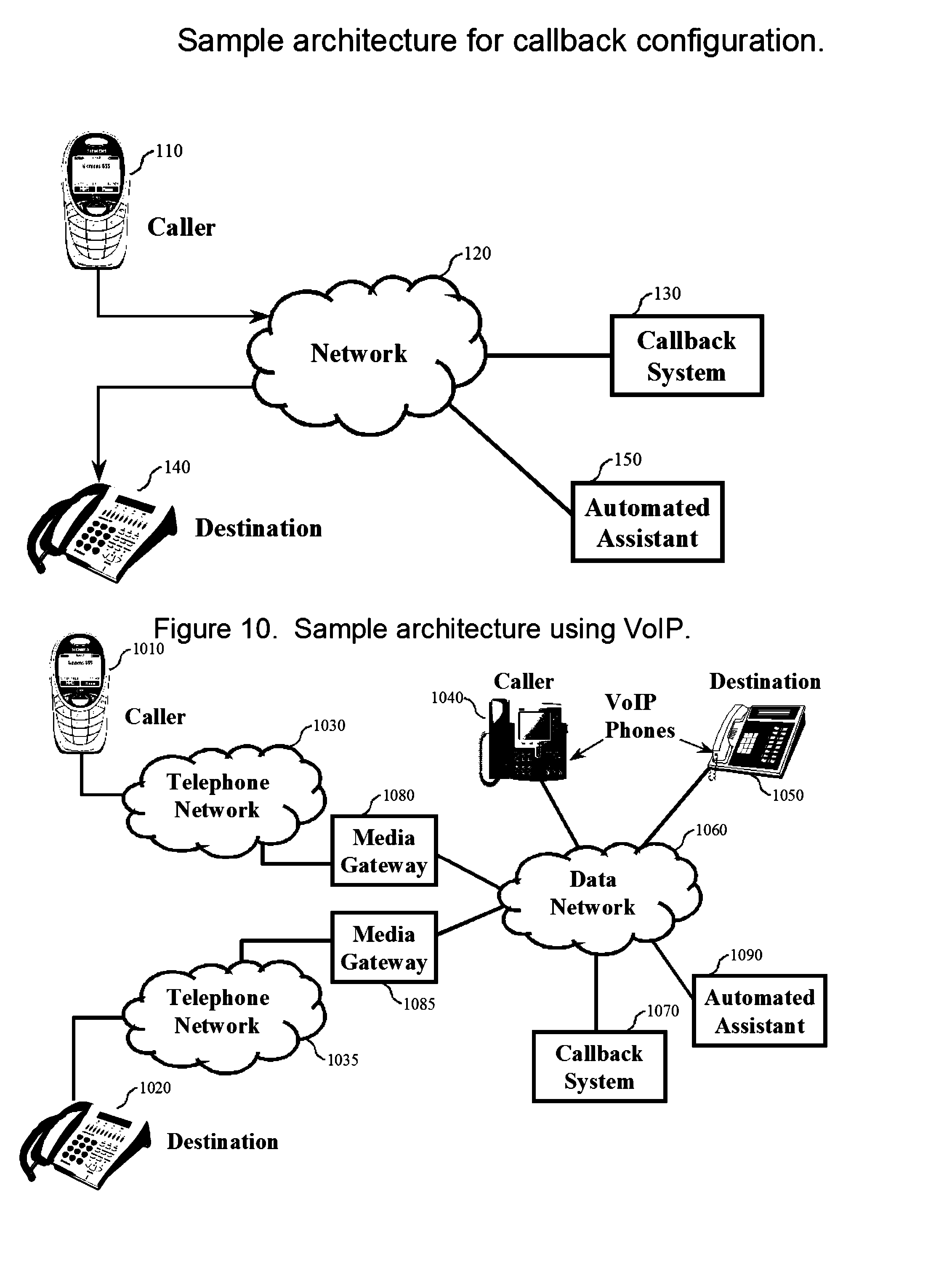

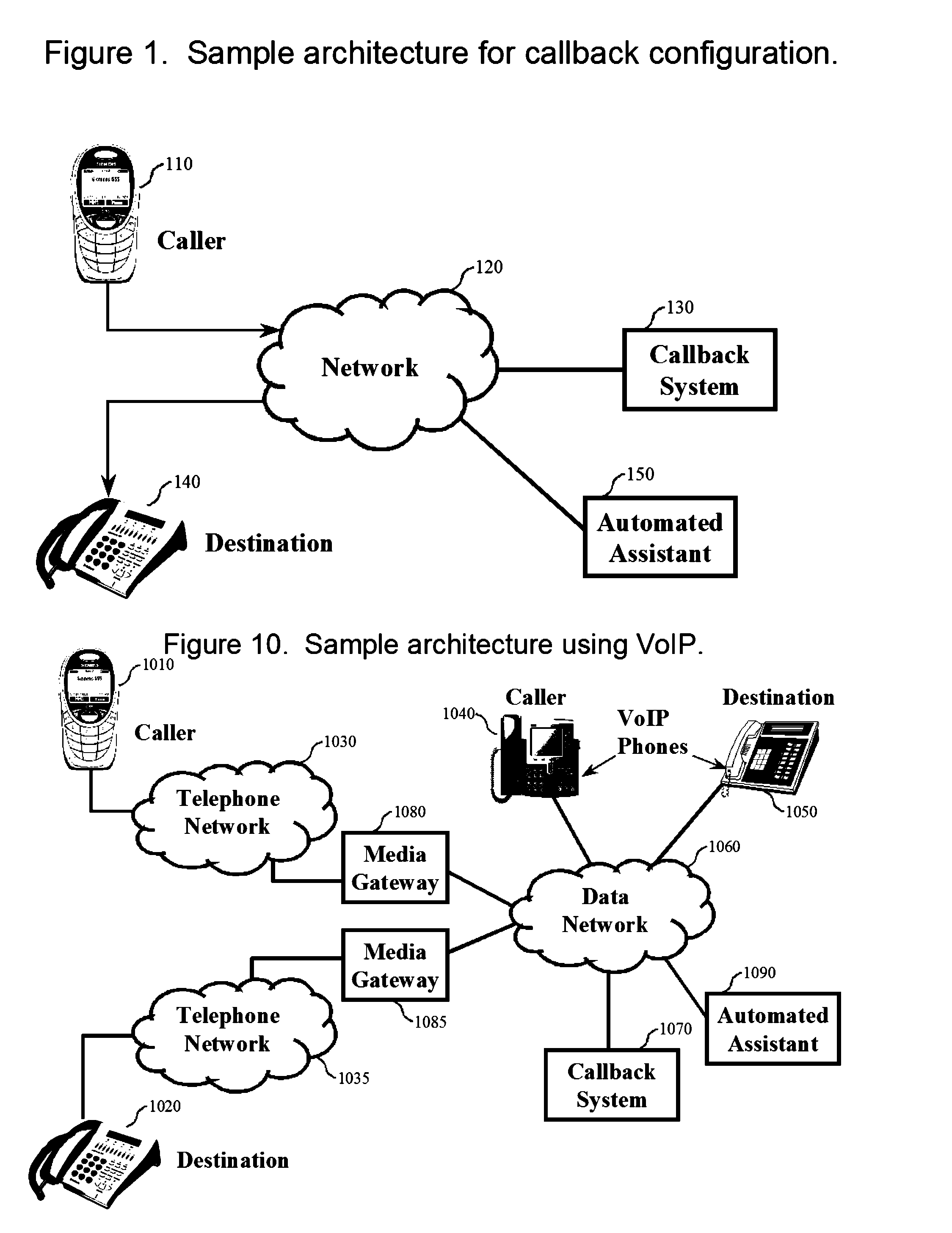

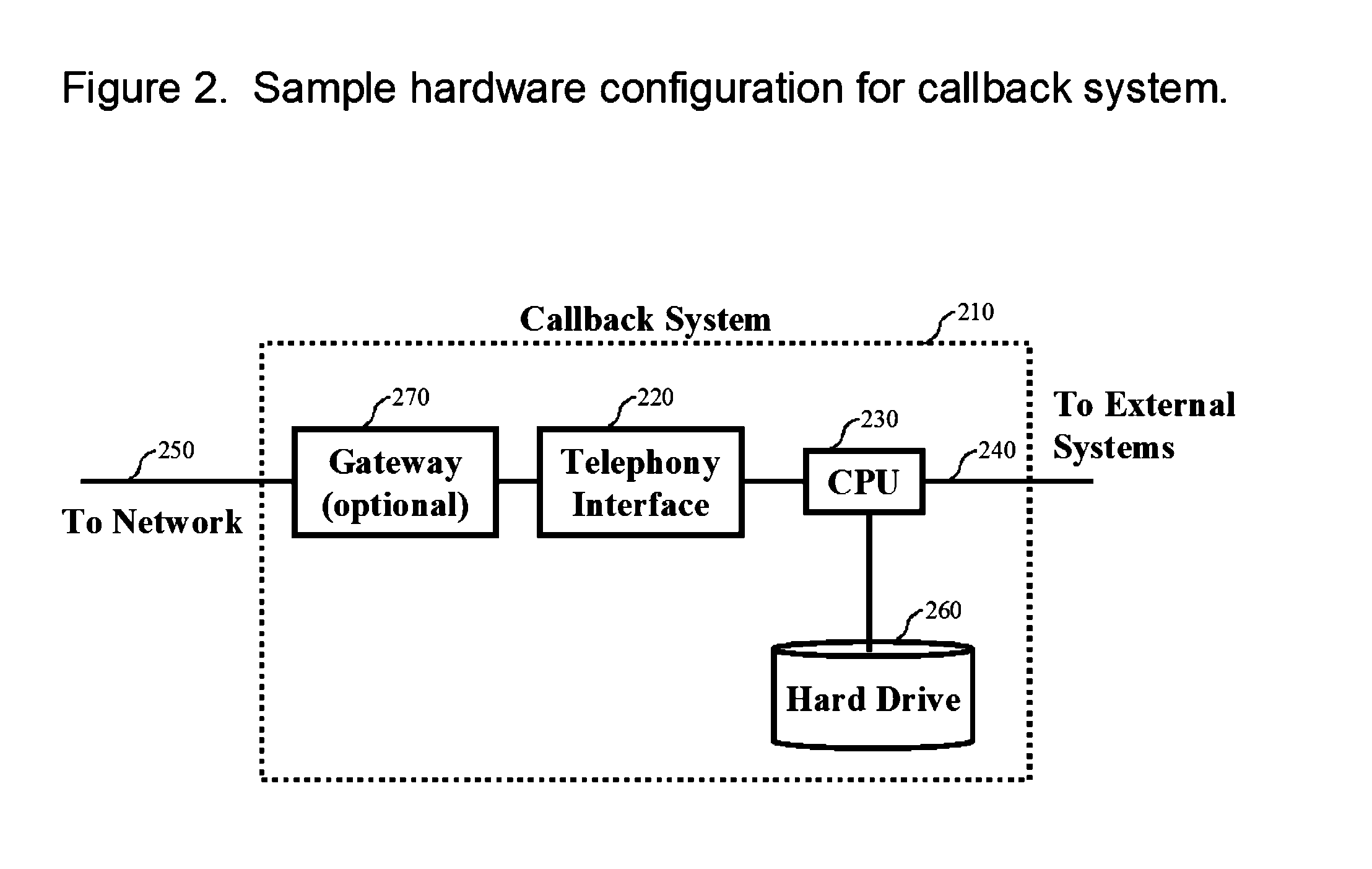

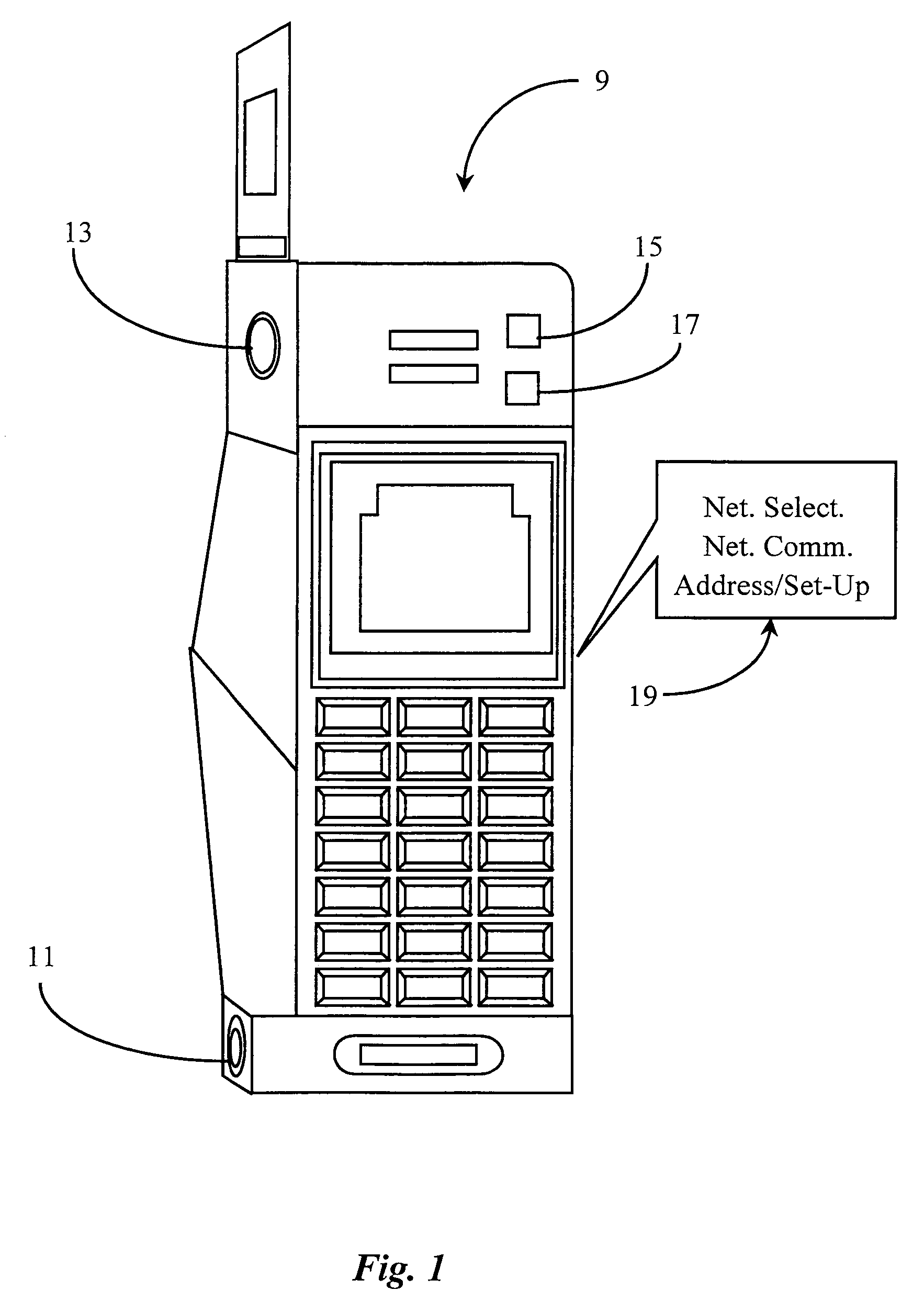

Callback Service

InactiveUS20070201646A1Minimizing service provider chargeMinimize chargeCalled number recording/indicationTelecommunications

A caller calls a callback system. If the caller is not a subscriber, the caller is offered a subscription, and if the caller provides proper billing information, the caller becomes a subscriber. When a subscriber calls a callback system, the system identifies the subscriber's ANI and calls the subscriber back. The system connects the subscriber to a destination chosen by the subscriber.

Owner:MDM INTPROP

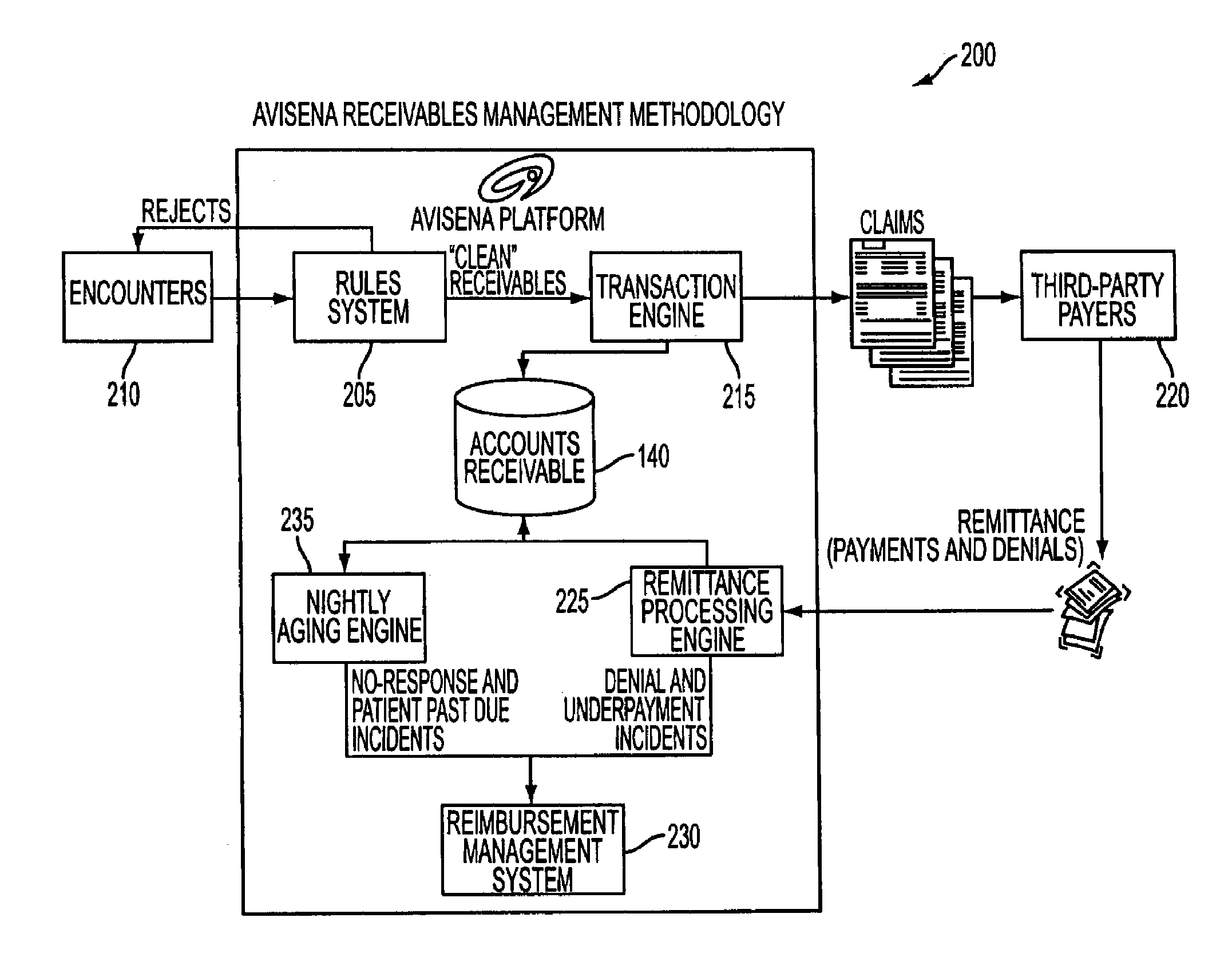

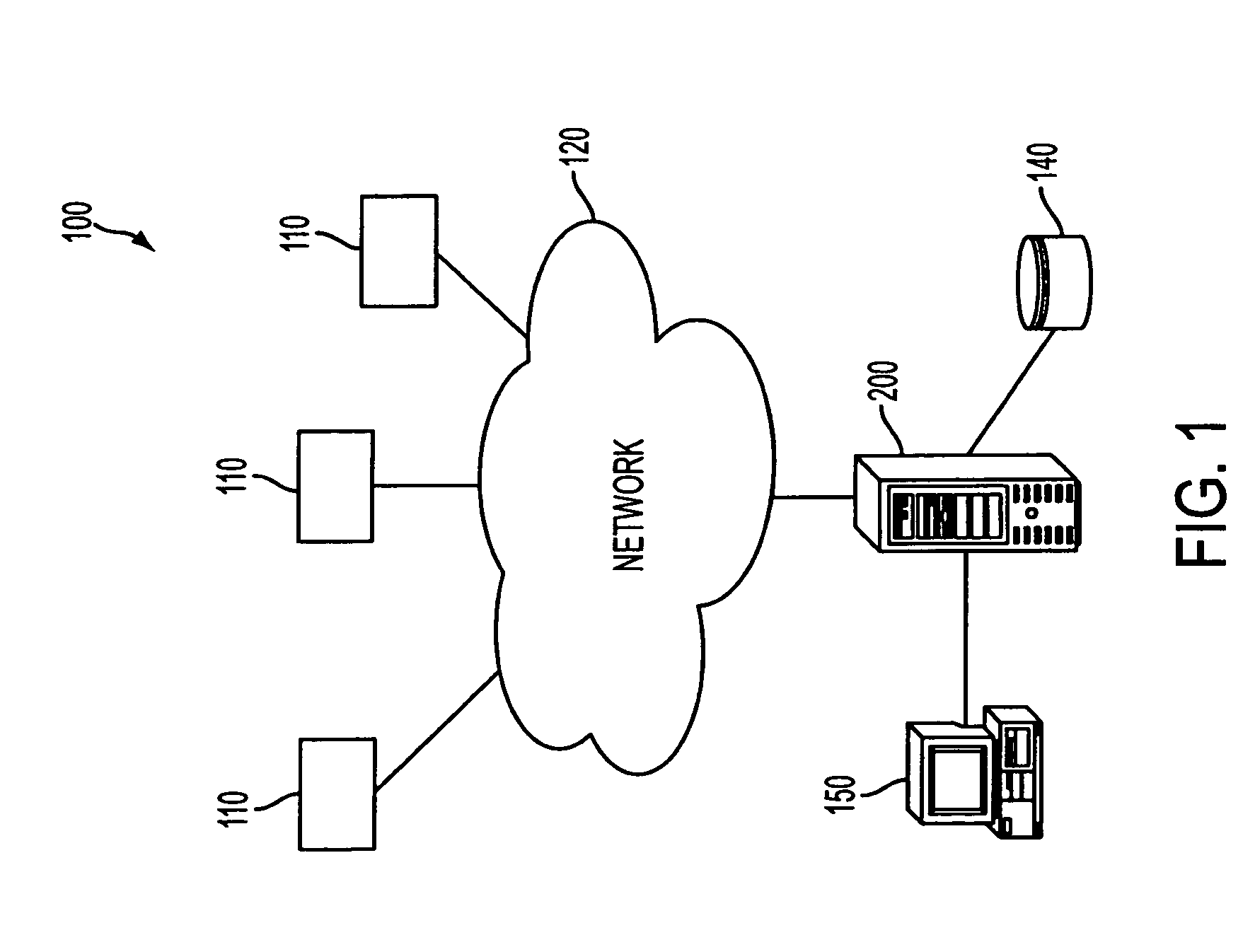

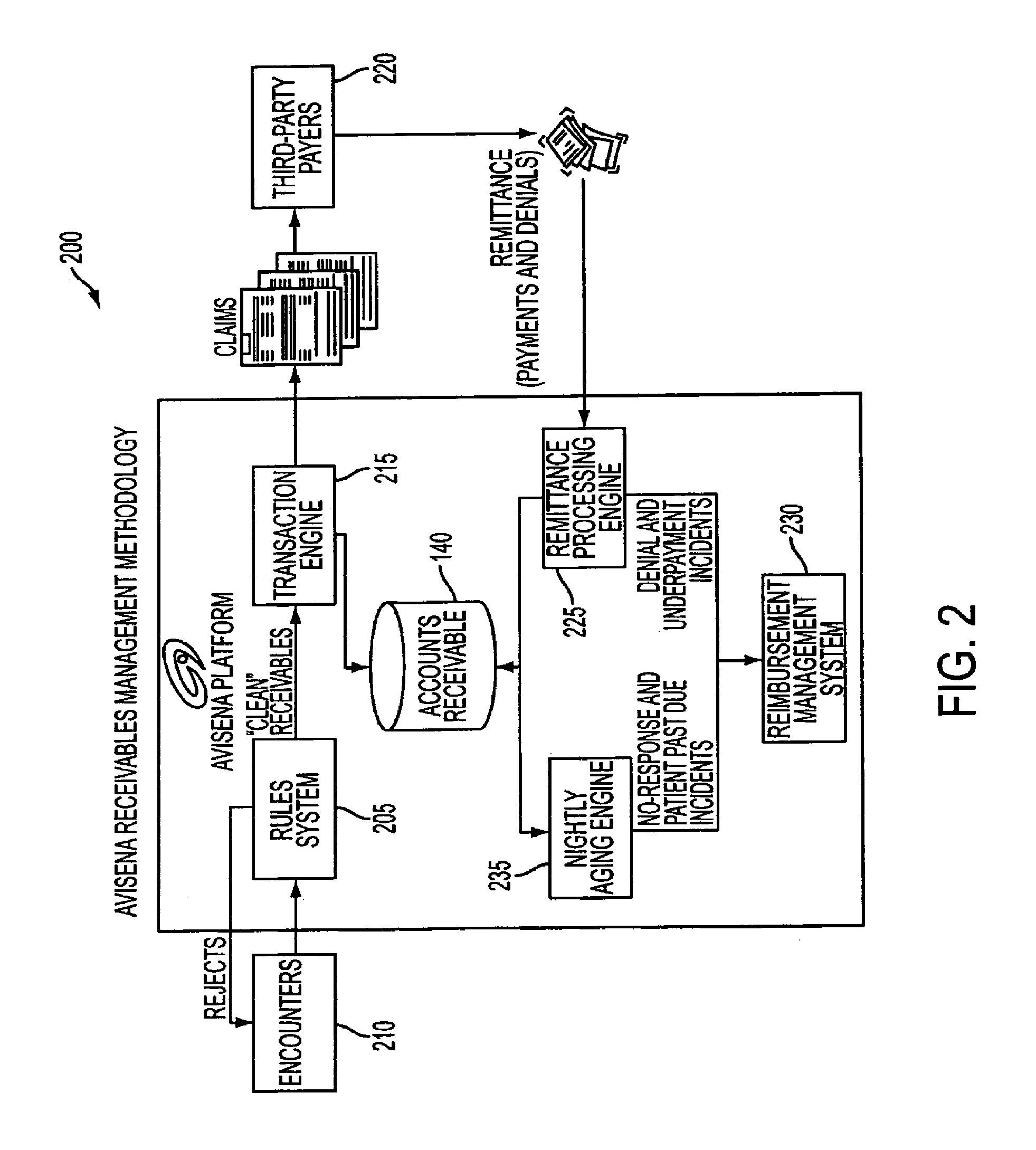

System and method for managing account receivables

ActiveUS7752096B2Efficient and timely collectionOvercomes drawbackComplete banking machinesFinanceData miningEngineering

A system for managing account receivables is provided. The system comprises a rules module or engine for receiving at least one encounter from a first party and for assessing the at least one encounter based on rules associated with a payer; and a transactions module or engine for outputting at least one claim to the payer based on the rule module's assessment of the at least one encounter.

Owner:MEDUSIND INC

Devices and methods for high frequency electroporation

ActiveUS20190256839A1Reduce adverse effectsMinimize charge buildupMedical simulationElectrotherapyElectrical impulseIrreversible electroporation

The present invention provides systems, methods, and devices for electroporation-based therapies (EBTs). Embodiments provide patient-specific treatment protocols derived by the numerical modeling of 3D reconstructions of target tissue from images taken of the tissue, and optionally accounting for one or more of physical constraints or dynamic tissue properties. The present invention further relates to systems, methods, and devices for delivering bipolar electric pulses for irreversible electroporation exhibiting reduced or no damage to tissue typically associated with an EBT-induced excessive charge delivered to the tissue.

Owner:VIRGINIA TECH INTPROP INC

Antenna and mobile terminal having the same

ActiveUS8995910B2Minimize chargeThickness minimizationNear-field transmissionSimultaneous aerial operationsMagnetic fluxLow frequency

An antenna and a mobile terminal having the antenna are discussed. According to an embodiment, the antenna can include a flexible board having a first region and a second region; a high frequency antenna pattern formed in the first region of the flexible board to transceive a wireless signal by detecting a magnetic flux; a low frequency antenna pattern formed in the second region of the flexible board to generate an induced current; and a magnetic sheet stacked on one surface of the flexible board to simultaneously cover both of the high frequency antenna pattern and the low frequency antenna pattern, the magnetic sheet having a high magnetic permeability for both a high frequency and a low frequency.

Owner:ROVI GUIDES INC

Integrated Product Inventory and Dispensing System, and Personal Dental Care Unit Having Disposable Containers with State-Sensitive Elements

InactiveUS20080210702A1Enhancing market appealMinimize chargeCoin-freed apparatus detailsHolders and dispensersE-commerceEngineering

The various aspects of the invention include embodiments of an integrated consumer or household product dispensing system which include one or more releasable product containers which are preferably disposable, and which include state-sensitive elements in communication with a processor, and which provide for the enhancement of the convenience, safety and efficiency of product use and re-supply. Certain embodiments of the dispensing system can automatically and / or semi-automatically manage a users inventory of one or more products and determine when re-supply is needed. Further embodiments of the dispensing system can automatically and / or semi-automatically place re-supply transactions with E-commerce suppliers and / or carry out related transactions with shippers and financial institutions, so as to provide for convenient product container re-supply. Further exemplary embodiments including a personal dental care dispenser system are described.

Owner:LOCHINGER ALEXANDER +4

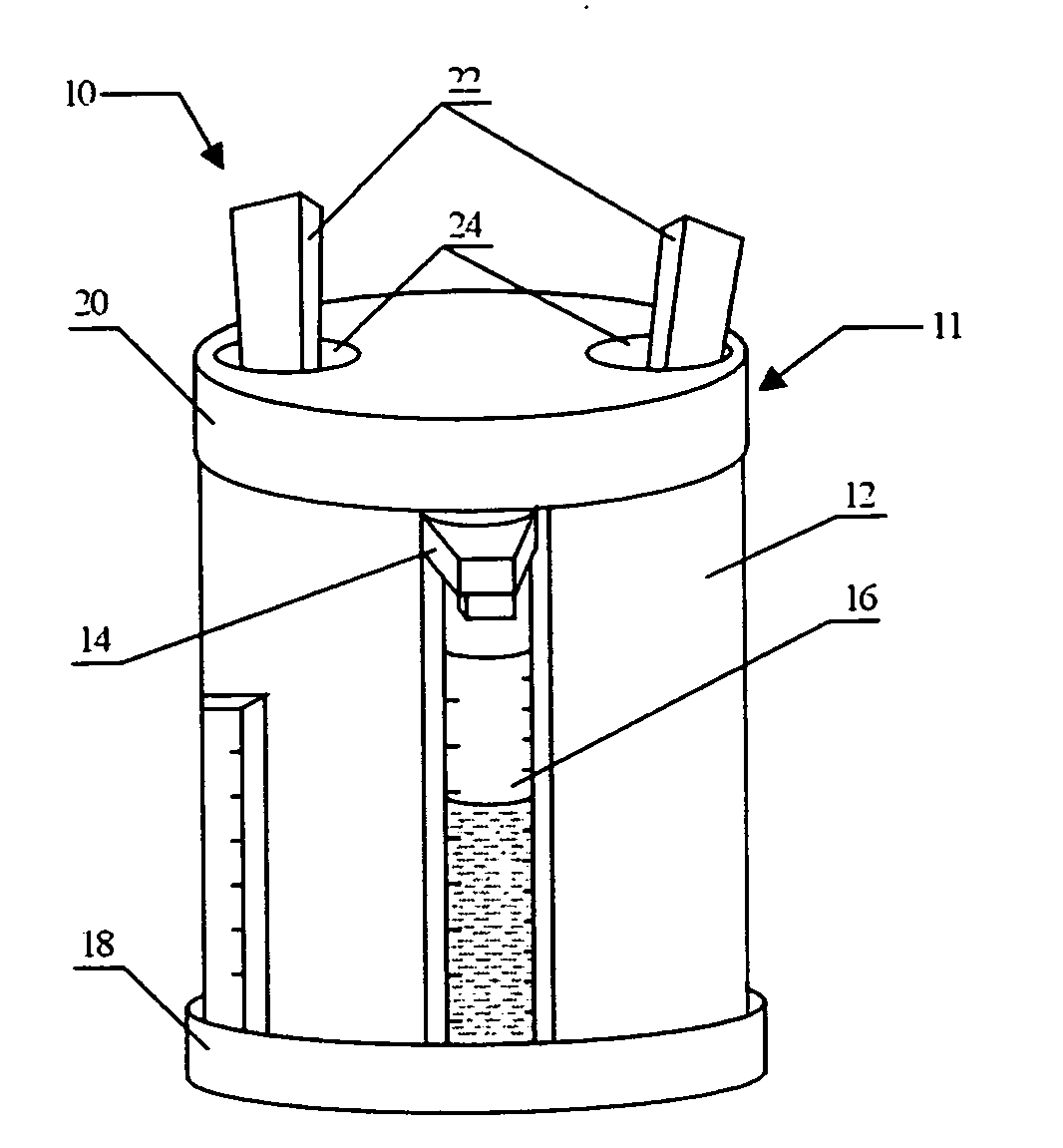

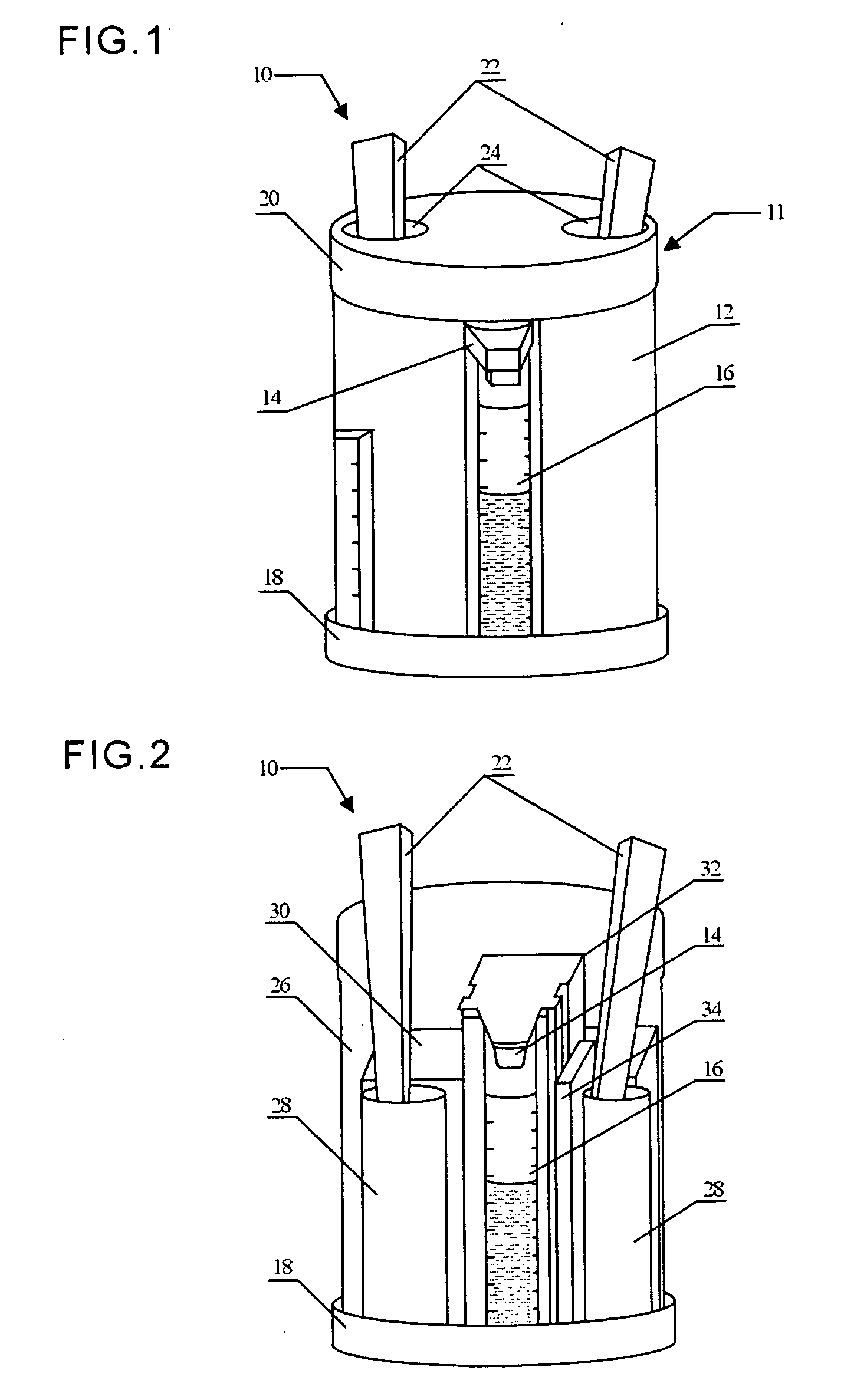

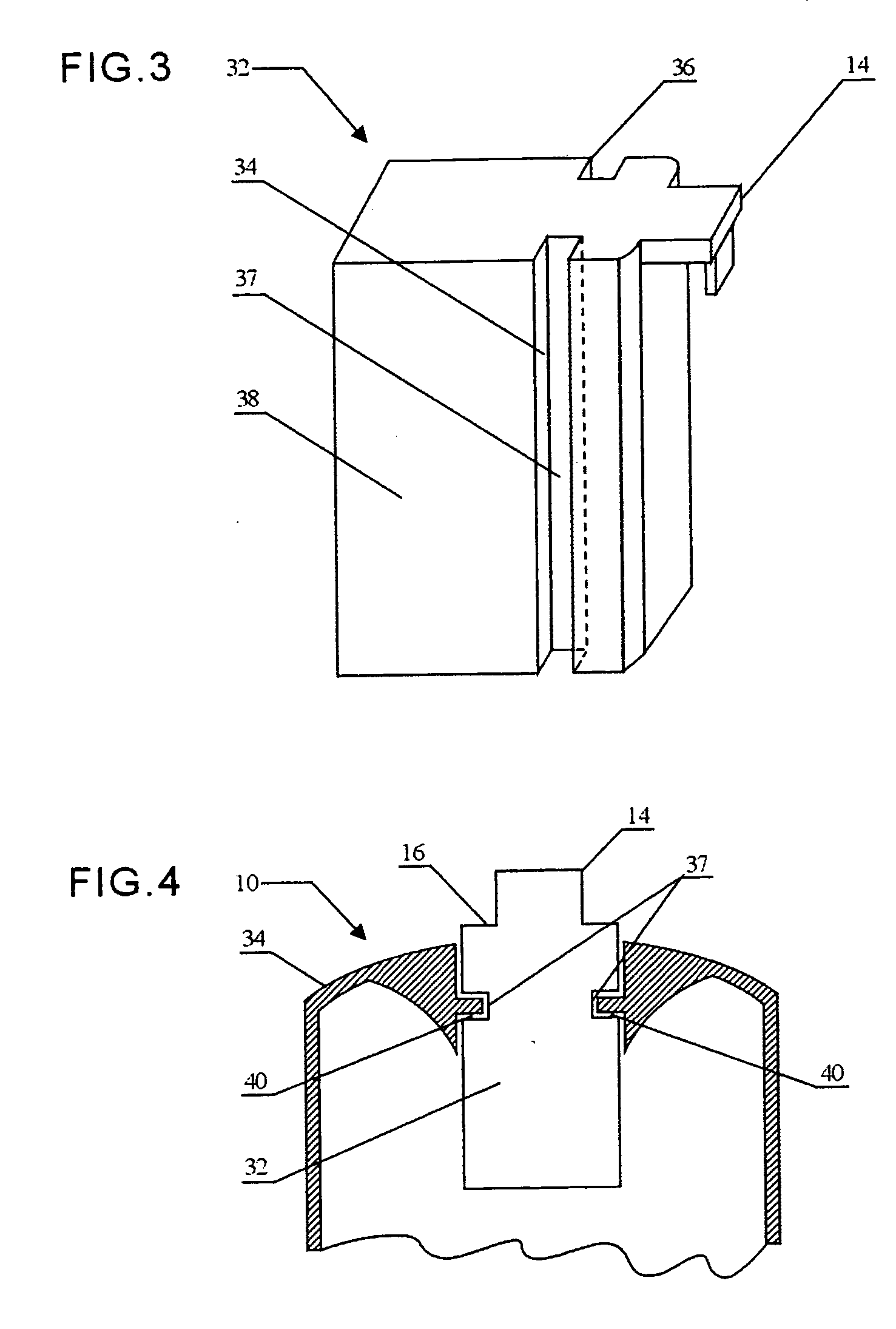

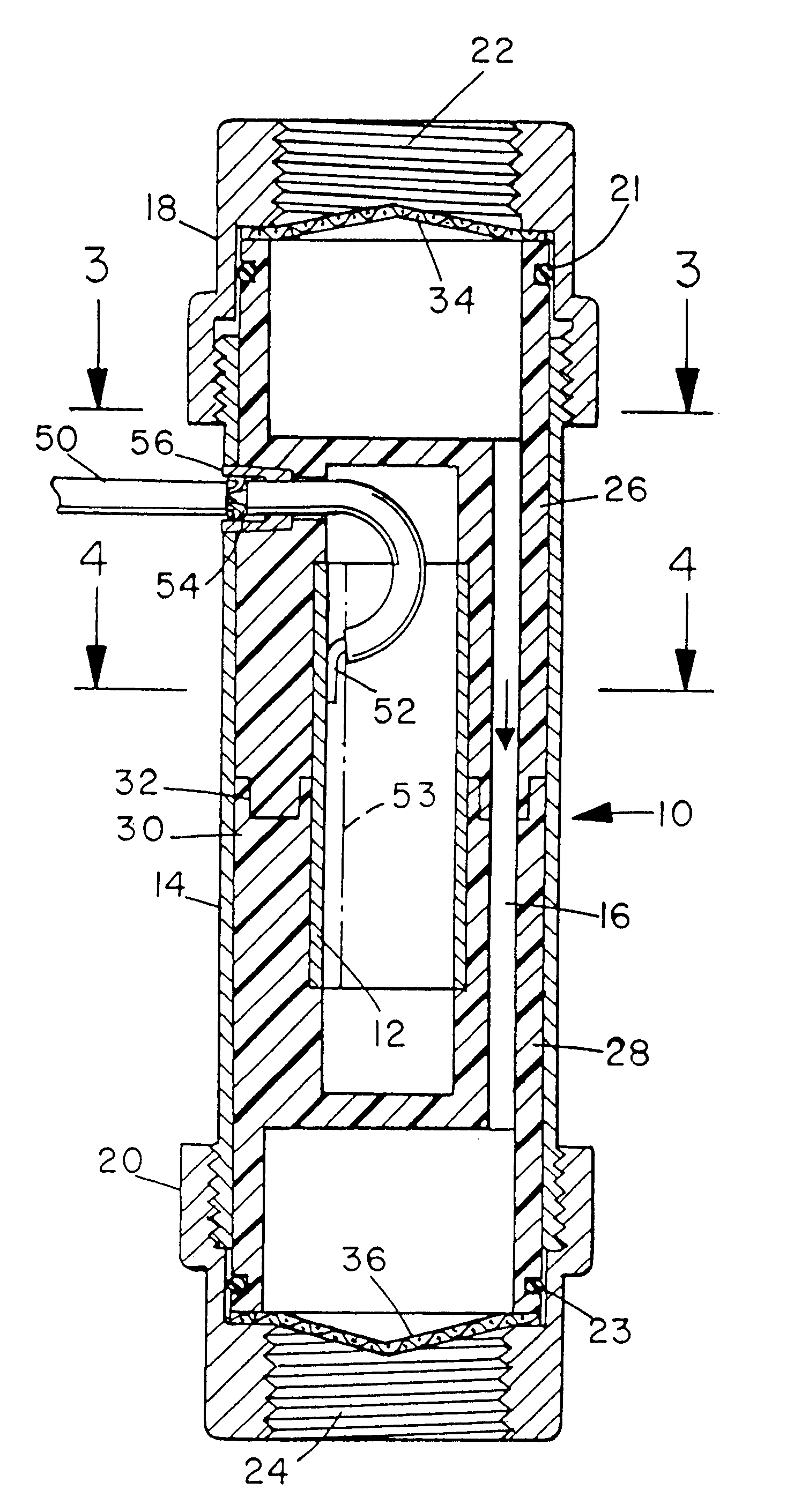

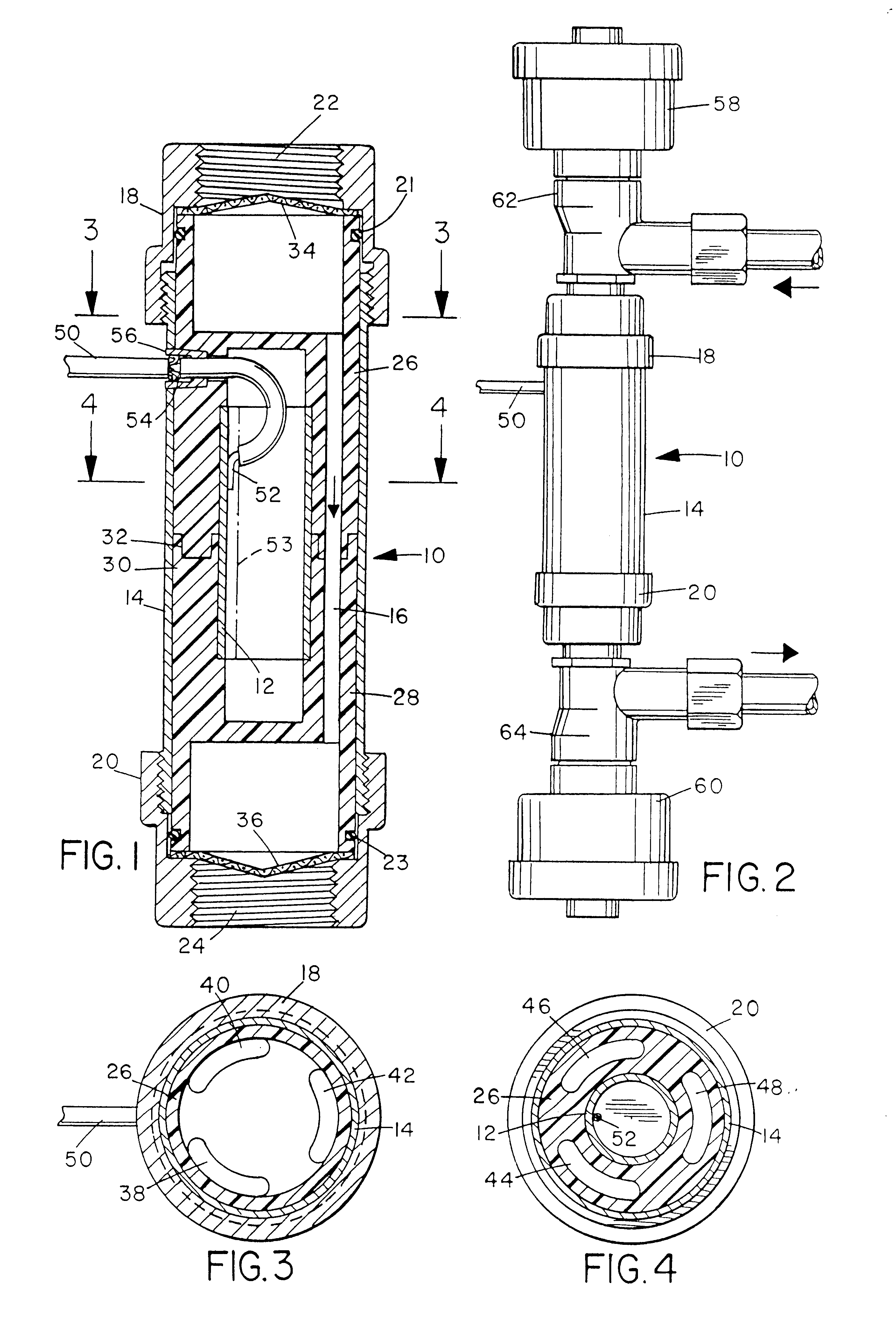

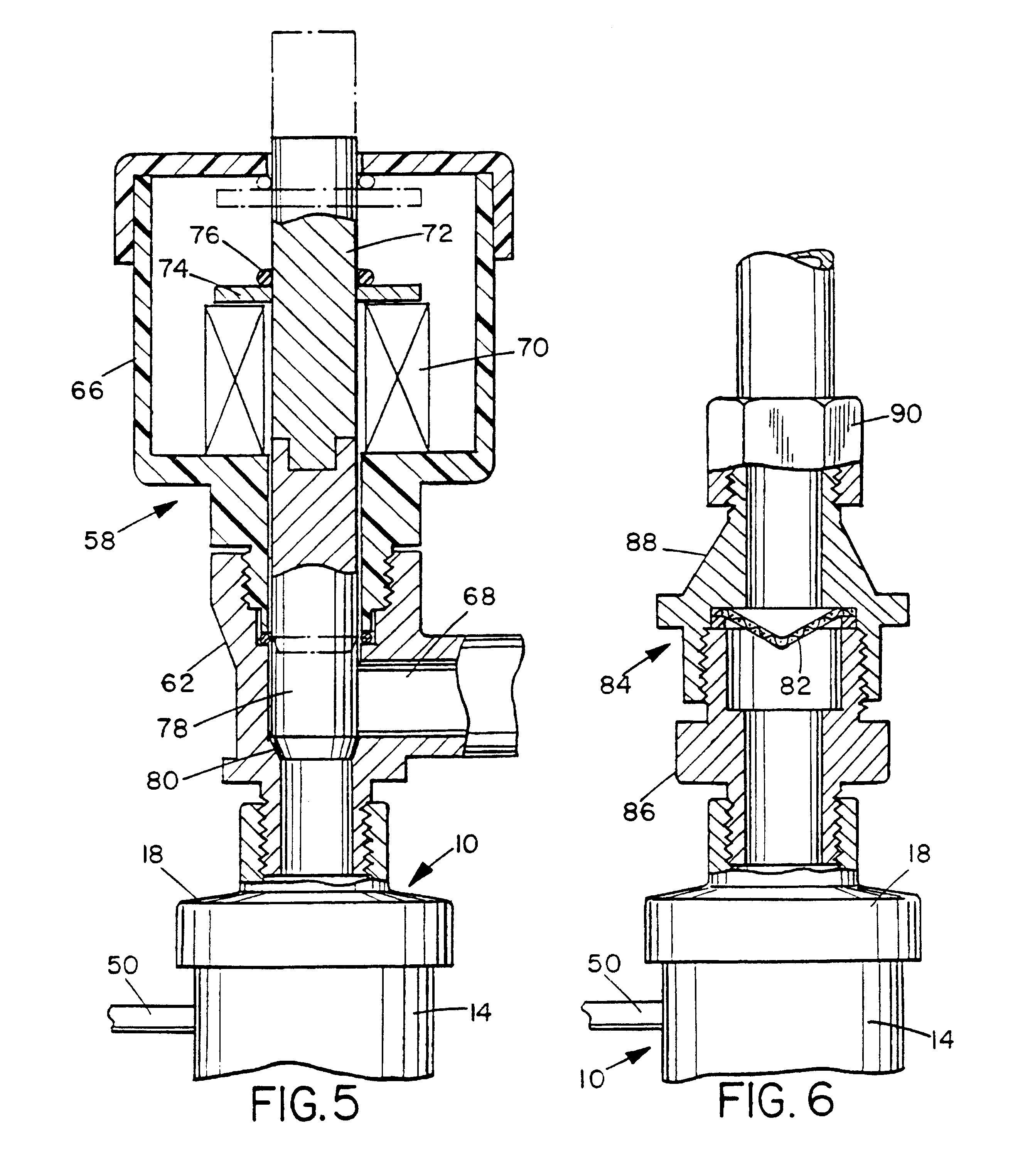

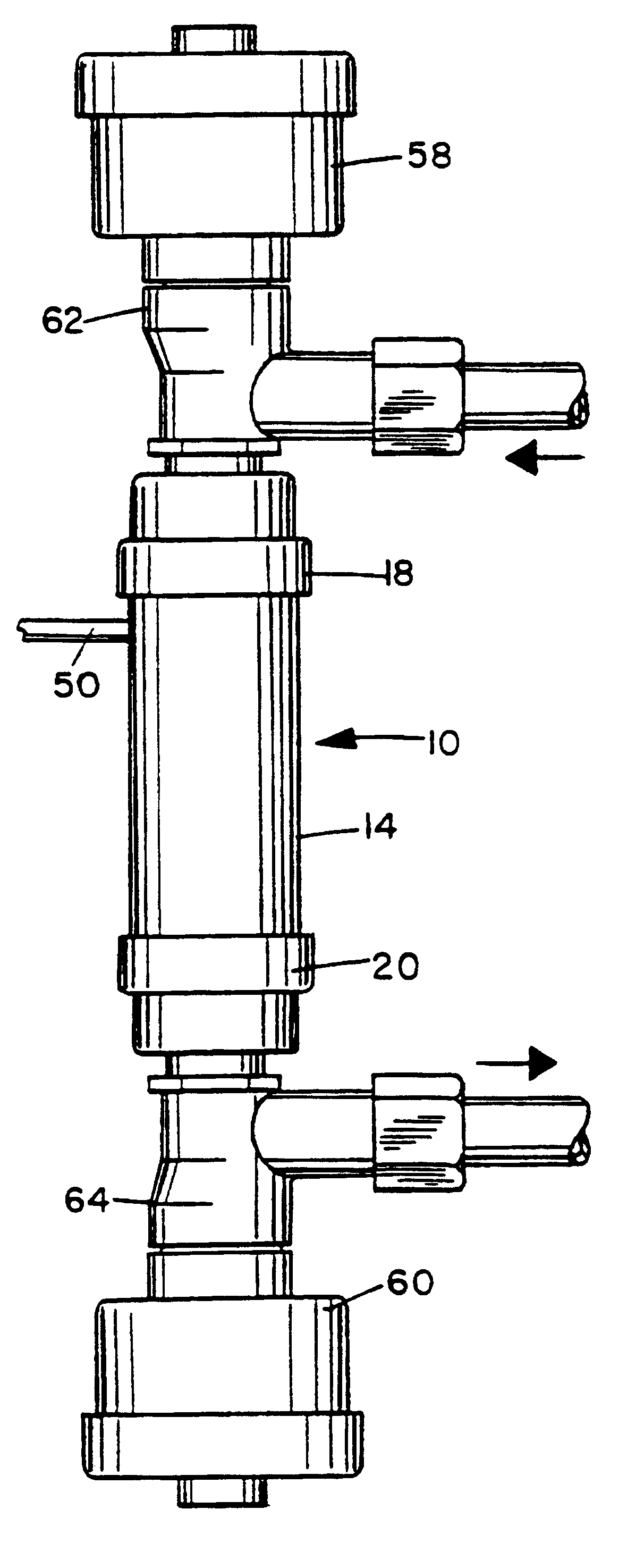

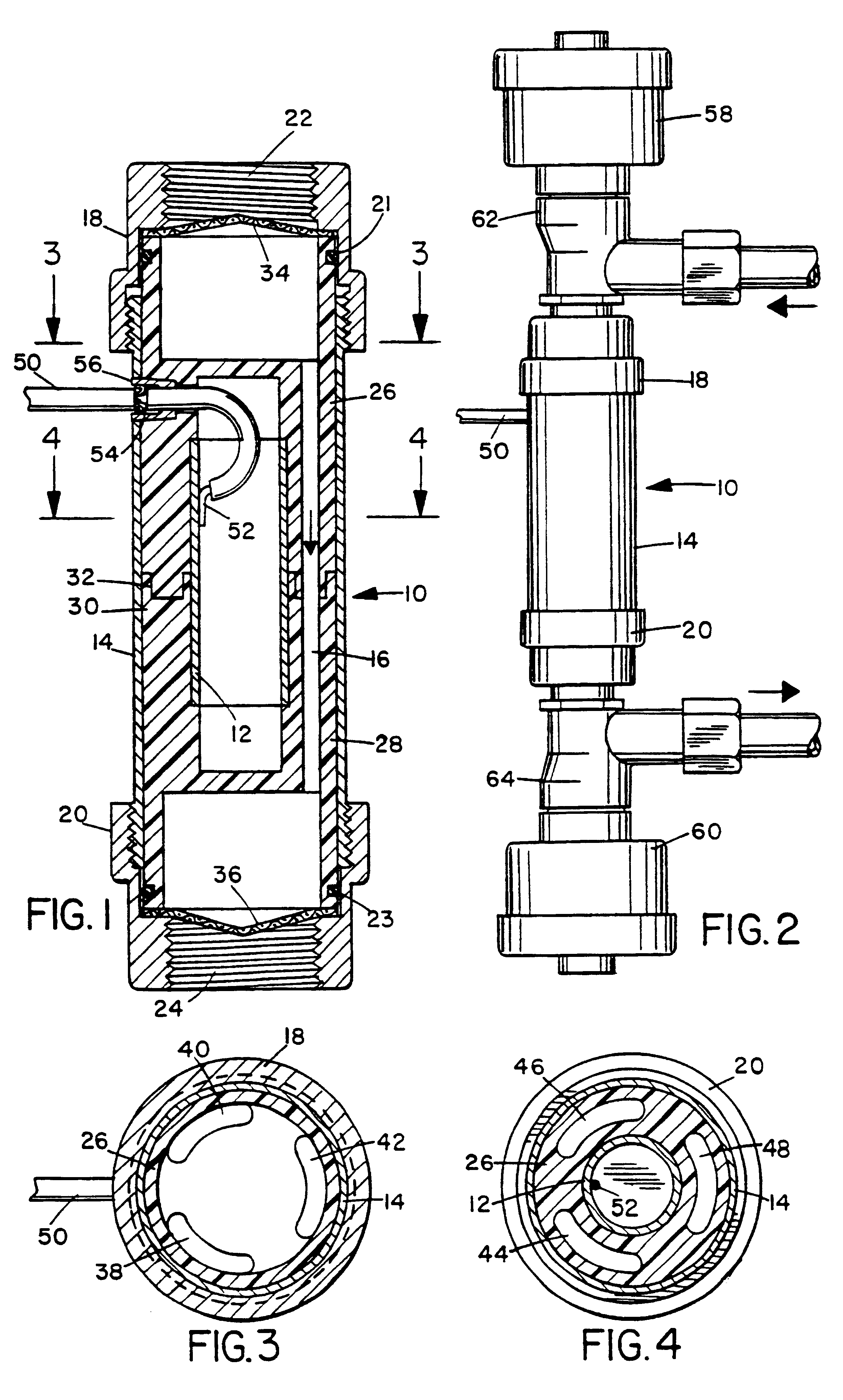

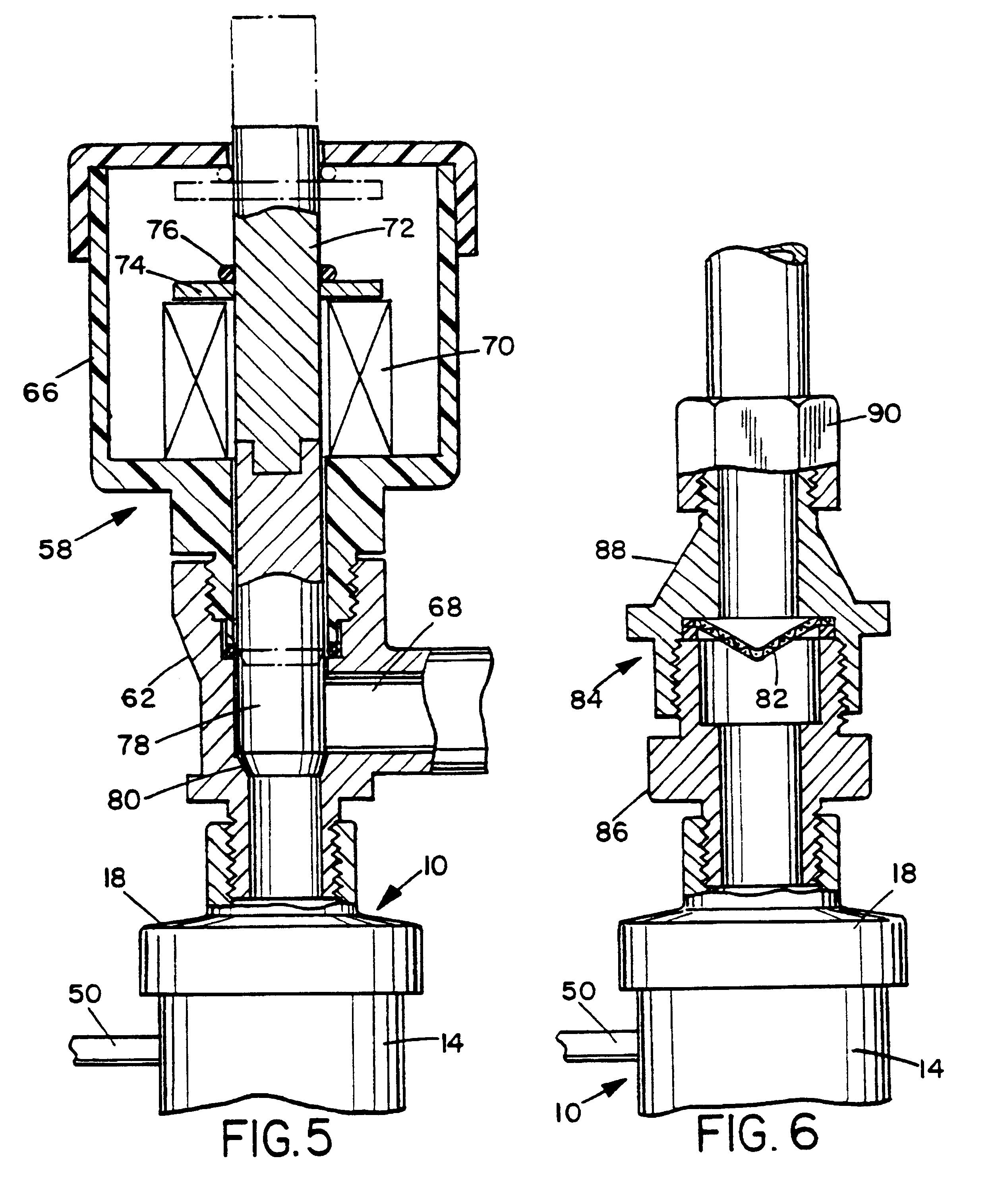

Volume charge density measuring system

InactiveUS6586949B1Eliminate the effects ofMinimizes shrinkageResistance/reactance/impedenceMaterial capacitanceElectrical conductorDisplay device

A capacitive sensor includes one or more chambers through which a material can flow. Two conductors are located to partially surround the flow chamber so that the material flows between the conductors. Where more than one chamber is used, additional conductors are provided. A measurement circuit connected to the conductors provides an output corresponding to a difference between test and reference frequencies. A display indicates the measured capacitance as a continuous-scale, proportional representation or a binary representation. The sensor system can measure volume charge density of a fluid or parameters responsive to changes in volume charge density, such as flow velocity.

Owner:JOFRACH L L C

Volume charge density measuring system

InactiveUS6586950B1Minimize chargeImprove linearityResistance/reactance/impedenceVoltage/current isolationCapacitanceElectrical conductor

A capacitive sensor is shielded against external electric fields to maximize measurement accuracy. The sensor may include two coaxial, tubular conductors with a chamber between them into which a material sample to be measured is introduced. A measurement circuit connected to the sensor may include a reference oscillator that oscillates at a constant frequency and a test oscillator that oscillates at a frequency responsive to sensor capacitance. The circuit may display a value responsive to the difference between the test and reference frequencies. The circuit may also reverse the polarity of the signal applied to the sensor to minimize charge buildup, a phase-locked loop frequency measuring circuit, a temperature compensating circuit, and a non-linearity compensating circuit. The indicating circuit that displays a representation of the measured capacitance may display a continuous-scale or proportional representation or may display a binary or "go-nogo" representation. An alternative sensor of the system includes coaxial, finned inner and outer conductors that intermesh to maximize capacitive surface area. Another alternative sensor includes two parallel, plate-like conductors. The sensor system may be used to measure volume charge density of a fluid or parameters responsive to changes in volume charge density, such as flow velocity.

Owner:JOFRACH L L C

Frame buffer pixel circuit for liquid crystal display

InactiveUS20060001634A1Increase contrastHigh quality imagingStatic indicating devicesCMOSLiquid-crystal display

An enhanced frame buffet pixel circuit with two control transistors and a separate capacitor put in as a memory capacitor before the memory transistor yields a high contrast ratio by removing induced charge and solving a charge sharing problem between the memory capacitor and the liquid crystal display (LCD) capacitor. The memory transistor may be made of either CMOS or PMOS. The frame buffer pixel can be used to drive binary displays which expresses ON and OFF only if a comparator is put in after the pixel electrode circuit to represent gray levels with reduced sub-frame frequency.

Owner:DUKE UNIV

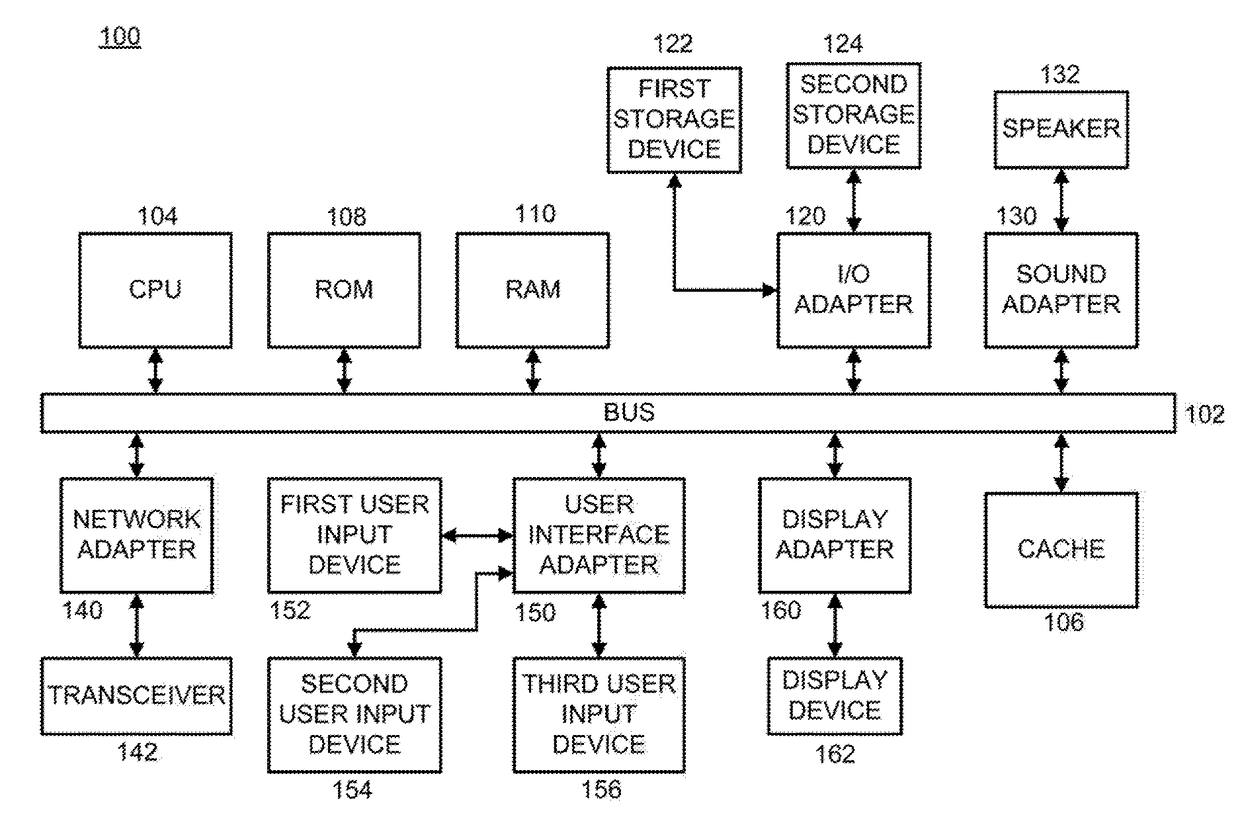

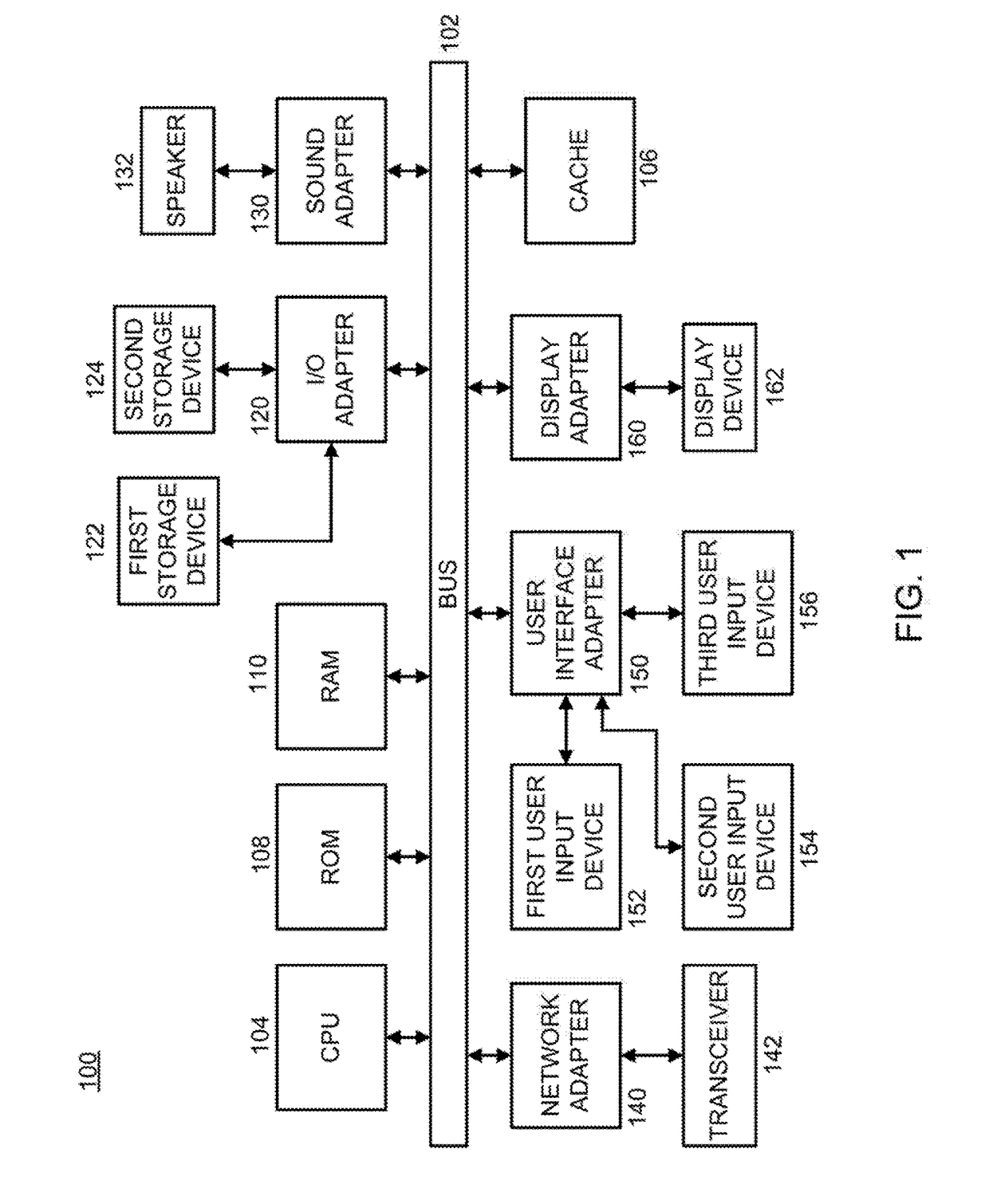

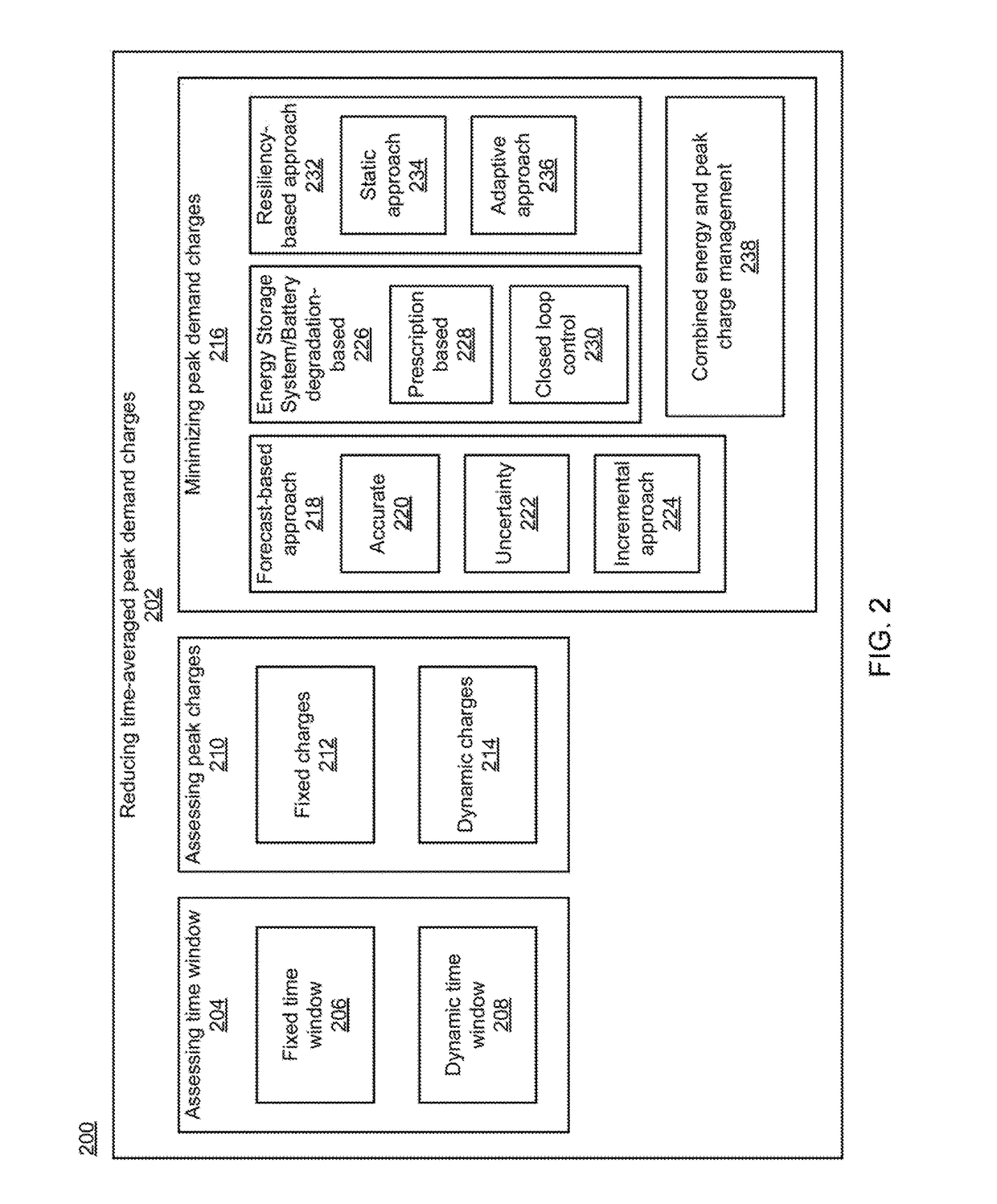

System and method for reducing time-averaged peak charges

InactiveUS20170310140A1Minimize demand chargeMinimize energyPower network operation systems integrationLoad forecast in ac networkUnit sizePeak value

Systems and methods for minimizing demand charges, including determining one or more optimal monthly demand charge thresholds based on historical load data, time of use charges, demand charges, and energy storage unit size for one or more end users. A grid power dispatch setpoint is calculated for a particular time step based on a daily load forecast and a daily economic dispatch solution based on the determined optimal monthly demand charge thresholds. A grid power dispatch setpoint for a subsequent time step is determined by iteratively solving the daily energy dispatch for the subsequent time step to determine an optimal grid power dispatch setpoint. Energy and demand charges are minimized by controlling charging and discharging operations for the energy storage unit in real-time based on the determined optimal grid power dispatch setpoint.

Owner:NEC LAB AMERICA

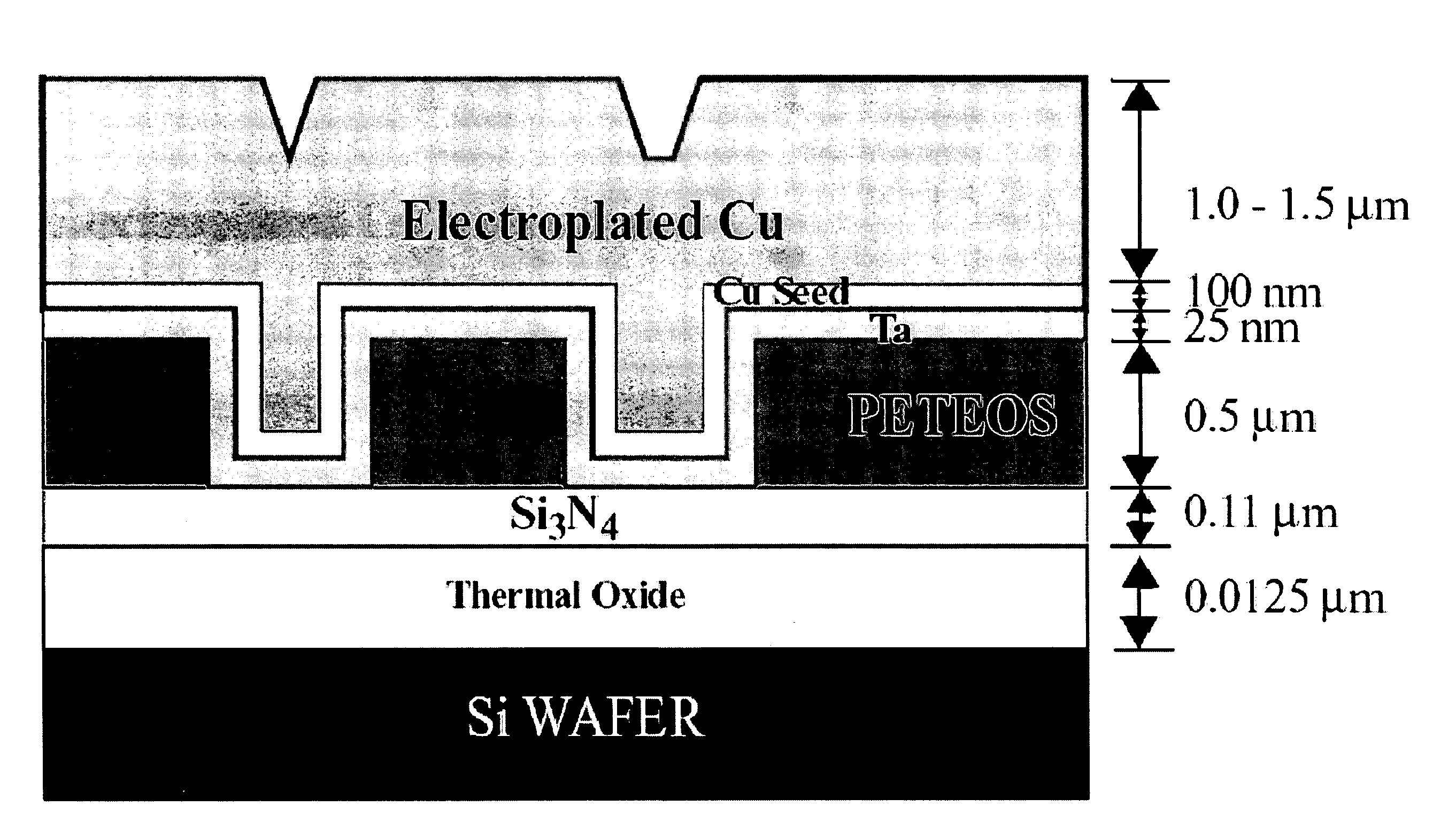

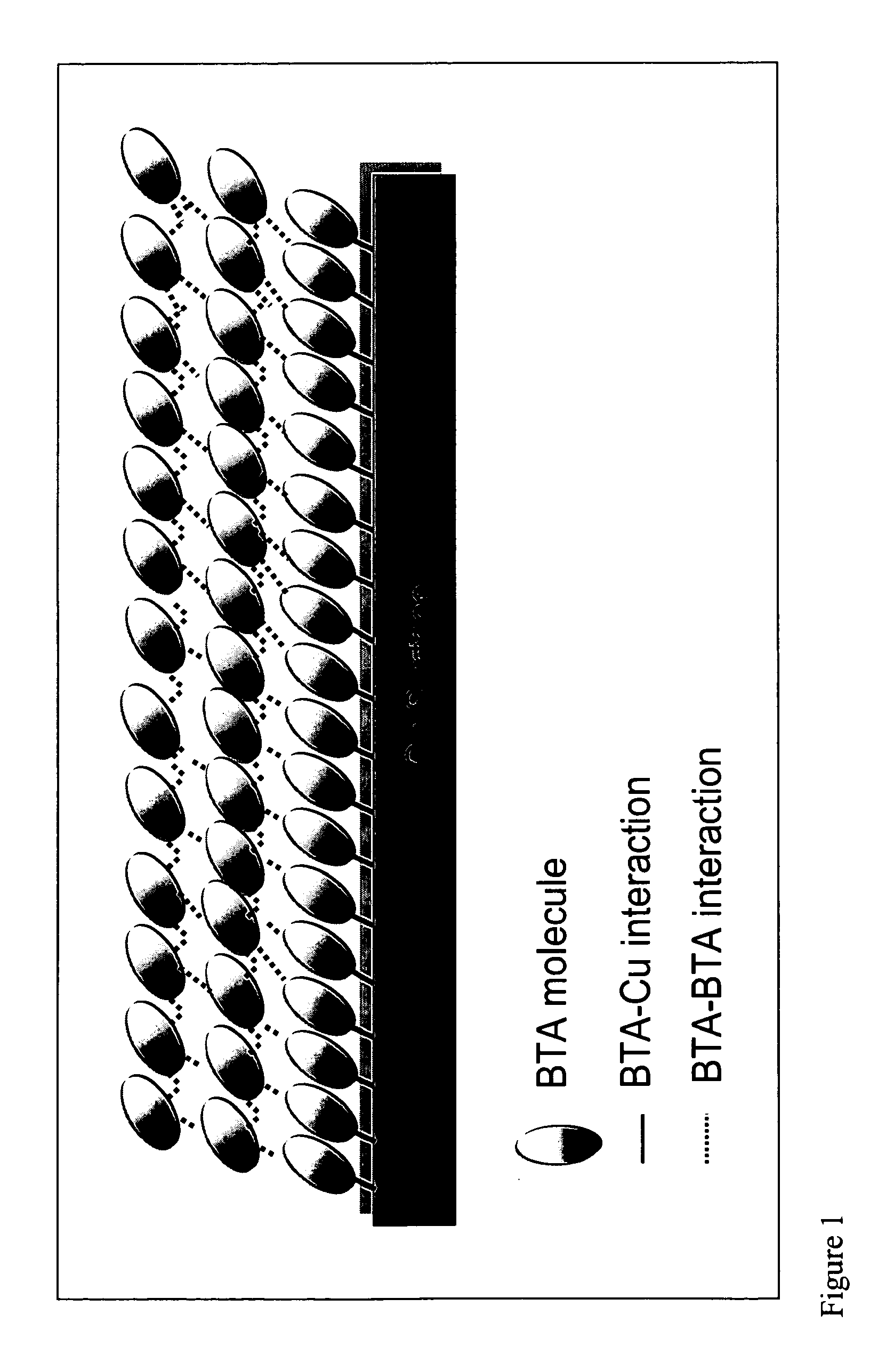

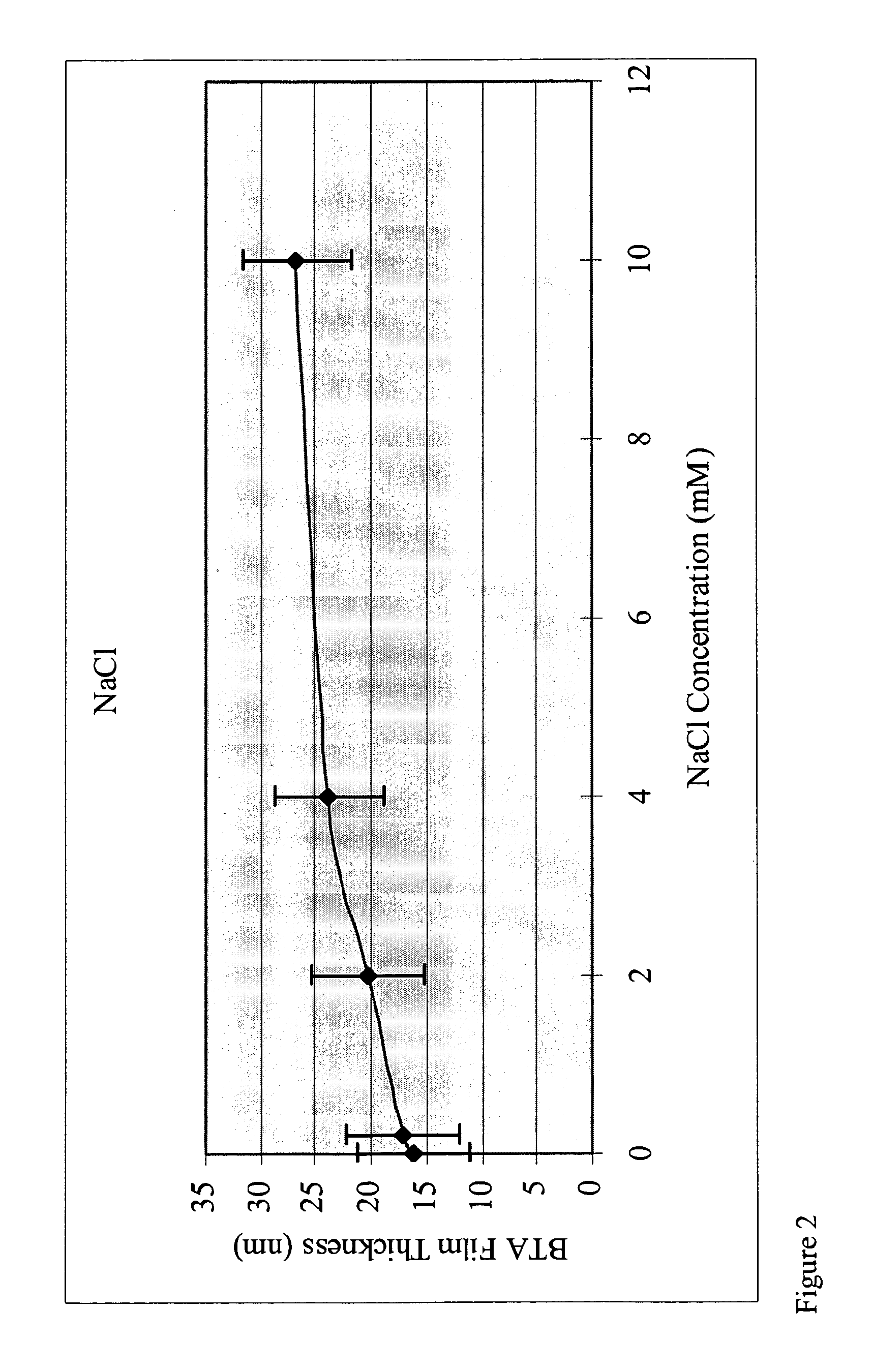

Controlling passivating film properties using colloidal particles, polyelectrolytes, and ionic additives for copper chemical mechanical planarization

InactiveUS20100178768A1Increase static etch rateLower static etch ratePigmenting treatmentOther chemical processesSlurryCopper

The present invention provides for a copper CMP slurry composition which comprises a complexing agent, an oxidizer, an abrasive and a passivating agent. The present invention also provides for a method of chemical mechanical planarization of a copper conductive structure which comprises administering the copper CMP slurry composition during the planarization process.

Owner:BASF AG

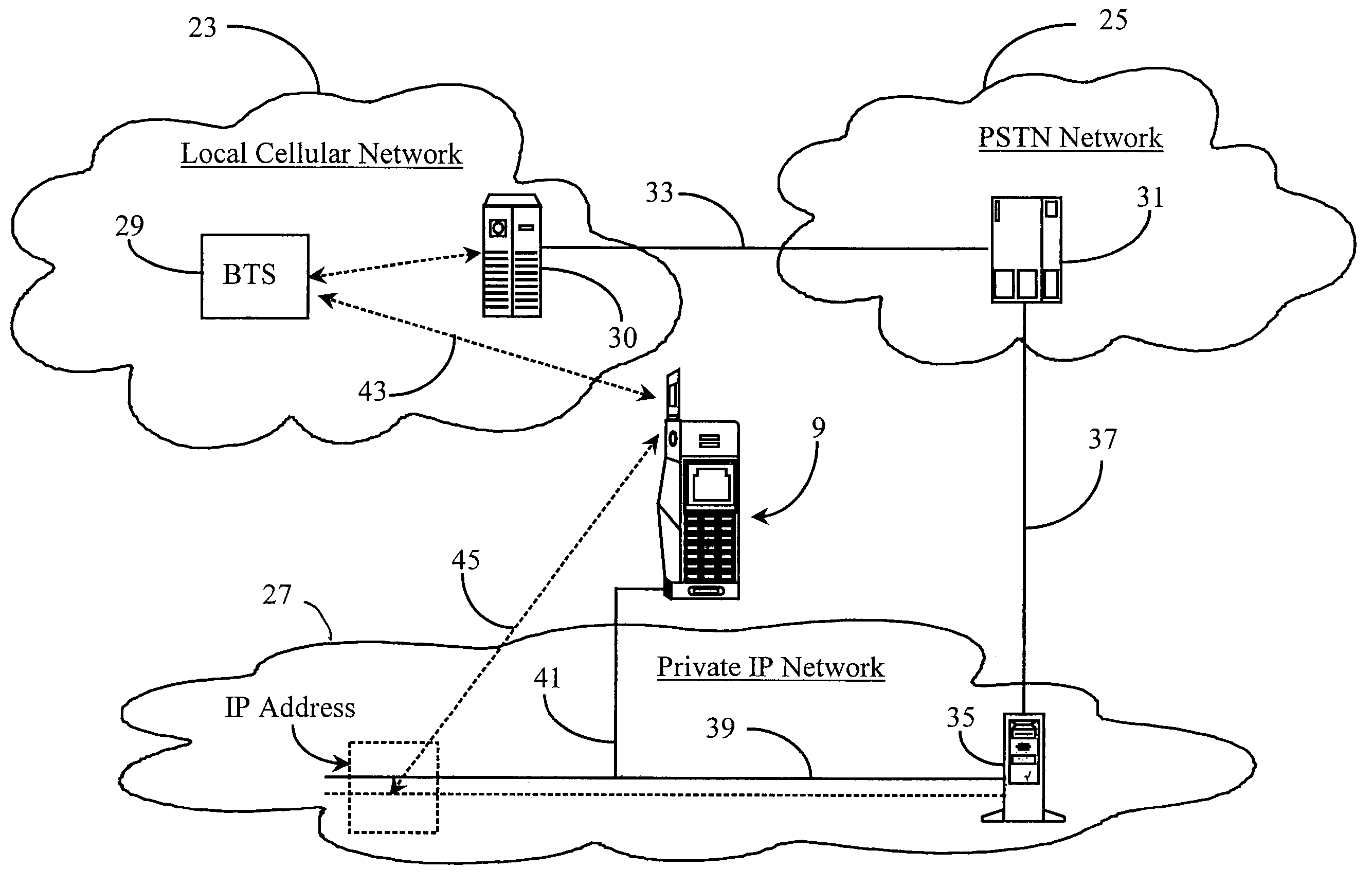

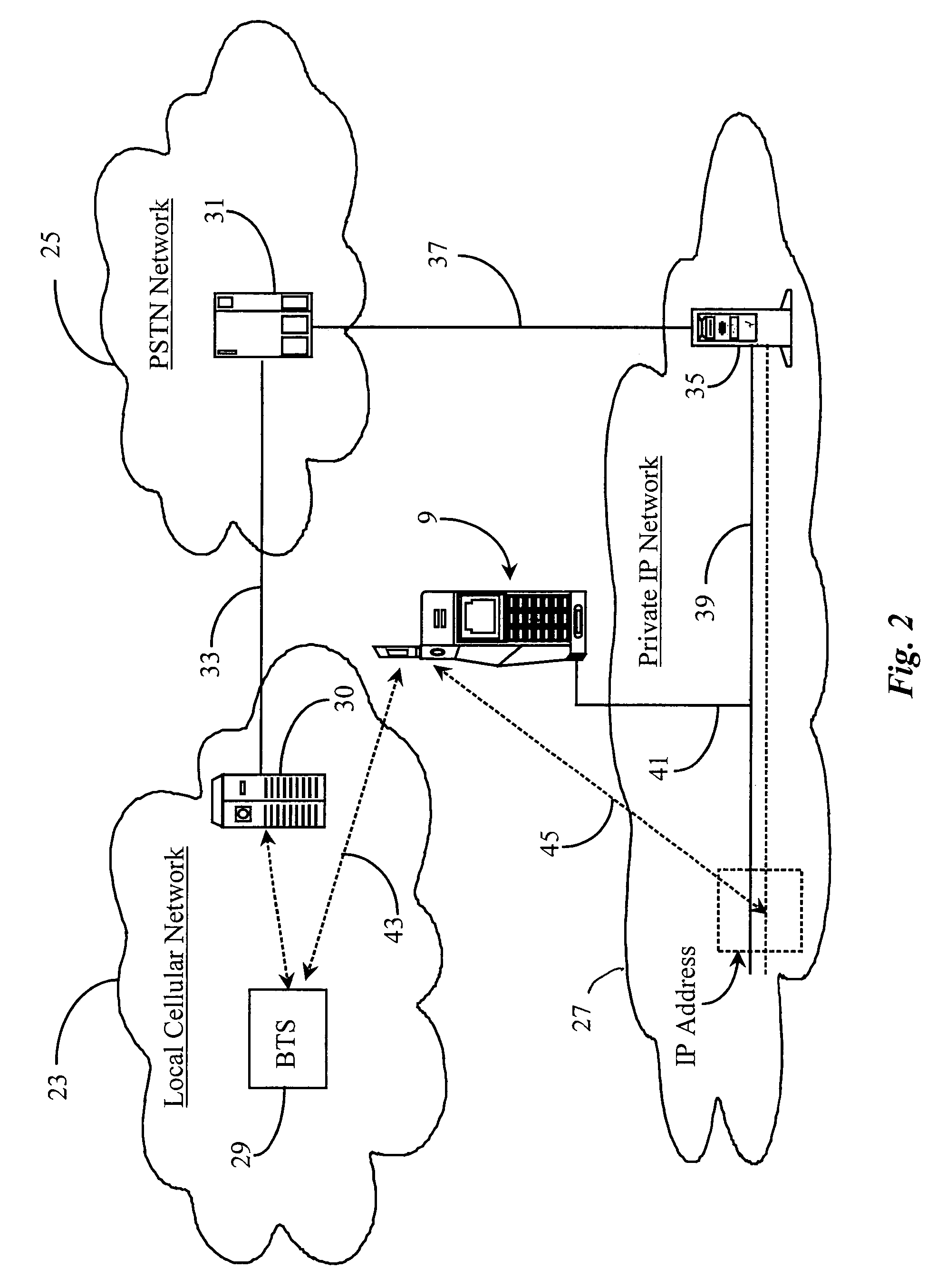

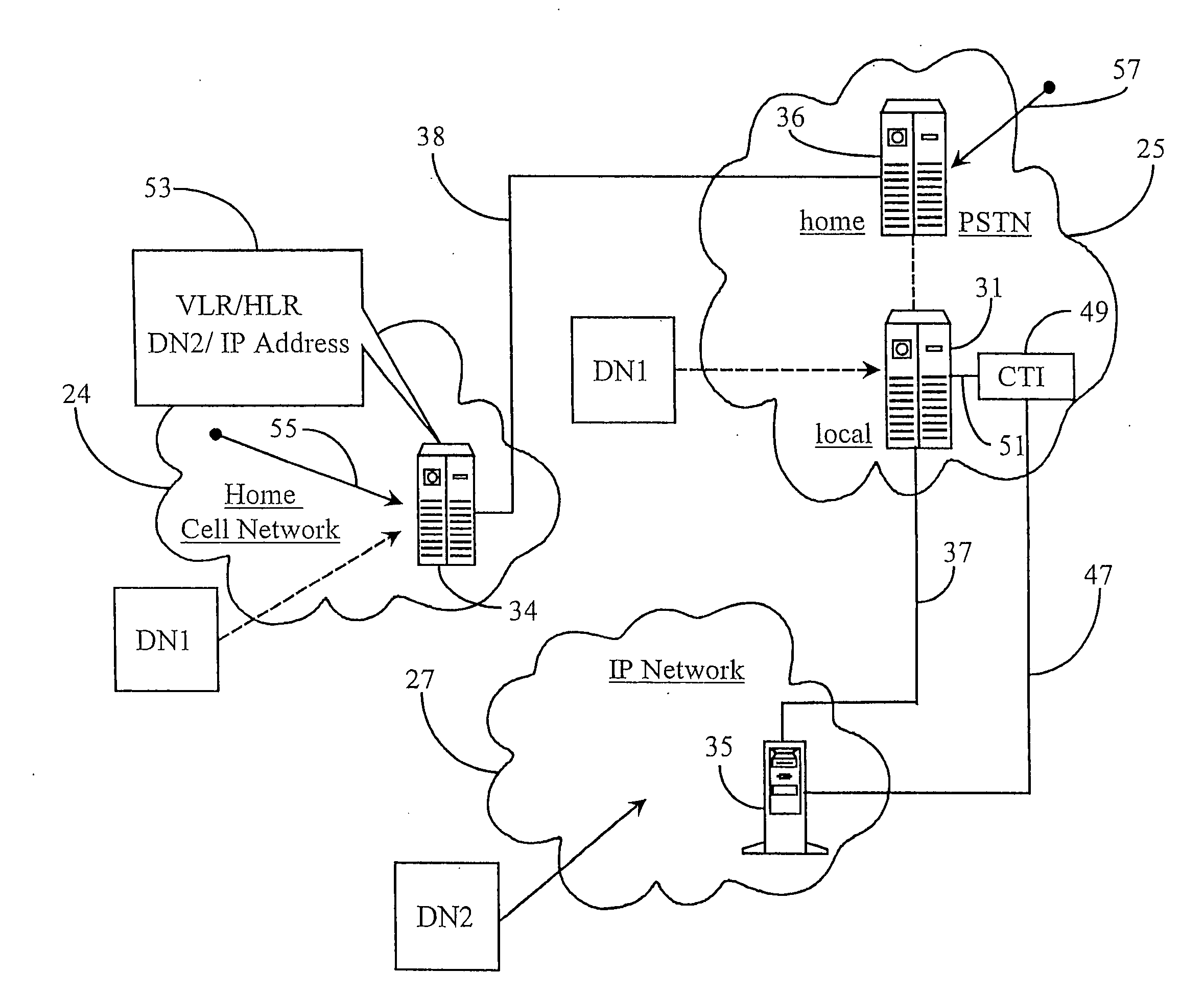

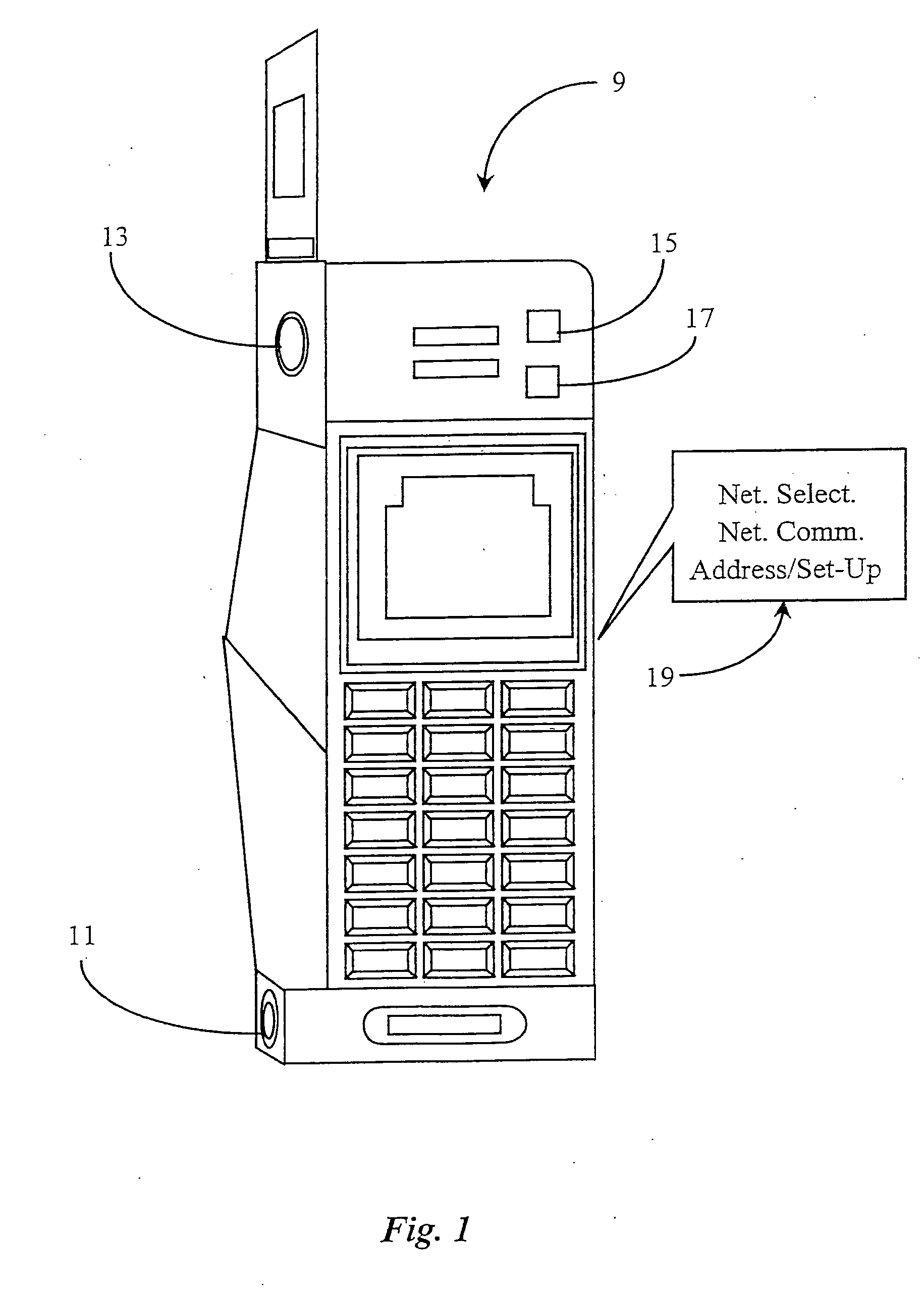

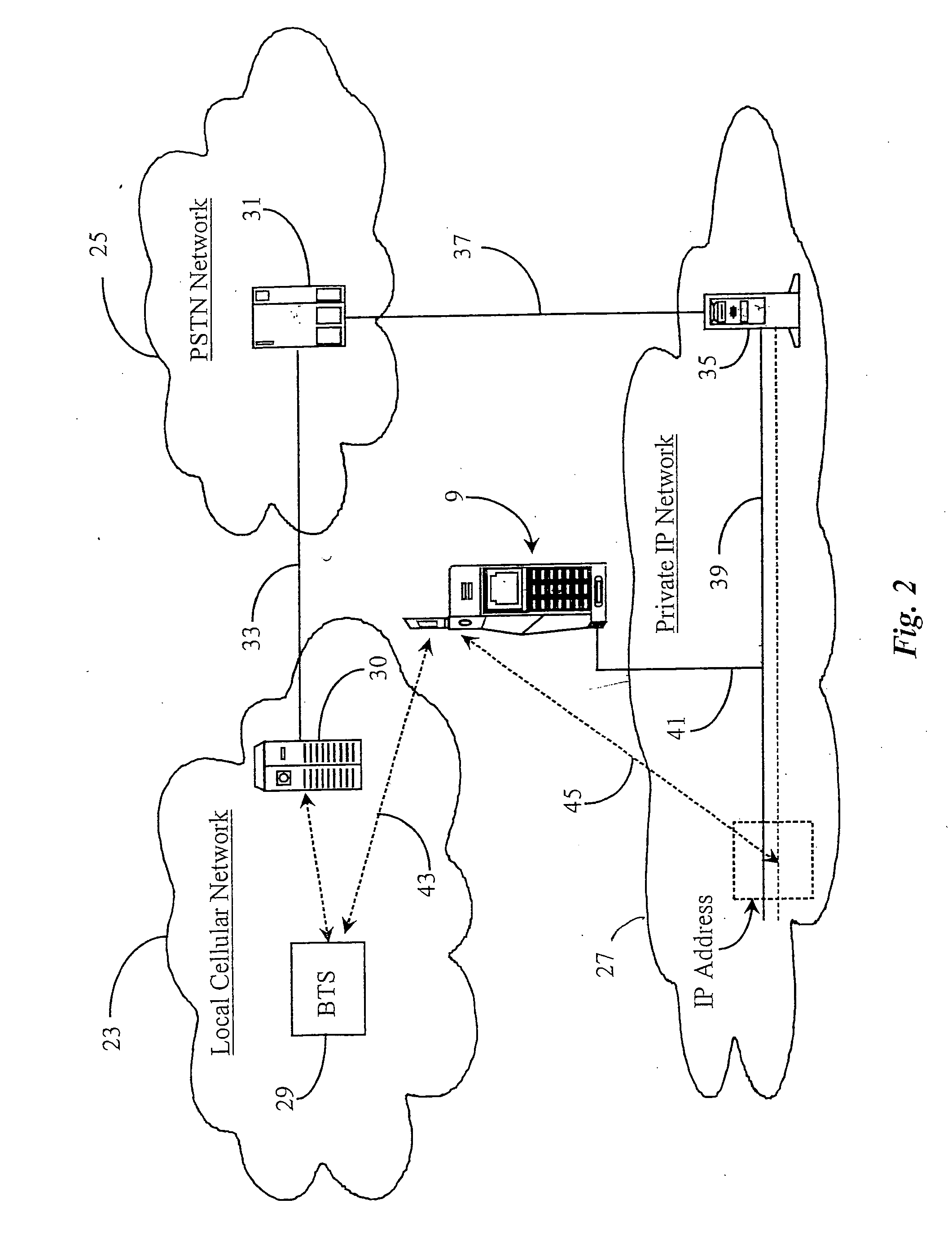

Telecommunication system for automatically locating by network connection and selectively delivering calls to mobile client devices

InactiveUS7116655B2Minimize chargeLow costData switching by path configurationRadio/inductive link selection arrangementsIp addressDual mode

A communication system for an organization having multiple sites uses a dual-mode device capable of both cell phone communication and telephone communication on a local area network (LAN). IP LANS are established at organization sites such that a temporary IP address is assigned to a dual-mode device that logs onto an organization LAN, and the IP address is associated at a PSTN-connected server on the LAN with the cell phone number of the communication device. The IP server notifies a PSTN-connected routing server when a device logs on to a LAN, and also provides a destination number for the IP server. Cell calls directed to the device are then redirected to the IP server and directed to the device connected to the LAN.

Owner:GENESYS TELECOMM LAB INC AS GRANTOR +3

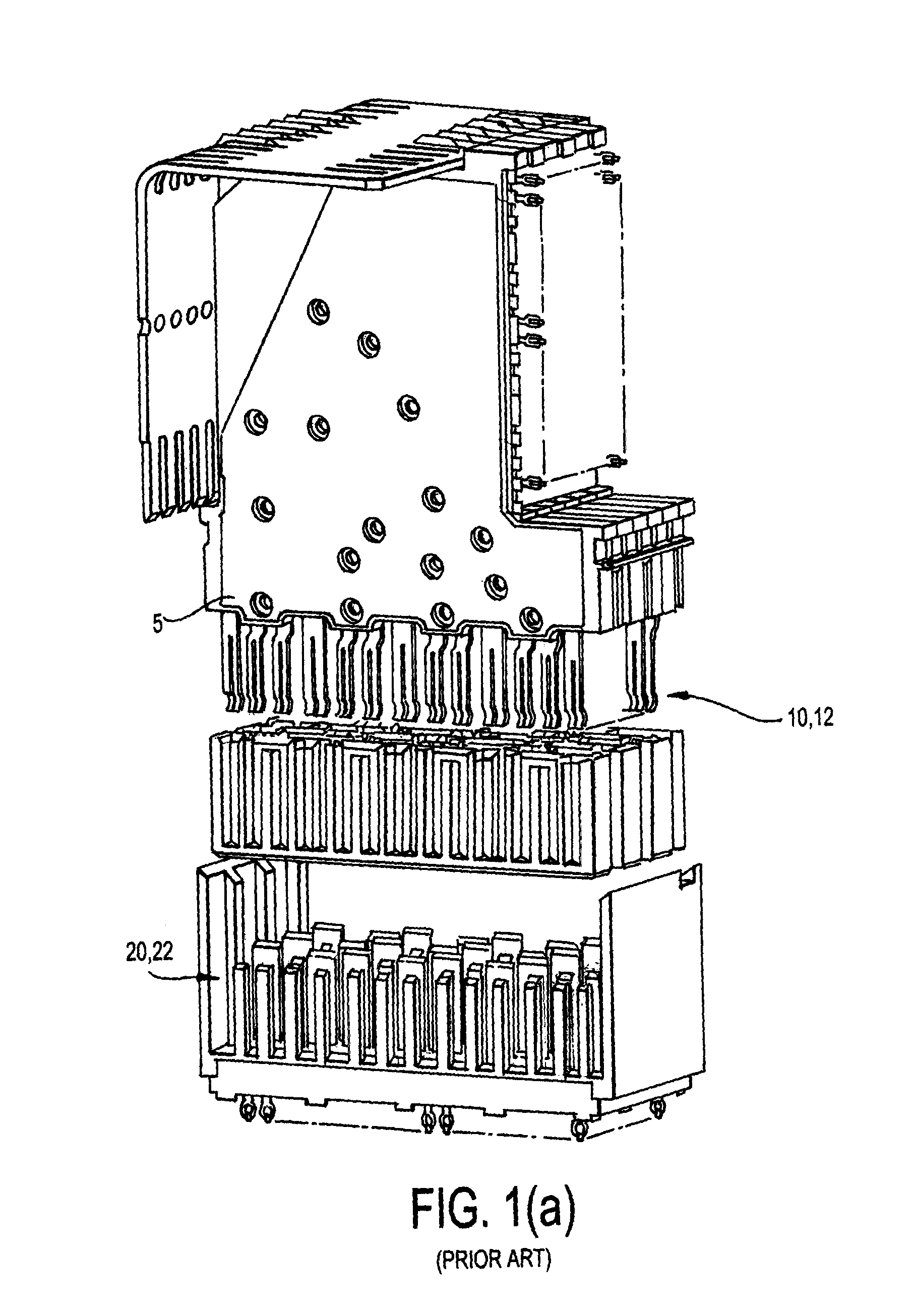

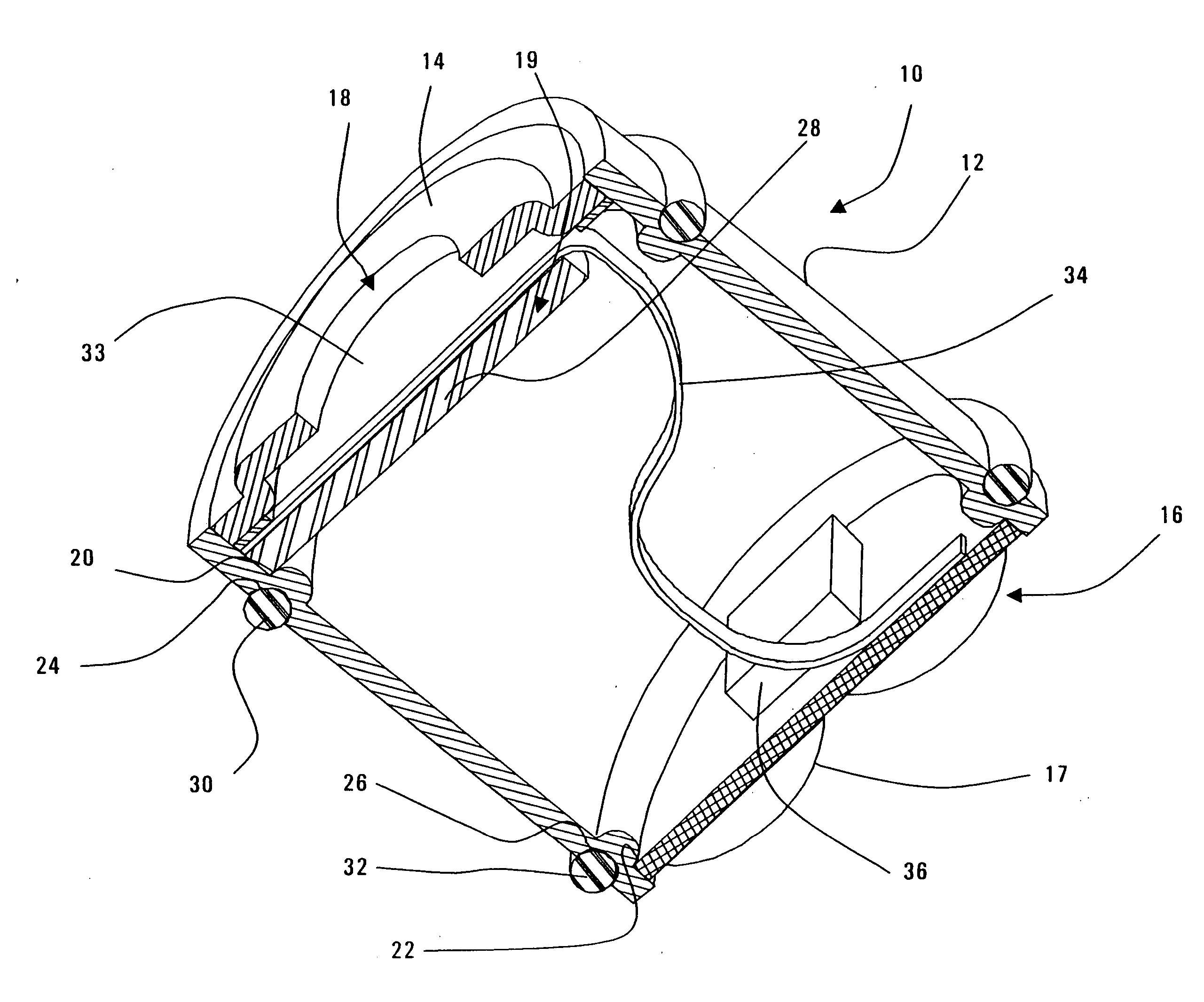

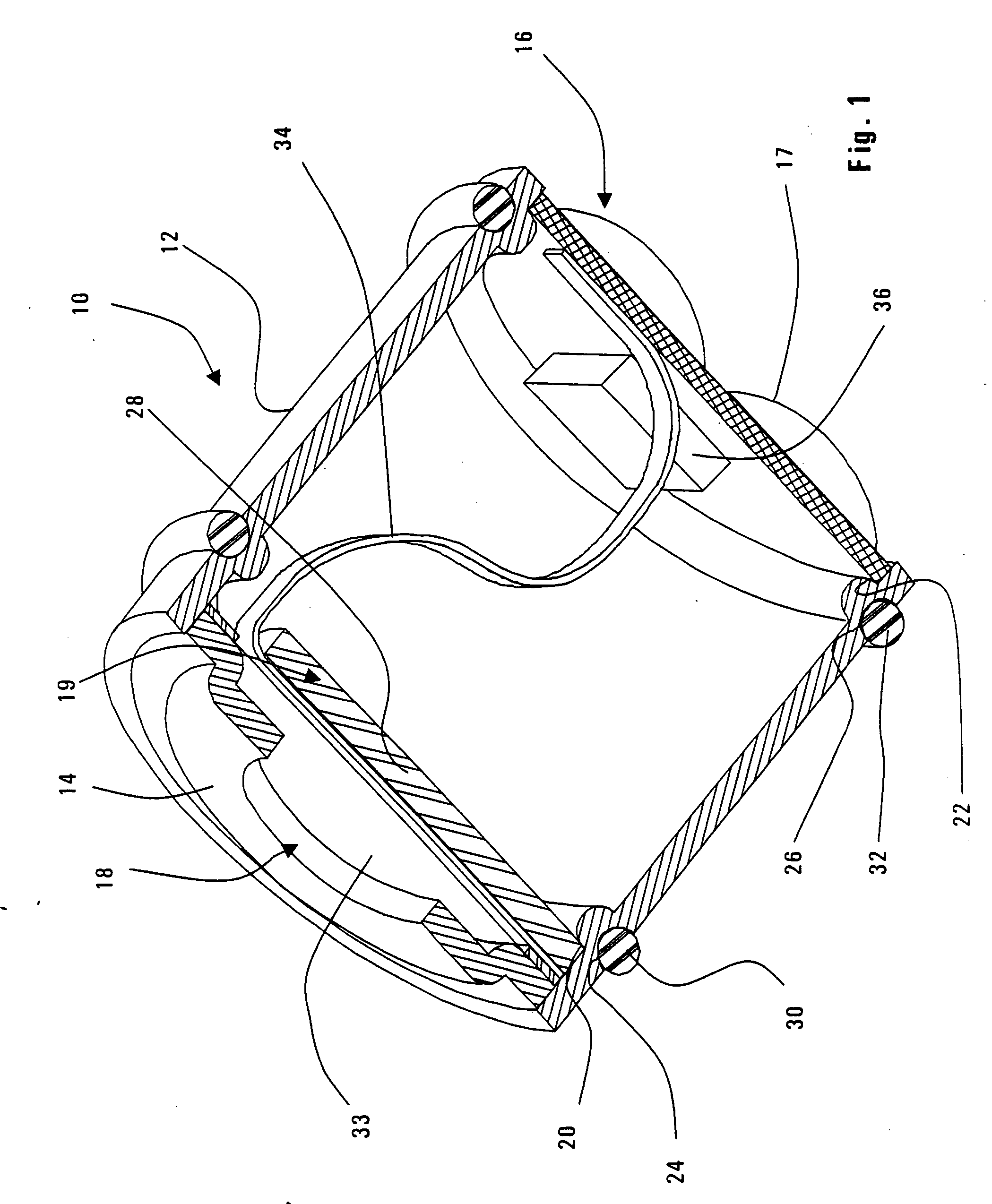

Connector having improved contacts

ActiveUS8961227B2Sufficient flexibilityReduce impactElectrically conductive connectionsCoupling contact membersElectrical conductorEngineering

An electrical connector for connecting a conductor of a daughter card connector wafer with a blade in the housing of a backplane connector. The daughter card conductor has a body with two elongated beams extending outward from the body. The two elongated beams each have an outer edge and an inner edge, whereby an opening is defined between the inner edges. The backplane conductor has a body with a narrowed tab portion extending outward from said second conductor body. The narrowed tab portion having outer opposite edges and is sized so that the narrowed tab portion fits between at least a portion of the outer edges of the two elongated beams, and in some cases between at least a portion of the inner edges of the two elongated beams.

Owner:AMPHENOL CORP

Telecommunication system for automatically locating by network connection and selectively delivering calls to mobile client devices

InactiveUS20060183499A1Minimizing cell phone chargeReduce communication costsAssess restrictionNetwork topologiesDual modeIp address

A communication system for an organization having multiple sites uses a dual-mode device capable of both cell phone communication and telephone communication on a local area network (LAN). IP LANS are established at organization sites such that a temporary IP address is assigned to a dual-mode device that logs onto an organization LAN, and the IP address is associated at a PSTN-connected server on the LAN with the cell phone number of the communication device. The IP server notifies a PSTN-connected routing server when a device logs on to a LAN, and also provides a destination number for the IP server. Cell calls directed to the device are then redirected to the IP server and directed to the device connected to the LAN.

Owner:GENESYS TELECOMM LAB INC AS GRANTOR +3

Devices and methods for high frequency electroporation

ActiveUS11254926B2Reduce adverse effectsMinimize charge buildupMedical simulationComputer-aided planning/modellingMedicineEngineering

The present invention provides systems, methods, and devices for electroporation-based therapies (EBTs). Embodiments provide patient-specific treatment protocols derived by the numerical modeling of 3D reconstructions of target tissue from images taken of the tissue, and optionally accounting for one or more of physical constraints or dynamic tissue properties. The present invention further relates to systems, methods, and devices for delivering bipolar electric pulses for irreversible electroporation exhibiting reduced or no damage to tissue typically associated with an EBT-induced excessive charge delivered to the tissue.

Owner:VIRGINIA TECH INTPROP INC

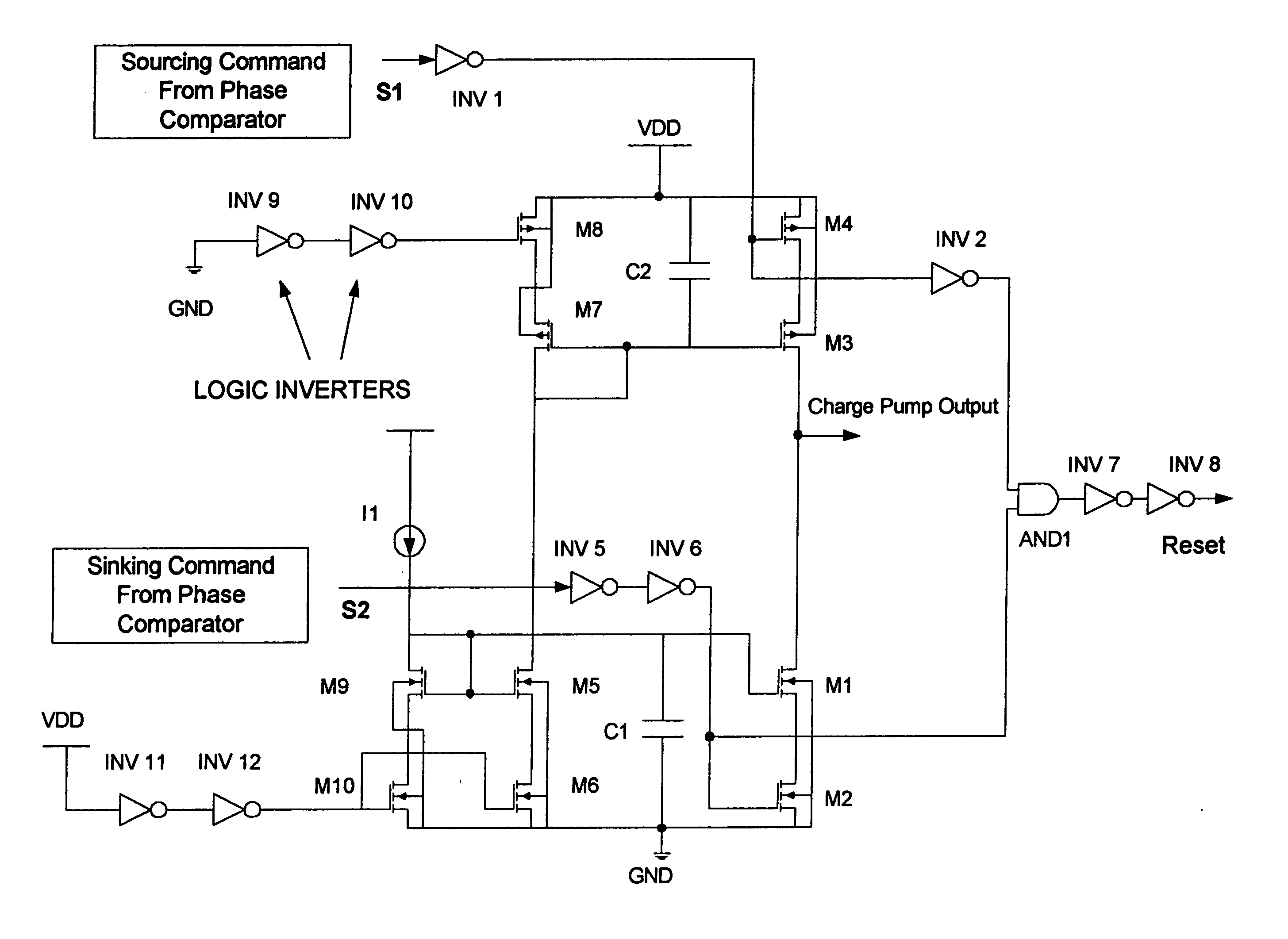

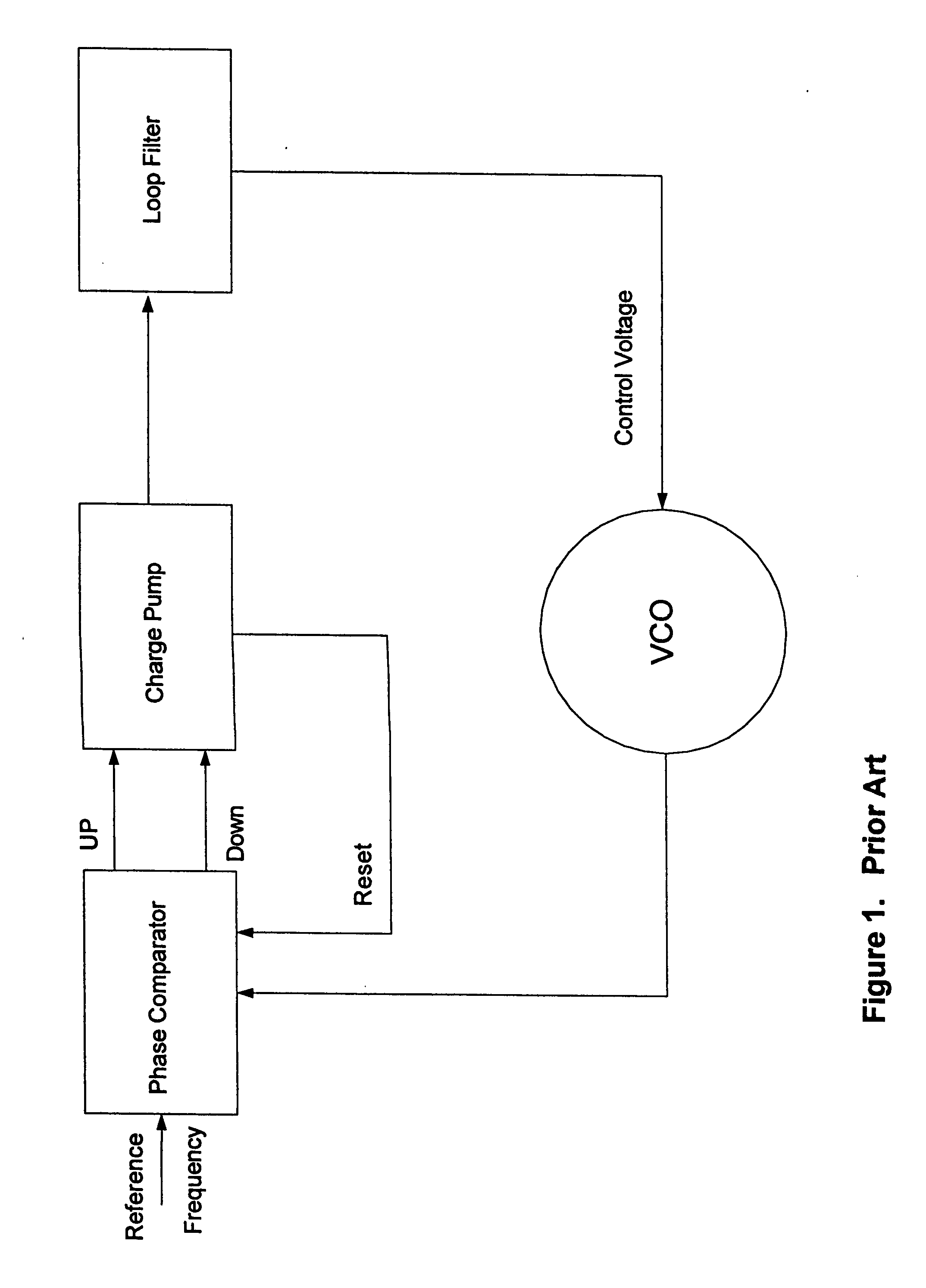

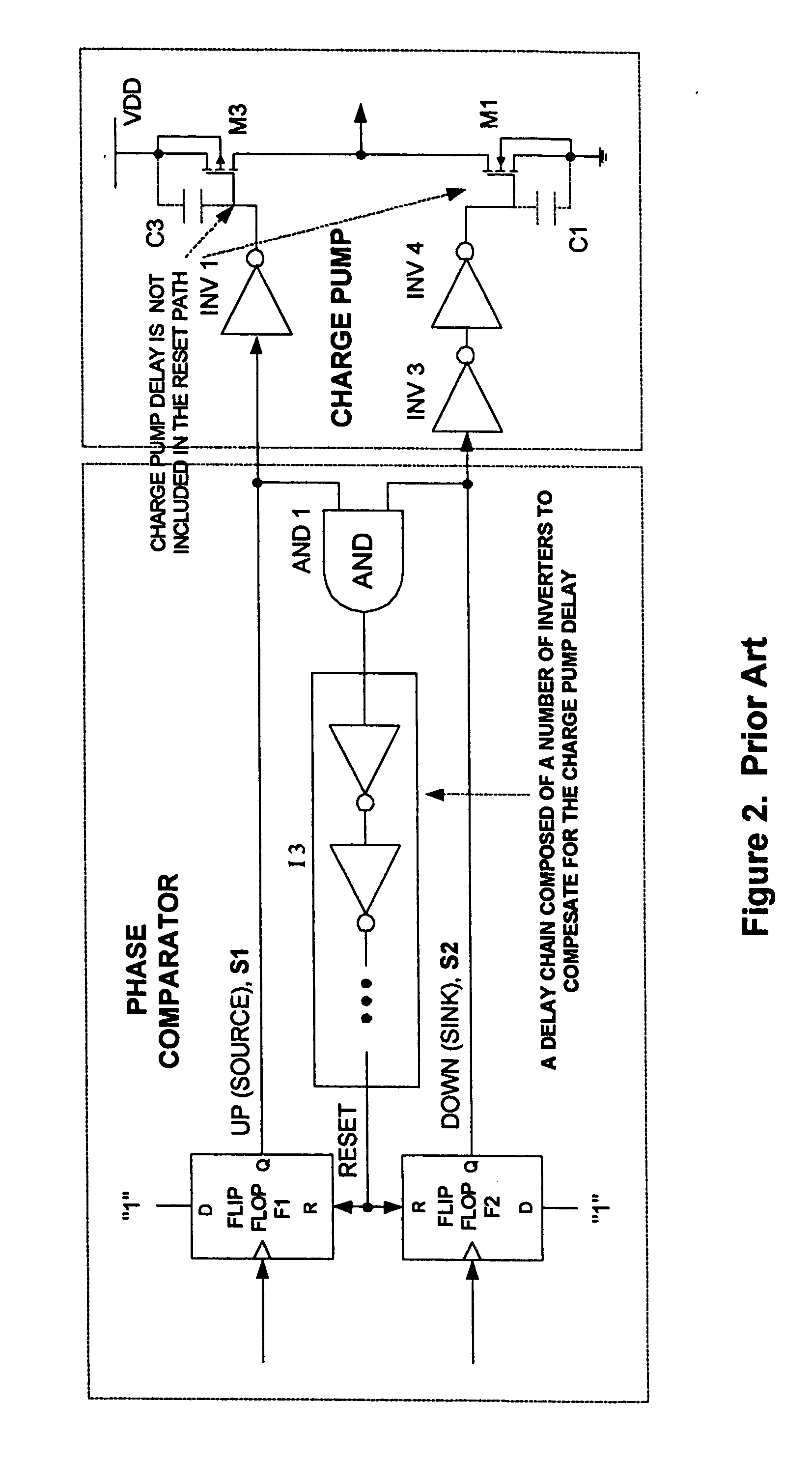

Charge pump for phase-locked loop

InactiveUS20050083136A1Minimize impactReduce phase noisePulse automatic controlVoltage-current phase angleMOSFETCapacitance

When both the sourcing command and the sinking command to the phase comparator are high, the charge pump phase detector creates a high impedance output dead period, which is undesirable. The dead zone can be minimized by resetting the phase comparator when both sourcing command and sinking command are high. Accurate timing of the reset signal is crucial to good PLL phase noise performance and also to the elimination of the dead zone problem. In our invention, accurate reset timing is achieved by including the charge pump delay time caused by the input gate capacitance of the output complementary MOSFETs in the reset signal path.

Owner:PROCOMM

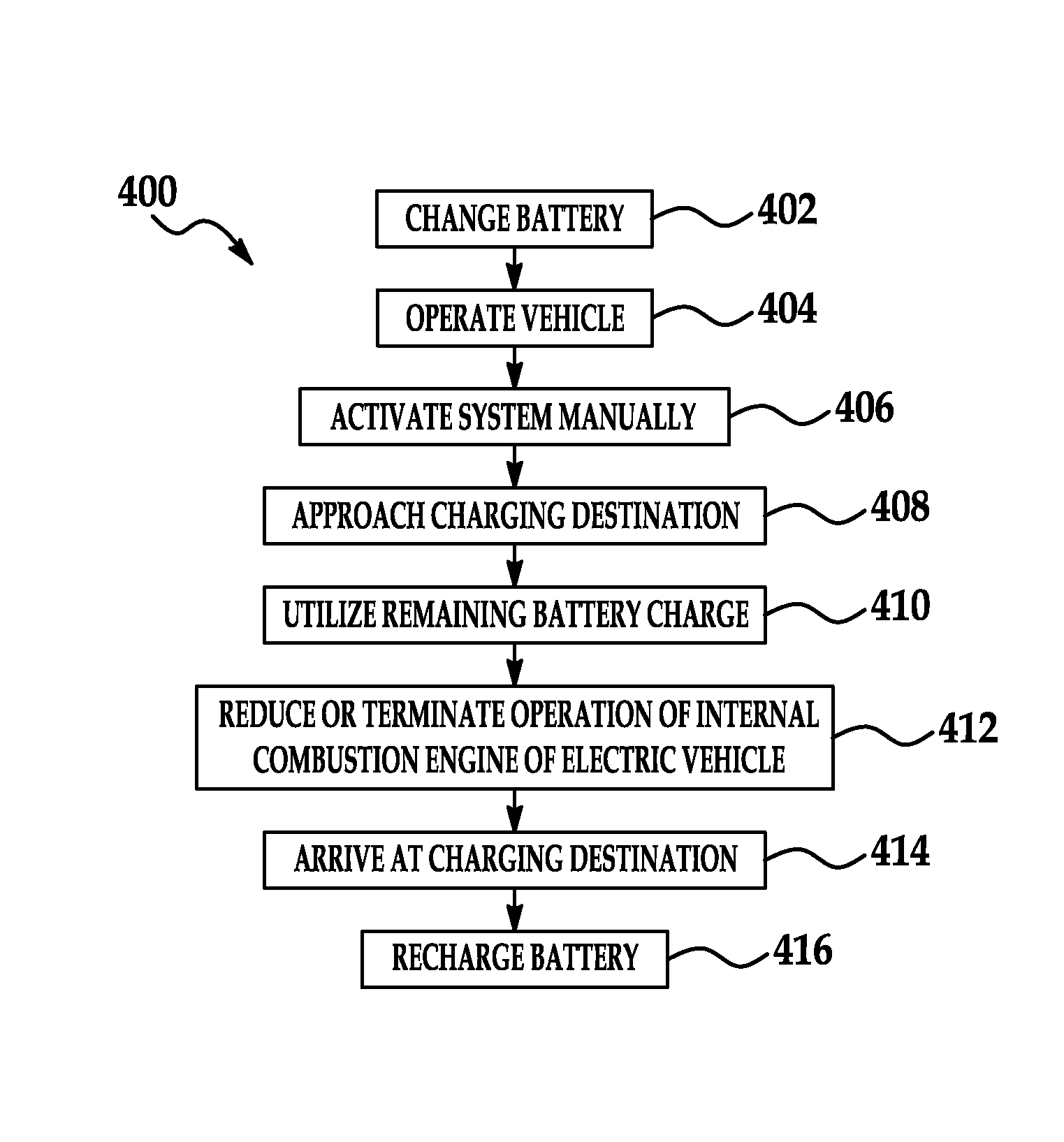

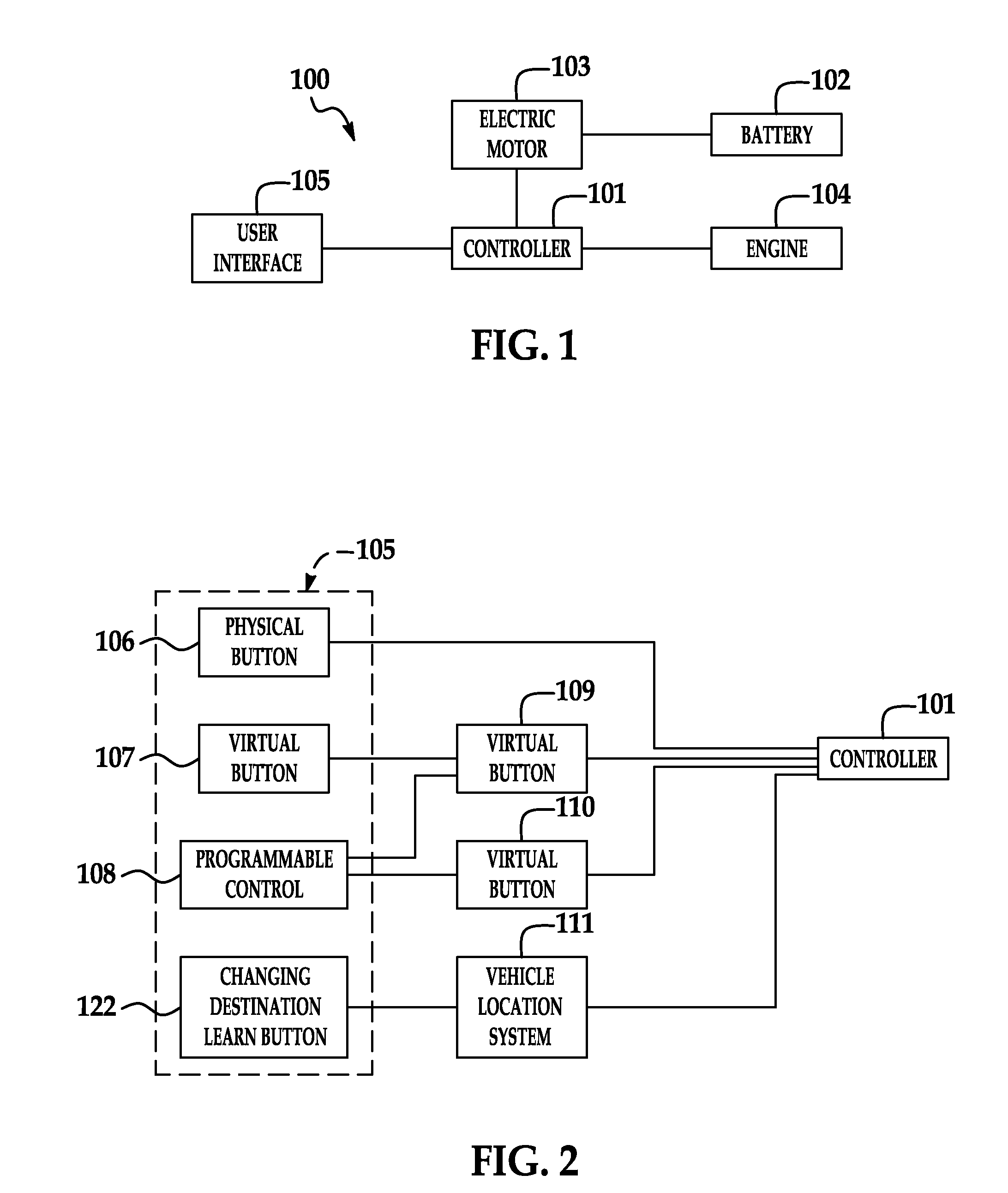

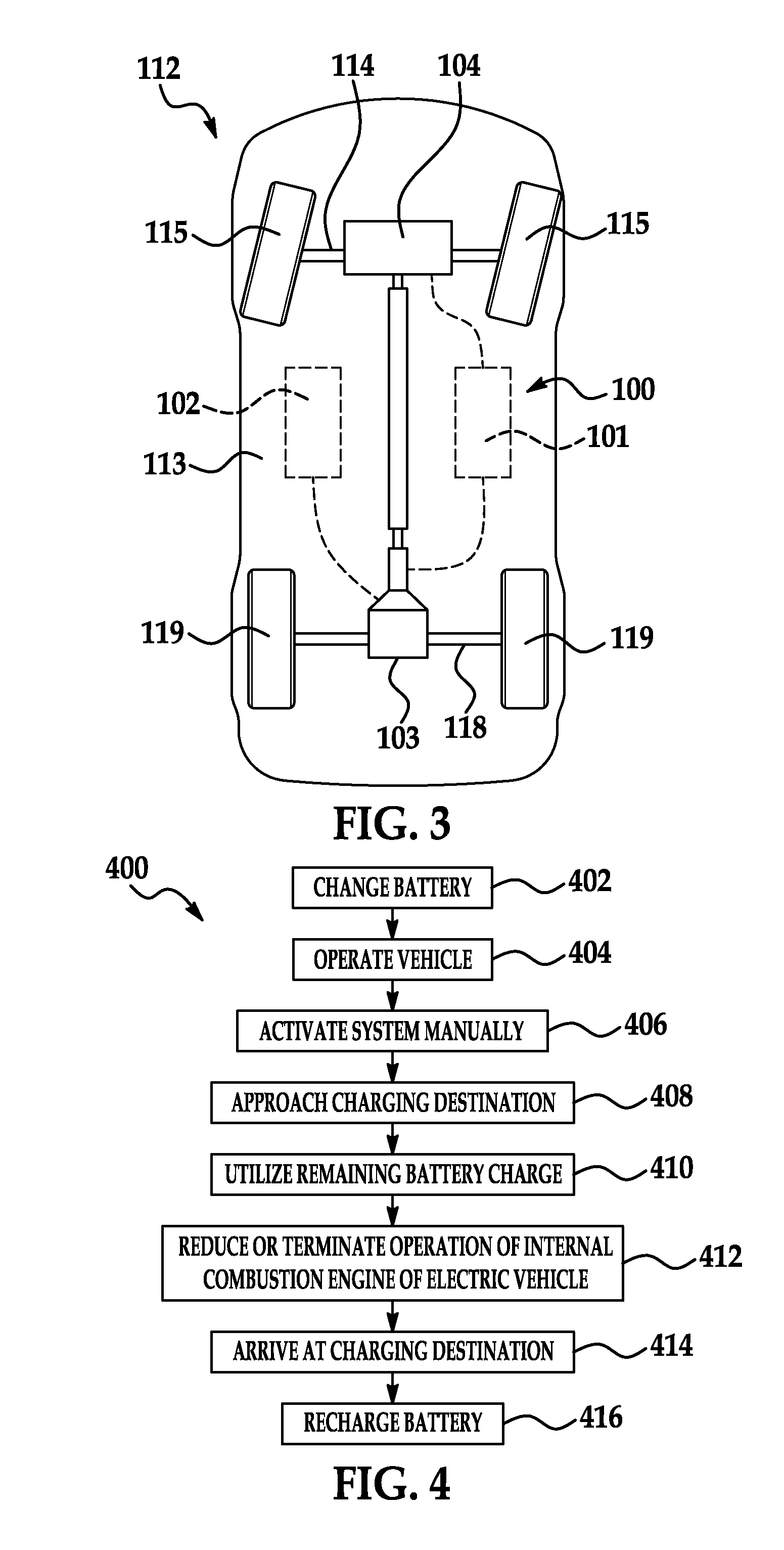

Charge utilization control system and method

ActiveUS8463473B2Minimize electric chargeReduce stepsDigital data processing detailsPropulsion using engine-driven generatorsElectrical batteryControl system

A charge utilization control system for an electric vehicle includes a controller, an electric motor connected to the controller, a battery connected to the electric motor and an internal combustion engine connected to the controller. The controller is adapted to minimize electric charge stored in the battery as the electric vehicle approaches a charging destination for the battery.

Owner:FORD GLOBAL TECH LLC

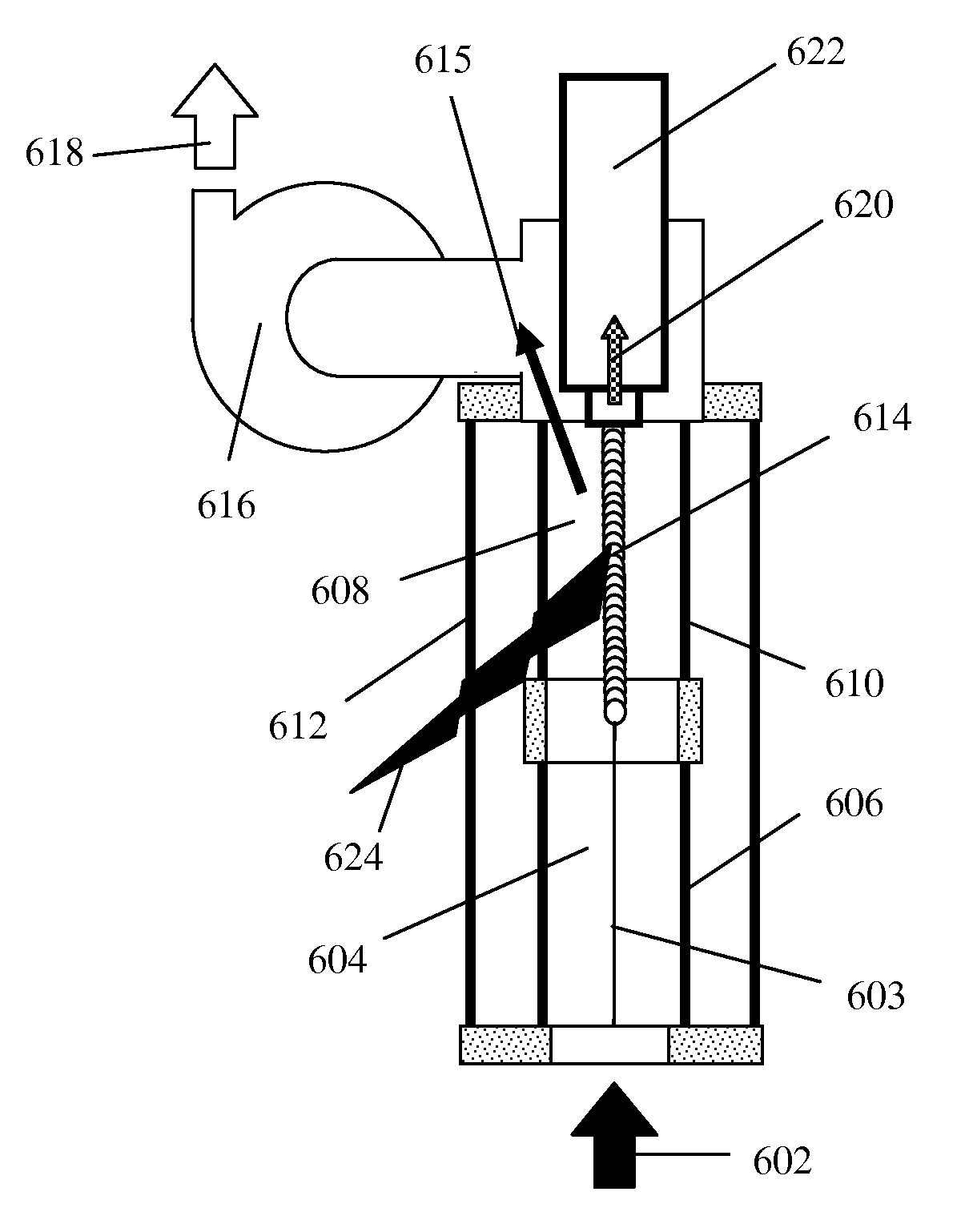

Electrostatic charging and collection

InactiveUS20100132561A1Reduce depositionEasy to chargeWithdrawing sample devicesIsotope separationParticulatesIon-mobility spectrometry

The present invention describes directly using particles collected with an electrostatic precipitator for the detection of explosives and other compounds of interest. The method and apparatus of analyzing particles involves directly measuring particles on the collection electrodes or thermally desorbing them into an ion mobility spectrometer and / or other analytical instruments. One aspect of the present invention is a particulate charging method. Another aspect of the present invention provides a means of high charging of the particulates while minimizing their collection in the charging stage. The present invention also provides a means for efficiently collecting the particulates in a second stage for sampling in a compact electrode.

Owner:EXCELLIMS CORP

Electret Assembly For A Microphone Having A Backplate With Improved Charge Stability

InactiveUS20100172521A1Minimize charge degradationMinimize water absorptionWave amplification devicesElectrets selectrostatic transducerElectrical conductorCharge layer

The present invention relates to a microphone that includes a housing and a diaphragm and backplate located with the housing. The housing has a sound port for receiving the sound. The diaphragm undergoes movement relative to the backplate, which it opposes, in response to the incoming sound. The backplate has a charged layer with a first surface that is exposed to the diaphragm and a second surface opposite the first surface. The backplate further includes a conductor for transmitting a signal from the backplate to electronics in the housing. The conductor faces the second surface of the charged layer. To minimize the charge degradation created by contact with or infiltration of foreign materials, the first surface, the second surface, or both surfaces of the charged layer includes a protective layer thereon.

Owner:SONION NEDERLAND

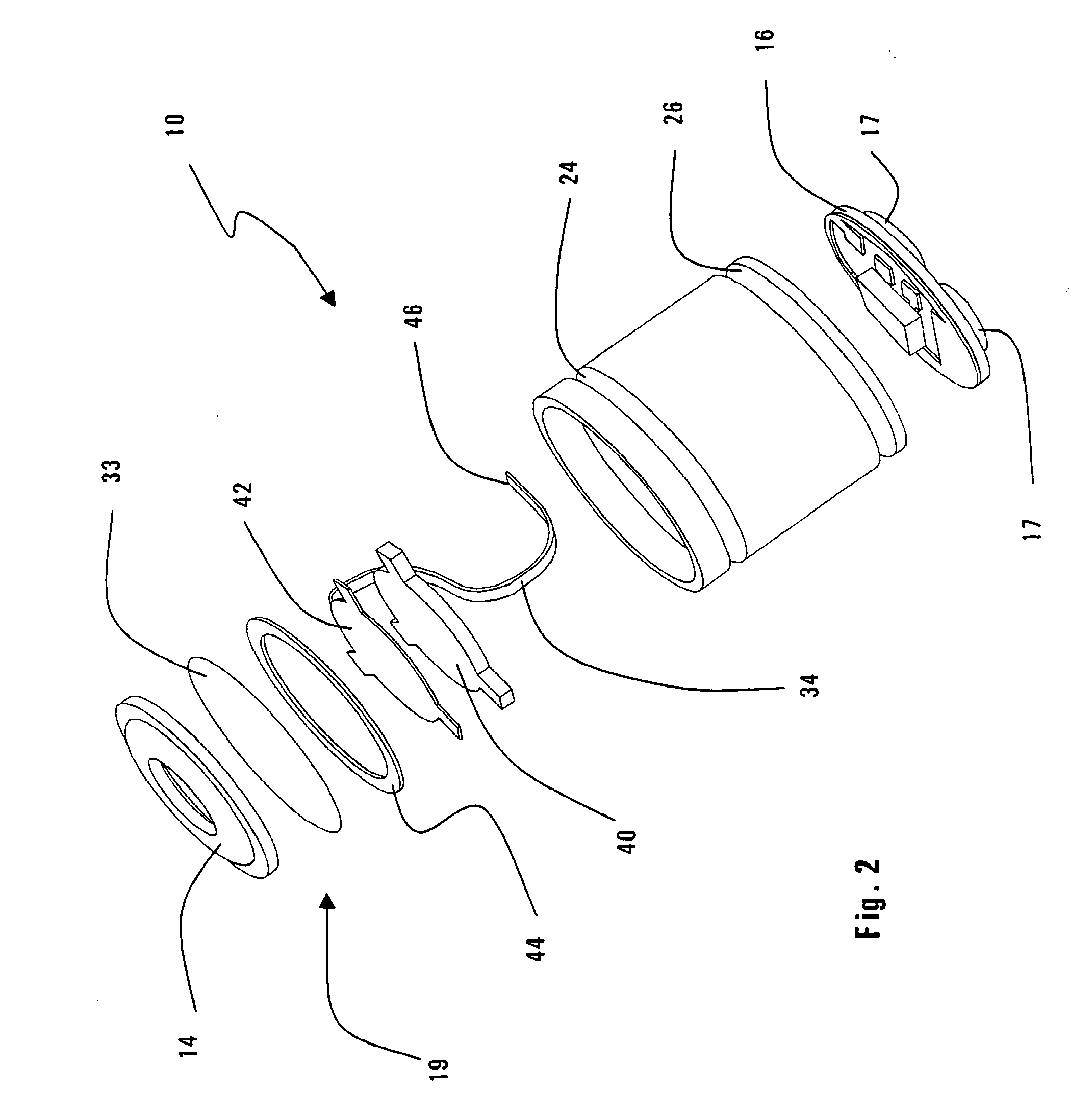

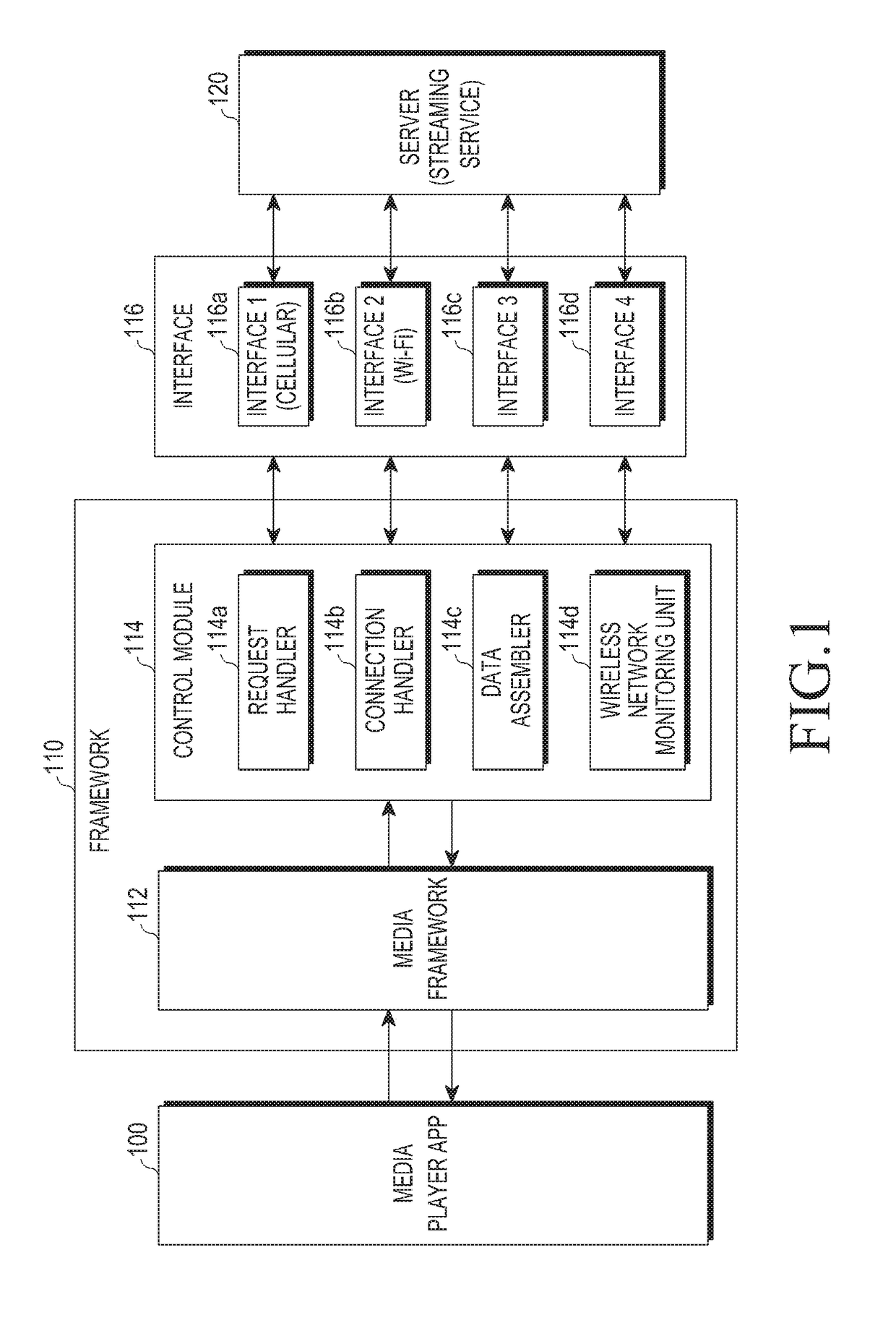

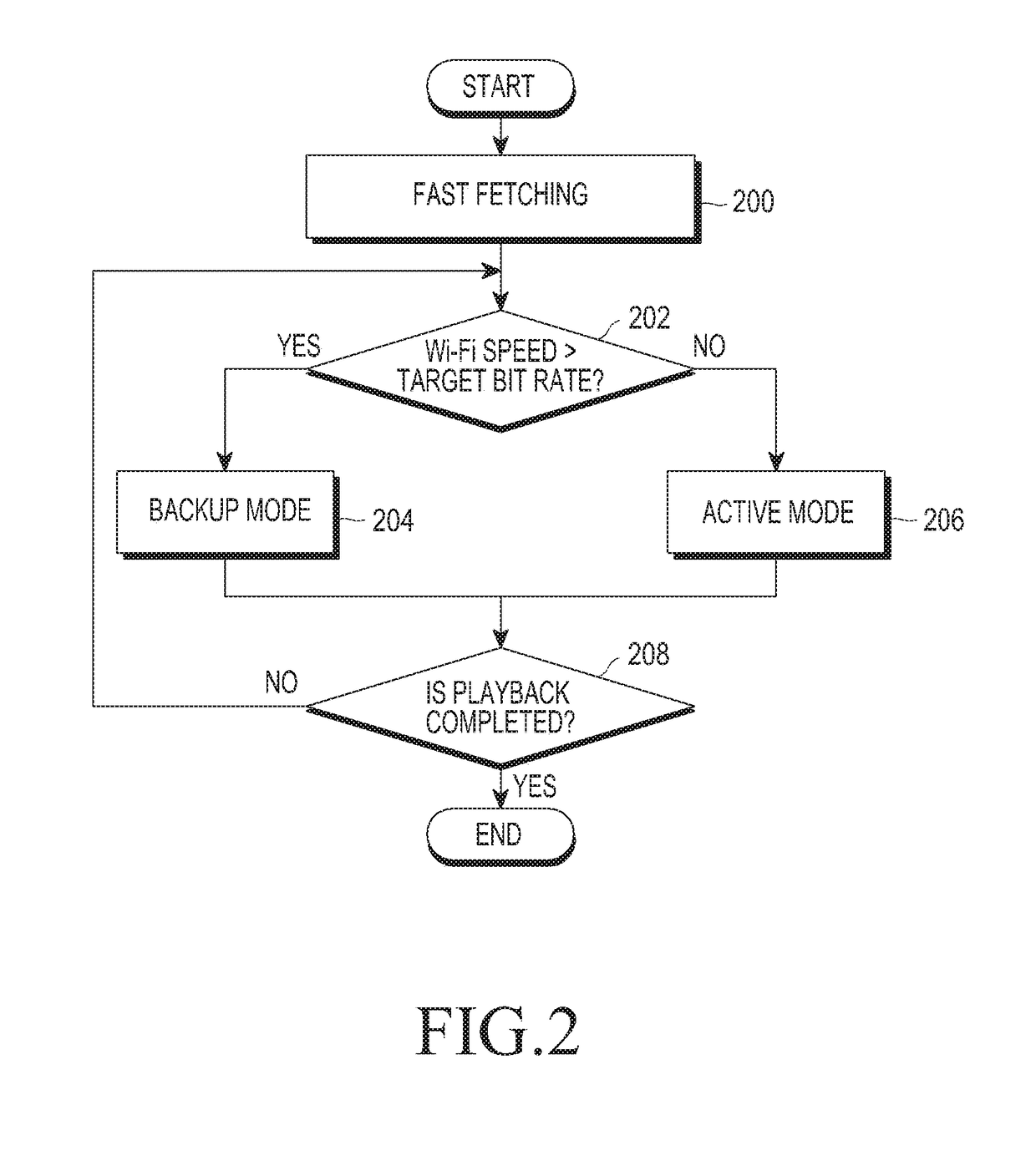

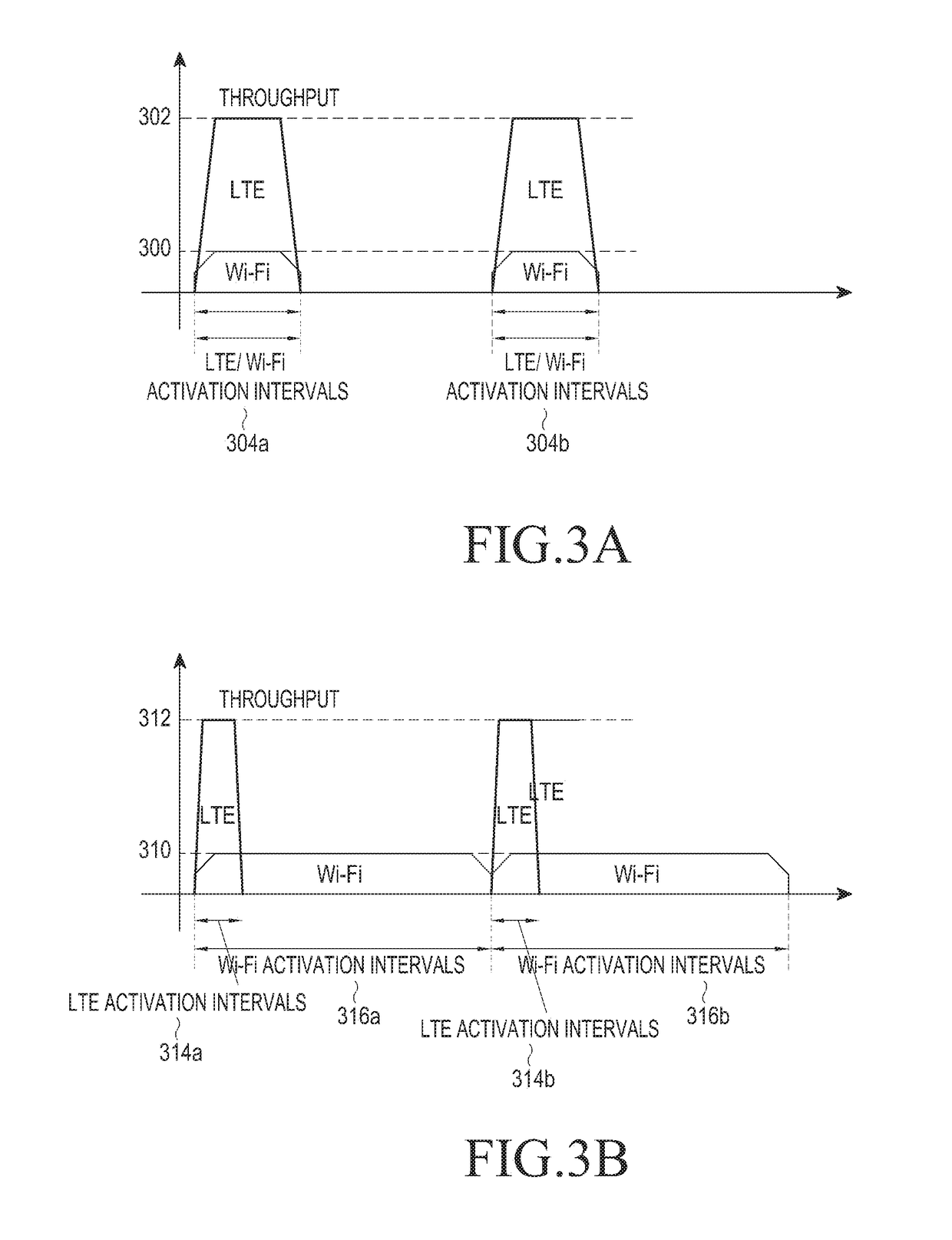

Device and method for receiving streaming service data in mobile communication system supporting plurality of radio access interfaces

ActiveUS20190082348A1Improve performanceMinimize chargeMetering/charging/biilling arrangementsAccounting/billing servicesTelecommunicationsRadio networks

Disclosed is a method for receiving streaming service data in a mobile communication system supporting a plurality of radio access interfaces, comprising the steps of: operating in a first mode for receiving, from a server, streaming service data through a first interface among the plurality of radio access interfaces; and determining a transition to a second mode for receiving the streaming service data by using at least two radio access interfaces according to a radio network currently being used in the first mode.

Owner:SAMSUNG ELECTRONICS CO LTD

Electret assembly for a microphone having a backplate with improved charge stability

ActiveUS20070121982A1Minimize chargeMinimize water absorptionPiezoelectric/electrostrictive microphonesMicrophone structural associationElectrical conductorCharge layer

The present invention relates to a microphone that includes a housing and a diaphragm and backplate located with the housing. The housing has a sound port for receiving the sound. The diaphragm undergoes movement relative to the backplate, which it opposes, in response to the incoming sound. The backplate has a charged layer with a first surface that is exposed to the diaphragm and a second surface opposite the first surface. The backplate further includes a conductor for transmitting a signal from the backplate to electronics in the housing. The conductor faces the second surface of the charged layer. To minimize the charge degradation created by contact with or infiltration of foreign materials, the first surface, the second surface, or both surfaces of the charged layer includes a protective layer thereon.

Owner:SONION NEDERLAND

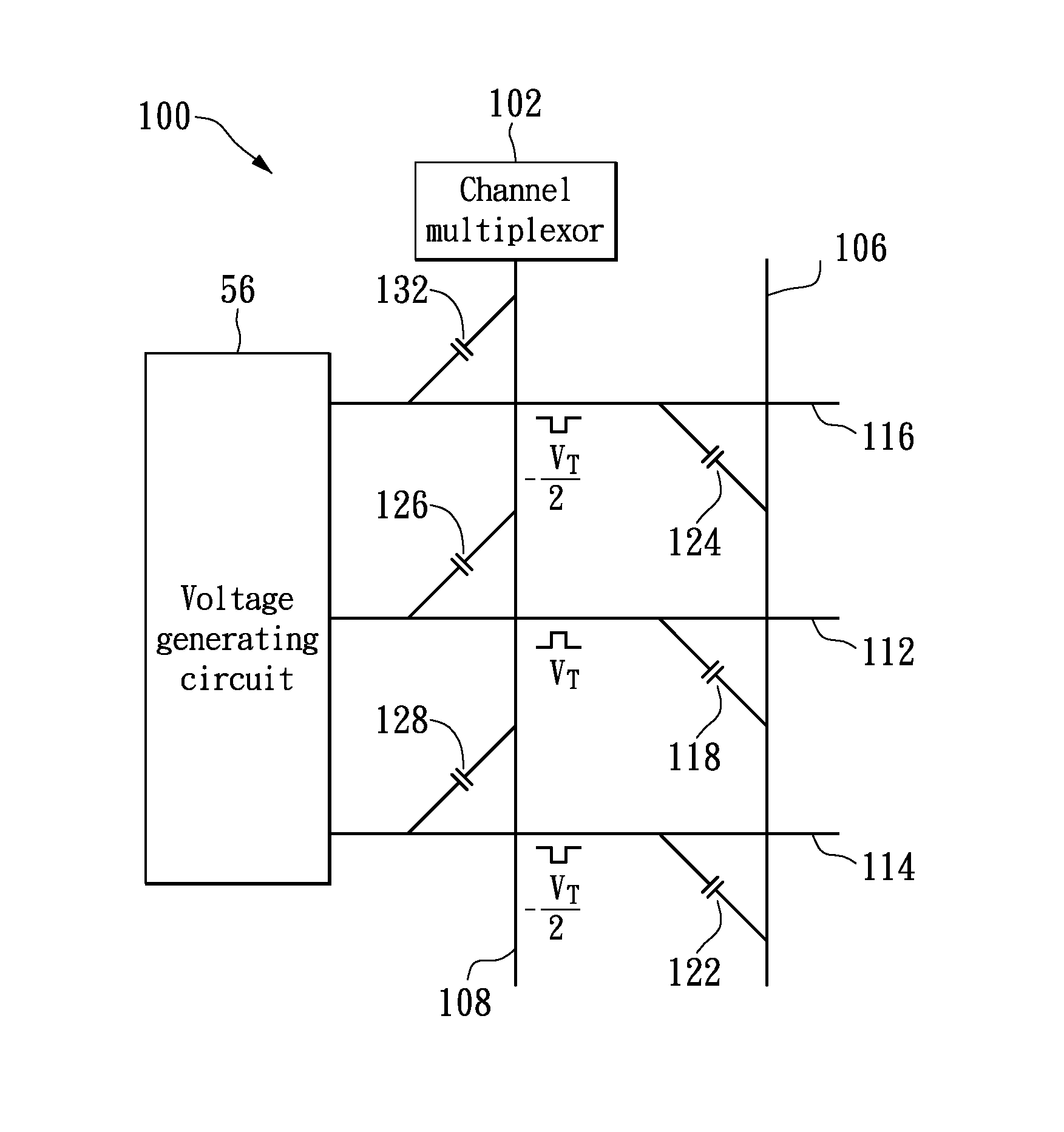

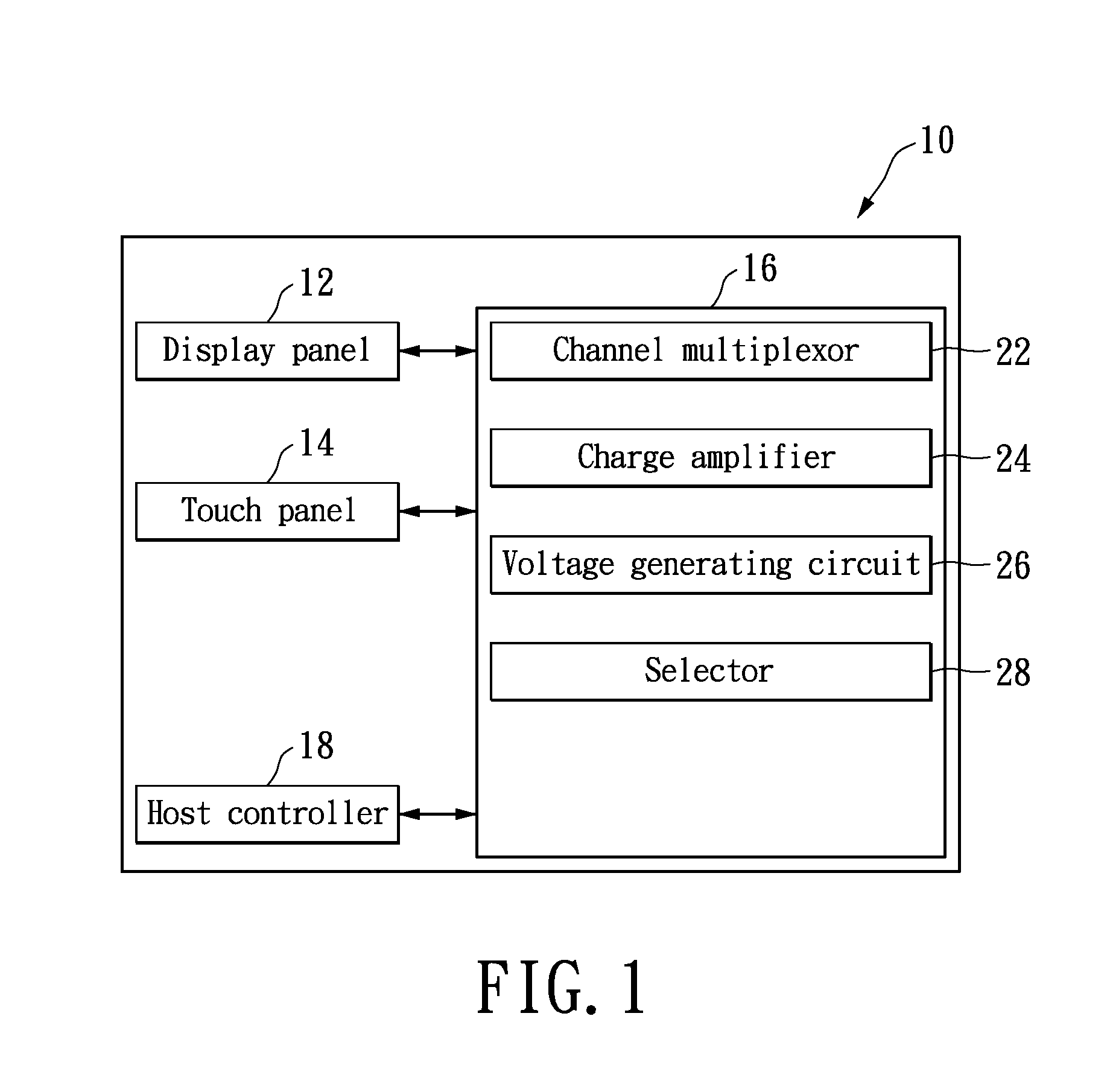

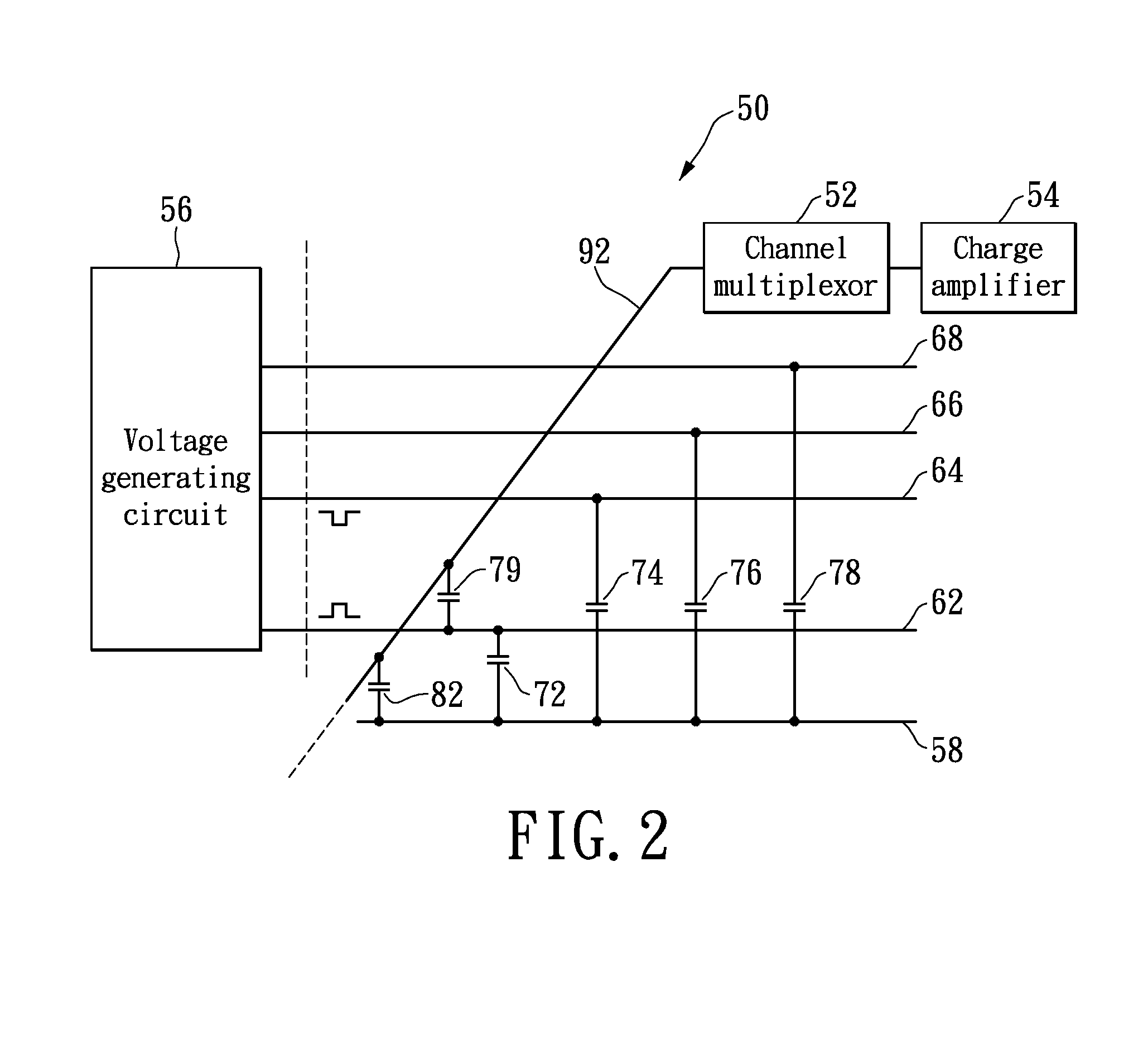

Method of minimizing charges accumulated at common electrode of display panel

ActiveUS9030426B2Minimize chargeInput/output processes for data processingElectrical polarityEngineering

Owner:INNOLUX CORP +1

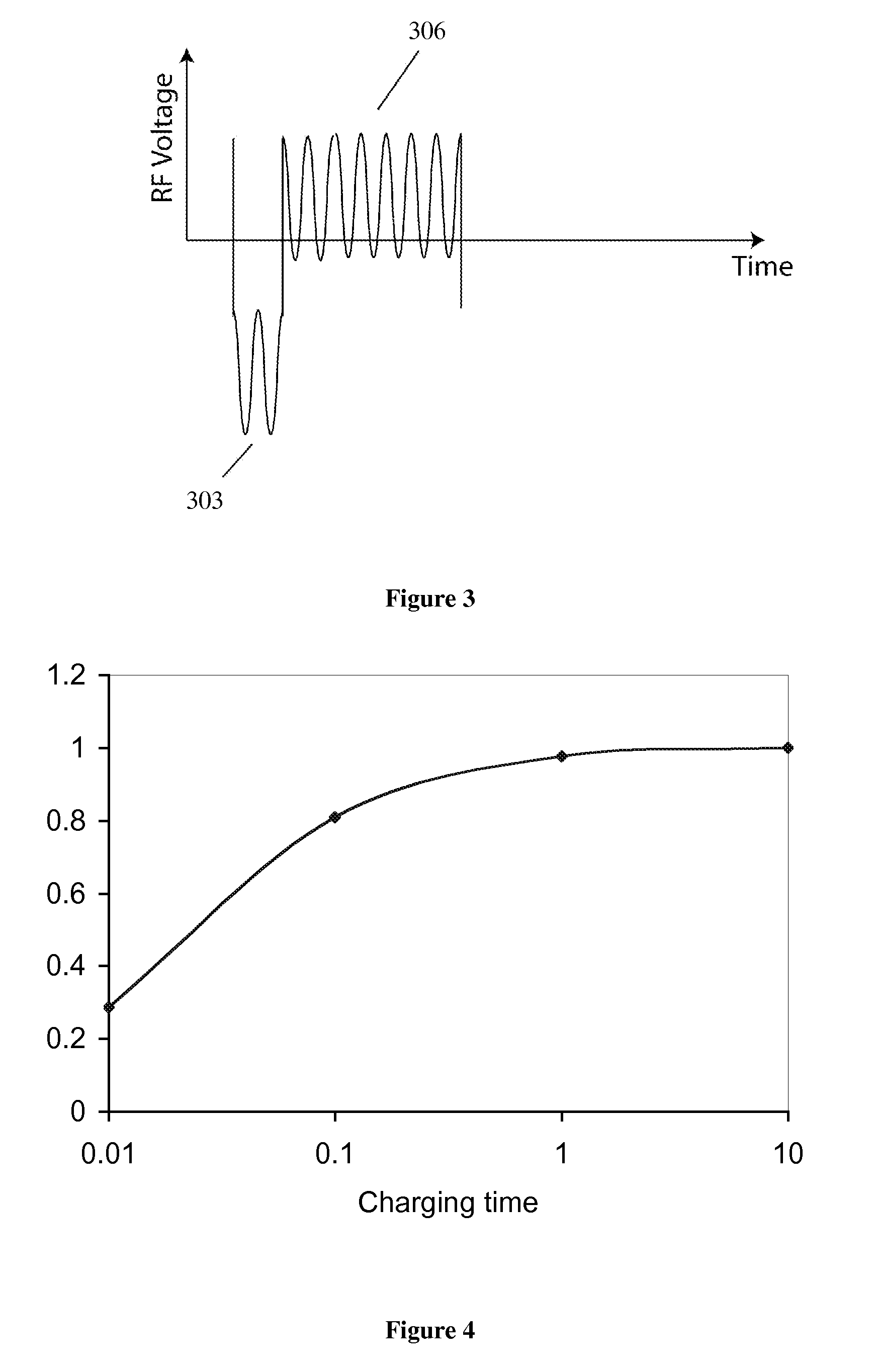

Electrophoresis display apparatus and drive method thereof

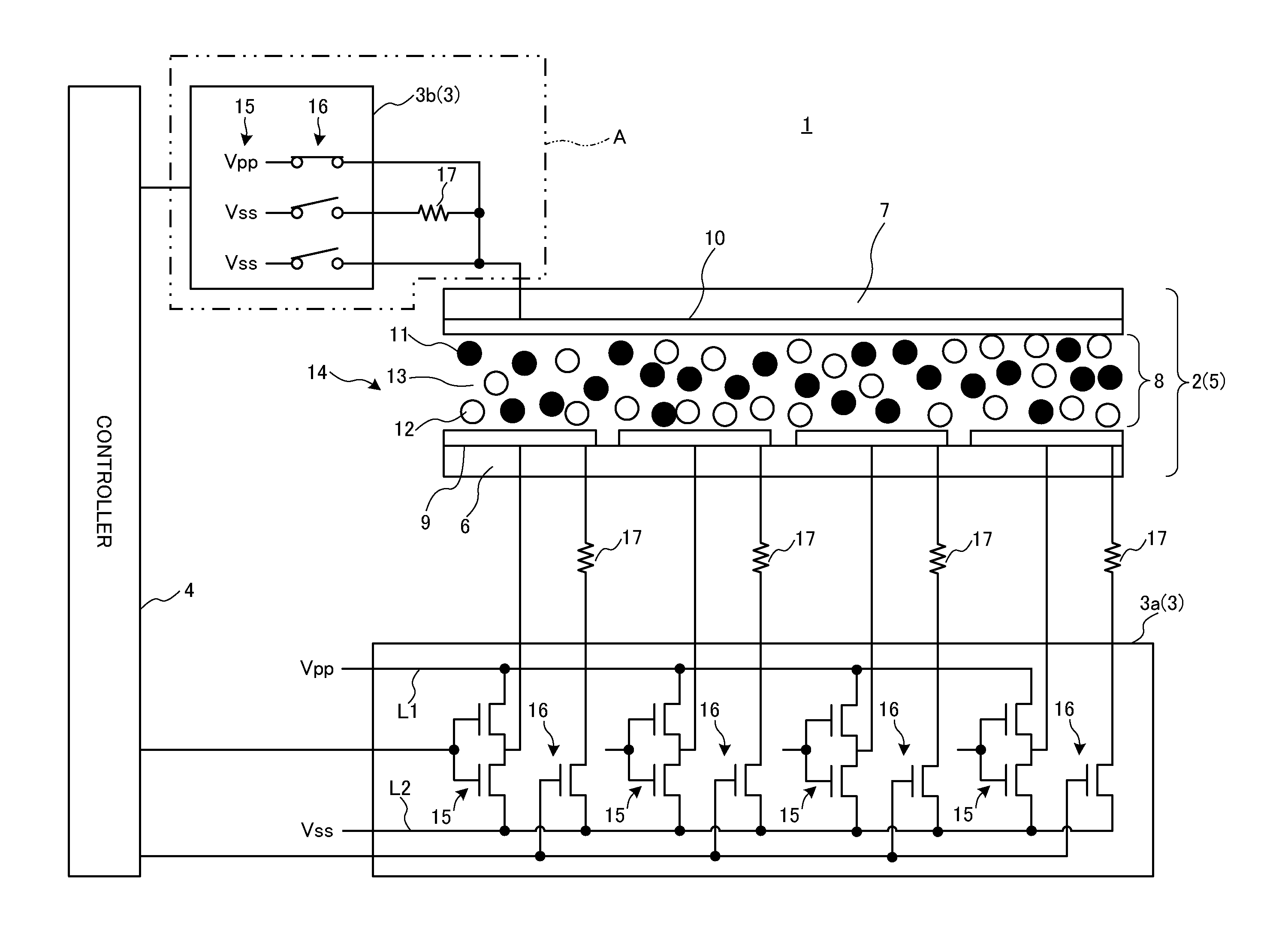

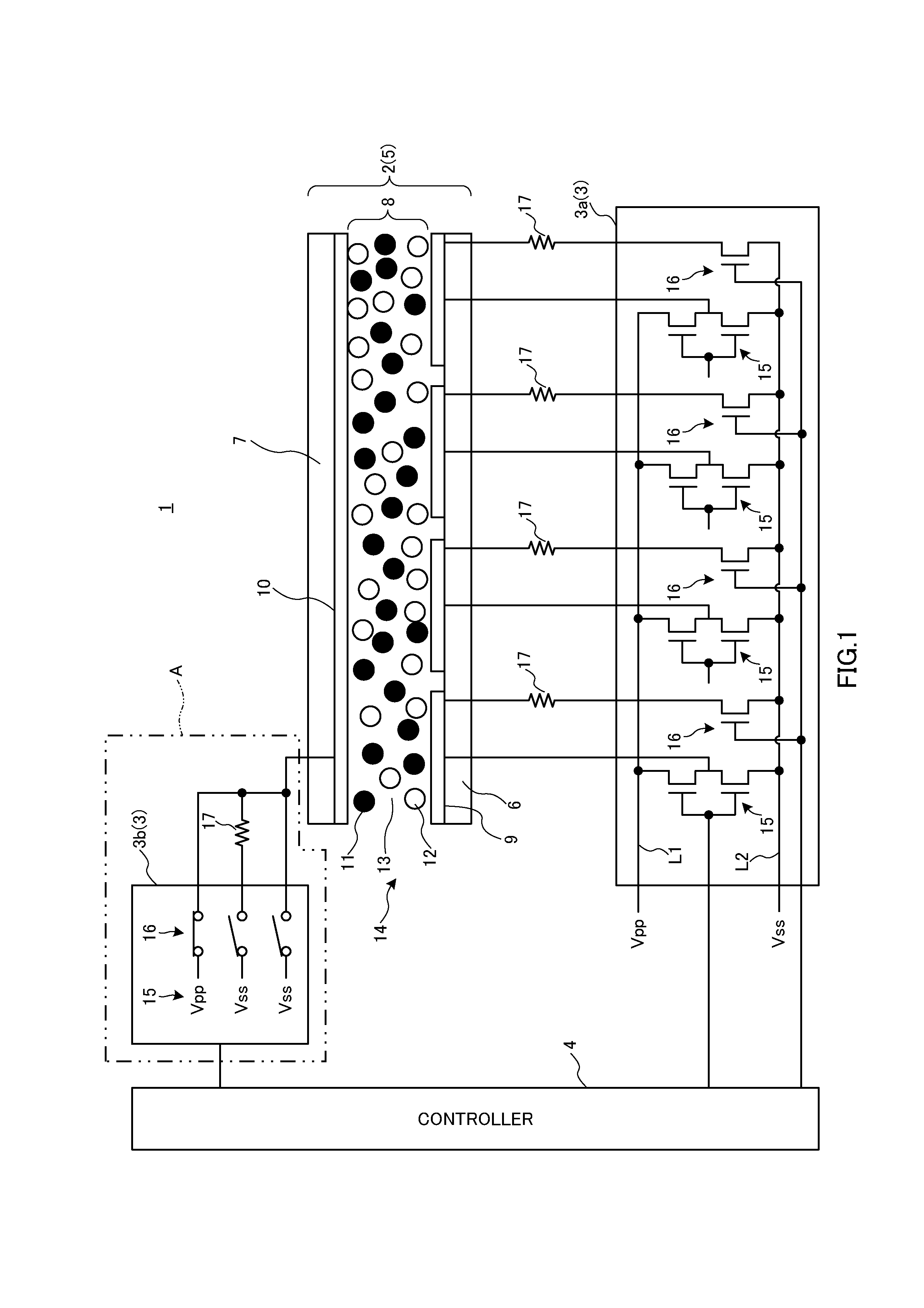

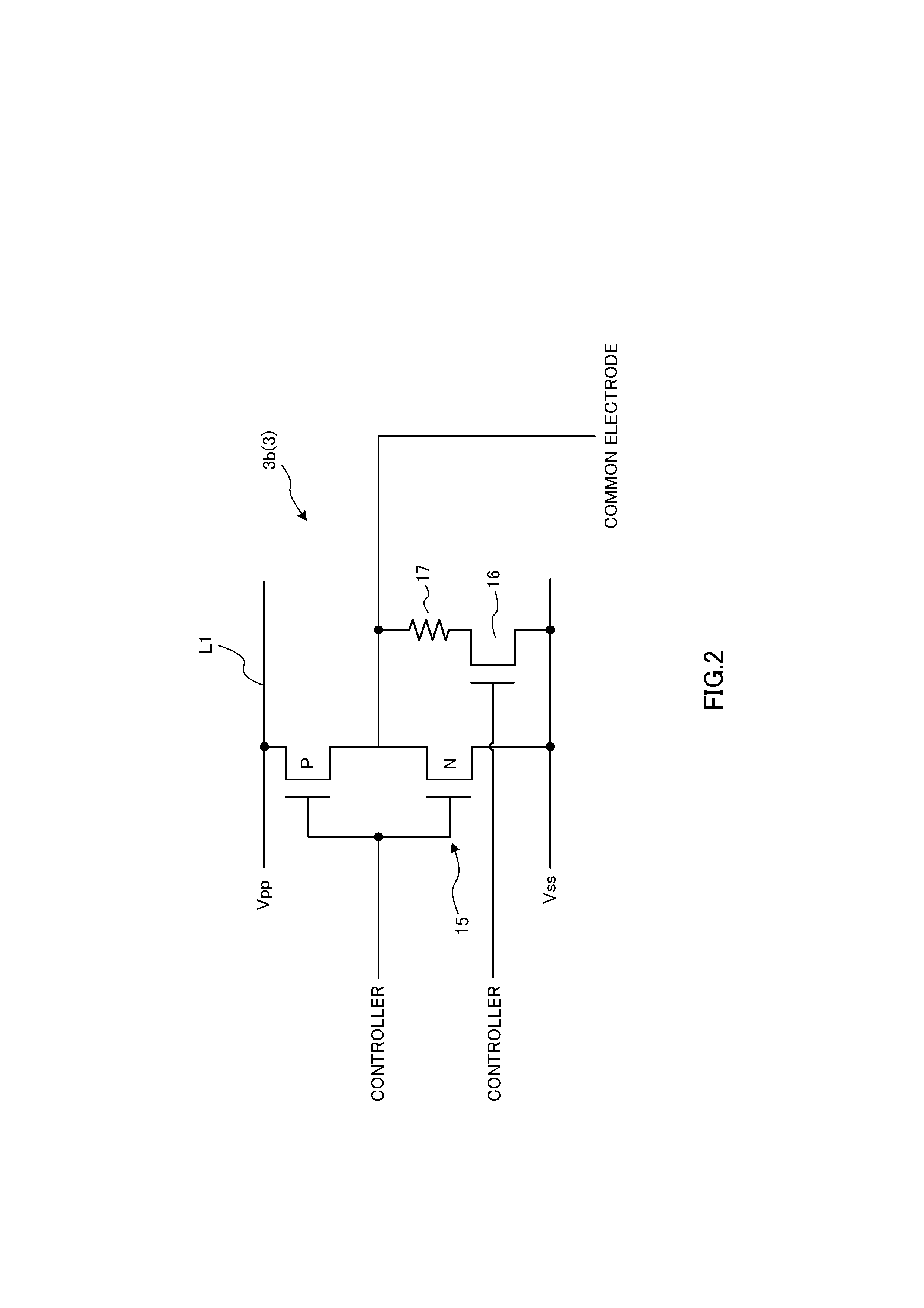

InactiveUS20130176613A1Minimize occurrenceSuppress contrast deteriorationStatic indicating devicesNon-linear opticsElectrophoresisPotential difference

An electrophoresis display apparatus (1) is provided with a pair of substrates (6, 7), a plurality of pixel electrodes (9) formed on the substrate surface of one substrate (6), a common electrode (10) formed opposite to the plurality of pixel electrodes (9) on the substrate surface of the other substrate (7), a liquid body (14) in which two charged particles (11, 12) having different colors and polarities sealed and dispersed between the pair of substrates, and a controller (4) that generates a write pulse to generate a potential difference for causing the charged particles (11, 12) to move between the pixel electrode (9) and the common electrode (10). The controller (4) applies a write pulse to the pixel electrode (9) and the common electrode (10), and then connects the pixel electrode (9) and the common electrode (10) via a resistance (17).

Owner:MITSUBISHI PENCIL CO LTD

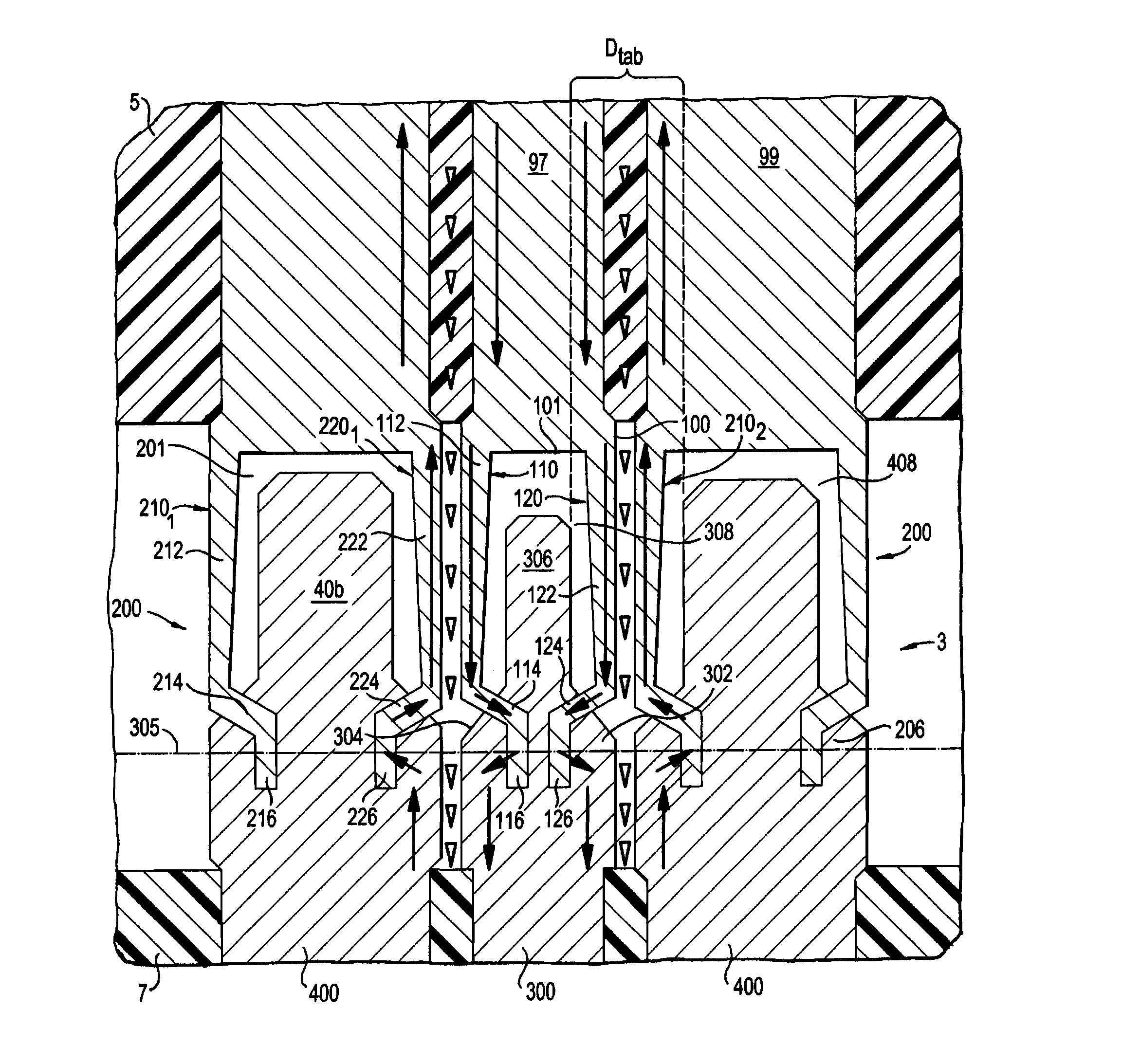

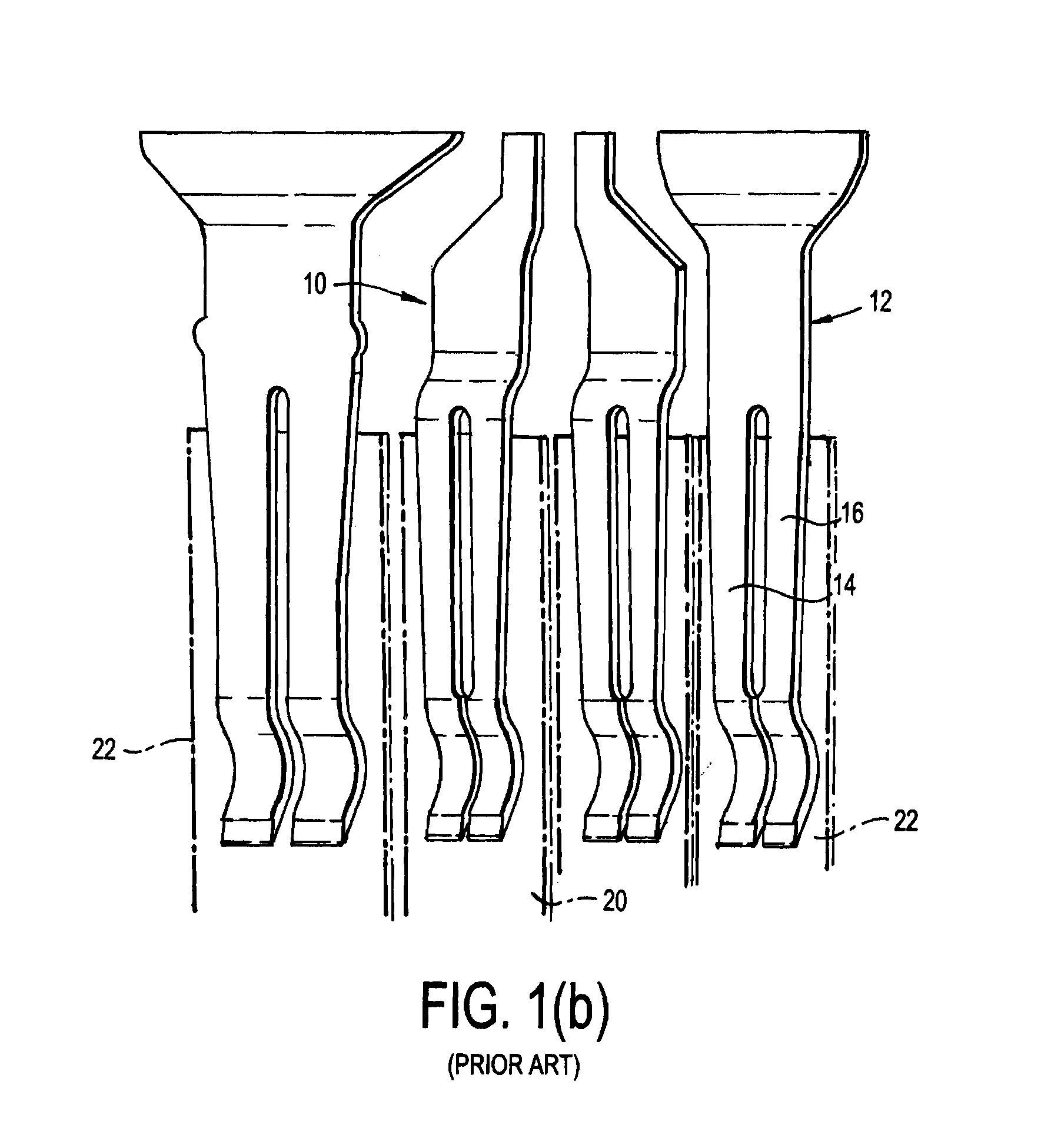

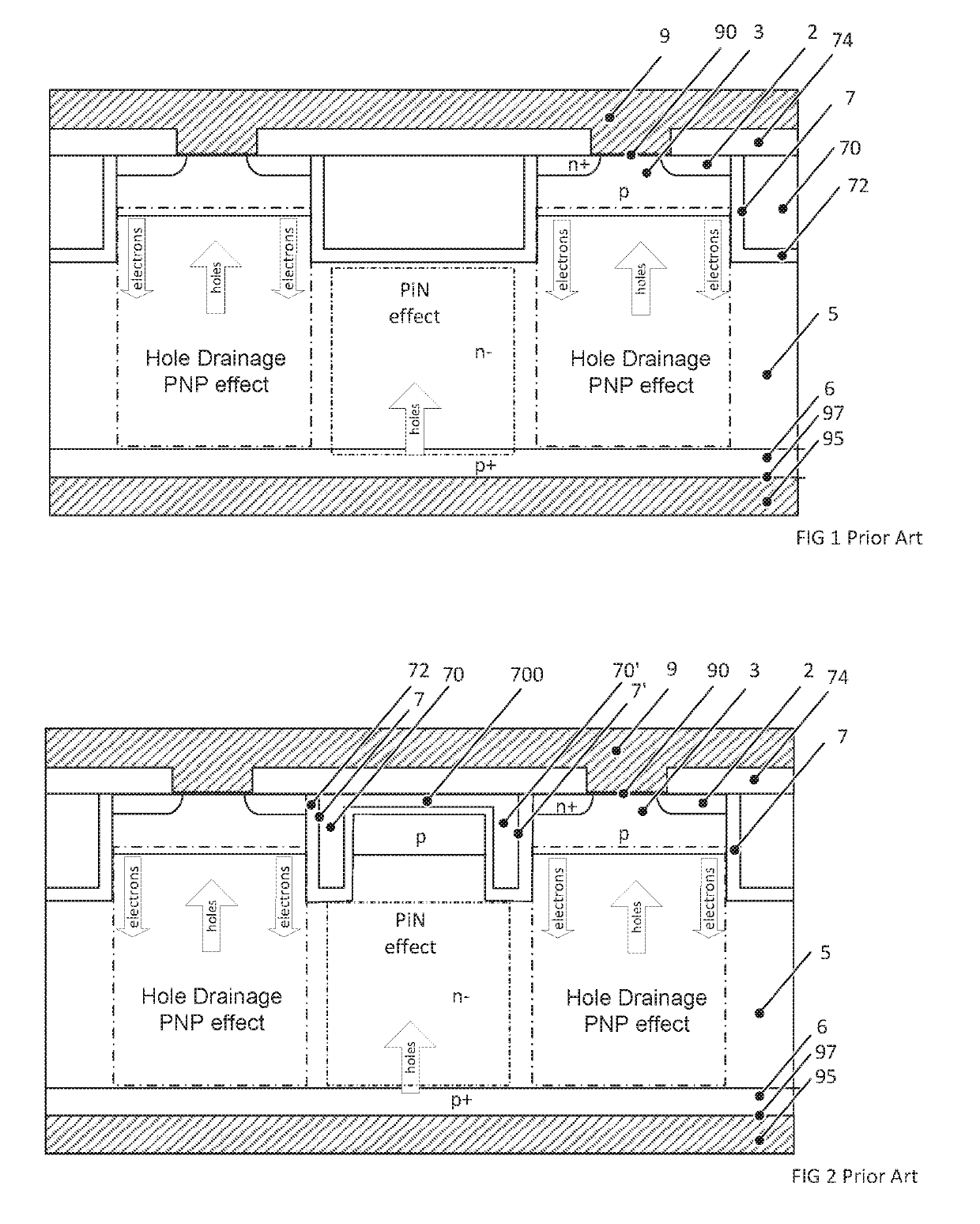

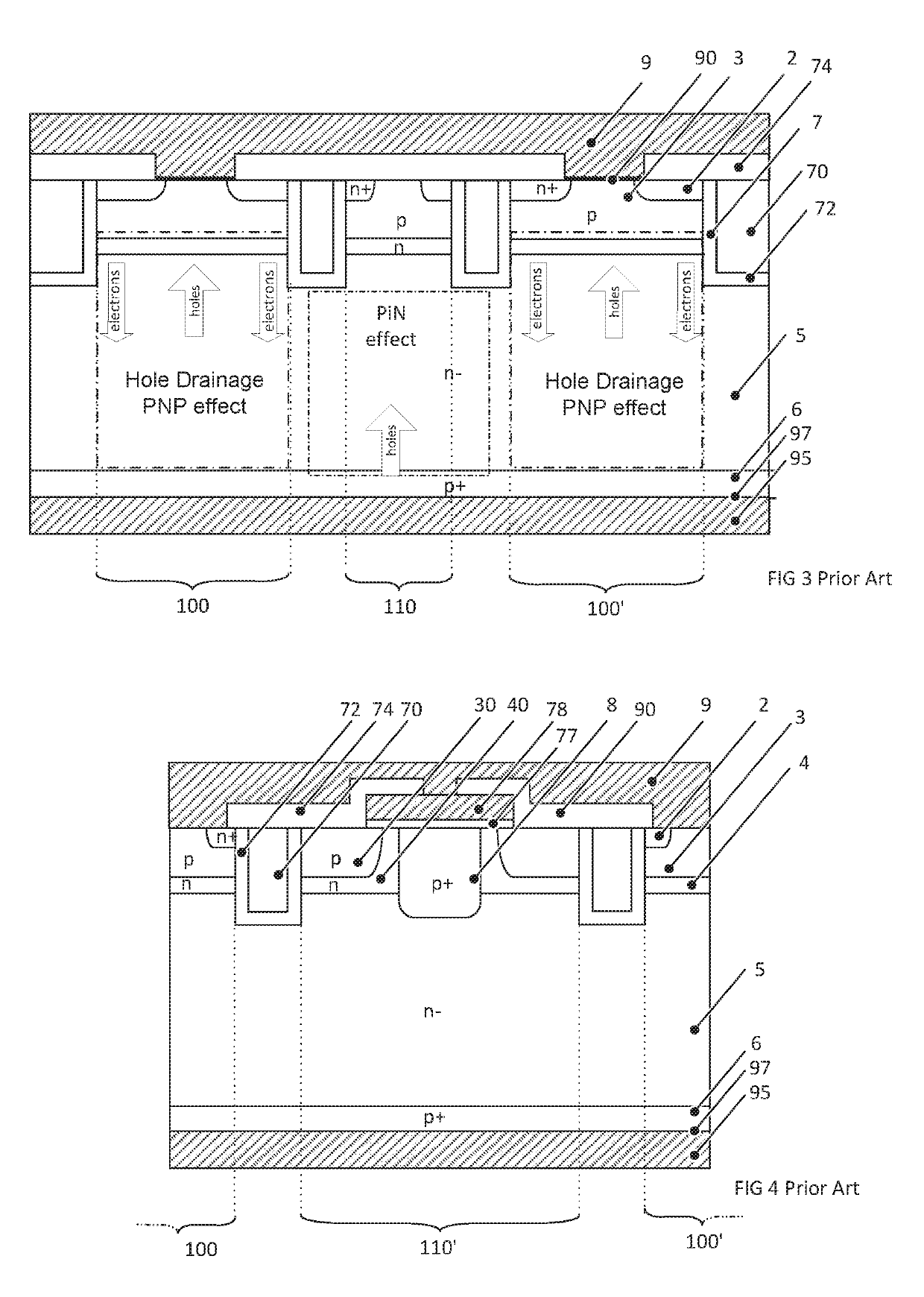

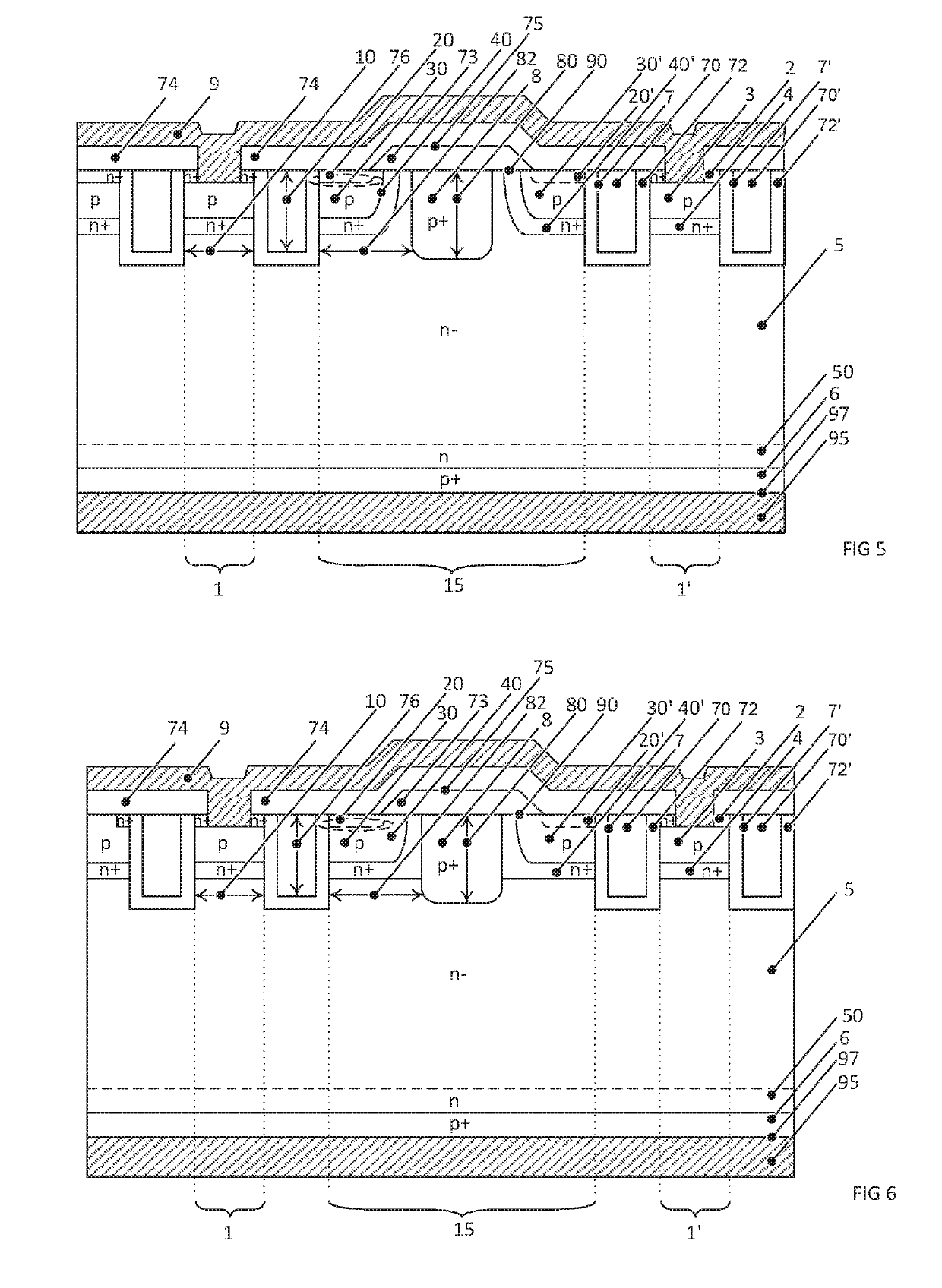

Insulated gate bipolar transistor

ActiveUS20190109218A1Improve performanceReduced on-stateSemiconductor/solid-state device manufacturingSemiconductor devicesLayer thicknessTrench gate

An IGBT is provided comprising at least two first cells (1, 1′), each of which having an n doped source layer (2), a p doped base layer (3), an n doped enhancement layer (4), wherein the base layer (3) separates the source layer (2) from the enhancement layer (4), an n− doped drift layer (5) and a p doped collector layer (6). Two trench gate electrodes (7, 7′) are arranged on the lateral sides of the first cell (1, 1′).The transistor comprises at least one second cell (15) between the trench gate electrodes (7, 7′) of two neighboured first cells (1, 1′), which has on the emitter side (90) a p+ doped well (8) and a further n doped enhancement layer (40, 40′) which separates the well (8) from the neighboured trench gate electrodes (7, 7′). An insulator layer stack (75) is arranged on top of the second cell (15) on the emitter side (90) to insulate the second cell (15) and the neighboured trench gate electrodes (7, 7′) from the metal emitter electrode (9), which consists of a first insulating layer (73) and a second insulating layer (74), wherein the insulator stack (75) has a thickness on top of the well (8) of a first layer thickness plus the second insulating layer thickness and a thickness on top of the gate layer (70, 70′) of the second insulating layer thickness, wherein each thickness of the first insulating layer (73) and the second insulating layer (74) is at least 700 nm.

Owner:HITACHI ENERGY SWITZERLAND AG