Patents

Literature

522 results about "Gate capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Answer Wiki. Gate charge is not capacitance. It is a measure of capacitance. One can use gate charge to determine gate capacitance. In fact capacitance measurements are typically done with charge measurements. Typically only ½ of this capacitance is allocated to gate to source capacitance; the other half is allocated to gate to drain capacitance.

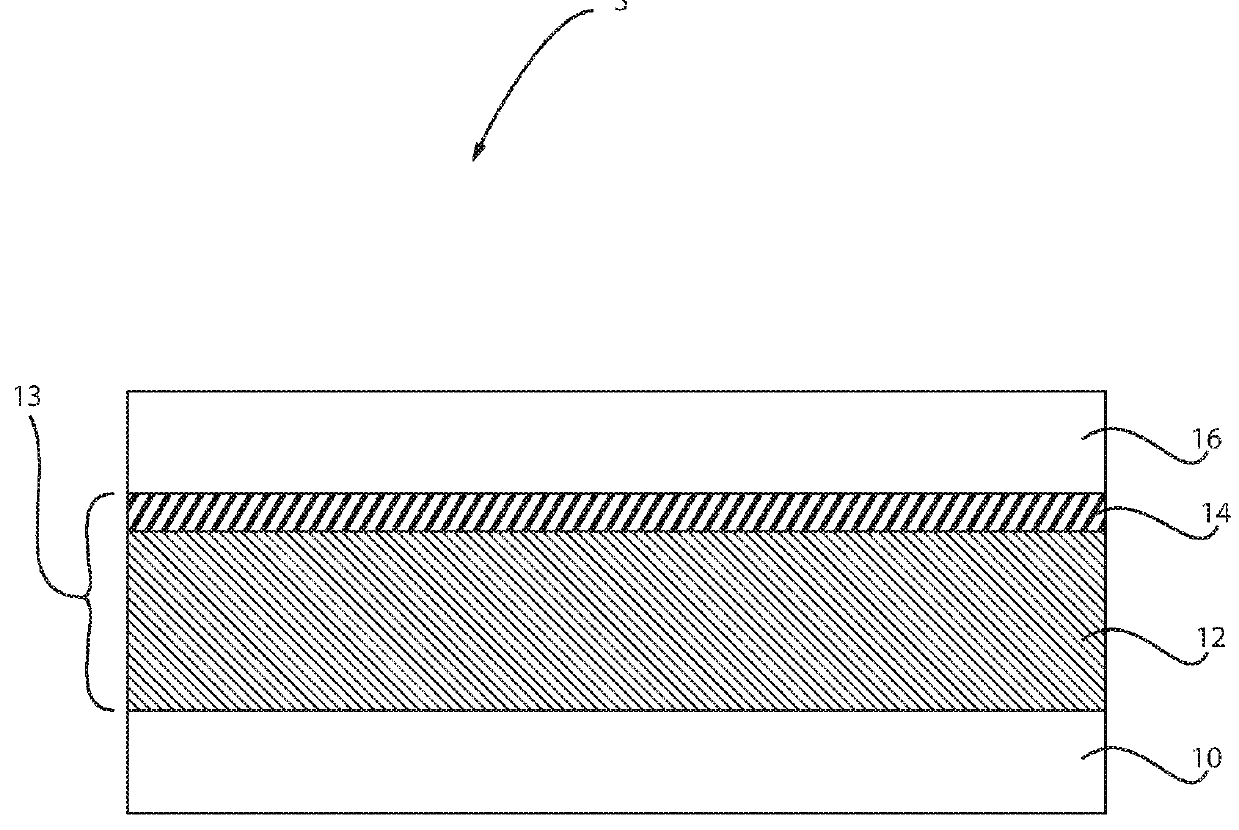

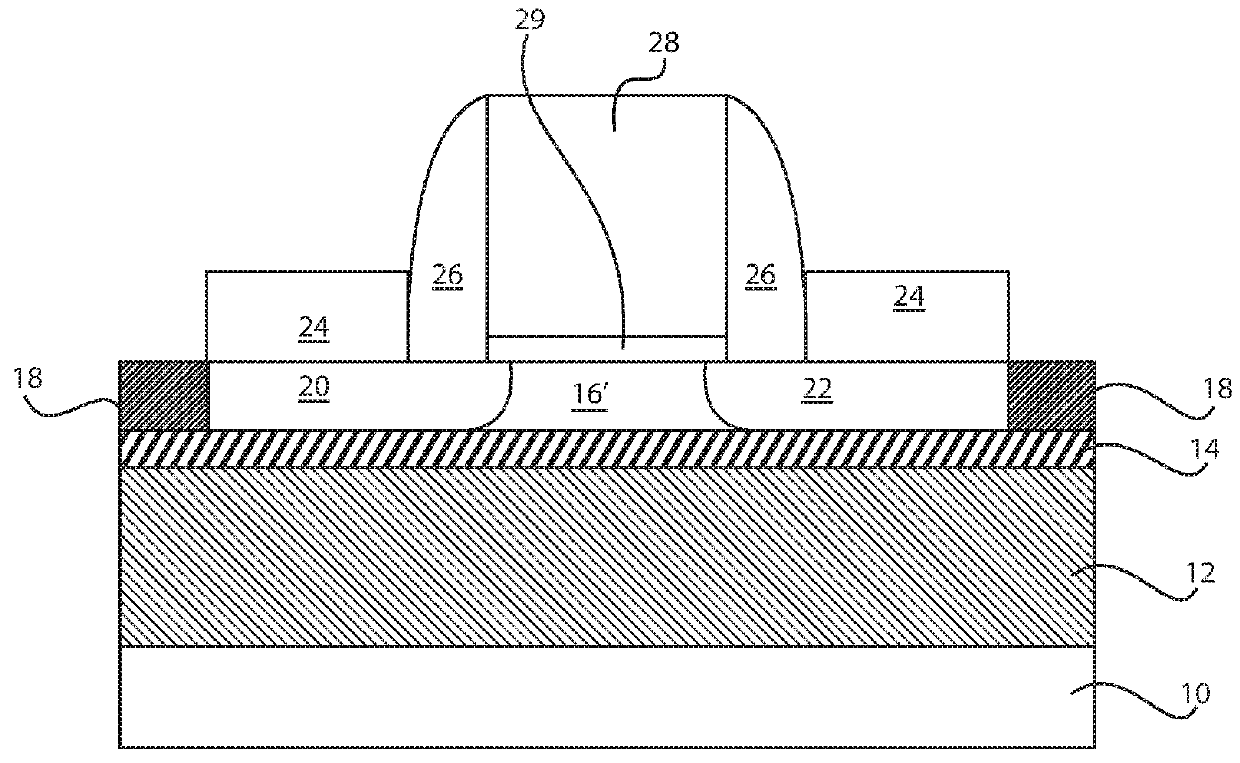

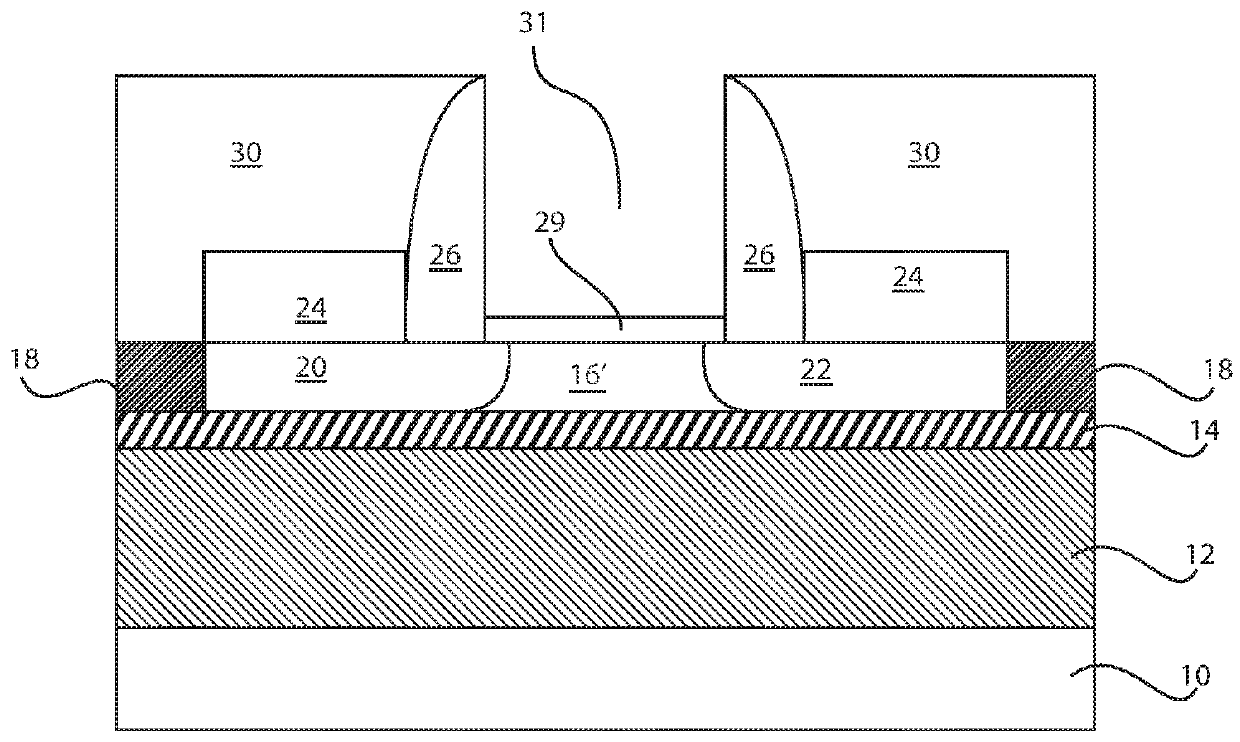

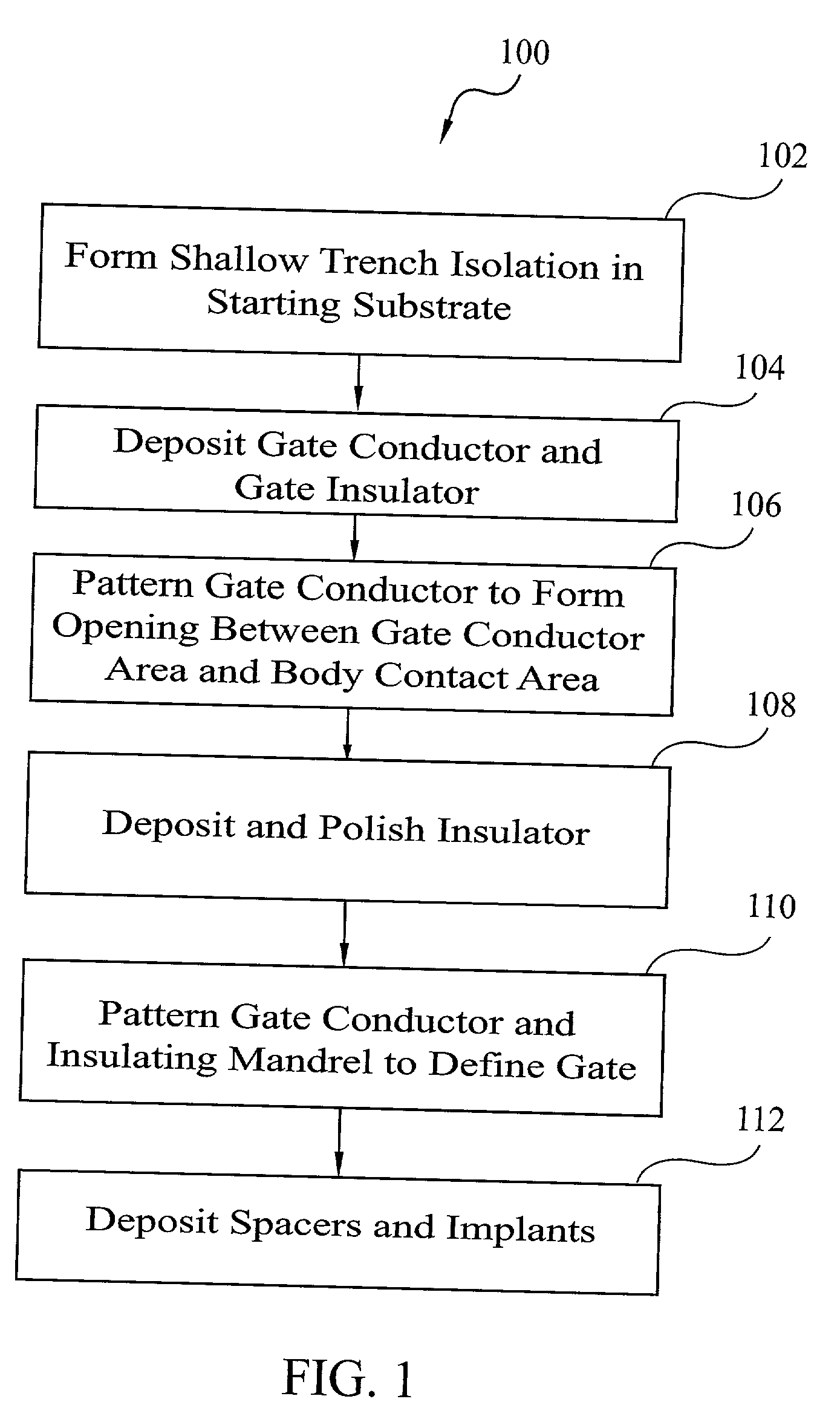

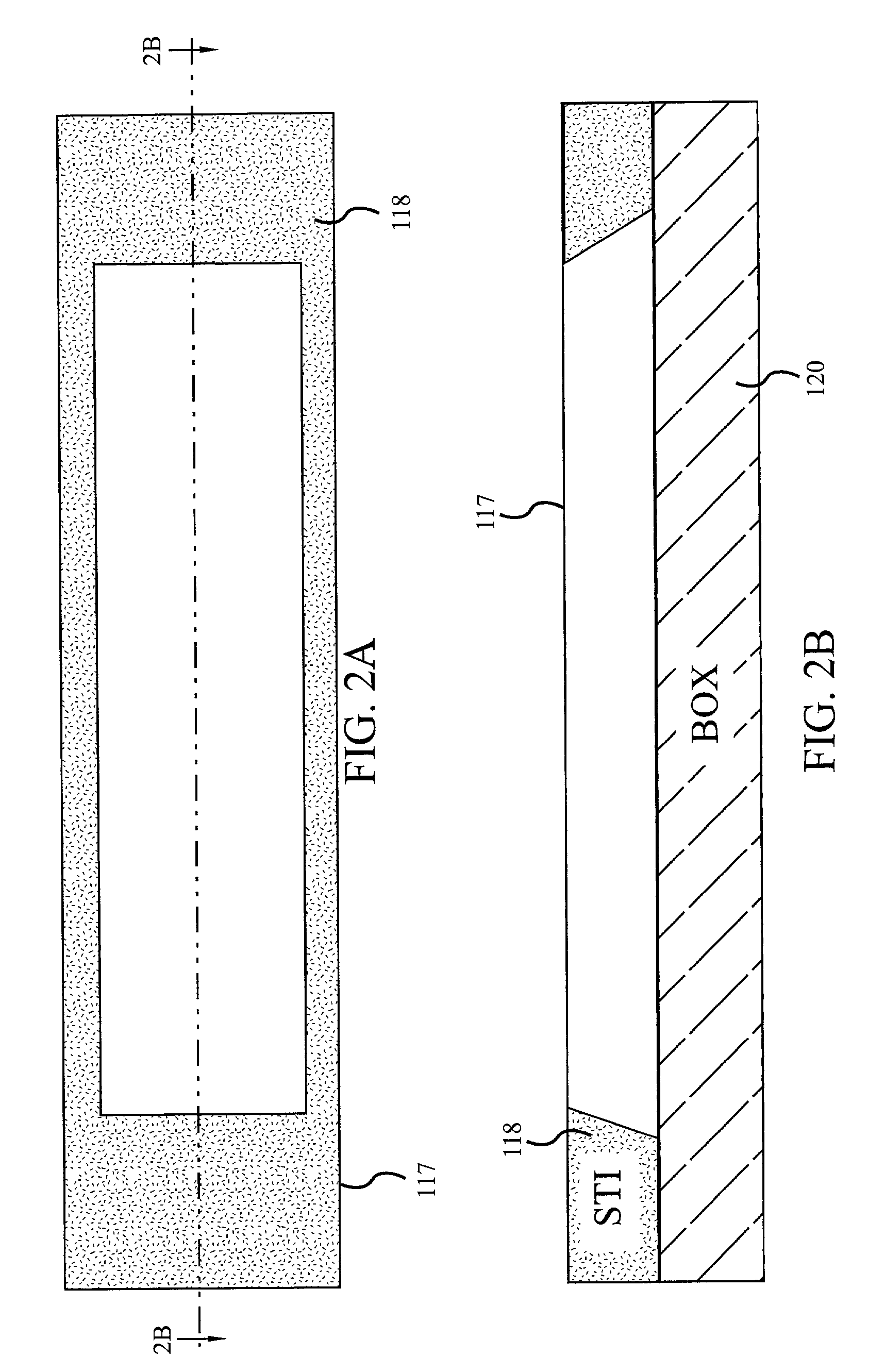

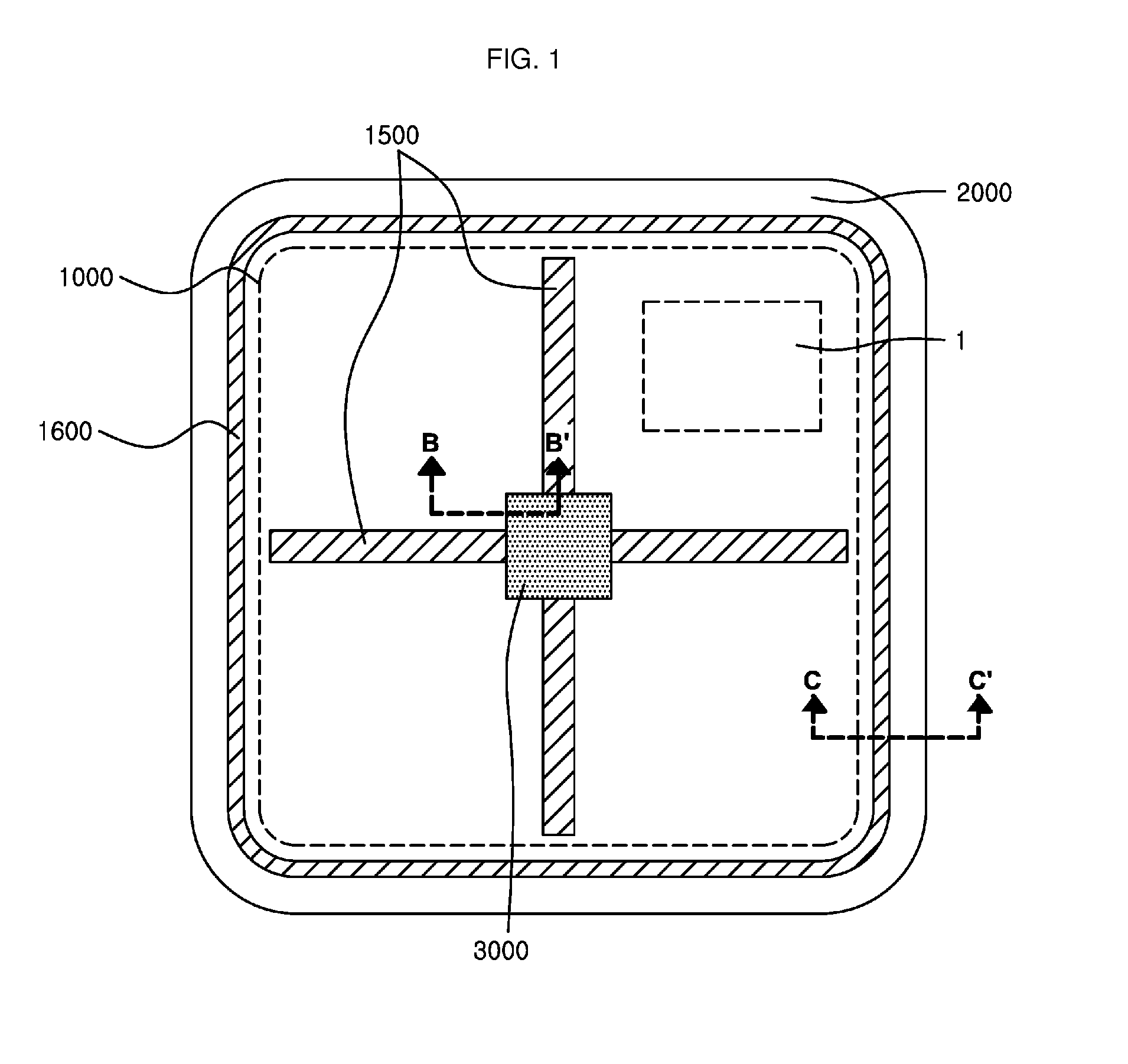

Fully depleted soi device for reducing parasitic back gate capacitance

ActiveUS20180097076A1Semiconductor/solid-state device detailsSolid-state devicesCapacitanceGate dielectric

A method is presented for forming a semiconductor structure. The method includes forming a bilayer buried insulator over a substrate, forming an extremely thin silicon-on-insulator (ETSOI) over the bilayer buried insulator, forming a dummy gate, and forming a source / drain next to the dummy gate, the source / drain defining a raised source / drain region. The method further includes depositing a dielectric material over the raised source / drain regions, removing the dummy gate to define a recess, implanting a species within a first layer of the bilayer buried insulator, and depositing a gate dielectric and a conducting material within the recess. The method further includes removing the substrate, etching the implanted portion of the first layer of the bilayer buried insulator to expose a surface of a second layer of the bilayer buried insulator, and forming a back gate over the exposed second layer, the back gate self-aligned to the ETSOI channel.

Owner:IBM CORP

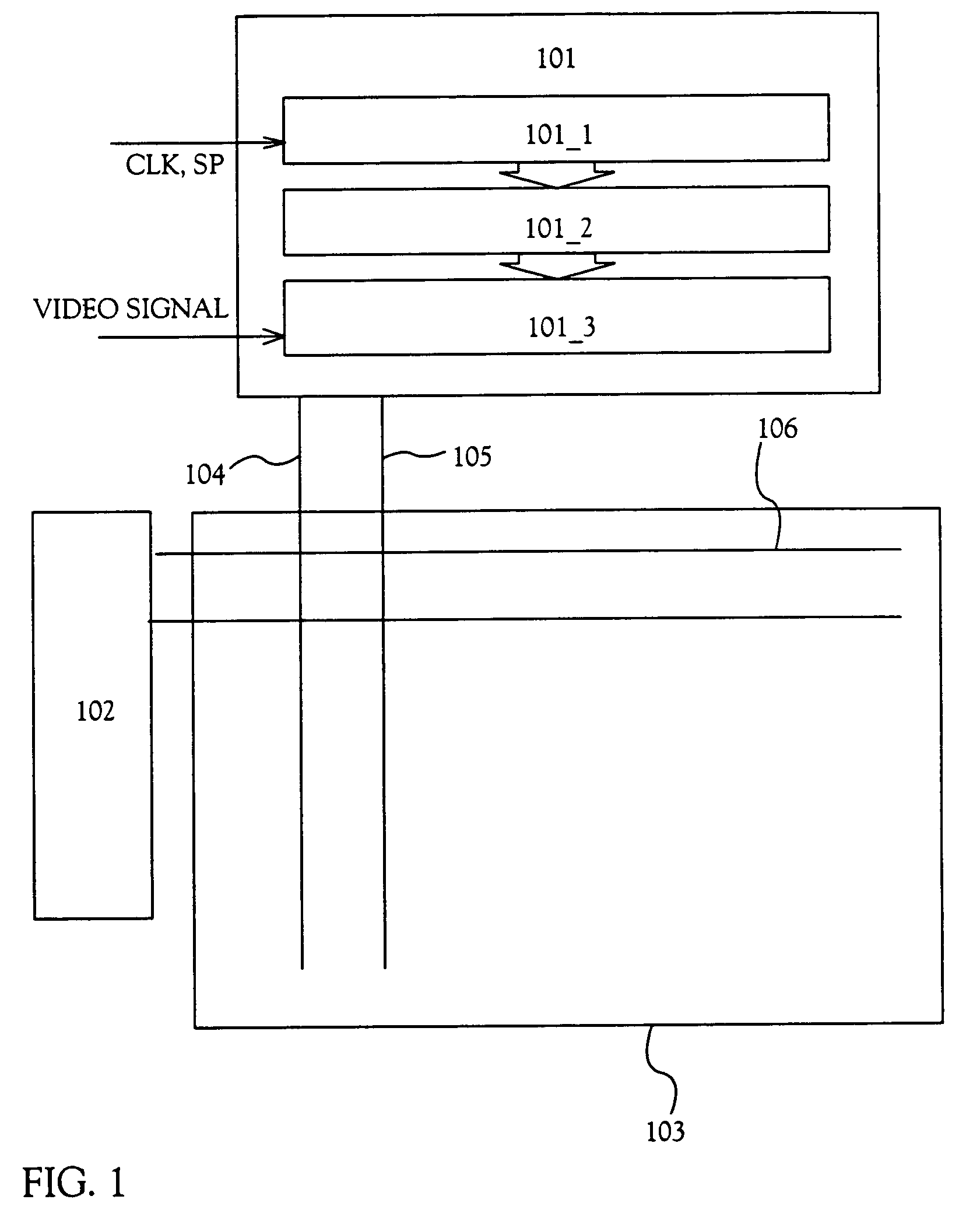

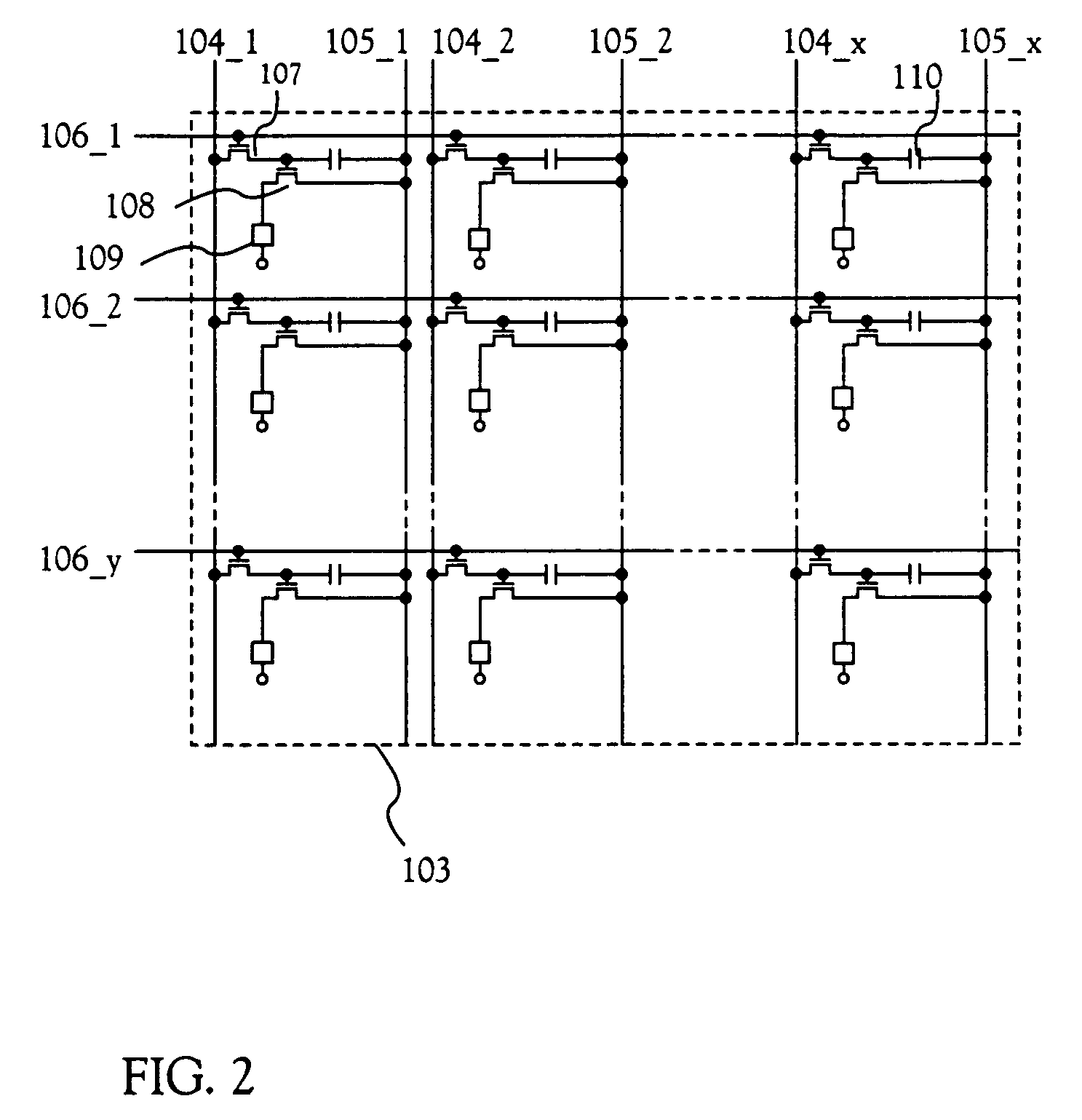

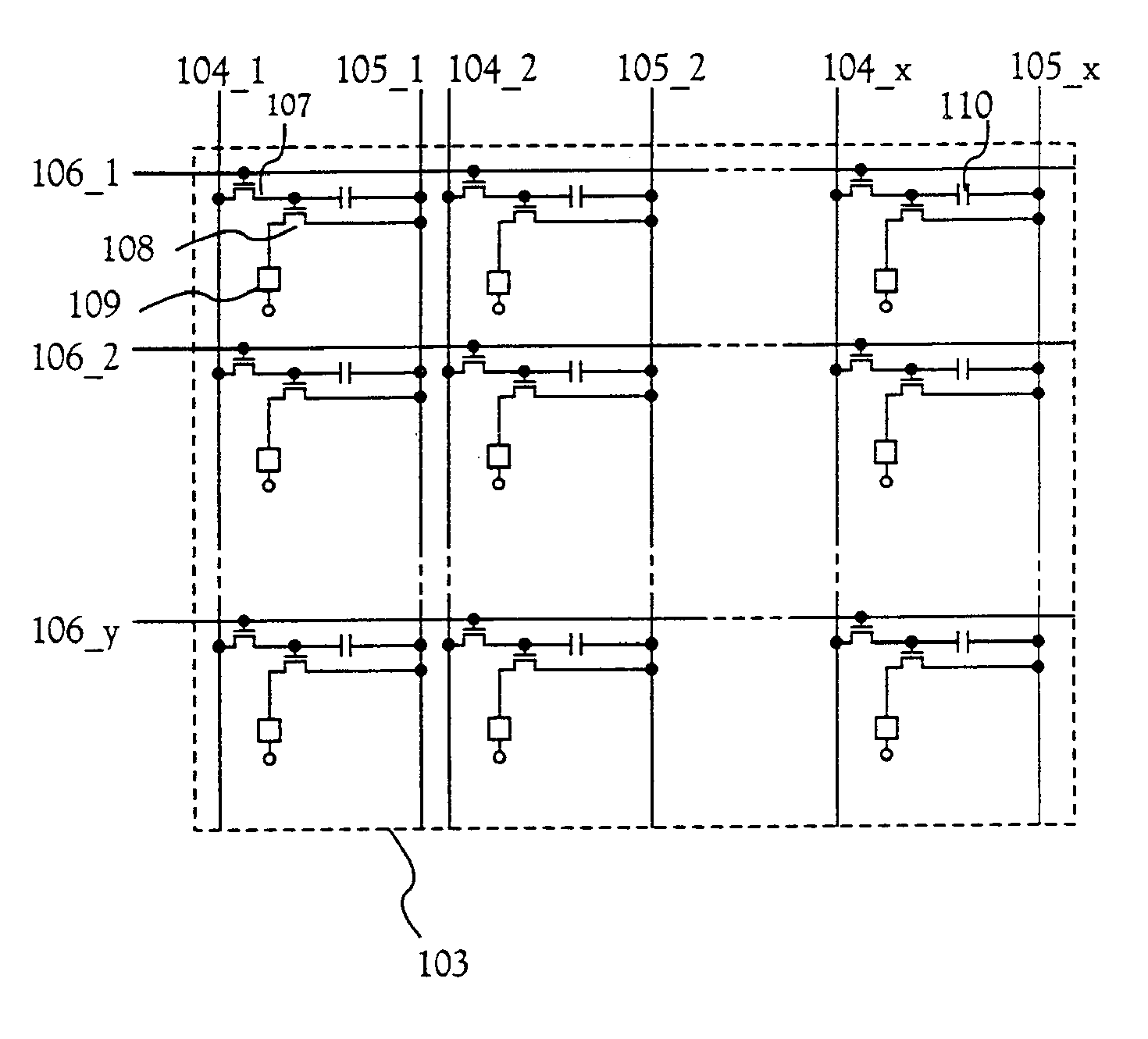

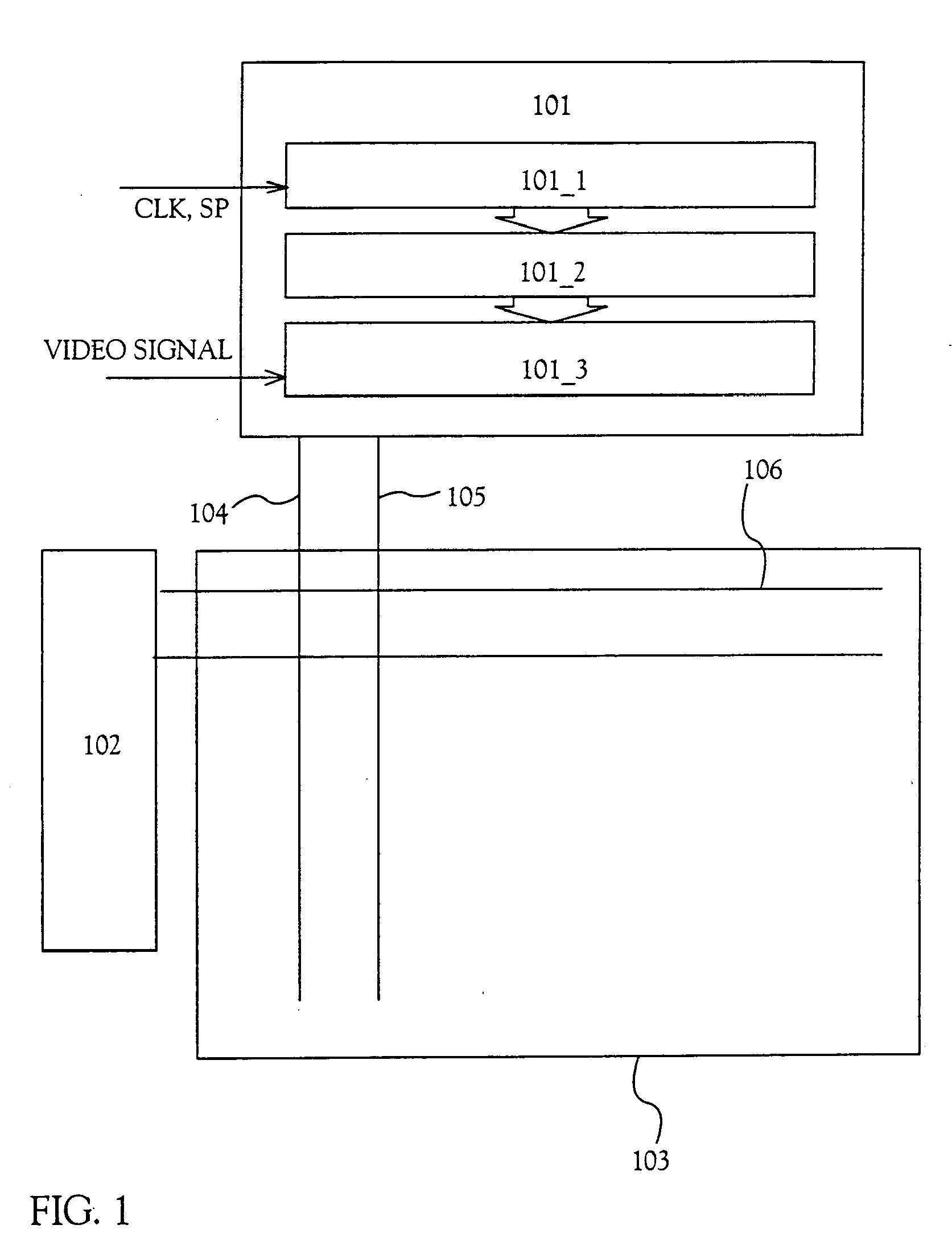

Light-emitting device

InactiveUS7129917B2Drop in opening ratioSuppression of uneven brightnessTransistorDischarge tube luminescnet screensDisplay deviceEngineering

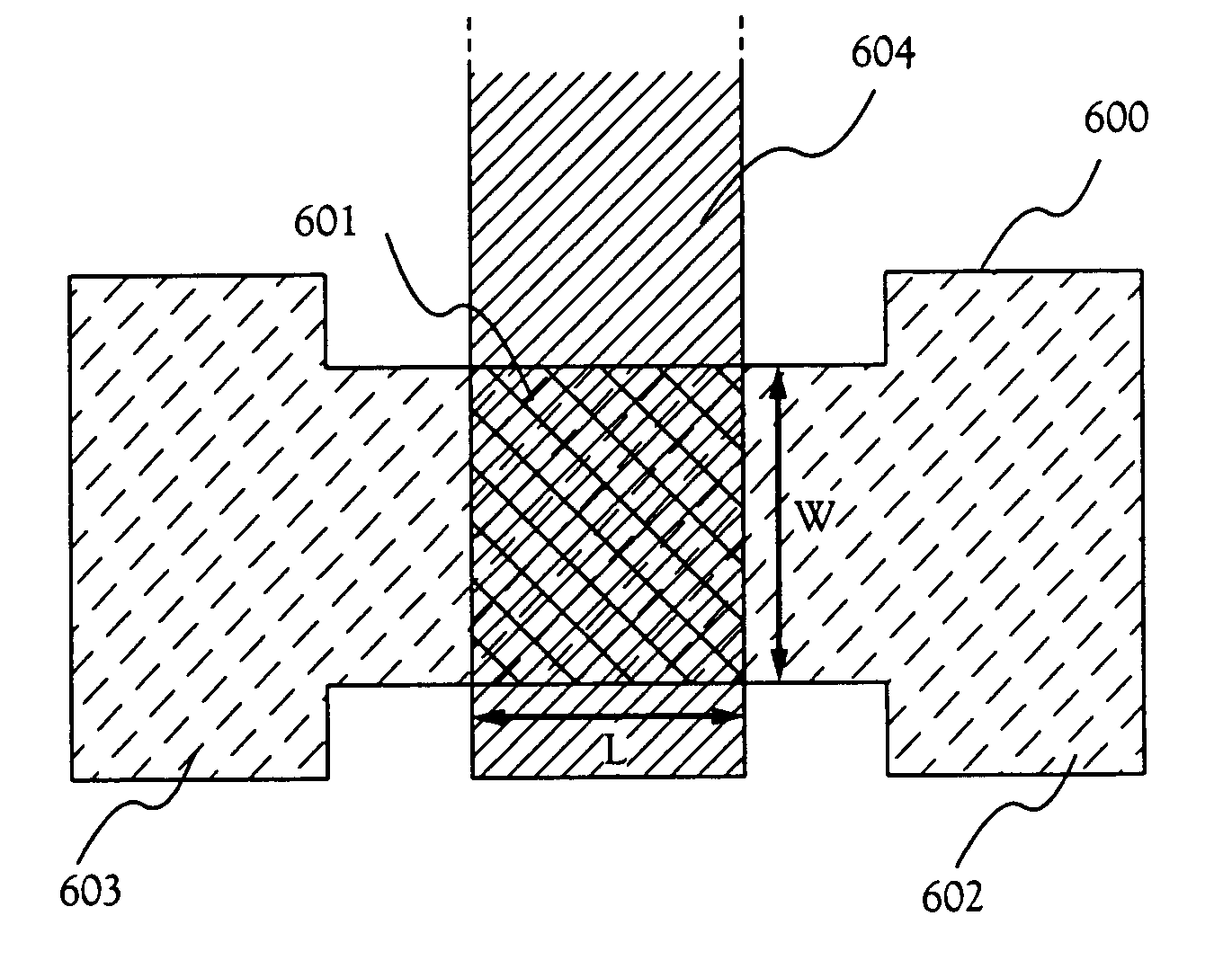

There is provided an EL light-emitting device with less uneven brightness. When a drain current of a plurality of current controlling TFTs is Id, a mobility is μ, a gate capacitance per unit area is Co, a maximum gate voltage is Vgs(max), a channel width is W, a channel length is L, an average value of a threshold voltage is Vth, a deviation from the average value of the threshold voltage is ΔVth, and a difference in emission brightness of a plurality of EL elements is within a range of ±n %, a semiconductor display device is characterized in thatA=2Idμ*C0A(Vgs(max)-Vth)2≦WL≦(1+n100-1)2*AΔVth2ΔVth≦(1+n100-1)*A*L / W

Owner:SEMICON ENERGY LAB CO LTD

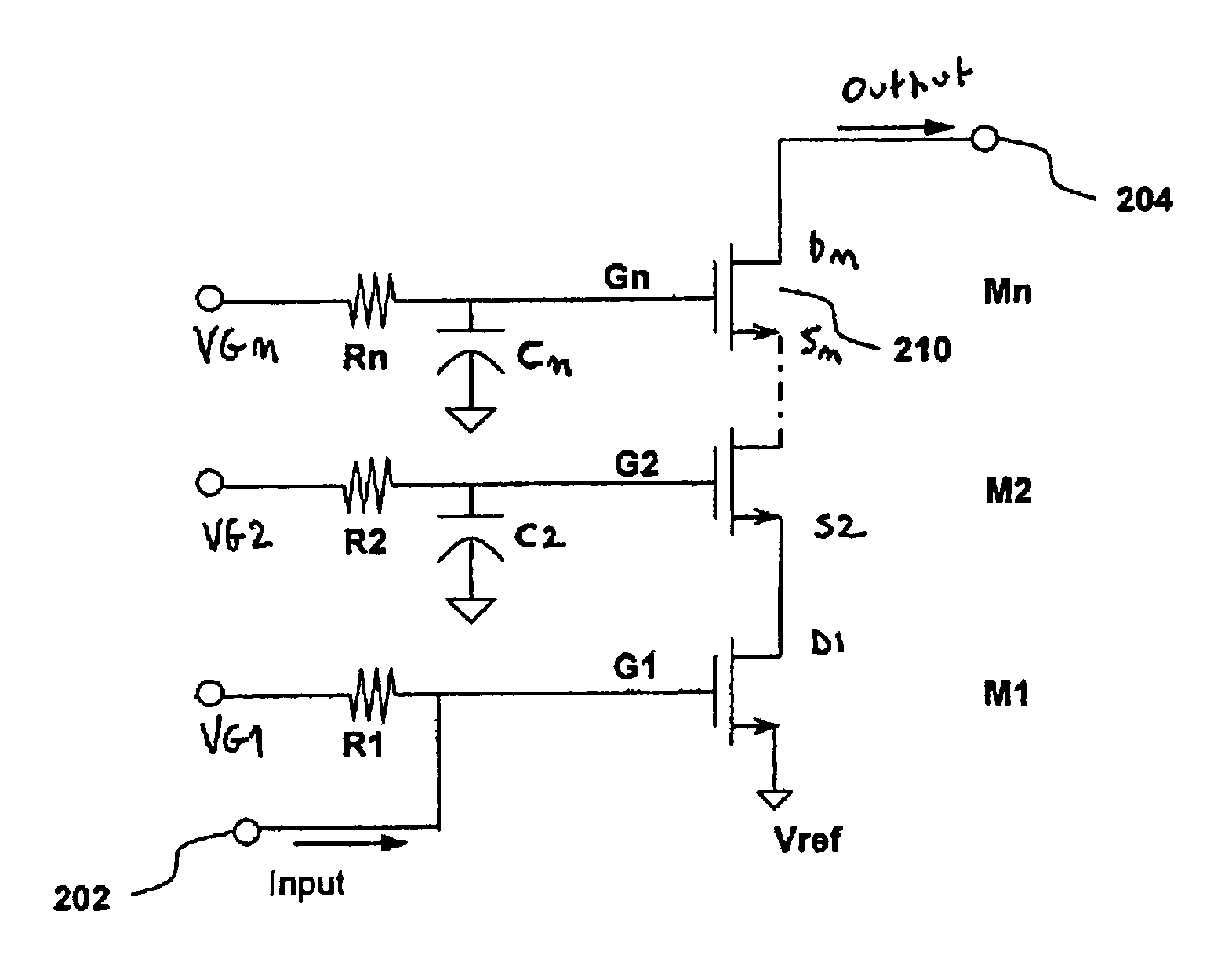

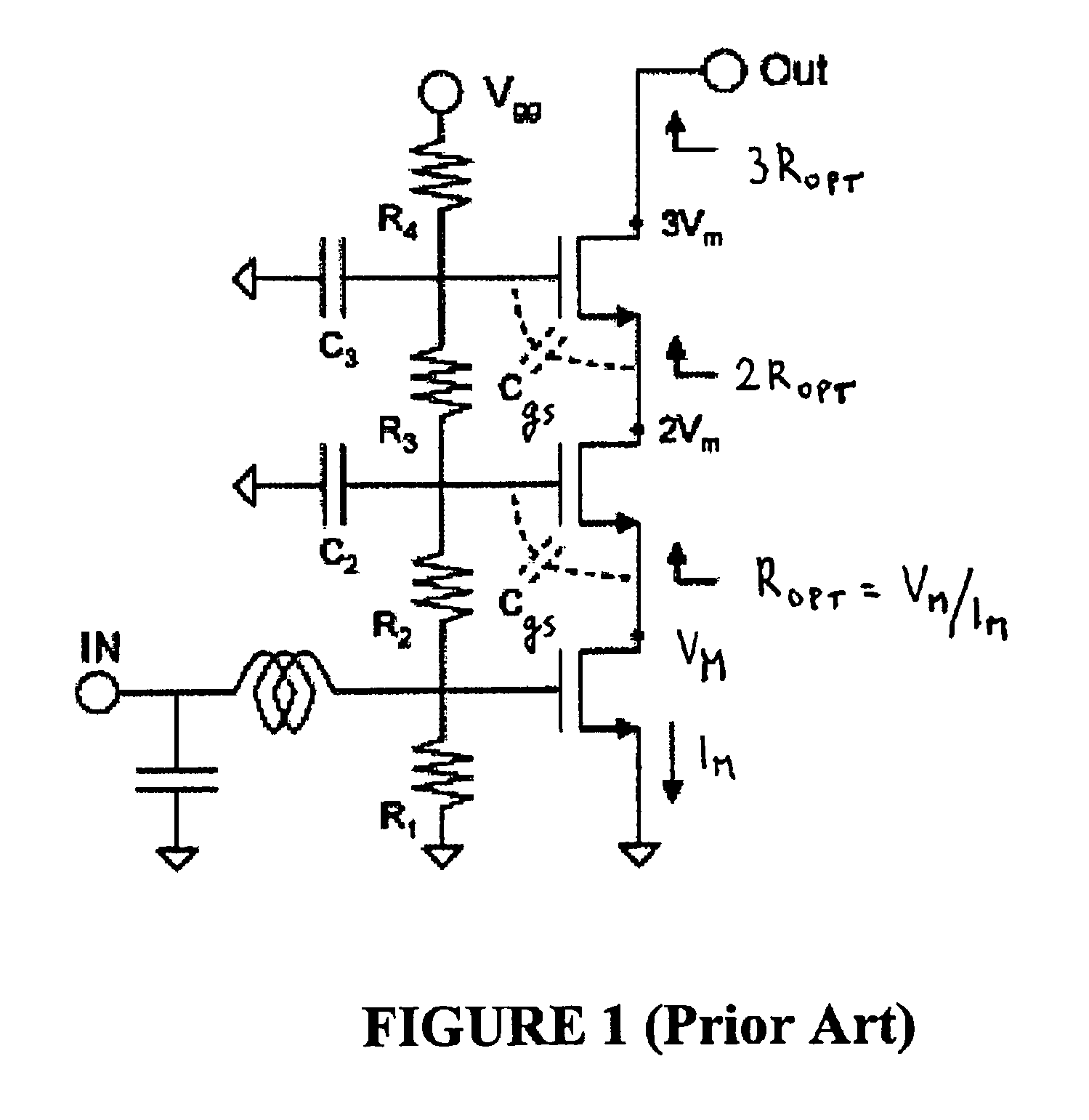

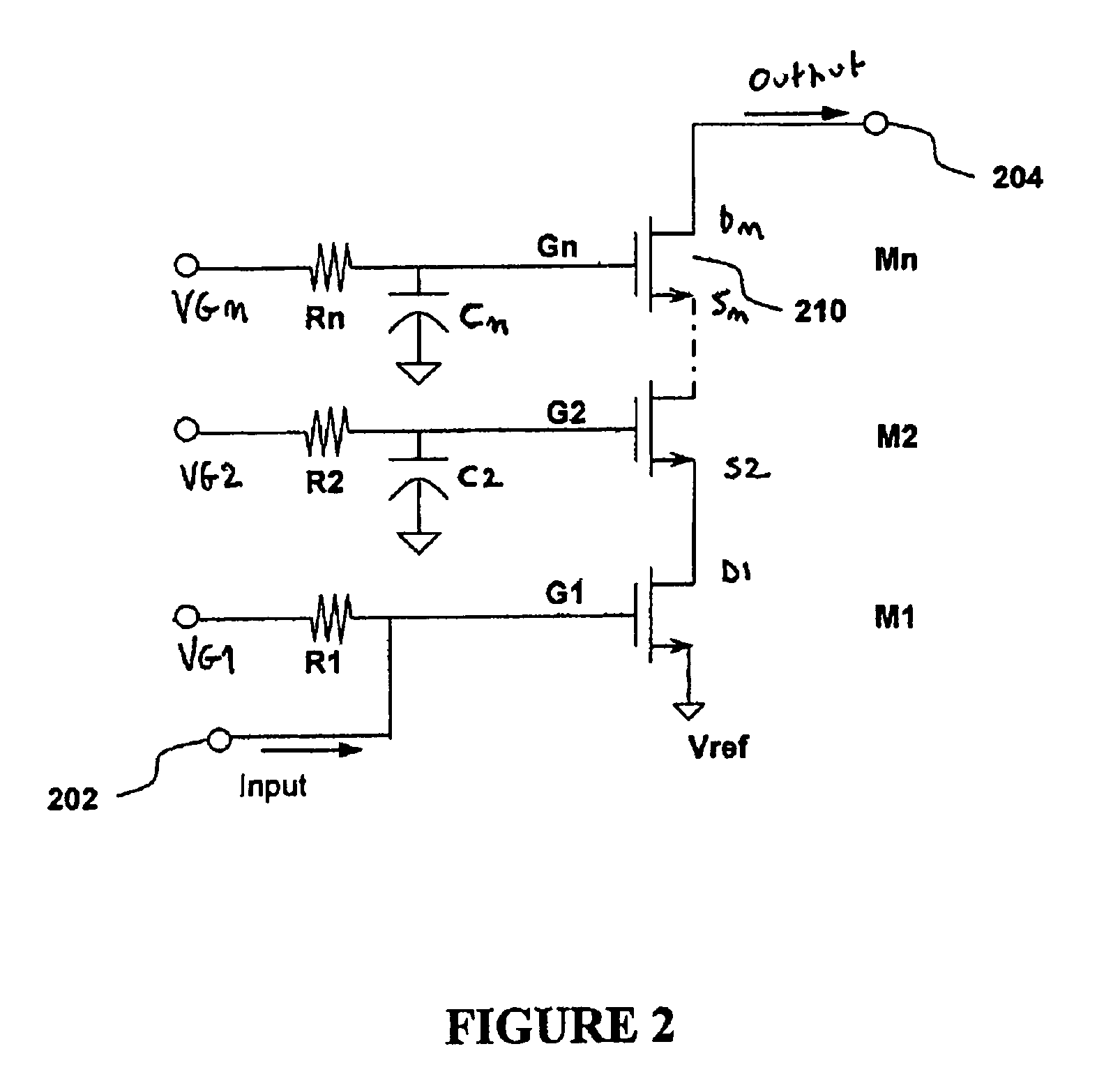

Stacked linear power amplifier with capacitor feedback and resistor isolation

ActiveUS8487706B2MinimizationMaximizeAmplifier combinationsAmplififers with field-effect devicesCapacitanceLinear power amplifier

A power amplifier with stacked, serially connected, field effect transistors is described. DC control voltage inputs are fed to the gates of each transistor. Capacitors are coupled to the transistors. The inputs and the capacitors are controlled to minimize generation of non-linearities of each field effect transistor and / or to maximize cancellation of distortions between the field effect transistors of the power amplifier in order to improve linearity of the power amplifier output.

Owner:PSEMI CORP

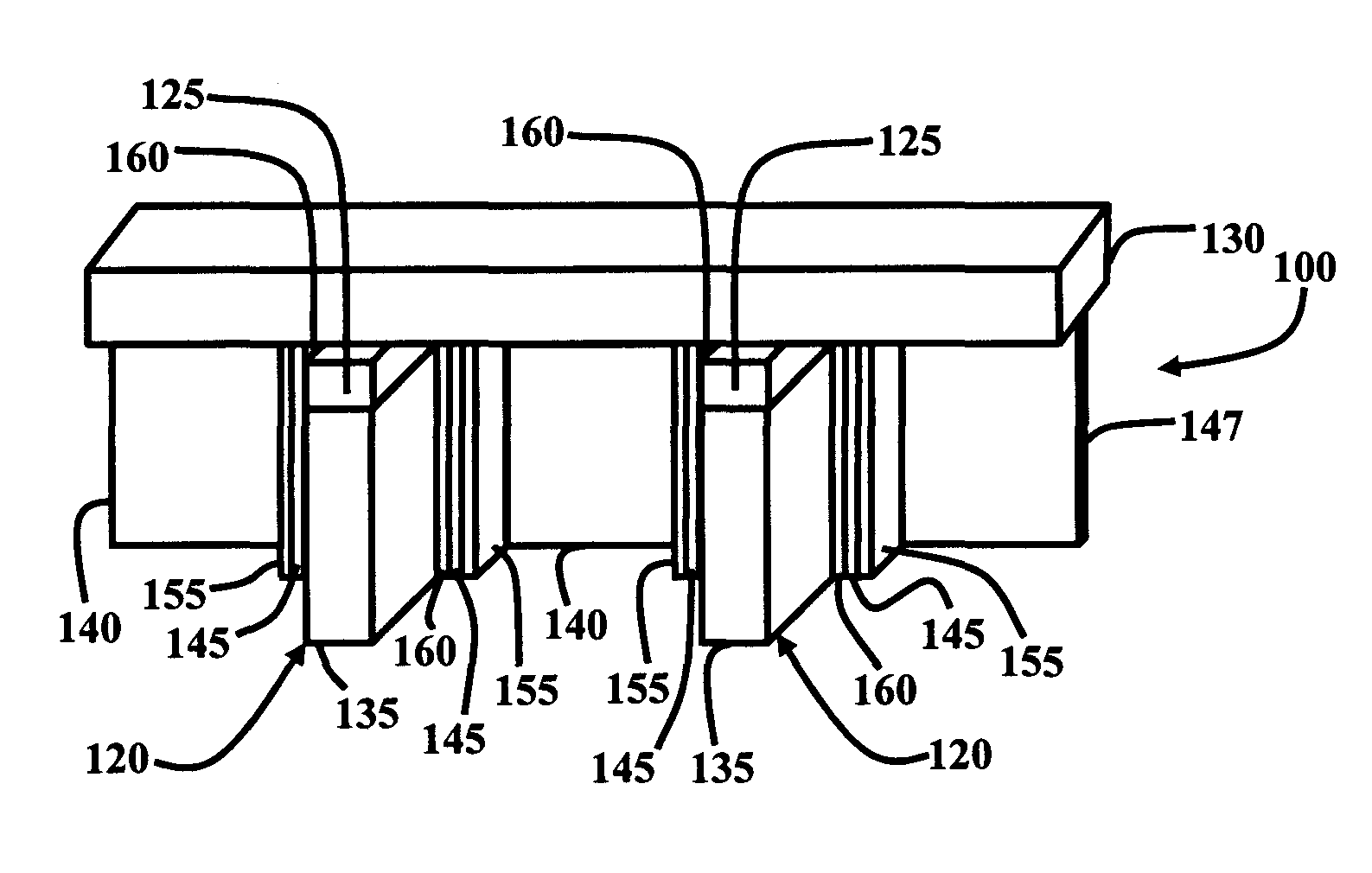

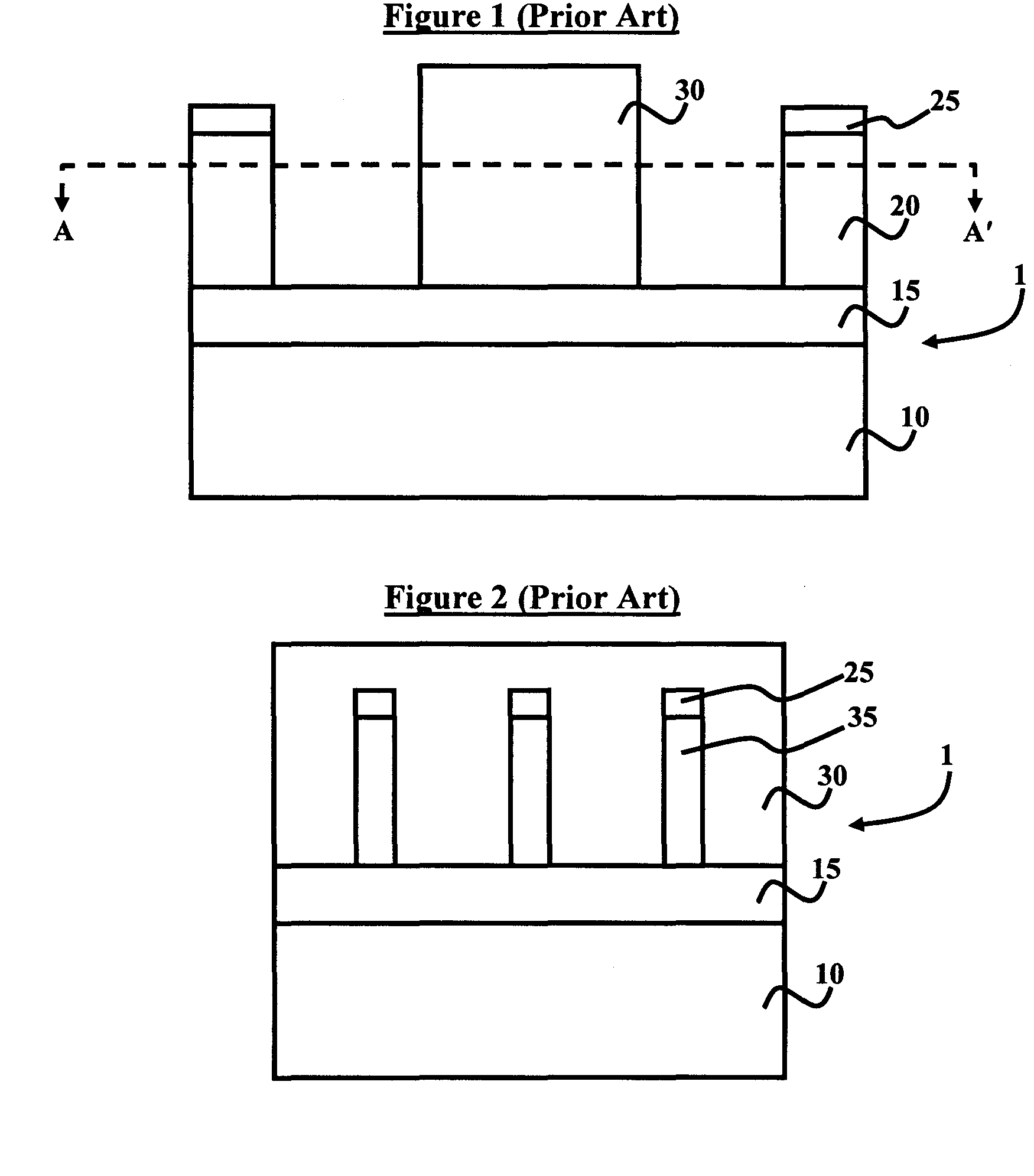

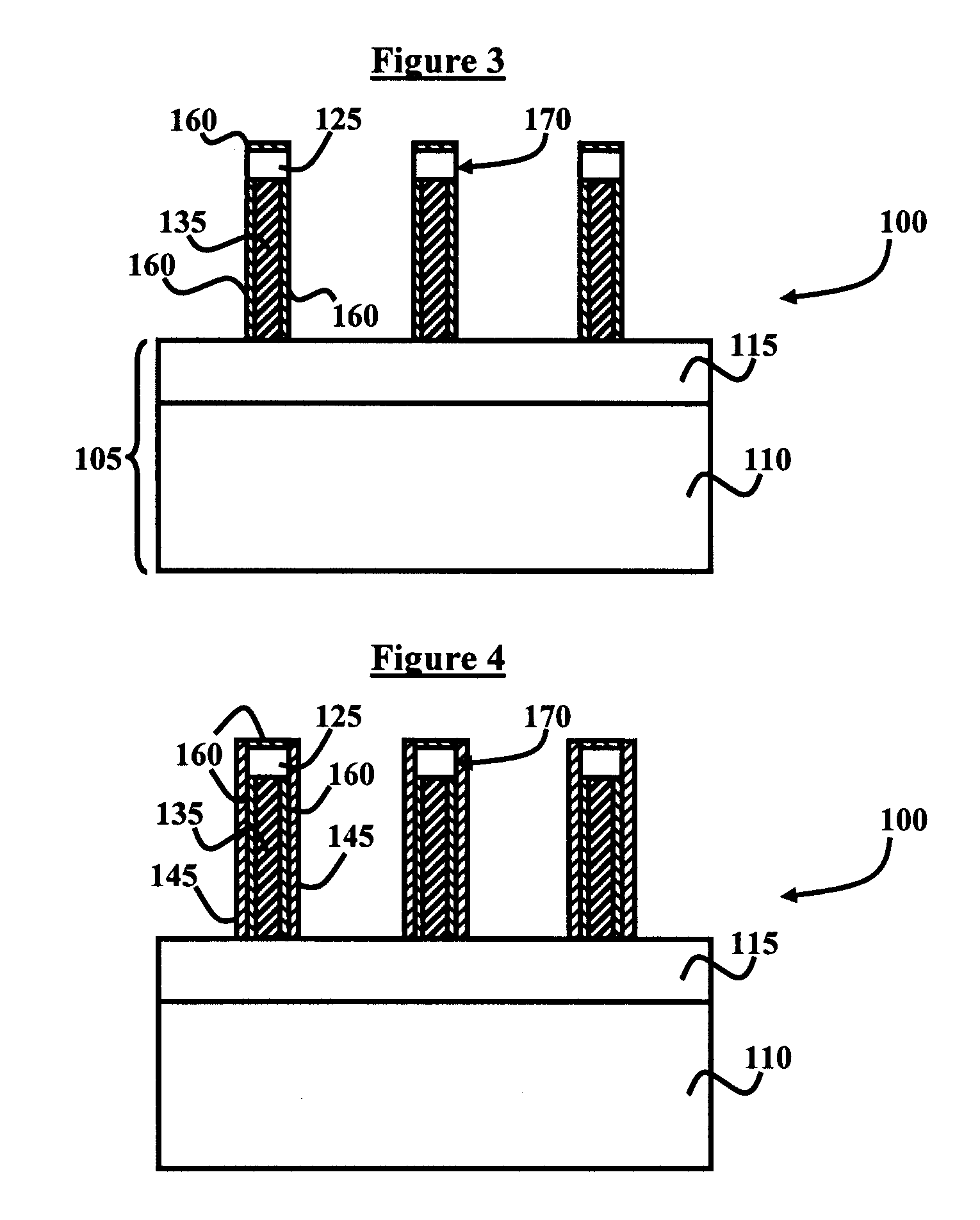

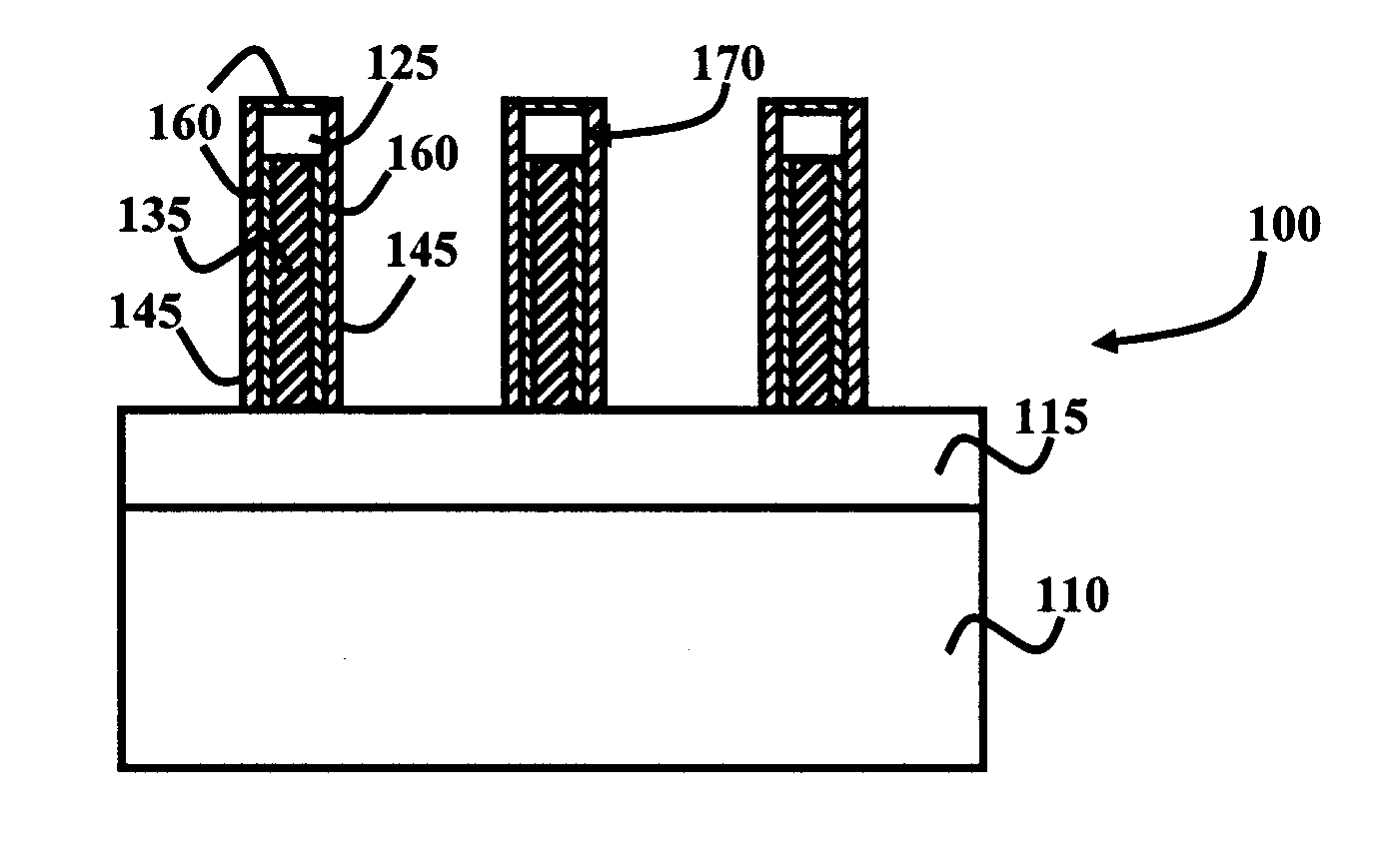

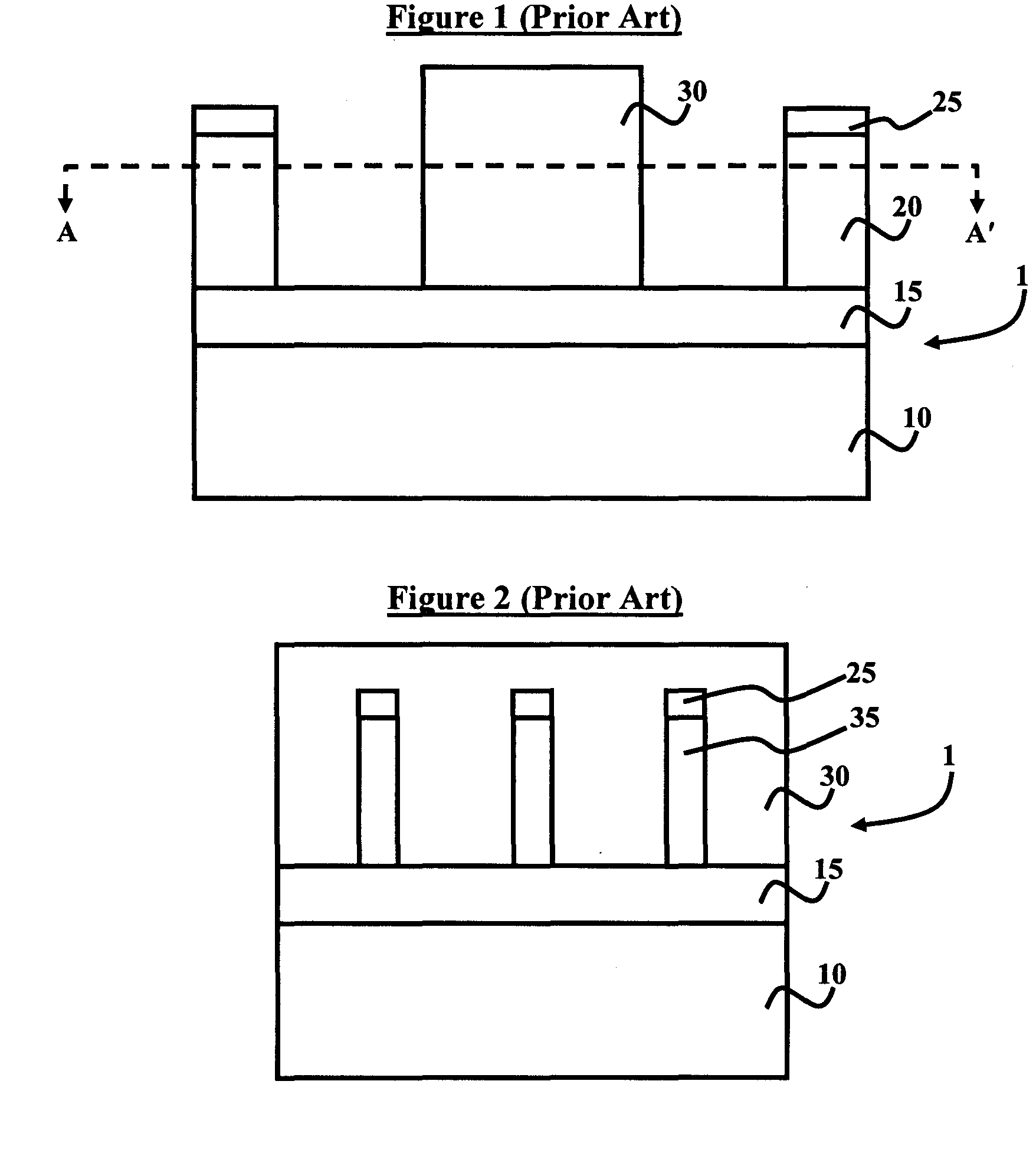

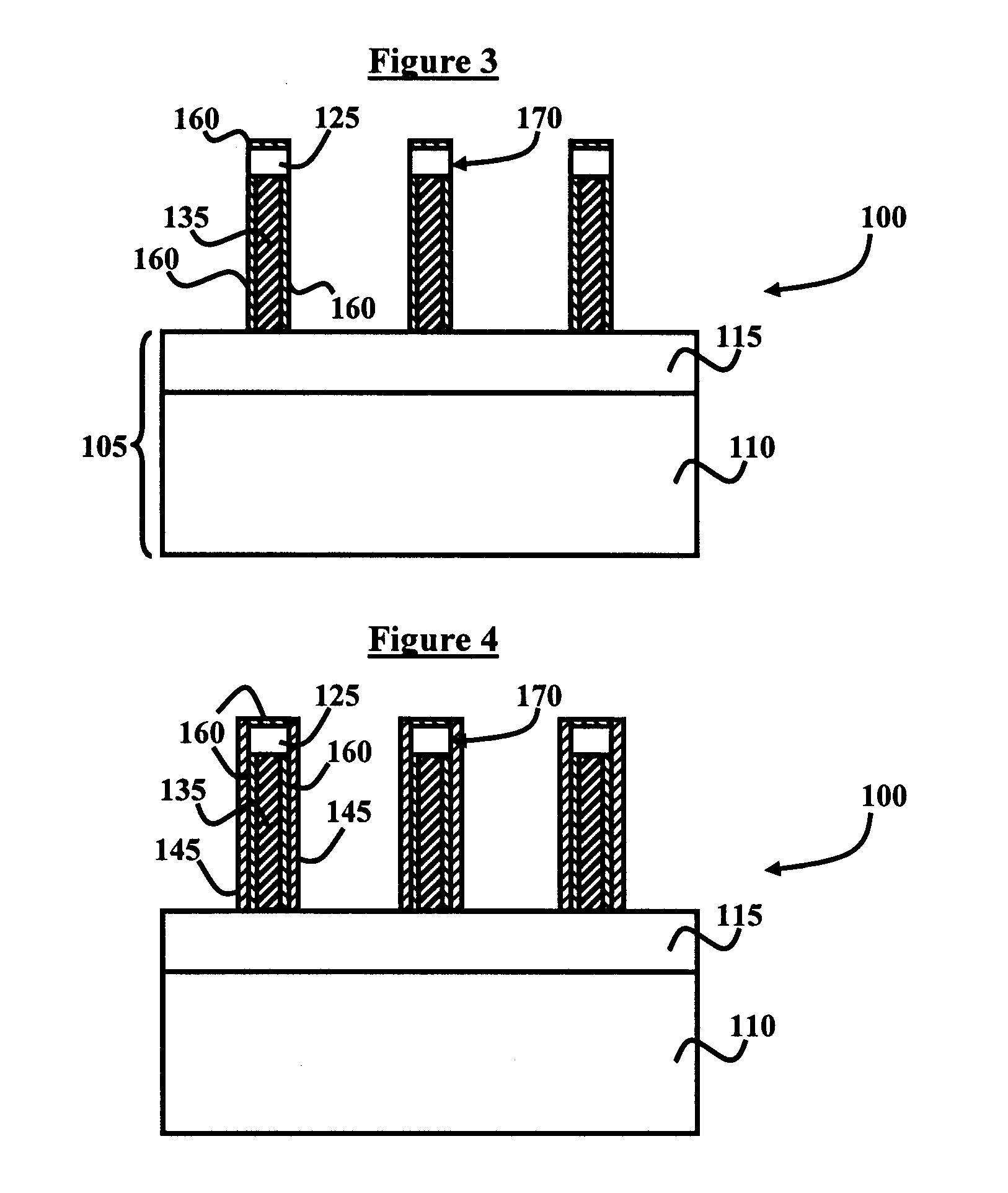

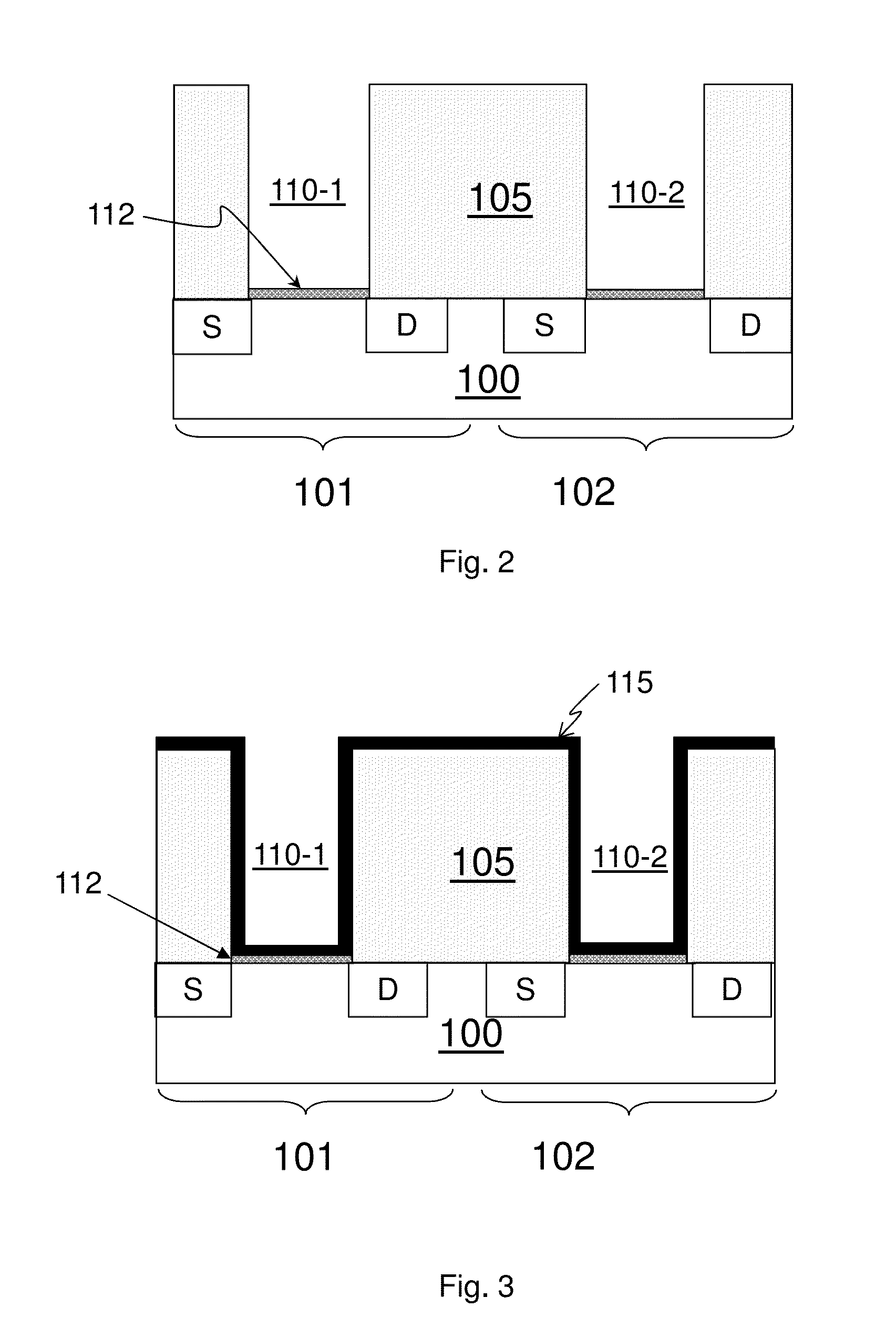

FinFET with low gate capacitance and low extrinsic resistance

ActiveUS7105934B2Reduce gate capacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate insulator

A FinFET device and a method of lowering a gate capacitance and extrinsic resistance in a field effect transistor, wherein the method comprises forming an isolation layer comprising a BOX layer over a substrate, configuring source / drain regions above the isolation layer, forming a fin structure over the isolation layer, configuring a first gate electrode adjacent to the fin structure, disposing a gate insulator between the first gate electrode and the fin structure, positioning a second gate electrode transverse to the first gate electrode, and depositing a third gate electrode on the fin structure, the first gate electrode, and the second gate electrode, wherein the isolation layer is formed beneath the insulator, the first gate electrode, and the fin structure. The method further comprises sandwiching the second gate electrode with a dielectric material. The fin structure is formed by depositing an oxide layer over a silicon layer.

Owner:MICROSOFT TECH LICENSING LLC

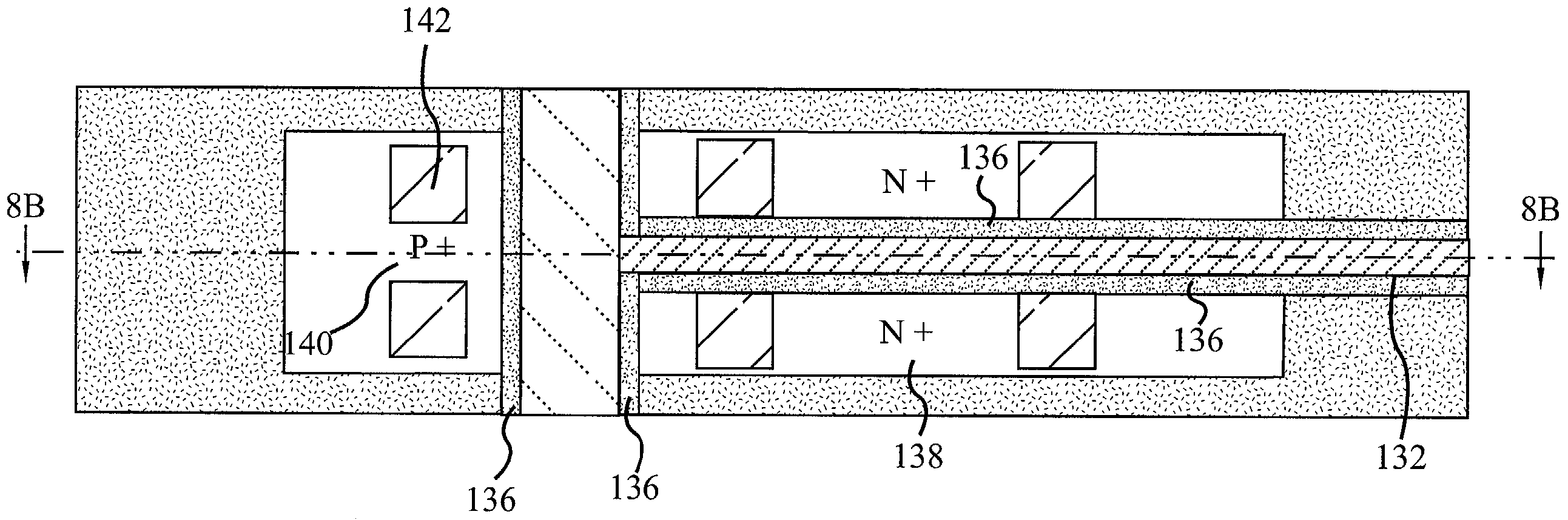

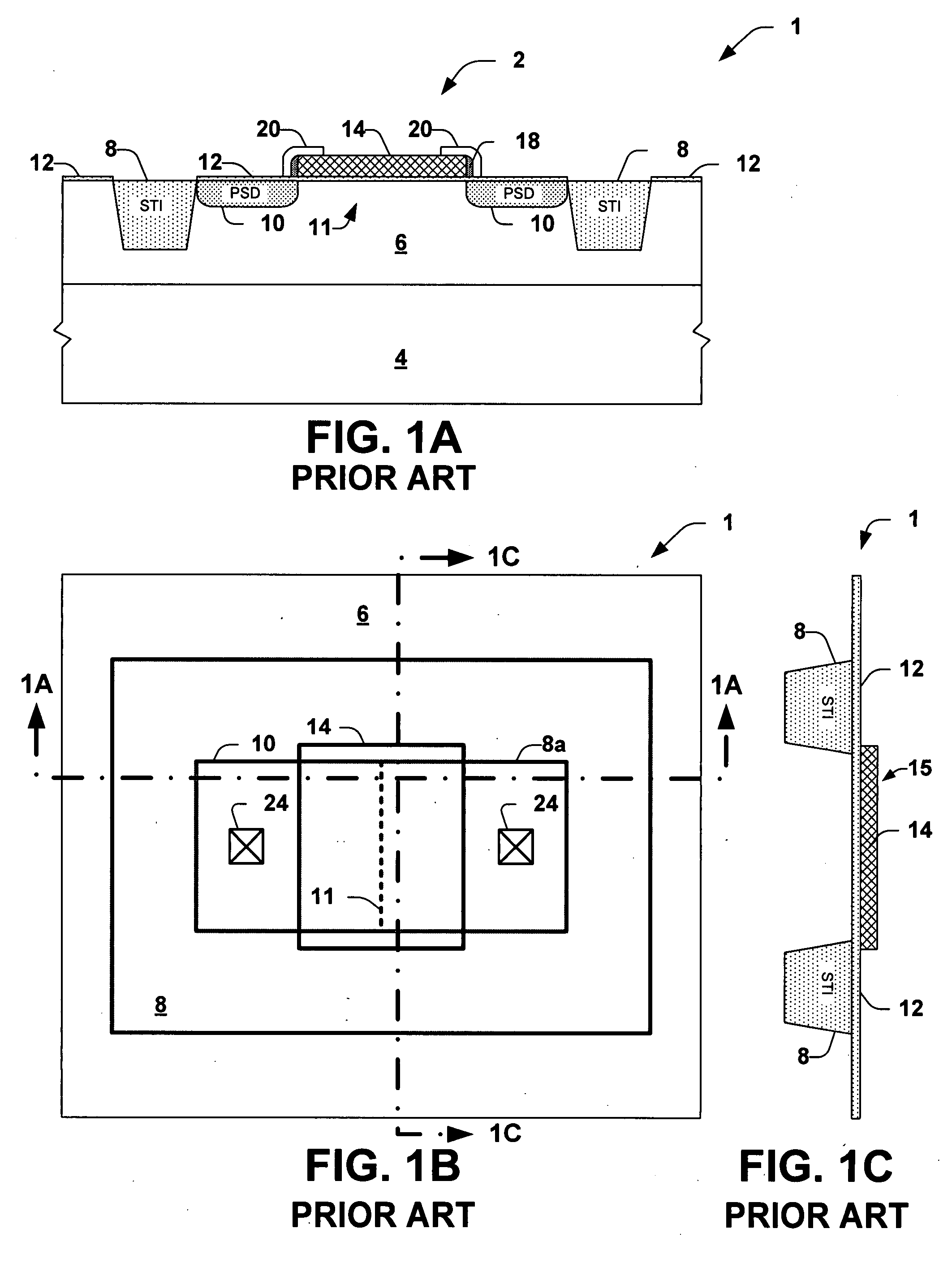

Body contact mosfet

A body contact structure utilizing an insulating structure between the body contact portion of the active area and the transistor portion of the active area is disclosed. In one embodiment, the present invention substitutes an insulator for at least a portion of the gate layer in the regions between the transistor and the body contact. In another embodiment, a portion of the gate layer is removed and replaced with an insulative layer in regions between the transistor and the body contact. In still another embodiment, the insulative structure is formed by forming multiple layers of gate dielectric between the gate and the body in regions between the transistor and the body contact. The body contact produced by these methods adds no significant gate capacitance to the gate.

Owner:GLOBALFOUNDRIES US INC

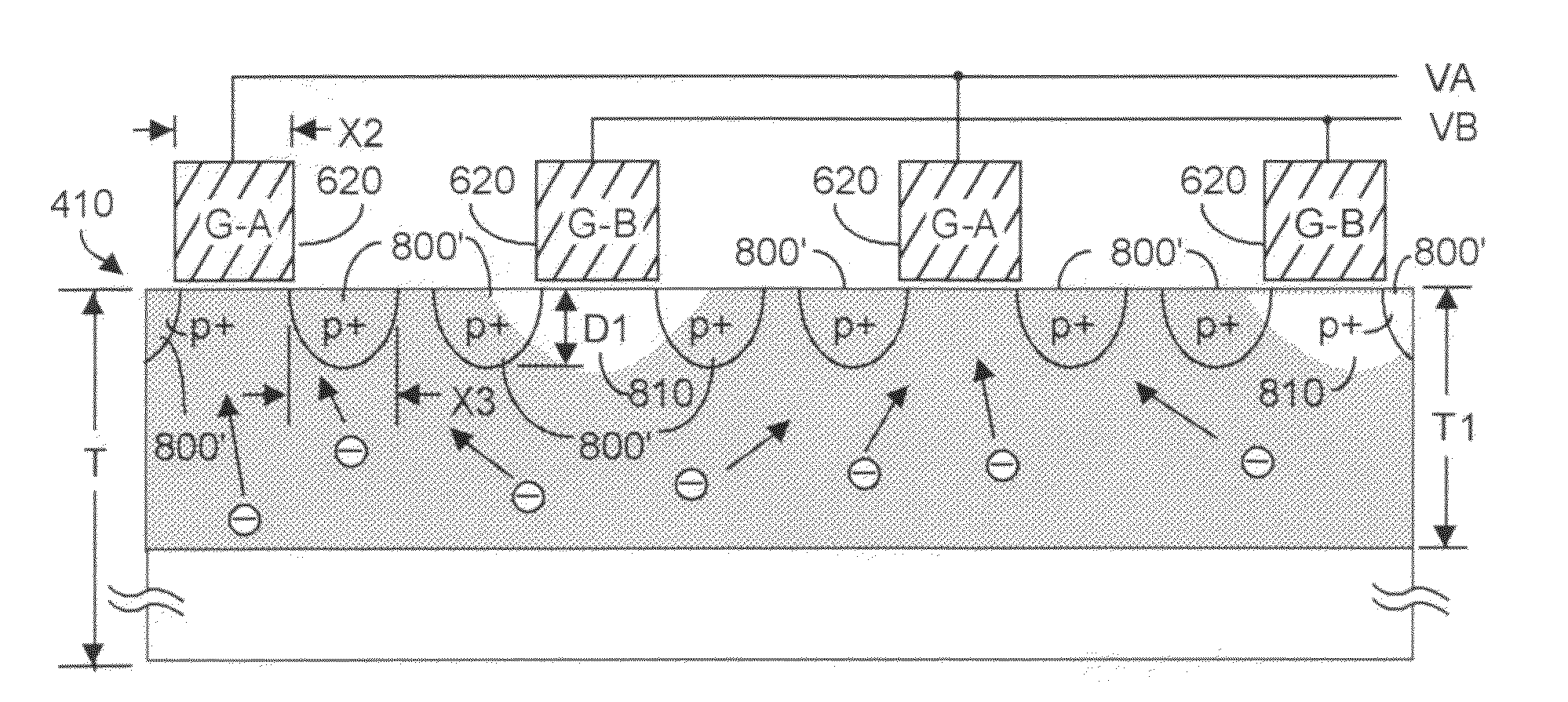

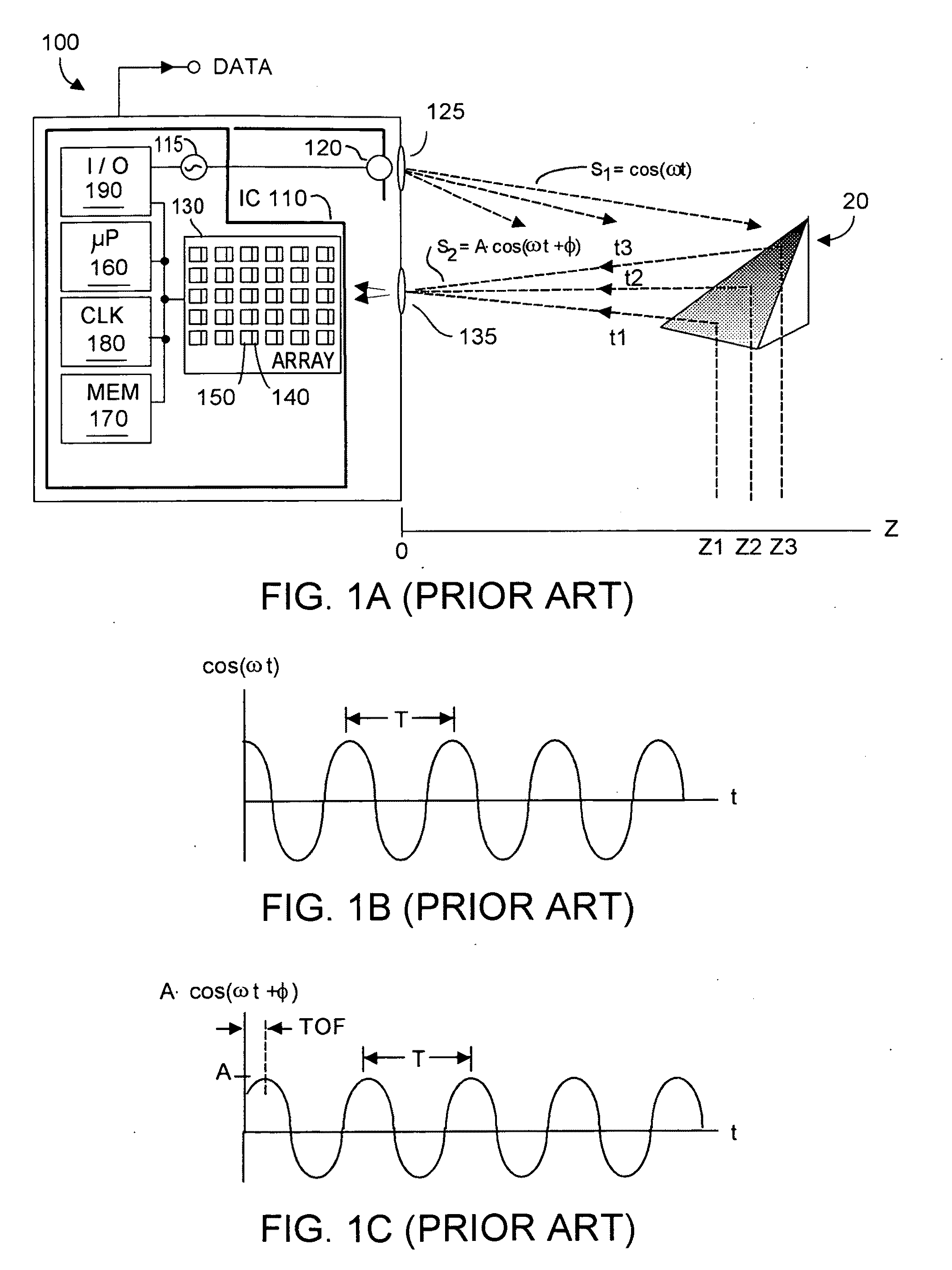

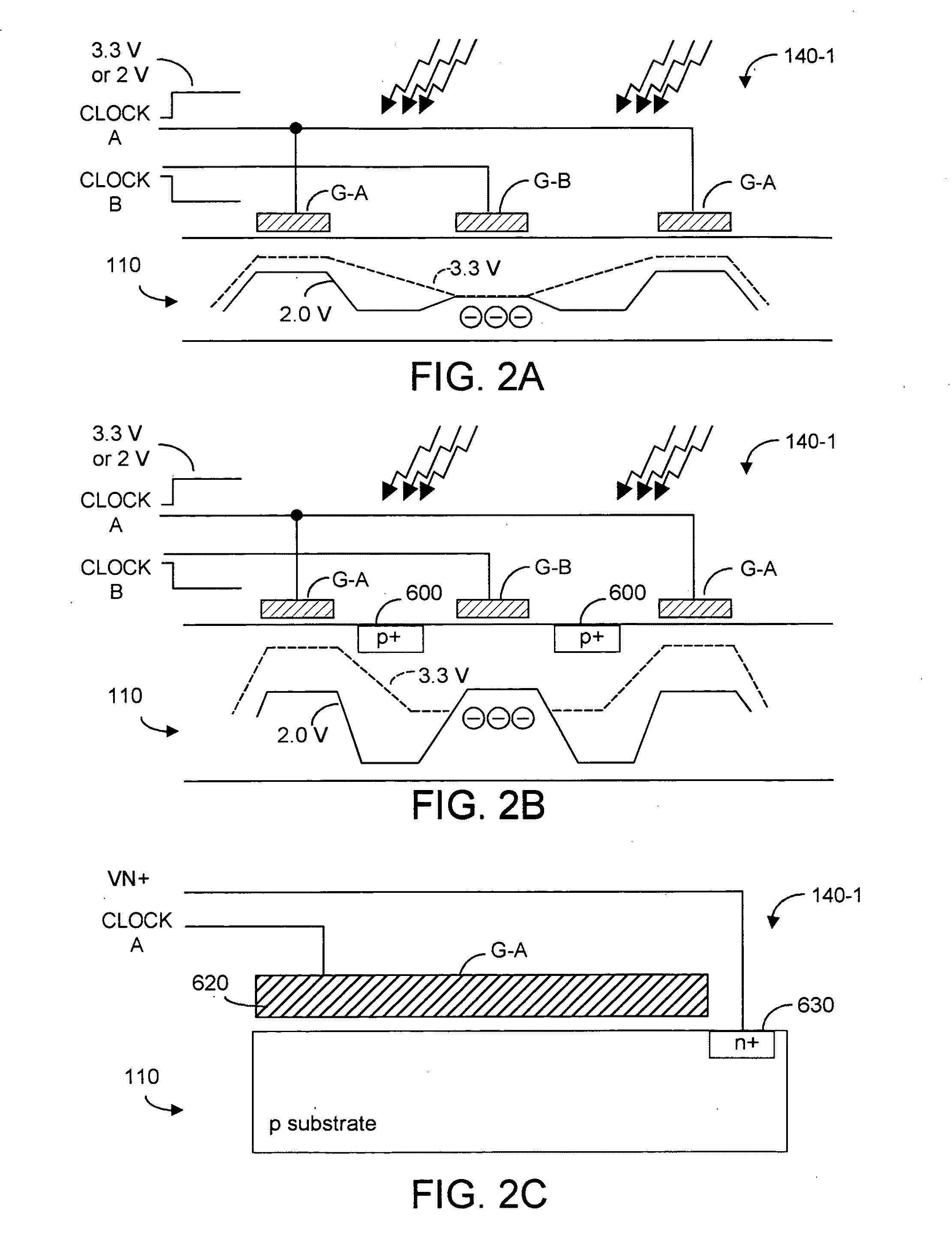

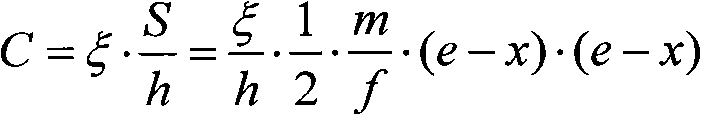

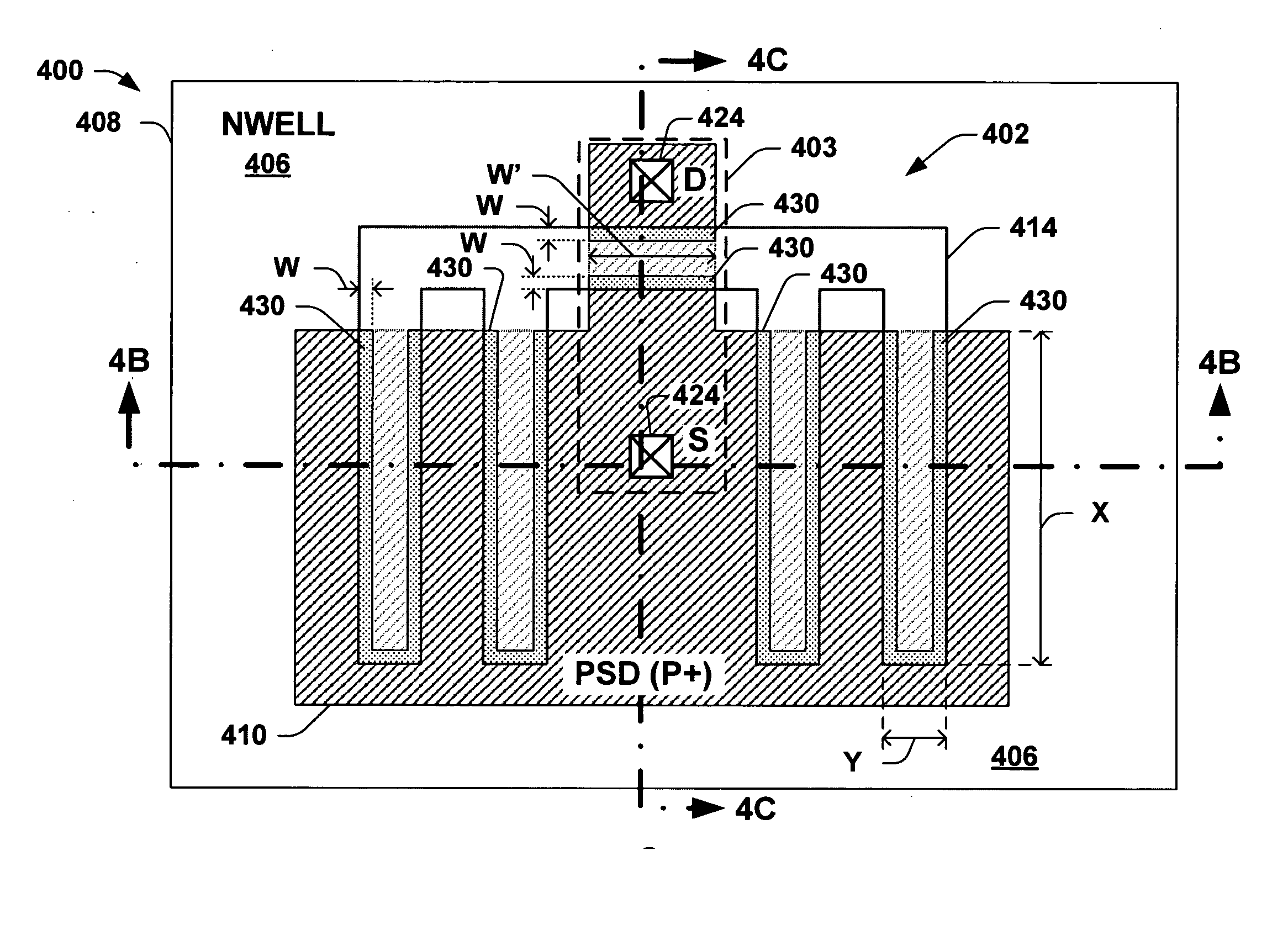

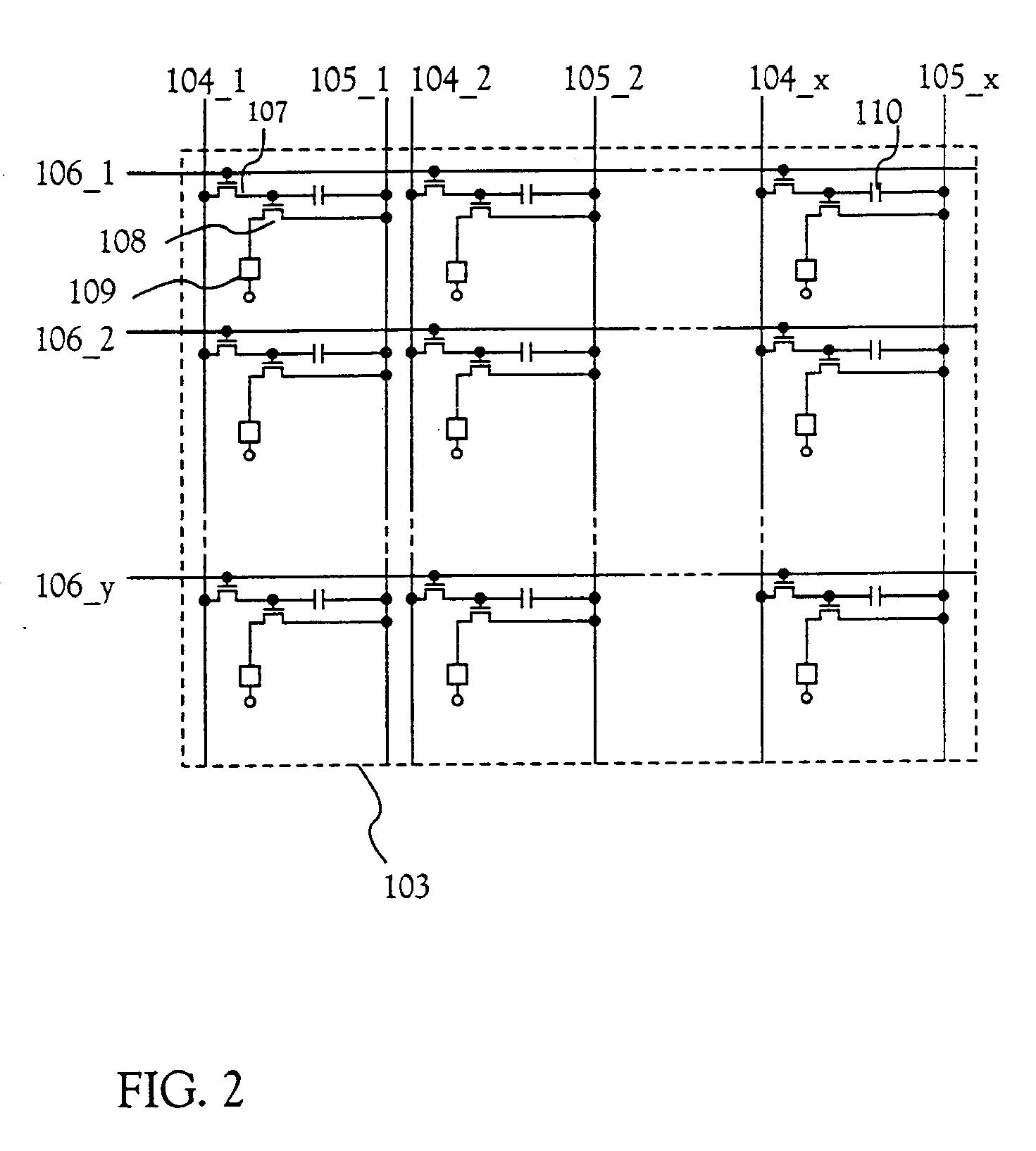

CMOS three-dimensional image sensor detectors having reduced inter-gate capacitance, and enhanced modulation contrast

A CMOS detector with pairs of interdigitated elongated finger-like collection gates includes p+ implanted regions that create charge barrier regions that can intentionally be overcome. These regions steer charge to a desired collection gate pair for collection. The p+ implanted regions may be formed before and / or after formation of the collection gates. These regions form charge barrier regions when an associated collection gate is biased low. The barriers are overcome when an associated collection gate is high. These barrier regions steer substantially all charge to collection gates that are biased high, enhancing modulation contrast. Advantageously, the resultant structure has reduced power requirements in that inter-gate capacitance is reduced in that inter-gate spacing can be increased over prior art gate spacing and lower swing voltages may be used. Also higher modulation contrast is achieved in that the charge collection area of the low gate(s) is significantly reduced.

Owner:MICROSOFT TECH LICENSING LLC

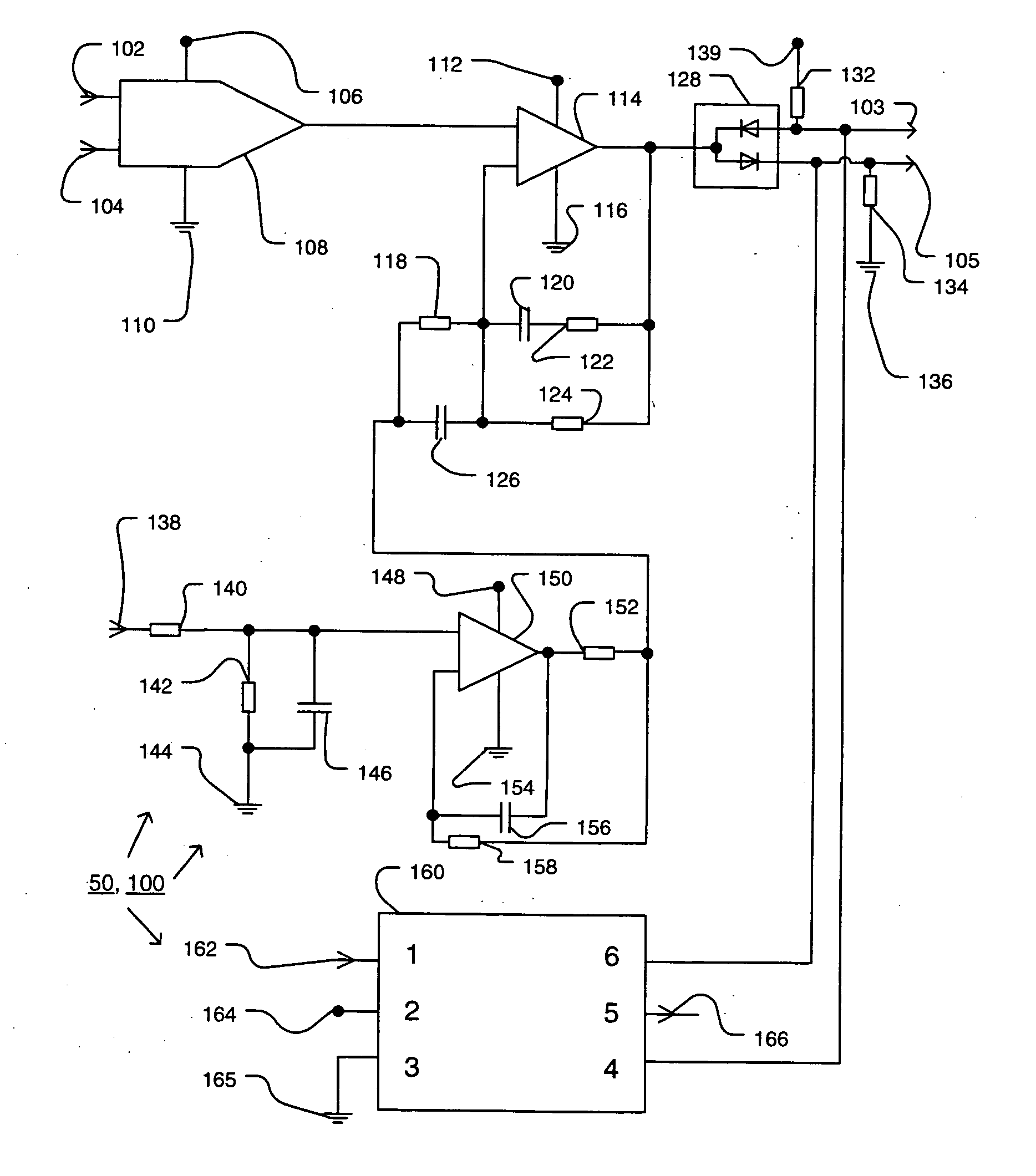

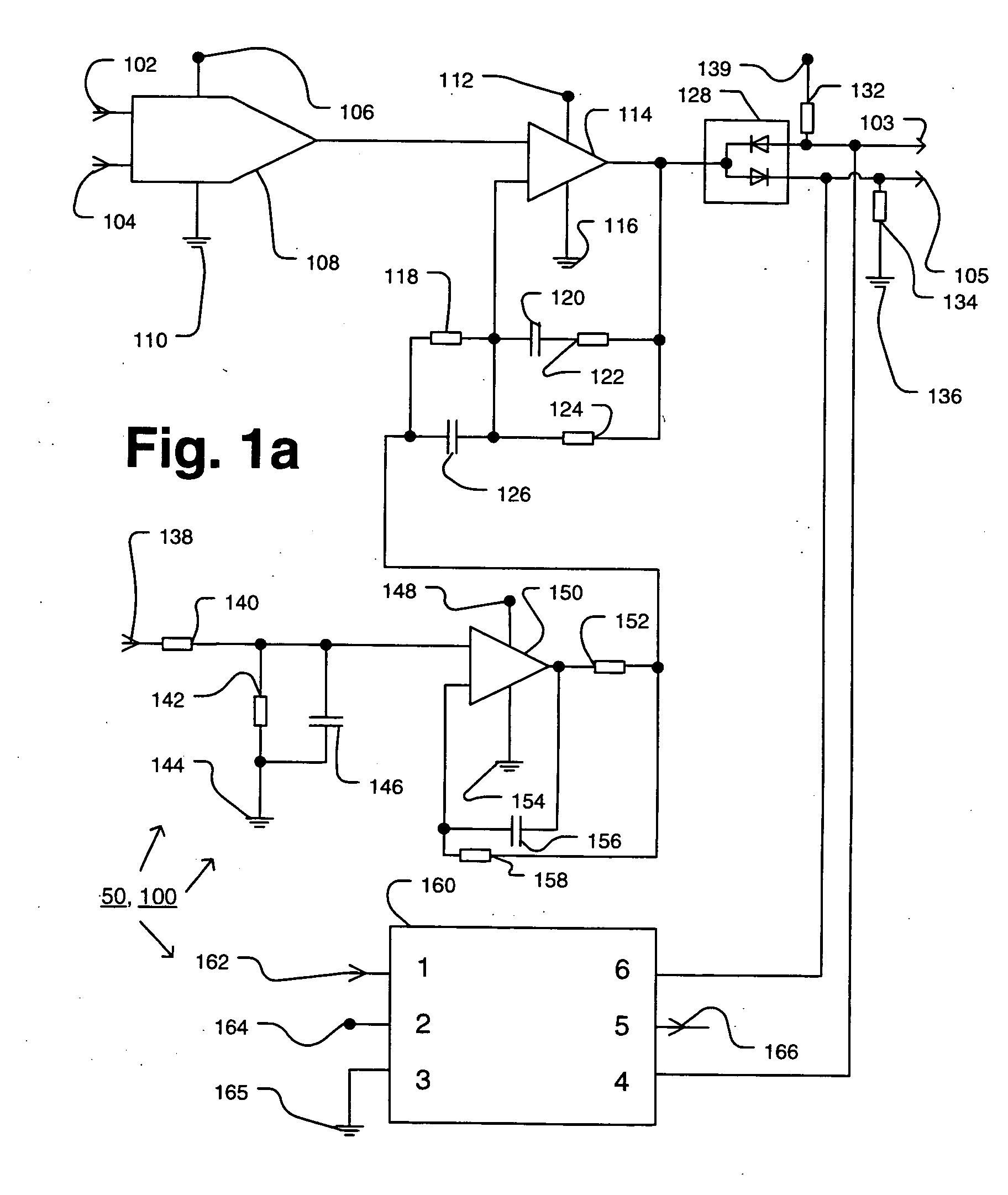

Current prediction in a switching power supply

ActiveUS20060119331A1Reliable supplyReduces and eliminates switchingTransistorEfficient power electronics conversionMicrocontrollerCapacitance

A high efficiency switching power supply including an analog front end, a battery control circuitry portion, a display and equalization circuitry portion, field effect transistor (FET) drivers, an isolated power supply transformer circuitry (and three associated sets of tap circuitry), microcontroller circuitry, oscillator circuitry, overcharge protection circuitry, programmable logic circuitry portion, and a zero current predictor. Overbiasing of the FET power supply switches, and / or other various circuitry features disclosed herein, helps achieve electrical power efficiencies of preferably greater than 95%, even more preferably greater than 98% and even more preferably greater than 99%. Preferably, the switching power supply has one or more of the following: (1) high electrical power efficiency (>95%. >98%, >99%); (2) overbiasing of a gate of a power supply switch; (3) a power supply switch with a low gate capacitance ratio; (4) multiple modes of operation; and (5) current prediction wherein an inductor voltage is used to control a constant current capacitor whose voltage indicates the level of current in the inductor.

Owner:ELECTROVAYA

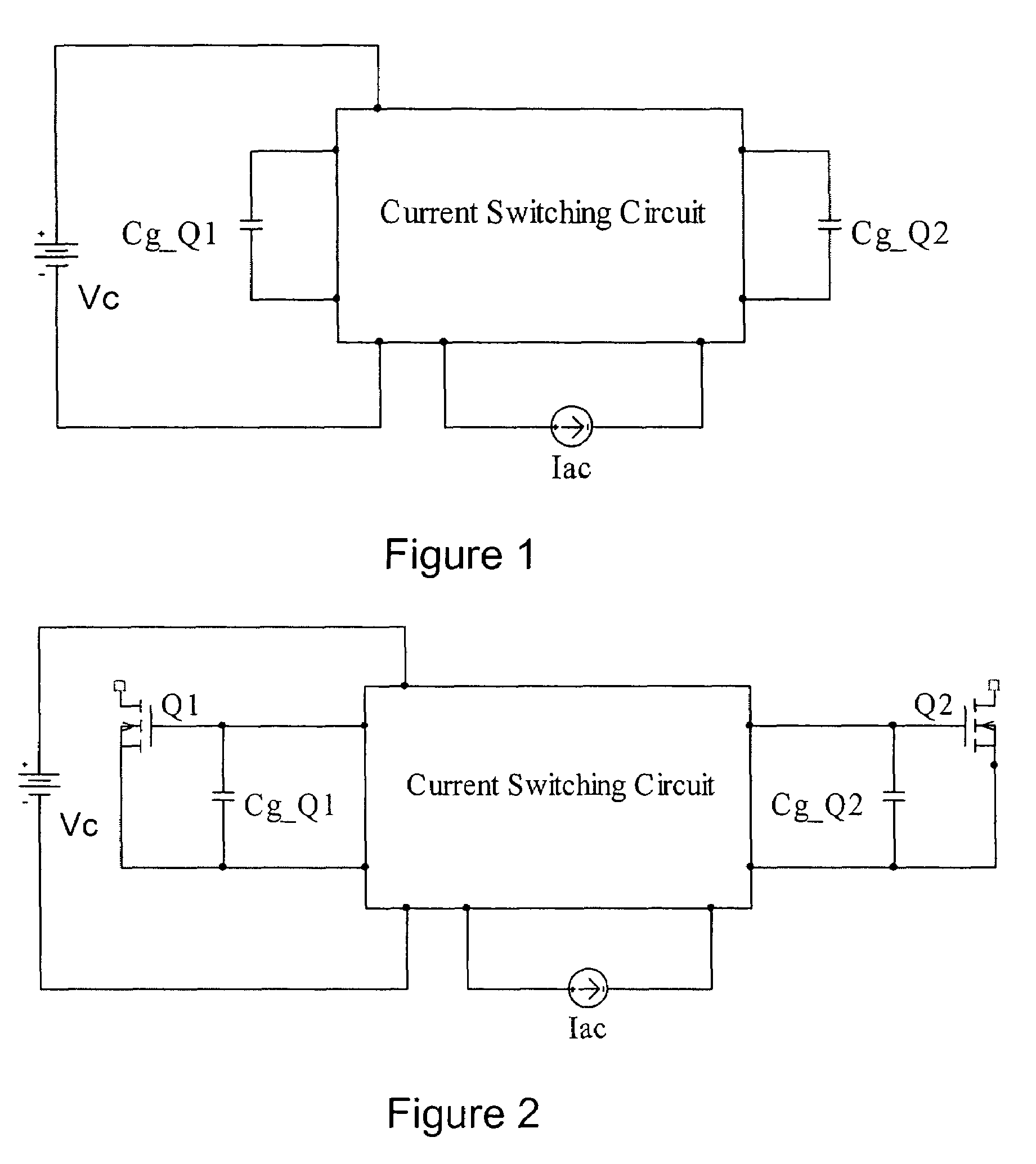

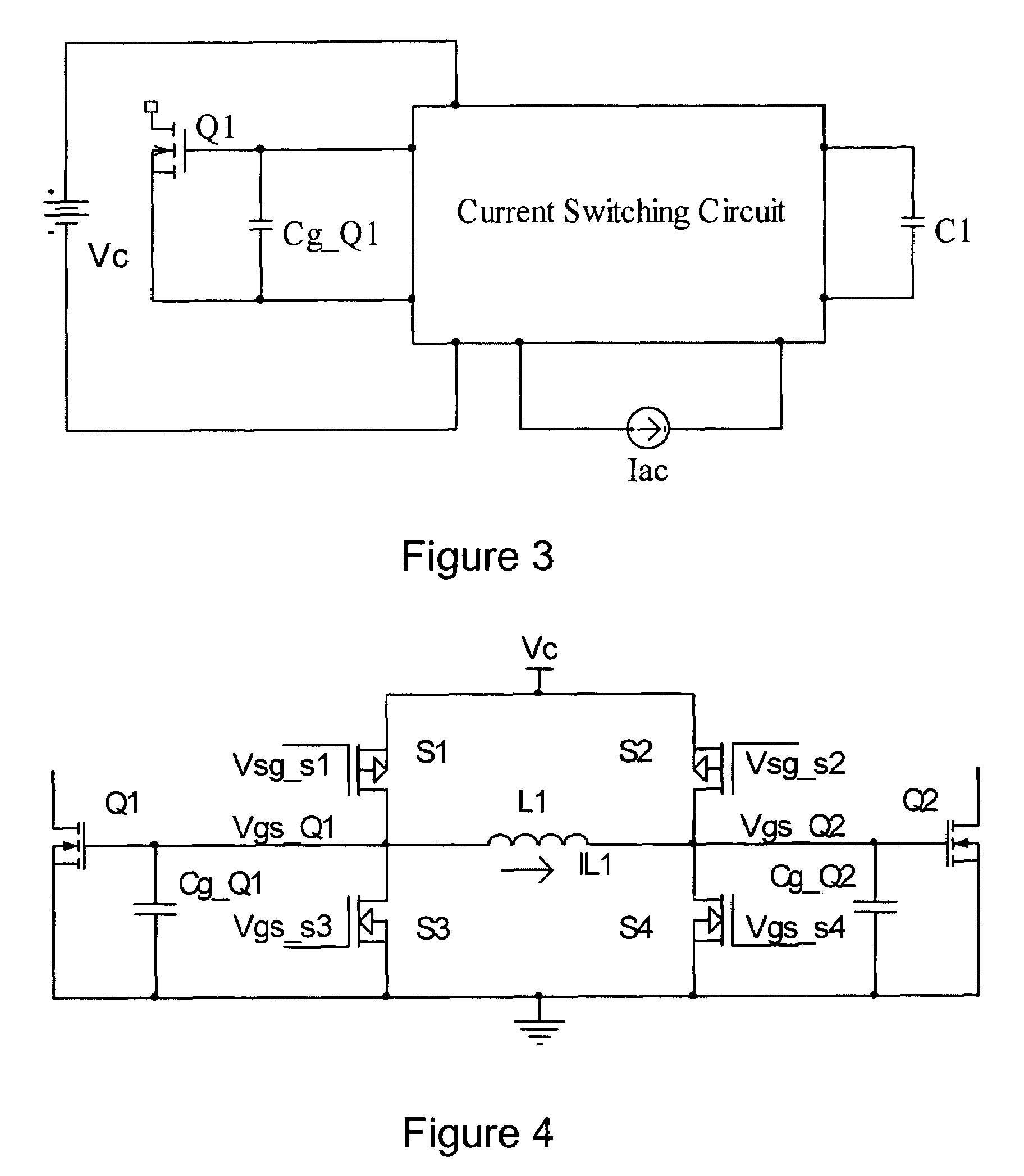

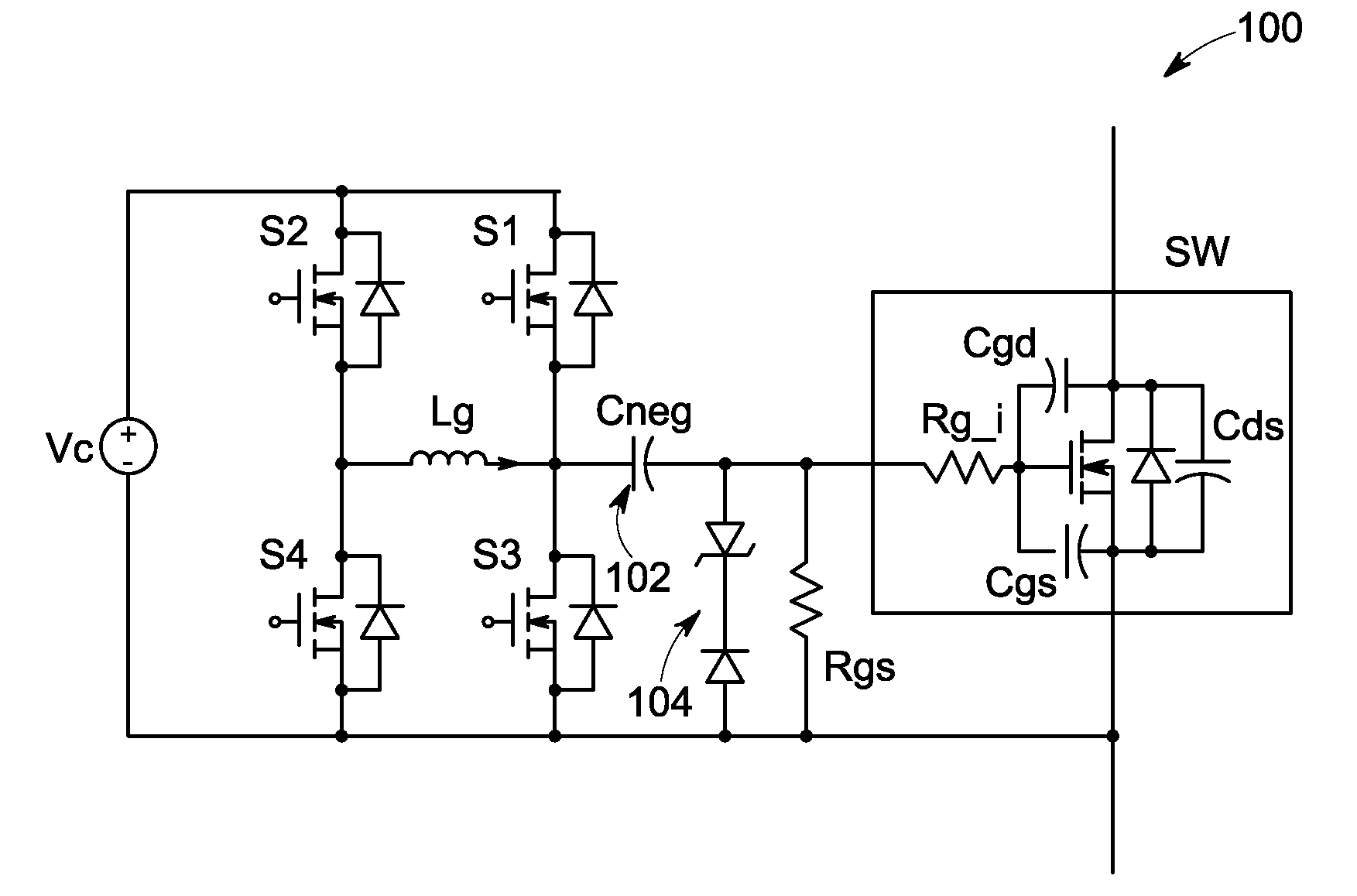

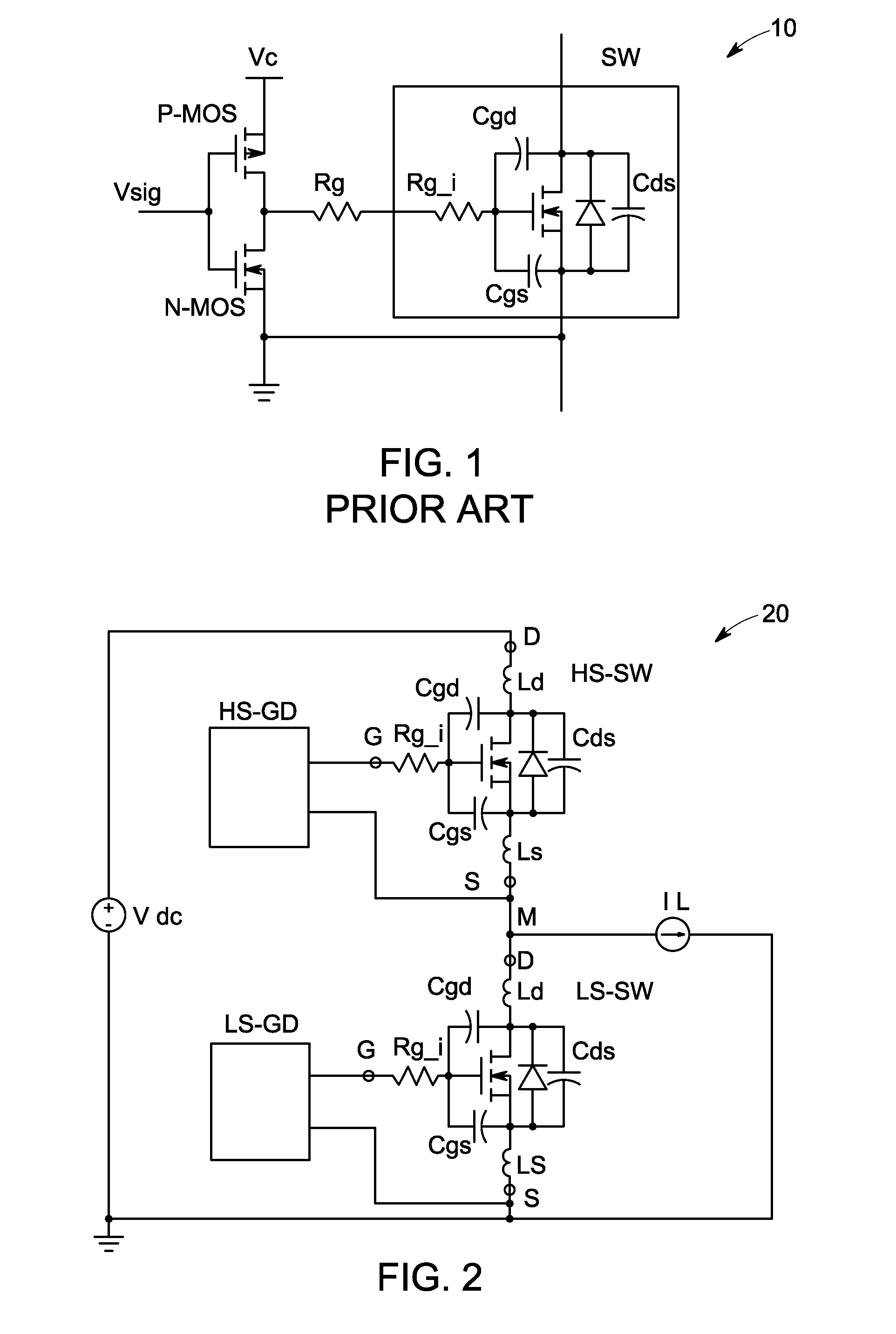

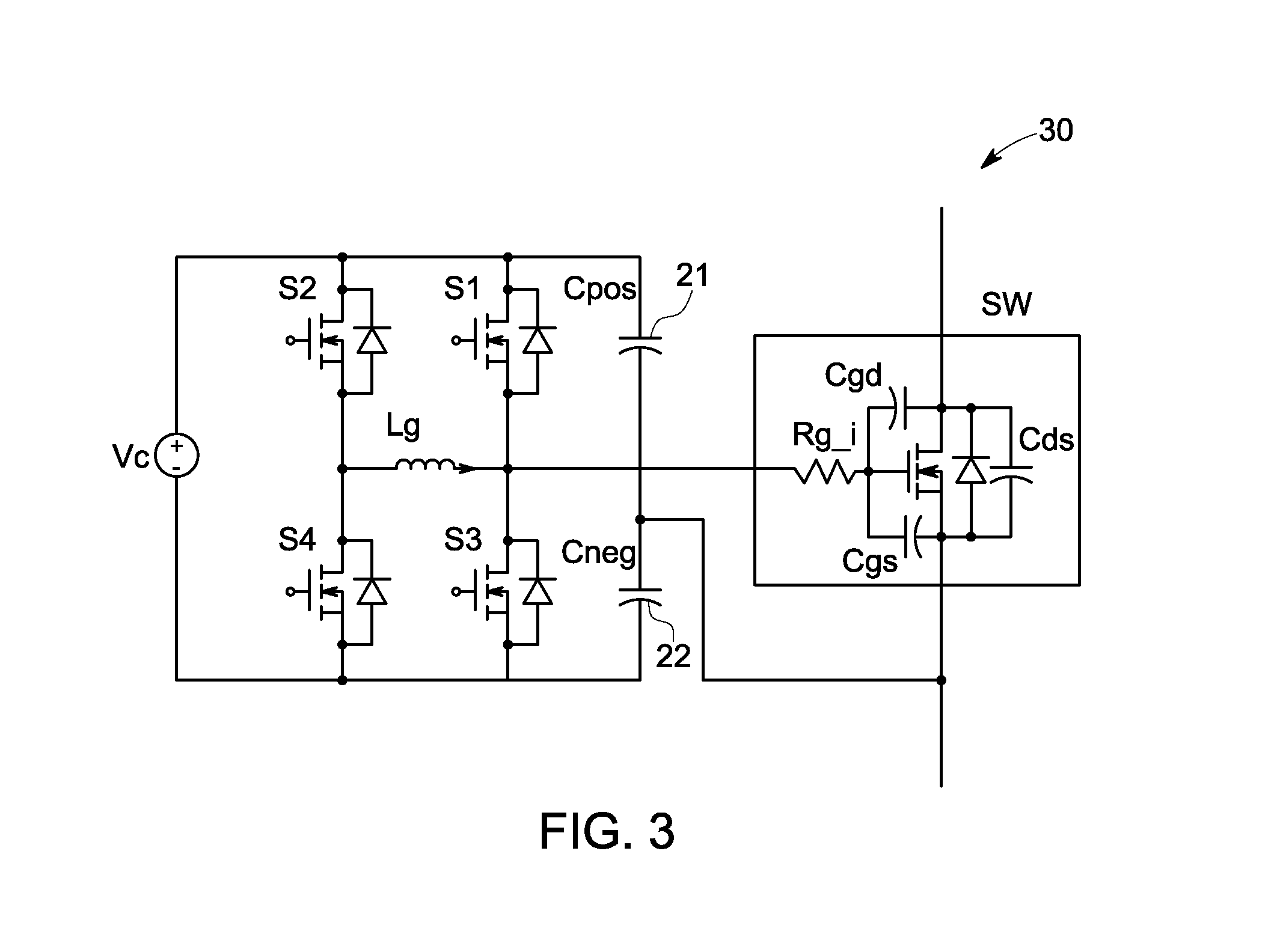

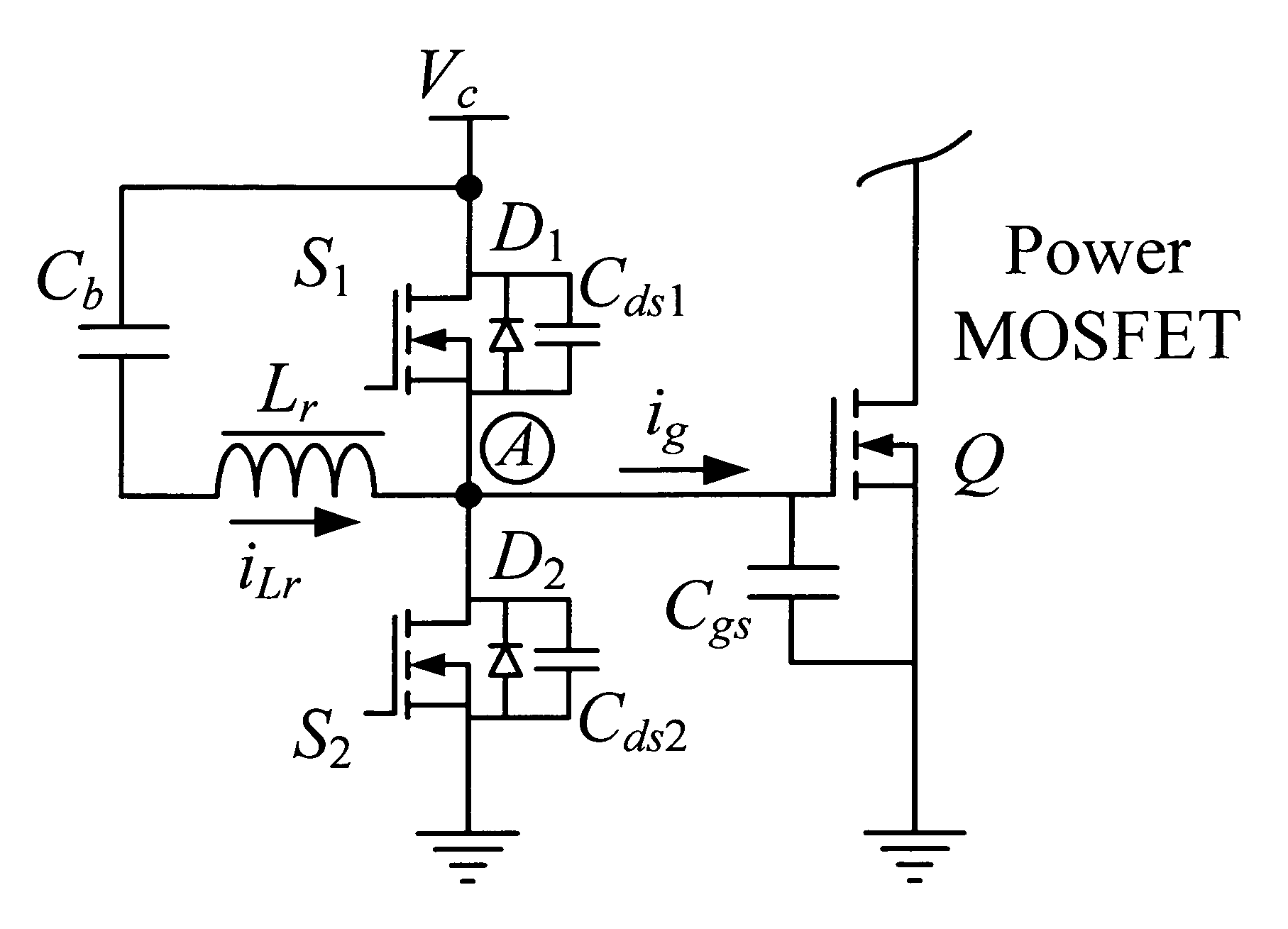

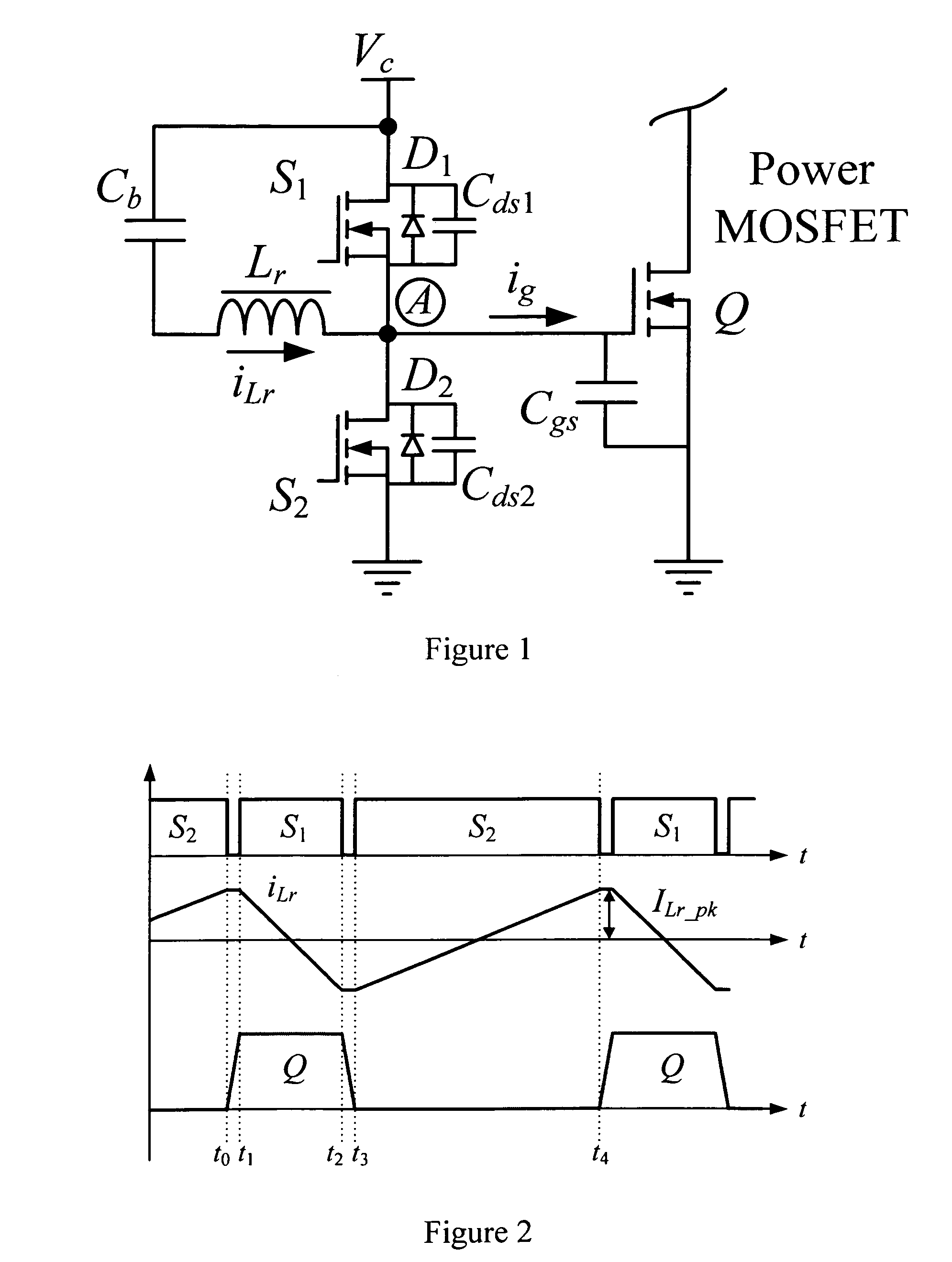

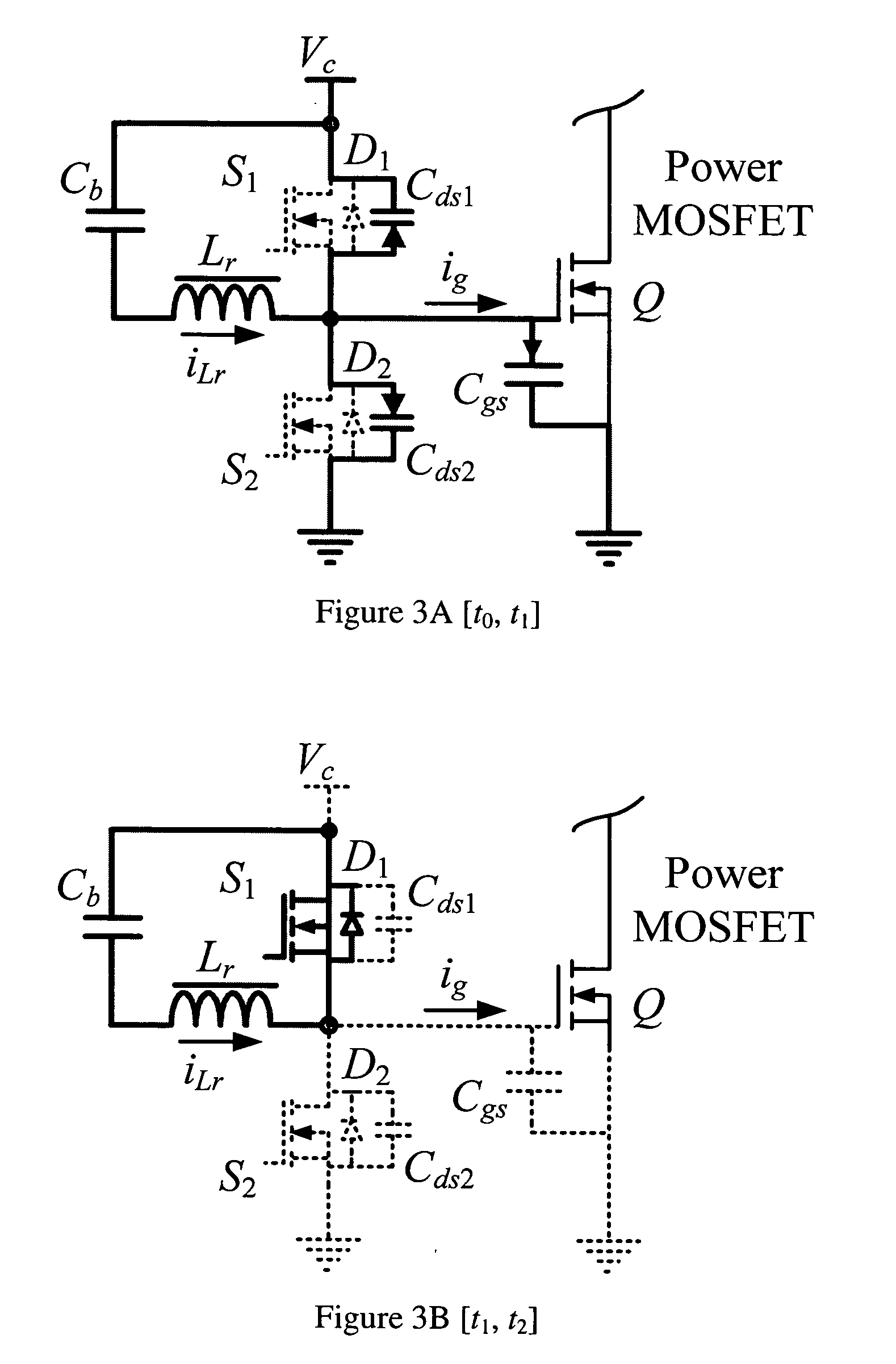

Resonant gate drive circuits

InactiveUS20060170043A1Reduce gate drive loss lossReduce loss other lossEfficient power electronics conversionAc-dc conversionCapacitanceDriver circuit

Owner:GANPOWER SEMICON FOSHAN LTD

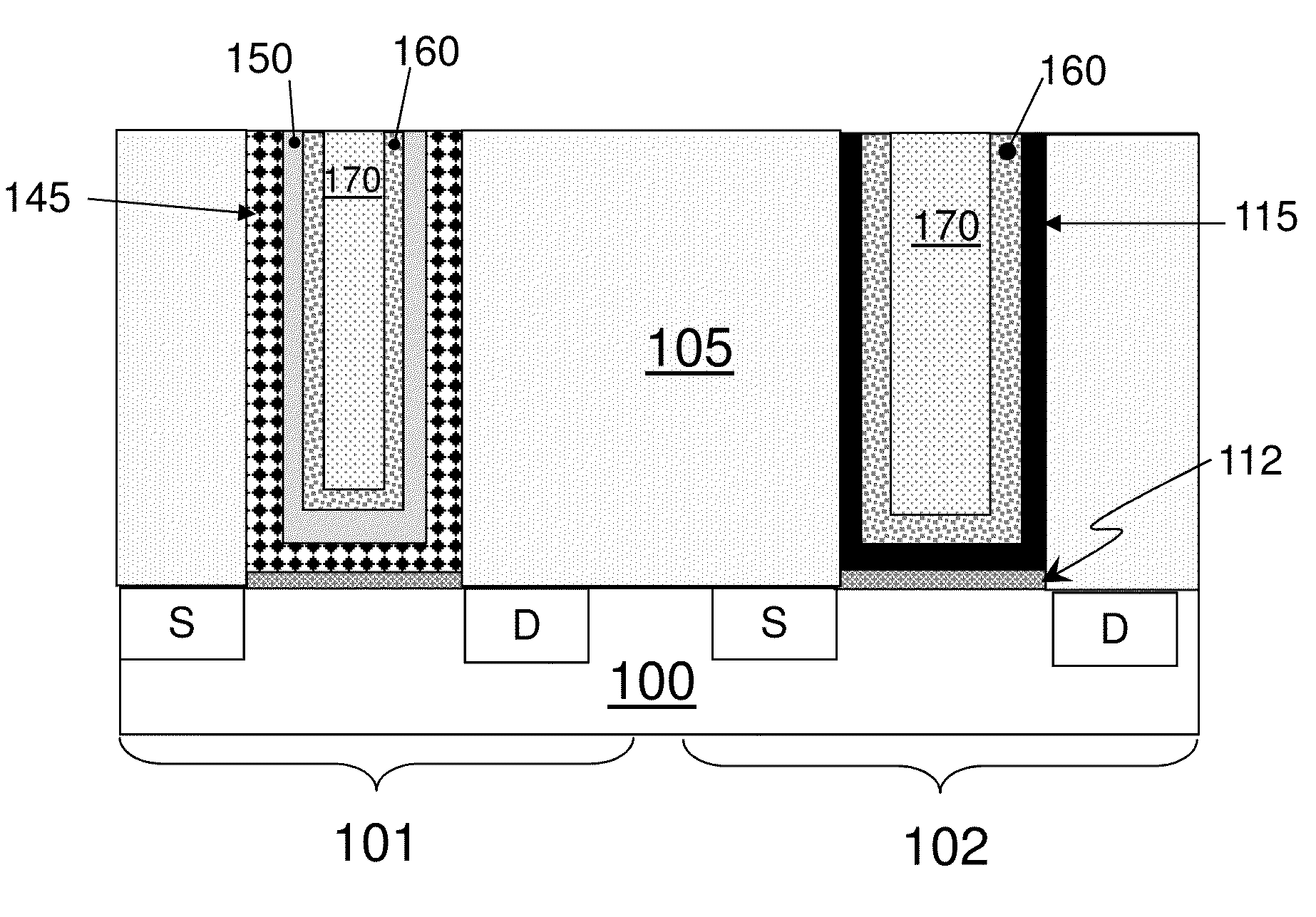

Semiconductor device and the method of manufacturing the same

ActiveUS20110303925A1Lower on-state resistanceLow impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing cost reductionPower semiconductor device

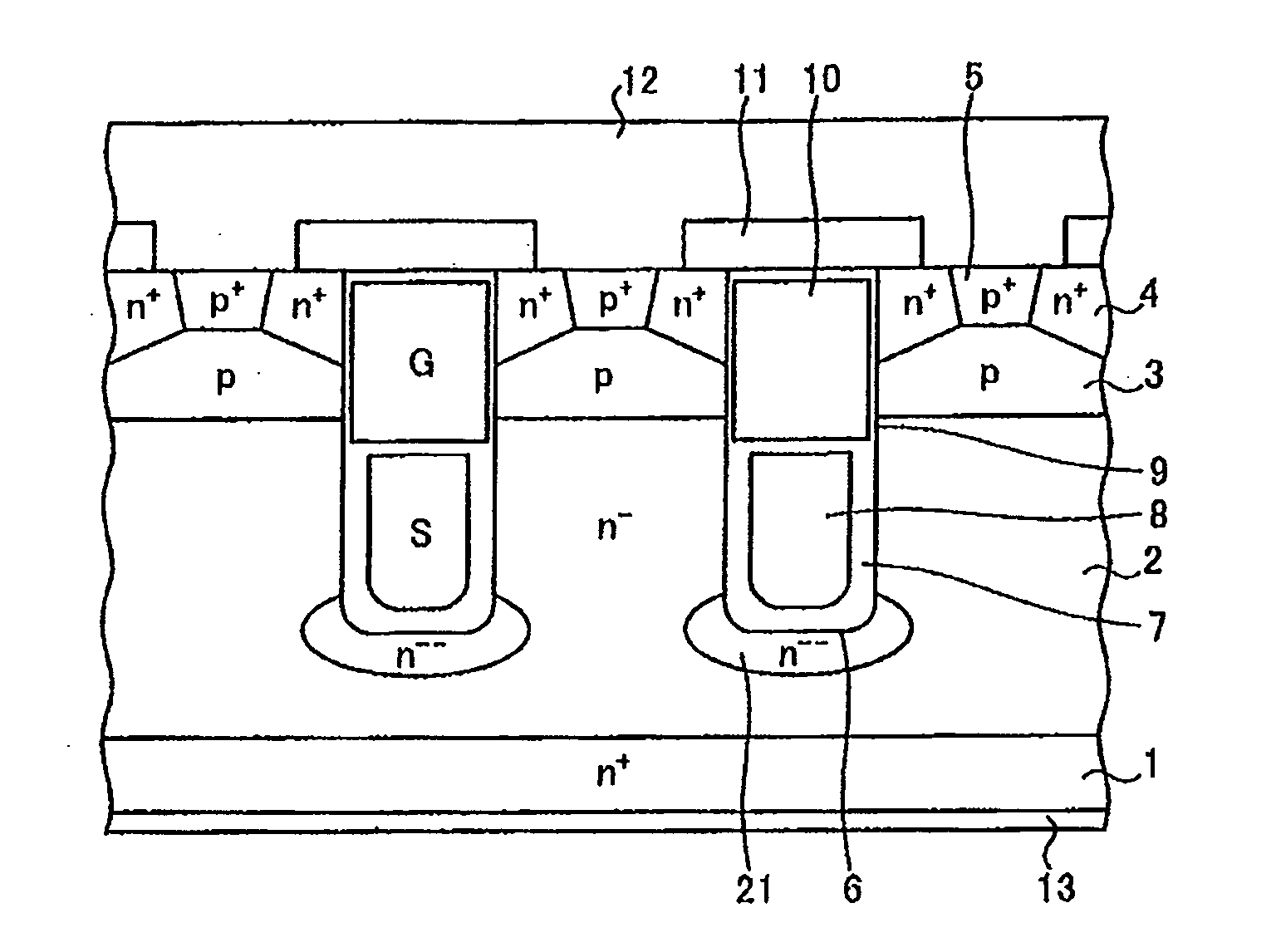

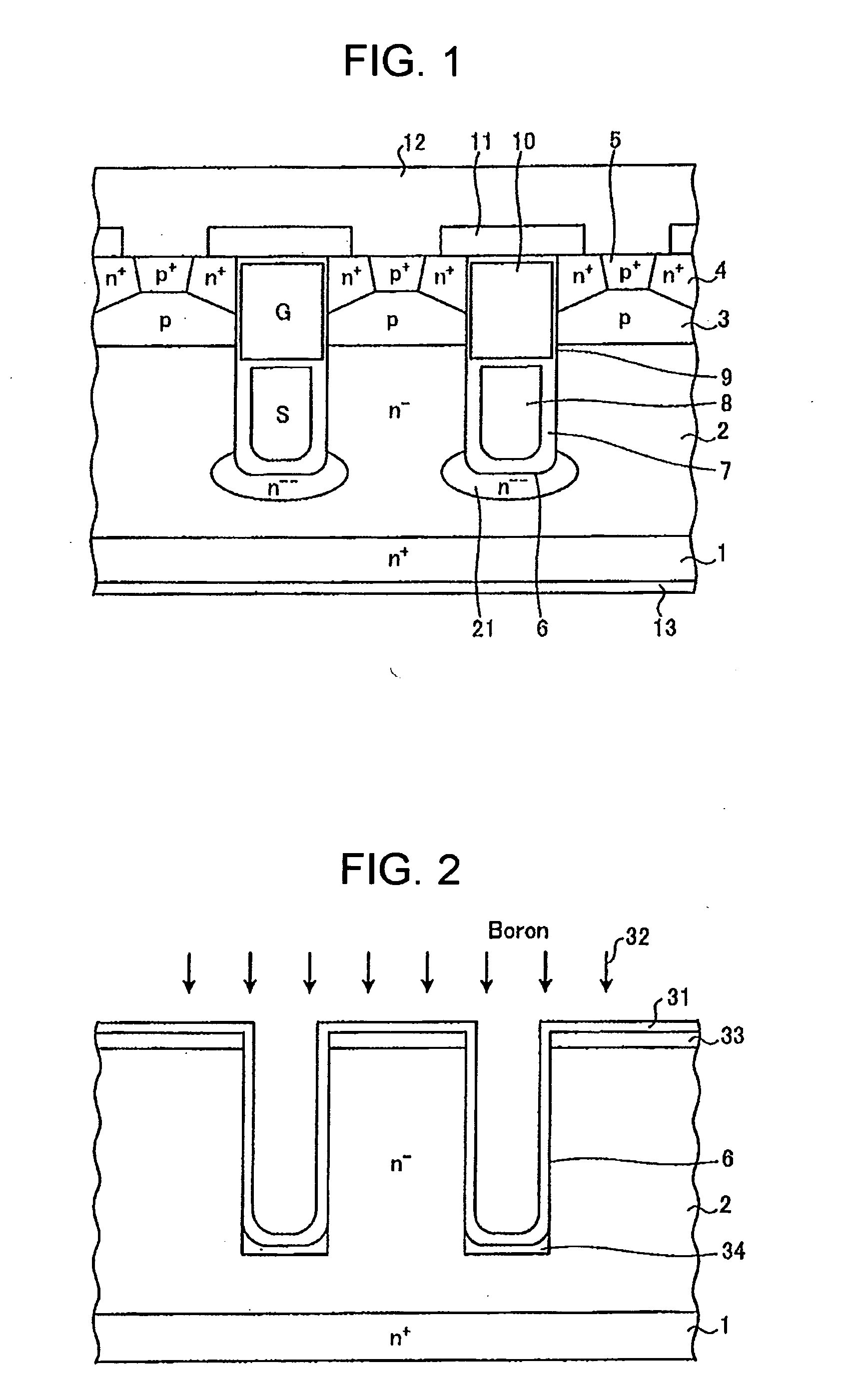

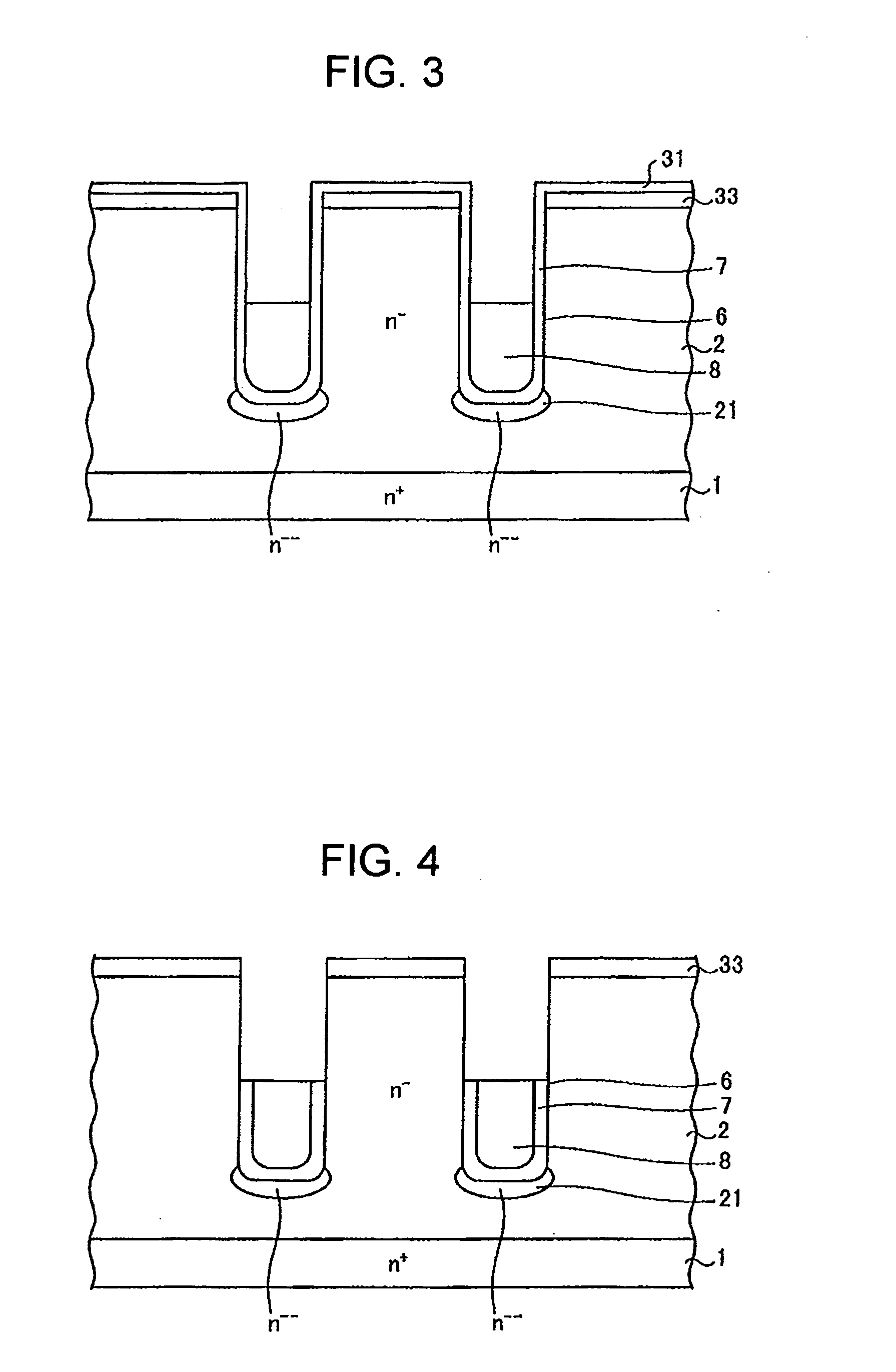

A semiconductor device according to the invention includes p-type well region 3 and n+ source region 4, both formed selectively in the surface portion of n− drift region 2; trench 6 in contact with n+ source region 4 and extending through p-type well region 3 into n− drift region 2; field plate 8 formed in trench 6 with first insulator film 7 interposed between the trench 6 inner surface and field plate 8; gate electrode 10 formed in trench 6 with second insulator film 9 interposed between the trench 6 side wall and gate electrode 10, gate electrode 10 being formed above field plate 8; first insulator film 7 being thicker than second insulator film 9; and n−− lightly doped region 21 in n− drift region 2, n−− lightly doped region 21 crossing under the bottom surface of trench 6 from the corner portion thereof, n−− lightly doped region 21 covering the bottom surface of trench 6.The semiconductor device according to the invention and the method of manufacturing the semiconductor device according to the invention facilitate lowering the ON-state voltage, preventing the breakdown voltage from lowering, lowering the gate capacitance, and reducing the manufacturing costs.

Owner:FUJI ELECTRIC CO LTD

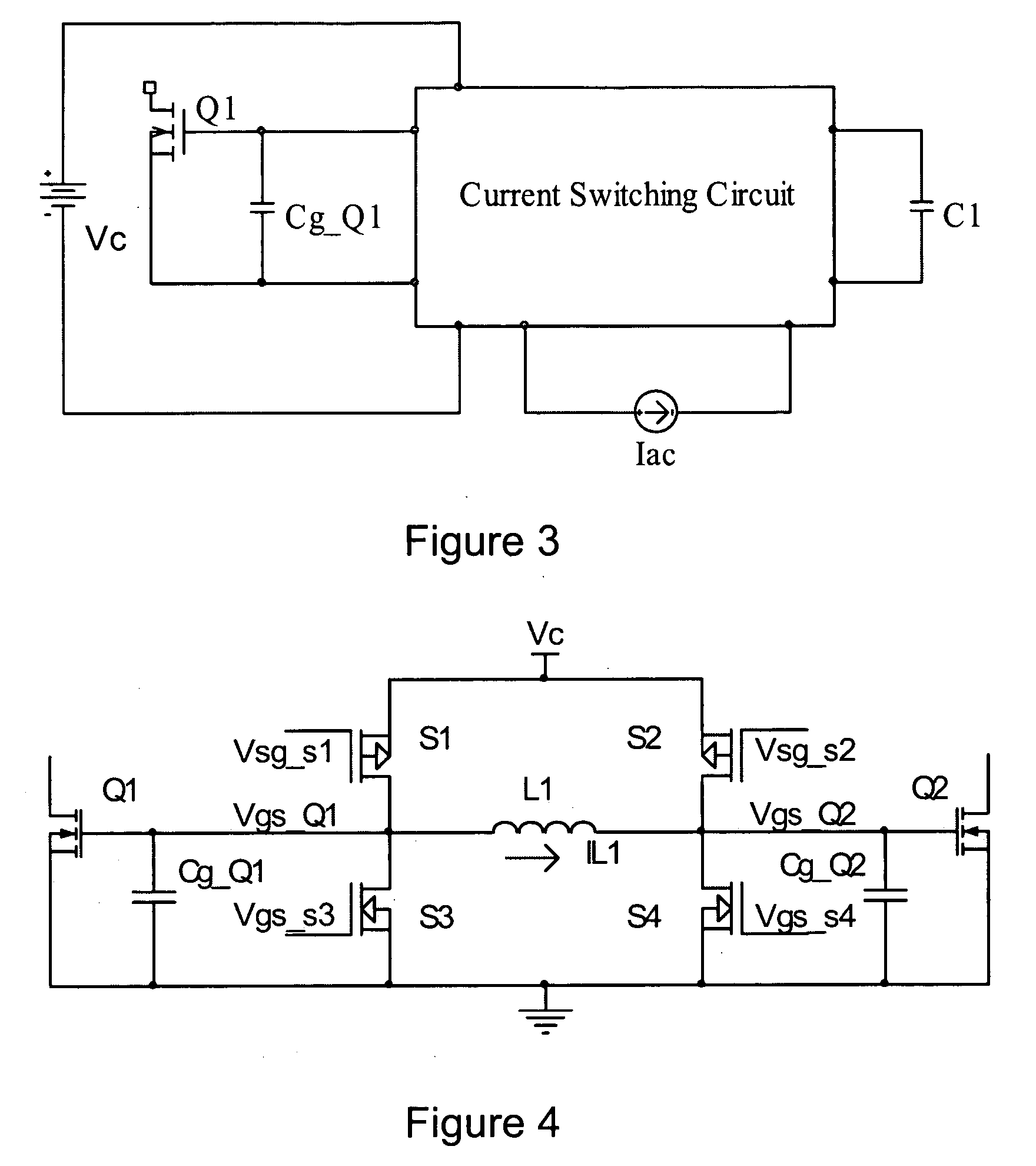

Resonant gate drive circuits

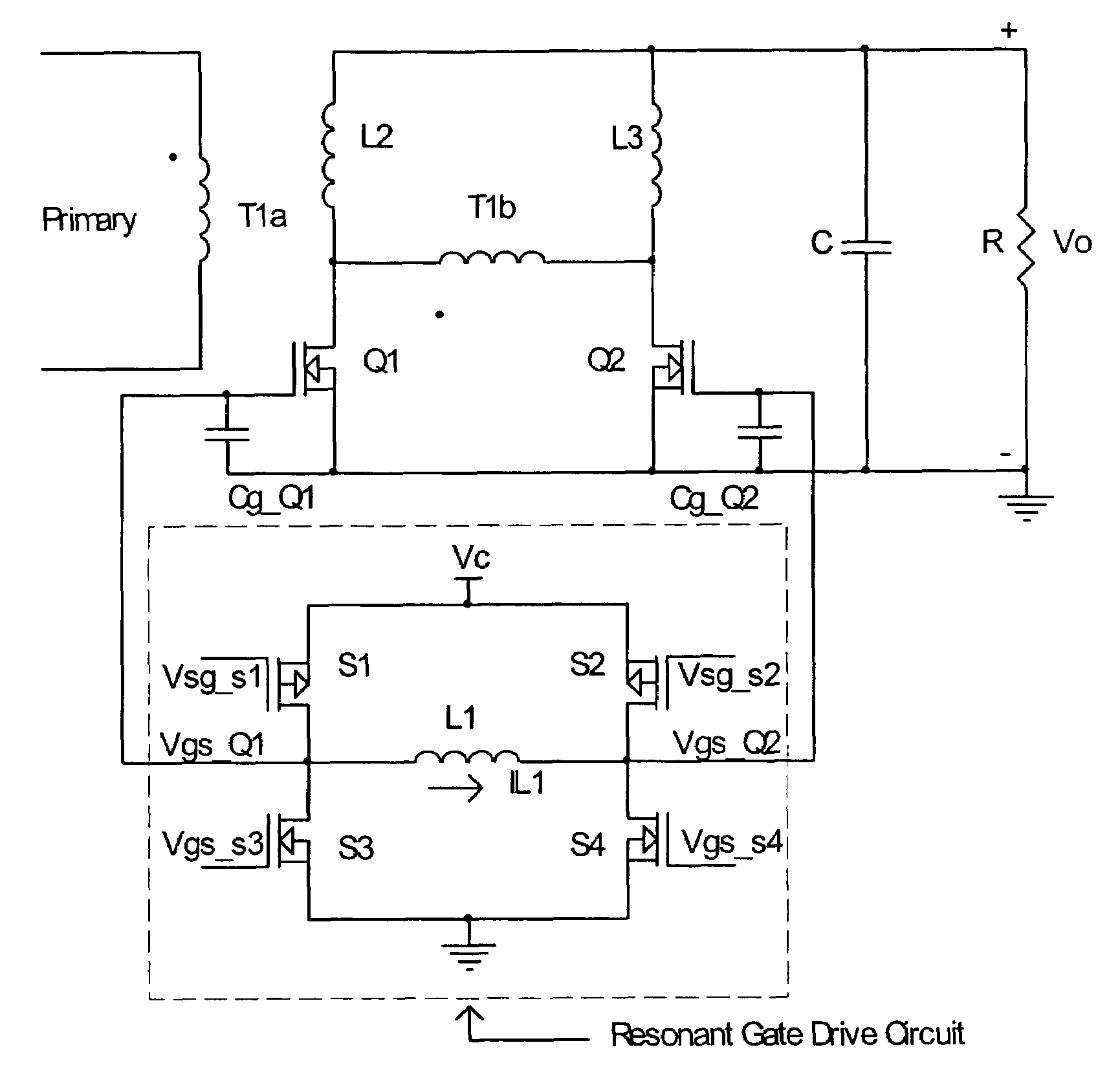

ActiveUS7612602B2Reduce gate drive loss and other lossReduce gate drive loss and conduction lossTransistorAc-dc conversionCapacitanceFull bridge

A resonate gate drive circuit for driving at least one power switching devices recovers energy loss for charging and discharging the input capacitance of the power switching devices. The gate drive circuit charging and discharging the gate capacitor with a high level current, so the switching loss of the power switching devices can also be reduced. The gate drive circuit can clamp and keep the voltage across the gate capacitor to a certain level while the power switching devices turn on, and it can also clamp and keep the voltage across the gate capacitor to almost zero while the power switching devices turn off. The gate drive circuit comprises four small semiconductor bidirectional conducting switching devices connected in full-bridge configuration. An inductor is connected to the two junctions of the full-bridge configuration to help switching the current direction. A capacitor in series with the inductor is necessary for some applications. A bootstrap circuit, which is widely used in conventional gate drive circuitry, is also necessary for this resonant gate drive circuit when it is adopted for high-side and low-side applications.

Owner:GANPOWER INT INC

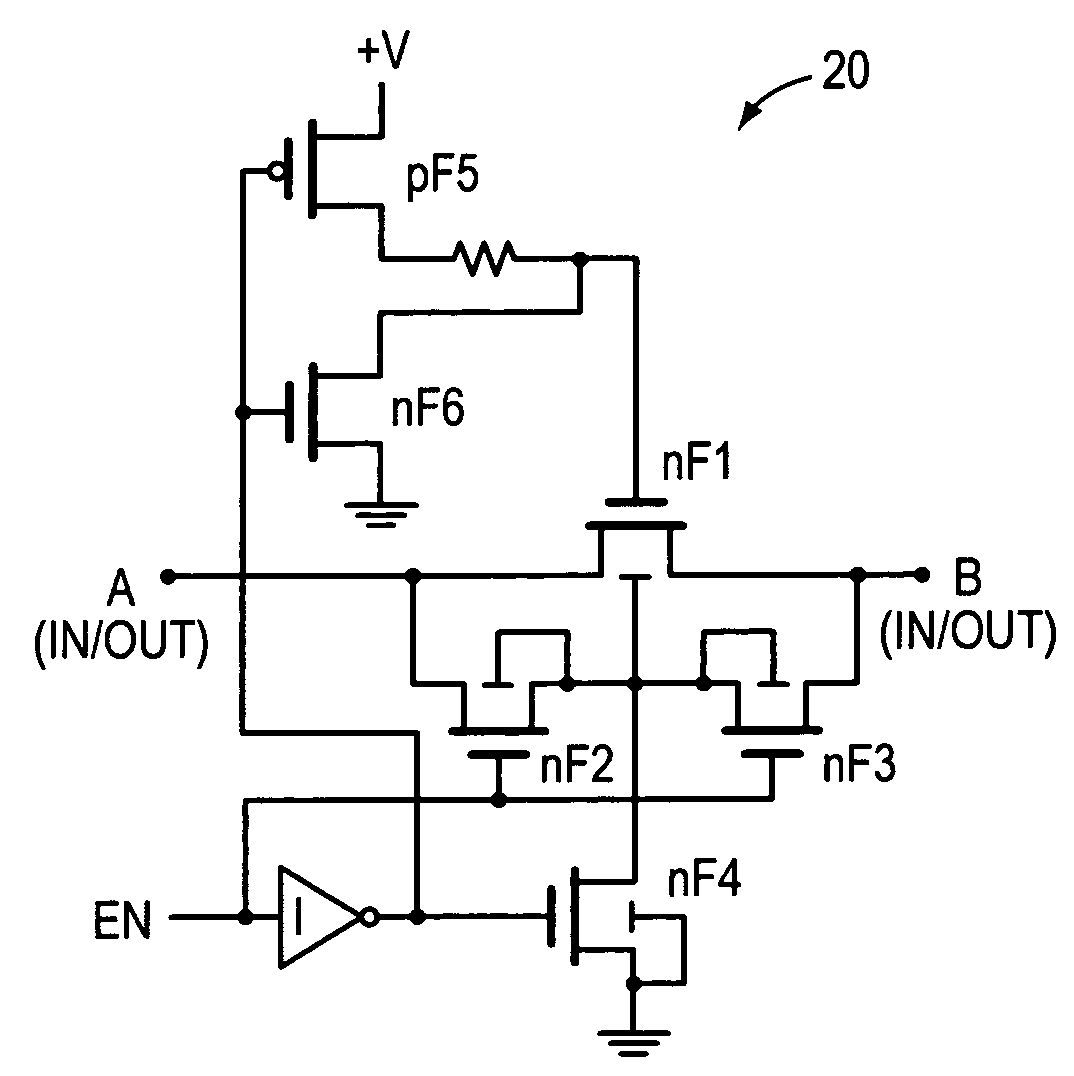

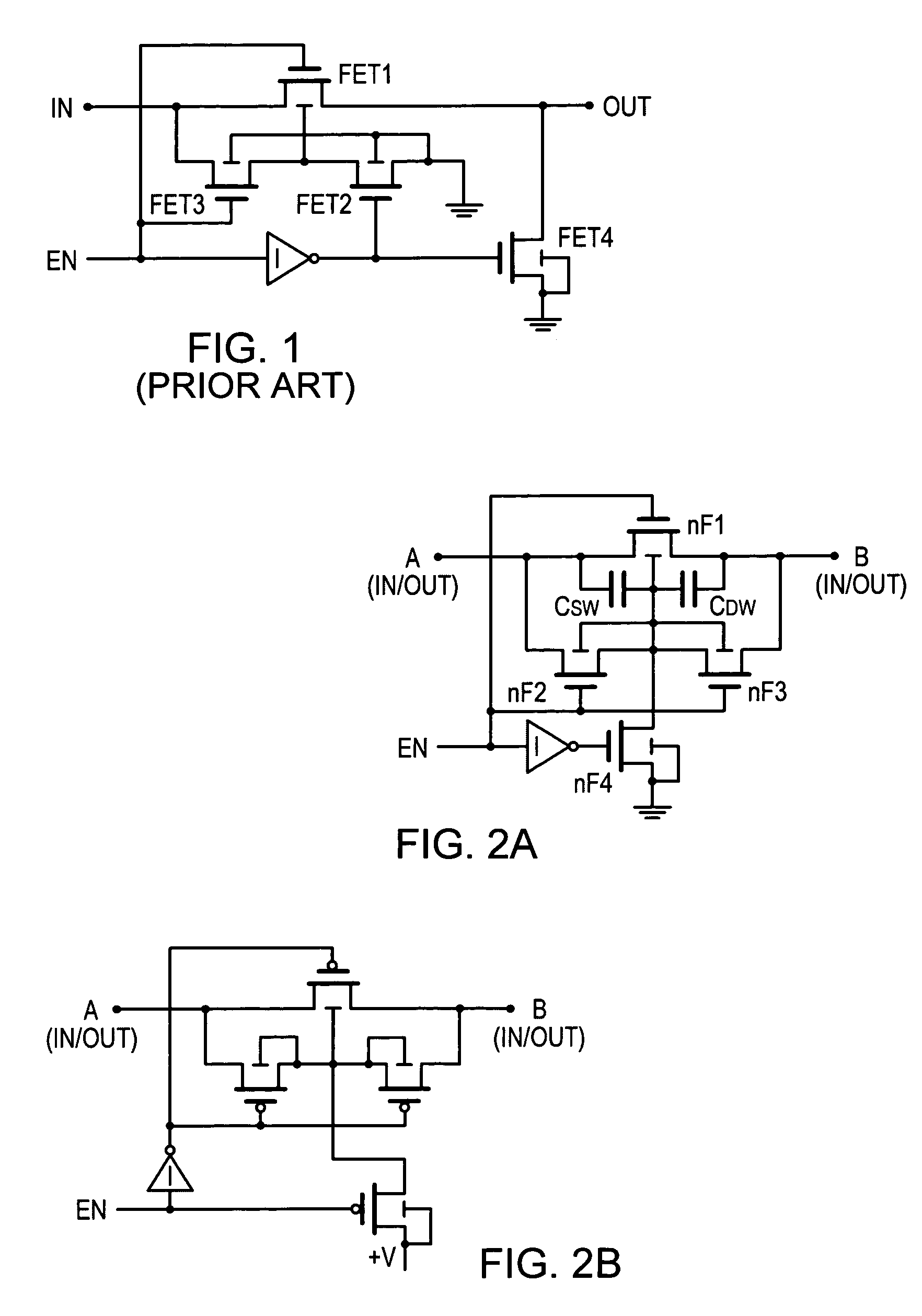

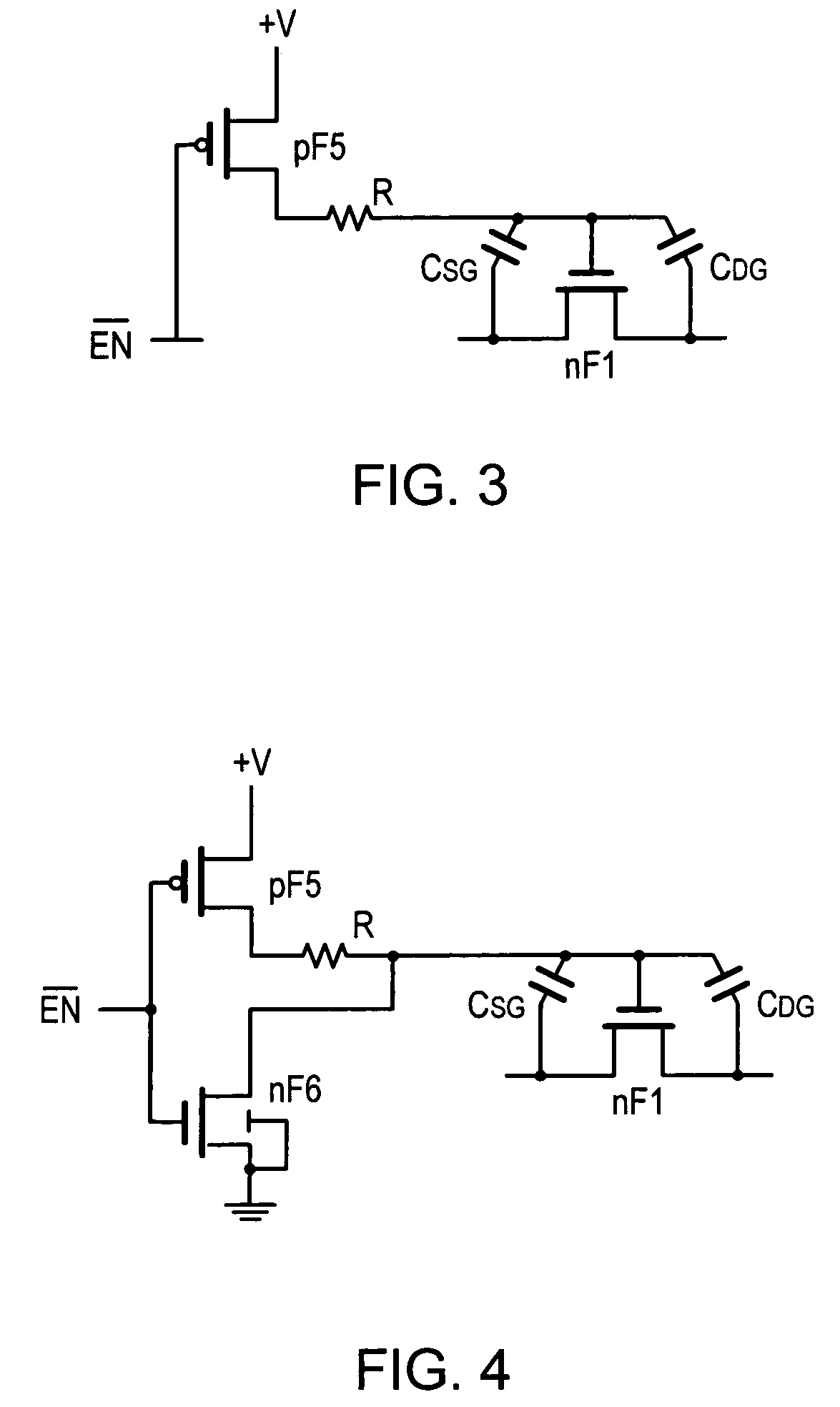

Circuit and method for lowering insertion loss and increasing bandwidth in MOSFET switches

A DC symmetrical FET switch includes second and third switches connecting the well of the symmetrical FET switch to the drains and the source when the symmetrical FET switch is on. When the three FET's are on, the well, source and drain of the symmetric FET switch all exhibit the same input signal, wherein the drains and source to well capacitances are substantially prevented from draining off any of the input signal, thereby increasing the bandwidth and decreasing the insertion loss of the switch. The second and third switches are also FET switches. An enable signal is connected to the gates of all three FET's turning them on and off together. When the enable is false the FET switches are turned off and their wells are driven to a potential a proper potential. When the FET's are n-type the potential is low and when the FET's are p-types the potential is high. A resistor is provided in the gate drive of the first FET switch that further increases bandwidth and decreases insertion loss of the switch by moving the break frequency of the drain and source to gate capacitances.

Owner:SEMICON COMPONENTS IND LLC

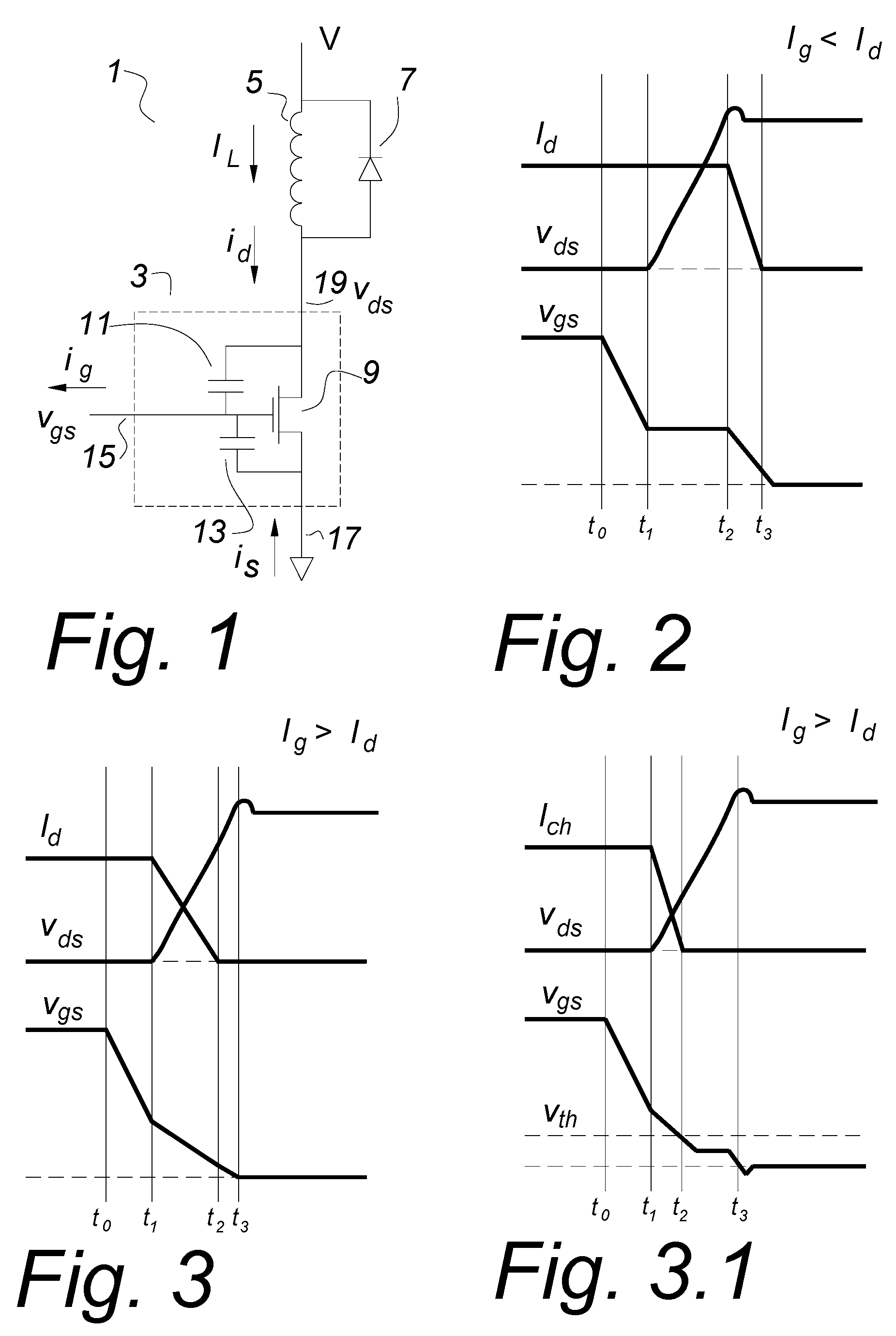

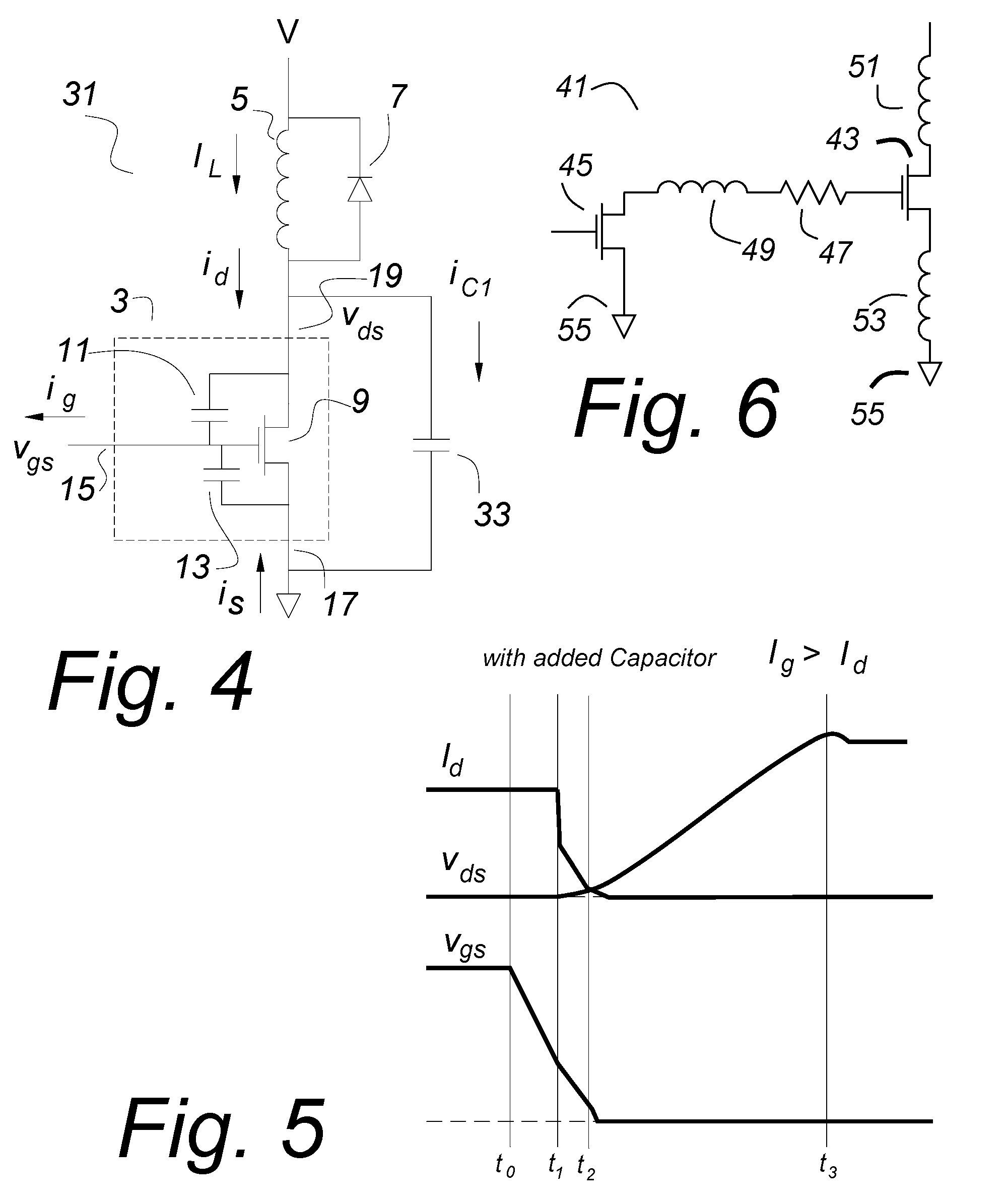

Gate drive method and apparatus for reducing losses in the switching of MOSFETs

InactiveUS6992520B1Reduces and eliminates consequenceLower impedanceTransistorSolid-state devicesMOSFETLower limit

Usually, in power converters, the load on a MOSFET is inductive, and the current cannot change rapidly. The drain current is the upper limit of the Miller current, so that if the gate current is larger than the drain current, the gate capacitance will continue to discharge and there can be no Miller shelf. If a parallel capacitor is used with a MOSFET, once the drain voltage starts to rise, the load current divides, placing a new lower limit on the Miller current. To drive a MOSFET with a gate current that exceeds the drain current, the circuit impedances have to be very low, suggesting a new geometry and packaging arrangement for the MOSFET and gate drive. A compatible gate turn of circuit is also disclosed.

Owner:HERBERT EDWARD

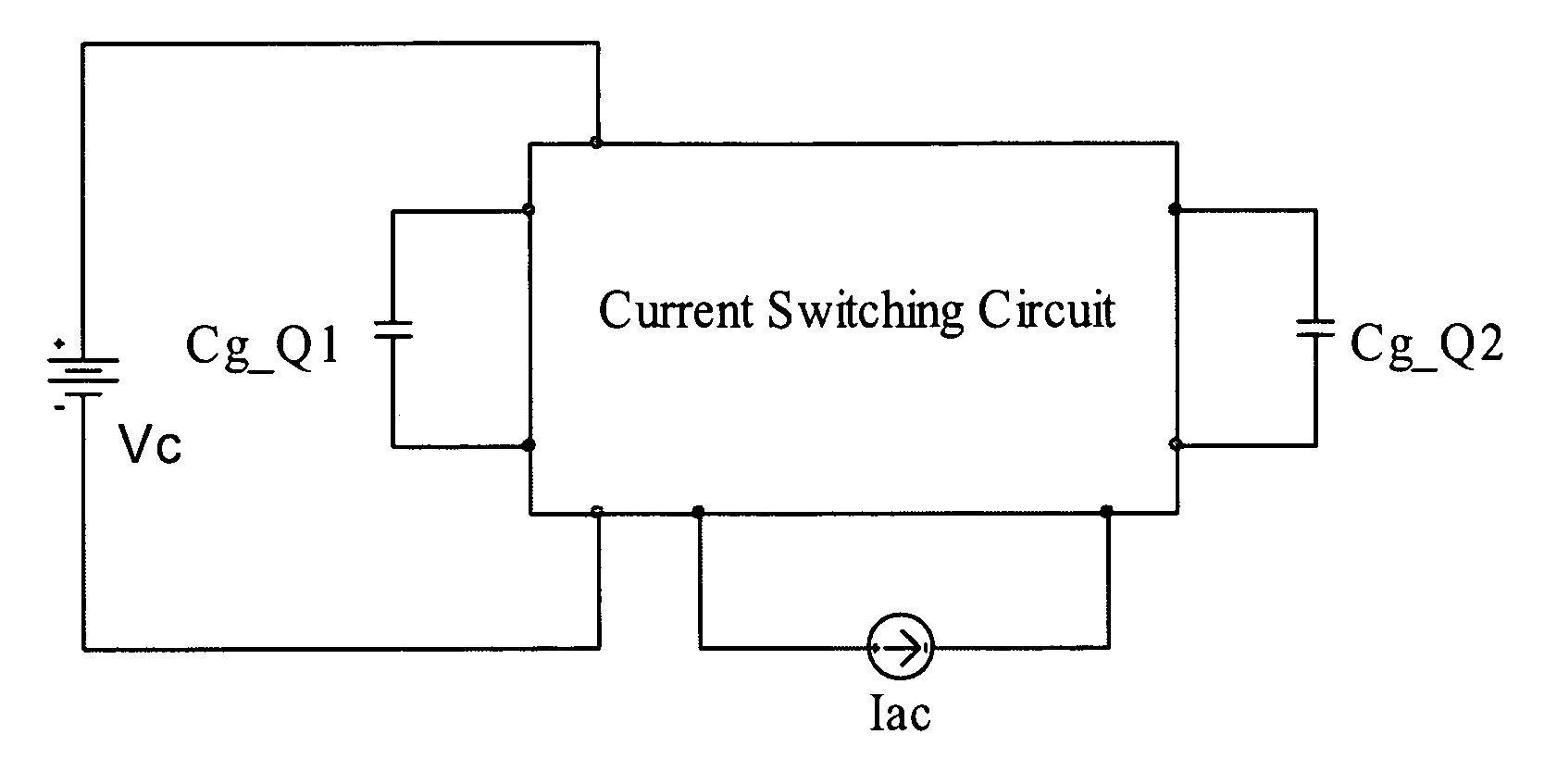

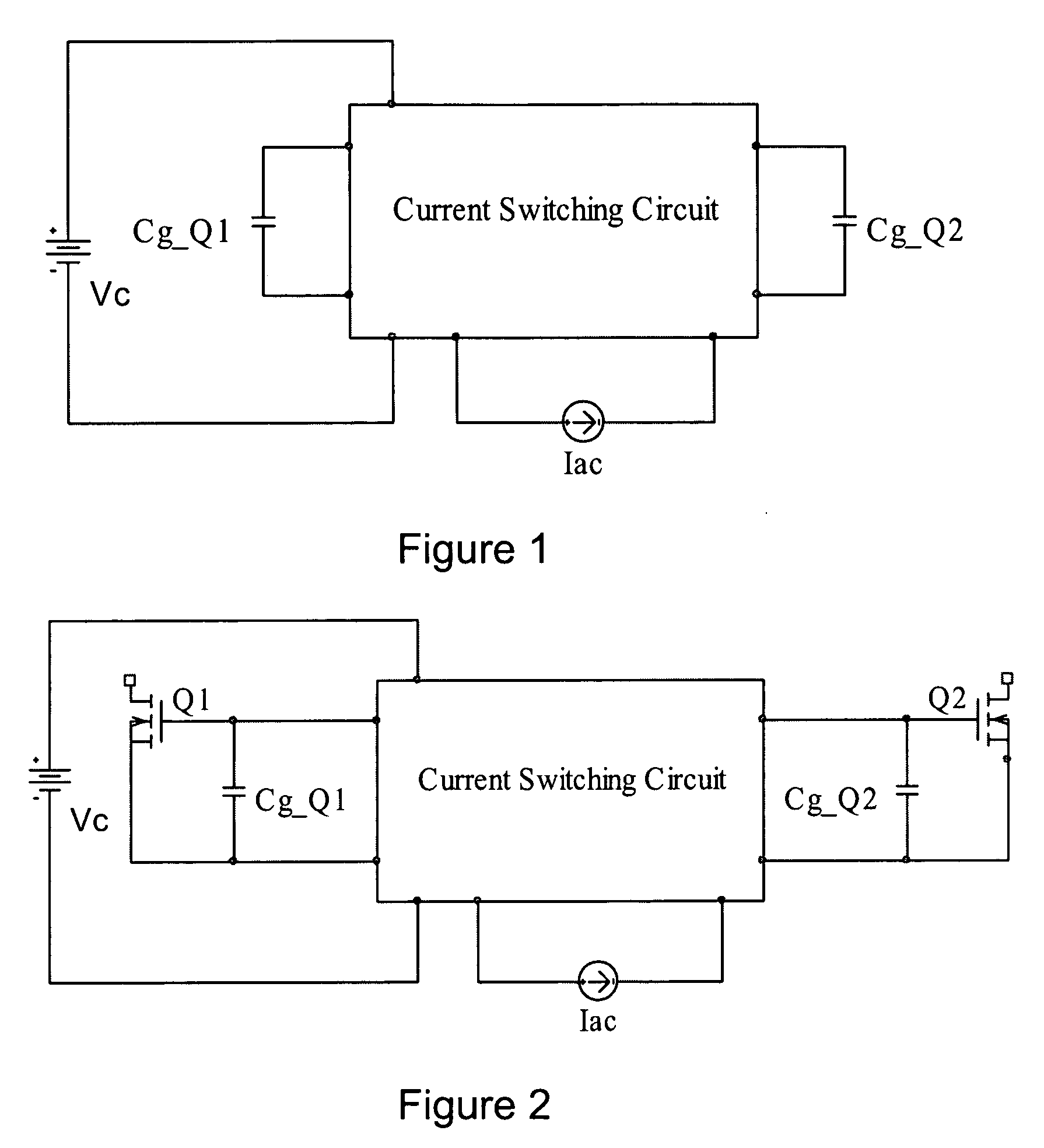

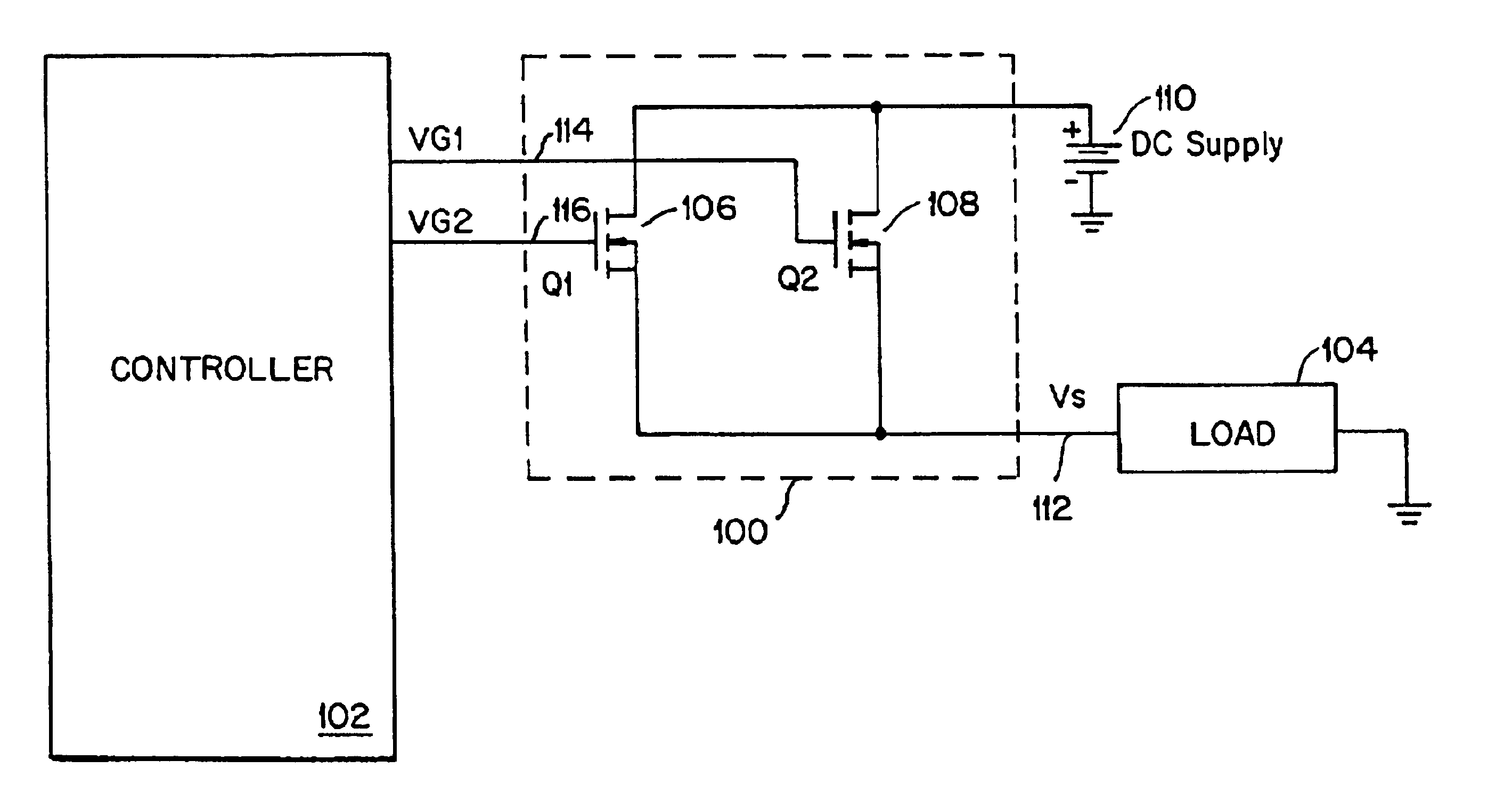

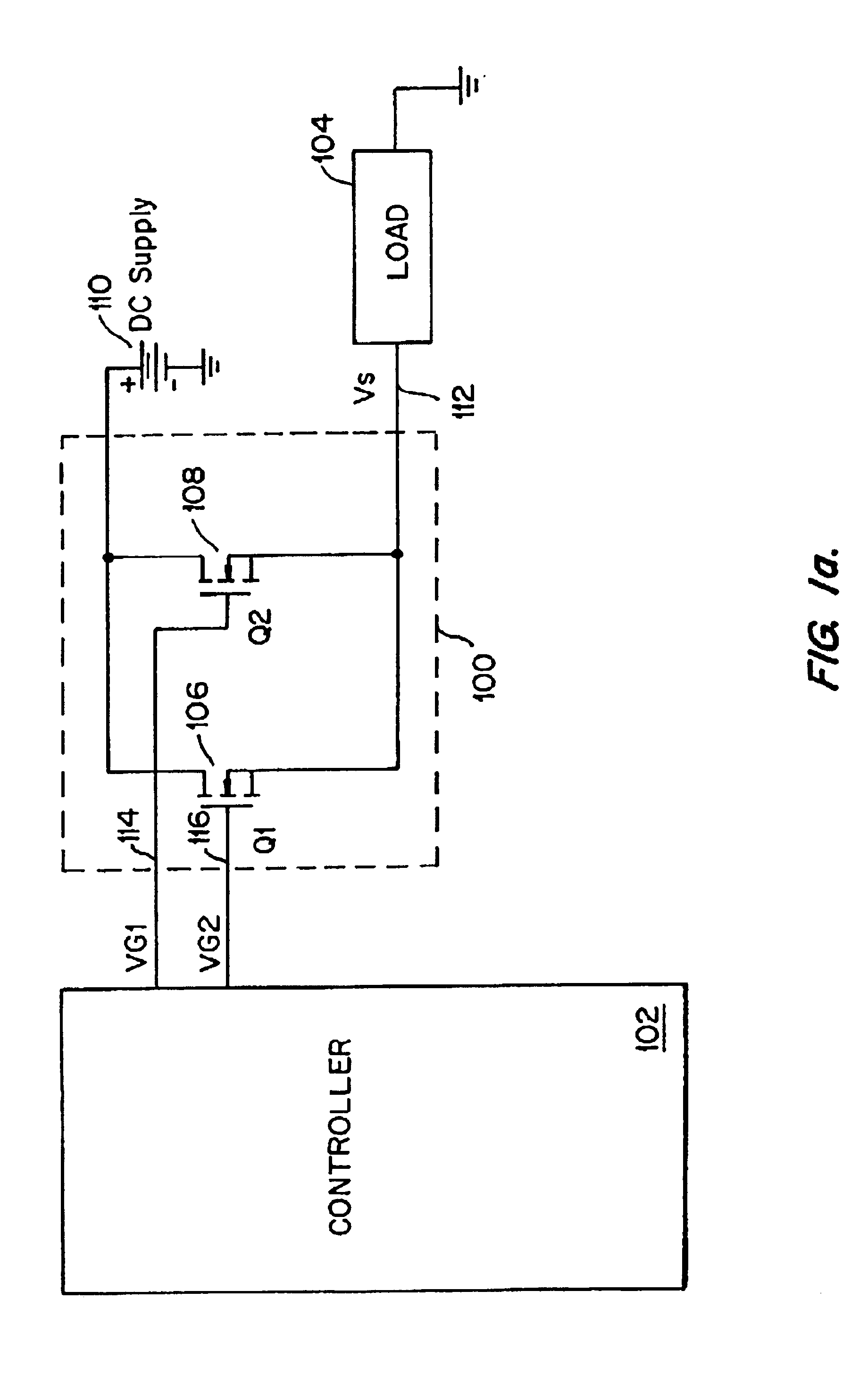

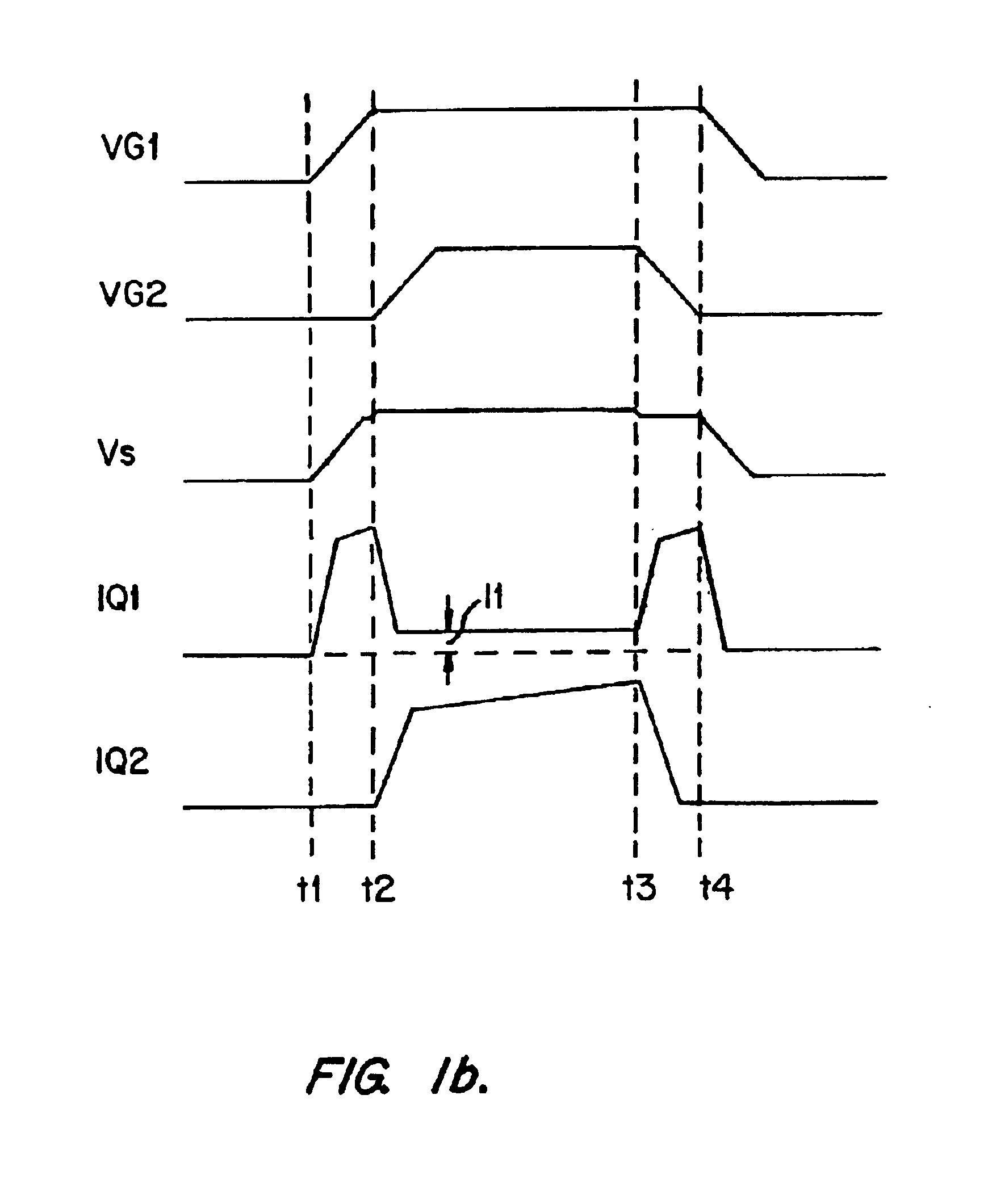

Method and circuit for reducing losses in DC-DC converters

InactiveUS6930473B2Reduction of gate capacitance switching lossReduce conduction lossElectronic switchingApparatus without intermediate ac conversionCapacitanceLow load

In accordance with the present invention, a switching converter includes two transistors Q1 and Q2 parallel-connected between two terminals. Transistor Q1 is optimized to reduce the dynamic loss and transistor Q2 is optimized to reduce the conduction loss. Q1 and Q2 are configured and operated such that the dynamic loss of the converter is dictated substantially by Q1 and the conduction loss of the converter is dictated substantially by Q2. Thus, the tradeoff between these two types of losses present in conventional techniques is eliminated, allowing the dynamic and conduction losses to be independently reduced. Further, the particular configuration and manner of operation of Q1 and Q2 enable reduction of the gate capacitance switching loss when operating under low load current conditions.

Owner:SEMICON COMPONENTS IND LLC

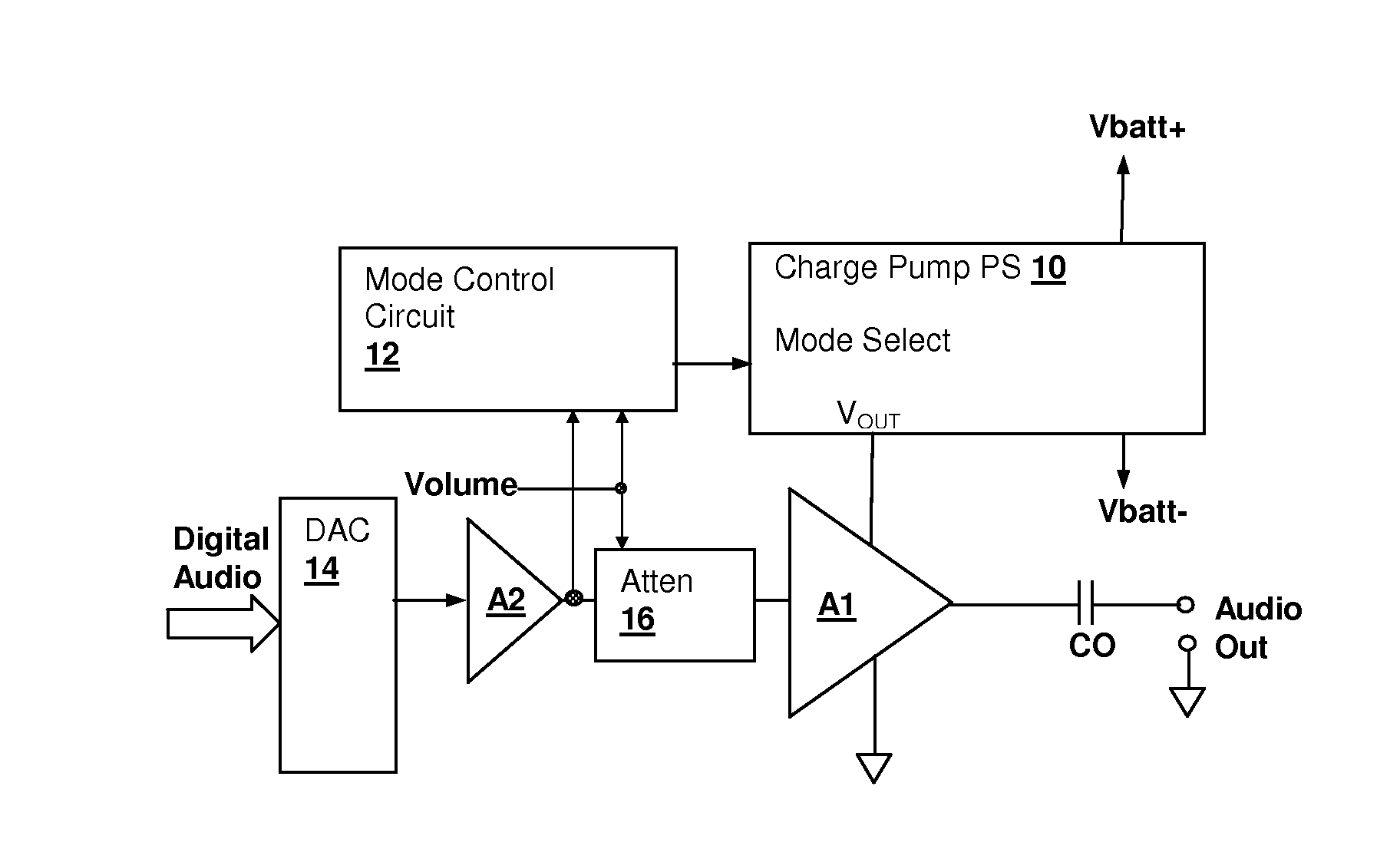

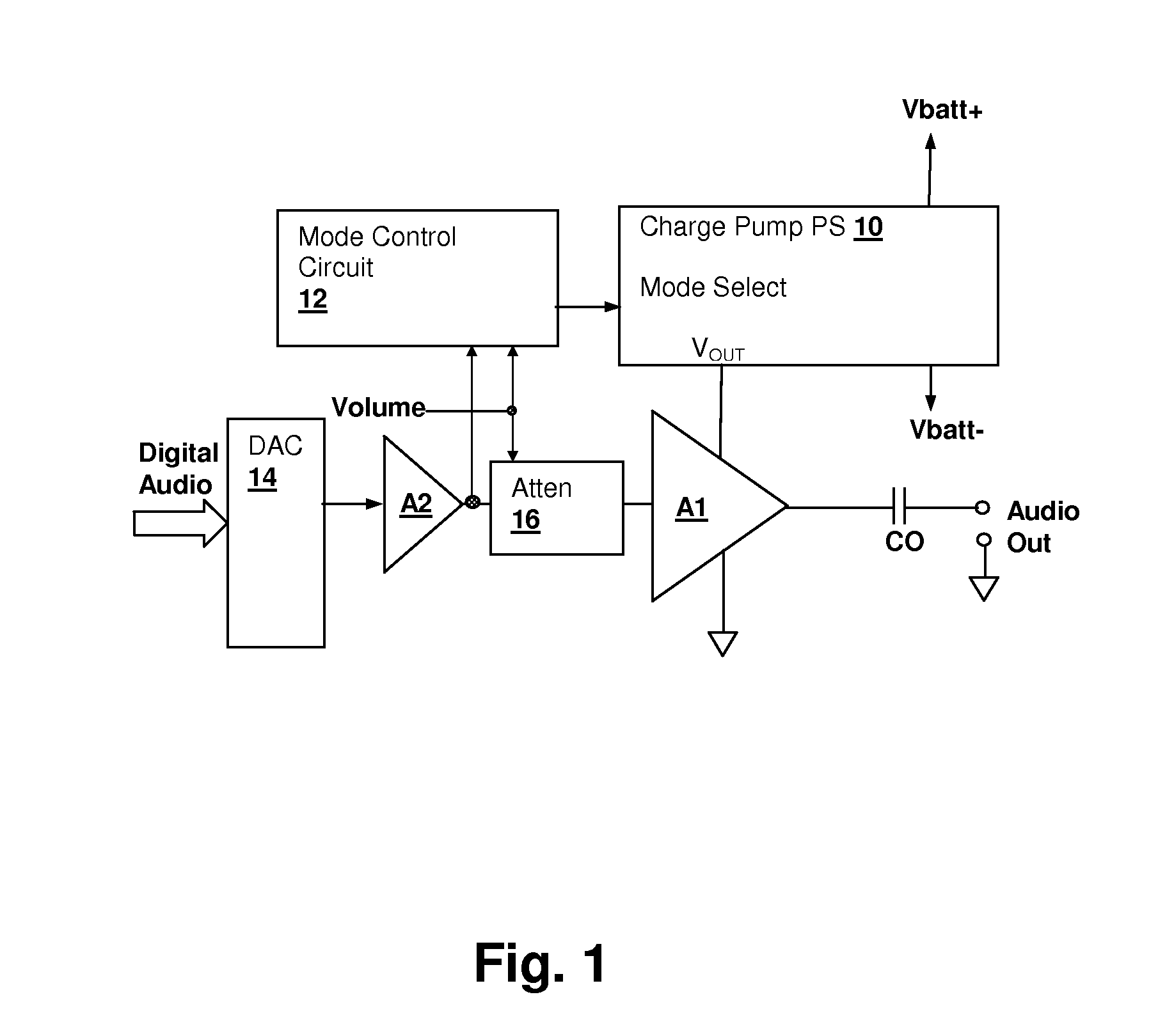

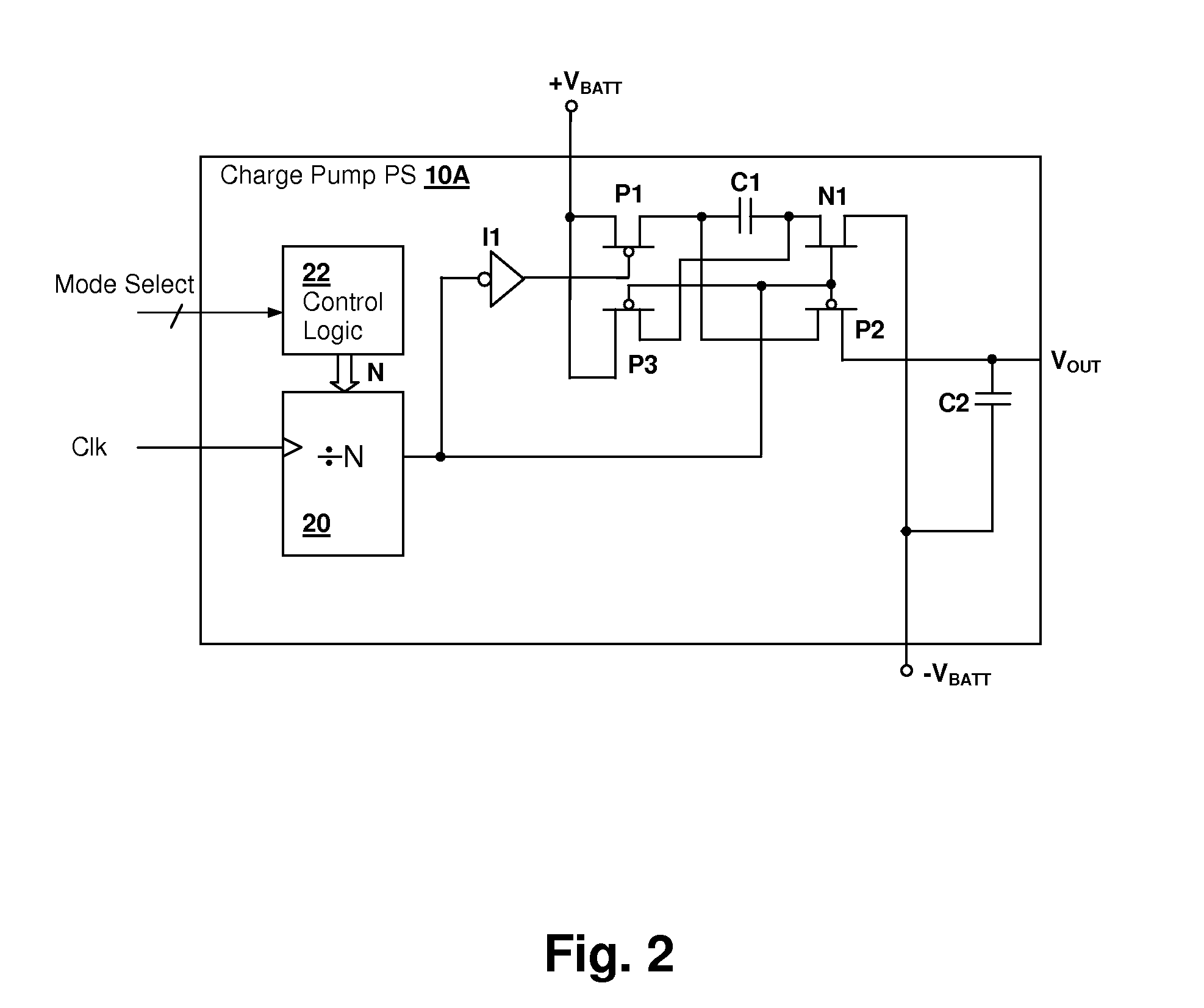

Signal level selected efficiency in a charge pump power supply for a consumer device audio power output stage

ActiveUS7830209B1Improve efficiencyIncreased power output capabilityManually-operated gain controlLow frequency amplifiersCapacitanceDriver circuit

Owner:CIRRUS LOGIC INC

Finfet with low gate capacitance and low extrinsic resistance

ActiveUS20060043616A1Reduce gate capacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate insulator

A FinFET device and a method of lowering a gate capacitance and extrinsic resistance in a field effect transistor, wherein the method comprises forming an isolation layer comprising a BOX layer over a substrate, configuring source / drain regions above the isolation layer, forming a fin structure over the isolation layer, configuring a first gate electrode adjacent to the fin structure, disposing a gate insulator between the first gate electrode and the fin structure, positioning a second gate electrode transverse to the first gate electrode, and depositing a third gate electrode on the fin structure, the first gate electrode, and the second gate electrode, wherein the isolation layer is formed beneath the insulator, the first gate electrode, and the fin structure. The method further comprises sandwiching the second gate electrode with a dielectric material. The fin structure is formed by depositing an oxide layer over a silicon layer.

Owner:MICROSOFT TECH LICENSING LLC

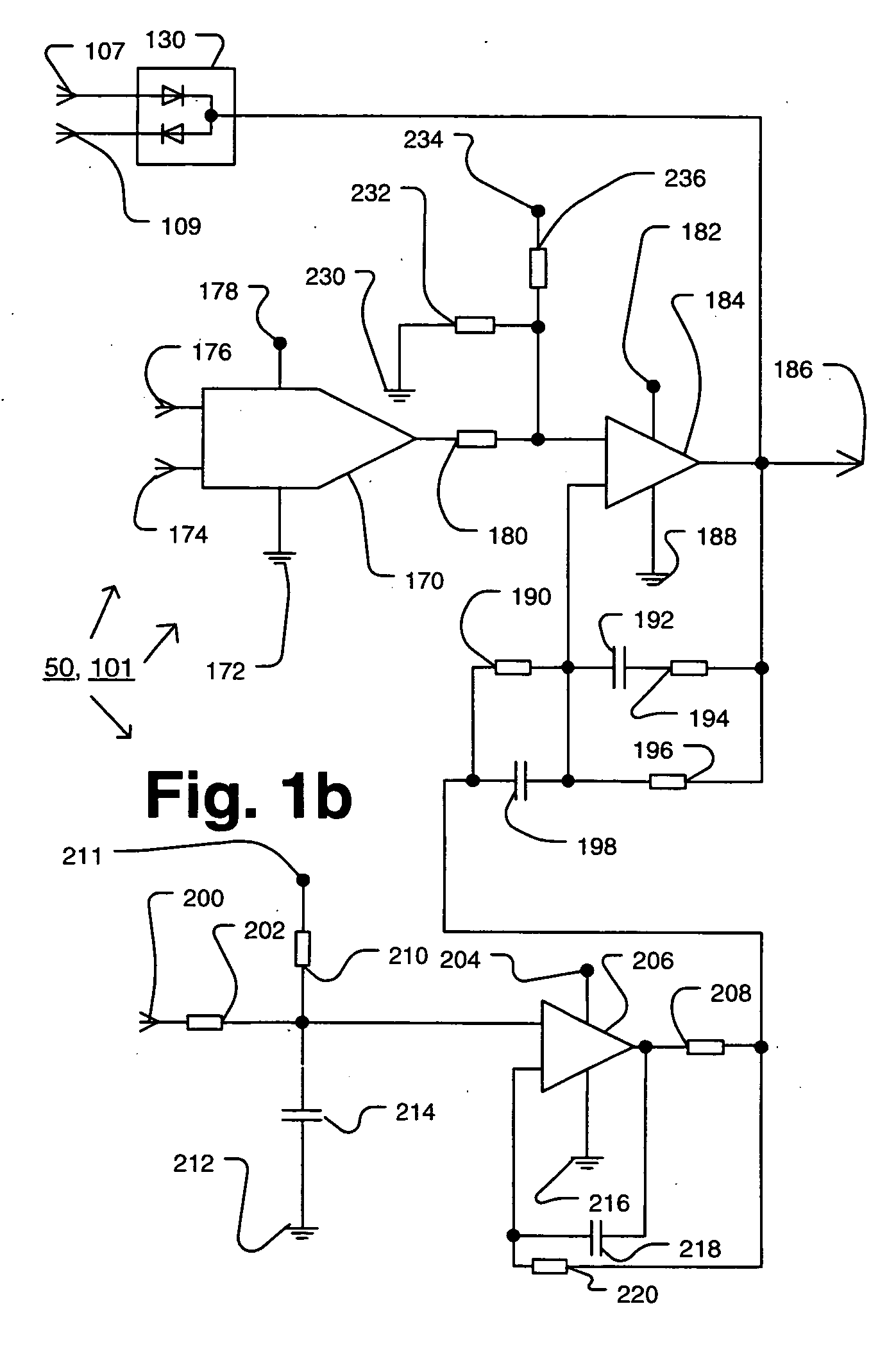

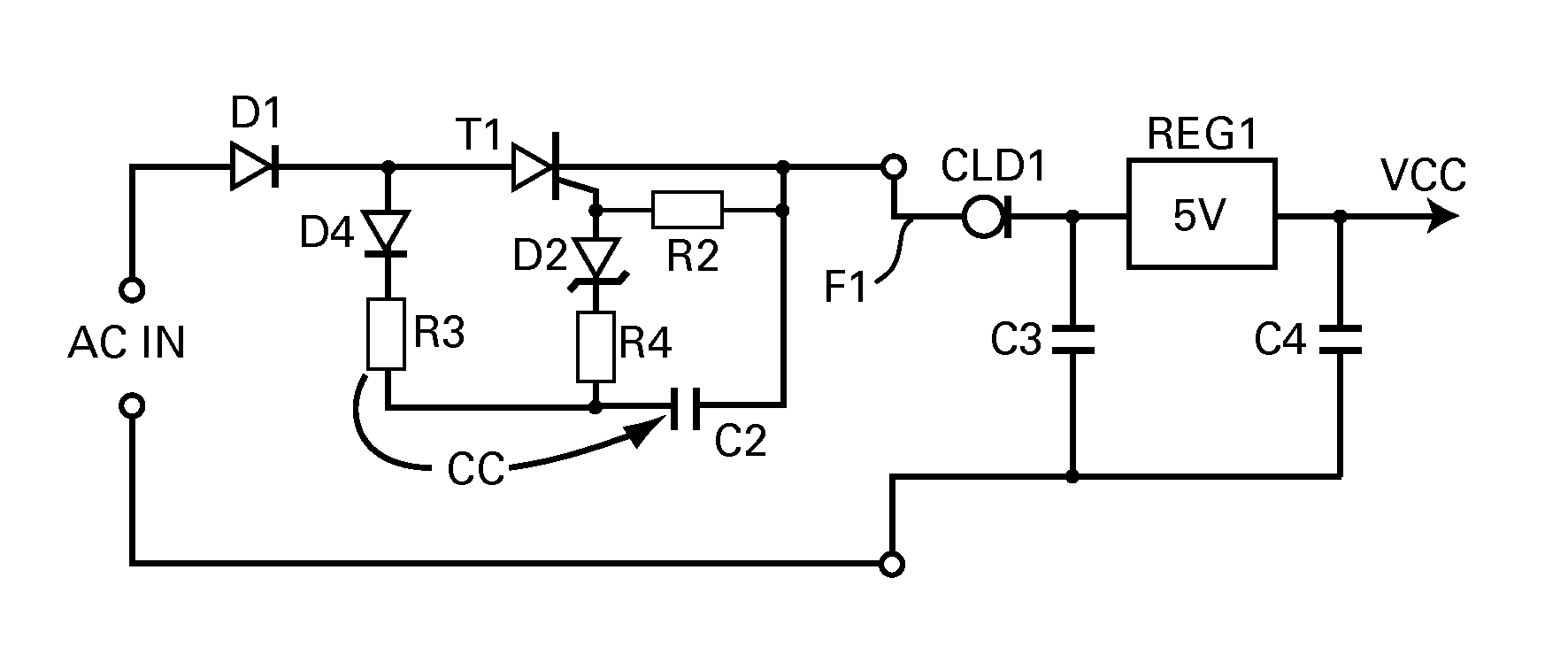

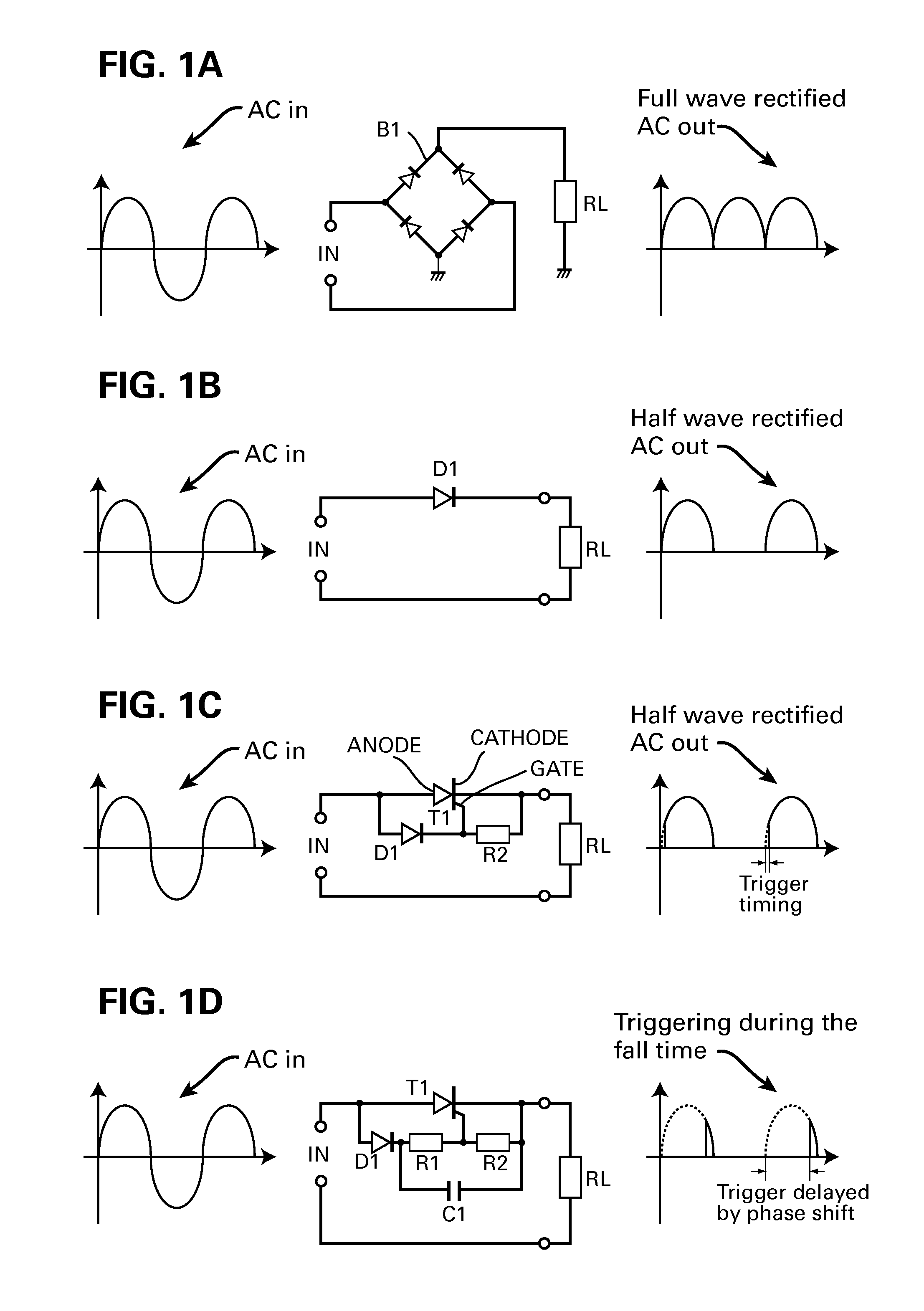

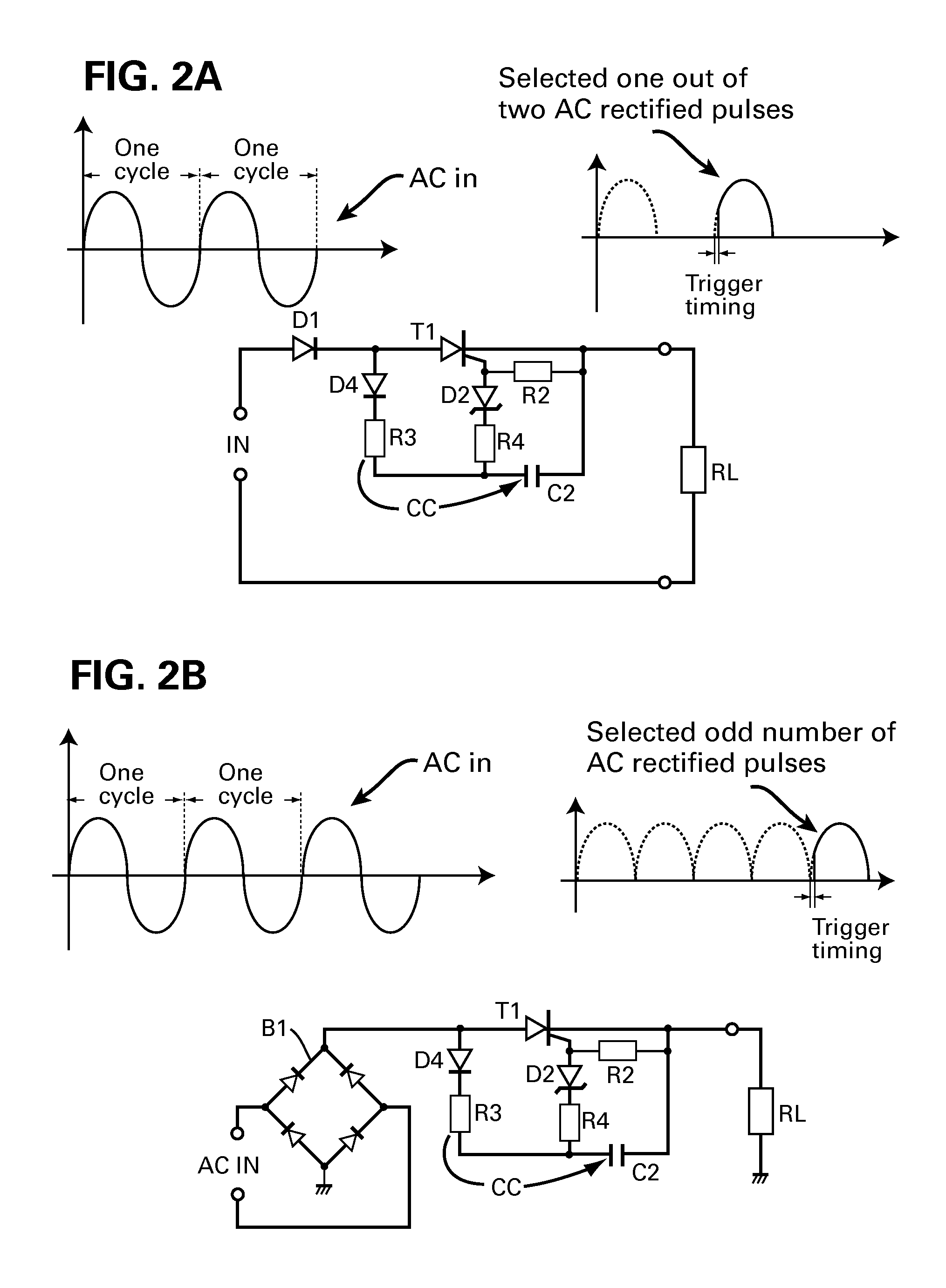

Method and apparatus for regulating AC-DC adaptor for low current drain

A method and apparatus for controlling the feed rate of a rectified AC pulses via a gated rectifier in a low DC voltage and current power supply is disclosed. The gated rectifier outputs gated AC pulses to an input capacitor via a current control diode and / or a zener diode and / or a resistor for charging the input capacitor to a voltage level and a charge capacity commensurate with the low voltage regulator and the low DC current drain. A gate capacitor for accumulating incremental charges of rectified AC pulses fed via a divider network is pre-configured to trigger the gated rectifier, timed by discharging the aggregated charge of a predetermined number of charges to the gate. The input capacitor charged by the gated AC pulses at a rate of one per said determined number to the input capacitor feeds the voltage regulator for powering a low DC current consuming device.

Owner:ELBEX VIDEO LTD

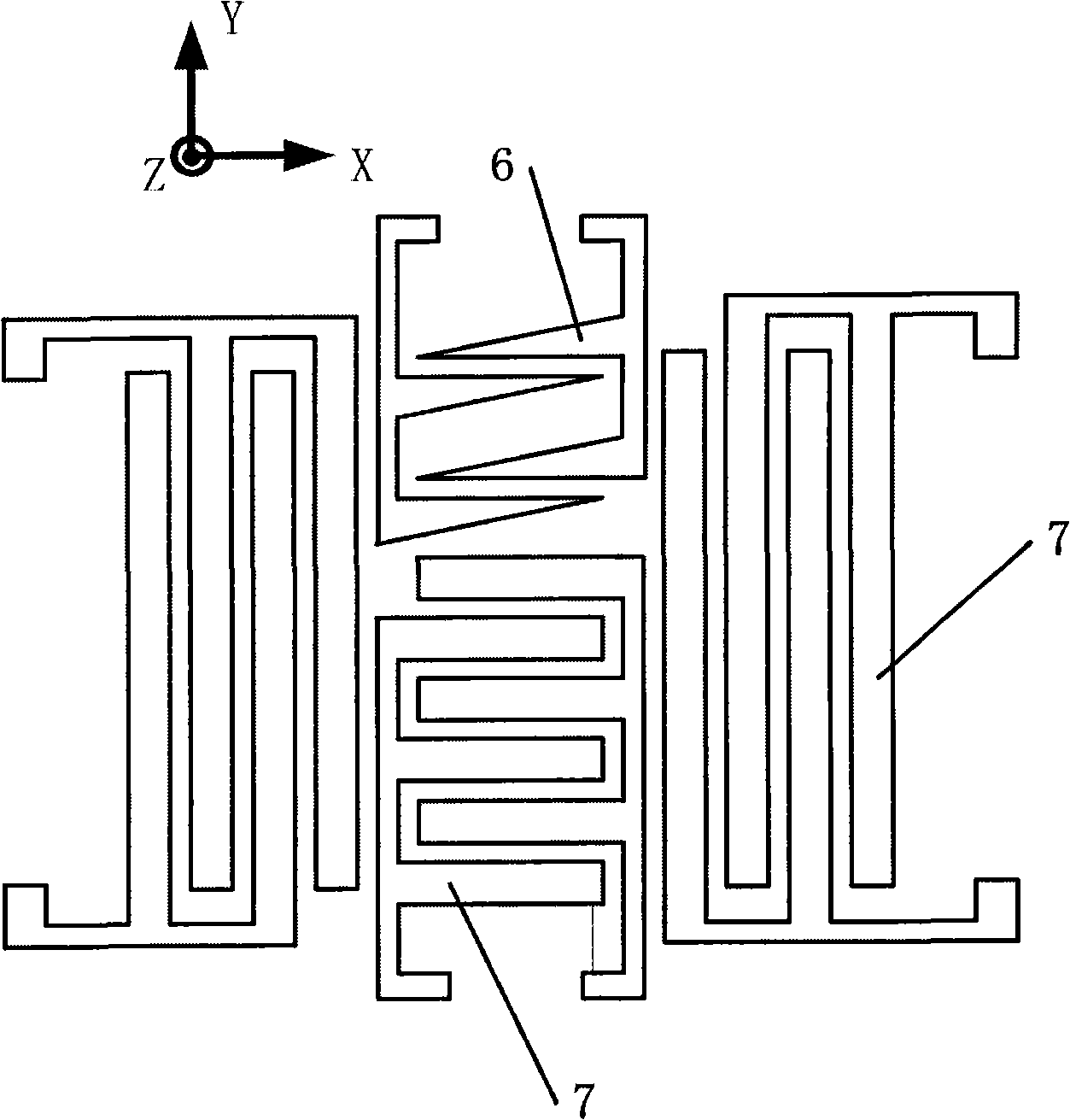

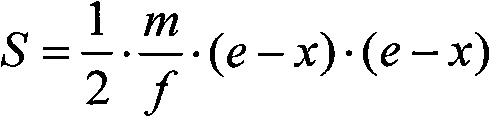

Micro-mechanics comb-typed gate capacitance top having electric tuning function

ActiveCN101813480AOvercome the defect of low sensitivityHigh sensitivitySpeed measurement using gyroscopic effectsTurn-sensitive devicesCapacitanceElectricity

The invention discloses a micro-mechanics comb-typed gate capacitance top having an electric tuning function, and belongs to the field of micro-mechanics inertial sensors. An electric tuning variable area capacitor is distributed in a driving or detecting direction of the top; in each unit capacitor of the electric tuning variable area capacitor, the positive surface of a movable electrode is parallel to the positive surface of a fixed electrode, wherein the positive surface of the movable electrode is rectangular and the positive surface of the fixed electrode is triangular or saw tooth-shaped, or the positive surface of the movable electrode is triangular or saw tooth-shaped and the positive surface of the fixed electrode is rectangular, and the triangular positive surface and a long edge of the rectangular positive surface are overlapped. The top tunes a resonance frequency in the driving or detecting direction by the electric tuning variable area capacitor distributed in the driving or detecting direction of the top, so that the top devices in the same batch have similar properties; and the resonance frequencies in the driving and detecting directions are close or even equal, and the sensitivity of the top is greatly improved.

Owner:ZHEJIANG UNIV

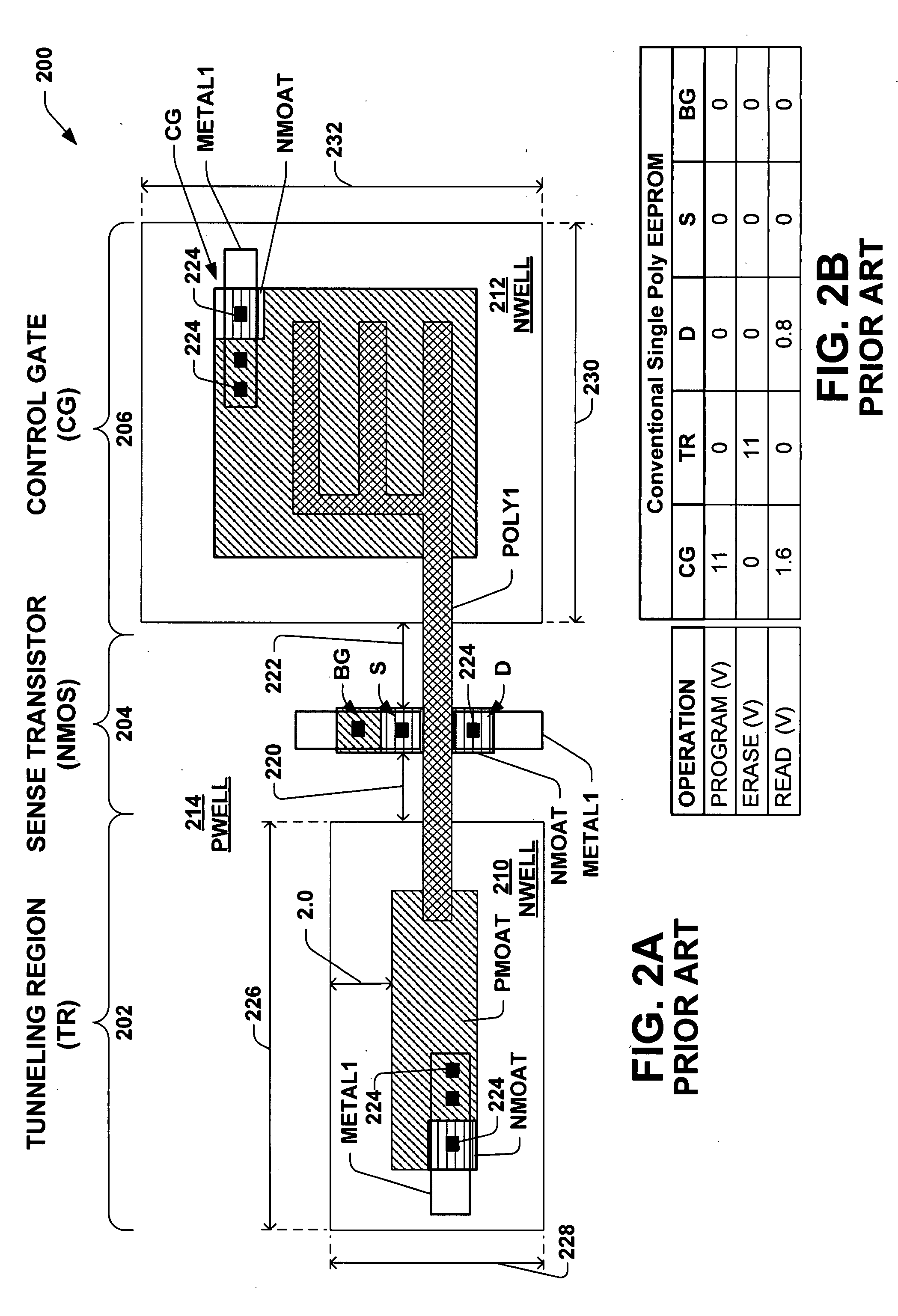

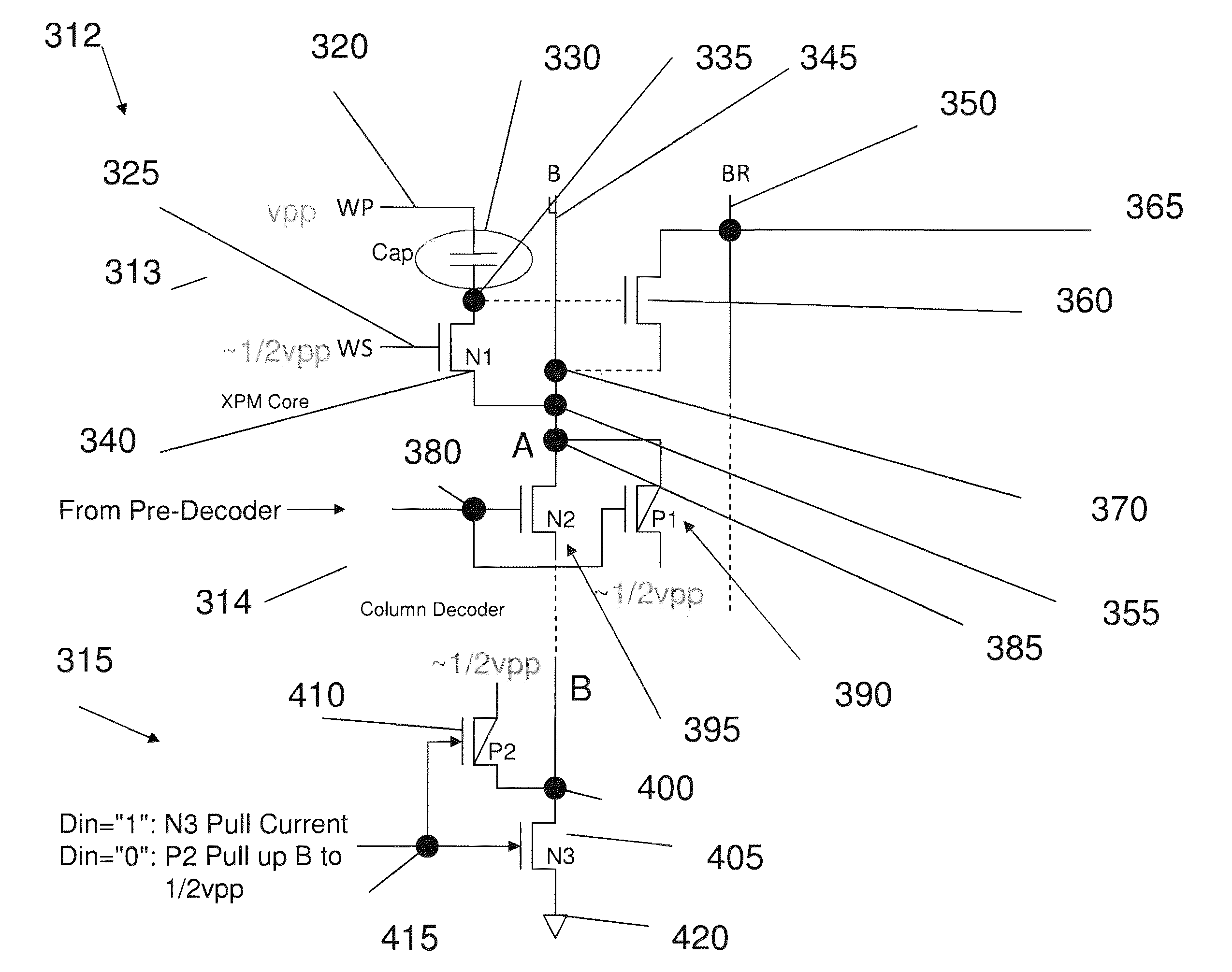

Single poly EEPROM without separate control gate nor erase regions

ActiveUS20080225593A1Small sizeReduce manufacturing costTransistorSolid-state devicesCapacitanceSemiconductor

A single-poly EEPROM memory device comprises source and drain regions in a semiconductor body, a floating gate overlying a portion of the source and drain regions, which defines a source-to-floating gate capacitance and a drain-to-floating gate capacitance, wherein the source-to-floating gate capacitance is substantially greater than the drain-to-floating gate capacitance. The source-to-floating gate capacitance is, for example, at least about three times greater than the drain-to-floating gate capacitance to enable the memory device to be electrically programmed or erased by applying a potential between a source electrode and a drain electrode without using a control gate. A current path between the source and drain electrodes generally defines current carrying portions of the source and drain regions, and a non-current carrying portion of the source region residing outside the current carrying portion, wherein substantially more of the floating gate overlies the non-current carrying portion than the current carrying portions.

Owner:TEXAS INSTR INC

Light-Emitting Device

InactiveUS20070052634A1Suppression of uneven brightnessTransistorStatic indicating devicesDisplay deviceEngineering

There is provided an EL light-emitting device with less uneven brightness. When a drain current of a plurality of current controlling TFTs is Id, a mobility is μ, a gate capacitance per unit area is Co, a maximum gate voltage is Vgs(max), a channel width is W, a channel length is L, an average value of a threshold voltage is Vth, a deviation from the average value of the threshold voltage is ΔVth, and a difference in emission brightness of a plurality of EL elements is within a range of ±n %, a semiconductor display device is characterized in that A=2Idμ*C0A(Vgs(max)-Vth)2≦WL≦(1+n100-1)2*AΔ Vth2Δ Vth≦(1+n100-1)*A*L / W

Owner:SEMICON ENERGY LAB CO LTD

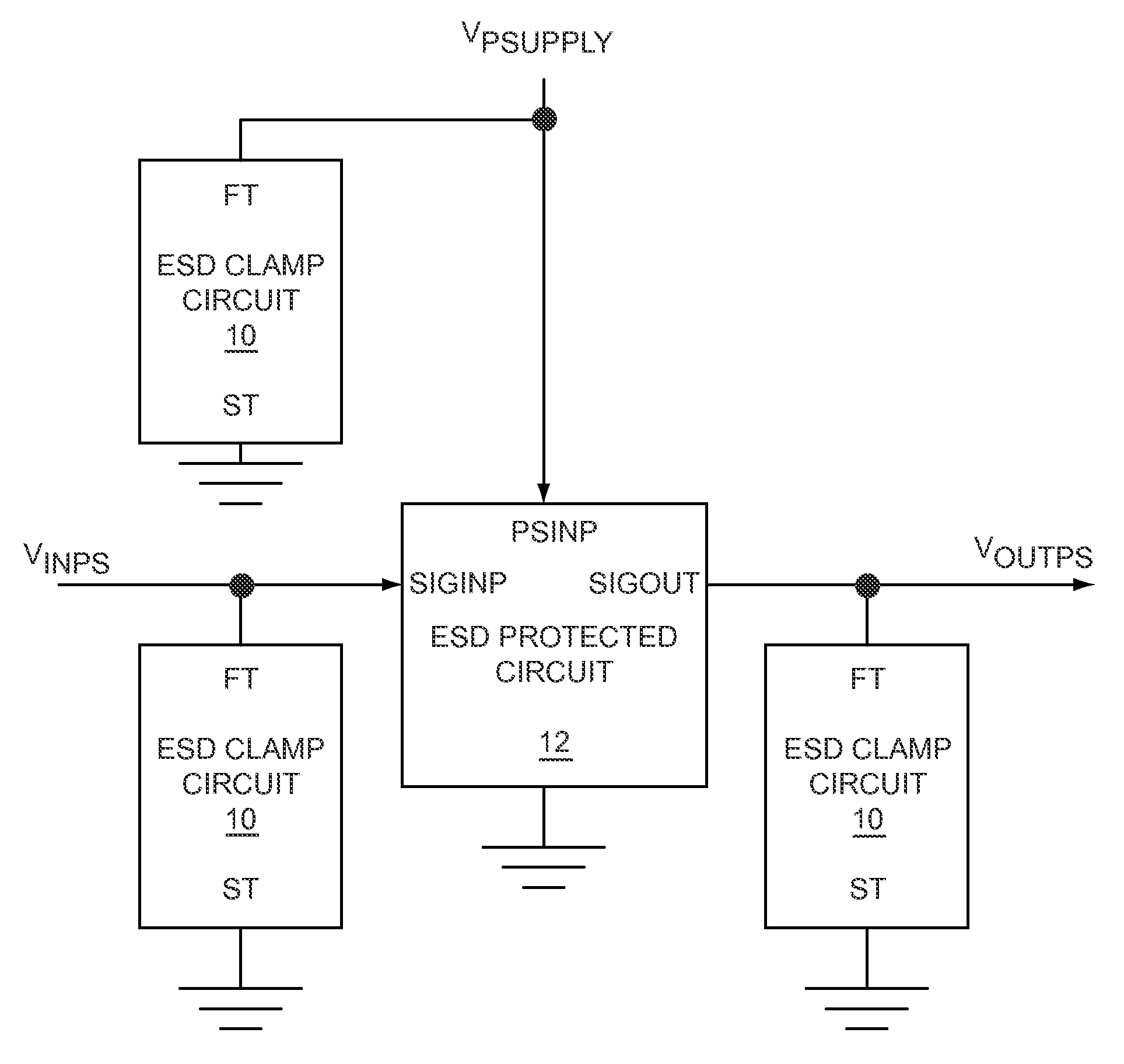

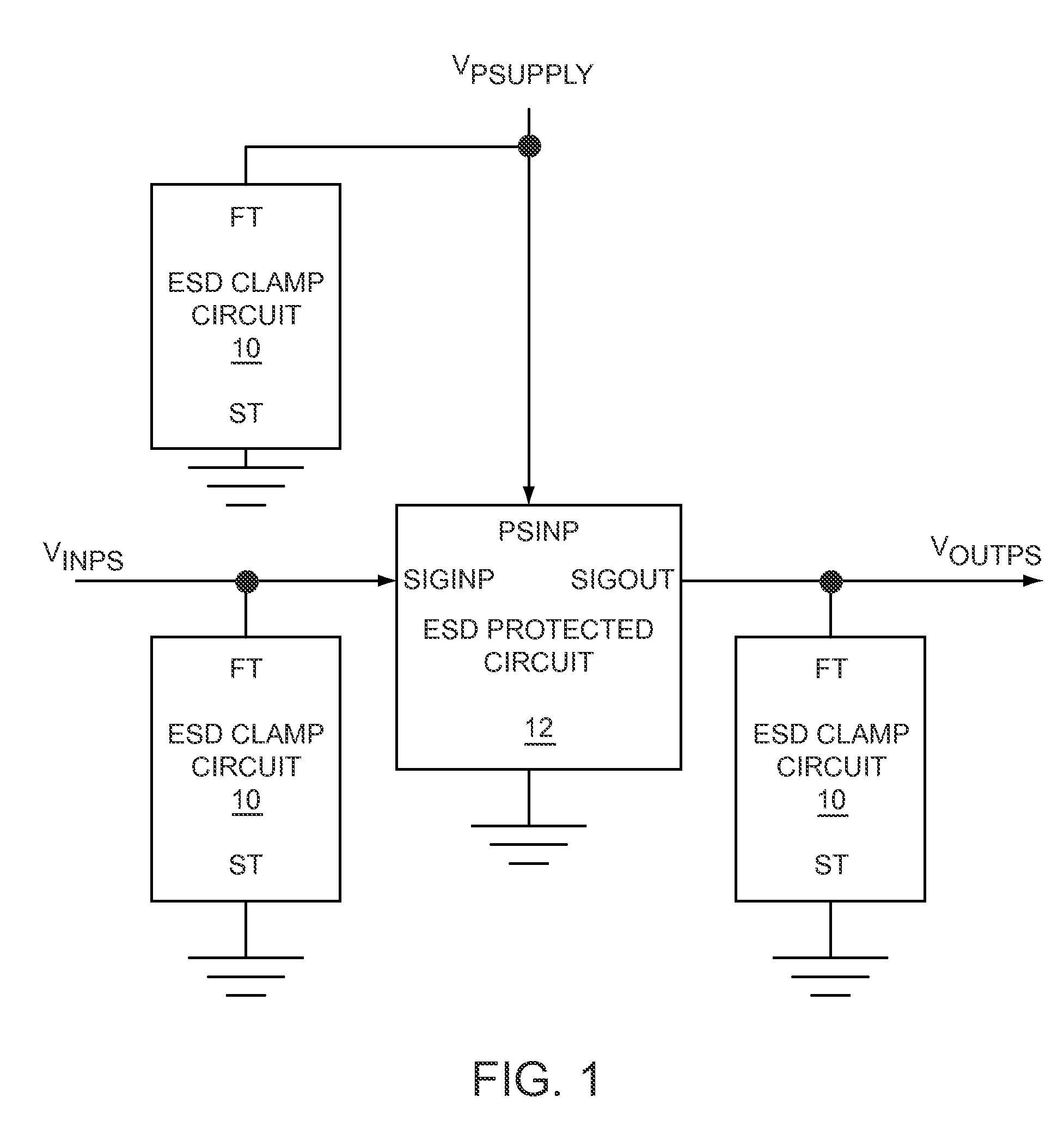

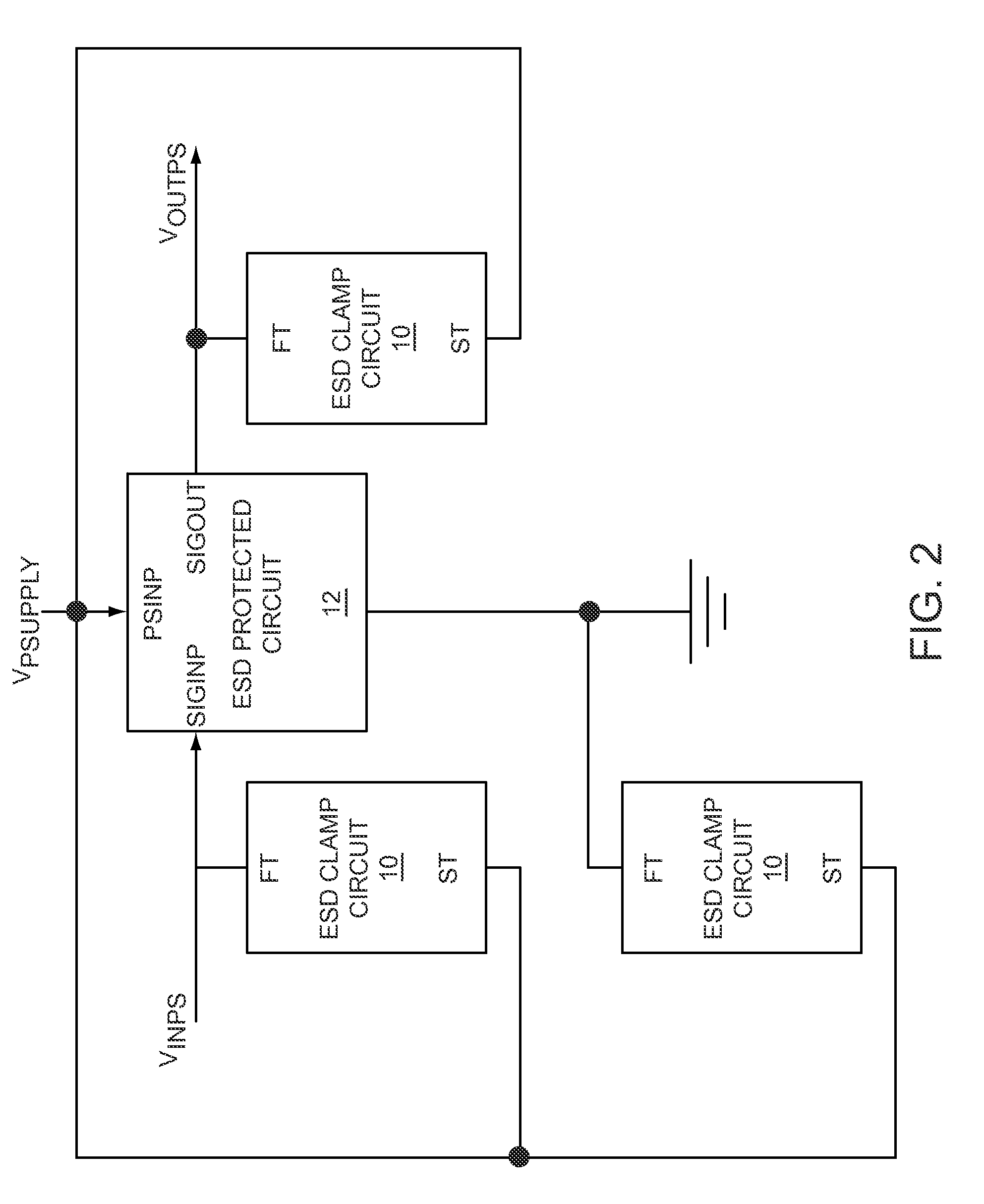

Depletion-mode field effect transistor based electrostatic discharge protection circuit

InactiveUS7881029B1Minimize parasitic capacitanceMaximize linearityAntennas earthing switches associationAmplifier protection circuit arrangementsLevel shiftingEngineering

The present invention relates to an electrostatic discharge (ESD) clamp circuit that is used to protect other circuitry from high voltage ESD events. The ESD clamp circuit may include a field effect transistor (FET) element as a clamping element, which is triggered by using a drain-to-gate capacitance and a drain-to-gate resistance of the FET element and a resistive element as a voltage divider to divide down an ESD voltage to provide a triggering gate voltage of the FET element. In its simplest embodiment, the ESD clamp circuit includes only an FET element, a resistive element, a source-coupled level shifting diode, and a reverse protection diode. Therefore, the ESD clamp circuit may be small compared to other ESD protection circuits. The simplicity of the ESD clamp circuit may minimize parasitic capacitances, thereby maximizing linearity of the ESD clamp circuit over a wide frequency range.

Owner:QORVO US INC

High speed low loss gate drive circuit

ActiveUS20130162322A1Maximize dv/dt immunityReduce switching lossesTransistorElectronic switchingCapacitanceEngineering

A gate drive circuit includes an insulated gate semiconductor switch. A controlled current source is connected to the semiconductor switch gate terminal to provide a gate drive circuit that is responsive to recycled gate charge corresponding to an internal gate capacitance of the insulated gate semiconductor switch.

Owner:GENERAL ELECTRIC CO

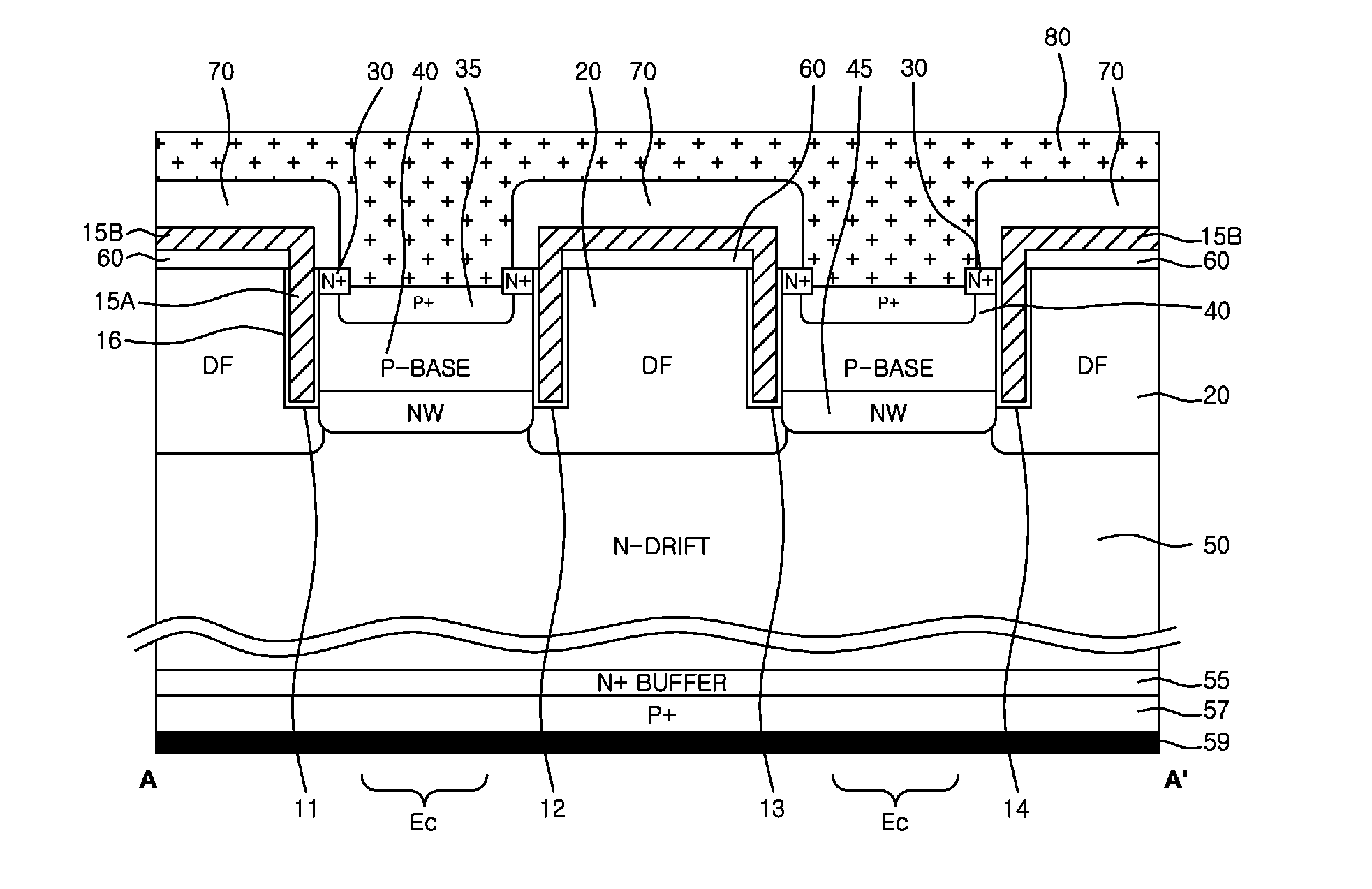

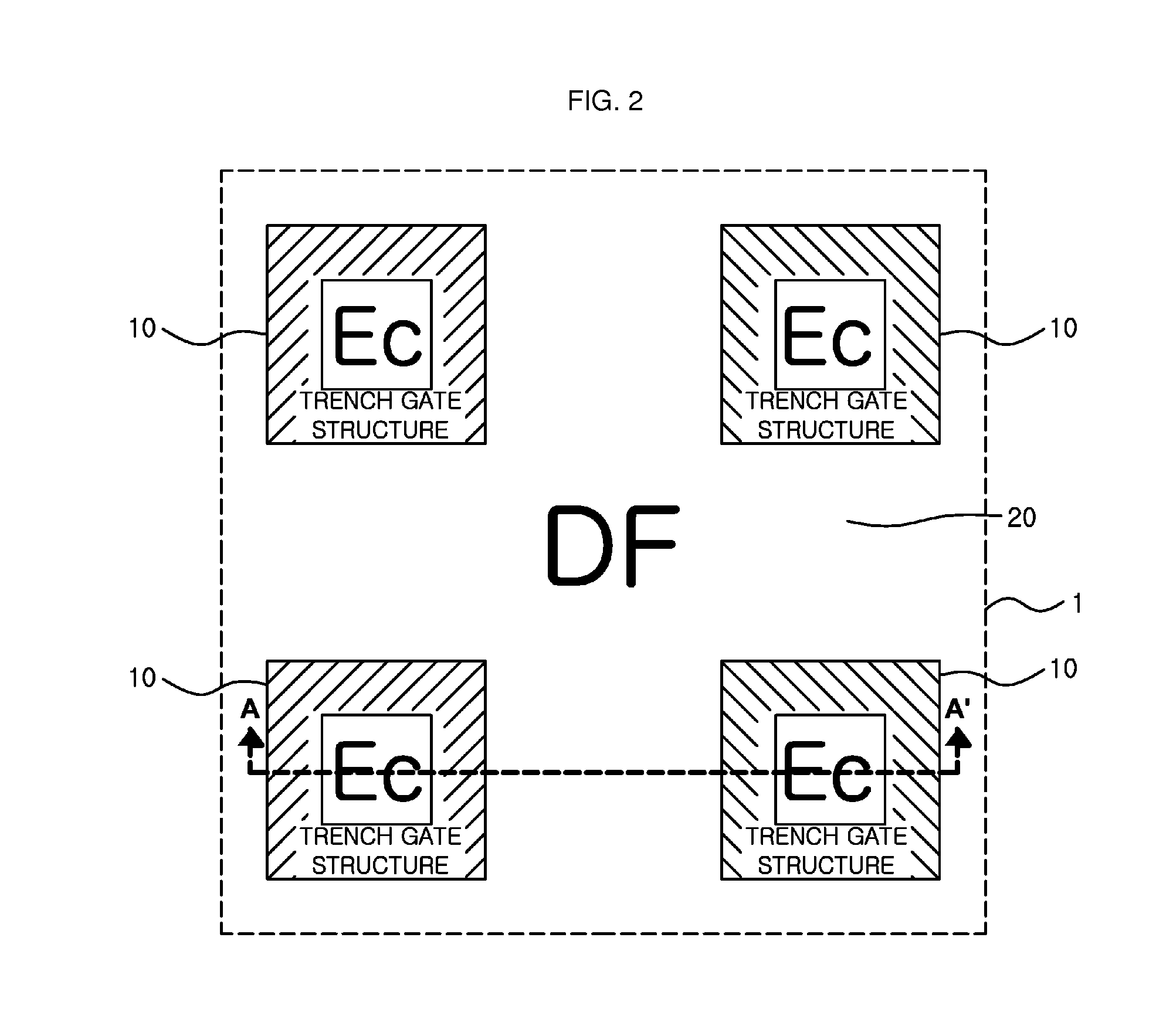

Power semiconductor device

ActiveUS20160336393A1Reduce gate capacitanceSolve the large consumptionSemiconductor/solid-state device detailsSolid-state devicesCapacitancePower semiconductor device

The present examples relate to a power semiconductor device. The present examples also relate to a power semiconductor device that maintains a breakdown voltage and reduces a gate capacitance through improving the structure of an Injection Enhanced Gate Transistor (IEGT), and thereby reduces strength of an electric field compared to alternative technologies. Accordingly, the present examples provide a power semiconductor device with a small energy consumption and with an improved switching functionality.

Owner:MAGNACHIP SEMICONDUCTOR LTD

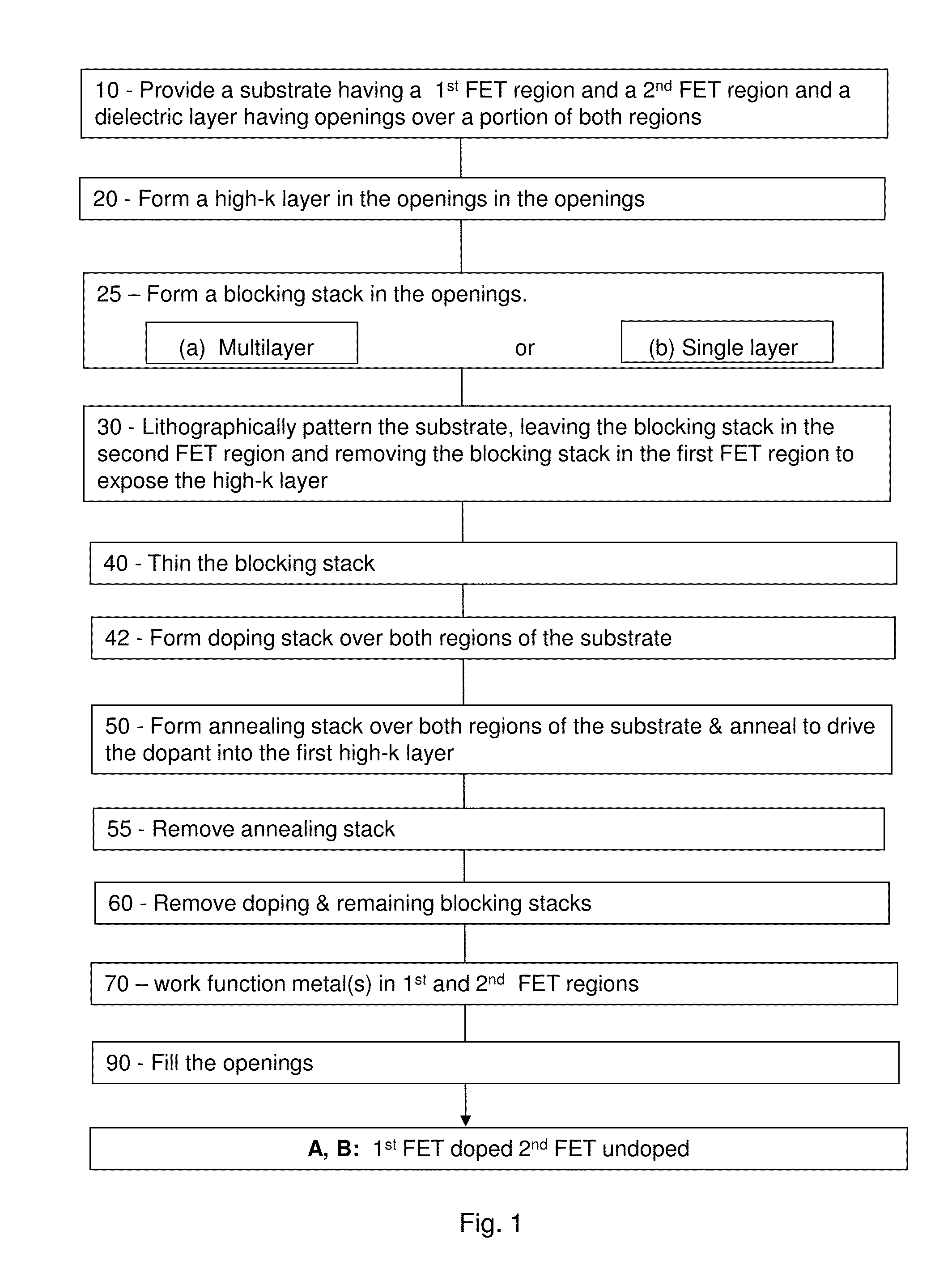

Method of patterning dopant films in high-k dielectrics in a soft mask integration scheme

ActiveUS20160027664A1Improve performanceReduce adverse effectsSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceDielectric

A method of fabricating advanced node field effect transistors using a replacement metal gate process. The method includes dopant a high-k dielectric directly or indirectly by using layers composed of multi-layer thin film stacks, or in other embodiments, by a single blocking layer. By taking advantage of unexpected etch selectivity of the multi-layer stack or the controlled etch process of a single layer stack, etch damage to the high-k may be avoided and work function metal thicknesses can be tightly controlled which in turn allows field effect transistors with low Tiny (inverse of gate capacitance) mismatch.

Owner:IBM CORP

Current-source gate driver

ActiveUS20100019807A1Electronic switchingElectric pulse generatorCapacitanceVoltage regulator module

Provided is a current-source gate driver for use with a switching device having a gate capacitance, including an input terminal for receiving a DC voltage; a first switch connected between the input terminal and an output terminal; a second switch connected between the output terminal and a circuit common; a series circuit comprising a first capacitor and an inductor, the series circuit connected between the input terminal and the output terminal; wherein the gate capacitance of the switching device is connected between the output terminal and the circuit common. The current-source gate driver improves efficiency of the power switching devices of a voltage regulator module or other switching converter.

Owner:GANPOWER SEMICON FOSHAN CO LTD

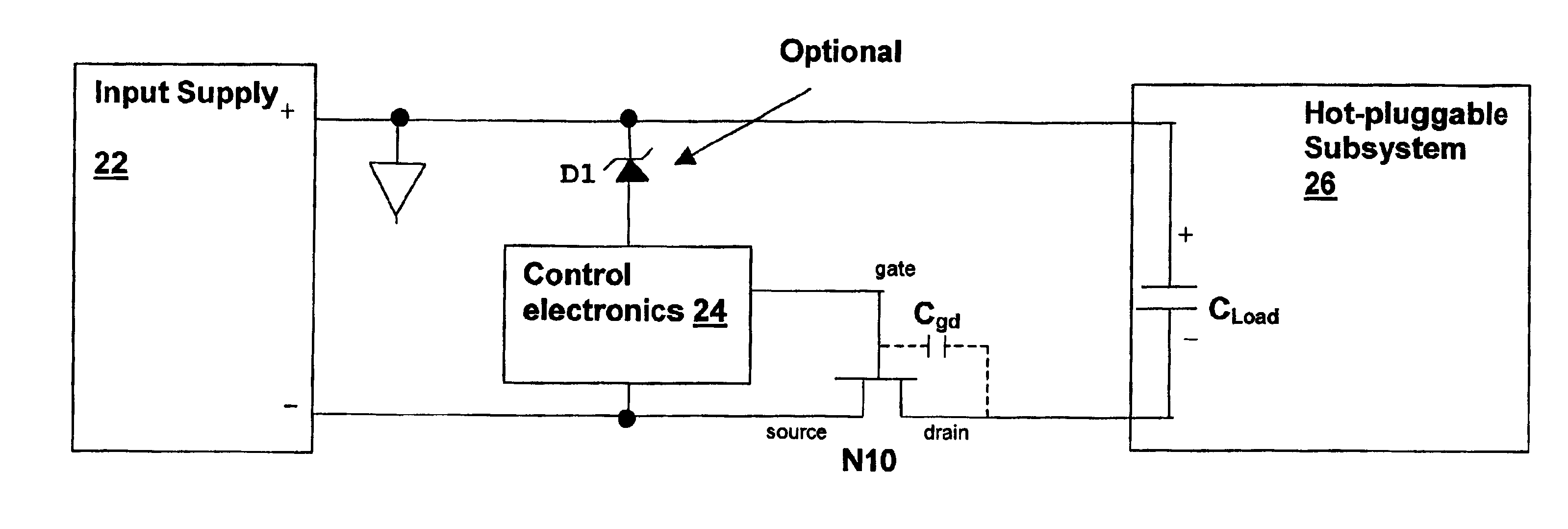

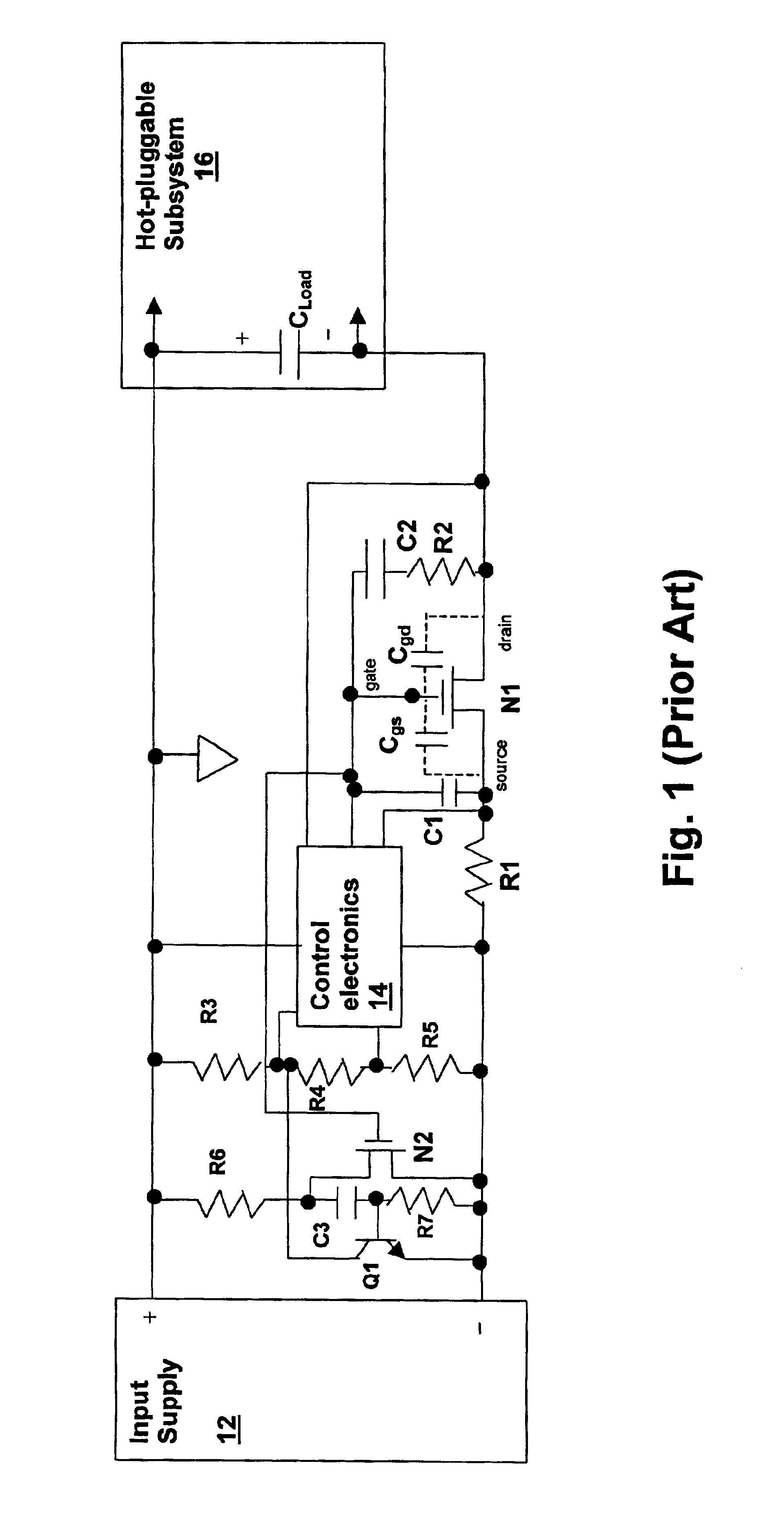

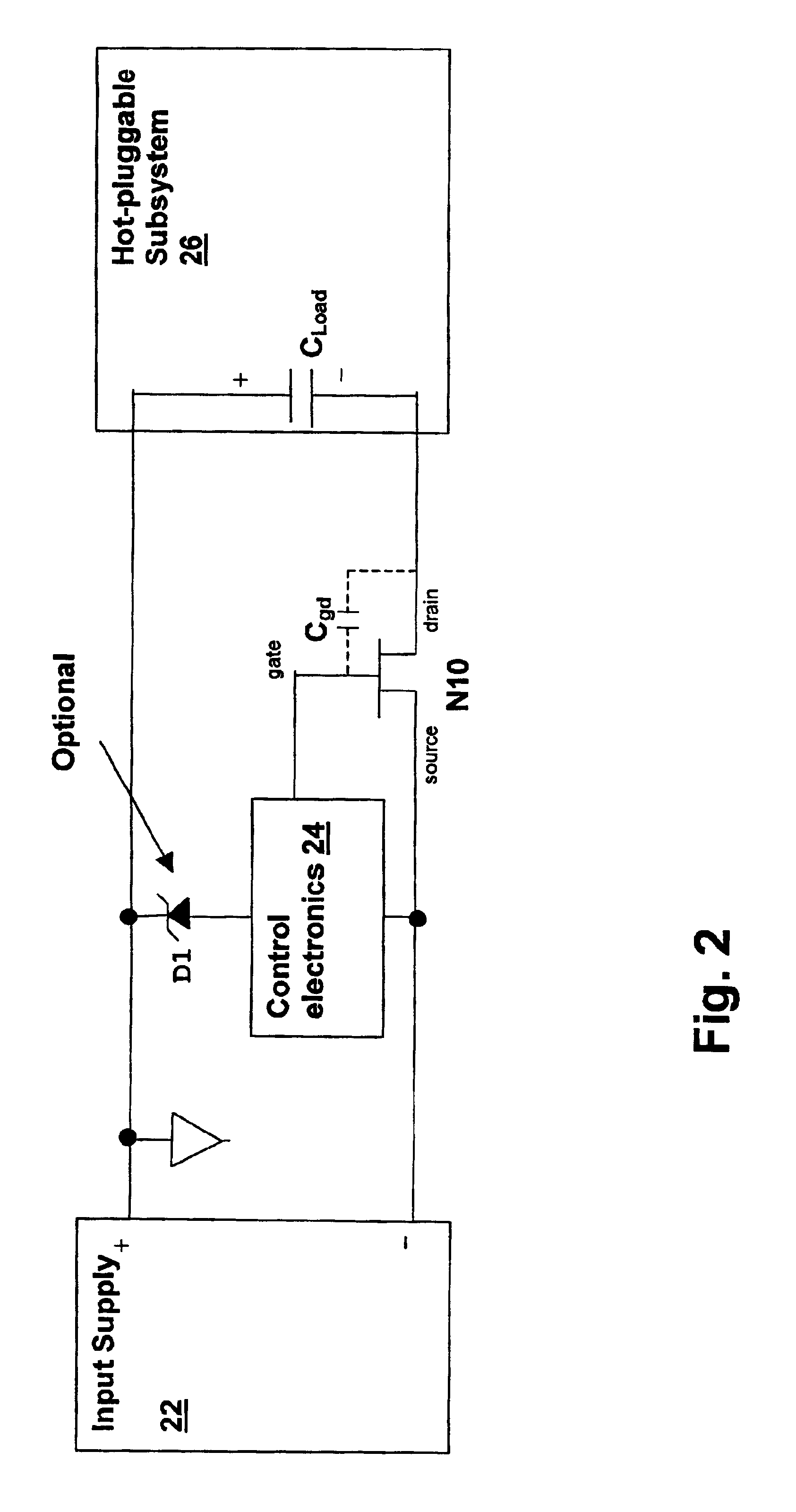

Apparatus and method for adaptively controlling power supplied to a hot-pluggable subsystem

InactiveUS6917504B2Volume/mass flow measurementPower supply for data processingPower-on resetCapacitance

An apparatus and method for adaptively controlling power supplied to a hot-pluggable subsystem controls the inrush current of the hot-pluggable subsystem when the subsystem is coupled to another system that supplies power, and optionally other signal connections. The apparatus and method adaptively control a pass device by detecting the voltage at the gate of the pass device during initial charging of the gate. The gate voltage may be sampled and used subsequently to control the operation of the pass device, and short-circuit conditions may be detected by determining that the miller effect does not change the charging of the gate capacitance. Automatic restart circuitry can be included to generate multiple startup attempts, and under-voltage lockout circuitry and power-on-reset timers can be used to provide a robust solution. The apparatus and method can be adapted to provide a three terminal device that does not require a feedback connection from a power supply output. The three terminal device may include the pass device, or may control an external pass device.

Owner:MICROCHIP TECH INC

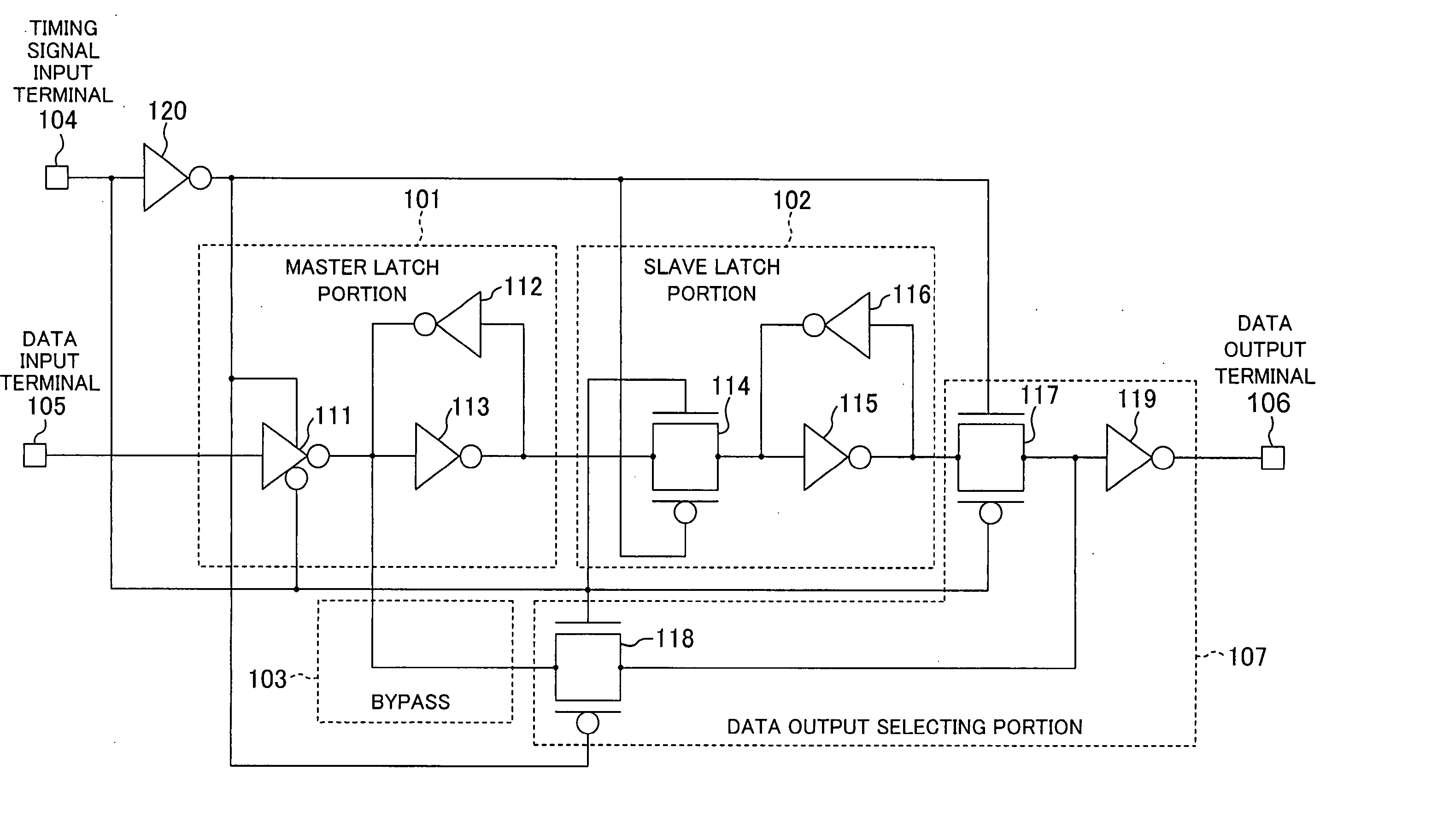

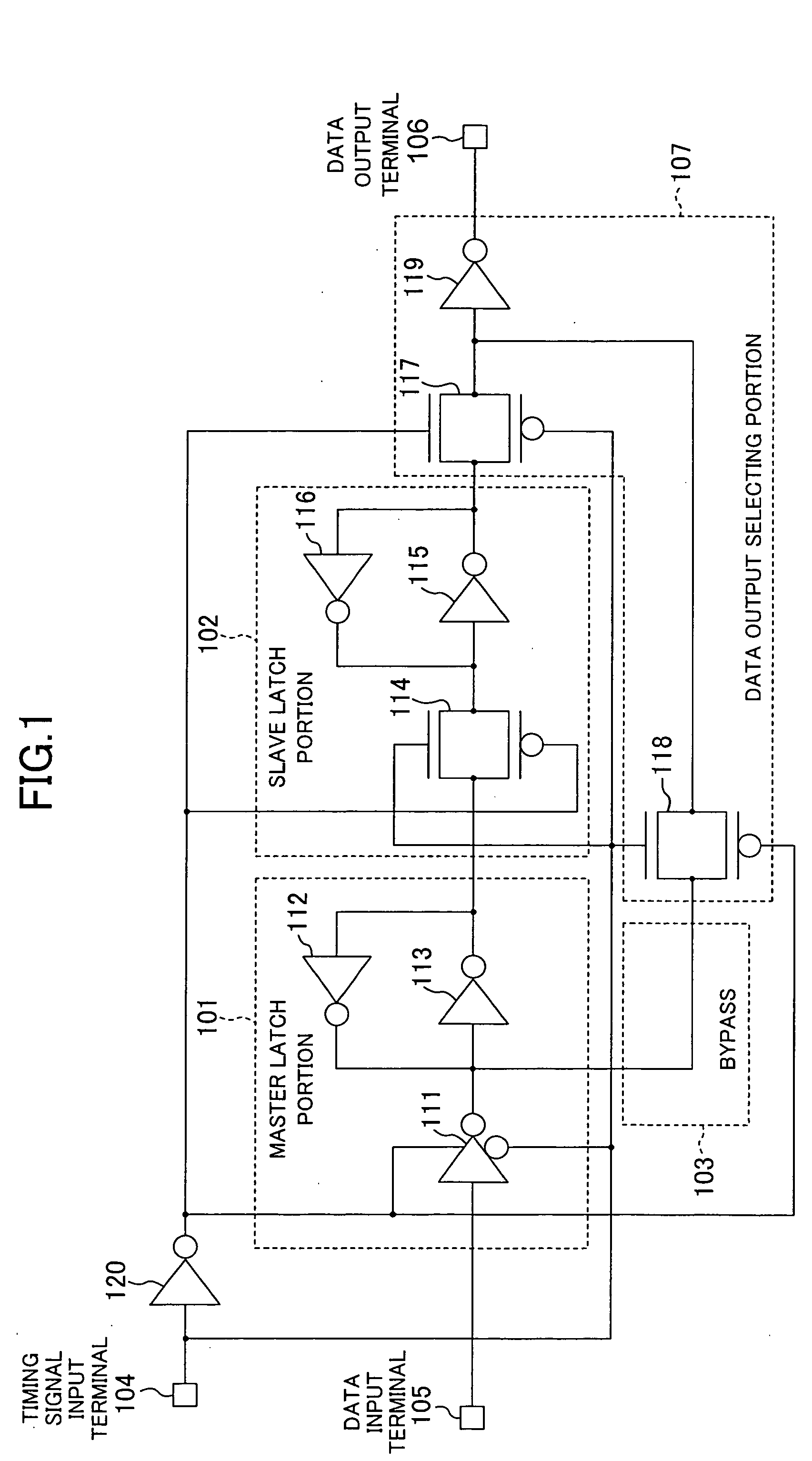

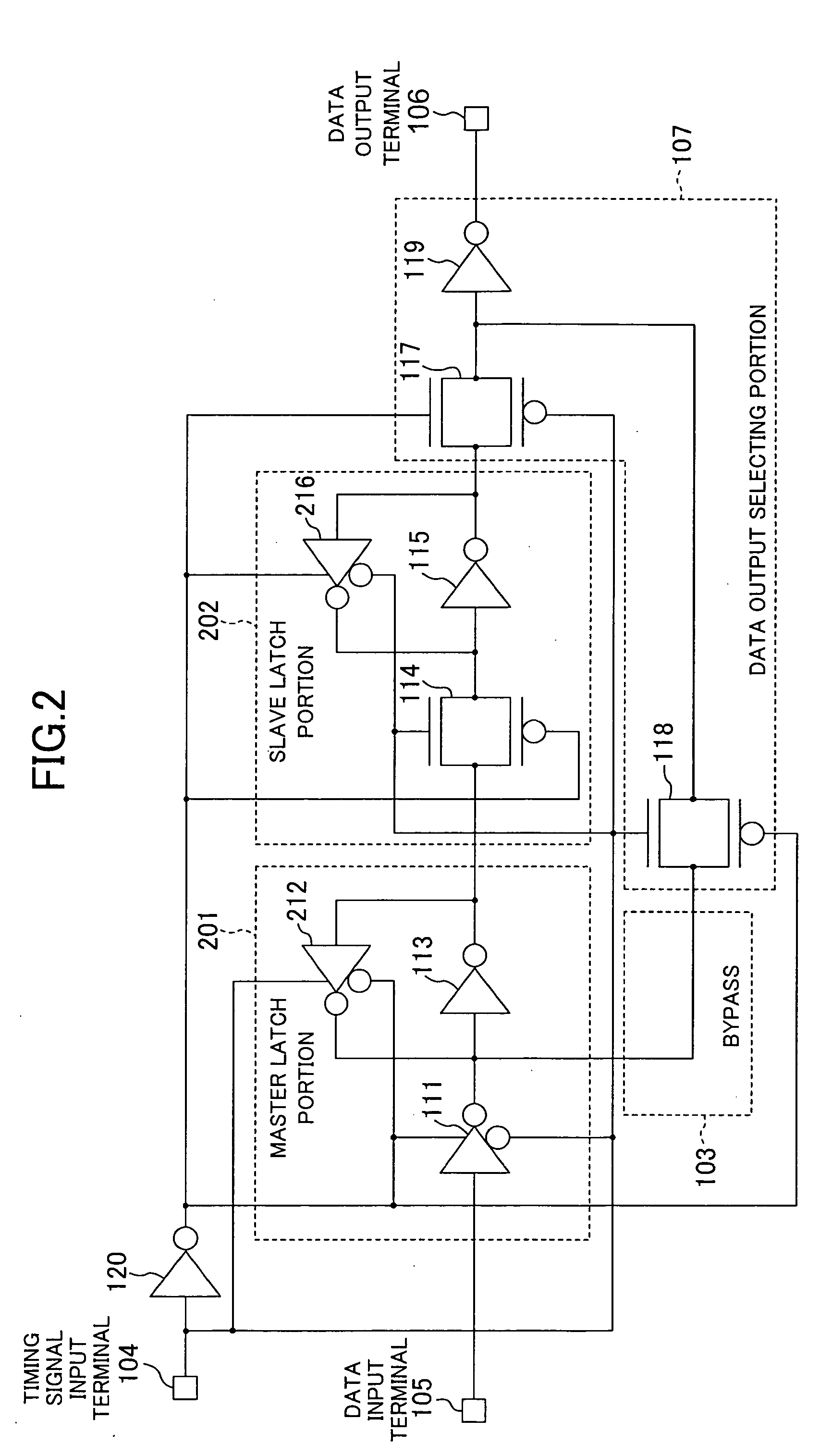

Flip-flop circuit

InactiveUS20050280459A1Easy to holdWithout usingElectric pulse generatorPulse manipulationCapacitanceGate capacitance

To keep input capacitance and driving capability at respective data input and output terminals of a flip-flop circuit, the flip-flop includes: a mater latch portion; a slave latch portion; and a data output selecting portion. The master latch portion includes a tri-state inverter, which is connected to the input terminal. The data output selecting portion is constituted by two pass gates and an inverter, which is connected to the output terminal. The input capacitance of the flip-flop circuit is determined by gate capacitances of transistors constituting the tri-state inverter connected to the input terminal. The driving capability of the flip-flop circuit is determined by the driving capability of the inverter connected to the output terminal. Accordingly, both the input capacitance and the driving capability are kept constant, irrespective of the state of a timing signal such as a clock signal.

Owner:PANASONIC CORP

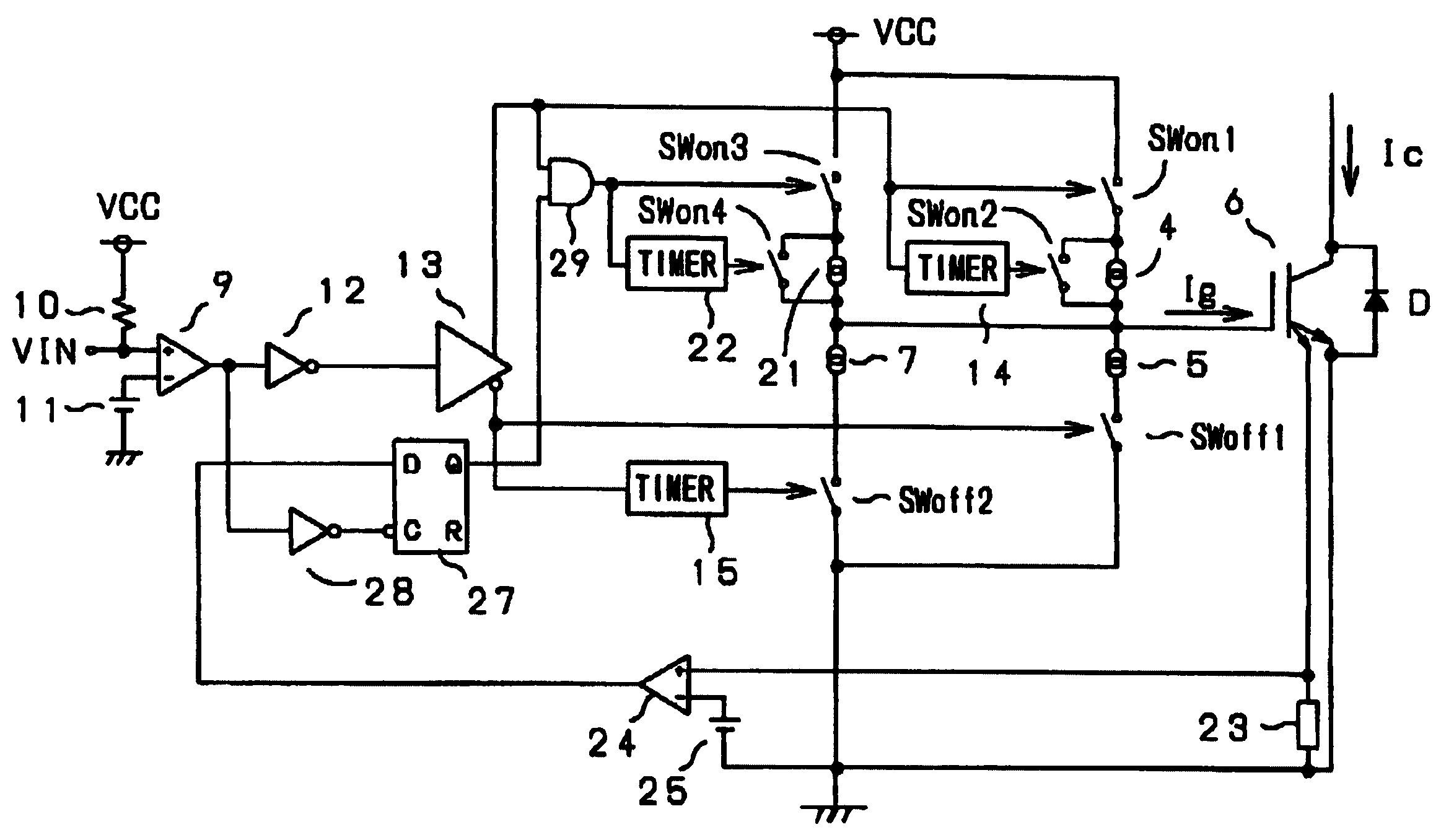

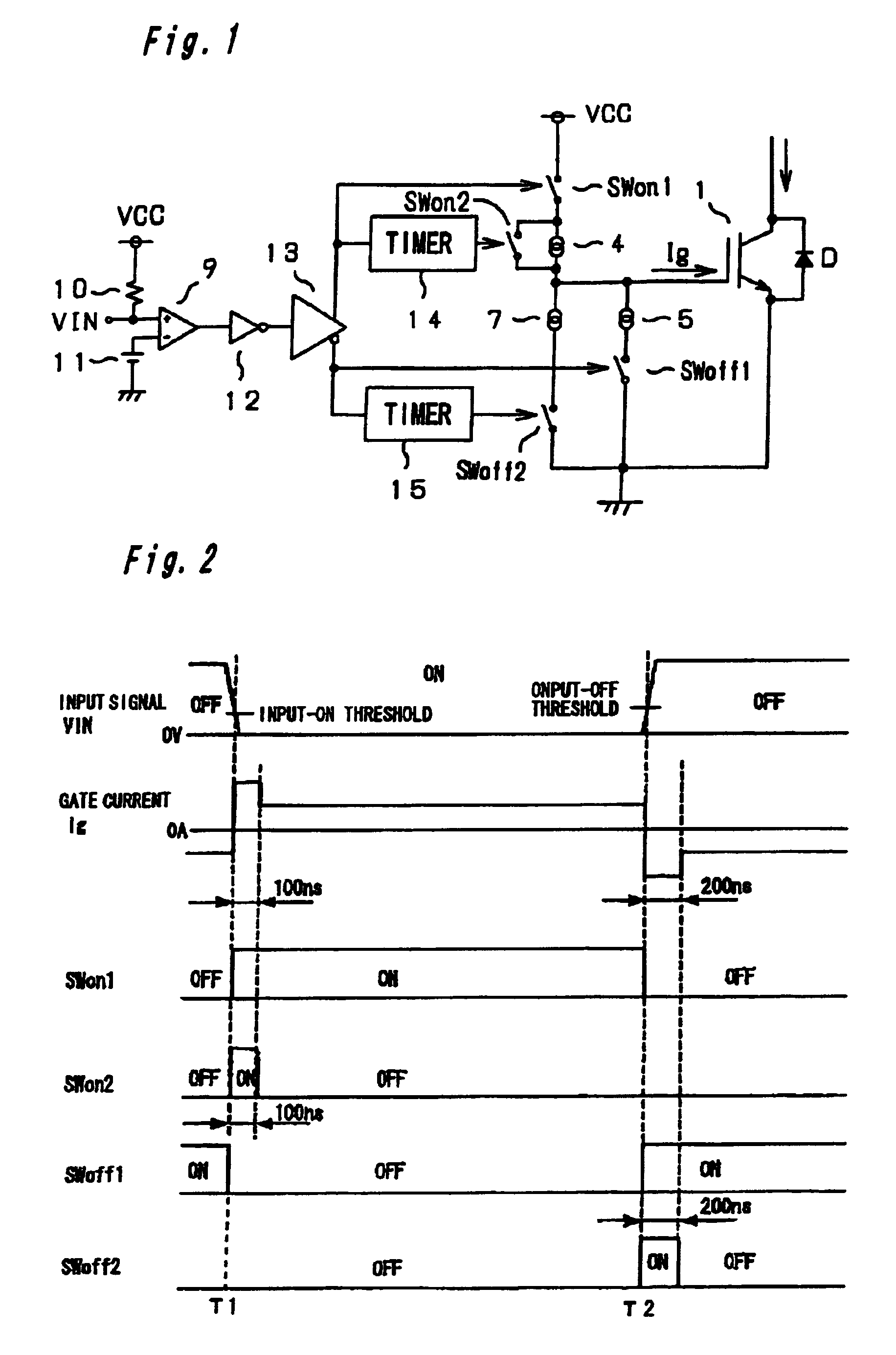

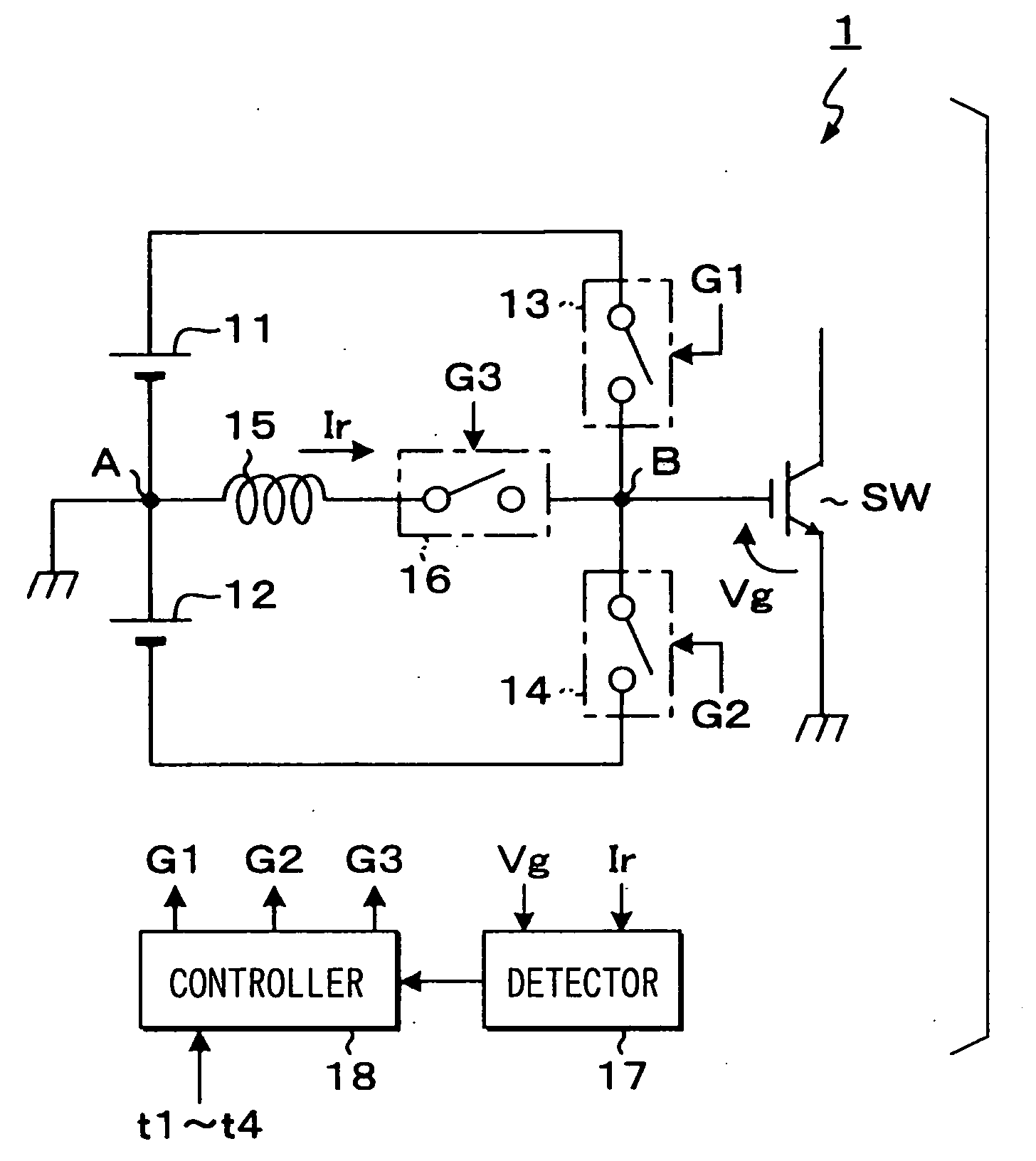

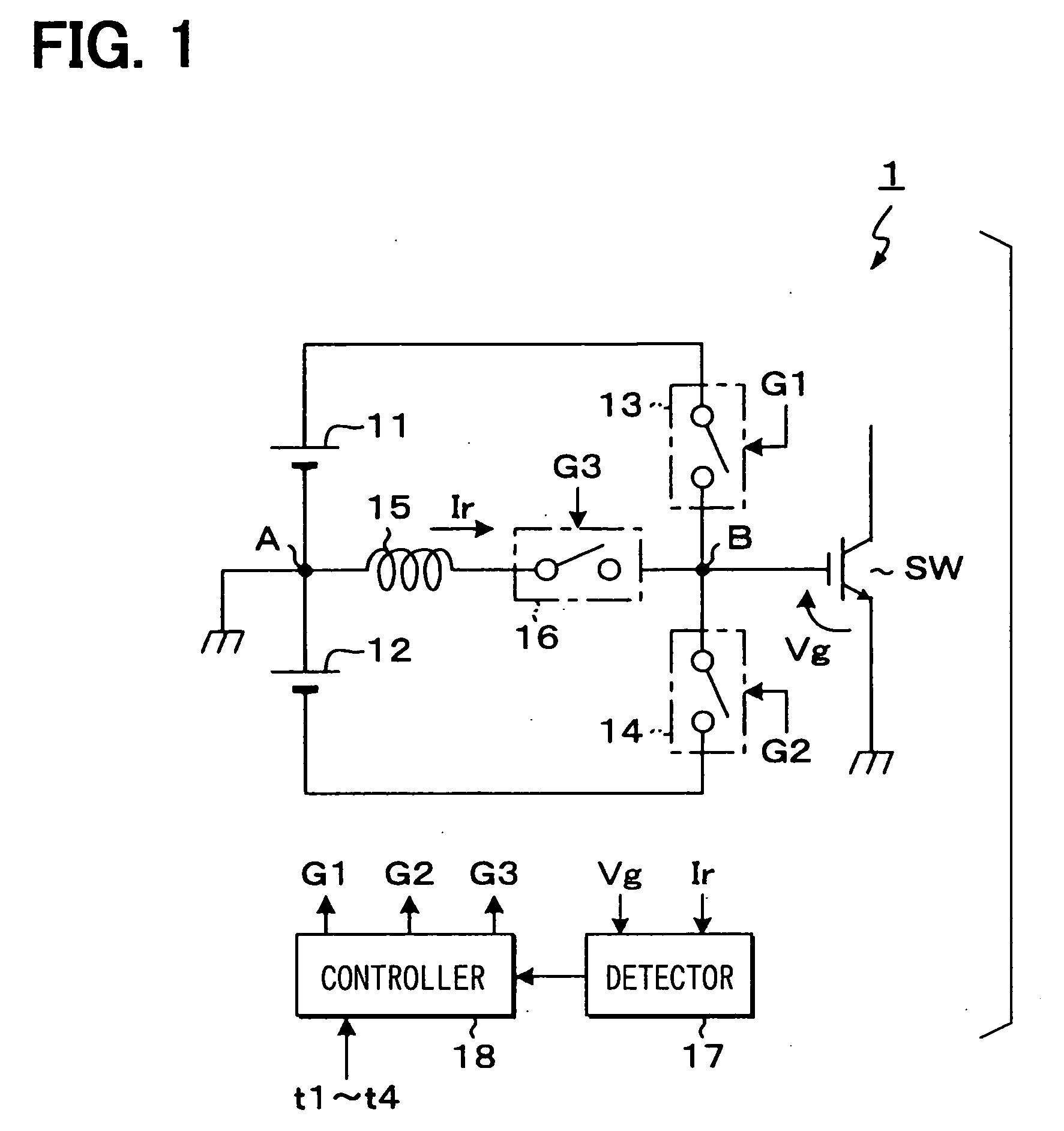

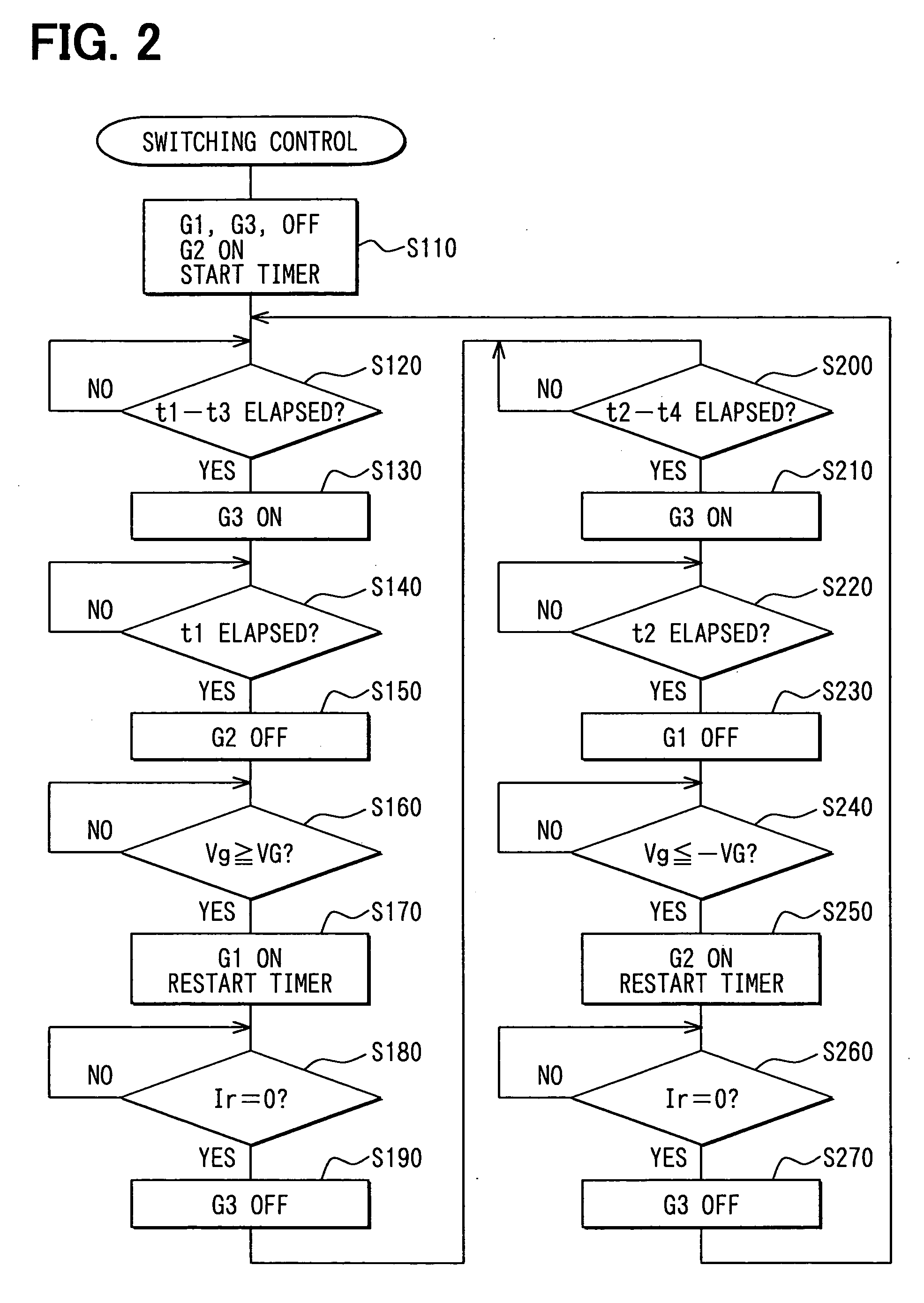

Semiconductor apparatus

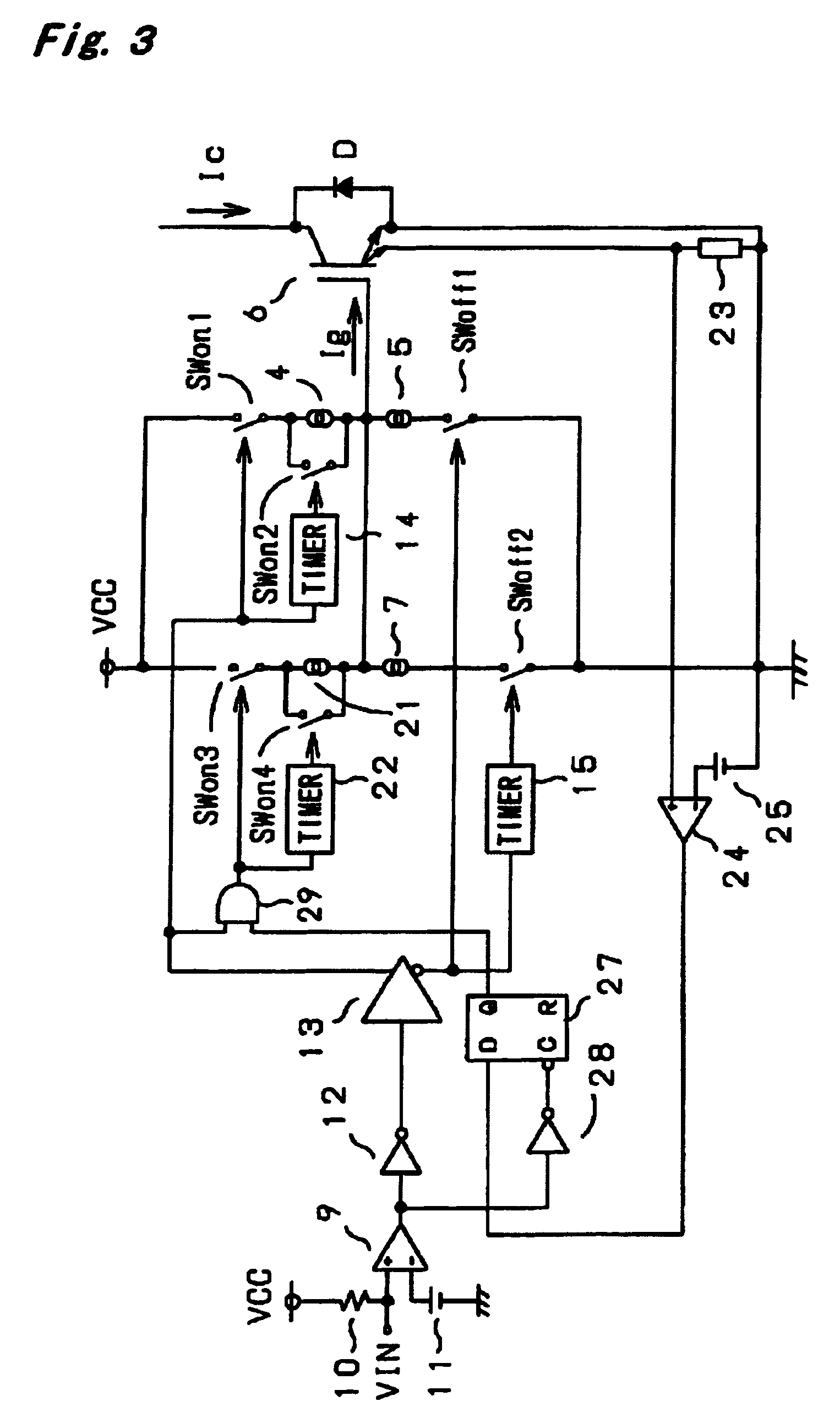

Disclosed is a semiconductor apparatus having an IGBT, which includes a switch SWon 1 for supplying a gate current during an operation for turning on the gate of the IGBT, a switch SWoff 1 for discharging a gate capacitance during an operation for turning off the gate, a switch SWon 2 for increasing the gate current, a timer 14 for turning on the switch SWon 2 in conjunction with the turn-on of the switch SWon 1 and then maintaining the turn-on of the switch SWon 2 only for a first predetermined time, a switch SWoff 2 for increasing the discharge current during the gate turn-off operation, and a timer 15 for turning on the switch SWoff 2 in conjunction with the turn-on of the switch SWoff 1 and then maintaining the turn-on of the switch SWoff 2 only for a second predetermined time.

Owner:MITSUBISHI ELECTRIC CORP

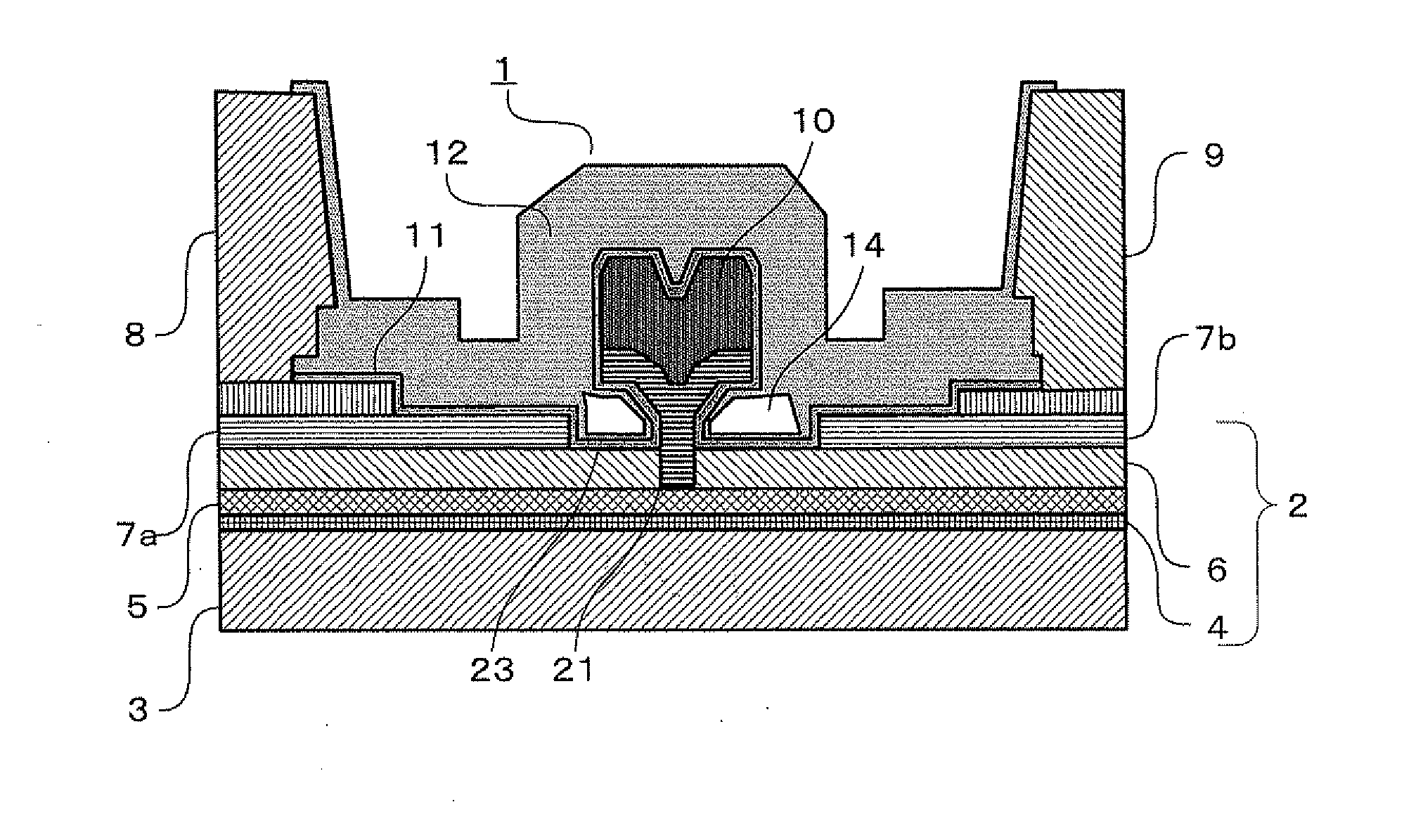

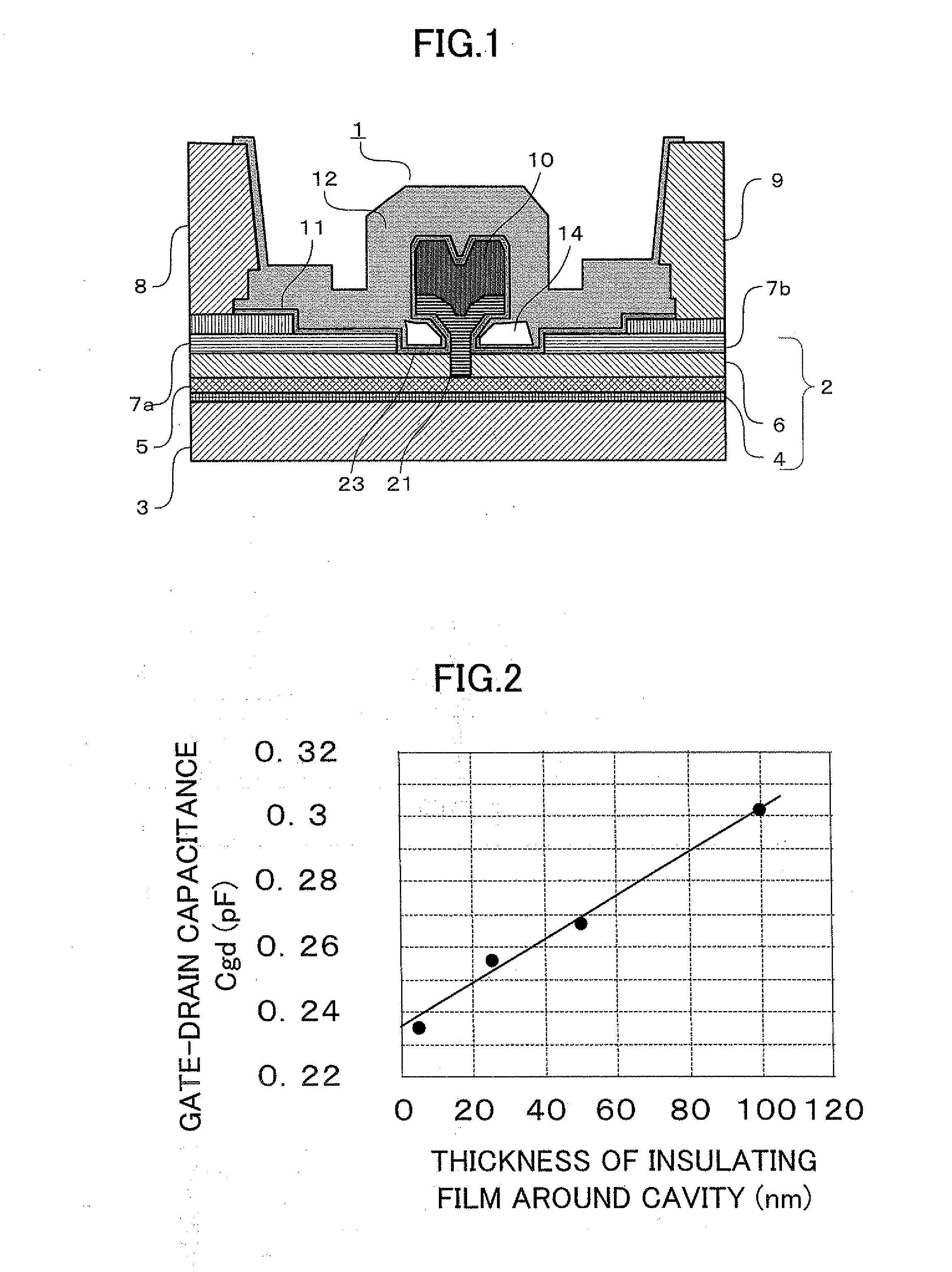

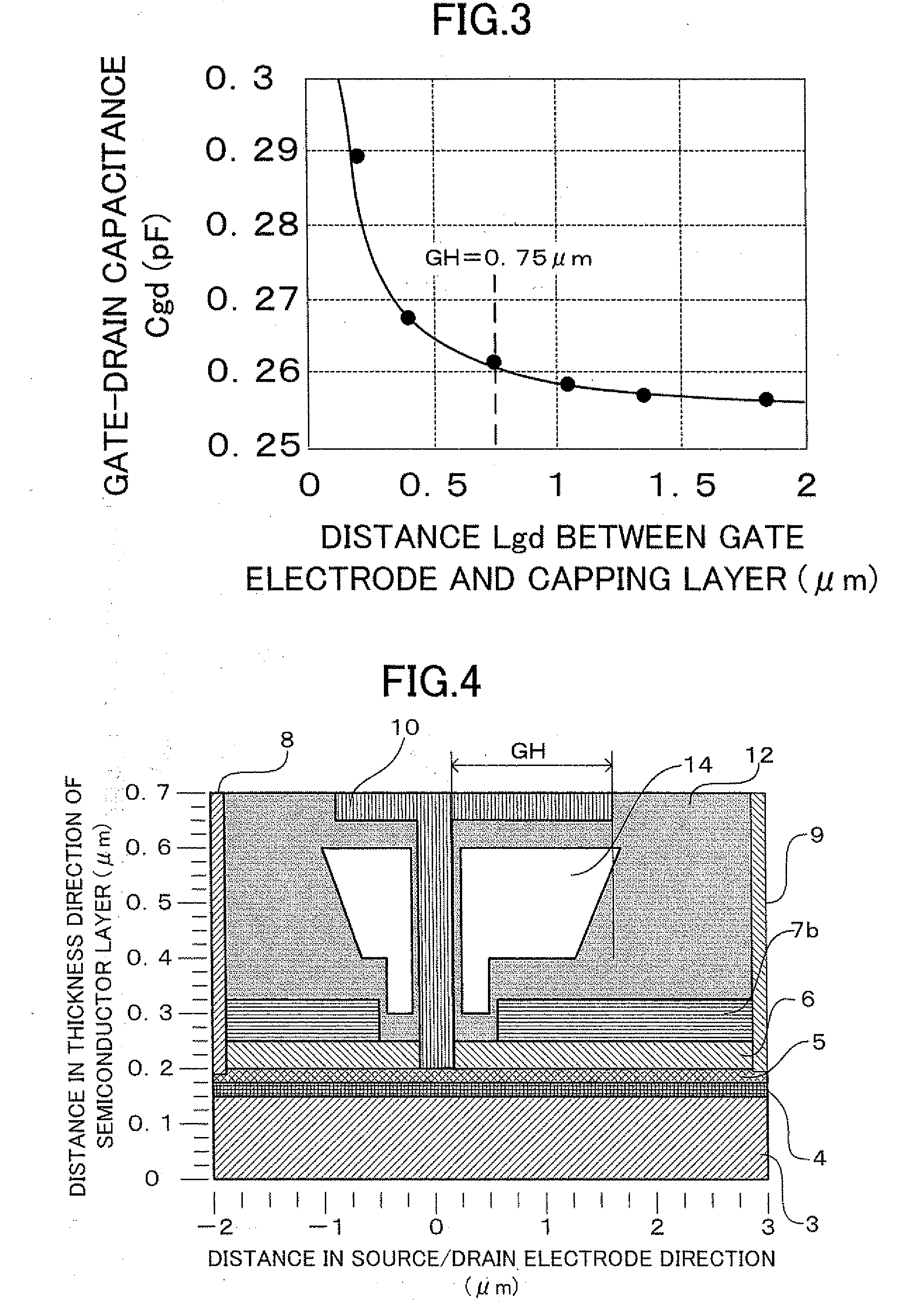

Field-effect transistor and method of manufacturing the same

ActiveUS20080087916A1Increase capacitanceEliminate processing stepsTransistorSemiconductor/solid-state device manufacturingCapacitanceEngineering

A low-cost field-effect transistor with a moisture-resistant gate covered by a thick moisture-resistant insulating film which suppresses an increase in gate capacitance, and a method of manufacturing the field-effect transistor. The field-effect transistor, has one of a T-shaped gate electrode and Γ-shaped gate electrode, a drain electrode, and a source electrode, the source electrode and the drain electrode being electrically connected through an n-doped semiconductor region. The gate, source, and drain electrodes are located on a semiconductor layer which includes an insulating film having a thickness of 50 nm or less and covering a surface of the gate electrode and a surface of the semiconductor layer. A silicon nitride film, deposited by catalytic CVD, covers the insulating film and includes a void volume located between a portion of the gate electrode corresponding to a canopy of an open umbrella and the semiconductor layer.

Owner:MITSUBISHI ELECTRIC CORP

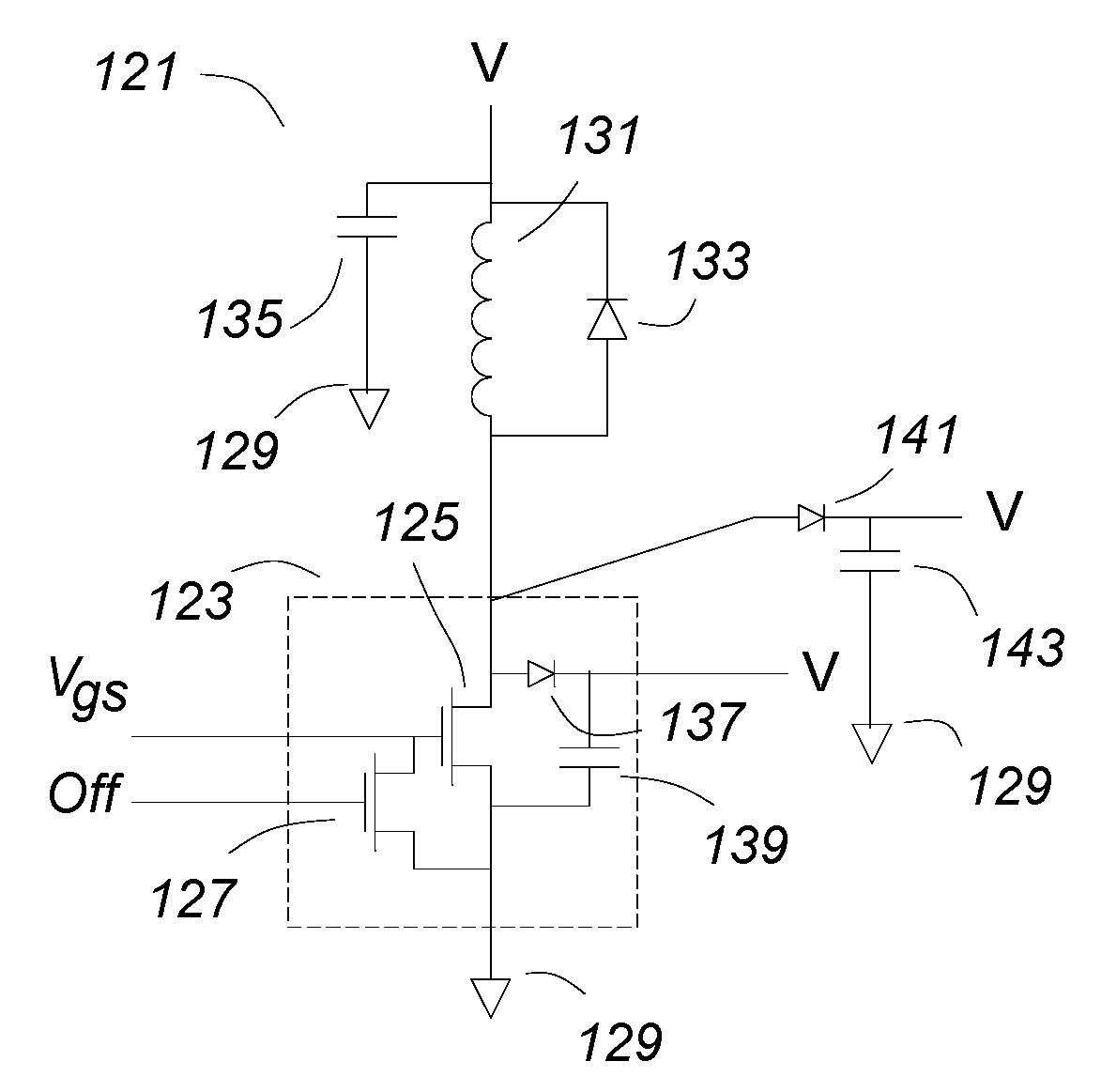

Gate driving circuit

ActiveUS20050001659A1Easy to controlLoss and noiseTransistorElectronic switchingCapacitanceResonance

In a gate driving circuit, when a driving target device is turned on, an auxiliary driving element is turned on to form a closed circuit comprising a DC power source, a reactor, an auxiliary driving element and an OFF-driving element, and make reactor current flow in the direction from a power source intermediate point to an output point in advance. Just before the driving target device is turned on, the OFF-driving element is turned off to form a resonance circuit comprising the reactor, the auxiliary driving element and the gate capacitance, and make gate current (reactor current) flow so that the gate capacitance is charged by using resonance phenomenon of the resonance circuit.

Owner:DENSO CORP

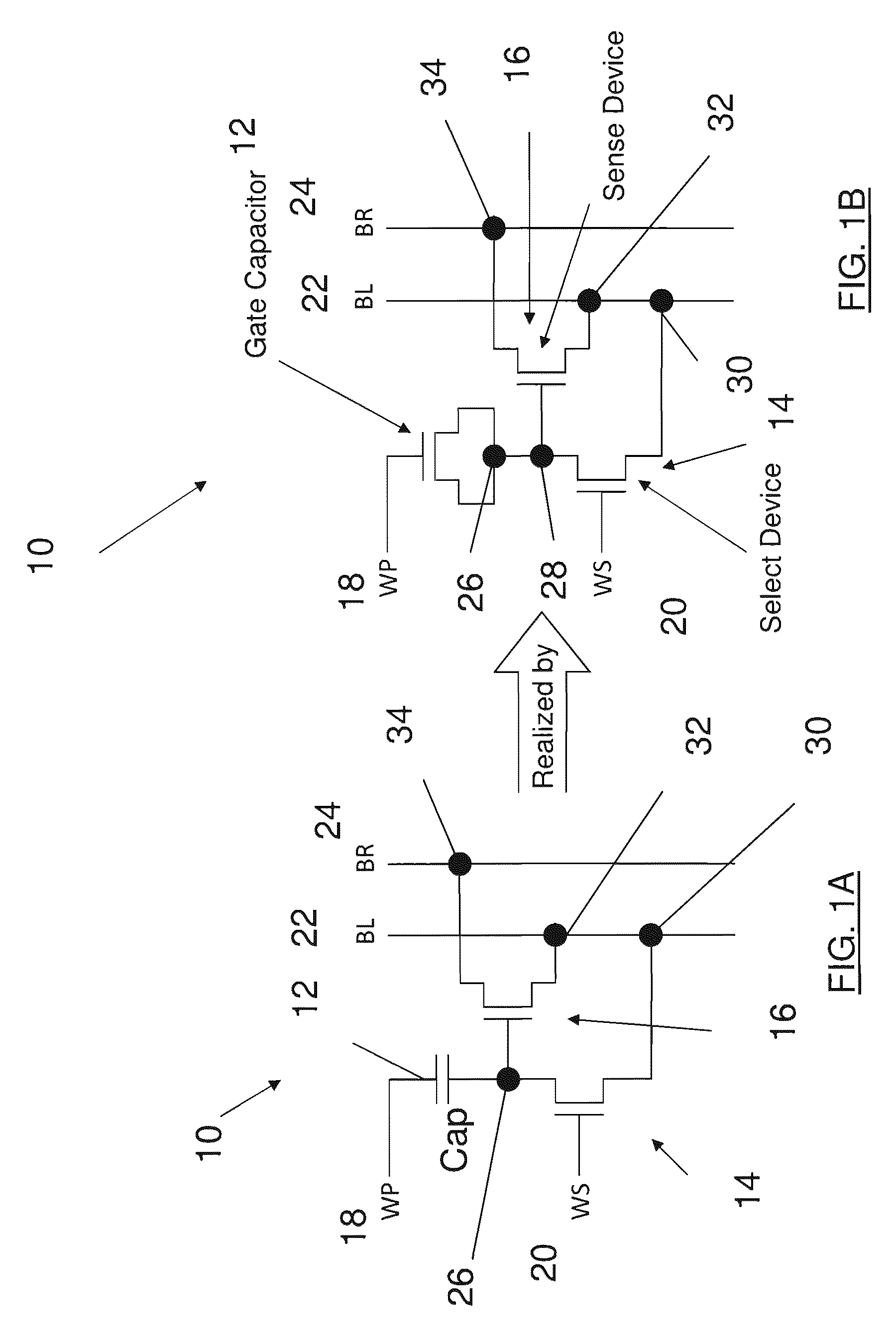

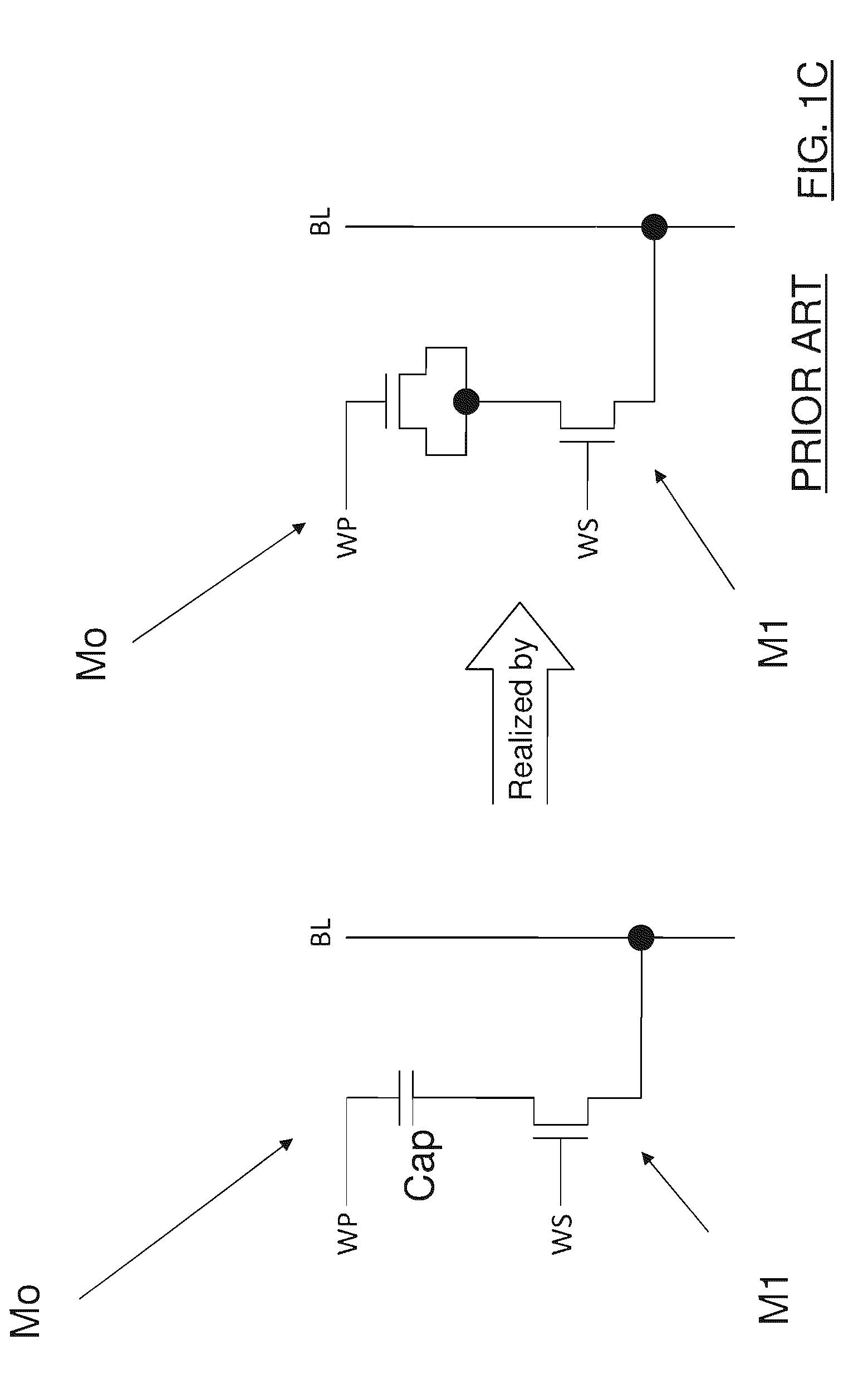

Low voltage and low power memory cell based on nano current voltage divider controlled low voltage sense MOSFET

A memory cell has at least two word lines and at least two bit lines. The cell also has a first select device being connected to at least one word line and one bit line and a gate capacitor element connected to at least one word line and the first select device. The cell also has a sense device being connected in series to the gate capacitor element and the first select device. The sense device is connected to at least two bit lines.

Owner:SICHUAN KILOWAY TECH CO LTD